Patents

Literature

3594results about "Amplifier combinations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

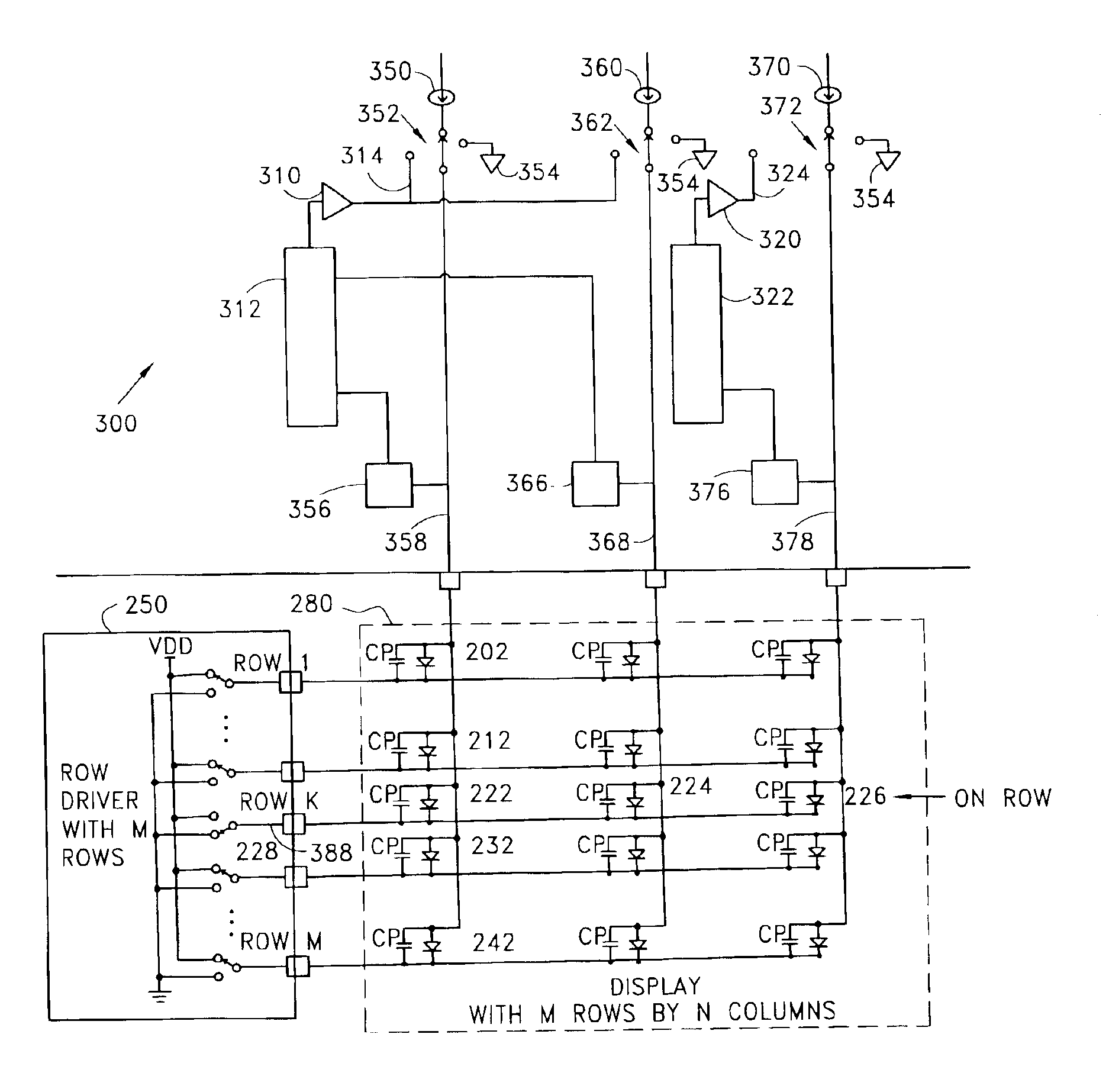

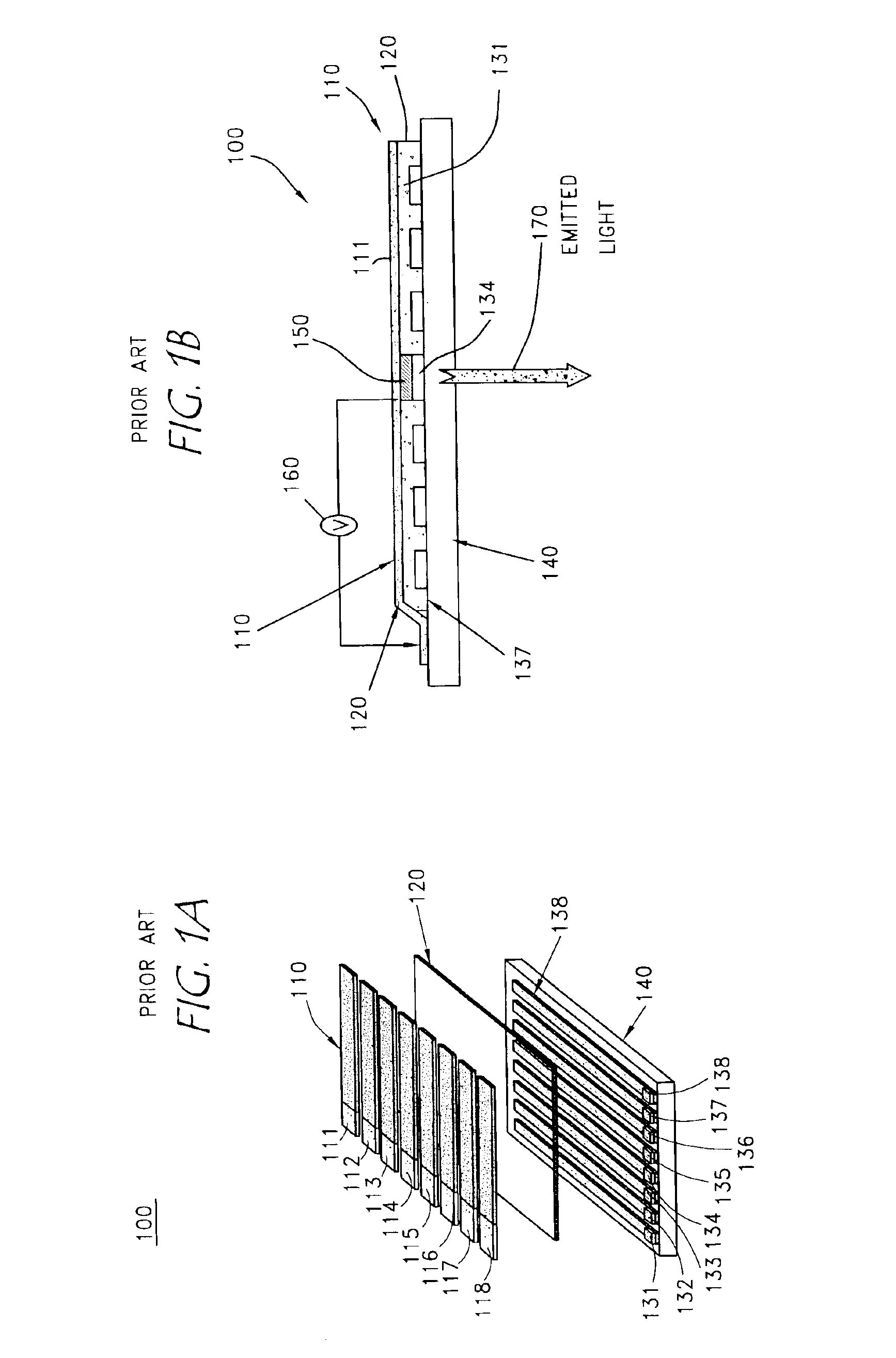

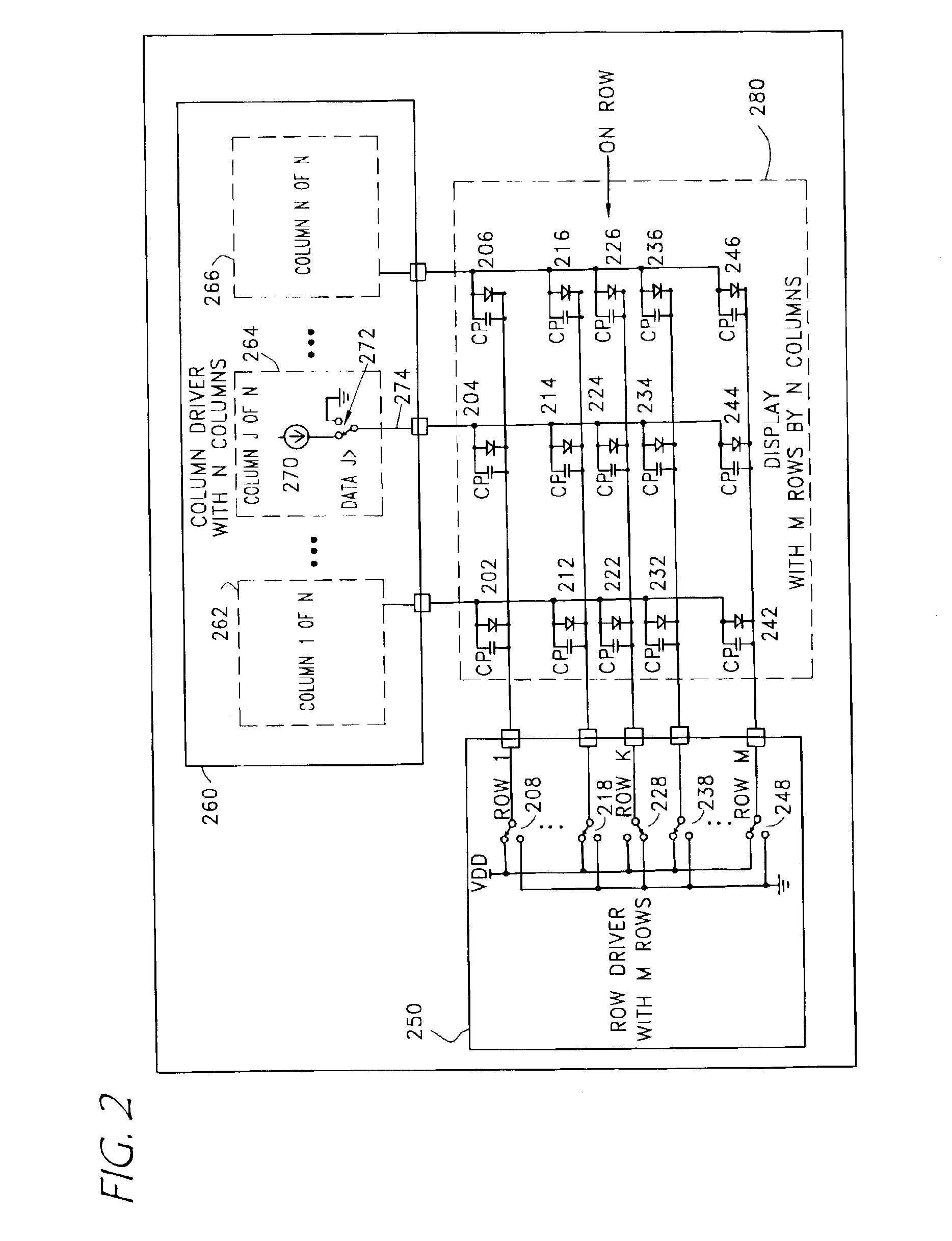

Matrix element precharge voltage adjusting apparatus and method

An apparatus for establishing and applying a voltage to precharge current-driven elements in a matrix. During ordinary scan cycles, a conduction voltage is sensed while the elements conduct a selected current. One or more such sensed conduction voltages are combined to provide a basis for a precharge voltage. Conduction and transient errors are determined, and are compensated for by offsetting the final precharge voltage from the conduction voltage basis. The final precharge voltage is provided to one or more columns during a precharge period of the scan cycle.

Owner:CLARE MICRONIX INTEGRATED SYST

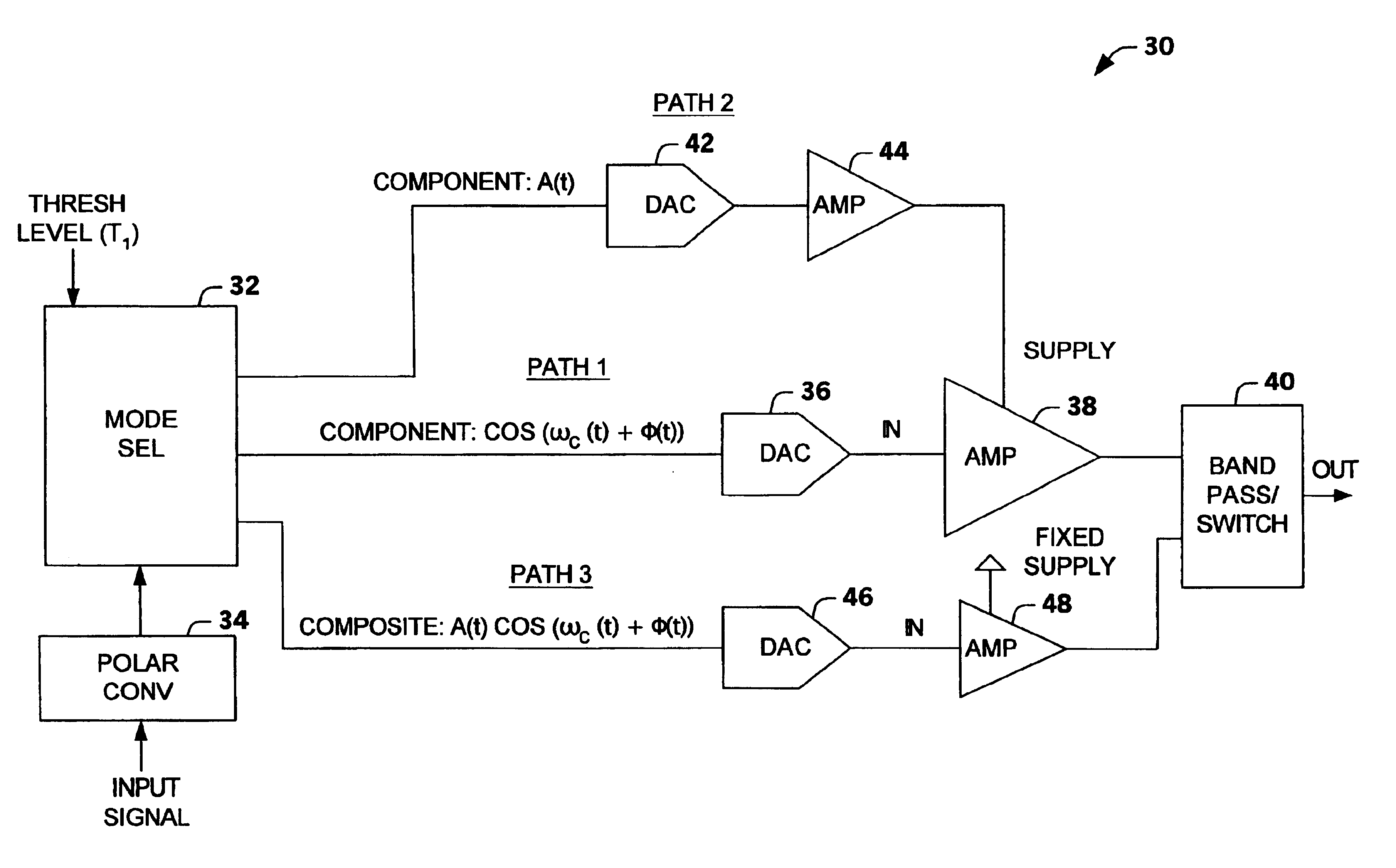

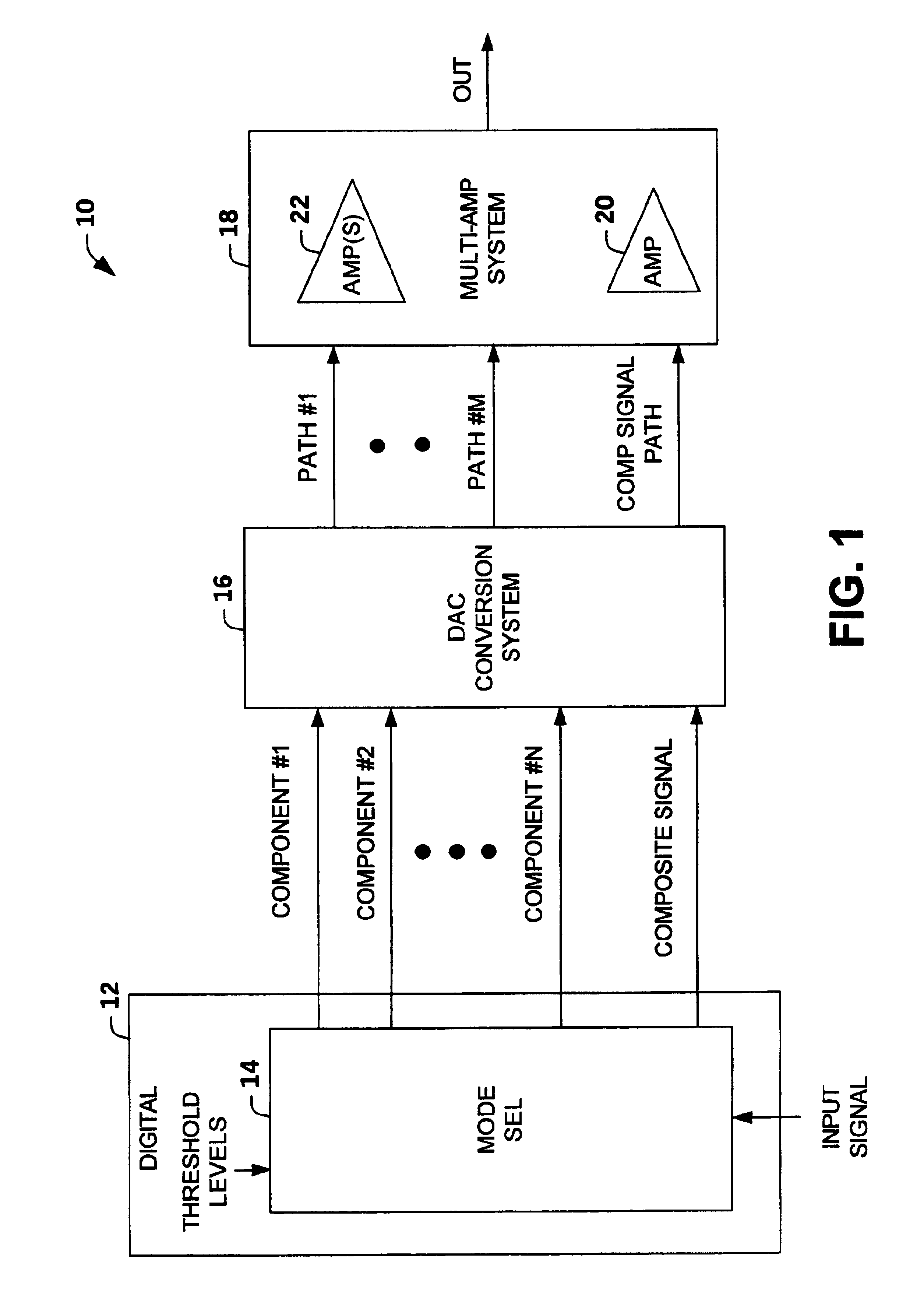

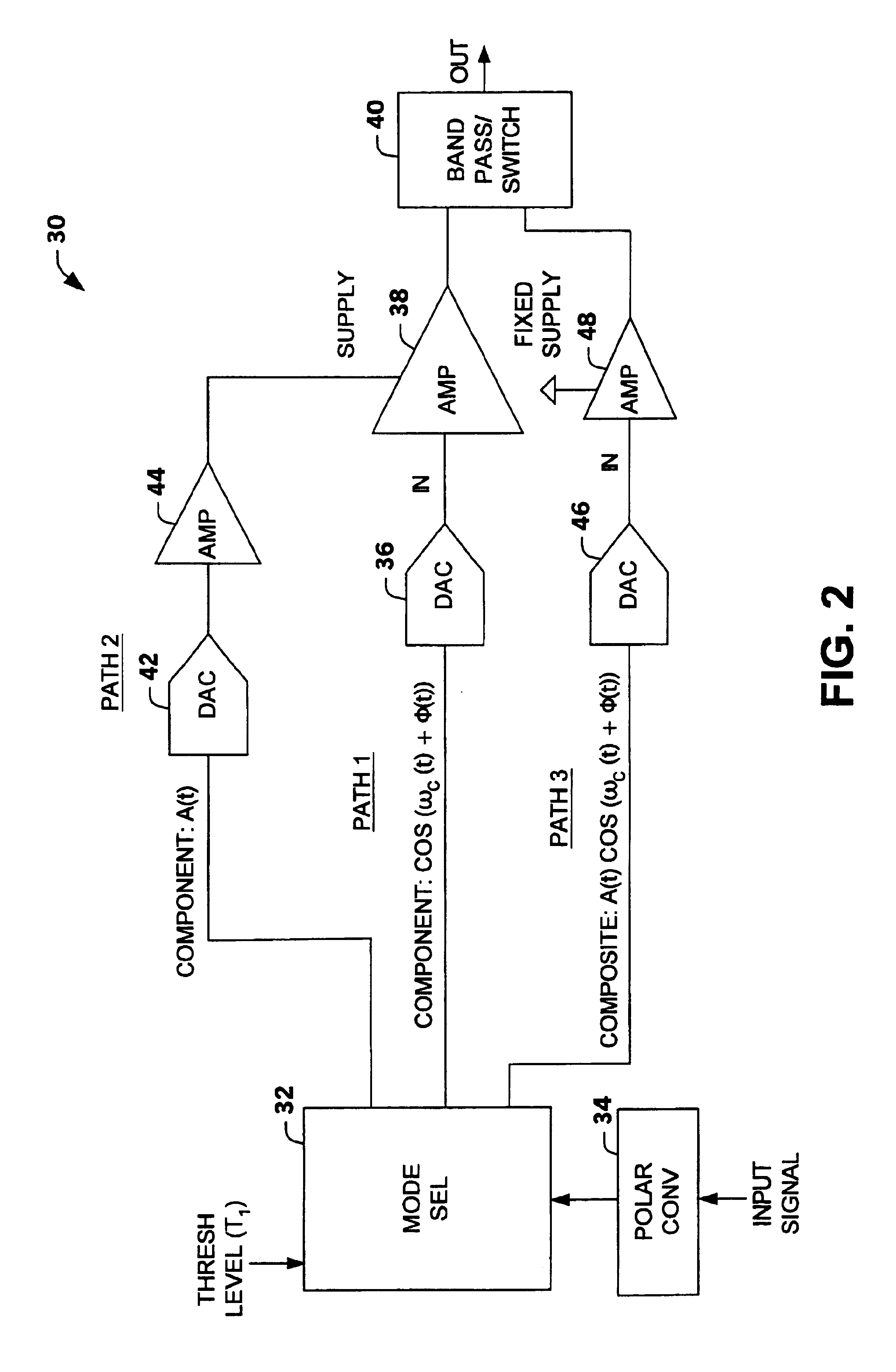

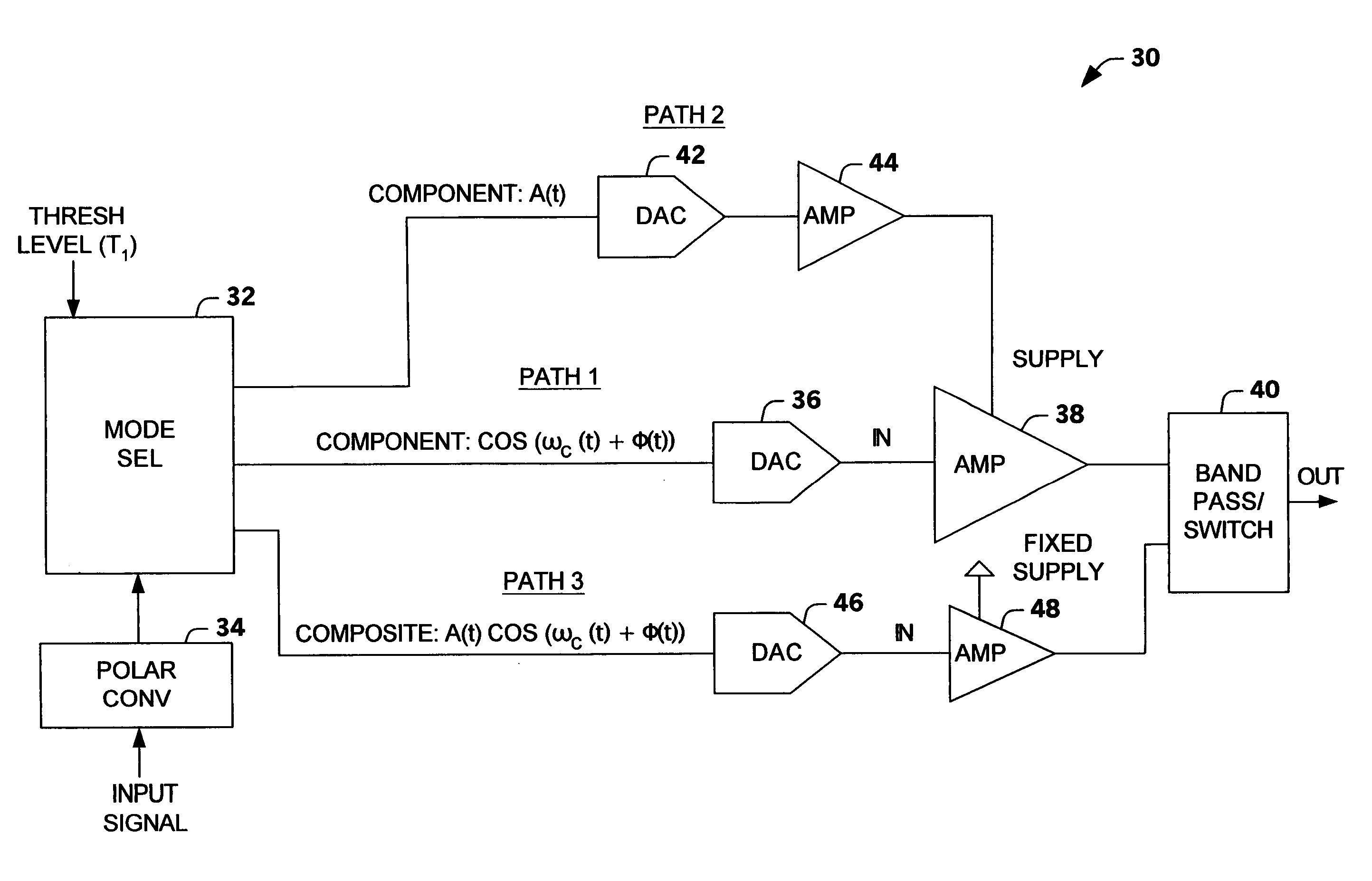

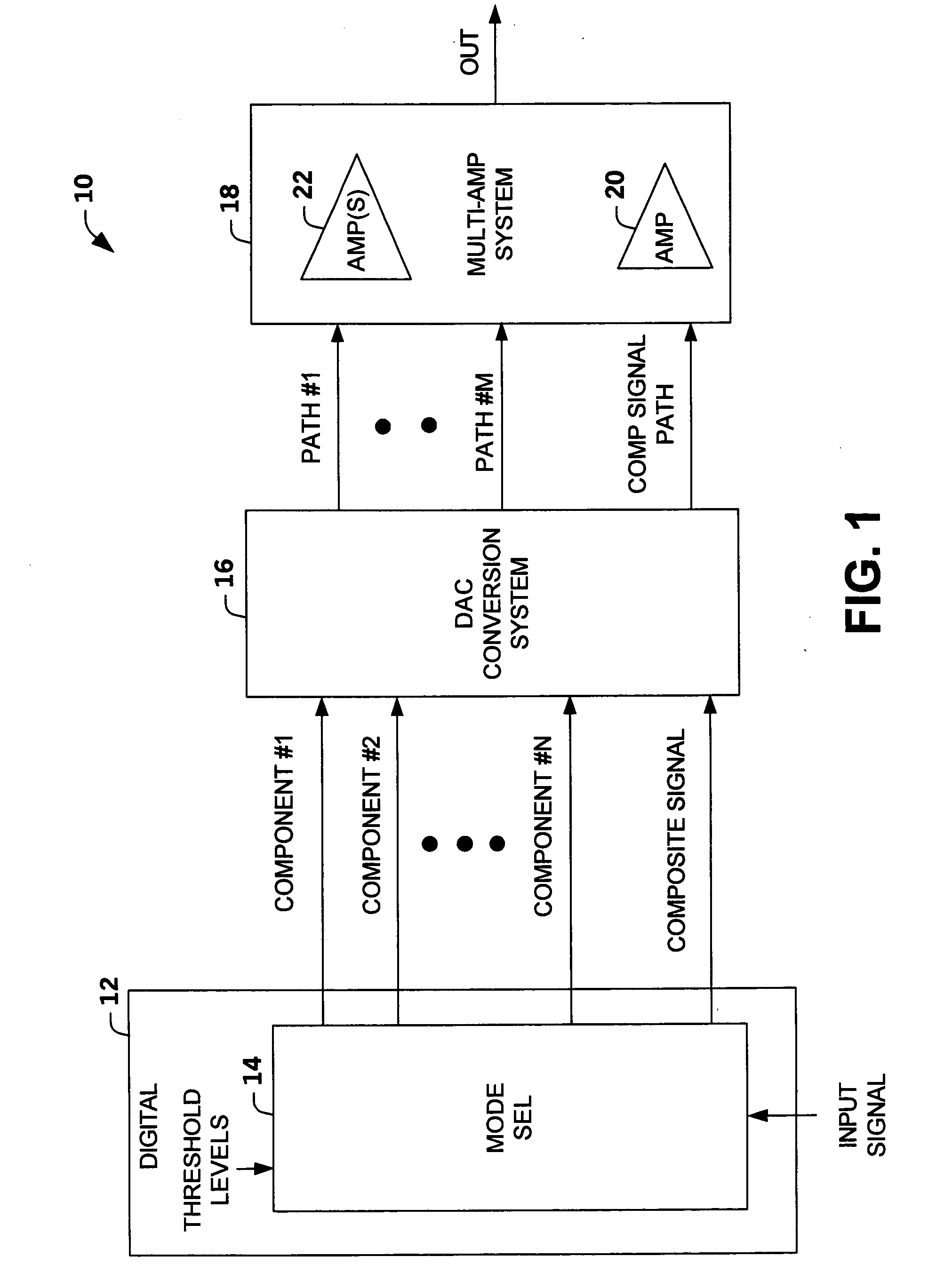

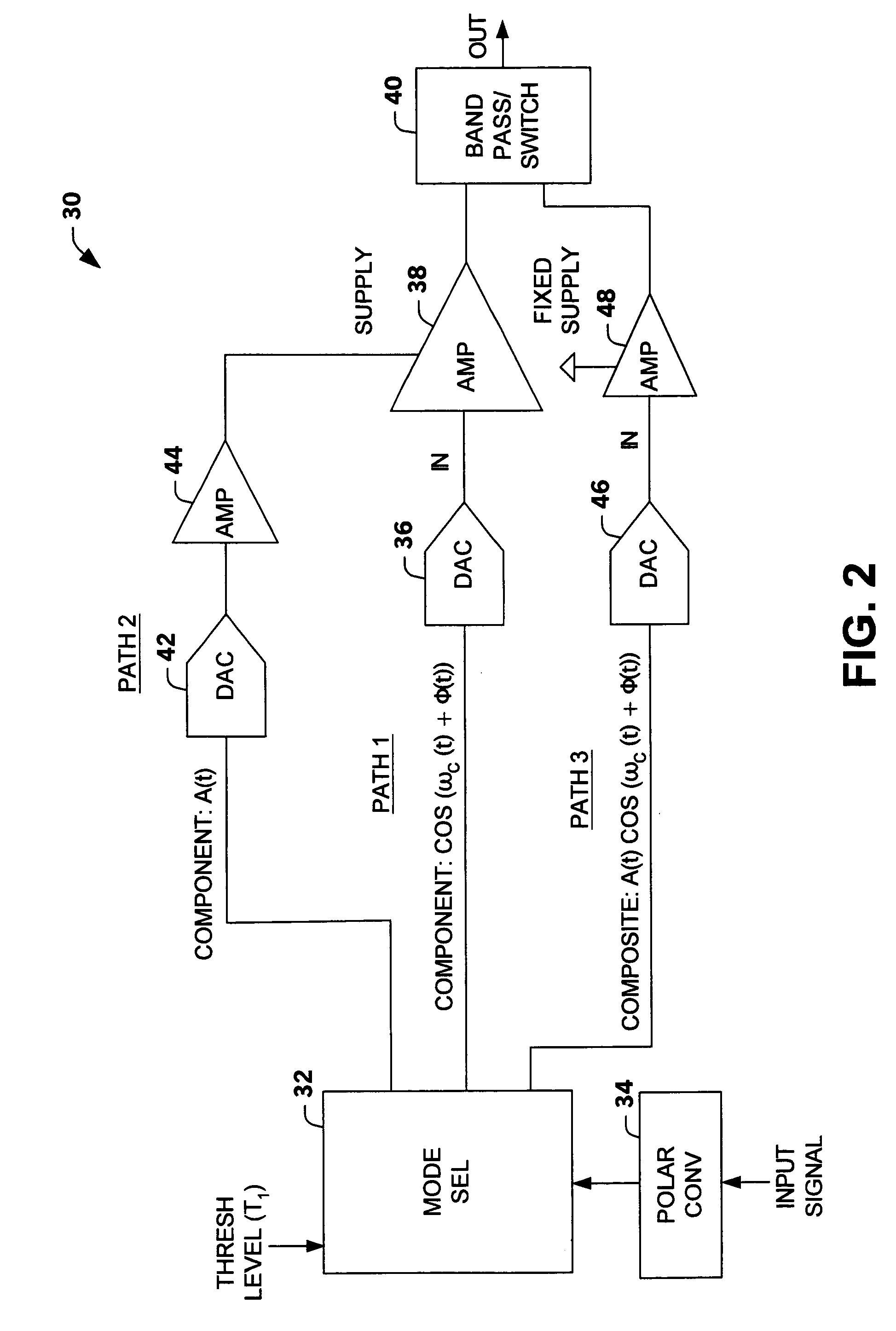

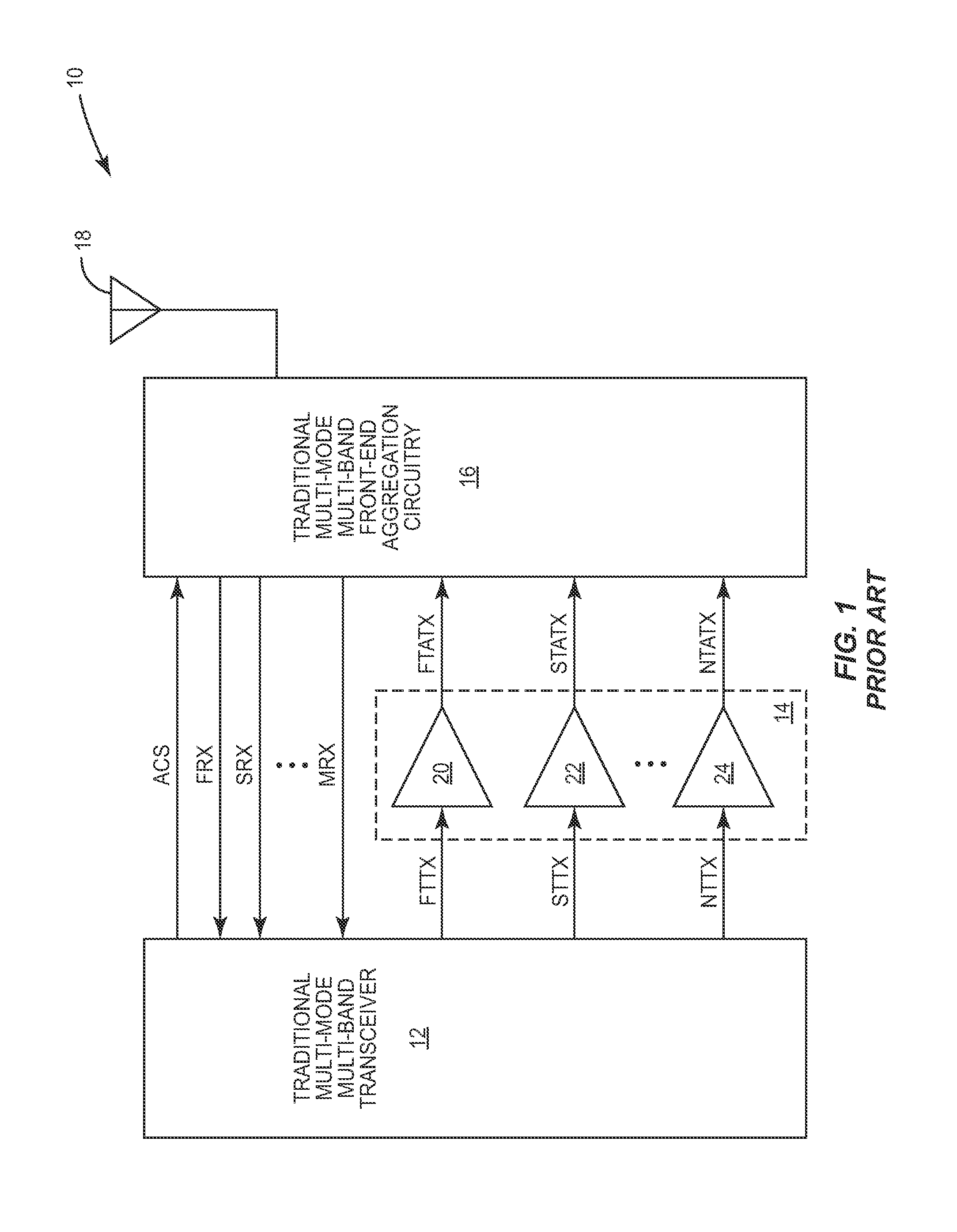

Multi-mode multi-amplifier architecture

InactiveUS6853244B2Amplifier modifications to reduce non-linear distortionGain controlAudio power amplifierEngineering

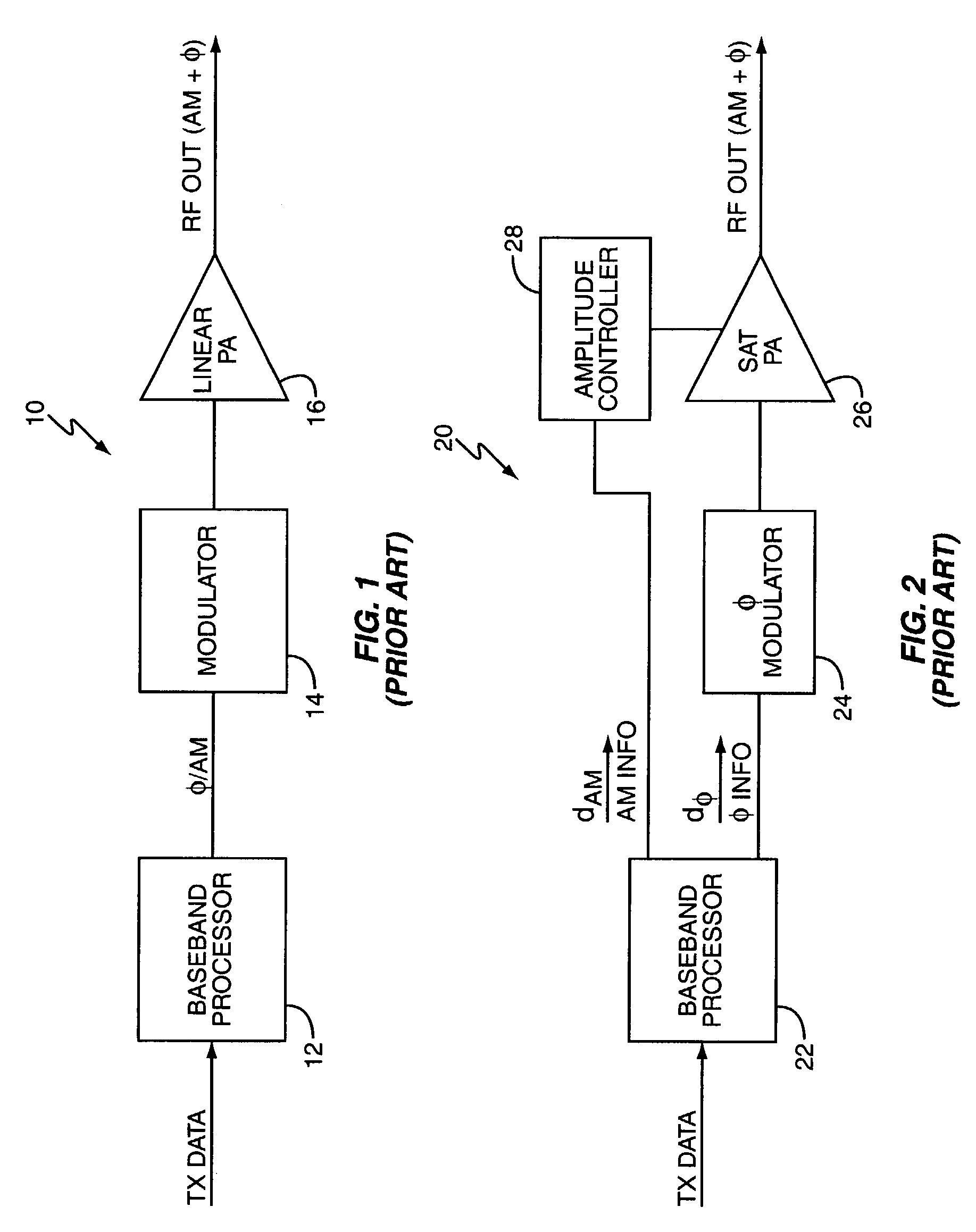

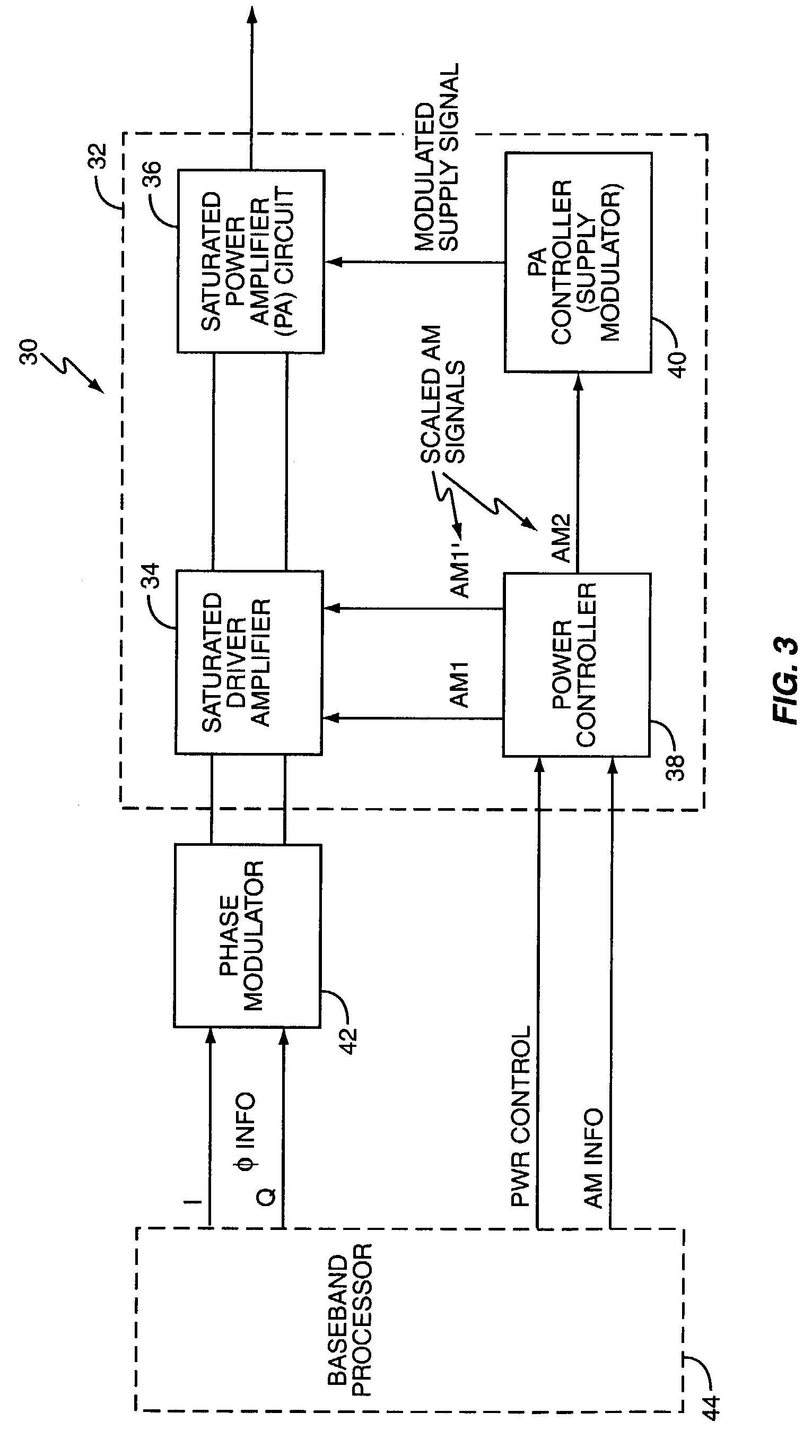

An amplification architecture or system is provided having a multiple amplifier system that switches modes of operation between operation in a component mode and a composite mode based on a characteristic of an input signal relative to a threshold level. In the component mode, the components of the input signal are employed to different terminals of the multiple amplifier system that provide a reconstructed amplified representation of the input signal. In the composite mode, the input signal is amplified to provide an amplified representation of the input signal.

Owner:NORTHROP GRUMMAN SYST CORP

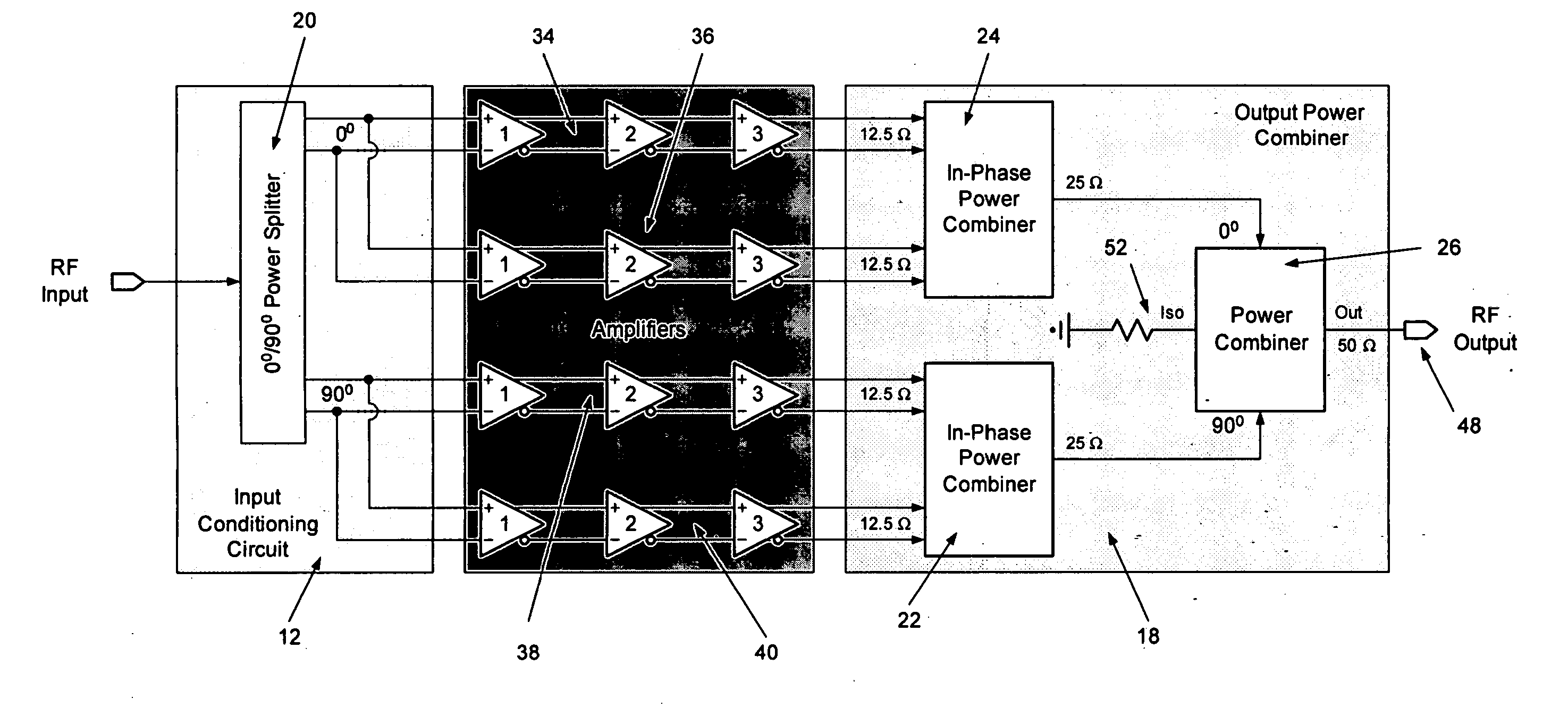

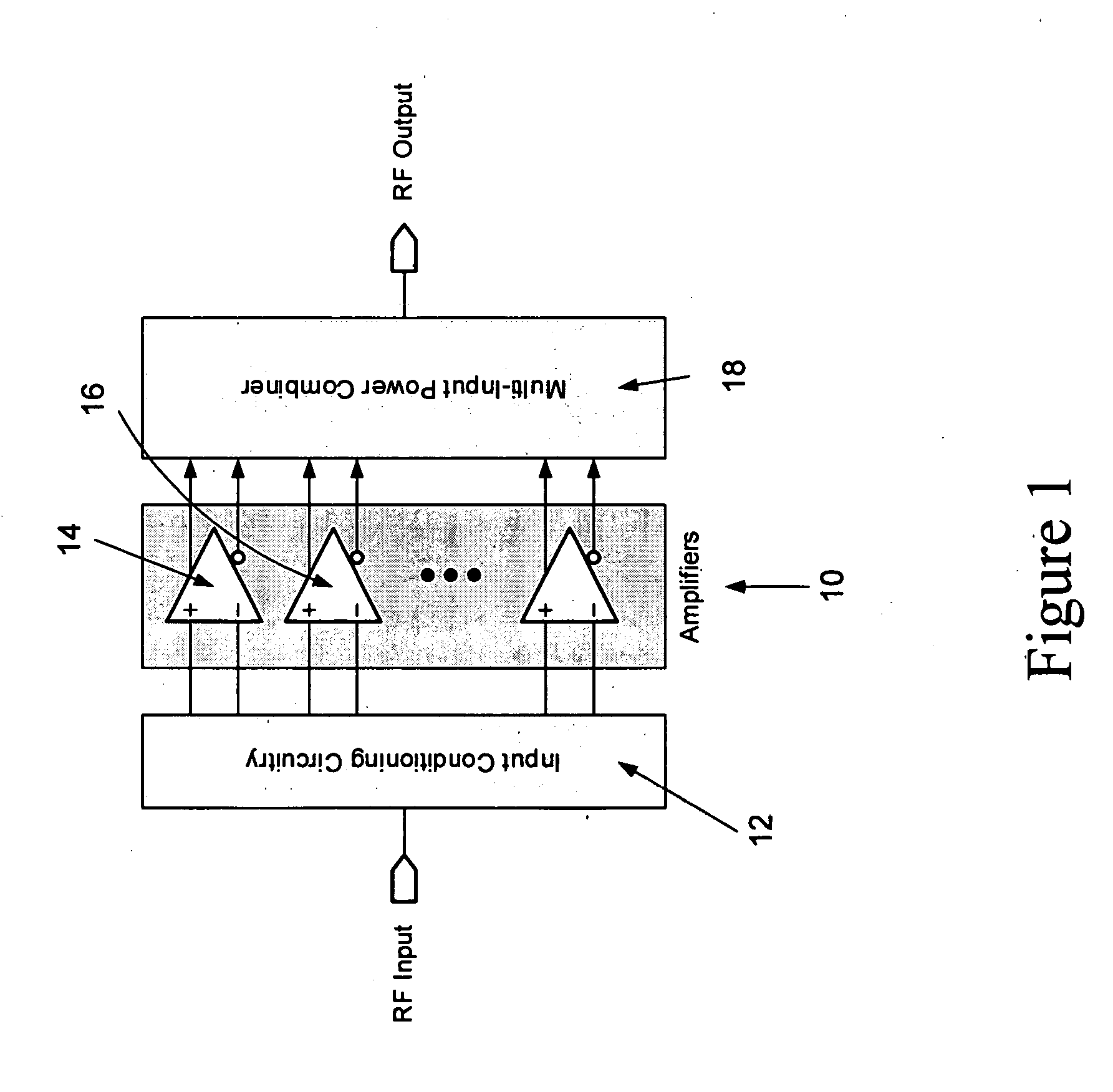

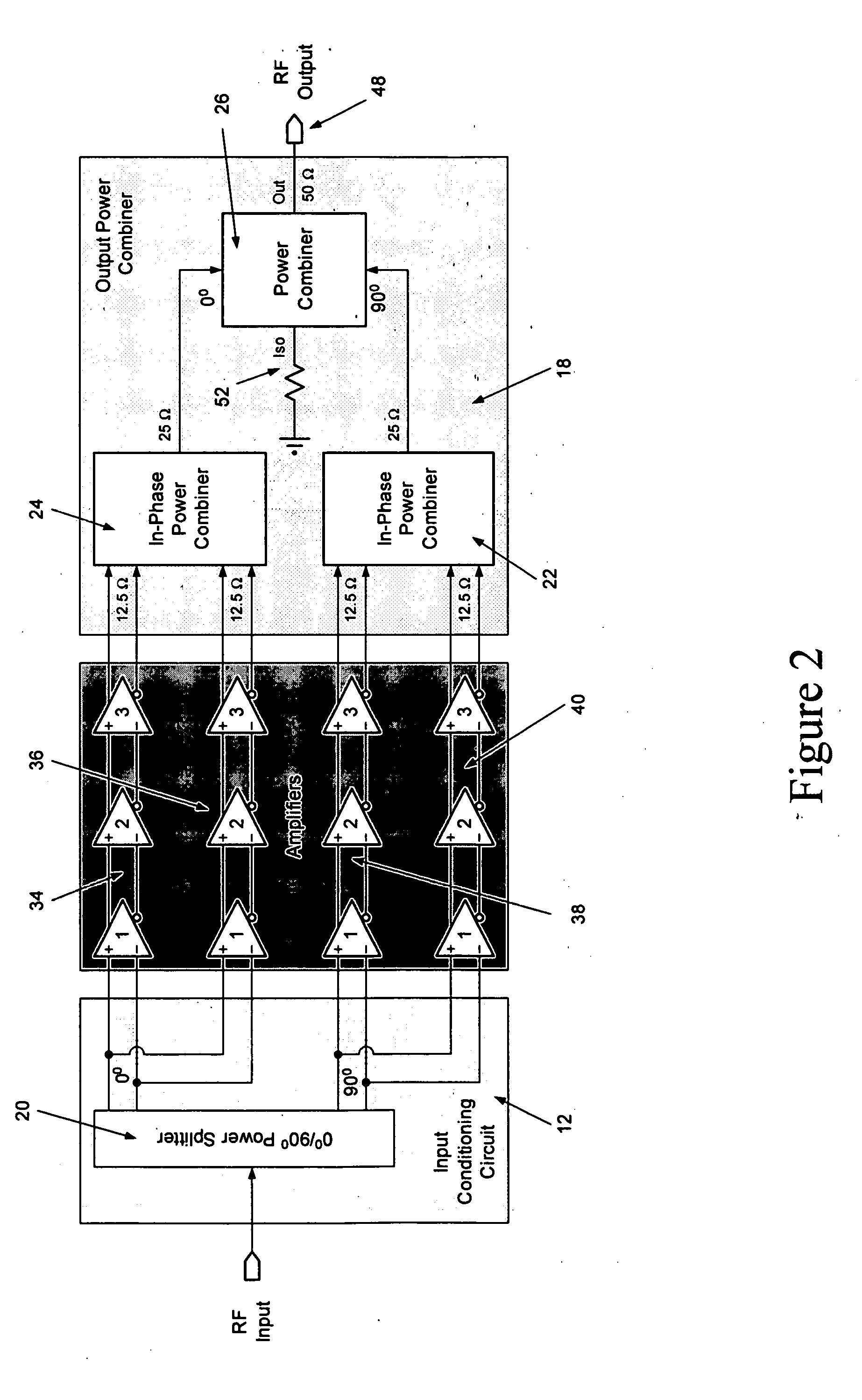

Method and apparatus for an improved power amplifier

ActiveUS20060006946A1Increase output powerImprove power added efficiencyAmplifier combinationsMulti inputAudio power amplifier

A power amplifier assembly has a first power amplifier with a first input conditioning circuit. At least first and second amplifiers are in parallel with each other and having inputs and outputs. An input signal is coupled to the inputs of the first and second amplifiers. A first multi-input power combiner is provided. The outputs of the at least first and second parallel amplifiers are combined by the first multi-input power combiner to add signals of the outputs constructively. A second power amplifier has a first input conditioning circuit. At least first and second amplifiers are in parallel with each other and having inputs and outputs. An input signal is coupled to the inputs of the first and second amplifiers. A second multi-input power combiner is provided. The outputs of the at least first and second parallel amplifiers are combined by the second multi-input power combiner to add signals of the outputs constructively.

Owner:QORVO INT PTE LTD

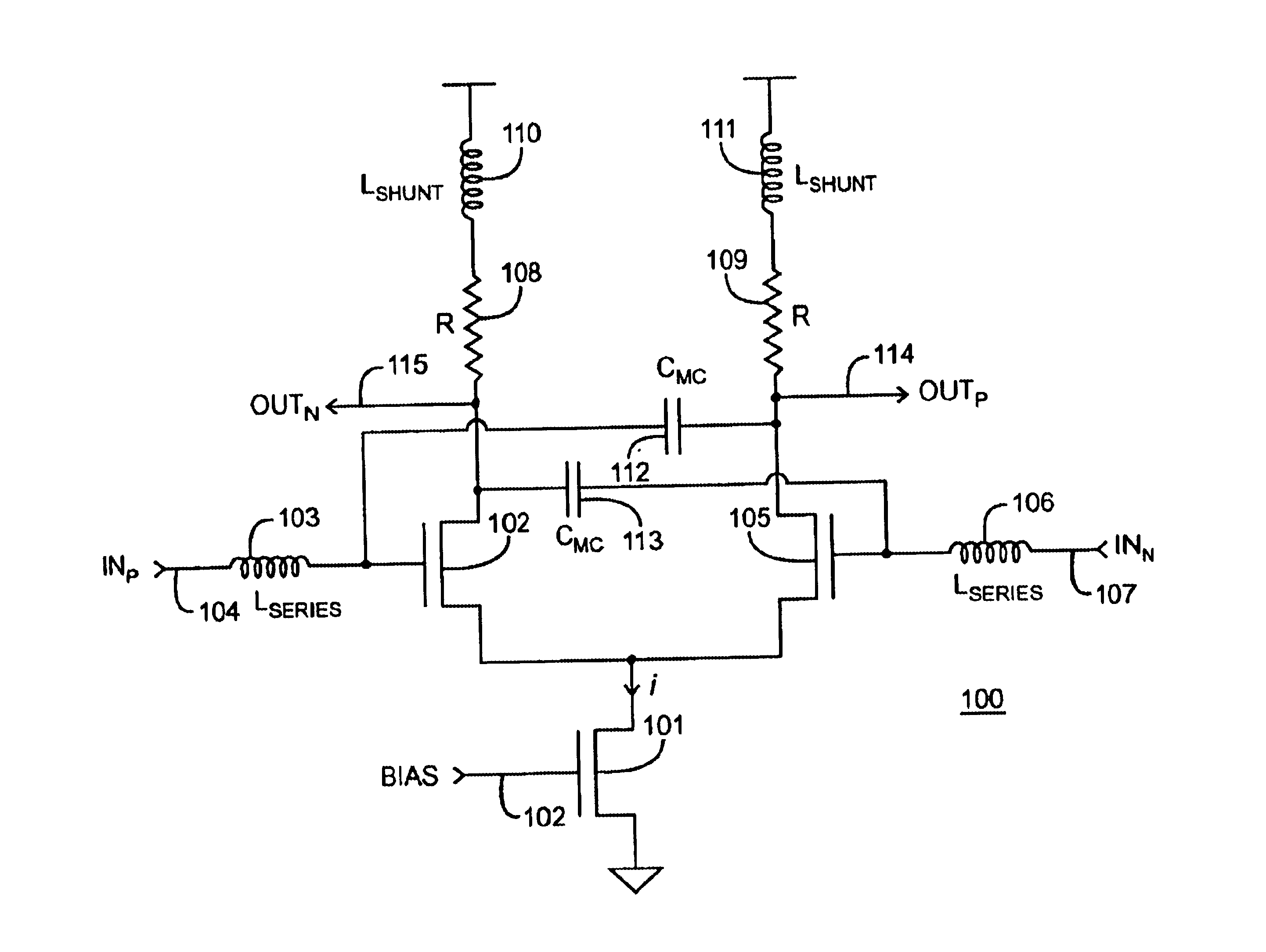

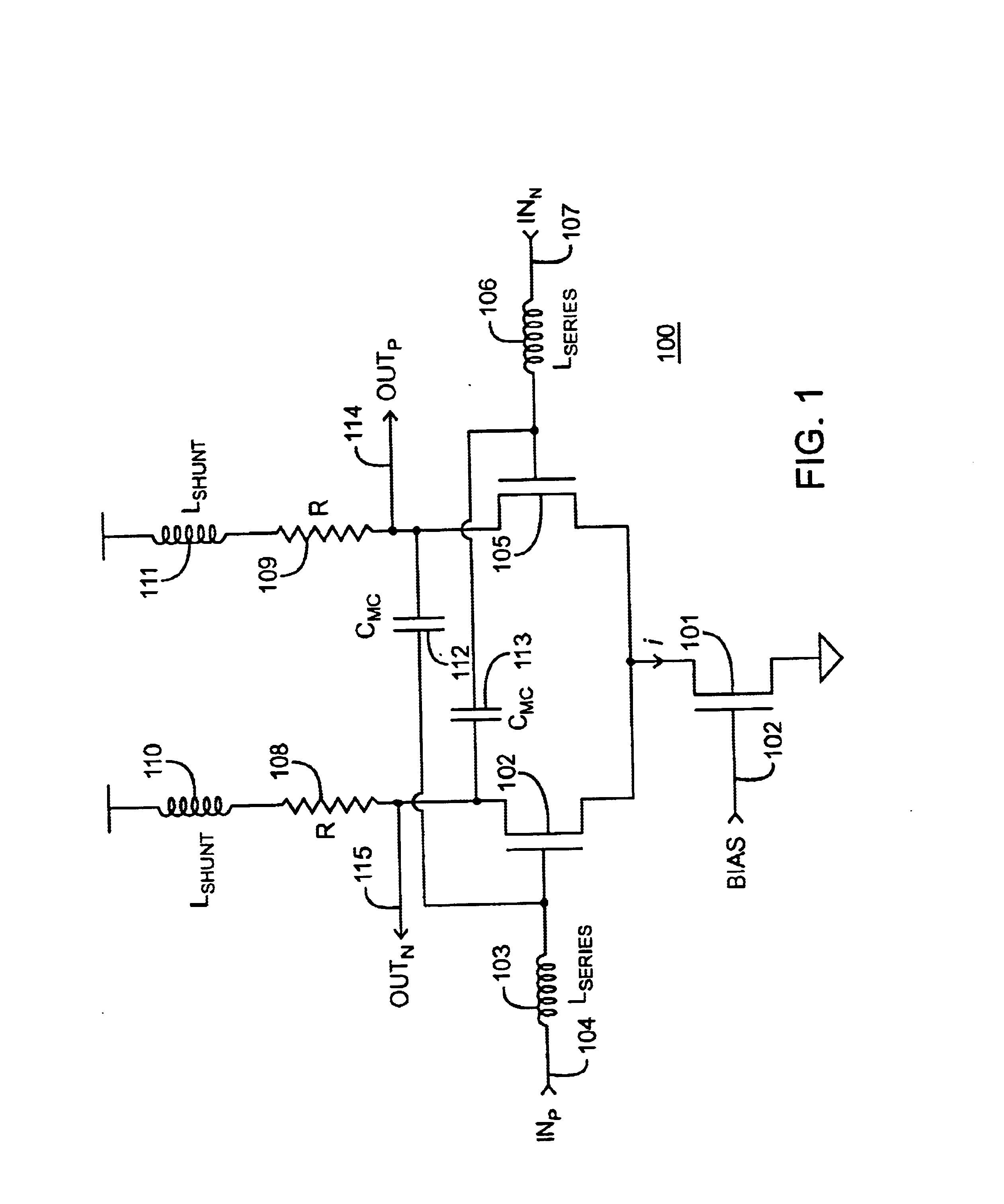

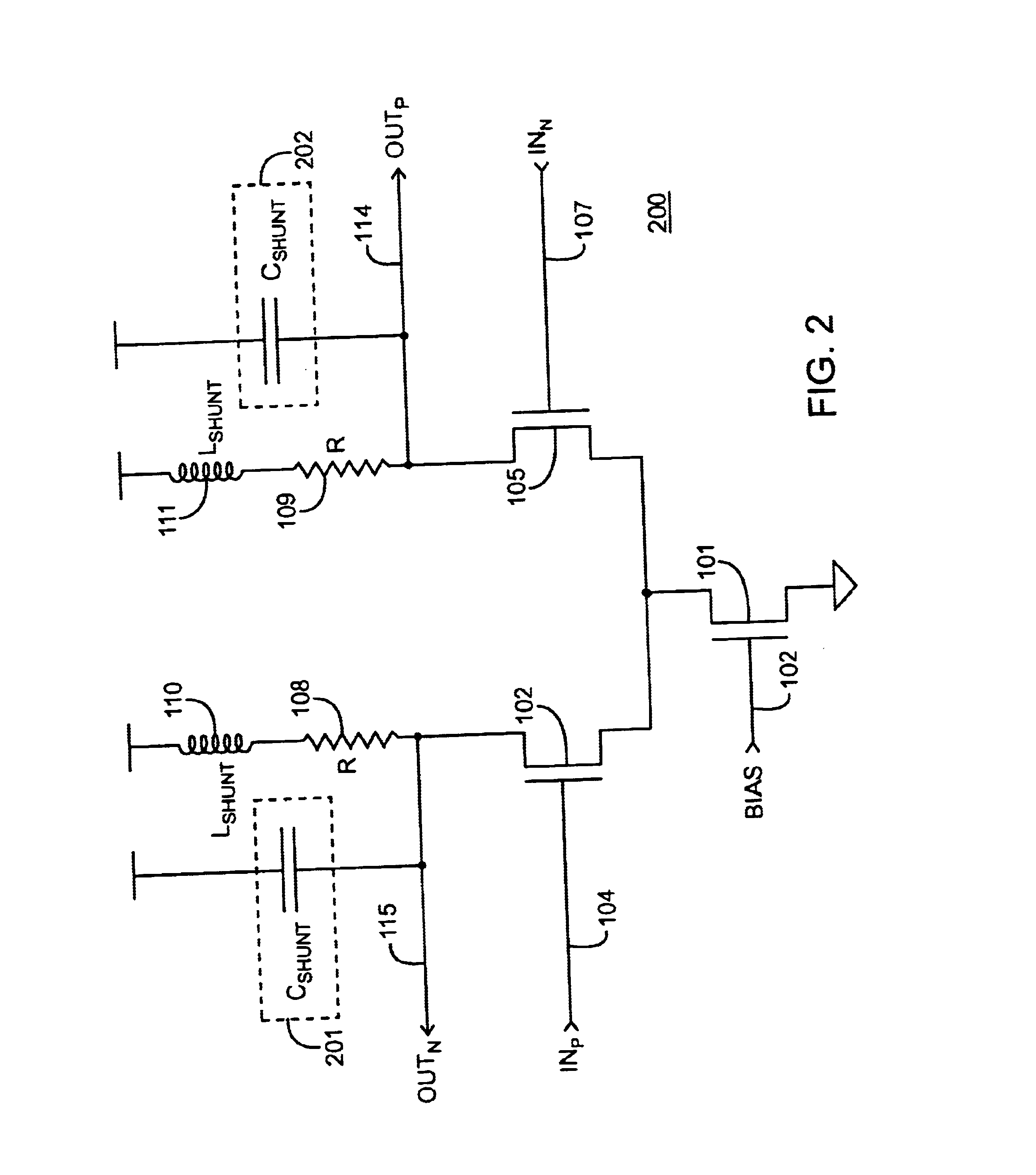

Current-controlled CMOS wideband data amplifier circuits

InactiveUS6624699B2Maximum bandwidth expansionReduced Miller CapacitanceAmplifier combinationsAmplifier modifications to reduce detrimental impedenceCapacitanceCMOS

Expansion of the bandwidth of a wideband CMOS data amplifier is accomplished using various combinations of shunt peaking, series peaking, and miller capacitance cancellation. These various combinations are employed in any of the amplifier input stage, in intermediate stages, or in the last stage.

Owner:AVAGO TECH INT SALES PTE LTD

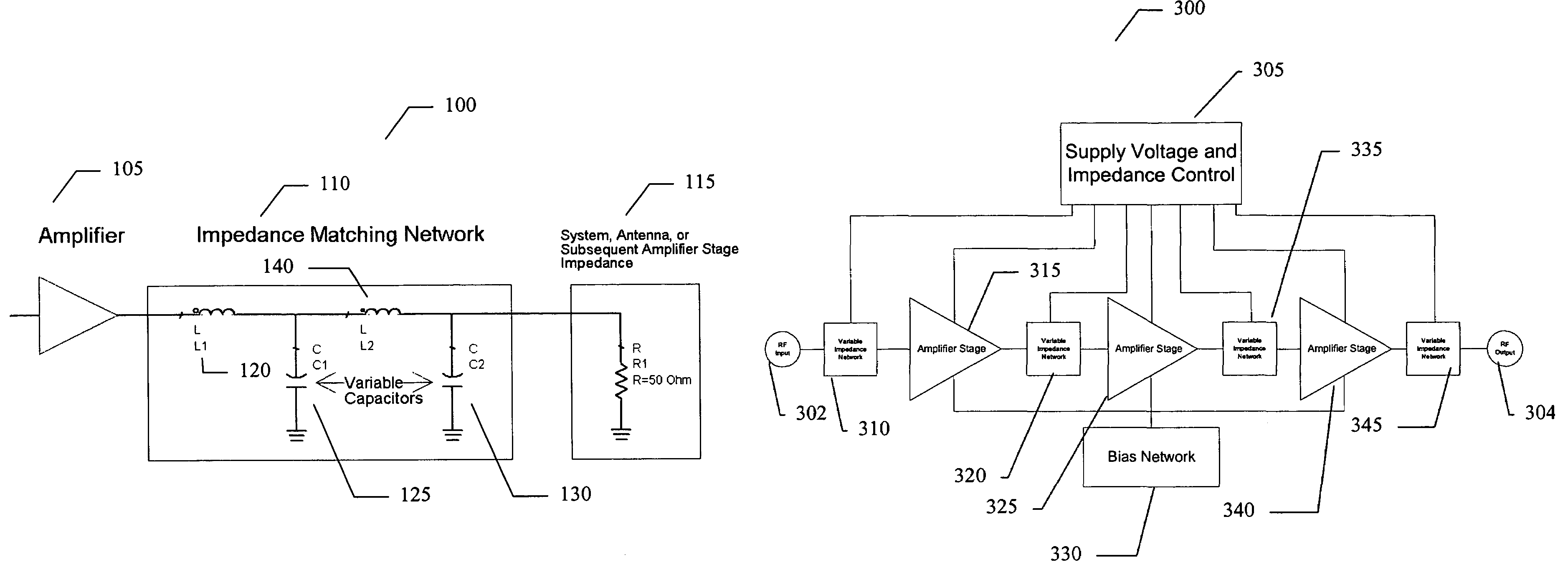

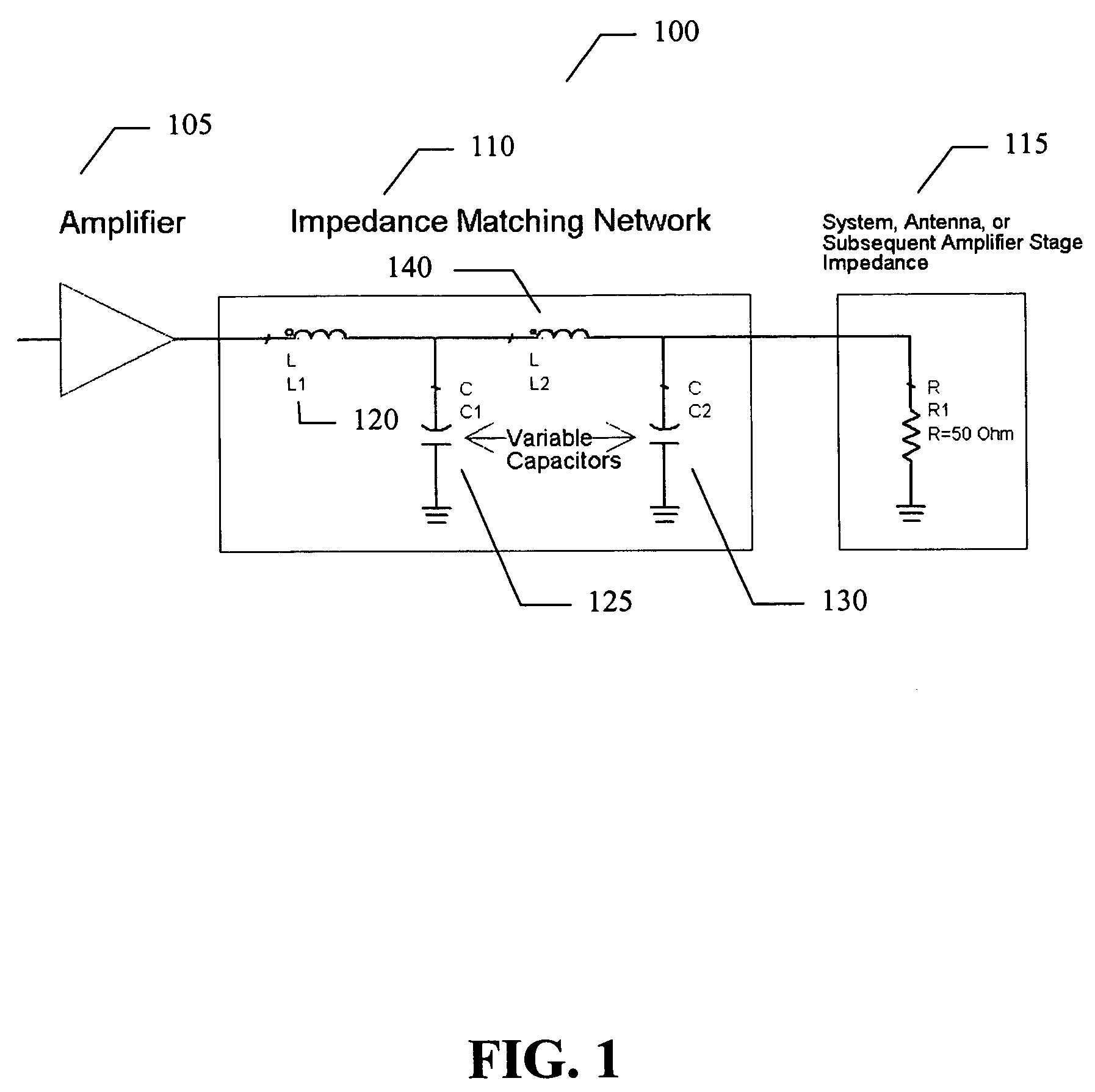

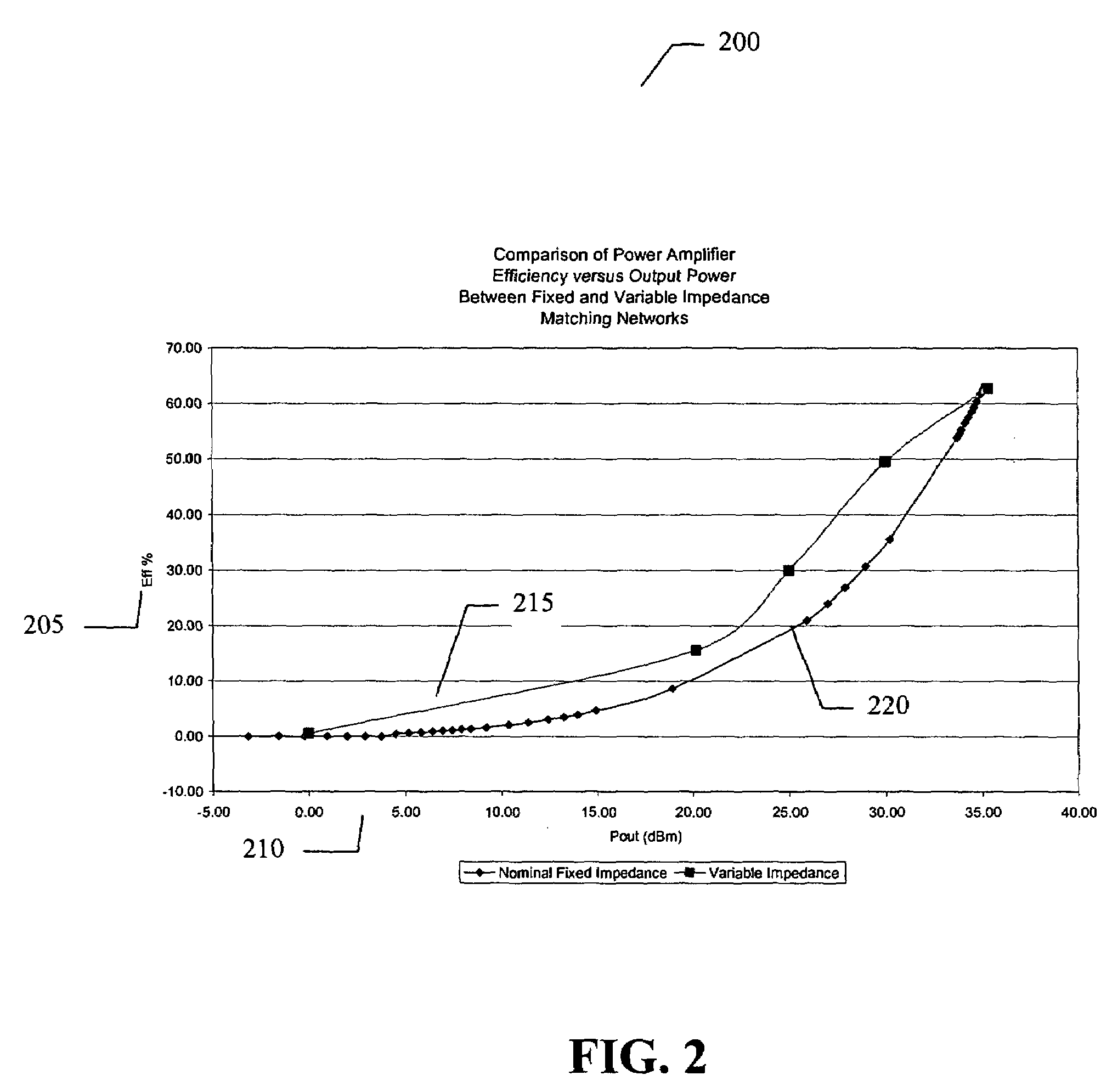

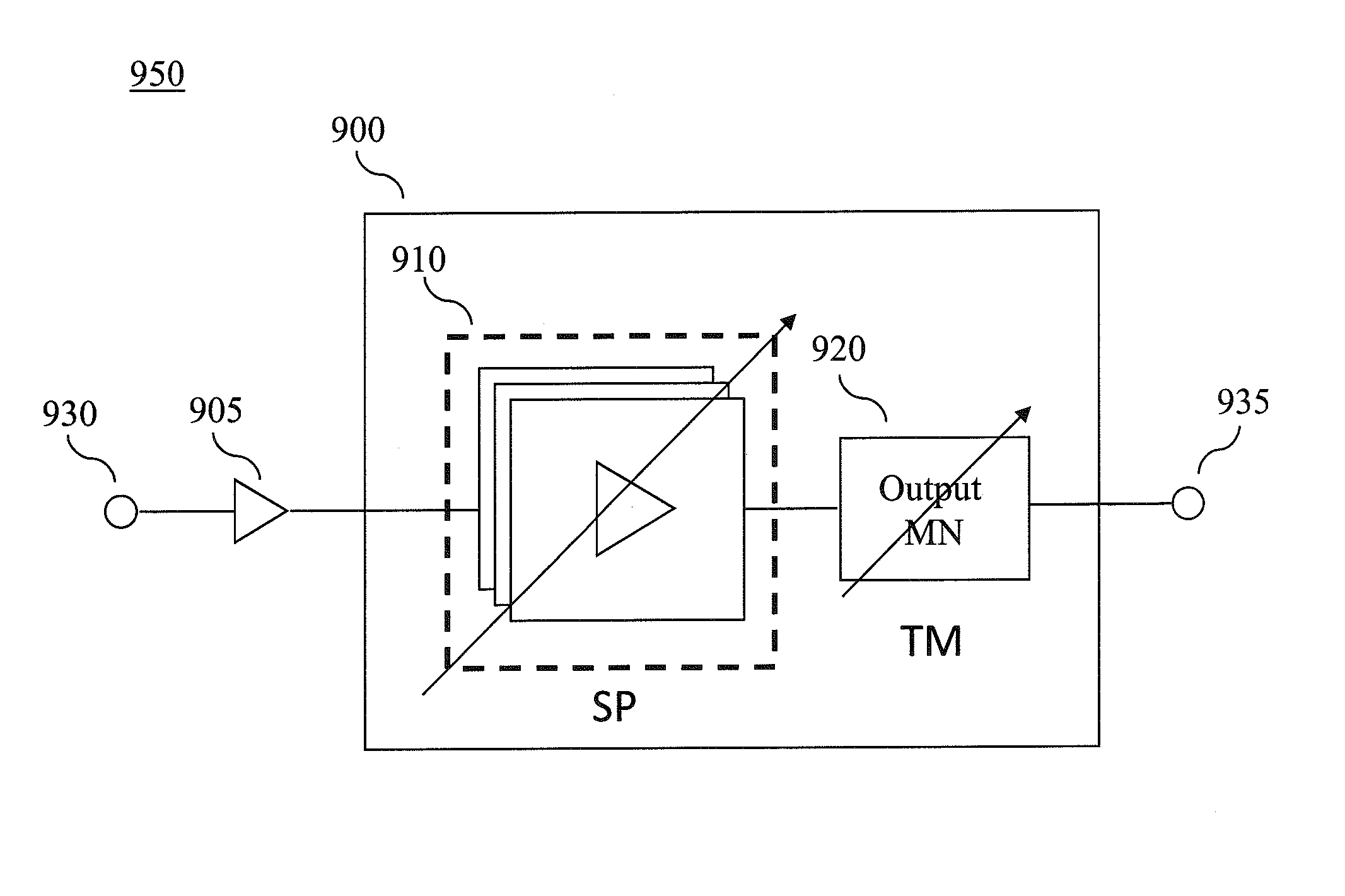

Amplifier system and method

ActiveUS7151411B2High frequency amplifiersAmplifier modifications to raise efficiencyAudio power amplifierImpedance matching

An embodiment of the present invention provides an amplifier system, comprising at least one variable impedance matching network, the output of which provides the input to at least one amplifier stage or provides an output of the power amplifier itself, and a bias network associated with the at least one amplifier stage. The amplifier system may further comprise a controller enabling impedance control to the at least one variable impedance matching network and a supply voltage provided to the at least one variable impedance network and / or the at least one amplifier stage and wherein the at least one variable impedance network and the at least one amplifier stage may be a plurality of impedance networks connected to a plurality of amplifier stages. The at least one variable impedance network may include at least one variable capacitor and the at least one variable capacitor may be a voltage tunable dielectric capacitor which may include Parascan® voltage tunable dielectric material.

Owner:NXP USA INC

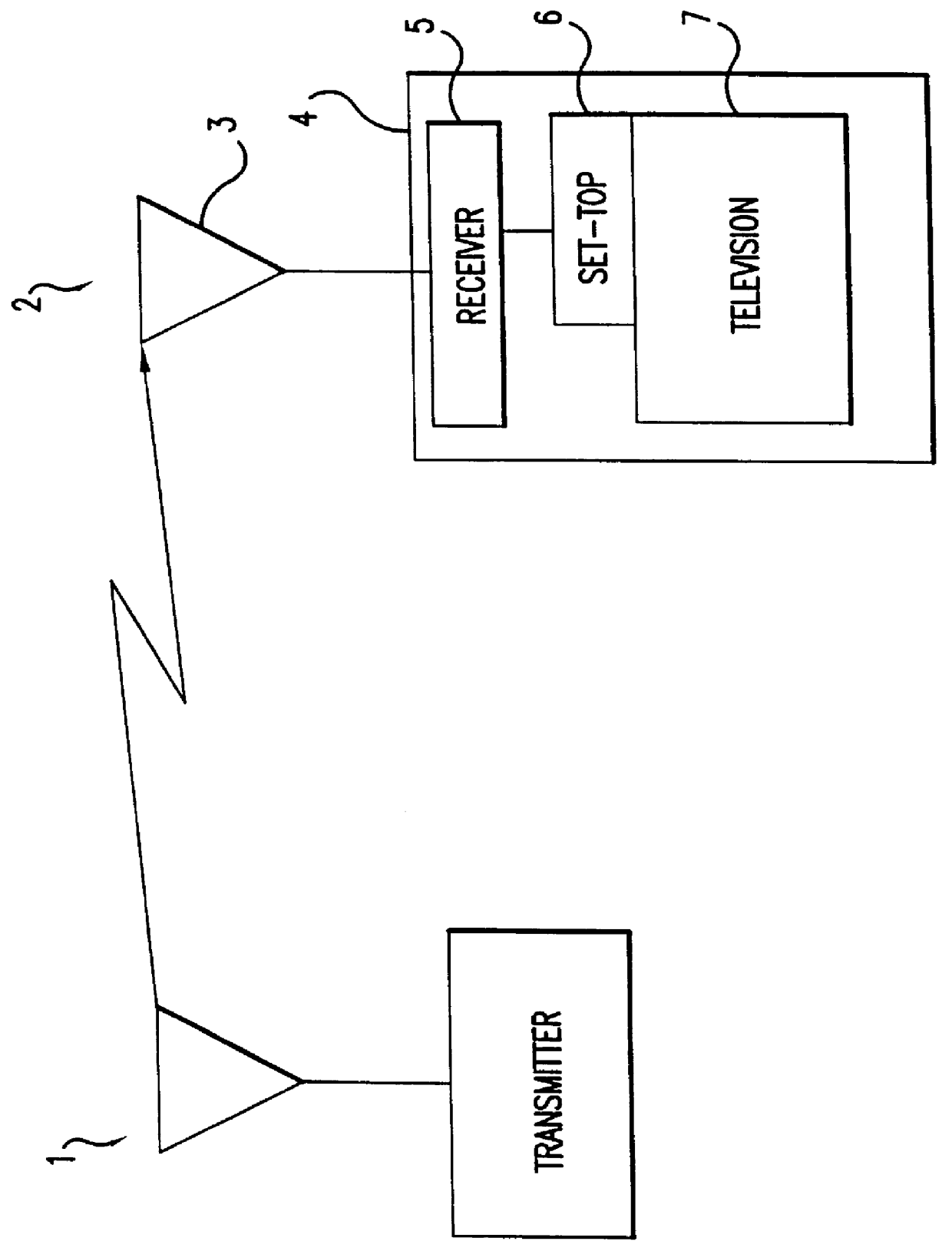

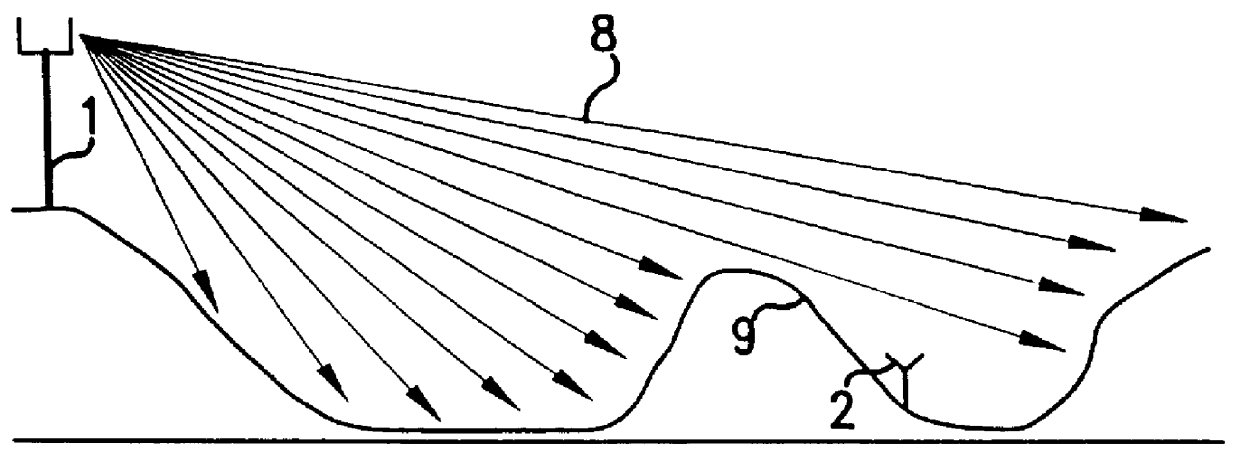

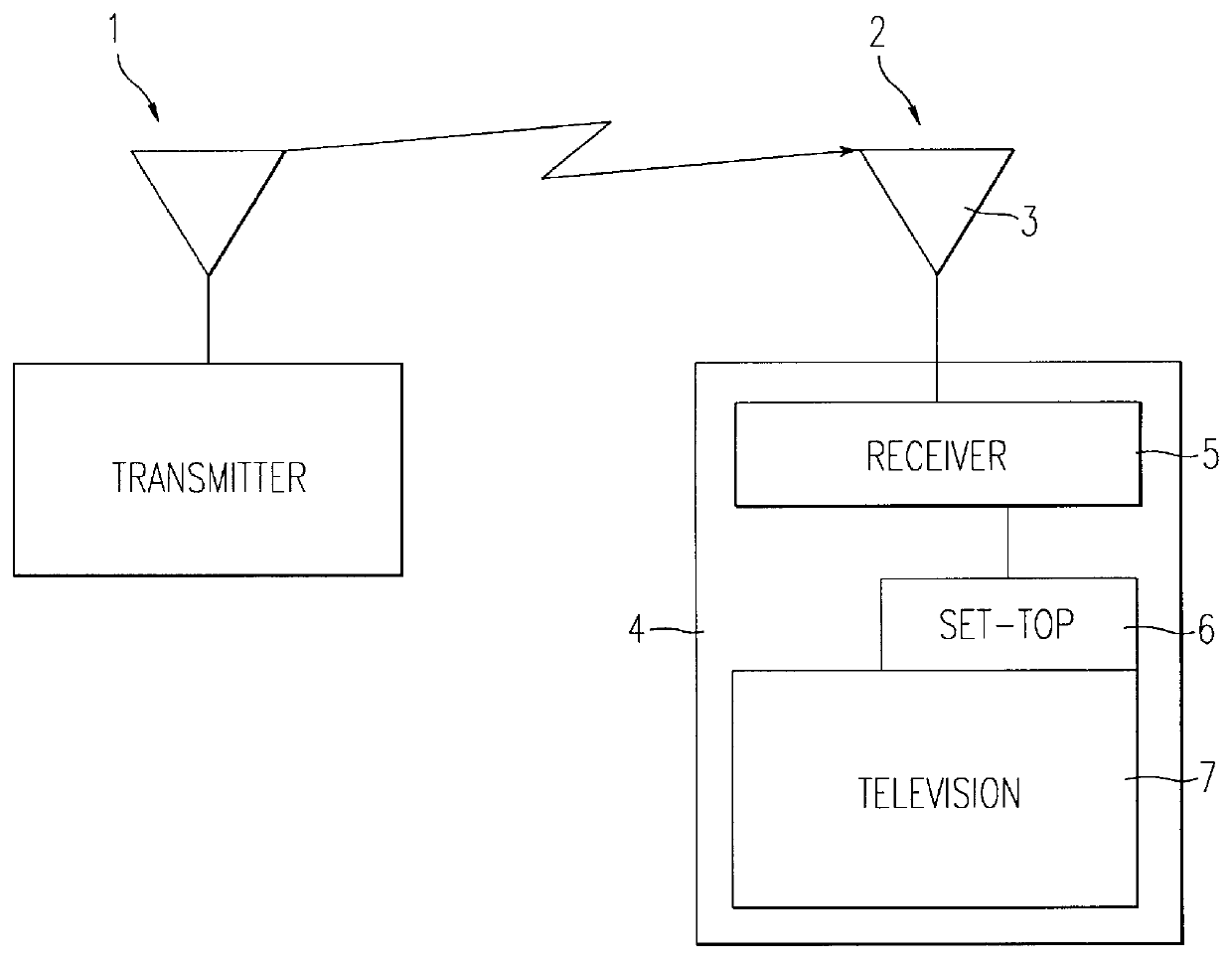

Modular transmission system and method

A modular broadband transmission system and method include an input signal connector that receives an input signal which is then divided into N parts and amplified with an amplifier have N power amplifier modules. Outputs of the N power amplifier modules are passed through transmission lines and to a radial combiner that combines the outputs. The radial combiner, transmission lines and power amplifier modules are configured such that if one of the power amplifier modules fails, the other power amplifier modules may still operate acceptable well, with minimal impact on total output power. An output of the amplifier is provided to a coupler that measures a power level of the output signal and feeds the measured power level back to a controller where the controller adjust an overall output power based on the number of the power amplifier modules that are functioning properly. Each of the power amplifier modules have a processor such that respective of the power amplifier modules may be taken off-line, and replaced while the other power amplifier modules continue to operate in a transmit mode of operation. The modular broadband transmission system and method may conveniently be used as either a broadband booster for amplifying a plurality of input signals, or a head and transmitter configured to amplify one or more different input signals.

Owner:THALES BROADCAST & MULTIMEDIA

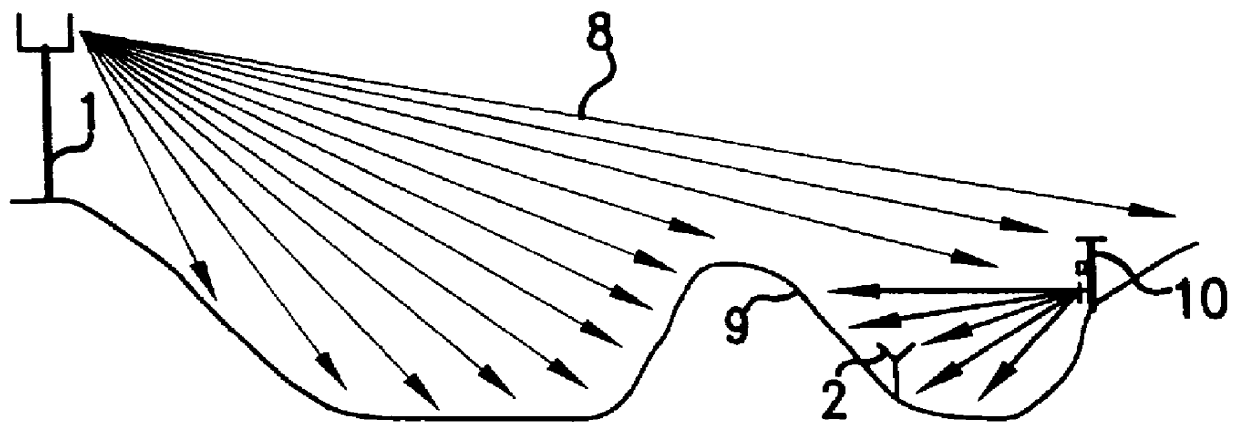

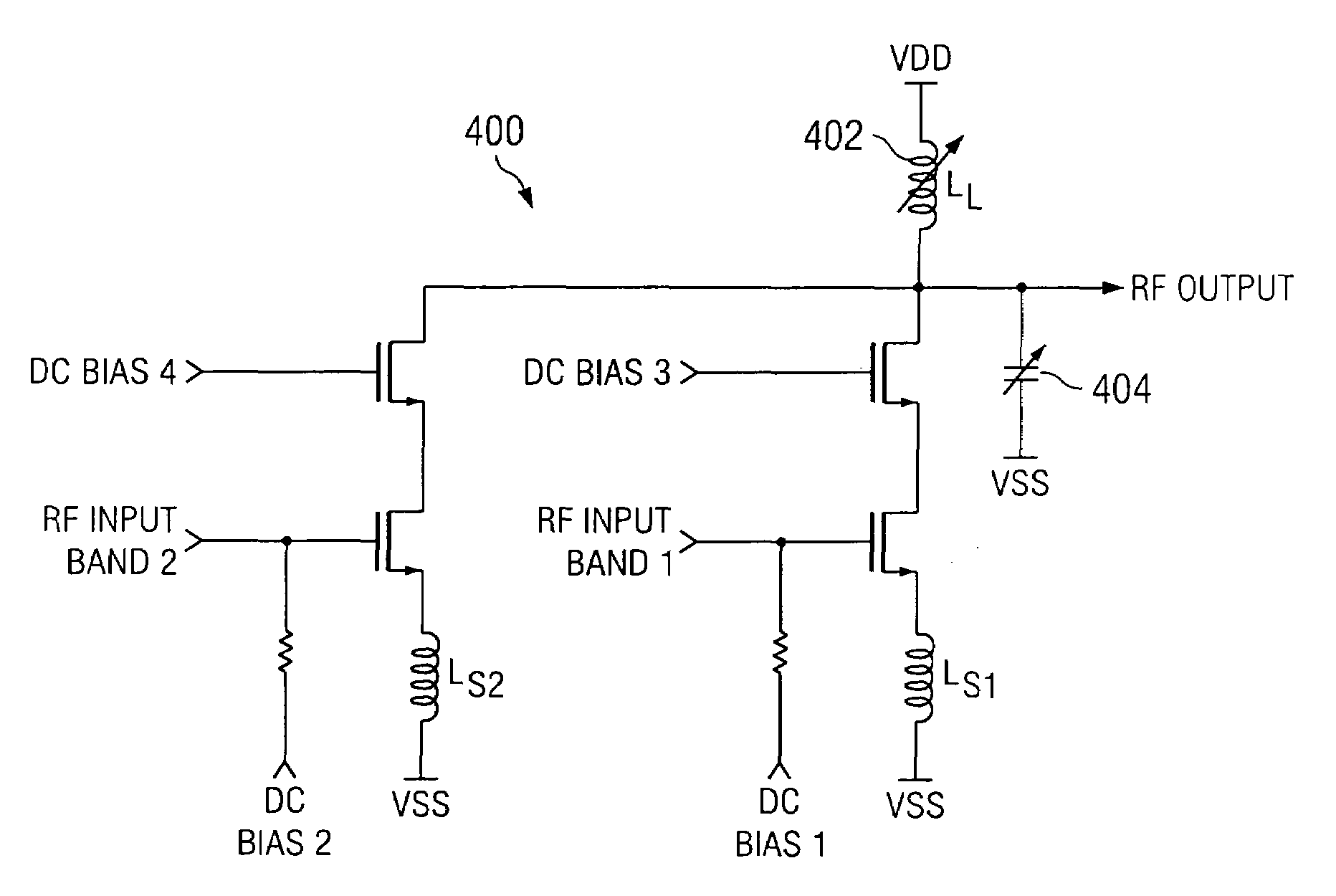

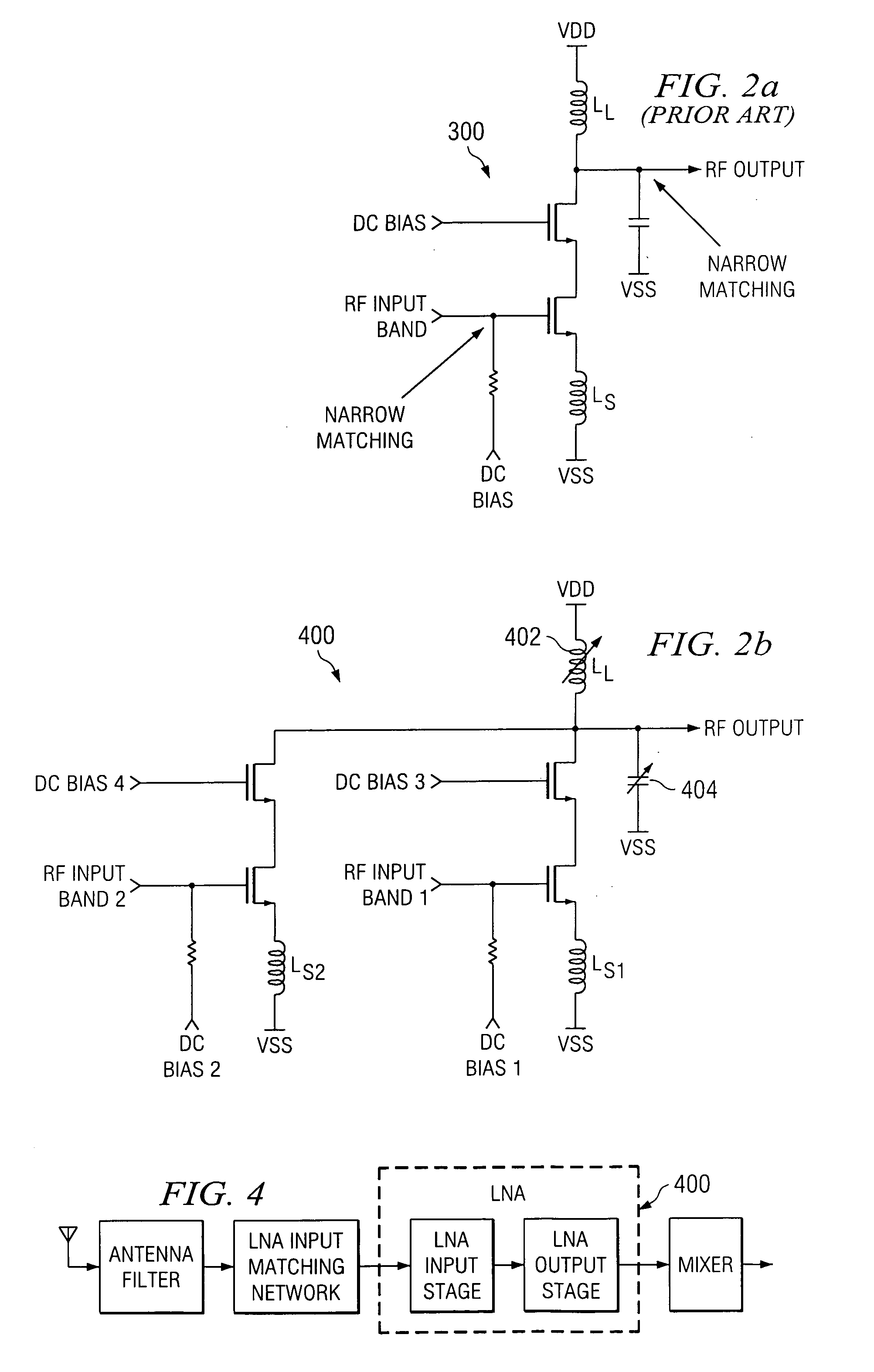

Multi-band low noise amplifier system

ActiveUS7023272B2Reduce areaIncrease/decrease the effective inductanceAmplifier modifications to reduce noise influenceAmplifier combinationsMulti bandAudio power amplifier

Owner:TEXAS INSTR INC

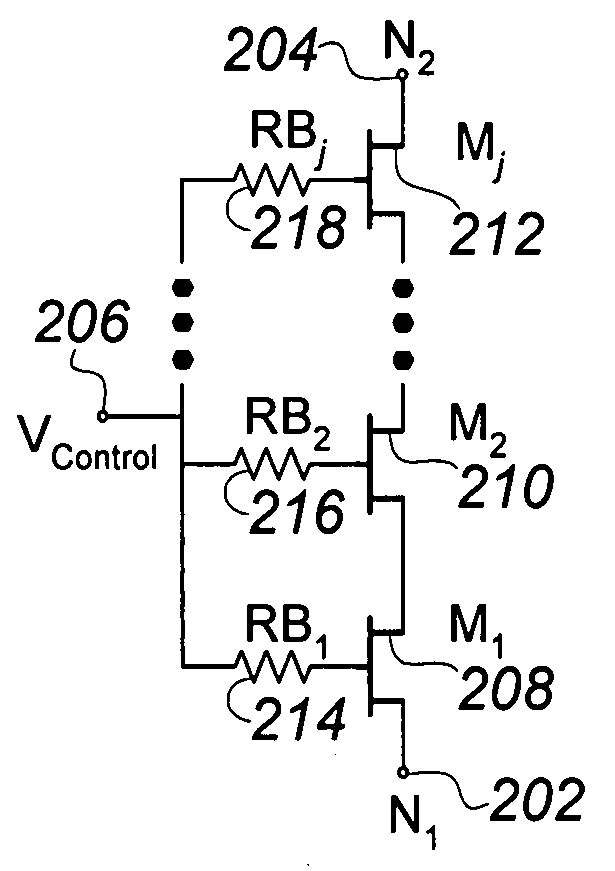

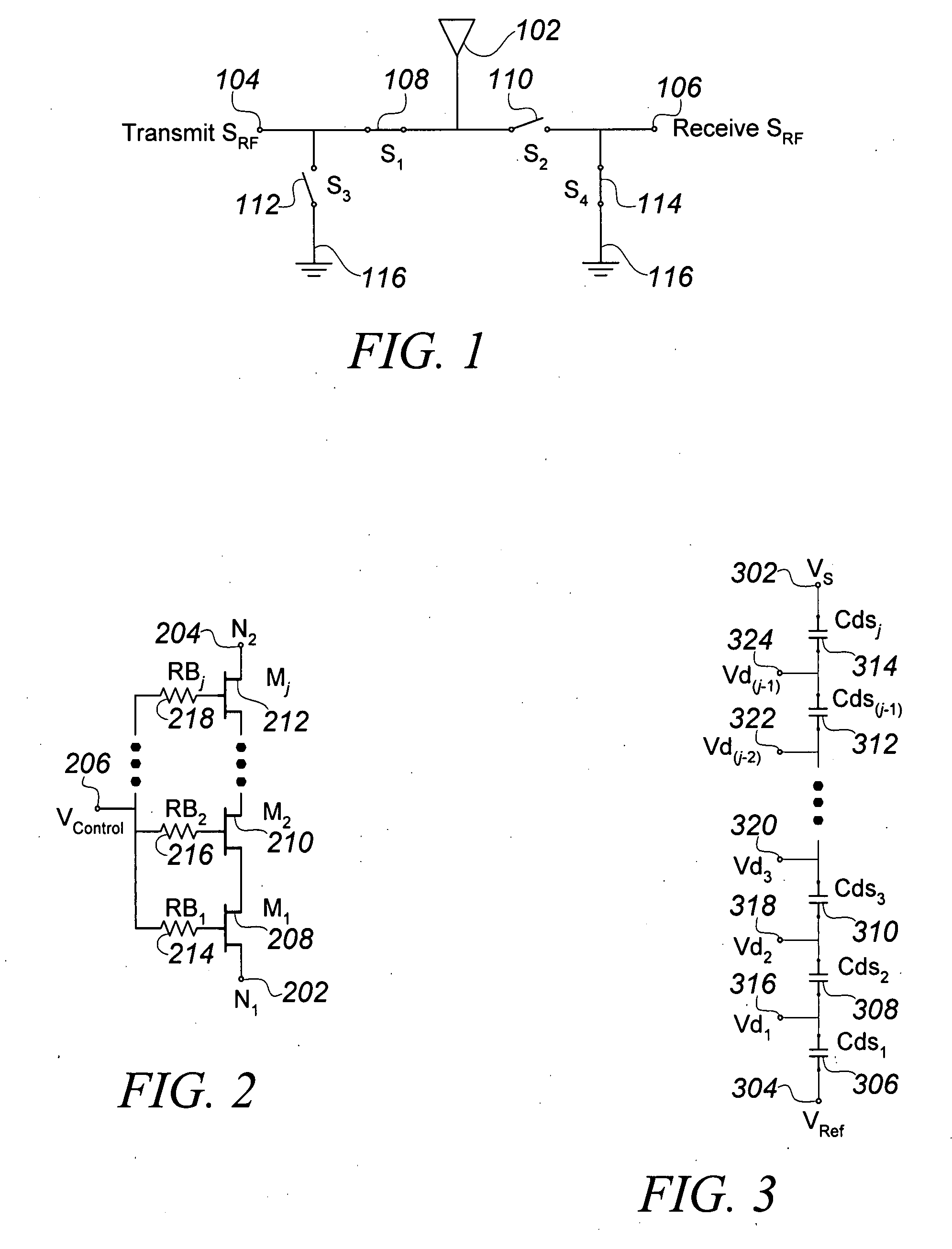

Tuning capacitance to enhance FET stack voltage withstand

An RF switch to controllably withstand an applied RF voltage Vsw, or a method of fabricating such a switch, which includes a string of series-connected constituent FETs with a node of the string between each pair of adjacent FETs. The method includes controlling capacitances between different nodes of the string to effectively tune the string capacitively, which will reduce the variance in the RF switch voltage distributed across each constituent FET, thereby enhancing switch breakdown voltage. Capacitances are controlled, for example, by disposing capacitive features between nodes of the string, and / or by varying design parameters of different constituent FETs. For each node, a sum of products of each significant capacitor by a proportion of Vsw appearing across it may be controlled to approximately zero.

Owner:PSEMI CORP

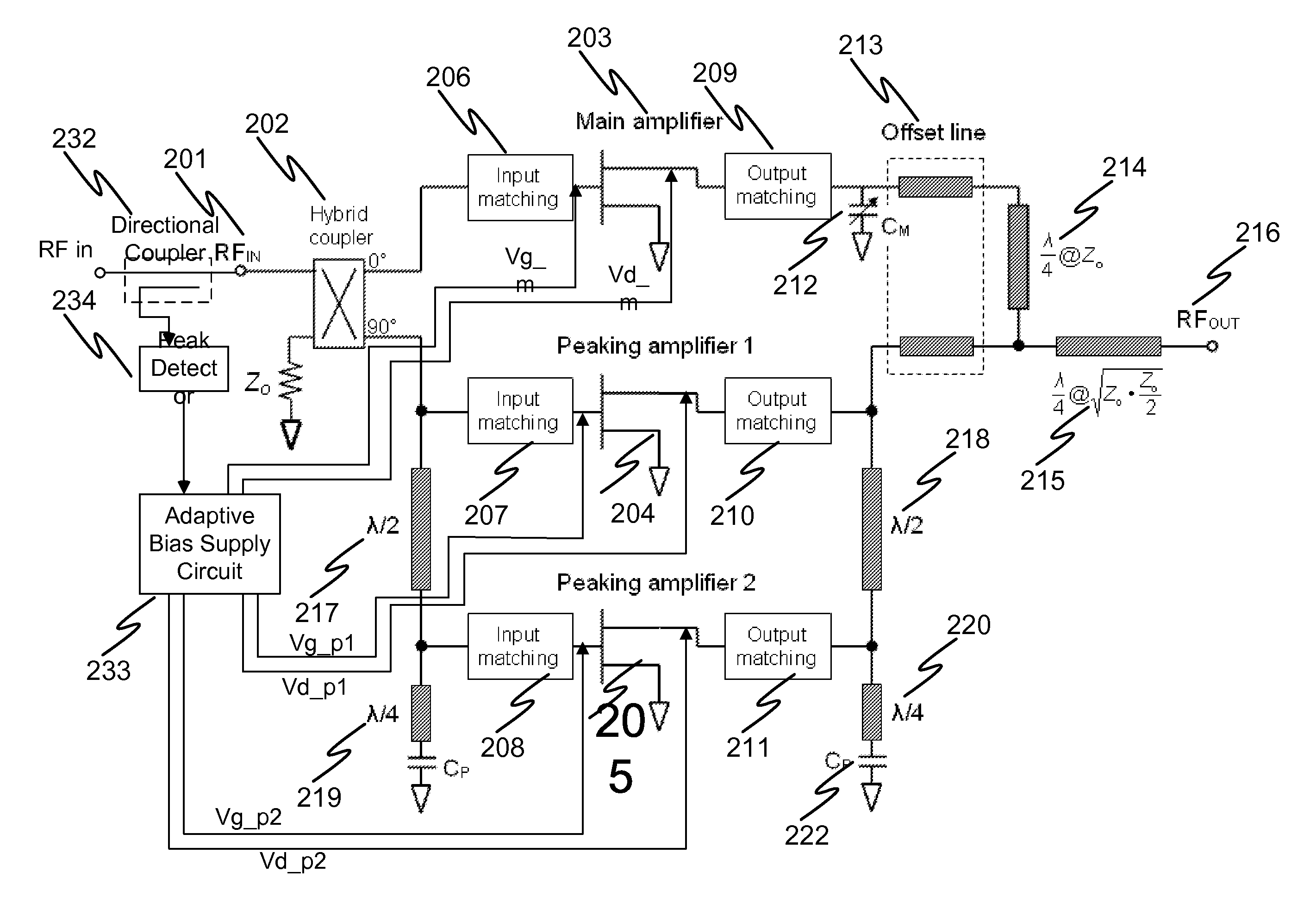

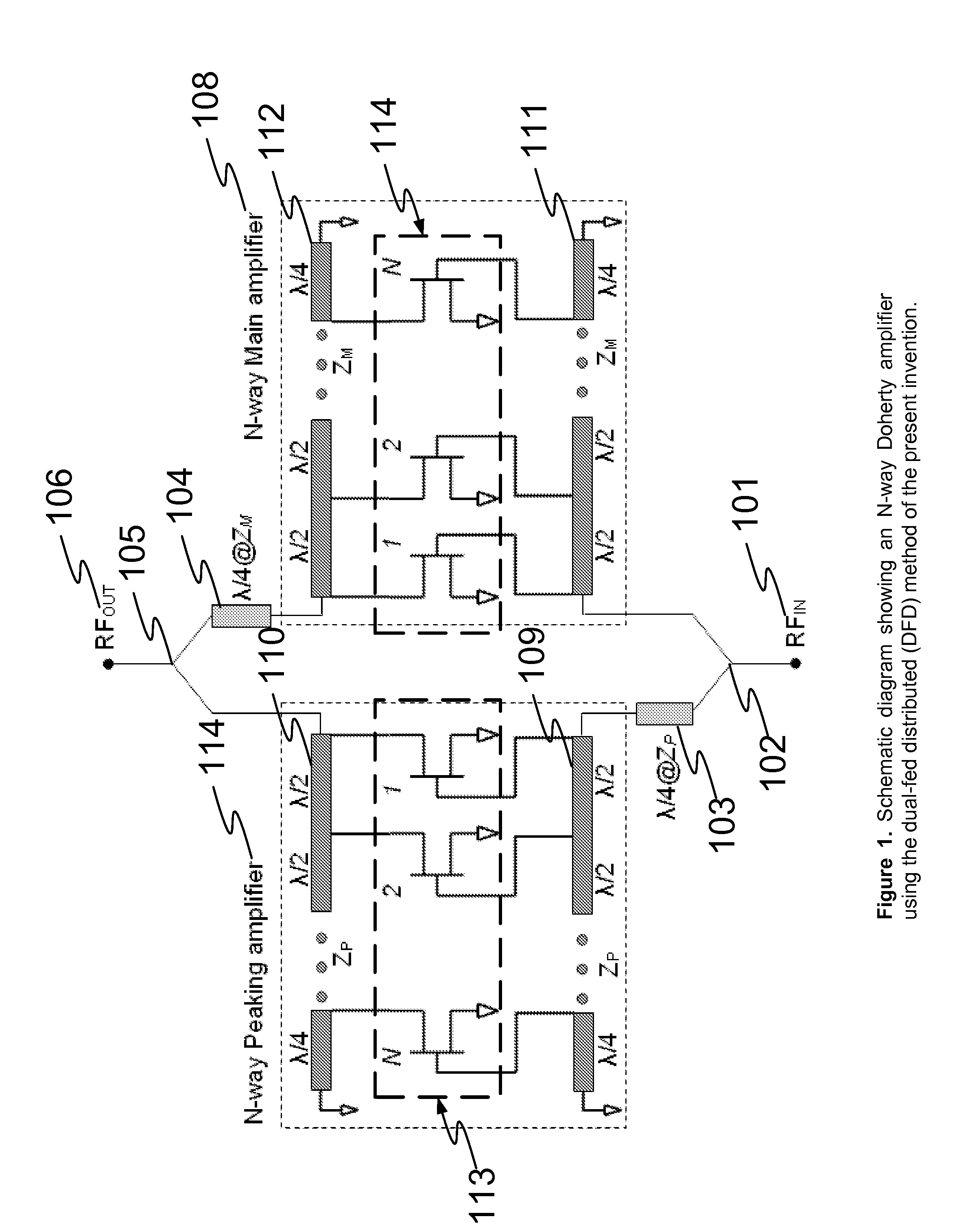

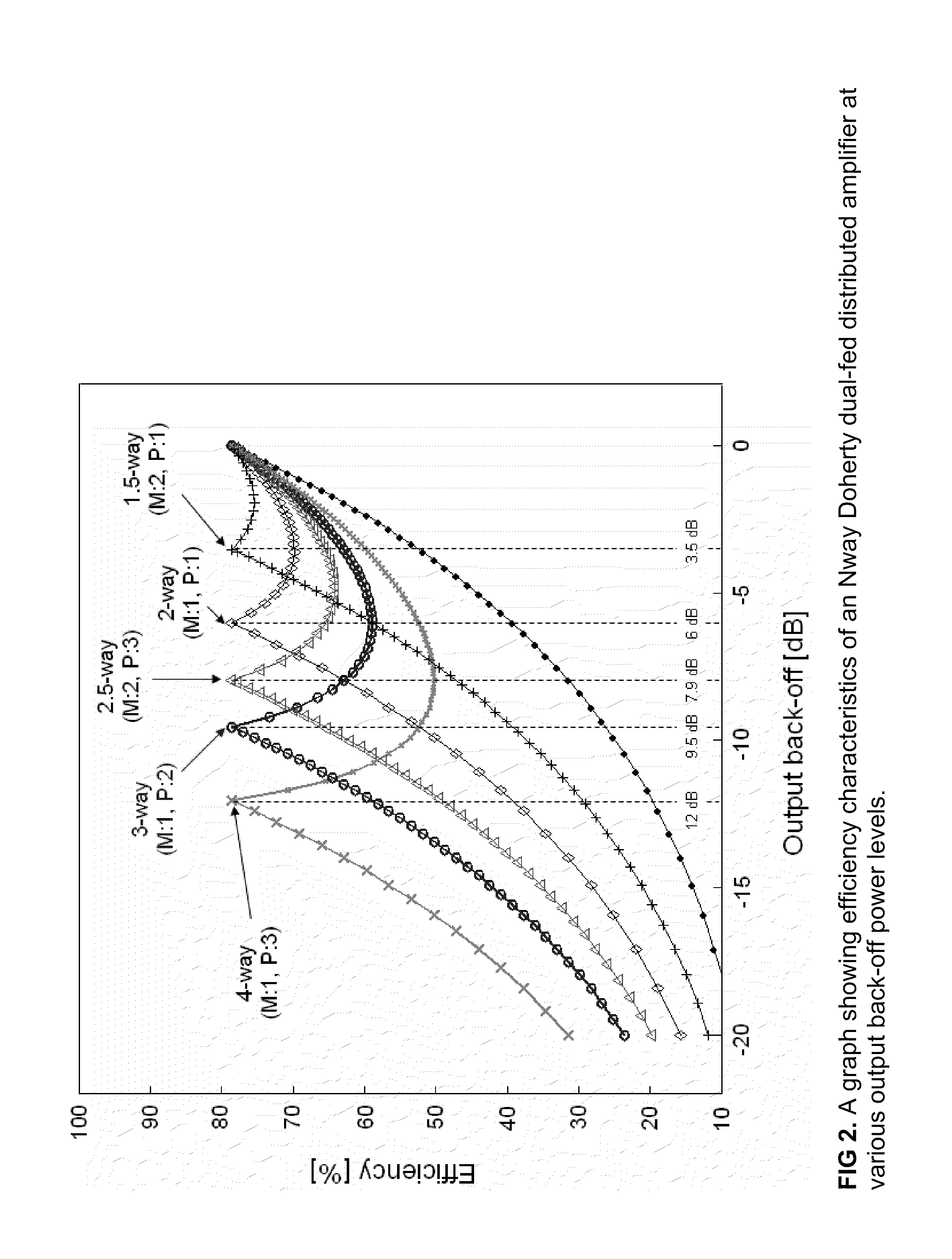

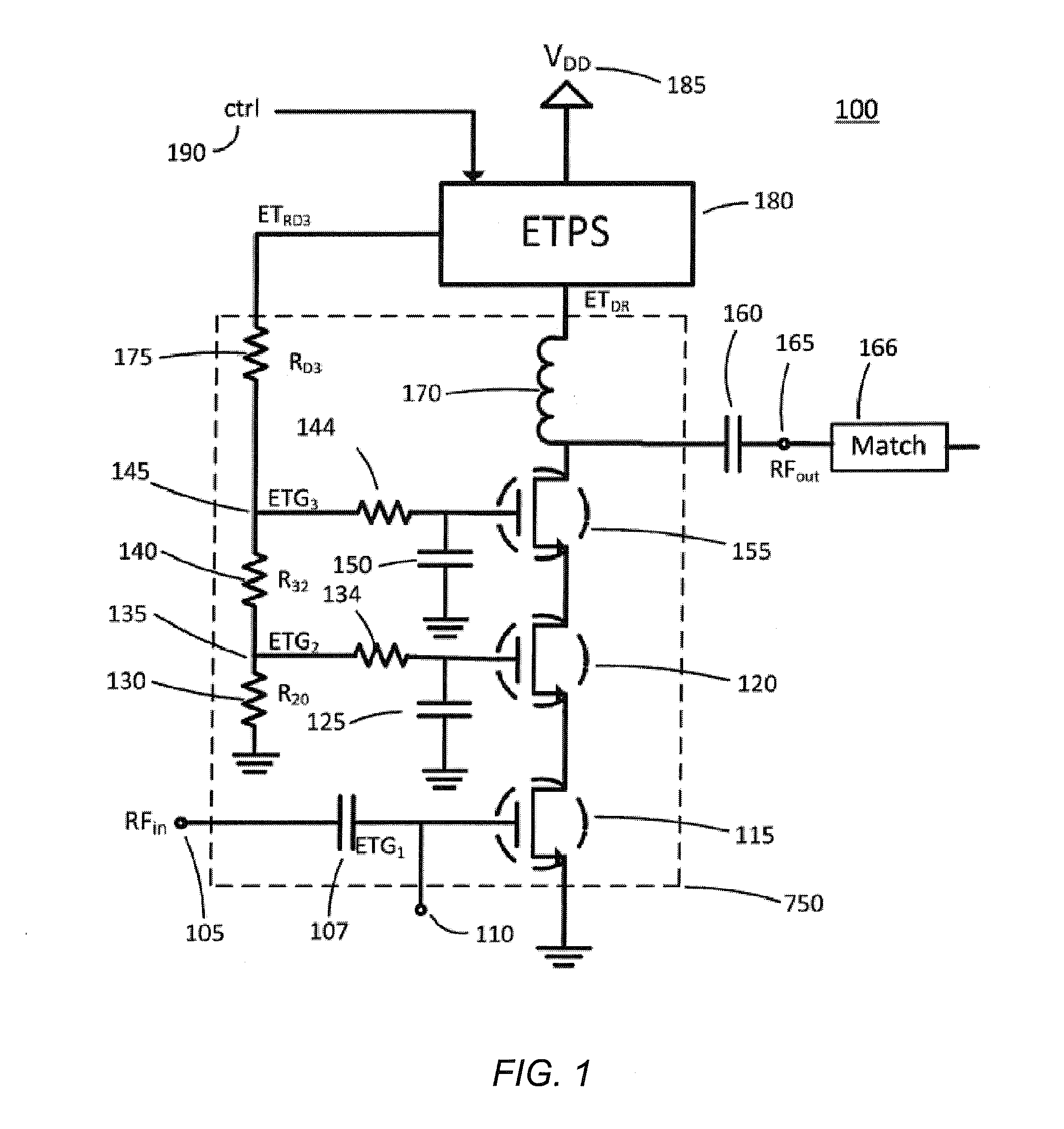

N-way Doherty distributed power amplifier with power tracking

ActiveUS8274332B2Improve performanceIncrease productionNegative-feedback-circuit arrangementsAmplifier combinationsAdaptive biasMultiplexing

Owner:DALI SYST LTD

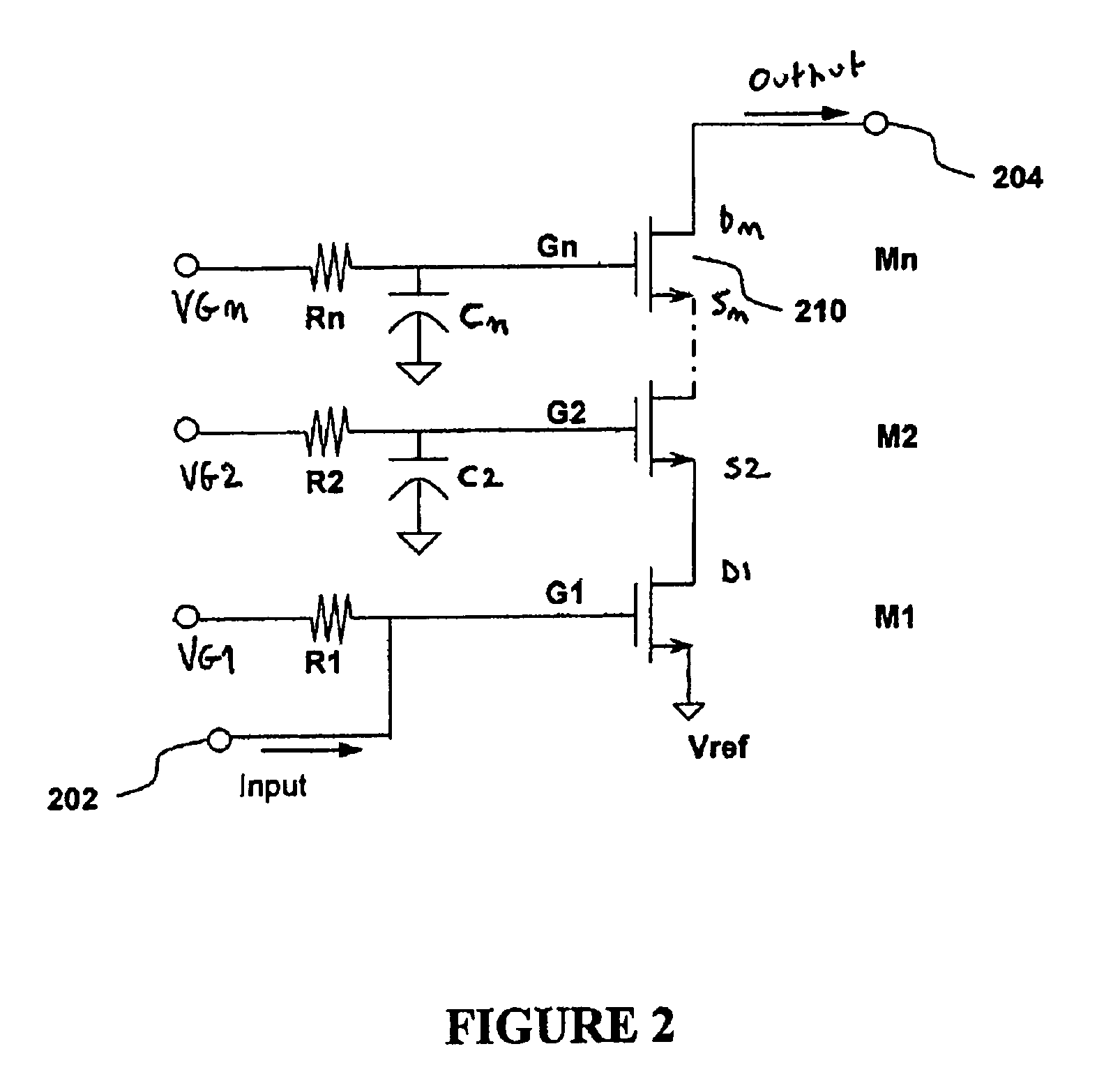

Stacked linear power amplifier with capacitor feedback and resistor isolation

ActiveUS8487706B2MinimizationMaximizeAmplifier combinationsAmplififers with field-effect devicesCapacitanceLinear power amplifier

A power amplifier with stacked, serially connected, field effect transistors is described. DC control voltage inputs are fed to the gates of each transistor. Capacitors are coupled to the transistors. The inputs and the capacitors are controlled to minimize generation of non-linearities of each field effect transistor and / or to maximize cancellation of distortions between the field effect transistors of the power amplifier in order to improve linearity of the power amplifier output.

Owner:PSEMI CORP

Multi-mode multi-amplifier architecture

InactiveUS20040263246A1Amplifier modifications to reduce non-linear distortionGain controlAudio power amplifierEngineering

An amplification architecture or system is provided having a multiple amplifier system that switches modes of operation between operation in a component mode and a composite mode based on a characteristic of an input signal relative to a threshold level. In the component mode, the components of the input signal are employed to different terminals of the multiple amplifier system that provide a reconstructed amplified representation of the input signal. In the composite mode, the input signal is amplified to provide an amplified representation of the input signal.

Owner:NORTHROP GRUMMAN SYST CORP

Scalable Periphery Tunable Matching Power Amplifier

A scalable periphery tunable matching power amplifier is presented. Varying power levels can be accommodated by selectively activating or deactivating unit cells of which the scalable periphery tunable matching power amplifier is comprised. Tunable matching allows individual unit cells to see a constant output impedance, reducing need for transforming a low impedance up to a system impedance and attendant power loss. The scalable periphery tunable matching power amplifier can also be tuned for different operating conditions such as different frequencies of operation or different modes.

Owner:PSEMI CORP

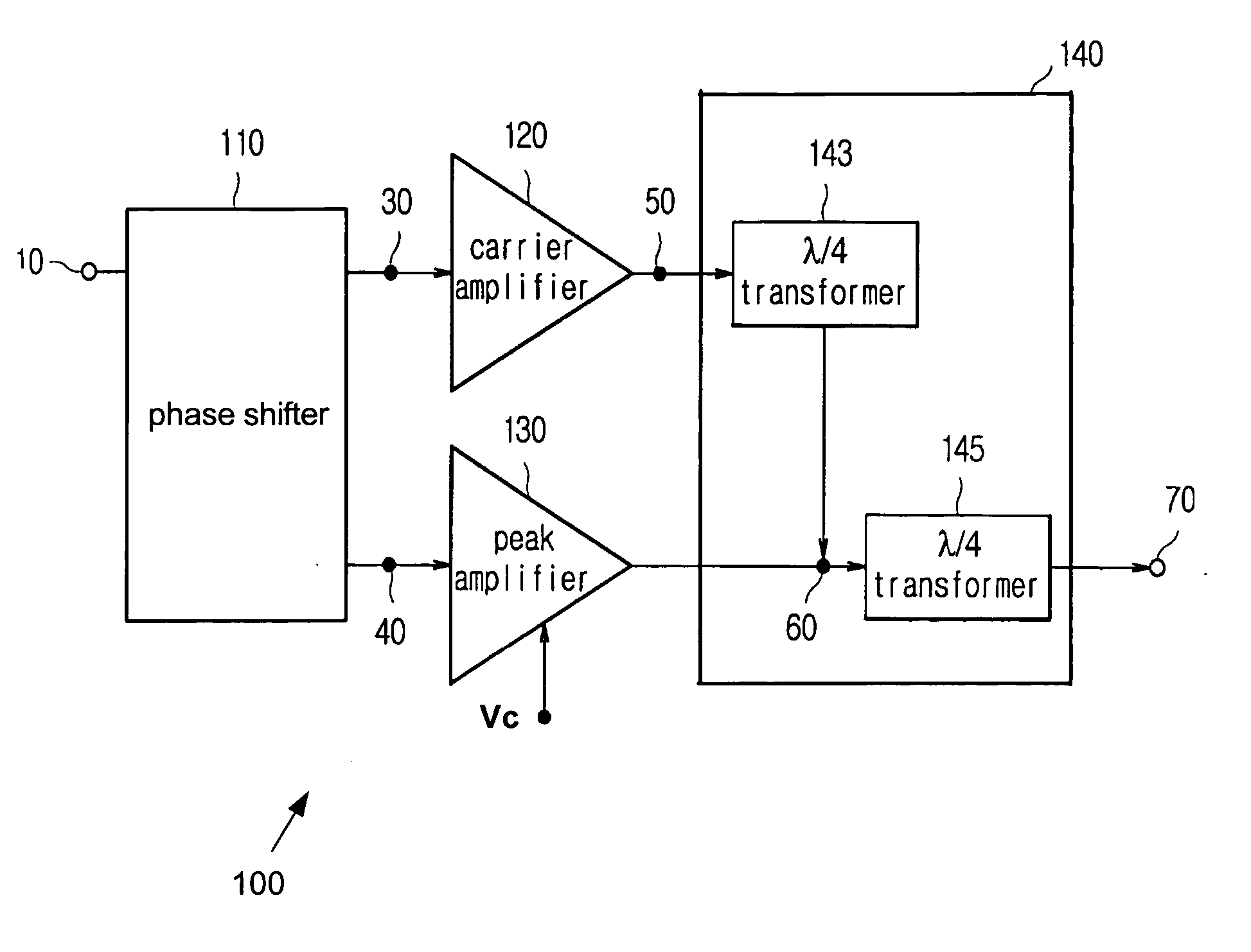

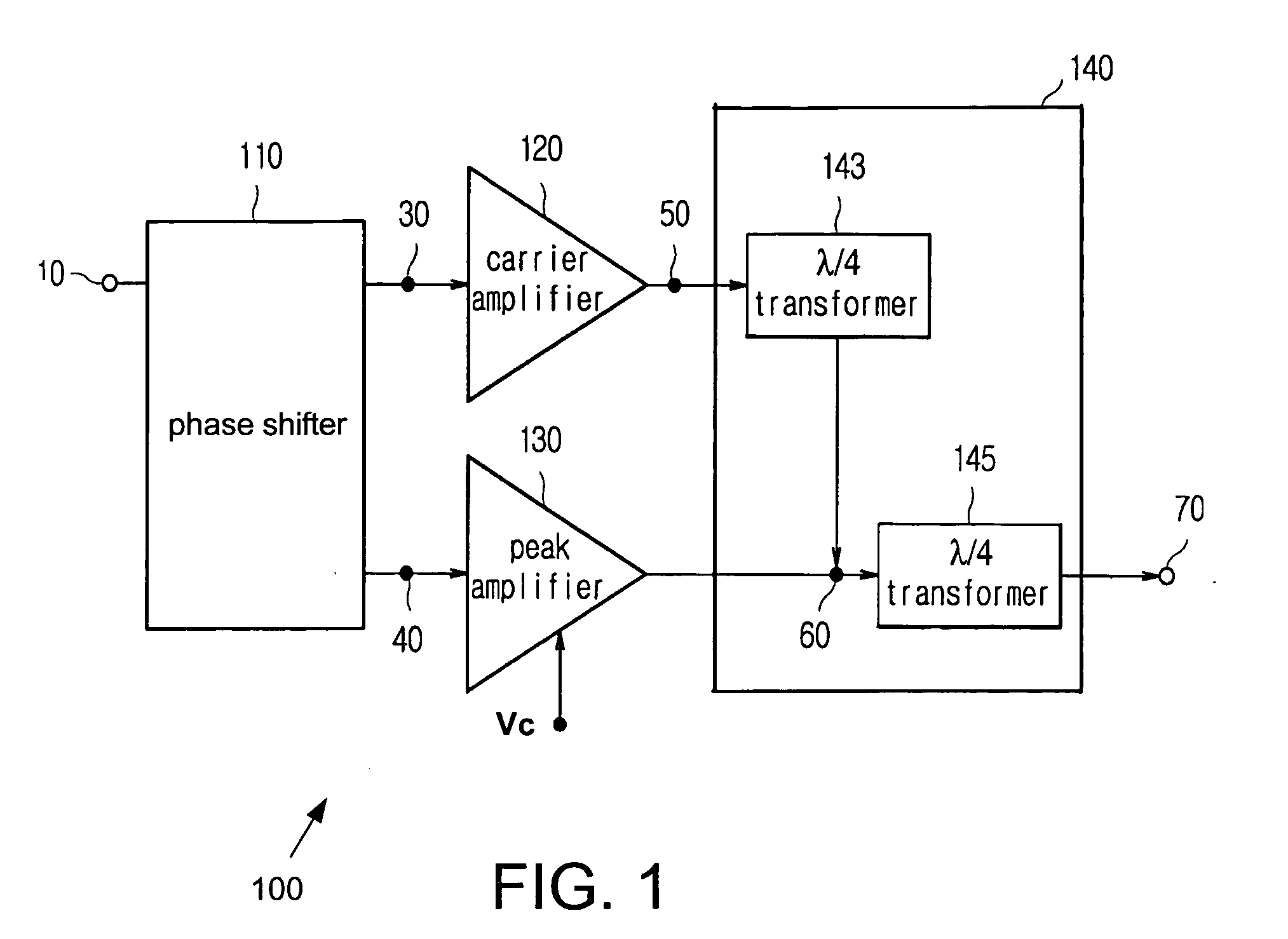

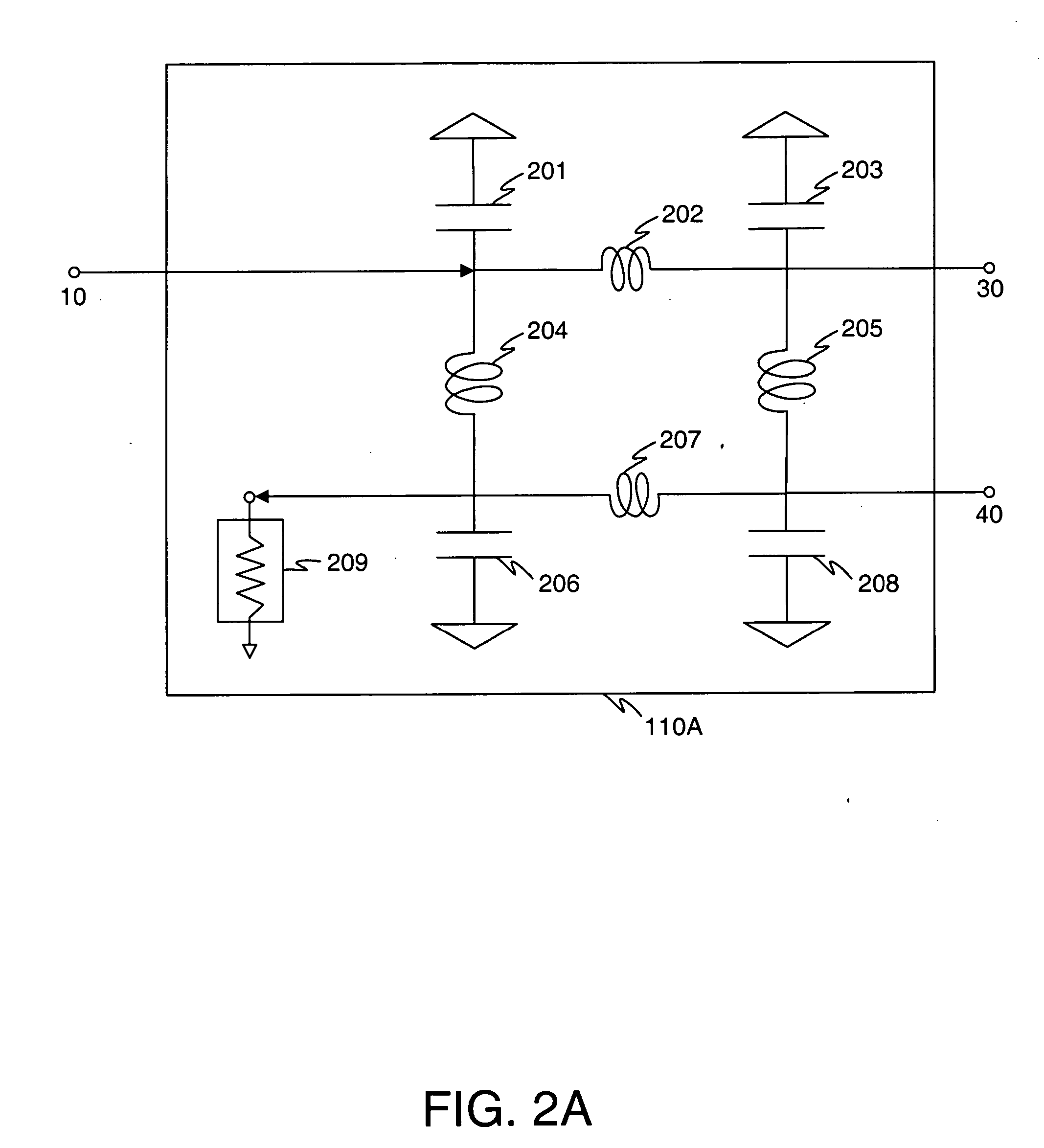

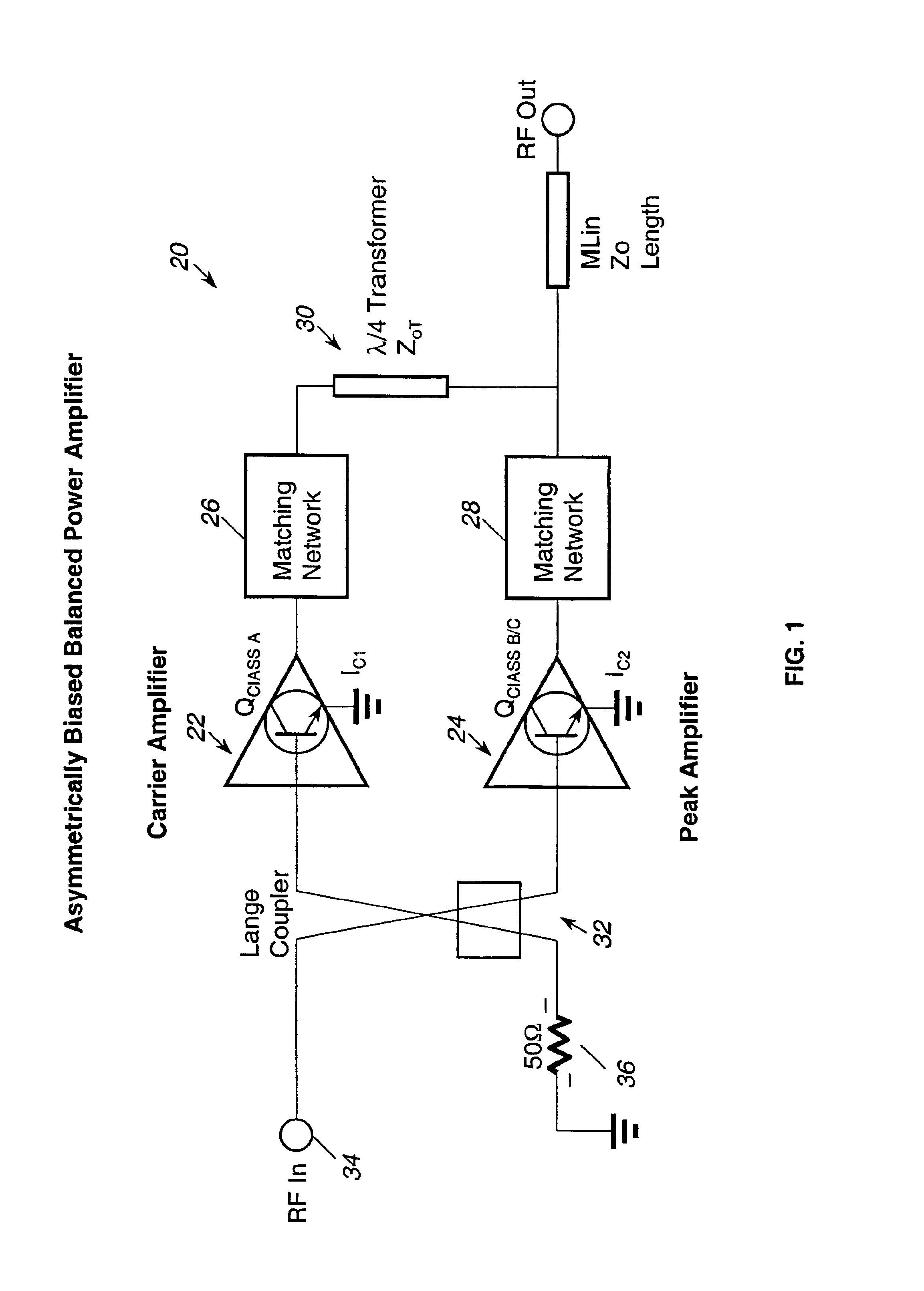

High linearity doherty communication amplifier with phase control

InactiveUS20050012547A1Satisfactory characteristicEnergy efficient ICTAmplifier modifications to reduce non-linear distortionAudio power amplifierActive component

A high linearity Doherty power amplifier with phase delay generation and control via passive and active components. In one embodiment, phase delay generation and control is implemented by an active phase shifter comprising a lower differential unit for generating a first differential output signal, an upper differential unit for generating a second differential output signal, and a phase control unit for tuning a phase difference between the first and second differential output signals within a phase tolerance. In addition, to improve efficiency and linearity characteristics, the power amplifier receives a voltage control signal to bias a supplemental amplifier so that the power amplifier operates in a Doherty mode in a low output power range and in a non-Doherty mode in a high output power range.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE +1

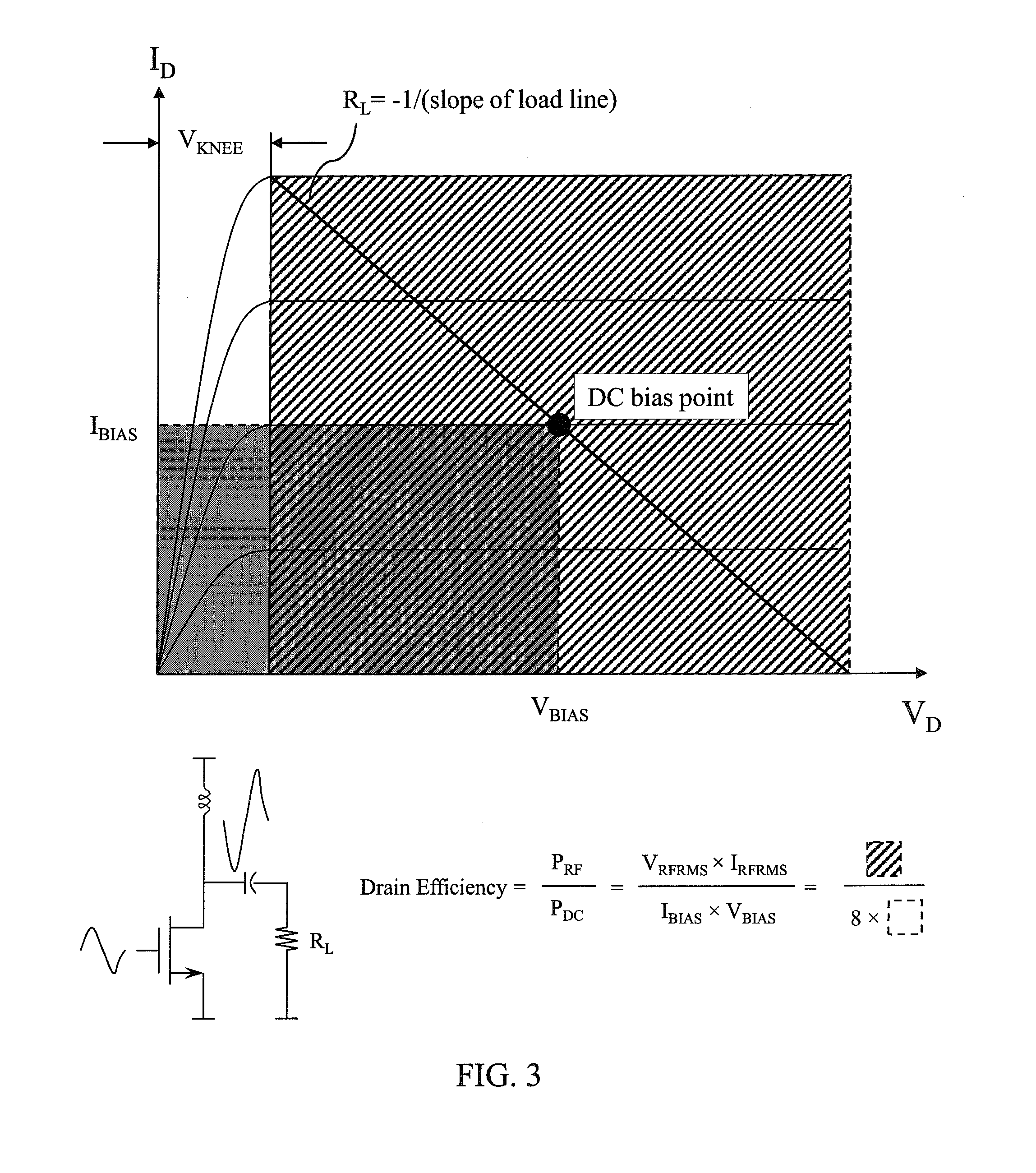

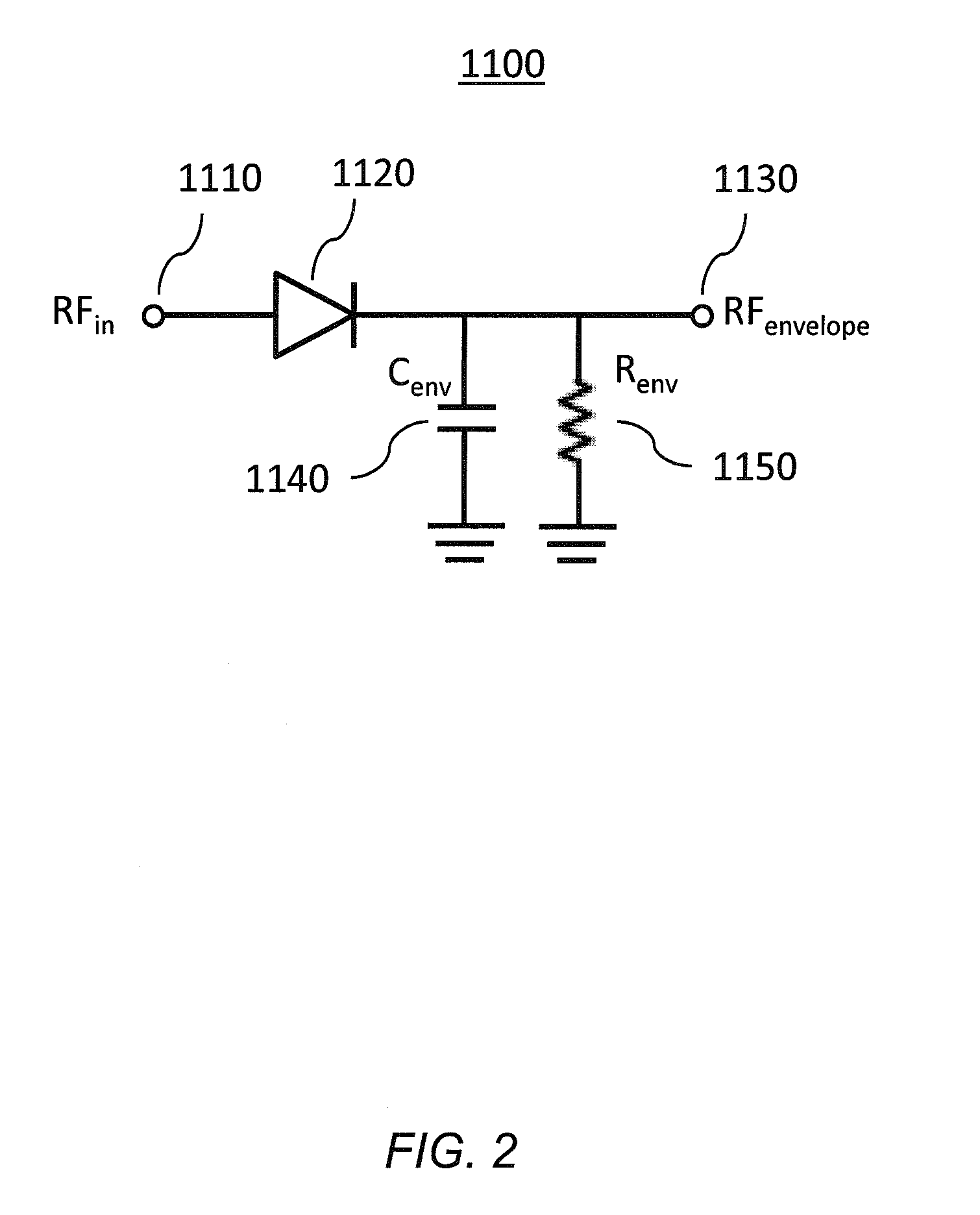

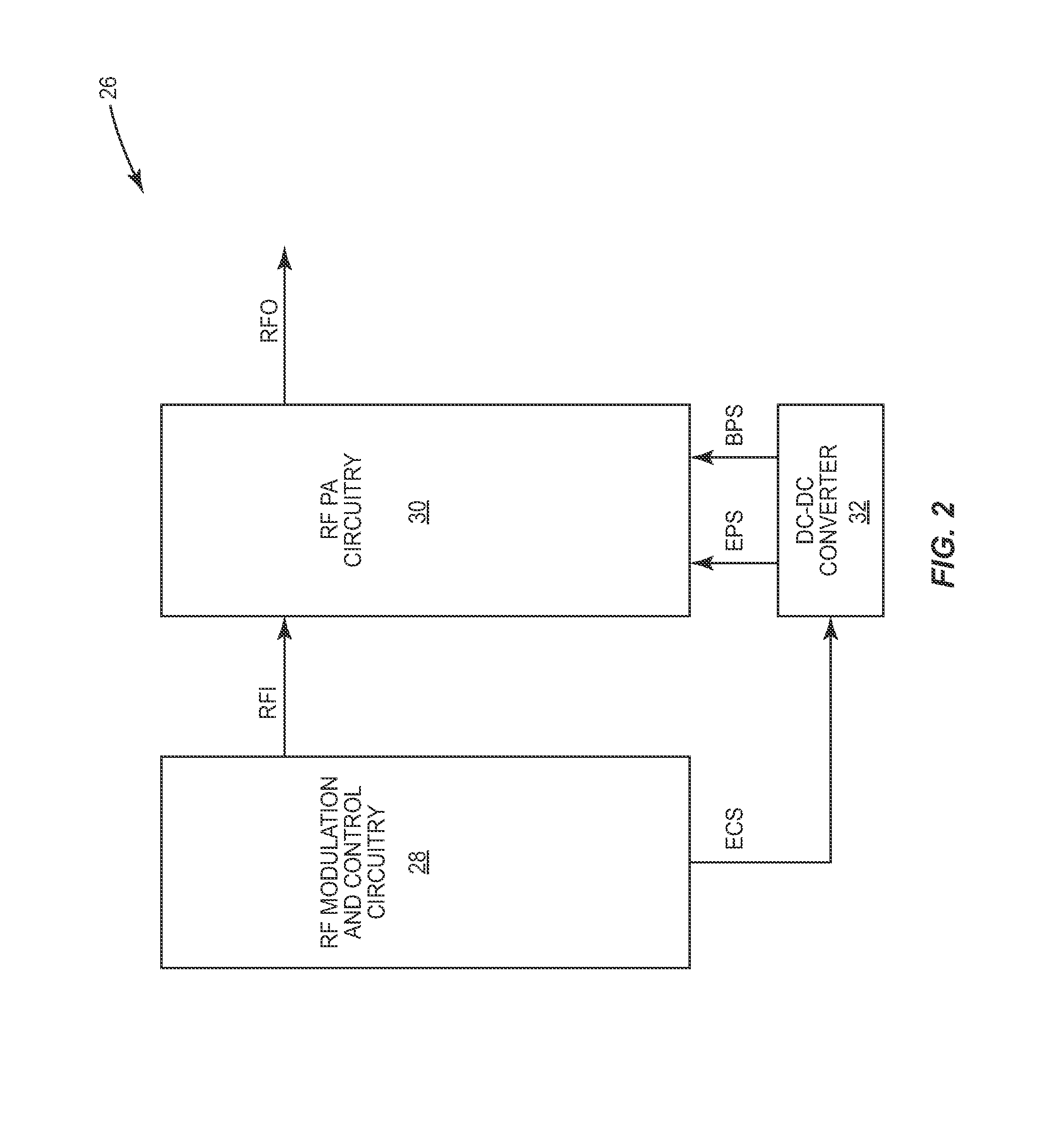

Optimization Methods for Amplifier with Variable Supply Power

ActiveUS20140184334A1Affecting responseAmplifier modifications to reduce non-linear distortionPower amplifiersAudio power amplifierLinear region

Optimization methods via various circuital arrangements for amplifier with variable supply power are presented. In one embodiment, a switch can be controlled to include or exclude a feedback network in a feedback path to the amplifier to adjust a response of the amplifier dependent on a region of operation of the amplifier arrangement (e.g. linear region or compression region).

Owner:PSEMI CORP

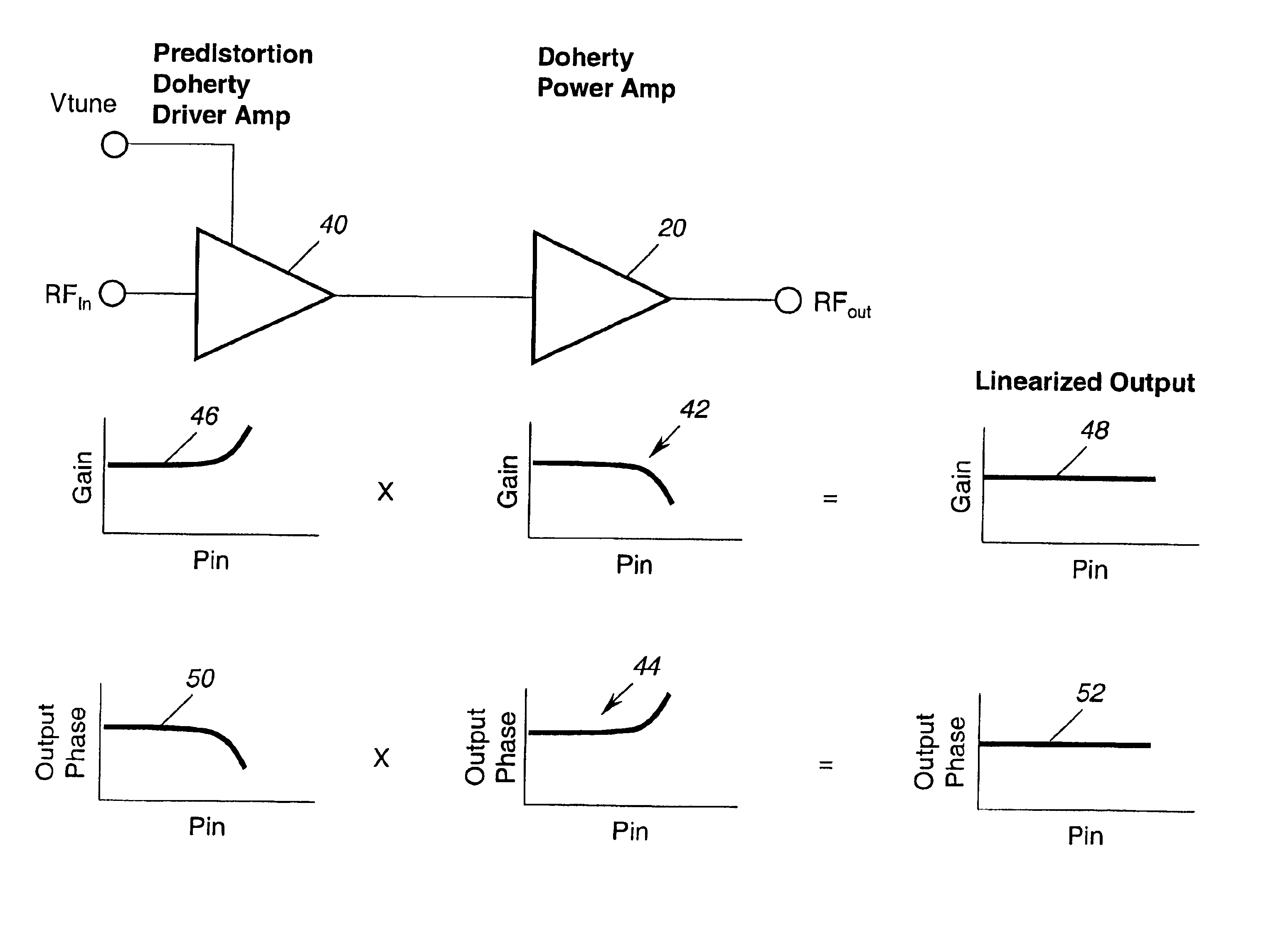

Application of the doherty amplifier as a predistortion circuit for linearizing microwave amplifiers

InactiveUS6864742B2Reducing intermodulation (IM) distortionImprove power added efficiencyAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influencePower-added efficiencyAudio power amplifier

A predistortion circuit for a microwave amplifier and more particularly to predistortion circuit configured as a Doherty amplifier. The predistortion circuit is adapted to be coupled to a downstream Doherty amplifier to precompensate for the gain compression and phase expansion of the downstream Doherty amplifier as the input power level is increased while simultaneously reducing the intermodulation (IM) distortion. In order to provide precompensation, the precompensation circuit is operated at bias level to provide gain expansion and phase compression to cancel out the gain compression and phase expansion of the downstream Doherty amplifier to provide a higher overall linear power added efficiency (PAE).

Owner:NORTHROP GRUMMAN SYST CORP

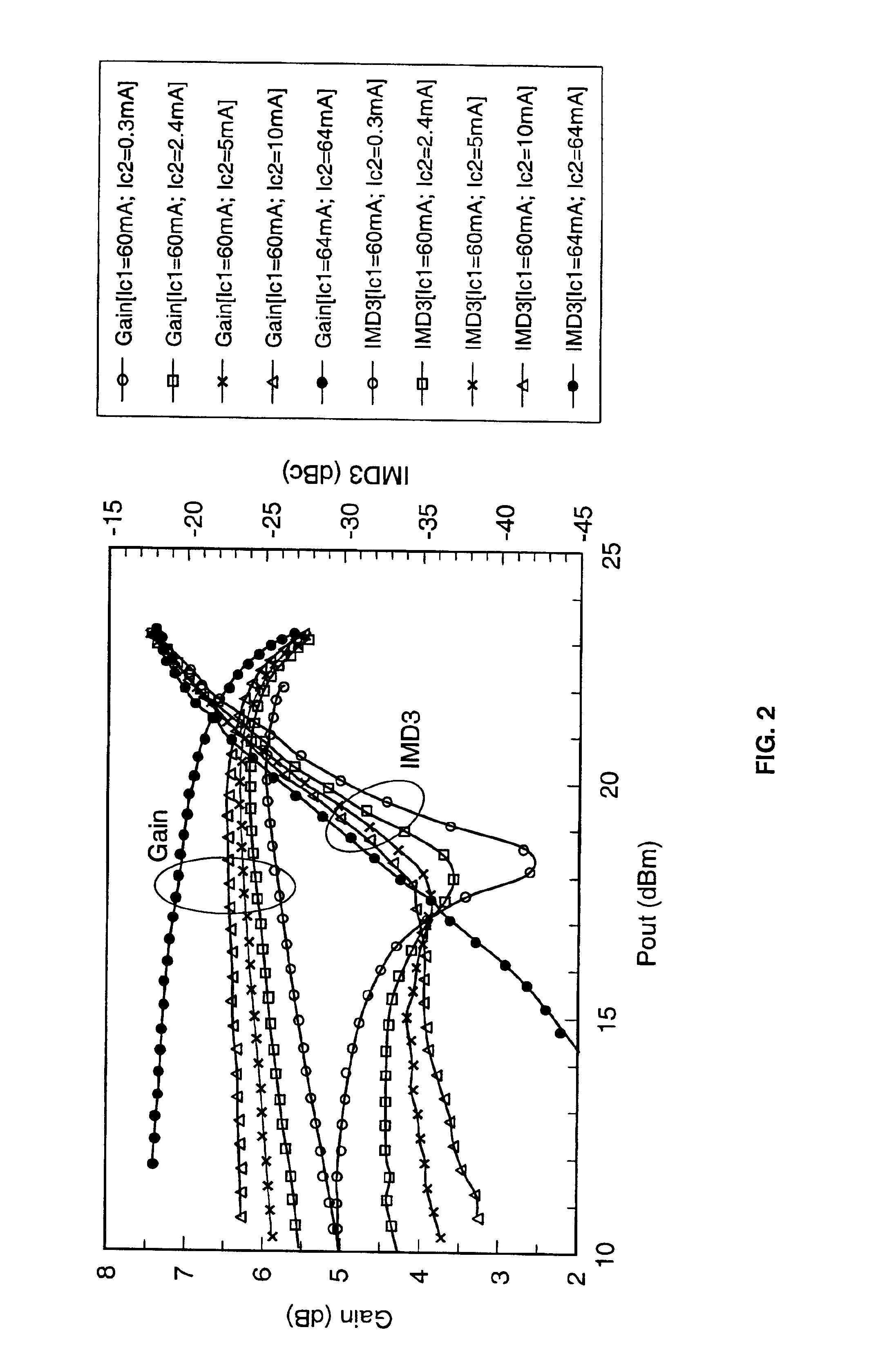

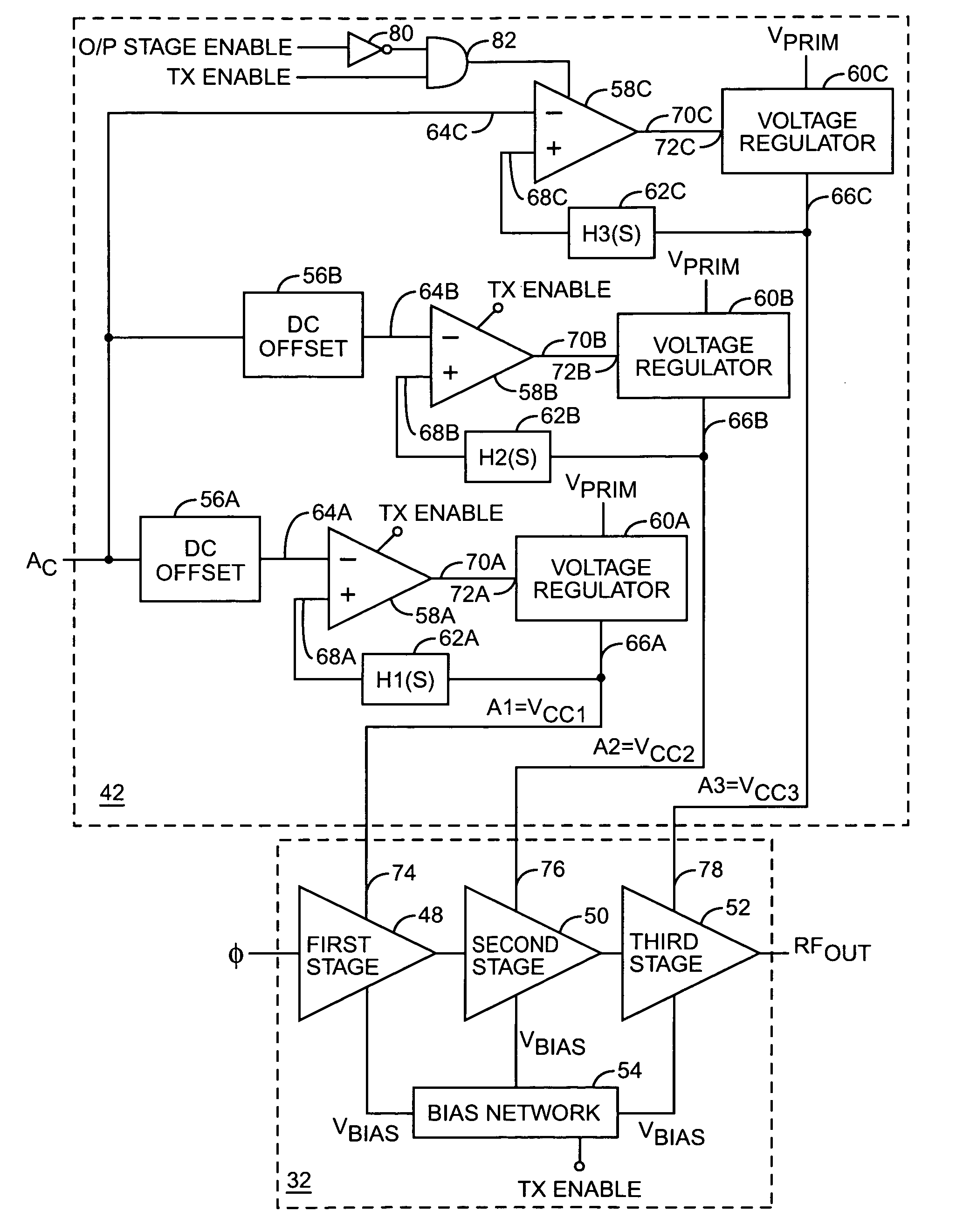

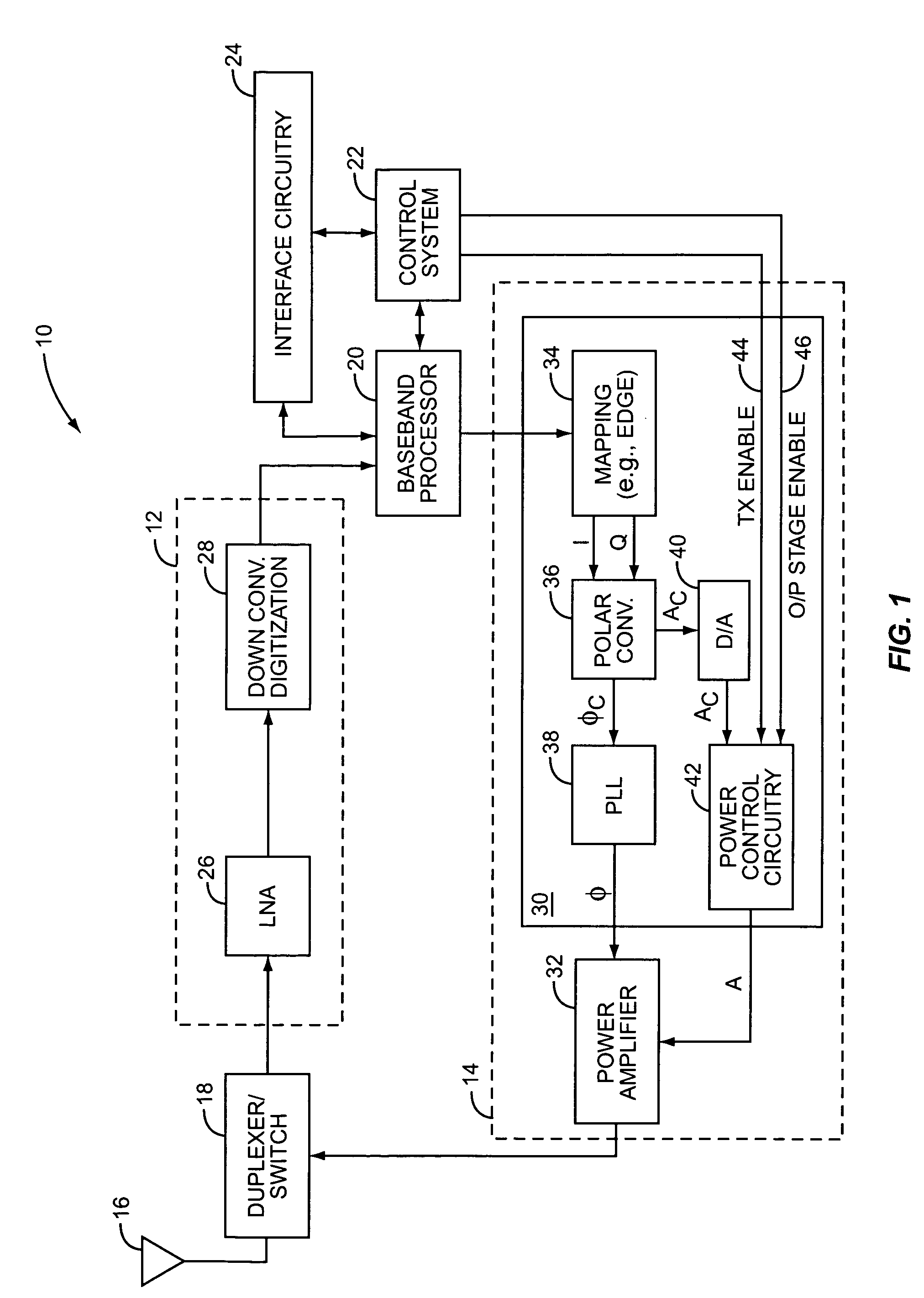

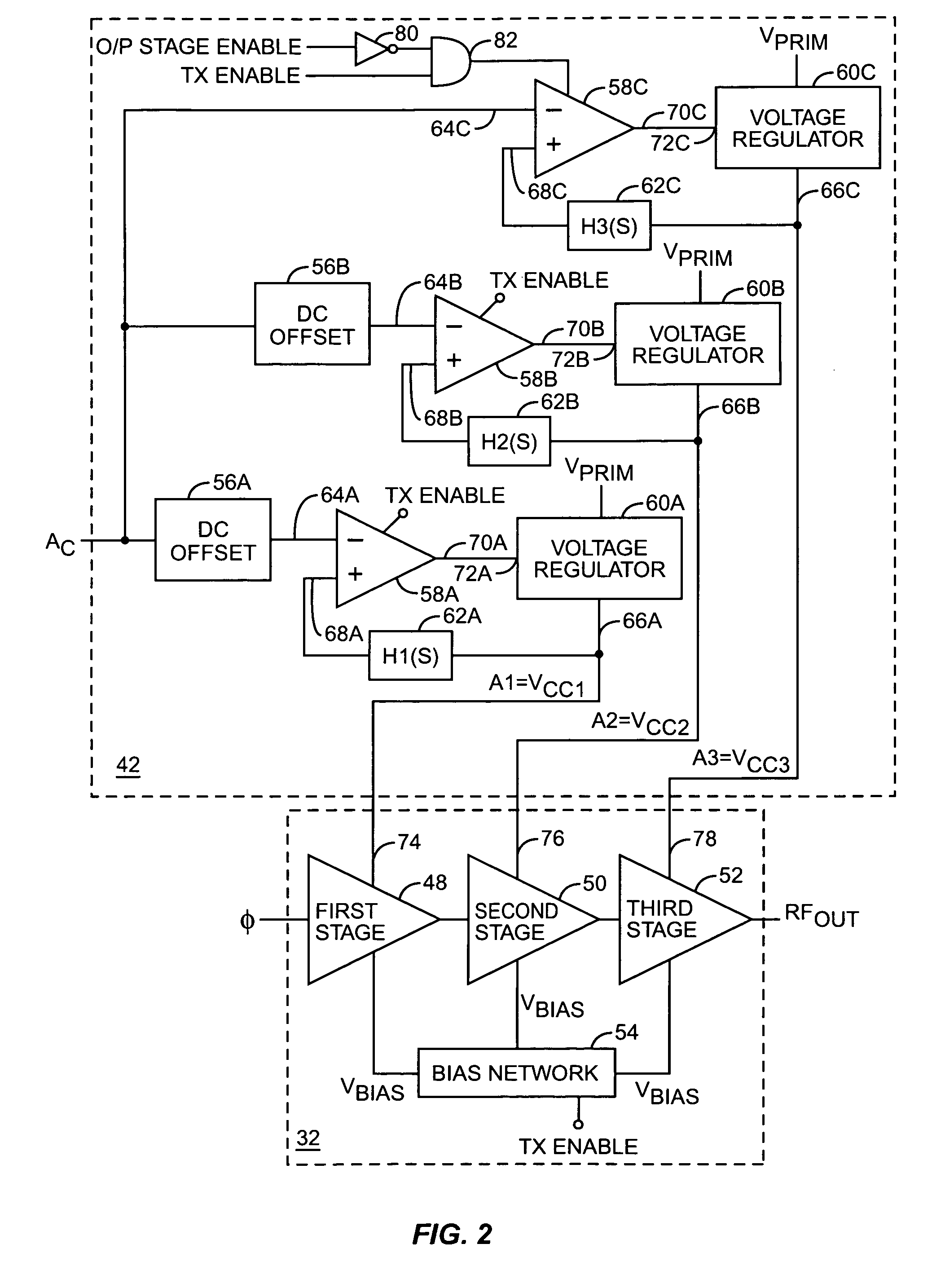

Tailored collector voltage to minimize variation in AM to PM distortion in a power amplifier

ActiveUS7109791B1Reduce variationAmplifier modifications to reduce non-linear distortionPulse automatic controlAudio power amplifierControl signal

A system is provided for substantially reducing variation in AM to PM distortion of a power amplifier caused by variations in RF drive power and temperature. The system includes power control circuitry and power amplifier circuitry. The power amplifier circuitry includes an input amplifier stage and at least one additional amplifier stage coupled in series with the input amplifier stage. The power control circuitry provides a first supply voltage to the input amplifier stage based on a control signal such that the first supply voltage has a predetermined DC offset with respect to the control signal. The first supply voltage is provided such that the predetermined DC offset substantially reduces variations in the AM to PM distortion of the power amplifier due to variations in radio frequency (RF) drive power.

Owner:QORVO US INC

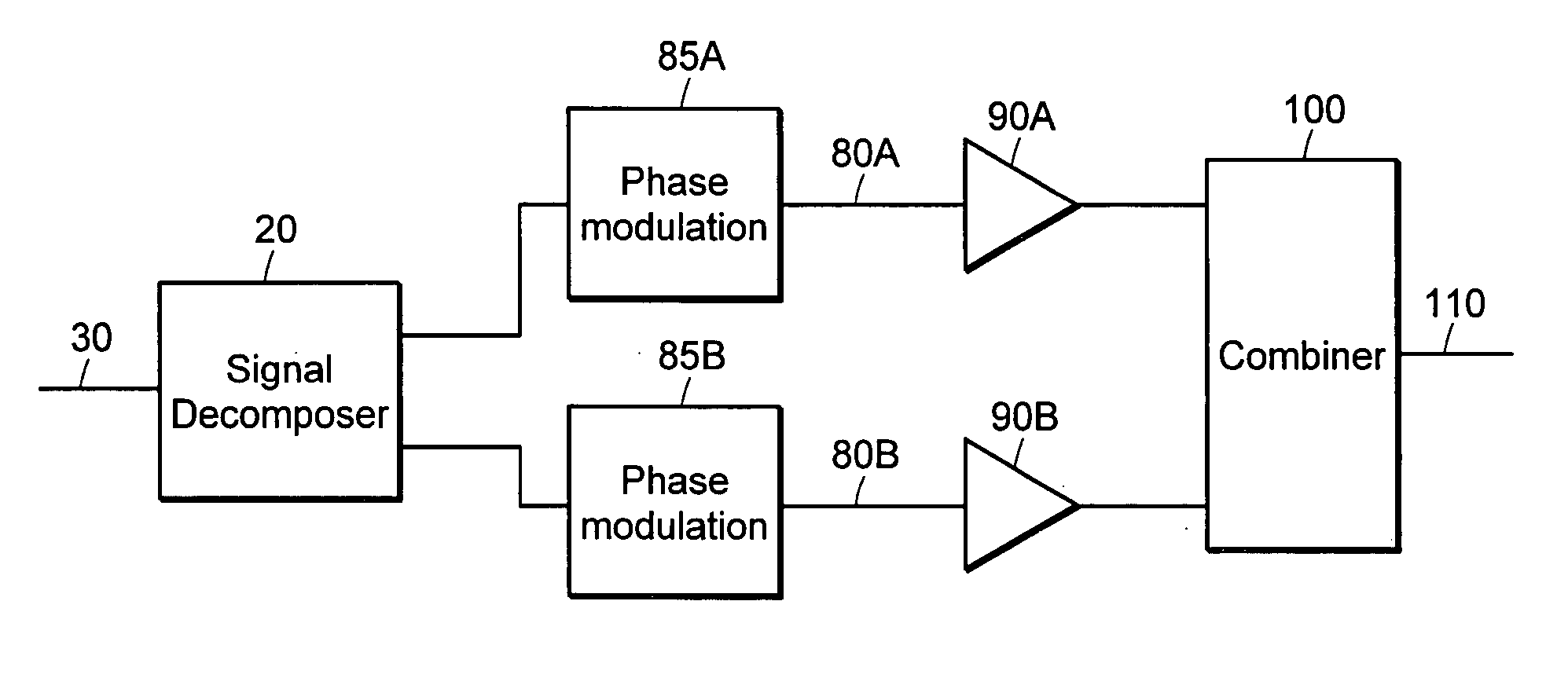

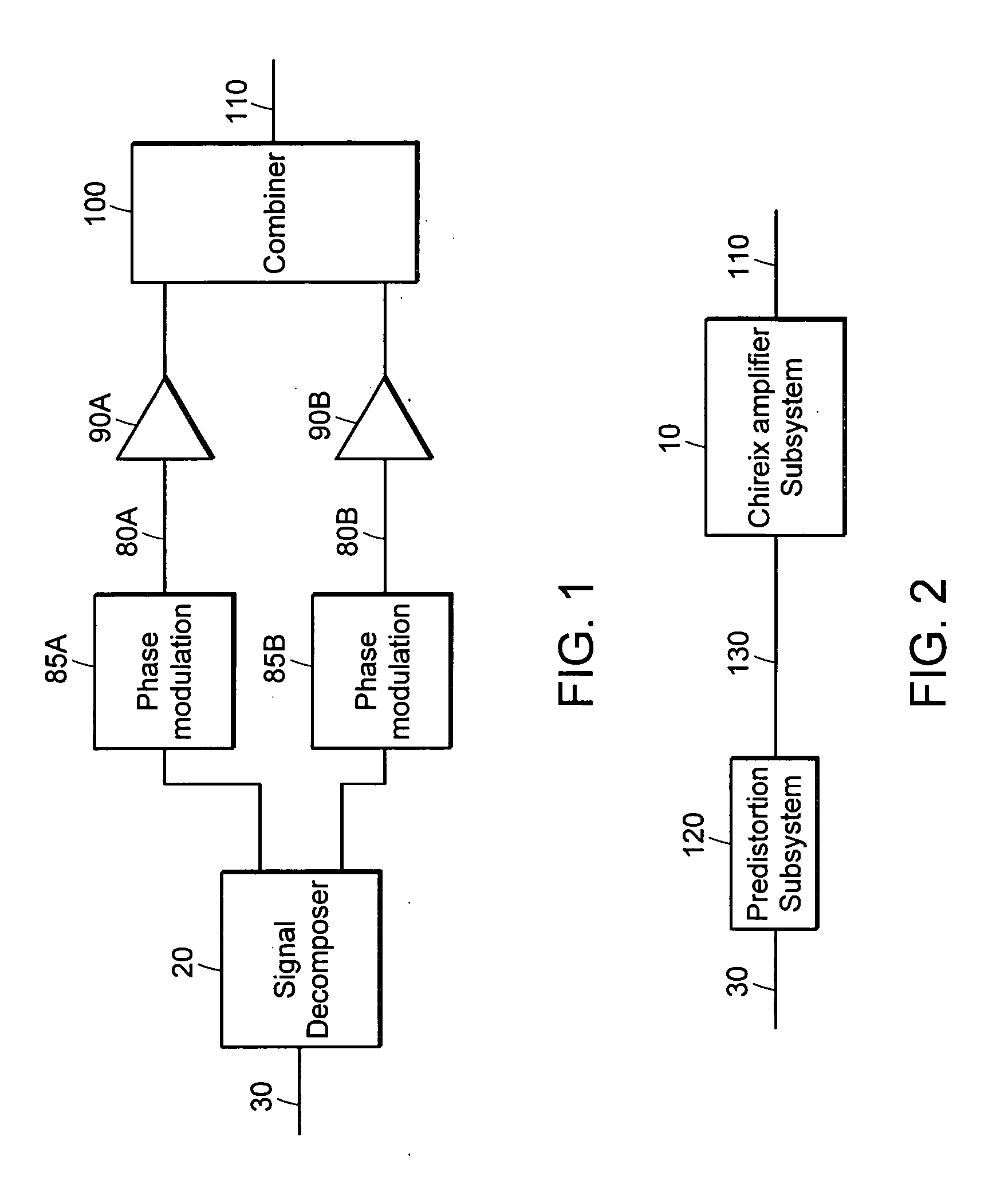

Switched-mode power amplifier using lumped element impedance inverter for parallel combining

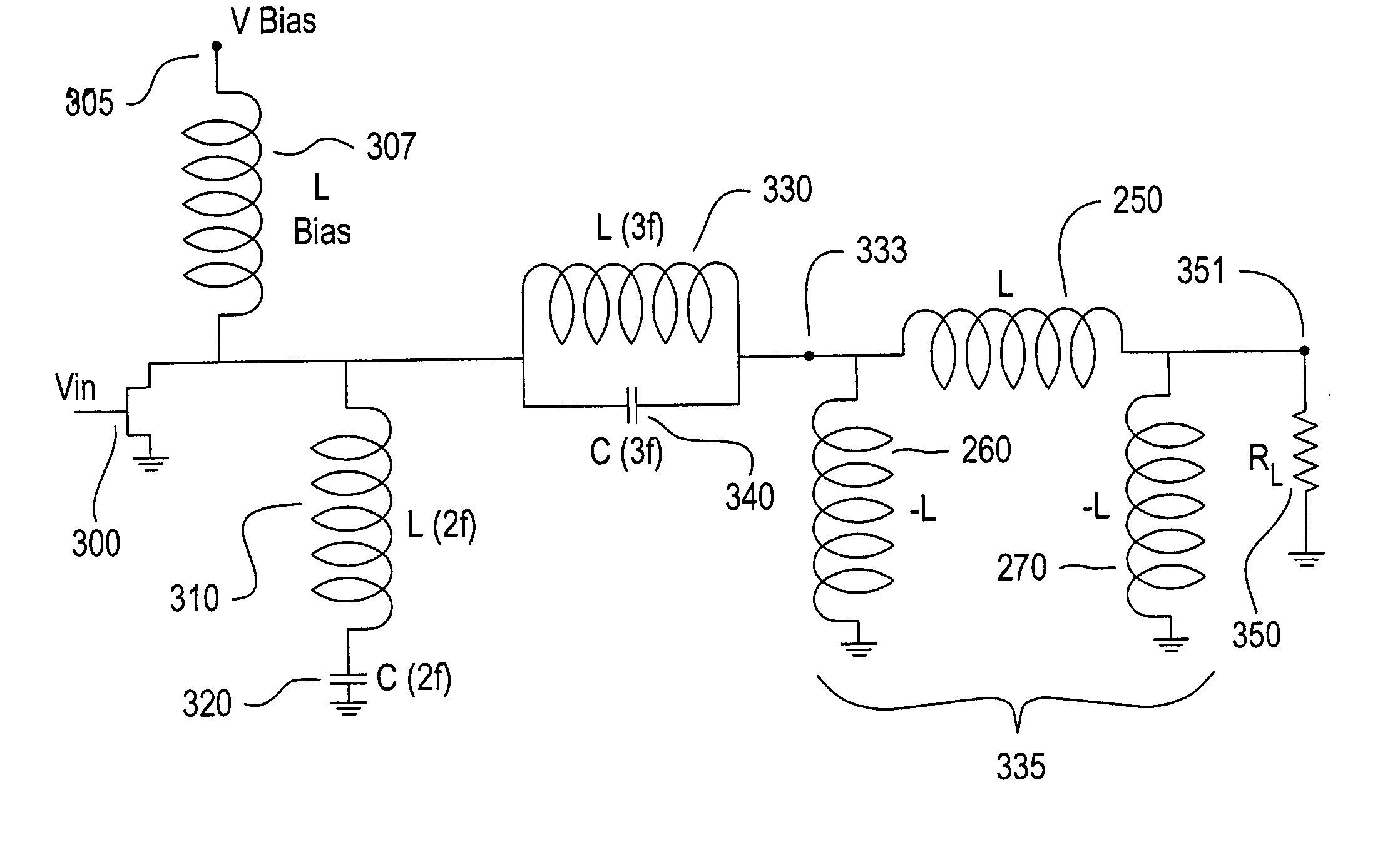

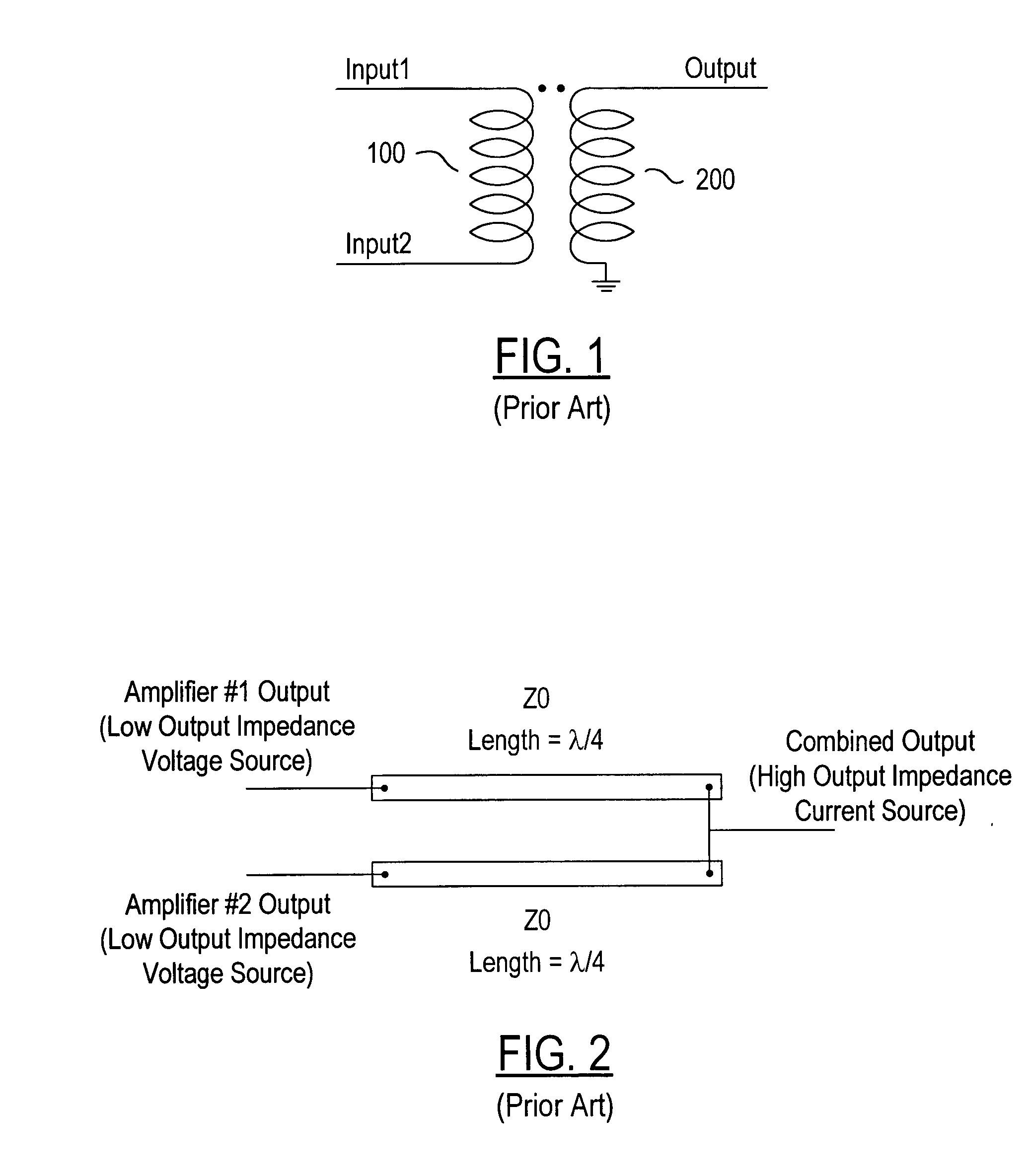

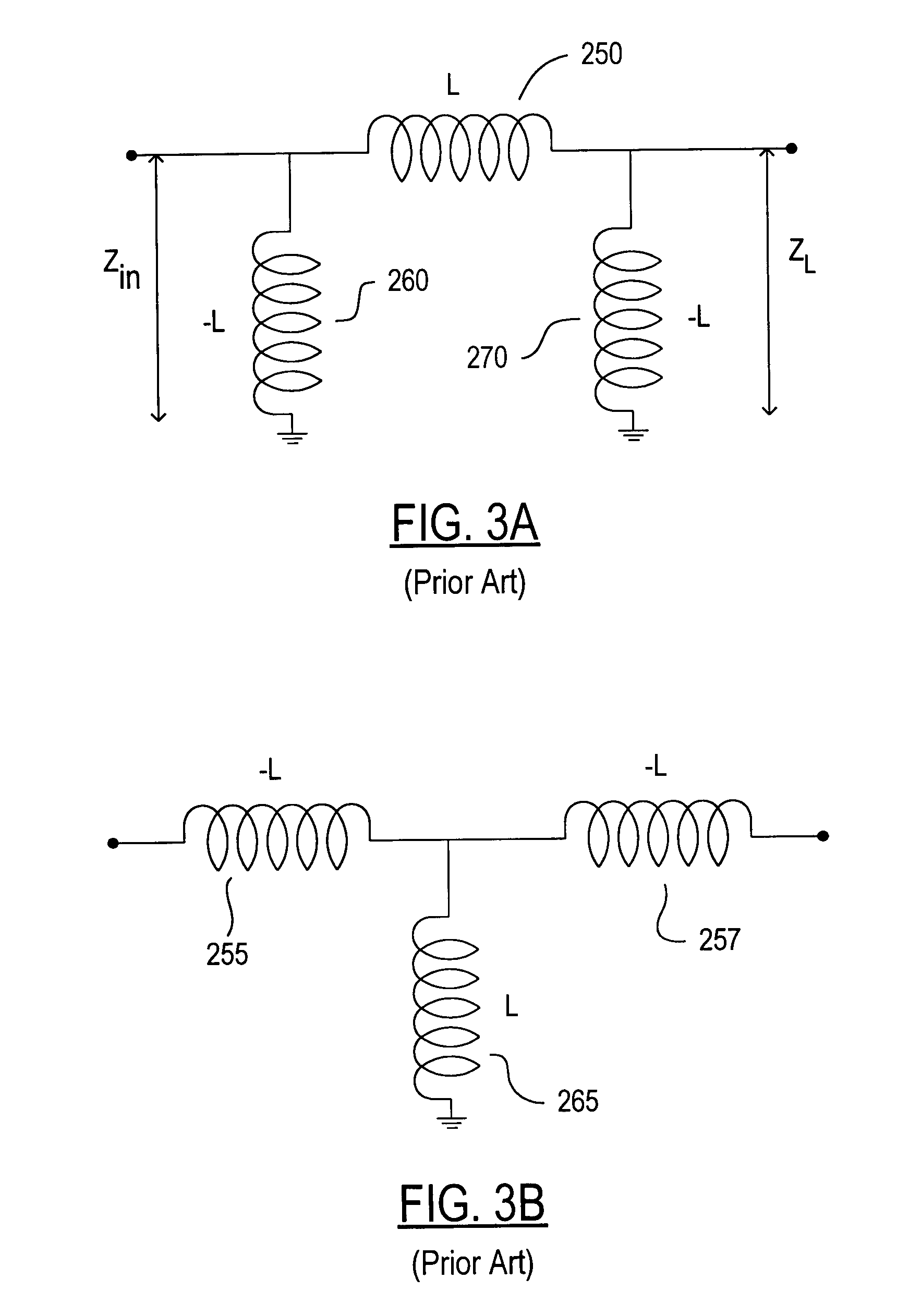

InactiveUS20050007194A1Effective compensationAmplifier combinationsAmplifier input/output impedence modificationAudio power amplifierParasitic capacitance

A switched-mode Class F power amplifier is provided for parallel connection with at least one other like amplifier, within a Chireix architecture, for combining the signals output therefrom. An input component includes at least one active device configured to be alternately switched by a signal input thereto to present an amplified signal corresponding to the input signal and constituting a low output impedance voltage source. A lumped element impedance inverter is provided between the input component and an output resonator component, the impedance inverter being configured for transforming the low output impedance voltage source to instead constitute a high output impedance current source configured for said parallel connection. In accordance with the invention, the negative reactive component values required by the impedance inverter are eliminated and effectively provided by incorporating those values into pre-selected reactive components of the input and output components. Further, a source-drain parasitic capacitance across the active device is eliminated by one or more pre-selected reactive components of the input component, the value(s) of which effectively compensate for the parasitic capacitance.

Owner:ZARBANA DIGITAL FUND

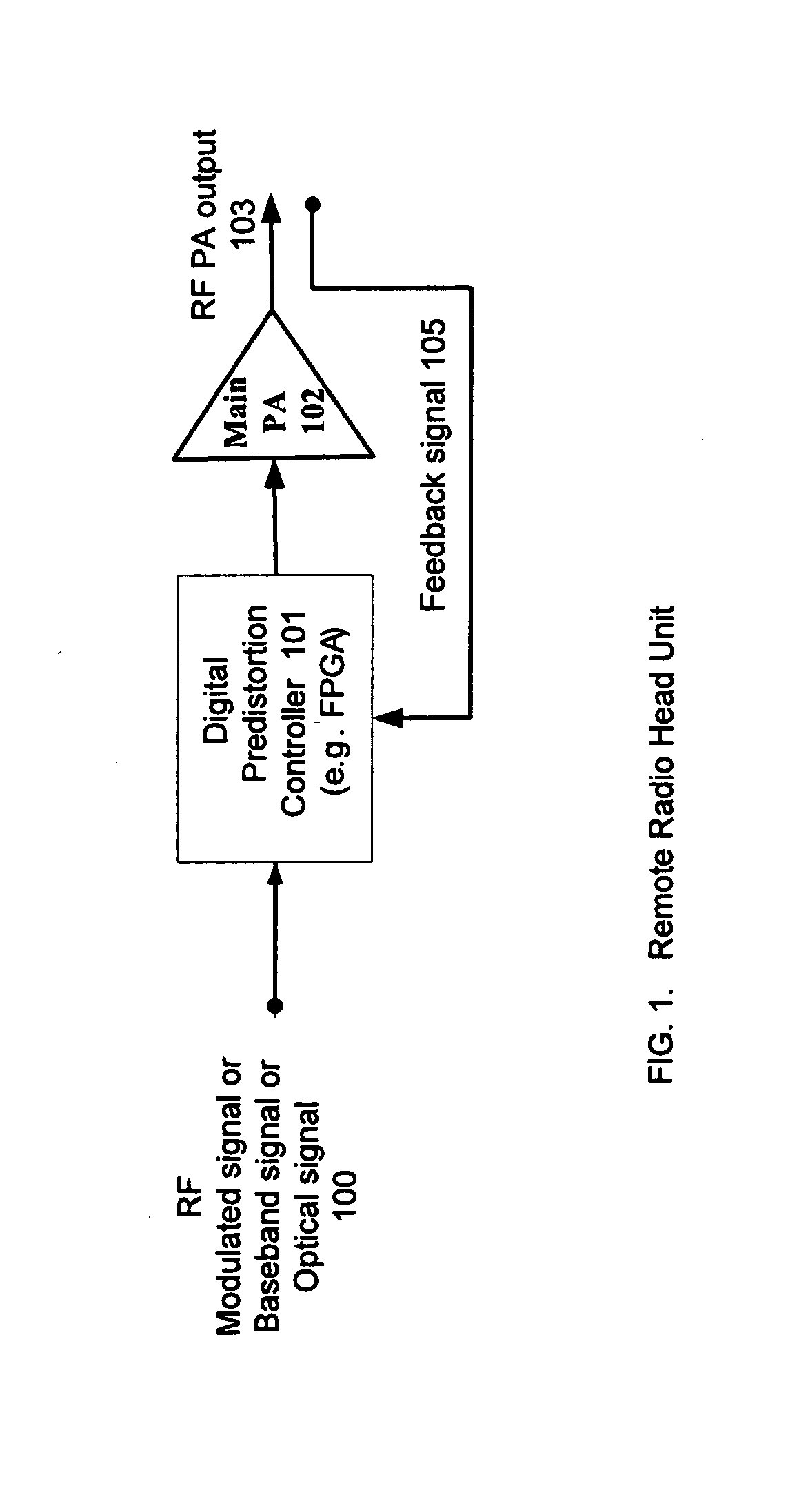

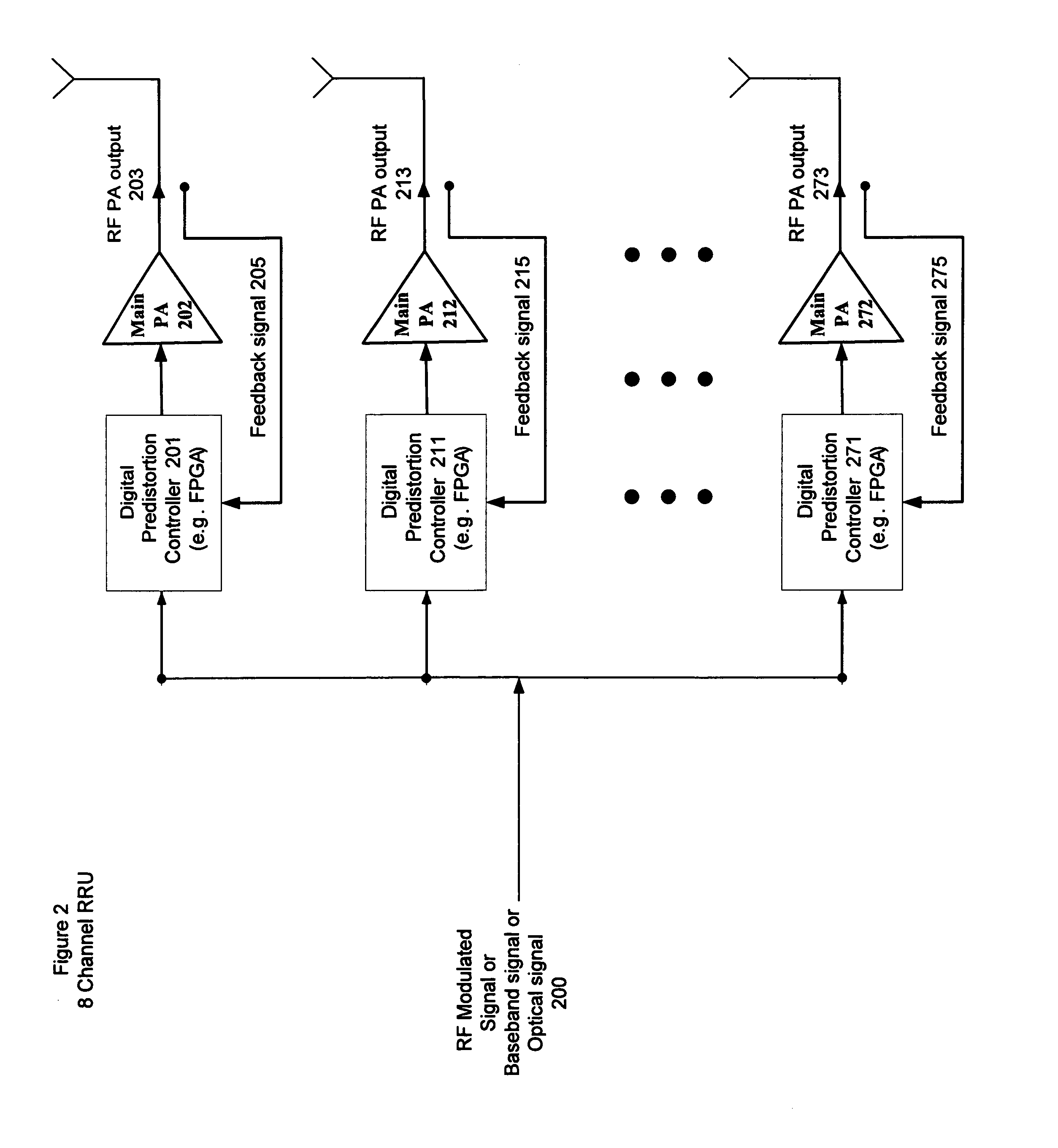

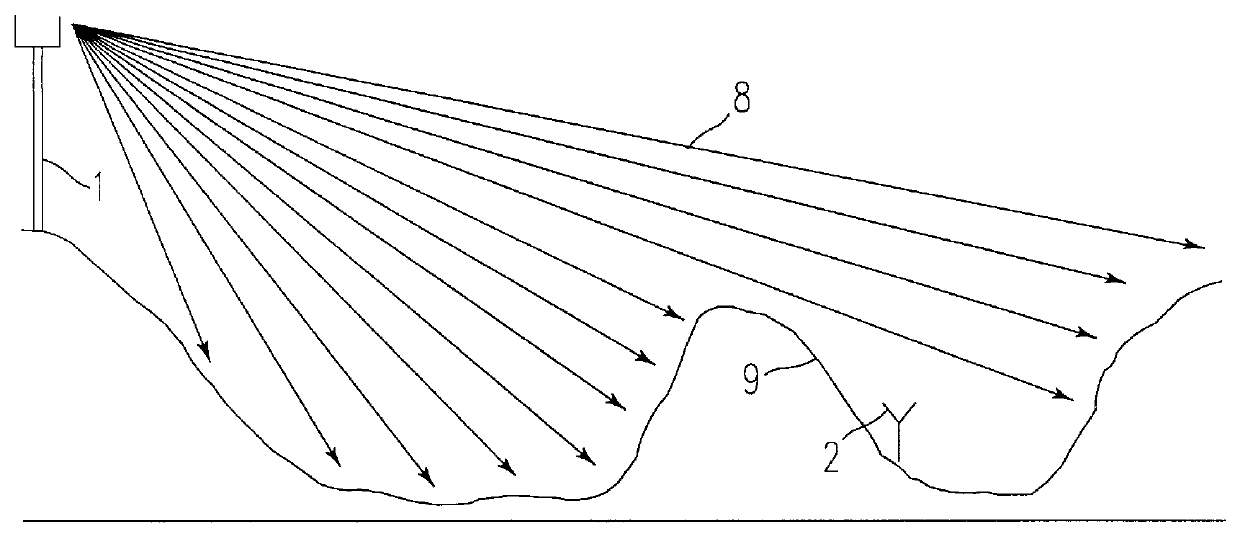

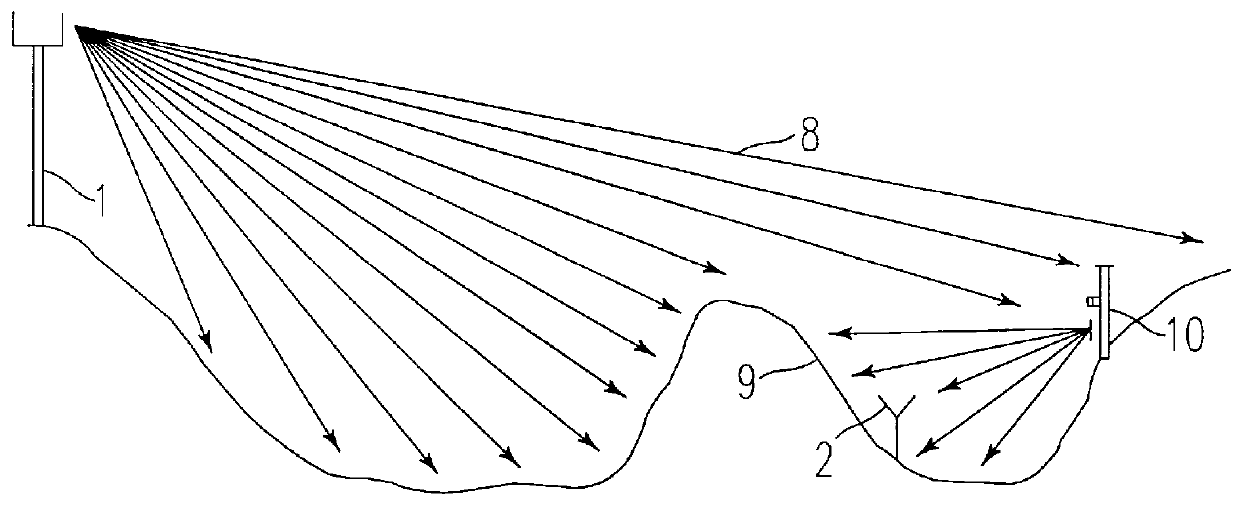

High efficiency, remotely reconfigurable remote radio head unit system and method for wireless communications

ActiveUS20120155572A1High performance and cost-effectiveImprove linearityEnergy efficient ICTPower amplifiersUnit systemEngineering

A remote radio head unit (RRU) system for achieving high efficiency and high linearity in wideband communication systems is disclosed. The present invention is based on the method of adaptive digital predistortion to linearize a power amplifier inside the RRU. The power amplifier characteristics such as variation of linearity and asymmetric distortion of the amplifier output signal are monitored by a wideband feedback path and controlled by the adaptation algorithm in a digital module. Therefore, embodiments of the present invention can compensate for the nonlinearities as well as memory effects of the power amplifier systems and also improve performance, in terms of power added efficiency, adjacent channel leakage ratio and peak-to-average power ratio. The present disclosure enables a power amplifier system to be field reconfigurable and support multi-modulation schemes (modulation agnostic), multi-carriers, multi-frequency bands and multi-channels. As a result, the remote radio head system is particularly suitable for wireless transmission systems, such as base-stations, repeaters, and indoor signal coverage systems.

Owner:DALI SYST LTD

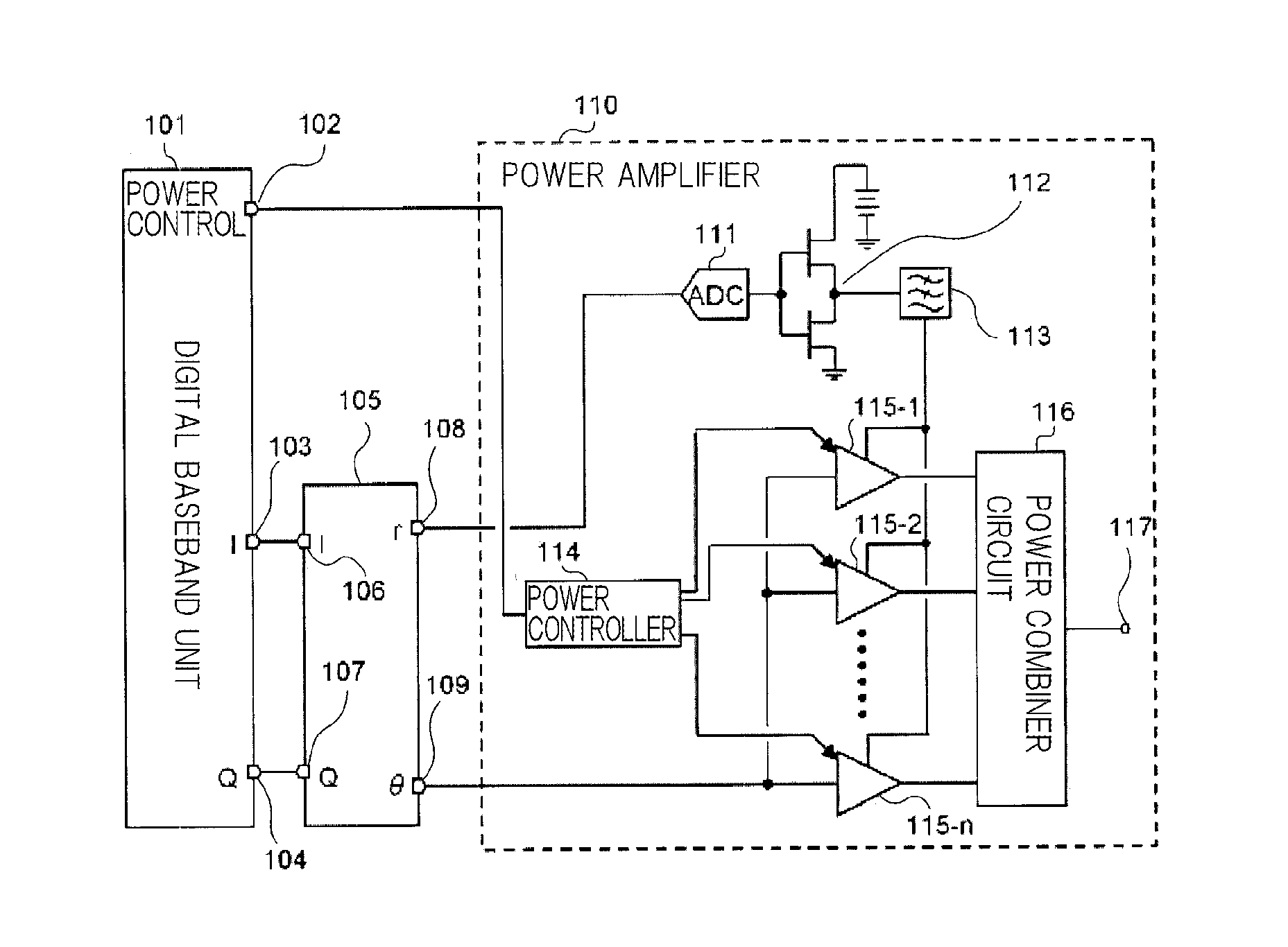

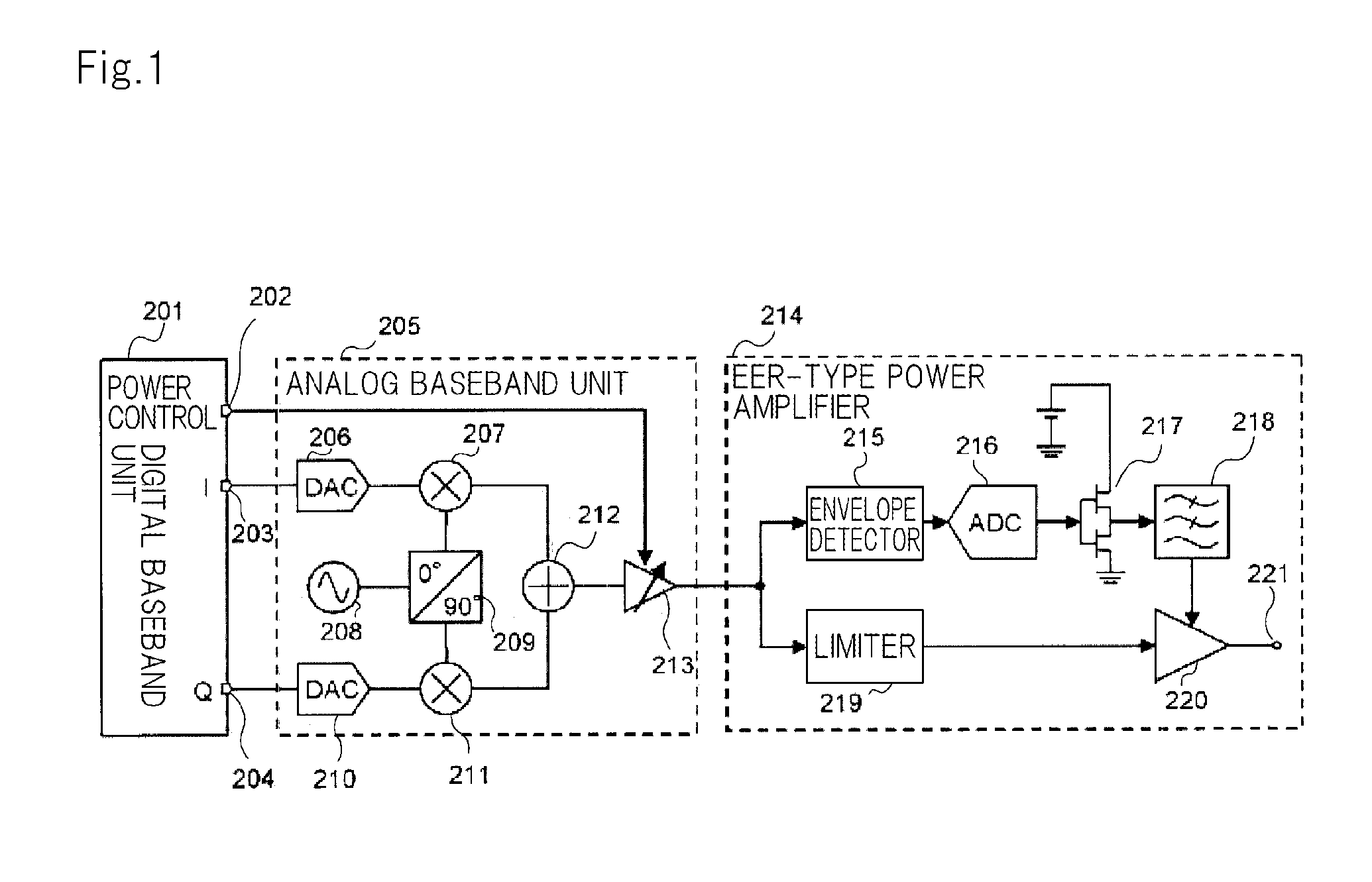

Power amplifier and radio wave transmitter having the same

ActiveUS20100266066A1Eliminate high frequency noiseNegative-feedback-circuit arrangementsModulated-carrier systemsPower controllerHigh frequency power

A power amplifier (10) comprises: an A / D converter (11) for converting, to a time discrete signal, an envelope signal included in a high-frequency modulated signal and including only an amplitude modulated component of the high-frequency modulated signal; a switching amplifier (12) for amplifying the output signal of the A / D converter (11); a low-pass filter (13) for removing high frequency noise from the output signal of the switching amplifier (12); a plurality of high-frequency power amplifiers (15-1 to 15-n) for receiving the output signal of the low-pass filter (13) as a power supply and for amplifying a carrier signal included in the high-frequency modulated signal; and a power controller (14) for adjusting the average power of the output signal of the power amplifier (10) by controlling the total gains of the plurality of high-frequency power amplifiers (15-1 to 15-n).

Owner:NEC CORP

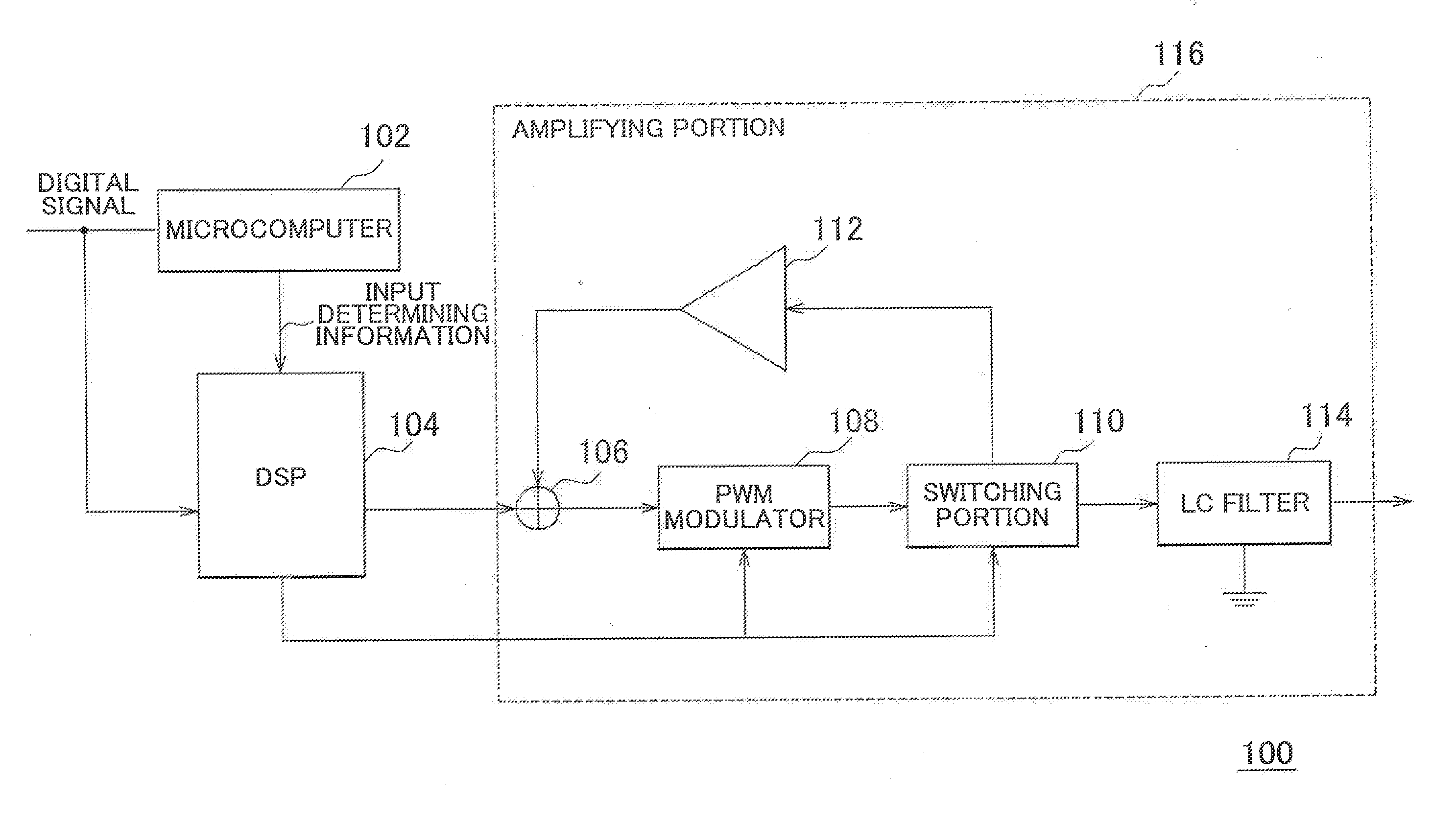

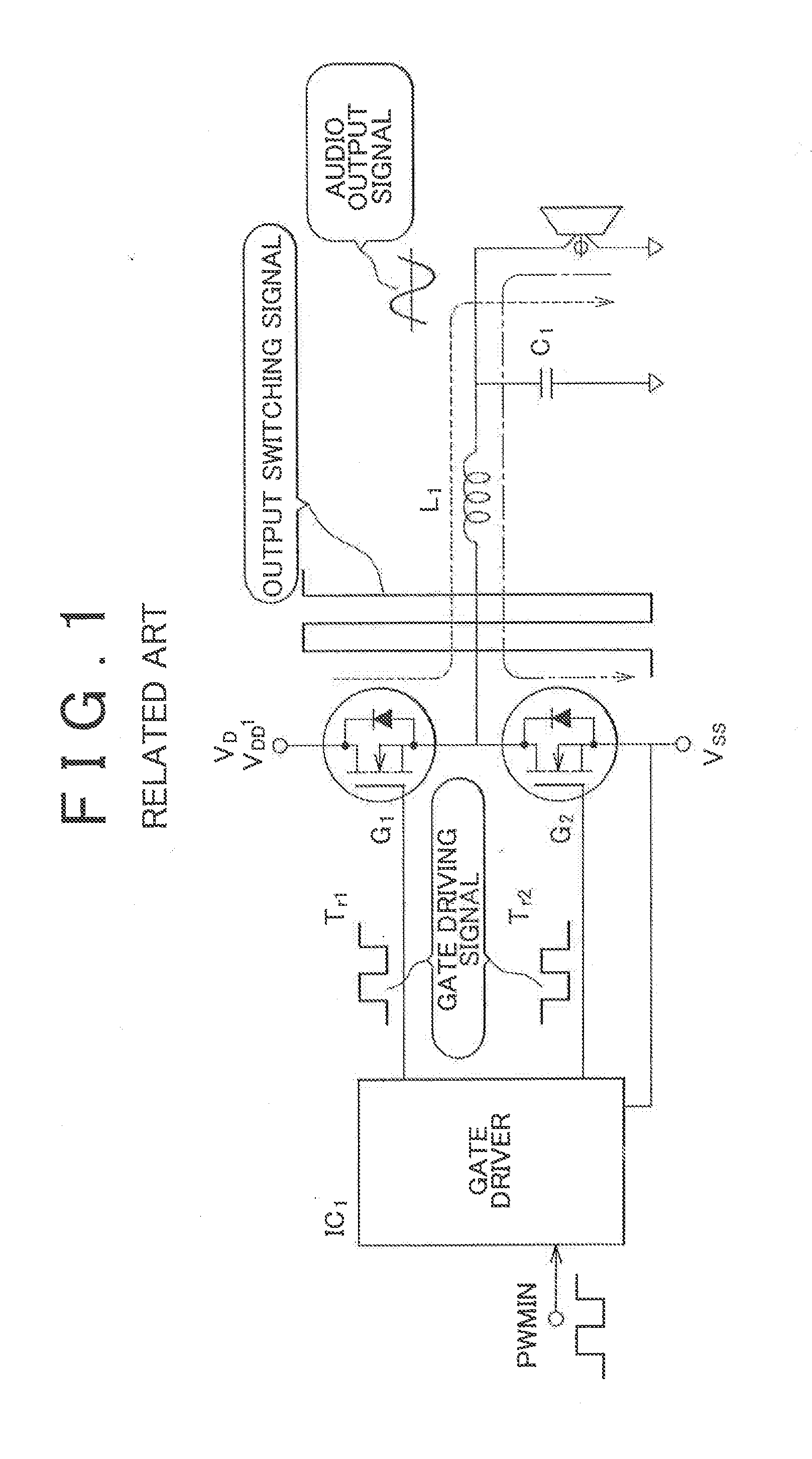

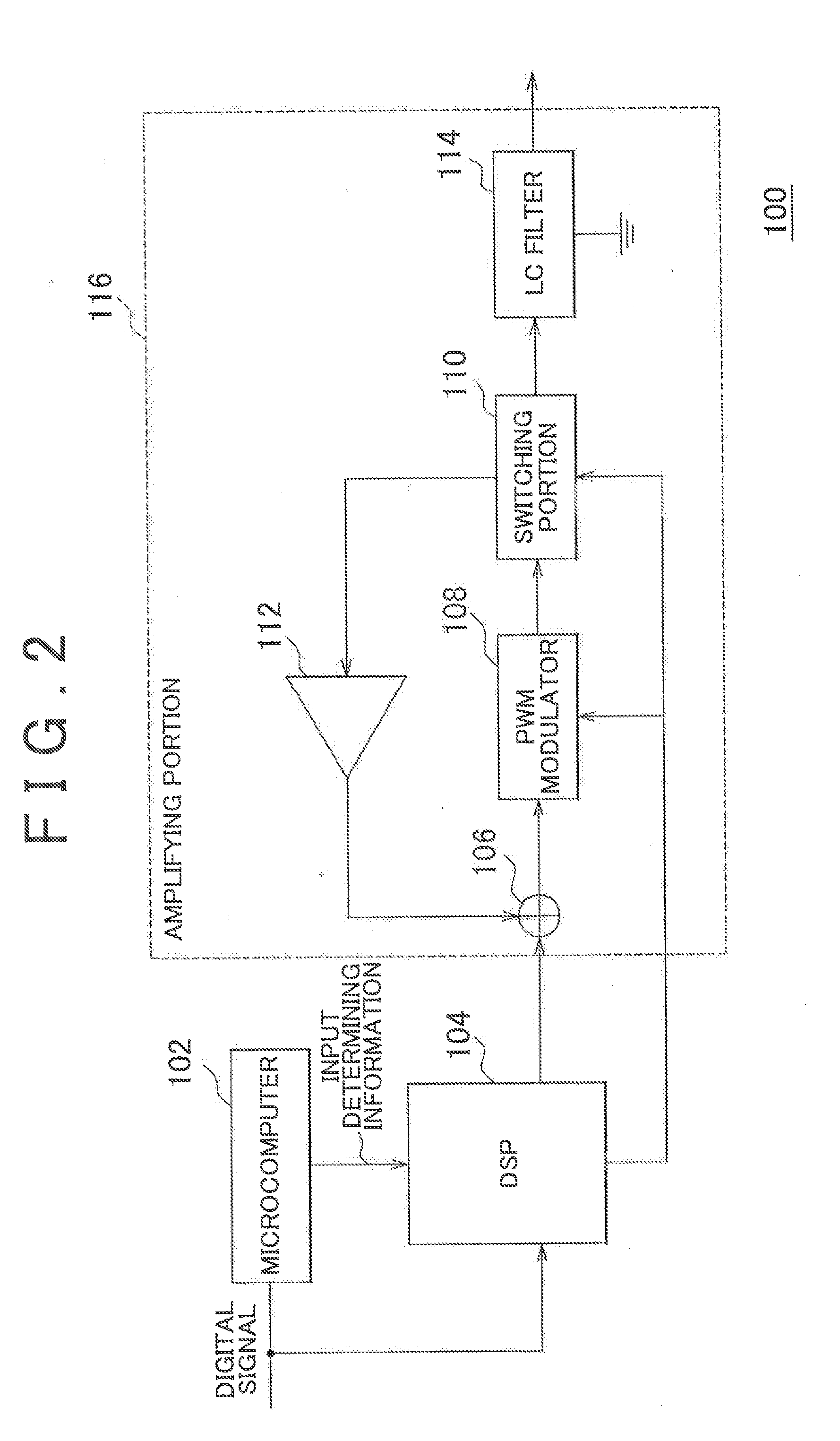

Amplifier and amplifying method

InactiveUS20130163789A1Reduce power consumptionAmplifier combinationsTransducer casings/cabinets/supportsAudio power amplifierSound sources

An amplifier that modulates a carrier frequency according to a digital signal and amplifies the modulated signal includes a determining portion that determines at least one of a sound quality required for the digital signal, a sound source of the digital signal, and a type of sound of the digital signal, a carrier frequency setting portion that sets a carrier frequency according to a result of the determination, and a pulse-width modulating portion that pulse-width modulates the carrier frequency according to the digital signal.

Owner:HARMAN INT JAPAN +1

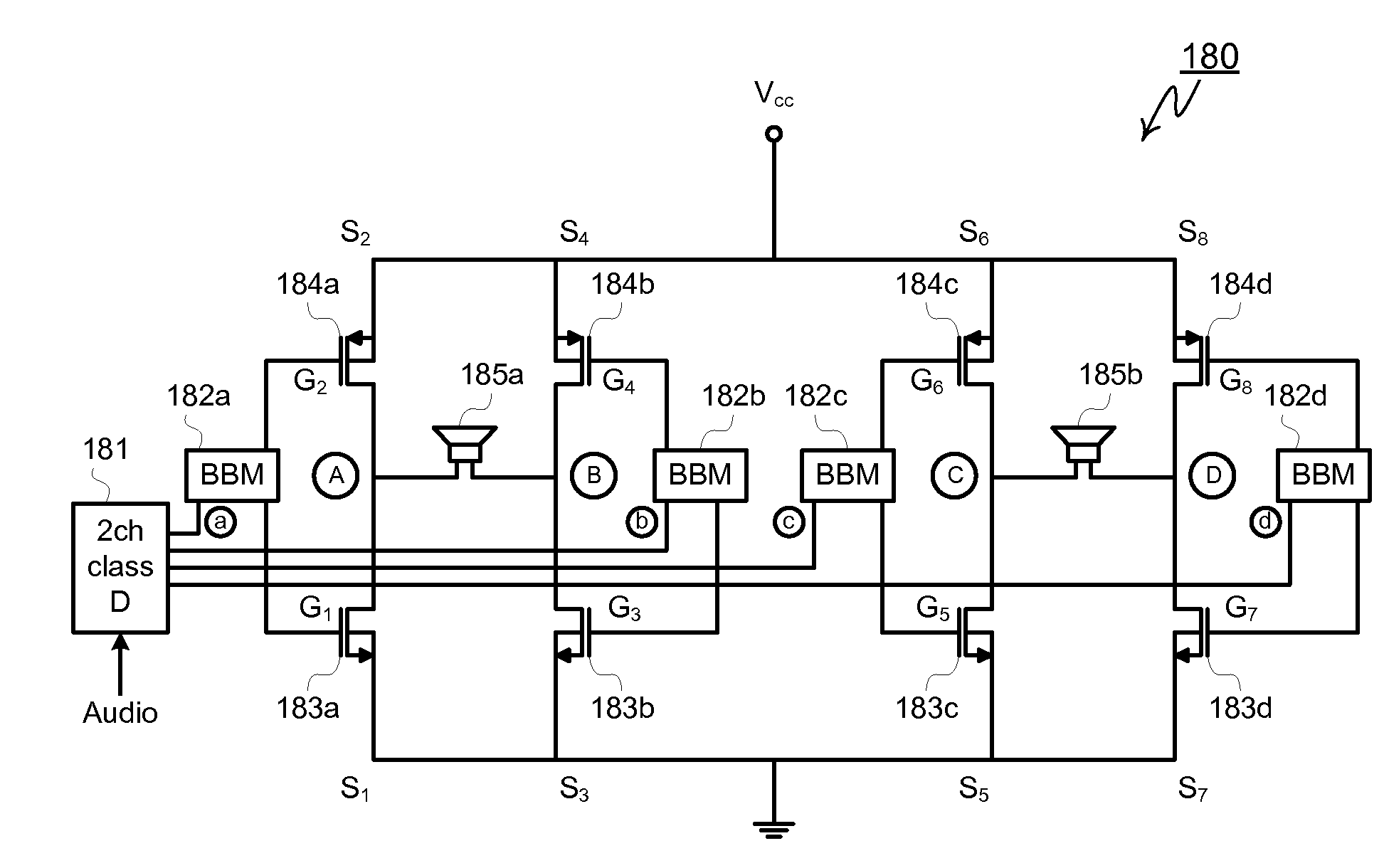

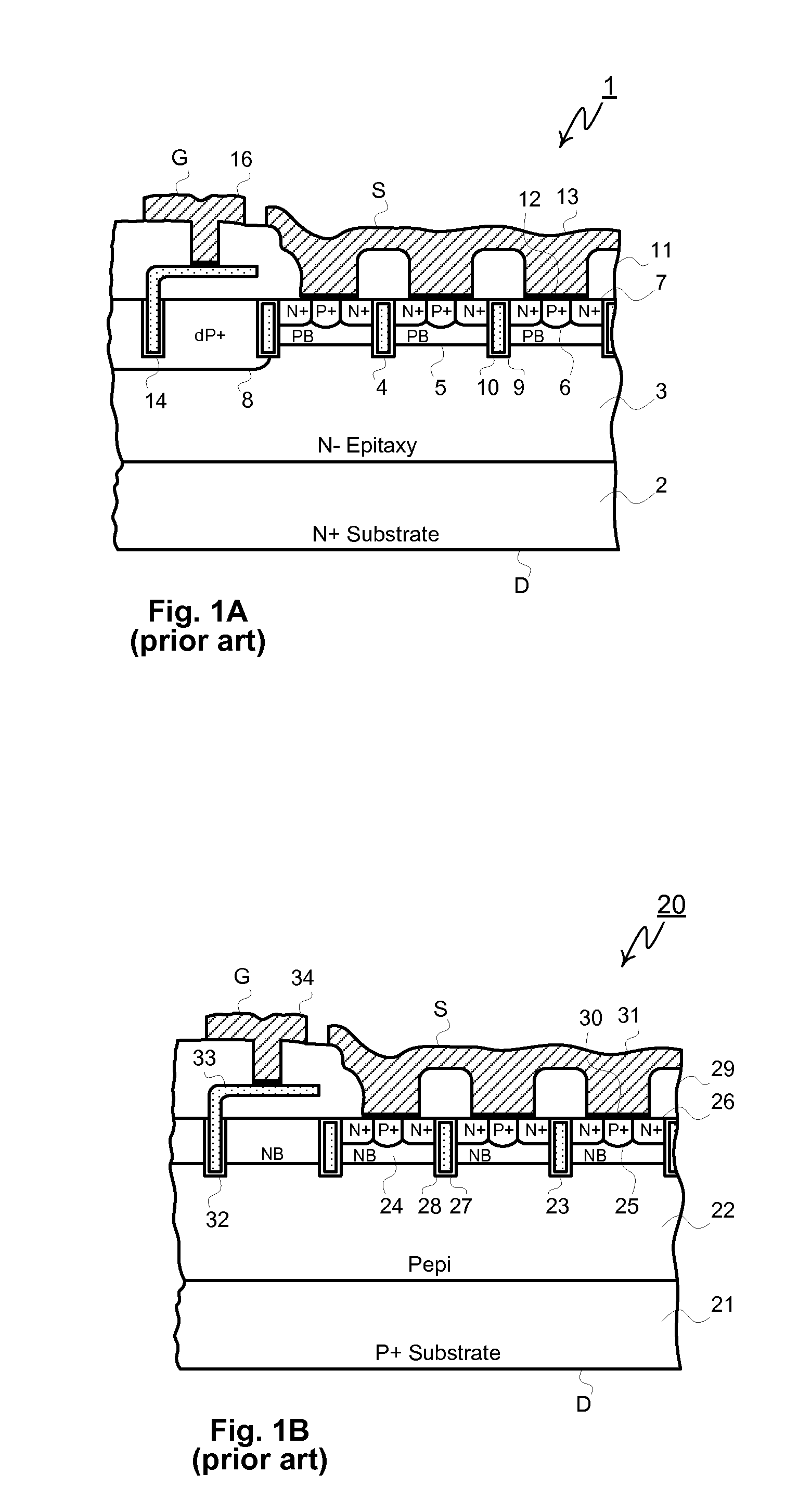

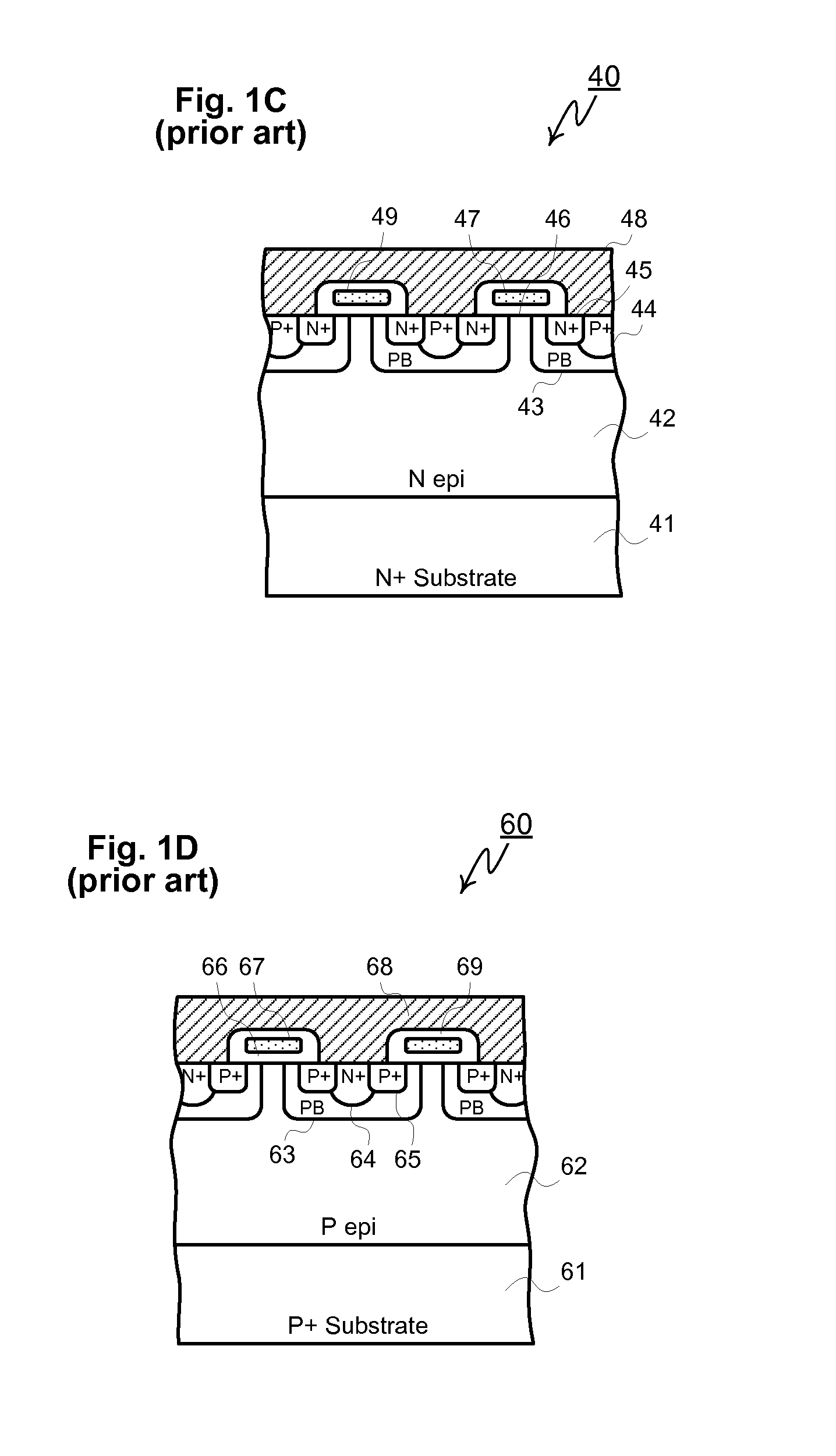

Power-MOSFETs with Improved Efficiency for Multi-channel Class-D Audio Amplifiers and Packaging Thereof

InactiveUS20080252372A1Lower on-resistanceSimple preparation techniqueTransistorSemiconductor/solid-state device detailsGround contactAudio power amplifier

A stereo class-D audio system includes a first die including four monolithically integrated NMOS high-side devices and a second a second die including four monolithically integrated PMOS low-side devices. The audio system also includes a set of electrical contacts for connecting the high and low-side devices to components within the a stereo class-D audio system, the set of electrical contacts including at least one supply contact for connecting the drains of the high-side devices to a supply voltage (Vcc) and at least one ground contact for connecting the drains of the low-side devices to ground, the electrical contacts also including respective contacts for each source of the high and low-side devices allowing the source of each high-side device to be connected to the source of a respective low-side device to form two H-bridge circuits.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Direct current (DC)-dc converter having a multi-stage output filter

ActiveUS20130271221A1Negative-feedback-circuit arrangementsHigh frequency amplifiersCapacitanceDc dc converter

A direct current (DC)-DC converter that includes a first switching converter and a multi-stage filter is disclosed. The multi-stage filter includes at least a first inductance (L) capacitance (C) filter and a second LC filter coupled in series between the first switching converter and a DC-DC converter output. The first LC filter has a first LC time constant and the second LC filter has a second LC time constant, which is less than the first LC time constant. The first switching converter and the multi-stage filter form a feedback loop, which is used to regulate the first switching power supply output signal based on the setpoint. The first LC filter includes a first capacitive element having a first self-resonant frequency, which is about equal to a first notch frequency of the multi-stage filter.

Owner:QORVO US INC

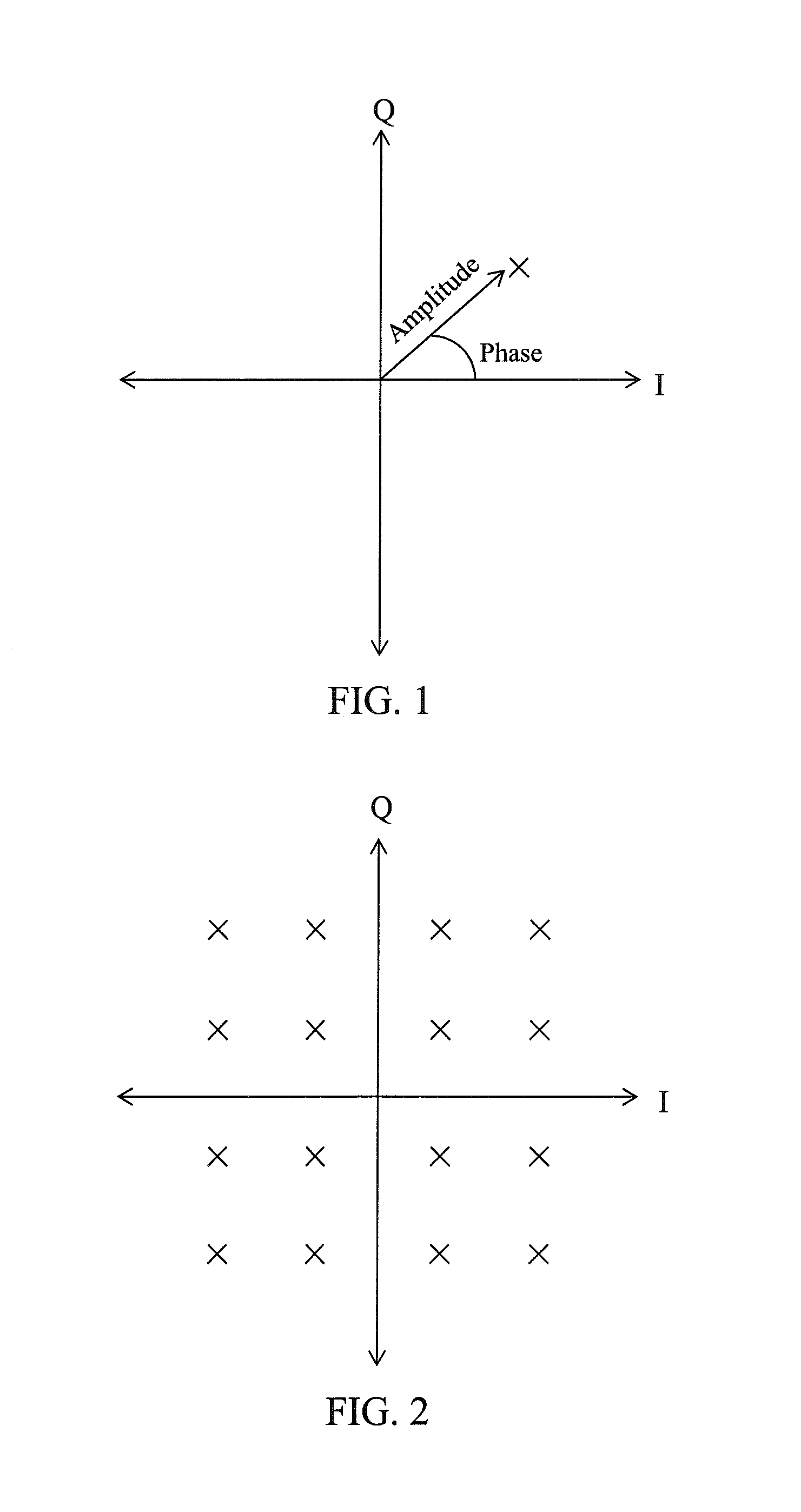

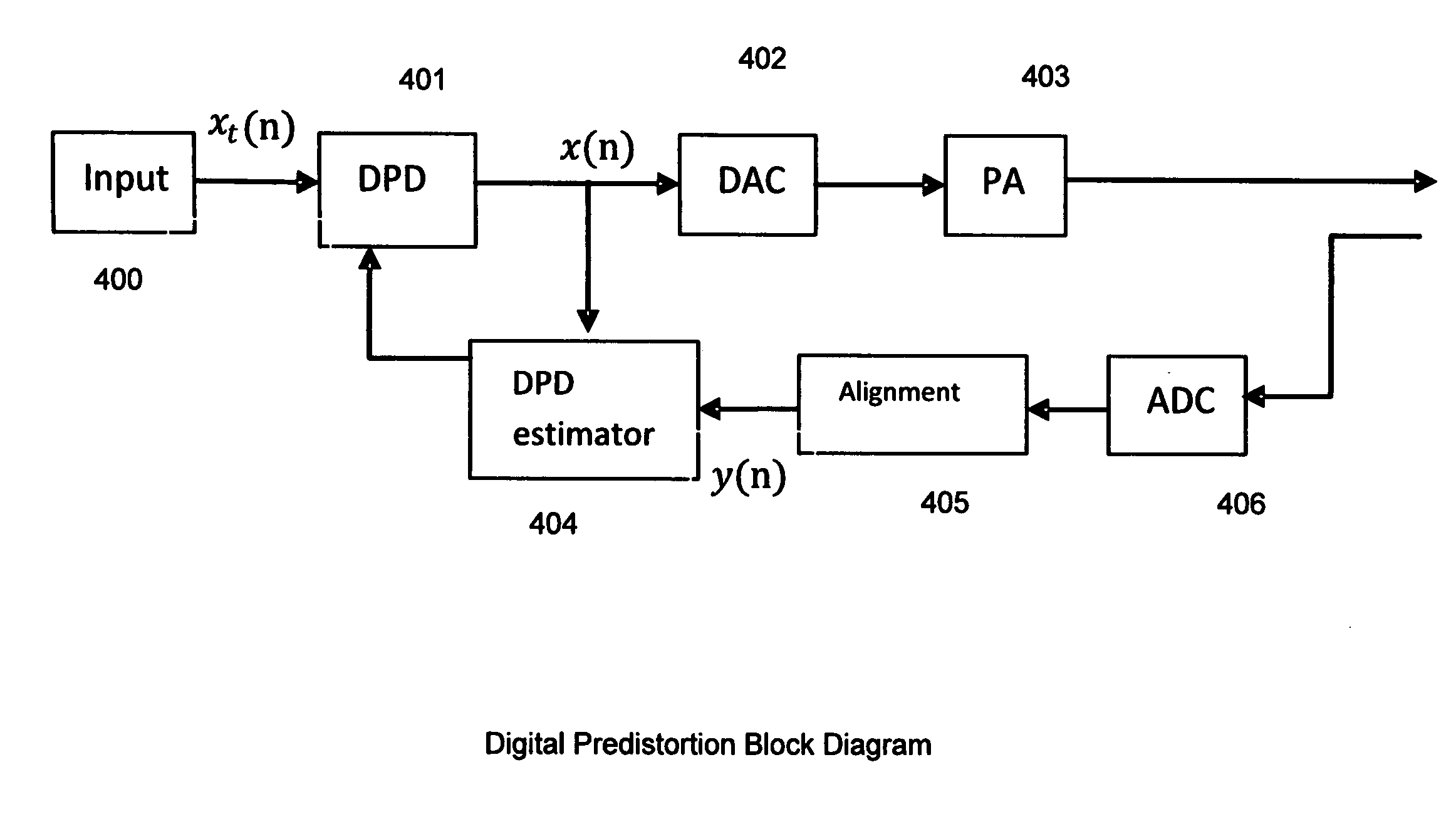

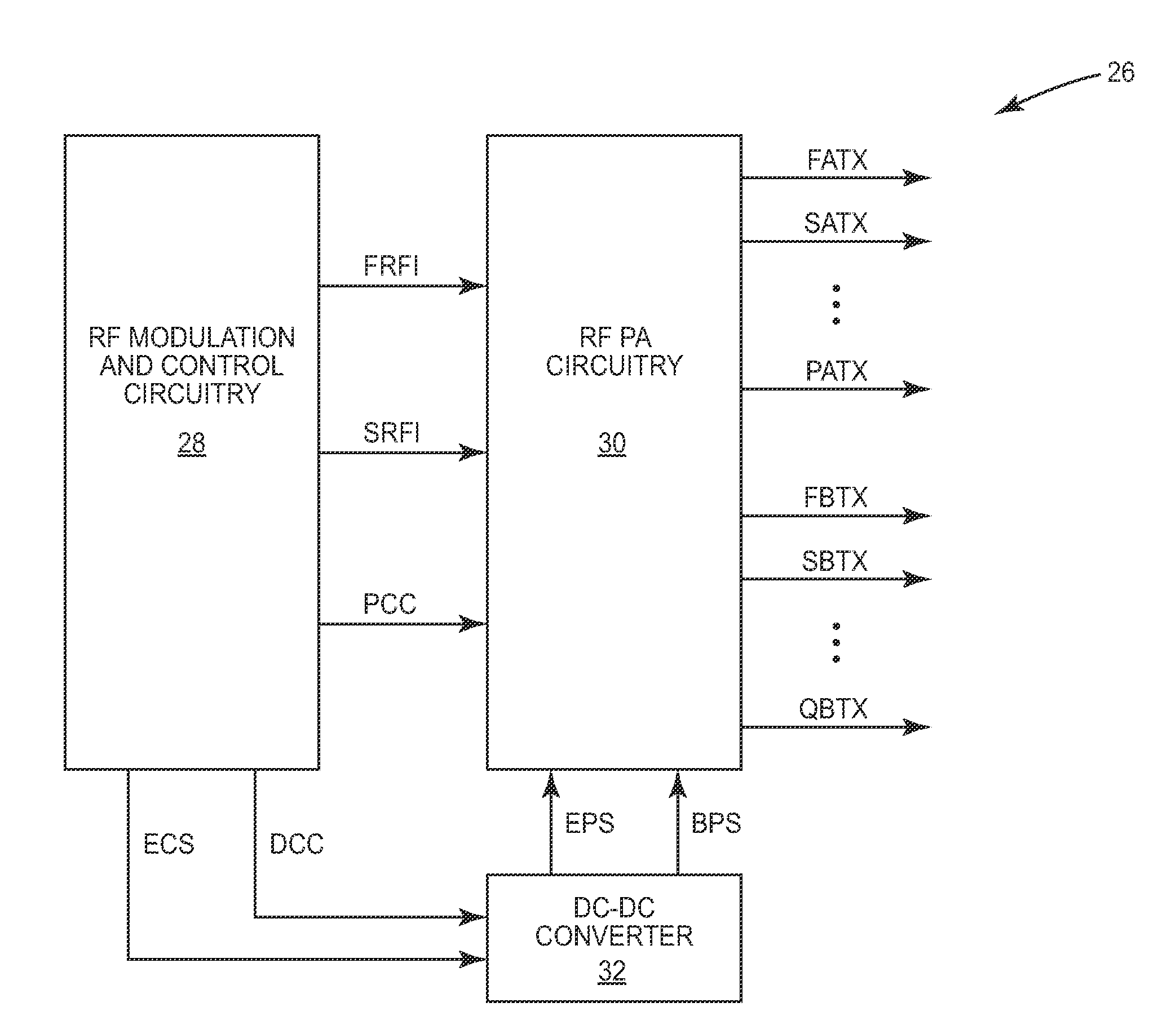

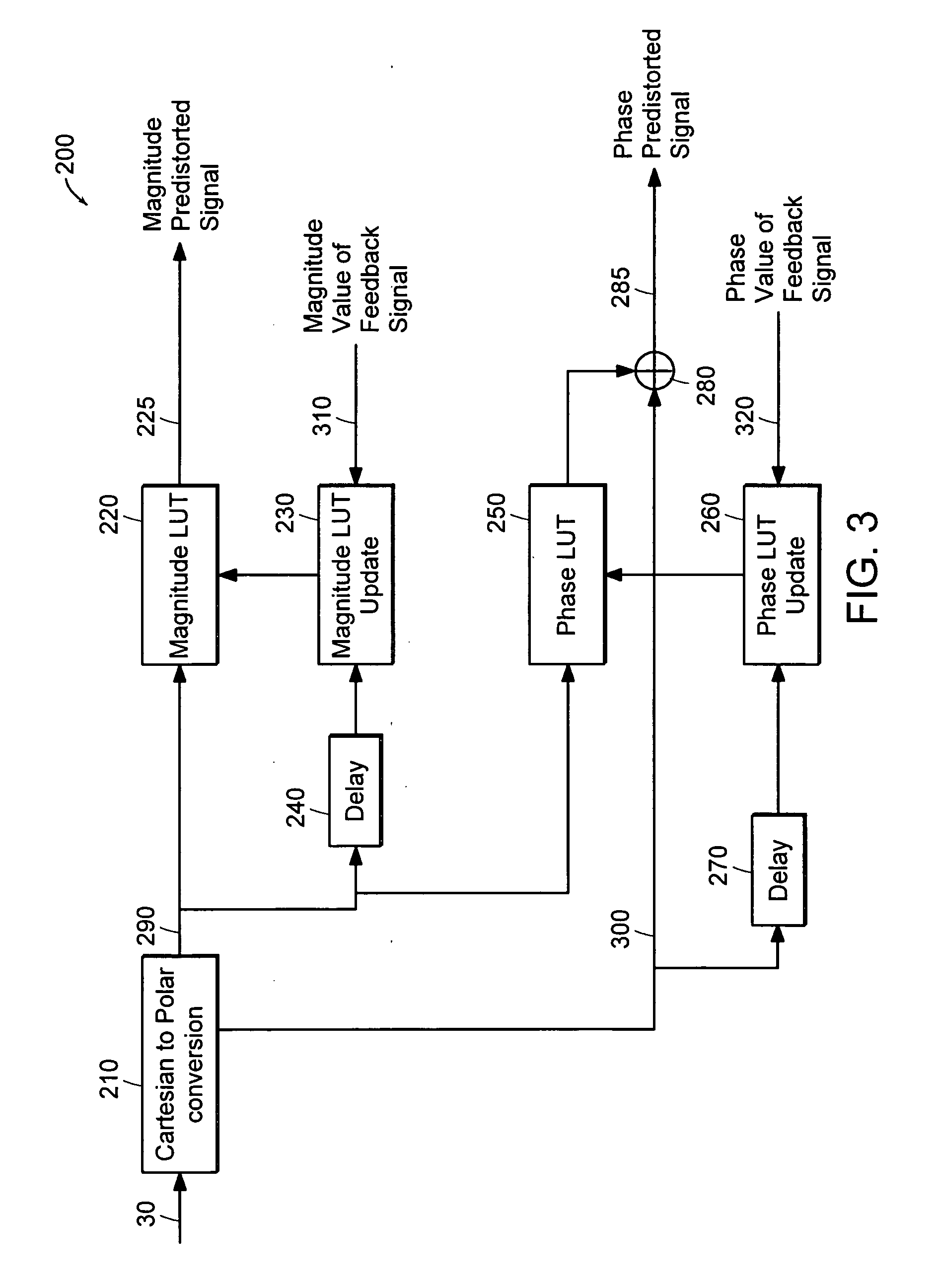

Adaptive predistortion for a transmit system

ActiveUS20050001674A1Amplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsTransfer systemEngineering

Systems, methods, and devices relating to the provision of deliberate predistortion to an input signal to compensate for distortions introduced by an amplifier subsystem. An input signal is received by a predistortion subsystem which applies deliberate predistortions to the input signal to arrive at a predistorted signal. The predistorted signal is received by an amplifier subsystem which decomposes the signal, processes the decomposed signal, and then recombines the components to arrive at a system output signal. The predistortion subsystem adaptively adjusts the predistortions based on characteristics of the system output signal. A feedback signal, a replica of the system output signal, is used in updating lookup table entries used to determine the predistortion.

Owner:ZARBANA DIGITAL FUND

Computer program product configured to control modular transmission system components

A computer program product is configured to control a modular transmission system having a control processor and at least N power amplifier modules, each having a controller submodule, wherein the system receives an input signal which may be a single carrier or multiple carriers. The signal is passed to a one-by-N divider which divides the signal N ways. Each of the N divided signals are independently amplified by the power amplifier (PA) modules "slices" (i.e., PA modules) that includes an RF amplifier module, a microcontroller module, and a power supply module, all of which are tightly coupled via a plurality of signal, power, control, and status connections. Each the PA slices amplifies its respective input signal and outputs a respective radio frequency output signal at a predetermined power level as controlled by the microcontrol module, the driver, and the system controller, or a network manager via a system input / output interface. The output coupler provides power coupling and status monitoring via feedback lines to support control at a module-level, a system-level, and a network-level.

Owner:THALES BROADCAST & MULTIMEDIA

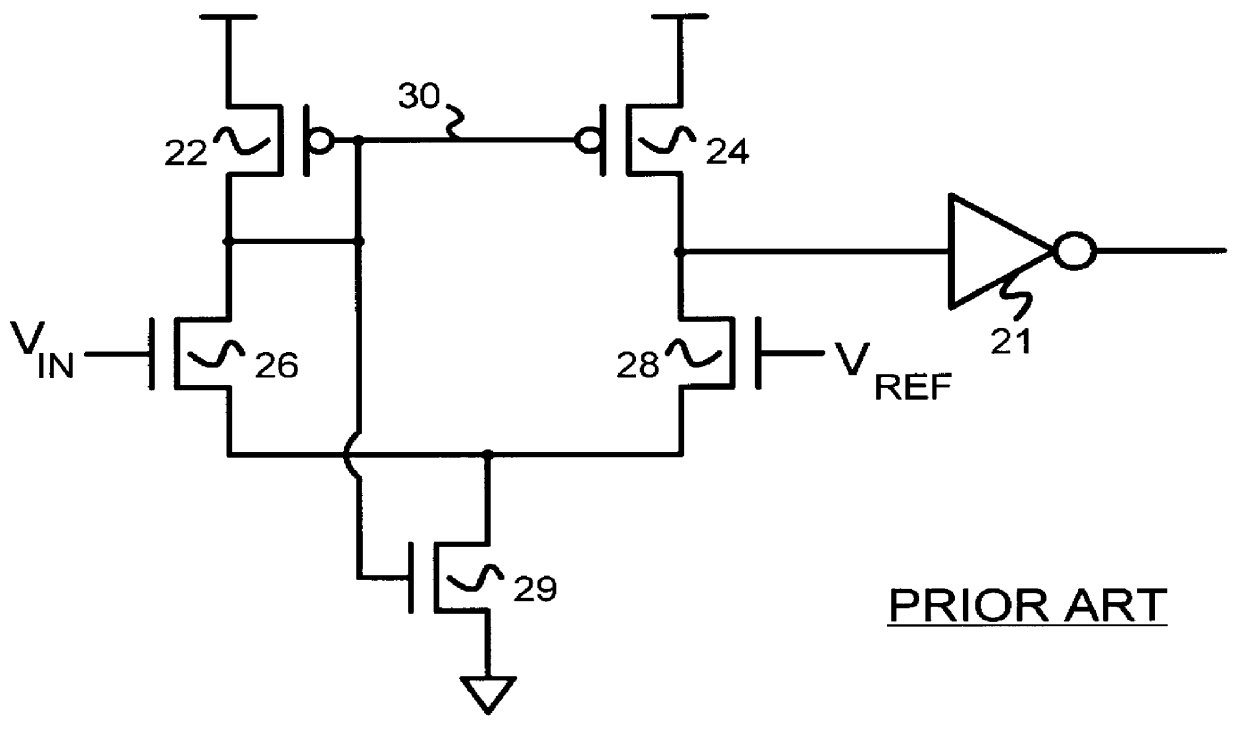

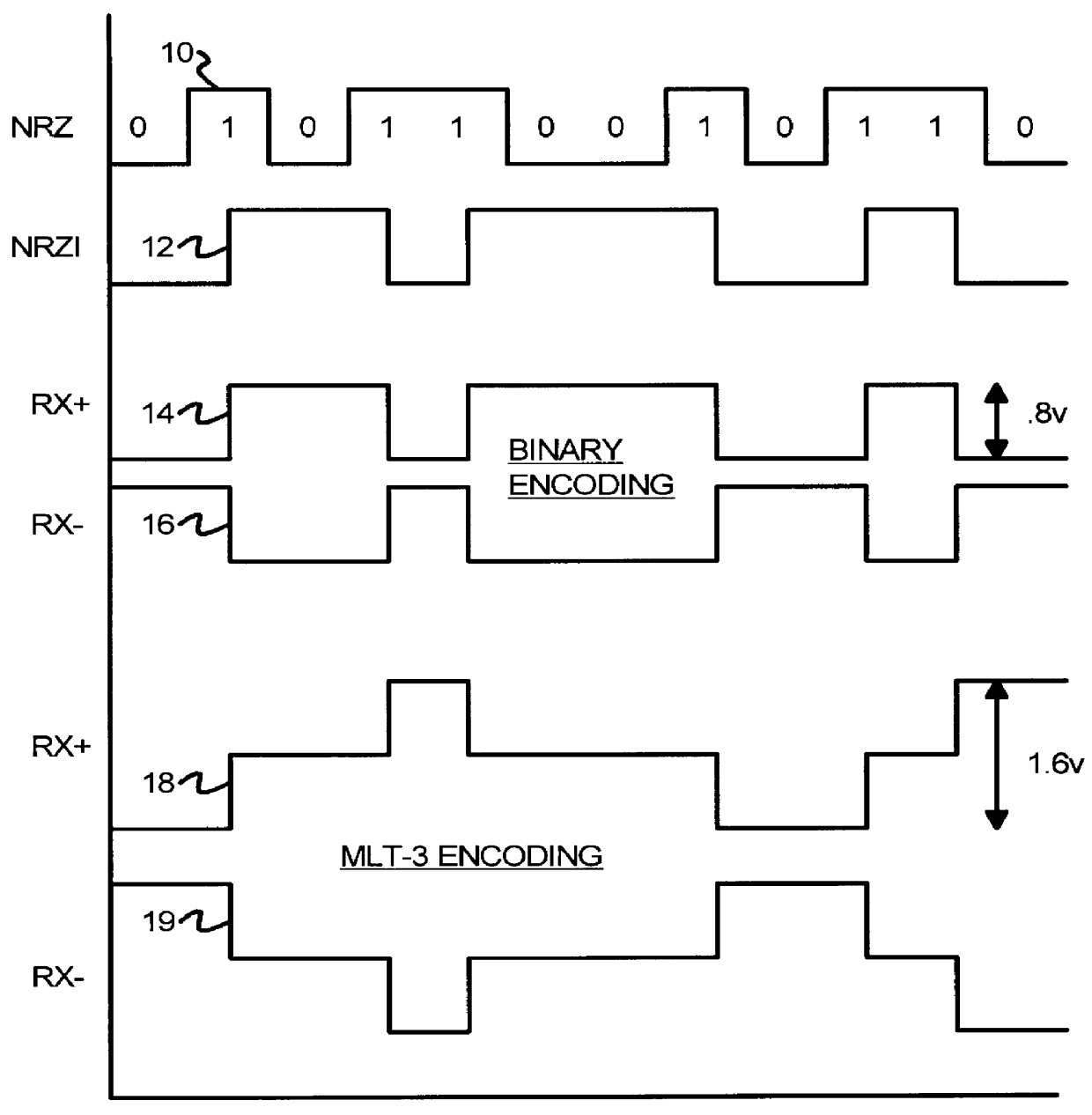

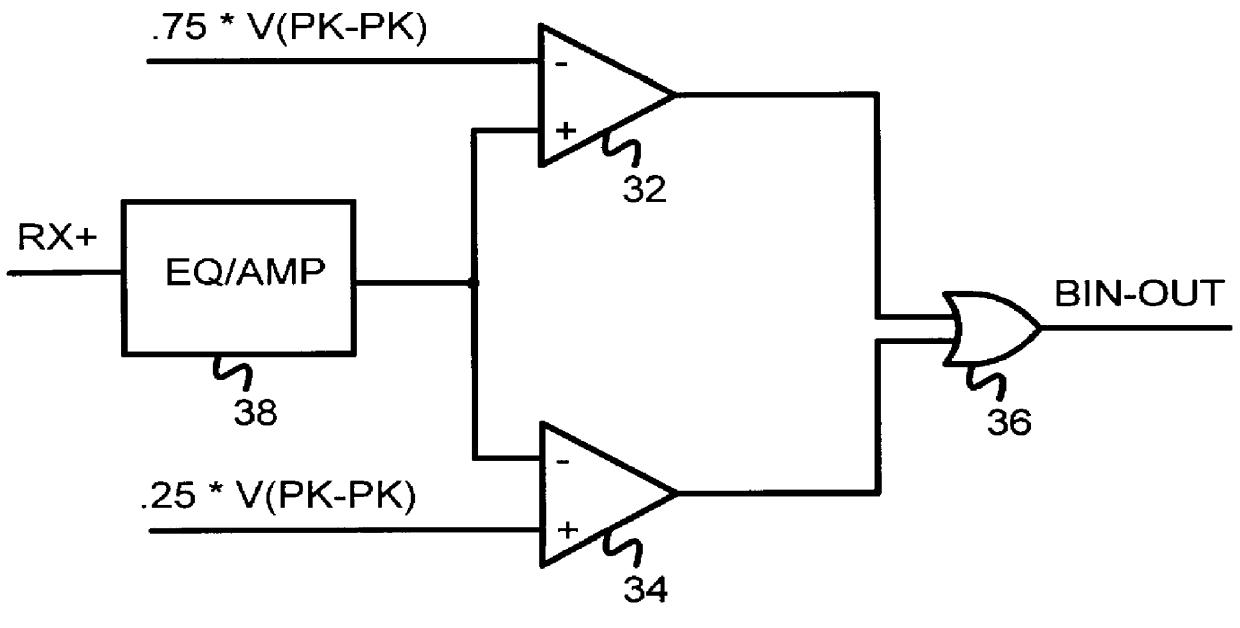

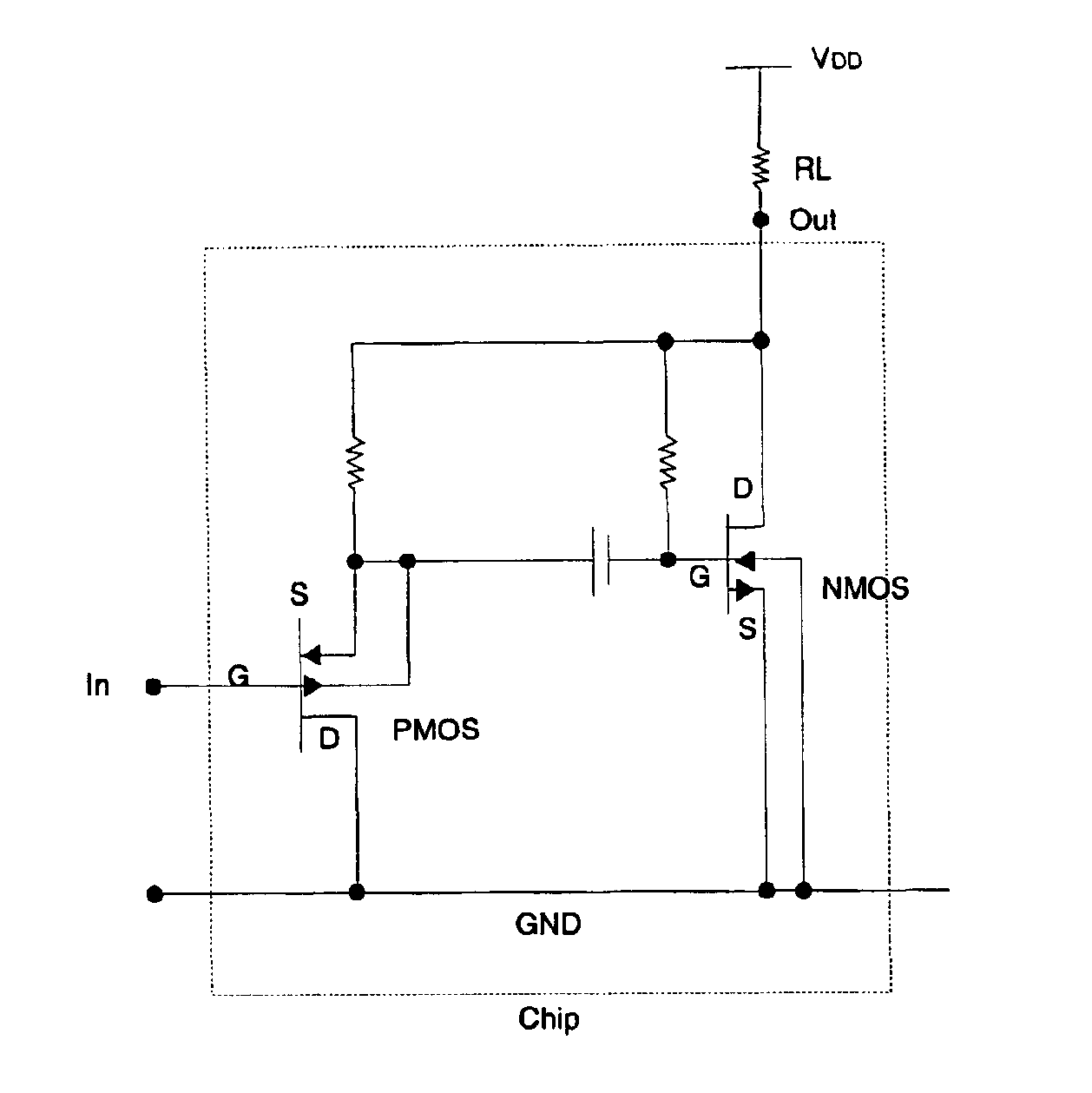

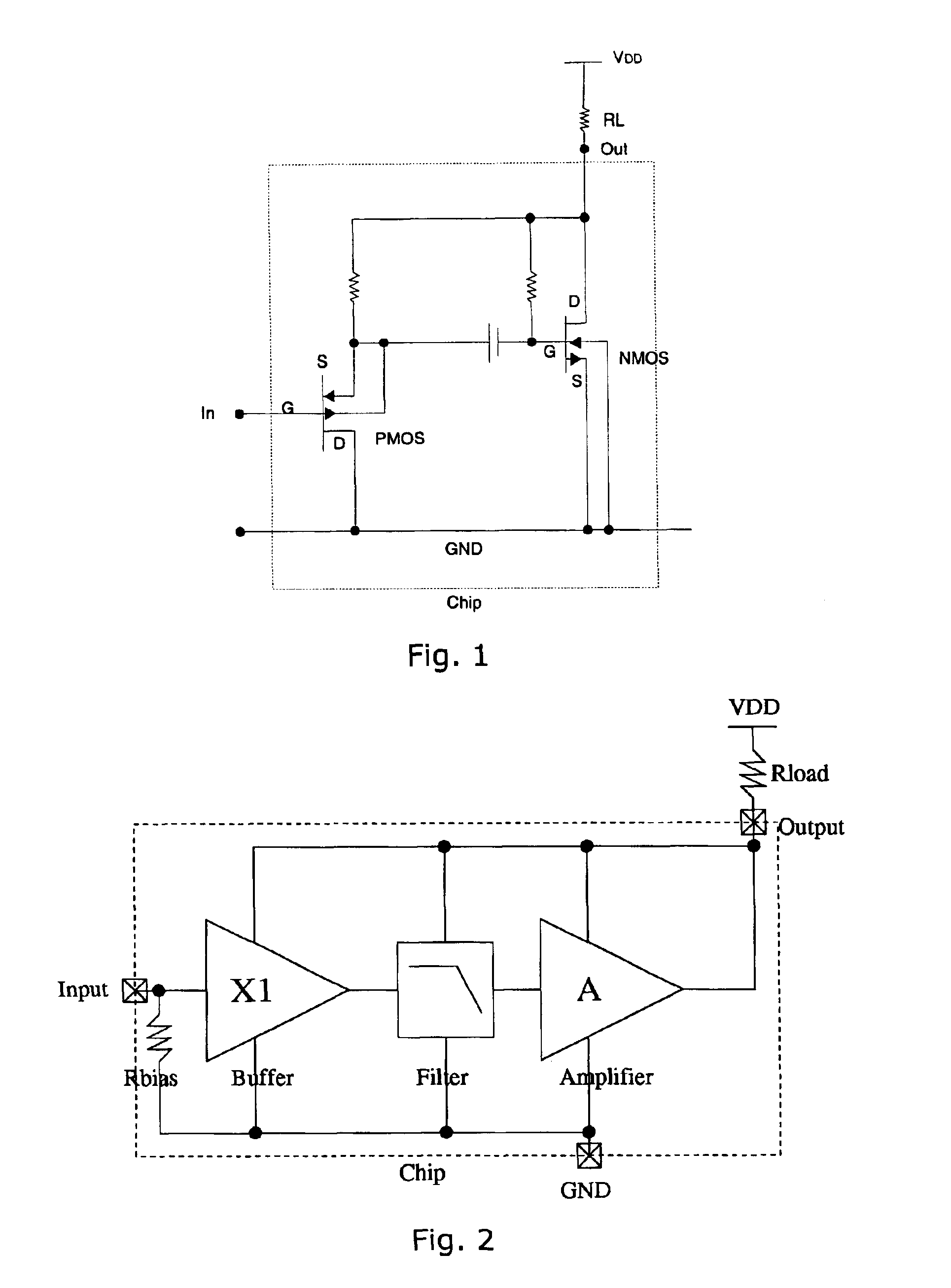

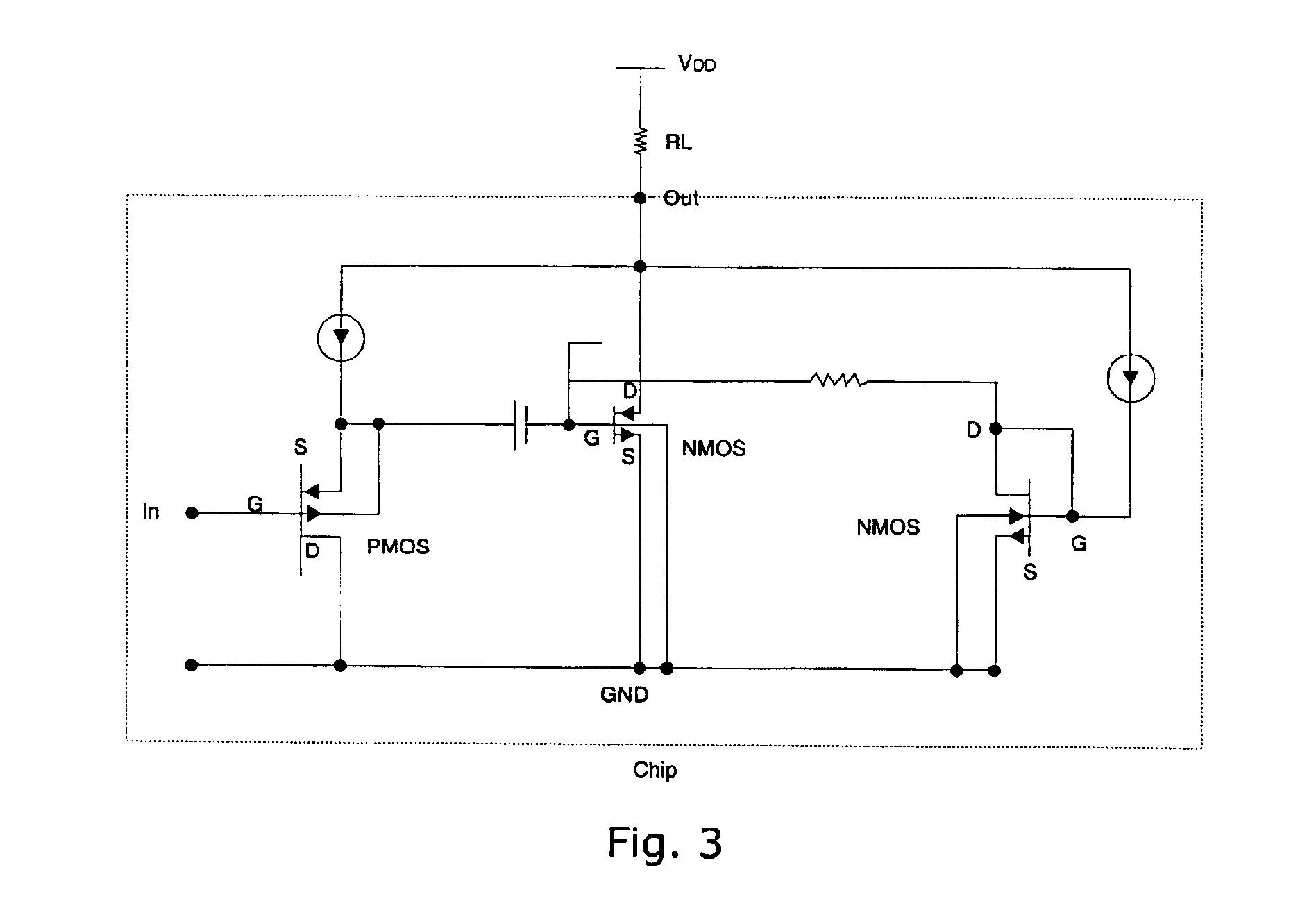

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

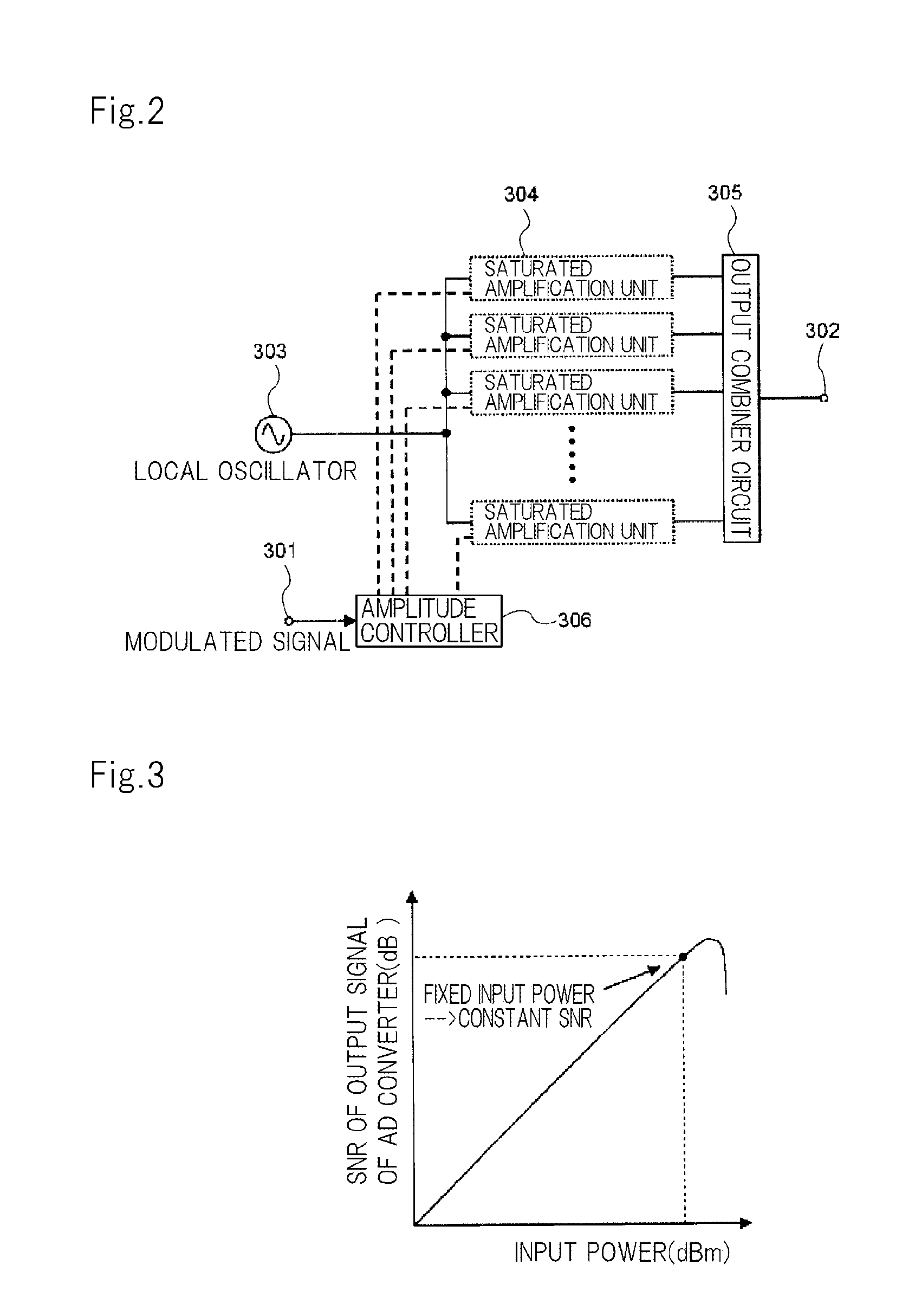

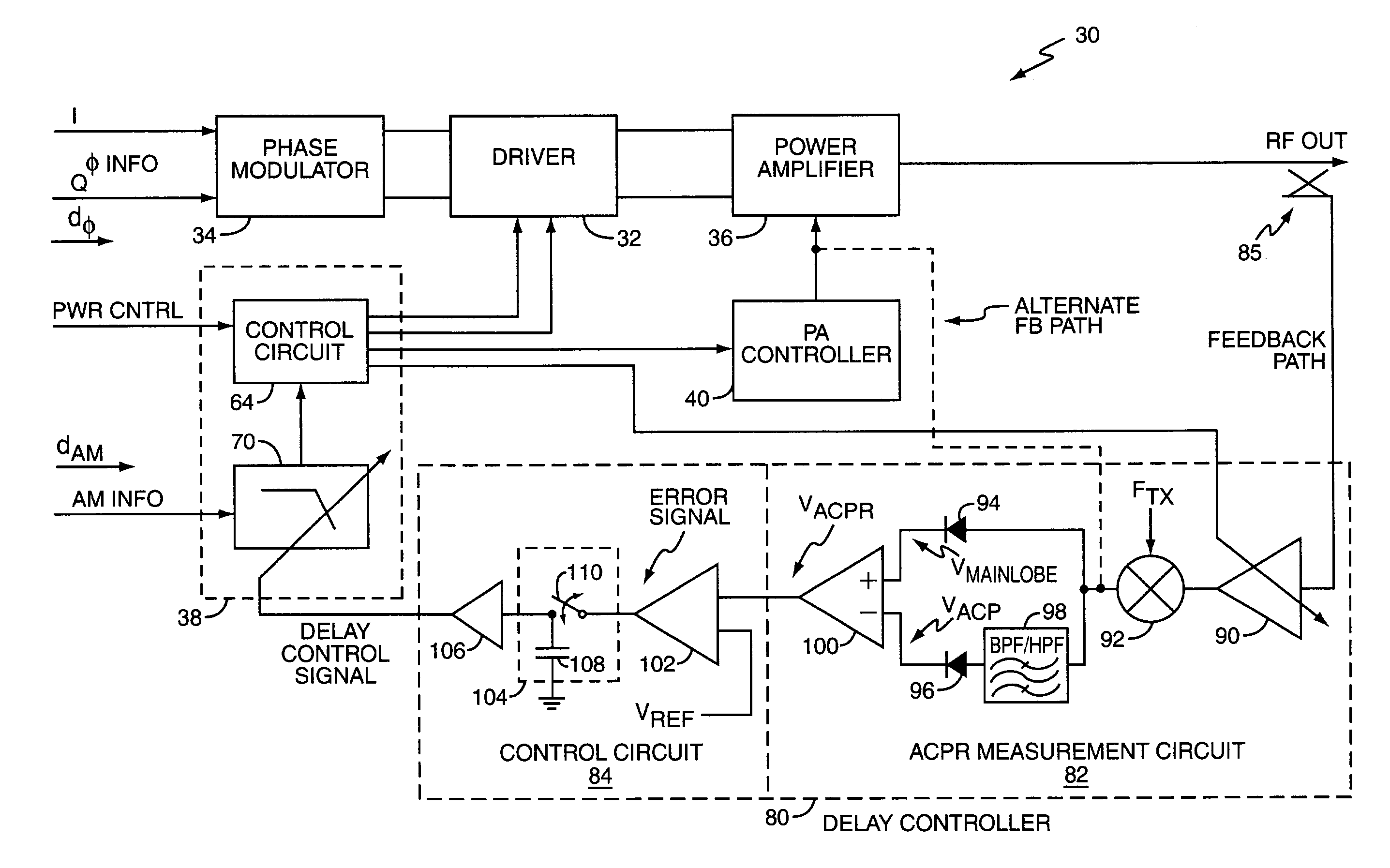

Polar modulation transmitter

ActiveUS7072626B2Improve performanceReduce ratio of average powerResonant long antennasPower amplifiersTransceiverAudio power amplifier

A polar modulation transmitter circuit provides reduced ACPR in its output signal by controlling the relative delay between its envelope and phase modulation operations based on direct or indirect feedback measurement the output signal's ACPR. Such measurement and associated control may be based on a delay controller that includes an ACPR measurement circuit and a delay control circuit. Additionally, or alternatively, the polar modulation transmitter circuit provides a greatly extended transmit power control range by using a staged amplifier circuit that includes a driver amplifier circuit operating in combination with a power amplifier circuit to impart desired envelope modulation. In an exemplary embodiment, the driver amplifier circuit is implemented as differential transistor pairs responsive to tail current modulation. As such, the driver amplifier circuit is suited in particular for economical and space saving integration within a transmitter or transceiver integrated circuit (IC).

Owner:UNWIRED PLANET

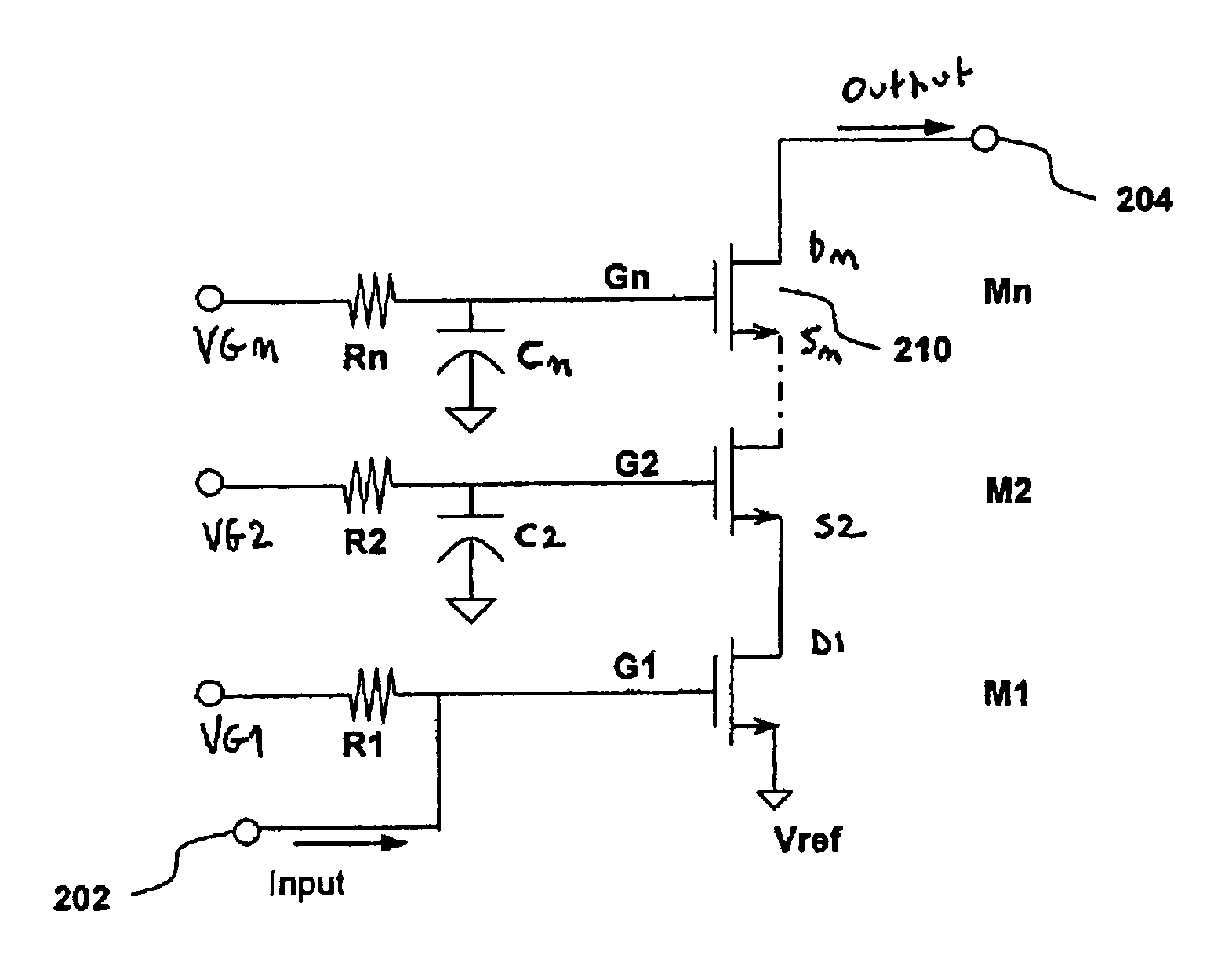

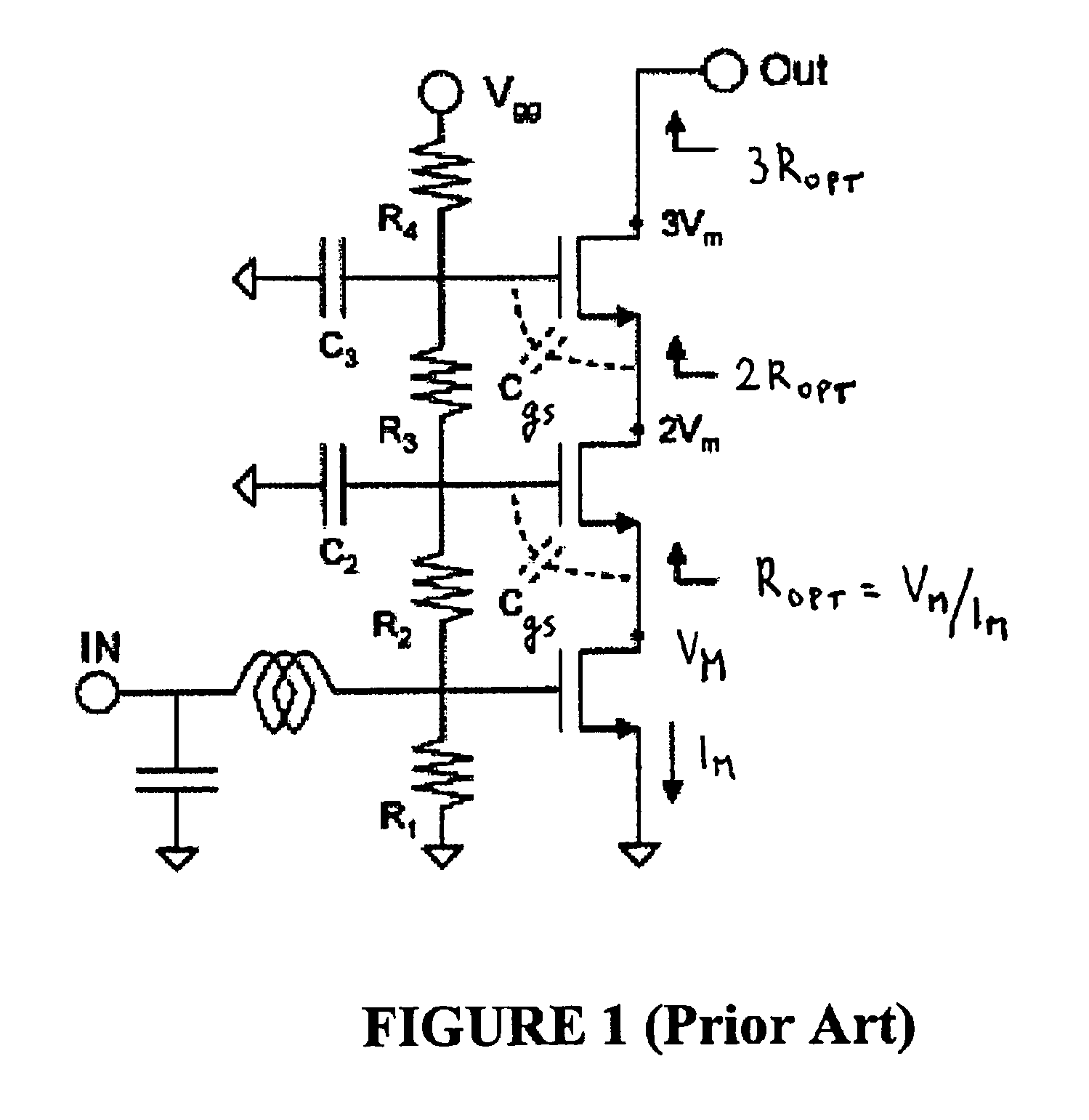

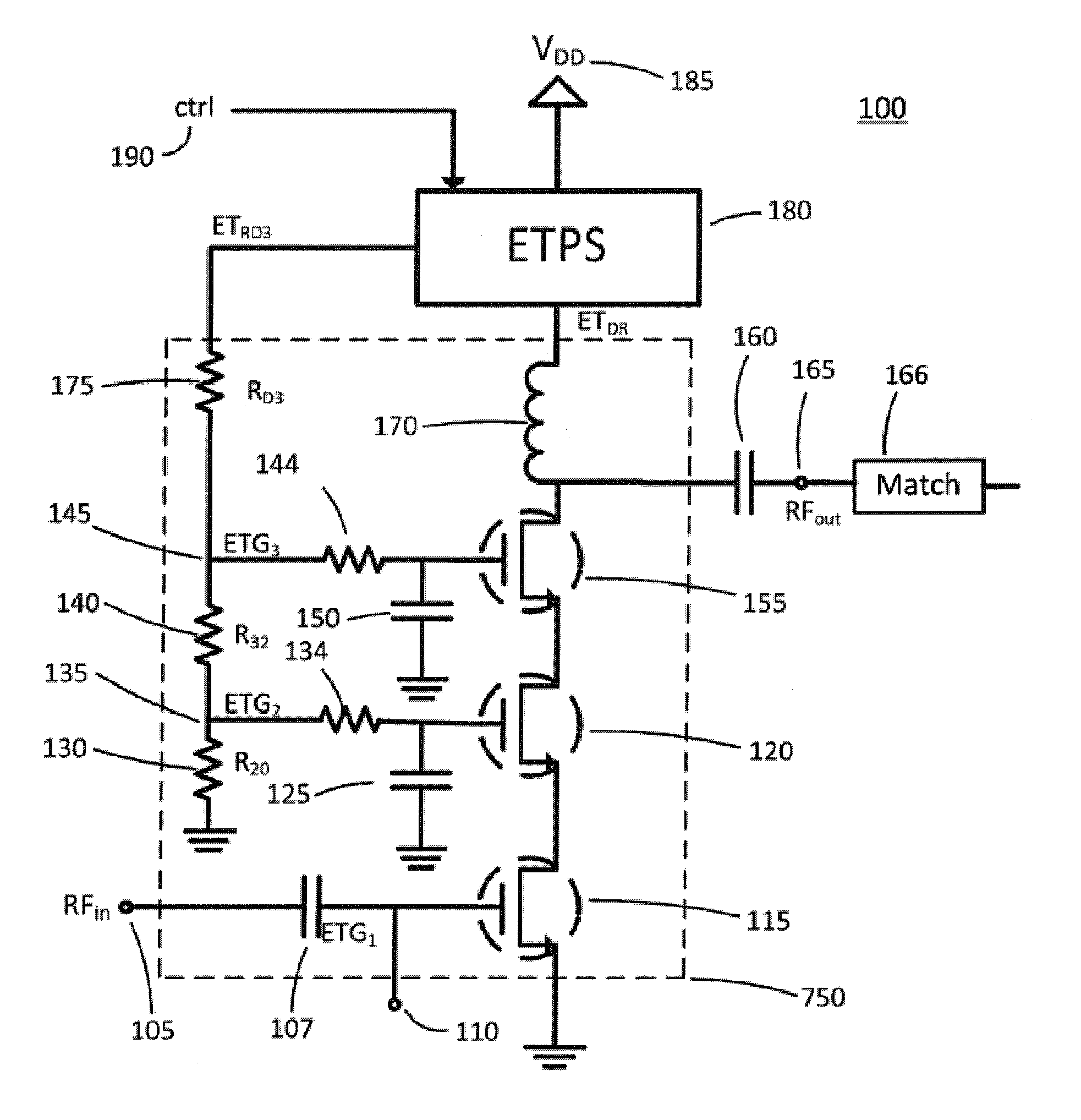

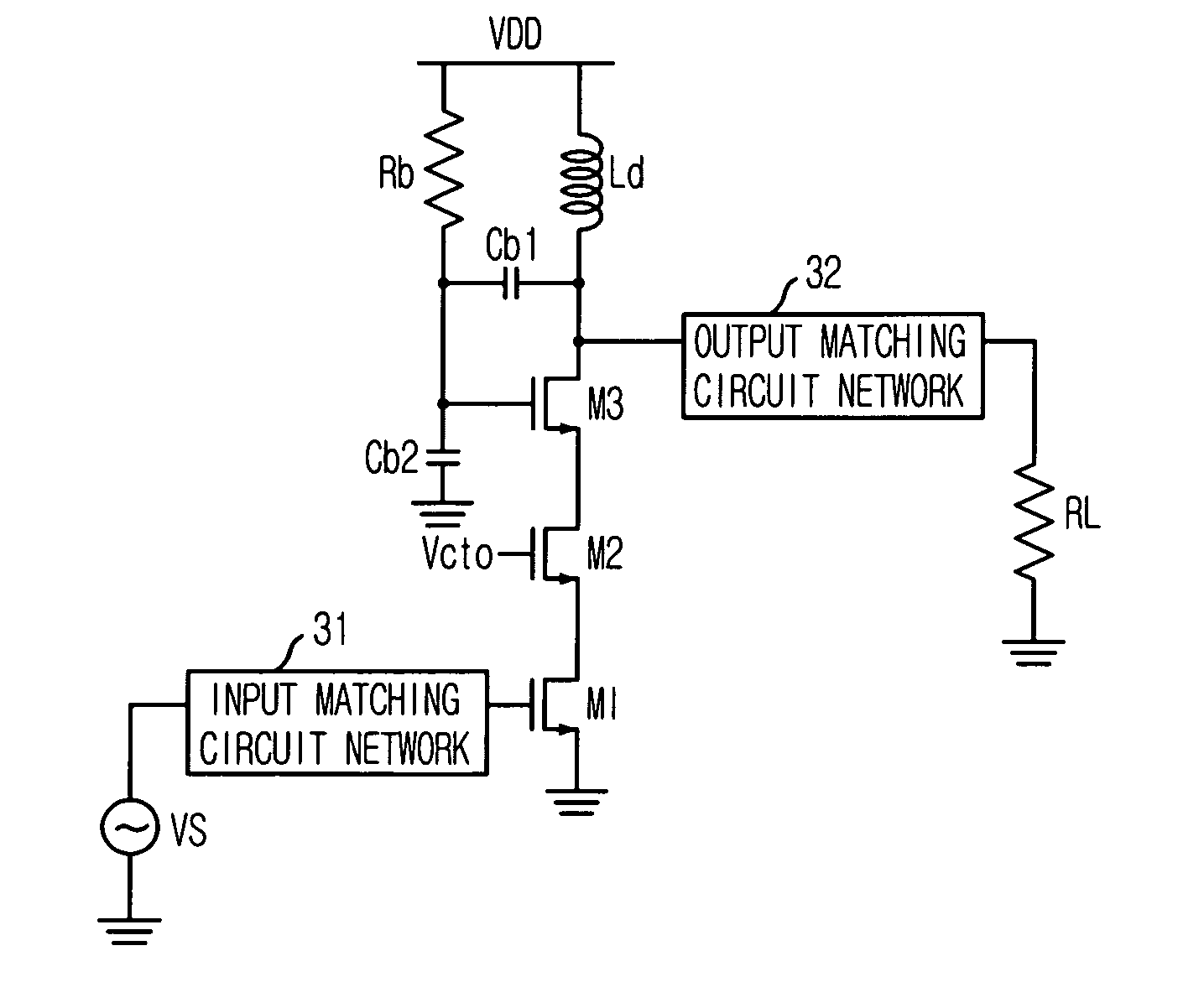

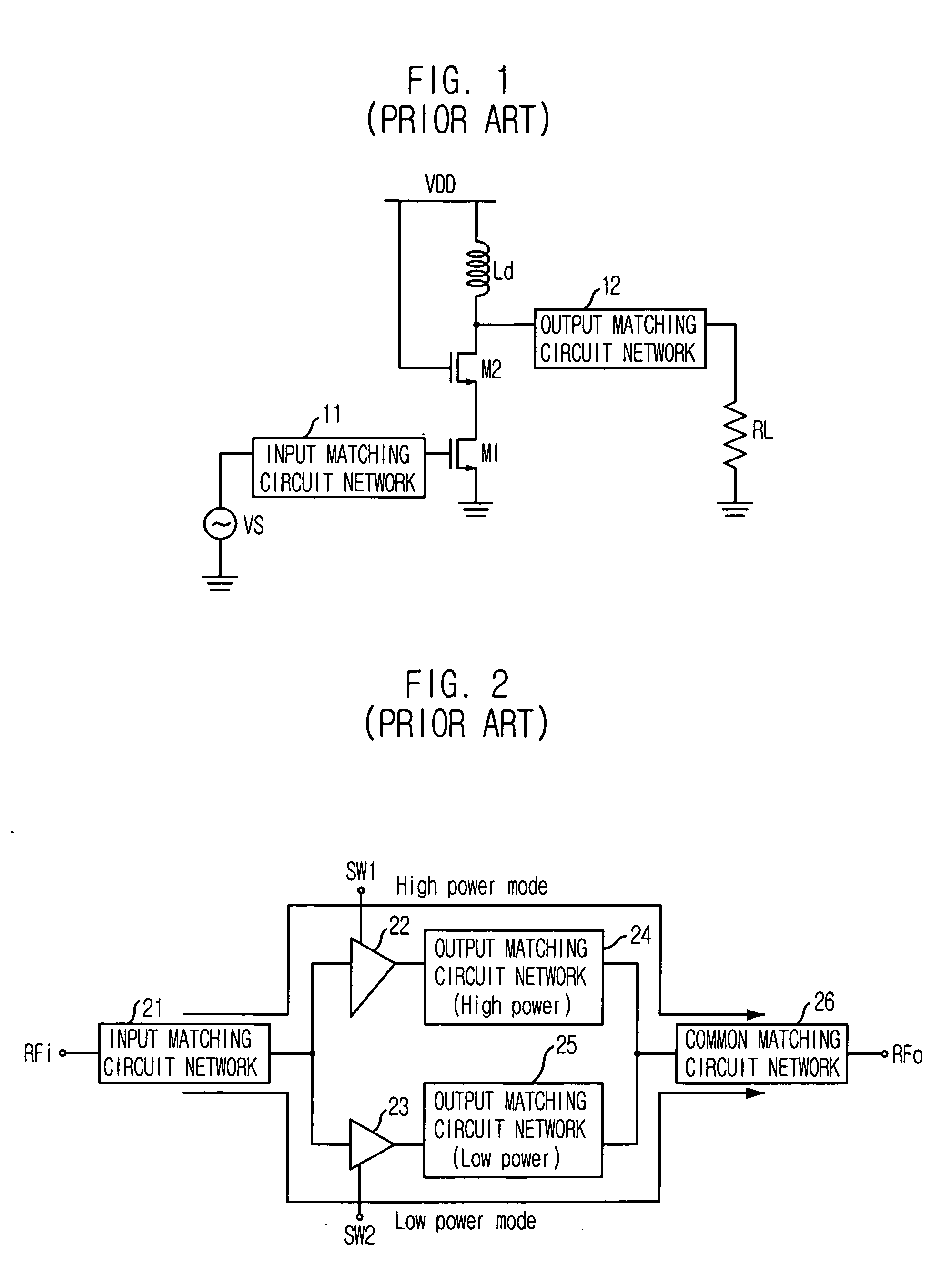

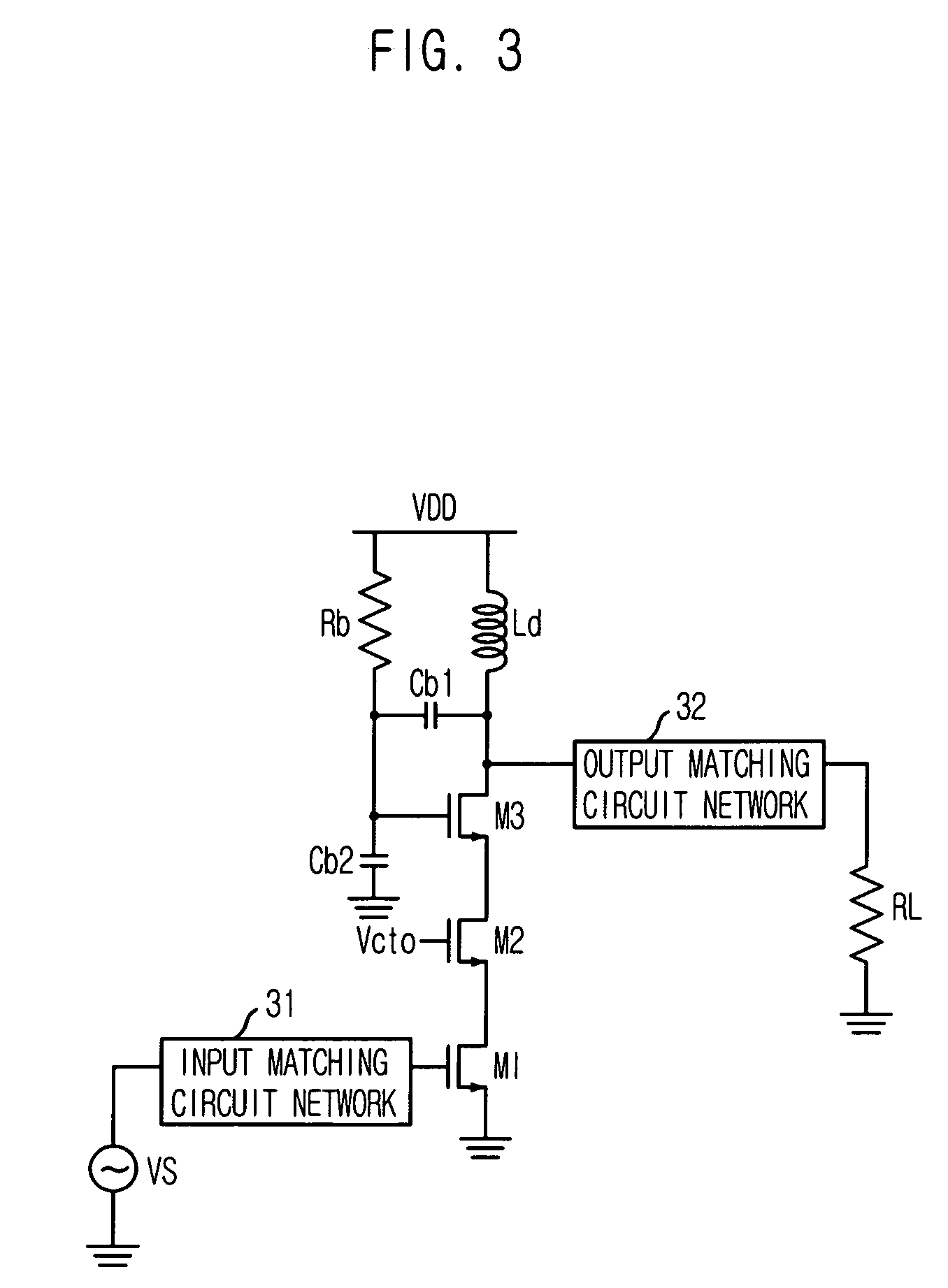

Triple cascode power amplifier of inner parallel configuration with dynamic gate bias technique

InactiveUS20060119435A1Easily embodiedIncrease output powerGated amplifiersAmplifier combinationsAudio power amplifierCascode

Provided is a power amplifier which fits to a deep-submicron technology in radio frequency wireless communication. The power amplifier includes a cascode including a first transistor which receives and amplifies an input signal, and a second transistor which is connected to the first transistor in series and operated by a DC bias voltage; a third transistor which is connected between the cascode and an output end, operated by a dynamic gate bias and outputting a signal; and a voltage divider which includes first and second capacitors that are connected between the output end, i.e. a drain of the third transistor, and a ground in series, and provides the dynamic bias to a gate of the third transistor.

Owner:ELECTRONICS & TELECOMM RES INST

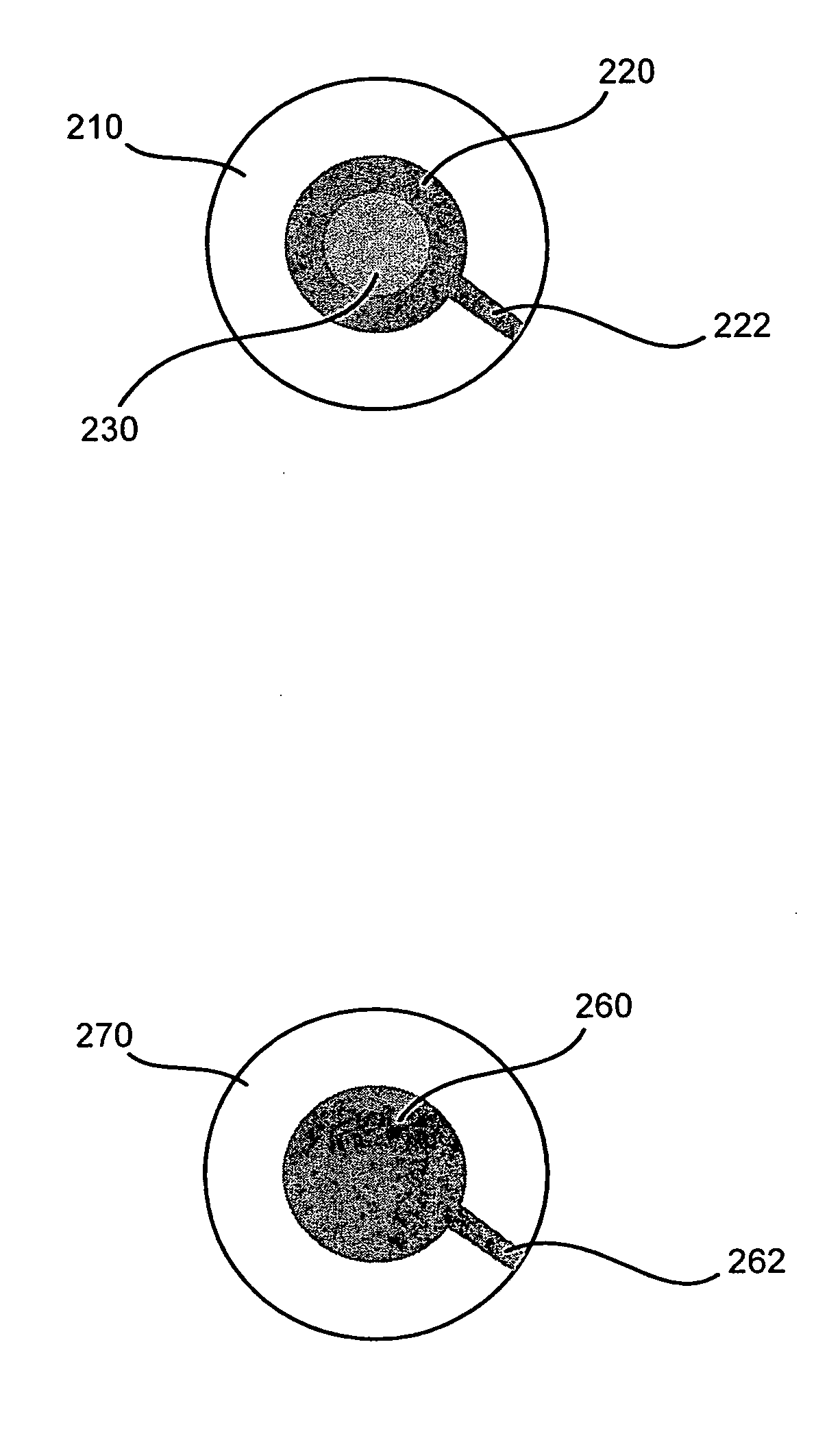

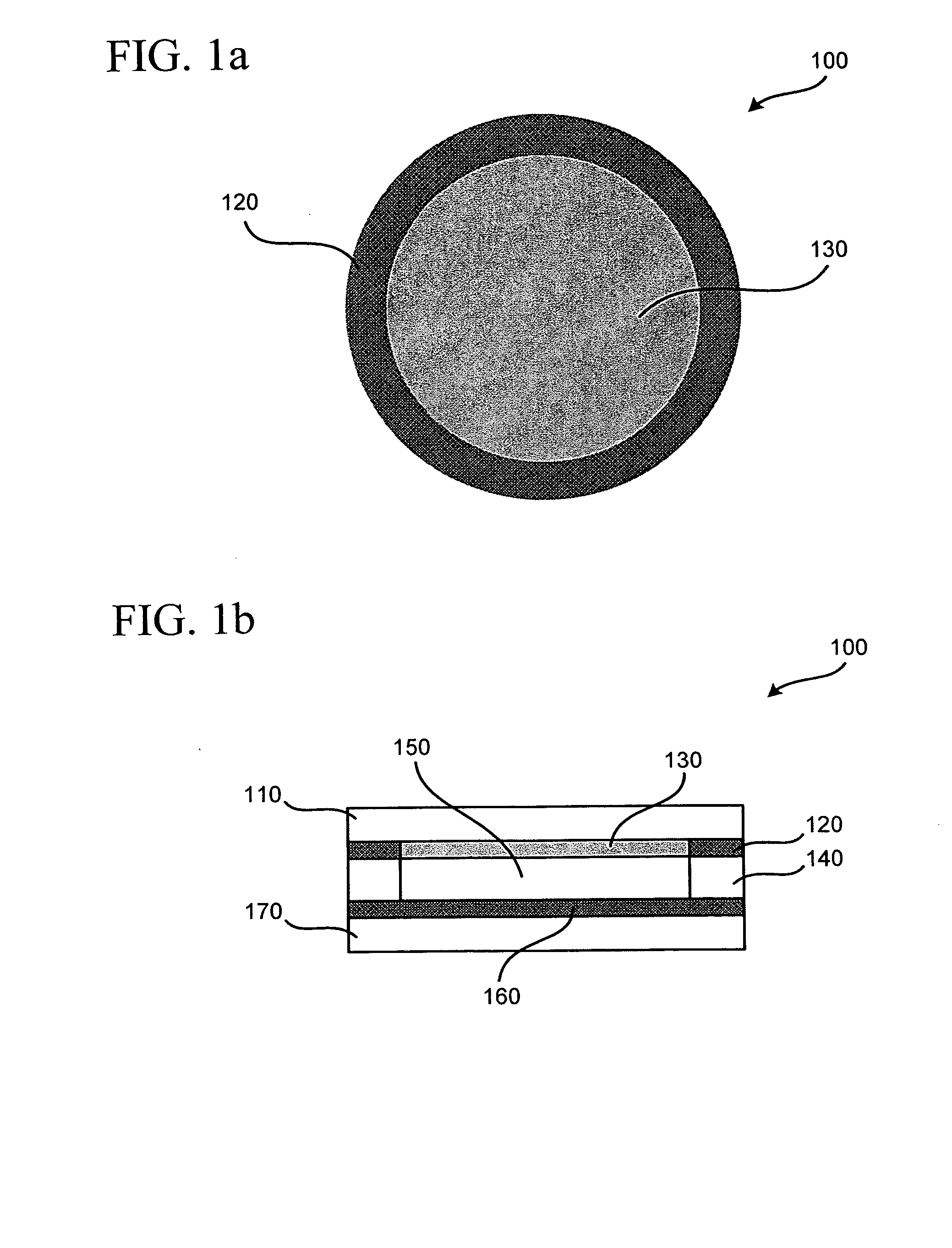

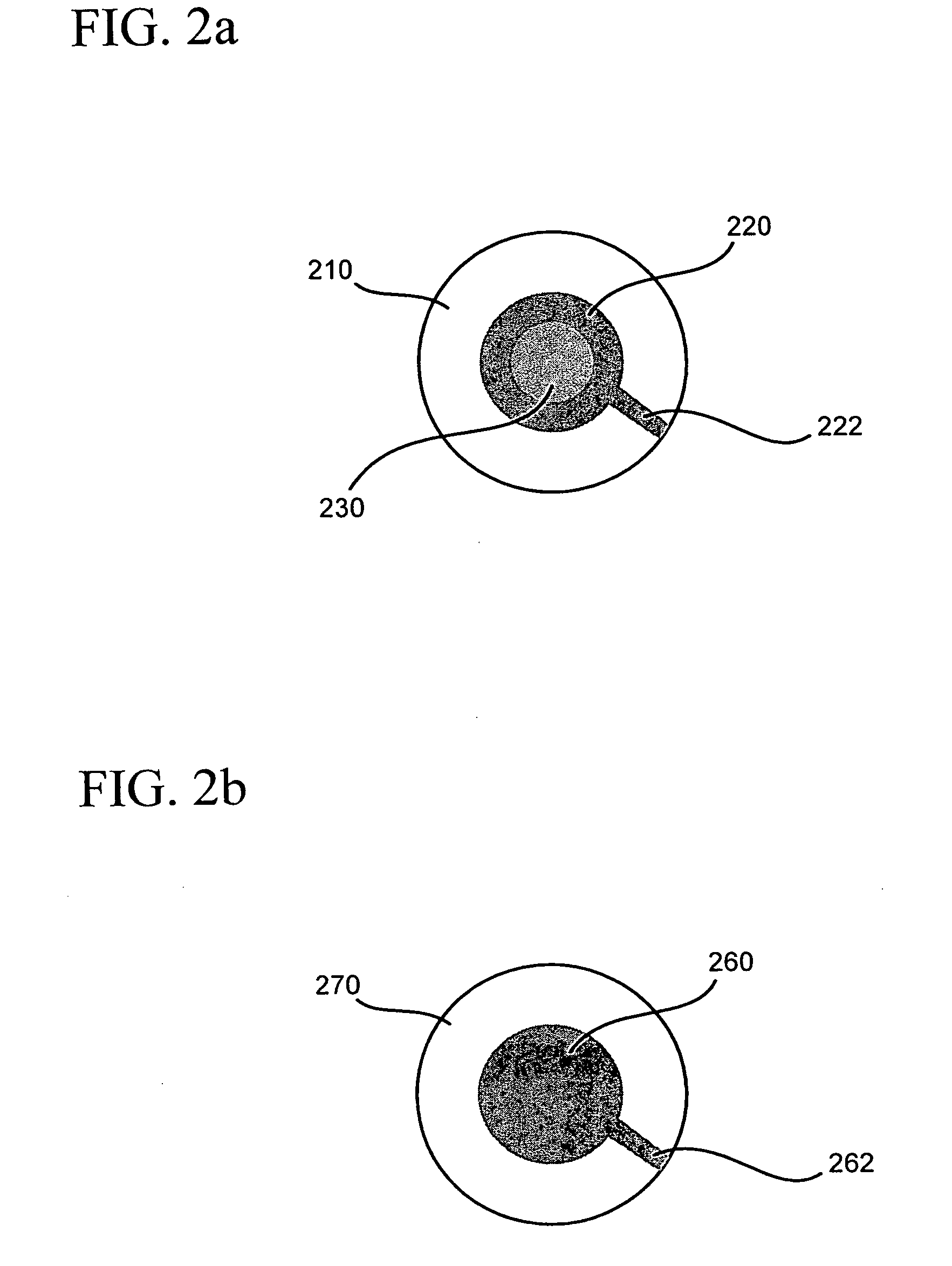

Electro-active spectacle employing modal liquid crystal lenses

An electro-active spectacle lens is disclosed. The spectacle lens comprises a first substrate having a first outer region and first inner region, a first electrode layer disposed adjacent to the first inner region, the first electrode layer including an outer electrode region having a first conductivity and an inner electrode region having a second conductivity, the first conductivity being greater than the second conductivity, a second substrate having a second outer region and second inner region, a second electrode layer disposed adjacent to the second inner region, the second electrode layer having a third conductivity, and an electro-active cell disposed between the first electrode layer and the second electrode layer, the electro-active cell containing an electro-active material. The first outer region and second outer region are configurable for fitting the spectacle lens within a lens frame without altering the electro-active cell.

Owner:E VISION LLC

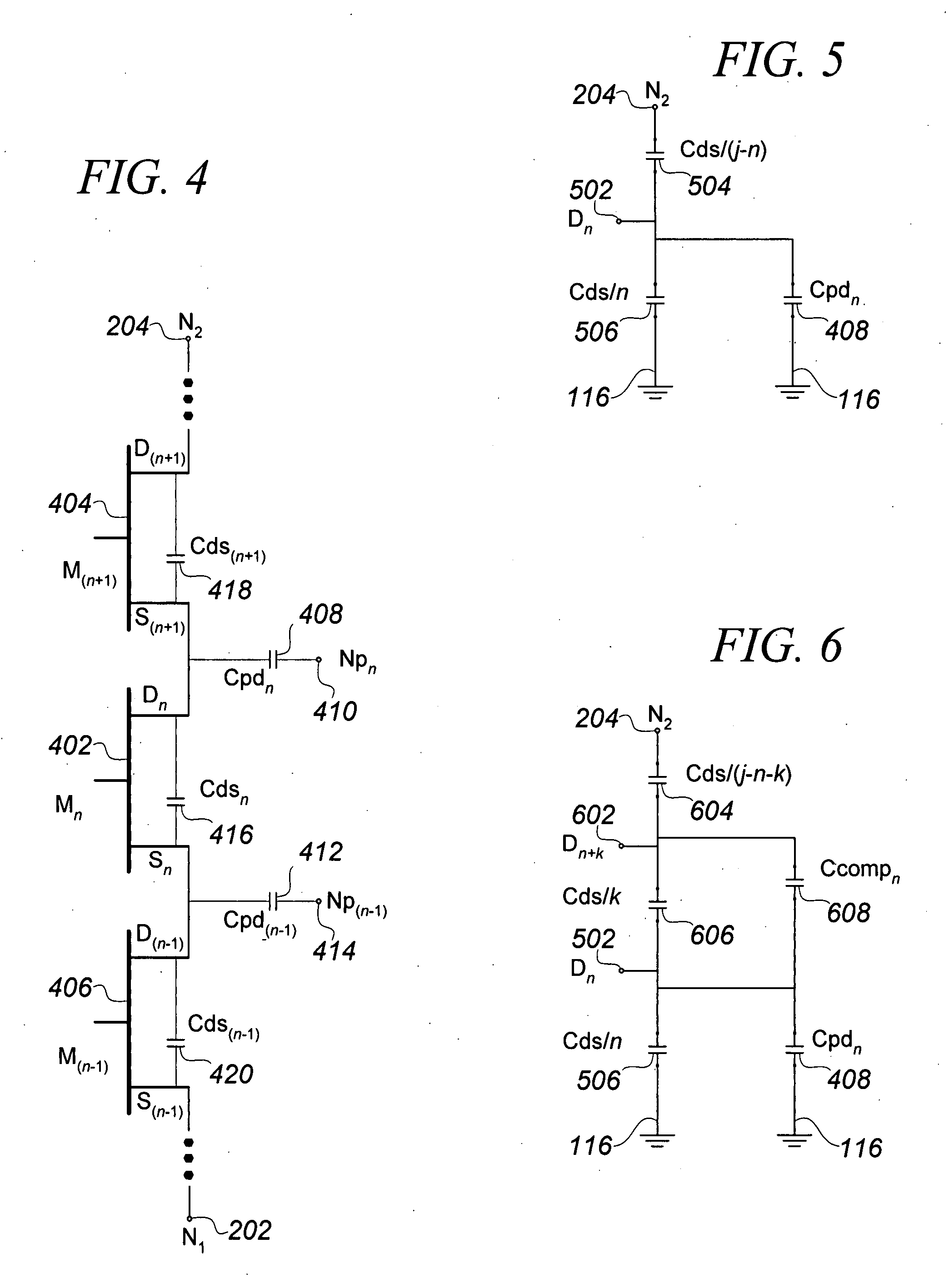

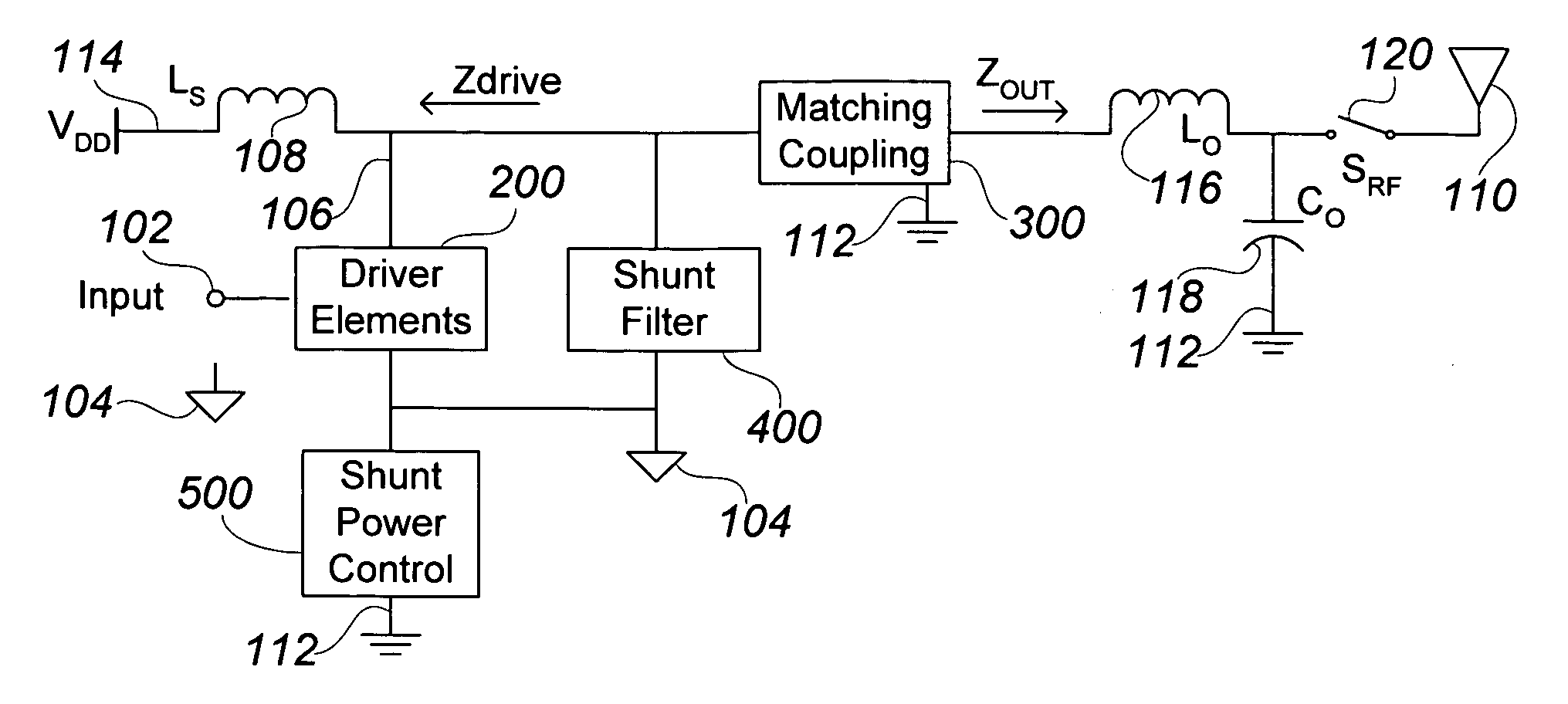

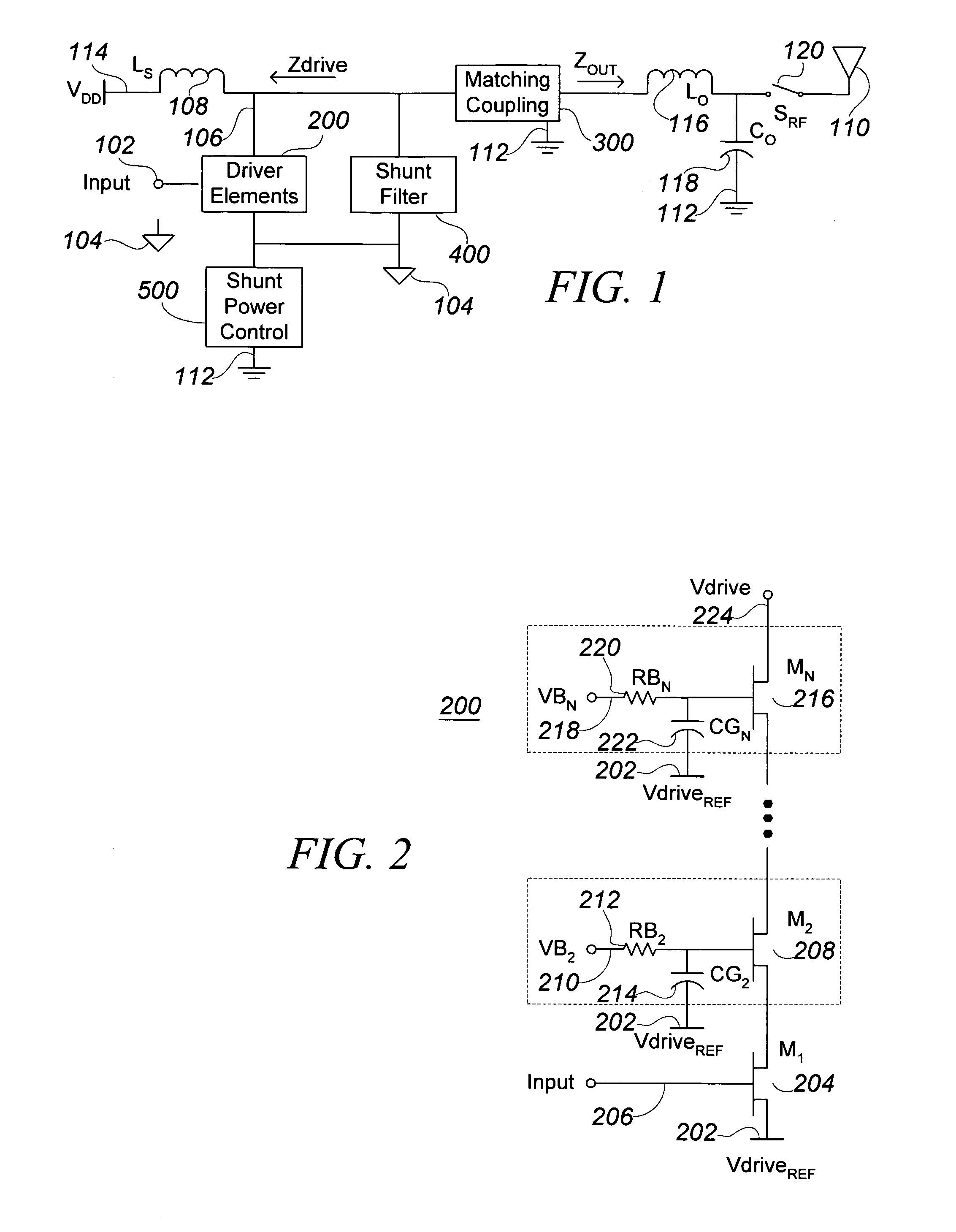

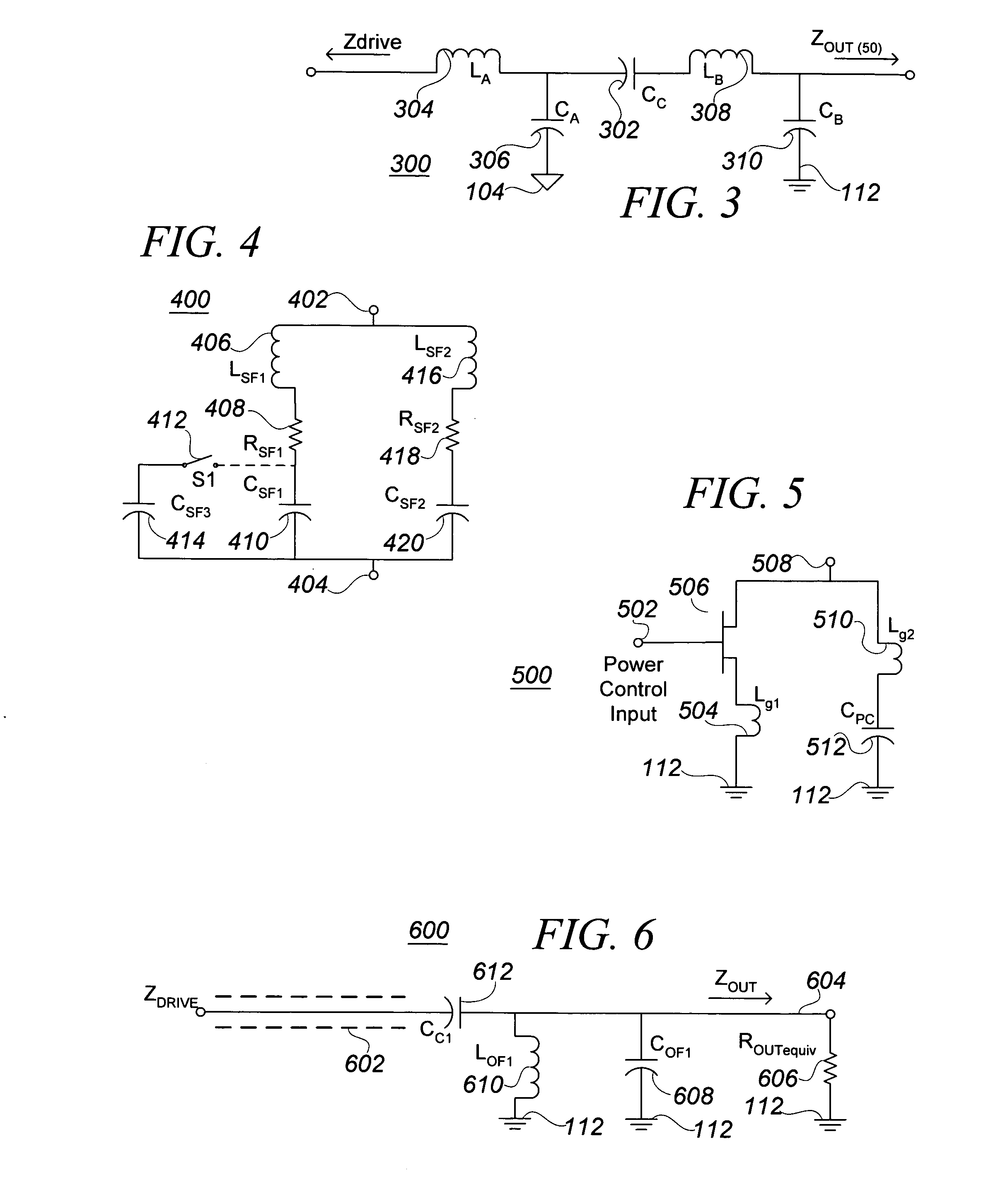

Integrated RF front end

ActiveUS7088971B2Effective protectionResonant long antennasHigh frequency amplifiersVoltage amplitudeTransceiver

A monolithic integrated circuit (IC), and method of manufacturing same, that includes all RF front end or transceiver elements for a portable communication device, including a power amplifier (PA), a matching, coupling and filtering network, and an antenna switch to couple the conditioned PA signal to an antenna. An output signal sensor senses at least a voltage amplitude of the signal switched by the antenna switch, and signals a PA control circuit to limit PA output power in response to excessive values of sensed output. Preferred fabrication techniques include stacking multiple FETs to form switching devices. An iClass PA architecture is described that dissipatively terminates unwanted harmonics of the PA output signal. A preferred embodiment of the RF transceiver IC includes two distinct PA circuits, two distinct receive signal amplifier circuits, and a four-way antenna switch to selectably couple a single antenna connection to any one of the four circuits.

Owner:PSEMI CORP

Preamplifier for two terminal electret condenser microphones

ActiveUS6888408B2Low costLimited space availableLow frequency amplifiersAmplifier combinationsCapacitanceAudio power amplifier

The present invention relates to a preamplifier suitable for use with Electret Condenser Microphones such as used within telecommunication equipment. More particularly the invention relates to a preamplifier specially suited for the demands to such a preamplifier within telecommunication equipment: low input capacitance, gain and a combined terminal for output and supply voltage, thus making the preamplifier suitable for two terminal microphone assemblies. These features are obtained with a two stage amplifier with a first stage optimised for low input capacitance and the second stage being able to provide gain. The preamplifier may be implemented using an ASIC, thus making the preamplifier suitable for applications with very limited space available, such as for integration within microphone assemblies.

Owner:SONION

Popular searches

Apparatus without intermediate ac conversion Cathode-ray tube indicators Differential amplifiers Electric variable regulation Dc-amplifiers with dc-coupled stages Transmission Amplifier modifications to extend bandwidth Amplifiers with semiconductor devices only RF amplifier Transmission control/equalising