Patents

Literature

1065 results about "Cascode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

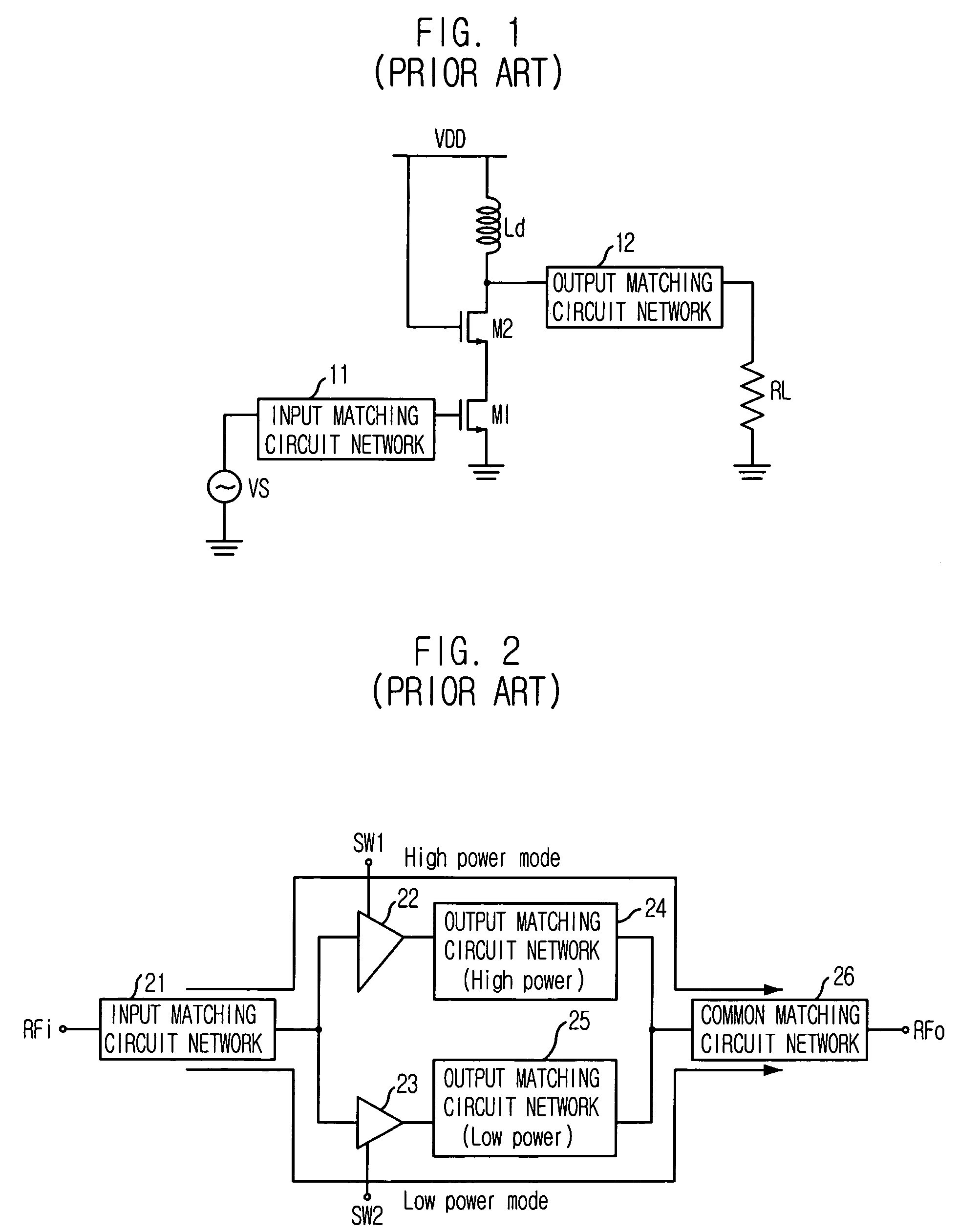

The cascode is a two-stage amplifier that consists of a common-emitter stage feeding into a common-base stage. Compared to a single amplifier stage, this combination may have one or more of the following characteristics: higher input–output isolation, higher input impedance, high output impedance, higher bandwidth.

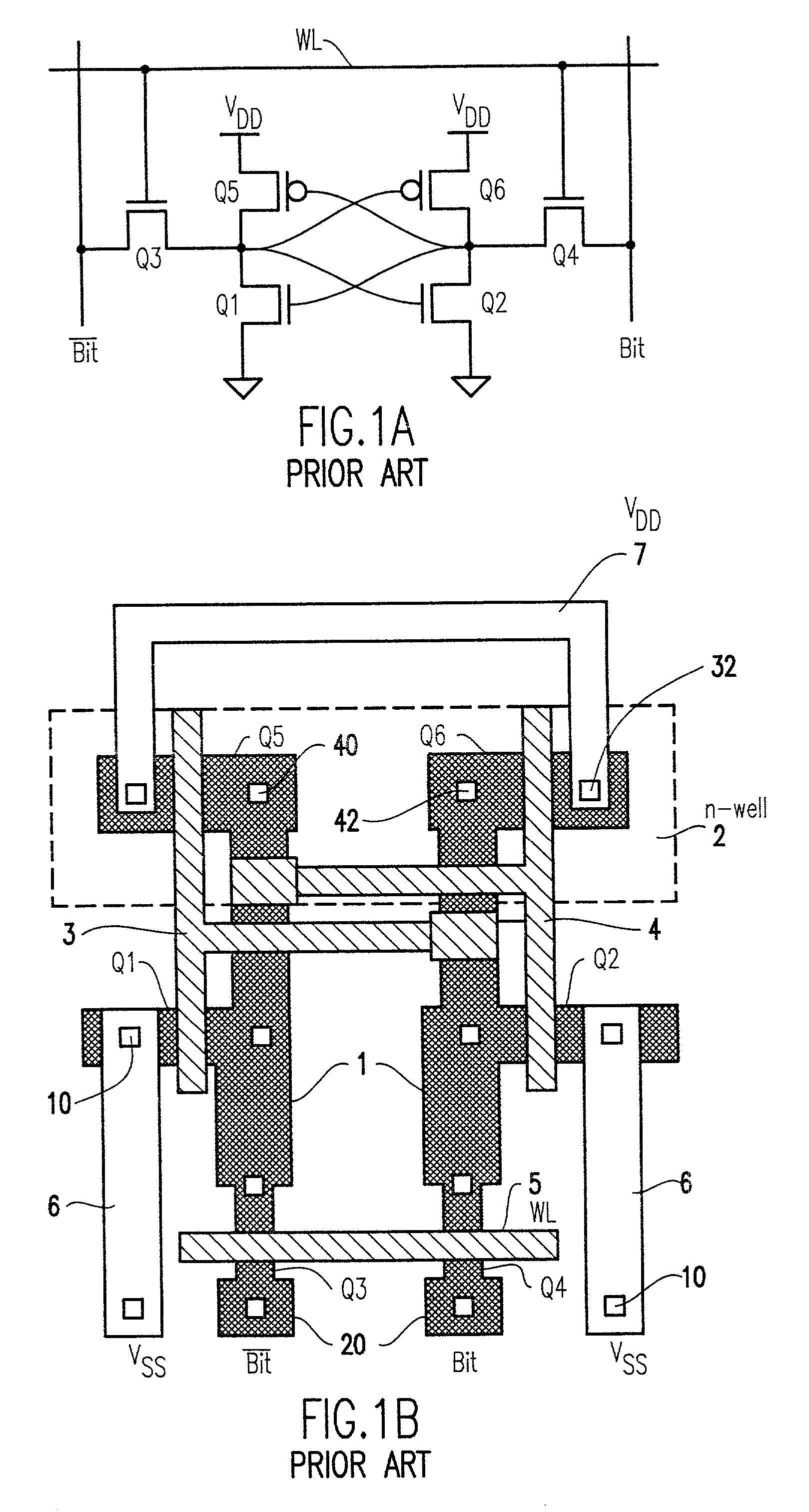

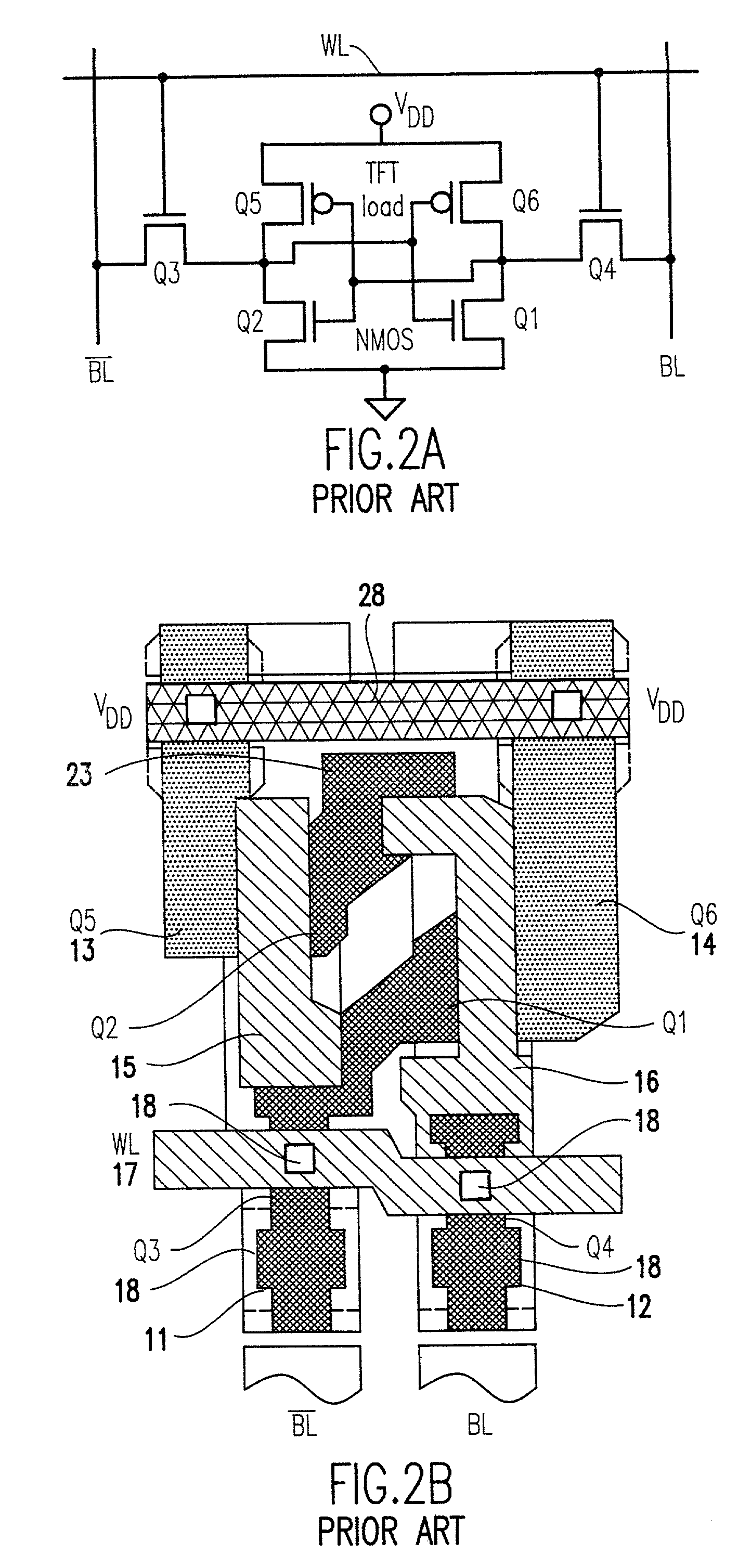

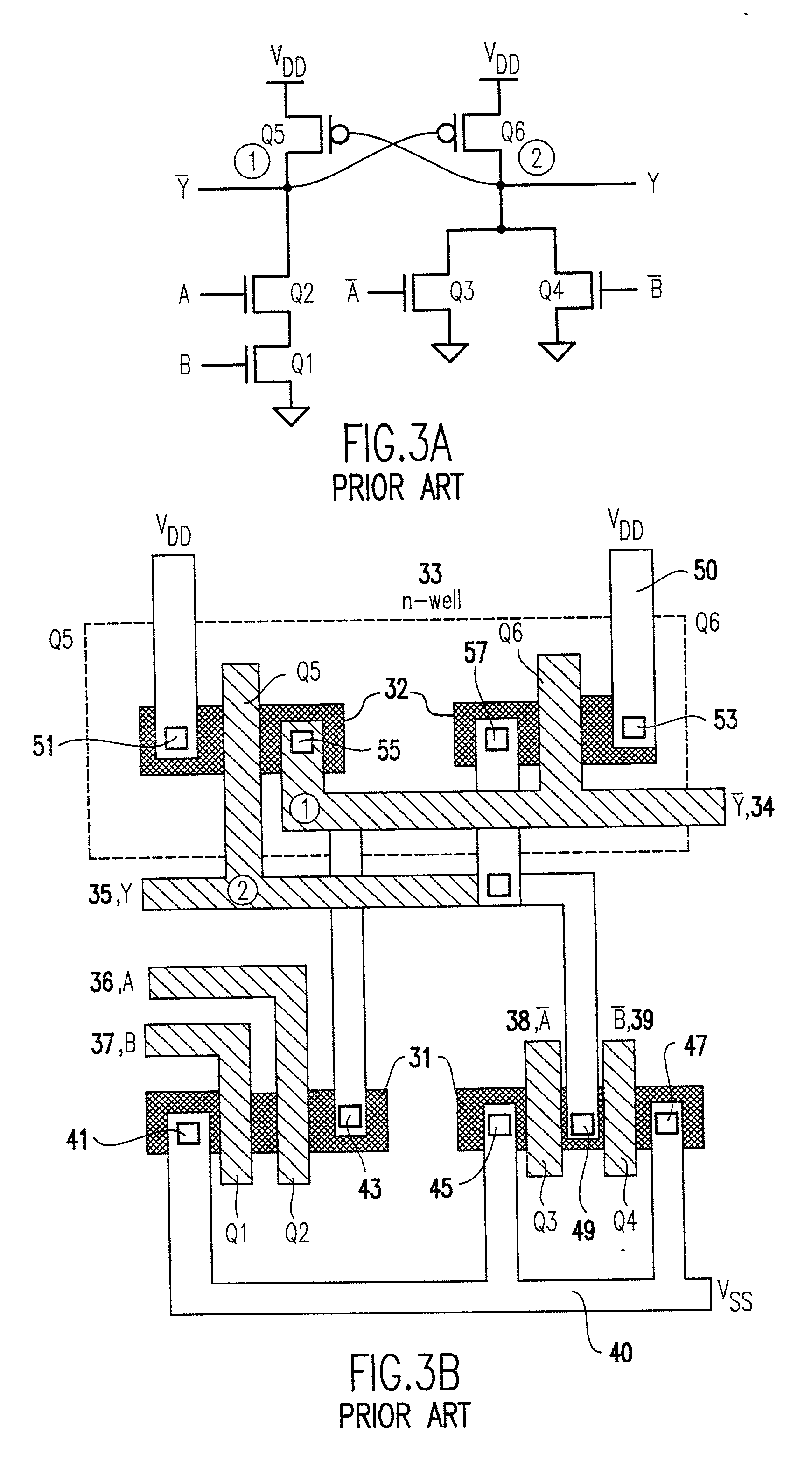

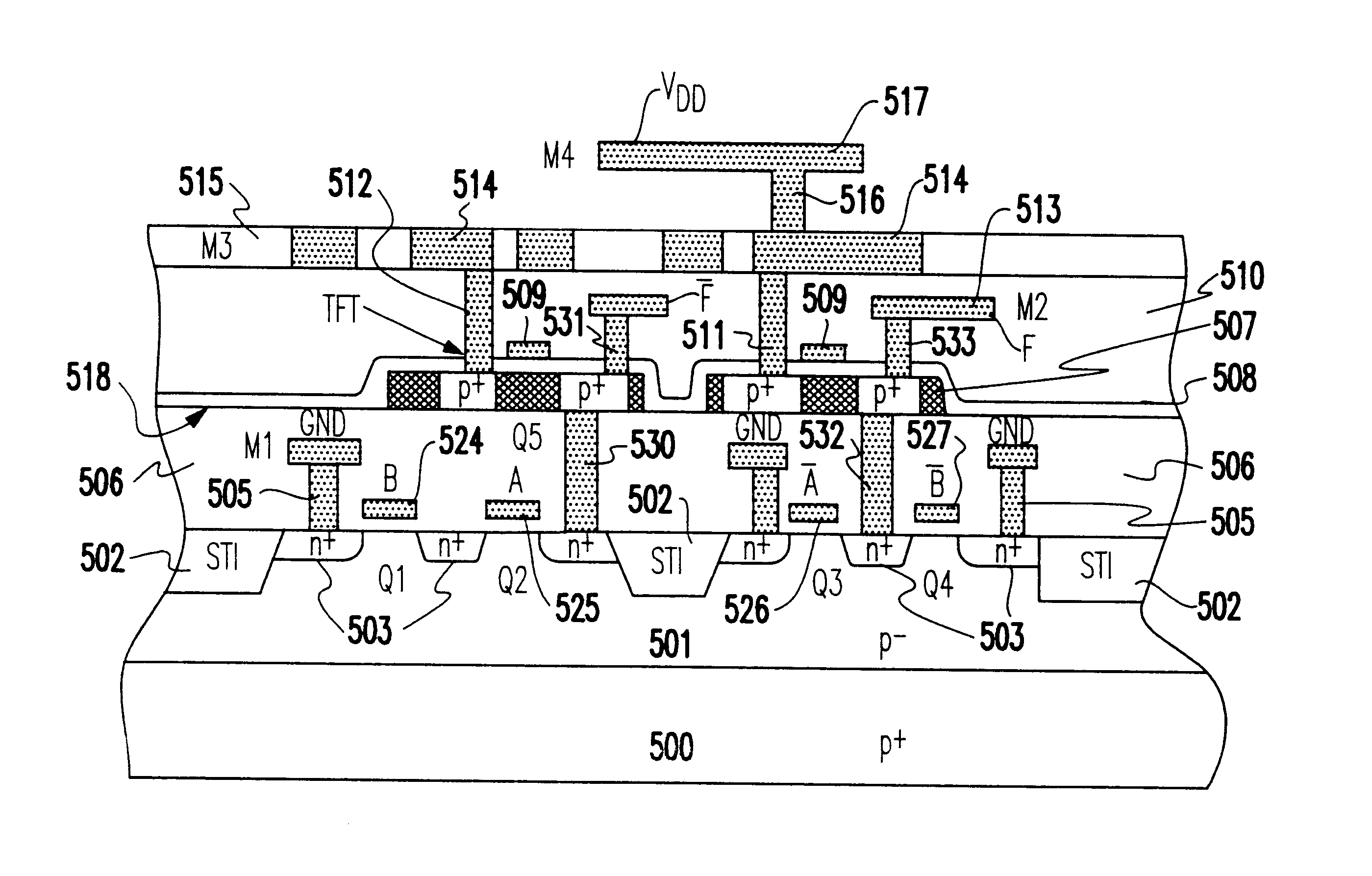

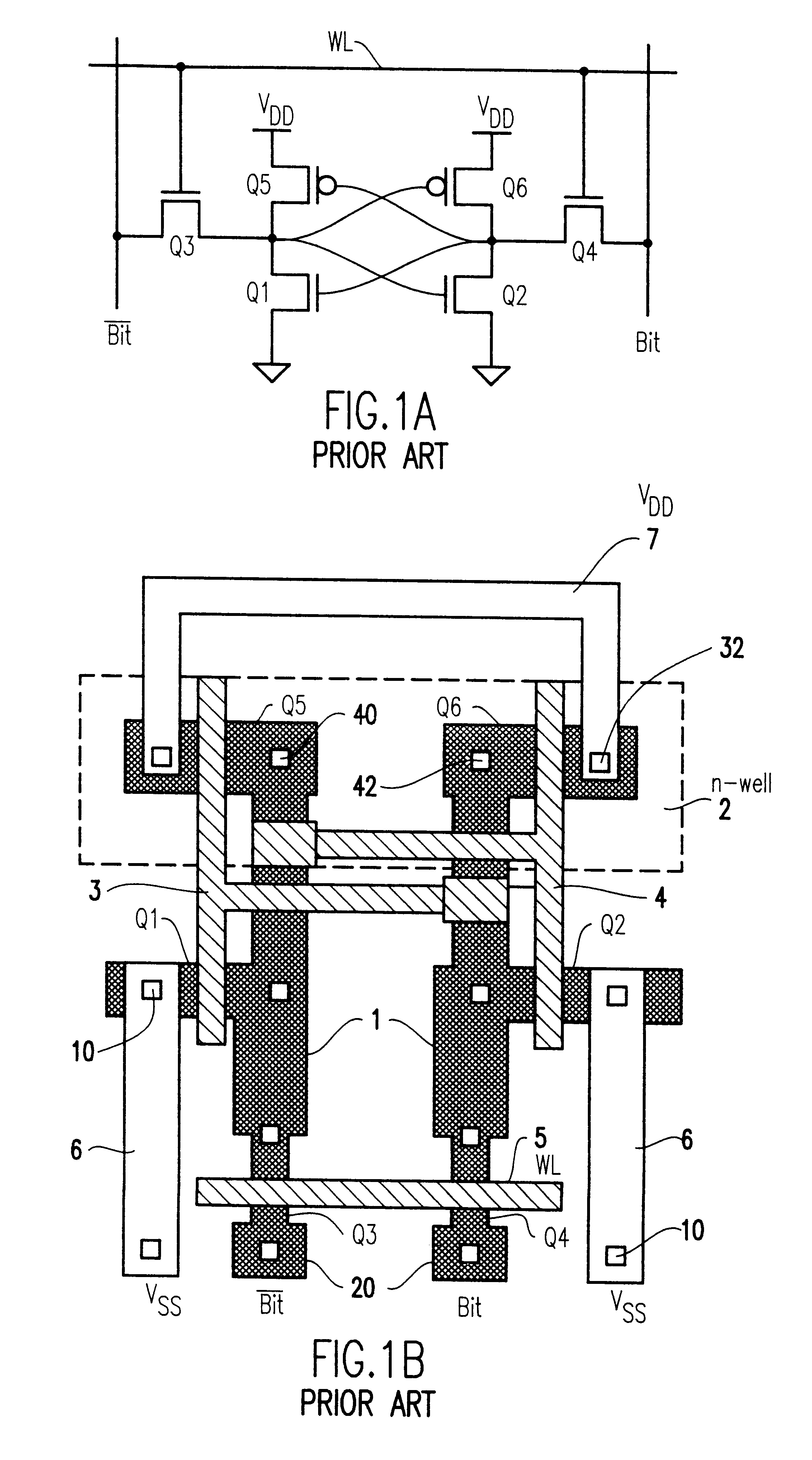

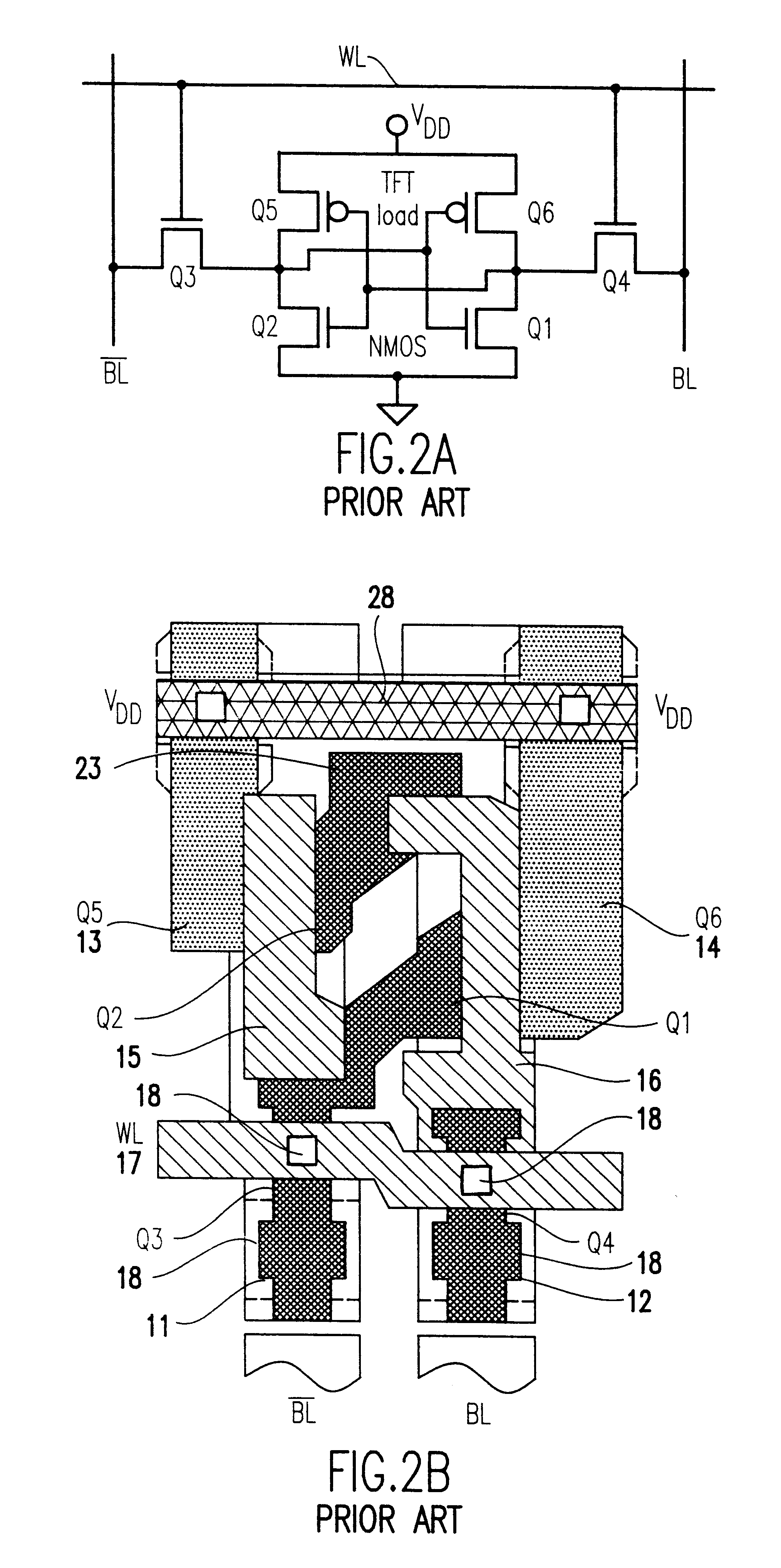

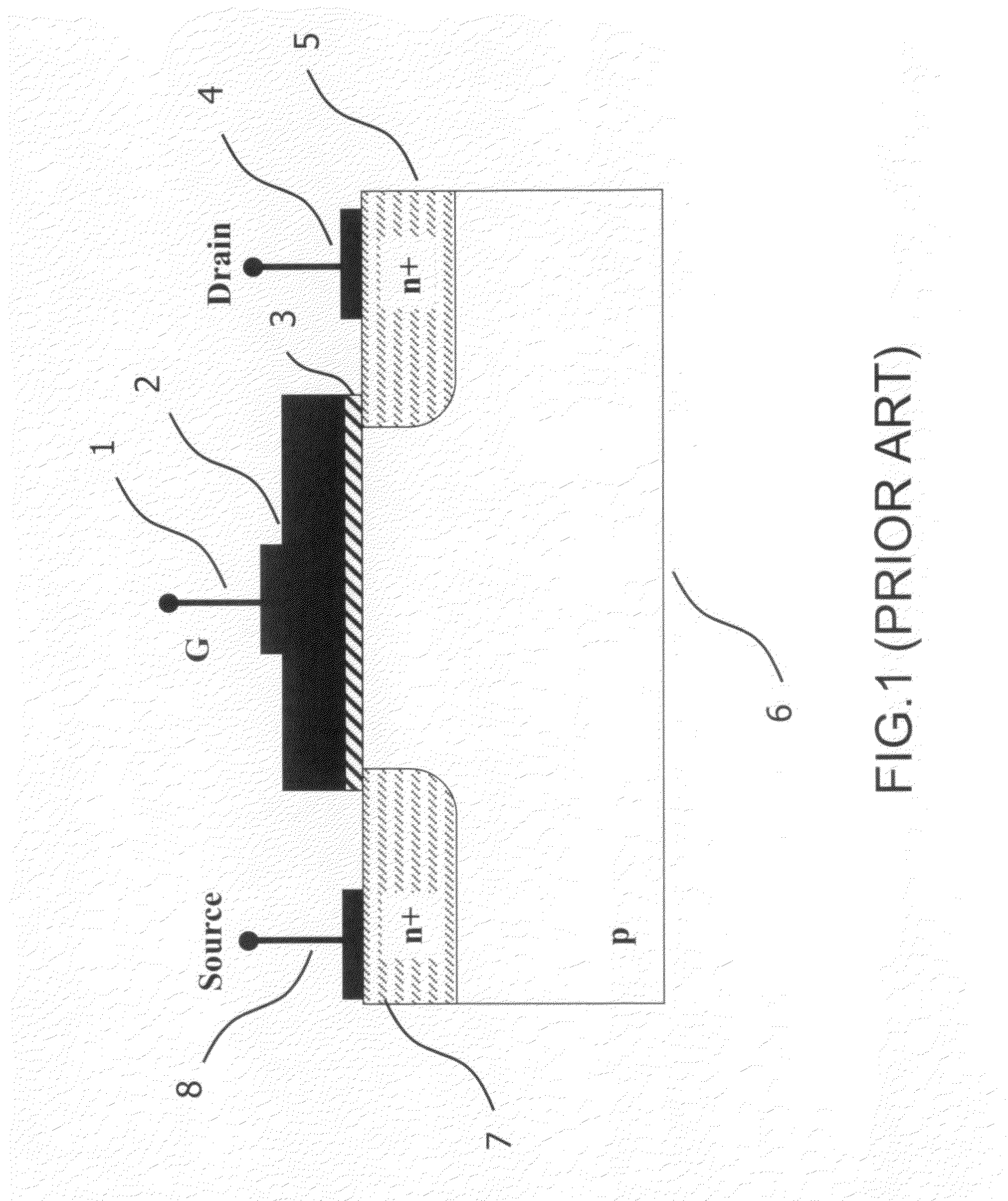

Merged logic and memory combining thin film and bulk Si transistors

InactiveUS20010028059A1Compact and economicalTransistorSolid-state devicesHigh densitySingle process

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

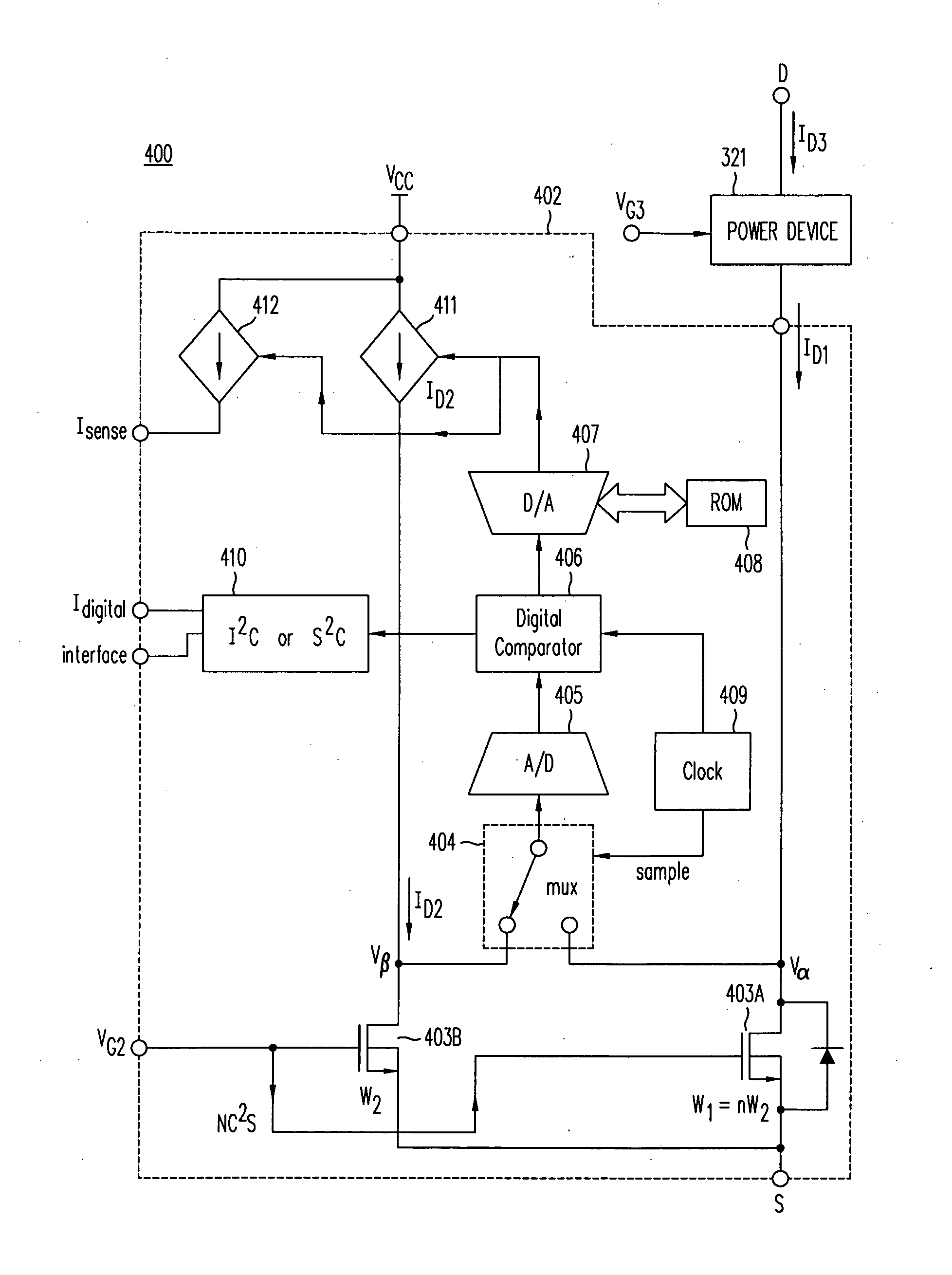

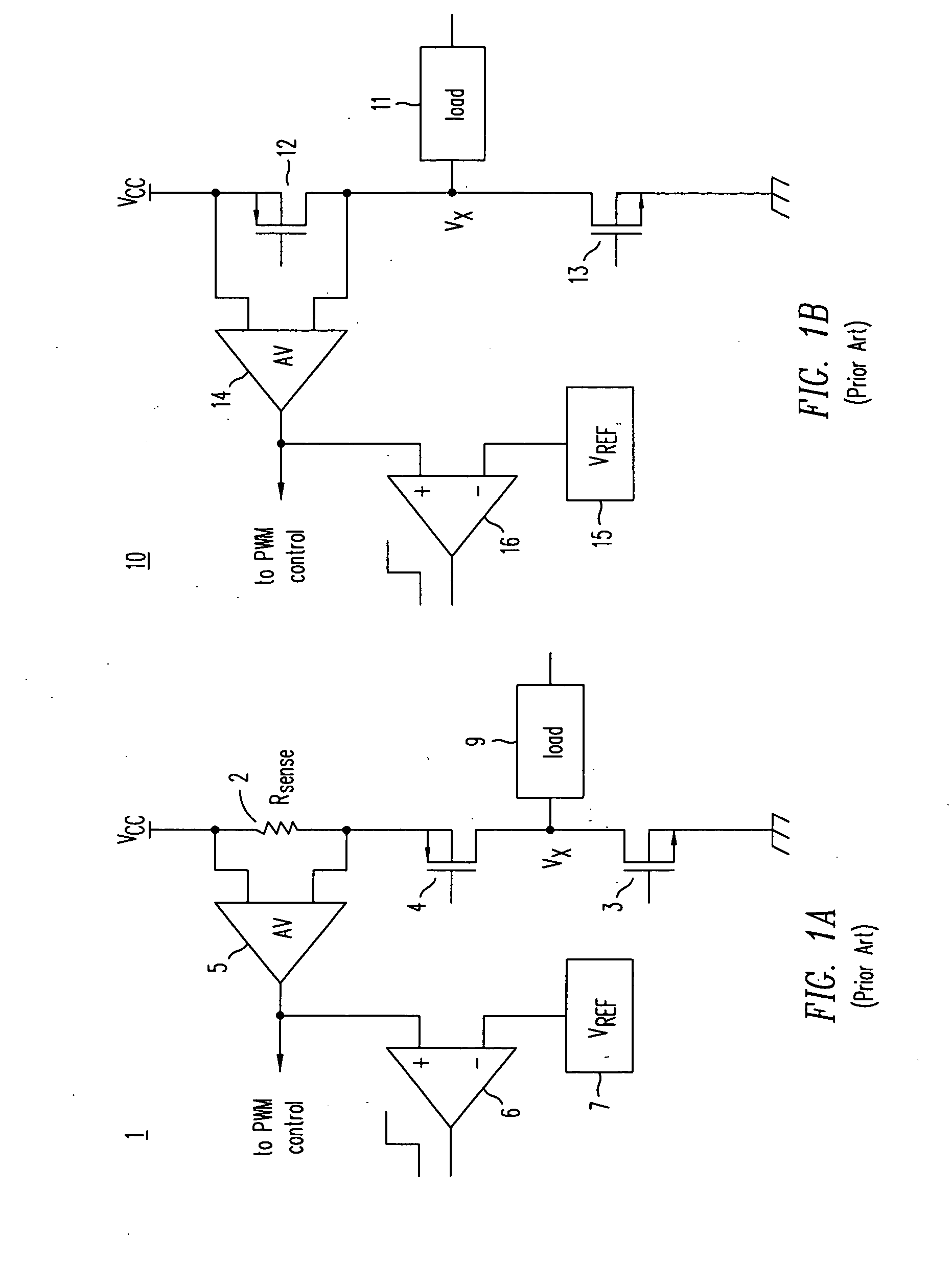

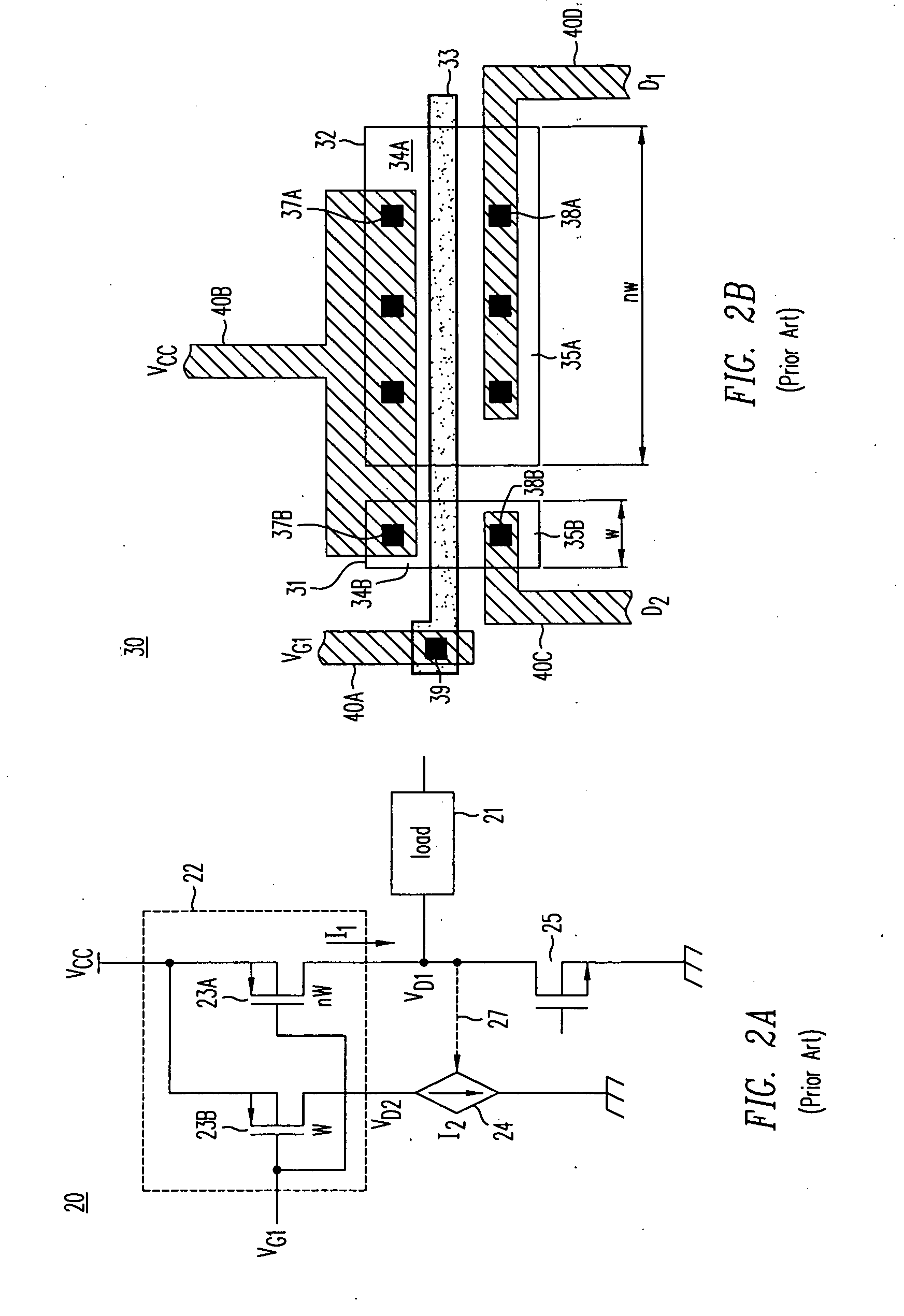

Cascode Current Sensor For Discrete Power Semiconductor Devices

InactiveUS20090039869A1Accurate detectionTransistorElectrical measurement instrument detailsMOSFETCascode

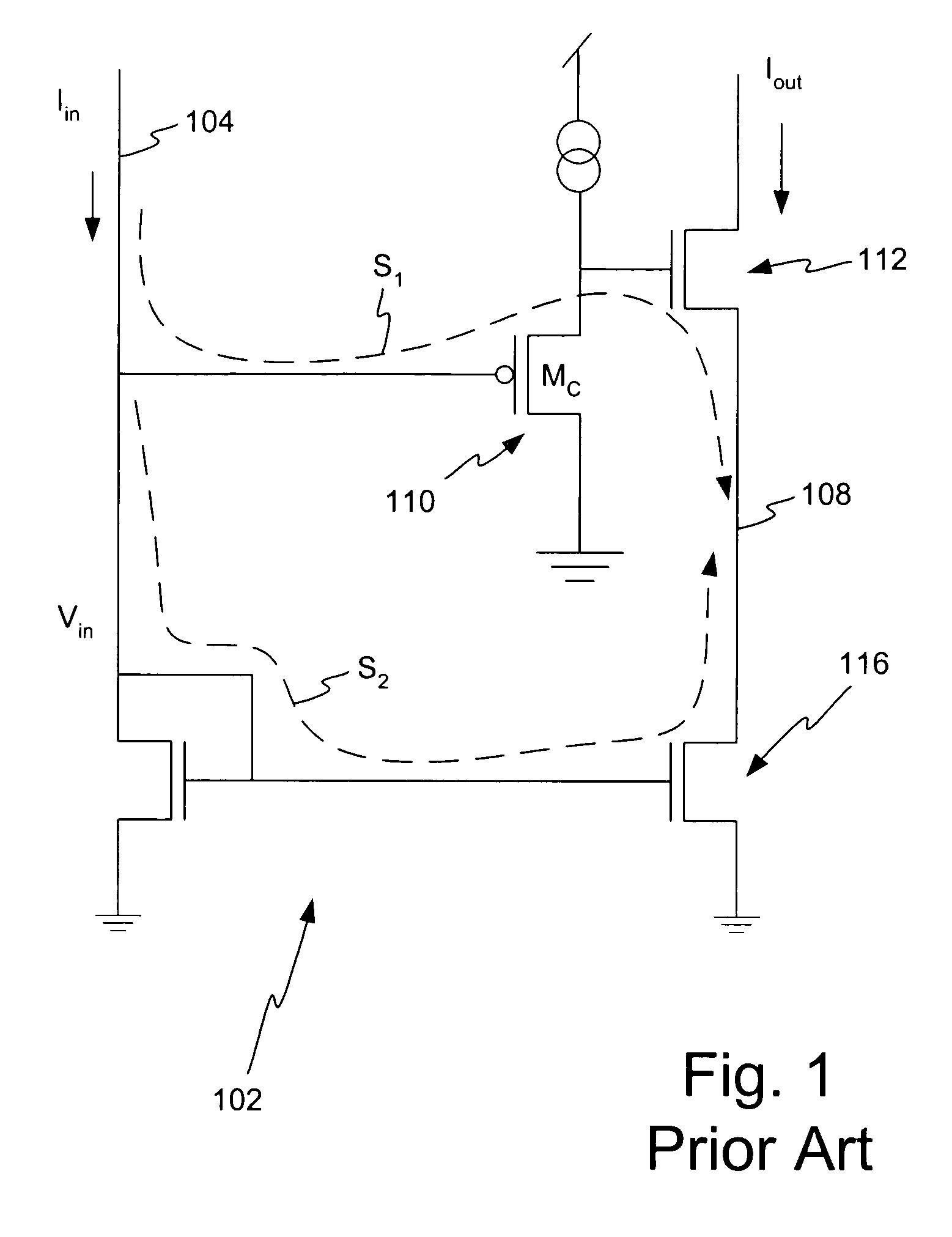

A cascode current sensor includes a main MOSFET and a sense MOSFET. The drain terminal of the main MOSFET is connected to a power device whose current is to be monitored, and the source and gate terminals of the main MOSFET are connected to the source and gate terminals, respectively, of the sense MOSFET. The drain voltages of the main and sense MOSFETs are equalized, in one embodiment by using a variable current source and negative feedback. The gate width of the main MOSFET is typically larger than the gate width of the sense MOSFET. Using the size ratio of the gate widths, the current in the main MOSFET is measured by sensing the magnitude of the current in the sense MOSFET. Inserting the relatively large MOSFET in the power circuit minimizes power loss.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

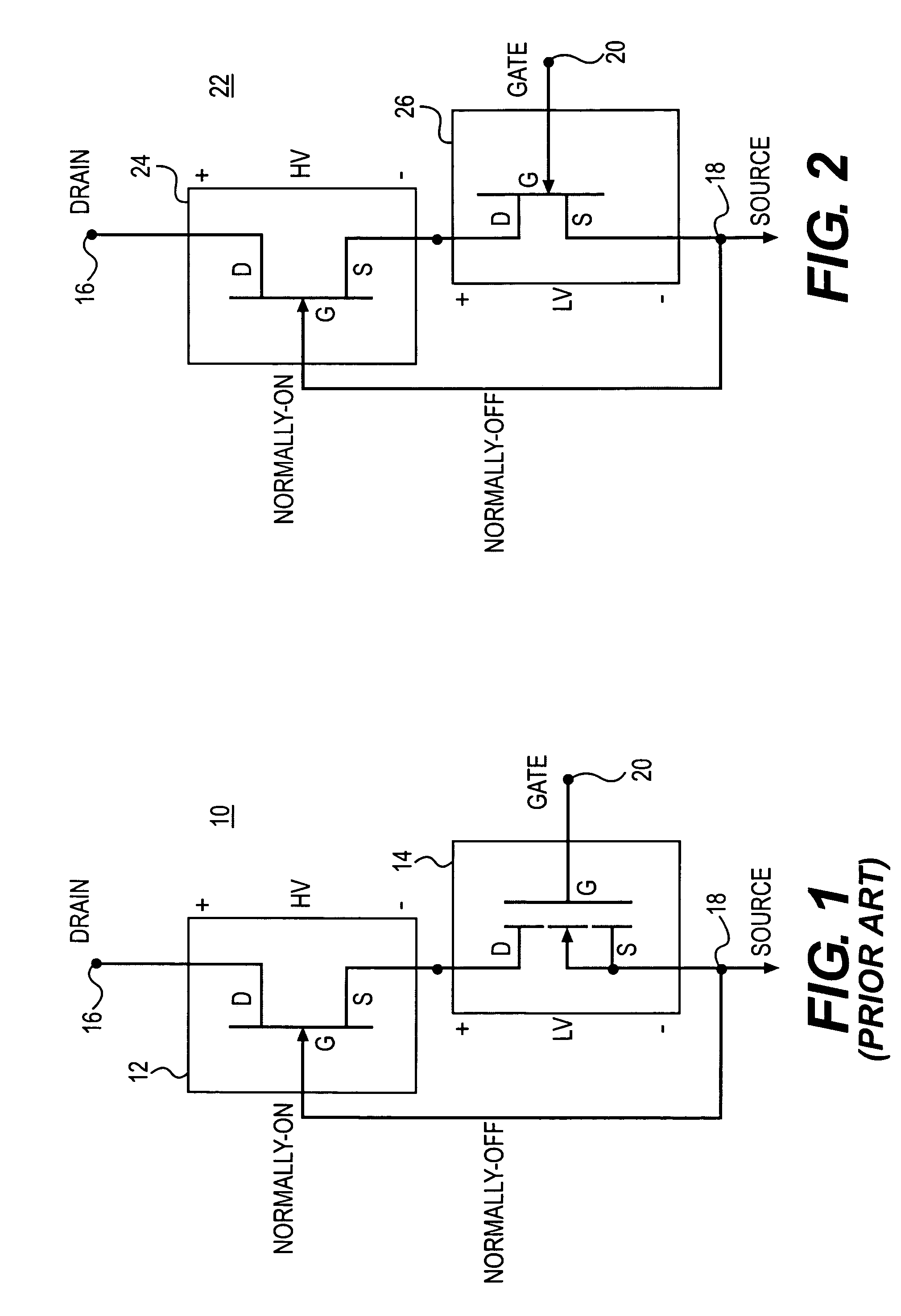

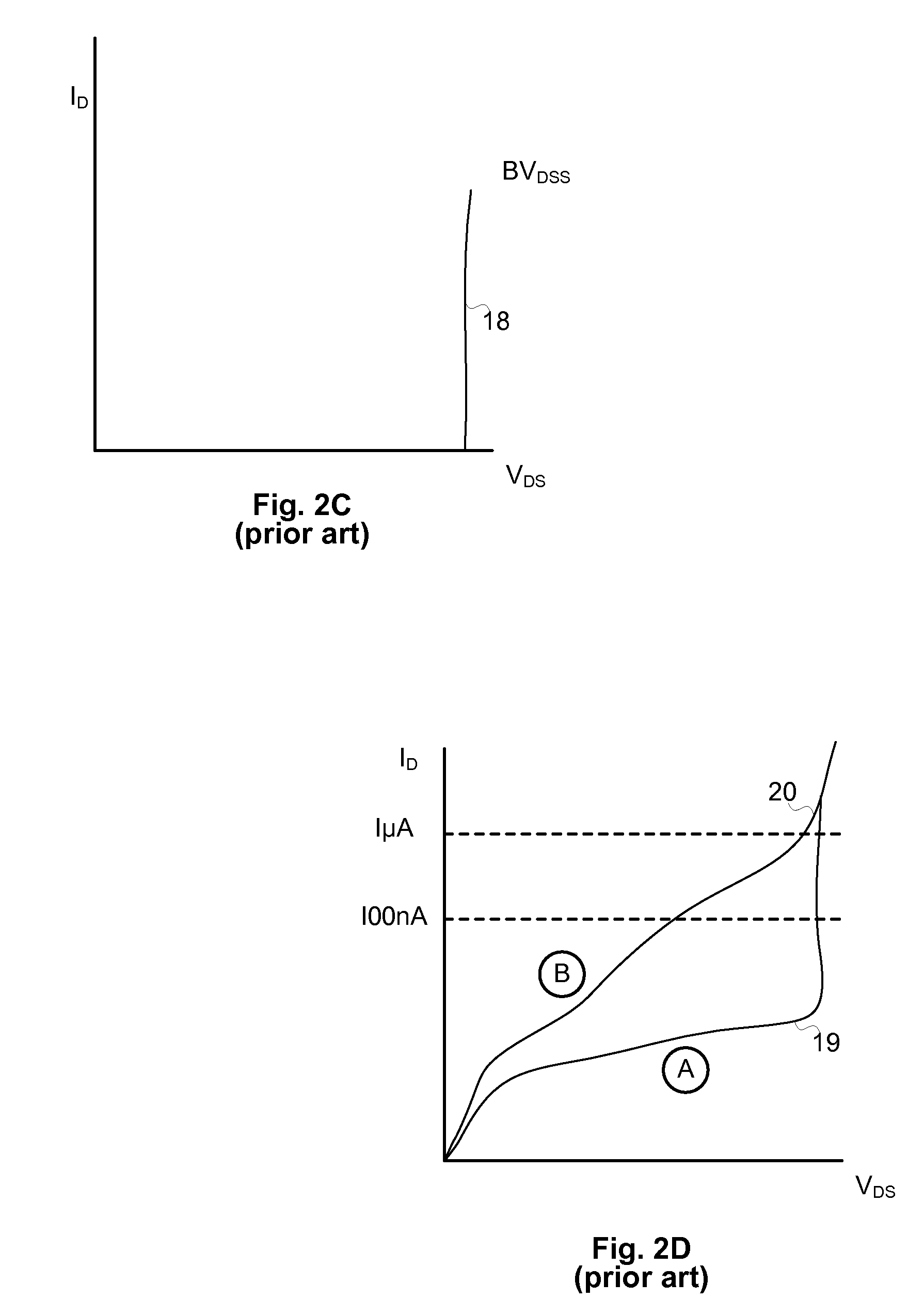

Cascode power switch topologies

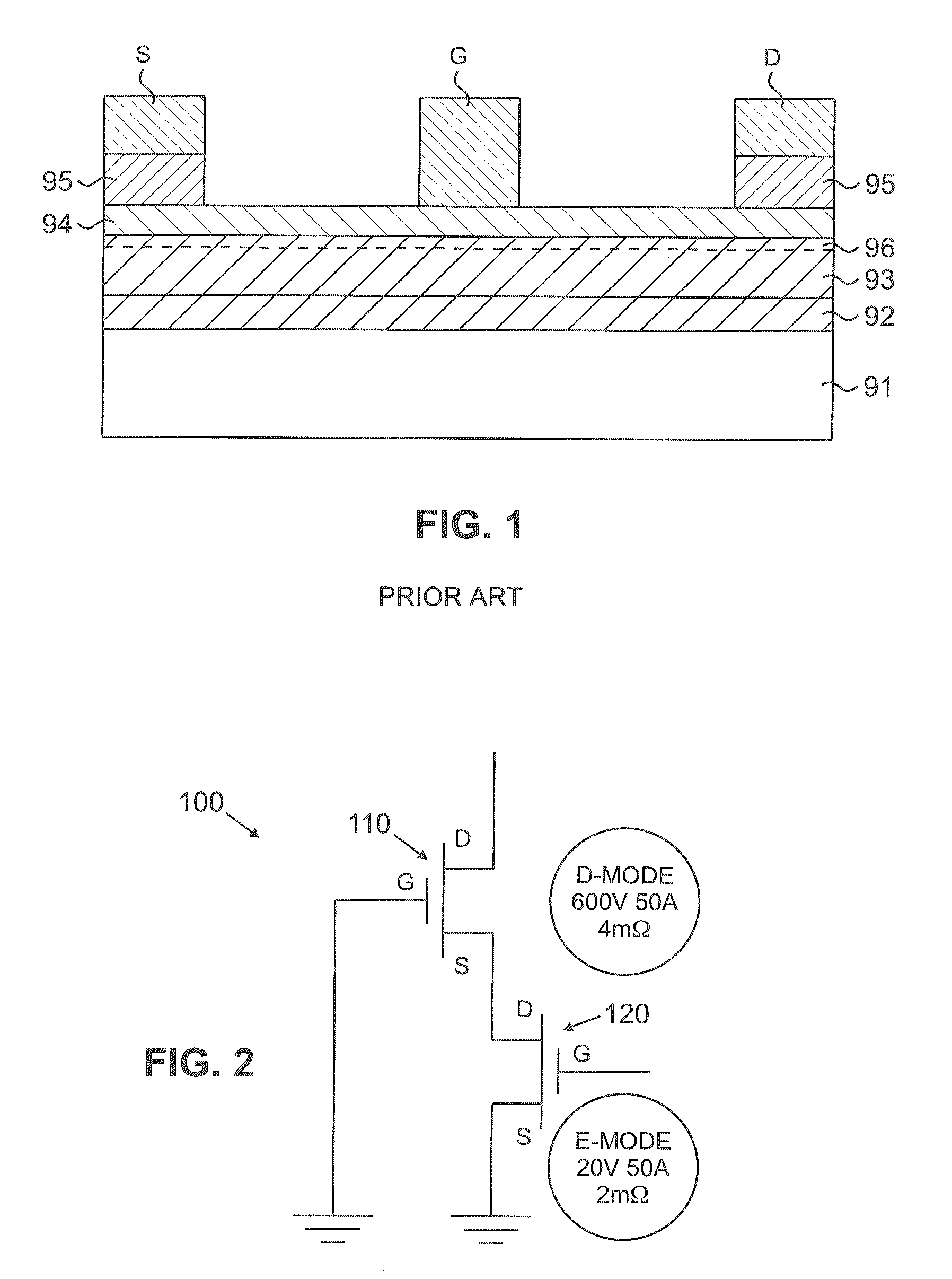

ActiveUS7719055B1Increase temperatureHigh blocking voltageElectronic switchingSemiconductor devicesCascodeGallium nitride

A normally-off cascode power switch circuit is disclosed fabricated in wide bandgap semiconductor material such as silicon carbide or gallium nitride and which is capable of conducting current in the forward and reverse direction under the influence of a positive gate bias. The switch includes cascoded junction field effect transistors (JFETs) that enable increased gain, and hence blocking voltage, while minimizing specific on-resistance.

Owner:NORTHROP GRUMMAN SYST CORP

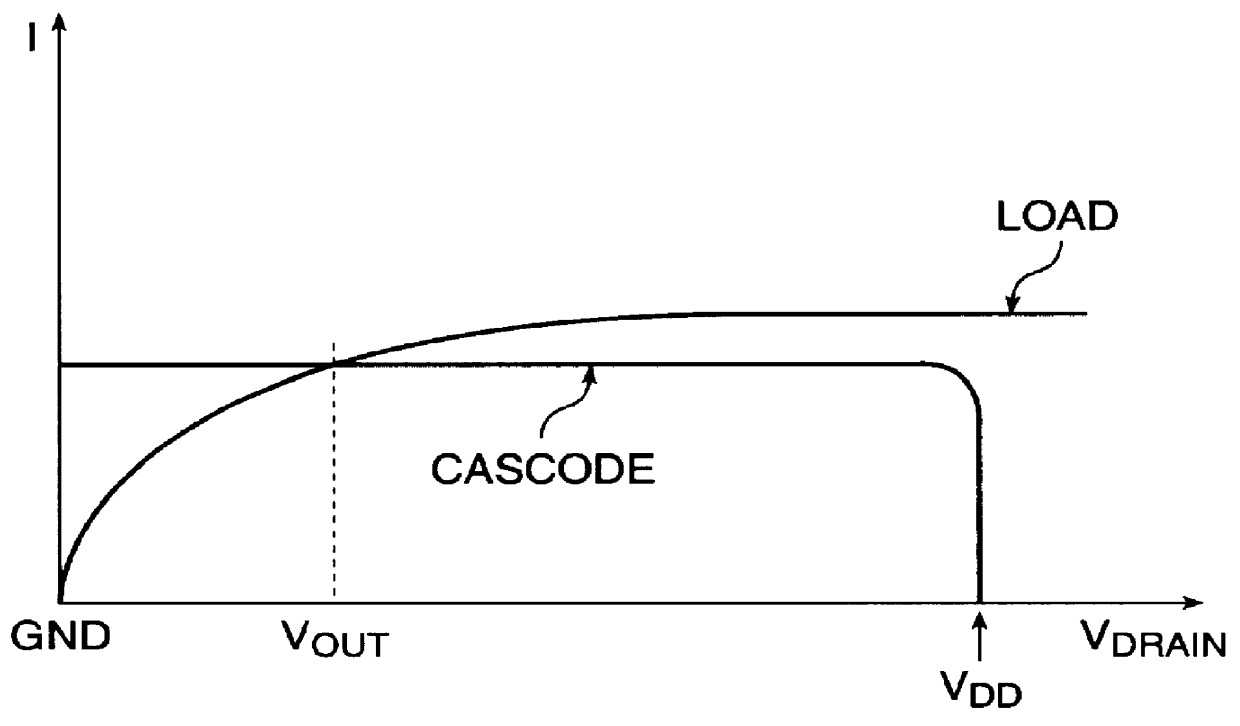

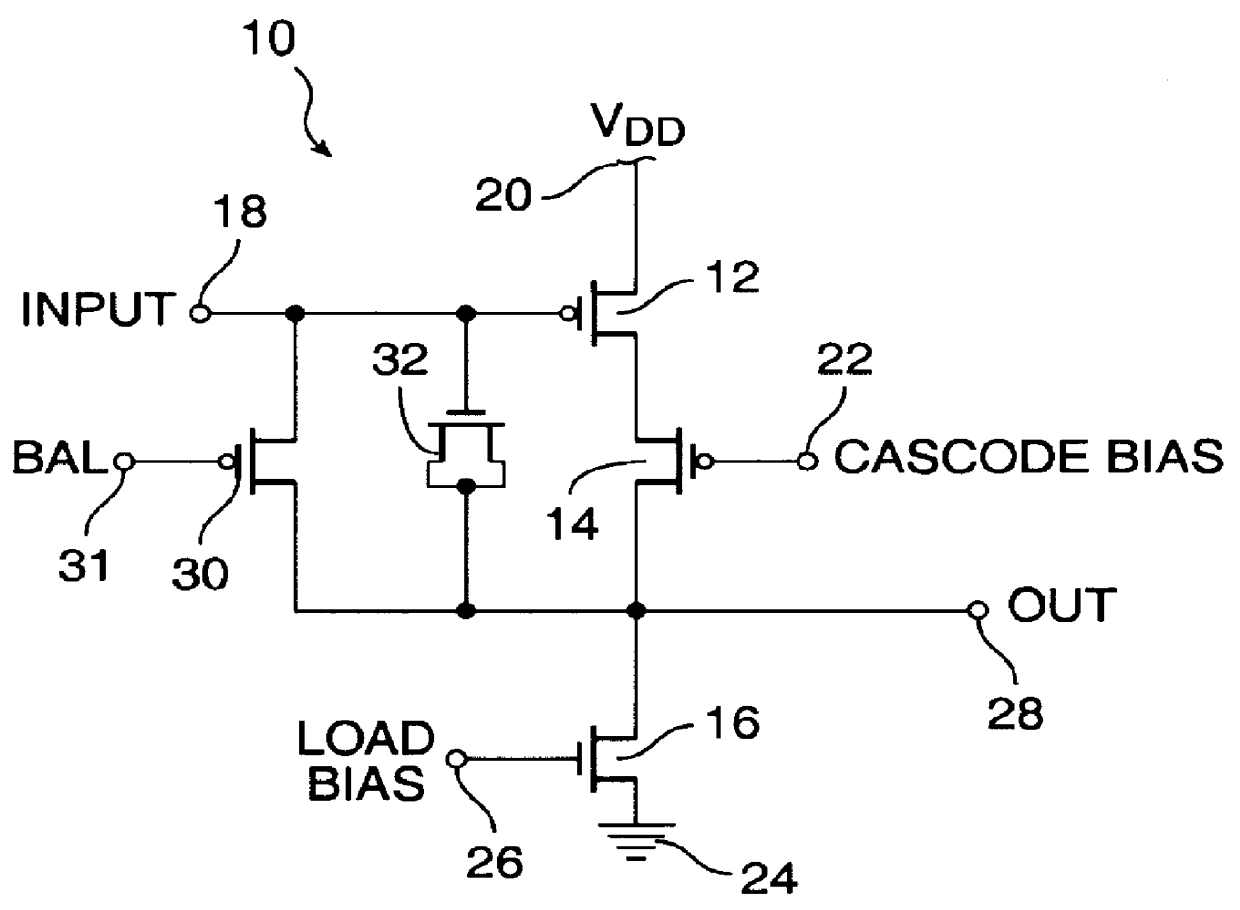

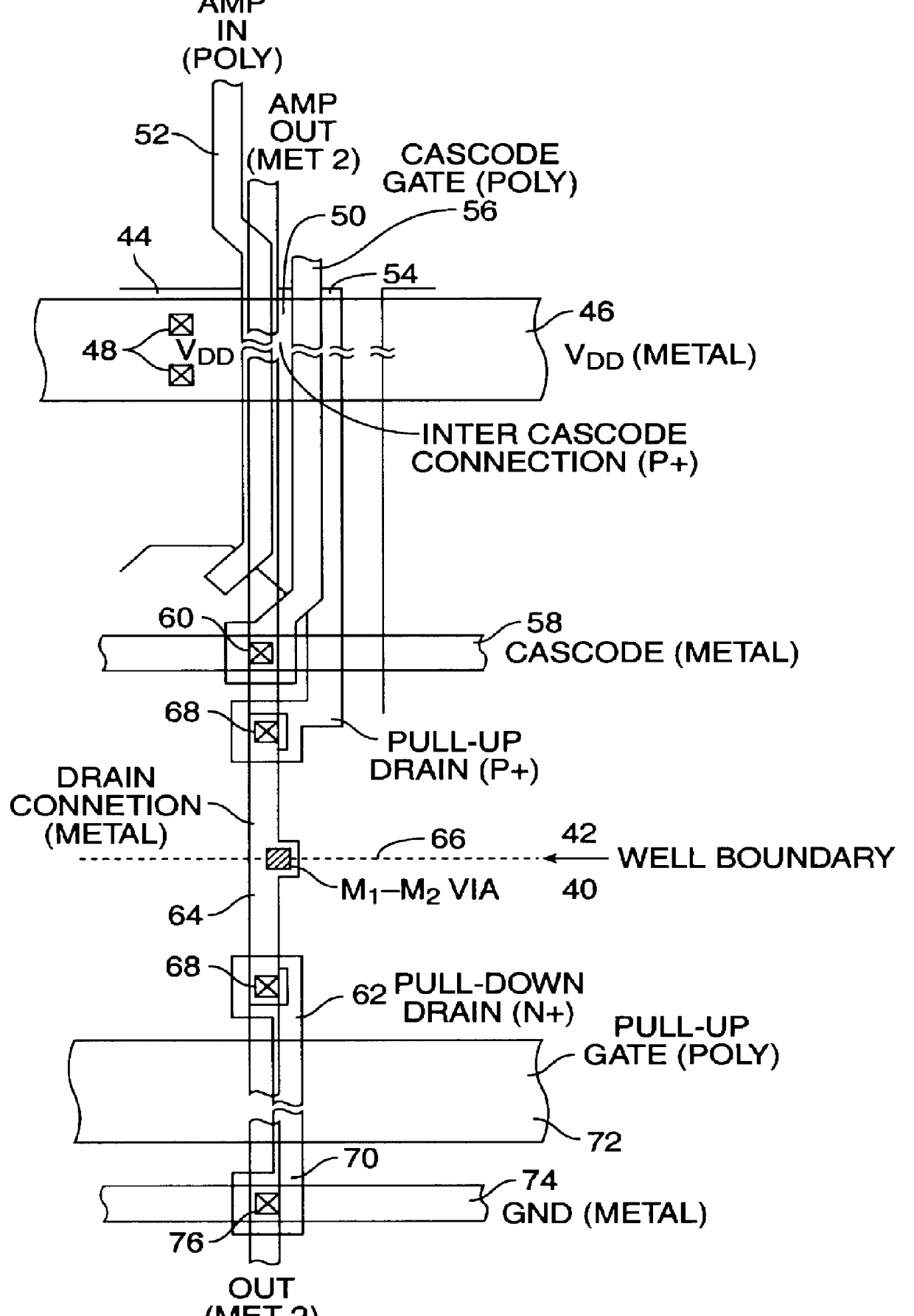

Sense amplifier for high-density imaging array

InactiveUS6097432ATelevision system detailsTelevision system scanning detailsHigh densityAudio power amplifier

A sense amplifier comprises an input node and an output node. An input transistor has a gate connected to the input node, a source connected to a first supply voltage rail, and a drain. A cascode transistor has a gate connected to a cascode node, a source connected to the drain of the input transistor, and a drain connected to the output node. A load transistor has a gate connected to a bias node, a drain connected to the output node, and a source connected to a second supply voltage rail. The gates of the cascode transistor and the load transistor are biased such that the input transistor and the cascode transistor are operated near their threshold and the load transistor is operated above threshold. In a presently preferred embodiment of the present invention, the input transistor and the cascode transistor of the sense amplifier are wide and short, such that they operate in below threshold, whereas the load transistor is made long and relatively narrow, so that it operates above threshold.

Owner:FOVEON

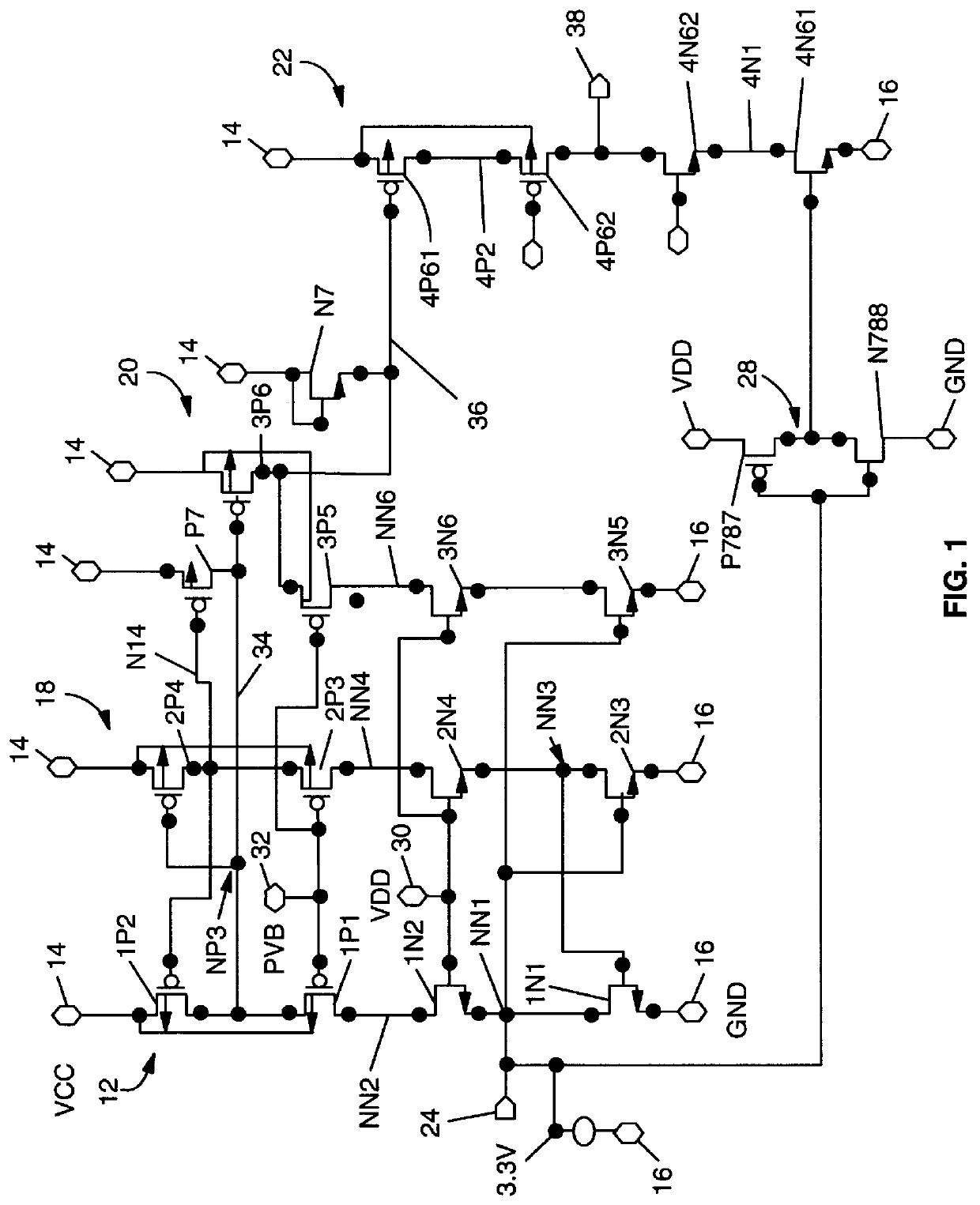

Merged logic and memory combining thin film and bulk Si transistors

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

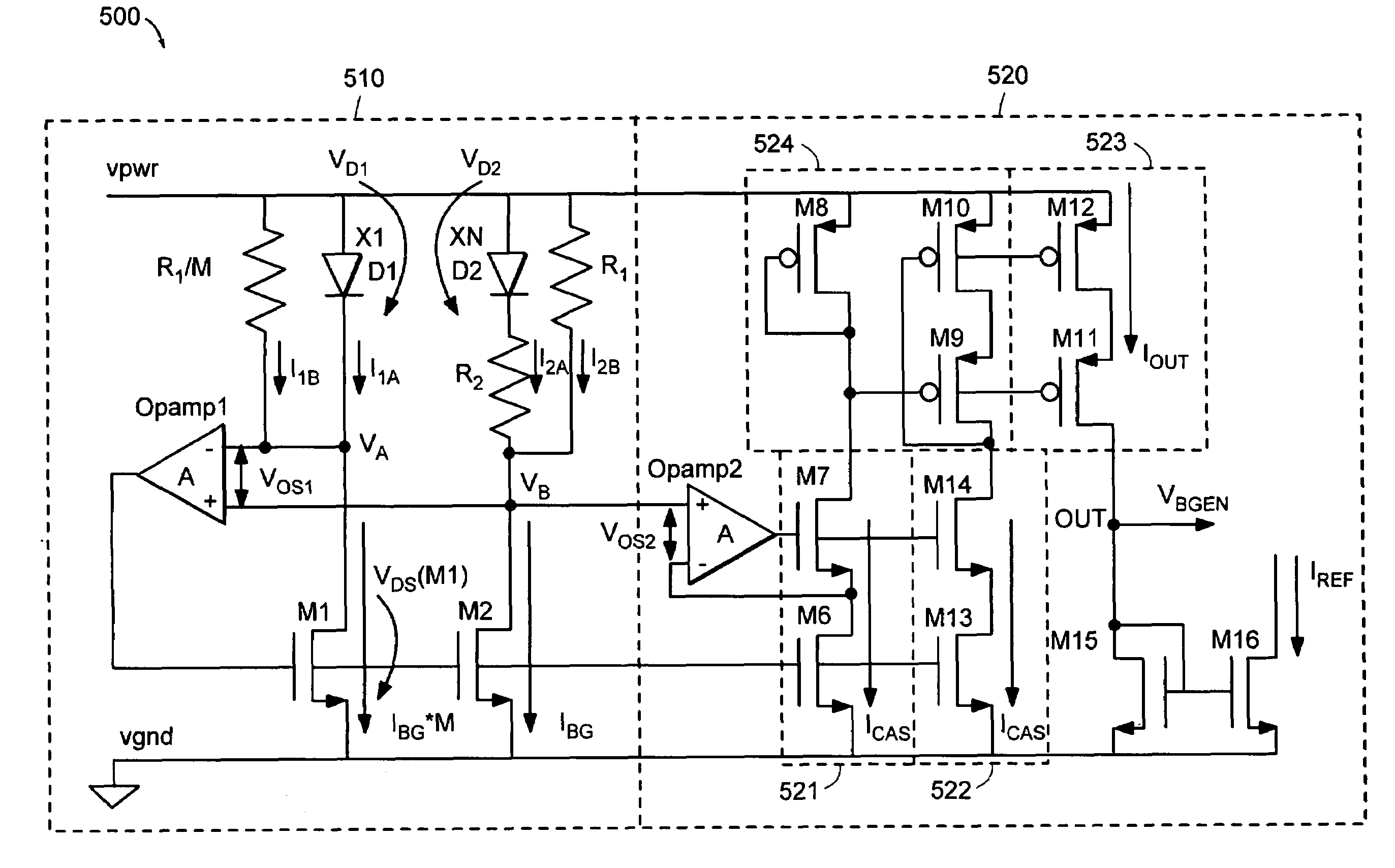

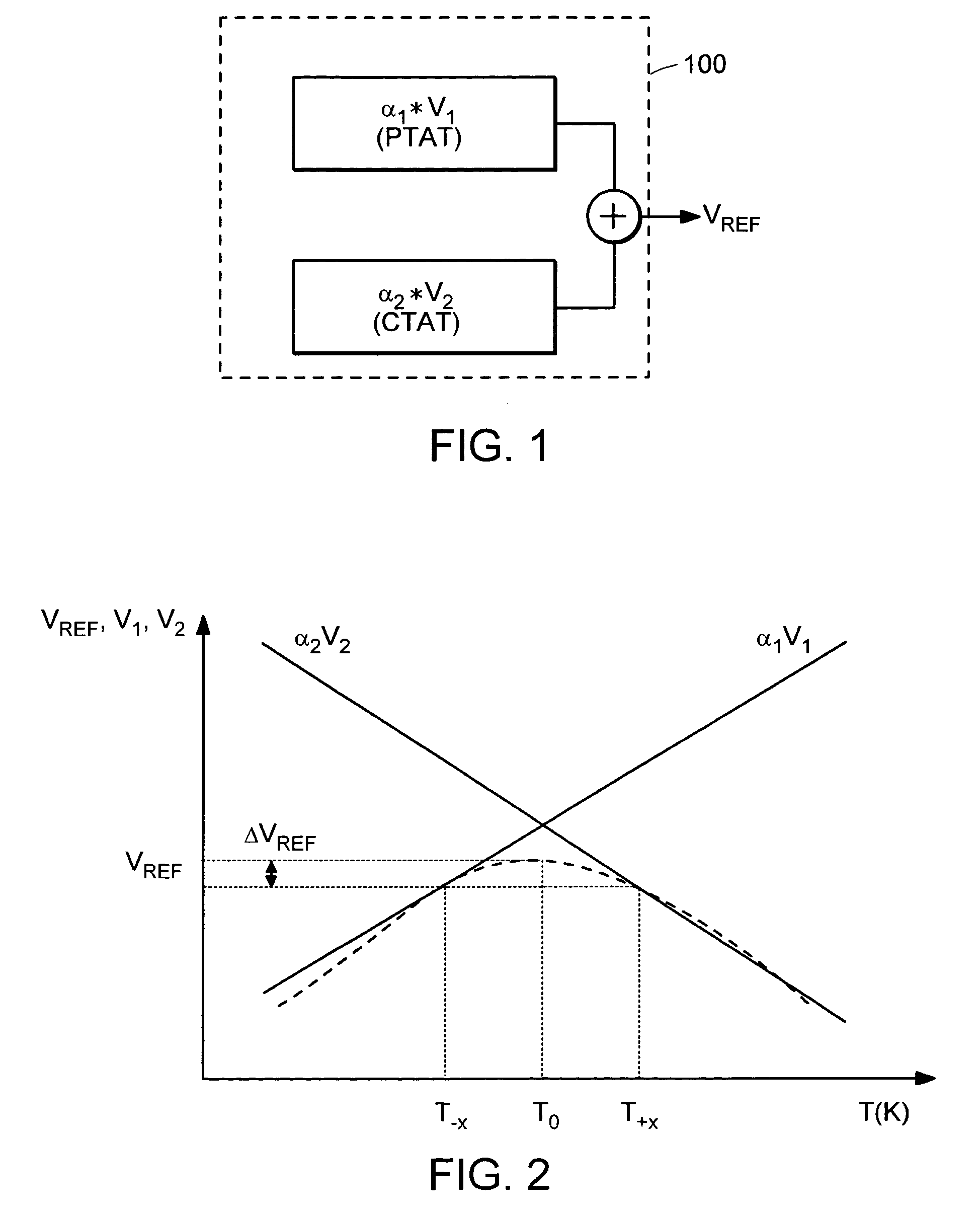

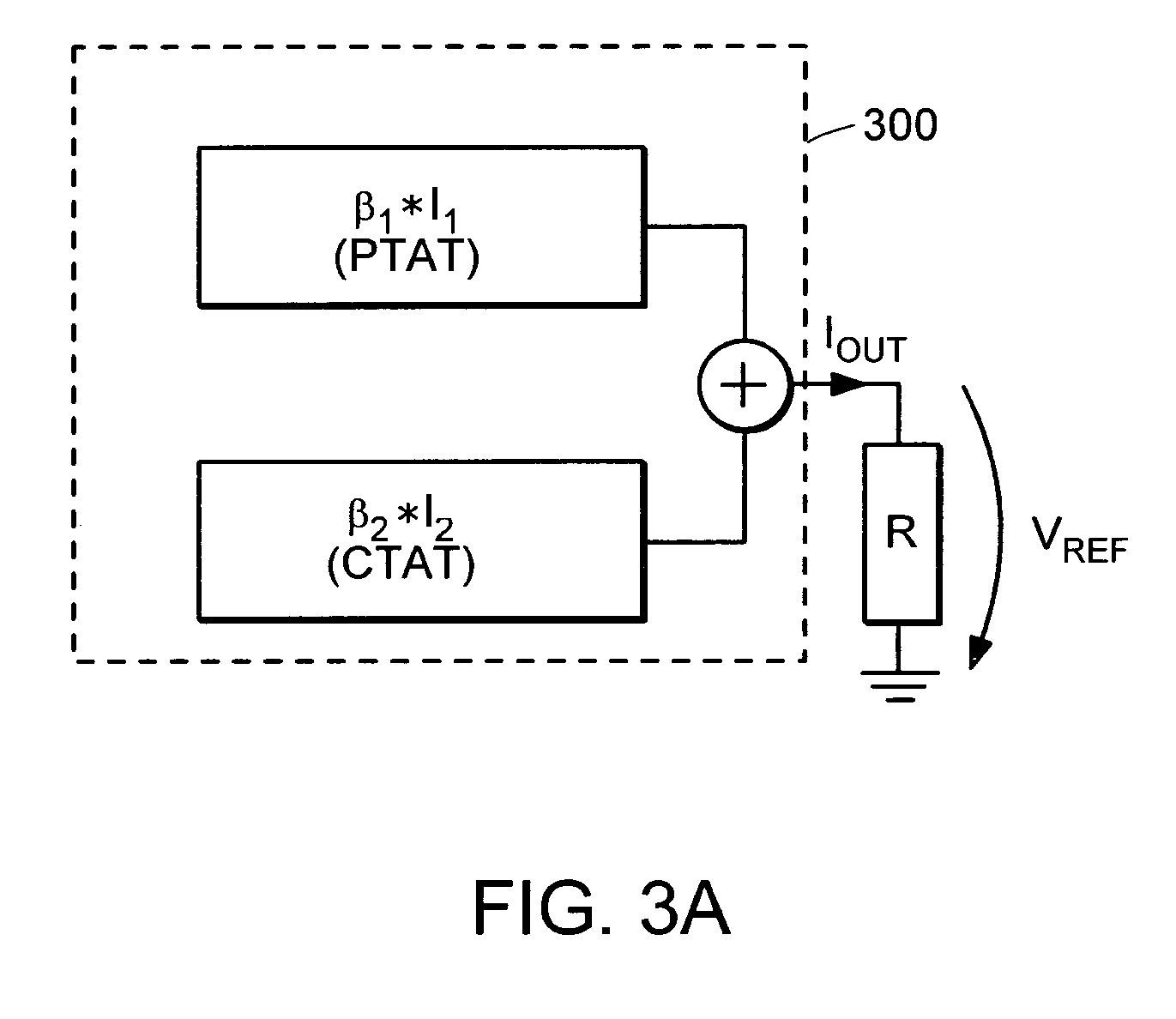

High PSRR, high accuracy, low power supply bandgap circuit

ActiveUS7199646B1Improve accuracyIncrease output impedanceElectric variable regulationAudio power amplifierCascode

A bandgap circuit comprising a current generation circuit and a current replication circuit is provided herein. The output current of the current generation circuit is generated as a weighted sum of two currents. The circuit configuration of the current generation circuit allows it to function at low power supply voltages, e.g., on the order of 1 V. The current replication circuit includes an operational amplifier, which when configured in conjunction with MOS cascode current sources and the current generation circuit, significantly increases the accuracy and insensitivity to power supply noise of the bandgap circuit output current. A resistor may be included between the bandgap circuit output node and ground for generating a reference voltage with increased accuracy and insensitivity to power supply noise.

Owner:MONTEREY RES LLC

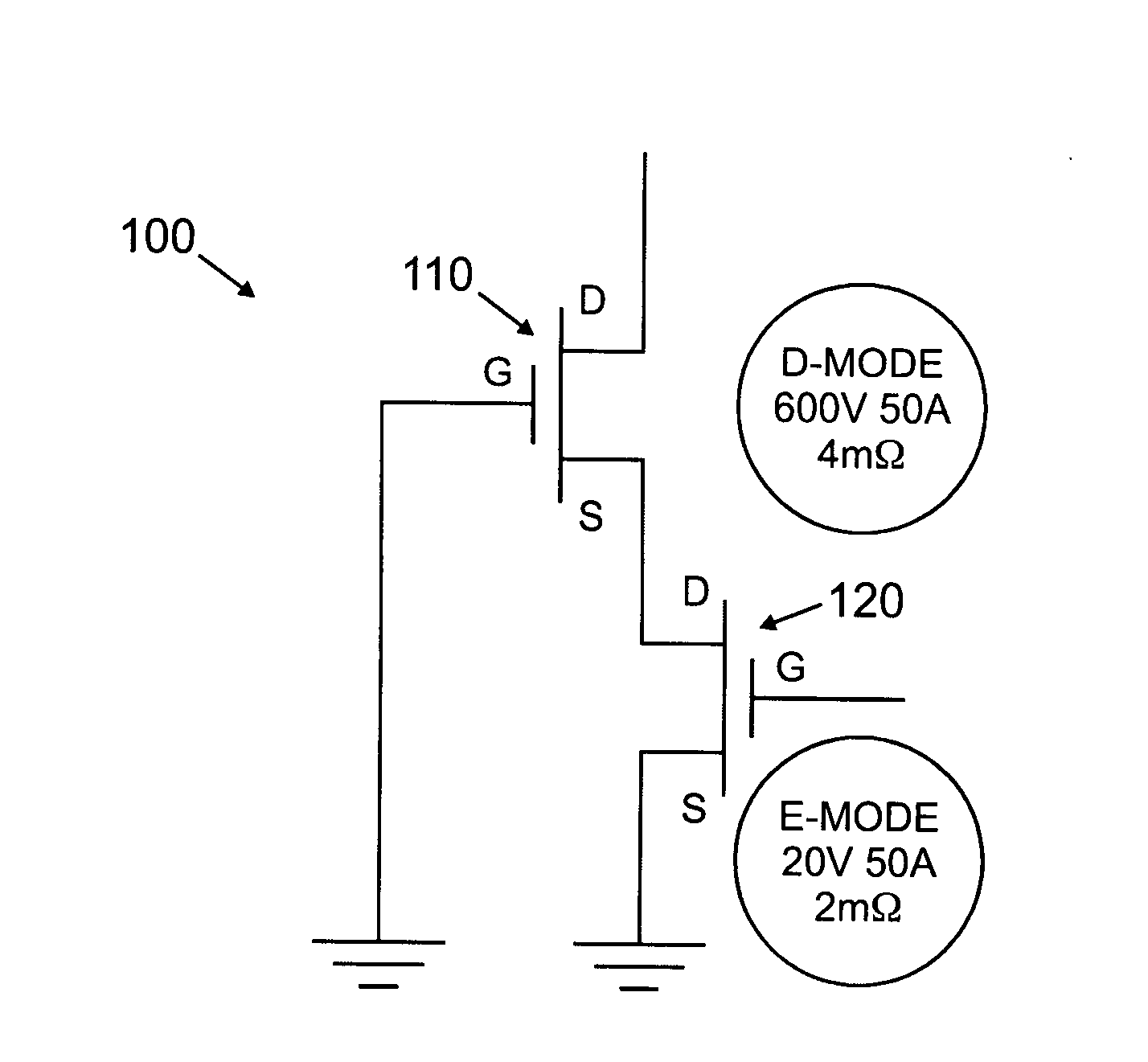

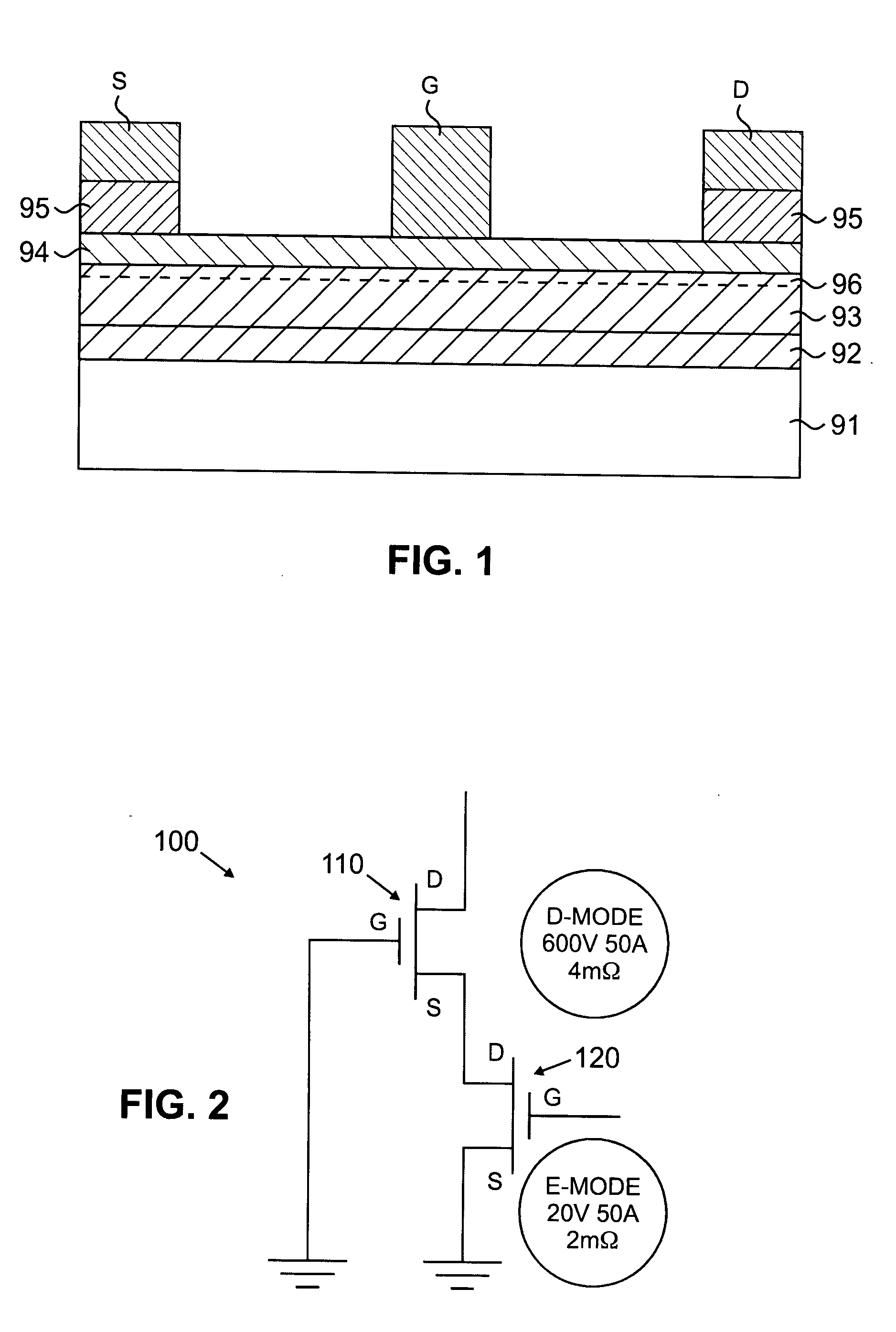

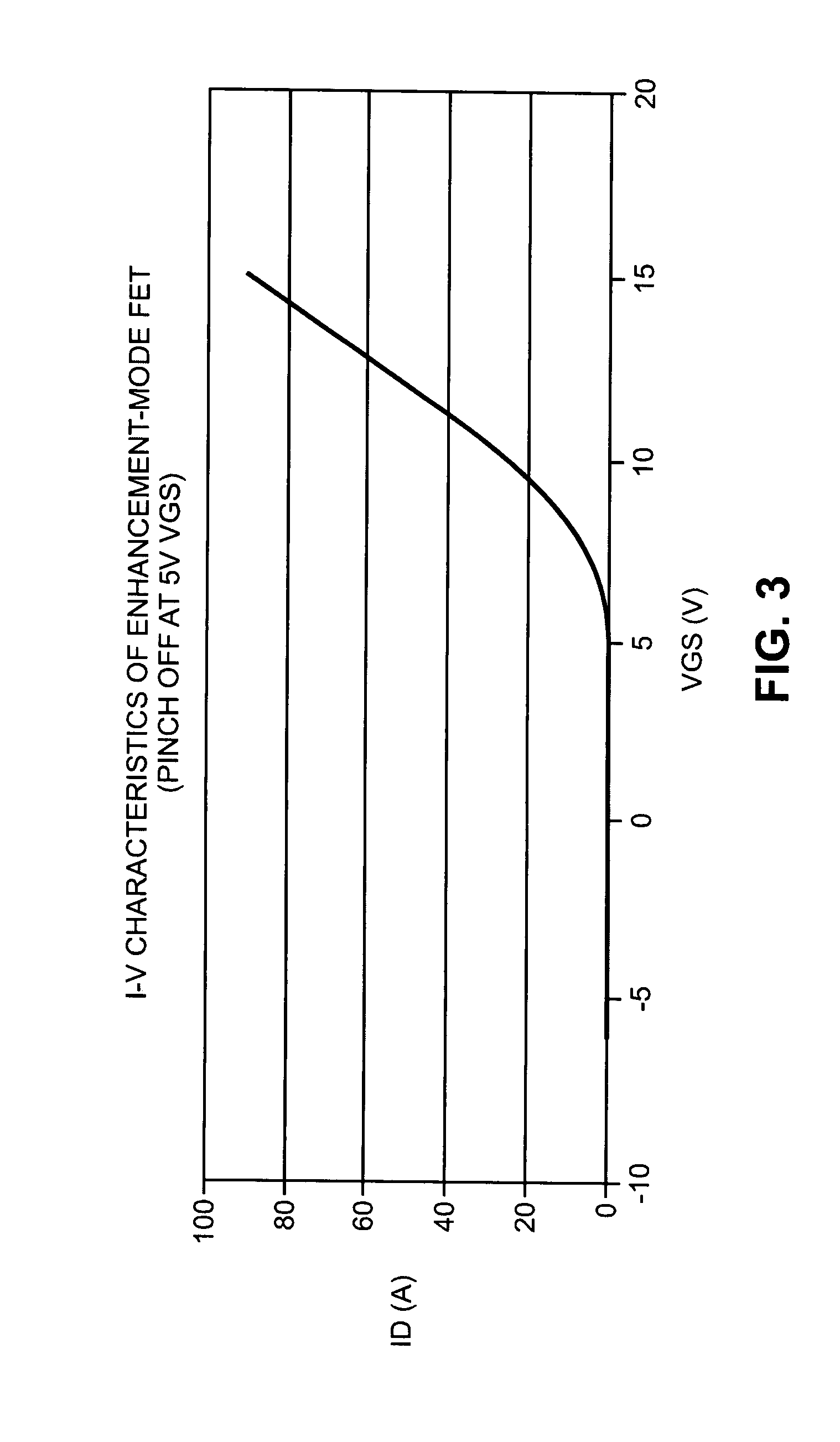

Cascode circuit employing a depletion-mode, GaN-based fet

A circuit includes an input drain, source and gate nodes. The circuit also includes a group III nitride depletion mode FET having a source, drain and gate, wherein the gate of the depletion mode FET is coupled to a potential that maintains the depletion mode FET in its on-state. In addition, the circuit further includes an enhancement mode FET having a source, drain and gate. The source of the depletion mode FET is serially coupled to the drain of the enhancement mode FET. The drain of the depletion mode FET serves as the input drain node, the source of the enhancement mode FET serves as the input source node and the gate of the enhancement mode FET serves as the input gate node.

Owner:POWER INTEGRATIONS INC

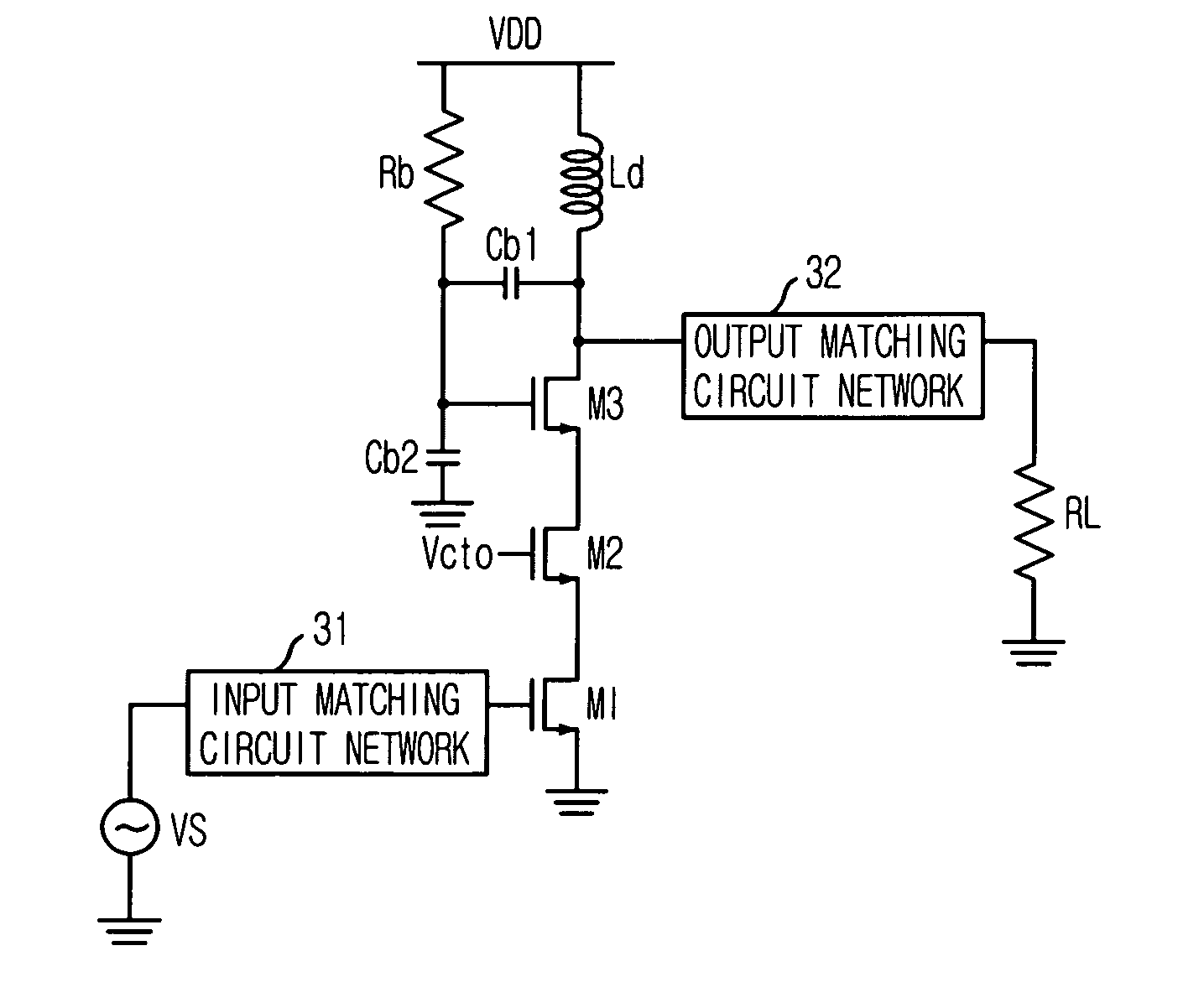

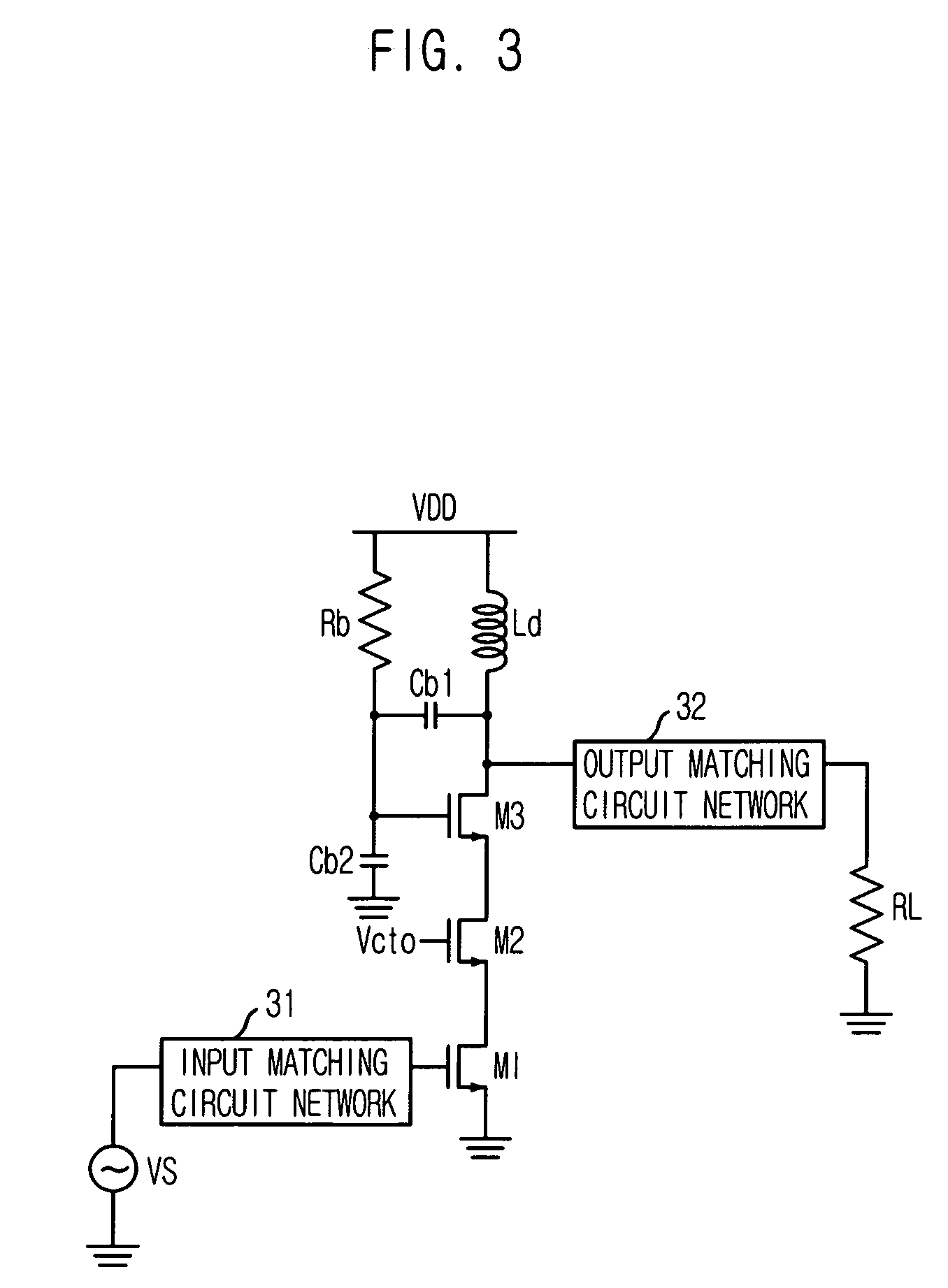

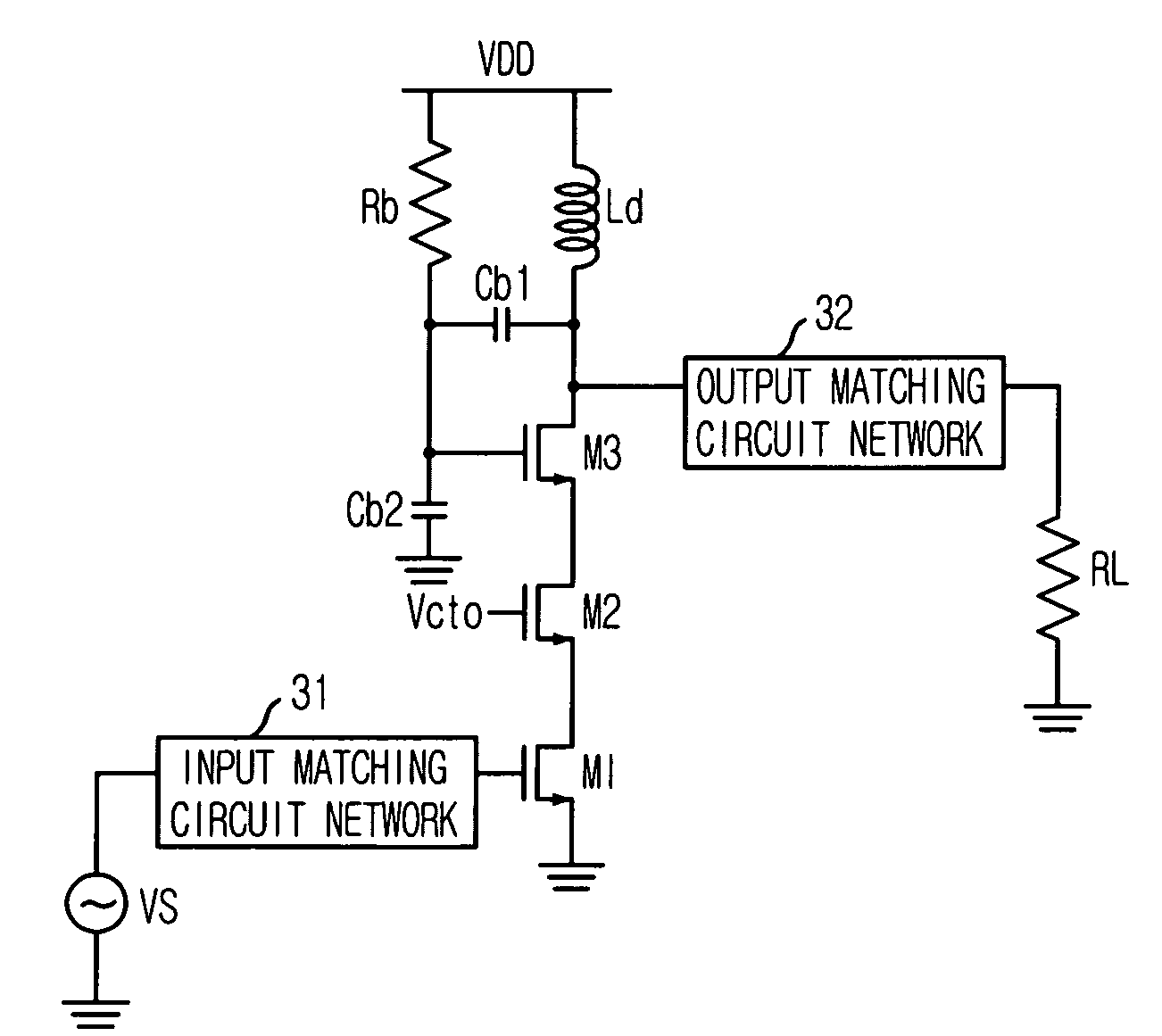

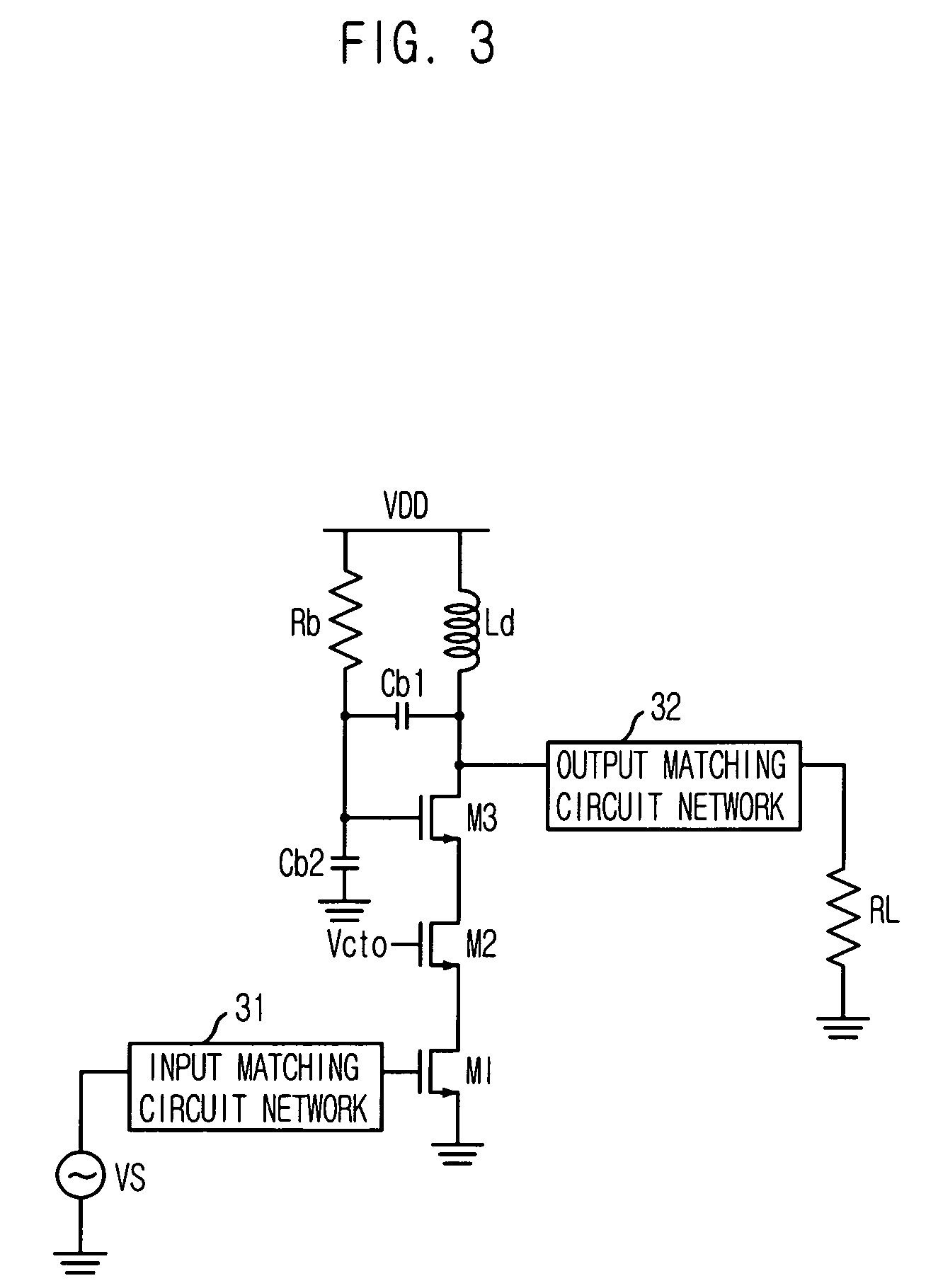

Triple cascode power amplifier of inner parallel configuration with dynamic gate bias technique

InactiveUS20060119435A1Easily embodiedIncrease output powerGated amplifiersAmplifier combinationsAudio power amplifierCascode

Provided is a power amplifier which fits to a deep-submicron technology in radio frequency wireless communication. The power amplifier includes a cascode including a first transistor which receives and amplifies an input signal, and a second transistor which is connected to the first transistor in series and operated by a DC bias voltage; a third transistor which is connected between the cascode and an output end, operated by a dynamic gate bias and outputting a signal; and a voltage divider which includes first and second capacitors that are connected between the output end, i.e. a drain of the third transistor, and a ground in series, and provides the dynamic bias to a gate of the third transistor.

Owner:ELECTRONICS & TELECOMM RES INST

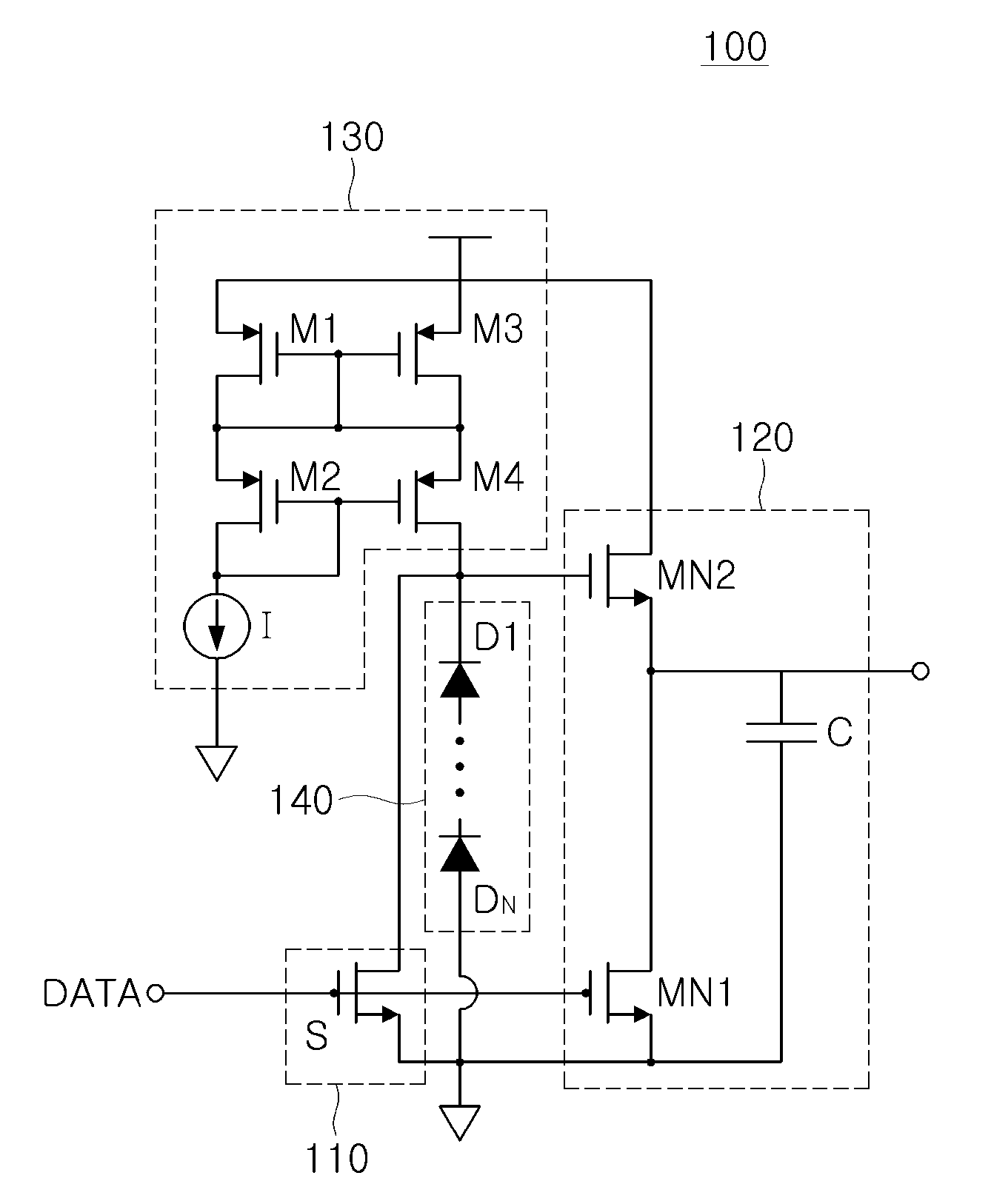

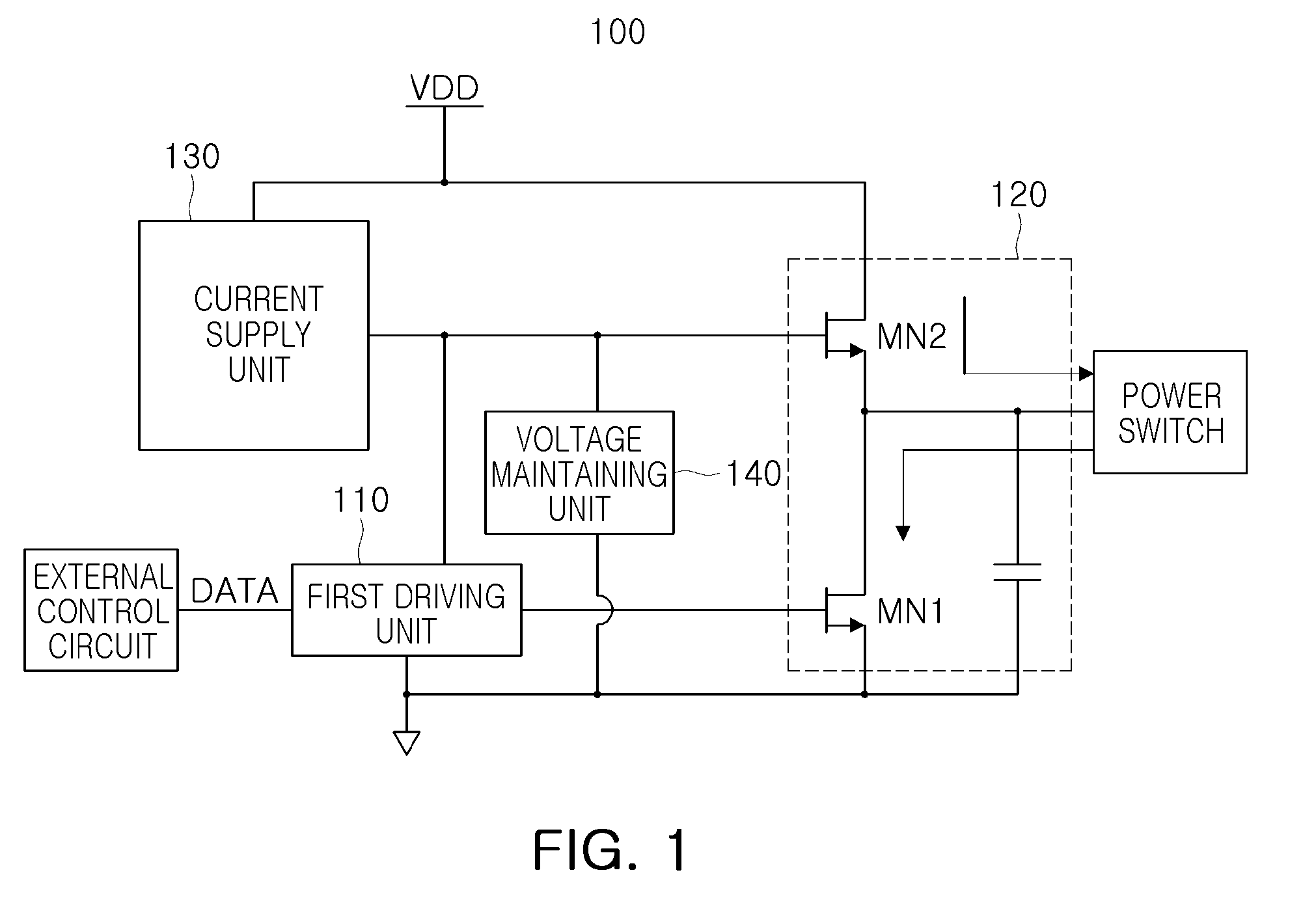

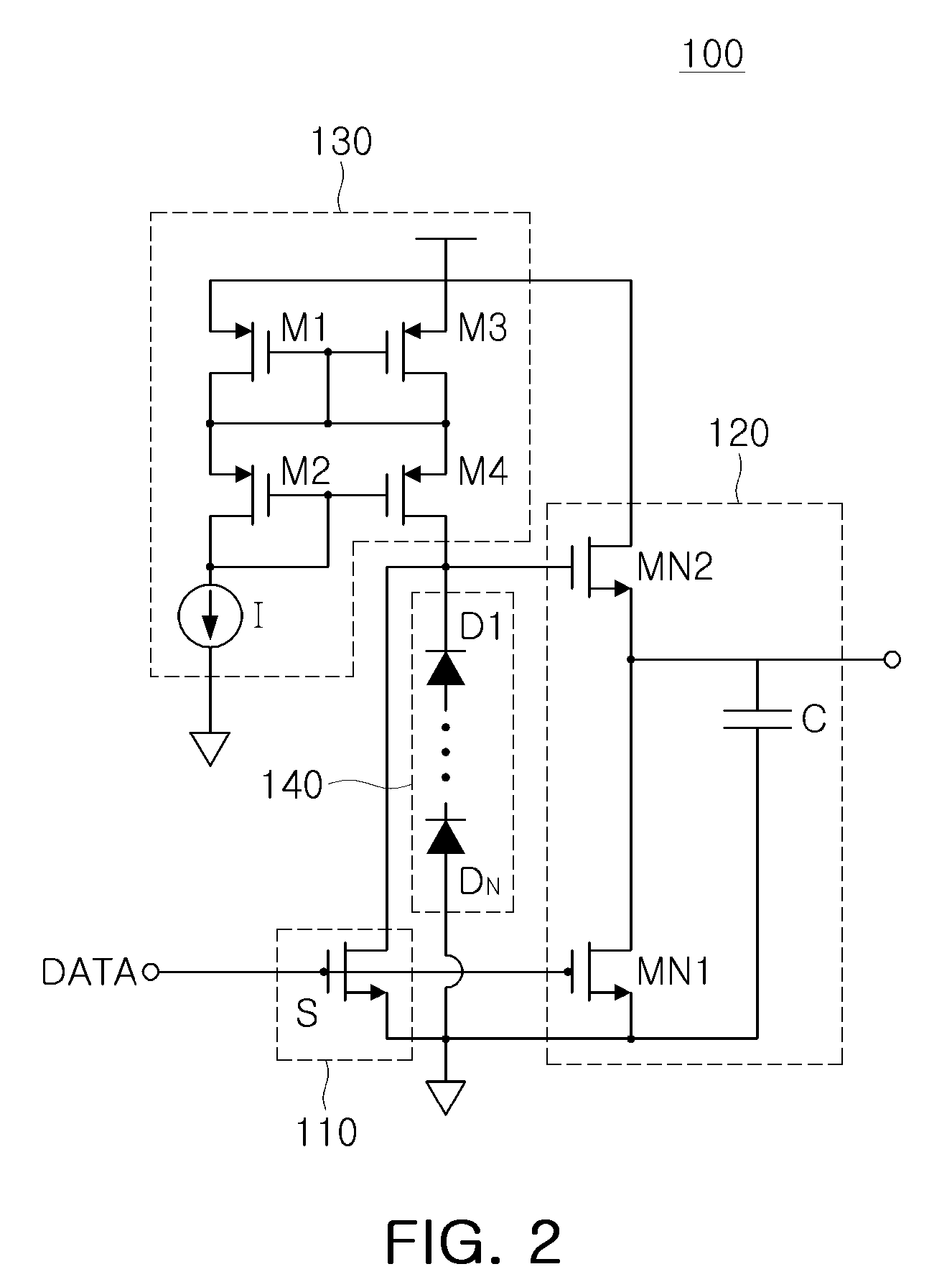

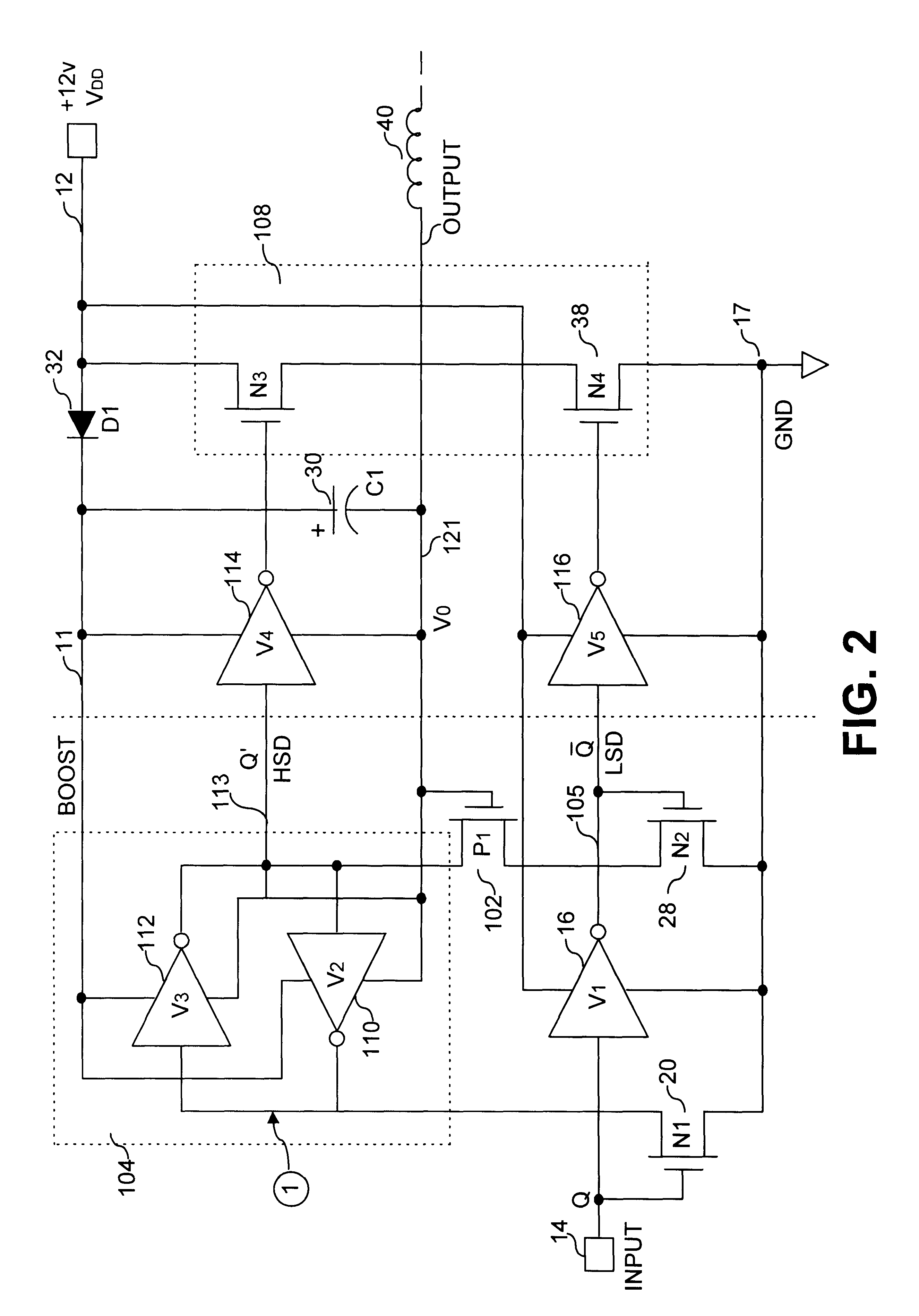

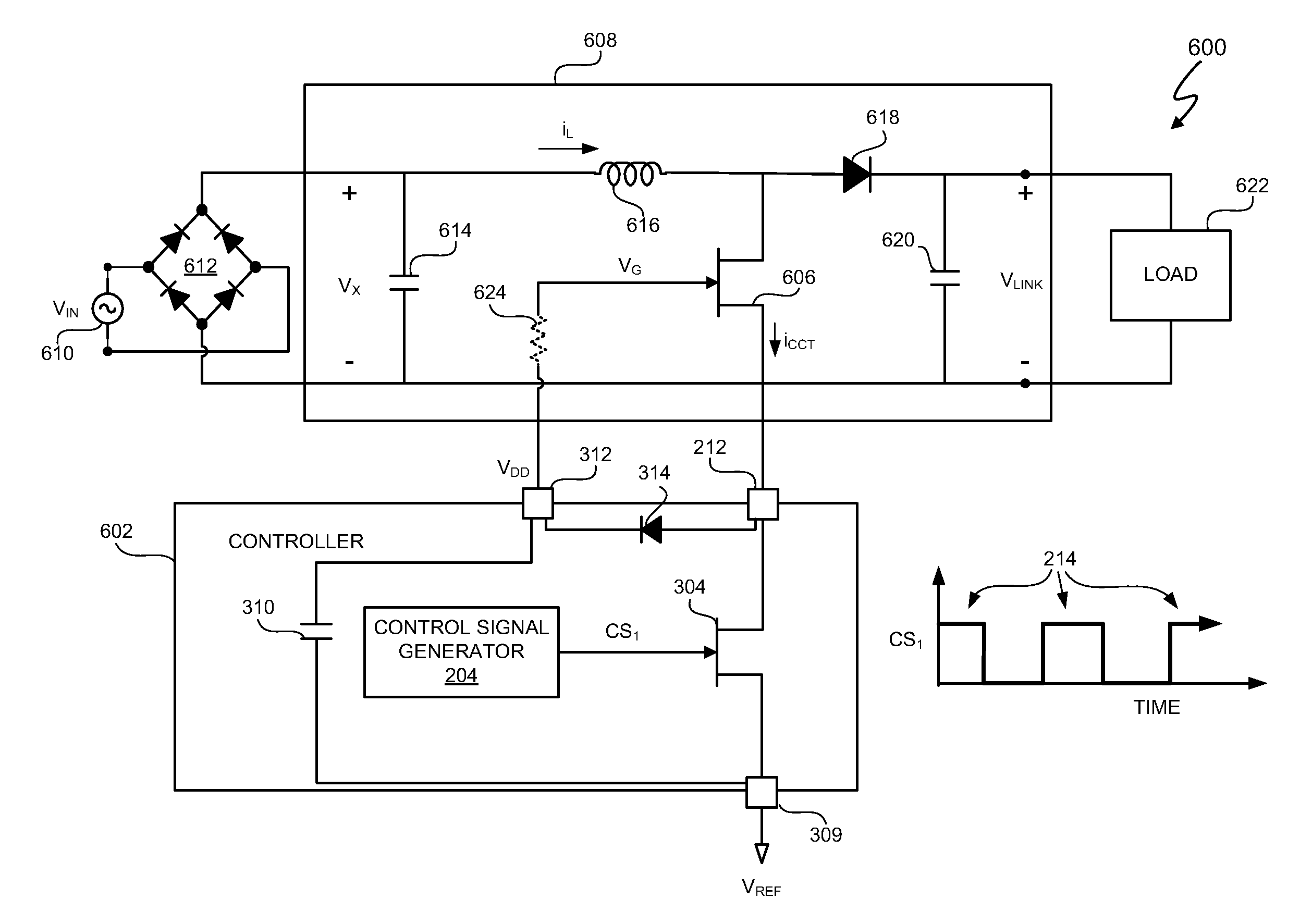

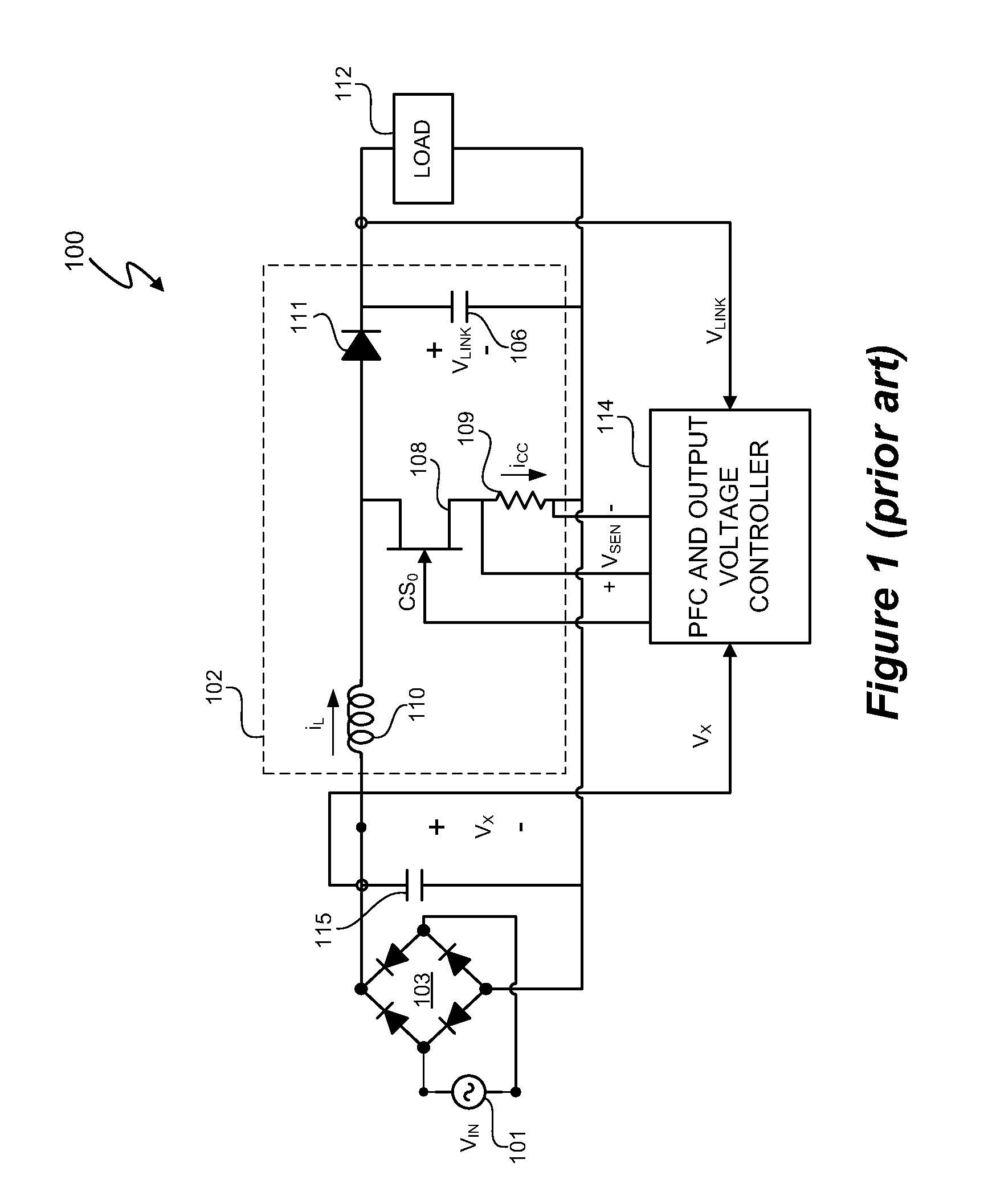

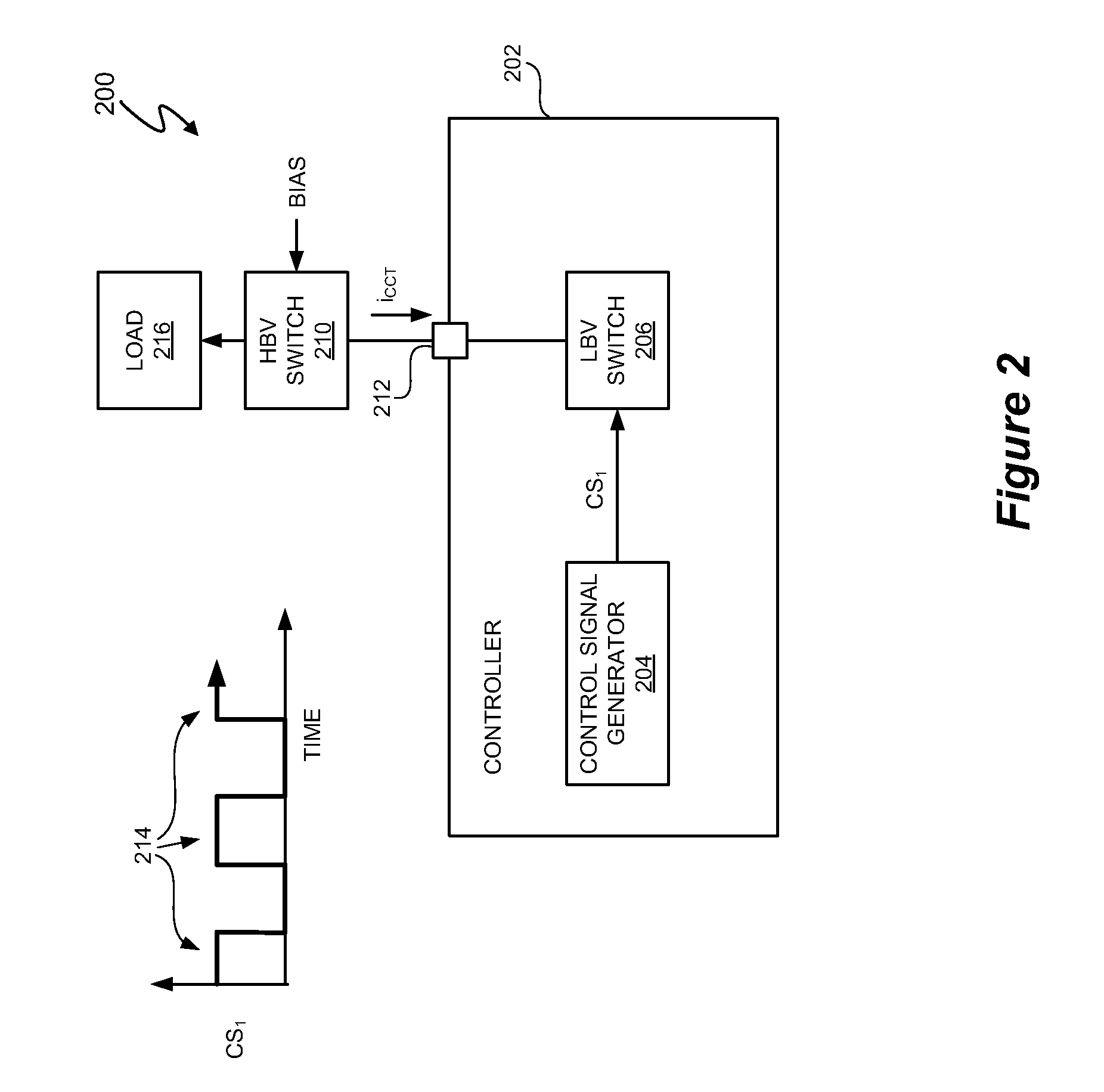

Power switching driving apparatus, and power factor correction device and power supply device having the same

InactiveUS20130163289A1Reduce circuit areaIncrease driving speedEfficient power electronics conversionEnergy industryControl signalPower switching

There are provided a power switching driving apparatus able to reduce a circuit area and increase a driving speed, and a power factor correction device and a power supply device having the same. The power switching driving apparatus includes: a first driving unit providing a switching signal in response to a control signal from the outside; a second driving unit including first and second NMOS FETs cascode-connected between an operational power source terminal supplying pre-set operation power and a ground, and performing switching complimentarily in response to the switching signal to provide a switching control signal controlling power switching; a current supply unit supplying a current for driving the second driving unit; and a voltage maintaining unit maintaining a voltage for driving the second driving unit.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

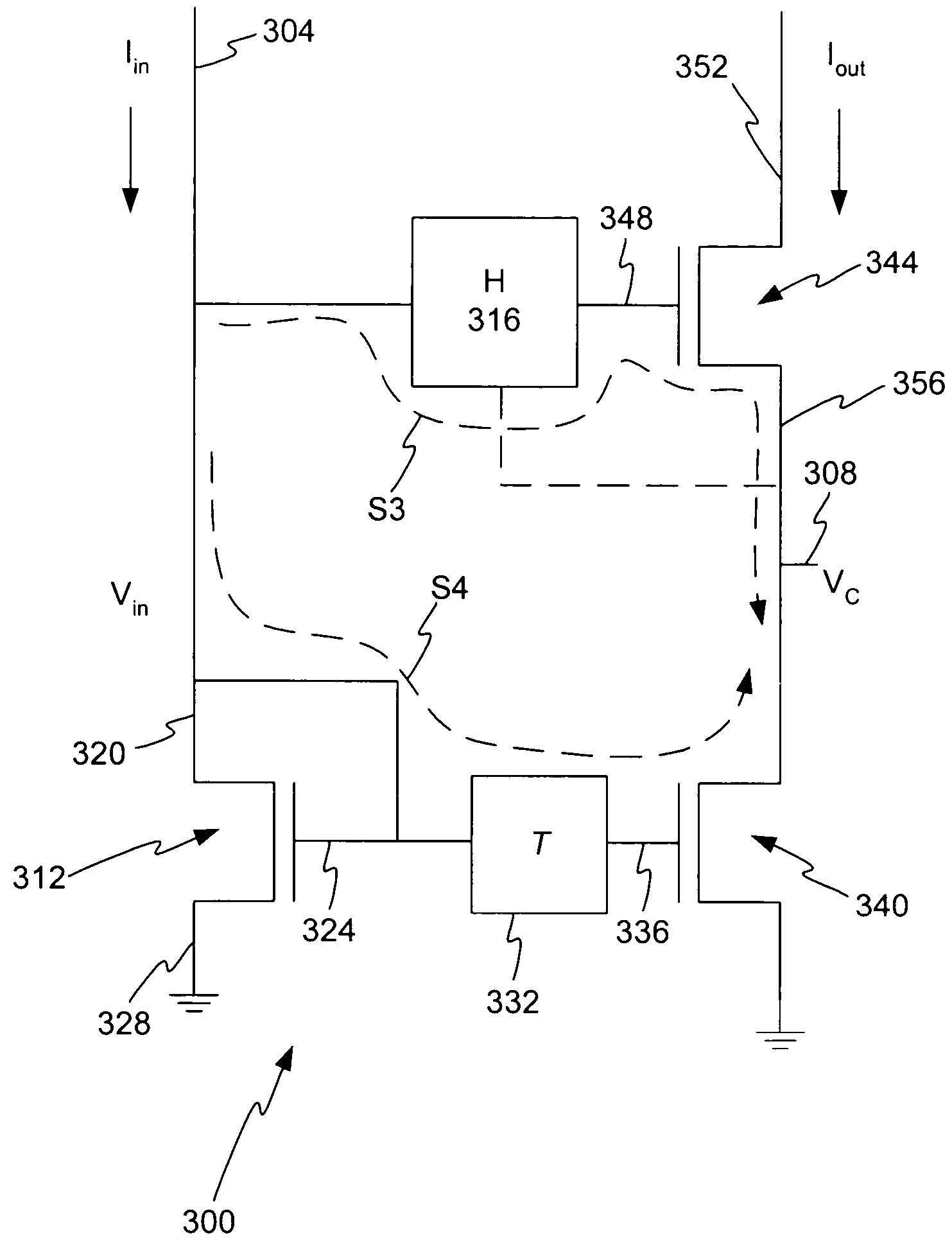

Method and apparatus for increasing the linearity and bandwidth of an amplifier

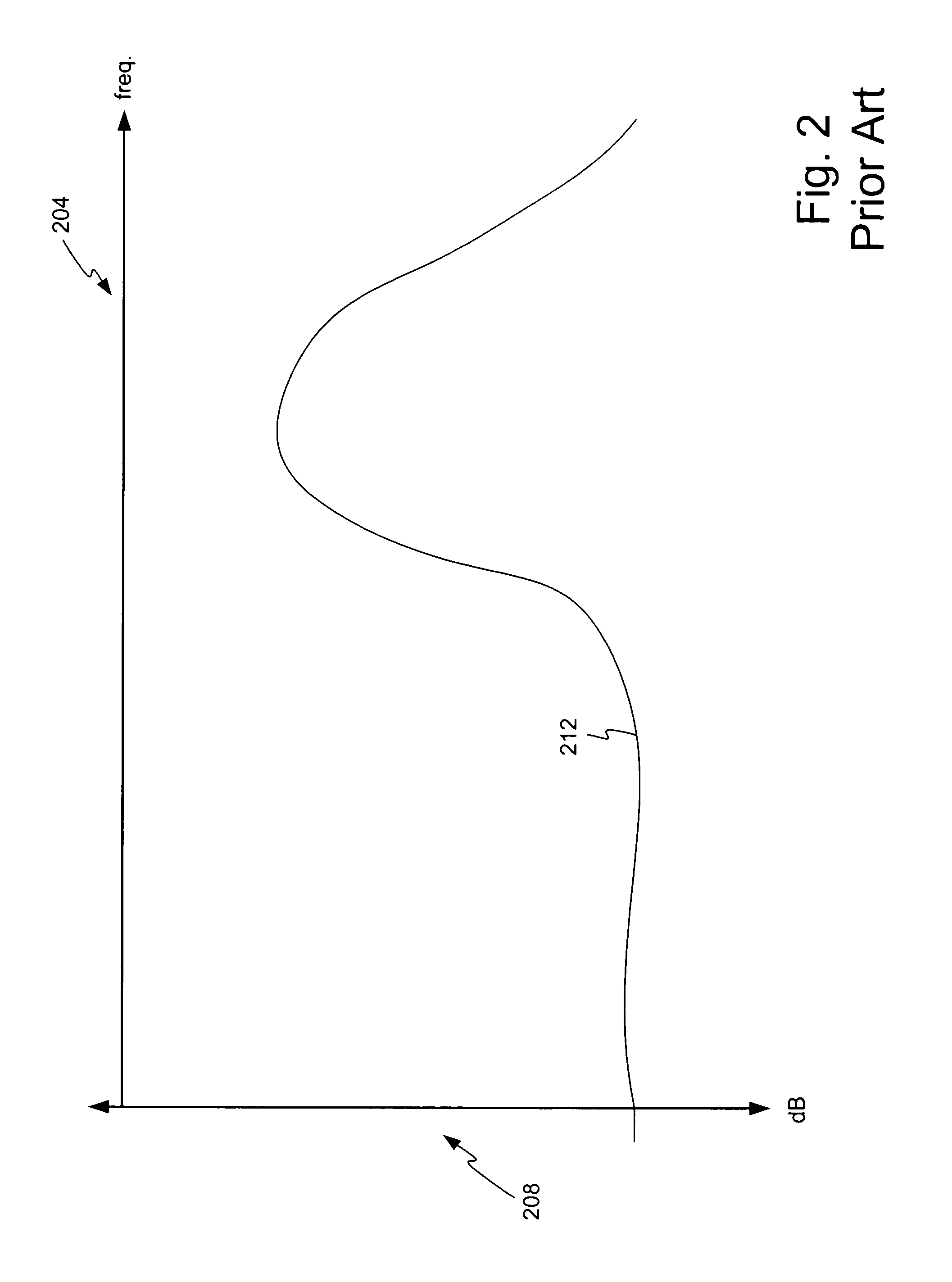

ActiveUS20050083130A1Amplifier modifications to reduce non-linear distortionElectric variable regulationCascodeEngineering

A method and apparatus is disclosed for improving high frequency performance of an amplifier, such as for example, a current mirror. In one embodiment, a delay element is introduced in a current mirror signal path to account for signal propagation delay that may exist in one or more alternative signal paths. The delay element maintains desired phase alignment at a cascade node of the current mirror thereby establishing, in one embodiment, the cascode node (Vc) in an AC ground state. To extend current mirror high frequency capability an embodiment is disclosed having cross-coupled capacitors, active elements, or one or more other devices configured to provide positive feedback to one or more current mirror inputs. The positive feedback may be selectively configured to increase the operational bandwidth of the current mirror.

Owner:MARVELL ASIA PTE LTD

Clamped cascode level shifter circuit

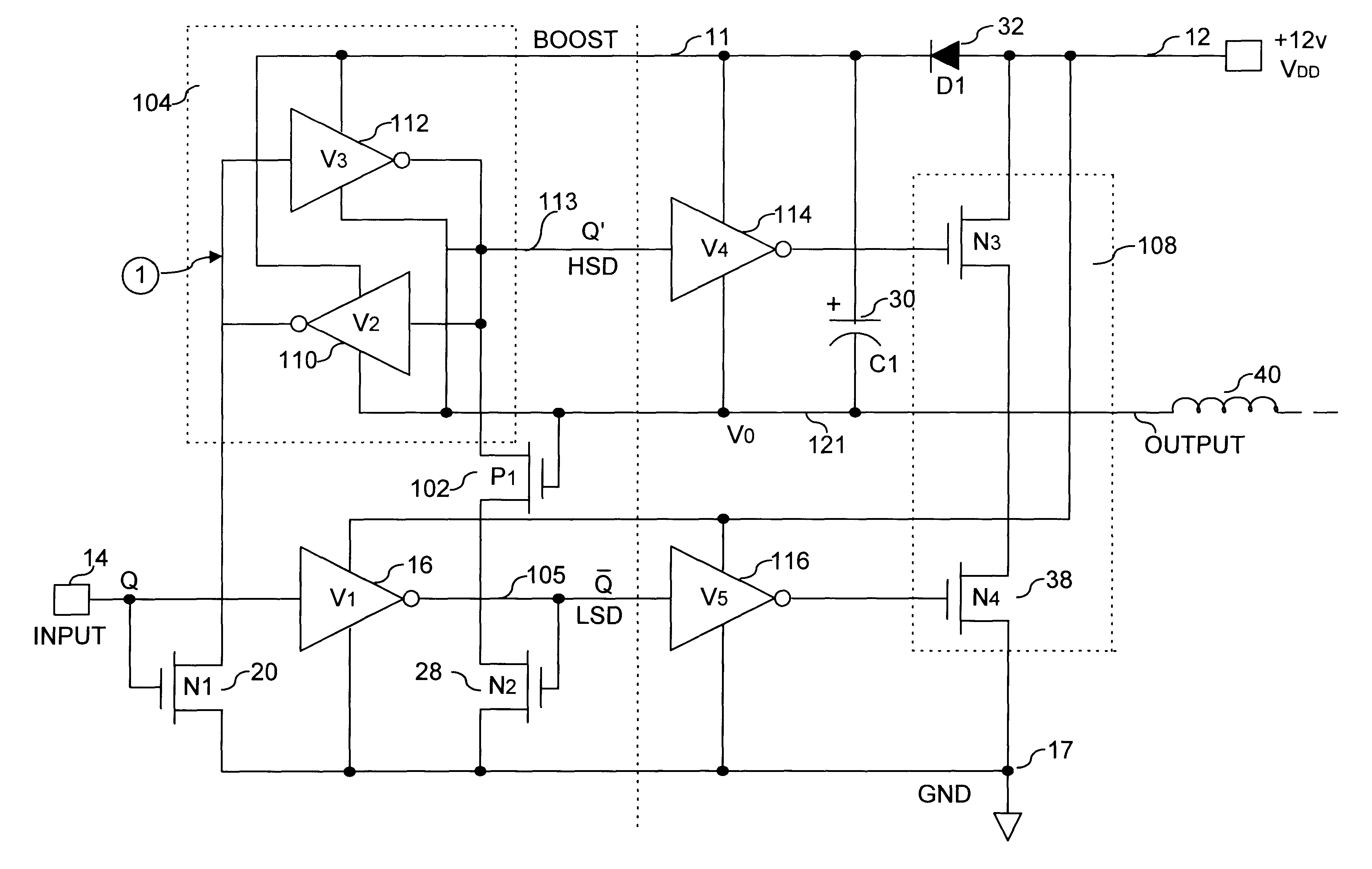

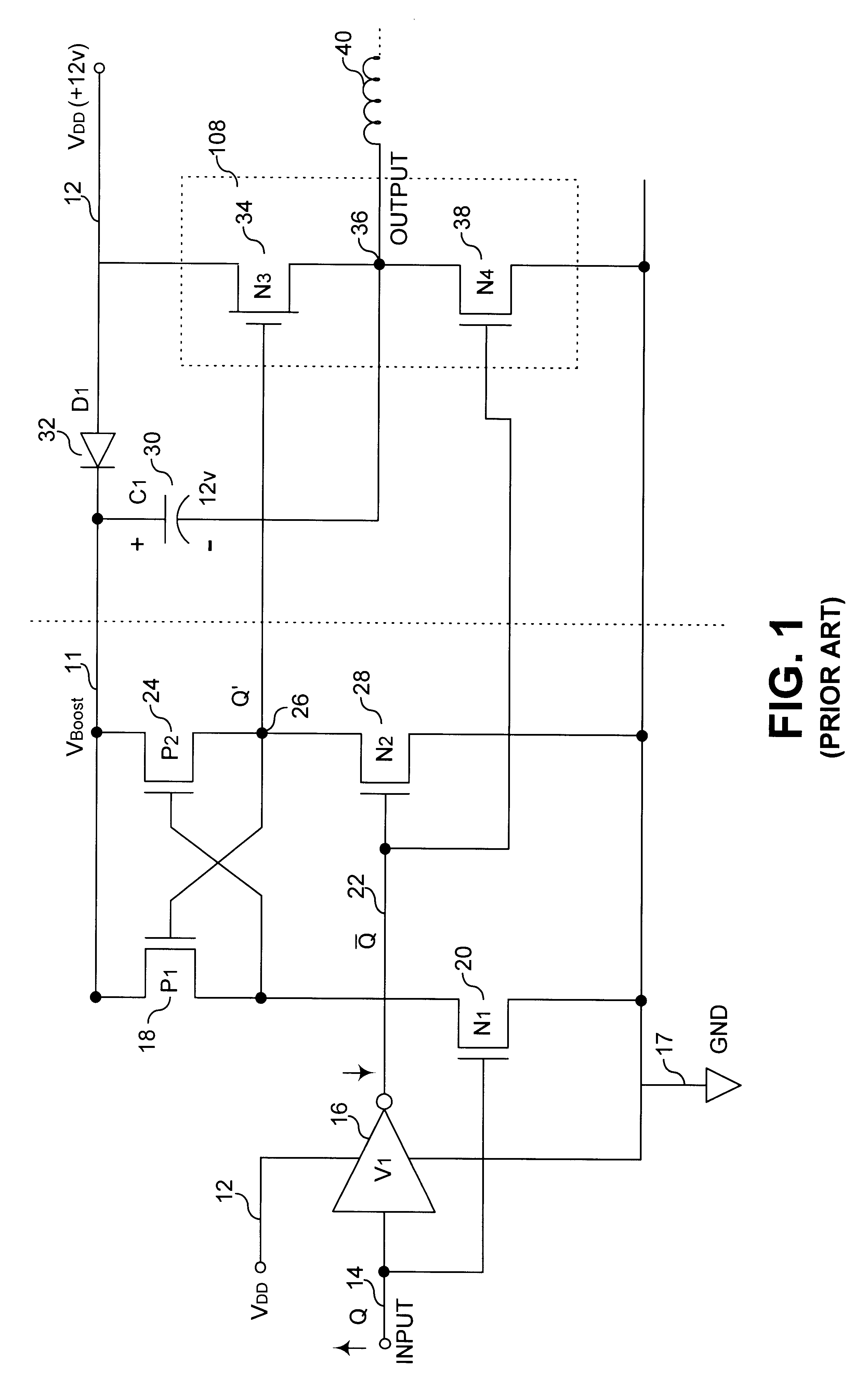

InactiveUS6201429B1Preventing continuous current conductionHysteretic SwitchingPower reduction in field effect transistorsPulse automatic controlCascodeEngineering

An improved level shifter circuit that toggles a "flying Flip-Flop" comprising a cross-coupled inverter pair with control devices driven out of phase through a pair of cascode transistors. The cross-coupled inverter pair provides pull-up to the positive rail, clamping to a High Side-Common (HSC), and providing Hysteretic Switching. The cascode transistors restrict the pull-down of the control devices, thereby preventing continuous current conduction.

Owner:AME

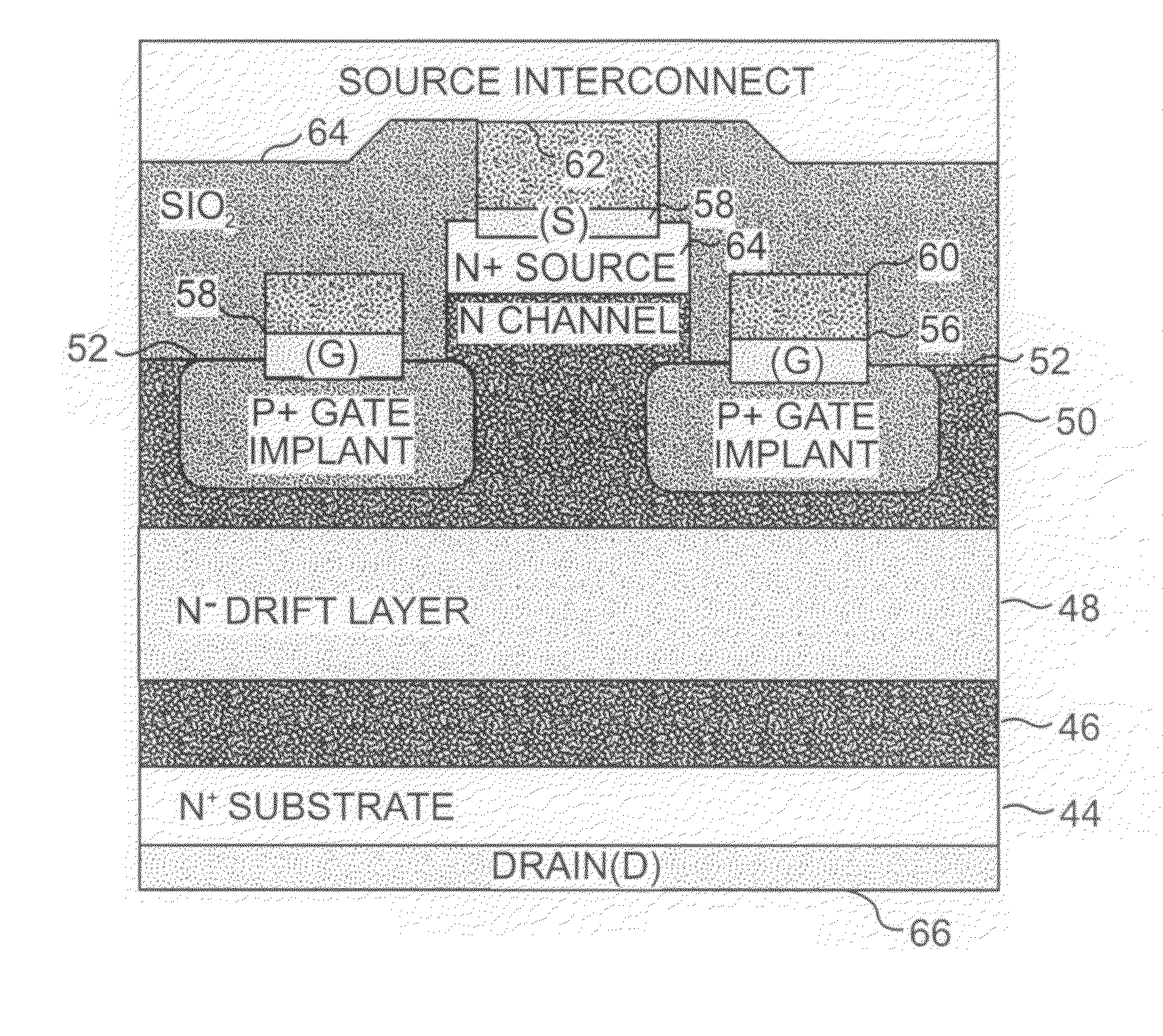

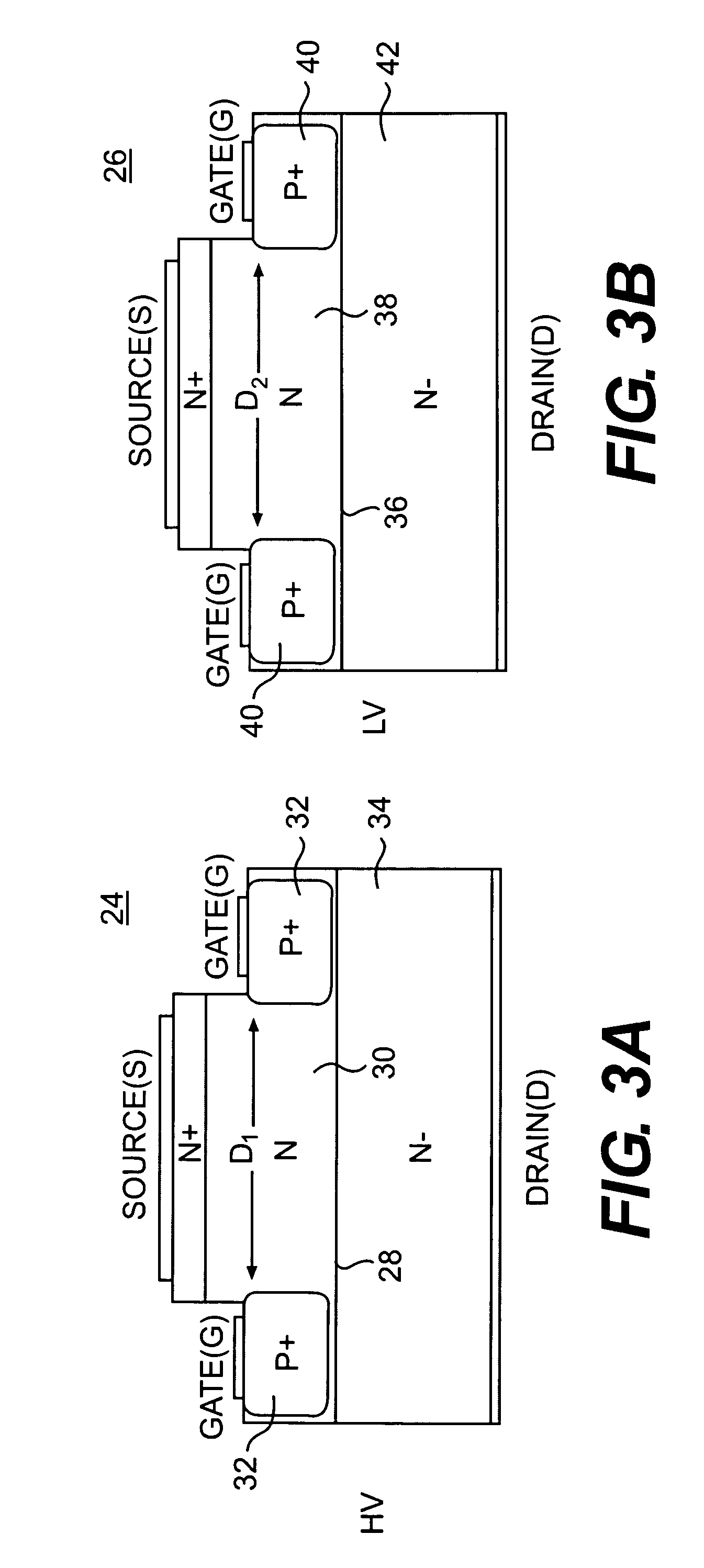

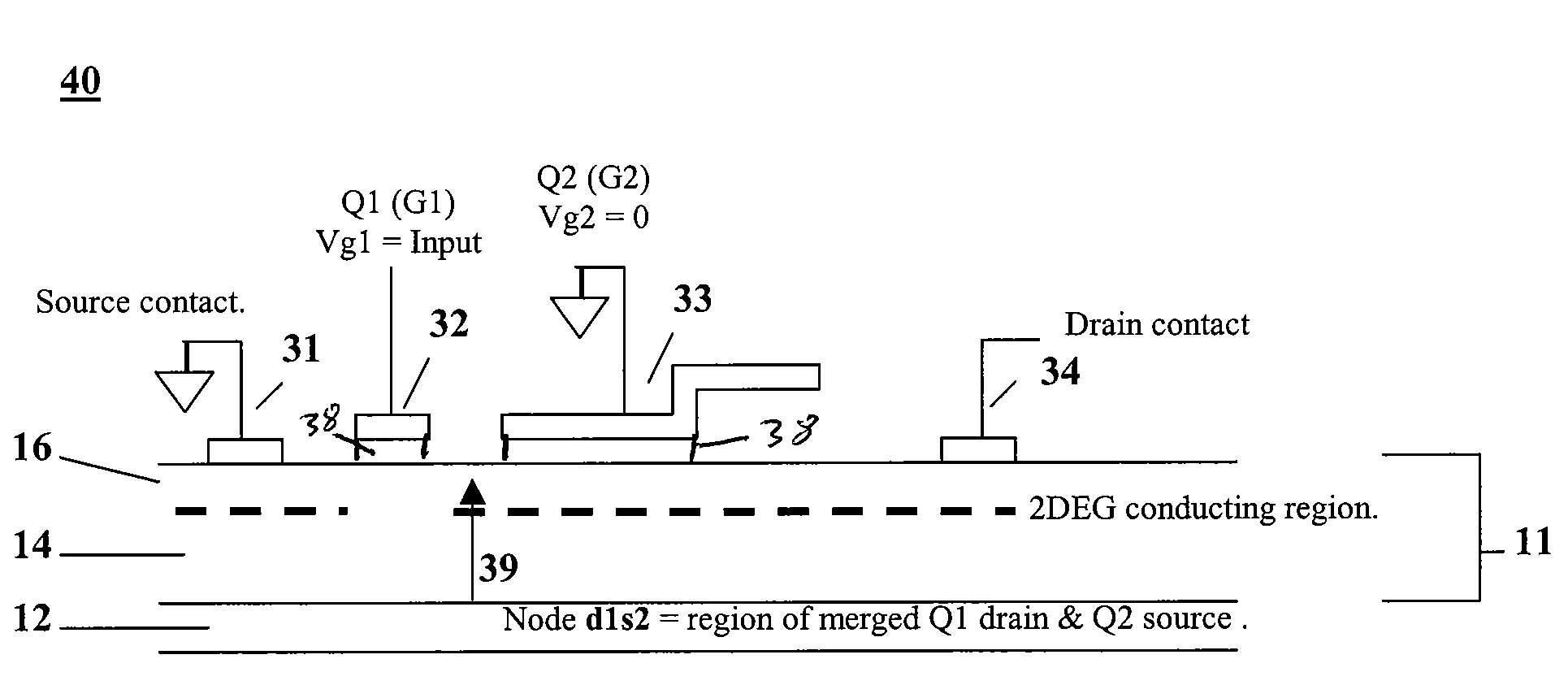

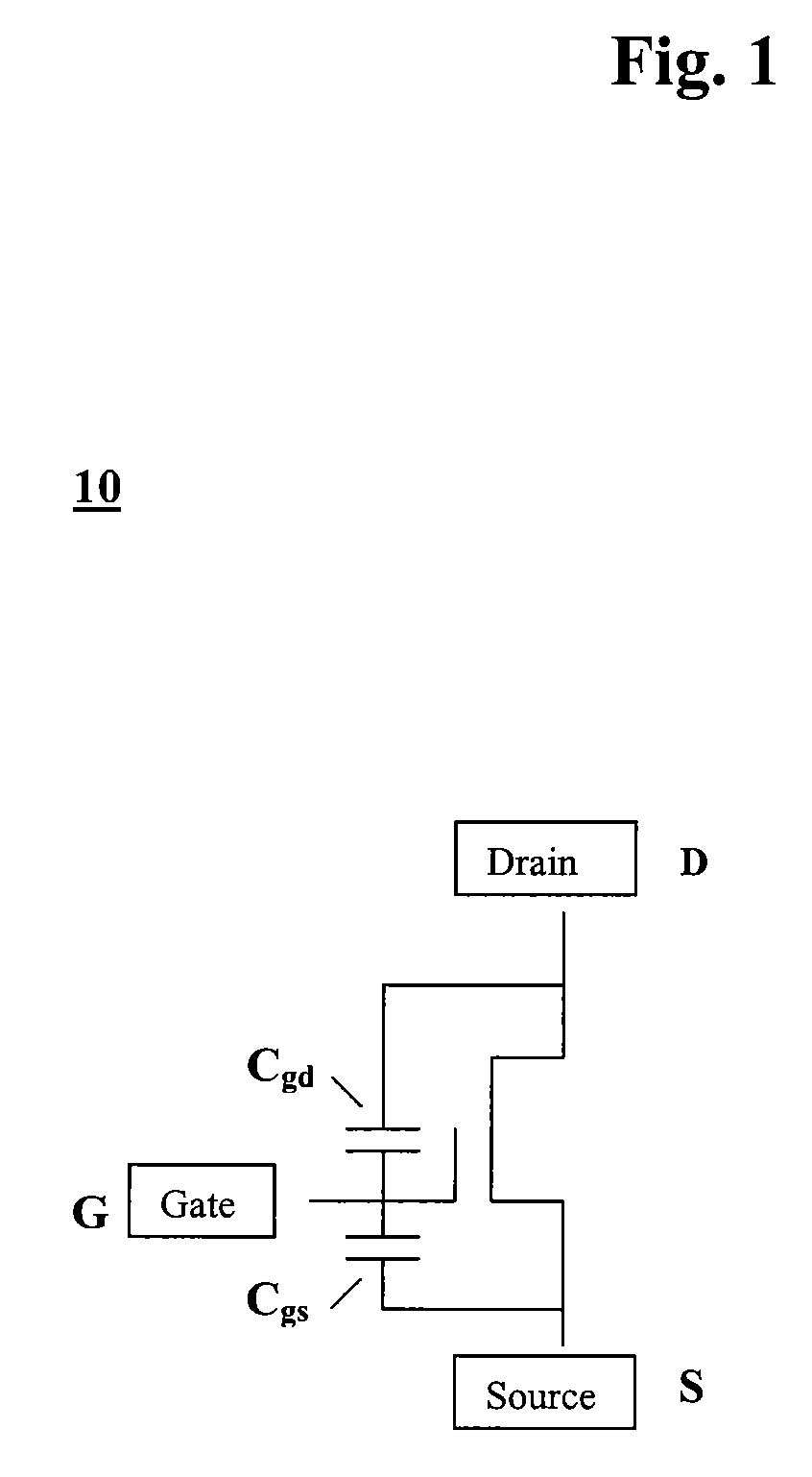

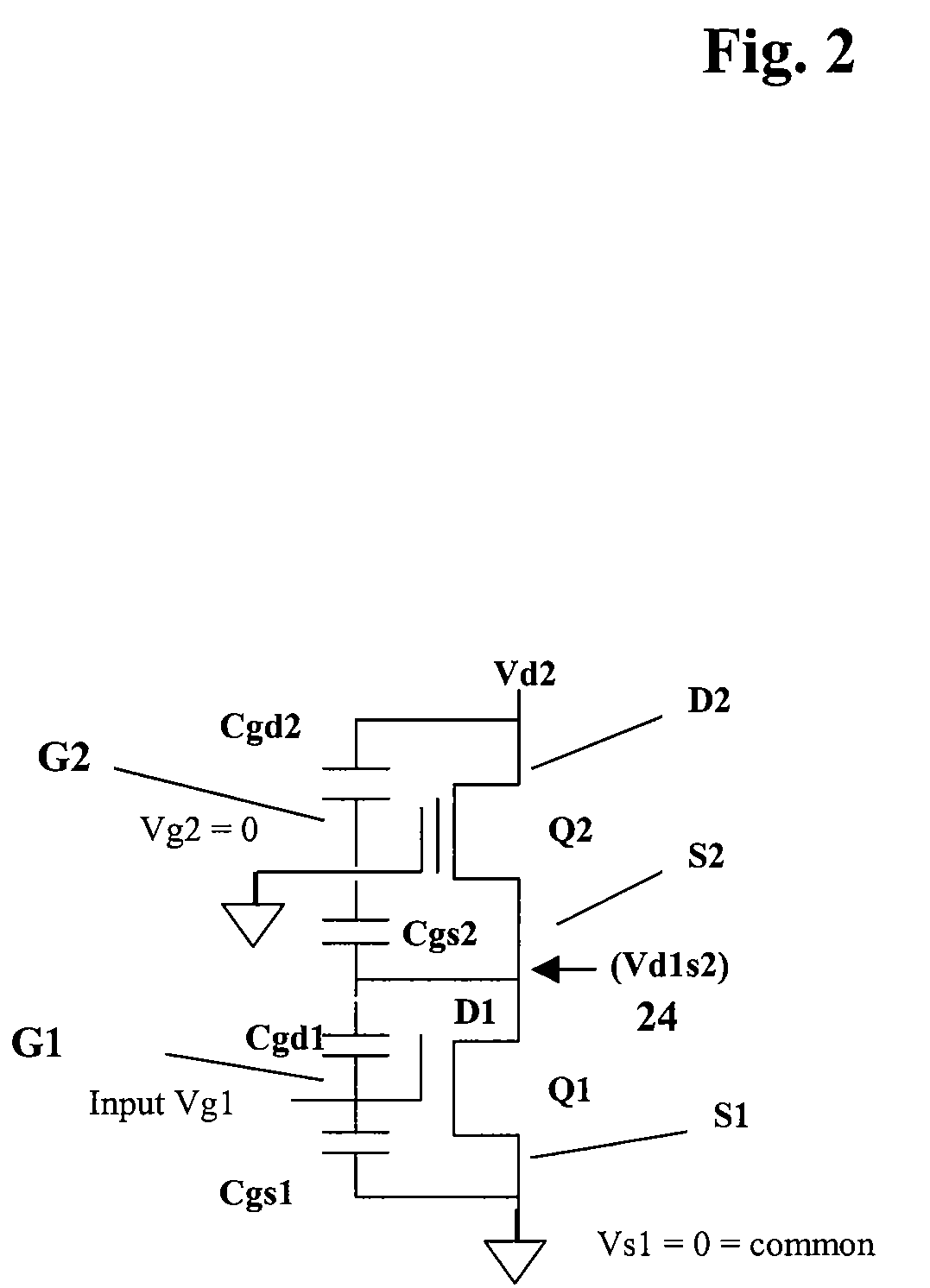

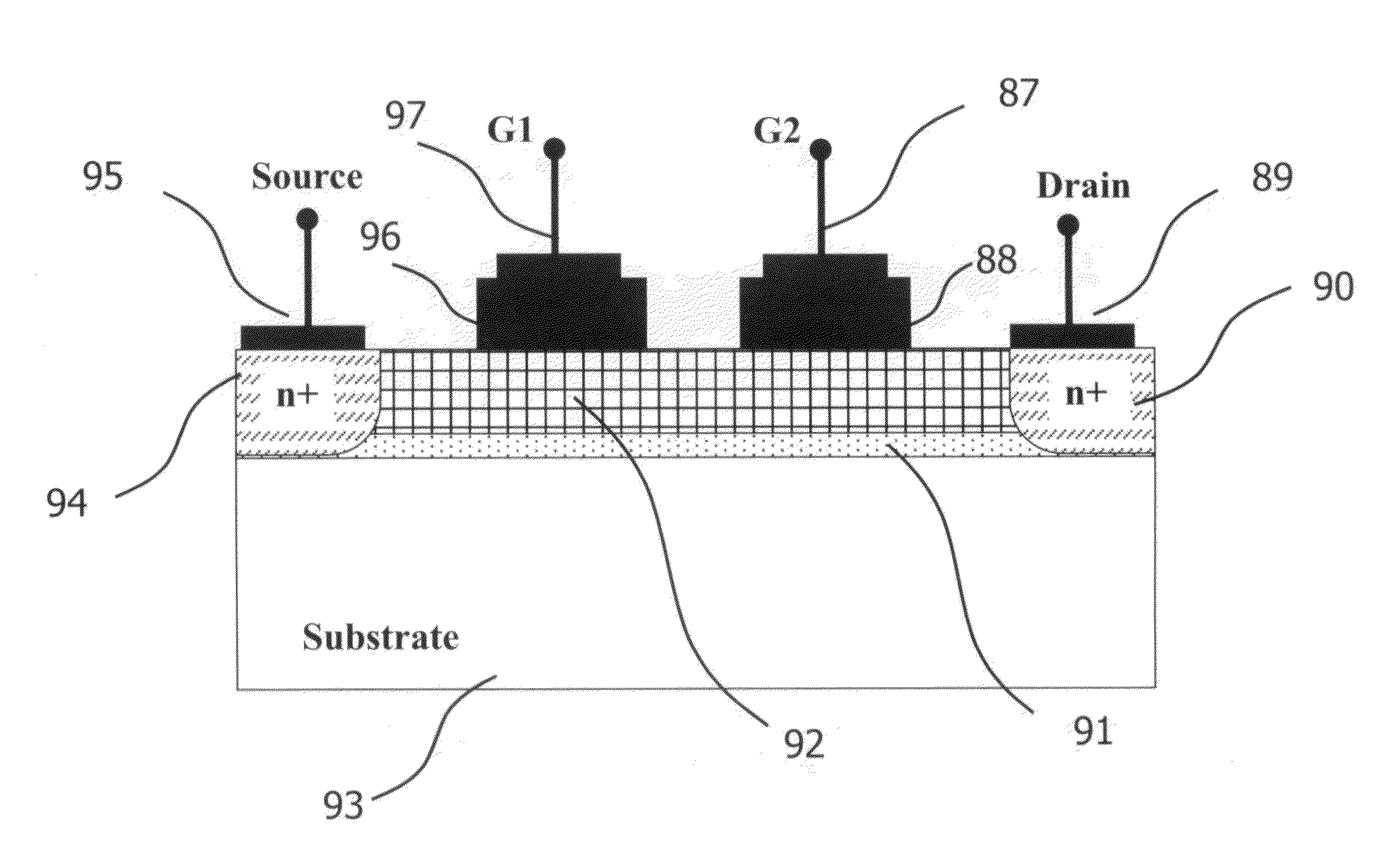

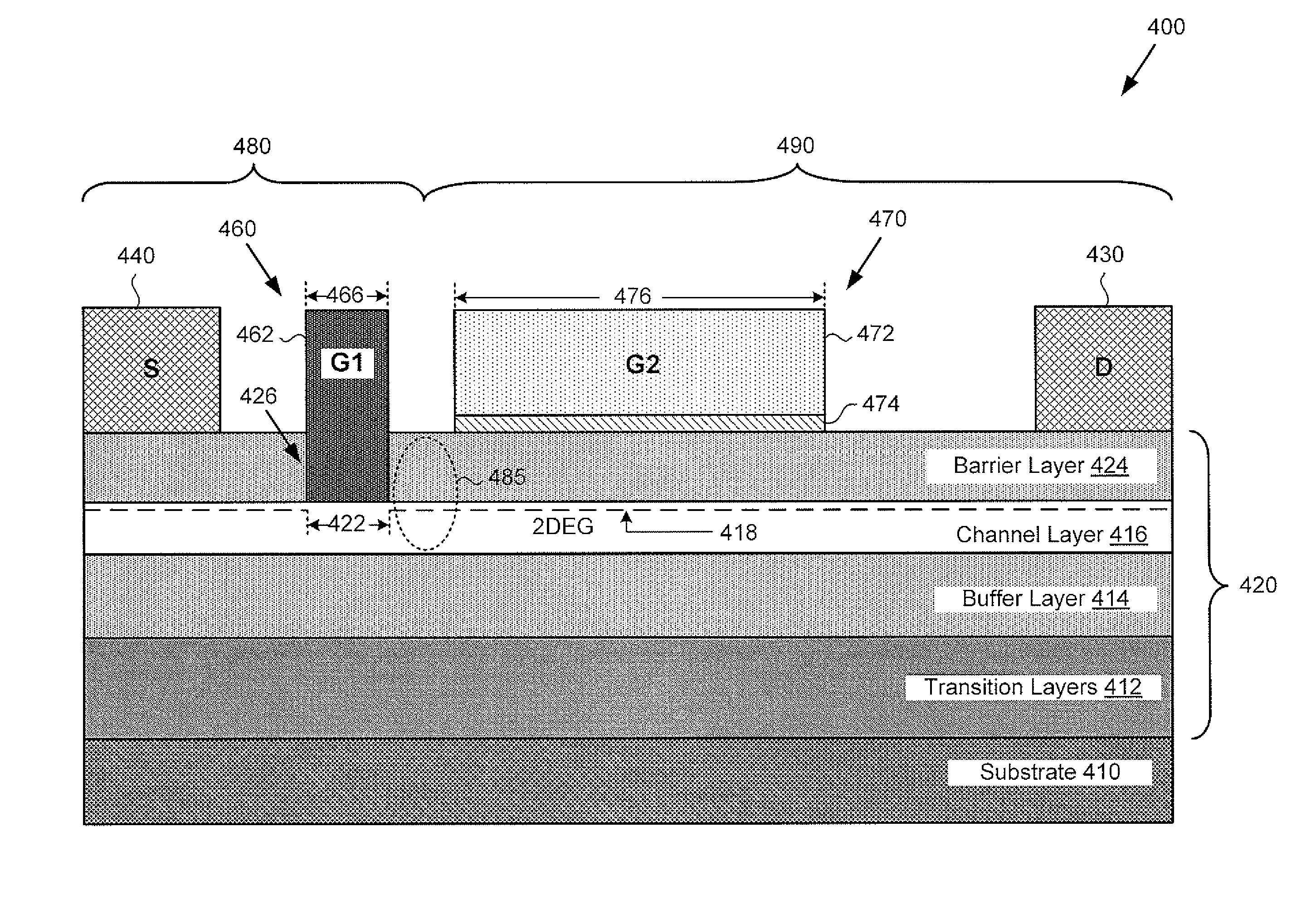

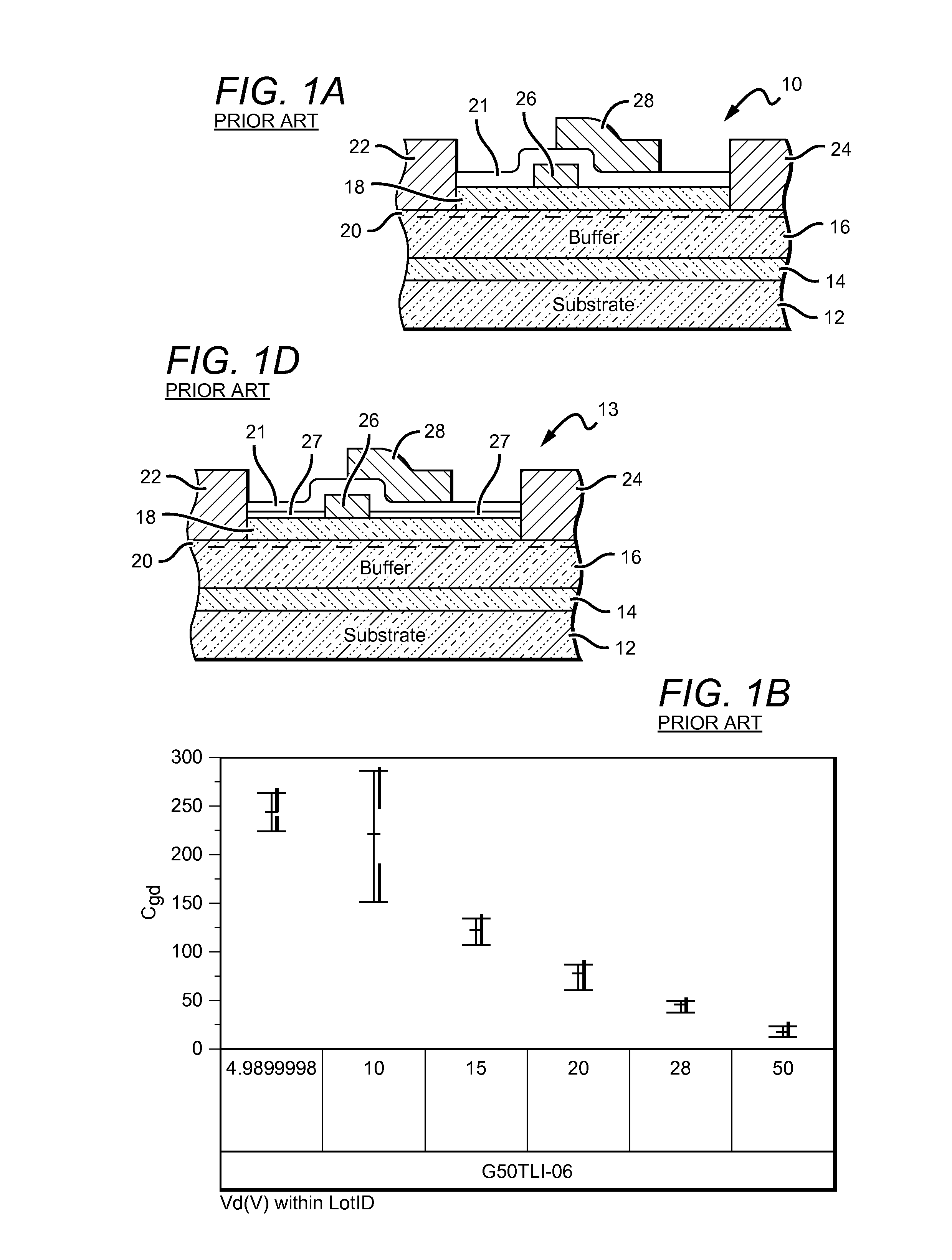

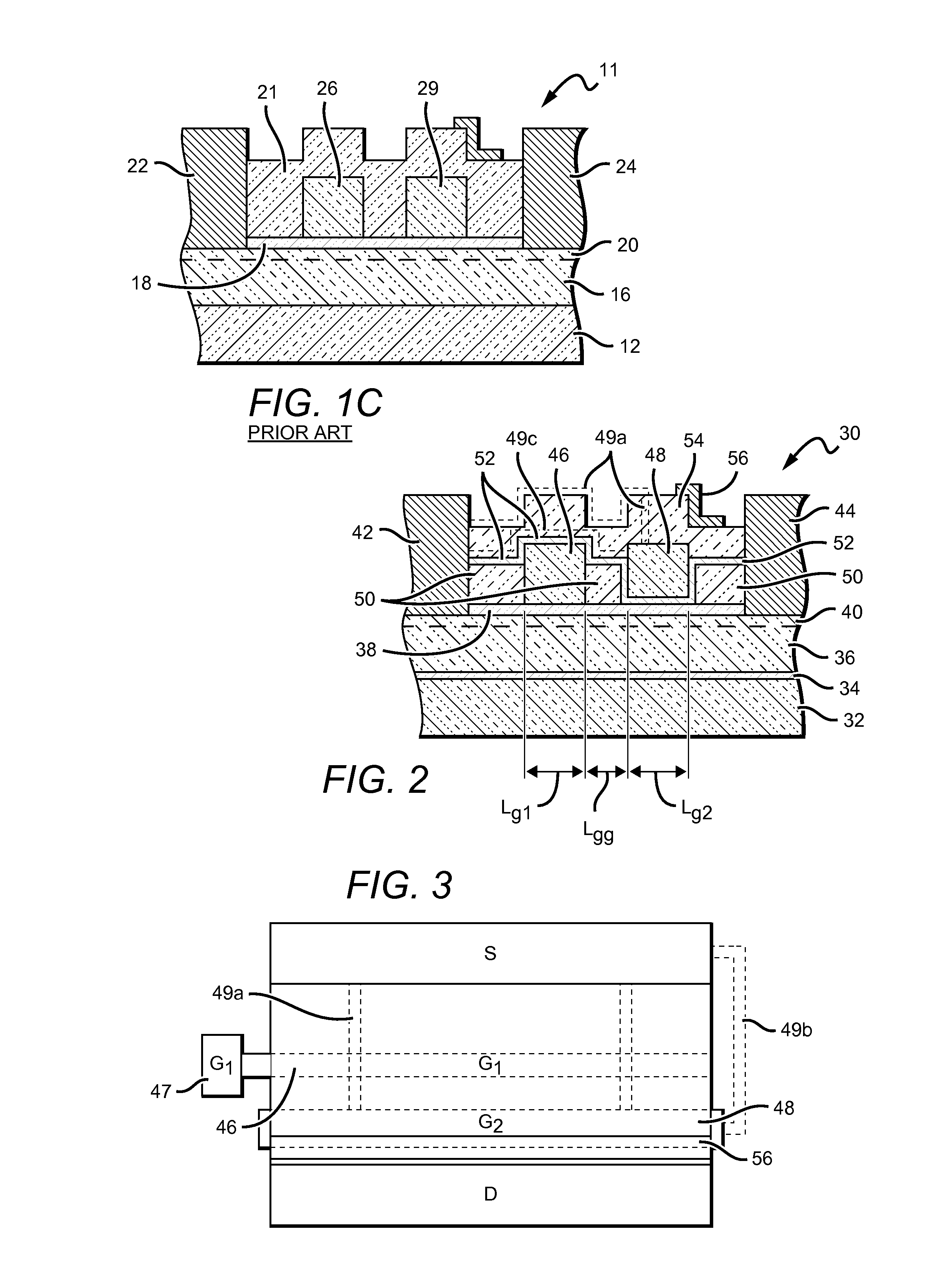

Merged gate cascode transistor

ActiveUS20070215899A1High electron mobilityThyristorSolid-state devicesCapacitanceCapacitive coupling

A merged gate transistor in accordance with an embodiment of the present invention includes a semiconductor element, a supply electrode electrically connected to a top surface of the semiconductor element, drain electrode electrically connected to the top surface of the semiconductor element and spaced laterally away from the supply electrode, a first gate positioned between the supply electrode and the drain electrode and capacitively coupled to the semiconductor element to form a first portion of the transistor and a second gate positioned adjacent to the first gate, and between the supply electrode and the drain electrode to form a second portion of the transistor, wherein the second gate is also capacitively coupled to the semiconductor element. The first gate is connected to an input voltage signal such that conduction of the first portion is based on a value of the input voltage signal and the second gate is connected to a predetermined constant voltage such that the second portion of the transistor conducts until a voltage difference between the predetermined constant voltage and a voltage at the source electrode reaches a predetermined level.

Owner:INFINEON TECH AMERICAS CORP

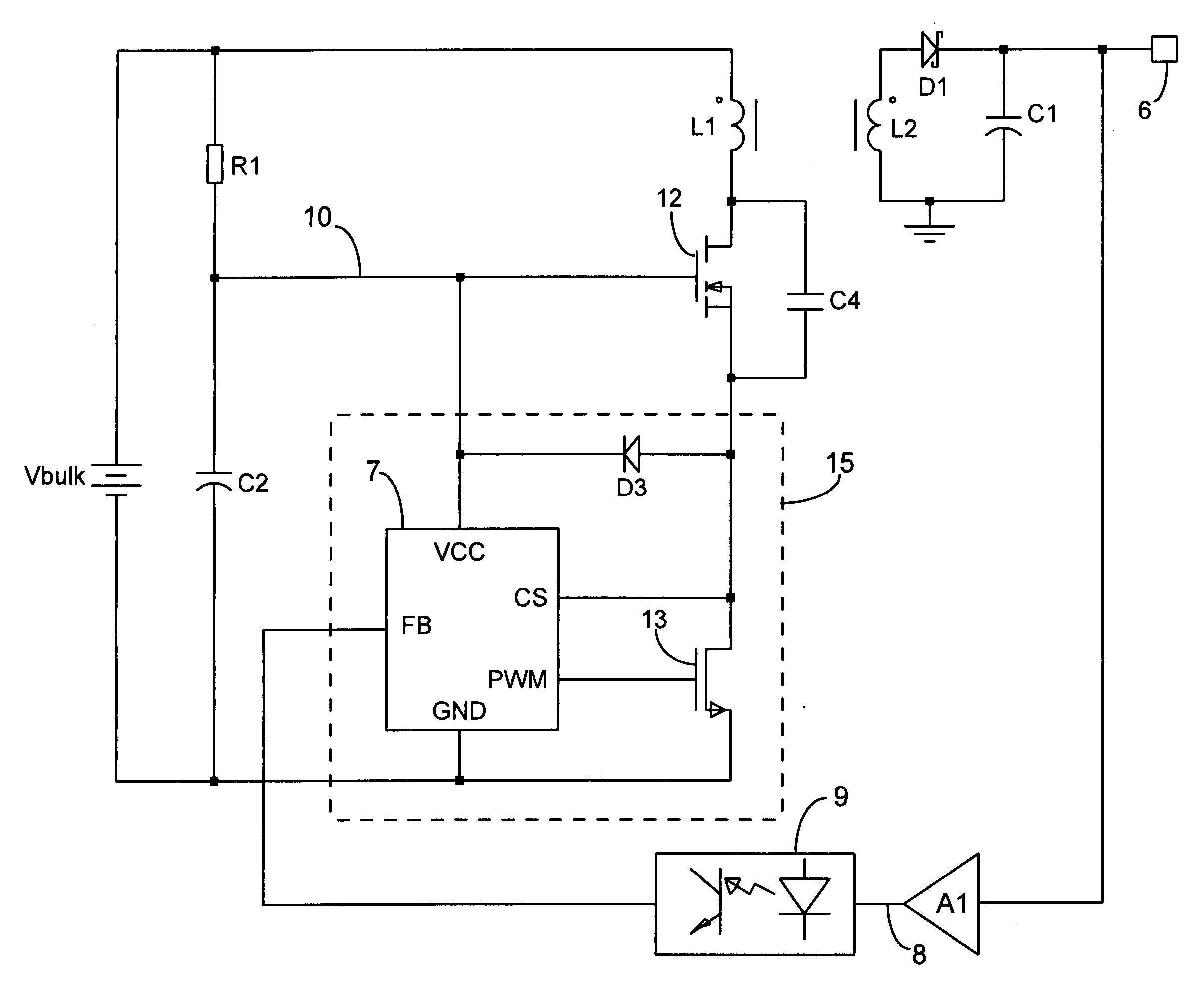

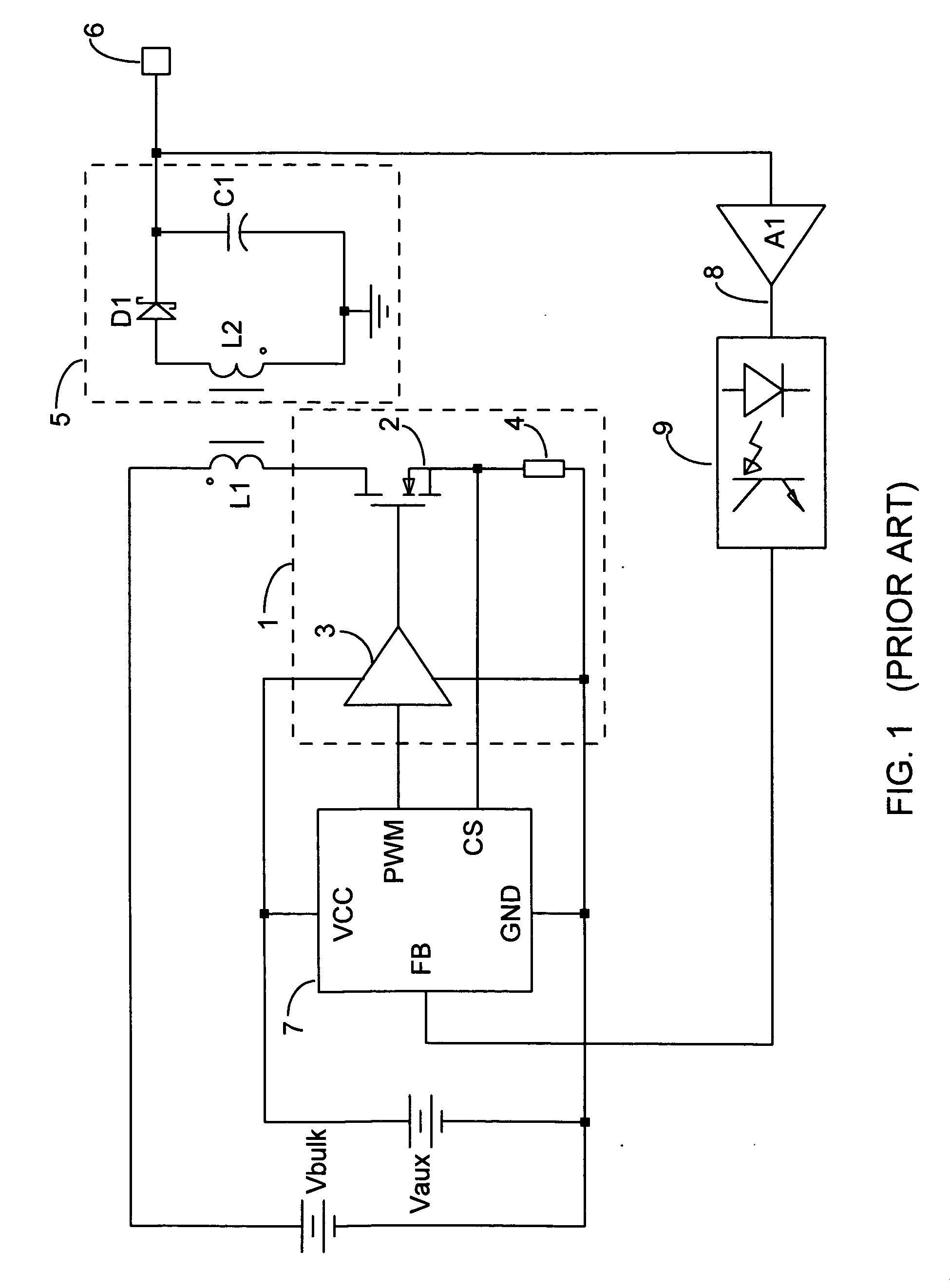

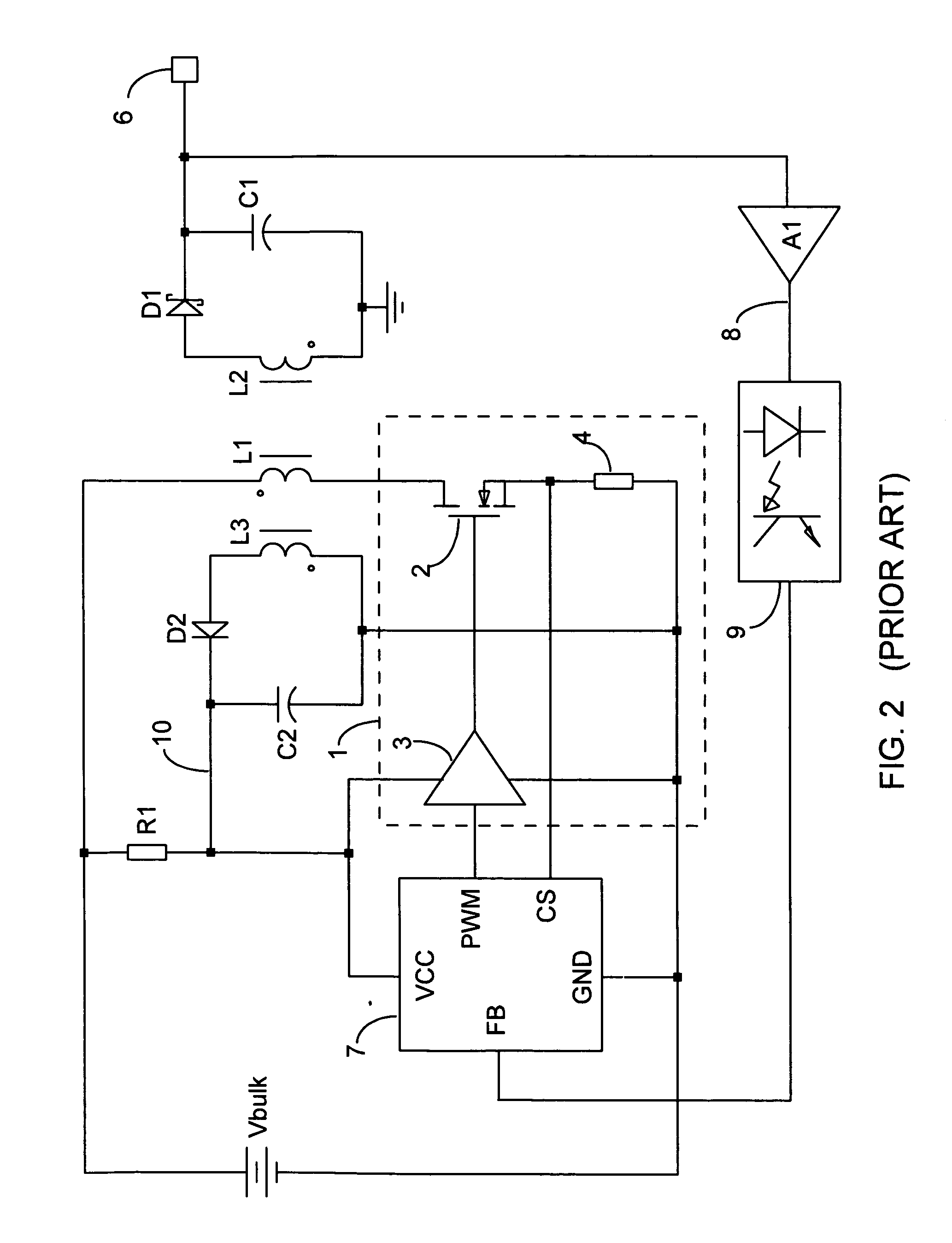

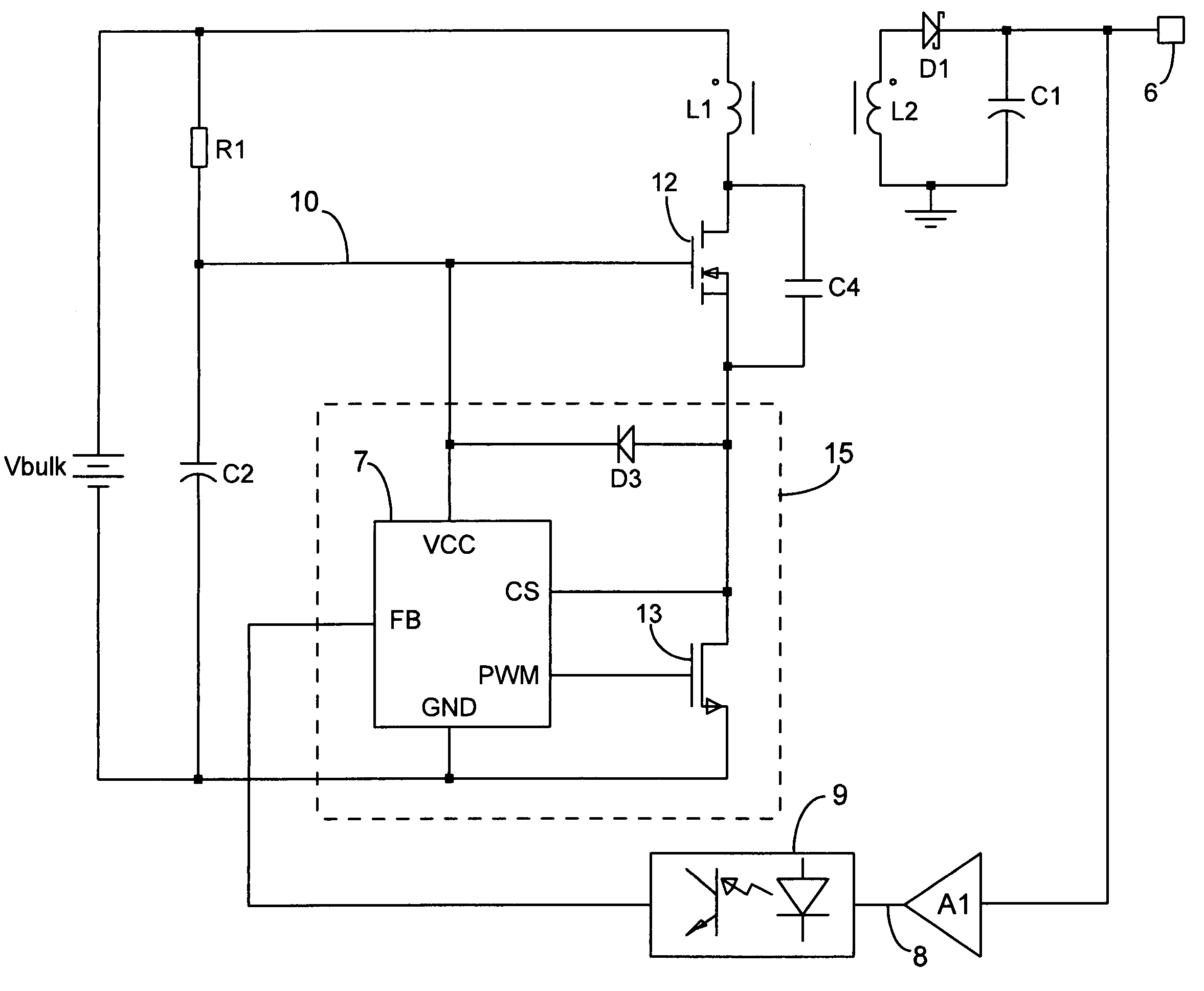

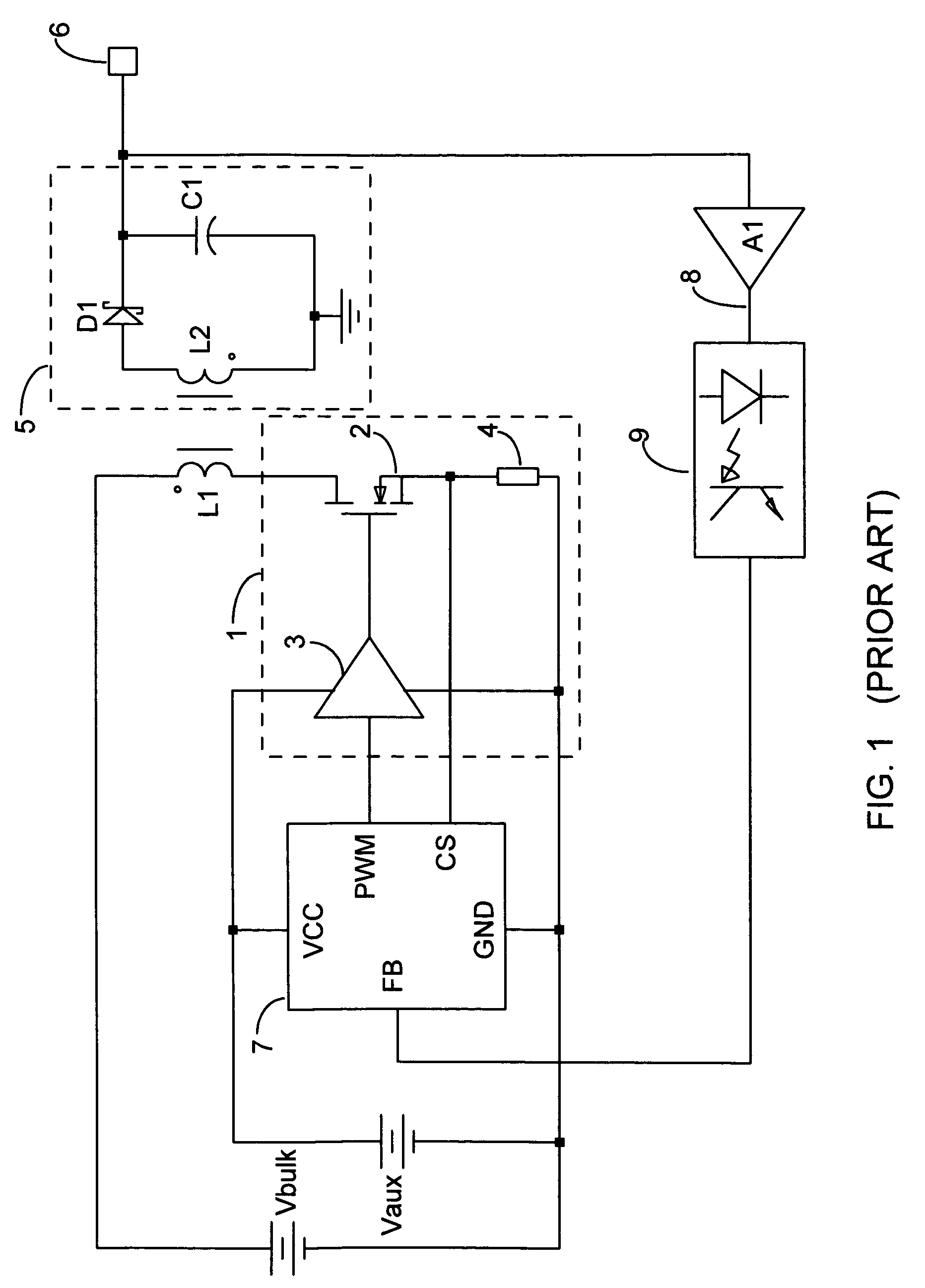

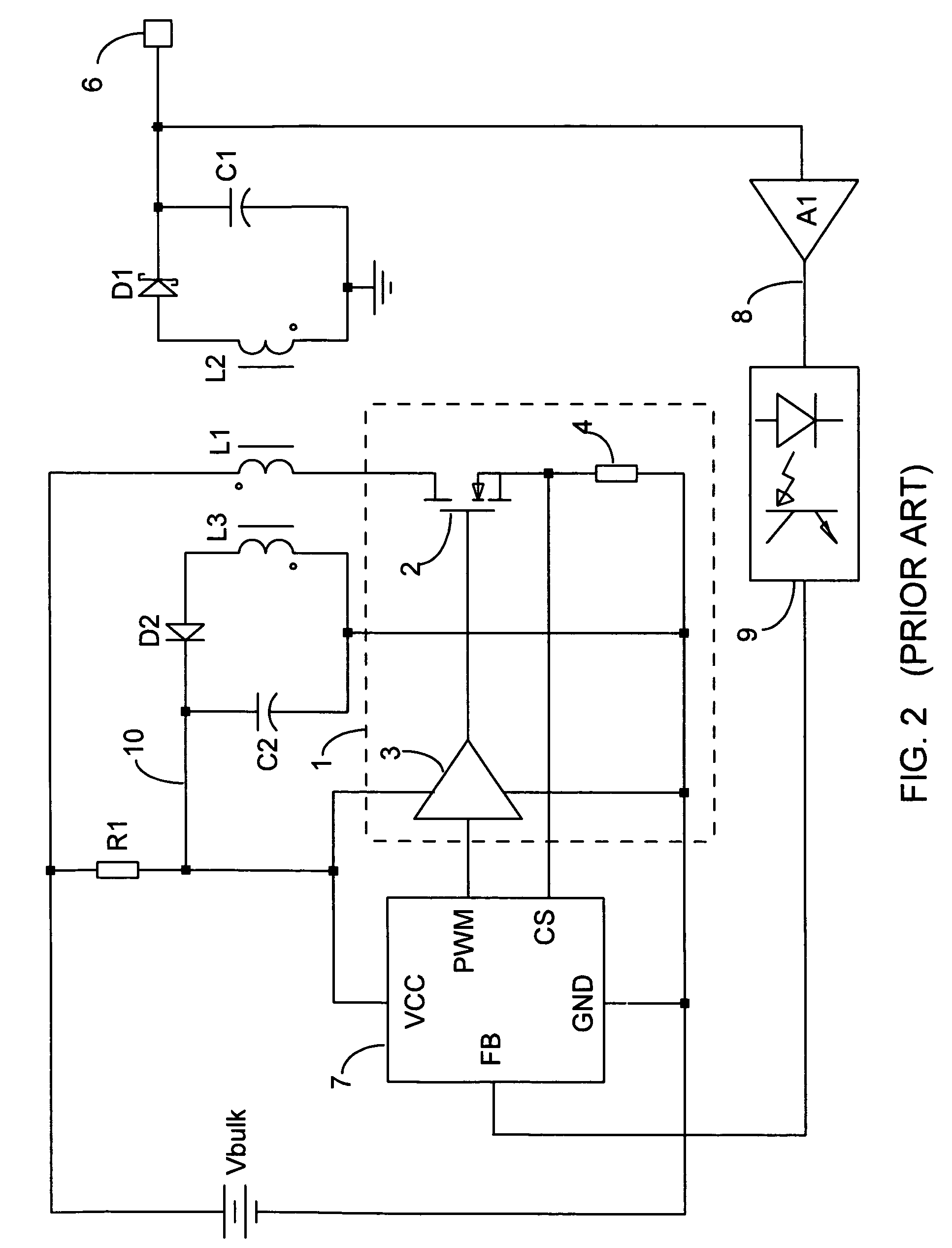

Cascode switch power supply

ActiveUS20070070659A1Reduce power lossMinimum of componentDc-dc conversionElectric variable regulationLow voltageCascode

A switching power supply is disclosed for improving the no-load power drain of low-power mains operated supplies. The power converter utilizes a cascoded switch arrangement with a conventional high voltage power MOSFET and a low voltage, low gate charge MOSFET. Driving only the small low voltage device reduces the power required for gate drive. The disclosed configuration is also capable of generating a non-isolated auxiliary rail for powering its control circuitry utilizing the parasitic capacitance of the high voltage power devices as an element in a charge pump. The resulting power supply requires significantly fewer components.

Owner:DIALOG SEMICONDUCTOR GMBH

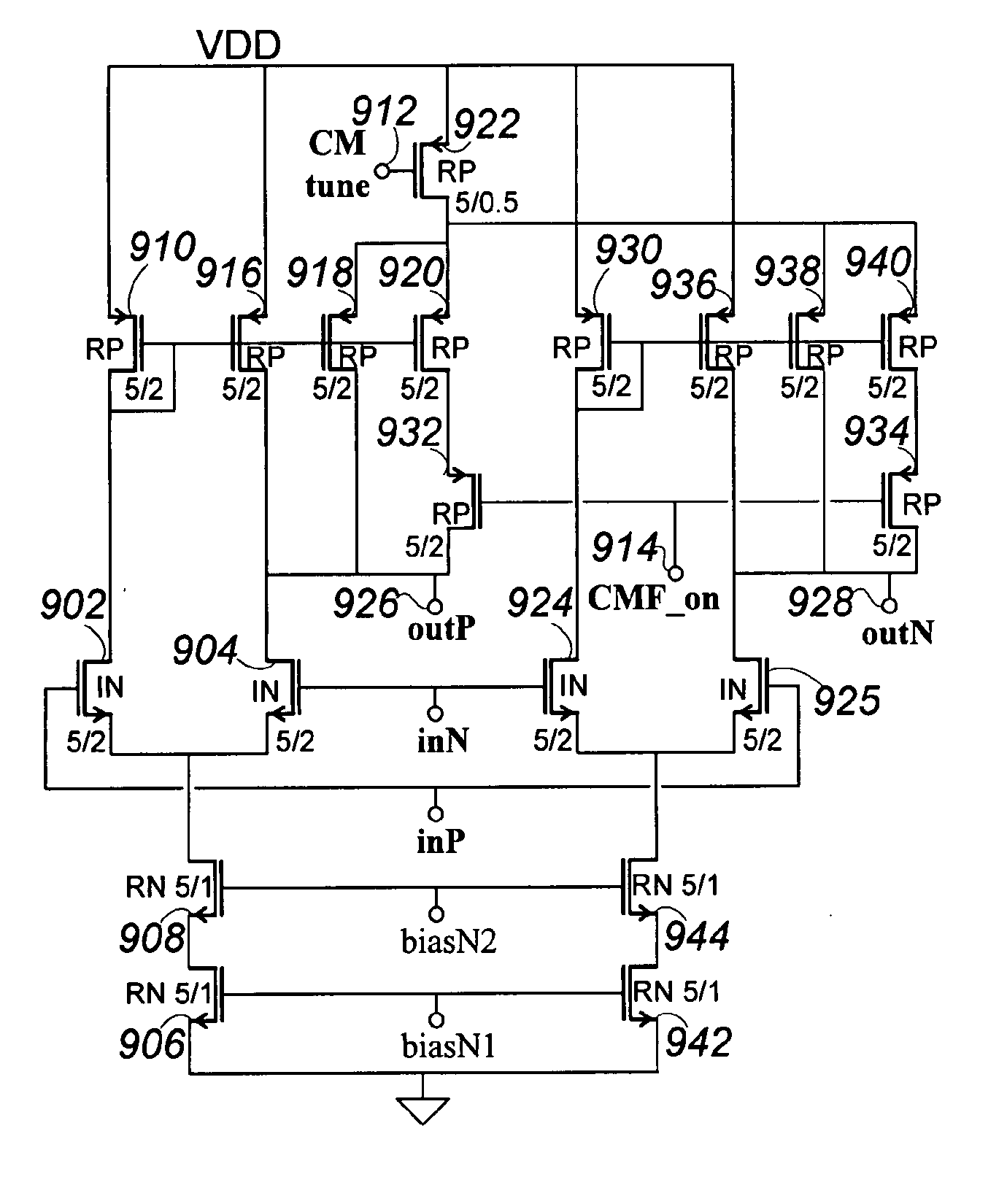

Low-Noise High Efficiency Bias Generation Circuits and Method

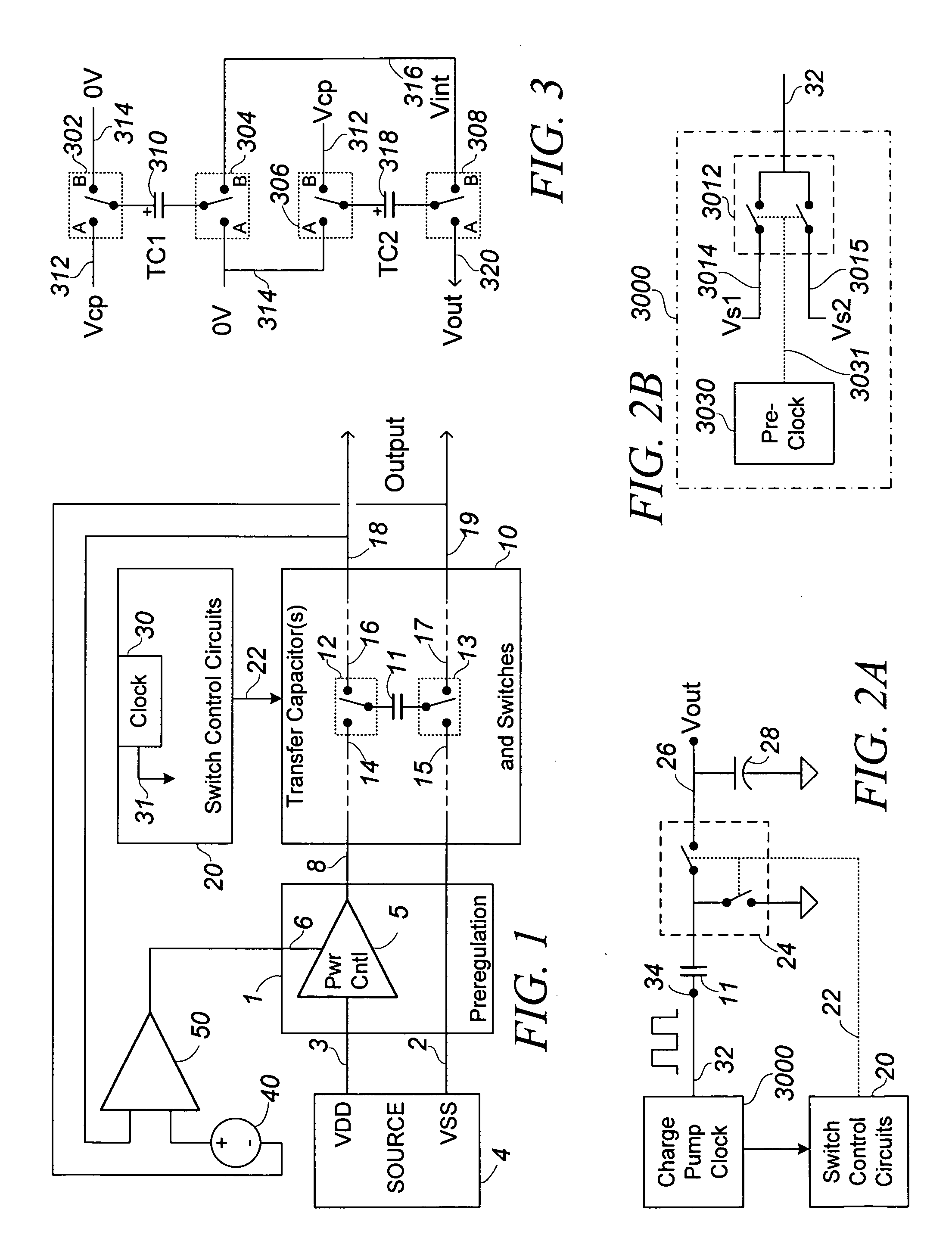

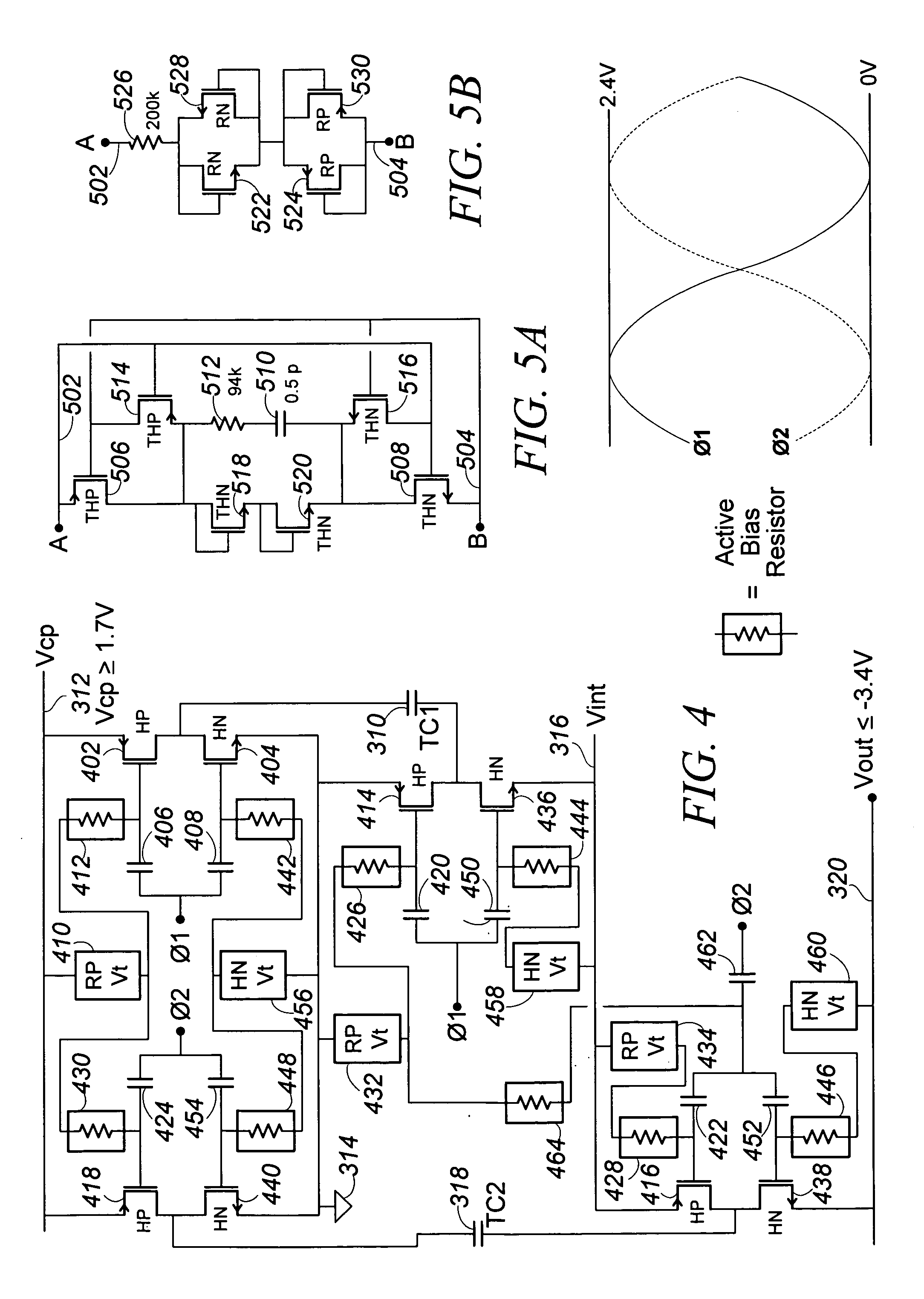

ActiveUS20110156819A1Reduce voltageAvoid problemsAmplifier modifications to reduce noise influenceActive element networkLow noiseCapacitance

A bias generation method or apparatus defined by any one or any practical combination of numerous features that contribute to low noise and / or high efficiency biasing, including: having a charge pump control clock output with a waveform having limited harmonic content or distortion compared to a sine wave; having a ring oscillator to generating a charge pump clock that includes inverters current limited by cascode devices and achieves substantially rail-to-rail output amplitude; having a differential ring oscillator with optional startup and / or phase locking features to produce two phase outputs suitably matched and in adequate phase opposition; having a ring oscillator of less than five stages generating a charge pump clock; capacitively coupling the clock output(s) to some or all of the charge transfer capacitor switches; biasing an FET, which is capacitively coupled to a drive signal, to a bias voltage via an “active bias resistor” circuit that conducts between output terminals only during portions of a waveform appearing between the terminals, and / or wherein the bias voltage is generated by switching a small capacitance at cycles of said waveform. A charge pump for the bias generation may include a regulating feed back loop including an OTA that is also suitable for other uses, the OTA having a ratio-control input that controls a current mirror ratio in a differential amplifier over a continuous range, and optionally has differential outputs including an inverting output produced by a second differential amplifier that optionally includes a variable ratio current mirror controlled by the same ratio-control input. The ratio-control input may therefore control a common mode voltage of the differential outputs of the OTA. A control loop around the OTA may be configured to control the ratio of one or more variable ratio current mirrors, which may particularly control the output common mode voltage, and may control it such that the inverting output level tracks the non-inverting output level to cause the amplifier to function as a high-gain integrator.

Owner:PSEMI CORP

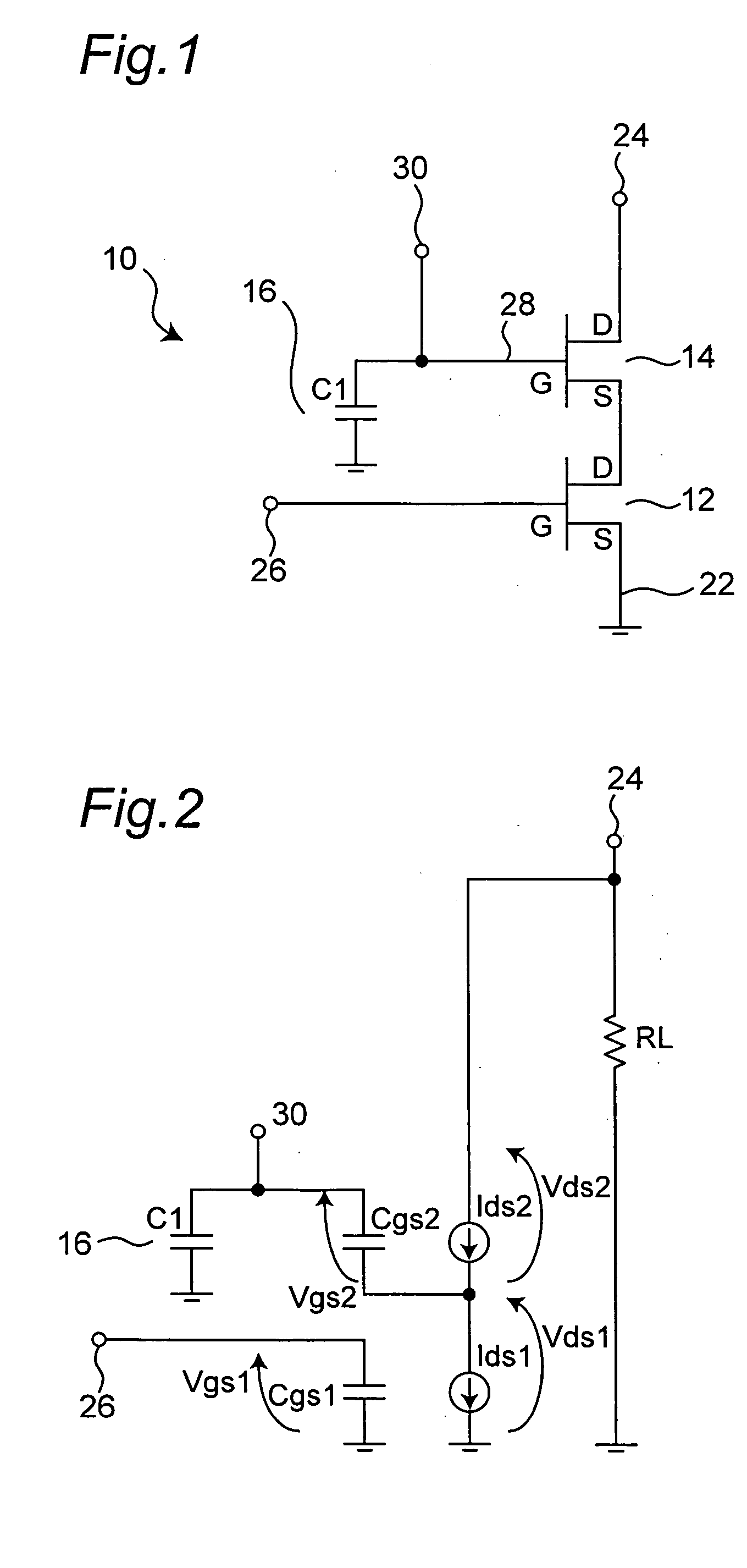

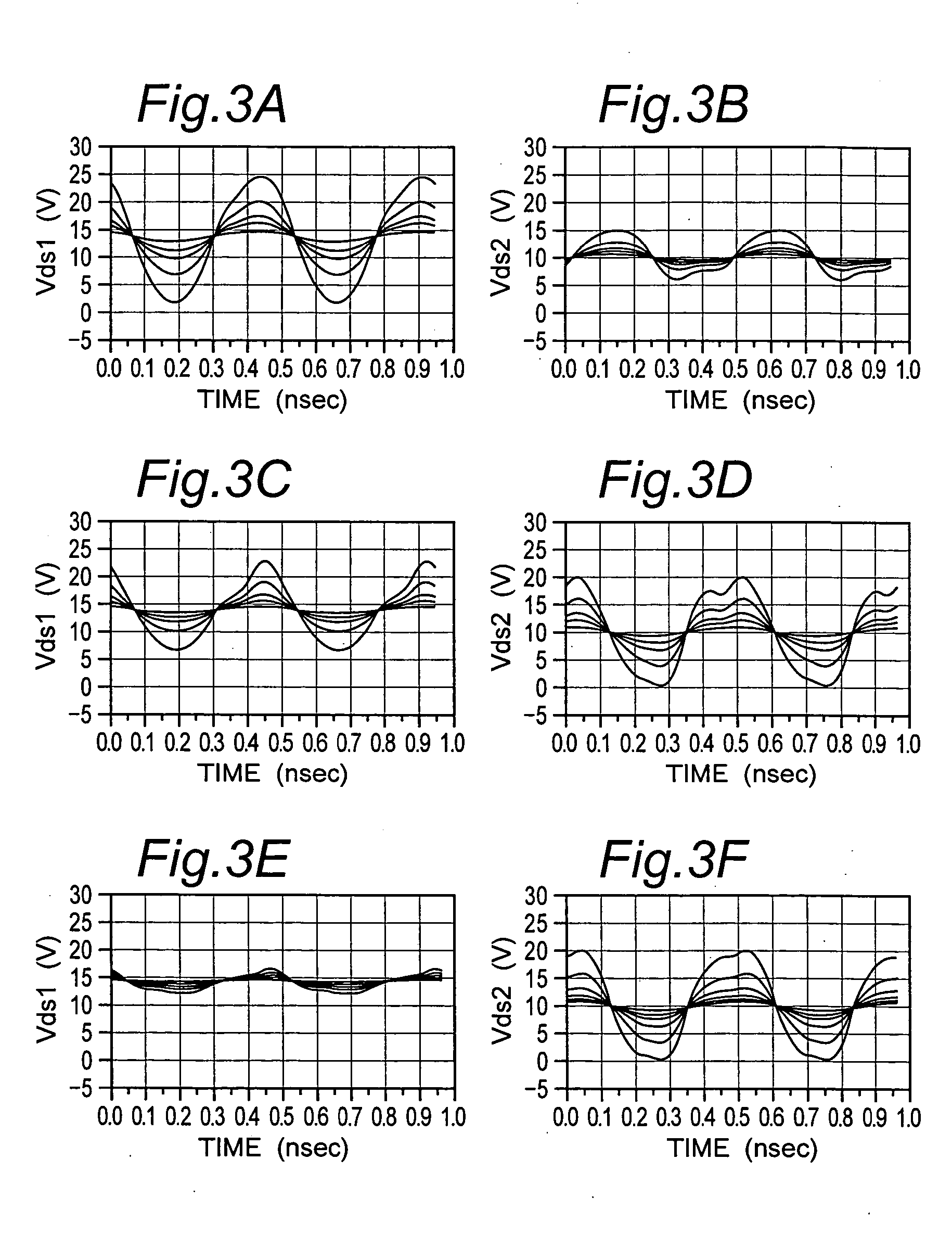

Cascode circuit and integrated circuit having it

ActiveUS7071786B2Increase powerImprove efficiencyTransistorHigh frequency amplifiersCapacitanceCascode

A cascode circuit includes a first field effect transistor which has a source terminal grounded, a second field effect transistor which has a source terminal connected to a drain terminal of the first field effect transistor, and a first capacitor connected between the source terminal of the first field effect transistor and a gate terminal of the second field effect transistor. The first field effect transistor and the second field effect transistor are cascode-connected successively. A capacitance value of the first capacitor is 0.01 to 10 times that between the gate and source terminals of the second field effect transistor.

Owner:MITSUBISHI ELECTRIC CORP

Multi-cascode transistors

InactiveUS6888396B2Boards/switchyards circuit arrangementsAmplifier modifications to reduce detrimental impedenceMOSFETCascode

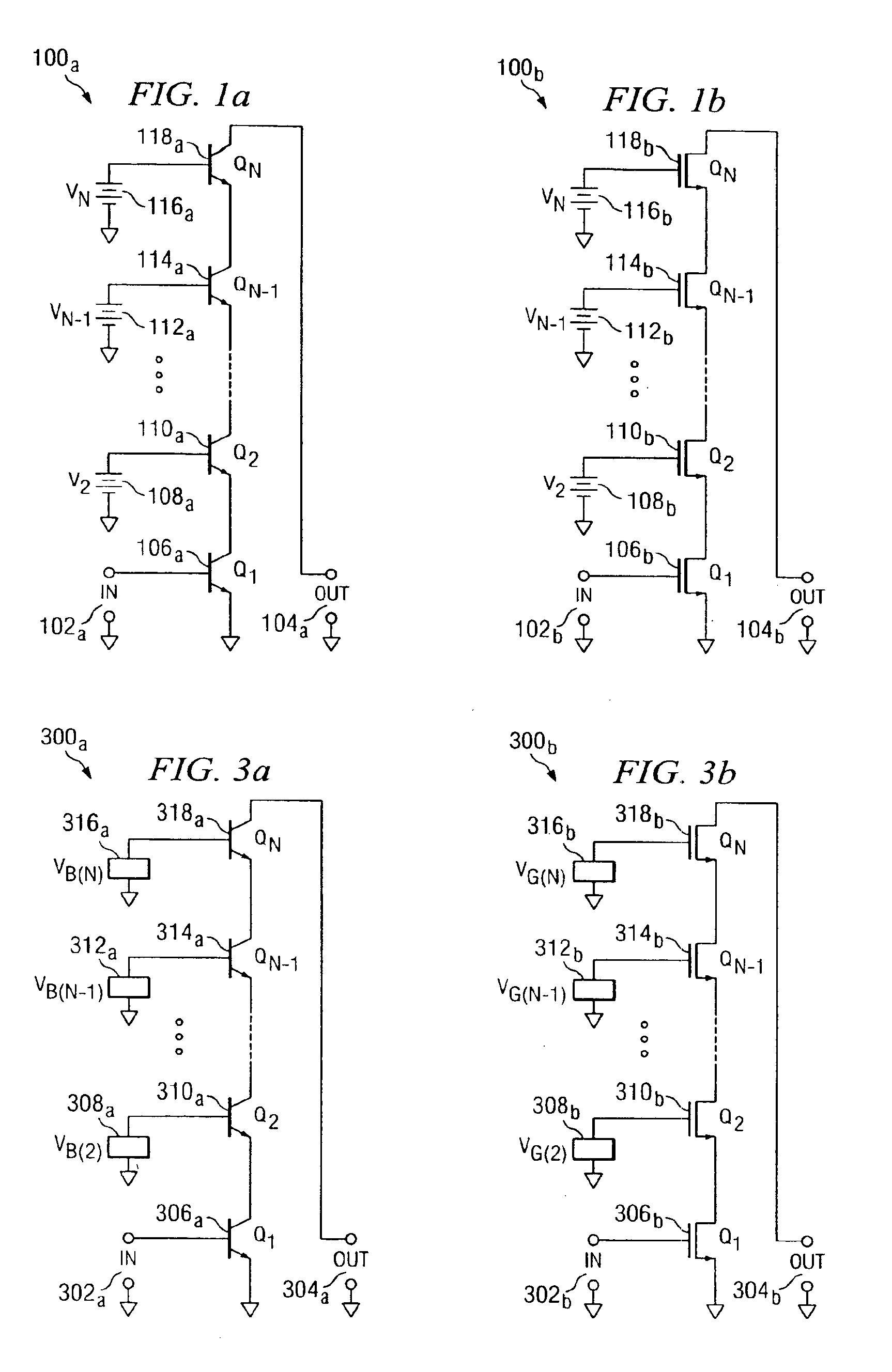

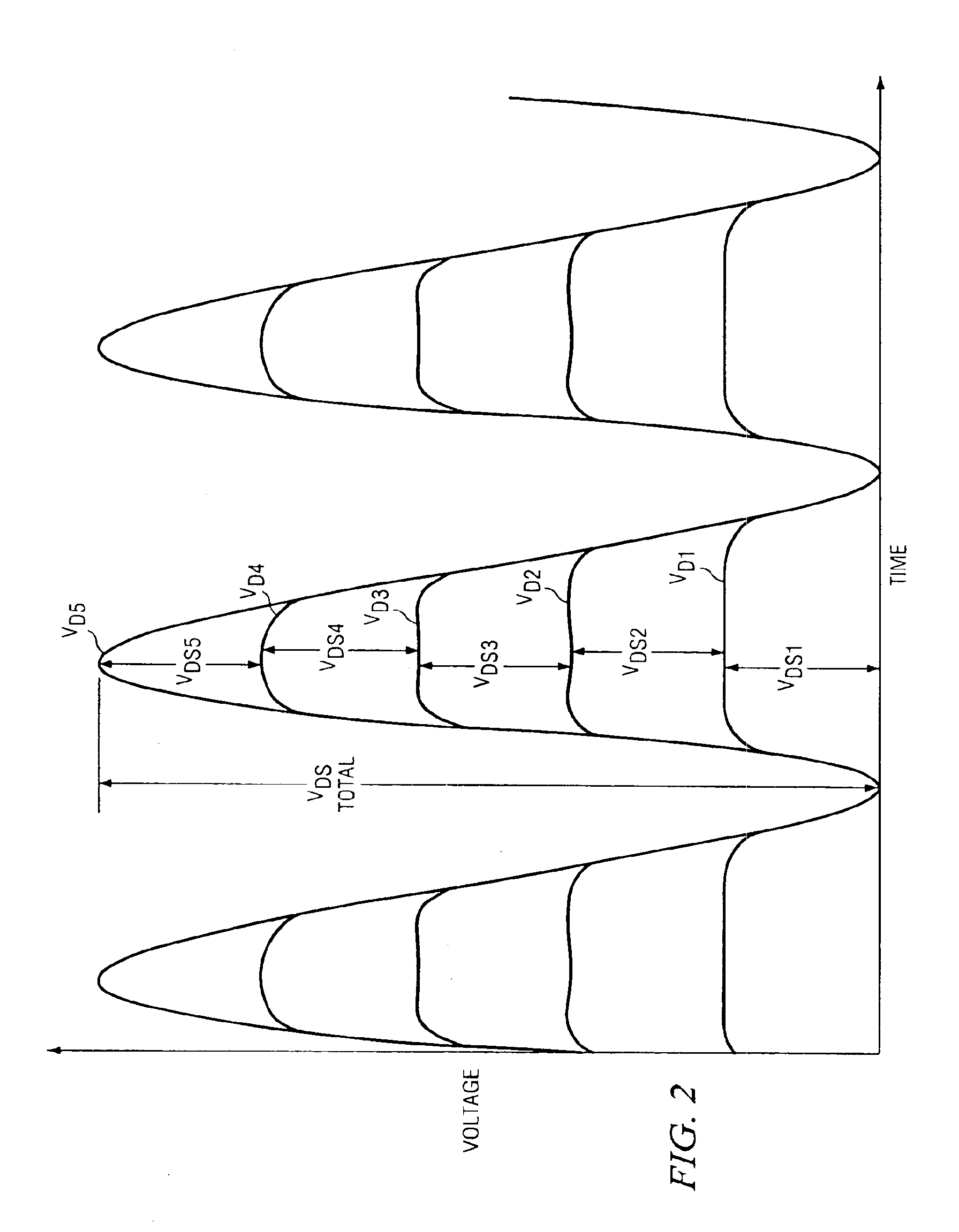

A cascode circuit with improved withstand voltage is provided. The cascode circuit includes three or more transistors, such as MOSFET transistors. Each transistor has a control terminal, such as a gate, and two conduction terminals, such as a drain and a source. The conduction terminals are coupled in series between two output terminals, such as where the drain of each transistor is coupled to the source of another transistor. A signal input is provided to the gate for the first transistor. Two or more control voltage sources, such as DC bias voltages, are provided to the gate of the remaining transistors. The DC bias voltages are selected so as to maintain the voltage across each transistor to a level below a breakdown voltage level.

Owner:CALIFORNIA INST OF TECH

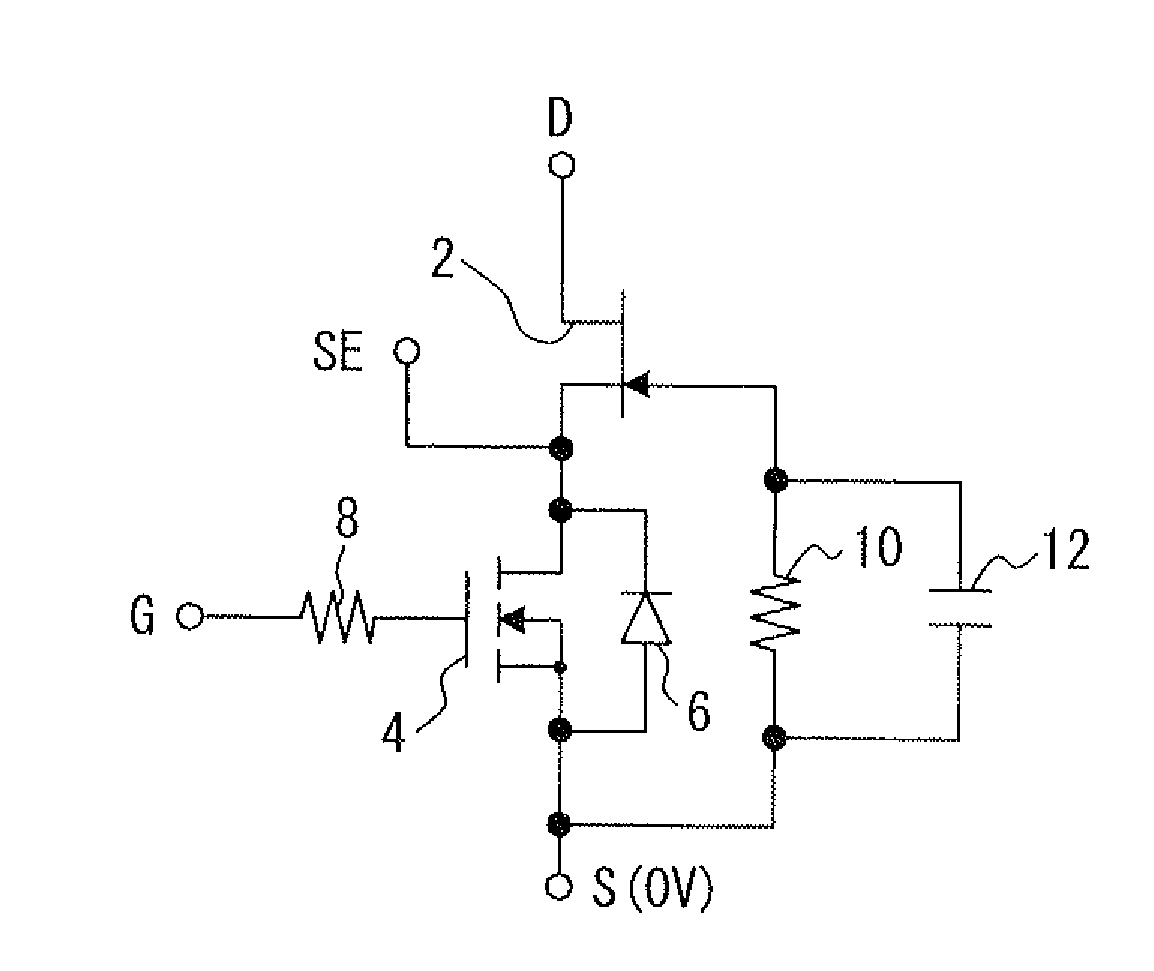

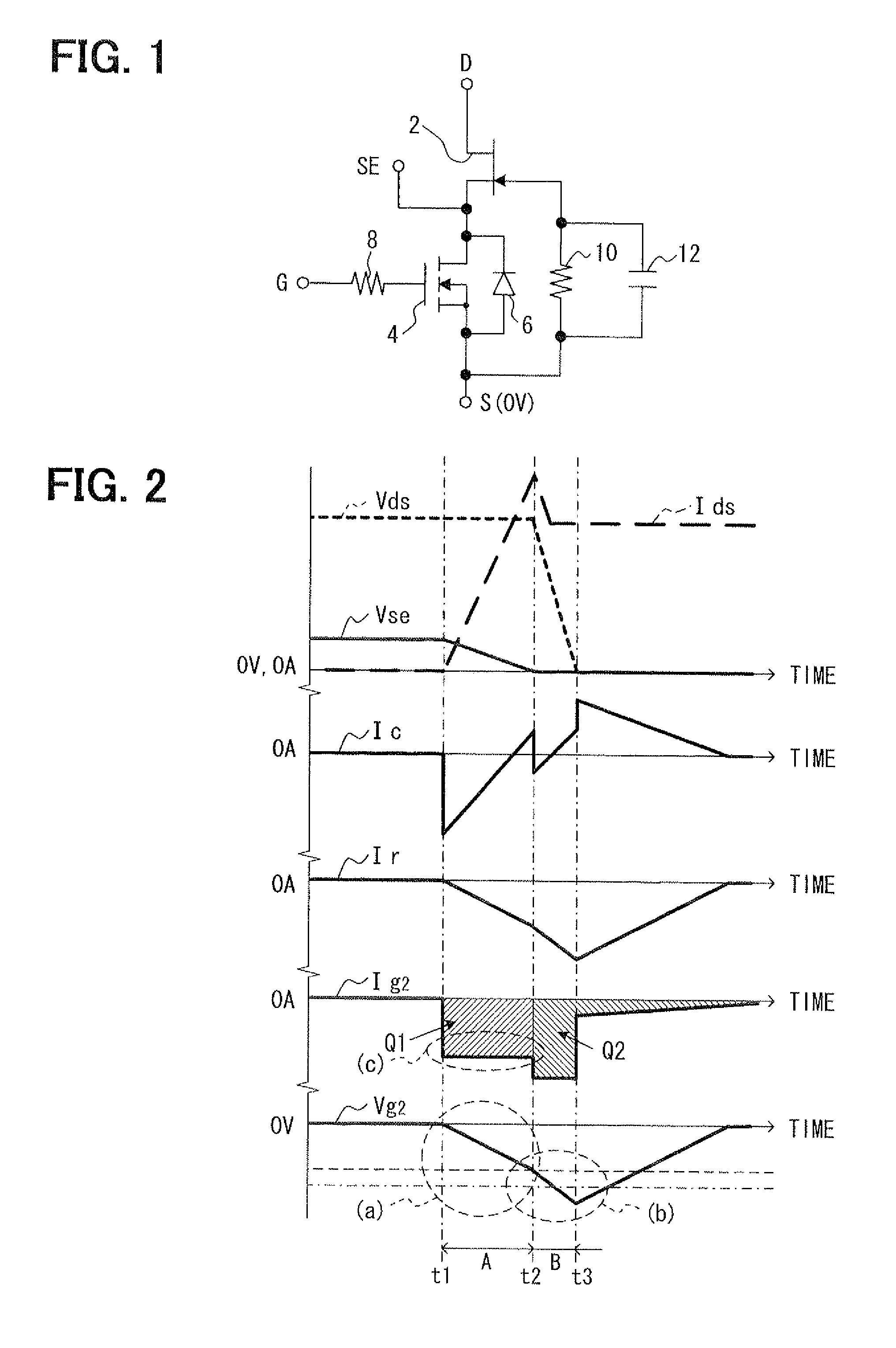

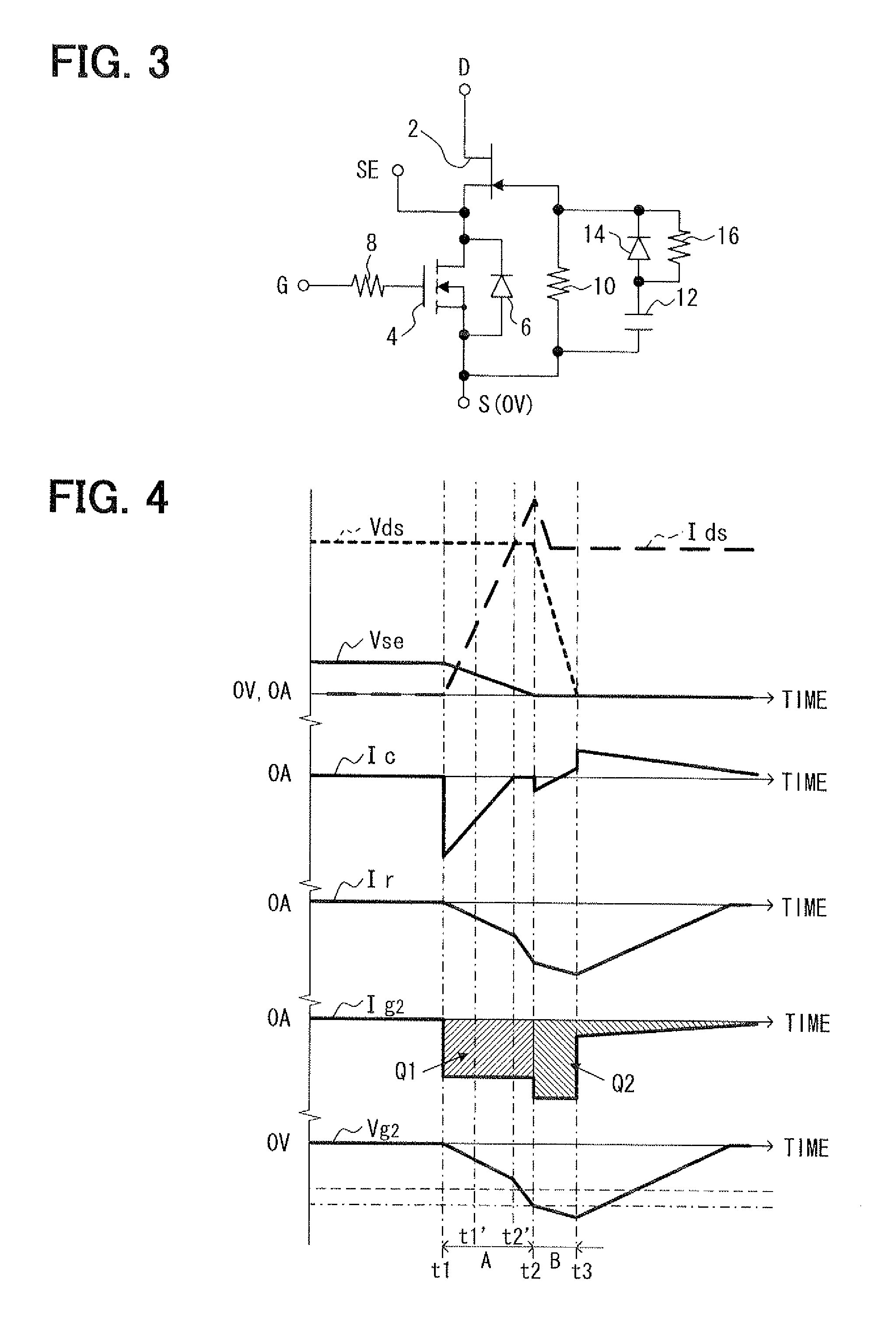

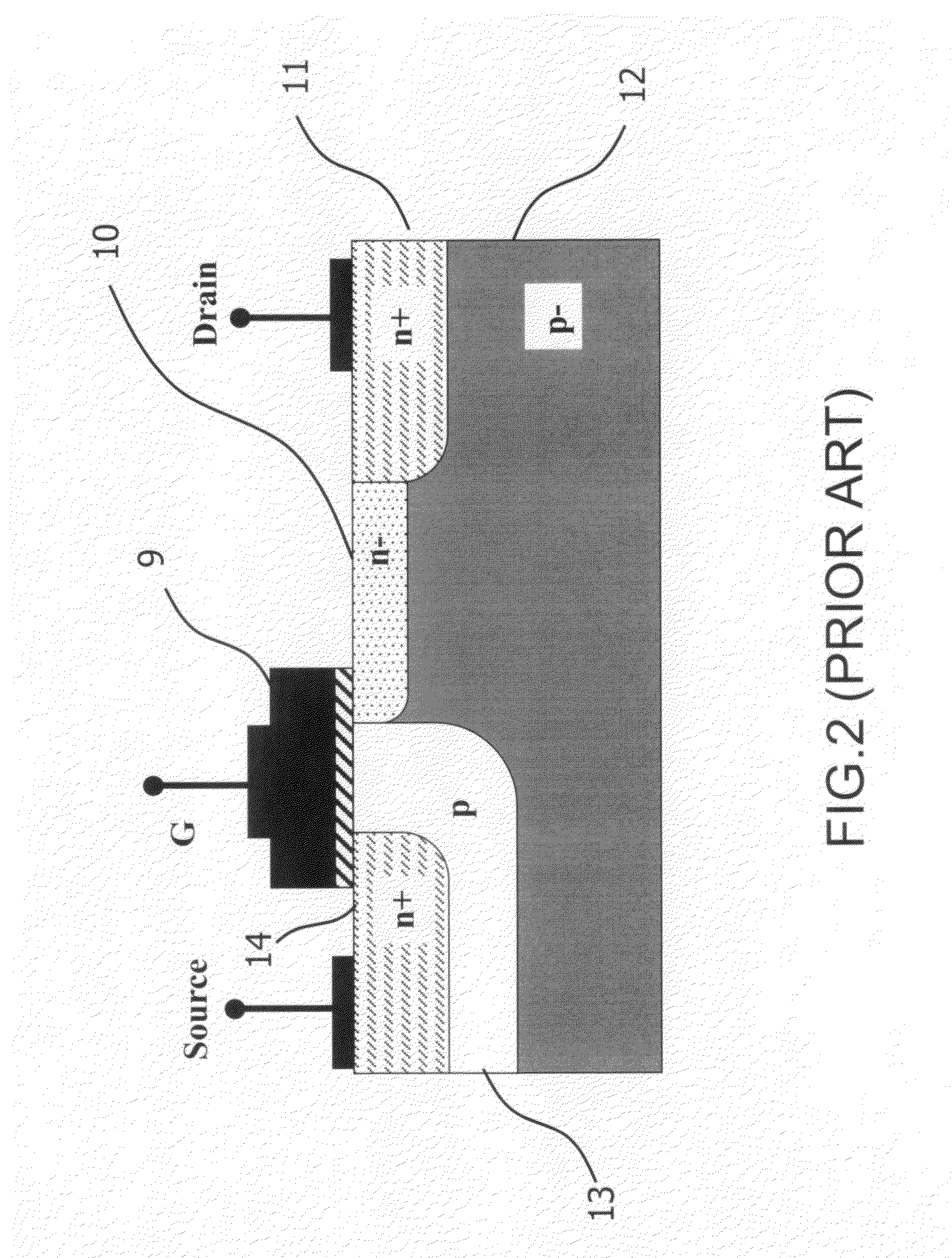

Hybrid power device

ActiveUS20110199148A1Suppress resonanceReduce switching lossesElectronic switchingElectric pulse generatorMOSFETCascode

A hybrid power device is formed of a normally-on type SiC-JFET and a normally-off type Si-MOSFET, which are connected in cascode with a source of the SiC-JFET and a drain of the Si-MOSFET being connected to each other thereby forming a hybrid power FET. A gate of the SiC-JFET and a source of the Si-MOSFET are connected via a switching speed regulating resistor. A capacitor is connected to the switching speed regulating resistor in parallel to control a switching speed to a first speed in a former part of the switching period of the hybrid power FET and to a second switching speed in a latter part of the switching period. The second switching speed is lower than the first switching speed.

Owner:DENSO CORP

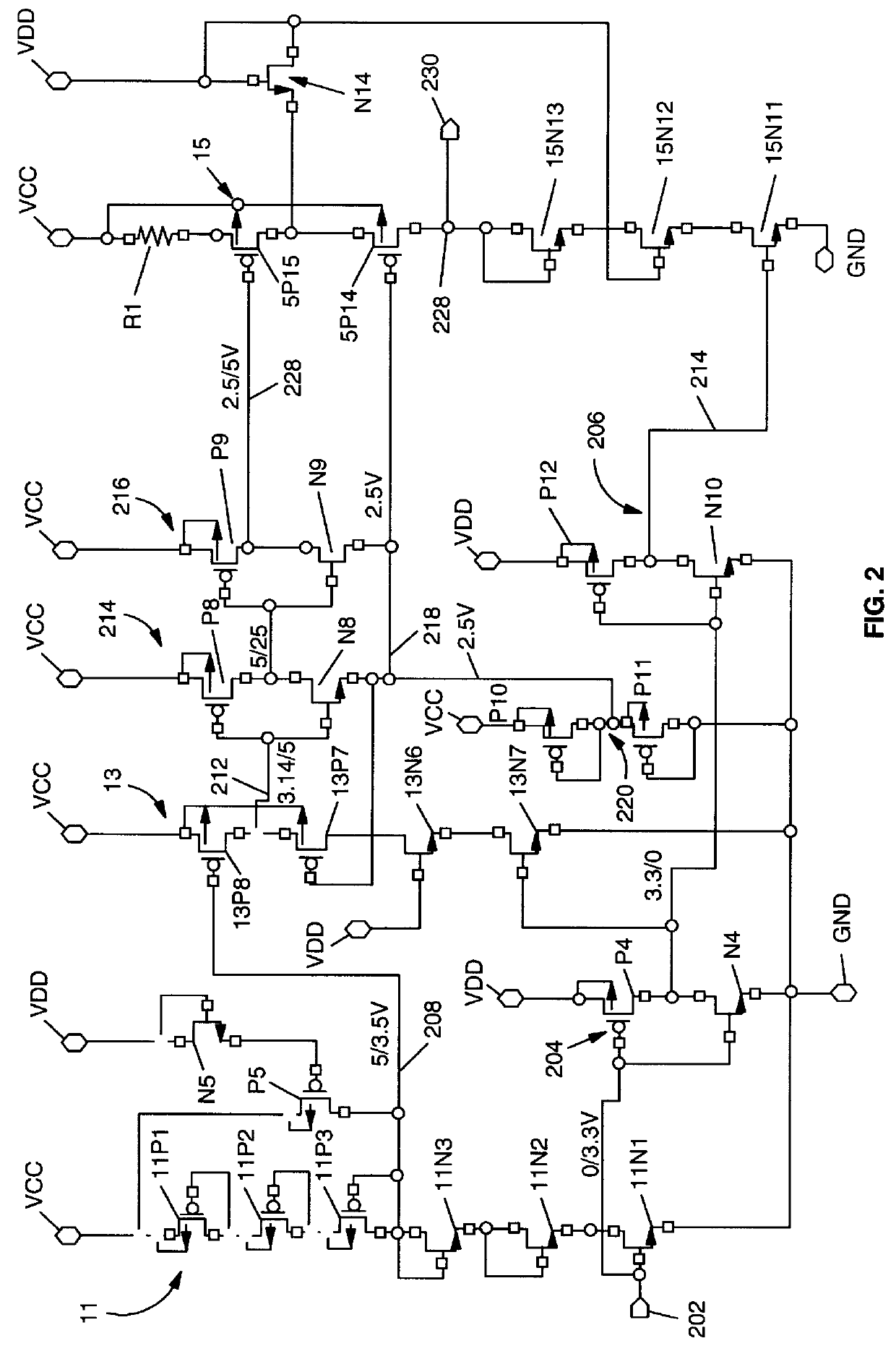

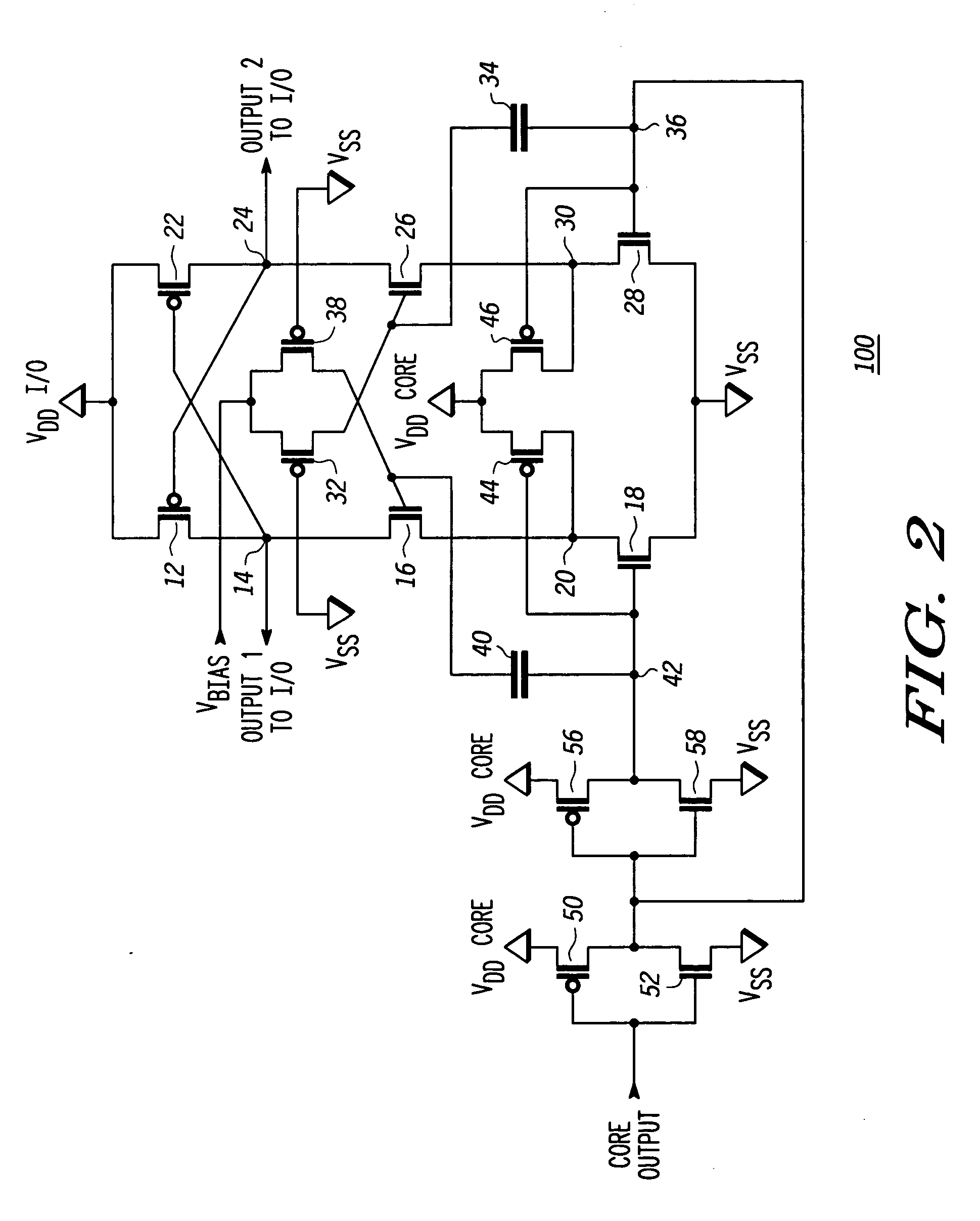

Low voltage CMOS circuit for on/off chip drive at high voltage

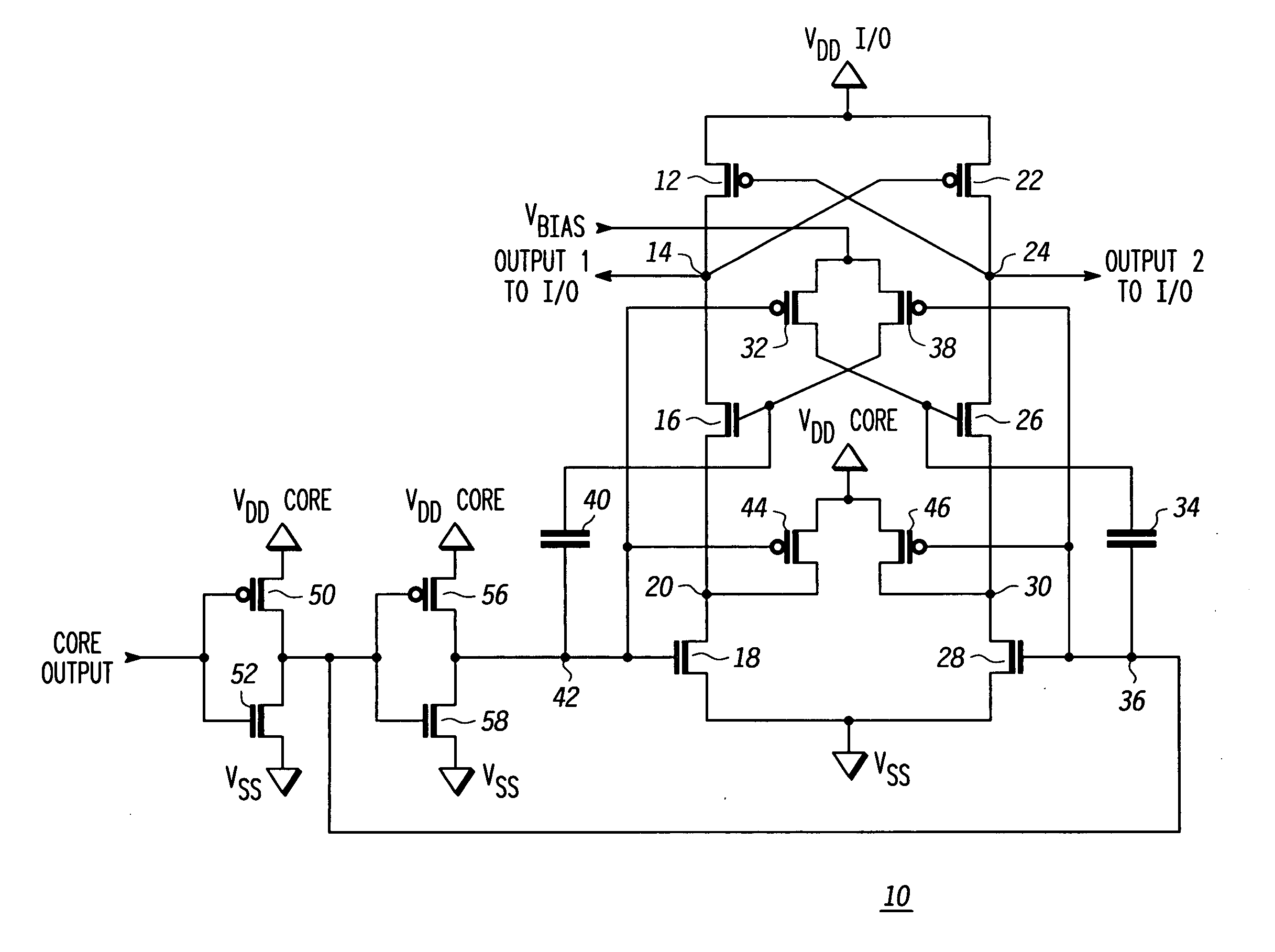

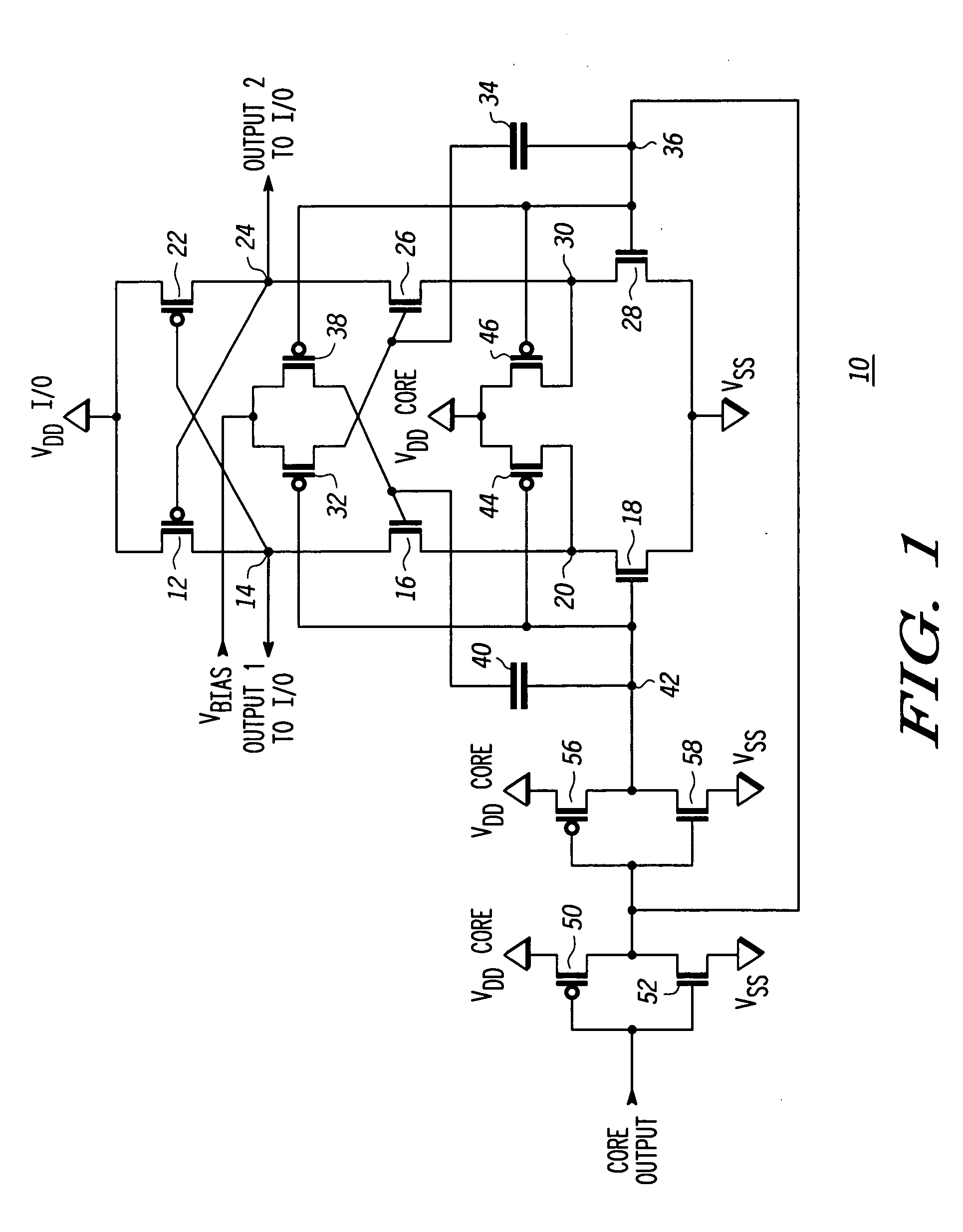

InactiveUS6031394AAvoid failureReliability increasing modificationsLogic circuits characterised by logic functionCMOSCascode

A low voltage CMOS circuit and method provide output current ability meeting multimode requirements of high voltage off-chip drivers while protecting the CMOS devices from various breakdown mechanisms. The circuit and method utilize intermediate voltages between two power rails and voltage division techniques to limit the voltages to acceptable limits for drain-to-source, gate-to-drain, and gate-to-source of CMOS devices in any chosen technology. The circuit comprises first and second CMOS cascode chains connected between a high voltage power rail, e.g 5 volt and a reference potential power rail, e.g. ground. Each CMOS cascode chain comprises first and second p-type MOS devices in series with first and second n-type MOS devices. An input circuit is coupled to a node at the midpoint of the first CMOS cascode chain. A bias voltage, typically 3.3 volts is connected to the NMOS devices in the first and CMOS cascode chains. A second bias voltage is coupled to the PMOS devices in the first and second CMOS cascode chains. An output is provided from the second CMOS cascode chain to a third CMOS cascode chain for purposes of providing sufficient pullup capability to drive an output circuit comprising a fourth CMOS cascode chain between the high and reference potentials without exceeding the breakdown mechanisms for any MOS device in the CMOS cascode chains.

Owner:GOOGLE LLC

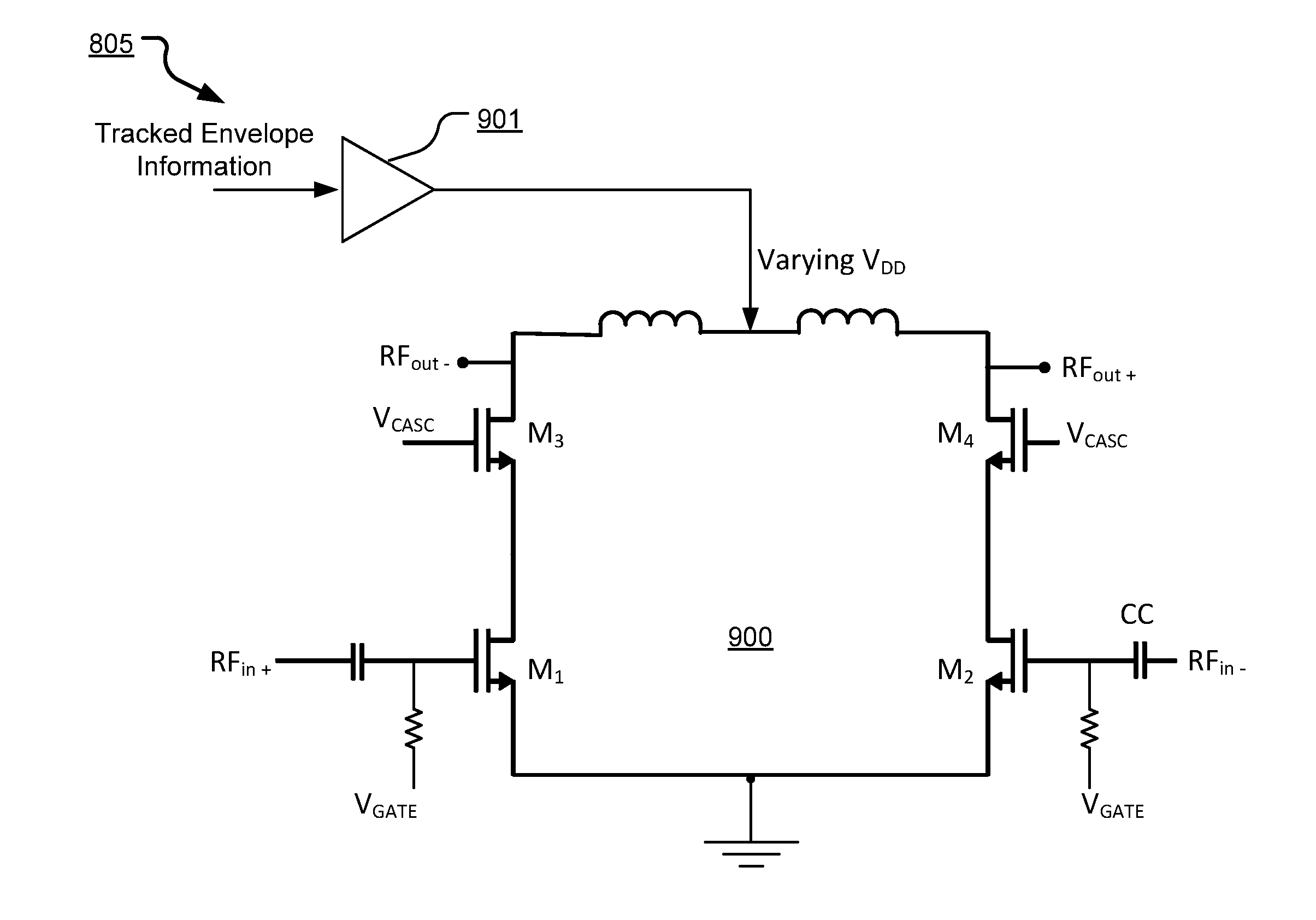

Supply tracking

ActiveUS20130285750A1Amplifier detailsAmplifiers with semiconductor devices onlyAudio power amplifierCascode

A power amplifier includes generation, tracking and usage of an envelope of an input RF signal. To improve upon the efficiency of the power amplifier, various configurations include using the tracked envelope, for example, an OFDM signal, to improve the average efficiency. Suitable hardware / software in the form of circuitry, logic gates, and / or code functions to generate and track an envelope of an input RF signal and modulate one or more of the input supply voltage, cascode gate bias or parallel PA branches using the tracked envelope.

Owner:AVAGO TECH INT SALES PTE LTD

Triple cascode power amplifier of inner parallel configuration with dynamic gate bias technique

InactiveUS7276976B2Increase output powerImprove efficiencyGated amplifiersAmplifier combinationsAudio power amplifierCascode

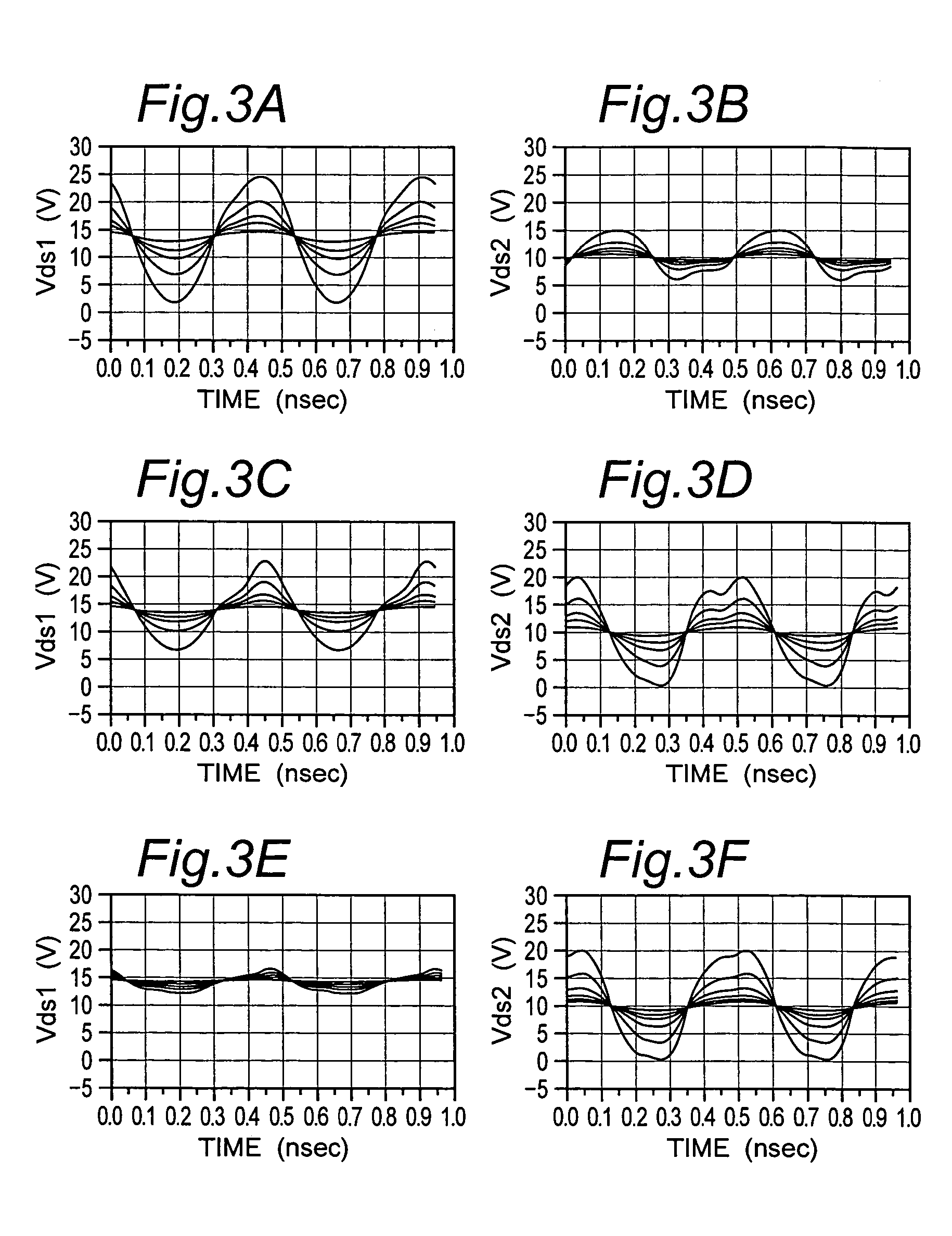

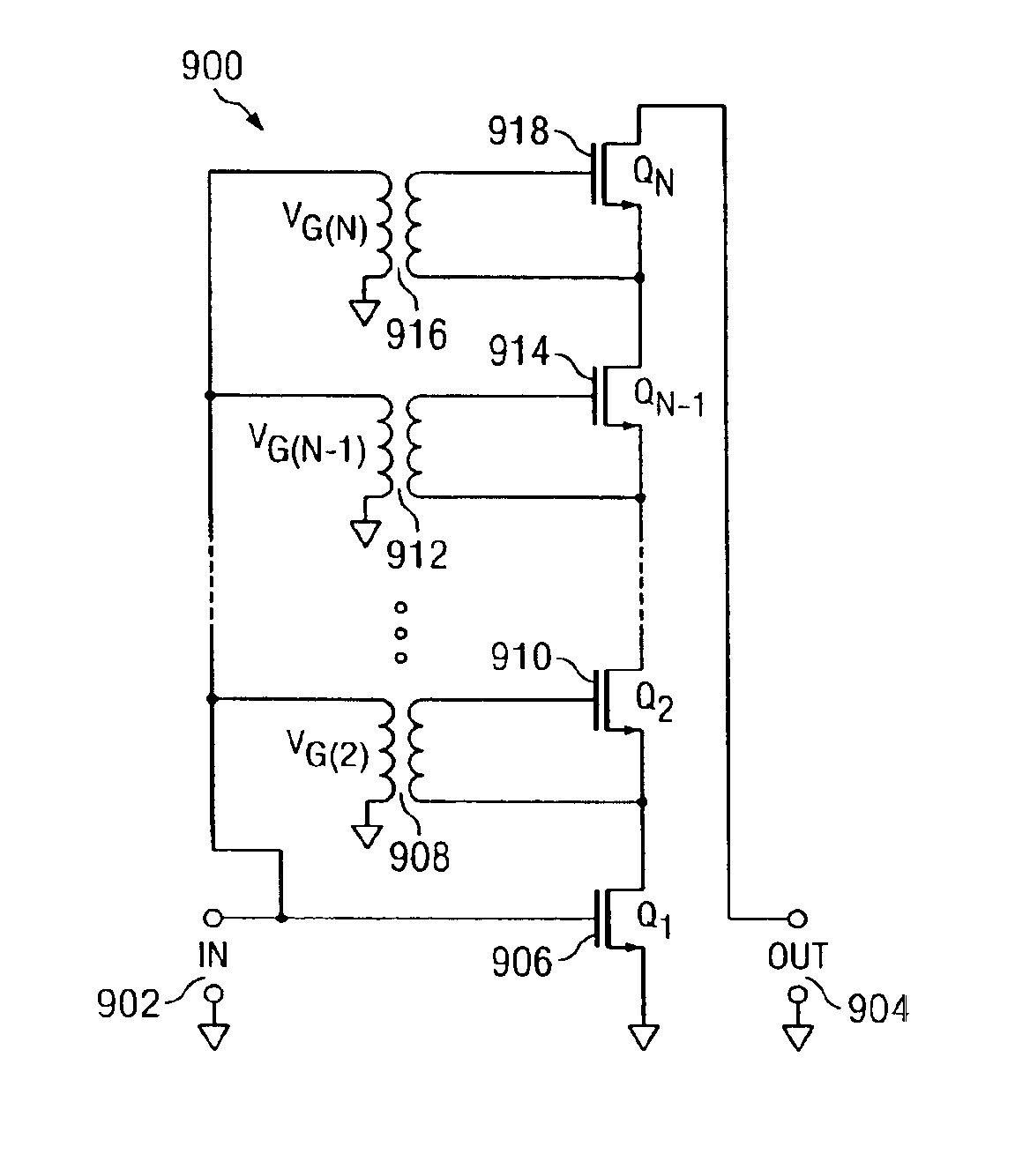

Provided is a power amplifier which fits to a deep-submicron technology in radio frequency wireless communication. The power amplifier includes a cascode including a first transistor which receives and amplifies an input signal, and a second transistor which is connected to the first transistor in series and operated by a DC bias voltage; a third transistor which is connected between the cascode and an output end, operated by a dynamic gate bias and outputting a signal; and a voltage divider which includes first and second capacitors that are connected between the output end, i.e. a drain of the third transistor, and a ground in series, and provides the dynamic bias to a gate of the third transistor.

Owner:ELECTRONICS & TELECOMM RES INST

Single structure cascode device

InactiveUS20120175679A1Without increasing device on-resistanceReduce voltageTransistorSemiconductor/solid-state device manufacturingCMOSSemiconductor structure

A novel semiconductor power transistor is presented. The semiconductor structure is simple and is based on a MOS configuration with a drift region and an additional gate that modulates the carrier density in the drift region, so that the control on the carrier transport is enhanced and the specific on-resistance per area is reduced. This characteristic enables the use of short gate lengths while maintaining the electric field under the gate within reasonable values in high voltage applications, without increasing the device on-resistance. It offers the advantage of extremely lower on-resistance for the same silicon area while improving on its dynamic performances with respect to the standard CMOS technology. Another inherent advantage is that the switching gate losses are smaller due to lower VGS voltages required to operate the device.

Owner:QUALCOMM INC

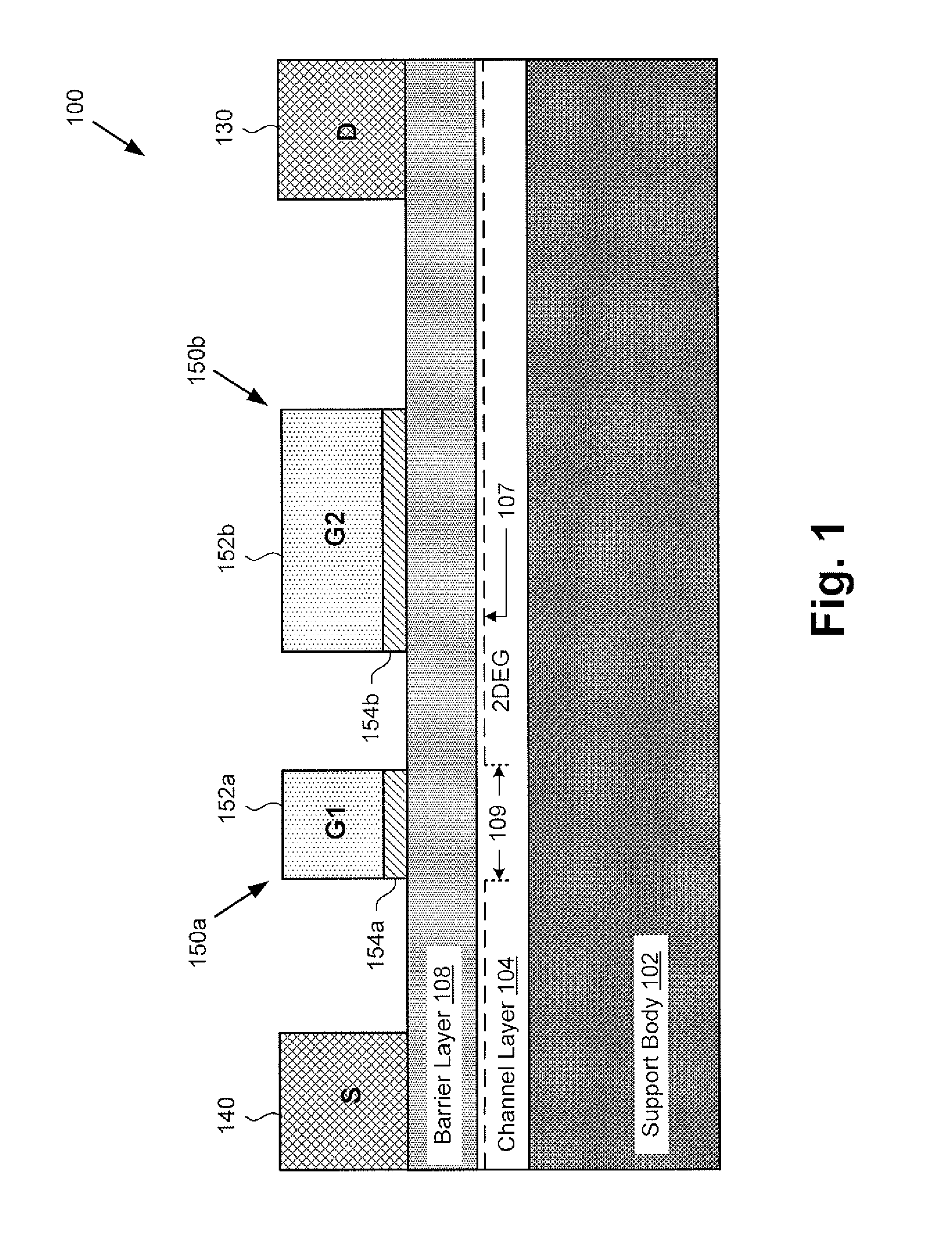

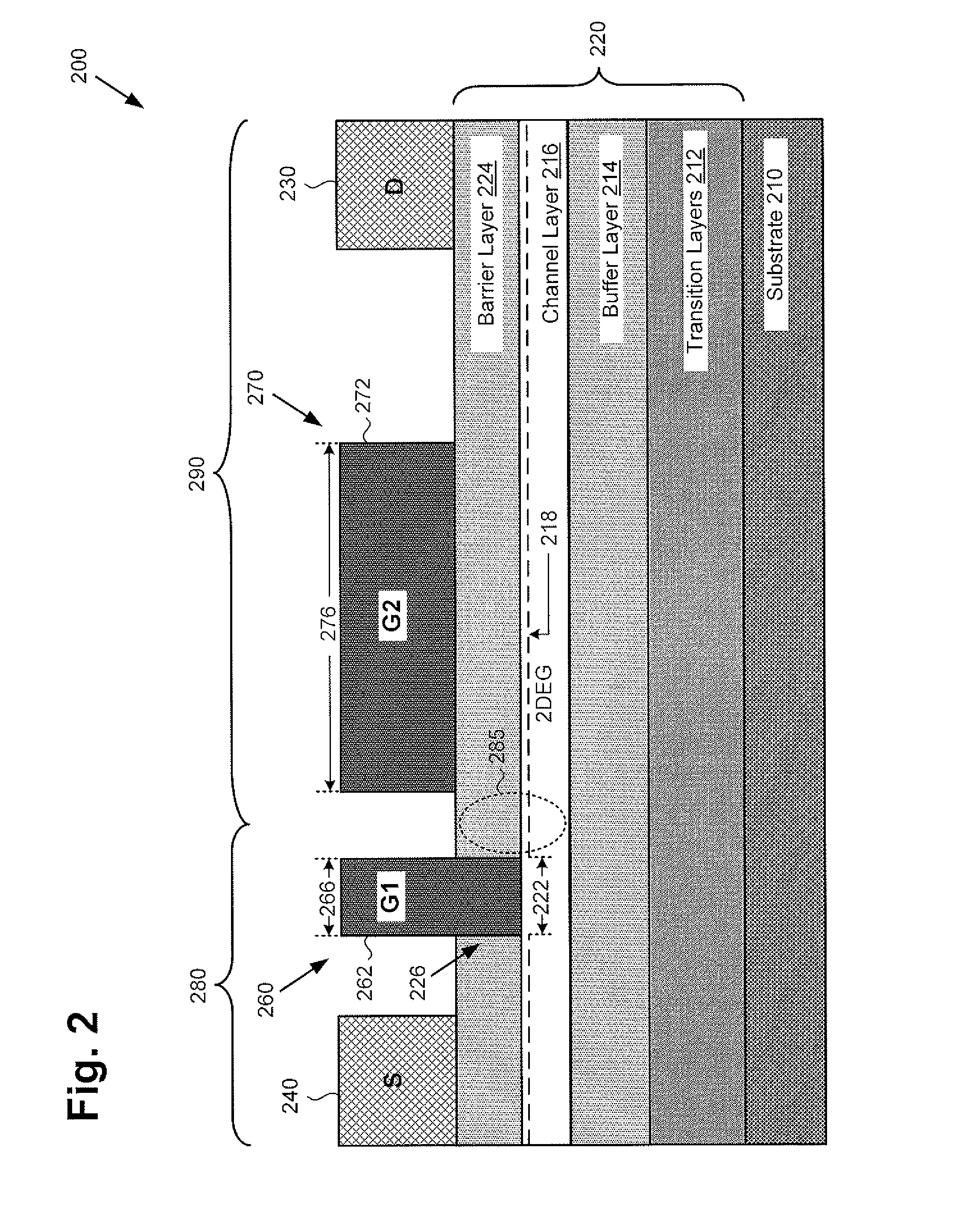

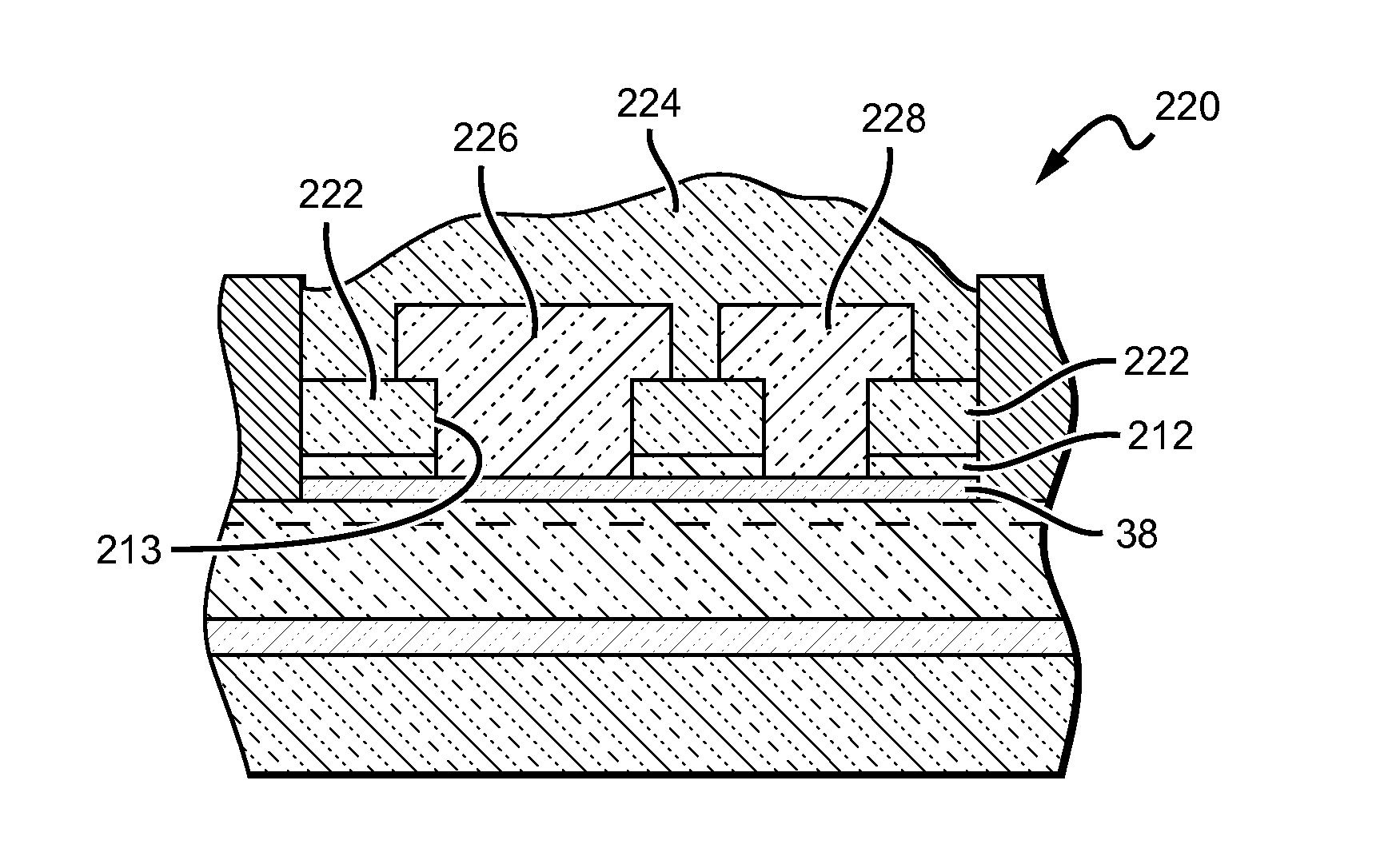

Dual-Gated Group III-V Merged Transistor

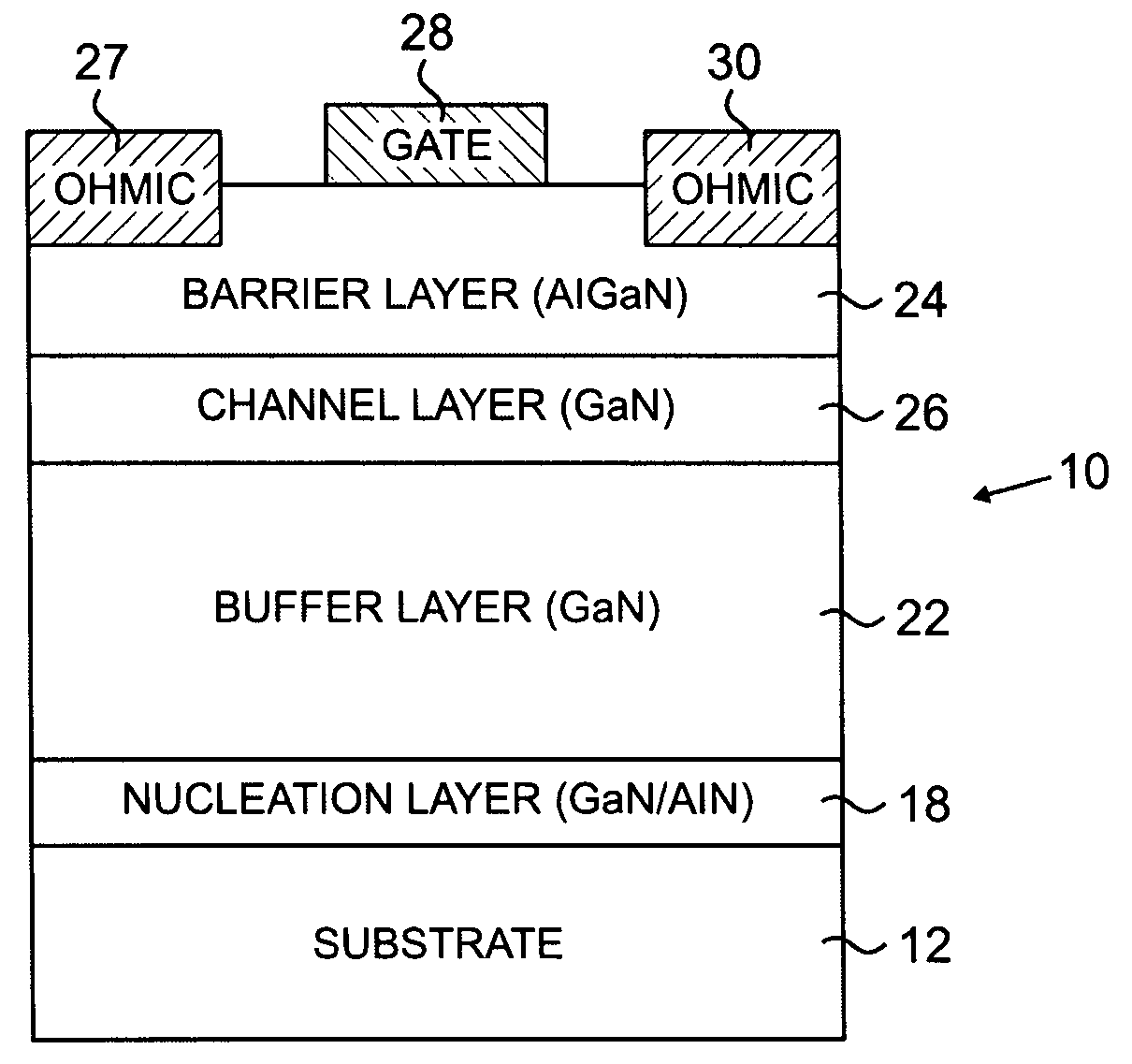

There are disclosed herein various implementations of a group III-V merged cascode transistor. Such a group III-V merged cascode transistor includes a group III-V body disposed over a substrate and configured to produce a two-dimensional electron gas (2DEG). The group III-V body includes a group III-V barrier layer situated over a group III-V channel layer, and a source electrode and a drain electrode. The group III-V merged cascode transistor also includes an enable gate disposed in a recess extending substantially through the group III-V barrier layer, and an operational gate disposed over the group III-V barrier layer, the operational gate not being in physical contact with the enable gate.

Owner:INFINEON TECH AMERICAS CORP

Cascode circuit and integrated circuit having it

ActiveUS20050007200A1Increase powerEasy to operateTransistorHigh frequency amplifiersCapacitanceCascode

A cascode circuit includes a first field effect transistor which has a source terminal grounded, a second field effect transistor which has a source terminal connected to a drain terminal of the first field effect transistor, and a first capacitor connected between the source terminal of the first field effect transistor and a gate terminal of the second field effect transistor. The first field effect transistor and the second field effect transistor are cascode-connected successively. A capacitance value of the first capacitor is 0.01 to 10 times that between the gate and source terminals of the second field effect transistor.

Owner:MITSUBISHI ELECTRIC CORP

Cascode circuit employing a depletion-mode, GaN-based FET

Owner:POWER INTEGRATIONS INC

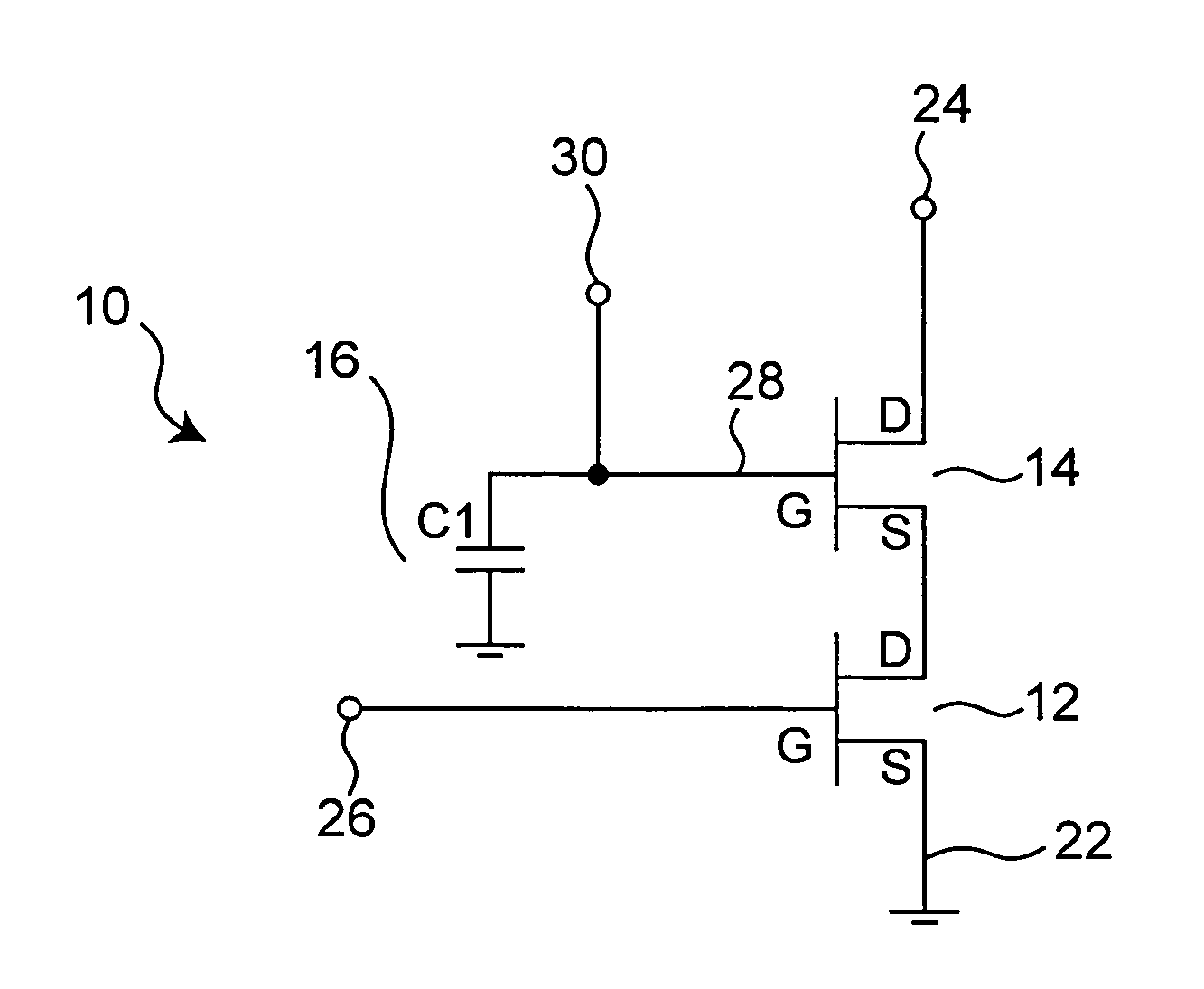

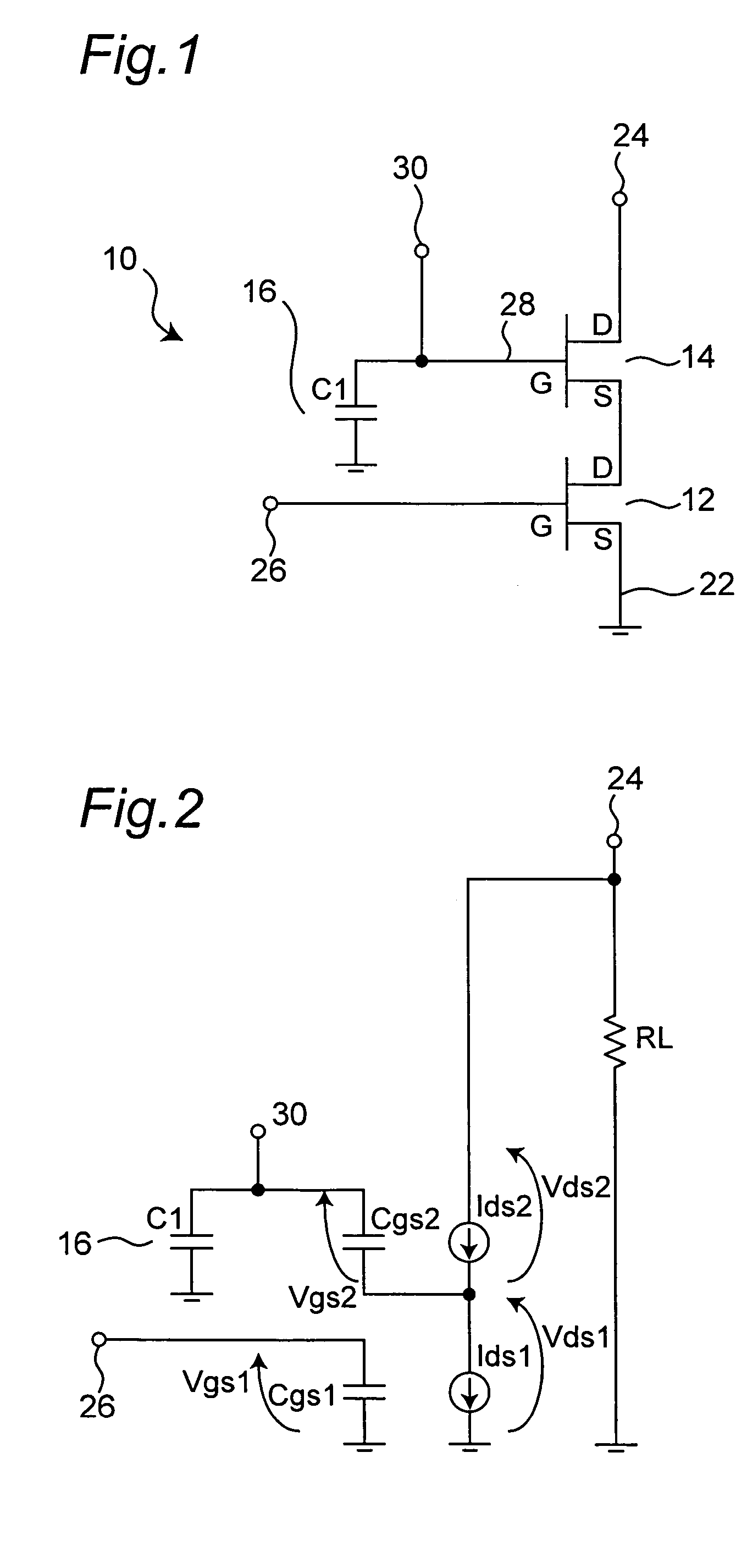

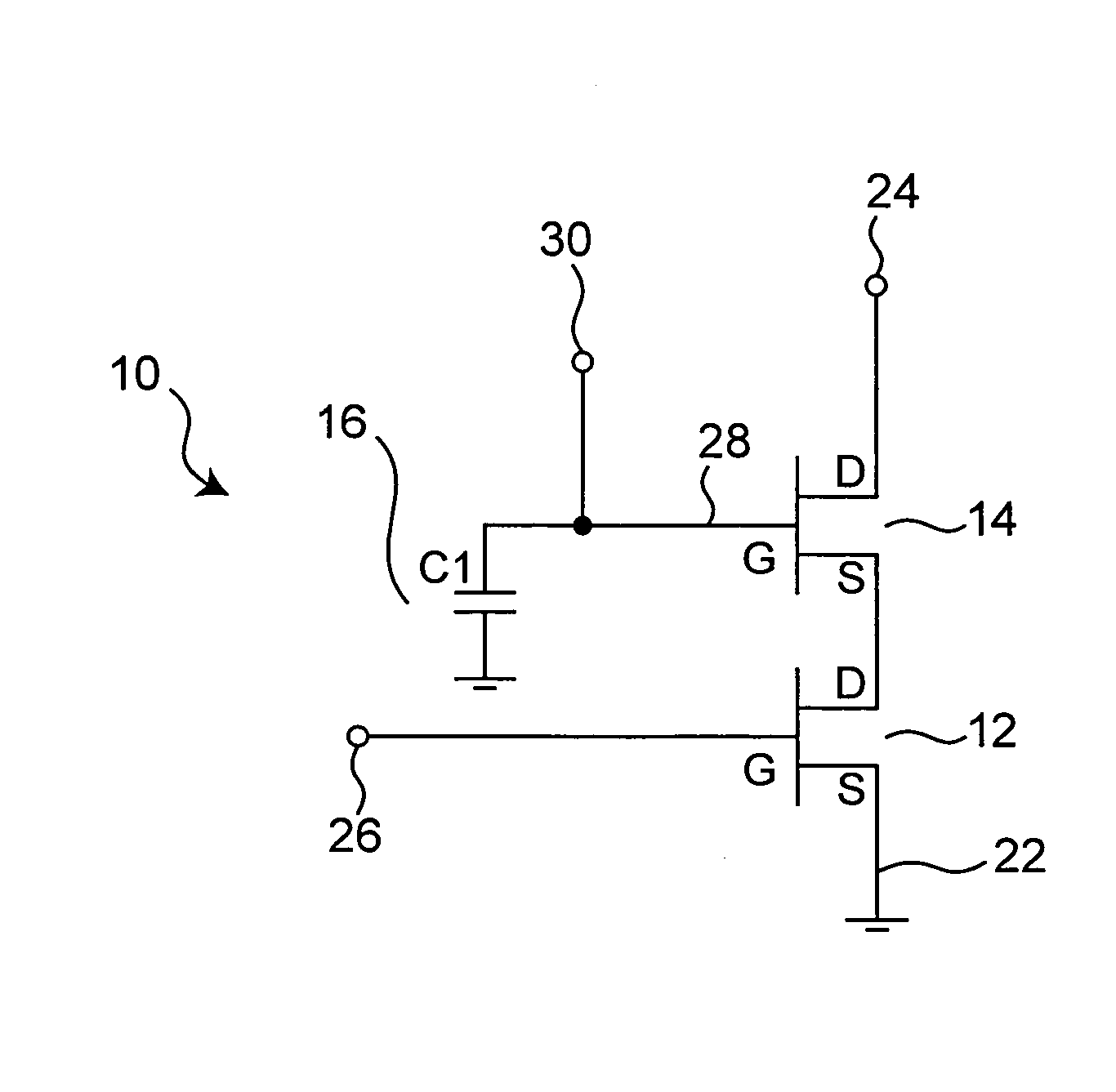

Level shifter with reduced duty cycle variation

InactiveUS20050285658A1Pulse automatic controlAmplifier modifications to reduce noise influenceLevel shiftingCapacitance

A voltage level shifting circuit (10) transitions an input signal at a first voltage to a second voltage higher than the first voltage. A cross-coupled latch provides the second voltage. Cascode configured transistors (16, 26) are connected in series with input transistors (18, 28) that receive the first voltage in complementary form. Capacitive devices (34, 40) are connected between the first voltage and gates of the cascode configured transistors for allowing independent small signal variations to occur on the gates of the cascode configured transistors for better control of duty cycle and rise and fall time matching of the level shifting circuit. Isolation devices (32, 38) permit independent modification of small signal voltages to occur on the gates of the cascode configured transistors.

Owner:FREESCALE SEMICON INC

Cascode switch power supply

ActiveUS7345894B2Reduce power lossMinimum of componentDc-dc conversionElectric variable regulationLow voltageCascode

A switching power supply is disclosed for improving the no-load power drain of low-power mains operated supplies. The power converter utilizes a cascoded switch arrangement with a conventional high voltage power MOSFET and a low voltage, low gate charge MOSFET. Driving only the small low voltage device reduces the power required for gate drive. The disclosed configuration is also capable of generating a non-isolated auxiliary rail for powering its control circuitry utilizing the parasitic capacitance of the high voltage power devices as an element in a charge pump. The resulting power supply requires significantly fewer components.

Owner:DIALOG SEMICONDUCTOR GMBH

CASCODE STRUCTURES WITH GaN CAP LAYERS

A transistor device including a cap layer is described. One embodiment of such a device includes cap layer between a gate and a semiconductor layer. In one embodiment, the thickness of the cap layer is between 5 nm and 100 nm. In another embodiment, the cap layer can be doped, such as delta-doped or doped in a region remote from the semiconductor layer. Devices according to the present invention can show capacitances which are less drain bias dependent, resulting in improved linearity.

Owner:CREE INC

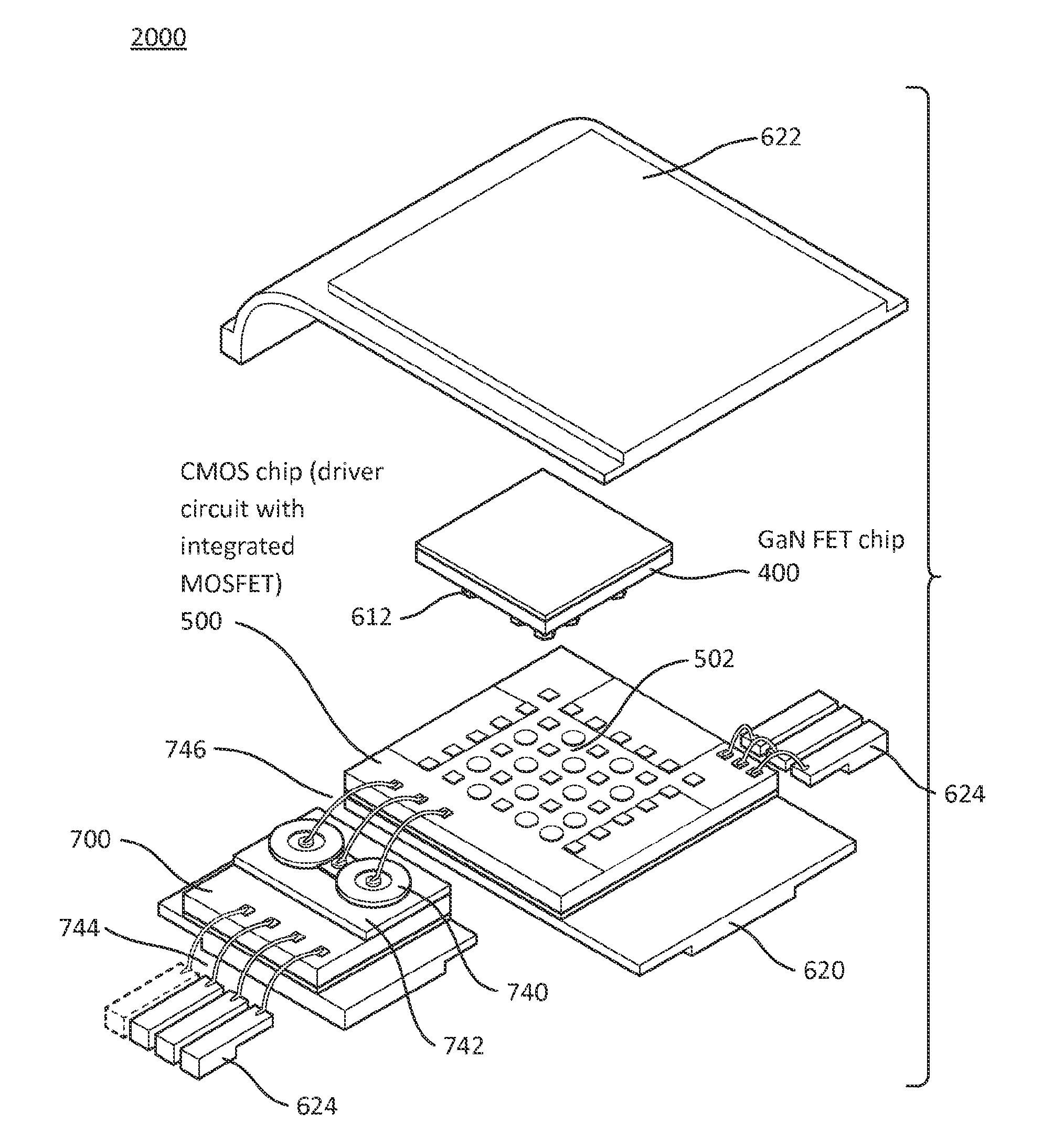

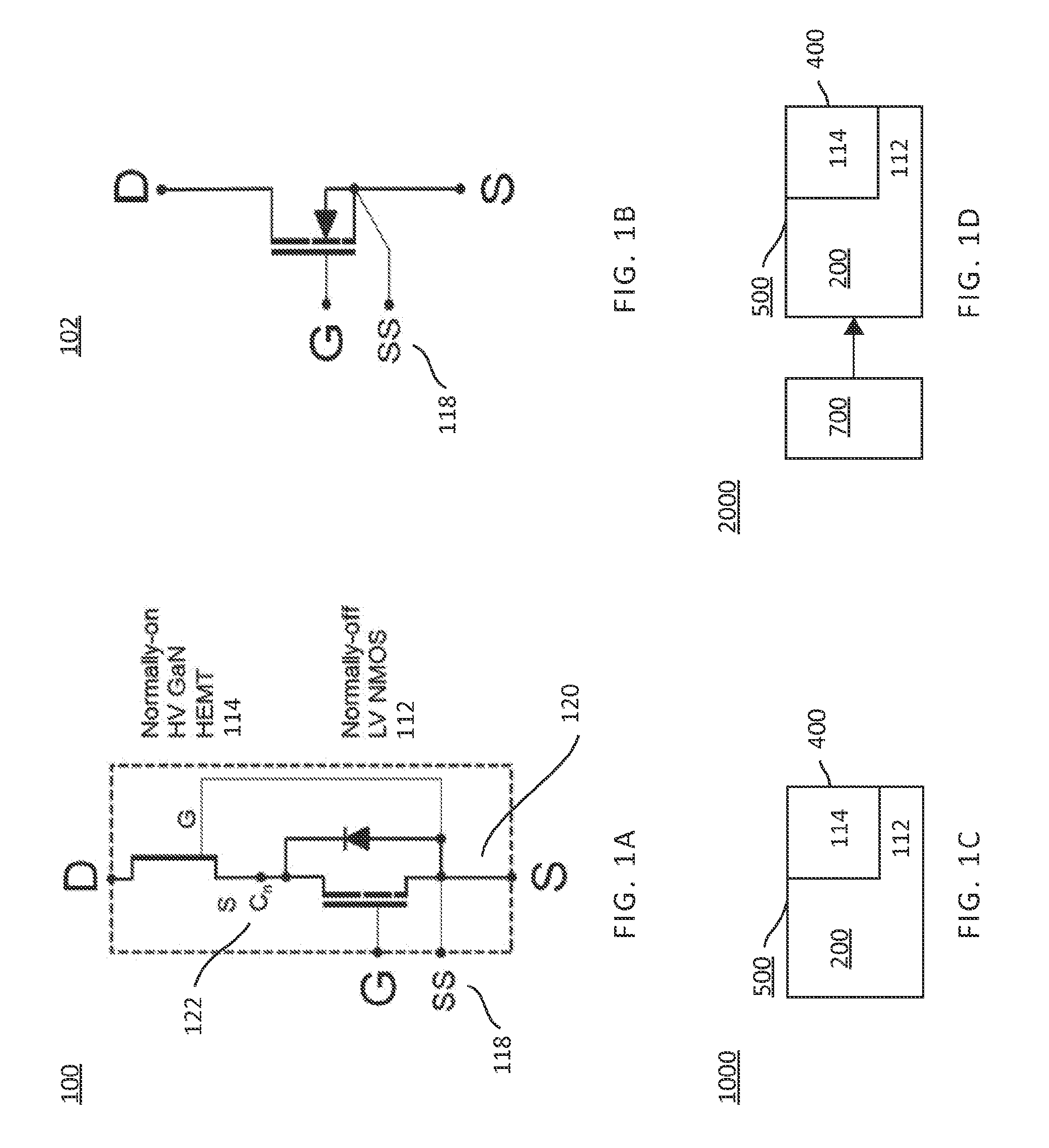

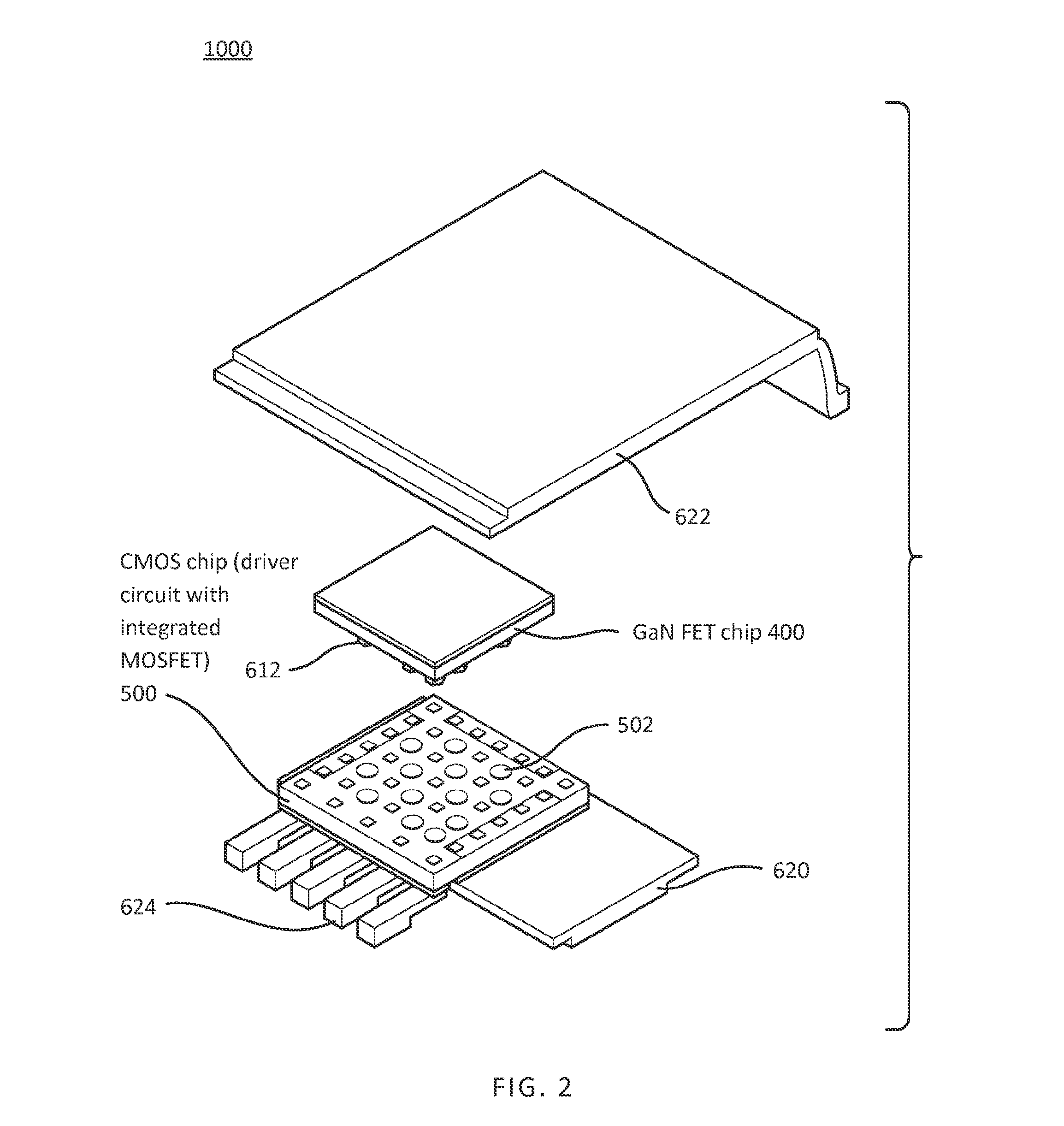

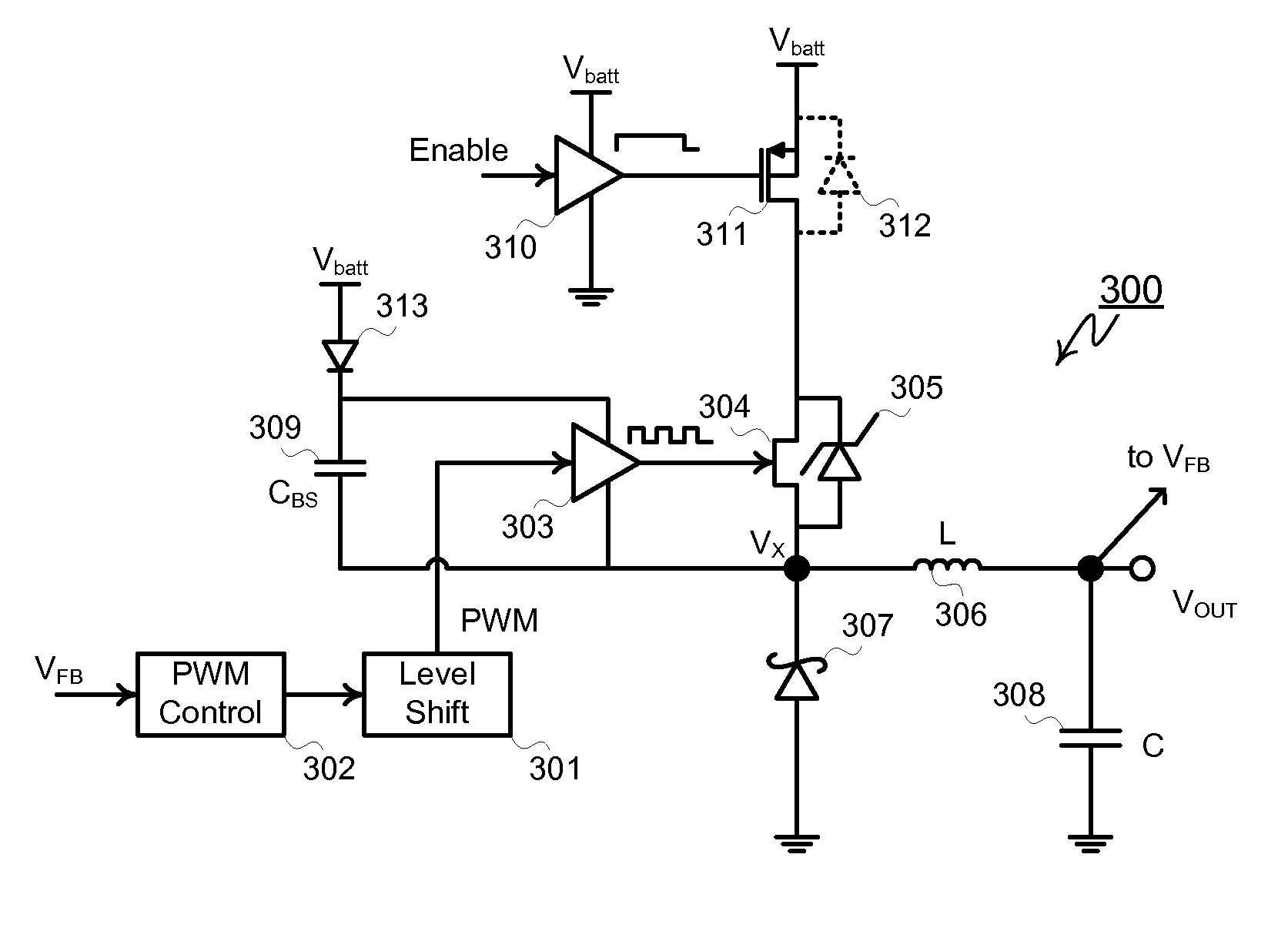

Devices and systems for power conversion circuits

ActiveUS20140175454A1Reduces series inductanceReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETLow voltage

Devices and systems comprising driver circuits are disclosed for MOSFET driven, normally-on gallium nitride (GaN) power transistors. Preferably, a low power, high speed CMOS driver circuit with an integrated low voltage, lateral MOSFET driver is series coupled, in a hybrid cascode arrangement to a high voltage GaN HEMT, for improved control of noise and voltage transients. Co-packaging of a GaN transistor die and a CMOS driver die using island topology contacts, through substrate vias, and a flip-chip, stacked configuration provides interconnections with low inductance and resistance, and provides effective thermal management. Co-packaging of a CMOS input interface circuit with the CMOS driver and GaN transistor allows for a compact, integrated CMOS driver with enhanced functionality including shut-down and start-up conditioning for safer operation, particularly for high voltage and high current switching. Preferred embodiments also provide isolated, self-powered, high speed driver devices, with reduced input losses.

Owner:GAN SYST

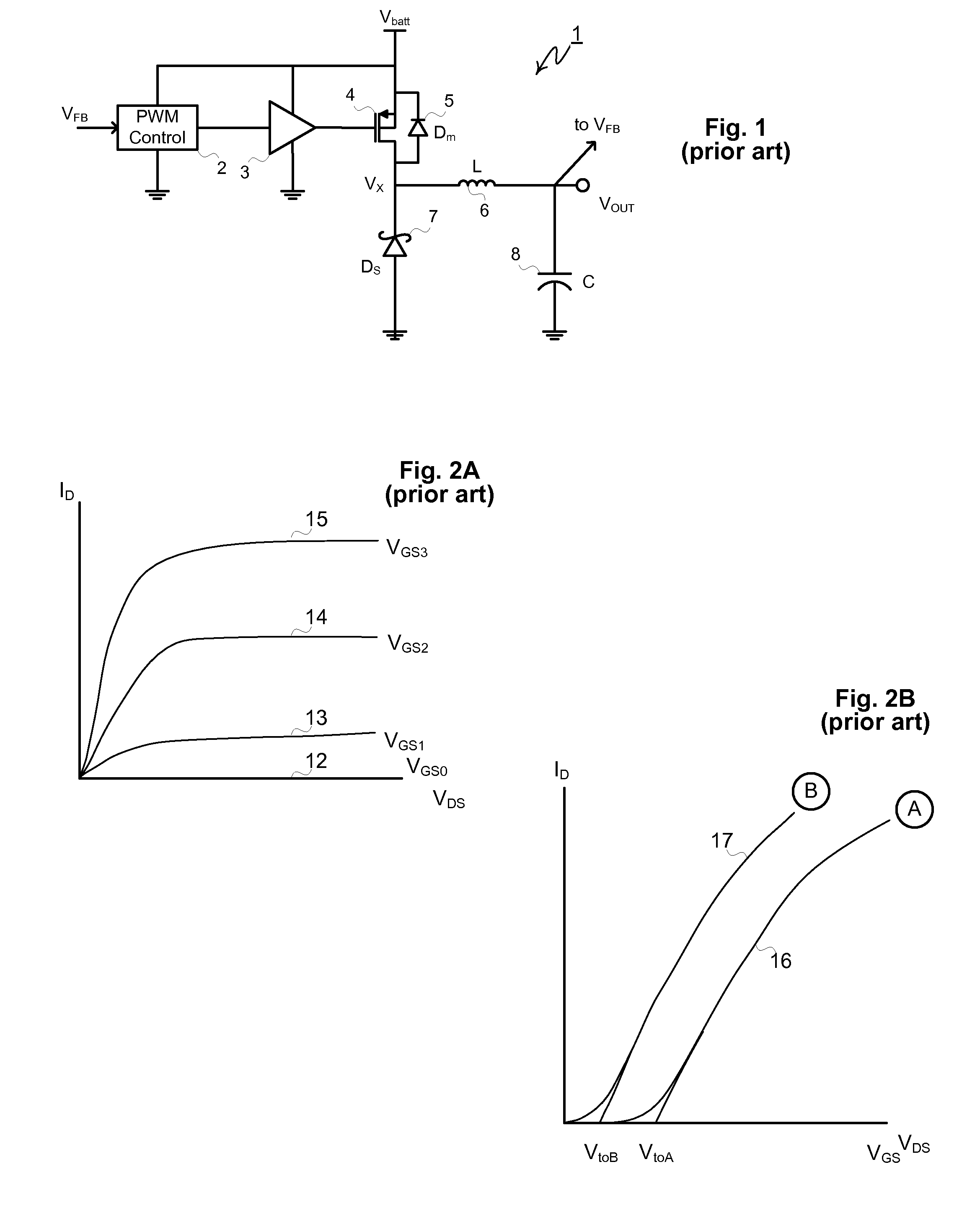

High-Frequency Buck Converter that Includes a Cascode MESFET-MOSFET Power Switch

InactiveUS20080191679A1Lower on-resistanceLow off-state drain leakageDc-dc conversionElectric variable regulationMOSFETElectrical battery

A Buck converter that includes a cascode switch comprising a series connected MESFET and MOSFET power switch. The cascode power switch is typically connected in between a power source and a node Vx. The node Vx is connected to an output node via an inductor and to ground via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to the battery and to ground. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED