Patents

Literature

178 results about "MESFET" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A MESFET (metal–semiconductor field-effect transistor) is a field-effect transistor semiconductor device similar to a JFET with a Schottky (metal-semiconductor) junction instead of a p-n junction for a gate.

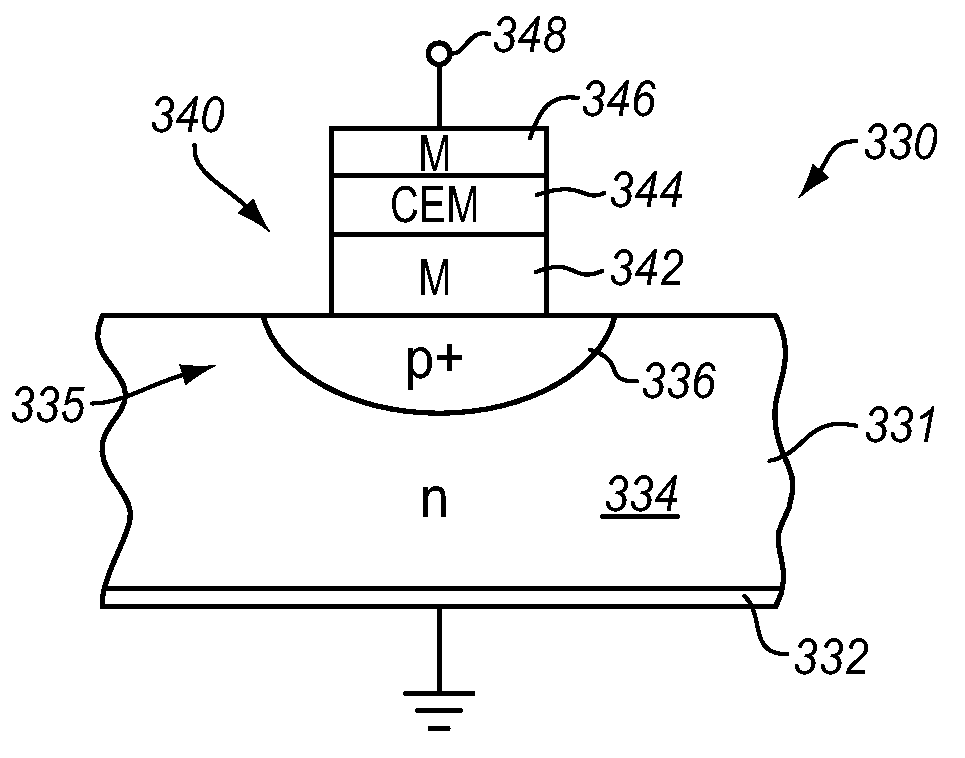

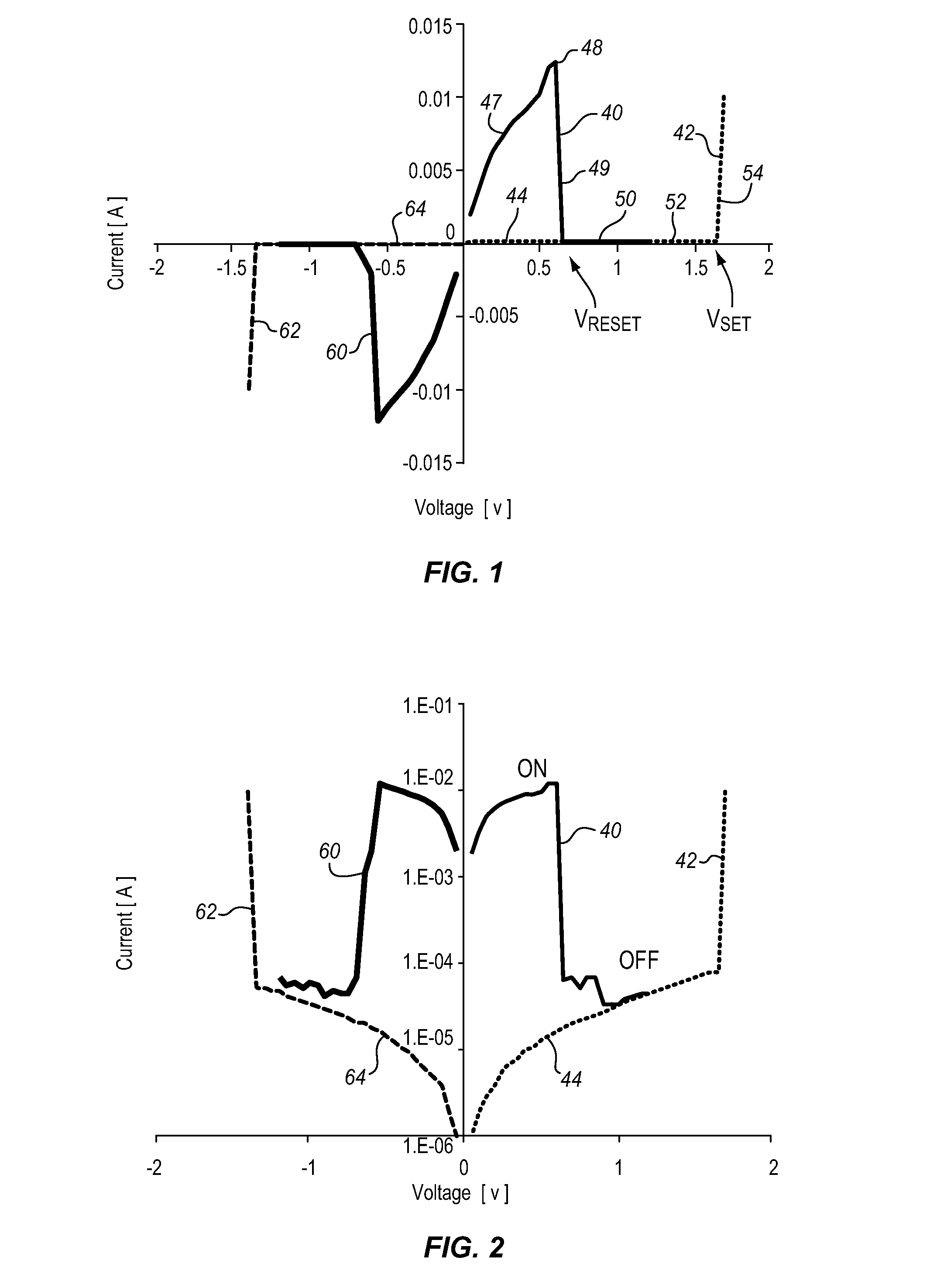

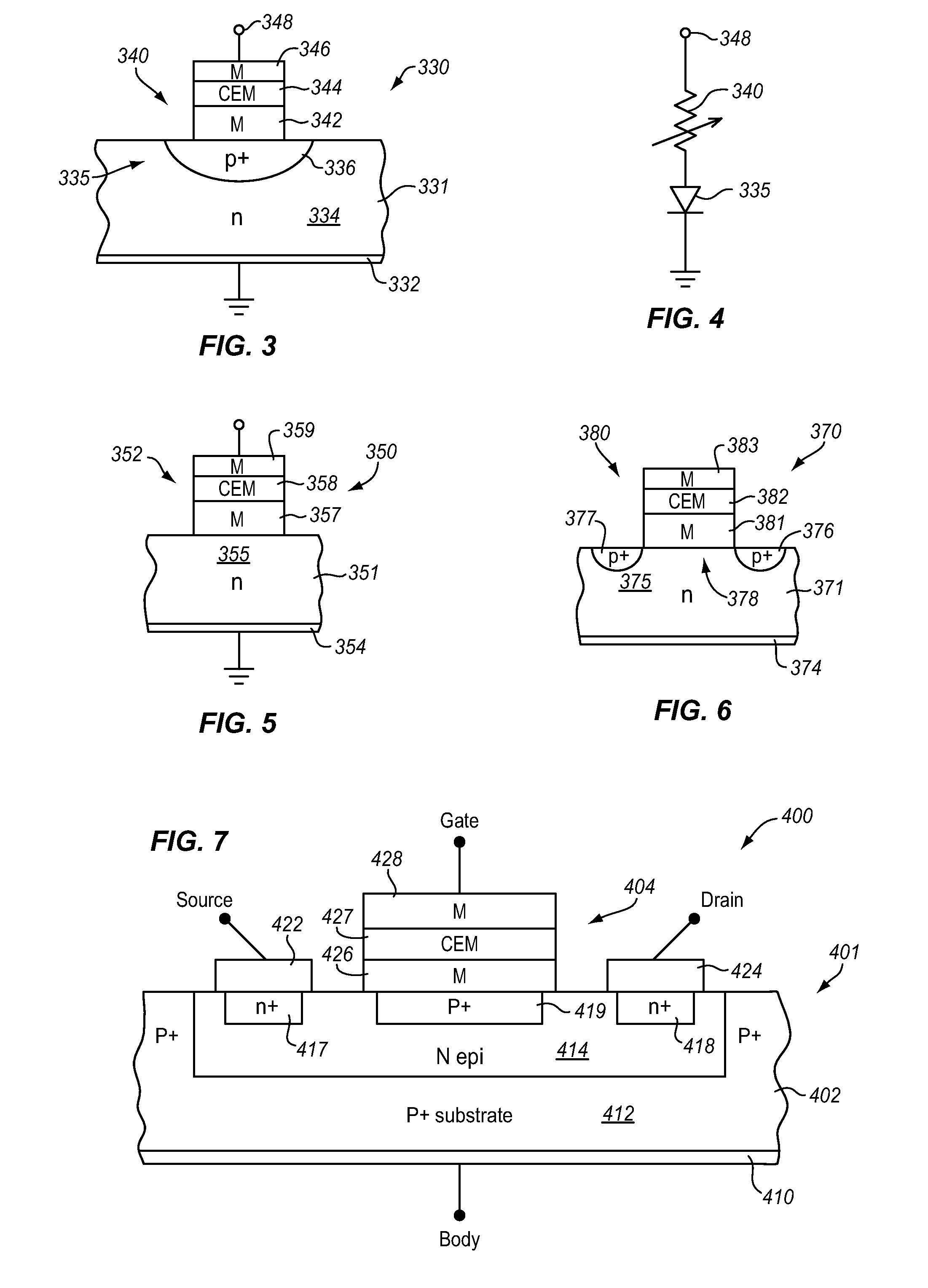

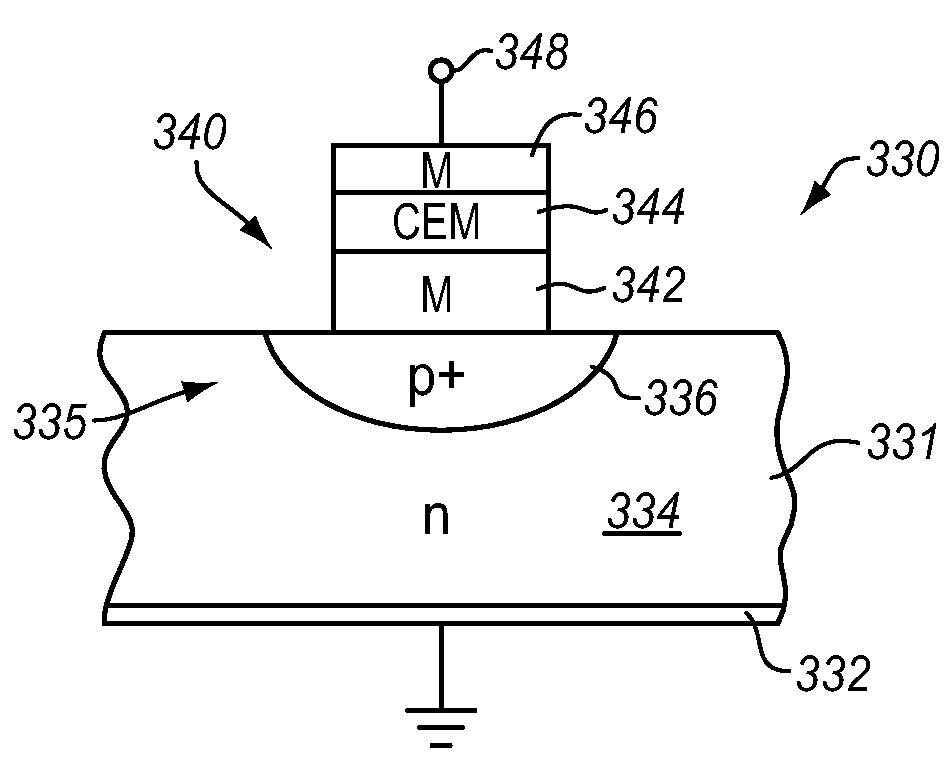

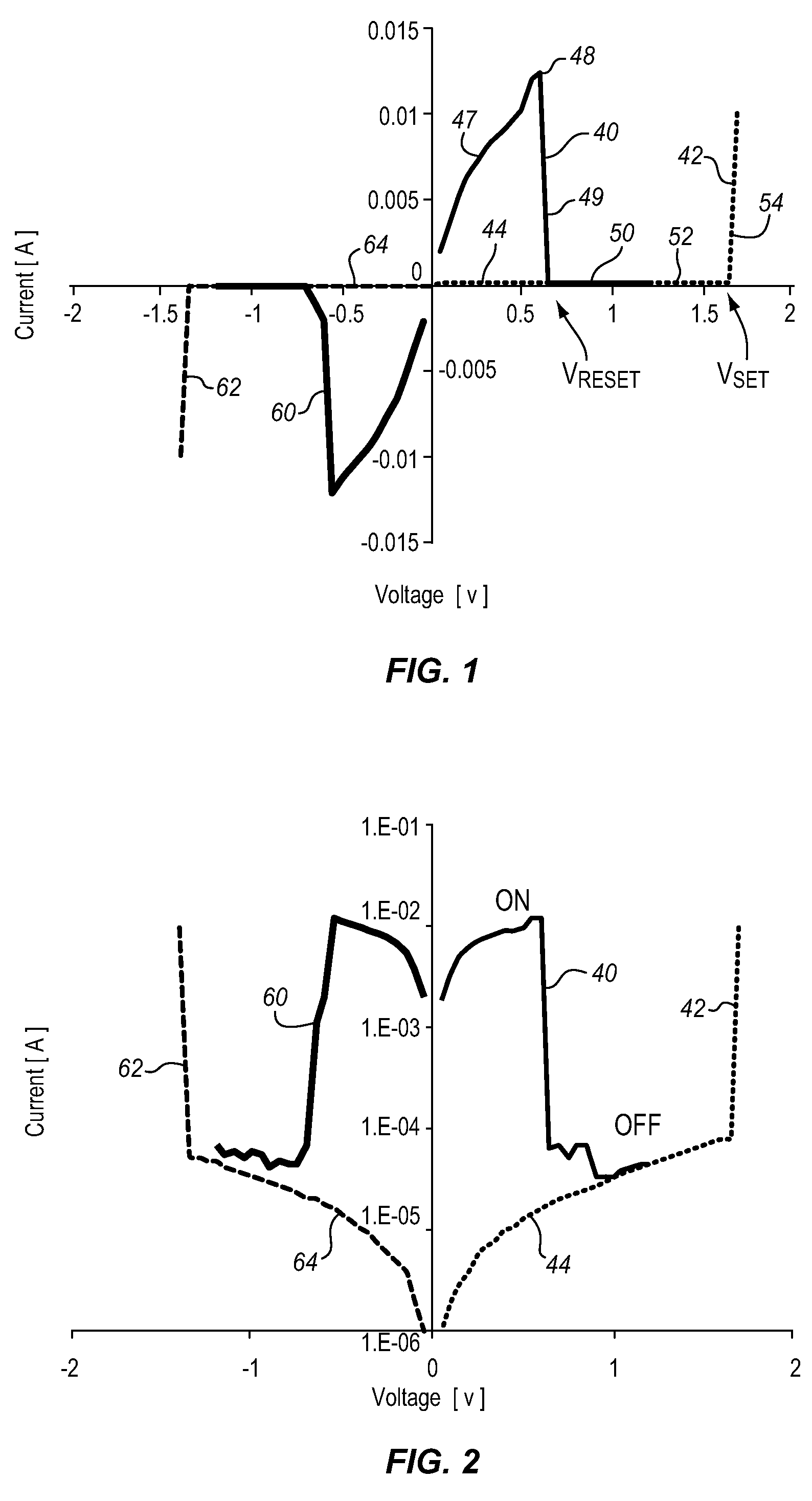

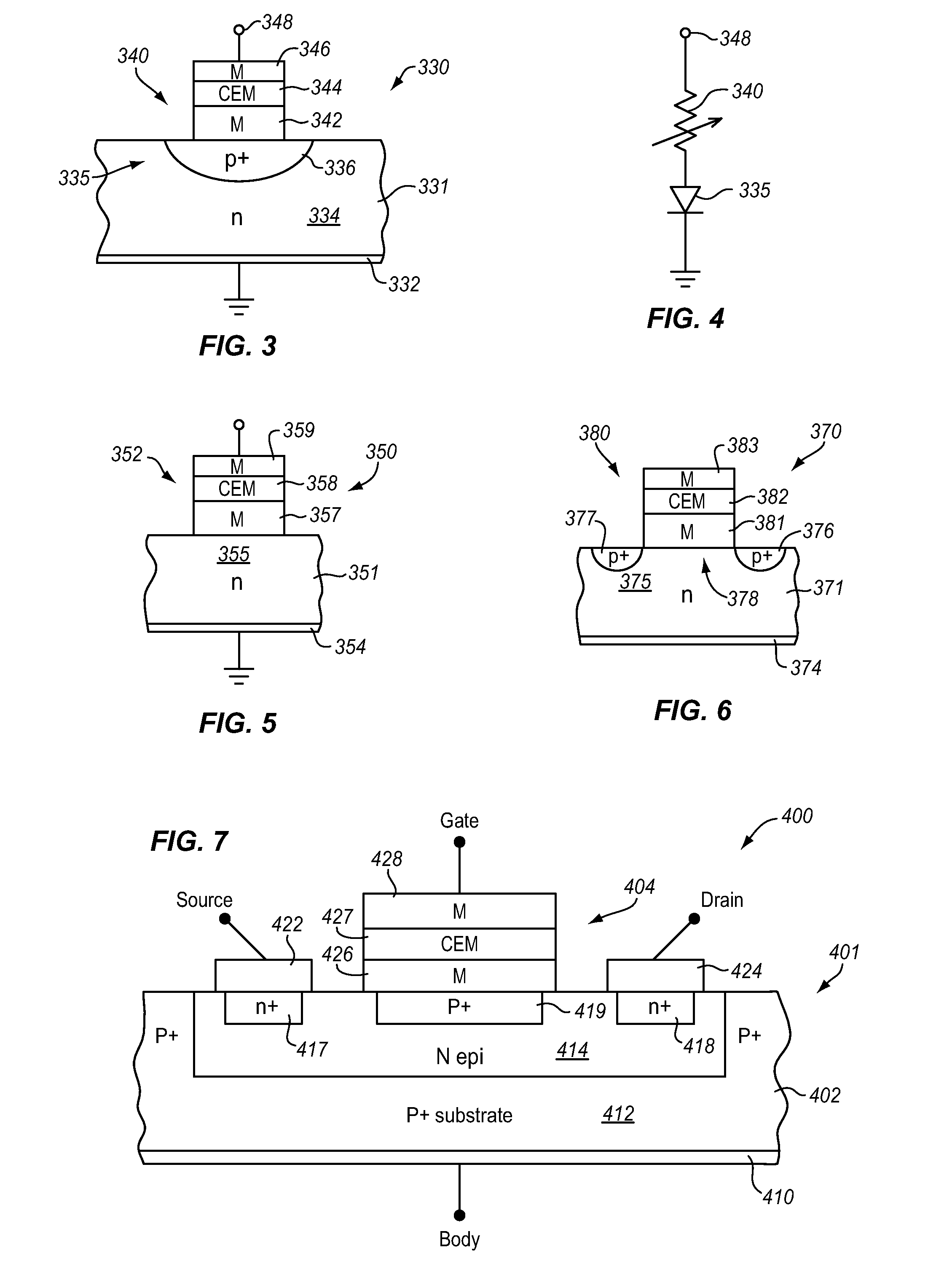

Non-volatile resistance switching memories and methods of making same

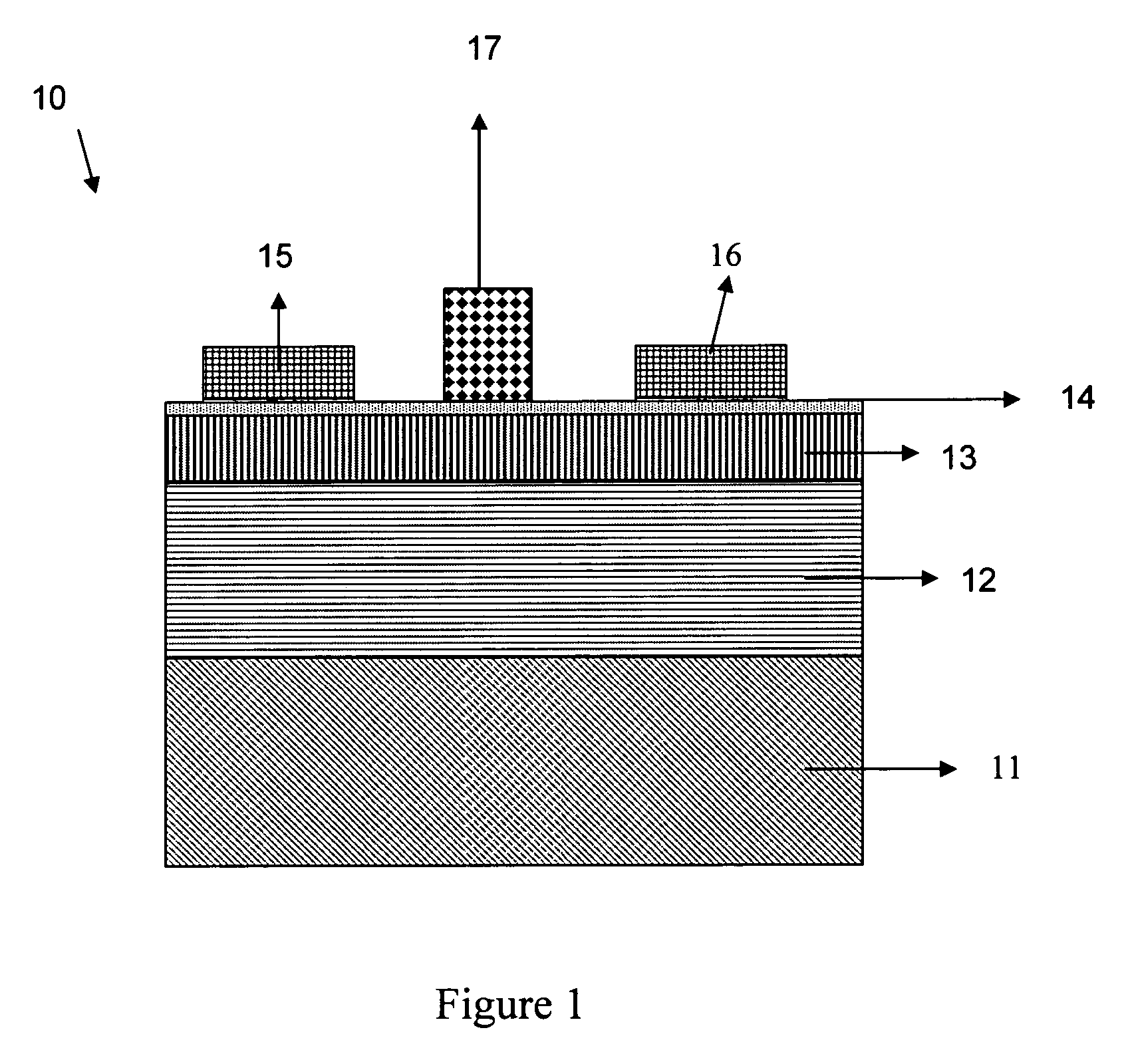

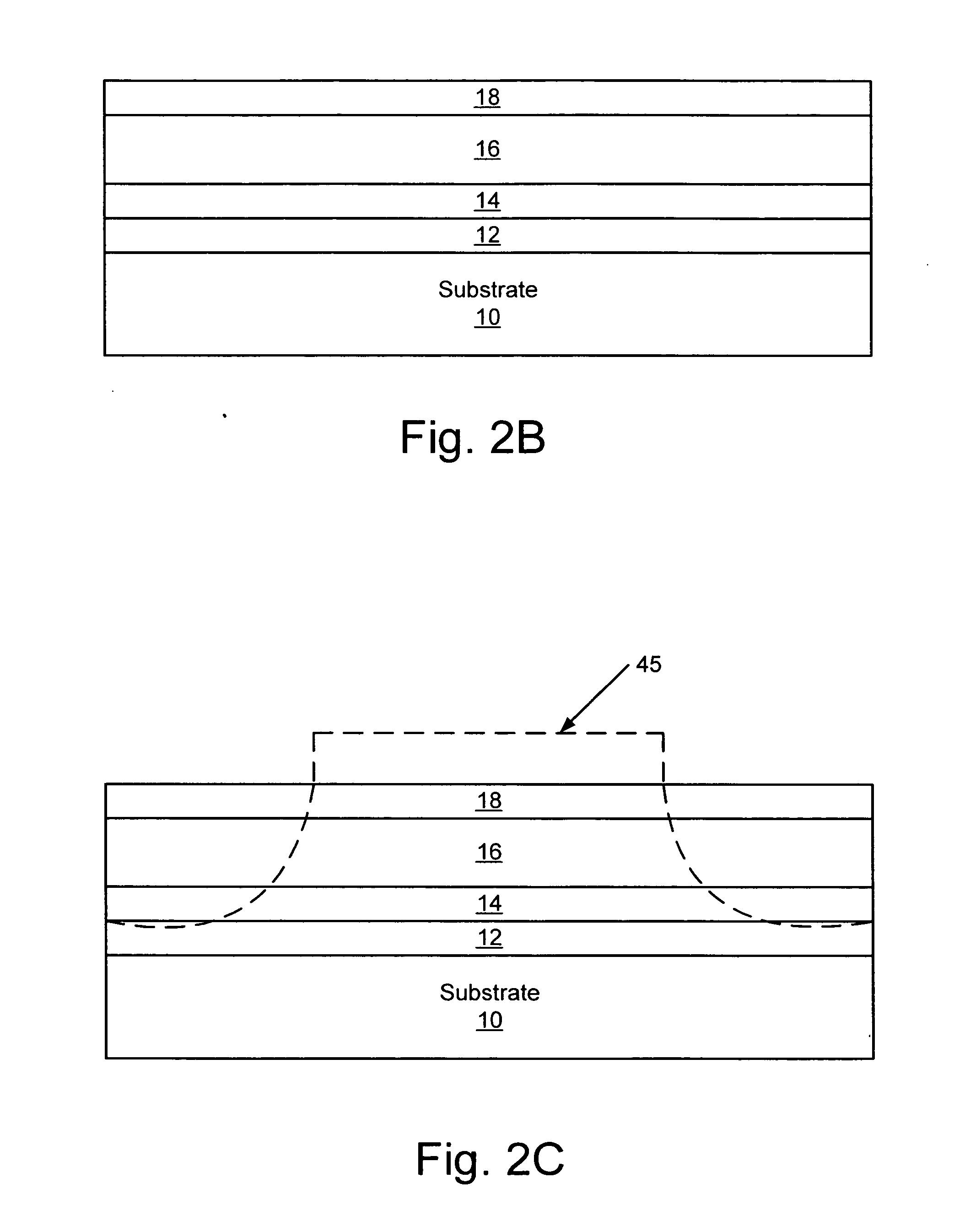

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

Non-volatile resistance switching memories and methods of making same

An integrated circuit memory cell including: a semiconductor having a first active area, a second active area, and a channel between the active areas; and a layer of a variable resistance material (VRM) directly above the channel. In one embodiment, there is a first conductive layer between the VRM and the channel and a second conductive layer directly above the VRM layer. The VRM preferably is a correlated electron material (CEM). The memory cell comprises a FET, such as a JFET or a MESFET. In another embodiment, there is a layer of an insulating material between the VRM and the channel. In this case, the memory cell may include a MOSFET structure.

Owner:SYMETRIX MEMORY

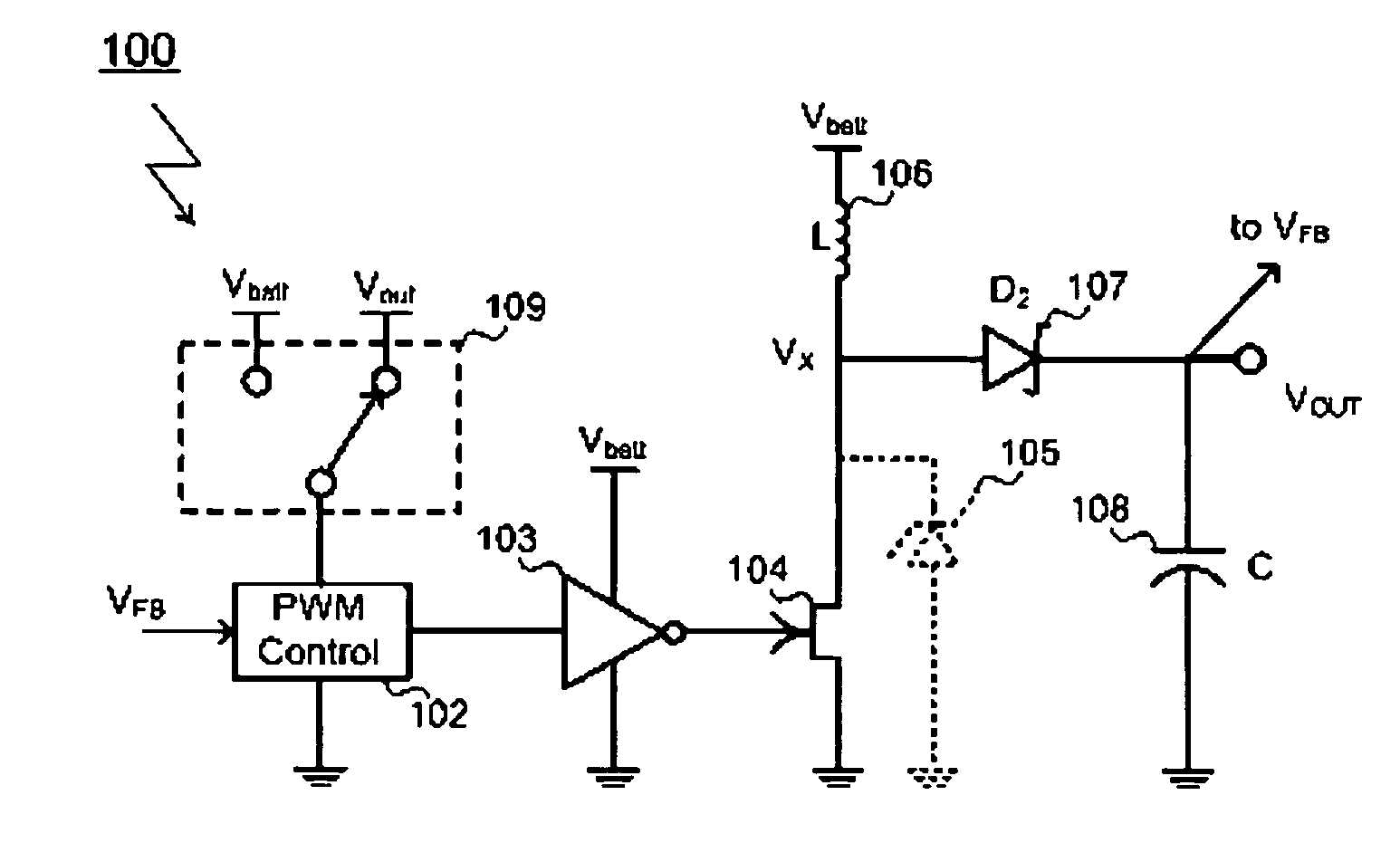

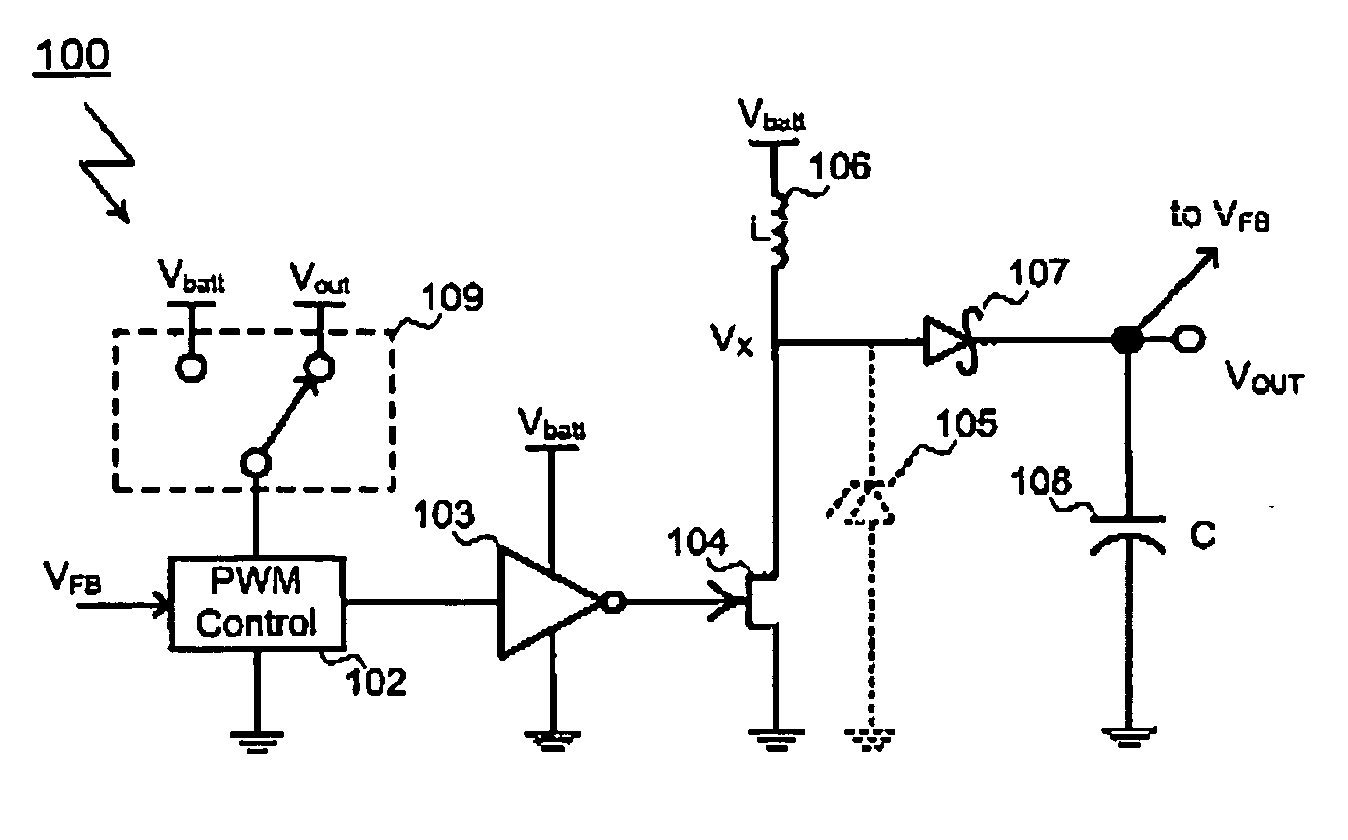

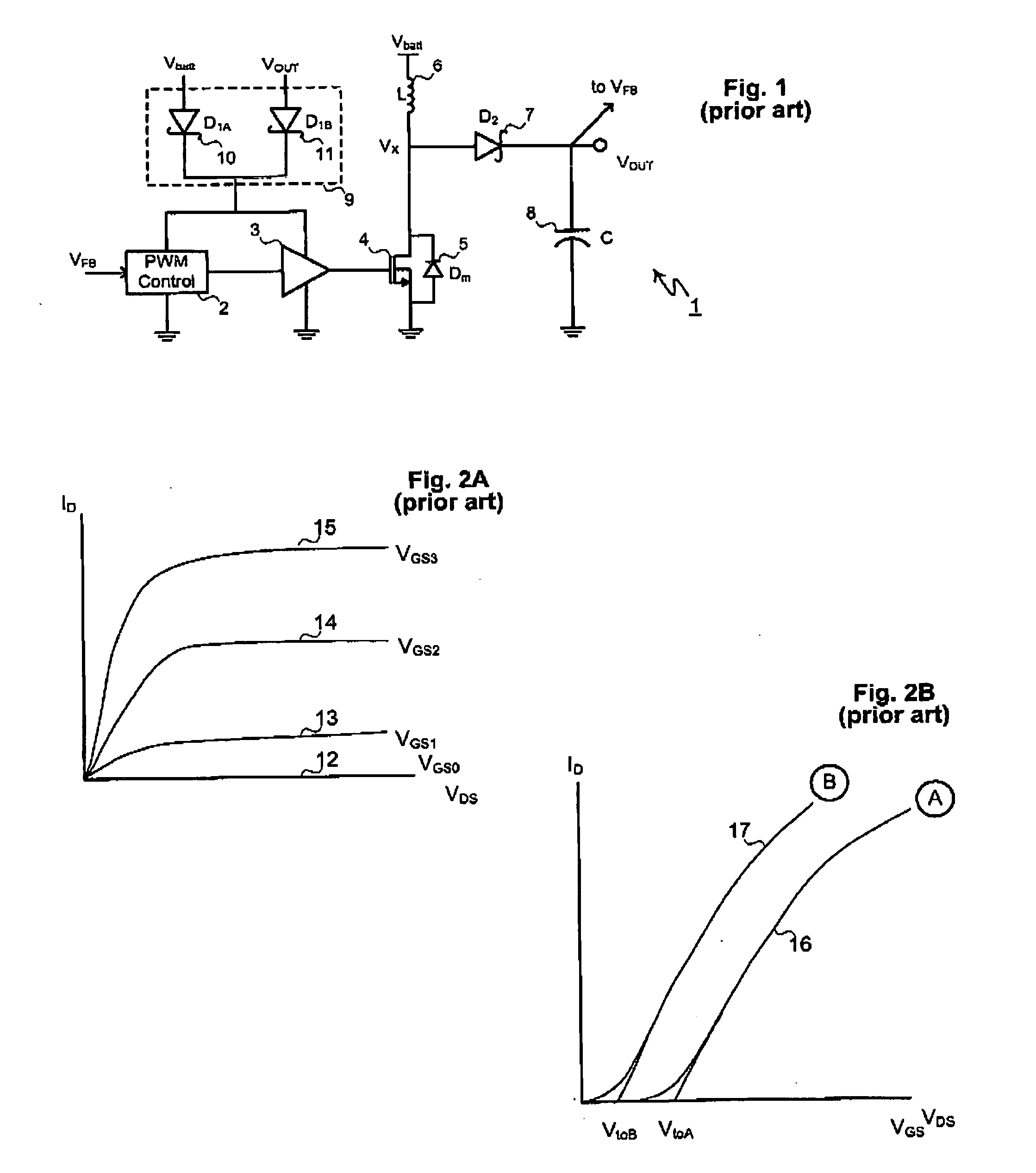

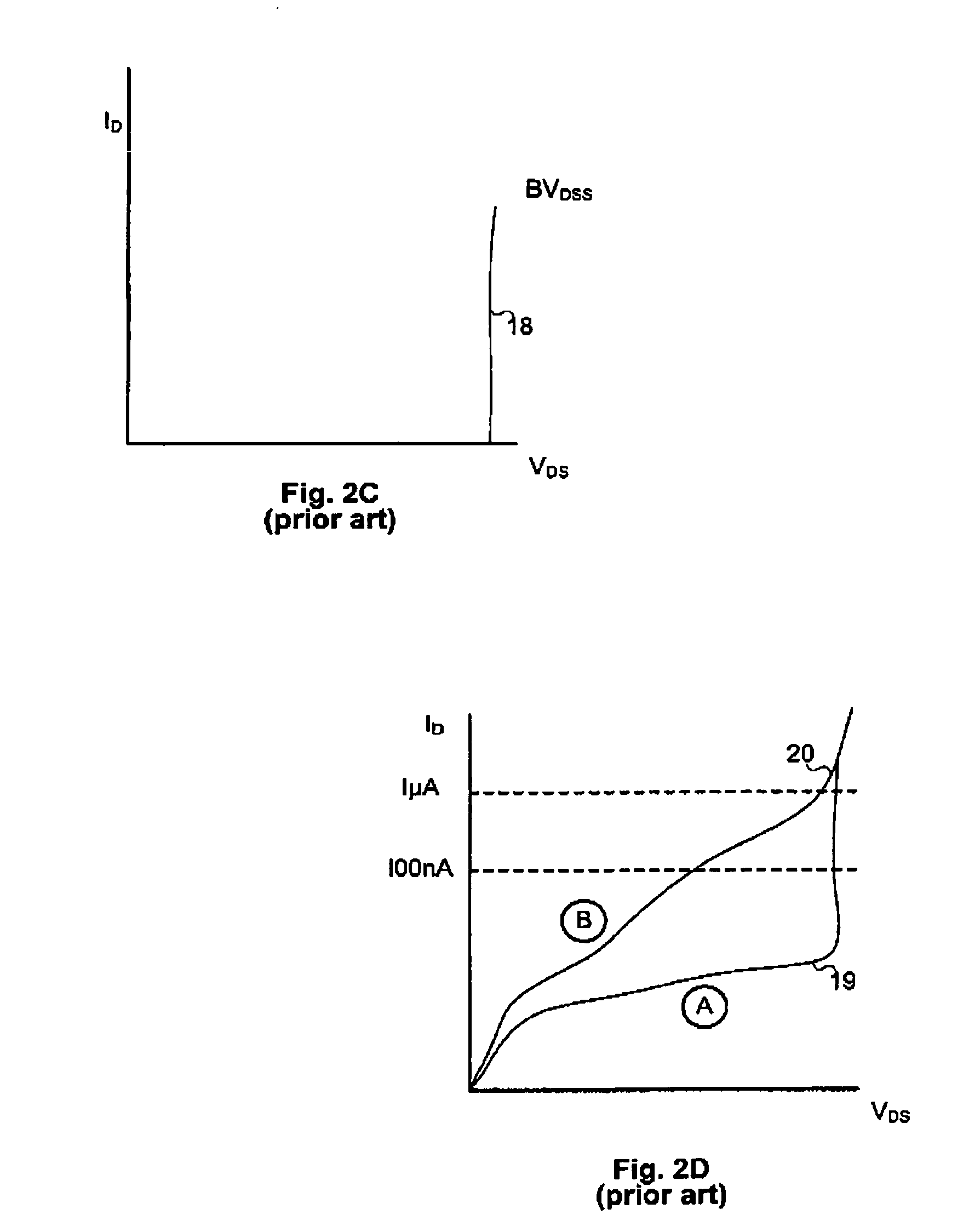

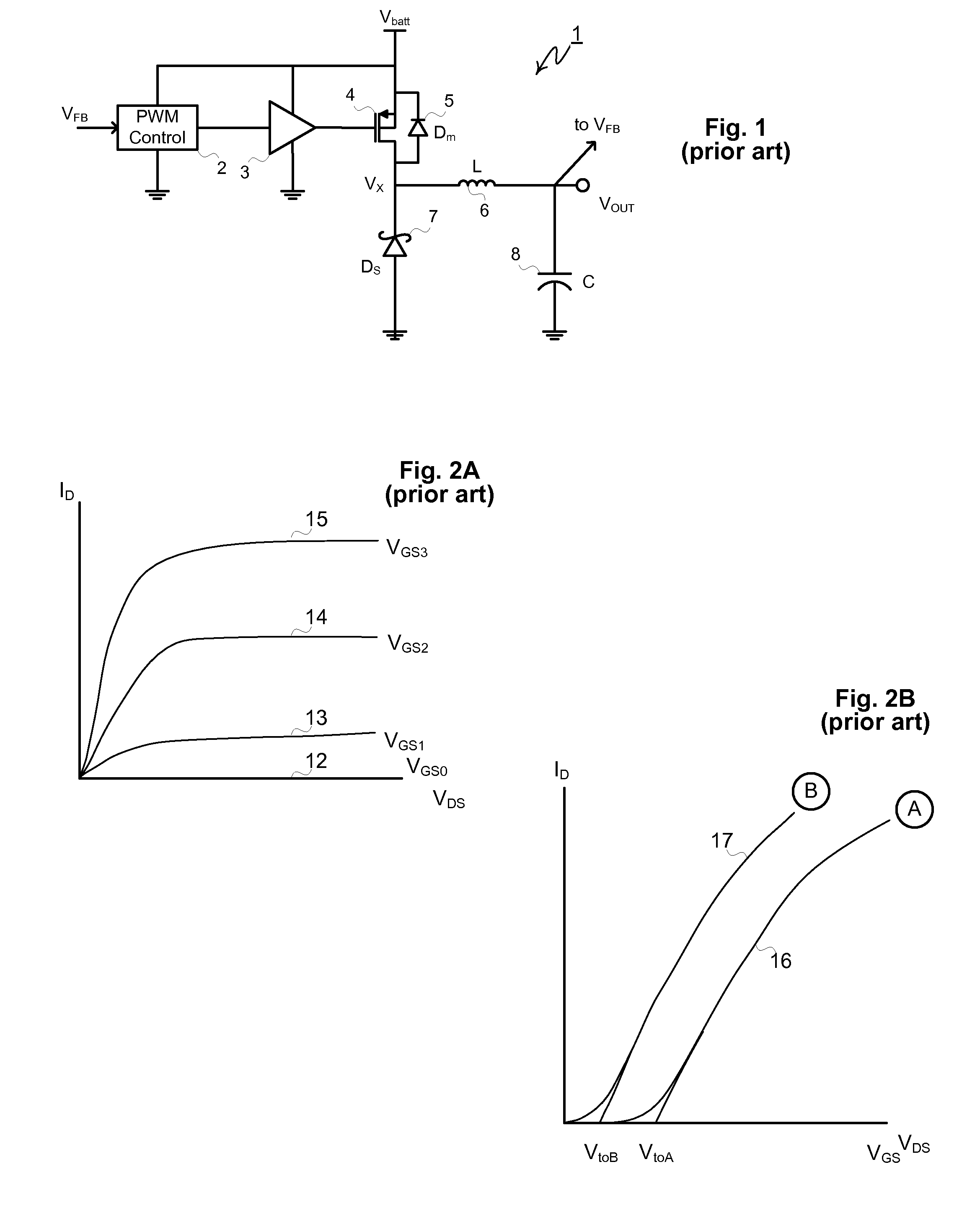

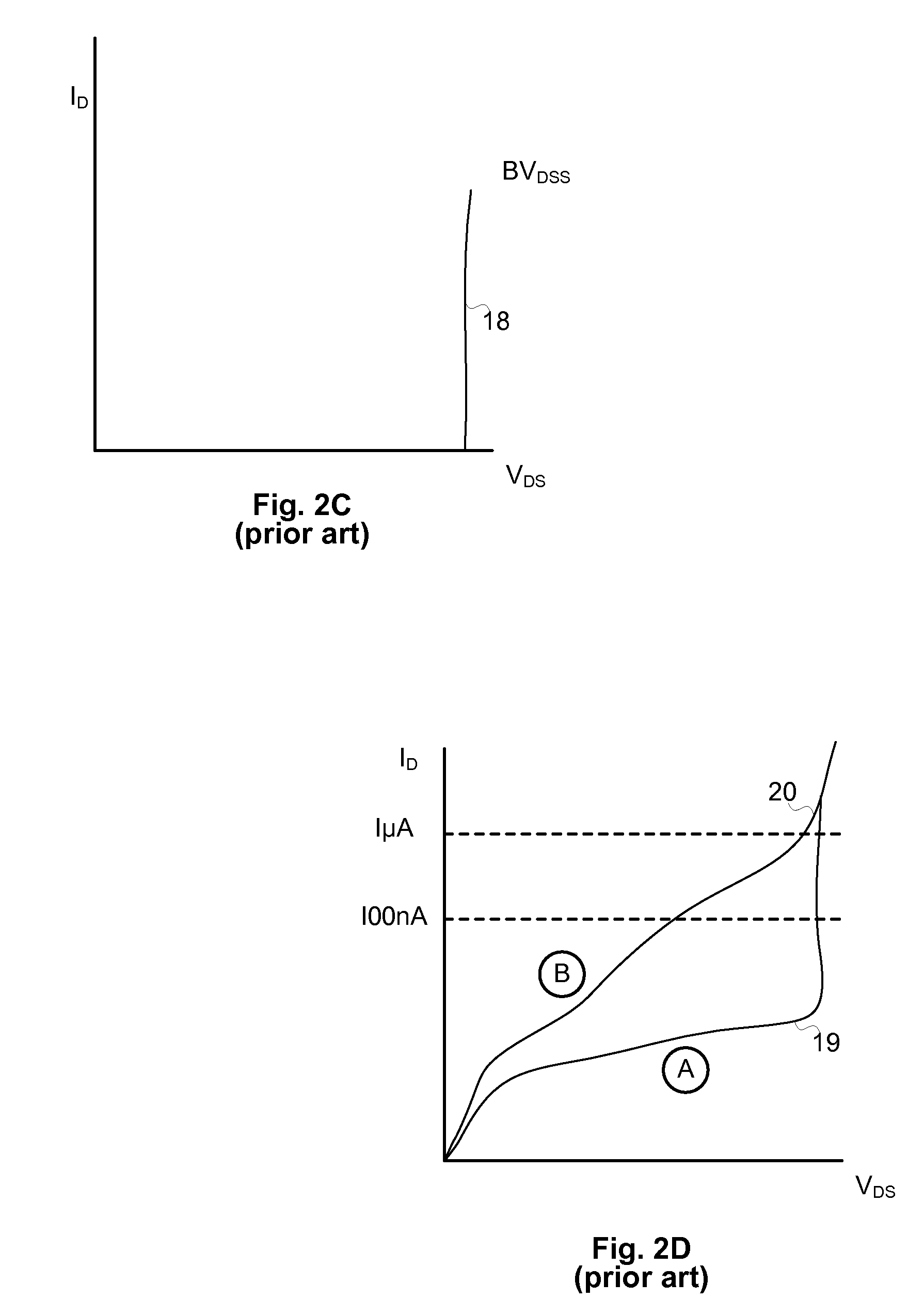

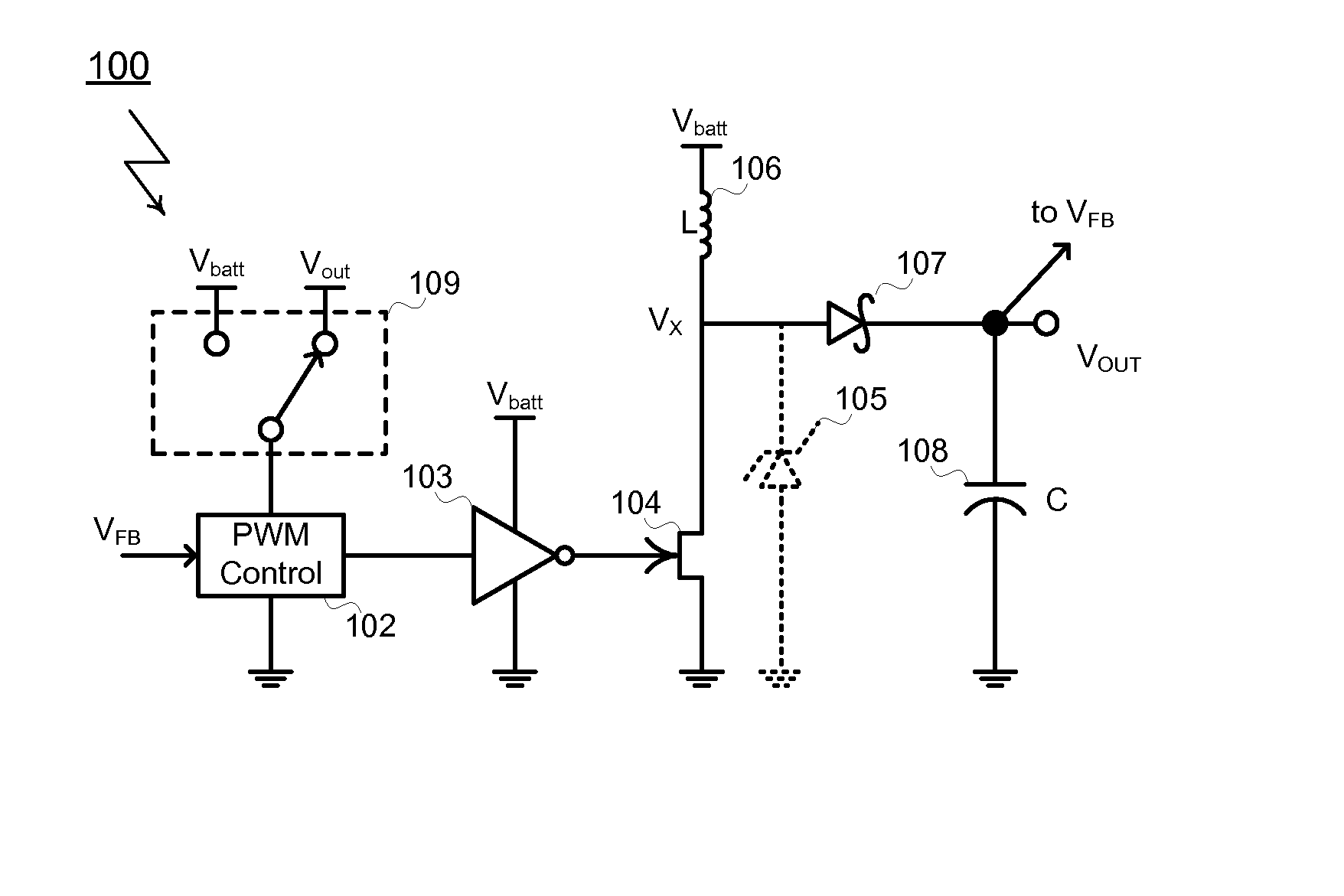

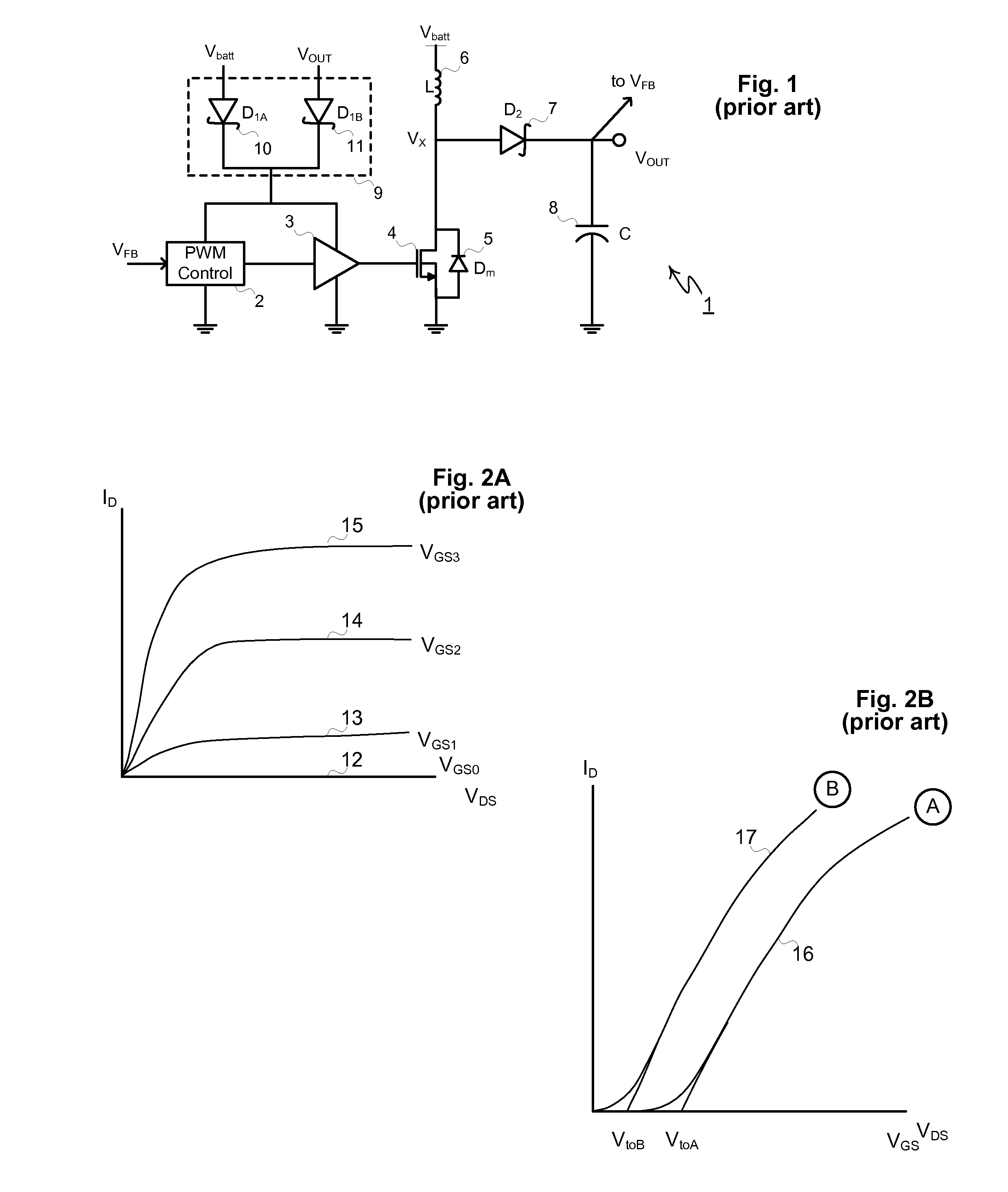

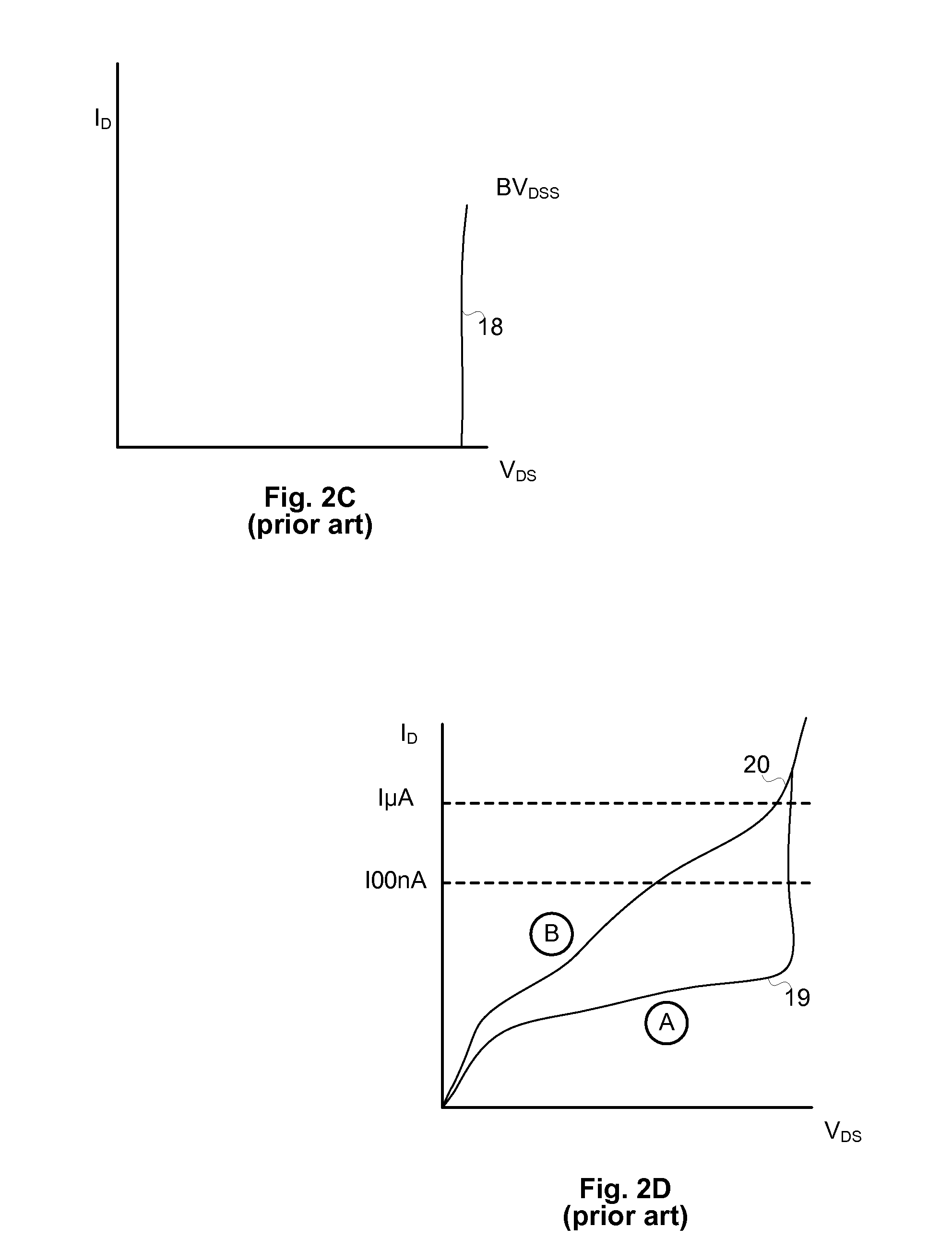

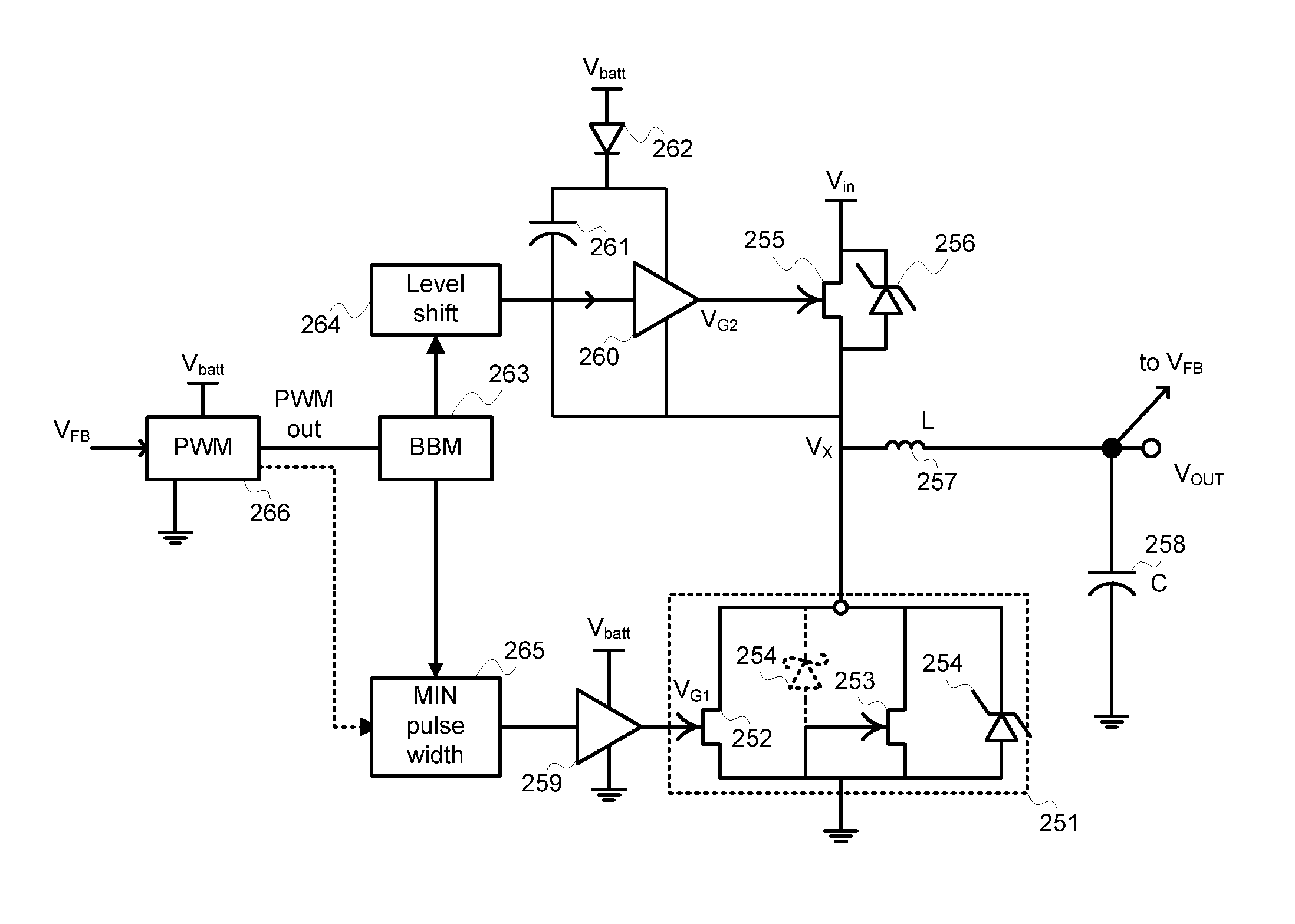

High-Frequency Power MESFET Boost Switching Power Supply

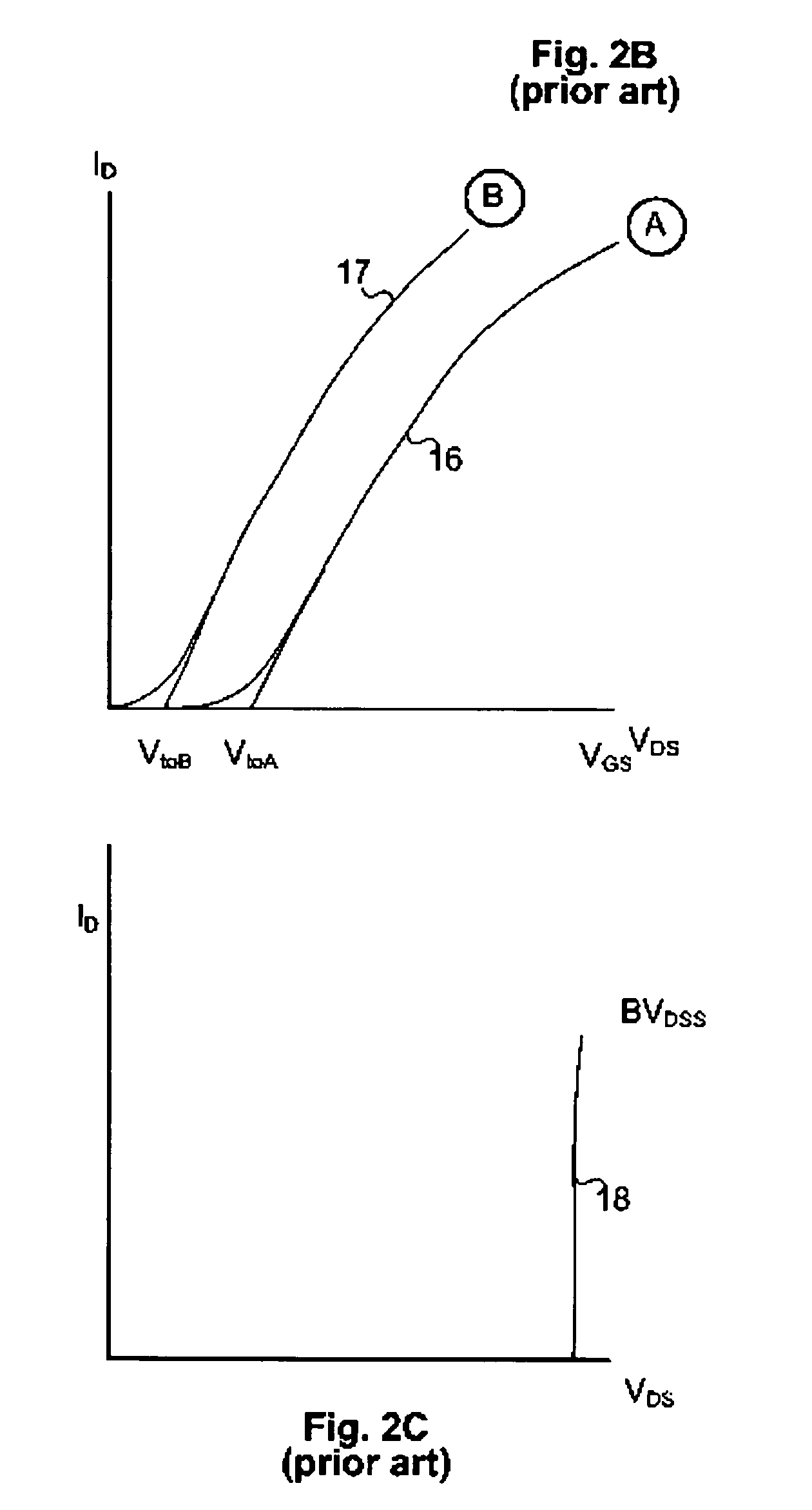

InactiveUS20080186004A1Lower on-resistanceLow off-state drain leakageTransistorDc-dc conversionMOSFETHigh frequency power

A MESFET based boost converter includes an N-channel MESFET connected to a node Vx. An inductor connects the node Vx to a battery or other power source. The node Vx is also connected to an output node via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to ground and to the output node. The maximum voltage impressed across the low side MESFET is optionally clamped by a Zener diode. In some implementations, the MESFET is connected in series with a MOSFET. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter. In other implementations, more than one MESFET is connected in series with a MOSFET, the MOSFETs being switched off during periods of inactivity to suppress leakage currents.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

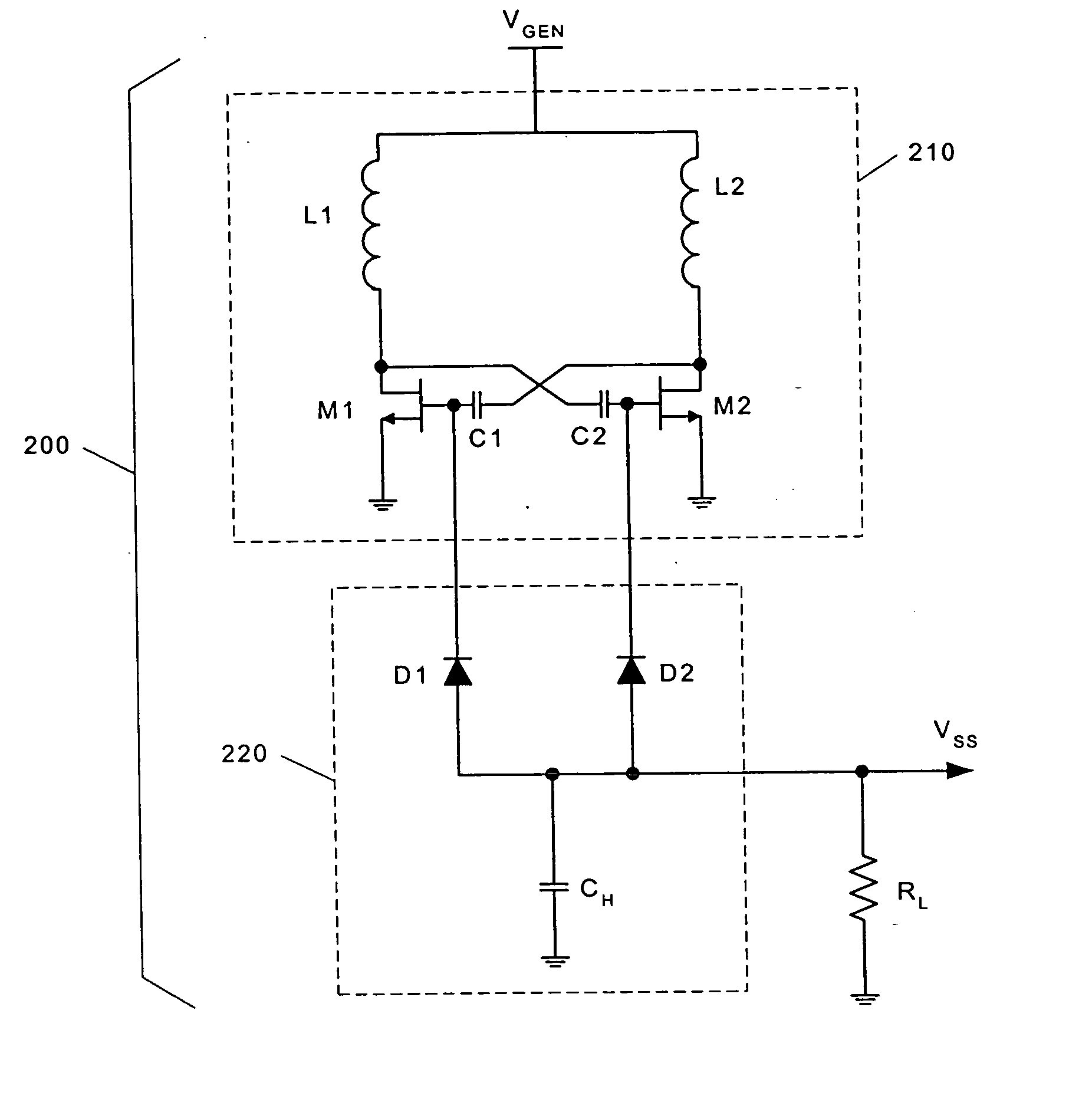

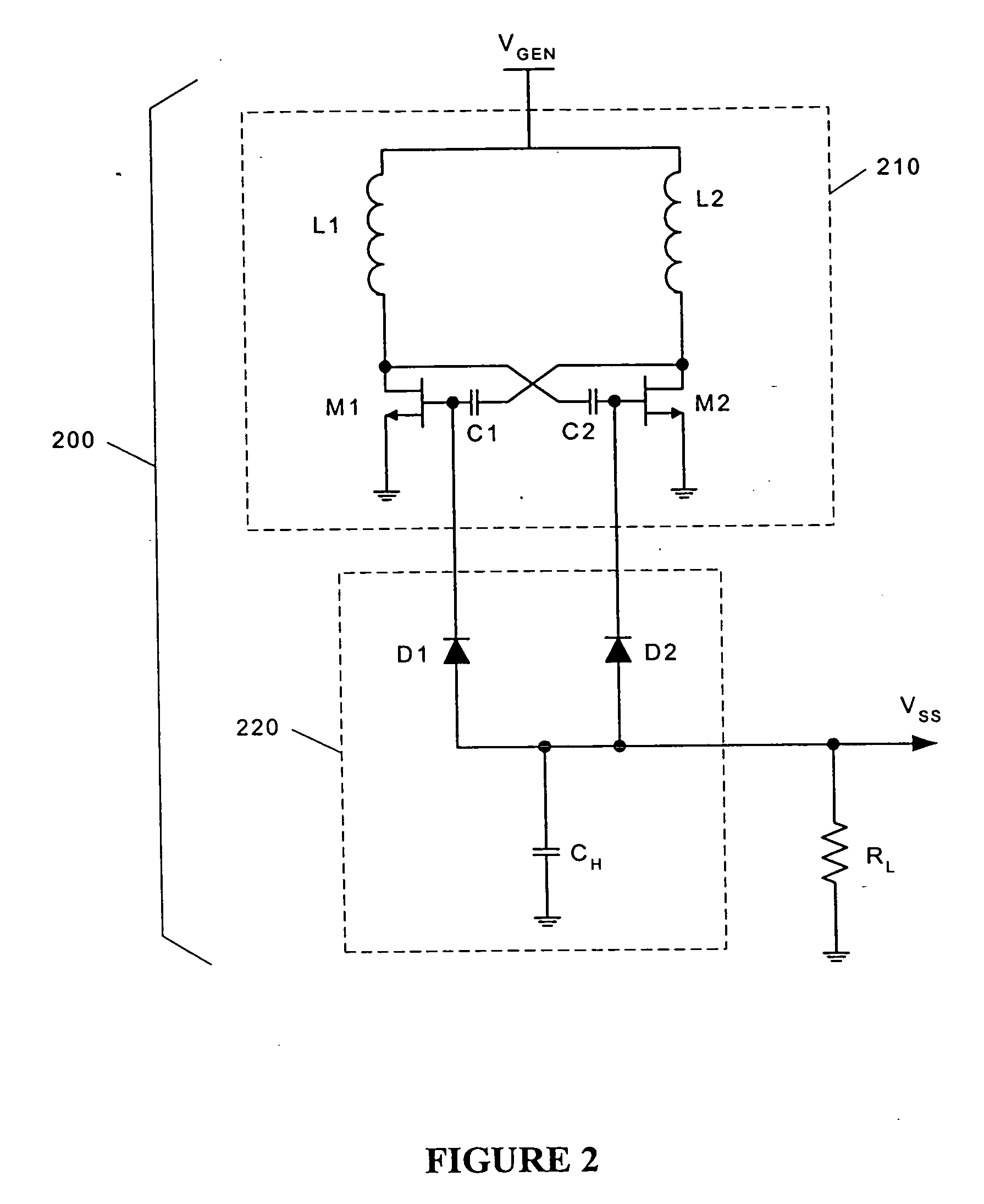

MMIC DC-to-DC converter

InactiveUS20050242795A1Improve efficiencyImprove reliabilityDc-dc conversionElectric variable regulationConvertersLow noise

An improved Monolithic Microwave Integrated Circuit DC-to-DC voltage converter fabricated in GaAs MESFET technology is introduced. The converter comprises a differential oscillator having crossed-coupled symmetrical inductors that ensure low-noise operation. The converter further comprises a highly-efficient synchronous rectifier and a start-up enable circuit.

Owner:AL KURAN SHIHAB +1

Integrated nitride-based acoustic wave devices and methods of fabricating integrated nitride-based acoustic wave devices

ActiveUS7112860B2Reduce unwanted reflectionReduce reflectionPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostriction/magnetostriction machinesMOSFETMESFET

A monolithic electronic device includes a substrate, a semi-insulating, piezoelectric Group III-nitride epitaxial layer formed on the substrate, a pair of input and output interdigital transducers forming a surface acoustic wave device on the epitaxial layer and at least one electronic device (such as a HEMT, MESFET, JFET, MOSFET, photodiode, LED or the like) formed on the substrate. Isolation means are disclosed to electrically and acoustically isolate the electronic device from the SAW device and vice versa. In some embodiments, a trench is formed between the SAW device and the electronic device. Ion implantation is also disclosed to form a semi-insulating Group III-nitride epitaxial layer on which the SAW device may be fabricated. Absorbing and / or reflecting elements adjacent the interdigital transducers reduce unwanted reflections that may interfere with the operation of the SAW device.

Owner:CREE INC

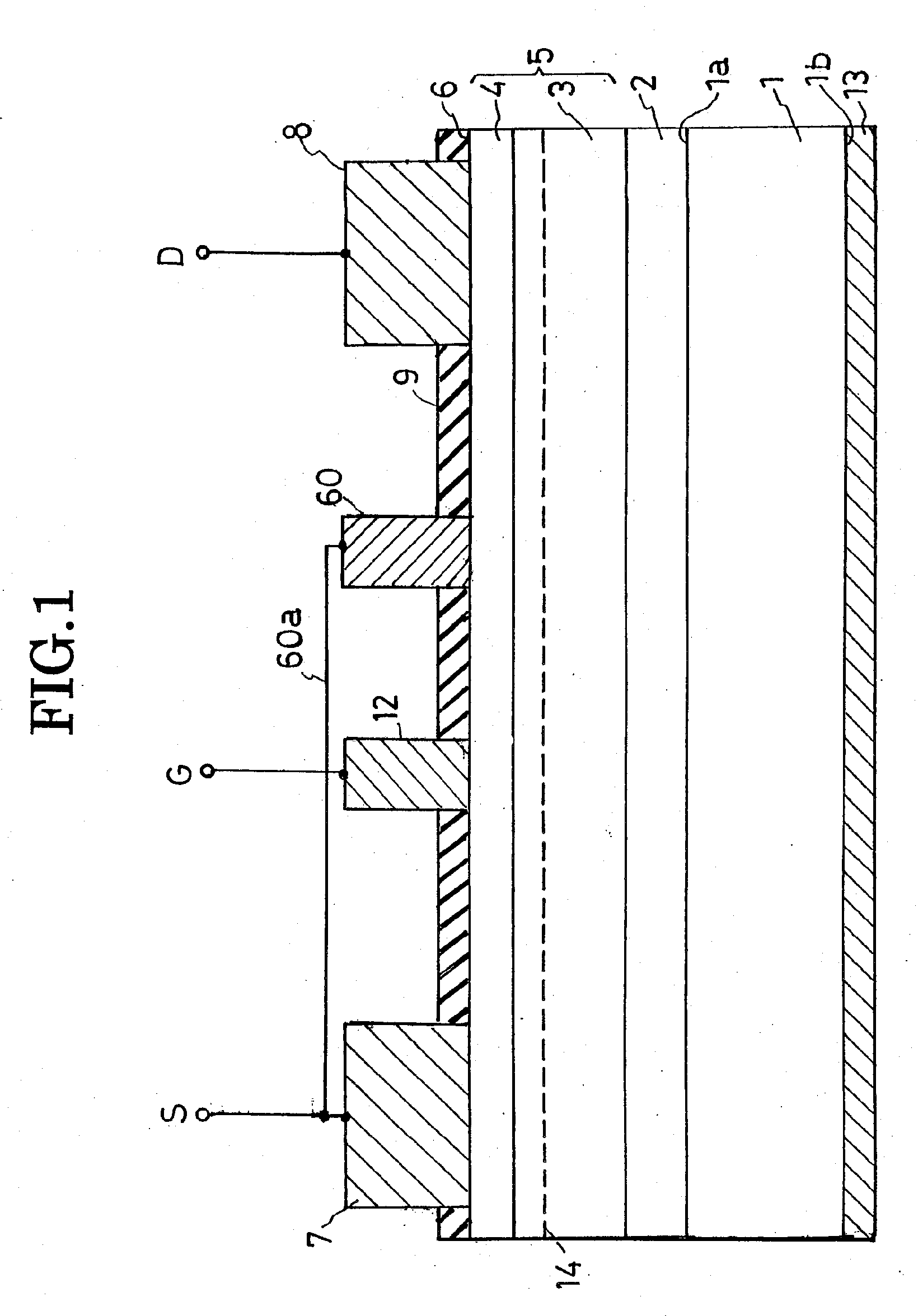

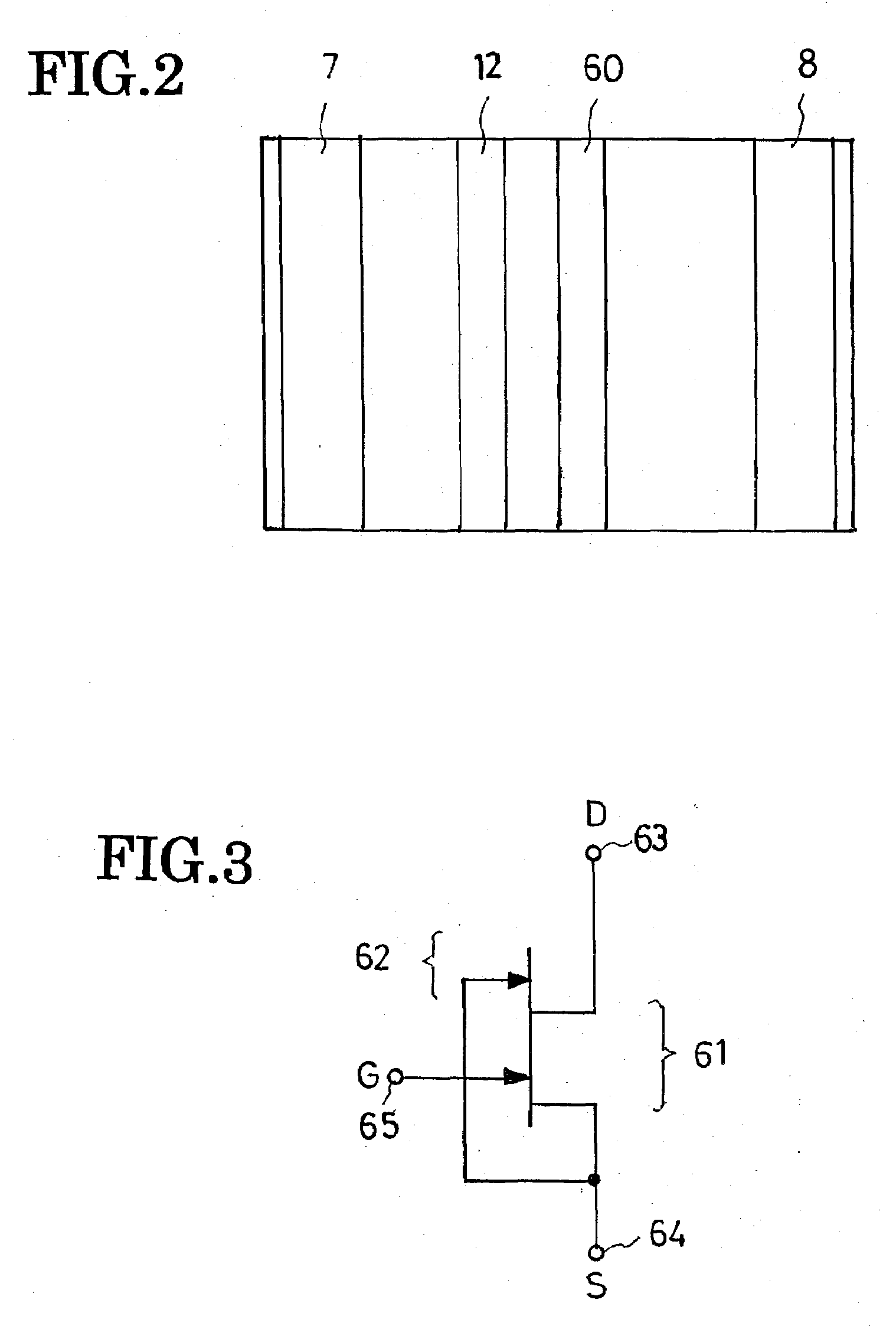

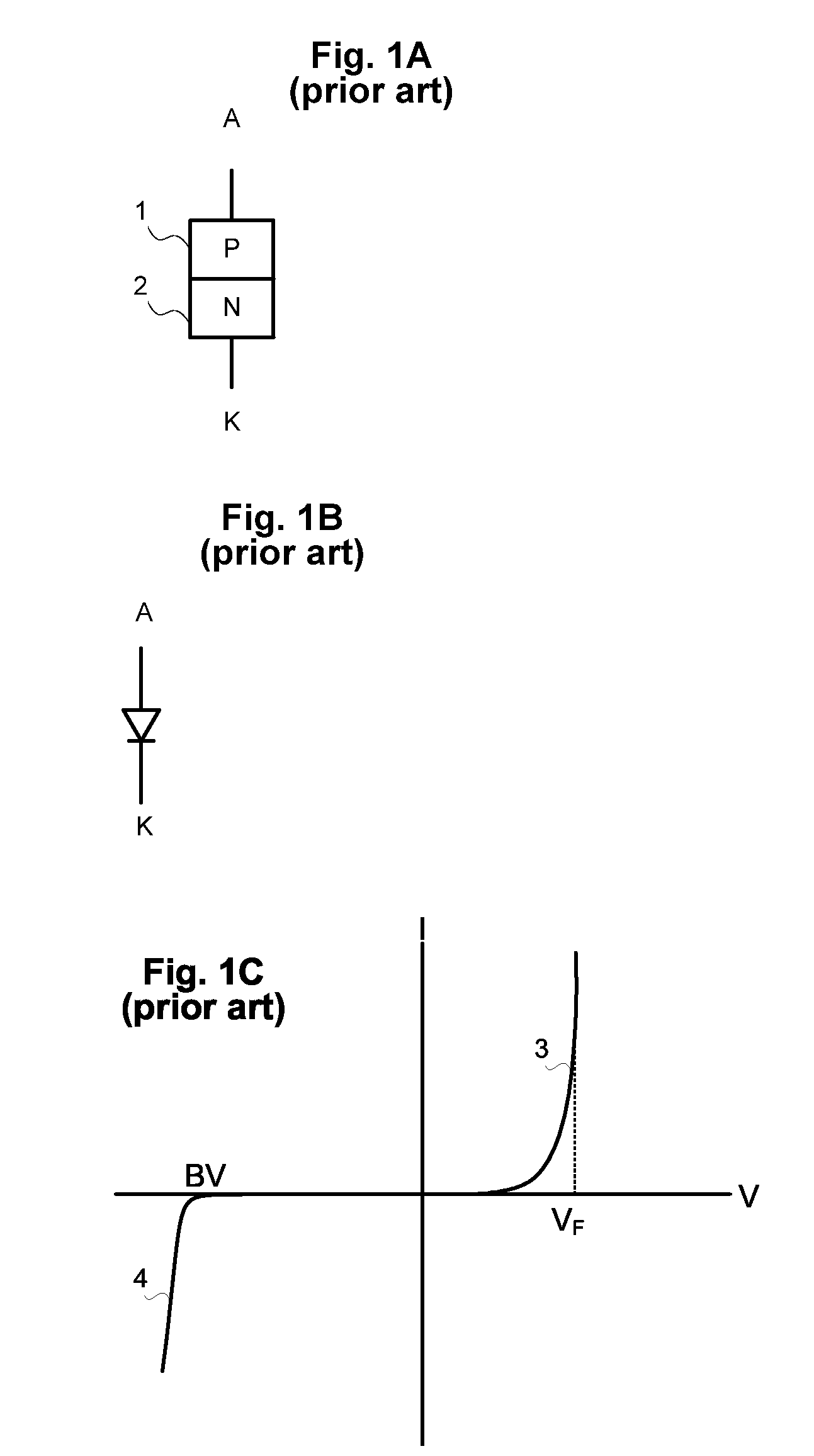

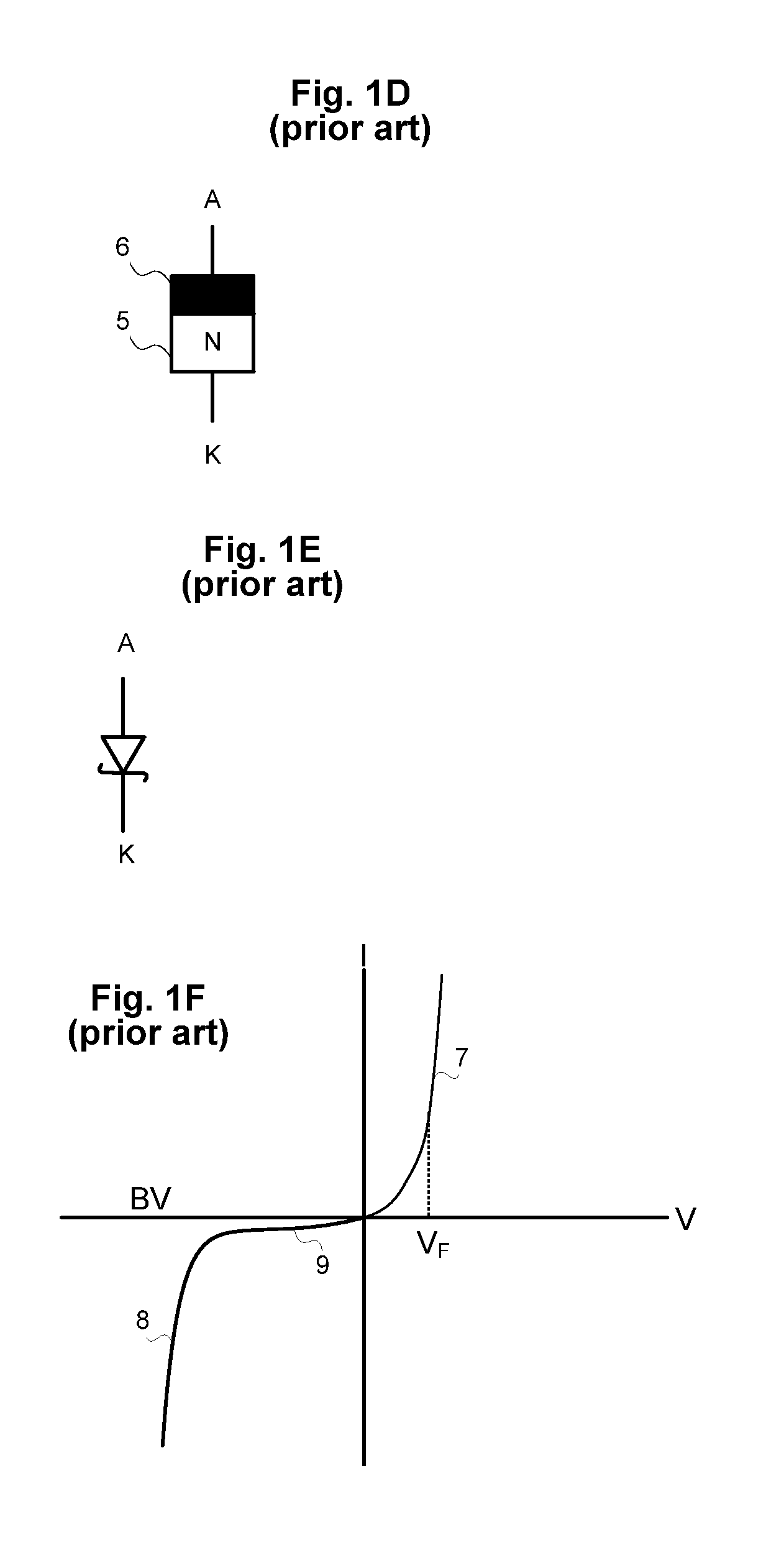

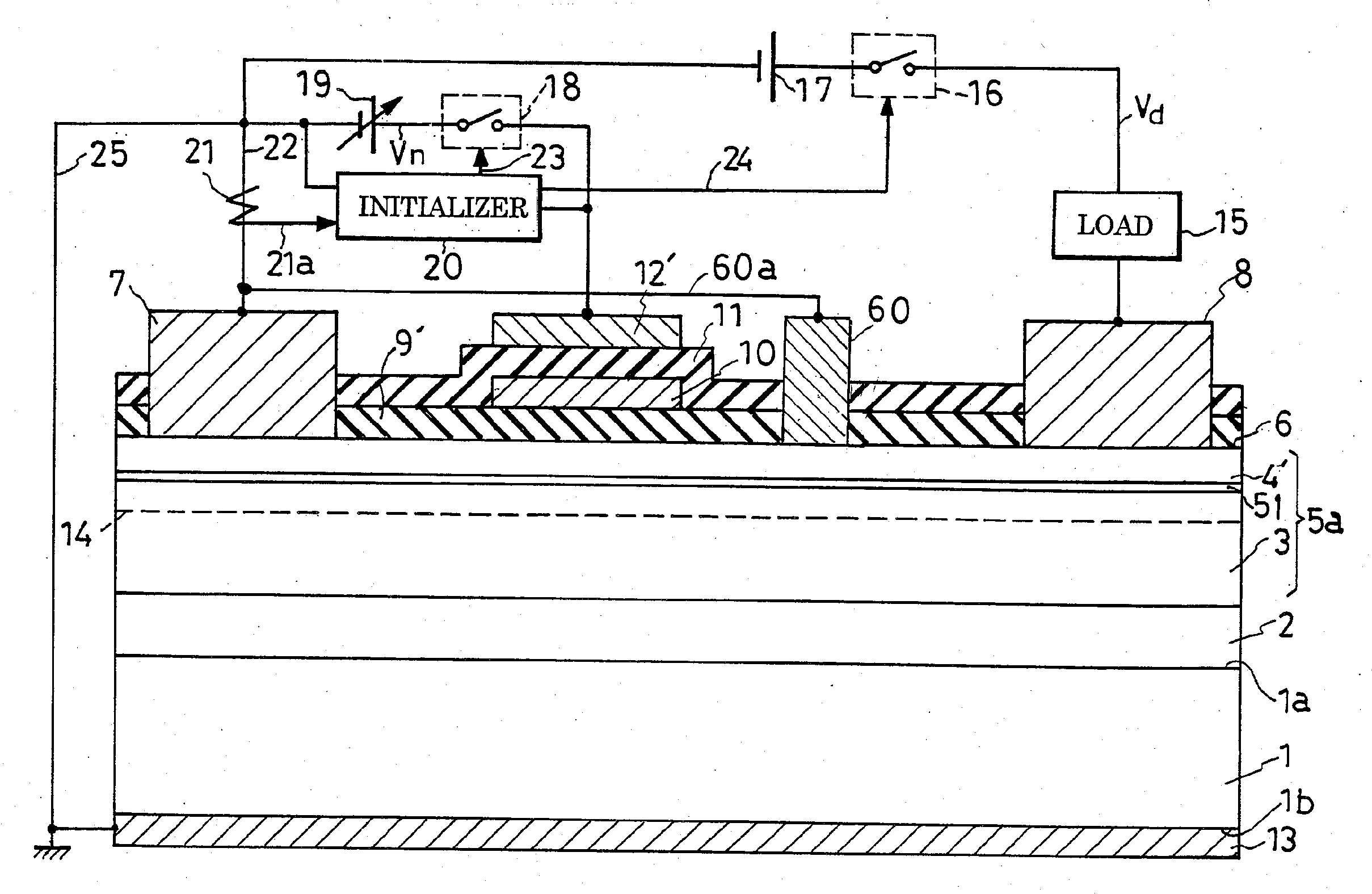

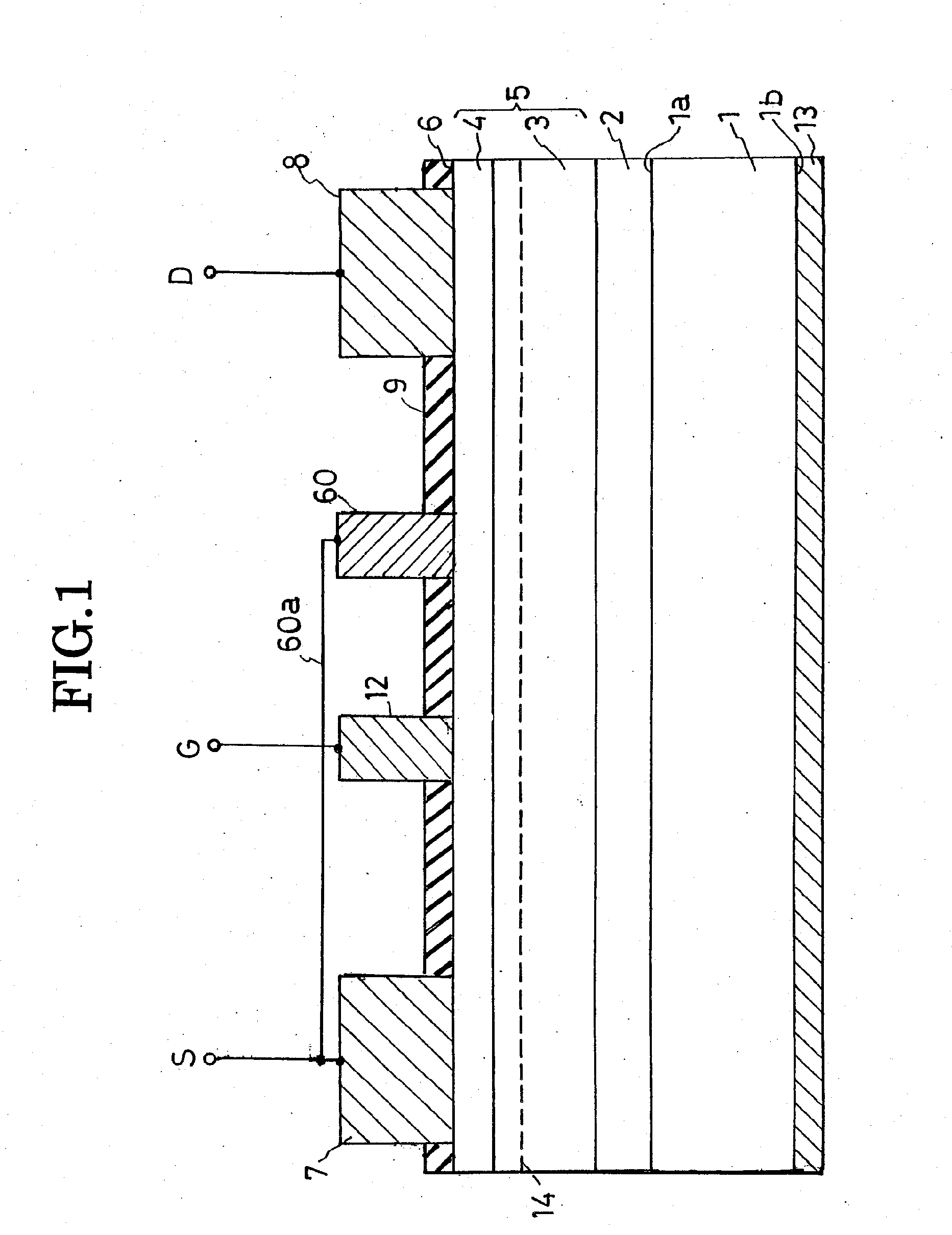

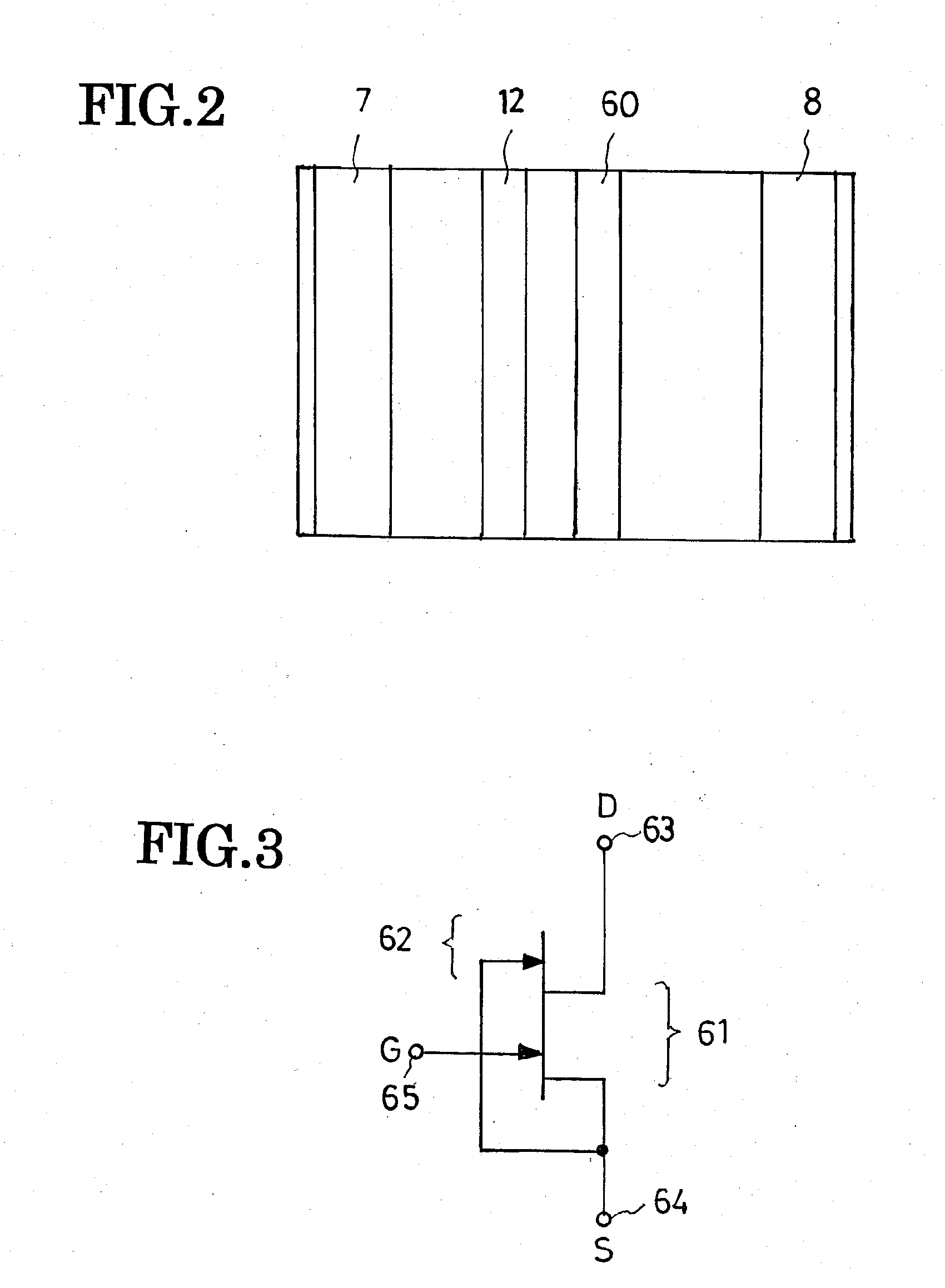

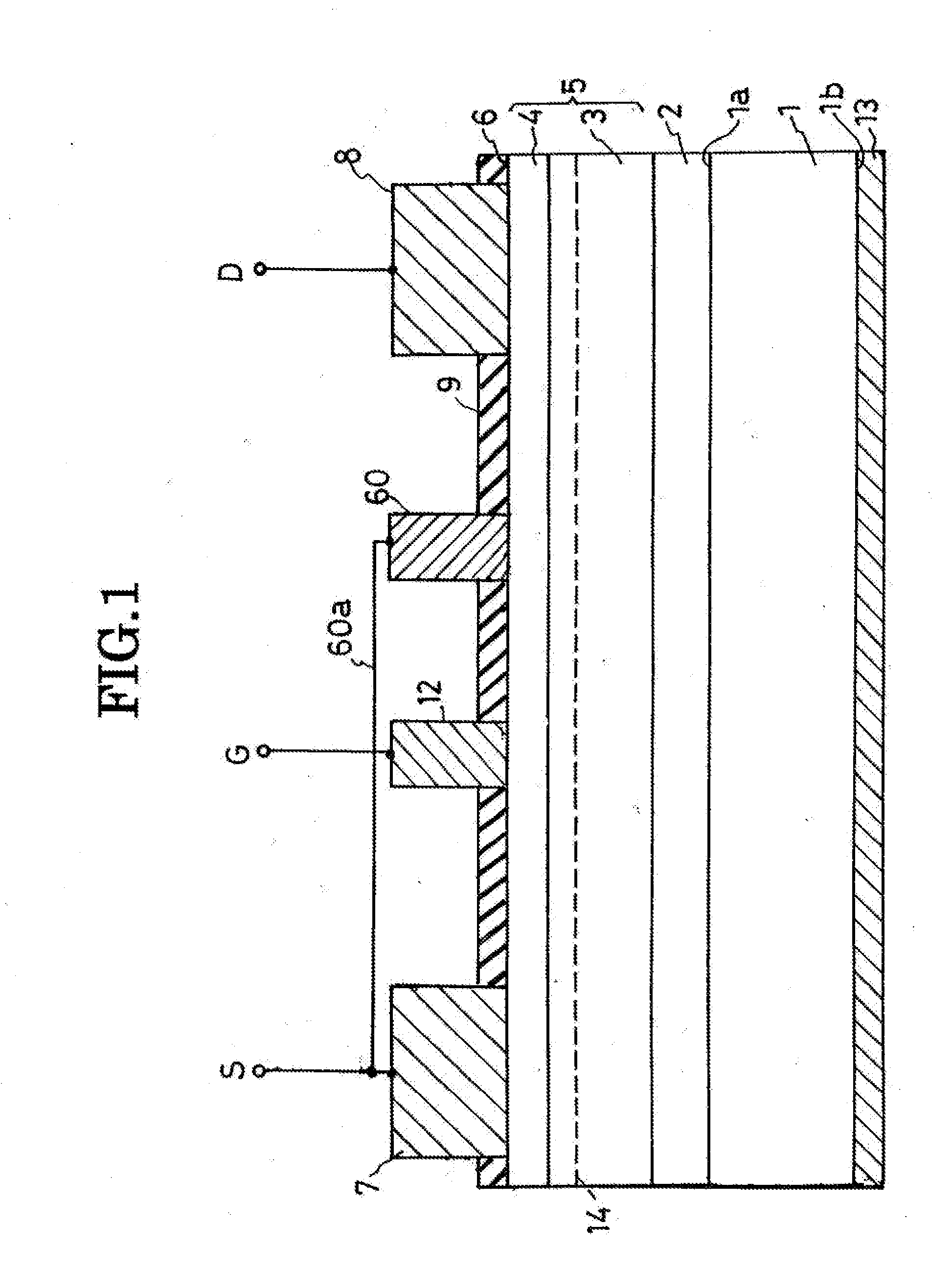

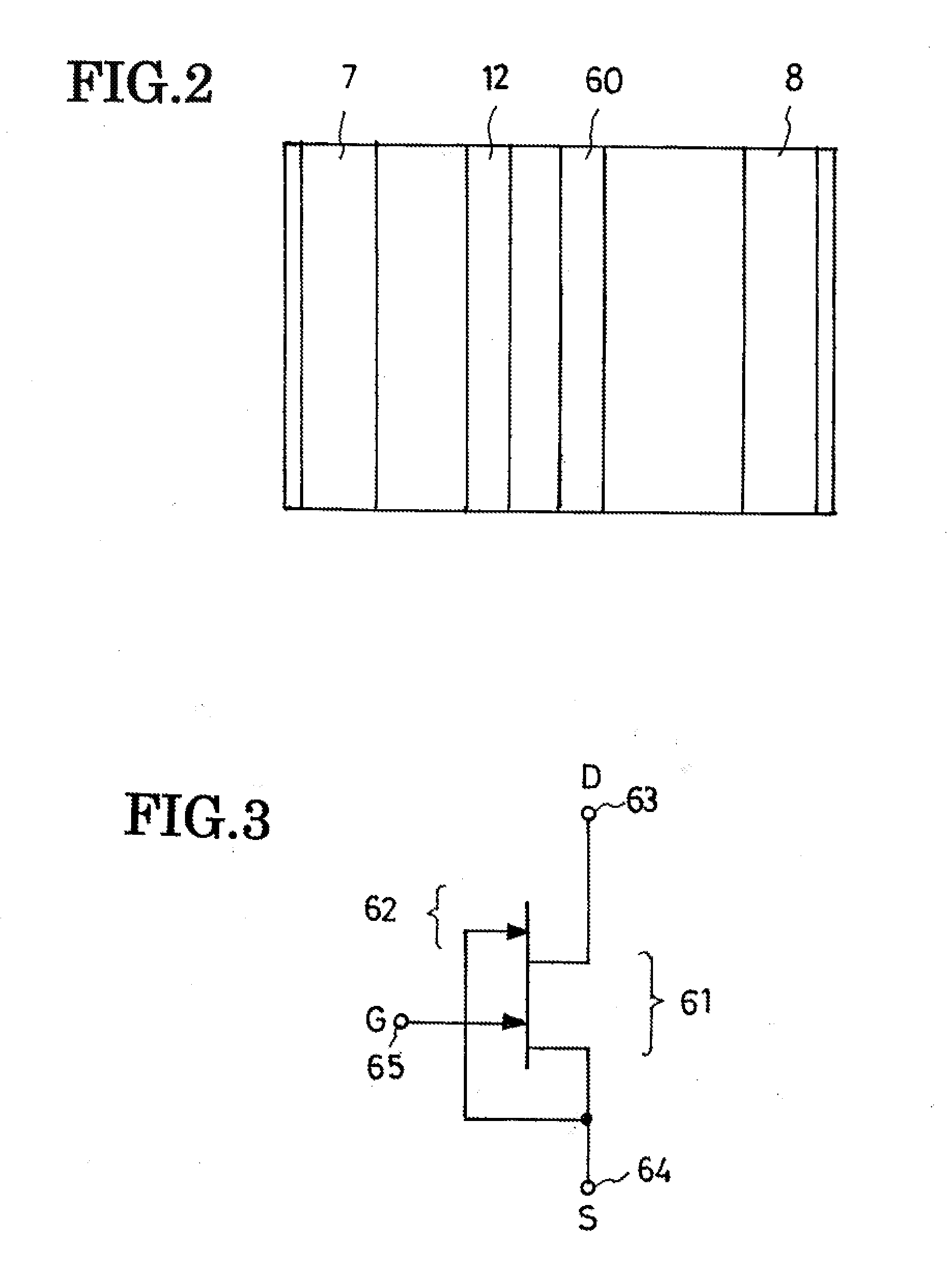

Monolithic integrated circuit of a field-effect semiconductor device and a diode

InactiveUS20070228477A1Flow assuranceEasy to FeedbackTransistorSolid-state devicesMESFETField effect

A field-effect semiconductor device such as a HEMT or MESFET is monolithically integrated with a Schottky diode for feedback, regeneration, or protection purposes. The field-effect semiconductor device includes a main semiconductor region having formed thereon a source, a drain, and a gate between the source and the drain. Also formed on the main semiconductor region, preferably between gate and drain, is a Schottky electrode electrically coupled to the source. The Schottky electrode provides a Schottky diode in combination with the main semiconductor region. A current flow is assured from Schottky electrode to drain without interruption by a depletion region expanding from the gate.

Owner:SANKEN ELECTRIC CO LTD

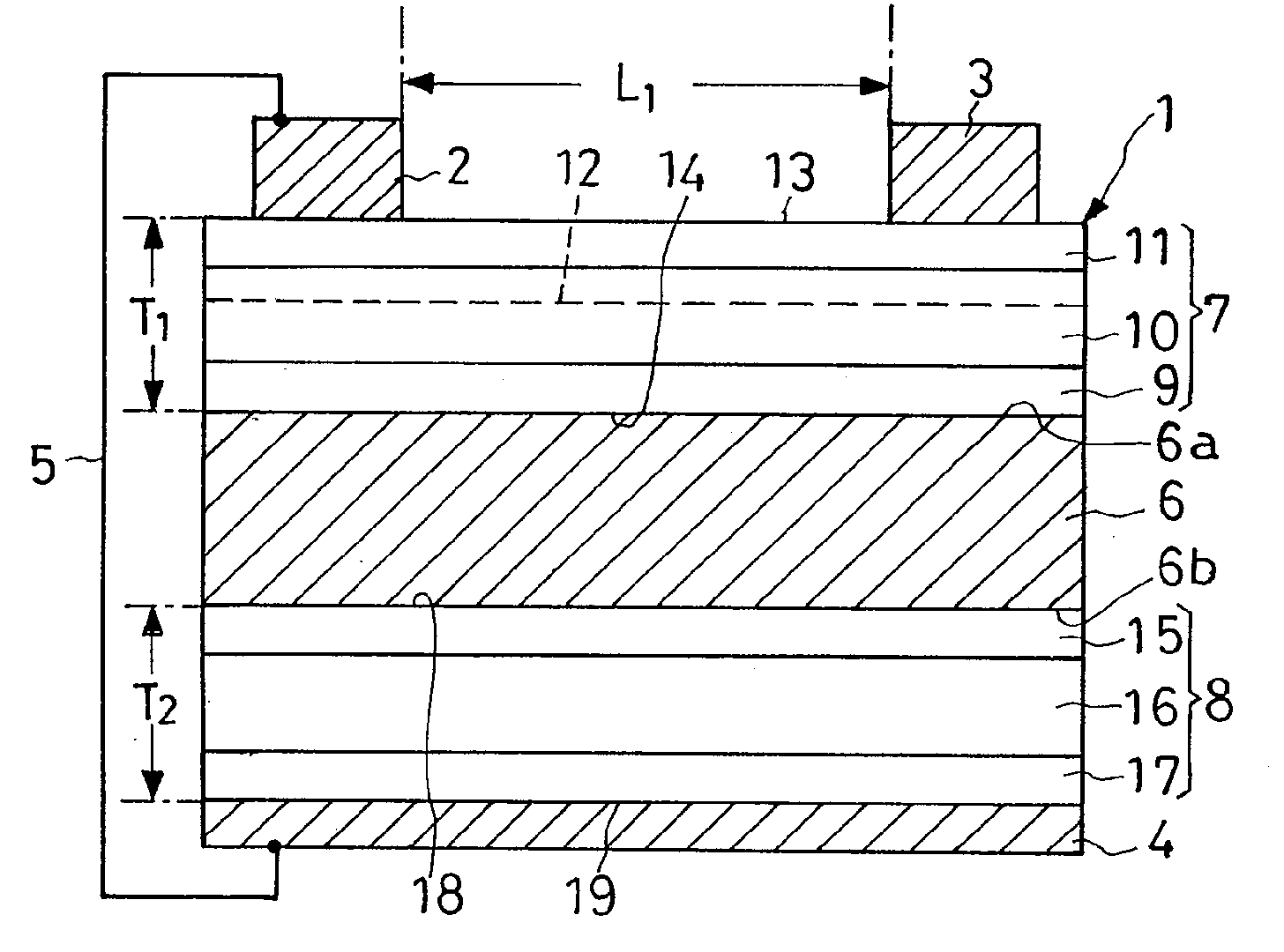

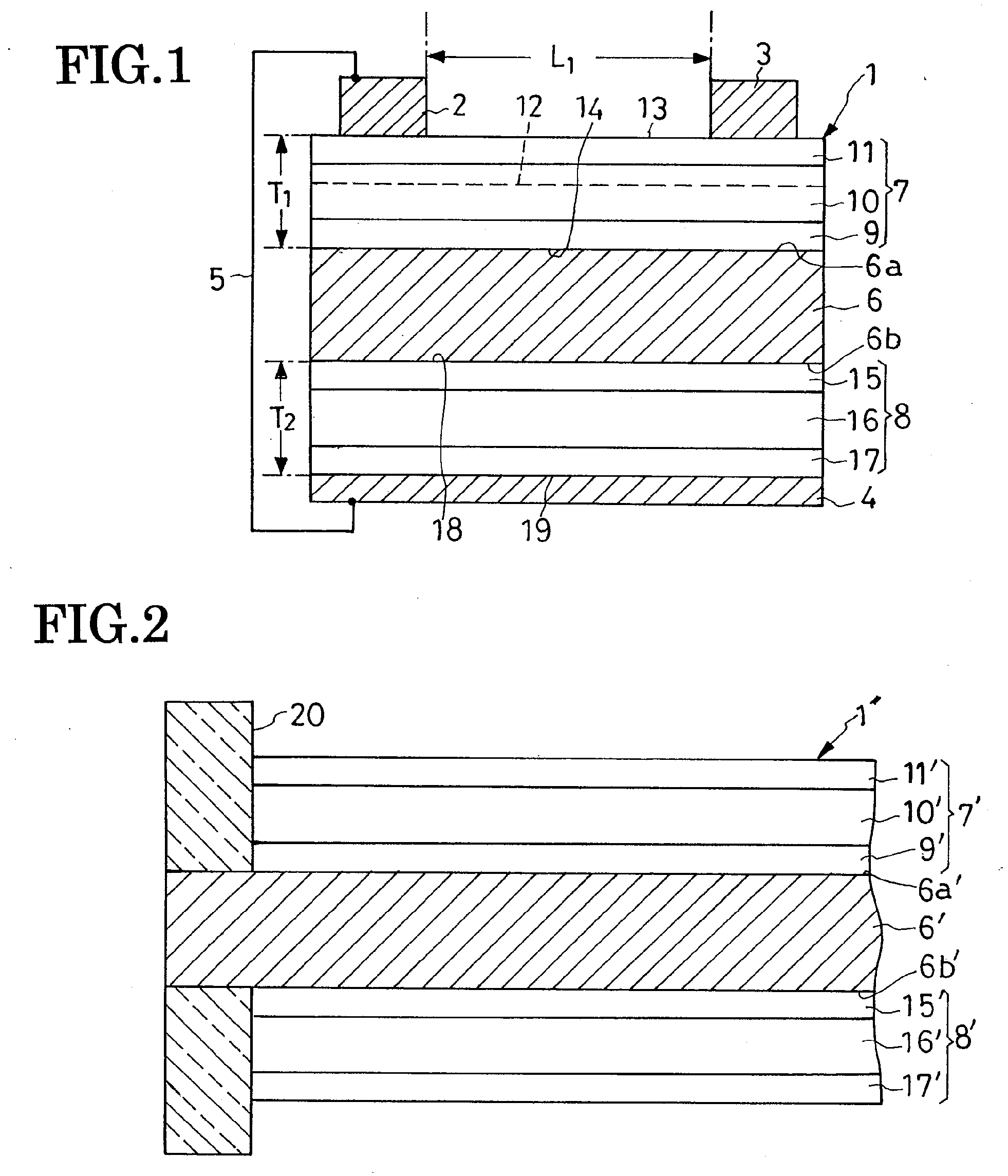

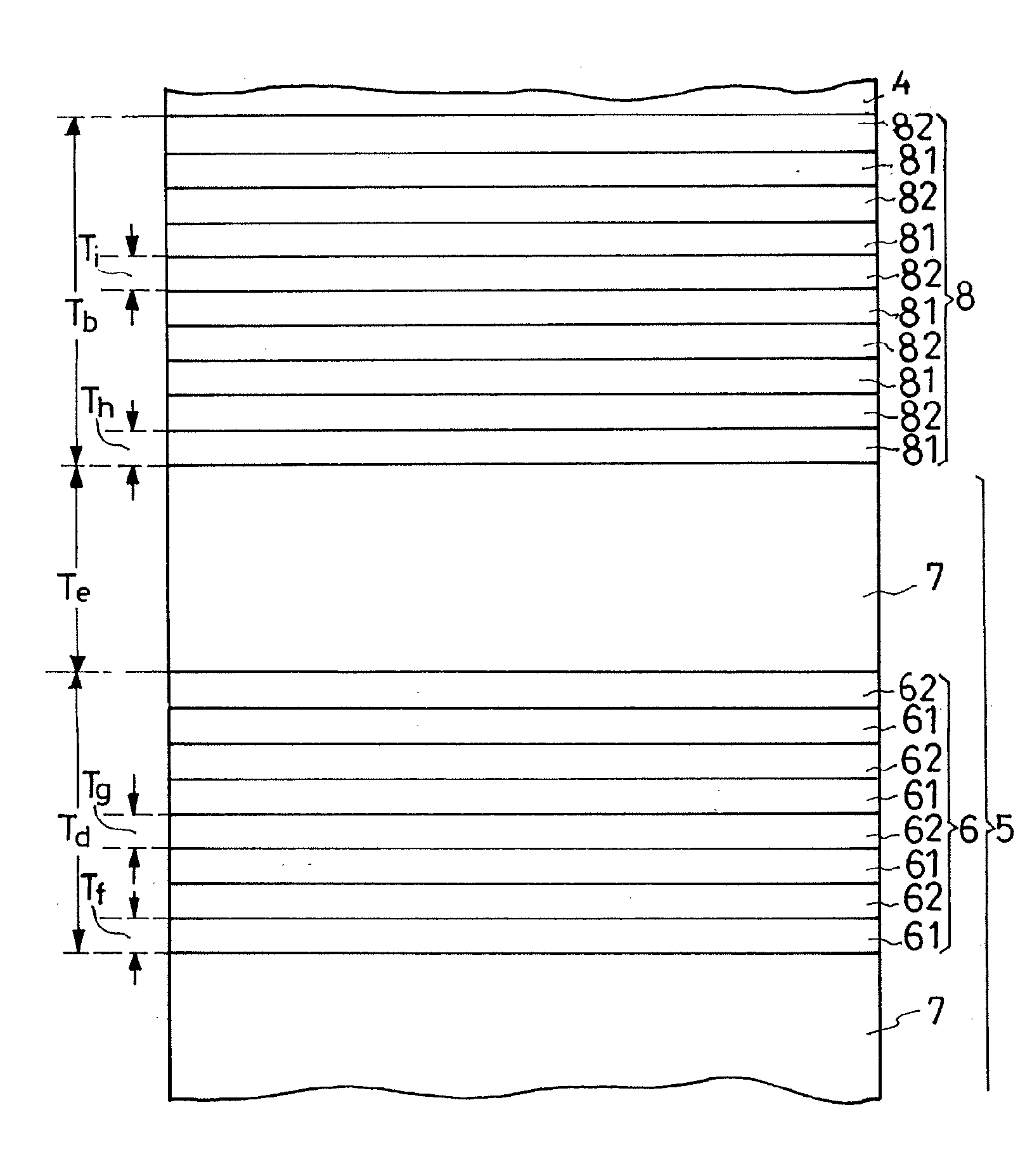

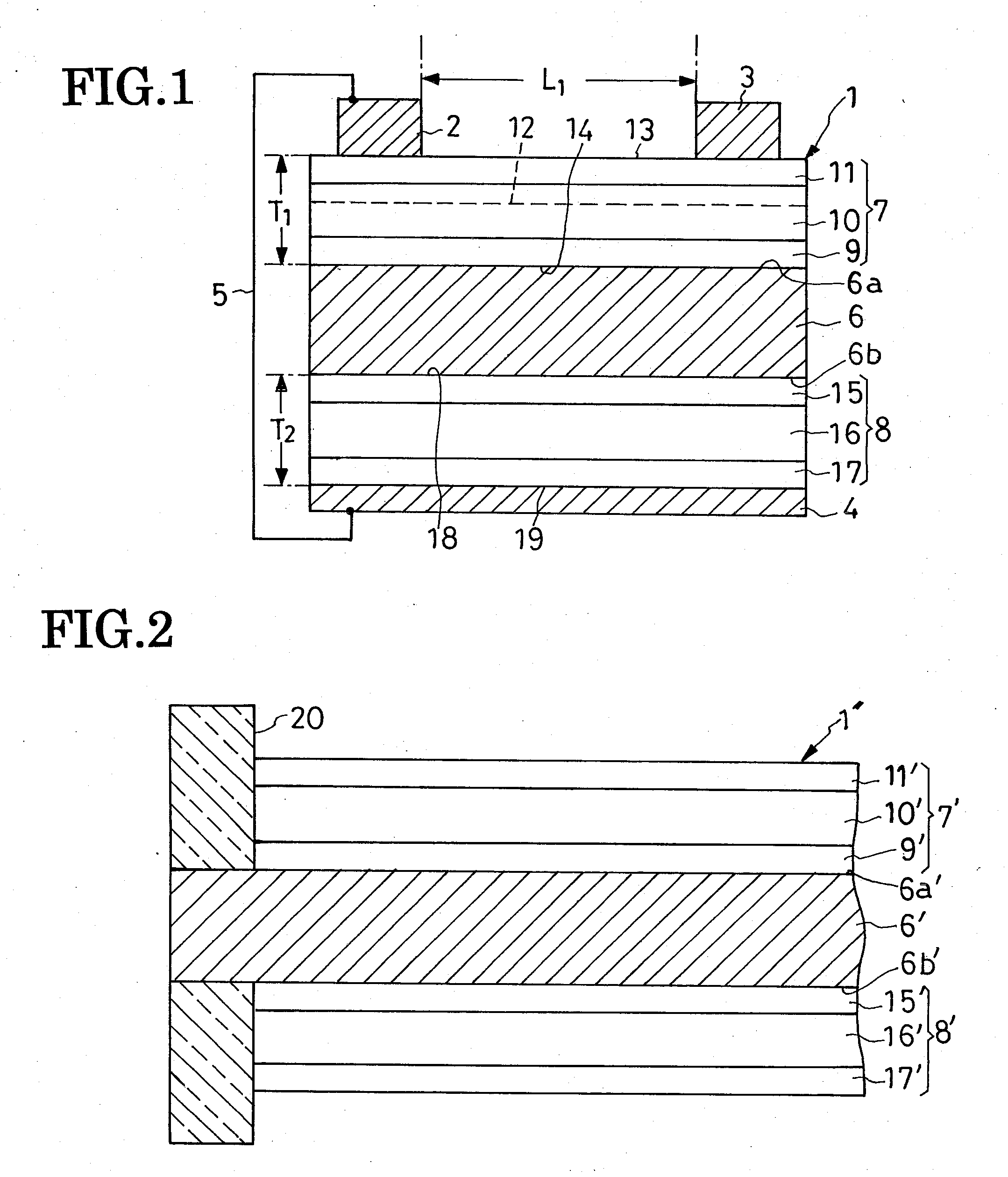

Warp-free semiconductor wafer, and devices using the same

A semiconductor wafer to be diced into individual SBDs, HEMTs or MESFETs has a substrate with a main semiconductor region and counter semiconductor region formed on its opposite surfaces. The main semiconductor region is configured to provide the desired semiconductor devices. In order to counterbalance the warping effect of the main semiconductor region on the substrate, as well as to enhance the voltage strength of the devices made from the wafer, the counter semiconductor region is made similar in configuration to the main semiconductor region. The main semiconductor region and counter semiconductor region are arranged in bilateral symmetry as viewed in a cross-sectional plane at right angles with the substrate surfaces.

Owner:SANKEN ELECTRIC CO LTD

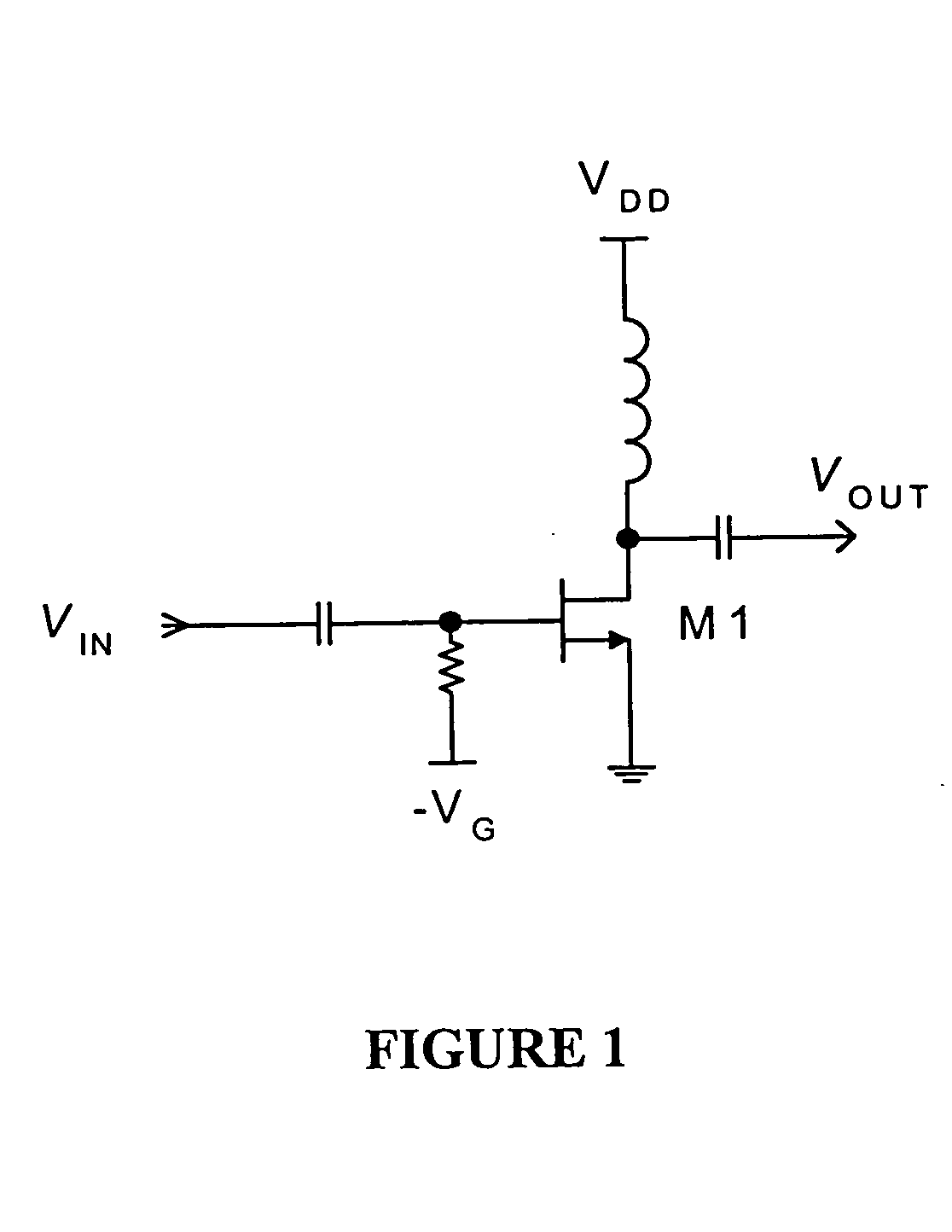

High Frequency Power MESFET Gate Drive Circuits

InactiveUS20070146020A1Lower on-resistanceRobust avalancheTransistorDc-dc conversionDriver circuitHigh frequency power

A series of gate drive circuits for MESFETs are provided. The gate drive circuits are intended to be used in switching regulators where at least one switching device is an N-channel MESFET. For regulators of this type, the gate drive circuits provide gate drive at the correct voltage to ensure that MESFETs are neither under driven (resulting in incorrect circuit operation) nor over driven (resulting in MESFET damage or excess current or power loss).

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

AlGaN/GaN high electron mobility transistor devices

ActiveUS20060006414A1Avoid crackingReduce the appearance of cracksSolid-state devicesSemiconductor/solid-state device manufacturingMESFETCooling down

The present invention recites a new method for manufacturing Group III-N field-effect devices, such as HEMT, MOSHFET, MISHFET devices or MESFET devices, grown by Metal-Organic Vapor Phase Expitaxy, with higher performance (power), by covering the surface with a thin SiN layer on the top AlGaN layer, in the reactor where the growth takes place at high temperature, prior cooling down the structure and loading the sample out of the reactor, as well as a method to produce some HEMT transistors on those heterostructures, by depositing the contact on the surface without any removal of the SiN layer by MOCVD. The present invention recites also a device.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

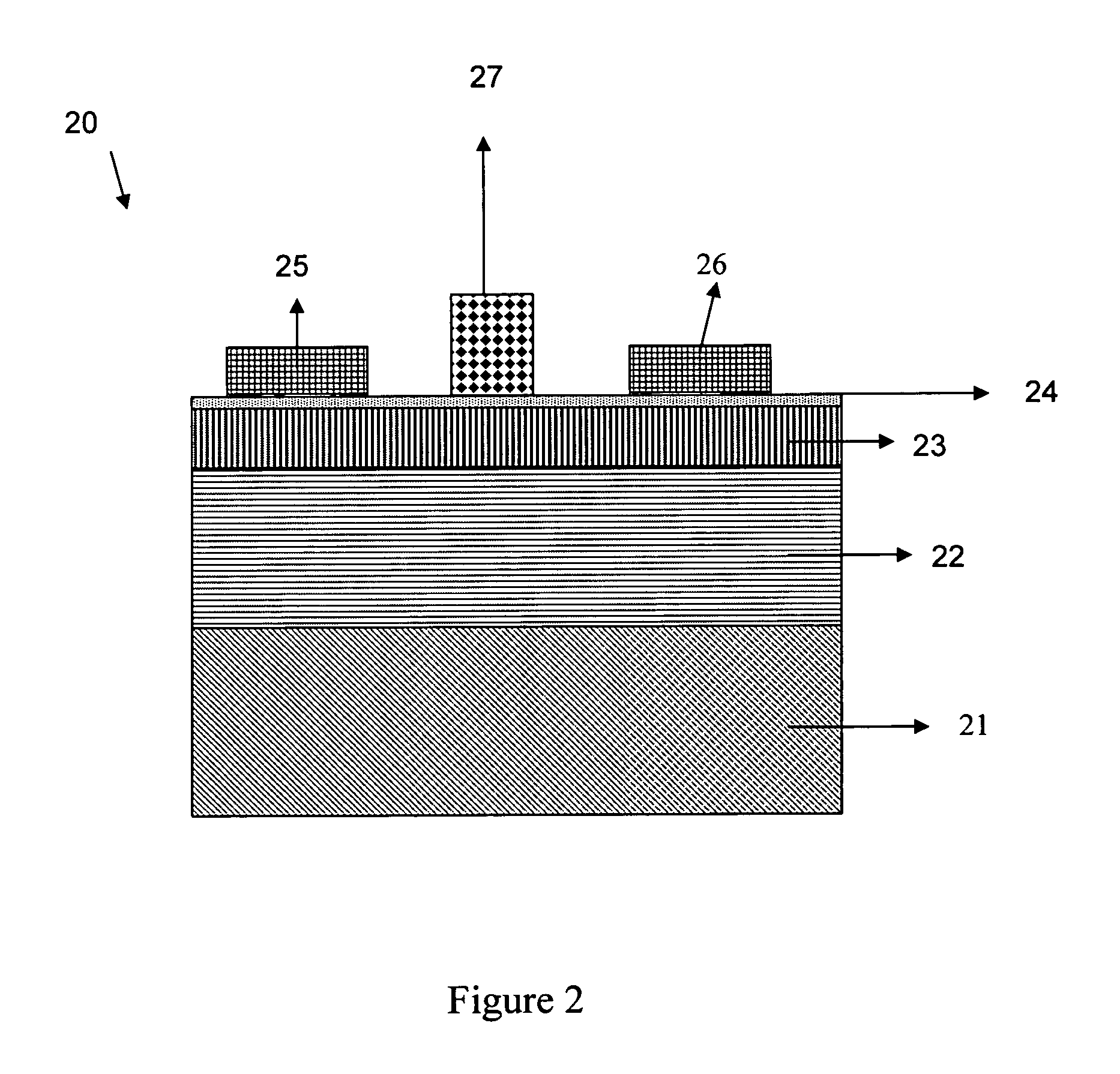

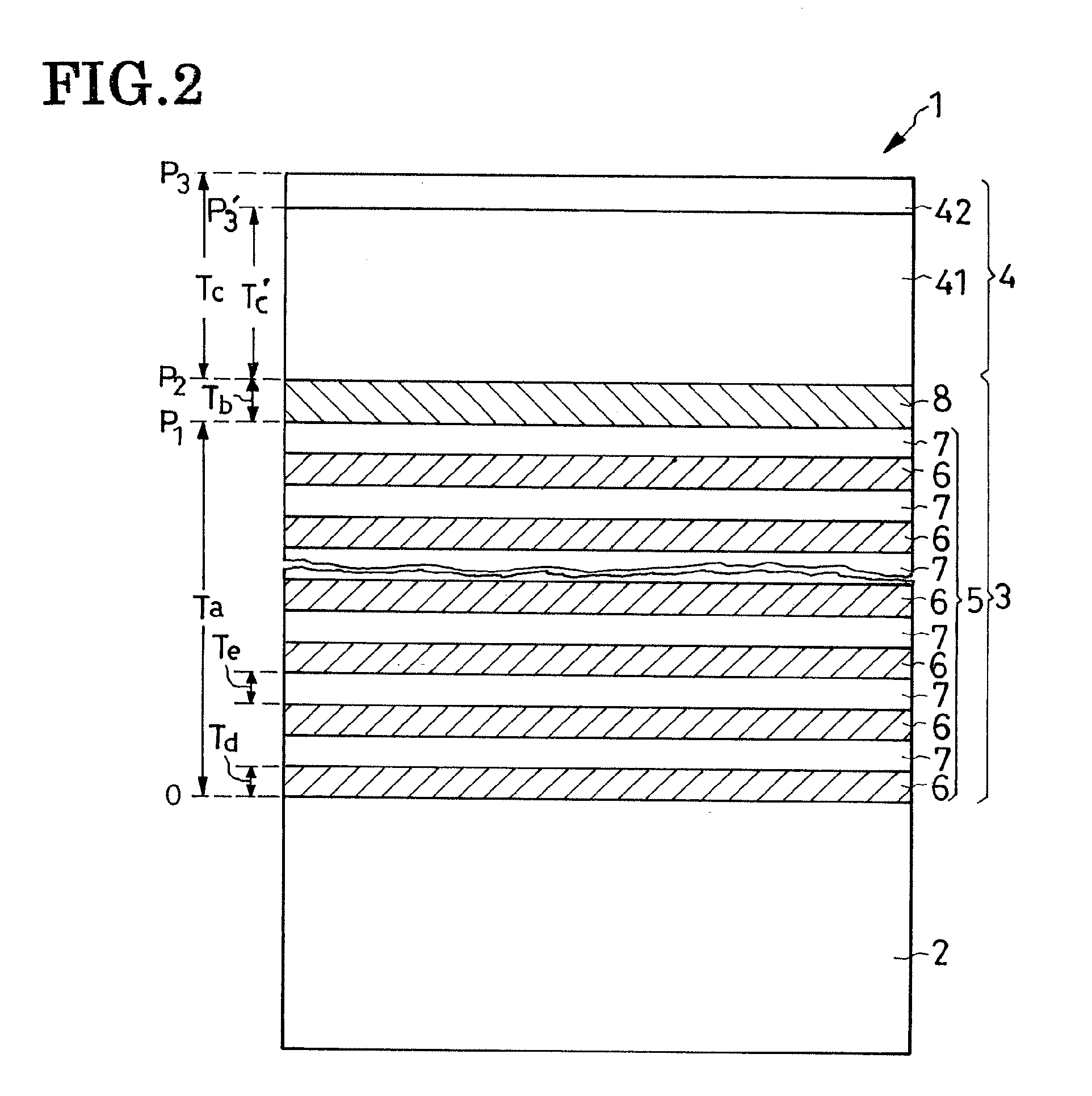

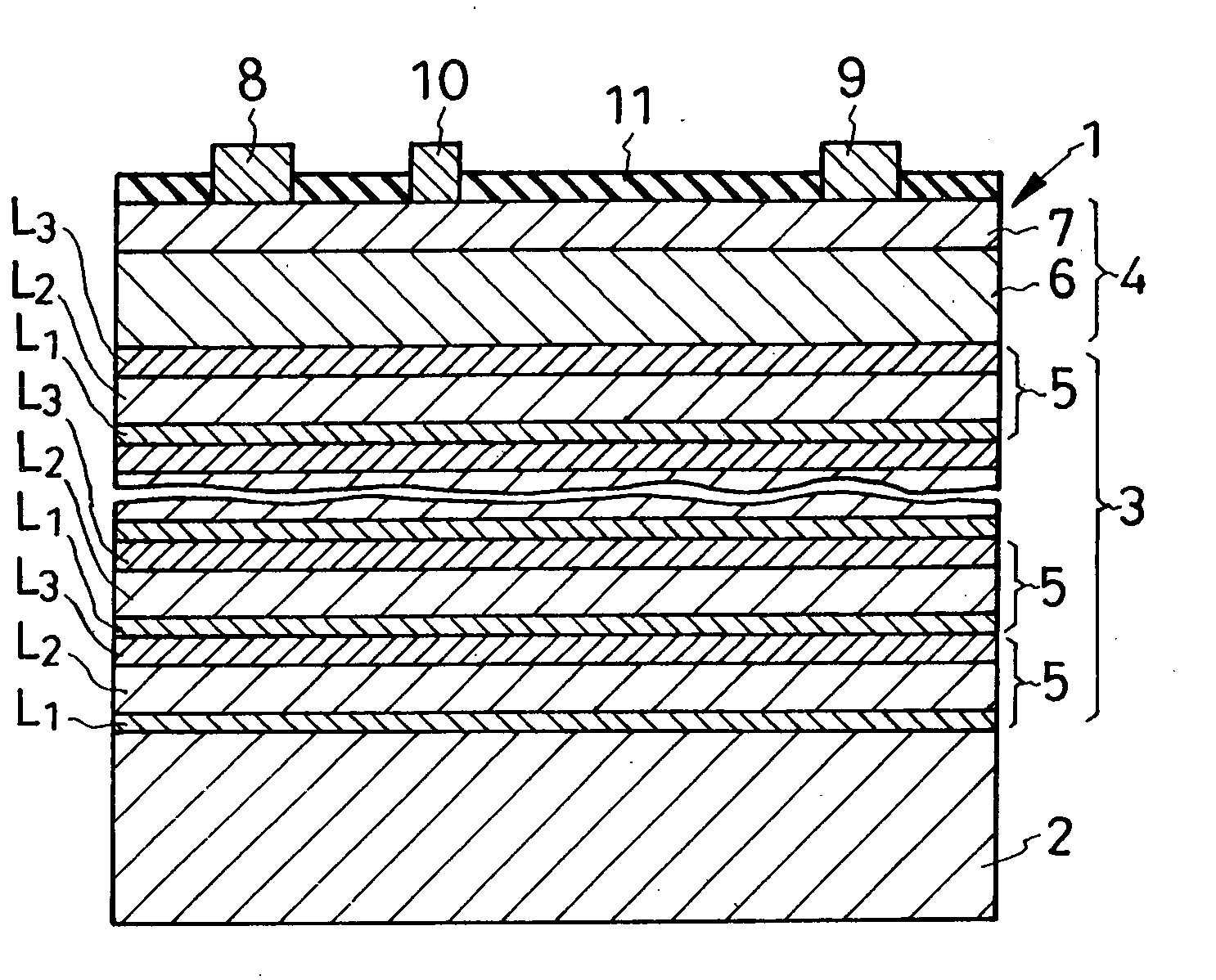

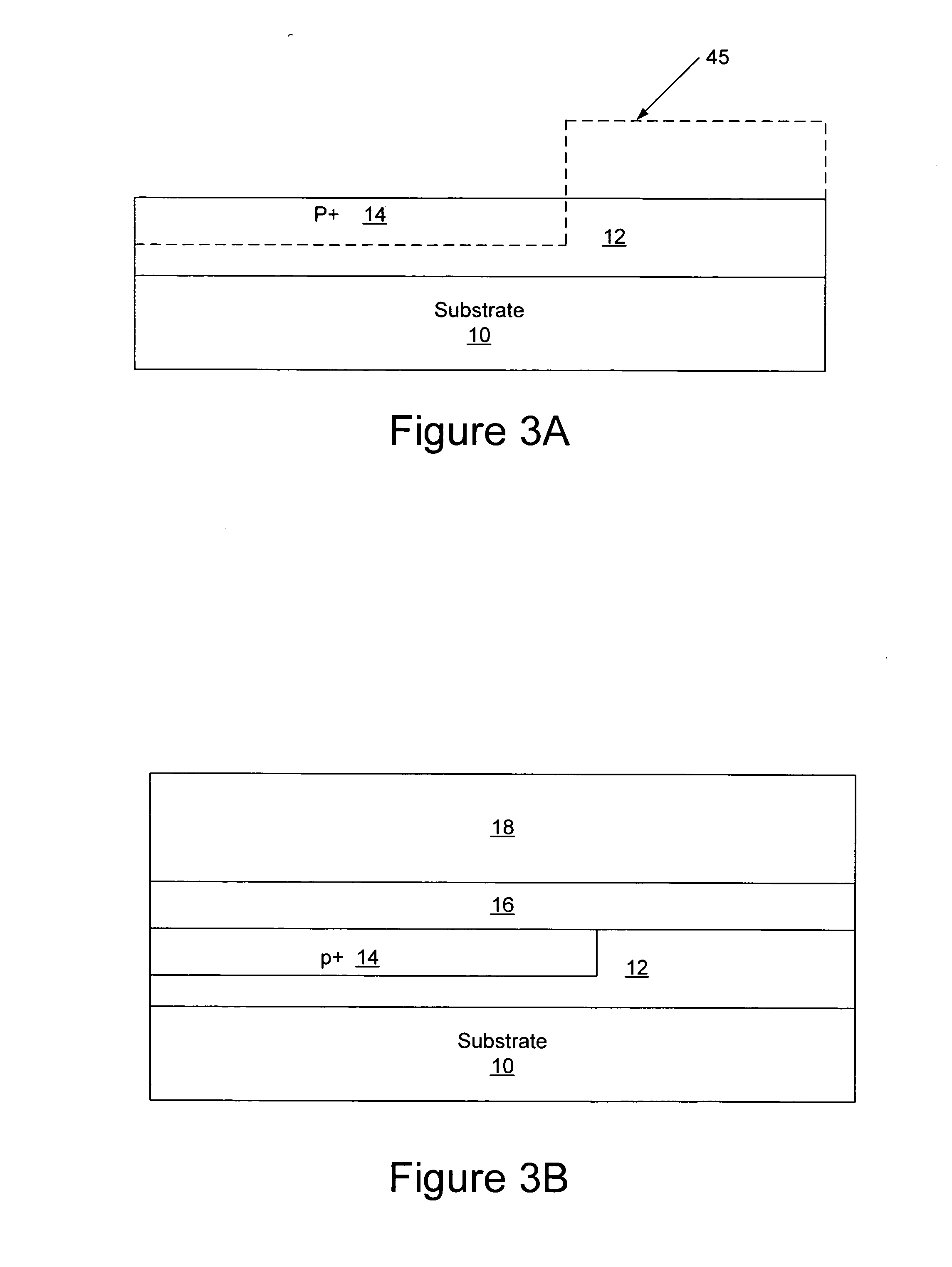

Semiconductor wafer, devices made therefrom, and method of fabrication

ActiveUS20080203382A1Reduce warpageReduce volatilitySemiconductor/solid-state device manufacturingSemiconductor devicesMESFETComputer science

A main semiconductor region of semiconducting nitrides is formed on a silicon substrate via a buffer region of semiconducting nitrides to provide devices such as HEMTs, MESFETs and LEDs. In order to render the wafer proof against warping, the buffer region is divided into a first and a second multilayered buffer subregion. The first buffer subregion comprises multiple alterations of a multi-sublayered first buffer layer and a non-sublayered second buffer layer. Each multi-sublayered first buffer layer of the first buffer subregion comprises multiple alternations of a first and a second buffer sublayer. The second buffer sublayers of each multi-sublayered first buffer layer either do not contain aluminum or do contain it in a higher proportion than do the first buffer sublayers. The second multilayered buffer subregion comprises multiple alternations of a first and a second buffer layer. The first buffer layers of the second multilayered buffer subregion are less in aluminum proportion than the fourth buffer layers of the second multilayered buffer subregion.

Owner:SANKEN ELECTRIC CO LTD

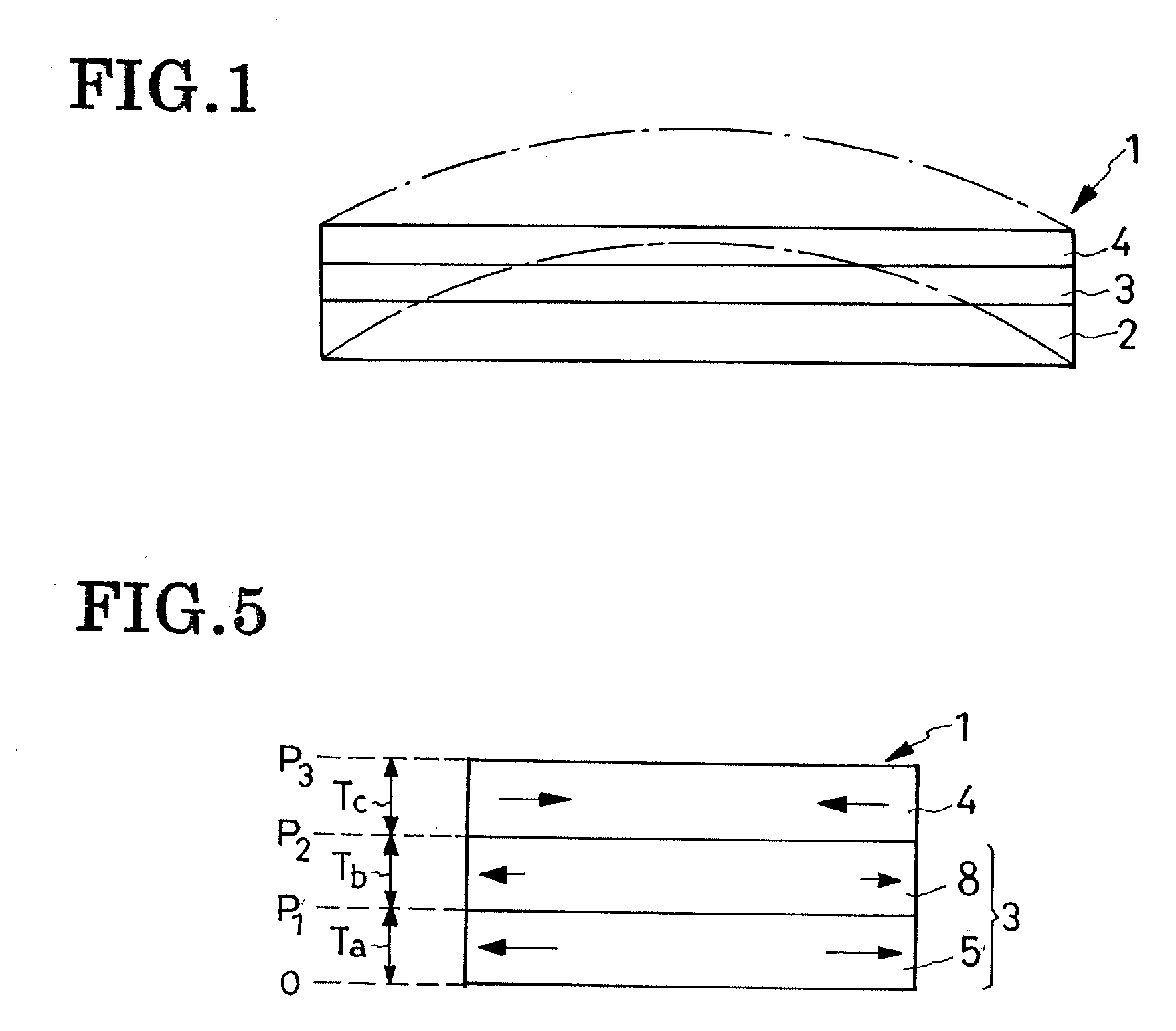

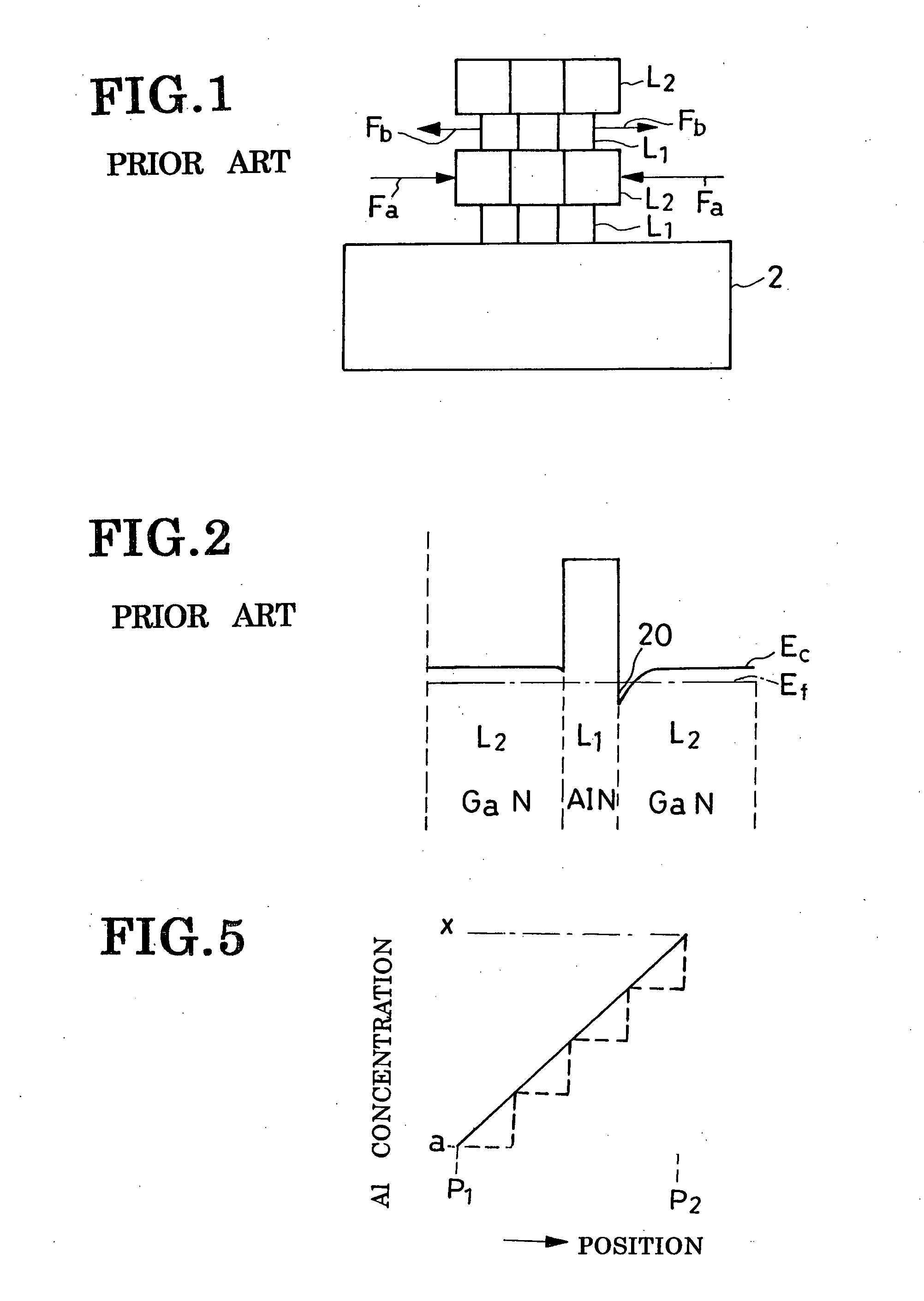

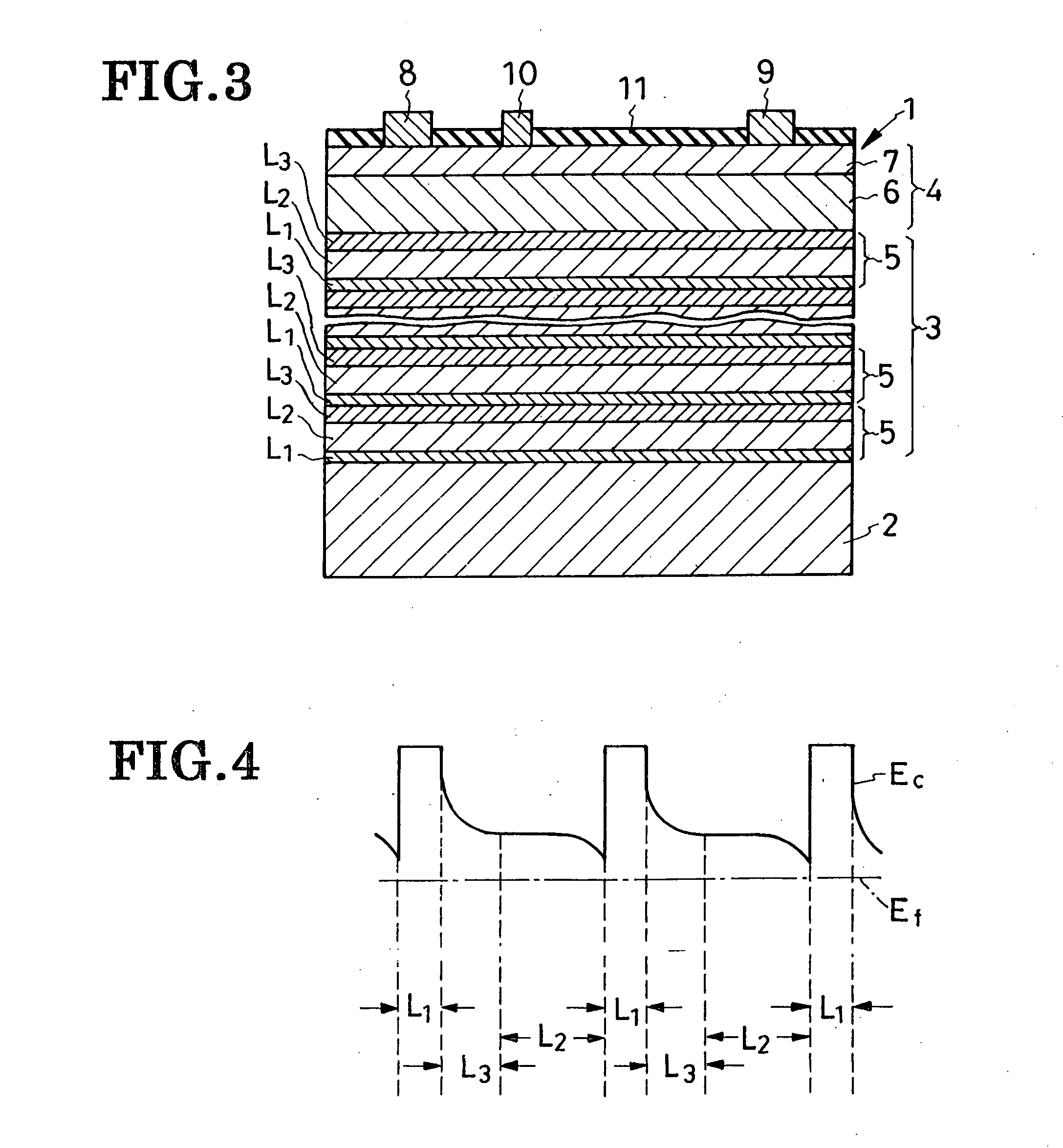

Nitride semiconductor substrate, method of fabrication thereof, and semiconductor element built thereon

ActiveUS20050110043A1Reduce the amount requiredLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMESFETSilicon

A substrate system of the kind having a buffer region interposed between a silicon substrate proper and a nitride semiconductor region in order to make up for a difference in linear expansion coefficient therebetween. Electrodes are formed on the nitride semiconductor layer or layers in order to provide HEMTs or MESFETs. The buffer region is a lamination of a multiplicity of buffer layers each comprising a first, a second, and a third buffer sublayer of nitride semiconductors, in that order from the silicon substrate proper toward the nitride semiconductor region. The three sublayers of each buffer layer contain aluminum in varying proportions including zero. The aluminum proportion of the third buffer sublayer is either zero or intermediate that of the first buffer sublayer and that of the second. The low aluminum proportion of the third buffer sublayer serves to prevent two-dimensional electron gas from generating in the buffer region and hence to make this region sufficiently high in resistance to inhibit current leakage from the HEMTs or MESFETs.

Owner:SANKEN ELECTRIC CO LTD

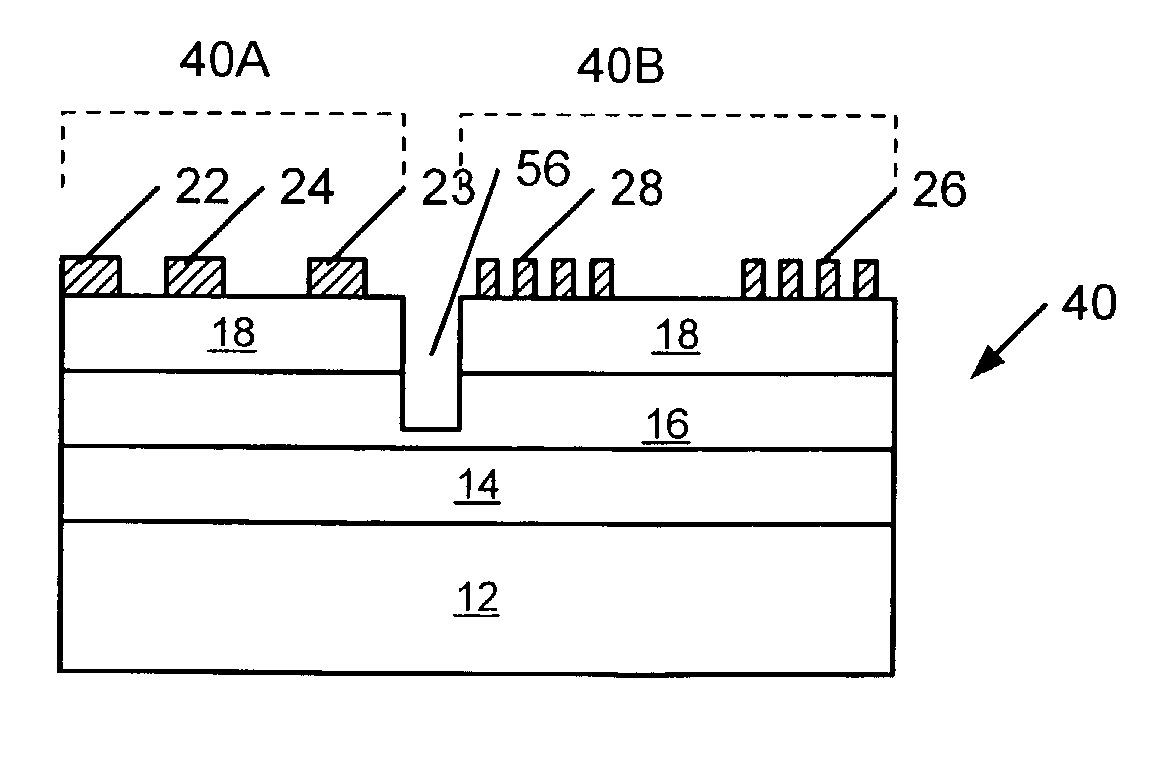

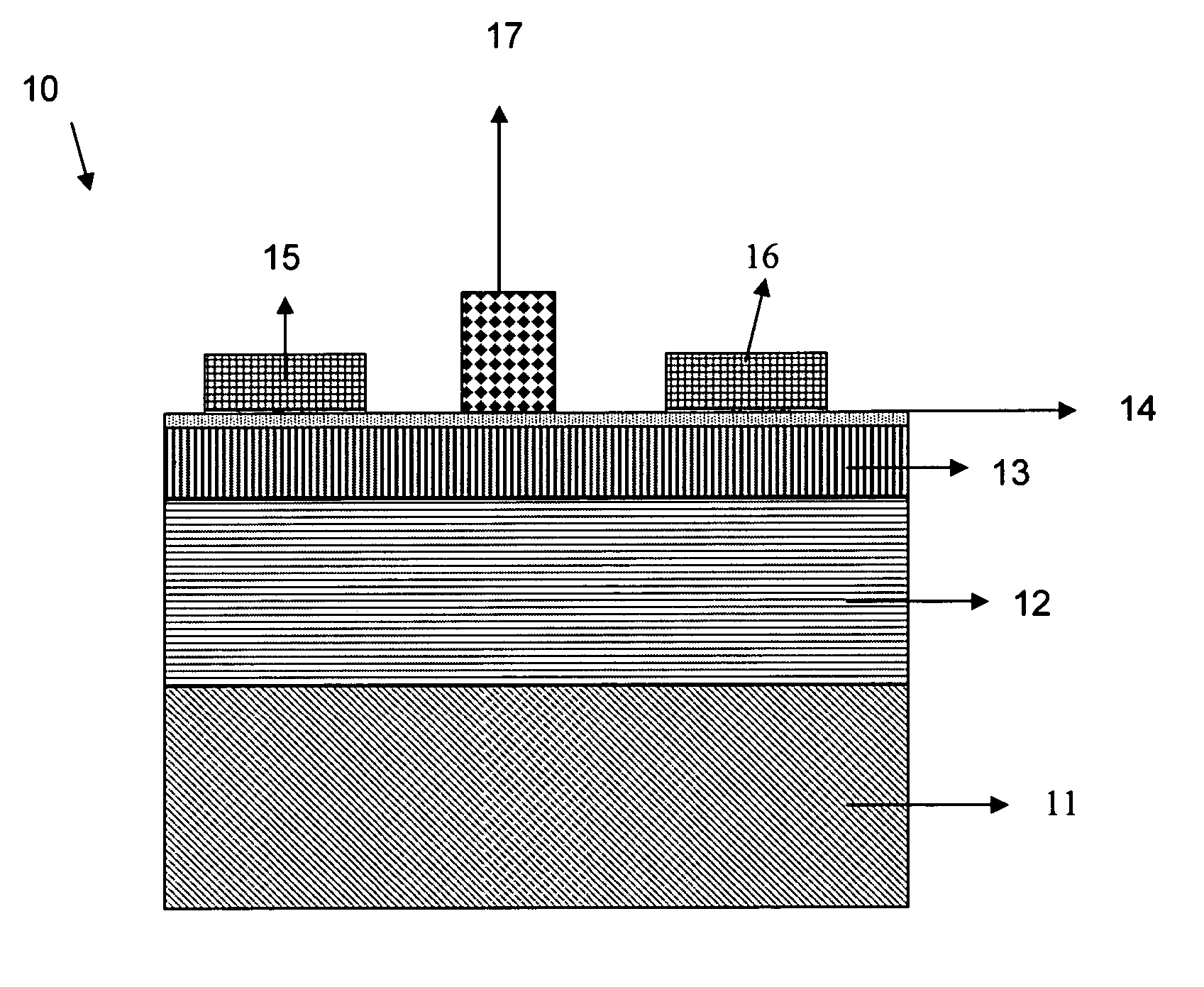

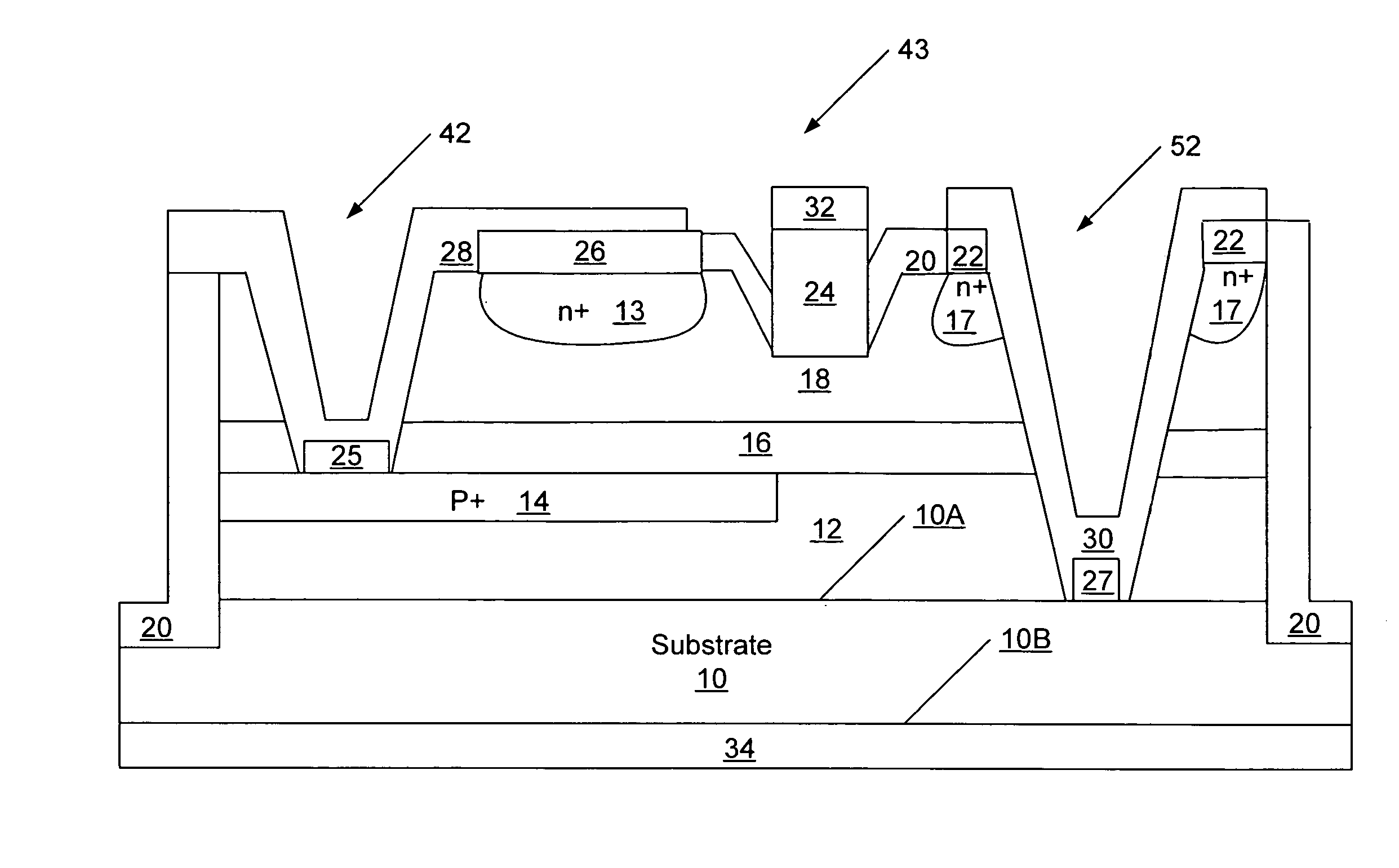

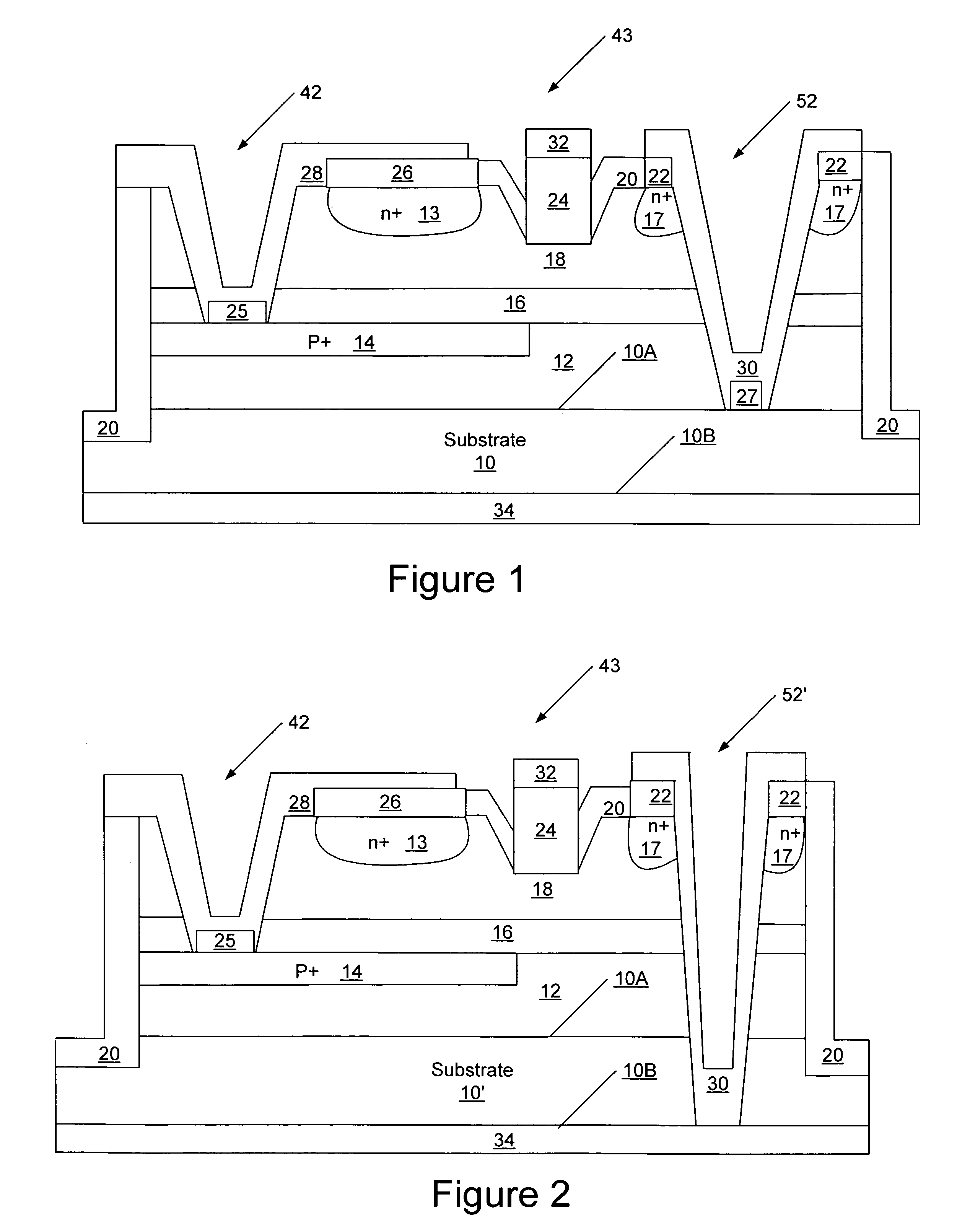

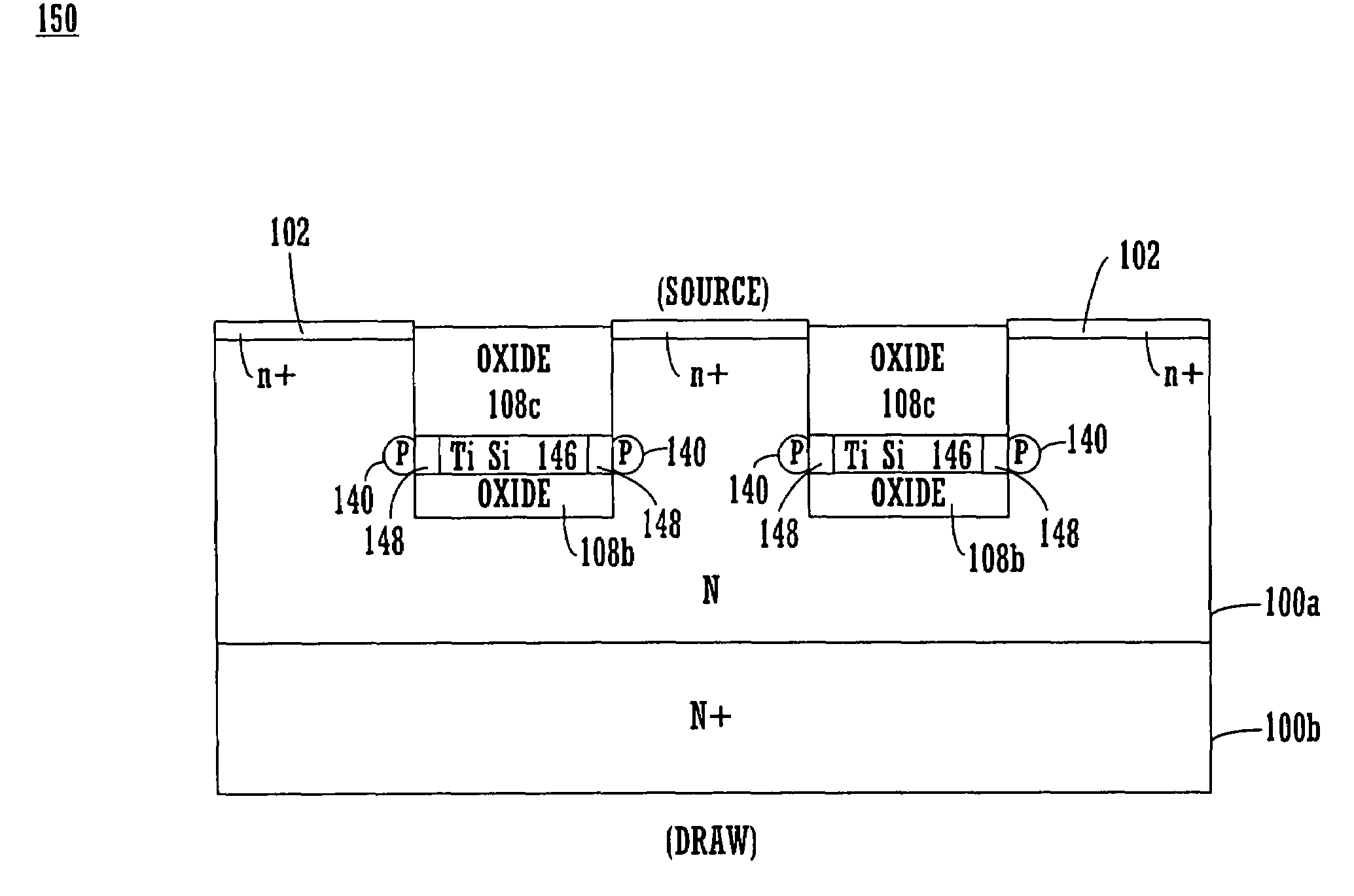

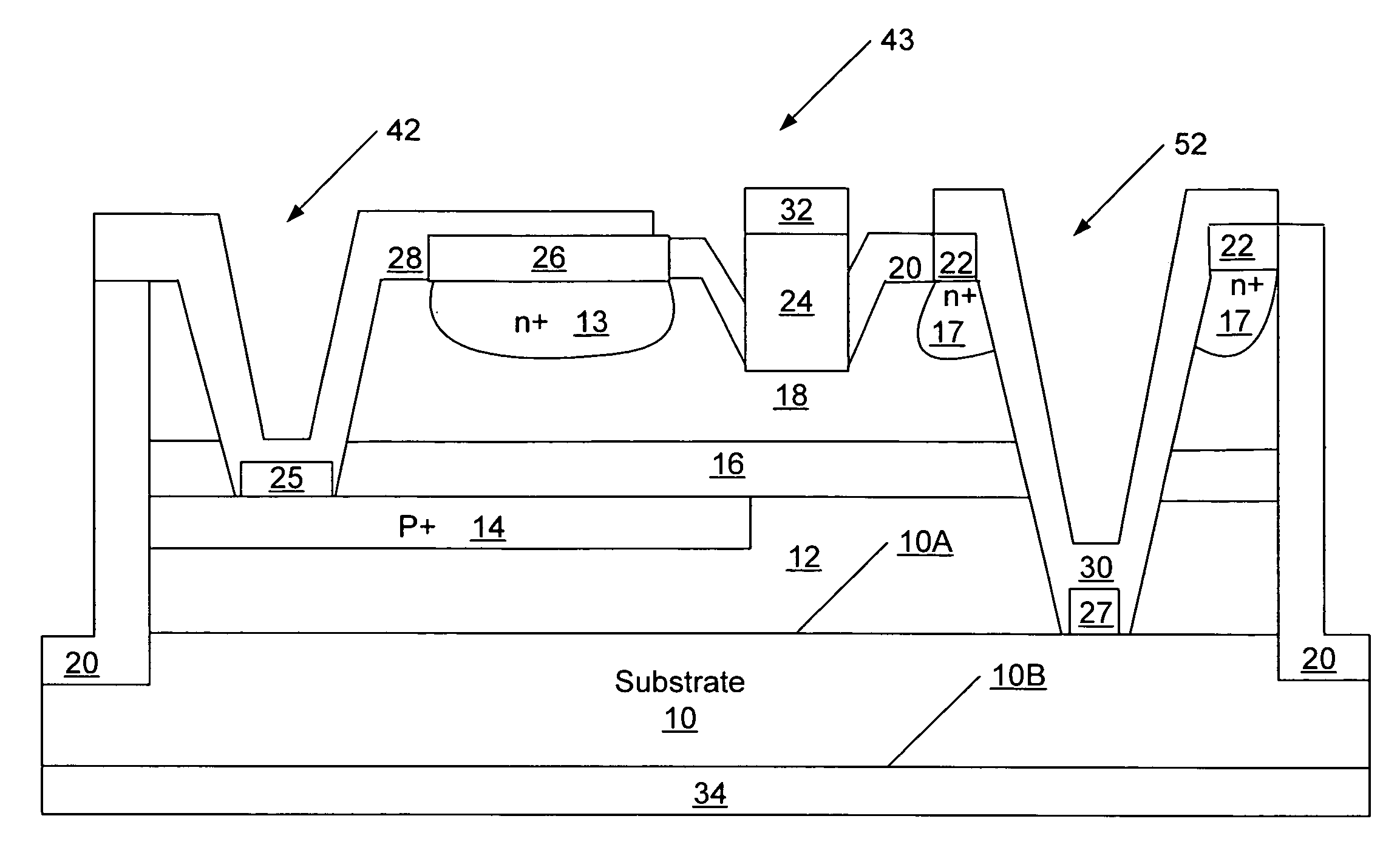

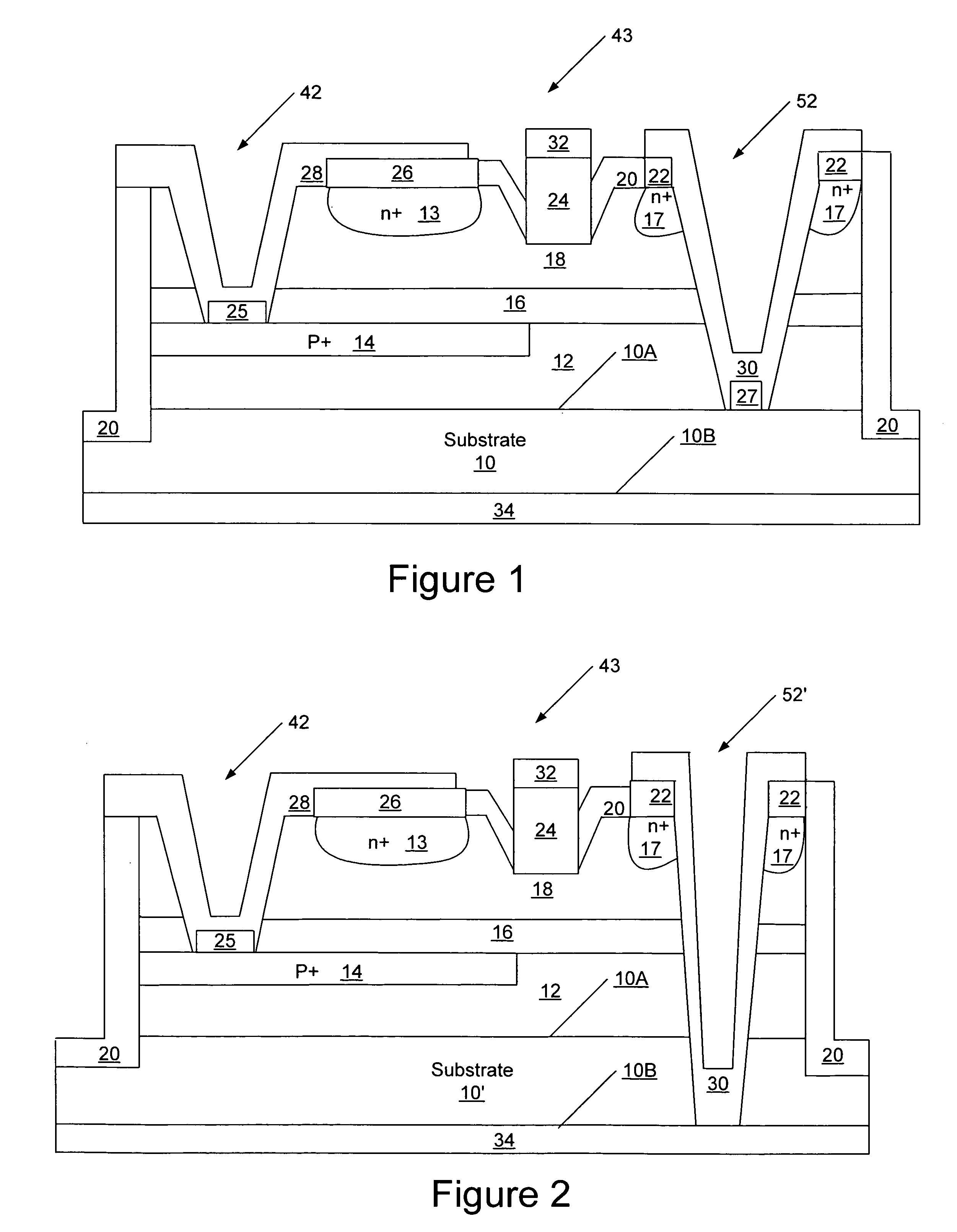

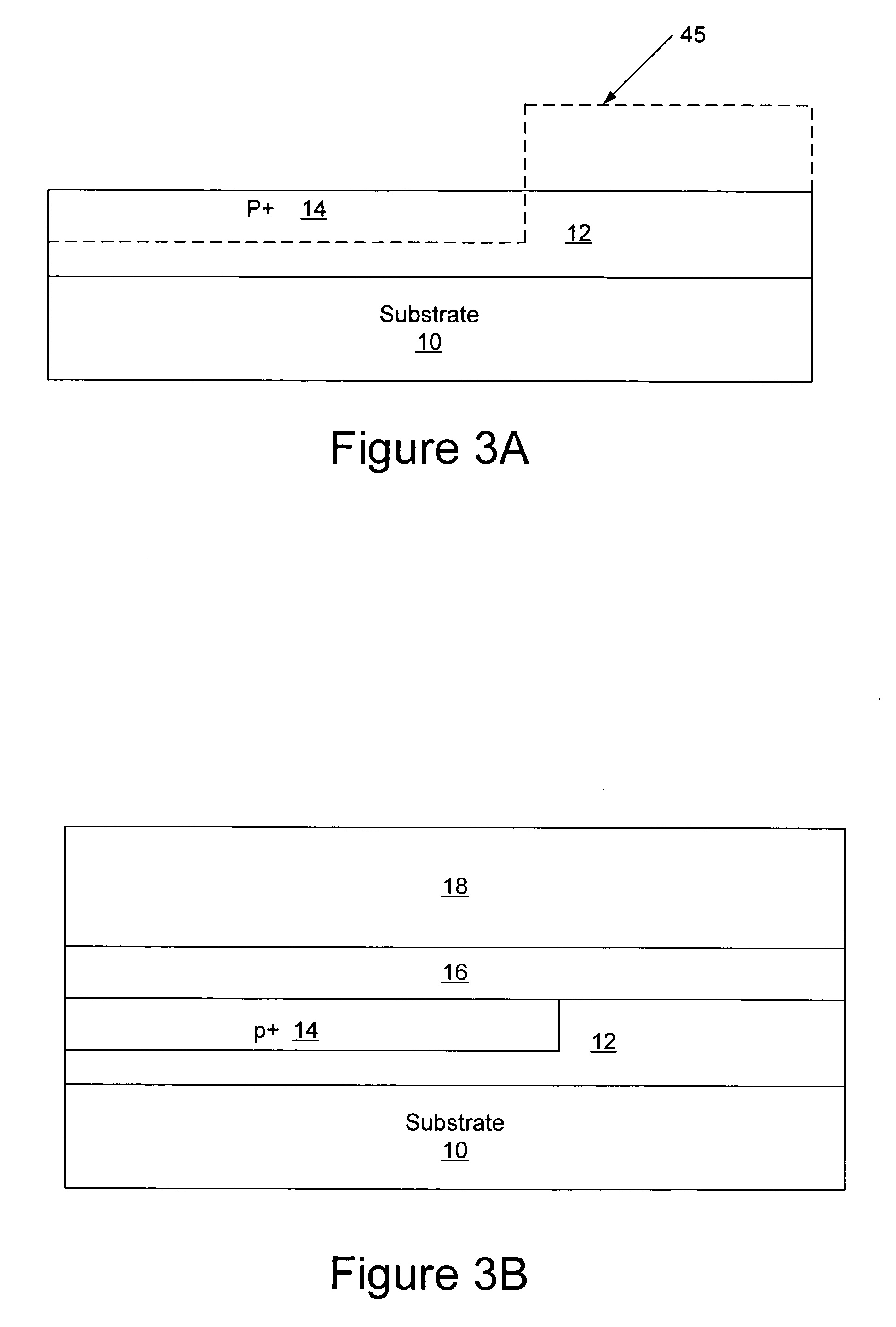

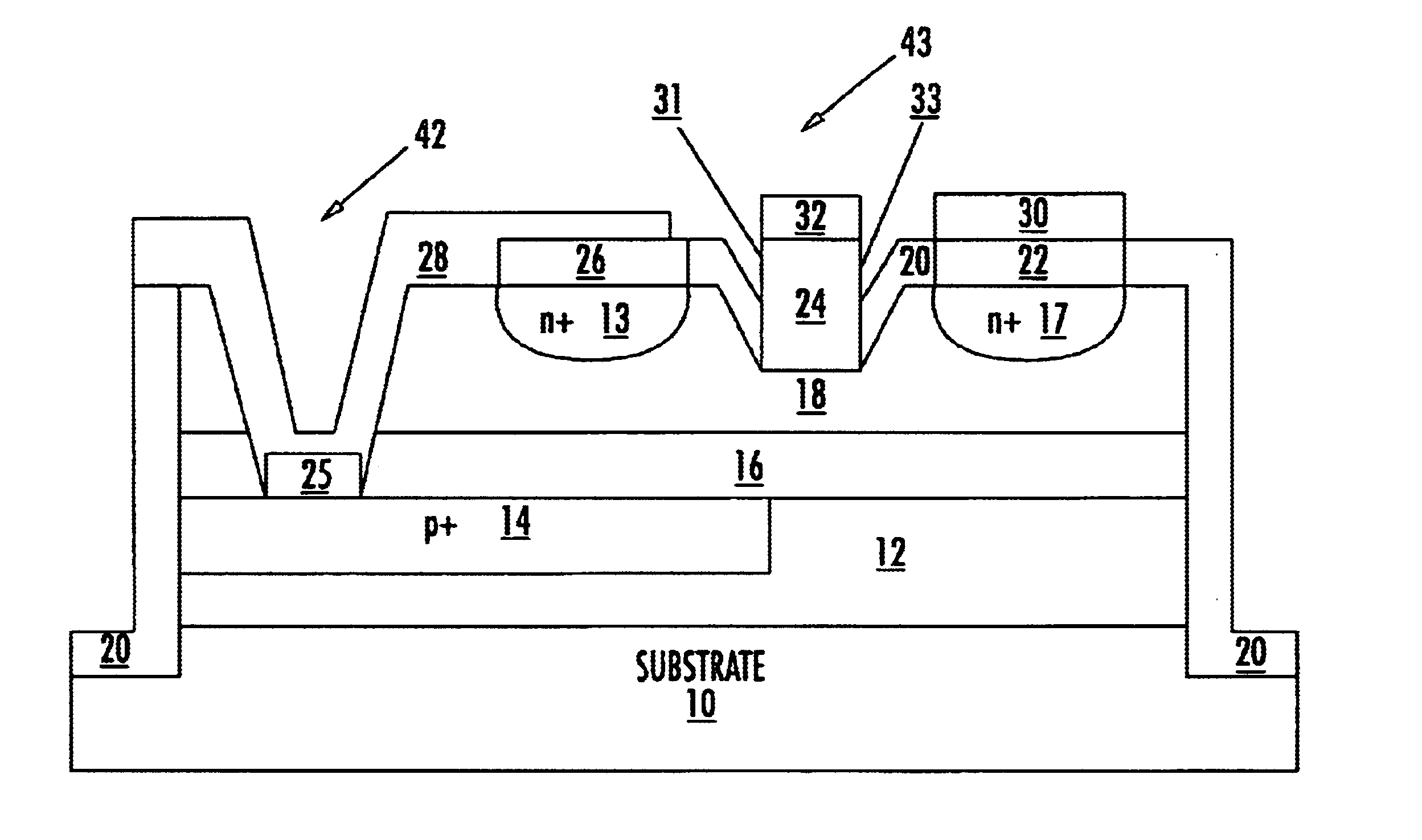

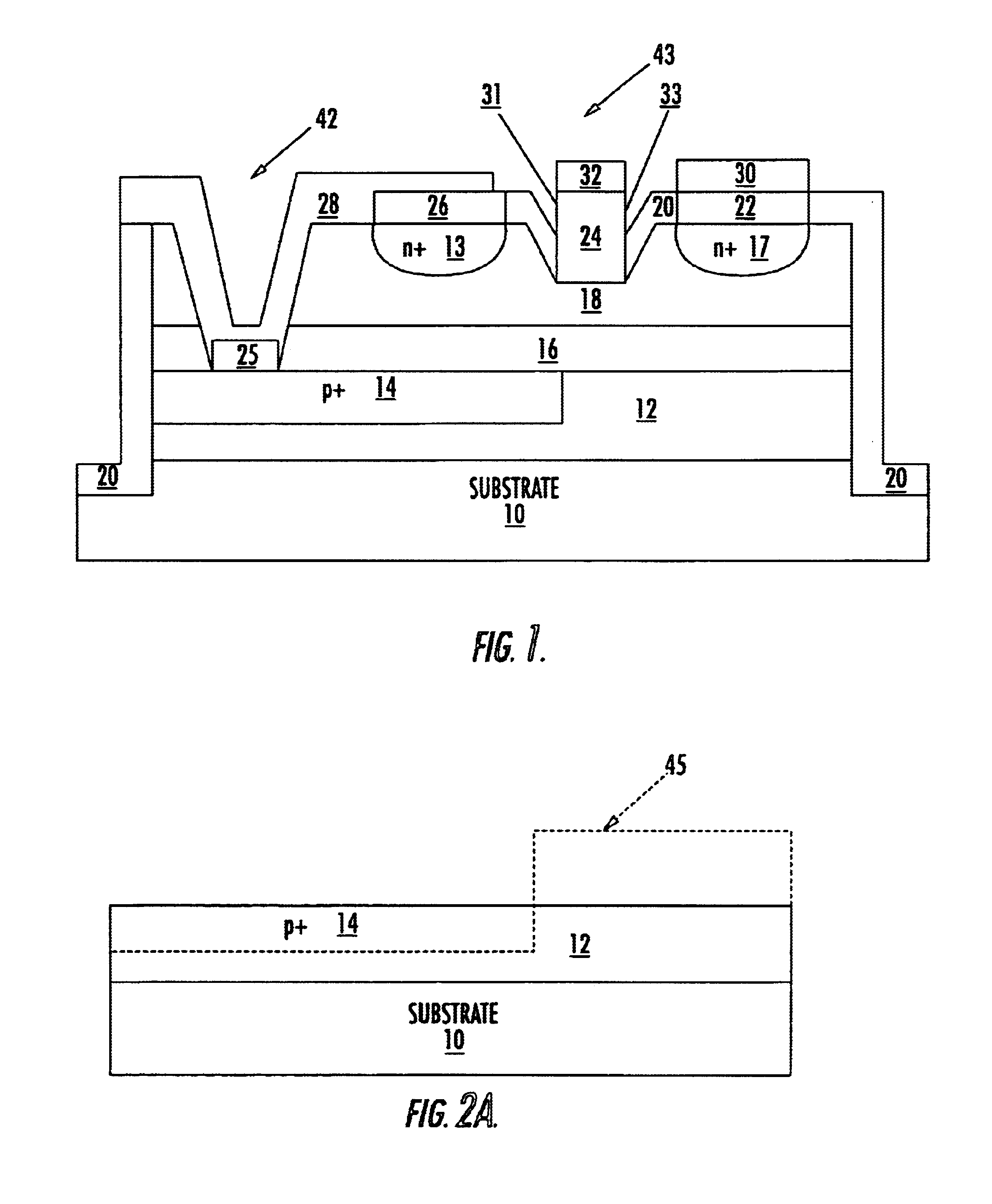

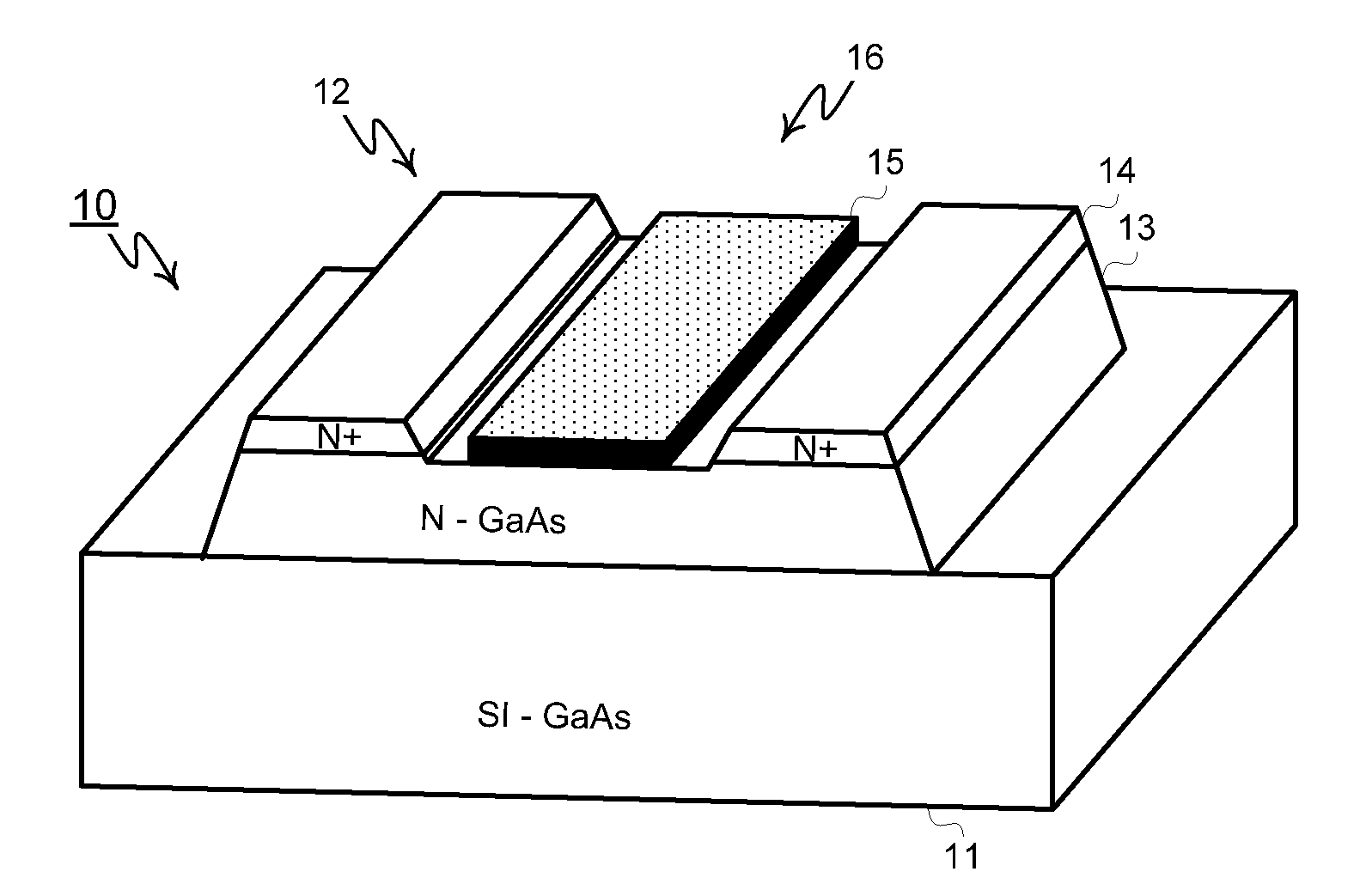

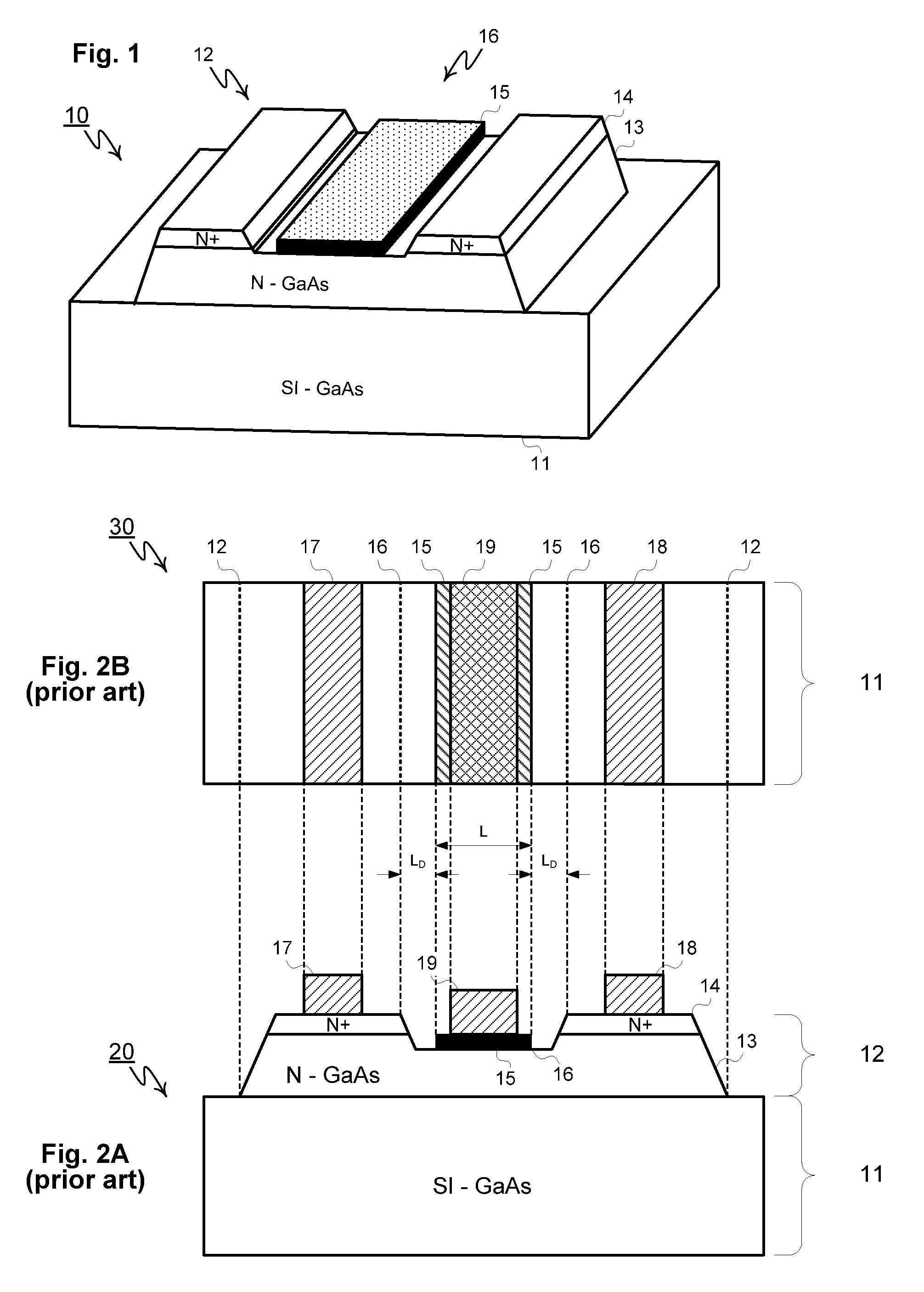

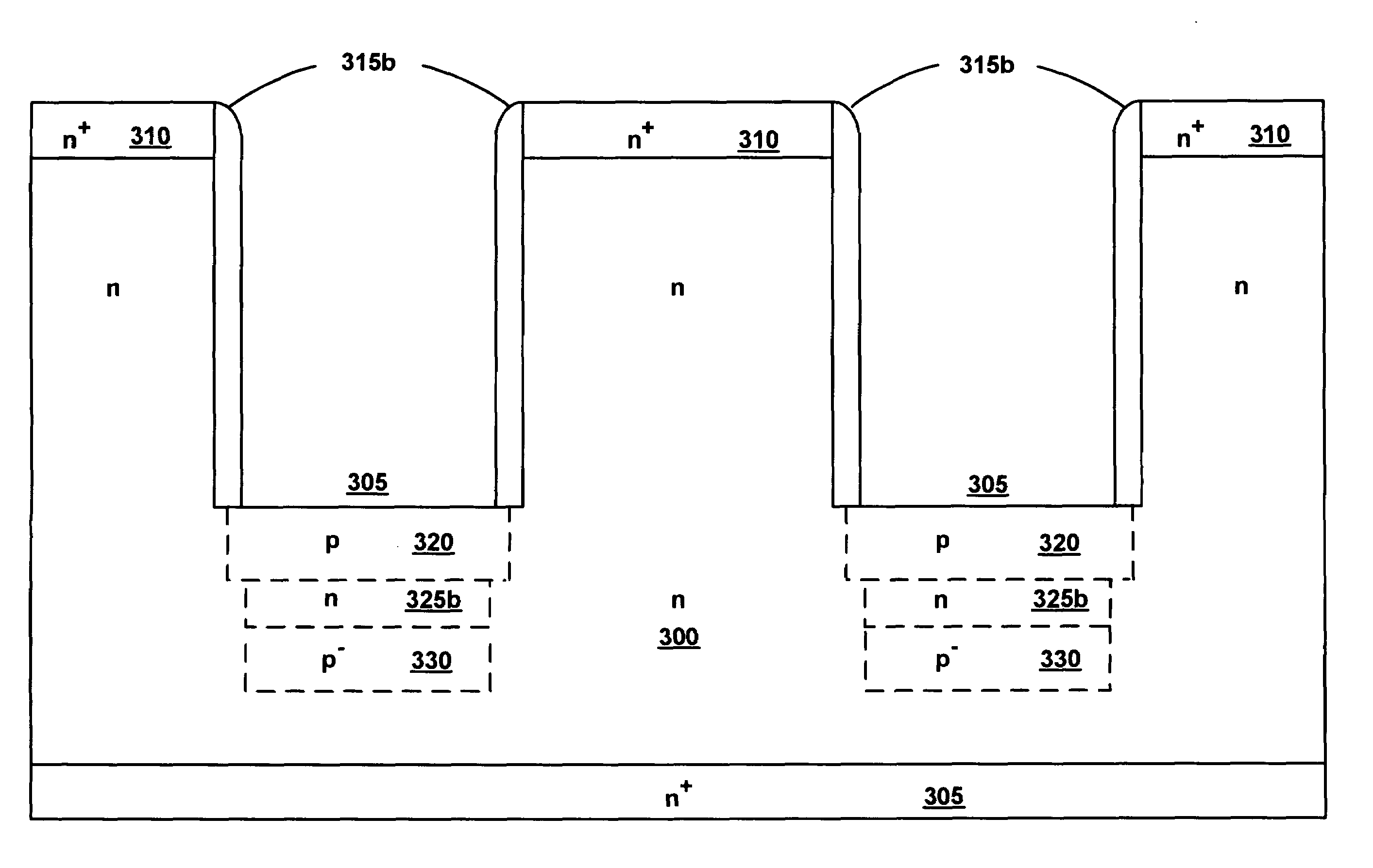

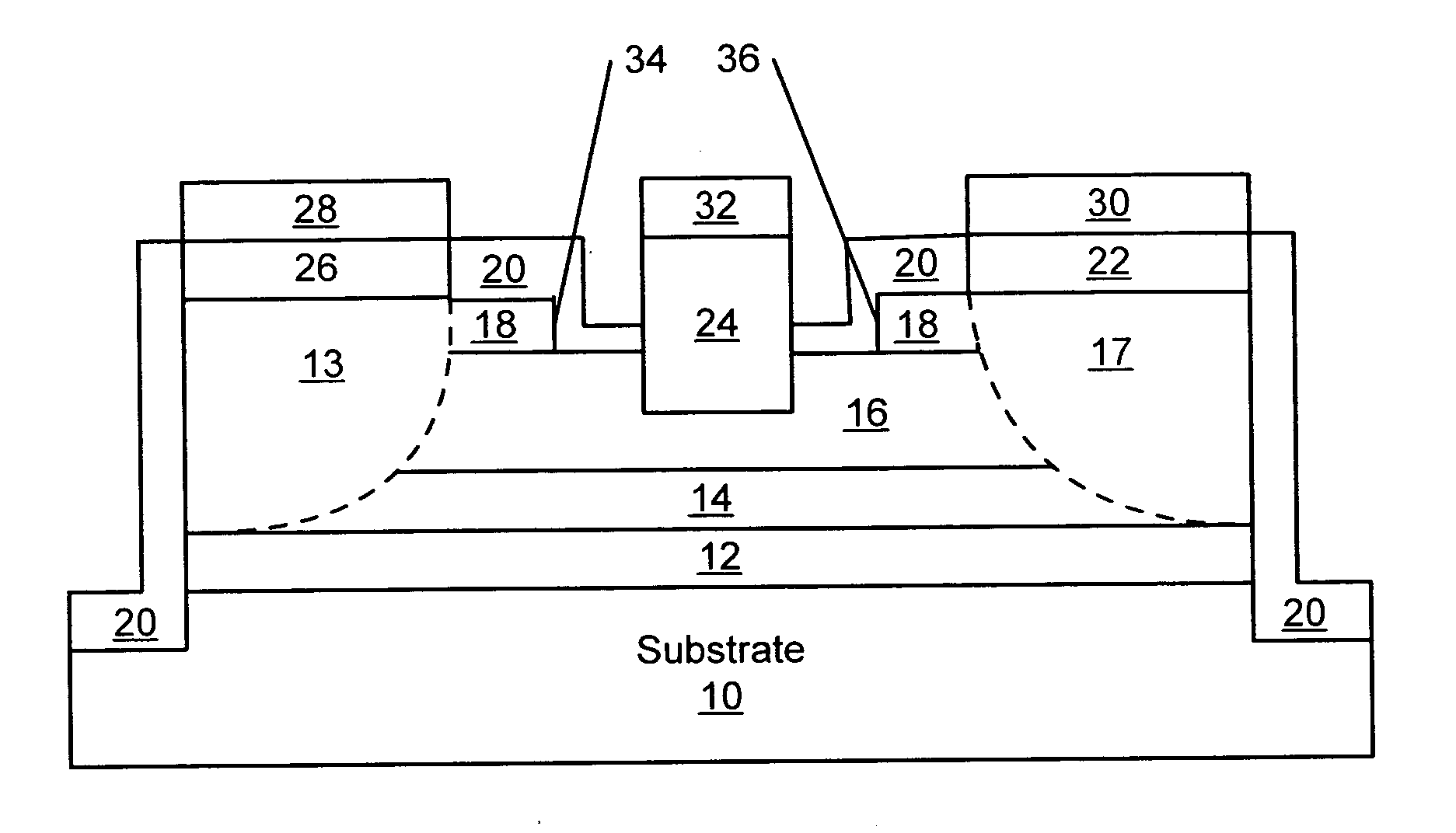

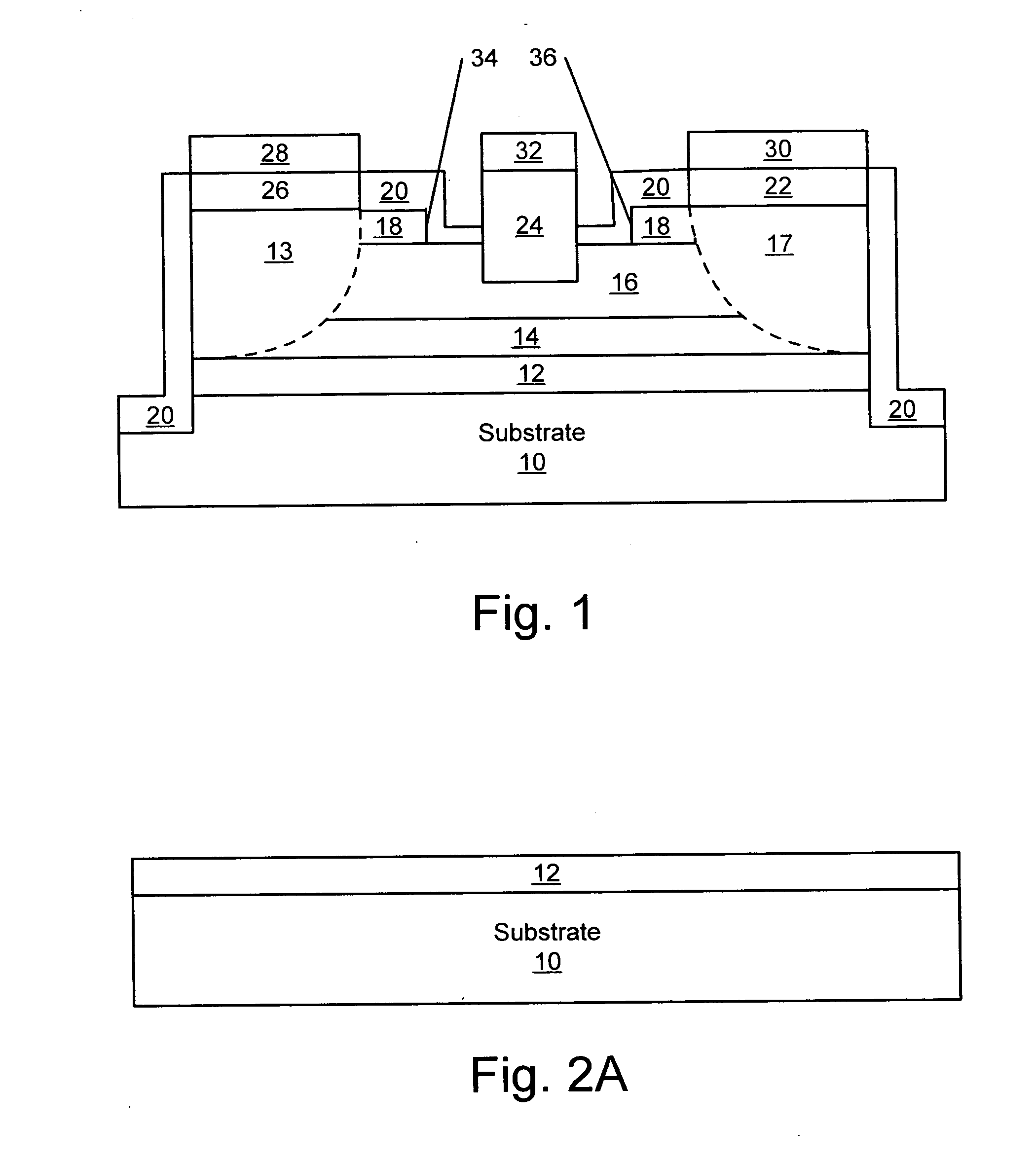

Metal-semiconductor field effect transistors (MESFETs) having drains coupled to the substrate and methods of fabricating the same

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a MESFET having a source region, a drain region and a gate contact. The gate contact is disposed between the source region and the drain region. The drain region is electrically coupled to the substrate through a contact via hole to the substrate. Related methods of fabricating MESFETs are also provided herein.

Owner:CREE INC

Warp-free semiconductor wafer, and devices using the same

A semiconductor wafer to be diced into individual SBDs, HEMTs or MESFETs has a substrate with a main semiconductor region and counter semiconductor region formed on its opposite surfaces. The main semiconductor region is configured to provide the desired semiconductor devices. In order to counterbalance the warping effect of the main semiconductor region on the substrate, as well as to enhance the voltage strength of the devices made from the wafer, the counter semiconductor region is made similar in configuration to the main semiconductor region. The main semiconductor region and counter semiconductor region are arranged in bilateral symmetry as viewed in a cross-sectional plane at right angles with the substrate surfaces.

Owner:SANKEN ELECTRIC CO LTD

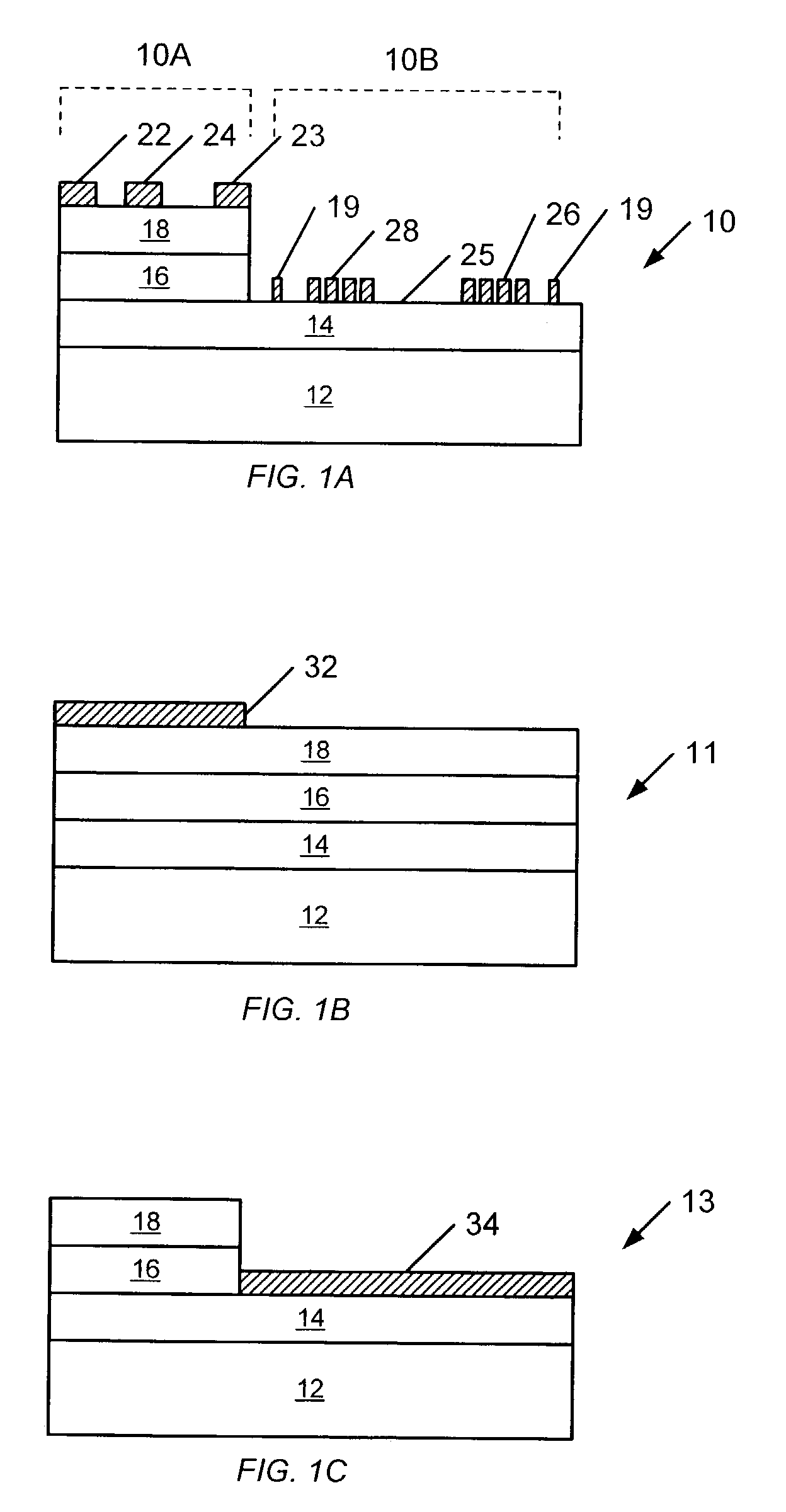

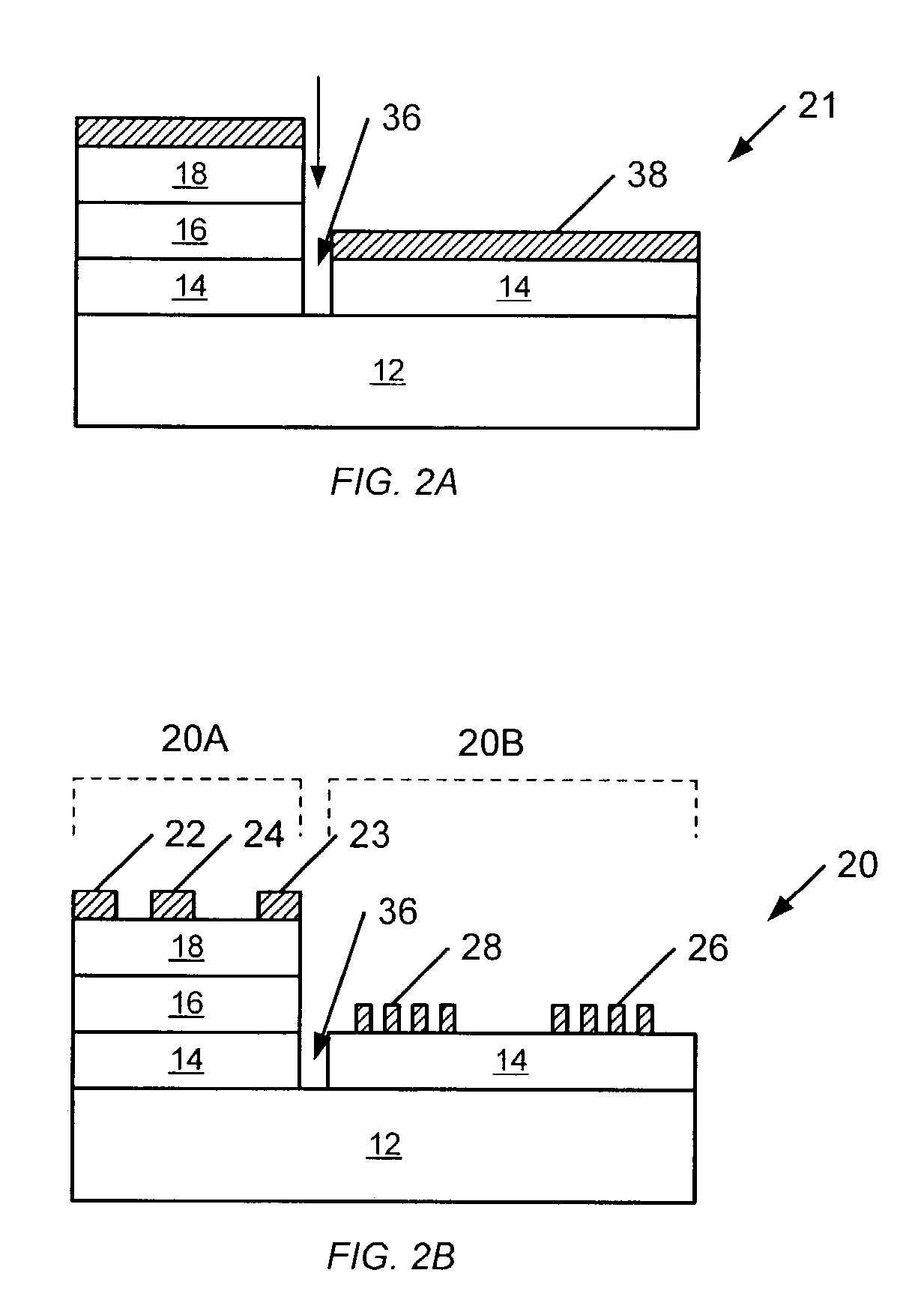

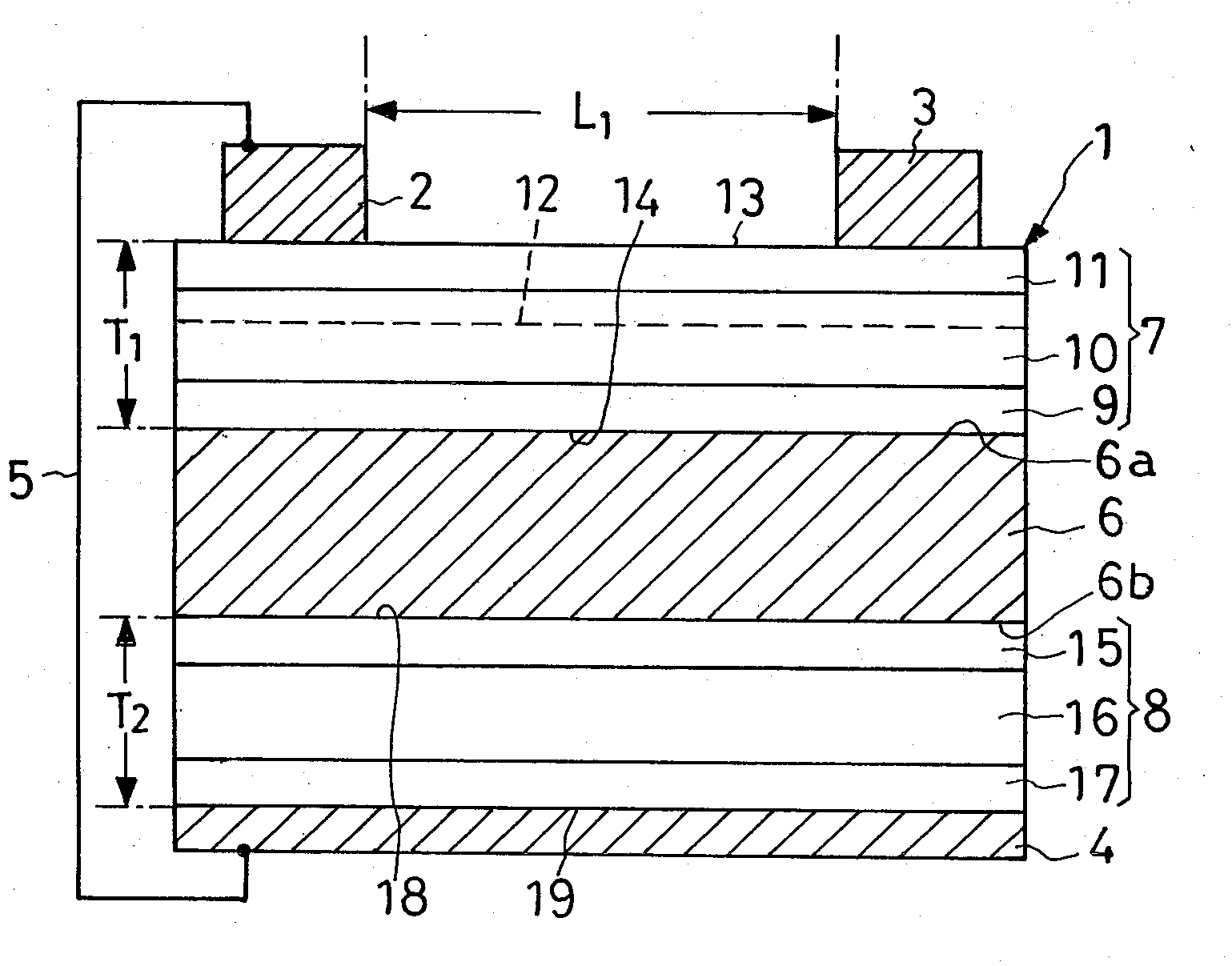

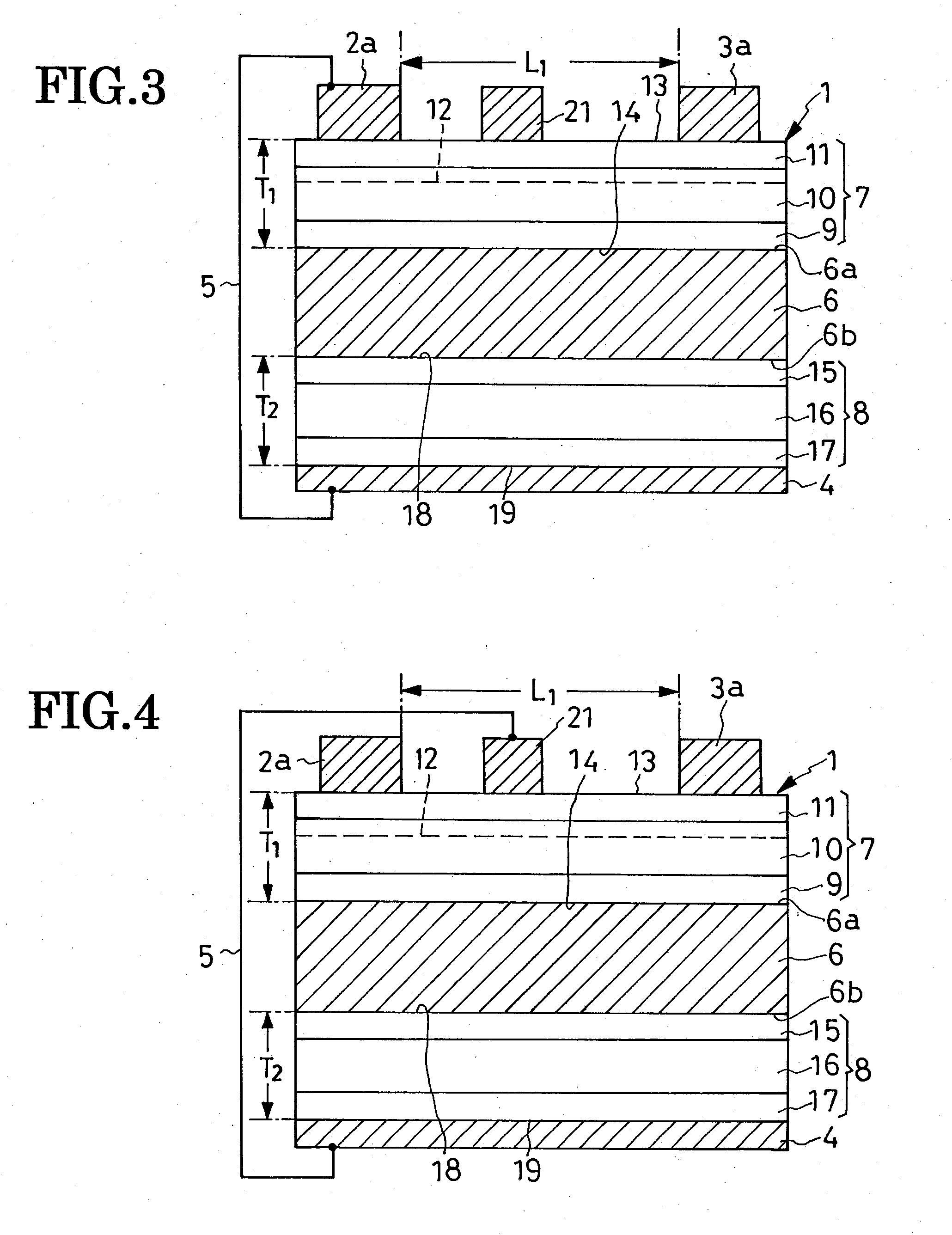

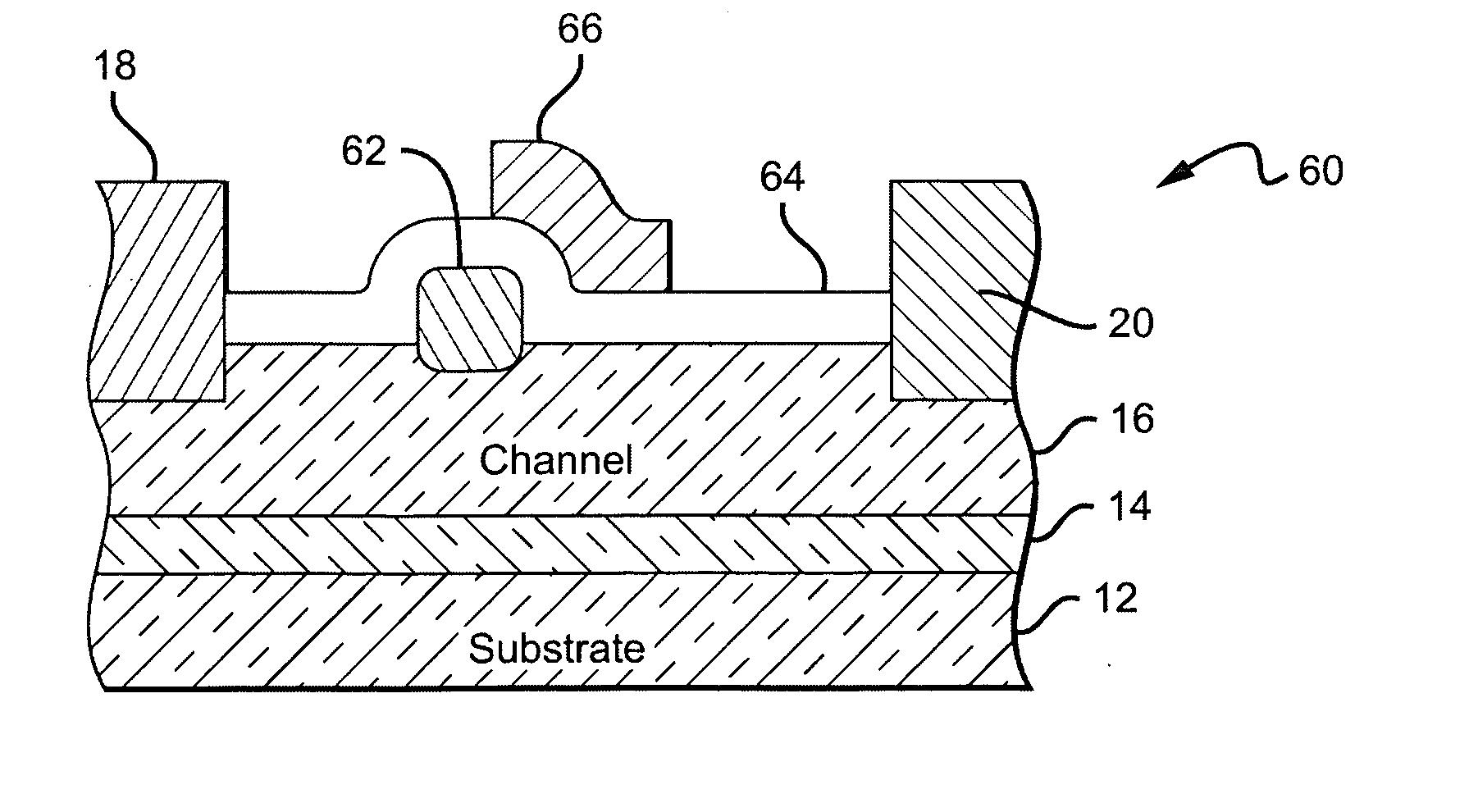

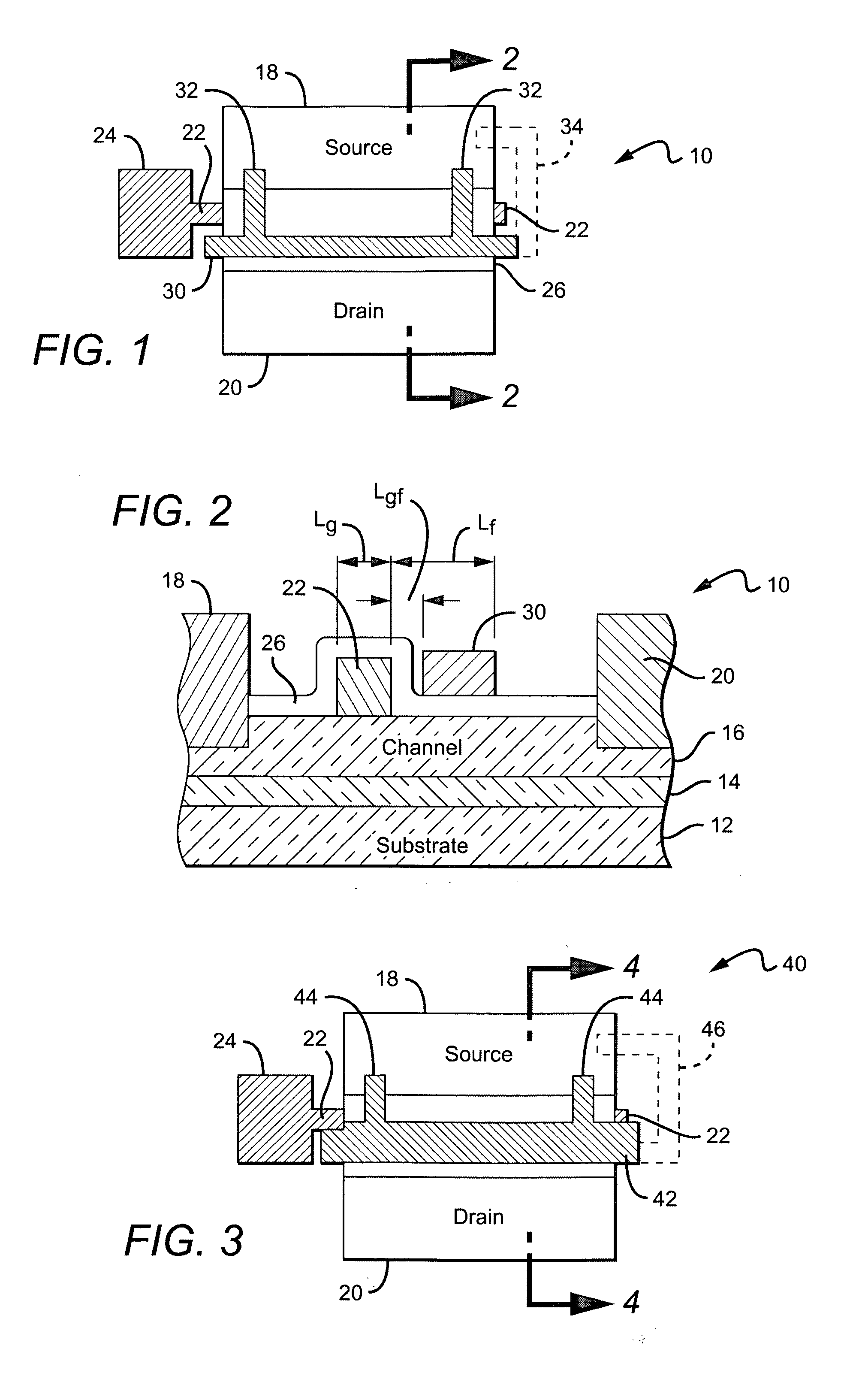

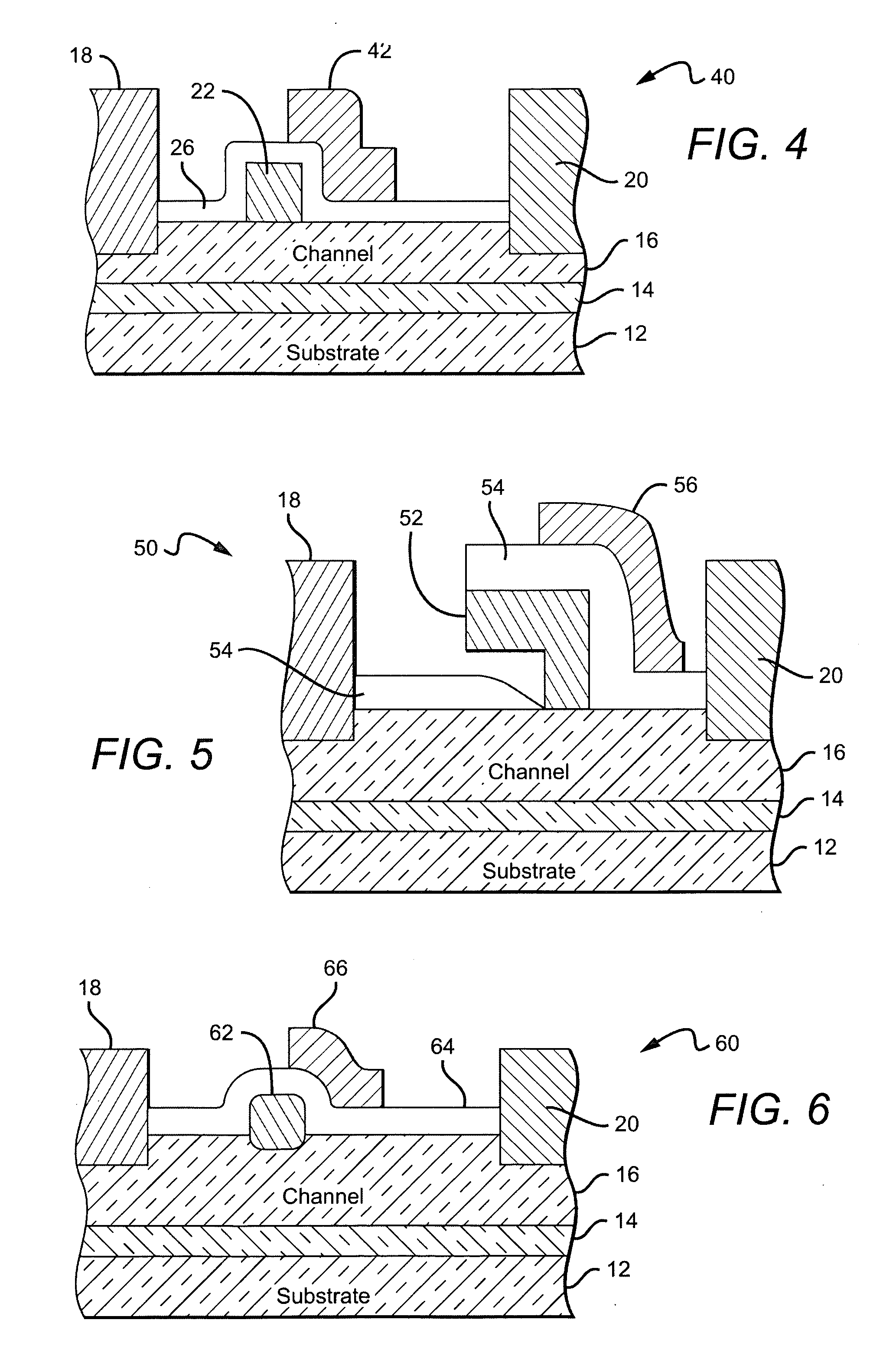

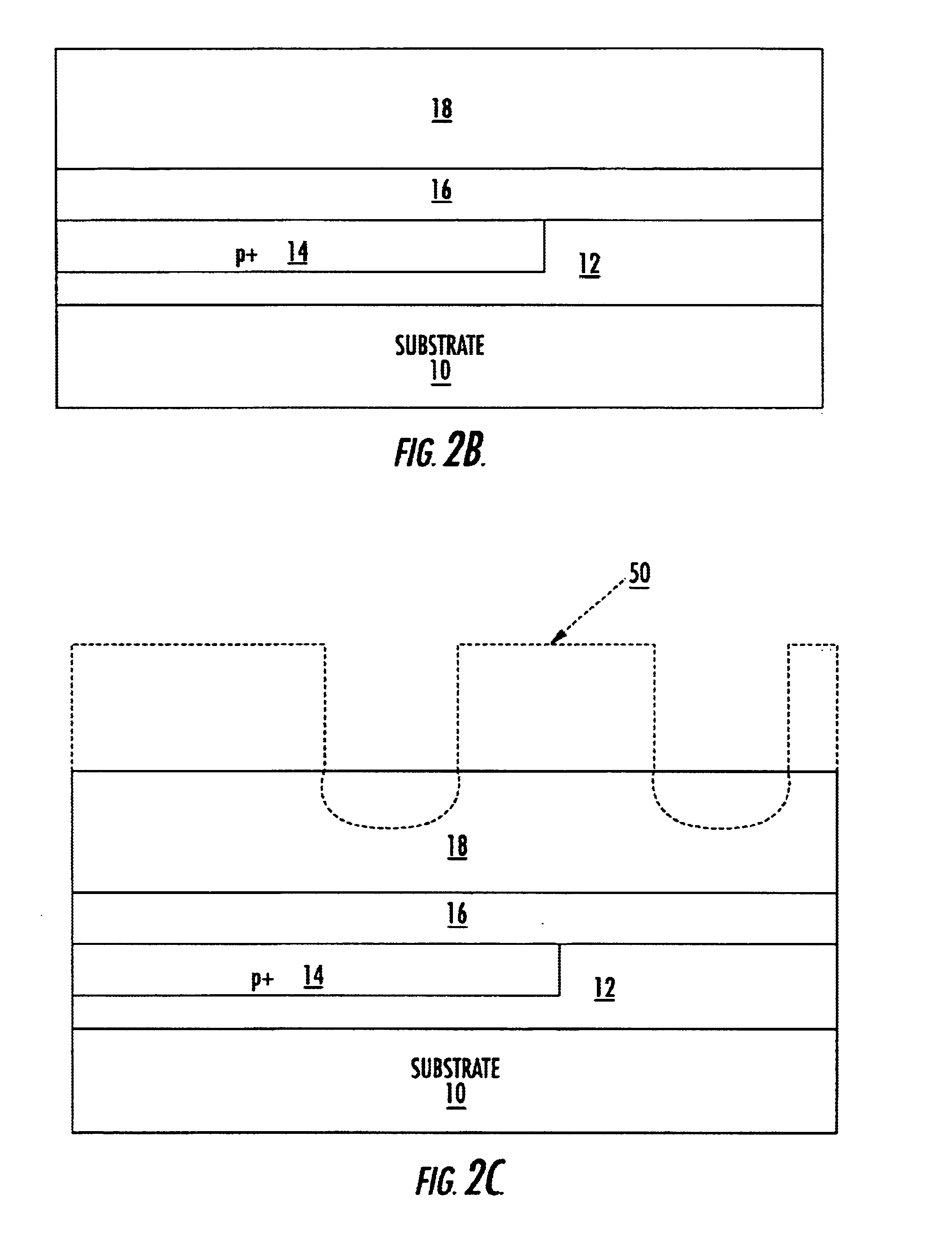

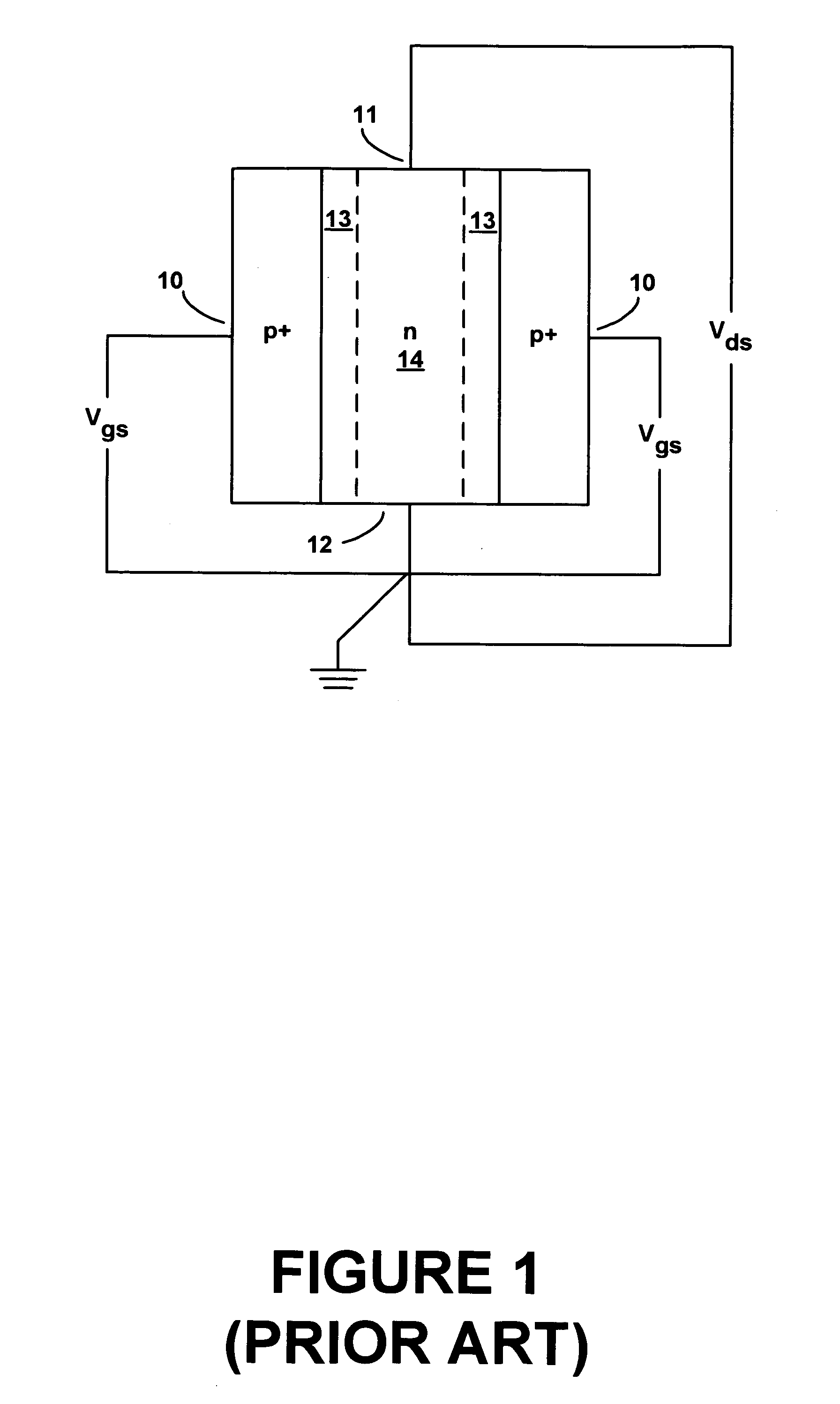

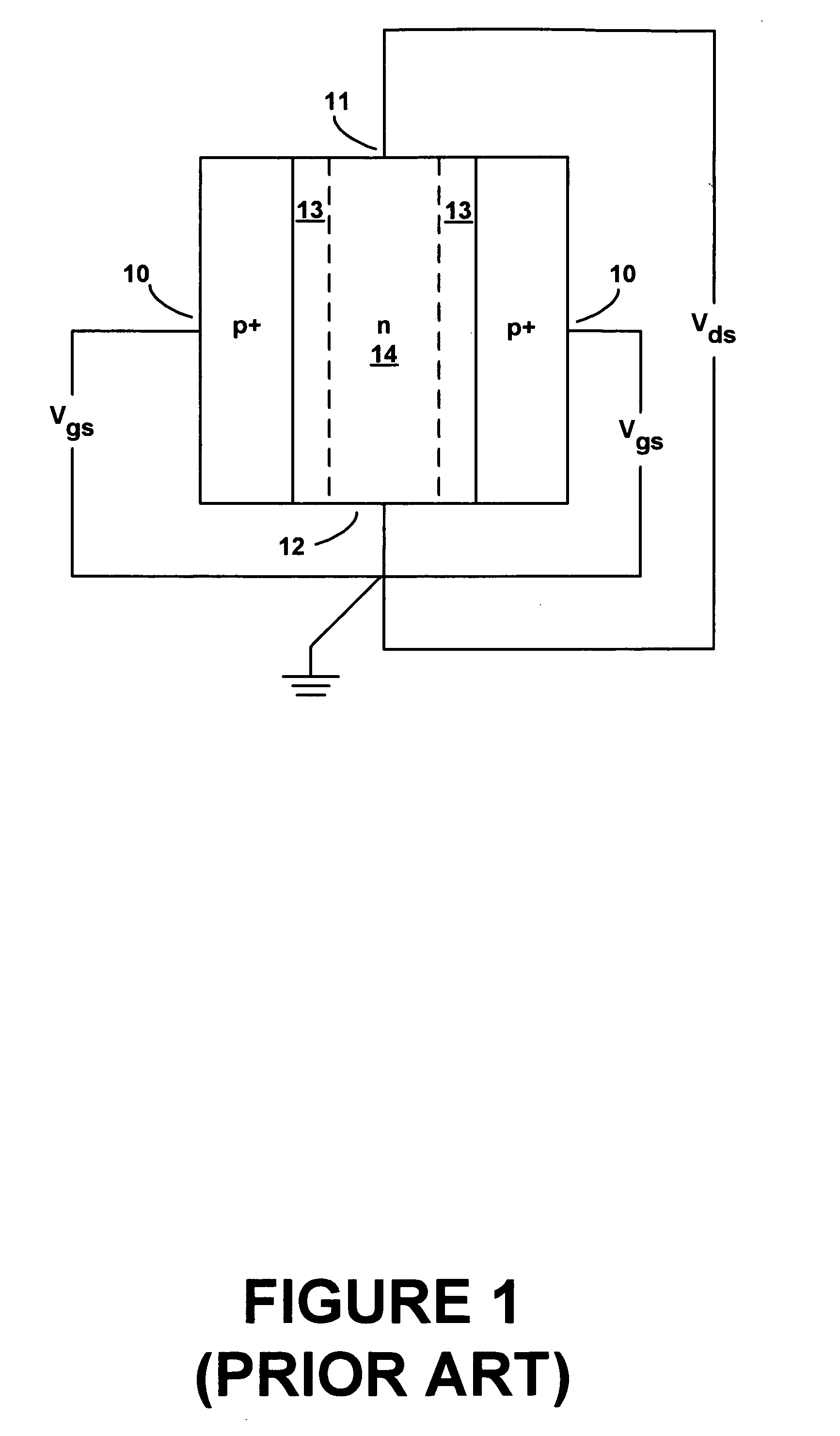

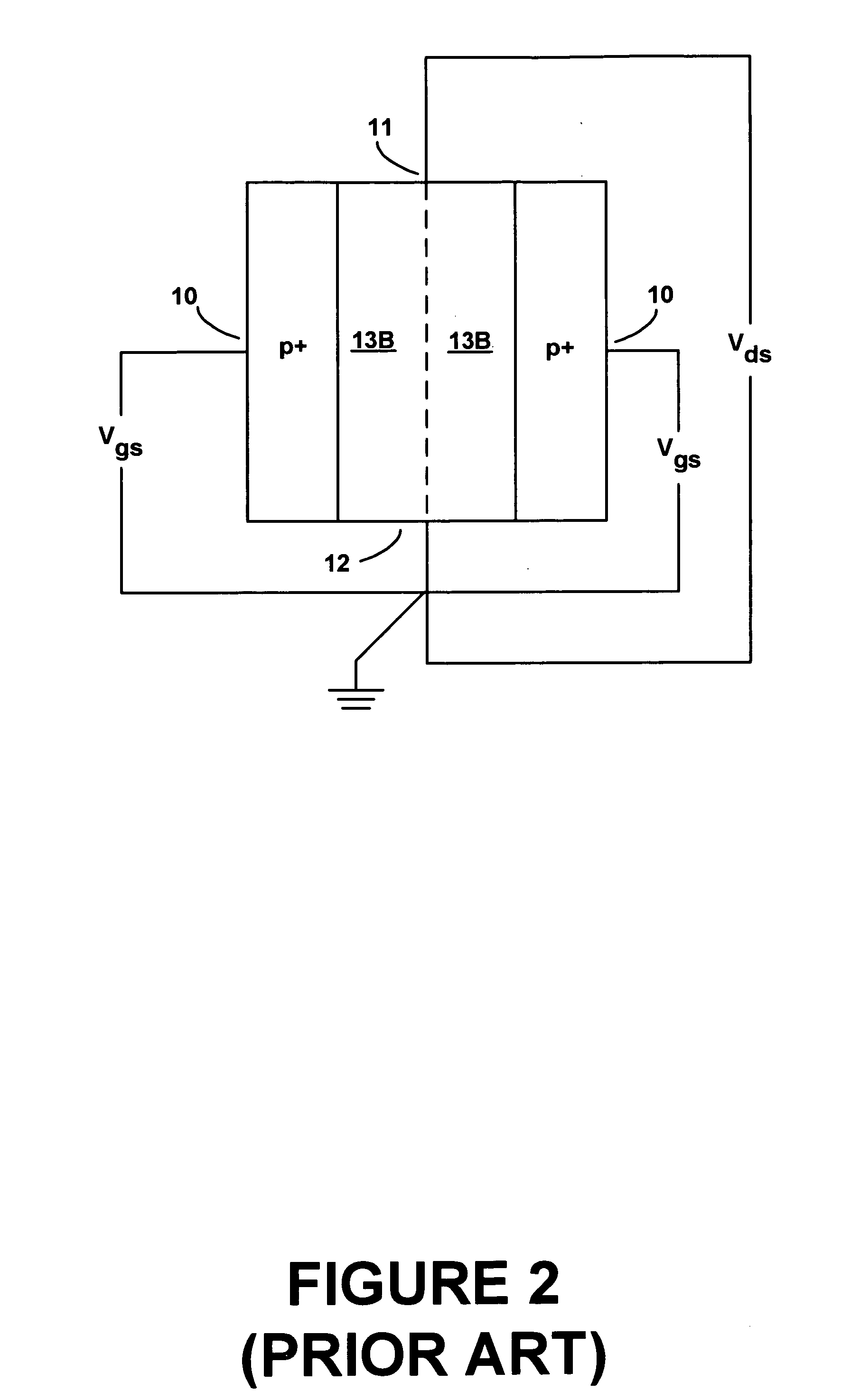

JFET and MESFET structures for low voltage high current and high frequency applications

InactiveUS7045397B1Easy to controlLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

Wide bandgap field effect transistors with source connected field plates

ActiveUS20050253167A1Reduces peak operating electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueMESFET

A field effect transistor comprising a buffer and channel layer formed successively on a substrate. A source electrode, drain electrode, and gate are all formed in electrical contact with the channel layer, with the gate between the source and drain electrodes. A spacer layer is formed on at least a portion of a surface of the channel layer between the gate and drain electrode and a field plate is formed on the spacer layer isolated from the gate and channel layer. The spacer layer is electrically connected by at least one conductive path to the source electrode, wherein the field plate reduces the peak operating electric field in the MESFET.

Owner:CREE INC

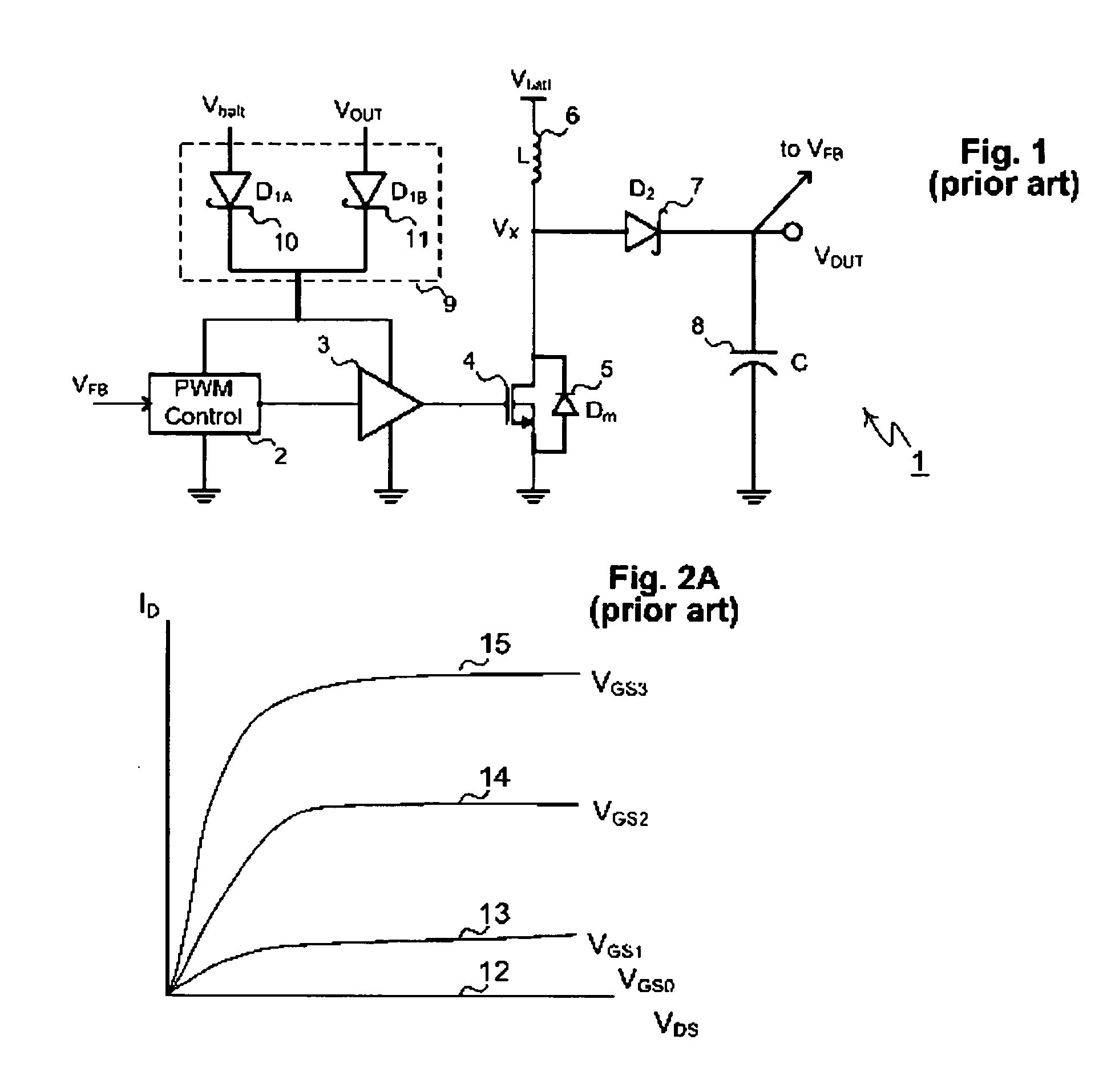

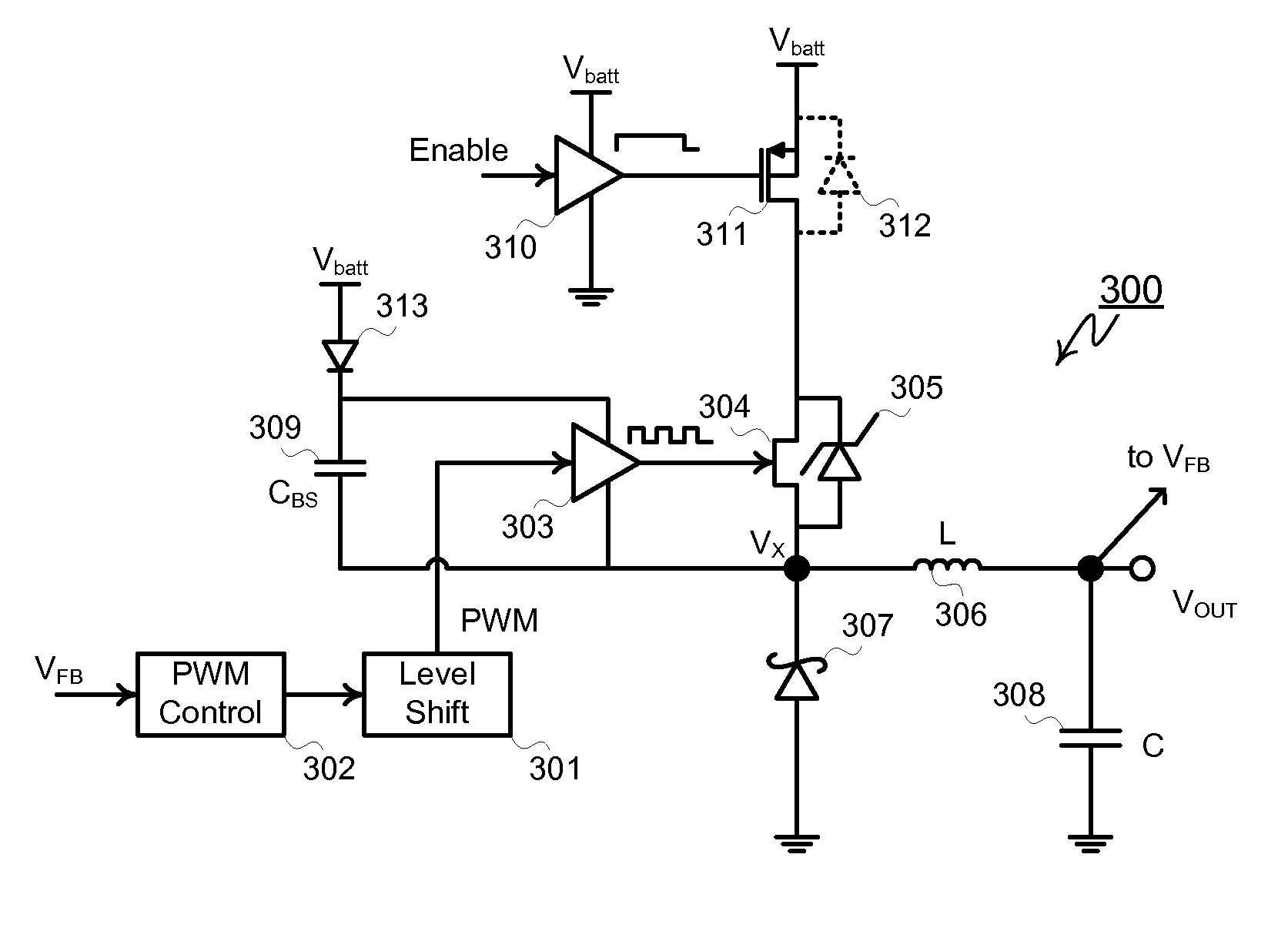

High-Frequency Buck Converter that Includes a Cascode MESFET-MOSFET Power Switch

InactiveUS20080191679A1Lower on-resistanceLow off-state drain leakageDc-dc conversionElectric variable regulationMOSFETElectrical battery

A Buck converter that includes a cascode switch comprising a series connected MESFET and MOSFET power switch. The cascode power switch is typically connected in between a power source and a node Vx. The node Vx is connected to an output node via an inductor and to ground via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to the battery and to ground. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

DC-DC Converter that Includes a High Frequency Power MESFET Gate Drive Circuit

InactiveUS20080203991A1Lower on-resistanceLow off-state drain leakageTransistorDc-dc conversionDc dc converterHigh frequency power

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

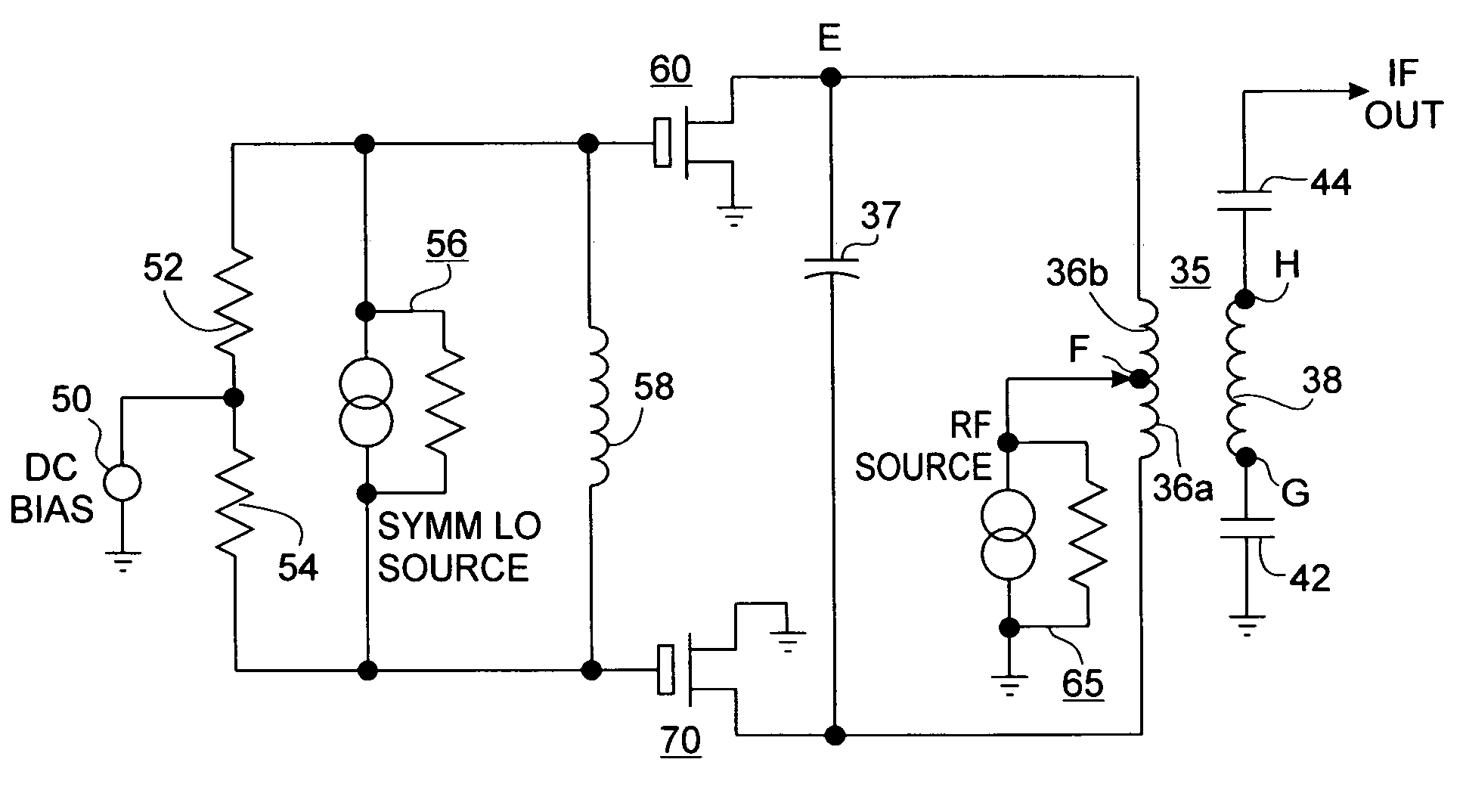

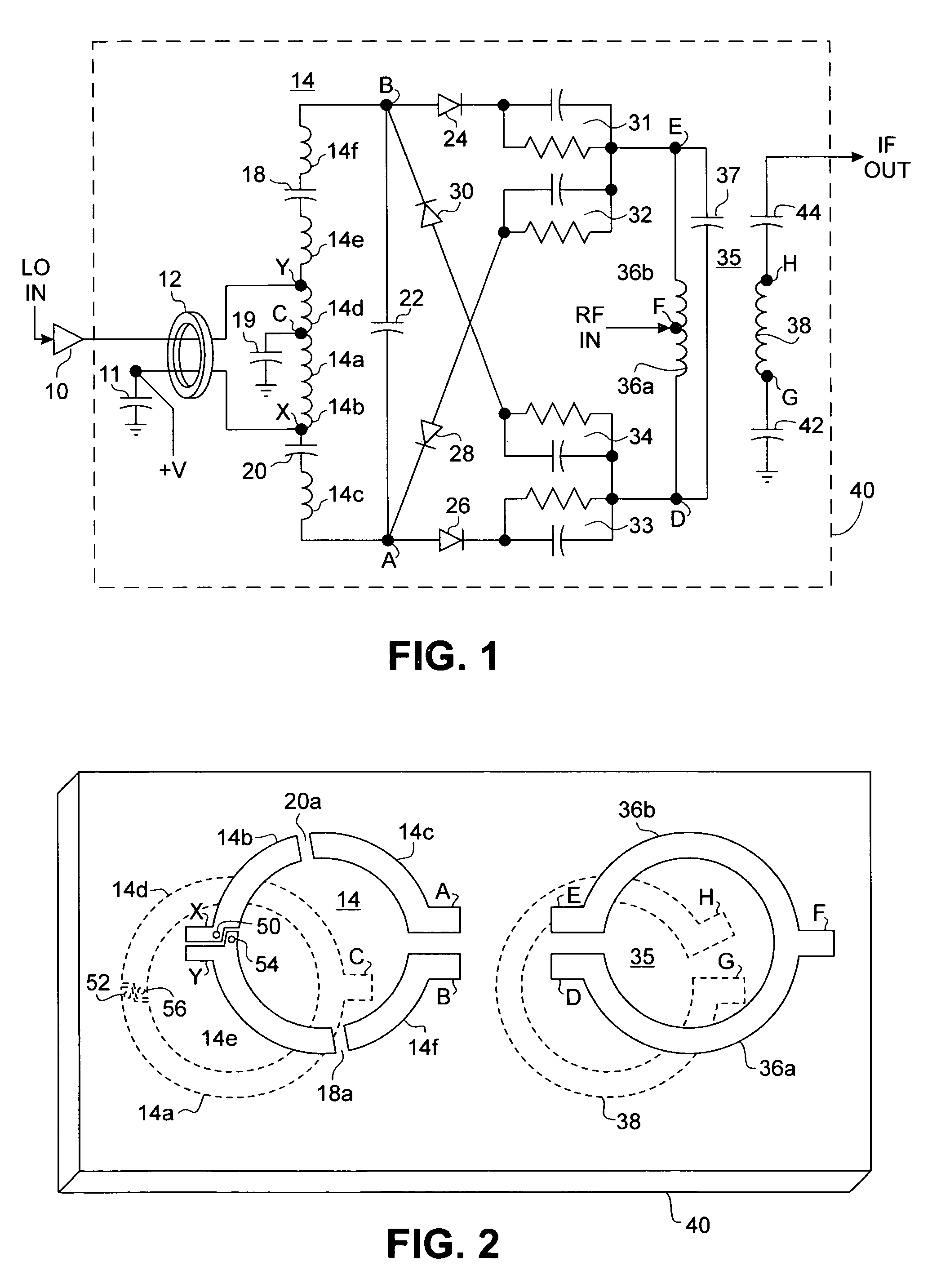

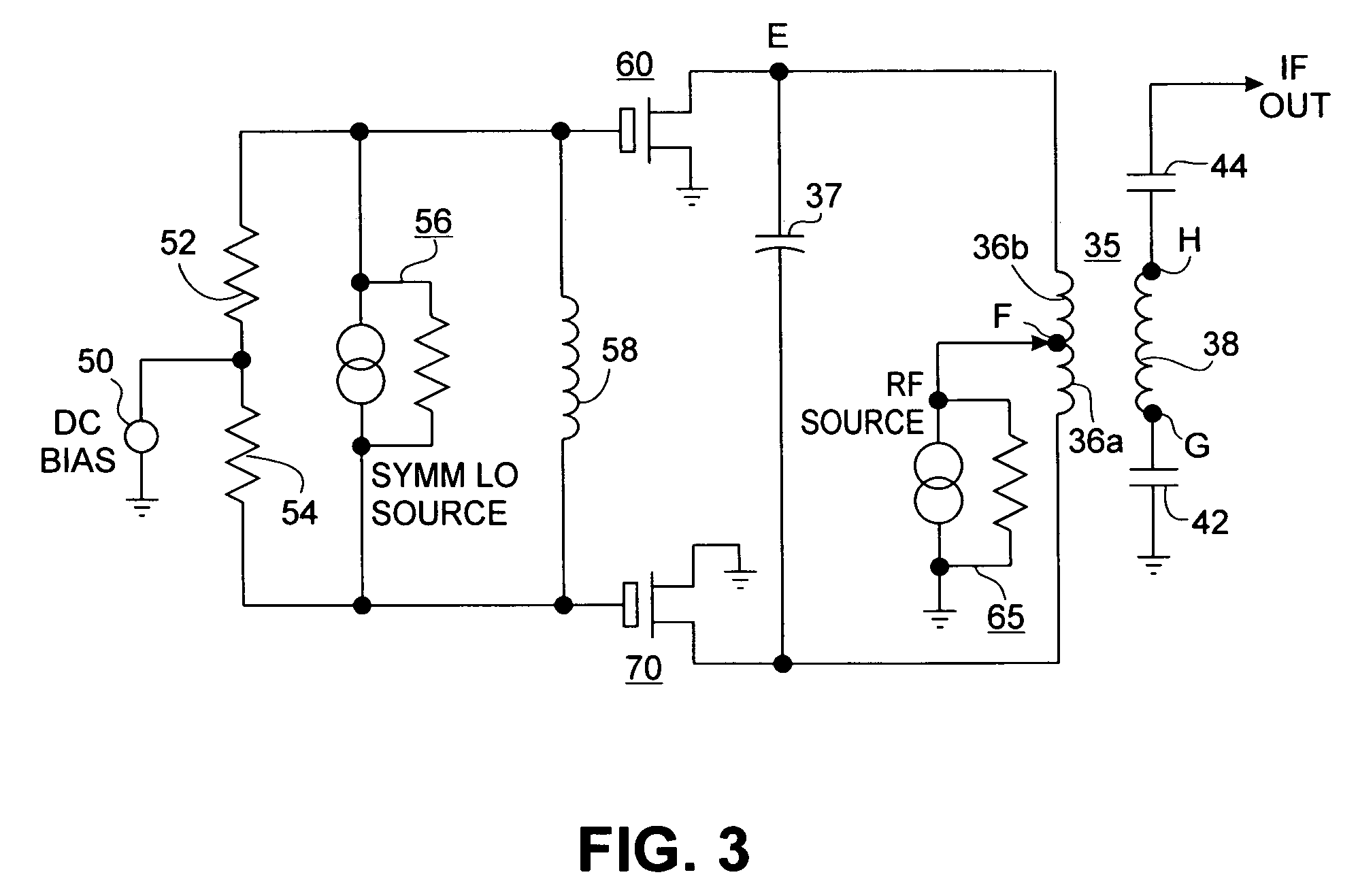

Printed circuit doubly balanced mixer for upconverter

InactiveUS7072636B2Minimization requirementsModulation transference balanced arrangementsTransmission noise suppressionBalanced mixerLocal oscillator signal

A doubly balanced upconverter mixer includes a local oscillator balun circuit comprising juxtaposed foil elements on opposite sides of an insulated substrate with electrical interconnections between the foil elements. An IF balun circuit also comprises series tuned and parallel tuned foil elements on opposite sides of the substrate in juxtaposition to each other. A diode switching network interconnects the baluns. A local oscillator signal is connected to the foil elements of the local oscillator balun circuit, an RF signal is coupled to one foil element of the IF balun circuit and an IF signal is taken from the other foil element of the IF balun circuit. Another embodiment incorporates MESFET type switches, the gates of which are supplied directly with a symmetrical local oscillator signal. This arrangement eliminates the need for the local oscillator balun.

Owner:ZENITH RADIO CORP

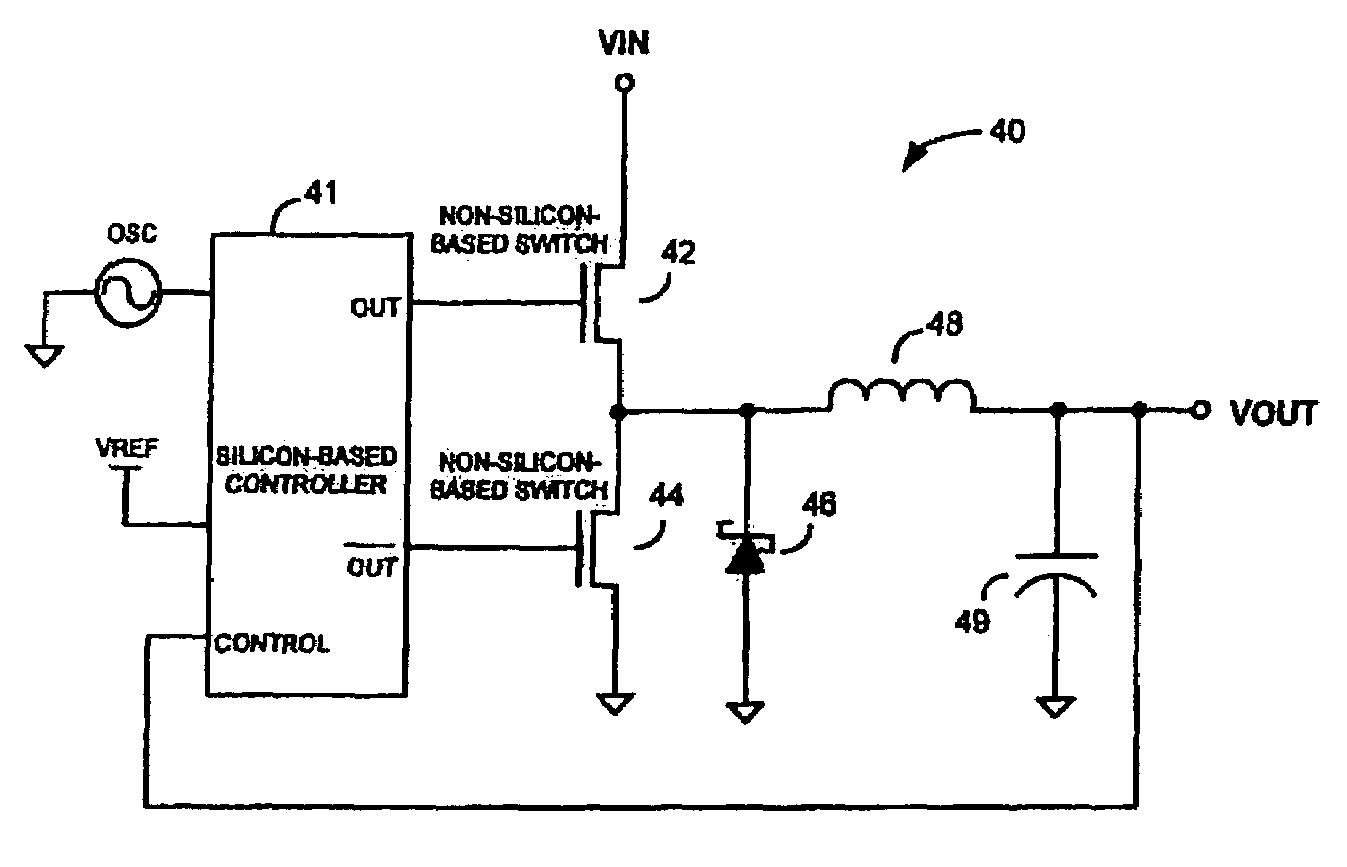

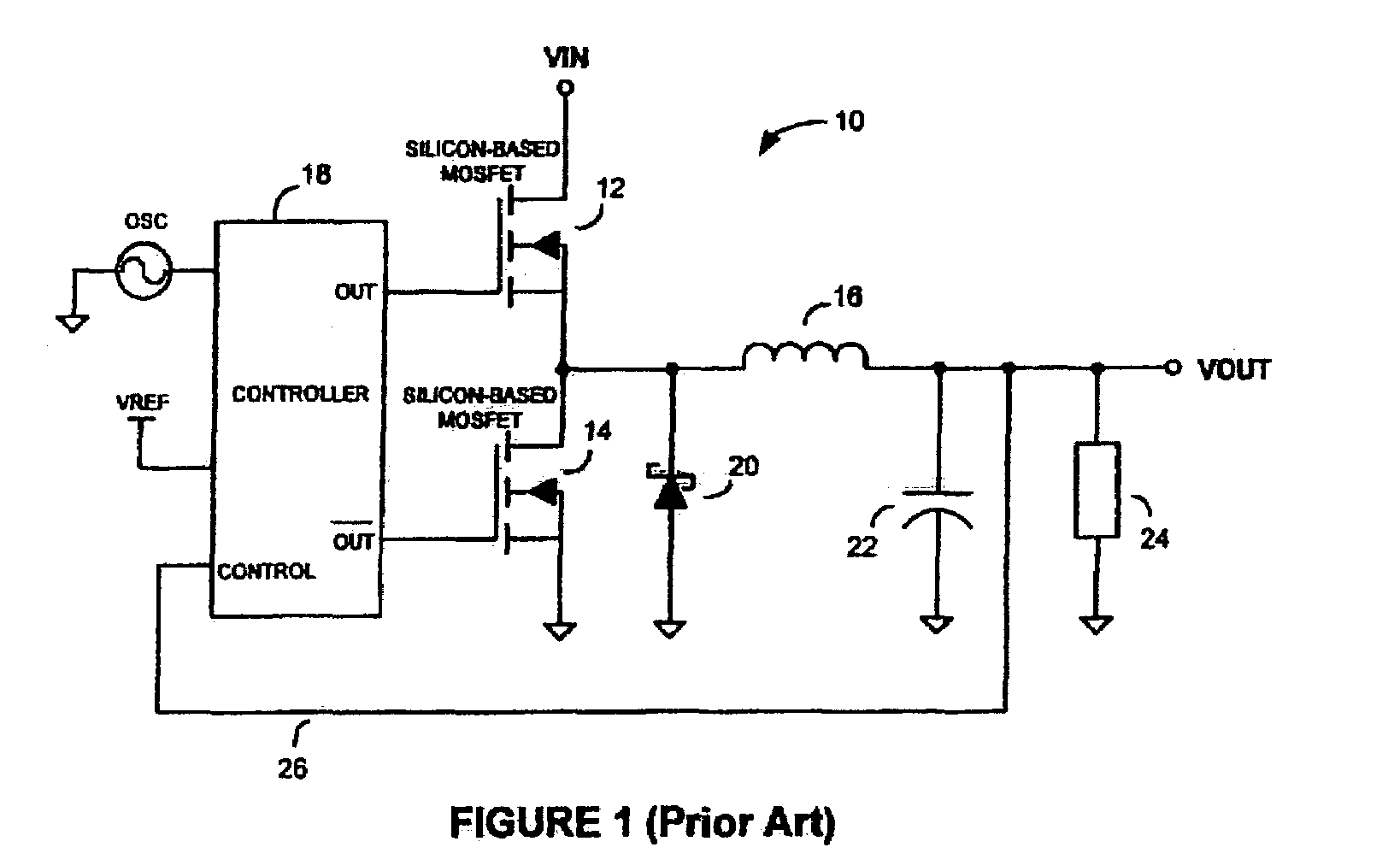

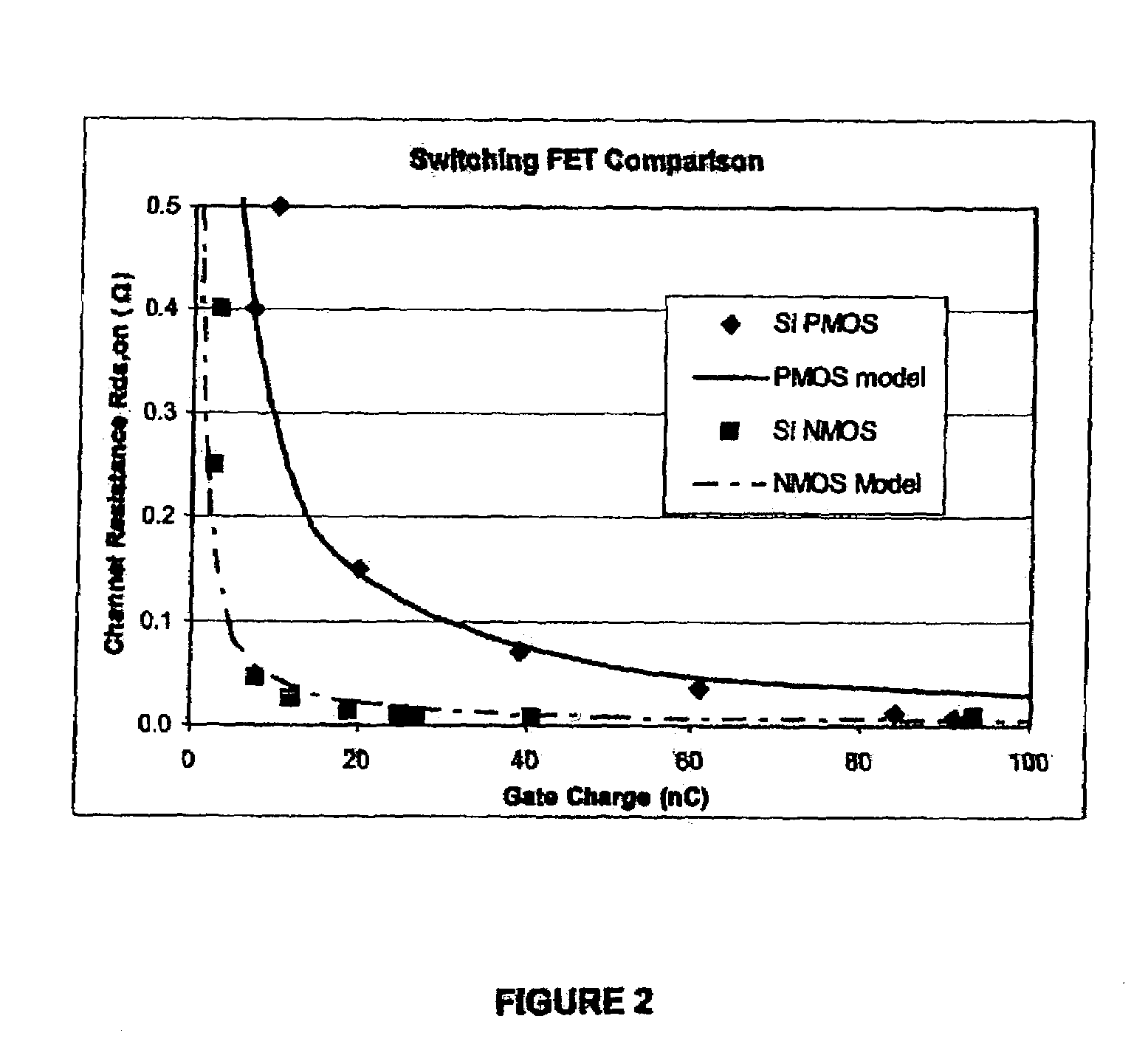

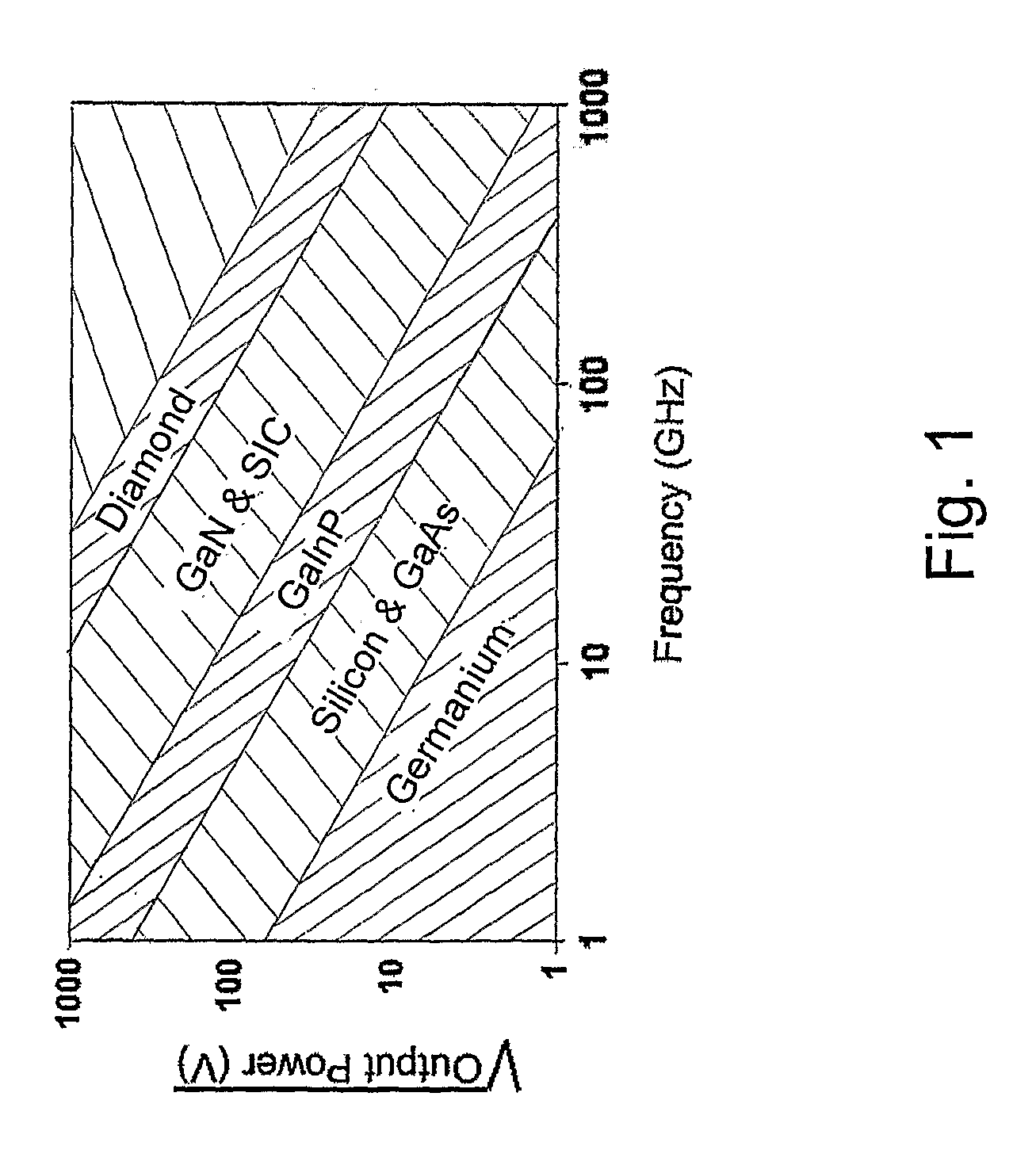

Extremely high-speed switchmode DC-DC converters

InactiveUS7026797B2Improve efficiencyImproving efficiency and battery savingResonant long antennasEfficient power electronics conversionFigure of meritCMOS

Switchmode DC—DC power converters using one or more non-Silicon-based switching transistors and a Silicon-based (e.g. CMOS) controller are disclosed. The non-Silicon-based switching transistors may comprise, but are not necessarily limited to, III-V compound semiconductor devices such as gallium arsenide (GaAs) metal-semiconductor field effect transistors (MESFETS) or heterostructure FETs such as high electron mobility transistors (HEMTs). According to an embodiment of the invention, the low figure of merit (FoM), τFET, of the non-Silicon-based switching transistors allows the converters of the present invention to be employed in envelope tracking amplifier circuits of wireless devices designed for high-bandwidth technologies such as, for example, EDGE and UMTS, thereby improving the efficiency and battery saving capabilities of the wireless devices.

Owner:MURATA MFG CO LTD +1

Metal-semiconductor field effect transistors (MESFETs) having drains coupled to the substrate and methods of fabricating the same

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a MESFET having a source region, a drain region and a gate contact. The gate contact is disposed between the source region and the drain region. The drain region is electrically coupled to the substrate through a contact via hole to the substrate. Related methods of fabricating MESFETs are also provided herein.

Owner:CREE INC

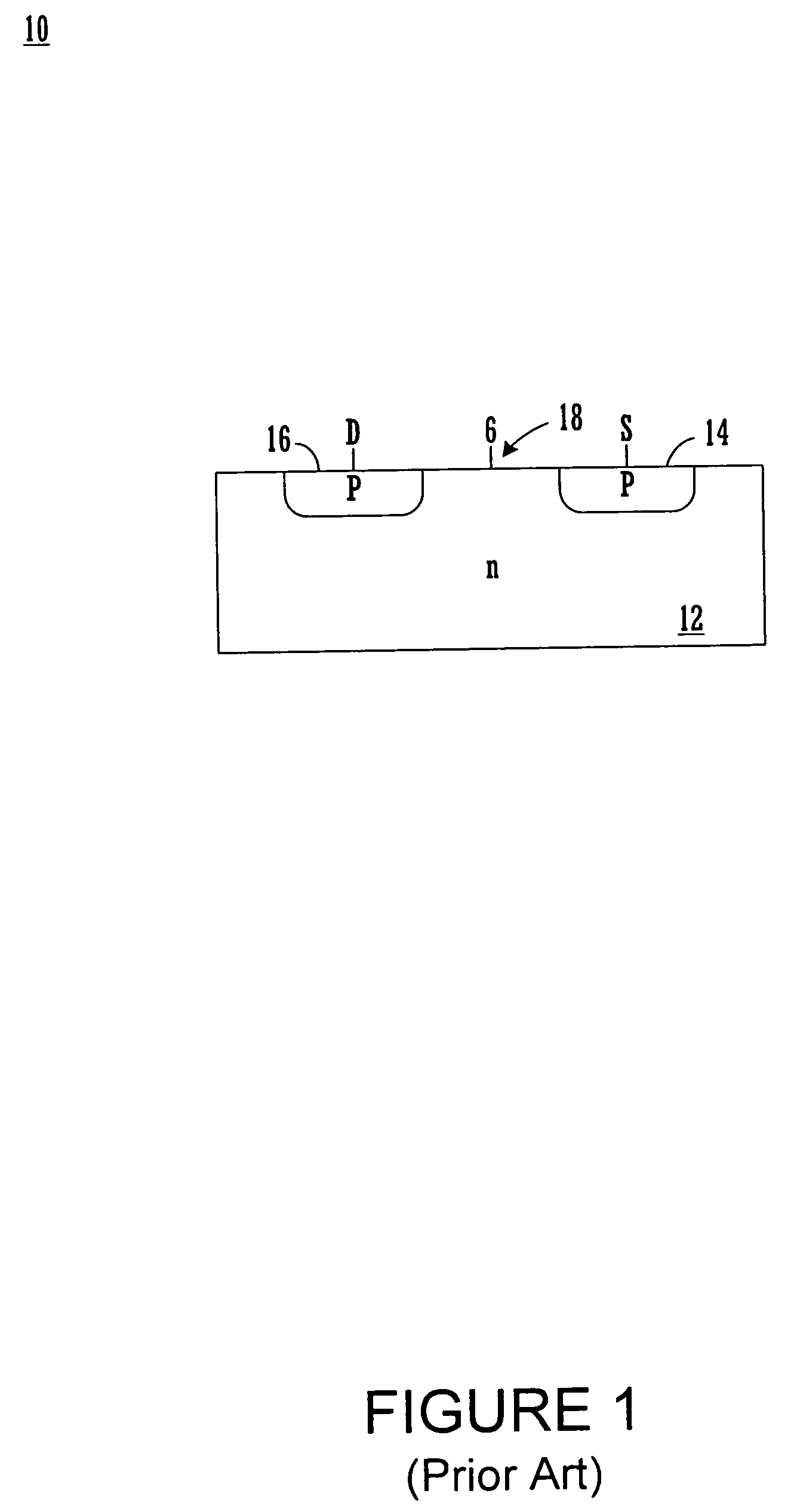

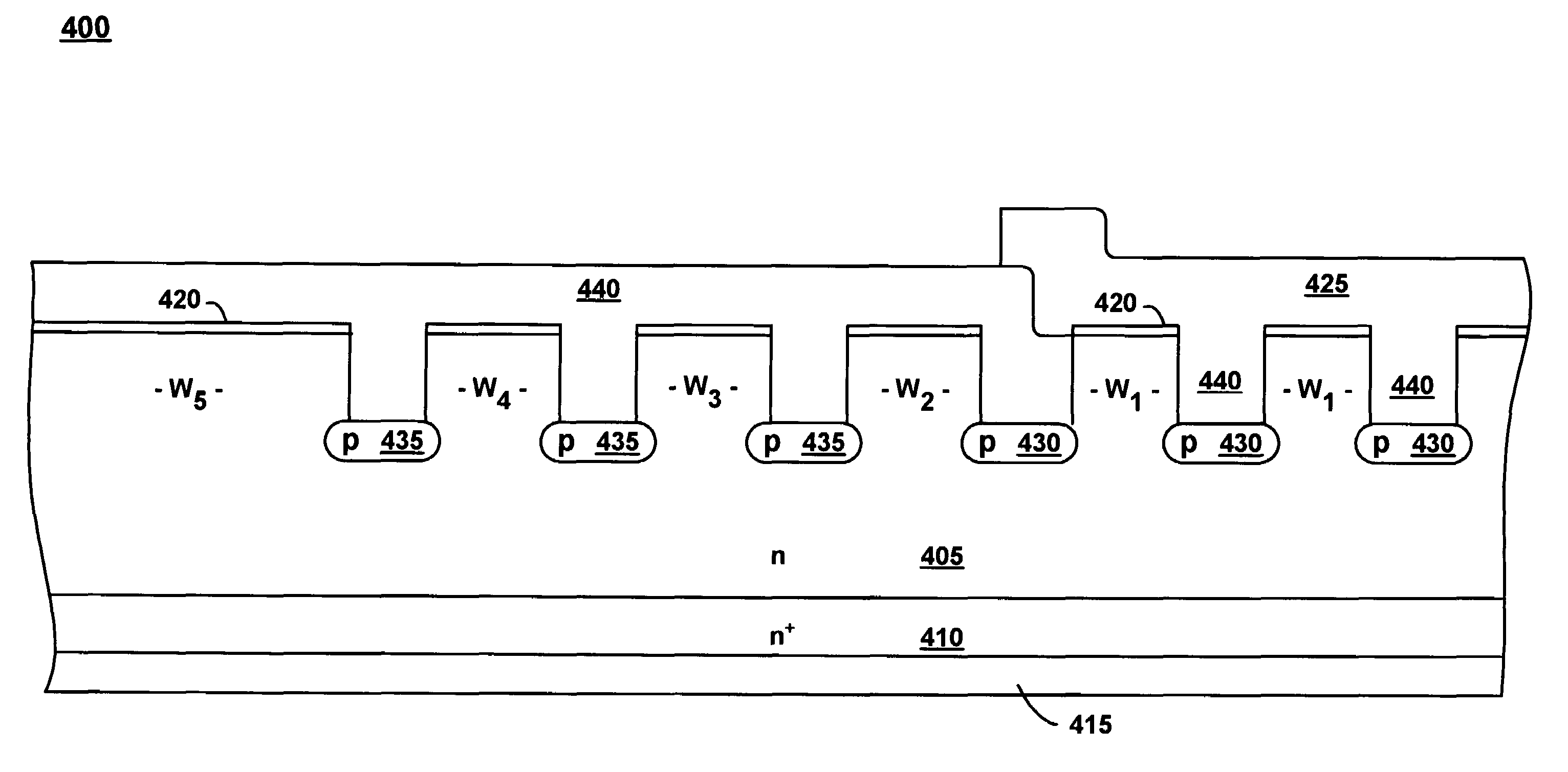

Transistors having buried p-type layers beneath the source region

InactiveUS6956239B2Semiconductor/solid-state device manufacturingSemiconductor devicesMESFETEngineering

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a source, a drain and a gate. The gate is disposed between the source and the drain and on an n-type conductivity channel layer. A p-type conductivity region is provided beneath the source and has an end that extends towards the drain. The p-type conductivity region is spaced apart from the n-type conductivity channel region and is electrically coupled to the source.

Owner:CREE INC

Power MESFET Rectifier

InactiveUS20080068868A1Shorten the timeIncreases—time available for deadtime decreasesEfficient power electronics conversionDc-dc conversionHigh resistanceZener diode

A rectifier MESFET includes an N-channel MESFET having its gate connected to its source, and at the same current density having a voltage drop lower than the gate Schottky diode. A Schottky diode may be connected in parallel with the N-channel device to provide over current protection. A Zener may also be connected in parallel to provide reverse voltage protection. A second N-channel device may be connected in parallel. The addition of the second N-channel provides two different operational mode: synchronous rectification where the majority of current flows through the low resistance first N-channel device and asynchronous rectification where the majority of current flows through the somewhat higher resistance first N-channel device.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Monolithic integrated circuit of a field-effect semiconductor device and a diode

InactiveUS20070228422A1Flow assuranceEasy to FeedbackTransistorSolid-state devicesField effectMESFET

A field-effect semiconductor device such as a HEMT or MESFET is monolithically integrated with a Schottky diode for feedback, regeneration, or protection purposes. The field-effect semiconductor device includes a main semiconductor region having formed thereon a source, a drain, and a gate between the source and the drain. Also formed on the main semiconductor region, preferably between gate and drain, is a Schottky electrode electrically coupled to the source. The Schottky electrode provides a Schottky diode in combination with the main semiconductor region. A current flow is assured from Schottky electrode to drain without interruption by a depletion region expanding from the gate.

Owner:SANKEN ELECTRIC CO LTD

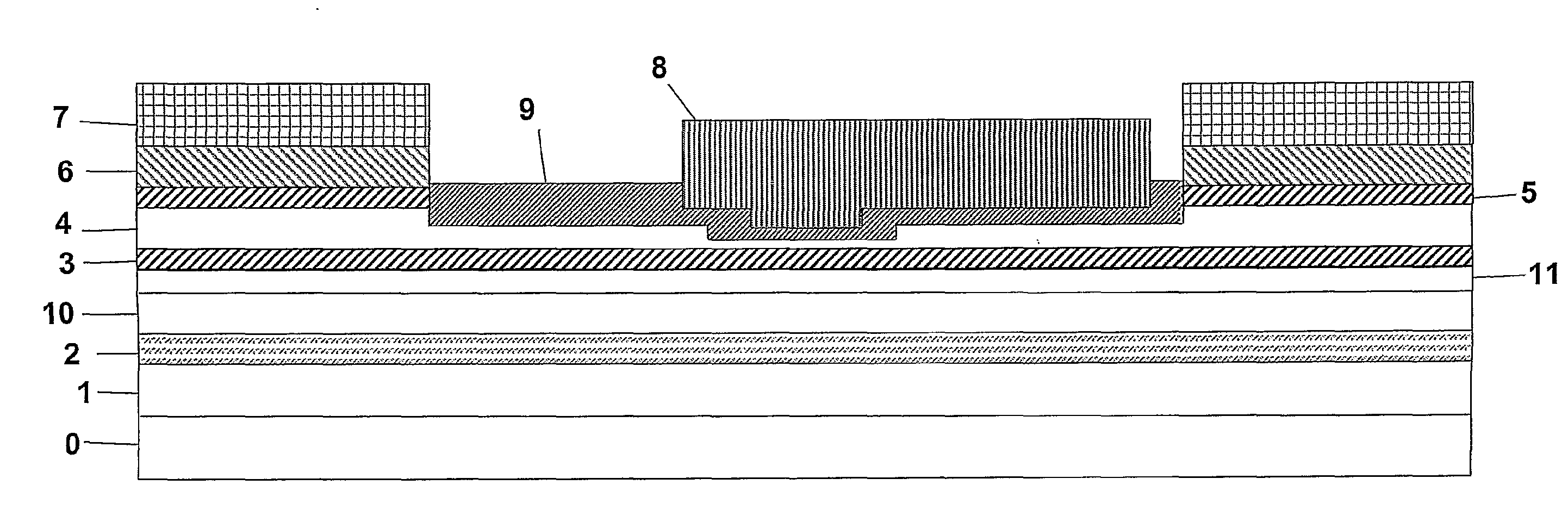

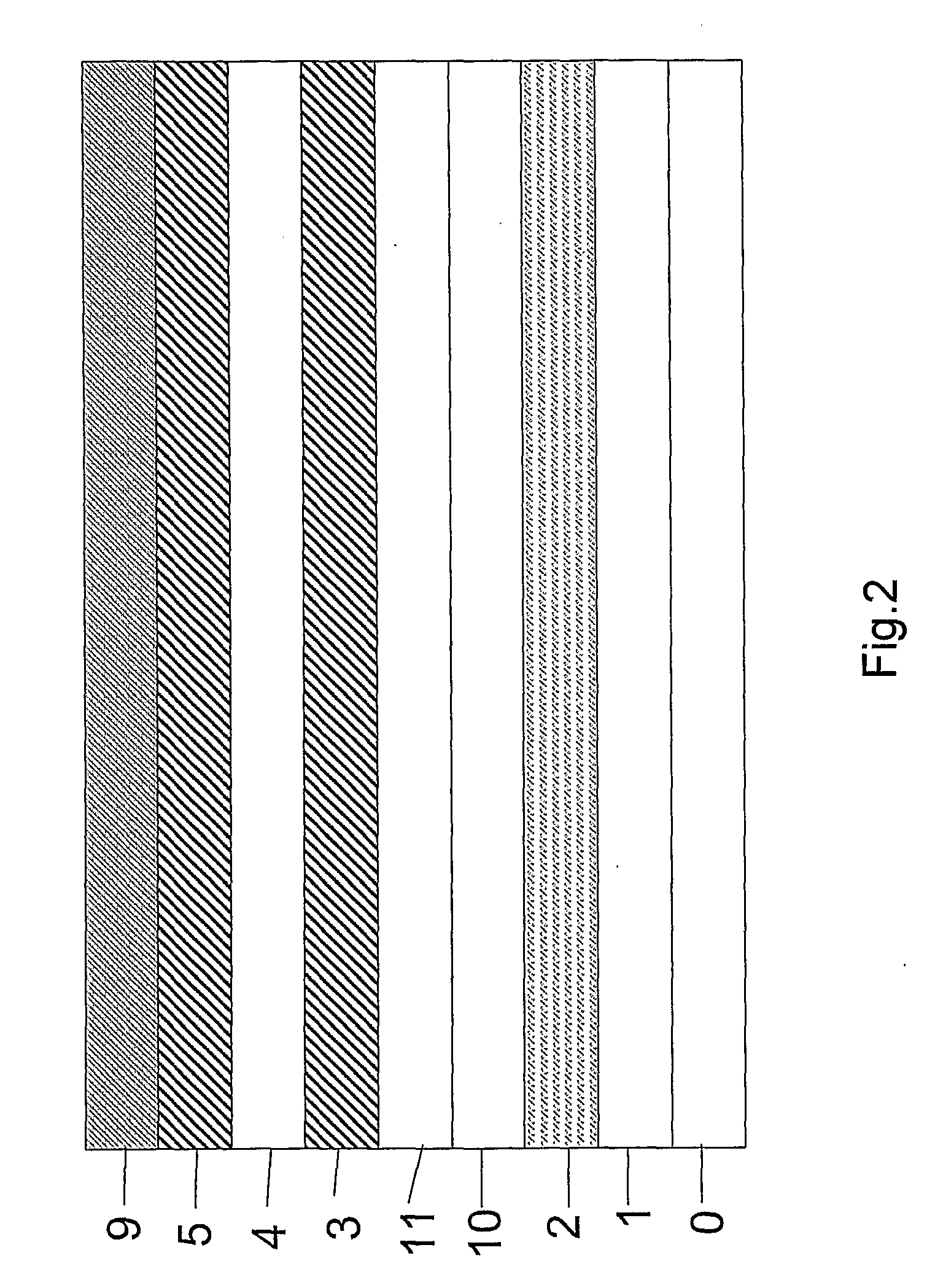

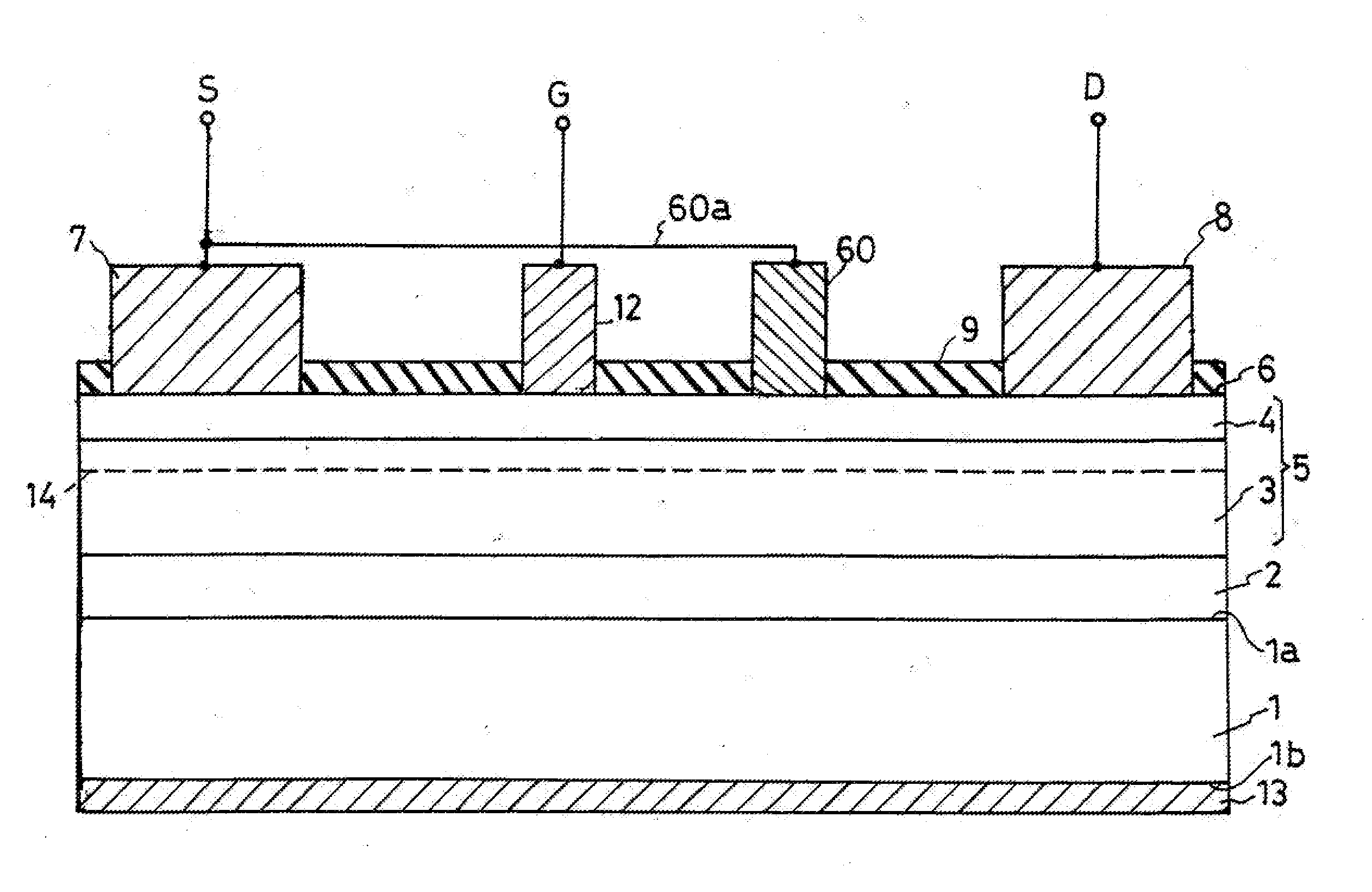

Diamond Transistor And Method Of Manufacture Thereof

InactiveUS20080099768A1Reduce surface roughnessLower step heightTransistorPolycrystalline material growthDelta dopingSingle crystal

Owner:DIAMOND MICROWAVE DEVICES

Monolithic integrated circuit of a field-effect semiconductor device and a diode

A field-effect semiconductor device such as a HEMT or MESFET is monolithically integrated with a Schottky diode for feedback, regeneration, or protection purposes. The field-effect semiconductor device includes a main semiconductor region having formed thereon a source, a drain, and a gate between the source and the drain. Also formed on the main semiconductor region, preferably between gate and drain, is a Schottky electrode electrically coupled to the source. The Schottky electrode provides a Schottky diode in combination with the main semiconductor region. A current flow is assured from Schottky electrode to drain without interruption by a depletion region expanding from the gate.

Owner:SANKEN ELECTRIC CO LTD

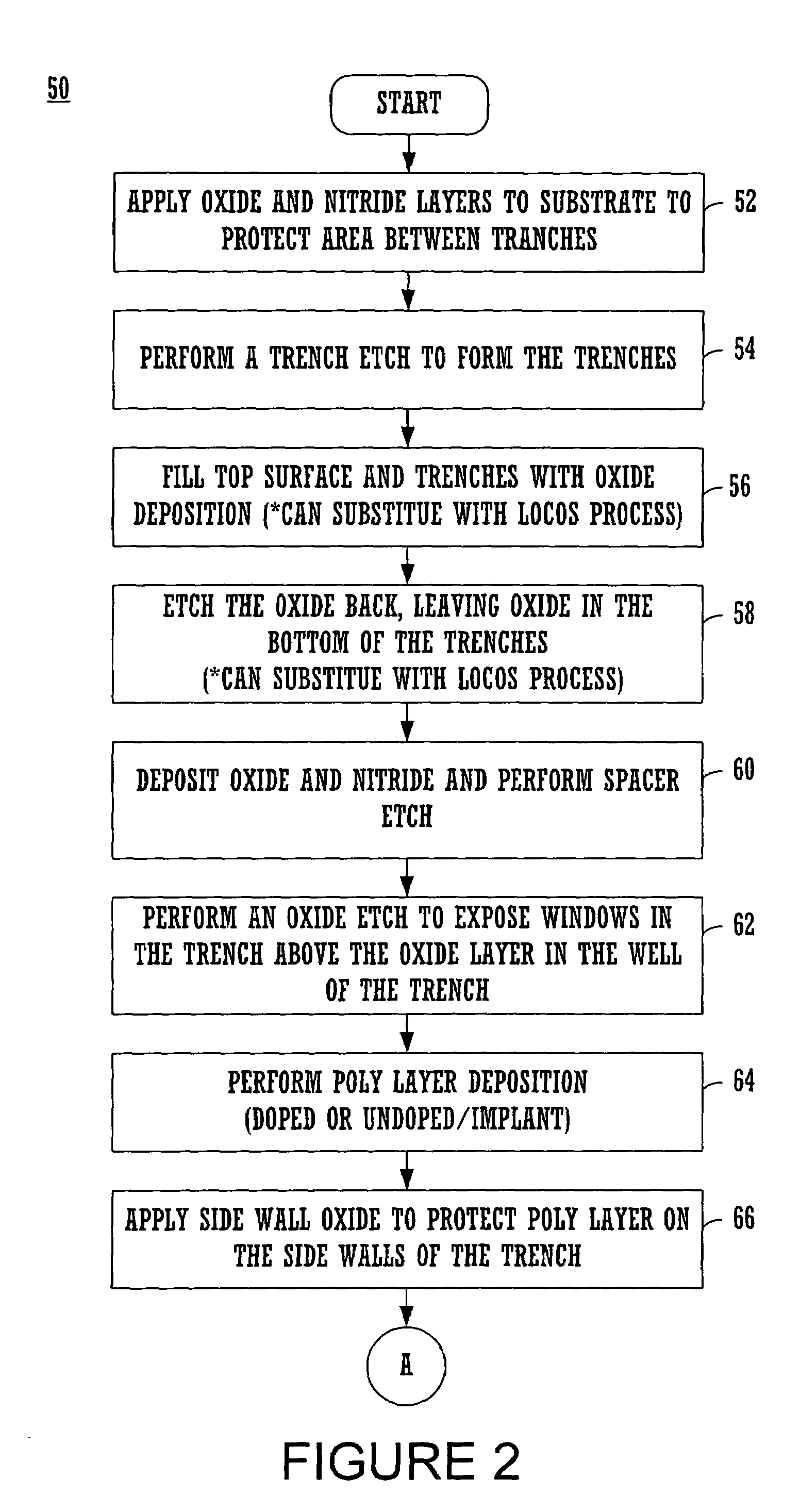

Guard ring structure and method for fabricating same

A method for fabricating a guard ring structure for JFETs and MESFETs. Trenches are etched in a semiconductor substrate for fabrication of a gate structure for a JFET or MESFET. At time the gate trenches are etched, concentric guard ring trenches are also etched. The process used to fabricate the gate p-h junction or Schottky barrier at the bottom of the gate trenches is also used to fabricate the guard ring at bottom of the guard ring trenches. The separation between the guard ring trenches is 1.0 to 3.0 times greater than the separation between the gate trenches.

Owner:POWER INTEGRATIONS INC

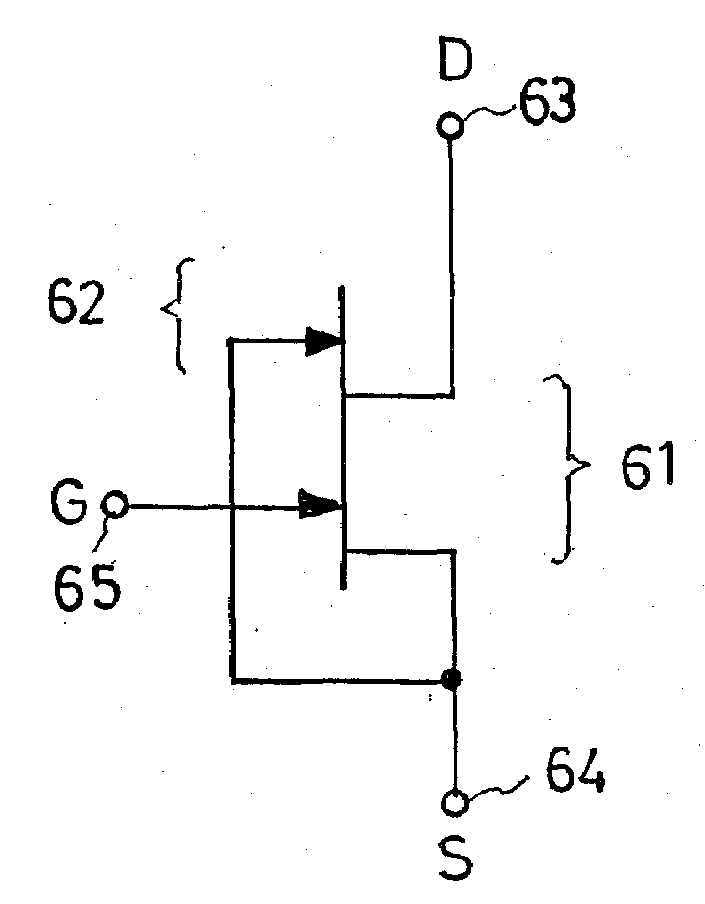

Merged and Isolated Power MESFET Devices

InactiveUS20070131938A1Maximize efficiencyReduce conduction lossTransistorSolid-state devicesEngineeringMESFET

A first type of merged power MESFET device includes two monolithically integrated MESFETS. The MESFETS share common sources and gates, and are sized so that one MESFET may be used as a power device while the other is used as a current-sense device. A second type of merged power MESFET device includes two monolithically integrated MESFETS. The MESFETS share a common region which serves as the source for one MESFET and the drain for the second MESFET. This allows the two MESFETS to function as the high and low-side switches for a buck or boost regulator. A third type of merged power MESFET device combines the high and low-side switches with a current-sensing device.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Dual gate structure for a FET and method for fabricating same

InactiveUS7038260B1Reduces the effective channel length, leakage current, and parasitic capacitanceEasy to controlTransistorSemiconductor/solid-state device manufacturingDopantMESFET

A method for fabricating a dual gate structure for JFETs and MESFETs and the associated devices. Trenches are etched in a semiconductor substrate for fabrication of a gate structure for a JFET or MESFET. A sidewall spacer may be formed on the walls of the trenches to adjust the lateral dimension for a first gate. Following the formation of the first gate by implantation or deposition, a buffer region is implanted below the first gate using a complementary dopant and a second sidewall spacer with a thickness that may be the same or greater than the thickness of the first sidewall spacer. Subsequent to the buffer implant, a second gate is implanted beneath the buffer layer using a third sidewall spacer with a greater thickness than the first sidewall spacer.

Owner:POWER INTEGRATIONS INC

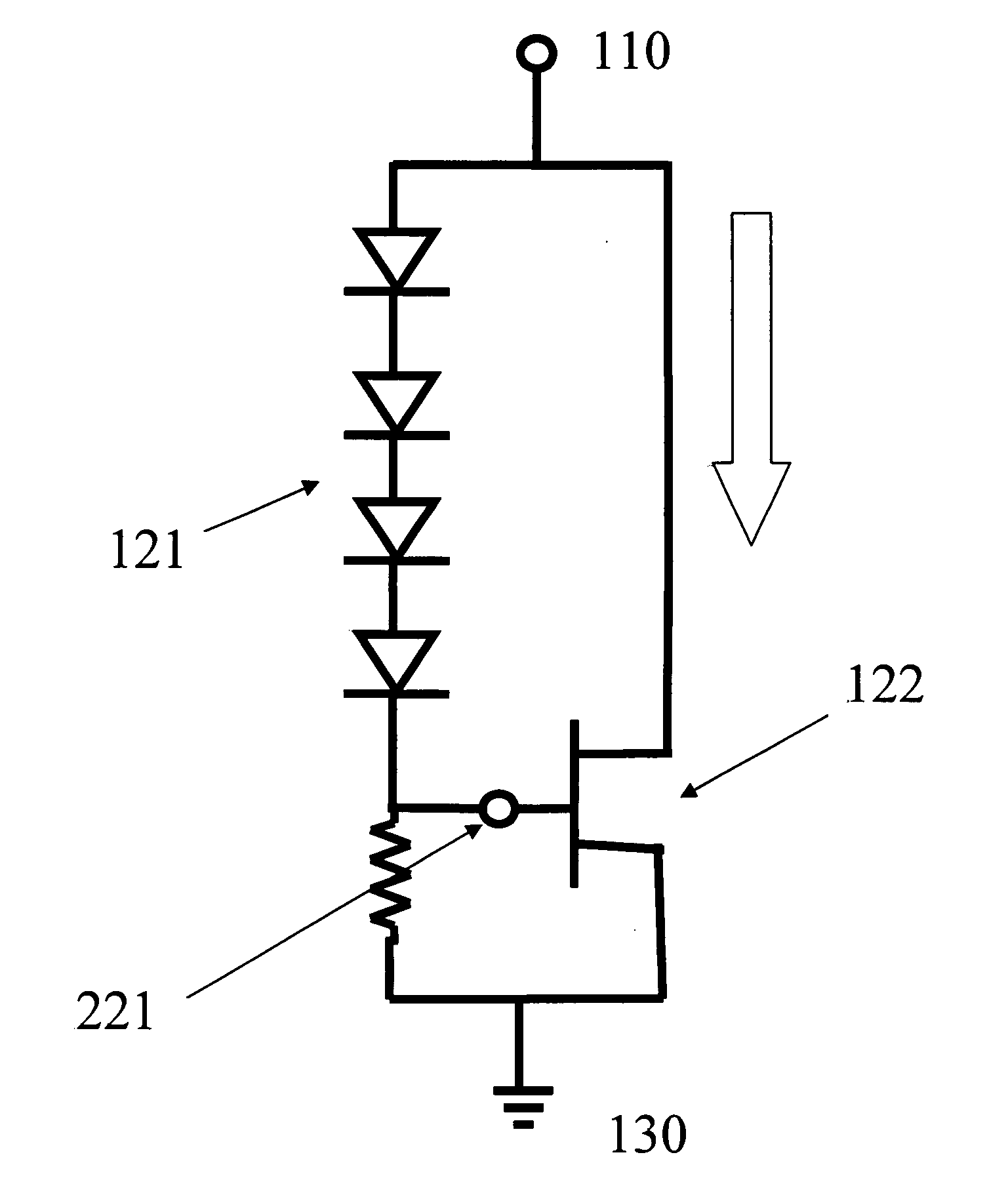

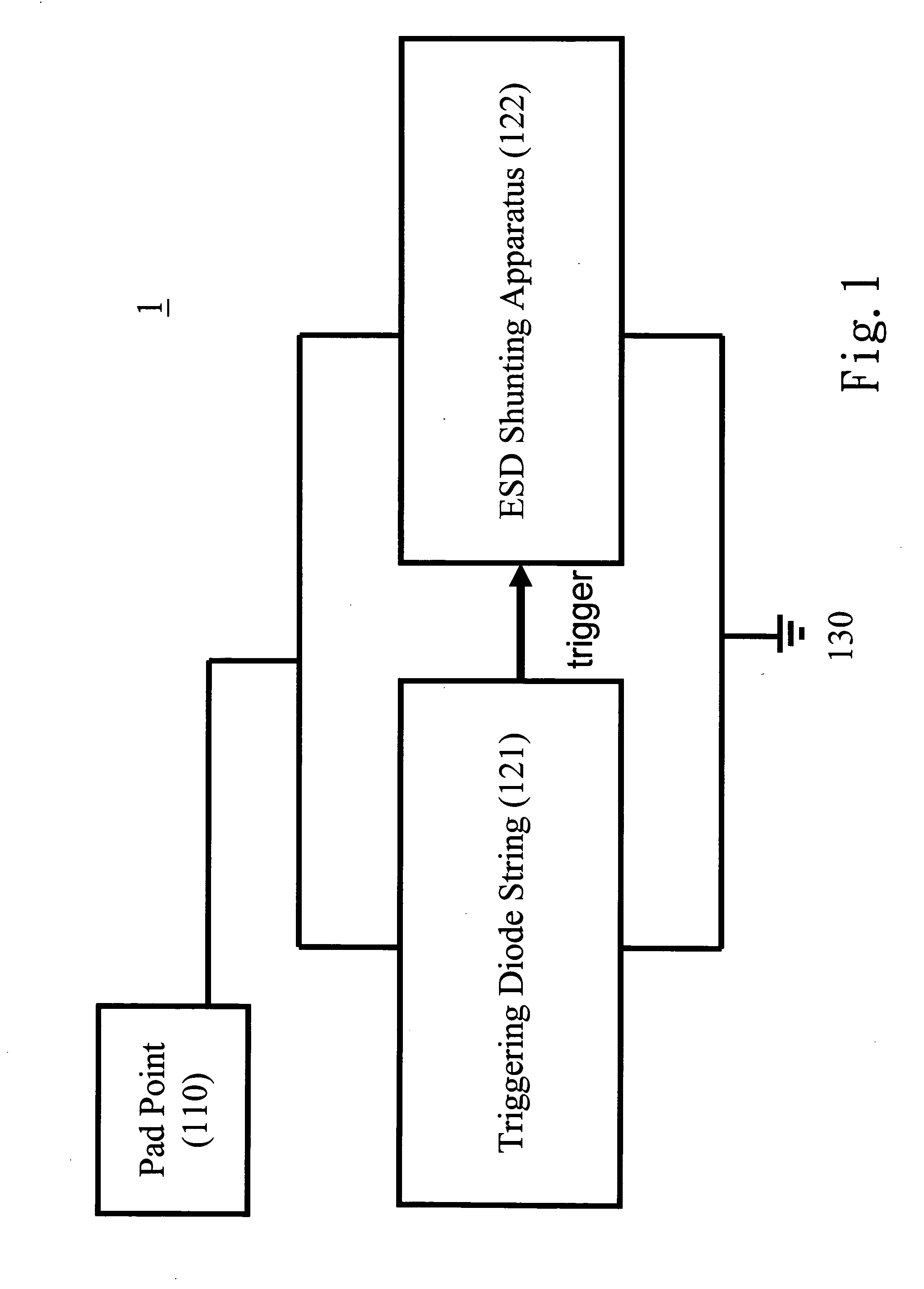

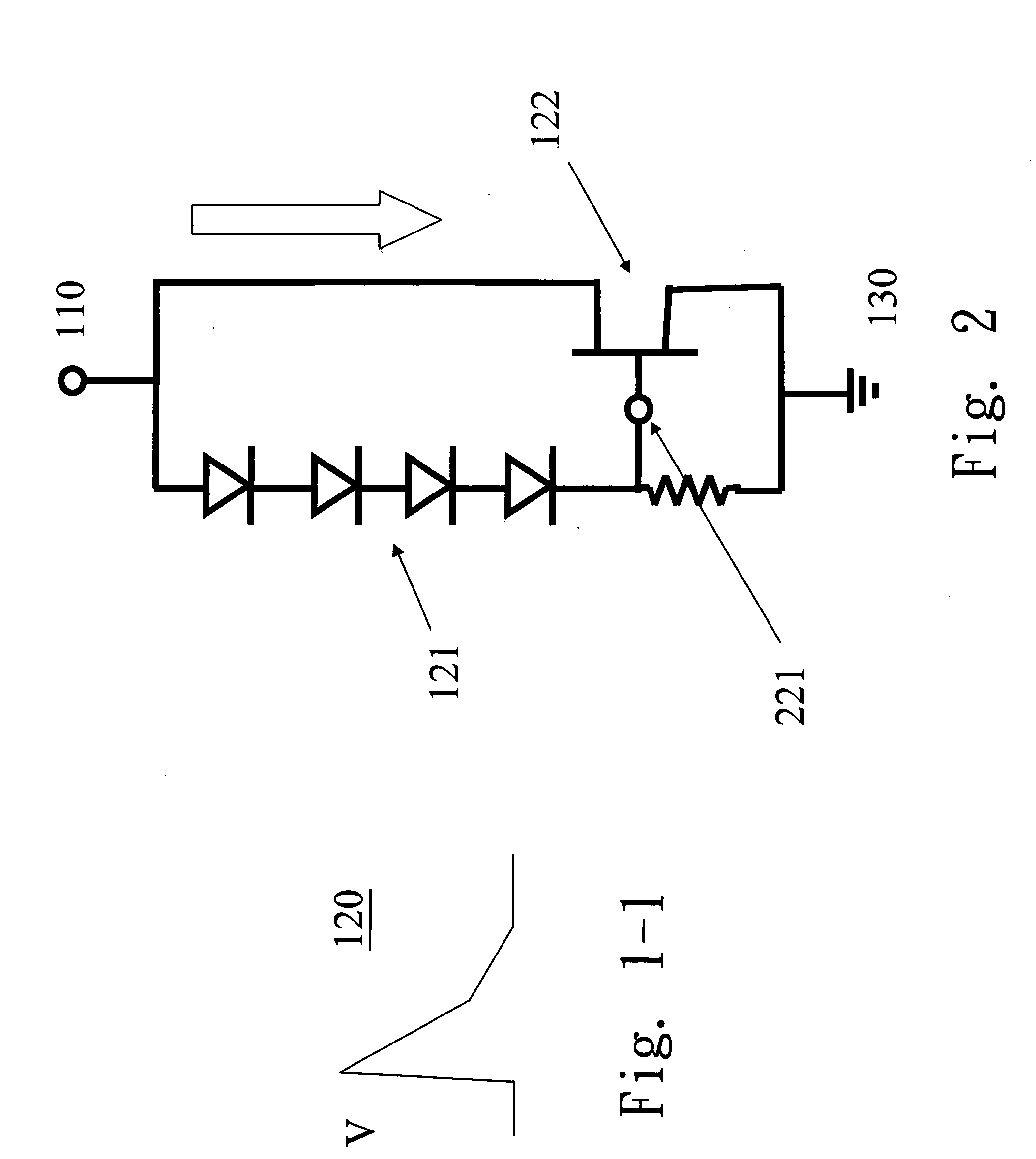

On-chip ESD protection circuit using enhancement-mode HEMT/MESFET technology

ActiveUS20080080108A1Low costSave spaceTransistorEmergency protective arrangements for limiting excess voltage/currentParasitic capacitanceMESFET

An on-chip circuit for protection against electrostatic discharge (ESD) is disclosed. Unlike conventional ESD protection circuit using high turn-on voltage diode string, the circuit uses a plural of enhancement-mode HEMT / MESFET triggered by a shorter diode string to shunt large ESD current for protected susceptive RF circuit. Further, by using dual-gate technology of enhancement-mode HEMT / MESFET, the on-chip ESD protection circuit has the less parasitic capacitance without expanding device size for vulnerable RF circuit.

Owner:WIN SEMICON

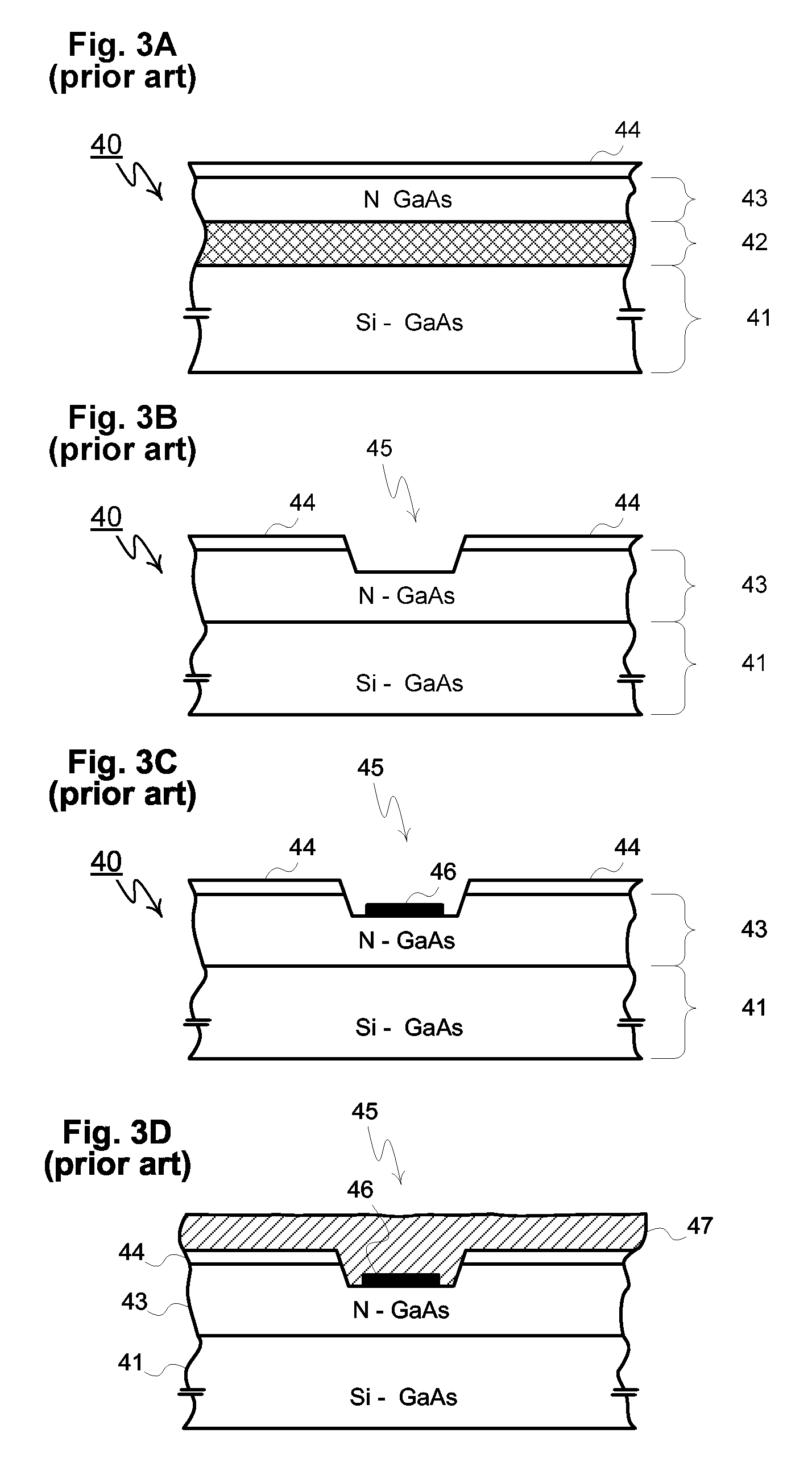

Methods of fabricating delta doped silicon carbide metal-semiconductor field effect transistors having a gate disposed in a double recess structure

InactiveUS20050023535A1Improve breakdown voltageReduce resistanceTransistorSemiconductor/solid-state device manufacturingDelta dopingMESFET

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a delta doped silicon carbide MESFET having a source, a drain and a gate. The gate is situated between the source and the drain and extends into a doped channel layer of a first conductivity type. Regions of silicon carbide adjacent to the source and the drain extend between the source and the gate and the drain and the gate, respectively. The regions of silicon carbide have carrier concentrations that are greater than a carrier concentration of the doped channel layer and are spaced apart from the gate.

Owner:CREE INC