Patents

Literature

276results about How to "Lower junction capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

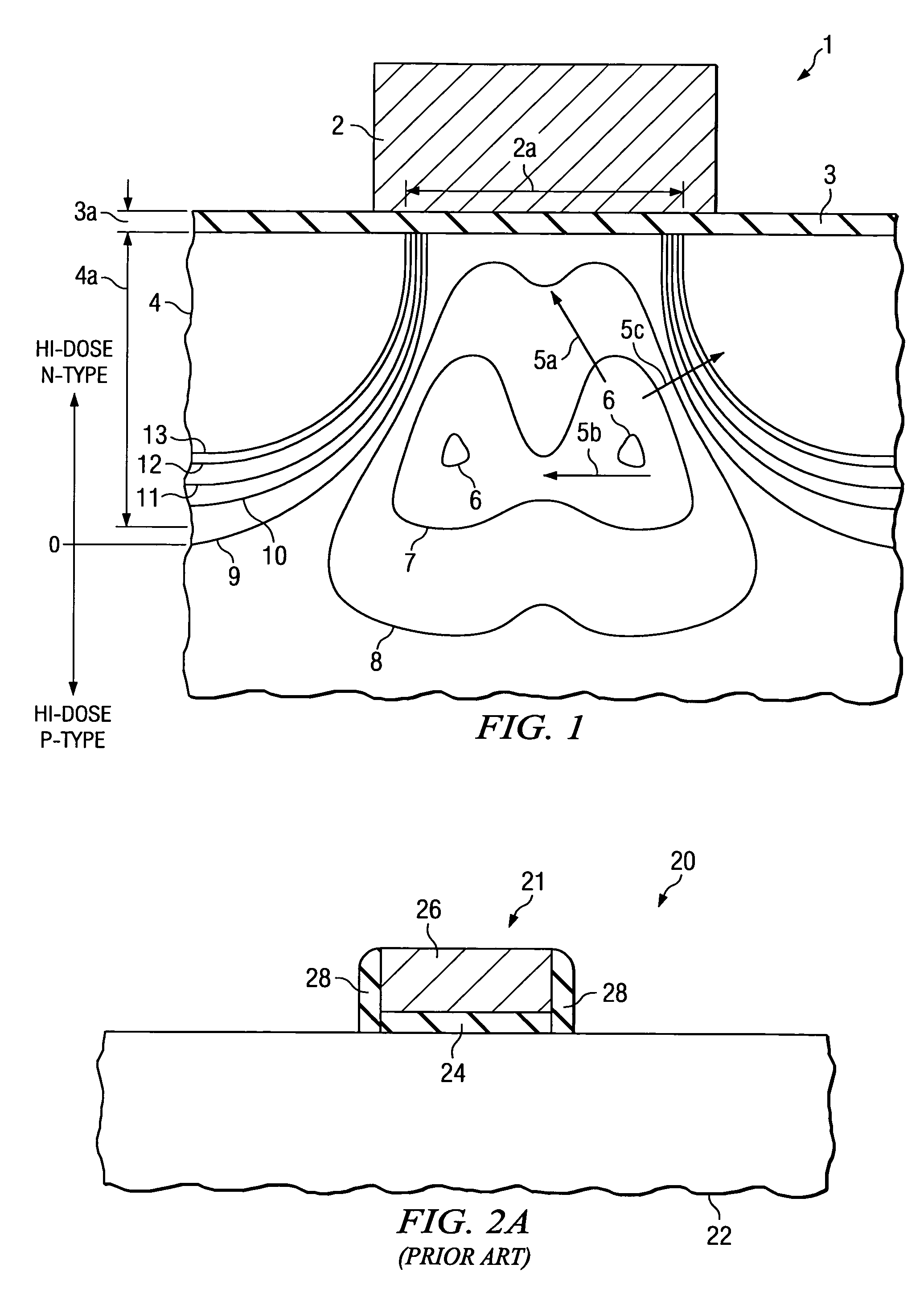

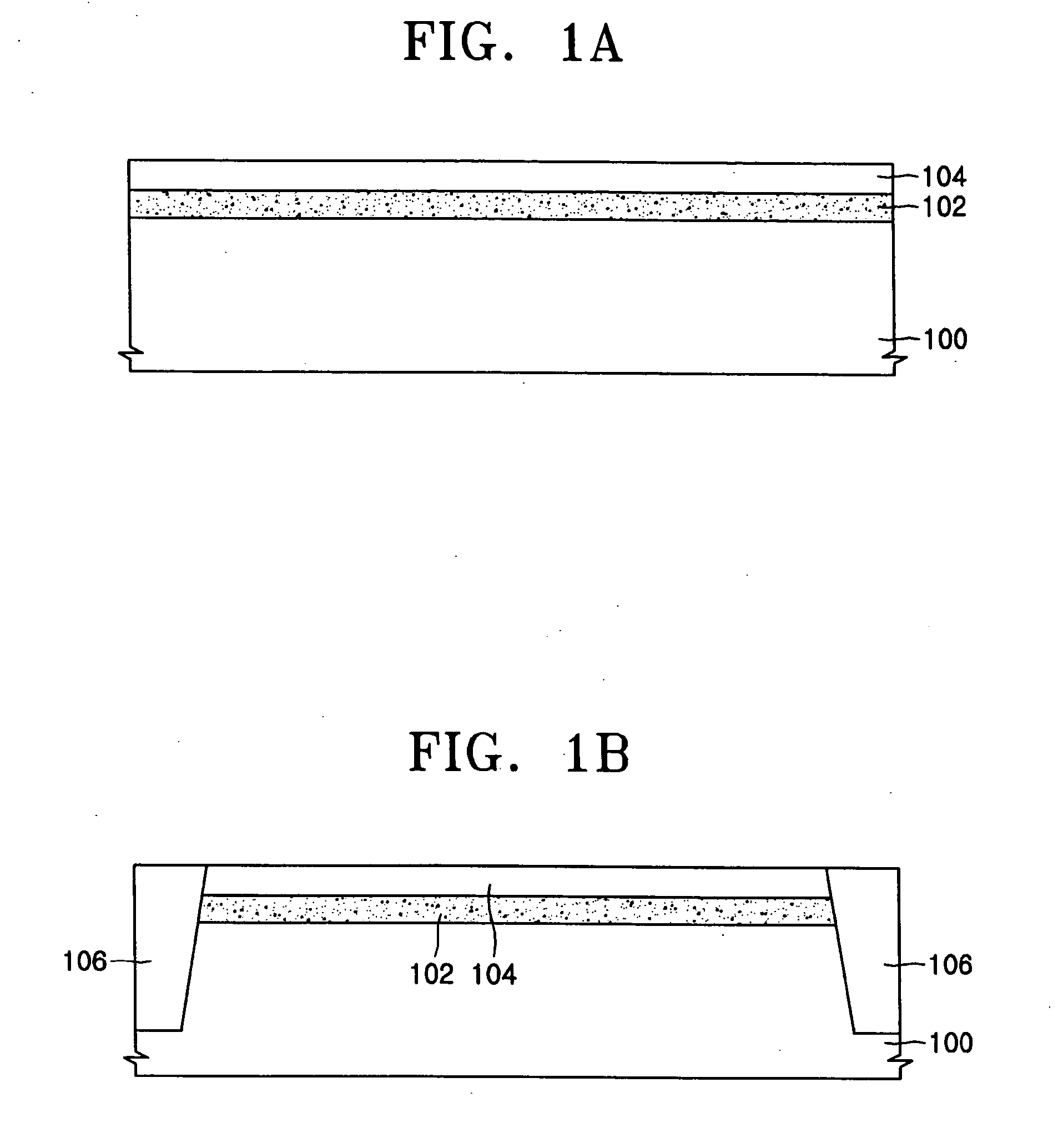

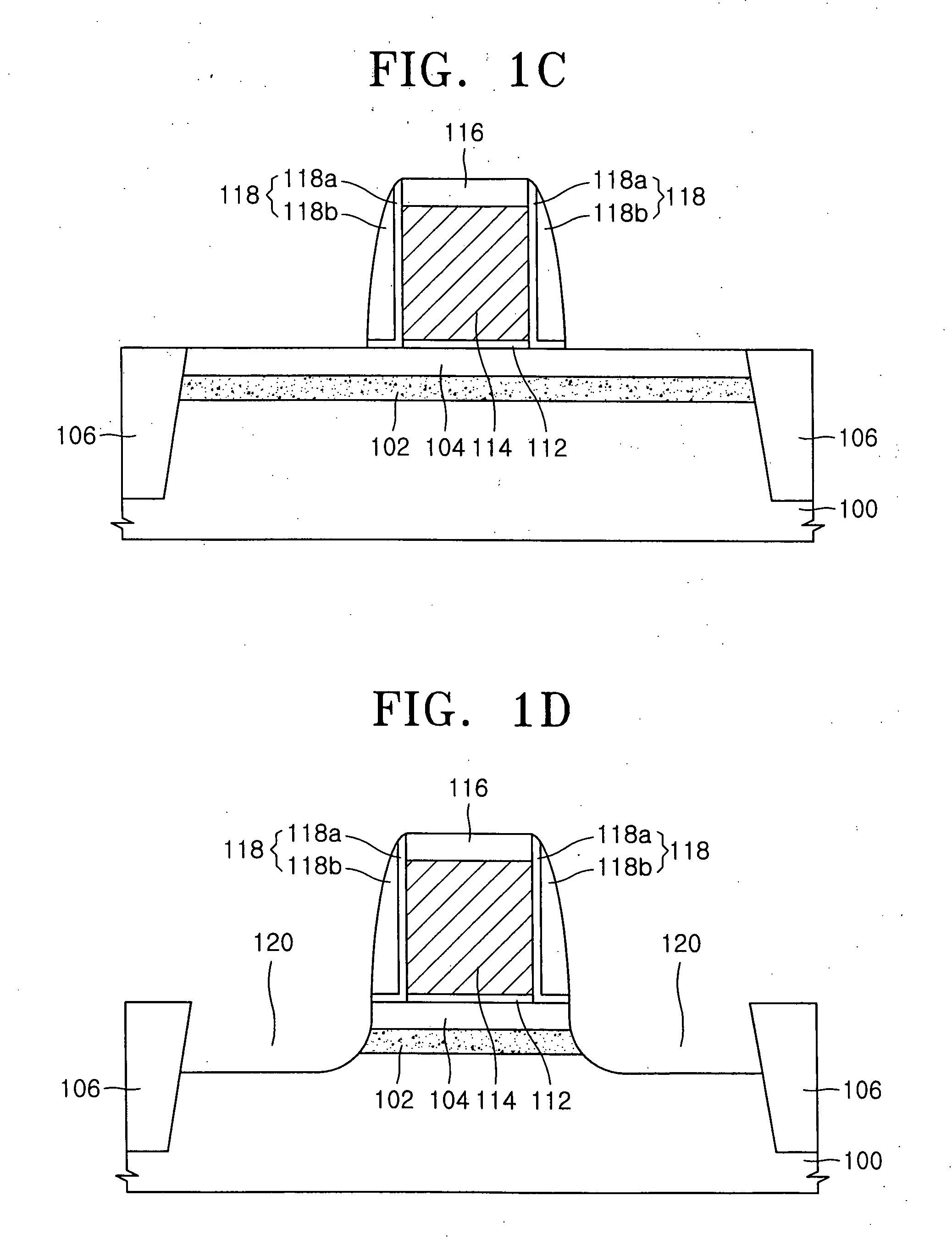

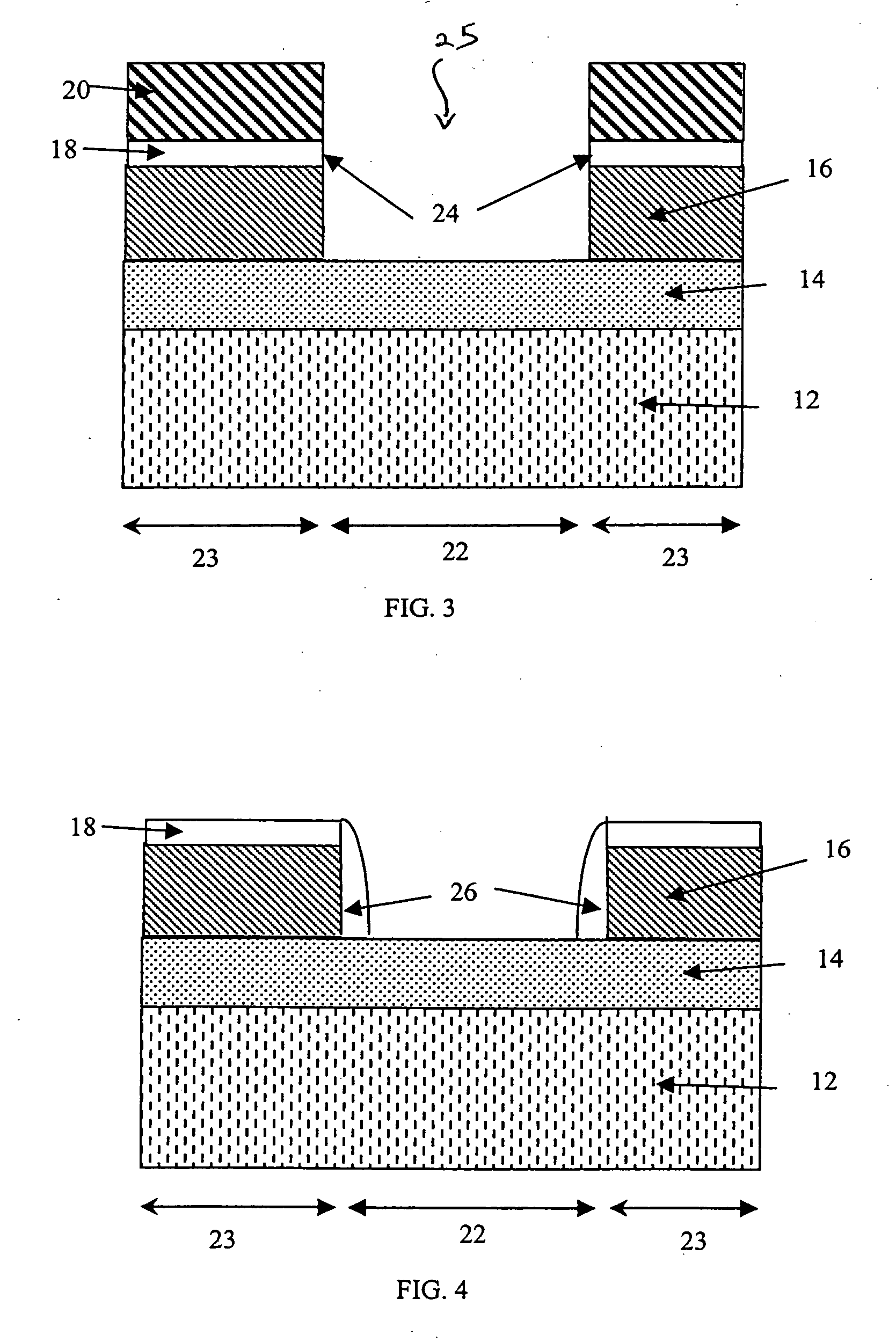

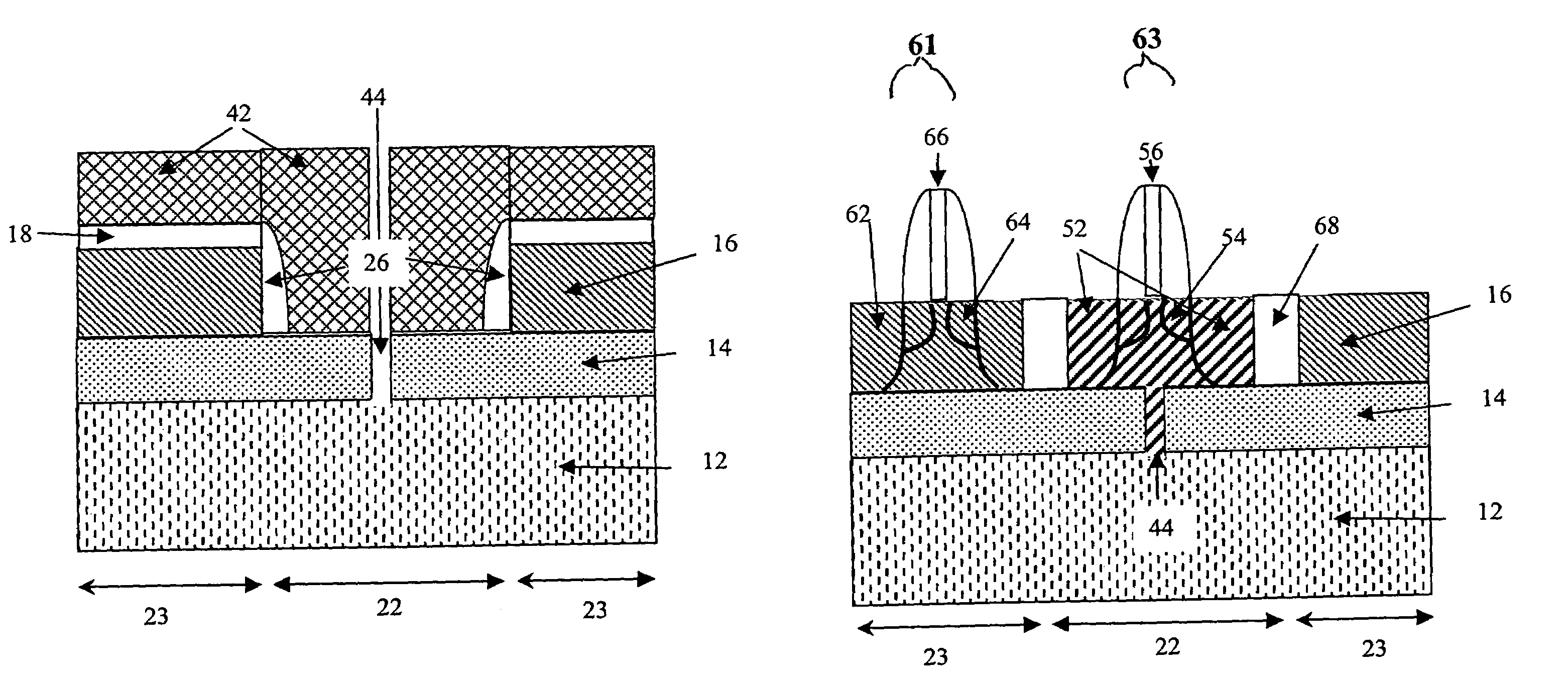

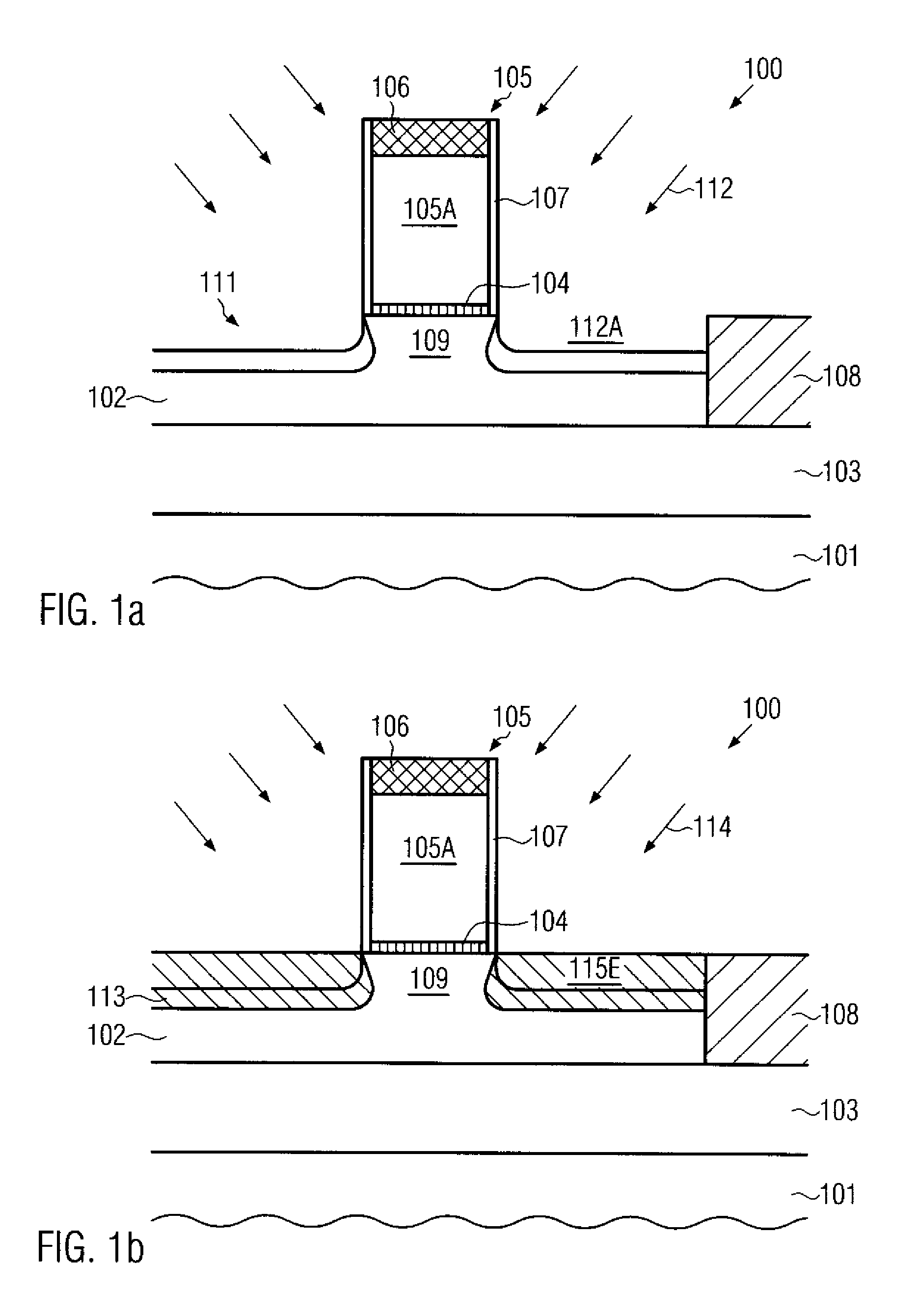

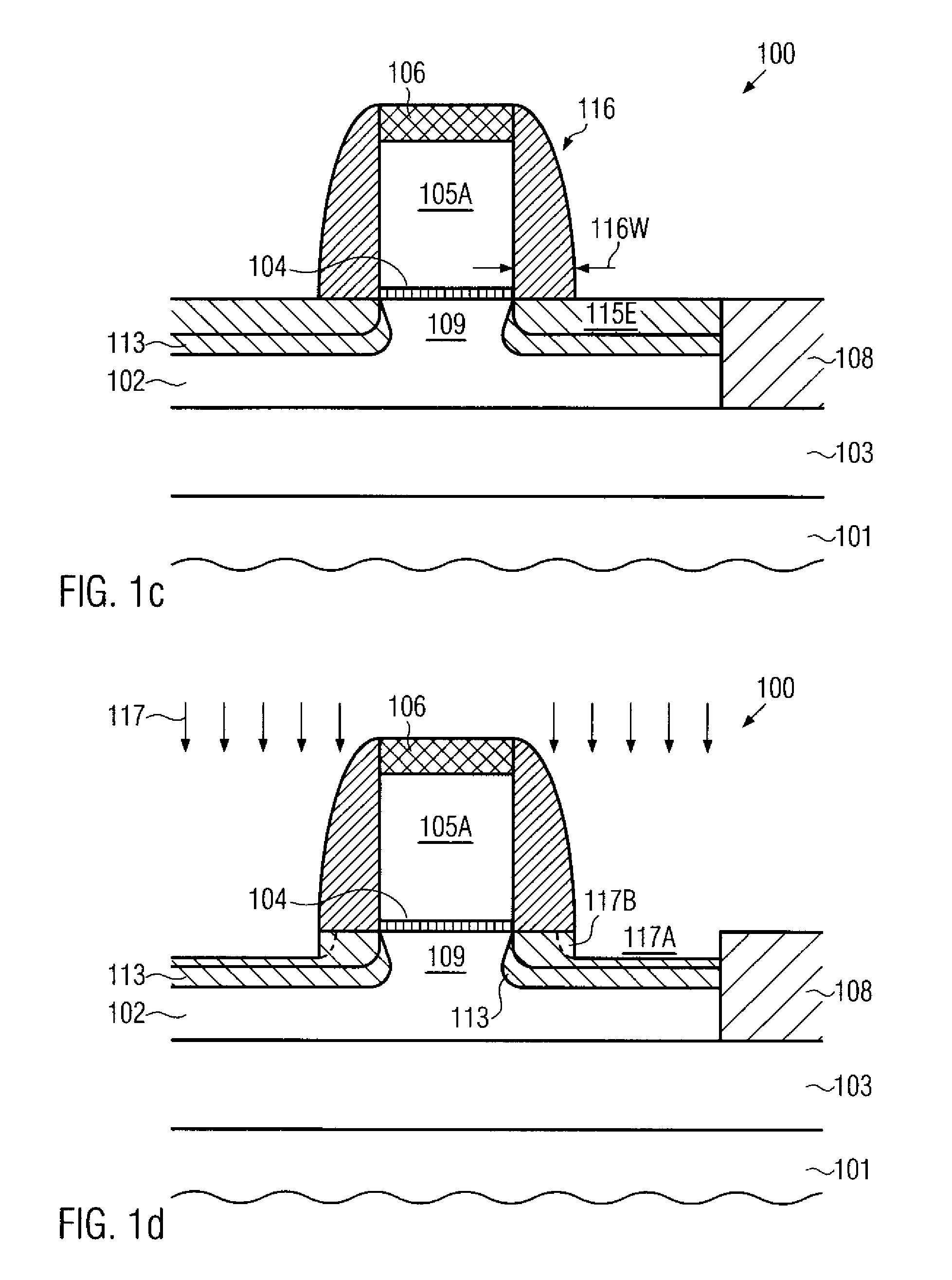

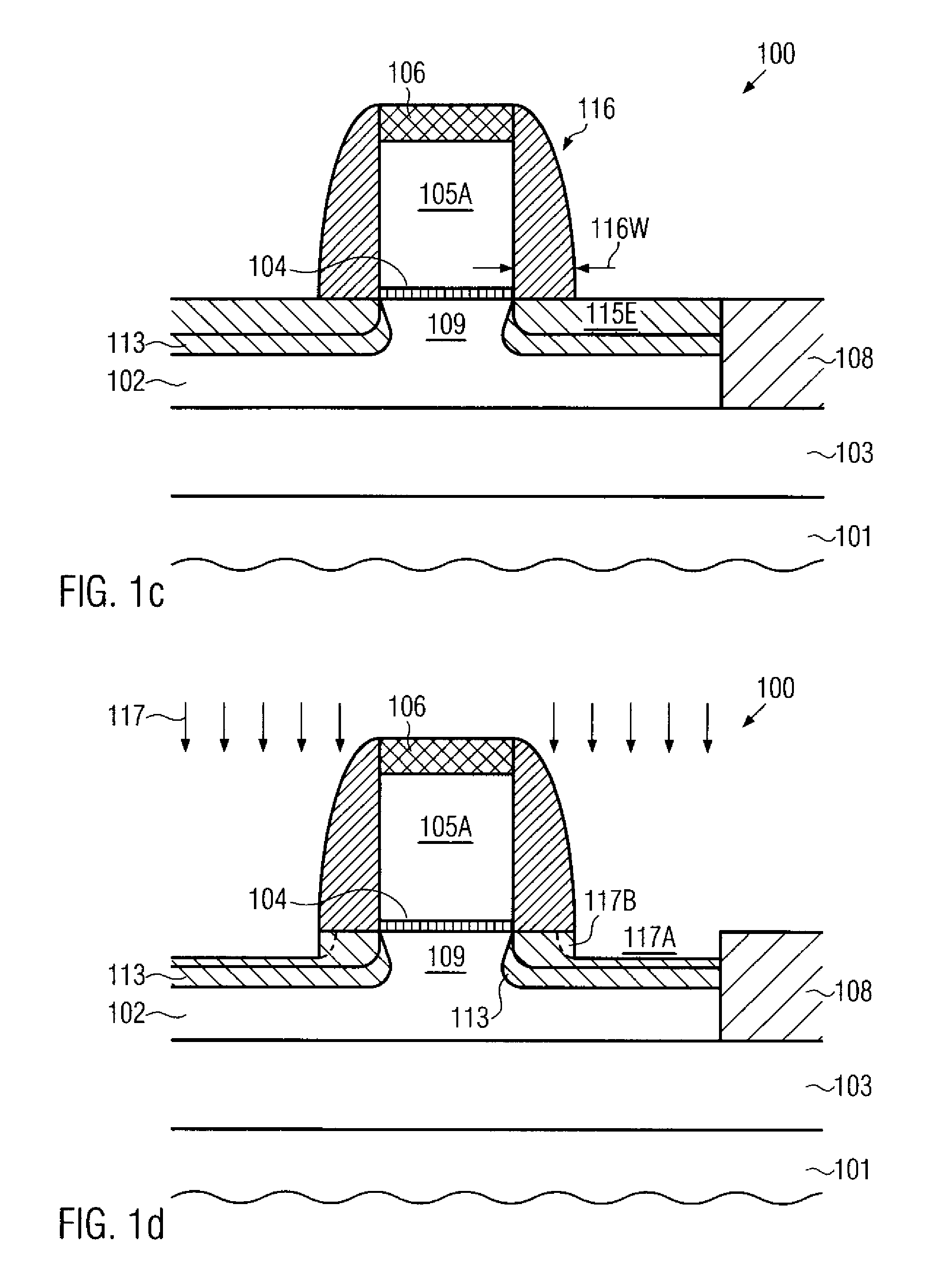

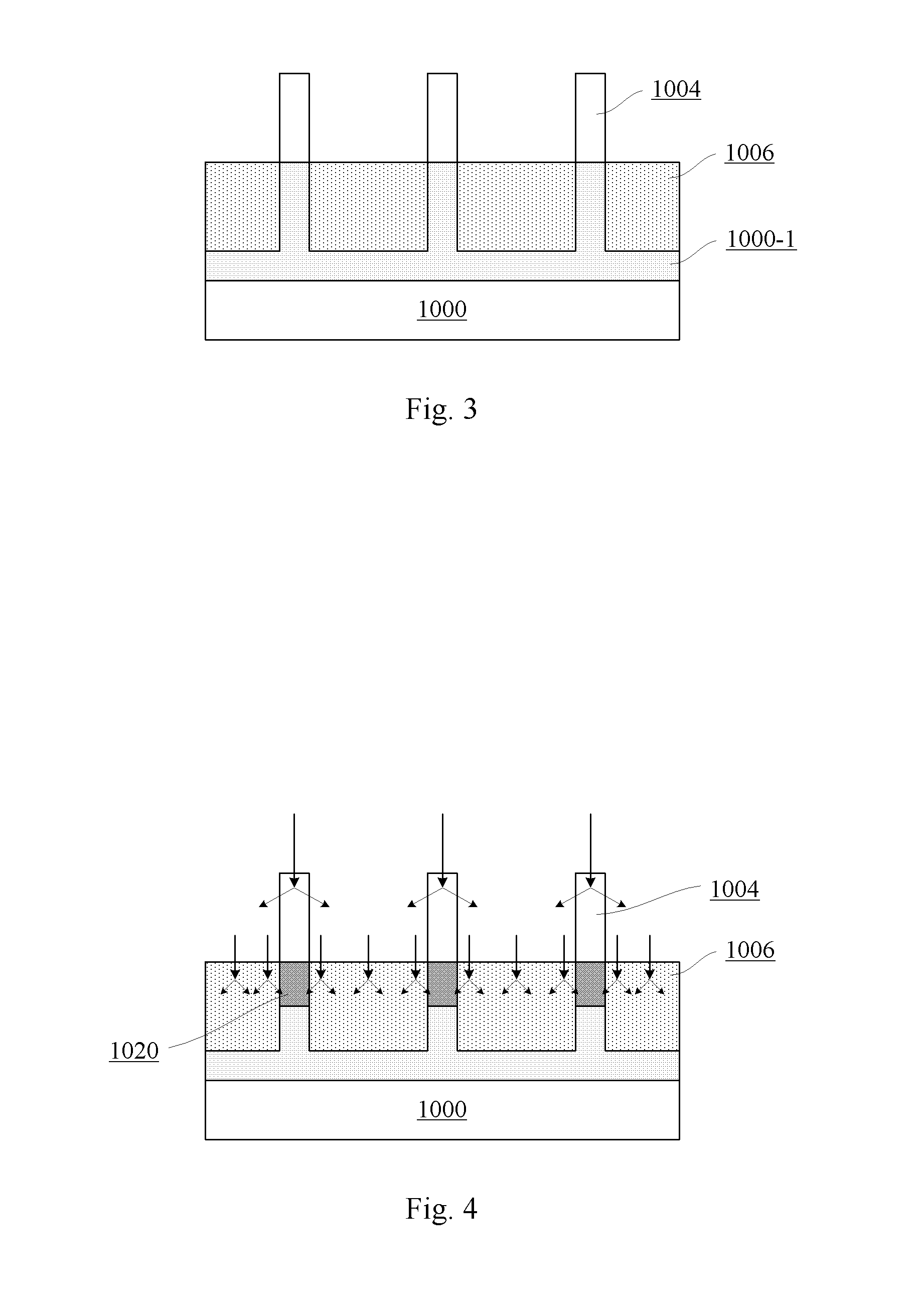

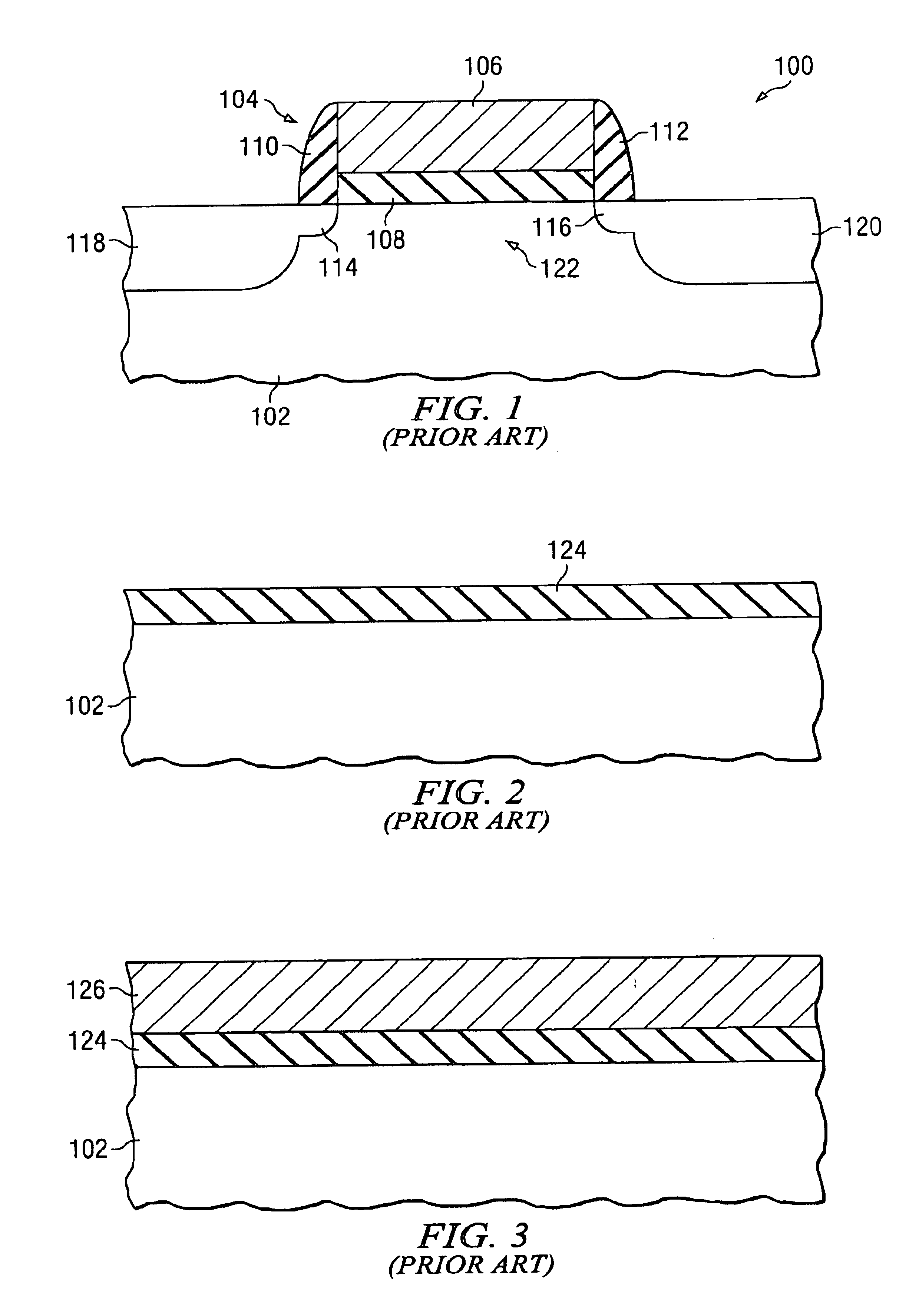

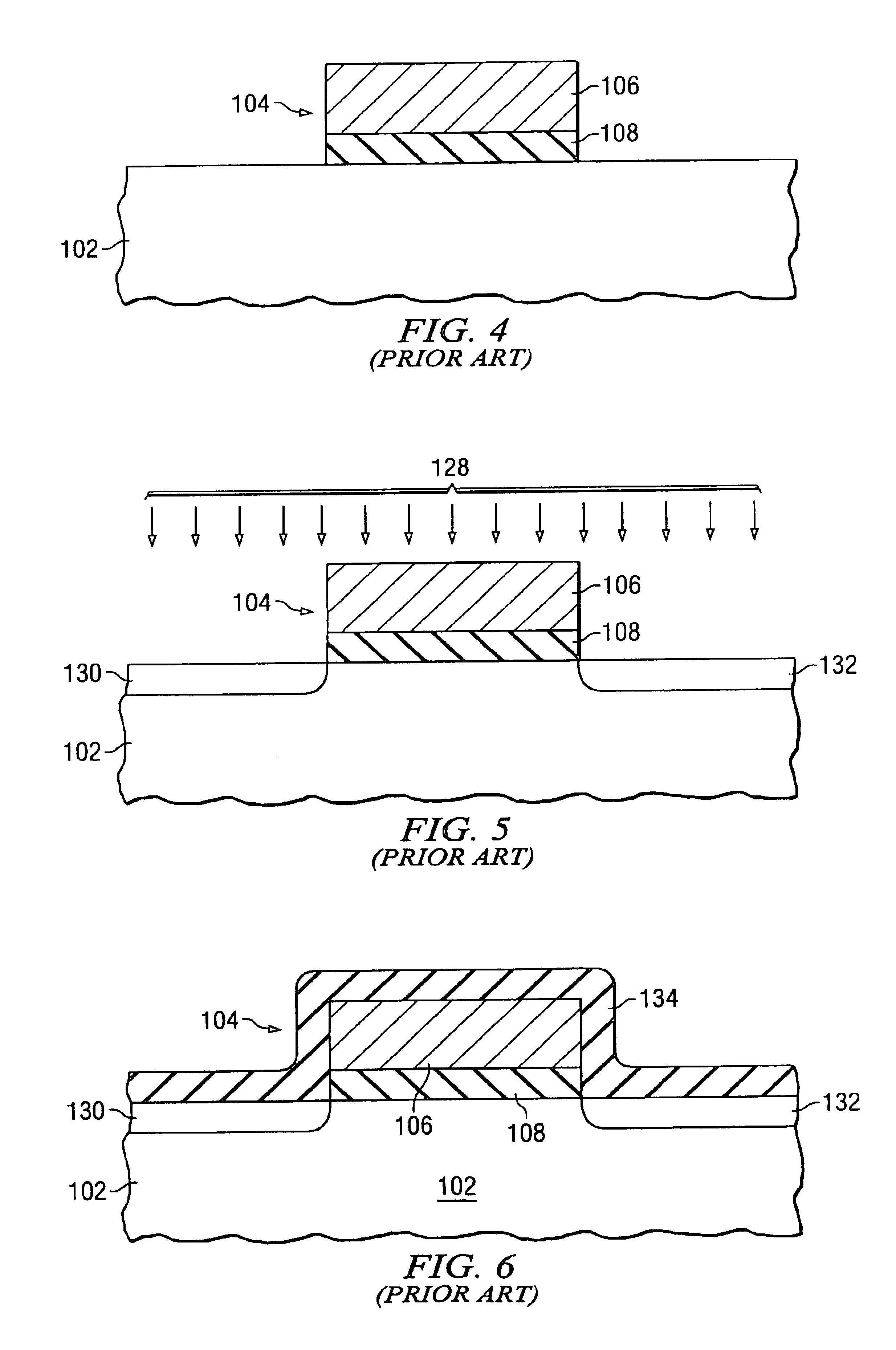

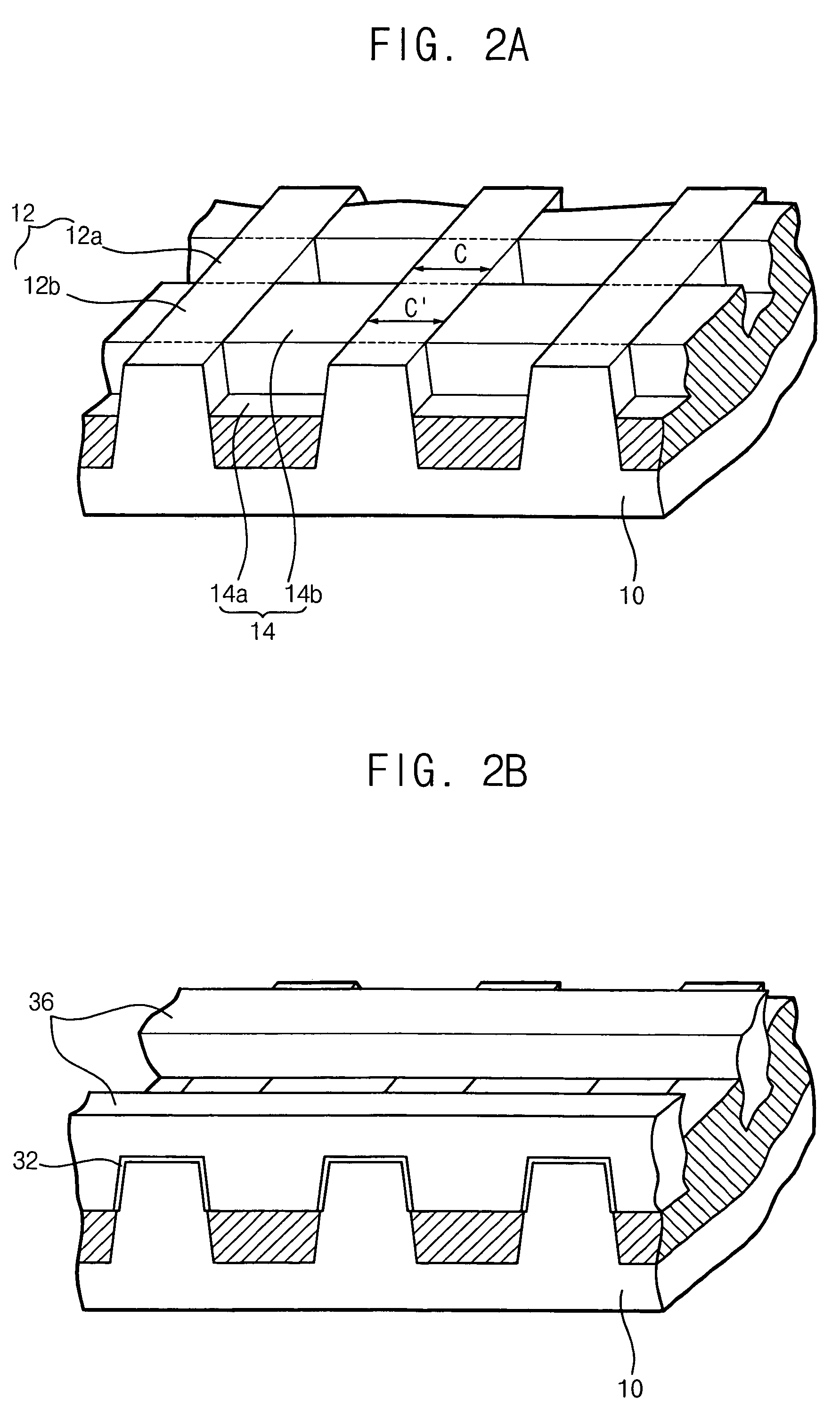

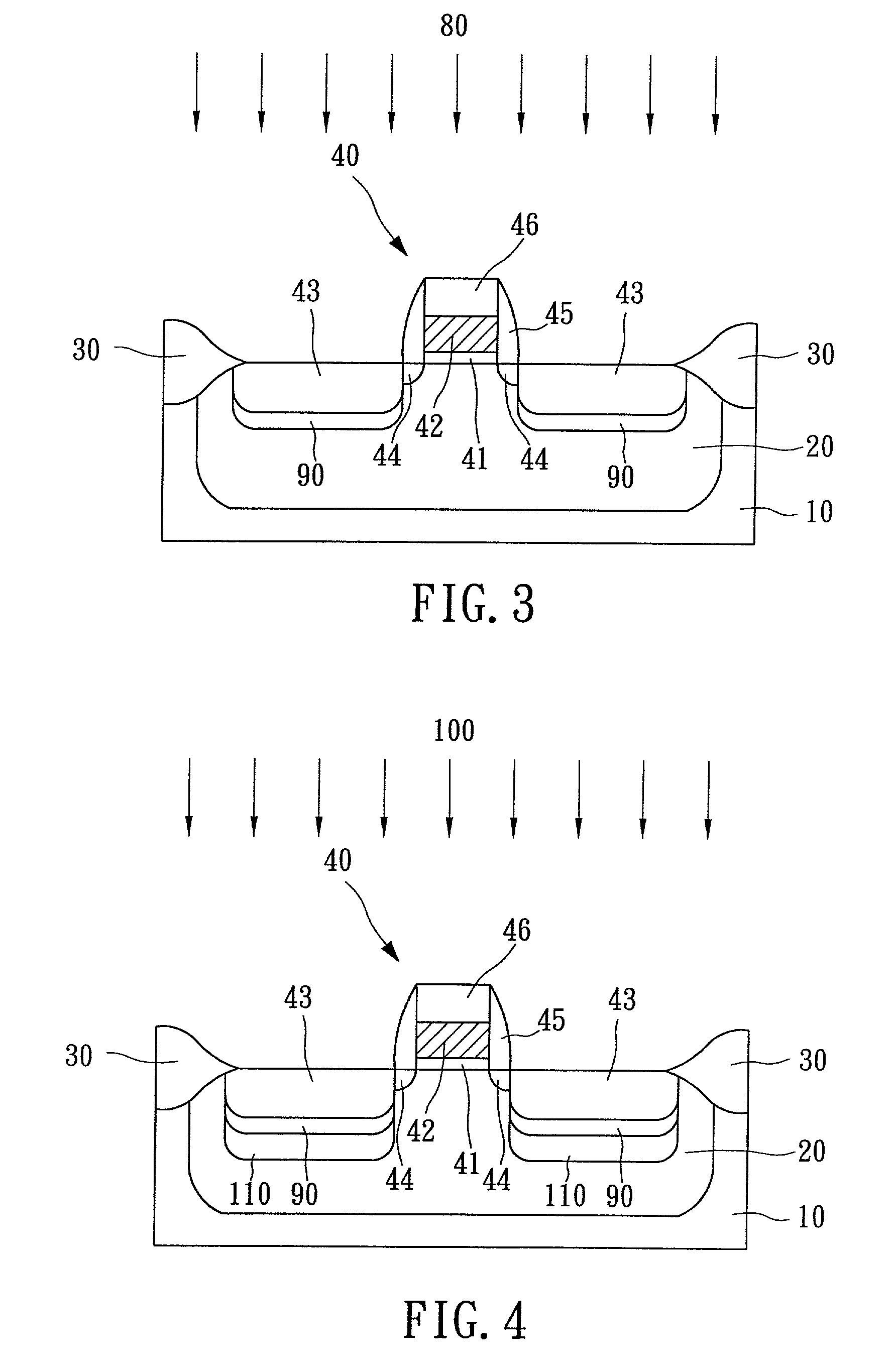

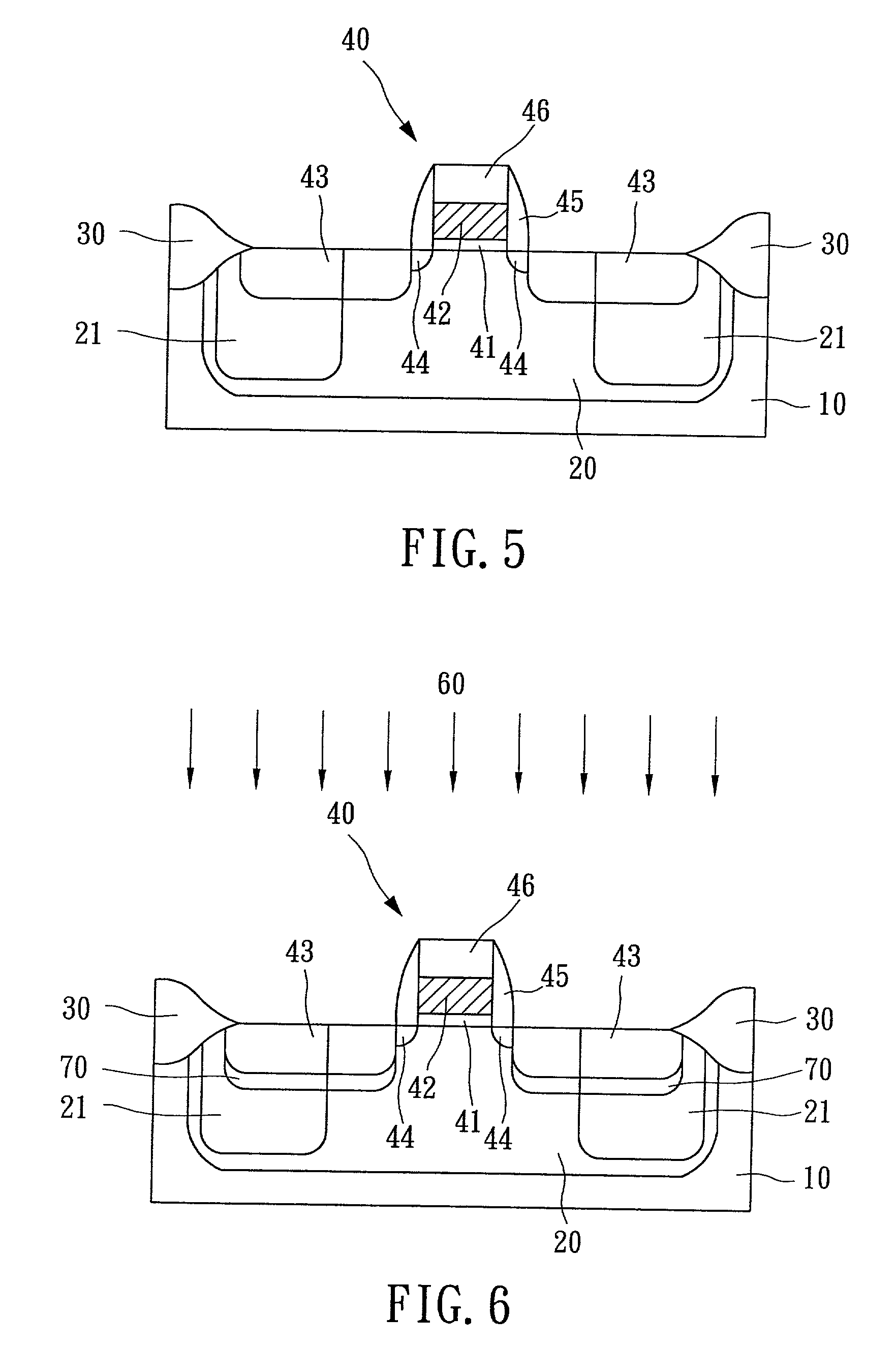

Method to produce localized halo for MOS transistor

InactiveUS7064039B2Accurate and repeatable formationLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSilicon

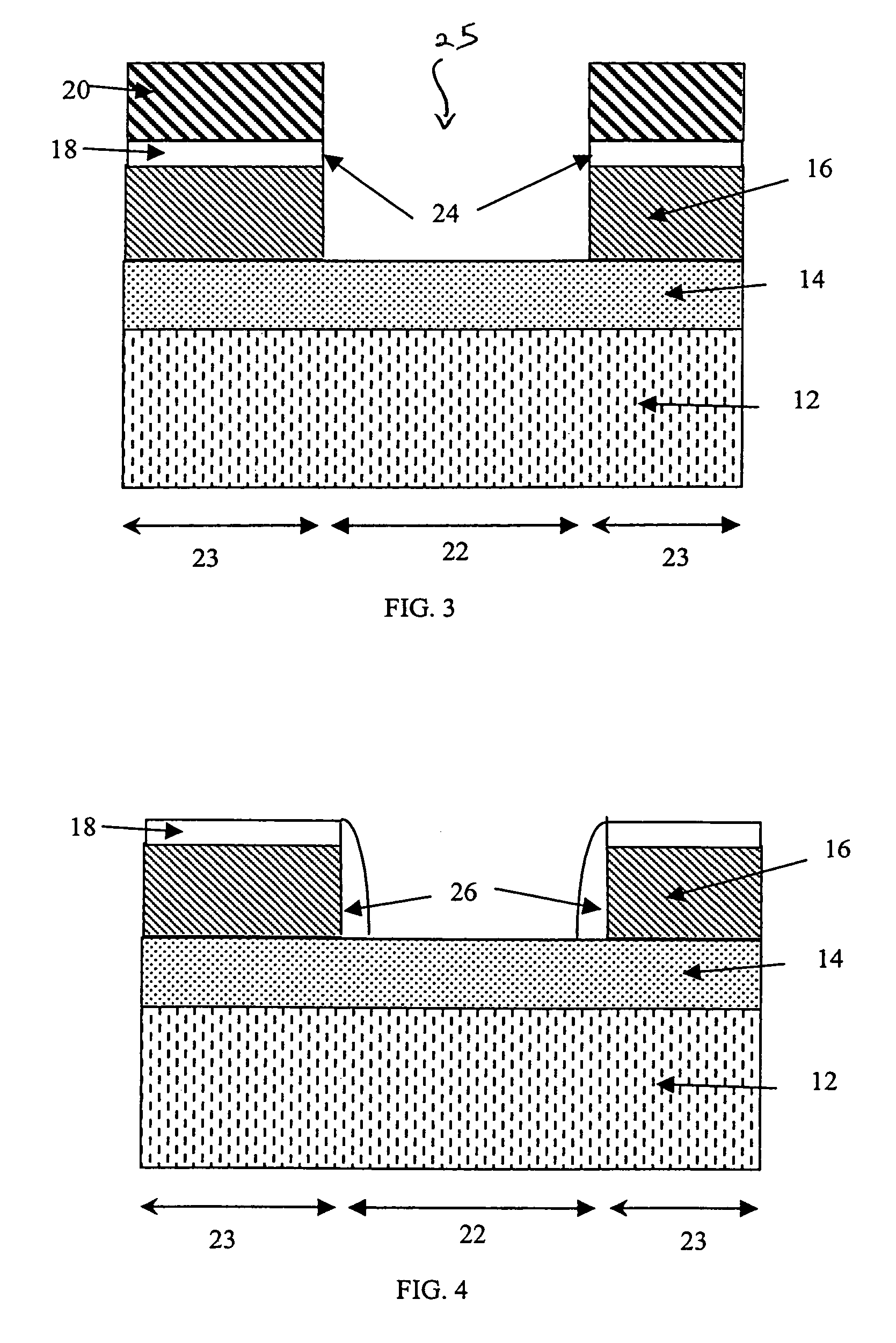

Methods are discussed for forming a localized halo structure and a retrograde profile in a substrate of a semiconductor device. The method comprises providing a gate structure over the semiconductor substrate, wherein a dopant material is implanted at an angle around the gate structure to form a halo structure in a source / drain region of the substrate and underlying a portion of the gate structure. A trench is formed in the source / drain region of the semiconductor substrate thereby removing at least a portion of the halo structure in the source / drain region. A silicon material layer is then formed in the trench using an epitaxial deposition.

Owner:TEXAS INSTR INC

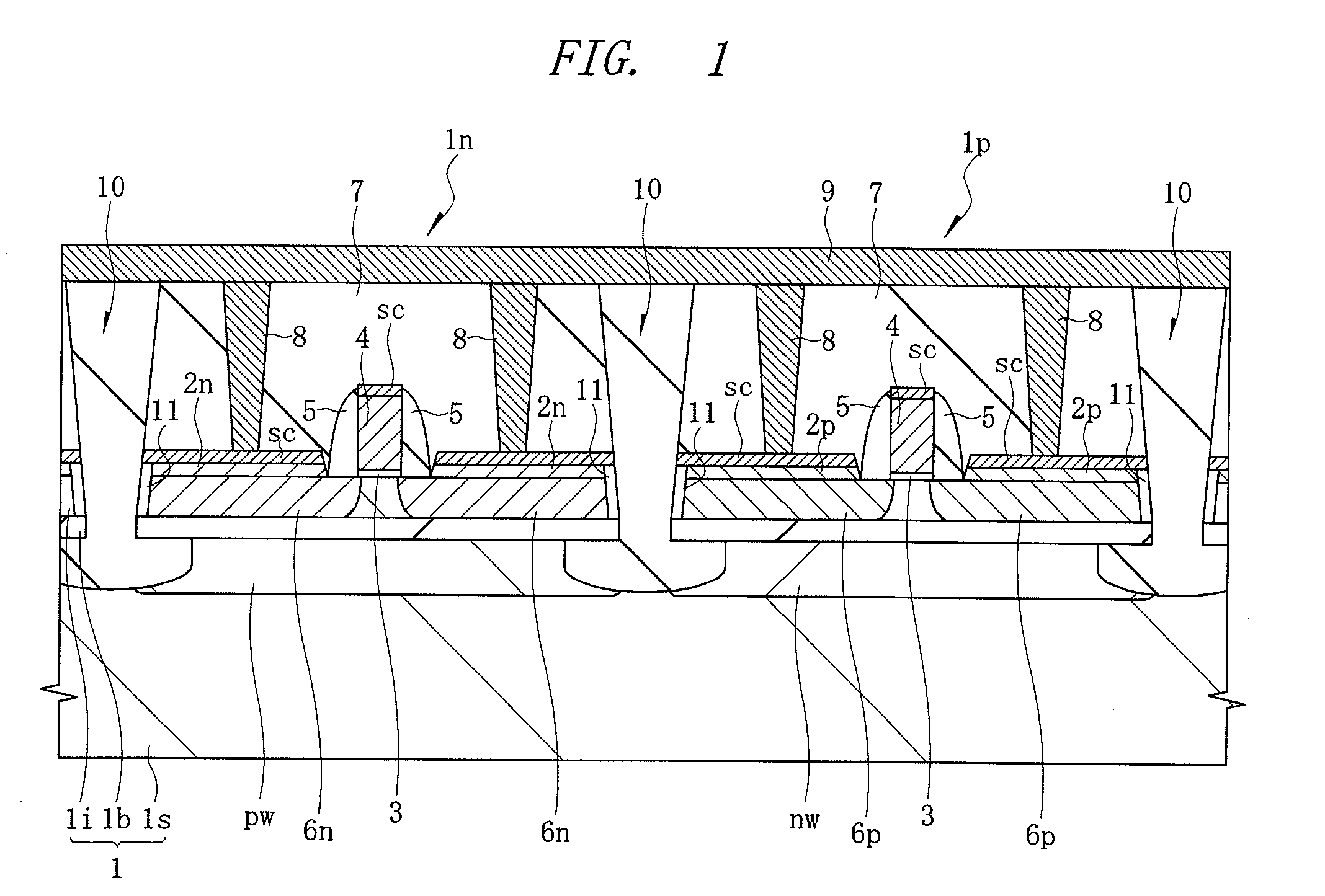

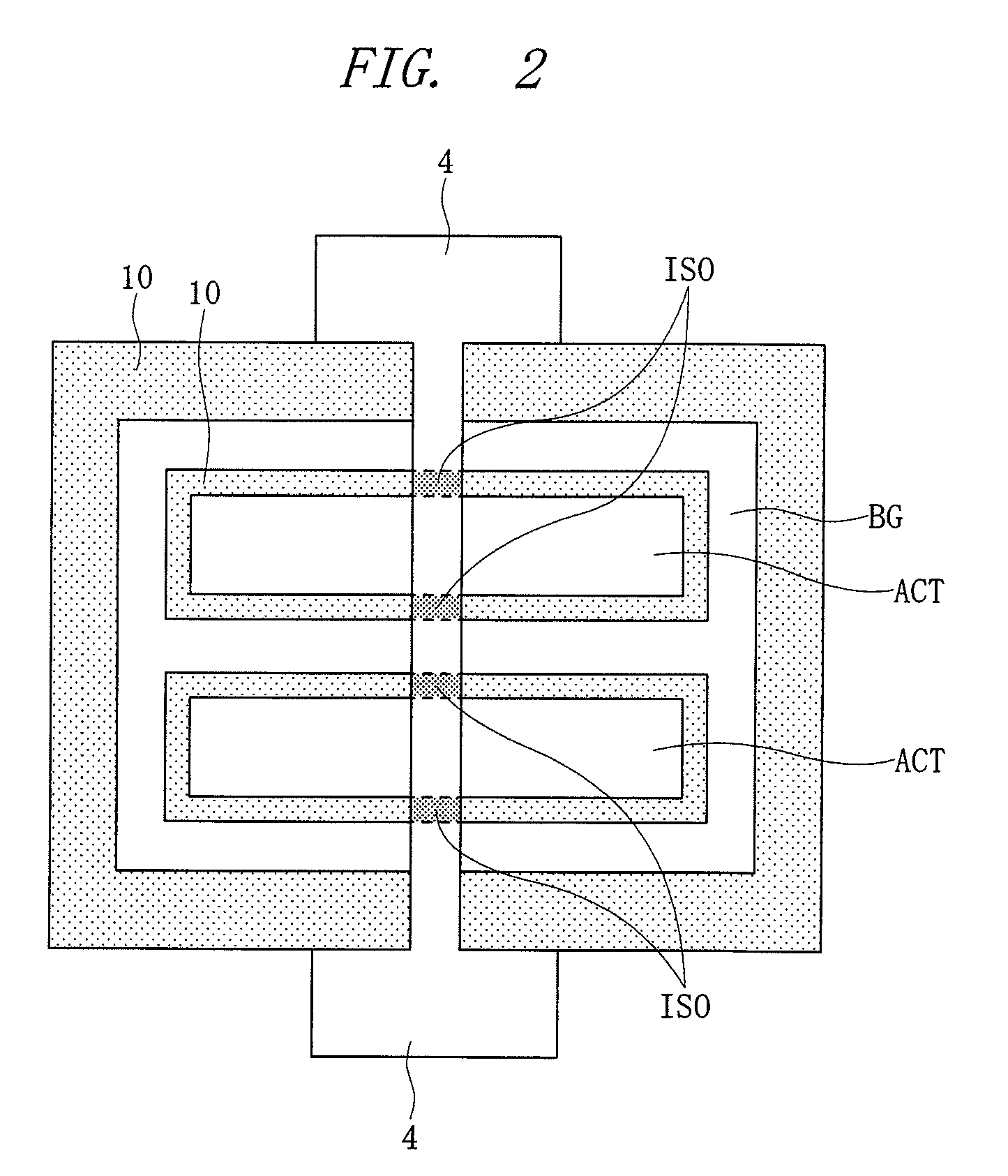

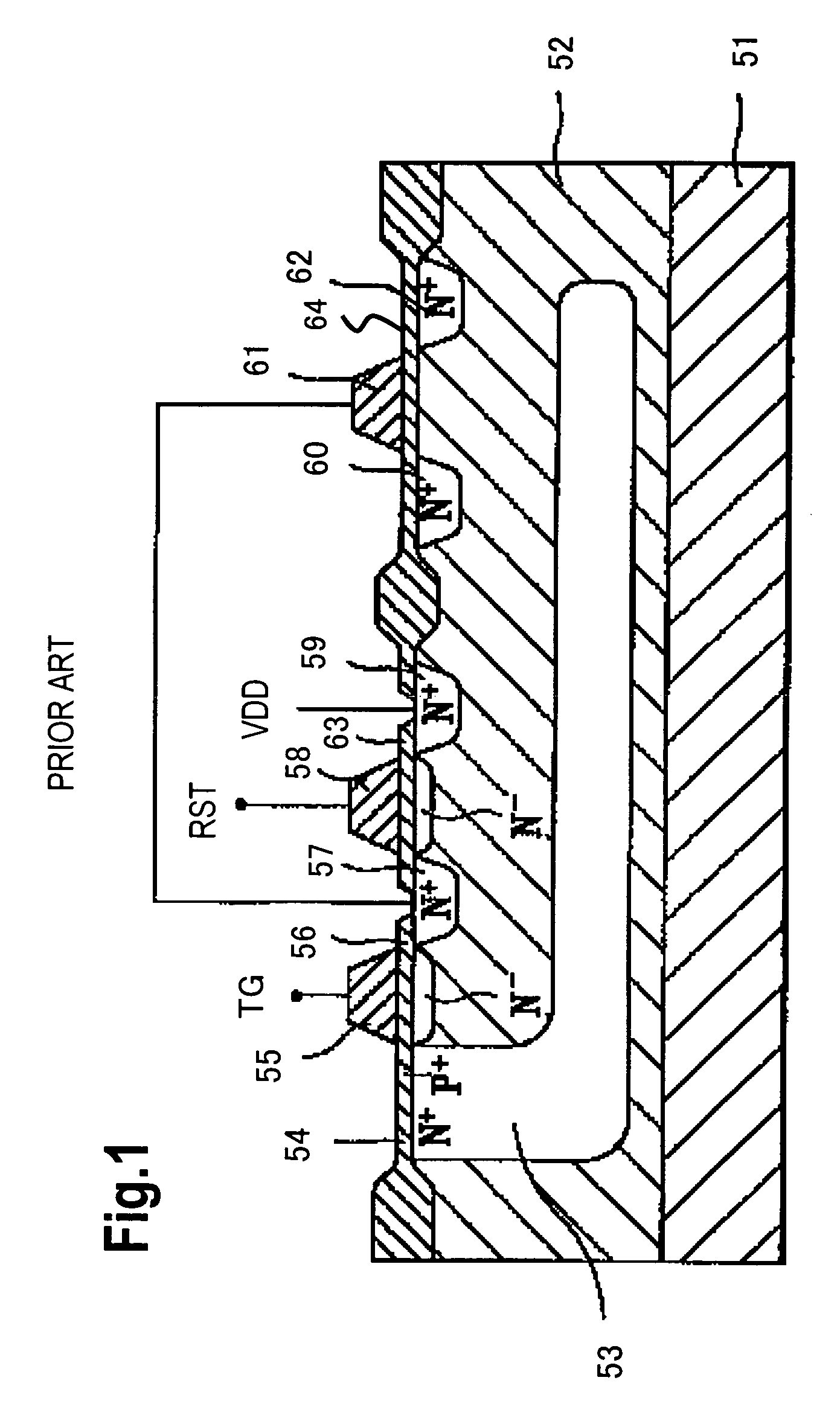

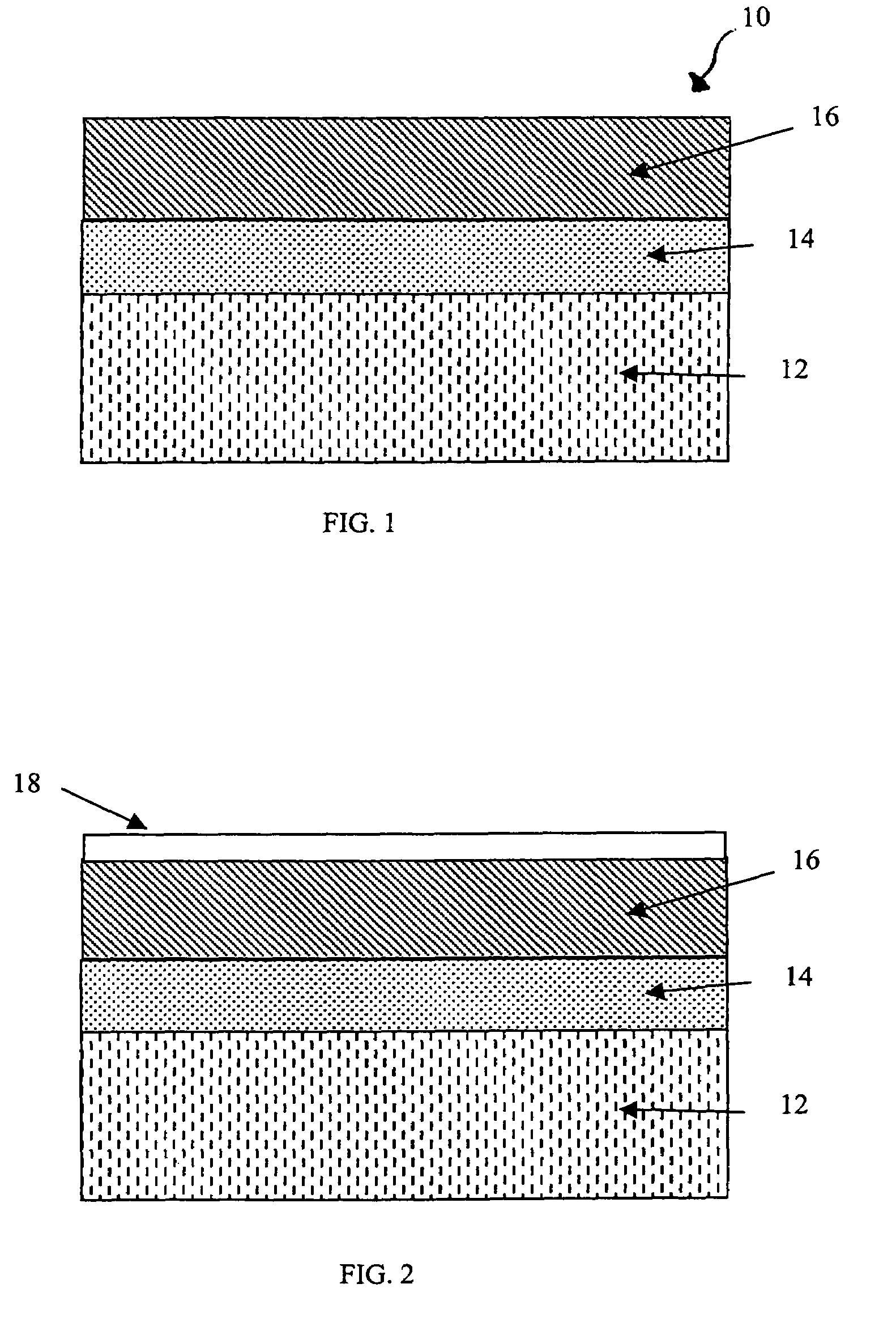

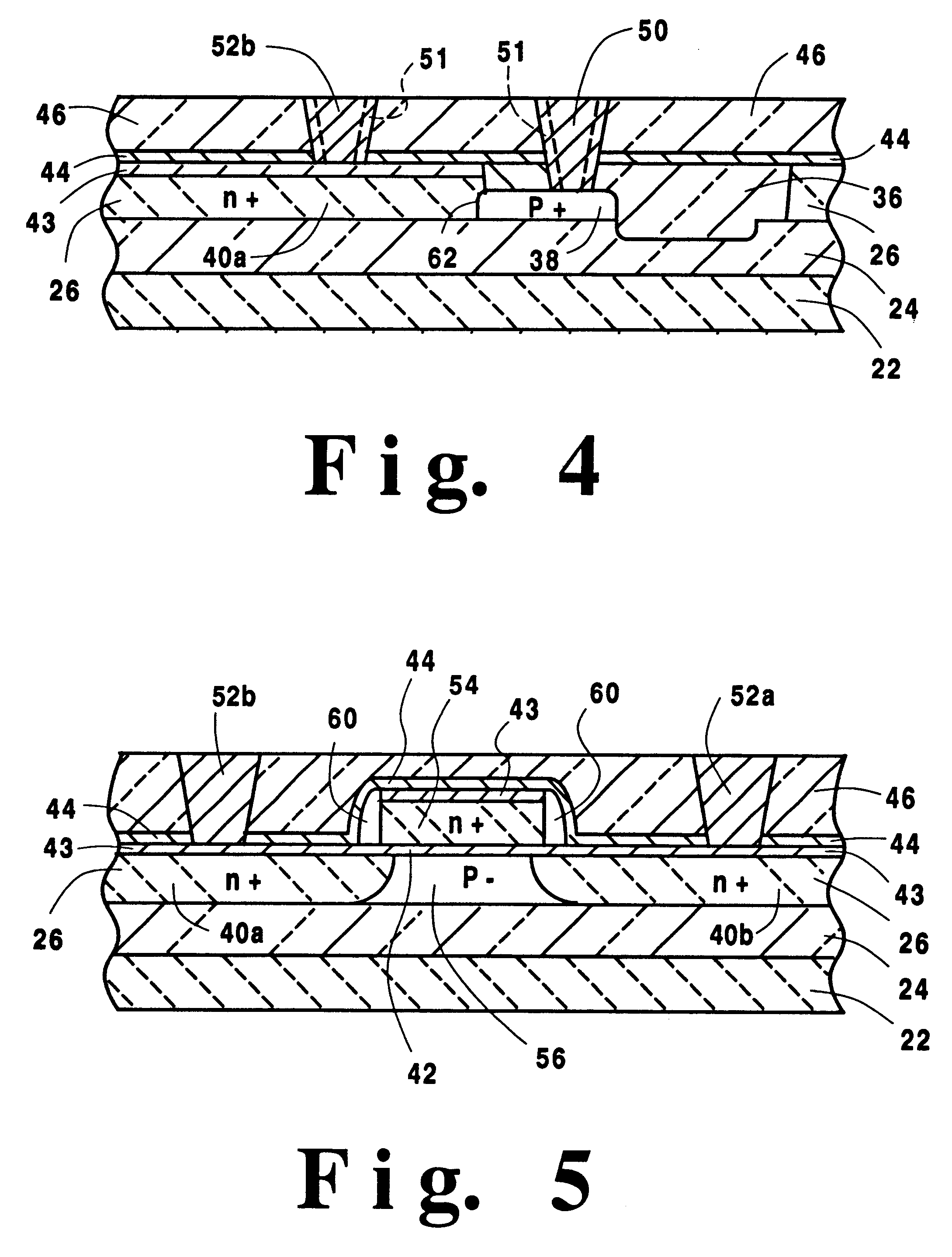

Semiconductor device and manufacturing method thereof

InactiveUS20100258869A1Inhibit currentLower junction capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateSemiconductor

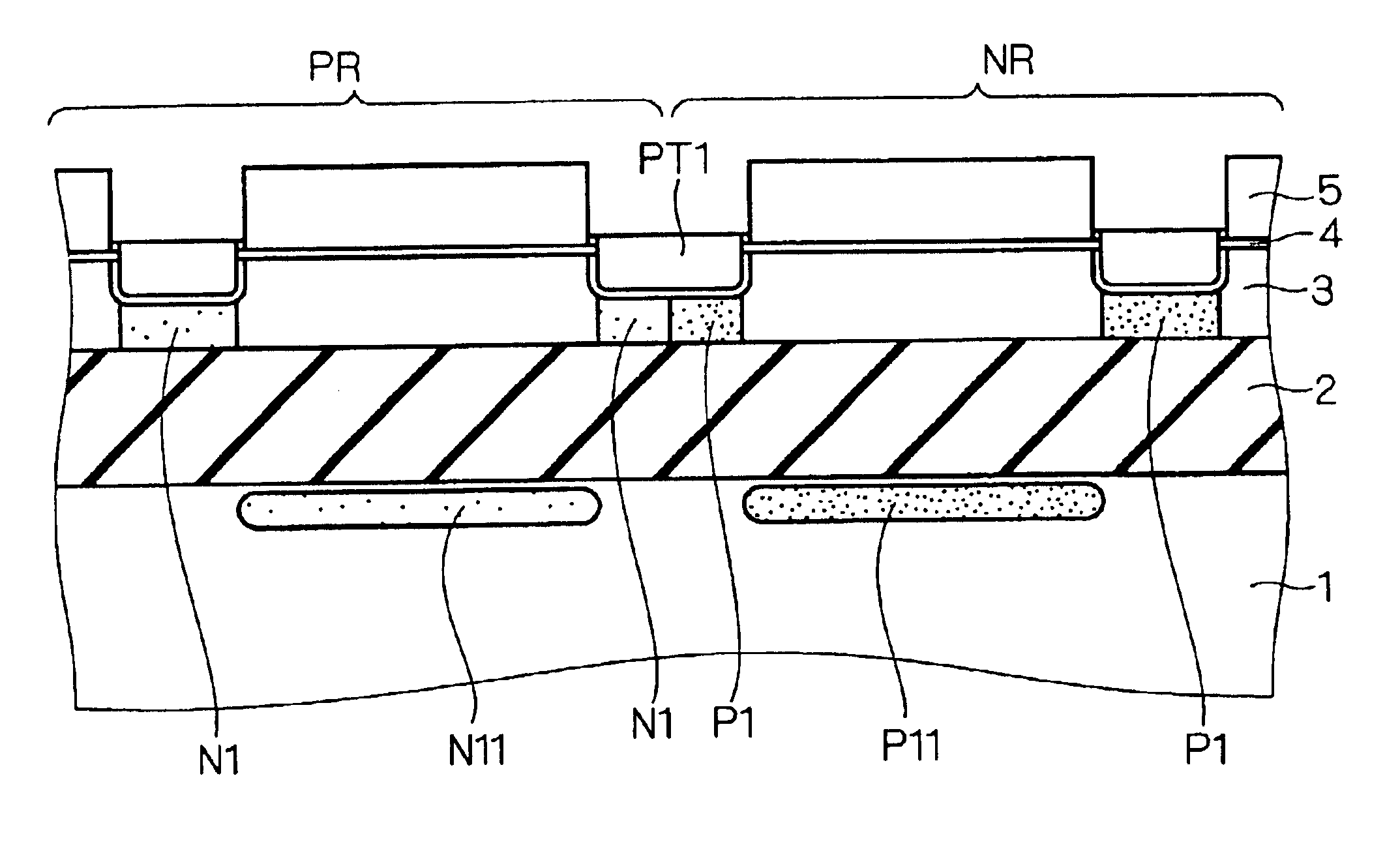

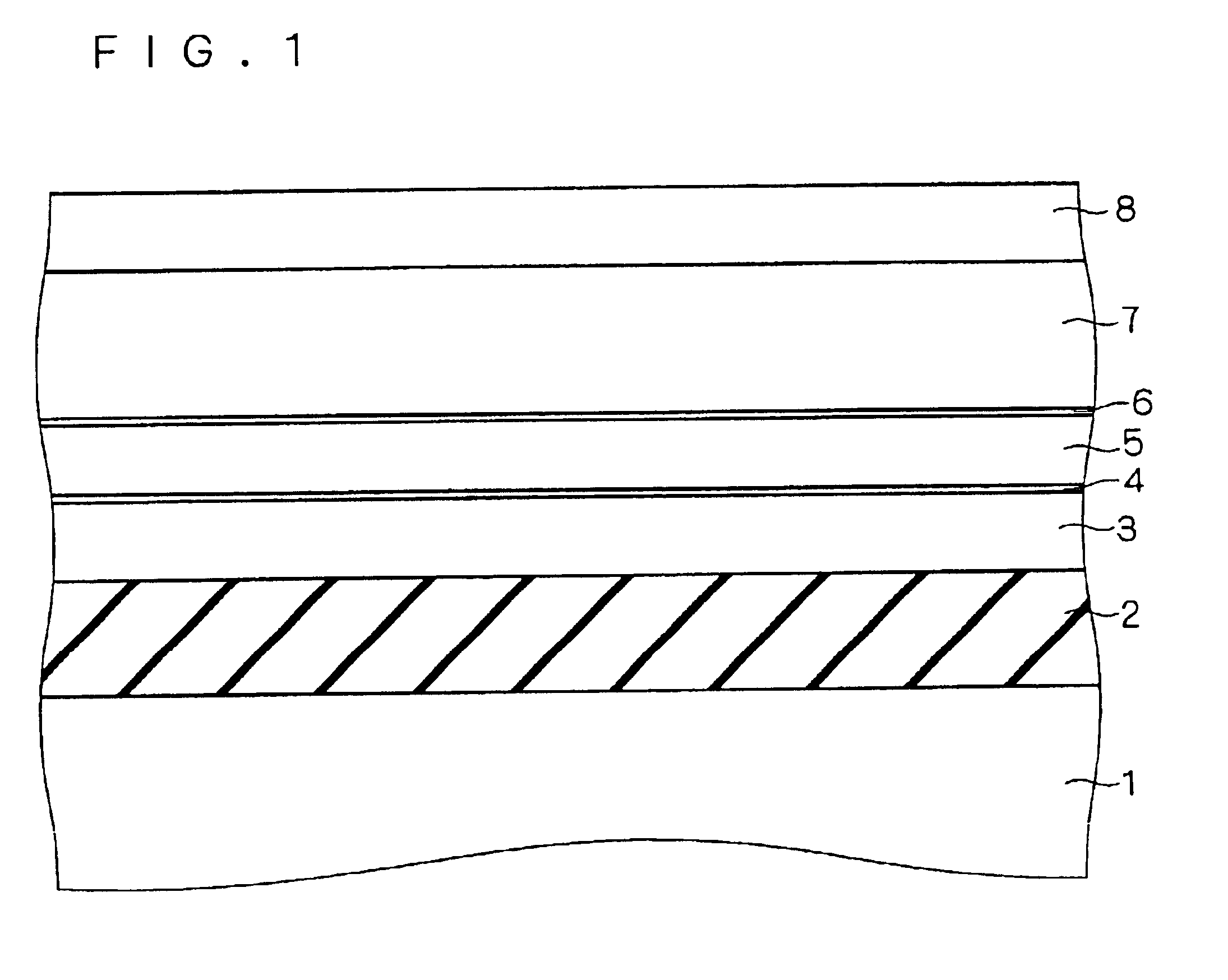

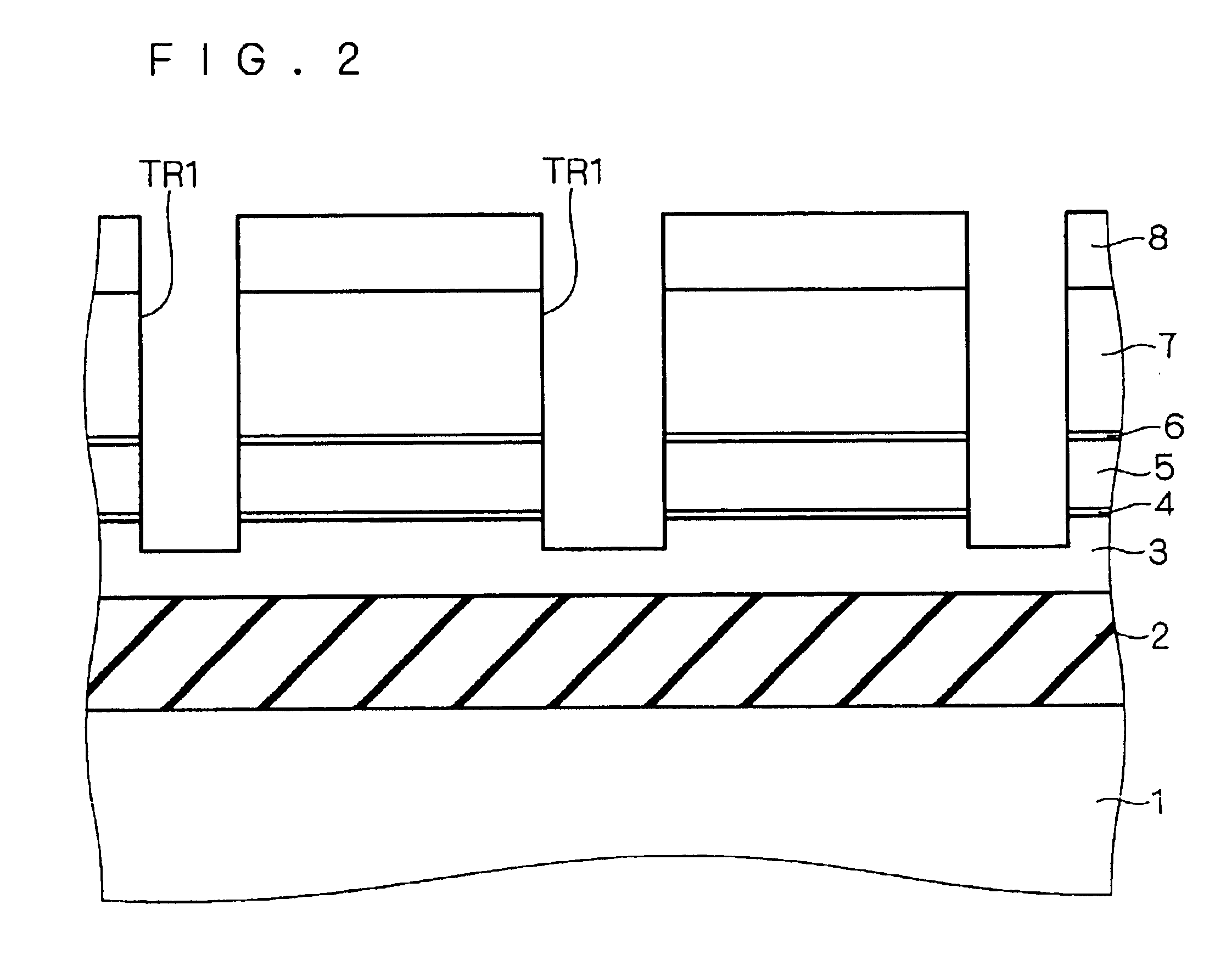

An n well and a p well disposed at a predetermined interval on a main surface of a SOI substrate with a thin BOX layer are formed, and an nMIS formed on the p well has a pair of n-type source / drain regions formed on semiconductor layers stacked on a main surface of the SOI layer at a predetermined distance, a gate insulating film, a gate electrode and sidewalls sandwiched between the pair of n-type source / drain regions. A device isolation is formed between the n well and the p well, and a side edge portion of the device isolation extends toward a gate electrode side more than a side edge portion of the n-type source / drain region (sidewall of the BOX layer).

Owner:HITACHI LTD

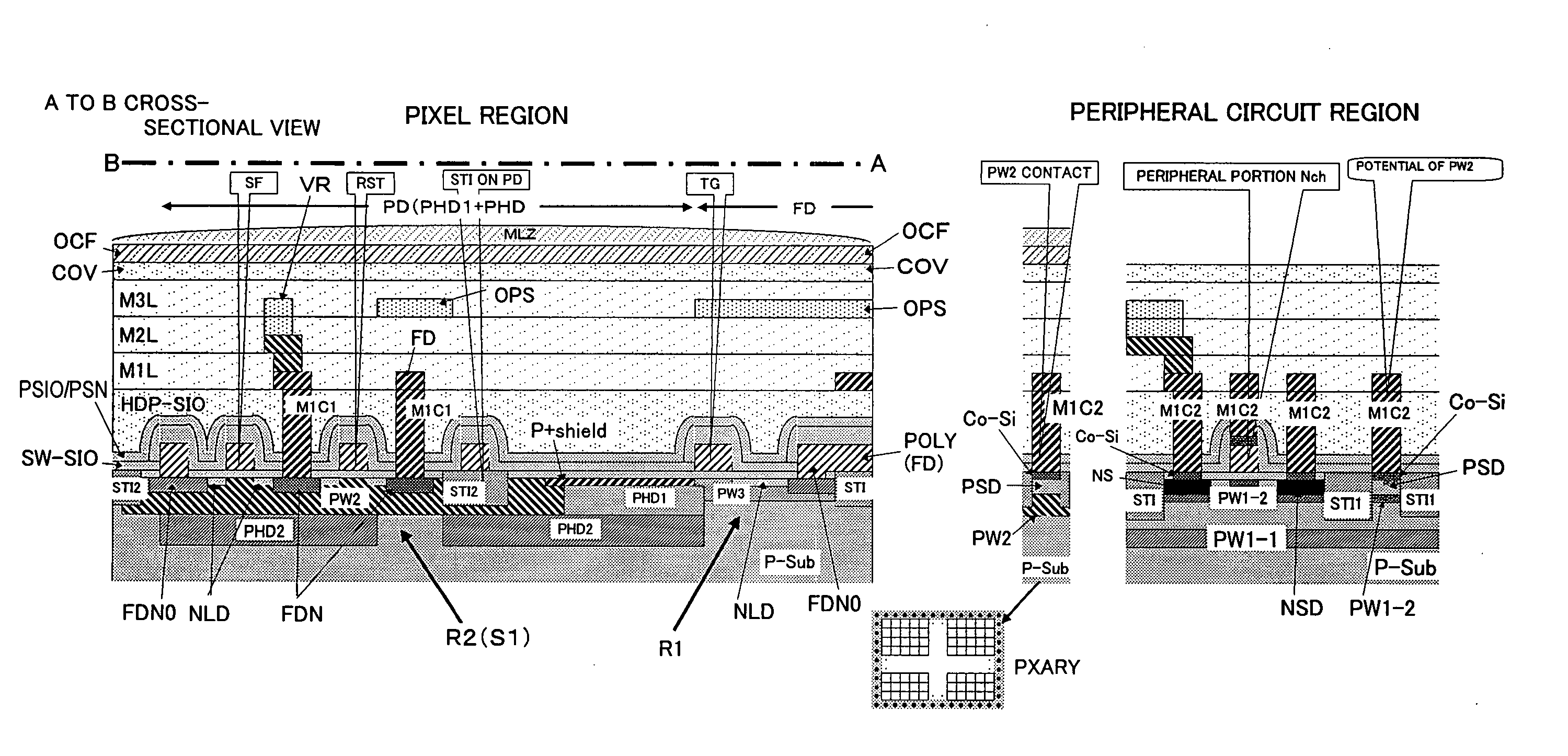

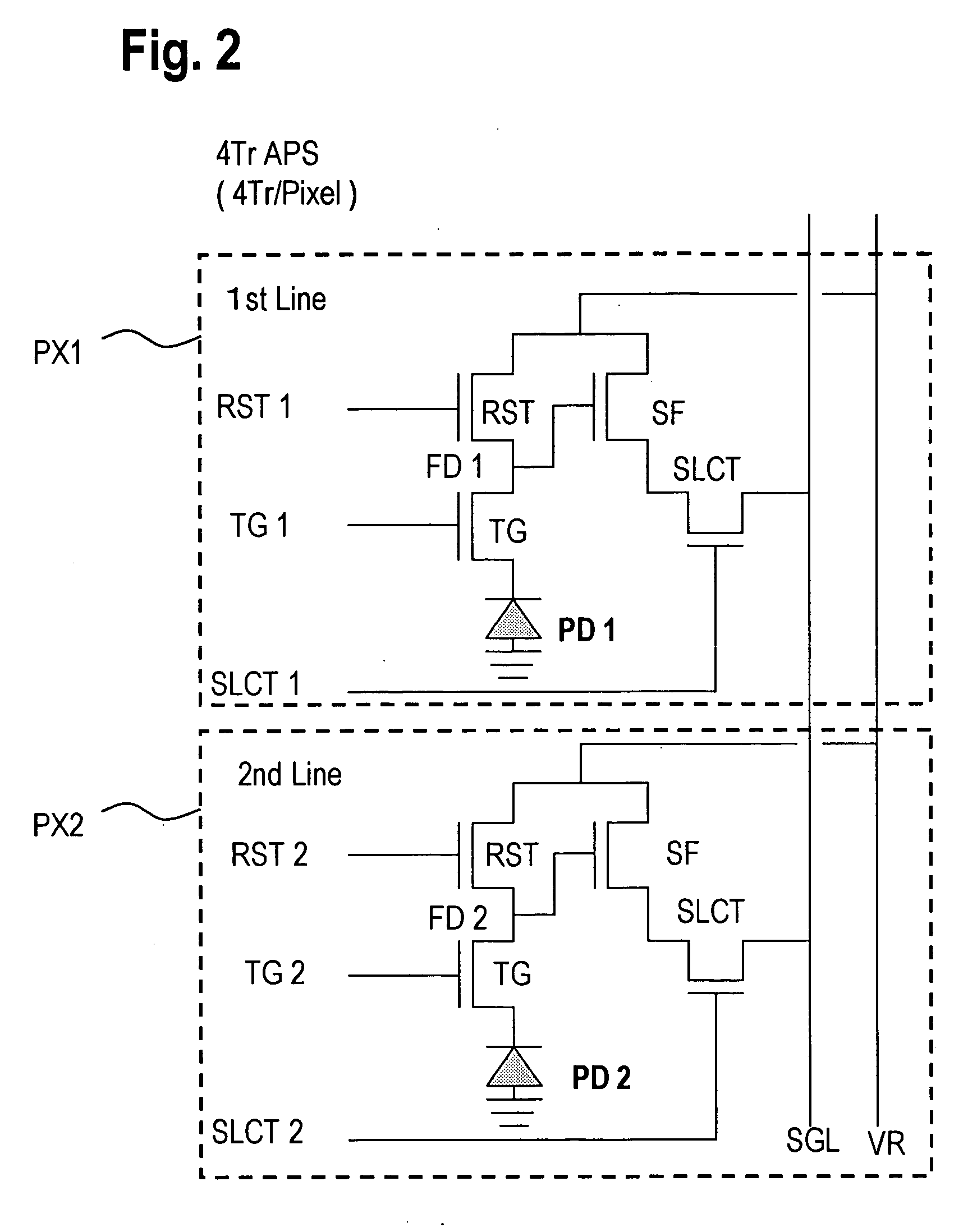

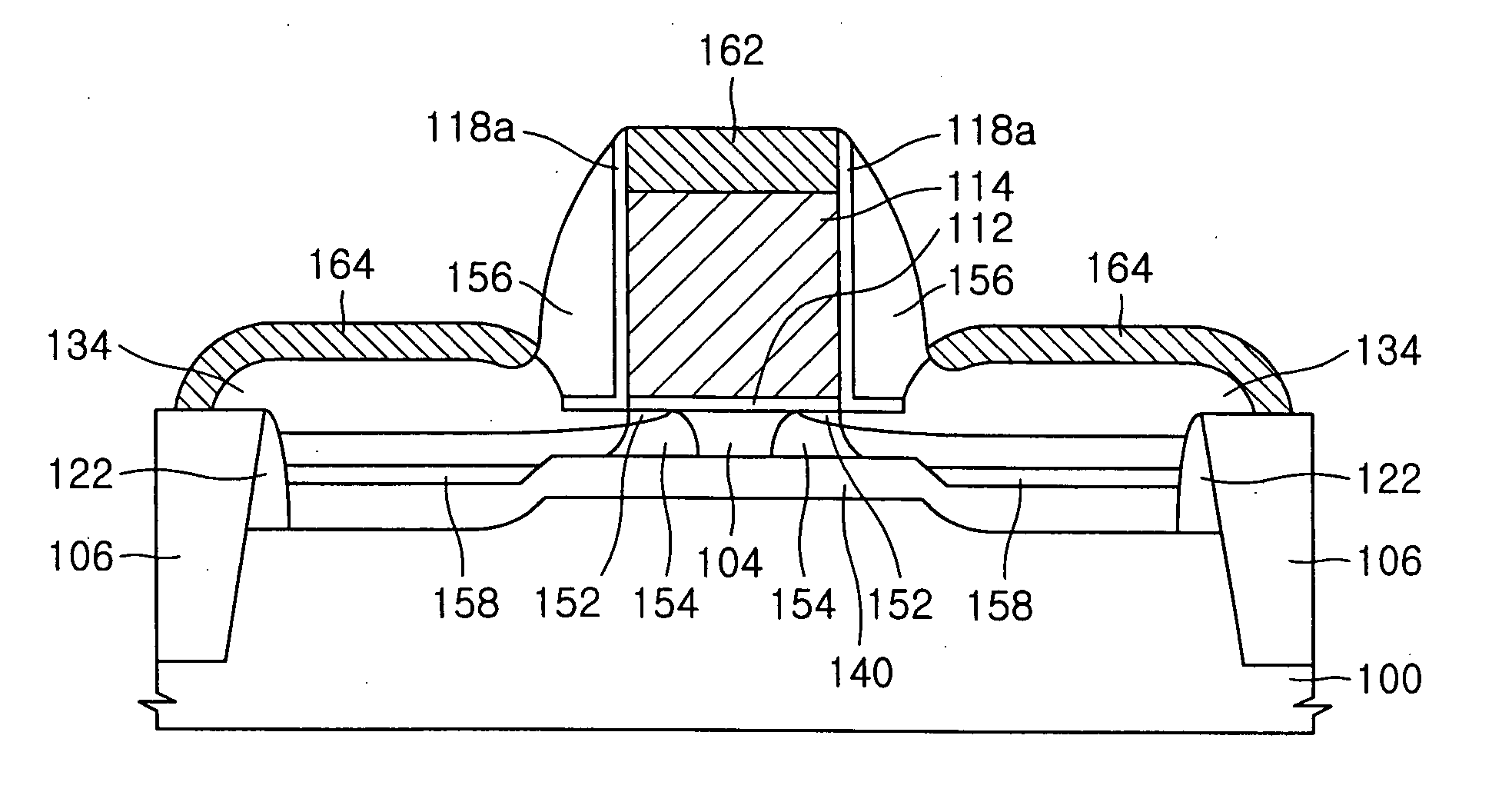

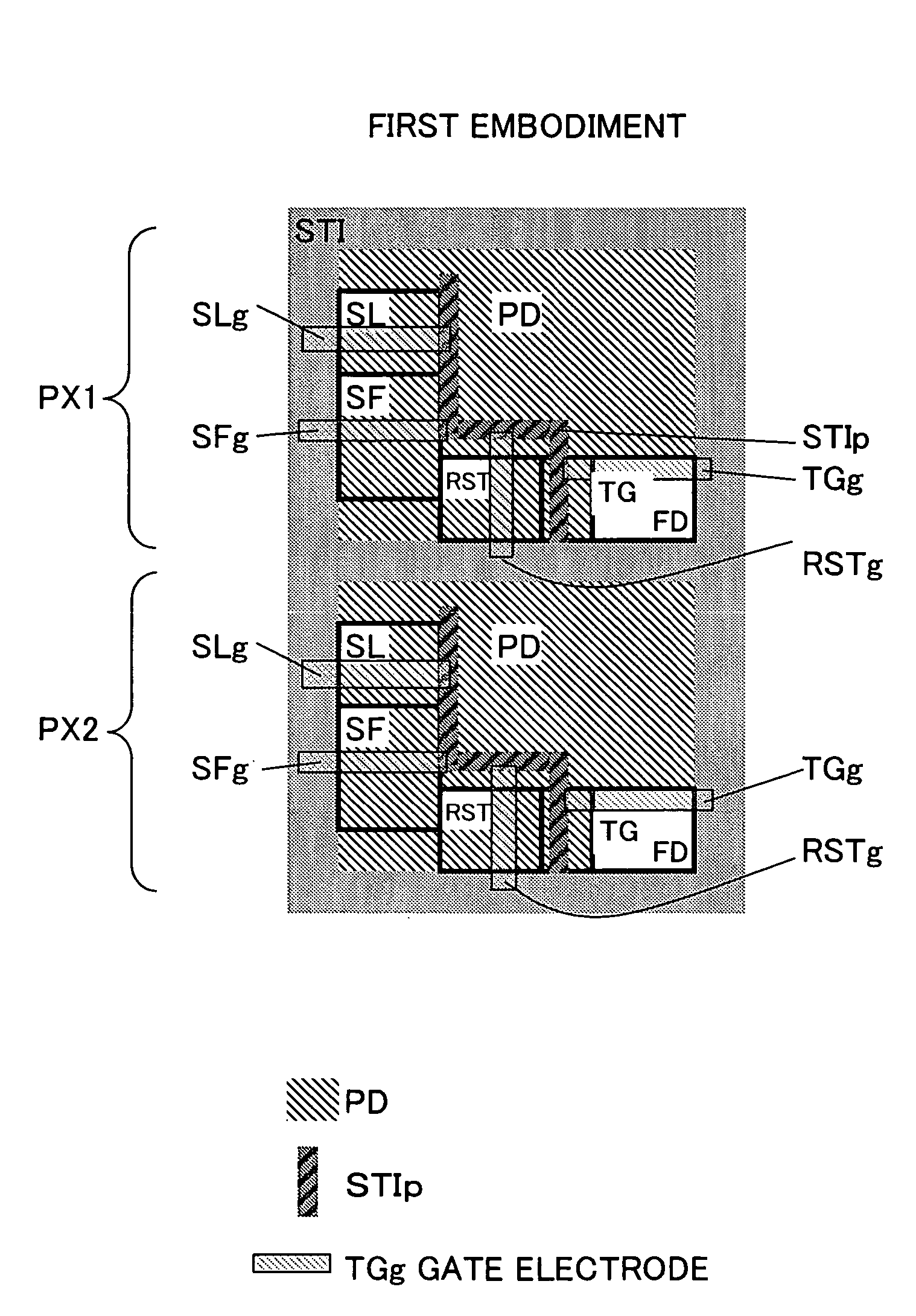

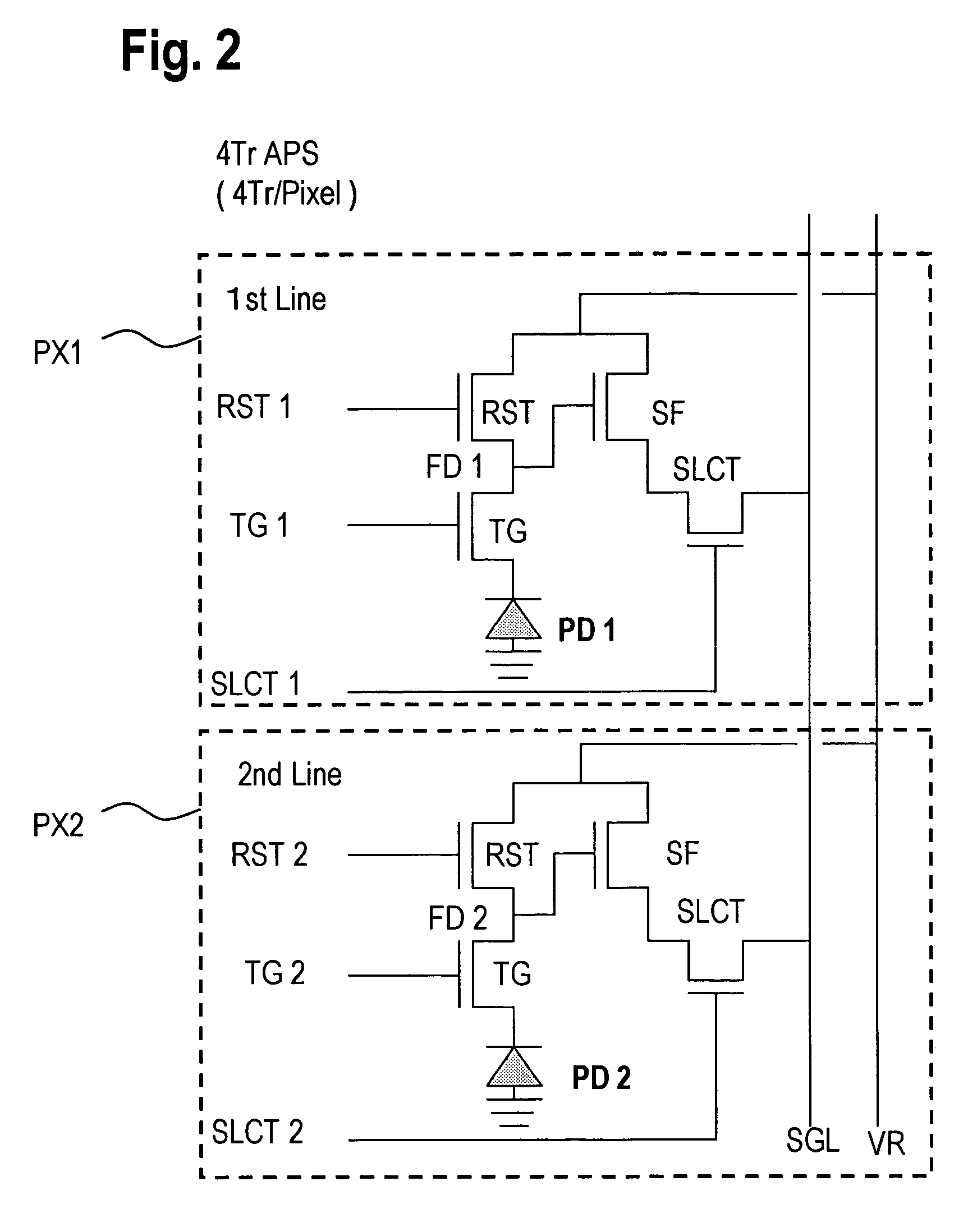

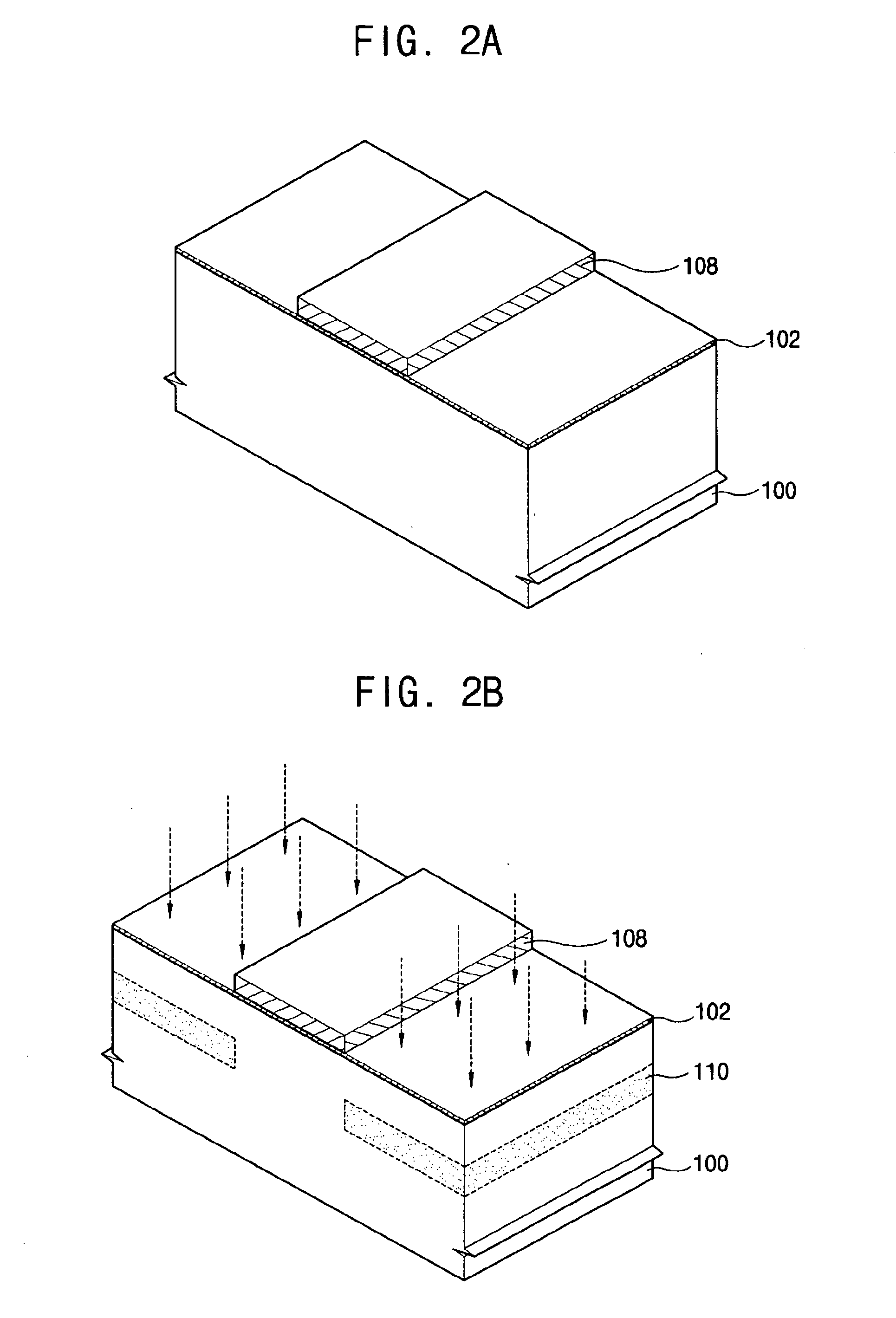

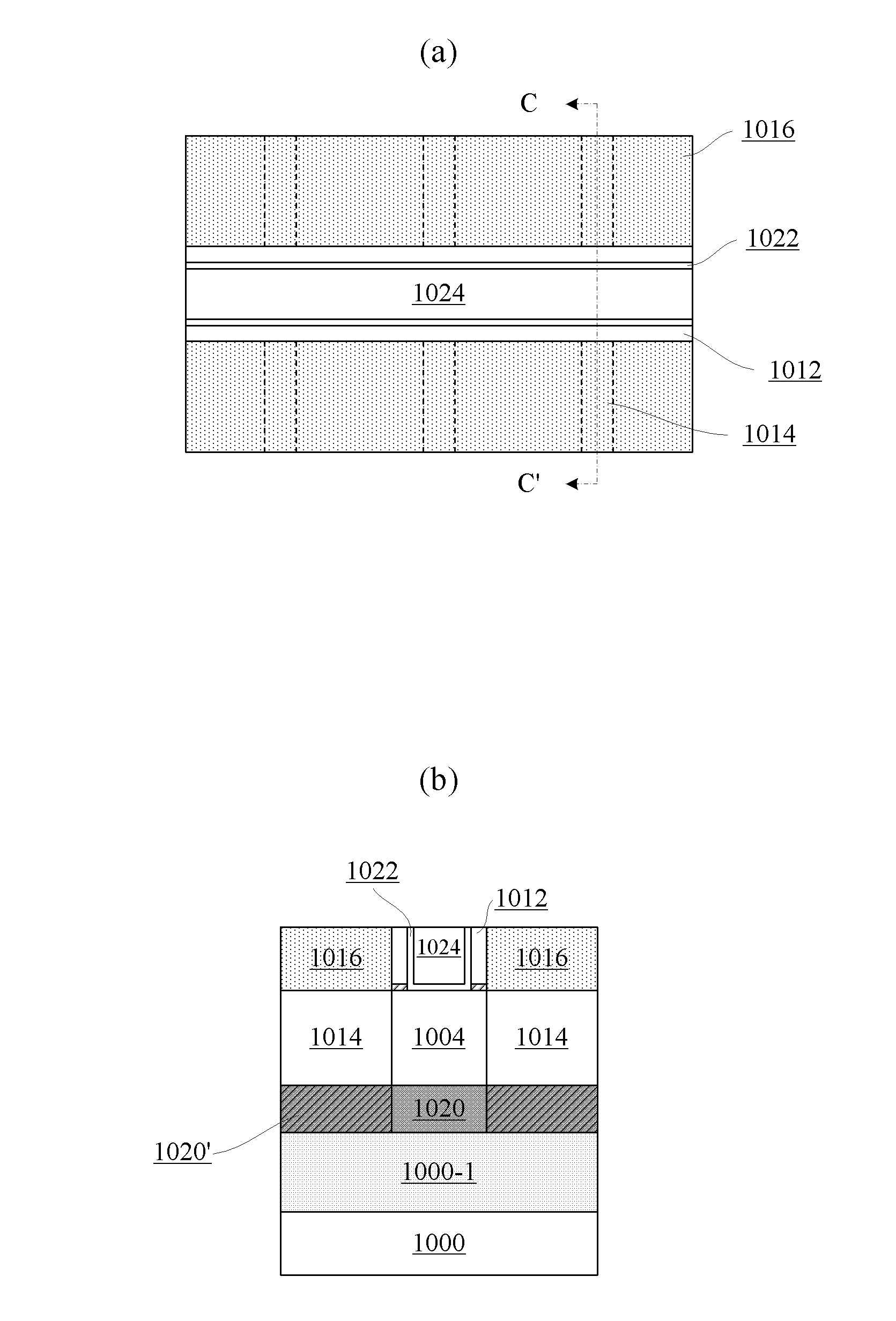

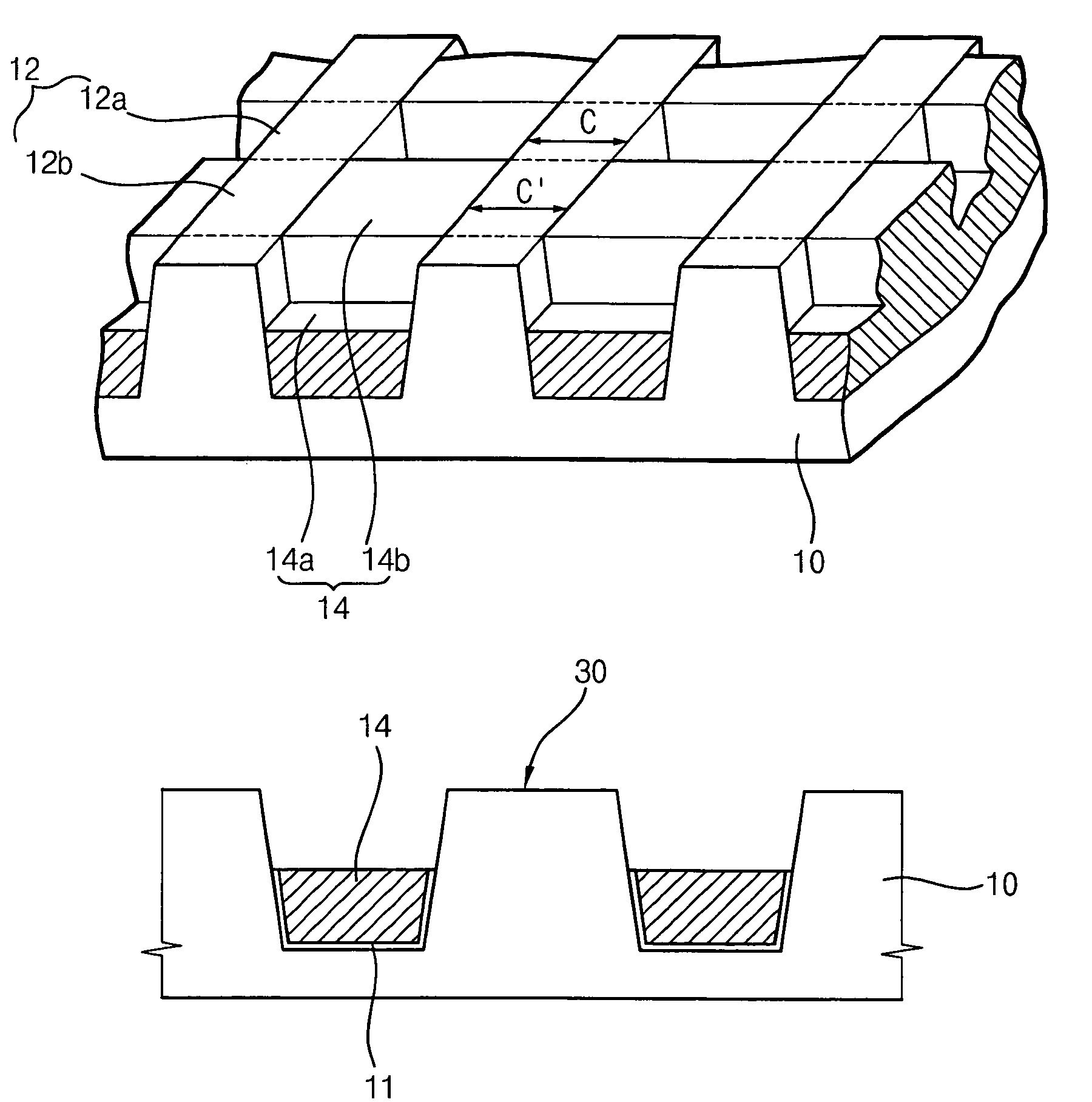

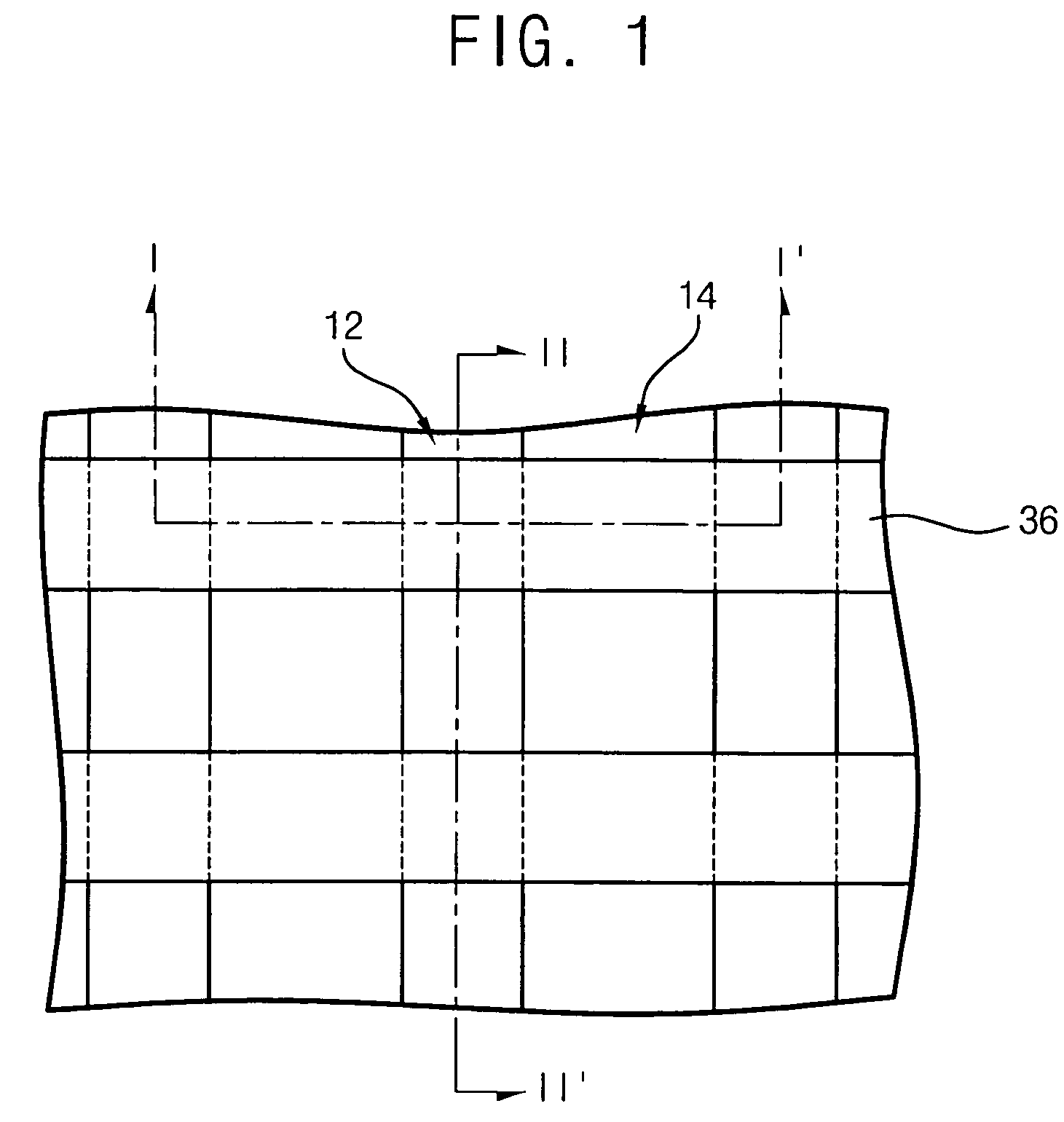

Image sensor with embedded photodiode region and fabrication method thereof

ActiveUS20060208285A1Addition of noise to detection can be suppressedSuppress noiseTelevision system detailsSolid-state devicesFloating diffusionPhotodiode

An image sensor in which a plurality of pixels having at least a photodiode, a reset transistor, and source follower transistor are formed, wherein each pixel comprises an electrical-charge transfer gate transistor between the photodiode and reset transistor, and a floating diffusion region constituting a node connecting the reset transistor and transfer gate transistor is connected to the gate of the source follower transistor. Further, a photodiode region is embedded below a well region in which the reset transistor and source follower transistor of each pixel are formed. In addition, the photodiode region is not formed below at least a partial region of the floating diffusion region.

Owner:SOCIONEXT INC

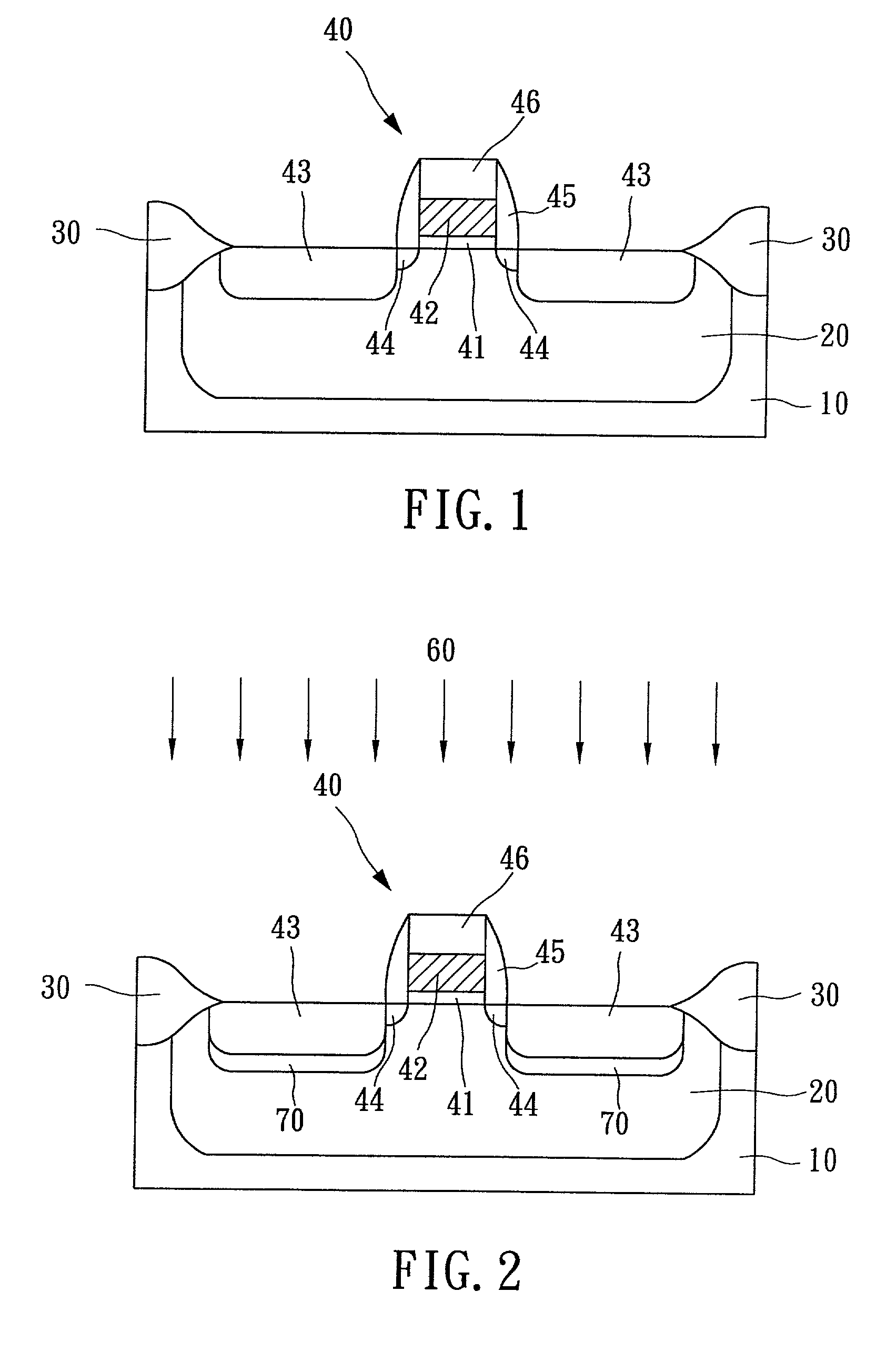

Semiconductor device and method of manufacturing same

InactiveUS20050285193A1Efficient solutionHigh carrier mobilityTransistorSolid-state devicesDevice materialEngineering

A semiconductor device and related method of manufacture are disclosed. The semiconductor device comprises a gate electrode formed on a semiconductor substrate, an active region containing spaces formed below the gate electrode, a channel region formed between the gate electrode and the spaces, and source and drain regions formed on opposite sides of the gate electrode within the active region. The spaces are formed by etching a semiconductor layer formed below the gate electrode in the active region.

Owner:SAMSUNG ELECTRONICS CO LTD

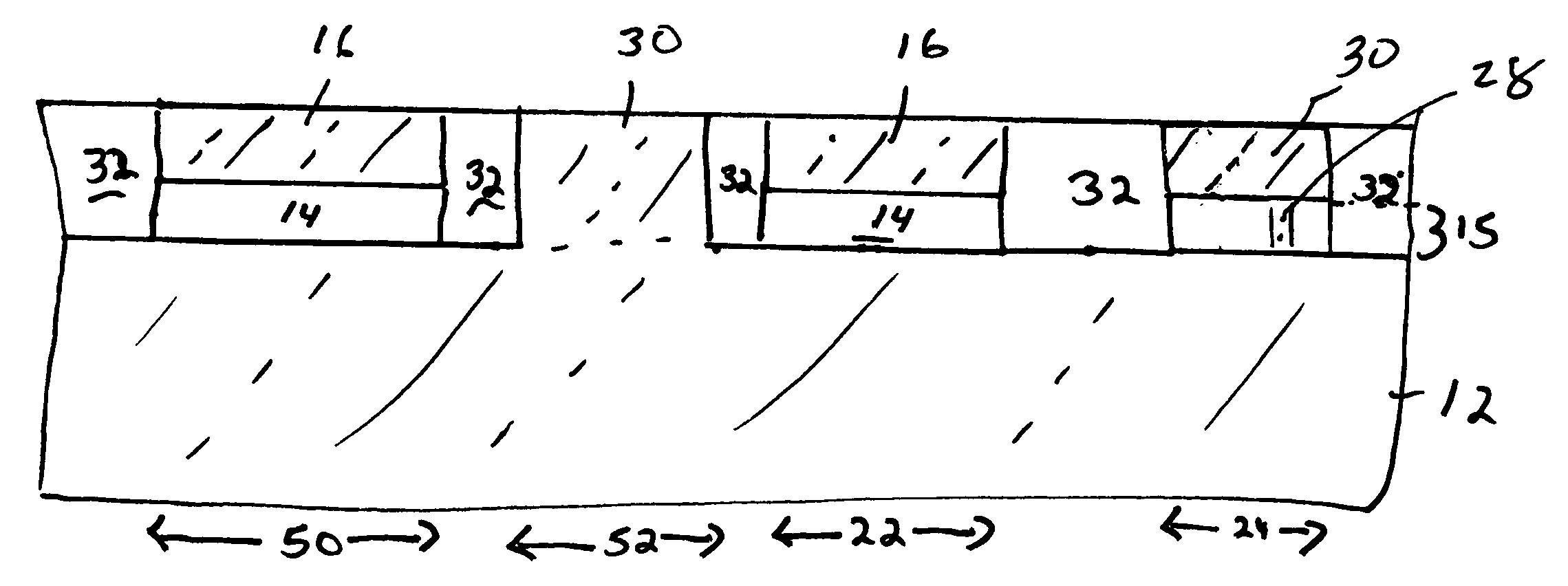

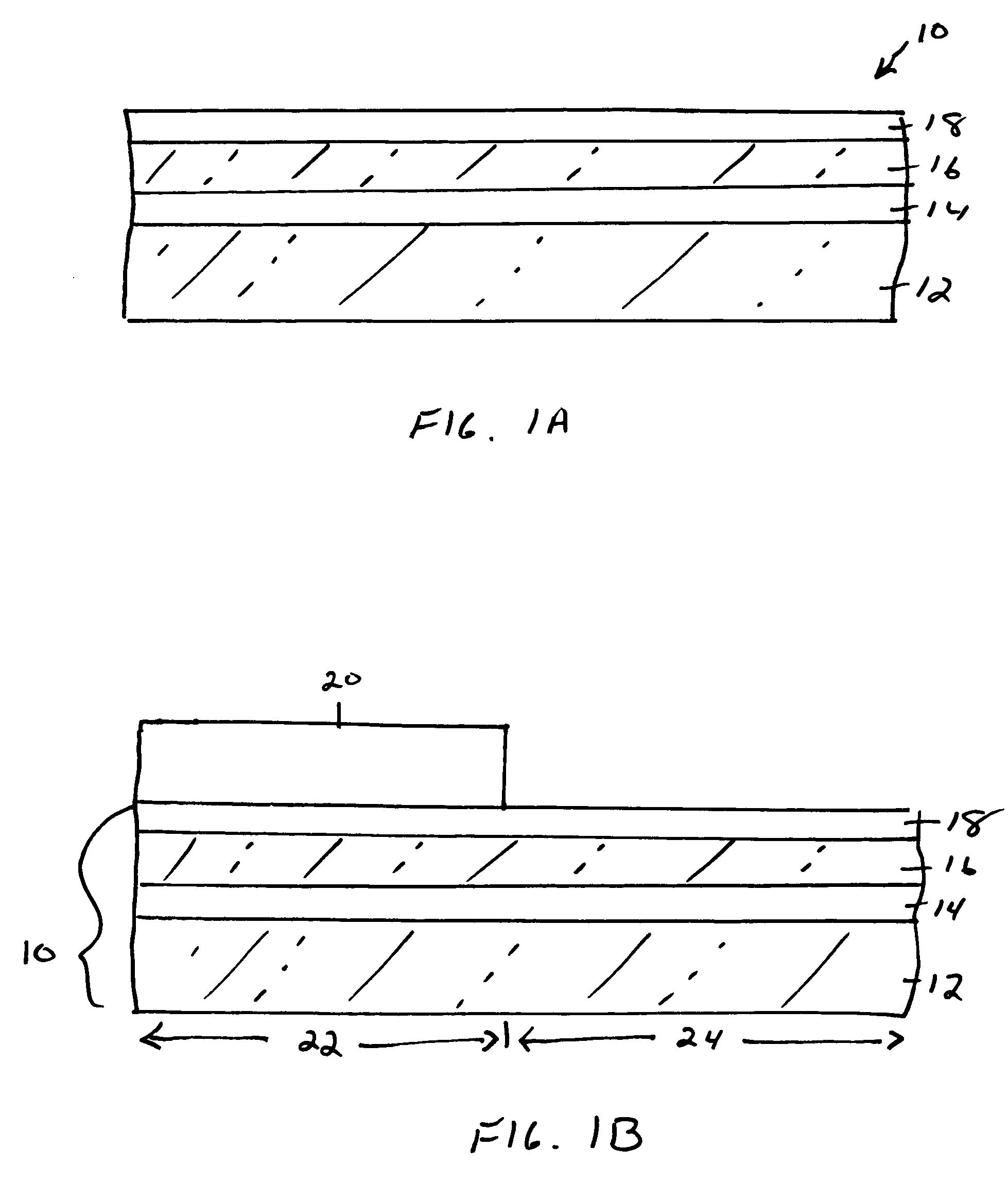

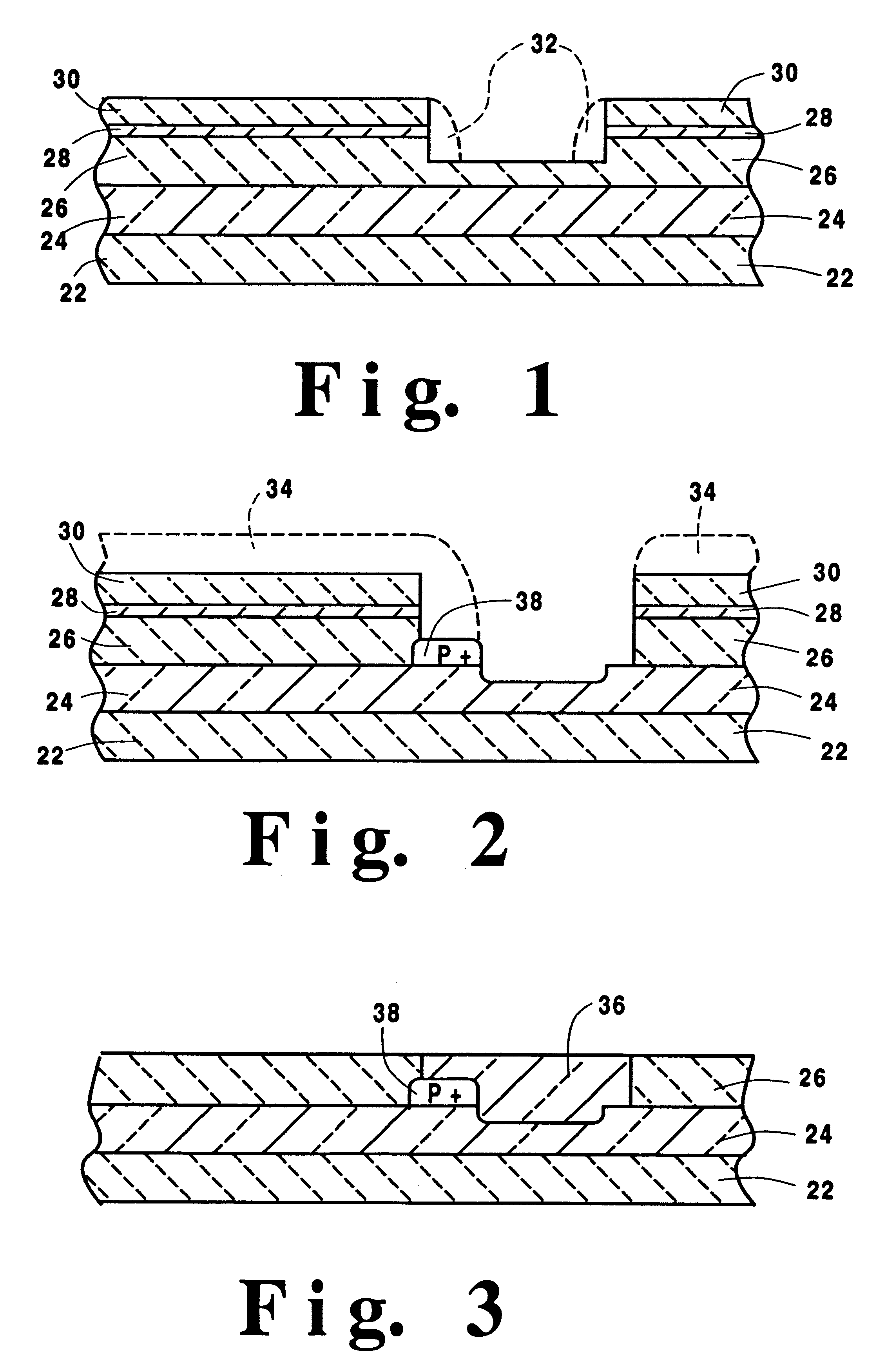

Hybrid orientation CMOS with partial insulation process

InactiveUS20060073646A1Improve performanceImprove device performanceTransistorSolid-state devicesCapacitanceSemiconductor materials

The present invention provides a method of integrated semiconductor devices such that different types of devices are formed upon a specific crystallographic orientation of a hybrid substrate. In accordance with the present invention, junction capacitance of one of the devices is improved in the present invention by forming the source / drain diffusion regions of the device in an epitiaxial semiconductor material such that they are situated on a buried insulating layer that extends partially underneath the body of the second semiconductor device. The second semiconductor device, together with the first semiconductor device, is both located atop the buried insulating layer. Unlike the first semiconductor device in which the body thereof is floating, the second semiconductor device is not floating. Rather, it is in contact with an underlying first semiconducting layer.

Owner:GLOBALFOUNDRIES INC

Metal oxide semiconductor (MOS) transistor and formation method thereof

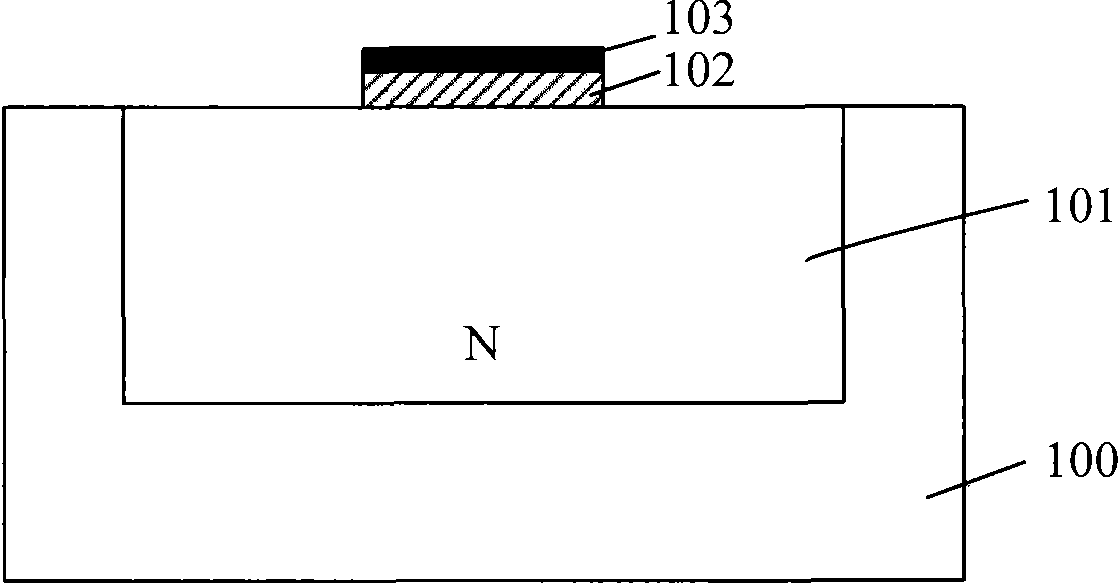

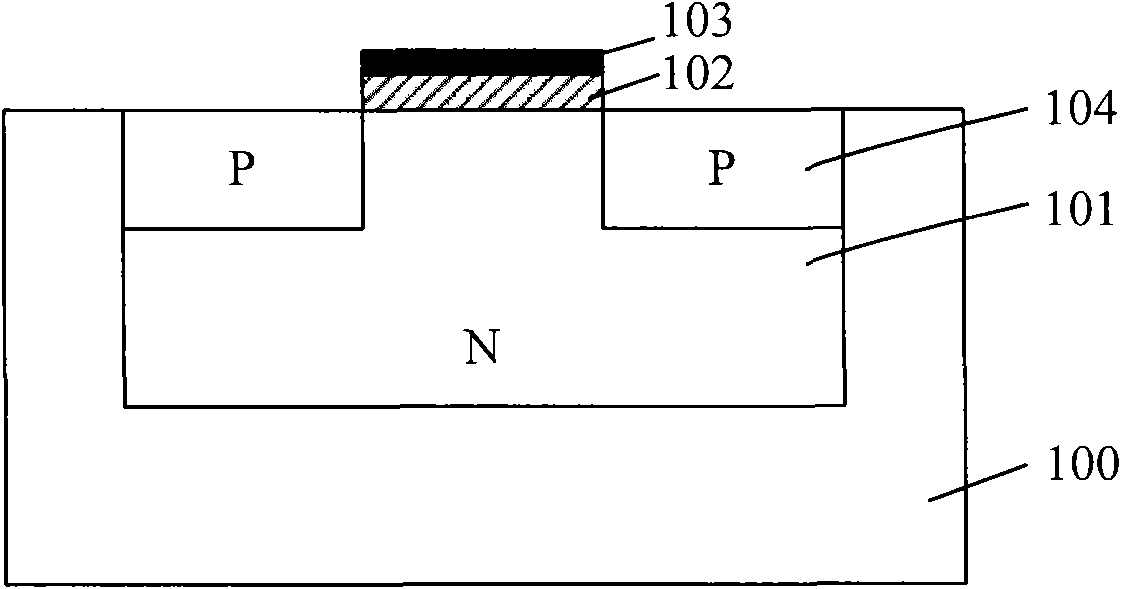

InactiveCN101789447AAvoid affecting basic performanceReduce doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceIon implantation

The invention provides a metal oxide semiconductor (MOS) transistor and a formation method thereof. The formation method of the transistor comprises the following steps of: forming an isolated well on a semiconductor substrate through repeated ion injection; carrying out reversed-phase ion injection on the isolated well; and forming a grid electrode, a source region and a drain region of the MOS transistor on the isolated well. The invention reduces the doping concentration nearby the interface of the source and the drain regions and the isolated well so as to weaken the junction capacitance and further reduce the influence of the parasitic junction capacitance on transistor devices, and also keeps the doping concentration on the surface of the isolated well and nearby the interface of the isolated well and the substrate so as to avoid affecting the original properties of the transistor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

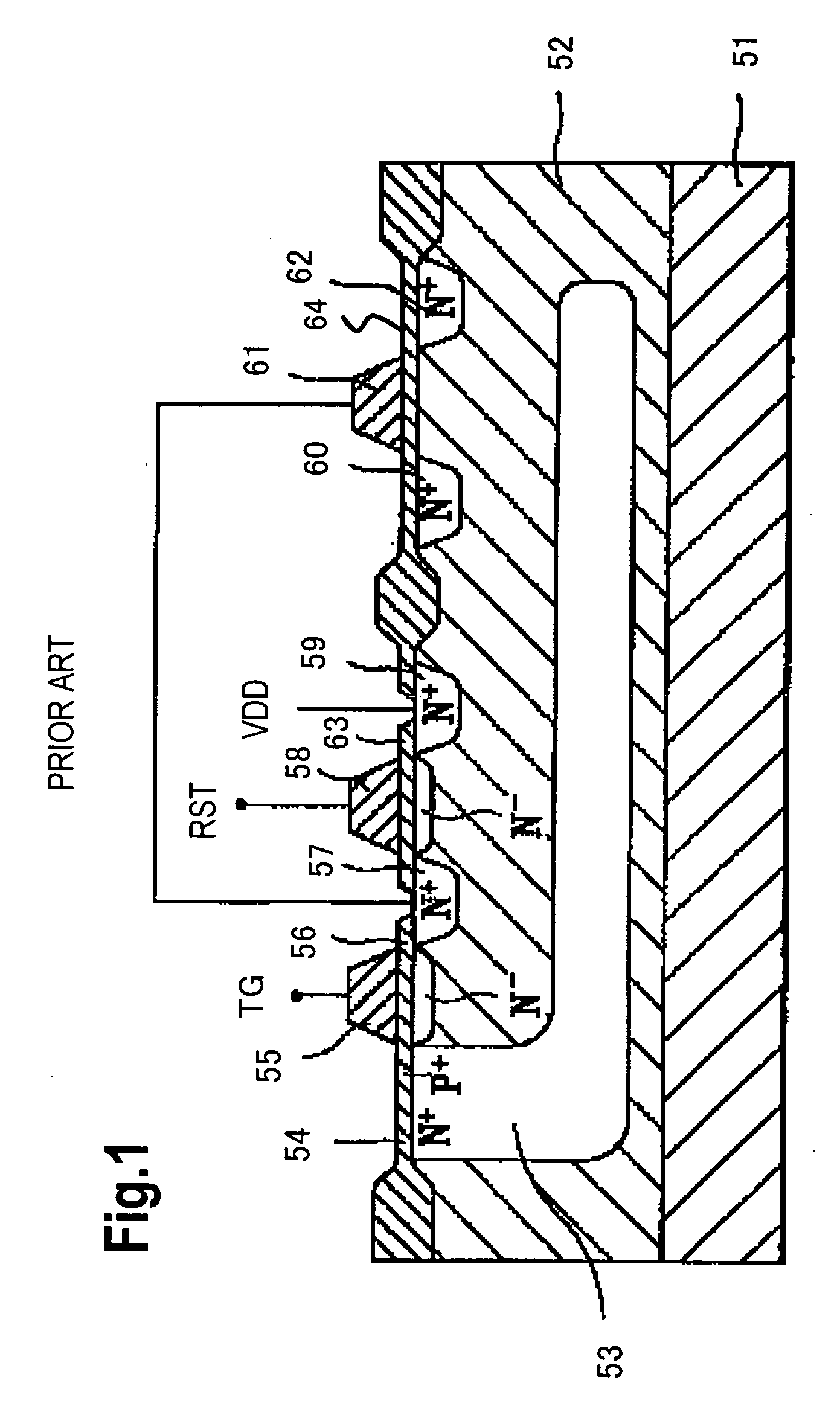

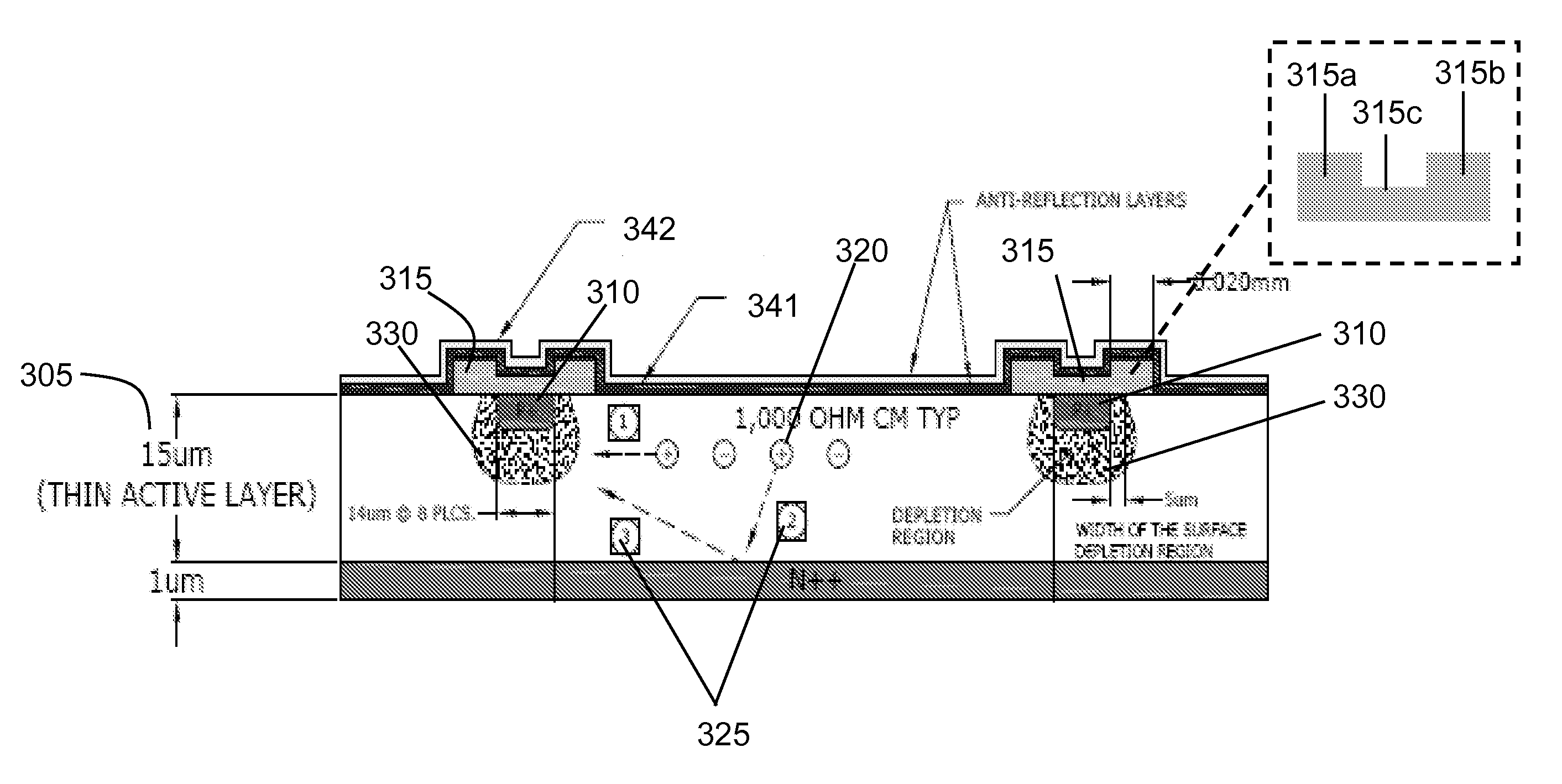

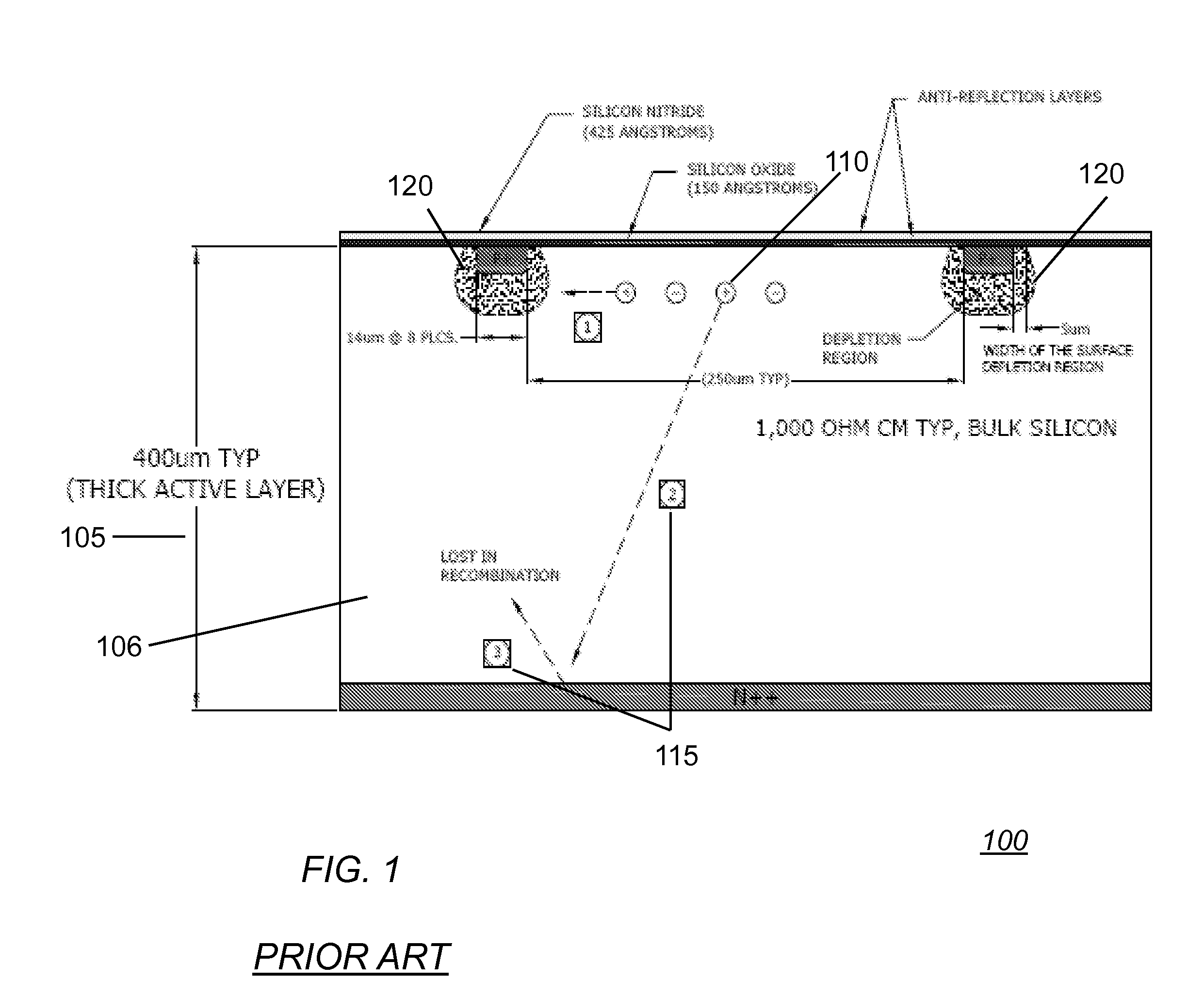

Thin active layer fishbone photodiode and method of manufacturing the same

ActiveUS20080277753A1Improves Structural IntegrityReduce junctionSolid-state devicesSemiconductor/solid-state device manufacturingDetector arrayRadiation damage

The present invention is directed toward a detector structure, detector arrays, and a method of detecting incident radiation. The present invention comprises a photodiode array and method of manufacturing a photodiode array that provides for reduced radiation damage susceptibility, decreased affects of crosstalk, reduced dark current (current leakage) and increased flexibility in application.

Owner:OSI OPTOELECTRONICS

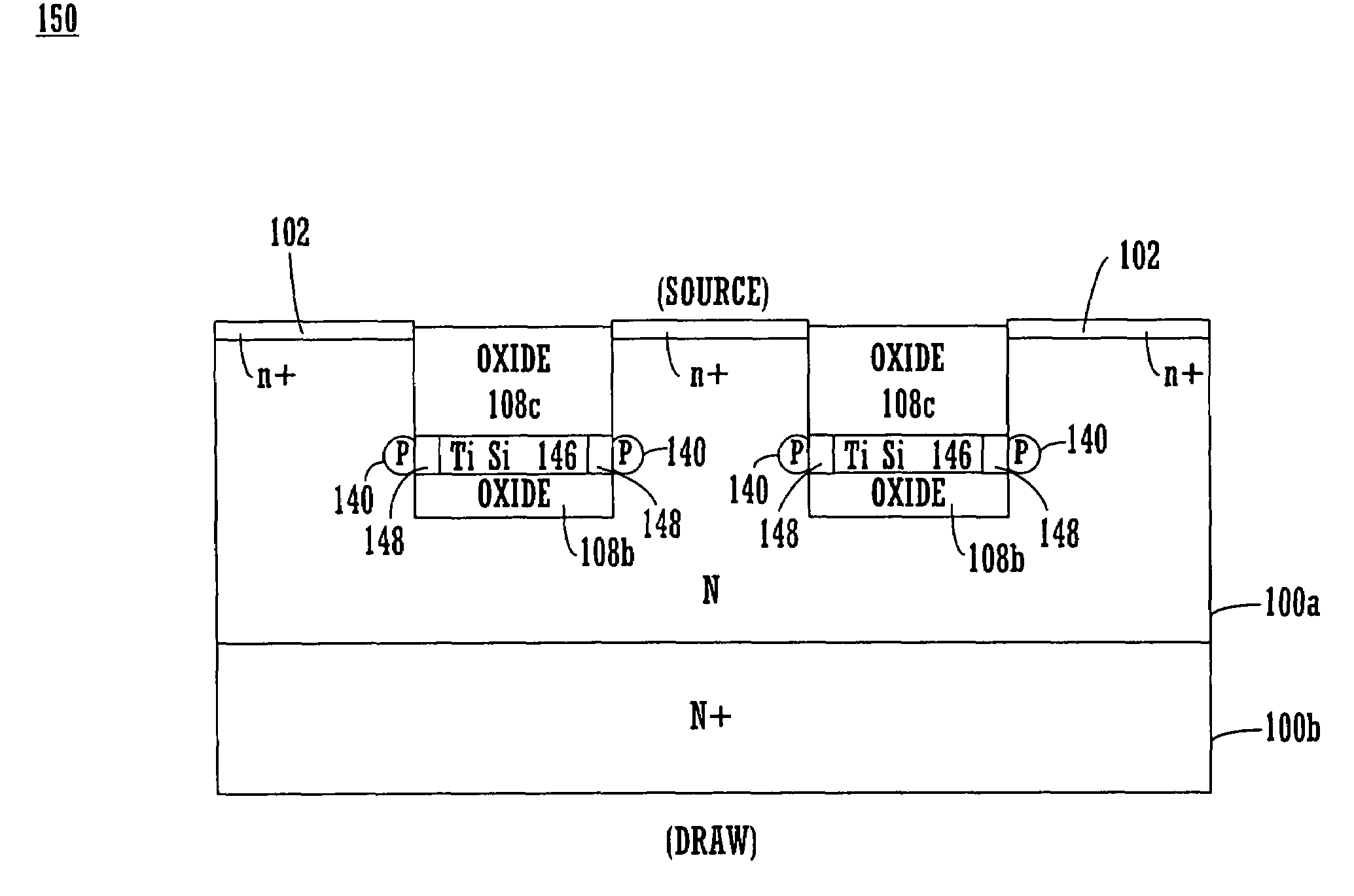

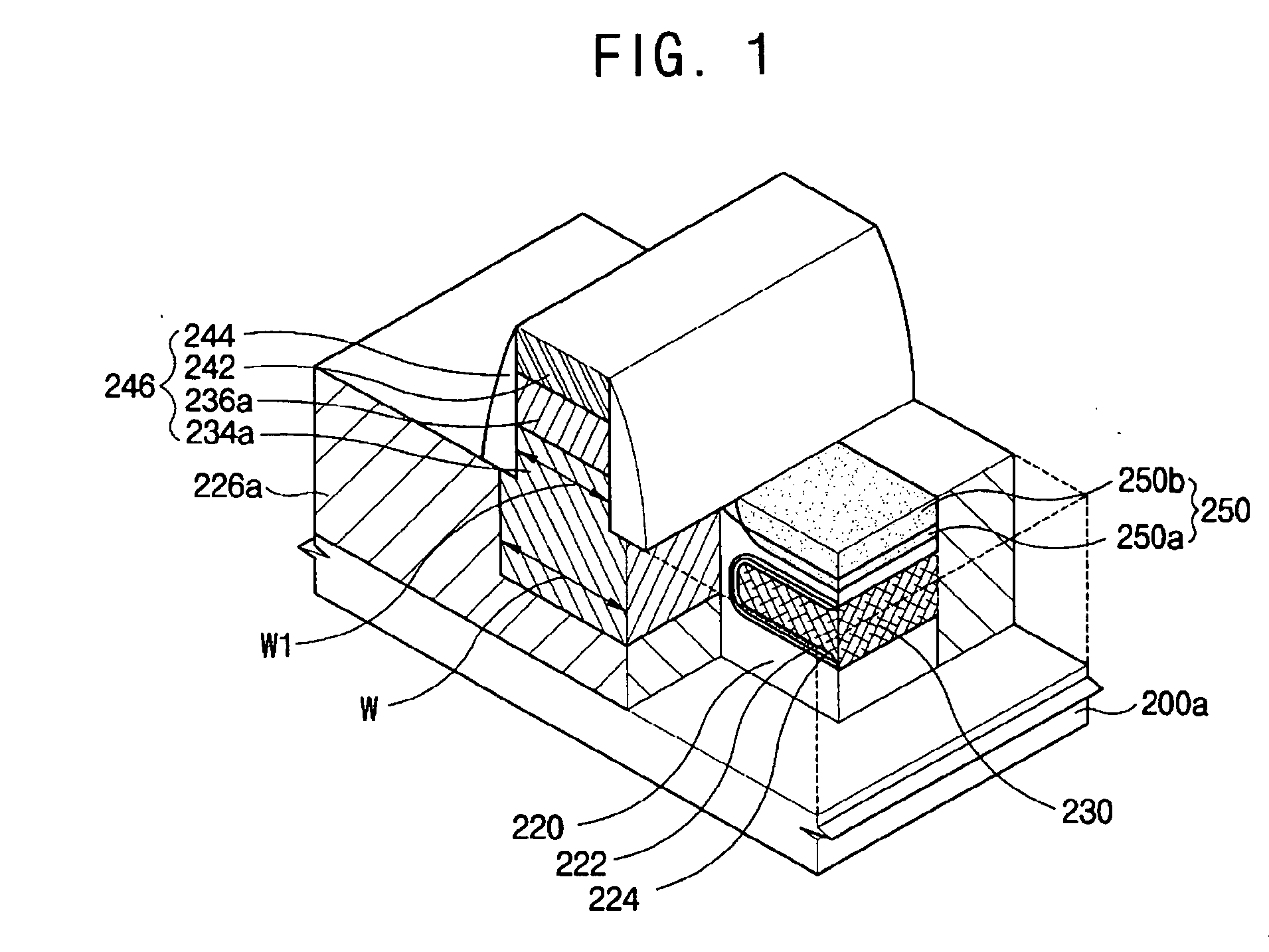

JFET and MESFET structures for low voltage high current and high frequency applications

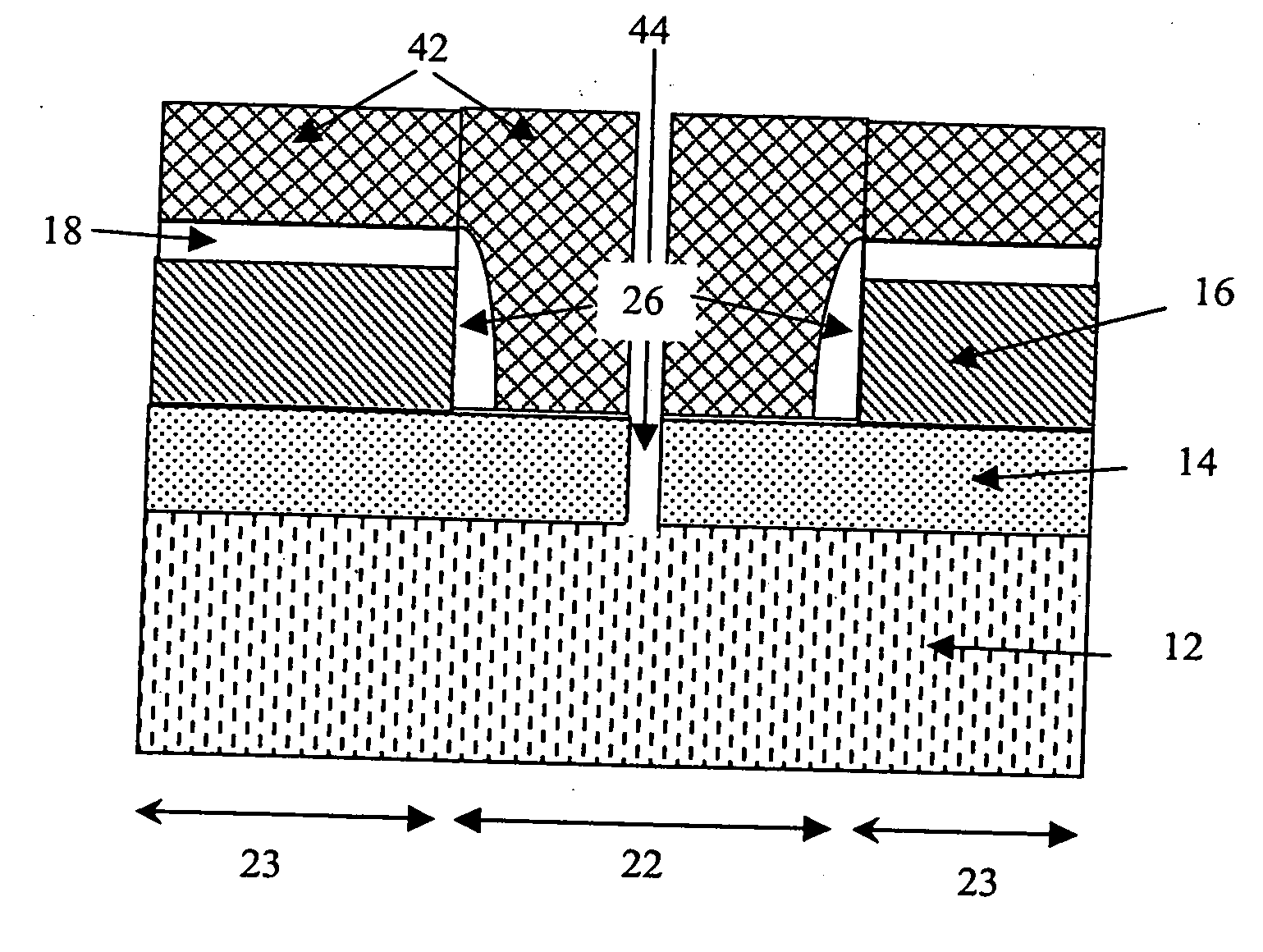

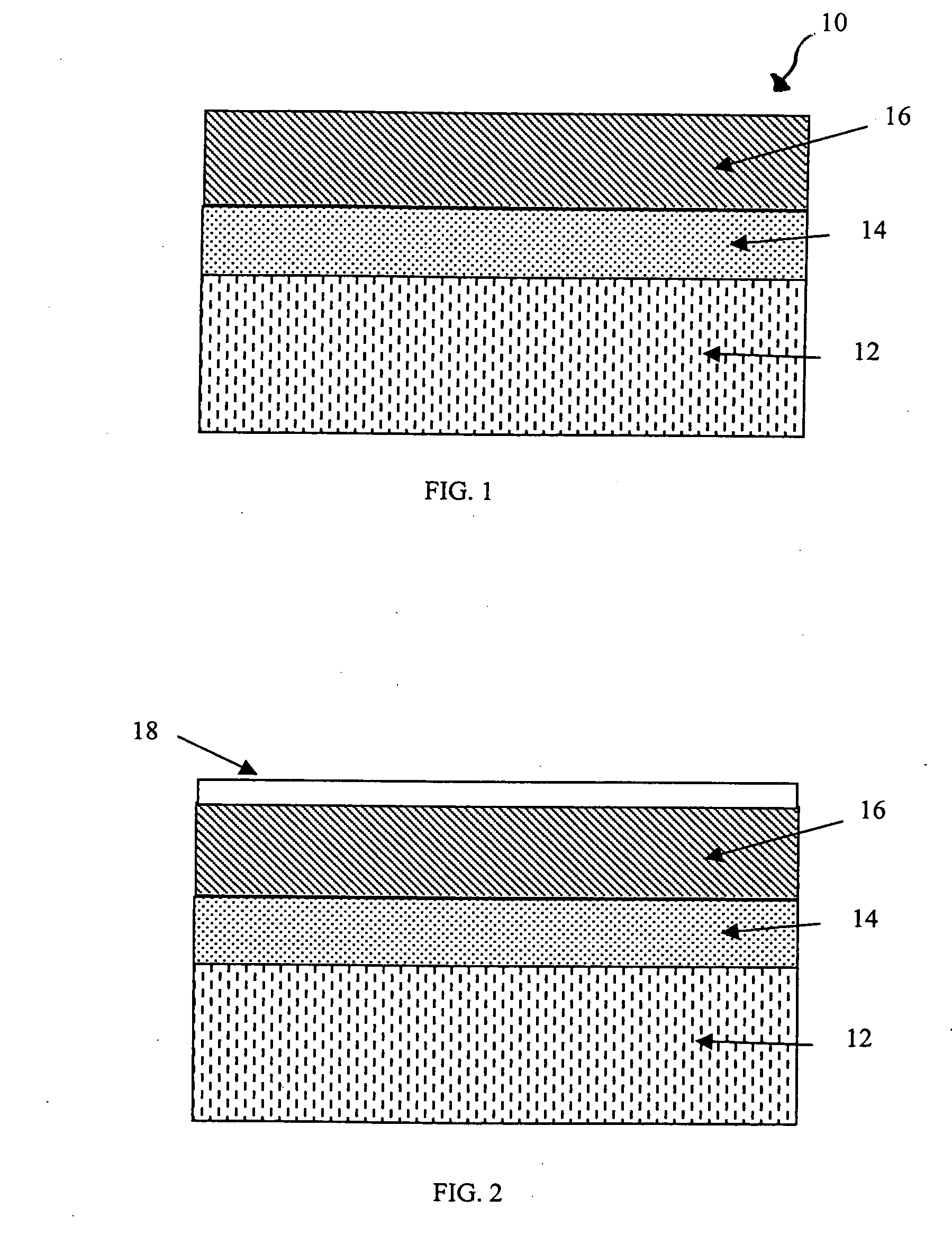

InactiveUS7045397B1Easy to controlLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

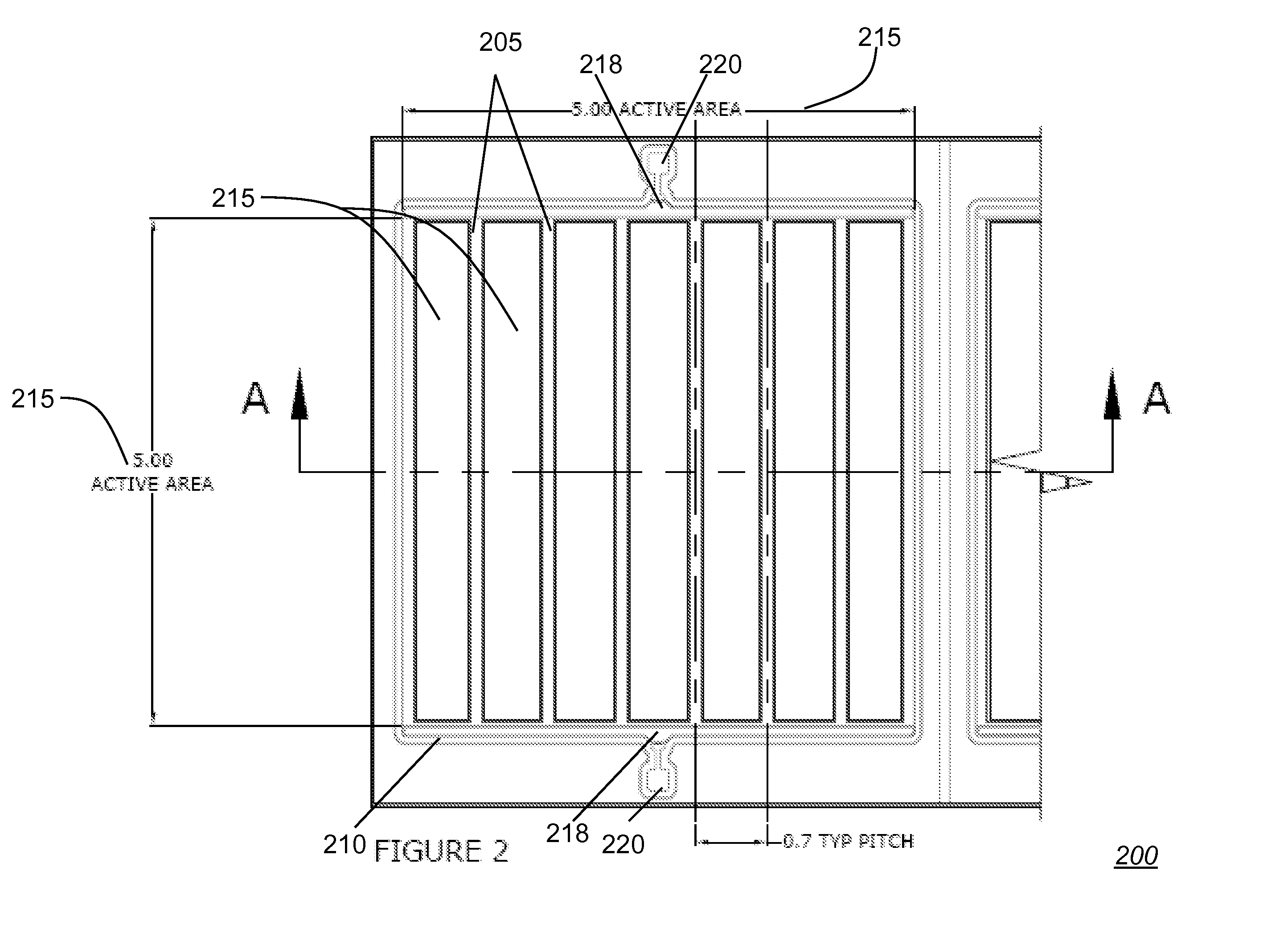

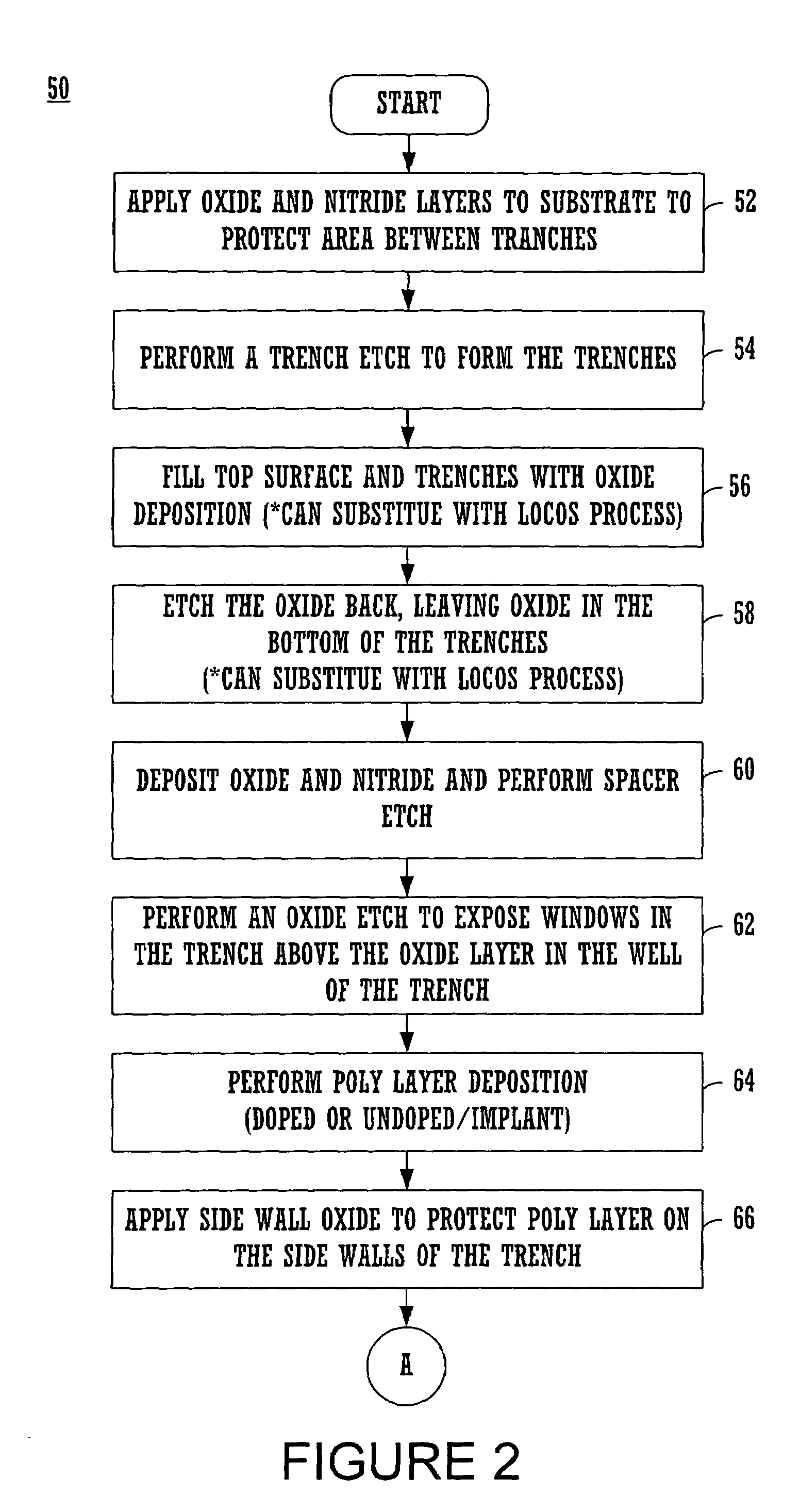

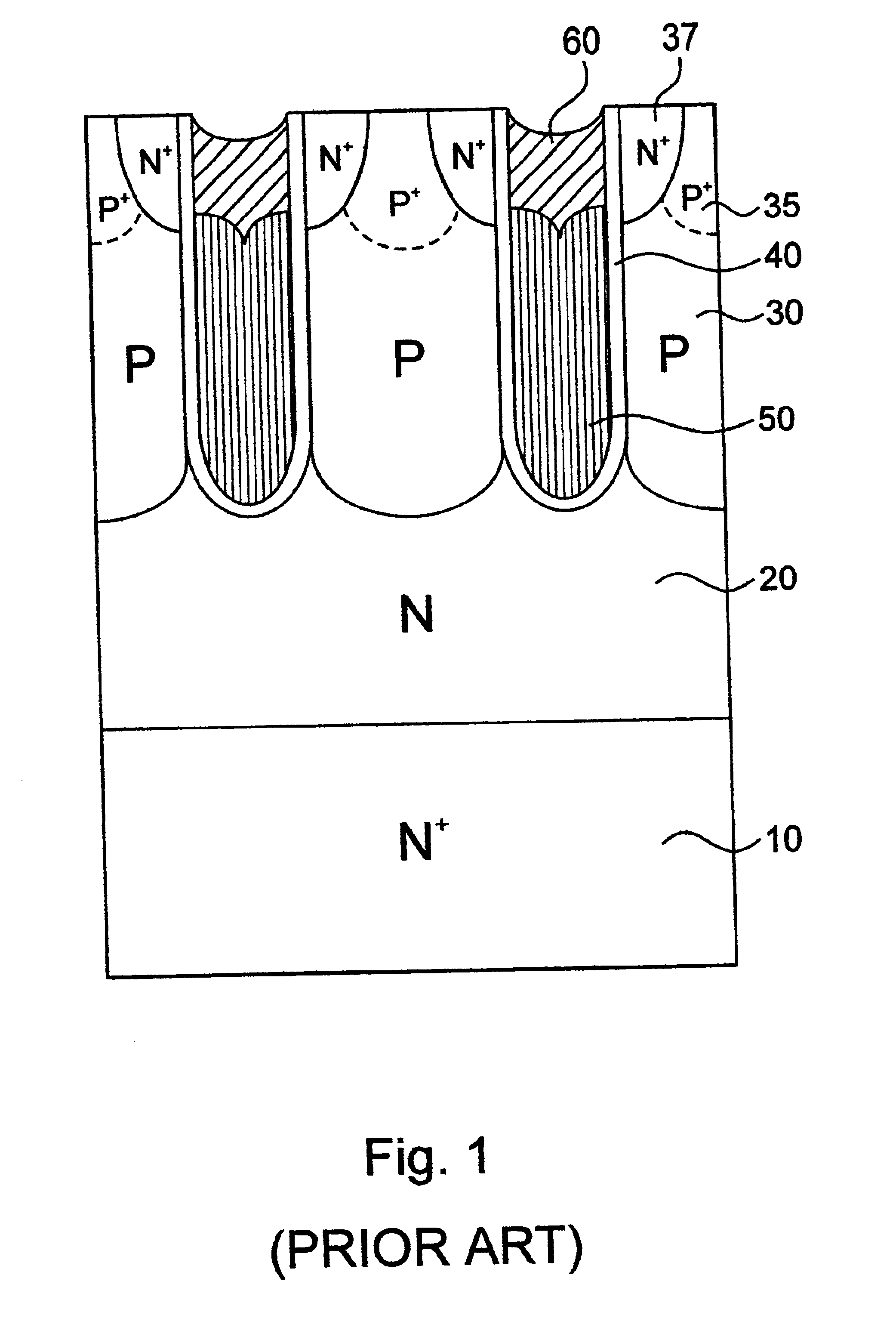

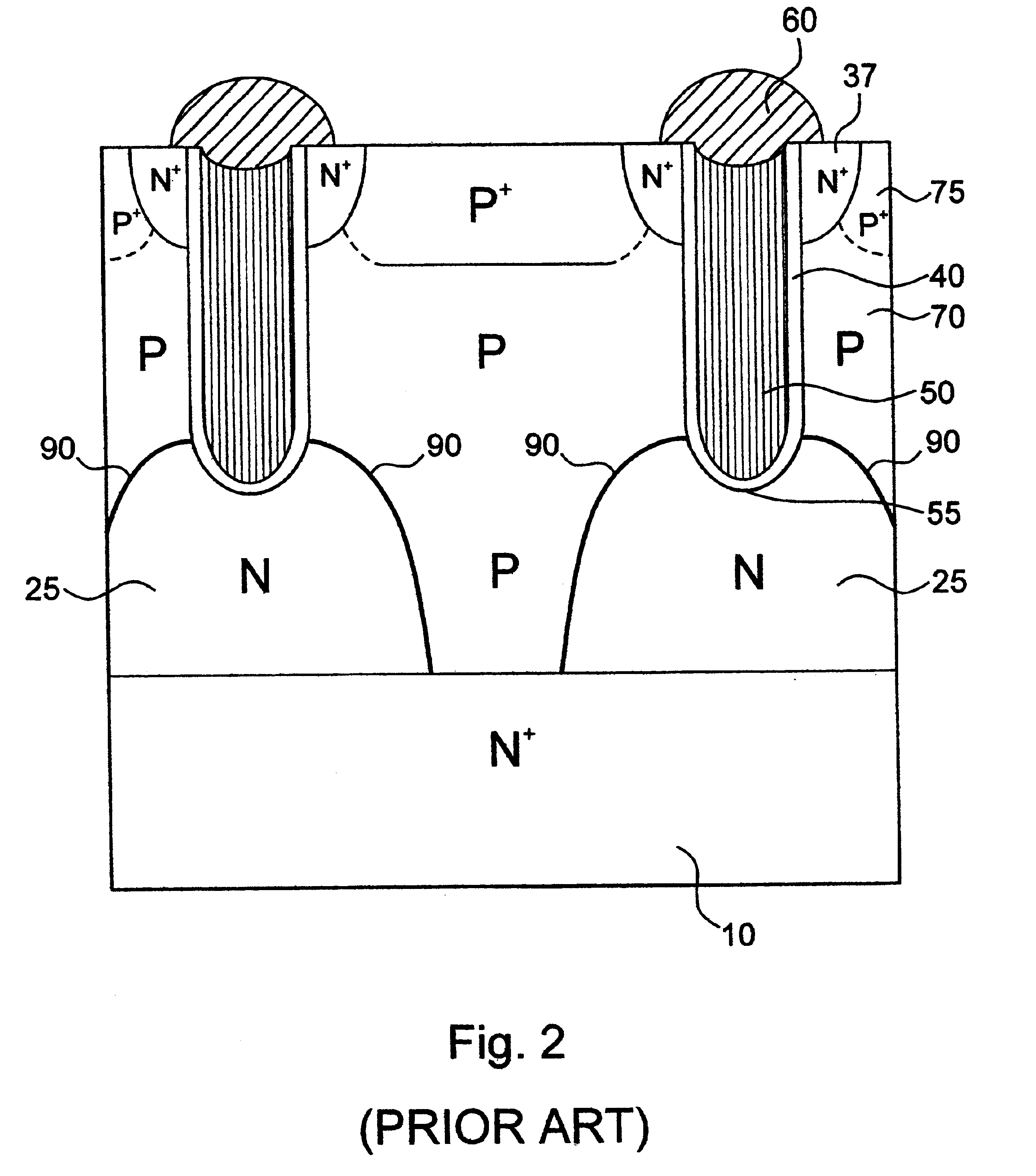

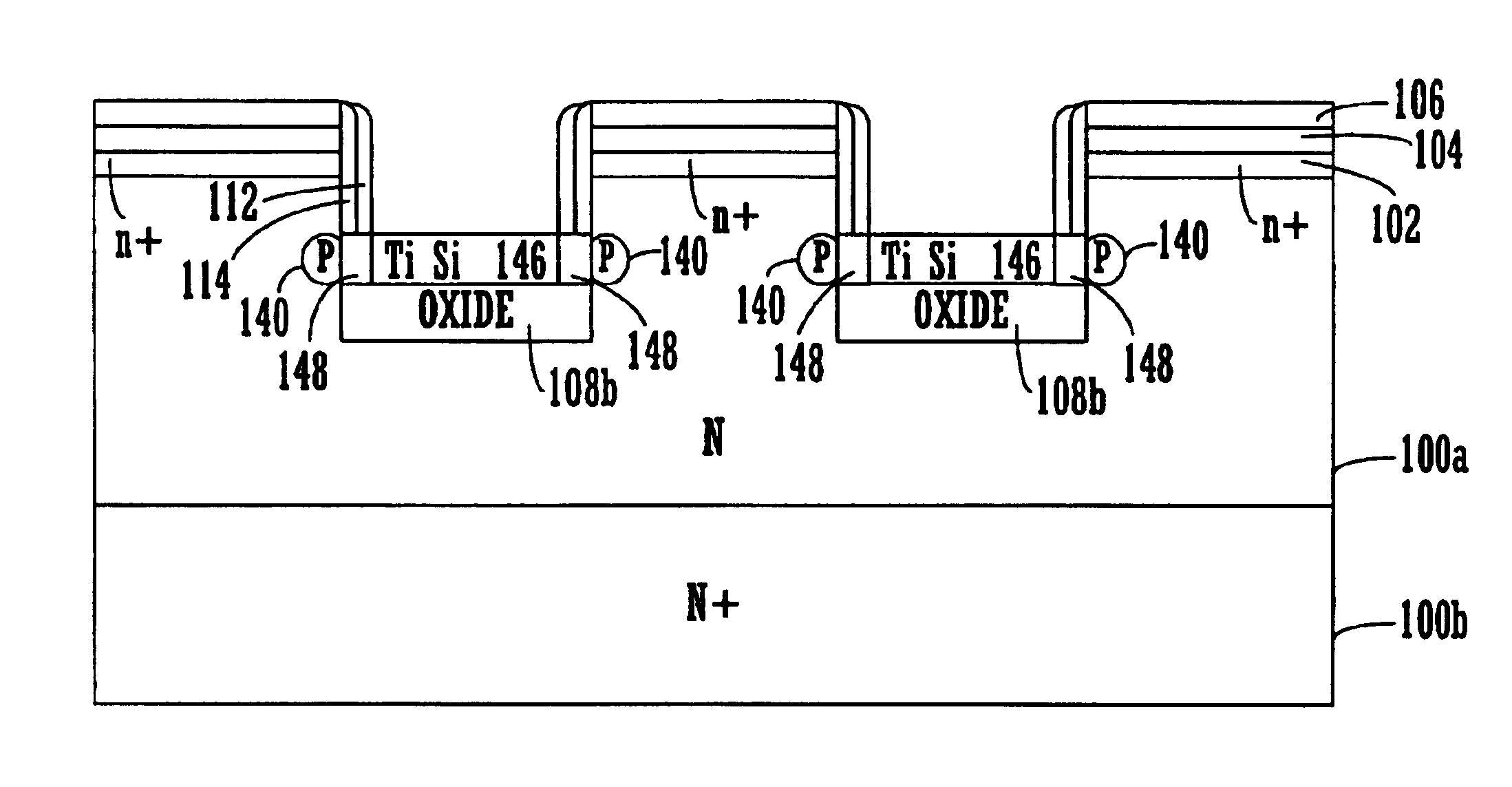

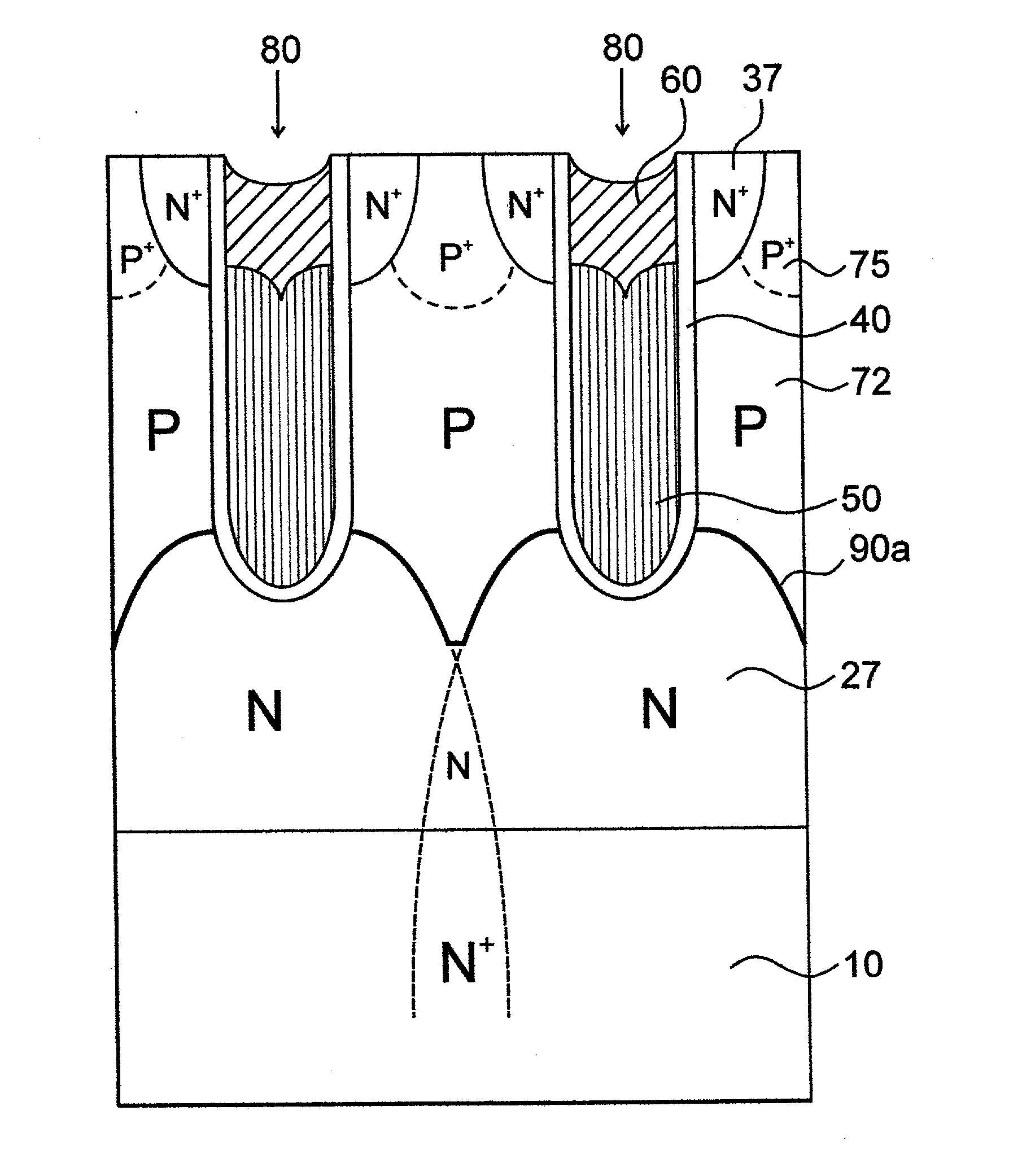

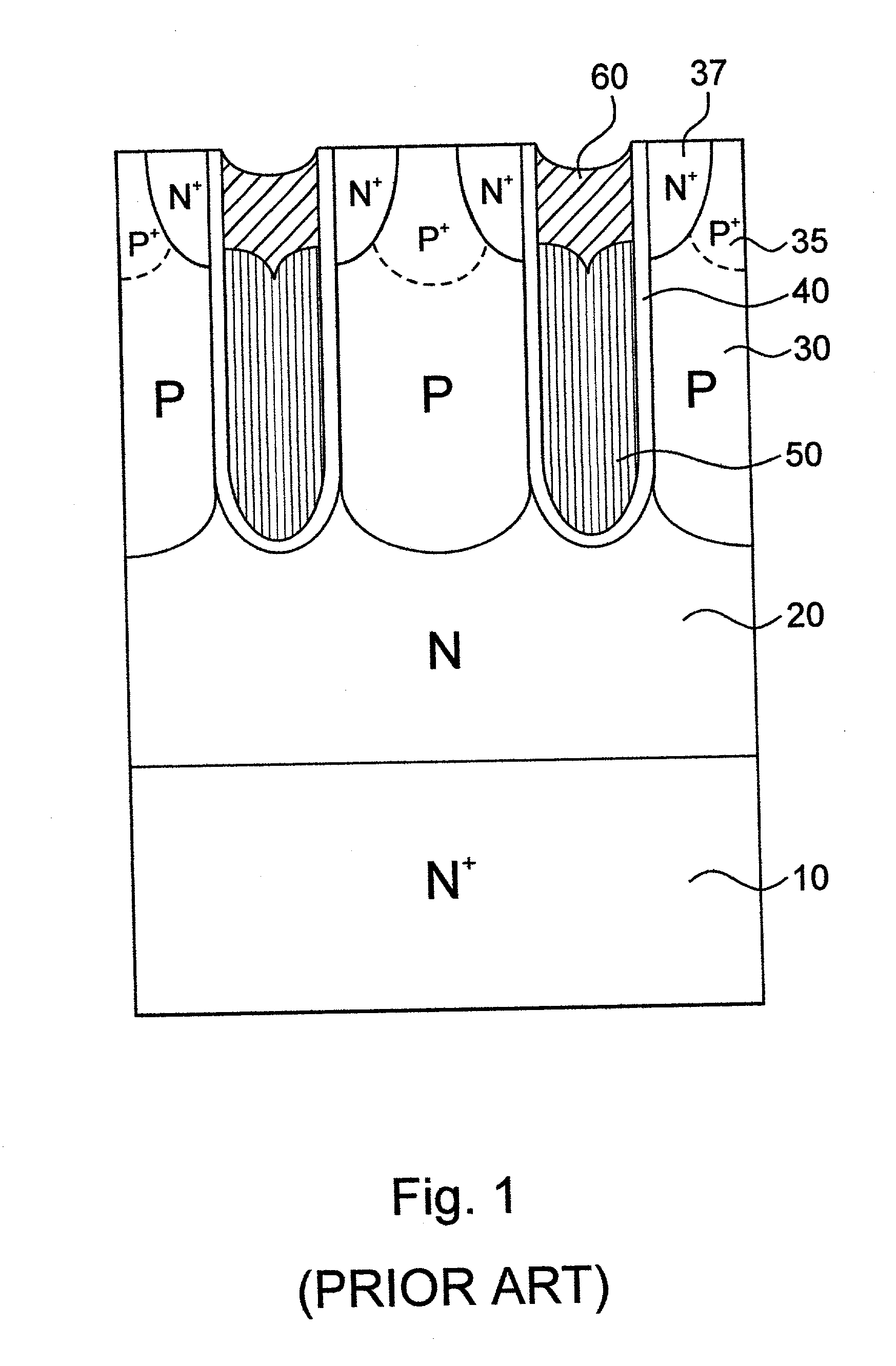

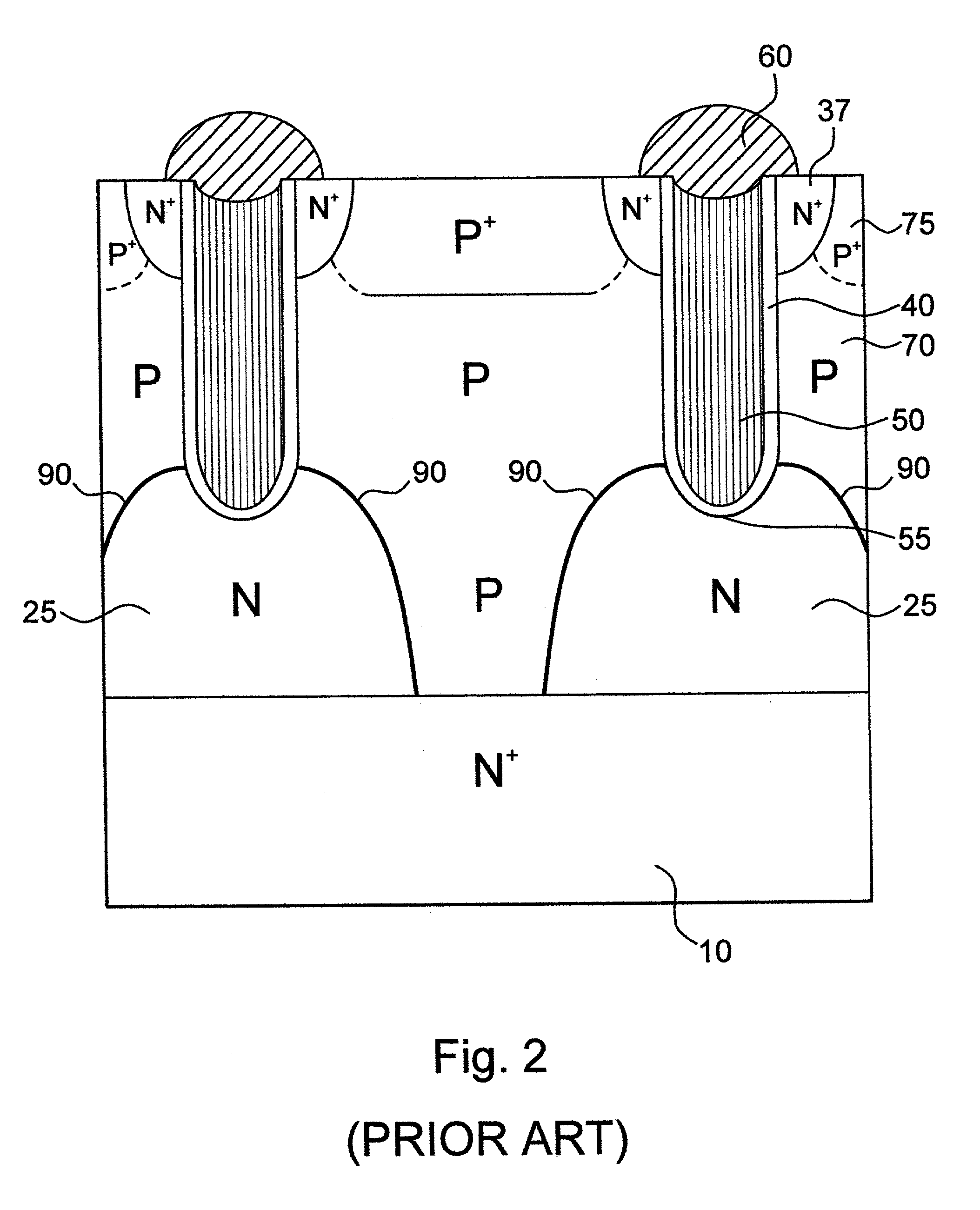

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS6784505B2Increase reverse voltageLow densityTransistorSolid-state devicesDopantChannel density

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

Image sensor with embedded photodiode region and fabrication method thereof

ActiveUS7417273B2Raise the ratioHigh light sensitivityTelevision system detailsSolid-state devicesEngineeringFloating diffusion

Owner:SOCIONEXT INC

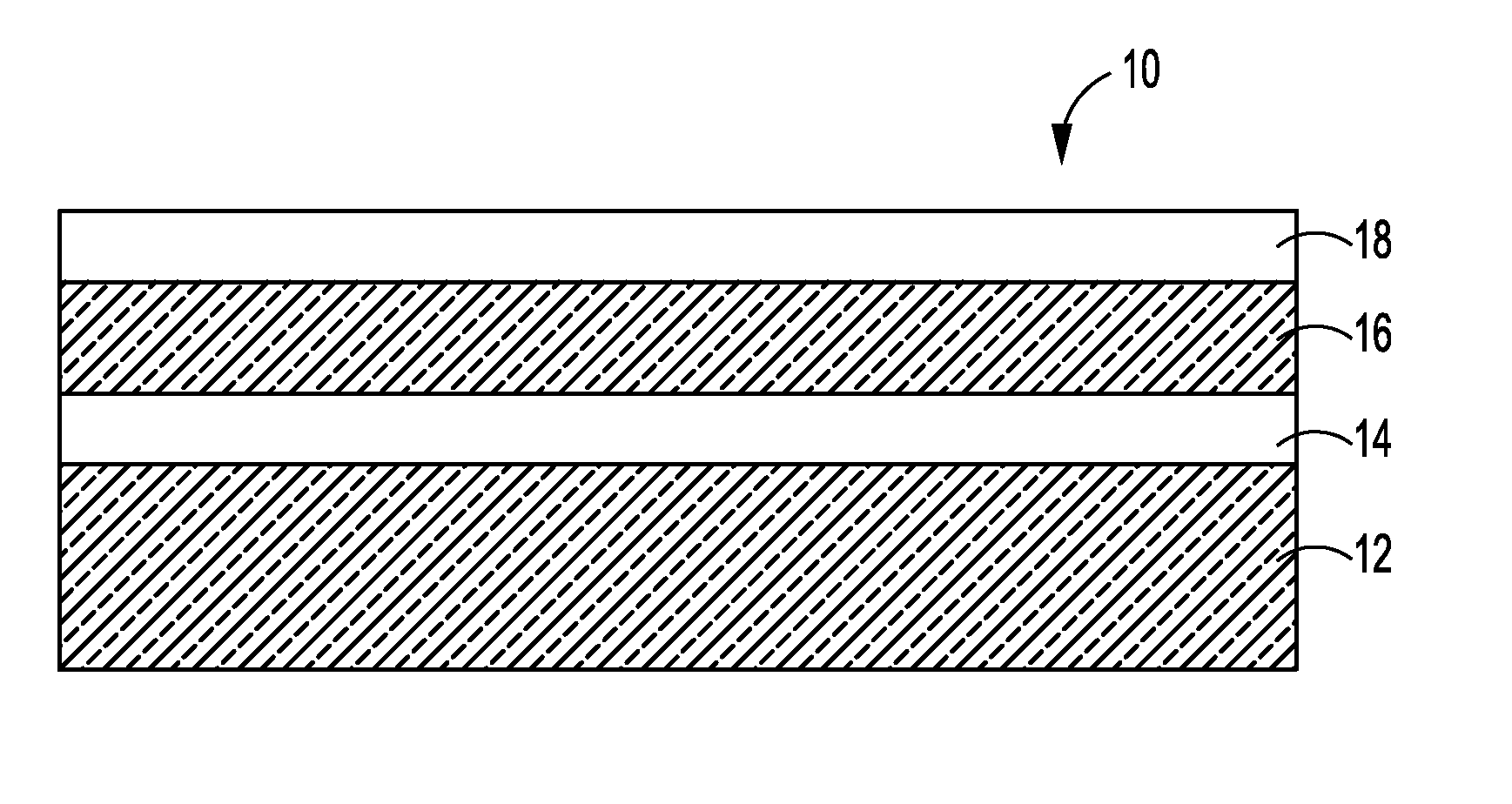

Structure and method of fabricating a hybrid substrate for high-performance hybrid-orientation silicon-on-insulator CMOS devices

InactiveUS20060194421A1Improve performanceLower junction capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCMOSDevice material

The present invention provides a method of integrating semiconductor devices such that different types of devices are formed upon a specific crystal orientation of a hybrid substrate that enhances the performance of each type of device. Specifically, the present invention provides a method of integrating semiconductor devices such that pFETs are located on a (110) crystallographic plane, while nFETs are located on a (100) crystallographic plane of a planar hybrid substrate. The method of the present invention also improves the performance of creating SOI-like devices with a combination of a buried insulator and counter-doping layers. The present invention also relates to semiconductor structures that are formed utilizing the method of the present invention.

Owner:GLOBALFOUNDRIES INC

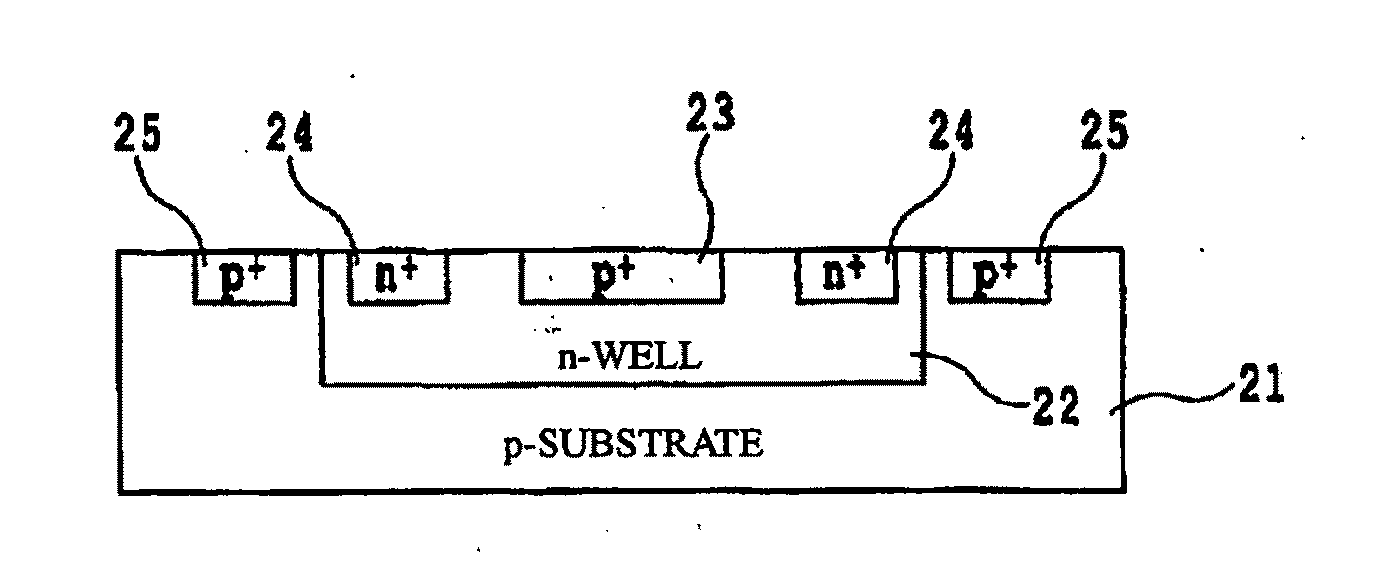

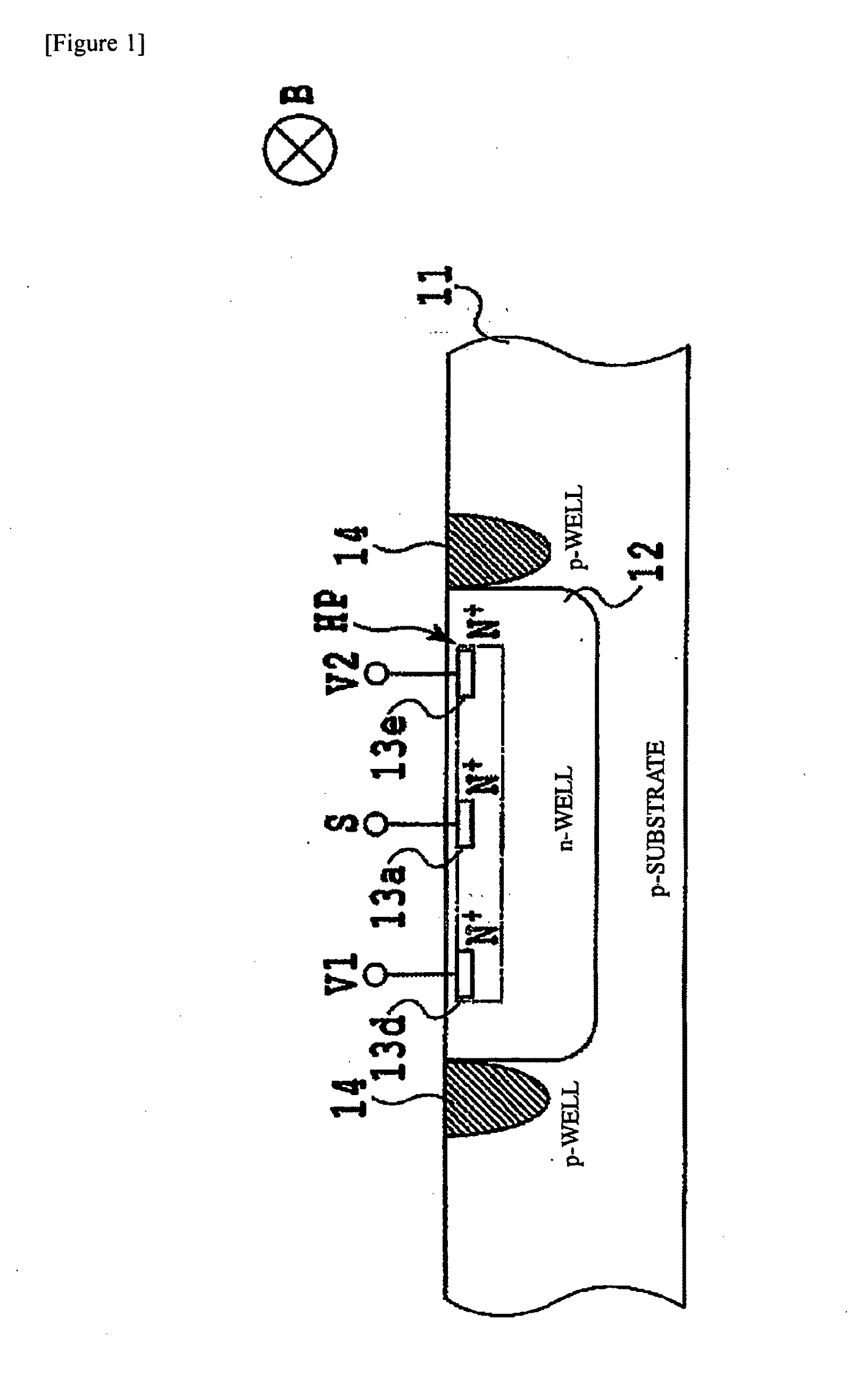

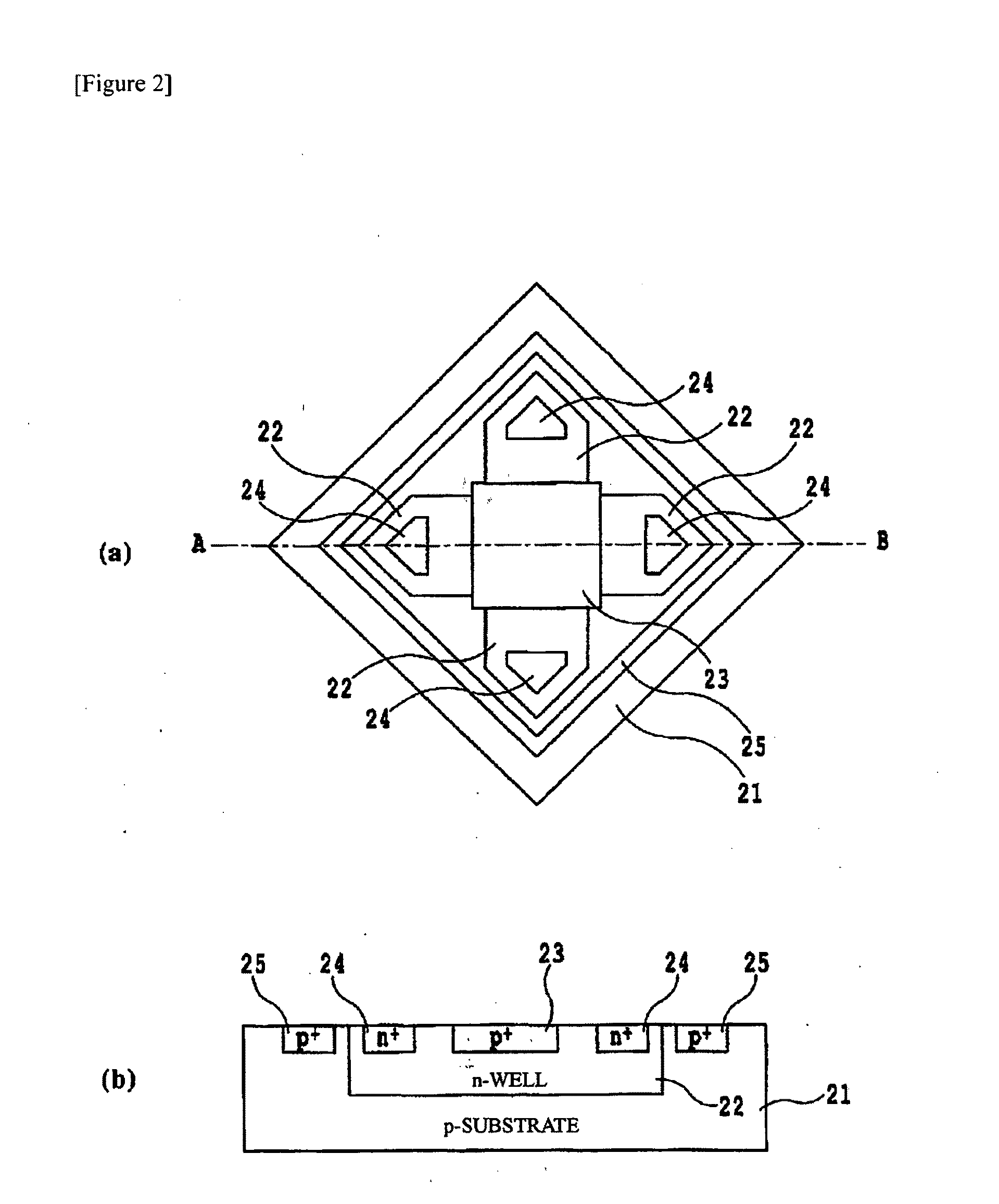

Hall Element and Magnetic Sensor

ActiveUS20100164483A1High sensitivityImprovement in S/N ratio per currentSolid-state devicesMagnetic field measurement using galvano-magnetic devicesHall elementOptoelectronics

A Hall element is provided which has a high sensitivity and contributes to an improvement in S / N ratio per current by using a low-concentration n-well within a suitable range. The Hall element includes a p-type semiconductor substrate layer 21 of p-type silicon, and an n-type impurity region 22 located in a surface of the p-type semiconductor substrate layer 21, the n-type impurity region 22 functioning as a magnetic sensing part 26. A p-type impurity region 23 is located in a surface of the n-type impurity region 22, and n-type regions 24 are located laterally of the p-type impurity region 23. A p-type substrate region 21a having a resistivity equal to that of the p-type semiconductor substrate layer 21 is located to extend around the n-type impurity region 22. An impurity concentration N in the n-type impurity region 22 functioning as the magnetic sensing part 26 is preferably from 1×1016 to 3×1016 (atoms / cm3), and a distribution depth D of the impurity concentration is preferably from 3.0 μm to 5.0 μm.

Owner:ASAHI KASEI ELECTRONICS CO LTD

Semiconductor device having a trench isolation and method of fabricating the same

InactiveUS6875663B2Prevent characteristic deteriorationInhibit deteriorationTransistorSolid-state devicesResistPeak value

The present invention provides a method of fabricating a semiconductor device in which deterioration in a transistor characteristic is prevented by preventing a channel stop implantation layer from being formed in an active region. A resist mask is formed so as to have an opening over a region in which a PMOS transistor is formed. Channel stop implantation is performed with energy by which ions pass through a partial isolation oxide film and a peak of an impurity profile is generated in an SOI layer, thereby forming a channel stop layer in the SOI layer under the partial isolation oxide film, that is, an isolation region. An impurity to be implanted here is an N-type impurity. In the case of using phosphorus, its implantation energy is set to, for example, 60 to 120 keV, and the density of the channel stop layer is set to 1×1017 to 1×1019 / cm3. At this time, the impurity of channel stop implantation is not stopped in the SOI layer corresponding to the active region.

Owner:RENESAS ELECTRONICS CORP

Transistor and method of forming the same

ActiveUS20050194616A1Improve breakdown voltageEffective channel length can be sufficientlySemiconductor/solid-state device manufacturingSemiconductor devicesBreakdown voltageShort-channel effect

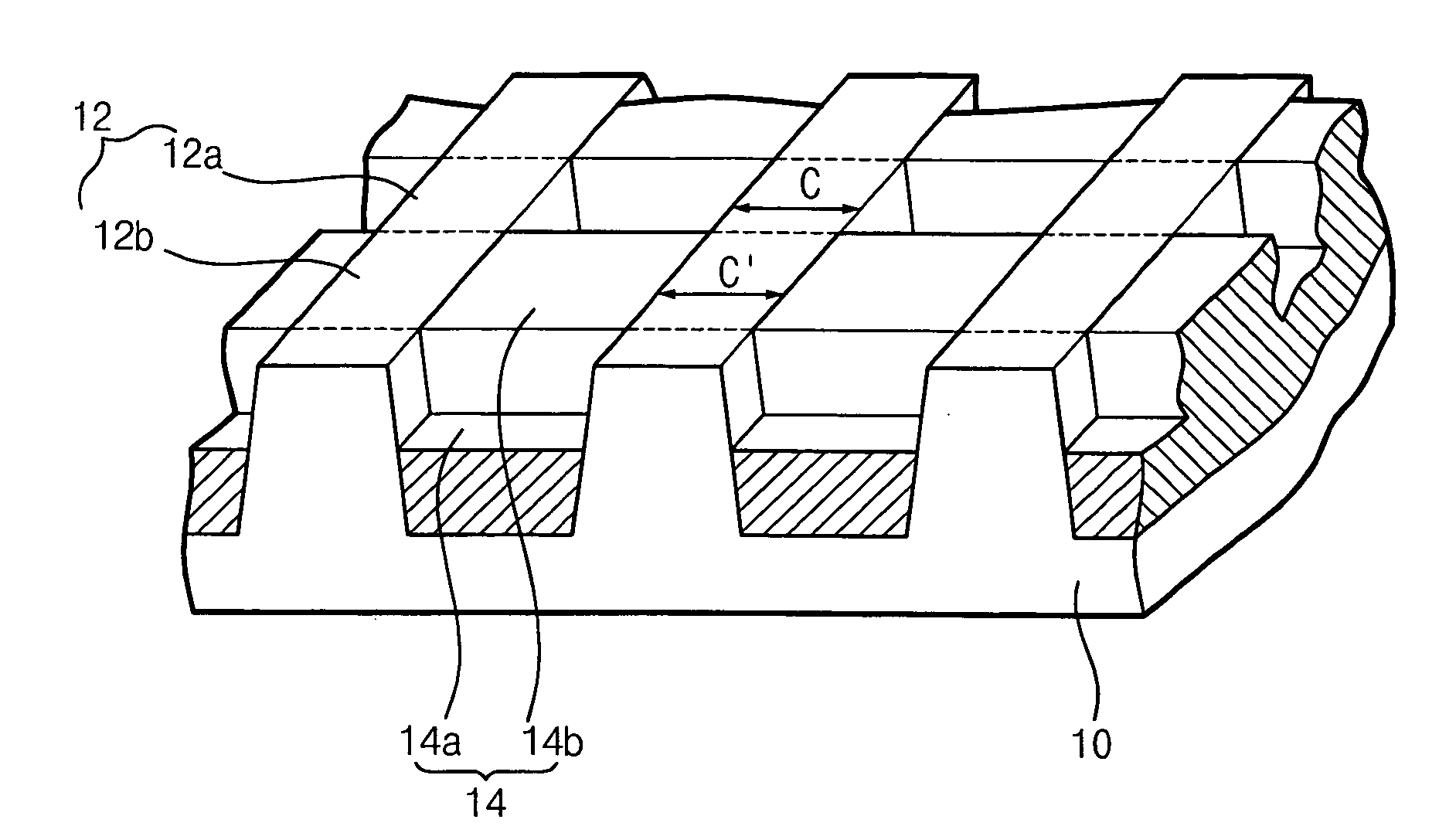

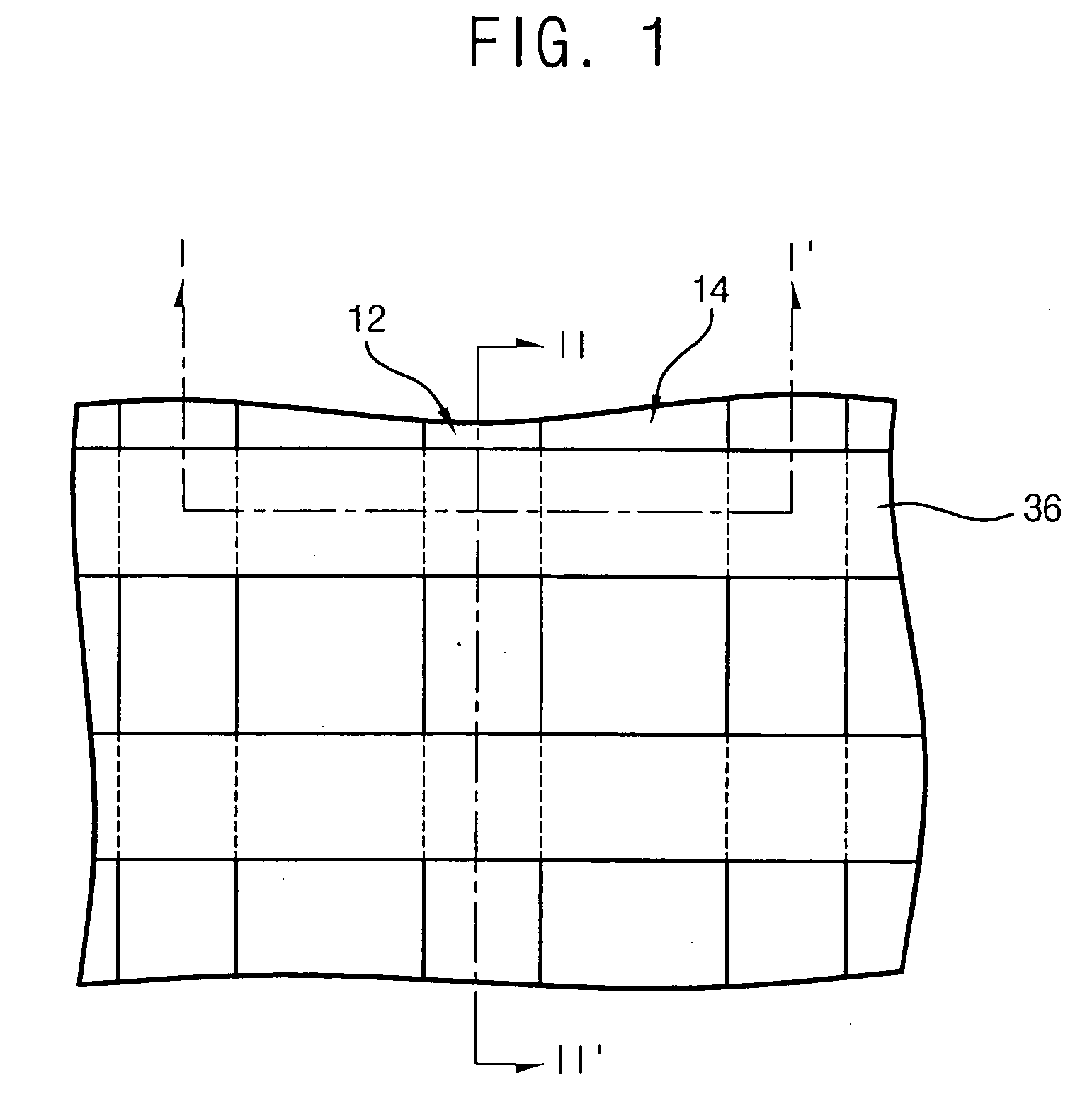

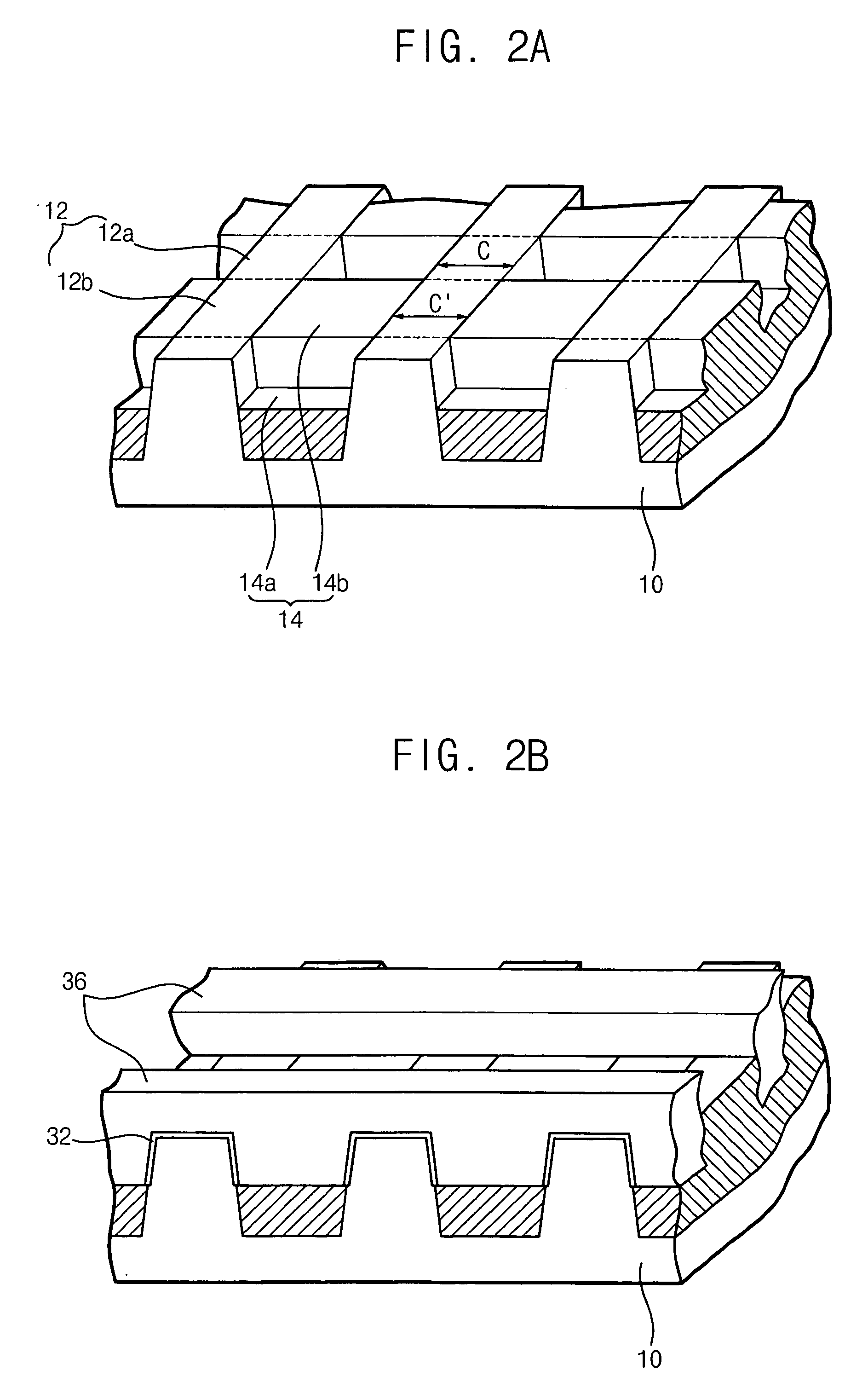

According to some embodiments of the invention, a fin type transistor includes an active structure integrally formed with a silicon substrate. The active structure includes grooves that form blocking regions under source / drain regions. A gate structure is formed to cross the upper face of the active structure and to cover the exposed side surfaces of the lateral portions of the active structure. An effective channel length of a fin type transistor may be sufficiently ensured so that a short channel effect of the transistor may be prevented and the fin type transistor may have a high breakdown voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

JFET and MESFET structures for low voltage, high current and high frequency applications

InactiveUS6921932B1Easy to controlLower junction capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

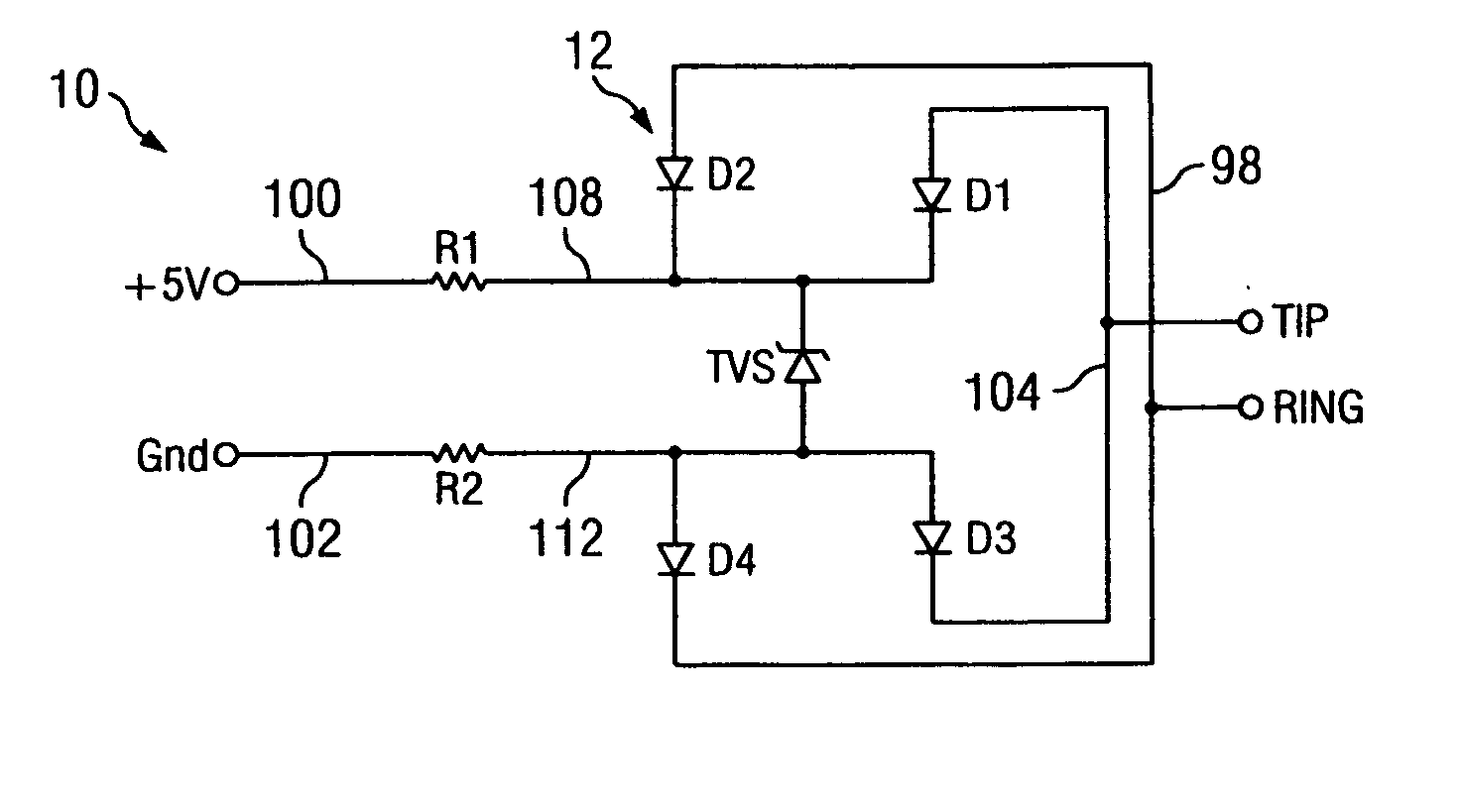

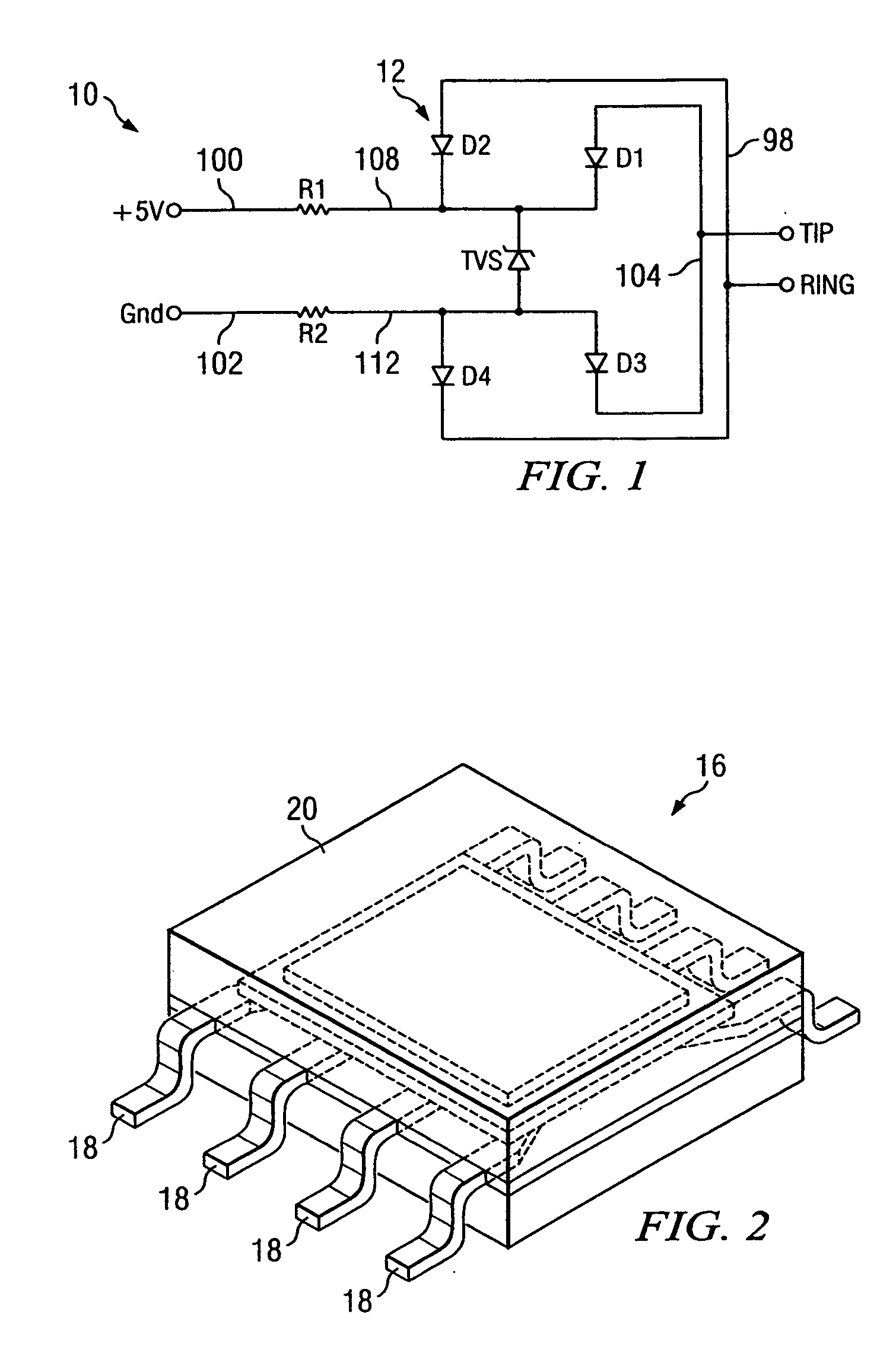

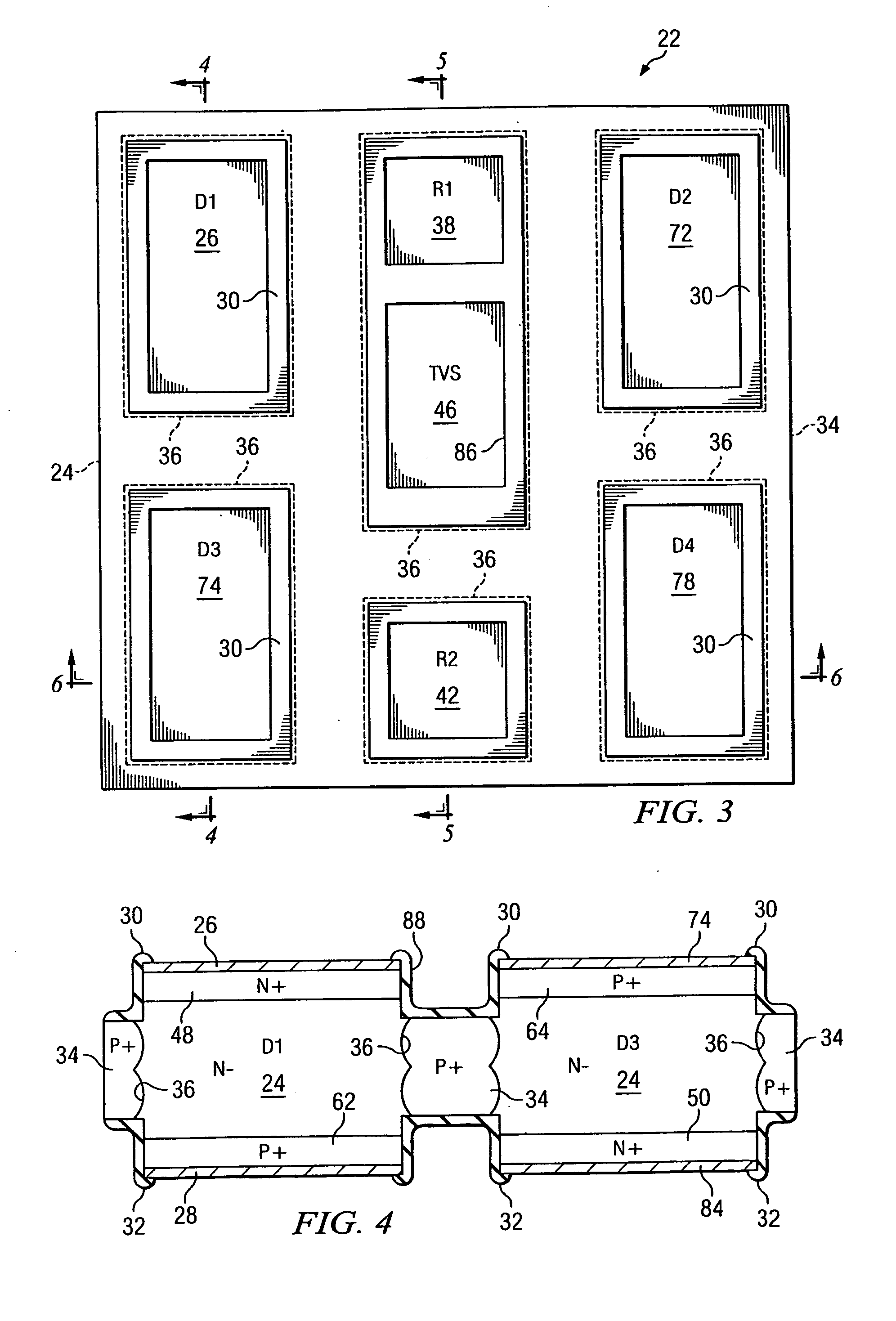

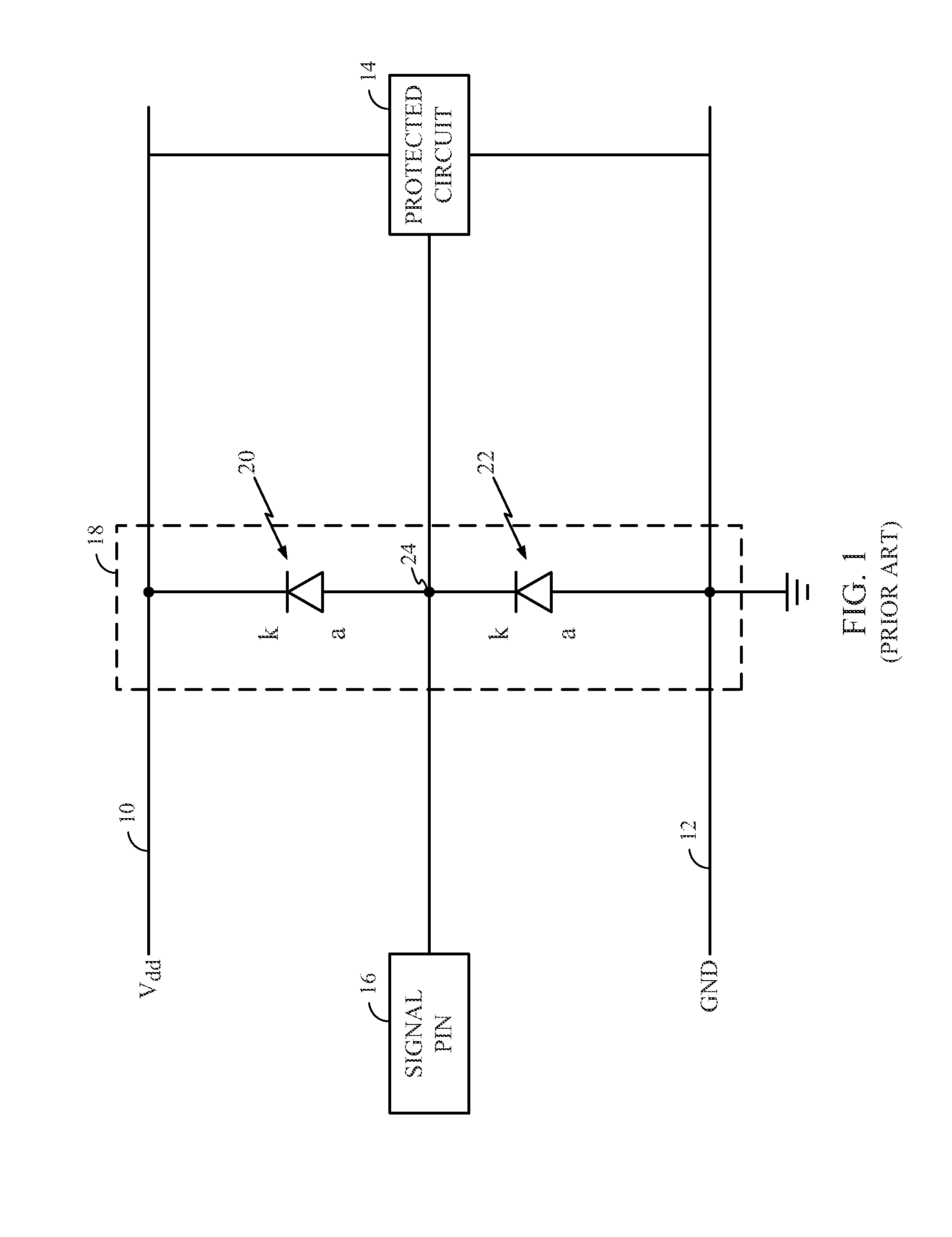

Integrated circuit providing overvoltage protection for low voltage lines

ActiveUS20070086129A1Lower junction capacitanceSafe to carrySemiconductor/solid-state device detailsSolid-state devicesOvervoltageCapacitance

An overvoltage protection circuit for protecting low voltage, high speed digital communication lines. The circuit is integrated into a semiconductor chip and includes a diode bridge, a transient voltage suppressor (TVS) device and resistors through which a bias voltage can be applied to the TVS device to reduce the capacitance hereof.

Owner:LITTELFUSE INC

Structure and method of fabricating a hybrid substrate for high-performance hybrid-orientation silicon-on-insulator CMOS devices

InactiveUS7268377B2Improve performanceLower junction capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor structure

The present invention provides a method of integrating semiconductor devices such that different types of devices are formed upon a specific crystal orientation of a hybrid substrate that enhances the performance of each type of device. Specifically, the present invention provides a method of integrating semiconductor devices such that pFETs are located on a (110) crystallographic plane, while nFETs are located on a (100) crystallographic plane of a planar hybrid substrate. The method of the present invention also improves the performance of creating SOI-like devices with a combination of a buried insulator and counter-doping layers. The present invention also relates to semiconductor structures that are formed utilizing the method of the present invention.

Owner:GLOBALFOUNDRIES INC

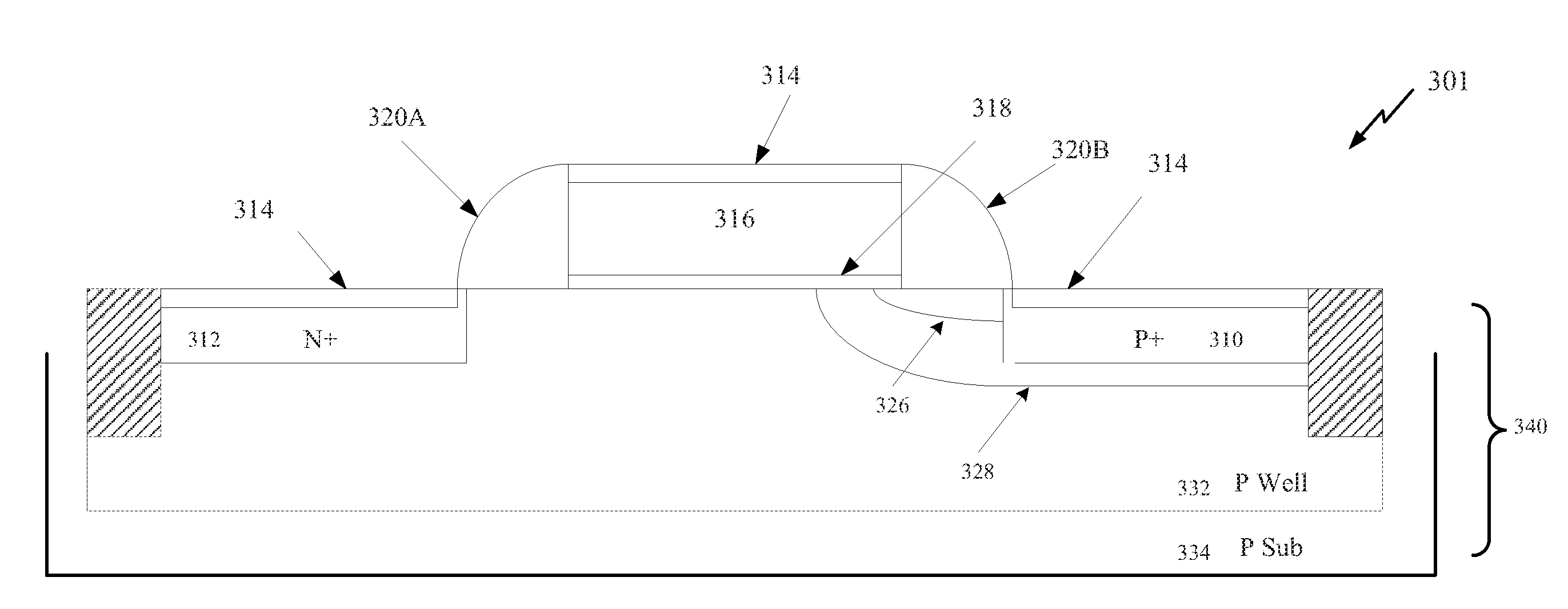

Diode Having A Pocket Implant Blocked And Circuits And Methods Employing Same

ActiveUS20120074496A1Reducing area junction capacitanceLower junction capacitanceLiquid surface applicatorsSemiconductor/solid-state device detailsCapacitanceEngineering

Diodes, including gated diodes and shallow trench isolation (STI) diodes, manufacturing methods, and related circuits are provided without at least one halo or pocket implant thereby reducing capacitance of the diode. In this manner, the diode may be used in circuits and other devices having performance sensitive to load capacitance while still obtaining the performance characteristics of the diode. Such characteristics for a gated diode include fast turn-on times and high conductance, making the gated diodes well-suited for electro-static discharge (ESD) protection circuits as one example. Diodes include a semiconductor substrate having a well region and insulating layer thereupon. A gate electrode is formed over the insulating layer. Anode and cathode regions are provided in the well region. A P-N junction is formed. At least one pocket implant is blocked in the diode to reduce capacitance.

Owner:QUALCOMM INC

Hybrid orientation CMOS with partial insulation process

InactiveUS7439542B2Improve performanceImprove device performanceTransistorSolid-state devicesCapacitanceElectrical conductor

The present invention provides a method of integrated semiconductor devices such that different types of devices are formed upon a specific crystallographic orientation of a hybrid substrate. In accordance with the present invention, junction capacitance of one of the devices is improved in the present invention by forming the source / drain diffusion regions of the device in an epitiaxial semiconductor material such that they are situated on a buried insulating layer that extends partially underneath the body of the second semiconductor device. The second semiconductor device, together with the first semiconductor device, is both located atop the buried insulating layer. Unlike the first semiconductor device in which the body thereof is floating, the second semiconductor device is not floating. Rather, it is in contact with an underlying first semiconducting layer.

Owner:GLOBALFOUNDRIES INC

Semiconductor device and method of manufacturing the same

ActiveUS20050167754A1Reduce widthAdvantageously adjust widthTransistorSolid-state devicesMOSFETDevice material

A fin type MOSFET and a method of manufacturing the fin type MOSFET are disclosed. Gate structures in the fin type MOSFET are formed by a damascene process without a photolithography process. Impurities used to form a channel region are selectively implanted into portions of a semiconductor substrate adjacent to the gate structures.

Owner:SAMSUNG ELECTRONICS CO LTD

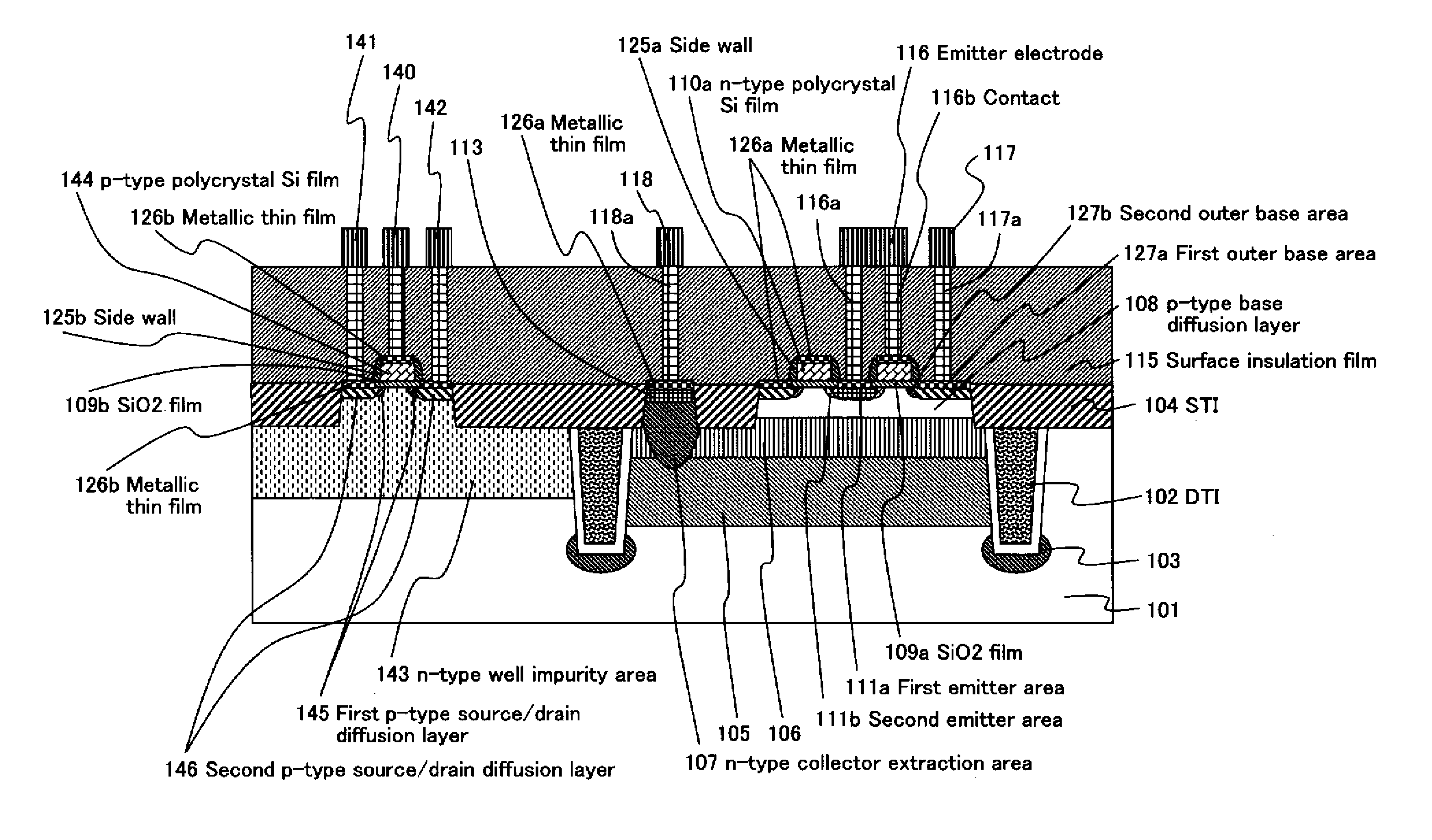

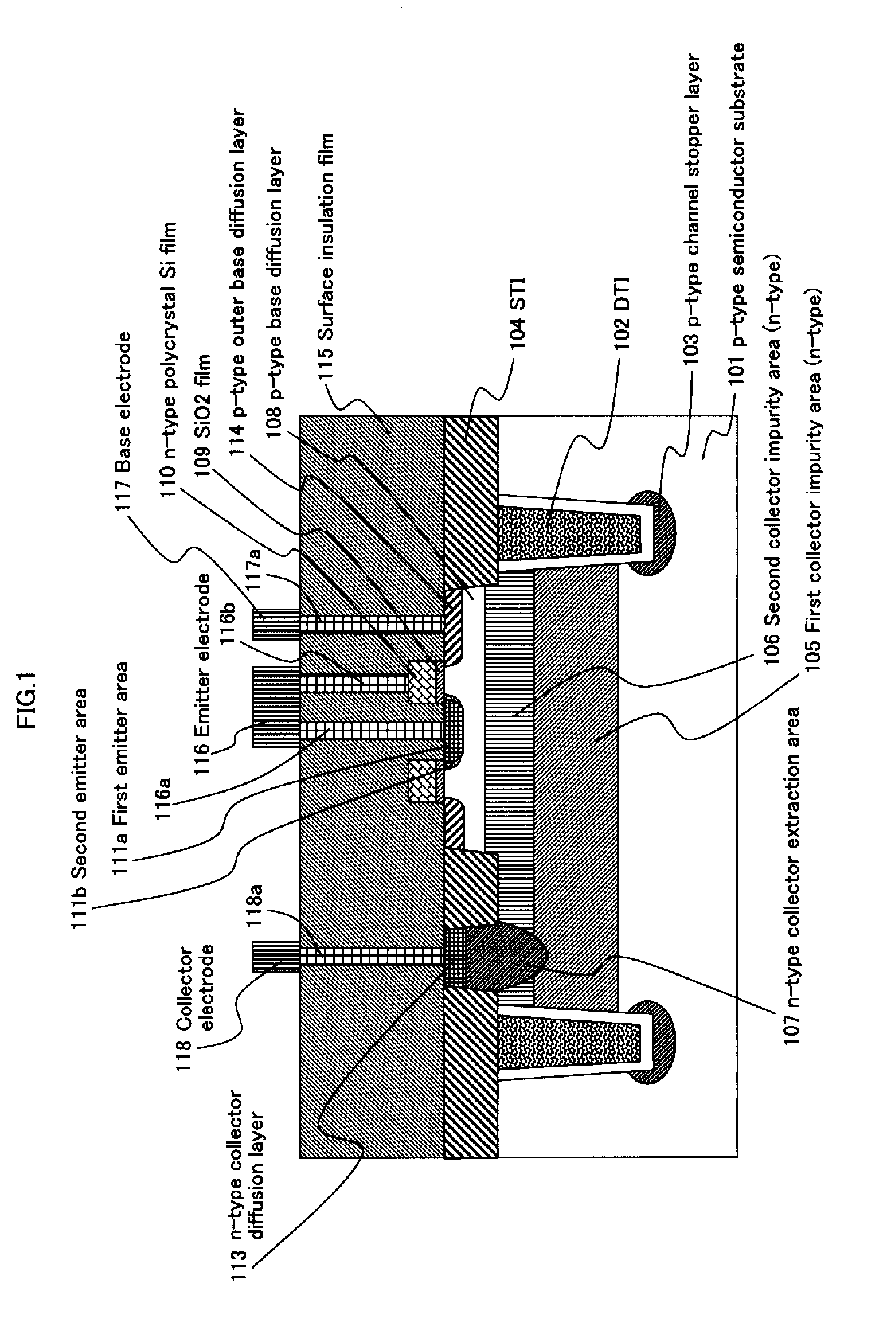

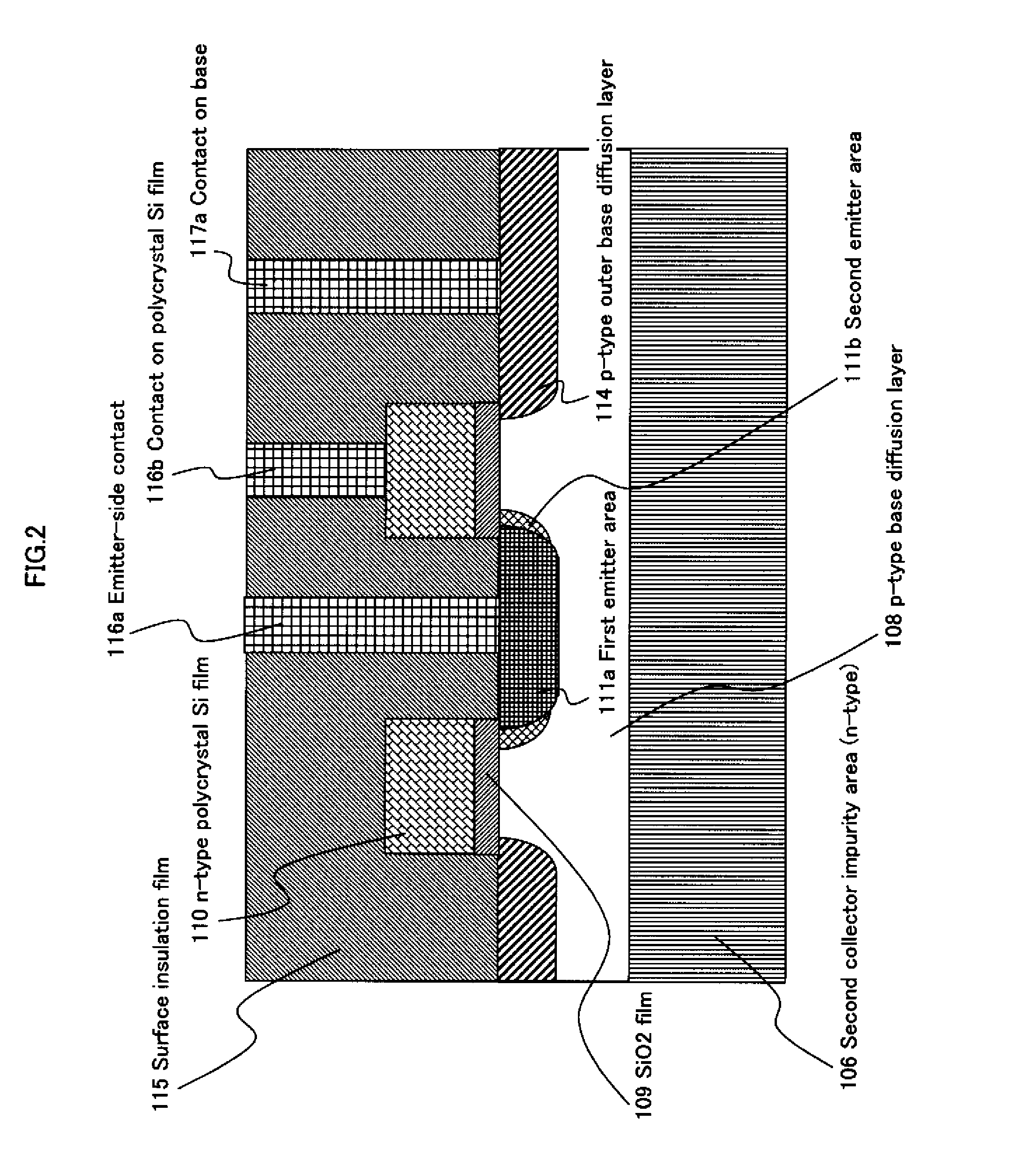

Semiconductor apparatus and manufacturing method thereof

InactiveUS20110127615A1Reduce leakage currentReduce electric field strengthTransistorSolid-state devicesElectrical field strengthImpurity ions

A high-performance semiconductor apparatus which can be easily introduced into the MOS process, reduces the leakage current (electric field strength) between the emitter and the base, and is insusceptible to noise or surge voltage, and a manufacturing method of the semiconductor apparatus. The emitter 111 is formed by performing the ion implantation twice by using the conductive film (109) as a mask. The second emitter area (111b) is formed by ion implantation of a low impurity density impurity ion, and the first emitter area (111a) is formed by ion implantation of a high impurity density impurity ion. As a result, the low impurity density second emitter area is formed in the circumference of the emitter 111, which lowers the electric field strength, and reduces the leakage current. Also the conductive film is connected with the emitter electrode (116), which makes the apparatus insusceptible to noise.

Owner:PANASONIC CORP

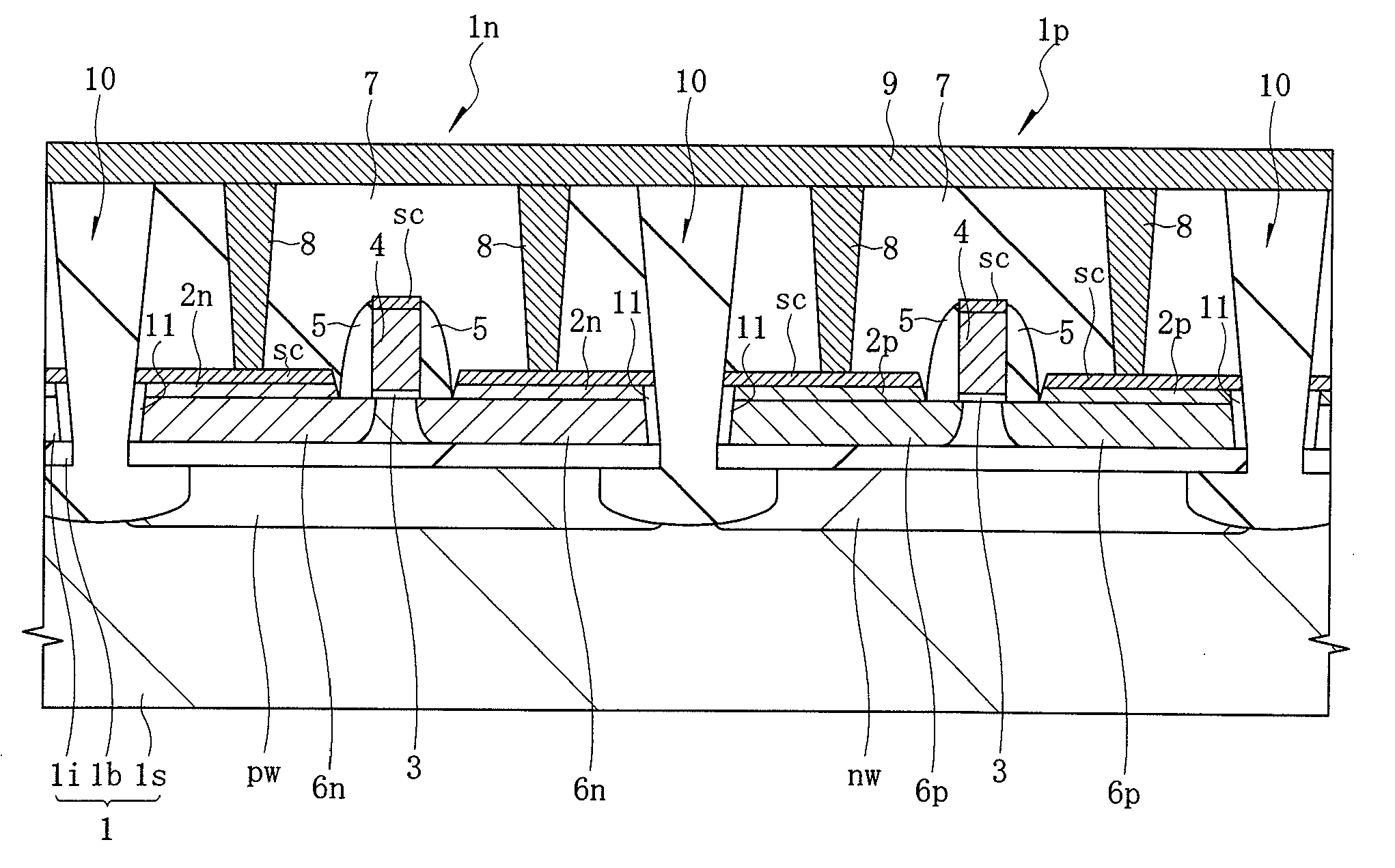

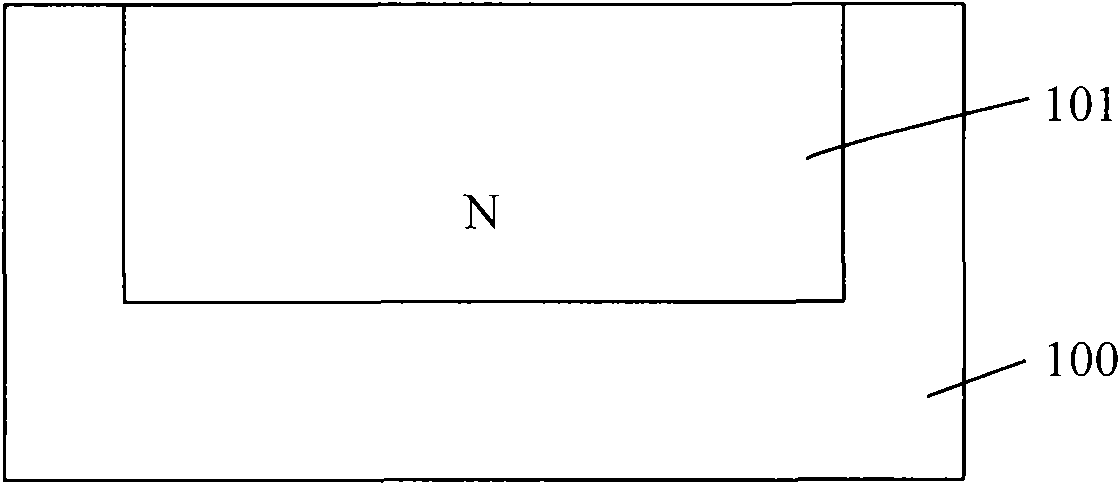

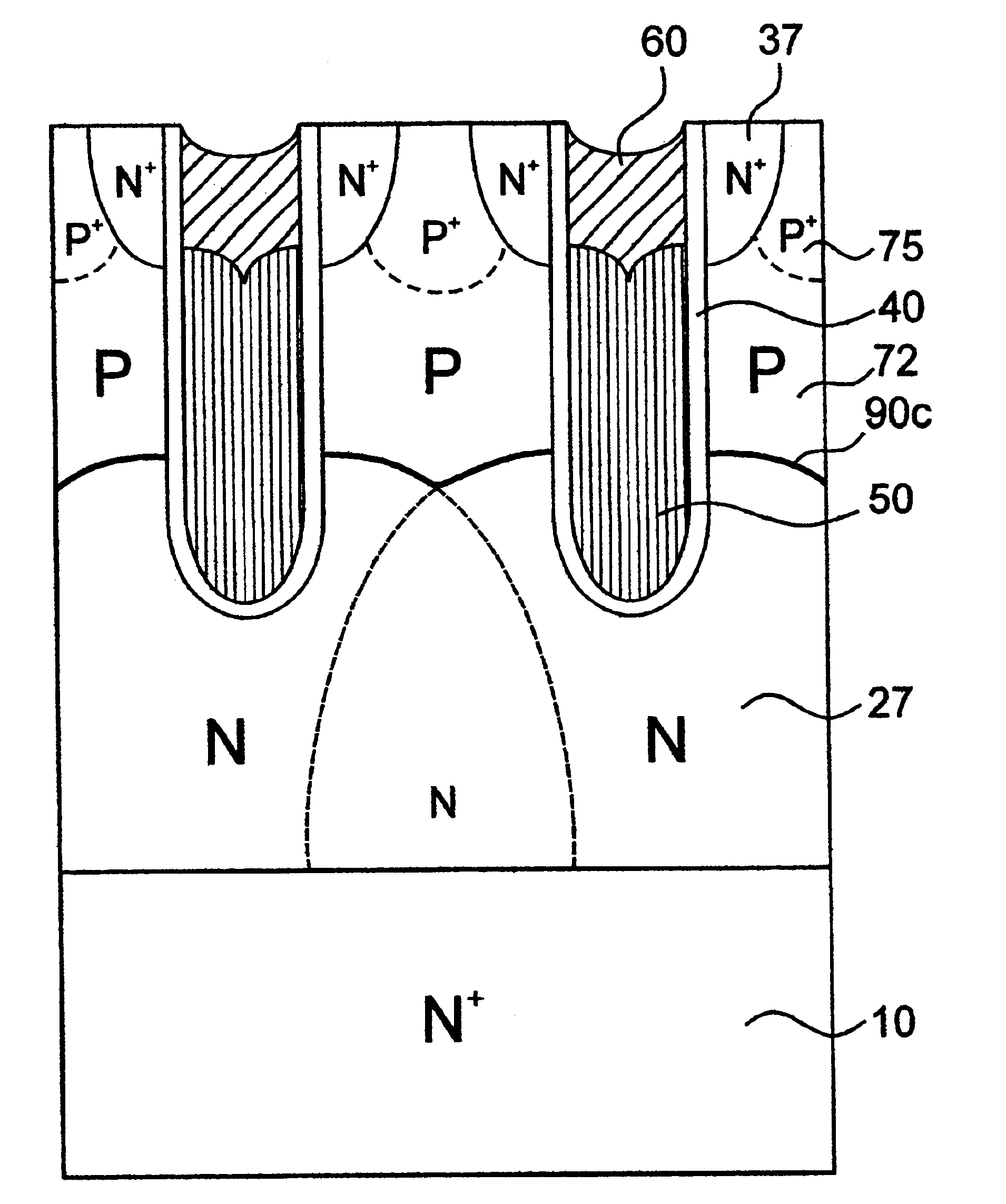

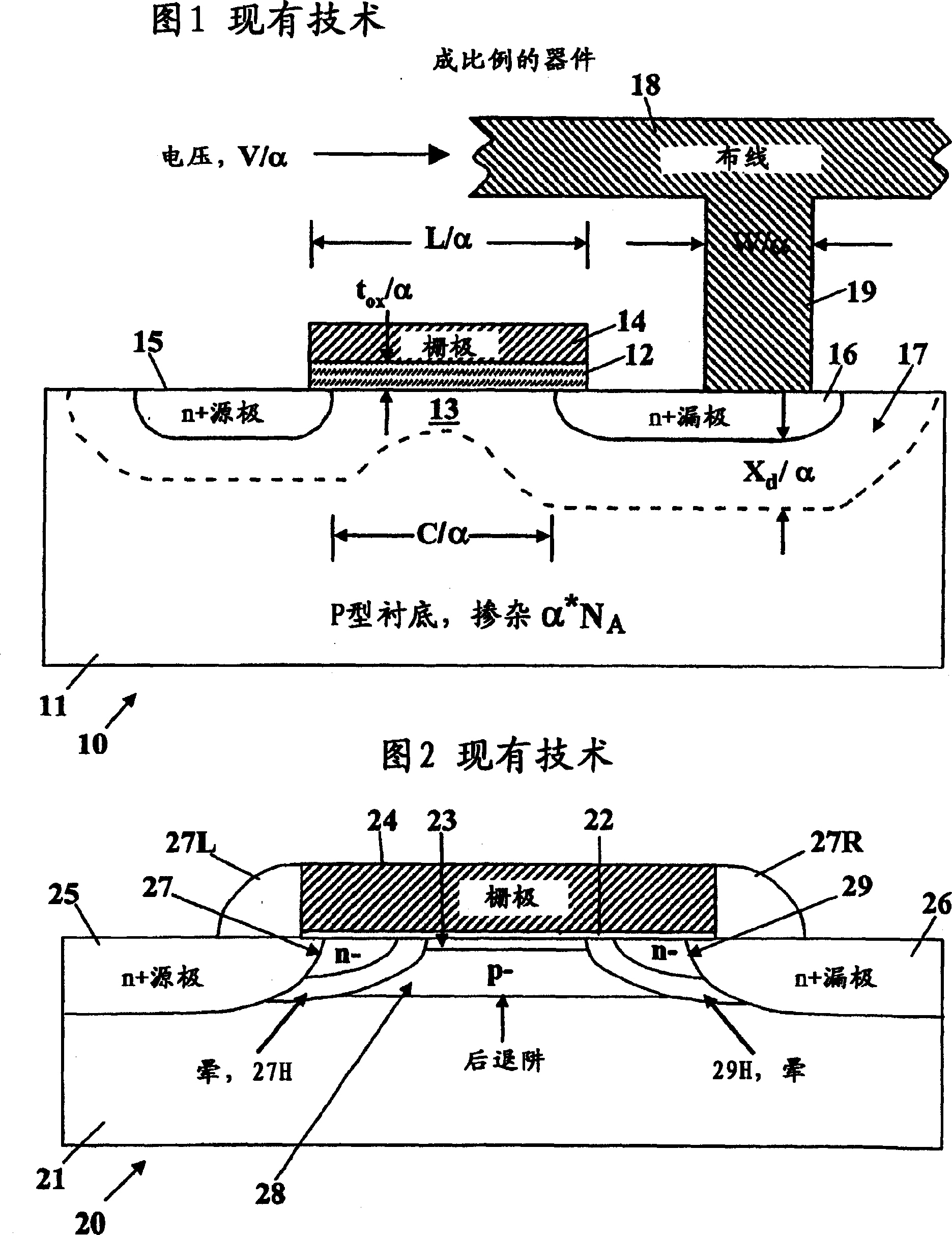

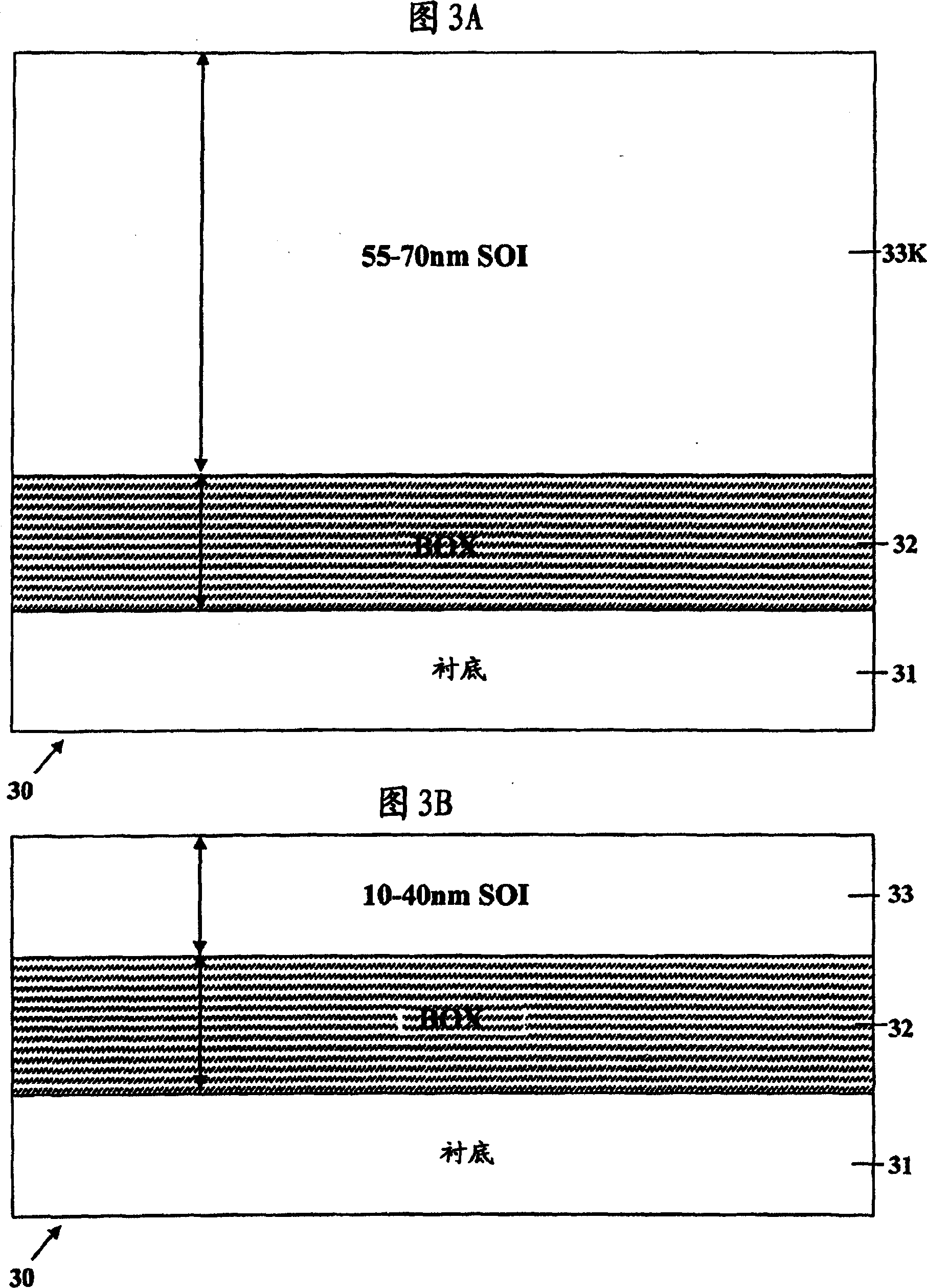

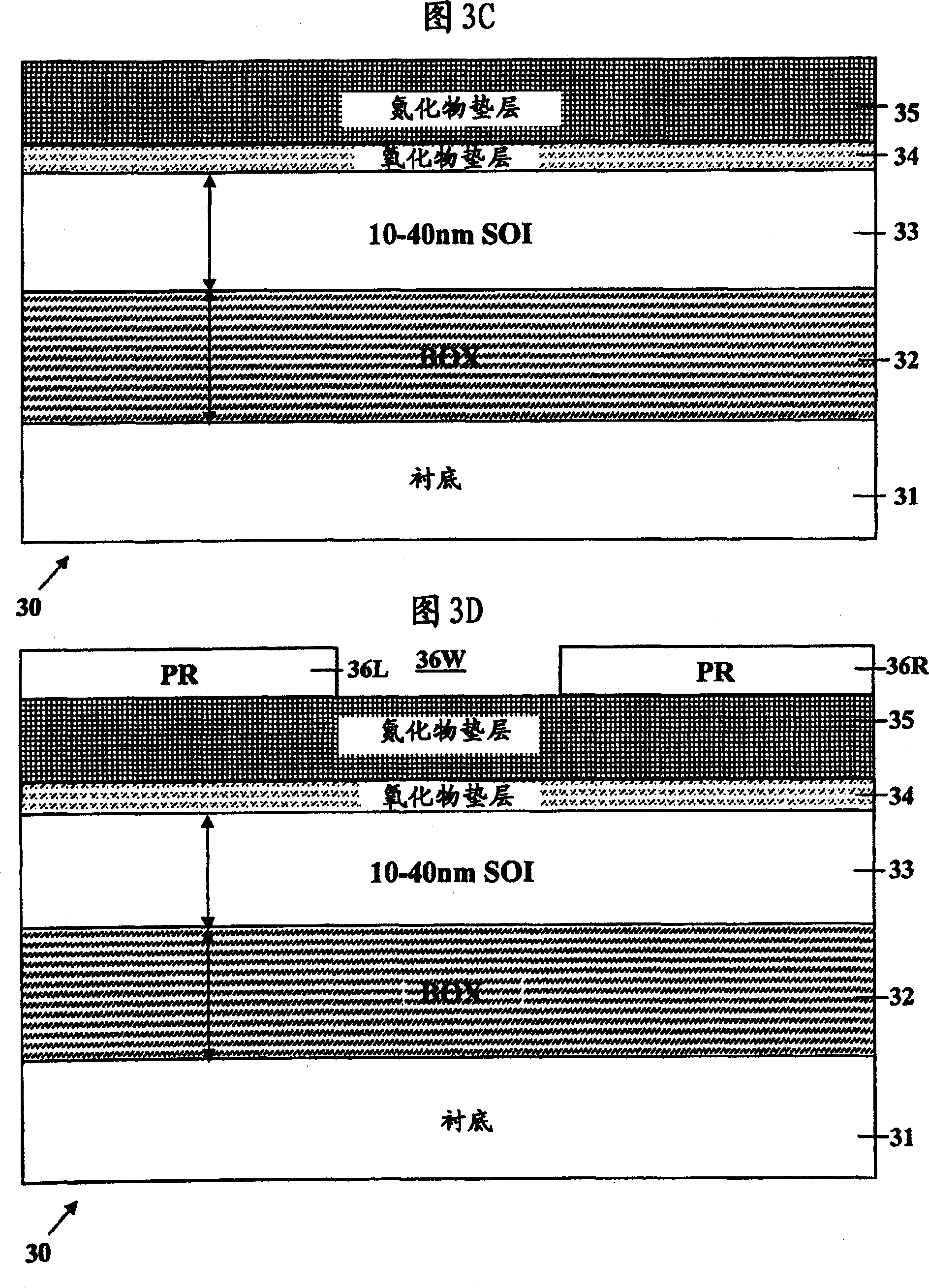

Ultra-thin body super-steep retrograde well (ssrw) fet devices

ActiveCN1728402AGuaranteed normal transmissionEasy to controlTransistorSolid-state devicesDopantGround plane

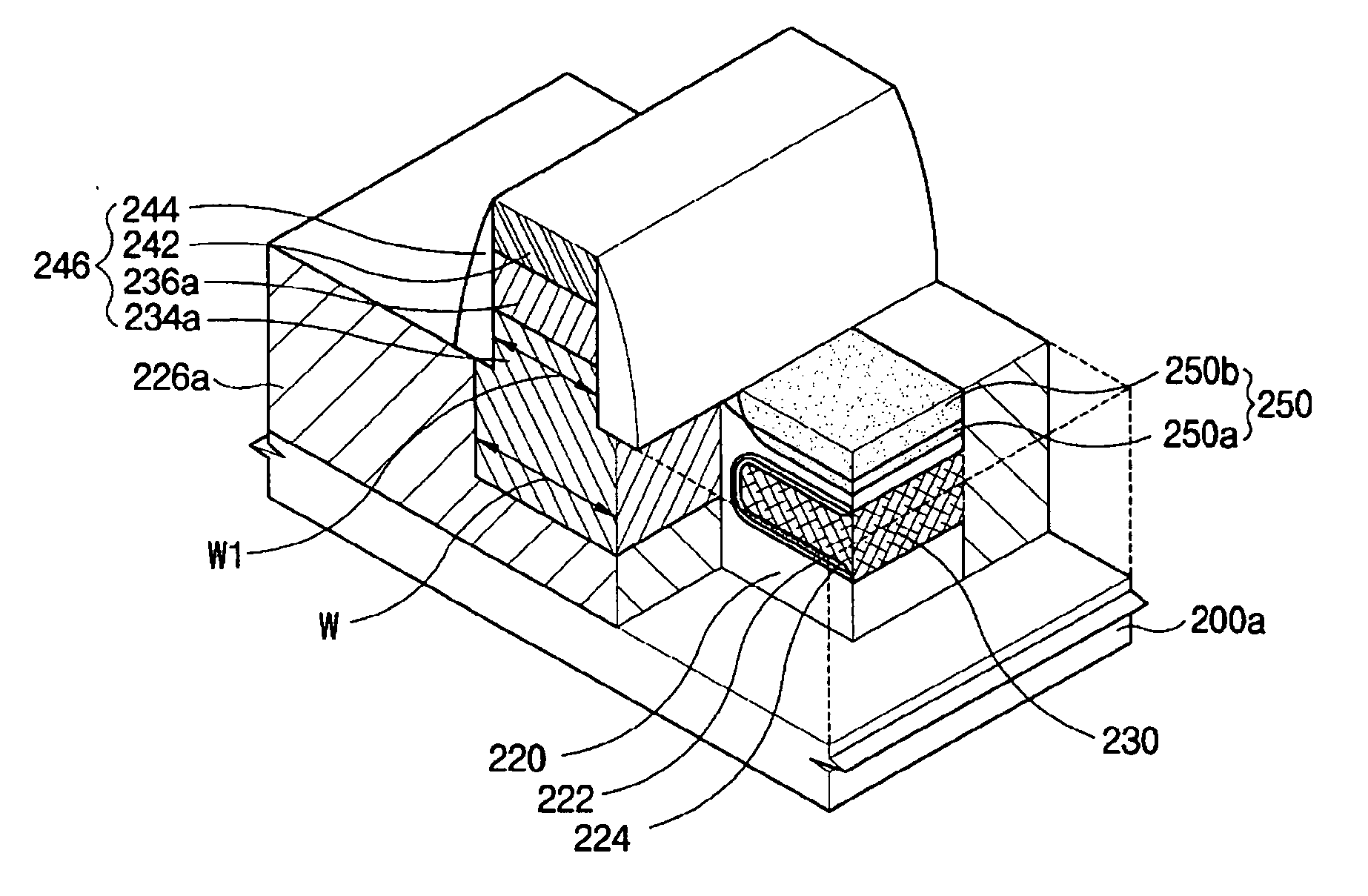

The present invention provides a method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES INC

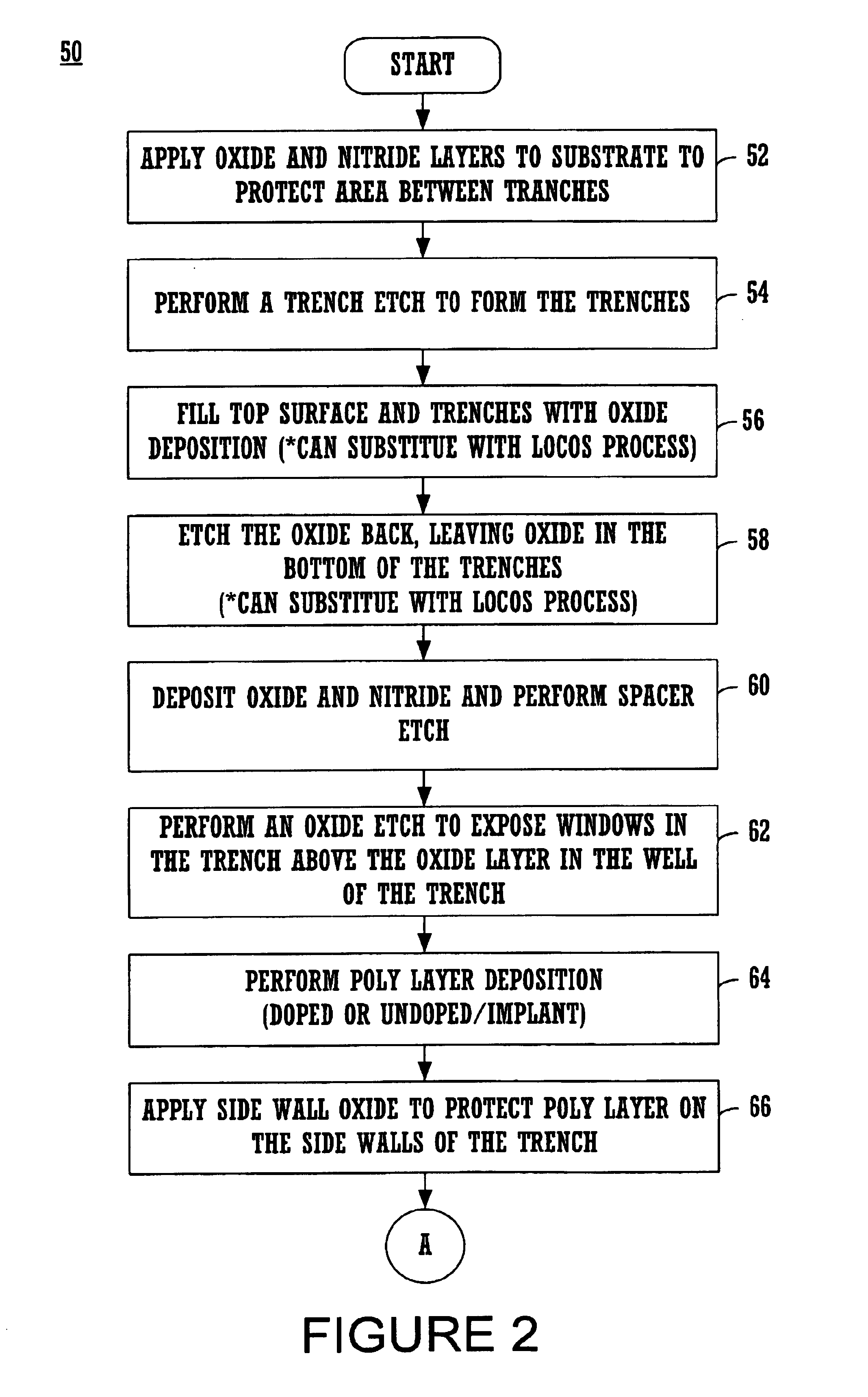

Low voltage high density trench-gated power device with uniformly doped channel and its edge termination technique

InactiveUS20030205758A1Increase reverse voltageLow densityTransistorSolid-state devicesChannel densityLow voltage

Merging together the drift regions in a low-power trench MOSFET device via a dopant implant through the bottom of the trench permits use of a very small cell pitch, resulting in a very high channel density and a uniformly doped channel and a consequent significant reduction in the channel resistance. By properly choosing the implant dose and the annealing parameters of the drift region, the channel length of the device can be closely controlled, and the channel doping may be made highly uniform. In comparison with a conventional device, the threshold voltage is reduced, the channel resistance is lowered, and the drift region on-resistance is also lowered. Implementing the merged drift regions requires incorporation of a new edge termination design, so that the PN junction formed by the P epi-layer and the N<+> substrate can be terminated at the edge of the die.

Owner:SEMICON COMPONENTS IND LLC

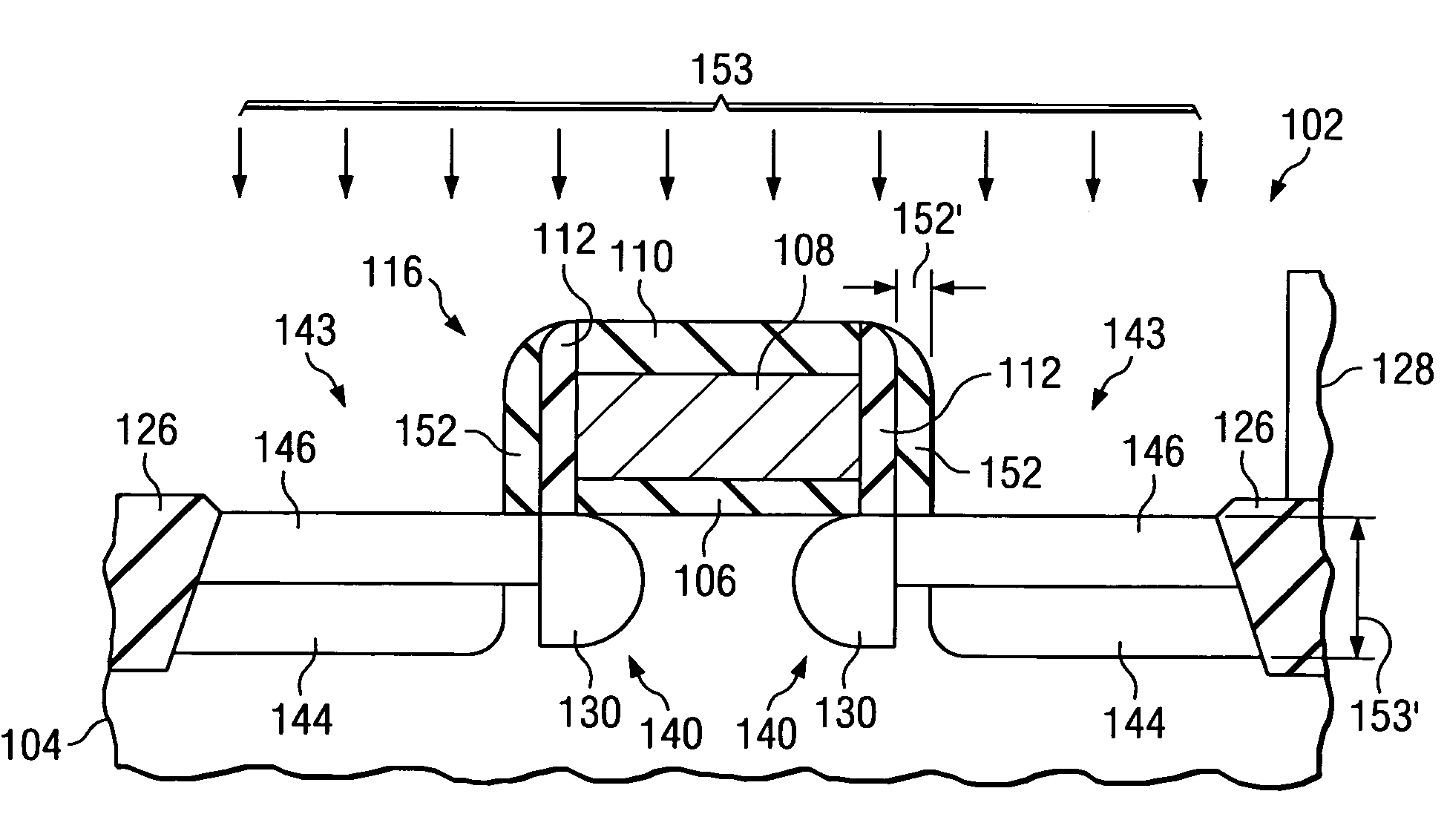

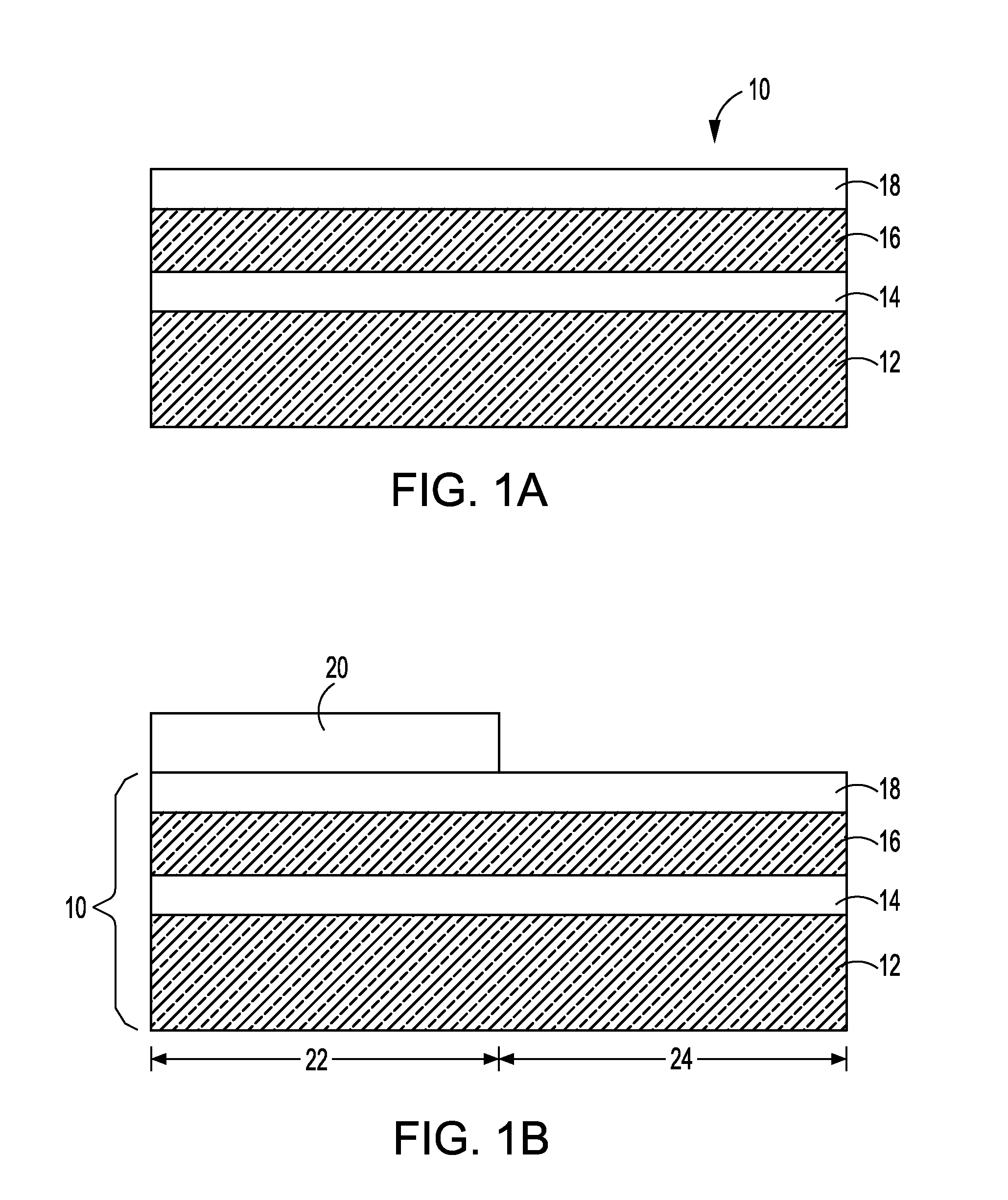

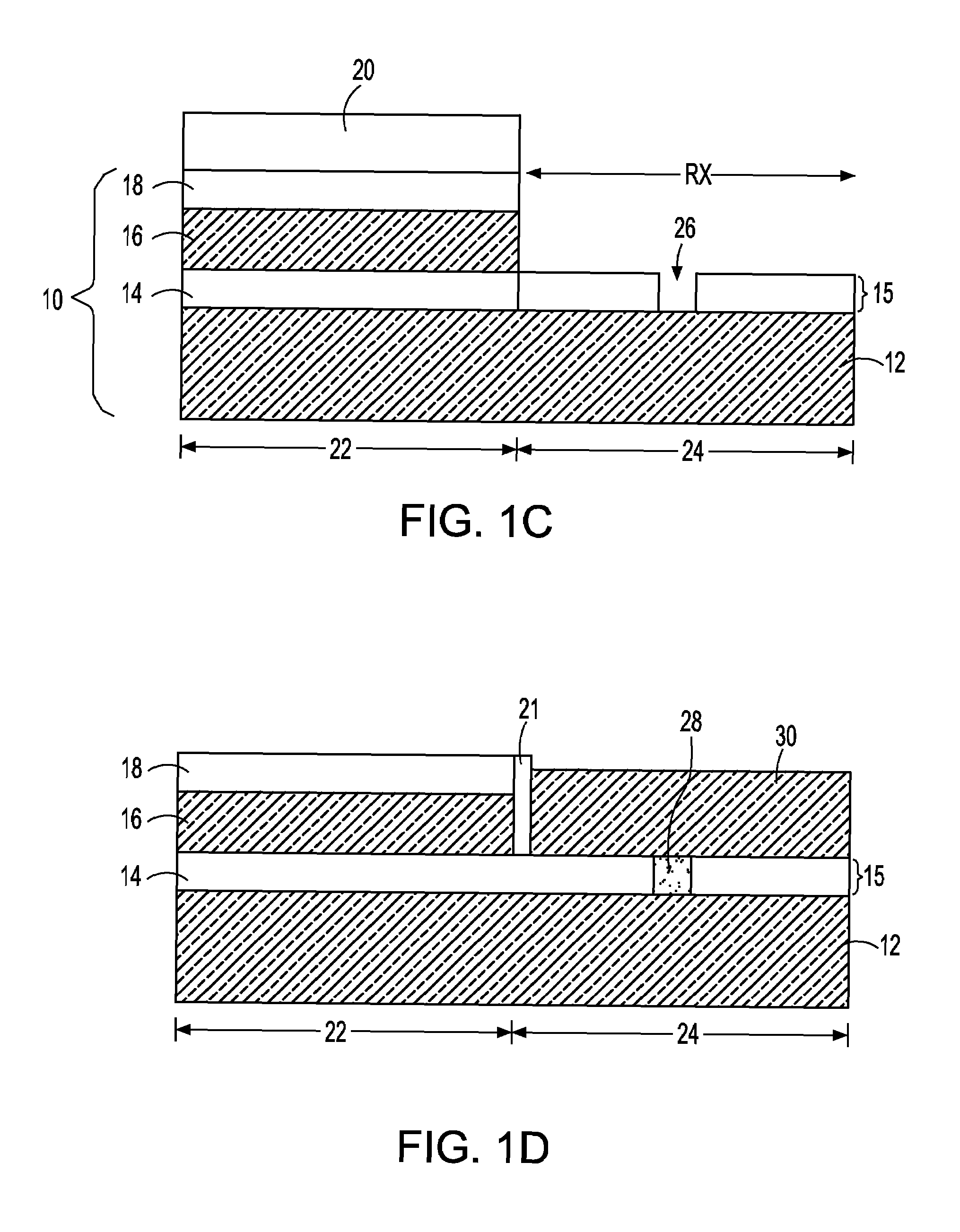

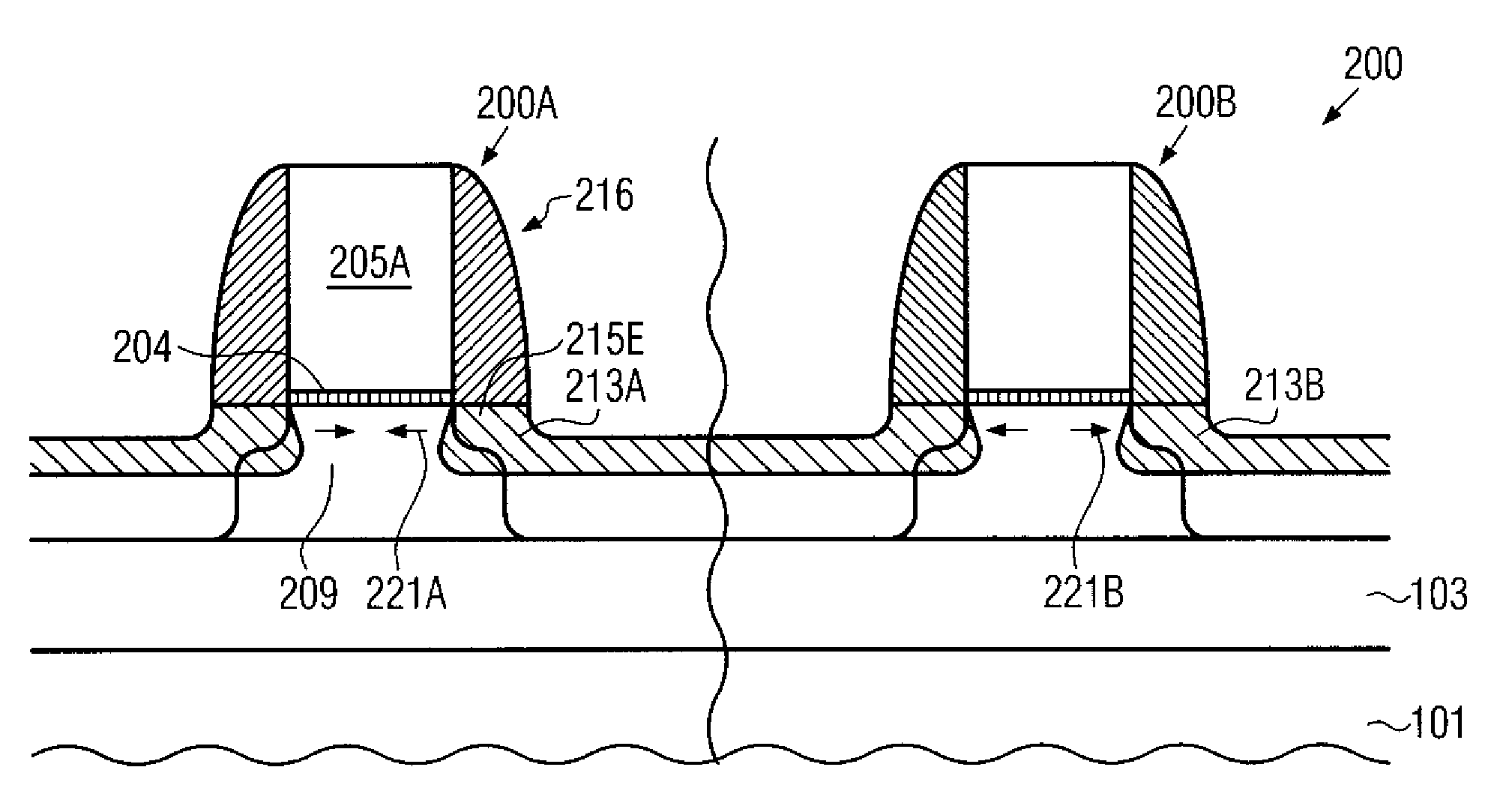

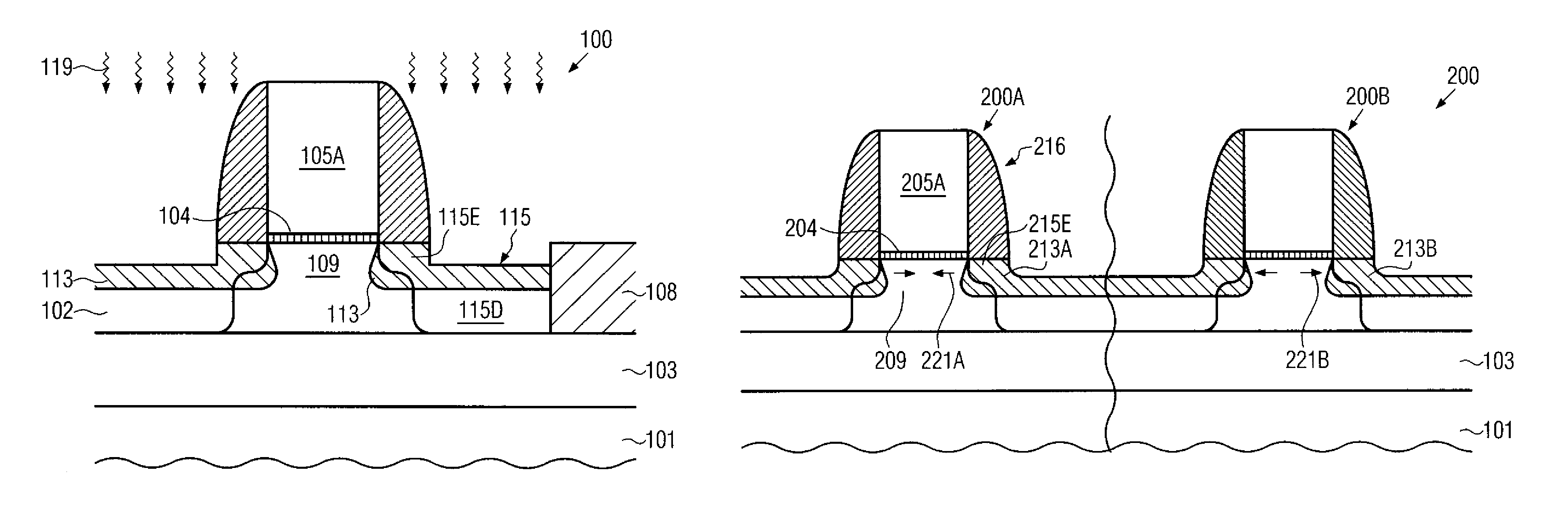

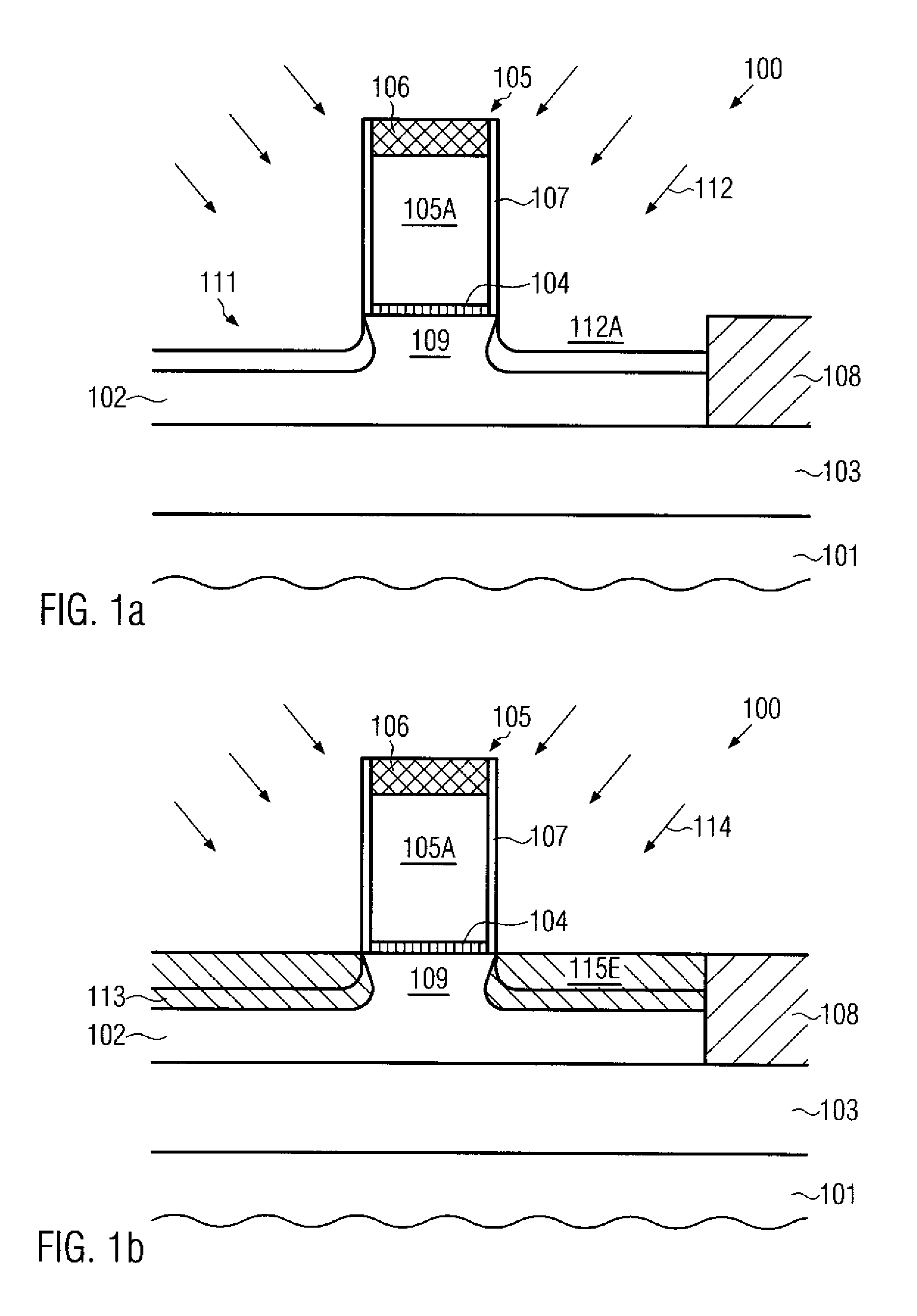

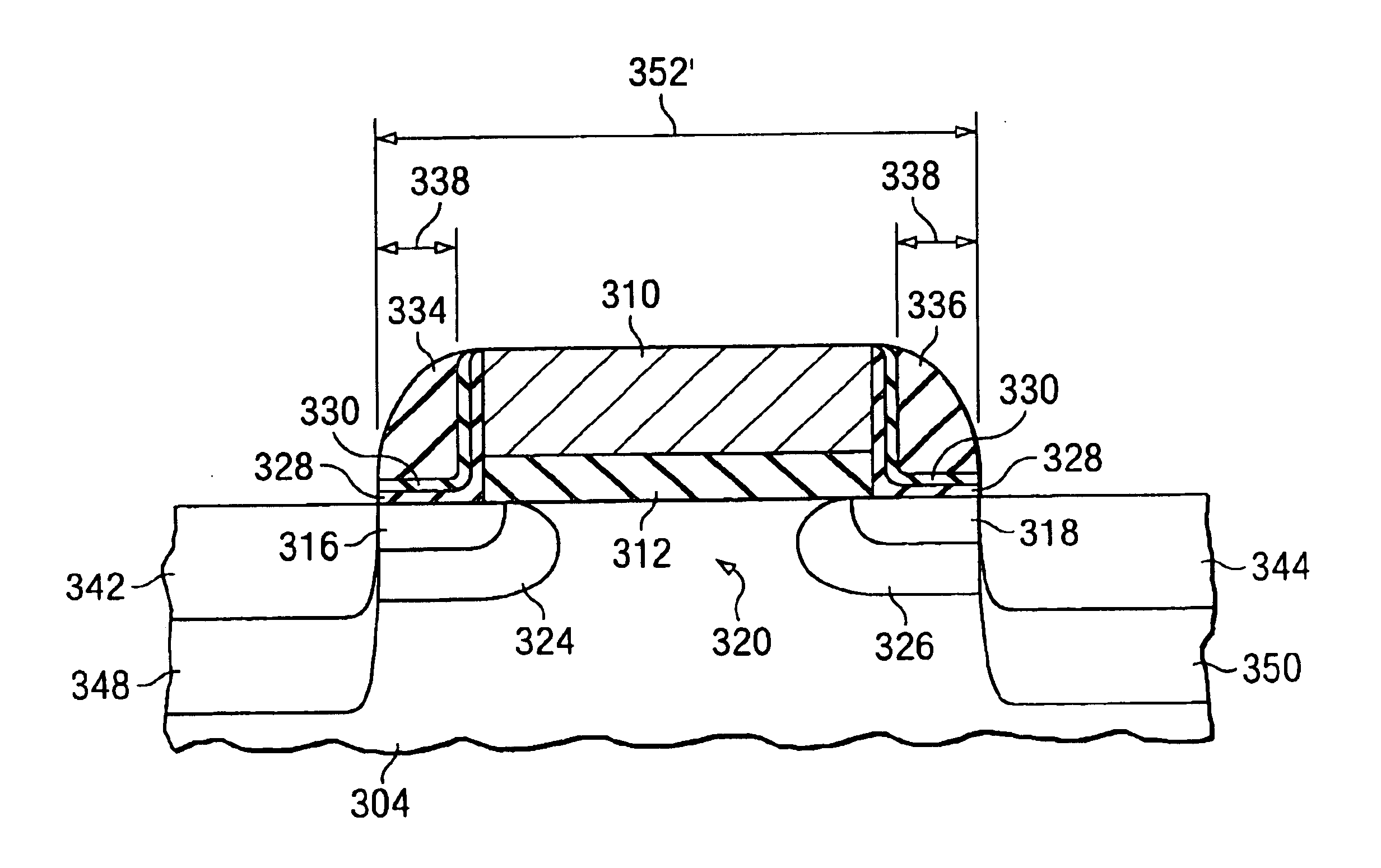

Reducing transistor junction capacitance by recessing drain and source regions

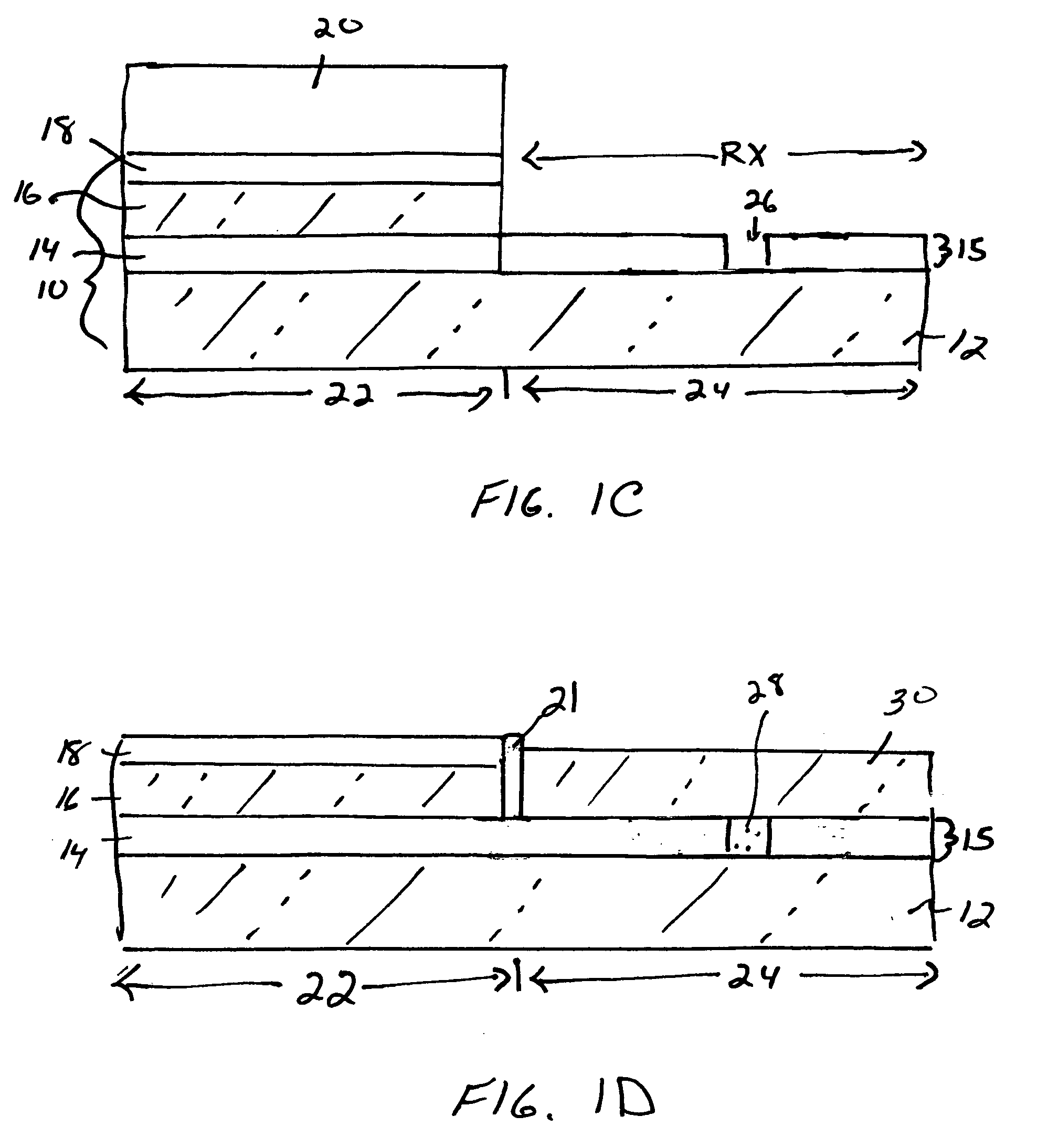

By recessing portions of the drain and source areas on the basis of a spacer structure, the subsequent implantation process for forming the deep drain and source regions may result in a moderately high dopant concentration extending down to the buried insulating layer of an SOI transistor. Furthermore, the spacer structure maintains a significant amount of a strained semiconductor alloy with its original thickness, thereby providing an efficient strain-inducing mechanism. By using sophisticated anneal techniques, undue lateral diffusion may be avoided, thereby allowing a reduction of the lateral width of the respective spacers and thus a reduction of the length of the transistor devices. Hence, enhanced charge carrier mobility in combination with reduced junction capacitance may be accomplished on the basis of reduced lateral dimensions.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Reducing transistor junction capacitance by recessing drain and source regions

By recessing portions of the drain and source areas on the basis of a spacer structure, the subsequent implantation process for forming the deep drain and source regions may result in a moderately high dopant concentration extending down to the buried insulating layer of an SOI transistor. Furthermore, the spacer structure maintains a significant amount of a strained semiconductor alloy with its original thickness, thereby providing an efficient strain-inducing mechanism. By using sophisticated anneal techniques, undue lateral diffusion may be avoided, thereby allowing a reduction of the lateral width of the respective spacers and thus a reduction of the length of the transistor devices. Hence, enhanced charge carrier mobility in combination with reduced junction capacitance may be accomplished on the basis of reduced lateral dimensions.

Owner:CONVERSANT INTPROP MANAGEMENT INC

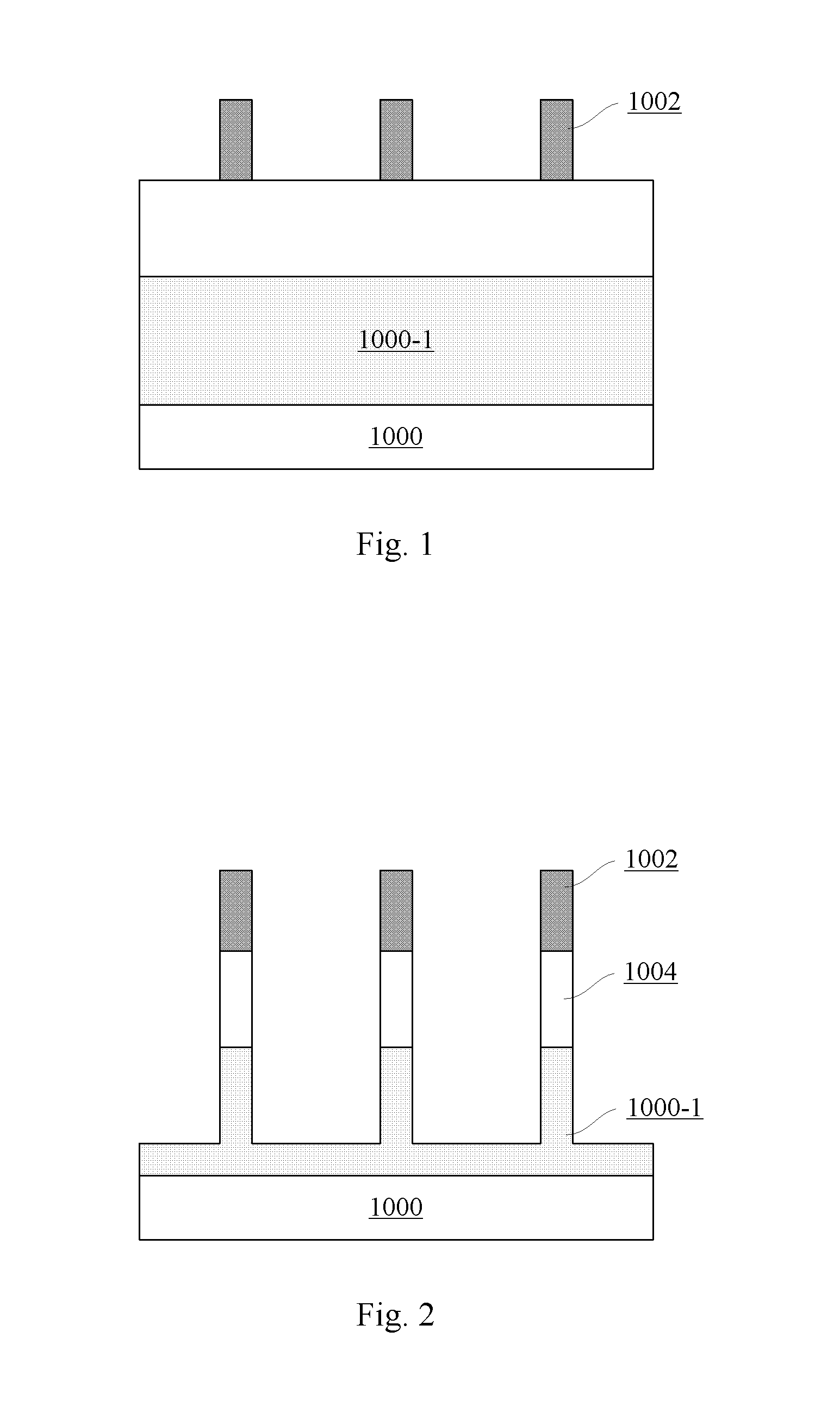

Semiconductor device and method of manufacturing the same

ActiveUS20150318397A1Reduce leakageLower junction capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingIsolation layerGate stack

Provided are a semiconductor device and a method of manufacturing the same. An example device may include: a fin formed on a substrate; a gate stack formed on the substrate and intersecting the fin, wherein the gate stack is isolated from the substrate by an isolation layer, and a Punch-Through Stopper (PTS) formed under the fin, including a first section directly under a portion of the fin where the fin intersects the gate stack and second sections on opposite sides of the first section, wherein the second sections each have a doping concentration lower than that of the first section.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

SOI low capacitance body contact

InactiveUS6368903B1Lower junction capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceBody contact

An FET device and method of making comprising a first dielectric layer; a substrate layer on the dielectric layer; a channel region of a first conductivity type formed in the substrate layer; a gate formed above the substrate layer over the channel region; FET diffusion regions of a second conductivity type formed in the substrate layer, the diffusion regions each having edges, the edges of the FET diffusion regions being separated by the channel region; and a body contact region of the first conductivity type extending continuously from the channel region. The first conductivity type material in the body contact region is thinner than the first conductivity type material in the channel region. The FET also includes a second dielectric layer formed on the body contact region.

Owner:IBM CORP

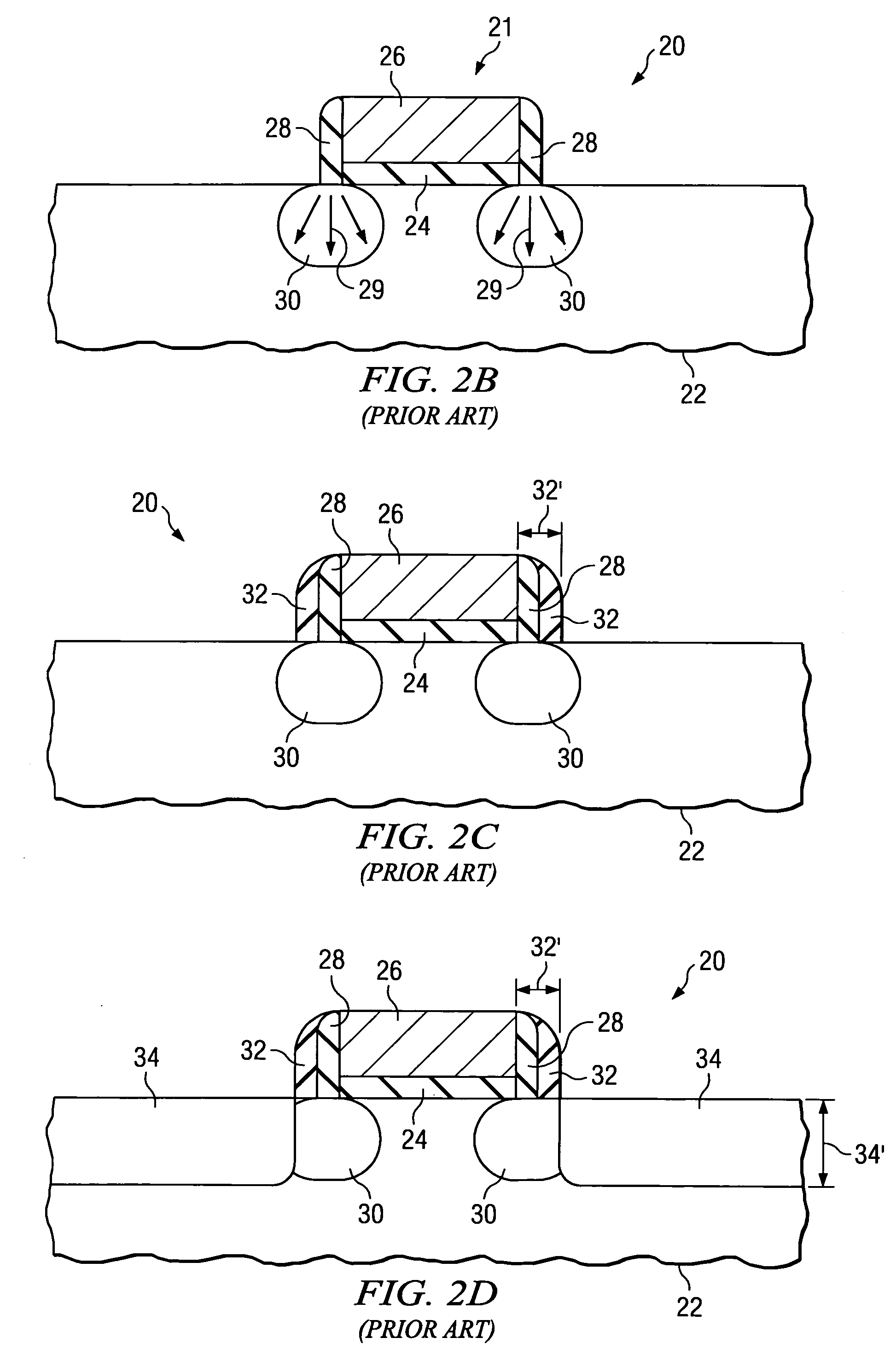

Process method of source drain spacer engineering to improve transistor capacitance

InactiveUS6913980B2Suppression of short channel effectsMitigates junction capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceDopant

A method of forming an associated transistor is presented whereby short channel effects and junction capacitances are mitigated and enhanced switching speeds are thereby facilitated. Compensation regions are formed within a substrate by implanting dopants relatively deeply over source and drain regions formed within the substrate. The compensation regions are spaced apart slightly less than are the source and drain regions. This spacing affects potential contours and reduces junction capacitances within the transistor. The different distances between the source and drain regions and the compensation regions are achieved by forming and selectively adjusting sidewall spacers adjacent to a gate structure of the transistor. These spacers serve as guides for the dopants implanted into the substrate to form the source and drain regions and the compensation regions.

Owner:TEXAS INSTR INC

Semiconductor device and method of manufacturing the same

ActiveUS7166514B2Improve reliabilityLower junction capacitanceTransistorSolid-state devicesMOSFETDevice material

A fin type MOSFET and a method of manufacturing the fin type MOSFET are disclosed. Gate structures in the fin type MOSFET are formed by a damascene process without a photolithography process. Impurities used to form a channel region are selectively implanted into portions of a semiconductor substrate adjacent to the gate structures.

Owner:SAMSUNG ELECTRONICS CO LTD

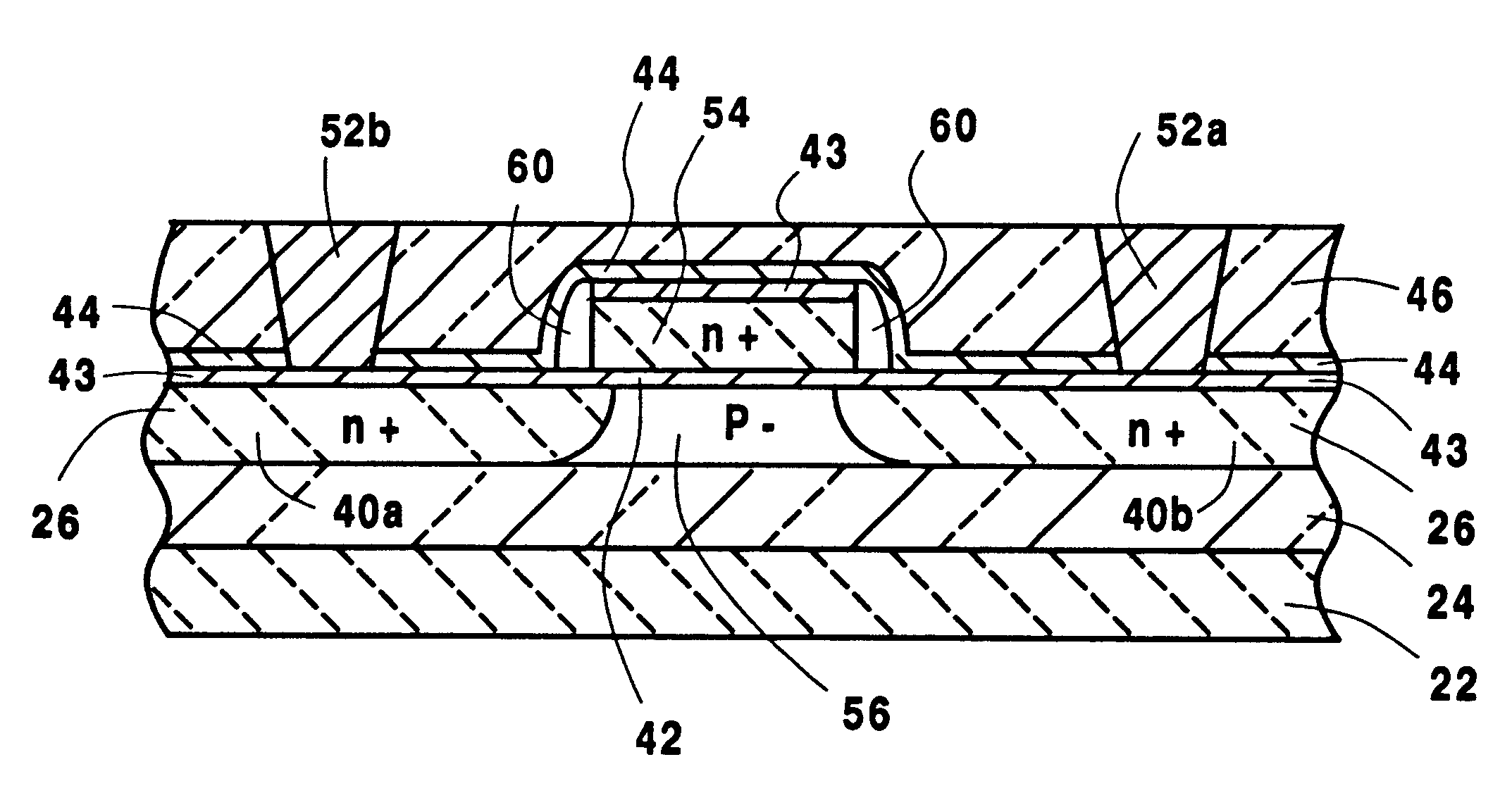

Method of forming an ESD protection device

InactiveUS20010010954A1Lower breakdown voltageLower junction capacitanceTransistorThyristorCapacitanceEngineering

The invention discloses a method of forming an ESD protection device without adding the extra mask layers into the traditional CMOS process. At first, P-wells, N-wells, and isolations are formed in a semiconductor substrate. Next, an NMOS transistor with a gate dielectric layer, a gate electrode, source / drain regions, lightly doped source / drain regions, and insulator spacers is formed on the substrate. Particularly, N-wells are also formed in a part of the source / drain regions of the NMOS transistor. Thereafter, ESD protection regions are formed under the source / drain regions by performing P+ ESD protection implantation. Such ESD protection device has a low junction breakdown voltage, quick response speed, and a small junction capacitance.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION