Patents

Literature

557results about How to "Lower breakdown voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Ultrapure synthetic carbon materials

ActiveUS8404384B2Short lifeEasy to operateNon-insulated conductorsElectrolytic capacitorsPorosityPolymer science

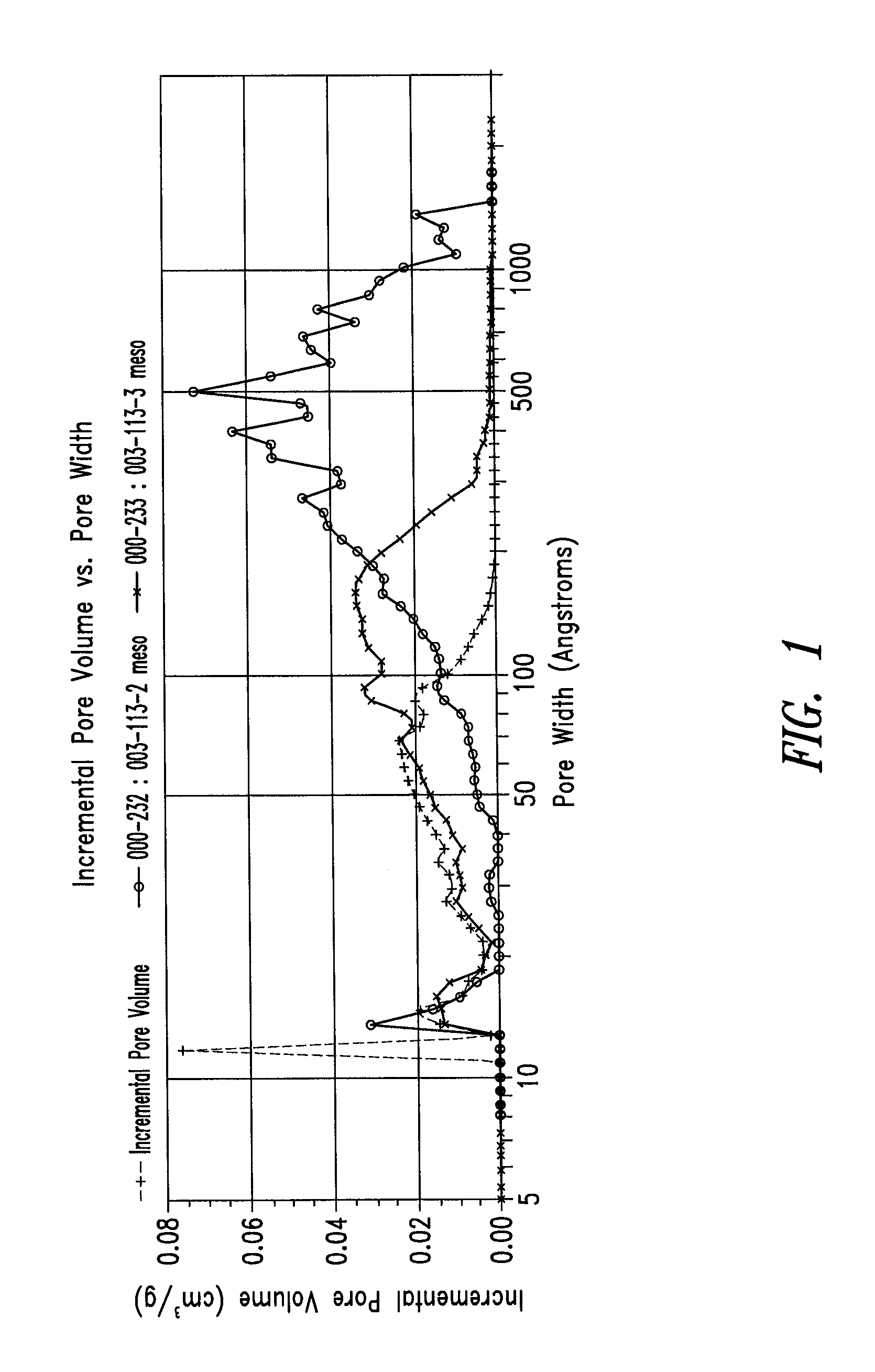

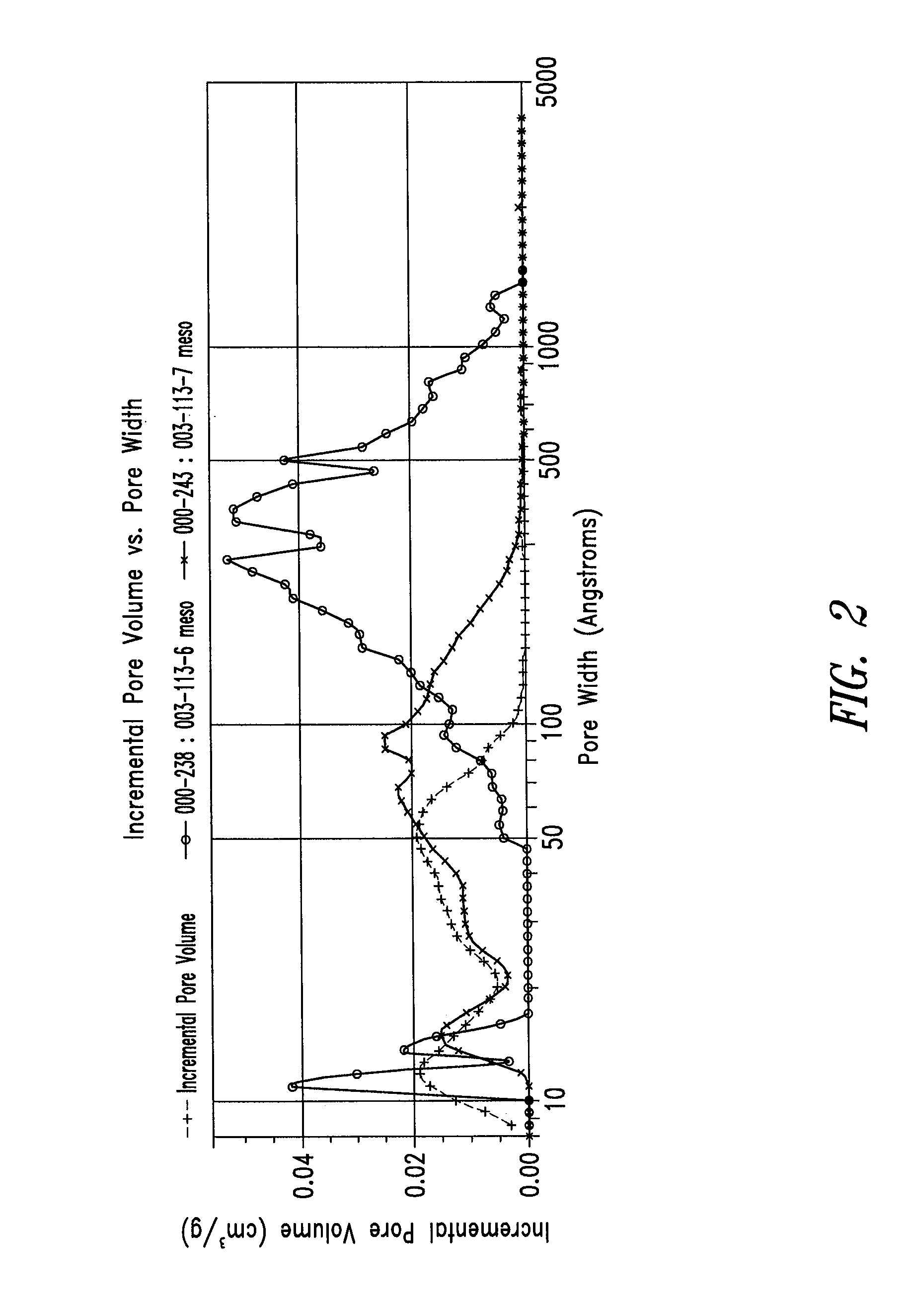

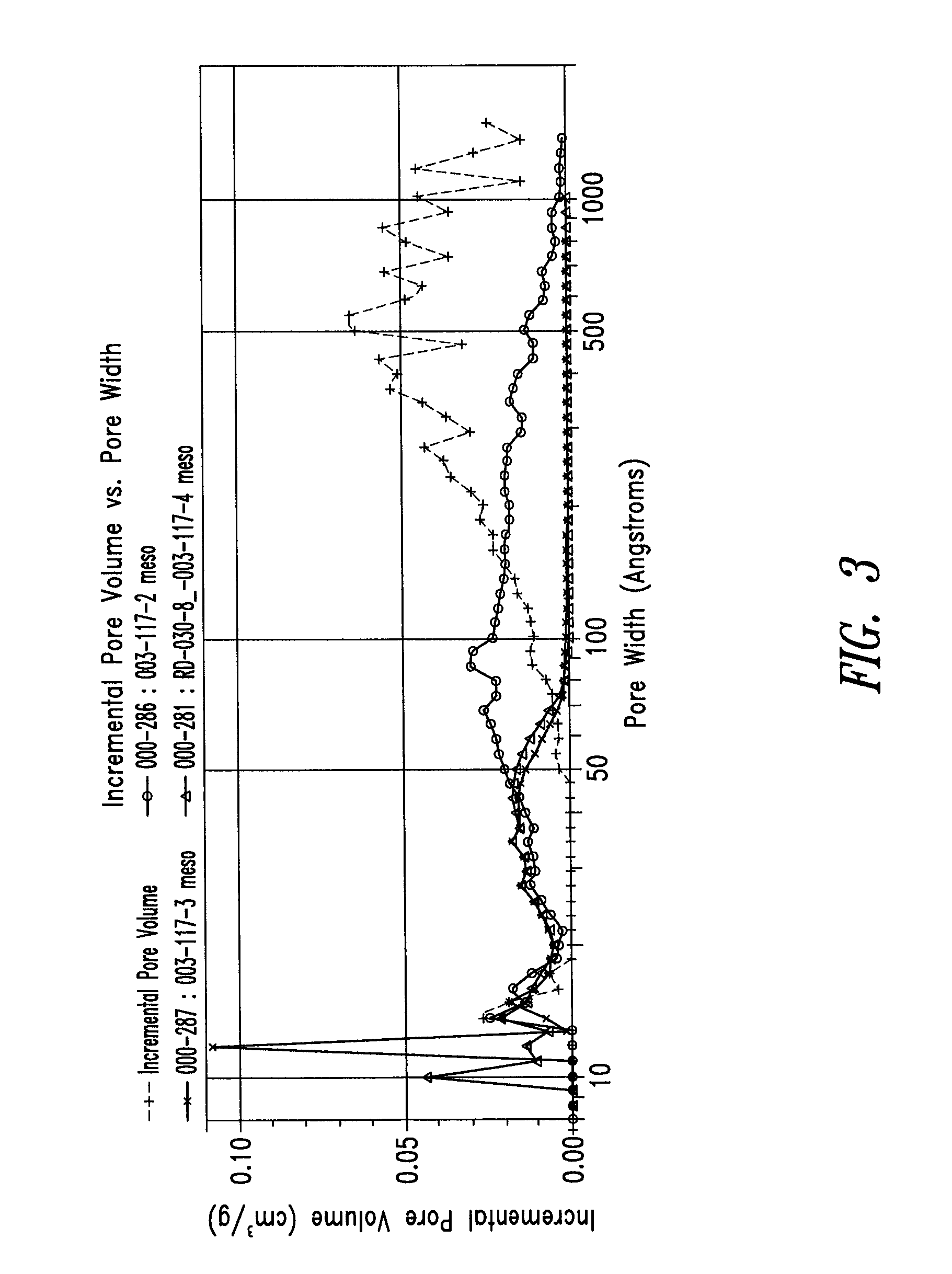

The present application is generally directed to ultrapure synthetic carbon materials having both high surface area and high porosity, ultrapure polymer gels and devices containing the same. The disclosed ultrapure synthetic carbon materials find utility in any number of devices, for example, in electric double layer capacitance devices and batteries. Methods for making ultrapure synthetic carbon materials and ultrapure polymer gels are also disclosed.

Owner:BASF SE

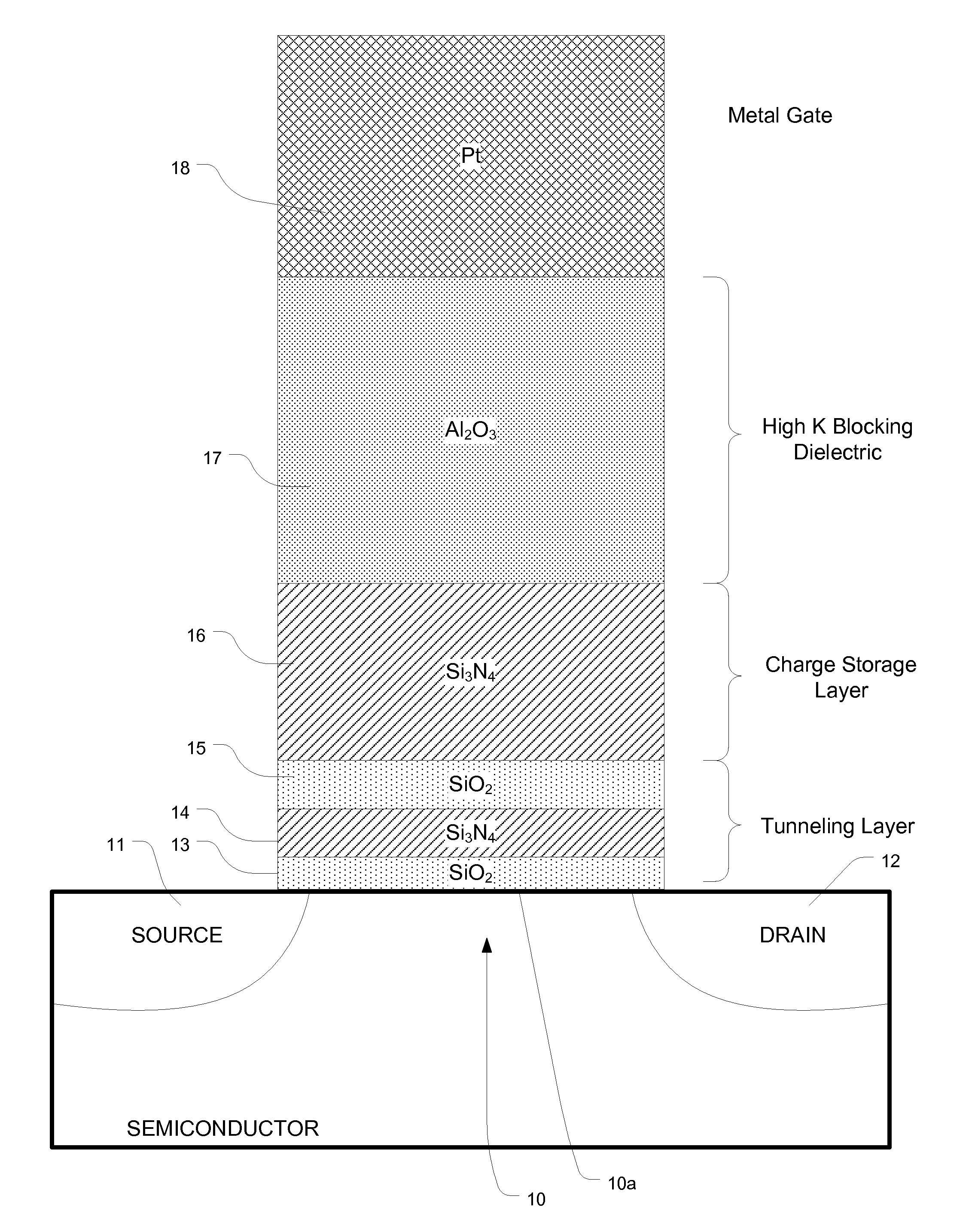

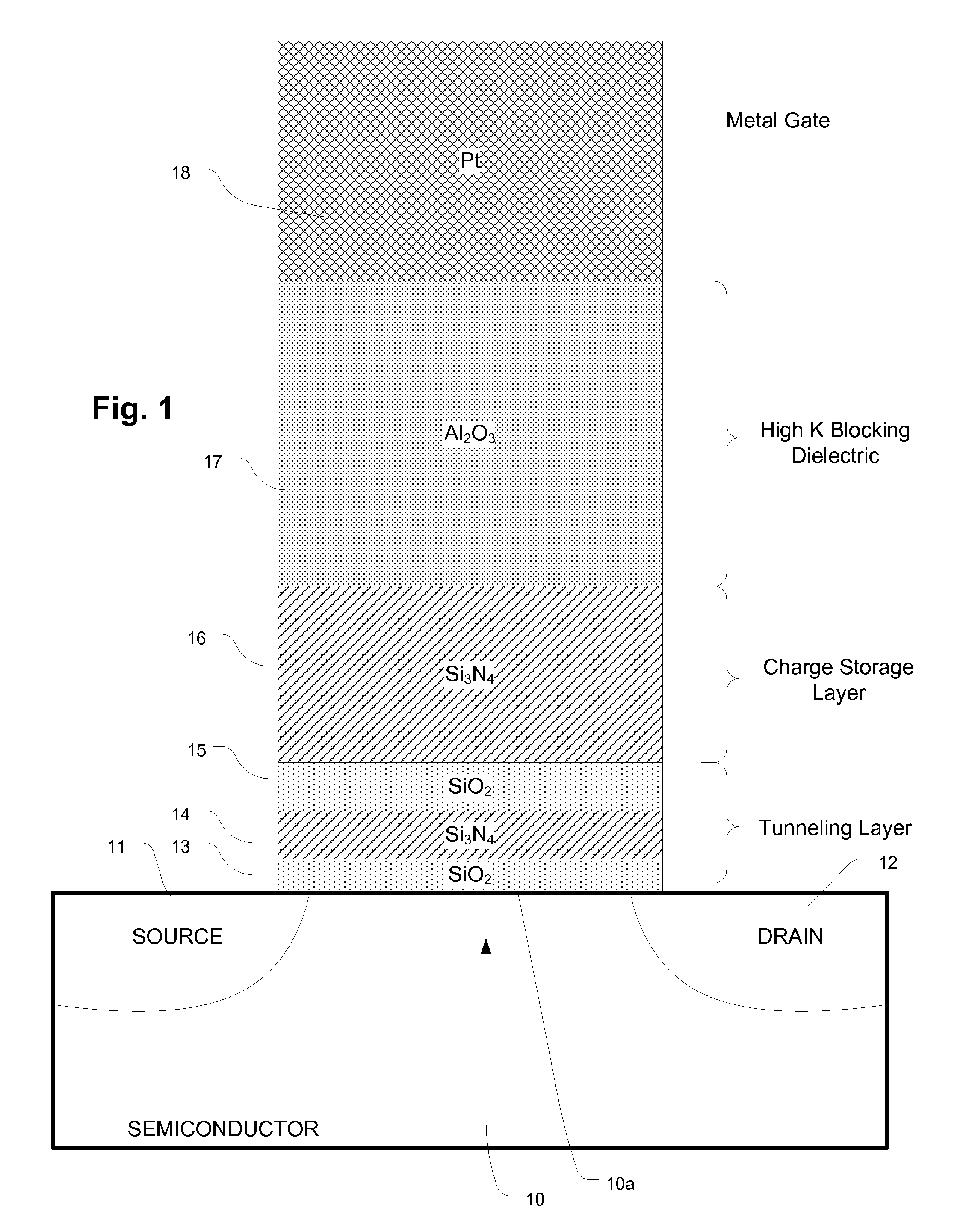

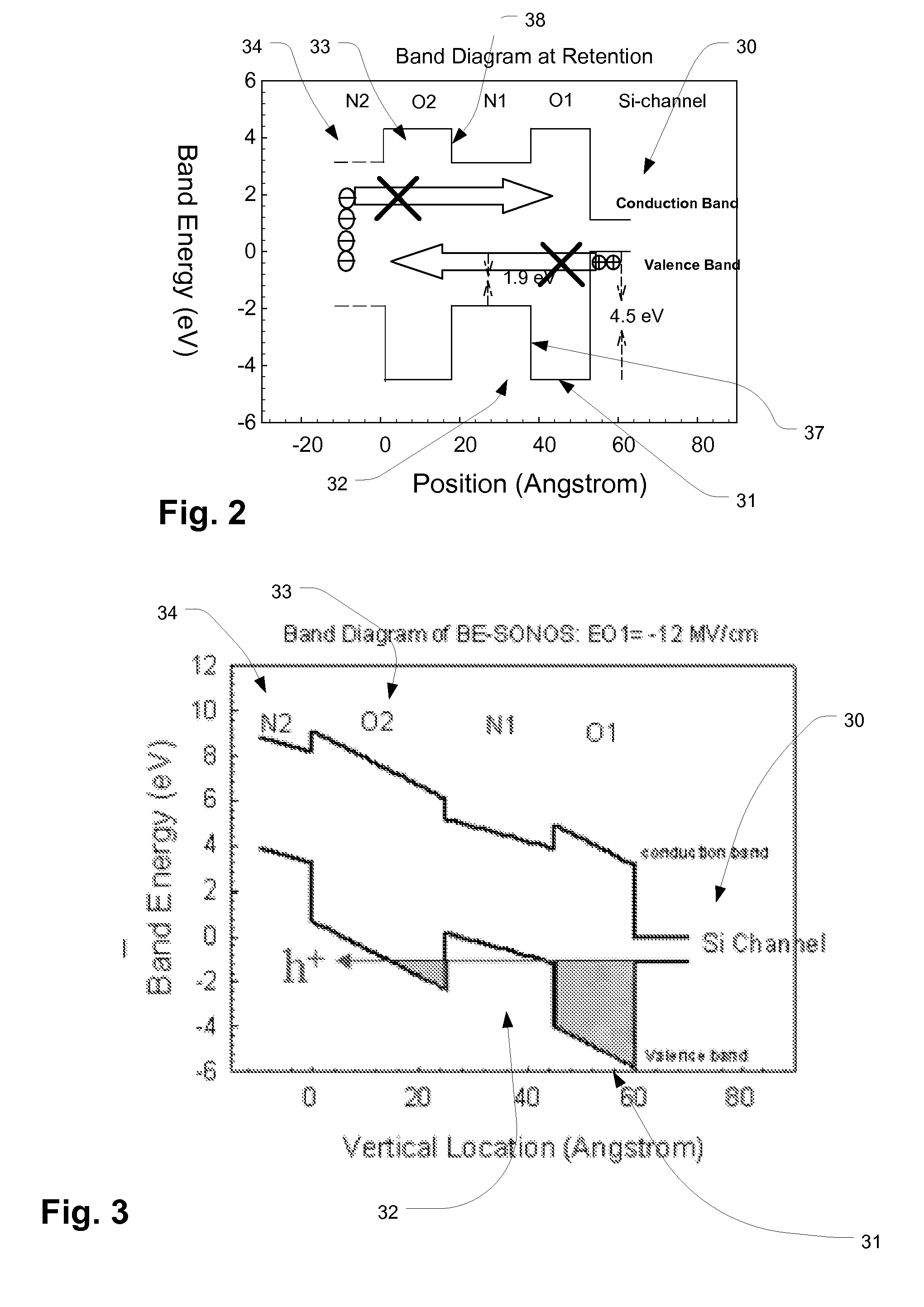

Charge trapping memory cell with high speed erase

InactiveUS20090039414A1Eliminates hole tunneling barrierEffectively preventing charge leakageSolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a metal or metal compound gate, such as a platinum gate, by a blocking layer of material having a high dielectric constant, such as aluminum oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric. Fast program and erase speeds with memory window as great as 7 V are achieved.

Owner:MACRONIX INT CO LTD

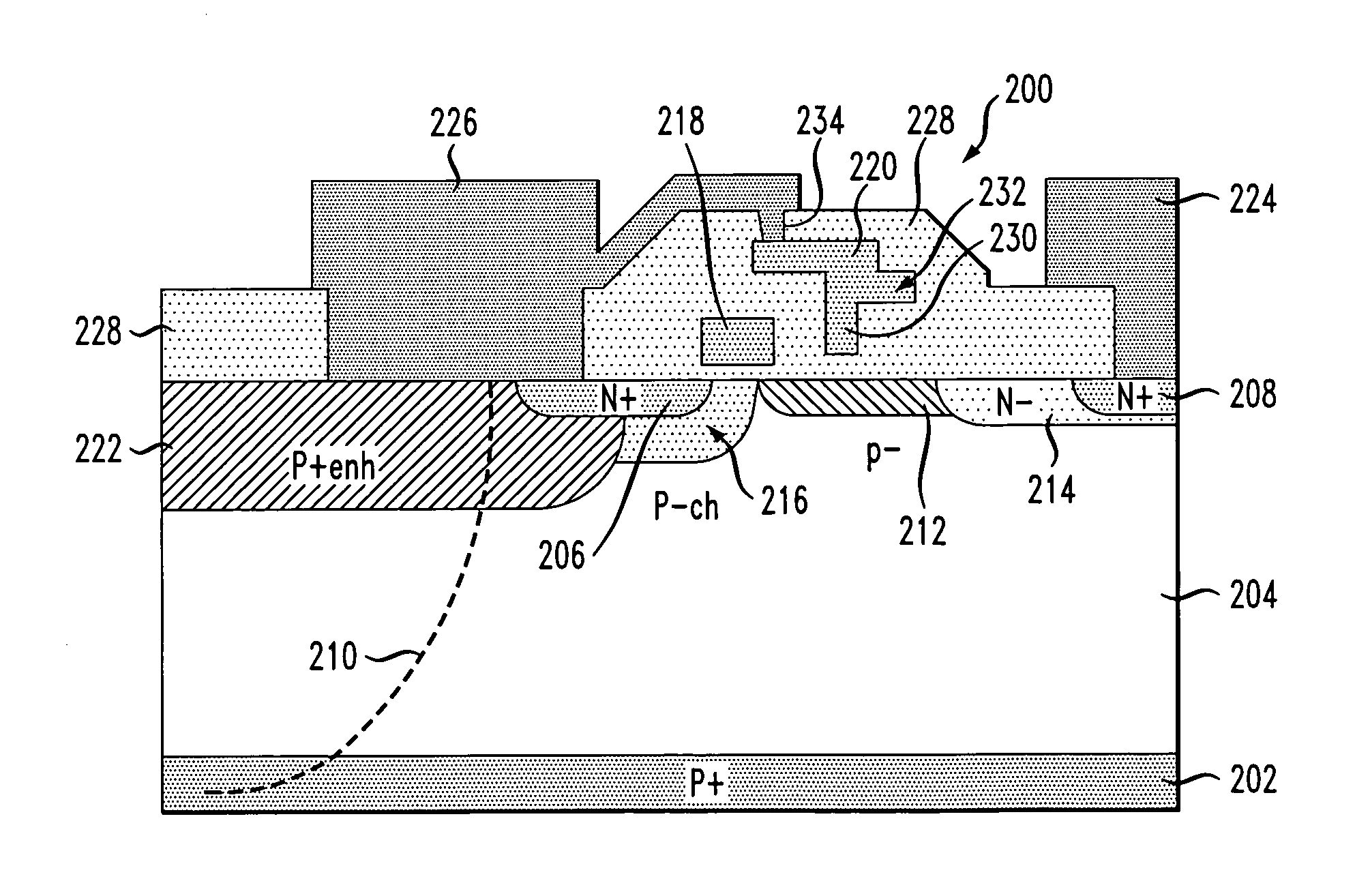

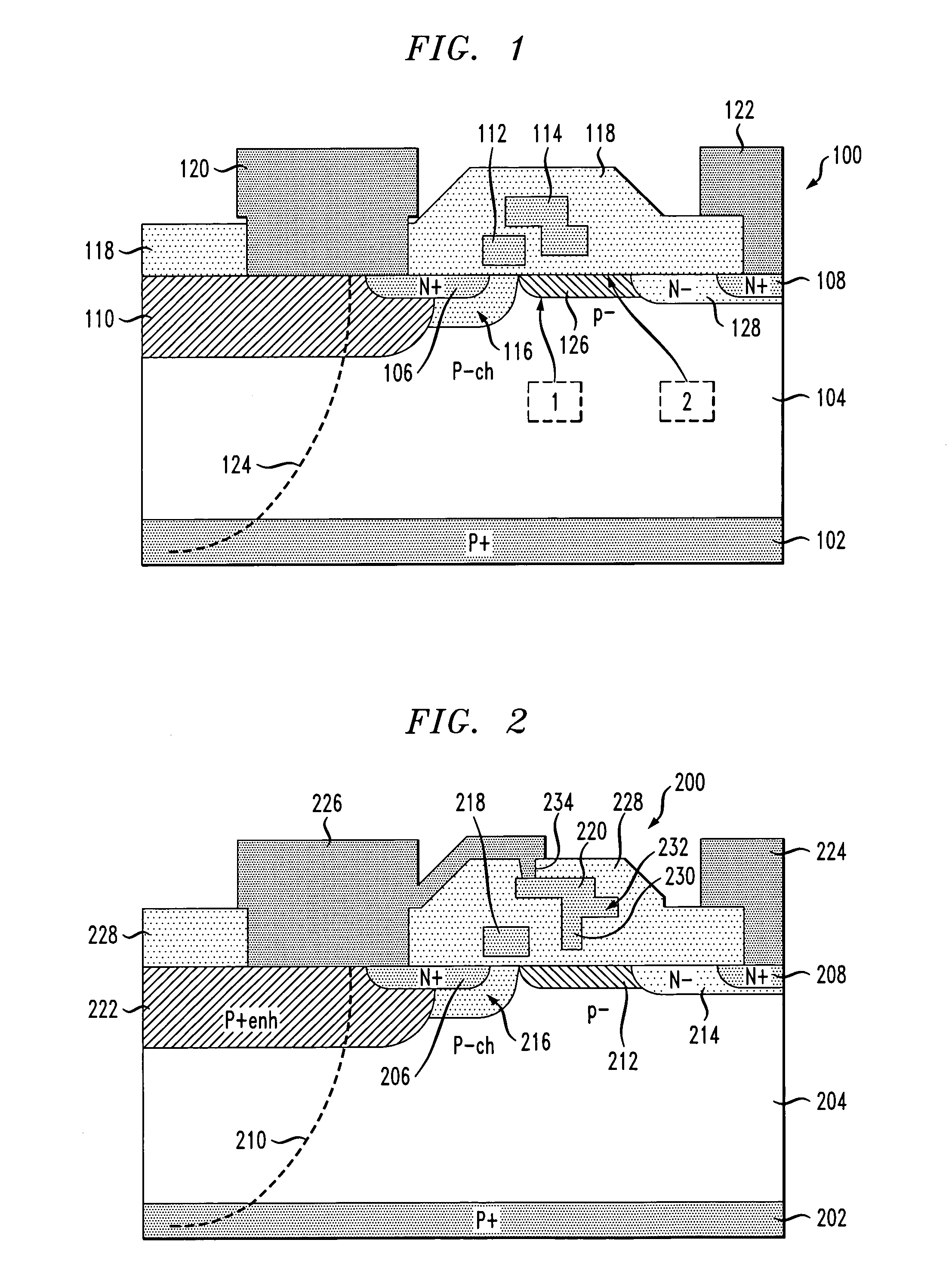

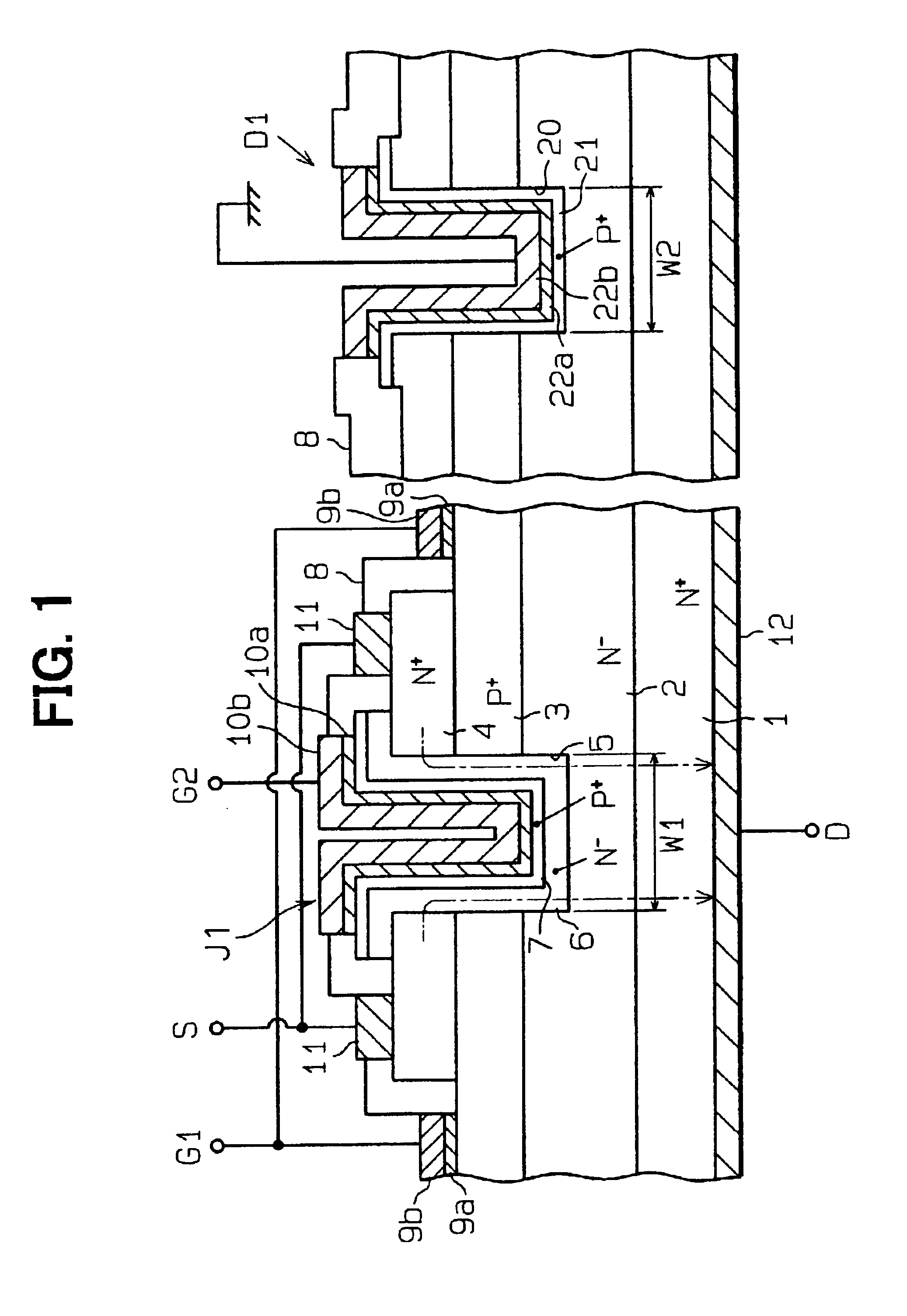

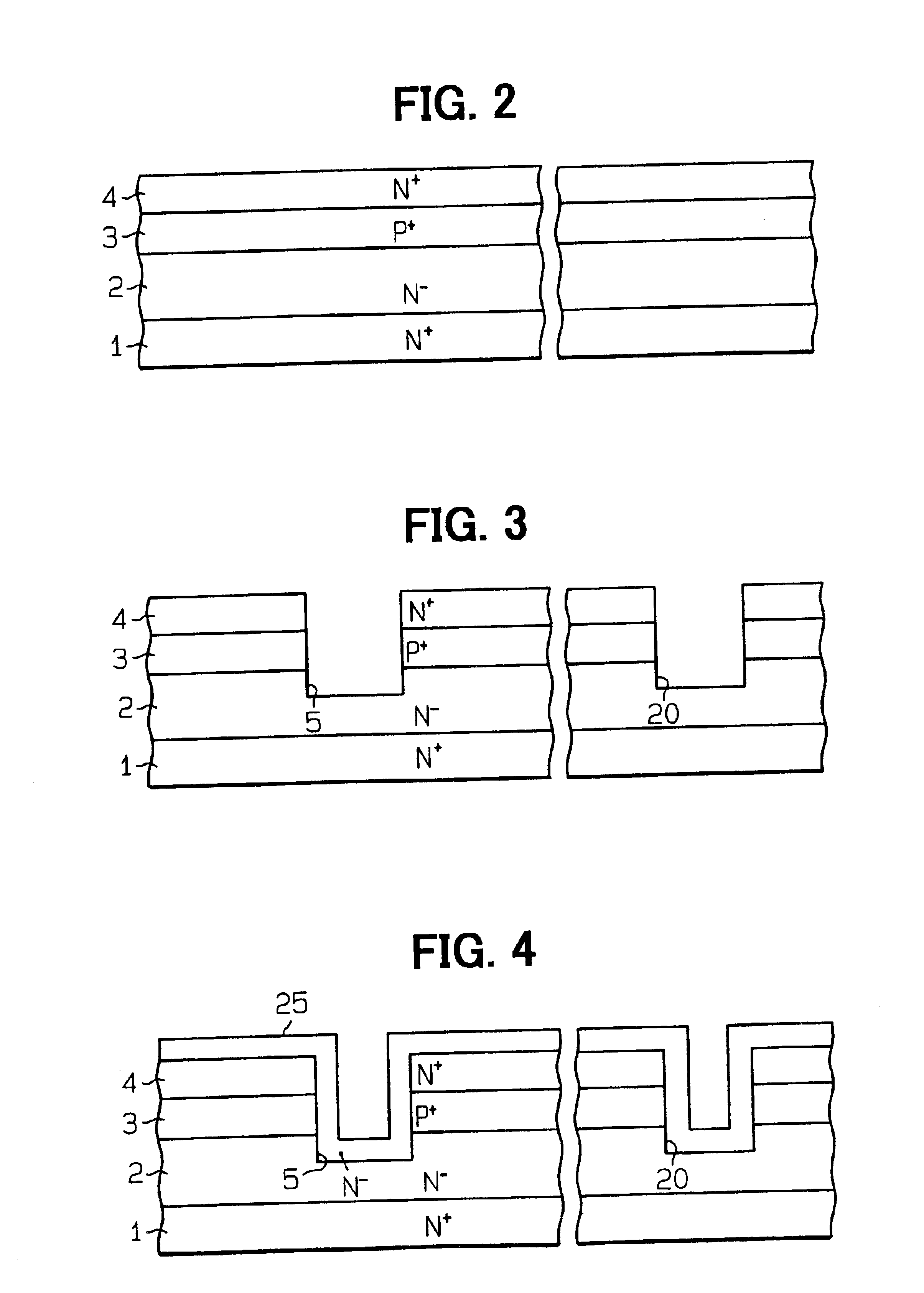

Power semiconductor device having RESURF layer

InactiveUS6919610B2Lower breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceImpurity

A semiconductor device including a drain layer having a first conductivity type, a drift layer having the first conductivity type, which is formed on the drain layer and has an impurity concentration lower than that in the drain layer, and a RESURF layer having a second conductivity type and formed to extend from a surface of the drift layer into the drain layer, the RESURF layer forming a superjunction structure together with the drift layer and forming a depletion layer in the drift layer.

Owner:AMANO CINCINNATI

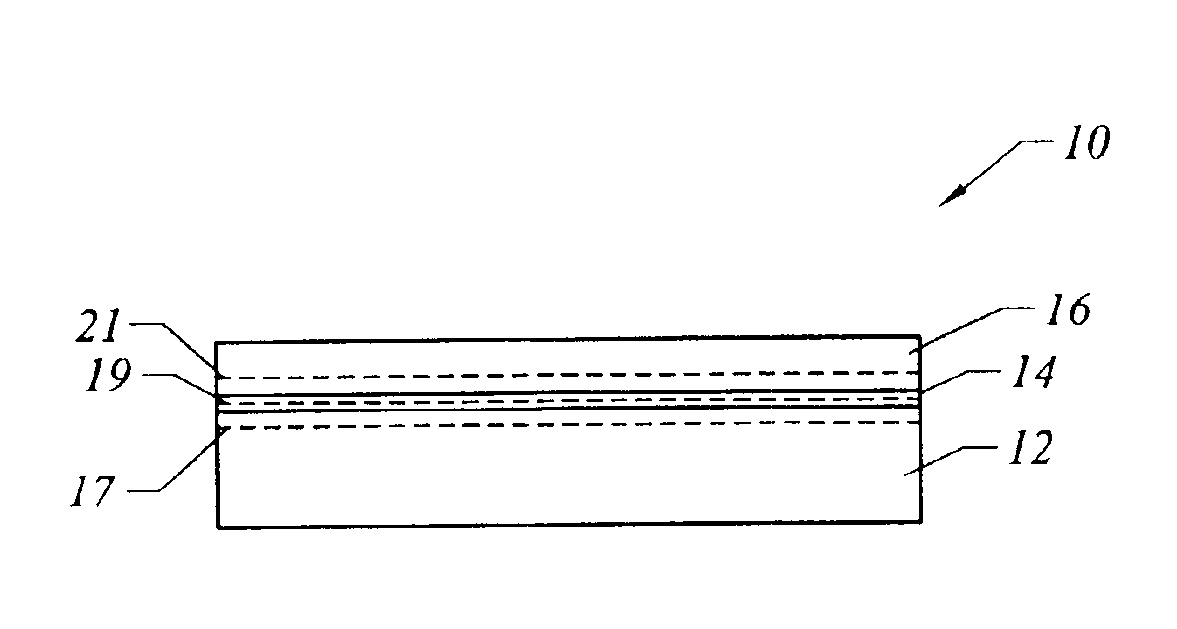

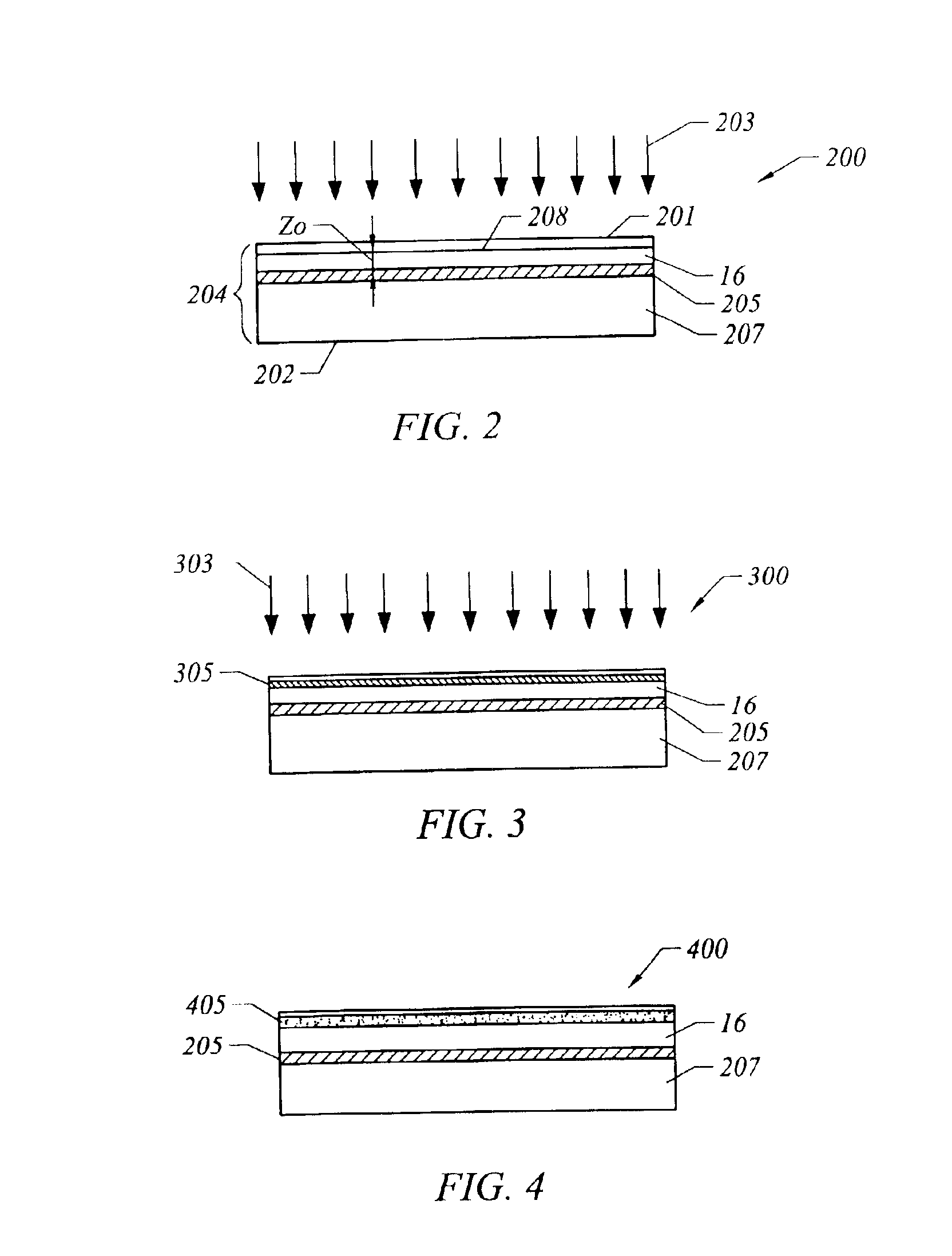

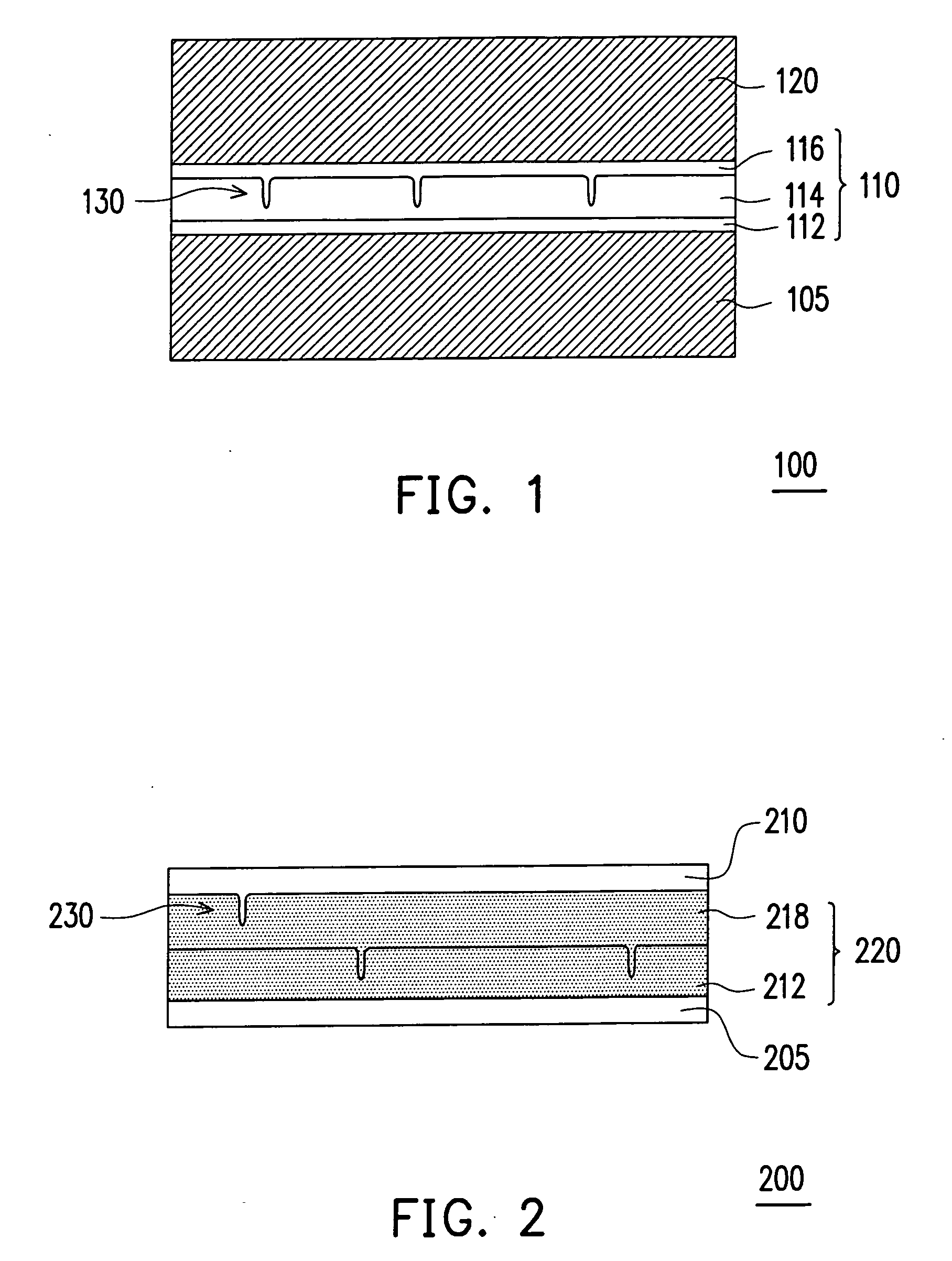

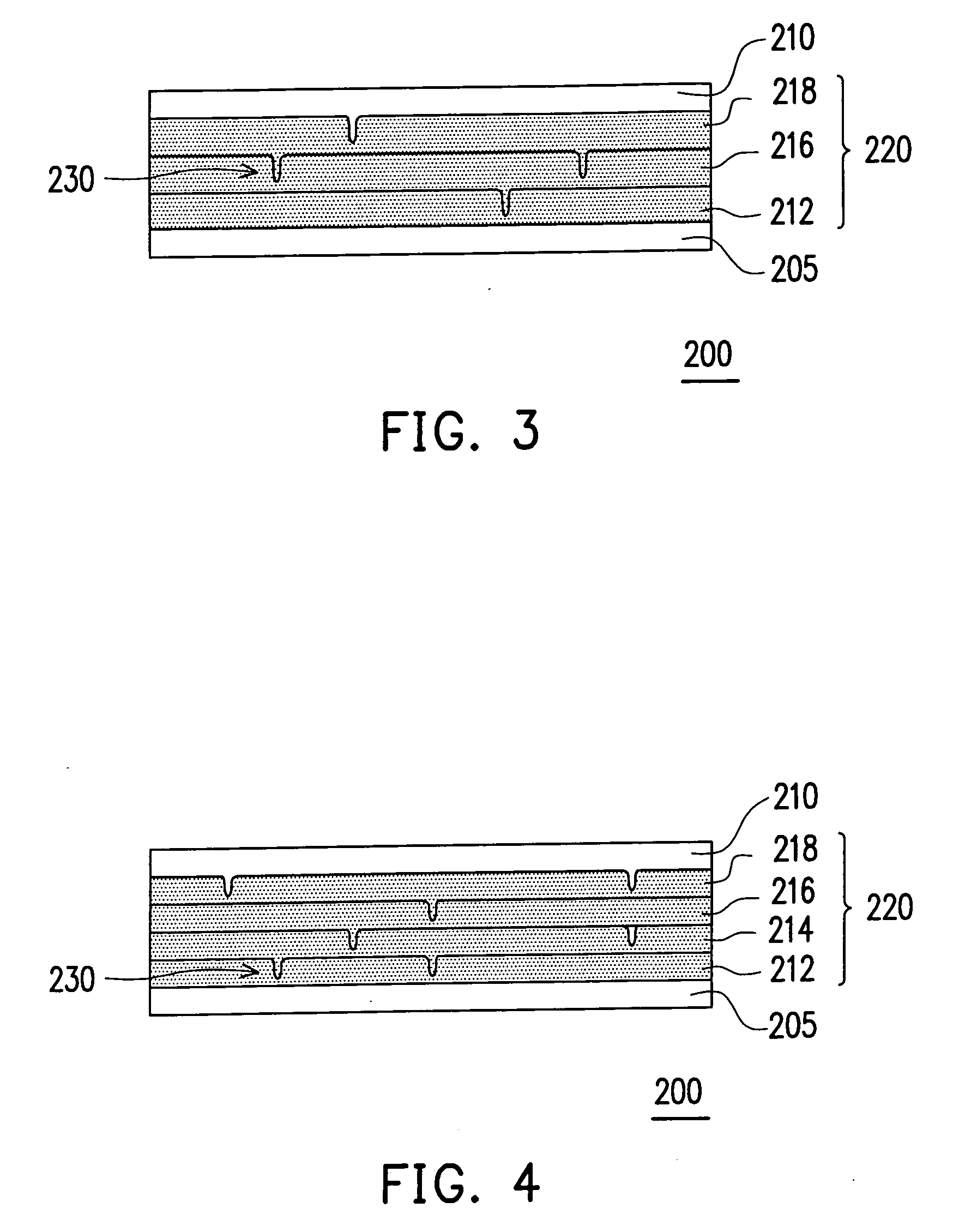

Gettering technique for wafers made using a controlled cleaving process

InactiveUS6890838B2Lower breakdown voltageImprove leakage currentSemiconductor/solid-state device manufacturingIntegrated circuitPlasma-immersion ion implantation

A technique for forming a gettering layer in a wafer made using a controlled cleaving process. The gettering layer can be made by implanting using beam line or plasma immersion ion implantaion, or made by forming a film of material such as polysilicon by way of chemical vapor deposition. A controlled cleaving process is used to form the wafer, which is a multilayered silicon on insulator substrate. The gettering layer removes and / or attracts impurities in the wafer, which can be detrimental to the functionality and reliability of an integrated circuit device made on the wafer.

Owner:SILICON GENERAL CORPORATION

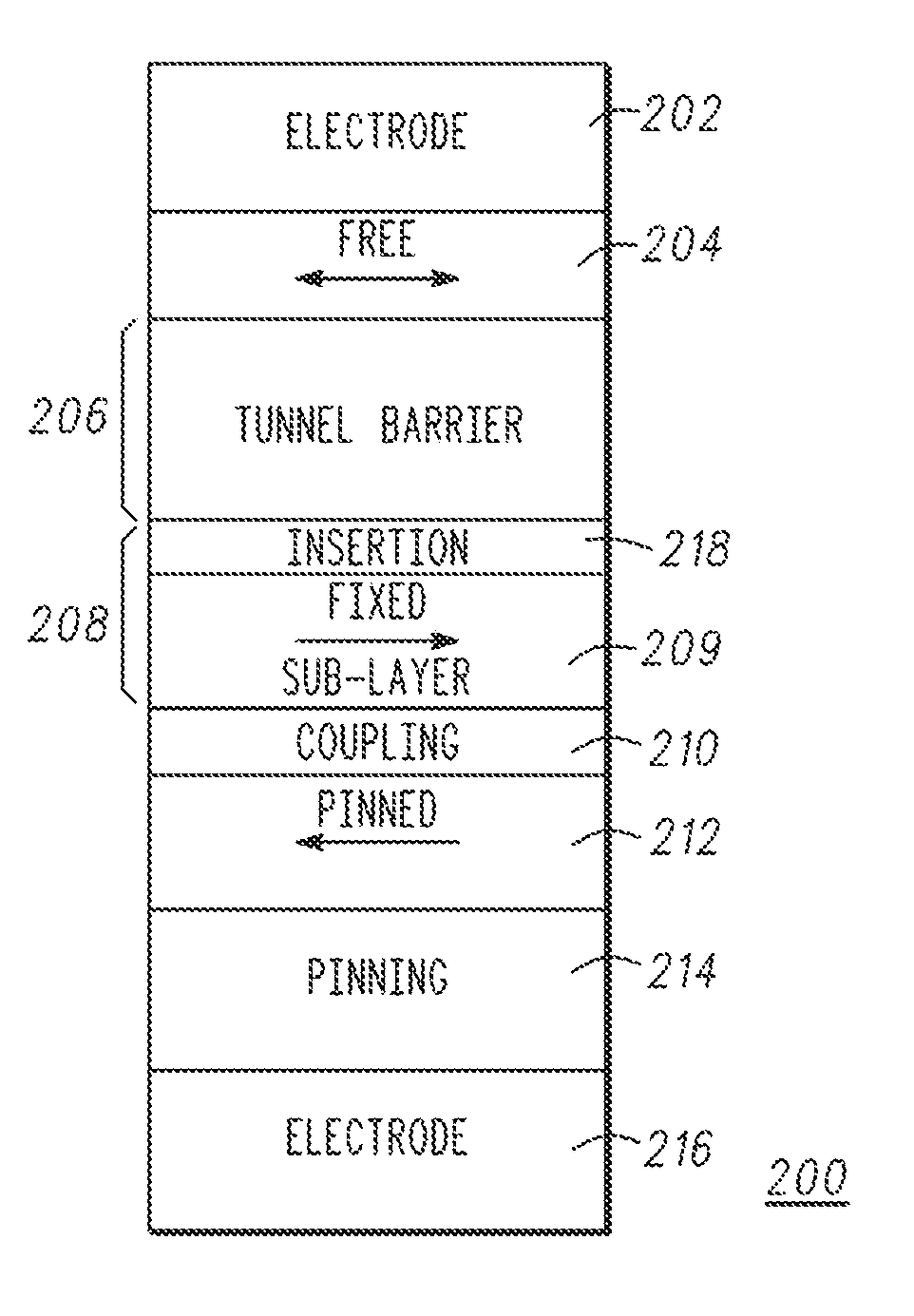

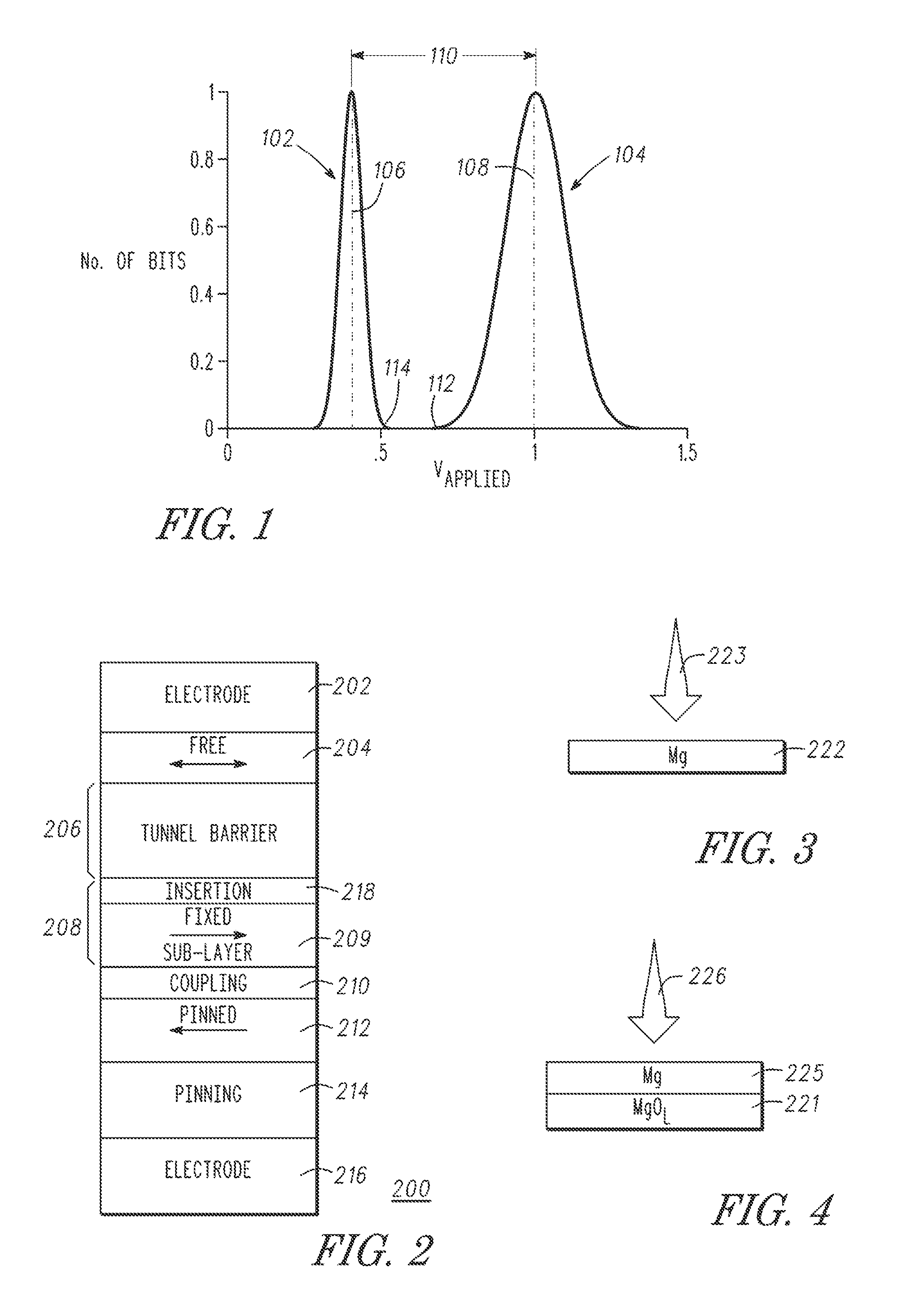

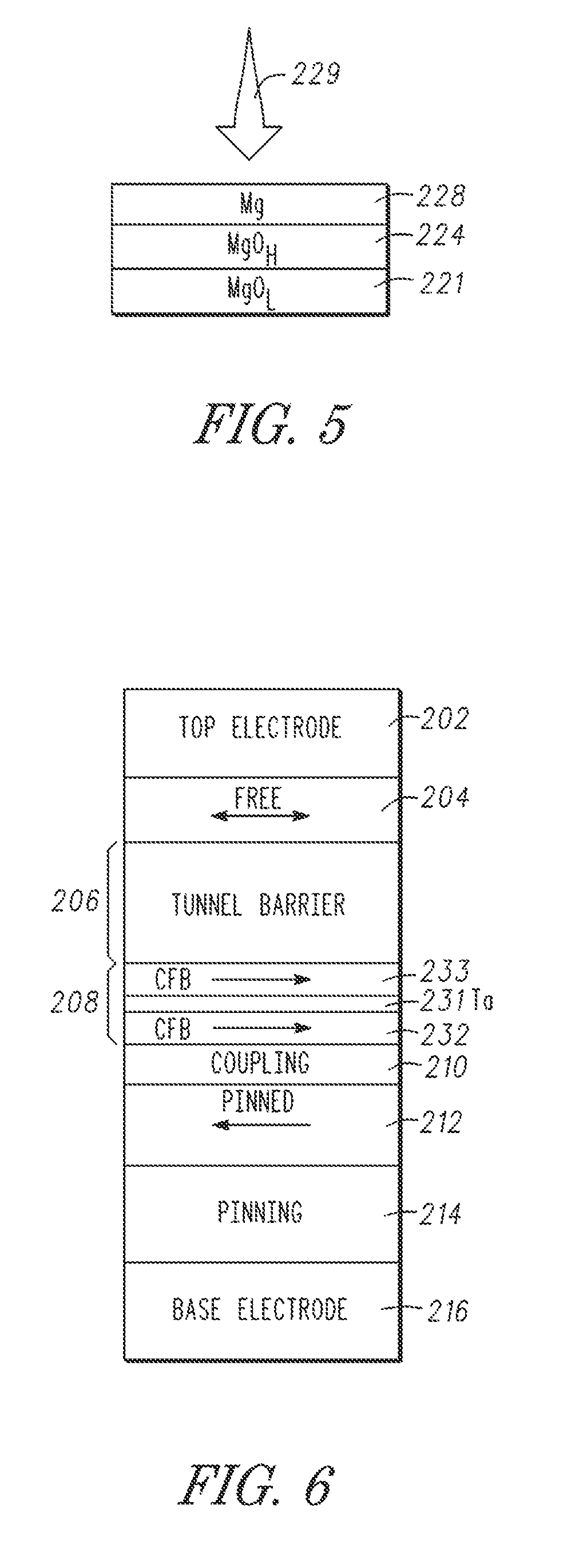

Apparatus and process for manufacturing ST-MRAM having a metal oxide tunnel barrier

ActiveUS9136464B1Improved breakdown distributionReduce in quantityNanoinformaticsGalvano-magnetic device detailsBreakdown voltageMetal

An MRAM device, and a process for manufacturing the device, provides improved breakdown distributions, a reduced number of bits with a low breakdown voltage, and an increased MR, thereby improving reliability, manufacturability, and error-free operation. A tunnel barrier is formed between a free layer and a fixed layer in three repeating steps of forming a metal material, interceded by oxidizing each of the metal materials. The oxidization of the third metal material is greater than the dose of the first metal, but less than the dose of the second metal. The fixed layer may include a discontinuous layer of a metal, for example, Ta, in the fixed layer between two layers of a ferromagnetic material.

Owner:EVERSPIN TECHNOLOGIES

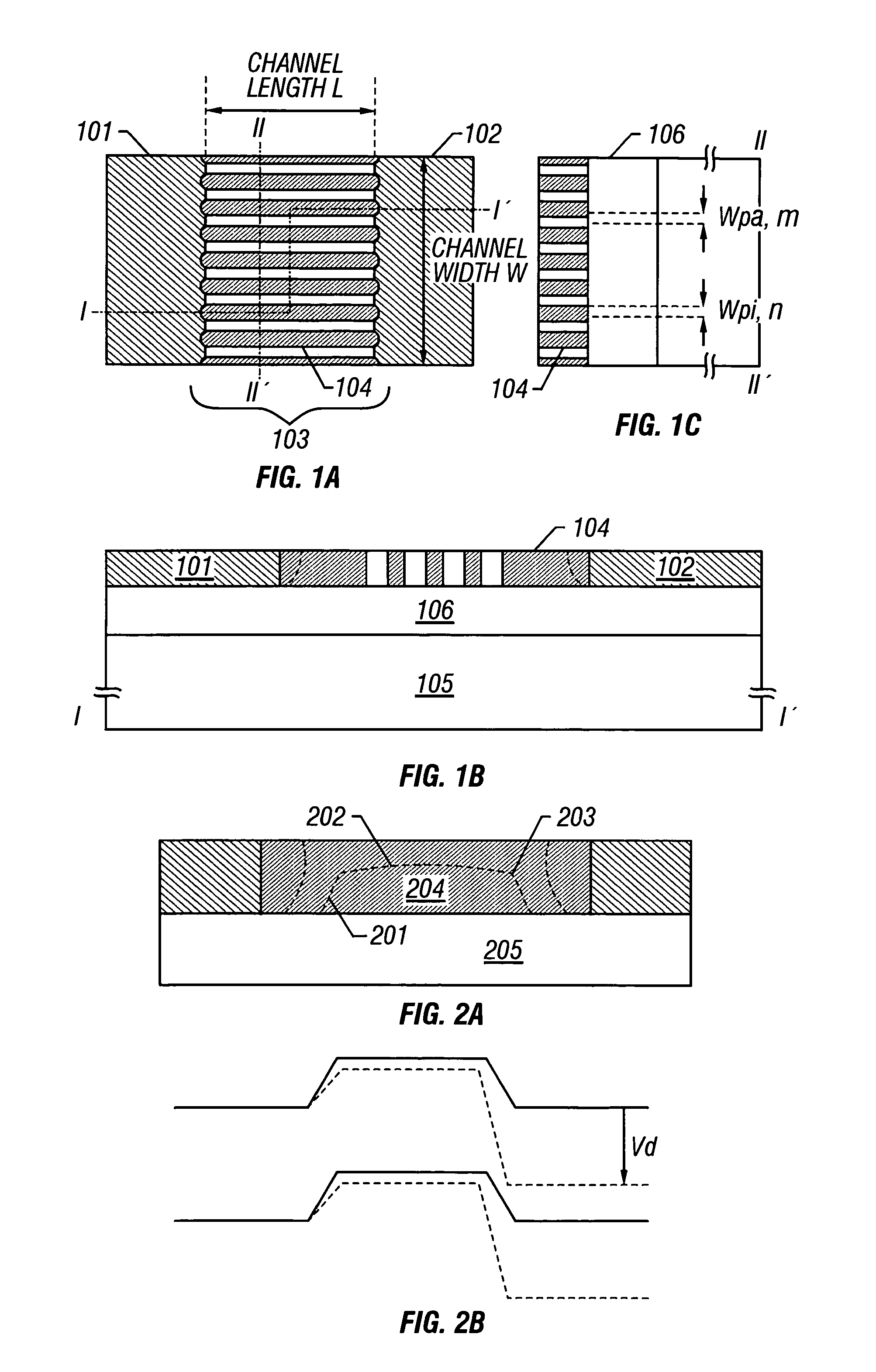

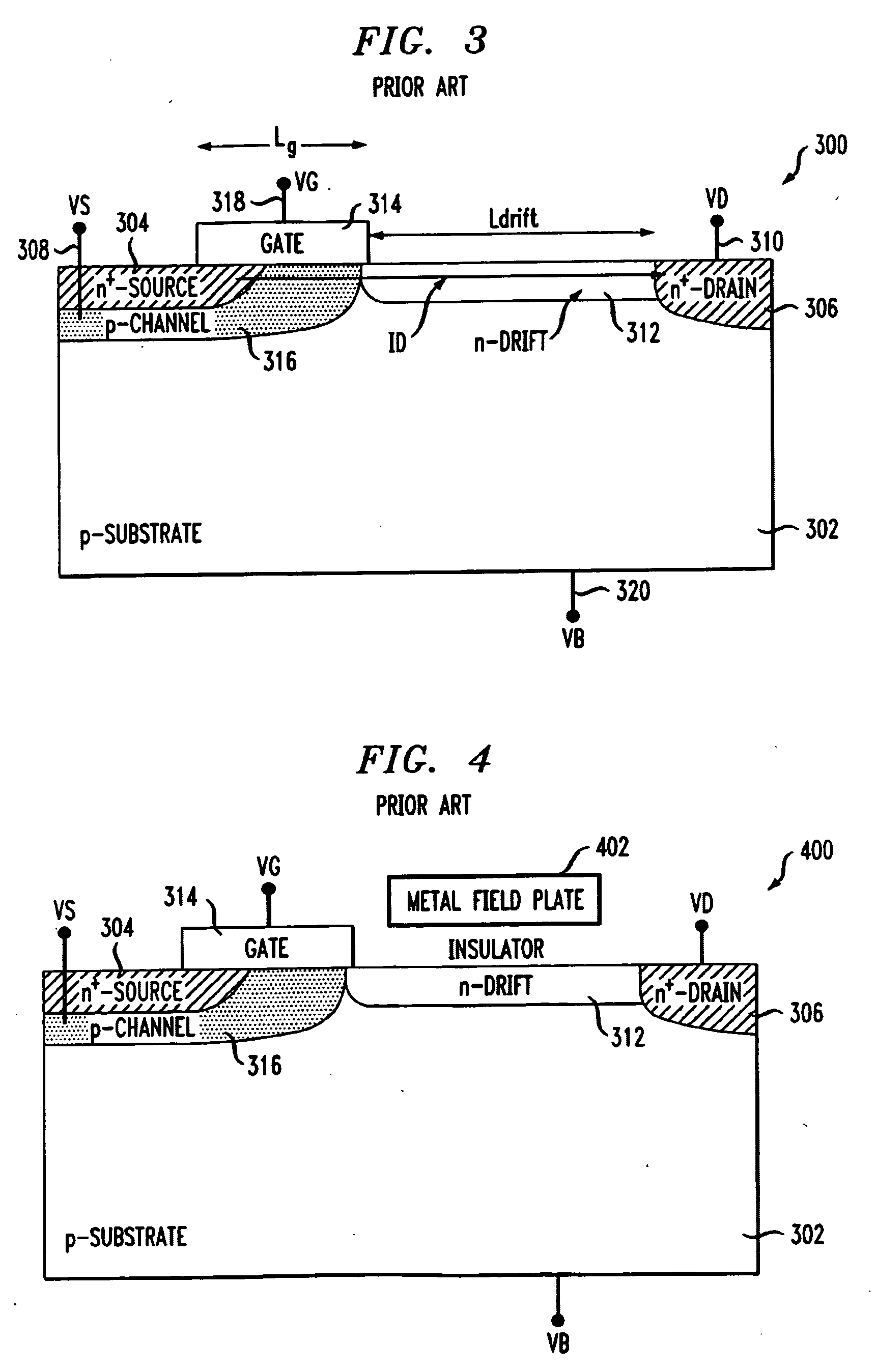

Graded conductive structure for use in a metal-oxide-semiconductor device

ActiveUS7148540B2Improve high frequency performanceLower breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesSemiconductorMetal

An MOS device comprises a semiconductor layer of a first conductivity type and source and drain regions of a second conductivity type formed in the semiconductor layer, the source and drain regions being spaced apart from one another. A drift region is formed in the semiconductor layer proximate an upper surface of the semiconductor layer and between the source and drain regions, and a insulating layer is formed on the semiconductor layer above at least a portion of the drift region. A gate is formed on the insulating layer and at least partially between the source and drift regions. The MOS device further includes a conductive structure comprising a first end formed on the insulating layer and spaced apart from the gate, and a second end formed on the insulating layer and extending laterally toward the drain region above at least a portion of the drift region. The conductive structure is configured such that a thickness of the insulating layer under the second end of the conductive structure increases as the second end extends toward the drain region.

Owner:BELL SEMICON LLC

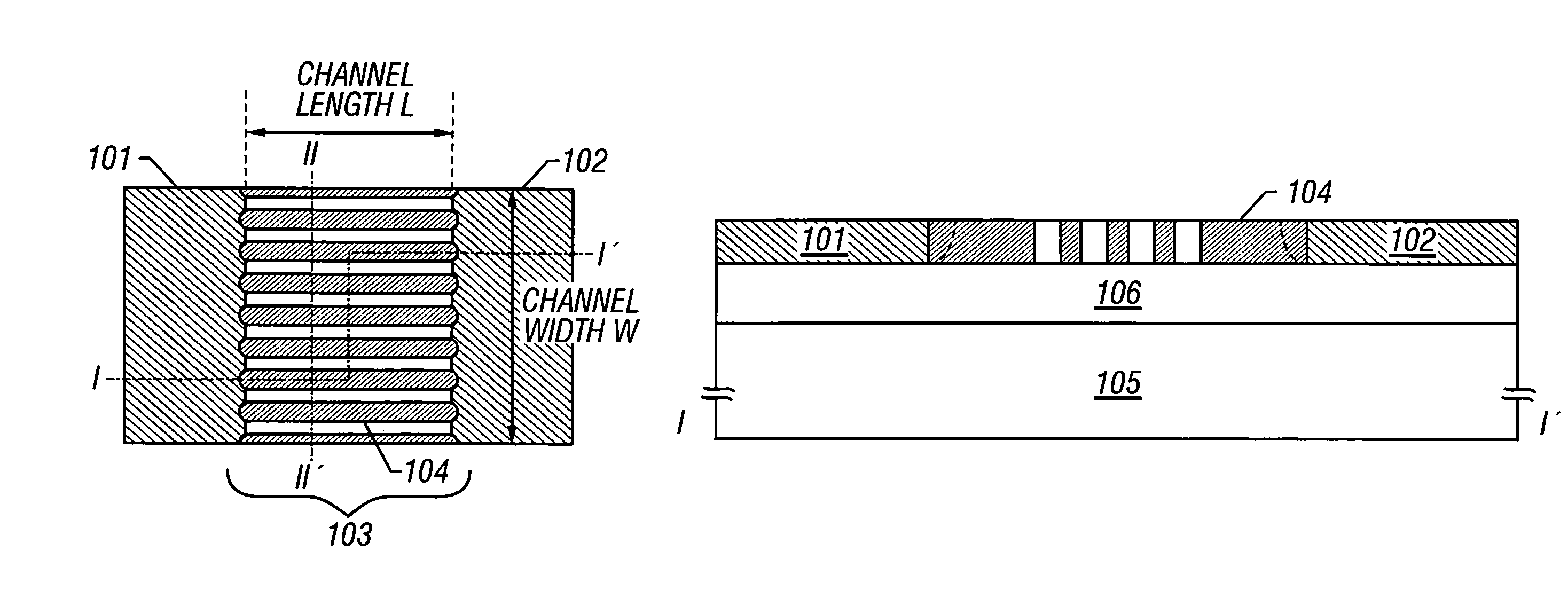

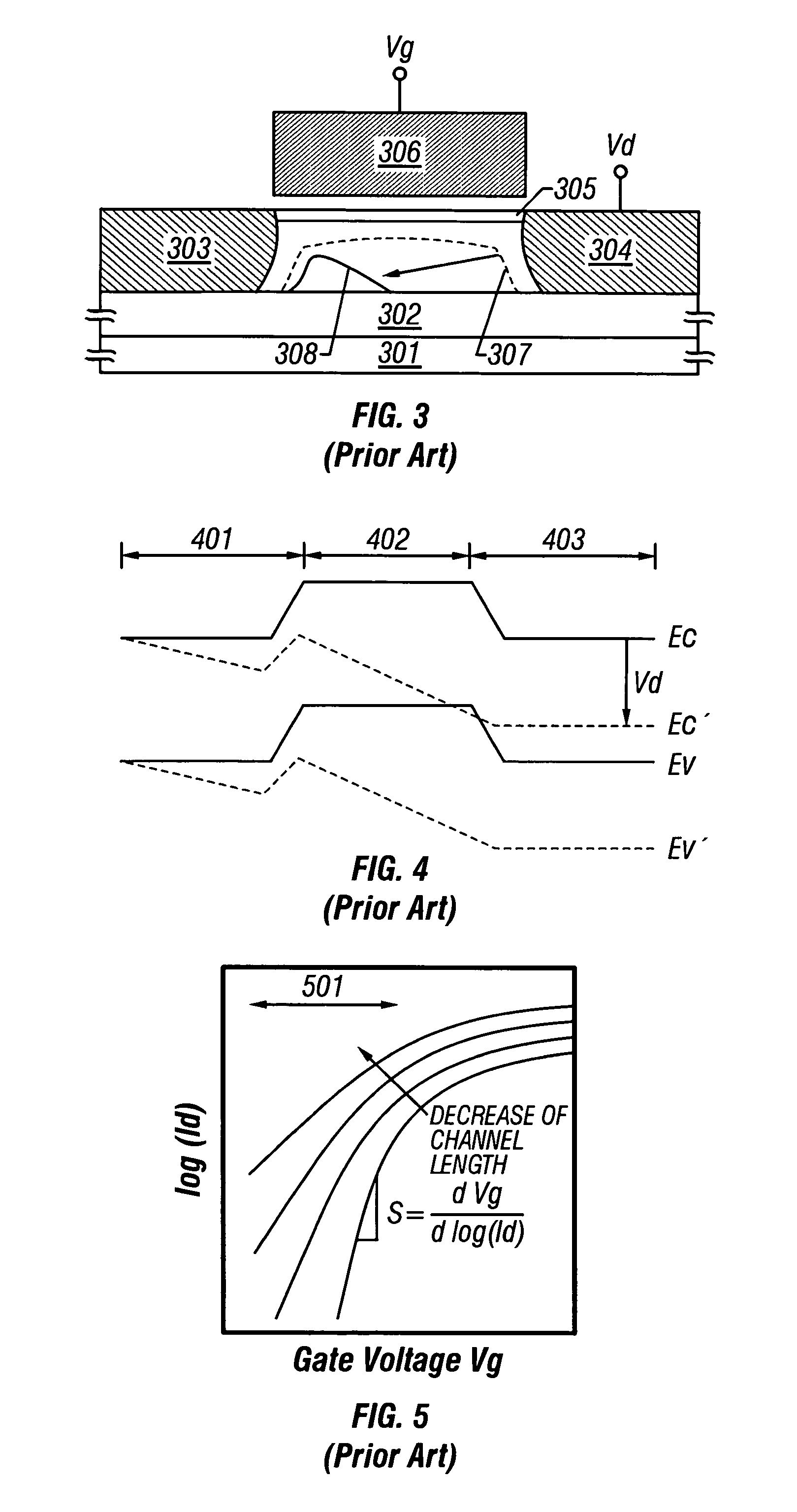

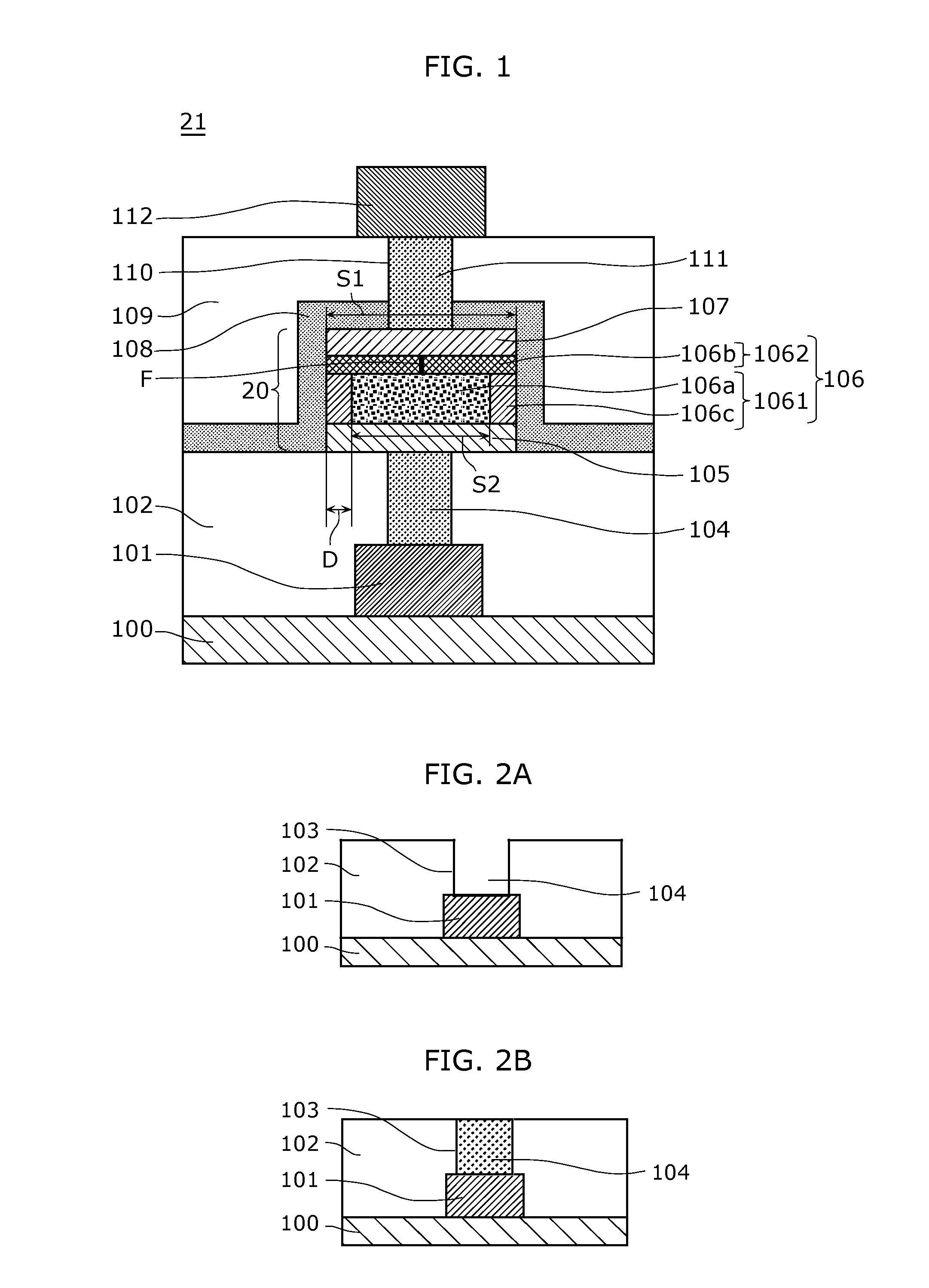

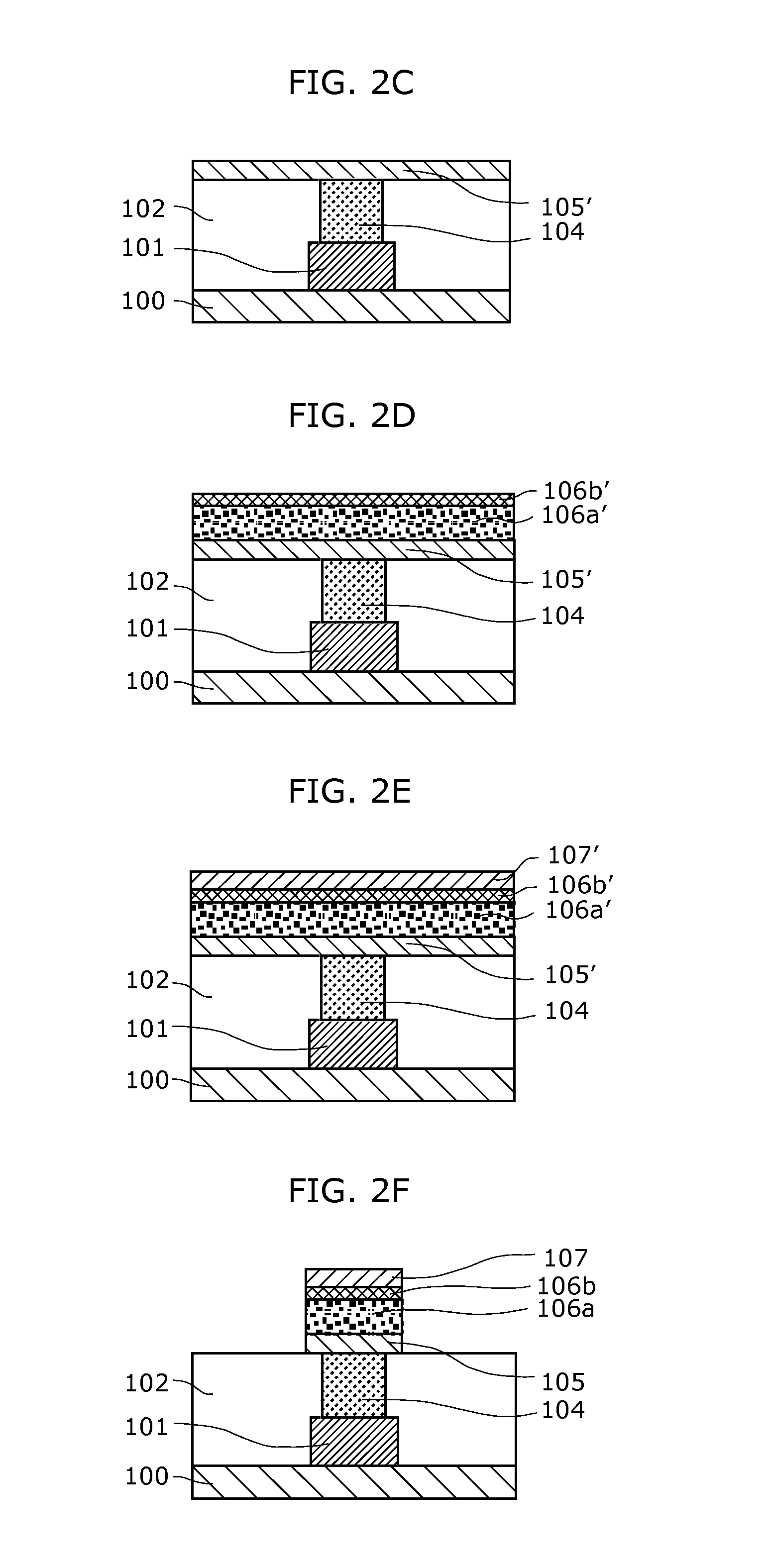

Semiconductor device having SOI structure and manufacturing method thereof

InactiveUS7339235B1Suppression of short channel effectsEffectively suppress a depletion layerTransistorIndividual molecule manipulationEngineeringSemiconductor

A fine semiconductor device having a short channel length while suppressing a short channel effect. Linearly patterned or dot-patterned impurity regions 104 are formed in a channel forming region 103 so as to be generally parallel with the channel direction. The impurity regions 104 are effective in suppressing the short channel effects. More specifically, the impurity regions 104 suppress expansion of a drain-side depletion layer, so that the punch-through phenomenon can be prevented. Further, the impurity regions cause a narrow channel effect, so that reduction in threshold voltage can be lessened.

Owner:SEMICON ENERGY LAB CO LTD

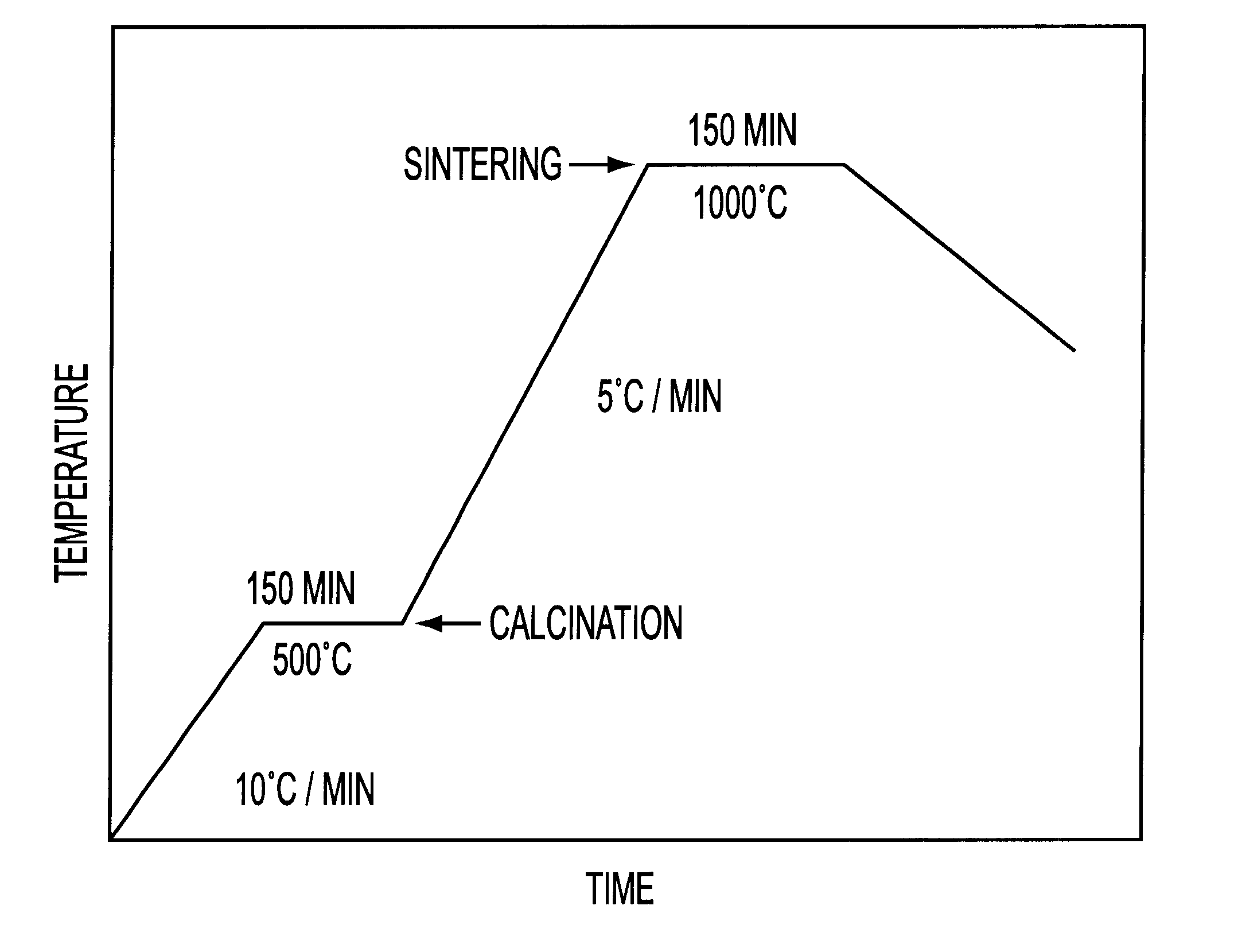

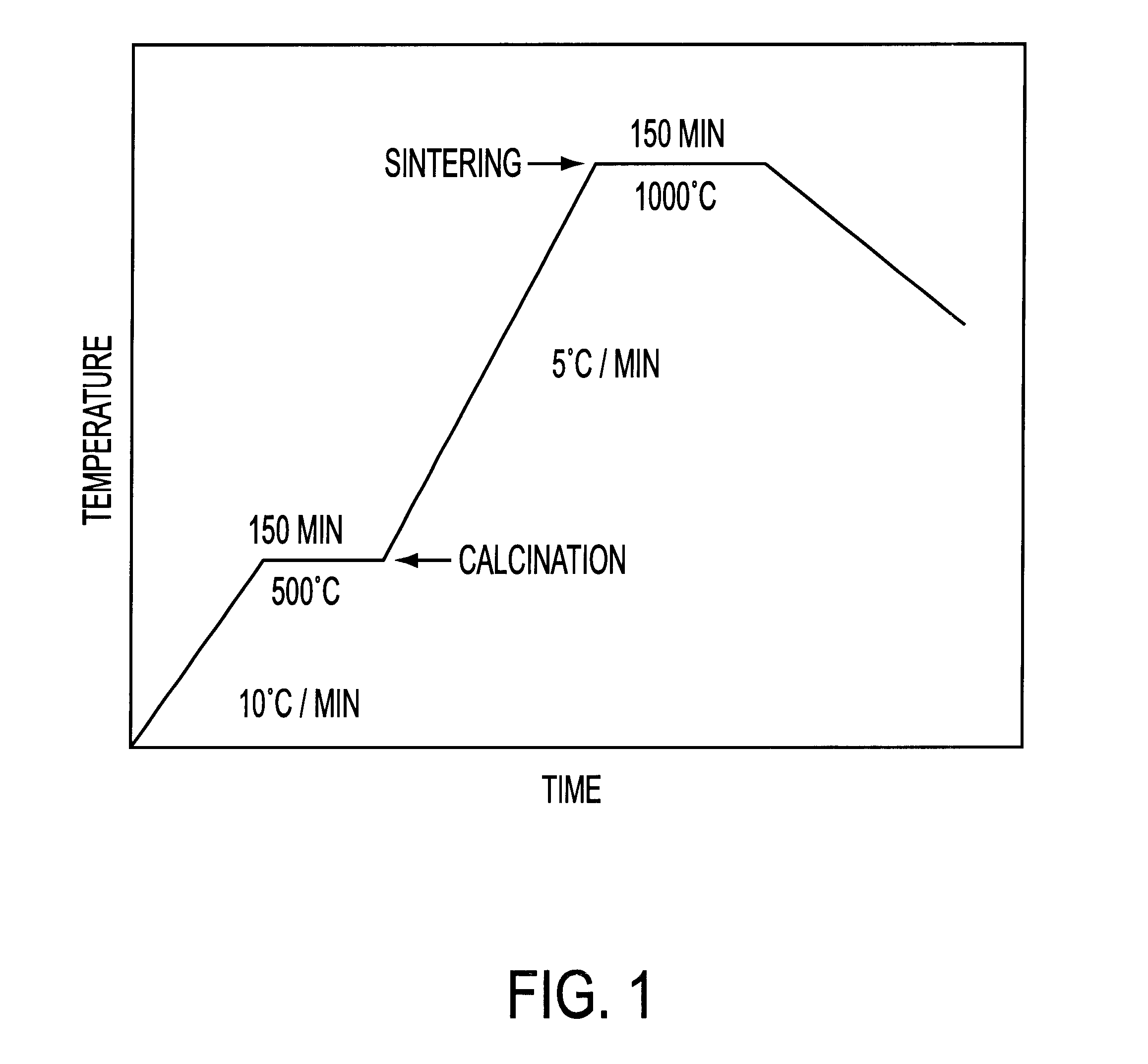

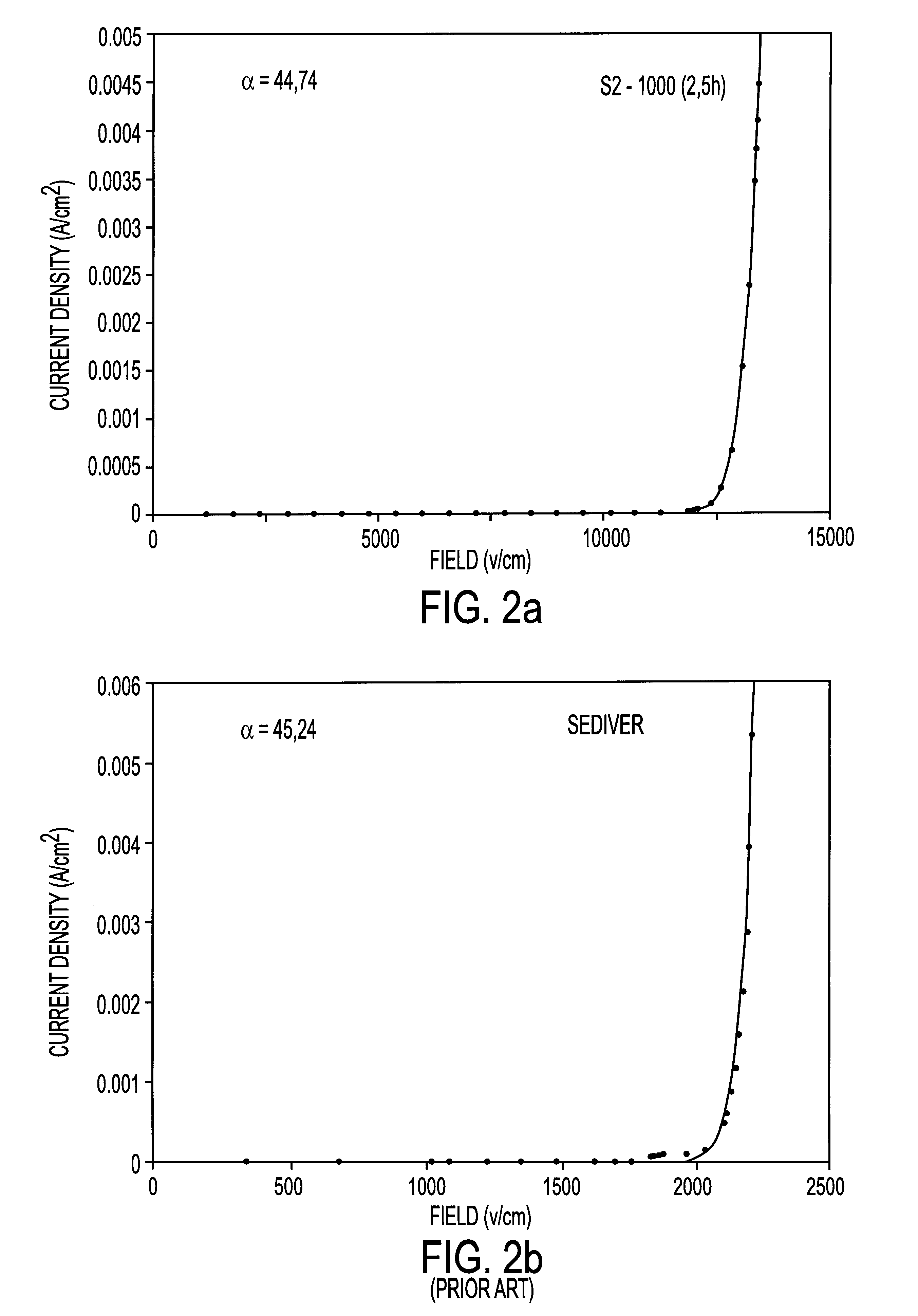

Varistors based on nanocrystalline powders produced by mechanical grinding

InactiveUS6620346B1Lower breakdown voltageImprove breakdown voltageMaterial nanotechnologyConductive materialGrain boundaryBreakdown voltage

The invention concerns novel varistors based on zinc oxide and a method for making same, which consists in using as base products nanocrystalline powders obtained by high-intensity mechanical grinding and in subjecting the mixture resulting from said nanocrystalline powders a consolidating treatment such as sintering, in suitably selected temperature and time conditions so as to retain the smallest possible grain size of ZnO. The resulting varistors have a very fine homogeneous microstructure and an average grain size characteristically not more than 3pm, i.e. five times smaller than standard materials. Said novel varistors have a larger number of grain boundaries per unit length unit and therefore a much higher breakdown voltage. Said voltage is characteristically higher than 10 kV / cm and can reach 17 kV / cm which is almost one order of magnitude above the breakdown voltage of standard varistors. The non-linearity coefficient of the current-voltage curve is also improved, and is greater than 20 and can reach values as high as 60. Moreover, the leakage currents below the breakdown voltage of said varistors, are much lower.

Owner:HYDRO QUEBEC CORP

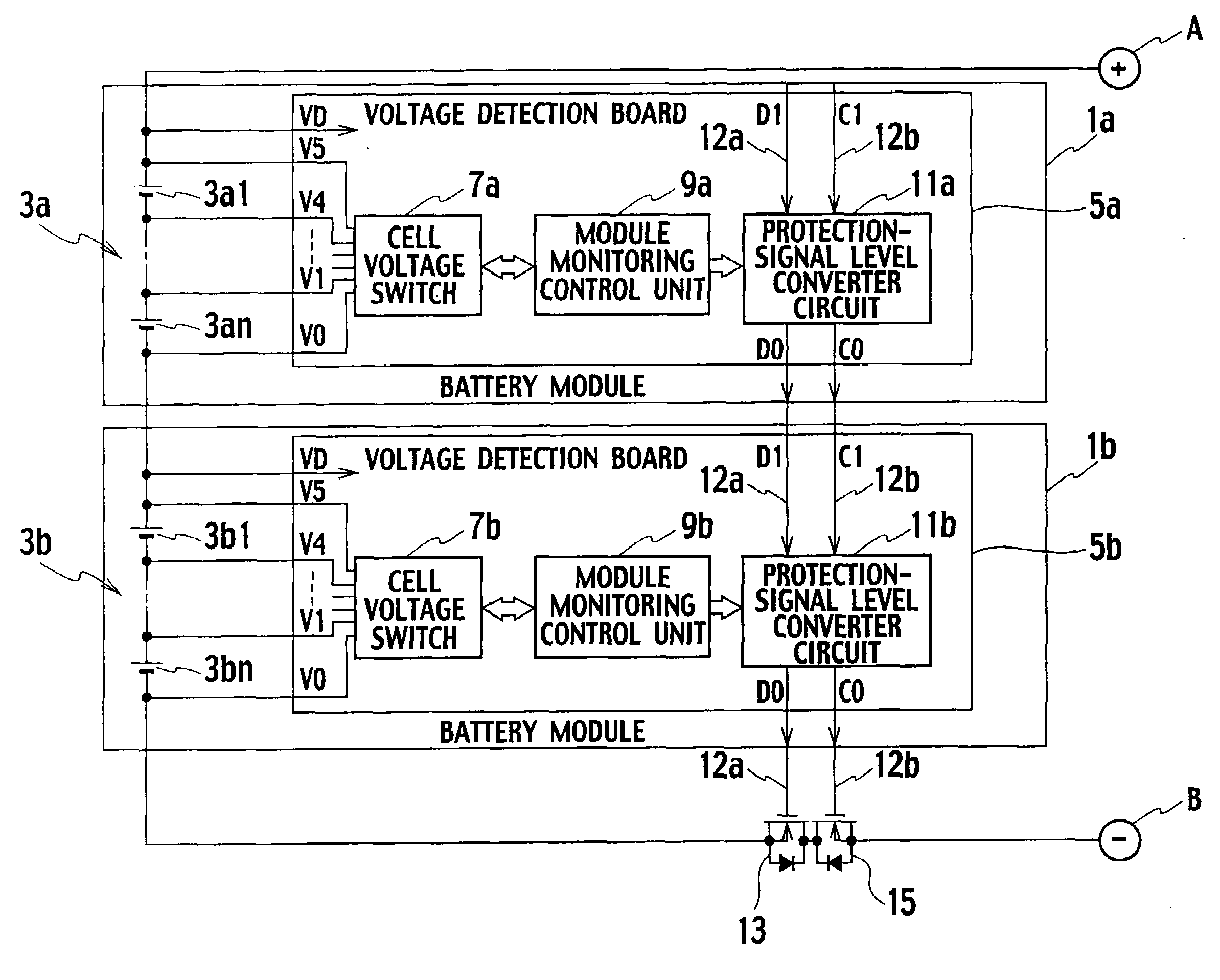

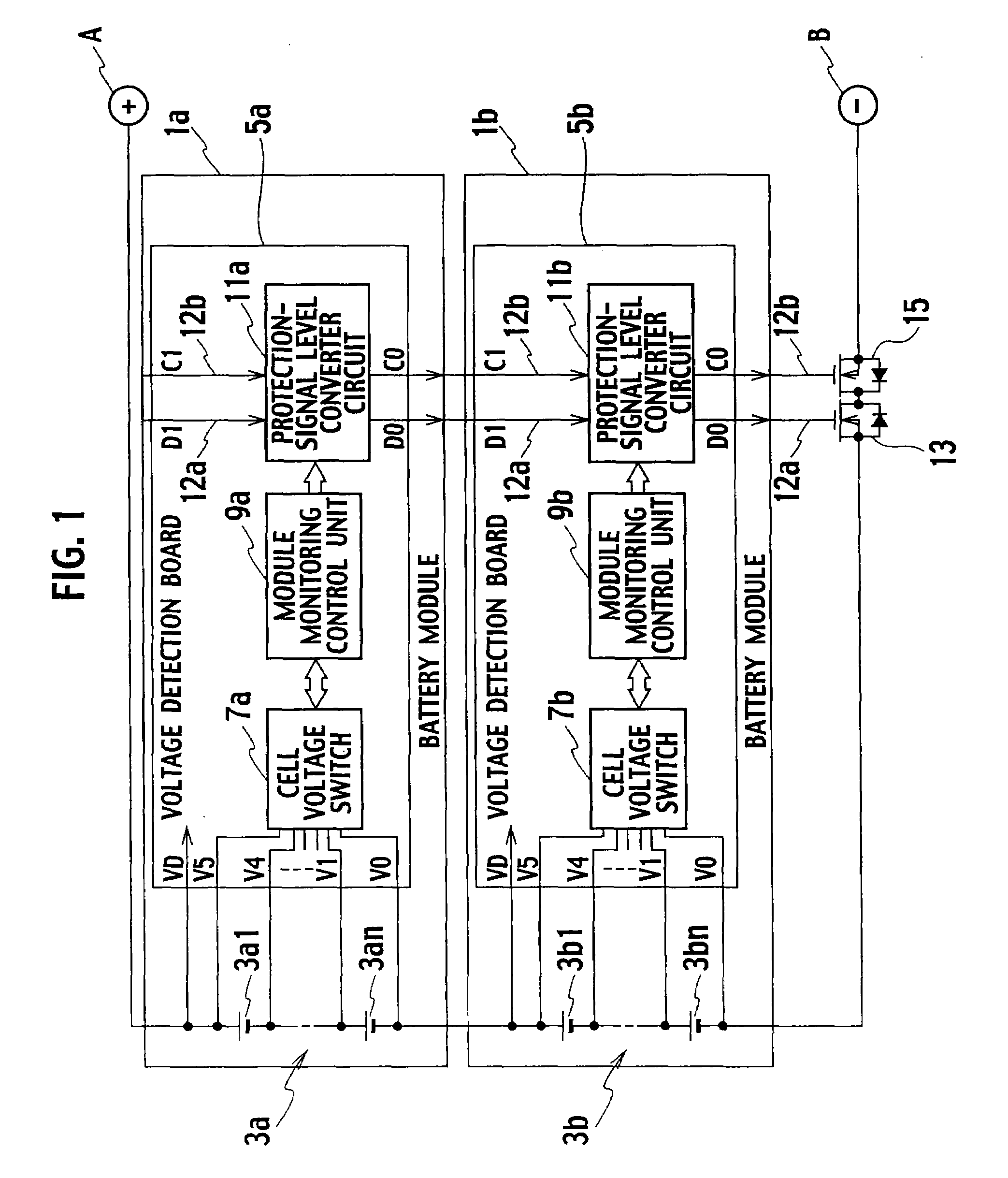

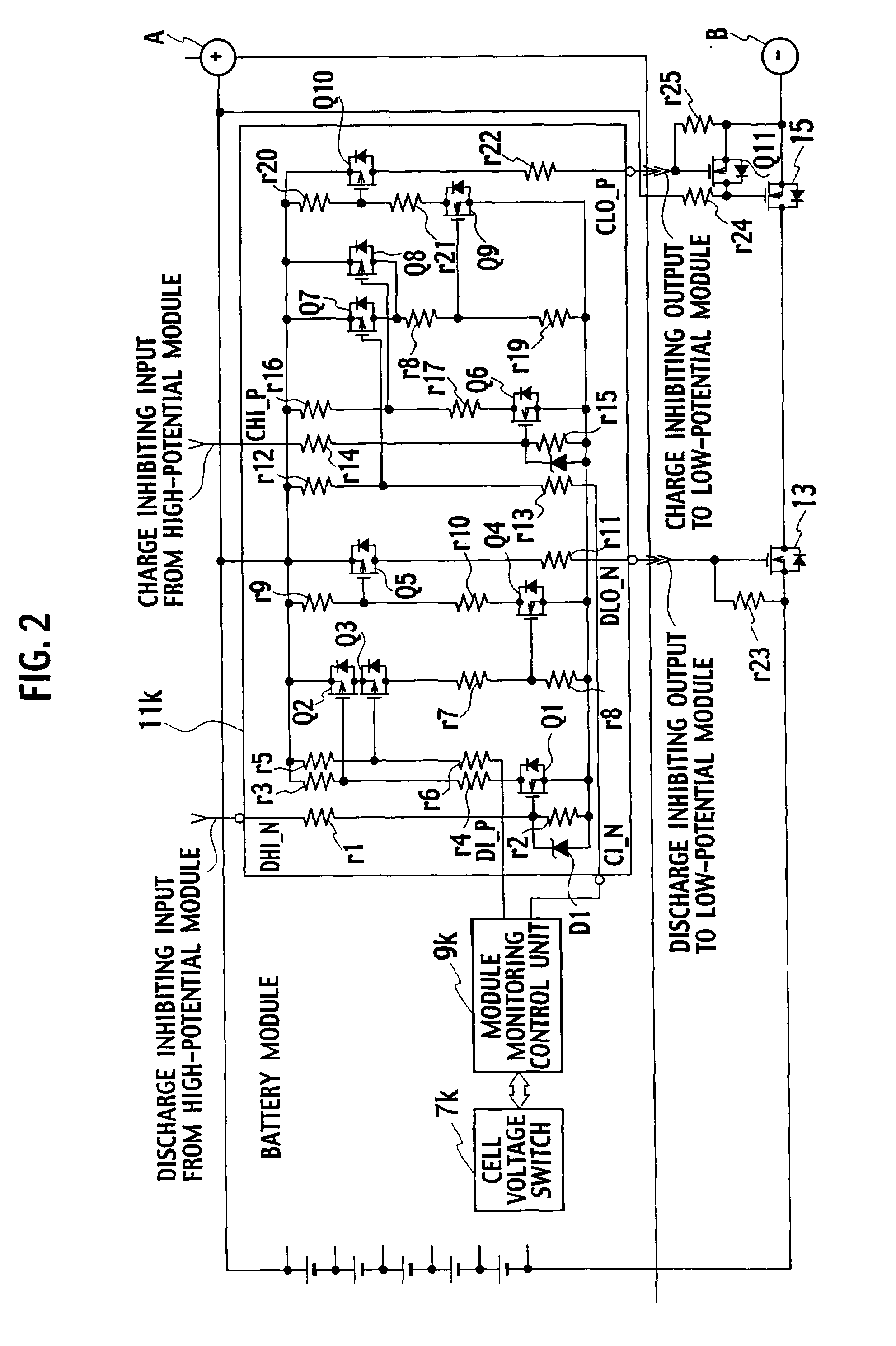

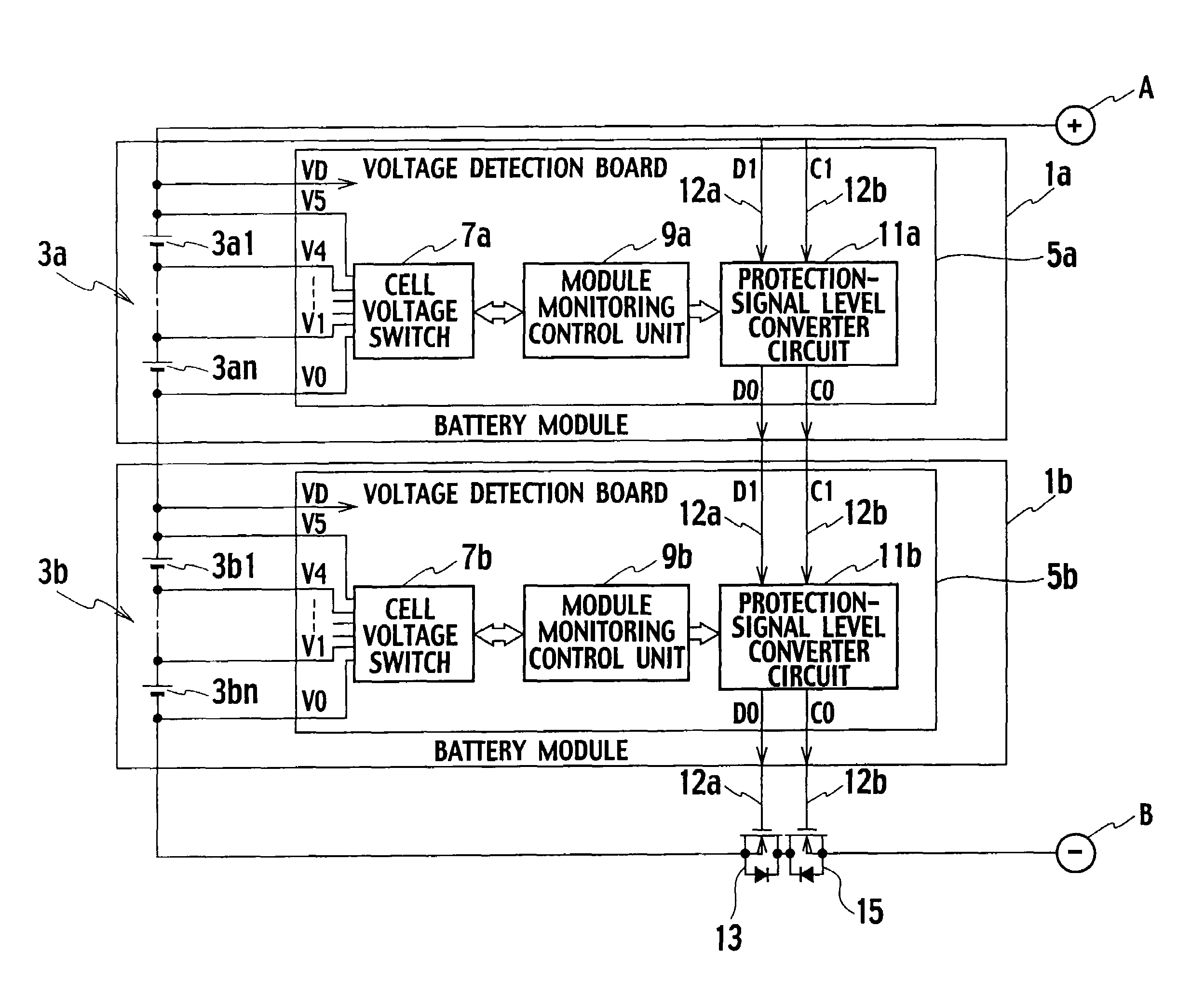

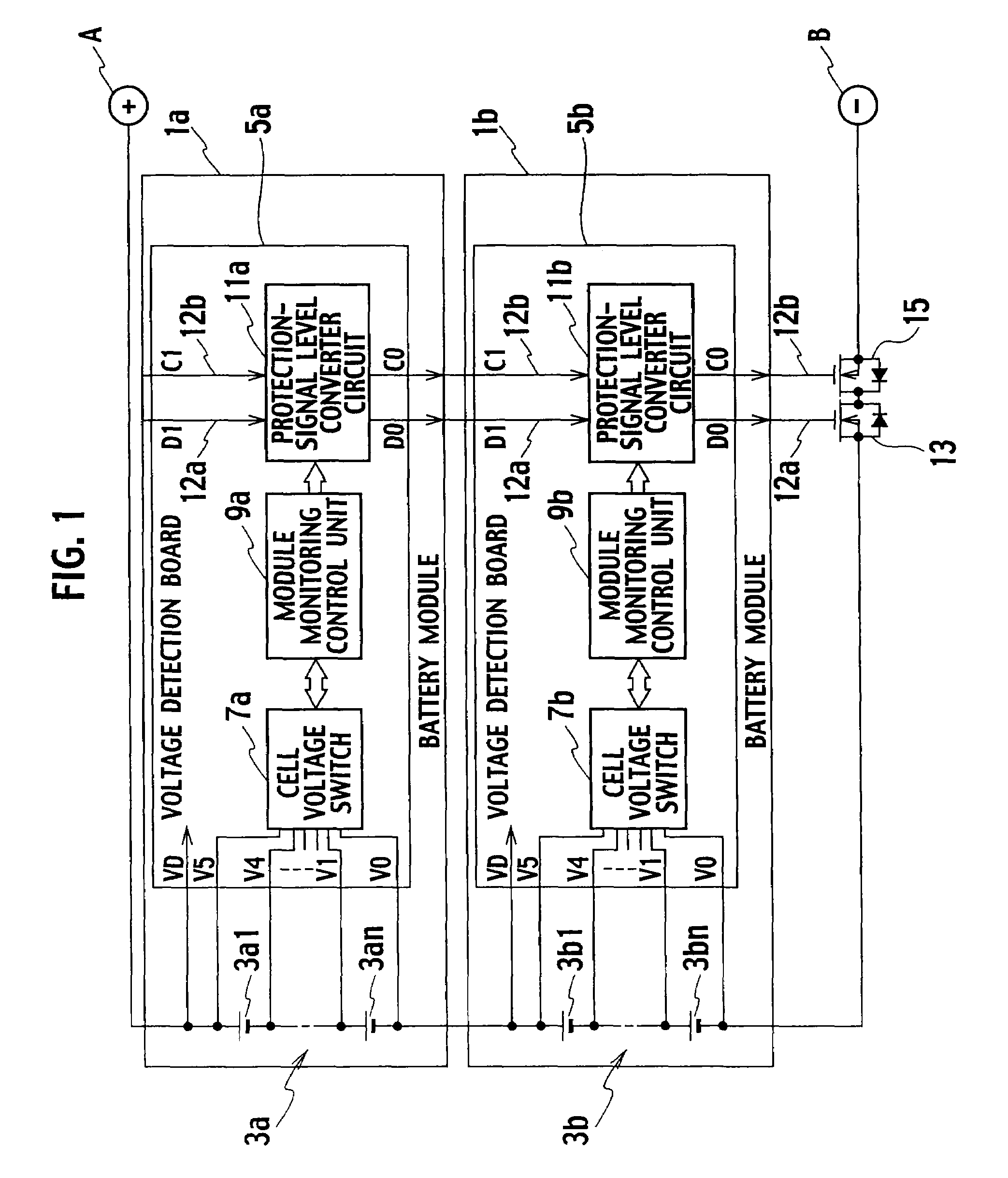

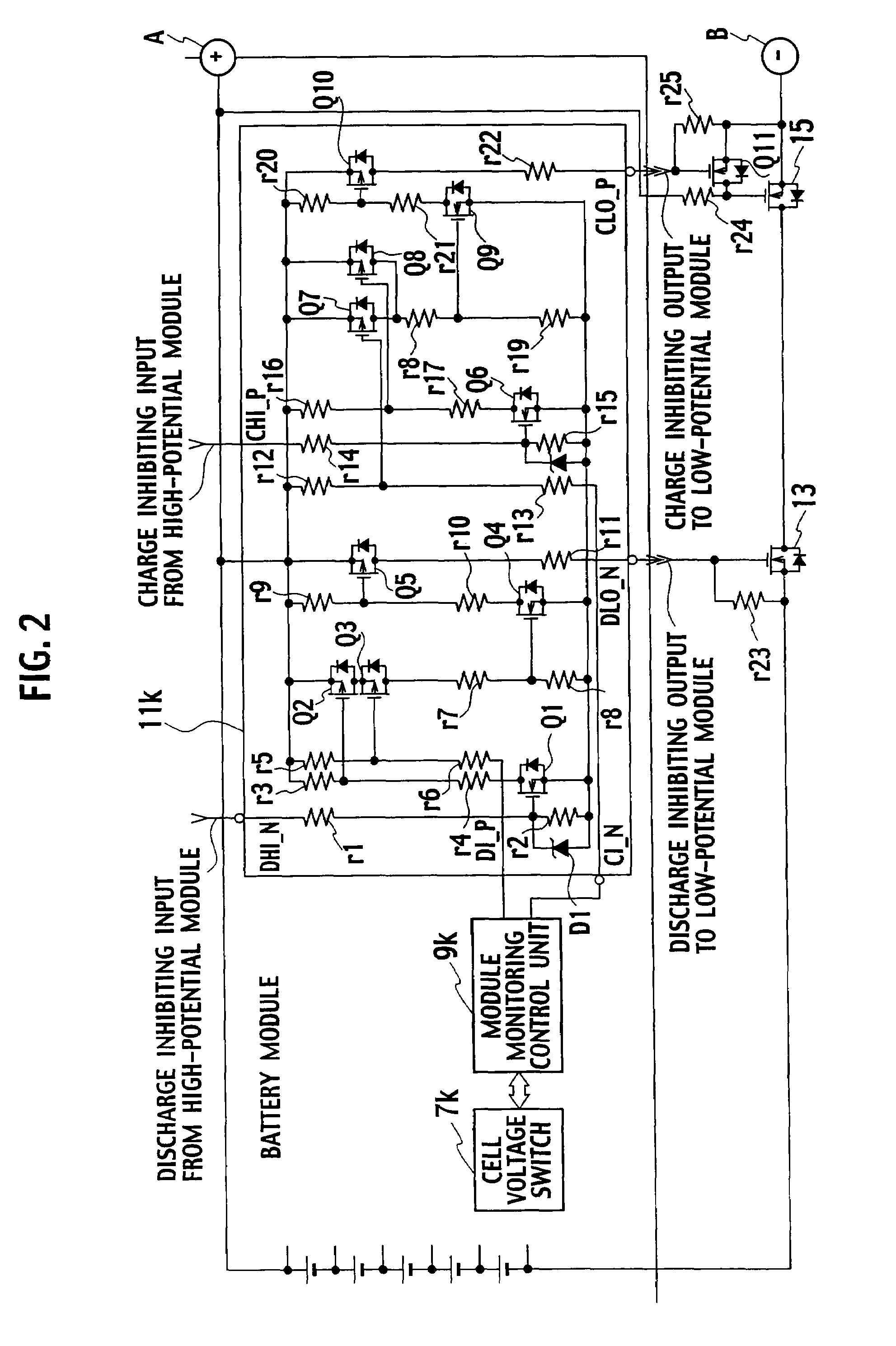

Battery system

InactiveUS20090208821A1Lower breakdown voltageCircuit monitoring/indicationCharge equalisation circuitHigh potentialCell voltage

In a battery system, battery modules (3a, 3b) connected to each other in series respectively include: one or more single cells (3a1 to 3an, 3b1 to 3b-n) connected to one another in any one of series, parallel, and series-parallel; cell voltage switches (7a, 7b) for detecting voltages respectively of the one or more single cells; module monitoring control units (9a, 9b) each for monitoring the detected voltages respectively of the one or more signal cells; and communications level converter circuits (14a, 14b). The battery system includes a master unit (8a) for receiving information on the voltages respectively of the one or more single cells from the module monitoring control units via the communications level converter circuits. One of the communications level converter circuits includes a switch element (Q32) for transmitting a signal of a low-potential battery module to a high-potential battery module. A series circuit includes resistors R1′, R2′ and R5 as well as the switch element is connected between a positive electrode of the highest-potential single cell in the high potential battery module and a negative electrode of the lowest-potential single cell in the low-potential battery cell.

Owner:KK TOSHIBA

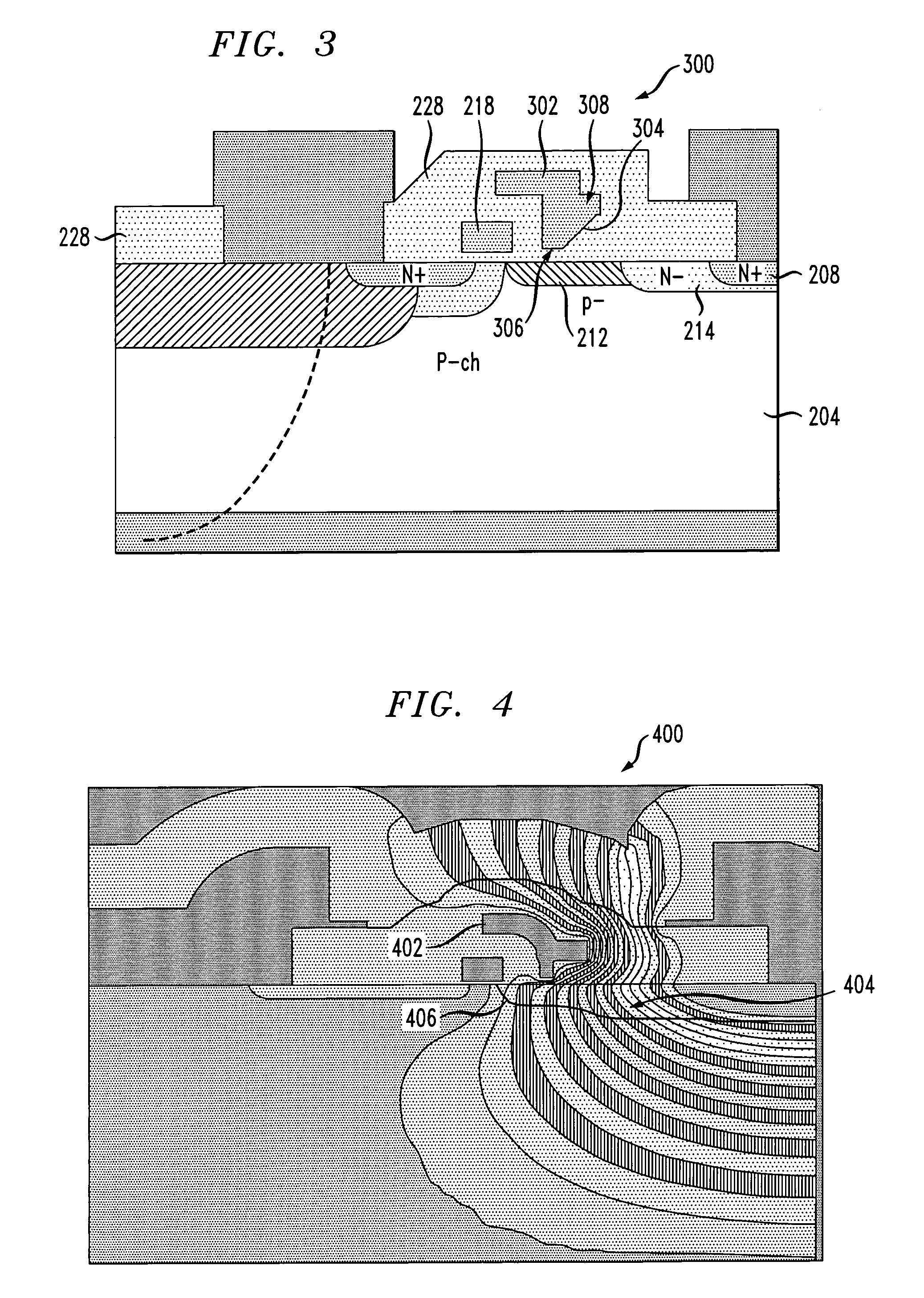

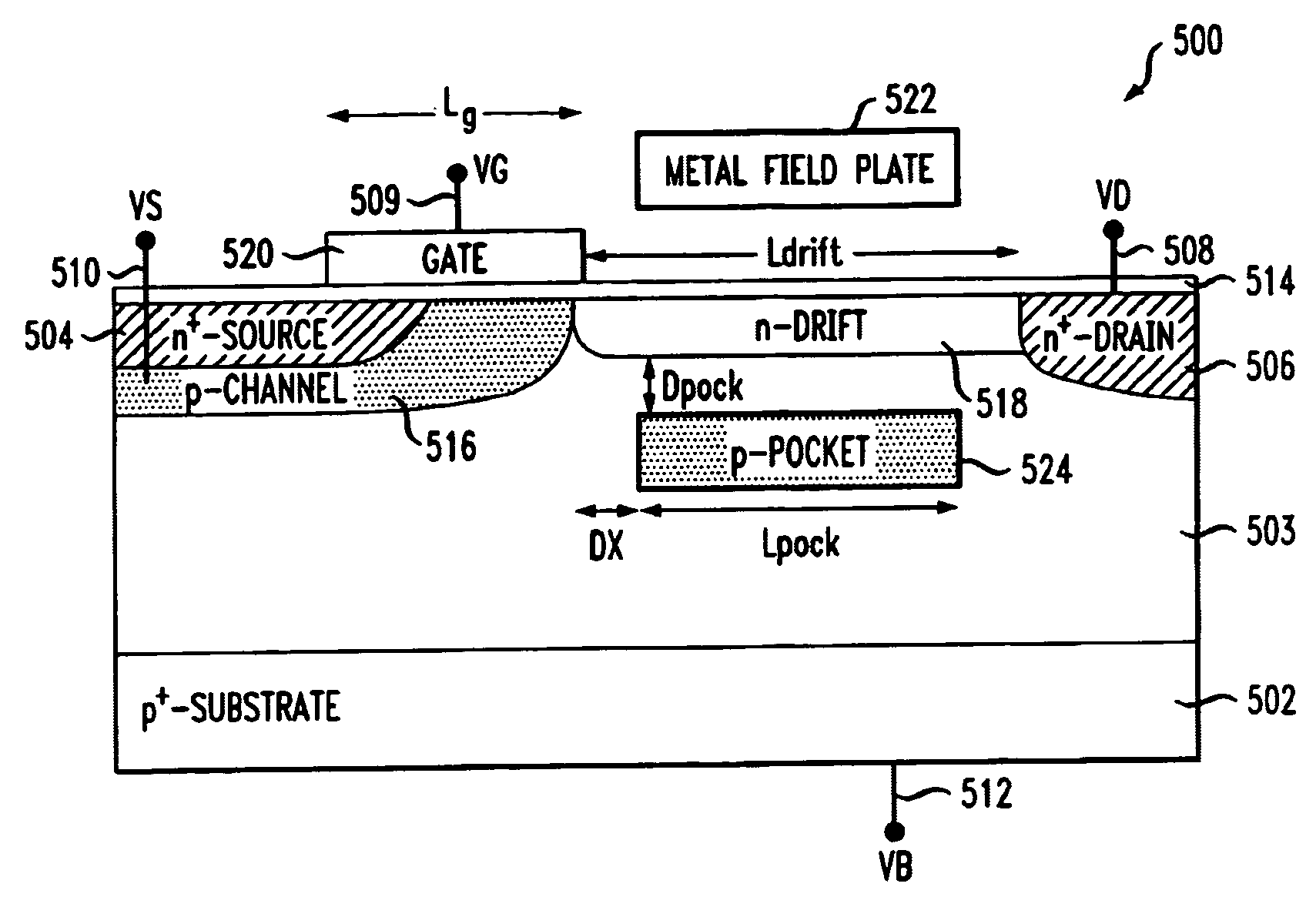

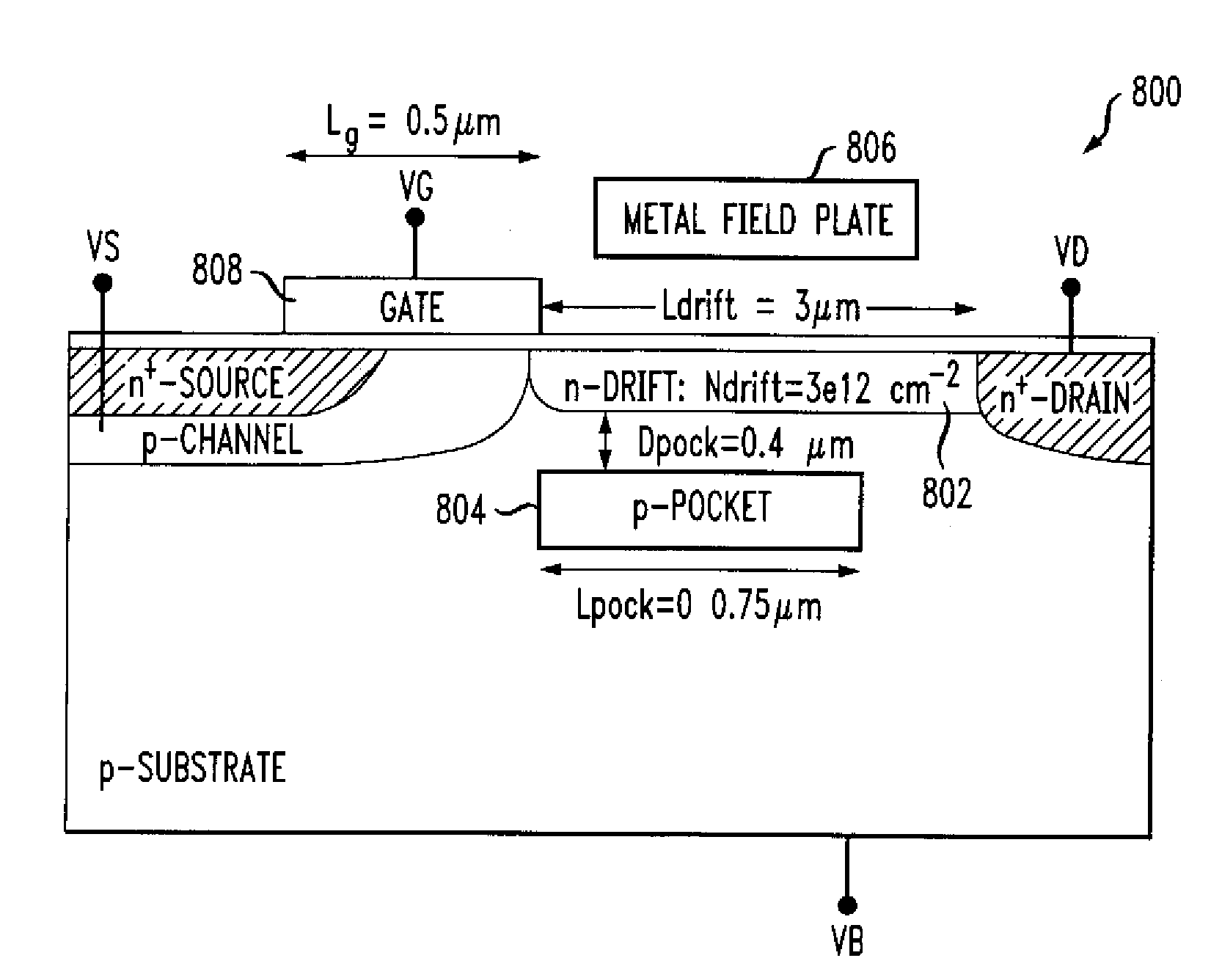

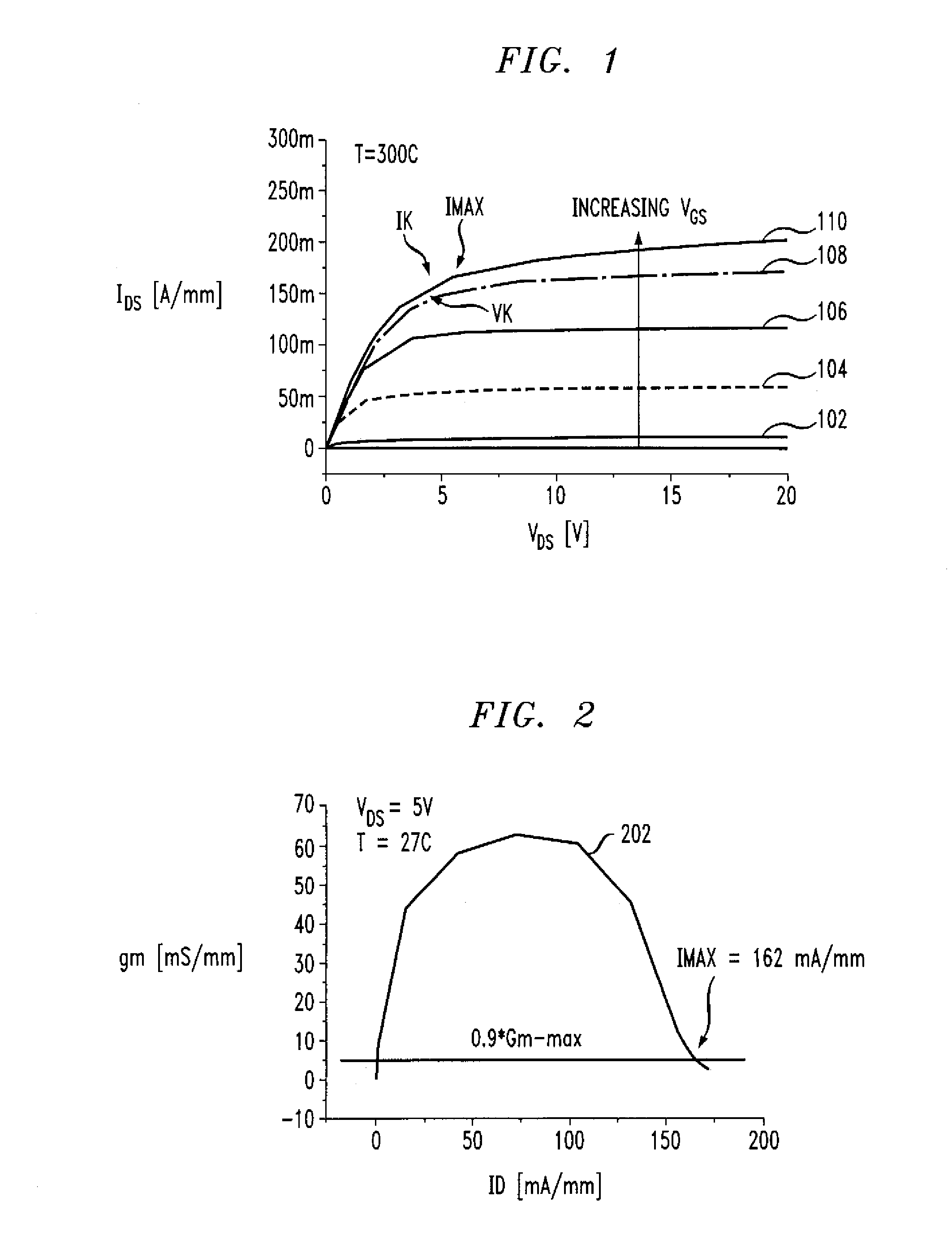

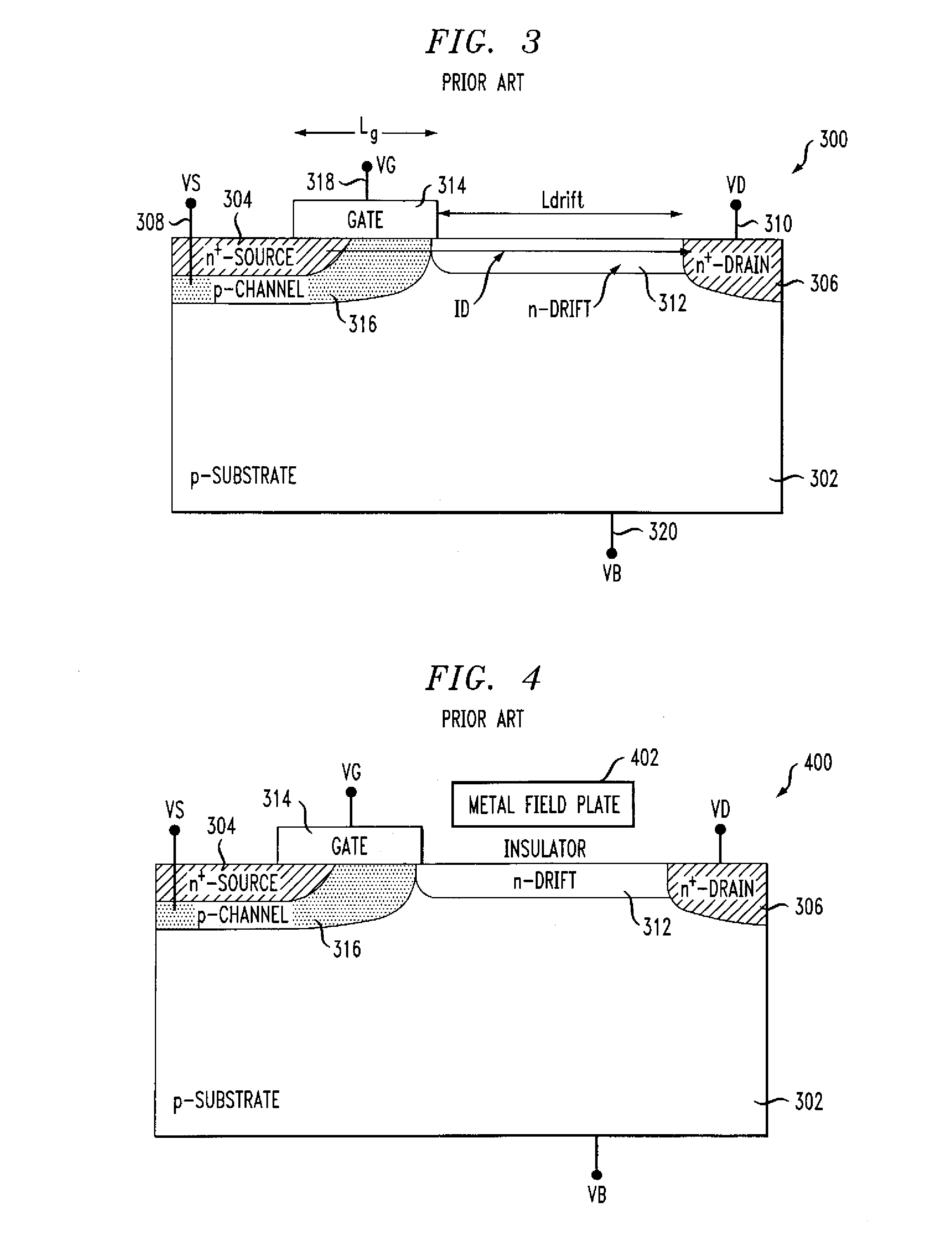

Semiconductor device having improved power density

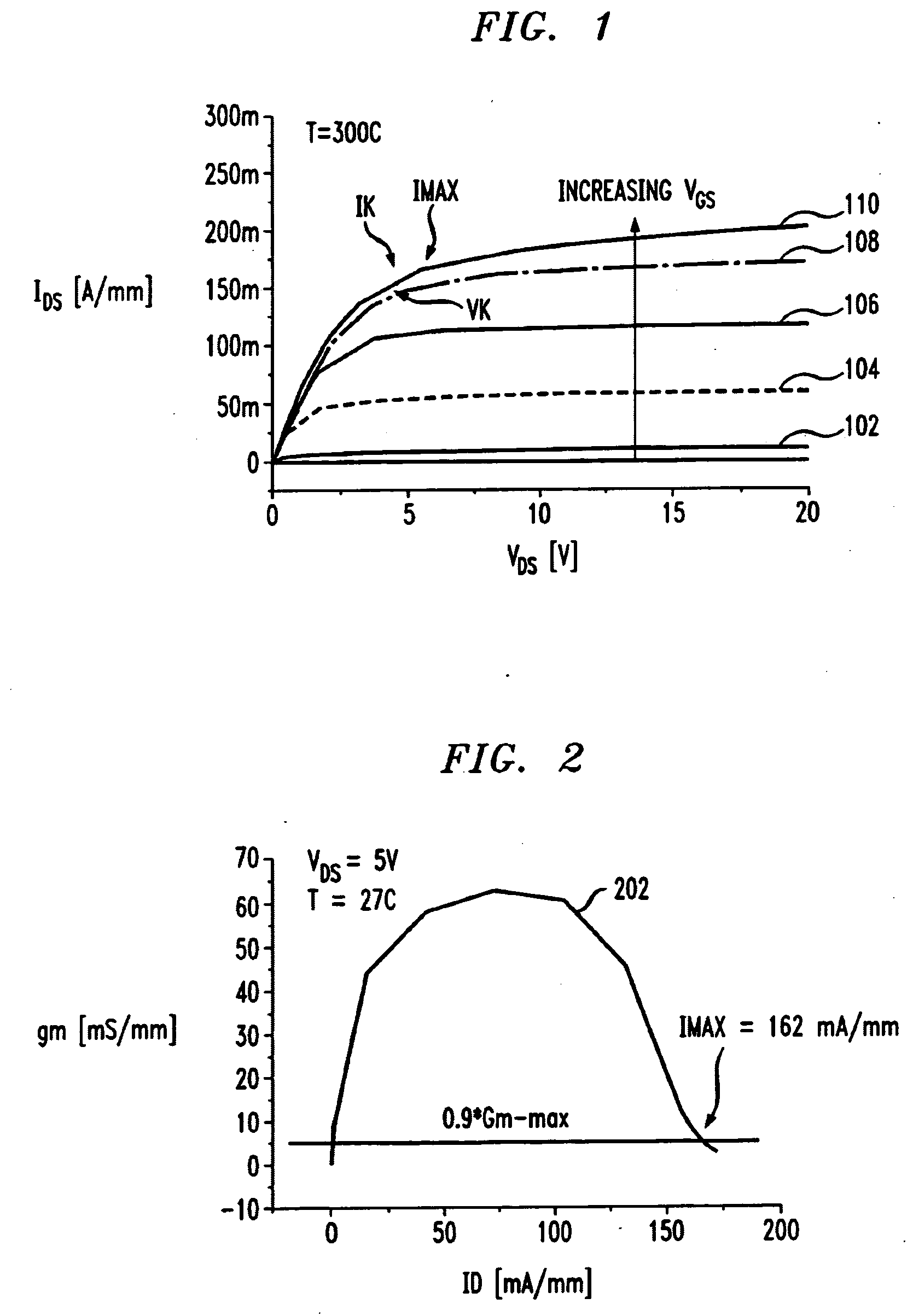

ActiveUS20060113625A1Improve power densityIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesClose relativesImpurity doping

An MOS device is formed including a semiconductor layer of a first conductivity type, and source and drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The source and drain regions are spaced apart relative to one another. A drift region of the second conductivity type is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the source and drain regions, the drift region having an impurity doping concentration greater than about 2.0e12 atoms / cm2. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer. The device further includes a gate formed on the insulating layer at least partially between the source and drain regions, and a buried layer of the first conductivity type formed in the semiconductor layer in close relative proximity to and beneath at least a portion of the drift region. A substantially vertical distance between the buried layer and the drift region, and / or one or more physical dimensions of the buried layer are configured so as to optimize a power density of the device relative to at least one of an on-resistance and a maximum drain current of the device.

Owner:BELL SEMICON LLC

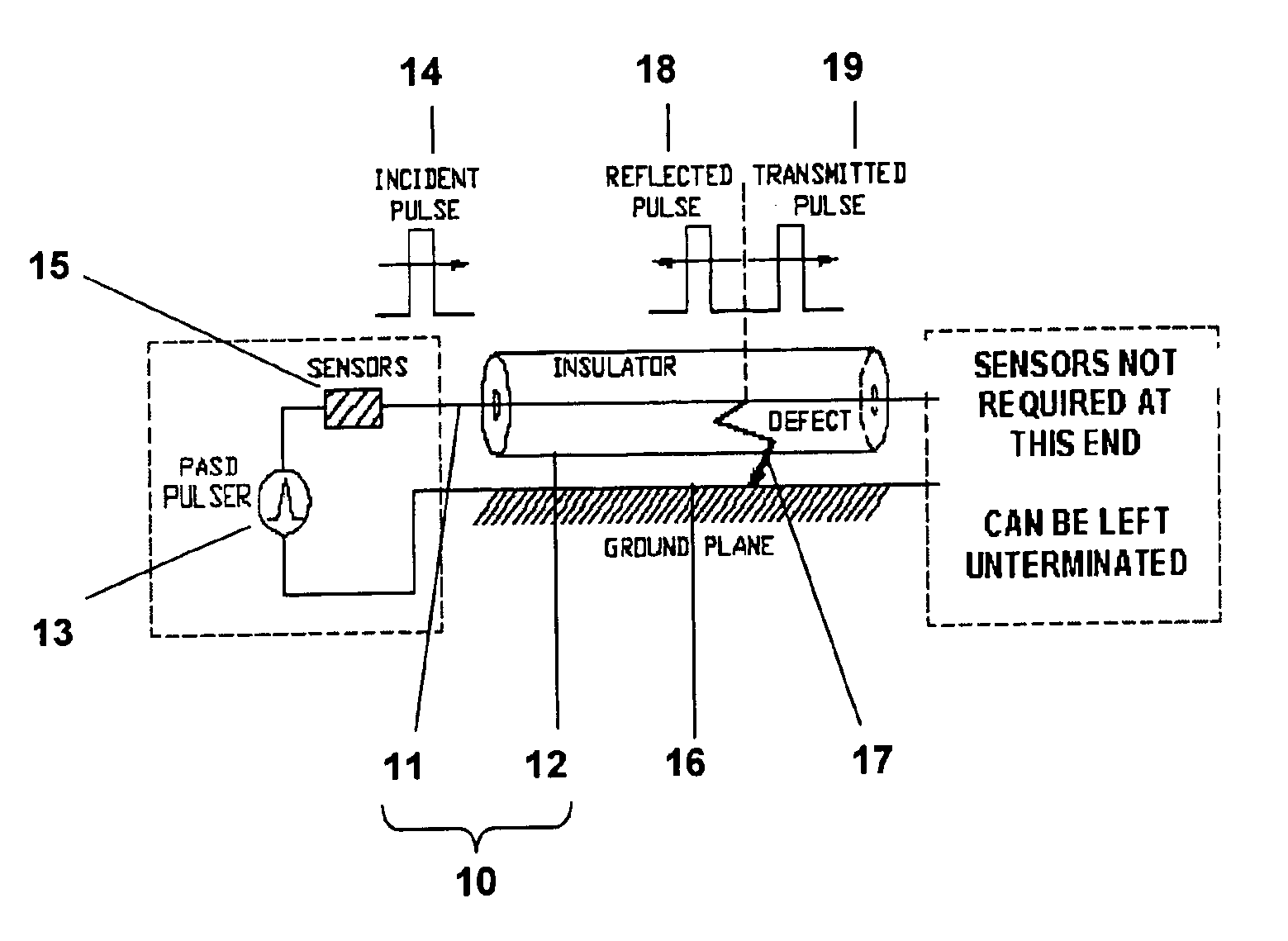

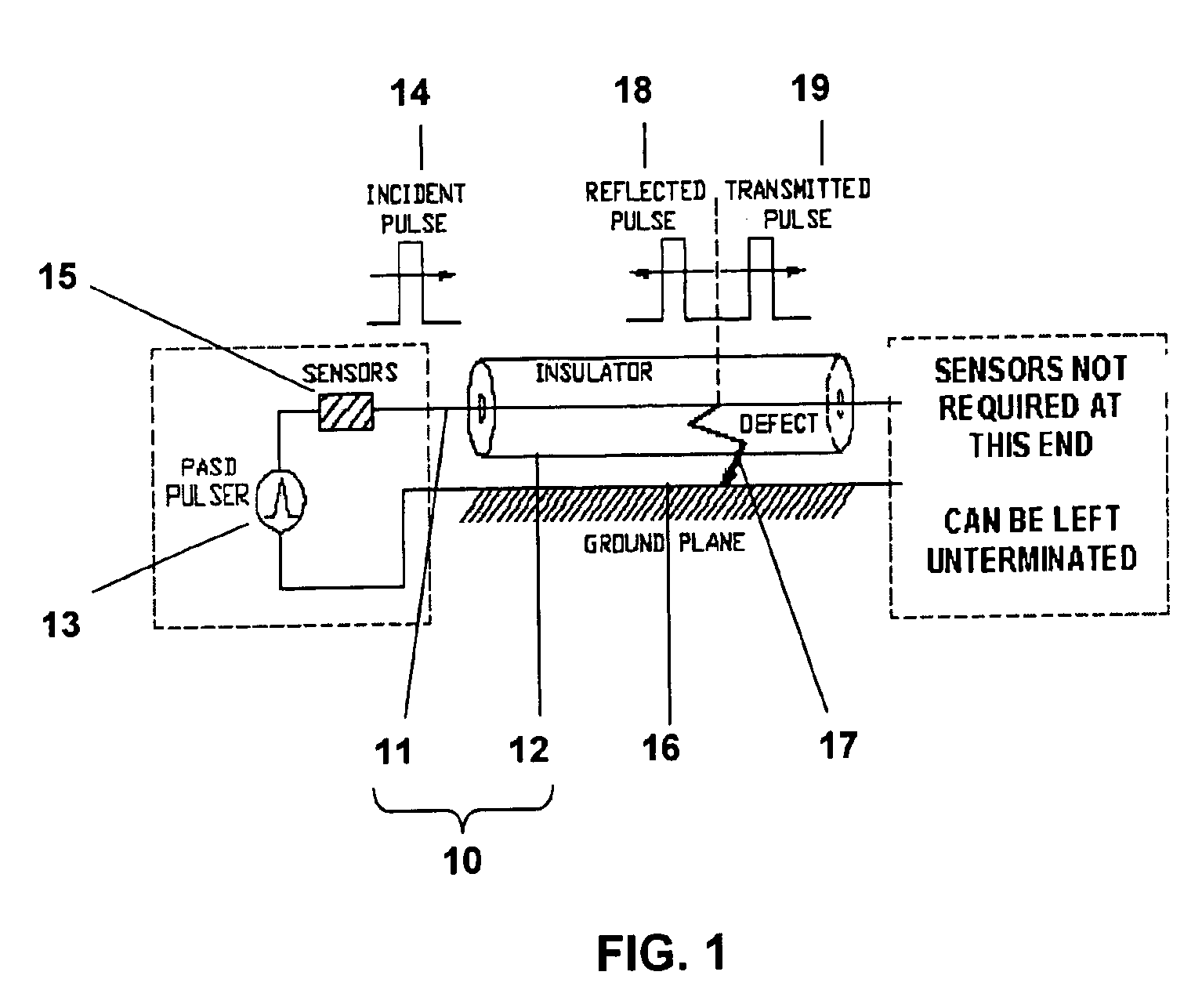

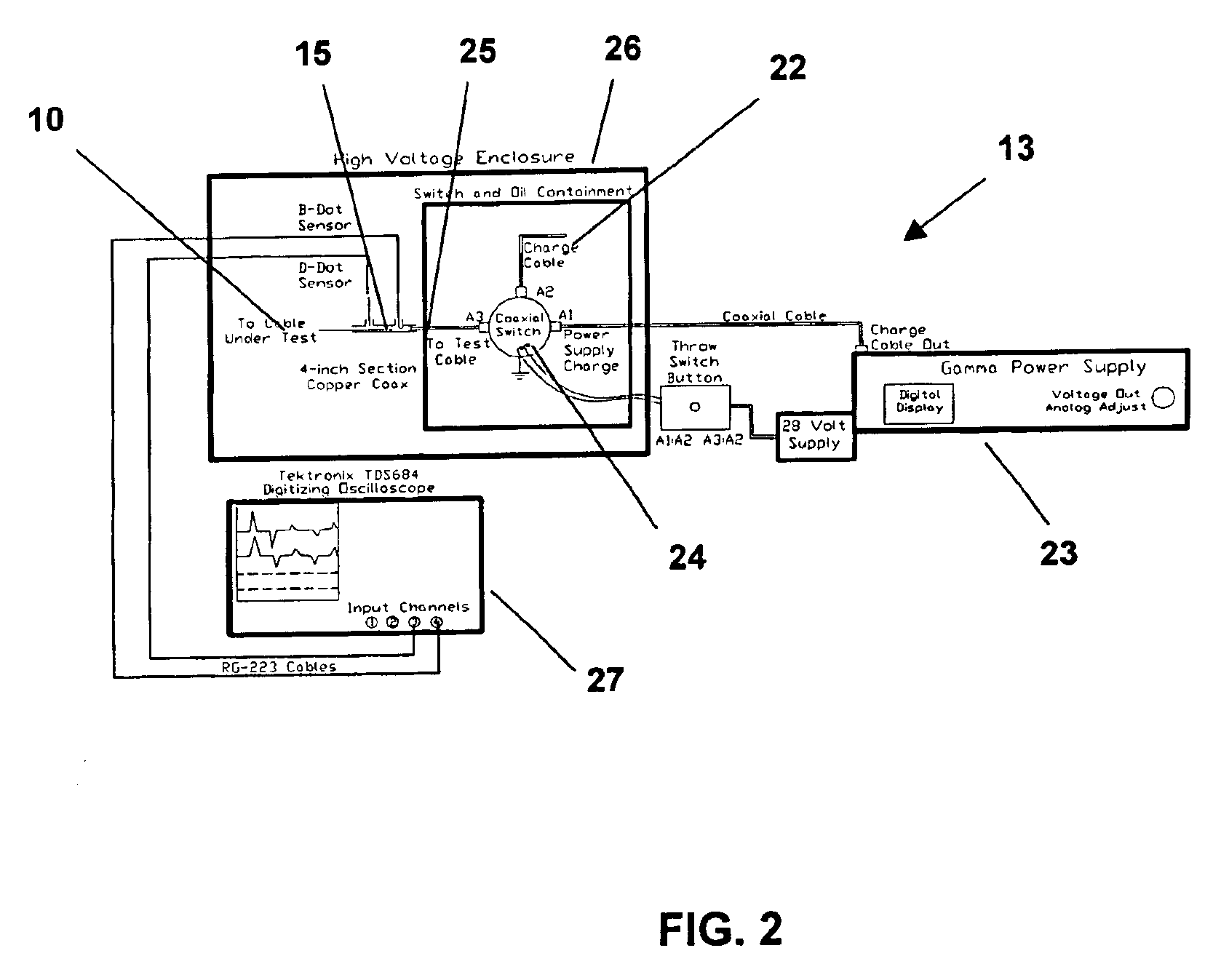

Method and apparatus for electrical cable testing by pulse-arrested spark discharge

InactiveUS6853196B1Enhance and inhibit onsetLower breakdown voltageResistance/reactance/impedenceFault location by pulse reflection methodsElectricityNuclear power

A method for electrical cable testing by Pulse-Arrested Spark Discharge (PASD) uses the cable response to a short-duration high-voltage incident pulse to determine the location of an electrical breakdown that occurs at a defect site in the cable. The apparatus for cable testing by PASD includes a pulser for generating the short-duration high-voltage incident pulse, at least one diagnostic sensor to detect the incident pulse and the breakdown-induced reflected and / or transmitted pulses propagating from the electrical breakdown at the defect site, and a transient recorder to record the cable response. The method and apparatus are particularly useful to determine the location of defect sites in critical but inaccessible electrical cabling systems in aging aircraft, ships, nuclear power plants, and industrial complexes.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

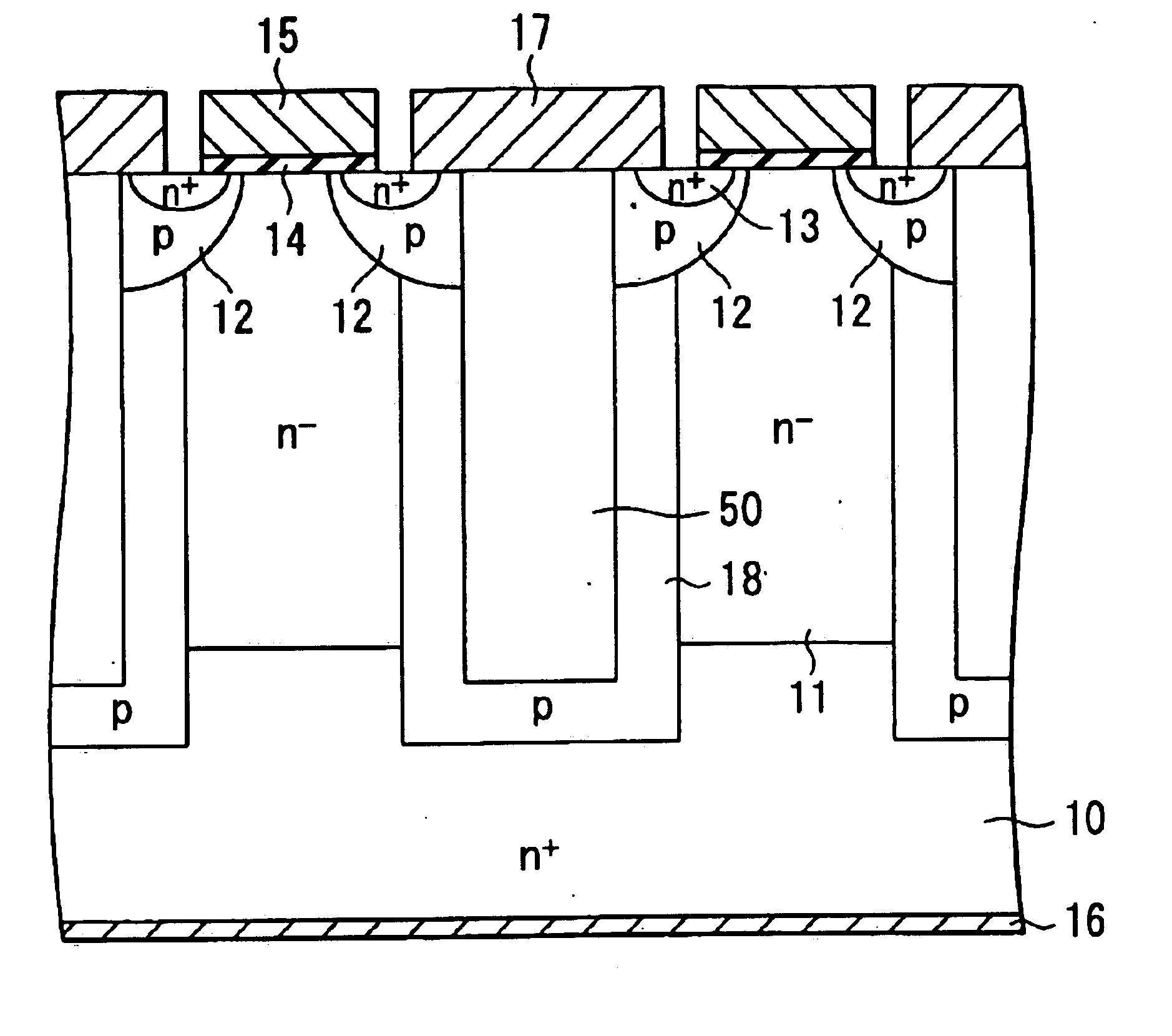

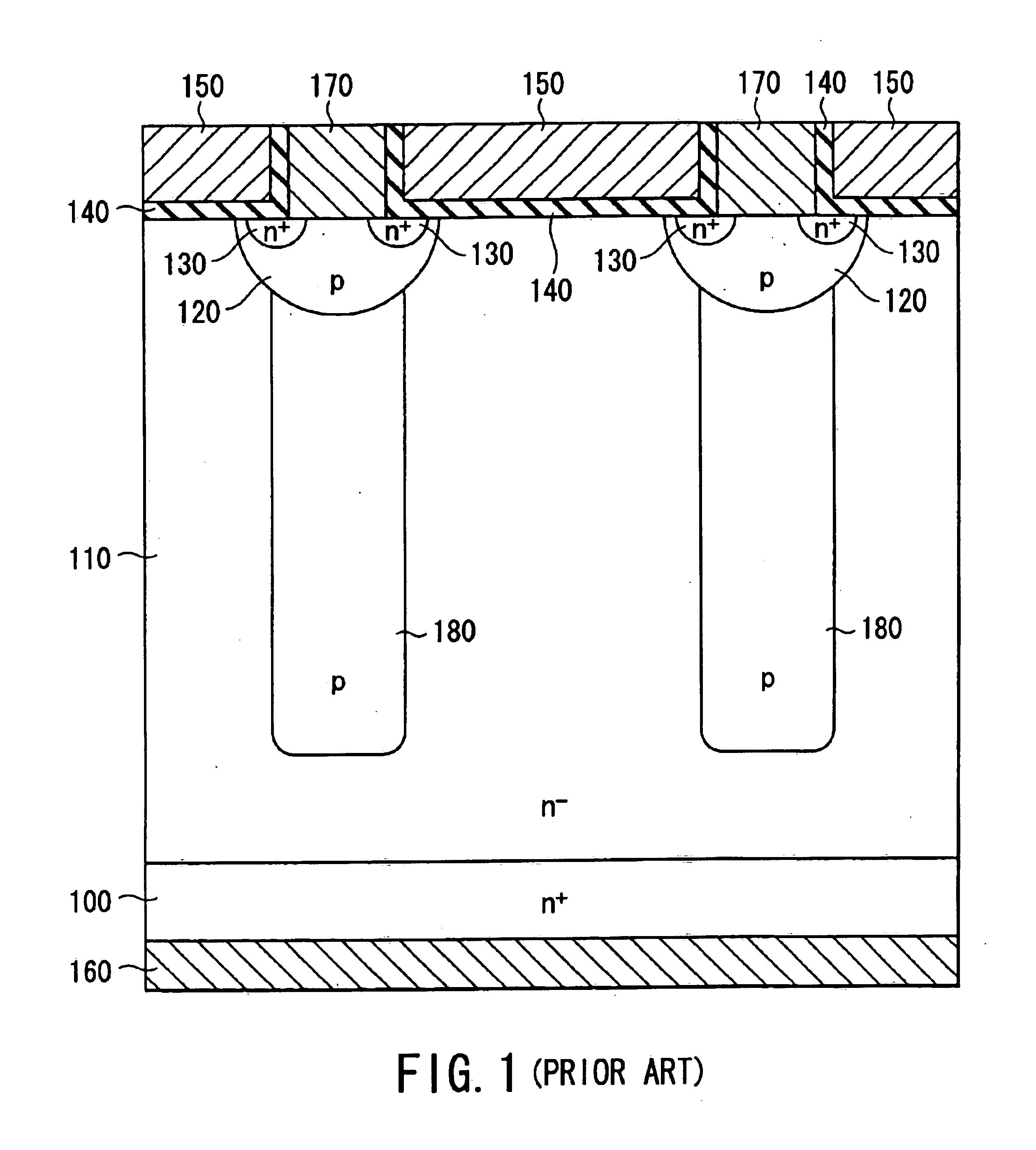

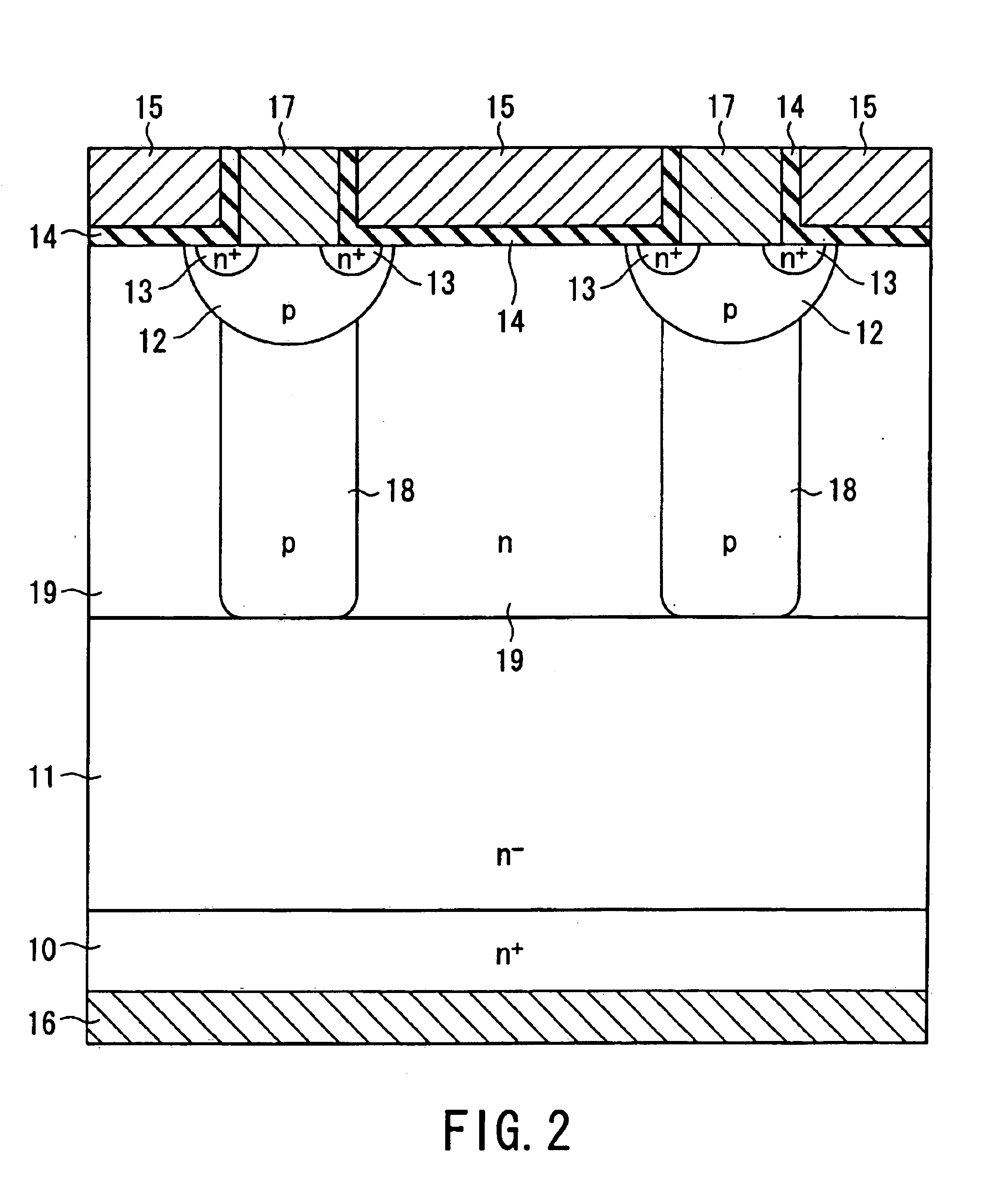

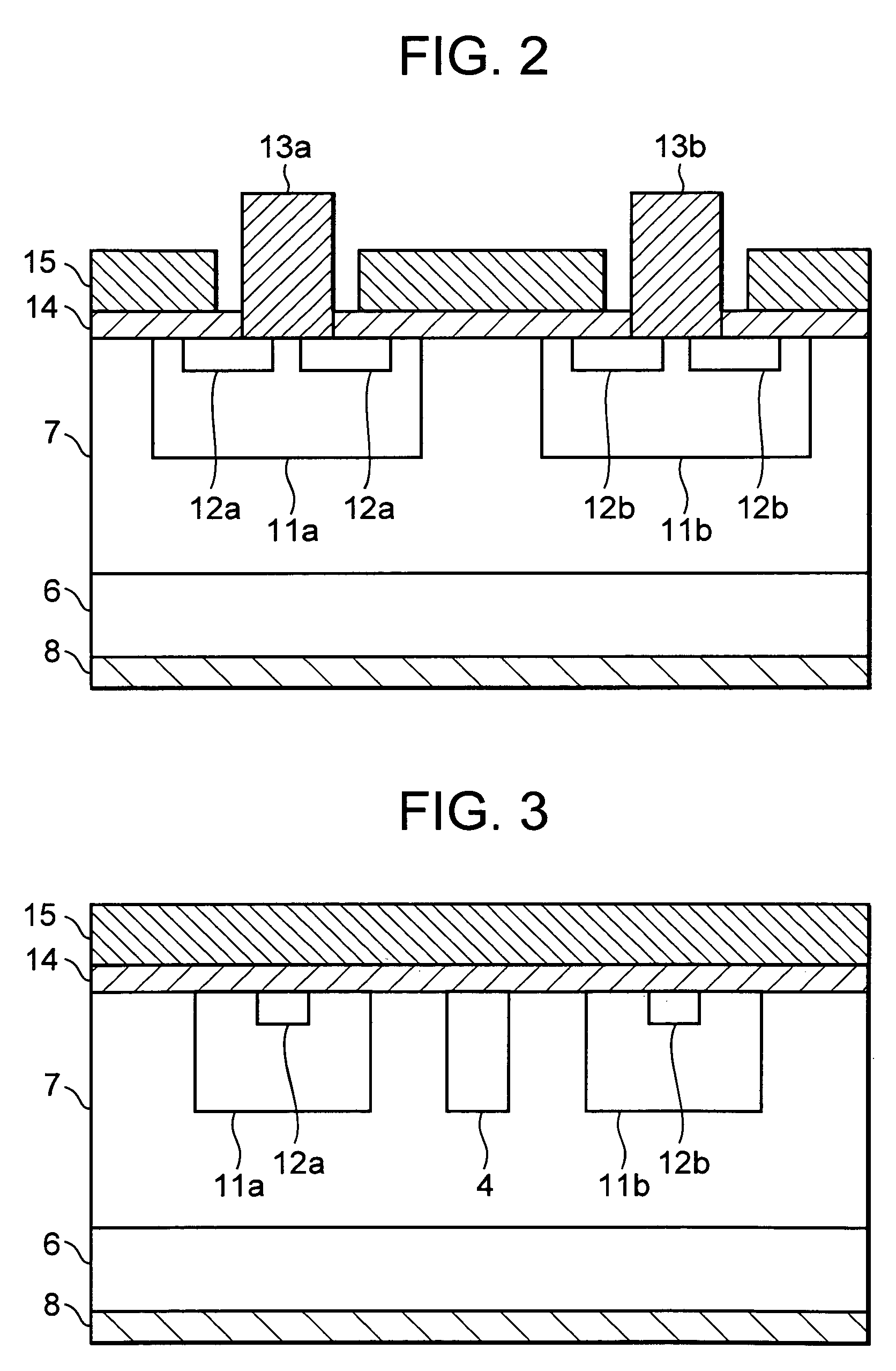

Trech-type vertical semiconductor device having gate electrode buried in rounded hump opening

InactiveUS20060267085A1Lower breakdown voltageIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

In a semiconductor device including a gate electrode buried in a trench of the device, the trench is constructed by a first opening with a uniform width the same as that of an upper portion of the first opening and a second opening beneath the first opening with a width larger than the uniform width. A bottom of a base region adjacent to the trench is adjacent to the second opening.

Owner:RENESAS ELECTRONICS CORP

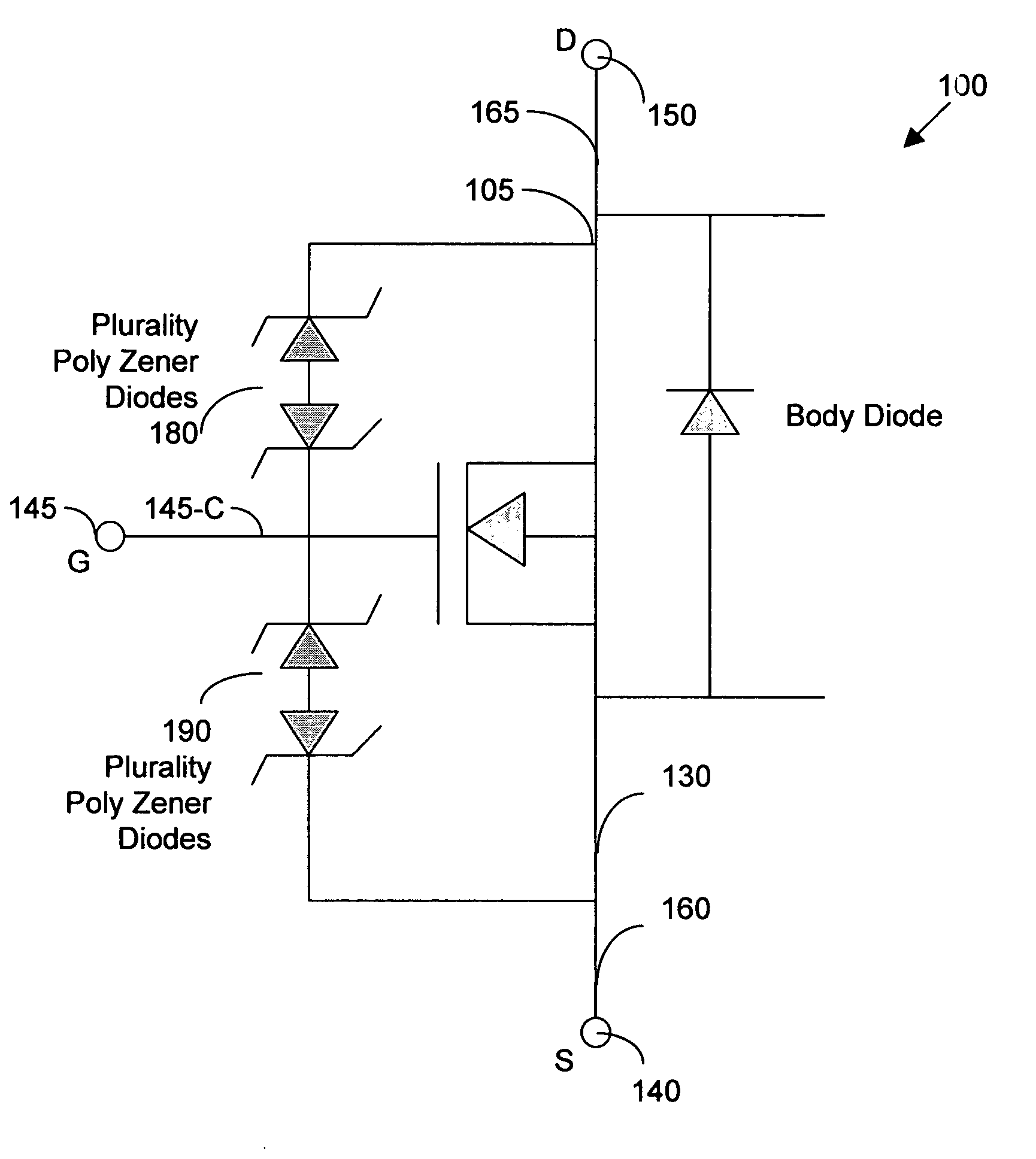

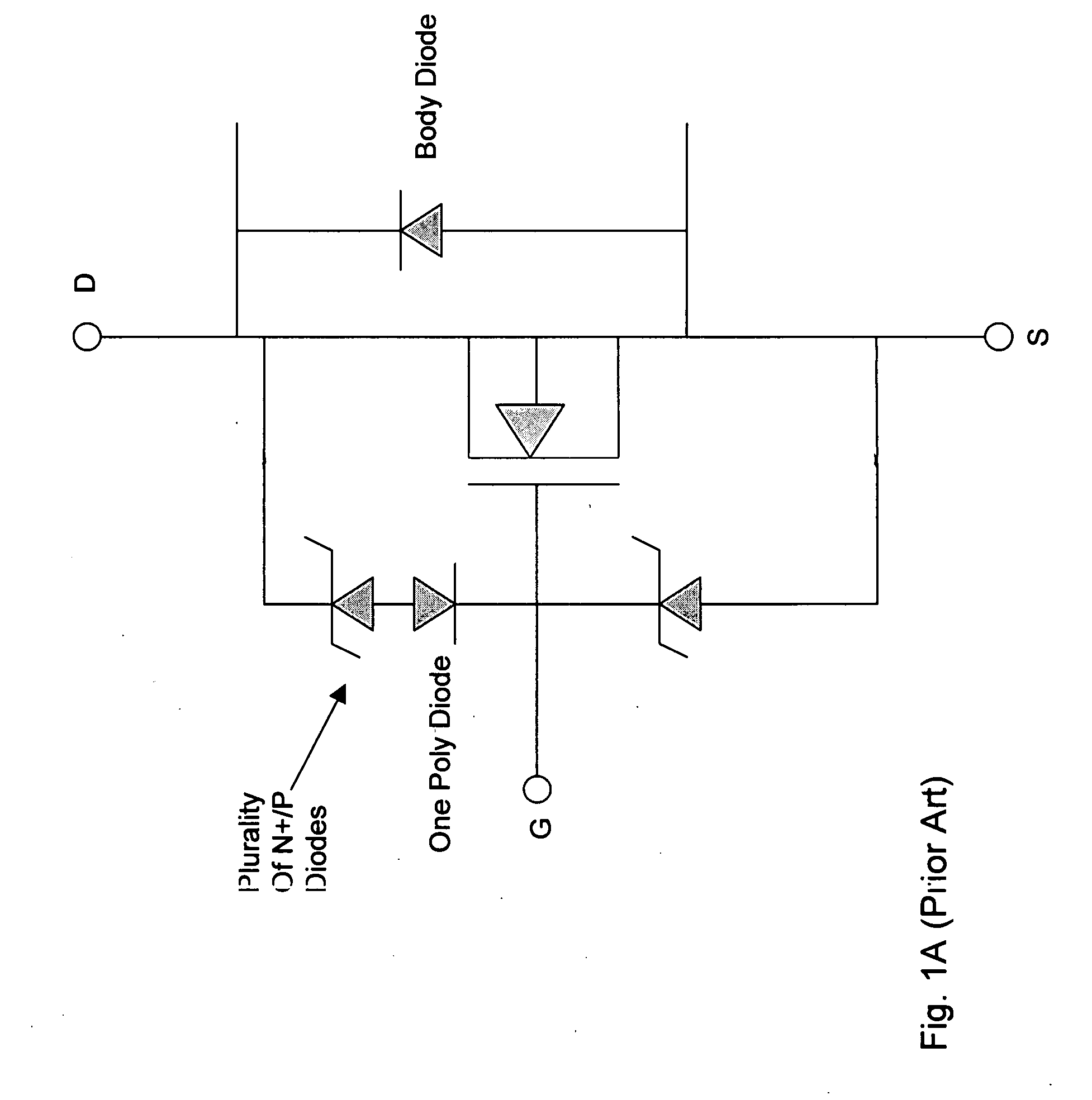

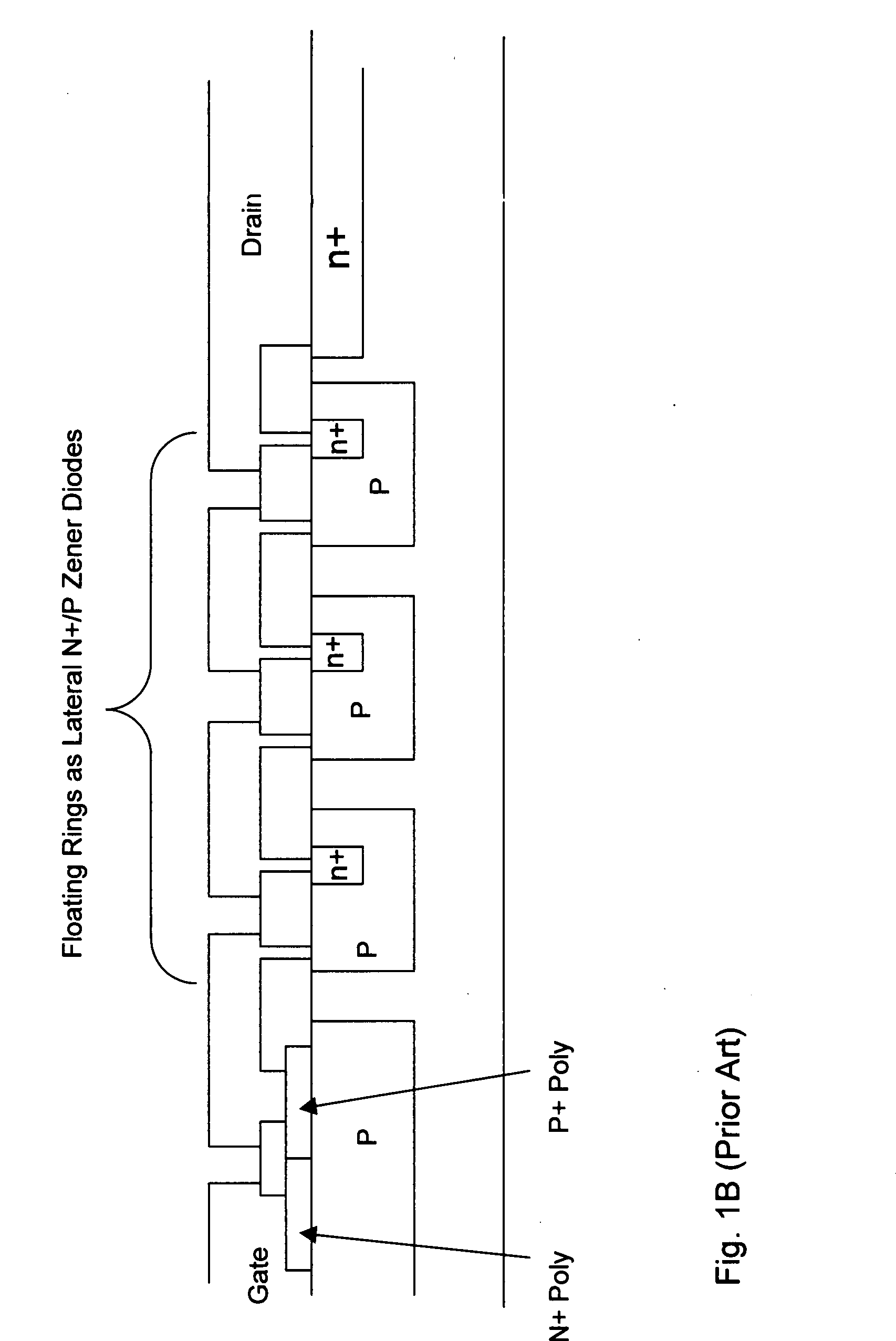

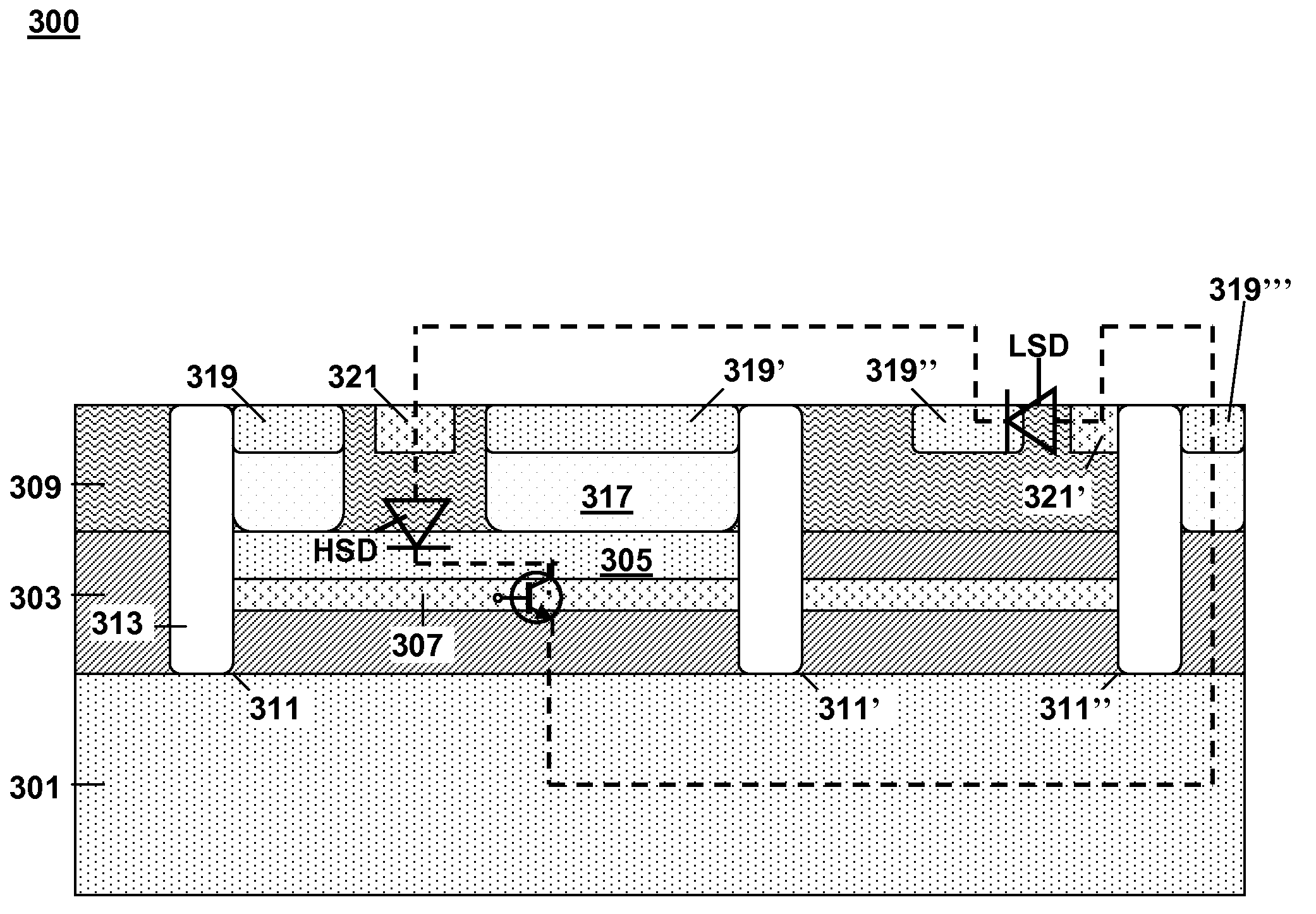

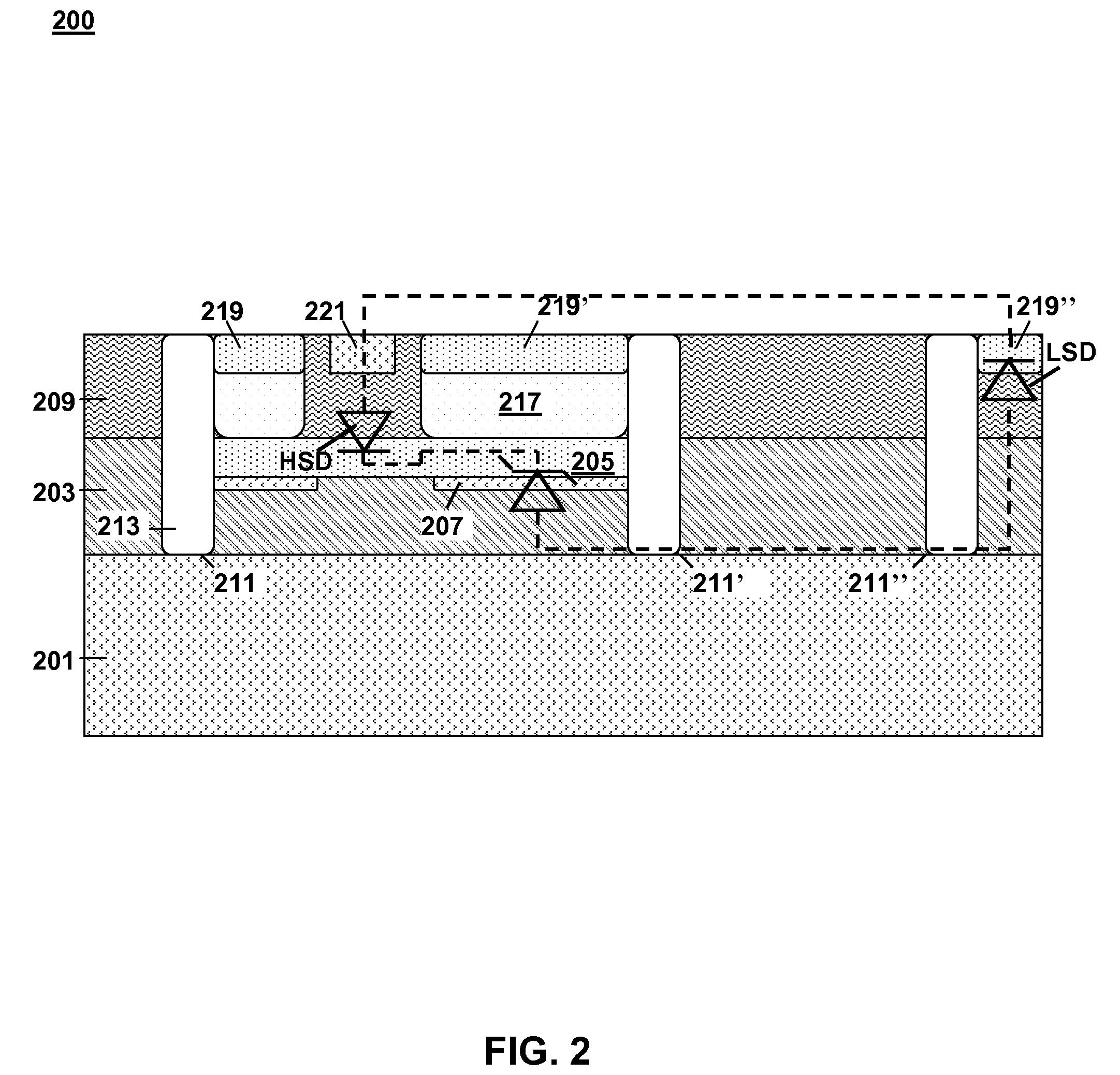

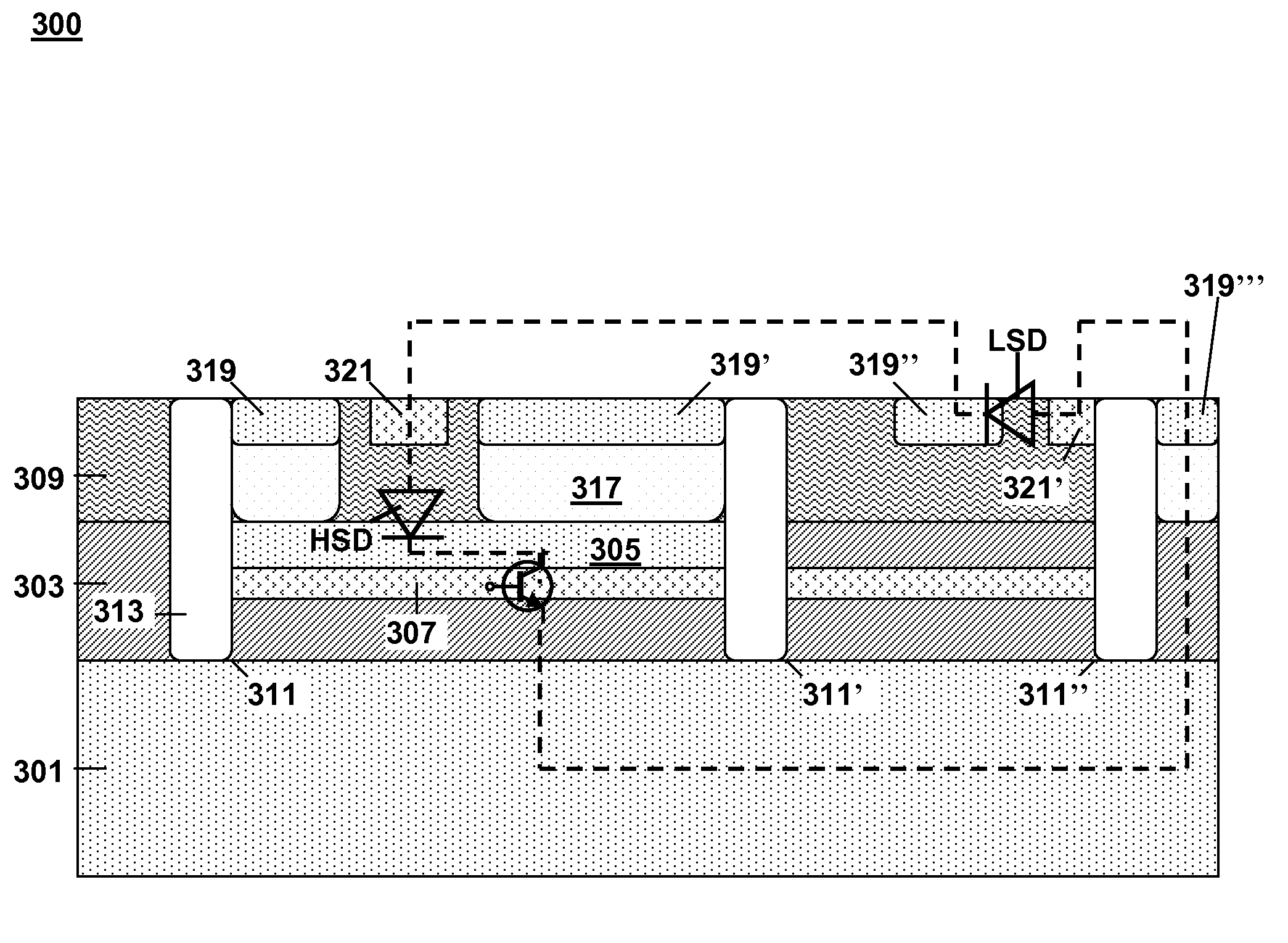

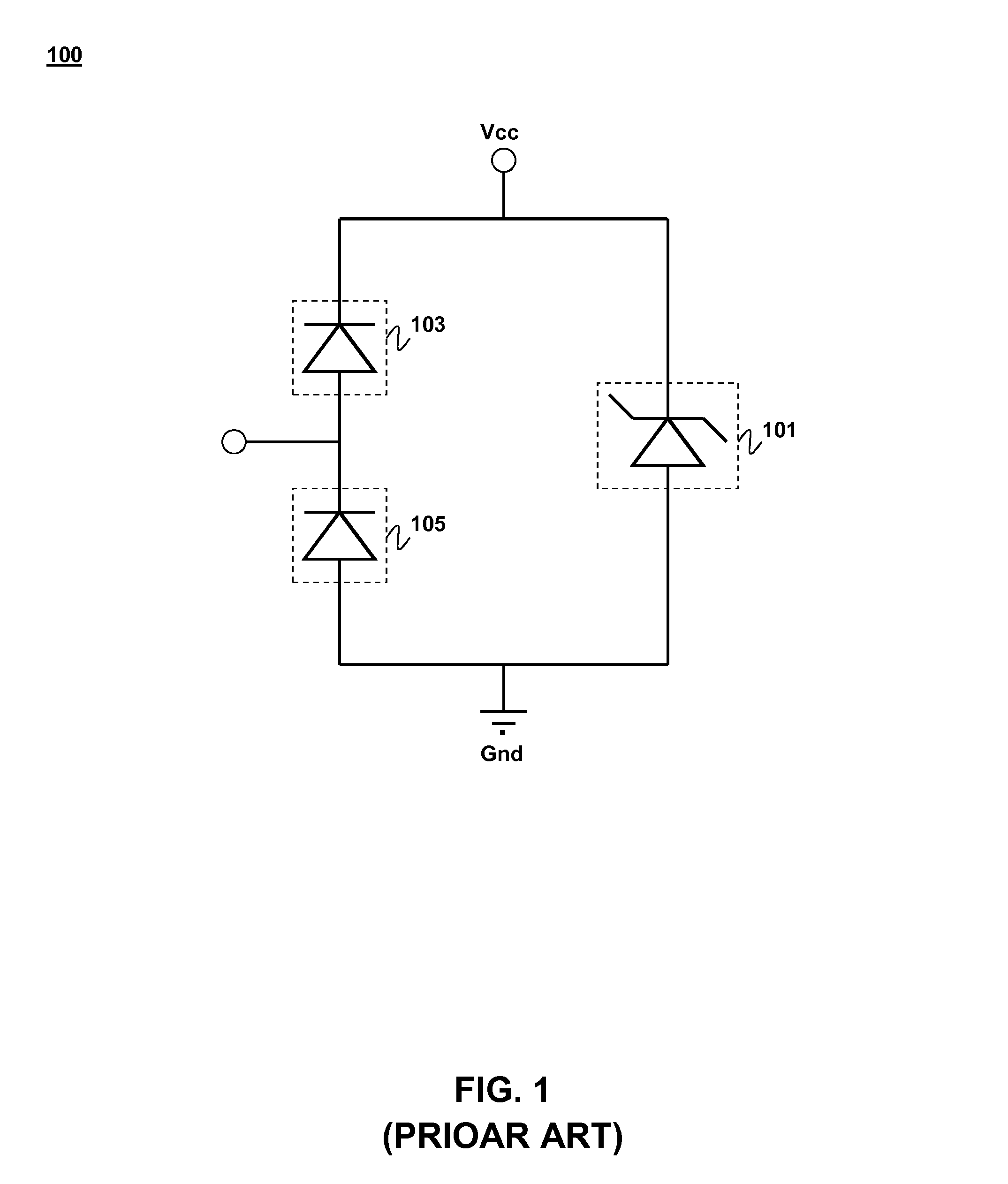

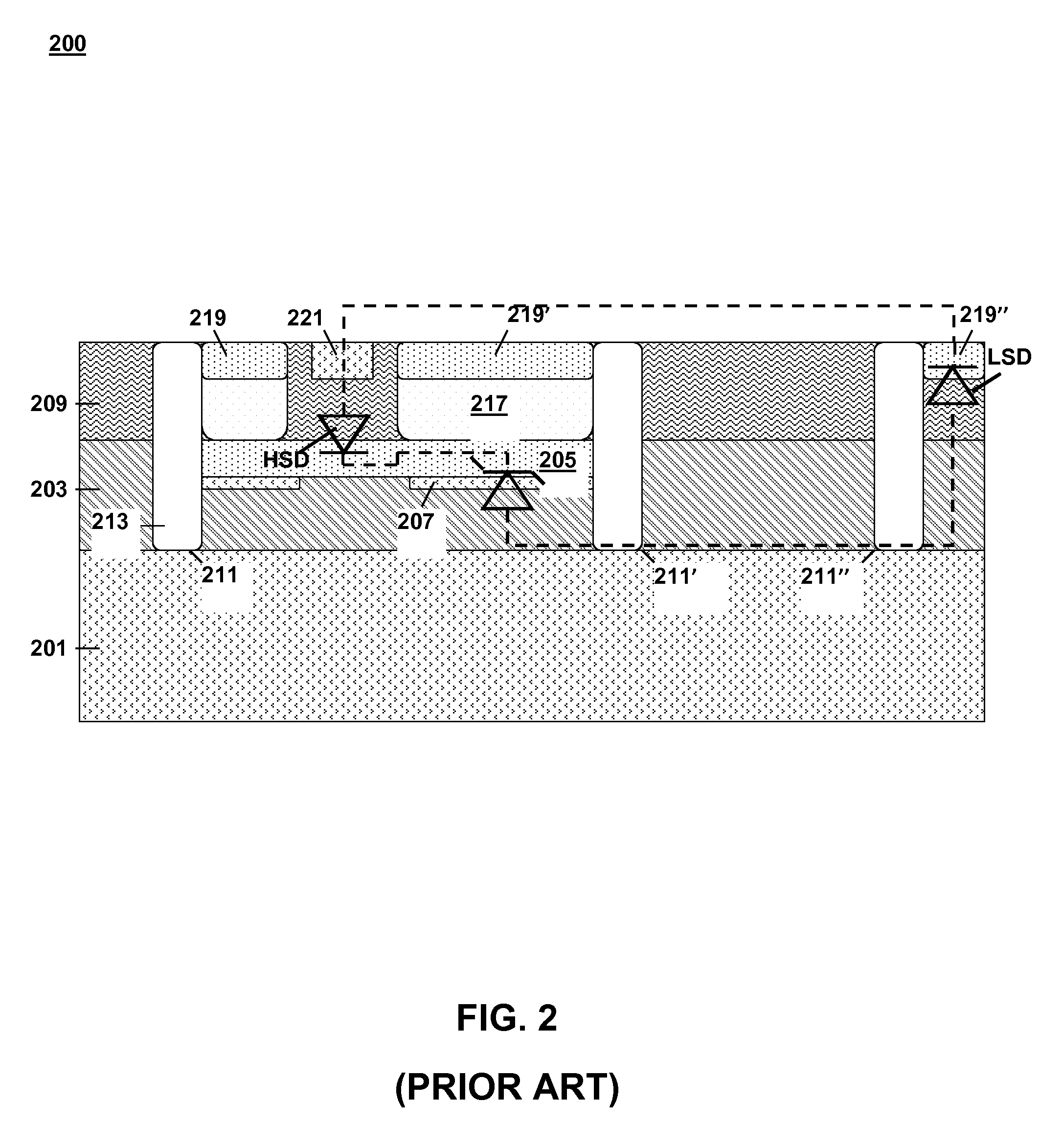

Trenched MOSFETs with improved gate-drain (GD) clamp diodes

ActiveUS20080258224A1Prevent channelingLower breakdown voltageTransistorSemiconductor/solid-state device detailsDopantInsulation layer

A MOSFET device that includes a first Zener diode connected between a gate metal and a drain metal of said semiconductor power device for functioning as a gate-drain (GD) clamp diode. The GD clamp diode includes multiple back-to-back doped regions in a polysilicon layer doped with dopant ions of a first conductivity type next to a second conductivity type disposed on an insulation layer above the MOSFET device, having an avalanche voltage lower than a source / drain avalanche voltage of the MOSFET device wherein the Zener diode is insulated from a doped region of the MOSFET device for preventing a channeling effect. The MOSFET device further includes a second Zener diode connected between a gate metal and a source metal of the MOSFET device for functioning as a gate-source (GS) clamp diode, wherein the GD clamp diode includes multiple back-to-back doped regions in the polysilicon layer doped with dopant ions of a first conductivity type next to a second conductivity type disposed on the insulation layer above the MOSFET device having a lower breakdown voltage than a gate oxide rupture voltage of the MOSFET device.

Owner:FORCE MOS TECH CO LTD

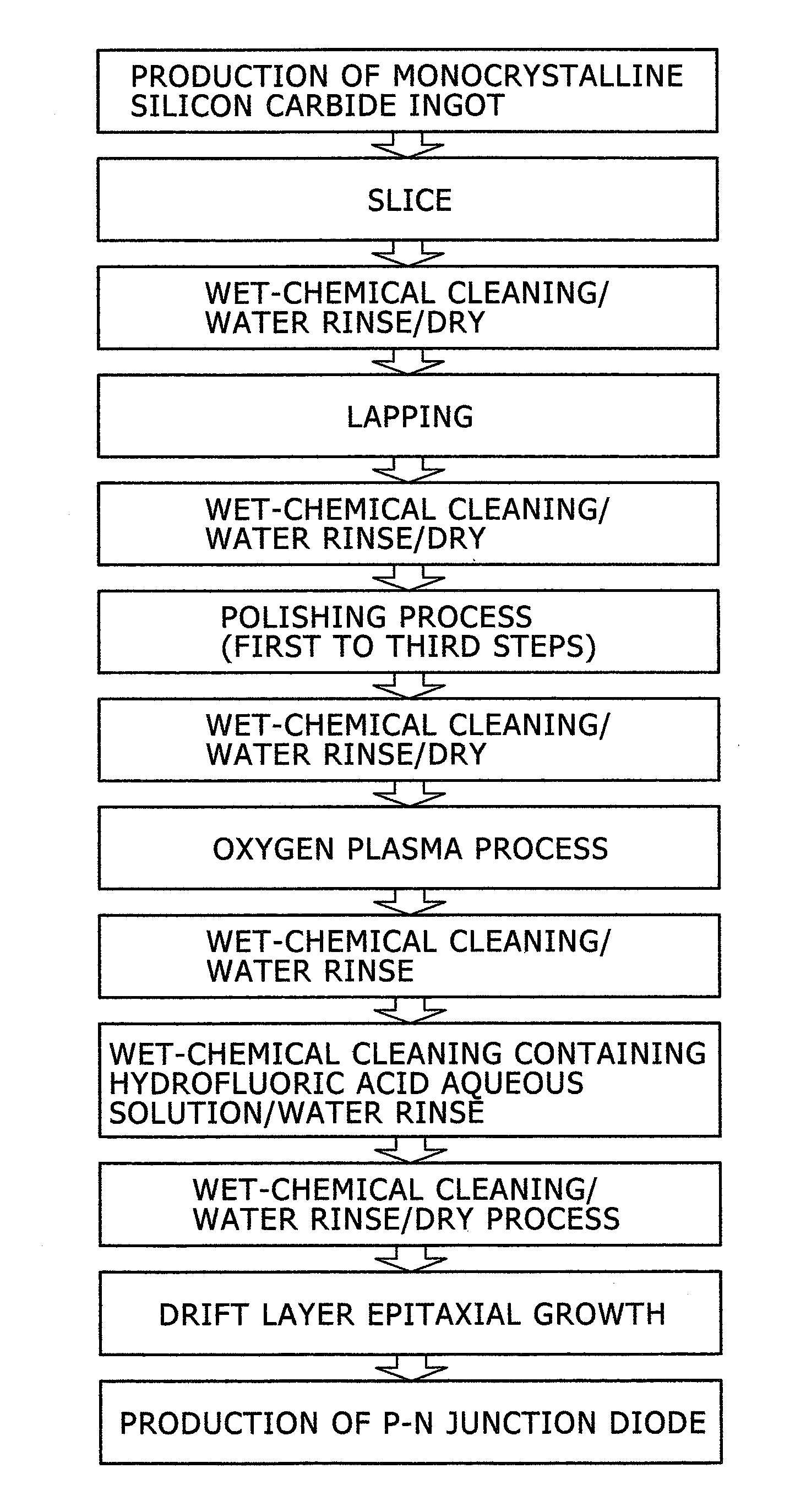

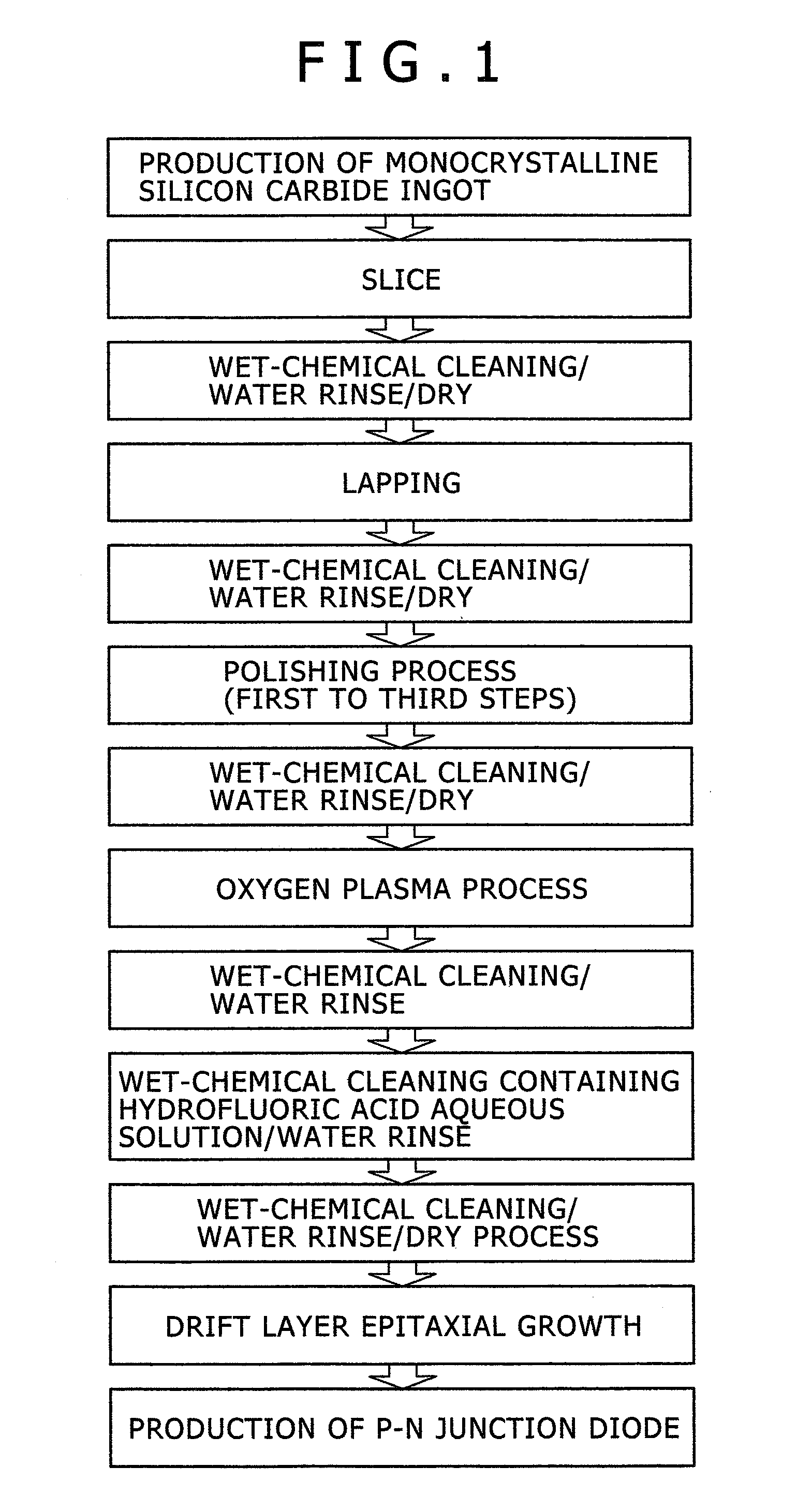

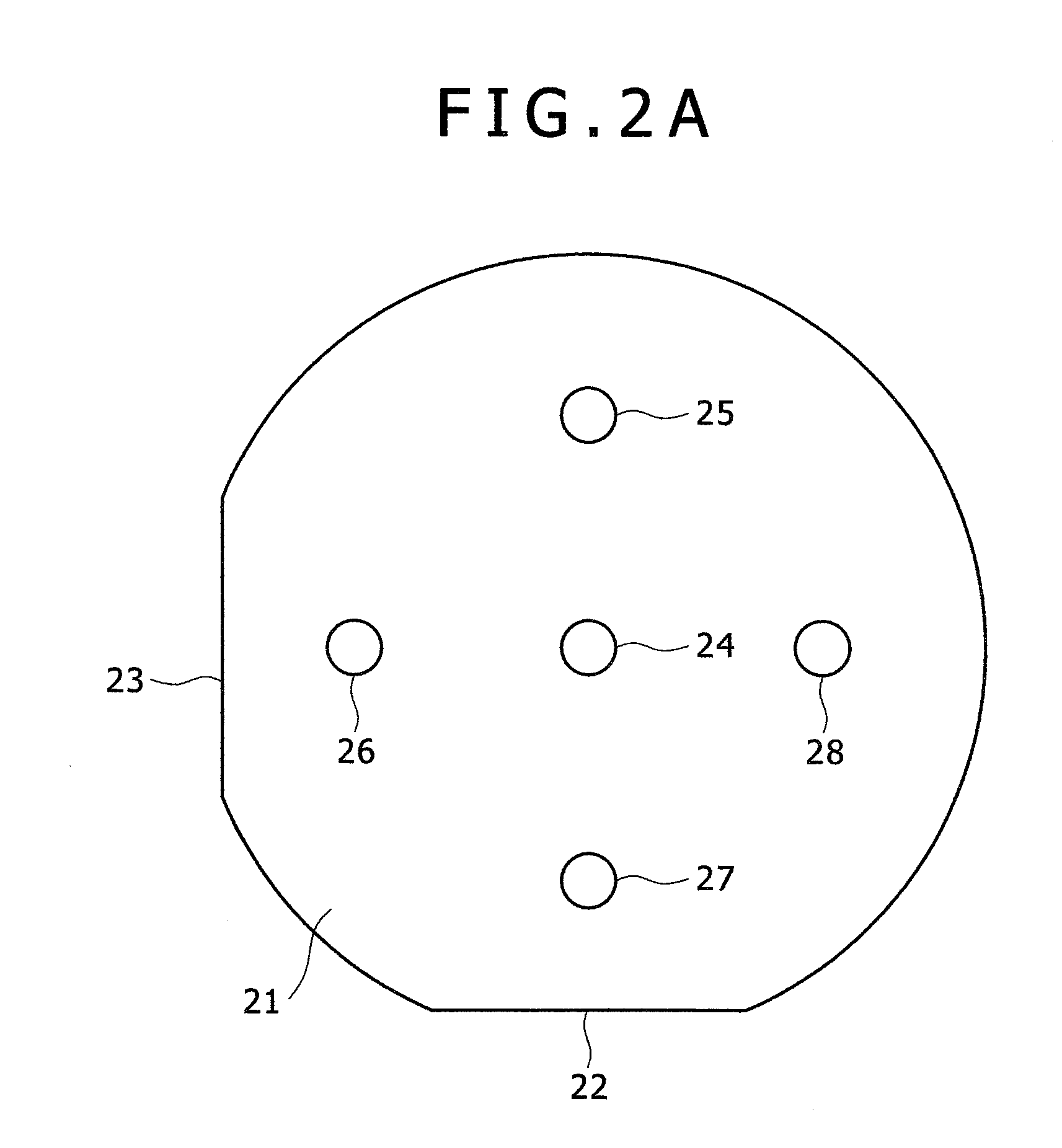

Manufacturing method of semiconductor device

ActiveUS20090209090A1Surface cleaningEasy to spreadSemiconductor/solid-state device manufacturingSemiconductor devicesMetal contaminationMonocrystalline silicon

A problem in the conventional technique is that metal contamination on a silicon carbide surface is not sufficiently removed in a manufacturing method of a semiconductor device using a monocrystalline silicon carbide substrate. Accordingly, there is a high possibility that the initial characteristics of a manufactured silicon carbide semiconductor device are deteriorated and the yield rate is decreased. Further, it is conceivable that the metal contamination has an adverse affect even on the long-term reliability of a semiconductor device. In a manufacturing method of a semiconductor device using a monocrystalline silicon carbide substrate, there is applied a metal contamination removal process, on a silicon carbide surface, including a step of oxidizing the silicon carbide surface and a step of removing a film primarily including silicon dioxide formed on the silicon carbide surface by the step.

Owner:HITACHI POWER SEMICON DEVICE

Battery module

InactiveUS8174237B2Lower breakdown voltageCircuit monitoring/indicationCharge equalisation circuitSignal cellLevel converter

Owner:KK TOSHIBA

Semiconductor device having improved power density

ActiveUS7262476B2Improve power densityIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesClose relativesImpurity doping

An MOS device is formed including a semiconductor layer of a first conductivity type, and source and drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer. The source and drain regions are spaced apart relative to one another. A drift region of the second conductivity type is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the source and drain regions, the drift region having an impurity doping concentration greater than about 2.0e12 atoms / cm2. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer. The device further includes a gate formed on the insulating layer at least partially between the source and drain regions, and a buried layer of the first conductivity type formed in the semiconductor layer in close relative proximity to and beneath at least a portion of the drift region. A substantially vertical distance between the buried layer and the drift region, and / or one or more physical dimensions of the buried layer are configured so as to optimize a power density of the device relative to at least one of an on-resistance and a maximum drain current of the device.

Owner:BELL SEMICON LLC

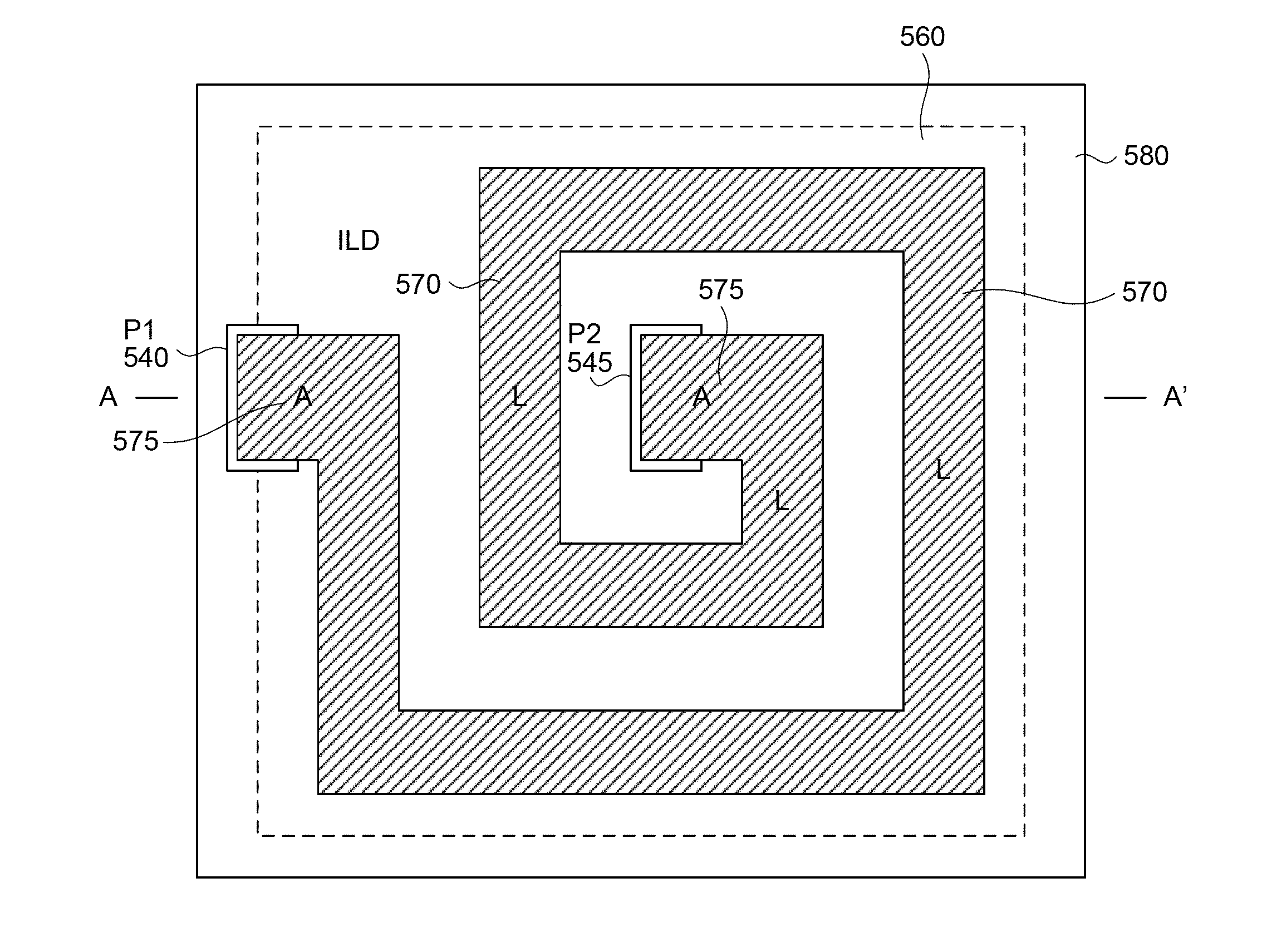

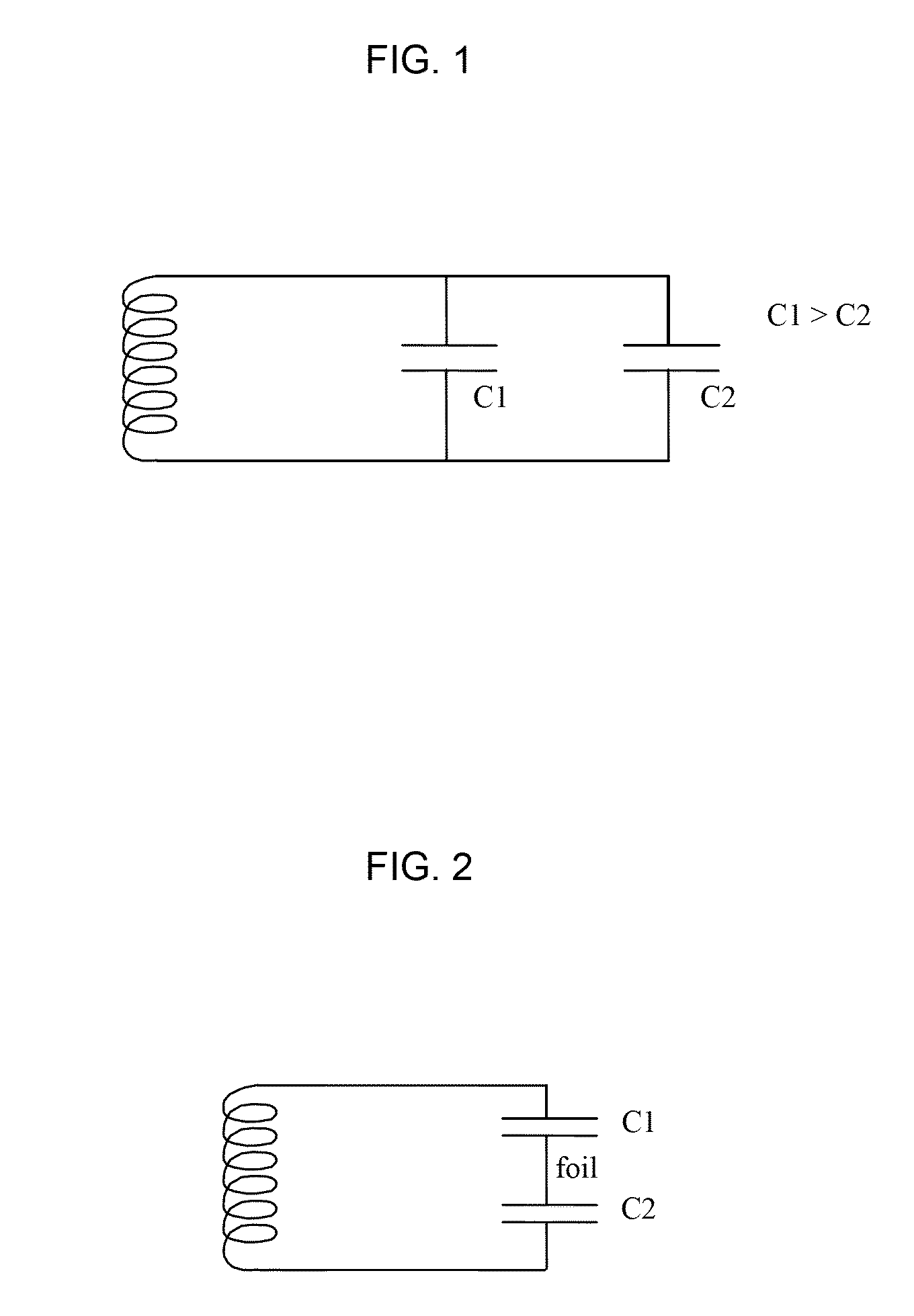

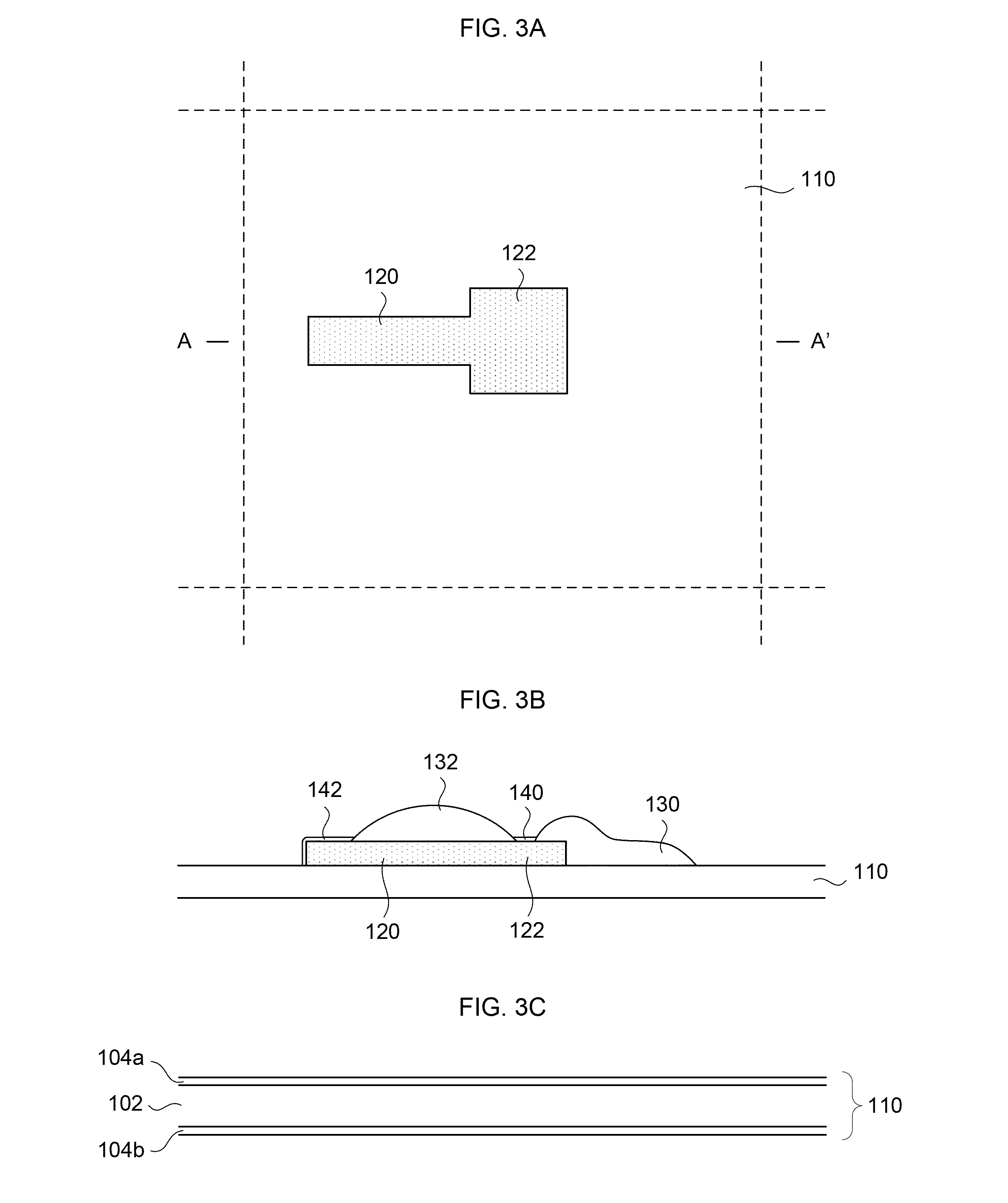

Surveillance Devices with Multiple Capacitors

ActiveUS20100123582A1Lower breakdown voltageReliable deactivationPrinted circuit assemblingPaper/cardboard articlesCapacitanceDielectric

The present invention relates to surveillance and / or identification devices having capacitors connected in parallel or in series, and methods of making and using such devices. Devices with capacitors connected in parallel, where one capacitor is fabricated with a relatively thick capacitor dielectric and another is fabricated with a relatively thin capacitor dielectric achieve both a high-precision capacitance and a low breakdown voltage for relatively easy surveillance tag deactivation. Devices with capacitors connected in series result in increased lateral dimensions of a small capacitor. This makes the capacitor easier to fabricate using techniques that may have relatively limited resolution capabilities.

Owner:ENSURGE MICROPOWER ASA

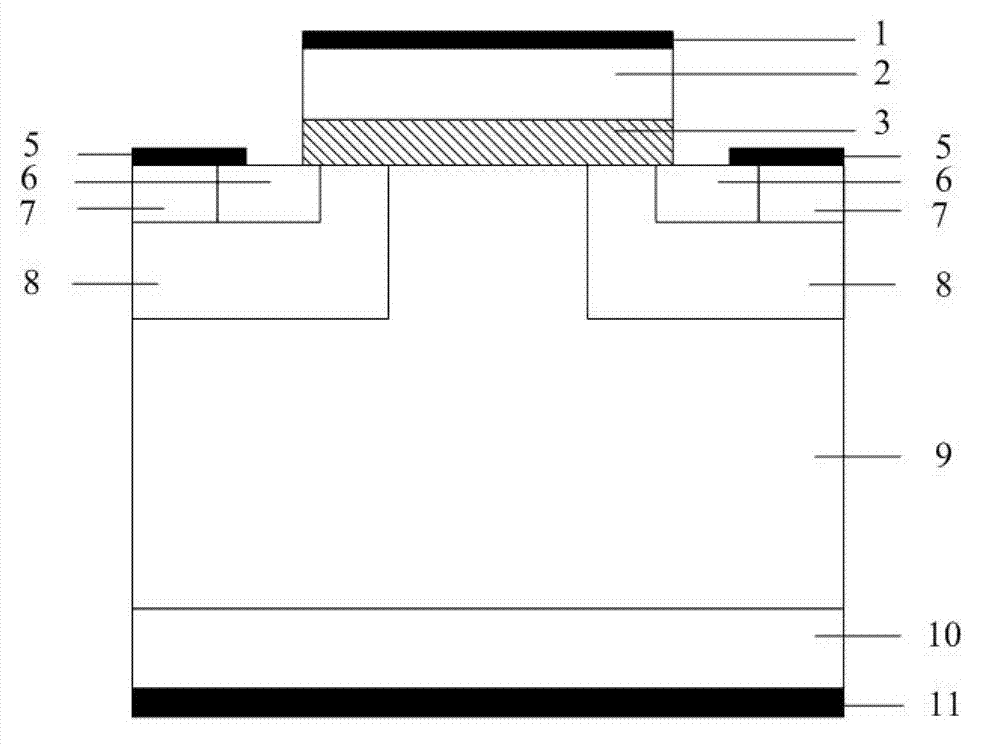

SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with composite gate dielectric structure

InactiveCN102779852ALower breakdown voltageAvoid premature breakdownSemiconductor devicesDielectricGate dielectric

The invention discloses a SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with a composite gate dielectric structure, and belongs to the technical field of power semiconductor devices. A thought of differentiating modulation of electric fields is adopted according to difference of intensities of electric fields and difference of defect concentrations of gate dielectrics in different areas, namely, high-k gate dielectrics are adopted in channel regions with high-defect concentration and a low electric field, so that a large quantity of trap states caused by using a SiO2 / SiC interface is avoided; the influence on Fowler-Nordheim (FN) tunneling current is obviously reduced; and meanwhile, because the electric field intensity in a channel injection area is small, the reduction on gate dielectric breakdown voltage caused by small offset of conduction band / valence band is weakened; and moreover, a SiO2 gate dielectric (a junction field-effect transistor (JFET) area is formed in a way of extension and is not subjected to ion injection, the surface quality of the JFET area is good, and the SiO2 / SiC interface state is low) is adopted by the JFET area with low defect concentration and a high electric field, and enough high conduction band offset is supplied by the SiO2 dielectric, so that the ahead breakdown of the gate dielectric is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

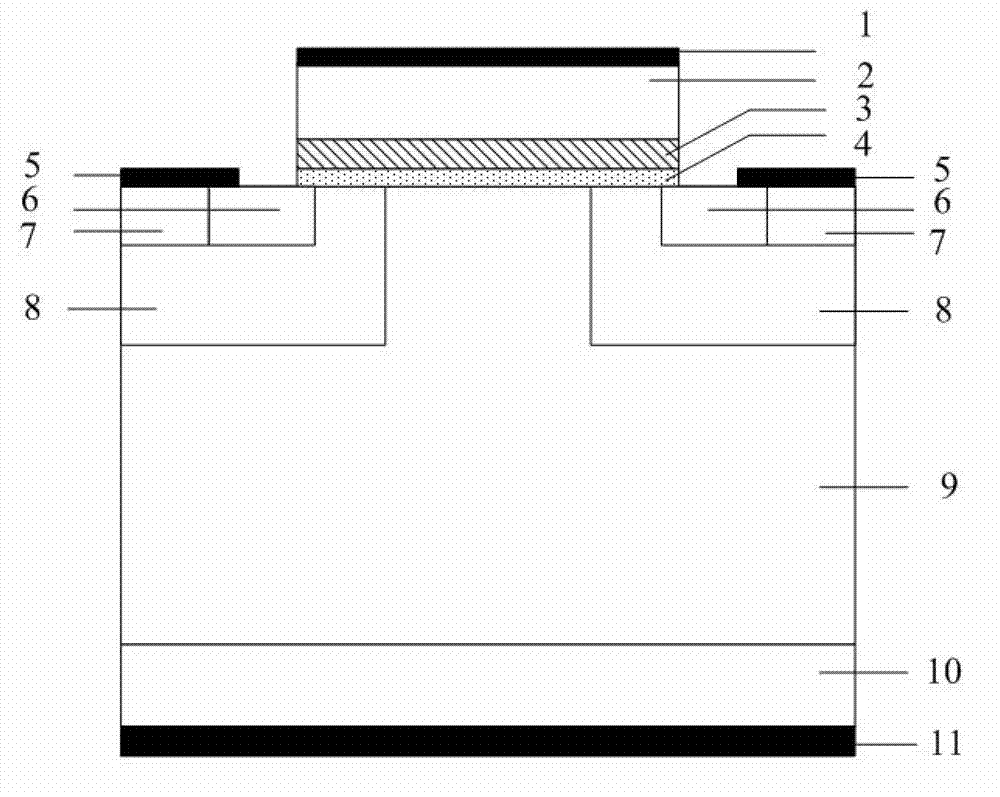

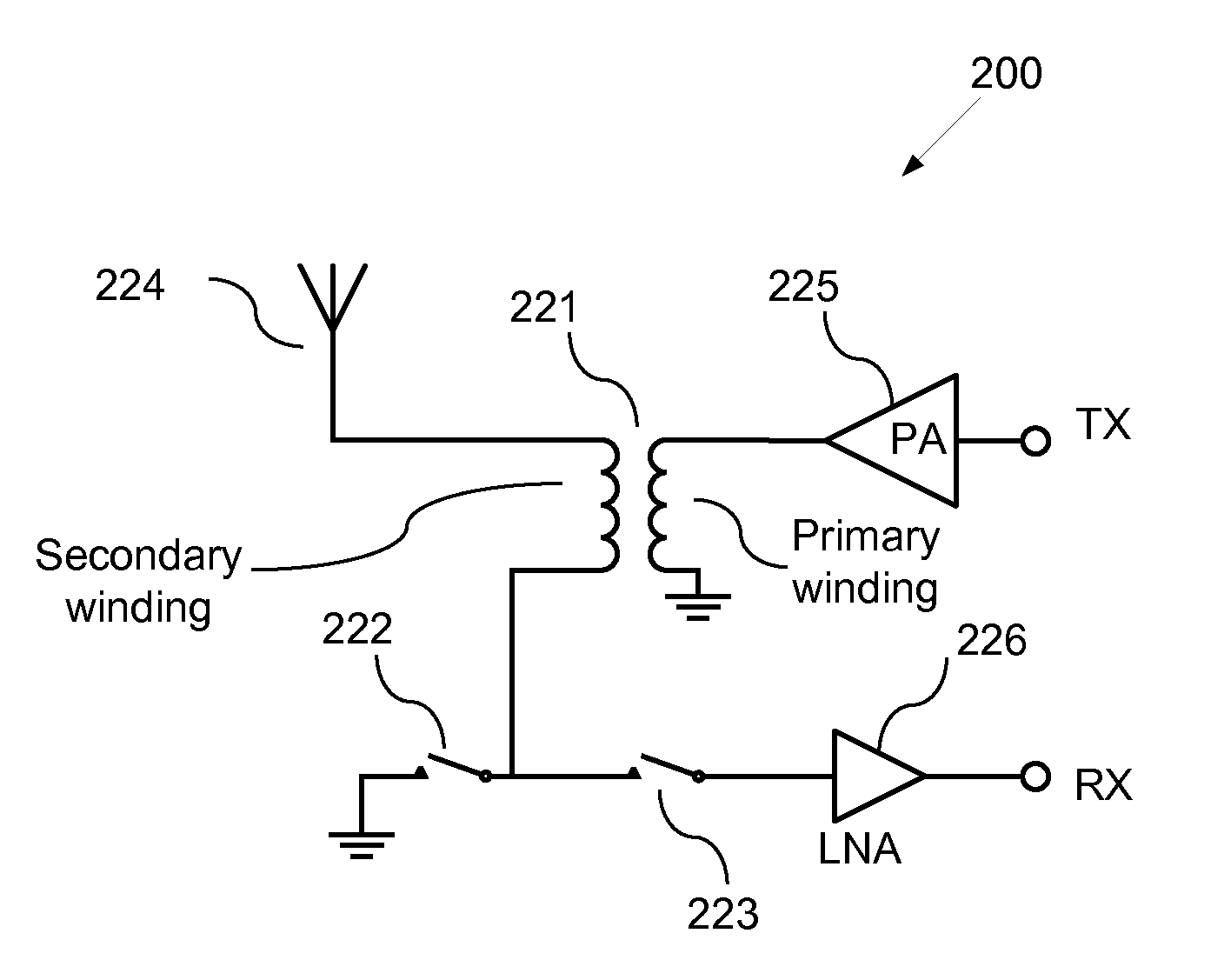

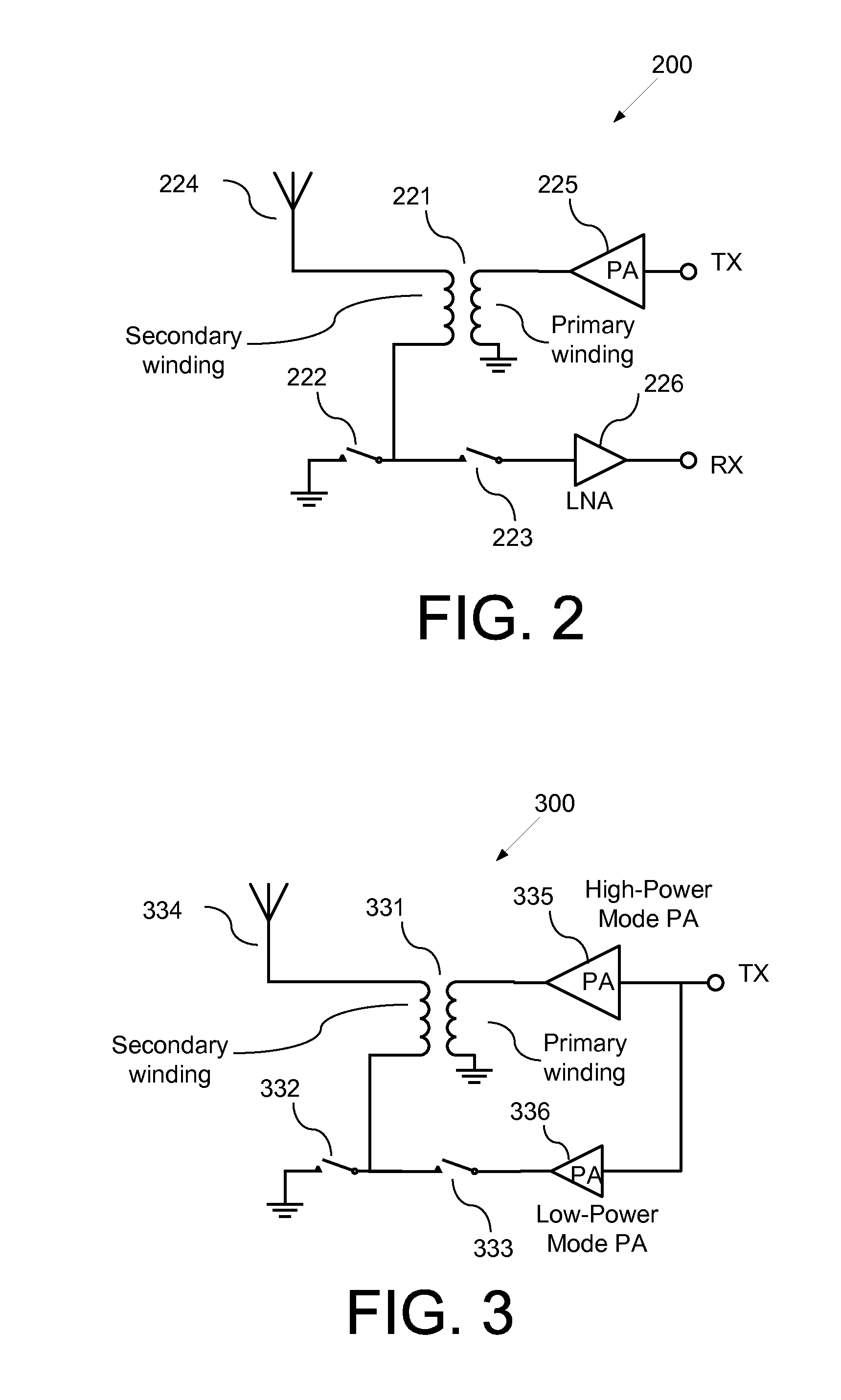

Systems and methods for a spdt switch or spmt switch with transformer

ActiveUS20110068636A1Low insertion lossLower breakdown voltageBoards/switchyards circuit arrangementsAmplifier with semiconductor-devices/discharge-tubesTransformerEngineering

A SPDT or SPMT switch may include a transformer having a primary winding and a secondary winding, where a first end of the secondary winding is connected to a single pole port, where a first end of the primary winding is connected to a first throw port; a first switch having a first end and a second end, where the first end is connected to ground; and a second switch, where a second end of the secondary winding is connected to both a second end of the first switch and a first end of the second switch, where a second end of the second switch is connected to a second throw port, where the first switch controls a first communication path between the single pole port and the first throw port, and where the second switch controls a second communication path between the second throw port and the single pole port.

Owner:GEORGIA TECH RES CORP +1

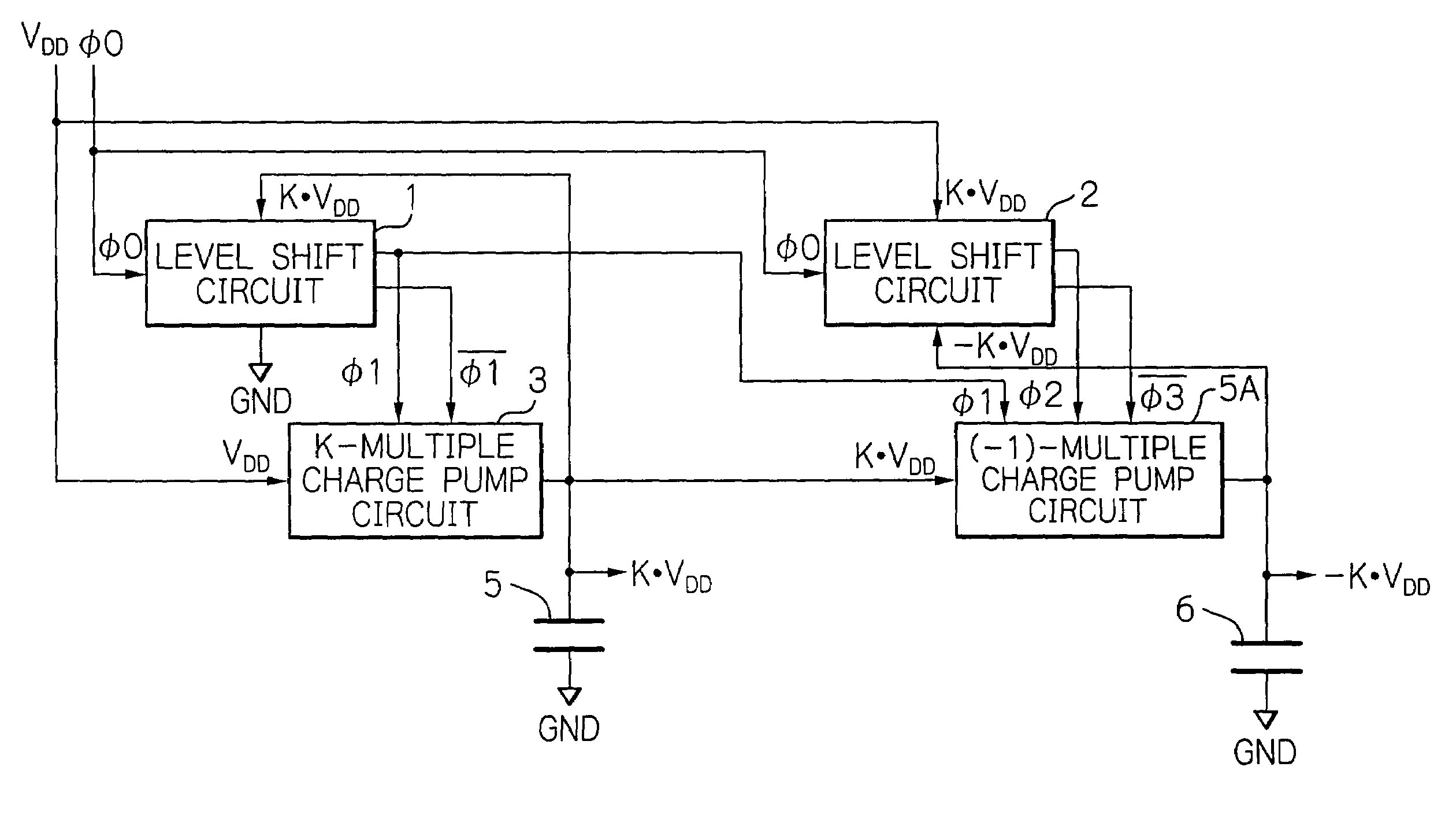

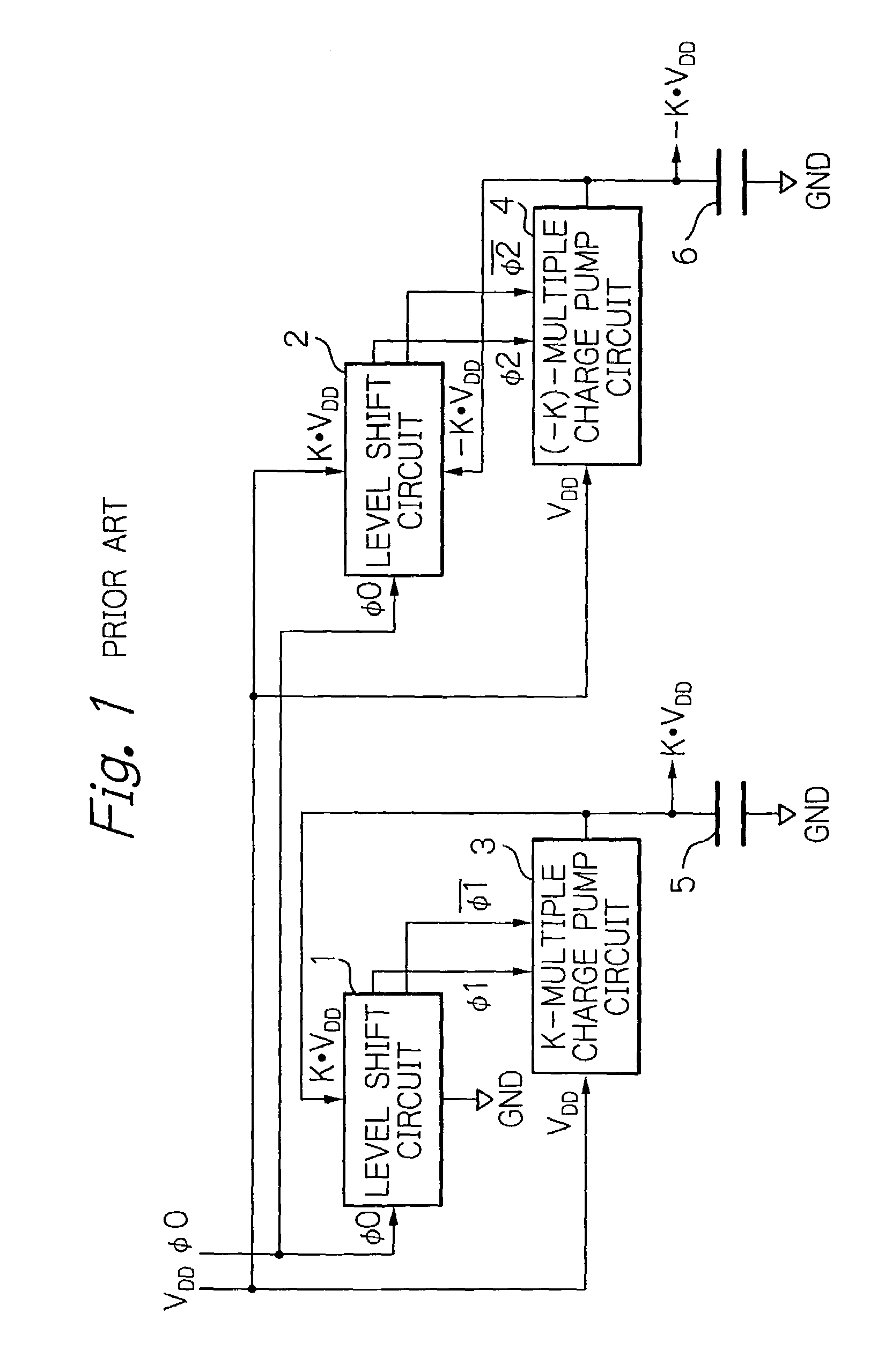

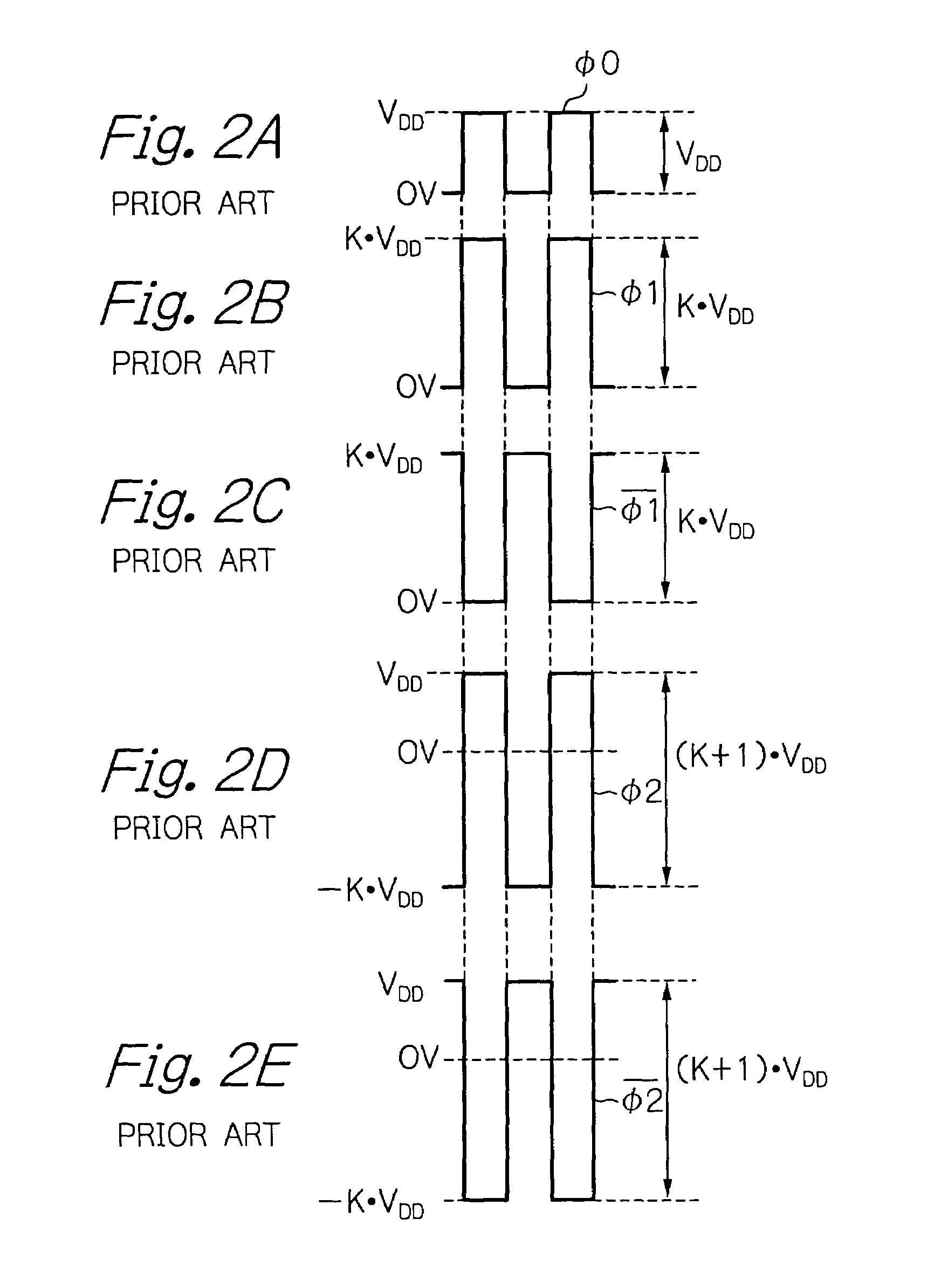

Simple step-up apparatus including level shift circuits capable of low breakdown voltage

ActiveUS7005912B2Lower breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingBreakdown voltageVIT signals

In a step-up apparatus, a first level shift circuit receives a first clock signal to generate two phase-opposite second clock signals, and a second level shift circuit receives the first clock signal to generate two phase-opposite third clock signals. A charge pump circuit steps up a power supply voltage at a power supply voltage terminal using the second clock signals to generate a positive voltage, and a polarity inverting circuit inverts the positive voltage using the third clock signals to generate a negative voltage whose absolute value is the same as the positive voltage. A high level of the second clock signals is not higher than the positive voltage, and a low level of the second clock signals is not lower than a voltage at a ground terminal. A high level of the third clock signals is not higher than the power supply voltage, and a low level of the third clock signals is not lower than the negative voltage.

Owner:NEC LCD TECH CORP

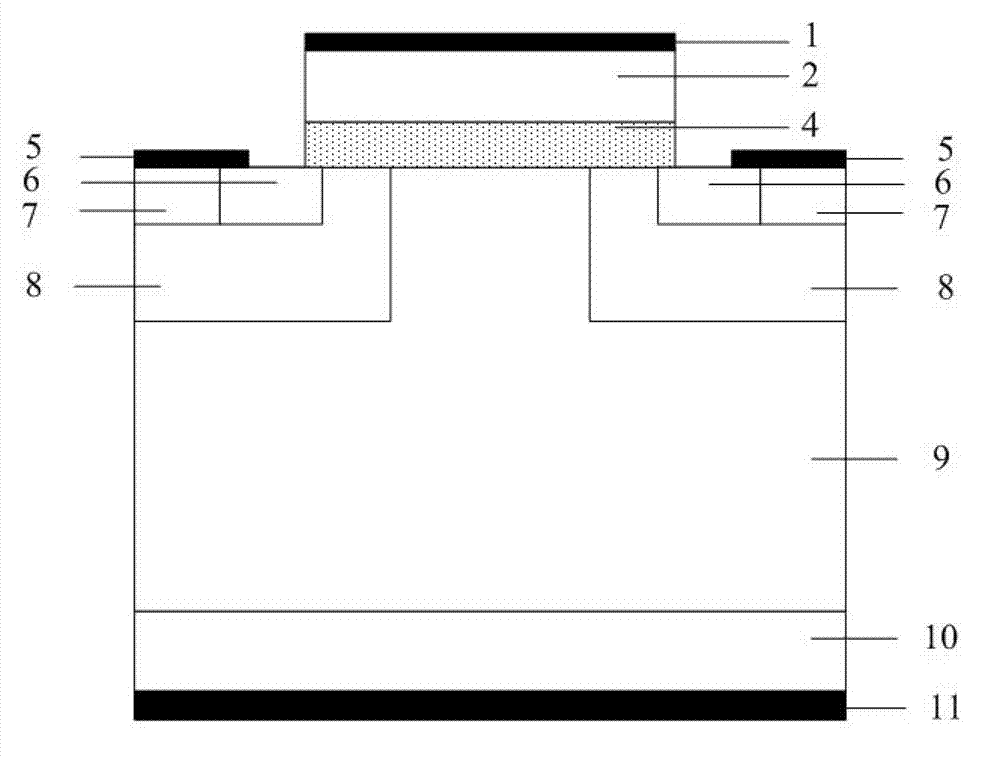

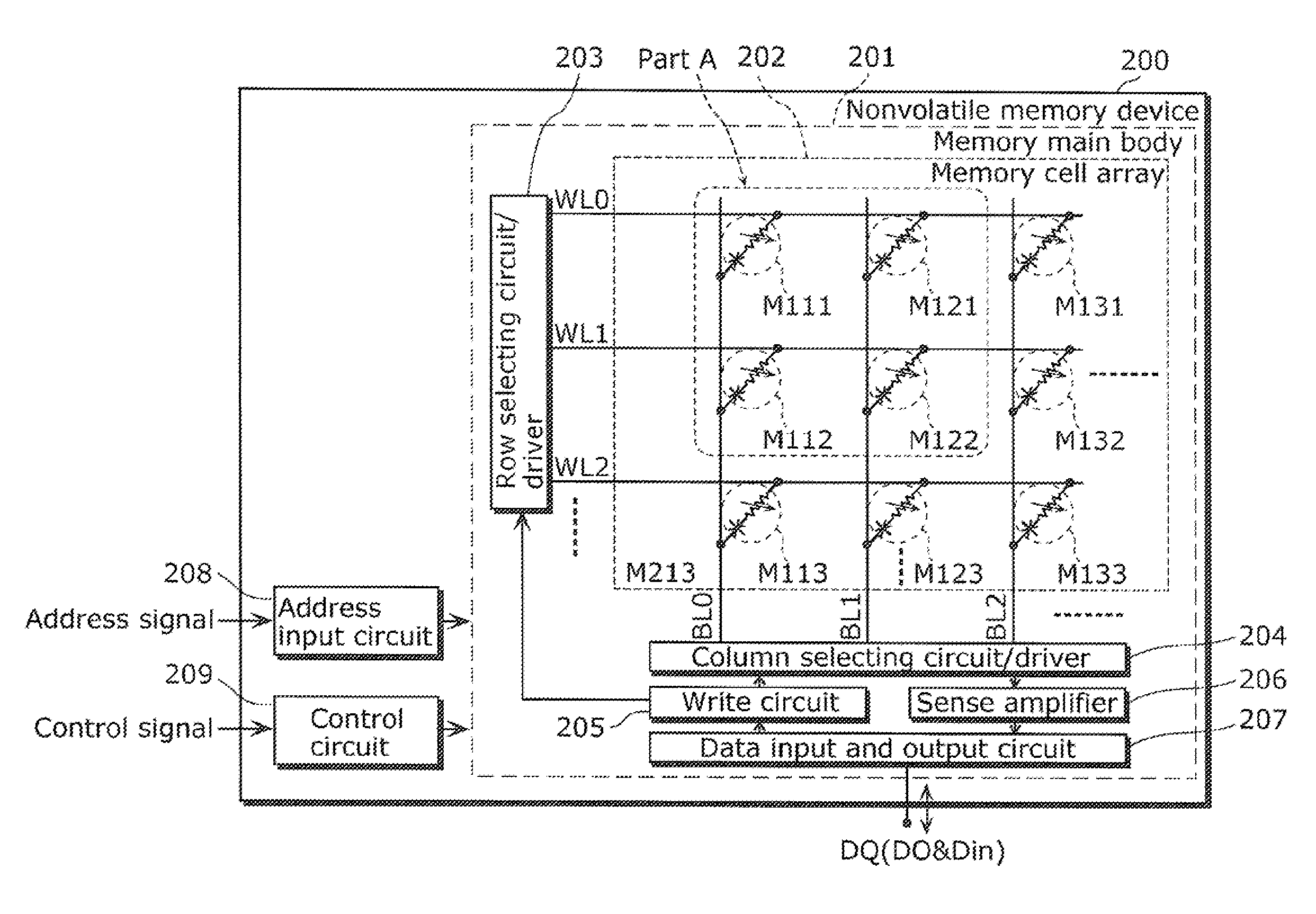

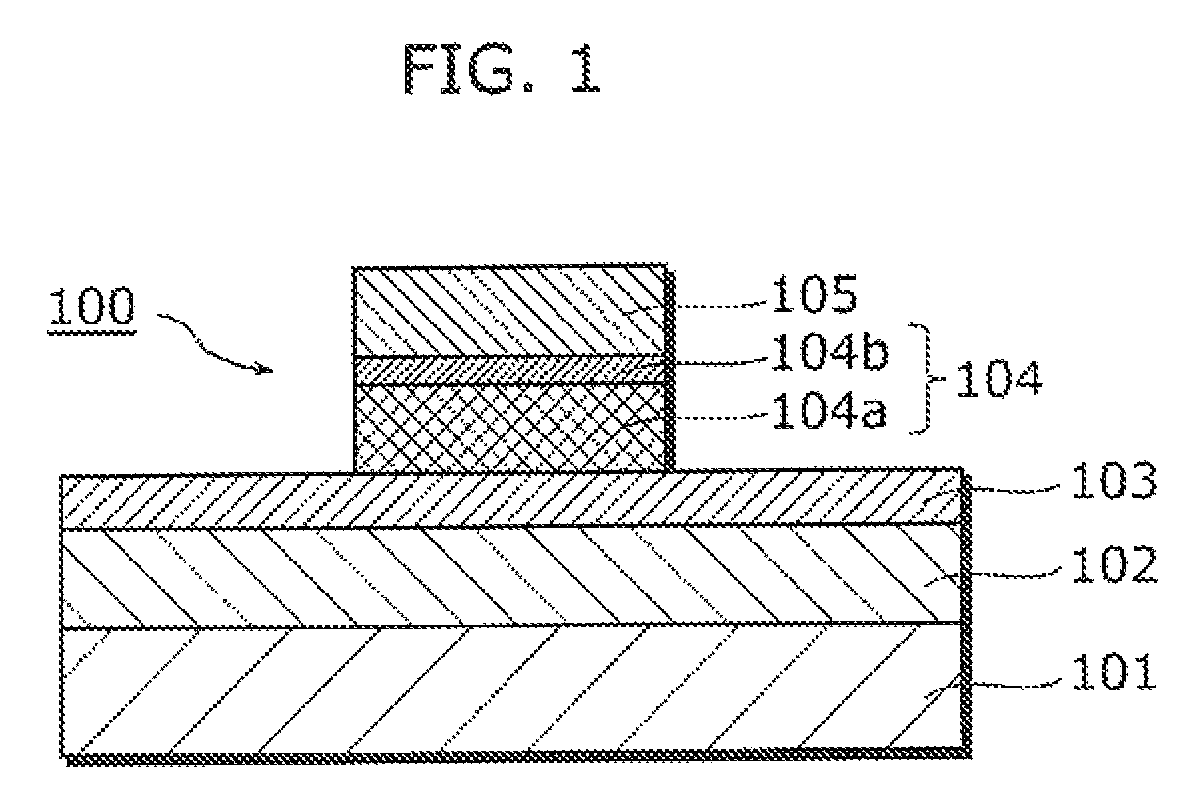

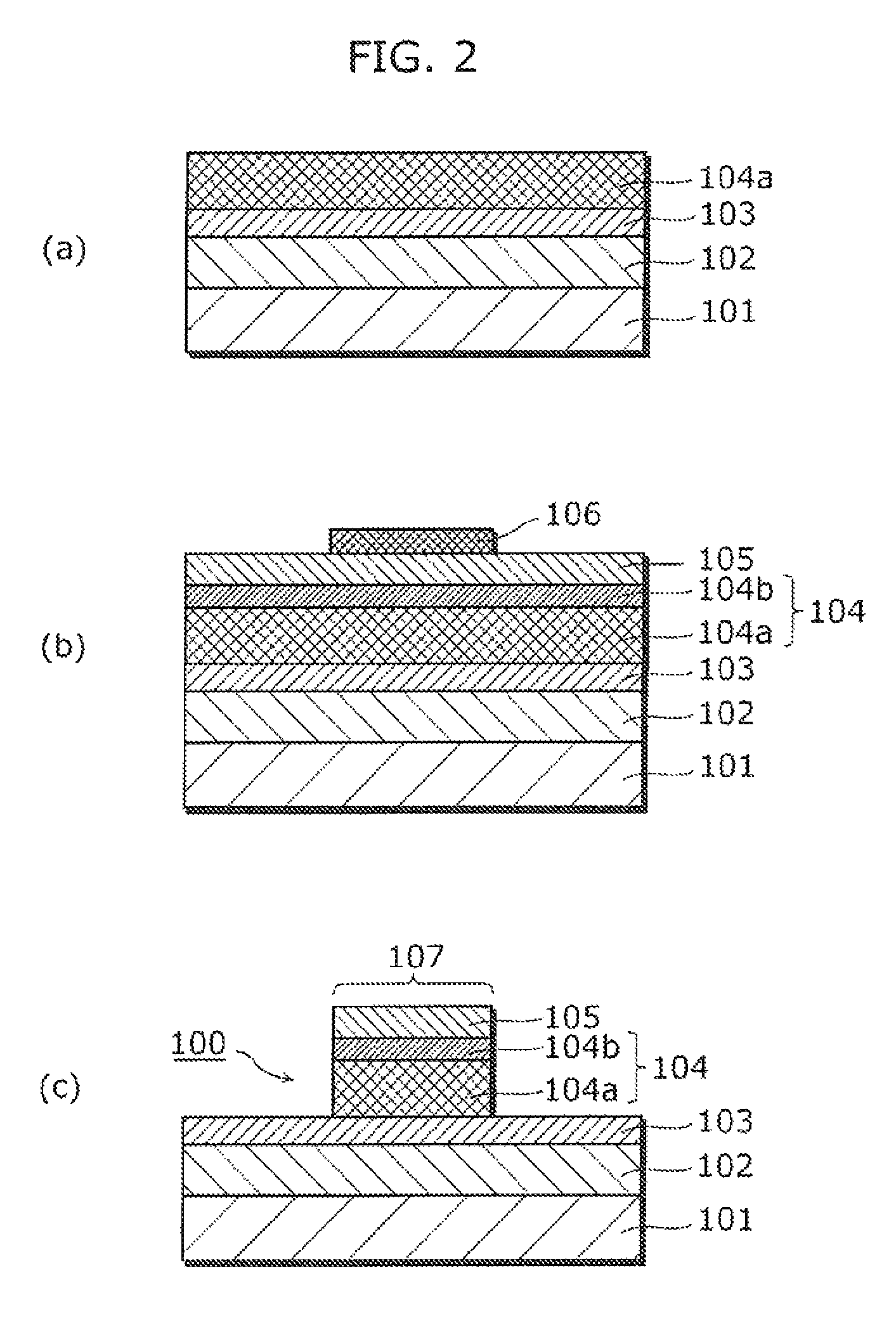

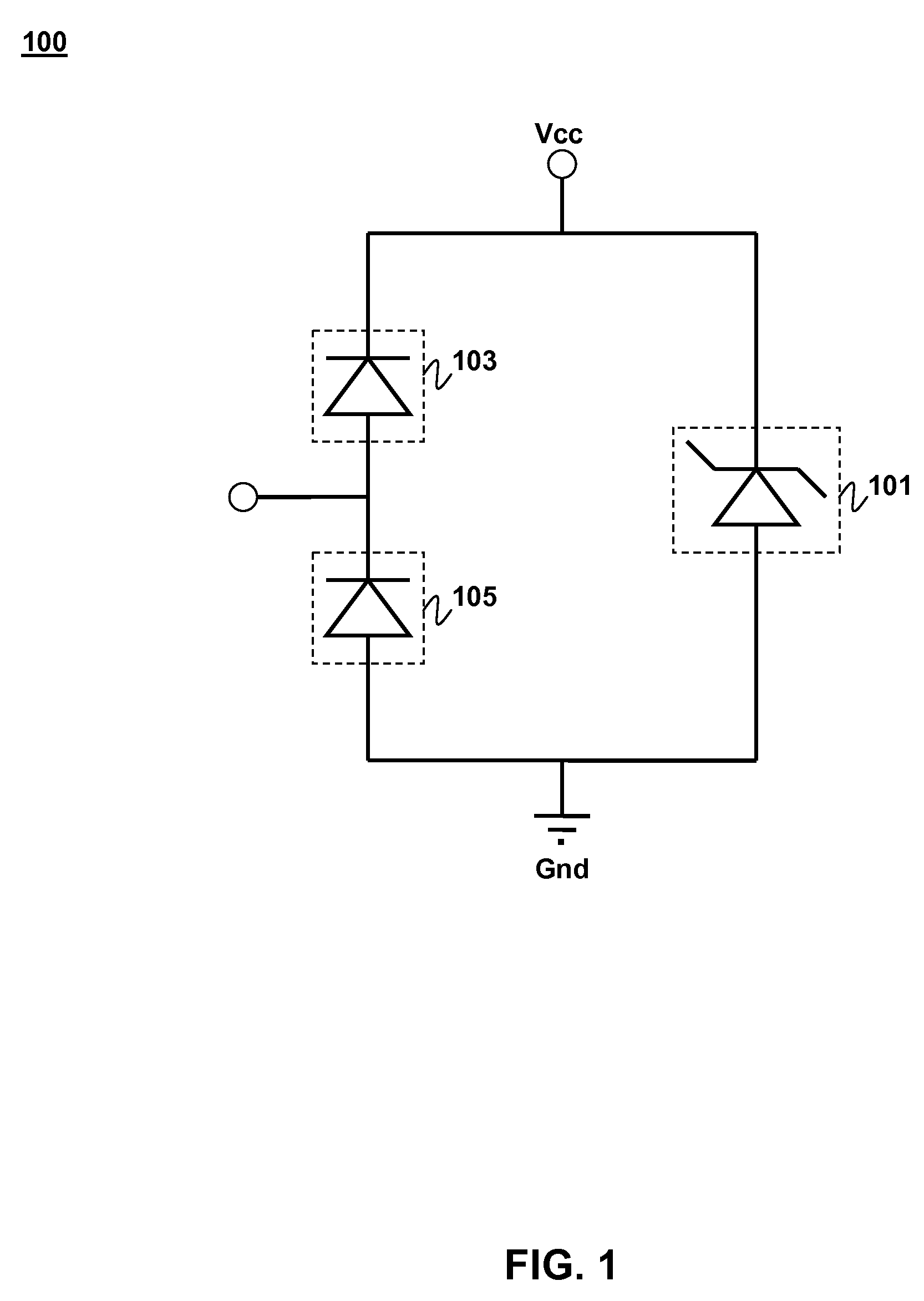

Nonvolatile memory element and nonvolatile memory device

ActiveUS8279657B2High resistivityHigh dielectric constantSolid-state devicesDigital storageElectrical resistance and conductanceElectrical polarity

Provided is a nonvolatile memory element which is capable of performing a stable resistance change operation at a low breakdown voltage.A nonvolatile memory element (100) includes: a first electrode layer (103); a second electrode layer (105); and a variable resistance layer (104) which is placed between the electrodes (103 and 105), and whose resistance state reversibly changes between a high resistance state and a low resistance state based on a polarity of a voltage applied between the electrodes (103 and 105). The variable resistance layer (104) is formed by stacking a first oxide layer (104a) including an oxide of a first transition metal and a second oxide layer (104b) including an oxide of a second transition metal which is different from the first transition metal. At least one of the following conditions is satisfied: (1) a dielectric constant of the second oxide layer (104b) is larger than a dielectric constant of the first oxide layer (104a); and (2) a band gap of the second oxide layer (104b) is smaller than a band gap of the first oxide layer (104a).

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

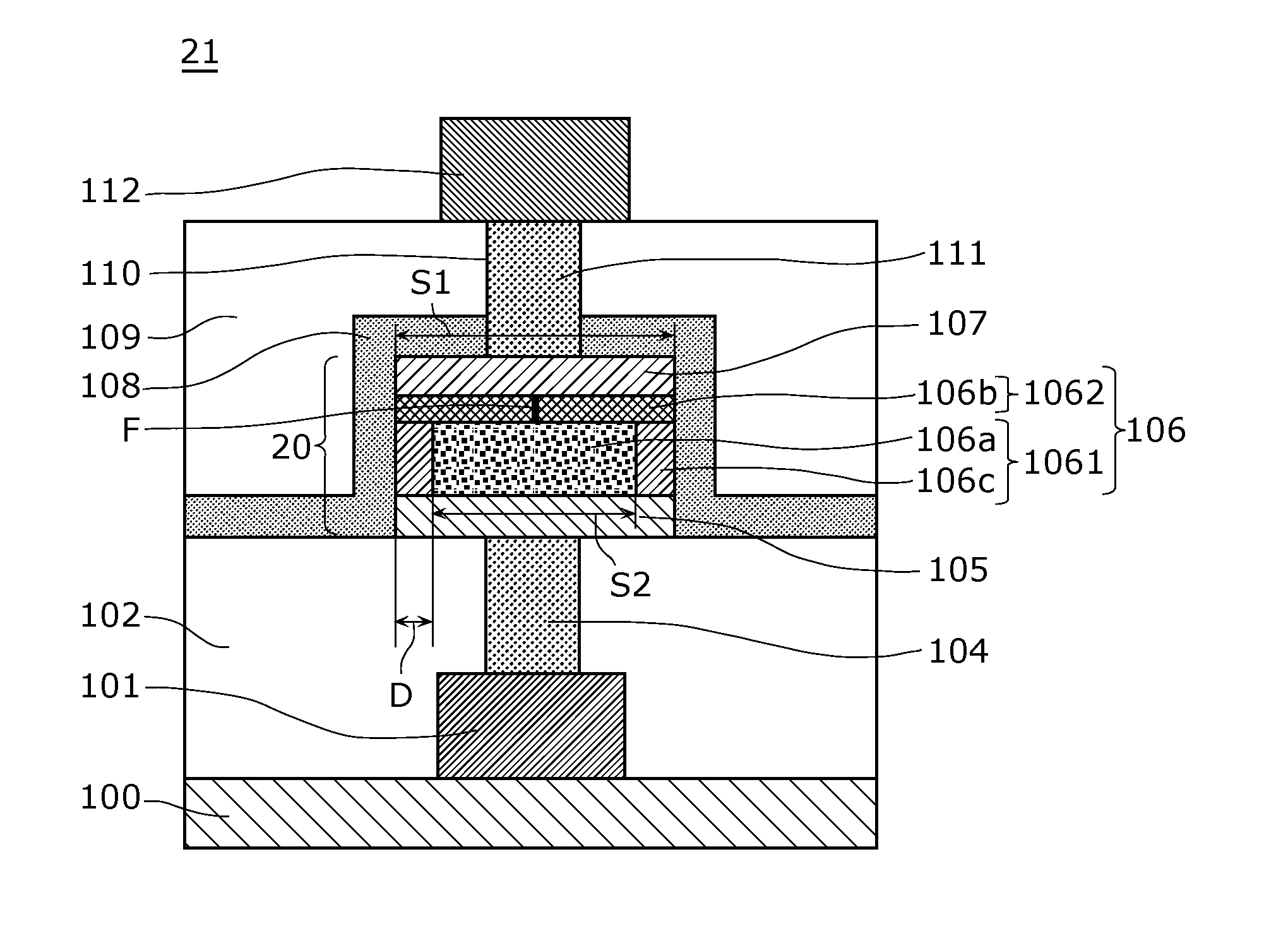

Nonvolatile memory element, nonvolatile memory device, nonvolatile memory element manufacturing method, and nonvolatile memory device manufacturing method

ActiveUS20140197368A1Decrease maximum areaReduce leakage currentSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesEngineeringOxygen barrier

A nonvolatile memory element including: a first electrode; a second electrode; a variable resistance layer that is between the first electrode and the second electrode and includes, as stacked layers, a first variable resistance layer connected to the first electrode and a second variable resistance layer connected to the second electrode; and a side wall protecting layer that has oxygen barrier properties and covers a side surface of the variable resistance layer. The first variable resistance layer includes a first metal oxide and a third metal oxide formed around the first metal oxide and having an oxygen deficiency lower than that of the first metal oxide, and the second variable resistance layer includes a second metal oxide having an oxygen deficiency lower than that of the first metal oxide.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

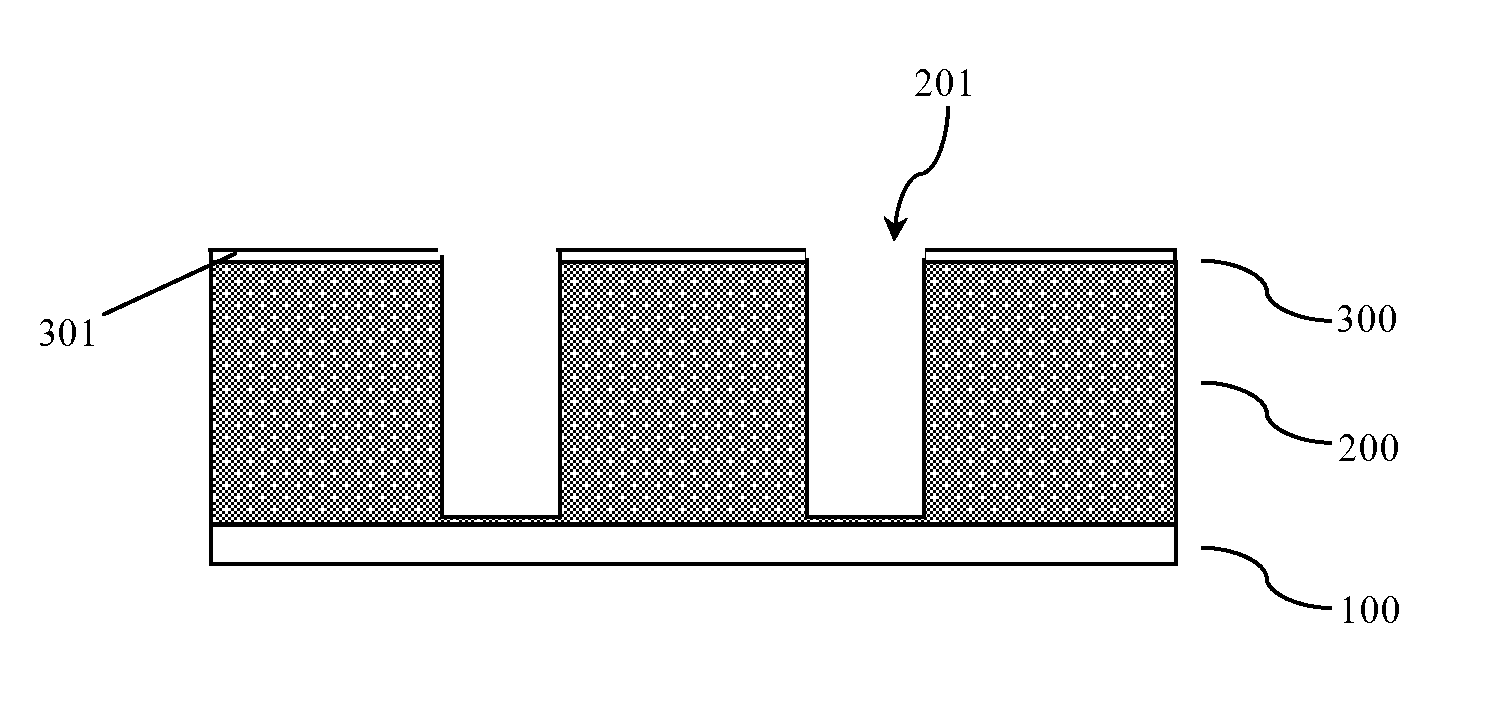

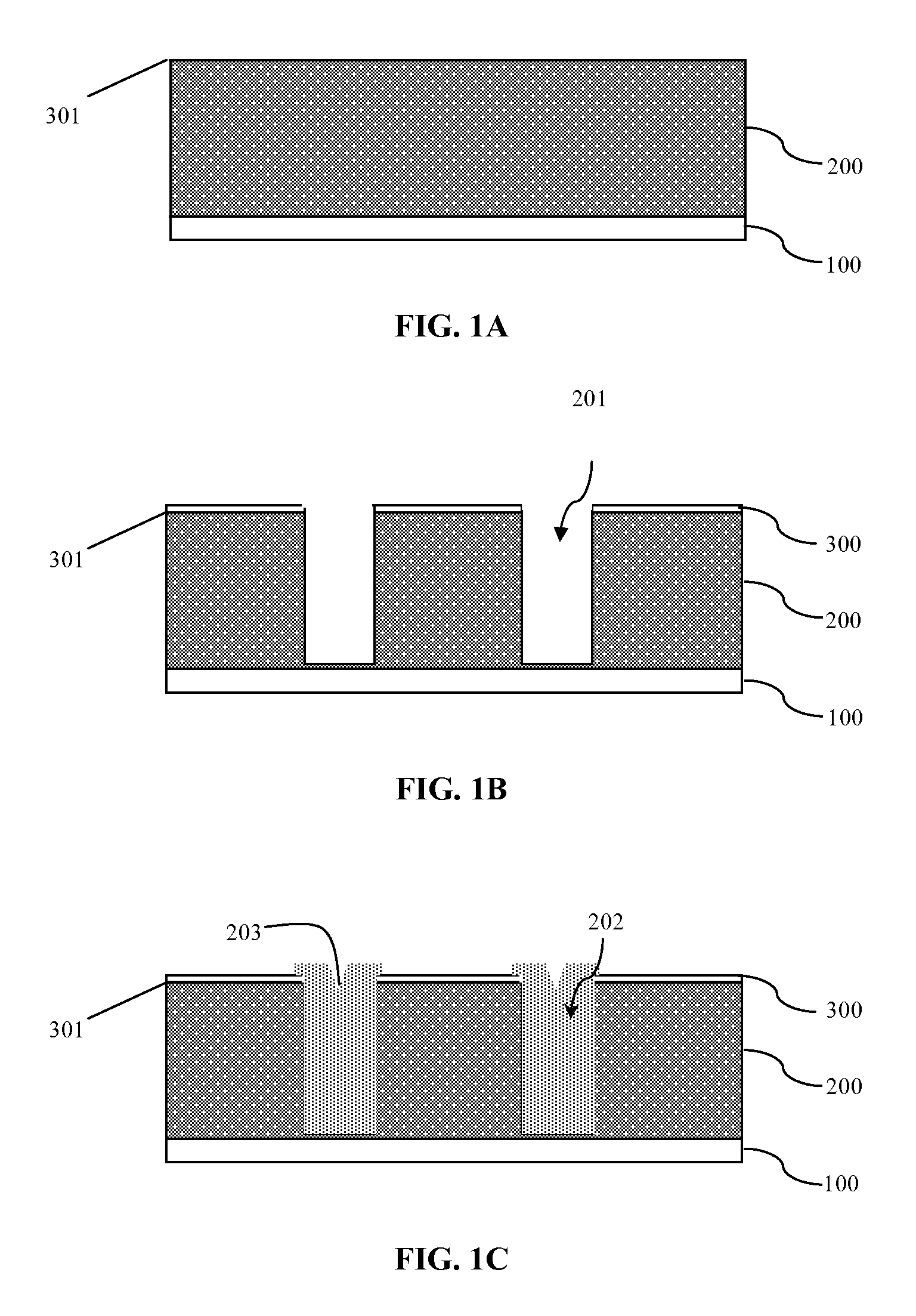

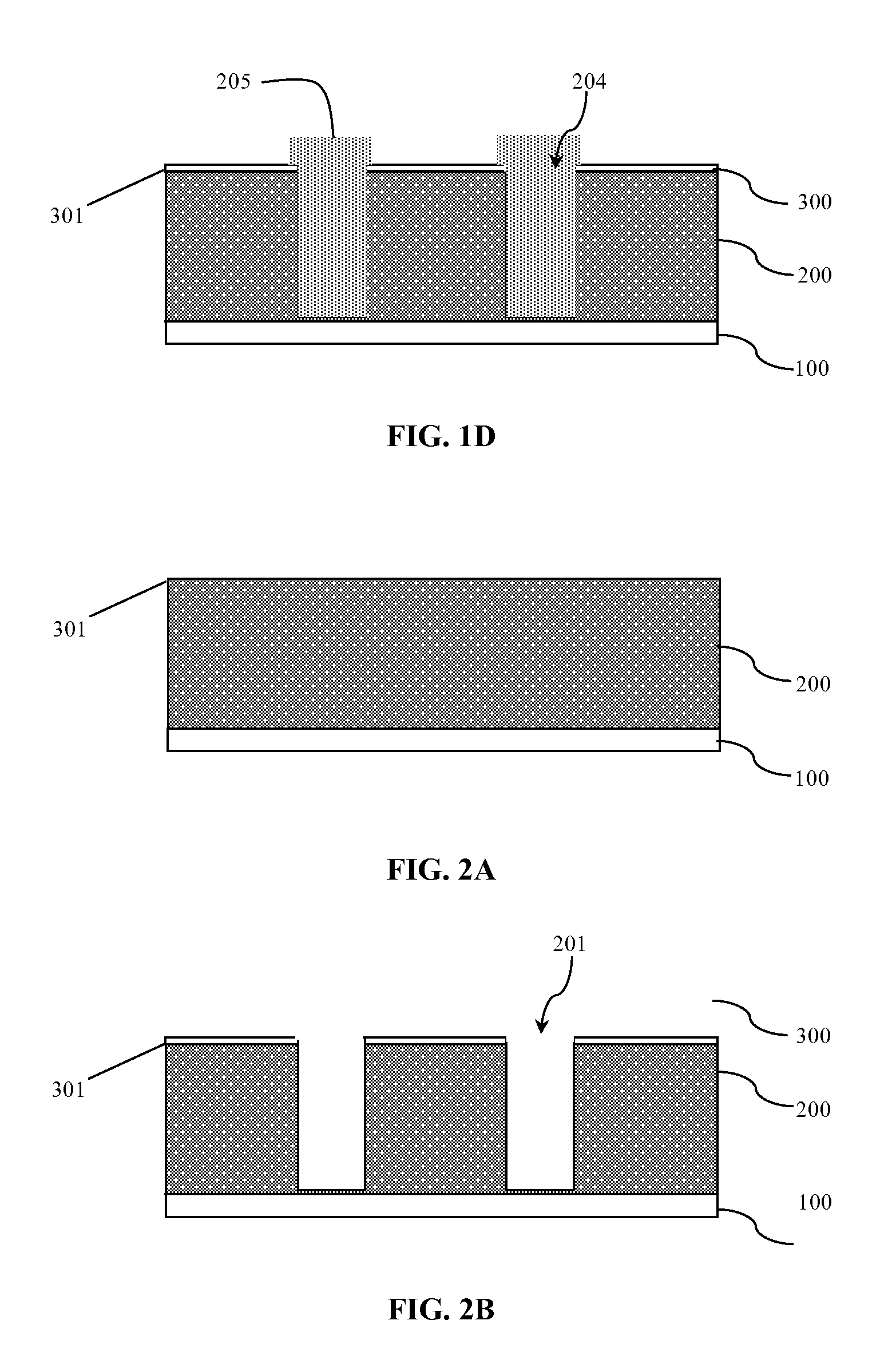

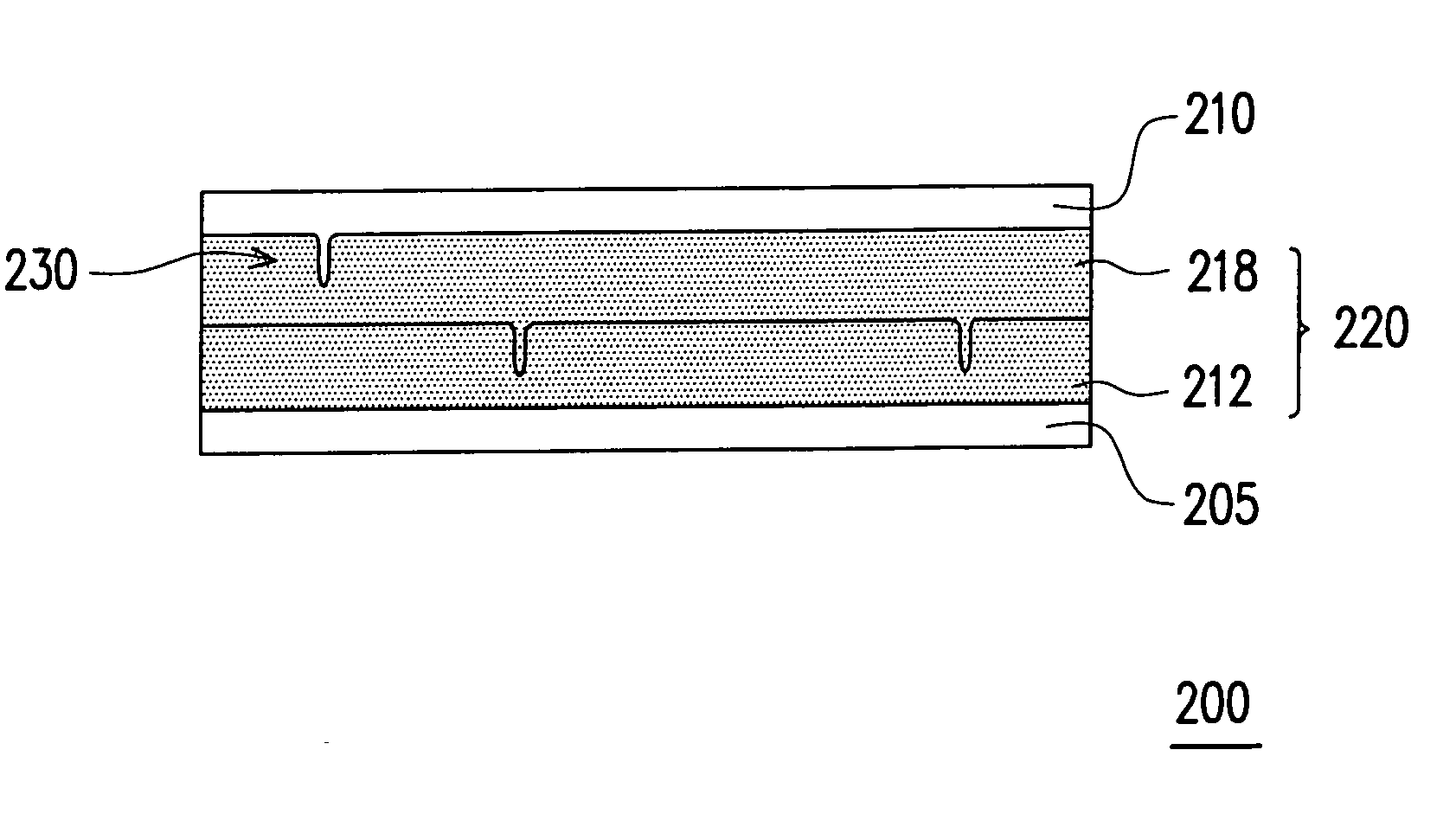

Semiconductor structures and fabrication method

ActiveUS20130105796A1Lower breakdown voltageDeterioration in electrical propertySemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringSemiconductor structure

A method is provided for fabricating a semiconductor structure. The method includes providing a semiconductor substrate, forming an epitaxial layer on a top surface of the semiconductor substrate and having a predetermined thickness, and forming a plurality of trenches in the epitaxial layer. The trenches are formed in the epitaxial layer and have a predetermined depth, top width, and bottom width. Further, the method includes performing a first trench filling process to form a semiconductor layer inside of the trenches using a mixture gas containing at least silicon source gas and halogenoid gas, stopping the first trench filling process when at least one trench is not completely filled, and performing a second trench filling process, different from the first trench filling process, to fill the plurality of trenches completely.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

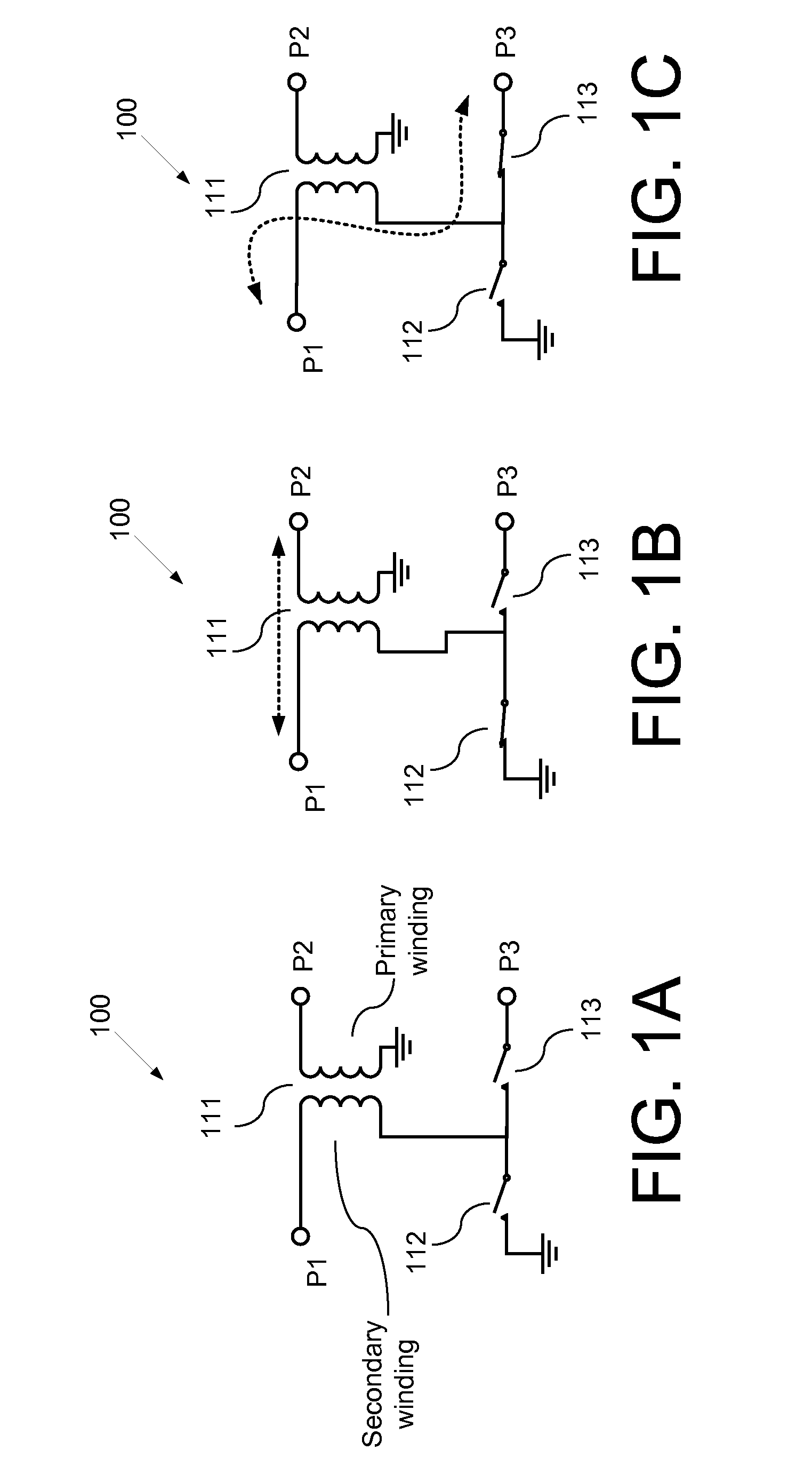

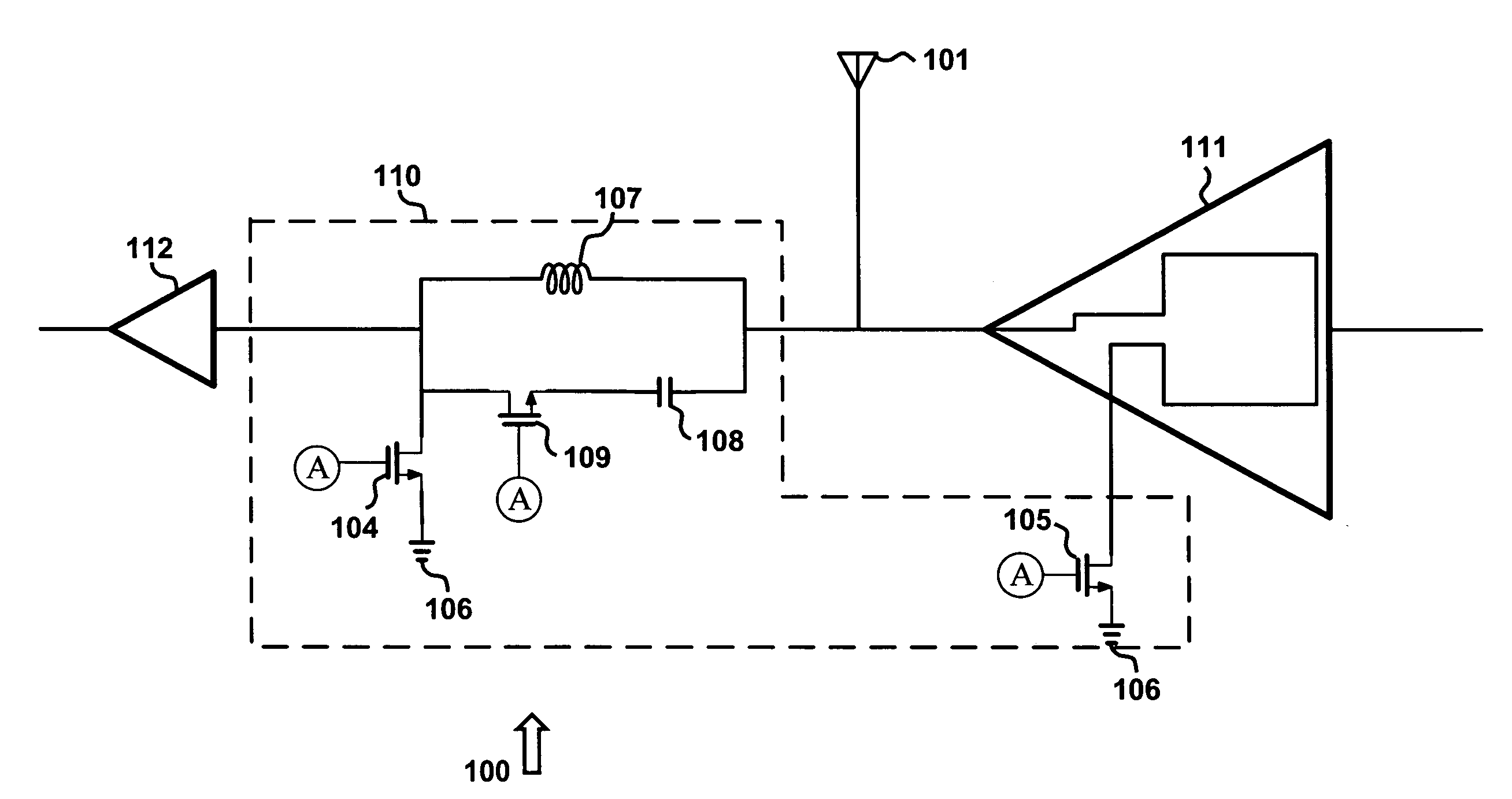

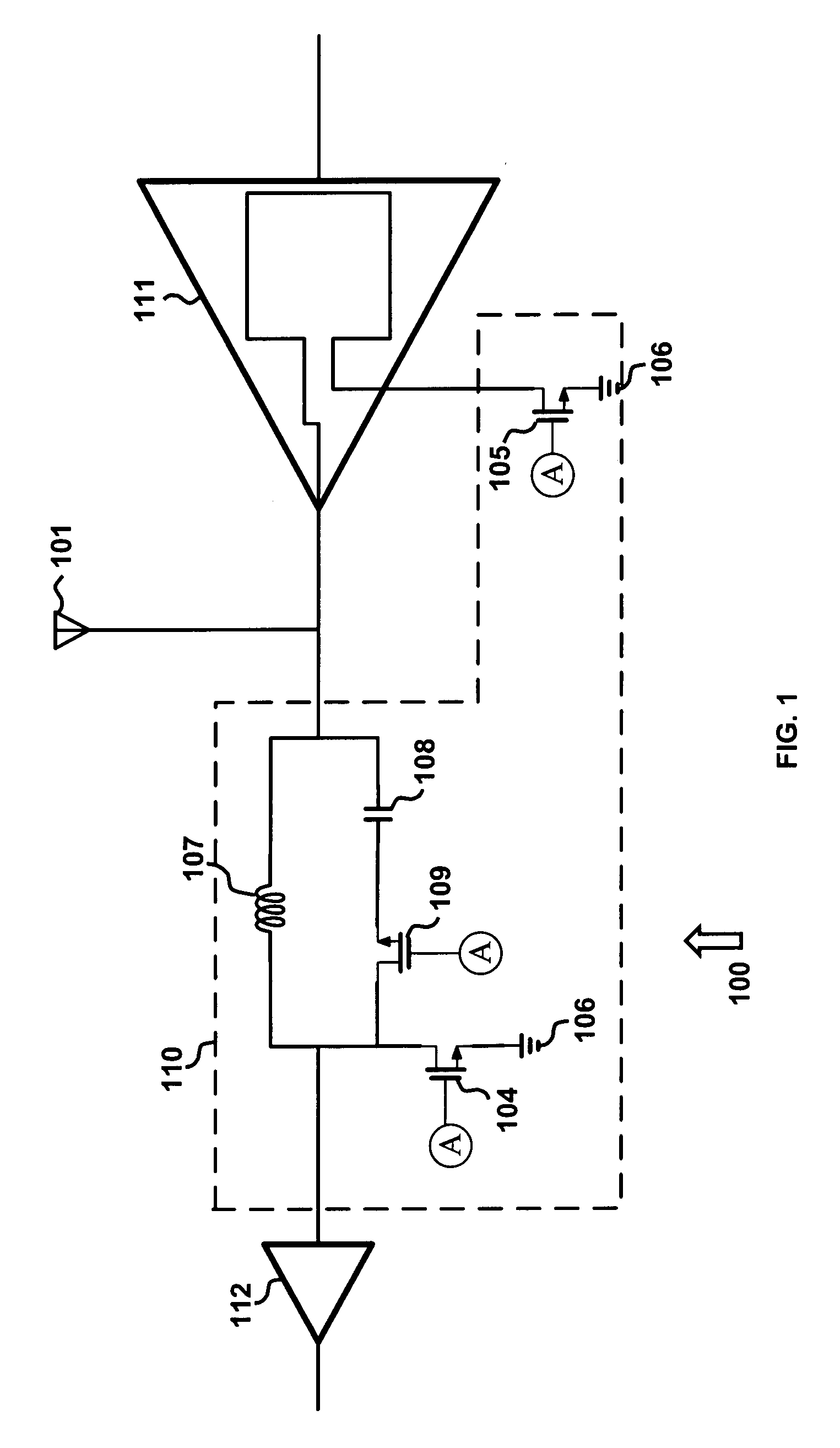

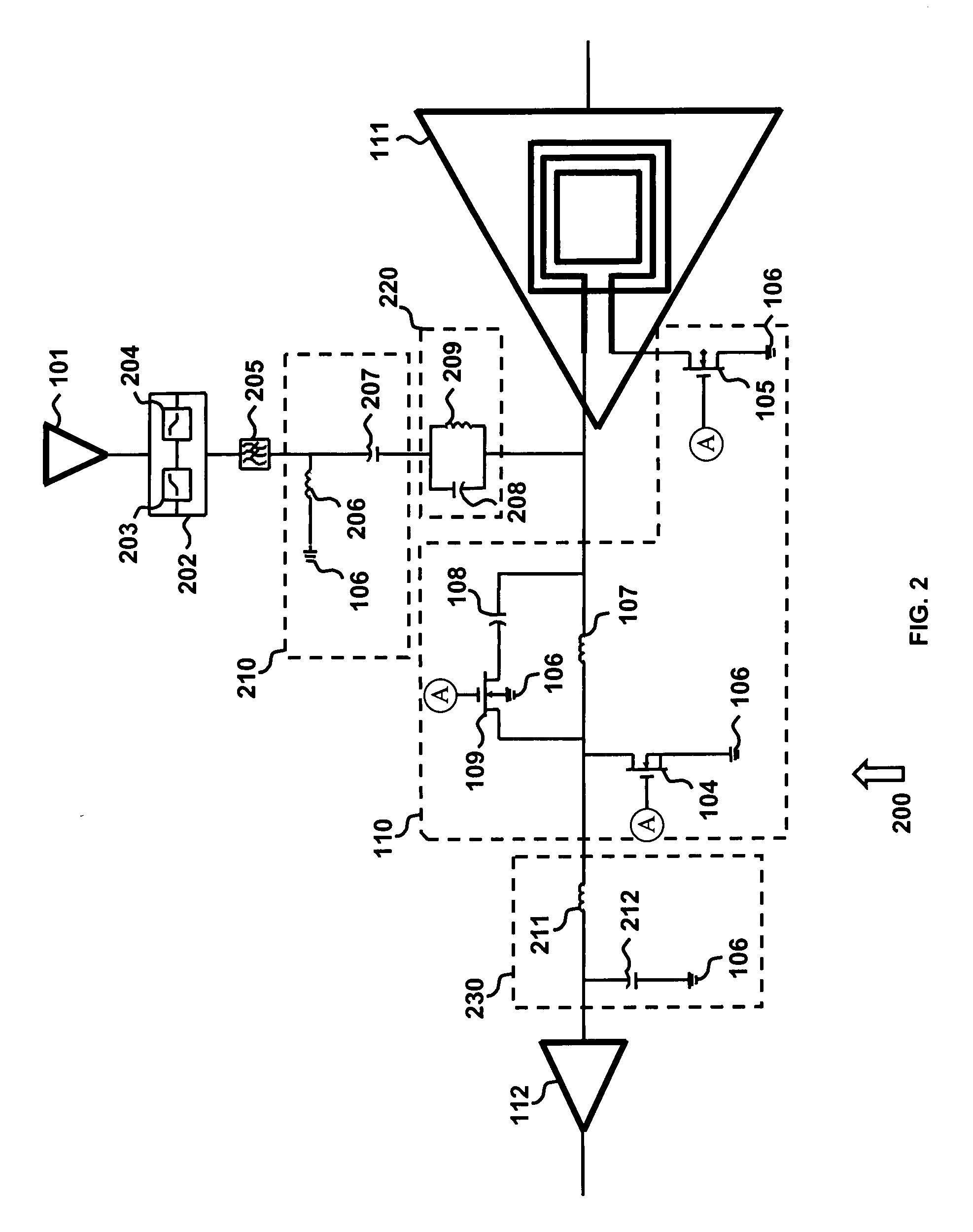

Radio front end with resonant transmit/receive switch

ActiveUS20090017775A1Improve the immunityEasy to integrateTransmissionAudio power amplifierTransmitted power

A device having a radio front end is provided. The radio front end includes an inductor having a first end and a second end. A capacitor having a first end and a second end is connected to the second end of the inductor. An antenna is connected to the second end of the inductor and the second end of the capacitor. A first switch is connected to the first end of the inductor and the first end of the capacitor, wherein the inductor and capacitor form a resonant circuit when the first switch is closed. A second switch is connected to the resonant circuit, the second switch connecting the resonant circuit to ground through a low impedance when the first switch is closed. A third switch is connected to a transmit power amplifier connecting the transmit power amplifier to ground through a low impedance when the first switch is closed.

Owner:AXIOM MICRODEVICES

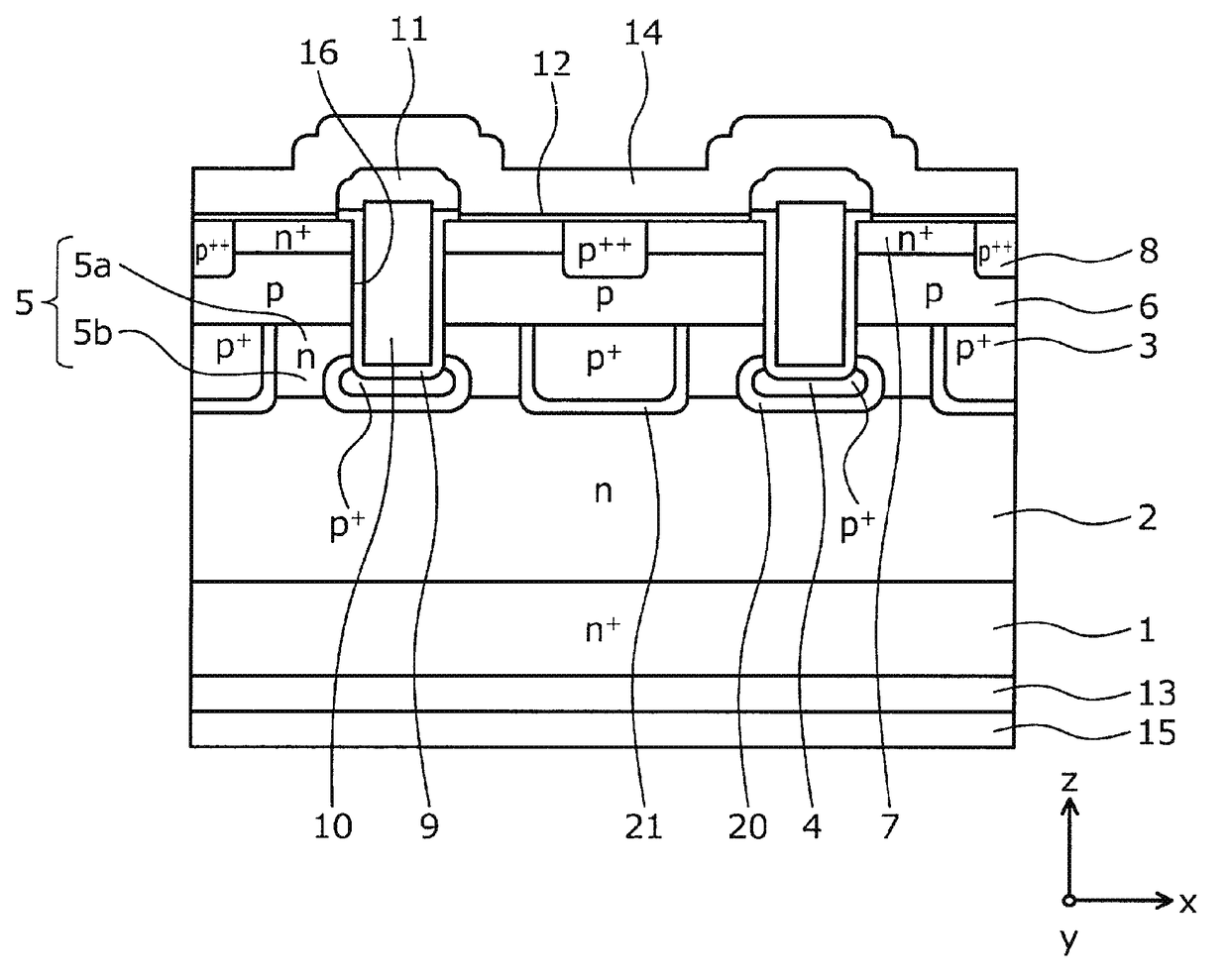

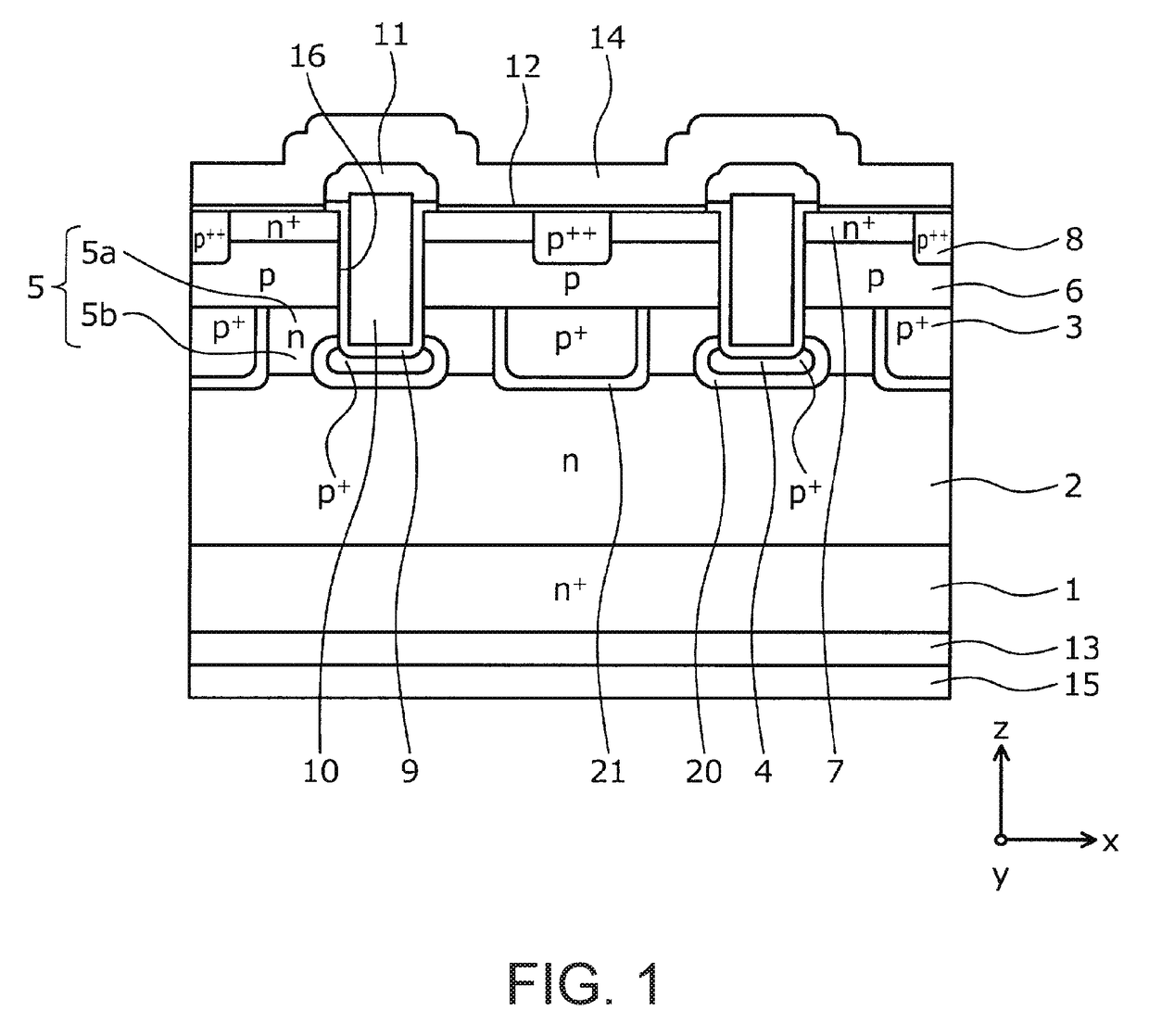

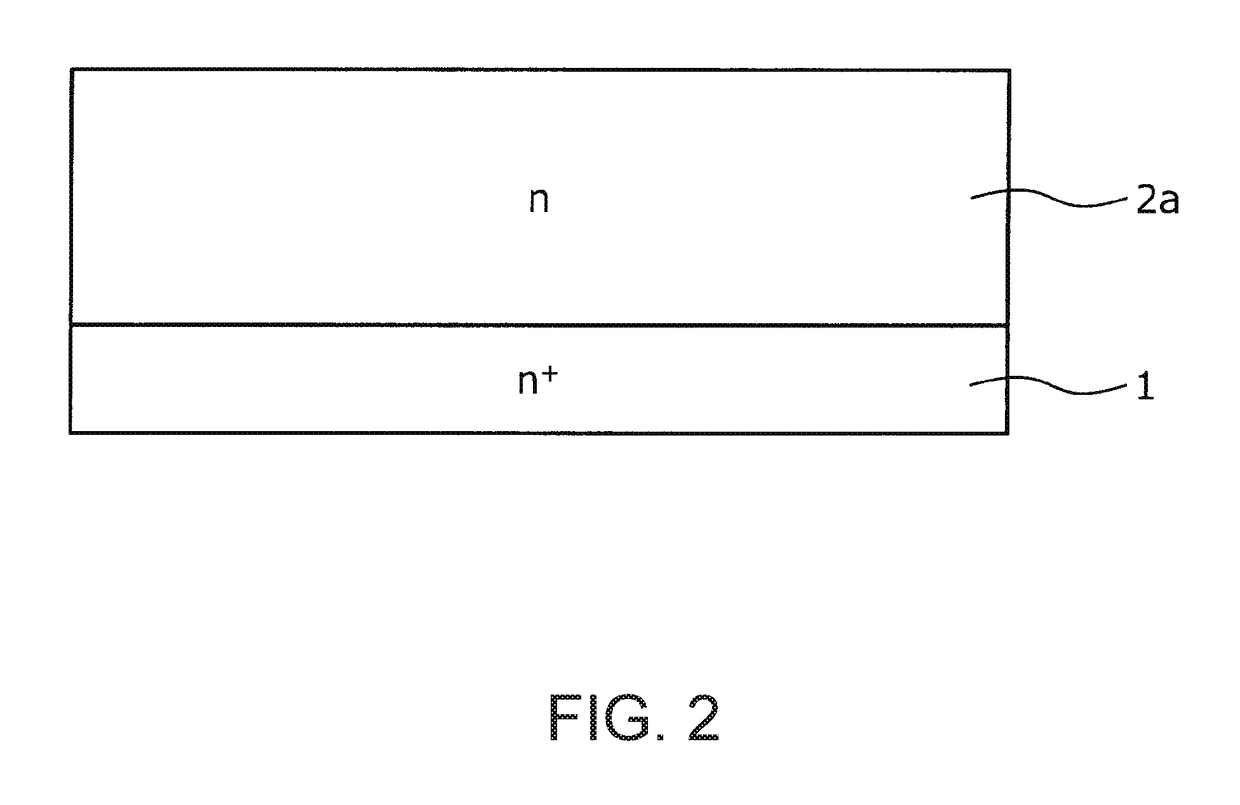

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20170141223A1Increase the on-resistanceLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialOptoelectronics

Trenches and n+ high impurity concentration regions are formed in a first principal surface side of a silicon carbide semiconductor substrate. In the n+ high impurity concentration regions, third n-type regions that respectively surround first p+ base regions contacting a p-type base layer and have a higher impurity concentration than the n+ high impurity concentration regions, as well as fourth n-type regions that respectively surround second p+ base regions formed at the bottoms of the trenches and also have a higher impurity concentration than the n+ high impurity concentration regions, are formed.

Owner:FUJI ELECTRIC CO LTD

Silicon carbide power device having protective diode

InactiveUS6855981B2Avoid damageLower breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesSchottky barrierZener diode

A silicon carbide power device includes a junction field effect transistor and a protective diode, which is a Zener or PN junction diode. The PN junction of the protective diode has a breakdown voltage lower than the PN junction of the transistor. Another silicon carbide power device includes a protective diode, which is a Schottky diode. The Schottky diode has a breakdown voltage lower than the PN junction of the transistor by adjusting Schottky barrier height or the depletion layer formed in the semiconductor included in the Schottky diode. Another silicon carbide power device includes three protective diodes, which are Zener diodes. Two of the protective diodes are used to clamp the voltages applied to the gate and the drain of the transistor due to surge energy and used to release the surge energy. The last diode is a thermo-sensitive diode, with which the temperature of the JFET is measured.

Owner:DENSO CORP

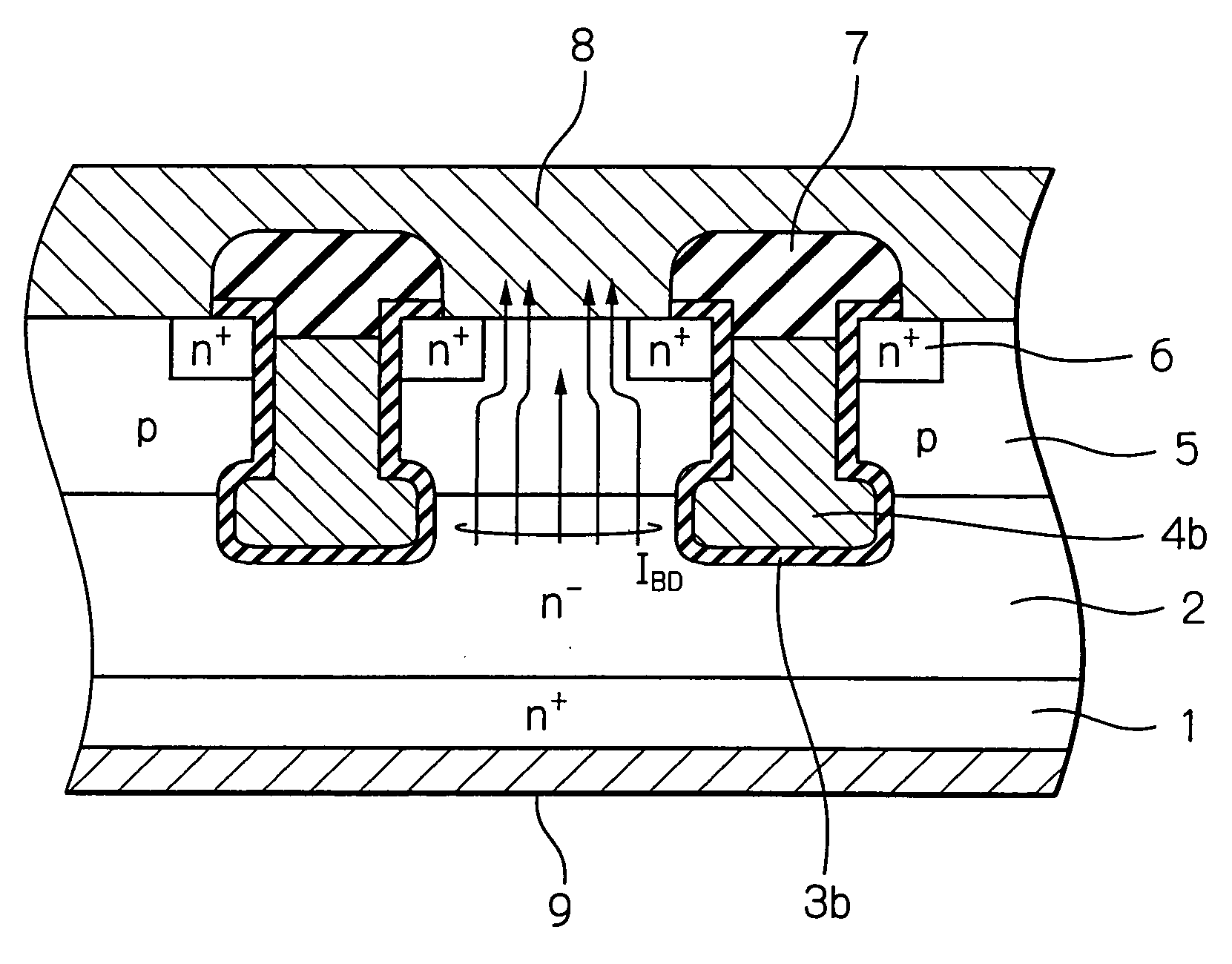

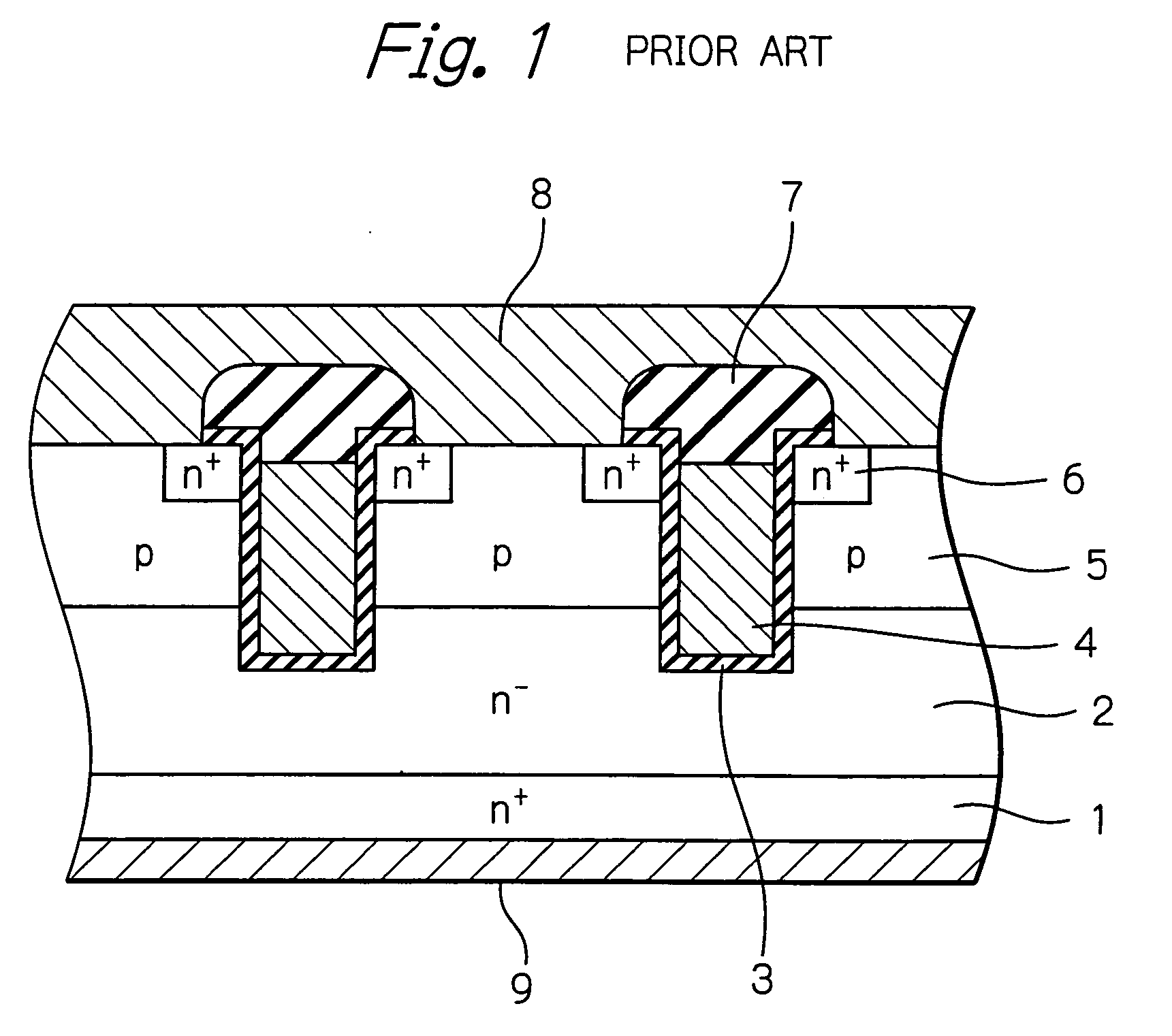

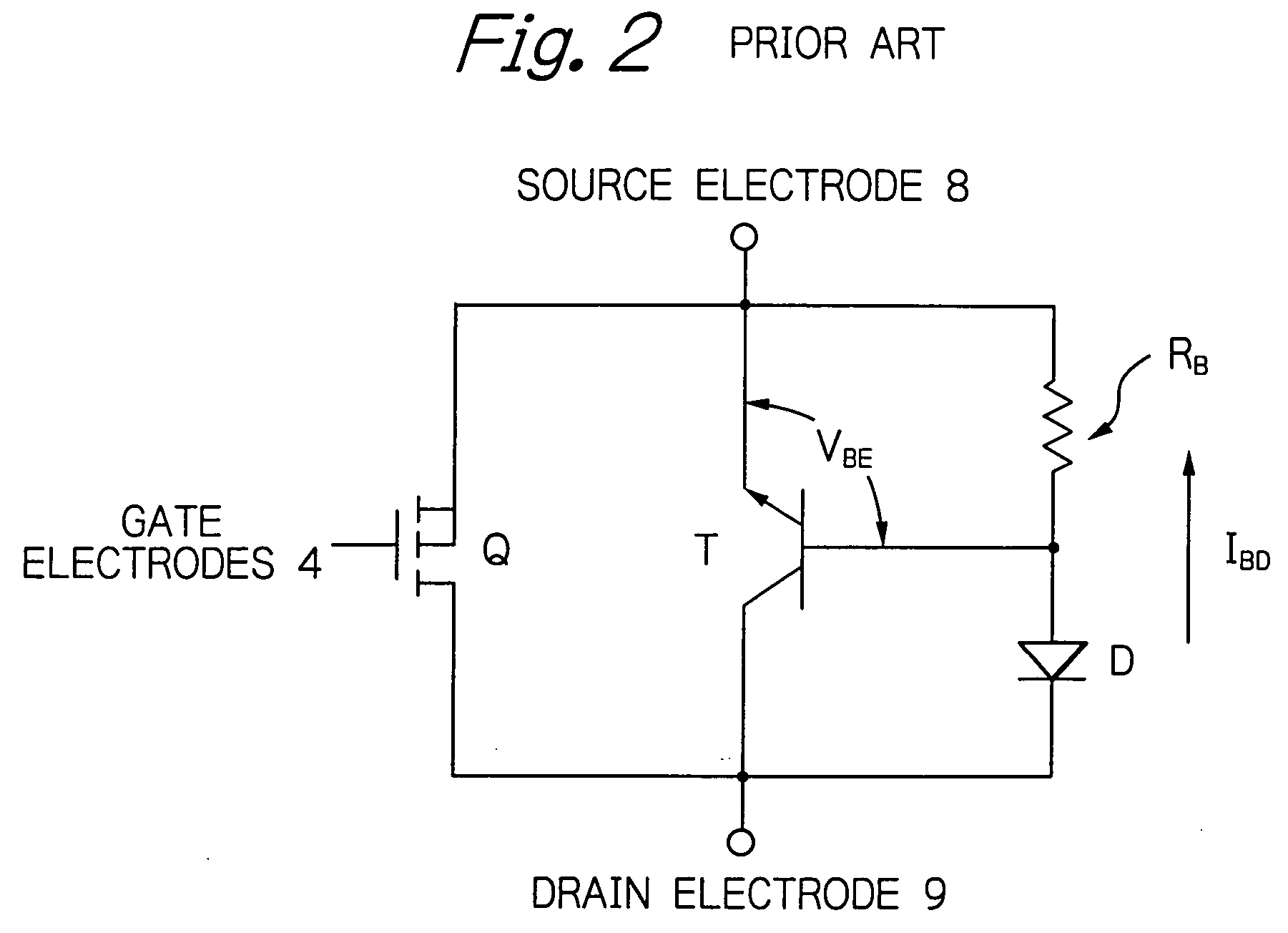

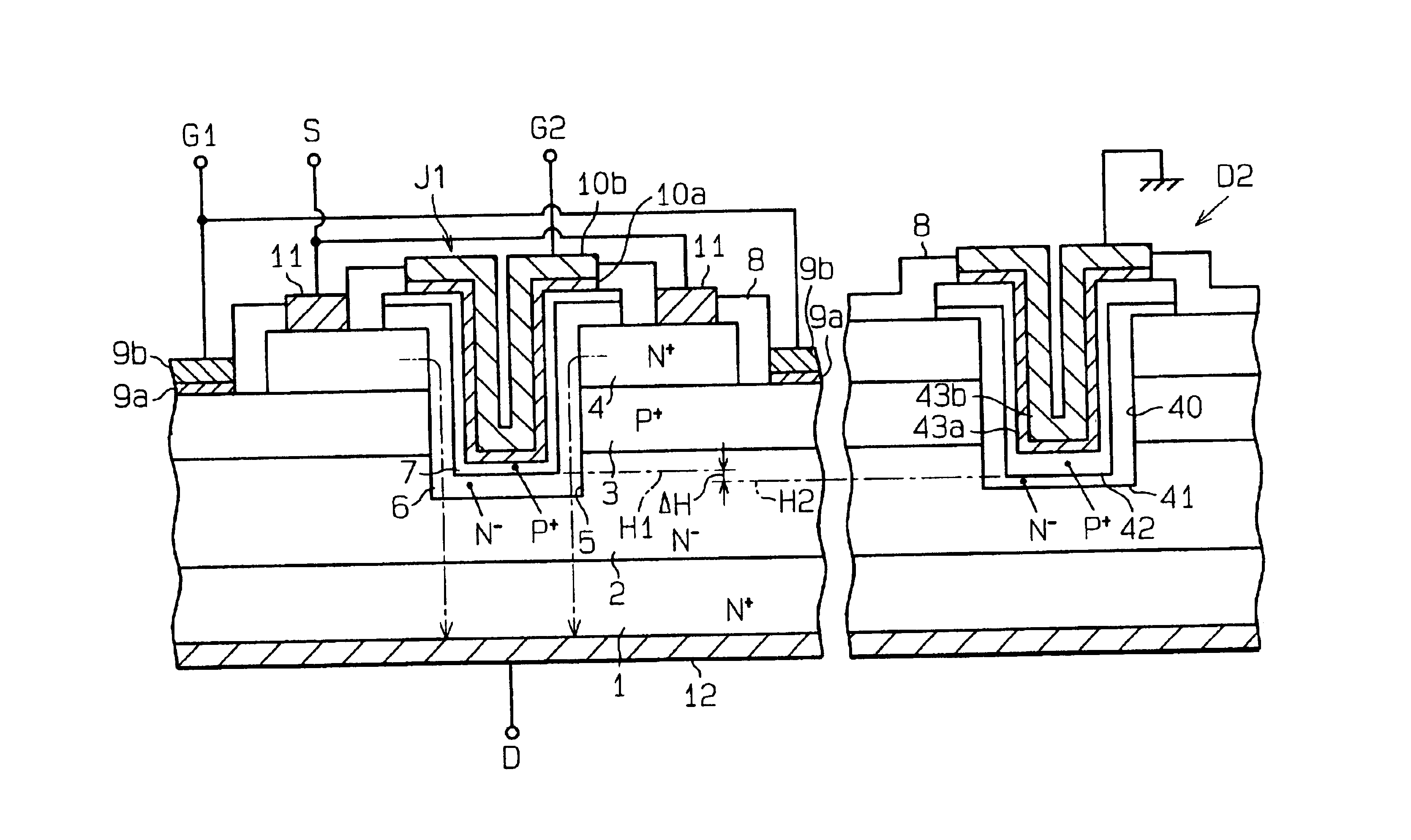

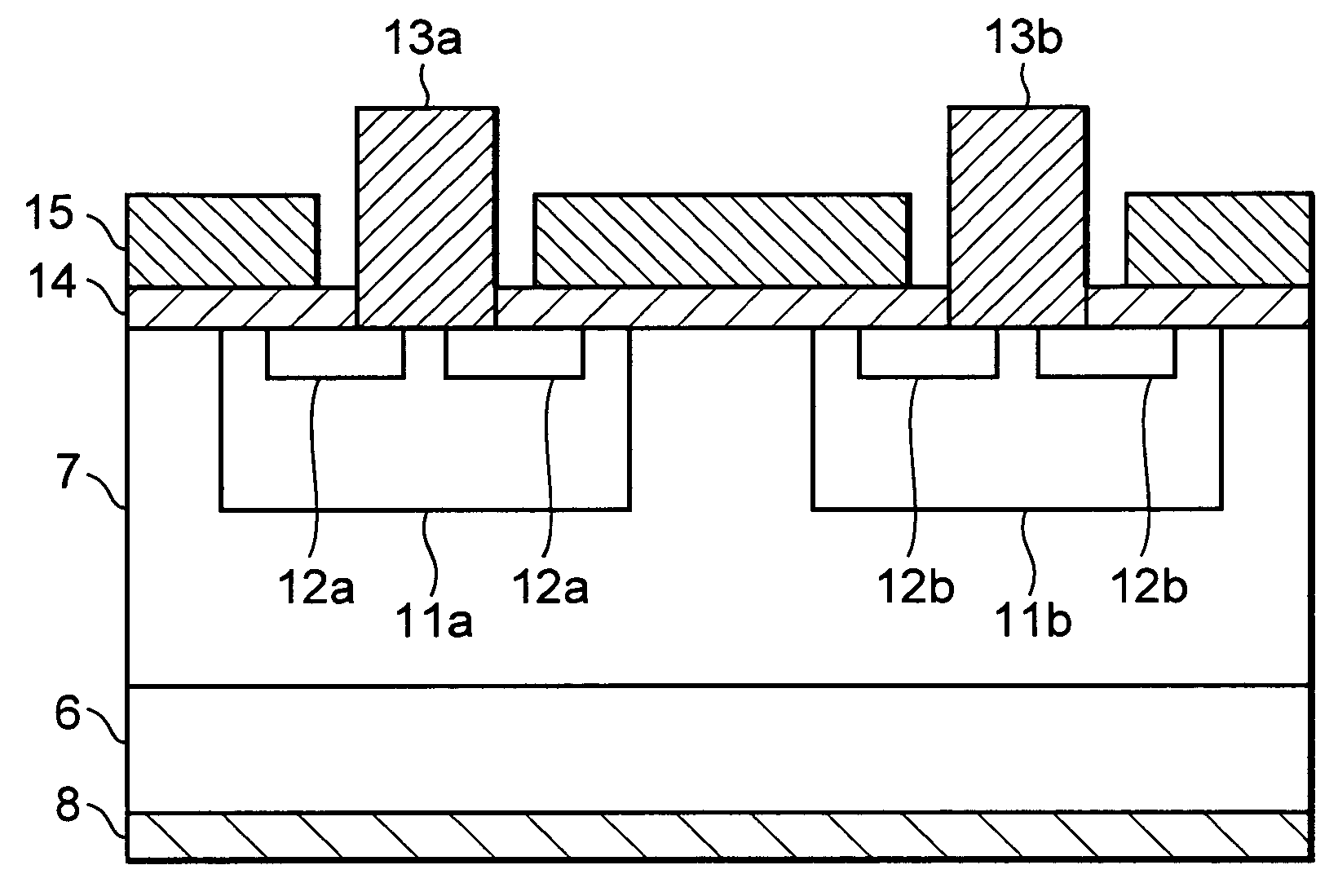

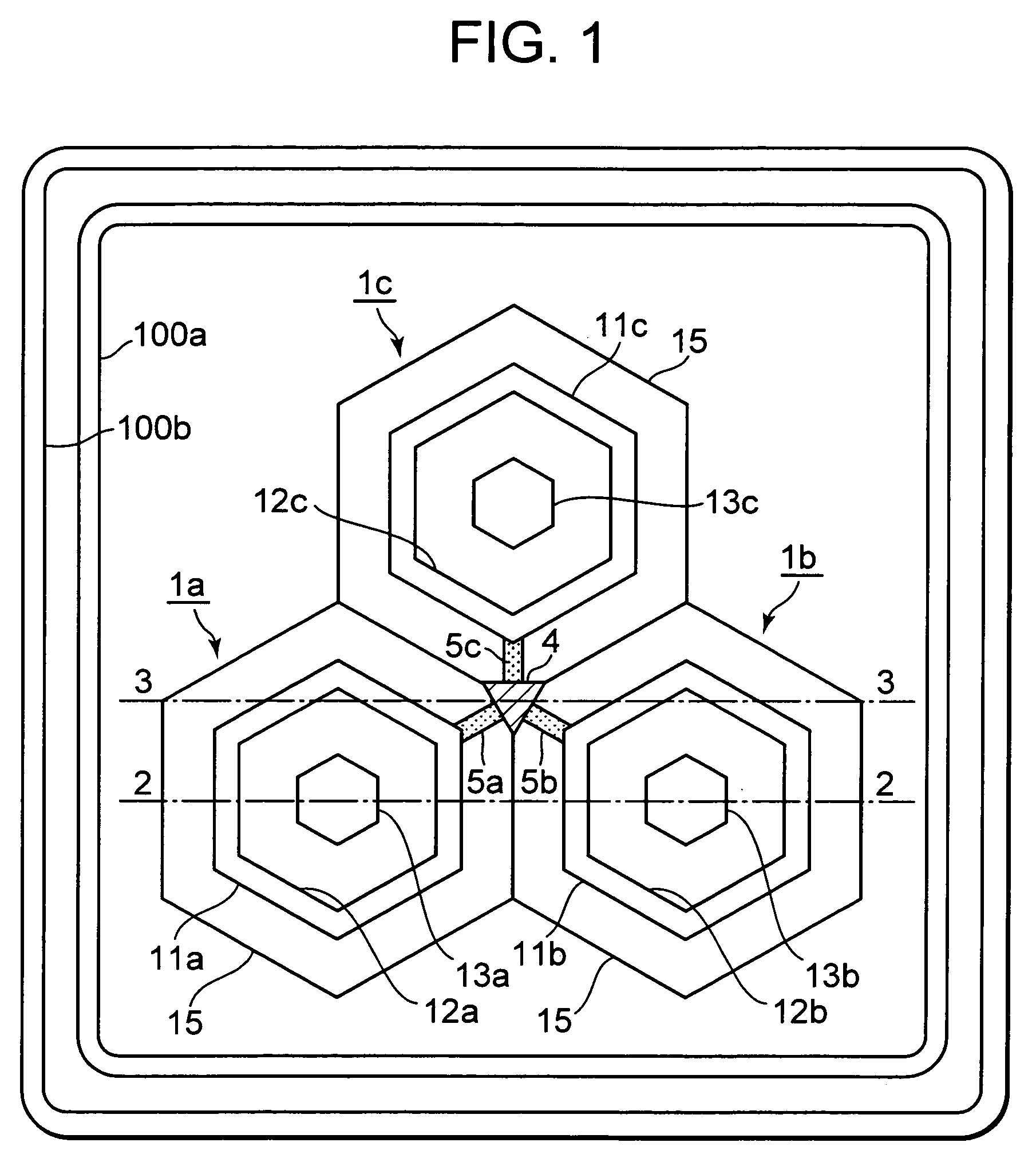

Semiconductror device and manufacturing method thereof

ActiveUS20090096020A1Lower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerField-effect transistor

A semiconductor device includes field effect transistors, each having a semiconductor layer formed on a major surface of a semiconductor substrate, a base region formed in a surface layer portion of a semiconductor layer, a source region formed in a surface layer portion of the base region, a source electrode formed on the base region and the source region, a gate electrode formed on the semiconductor layer and the base region via a gate insulating film interposed therebetween, and a drain electrode formed on a back surface of the semiconductor substrate, and which are placed side by side. A columnar intermediate region is formed in its corresponding predetermined region of the surface layer portion of the semiconductor layer placed below each gate electrode. Connection regions are formed in the surface layer portion of the semiconductor layer to contact the intermediate region and the base regions.

Owner:LAPIS SEMICON CO LTD

Low capacitance transient voltage suppressor (TVS) with reduced clamping voltage

ActiveUS20130001694A1Improve clamping effectEasy to integrateSemiconductor/solid-state device detailsSolid-state devicesCapacitanceTransient voltage suppressor

A low capacitance transient voltage suppressor with reduced clamping voltage includes an n+ type substrate, a first epitaxial layer on the substrate, a buried layer formed within the first epitaxial layer, a second epitaxial layer on the first epitaxial layer, and an implant layer formed within the first epitaxial layer below the buried layer. The implant layer extends beyond the buried layer. A first trench is at an edge of the buried layer and an edge of the implant layer. A second trench is at another edge of the buried layer and extends into the implant layer. A third trench is at another edge of the implant layer. Each trench is lined with a dielectric layer. A set of source regions is formed within a top surface of the second epitaxial layer. The trenches and source regions alternate. A pair of implant regions is formed in the second epitaxial layer.

Owner:ALPHA & OMEGA SEMICON INC

Low capacitance transient voltage suppressor (TVS) with reduced clamping voltage

ActiveUS8698196B2Improve clamping effectReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

A low capacitance transient voltage suppressor with reduced clamping voltage includes an n+ type substrate, a first epitaxial layer on the substrate, a buried layer formed within the first epitaxial layer, a second epitaxial layer on the first epitaxial layer, and an implant layer formed within the first epitaxial layer below the buried layer. The implant layer extends beyond the buried layer. A first trench is at an edge of the buried layer and an edge of the implant layer. A second trench is at another edge of the buried layer and extends into the implant layer. A third trench is at another edge of the implant layer. Each trench is lined with a dielectric layer. A set of source regions is formed within a top surface of the second epitaxial layer. The trenches and source regions alternate. A pair of implant regions is formed in the second epitaxial layer.

Owner:ALPHA & OMEGA SEMICON INC

Capacitance dielectric layer, capacitor and forming method thereof

ActiveUS20070196977A1Increase currentLower breakdown voltageTransistorSemiconductor/solid-state device detailsCapacitanceDrain current

A capacitance dielectric layer is provided. The capacitance dielectric layer includes a first dielectric layer, a second dielectric layer and a silicon nitride stacked layer. The silicon nitride stacked layer is disposed between the first dielectric layer and the second dielectric layer. The structure of the capacitance dielectric layer permits an increase in the capacitance per unit area by decreasing the thickness of the capacitance dielectric layer and eliminates the problems of having a raised leakage current and a diminished breakdown voltage.

Owner:MARLIN SEMICON LTD