Patents

Literature

83results about How to "Avoid premature breakdown" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

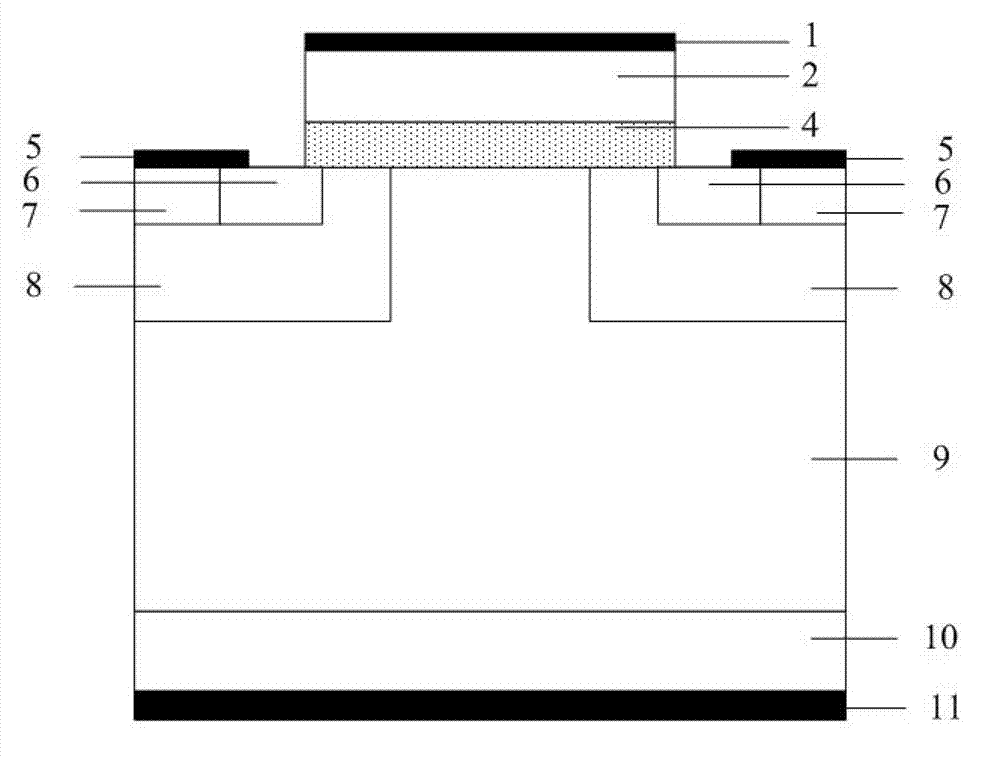

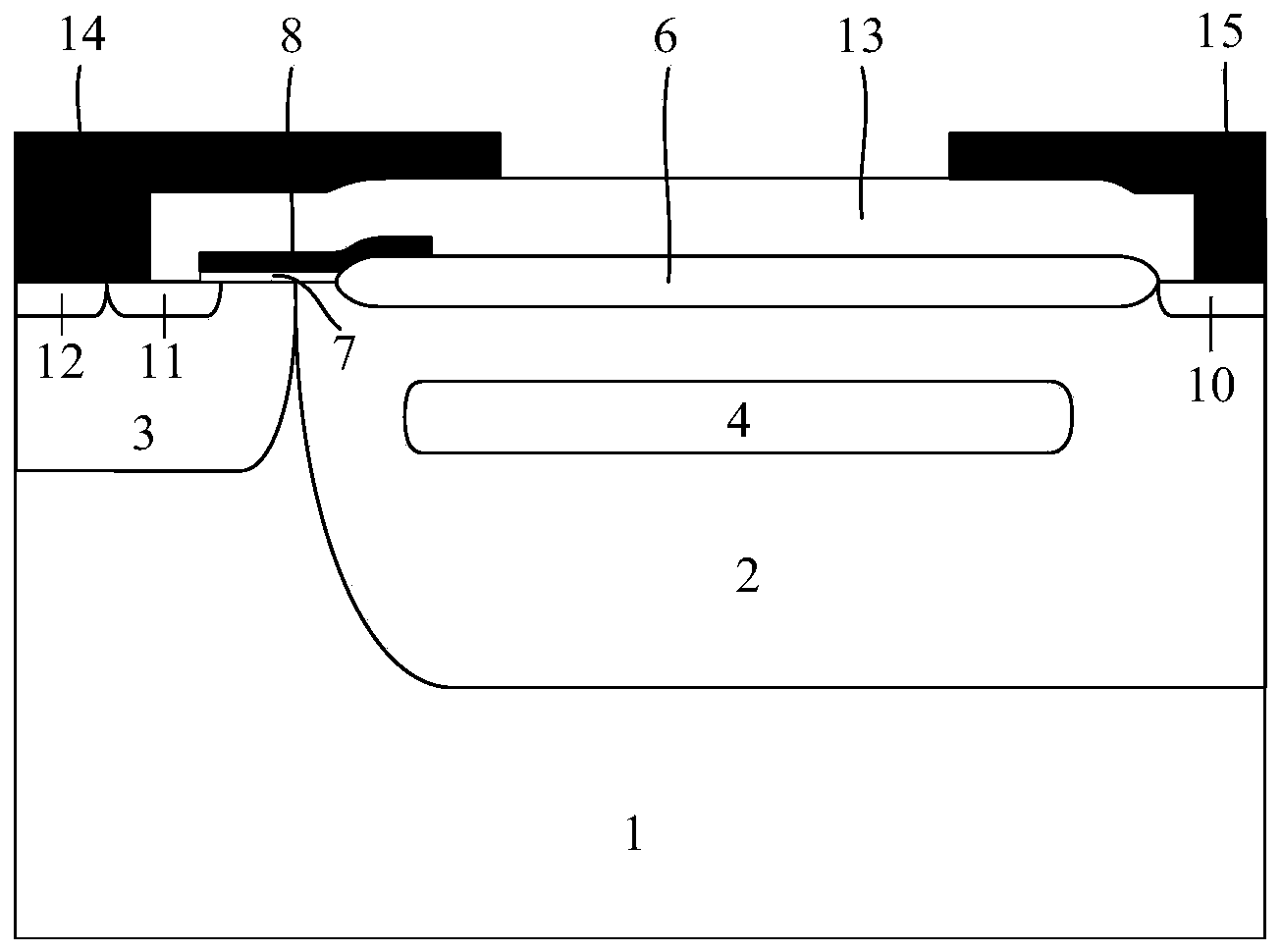

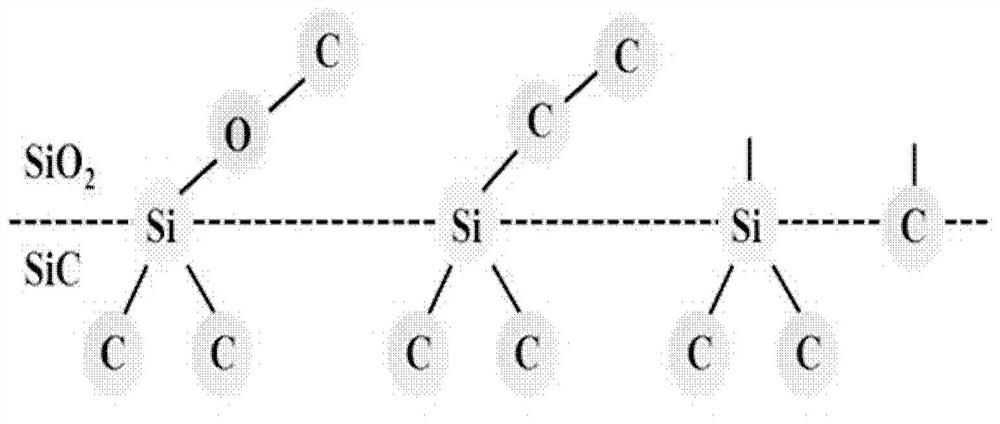

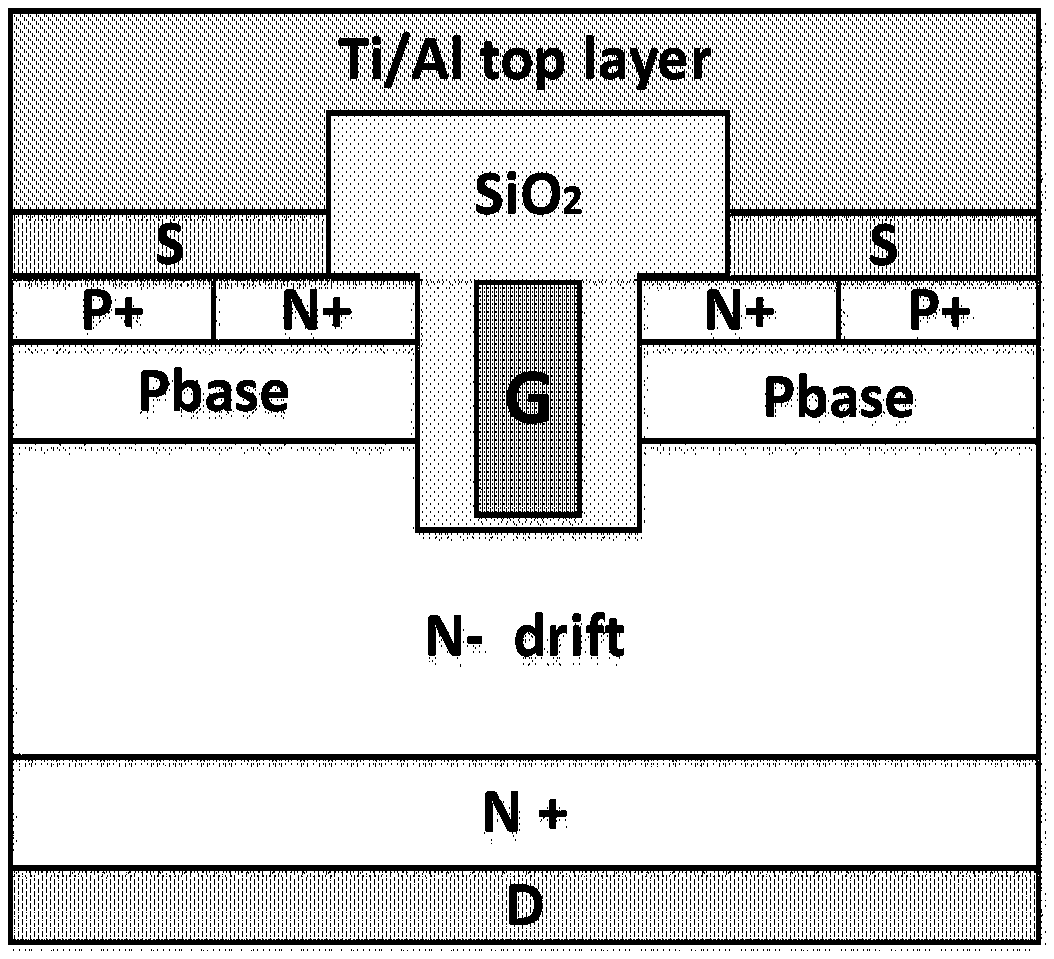

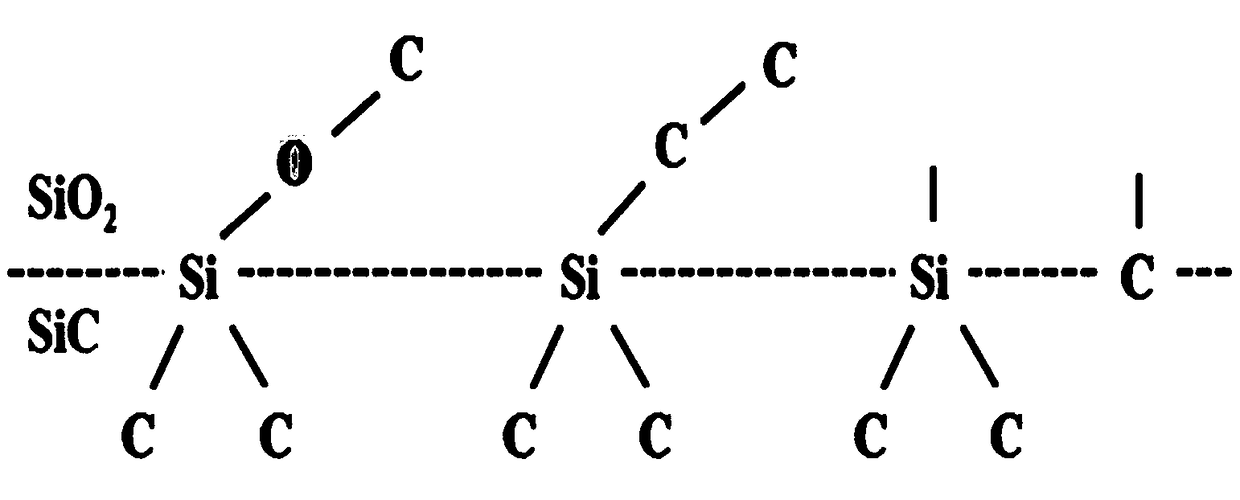

SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with composite gate dielectric structure

InactiveCN102779852ALower breakdown voltageAvoid premature breakdownSemiconductor devicesDielectricGate dielectric

The invention discloses a SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with a composite gate dielectric structure, and belongs to the technical field of power semiconductor devices. A thought of differentiating modulation of electric fields is adopted according to difference of intensities of electric fields and difference of defect concentrations of gate dielectrics in different areas, namely, high-k gate dielectrics are adopted in channel regions with high-defect concentration and a low electric field, so that a large quantity of trap states caused by using a SiO2 / SiC interface is avoided; the influence on Fowler-Nordheim (FN) tunneling current is obviously reduced; and meanwhile, because the electric field intensity in a channel injection area is small, the reduction on gate dielectric breakdown voltage caused by small offset of conduction band / valence band is weakened; and moreover, a SiO2 gate dielectric (a junction field-effect transistor (JFET) area is formed in a way of extension and is not subjected to ion injection, the surface quality of the JFET area is good, and the SiO2 / SiC interface state is low) is adopted by the JFET area with low defect concentration and a high electric field, and enough high conduction band offset is supplied by the SiO2 dielectric, so that the ahead breakdown of the gate dielectric is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

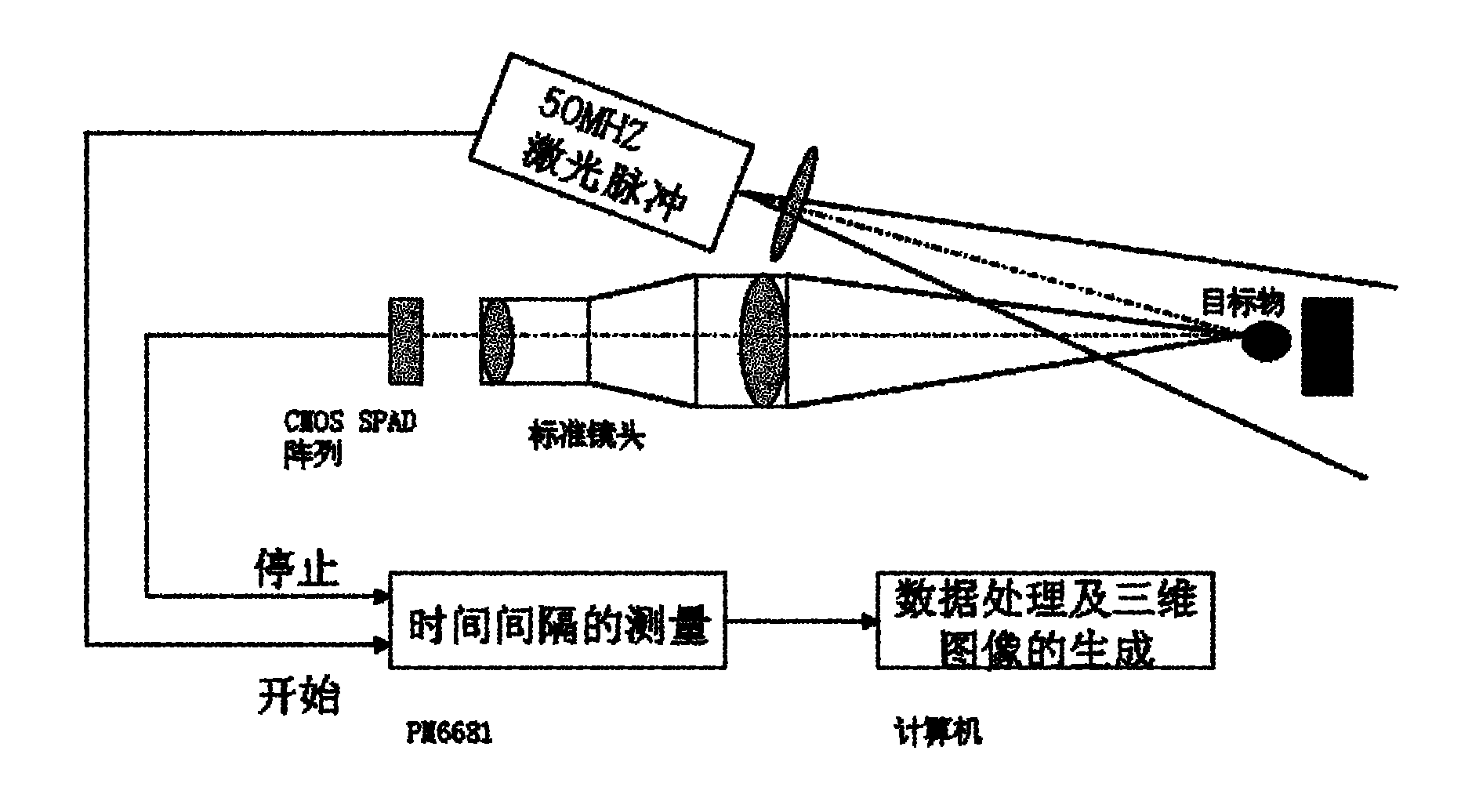

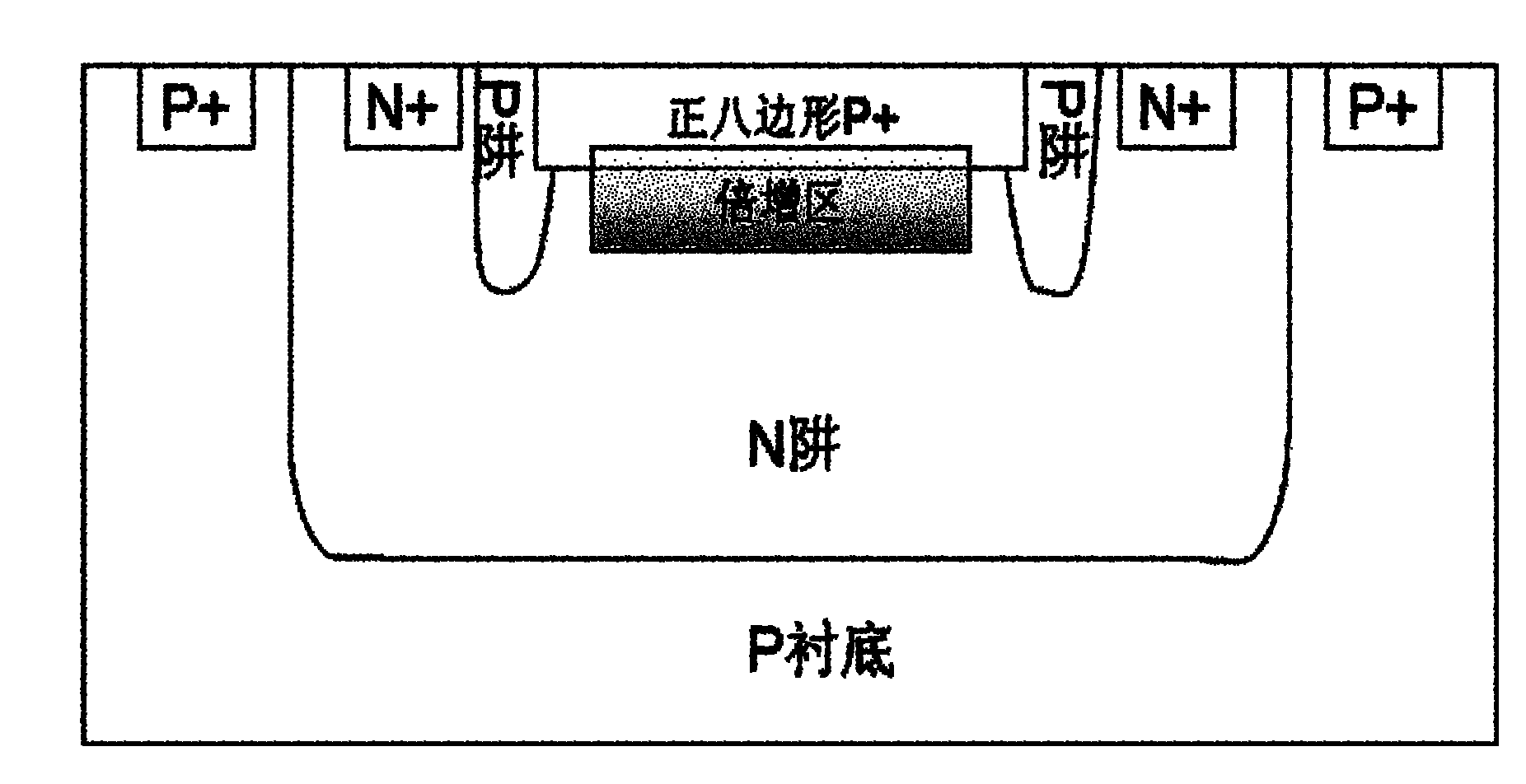

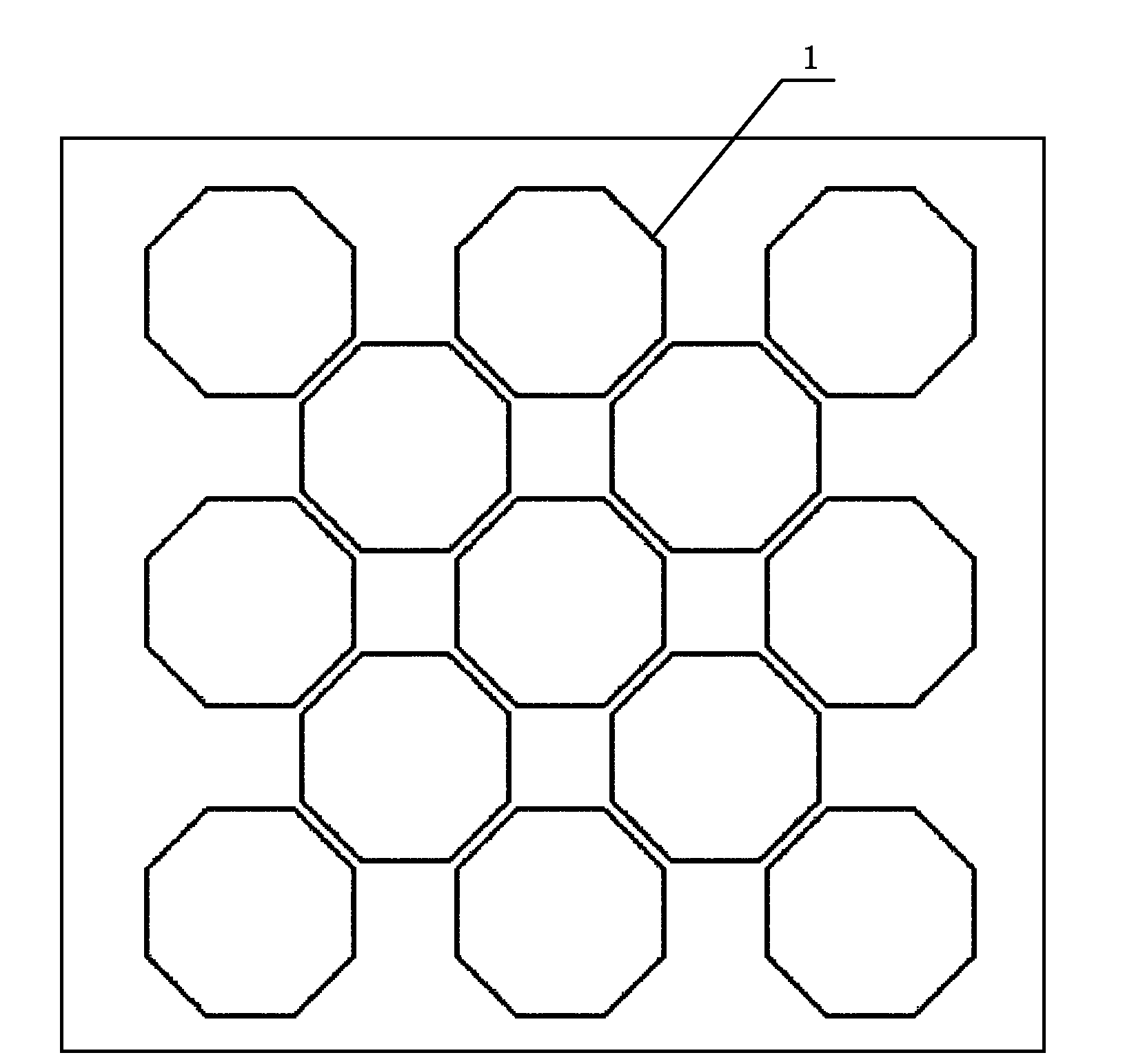

Single-photon avalanche diode and three-dimensional CMOS (Complementary Metal Oxide Semiconductor) image sensor based on same

InactiveCN101931021AImprove uniformityFully magnifiedTelevision system detailsFinal product manufactureHorizontal and verticalElectron

The invention belongs to the technical field of electronic technologies and photoelectronic imaging technologies, in particular relates to a single-photon avalanche diode and a three-dimensional CMOS (Complementary Metal Oxide Semiconductor) image sensor based on the diode. The single-photon avalanche diode of the invention improves the traditional rectangular photosensitive PN junction into a regular octagon and can conveniently and simply weaken edge breakdown and improve gain uniformity. A two-dimensional pixel array of the three-dimensional CMOS image sensor based on the diode comprises unit pixels of the regular octagon-shaped single-photon avalanche diode and is arrayed in a honeycomb-shape, thereby being convenient for interpolation and improving resolution in horizontal and vertical direction.

Owner:XIANGTAN UNIV

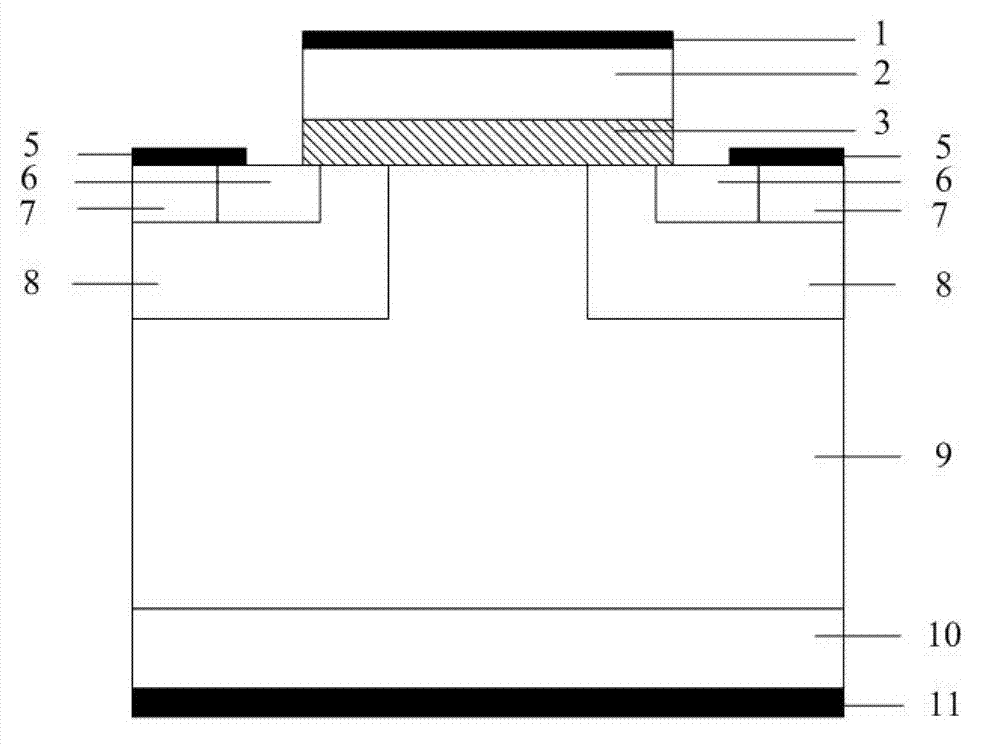

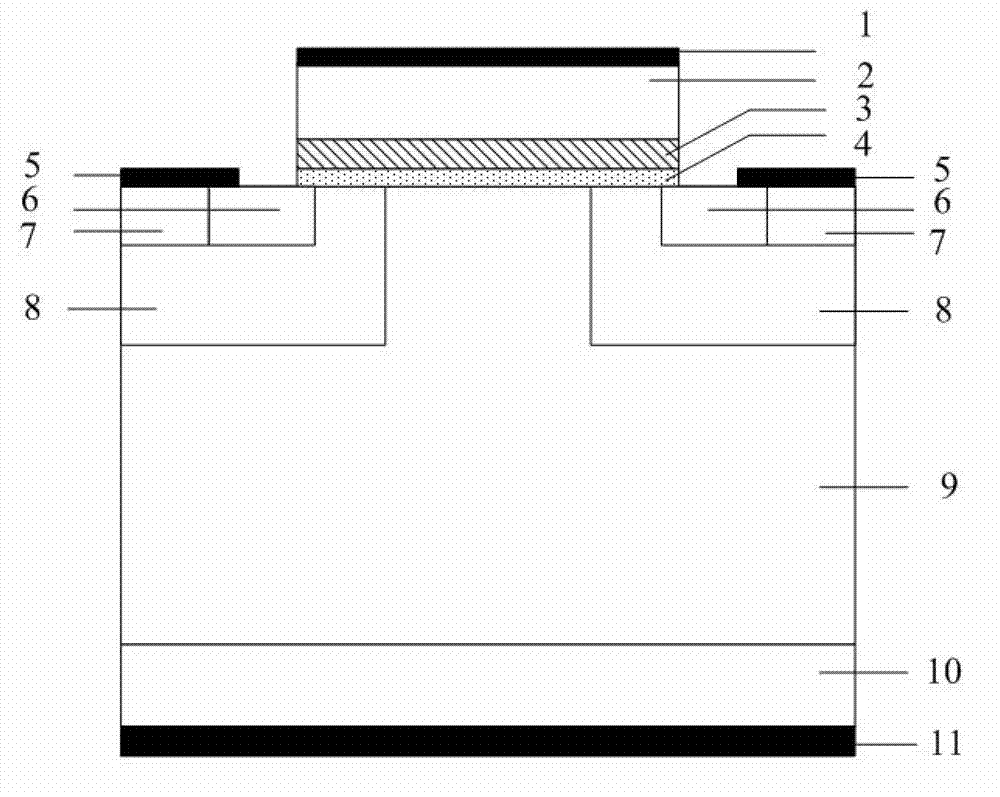

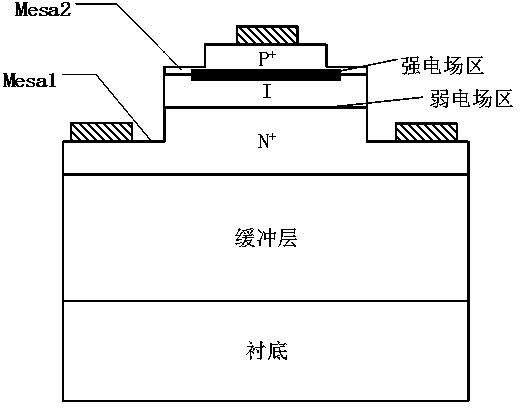

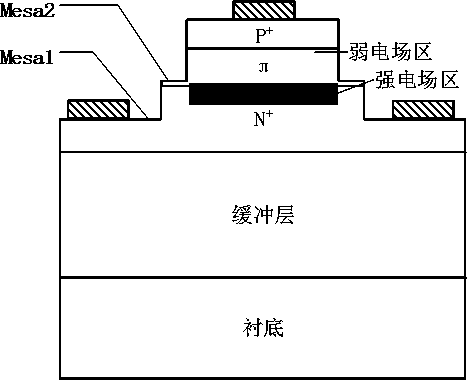

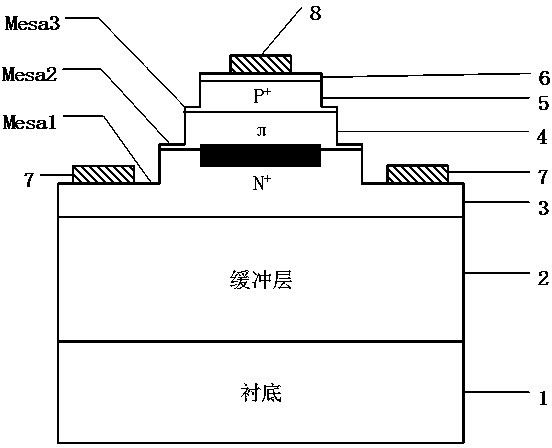

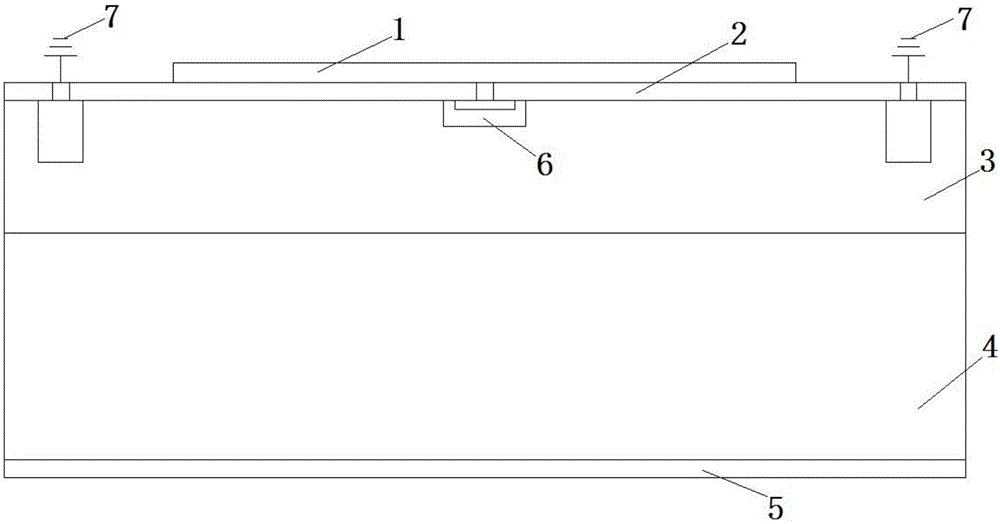

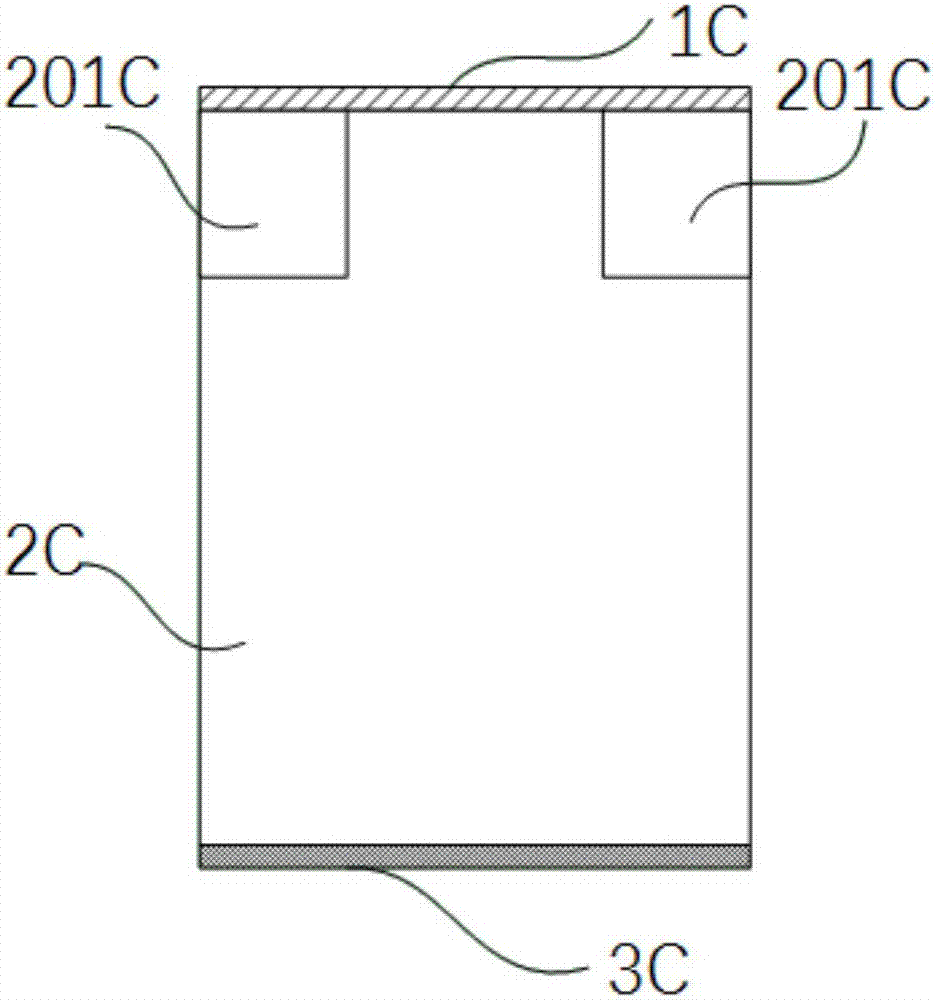

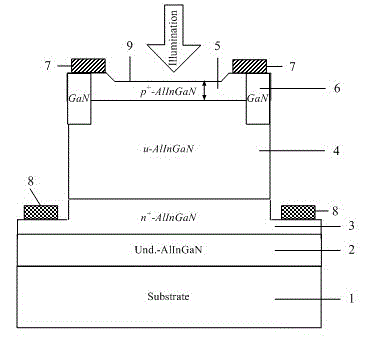

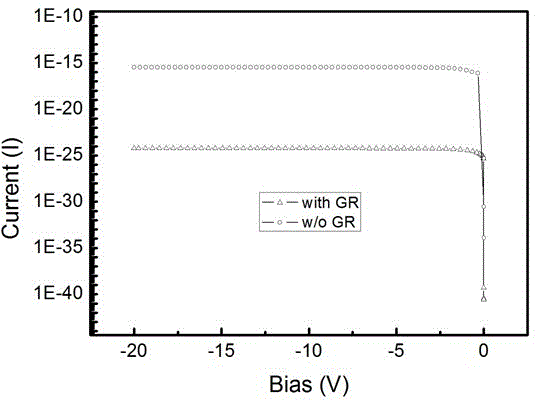

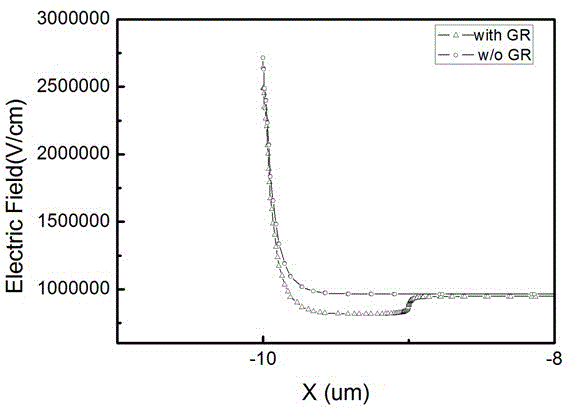

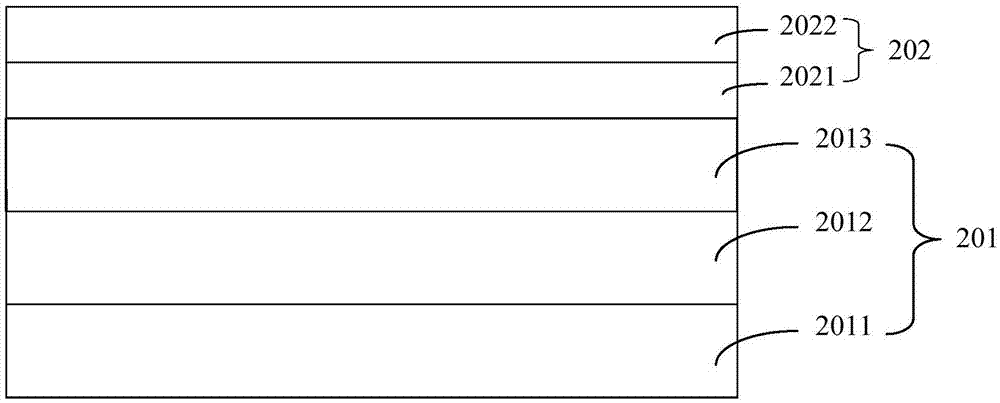

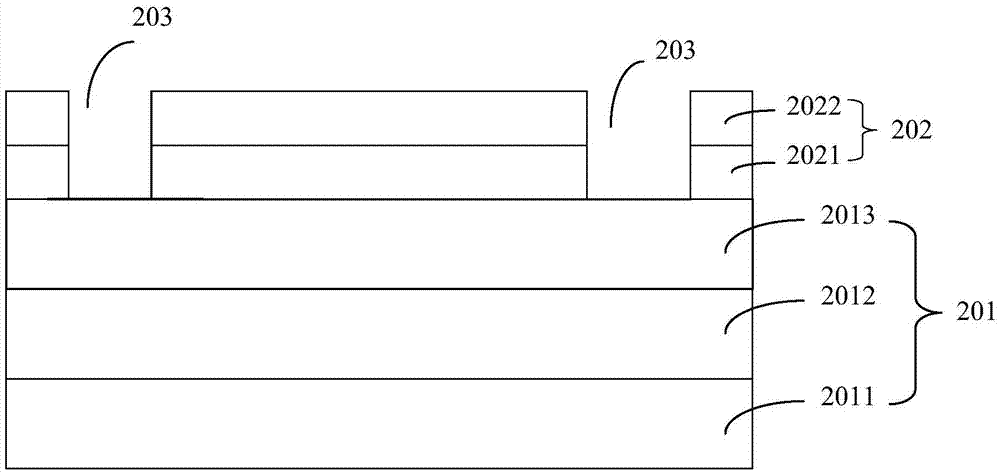

Three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector and preparation method thereof

InactiveCN104282793AAvoid premature breakdownSolve the problem of reverse premature breakdownFinal product manufactureSemiconductor devicesPhotodetectorElectrode Contact

The invention relates to the technical field of detectors, in particular to a three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector and a preparation method of the three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector. The three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector comprises a substrate, a buffer layer, an n-type doping nitride ohmic electrode contact layer, a Pi-type nitride active layer, a p-type doping nitride layer, a p-type heavy-doping nitride ohmic contact layer, n-type ohmic contact electrodes and a p-type ohmic contact electrode, wherein the buffer layer, the n-type doping nitride ohmic electrode contact layer, the Pi-type nitride active layer, the p-type doping nitride layer and the p-type heavy-doping nitride ohmic contact layer are sequentially grown on the substrate through epitaxial growth methods such as a molecular beam epitaxial method or an organometallic chemical vapor deposition epitaxial method; the n-type ohmic contact electrodes are manufactured on the n-type layer, and the p-type ohmic contact electrode is manufactured on the p-type layer. The three-mesa p-Pi-n structured III-nitride semiconductor avalanche photodetector can solve the problems that a traditional p-i-n structured device leaks a large number of currents and the edge of the traditional p-i-n structured device can be broken through easily in advance; moreover, a three-mesa structure conducts double-suppression protection on edge electric fields of a strong electric field region and a weak electric field region of a p-Pi-n structured device, so that the edge electric field is effectively prevented from being broken through in advance.

Owner:SUN YAT SEN UNIV

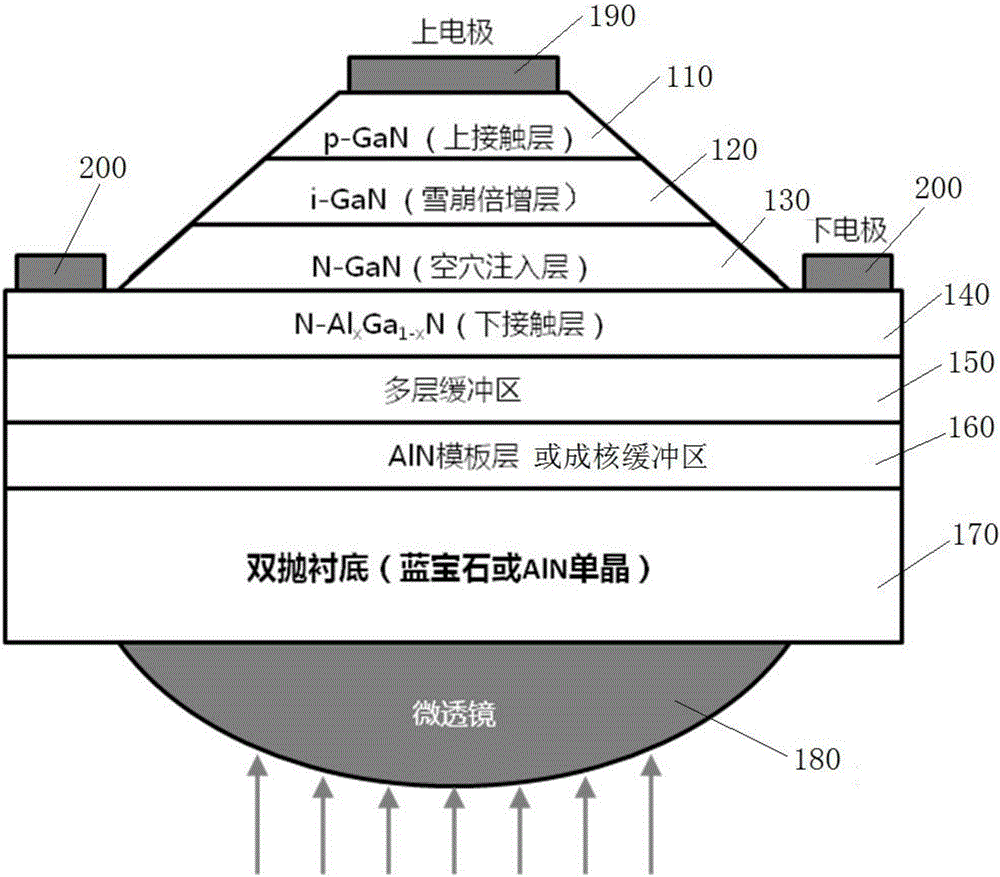

P-i-n-(-n)-type GaN single-photon avalanche detector

ActiveCN106409967AHigh Avalanche GainIncrease freedomSemiconductor devicesMinority carrier injectionHole injection layer

The present invention provides a p-i-n-(-n)-type GaN single-photon avalanche detector. The detector comprises a p-GaN upper contact layer, an i-GaN avalanche multiplication layer, an n<->-GaN hole-injection layer and an n-AlGaN lower contact layer arranged from up to down, wherein the n<->-GaN hole-injection layer is light doping. The p-i-n-(-n)-type GaN single-photon avalanche detector replaces an n-GaN layer with a traditional pin-type structure with the n<->GaN / n-AlGaN heterojunction, takes the n<->-GaN as an absorption injection layer, and takes the n-AlGaN as the lower contact layer so as to facilitate the improvement of the crystalline quality of epitaxial materials of an active region and improve the external quantum efficiency and the cavity minority carrier injection efficiency; and moreover, the parameters, such as doping concentration, thickness and the like, of the n<->-GaN layer are flexible and adjustable, and a very high avalanche gain can be obtained under the low work bias through compromise optimization.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

Silicon carbide avalanche photoelectric detector provided with graphene transparent electrode

InactiveCN108231919ATurn up the incident efficiencyGood ohmic contactPhotovoltaic energy generationSemiconductor devicesSputteringPhotovoltaic detectors

The invention discloses a silicon carbide avalanche photoelectric detector provided with a graphene transparent electrode and relates to a semiconductor photoelectric detector. The silicon carbide avalanche photoelectric detector is provided with a substrate, wherein a first N type epitaxial buffer layer, an N type epitaxial absorption layer, a second N<-> type epitaxial multiplication layer and aP<+> type ohmic contact layer which are homogeneous are sequentially arranged on the substrate; and multiple graphene transparent electrode layers grow on the surface of the P<+> type ohmic contact layer by virtue of an electrothermal decomposition process, and one height from the surface of a graphene layer to the surface of the first N type epitaxial buffer layer is etched by adopting a photolithography mask technology and an ICP etching process, so that the P<+> type ohmic contact layer, the second N type epitaxial multiplication layer and the N- type epitaxial absorption layer are circular truncated cones; and one compact SiOx / Si3N4 protection passivation layer is grown by virtue of a plasma enhanced chemical vapor deposition process. An N type ohmic contact electrode is sputtered onthe back of an N+ type substrate, and a bonding pad window is etched by virtue of a photolithography technology and a bonding pad for the graphene transparent electrode layers is prepared on the SiOx / Si3N4 protection passivation layer.

Owner:XIAMEN UNIV

High-voltage power device terminal structure

InactiveCN106024863AAvoid premature breakdownReduce electric field peaksSemiconductor devicesPeak valueComputer terminal

The invention belongs to semiconductor technology, and specifically relates to a high-voltage power device terminal structure. The high-voltage power device terminal structure comprises a groove in a silicon chip body and P-type protective rings, combination of the internal groove and the protective rings allows the peak value of an electric field to be transferred from the surface of the silicon chip into the body, and the breakdown points of a terminal area are transferred from the surface of the silicon chip to the two sides of a dielectric layer in the groove. Since the critical breakdown electric field (about 1e7V / cm) of the dielectric layer is far higher than a critical breakdown electric field (about 1e5V / cm) of silicone, P-type floating islands in staggered arrangement with the P-type protective rings reduce the peak values of the electric fields on the two sides of the P-type protective rings without reducing the reverse blockout voltage of a terminal area, thereby preventing premature breakdown of PN junctions in the silicon chip body.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

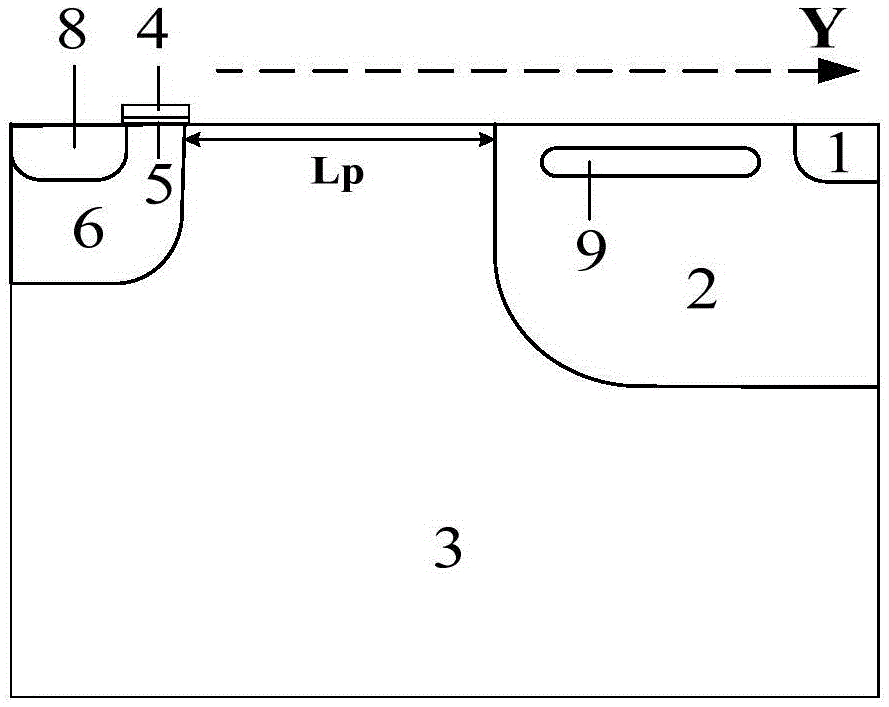

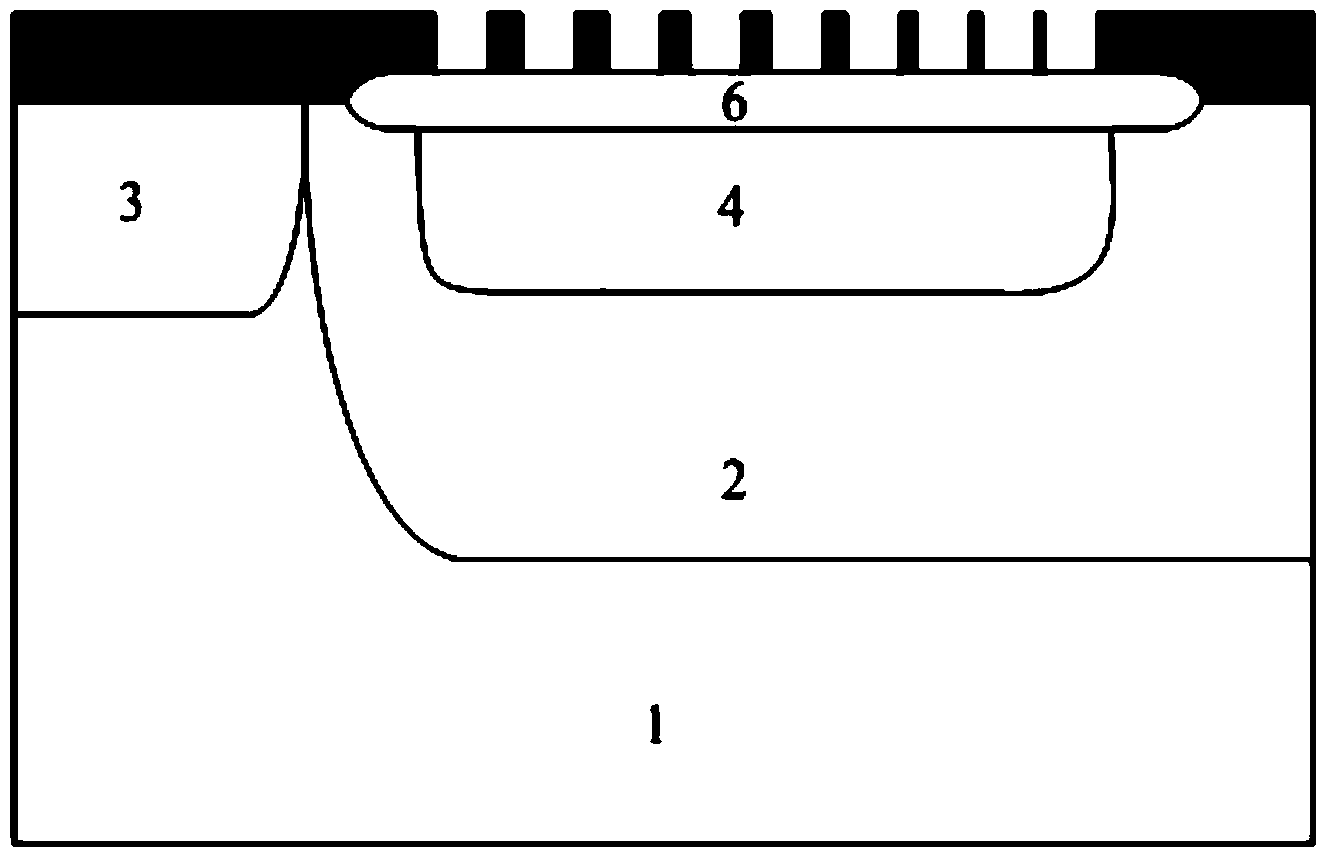

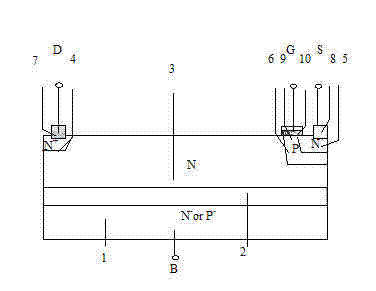

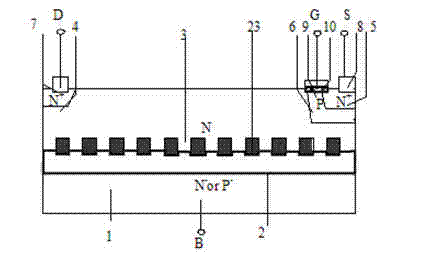

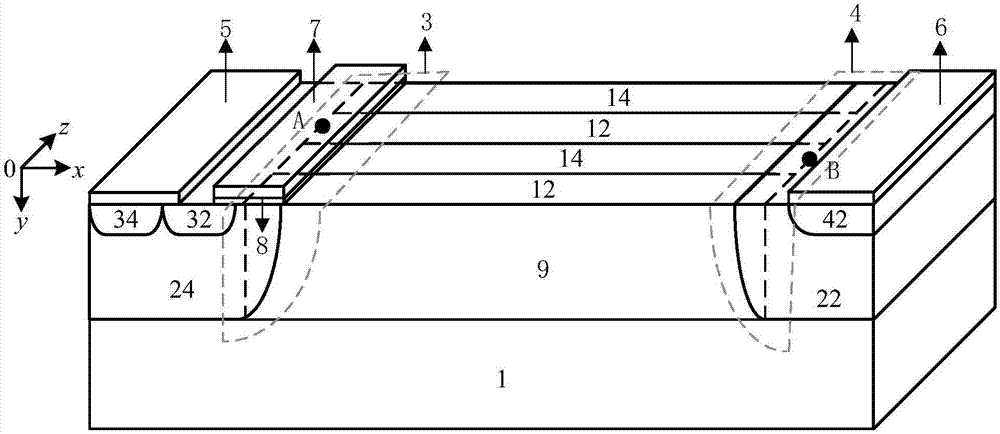

Junction terminal structure of transverse high-voltage power device

ActiveCN105047694AMitigation of curvature effectsImprove imbalanceSemiconductor devicesMicrometerHigh pressure

The invention belongs to the technical field of a semiconductor, in particular relates to a junction terminal structure of a transverse high-voltage power device. In the structure, the inner wall of an N-type shift region 2 and the inner wall of a P-type buried layer 9 in a curvature junction terminal structure respectively extend to the middle until to be connected with the inner wall of an N-type shift region 2 and the inner wall of a P-type buried layer 9 in a direct junction terminal structure, included angles of Alpha degrees are generated between the extension directions and the vertical directions of the inner walls of the N-type shift region 2 and the P-type buried layer 9 in the direct junction terminal structure, and the Alpha degrees is 45 degrees. By the junction terminal structure, the curvature effect of an electric field at a connection part can be effectively relieved; and on the vertical direction of the extension direction at the connection part, the distance of the P-type buried layer 9 exceeding the N-type shift region is 5 micrometers, and thus, the problem of charge unbalance is solved. The junction terminal structure has the advantages that the problems of charge unbalance in the connection part between the direct junction terminal structure and the curvature junction terminal structure and the curvature effect of the electric field at the connection part are solved, a device is prevented from being broken down in advance, and thus, optimal breakdown voltage is obtained.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

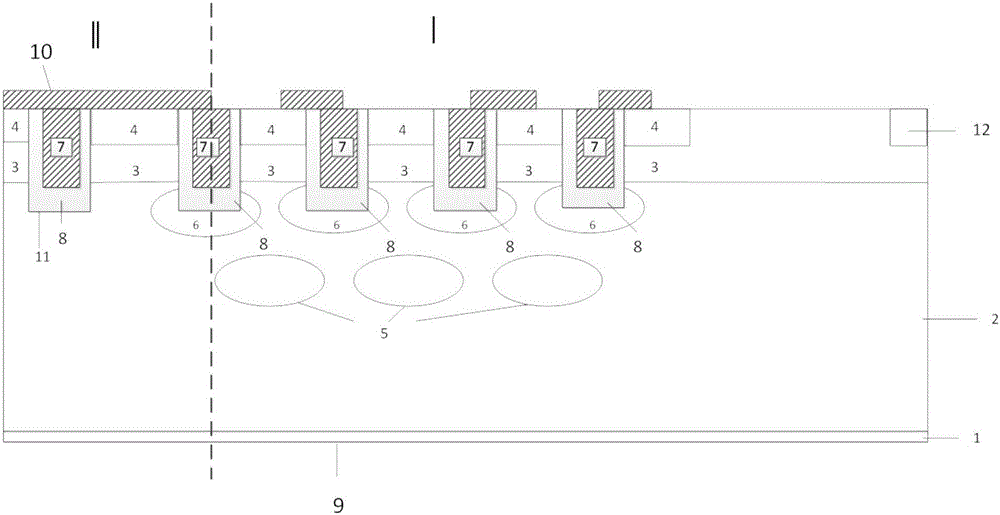

Ultraviolet avalanche photodiode detector and detection method thereof

InactiveCN106784054AHigh frequency responseReduce blockingPhotometry using electric radiation detectorsSemiconductor devicesSemiconductor materialsUltraviolet

The invention discloses an ultraviolet avalanche photodiode detector. Each device unit of the detector comprises a CE electrode, an SiO2 layer, a P-well or N-well, a substrate and a back surface electrode in sequence from top to bottom, wherein a point-shaped avalanche photodiode is arranged at the center of the upper part of the P-well or N-well; the point-shaped avalanche photodiode is electrically communicated with the CE electrode; a ground connector GND is peripherally arranged at the periphery of the SiO2 layer. The ultraviolet avalanche photodiode detector is manufactured by adopting a wide band gap semiconductor material, an avalanche region is separated from a photon collection region, and an avalanche multiplication nodal region is relatively small, so that a device with relatively low avalanche voltage can be manufactured, and the uniformity and controllability of an electric field of the avalanche region are good; while an avalanche multiplication high-field region is relatively small, a large-area optical detection region is guaranteed, so that the quantum efficiency is improved; the area of the avalanche region is reduced, and dark current and dark excitation are easy to reduce; meanwhile, the tolerance to the quality and defects of a wafer is improved, and breakdown of the large-area avalanche multiplication high-field region at a defect position is prevented in advance.

Owner:BEIJING CENTURY GOLDRAY SEMICON CO LTD

Horizontal high-voltage device and manufacturing method of horizontal high-voltage device

InactiveCN103413831ALower on-resistanceOptimizing Surface Electric FieldSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueEngineering

The invention relates to the semiconductor technology, in particular to a horizontal high-voltage device and a manufacturing method of the horizontal high-voltage device. The horizontal high-voltage device is characterized in that a first conduction type semiconductor filed reduction layer is formed through trap driving and an ion implantation technology in a second conduction type semiconductor drift region; through photoetching and the ion implantation technology, a second conduction type semiconductor heavy doping layer is formed on the surface of the second conduction type semiconductor drift region. The horizontal high-voltage device and the manufacturing method of the horizontal high-voltage device have the advantages that the on resistance of the horizontal high-voltage device can be greatly reduced under the condition that high breakdown withstand voltage is maintained; meanwhile, the electric field peak value on the source side of the horizontal high-voltage device is reduced, a high-field effect is avoided, the breakdown voltage of the horizontal high-voltage device is increased, and the on resistance of the horizontal high-voltage device is smaller; the chip area is smaller under the condition that the breakover capacity is the same, and a surface electric field of the horizontal high-voltage device is well optimized; meanwhile, the manufacturing method of the horizontal high-voltage device is simple and relatively low in process difficulty, thereby being particularly suitable for the horizontal high-voltage device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

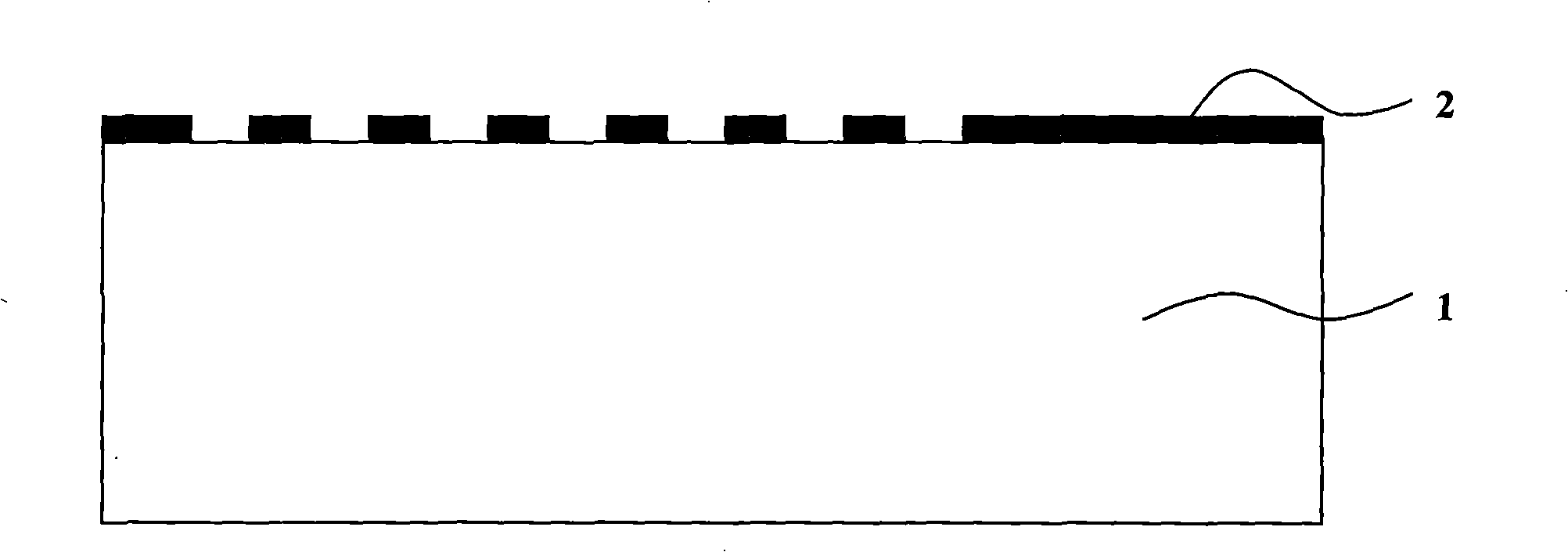

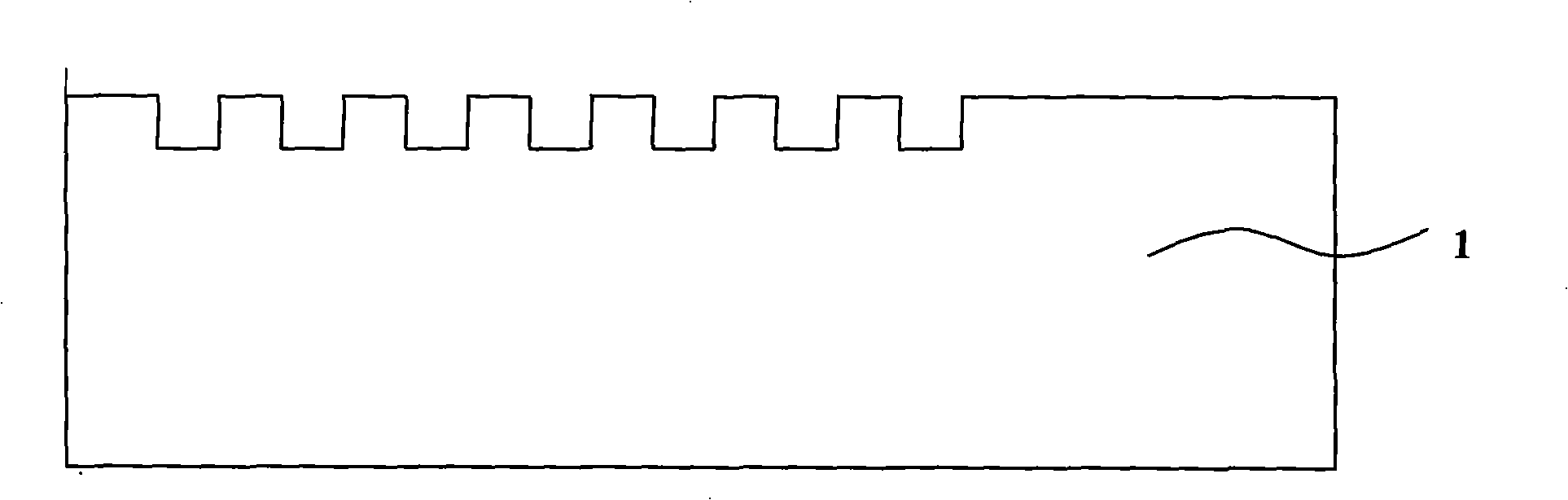

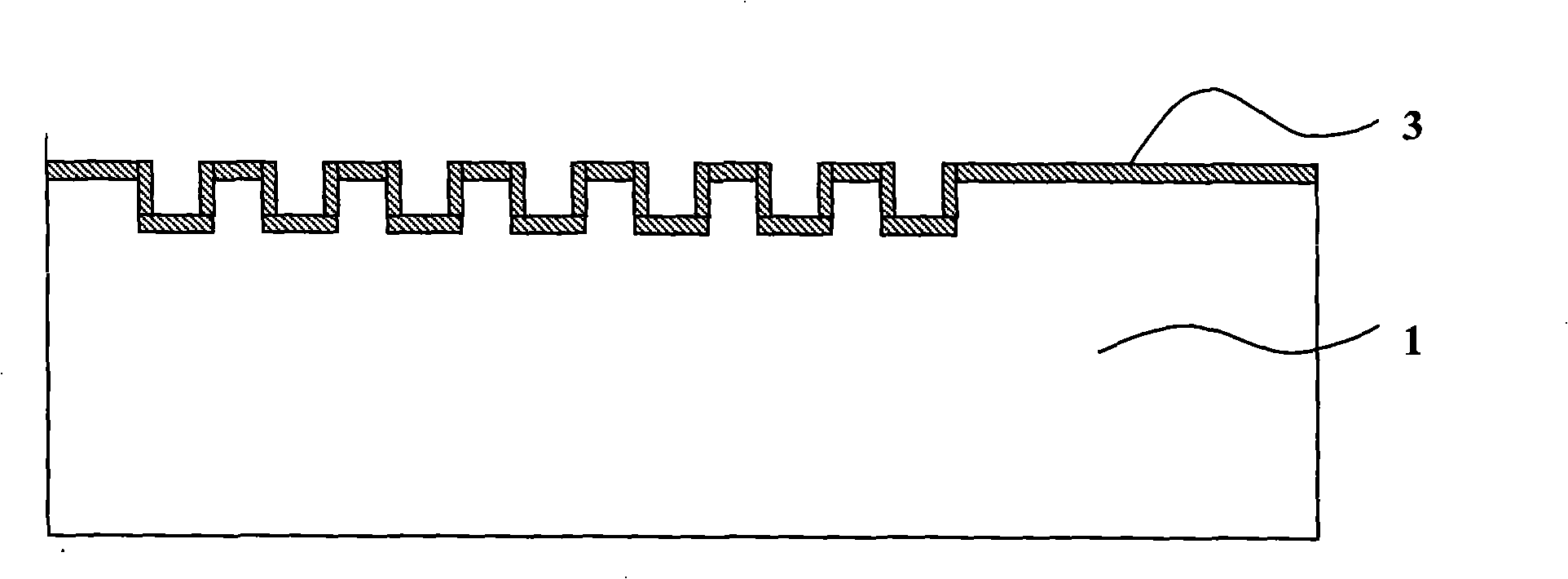

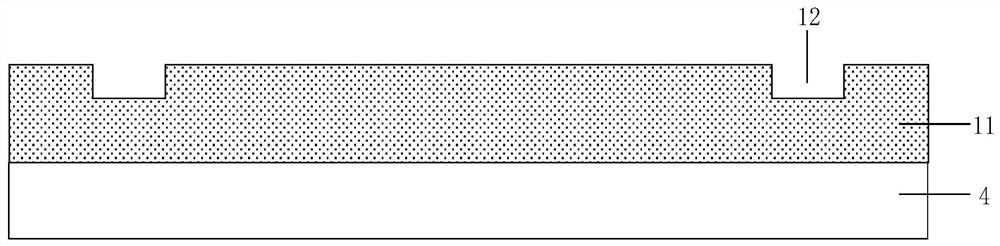

Method for preparing double side dielectric groove part SOI material

InactiveCN101527277AImprove pressure resistanceReduce self-heating effectSemiconductor/solid-state device manufacturingDielectricGas phase

The invention discloses a method for preparing double side dielectric groove part SOI material. Compared with the conventional bonding technology, before bonding, the method adds the following steps: 1. silicon groove etching on top layer silicon chip; 2. thermal growth and chemical vapor deposition of SiO2 layer; 3. removing the SiO2 layer positioned in a source area and under a channel region by etching; 4. deposition of polysilicon; 5. planarization of the polysilicon. As devices manufactured on the SOI material prepared by the method pass through reinforcing buried oxide layer electric field, the pressure resistance of the devices can be improved, and heat can be fully dispersed. Compared with devices with the conventional SOI structure, SOI devices prepared on the SOI material prepared by the method can utilize thinner top layer silicon and the buried oxide layer to reach the same pressure resistance, thus further reducing self-heating effect.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

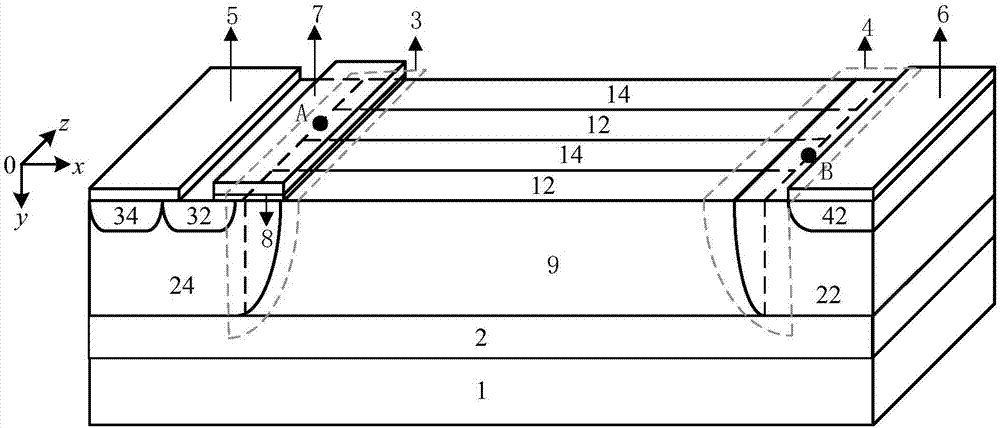

Junction termination structure of transverse high-voltage power device

ActiveCN105047693AImprove imbalanceAvoid premature breakdownSemiconductor devicesHigh pressureIon implantation

The invention belongs to the technical field of semiconductors, and particularly relates to a junction termination structure of a transverse high-voltage power device. According to the structure provided by the invention, in the connected part of a linear junction termination structure and a curvature junction termination structure, in the Y direction, a P-type buried layer exceeds an N-type drift region 5 microns; and meanwhile, the P-type buried layer also exceeds an N-type doped layer 3 microns. In an actual technology, an N-type drift region 2 is formed by ion injection; after annealing junction pushing, the N-type drift region diffuses towards the Y direction; and the P-type buried layer exceeds the N-type drift region 2 a certain distance, so that P-type impurities in the diffused N-type drift region are exhausted, therefore, the problem of unbalanced charge in the connected part of the linear junction termination structure and the curvature junction termination structure is solved, so as to obtain relatively optimized breakdown voltage. The junction termination structure has the beneficial effects that the problem of unbalanced charge in the connected part of the linear junction termination structure and the curvature junction termination structure is solved; and pre-breakdown of the device is avoided, so as to obtain the optimal breakdown voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

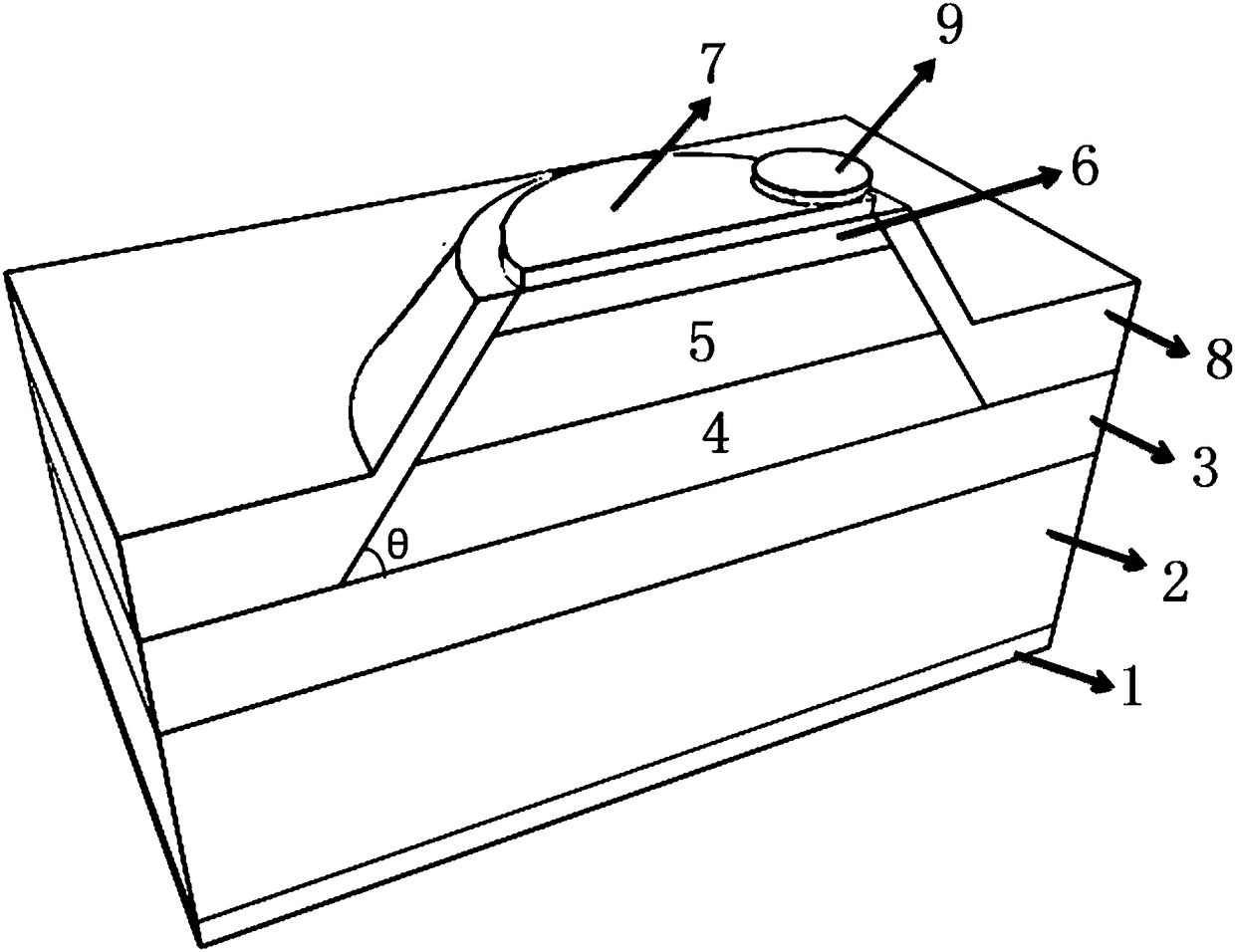

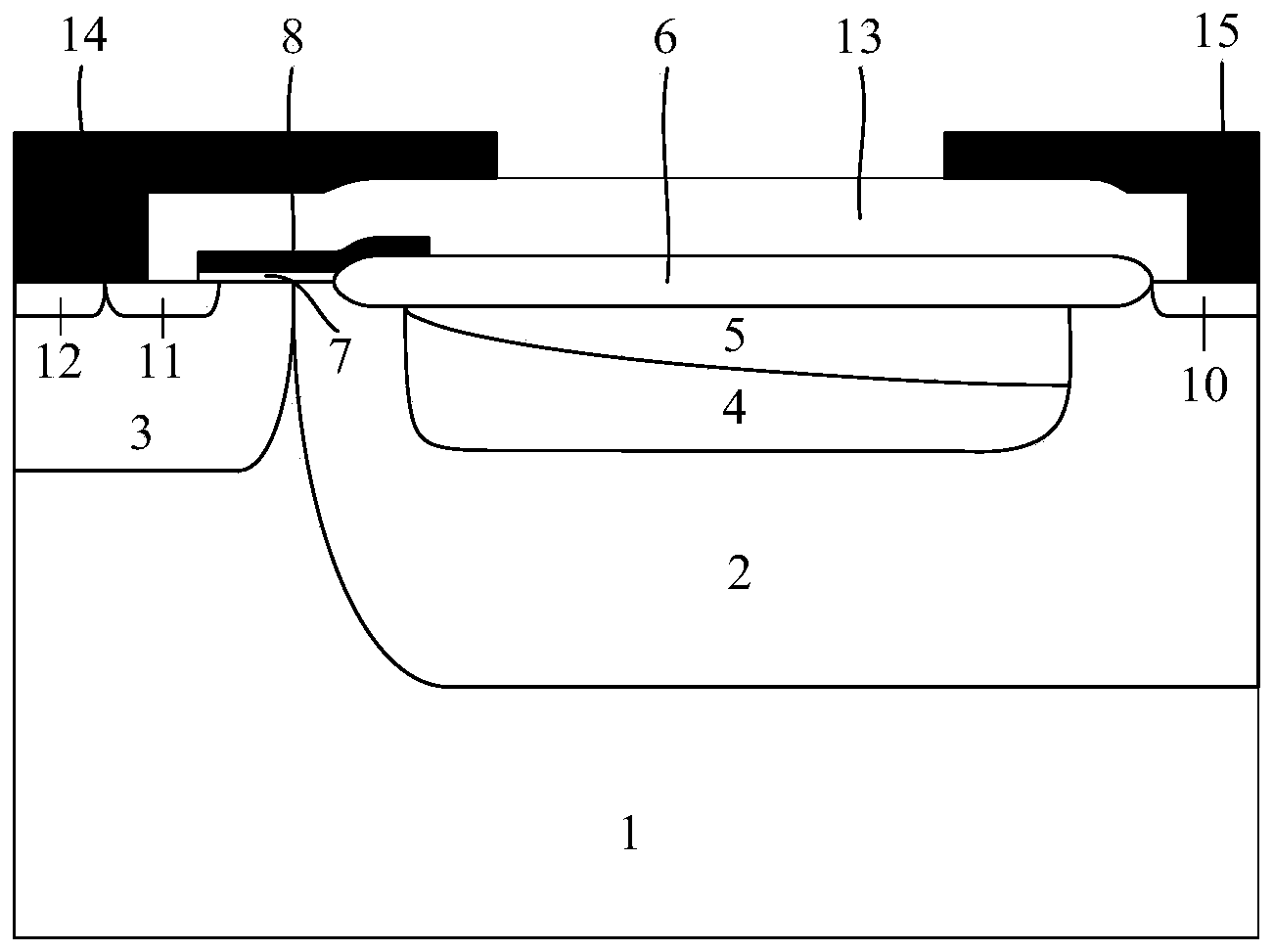

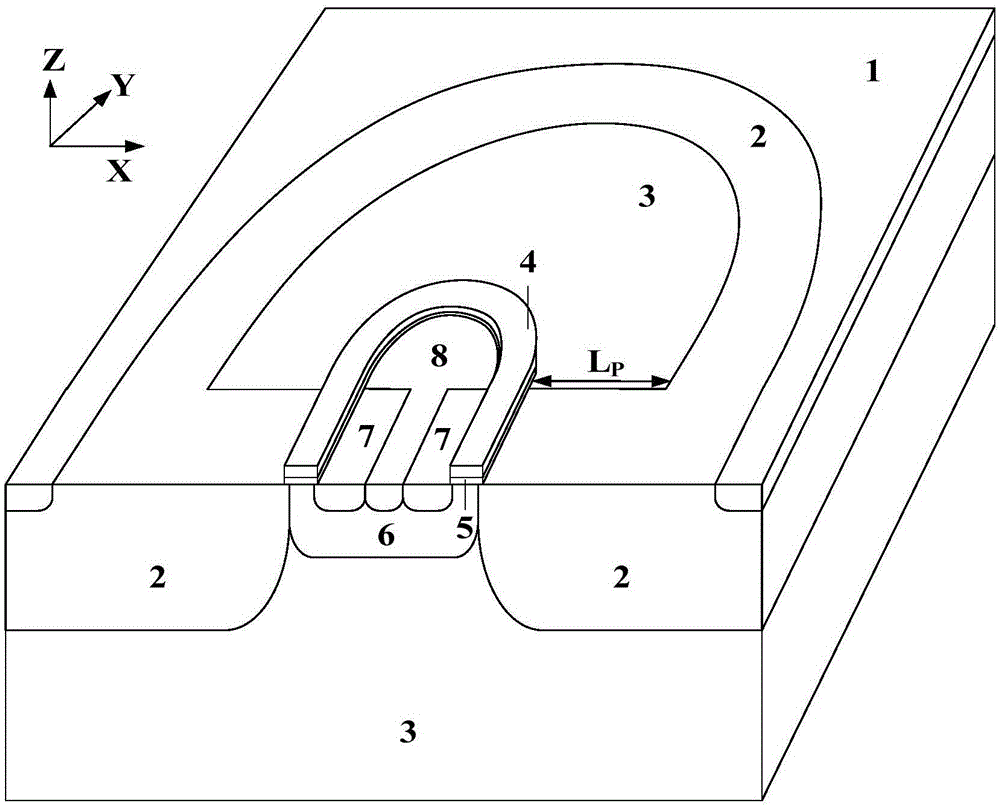

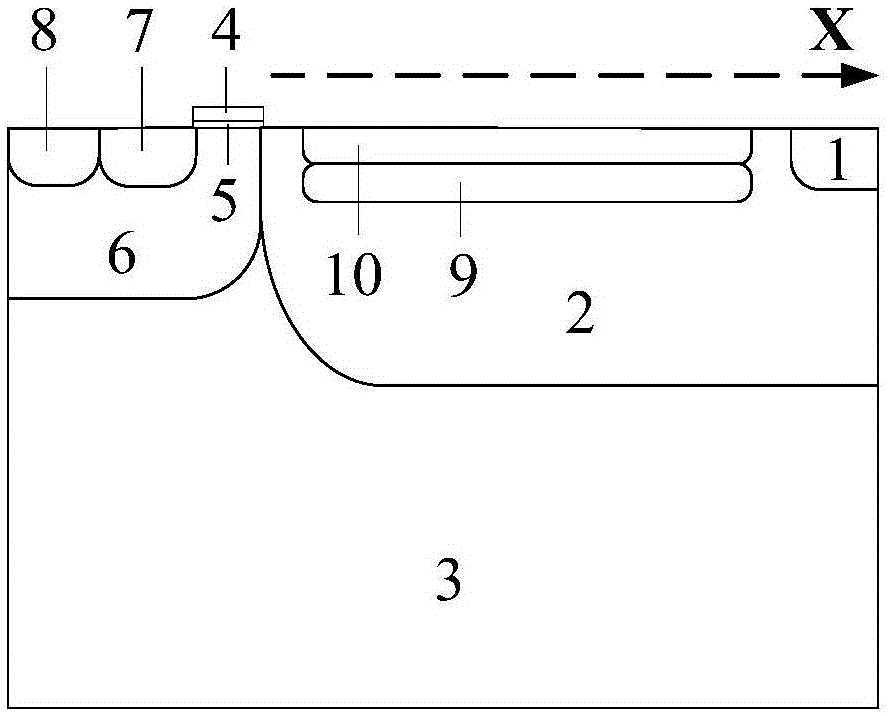

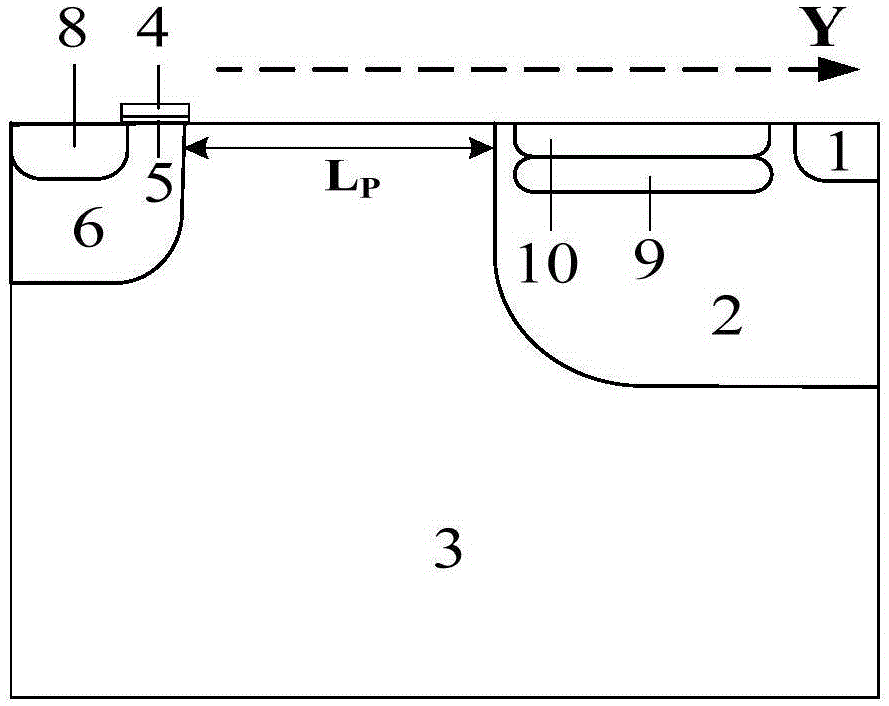

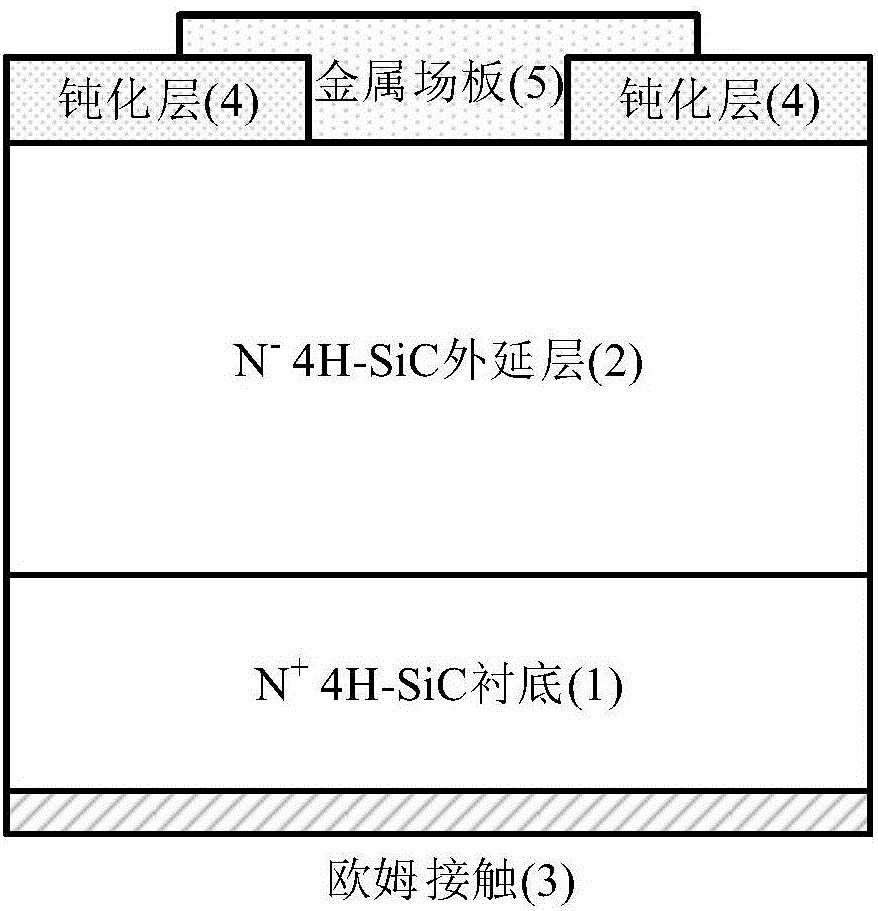

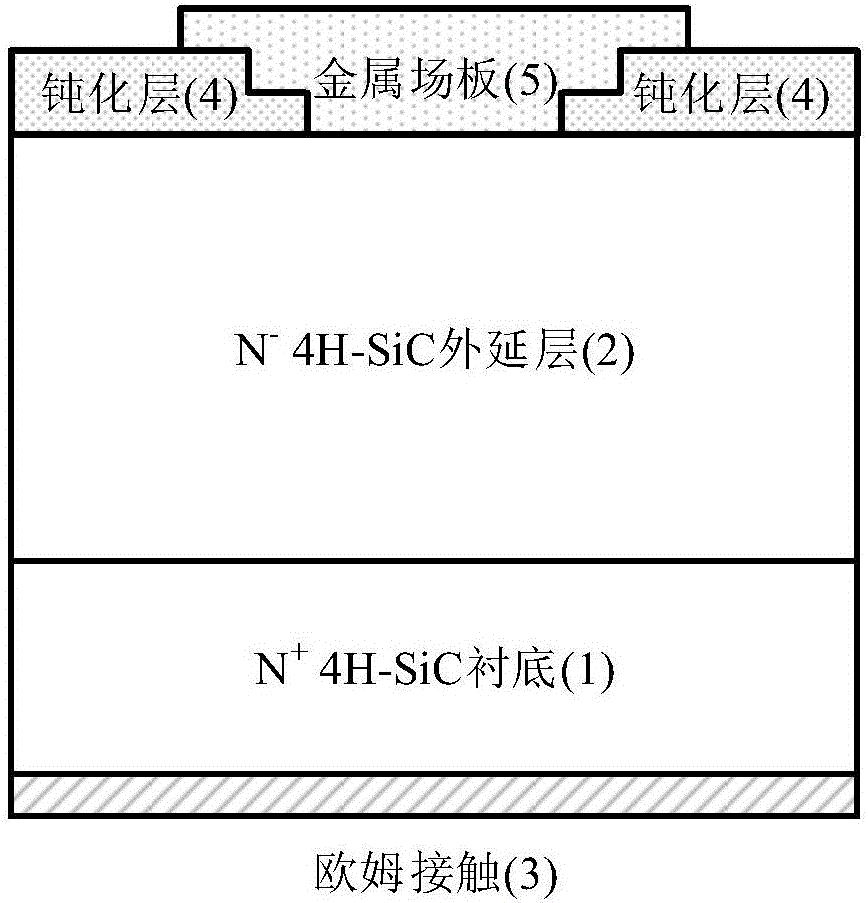

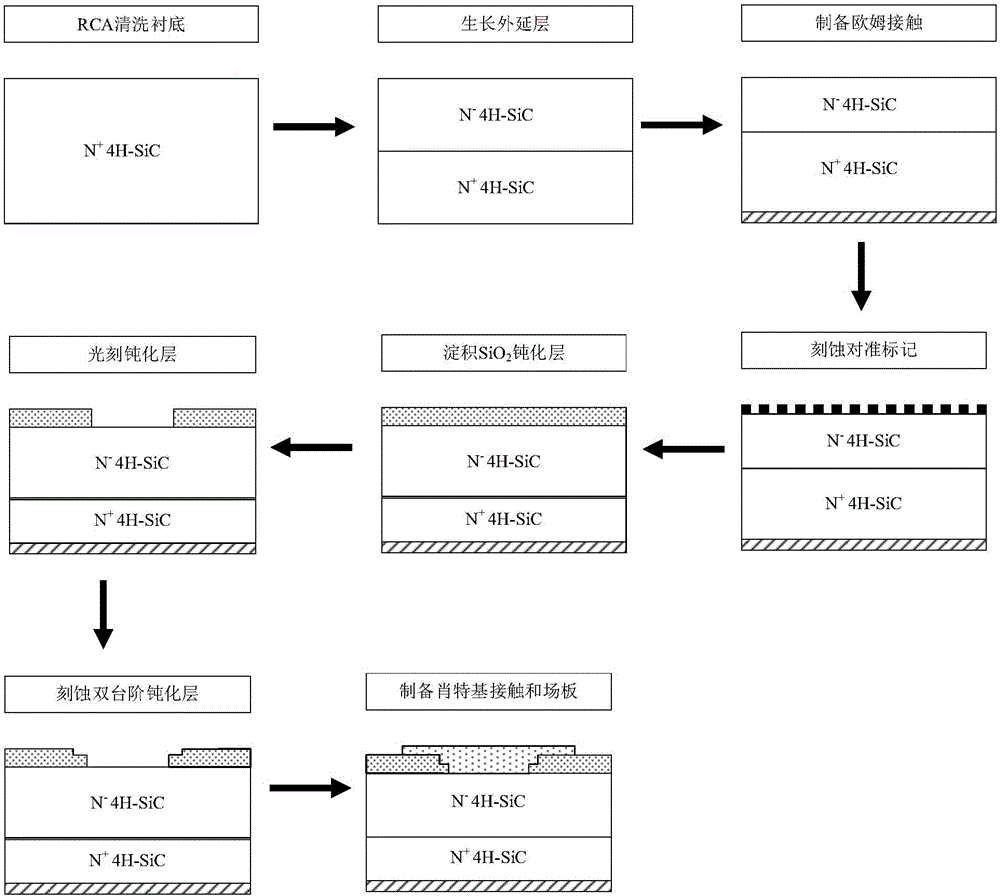

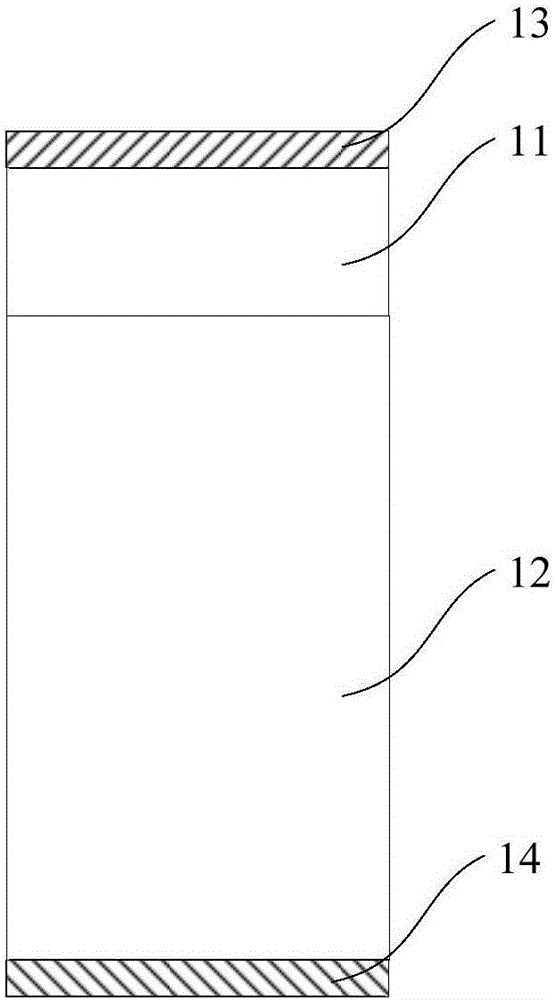

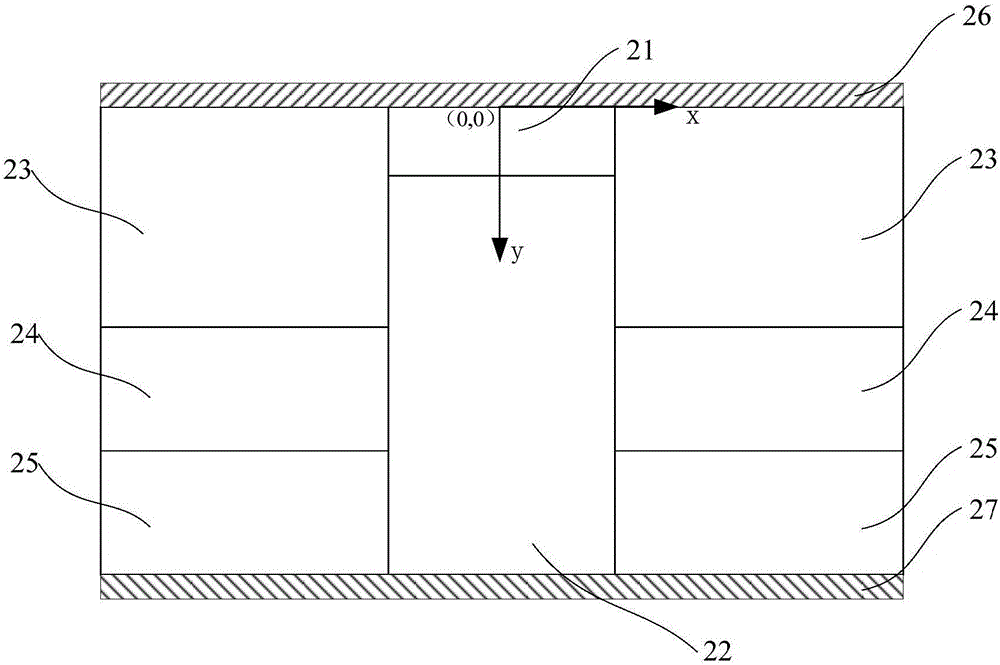

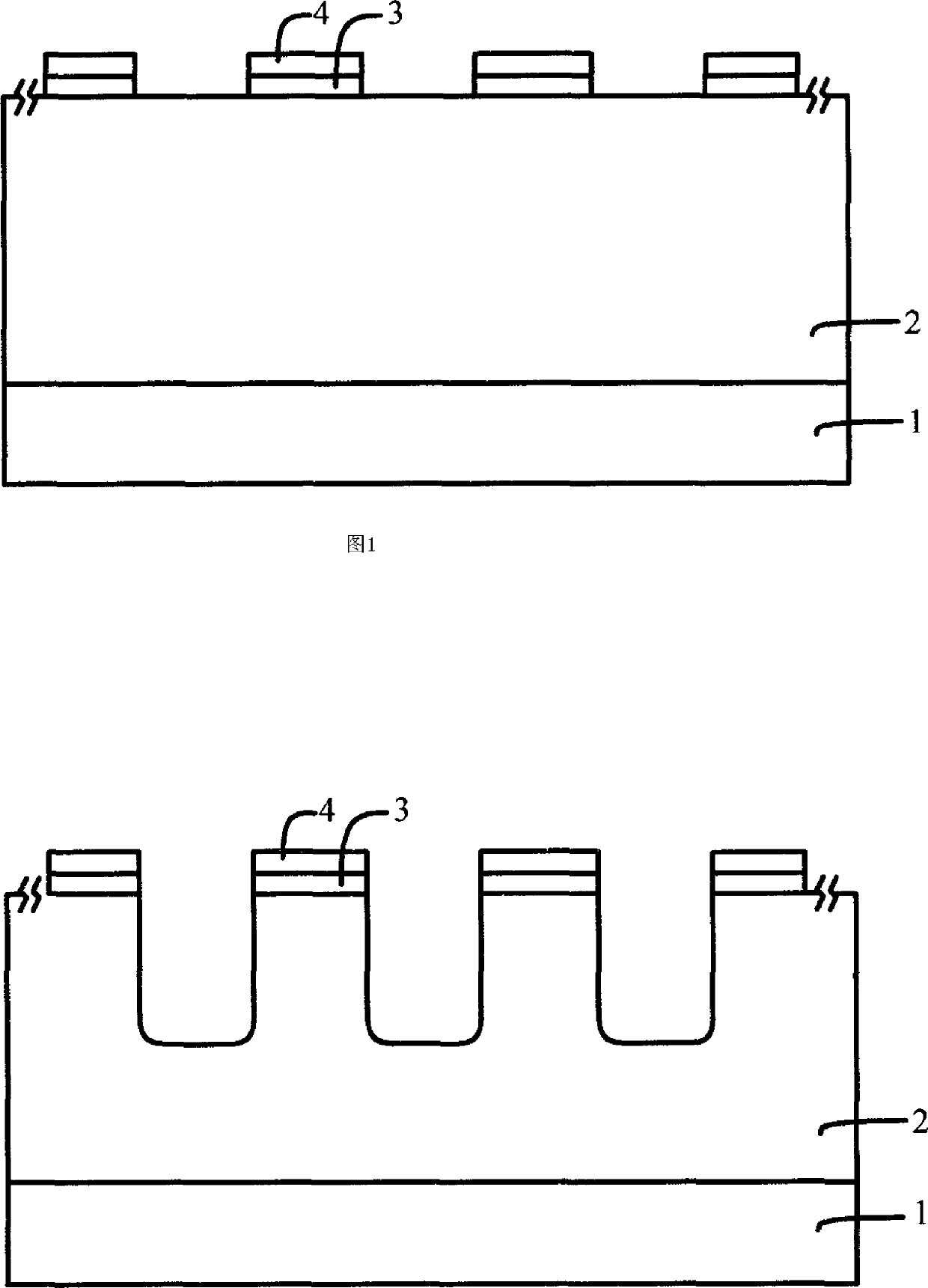

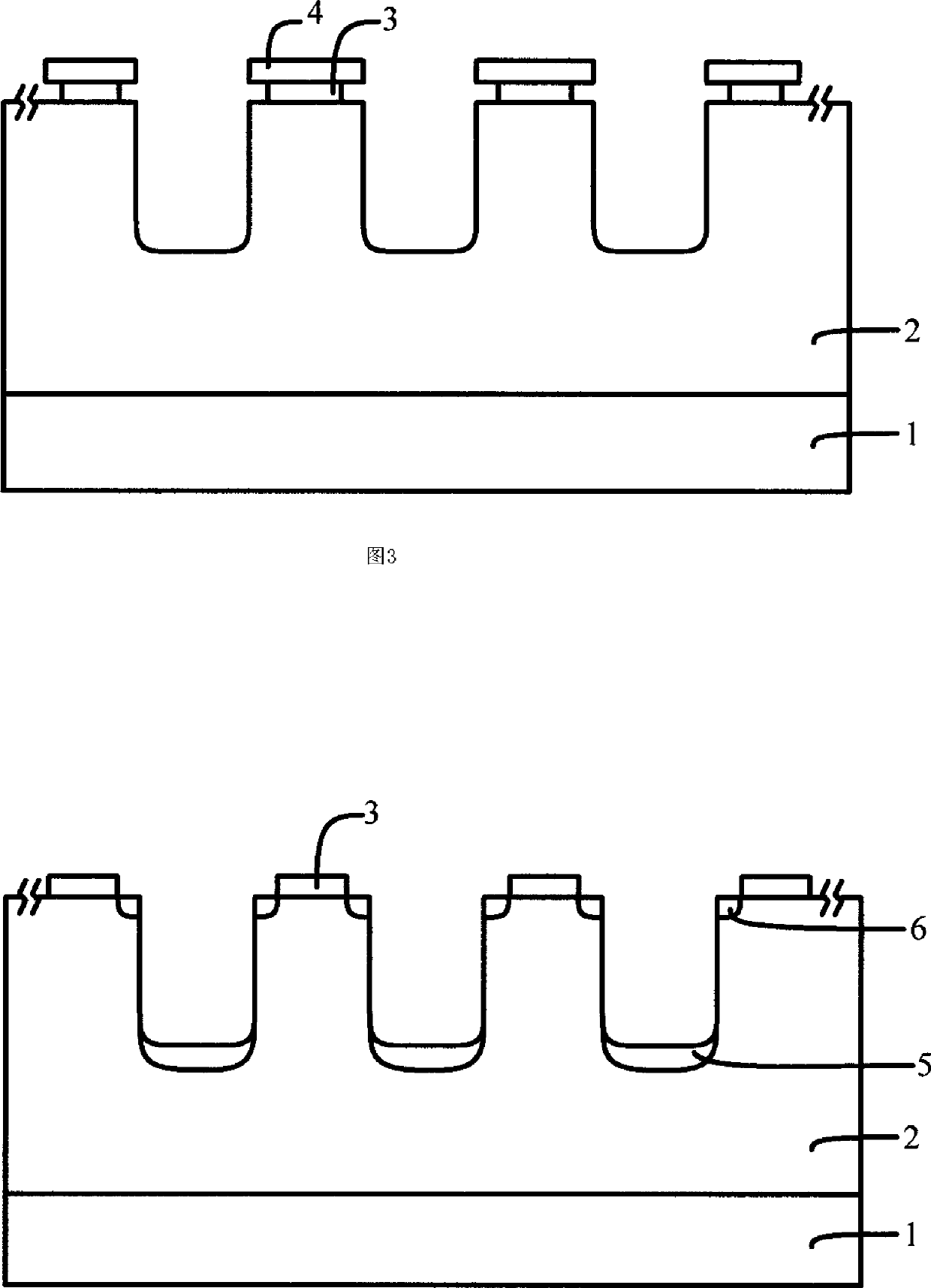

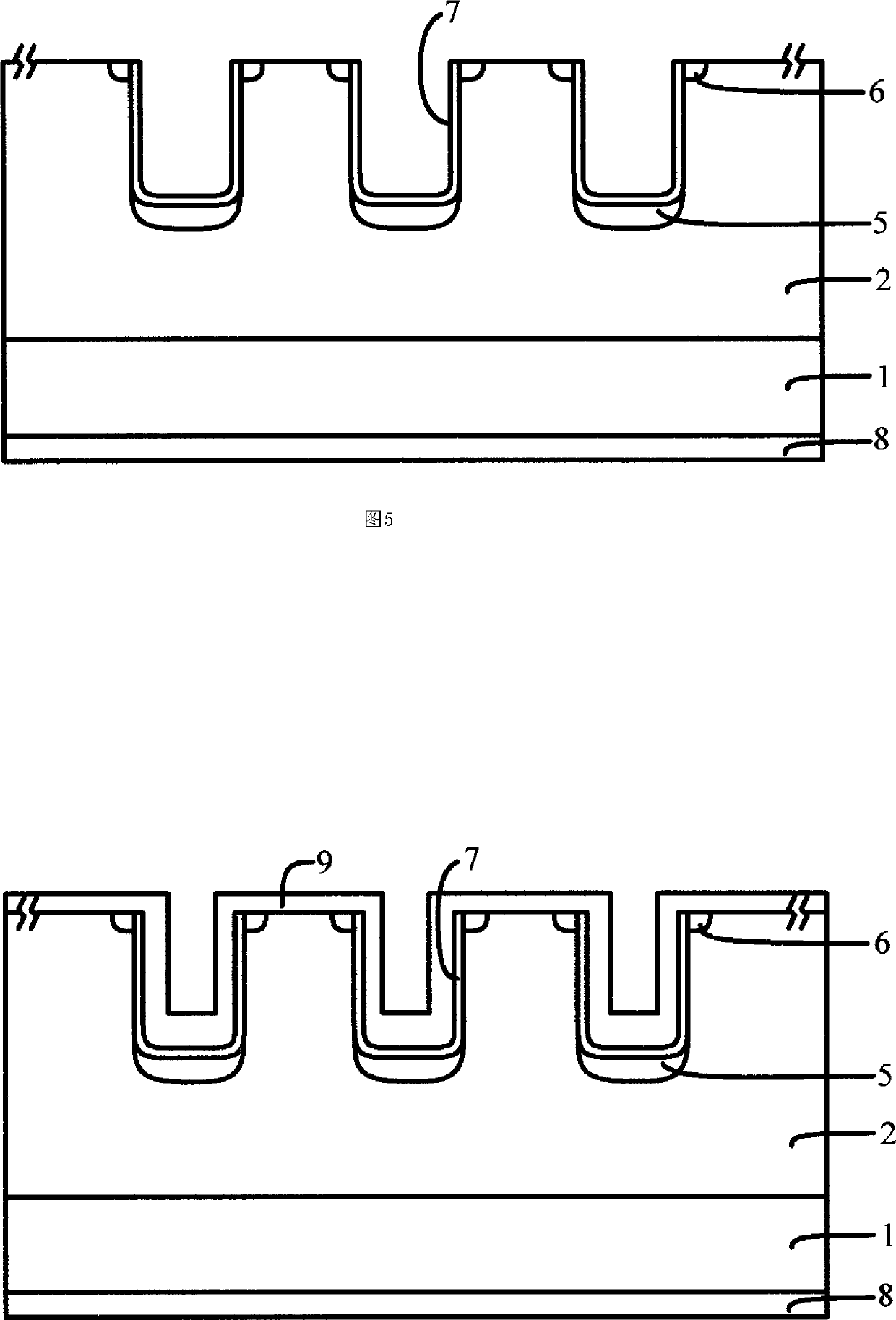

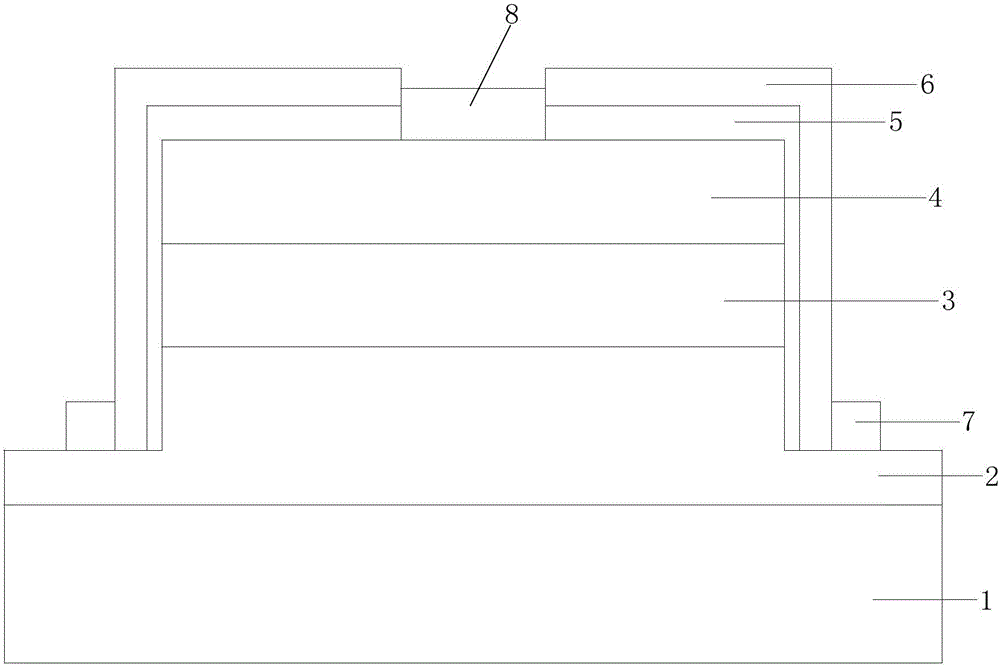

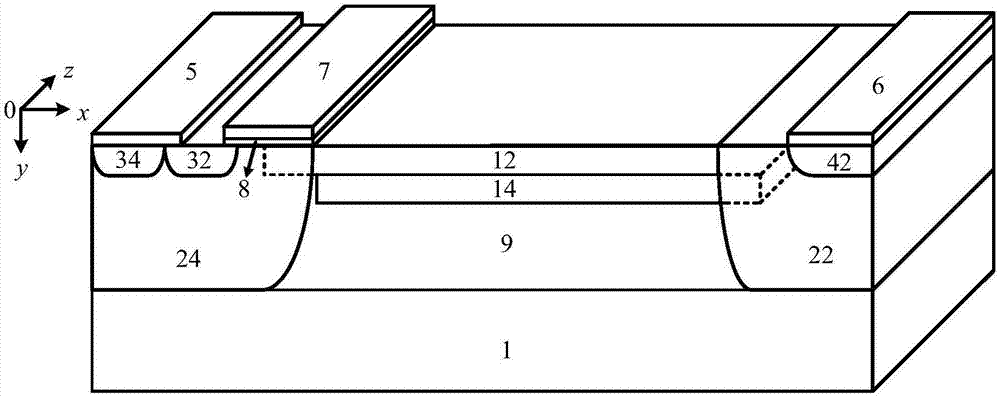

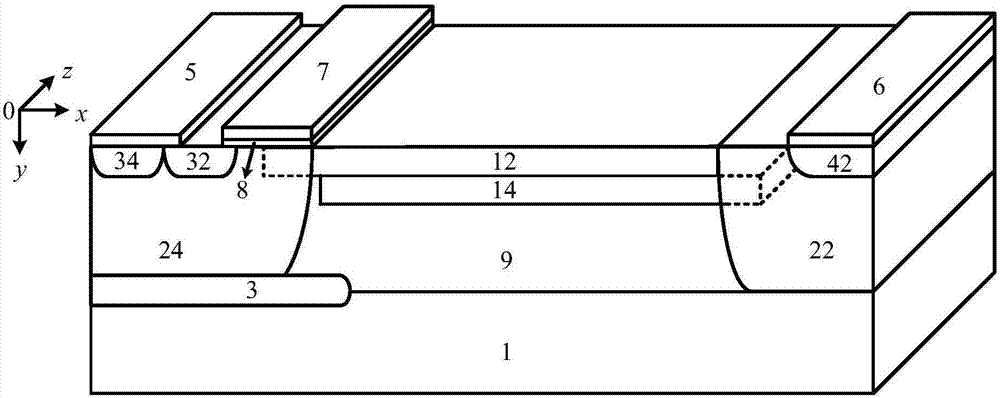

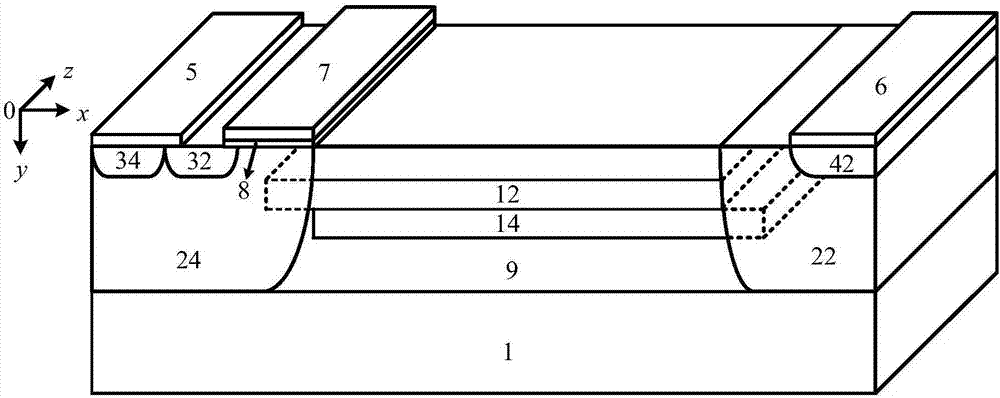

Double step field plate terminal based 4H-SiC Schottky diode and manufacturing method thereof

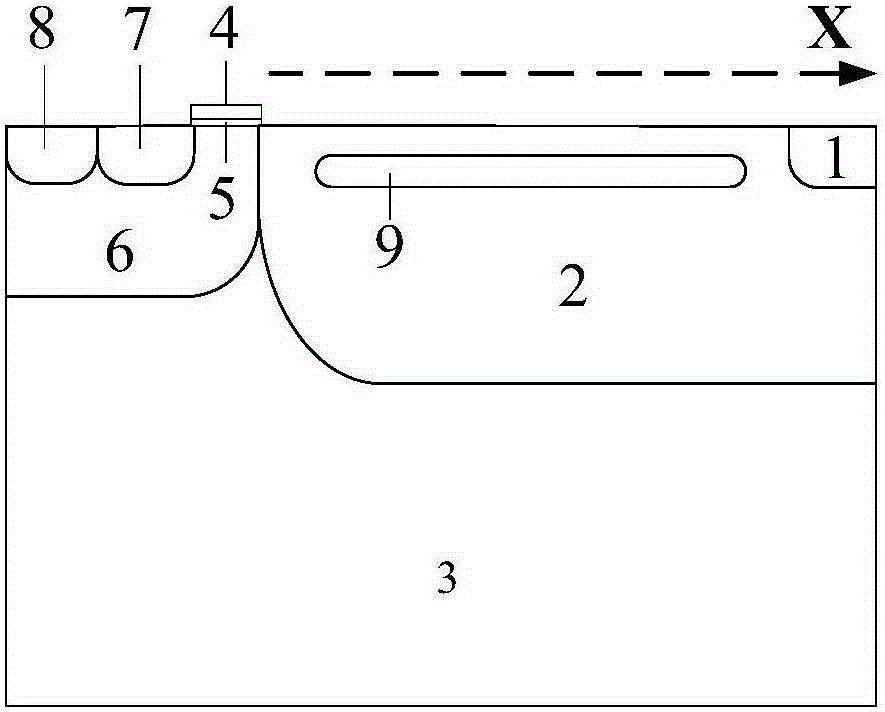

InactiveCN106057914AAvoid premature breakdownIncrease the lengthSemiconductor/solid-state device detailsSolid-state devicesOhmic contactTotal thickness

The invention discloses a double step field plate terminal based 4H-SiC Schottky diode, which mainly solves the problem that the breakdown voltage of a conventional double step field plate terminal based 4H-SiC Schottky diode is less than 1500V. The Schottky diode comprises an N + 4H-SiC substrate (1) and an N- 4H-SiC epitaxial layer (2). The back of the substrate is provided with an ohmic contact (3). The two sides of the epitaxial layer surface are provided with SiO2 passivation layers (4). The middle part of the epitaxial layer surface is provided with a metal field plate terminal (5). The schottky diode is characterized in that the passivation layers (4) and field plate terminal (5) are of a double step shape; the thickness of the double step passivation layers is identical to that of the double step field plate terminal, and the total thickness ranges from 350nm to 600nm. Because the field plate terminal is designed to be of a double step shape, the breakdown voltage of the 4H-SiC Schottky diode can reach 1800V or above; therefore, the diode breakdown ability improves, making it suitable for fabrications of large power integrated circuits.

Owner:XIDIAN UNIV

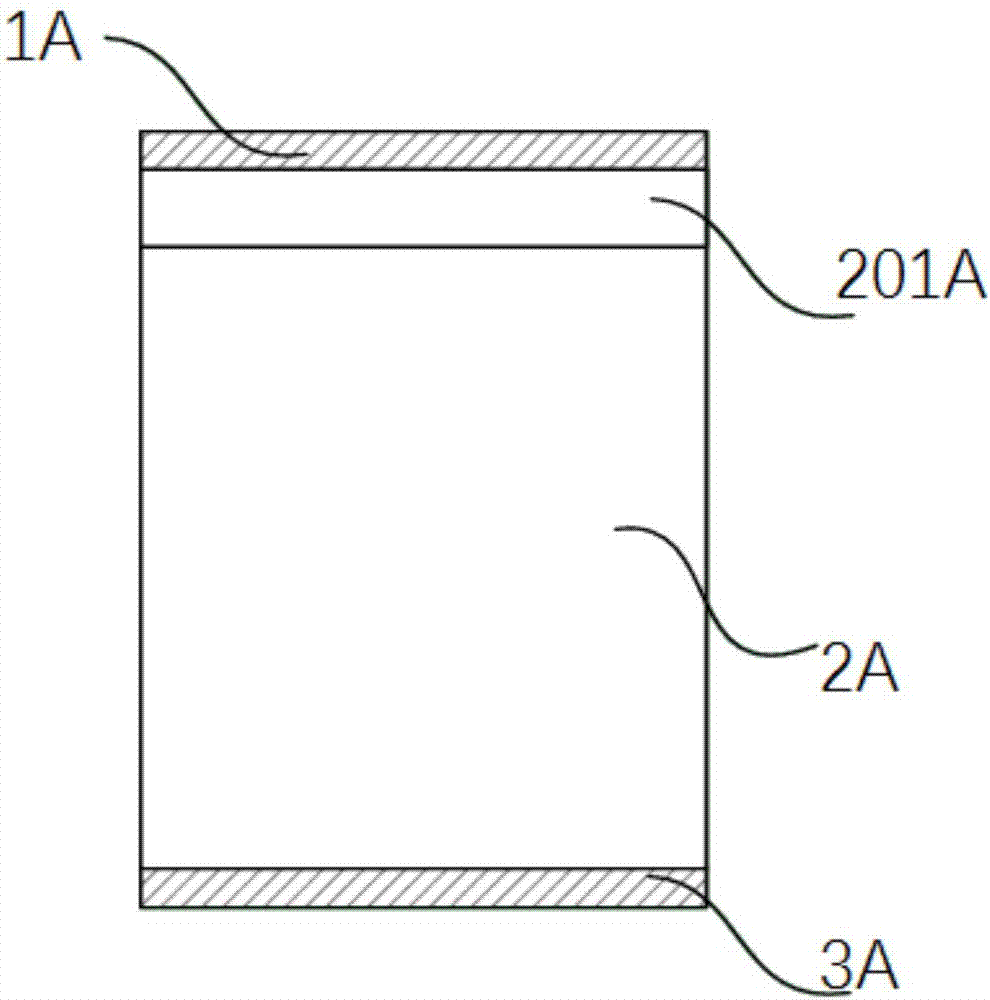

Semiconductor structure, semiconductor assembly and power semiconductor device

ActiveCN106129107AImprove electric field distributionImprove breakdown voltageSemiconductor/solid-state device detailsSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention provides a semiconductor structure, a semiconductor assembly and a power semiconductor device. The semiconductor structure comprises a P-type semiconductor material layer, an N-type semiconductor material layer and multiple insulating material layers, wherein the N-type semiconductor material layer is adhered to the P-type semiconductor material layer, and forms a PN junction together with the P-type semiconductor material layer; the multiple insulating material layers are positioned on the outer side of the PN junction and are distributed along the laminated direction of the P-type semiconductor material layer and the N-type semiconductor material layer, and the relative dielectric constants of the adjacent insulting material layers are different. According to the semiconductor structure provided by the invention, the electric field distribution when the device is resistant to voltage is obviously optimized, and the breakdown voltage of the device is greatly improved; device voltage resistance drop caused by a junction edge electric field concentration effect is avoided, and pre-breakdown of the device is prevented; and a field ring and a metal field plate structure are avoided from being used, so that the chip area is decreased, the cost of the device is reduced, and the reliability of the device is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Preparation method for semiconductor device with improved surge current resistance

InactiveCN103887169AImprove reliabilityAvoid premature breakdownSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLine width

The invention discloses a preparation method for a semiconductor device with improved surge current resistance. The semiconductor device is an improved TMBS diode. According to the semiconductor device, metal Cr is utilized to act as an etching mask film to form a deep groove structure on the surface of a SiC drift layer. Wet etching is performed so that line width of the Cr mask film is narrowed, two sides of a mesa which is not etched are exposed to act as an injection mask film to perform Al-ion injection on the surface of the SiC drift layer, and P-type injection regions are formed on the two sides of the mesa. A PN-junction is formed by the injection regions and an N-type drift region. The PN-junction participates in conduction under the condition of high current. The conductance modulation effect is formed by utilizing minority-carrier injection so that the semiconductor device is enabled to have surge current resistance. Besides, a P-injection region can be formed on the bottom part of a groove simultaneously. The bottom part of the groove can be protected by the P-region under the reverse blocking state of the device, the situation that electric field concentration is formed on a non-ideal etching surface can be avoided, early breakdown can be prevented and thus reliability of the device can be enhanced.

Owner:HANGZHOU ENNENG TECH

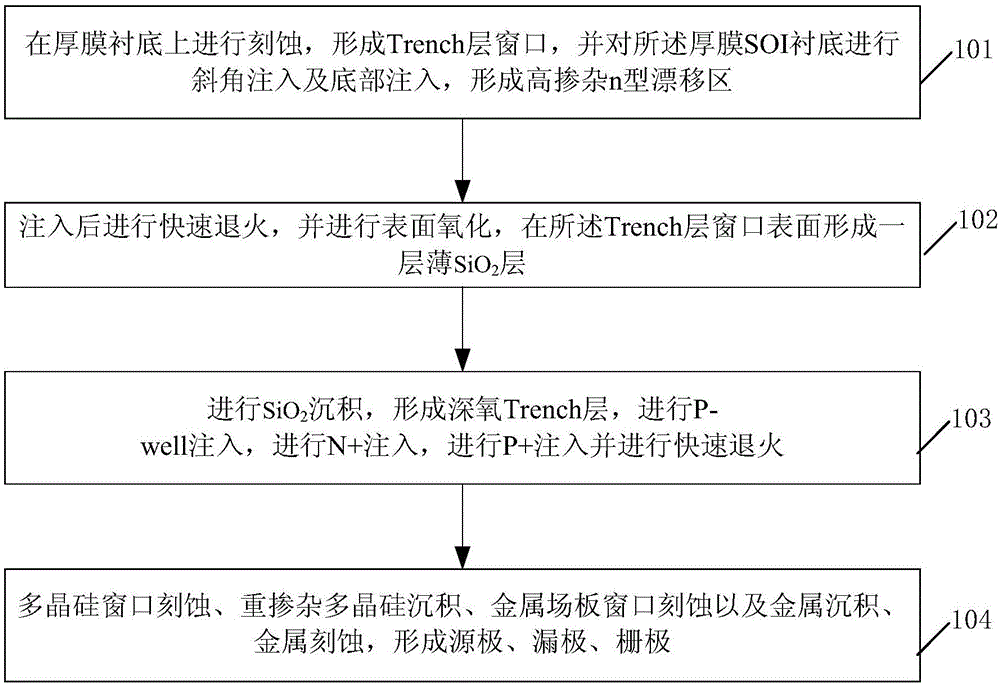

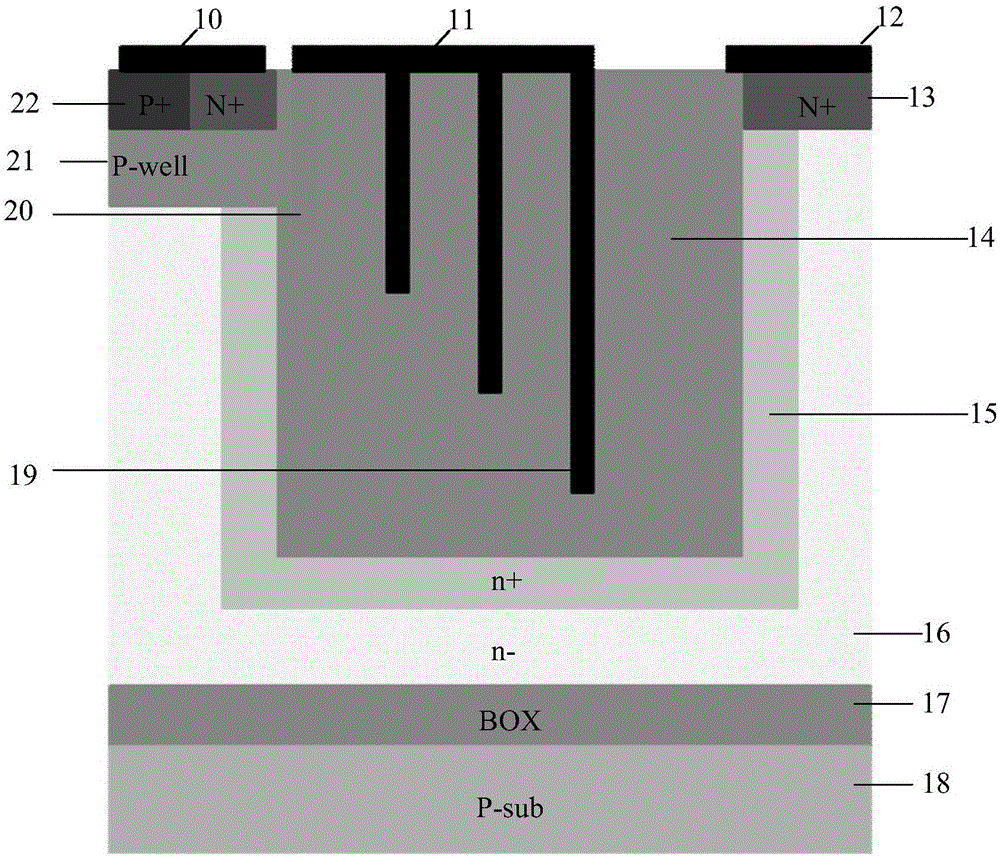

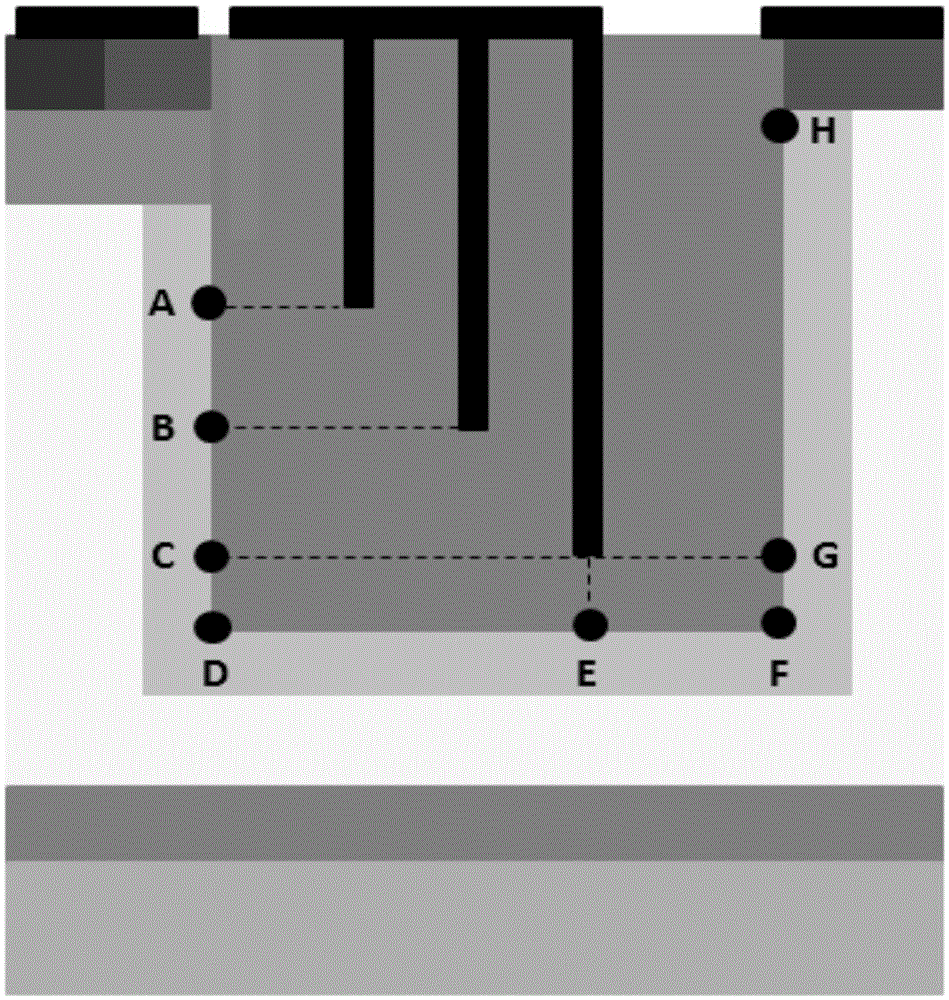

Preparation method for semiconductor power device structure, and structure

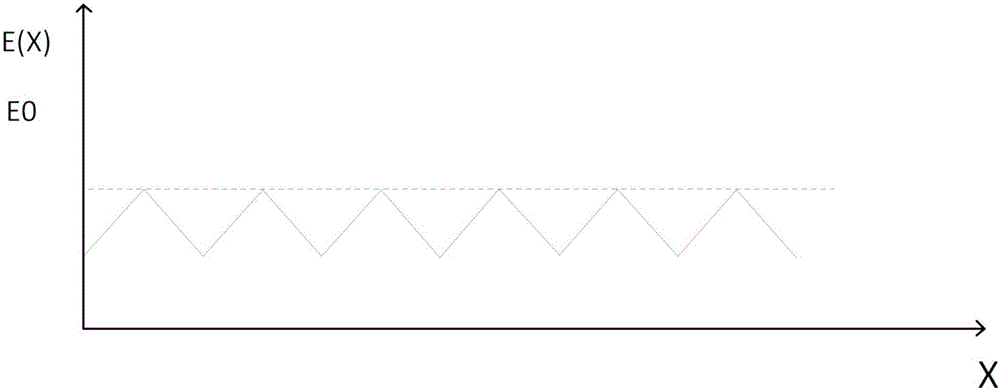

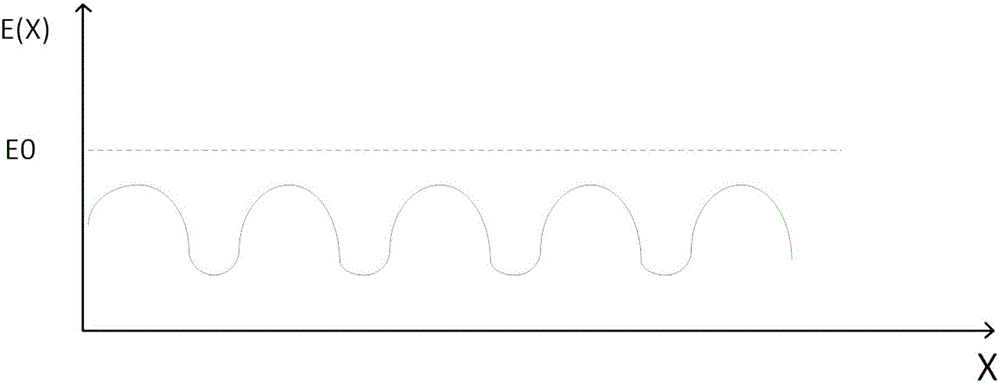

ActiveCN105070758AImprove breakdown voltageAvoid premature breakdownTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceLDMOS

The embodiment of the invention discloses a preparation method for a semiconductor power device structure, and a structure. A Trench layer of a conventional lateral power device Trench LDMOS structure is provided with a plurality of longitudinal metal field plates at different depths, and a drift region is provided with a heavily-doped n-type layer. In order to improve the breakdown voltage of a device, the metal field plates with different lengths at different layers can introduce a plurality of new electric field peak values in a drift region, and enables a surface high electric field to be introduced into a body, thereby protecting the surface of the device from being broken down in advance. After complete loss, the heavily-doped n-type layer improves the surface charge density of the Trench layer, improves the electric fields of the Trench layer and the drift region, and improves the breakdown voltage of the device. In order to reduce the conduction resistance of the device, a deep oxygen Trench layer reduces the length of the lateral drift region.

Owner:工业和信息化部电子第五研究所华东分所

Growth method of surface passivation layer of mesa detector

ActiveCN106356428AImprove yield rateImprove reliabilityPhotovoltaic energy generationSemiconductor devicesPolyimide membraneChemical vapor deposition

The invention discloses a growth method of a surface passivation layer of a mesa detector. The growth method comprises the following steps of: forming a SiO2 passivation film on the surface of the mesa structure of a wafer by using a plasma chemical vapor deposition process in a low-temperature environment; coating a polyimide film on the SiO2 passivation film and carrying out gradient curing to densify the polyimide film; spin-coating a photoresist on the polyimide film to form a photoresist layer, and forming an exposure region on the photoresist layer; developing the photoresist layer of the exposure region, etching the polyimide film of the exposure region, and then removing the photoresist layer; performing imidization treatment on the polyimide film so that the polyimide film is fixed to the surface of the SiO2 passivation film; and etching the exposed SiO2 passivation film to set apart an electrode position. The growth method disclosed by the invention can be used for improving the passivation quality of the mesa detector, effectively reducing the surface leakage current of a device, preventing the device from premature breakdown, and improving the reliability of the device.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

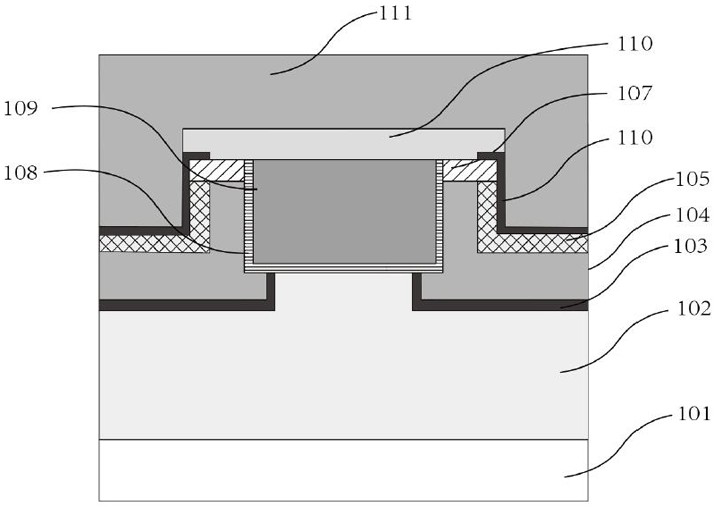

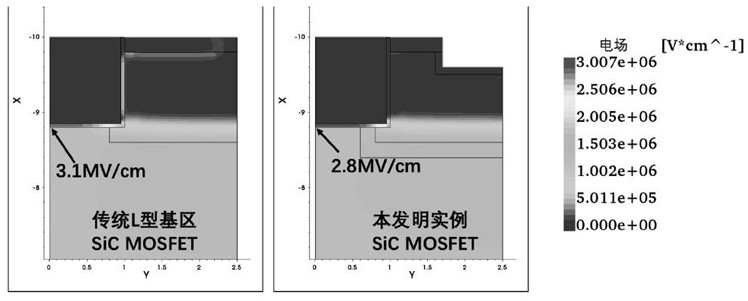

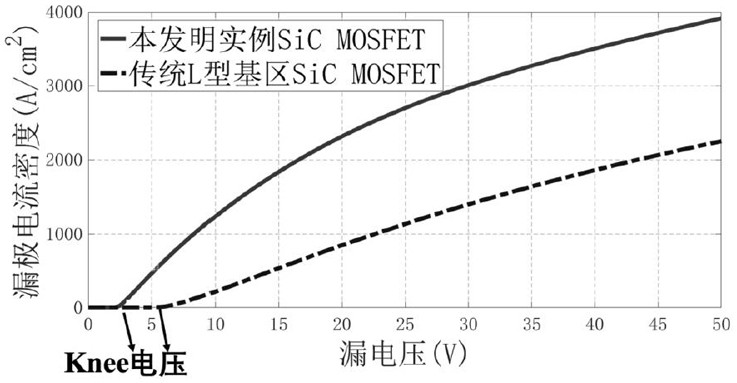

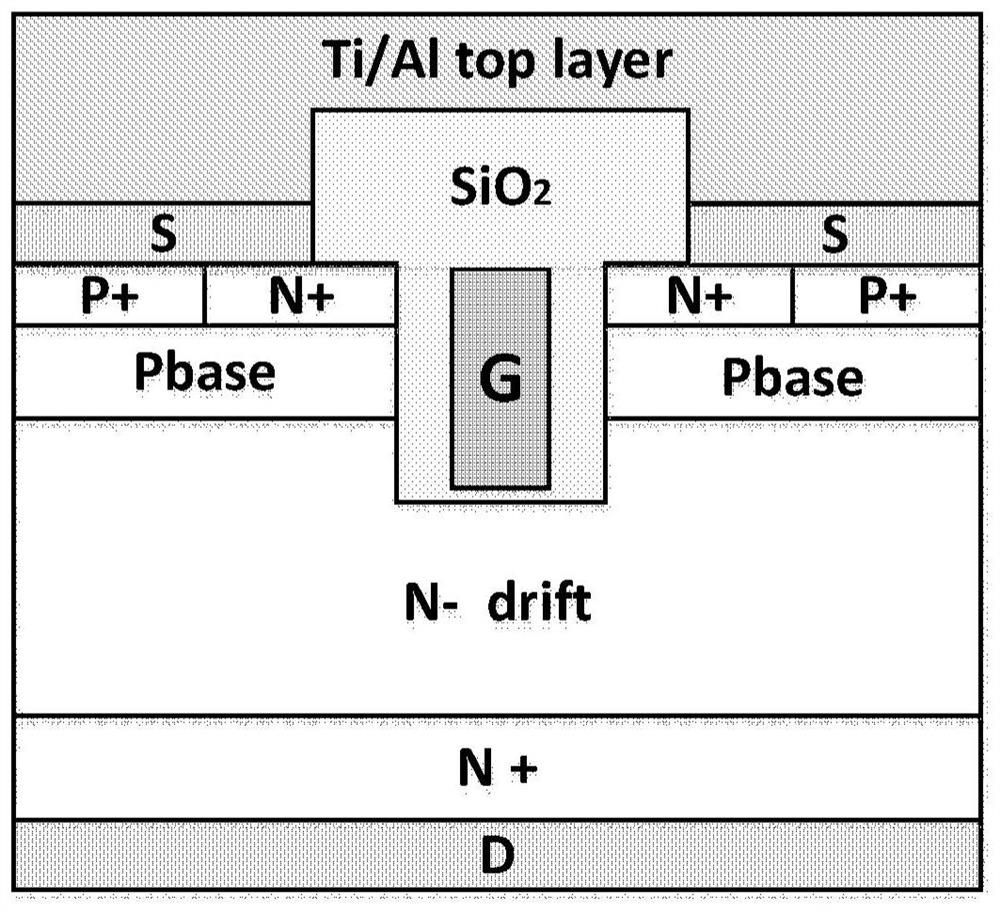

L-type base region SiC MOSFET cellular structure, device and manufacturing method

ActiveCN114023810AReduce horizontal expansionImprove shielding effectSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

The invention discloses an L-type base region SiC MOSFET cellular structure, a device and a manufacturing method. The L-type base region SiC MOSFET cellular structure comprises an N++ SiC substrate, an N- SiC drift layer, a P-type base region and an N+ source region. The N- SiC drift layer is located above the N++ SiC substrate, a source trench and a gate trench are formed in the N- SiC drift layer, and a gate dielectric layer and a gate electrode are arranged in the gate trench. The P-type base region and the N+ source region are positioned on the N- SiC drift layer between the source trench and the gate trench and are arranged from bottom to top, an N-type current conducting layer is arranged between the P-type base region and the N- SiC drift layer, and a source N+ ohmic contact region is arranged between the P-type base region and the source trench. According to the device structure, the on resistance and the gate-drain capacitance can be further reduced, the conduction loss and the switching loss can be reduced, the working frequency can be improved, the premature breakdown of the P-type base region can be avoided, and the reliability of the device can be ensured.

Owner:北京昕感科技有限责任公司

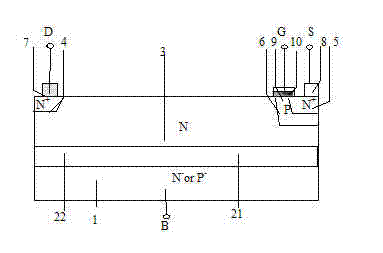

Junction termination structure of transverse high-voltage power device

ActiveCN105206659AImprove balanceAvoid premature breakdownSemiconductor devicesEngineeringHigh pressure

The invention belongs to the semiconductor technical field and relates to a junction termination structure of a transverse high-voltage power device. According to the structure of the invention, the inner wall of an N-type drift region 2 and the inner wall of a P type buried layer 9 in a curvature junction termination structure respectively extend to the middle so as to be connected with the inner wall of an N-type drift region 2 and the inner wall of a P type buried layer 9 in a direct junction termination structure, an extending route being a circular arc-shaped path; and therefore, curvature effects of electric fields at joints can be effectively alleviated; in a direction vertical to the extension direction of the joints, the P-type buried layers 9 exceed the N-type drift regions 2 by a certain distance, and therefore, the problem of charge imbalance can be solved. With the junction termination structure of the transverse high-voltage power device of the invention adopted, the problem of charge imbalance of the joints of the direct junction termination structure and the curvature junction termination structure and the problem of the curvature effects of the electric fields at the joints of the direct junction termination structure and the curvature junction termination structure can be solved, and pre-breakdown of the device can be avoided, and optimized breakdown voltage can be obtained.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

SOI LDMOS device with interface N<+> layer

ActiveCN102760753AAvoid premature breakdownImprove vertical pressure resistanceSemiconductor devicesHigh concentrationP type silicon

The invention discloses an SOI (Semiconductor ON Insulator) LDMOS (Laterally Diffused Metal Oxide Semiconductor) device with an interface N<+> layer, and relates to a semiconductor power device. The SOI LDMOS device comprises a substrate silicon layer, a medium buried layer and active top layer silicon, wherein the medium buried layer is arranged between the substrate silicon layer and the active top layer silicon; and the active top layer silicon is divided into an N-type silicon layer, a P-type silicon layer and an N<+> silicon layer from the surface of a semiconductor to the medium buried layer. According to the invention, as the N<+> silicon layer is arranged between the medium buried layer and the active top layer silicon, when the device is in a reverse blocking state, exhausted high-concentration ionized donor at the interface part enhances the electric field of the medium buried layer, the distribution of the electric field in the active top layer silicon is effectively modulated, and accordingly, the longitudinal voltage resistance and the transverse voltage resistance of the device are effectively improved. Meanwhile, the P-type silicon layer in the active top layer silicon can adjust the RESURF (Reduced SURface Field) condition of the device and relieve the contradiction between the breakdown voltage and the on resistance of the device.

Owner:NO 24 RES INST OF CETC

Device for eliminating high electric field

ActiveCN107359194AImprove breakdown voltageAvoid premature breakdownSemiconductor devicesElectrical resistance and conductanceGate oxide

The invention provides a device for eliminating a high electric field. A cellular structure comprises a substrate, a source contact electrode, a drain contact electrode, a grid electrode, a grid oxide layer, a second type drift region, a second type bar, a first type bar, a second type buffer region, a first type well region, a second type heavy-doped region, a first type heavy-doped region and a third type heavy-doped region. According to the device for eliminating the high electric field, the left end of the second type bar extends into the first type well and is not connected with the second type heavy-doped region; the right end of the first type bar extends into the second type buffer region, so that the second type bar at the left end is exhausted by a multi-surface first type impurity, and the first type bar at the right end is exhausted by a multi-surface second type impurity; therefore, the peak of an electric field at a super junction edge is weakened, in-advance breakdown of the device is avoided, and the breakdown voltage of a super junction device is further increased; and the left side of the second type bar extends into the first type well region, so that the channel resistance of the device in an on state is reduced, and the specific on-state resistance of the device is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

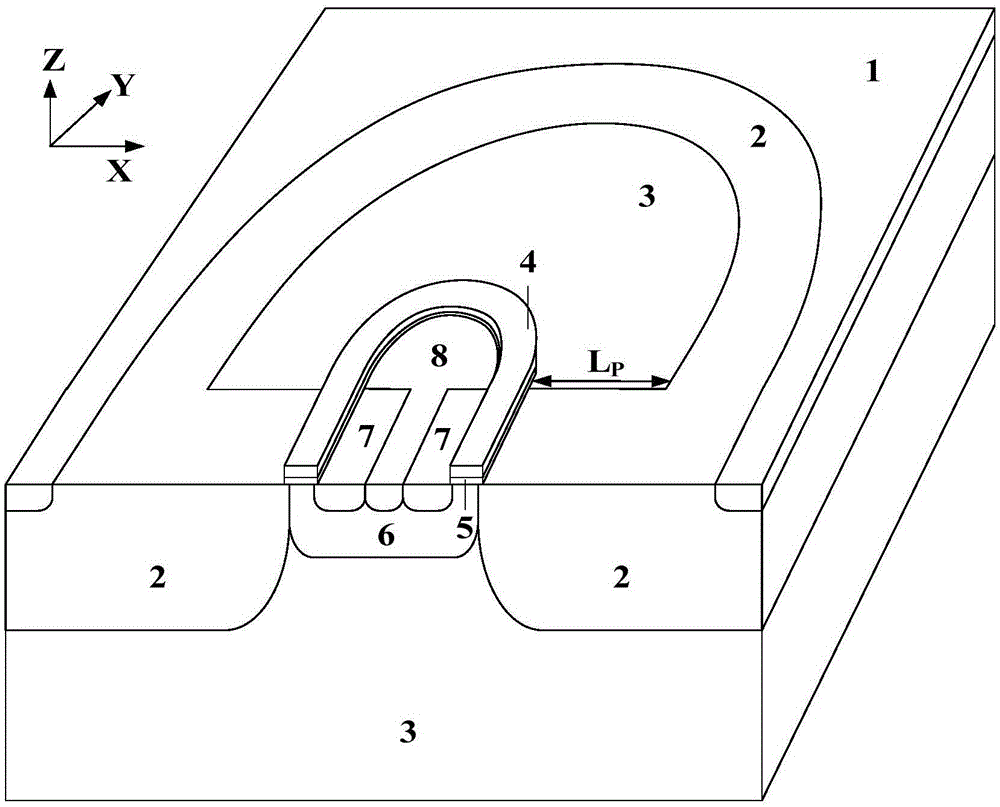

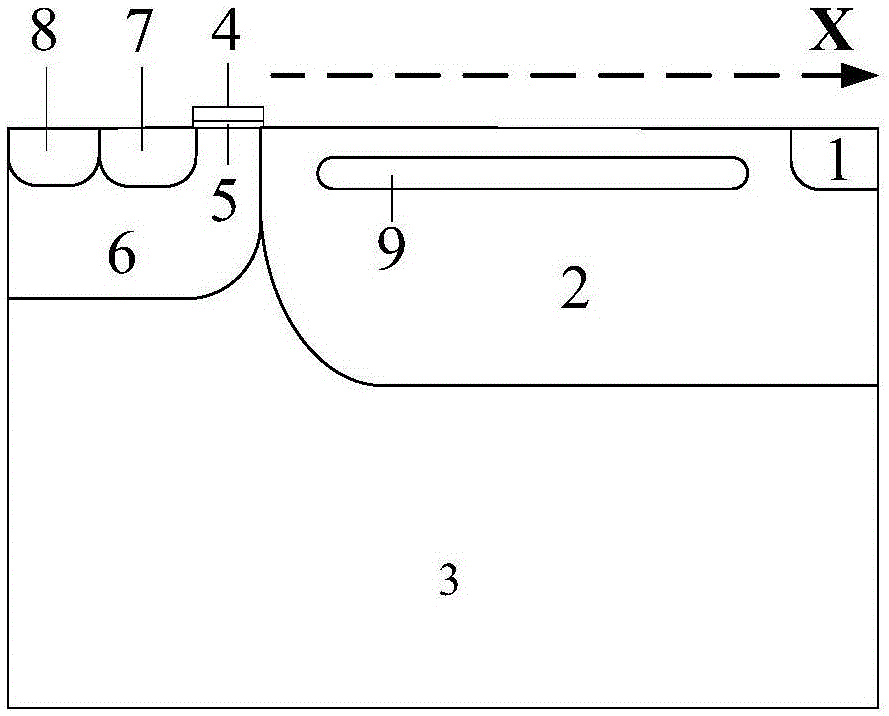

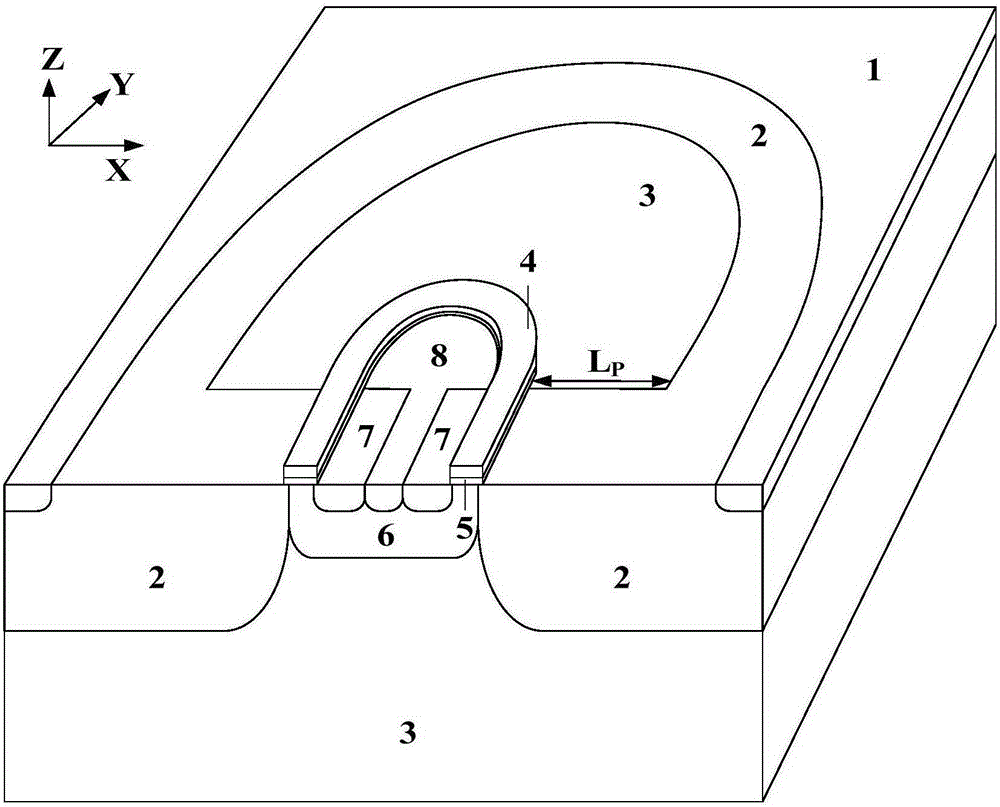

Junction termination structure of transverse high-voltage power device

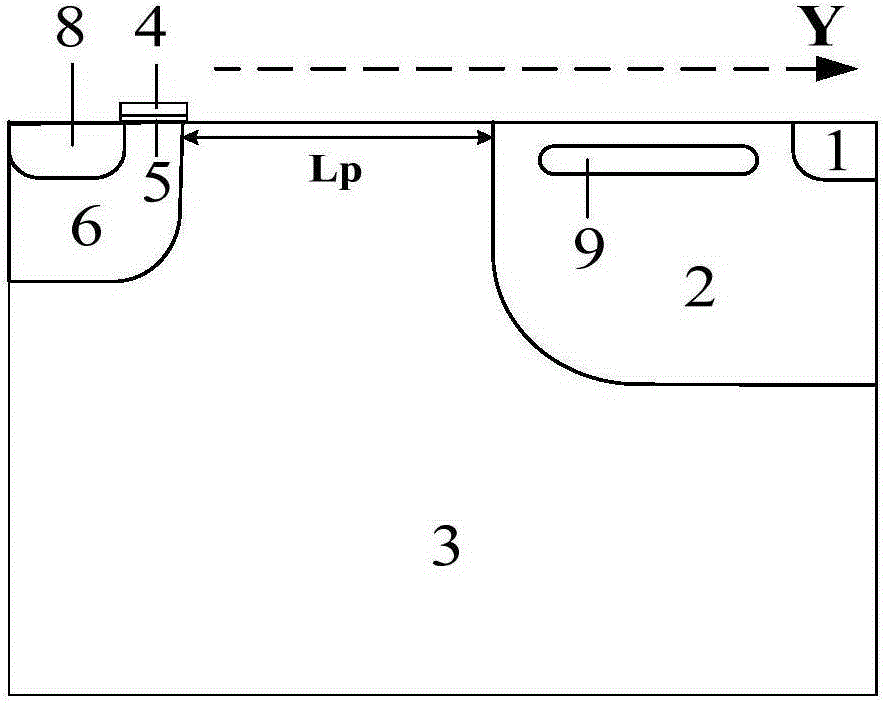

ActiveCN106098754AOptimize and improve the problem of early breakdownAvoid premature breakdownSemiconductor devicesEngineeringGate oxide

The invention provides a junction termination structure of a transverse high-voltage power device, wherein the junction termination structure comprises a linear junction termination structure and a curved junction termination structure. The curved junction termination structure comprises a drain N<+> contact region, an N-type drift region, a P-type substrate, a gate polycrystalline silicon, a gate oxide layer, a P-well region, a source P<+> contact region and insulating medium, wherein the insulating medium comprises sub-mediums which are separated from each other. Each sub-medium extends from outside of the P-well region to outside of the N-type drift region. The annular drain N<+> contact region surrounds the annular N-type drift region. The annular N-type drift region surrounds the annular insulating medium. The annular insulating medium is used for insulating the P-well region. The annular insulating medium is arranged between the P-well region and the N-type drift region. The P-well region is not connected with the N-type drift region, and furthermore the distance between the P-well region and the N-type drift region is LP. The junction termination structure settles problems of charge unbalance and electric field curvature effect at the connecting part between the linear junction termination structure and the curved junction termination structure, thereby obtaining an optimal breakdown voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

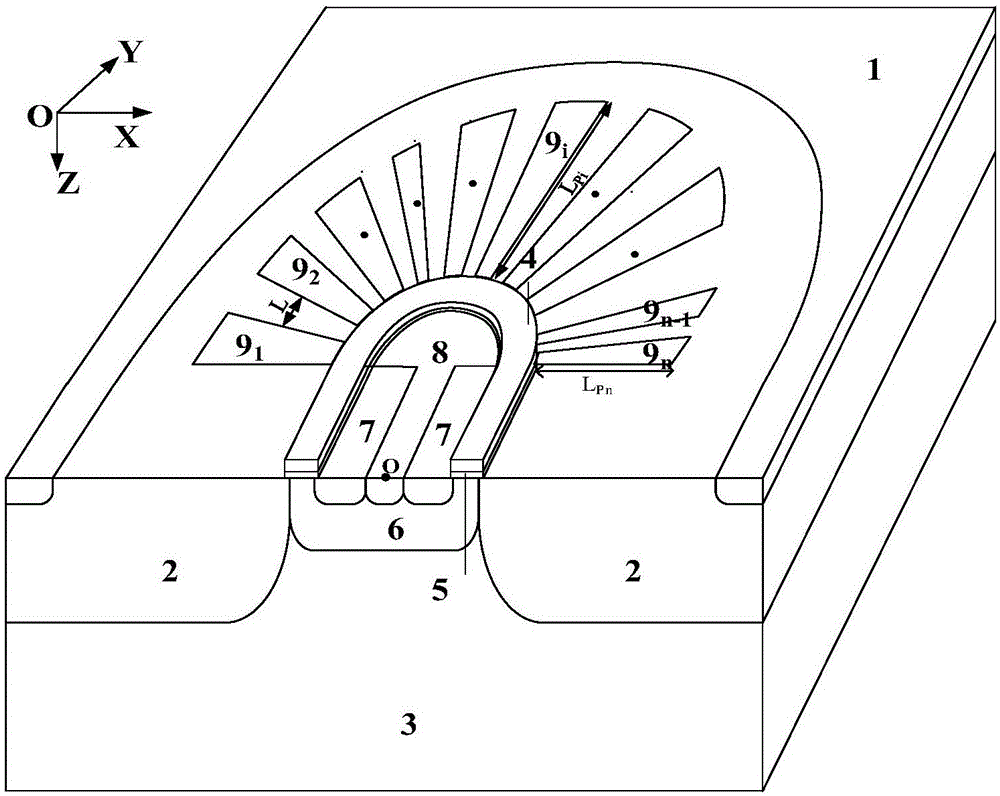

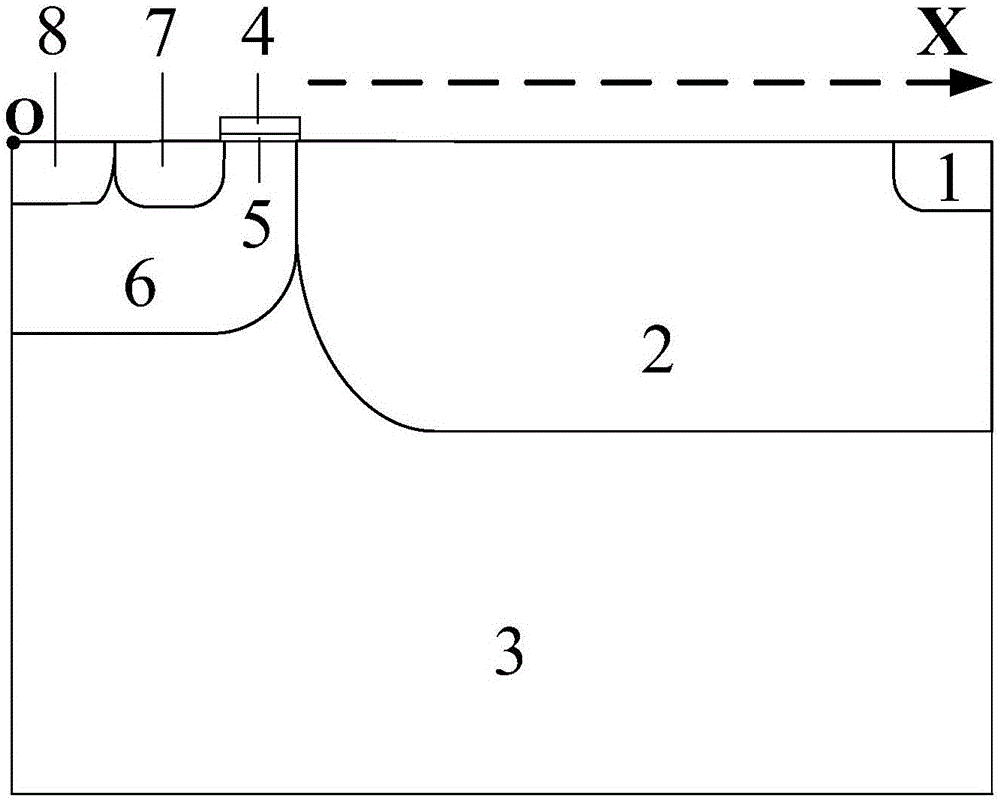

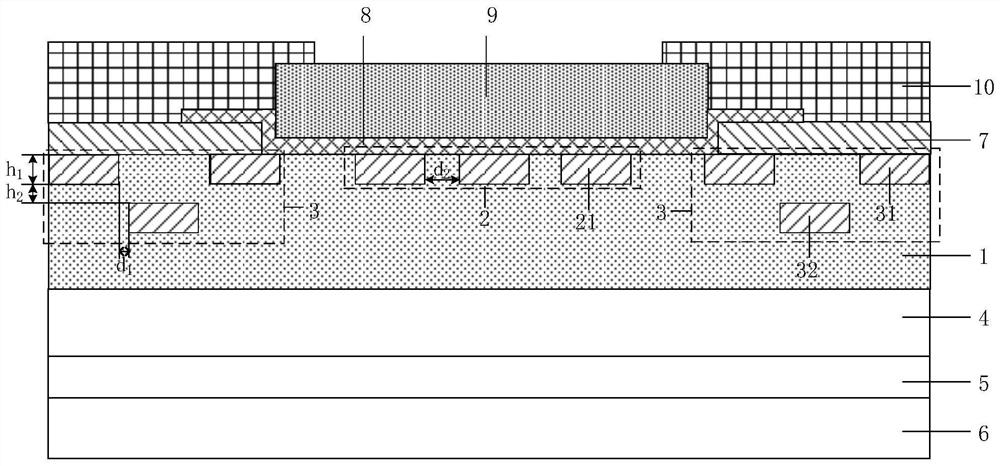

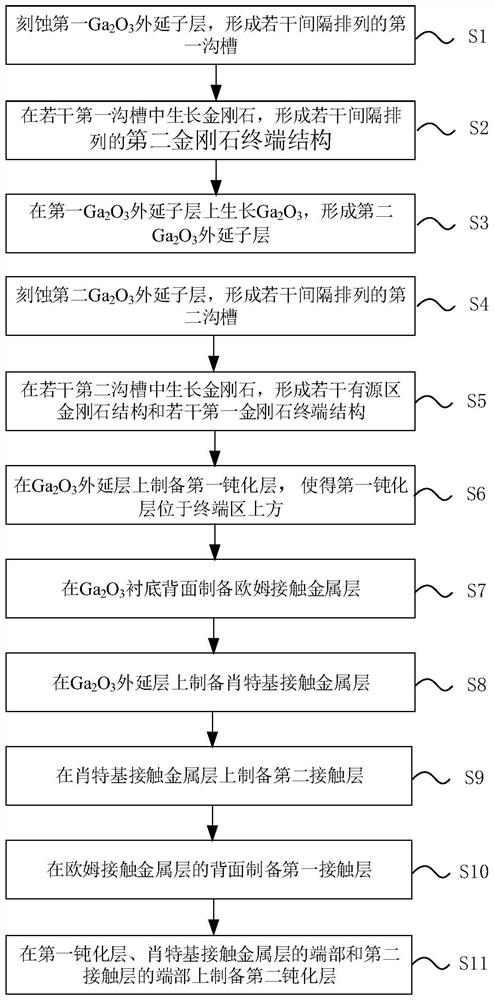

Ga2O3 Schottky diode based on diamond terminal structure and manufacturing method

ActiveCN113555446AHigh breakdown field strengthReduce leakage currentFinal product manufactureSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

Owner:ZHEJIANG XINKE SEMICON CO LTD

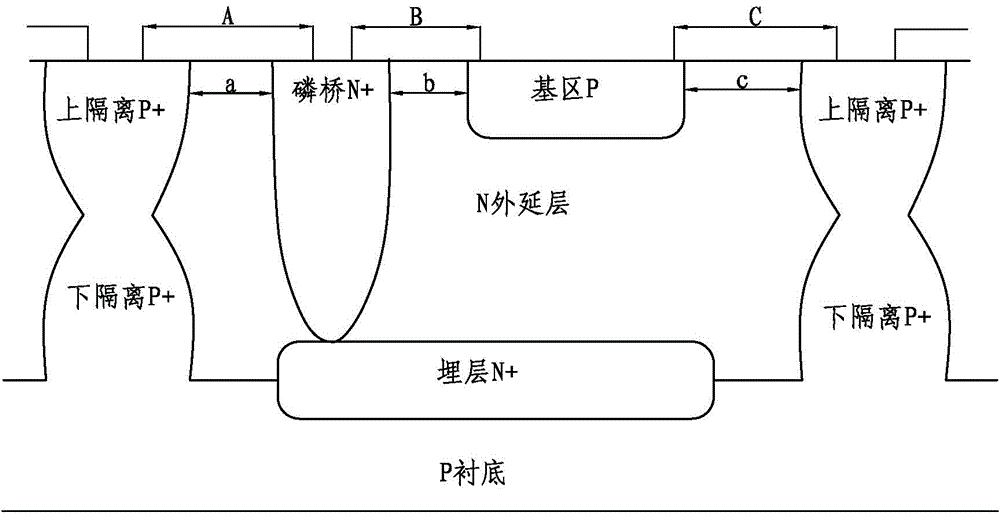

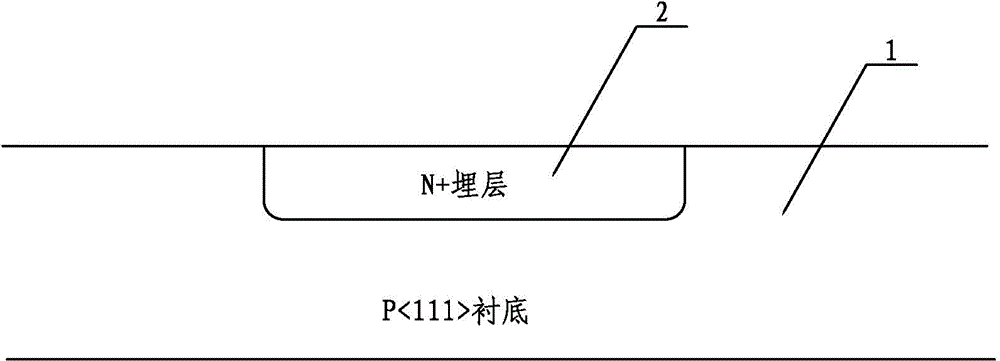

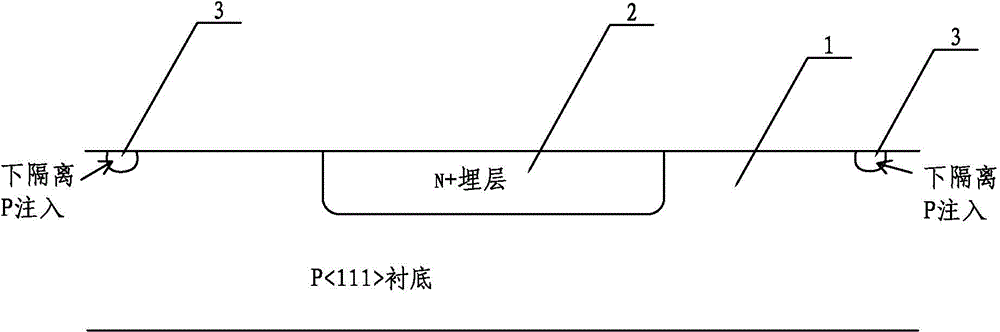

Bipolar integrated circuit chip based on groove dielectric isolation and production technology thereof

ActiveCN104064564AAvoid premature breakdownIncrease the areaTransistorSemiconductor/solid-state device manufacturingEngineeringElectrical performance

The invention discloses a bipolar integrated circuit chip based on groove dielectric isolation and a production technology thereof, and belongs to the field of integrated circuit design / manufacturing. The production technology sequentially comprises the steps of N+ buried layer forming, lower isolation area forming, epitaxial layer forming, phosphorus bridge area forming, upper isolation area forming, groove forming and the like. According to the bipolar integrated circuit chip based on groove dielectric isolation, which is manufactured by the production technology, the inner side of an upper isolation area, the outer side of the upper isolation area and the outer side of a base area are respectively provided with an annular groove, the design size is lowered to the high limit, meanwhile, the maximum withstanding voltage of BVCBO is improved, and electrical performance maximization between electrodes within minimum spacing is achieved.

Owner:HUAYUE MICROELECTRONICS

Structure for improving breakdown voltage of gallium nitride HEMT power device and preparation method thereof

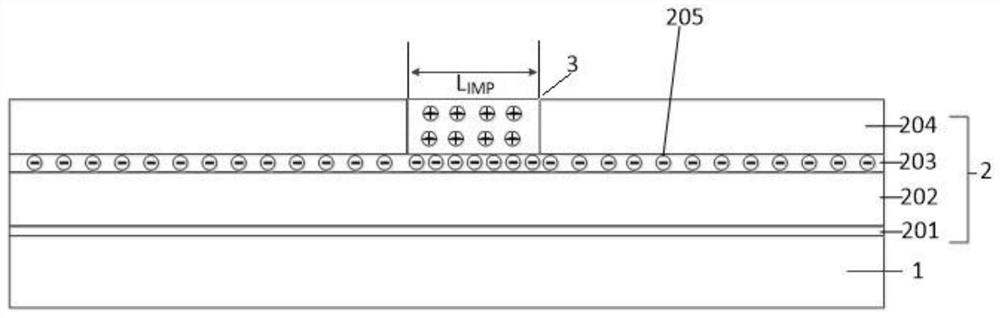

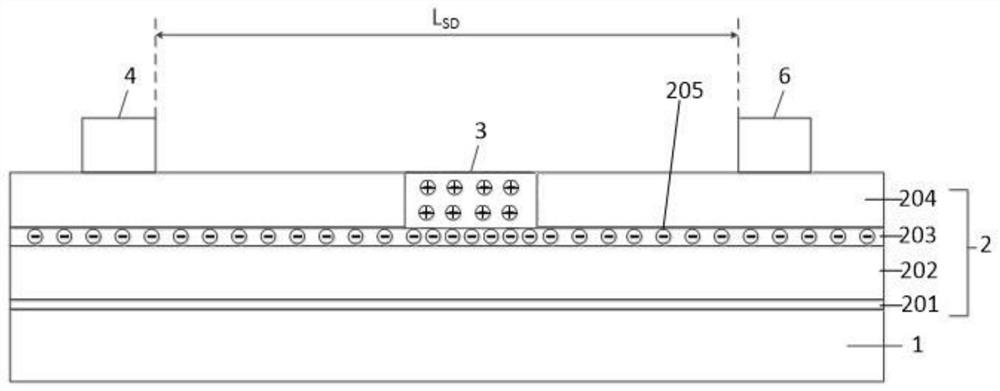

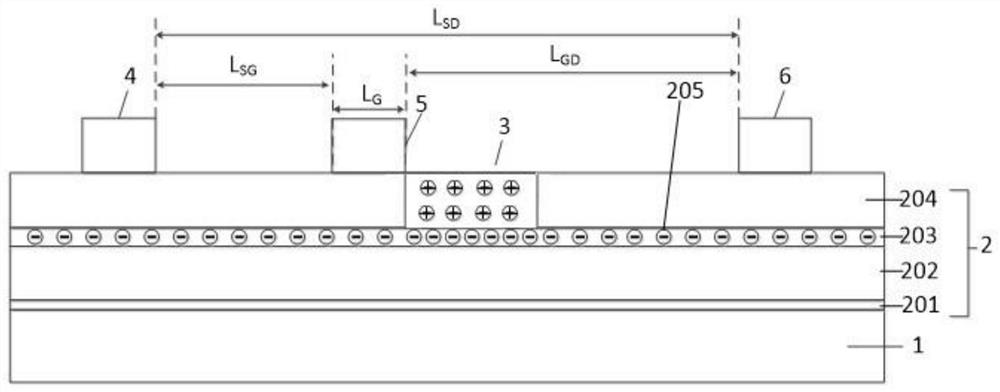

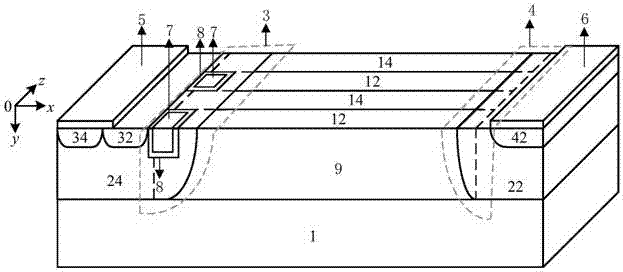

InactiveCN112885891AAvoid premature breakdownImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideMaterials science

The invention provides a structure for improving the breakdown voltage of a gallium nitride HEMT power device and a preparation method of the structure. The structure comprises a substrate, an epitaxial layer, a source electrode, a drain electrode and a grid electrode. The epitaxial layer is arranged above the substrate and comprises a nucleating layer, a first material layer, a channel layer and a barrier layer which are arranged from bottom to top; the channel layer is internally provided with two-dimensional electron gas, and the barrier layer is internally provided with an ion doped region. The ion doping region is introduced between the grid electrode and the drain electrode, the two-dimensional electron gas concentration of partial region in the channel is changed, the electric field distribution is changed on one side of the grid electrode, the peak electric field is obviously lower than that of a device without the ion doping region, the electric field uniformity between the grid electrode and the drain electrode is enhanced, and the electric field distribution is effectively improved; and advanced breakdown of the device caused by a grid edge electric field peak value is avoided, and the device can bear higher drain voltage. And finally, the breakdown voltage of the device is improved, and the frequency characteristic of the device is not reduced.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

High-voltage-withstand transverse super junction device

InactiveCN107359195AImprove pressure resistanceGuaranteed charge balanceSemiconductor devicesJunction pointPeak value

The invention provides a high-voltage-withstand transverse super junction device. First doped type bars and second doped type bars which are alternated form a super junction structure; a second doped type multi-surface exhausting region is formed at an intersection of a second doped type well region and a region where the second doped type bars and the first doped type bars appear alternately; the second doped type bars and the second doped type well region form a three-surface exhausted structure for the first doped type bars; the left side and the right side are based on the same way; a first doped type multi-surface exhausting region exists on the right; and therefore, influence of an edge region on the voltage withstand of the device is reduced, a charge balance is remained, and the aims of avoiding in-advance breakdown by eliminating a high electric field at a super junction point AB and enhancing the voltage withstand of the device are fulfilled. As the peak of edge voltage is suppressed, under a condition of remaining high voltage withstand, the on-state resistance is reduced by further increasing the doping concentration of super junction bars; and therefore, the aims of eliminating the high electric field at the super junction point AB, enhancing the voltage withstand of the device and reducing the specific on-state resistance are finally fulfilled.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Manufacturing method of groove MOSFET device based on microwave plasma oxidation

PendingCN112133634AImprove oxidation efficiencyReduce electronic defectsSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMOSFET

A manufacturing method of a groove MOSFET device based on microwave plasma oxidation comprises the step that after a groove gate is etched, silicon carbide on the surface of the groove gate is oxidized into silicon dioxide through microwave plasma to form a groove gate oxide layer. The step of forming the groove gate oxide layer comprises the steps as follows: placing a silicon carbide substrate subjected to groove gate etching in a microwave plasma generating device; introducing oxygen-containing gas to generate oxygen plasma; reacting the oxygen plasma with silicon carbide to generate silicon dioxide with a preset thickness; and stopping introducing the oxygen-containing gas, and ending the reaction; wherein the reaction temperature of the oxygen plasma and the silicon carbide is 500-900DEG C, and the reaction pressure is 400-1000 mTorr. The oxidation efficiency of silicon carbide can be remarkably improved, the interface quality is improved, and a uniform gate dielectric layer is formed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

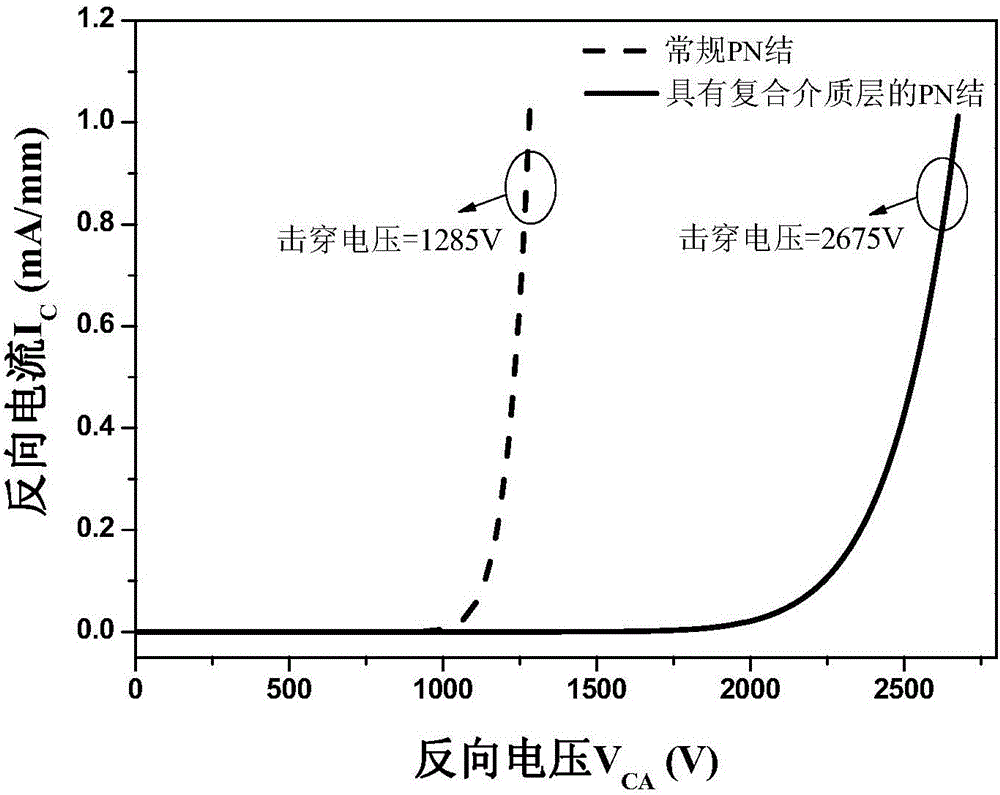

Junction barrier Schottky diode with composite dielectric layer structure

ActiveCN107393952AImprove electric field distributionUniform electric field distributionSemiconductor devicesElectrical field strengthGallium nitride

The invention provides a junction barrier Schottky diode with a composite dielectric layer structure, belonging to the field of power device technology. According to the junction barrier Schottky diode, composite dielectric layers that are formed by contacting high and low dielectric constants are separately arranged on outer walls of two sides of an N-type material layer, and a P-type gallium nitride region is arranged inside the N-type material layer to ensure that the distribution of a longitudinal electric field that is formed from the anode to the cathode is affected, the defect that the strength of the longitudinal electric field is greatly reduced existing in a traditional JBS device can be avoided, and meanwhile, the withstand voltage drop of the device caused by the junction edge electric field concentration effect can also be avoided, the early breakdown of the device can be prevented, and thus a high withstand voltage can be achieved on the basis of guaranteeing a small start voltage and a large conduction current. In addition, the junction barrier Schottky diode provided by the invention avoids the use of field ring structures and metal field plate structures, and thus the chip area can be reduced, the cost of the device can be reduced, and the reliability of the device can be improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

PIN structural ultraviolet photoelectric detector for avalanche and preparation method thereof

InactiveCN102800717BAvoid complexityReduce leakage currentFinal product manufactureSemiconductor devicesUltravioletIon implantation

The invention discloses a PIN structural ultraviolet photoelectric detector for avalanche and a preparation method of the PIN structural ultraviolet photoelectric detector. According to the PIN structural ultraviolet photoelectric detector, an extended p type GaN light doped protective ring under regional selective growing is adopted to reduce the current leakage of the detectora and suppress the edge from being punctured in advance, so as to achieve stable and high-gain ultraviolet photoelectric detecting on the avalanche. With adoption of the p type GaN light doped protective ring, the current leakage on the surface of the detector can be reduced, an electric field at the edge of the detector can be reduced, especially a high electric field area in the p-i node part is obviously improved, thus, the puncturing voltage of the detector can be increased, and high-performance ultraviolet photoelectric detector for avalanche can be obtained. By adopting the regional selective secondary growing technology, complex processes and expensive equipment for pouring ion can be saved, and the positions of the protective ring and an active area can be accurately controlled.

Owner:SUN YAT SEN UNIV

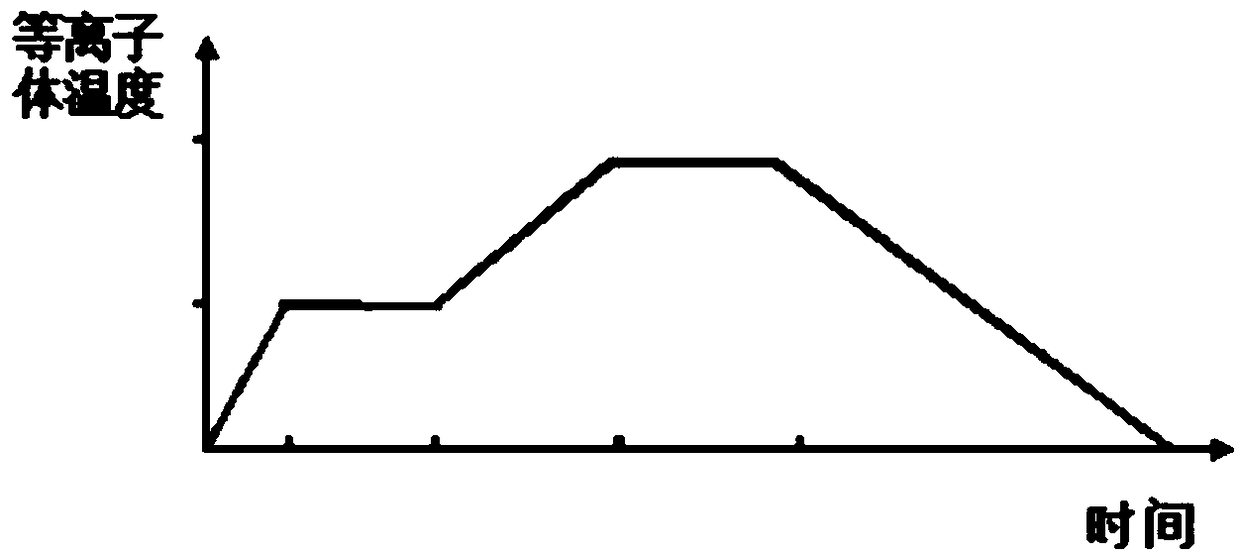

Method for manufacturing grooved MOSFET device on basis of two-step microwave plasma oxidation

ActiveCN108766887AImprove oxidation efficiencyReduce electronic defectsSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention provides a method for manufacturing a grooved MOSFET device on the basis of two-step microwave plasma oxidation. The method comprises the step that after a grooved gate is etched, silicon carbide on the surface of the grooved gate is oxidized into silicon dioxide by means of microwave plasmas to form a grooved gate oxide layer. The grooved gate oxide layer is formed through the stepsthat the silicon carbide substrate after the grooved gate is etched is placed in a microwave plasma generation device; first oxygen-containing gas is introduced, the temperature of generated oxygen plasmas rises to the first temperature at a first temperature rising speed, and low-temperature plasma oxidation is conducted at the first temperature under the first pressure; the temperature of the oxygen plasmas rises to the second temperature at a second temperature rising speed, second oxygen-containing gas is introduced, and high-temperature plasma oxidation is conducted at the second temperature under the second pressure until silicon dioxide with the predetermined thickness is generated; and the oxygen-containing gas stops being introduced, and the reaction is finished. According to themethod, the oxidation efficiency of silicon carbide can be significantly improved, the interface quality is improved, and the uniform gate dielectric layer is formed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

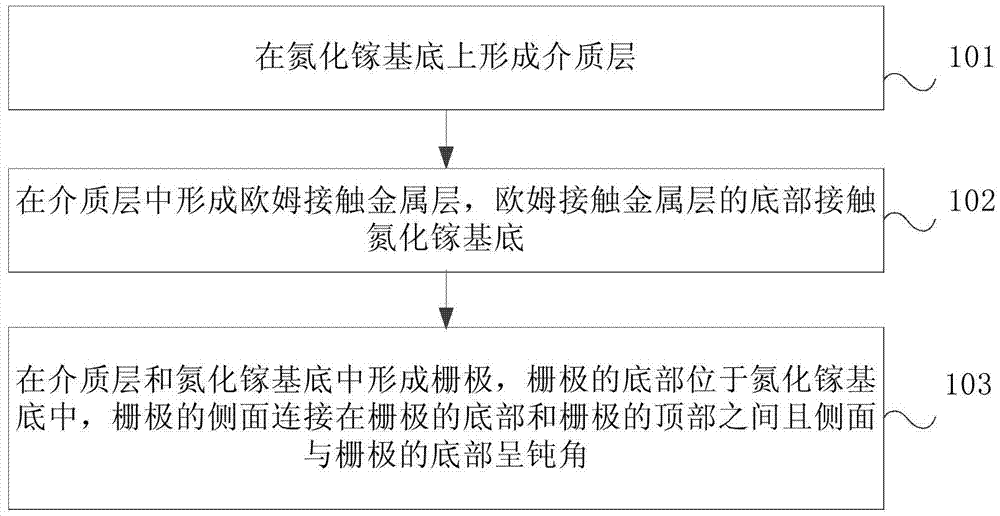

Gallium nitride field effect transistor manufacturing method and gallium nitride field effect transistor

InactiveCN107230629AAvoid premature breakdownImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactGallium nitride

The invention provides a manufacturing method of a gallium nitride field effect transistor and the gallium nitride field effect transistor. The method comprises the following steps: forming a dielectric layer on a gallium nitride substrate; forming an ohmic contact metal layer in the dielectric layer, wherein the bottom of the ohmic contact metal layer is in contact with the gallium nitride substrate; forming a grid electrode in the dielectric layer and the gallium nitride substrate, wherein the bottom of the grid electrode is located in the gallium nitride substrate, the side surface of the grid electrode is connected between the bottom of the grid electrode and the top of the grid electrode, and an obtuse angle is formed between the side surface and the bottom of the grid electrode. According to the manufacturing method of the gallium nitride field effect transistor, the voltage resistance of the gallium nitride field effect transistor can be improved.

Owner:PEKING UNIV +2