Patents

Literature

90results about How to "Reduce electric field peaks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Junction termination structure of transverse high-pressure power semiconductor device

InactiveCN102244092AImprove breakdown voltageReduce widthSemiconductor devicesPower semiconductor deviceCMOS

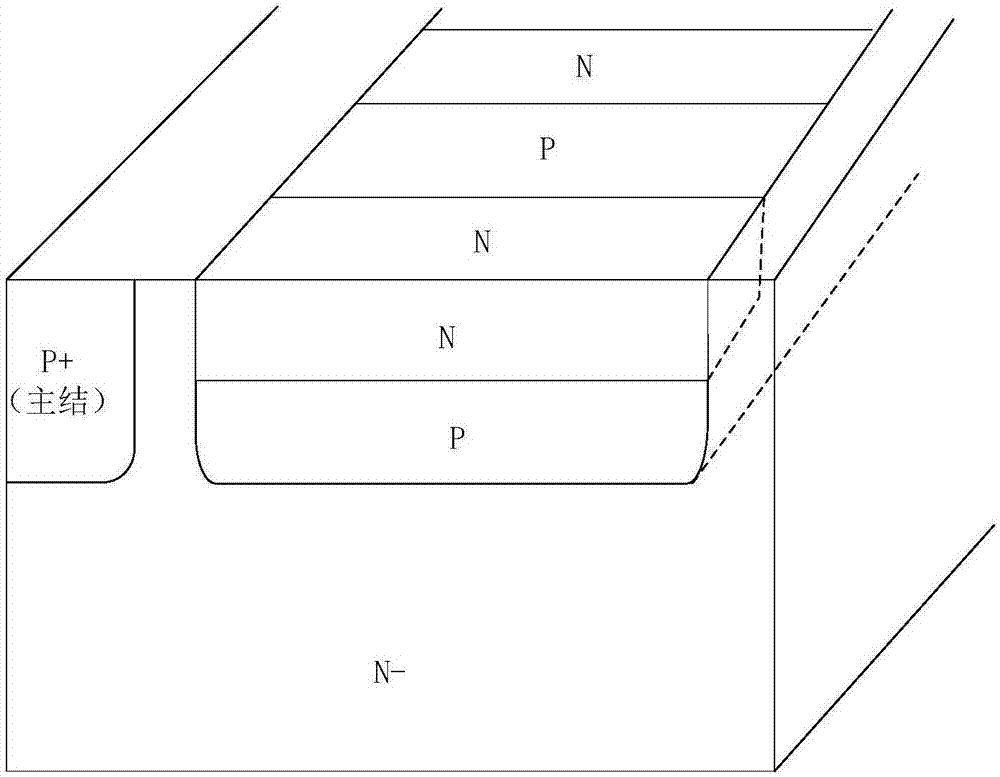

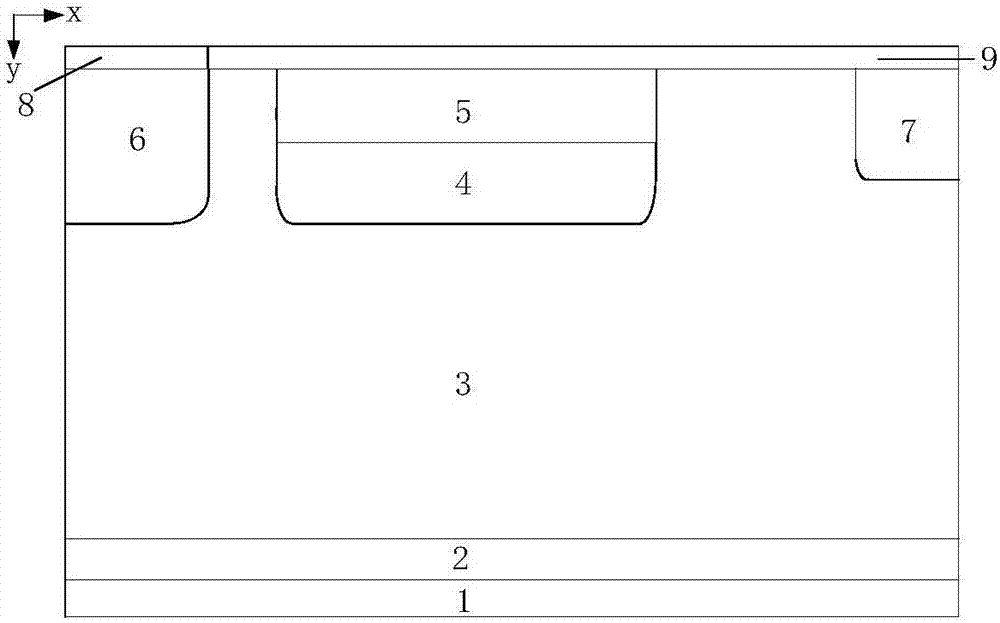

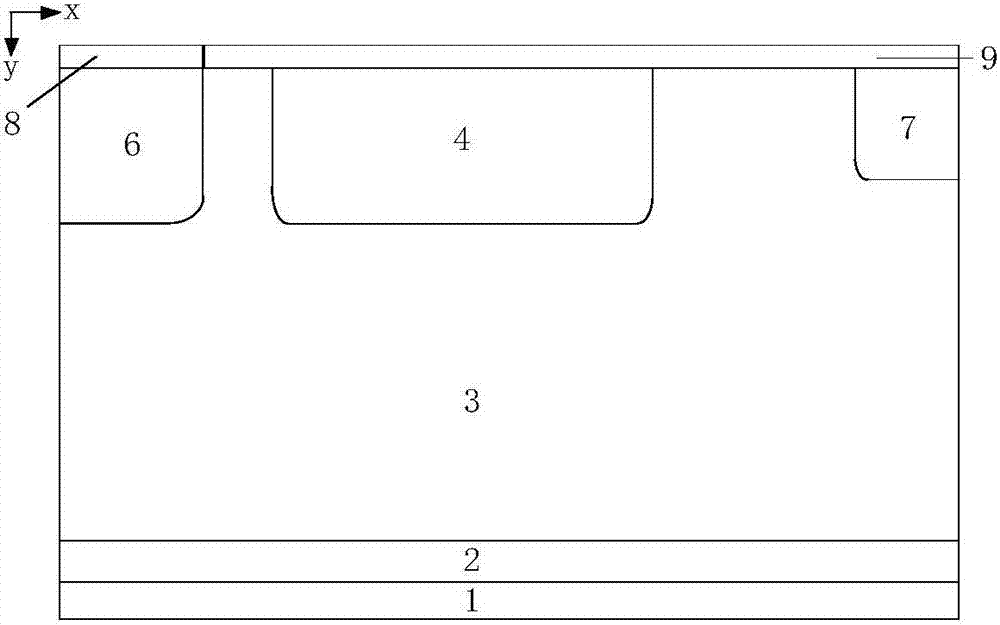

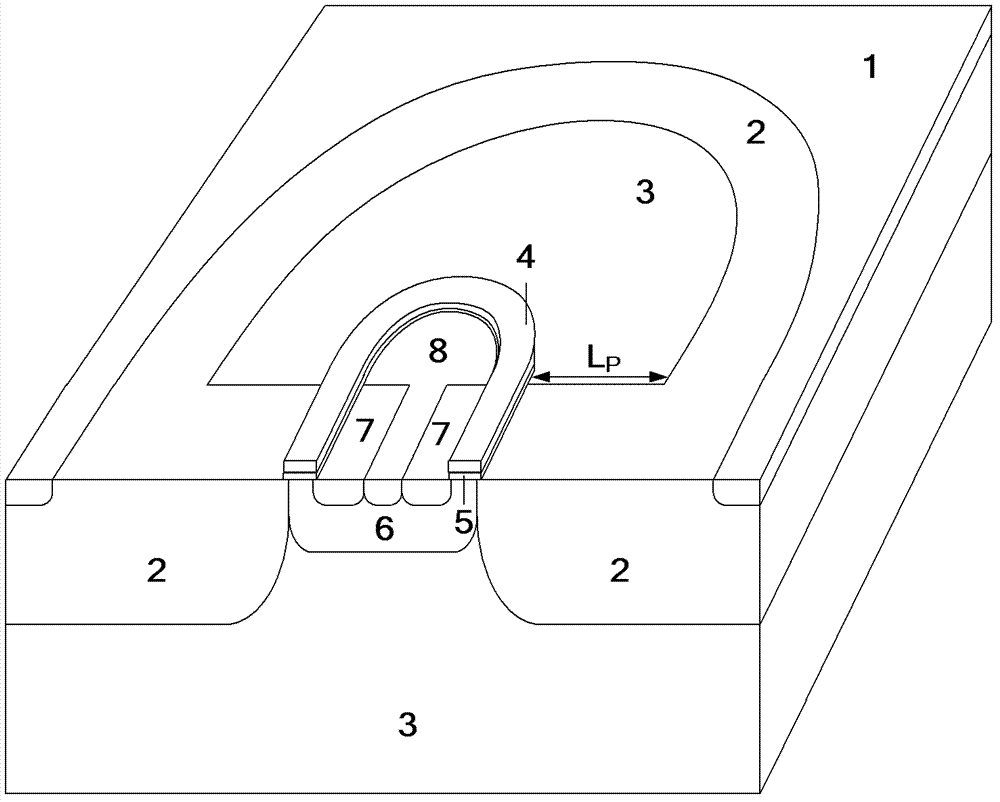

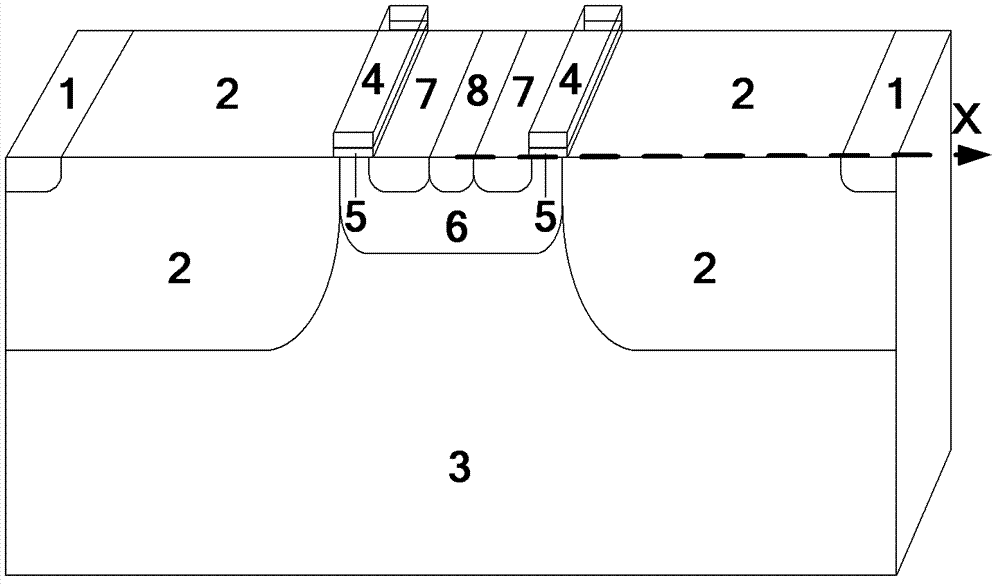

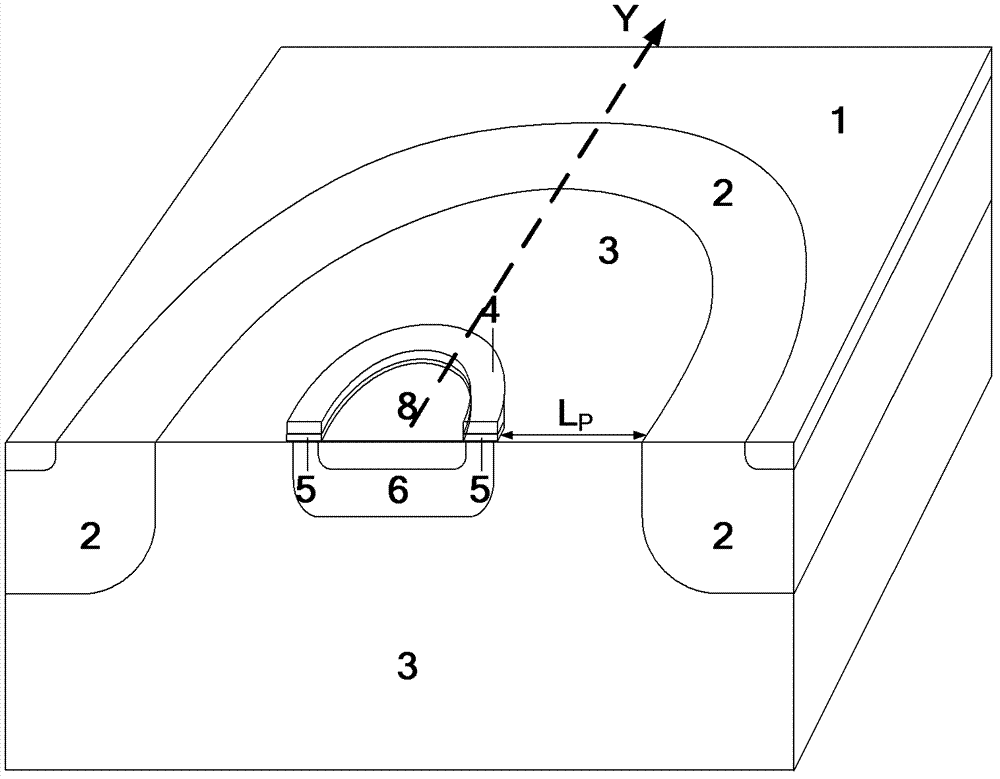

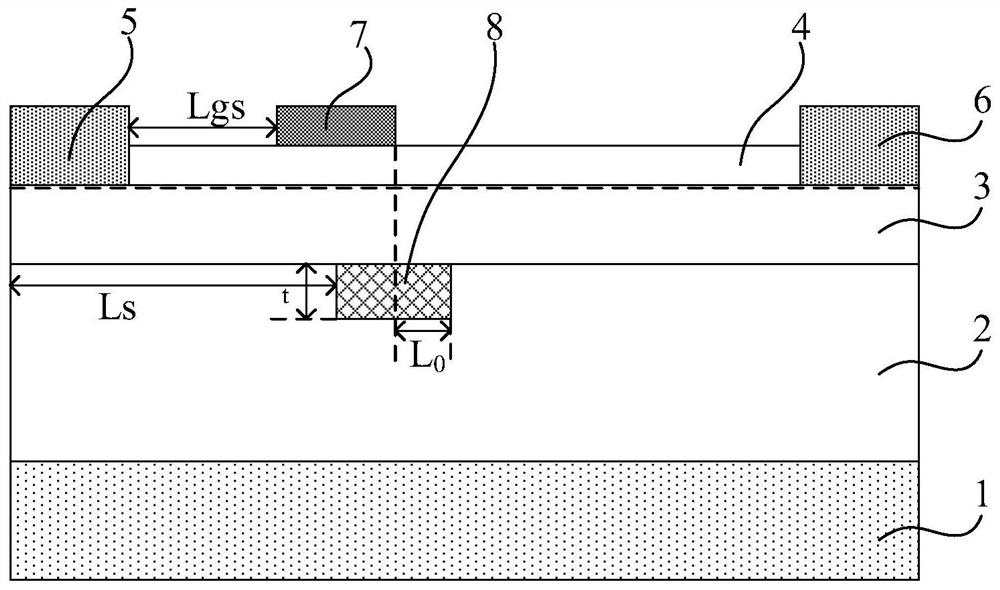

The invention relates to a junction termination structure of a transverse high-pressure power semiconductor device, belonging to the technical field of semiconductor power devices. An N-type drift region at a curvature termination of the transverse high-pressure power semiconductor device is shortened in length to ensure that the N-type drift region is spaced with a P-well region by a certain displace, wherein the spaced part is replaced by a P-type substrate, which is equivalent that additional electric charges of the P-type substrate are introduced so that the peak value of an electric field at a pn junction formed the original P-well region and the N-type drift region is reduced, meanwhile, a new peak value of the electric field is introduced at a pn junction formed by the P-type substrate and the N-type drift region, the radius of curvature of the curvature terminal is increased, the excessive concentration of a power line is avoided, and the puncture voltage of the device is increased, wherein the surface of the N-type drift region also can be combined with a surface RESURF structure or an ultra-junction structure. The junction termination structure has the advantages of being capable of decreasing the width of the curvature terminal of the device, saving the layout area of the device and being compatible with a CMOS (Complementary Metal-Oxide-semiconductor Transistor) process, and can be used for manufacturing the transverse high-pressure power device with the advantages of excellent performance, high voltage, high speed and low conduction loss.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

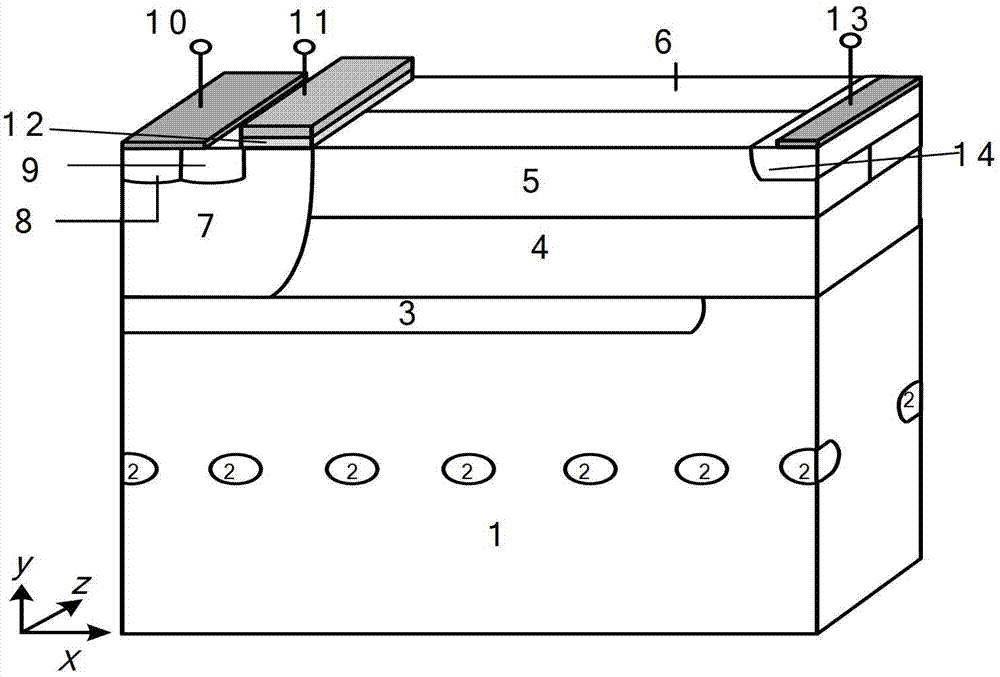

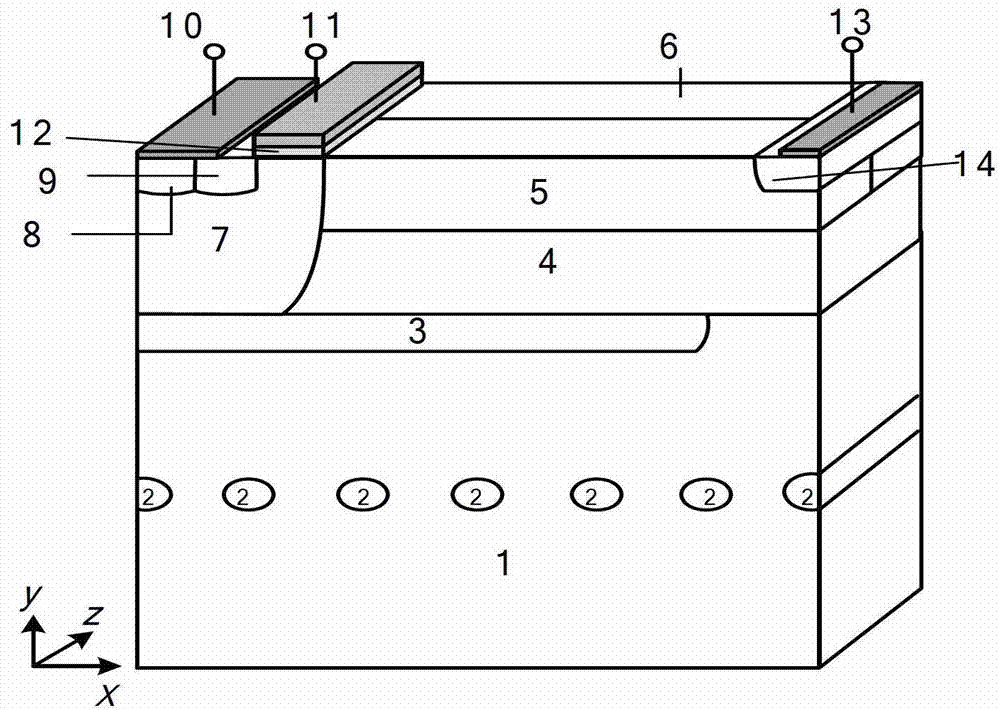

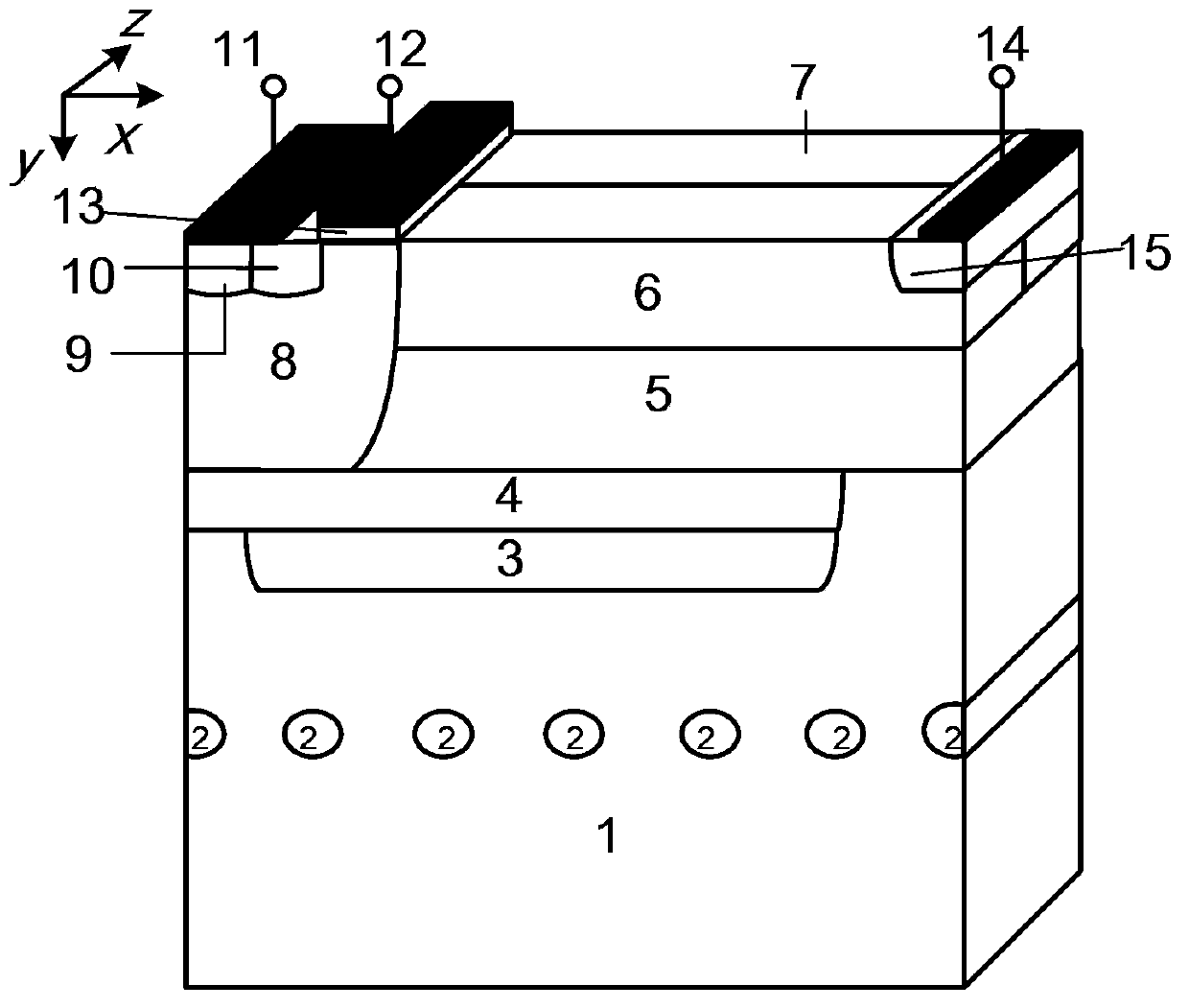

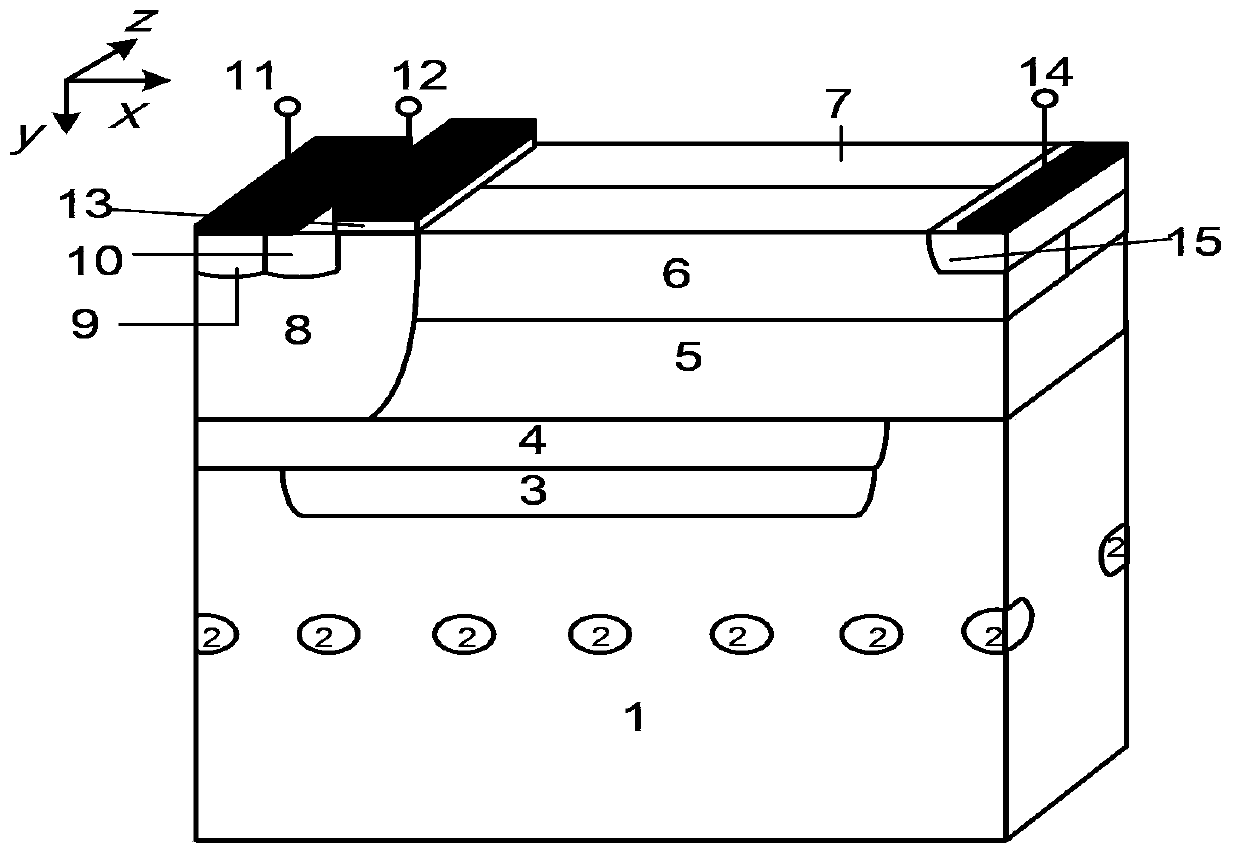

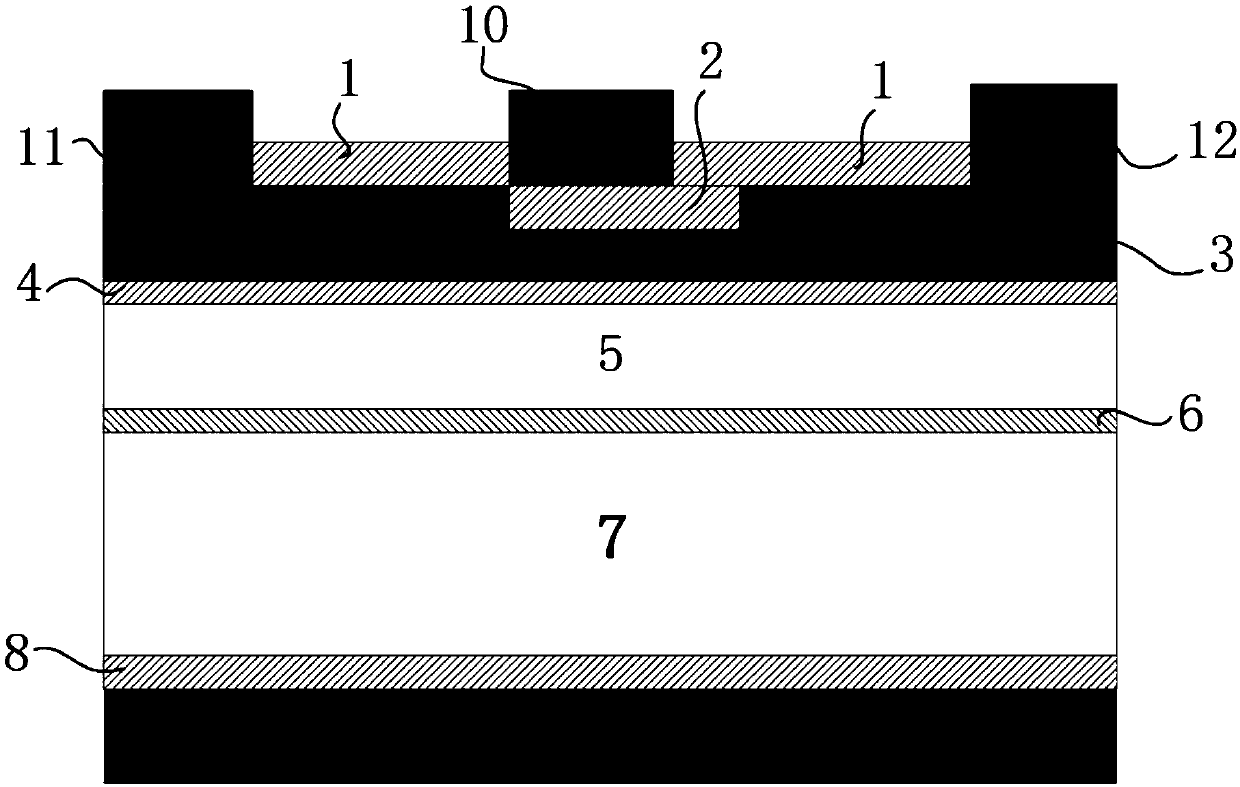

Super junction lateral double-diffused metal-oxide semiconductor (LDMOS) device

InactiveCN103165678AImprove vertical pressure resistanceImprove breakdown voltageSemiconductor devicesLDMOSPeak value

The invention relates to a super junction lateral double-diffused metal-oxide semiconductor (LDMOS) device and belongs to the field of semiconductor power devices. By means of the super junction LDMOS device, evenly distributed N+ islands are embedded in a P type substrate of a traditional super junction LDMOS device, and a P type electric field screening buried layer is added between an active area and the substrate. An N+ island (2) can improve longitudinal withstand voltage of the device by enhancing internal electric field, simultaneously generates extra electric charge to eliminate substrate auxiliary depletion effect, and further improves breakdown voltage of the device. The P type electric field screening buried layer (3) can screen high electric fields generated by an N+ island near an active end, lower electric field peak value near the active area, and form super junction with an N type cushion layer; and a super junction drift area is provided, the device is enabled to have multiple super junction structures, accordingly electric field distribution inside the device can be effectively improved, breakdown voltage of the device is improved, conduction ratio resistance of the device is simultaneously lowered by improving dosage concentration of the drift area, and finally the aim of effectively reducing device area and lower device cost can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

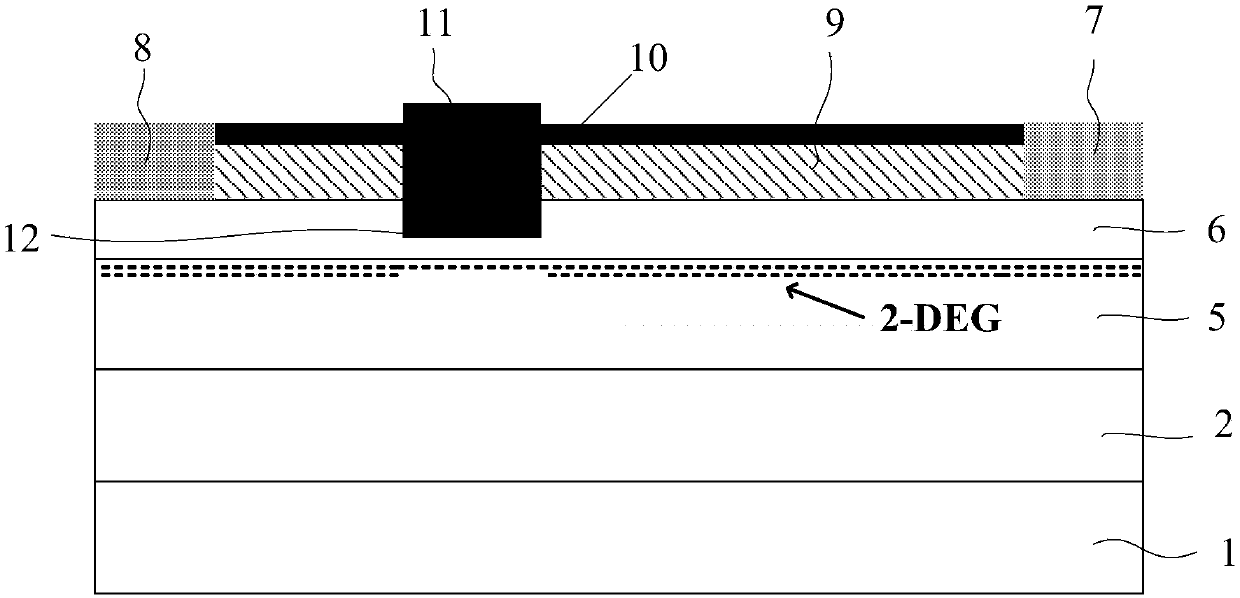

Field effect diode and manufacturing method thereof

ActiveCN104241400ALower forward conduction resistanceHigh densitySemiconductor/solid-state device manufacturingDiodeOhmic contactVoltage drop

The invention discloses a field effect diode and a manufacturing method of the field effect diode. The field effect diode sequentially comprises a substrate, a nucleating layer, a buffering layer, a back barrier layer, a channel layer, a first barrier layer and a second barrier layer. A groove, an anode and a cathode are arranged on the second barrier layer. The cathode is an ohmic contact electrode. The anode is of a composite structure and is composed of the ohmic contact electrode and a schottky electrode which is located in the groove and is connected with the ohmic contact electrode in a short circuit mode. The first barrier layer and the back barrier layer have similar constituent content, the second barrier layer is different from the first barrier layer in constituent content, and the lattice constant of the second barrier is smaller than that of the first barrier layer. The field effect diode has smaller positive conductive voltage drop, smaller reverse leakage current and larger breakdown voltage.

Owner:GPOWER SEMICON

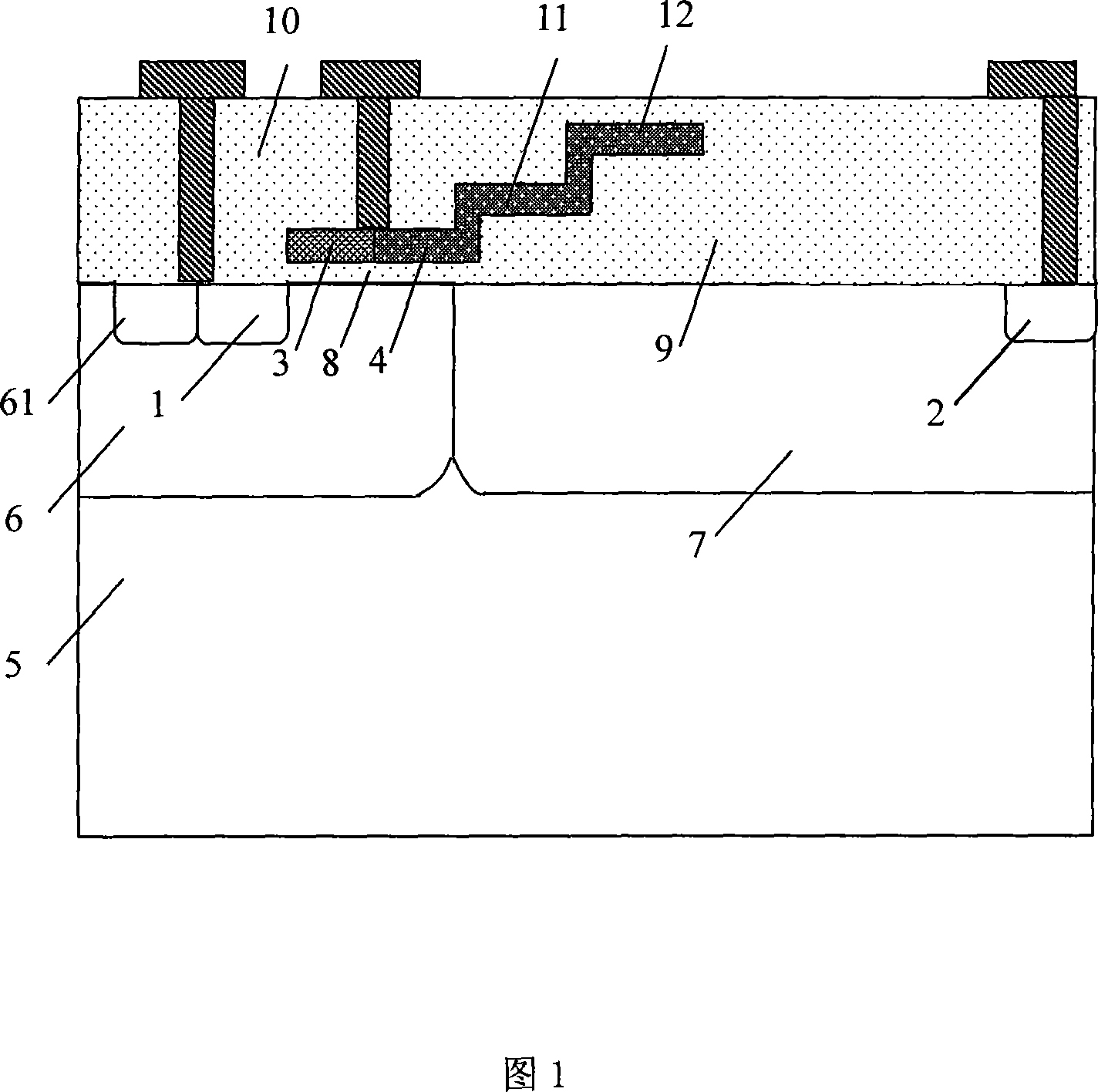

Horizontal dispersion oxide semiconductor of heterogeneous bar multi-step field electrode board

InactiveCN101079446AIncrease the number ofIncrease the average electric fieldSemiconductor devicesDouble diffusionTransconductance

The invention discloses a lateral double diffusion metal oxide semiconductor of a heterogeneous grip multi step field polar plate, which is characterized by the following: equipping with the heterogeneous double-grip structure of the source grip and the leakage grip; composing the multi step field polar plate of the first step field polar plate and the second step field polar plate, connecting with the source grip, the leakage grip, the first step field polar plate and the second step field polar plate orderly; equipping with the source and the leakage in the channel trap section and the trap drift section; equipping with grip oxide layer among the source grip, the leakage grip and the channel trap section, equipping with the trap contact hole in the channel trap section; equipping the field oxide layer among the first step field polar plate, the second step field polar plate and the trap draft section; covering the oxide layer on the multi step field polar plate; making the channel trap section and the trap draft section on the underlay. The invention improves the driving current and the transconductance, which reduces the conducting resistance and the power consumption.

Owner:ANHUI UNIVERSITY

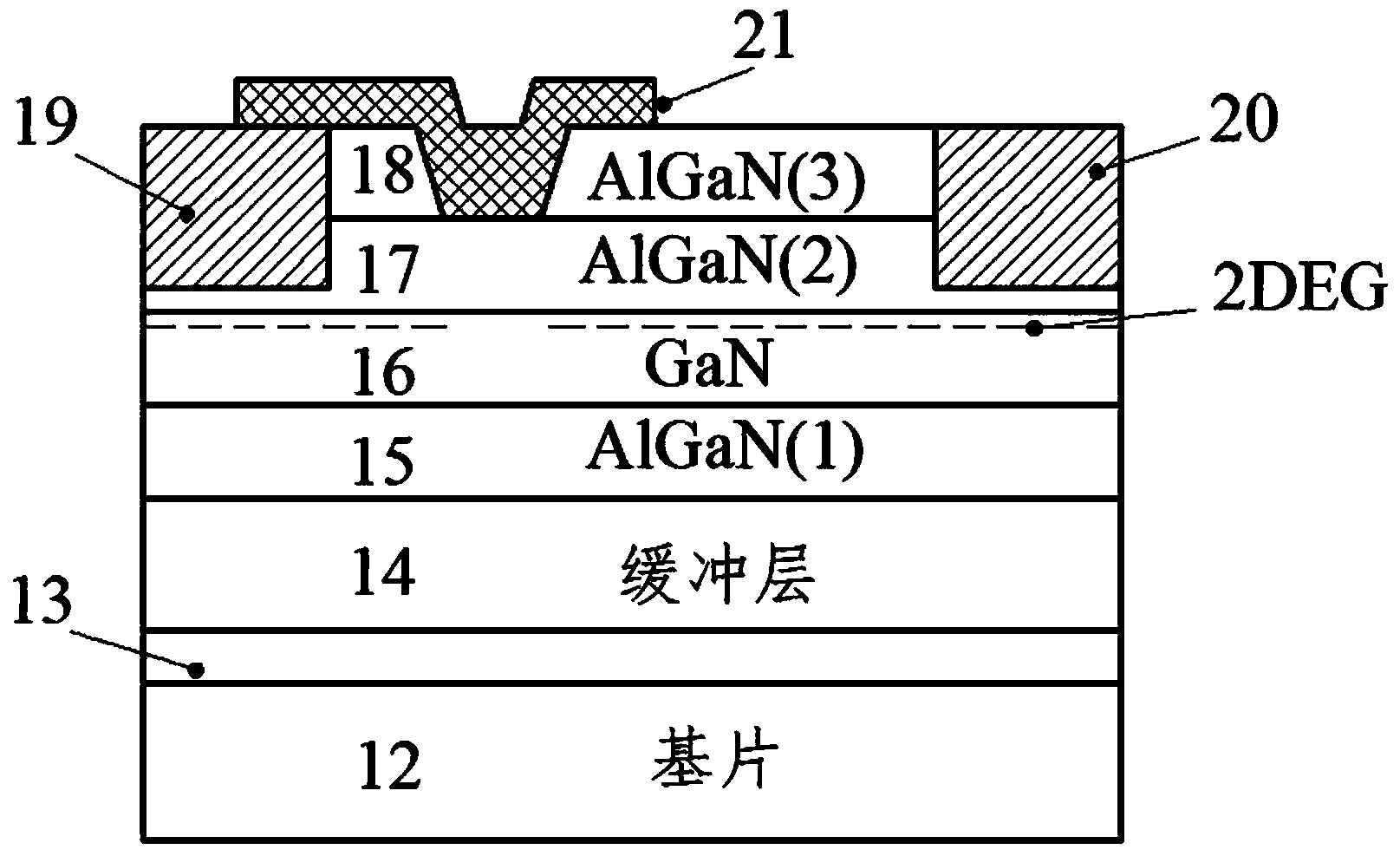

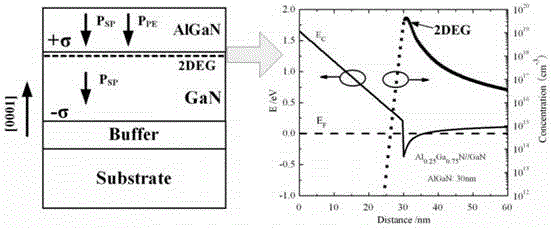

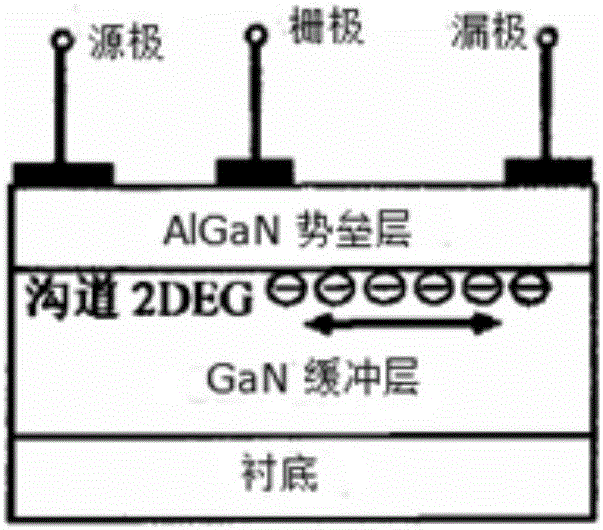

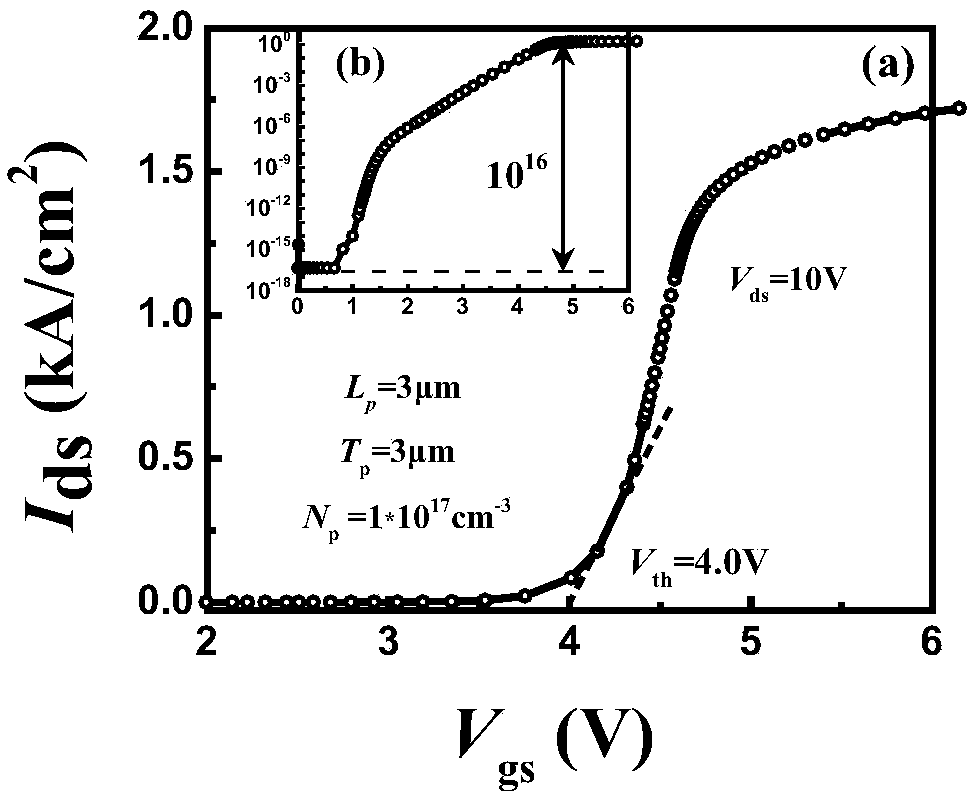

AlGaN/GaN heterojunction field effect transistor and preparation method thereof

InactiveCN105428412AAchieve conductionStrong and stable current transmission capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsDielectric layer

The invention relates to an AlGaN / GaN heterojunction field effect transistor and a preparation method thereof. The field effect transistor comprises a grid, a source, a drain, a substrate, an epitaxial structure and an insulated dielectric layer, wherein the drain, the substrate and the epitaxial structure are orderly arranged in a stacking form; the epitaxial structure comprises a n type GaN layer, a vertical super junction layer, a channel layer and a barrier layer, which are orderly stacked; the vertical super junction layer comprises alternatively arranged light-doped p type GaN layer and heavy-doped n type GaN layer, the heavy-doped n type GaN layer is thinner than the light-doped p type GaN layer, and the channel layer and the barrier layer are stacked on the light-doped p type GaN layer. The field effect transistor is simple in structure; performance deterioration of devices caused by complex device processing is avoided; stability is guaranteed; and relatively high forward current transmission ability and backward high voltage endurance of devices are realized simultaneously.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

High-voltage power device terminal structure

InactiveCN106024863AAvoid premature breakdownReduce electric field peaksSemiconductor devicesPeak valueComputer terminal

The invention belongs to semiconductor technology, and specifically relates to a high-voltage power device terminal structure. The high-voltage power device terminal structure comprises a groove in a silicon chip body and P-type protective rings, combination of the internal groove and the protective rings allows the peak value of an electric field to be transferred from the surface of the silicon chip into the body, and the breakdown points of a terminal area are transferred from the surface of the silicon chip to the two sides of a dielectric layer in the groove. Since the critical breakdown electric field (about 1e7V / cm) of the dielectric layer is far higher than a critical breakdown electric field (about 1e5V / cm) of silicone, P-type floating islands in staggered arrangement with the P-type protective rings reduce the peak values of the electric fields on the two sides of the P-type protective rings without reducing the reverse blockout voltage of a terminal area, thereby preventing premature breakdown of PN junctions in the silicon chip body.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

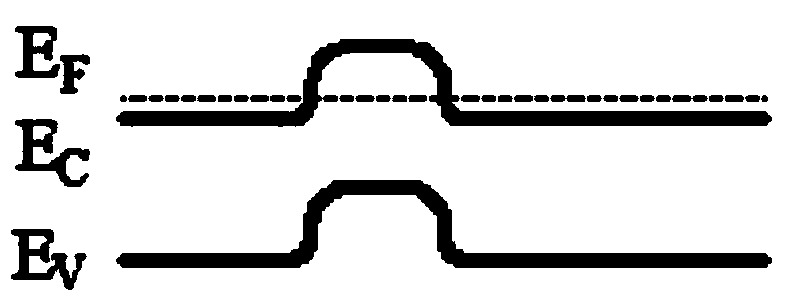

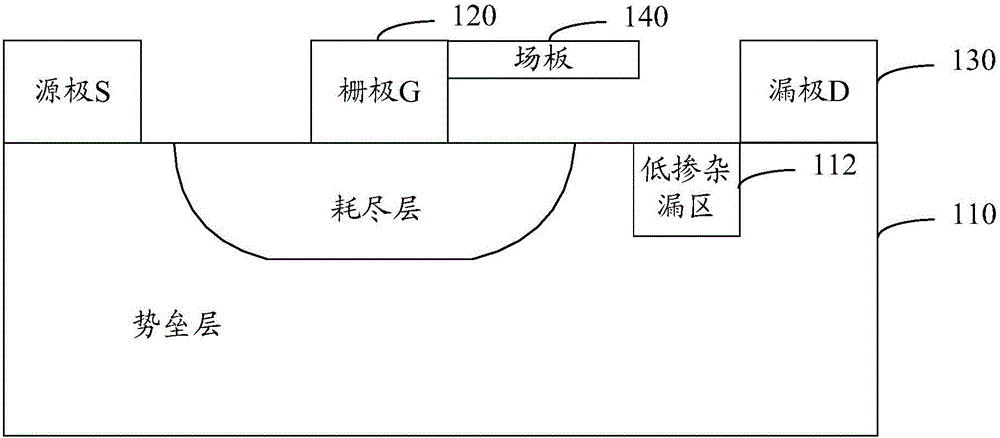

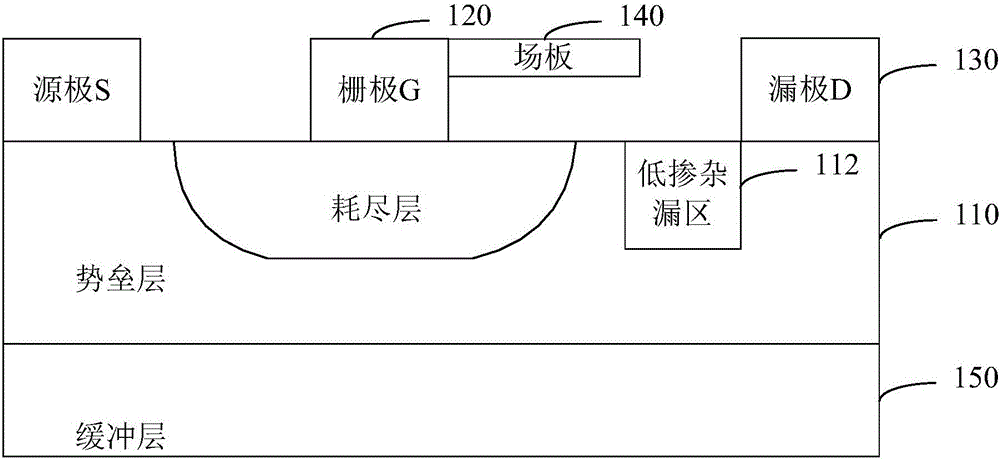

Transistor

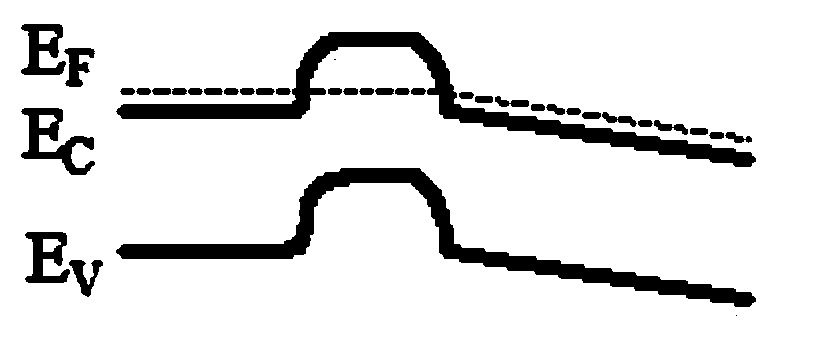

InactiveCN105826370AImprove breakdown voltageImprove stabilityTransistorSolid-state devicesElectronegativityJoint action

The invention relates to a transistor. A lowly-doped drain region is arranged in a barrier layer of the transistor. Due to the difference in electronegativity between the lowly-doped drain region and the region in the barrier layer except the lowly-doped drain region, the lowly-doped drain region can help adjust the two-dimensional electron gas in the barrier layer, change the electric field intensity of a depletion layer under a gate in the barrier layer, make the electric field re-distributed, reduce the peak of the electric field, reduce the trap effect, and improve the breakdown voltage. Meanwhile, a field plate is introduced, the bending degree of the boundary of the depletion layer at the edge of the gate is reduced, electric field distribution is modulated, the peak of the electric field is reduced, the trap effect is reduced, and the breakdown voltage is further improved. Under the joint action of the lowly-doped drain region and the field plate, the breakdown voltage of the transistor is improved greatly, and the working stability of the transistor is increased.

Owner:CHINA COMM TECH CO LTD +1

Laterally high-voltage MOSFET and manufacturing method thereof

ActiveCN103413830ALower specific on-resistanceLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueHigh voltage mosfet

The invention relates to semiconductor technologies, in particular to a laterally high-voltage MOSFET and a manufacturing method thereof. The laterally high-voltage MOSFET is characterized in that a first-kind conduction type semiconductor field dropping layer is formed in a second conduction type semiconductor drift region through photoetching and ion implantation technologies, and a second conduction type semiconductor heavy doping layer is formed on the surface of the second conduction type semiconductor drift region through the photoetching and ion implantation technologies. The laterally high-voltage MOSFET has the advantages that under the circumstance that high breakdown voltage is guaranteed, specific on-resistance of the MOSFET can be greatly reduced, meanwhile the electric field peak value of the source end of the laterally high-voltage MOSFET is reduced, high-field effects are avoided, breakdown voltage of the MOSFET is improved, the MOSFET has lower on-resistance and a smaller chip area under the condition of the same breakover capacity, and a surface electric field of the MOSFET is well optimized; meanwhile, the manufacturing method is simple, low in technological difficulty and especially suitable for the laterally high-voltage MOSFET.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

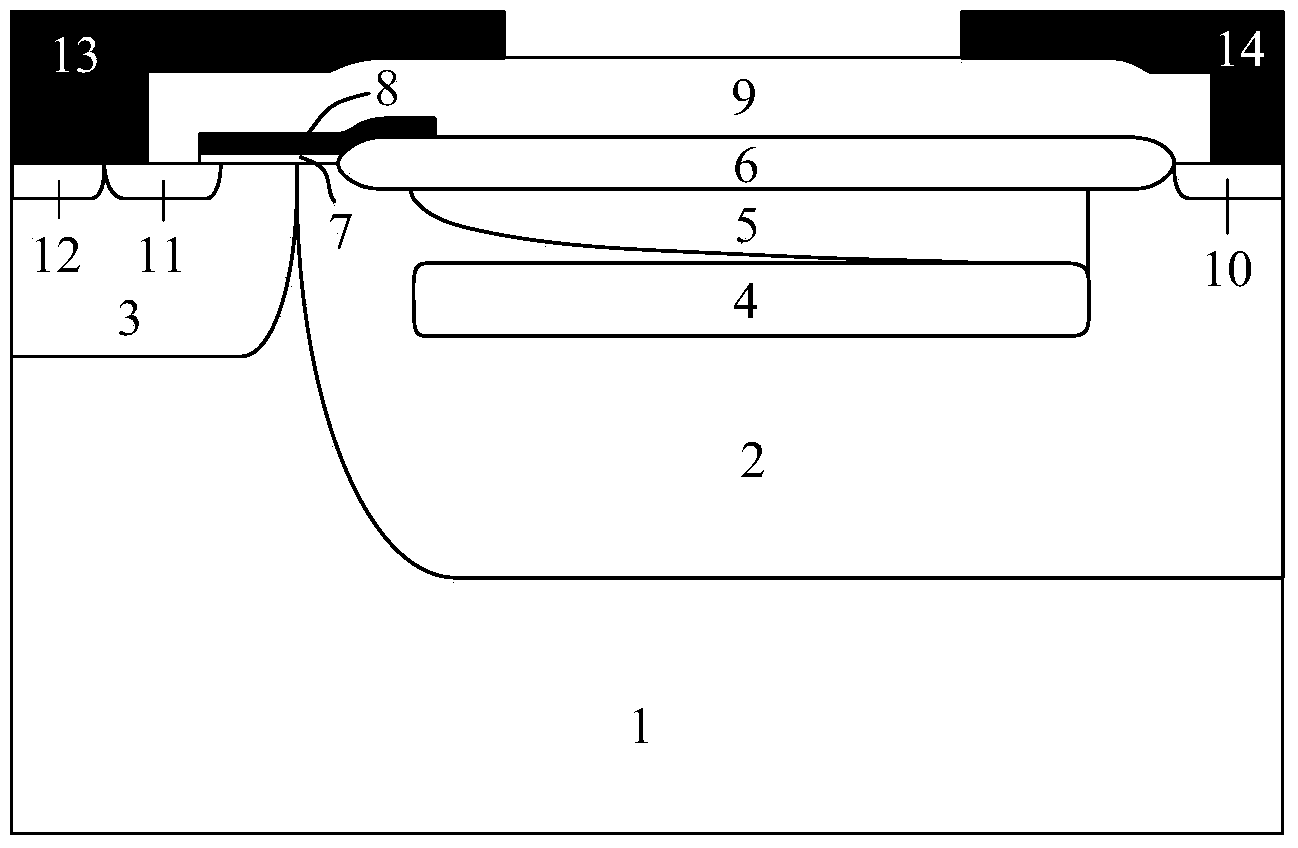

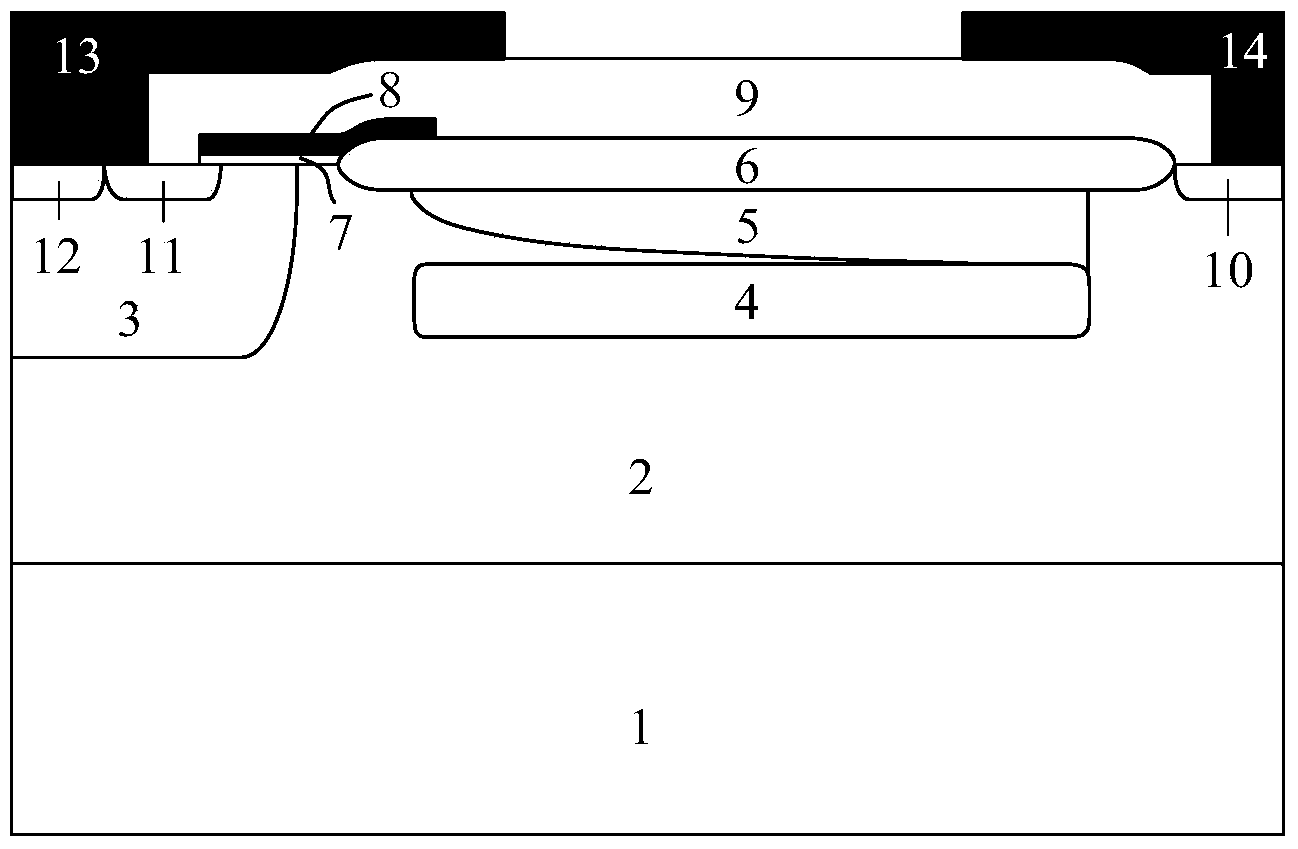

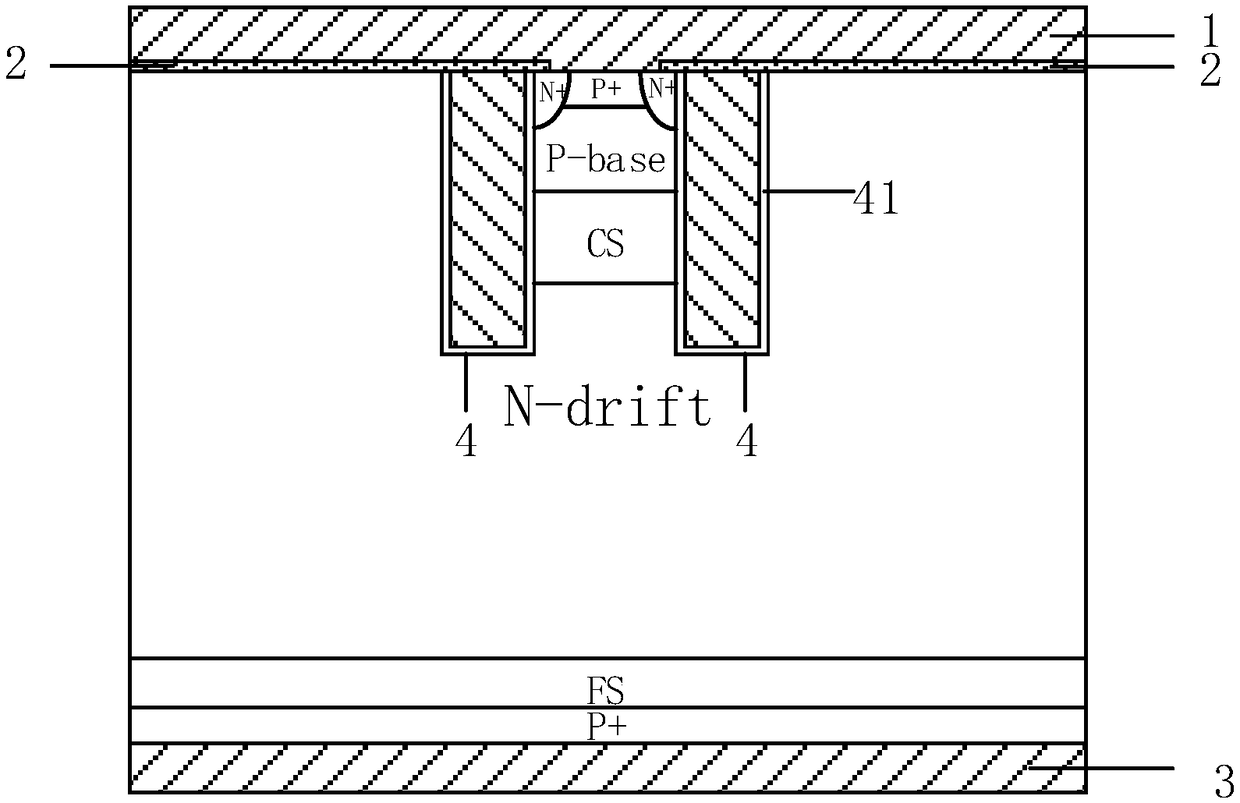

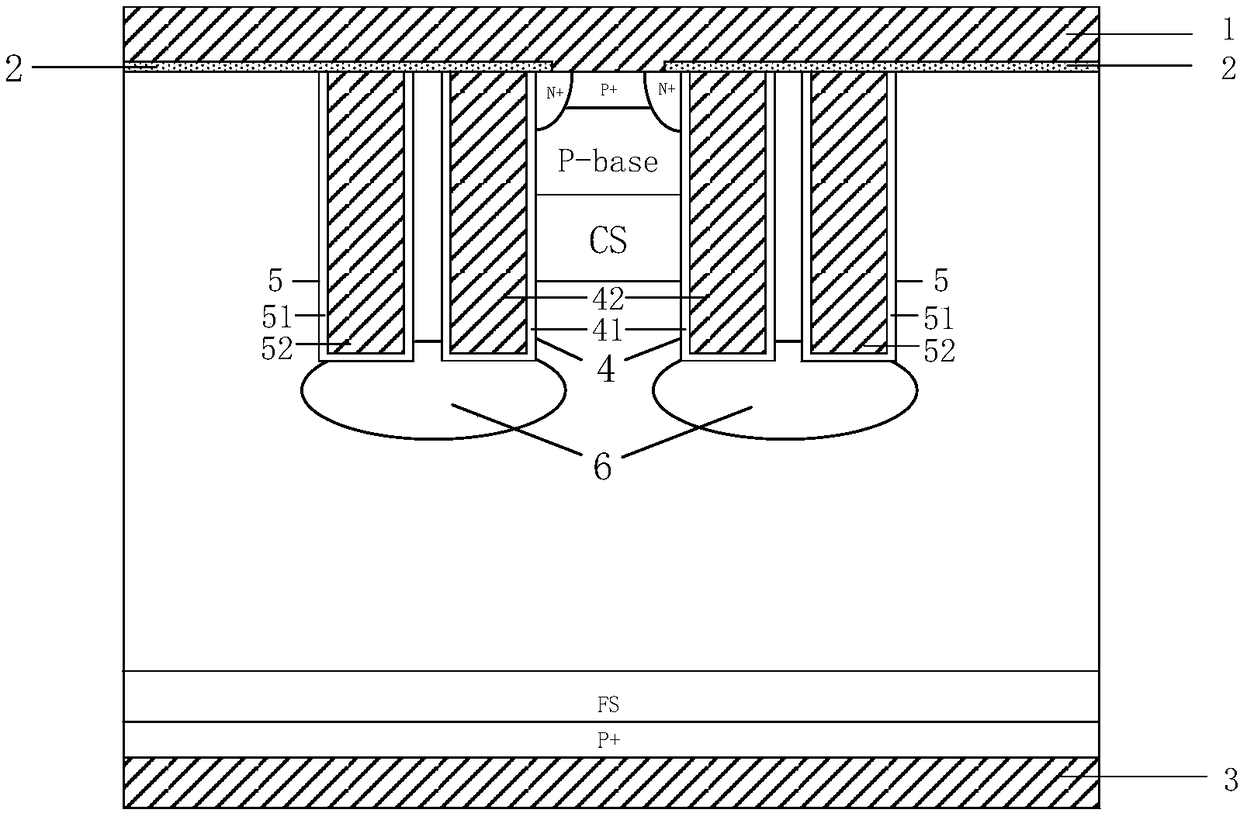

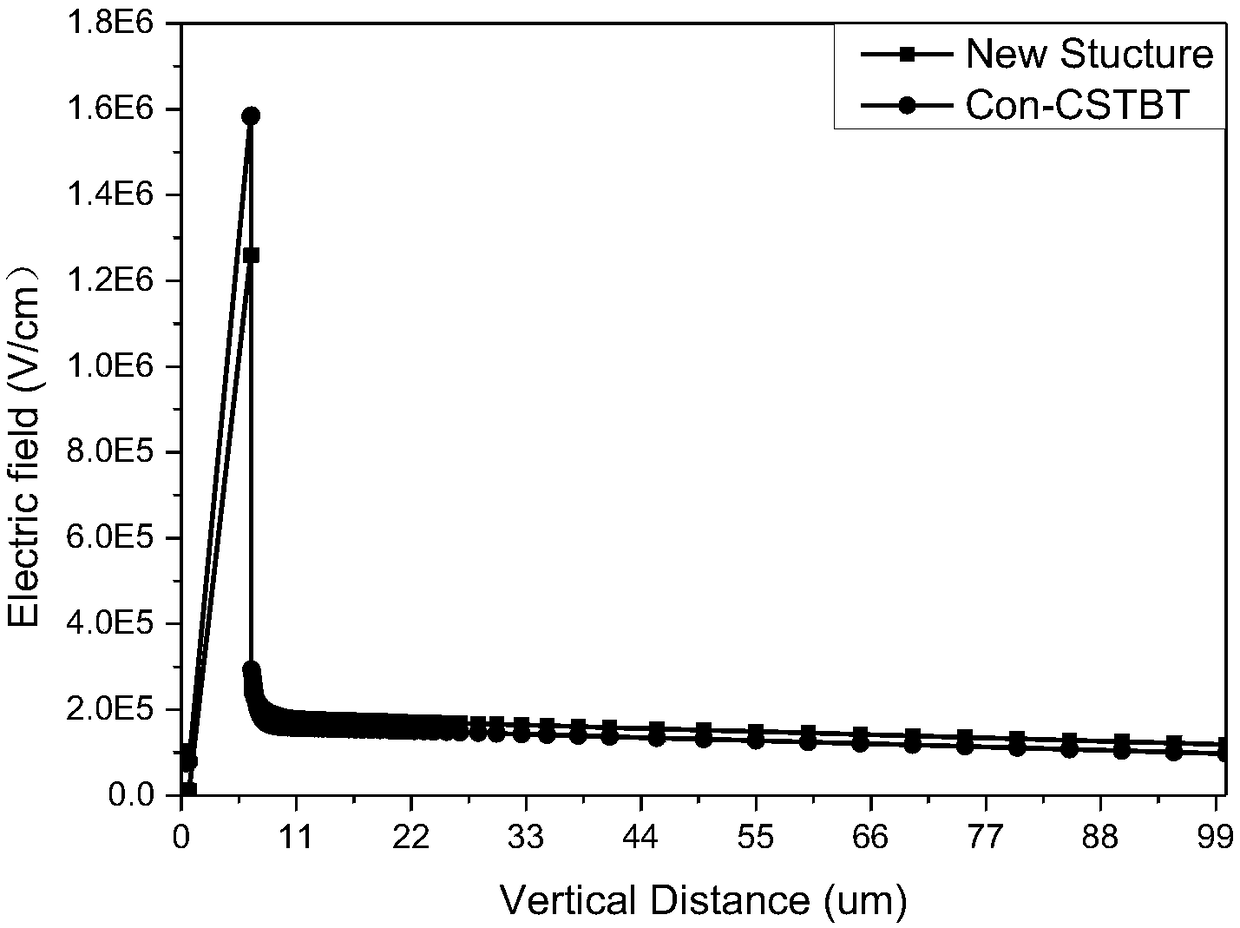

Dual-gate carrier stored IGBT device with P-type buried layer

InactiveCN108183130AReduce electric field peaksImprove breakdown voltageSemiconductor devicesHigh potentialElectric field

The invention provides a dual-gate carrier stored IGBT device with a P-type buried layer. A control gate and a shield gate are added to a conventional CSTBT trench gate and a P-type buried layer is added to the bottoms of the two gates. When the device operates, the control gate is configured to switch on the device to a high potential, the shield gate is configured to reduce device capacitance and control the device not to be connected to a potential. The P-type buried layer is configured to reduce the electric field peaks of the left and right control gates and the left and right shield gates. By reasonably adjusting the concentration and junction depth of a P-bury region and the distance between the shield gates, the electric field peak at the bottom of the trench can be reduced, the breakdown voltage of the device can be increased, and the gate-collector capacitance and the gate-emitter capacitance of the device can be reduced, thereby achieving an effect of increasing the switching speed.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

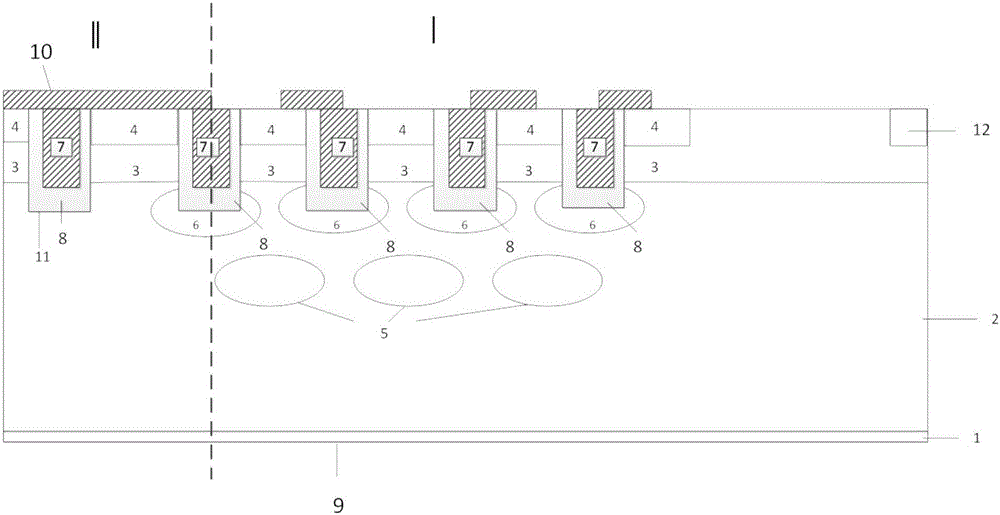

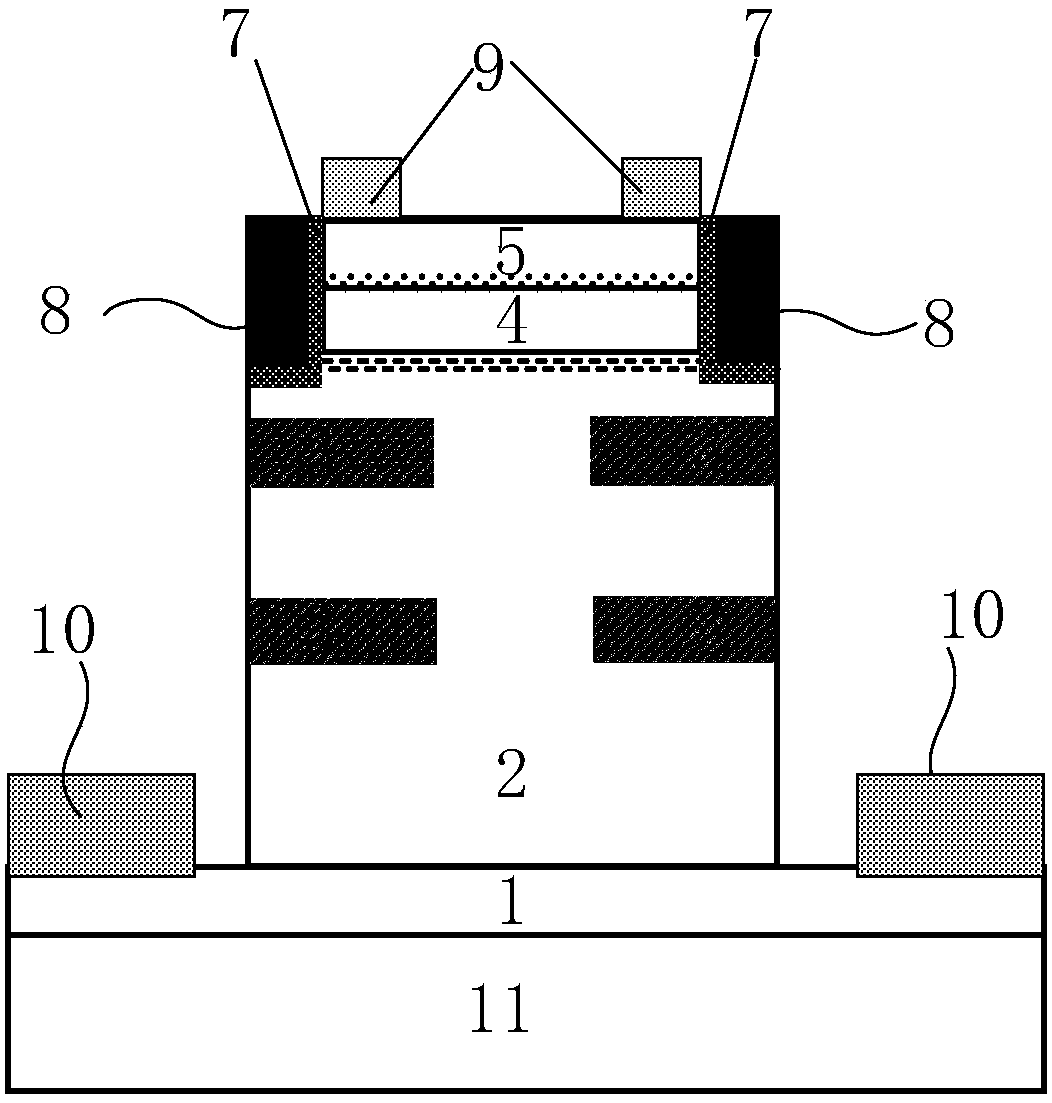

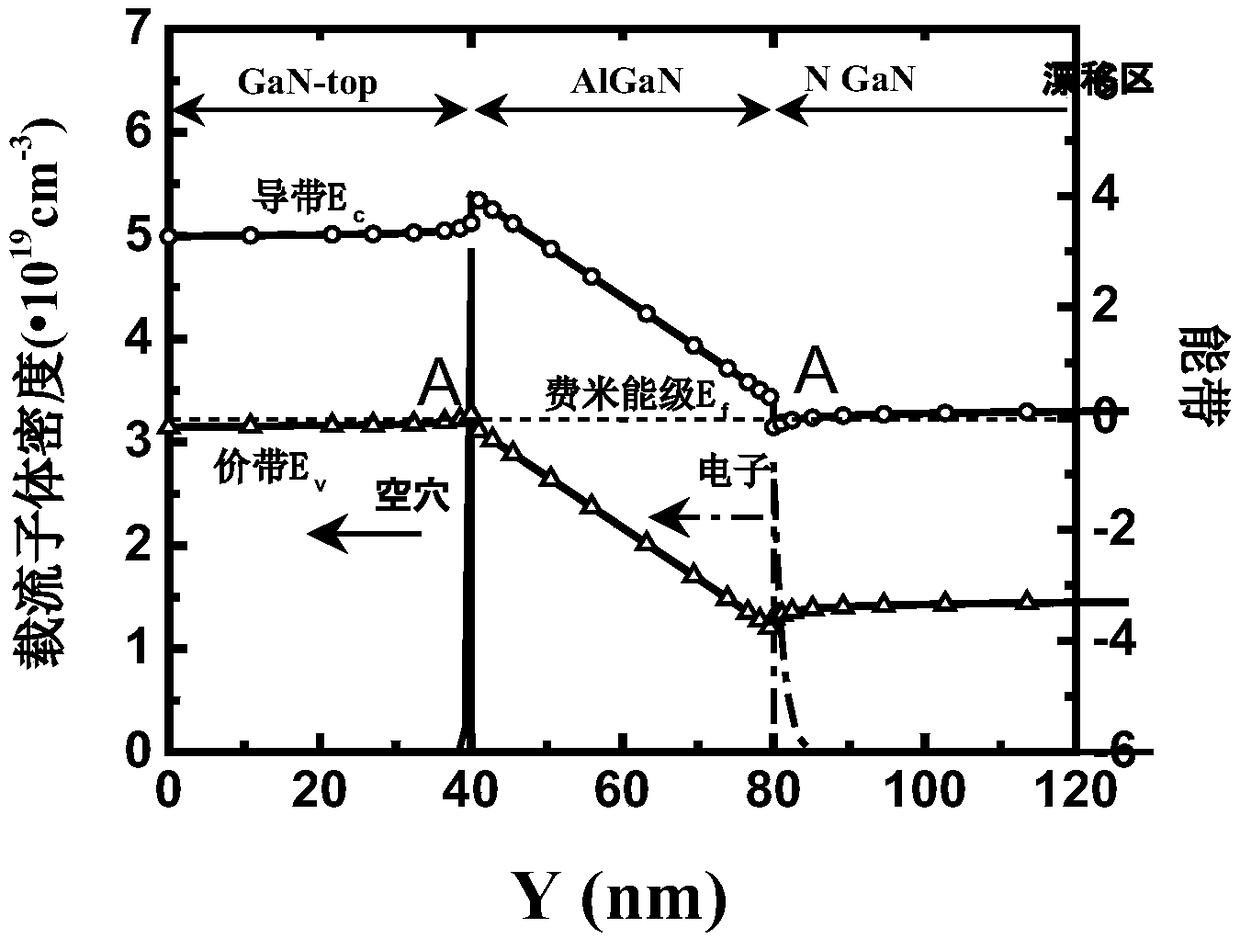

GaN heterojunction conductivity modulation field effect transistor

InactiveCN108649070AIncrease concentrationLower on-resistanceSemiconductor devicesHeterojunctionPower flow

The invention belongs to the technical field of power semiconductors and relates to a GaN heterojunction conductivity modulation field effect transistor. When the GaN heterojunction conductivity modulation field effect transistor is positively switched on, after positive voltage is applied to a drain, a large number of holes are injected into a lightly doped N-type GaN drift region from a P-type heavily doped GaN layer, a large injection phenomenon occurs in the lightly doped N-type GaN drift region, at that same time, a large number of electrons are injected into the drift region from a source electrode for maintaining charge balance, so that the carrier concentration in the orginally lightly doped drift region is increased, the conductivity modulation occurs in the lightly doped N-type GaN drift region, the drift region resistance of the lightly doped N-type GaN drift region is greatly reduced, and the novel structure can further obtain an excellent forward characteristic of low on-resistance and large on-current. During reverse voltage withstanding, a reverse-biased PN junction formed by the floating P-GaN and the N-type drift region is used as gate protection ring to reduce thepeak value of a gate electric field, and a depletion region of the reverse-biased PN junction expands continuously to uniformly distribute the device in the electric field when the reverse-biased PNjunction withstands reverse voltage, so that the reverse leakage current is reduced and the breakdown voltage of the device is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

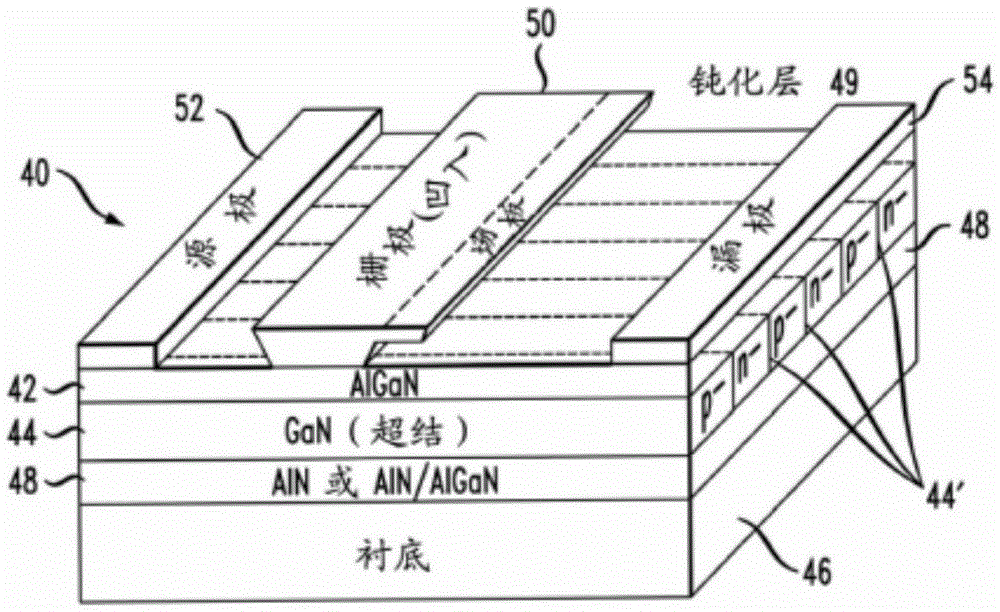

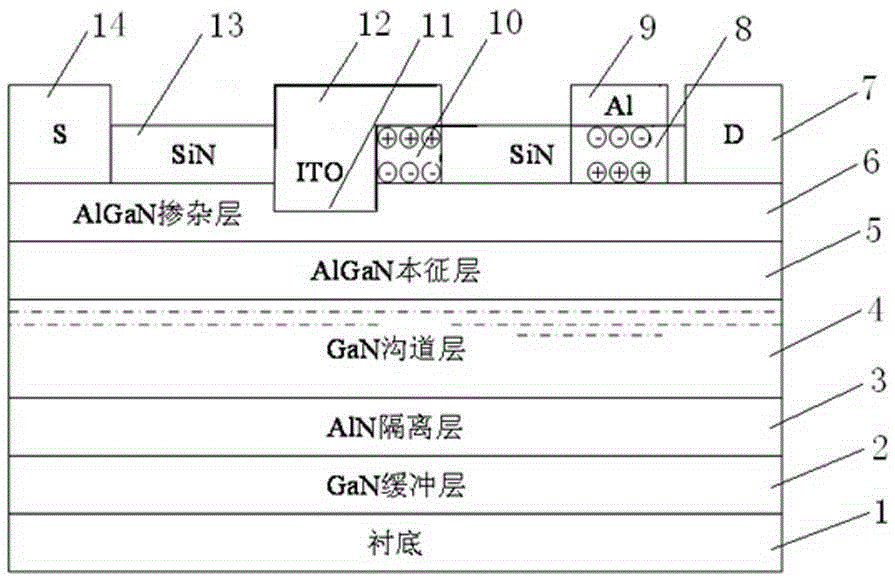

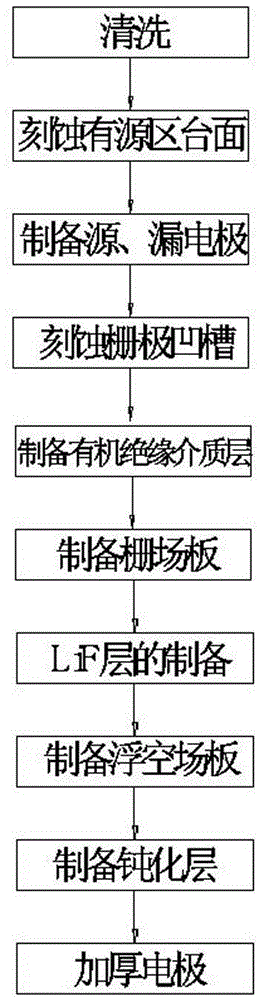

Trench-gate AlGaN/GaN HEMT device structure and manufacturing method

InactiveCN105355659AImprove breakdown voltageReduce concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesTrench gateDielectric layer

The invention discloses a composite gate floating field plate trench-gate AlGaN / GaN HEMT device structure and a manufacturing method thereof. The composite gate floating field plate trench-gate AlGaN / GaN HEMT device structure comprises a substrate, a GaN buffer layer, an AlN isolating layer, a GaN channel layer, an intrinsic AlGaN layer and an AlGaN doped layer which are sequentially compounded from bottom to top, wherein both ends on the AlGaN doped layer are respectively provided with a source and a drain, a LiF layer is arranged on the AlGaN doped layer at a position close to the drain, and a floating field plate is arranged on the LiF layer; an organic insulating dielectric layer is arranged between the LiF layer and the source, and a gate field plate is arranged on and beside the organic insulating dielectric layer; and a passivation layer is arranged in a bare area on the AlGaN doped layer. According to the trench-gate AlGaN / GaN HEMT device structure and the manufacturing method thereof, the breakdown voltage of a device is increased by utilizing the PTFE layer and the ITO gate field plate, the on resistance between the gate and the source of the device is decreased by utilizing the LiF layer and the Al floating field plate, and the breakdown voltage of the device is further increased by utilizing the gate field plate and the floating field plate.

Owner:XIDIAN UNIV

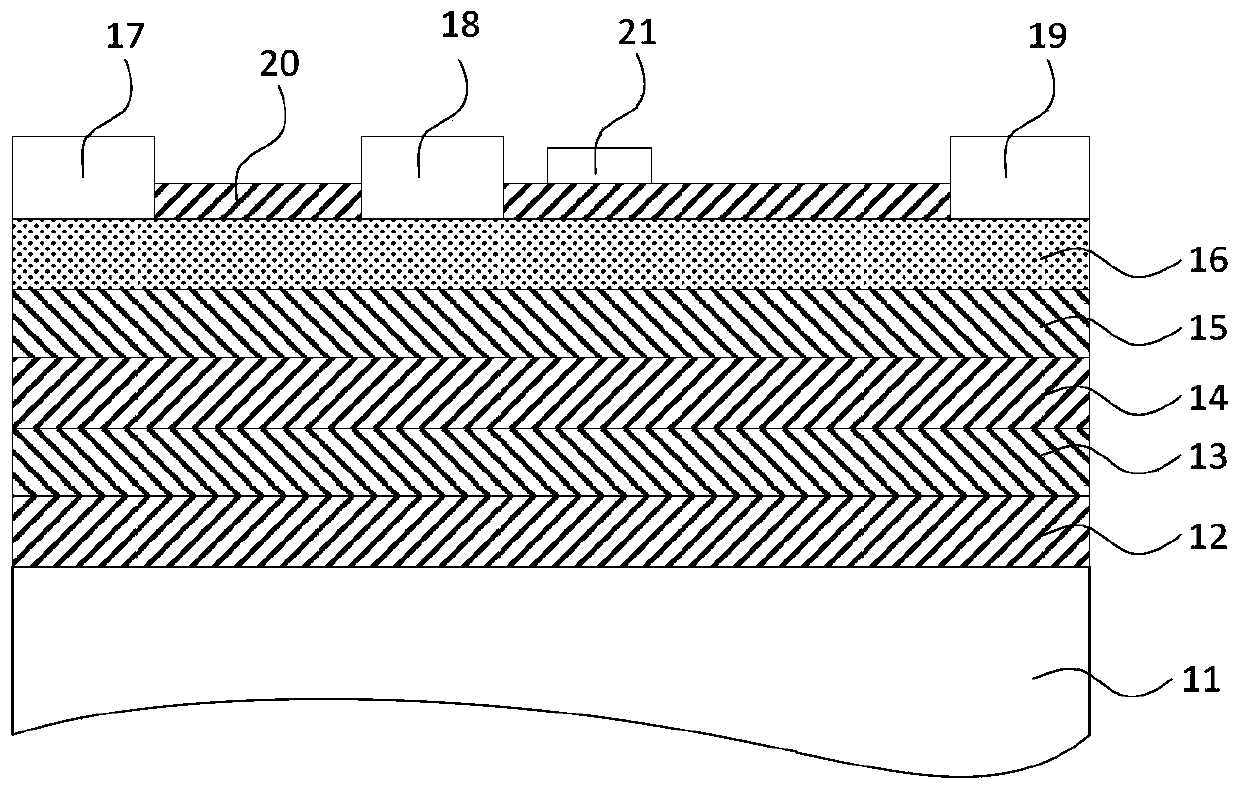

Partial P-type GaN cap layer RESURF GaN-based schottky barrier diode

PendingCN108711578AExcellent transient characteristicsReduce reverse leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactAnode

The invention relates to a partial P-type GaN cap layer RESURF GaN-based schottky barrier diode which is characterized by comprising a substrate layer, a buffer layer arranged on the substrate layer,a channel layer arranged on the buffer layer, a barrier layer arranged on the channel layer, a cathode and a composite anode which are arranged on the two ends of the barrier layer, a partial P-type GaN cap layer which is connected with the composite anode and arranged on the barrier layer, and a passivation layer which covers the barrier layer, the partial P-type GaN cap layer, the composite anode and the cathode. The channel layer and the barrier layer form heterojunctions. The P-type GaN cap layer and the barrier layer form PN junctions. The cathode is cathode ohmic contact. The composite anode comprises anode ohmic contact and anode schottky contact. The partial P-type GaN cap layer is introduced and the composite anode is used so as to prepare the GaN-based schottky barrier diode having low forward starting voltage and high reverse breakdown voltage.

Owner:XIDIAN UNIV

Schottky diode device

InactiveCN108807555AUniform electric field distributionIncrease the doping concentrationSemiconductor devicesPeak valueConduction loss

A Schottky diode belongs to the semiconductor power technology field. A metallized cathode, an N+ semiconductor substrate, an N-type semiconductor nanowire array, Schottky metal, and a metallized anode which are successively arranged from bottom to top are included. A composite insulating dielectric layer is filled among the gaps of N-type semiconductor nanowires. The composite interface formed byinsulating dielectric layers with different dielectric constants can introduce an electric field peak value, and the dielectric constant of the insulating dielectric layer near one side of the metalized anode is higher so that a surface electric field at a Schottky junction can be effectively reduced, and electric field distribution in the semiconductor nanowires is more uniform. The breakdown voltage of a device is increased and the doping concentration of the semiconductor nanowires is properly increased too so as to reduce an on resistance and conduction losses, and a contradictory relation between the breakdown voltage of the Schottky diode and a forward voltage drop is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

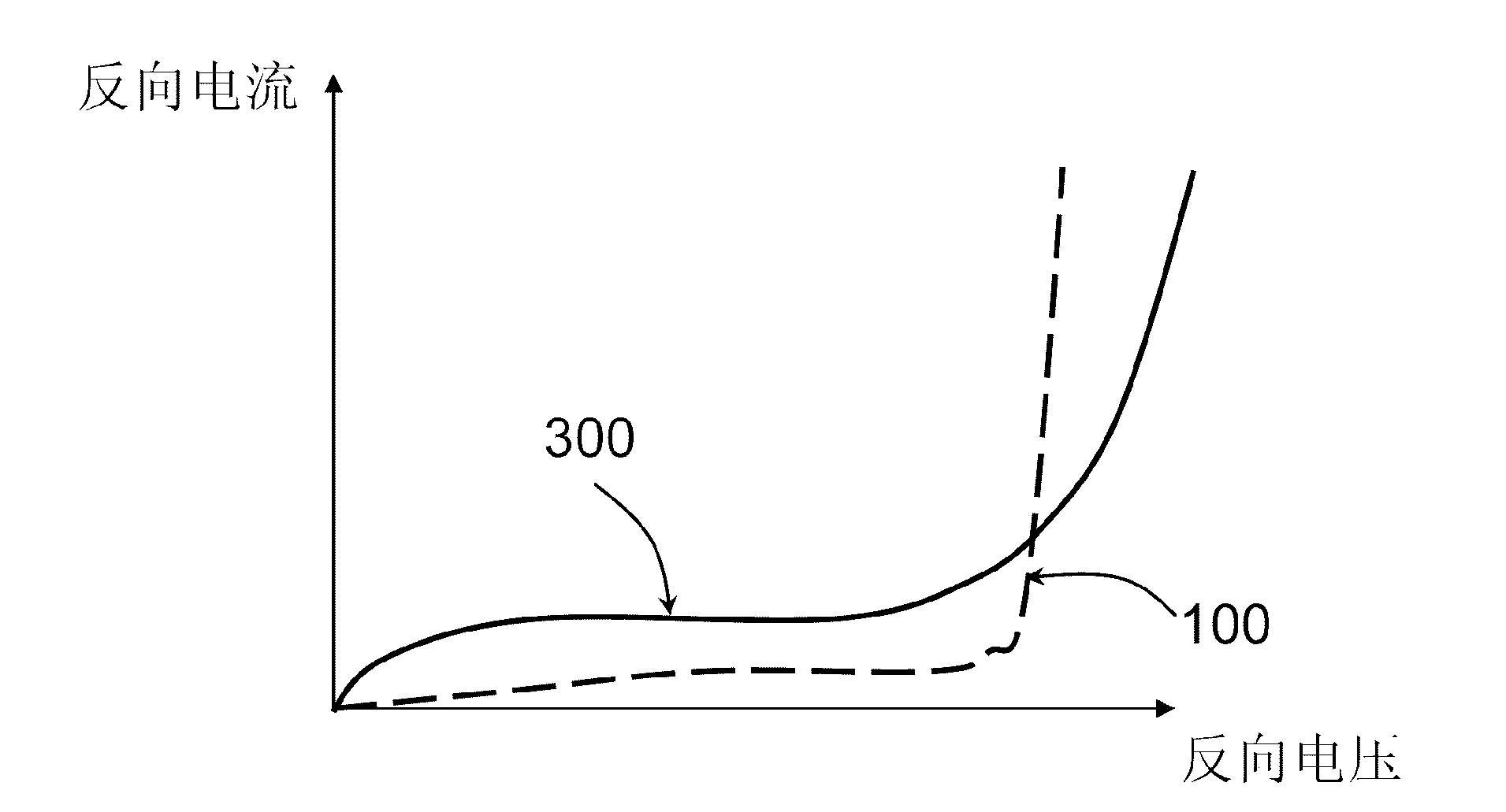

Fast recovery epitaxial diode (FRED) and preparation method thereof

InactiveCN103178120AImprove avalanche resistanceIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesFlyback diodeP–n junction

The invention provides an FRED and a preparation method thereof and belongs to the technical field of power apparatuses. A P-type semiconductor doping layer of an anode region for forming a PN junction of the FRED comprises a first P-type semiconductor region, a second P-type semiconductor region and a third P-type semiconductor region, and the doping concentration of the first P-type semiconductor region, the second P-type semiconductor region and the third P-type semiconductor region increases progressively successively. In a preparation method of the FRED, the first P-type semiconductor region, the second P-type semiconductor region and the third P-type semiconductor region are formed through three doping steps, and accordingly, the doping concentration of P-type semiconductor doping layers is redistributed. The FRED is high in the avalanche resistance and relatively 'soft' in the reverse breakdown characteristic and particularly suitable for being used in series or as fly-wheel diode of insulated gate bipolar translator (IGBT).

Owner:MACMIC SCIENCE & TECHNOLOGY CO LTD

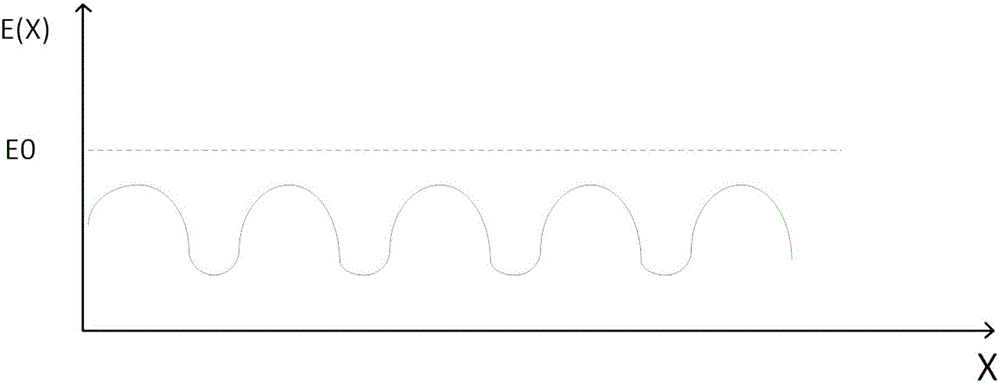

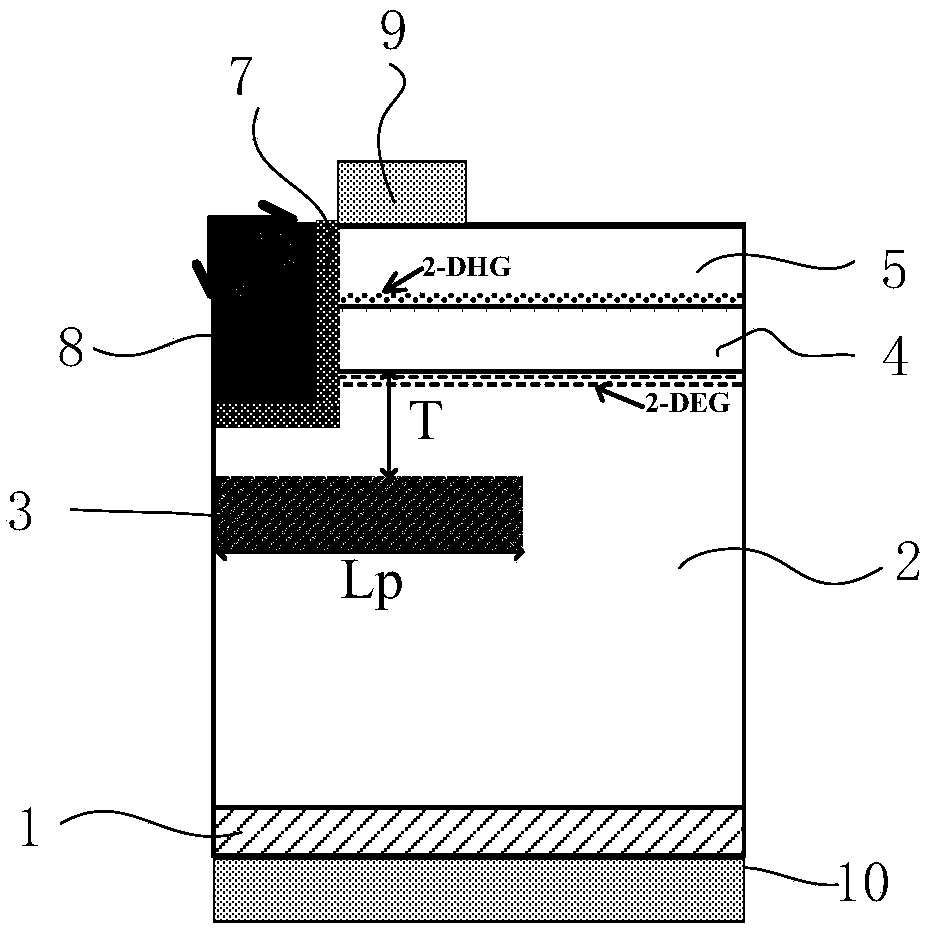

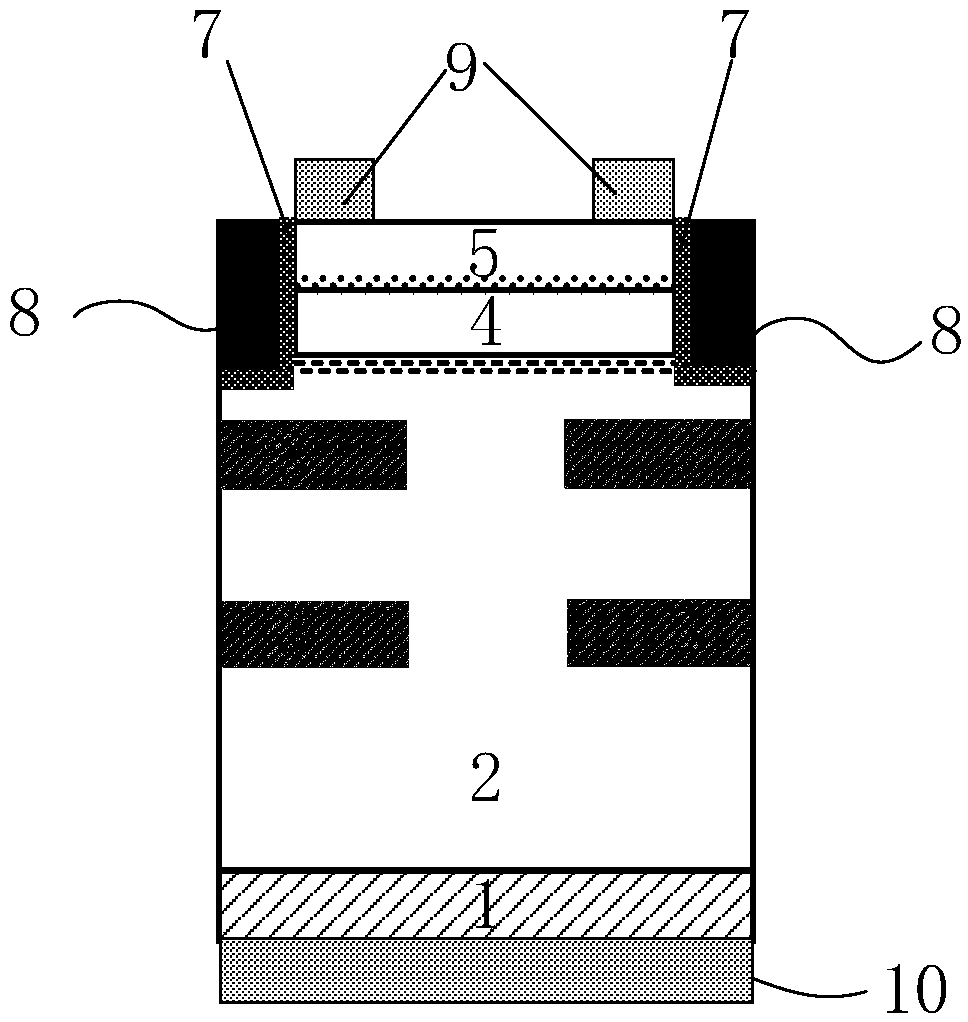

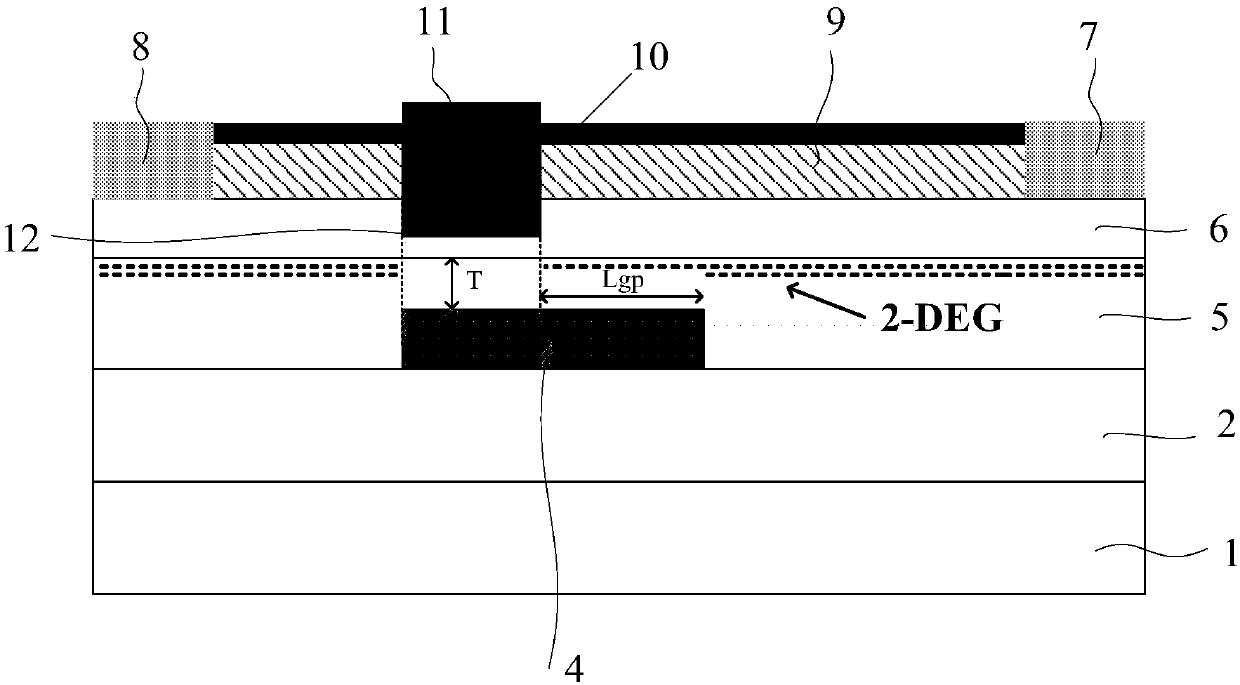

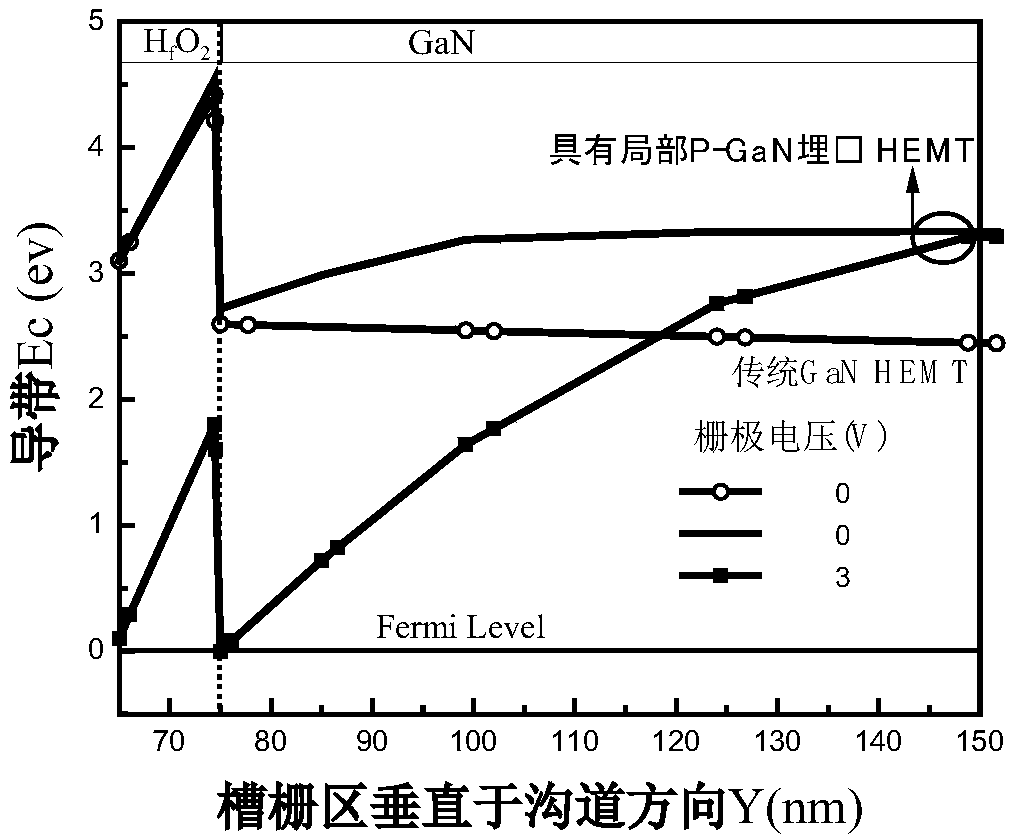

Novel GaN heterojunction field effect transistor

InactiveCN107623032AReduce electric field peaksReduced maximum peak electric fieldSemiconductor devicesElectric field modulationHeterojunction

The invention discloses a novel GaN heterojunction field effect transistor. According to the invention, a P-type GaN buried layer is introduced into a local area of a GaN channel layer of a field effect transistor. The P-type GaN buried layer can improve the heterojunction energy band of the area so as to reduce local channel 2-DEG concentration and a pn junction field board is introduced into theGaN channel layer along the current direction so as to modulate channel electric field. According to the invention, P-type GaN buried layer and groove technology are combined together, so that a threshold value voltage regulation scheme becomes more flexible and threshold value voltage regulation of a larger range can be realized. At the same time, by the electric field modulation effect of the P-type GaN buried layer in the GaN channel layer, the maximal peak value electric field in a device can be reduced effectively and electric field distribution uniformity can be improved. Besides, the P-type GaN buried layer introduces a barrier in a GaN Buffer, so that source and drain electrode punchthrough of the device caused by Buffer electric leakage can be inhibited effectively. Therefore, compared with a traditional groove gating GaN heterojunction field effect transistor, the new structure enlarges the threshold value voltage regulation range effectively and improves the voltage resistance of the device substantially.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

LDMOS device and manufacturing method thereof

ActiveCN106298935AReduced impact ionizationLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate oxide

The invention discloses an LDMOS device which comprises a P-type epitaxial layer, an N-well, a P-well, a first N-type drift region, a first P-type layer, a second N-type drift region, a second P-type layer, a gate oxide layer and gate polysilicon. The P-well, the second N-type drift region, the first N-type drift region and the N-well are sequentially contiguous from left to right at the upper part of the P-type epitaxial layer. The second N-type drift region is shallower than the first N-type drift region. The second P-type layer is adjacent to the lower part of the second N-type drift region. The first P-type layer is adjacent to the lower part of the first N-type drift region. The second P-type layer is shallower than the first P-type layer. The second P-type layer has a higher doping concentration than the first P-type layer. The invention further discloses a manufacturing method for the LDMOS device. According to the invention, the LDMOS device has lower on-resistance, and can satisfy off-state breakdown voltage and on-state breakdown voltage at the same time.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

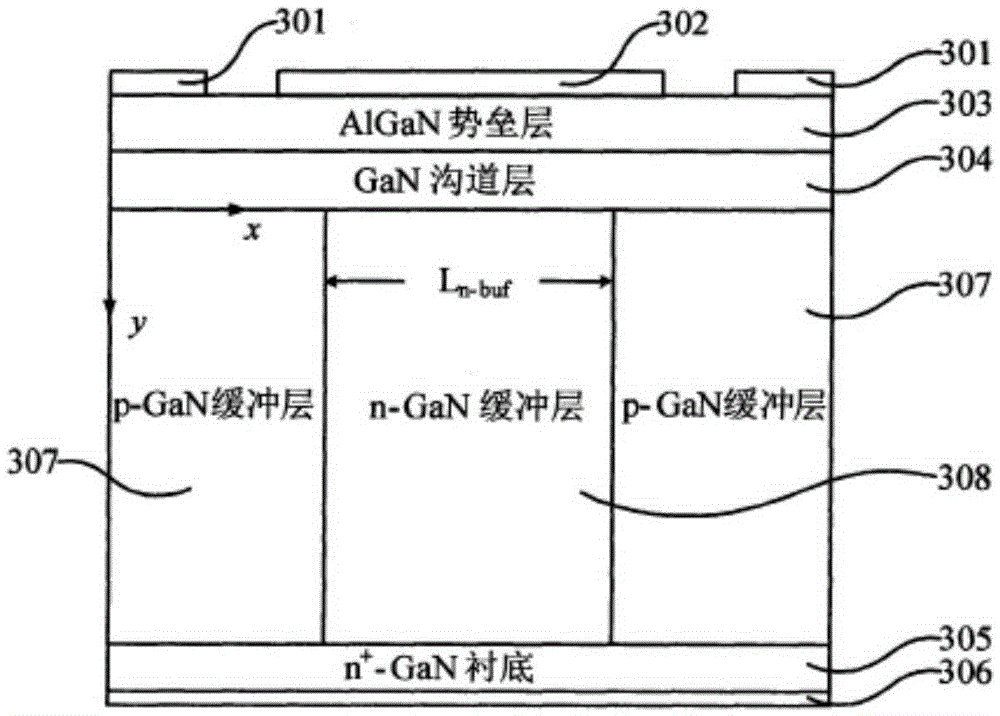

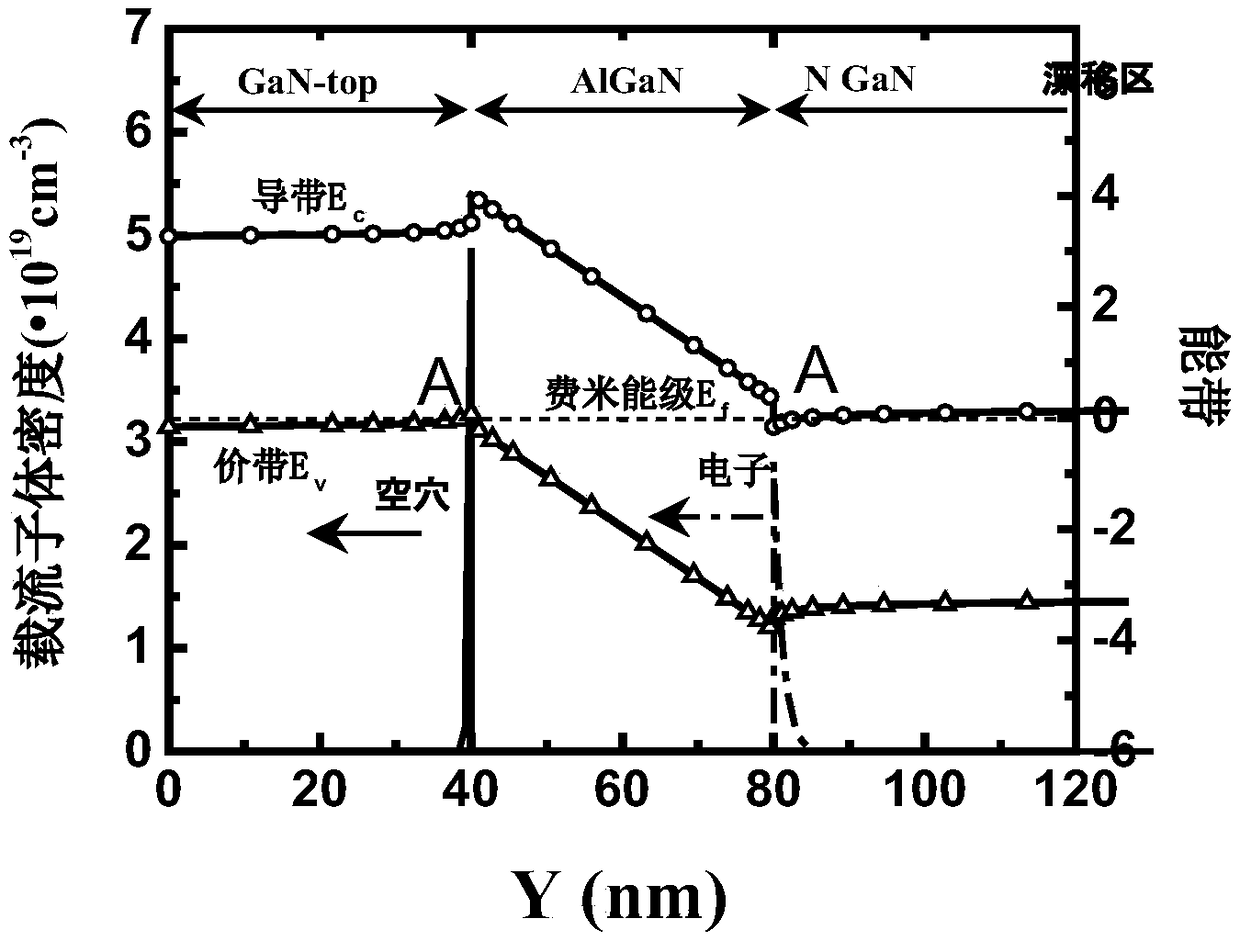

GaN heterojunction longitudinal power device

InactiveCN108598163AReduce electric field peaksUniform electric field distributionSemiconductor devicesHeterojunctionControl channel

The invention discloses a GaN heterojunction longitudinal power device. According to the GaN heterojunction longitudinal power device disclosed by the invention, source electrode electrons are prevented from being injected into a two-dimensional electron gas channel through a longitudinal grid control channel by using a two-dimensional hole gas, a device enhancement type is achieved, and the longitudinal device realizes low on resistance and large saturation current by using the two-dimensional electron gas channel with a high migration rate; meanwhile, a reverse biased PN junction is importedto a GaN drift region of a floating P-type GaN buried layer, an exhaustion region of the reverse biased PN junction continuously expands when the reverse biased PN junction withstands a reverse withstand voltage, so that the electric field in the device is uniformly distributed, so that the maximum peak electric field in the device is effectively reduced. By adjusting the doping concentration, the thickness and the length of P-GaN type drift region, the P-GaN drift region is almost simultaneously depleted with the N-type drift region, so that the exhaustion region between the reverse biased PN junctions of the P-GaN type drift region and the N type type drift region is expanded to a larger exhaustion region to withstand the reverse voltage, the advantages of a large forbidden band width and a high withstand voltage of a GaN body material are fully played, and the reliability and the stability of a power electronic circuit system are improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

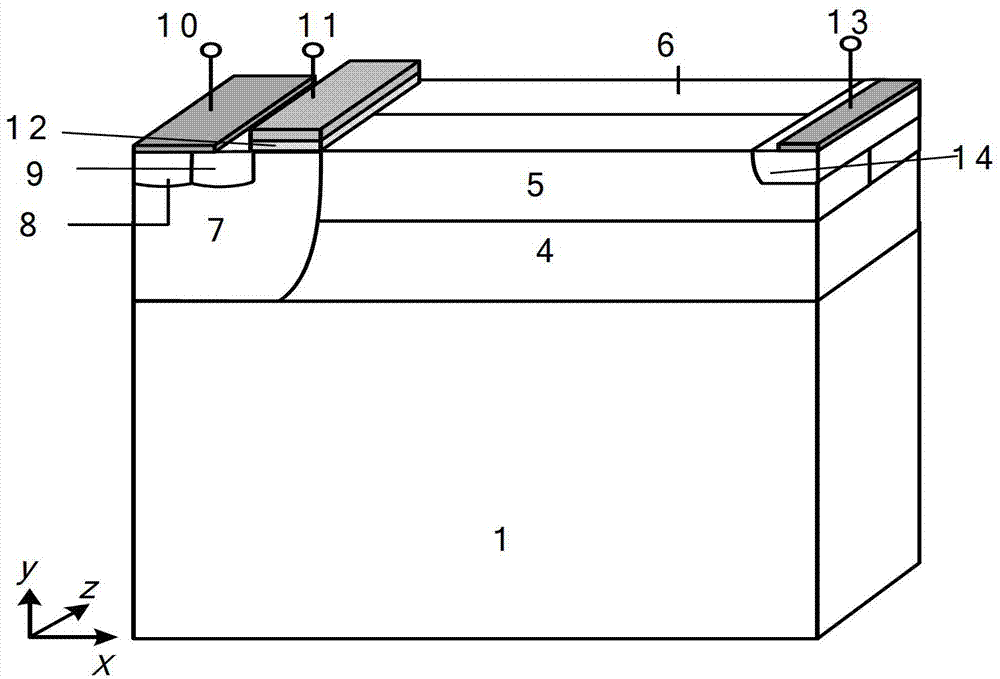

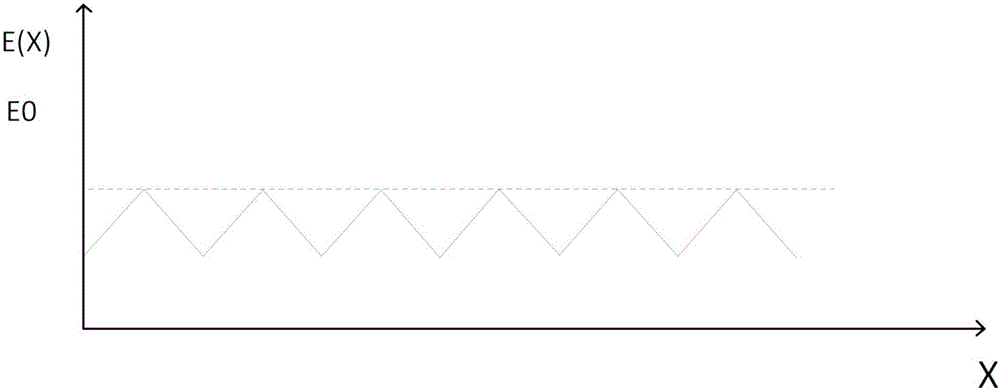

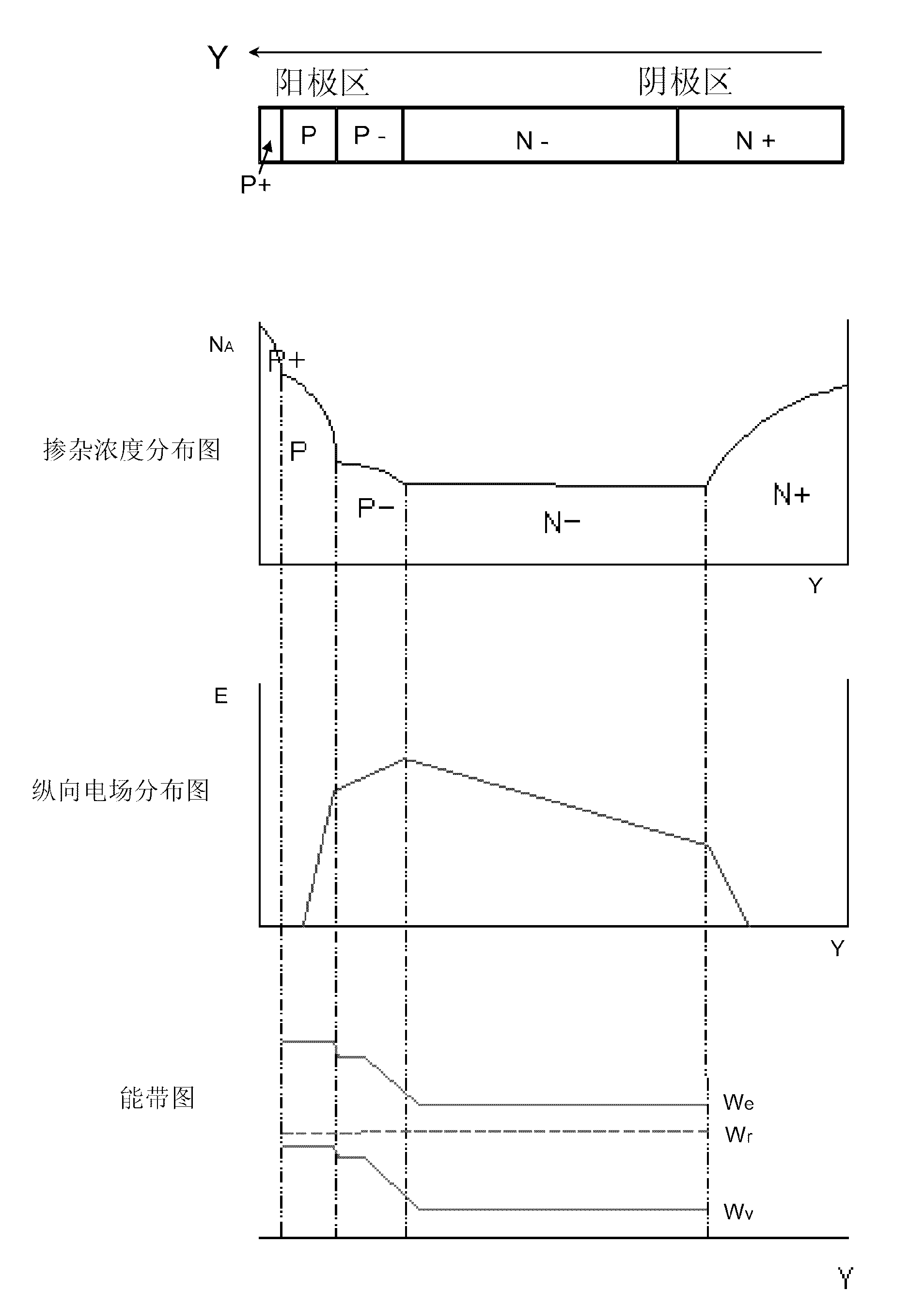

3D-RESURF terminal structure of power semiconductor device and manufacturing method thereof

InactiveCN107316896AReduced injection energy requirementsReduce electric field concentrationSemiconductor devicesPower semiconductor deviceEngineering

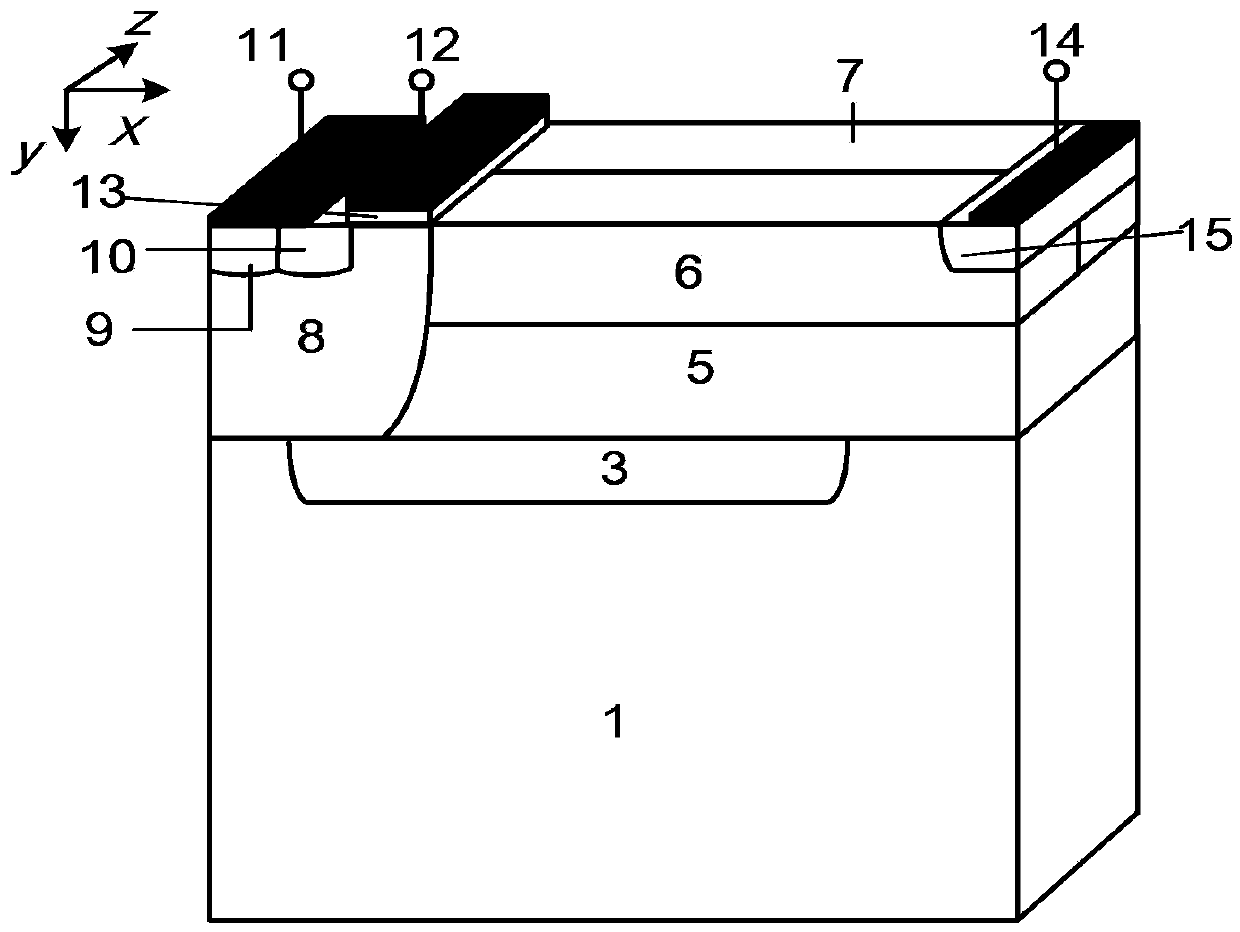

The invention provides a 3D-RESURF terminal structure of power semiconductor device and a manufacturing method thereof. The 3D-RESURF terminal structure comprises a metallizing cathode, a first conduction type heavily-doped semiconductor substrate, a first conduction type lightly-doped drift region, a field oxidation layer, a second conduction type semiconductor main knot and a first conduction type heavily-doped cut-off ring, wherein a second conduction type semiconductor RESURF layer is positioned between the second conduction type semiconductor main knot and the first conduction type semiconductor cut-off ring; a first conduction type semiconductor drift region is arranged above the second conduction type semiconductor RESURF layer. The second conduction type semiconductor lightly-doped RESURF layer near the second conduction type semiconductor main knot and the first conduction type semiconductor drift region above the second conduction type semiconductor main knot are exhausted mutually, a space charge region is formed, electric fields in y direction and z direction are introduced, and the distribution of the electric field in x direction is changed, so that triangular distribution of the electric field on the surface in x direction are changed into approximately trapezoidal distribution, the peak value of the electric value is reduced, and the breakdown voltage is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

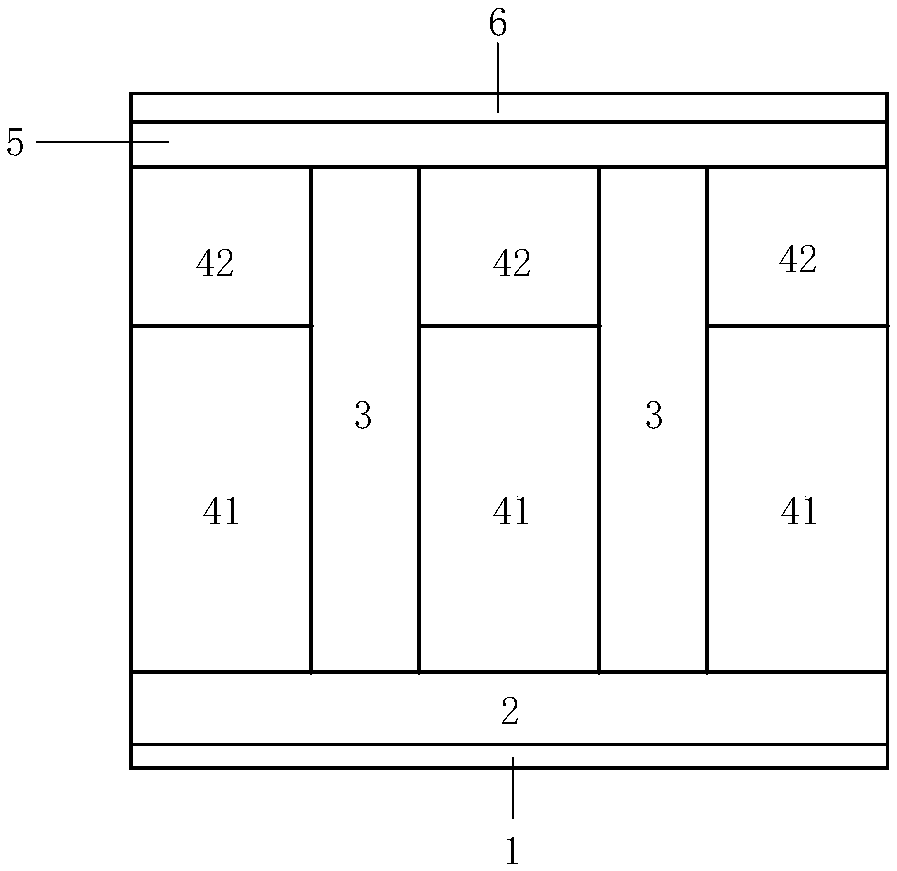

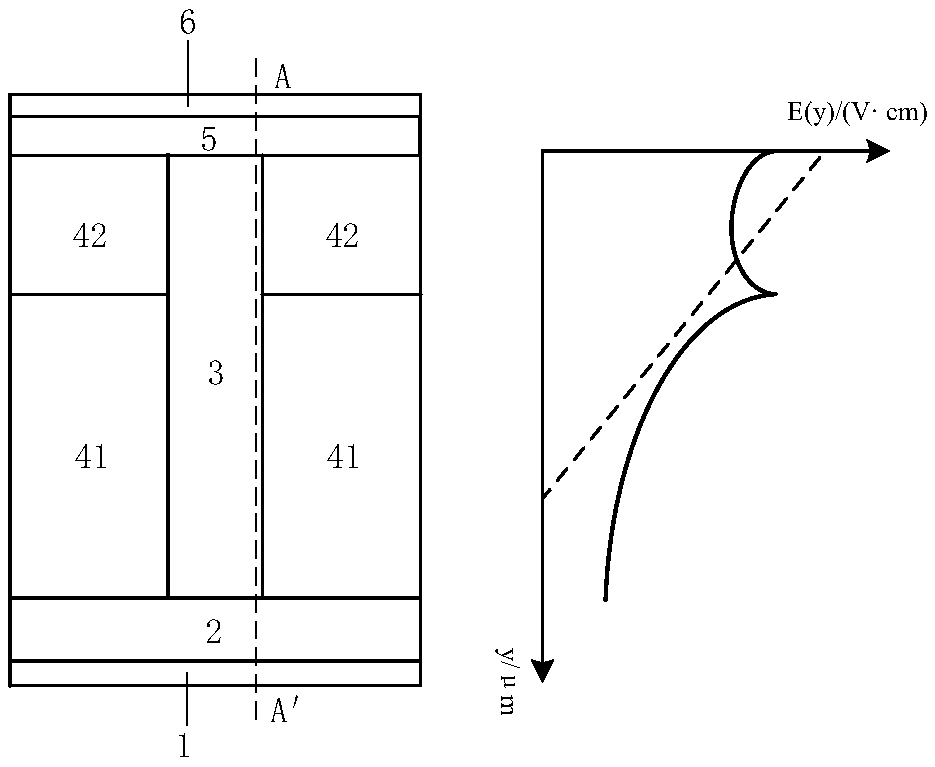

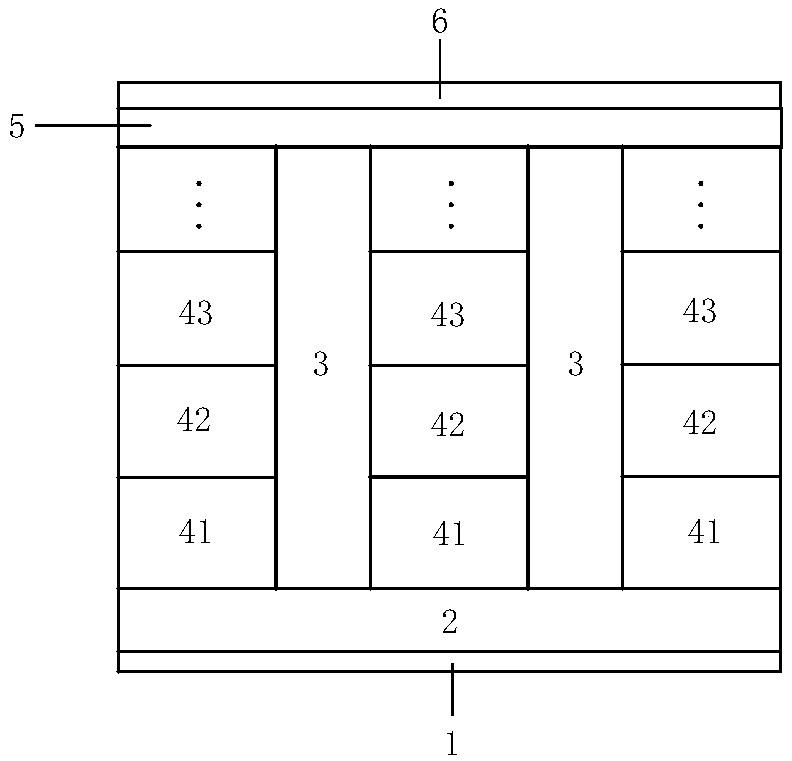

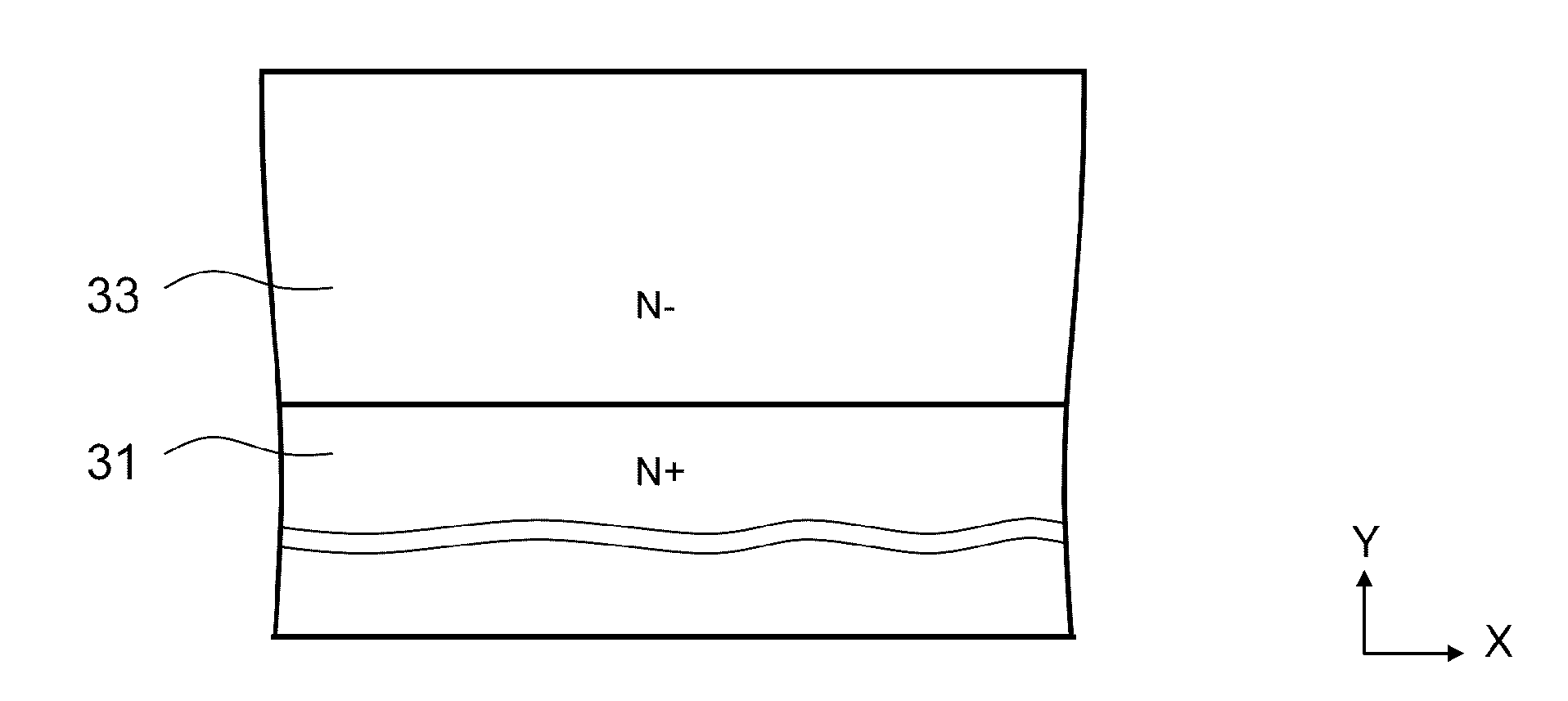

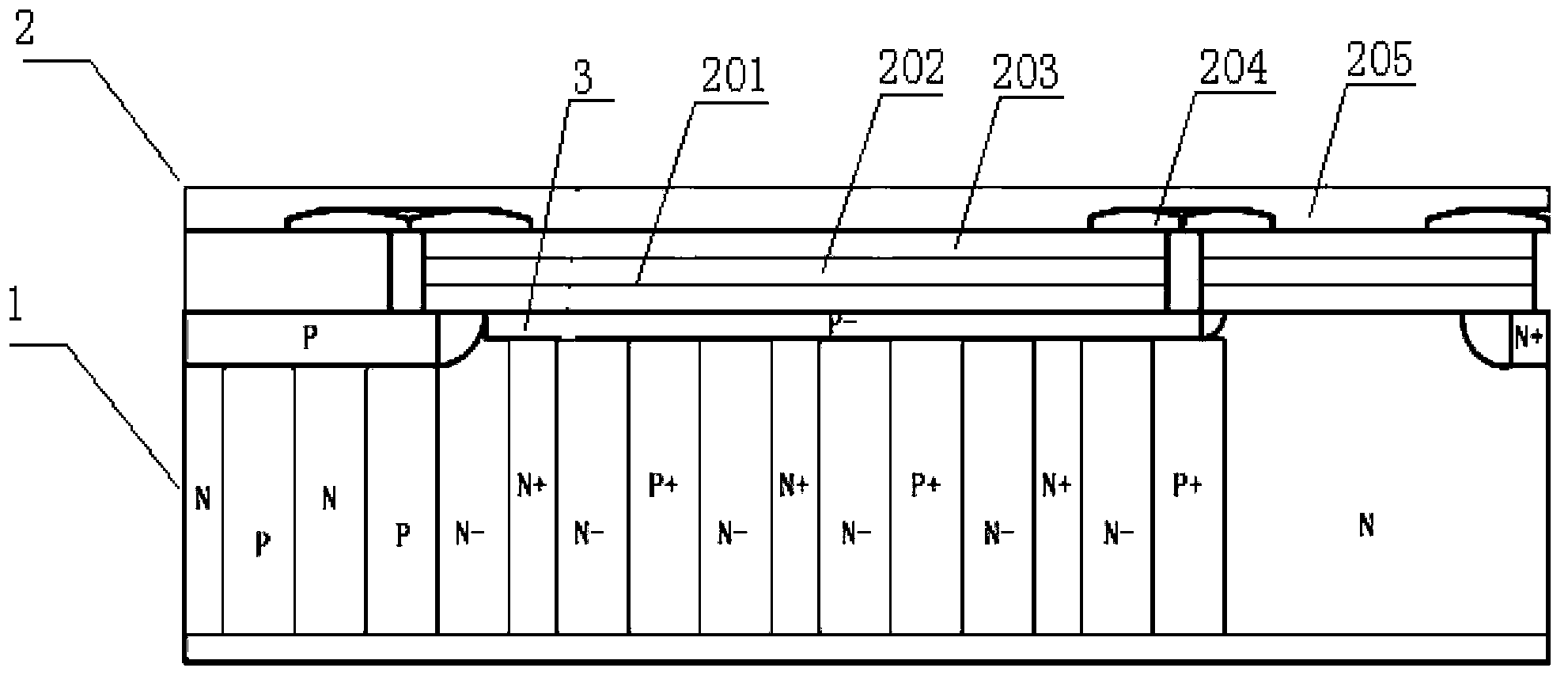

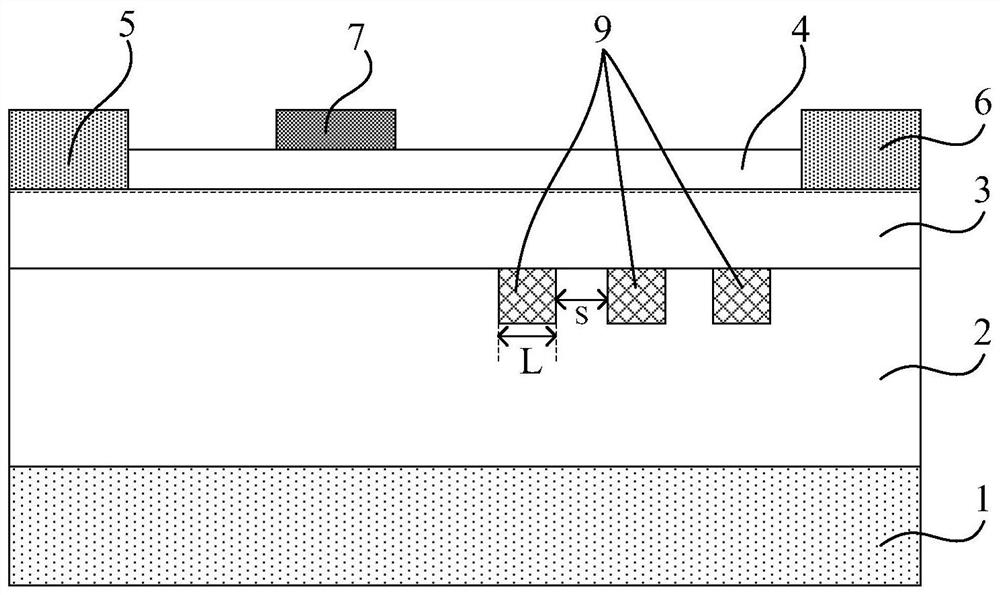

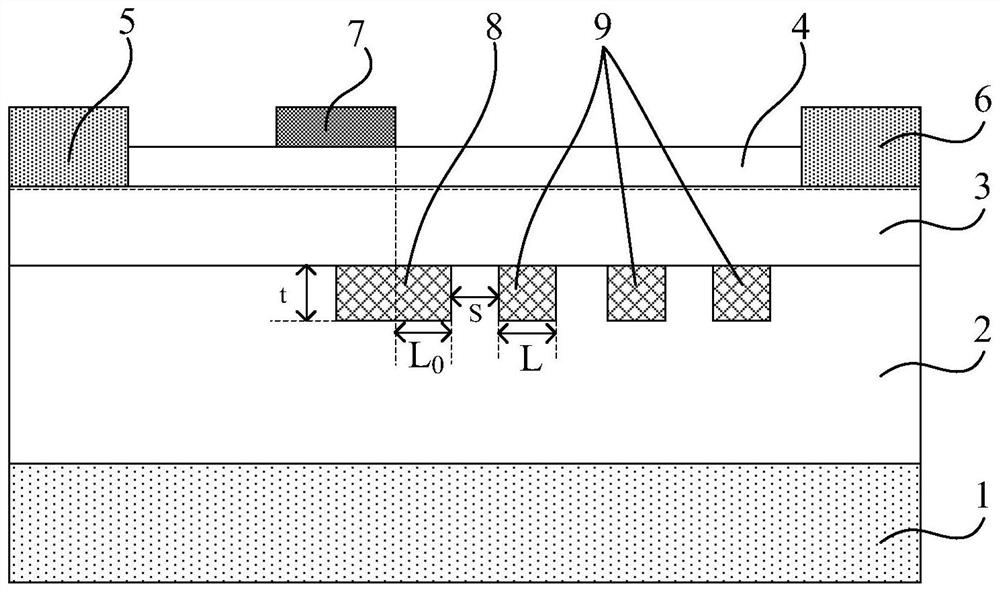

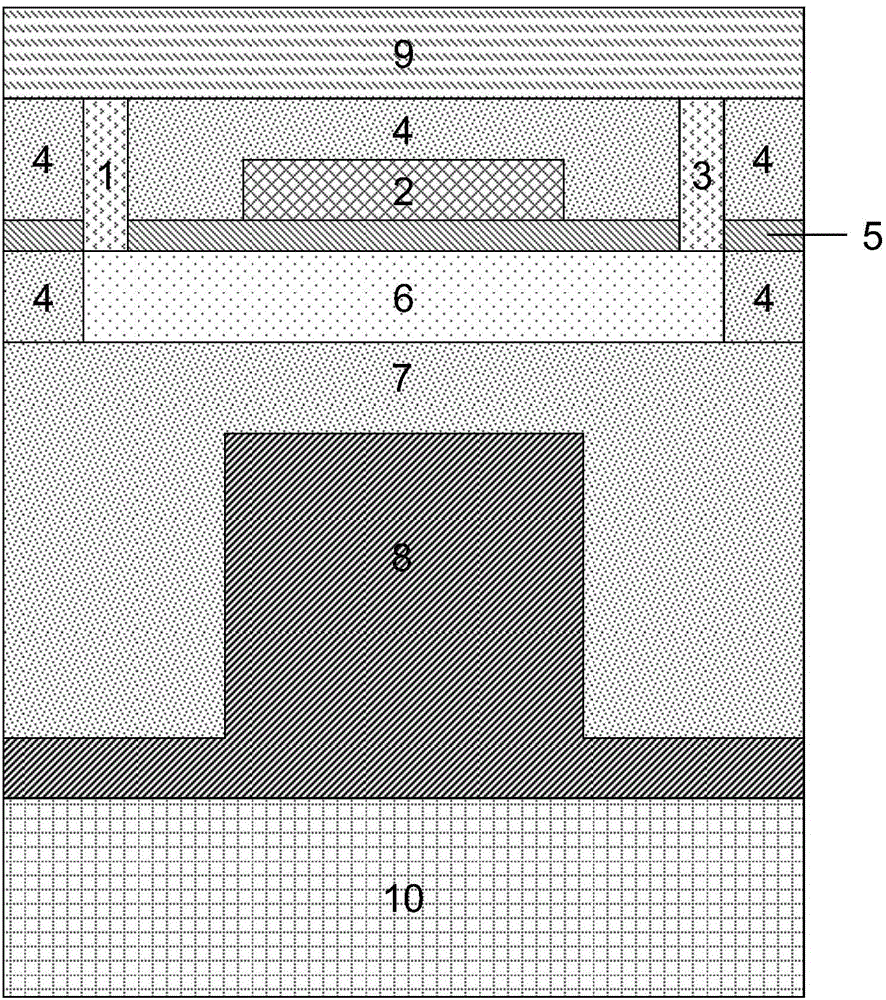

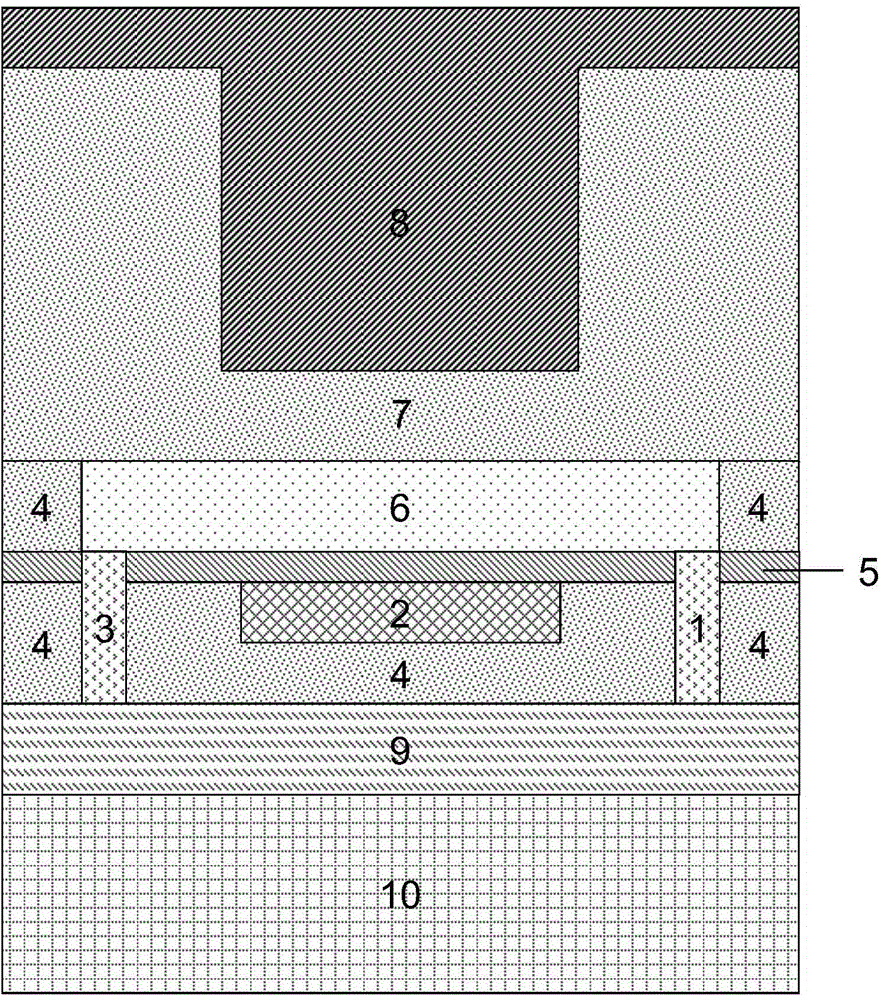

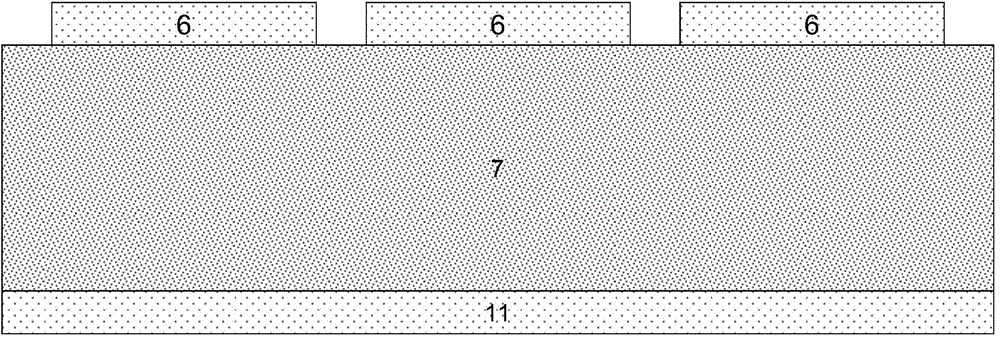

Partial SOI (silicon on insulator) super junction high-voltage power semiconductor device

InactiveCN103426913AUniform electric field distributionImprove electric field distributionSemiconductor devicesPower semiconductor deviceHigh pressure

The invention relates to semiconductor technology, in particular to a partial SOI (silicon on insulator) super junction high-voltage power semiconductor device. The partial SOI super junction high-voltage power semiconductor device is characterized by comprising a plurality of N+ pads and a P-type electric field shielding layer, the N+ pads are uniformly embedded into a P-type substrate, the P-type electric field shielding layer is arranged in the P-type substrate, the upper surface of the P-type electric field shielding layer is connected with a P-type body area and the lower surface of an N-type buffer area close to a source end, and the lower surface of the P-type electric field shielding layer is connected with the upper surface of a buried oxide layer. The partial SOI super junction high-voltage power semiconductor device has the advantages that the doping concentration of a drift region is increased by changing electric field distribution, the voltage resistance of the device is improved, on resistance is reduced, the area of the device is decreased, and cost is reduced. The invention is particularly applicable to the partial SOI super junction high-voltage power semiconductor device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

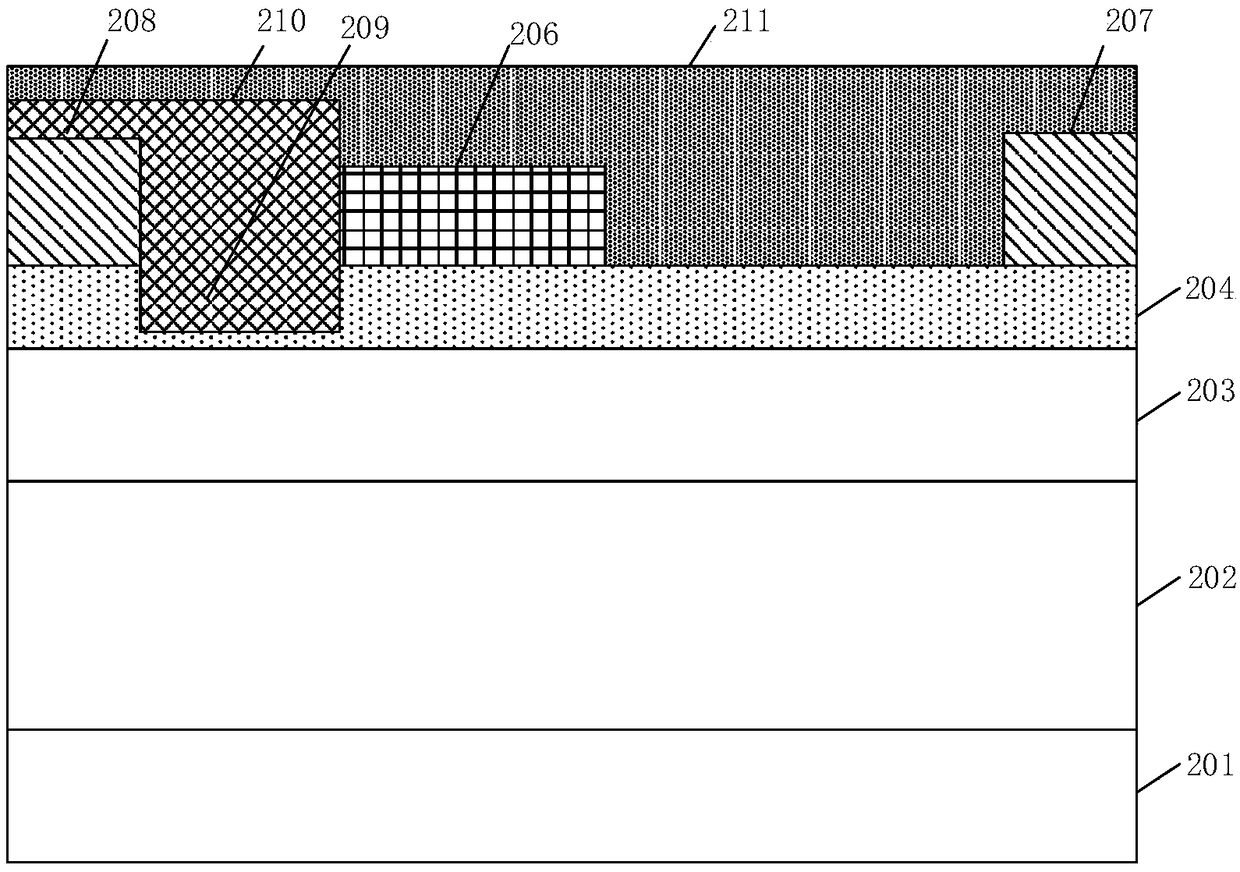

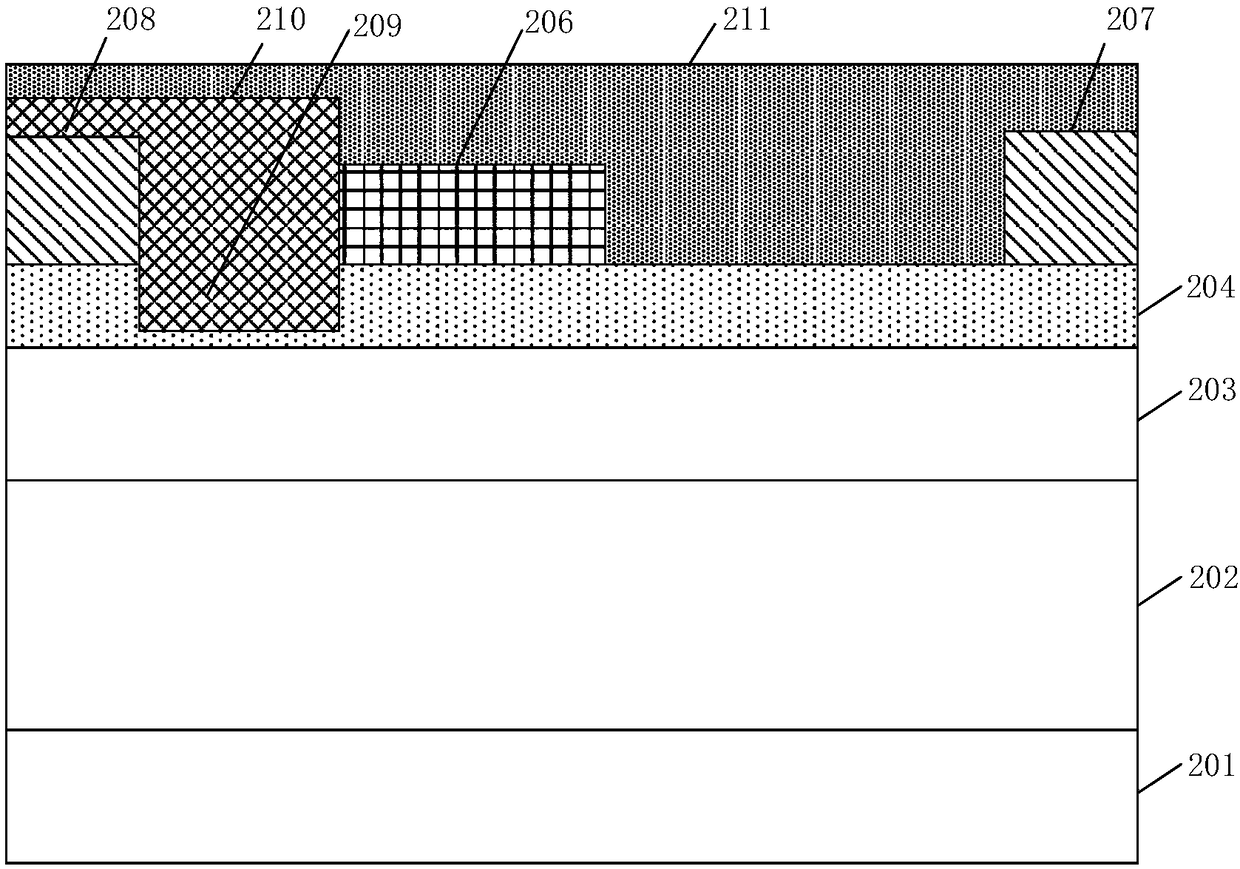

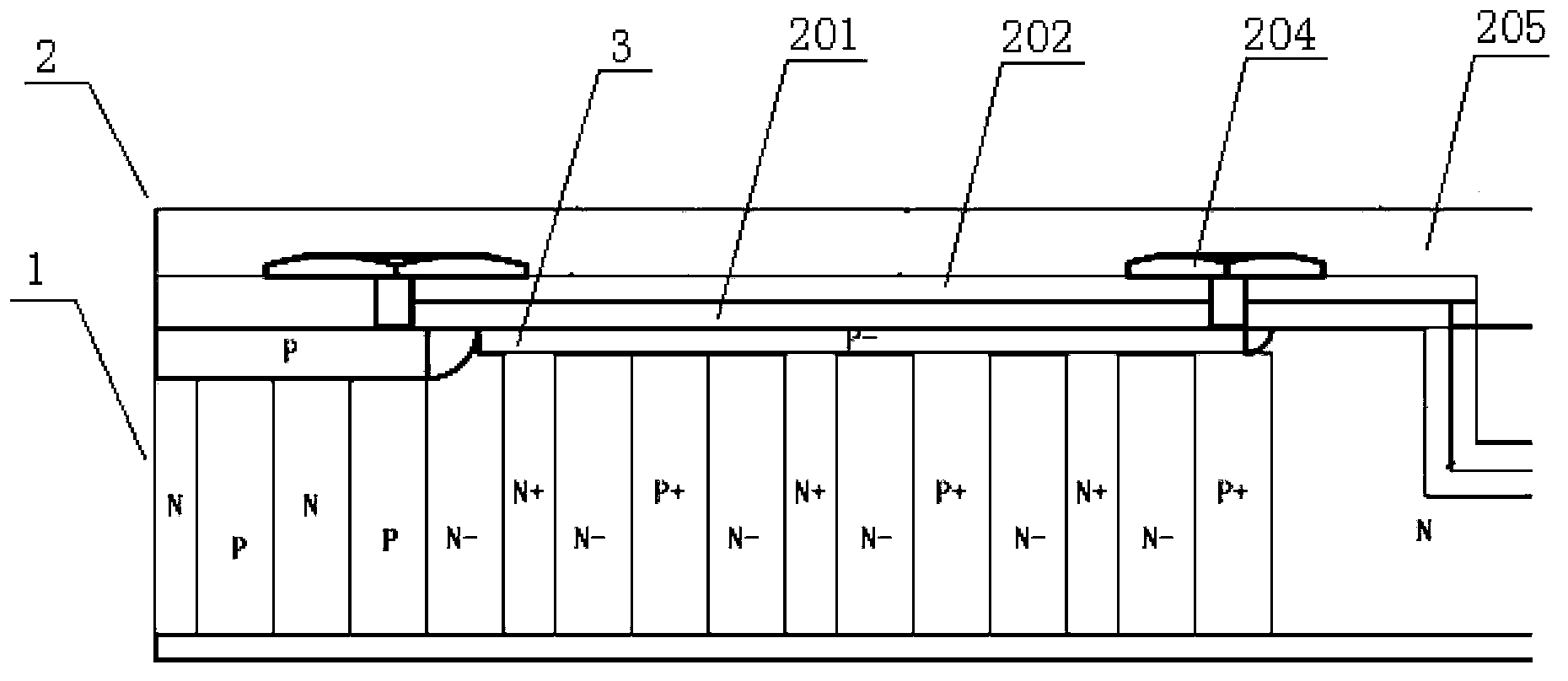

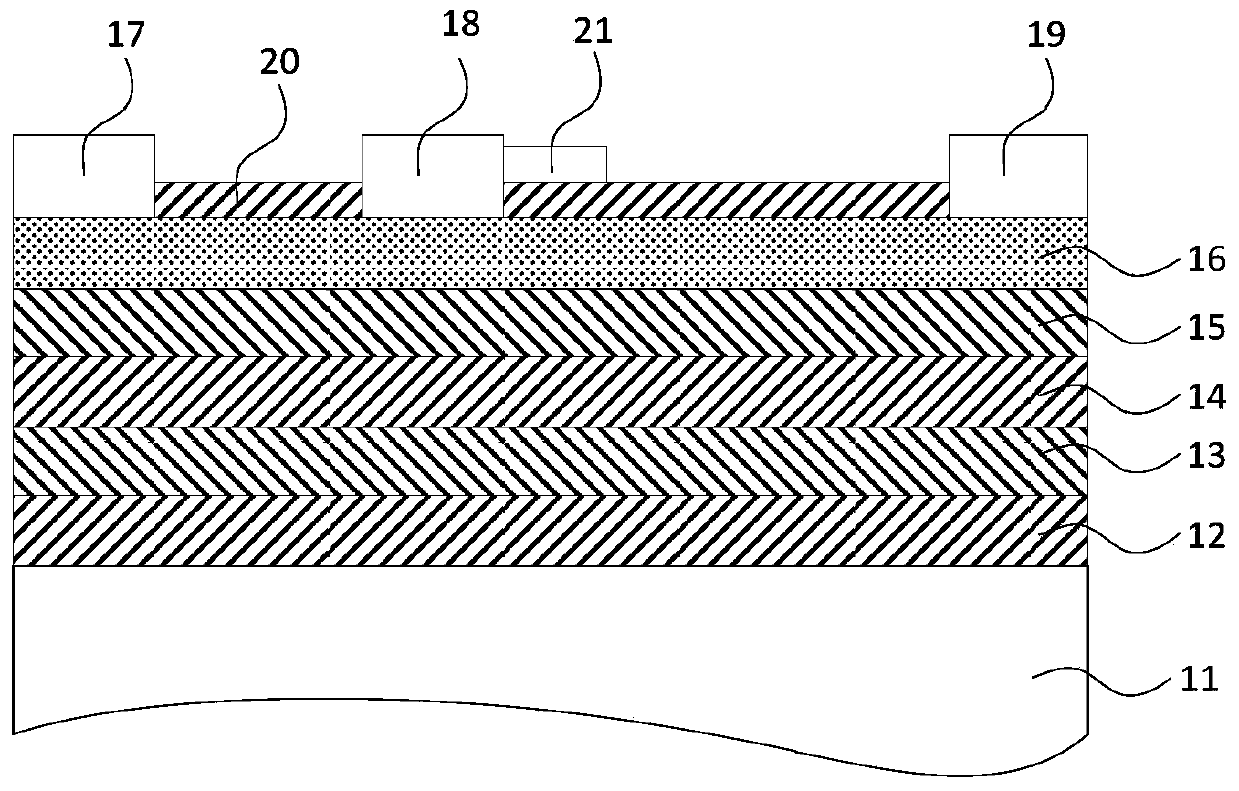

Partial intrinsic GaN cap layer RESURF (Reduced Surface Field) CaN-based Schottky barrier diode

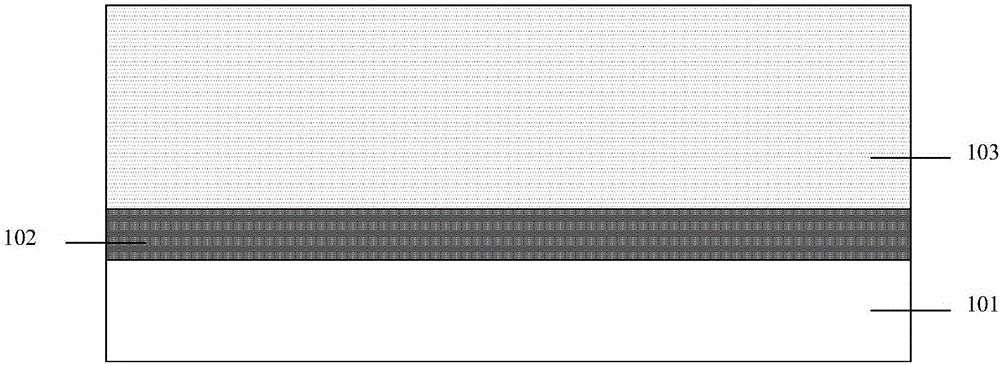

InactiveCN108598182AExcellent transient characteristicsReduce reverse leakage currentSemiconductor devicesPhysicsOhmic contact

The invention relates to a partial intrinsic GaN cap layer RESURF (Reduced Surface Field) CaN-based Schottky barrier diode which comprises a substrate layer, a buffer layer, a channel layer 203, a barrier layer, a cathode and a composite anode, a partial intrinsic GaN cap layer and a passivation layer, wherein the buffer layer is positioned on the substrate layer; the channel layer is positioned on the buffer layer; the barrier layer is positioned on the channel layer; the cathode and the composite anode are positioned at both ends of the barrier layer; the partial intrinsic GaN cap layer is connected with the composite anode and positioned on the barrier layer; the passivation layer is covered on the barrier layer, the partial intrinsic GaN cap layer, the composite anode and the cathode;the channel layer and the barrier layer forms a heterojunction; the cathode is cathode ohmic contact; and the composite anode comprises an anode ohmic contact and an anode Schottky contact. Accordingto the embodiment of the invention, the partial intrinsic GaN cap layer is introduced on the barrier layer and the composite anode is adopted, so that the CaN-based Schottky barrier diode with a low forward turn-on voltage and a high reverse breakdown voltage is prepared.

Owner:XIDIAN UNIV

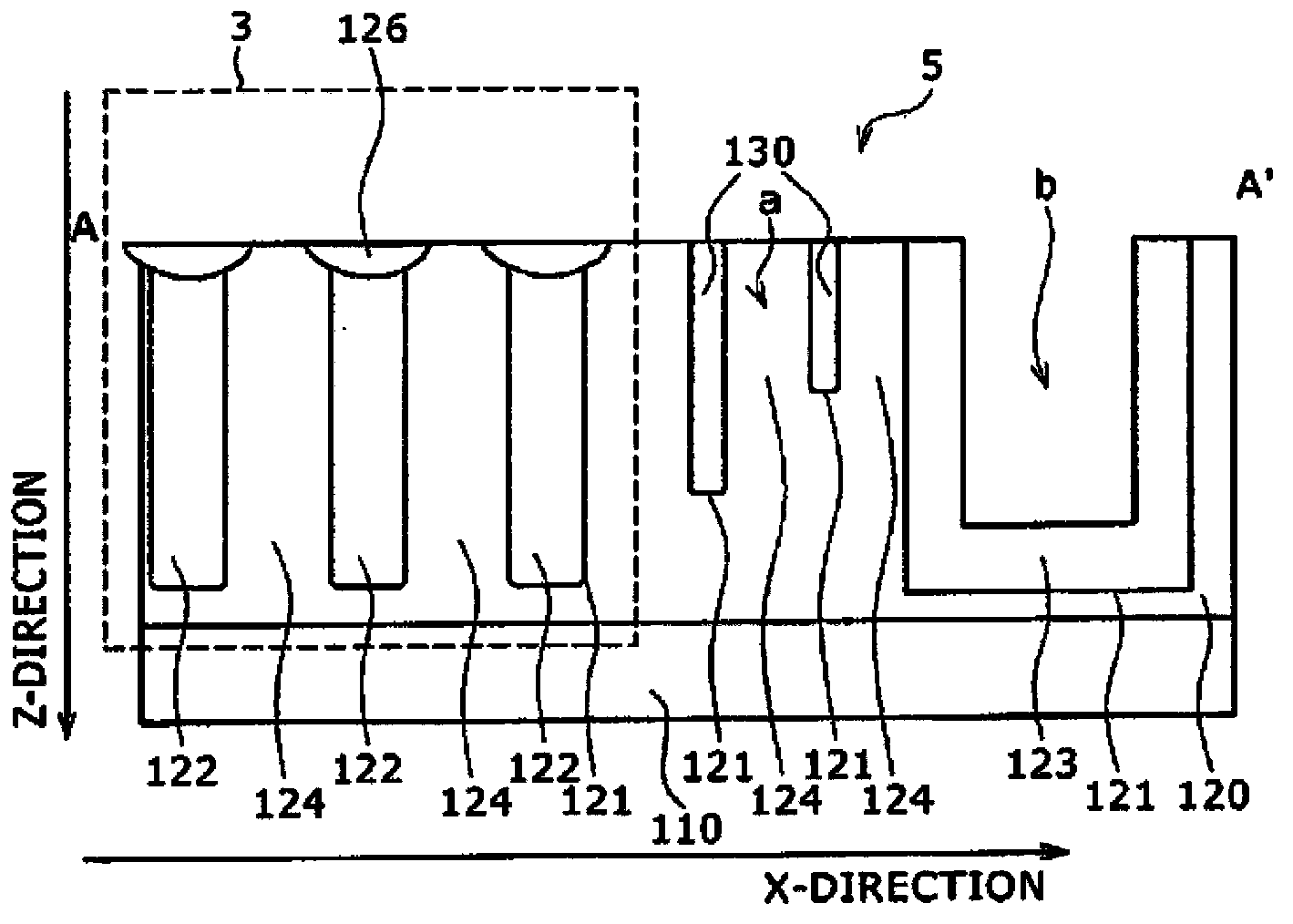

High-voltage super-junction terminal structure

ActiveCN103681780AImprove pressure resistanceImprove reliabilitySemiconductor devicesHigh resistanceHigh pressure

The invention provides a high-voltage super-junction terminal structure. The high-voltage super-junction terminal structure comprises a super-junction zone and a terminal surface structure, wherein the super-junction zone is formed through the spaced distribution of P+, N- and N+ poles; a metal field plate and an SIPOS (Semi-Insulating Polycrystalline Silicon) field plate are arranged on the terminal surface structure; a P- layer is arranged between the super-junction zone and the terminal surface structure; a high-resistance SIPOS layer, an SiO2 layer, a low-resistance SIPOS layer, the metal field plate and a nitrogen-doped SIPOS layer are sequentially deposited on the terminal surface structure from the bottom to the top, or the high-resistance SIPOS layer, the SiO2 layer, the metal field plate and the nitrogen-doped SIPOS layer are sequentially deposited on the terminal surface structure from the bottom to the top; the bottom end of the terminal surface structure is ended by a trench. The high-voltage super-junction terminal structure which is provided by the invention has the advantages that high voltage can be resisted, the reliability of the terminal is improved, and leaked current is reduced. The high-voltage super-junction terminal structure can be applied in the manufacture of the terminals of large power devices, such as an IGBT (Insulated Gate Bipolar Translator) and a VDMOS (Vertical Double Diffused Metal Oxide Semiconductor).

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

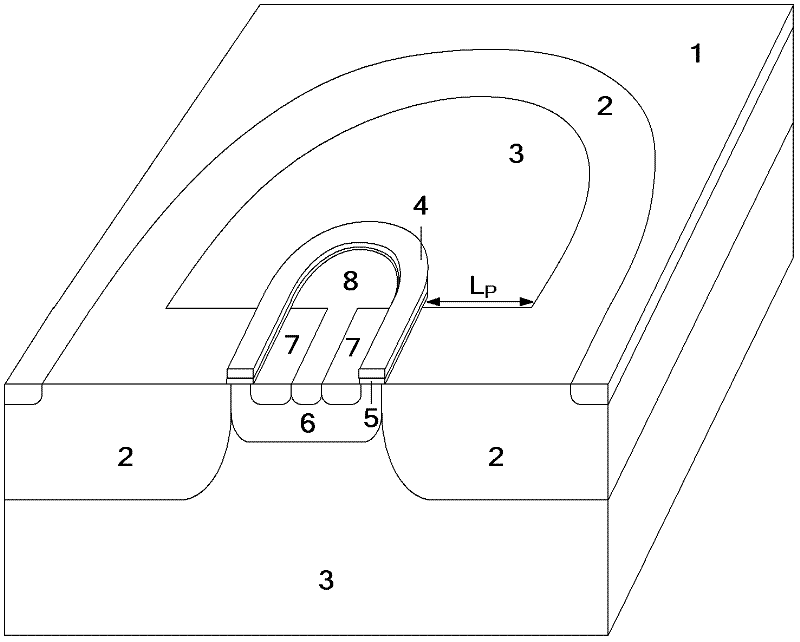

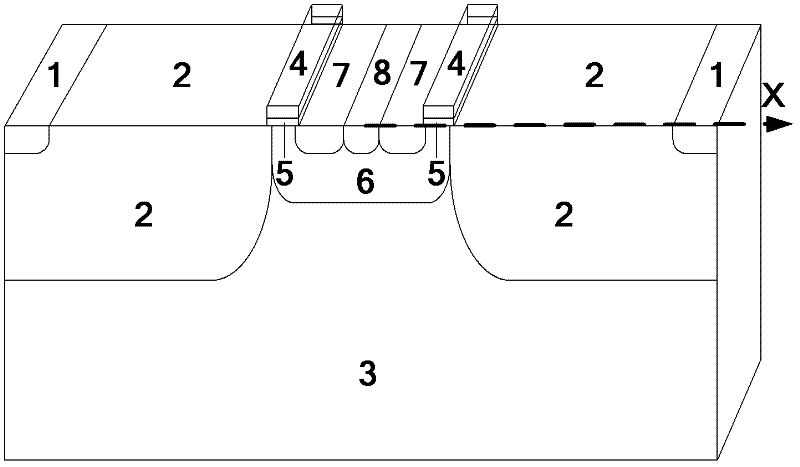

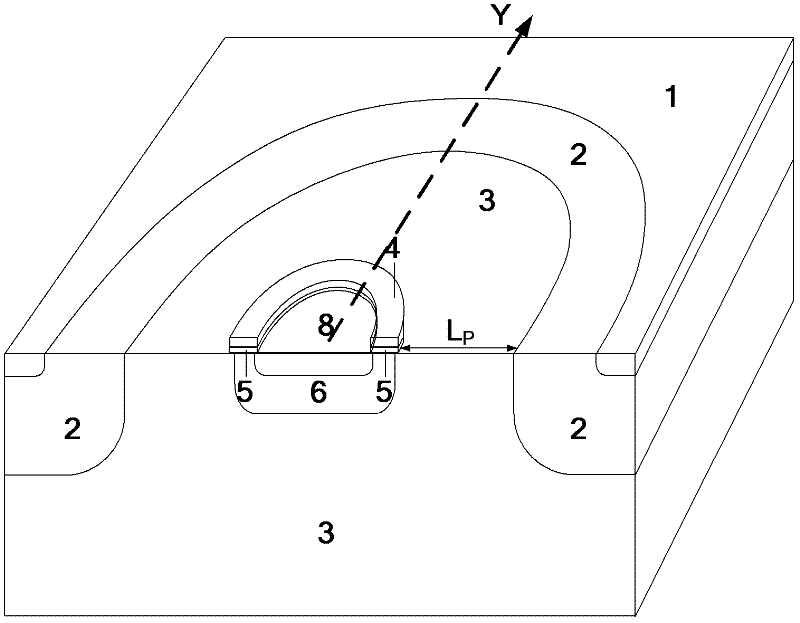

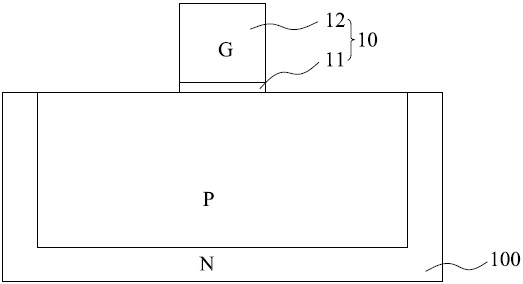

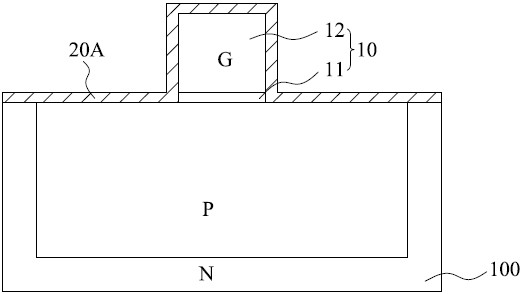

Junction termination structure of transverse high-pressure power semiconductor device

InactiveCN102244092BImprove breakdown voltageReduce widthSemiconductor devicesPower semiconductor deviceCMOS

A junction terminal structure of a lateral high-voltage power semiconductor device belongs to the technical field of semiconductor power devices. By shortening the length of the N-type drift region at the curvature terminal portion of the lateral high-voltage power semiconductor device, the N-type drift region is separated from the P-well region by a certain distance, and the spaced part is replaced by a P-type substrate, which is equivalent to introducing a P-type substrate. The additional charge reduces the peak value of the electric field at the pn junction formed by the original P-well region and the N-type drift region, and at the same time introduces a new peak value of the electric field at the pn junction formed by the P-type substrate and the N-type drift region, and increases The curvature radius of the curvature terminal is improved, the excessive concentration of the power line is avoided, and the breakdown voltage of the device is improved. The surface of the N-type drift region can also be combined with a surface RESURF structure or a super junction structure. The invention can reduce the width of the curvature terminal of the device, save the layout area of the device, and is compatible with the CMOS process. The invention can be used to manufacture high-voltage, high-speed, and low-conduction-loss lateral high-voltage power devices with excellent performance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

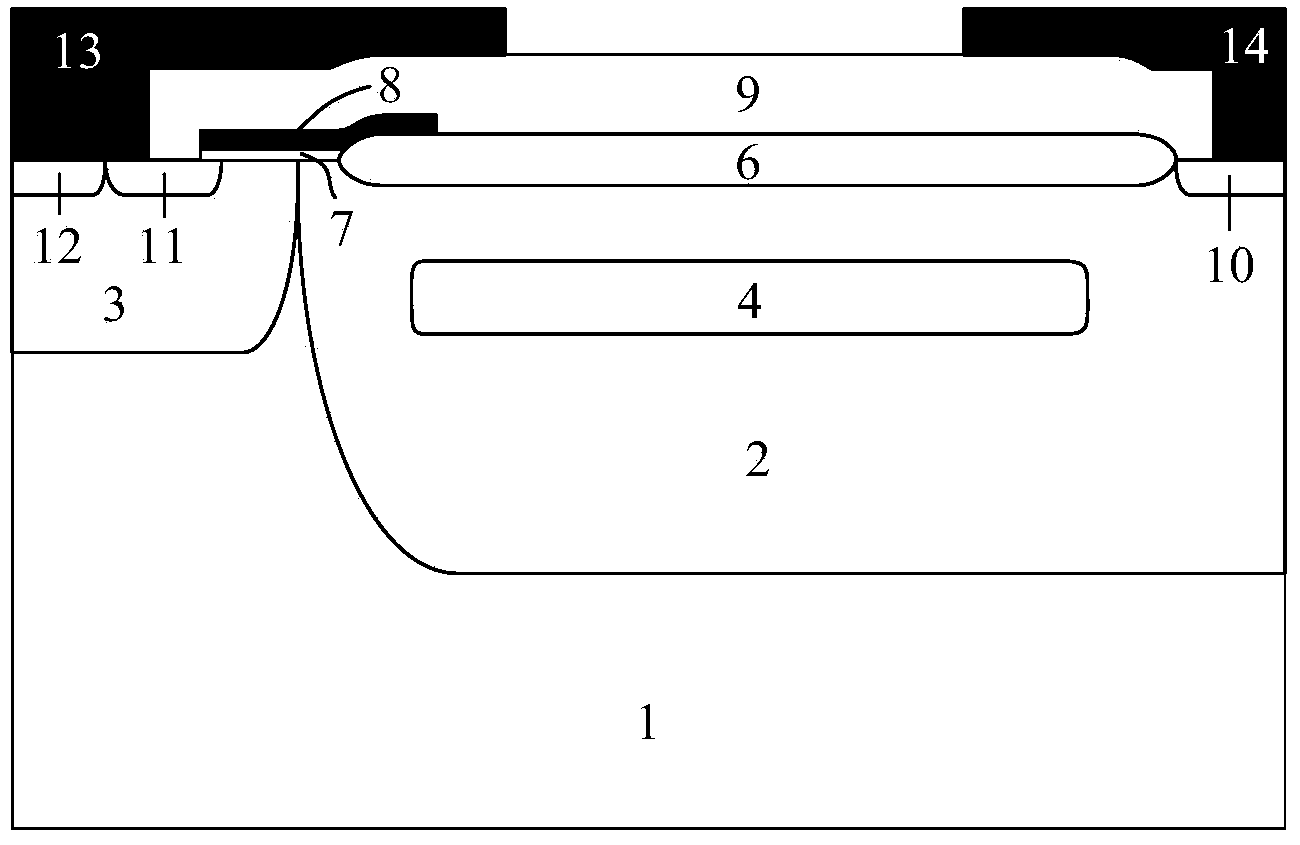

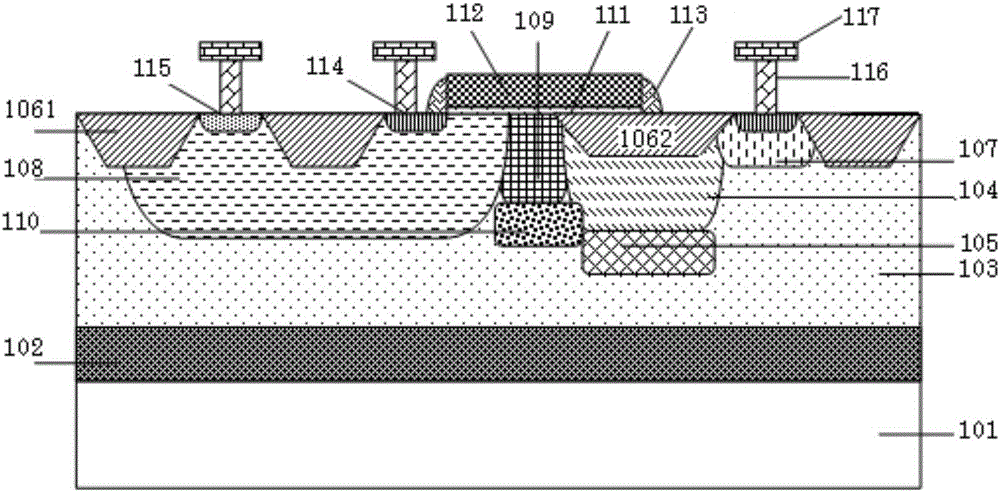

Semiconductor device and manufacturing method thereof

PendingCN112018176AImprove breakdown voltageUniform electric field distributionSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

The invention discloses a semiconductor device and a manufacturing method thereof. The semiconductor device comprises: a substrate; a semiconductor layer which is located on the substrate, wherein two-dimensional electron gas is formed in the semiconductor layer; and a source electrode and a drain electrode which are located on the side, away from the substrate, of the semiconductor layer, and a grid electrode which is located between the source electrode and the drain electrode, wherein a buried layer is formed in the semiconductor layer on one side, close to the substrate, of the two-dimensional electron gas, the buried layer and the semiconductor layer form a pn junction, the buried layer comprises a first buried layer and / or at least one second buried layer, the edge, close to the drain electrode, of the grid electrode is overlapped with the first buried layer, one part of the first buried layer extends from the edge, close to the drain electrode, of the grid electrode to the drainelectrode, and / or the second buried layer is located between the grid electrode and the drain electrode. According to the embodiment of the invention, the buried layer is formed in the semiconductorlayer, so that the breakdown voltage of the semiconductor device is improved.

Owner:GPOWER SEMICON

GaN-based heterojunction field effect transistor and manufacturing method thereof

PendingCN110444599AMeet application needsImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionPeak value

The invention is applicable to the technical field of semiconductor devices, and particularly relates to a GaN-based heterojunction field effect transistor and a manufacturing method thereof. The transistor sequentially comprises a substrate, a nucleating layer, a buffer layer, a channel layer, an insertion layer, a barrier layer, a source electrode, a grid electrode and a drain electrode from bottom to top, wherein the source electrode, the grid electrode and the drain electrode are arranged on the barrier layer. Passivation layers are arranged between the source electrode and the grid electrode and between the grid electrode and the drain electrode on the barrier layer. Field plates are arranged on the passivation layers. The forming material of the barrier layer includes: B (Al, Ga, In)N. The forbidden band width of the barrier layer is larger than the forbidden band width of the channel layer and smaller than the forbidden band width of the insertion layer. A heterojunction interface formed by the barrier layer made of the B (Al, Ga, In) N materials is large in band gap difference. The barrier layer has super-large polarization field intensity, very high two-dimensional electron gas concentration can be obtained, and the high-frequency requirement of a device is met. Through the field plates, the electric field peak value of the grid edge can be reduced, the channel electric field distribution uniformity of the device is improved, the breakdown voltage of the device is increased and the high-voltage requirements are met.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

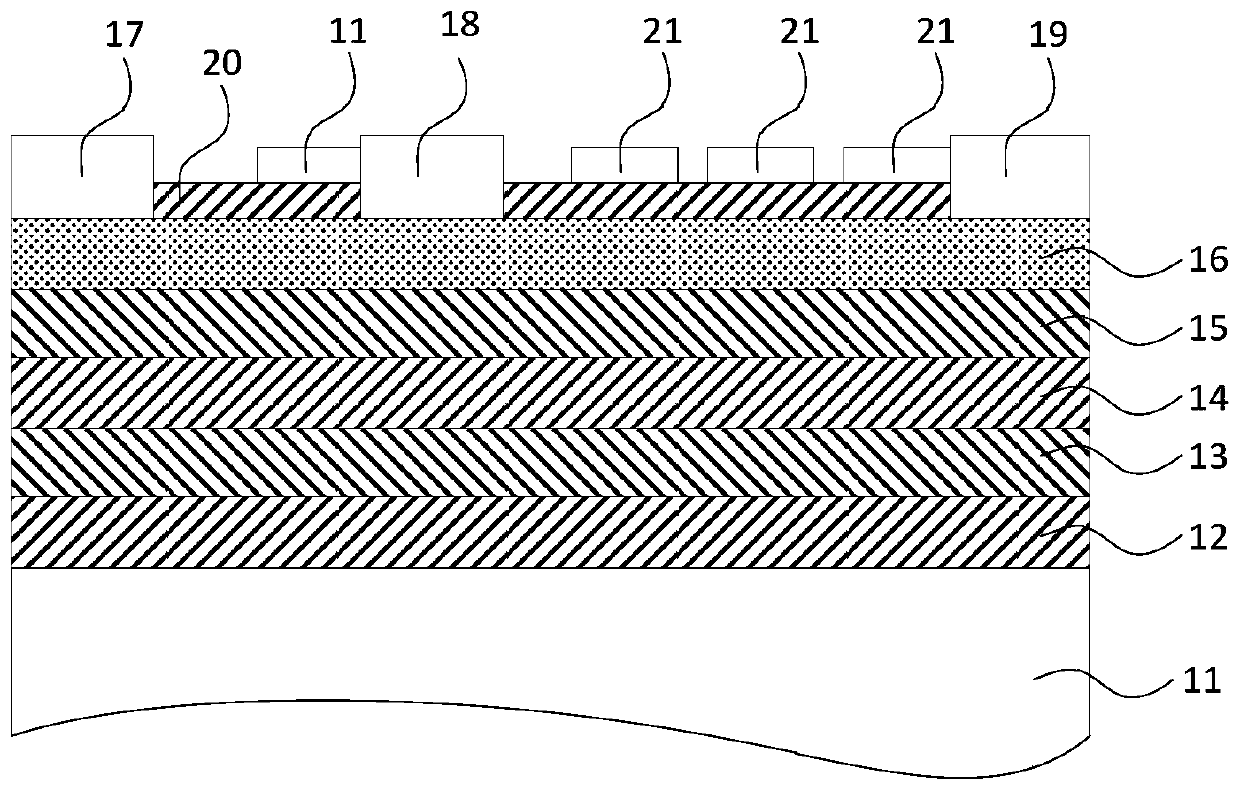

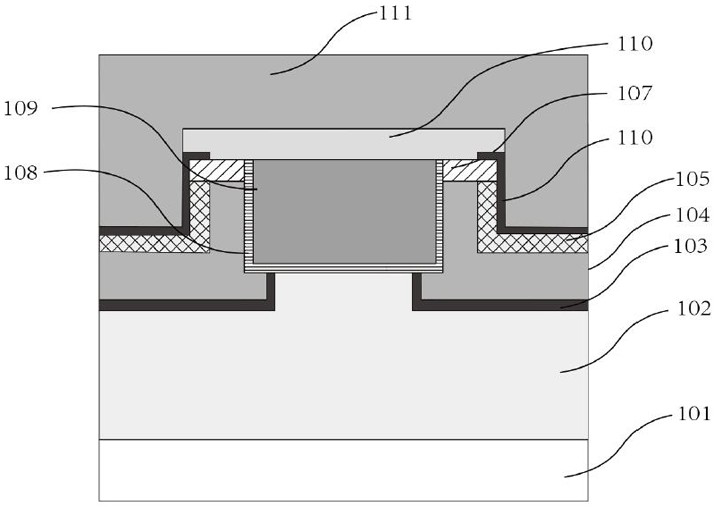

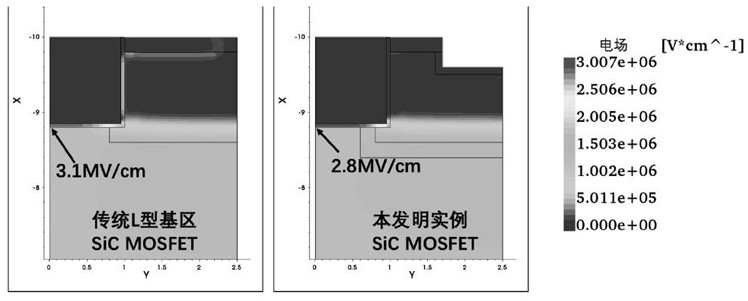

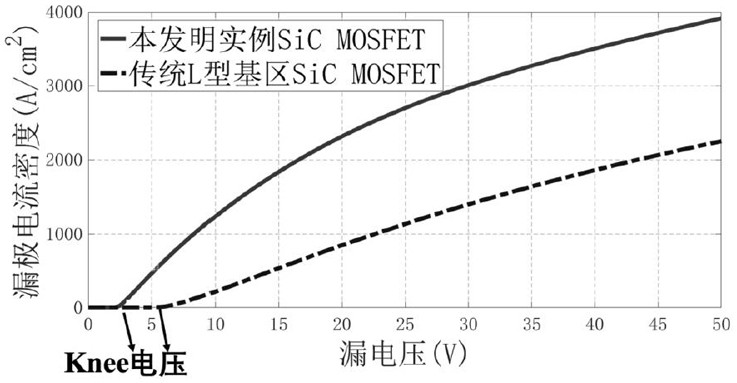

L-type base region SiC MOSFET cellular structure, device and manufacturing method

ActiveCN114023810AReduce horizontal expansionImprove shielding effectSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

The invention discloses an L-type base region SiC MOSFET cellular structure, a device and a manufacturing method. The L-type base region SiC MOSFET cellular structure comprises an N++ SiC substrate, an N- SiC drift layer, a P-type base region and an N+ source region. The N- SiC drift layer is located above the N++ SiC substrate, a source trench and a gate trench are formed in the N- SiC drift layer, and a gate dielectric layer and a gate electrode are arranged in the gate trench. The P-type base region and the N+ source region are positioned on the N- SiC drift layer between the source trench and the gate trench and are arranged from bottom to top, an N-type current conducting layer is arranged between the P-type base region and the N- SiC drift layer, and a source N+ ohmic contact region is arranged between the P-type base region and the source trench. According to the device structure, the on resistance and the gate-drain capacitance can be further reduced, the conduction loss and the switching loss can be reduced, the working frequency can be improved, the premature breakdown of the P-type base region can be avoided, and the reliability of the device can be ensured.

Owner:北京昕感科技有限责任公司

High performance SOI non-junction transistor of non-monolithic substrate insulation layer thickness

InactiveCN104538443AAchieve local enhancementReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerVoltage regulation

The invention relates to a high performance SOI non-junction transistor of a non-monolithic substrate insulation layer thickness. An employed SOI wafer insulation layer thickness is not single-valued in the unit length of a transistor. By properly increasing the thickness of the parts, near a source region and a drain region, of an SOI wafer insulation layer, the resistance of the source region and the drain region is greatly reduced, and the positive onset property of a component is greatly improved. By properly decreasing the thickness of the parts, under corresponding gate electrodes, of the SOI wafer insulation layer, local enhancement on the voltage regulating effect of a substrate can be achieved, the substrate voltage bias needed for auxiliary grid control can be lowered, and voltage control over the lower part of the substrate can be achieved. By optimizing the relative positions and sizes of the thicker part and the thinner part of the insulation layer of the SOI wafer, the reverse leakage current caused by band-to-band tunneling around the junctions of a component channel and drain electrodes when reversal of biasing of the gate electrodes occurs is effectively reduced. Therefore, the high performance SOI non-junction transistor is suitable for widespread application.

Owner:SHENYANG POLYTECHNIC UNIV

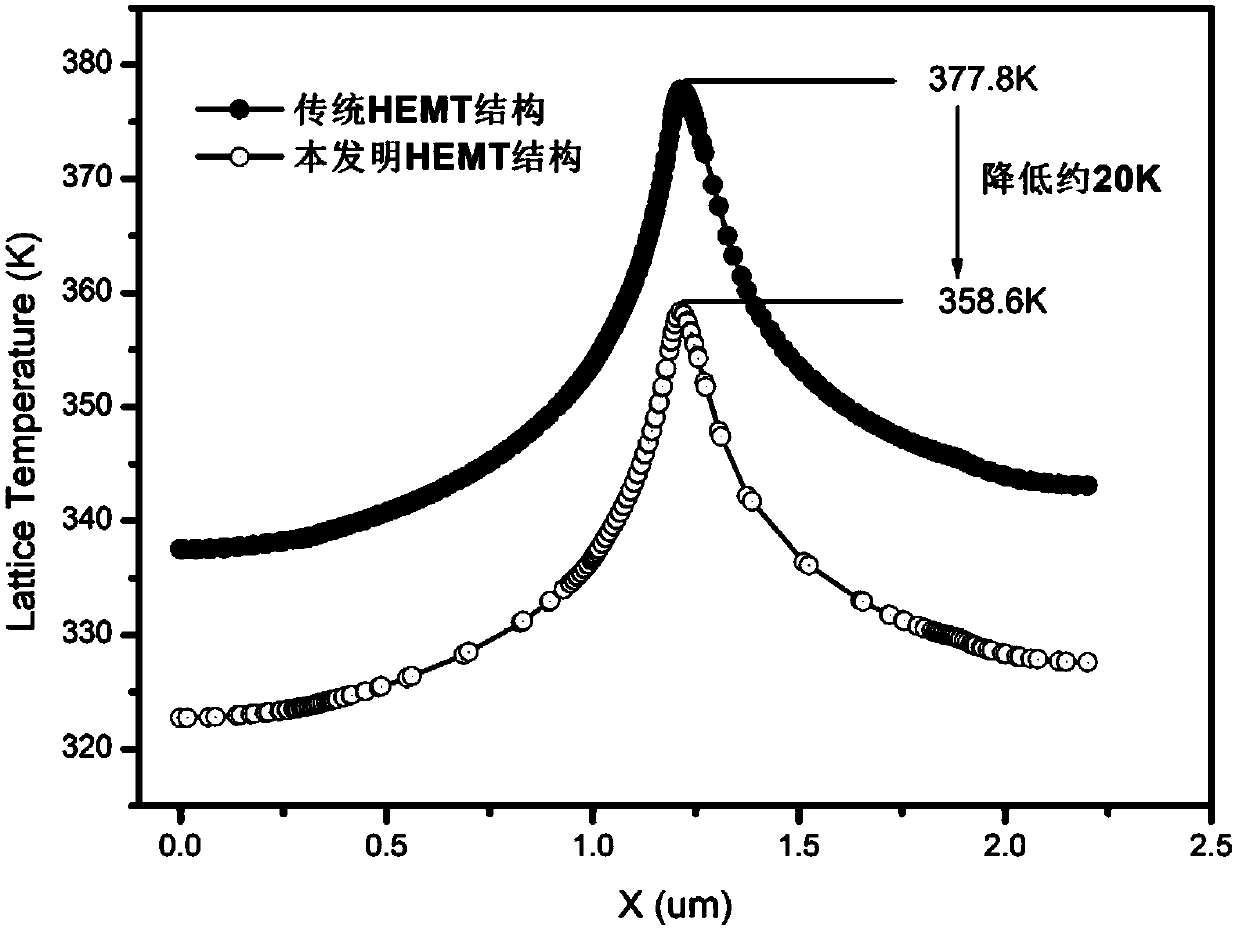

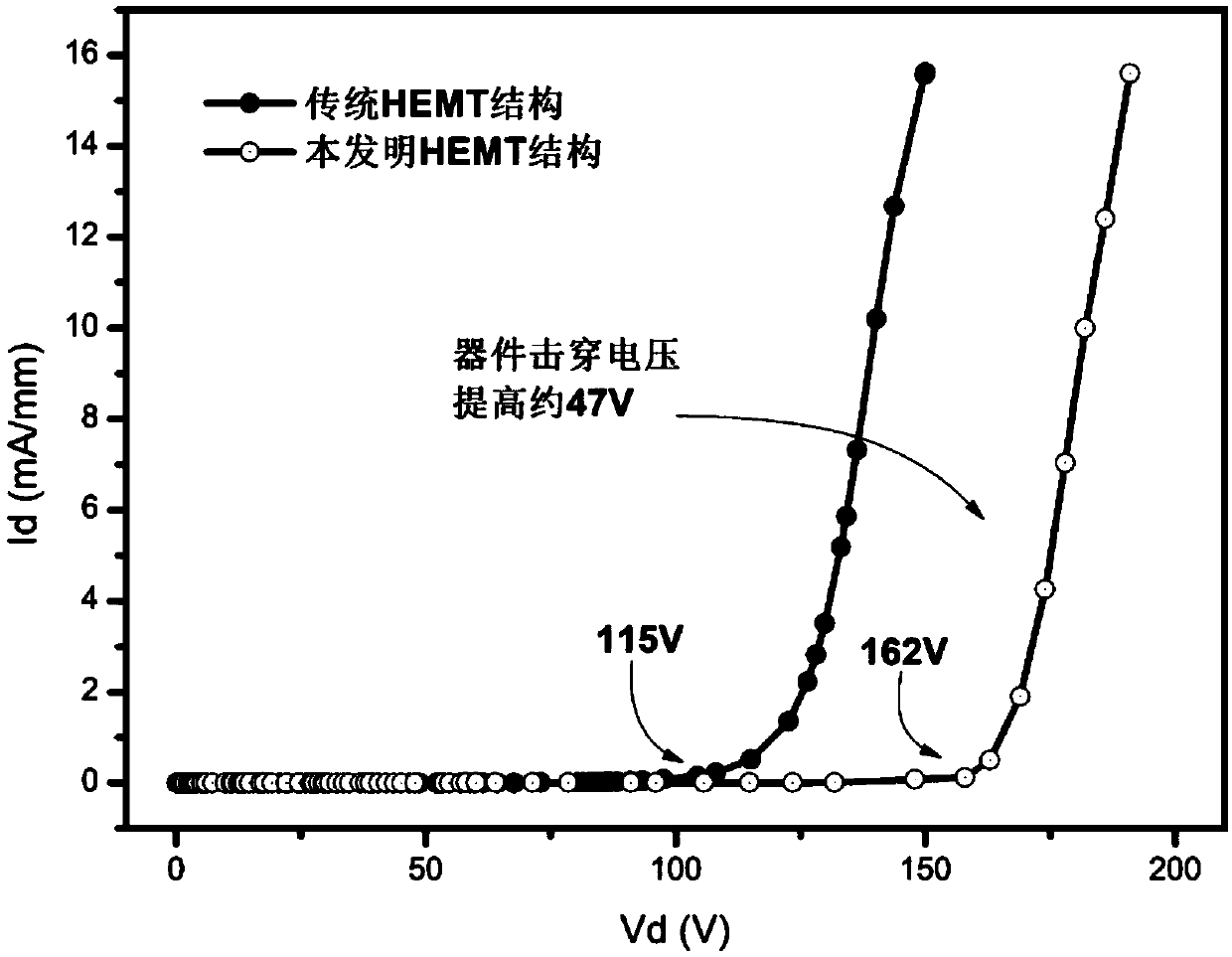

Low-junction-temperature and high-voltage-resistance GaN heterojunction field effect transistor

ActiveCN109671768AImprove efficiencyImprove linearityTransistorSemiconductor/solid-state device detailsHeat conductingJunction temperature

The invention relates to a power semiconductor technology, in particular to a low-junction-temperature and high-voltage-resistance GaN heterojunction field effect transistor. According to the low-junction-temperature and high-voltage-resistance GaN heterojunction field effect transistor provided by the invention, an AlN region is mainly inserted into a barrier layer to reduce a channel peak valveelectric field, so that the aims of increasing the voltage resistance and reducing the heat dissipation are realized. Furthermore, AlN with a good heat-conducting property is used as a passivation layer of a device, so that the current collapse is favorably inhibited and the effect of accelerating heat dissipation is also realized. The low-junction-temperature and high-voltage-resistance GaN heterojunction field effect transistor has the excellent effects that reverse voltage resistance of the device is improved, output properties of the device are improved and the channel temperature of the device is reduced, so that dangers caused by the current collapse and a self-heating effect are inhibited. The invention is especially applicable to the GaN heterojunction field effect transistor witha high-voltage-resistance capability and low channel temperature.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

HEMT device with multi-metal gate structure and preparation method thereof

PendingCN111403479AImprove breakdown voltageReduces the effects of current collapseSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention discloses an HEMT device with a multi-metal gate structure and a preparation method thereof. The device comprises an AlGaN / GaN epitaxy layer; the two ends of the upper surface of the AlGaN / GaN epitaxy layer are connected with a source electrode and a drain electrode respectively; a gate electrode is arranged between the source electrode and the drain electrode at the place close to the source electrode side; and a first layer of metal X of the gate electrode is deposited in an electron beam evaporation mode, a second layer of metal Y of the gate electrode is deposited in a magnetron sputtering mode, the work function of the second layer of metal Y of the gate electrode is higher than that of the first layer of metal X, photoetching is not needed, and a metal structure which is formed after the gate electrode is stripped and makes contact with (Al)GaN is Y / X / Y. The multi-metal gate structure is in contact with (Al)GaN, so that the electric field is redistributed, the peakvalue of the electric field at the gate edge near the drain is reduced, and the breakdown voltage of the device is improved; and meanwhile, the lower electric field peak value of the gate edge weakensgate injection electrons to form a virtual gate effect, so that current collapse of the device is reduced, and the dynamic performance of the device is improved.

Owner:ZHONGSHAN INST OF MODERN IND TECH SOUTH CHINA UNIV OF TECH +1

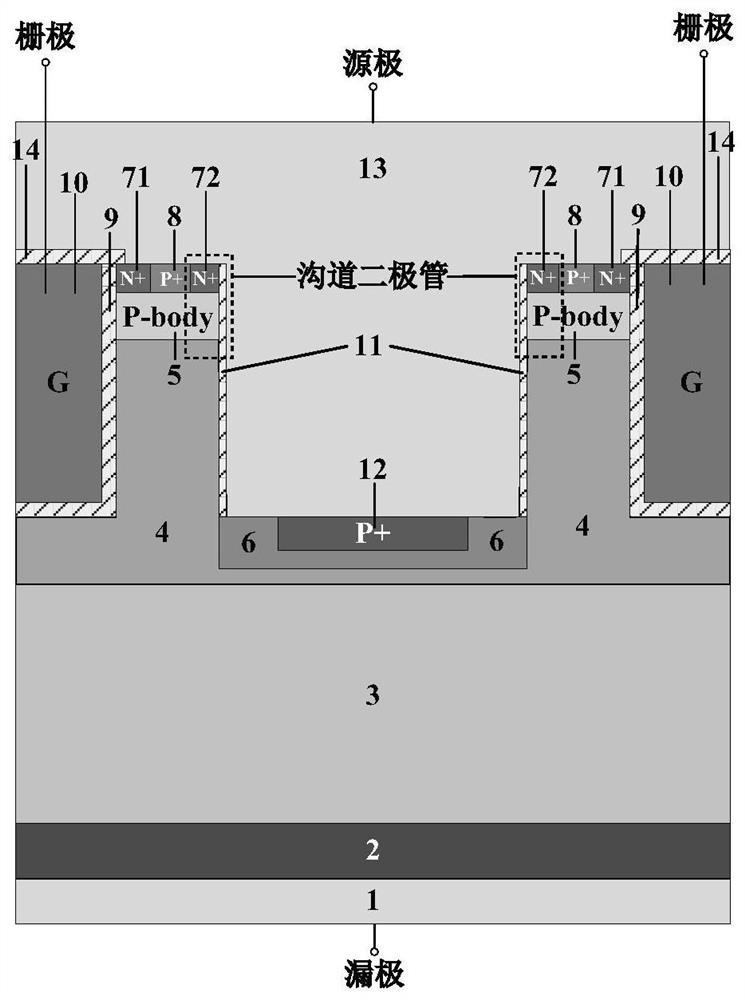

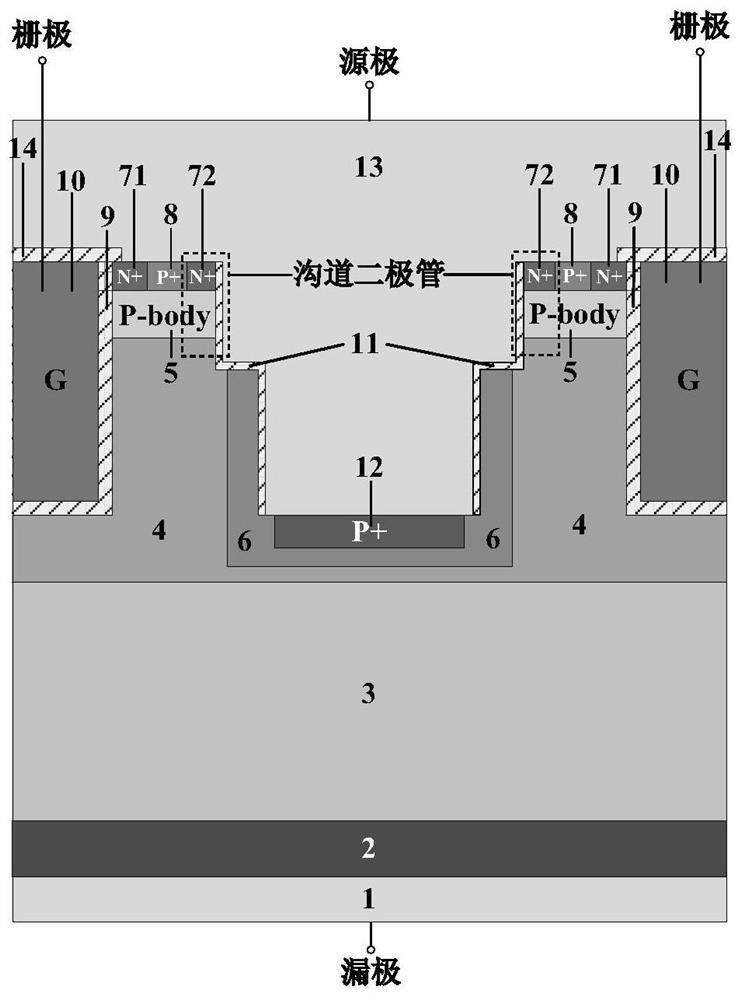

Silicon carbide double-groove MOSFET integrated with channel diode

ActiveCN113990923ASmall pressure dropImprove reliabilityEfficient power electronics conversionSolid-state devicesMOSFETCarbide silicon

The invention belongs to the technical field of power semiconductors, and particularly relates to a silicon carbide double-groove MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) integrated with an channel diode. The MOSFET is mainly characterized in that: firstly, a channel diode is integrated, when a device is in a follow current working mode, the channel diode is conducted to achieve a follow current function, conduction of a body diode is effectively restrained by reducing reverse conduction voltage drop, and meanwhile the influence caused by bipolar degradation is eliminated; and secondly, an electric field is modulated through a P-type region below the source groove, so that the peak of the electric field at the corner of silicon dioxide at the bottom of the gate groove is reduced, and the breakdown voltage and the reliability of the device in a blocking working mode are improved;.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

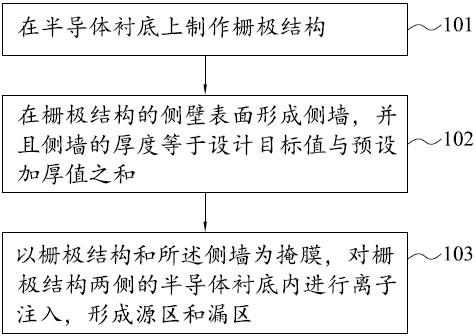

Semiconductor device forming method and semiconductor device

ActiveCN114334662AReduce electric field peaksImprove HCI effectSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

The invention discloses a forming method of a semiconductor device and the semiconductor device. The forming method comprises the following steps: manufacturing a gate structure on a semiconductor substrate; forming a side wall on the surface of the side wall of the gate structure, wherein the thickness of the side wall is equal to the sum of a design target value and a preset thickening value; and performing ion implantation in the semiconductor substrate at two sides of the gate structure by taking the gate structure and the side walls as masks to form a source region and a drain region. By thickening the side wall of the gate structure, the distance between the source and the drain of the semiconductor device is increased, so that the electric field peak value in a channel can be reduced, the HCI effect is improved, the method is simple to operate, and the cost is basically not increased.

Owner:GUANGZHOU CANSEMI TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com