Patents

Literature

85results about How to "Lower forward conduction resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

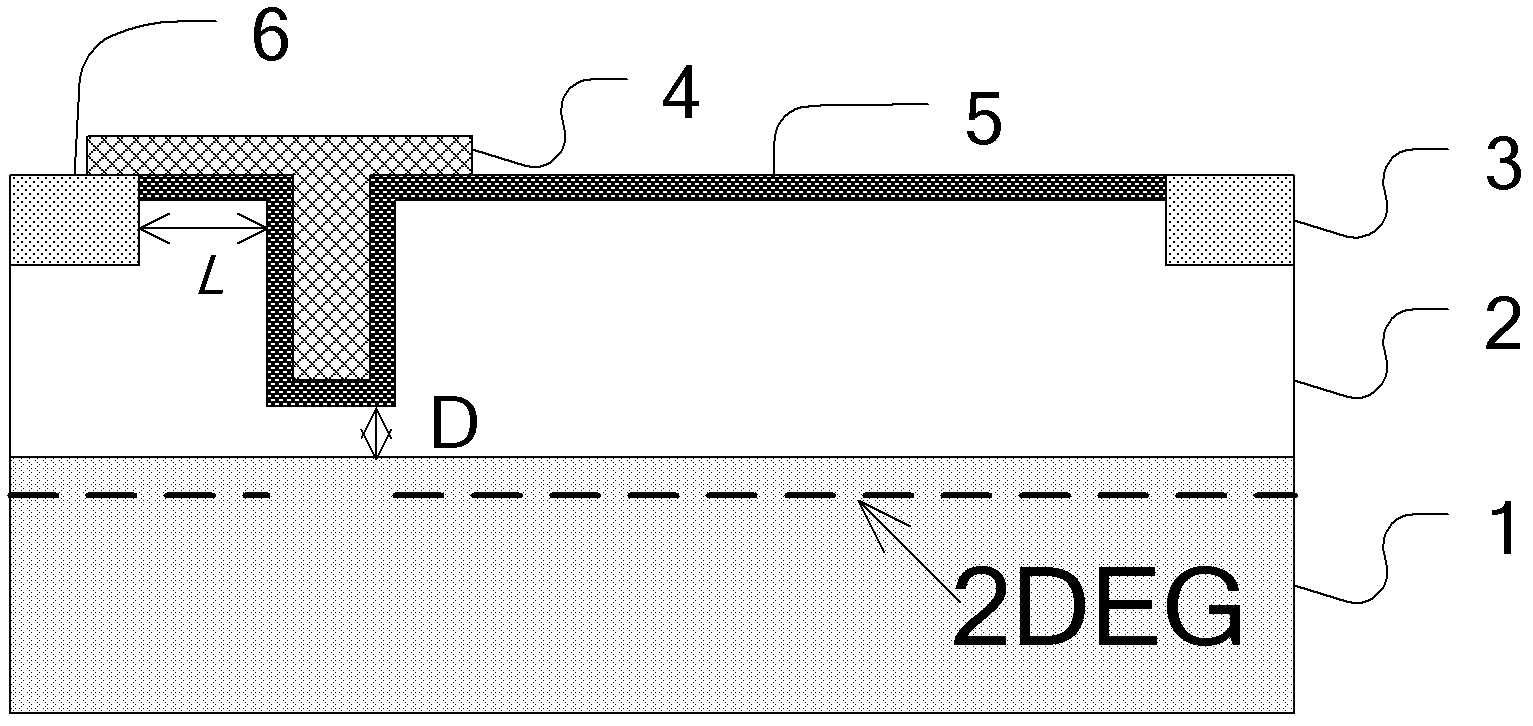

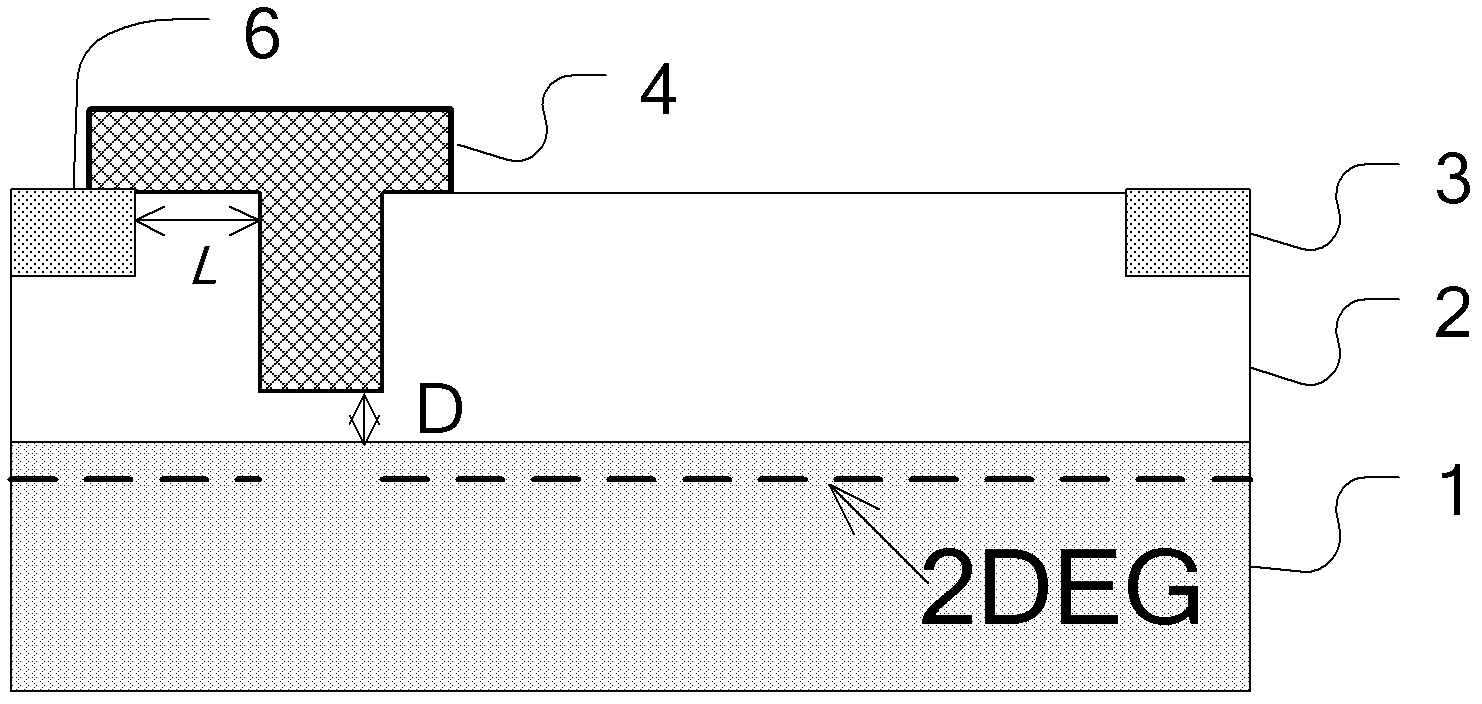

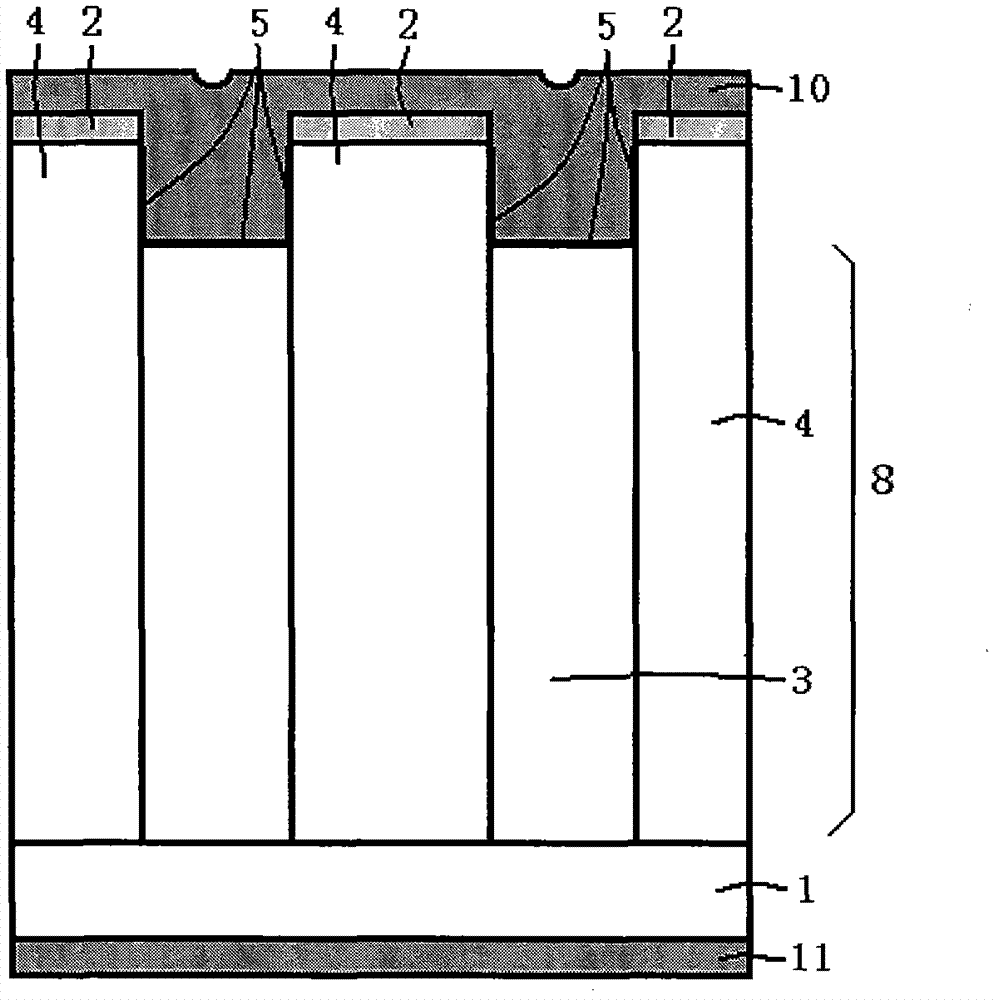

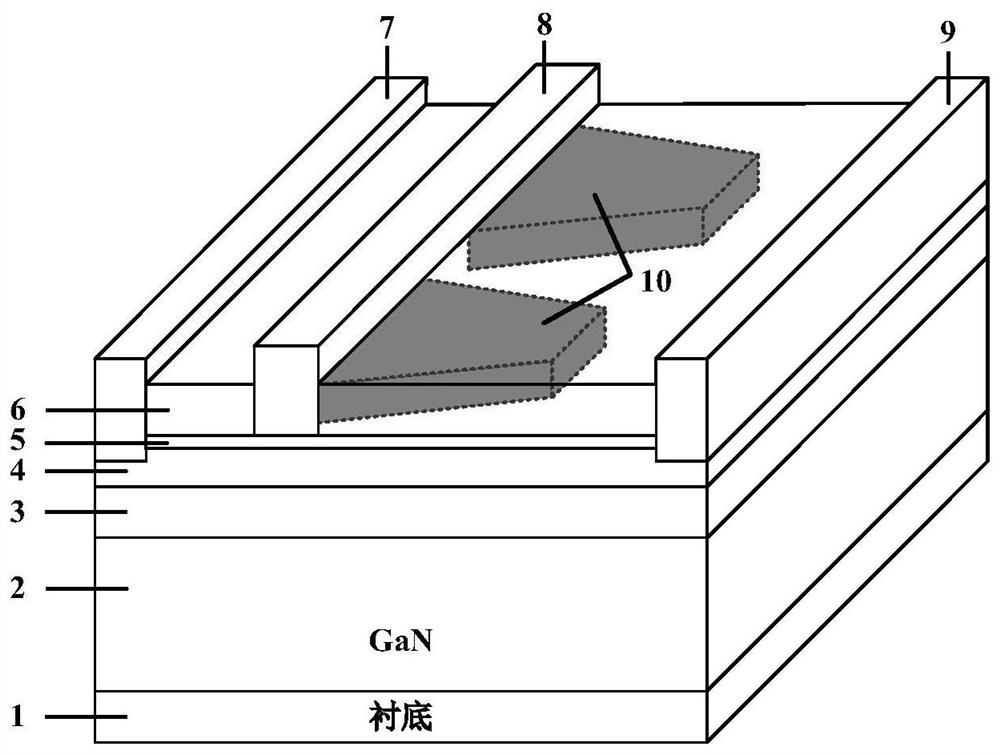

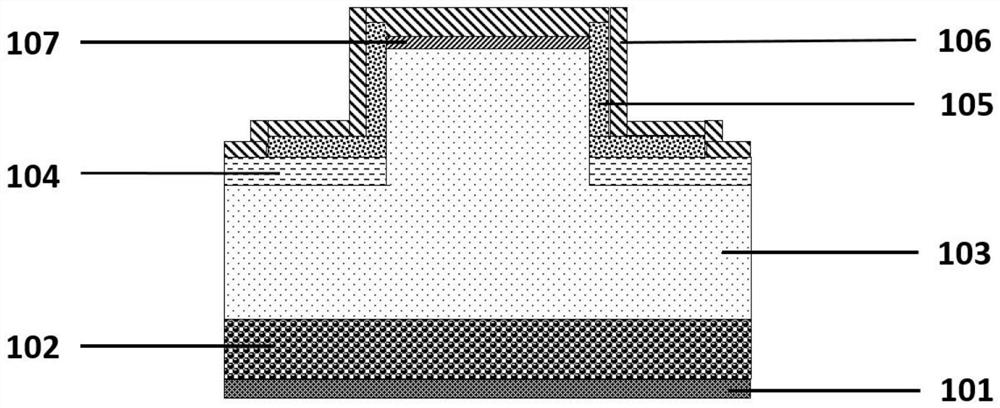

Normally-off field-controlled channel gan heterojunction diode

InactiveCN102280494AImplement field control featuresEfficient use ofSemiconductor devicesControl channelPositive power

A normally-off type field-controlled channel GaN heterojunction diode belongs to the technical field of semiconductor devices. The invention adopts the technology of combining insulating layer-groove, modulation doping and groove-modulation doping to change the conductive channel structure of the existing GaN heterojunction diode, and convert the original normally-on spontaneously polarized GaN heterojunction The junction conductive channel is changed into a normally-off field-controlled conductive channel combining spontaneous polarization and piezoelectric polarization in the present invention, which realizes the field-controlled characteristics of the GaN heterojunction diode conductive channel and reduces the forward conduction resistance and enhanced reverse cut-off capability. The invention has lower forward conduction resistance and power consumption, stronger reverse cut-off ability, and is compatible with AlGaN / GaN HEMT power switching device technology, which is beneficial to the application of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

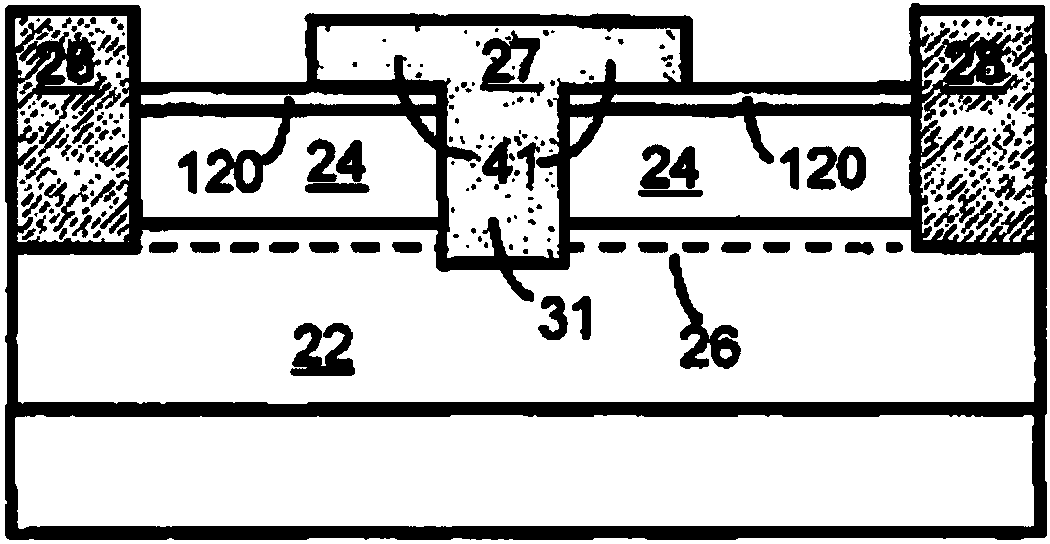

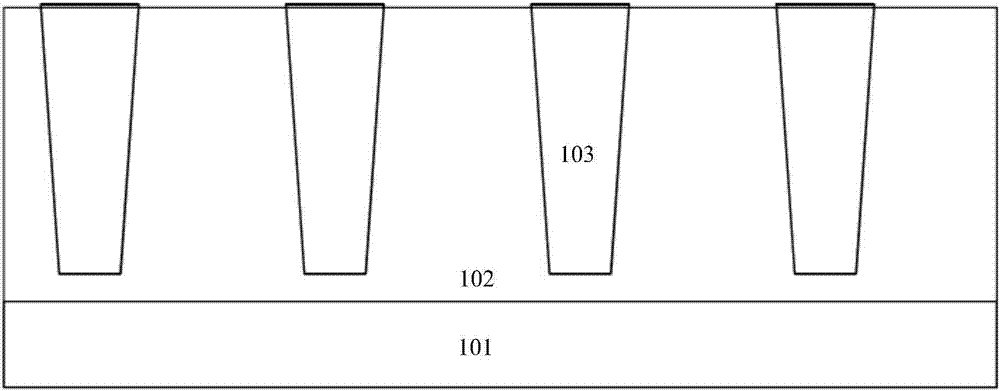

Schottky diode and manufacturing method for Schottky diode

InactiveCN104134704AIncrease widthReduce concentration effectSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSchottky diode

The invention provides a Schottky diode and a manufacturing method of the Schottky diode. The Schottky diode has the advantages that due to the fact that a groove structure with the wide upper portion and the narrow lower portion is mainly formed in a semiconductor layer, the concentration of two-dimensional electron gas below the Schottky metal inclined groove face can be effectively modulated, the Schottky barrier width and the Schottky barrier height can be increased, and therefore reverse electric leakage can be reduced; meanwhile, the concentration effect of an electric field at the edge of a groove can be further effectively improved, and the breakdown voltage of a device can be increased.

Owner:GPOWER SEMICON

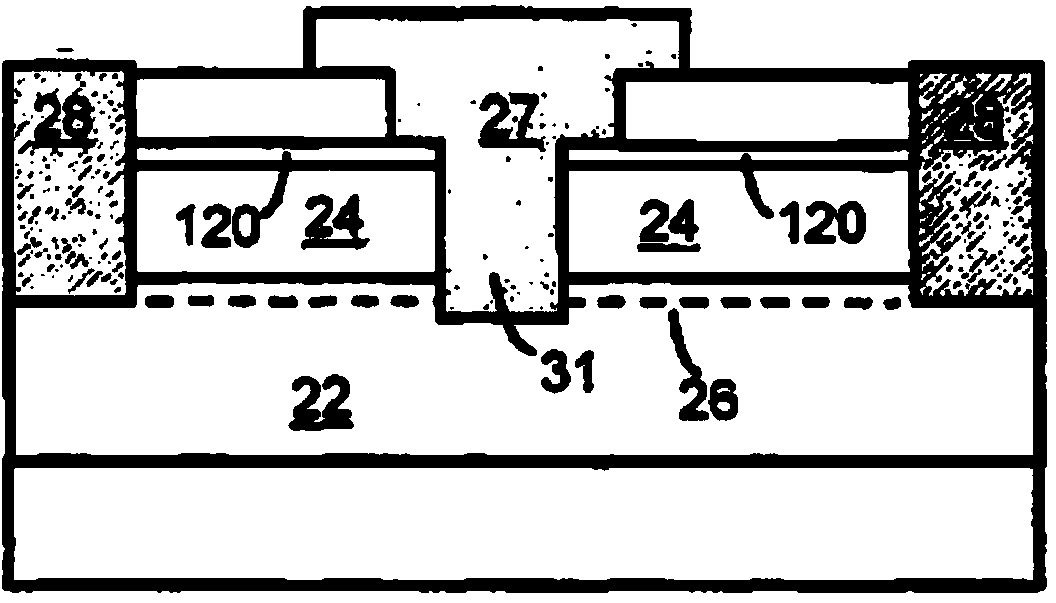

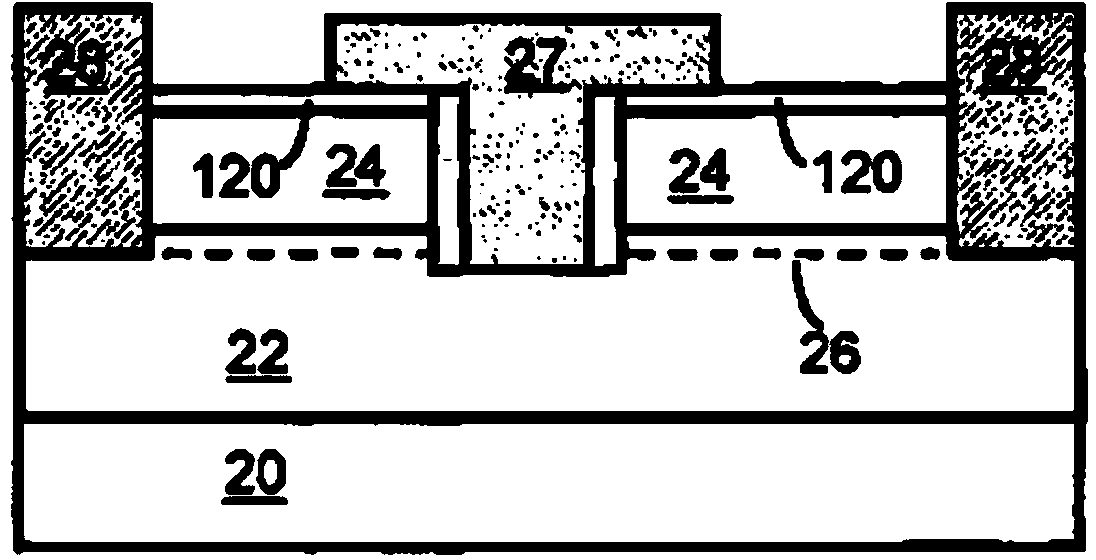

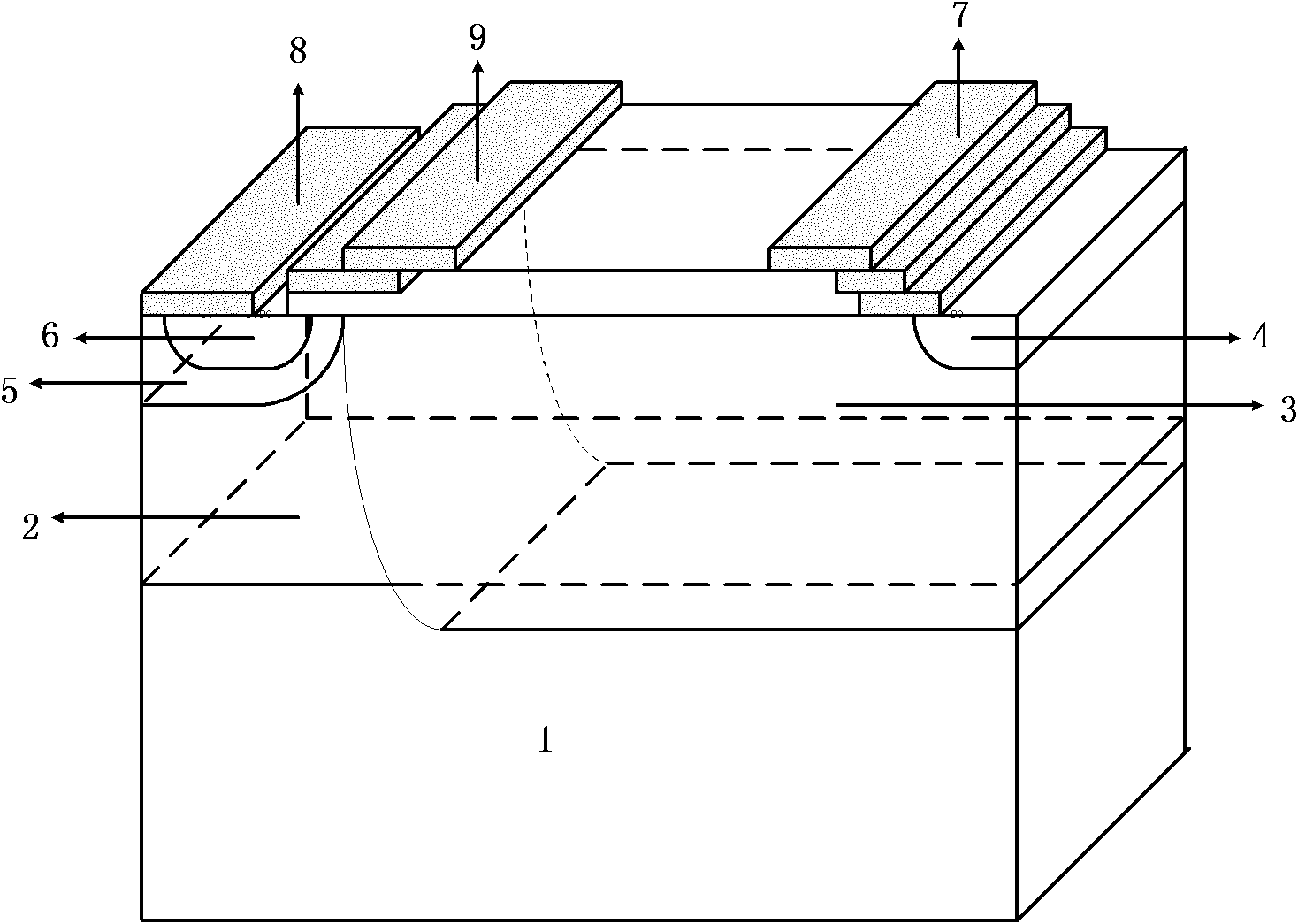

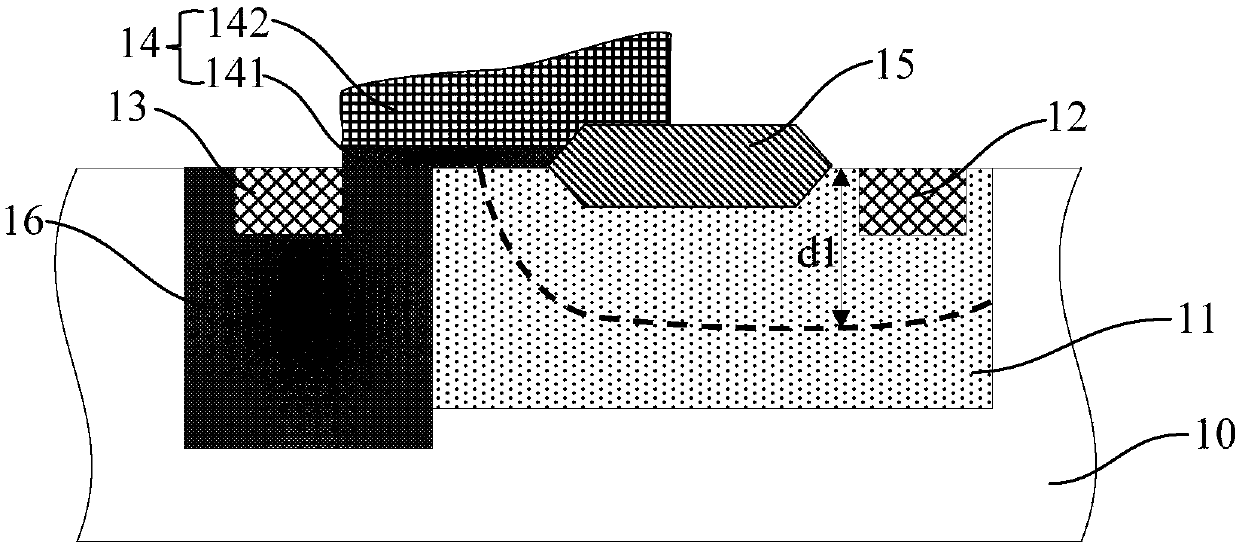

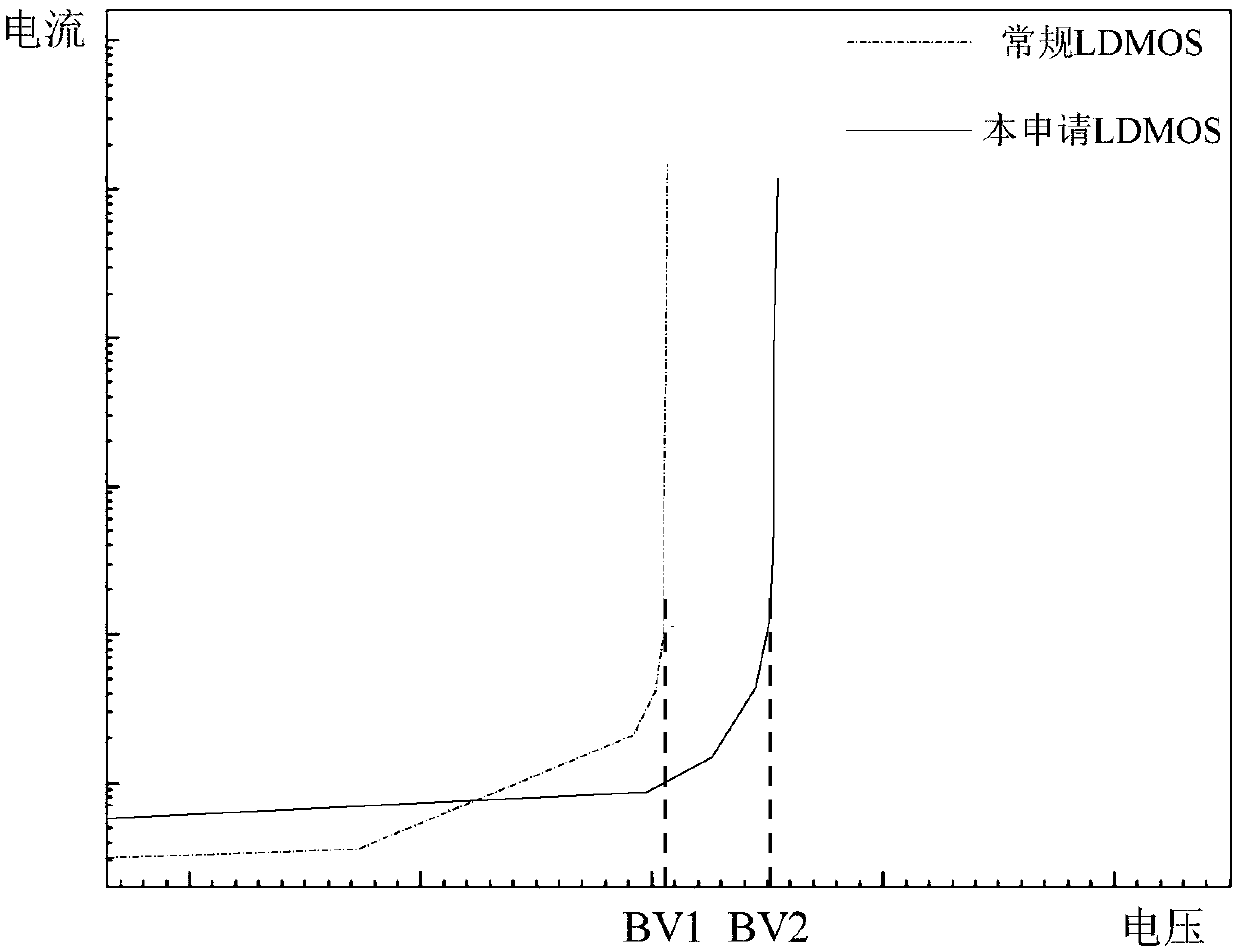

High-voltage LDMOS (landscape diffusion metal oxide semiconductor) device

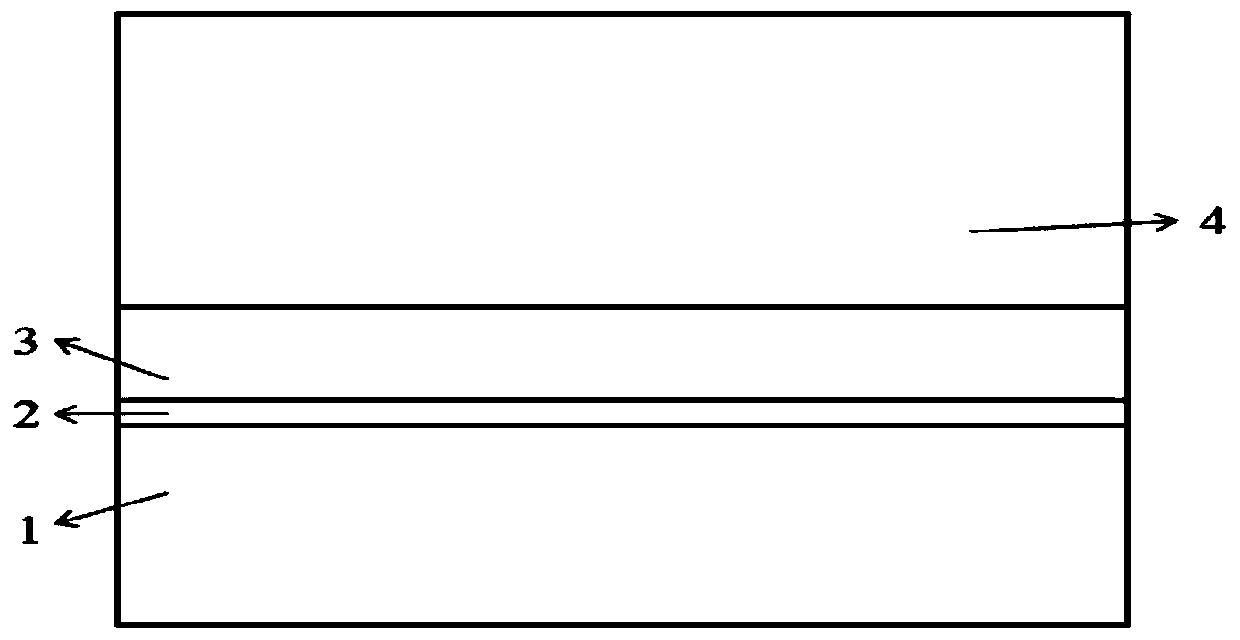

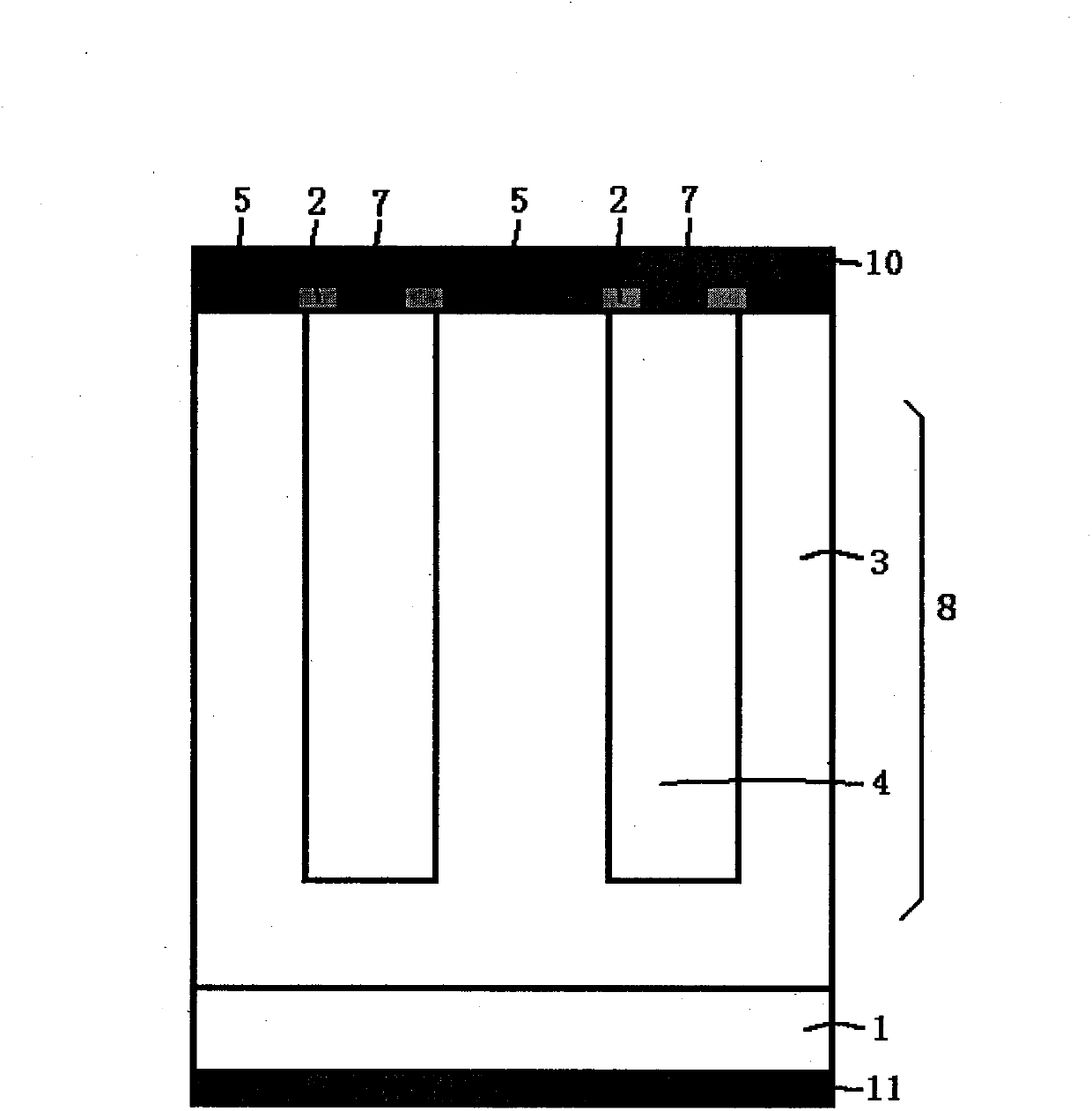

InactiveCN102157560ALower forward conduction resistanceImprove reverse withstand voltageSemiconductor devicesElectrical resistance and conductanceLDMOS

The invention relates to a high-voltage LDMOS (landscape diffusion metal oxide semiconductor) device which comprises a substrate, an epitaxial layer, a drift region, a drain region, a source region and at least one pair of n-type semiconductor regions and p-type semiconductor regions, wherein the epitaxial layer is positioned above the substrate; the drift region is positioned on one side, close to the drain region, of the epitaxial layer, and the lower surface of the drift region is coincided with the lower surface of the epitaxial layer; the drain region and the source region are positioned at two ends of the LDMOS device; at least one pair of the n-type semiconductor regions and the p-type semiconductor regions are arrayed alternatively, pass through the lower surface of the epitaxial layer on the border surface of the substrate and the epitaxial layer; the border surface of the n-type semiconductor regions and the p-type semiconductor regions is in parallel with the surface voltage drop direction of a power device in working; and the n-type semiconductor regions and the p-type semiconductor regions are arrayed closely, thus a PN junction is formed. The invention has the beneficial effects that the n-type semiconductor regions and the p-type semiconductor regions provided by the invention are named a bulk reduced surface field layer, and the contradiction of improving the reverse withstand voltage and reducing the positive conduction resistance of the existing LDMOS device is solved effectively by the LDMOS device with the bulk reduced surface field layer.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

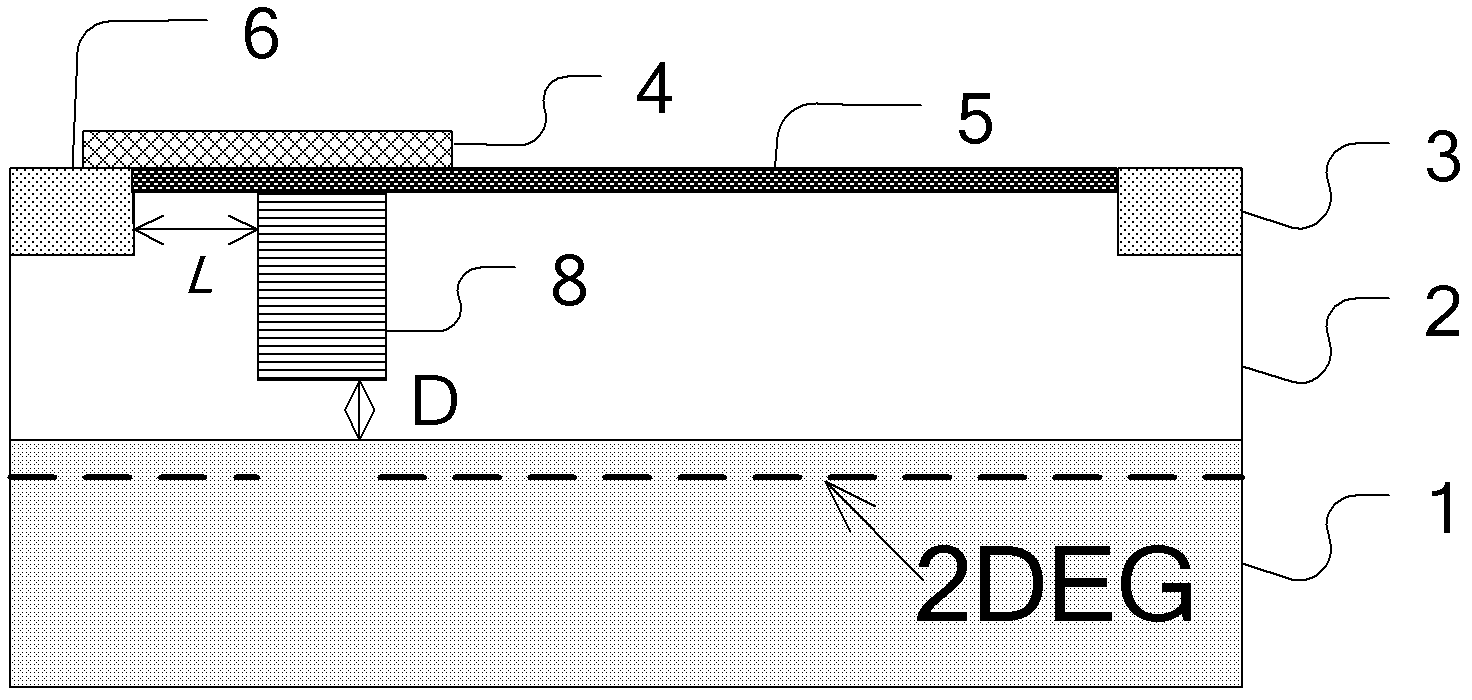

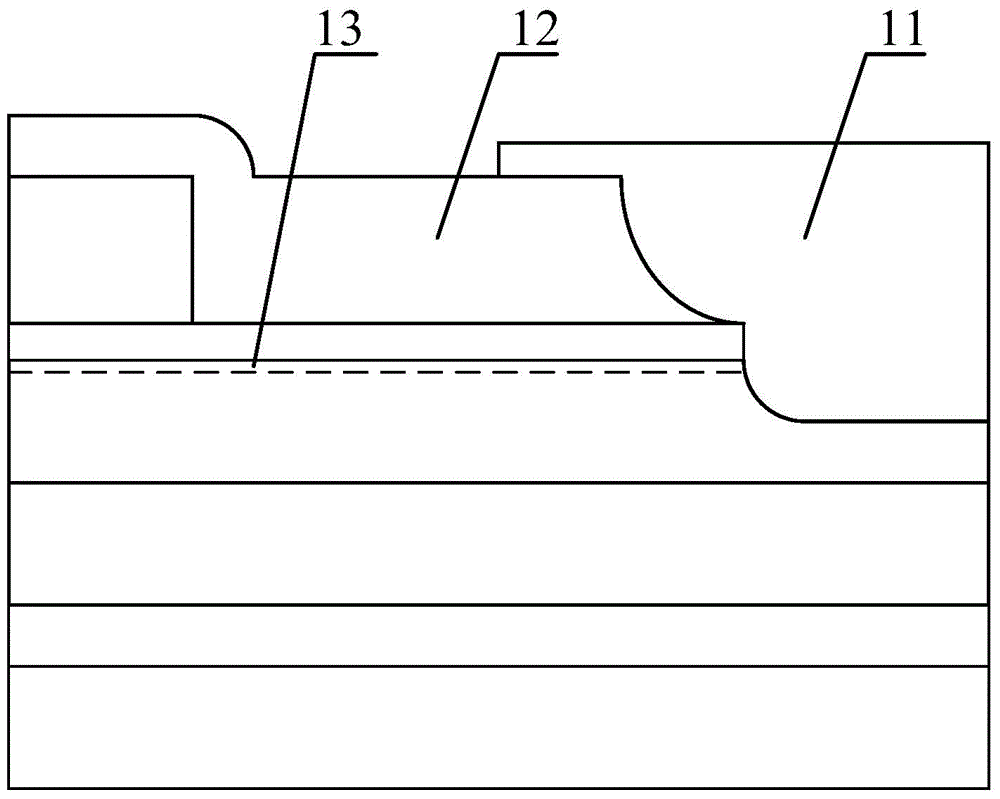

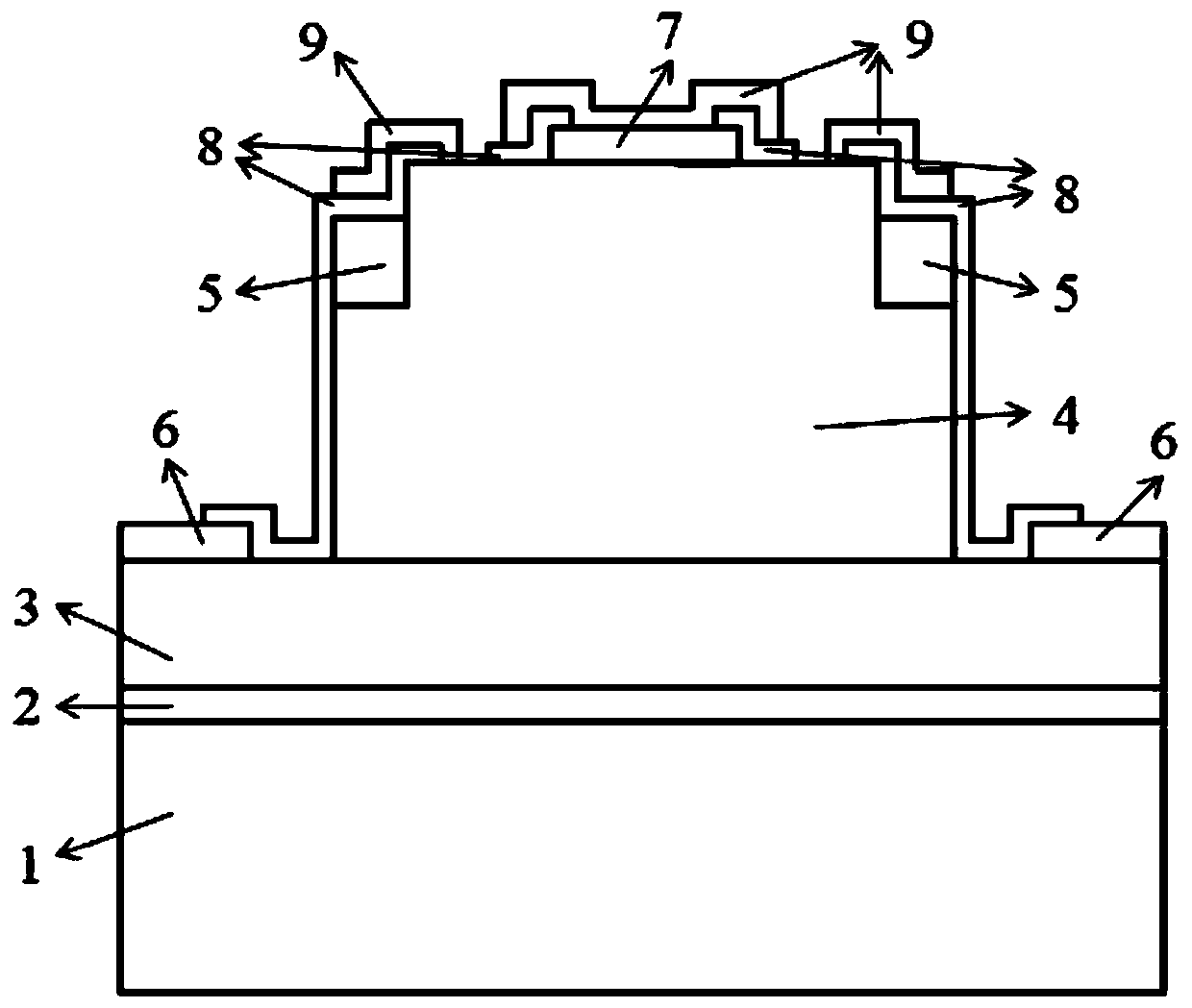

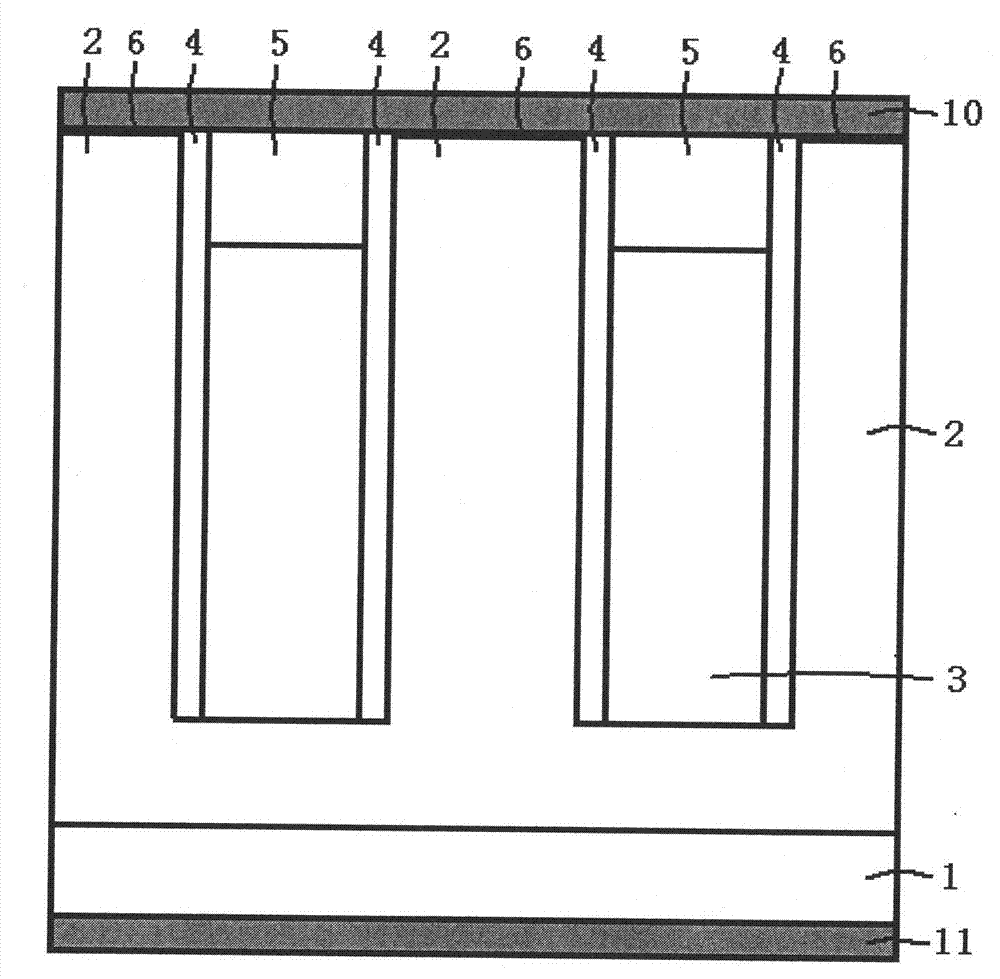

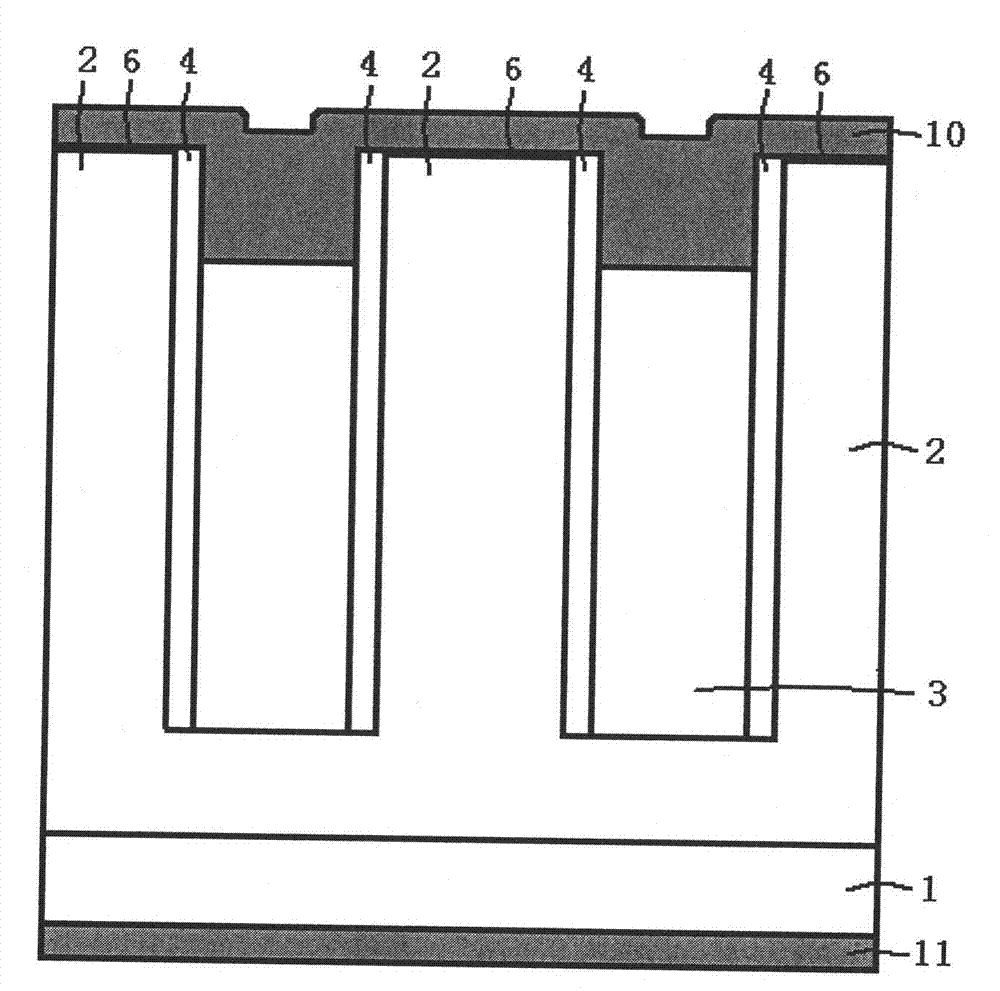

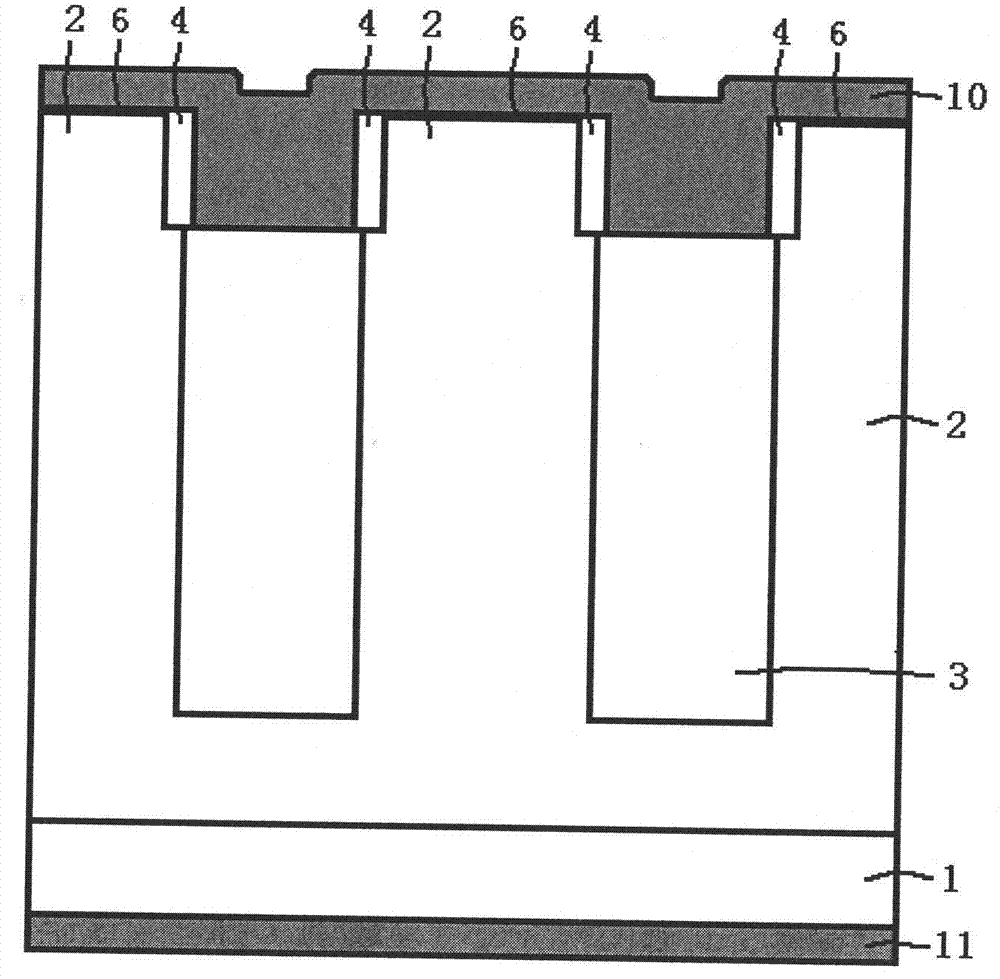

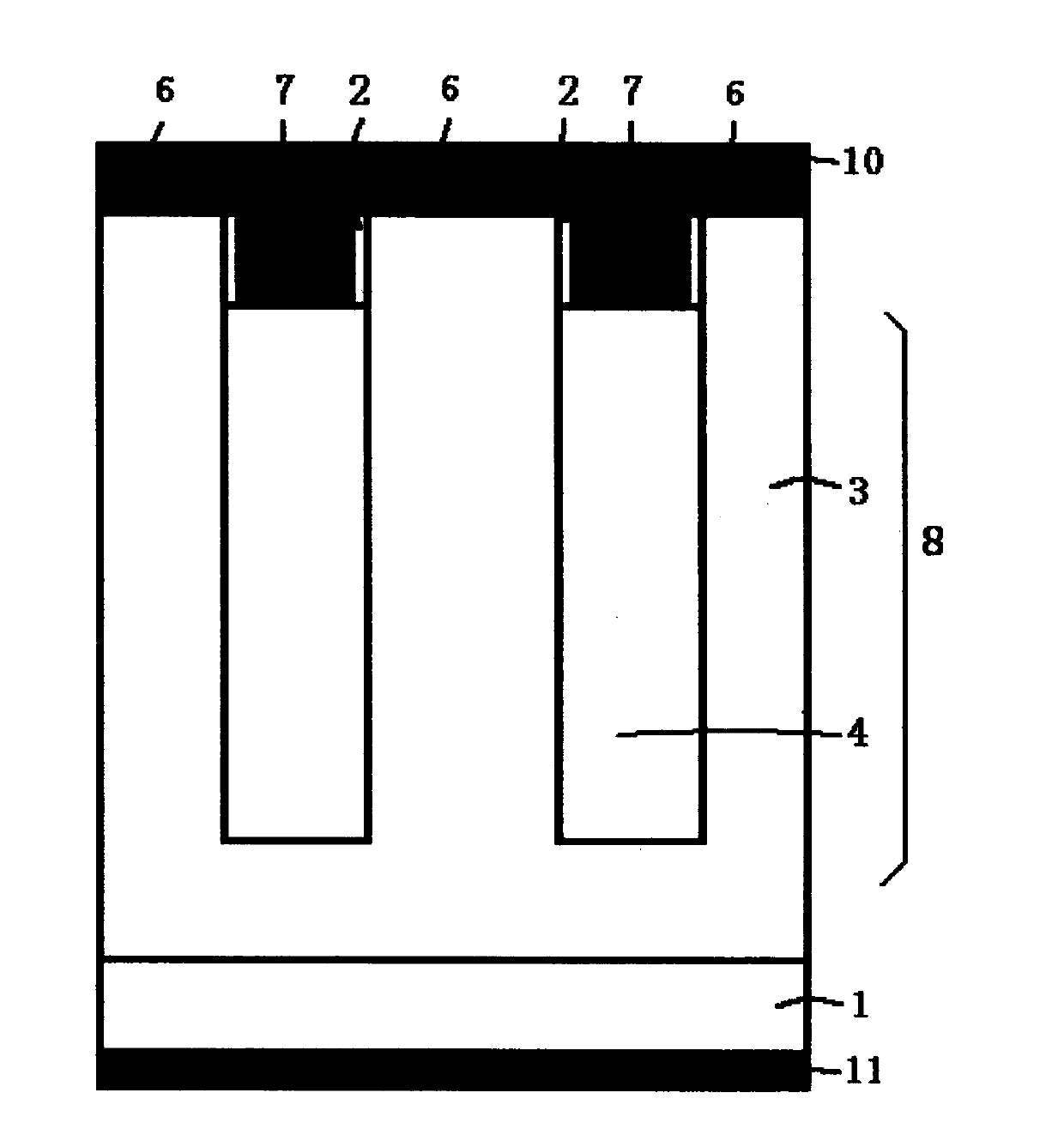

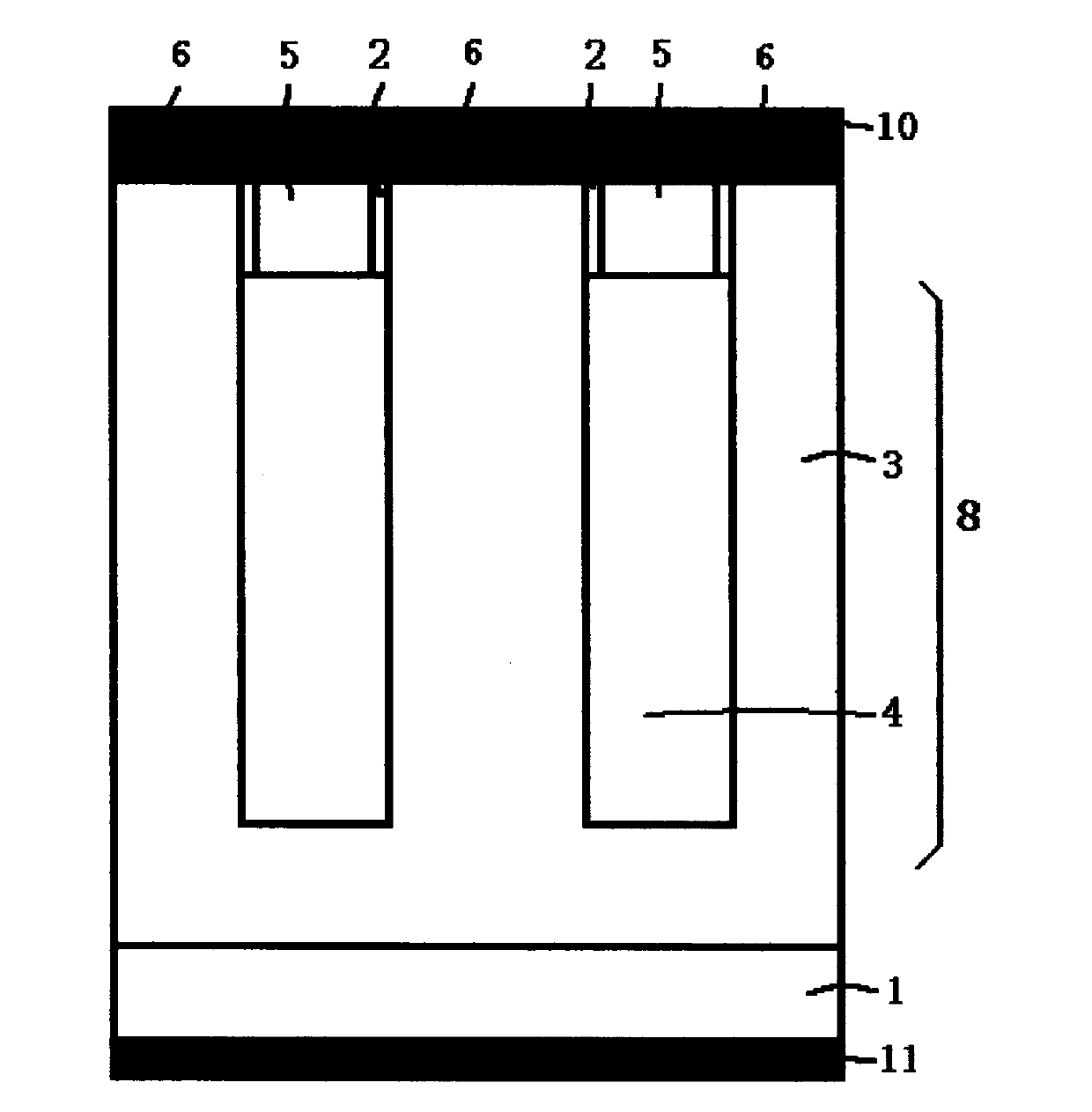

Schottky diode and manufacturing method thereof

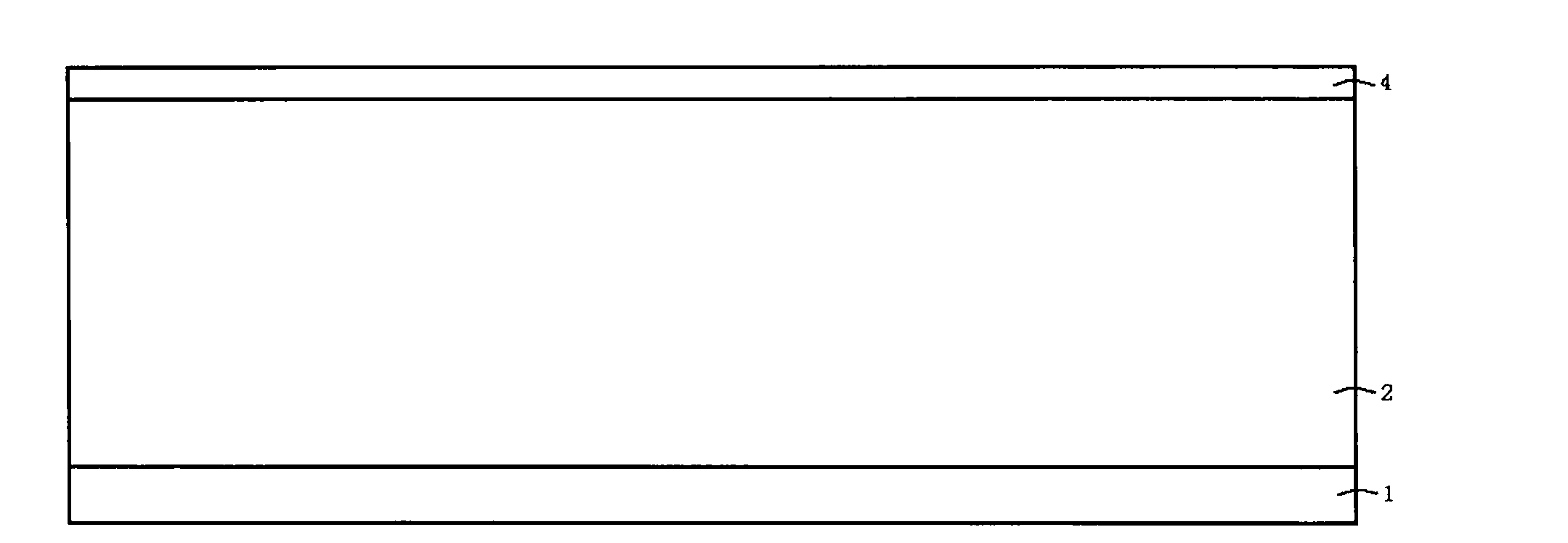

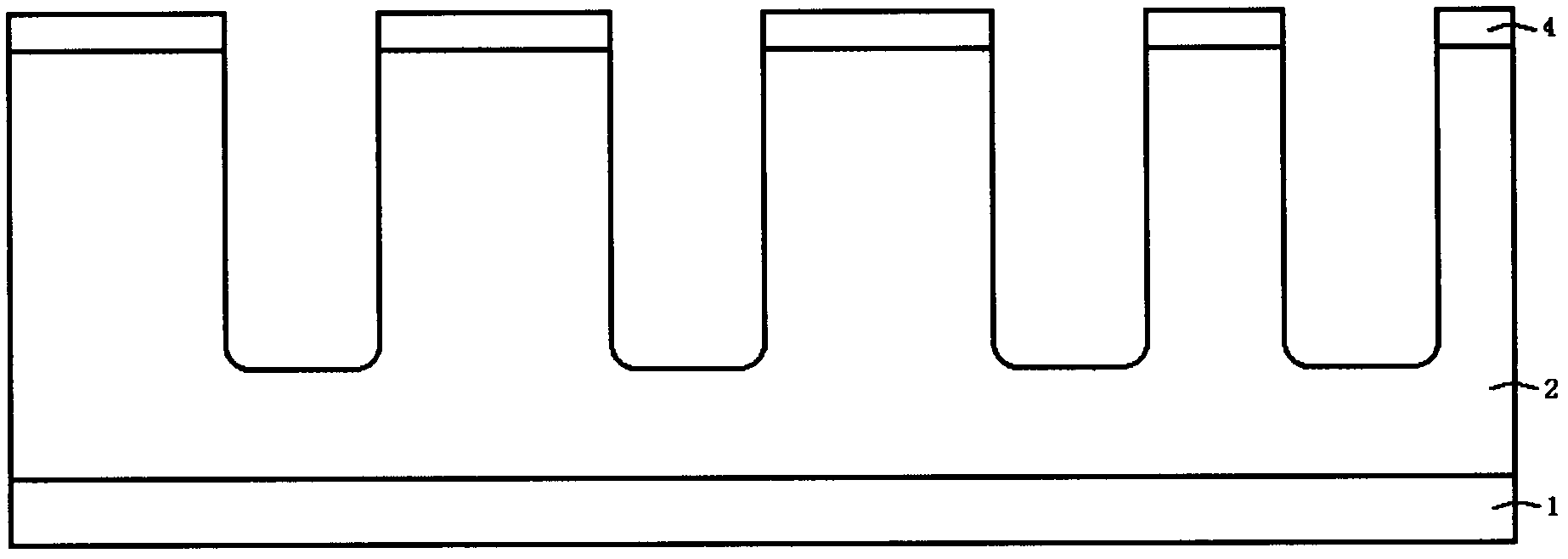

ActiveCN104465795ALow forward turn-on voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingDiodeElectrical conductorSchottky diode

The invention discloses a Schottky diode and a manufacturing method thereof. The Schottky diode comprises a substrate, a first semiconductor layer located on the substrate, a second semiconductor layer located on the first semiconductor layer, two-dimensional electron gas formed at the interface of the first semiconductor layer and the second semiconductor layer, a cathode located on the second semiconductor layer, a first passivation dielectric layer located on the second semiconductor layer, an anode groove located between the first passivation dielectric layer and the second semiconductor layer, a field plate groove located in the part, between the anode groove and the cathode, of the first passivation layer, and an anode covering the anode groove, the field plate groove and the part, between the anode groove and the field plate groove, of the first passivation dielectric layer. The Schottky diode has the advantages of being low in forward conduction voltage and reverse electric leakage and resistant to high voltage.

Owner:GPOWER SEMICON

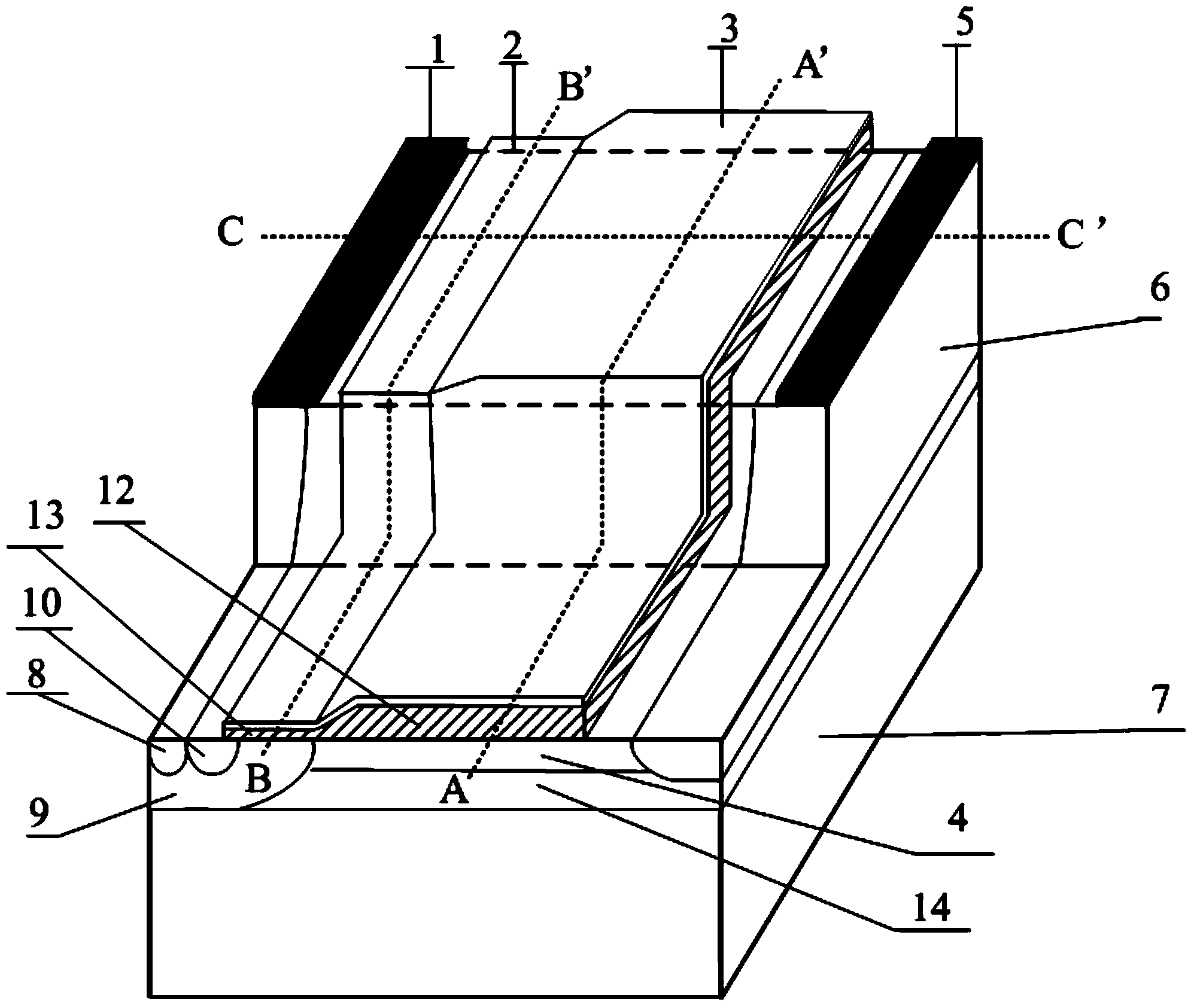

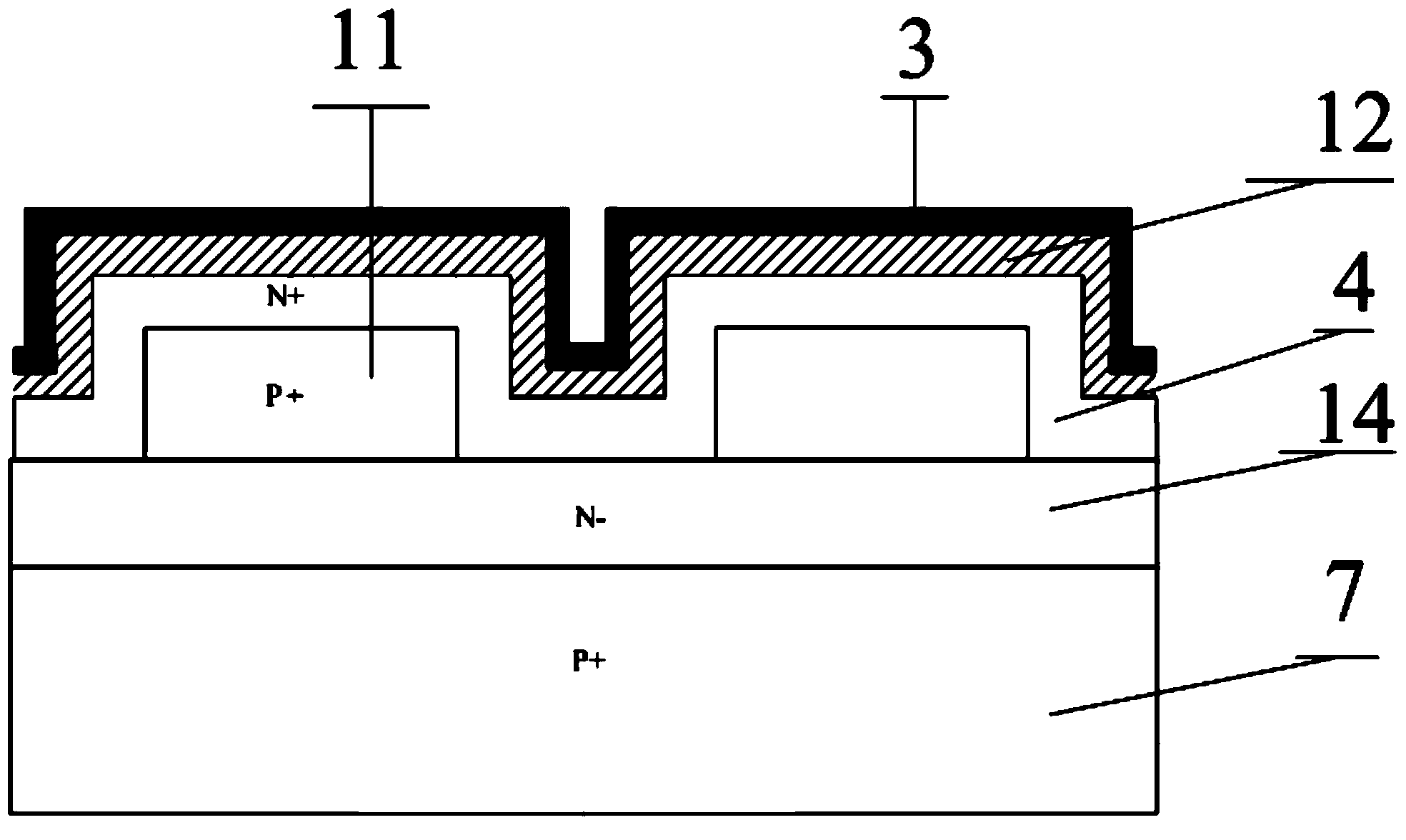

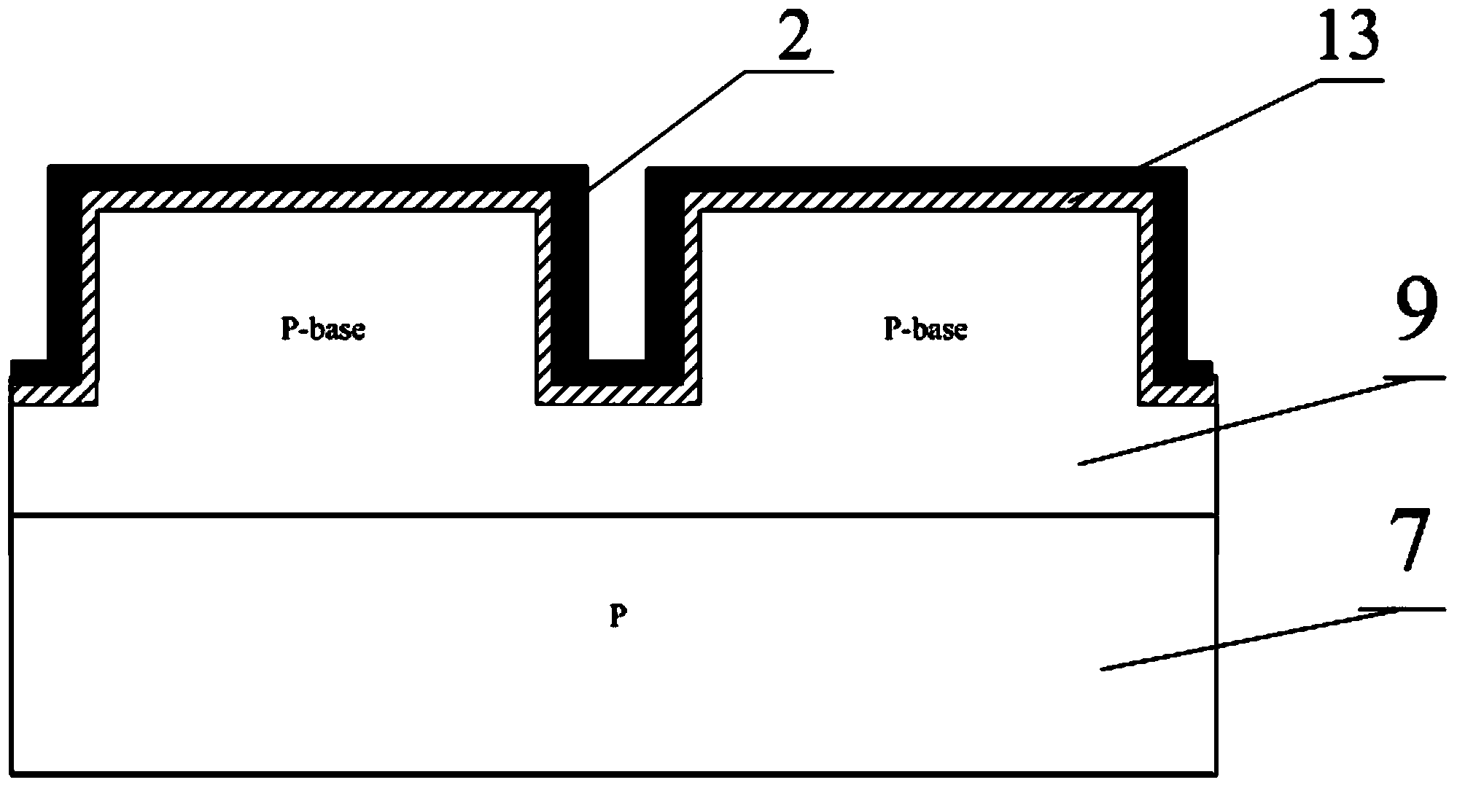

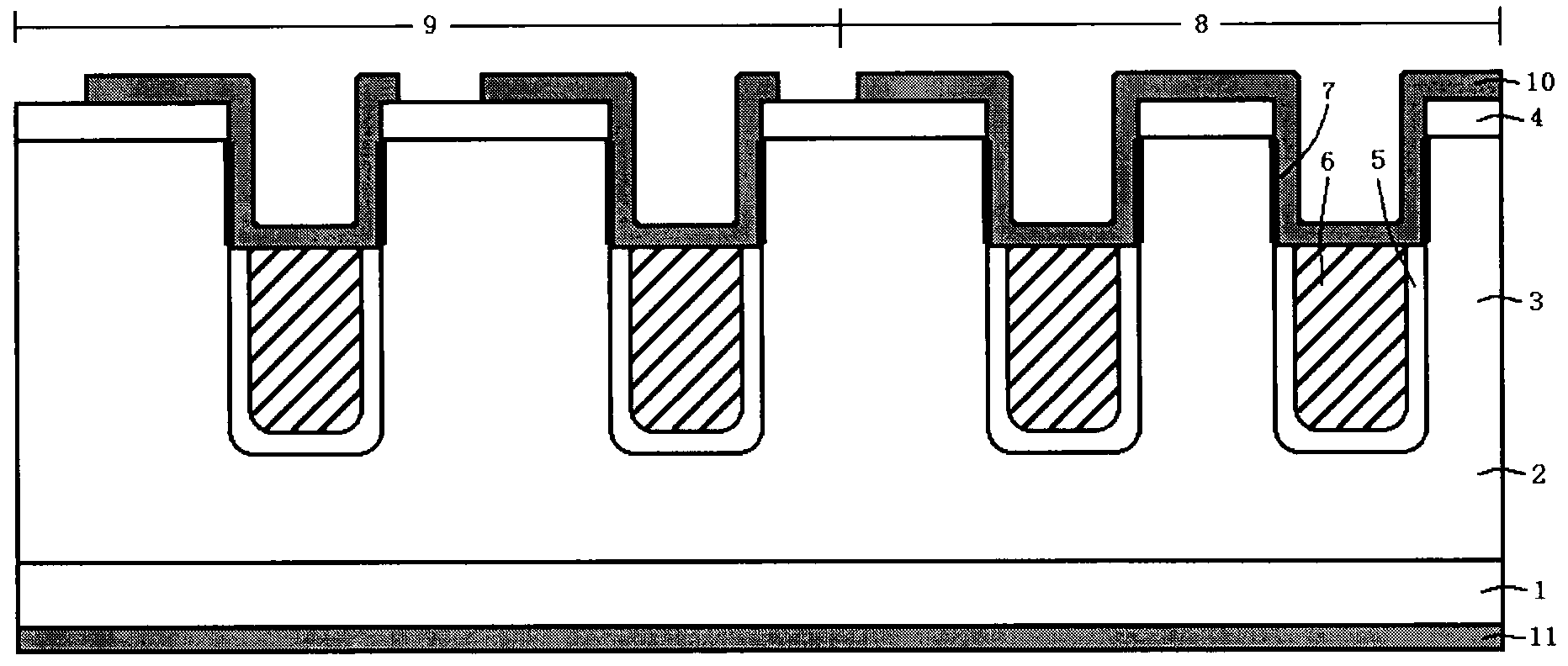

Super-junction power device and manufacturing method thereof

InactiveCN103515443AIncrease widthLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

The invention relates to technologies of power semiconductor devices, in particular to a transverse power device of a super junction structure and a manufacturing method of the transverse power device. The super-junction power device is characterized in that a second conductive type semiconductor drift region 4 and a first conductive type semiconductor body region 9 are provided with grooves, a thick oxidation layer 12 is arranged on the upper surface of the second conductive type semiconductor drift region 4 in a covering mode, a thin gate oxidation layer 13 is arranged on the upper surface of the first conductive type semiconductor body region 9 in a covering mode, and a gate electrode 2 is arranged on the upper surface of the thick oxidation layer 12 and the upper surface of the thin gate oxidation layer 13 in a covering mode. The super-junction power device has the advantages that the area of a channel of an accumulation layer of the surface of the drift region 4 is increased so that lower forward on-resistance can be achieved. The super-junction power device is particularly suitable for transverse power devices of the super junction structure.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Groove MOS (metal oxide semiconductor) structure Schottky diode and preparation method thereof

ActiveCN103022155AShorten the production cycleReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSemiconductor materials

The invention discloses a groove MOS (metal oxide semiconductor) structure Schottky diode. The electric field intensity distribution of a drifting region is changed through an MOS structure, so that a peak value electric field appears in a semiconductor material close to the bottom part of a groove, and does not appear close to a Schottky barrier junction. The invention also provides a preparation method, so that devices can be produced and manufactured through photolithographic processes twice.

Owner:ZHEJIANG UNIV

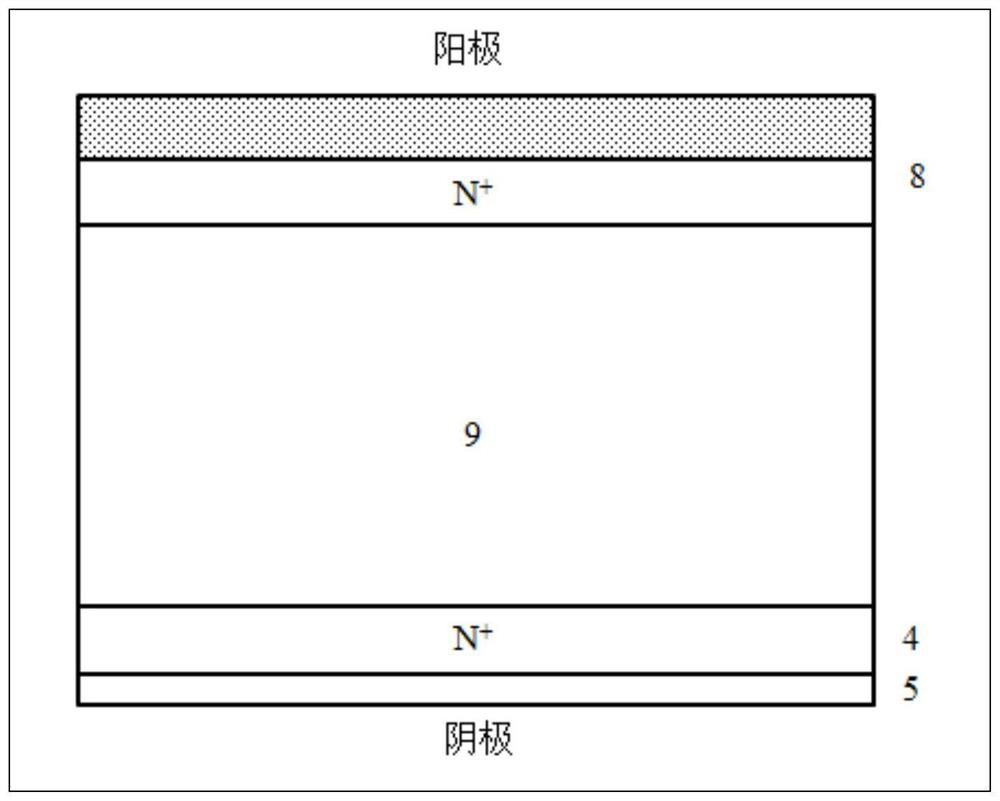

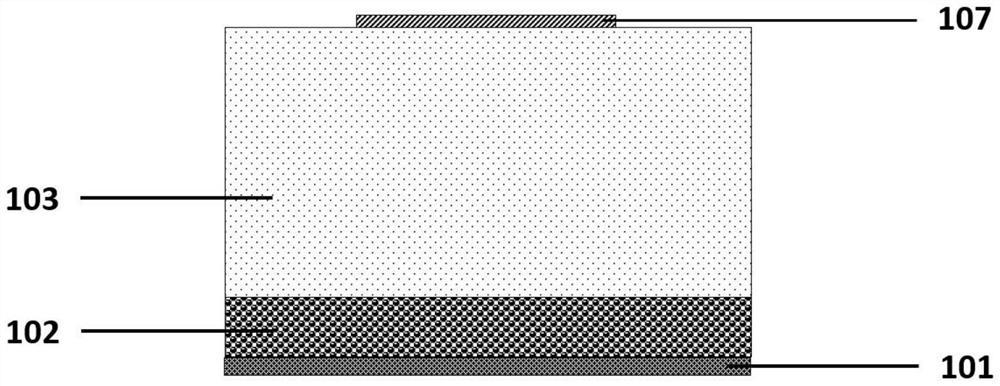

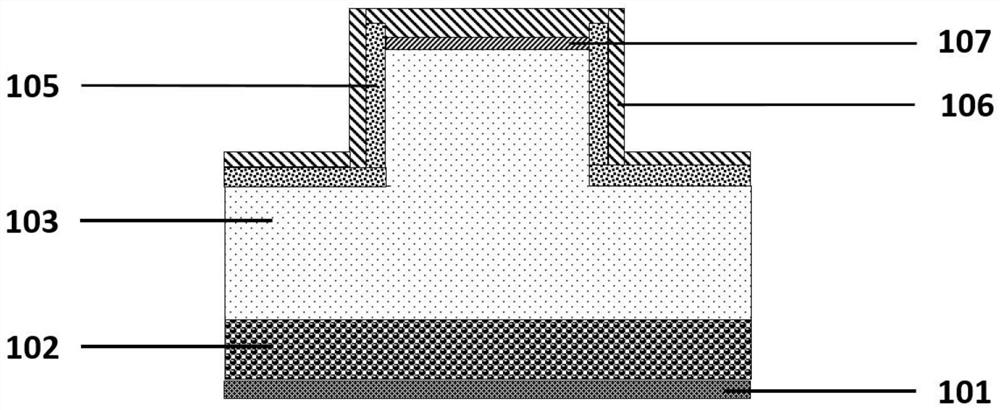

Vertical GaN Schottky device structure with high breakdown voltage and low reverse electric leakage

ActiveCN111192928AImprove breakdown voltageReduce reverse leakage currentSemiconductor devicesEtchingHigh field

The invention discloses a vertical GaN Schottky device structure with high breakdown voltage and low reverse electric leakage. The vertical GaN Schottky device structure comprises a first conductive type highly-doped GaN layer, a first conductive type low-doped GaN layer, a second conductive type NiO filling layer, a SiO2 and Si3N4 mixed dielectric layer, a floating metal field plate, an ohmic cathode, a Schottky anode, a sapphire substrate and an AlN nucleating layer. According to the device structure provided by the invention, a two-step etching process is applied, so that the operability problem of a deep etching technology is solved; the designed second conductive type NiO filling layer overcomes the technical problem of second conductive type doping of a GaN material, effectively shields a high electric field and protects a Schottky barrier, so that the reverse leakage current of the device is effectively reduced; the designed multi-field-plate structure effectively utilizes the advantage of high field plate contact area brought by a two-step etching process, weakens the fringe field concentration effect of the device, and effectively improves the reverse breakdown voltage ofthe device.

Owner:XI AN JIAOTONG UNIV

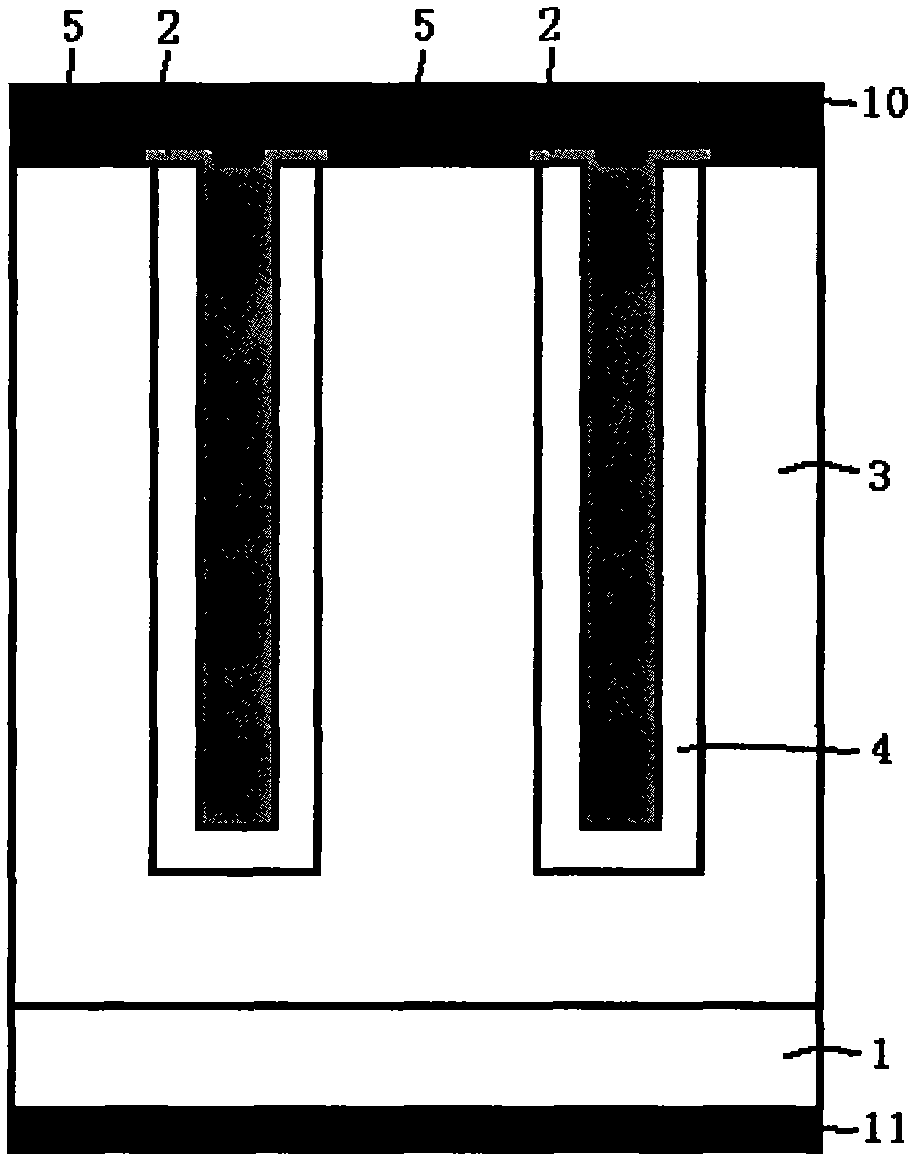

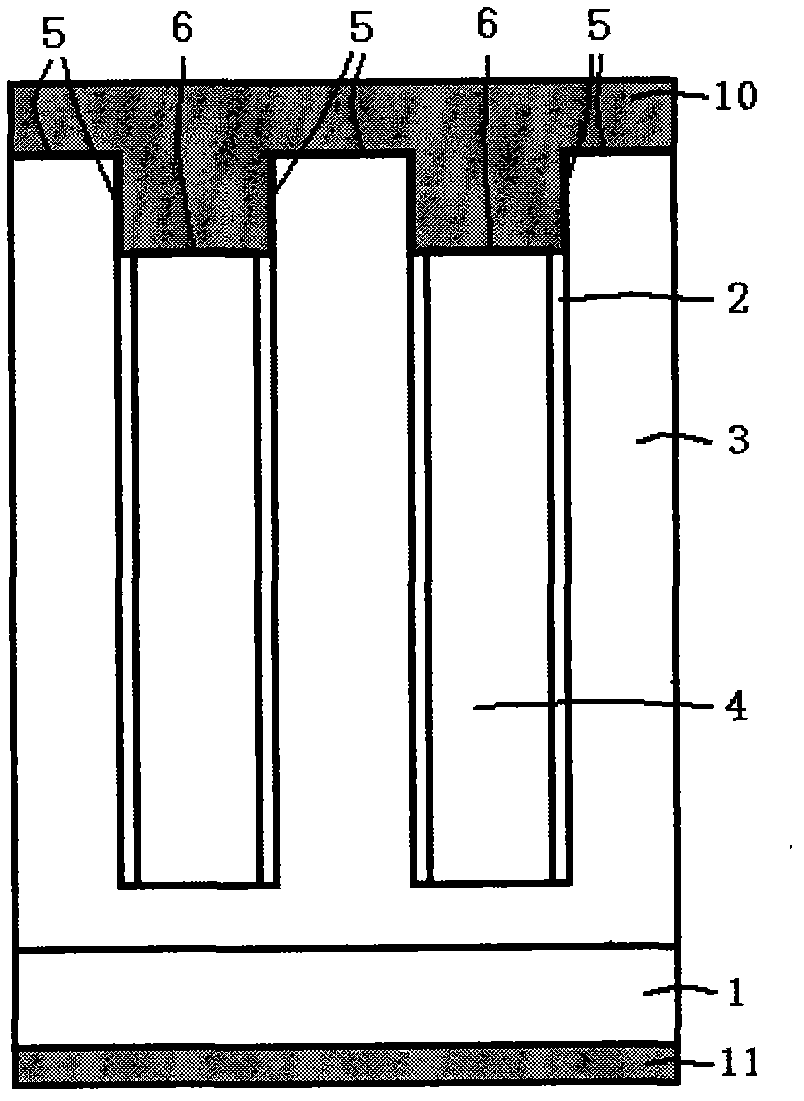

Groove schottky semiconductor device with super junction structure and manufacturing method thereof

ActiveCN103199119AImprove reverse breakdown voltageRealize manufacturingSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationSemiconductor materials

The invention discloses a groove schottky semiconductor device with a super junction structure. Charge compensation can be formed by second conductive semiconductor materials located on the lower portions inside grooves and first conductive semiconductor materials among the grooves, then the super junction structure is formed, and reverse breakdown voltages of devices are improved; meanwhile, when a semiconductor device is connected with a certain reverse bias voltage, a metal oxide semiconductor (MOS) structure is constructed by the second conductive semiconductor materials which are doped with metal or high-concentration impurities and arranged on the upper portions inside the grooves and insulating medium located on the side surfaces of the grooves, electric field intensity of drifting materials nearby schottky barrier can be restrained, the pheromone that the barrier height of the schottky barrier is reduced along with rising of the reverse bias voltage is reduced, accordingly reverse leakage current of the devices is reduced, and a reverse blocking characteristic of the devices is improved.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

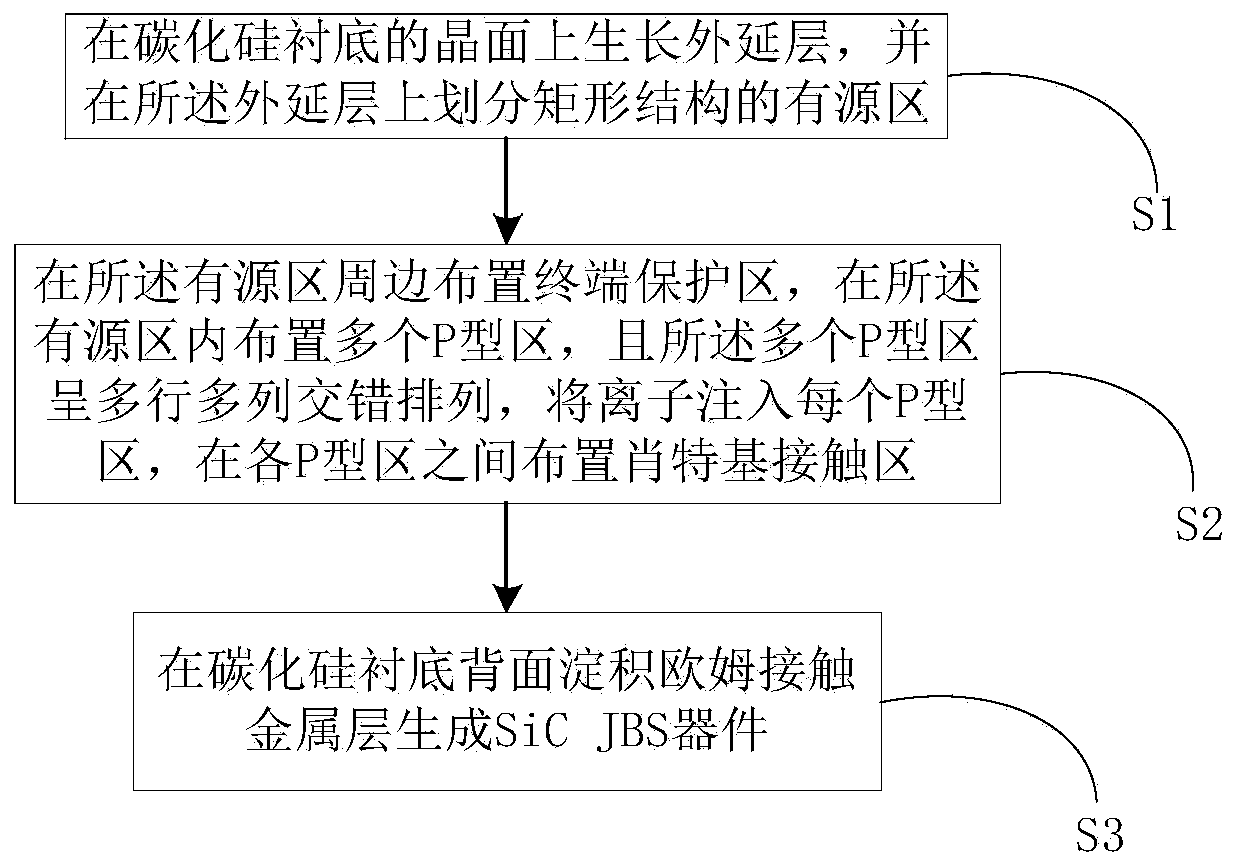

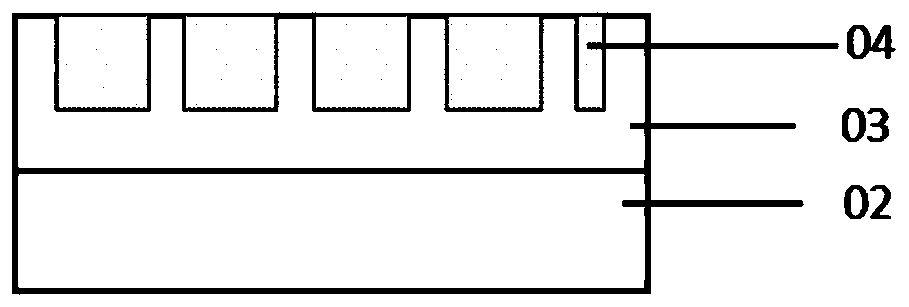

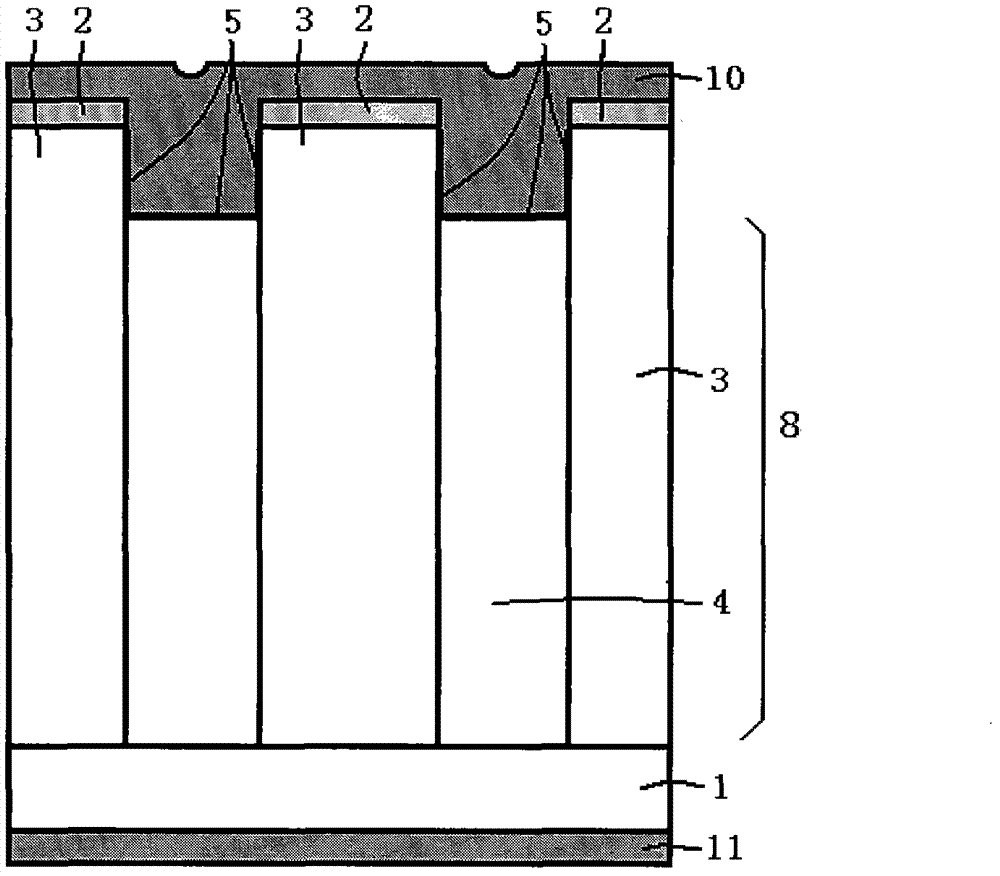

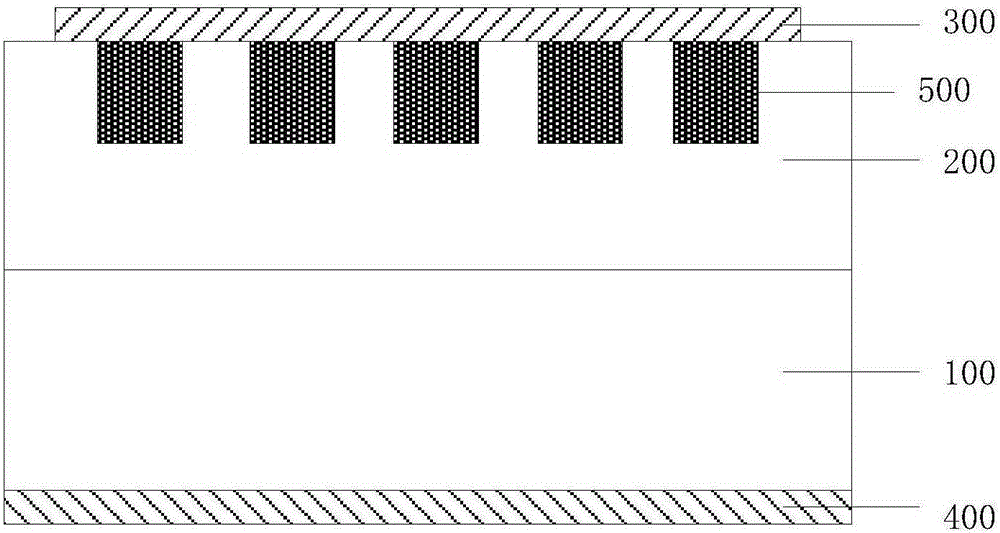

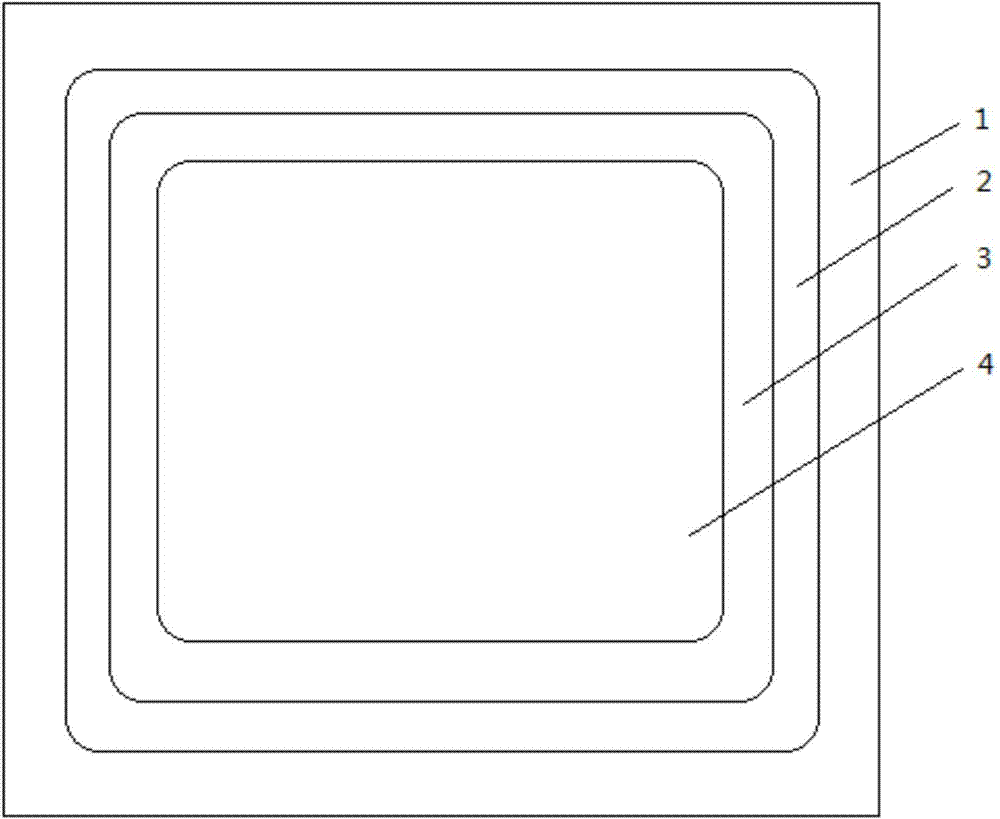

Layout method of SiC JBS device

PendingCN111261724AIncrease the area of the barrier regionGuaranteed reverse breakdown characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingCarbide siliconSchottky barrier

The invention provides a layout method of a SiC JBS device, which comprises the following steps of: growing an epitaxial layer on the crystal surface of a silicon carbide substrate, and dividing an active region with a rectangular structure on the epitaxial layer, arranging a terminal protection region at the periphery of the active region, arranging a plurality of P-type regions in the active region, arranging the plurality of P-type regions in a multi-row and multi-column staggered manner, implanting ions into each P-type region, and arranging Schottky contact regions between the P-type regions, and depositing an ohmic contact metal layer on the back surface of the silicon carbide substrate to generate the SiC JBS device. The plurality of P-type regions are arranged in the SiC JBS devicein a multi-row and multi-column staggered manner, so that the reverse breakdown characteristic of the SiC JBS device is ensured, the Schottky barrier region area is increased, and the conduction capability is improved.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD

Super junction Schottky semiconductor device and preparation method thereof

ActiveCN103367396AImprove reverse breakdown voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSchottky barrier

The invention discloses a super junction Schottky semiconductor device. When the semiconductor device is accessed to a certain reverse bias voltage, charge compensation is formed by a second conductive semiconductor material and a first conductive semiconductor material, a super junction structure is formed, the reverse breakdown voltage of the device is enhanced, and characteristics of conduction or blocking of the device are improved. Meanwhile, when the semiconductor device is accessed to a certain forward bias voltage, a first type Schottky barrier junction (assuming that the first conductive semiconductor layer adopts an N type semiconductor material) is in the forward bias conduction state, and a second type Schottky barrier junction (assuming that the second conductive semiconductor layer adopts a P type semiconductor material) is in the reverse bias cut-off state, therefore when in the forward conduction state, the device is still a conductive device with a single carrier, and minority carrier injection does not exist in the conductive device with the single carrier. The device has good switching characteristics. The invention also provides a preparation method of the super junction Schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

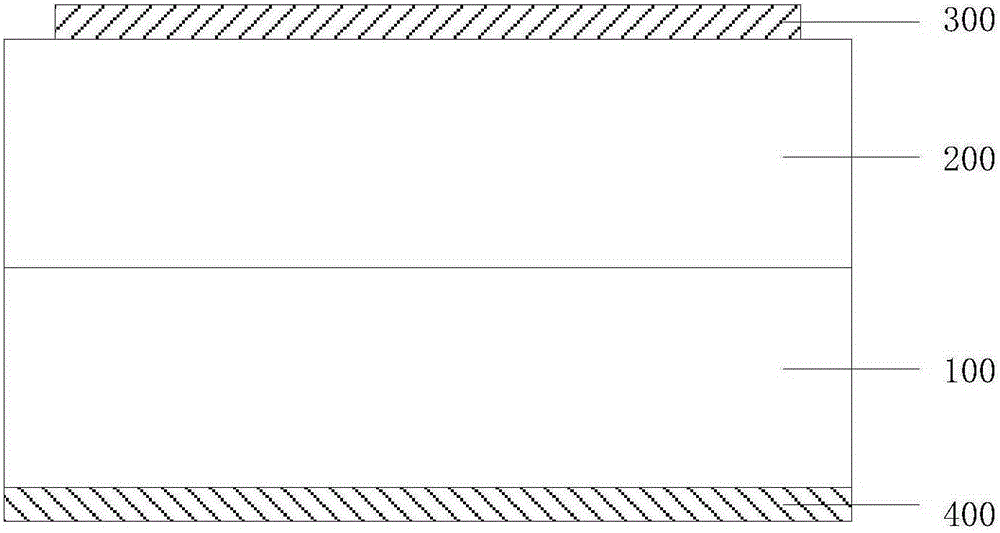

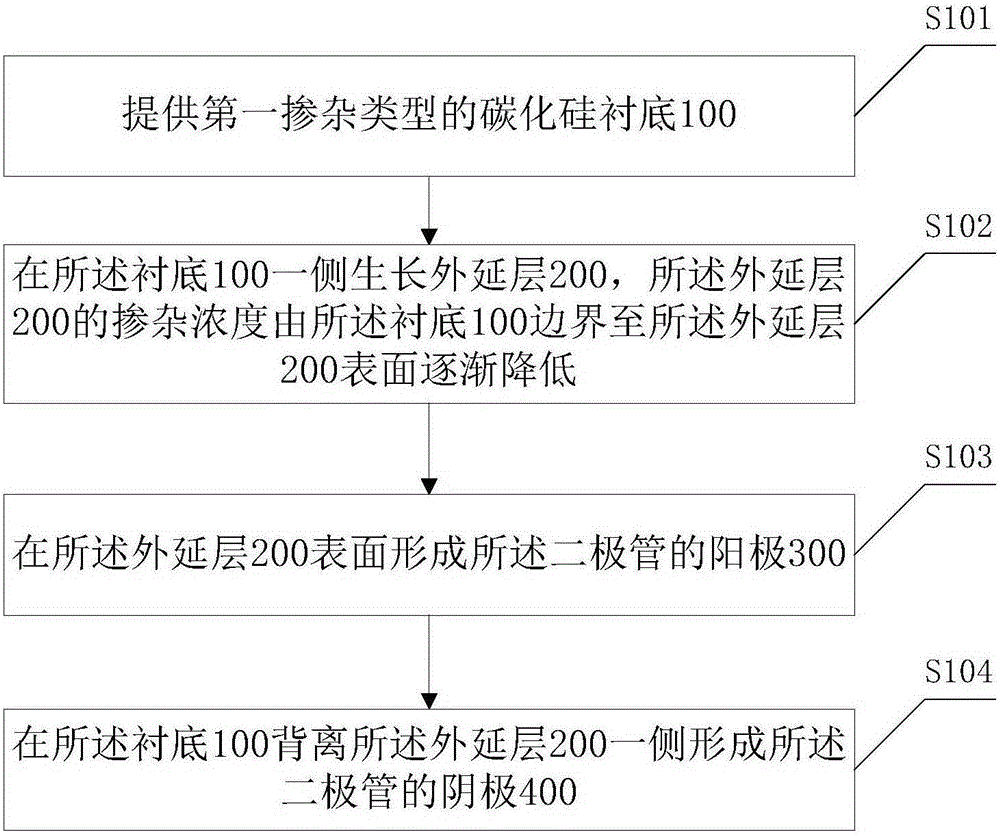

Silicon carbide schottky diode and preparation method thereof

ActiveCN105226104ALower on-resistanceImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationVoltage drop

The application discloses a silicon carbide schottky diode (SBD) and a preparation method thereof. The SBD comprises a first doped silicon carbide substrate; a cathode located on one side of the substrate; an epitaxial layer located on the side of the substrate distant from the cathode; and an anode located on the surface of the epitaxial layer, wherein the doping concentration of the epitaxial layer gradually increases from an anode boundary to a substrate boundary. For the epitaxial layer, a high concentration is in favor of reducing diode conduction resistance, and a low doping concentration is in favor of improving a diode voltage endurance capability. According to research, when a diode is in a reverse-bias state, the intensity of a built-in electric field gradually decreases from the diode anode boundary to the substrate boundary. Accordingly, the diode can reduce forward on-resistance under the condition of not changing the voltage endurance capability, and furthermore reduce conduction voltage drop and total power consumption.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Schottky semiconductor device with super junction and preparation method thereof

InactiveCN103378170AImprove reverse breakdown voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceElectricity

The invention discloses a Schottky semiconductor device with a super junction. When the semiconductor device is connected with certain reverse bias voltage, a first electricity-conductive semiconductor material and a second electricity-conductive semiconductor material can form charge compensation and form a super junction structure, and therefore the reverse breakdown voltage of a component can be increased, and the conduction character or the blocking character of the component can be improved. The invention further provides a preparation method of the Schottky semiconductor device with the super junction.

Owner:朱江

Groove charge compensation Schottky semiconductor device and manufacturing method thereof

ActiveCN103515450AImprove reverse breakdown voltageIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention discloses a groove charge compensation Schottky semiconductor device which is provided with a charge compensation structure. When the semiconductor device is connected with certain back bias voltage, a first conducting semiconductor material and a second conducting semiconductor material can form charge compensation and the back blocking property of a device is improved. A polycrystal semiconductor material is led into the upper portion of the groove so that strength of a peak electric field of Schottky junction surface can be reduced when the semiconductor device is connected with the back bias voltage and the back blocking property of the device is further improved. The invention further provides a manufacturing method of the groove charge compensation Schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

Interface charge compensation Schottky semiconductor device and manufacturing method for same

InactiveCN103383968AImprove reverse breakdown voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsCharge compensation

The invention discloses an interface charge compensation Schottky semiconductor device. When the semiconductor device is connected with a certain reverse biased voltage, charge compensation is generated by interface charge compensation regions and drifting semiconductor materials, depletion layers between the interface charge compensation regions are made to be overlapped, and therefore the reverse breakdown voltage of the device is improved, or the forward breakover resistance of the device is lowered, and the forward breakover feature of the device is improved. The invention further provides a manufacturing method for the interface charge compensation Schottky semiconductor device.

Owner:朱江

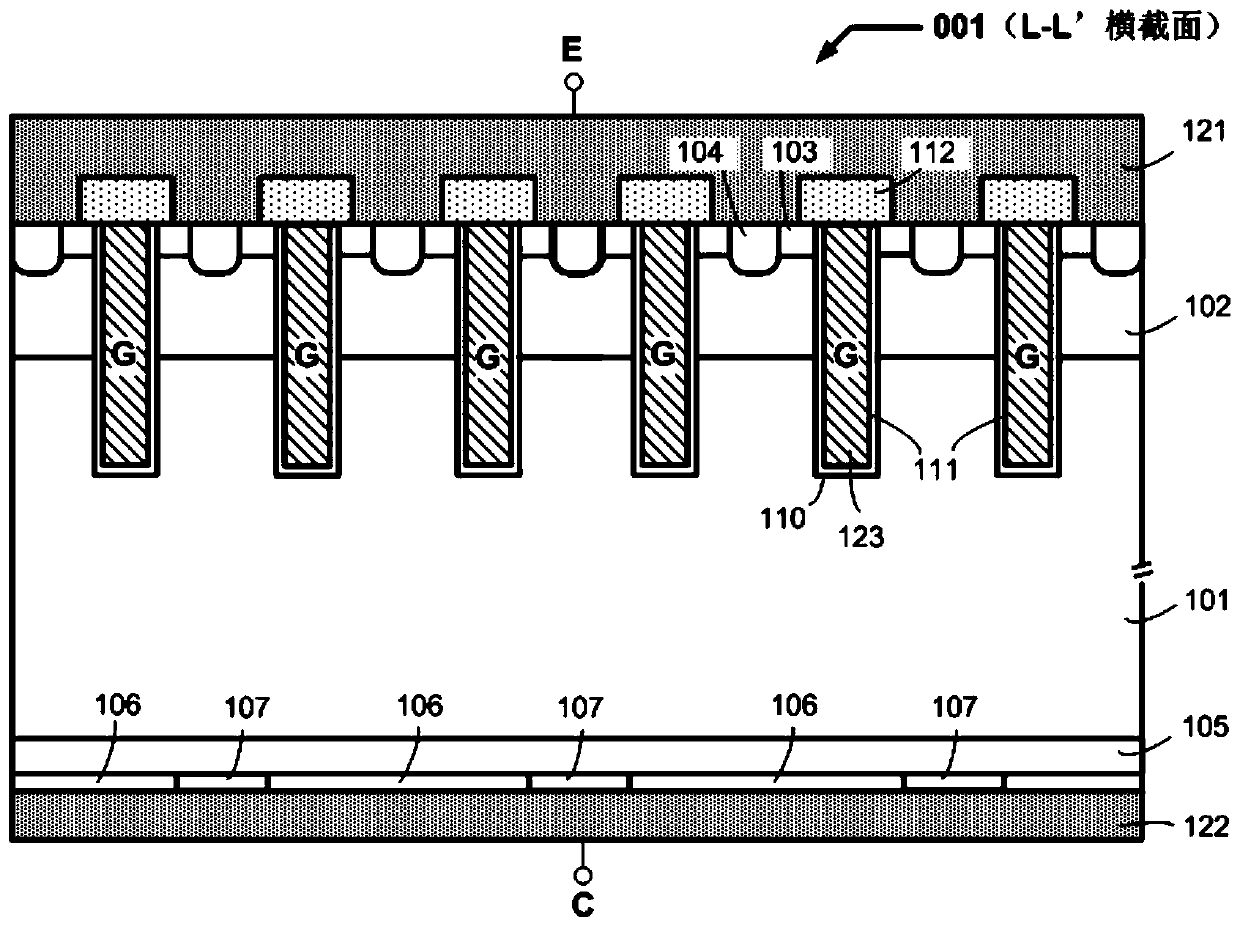

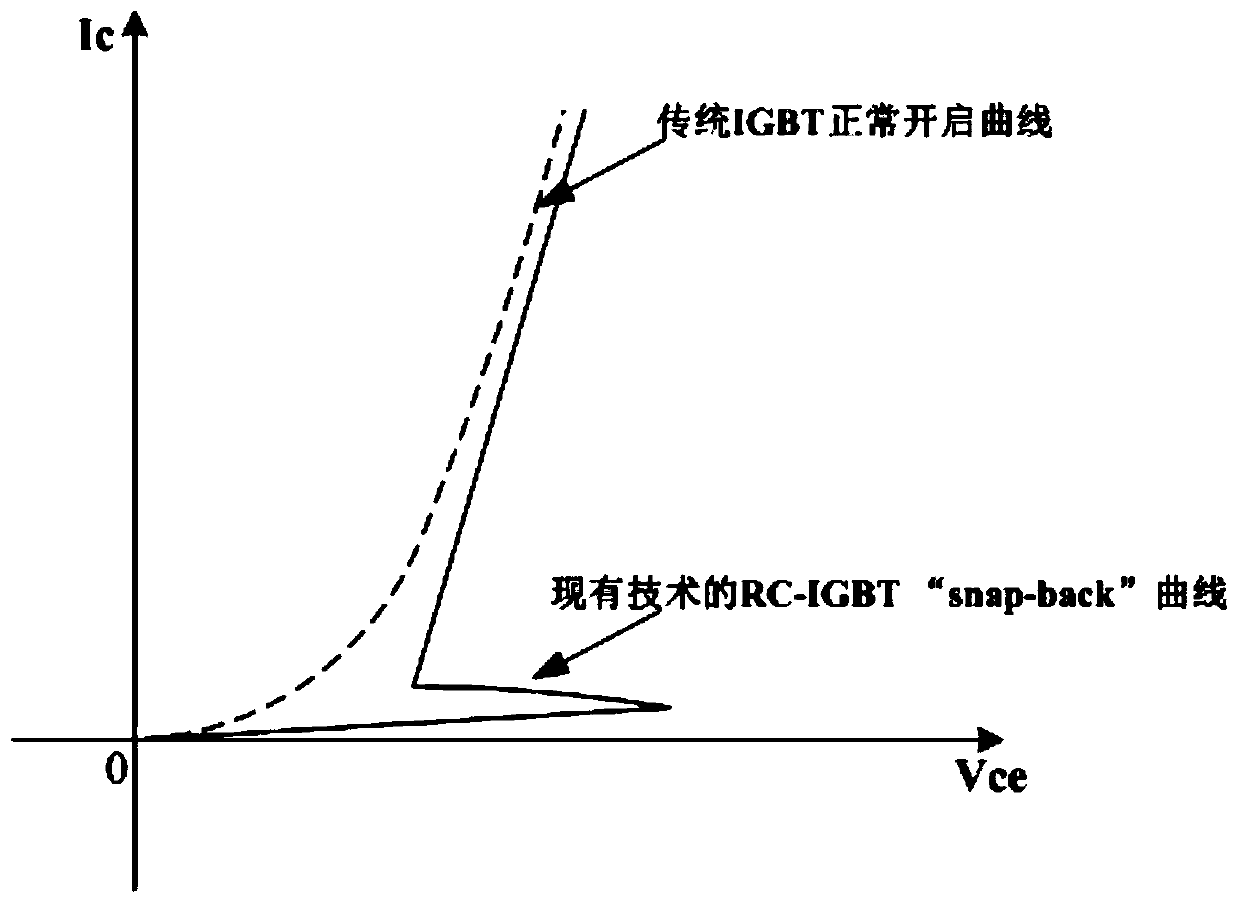

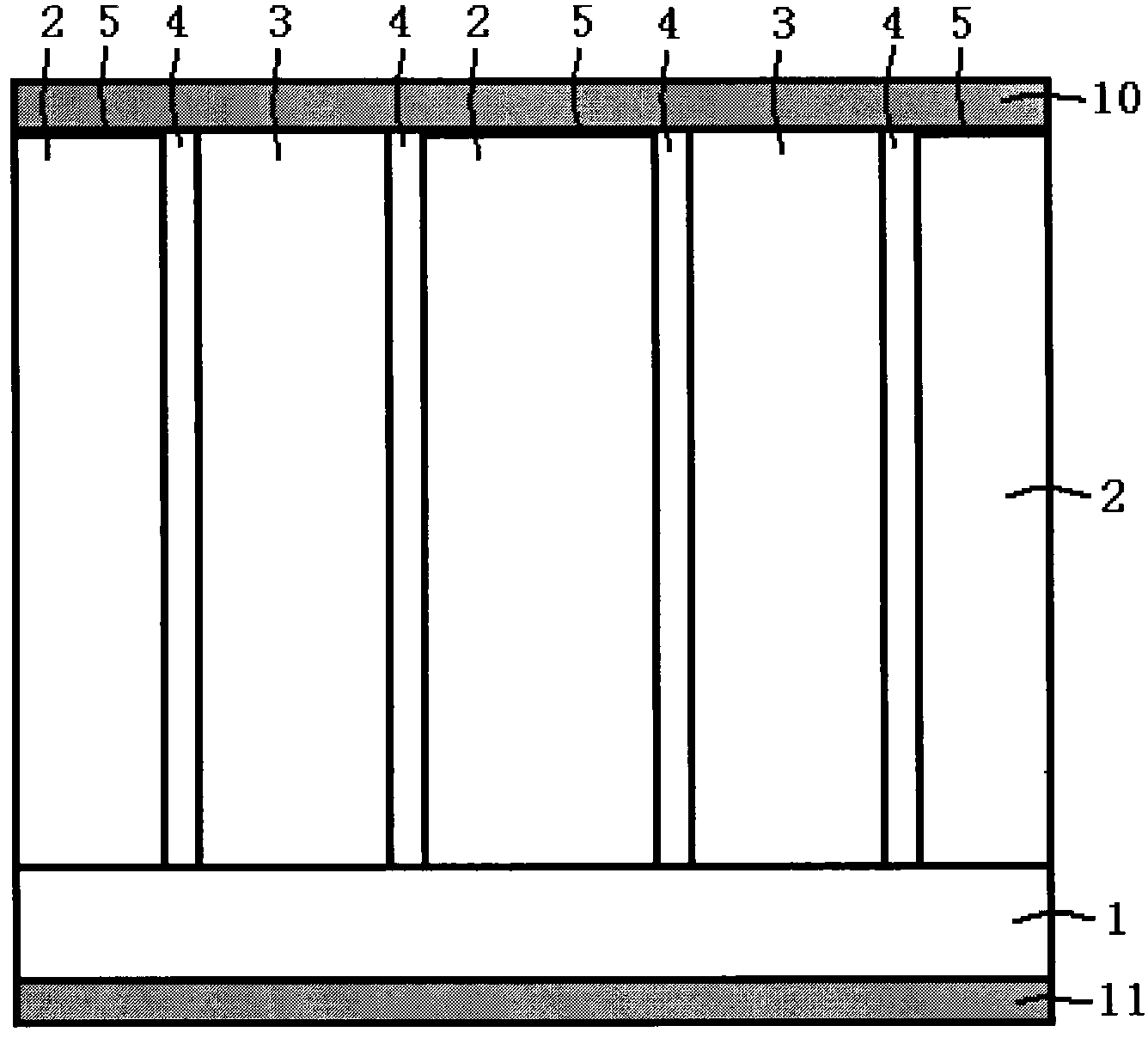

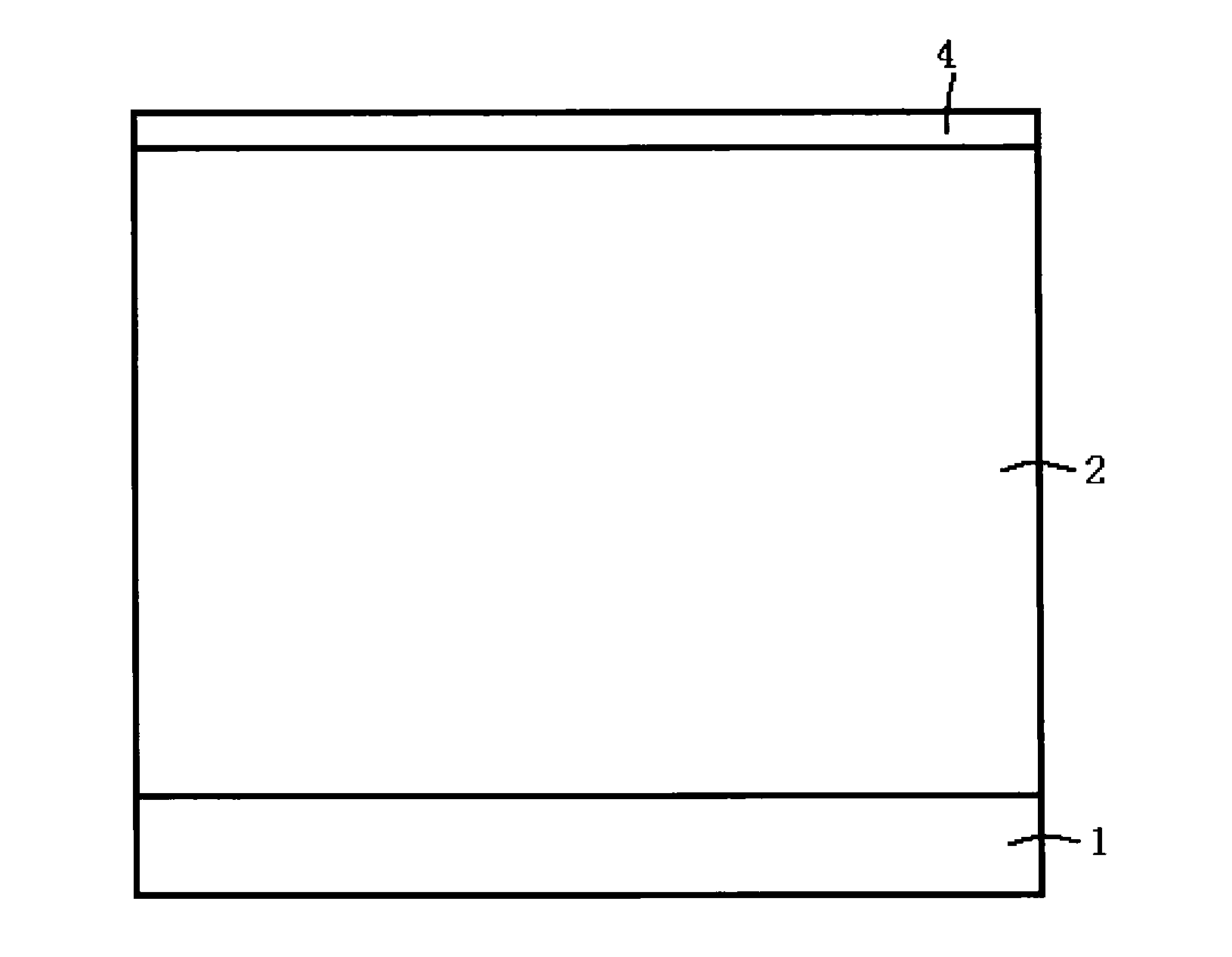

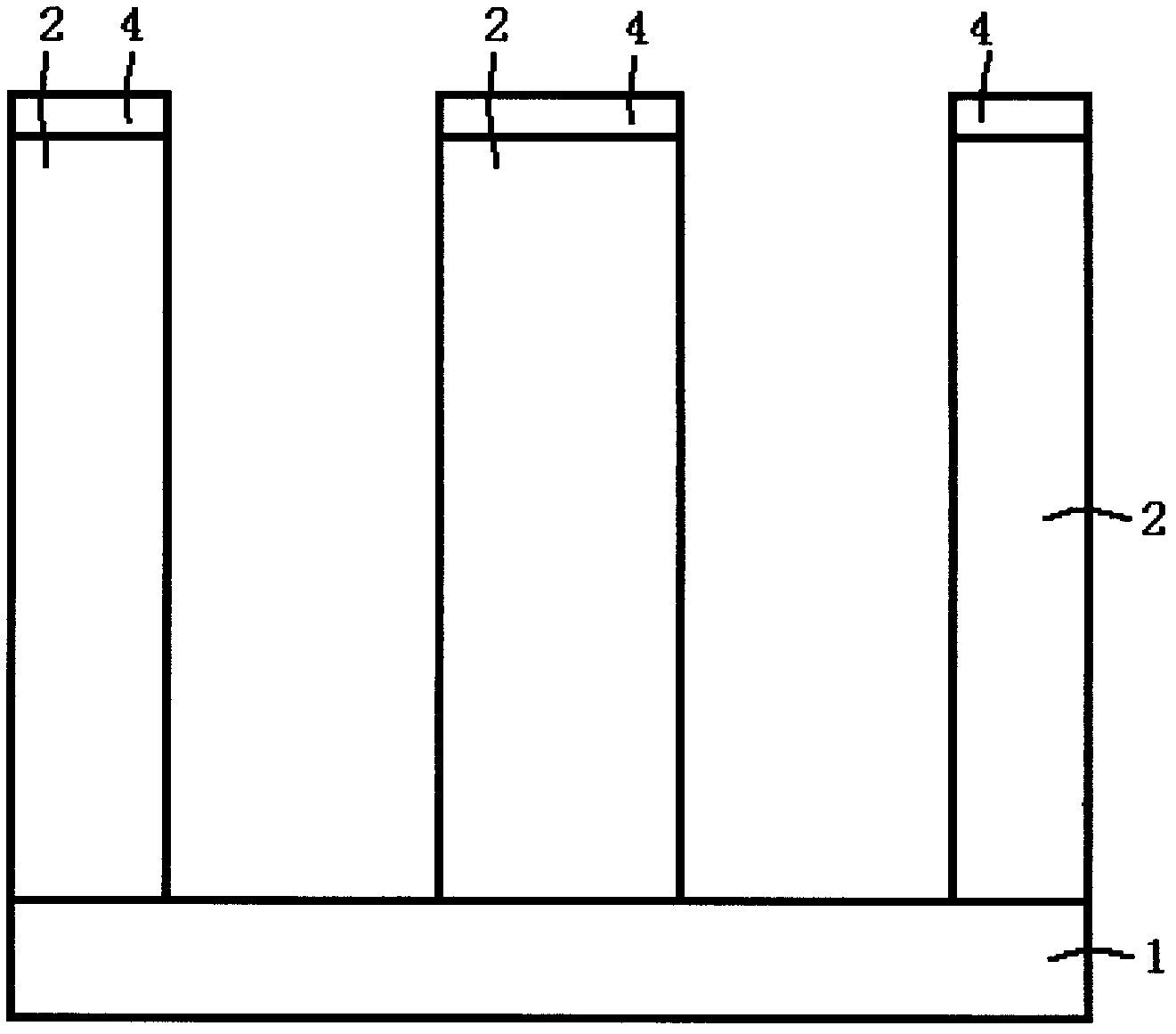

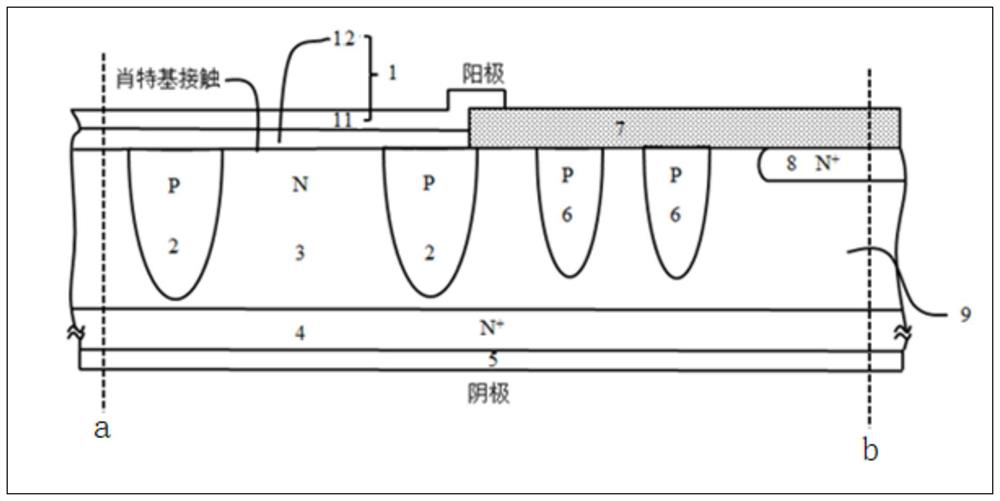

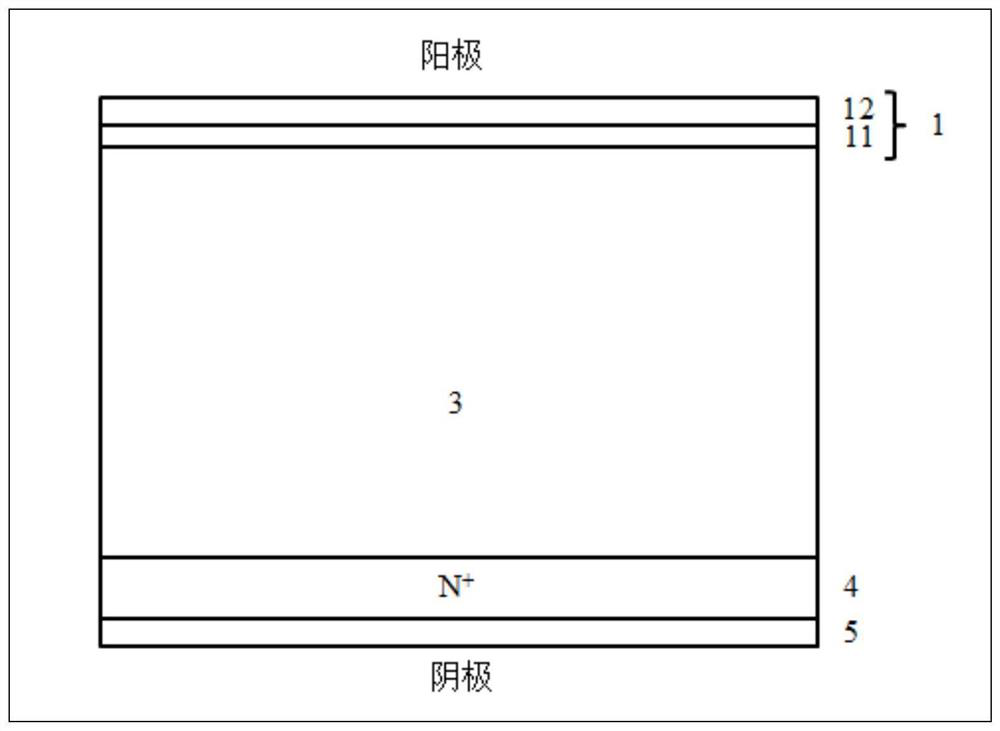

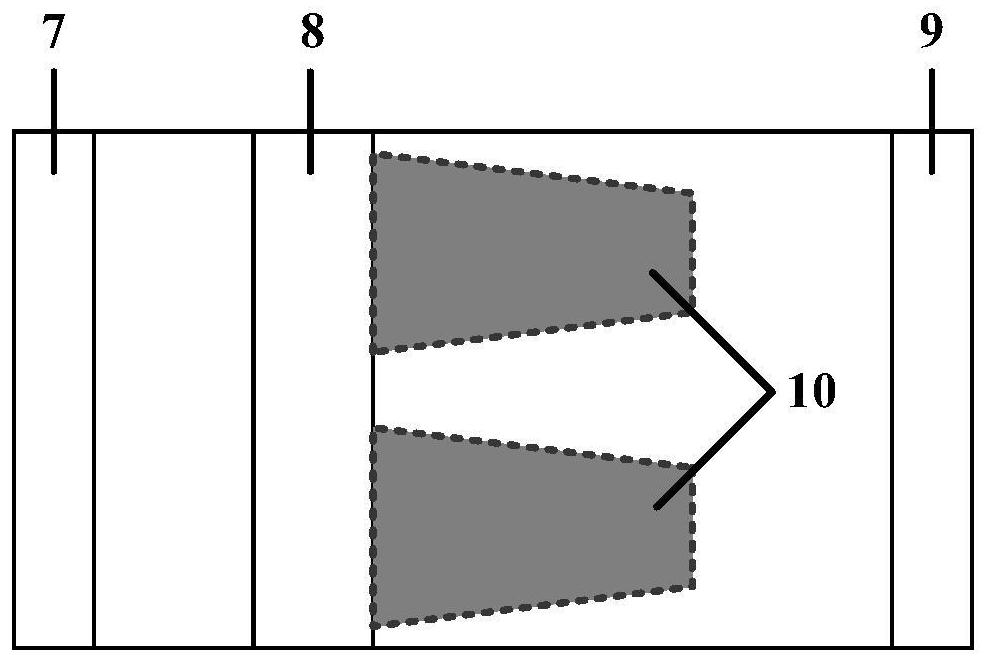

Reverse conducting insulated gate bipolar transistor

ActiveCN109728085ALower forward conduction resistanceHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceState of art

A reverse conducting insulated gate bipolar transistor (RC-IGBT) is provided. The present invention relates to a power semiconductor device. In view of the problem of an RC-IGBT device in the prior art, the present invention provides a design scheme which can solve the problem in the prior art by optimizing the distribution of the n+ cathode region on the back side of the RC-IGBT device. Comparedwith a conventional RC-IGBT device, the RC-IGBT device of the present invention, by special design of the back structure, can suppress the turn-on voltage jumpback problem of the device whiling maintaining the low forward and reverse on-state loss of the device and not increasing the process cost, and is beneficial to improvement in the reliability of the RC-IGBT in practical application.

Owner:安建科技(深圳)有限公司

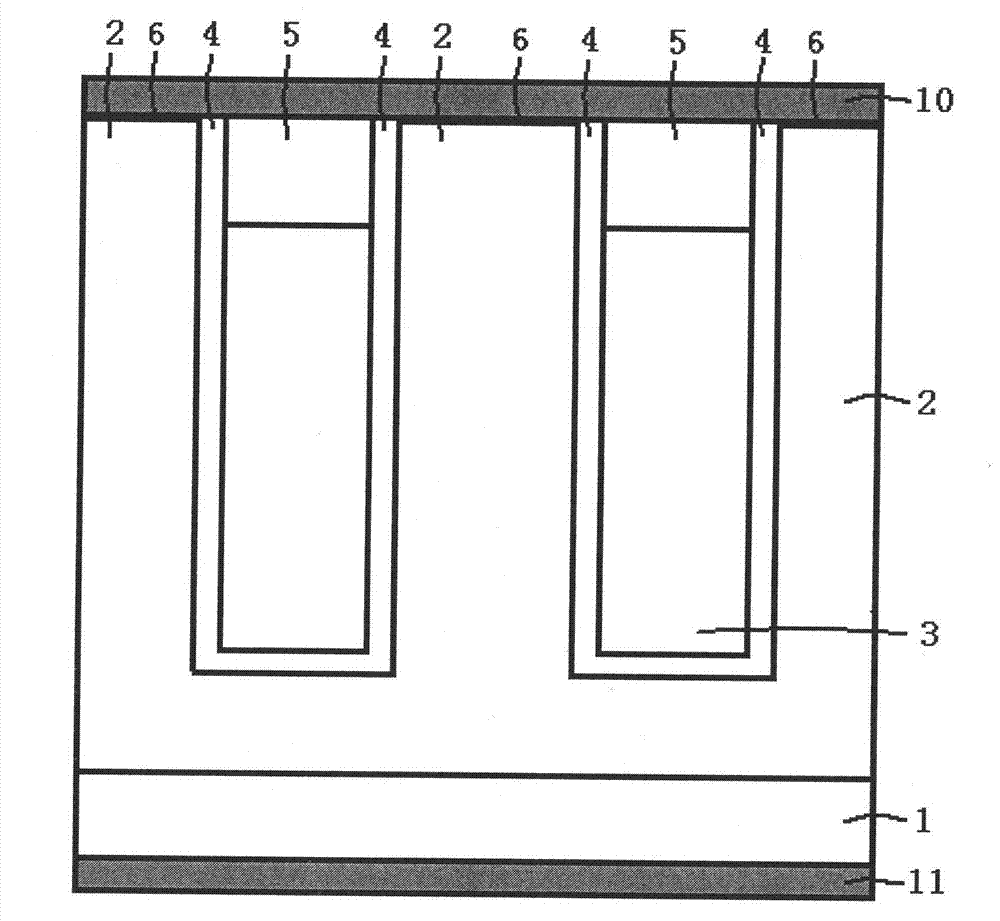

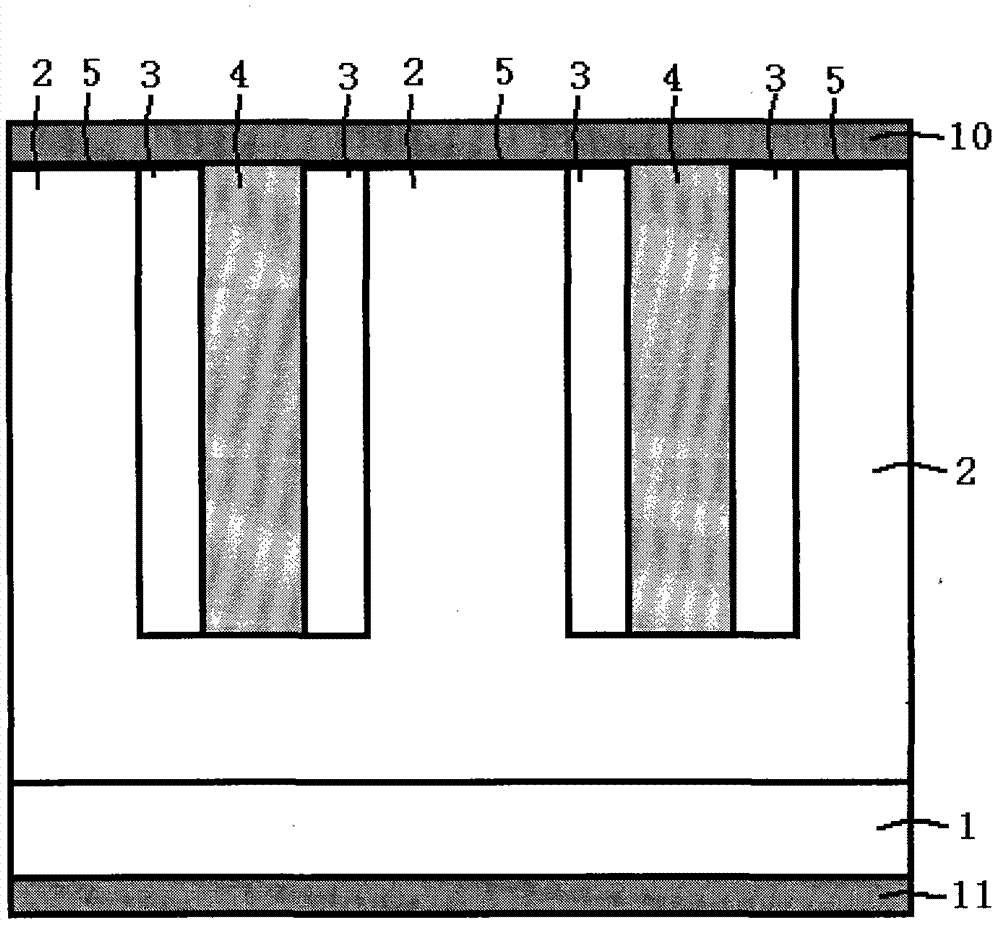

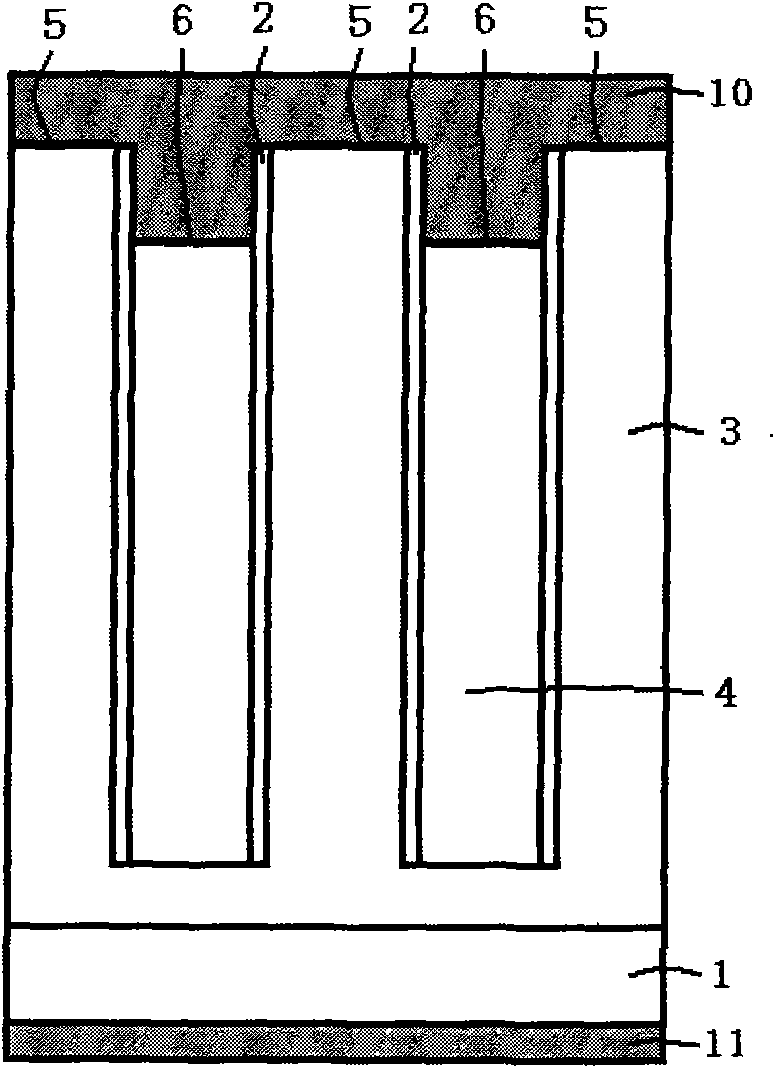

Schottky semiconductor device with insulating layer isolation structure and preparation method thereof

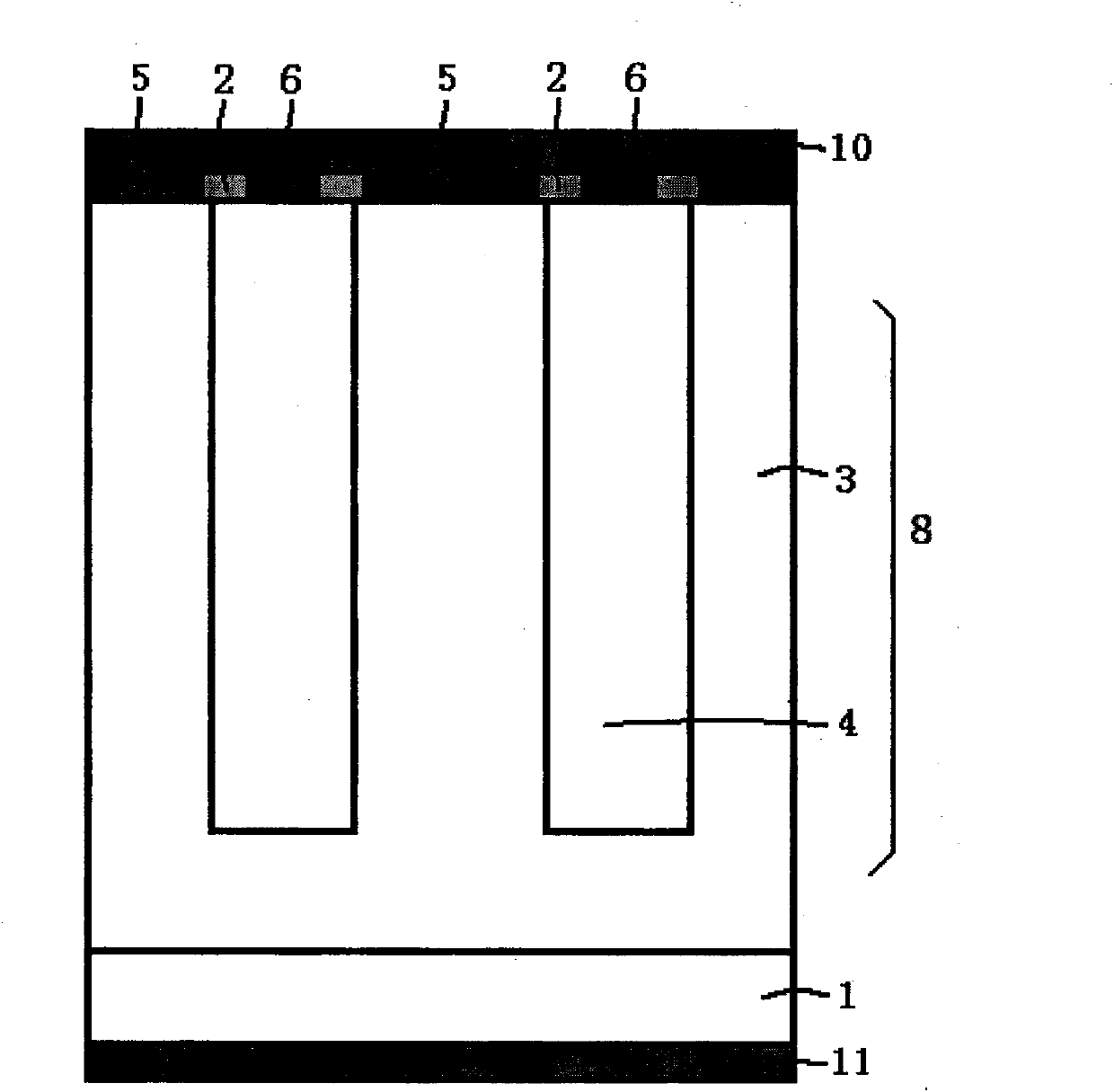

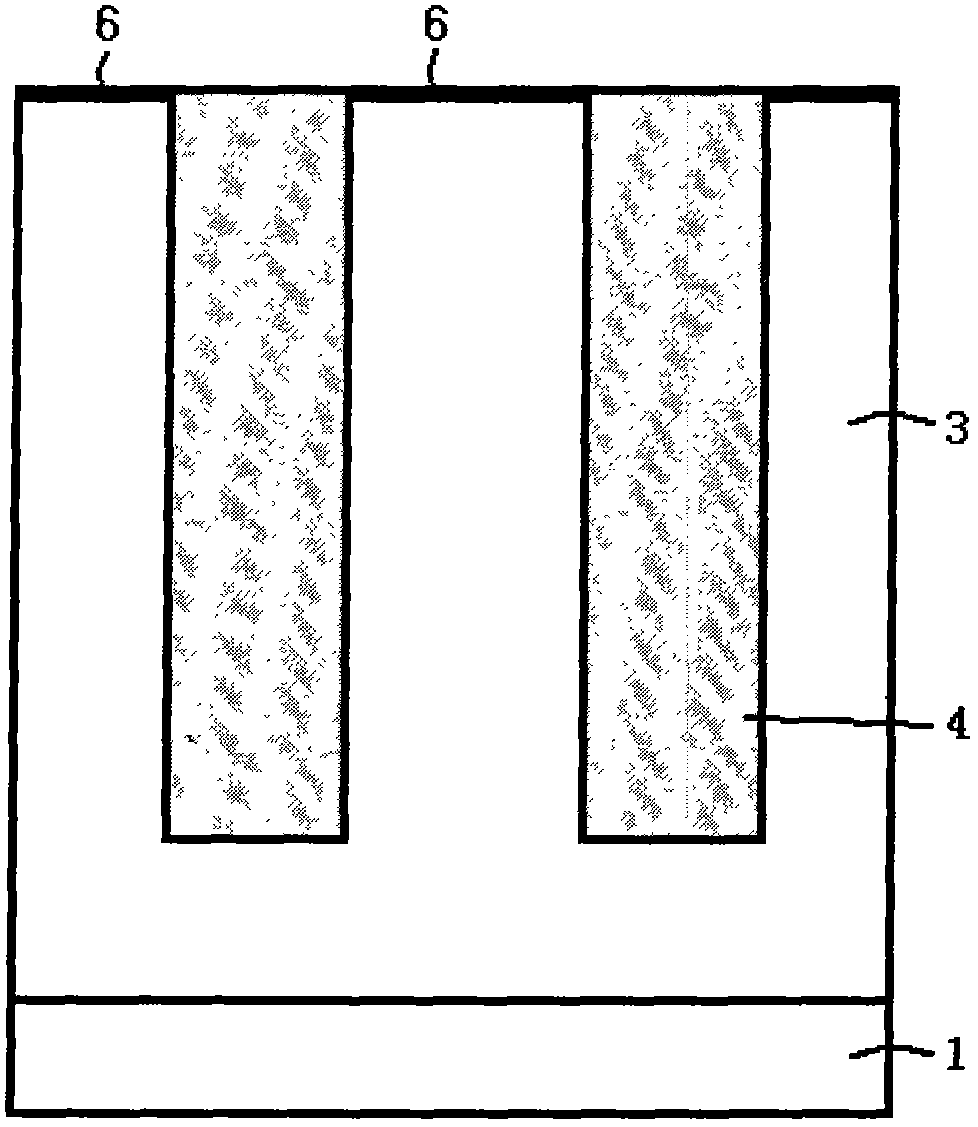

InactiveCN103137711AImprove reverse breakdown voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention discloses a Schottky semiconductor device with an insulating layer isolation structure. Through a trench structure, deep strip P-type semiconductor silicon materials 3 can be achieved, and ideal vertical strip semiconductor materials can be achieved through insulating layer isolation. When an apparatus is connected with a reverse bias voltage, the strip P-type semiconductor silicon materials 3 and strip N-type semiconductor silicon materials 2 form charge complementation to form a super-junction structure, and accordingly, the electric field intensity distribution of drift regions is changed, and flat field intensity distribution curves are formed. The invention further provides a preparation method of the Schottky semiconductor device with the insulating layer isolation structure.

Owner:朱江 +1

Schottky semiconductor device with super junction structure and manufacturing method thereof

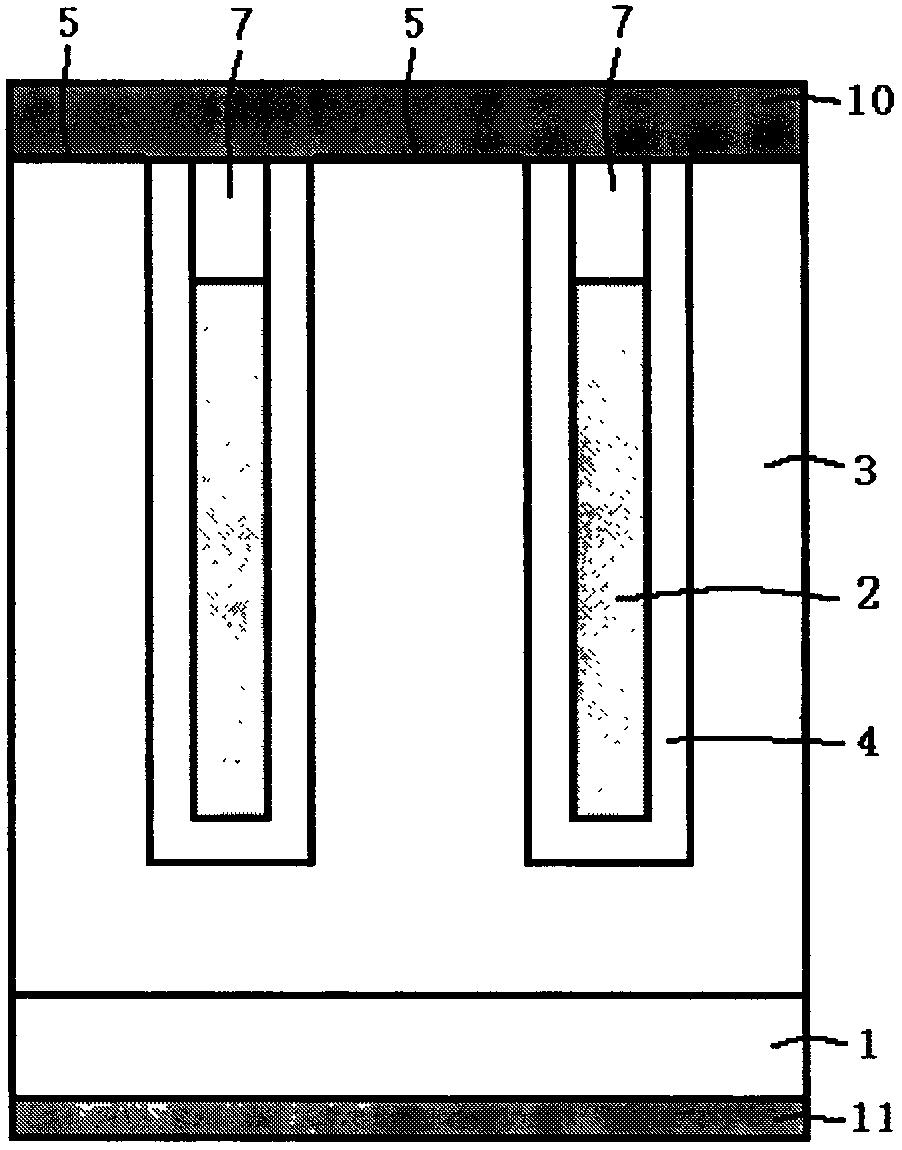

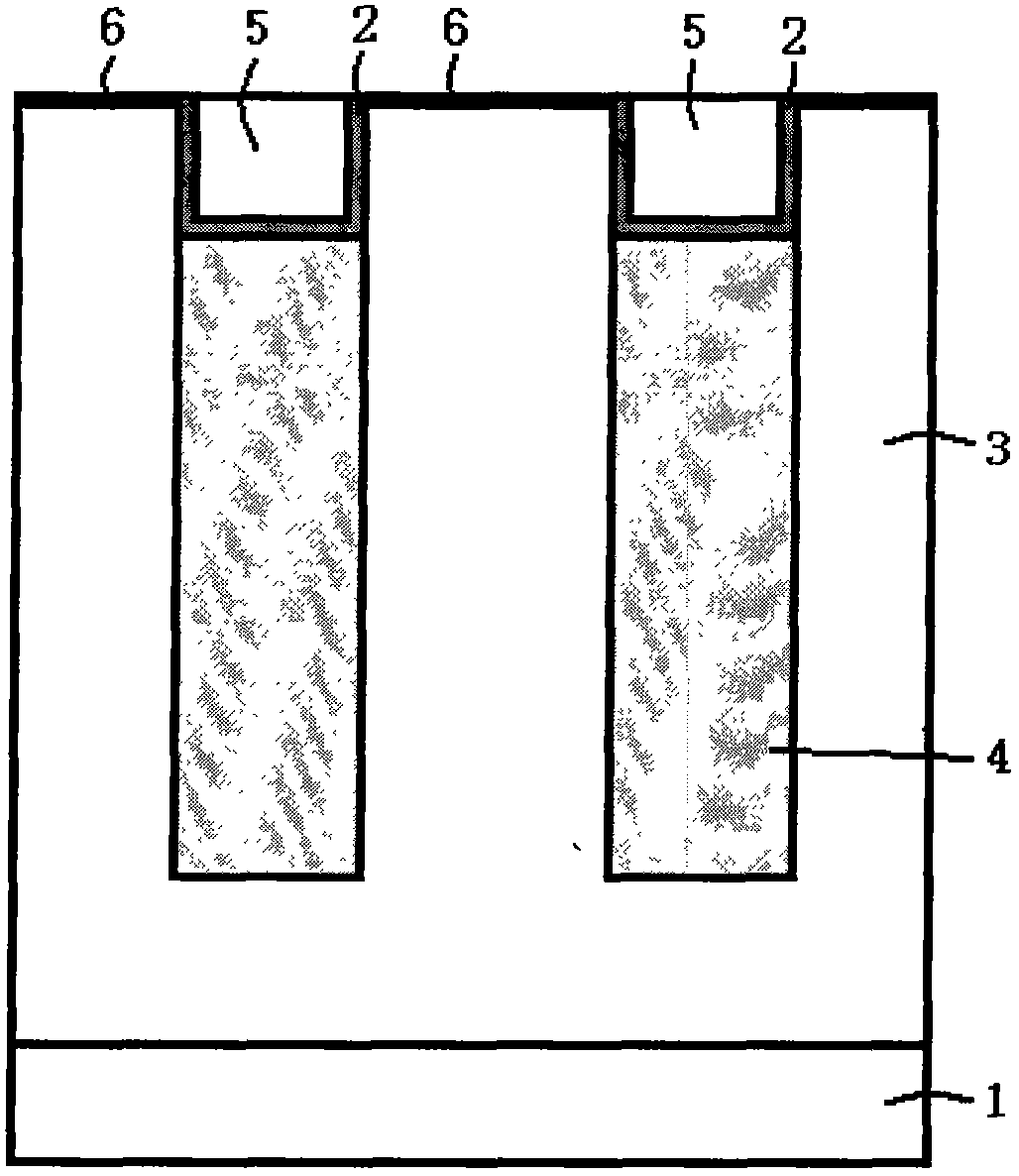

InactiveCN103199102AImprove reverse breakdown voltageRealize manufacturingSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationPower semiconductor device

The invention discloses a schottky semiconductor device with an insulating layer isolation structure and particularly discloses a schottky semiconductor device with a super junction structure and a manufacturing method thereof. Charge compensation can be formed by second conductive semiconductor materials located on the lower portions inside the grooves and first conductive semiconductor materials among the grooves, then the super junction structure is formed; when a semiconductor device is connected with a certain reverse bias voltage, a metal oxide semiconductor (MOS) structure is constructed by the second conductive semiconductor materials which are doped with metal or high-concentration impurities and arranged on the upper portions inside the grooves and insulating medium located on the side surfaces of the grooves, and the pheromone that the barrier height of a schottky barrier is reduced along with rising of the reverse bias voltage is reduced; and besides, the schottky barrier which is capable of forming semiconductor materials P is formed by metal located on the upper portions inside the grooves and the second conductive semiconductor materials located on the lower portions inside the grooves, when the semiconductor device is connected with a forward bias voltage, the schottky barrier is in a reverse bias state, so that forward communication of PN junctions can be effectively restrained, accordingly injection of minority carriers to a drift region is reduced, and a switching characteristic of a device is improved.

Owner:盛况 +1

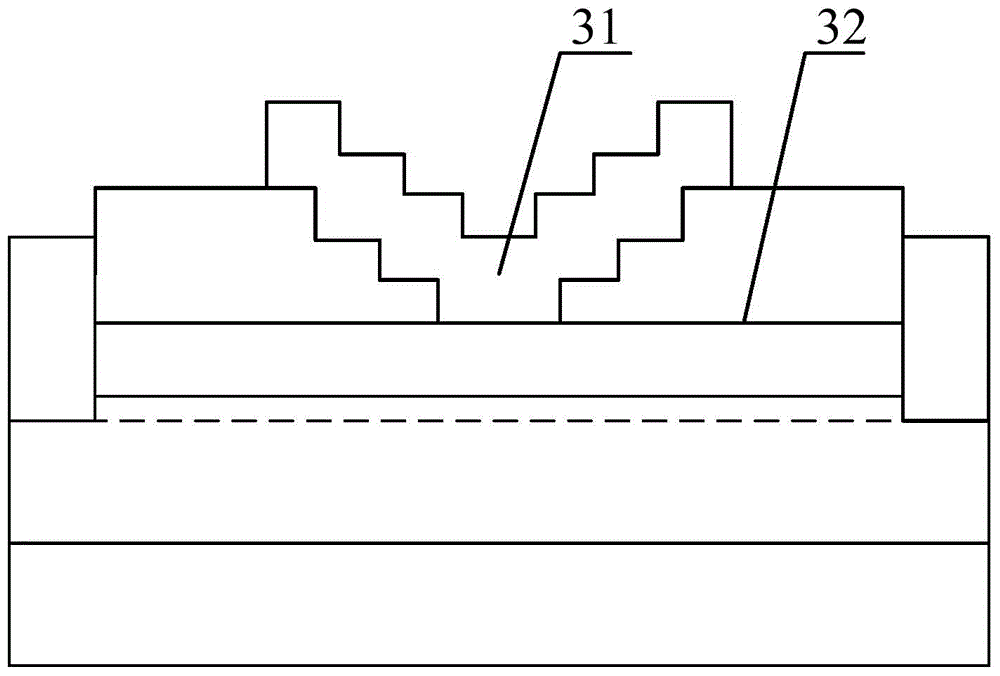

Low-power-consumption high-performance super-junction JBS diode and manufacturing method thereof

PendingCN112289848AGood reverse blocking propertiesReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse recovery

The invention belongs to the field of power semiconductor devices, and particularly relates to a low-power-consumption high-performance super-junction JBS diode and a manufacturing method thereof. Thelow-power-consumption high-performance super-junction JBS diode is manufactured by using a traditional silicon-based process technology, so that the manufacturing cost is low; a P heavily doped cylindrical region and an N cylindrical drift region which have the characteristics of large area, high concentration and large junction depth are adopted, so that the forward conduction resistance is reduced; a super junction is formed, and good reverse blocking characteristics are achieved by optimizing electric field distribution; by optimizing parameters of the super junction, higher blocking withstand voltage can be realized, and the on-state and off-state power consumption of the device is reduced; and optimal two-dimensional electric field distribution is obtained by optimizing the doping concentration and width of the P column region and the N column region, unification of high blocking voltage and low on-resistance and unification of high blocking voltage and rapid switching are achieved, compromise between forward on-state voltage drop and reverse blocking characteristics and compromise between reverse recovery characteristics and reverse blocking voltage are optimized, and the limit of a traditional silicon material is broken through.

Owner:SHENYANG POLYTECHNIC UNIV

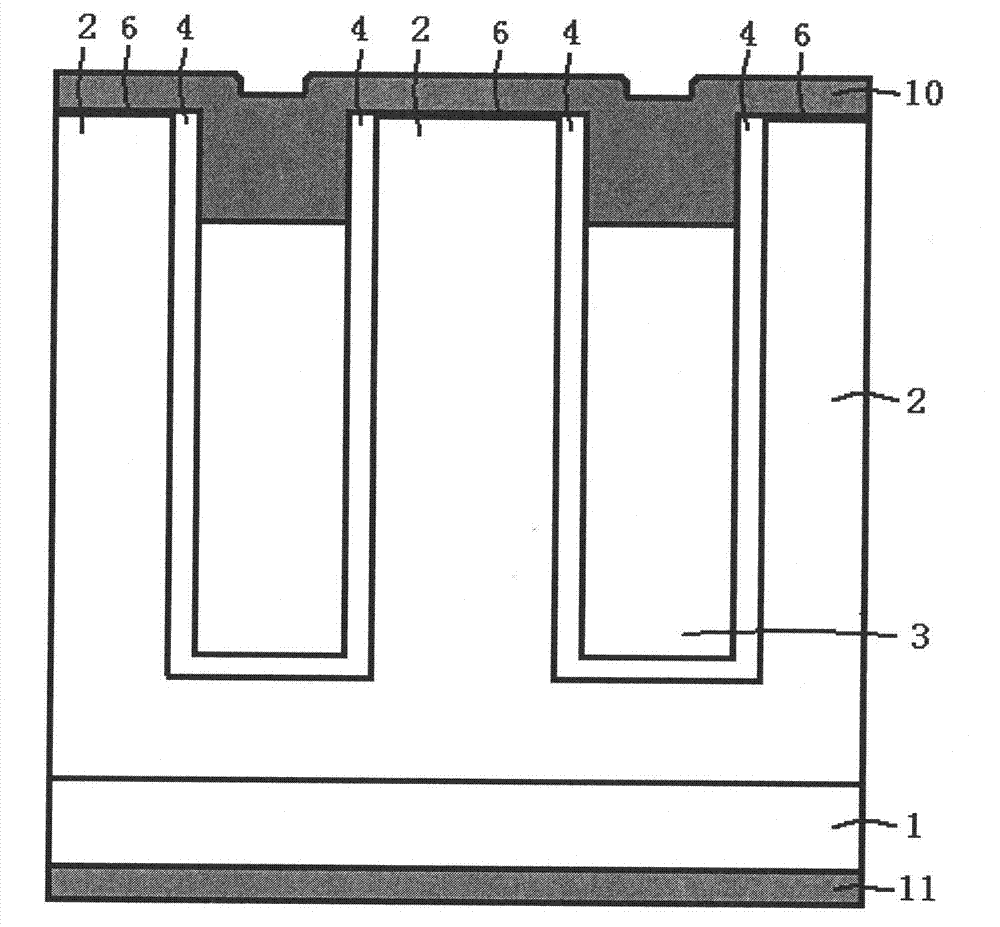

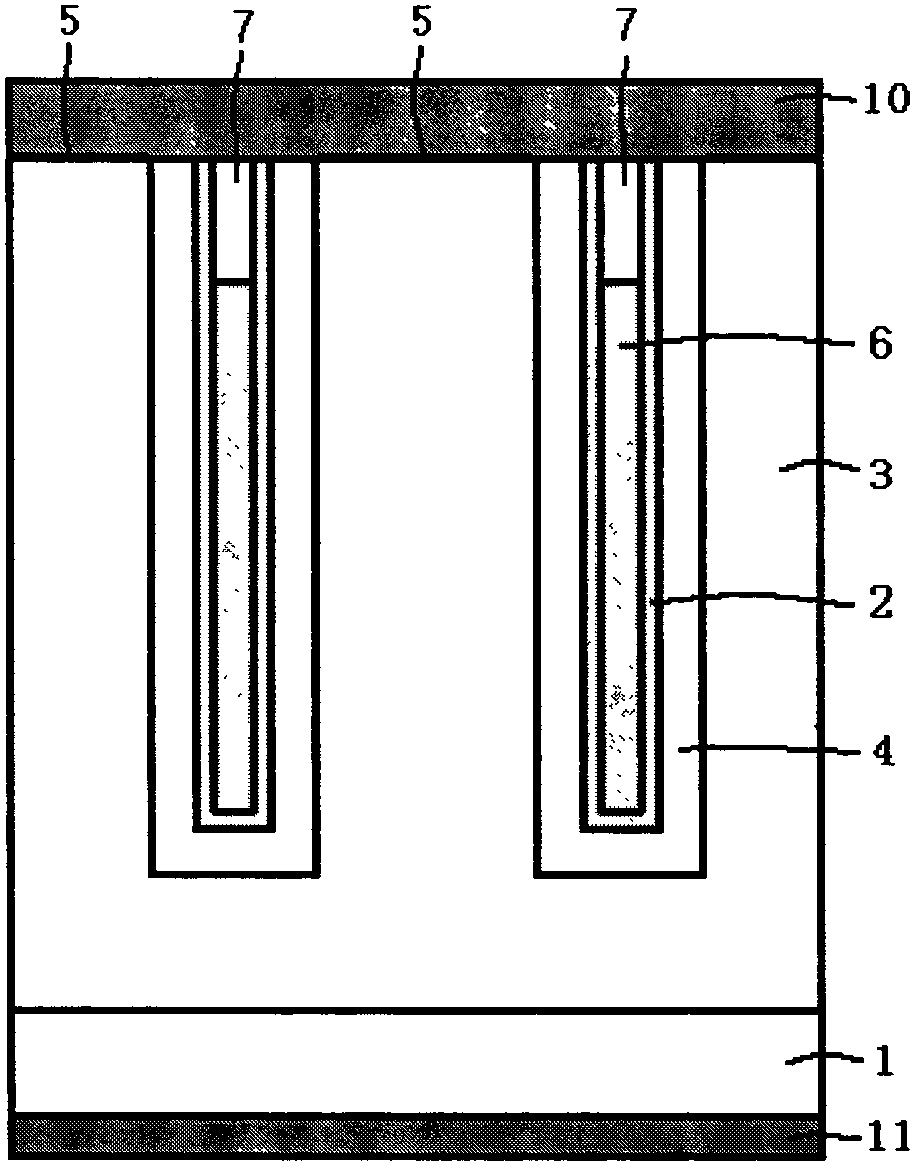

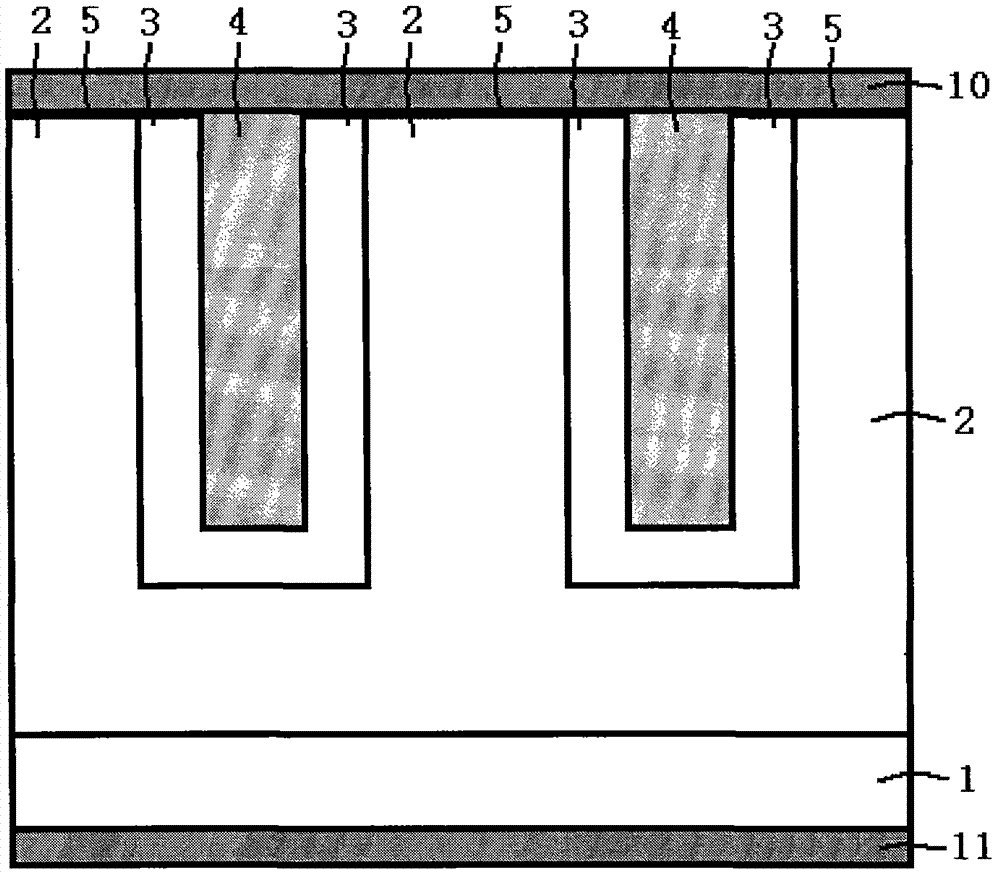

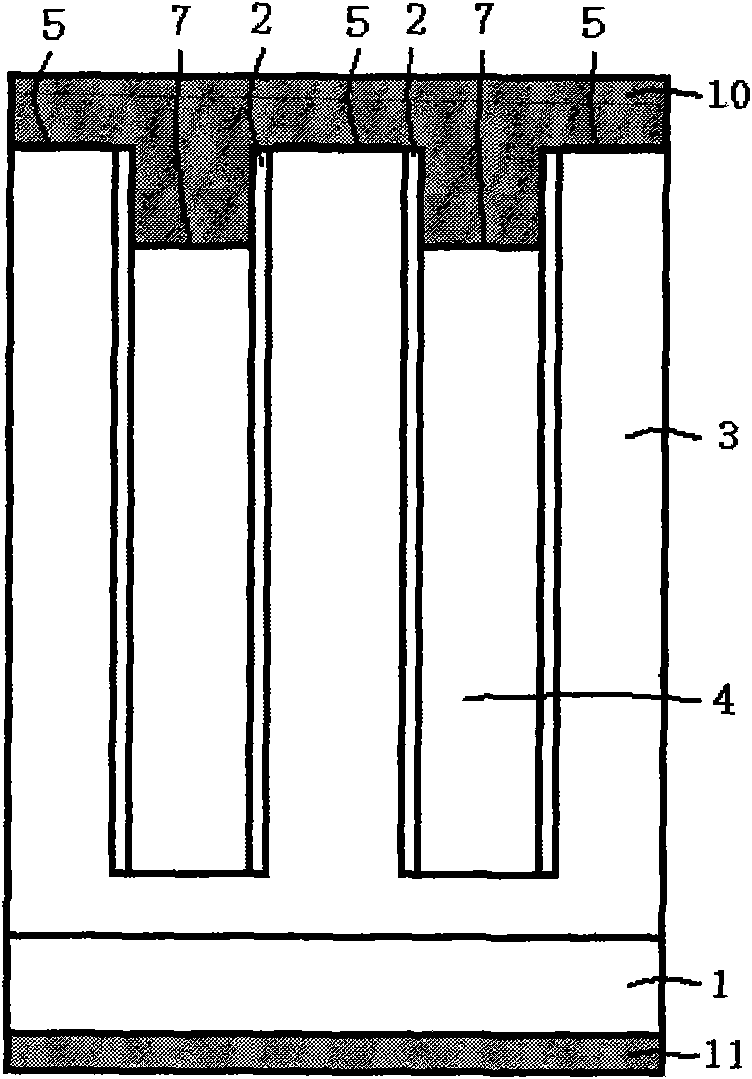

Schottky semiconductor device with insulating layer isolated super-junction structure and preparation method for Schottky semiconductor device

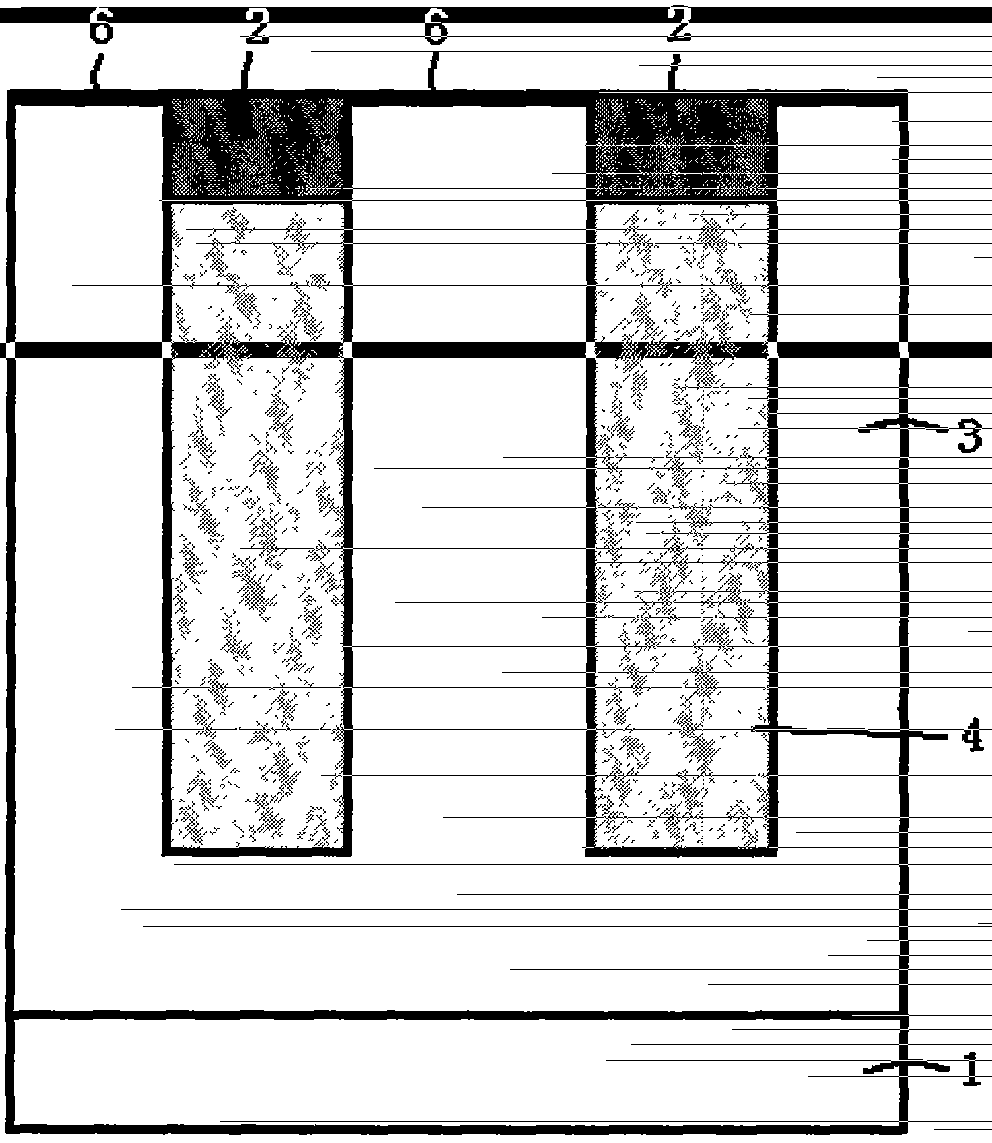

InactiveCN103367462AImprove reverse breakdown voltageLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse bias

The invention discloses a Schottky semiconductor device with an insulating layer isolated super-junction structure. By a groove structure, a deeper strip-shaped P-type semiconductor silicon material can be realized, when the device is connected with reverse bias, the strip-shaped P-type semiconductor silicon material and an N-type semiconductor silicon material form charge complementation to form the super-junction structure, and the electric field intensity distribution of a drift region is changed to form a flat electric field intensity distribution curve. The invention also provides a preparation method for the Schottky semiconductor device with the insulating layer isolated super-junction structure.

Owner:朱江

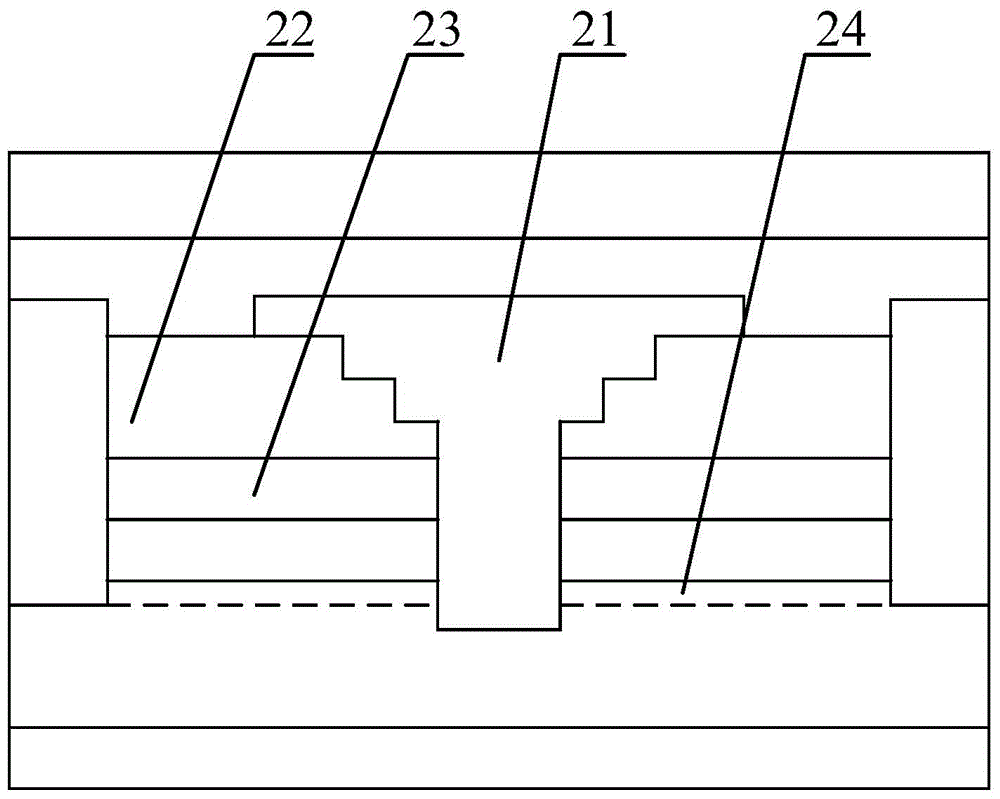

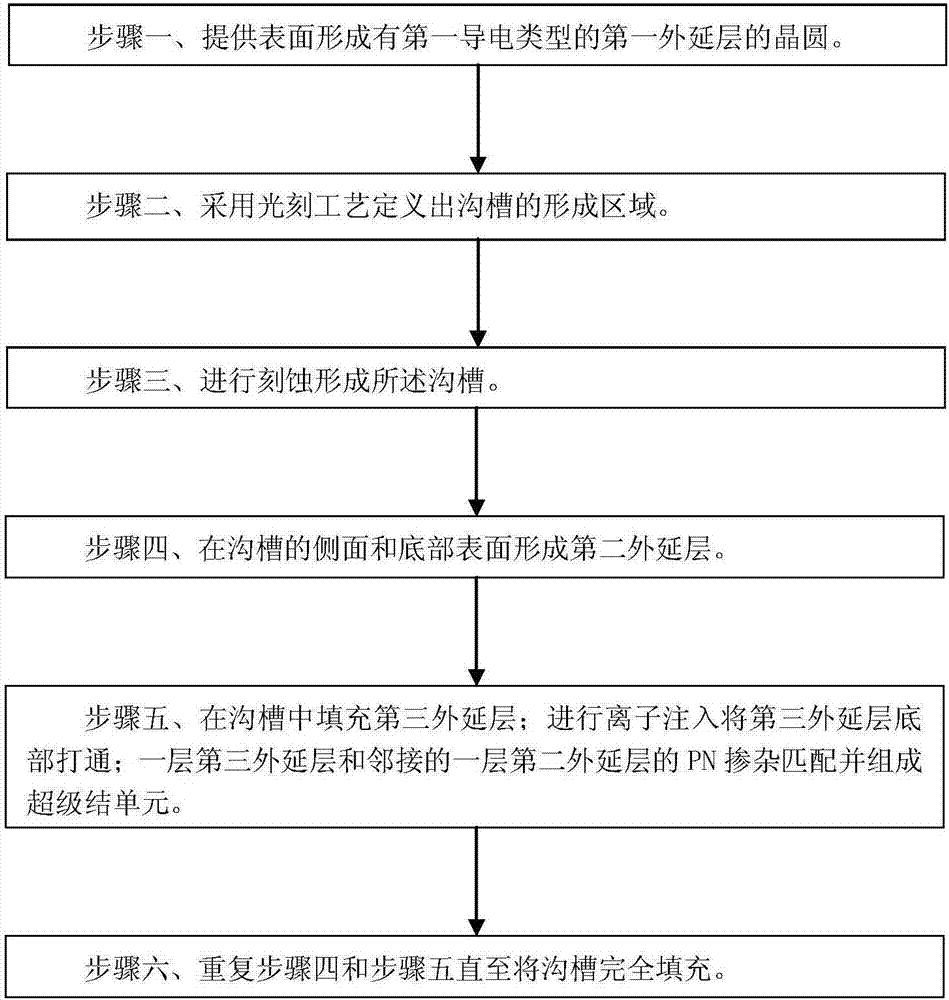

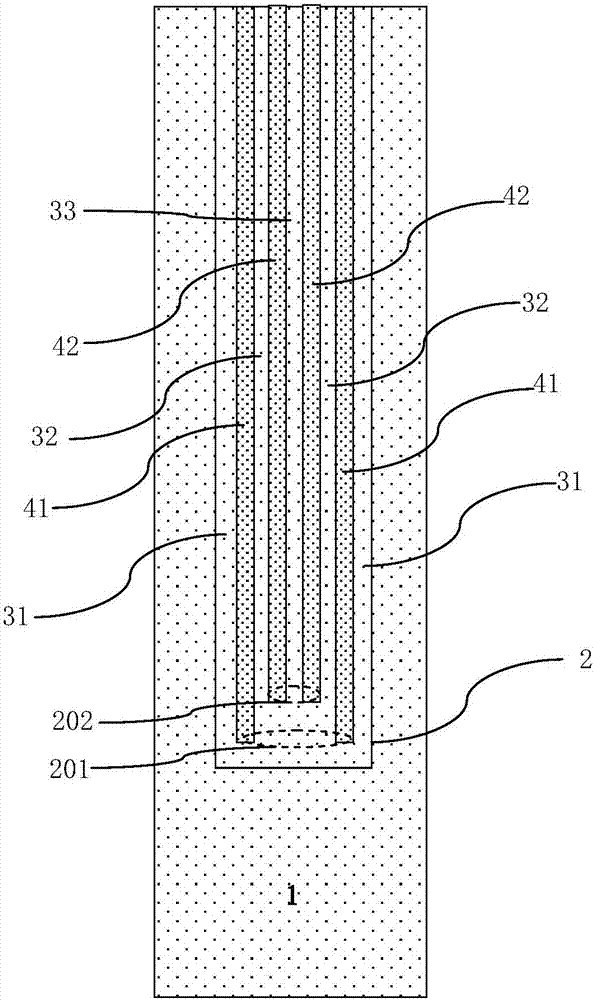

Manufacturing method of groove type super junction

InactiveCN107045973ASmall stepStep limitSemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationPhotolithography

The invention discloses a manufacturing method of a groove type super junction. The manufacturing method comprises the steps of: providing a wafer, wherein a first conduction type epitaxial layer is formed on the surface of the wafer; using a photolithography technique to define a groove forming region; carrying out etching to form a groove; forming second epitaxial layers on the side surfaces and the bottom part surface of the groove; filling third epitaxial layers in the groove; carrying out ion injection to get through the bottom part of the third epitaxial layer; carrying out PN doped matching of one layer of the third epitaxial layer and the adjacent one layer of the second epitaxial layer, and forming a super junction unit; and repeating the formation steps of the second epitaxial layers and the third epitaxial layers until the groove is completely filled up. The manufacturing method can reduce the stepping of the super junction unit, improve the in-surface evenness of PN doped matching of the super junction units on the same wafer, can improve the in-surface evenness of reverse breakdown voltage of the super junction device and improve the breakdown unit of the device, and can reduce the forward on resistance of the device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

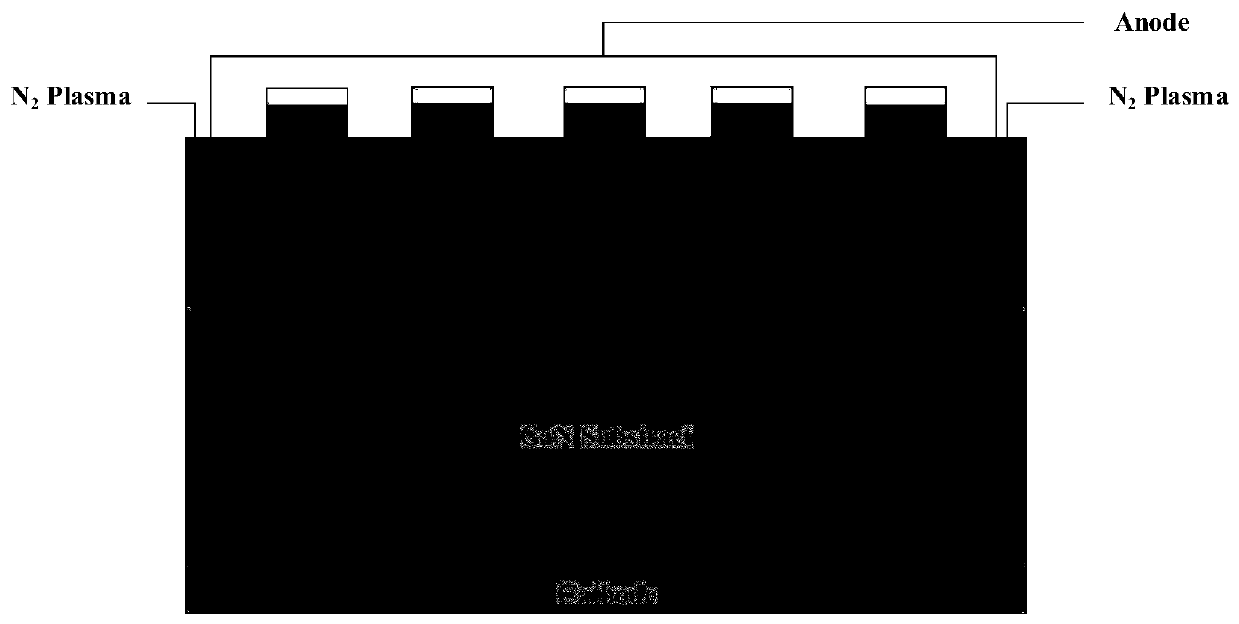

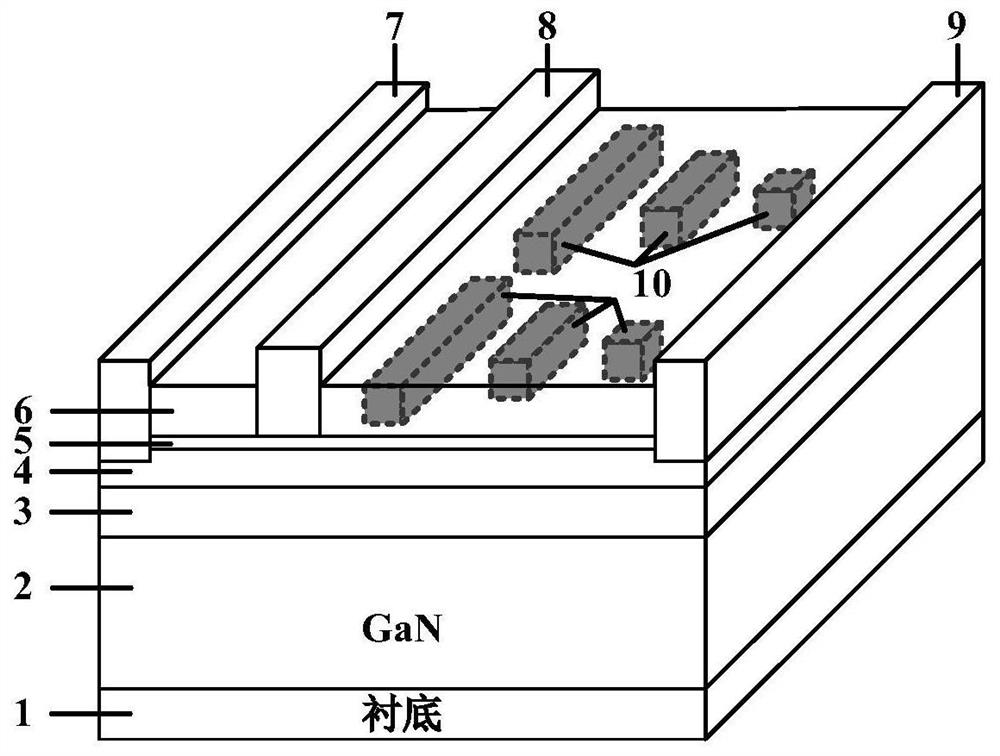

Novel GaN junction barrier Schottky diode and preparation method thereof

InactiveCN110752260AImprove performanceGood effectSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactSchottky diode

The invention discloses a novel GaN junction barrier Schottky diode and a preparation method thereof, which provides a new way for improving the performance of the Schottky diode by utilizing a noveldesign and a relatively simple and easily-achieved process. The novel GaN junction barrier Schottky diode sequentially comprises a cathode, a substrate, an n+ type GaN epitaxial layer, an n type GaN epitaxial layer, a high-resistance region, a comb-shaped p type GaN epitaxial layer, a comb-shaped p+ type GaN epitaxial layer and an anode from bottom to top, wherein plasmas are annularly injected into the outer edge of the n type GaN epitaxial layer to form the high-resistance region. According to the invention, p-type GaN does not need to be grown in the n-type GaN layer and a subsequent activation process is not needed, so that the process difficulty and the complexity are greatly reduced. Through the four layers of epitaxial GaN structures, good ohmic contact and better PN junctions can be formed, the forward on resistance is reduced, the reverse breakdown voltage is increased, and the performance of the device is effectively improved. In addition, the high-resistance region formed byN2 Plasma can effectively inhibit breakdown of the device at the edge of an electrode under high voltage, and the breakdown performance is enhanced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

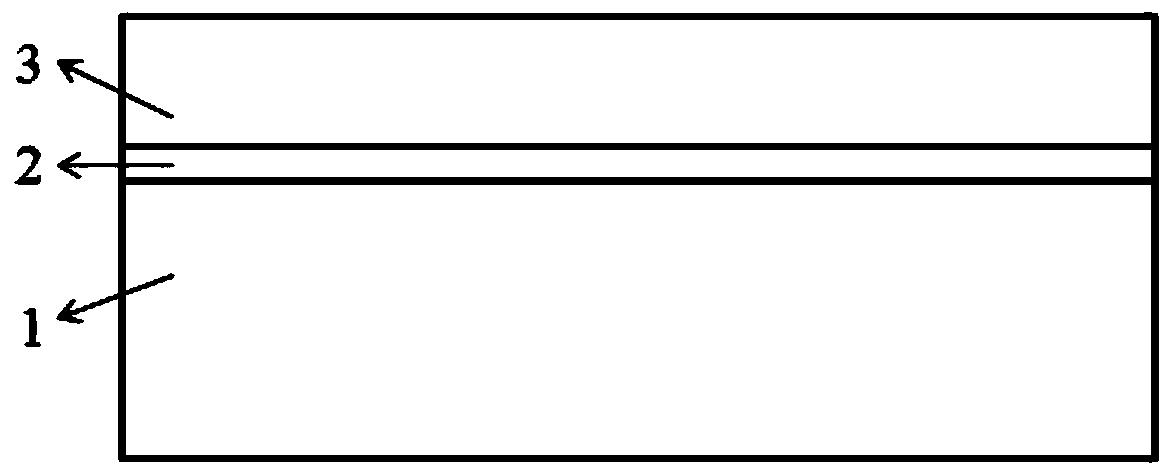

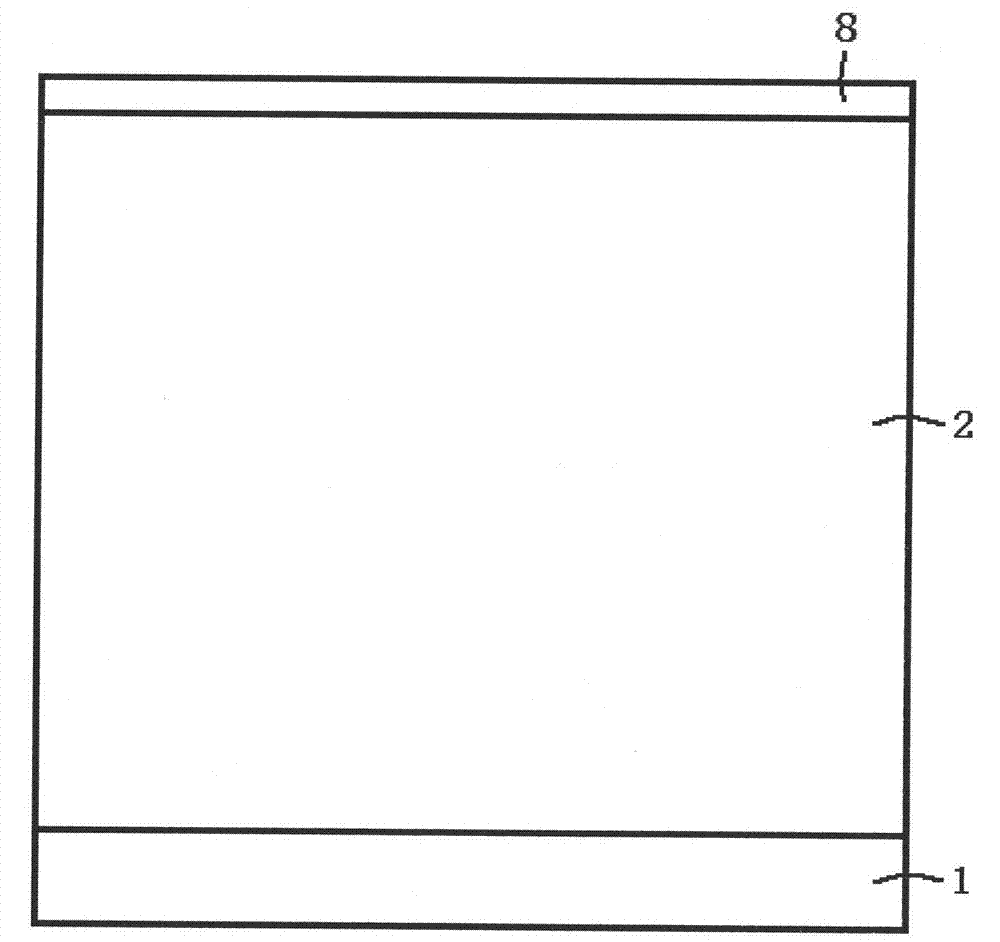

Manufacturing method of semiconductor device and semiconductor device manufactured by method

InactiveCN105529272ALower forward conduction resistanceLow Epitaxial ResistivitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The invention provides a manufacturing method of a semiconductor device and the semiconductor device manufactured by the method. The method comprises the following steps: (1) growing an N-type epitaxial layer on an N-type substrate; (2) growing an intrinsic epitaxial layer on the N-type epitaxial layer; (3) injecting N-type impurities into the intrinsic epitaxial layer; (4) injecting P-type impurities into the preset position of the intrinsic epitaxial layer; (5) repeating the steps (2) to (4); (6) carrying out thermal annealing; and (7) injecting a P-type well into the preset position. According to the manufacturing method, the process difficulty and the cost are reduced; meanwhile, the performance is not obviously weakened; and the cost performance is relatively high.

Owner:FUJIAN FUXIN ELECTRONICS TECH CO LTD

Charge compensation Schottky semiconductor device and manufacturing method thereof

InactiveCN103378131AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

The invention discloses a charge compensation Schottky semiconductor device. When a certain reverse bias voltage is connected to the semiconductor device, first electric conduction semiconductor material and second electric conduction semiconductor material can form charge compensation and improve reverse breakdown voltage of the device or improve the forward direction communication characteristic of the device. The invention further provides a manufacturing method of the super junction Schottky semiconductor device.

Owner:朱江

Groove schottky semiconductor device and manufacturing method thereof

ActiveCN103390651AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The invention discloses a groove schottky semiconductor device which is provided with a charge compensation structure. First conducting semiconductor materials and second conducting semiconductor materials can form charge compensation when the semiconductor device is connected with a certain reverse bias, so that positive conducting or reverse blocking characteristics of the device can be improved. The invention further provides a manufacturing method of the groove schottky semiconductor device.

Owner:北海惠科半导体科技有限公司

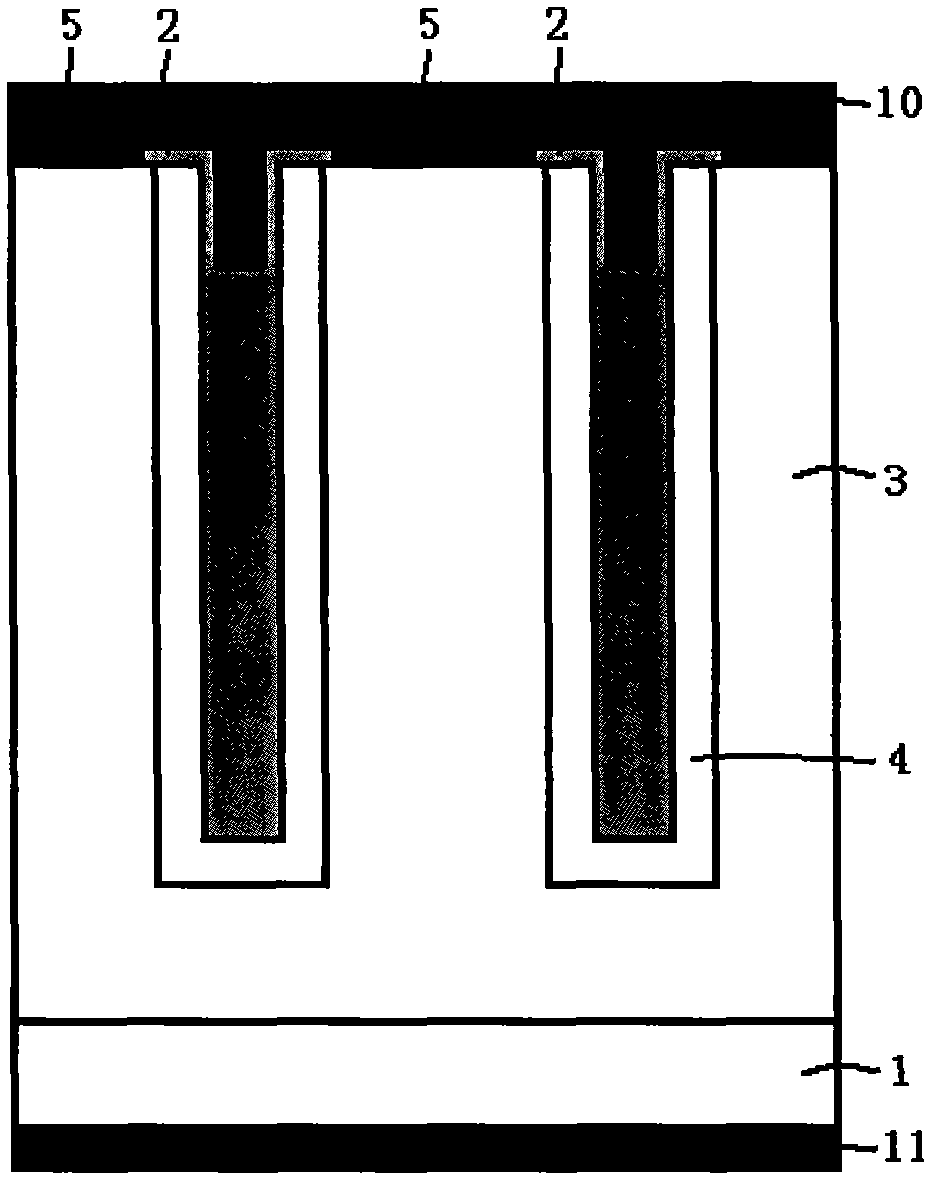

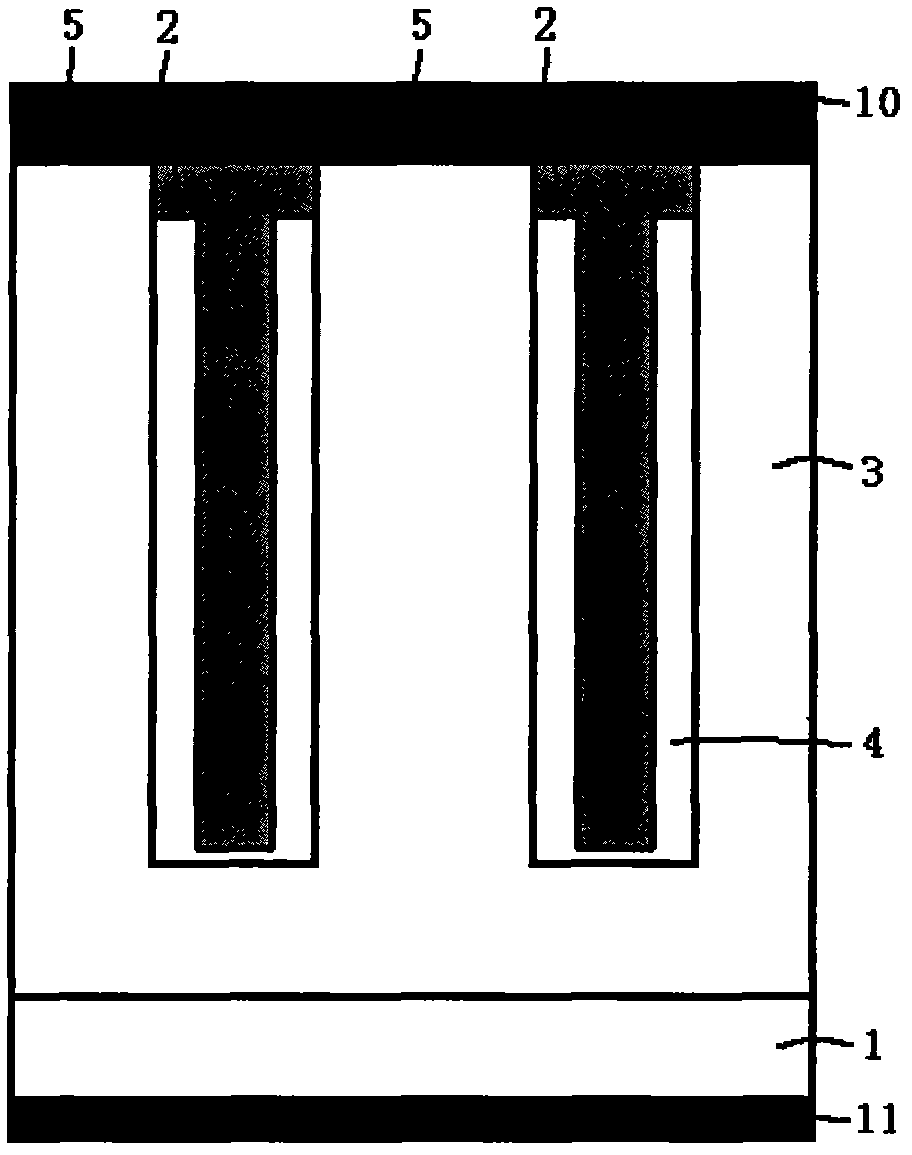

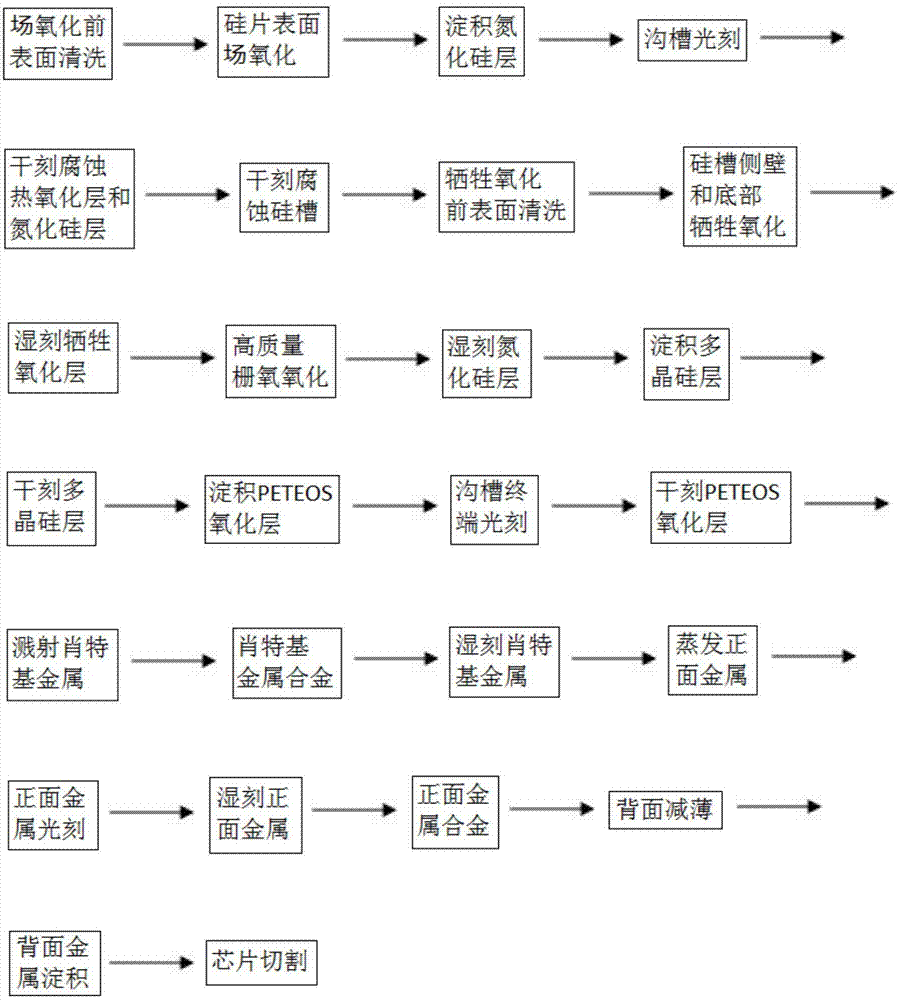

Schottky barrier diode chip and production technology thereof

ActiveCN104241285AReduce lossImprove stabilityTransistorSemiconductor/solid-state device manufacturingSchottky barrierSurface oxidation

The invention discloses a schottky barrier diode chip and a production technology thereof, and belongs to the field of semiconductor chip production. The schottky barrier diode chip comprises a chip body, a terminal groove, a protecting layer and an electrode. The chip body refers to a schottky barrier diode chip body. The chip section sequentially comprises the chip body, the germinal groove, the protecting layer and the electrode from bottom to top. The electrode refers to a groove gate-oxide polycrystal electrode and comprises a schottky area. The protecting layer refers to a PETEOS (plasma enhanced tetraethoxysilane) protecting layer. Methods such as field surface oxidation, sacrifice oxidation, gate-oxide oxidation, PETEOS oxidation layer deposition, schottky metal sputtering, front metal alloying and back thinning are applied to chip technology improvement. Low switching loss, forward break-over voltage and chip power consumption are achieved, voltage-withstanding stability and reliability of a diode are enhanced, and service life of the diode is prolonged.

Owner:桑德斯微电子器件(南京)有限公司

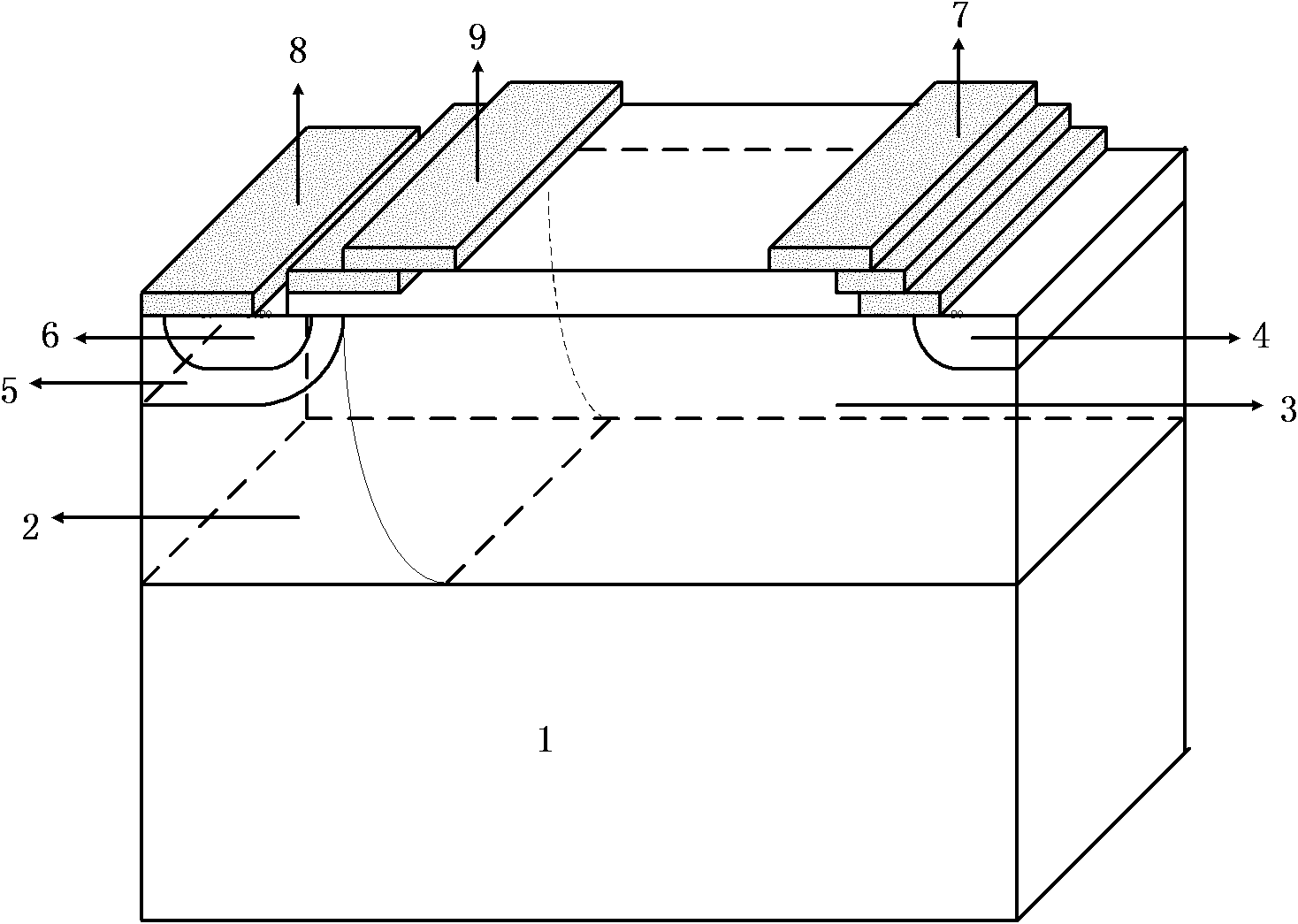

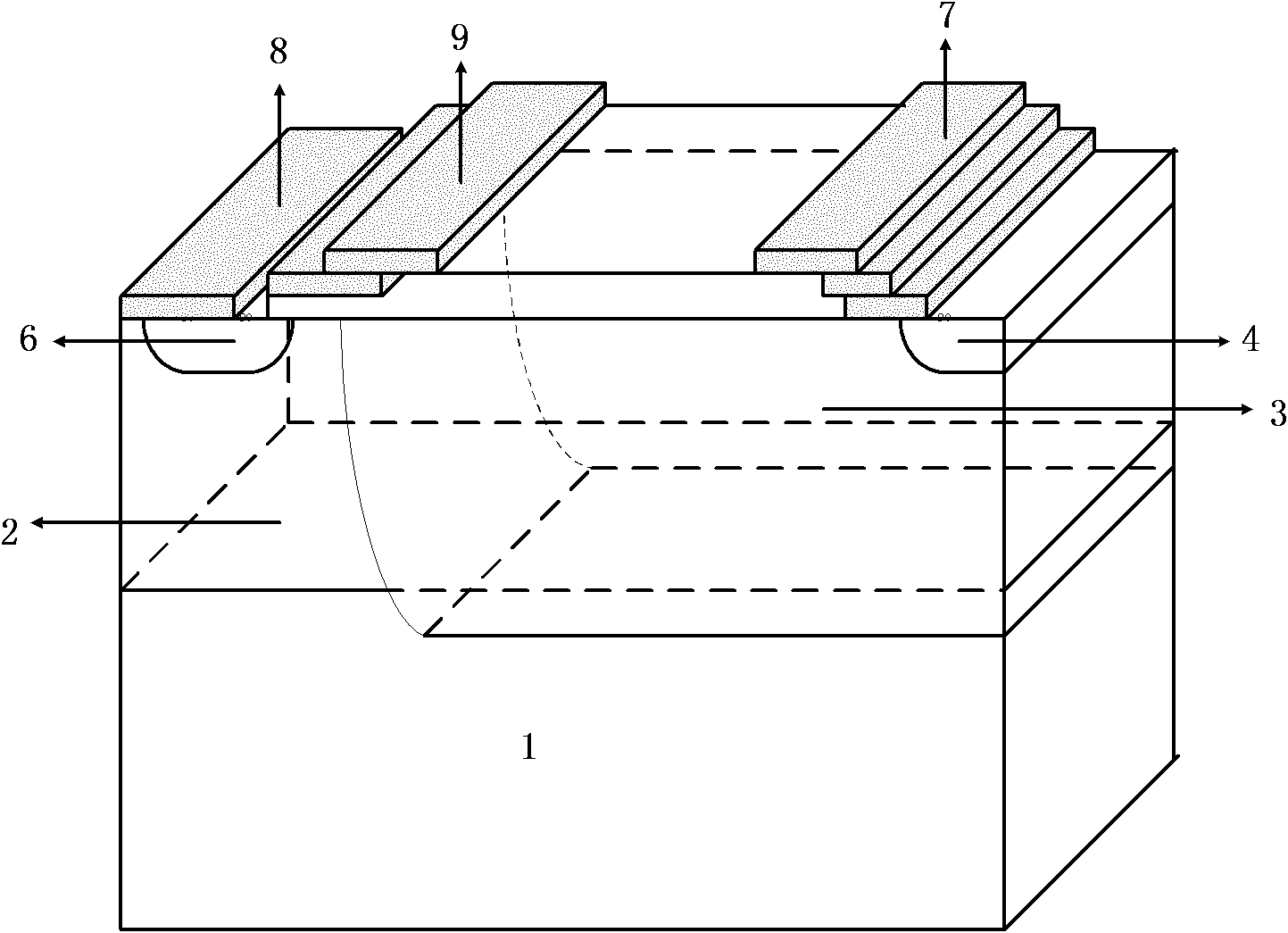

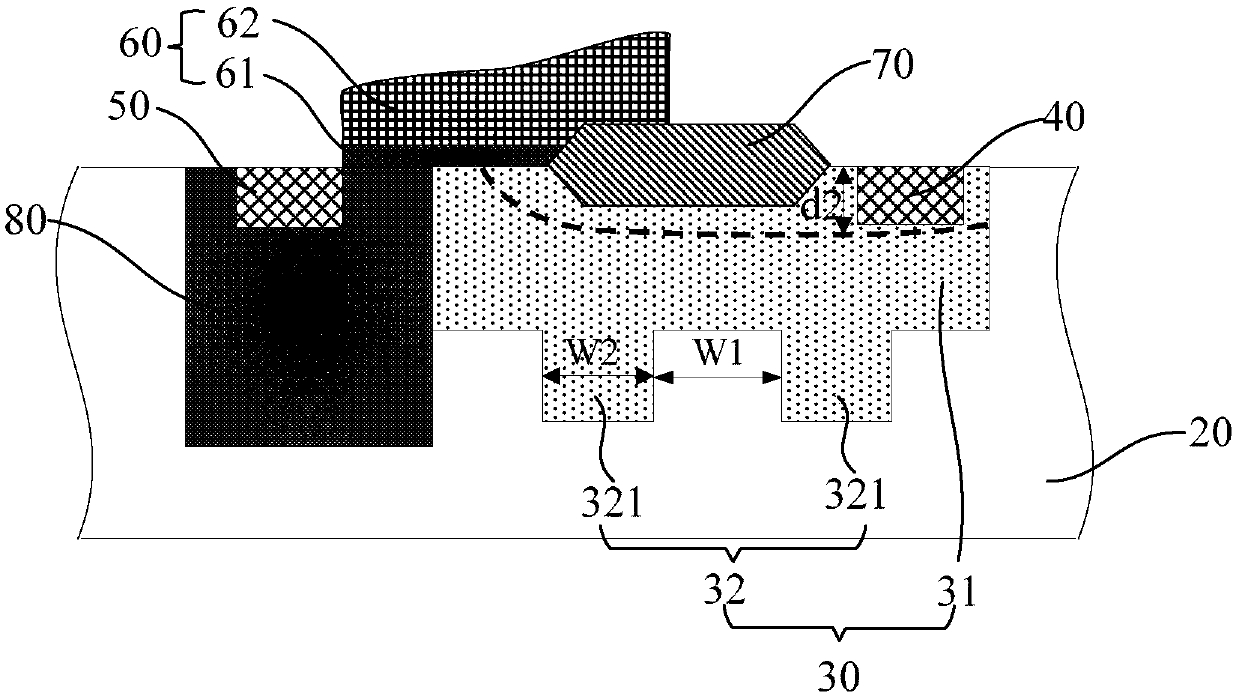

LDMOS device and manufacturing method thereof

InactiveCN109545854AImprove breakdown voltageImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSCondensed matter physics

The invention provides an LDMOS device and a manufacturing method thereof. The device comprises: a substrate, a drain electrode, a source electrode, a gate electrode, and a drift region. The drift region includes a first drift region and a second drift region under the first drift region, wherein the width of the second drift region is smaller than the width of the first drift region. Compared with the prior art, under the condition of the same doping concentration, depth of an undepleted region can be effectively reduced, thereby increasing area of a depletion region, so that breakdown voltage of the LDMOS device can be improved. Therefore, in the case of ensuring the same withstand voltage as in the prior art, performance of the LDMOS device is improved by increasing the doping concentration of the drift region and reducing forward conduction resistance of the drift region. The LDMOS device effectively solves a contradiction problem of improving breakdown voltage and reducing forwardconduction resistance of a LDMOS device in the prior art.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

GaN HMET device with gradually-change fluorine ion terminal in passivation layer

ActiveCN112864243AImprove pressure resistanceImprove reliabilitySemiconductor devicesIon implantationSemiconductor technology

The invention belongs to the technical field of power semiconductors, and relates to a GaN HMET device with a gradually-change fluorine ion terminal in a passivation layer. The GaN HMET device is mainly characterized in that a fluorine ion implantation terminal structure is introduced between a grid and a drain of the device, and the area of a fluorinion injection region is gradually reduced from the side, close to the grid, to the side of the drain, so an electric field peak of the edge of the grid is effectively reduced, and a new electric field peak is introduced into the middle of a drift region to modulate a transverse electric field of the device; and the fluorine ion implantation terminal structure is located in the thick passivation layer, so physical damage of ion implantation to an AlGaN material and influence of ion implantation to 2DEG mobility can be avoided, device characteristics are improved, and current collapse is inhibited. The beneficial effect of the invention is that the structure can realize higher withstand voltage and smaller specific on-resistance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Hybrid Schottky barrier diode structure with P-type nickel oxide material

ActiveCN112909076ASolve difficultySolve process problemsSemiconductor devicesSchottky barrierSemiconductor materials

The invention relates to a hybrid Schottky barrier diode structure with a P-type nickel oxide material. The structure comprises a bottom ohmic contact electrode, an N+ substrate, an N-drift layer, a groove, a P-type layer, a field plate dielectric layer, field plate metal and a Schottky contact electrode, the N-drift layer is of a step structure, and p-NiO materials are grown on selected areas on the two sides of a table top to replace P-type wide bandgap semiconductor materials. Therefore, the problem that a P-type epitaxial growth technology and an ion implantation technology of a wide bandgap semiconductor material at the present stage are immature can be well solved. The structure is high in operability, low in cost, simple and reliable in process and suitable for industrial application and popularization.

Owner:HEBEI UNIV OF TECH

Schottky semiconductor device with charge compensation groove and preparing method thereof

ActiveCN103515449AIncrease the doping concentrationLower forward conduction resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsEngineering

The invention discloses a Schottky semiconductor device with a charge compensation groove. According to the Schottky semiconductor device with the charge compensation groove, a charge compensation structure can be formed by a first conductive semiconductor material and a second conductive semiconductor material, electric field intensity which can reduce Schottky junctions on the surface of the first conductive semiconductor material exists in the groove in the surface of the device, and then reverse breakdown voltage of the device is improved. The invention further provides a preparing method of the Schottky semiconductor device with the charge compensation groove.

Owner:北海惠科半导体科技有限公司

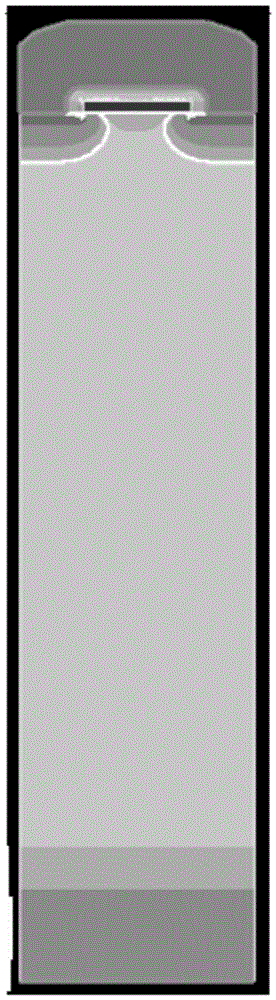

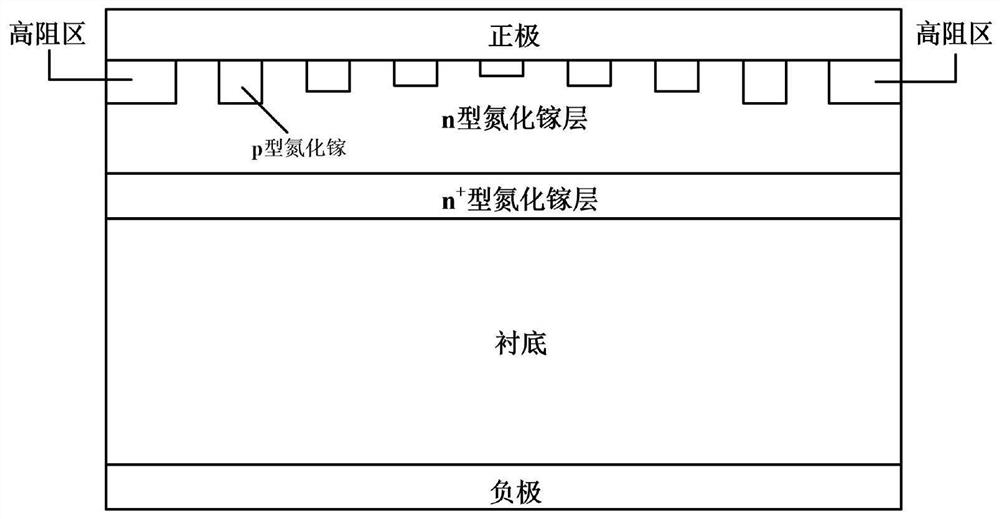

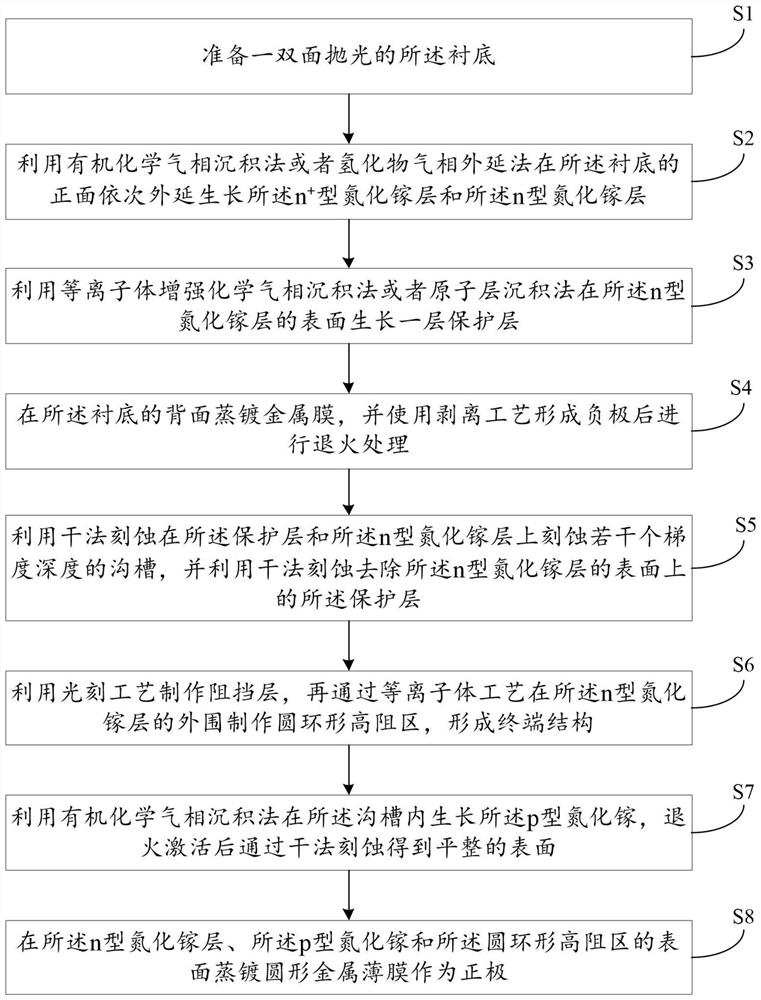

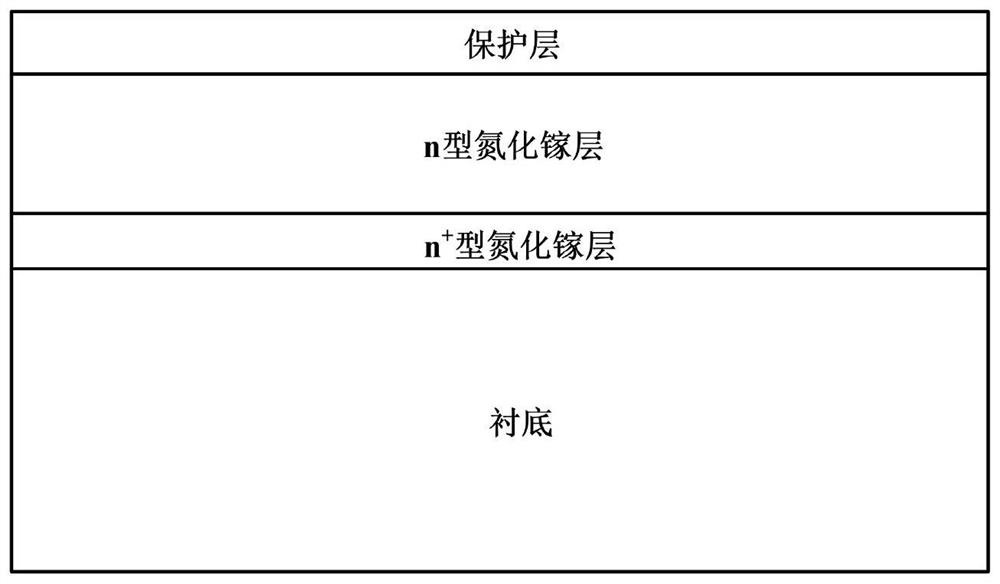

Junction barrier Schottky diode with gradient depth P type region and preparation method thereof

PendingCN112531007ASuppress breakdownImprove performanceSemiconductor/solid-state device manufacturingDiodeElectrical field strengthOhmic contact

The invention relates to a junction barrier Schottky diode with a gradient depth P type region and a preparation method thereof. The junction barrier Schottky diode comprises: a substrate; a negativeelectrode, which is manufactured on the back surface of the substrate; an n+ type gallium nitride layer, which epitaxially grows on the front surface of the substrate; an n type gallium nitride layer,which epitaxially grows on the n+ type gallium nitride layer, wherein an annular high-resistance region is arranged on the periphery of the n type gallium nitride layer, a plurality of grooves with gradient depths are etched in the n type gallium nitride layer, and p type gallium nitride grows in each groove; and a positive electrode, which is manufactured on the surfaces of the n type gallium nitride layer, the p type gallium nitride layer and the annular high-resistance region. The P type region with the gradient depth can adjust the electric field distribution of the high-electric-field-intensity region of the device; meanwhile, good ohmic contact and better PN junctions can be formed through the double-layer epitaxial gallium nitride structure, and the performance of the device is effectively improved; and in addition, the high-resistance region can effectively restrain breakdown of the device located on the edge of the electrode under high voltage, and the breakdown performance of the device is enhanced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI