Patents

Literature

5018 results about "Semiconductor technology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

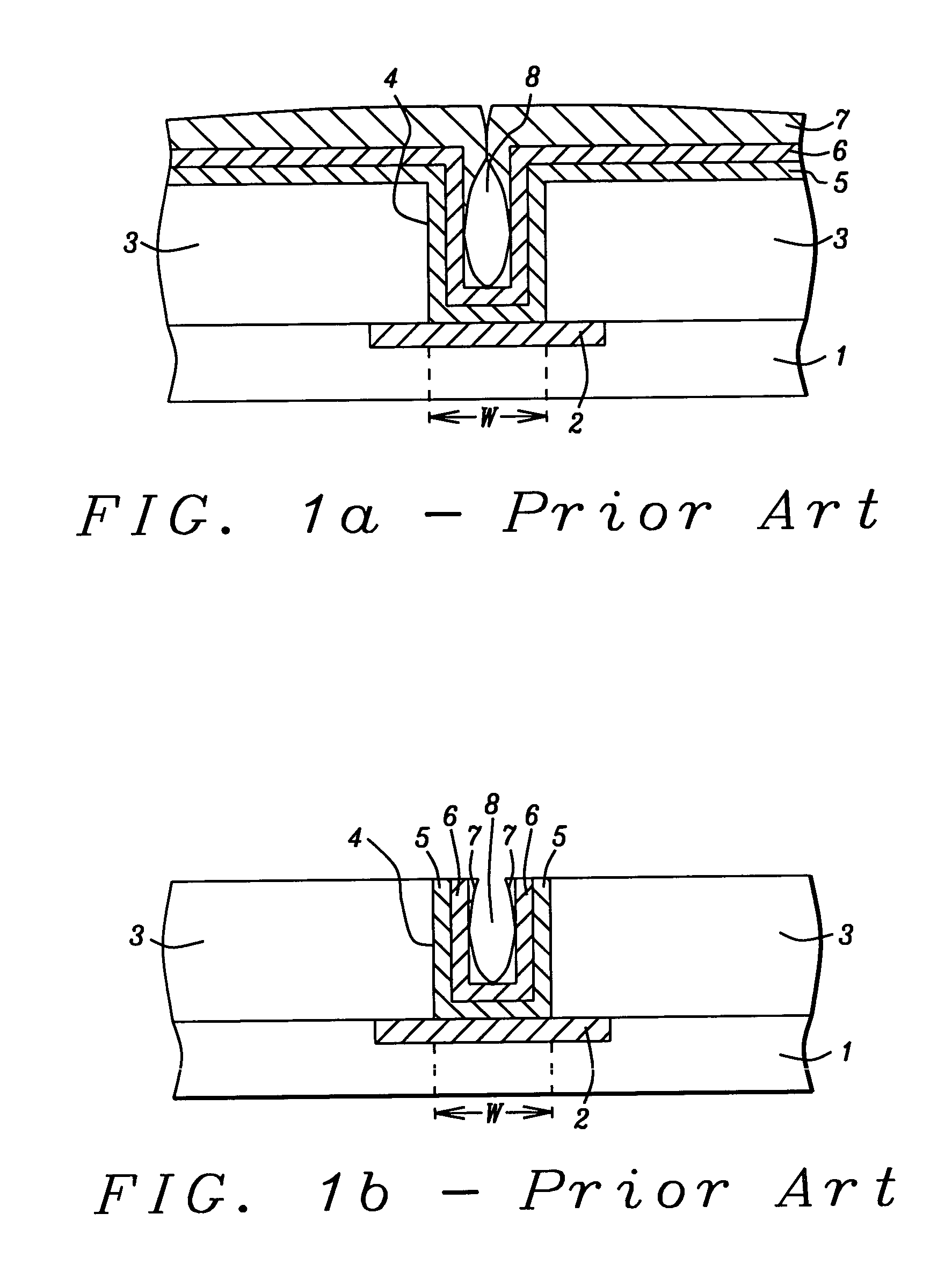

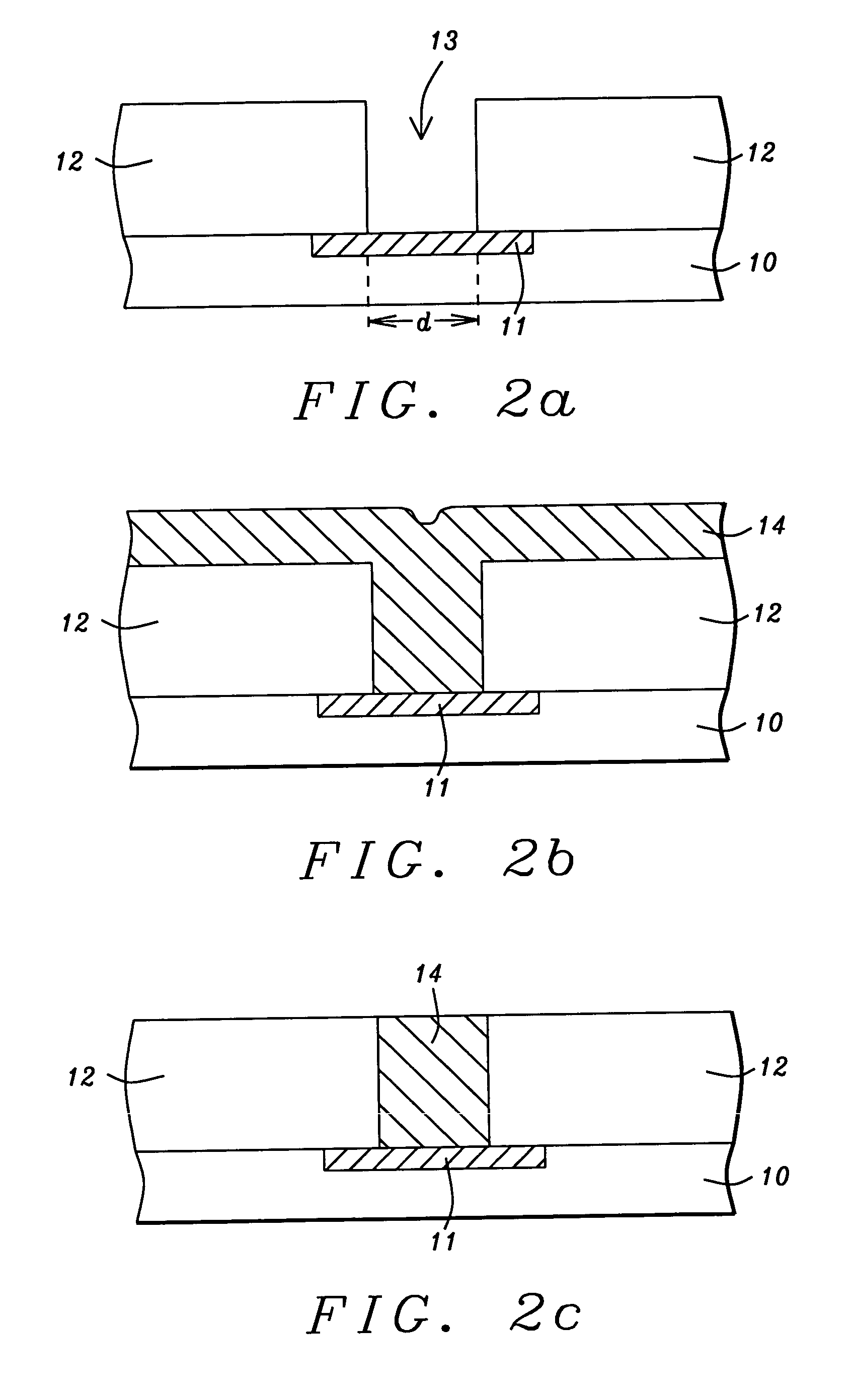

Method of manufacturing a contact interconnection layer containing a metal and nitrogen by atomic layer deposition for deep sub-micron semiconductor technology

ActiveUS7235482B2Good step coverageSafe handlingSemiconductor/solid-state device detailsSolid-state devicesAtomic layer depositionContamination

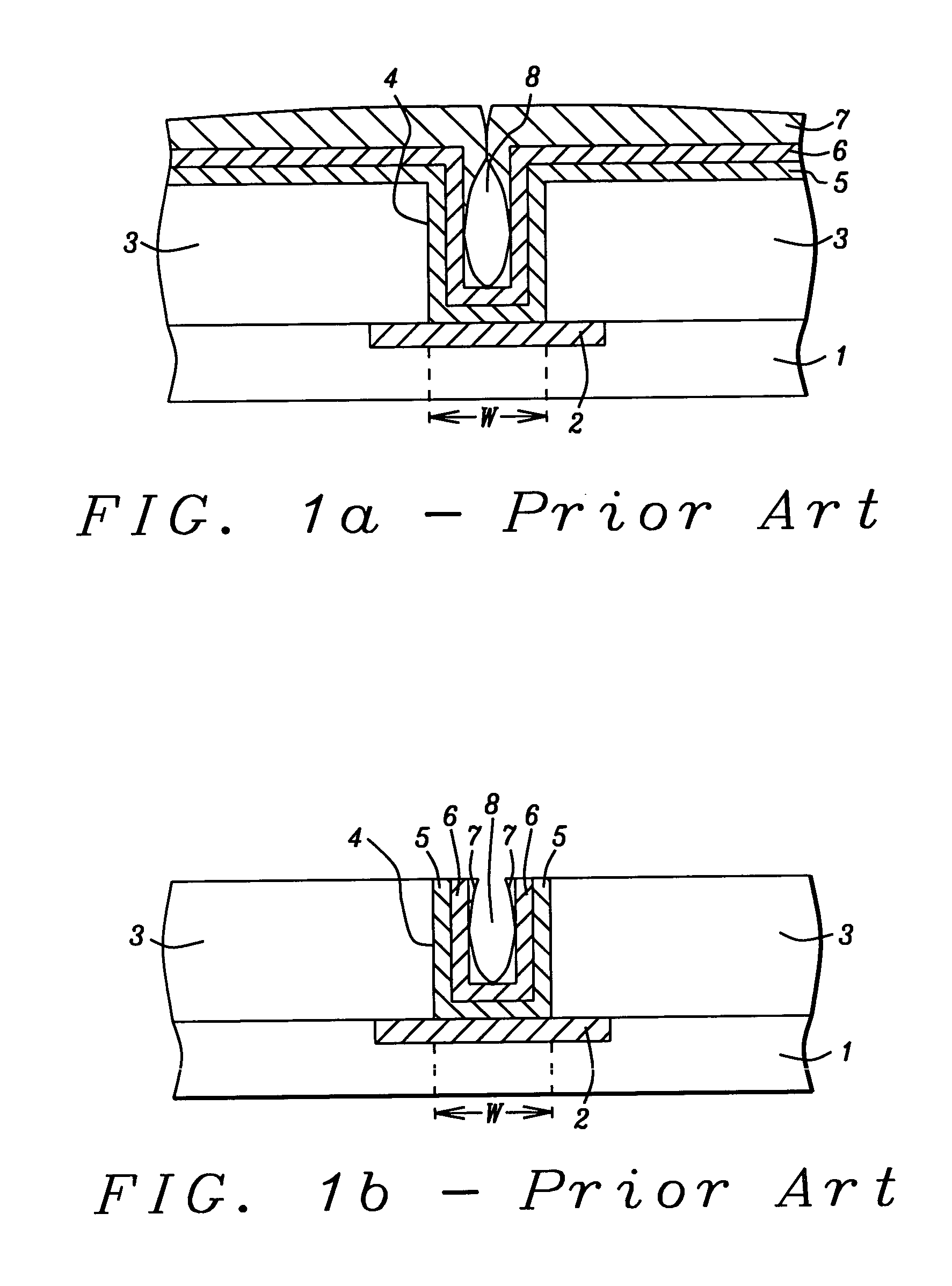

An atomic layer deposition method is used to deposit a TiN or TiSiN film having a thickness of about 50 nm or less on a substrat. A titanium precursor which is tetrakis(dimethylamido)titanium (TDMAT), tetrakis(diethylamido)titanium (TDEAT), or Ti{OCH(CH3)2}4 avoids halide contamination from a titanium halide precursor and is safer to handle than a titanium nitrate. After a monolayer of the titanium precursor is deposited on a substrate, a nitrogen containing reactant is introduced to form a TiN monolayer which is followed by a second purge. For TiSiN, a silicon source gas is fed into the process chamber after the TiN monolayer formation. The process is repeated several times to produce a composite layer comprised of a plurality of monolayers that fills a contact hole. The ALD method is cost effective and affords an interconnect with lower impurity levels and better step coverage than conventional PECVD or CVD processes.

Owner:TAIWAN SEMICON MFG CO LTD

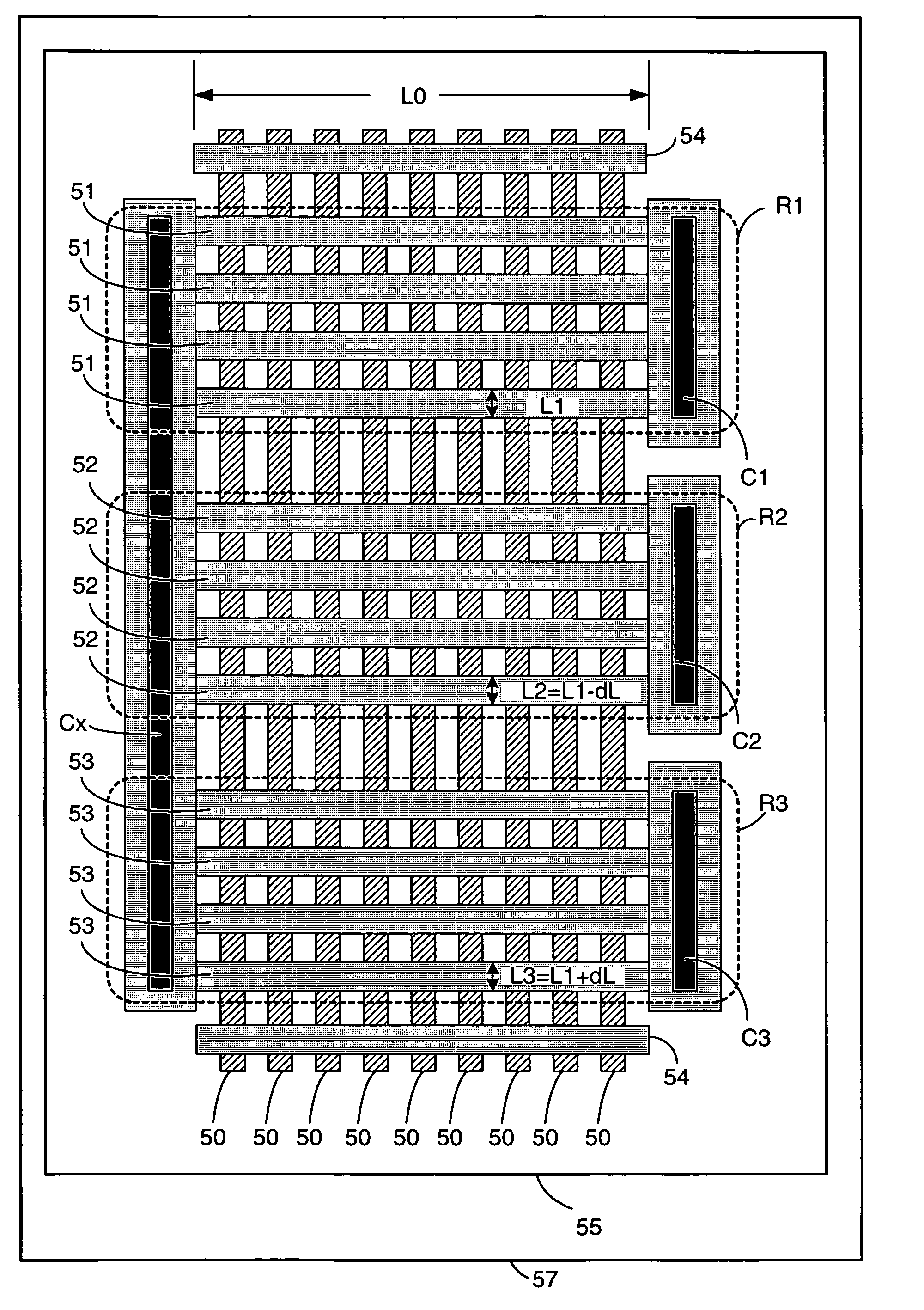

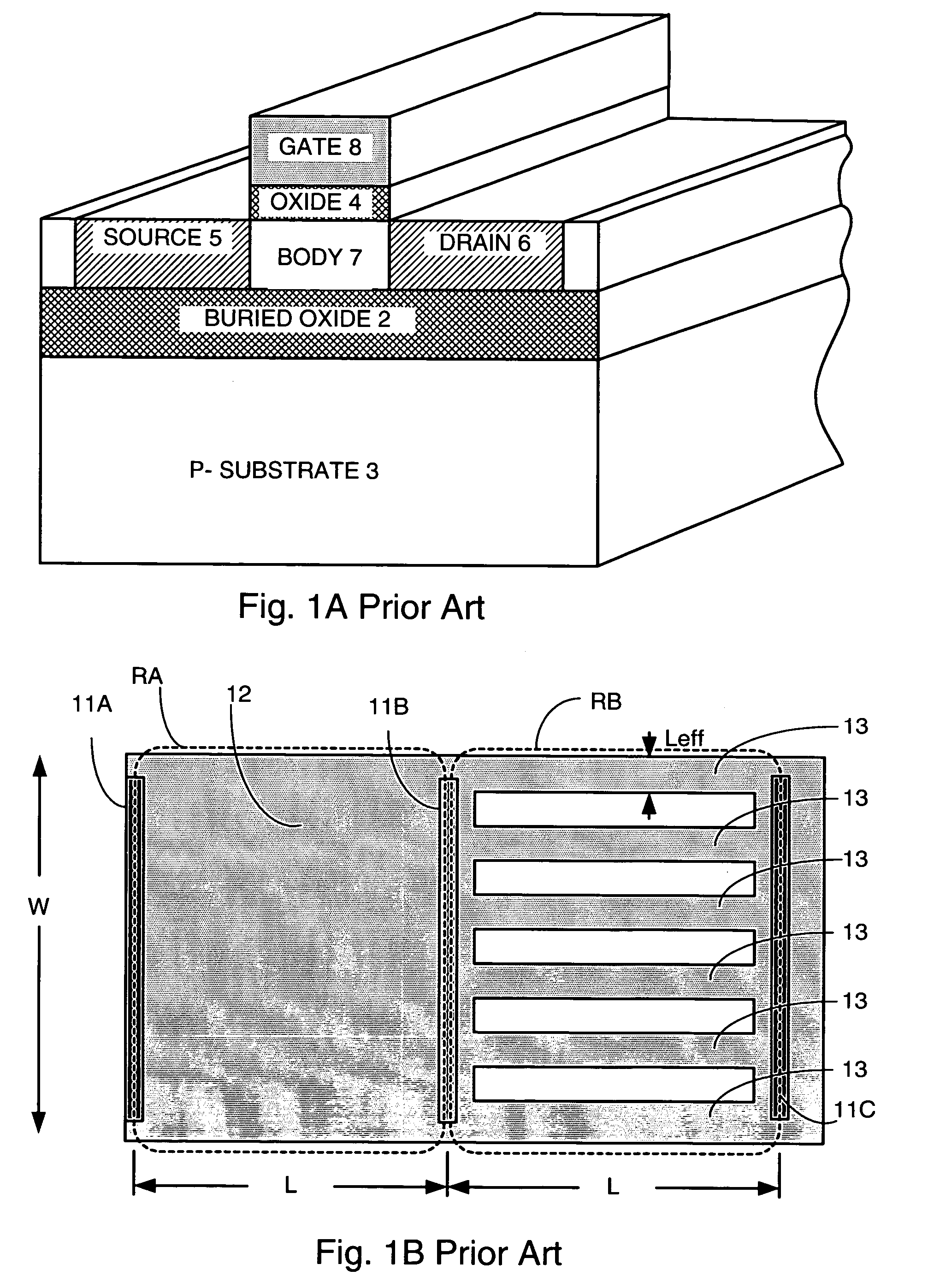

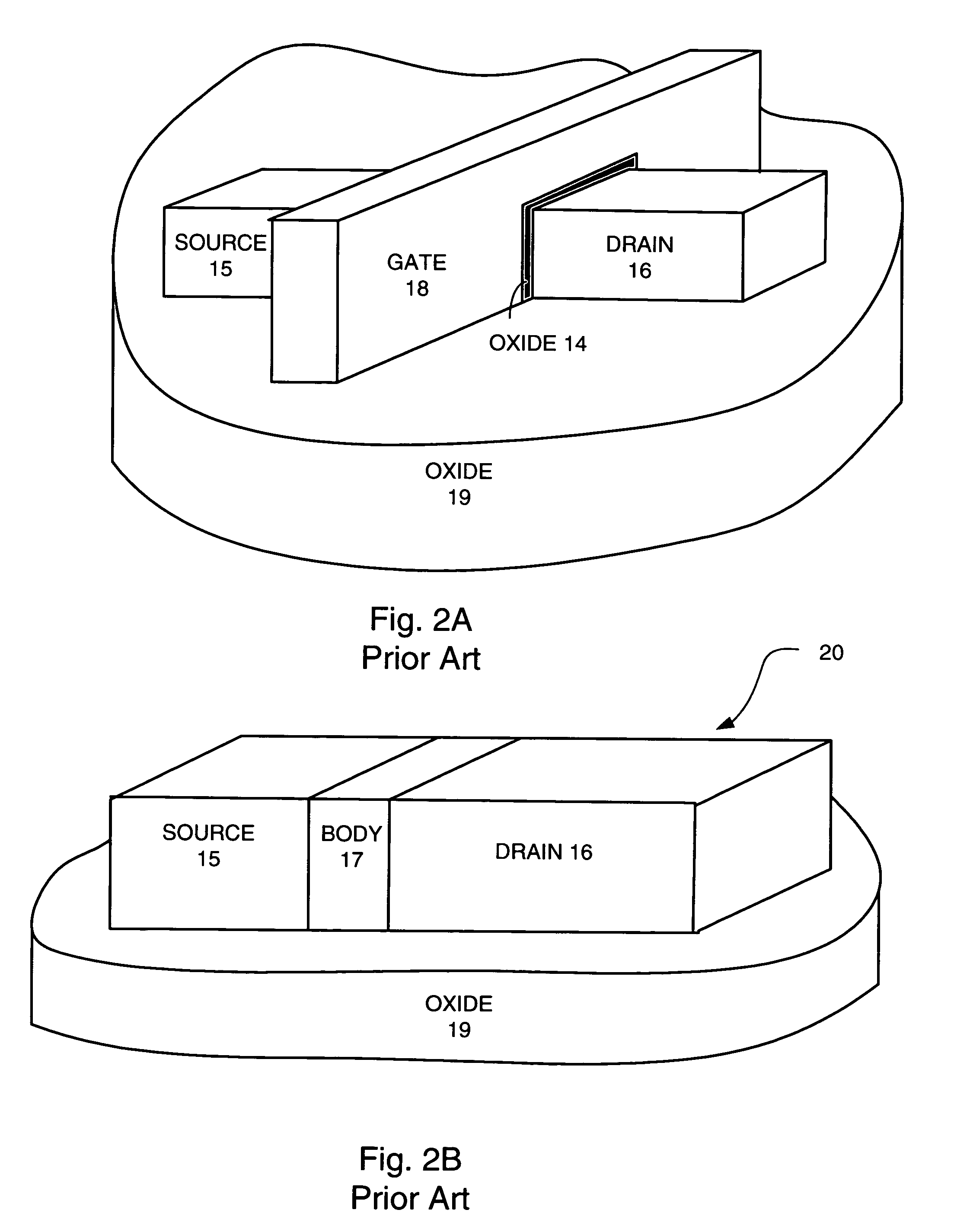

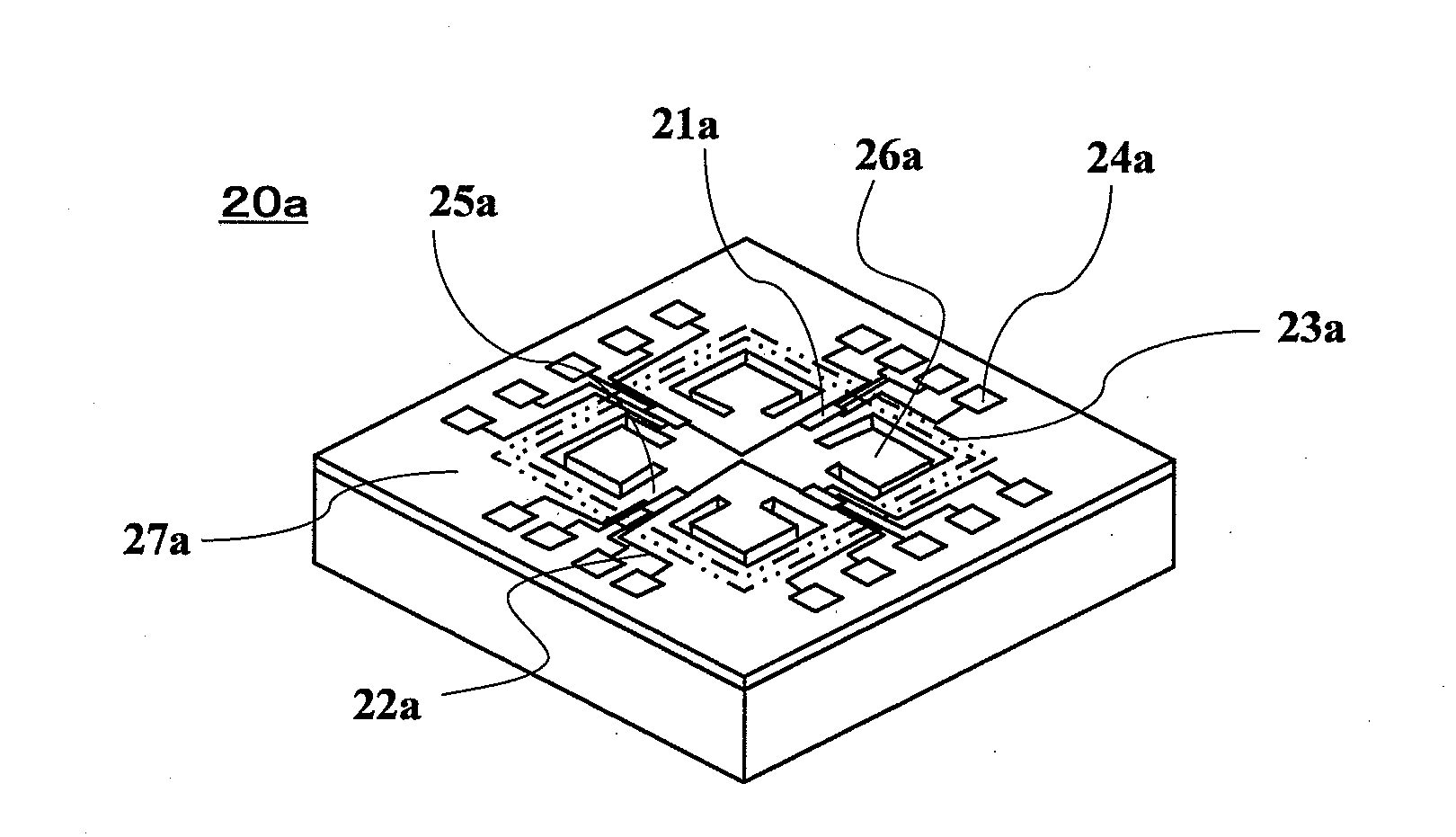

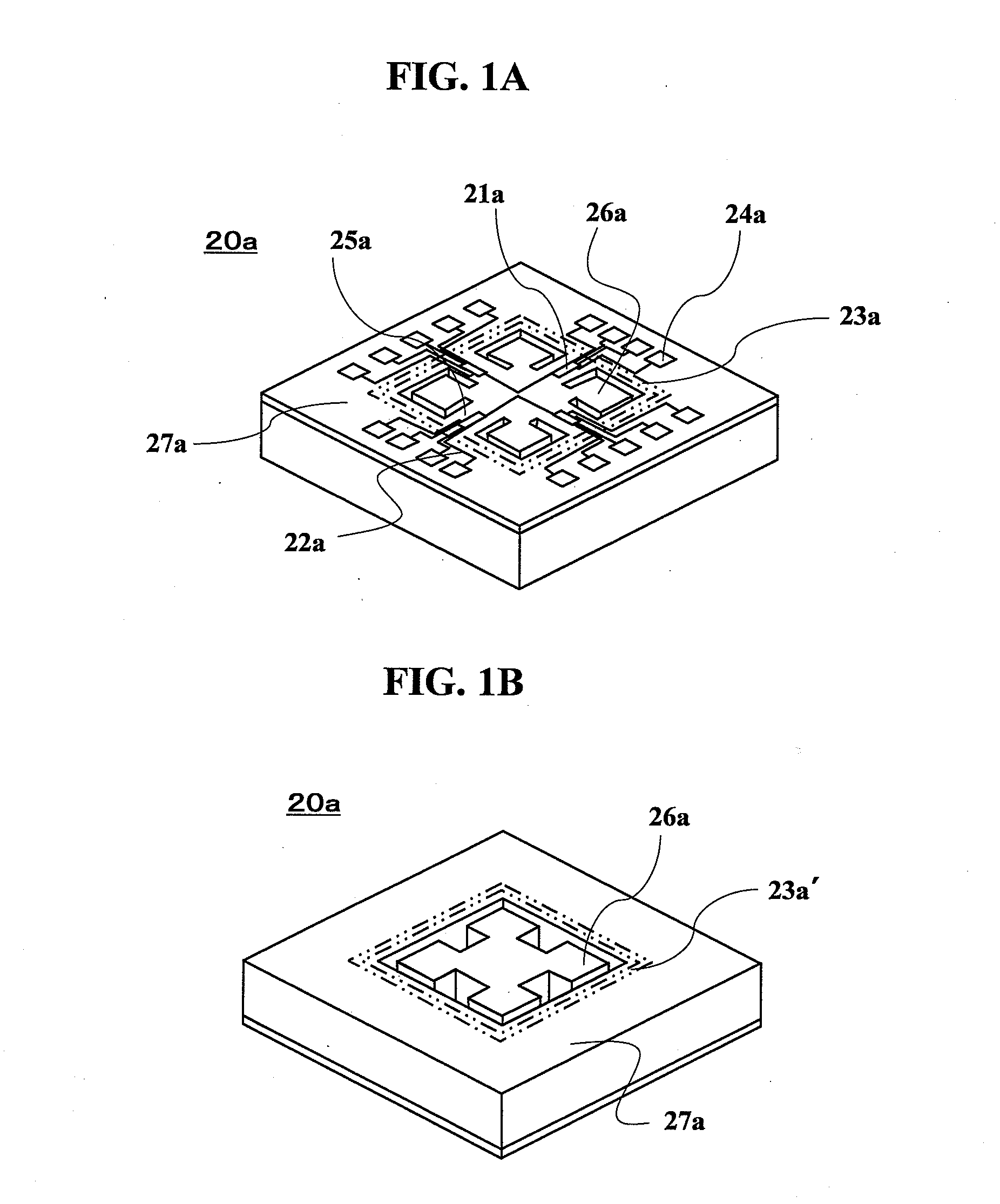

Polysilicon conductor width measurement for 3-dimensional FETs

InactiveUS7227183B2Sure easyImprove accuracyTransistorSemiconductor/solid-state device testing/measurementElectrical resistance and conductanceElectrical conductor

An apparatus and method is disclosed for determining polysilicon conductor width for 3-dimensional field effect transistors (FinFETs). Two or more resistors are constructed using a topology in which polysilicon conductors are formed over a plurality of silicon “fins”. A first resistor has a first line width. A second resistor has a second line width. The second line width is slightly different than the first line width. Advantageously, the first line width is equal to the nominal design width used to make FET gates in the particular semiconductor technology. Resistance measurements of the resistors and subsequent calculations using the resistance measurements are used to determine the actual polysilicon conductor width produced by the semiconductor process. A composite test structure not only allows calculation of the polysilicon conductor width, but provides proof that differences in the widths used in the calculations do not introduce objectionable etching characteristics of the polysilicon conductors.

Owner:IBM CORP

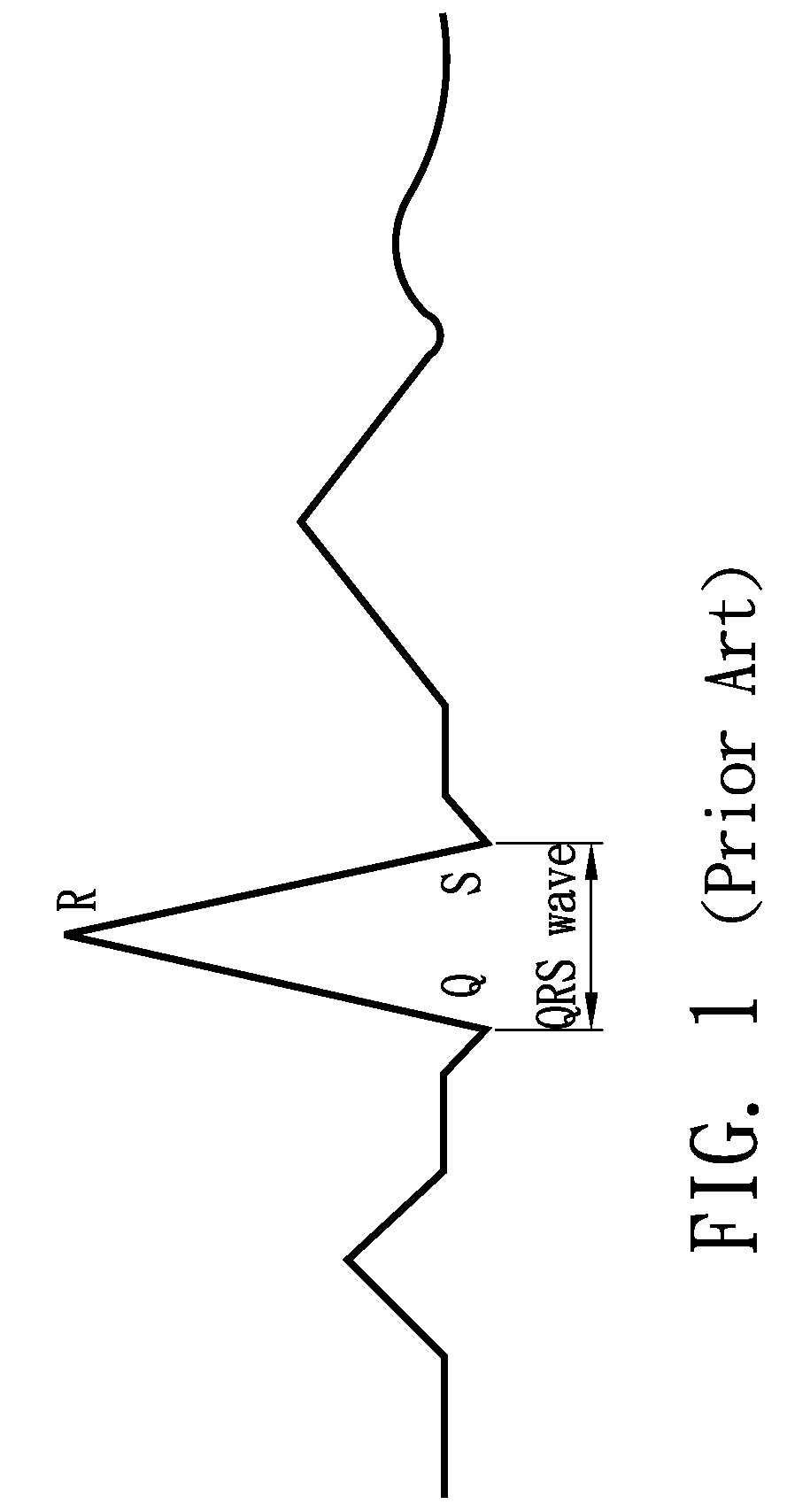

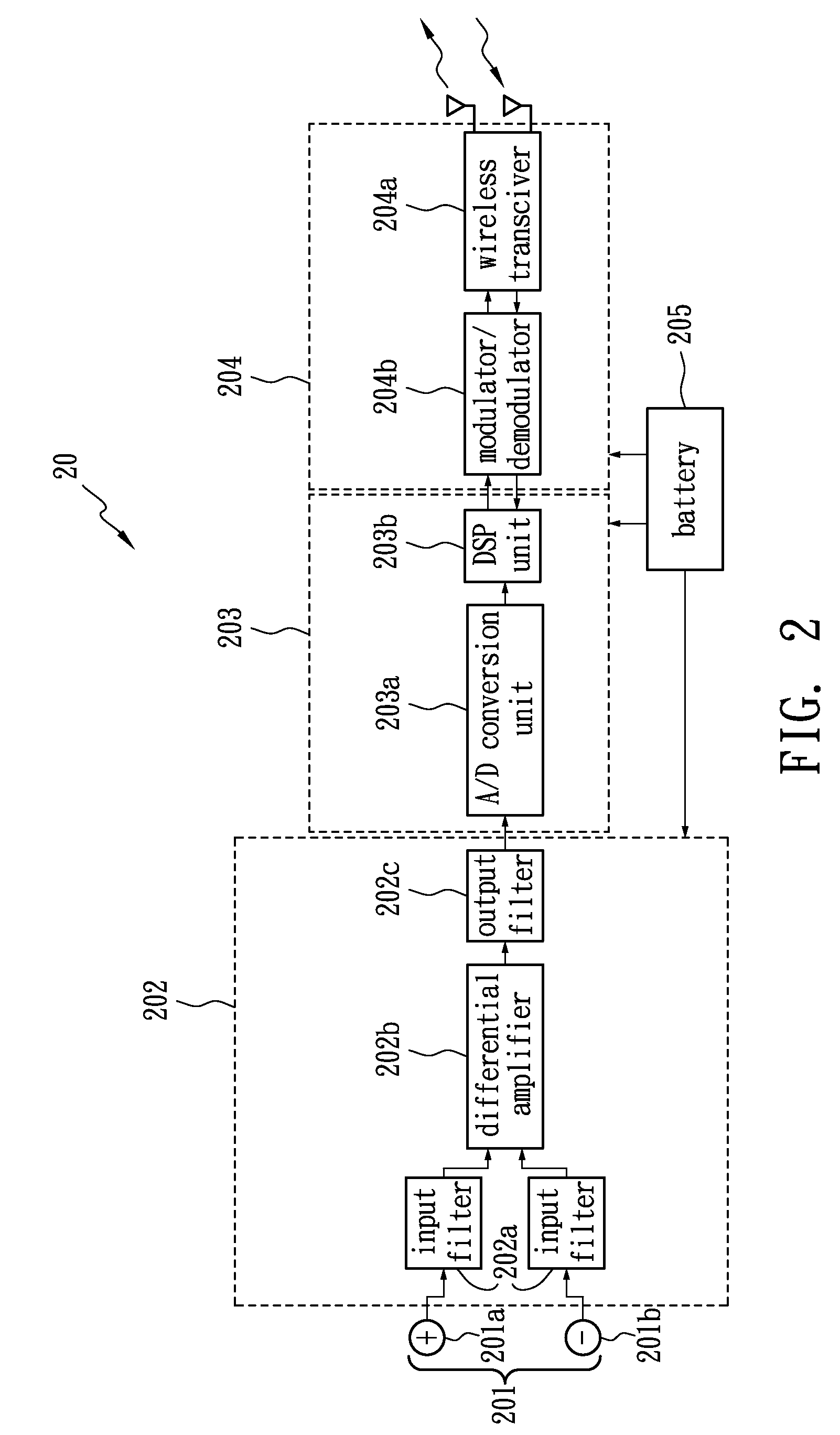

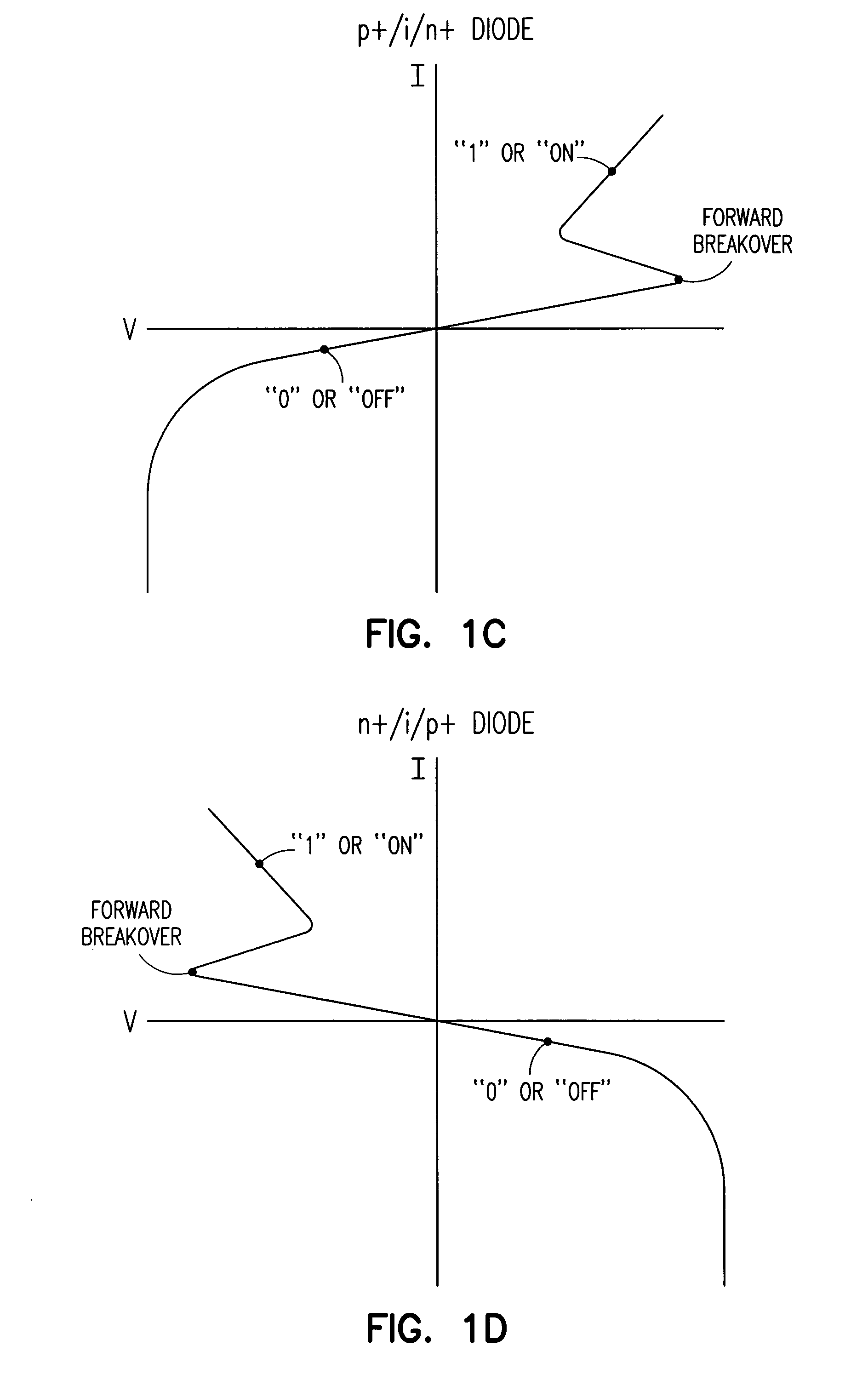

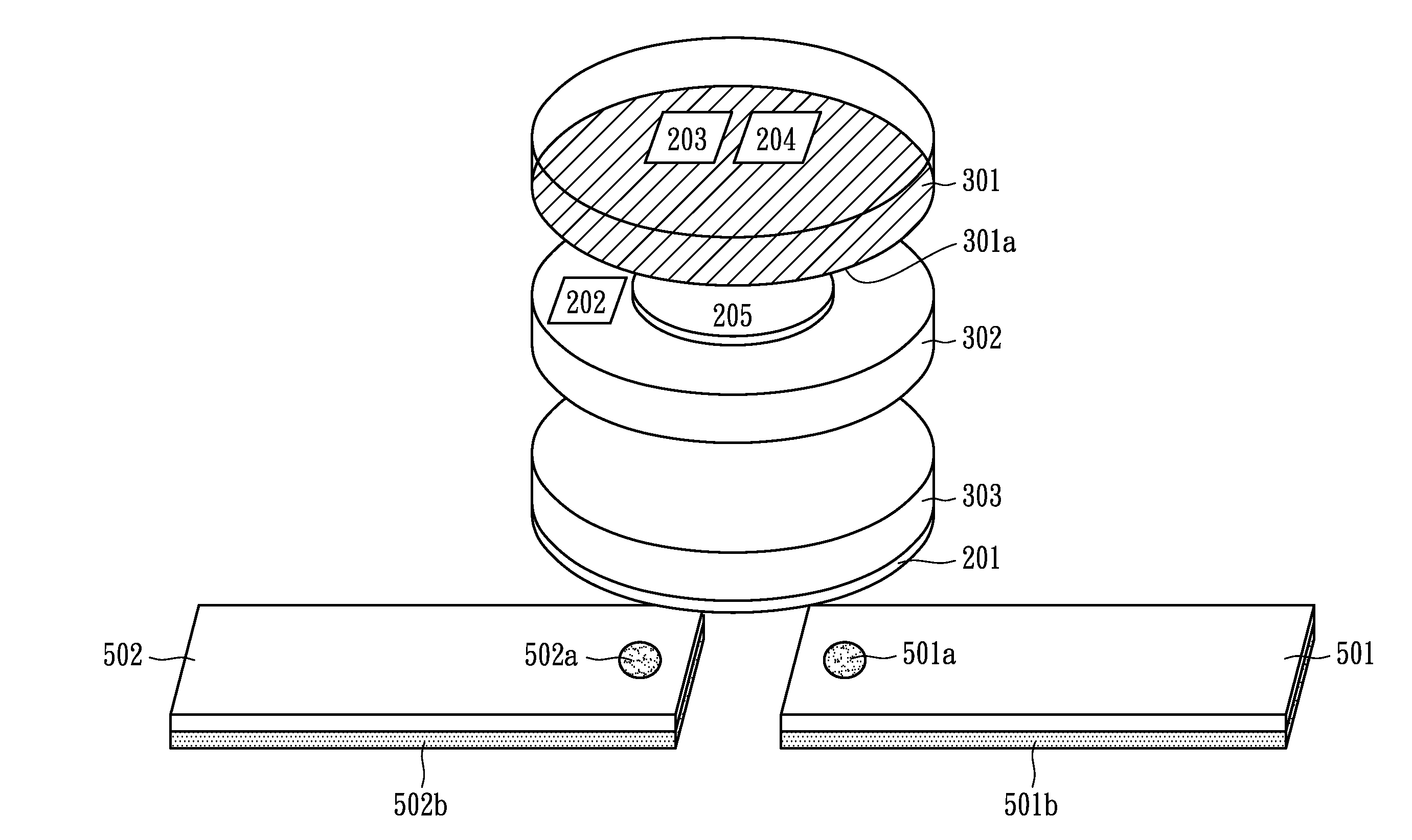

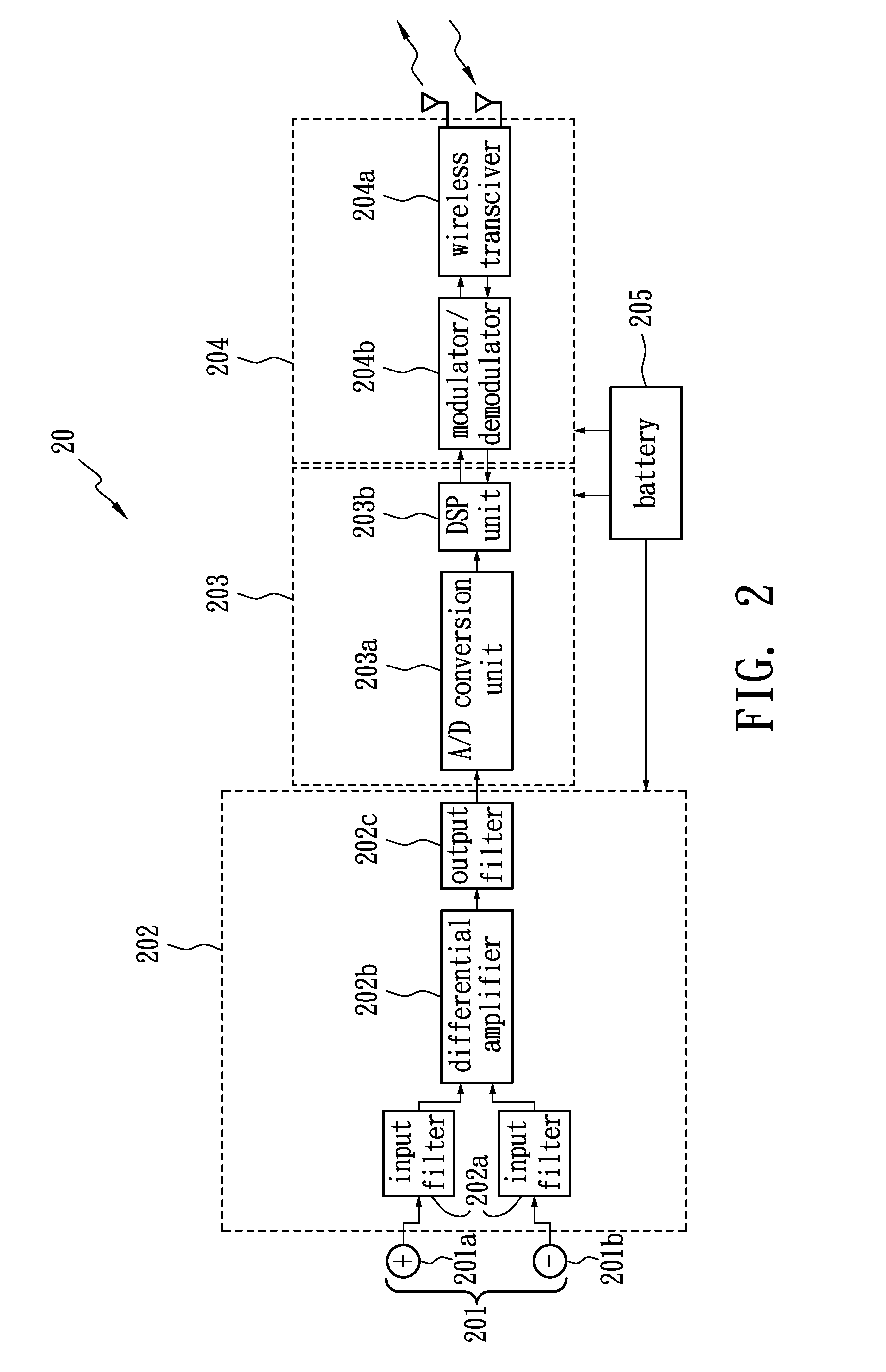

Miniature wireless apparatus for collecting physiological signals

InactiveUS7672714B2Simple materialLow costControlling membersElectrocardiographyMicrocontrollerData compression

Owner:KUO TERRY B J +2

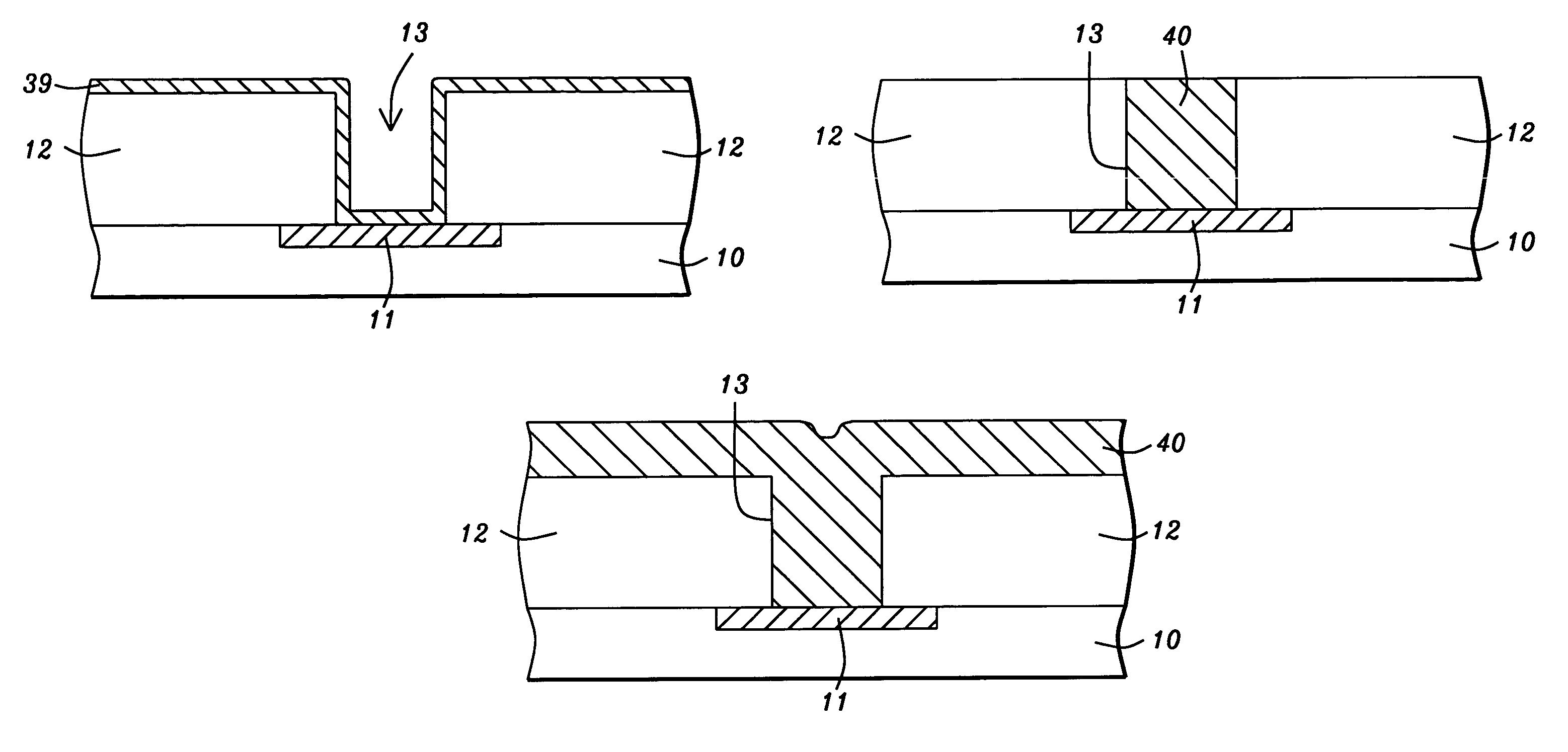

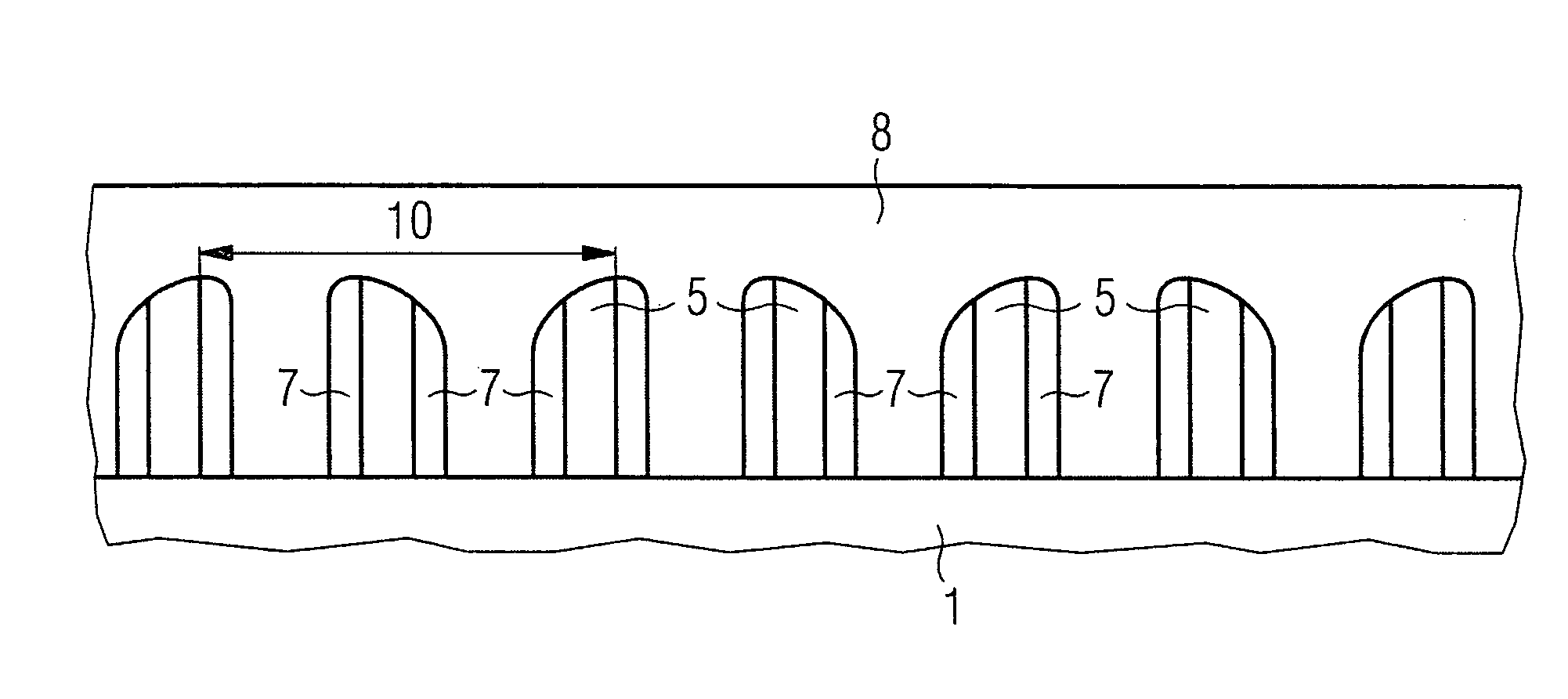

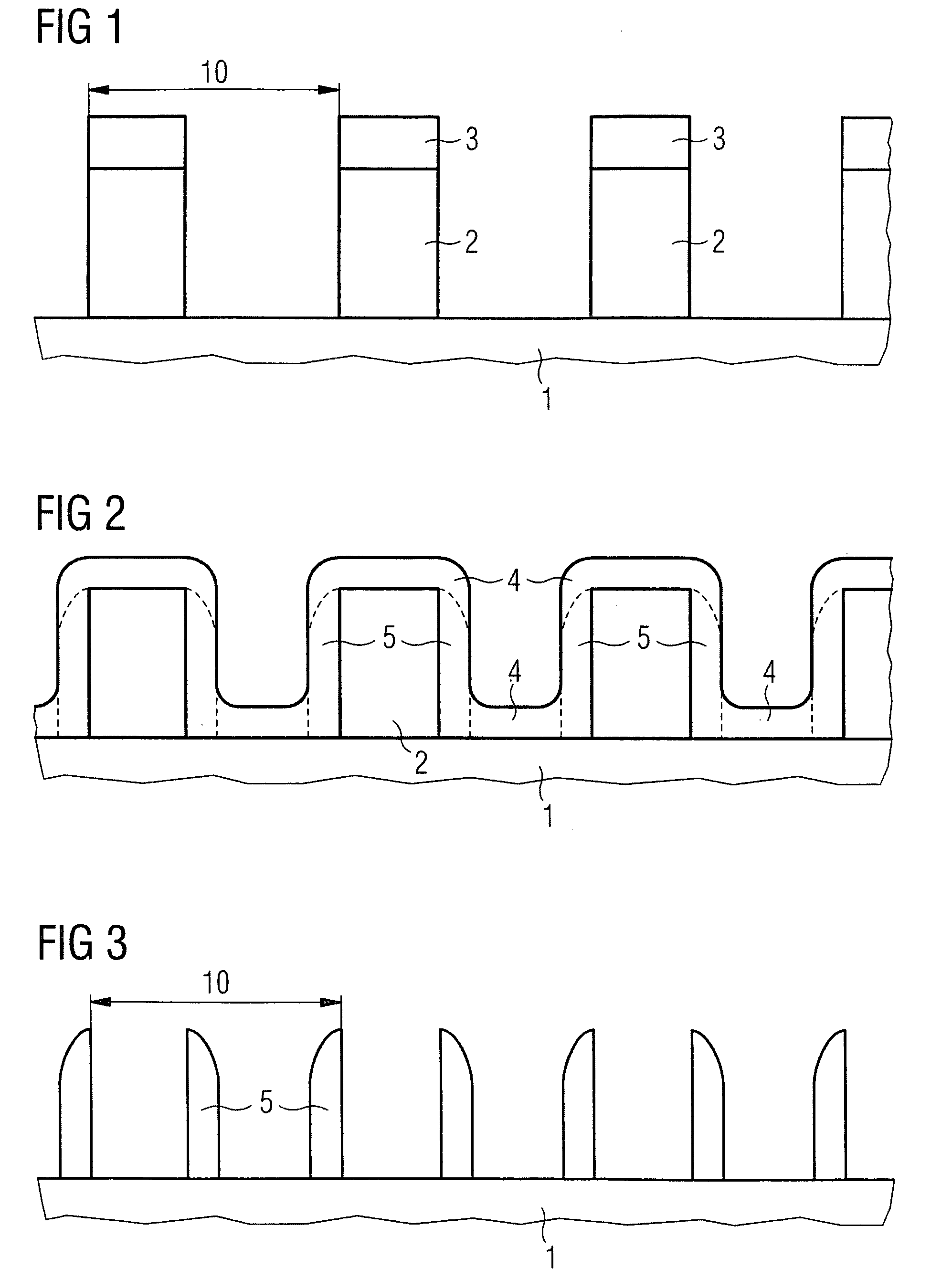

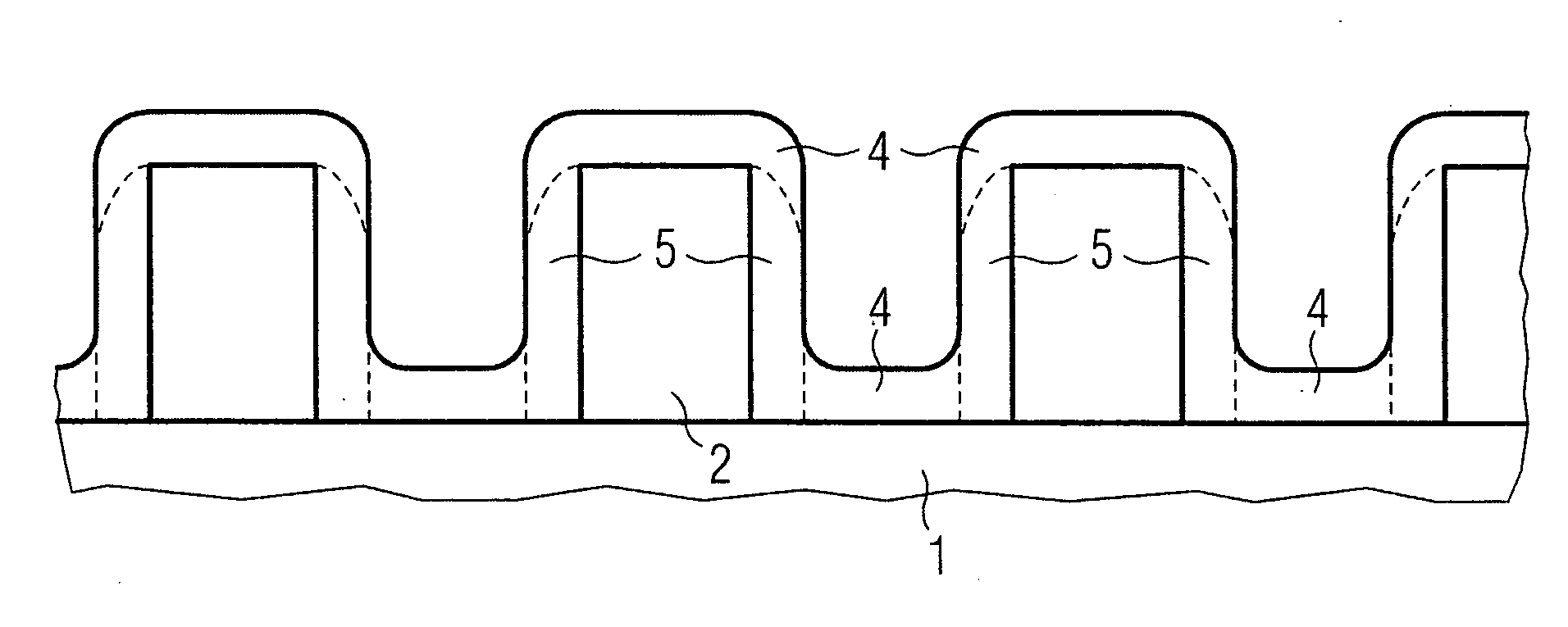

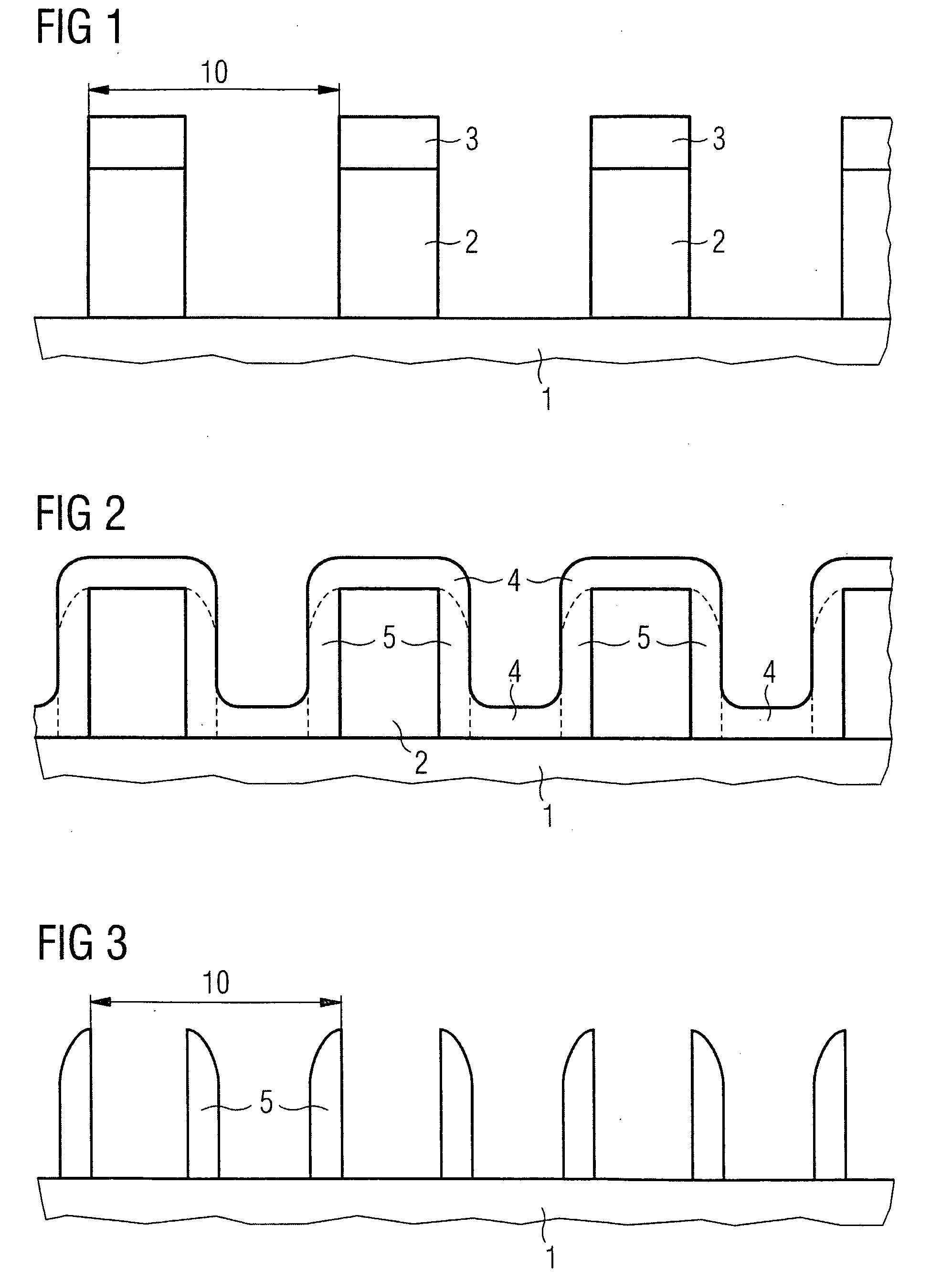

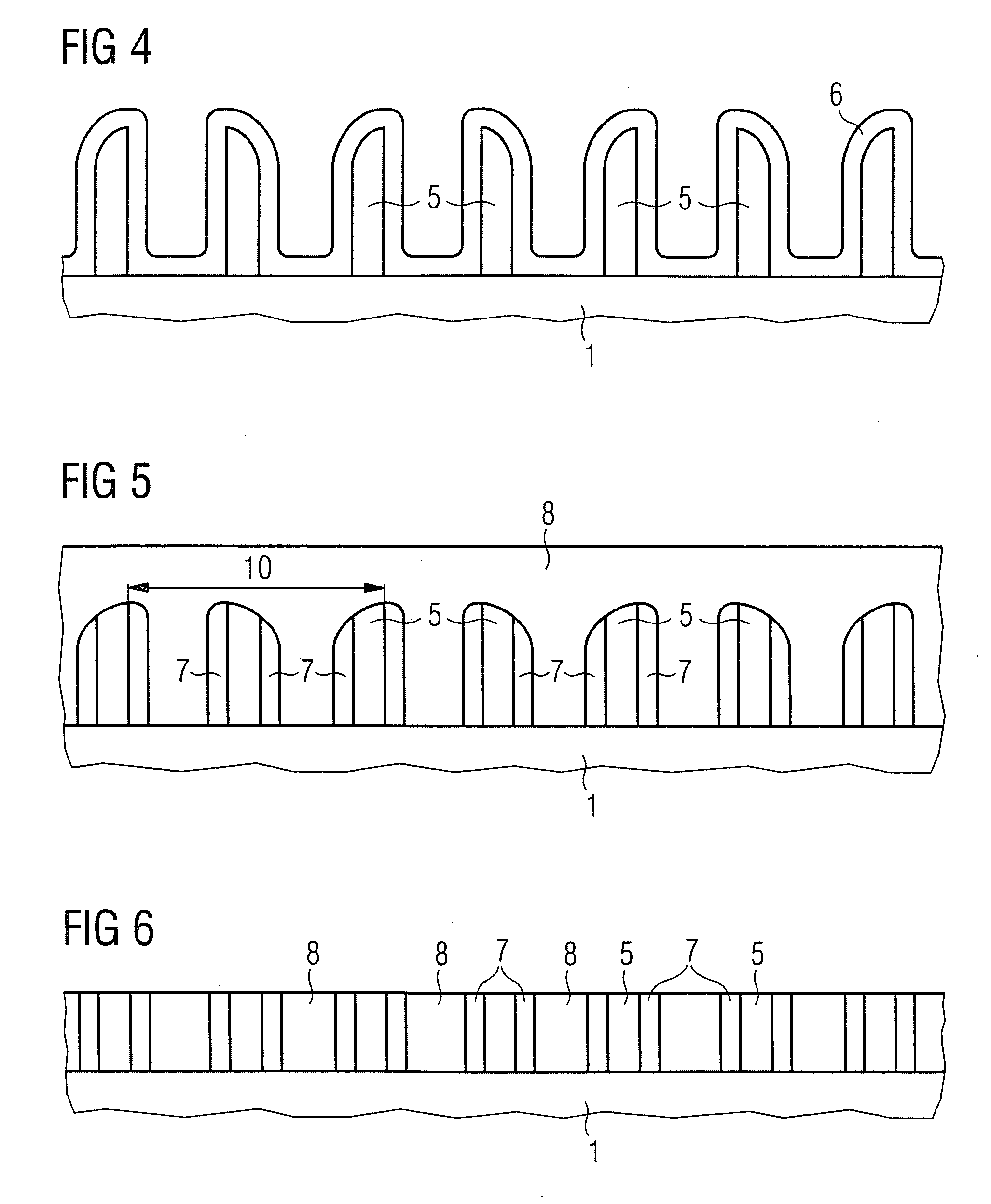

Method of production pitch fractionizations in semiconductor technology

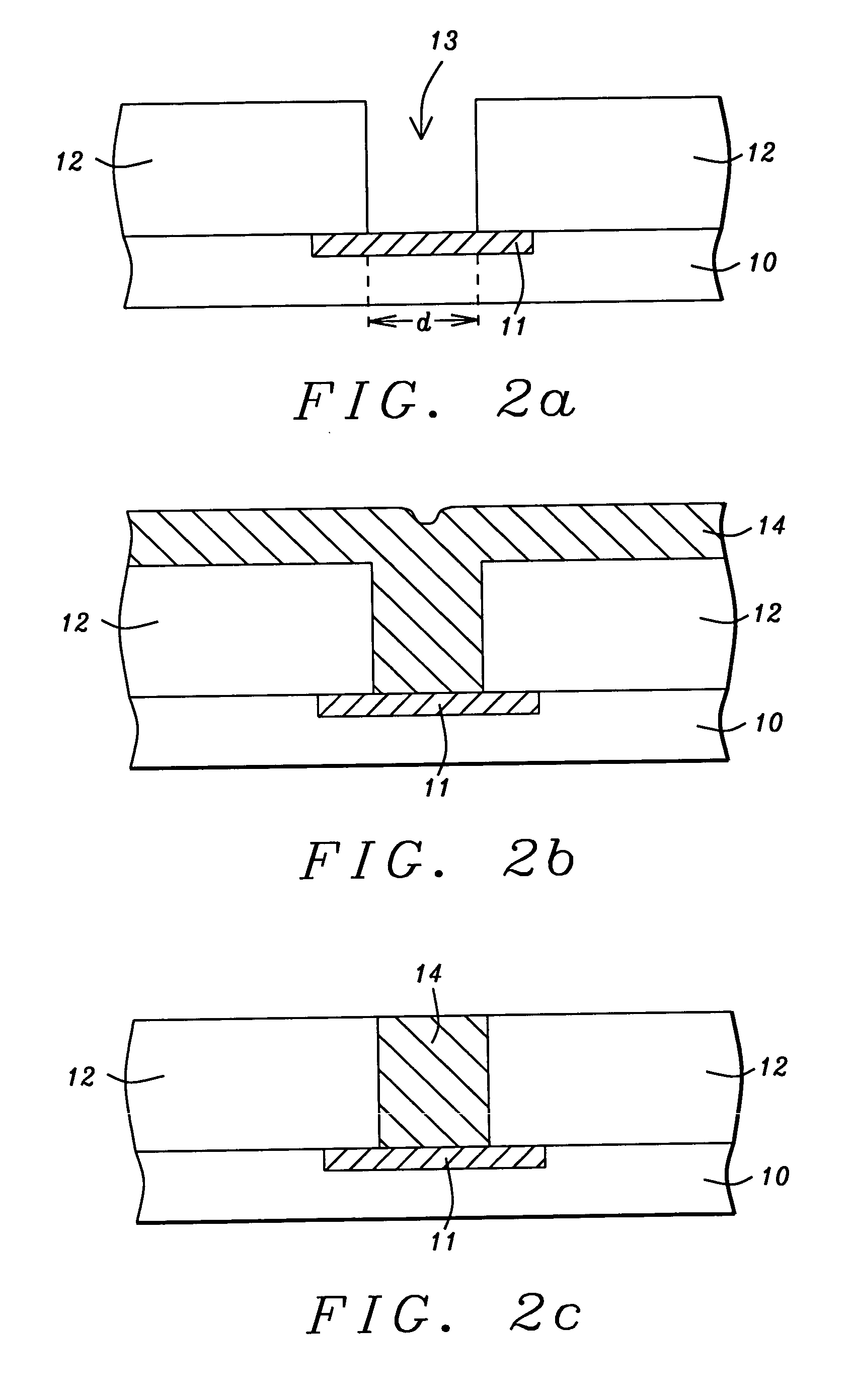

ActiveUS7291560B2Reduce spacingDecorative surface effectsSemiconductor/solid-state device manufacturingSurface levelEngineering

Spacers are formed on sidewalls of striplike parts of a pattern layer of periodic structure. The pattern layer is removed, and the spacers are covered with a further spacer layer, which is then structured to second sidewall spacers. Gaps between the spacers are filled with a complementary layer. The upper surface is planarized to a lower surface level, leaving a periodic succession of the first spacers, the second spacers and the residual parts of the complementary layer. The lateral dimensions are adapted in such a manner that a removal of one or two of the remaining layers renders a periodic pattern of smaller pitch.

Owner:CHANGXIN MEMORY TECH INC

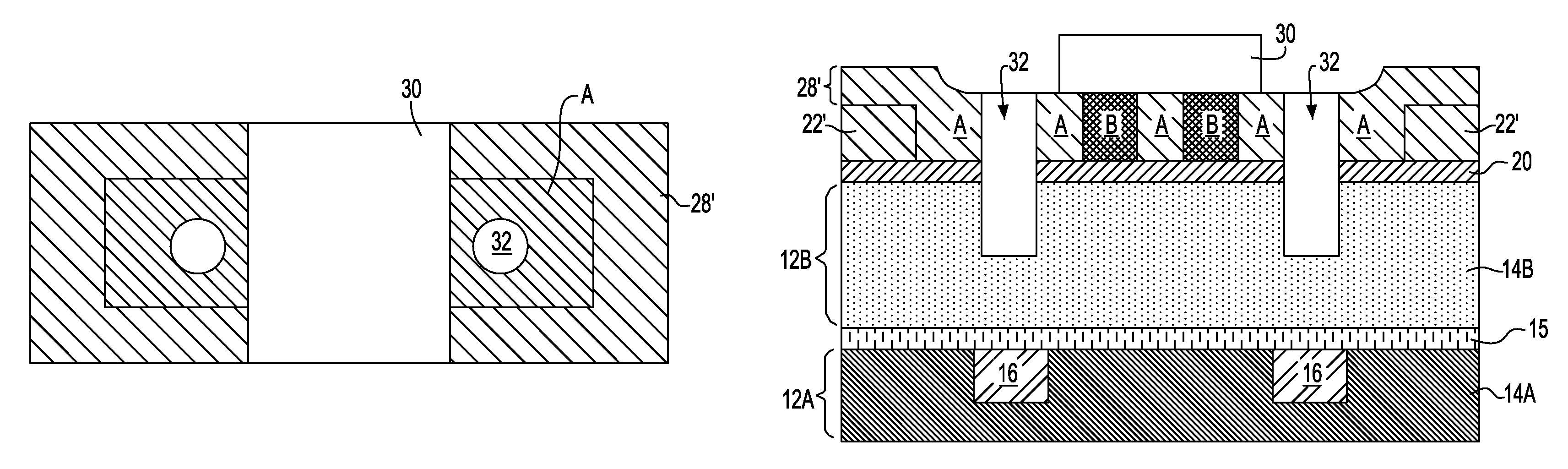

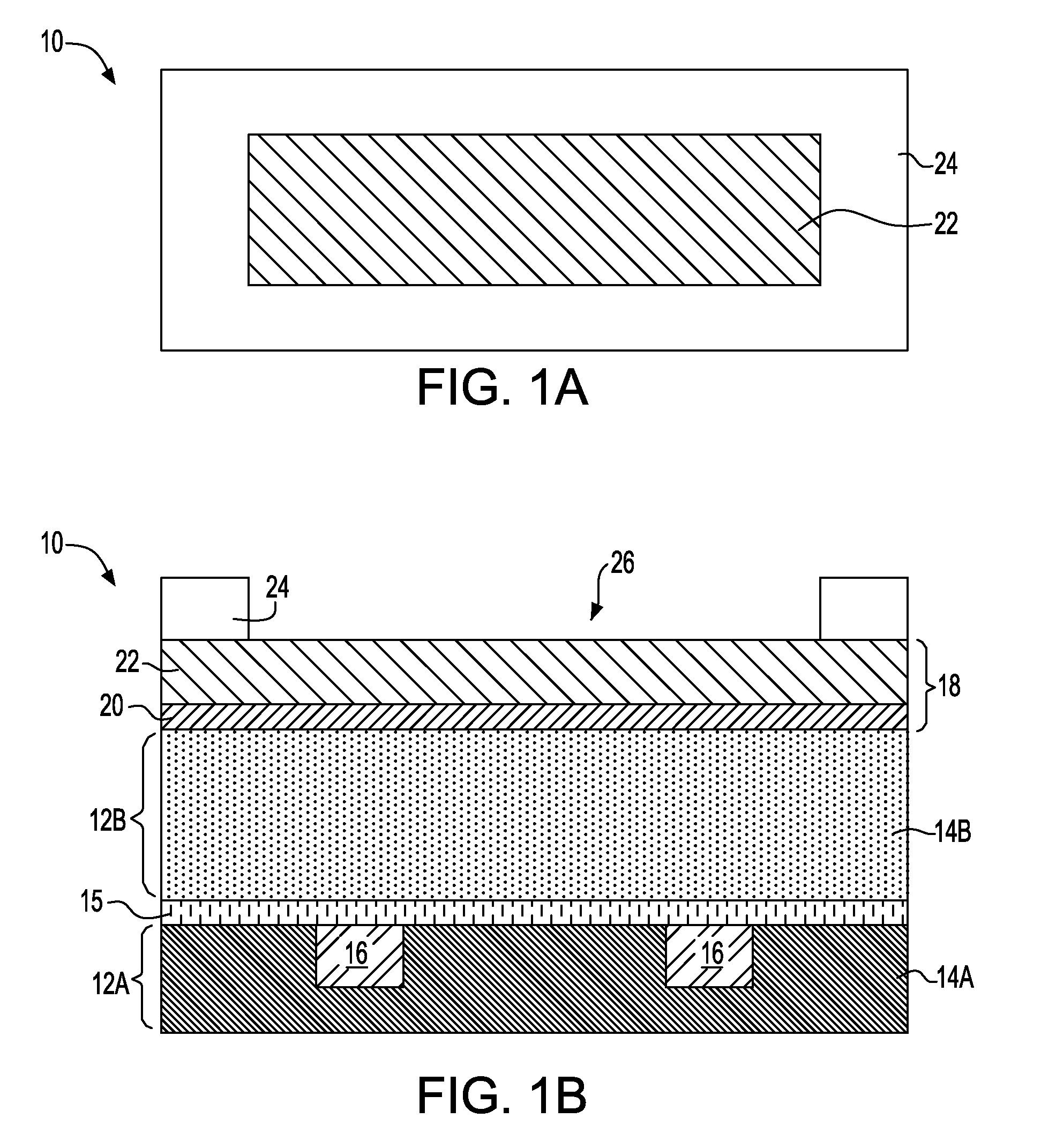

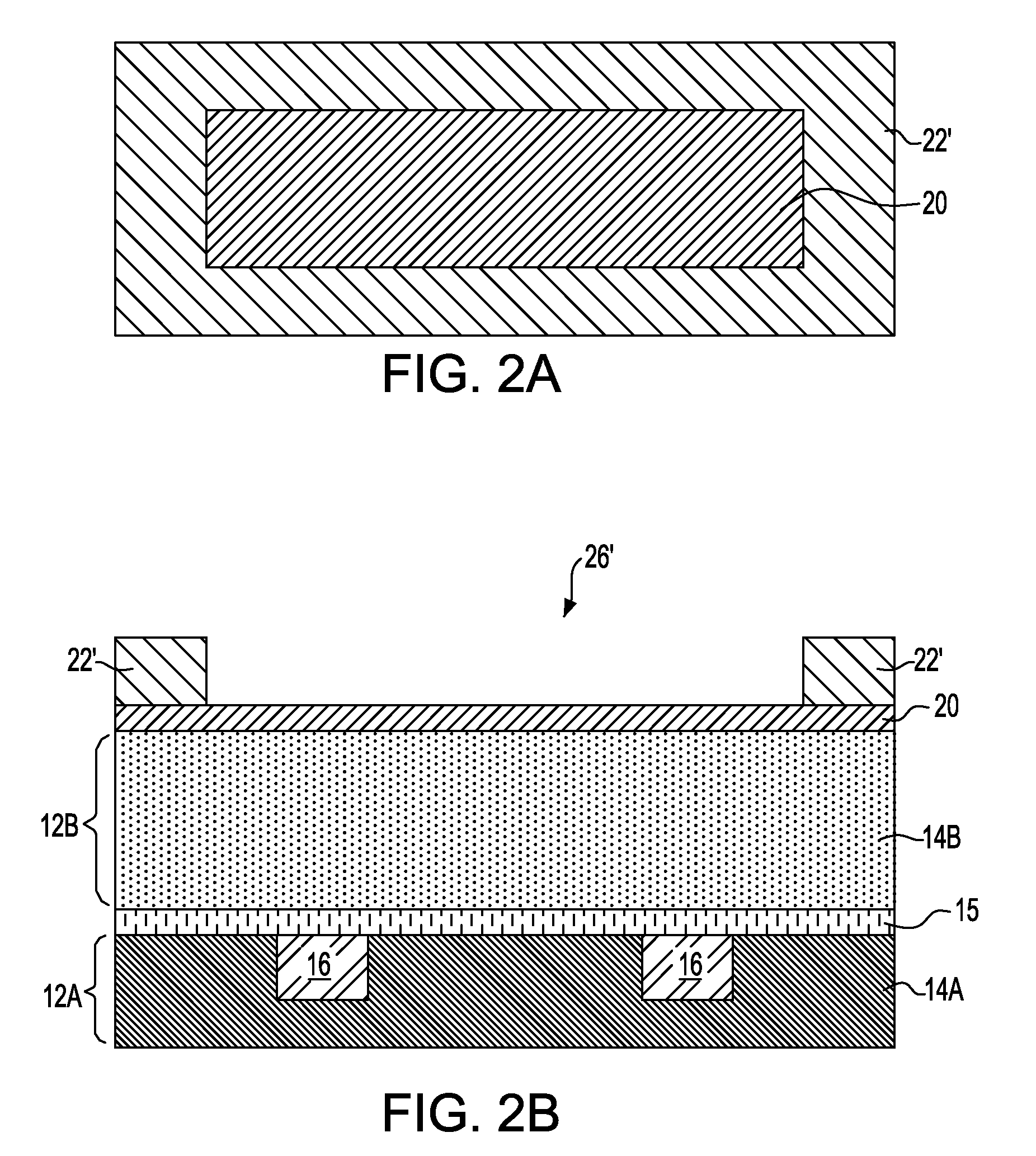

Sub-lithographic NANO interconnect structures, and method for forming same

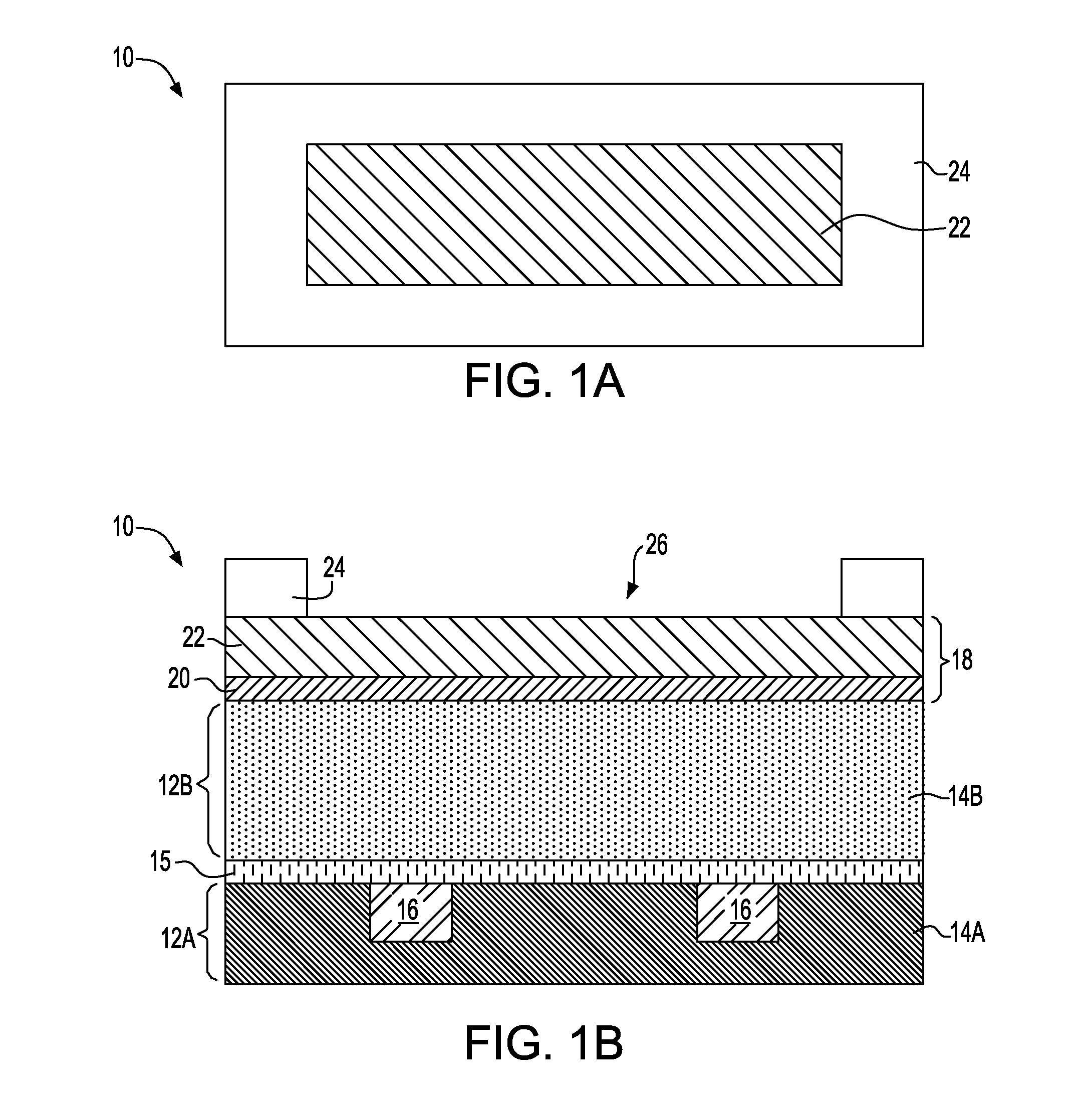

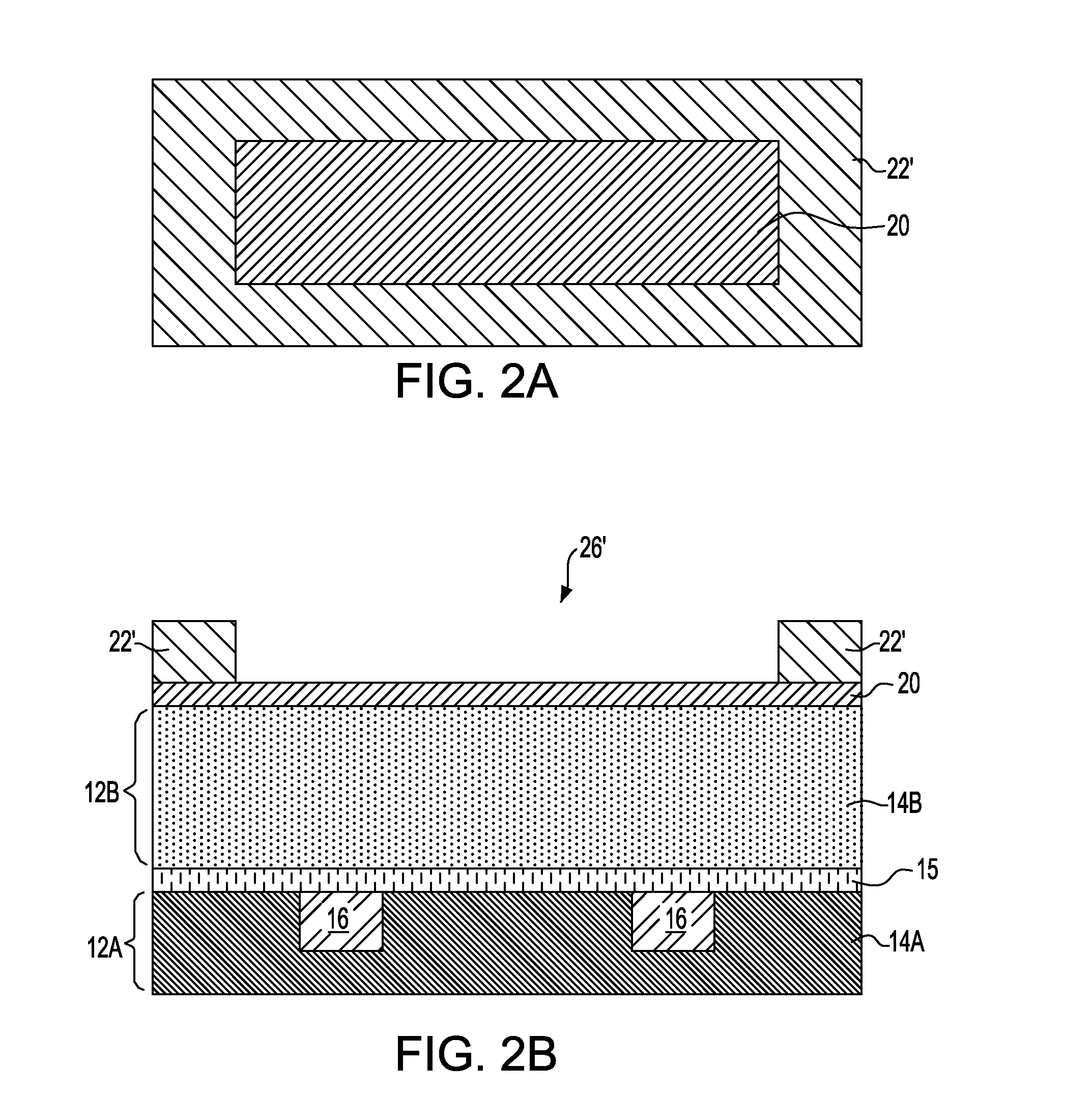

InactiveUS20080093743A1Alignment error be smallMaterial nanotechnologySemiconductor/solid-state device detailsEngineeringSelf-assembly

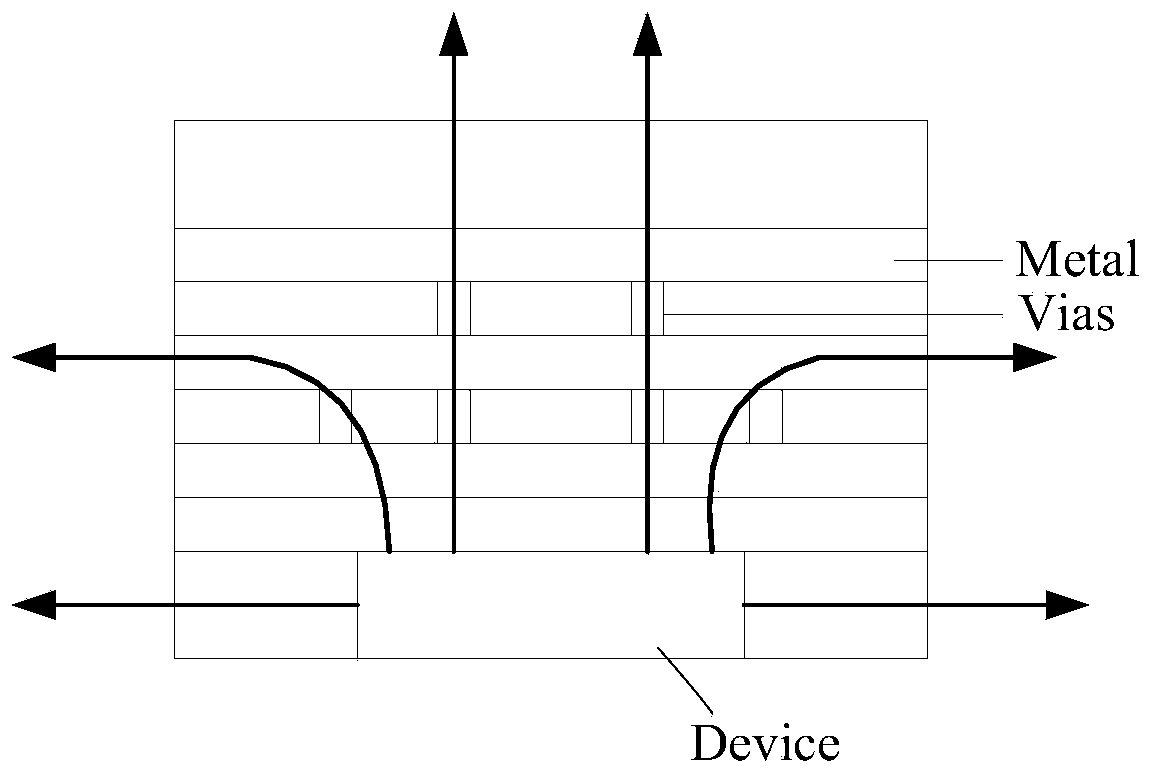

A method to form interconnect structures including nano-scale, e.g., sub-lithographic, lines and vias for future generation of semiconductor technology using self-assembly block copolymers that can be placed at a specific location using a pre-fabricated hard mask pattern is provided. The inventive method provides an interconnect structure in which the line is self-aligned to the via.

Owner:ELPIS TECH INC

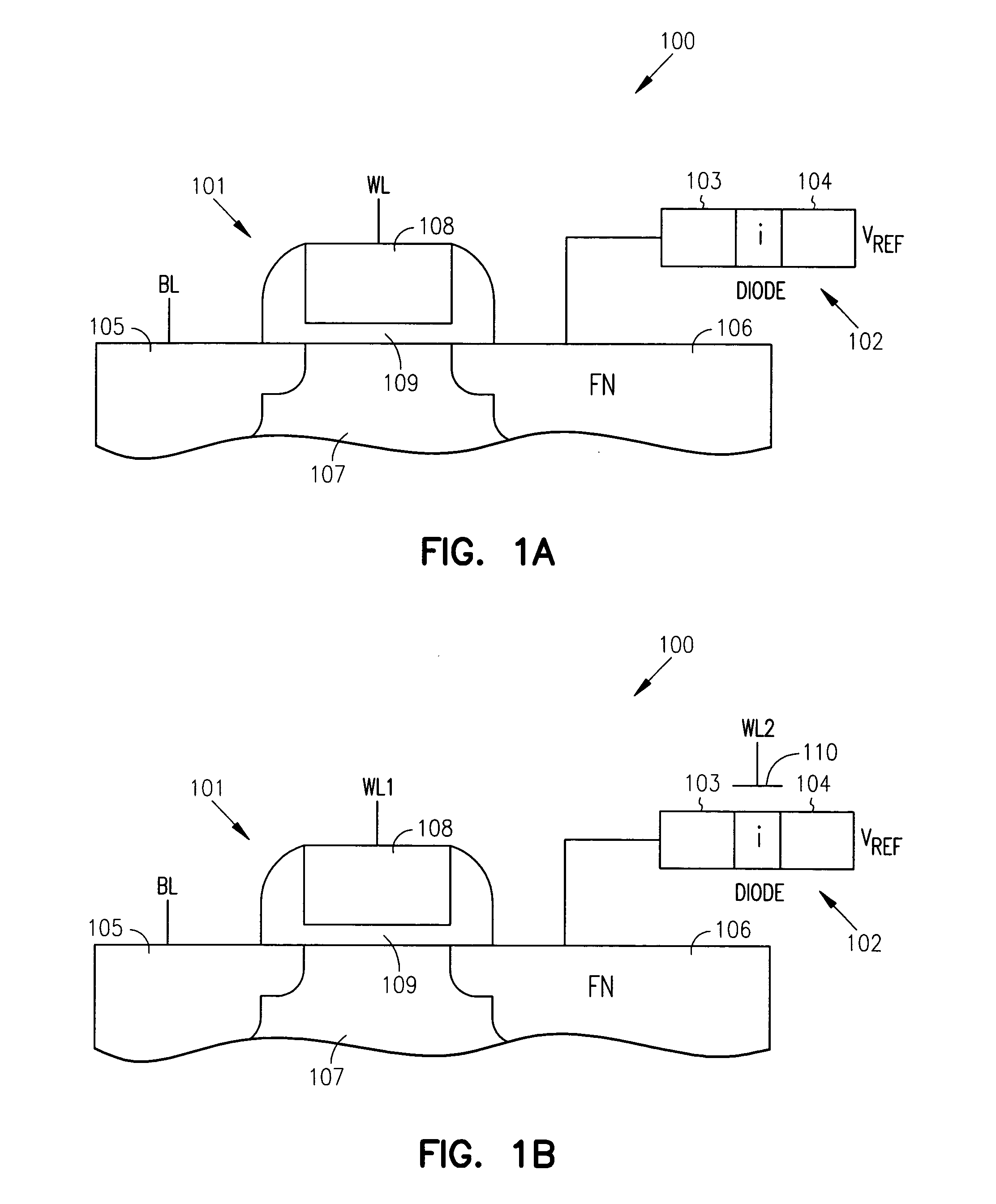

High-performance one-transistor memory cell

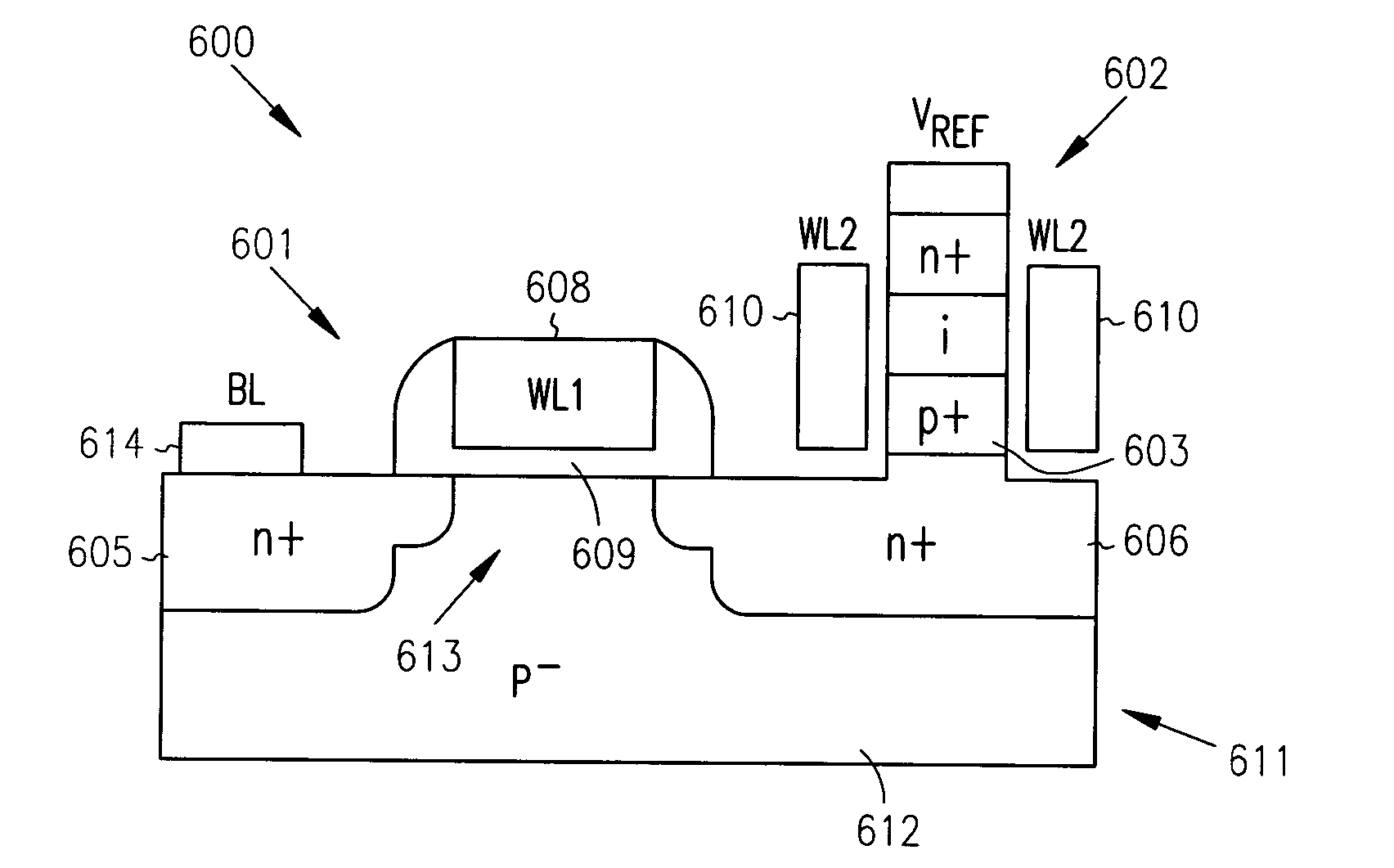

ActiveUS20050001232A1Reduce standby powerAddressing slow performanceTransistorThyristorCharge retentionSemiconductor

One aspect of this disclosure relates to a memory cell. In various embodiments, the memory cell includes an access transistor having a floating node, and a diode connected between the floating node and a diode reference potential line. The diode includes an anode, a cathode, and an intrinsic region between the anode and the cathode. A charge representative of a memory state of the memory cell is held across the intrinsic region of the diode. In various embodiments, the memory cell is implemented in bulk semiconductor technology. In various embodiments, the memory cell is implemented in semiconductor-on-insulator technology. In various embodiments, the diode is gate-controlled. In various embodiments, the diode is charge enhanced by an intentionally generated charge in a floating body of an SOI access transistor. Various embodiments include laterally-oriented diodes (stacked and planar configurations), and various embodiments include vertically-oriented diodes. Other aspects and embodiments are provided herein.

Owner:MICRON TECH INC

Miniature wireless apparatus for collecting physiological signals

InactiveUS20070167848A1Simple materialLow costControlling membersElectrocardiographyMicrocontrollerData compression

Owner:KUO TERRY B J +2

Sub-lithographic nano interconnect structures, and method for forming same

InactiveUS7553760B2Material nanotechnologySemiconductor/solid-state device detailsEngineeringSelf-assembly

Owner:ELPIS TECH INC

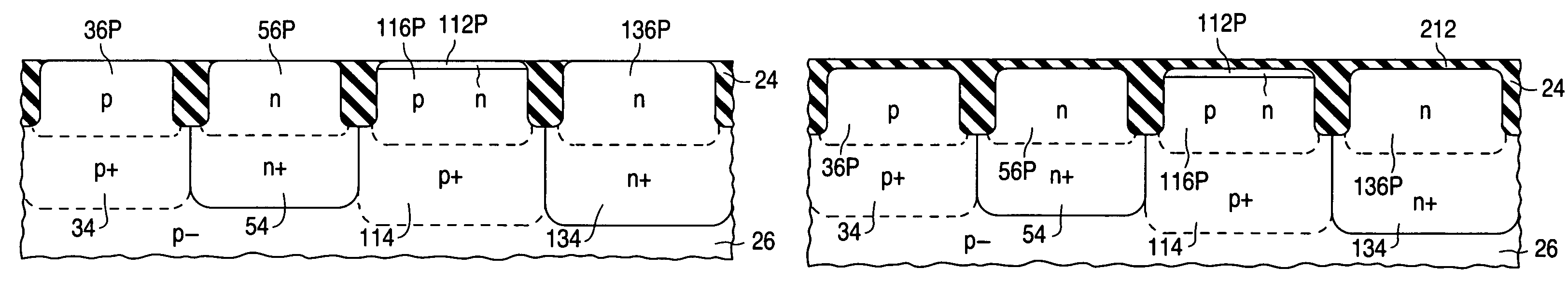

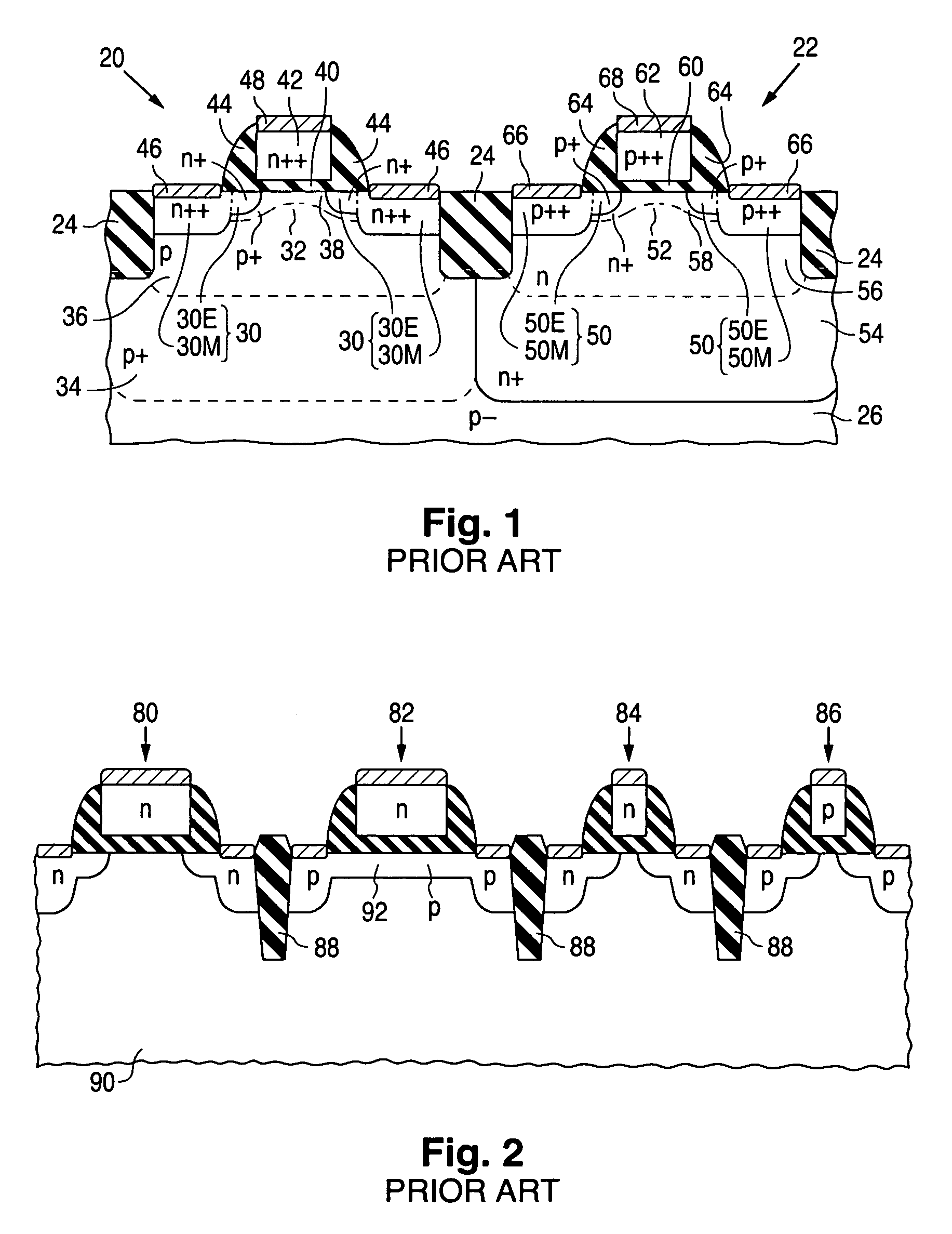

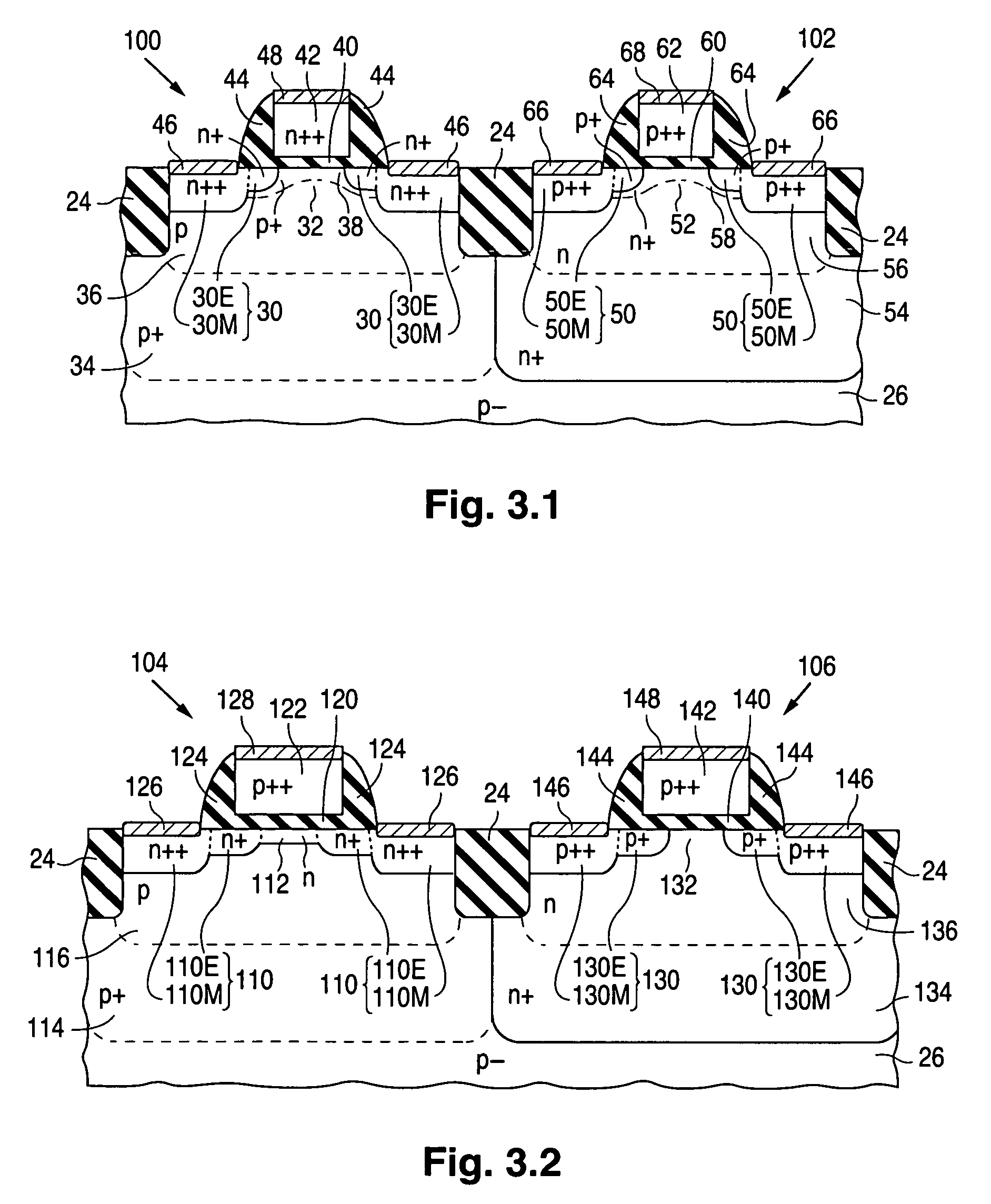

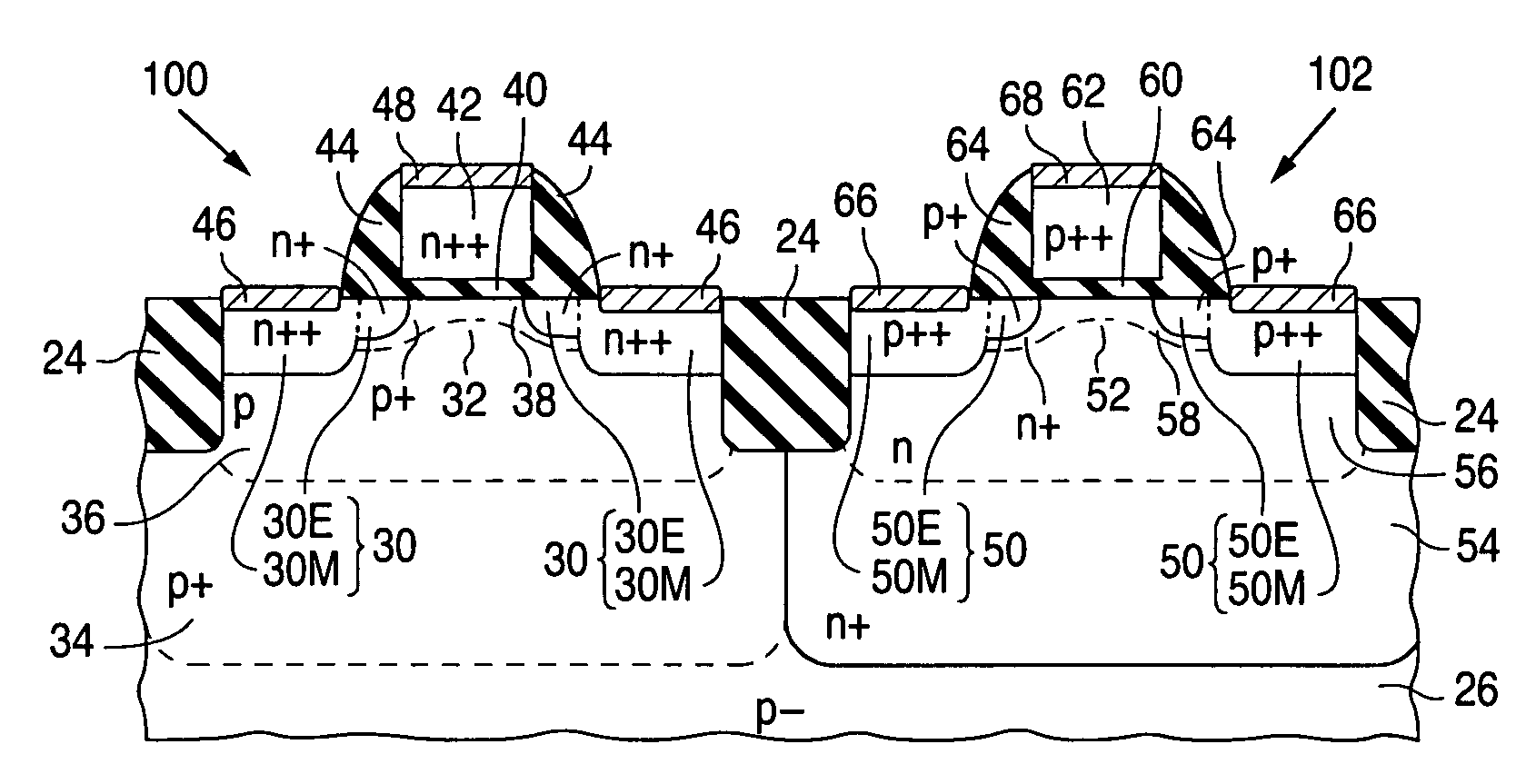

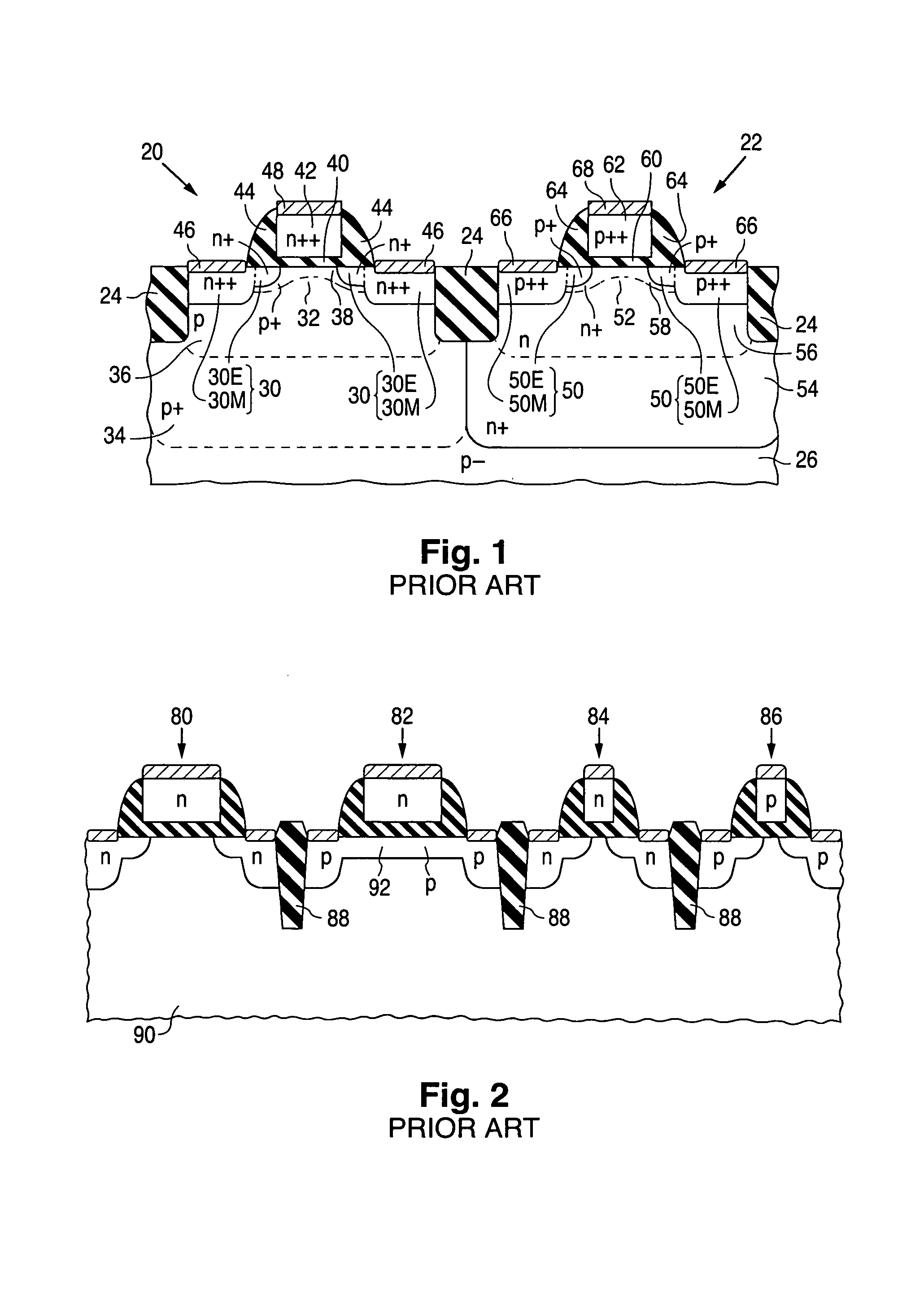

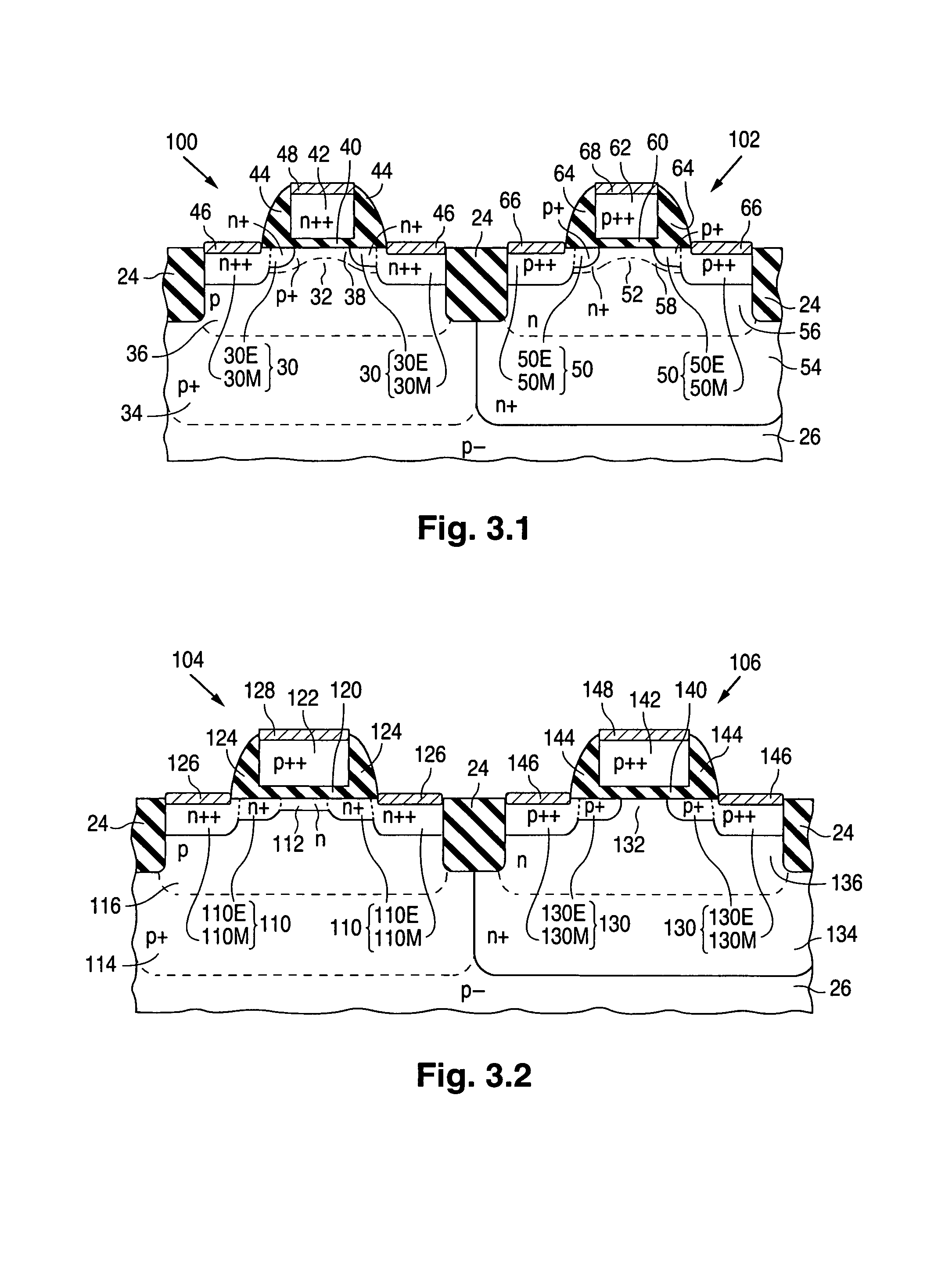

Fabrication of semiconductor structure having N-channel channel-junction field-effect transistor

ActiveUS7595243B1Performance characteristicHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally fabricated to be of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. A p-channel surface-channel IGFET (102 or 162), which is typically fabricated to be of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically fabricated to be of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

Method of producing pitch fractionizations in semiconductor technology

ActiveUS20070026684A1Reduce spacingDecorative surface effectsSemiconductor/solid-state device manufacturingEngineeringSurface level

Spacers are formed on sidewalls of striplike parts of a pattern layer of periodic structure. The pattern layer is removed, and the spacers are covered with a further spacer layer, which is then structured to second sidewall spacers. Gaps between the spacers are filled with a complementary layer. The upper surface is planarized to a lower surface level, leaving a periodic succession of the first spacers, the second spacers and the residual parts of the complementary layer. The lateral dimensions are adapted in such a manner that a removal of one or two of the remaining layers renders a periodic pattern of smaller pitch.

Owner:CHANGXIN MEMORY TECH INC

Semiconductor structure having n-channel channel-junction field-effect transistor

ActiveUS7176530B1Large noise reductionEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

A semiconductor technology combines a normally off n-channel channel-junction insulated-gate field-effect transistor (“IGFET”) (104) and an n-channel surface-channel IGFET (100 or 160) to reduce low-frequency 1 / f noise. The channel-junction IGFET is normally of materially greater gate dielectric thickness than the surface-channel IGFET so as to operate across a greater voltage range than the surface-channel IGFET. Alternatively or additionally, the channel-junction IGFET may conduct current through a field-induced surface channel. A p-channel surface-channel IGFET (102 or 162), which is typically of approximately the same gate-dielectric thickness as the n-channel surface-channel IGFET, is preferably combined with the two n-channel IGFETs to produce a complementary-IGFET structure. A further p-channel IGFET (106, 180, 184, or 192), which is typically of approximately the same gate dielectric thickness as the n-channel channel-junction IGFET, is also preferably included. The further p-channel IGFET can be a surface-channel or channel-junction device.

Owner:NAT SEMICON CORP

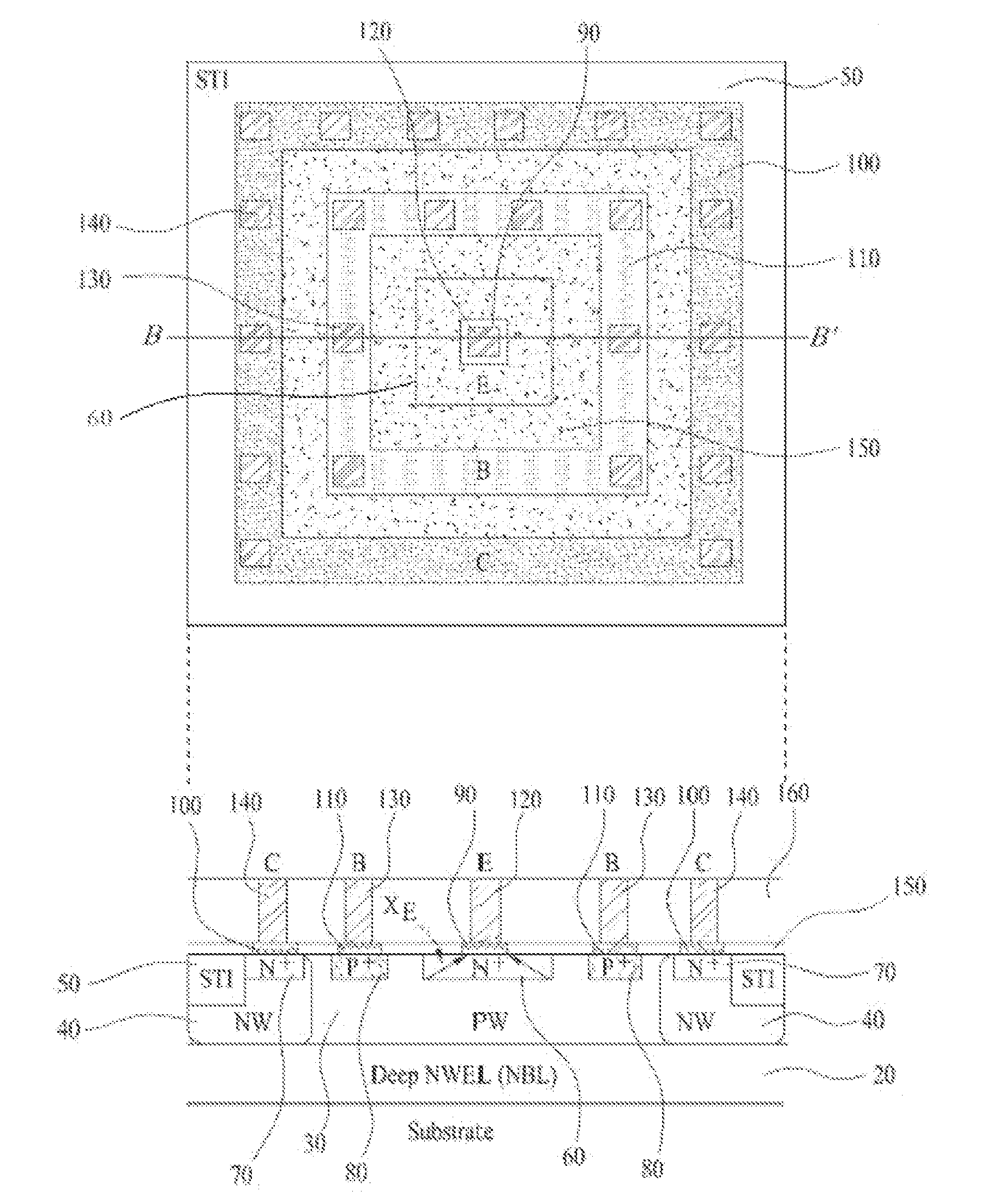

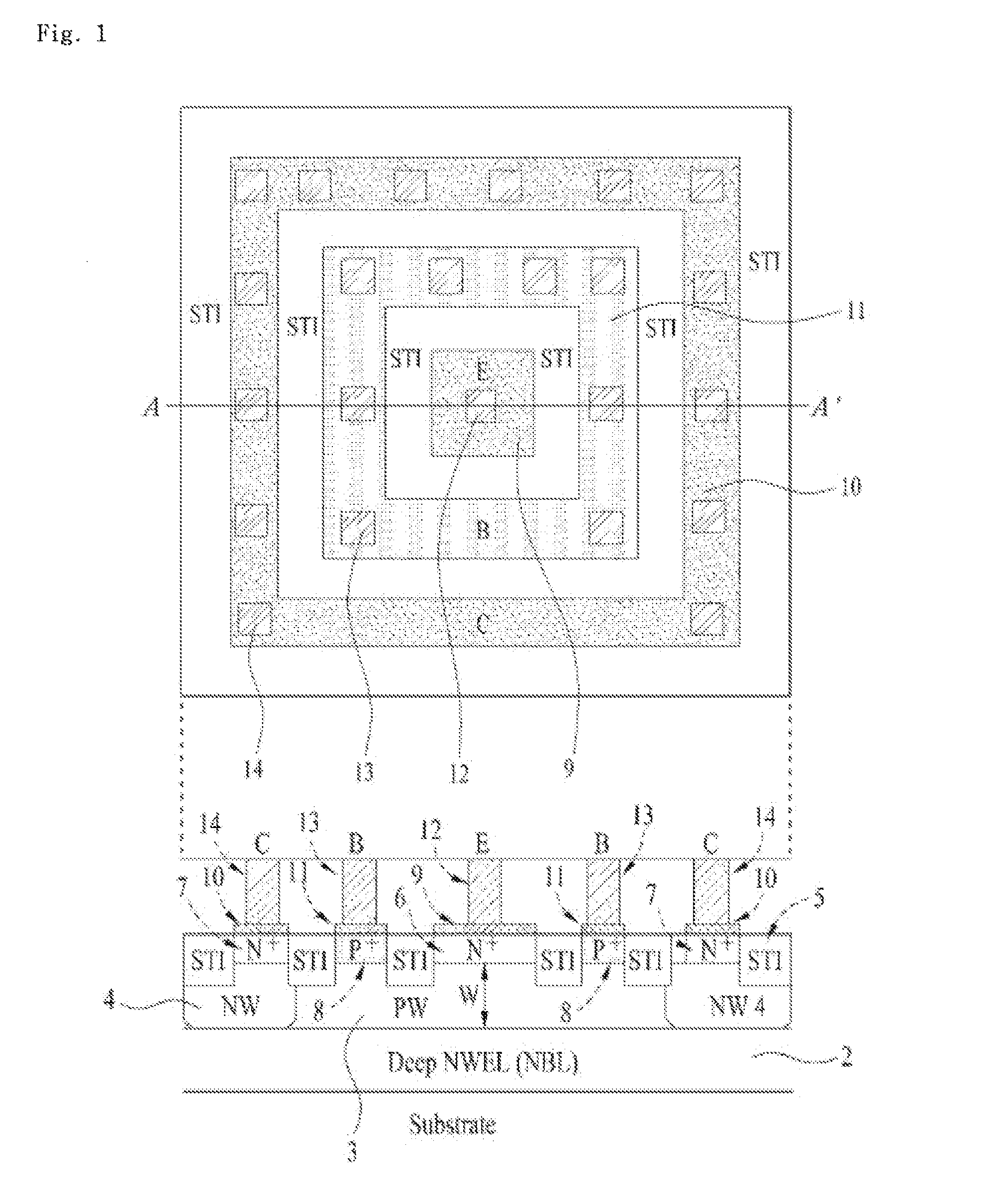

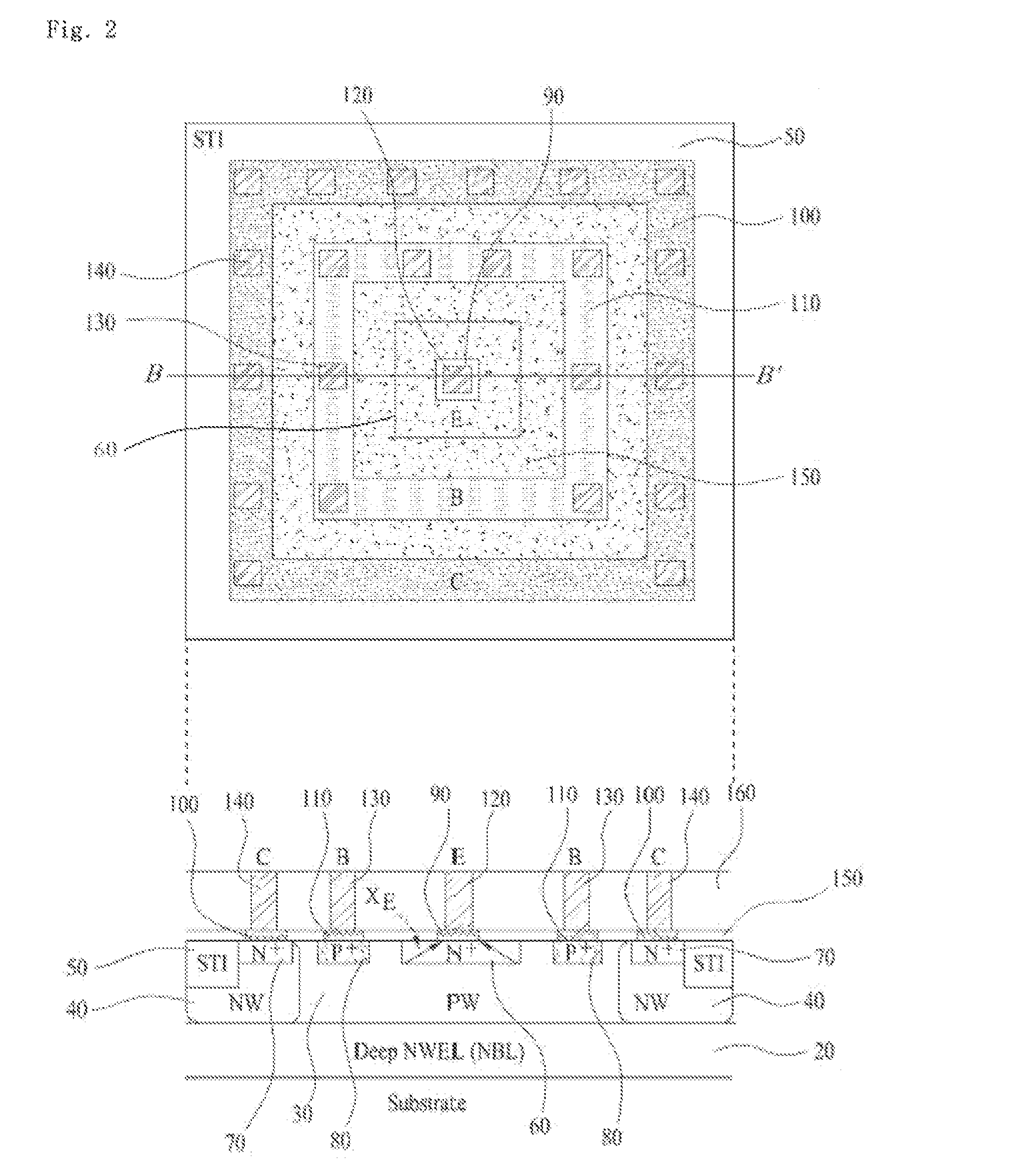

Bipolar Junction Transistor Based on CMOS Technology

InactiveUS20120032303A1Increase currentHigh base resistanceTransistorSemiconductor/solid-state device manufacturingCMOSEngineering

The present invention relates to semiconductor technologies, and more particularly to a bipolar junction transistor (BJT) in a CMOS base technology and methods of forming the same. The BJT includes a semiconductor substrate having an emitter region, a base having a first contact, and a collector having a second contact and a well plug; a first silicide film on the first contact; a second silicide film on the second contact; a first silicide blocking layer on or over the semiconductor substrate between the first and second silicide films, and a second silicide blocking layer on the semiconductor substrate between the first silicide film and the emitter region.

Owner:DONGBU HITEK CO LTD

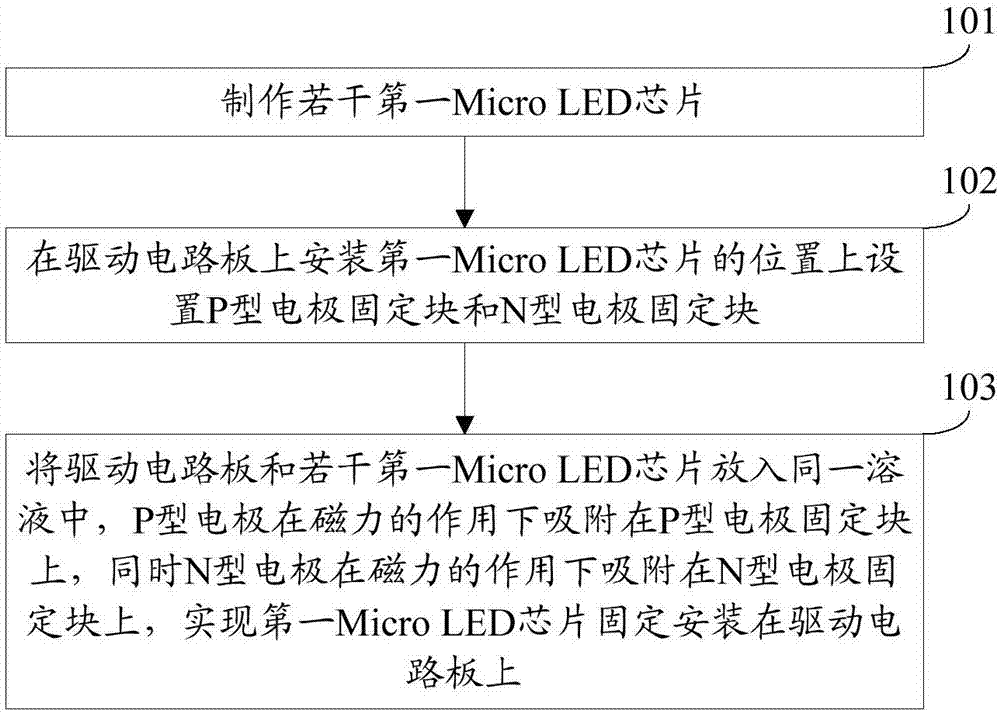

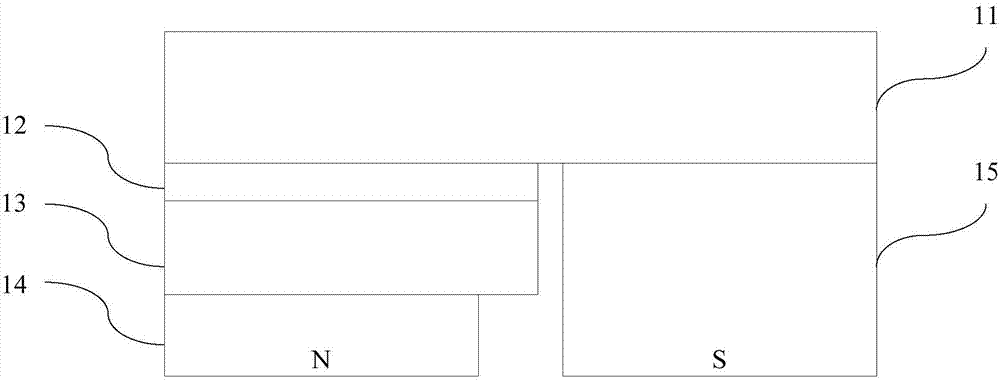

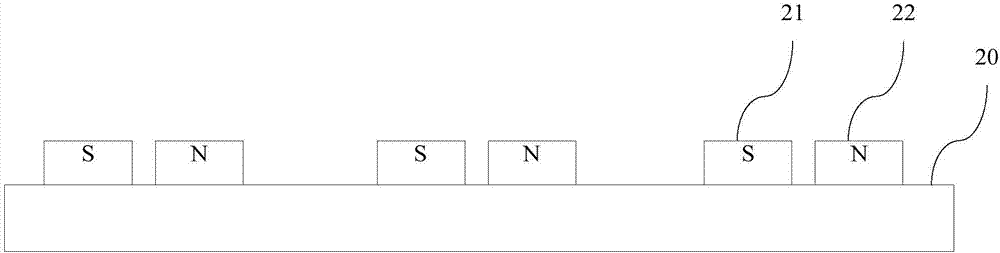

Mass transfer method of Micro LED (Light Emitting Diode) chips

ActiveCN107425101AMass transferIncrease productivityPrinted circuit aspectsSolid-state devicesMagnetic polesEngineering

The invention discloses a mass transfer method of Micro LED (Light Emitting Diode) chips, and belongs to the technical field of a semiconductor. The mass transfer method comprises the steps of: producing a plurality of first Micro LED chips, wherein the same sides of P-type electrodes and N-type electrodes of the first Micro LED chips are contrary name magnetic poles; arranging P-type electrode fixing blocks and N-type electrode fixing blocks at positions on a driving circuit board, where the first Micro LED chips are mounted, wherein the opposite sides of the P-type electrode fixing blocks and the P-type electrodes are contrary name magnetic poles, and the opposite sides of the N-type electrode fixing blocks and the N-type electrodes are contrary name magnetic poles; placing the driving circuit board and a plurality of first Micro LED chips into the same solution, and fixedly mounting the first Micro LED chips on the driving circuit board under the action of a magnetic force. The mass transfer method disclosed by the invention can implement mass transfer of the Micro LED chips, and does not have the problem that when one chip has defects, all chips need to be replaced; production efficiency is improved; and production cost is reduced.

Owner:HC SEMITEK ZHEJIANG CO LTD

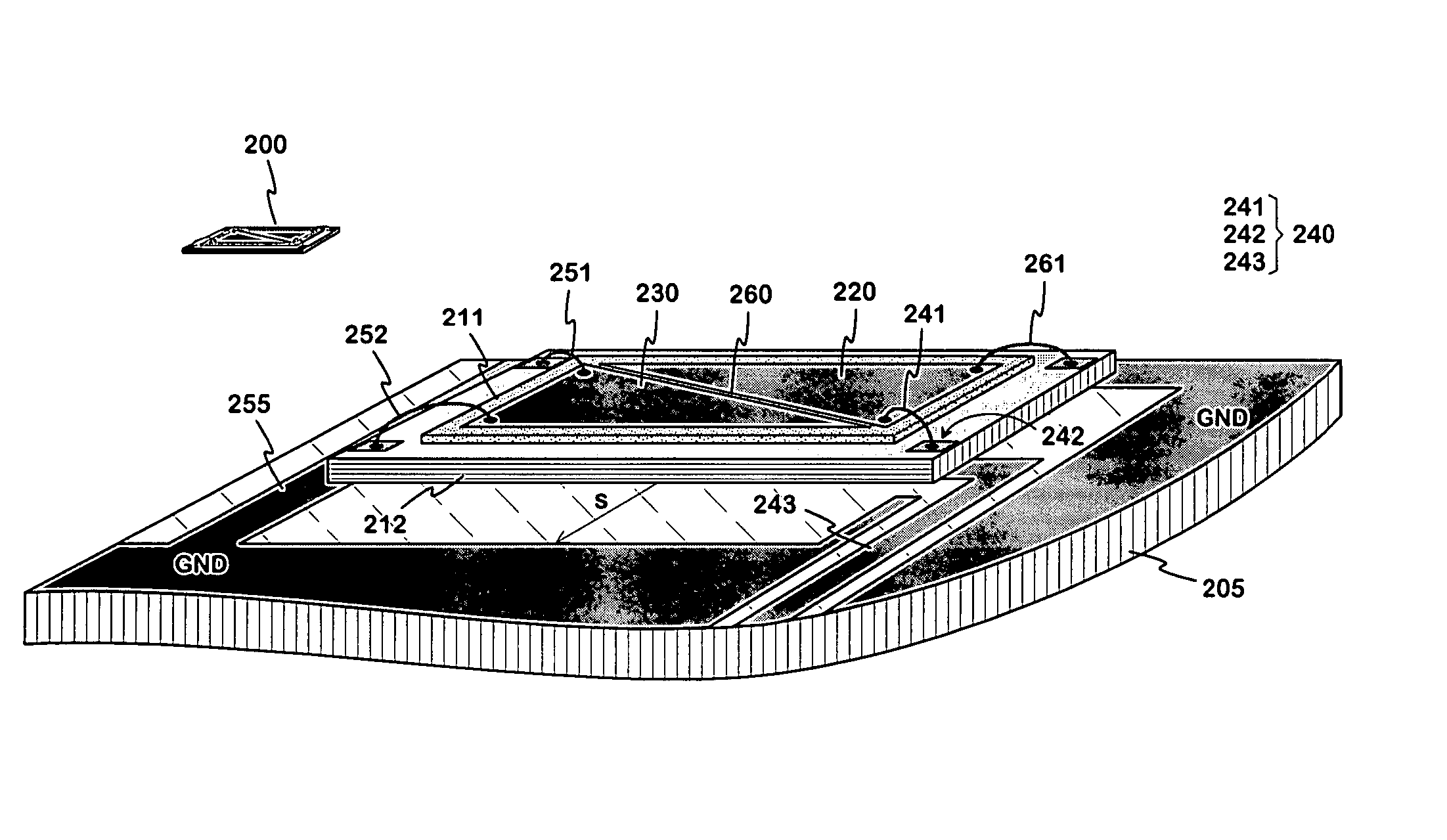

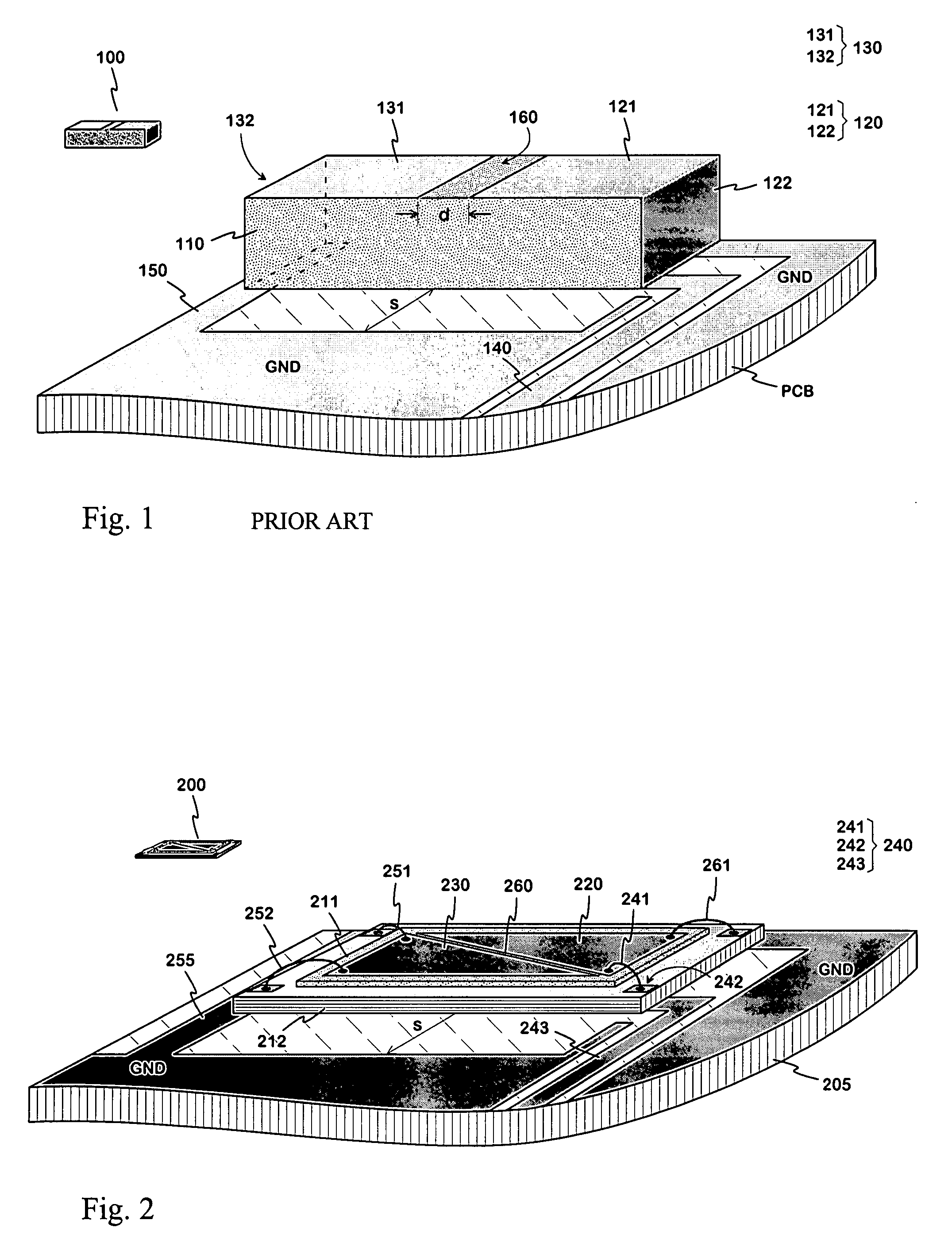

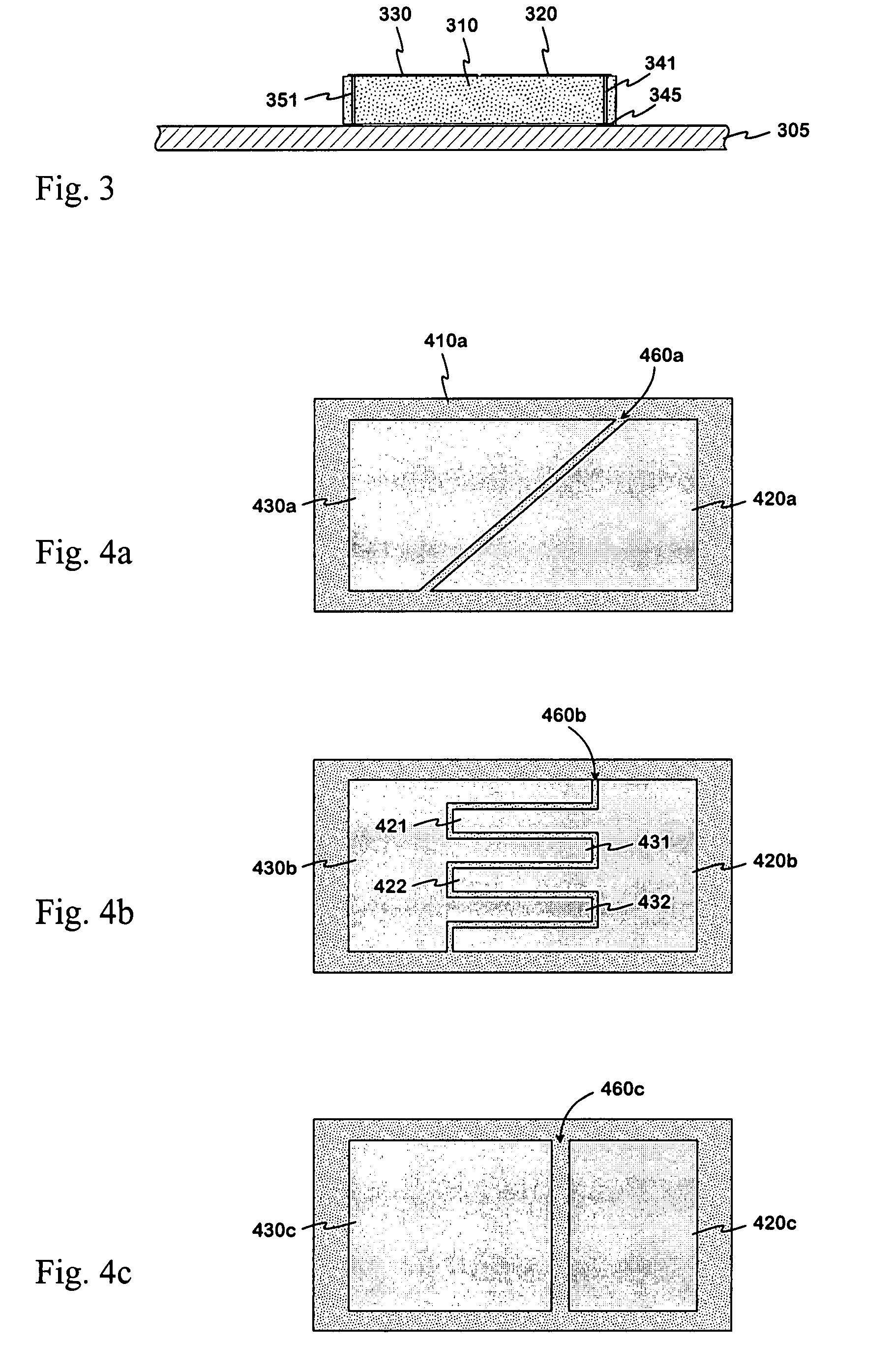

Antenna component and methods

InactiveUS20080088511A1High dielectric constantEfficient preparationSimultaneous aerial operationsRadiating elements structural formsElectrical conductorDielectric substrate

An antenna component (200) with a dielectric substrate and two radiating antenna elements. The elements are located on the upper surface of the substrate and there is a narrow slot (260) between them. The antenna feed conductor (241) is connected to the first antenna element (220), which is connected also to the ground by a short-circuit conductor (261). The second antenna element (230) is parasitic; it is galvanically connected only to the ground. The component is preferably manufactured by a semiconductor technique by growing a metal layer e.g. on a quartz substrate and removing a part of it so that the antenna elements remain. In this case the component further comprises supporting material (212) of the substrate chip. The antenna component is very small-sized because of the high dielectricity of the substrate to be used and mostly because the slot between the antenna elements is narrow. The efficiency of an antenna made by the component is high.

Owner:PULSE FINLAND

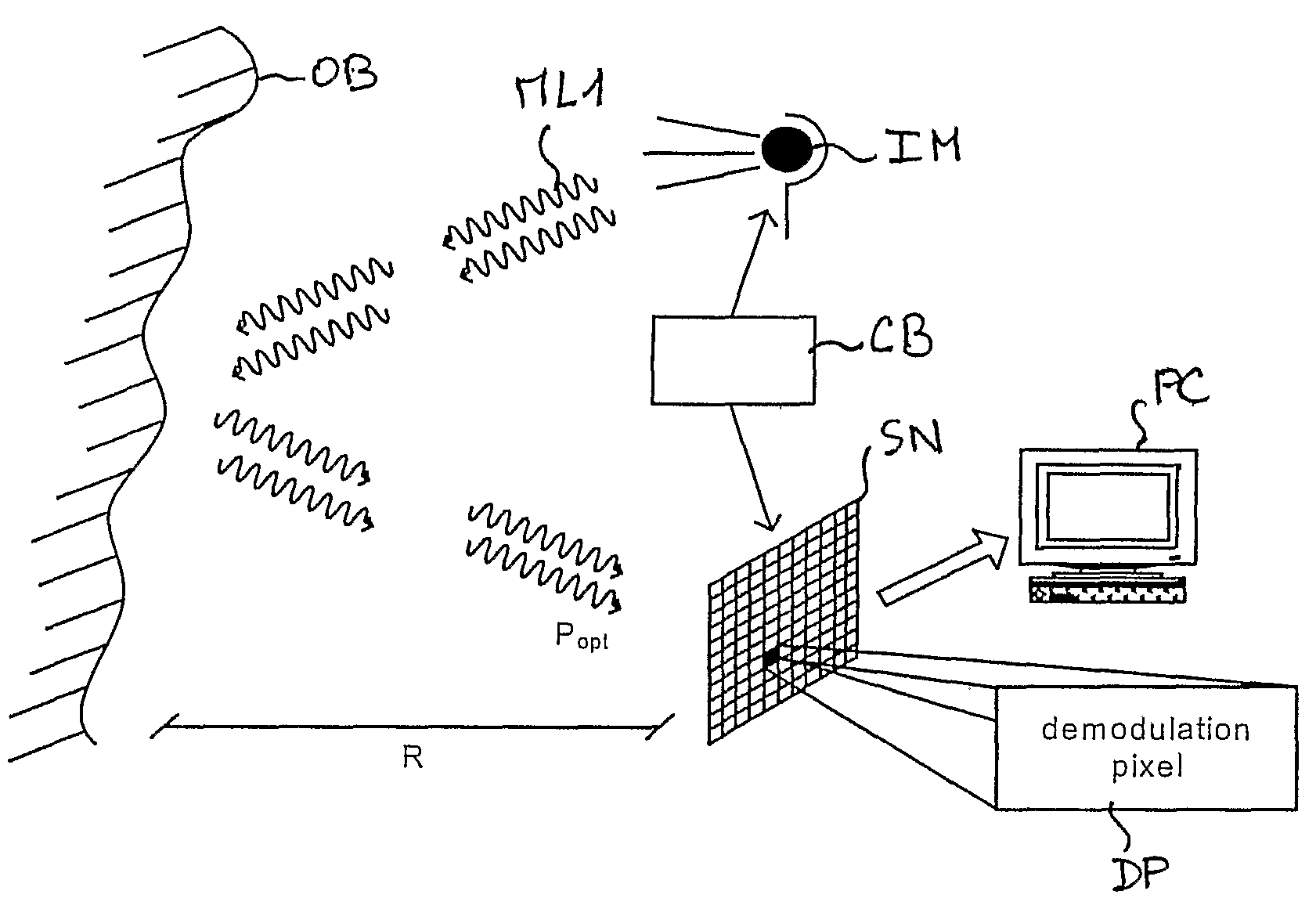

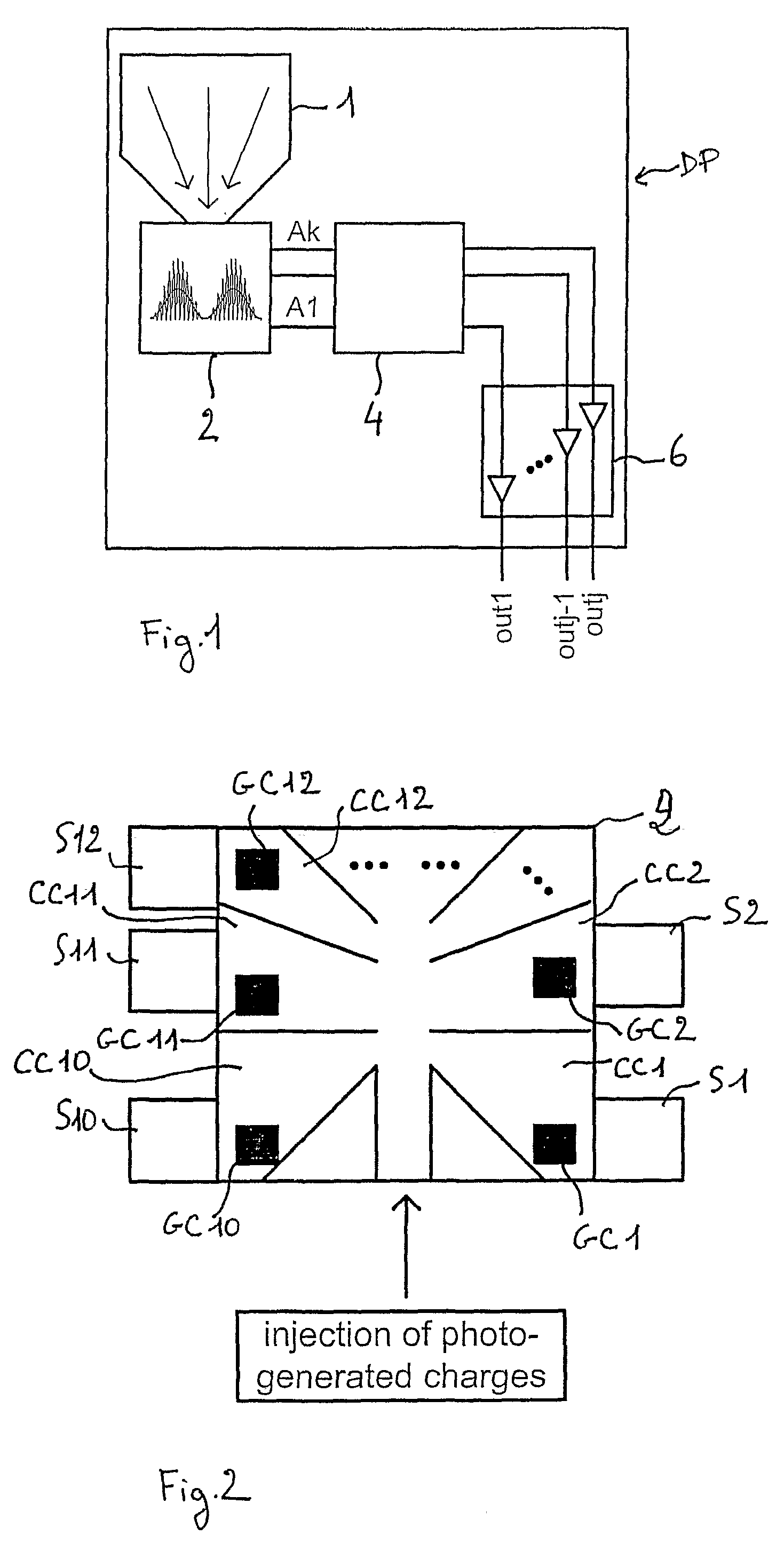

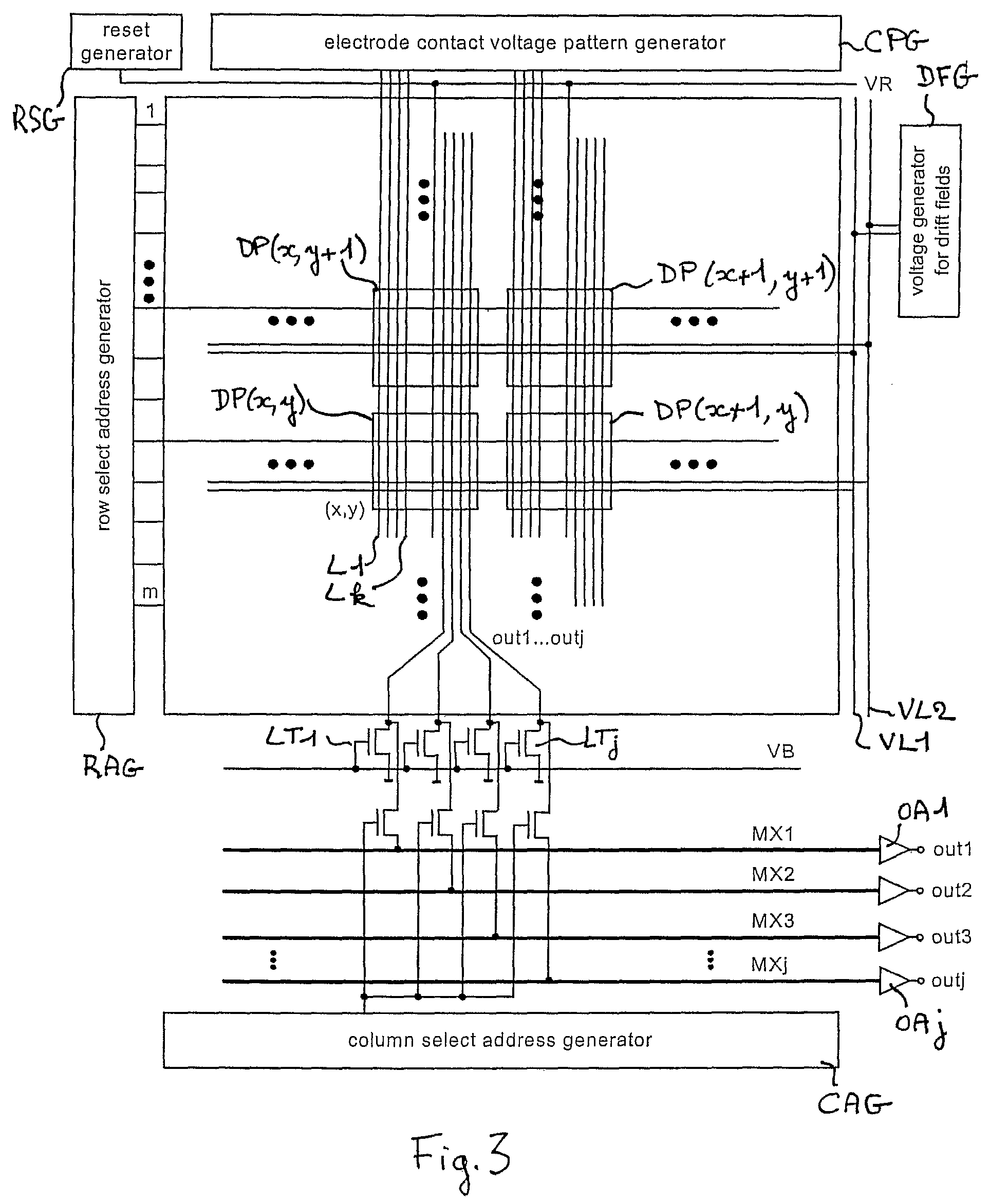

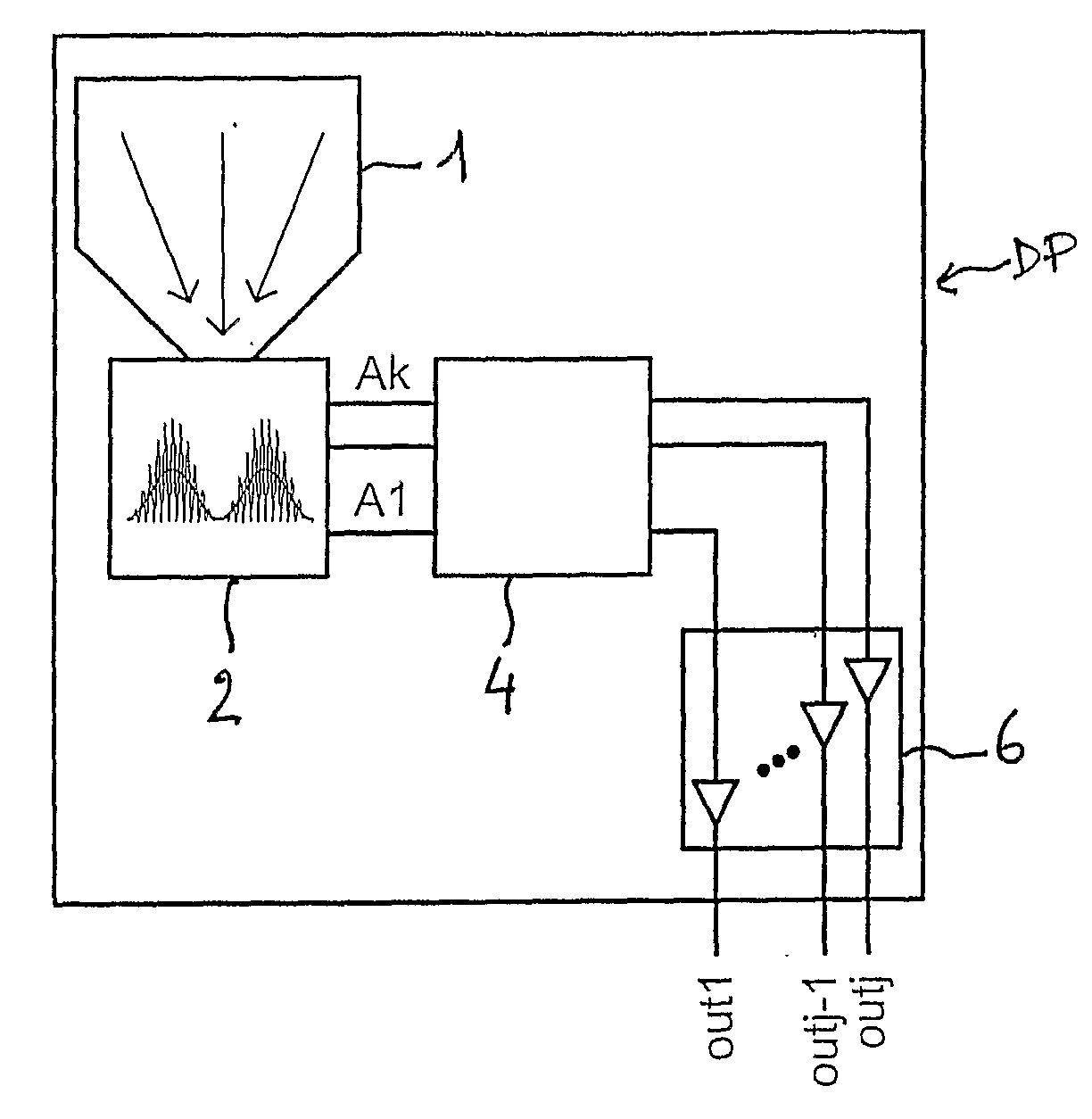

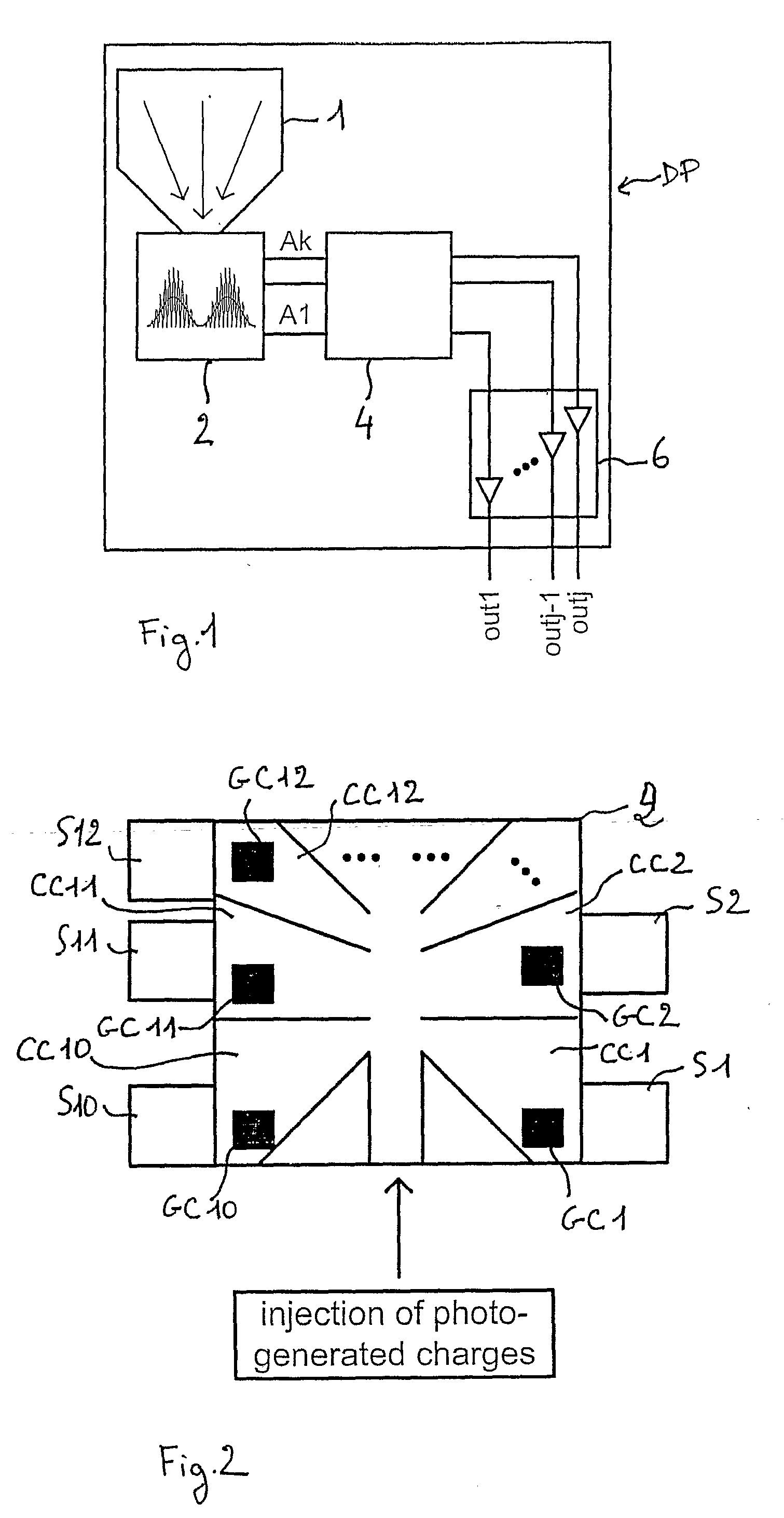

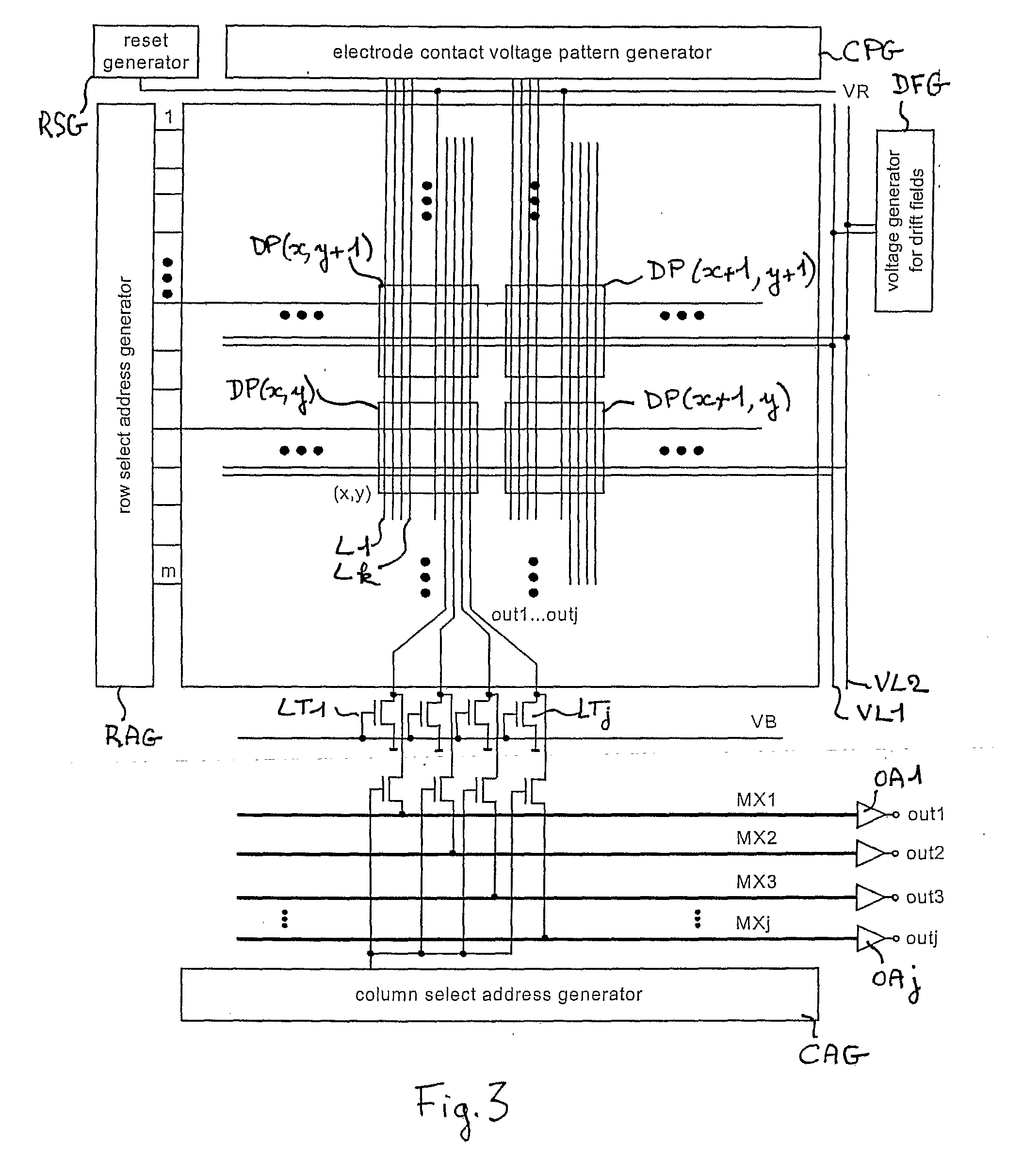

Device and method for the demodulation electromagnetic wave fields having separated detection and demodulation regions

ActiveUS7884310B2Increase speedFast shippingTelevision system detailsSolid-state devicesCharge currentWave field

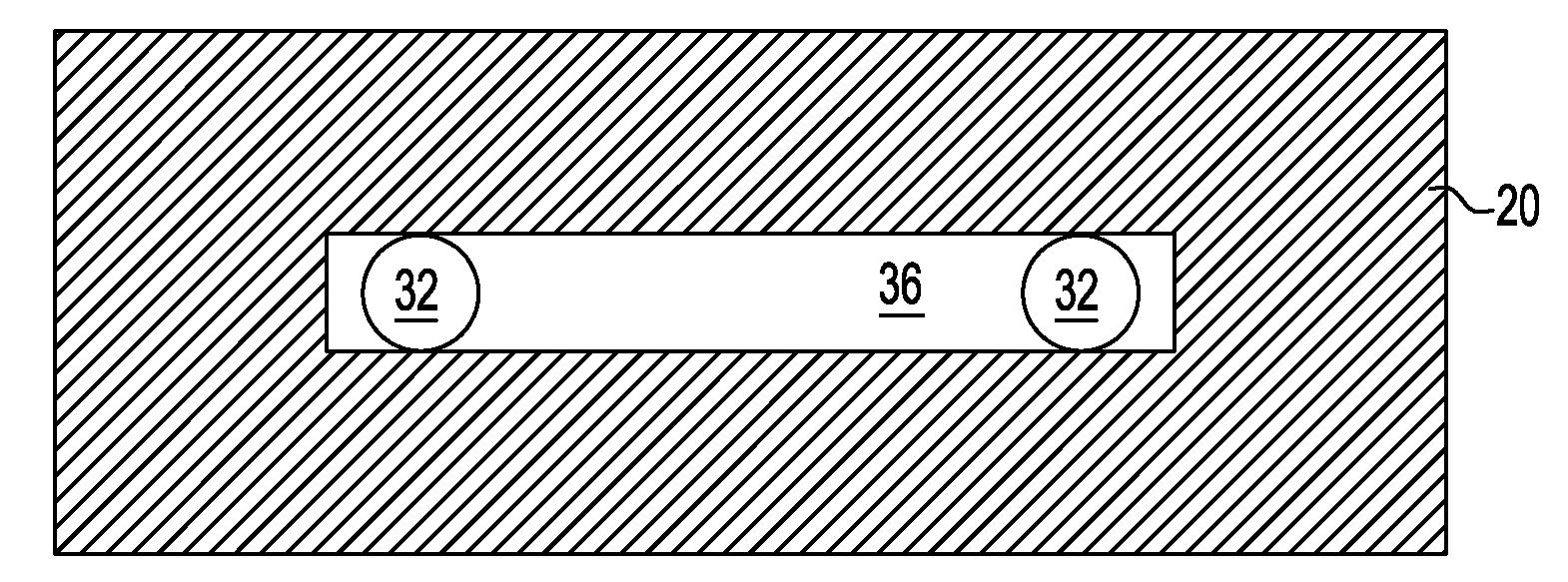

A new pixel in semiconductor technology comprises a photo-sensitive detection region (1) for converting an electromagnetic wave field into an electric signal of flowing charges, a separated demodulation region (2) with at least two output nodes (D10, D20) and means (IG10, DG10, IG20, DG20) for sampling the charge-current signal at least two different time intervals within a modulation period. A contact node (K2) links the detection region (1) to the demodulation region (2). A drift field accomplishes the transfer of the electric signal of flowing charges from the detection region to the contact node. The electric signal of flowing charges is then transferred from the contact node (K2) during each of the two time intervals to the two output nodes allocated to the respective time interval. The separation of the demodulation and the detection regions provides a pixel capable of demodulating electromagnetic wave field at high speed and with high sensitivity.

Owner:AMS SENSORS SINGAPORE PTE LTD

Method for preparing silicon thin film heterojunction solar cell

InactiveCN1588649AAvoid damageReduce hydrogen contentFinal product manufacturePhotovoltaic energy generationHeterojunctionSilicon thin film

A prepn. method of silicon thin film heterojunction solar cell includes following steps: cleaning substrate, semiconductor cleaning technology is used to do primary cleaing to substrate surface, then do ultrasonic cleaning in deionized water several times; nitrogen blow drying; prepare nitrinsic amorphous silicon layer by heater chemical vapour phase depositing technology, tungsten filament temp. is measured by pyrometer, temp of heater and sample are determined separately by two electric thermo-couples, temp. is controlled by electric temp. controller; to react and grow thin film on substrate surface; to redeposit a transmitting layer on intrinsic amorphous silicon thin film; front and back electrodes forming, sputtering technology is used to form front and back electrodes; finally to proceed vacuum heat annealing process. The thin film produced by the invention has illumination stability, the photoconduction gain can reach to 10 to the power 6 on Am1.5 100mW / cm2 standard illumination.

Owner:SHANGHAI JIAO TONG UNIV

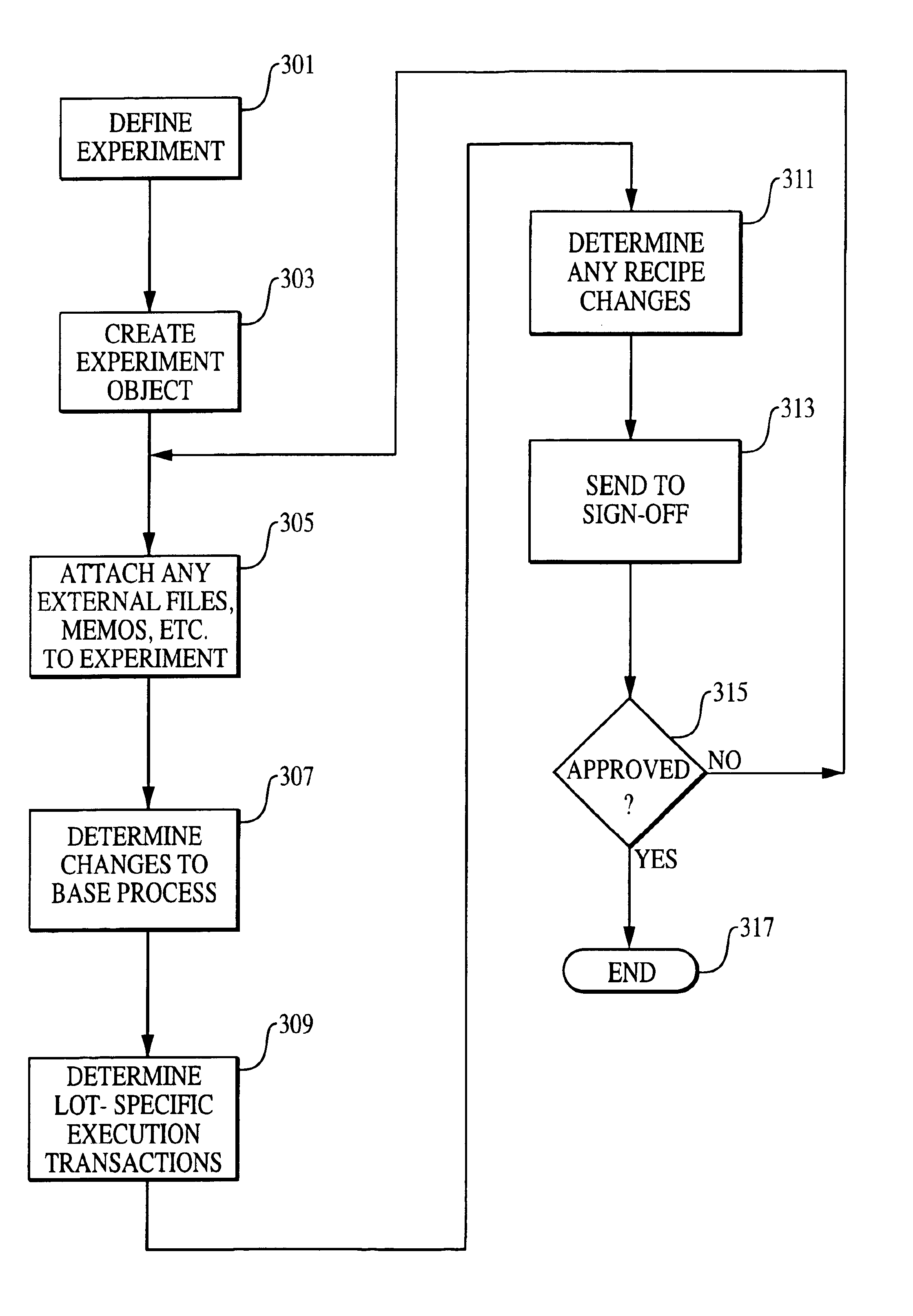

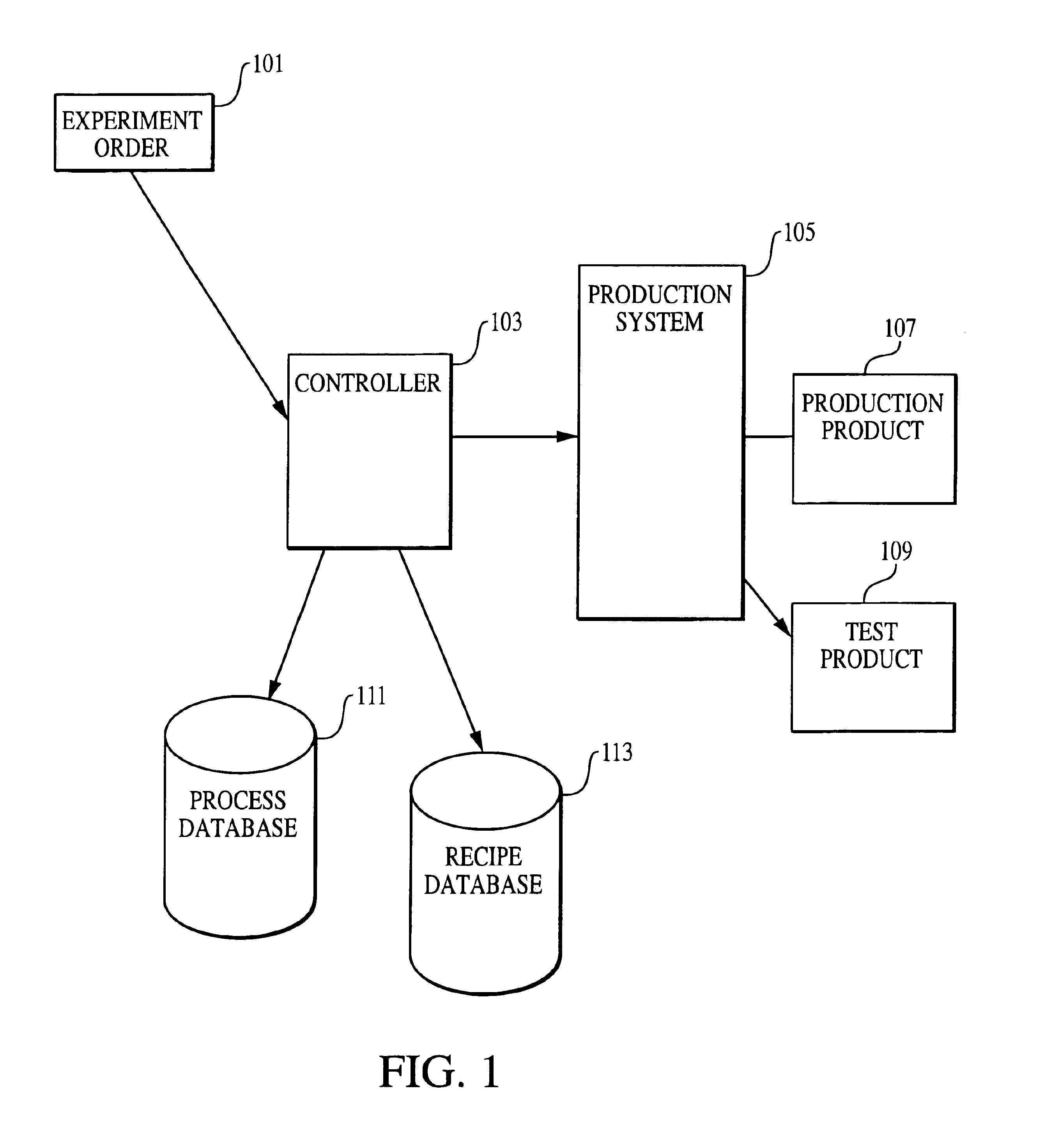

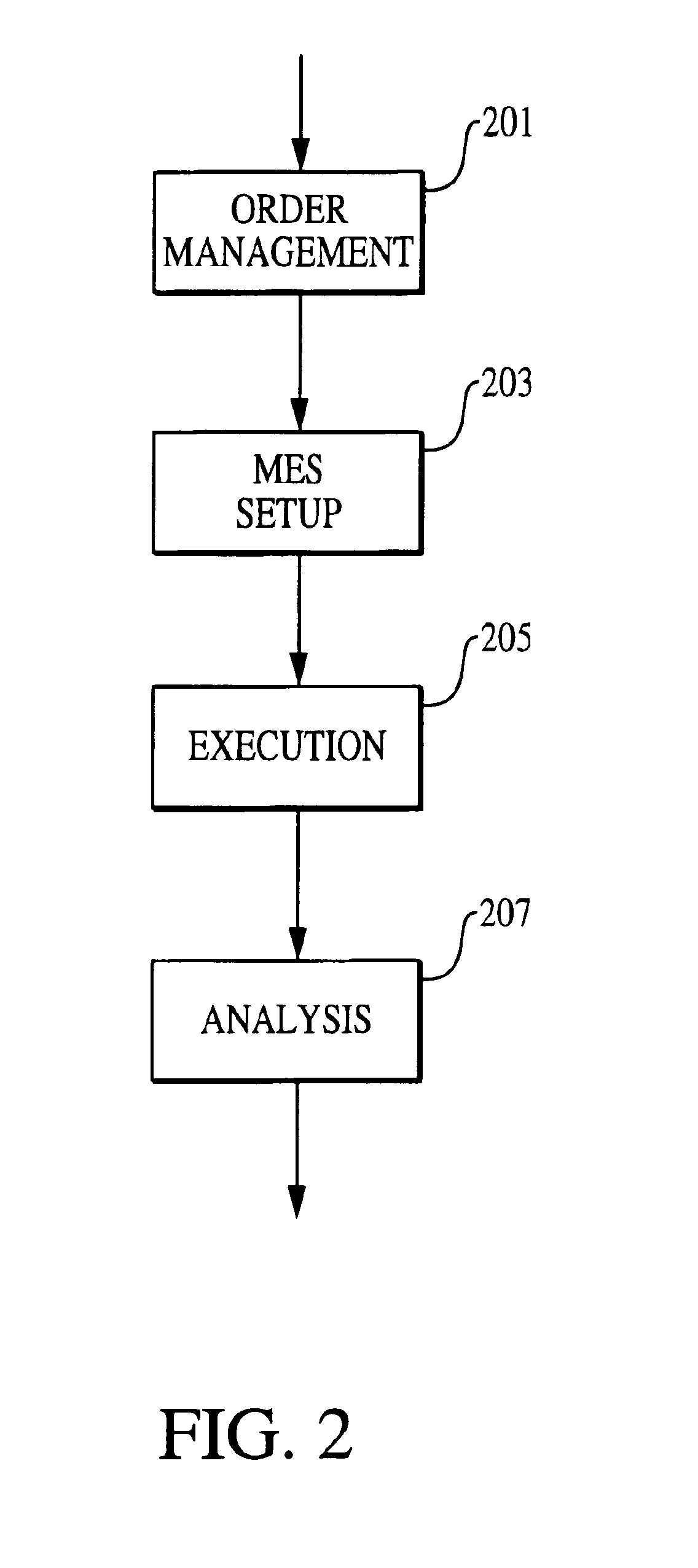

Experiment management system, method and medium

InactiveUS6984198B2Easy to implementSemiconductor/solid-state device testing/measurementComputer controlSemiconductor chipDocumentation

Systems, methods and mediums are provided for automating experiments within an automated environment without the need to disassociate the test subject (e.g., the semiconductor chip or chips) from that environment. An “experiment” may be a pre-planned deviation of an established (e.g., pre-defined) process utilizing the automated environment.A computer-implemented method, system and computer-readable medium for managing experiments, such as those relating to semiconductor technology. An experiment order includes some deviation from a base process capable of operating in an automated environment. An approval of the experiment order is obtained from a distribution list of users, while permitting the users to attach documents to the experiment order or perhaps modify the experiment. The experiment order is translated into processing data suitable for implementation by said automated environment, and stored. The experiment is caused to be executed in conjunction with at least some portion of said base process via the automated environment according to the processing data.

Owner:APPLIED MATERIALS INC

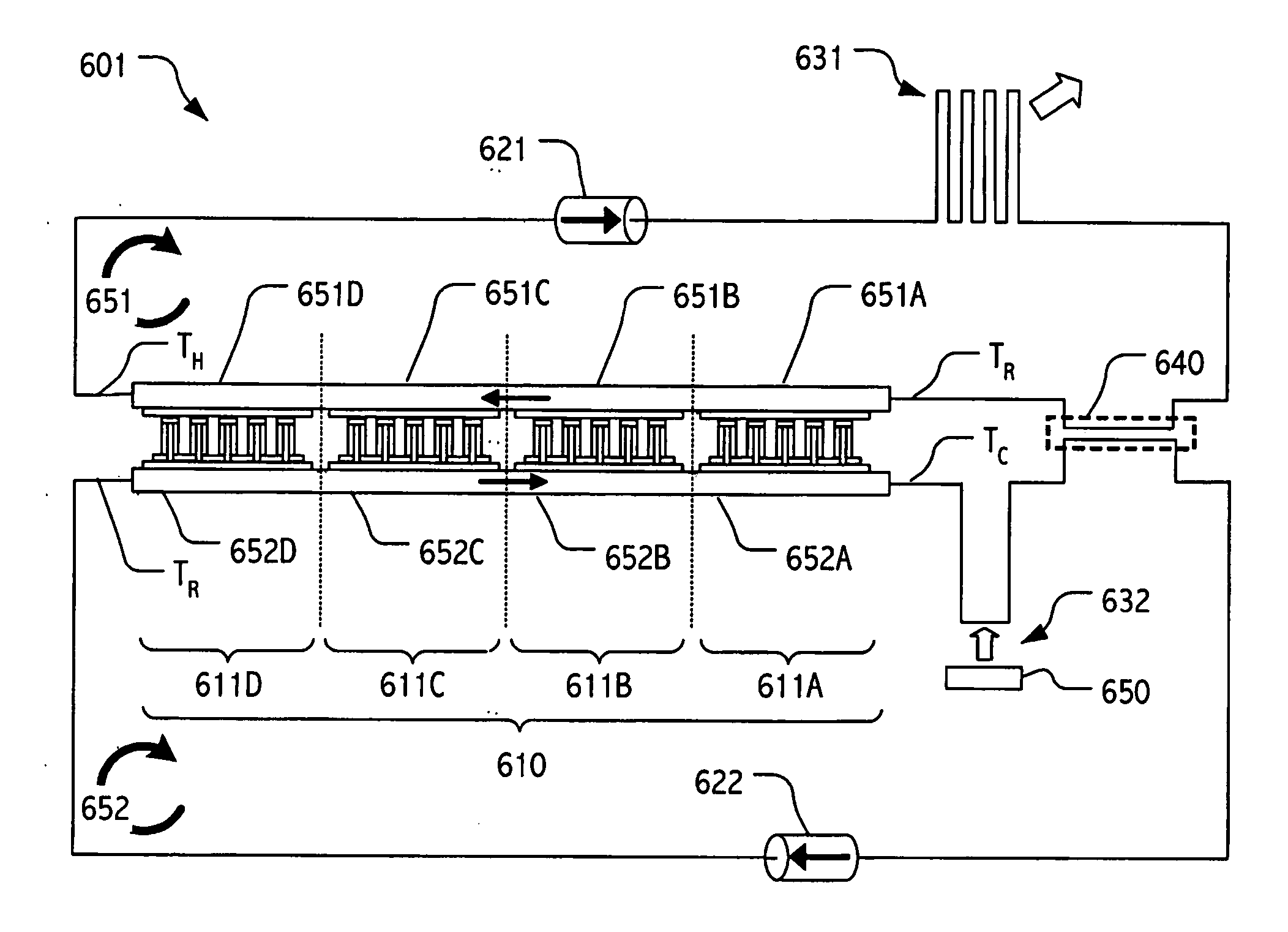

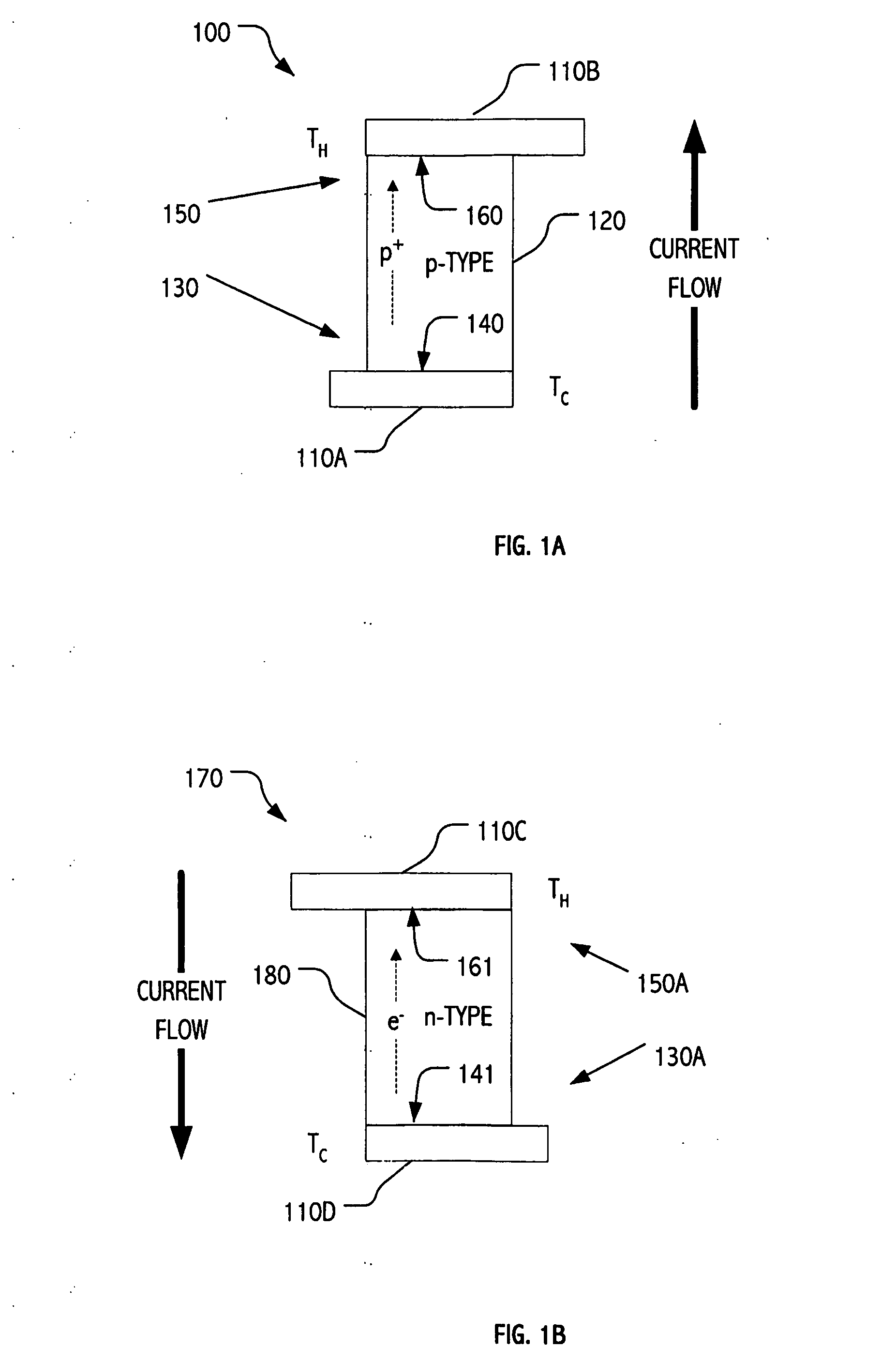

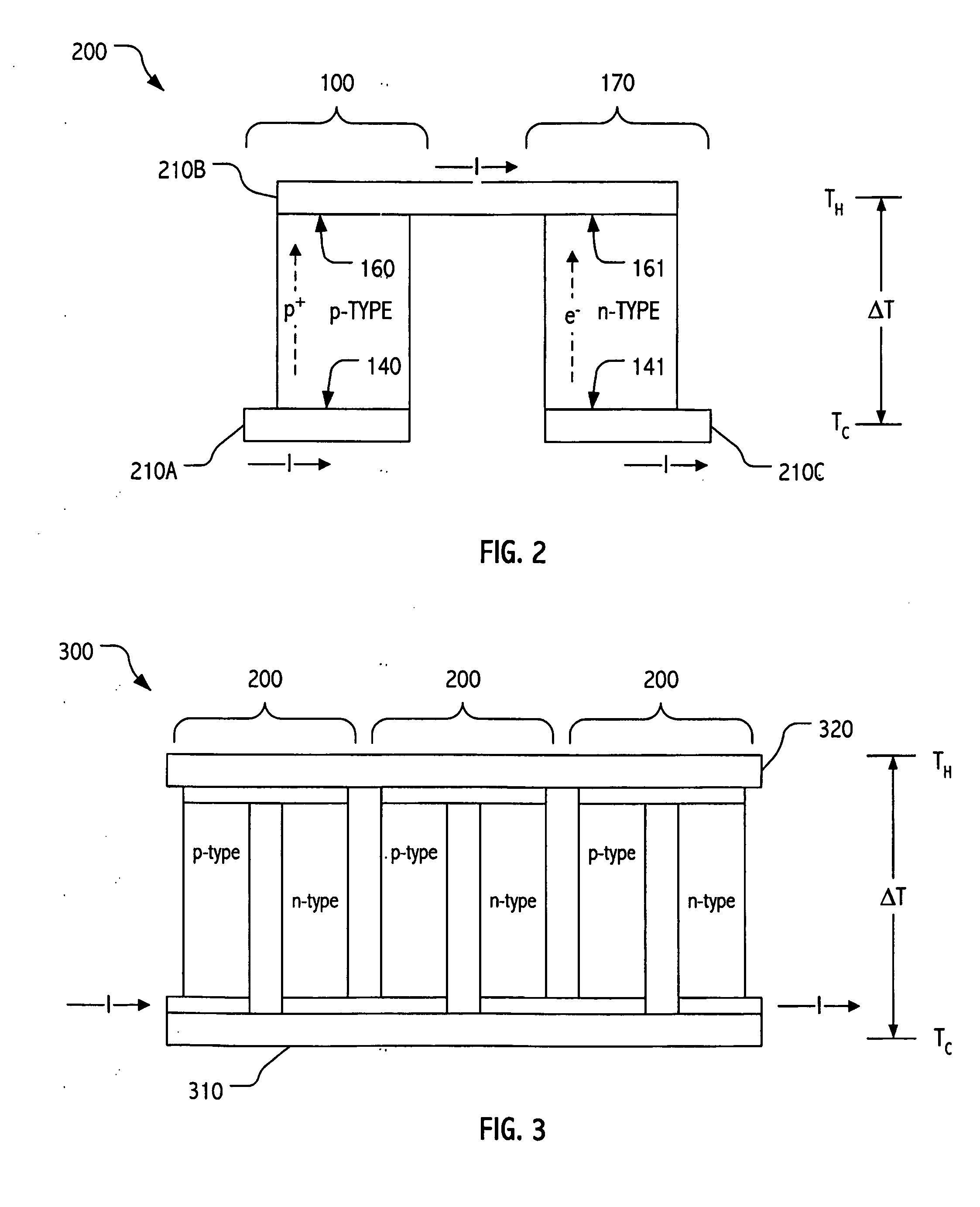

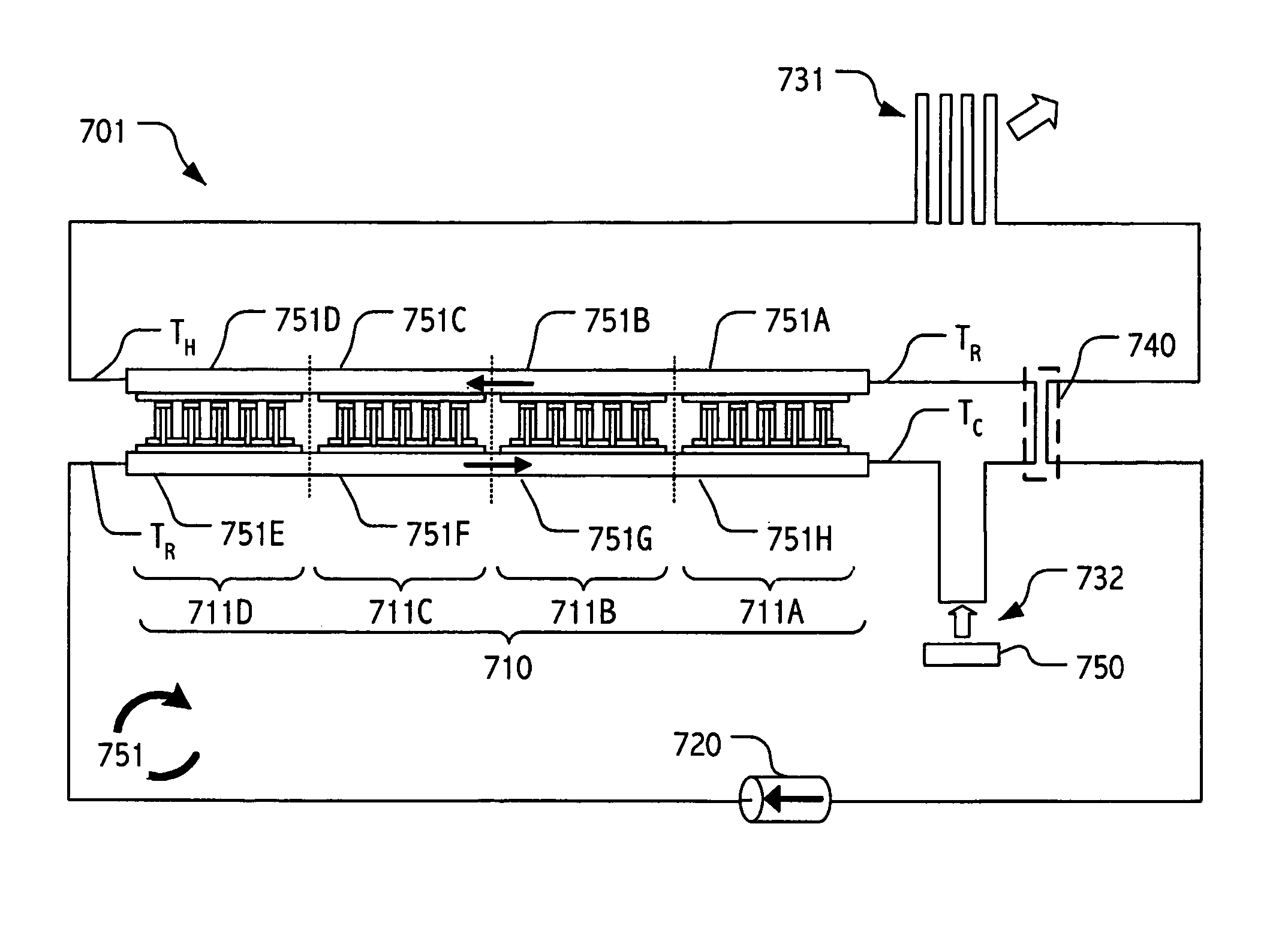

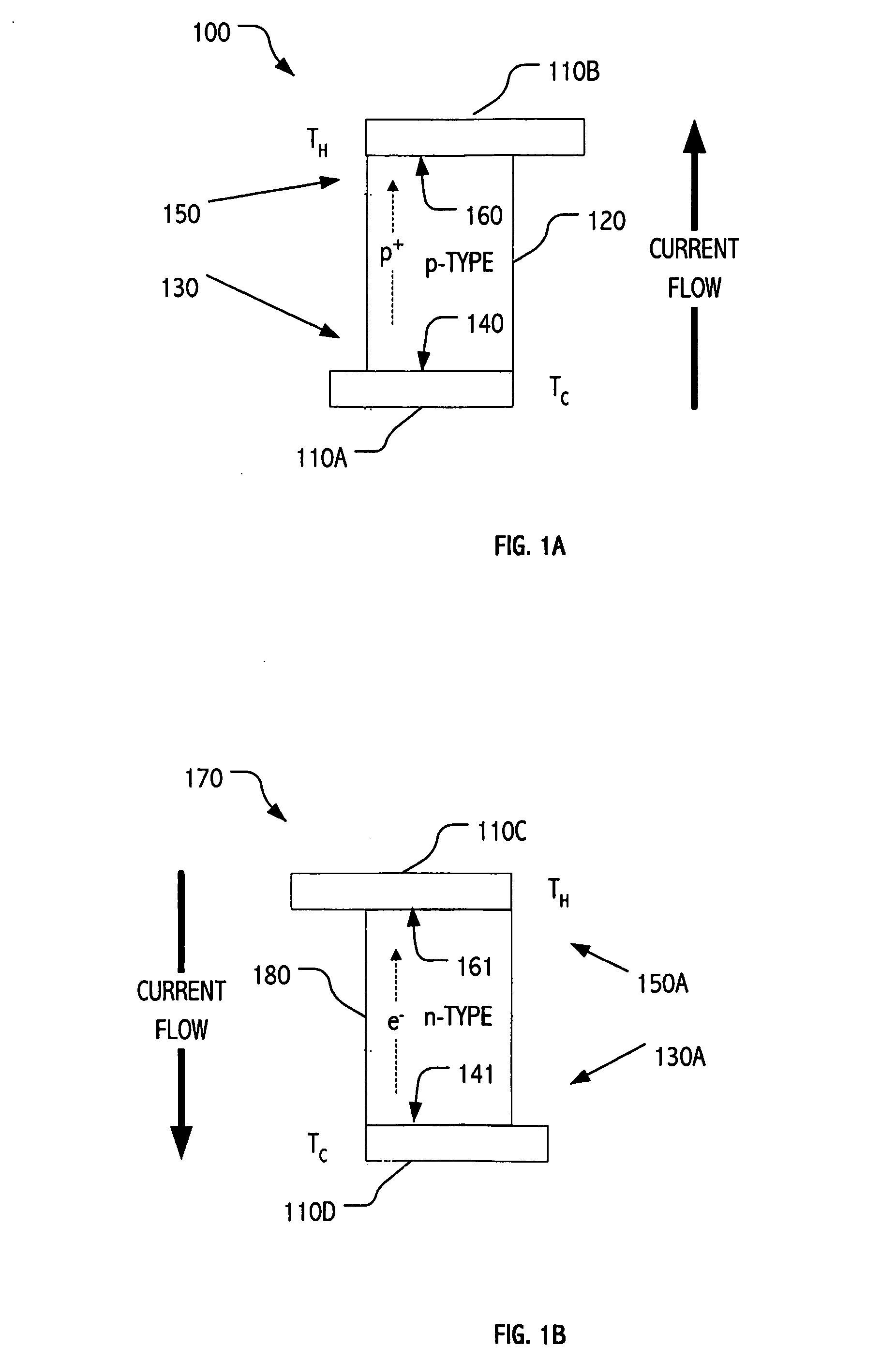

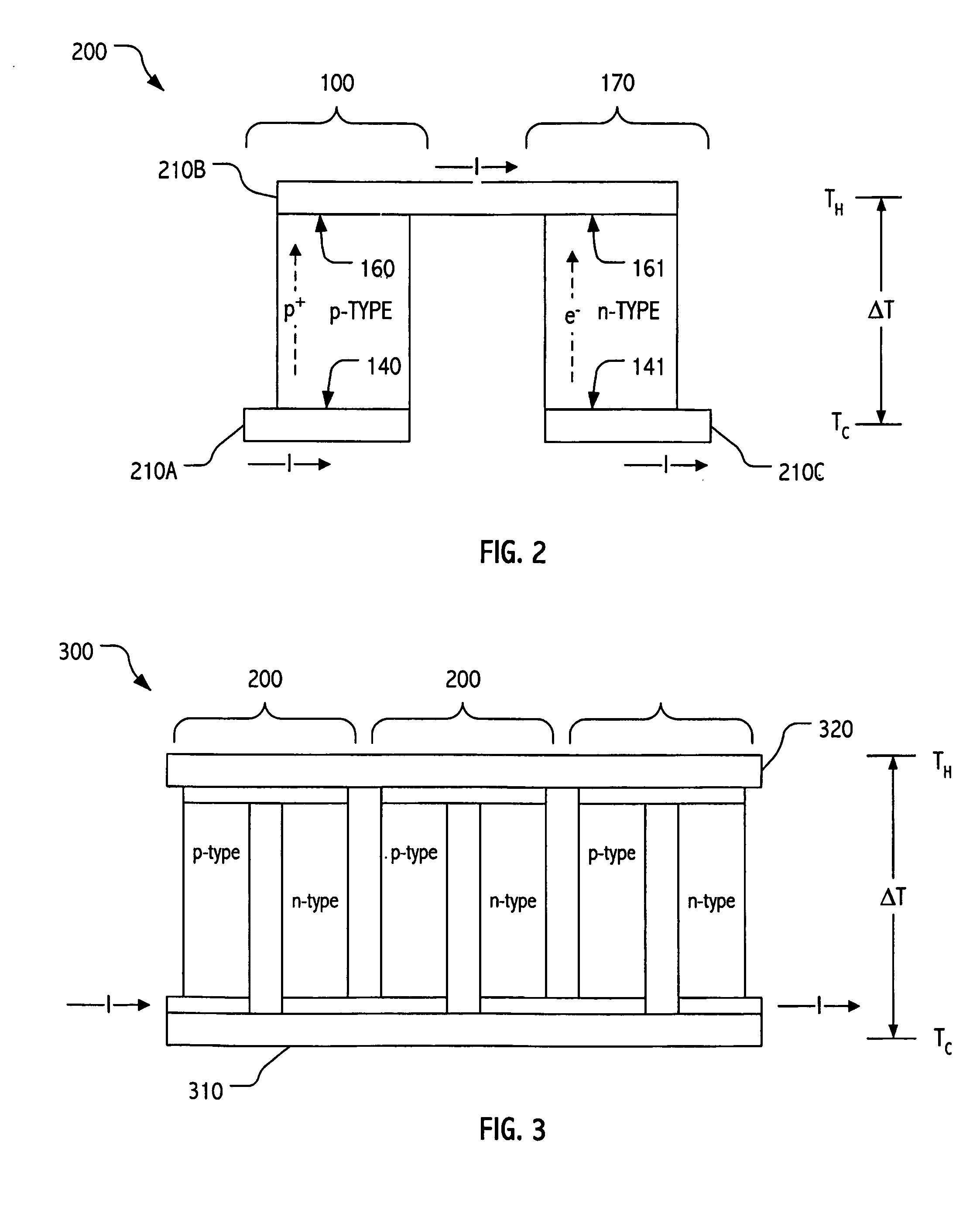

Counterflow thermoelectric configuration employing thermal transfer fluid in closed cycle

ActiveUS20060137359A1Cost-effectively employedCost-effectively configuredThermoelectric device with peltier/seeback effectMachines using electric/magnetic effectsNuclear engineeringActive cooling

Active cooling technologies such as thermoelectrics can be used to introduce thermal “gain” into a cooling system and, when employed in combination with forced flow liquid metal cooling loops, can provide an attractive solution for cooling high heat flux density devices and / or components. Total cooling power can be increased by employing multiple thermoelectric elements. Indeed, by employing modern semiconductor technologies, including e.g., thin-film technologies, thermoelectric elements may be cost-effectively employed and configured in large arrays.

Owner:SHEETAK INC

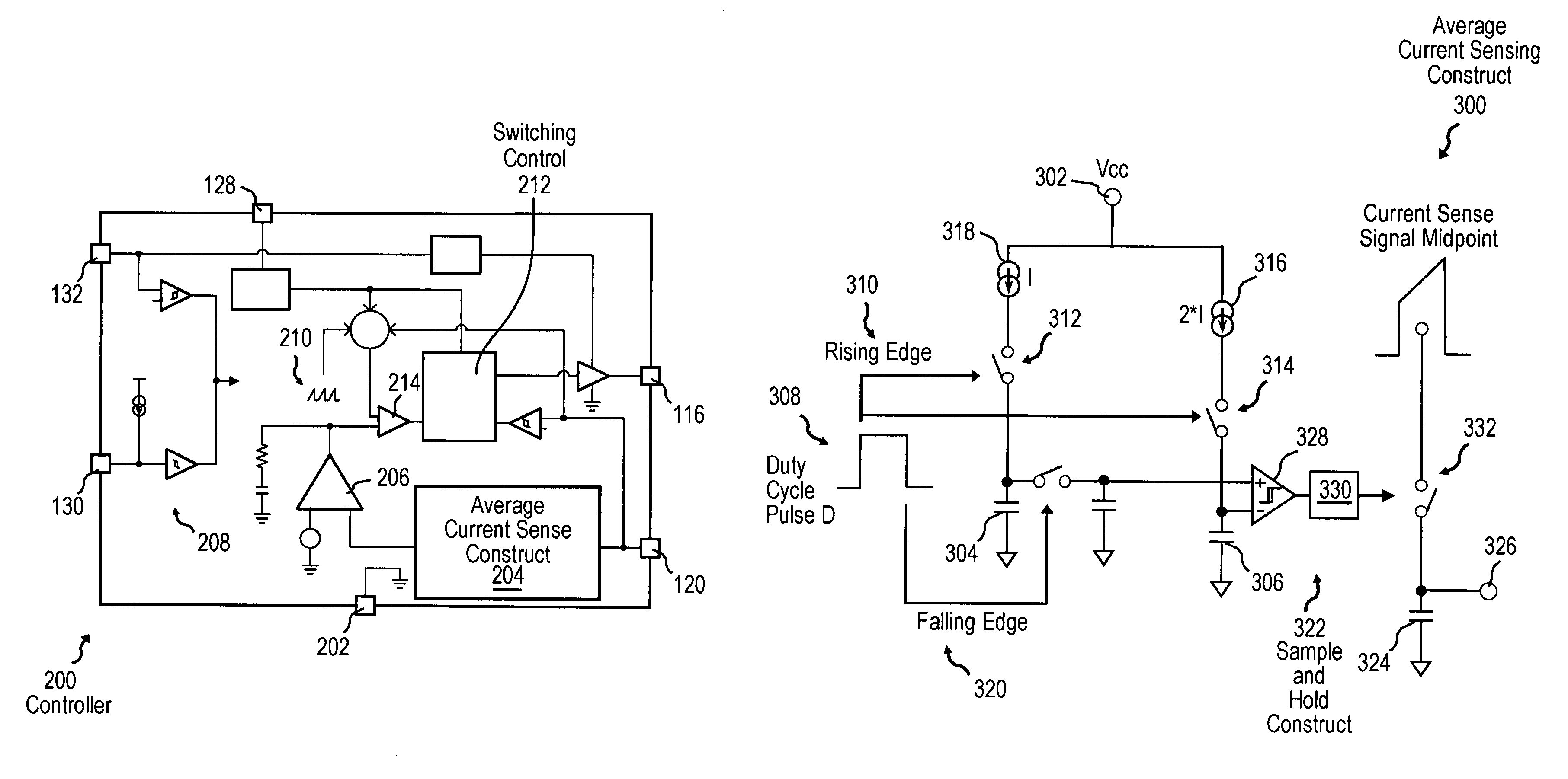

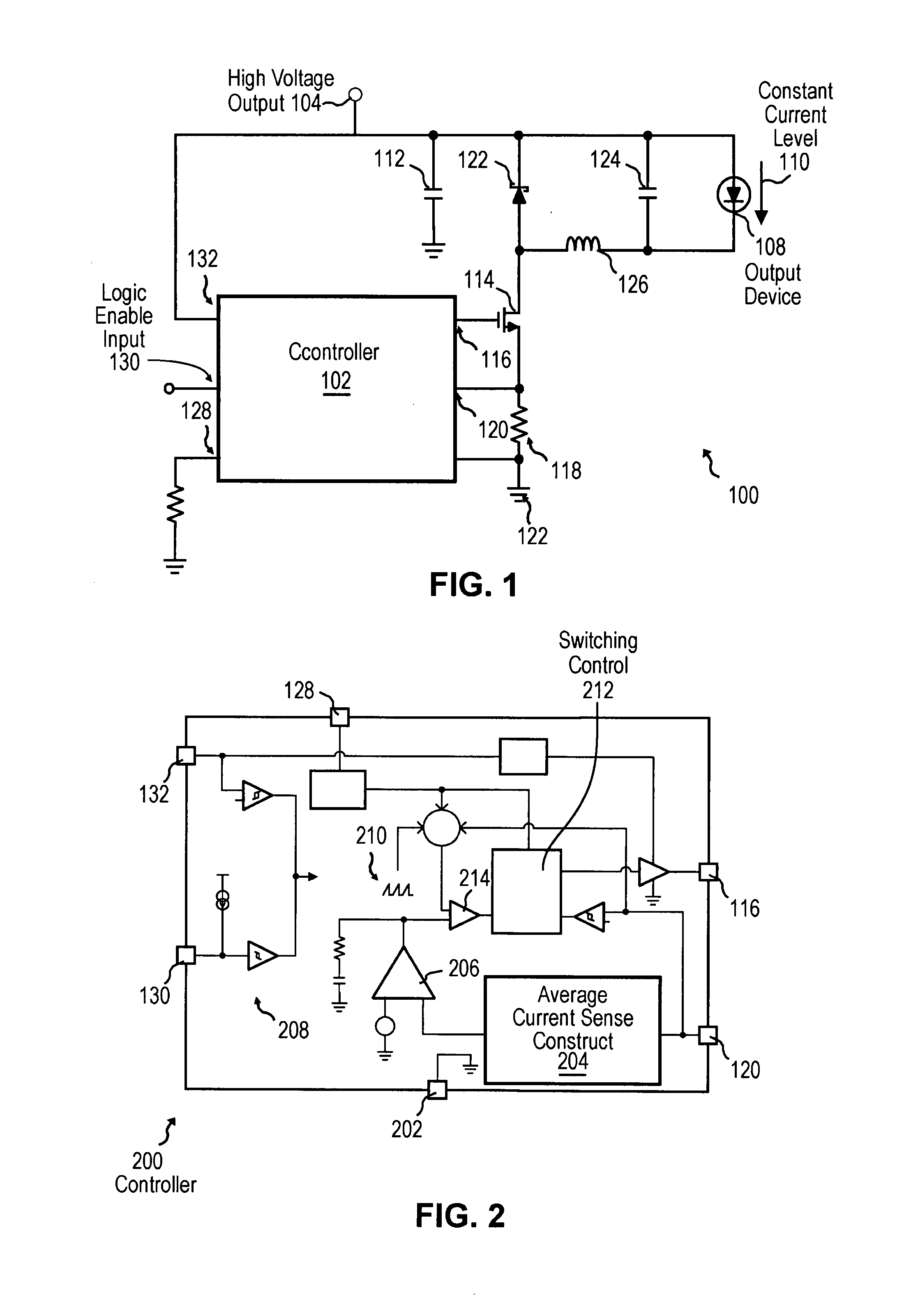

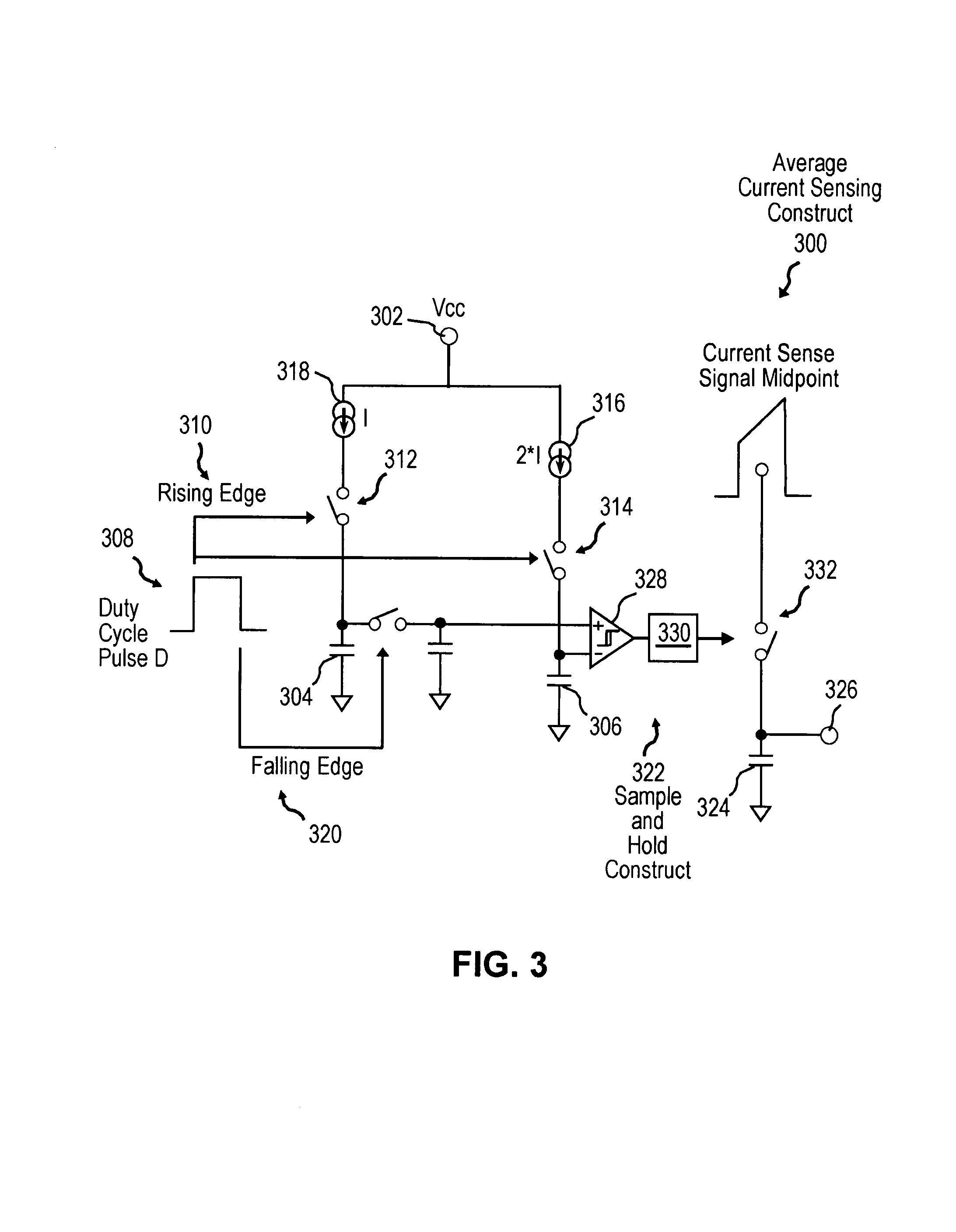

Versatile system for high-power switching controller in low-power semiconductor technology

The present invention provides a versatile system for providing a current-mode switching controller—in low voltage commercial semiconductor technologies—that is compatible with applications having very high input voltage ranges. The system provides an output transistor and a sense element coupled to the output transistor. A waveform representative of current charging across the sense element is recognized. First and second charging elements are provided, and the second charging element is adapted to charge at a rate twice as fast as the first charging element. First and second switching elements, coupled to the first and second charging elements, respectively, are adapted to activate the first and second charging elements responsive to a rising edge of the waveform. An output charge element is provided, and a sample and hold construct is adapted to transfer a charge value—to the output charge element—that corresponds to an average of the charge values of the first and second charging elements upon a falling edge of the waveform.

Owner:NAT SEMICON CORP

Counterflow thermoelectric configuration employing thermal transfer fluid in closed cycle

ActiveUS7293416B2Cost-effectively employedCost-effectively configuredThermoelectric device with peltier/seeback effectMachines using electric/magnetic effectsNuclear engineeringActive cooling

Active cooling technologies such as thermoelectrics can be used to introduce thermal “gain” into a cooling system and, when employed in combination with forced flow liquid metal cooling loops, can provide an attractive solution for cooling high heat flux density devices and / or components. Total cooling power can be increased by employing multiple thermoelectric elements. Indeed, by employing modern semiconductor technologies, including e.g., thin-film technologies, thermoelectric elements may be cost-effectively employed and configured in large arrays.

Owner:SHEETAK INC

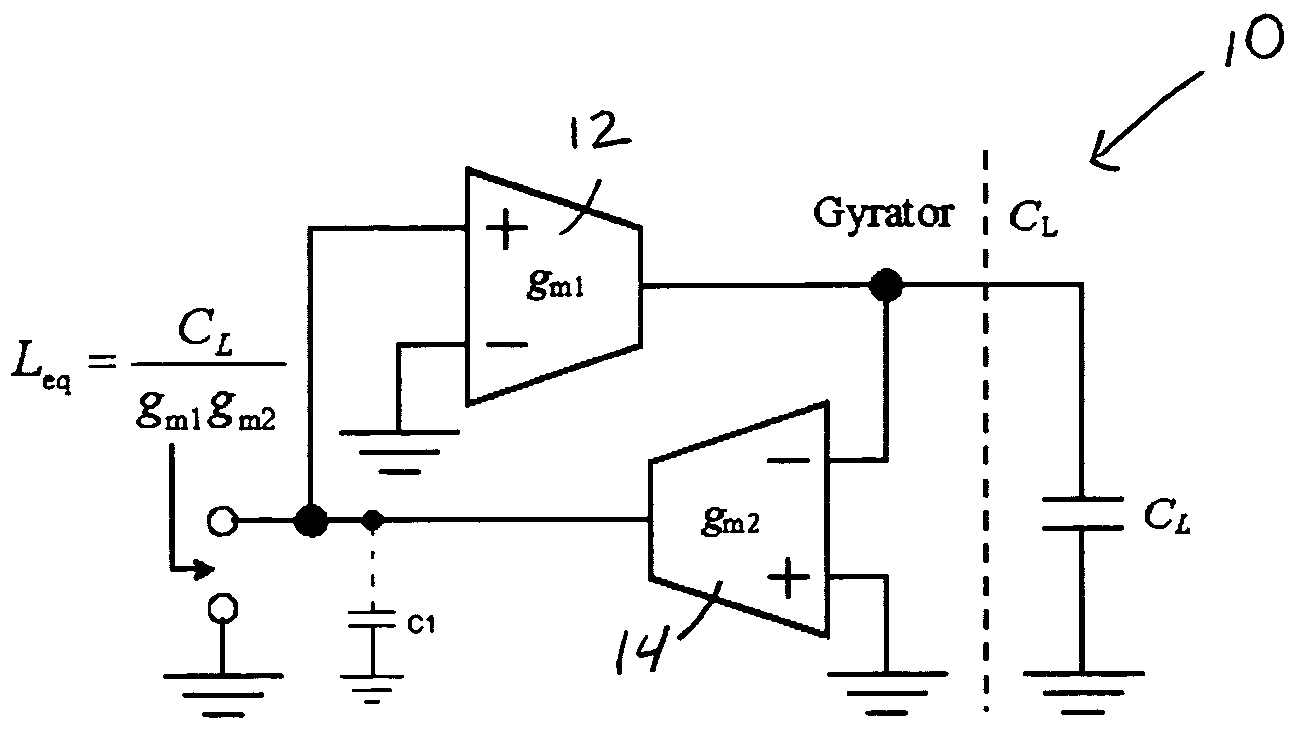

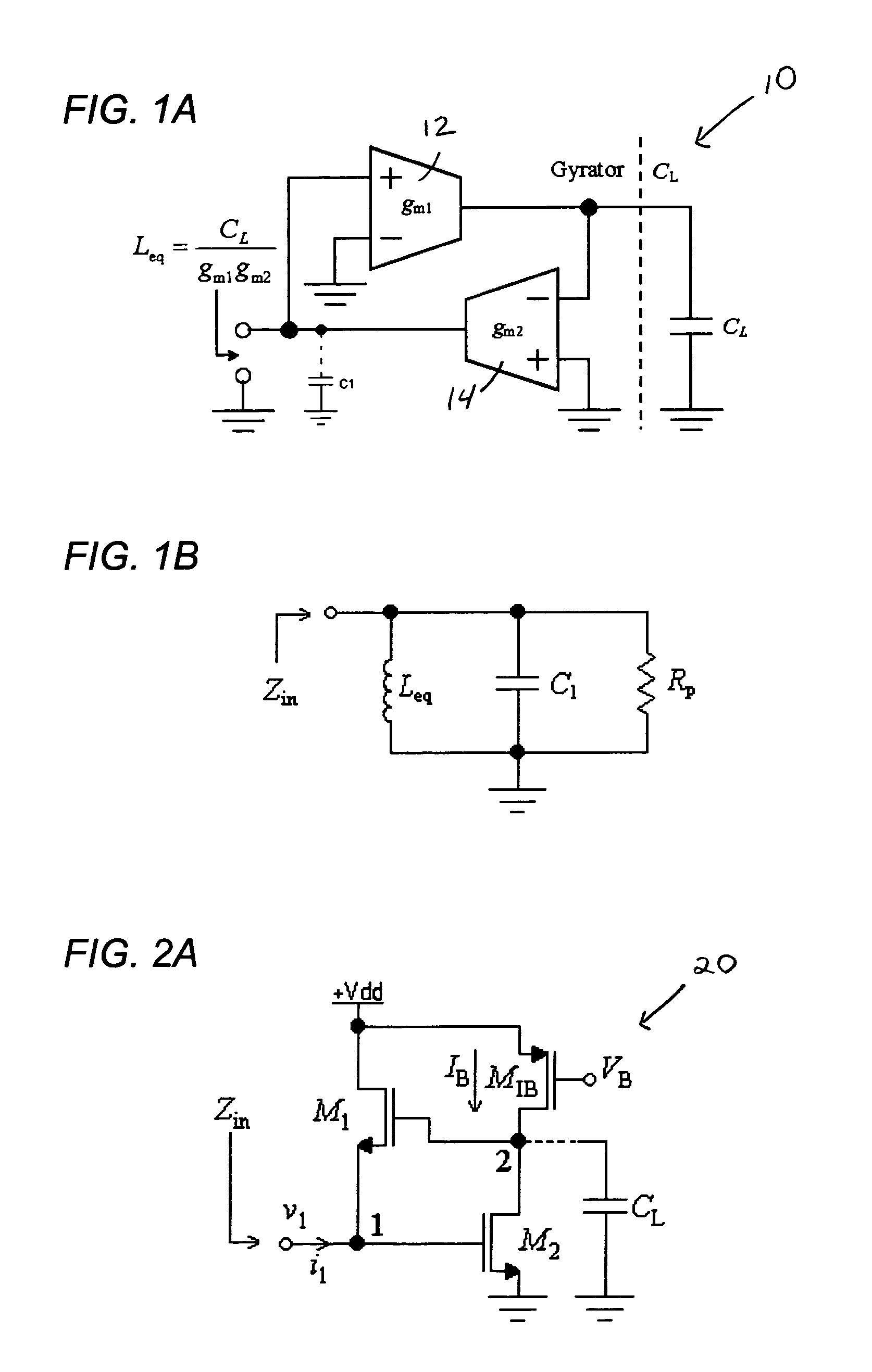

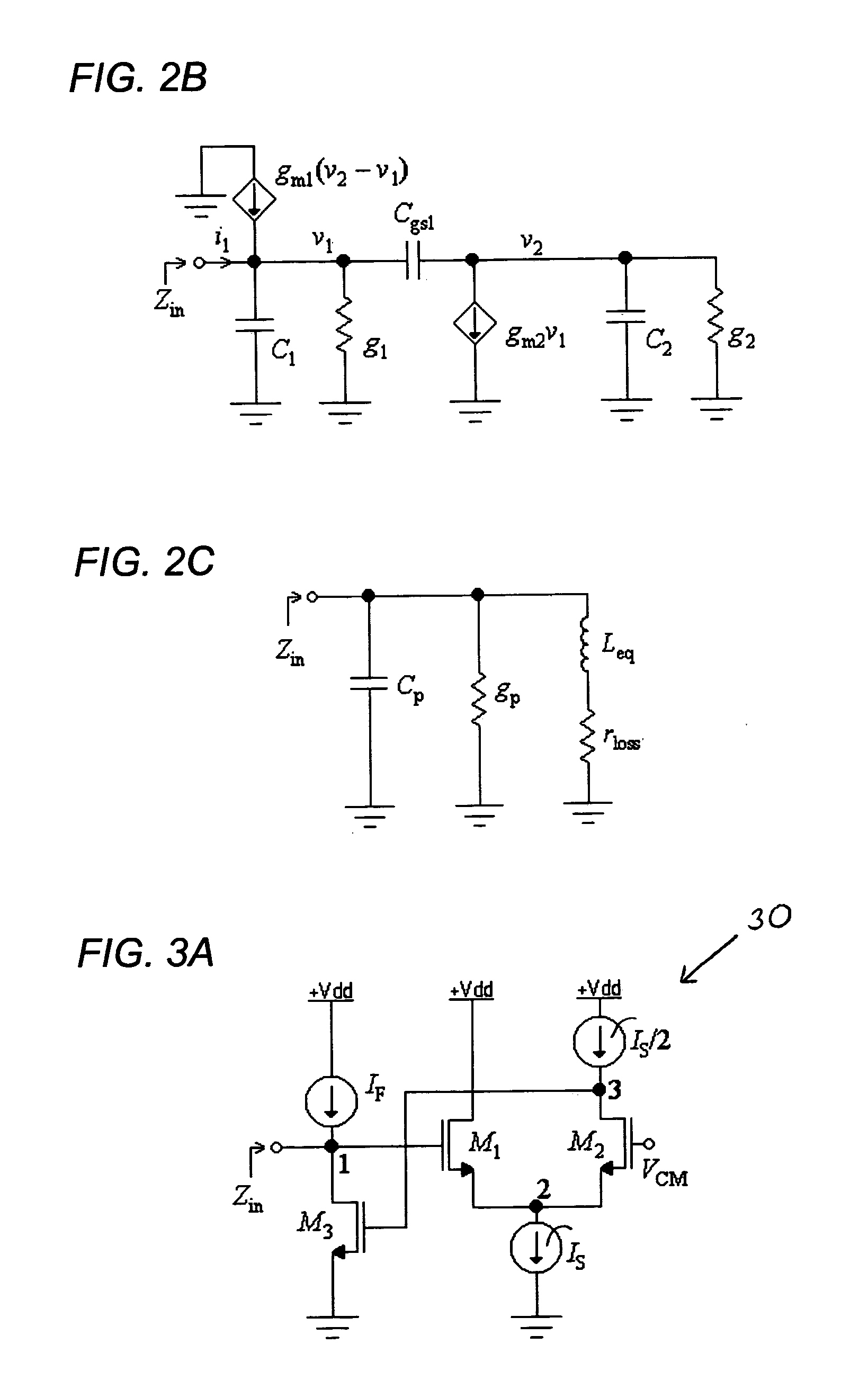

High-frequency active inductor

An active inductor circuit implemented in sub-micron CMOS semiconductor technology is usable at gigaHertz frequencies and includes an input node, a non-inverting transconductor circuit comprising a differential pair of NMOS transistors connected to the input node, an inverting transconductor circuit comprising an NMOS transistor connected to an output node of the non-inverting transconductor circuit and connected to the input node in a gyrator feedback configuration. Varactors coupled to the transconductor circuits tune the frequency and Q of the active inductor circuit.

Owner:PORTLAND STATE UNIV

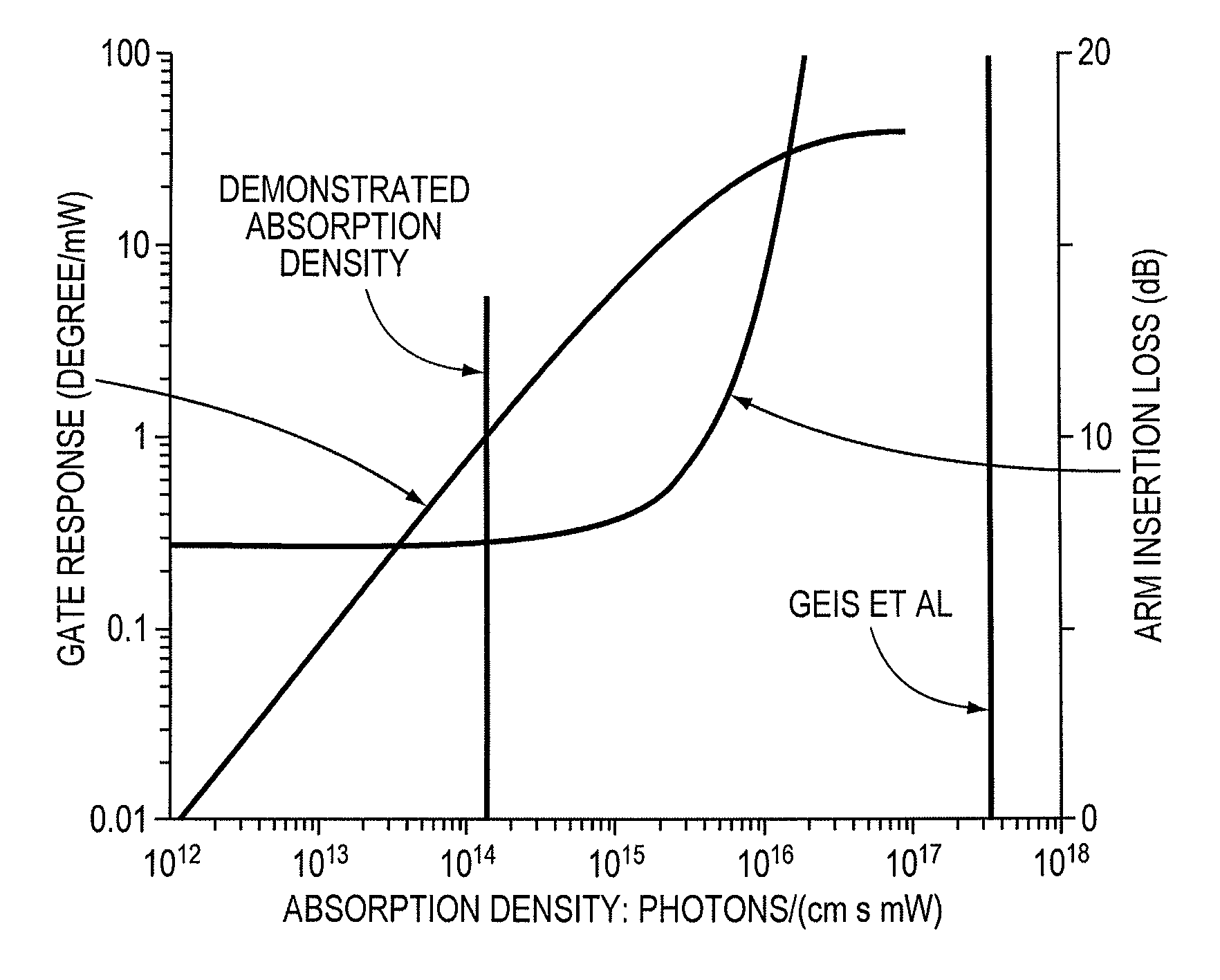

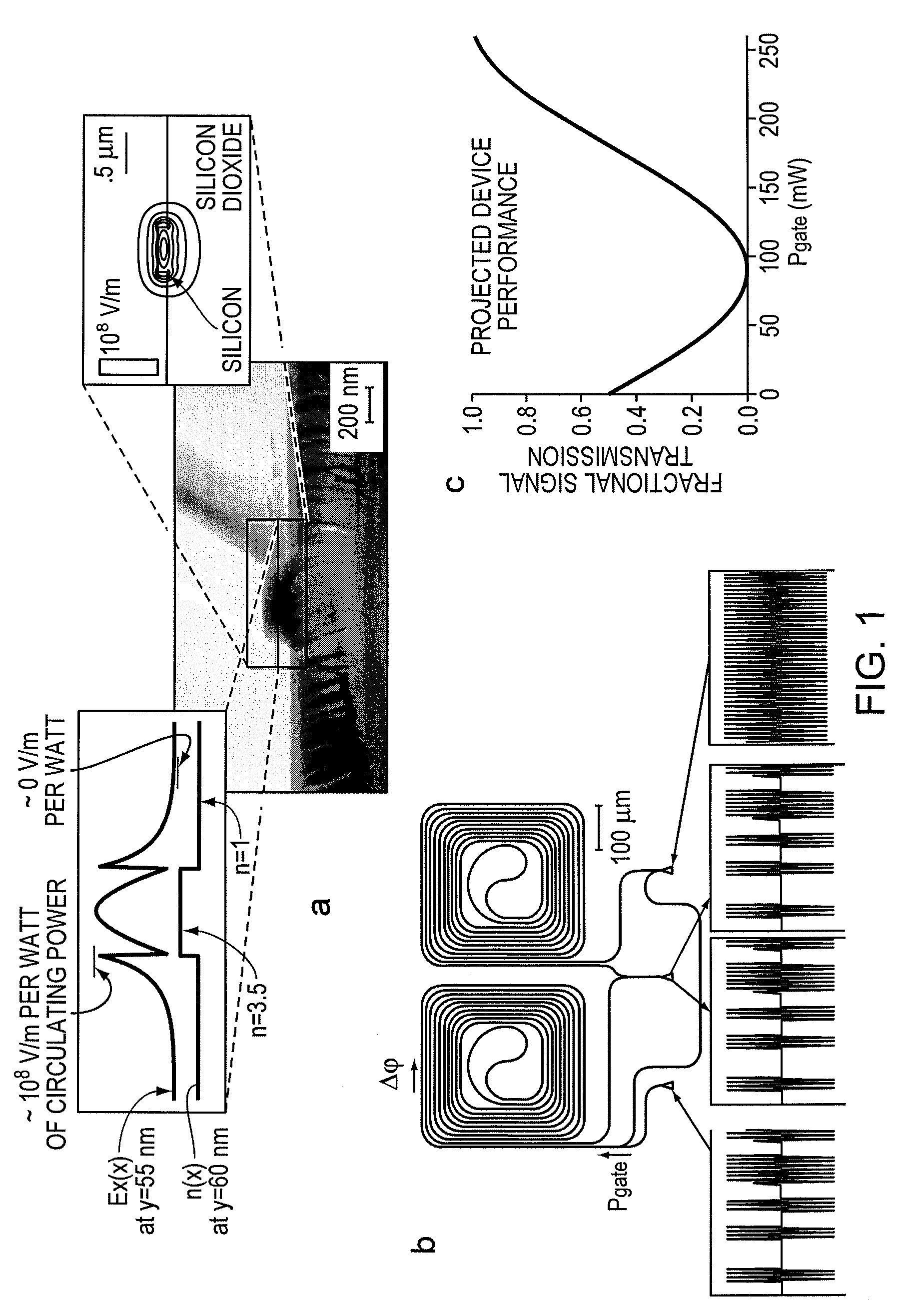

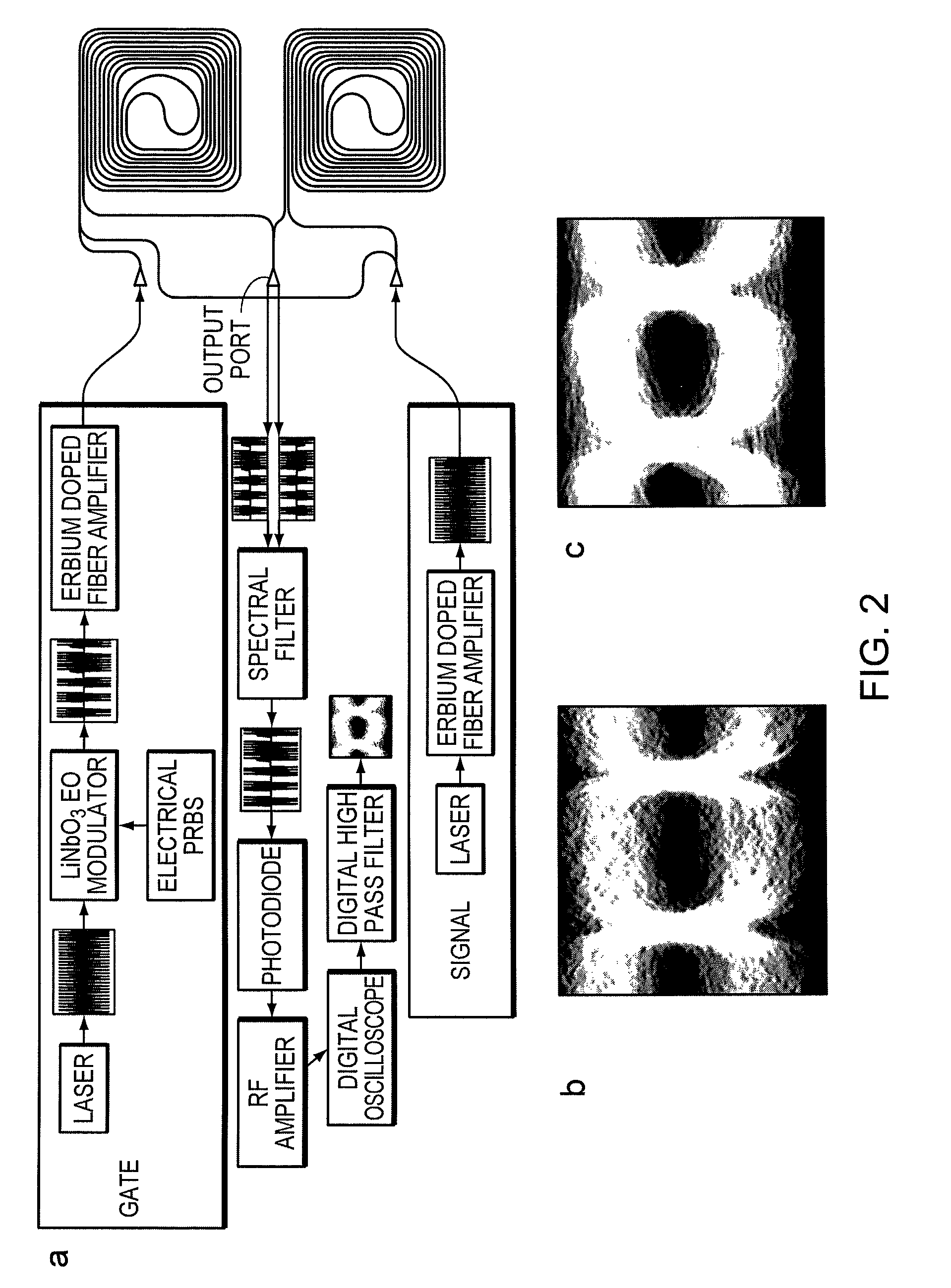

Single photon absorption all-optical modulator in silicon

A single-photon absorption all-optical modulator, systems employing the same, and methods of making and using the same. An illustrative example is provided based on silicon semiconductor technology that employs rectangular waveguides. In some embodiments, it is observed that the waveguides operate with an absorption density of less than 1017 cm−1s−1mW−1 to provide a single-photon absorption operation mode.

Owner:CALIFORNIA INST OF TECH

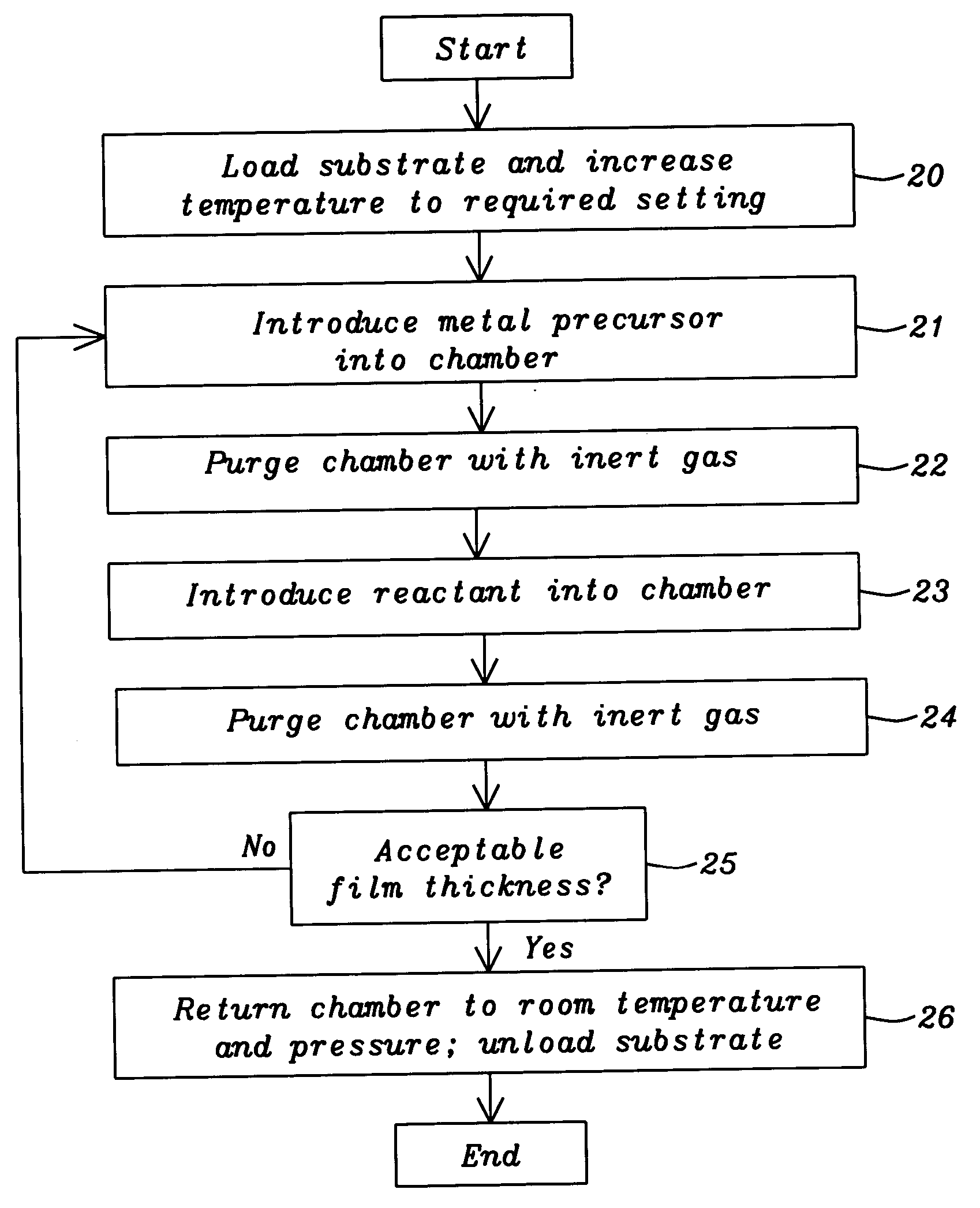

Method of manufacturing a contact interconnection layer containing a metal and nitrogen by atomic layer deposition for deep sub-micron semiconductor technology

ActiveUS20050054196A1Good step coverageSafe handlingSemiconductor/solid-state device detailsSolid-state devicesAtomic layer depositionImpurity

An atomic layer deposition method is used to deposit a TiN or TiSiN film having a thickness of about 50 nm or less on a substrate. A titanium precursor which is tetrakis(dimethylamido)titanium (TDMAT), tetrakis(diethylamido)titanium (TDEAT), or Ti{OCH(CH3)2}4 avoids halide contamination from a titanium halide precursor and is safer to handle than a titanium nitrate. After a monolayer of the titanium precursor is deposited on a substrate, a nitrogen containing reactant is introduced to form a TiN monolayer which is followed by a second purge. For TiSiN, a silicon source gas is fed into the process chamber after the TiN monolayer formation. The process is repeated several times to produce a composite layer comprised of a plurality of monolayers that fills a contact hole. The ALD method is cost effective and affords an interconnect with lower impurity levels and better step coverage than conventional PECVD or CVD processes.

Owner:TAIWAN SEMICON MFG CO LTD

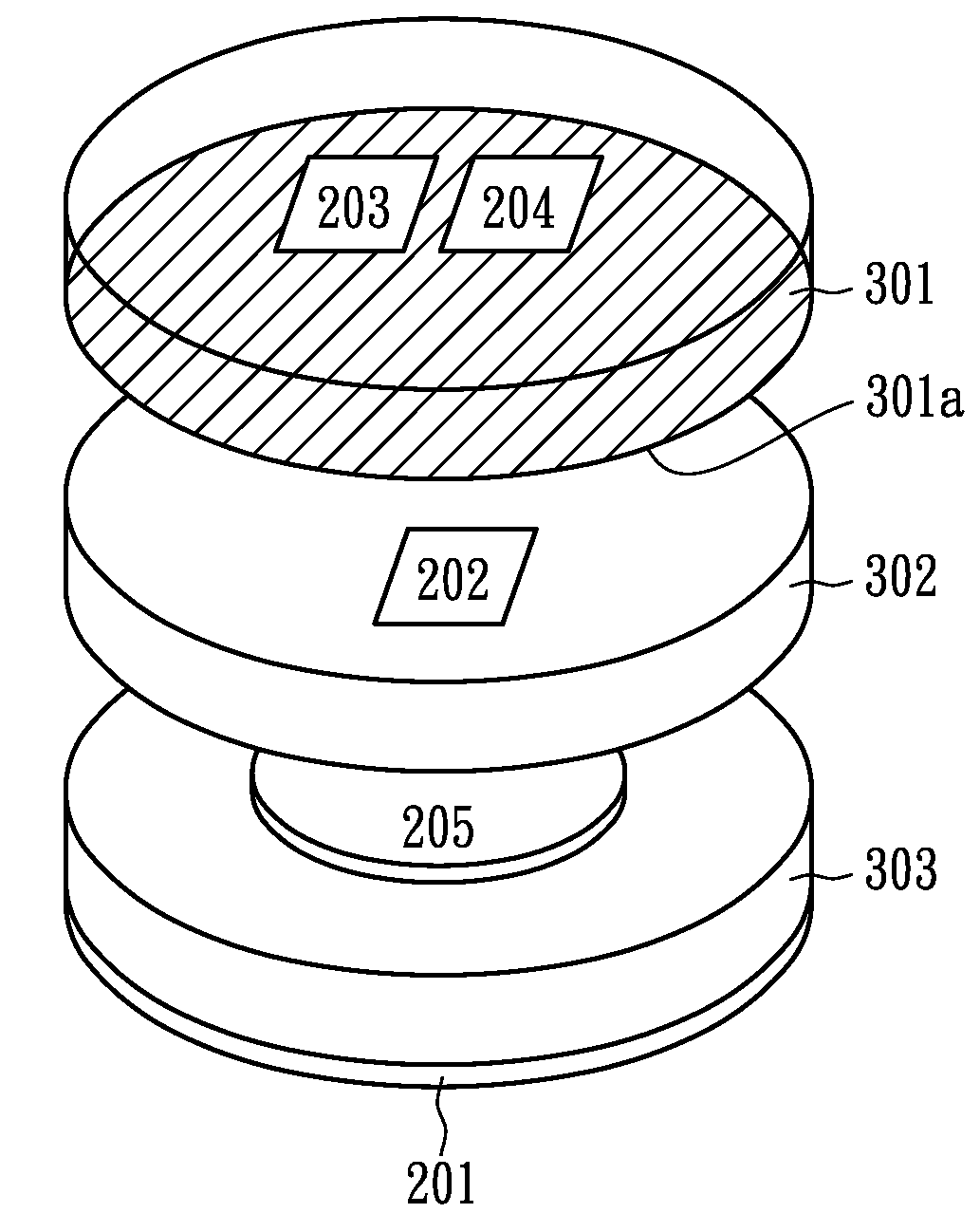

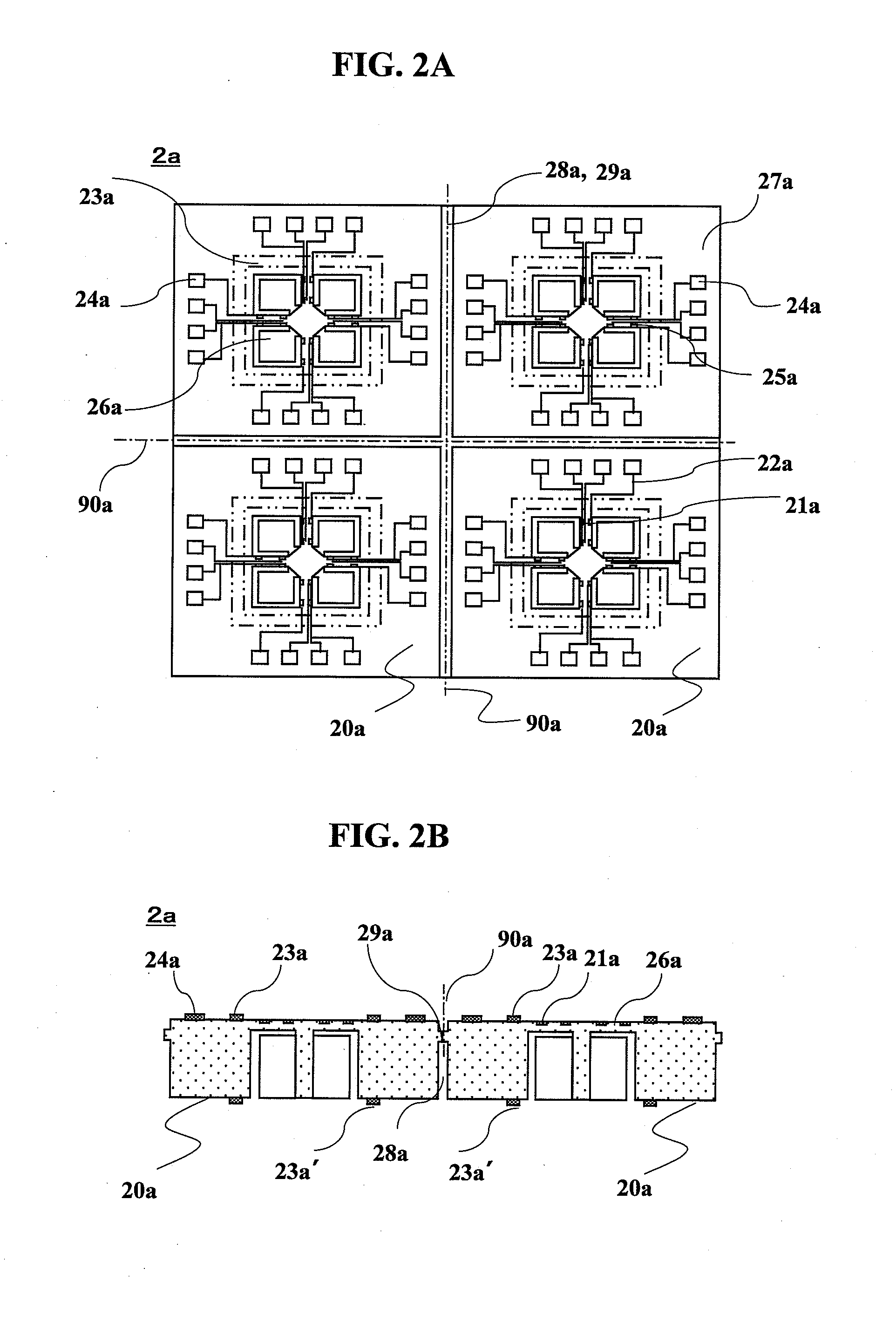

Semiconductor sensor device and method for manufacturing same

InactiveUS20090050990A1Ensure overall airtightnessAvoid failureSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor sensor

Provided is a semiconductor sensor device which is manufactured by an MEMS technology wherein machining technology and / or material technology is combined with semiconductor technology for detecting and measuring various physical quantities. In the semiconductor sensor device, cracks which generate in a cap chip and a molding resin are eliminated and air-tightness between a semiconductor sensor chip and the cap chip is ensured. The cracks due to vibration applied when being cut can be eliminated by having the circumference side surface of the cap chip as a wet-etched surface. Furthermore, insulation is ensured by coating the cap chip side surface with an insulating protection film.

Owner:HITACHI METALS LTD

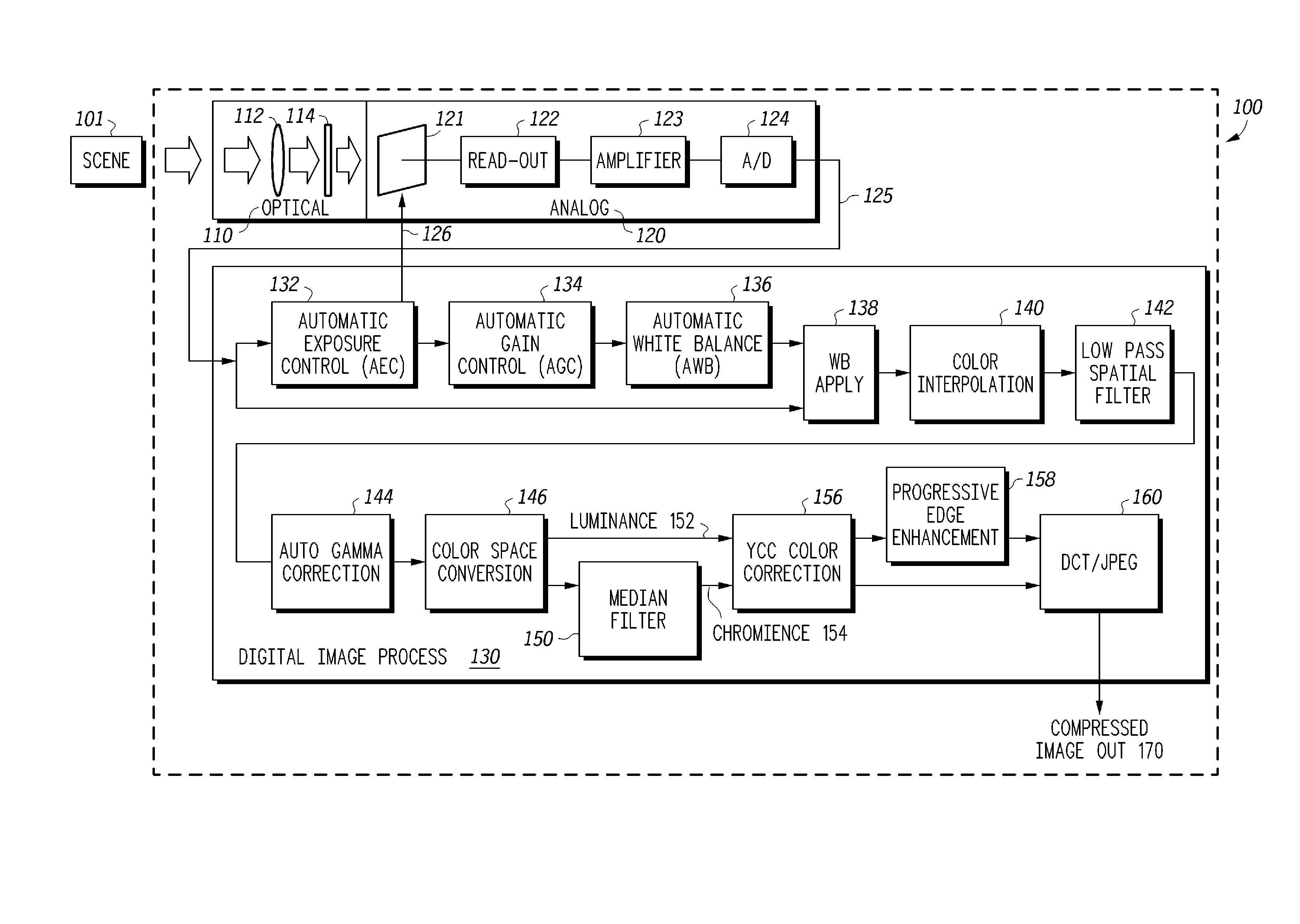

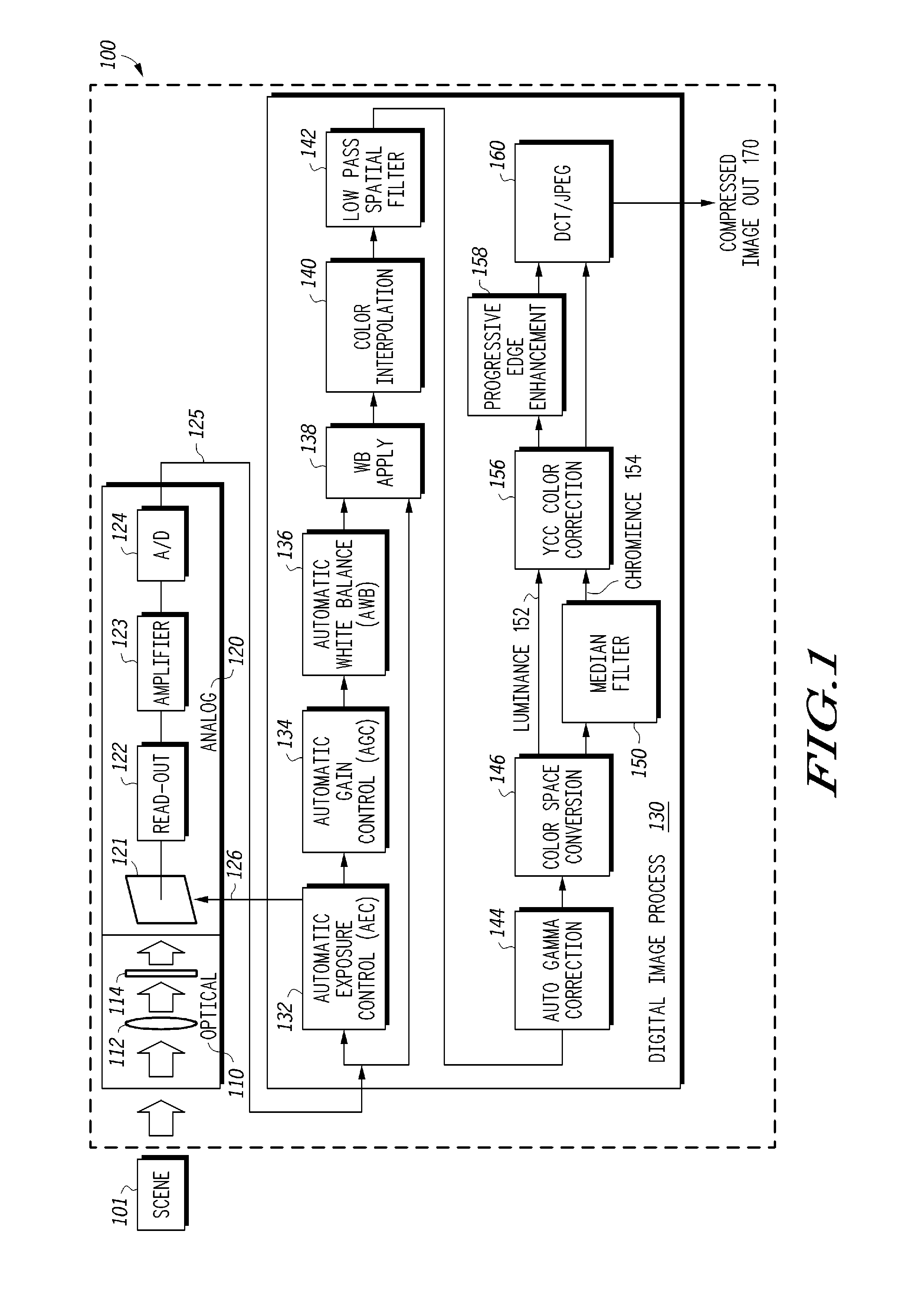

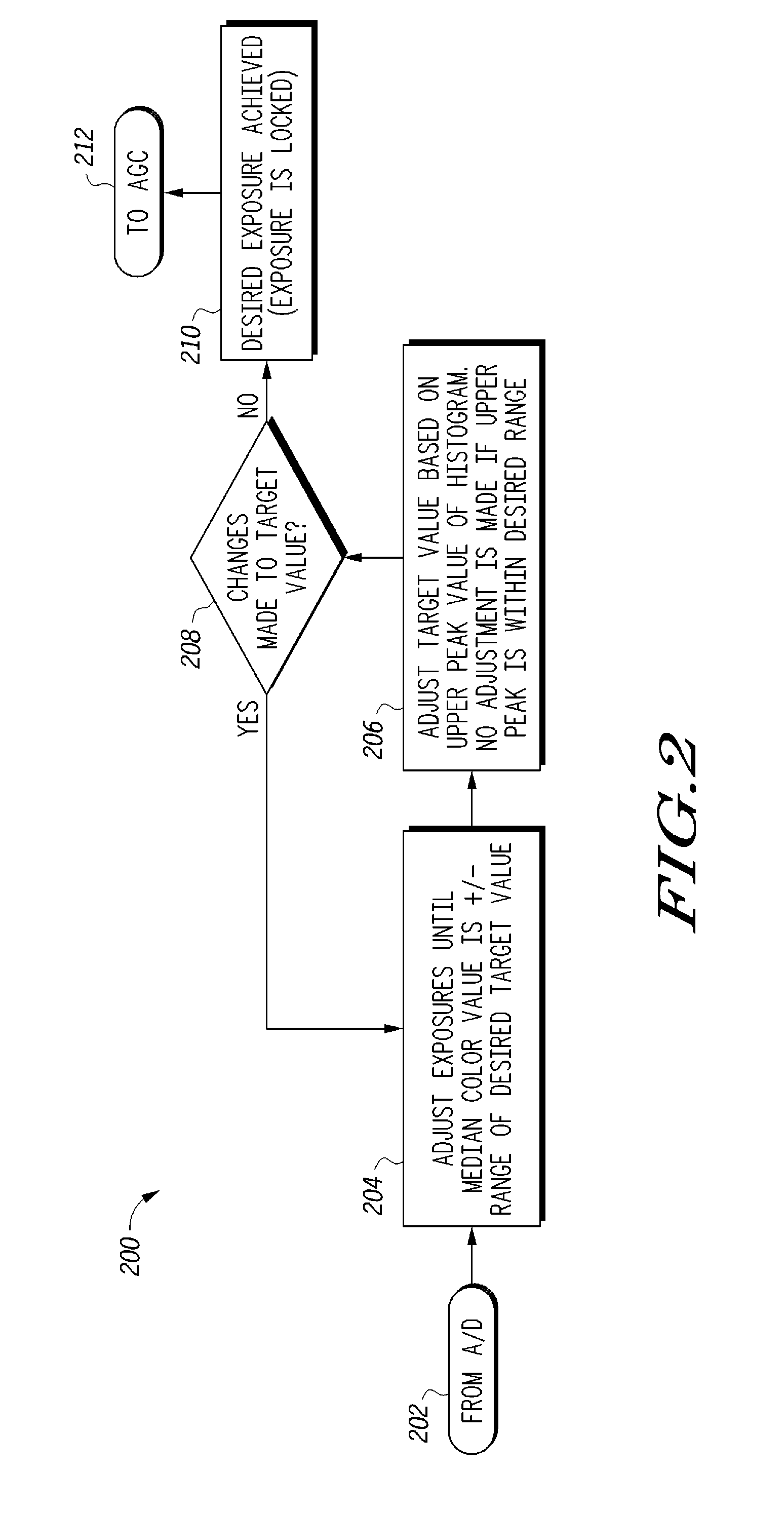

Digital image processing using white balance and gamma correction

A method and system for digital cameras provides improved automatic exposure control, improved automatic white balance, improved color interpolation, improved automatic gamma correction, and improved progressive edge enhancement. These improvements are preferably implemented in CMOS semiconductor technology for faster speed.

Owner:NXP USA INC

Device and Method for the Demodulation Electromagnetic Wave Fields

ActiveUS20080239466A1Less susceptibleLess susceptibilityTelevision system detailsSolid-state devicesCharge currentWave field

A new pixel in semiconductor technology comprises a photo-sensitive detection region (1) for converting an electromagnetic wave field into an electric signal of flowing charges, a separated demodulation region (2) with at least two output nodes (D10, D20) and means (IG10, DG10, IG20, DG20) for sampling the charge-current signal at at least two different time intervals within a modulation period. A contact node (K2) links the detection region (1) to the demodulation region (2). A drift field accomplishes the transfer of the electric signal of flowing charges from the detection region to the contact node. The electric signal of flowing charges is then transferred from the contact node (K2) during each of the two time intervals to the two output nodes allocated to the respective time interval. The separation of the demodulation and the detection regions provides a pixel capable of demodulating electromagnetic wave field at high speed and with high sensitivity.

Owner:AMS SENSORS SINGAPORE PTE LTD

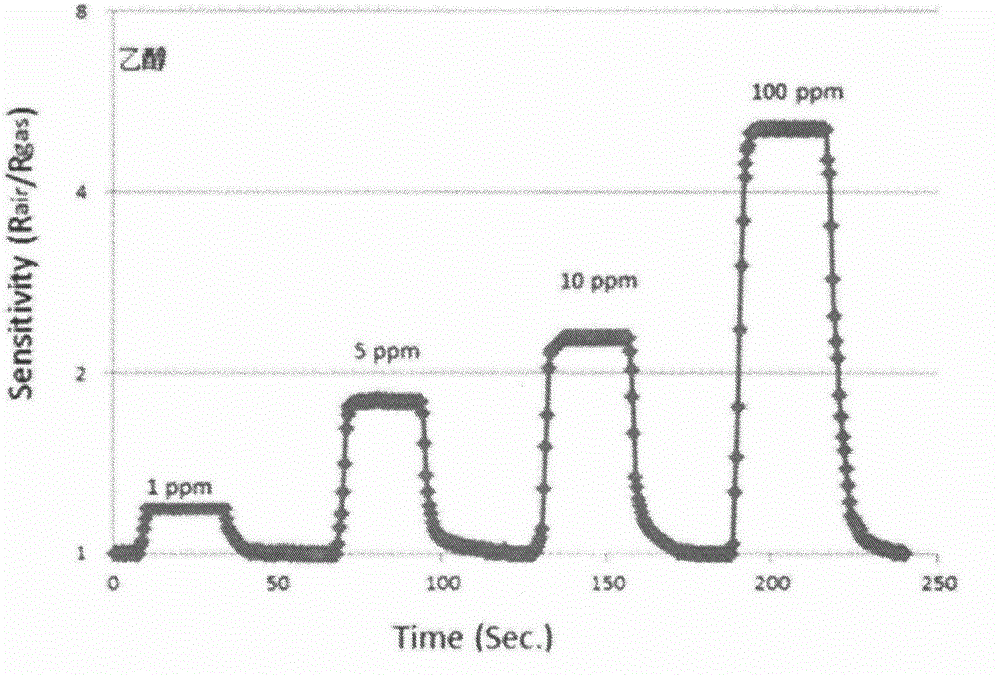

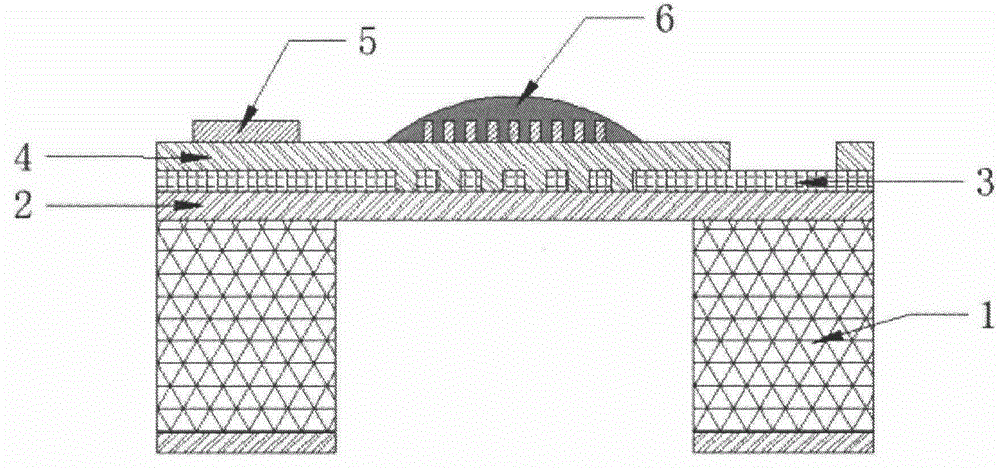

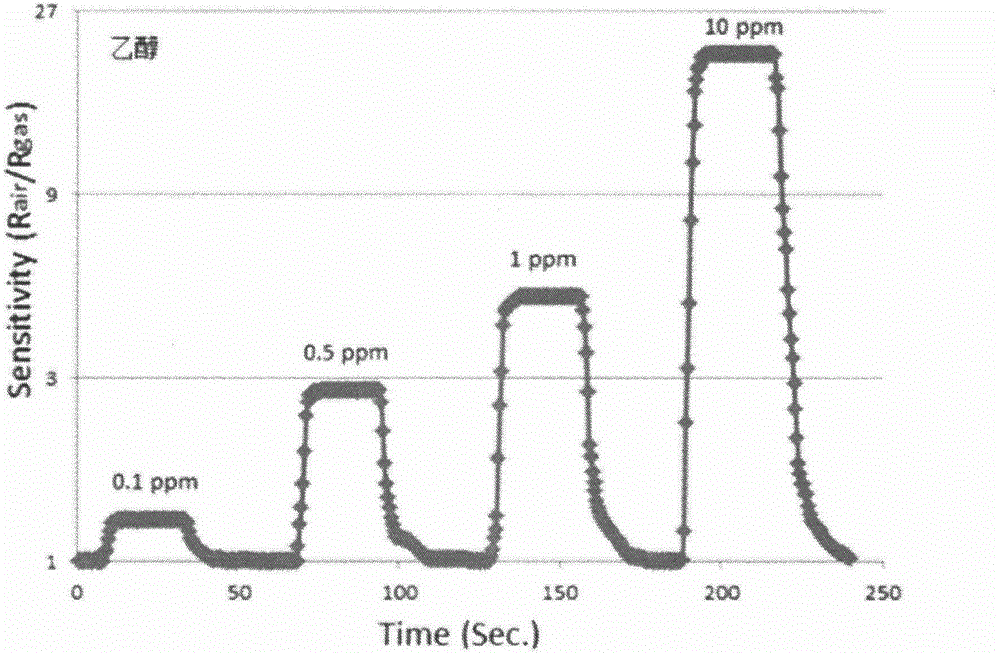

MEMS metal-oxide semiconductor gas sensor and manufacturing method thereof

InactiveCN105158297AImprove consistencyHigh sensitivityMaterial analysis by electric/magnetic meansSlurryUltrasonic dispersion

The invention provides an MEMS metal-oxide semiconductor gas sensor and a manufacturing method thereof. A sensitive material thin film is made of a hollow nanostructure material which includes at least one sort of metallic oxide. The manufacturing method includes the following steps that (a) an MEMS gentle heating disk is formed by the adoption of a semiconductor technology; (b) the hollow nanostructure material is synthesized through a hydrothermal method, and a solid nanostructure material is obtained through the methods of hydro-thermal synthesis, grinding and the like; (c) the hollow nanostructure material, the solid nanostructure material and a plurality of functional additives are prepared into slurry according to a certain proportion, and stable suspension liquid ink is obtained by means of stirring and ultrasonic dispersion; (d) the suspension liquid ink is printed in a sensitive electrode measuring area of the MEMS gentle heating disk; (e) low-temperature drying and high-temperature sintering are carried out, and accordingly the MEMS metal-oxide semiconductor gas sensor of a stable and reliable structure is formed. The MEMS metal-oxide semiconductor gas sensor has the advantages of being small in size, low in power consumption, high in sensitivity, short in response time, long in service life, capable of being integrated easily and the like.

Owner:武汉微纳传感技术有限公司

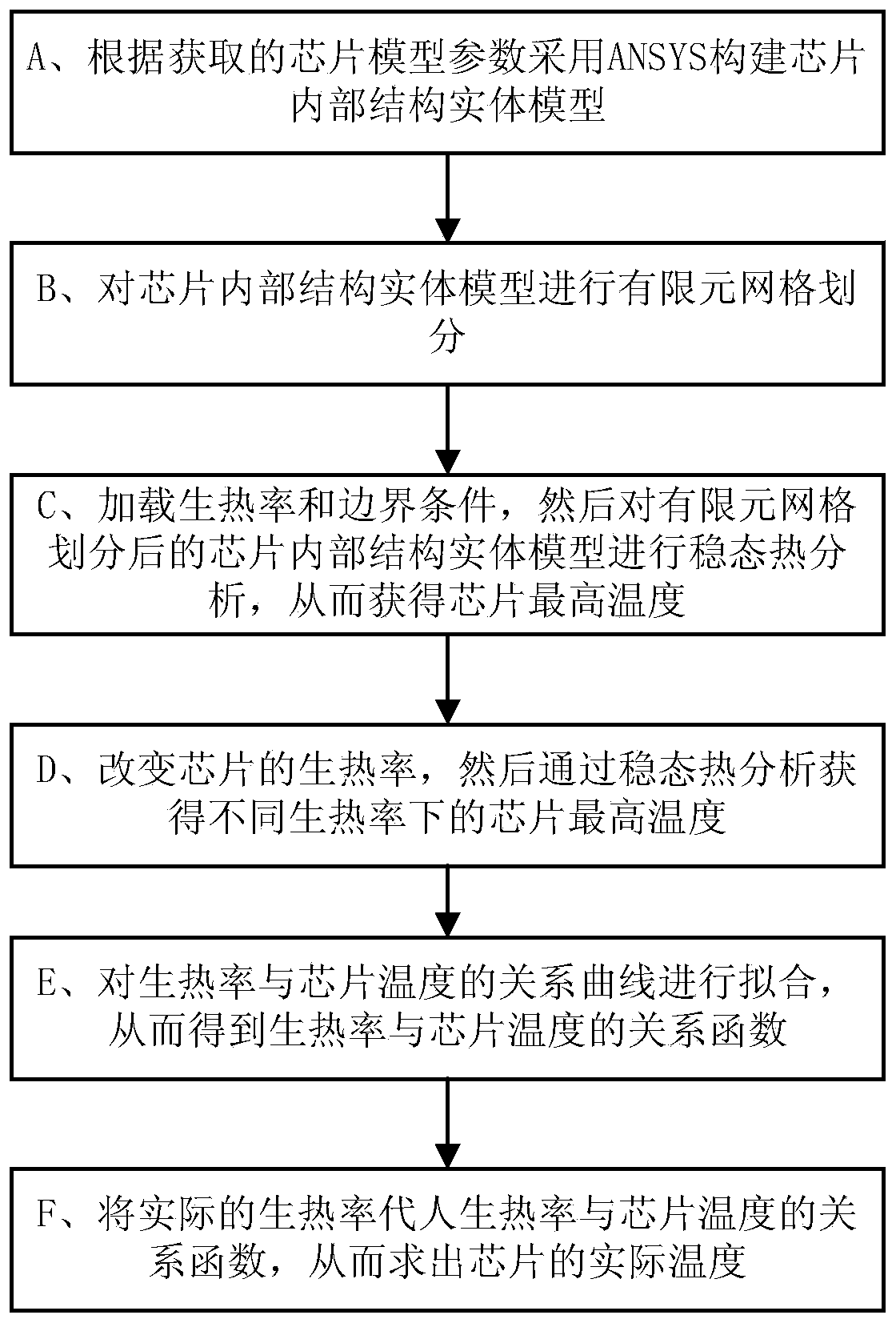

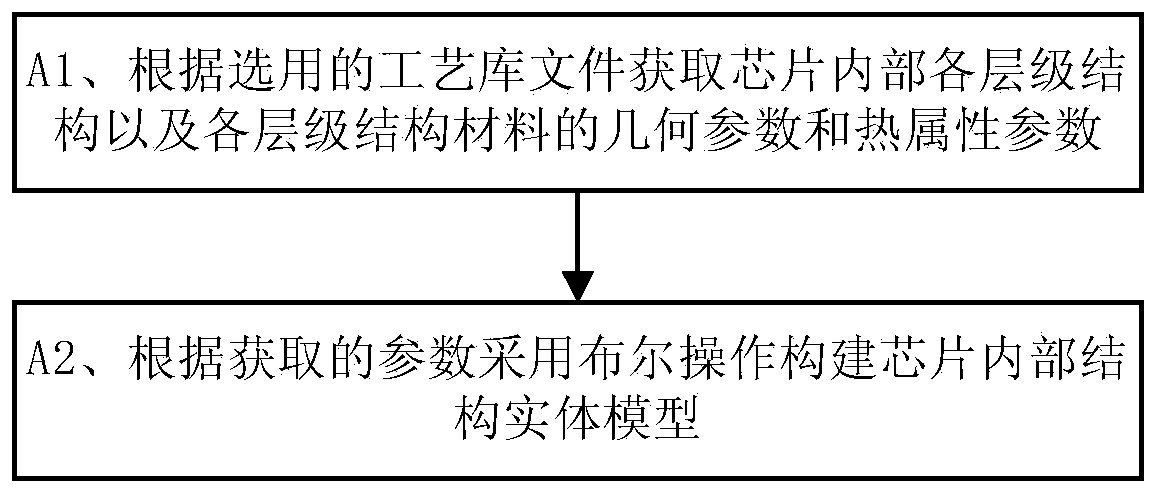

Chip temperature predicating method based on ANSYS finite element heat analysis

ActiveCN104182568ALow costEasy to operateSpecial data processing applicationsGeneration rateHeat analysis

The invention discloses a chip temperature predicating method based on ANSYS finite element heat analysis. The chip temperature predicating method comprise steps as follows: a chip interior structure solid model is established by ANSYS according to acquired chip model parameters; the chip interior structure solid model is subjected to finite element mesh generation; the heat generation rate and the boundary conditions are loaded, then, the chip interior structure solid model after finite element mesh generation is subjected to steady-state heat analysis, and the maximum temperature of a chip is obtained; the heat generation rate of the chip is changed, and the maximum temperature of the chip under different heat generation rates is acquired through steady-state heat analysis; the relation curve of the heat generation rate and the chip temperature is fitted, and a relation function of the heat generation rate and the chip temperature is obtained; and the actual heat generation rate is substituted into the relation function of the heat generation rate and the chip temperature, and the actual temperature of the chip is obtained. According to the method, the temperature predication is placed at the physical design stage of the chip, the cost is reduced and the operation is simple and convenient; and the method can be widely applied to the technical field of semiconductors.

Owner:SYSU CMU SHUNDE INT JOINT RES INST +1

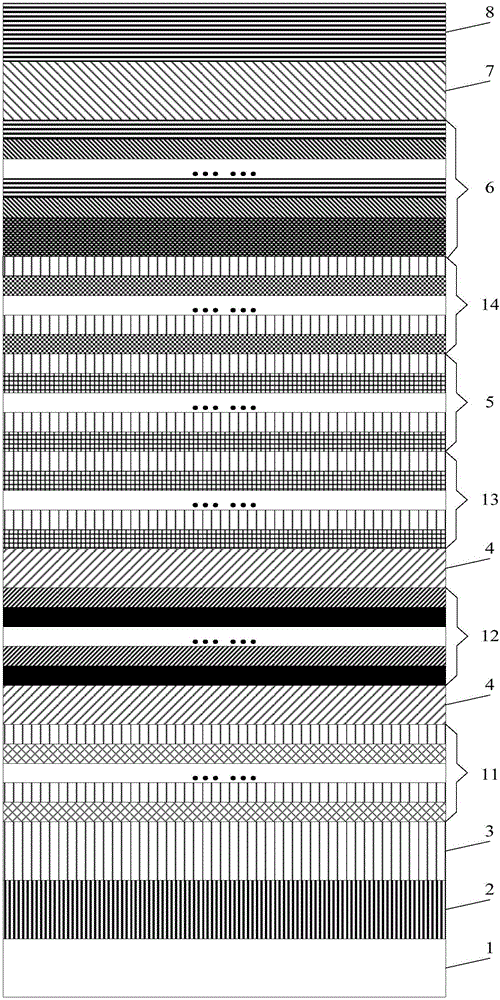

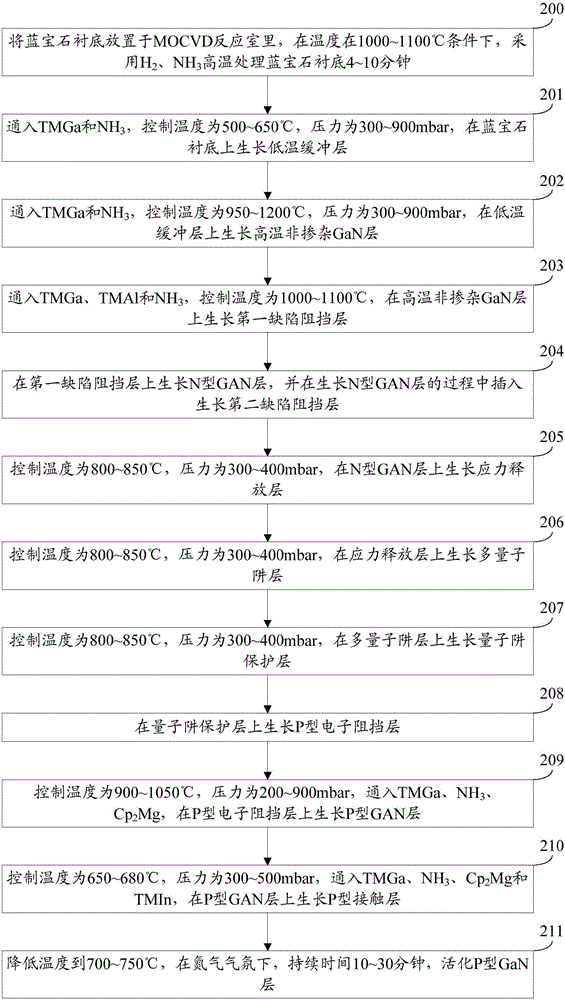

Light-emitting diode epitaxial wafer and preparation method thereof

The invention discloses a light-emitting diode epitaxial wafer and a preparation method thereof, and belongs to the technical field of semiconductors. The light-emitting diode epitaxial wafer comprises a sapphire substrate, a low-temperature buffer layer, a high-temperature non-doped GaN layer, a first defect barrier layer, an N-type GaN layer, a stress release layer, a multi-quantum well layer, a P-type electron blocking layer, a P-type GaN layer and a P-type contact layer, wherein the low-temperature buffer layer, the high-temperature non-doped GaN layer, the first defect barrier layer, the N-type GaN layer, the stress release layer, the multi-quantum well layer, the P-type electron blocking layer, the P-type GaN layer and the P-type contact layer are sequentially laminated on the sapphire substrate; a second defect barrier layer is inserted into the N-type GaN layer; the first defect barrier layer comprises alternately laminated AlGaN layers and GaN layers; the second defect barrier layer comprises alternately laminated SiN films and N-type AlGaN layers; and the stress release layer comprises alternately laminated InGaN layers and GaN layers. According to the light-emitting diode epitaxial wafer, extension of defects formed by lattice mismatch into the multi-quantum well layer is effectively suppressed; stress release is enhanced; the crystal quality is improved; leakage passages are reduced; the anti-static electricity capacity of an LED chip is improved; and the product yield is improved.

Owner:HC SEMITEK SUZHOU

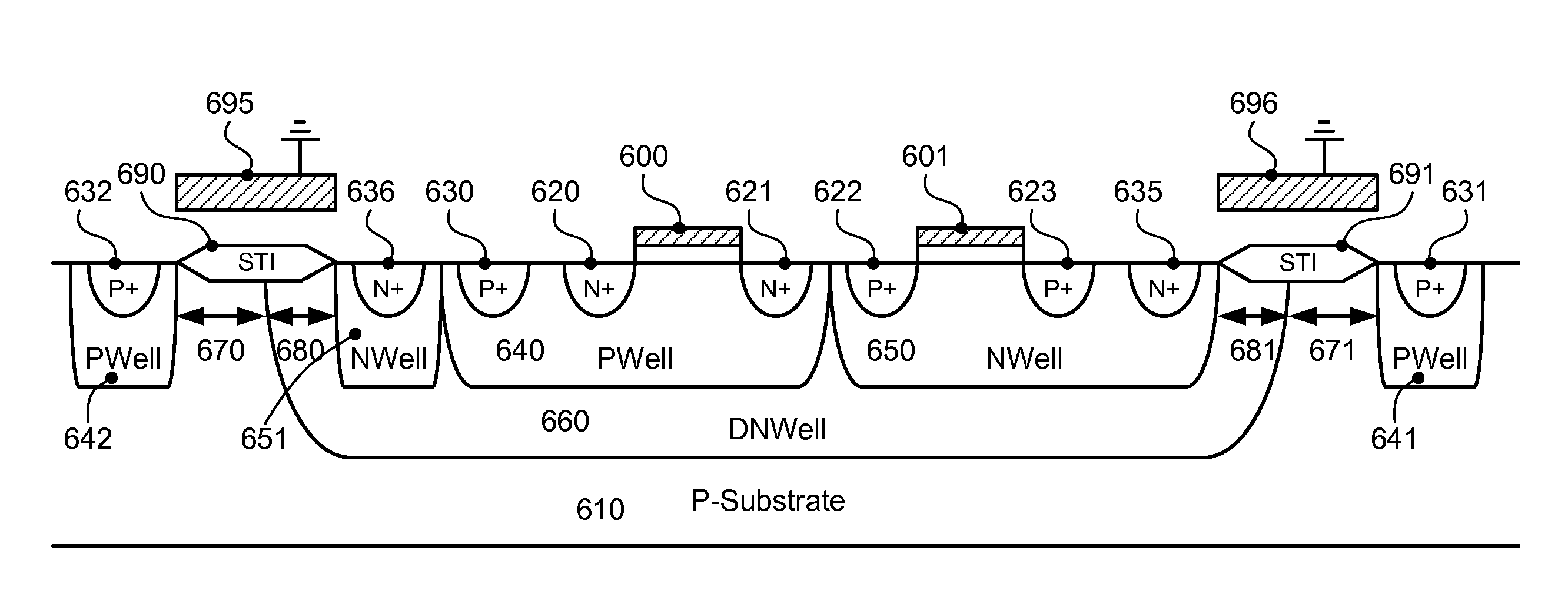

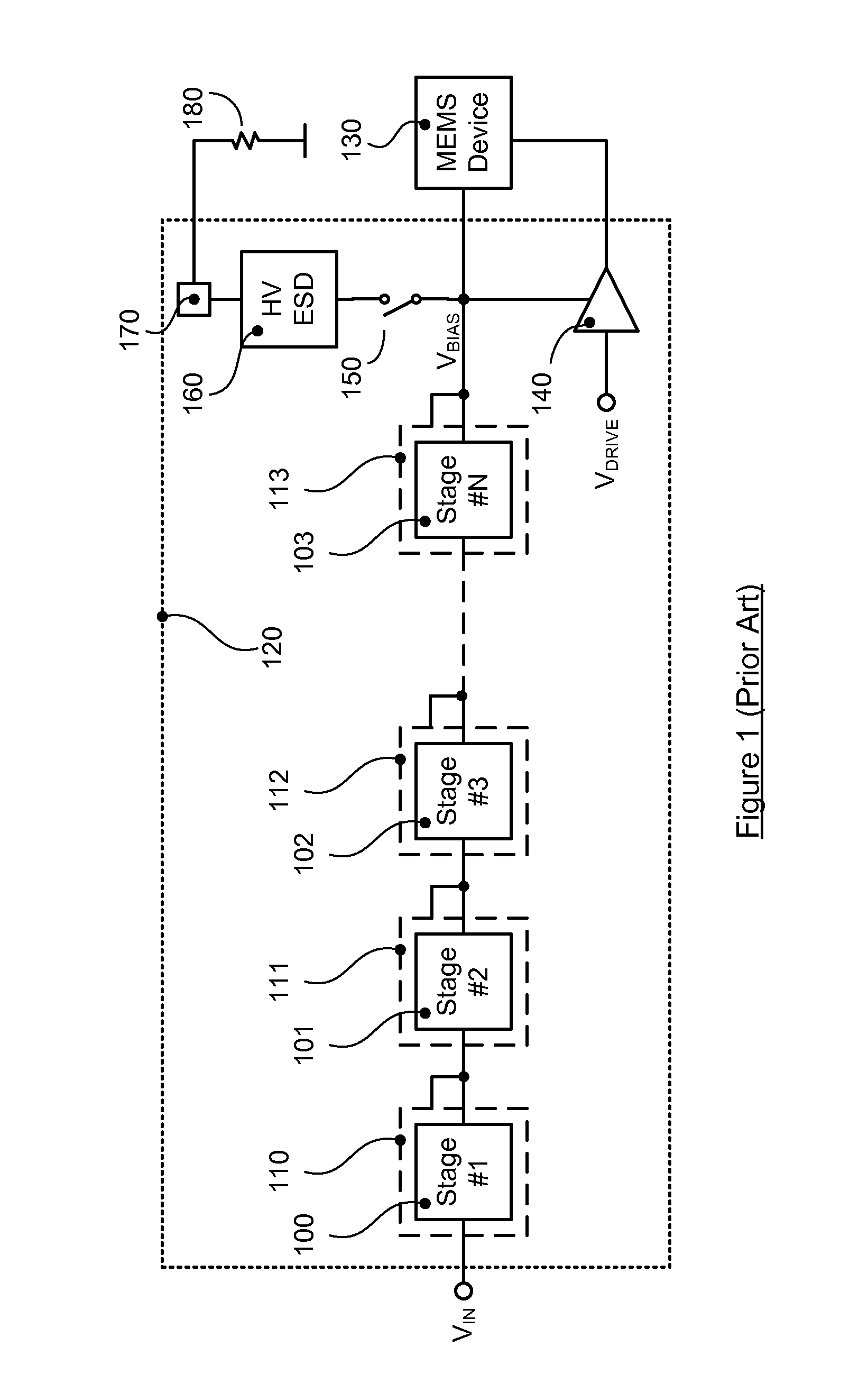

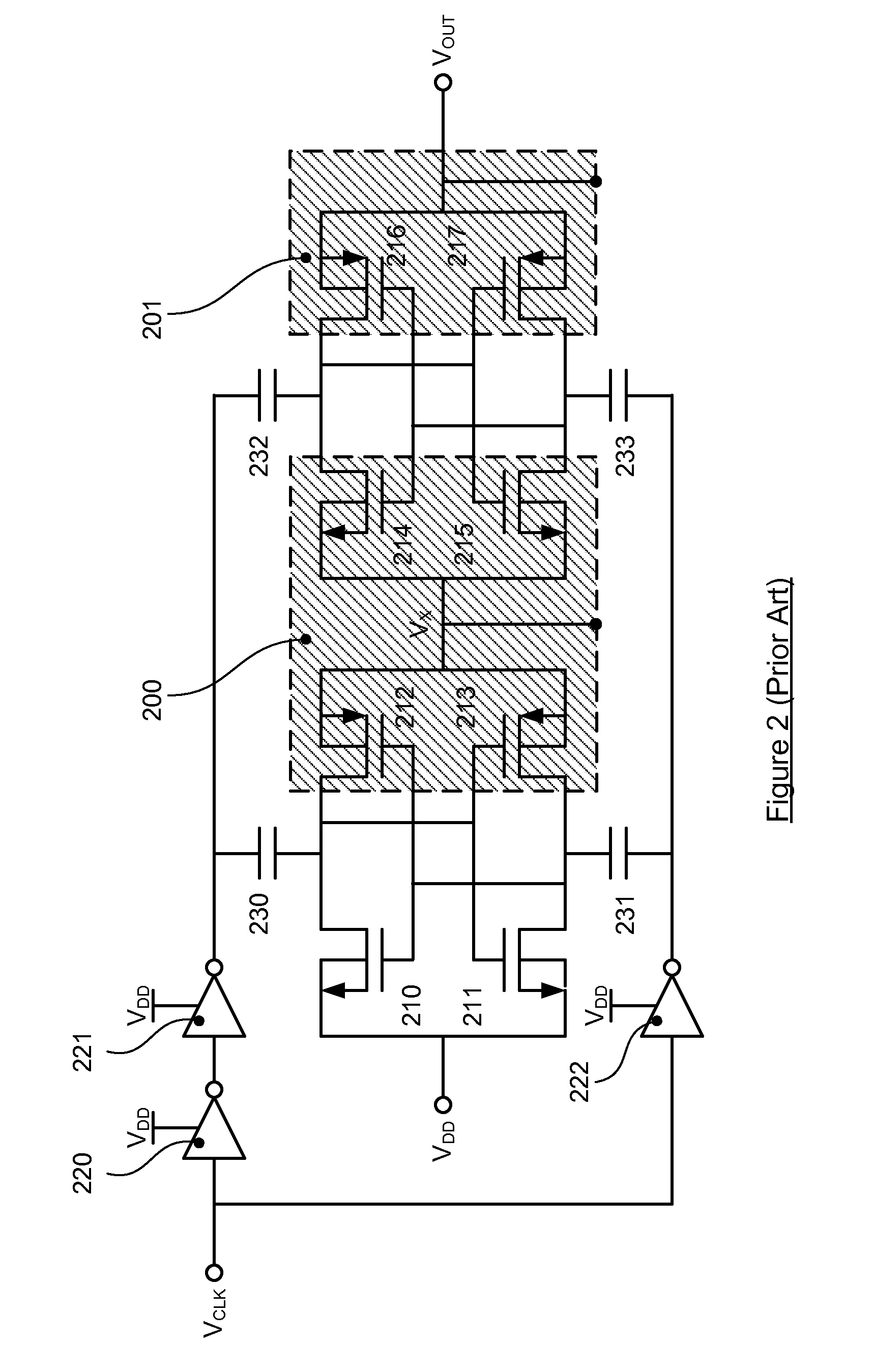

High-voltage MEMS apparatus and method

ActiveUS20120242400A1Reduce complexityReduce processing costsTransistorSemiconductor/solid-state device manufacturingHigh voltage transistorsEngineering

A high-voltage MEMS system compatible with low-voltage semiconductor process technology is disclosed. The system comprises a MEMS device coupled to a high-voltage bias generator employing an extended-voltage isolation residing in a semiconductor technology substrate. The system avoids the use of high-voltage transistors so that special high-voltage processing steps are not required of the semiconductor technology, thereby reducing process cost and complexity. MEMS testing capability is addressed with a self-test circuit allowing modulation of the bias voltage and current so that a need for external high-voltage connections and associated electro-static discharge protection circuitry are also avoided.

Owner:INVENSENSE