Light-emitting diode epitaxial wafer and preparation method thereof

A technology of light-emitting diodes and epitaxial wafers, which is applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve problems such as lattice mismatch and product yield decline, and achieve improved crystal quality, product yield, and antistatic ability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

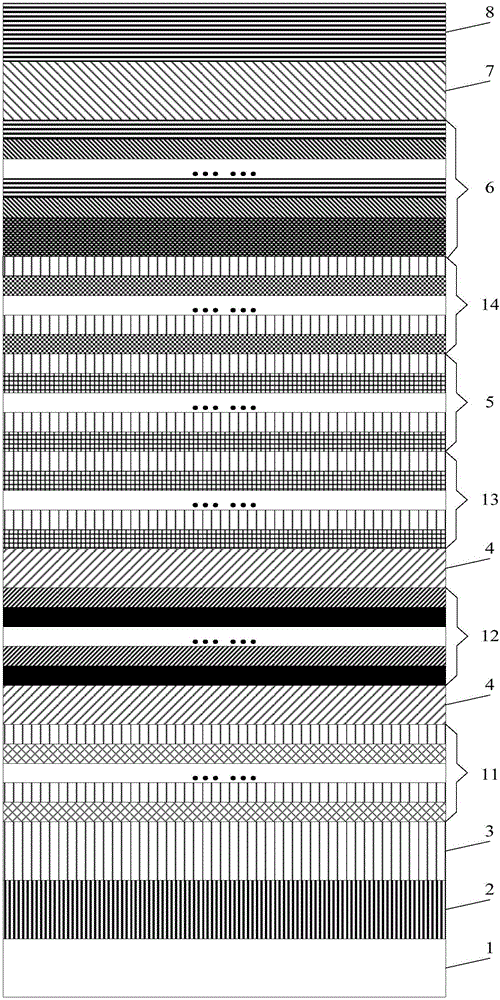

[0033] An embodiment of the present invention provides a light emitting diode epitaxial wafer, see figure 1 , the light-emitting diode epitaxial wafer includes a sapphire substrate 1, and a low-temperature buffer layer 2, a high-temperature non-doped GaN layer 3, an N-type GAN layer 4, a multi-quantum well layer 5, and a P-type electronic layer sequentially stacked on the sapphire substrate 1. Barrier layer 6, P-type GAN layer 7, P-type contact layer 8, the light-emitting diode epitaxial wafer also includes a first defect barrier layer 11 arranged between the high-temperature non-doped GaN layer 3 and the N-type GAN layer 4, inserted in the The second defect barrier layer 12 in the N-type GAN layer 4, the stress release layer 13 arranged between the N-type GAN layer 4 and the multi-quantum well layer 5, the first defect barrier layer 11 includes alternately stacked AlGaN layers and GaN layers , the second defect barrier layer 12 includes alternately stacked SiN film layers and...

Embodiment 2

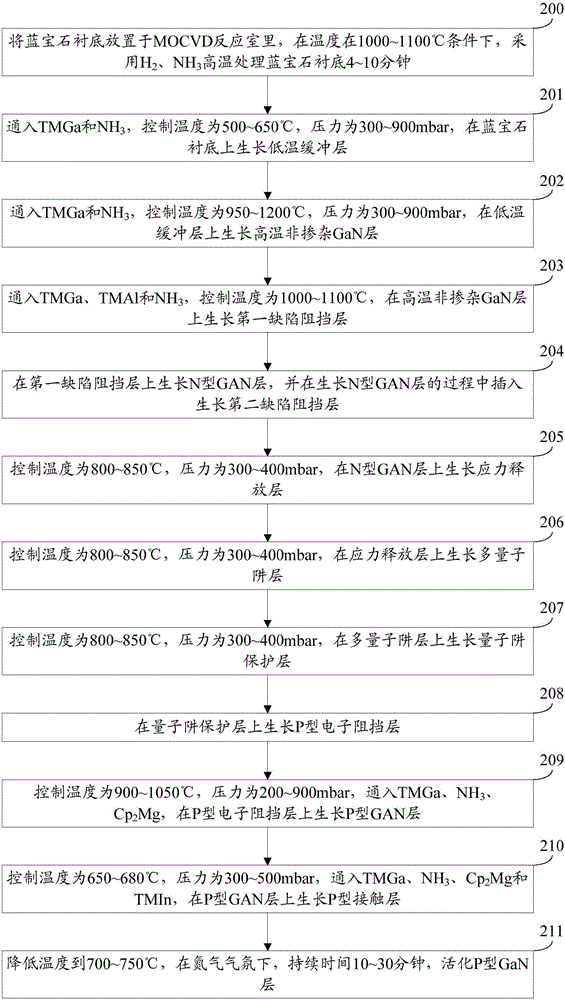

[0078] The embodiment of the present invention provides a method for preparing a light-emitting diode epitaxial wafer, see figure 2 , the preparation method comprises:

[0079] Step 200: Place the sapphire substrate in a Metal-organic Chemical Vapor Deposition (MOCVD) reaction chamber, and use H 2 , NH 3 Treat the sapphire substrate at high temperature for 4-10 minutes.

[0080] Step 201: Passing TMGa and NH 3 , the temperature is controlled at 500-650° C., the pressure is 300-900 mbar, and a low-temperature buffer layer is grown on the sapphire substrate.

[0081] Optionally, the low-temperature buffer layer may be a GaN layer or an AlGaN layer.

[0082] Optionally, the thickness of the low-temperature buffer layer may be 20-50 nm.

[0083] Preferably, after step 201, the preparation method may further include:

[0084]Raise the temperature to 950-1100° C., anneal at a high temperature for 60-300 s, and the low-temperature buffer layer becomes a GaN crystal nucleus.

...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More