Patents

Literature

525 results about "High voltage transistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

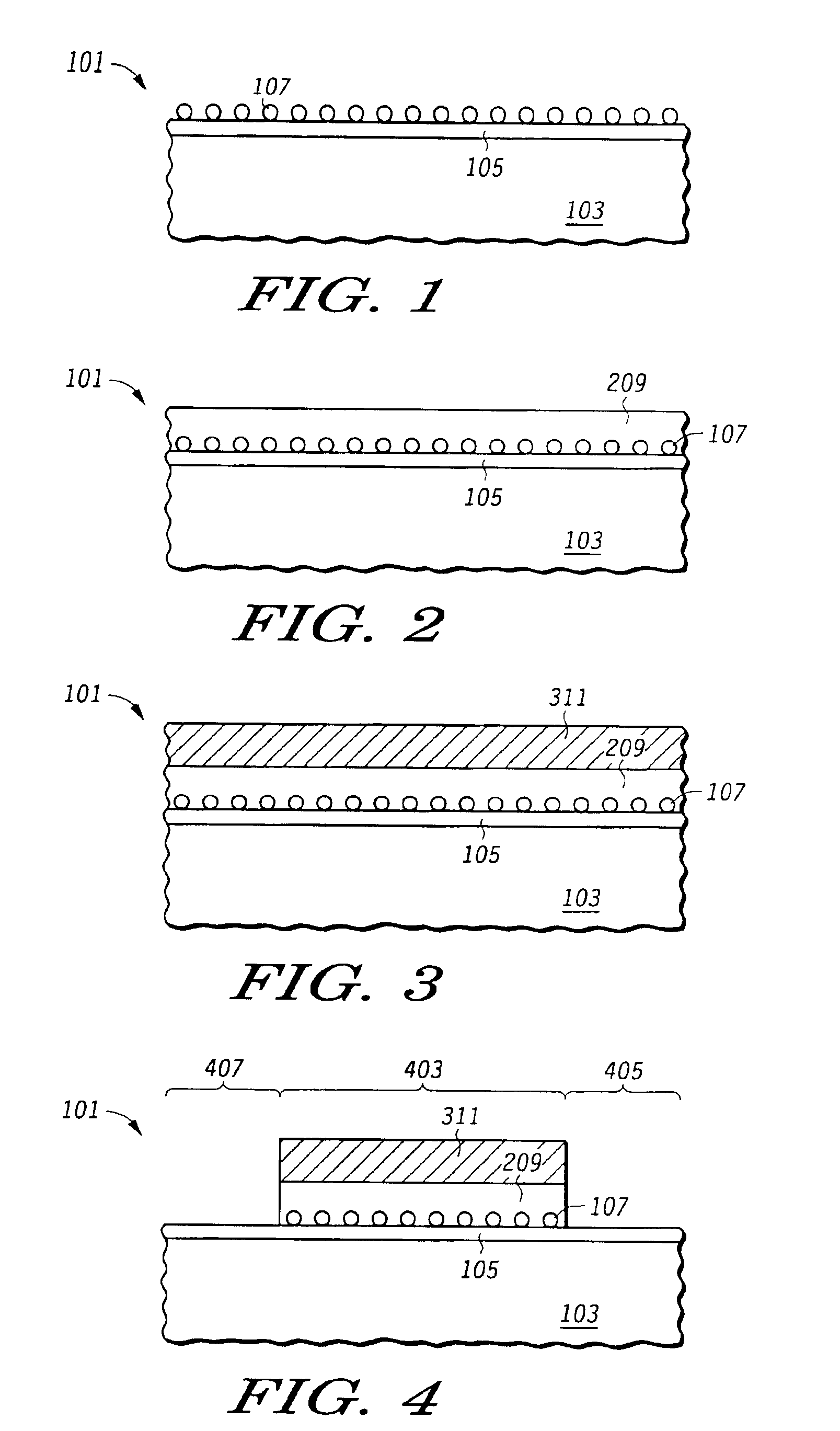

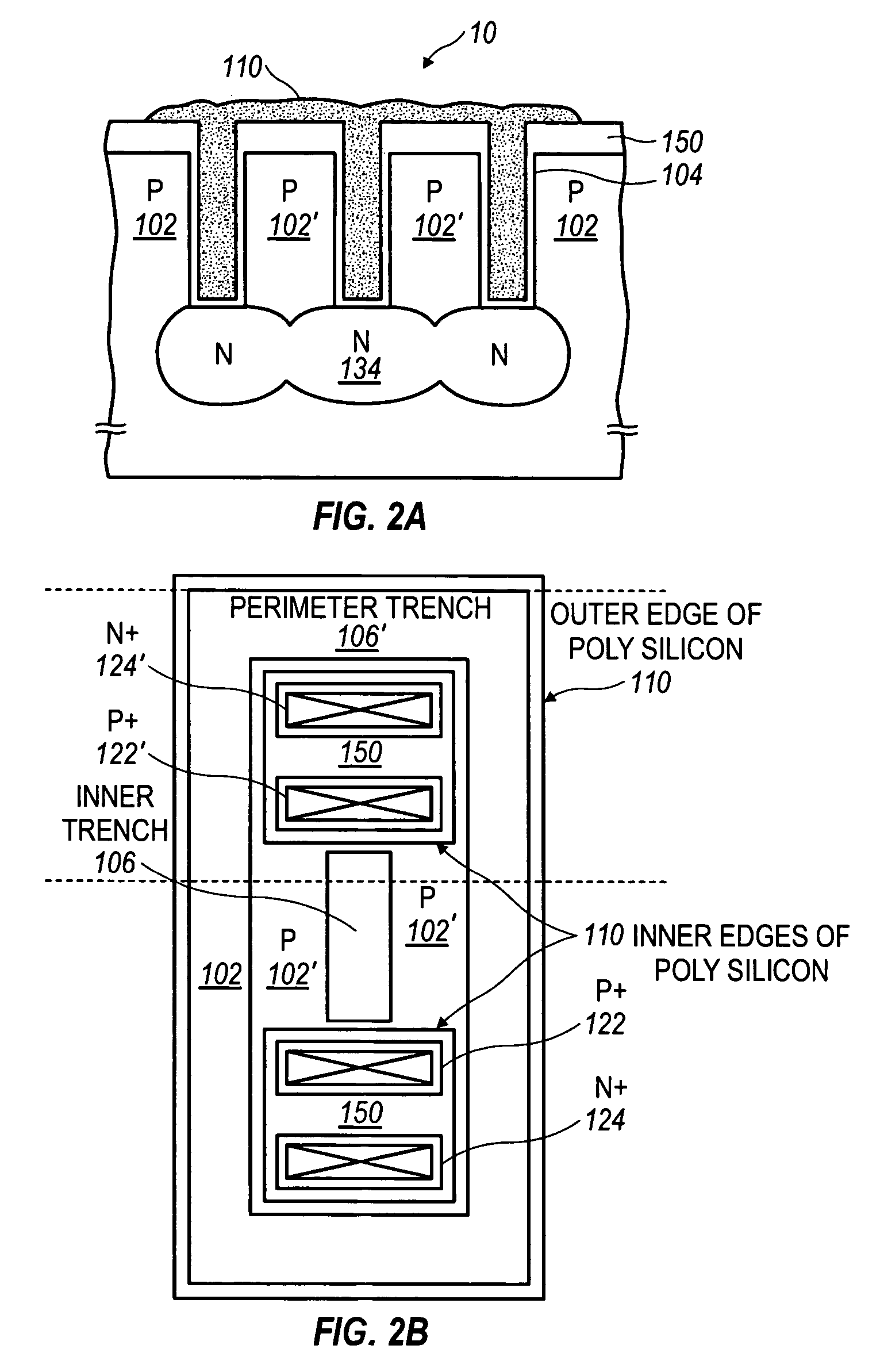

High-voltage vertical transistor with edge termination structure

InactiveUS20050167749A1Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsSubject matter

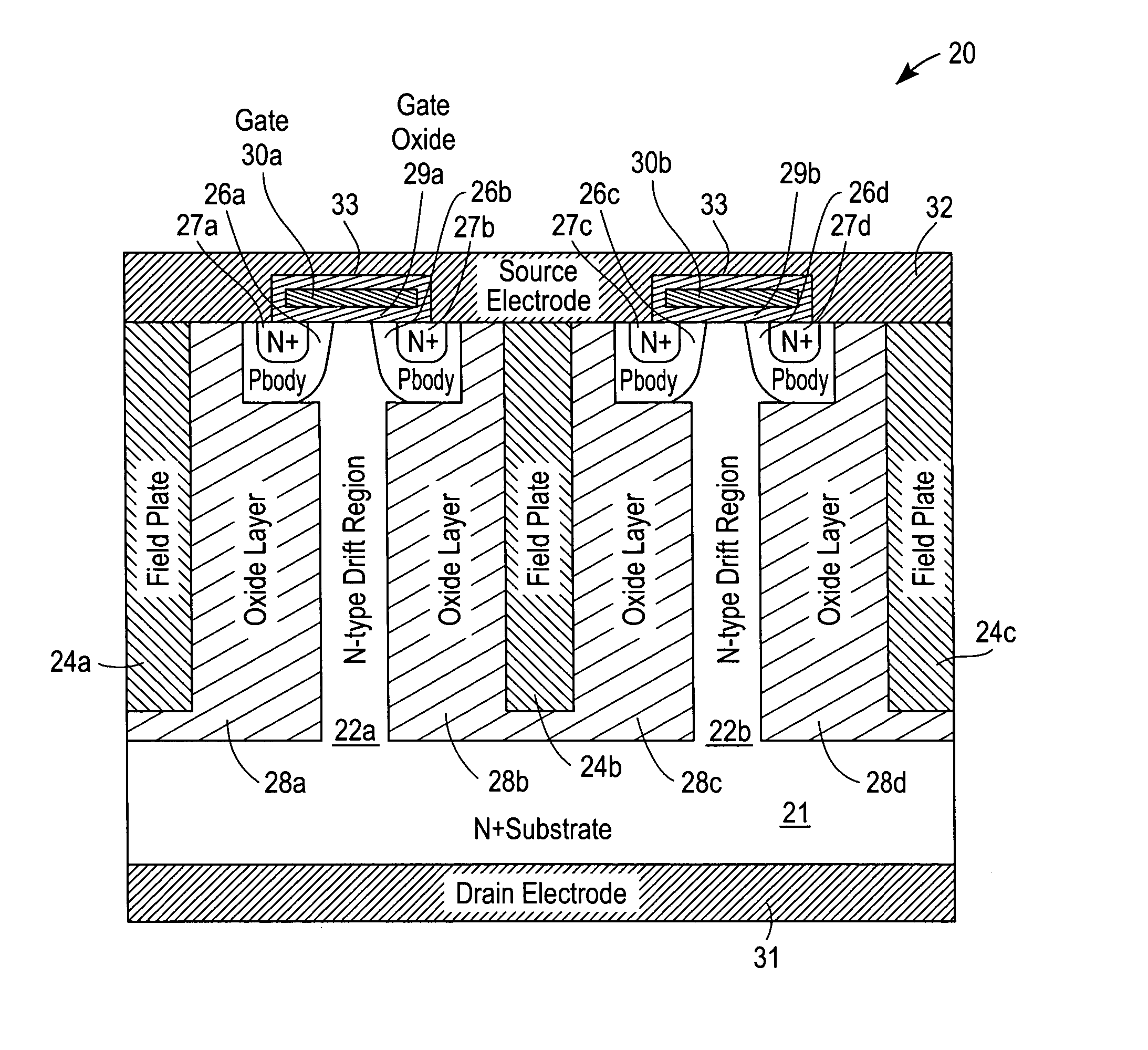

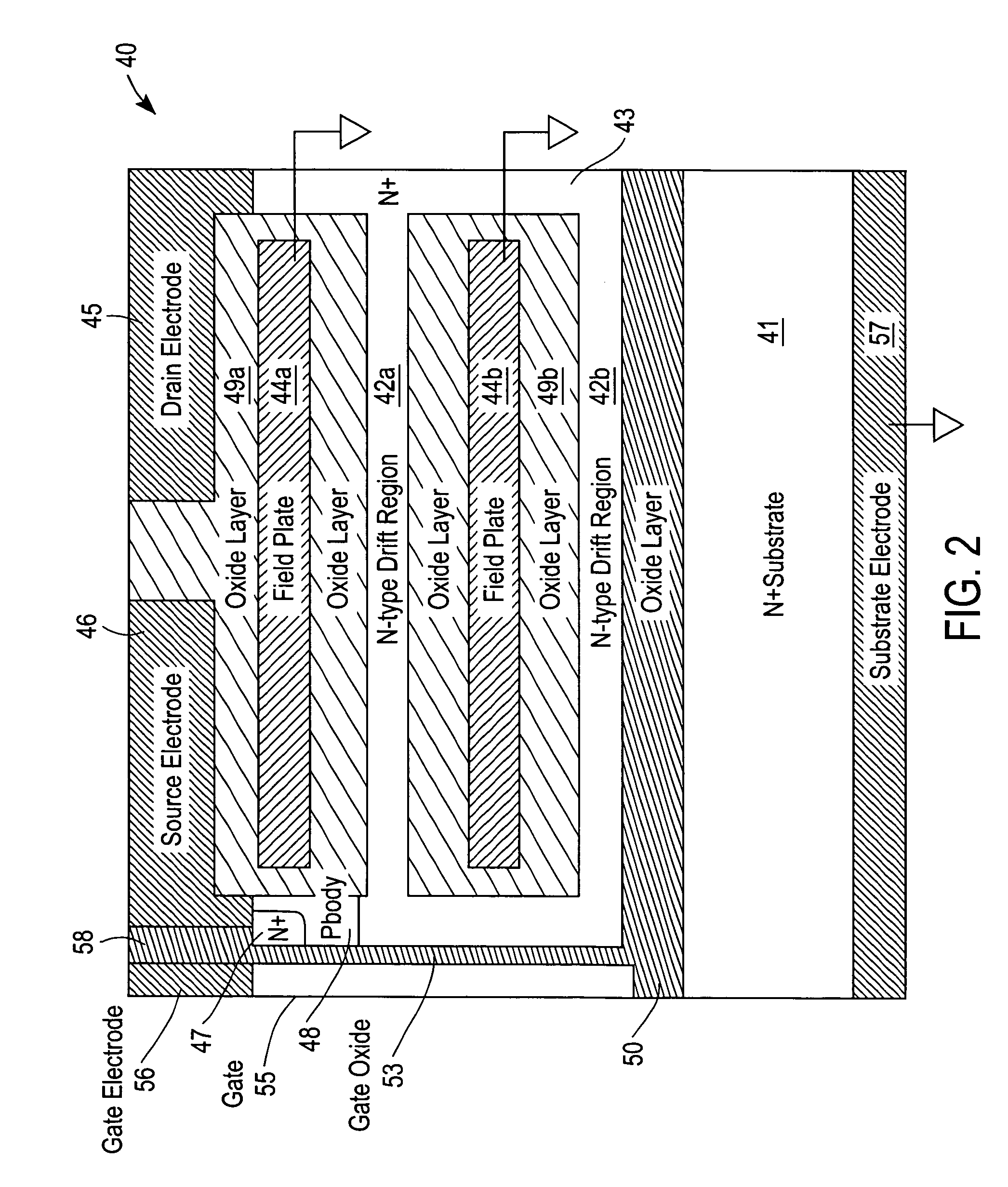

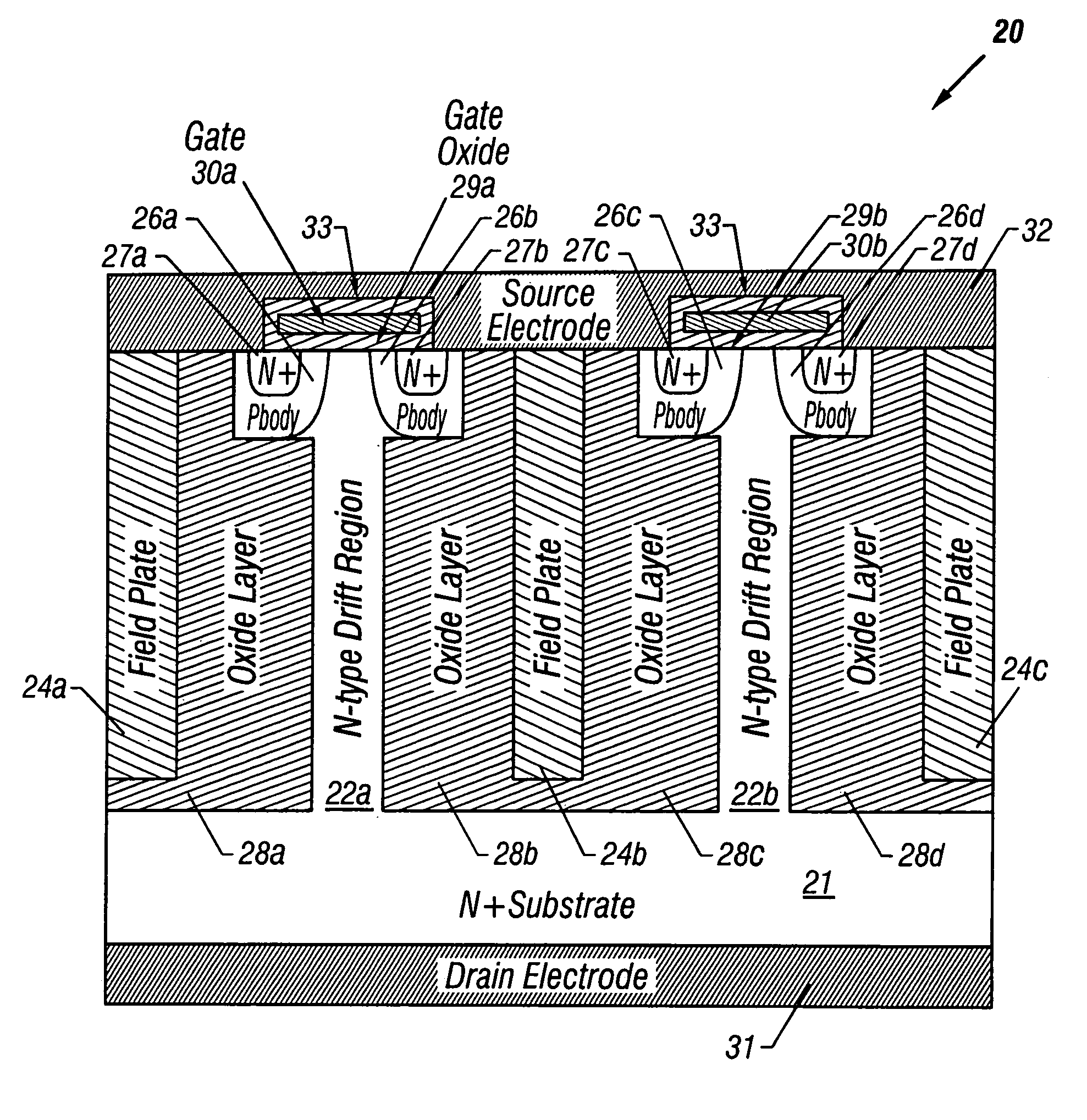

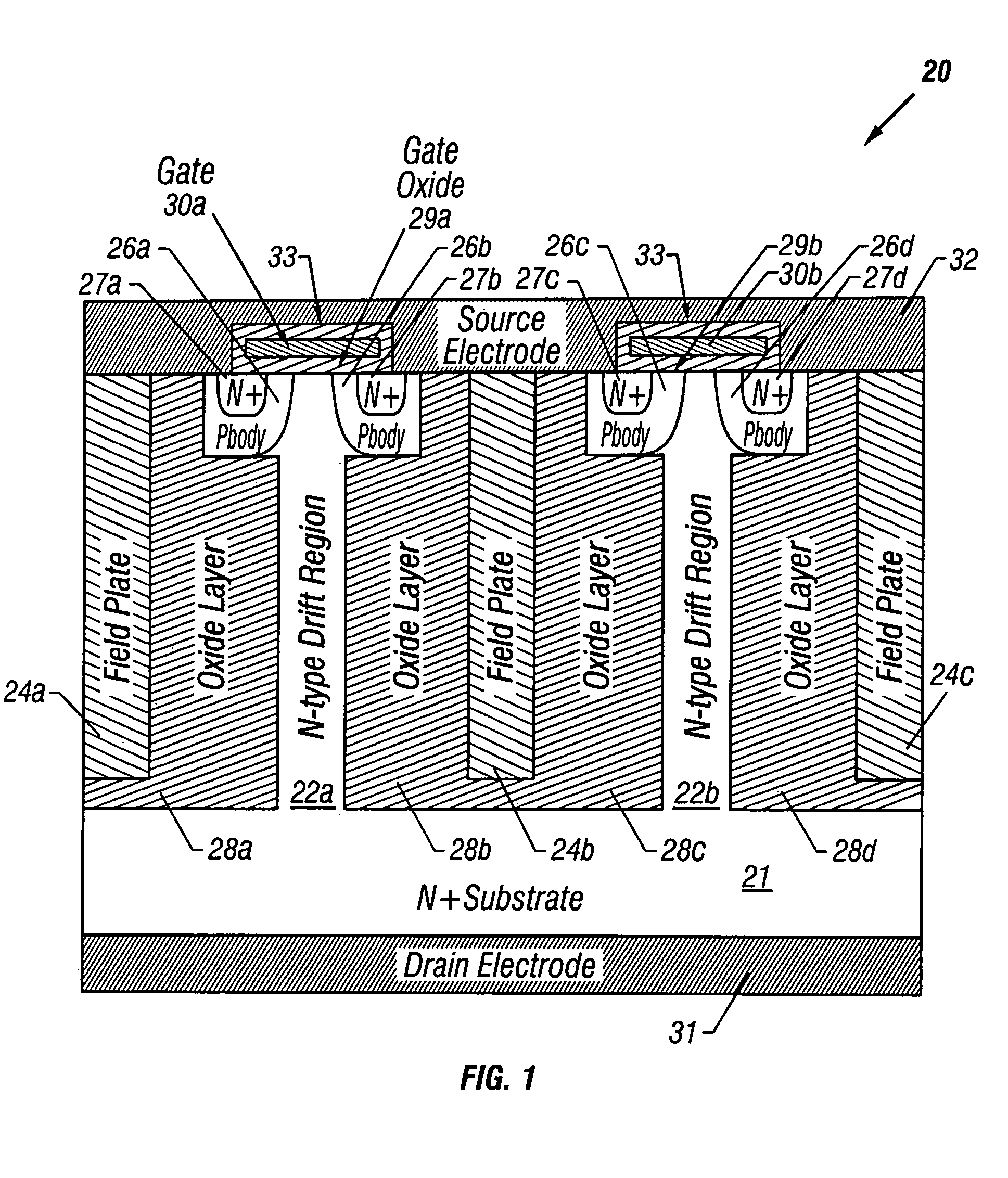

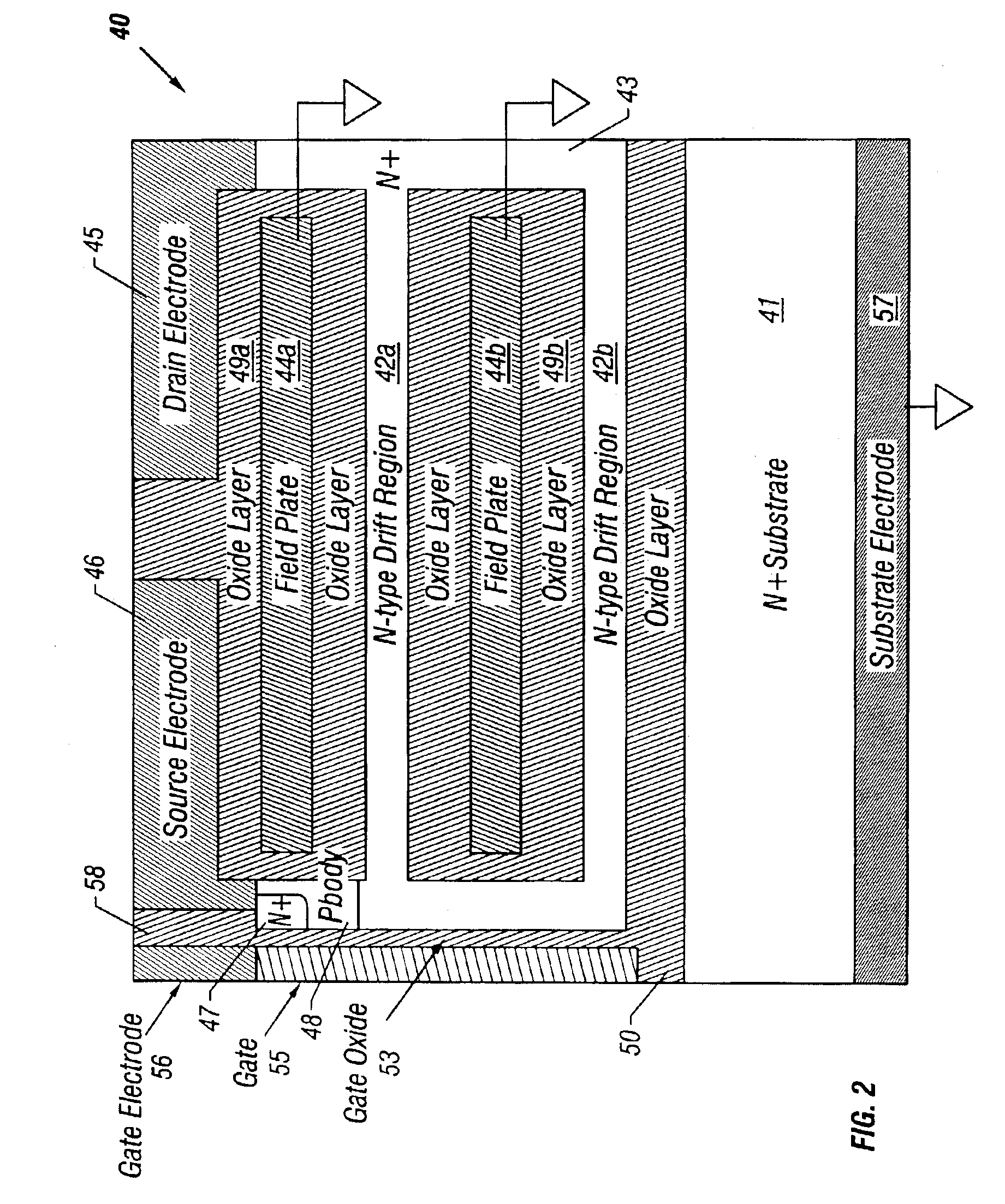

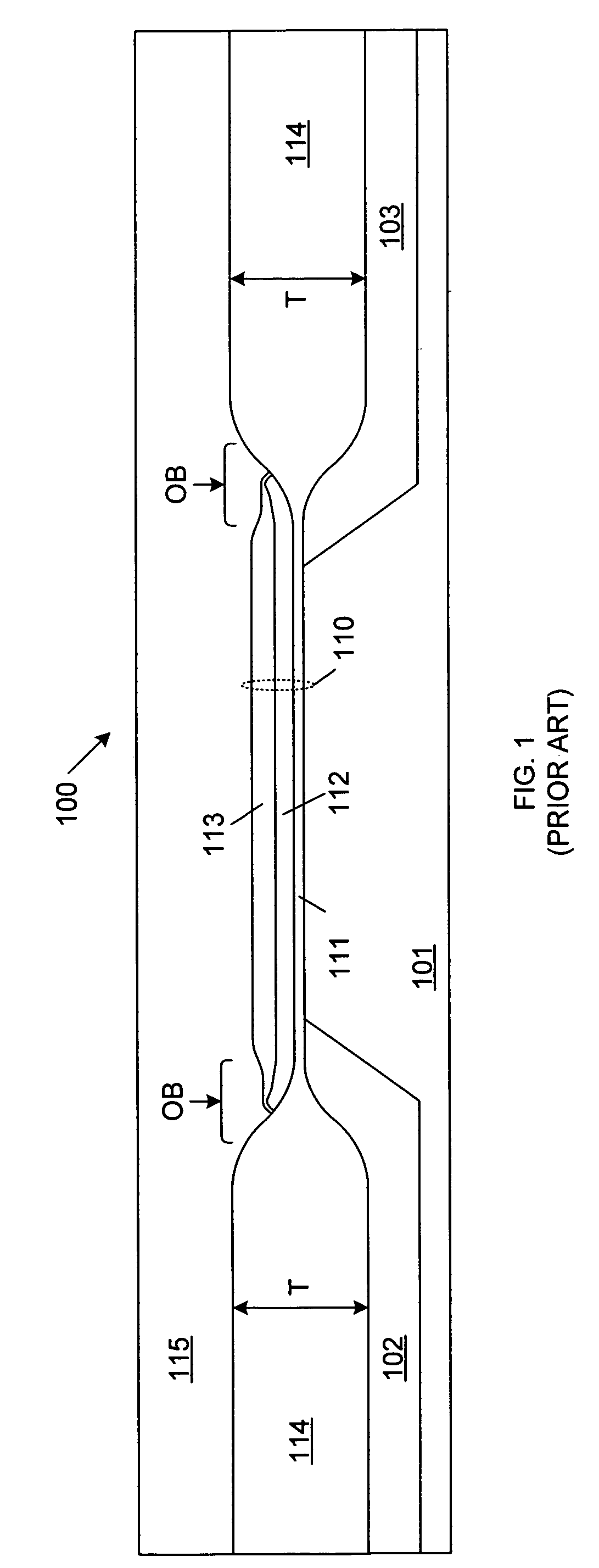

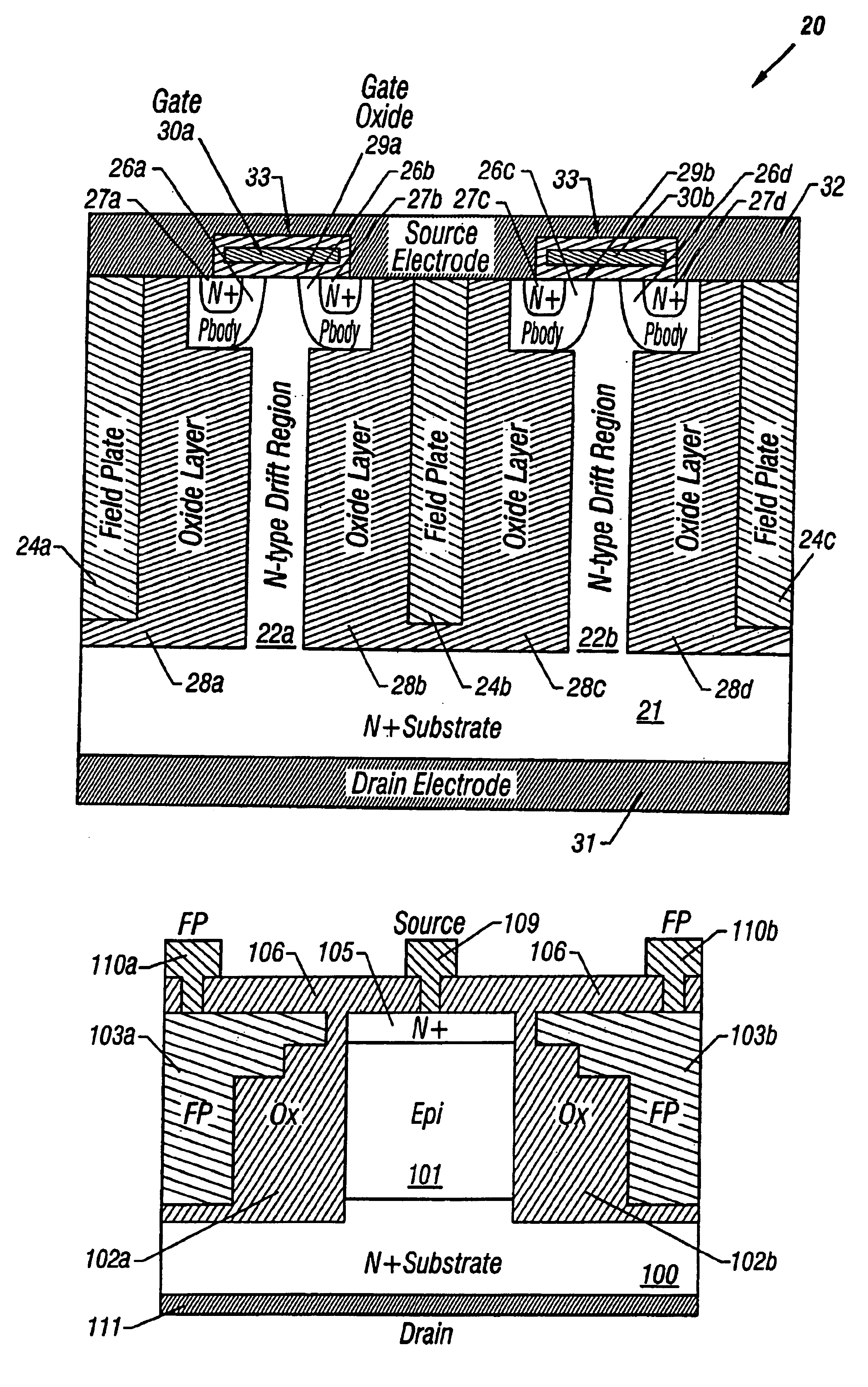

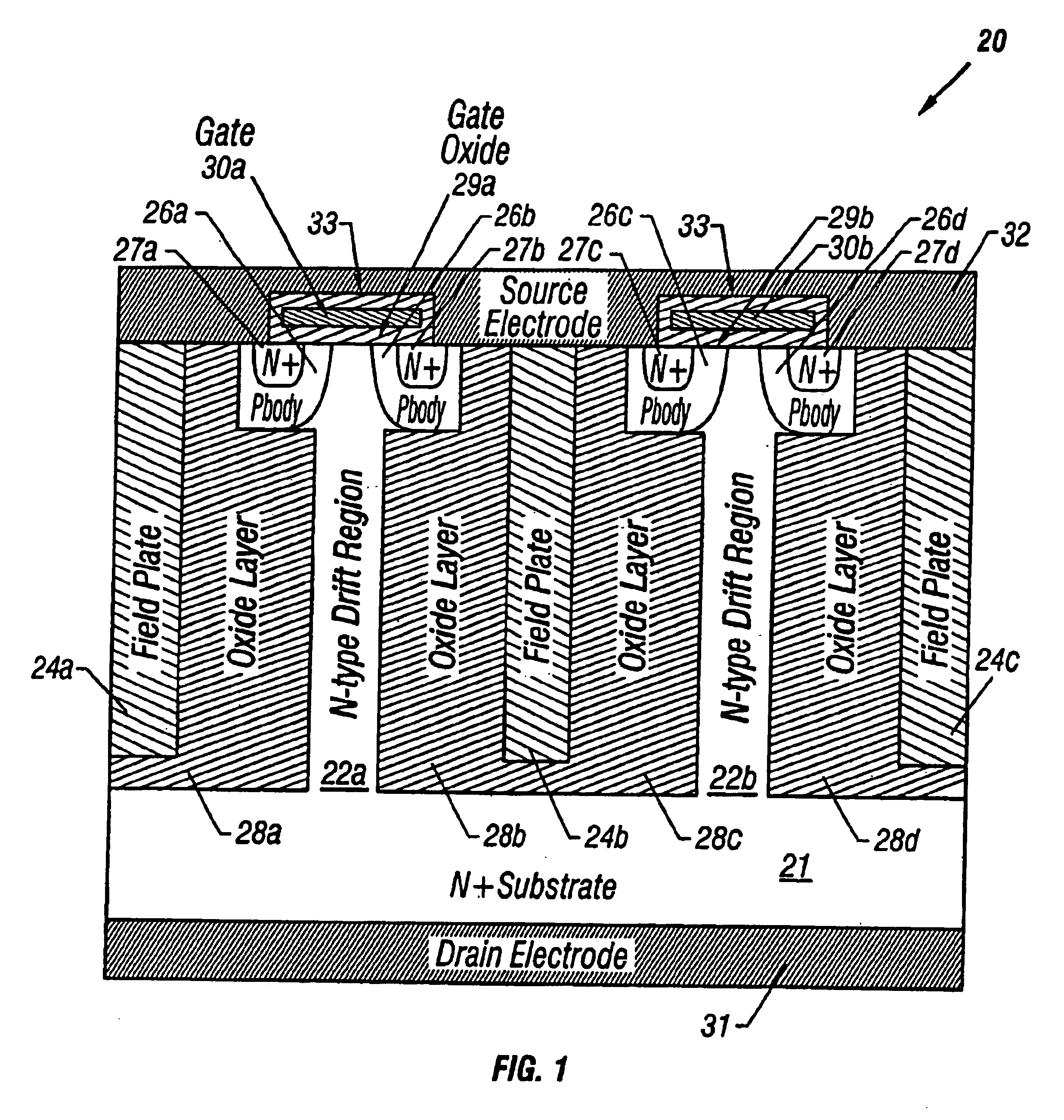

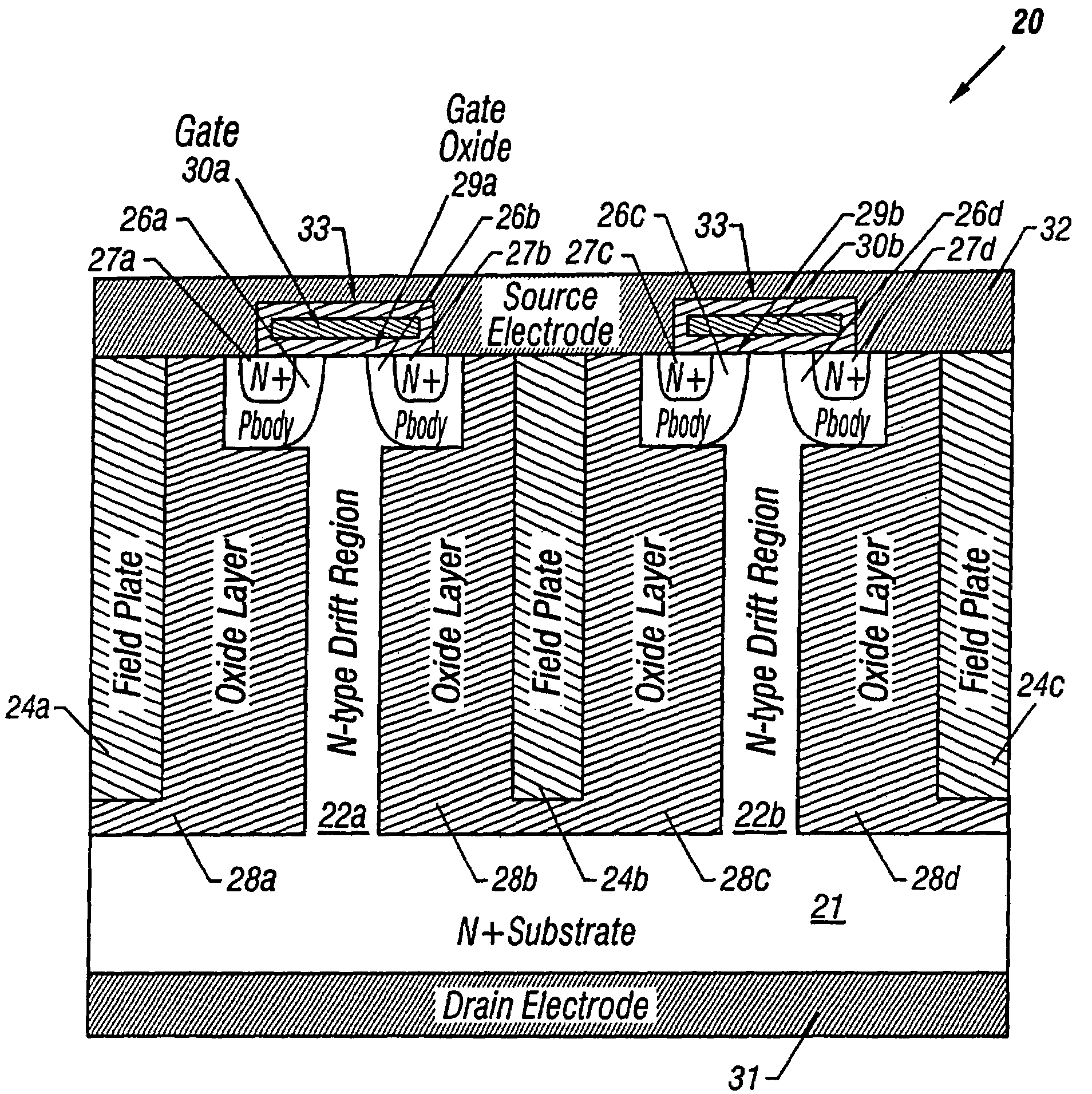

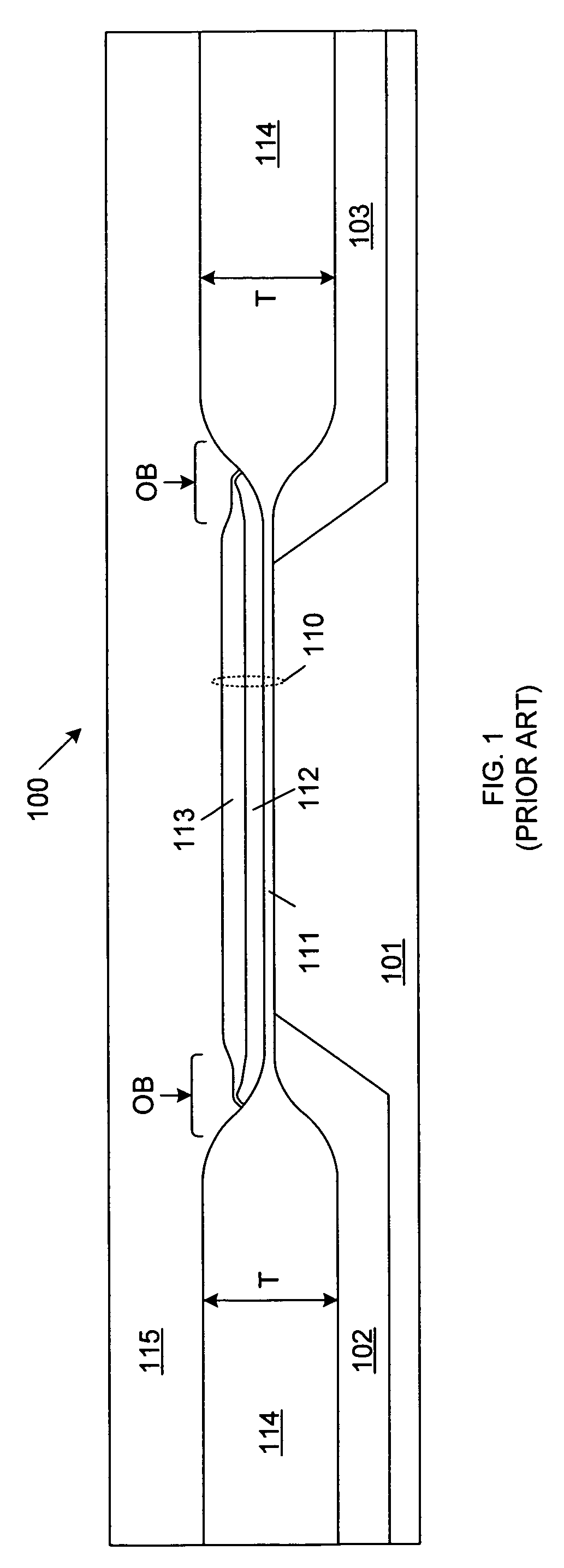

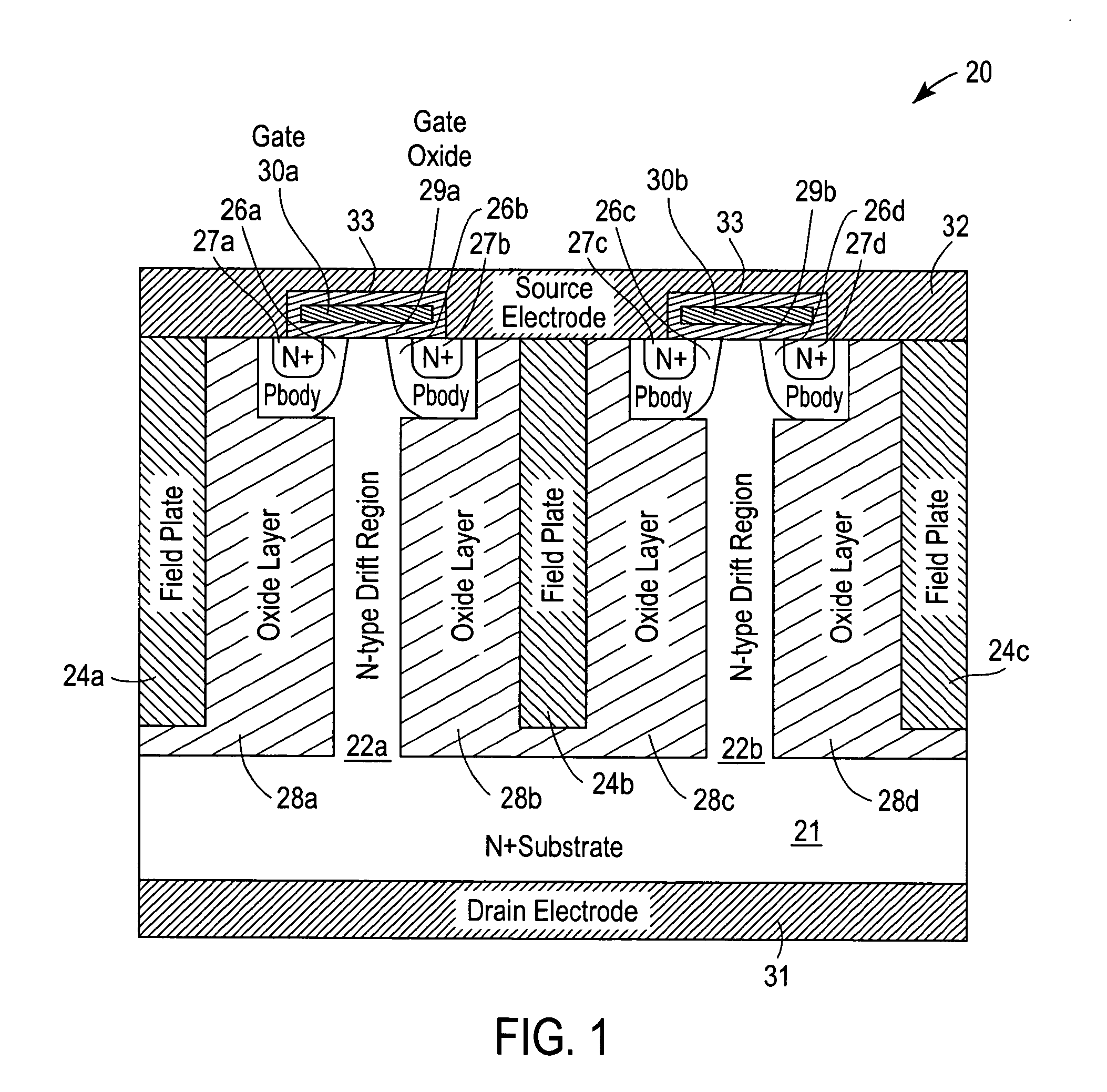

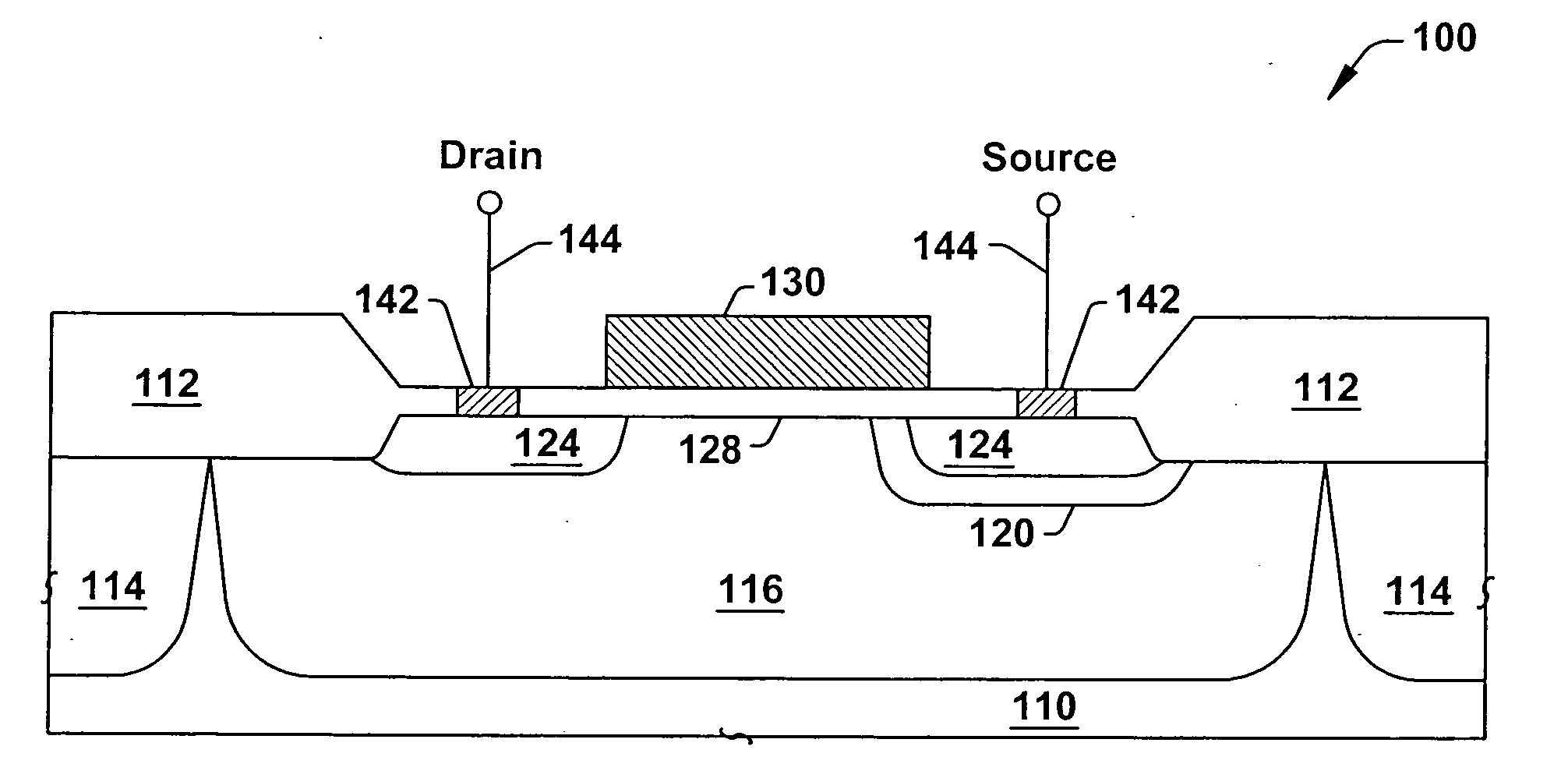

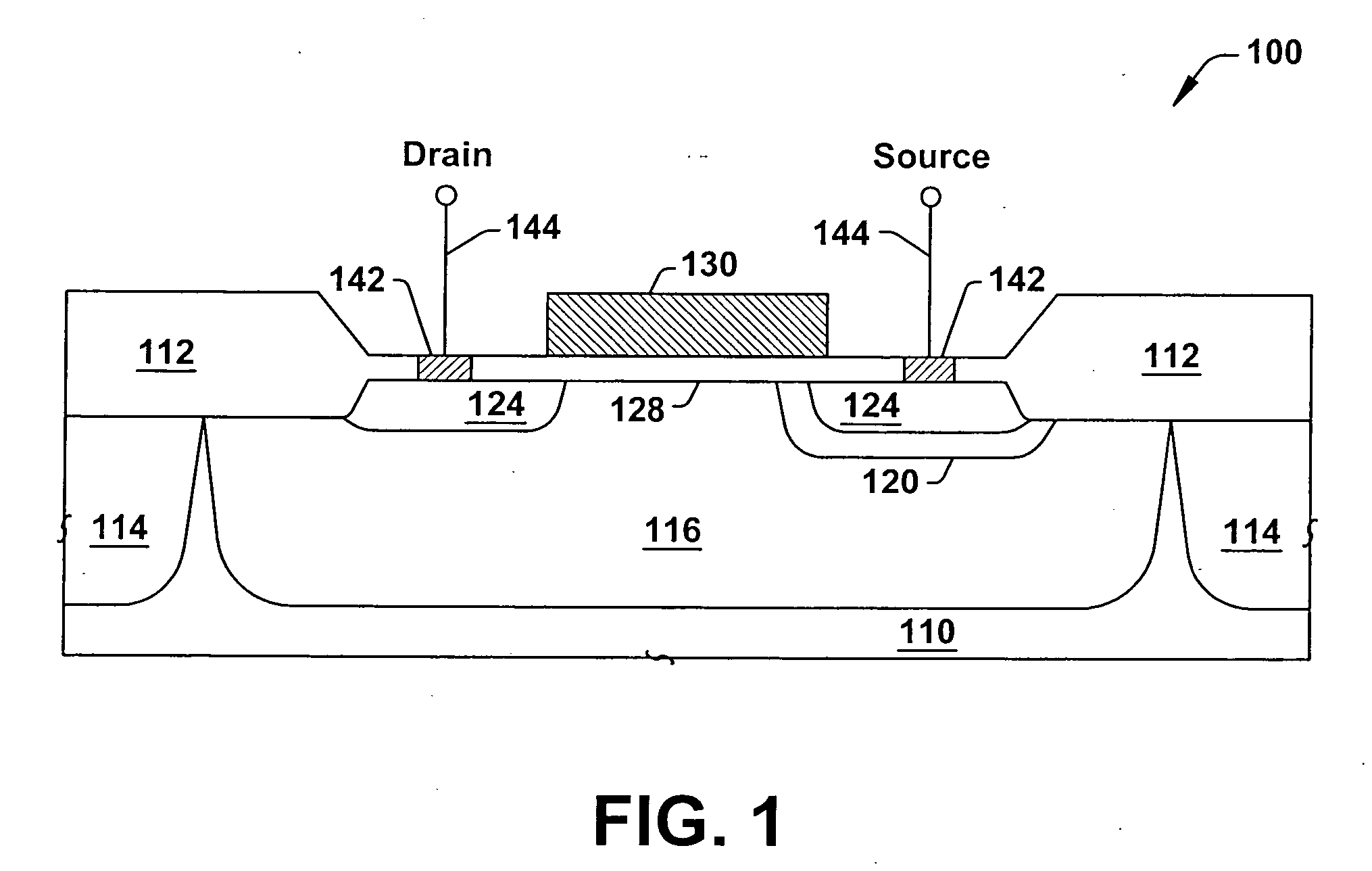

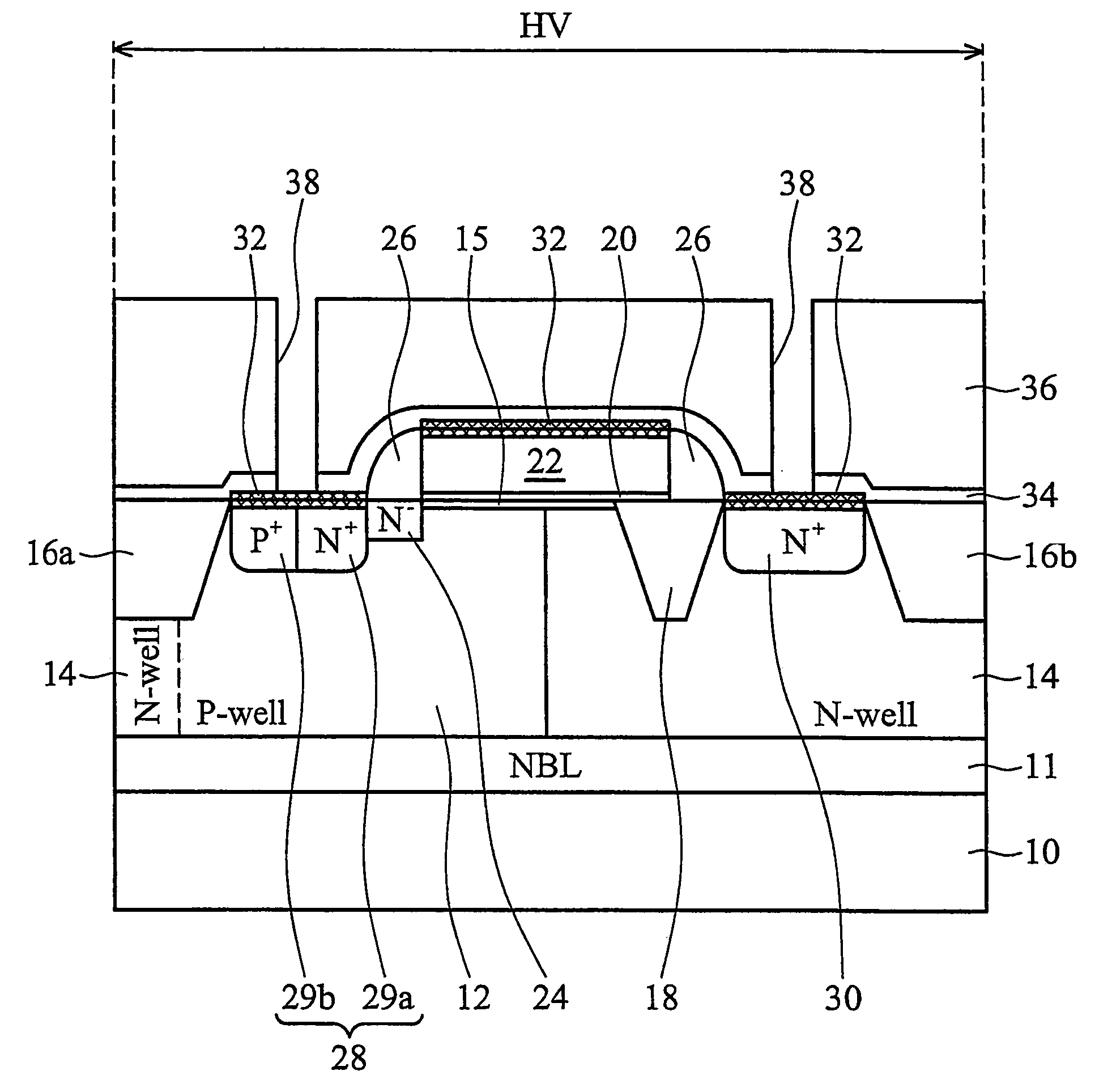

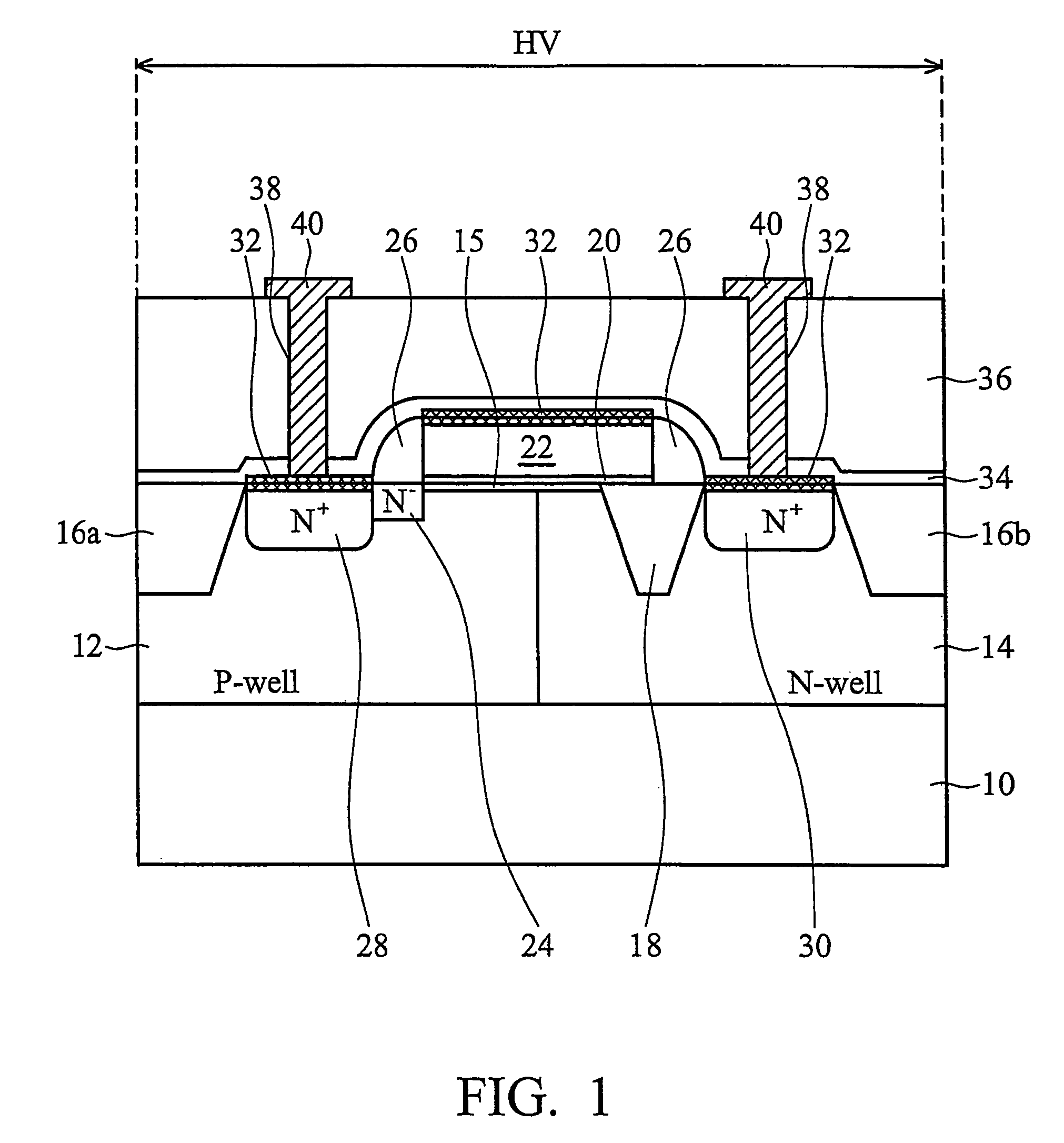

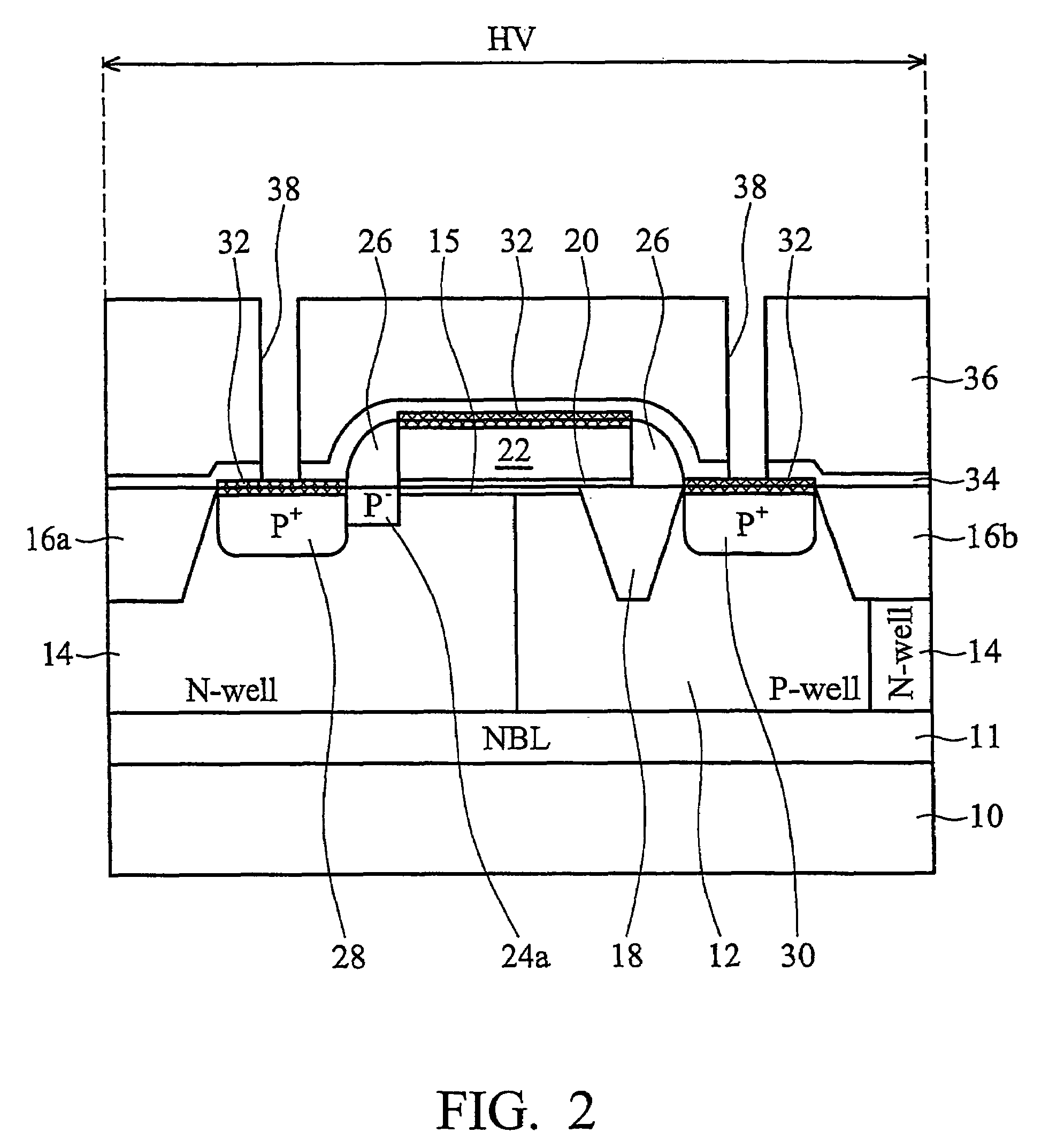

A high-voltage transistor includes a drain, a source, and one or more drift regions extending from the drain toward the source. A field plate member laterally surrounds the drift regions and is insulated from the drift regions by a dielectric layer. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:POWER INTEGRATIONS INC

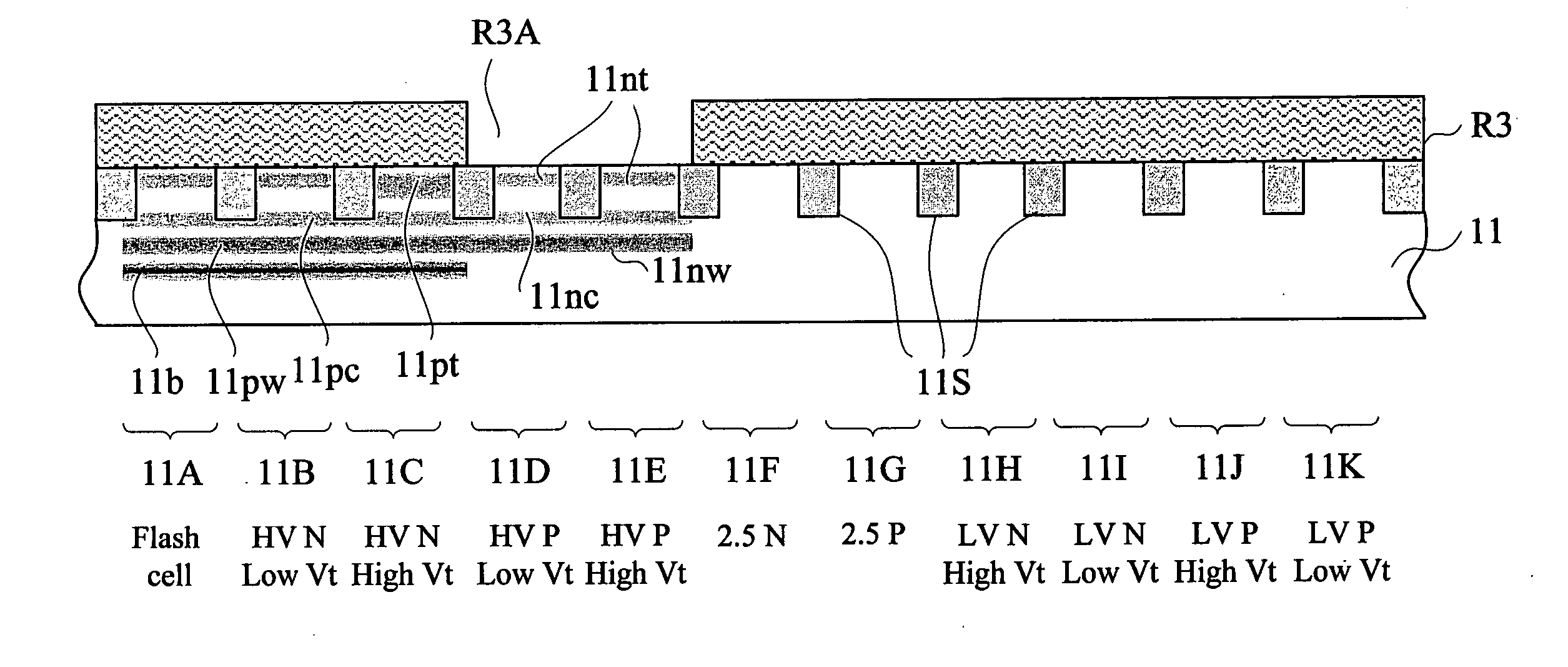

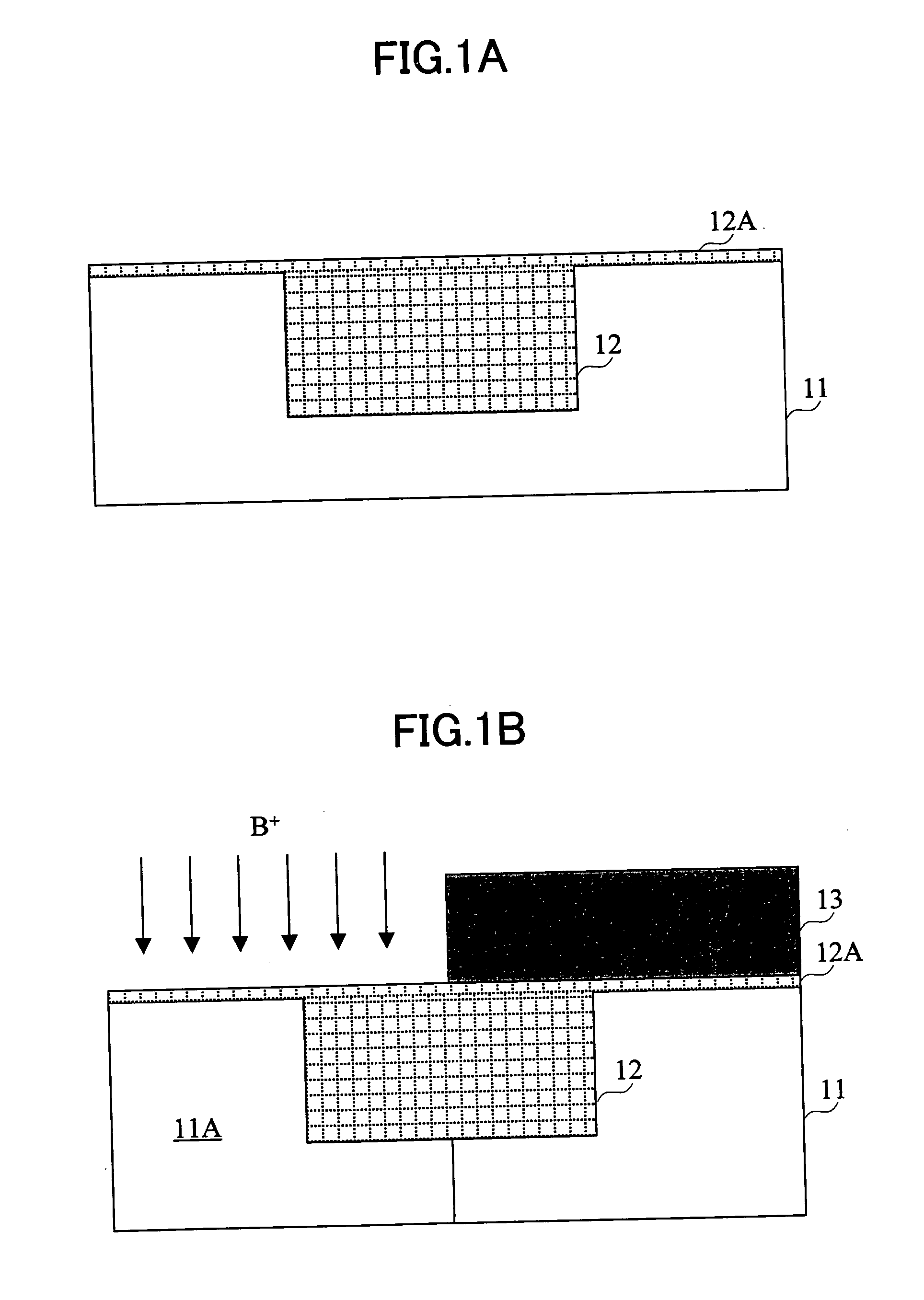

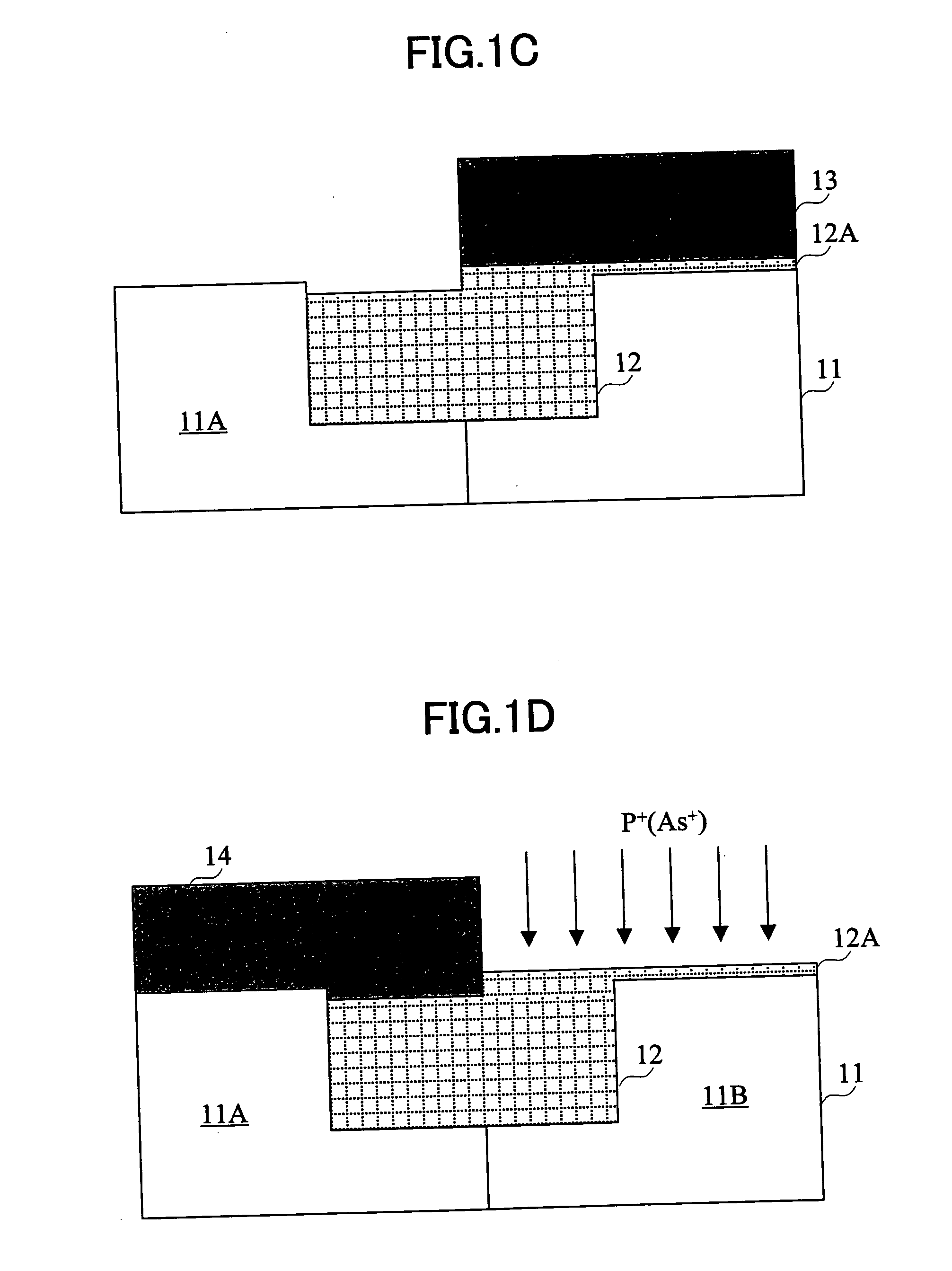

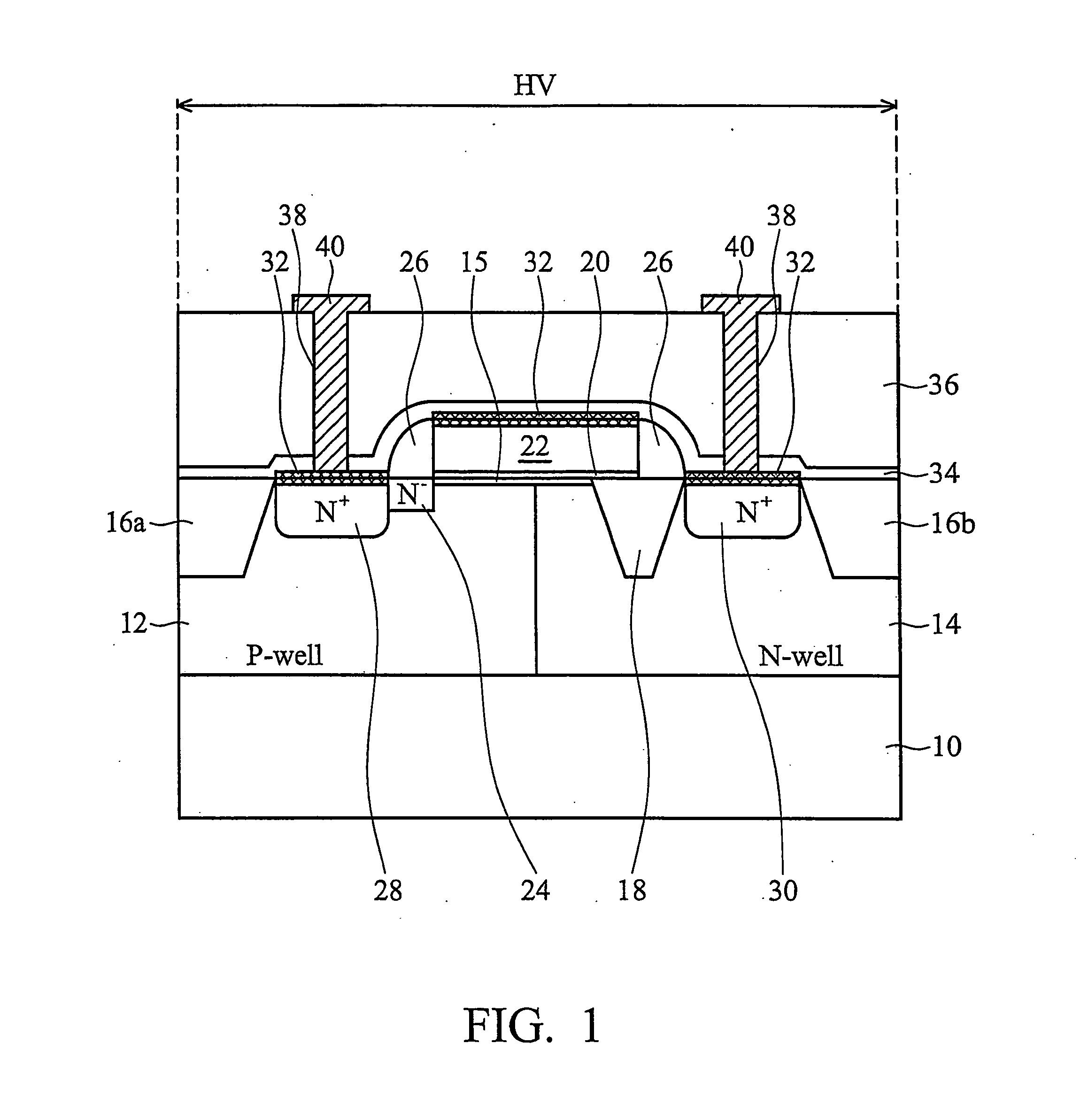

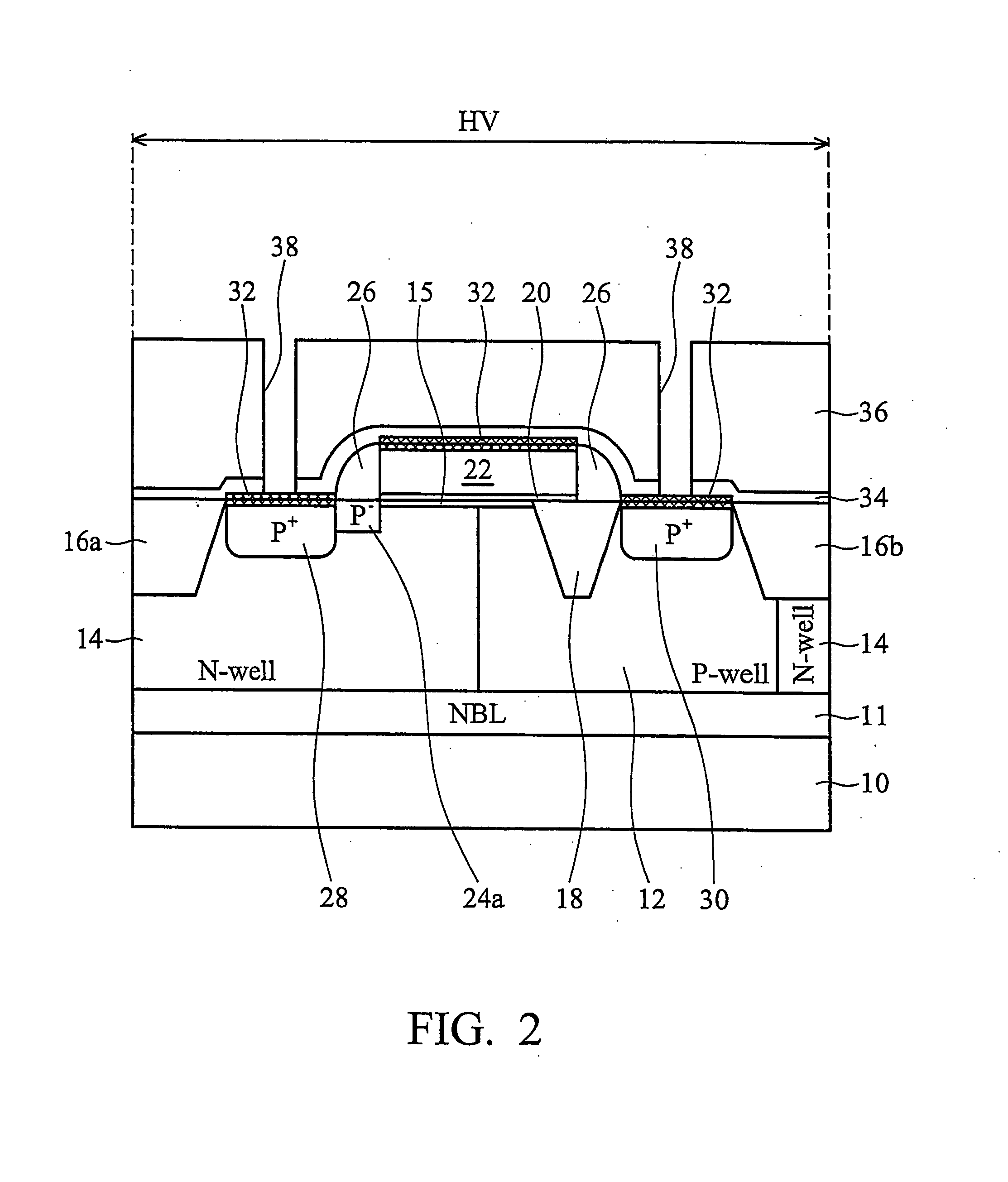

Semiconductor integrated circuit device having improved punch-through resistance and production method thereof, semiconductor integrated circuit device including a low-voltage transistor and a high-voltage transistor

InactiveUS20050280075A1Increase resistanceRaise the threshold voltageTransistorSolid-state devicesHigh voltage transistorsHigh pressure

An integrated circuit device comprises a memory cell well formed with a flash memory device, first and second well of opposite conductivity types for formation of high voltage transistors, and third and fourth wells of opposite conductivity types for low voltage transistors, wherein at least one of the fist and second wells and at least one of the third and fourth wells have an impurity distribution profile steeper than the memory cell well.

Owner:FUJITSU SEMICON LTD

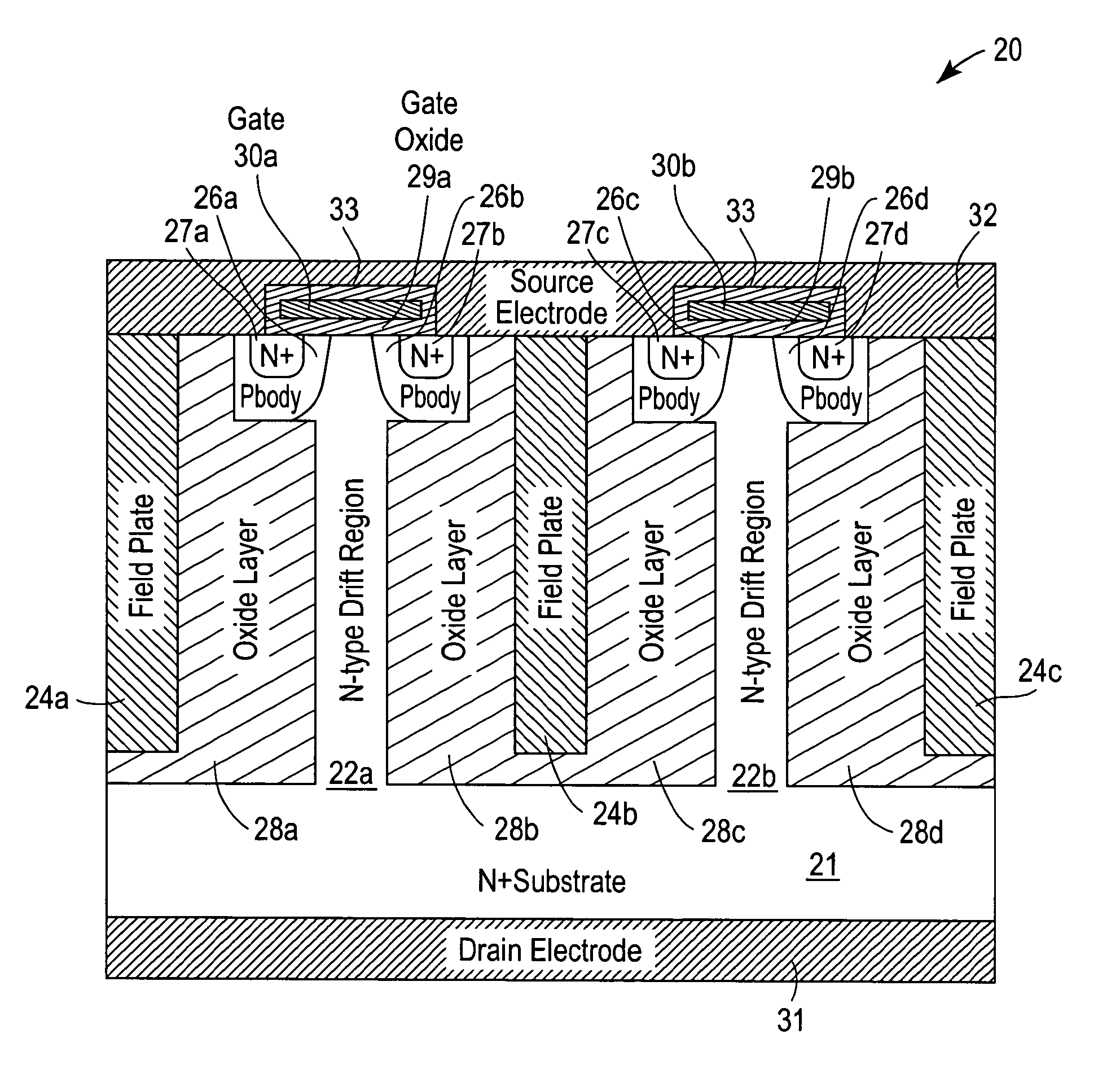

High-voltage vertical transistor with a multi-gradient drain doping profile

InactiveUS7221011B2Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsSubject matter

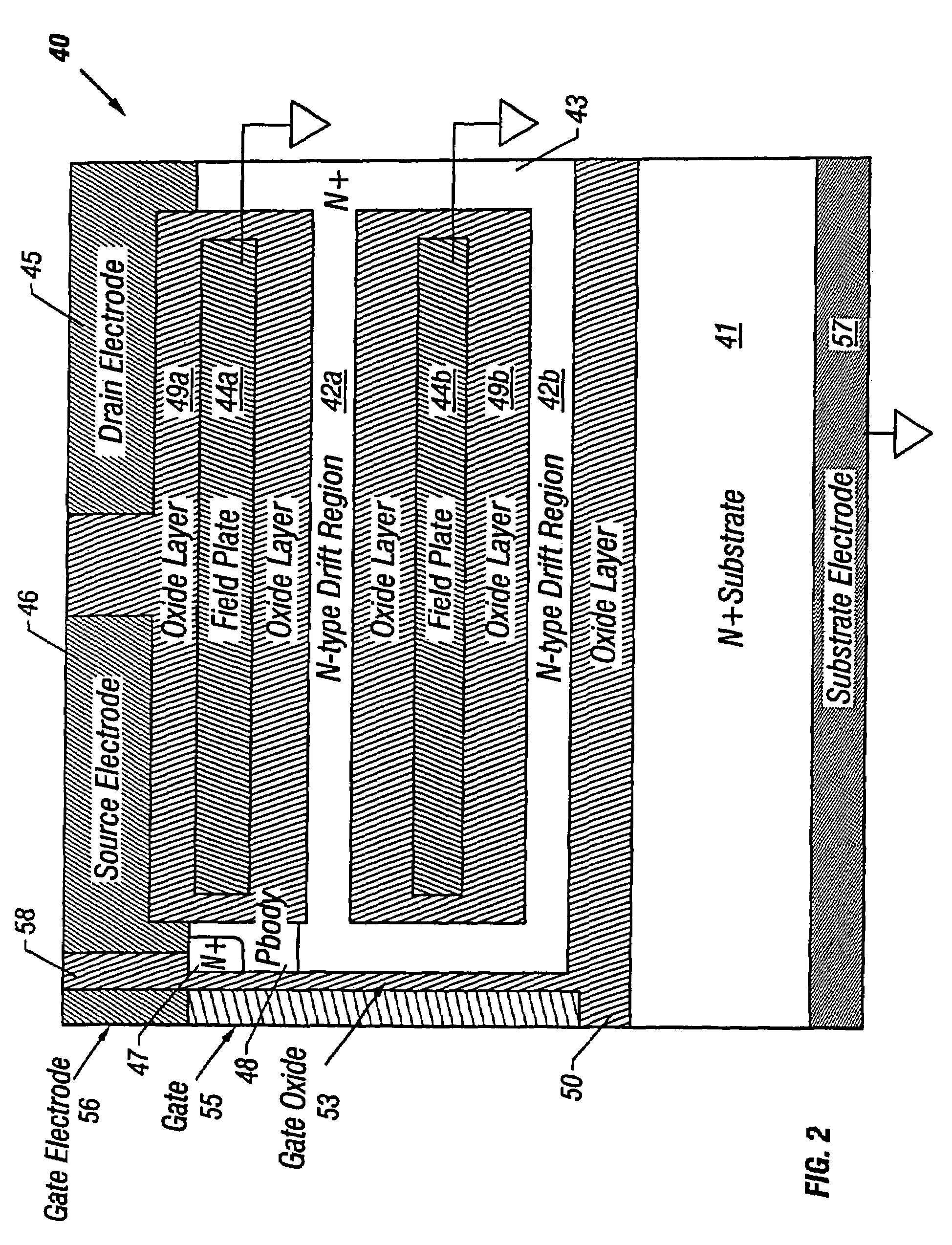

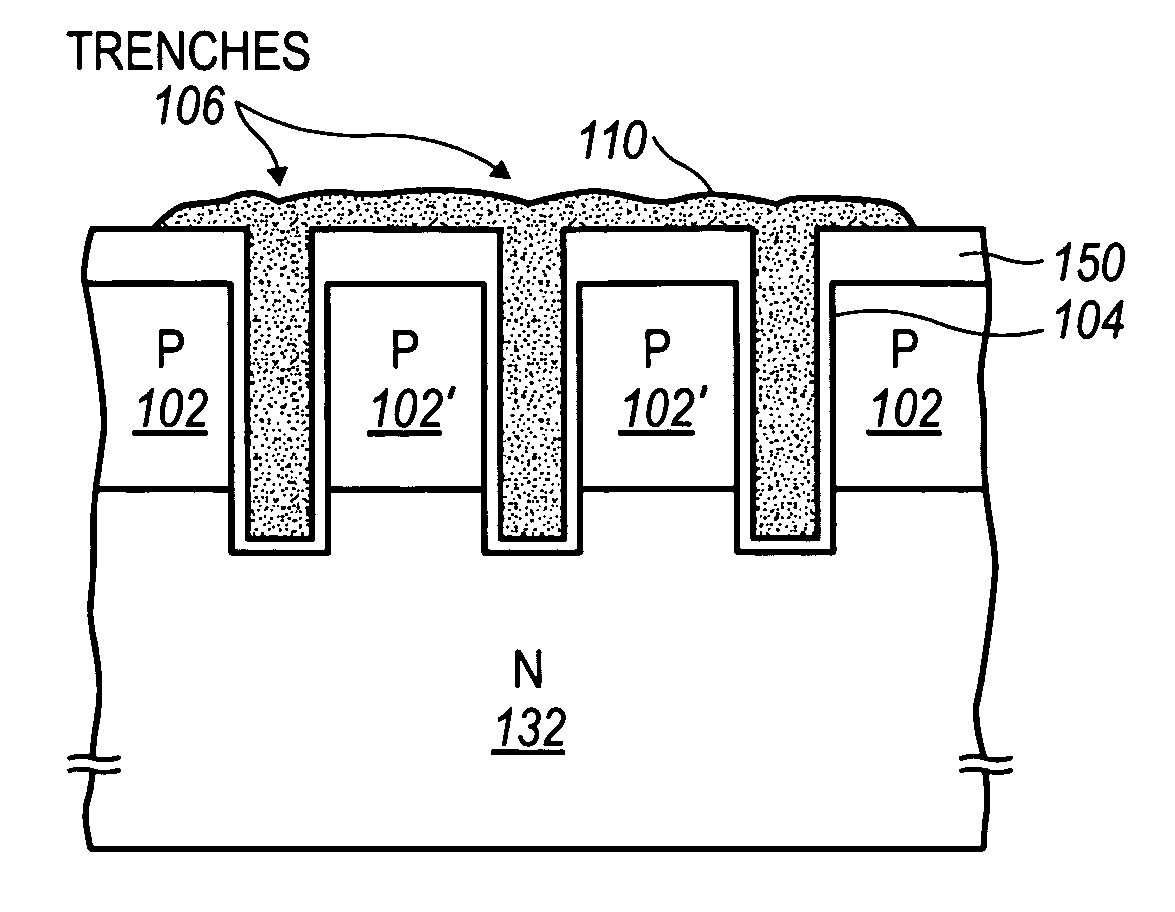

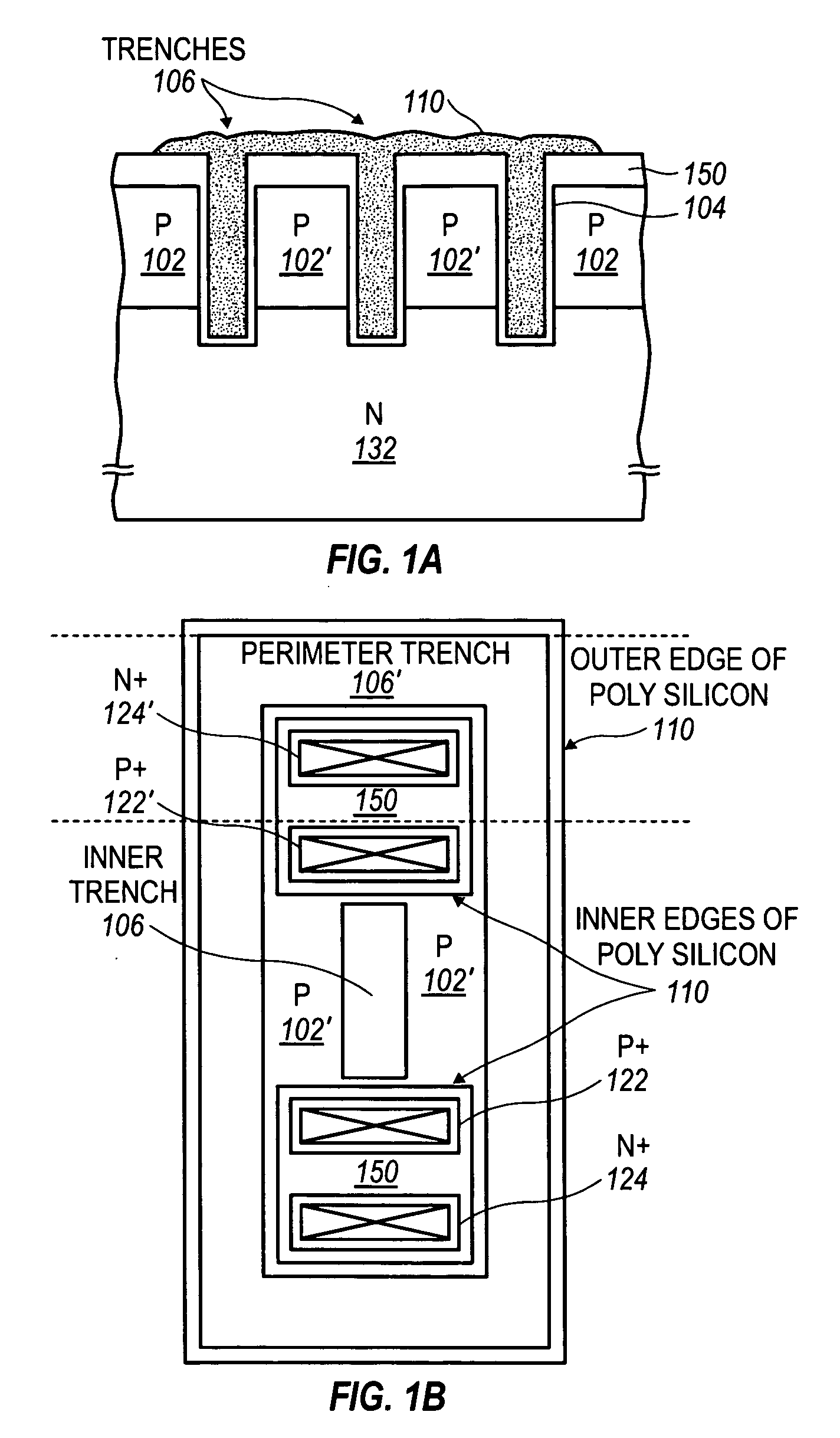

A high-voltage transistor includes first and second trenches that define a mesa in a semiconductor substrate. First and second field plate members are respectively disposed in the first and second trenches, with each of the first and second field plate members being separated from the mesa by a dielectric layer. The mesa includes a plurality of sections, each section having a substantially constant doping concentration gradient, the gradient of one section being at least 10% greater than the gradient of another section. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:POWER INTEGRATIONS INC

Semiconductor memory device and method of manufacturing the same

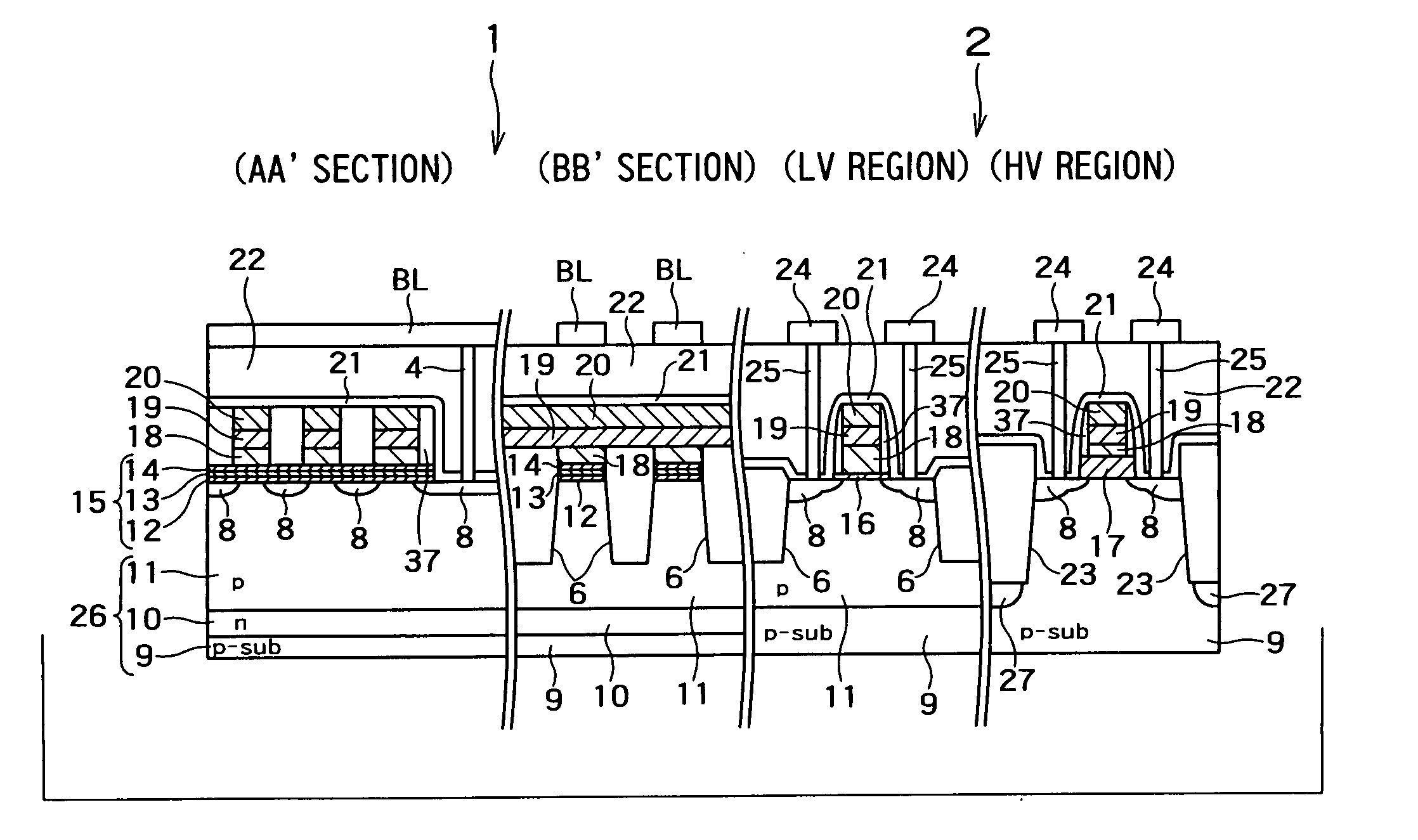

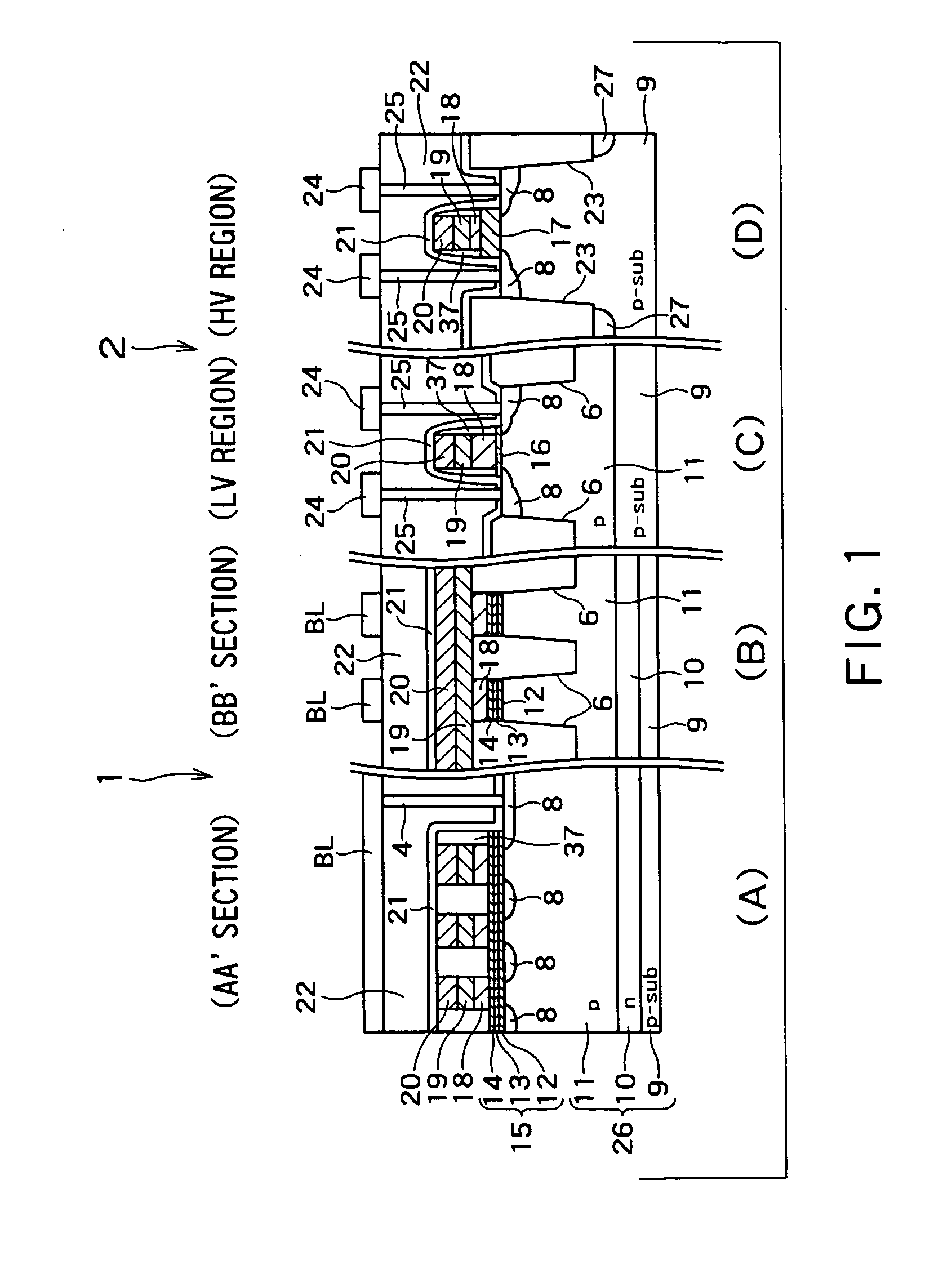

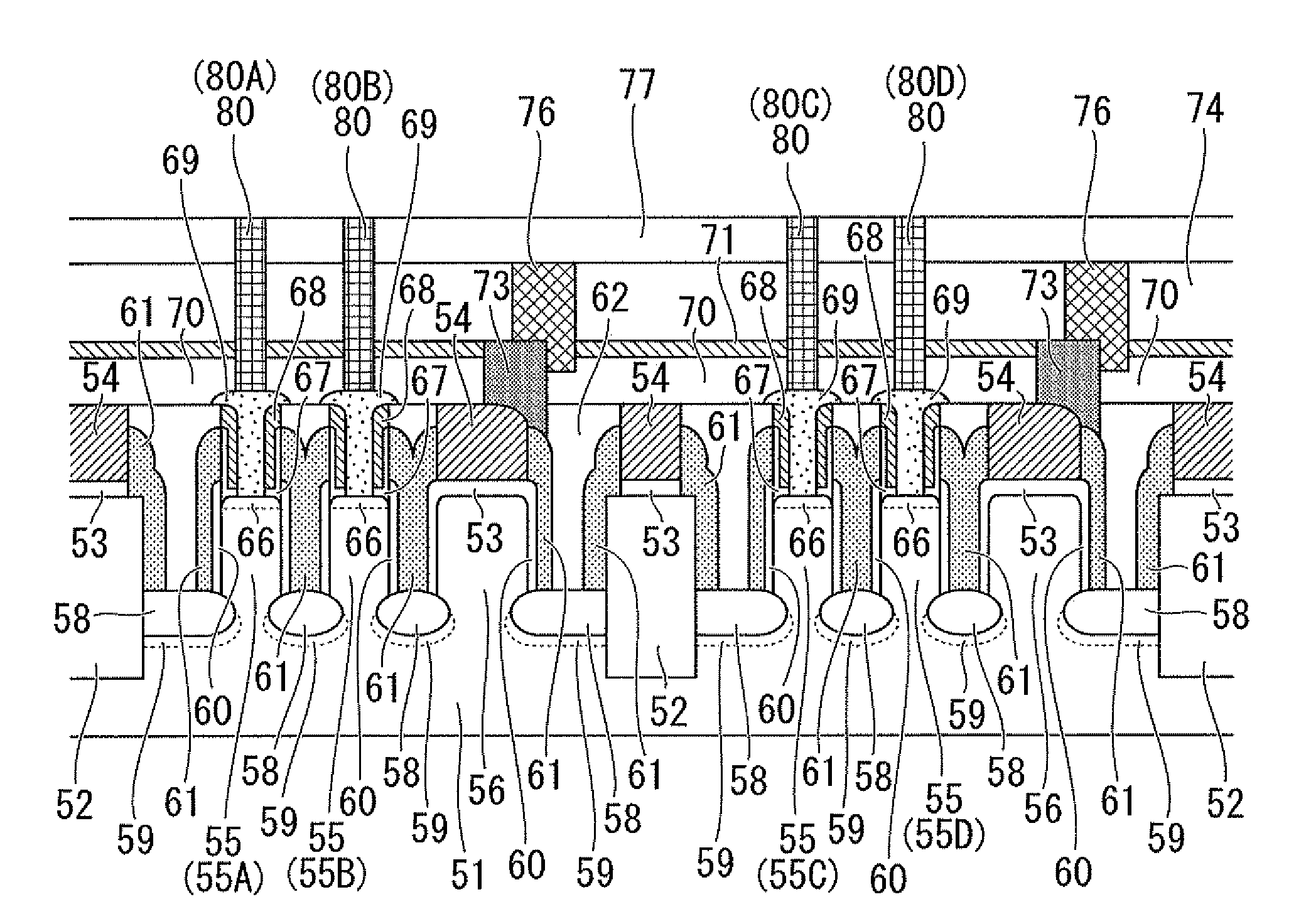

A semiconductor memory device having a memory cell region and a peripheral circuit region, and a method of manufacturing such a semiconductor memory device, are proposed, in which trench grooves are formed to be shallow in the memory cell region in order to improve the yield, and trench grooves are formed to be deep in the high voltage transistor region of the peripheral circuit region, in particular in a high voltage transistor region thereof, in order to improve the element isolation withstand voltage. A plurality of memory cell transistors having an ONO layer 15 serving as a charge accumulating insulating layer are provided in the memory cell region, where element isolation grooves 6 for these memory cell transistors are narrow and shallow. Two types of transistors, one for high voltage and the other for low voltage, having gate insulating layers 16 or 17, which are different from the ONO layer 15 in the memory cell region, are provided in the peripheral circuit region, where at least element isolation grooves 23 for high voltage transistors are wide and deep. In this way, it is possible to improve the degree of integration and yield in the memory cell region, and secure withstand voltage in the peripheral circuit region.

Owner:KK TOSHIBA

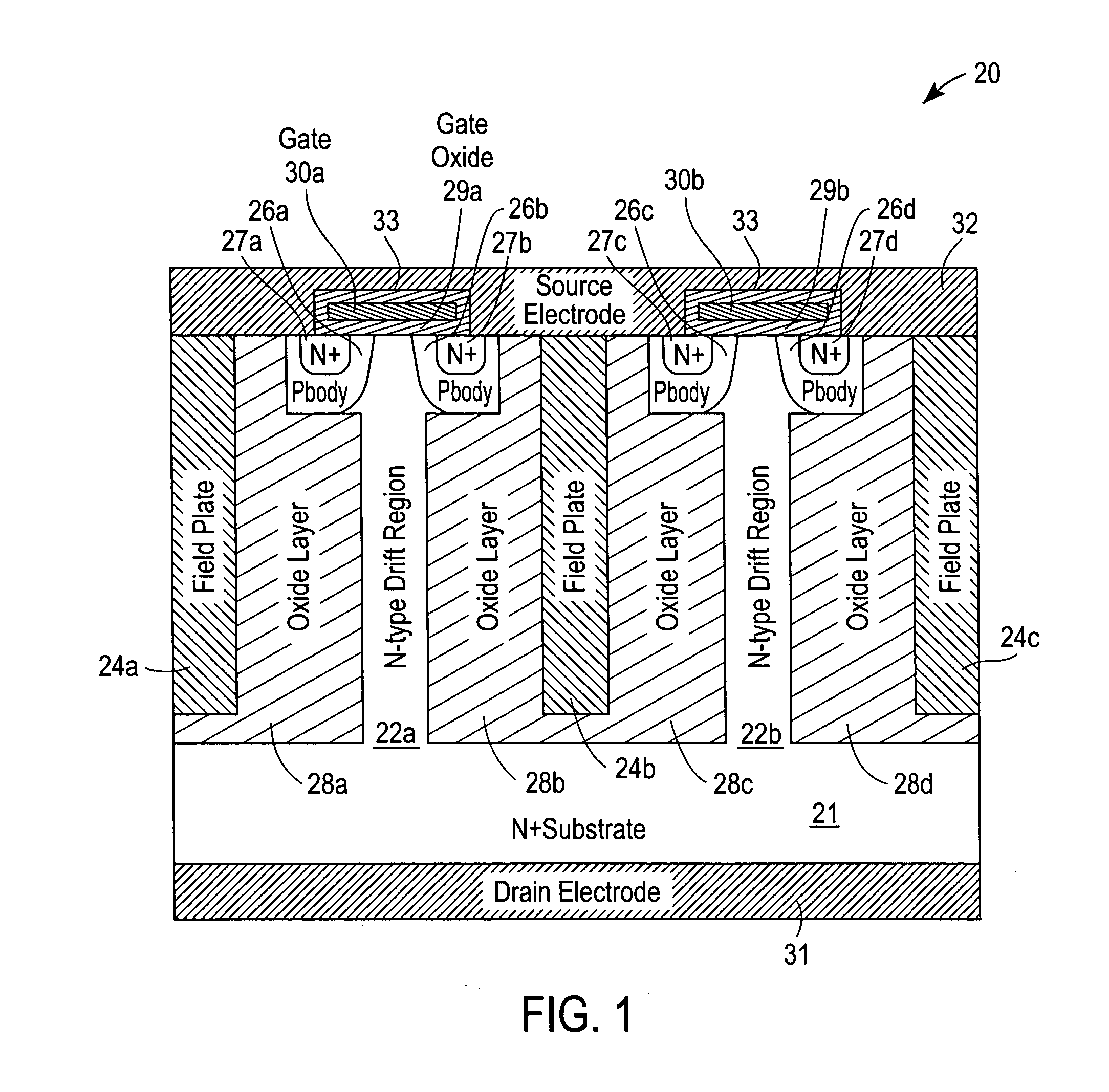

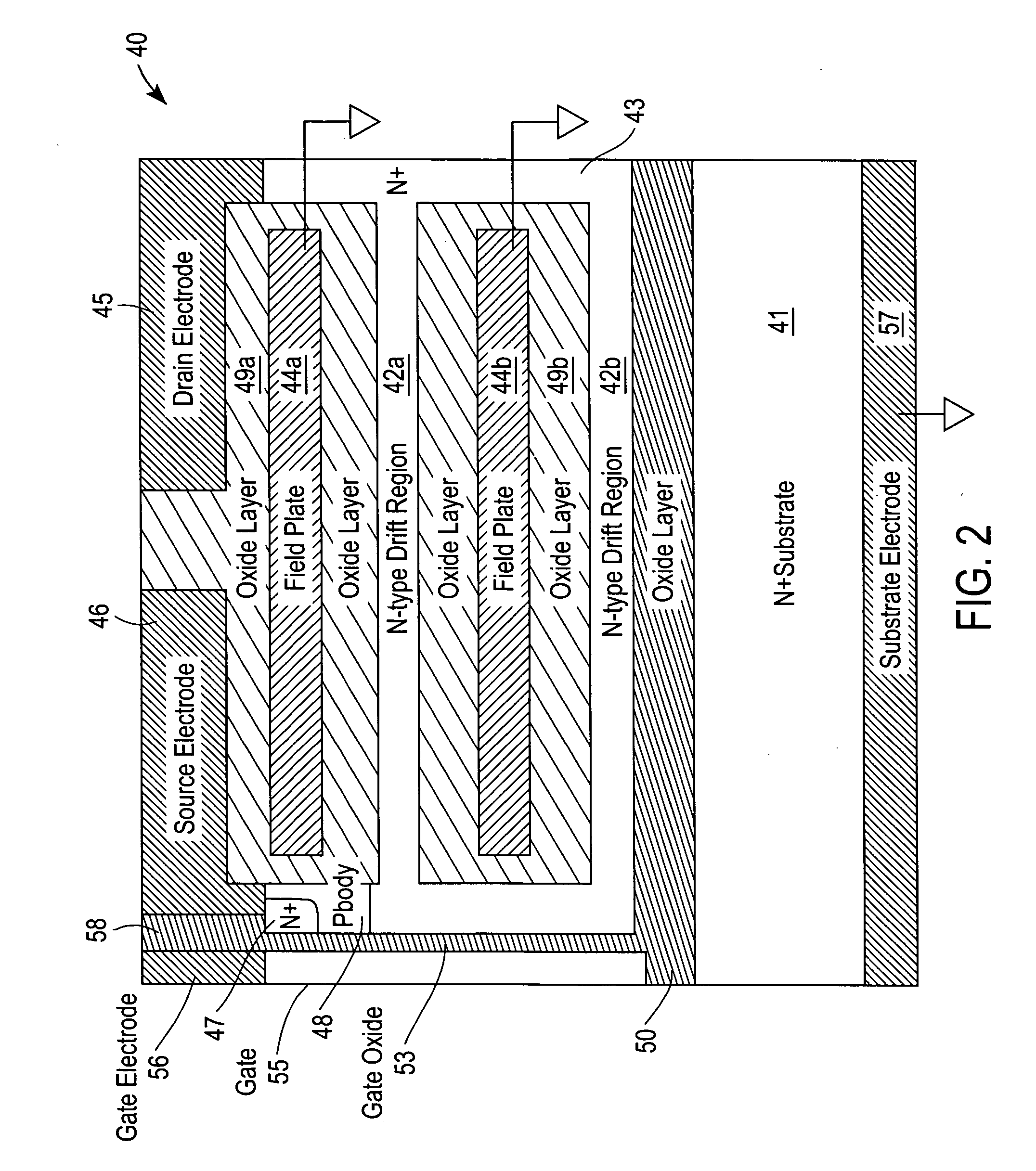

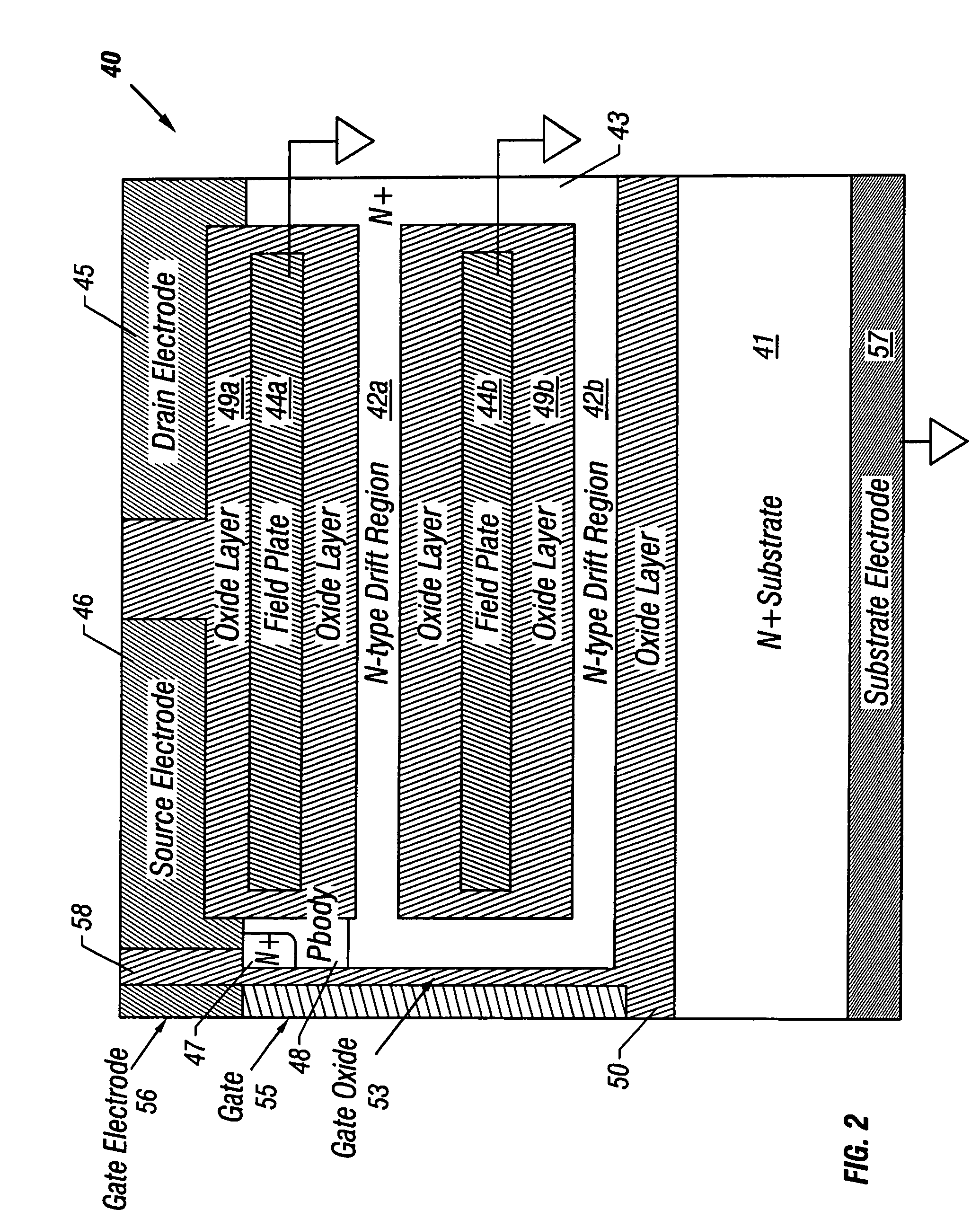

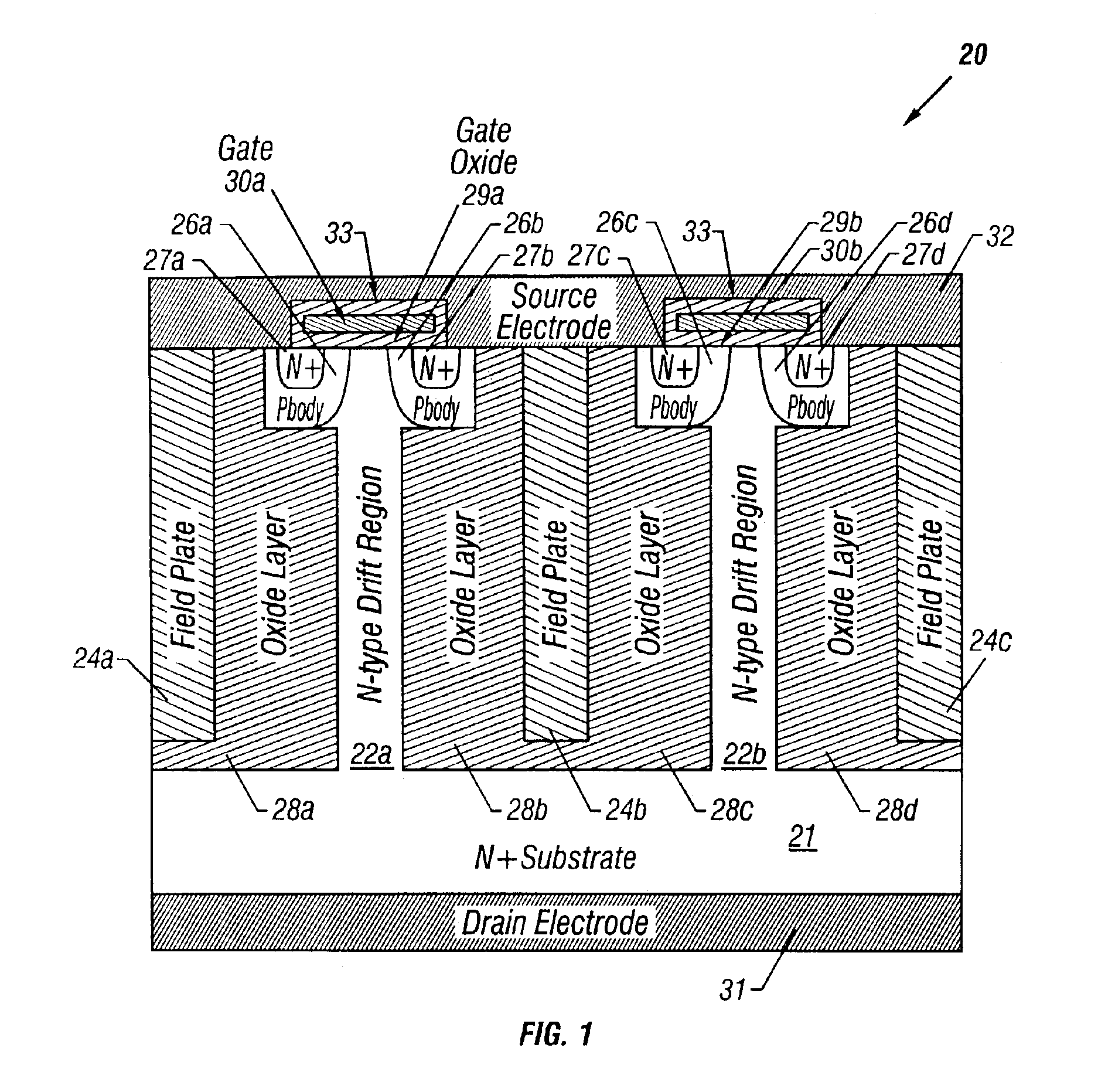

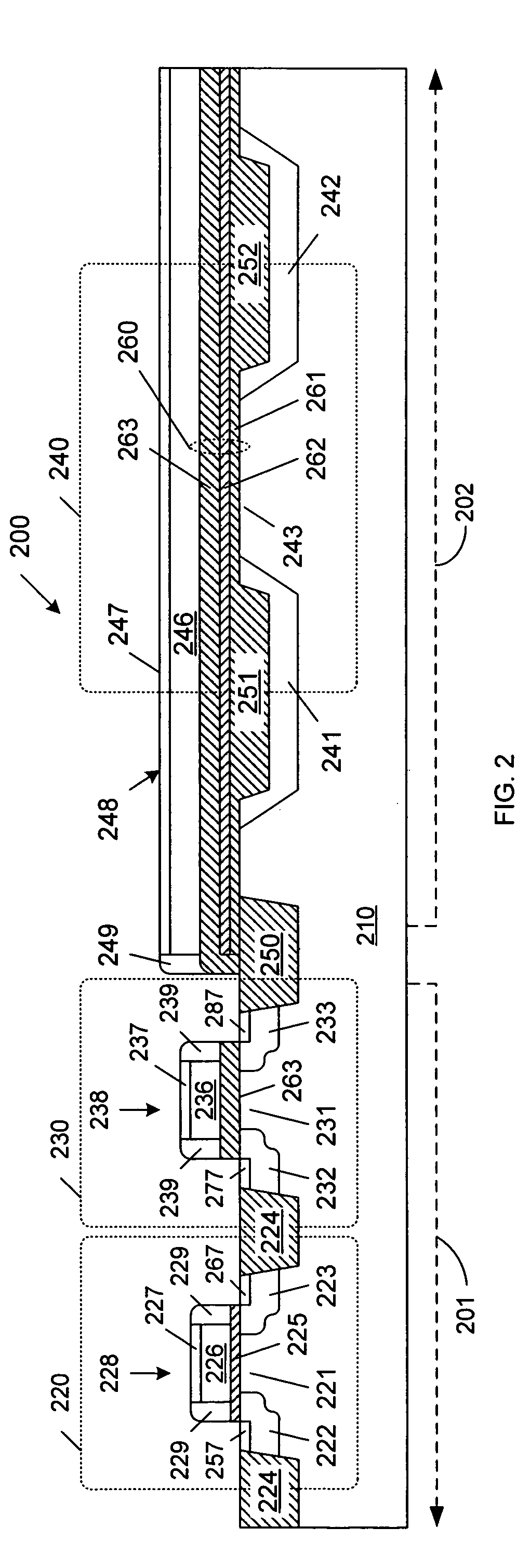

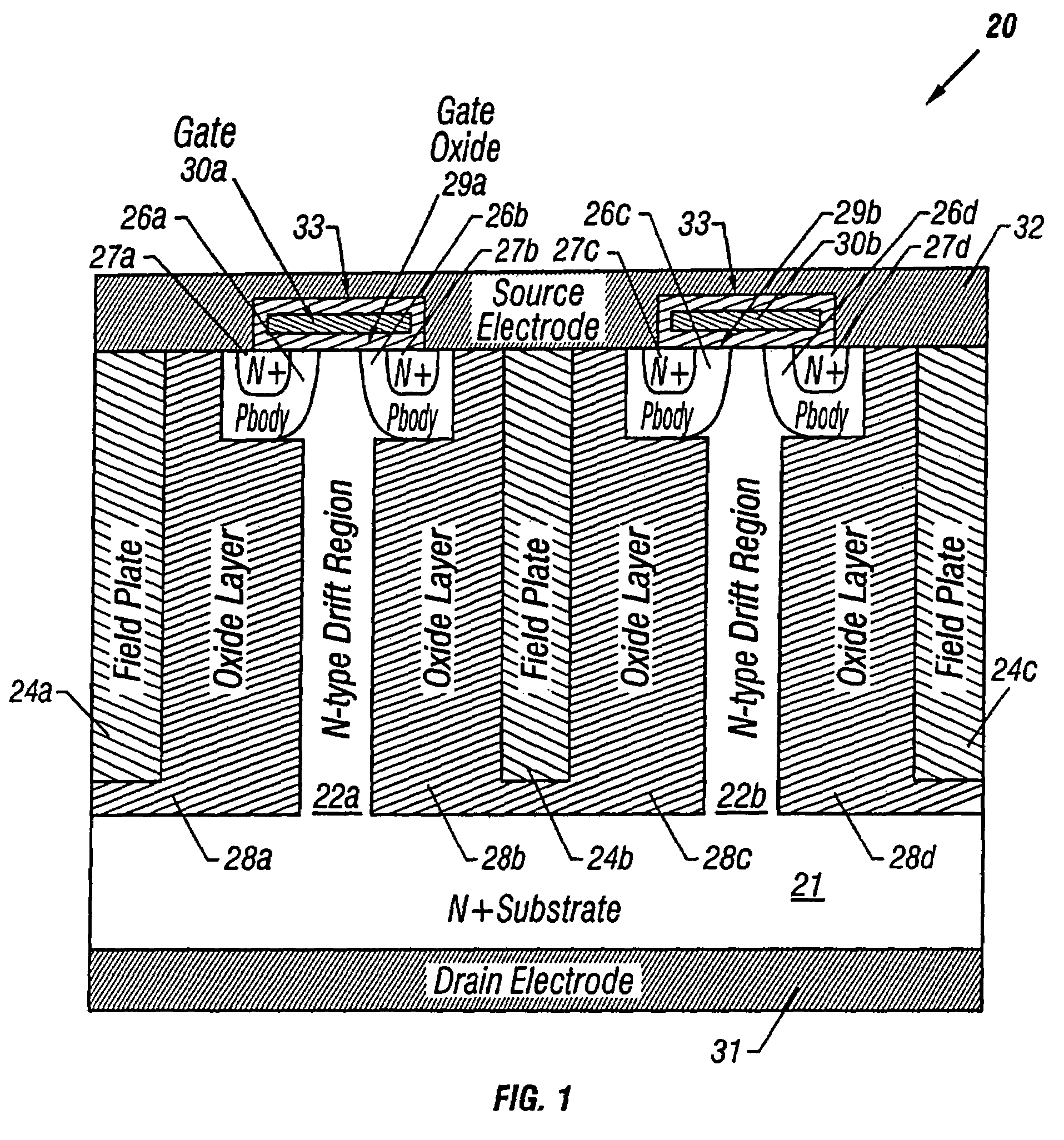

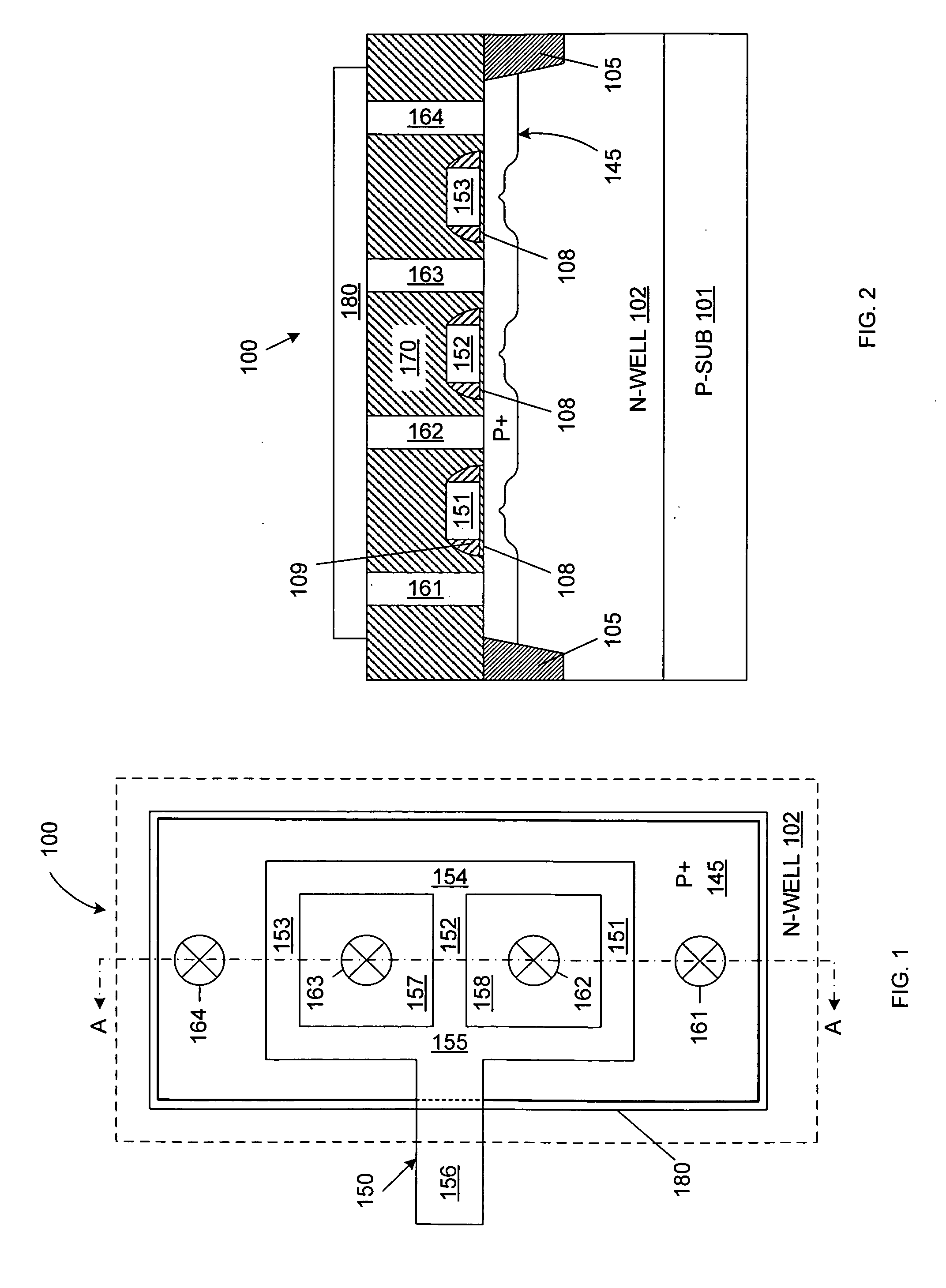

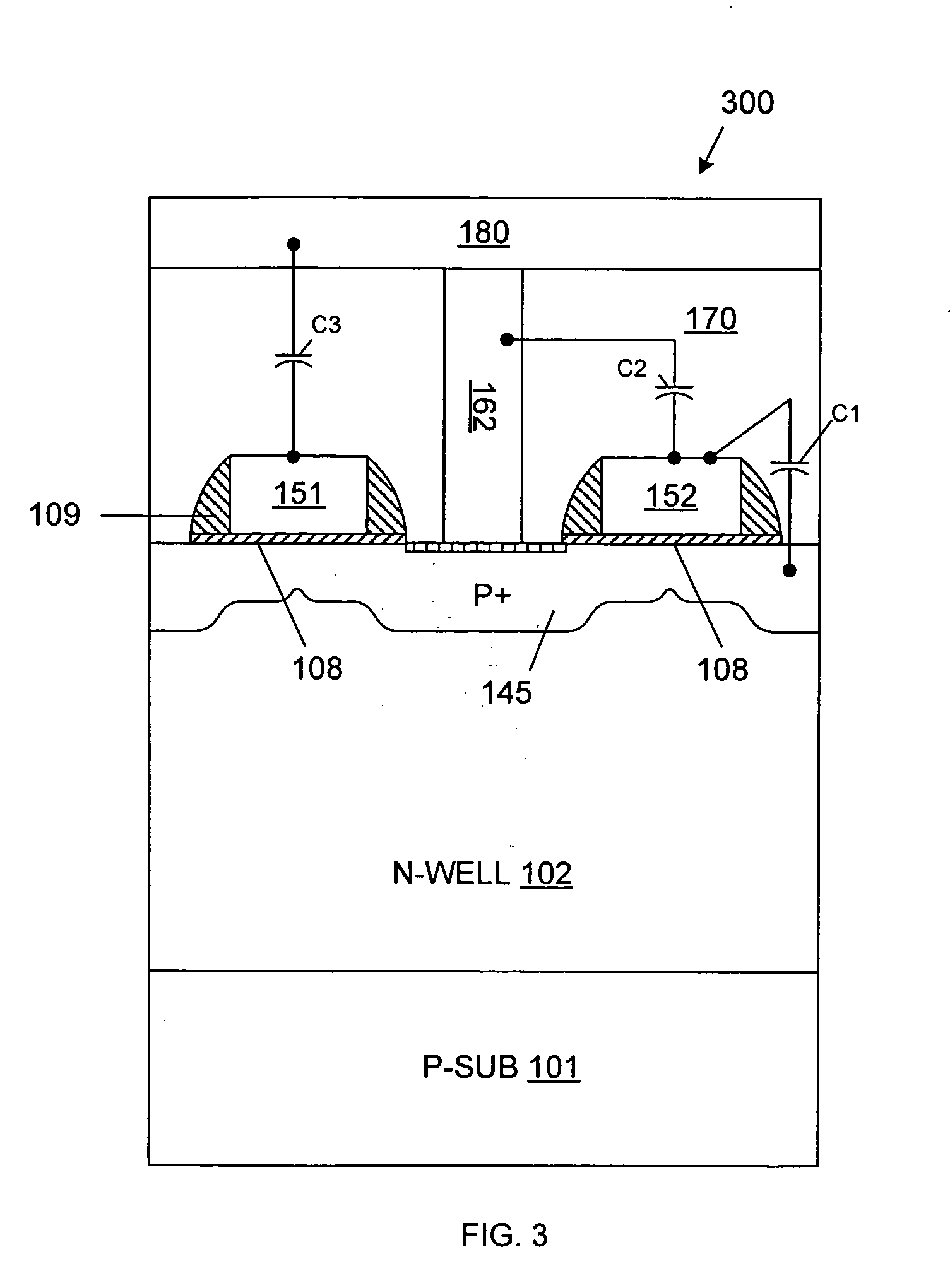

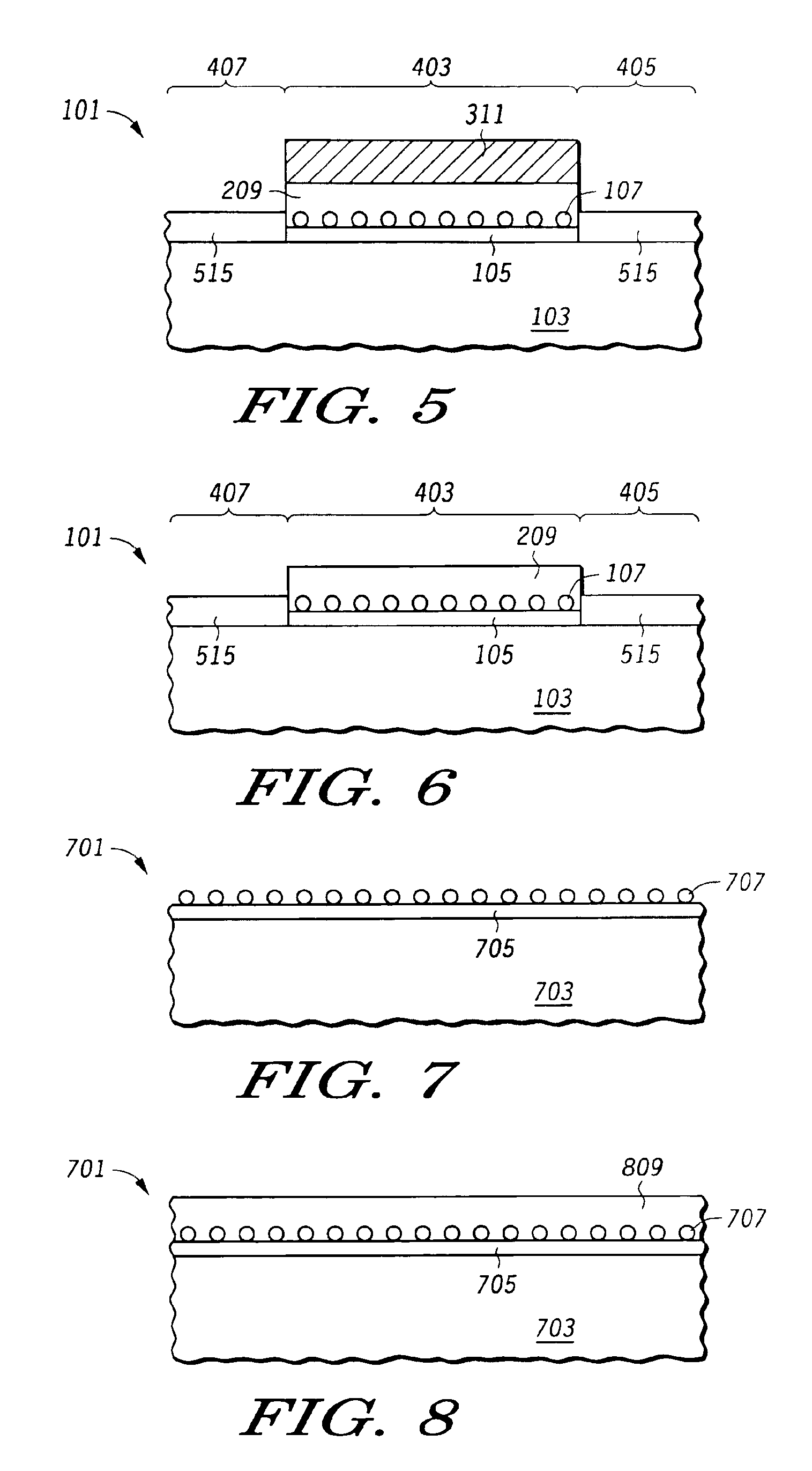

High-voltage lateral transistor with a multi-layered extended drain structure

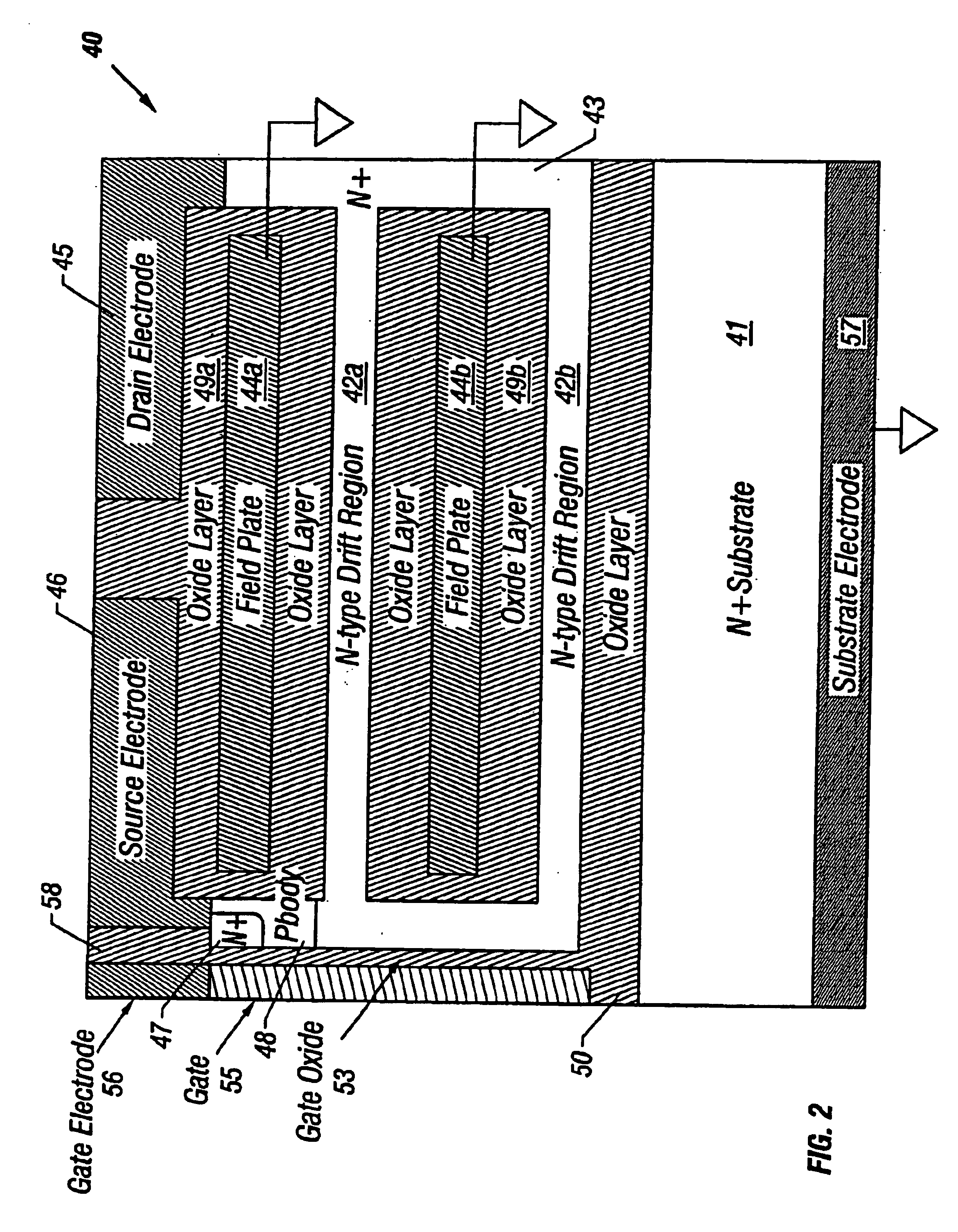

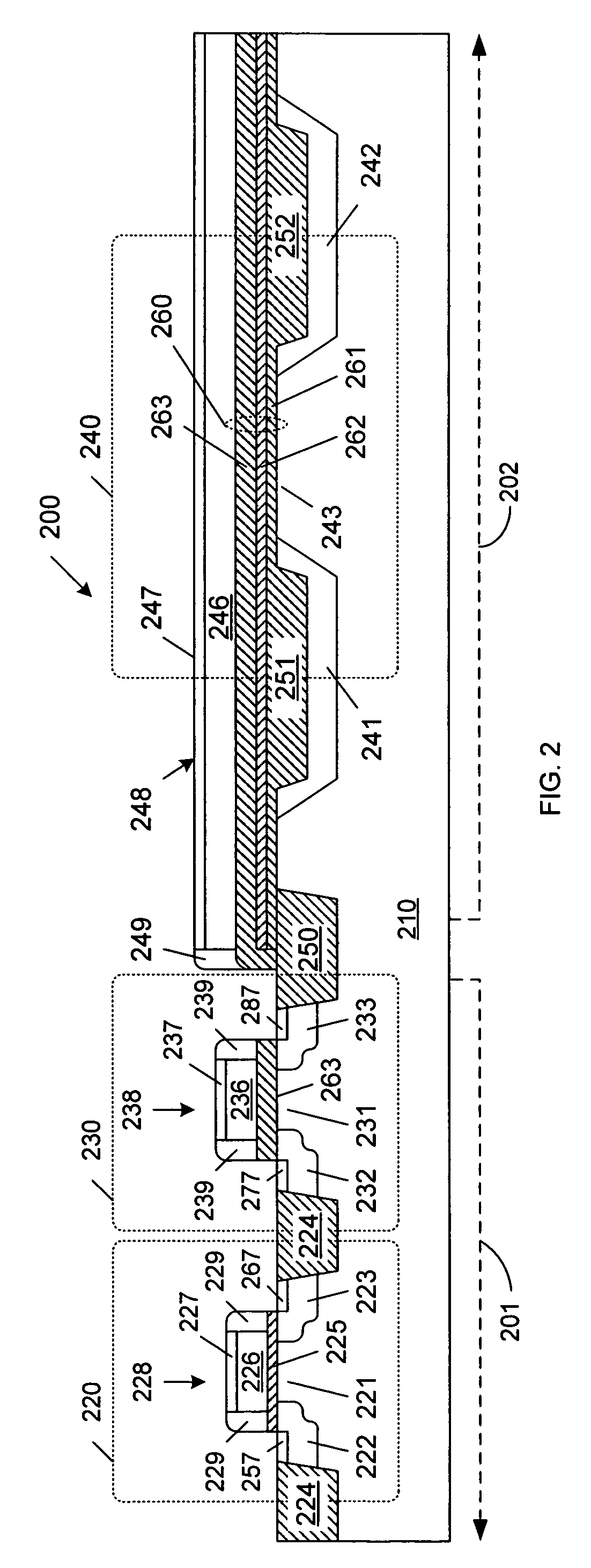

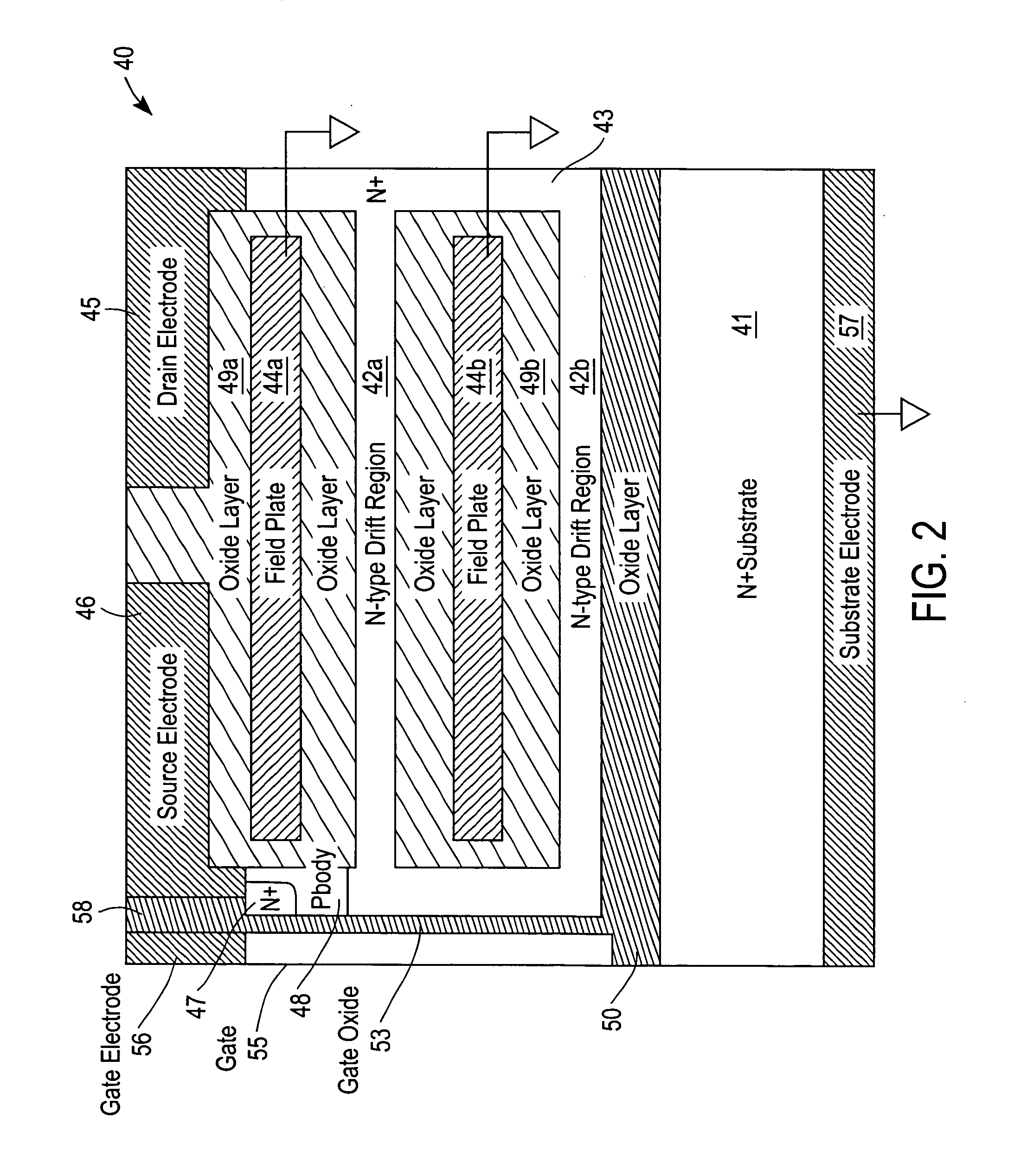

A high-voltage transistor with a low specific on-state resistance and that supports high voltage in the off-state includes one or more source regions disposed adjacent to a multi-layered extended drain structure which comprises extended drift regions separated from field plate members by one or more dielectric layers. The layered structure may be fabricated in a variety of orientations. A MOSFET structure may be incorporated into the device adjacent to the source region, or, alternatively, the MOSFET structure may be omitted to produce a high-voltage transistor structure having a stand-alone drift region. It is emphaized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims 37 CFR 1.72(b).

Owner:POWER INTEGRATIONS INC

High-voltage transistor device having an interlayer dielectric etch stop layer for preventing leakage and improving breakdown voltage

ActiveUS20060113627A1Prevent leakageImprove breakdown voltageTransistorSolid-state devicesDielectricHigh voltage transistors

A high-voltage transistor device with an interlayer dielectric (ILD) etch stop layer for use in a subsequent contact hole process is provided. The etch stop layer is a high-resistivity film having a resistivity greater than 10 ohm-cm, thus leakage is prevented and breakdown voltage is improved when driving a high voltage greater than 5V at the gate site. A method for fabricating the high-voltage device is compatible with current low-voltage device processes and middle-voltage device processes.

Owner:TAIWAN SEMICON MFG CO LTD

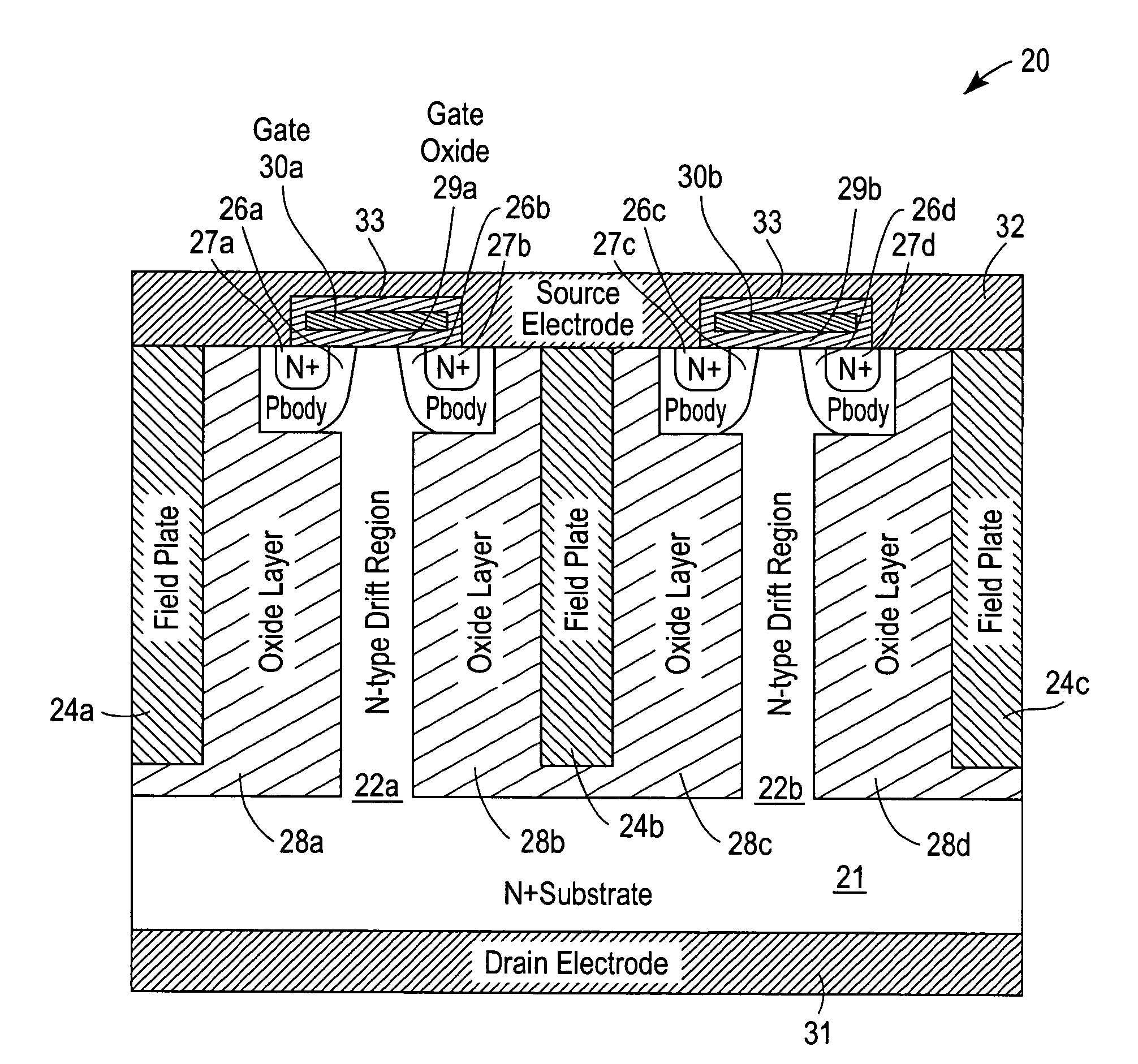

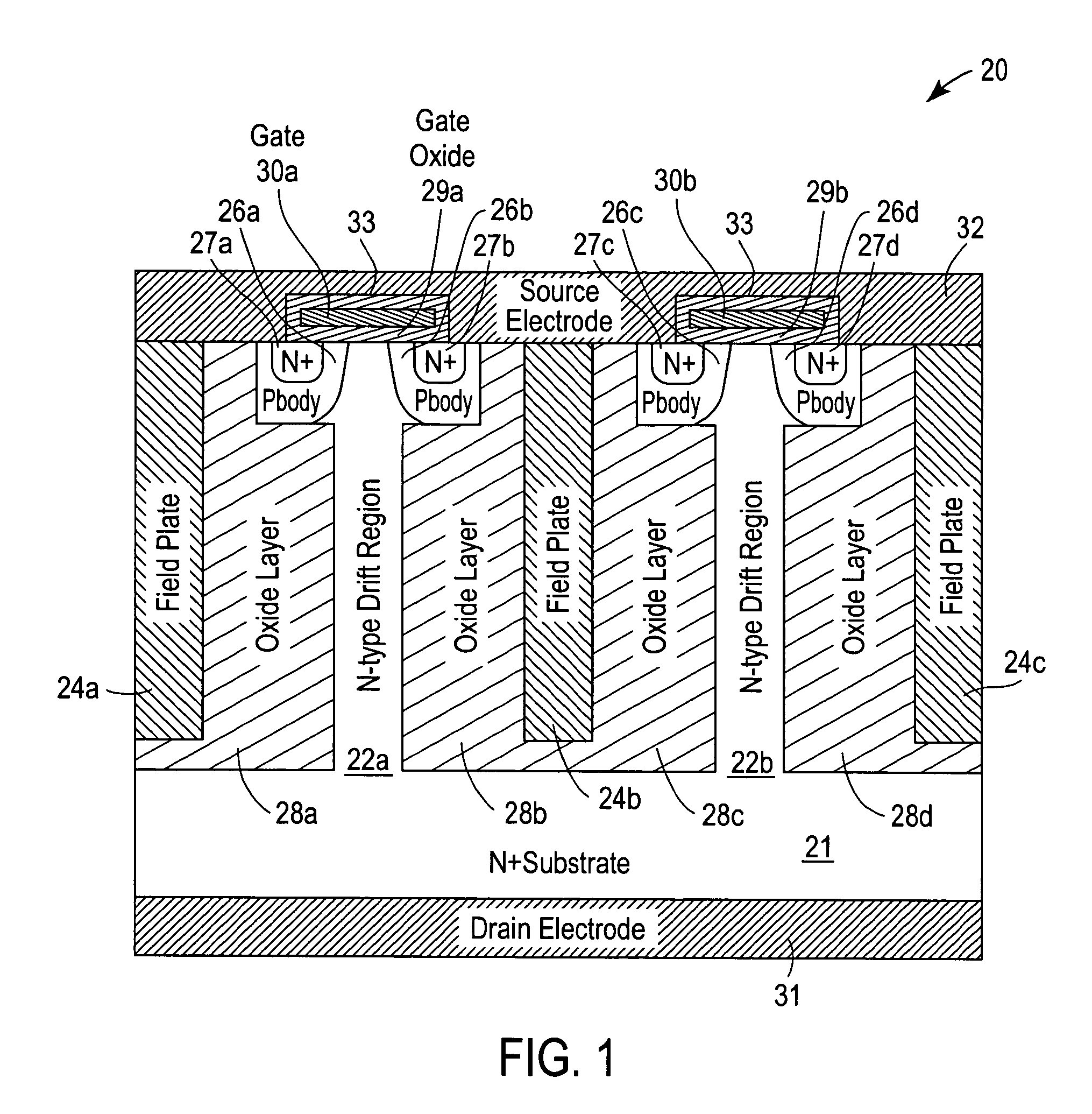

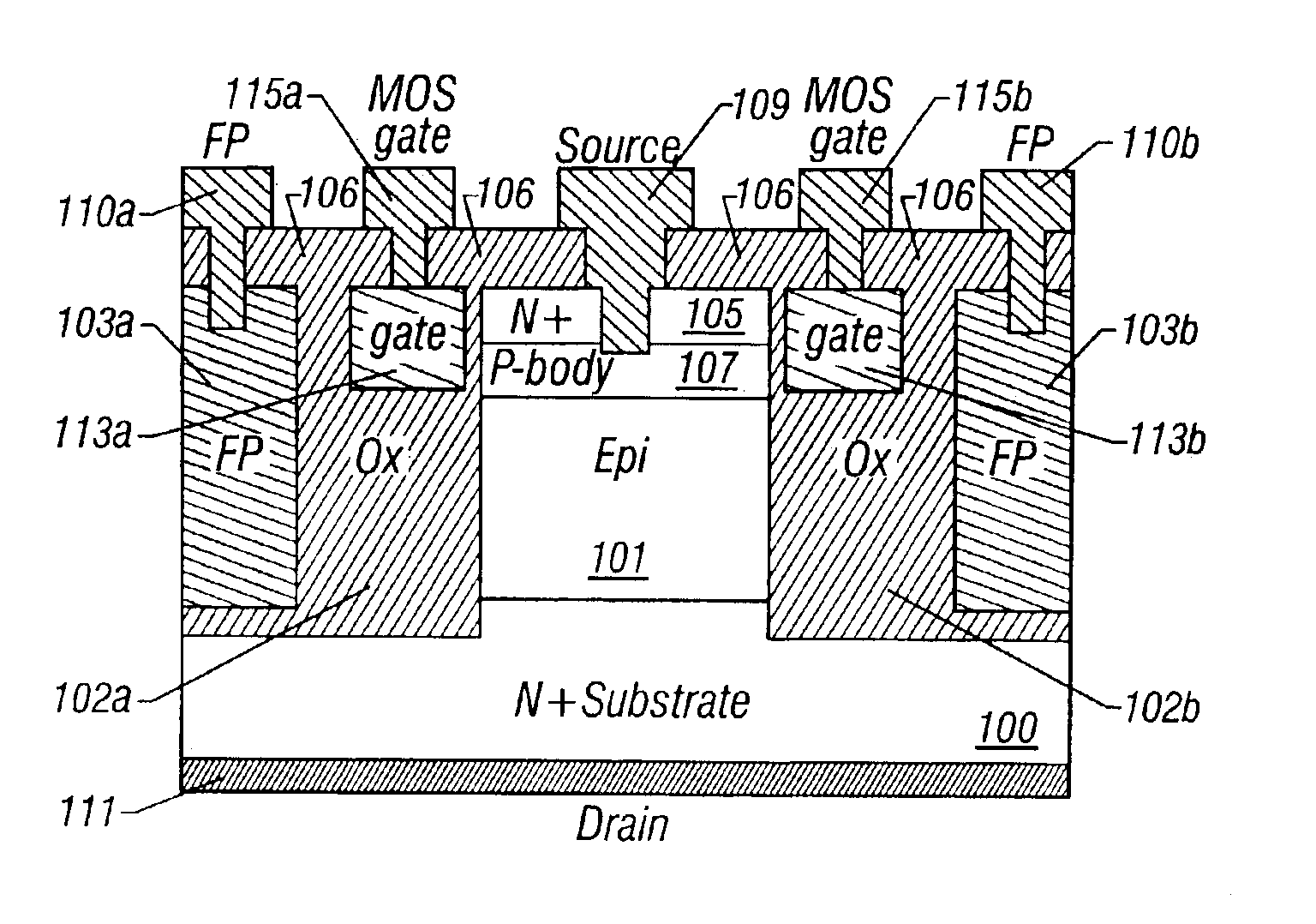

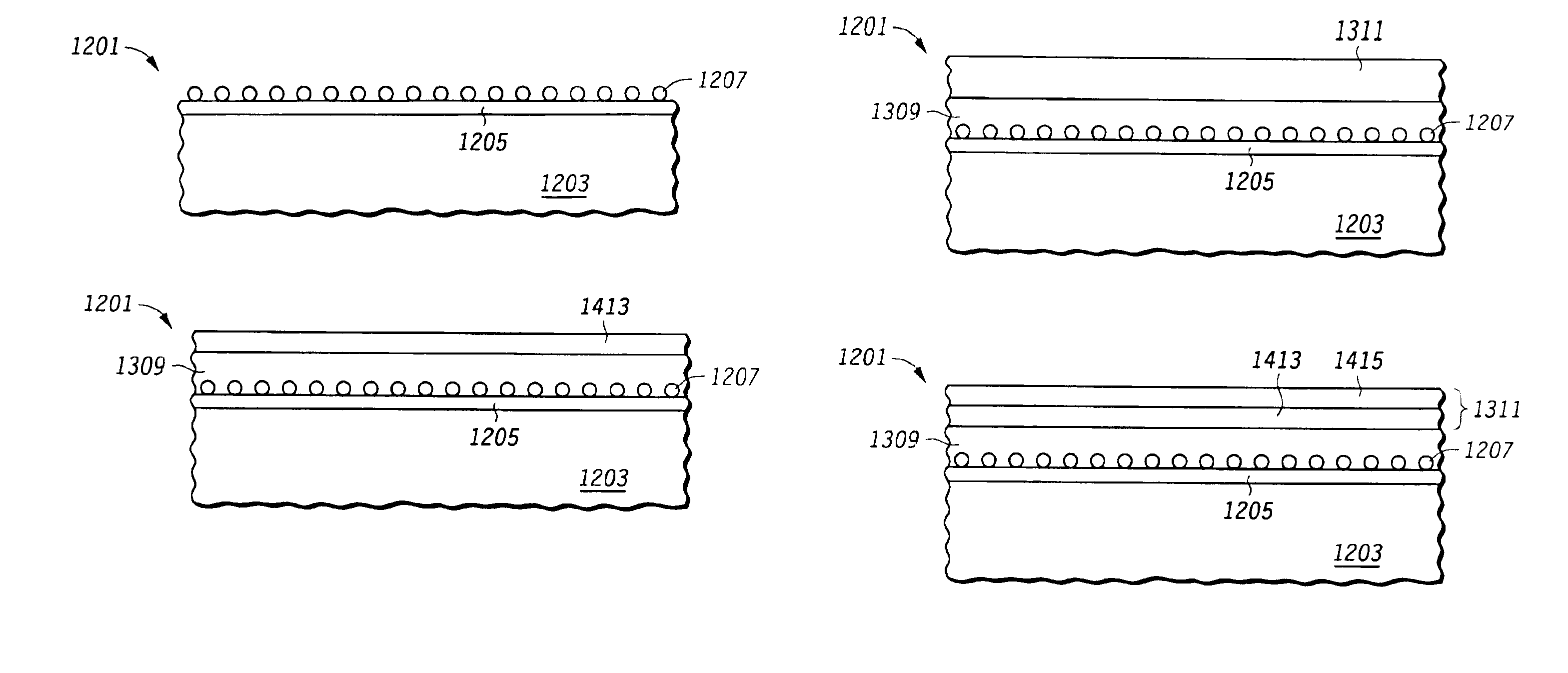

High-voltage vertical transistor with a multi-layered extended drain structure

A high-voltage transistor with a low specific on-state resistance and that supports high voltage in the off-state includes one or more source regions disposed adjacent to a multi-layered extended drain structure which comprises extended drift regions separated from field plate members by one or more dielectric layers. With the field plate members at the lowest circuit potential, the transistor supports high voltages applied to the drain in the off-state. The layered structure may be fabricated in a variety of orientations. A MOSFET structure may be incorporated into the device adjacent to the source region, or, alternatively, the MOSFET structure may be omitted to produce a high-voltage transistor structure having a stand-alone drift region.

Owner:POWER INTEGRATIONS INC

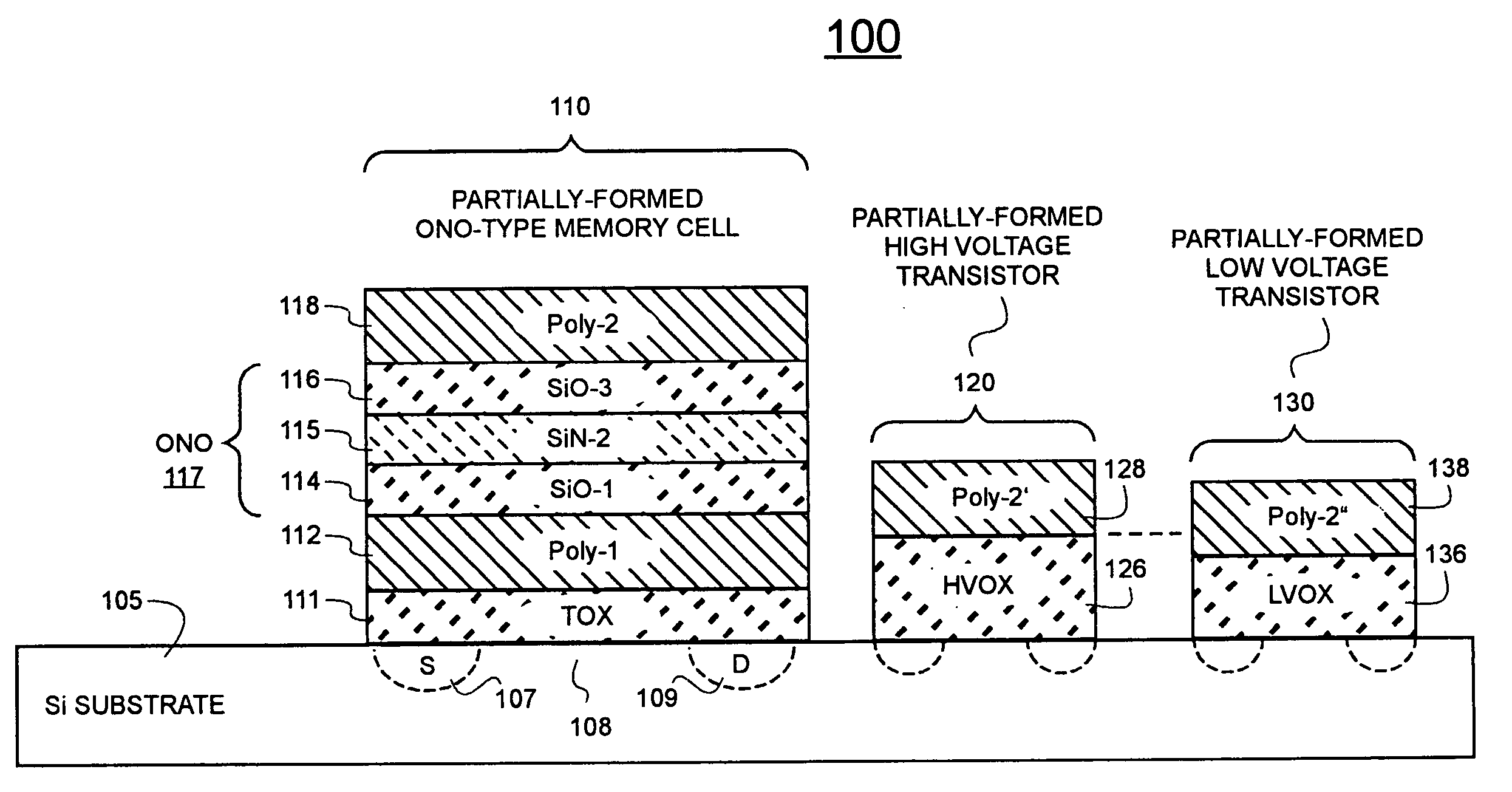

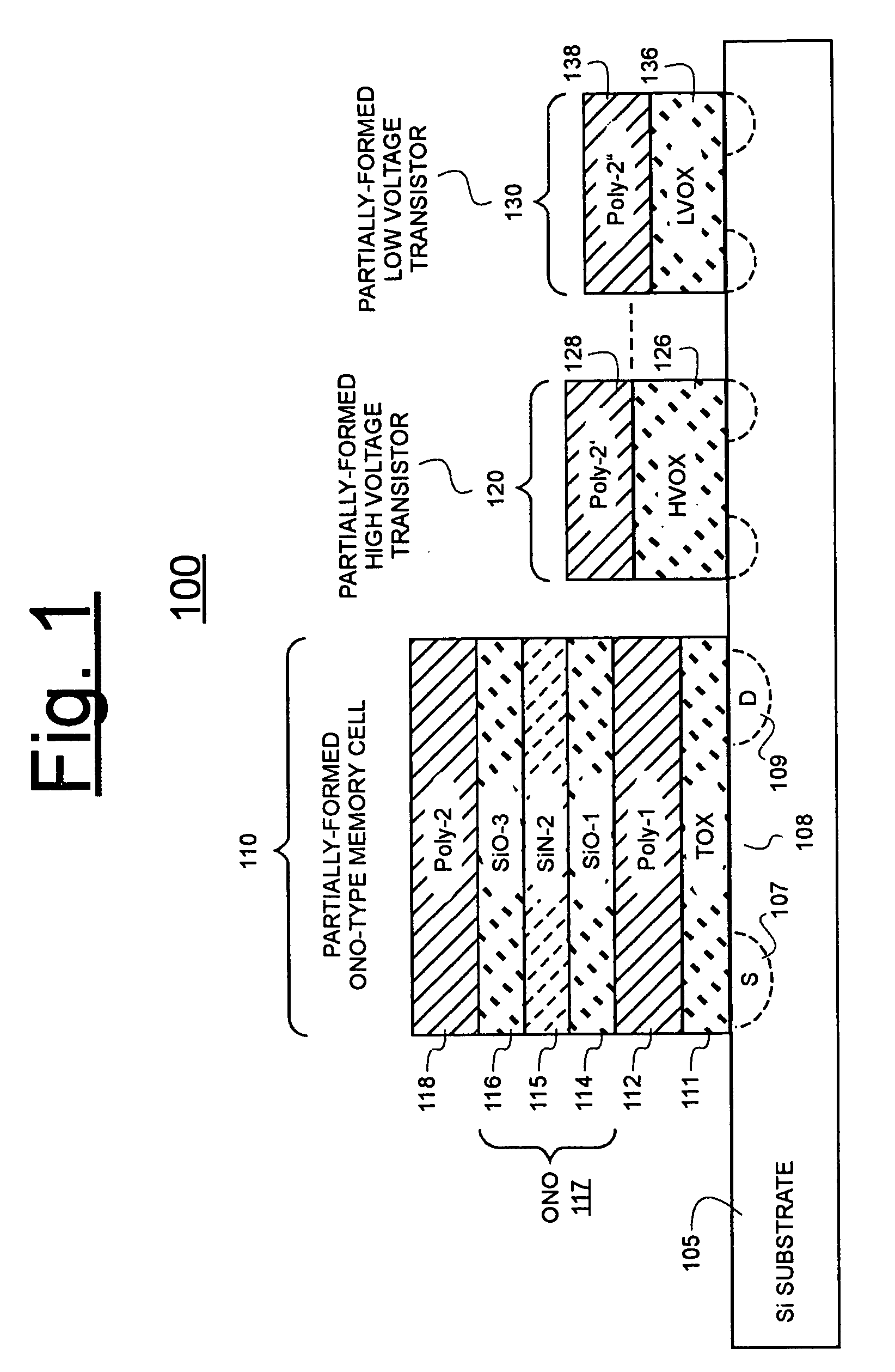

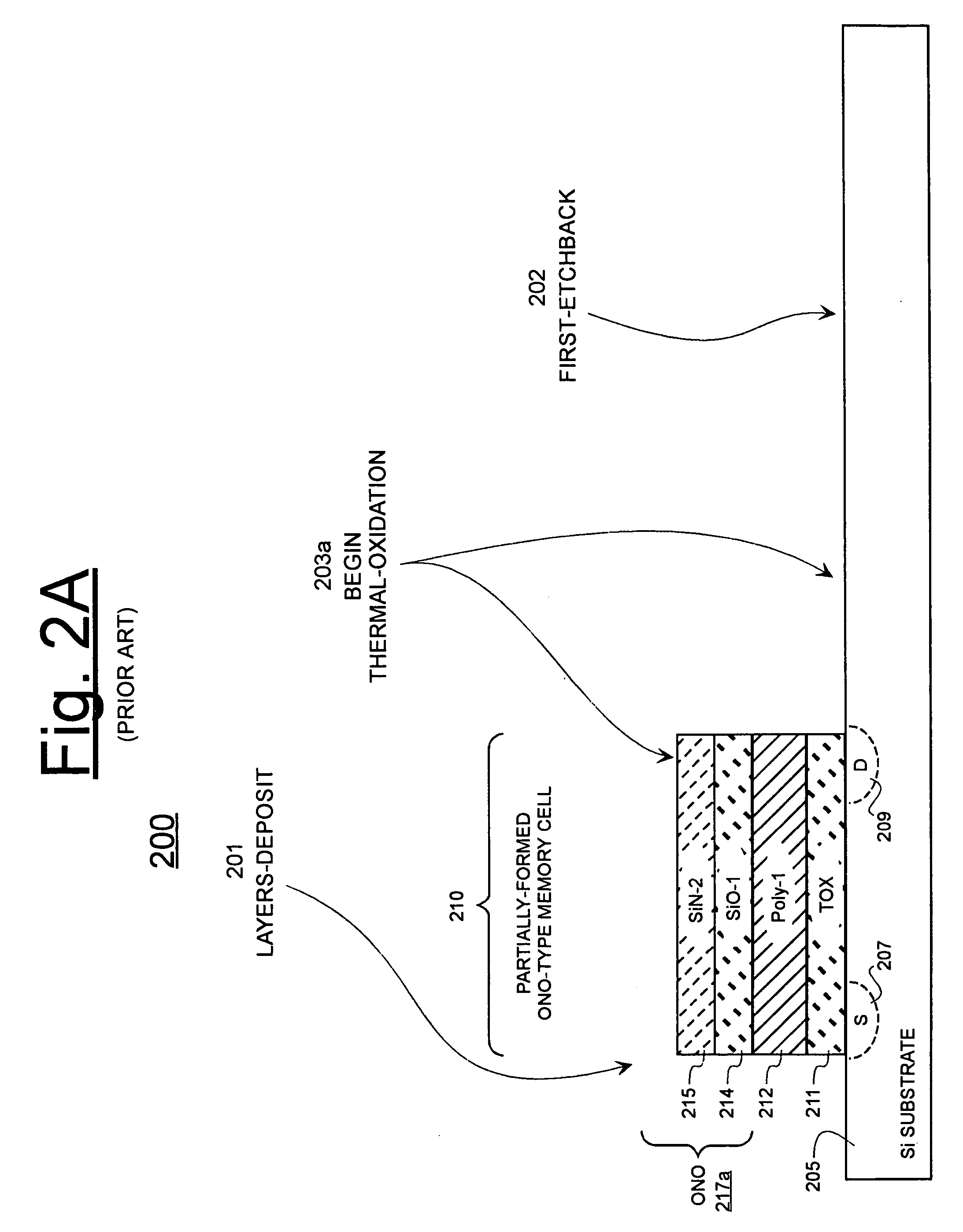

Method for simultaneously fabricating ONO-type memory cell, and gate dielectrics for associated high voltage write transistors and gate dielectrics for low voltage logic transistors by using ISSG

ActiveUS20060017092A1Solid-state devicesSemiconductor/solid-state device manufacturingDielectricGate dielectric

Conventional fabrication of top oxide in an ONO-type memory cell stack usually produces Bird's Beak. Certain materials in the stack such as silicon nitrides are relatively difficult to oxidize. As a result oxidation does not proceed uniformly along the multi-layered height of the ONO-type stack. The present disclosure shows how radical-based fabrication of top-oxide of an ONO stack (i.e. by ISSG method) can help to reduce formation of Bird's Beak. More specifically, it is indicated that short-lived oxidizing agents (e.g., atomic oxygen) are able to better oxidize difficult to oxidize materials such as silicon nitride and the it is indicated that the short-lived oxidizing agents alternatively or additionally do not diffuse deeply through already oxidized layers of the ONO stack such as the lower silicon oxide layer. As a result, a more uniform top oxide dielectric can be fabricated with more uniform breakdown voltages along its height. Additionally, adjacent low and high voltage transistors may benefit from simultaneous formation of their gate dielectrics with use of the radical-based oxidizing method.

Owner:PROMOS TECH INC

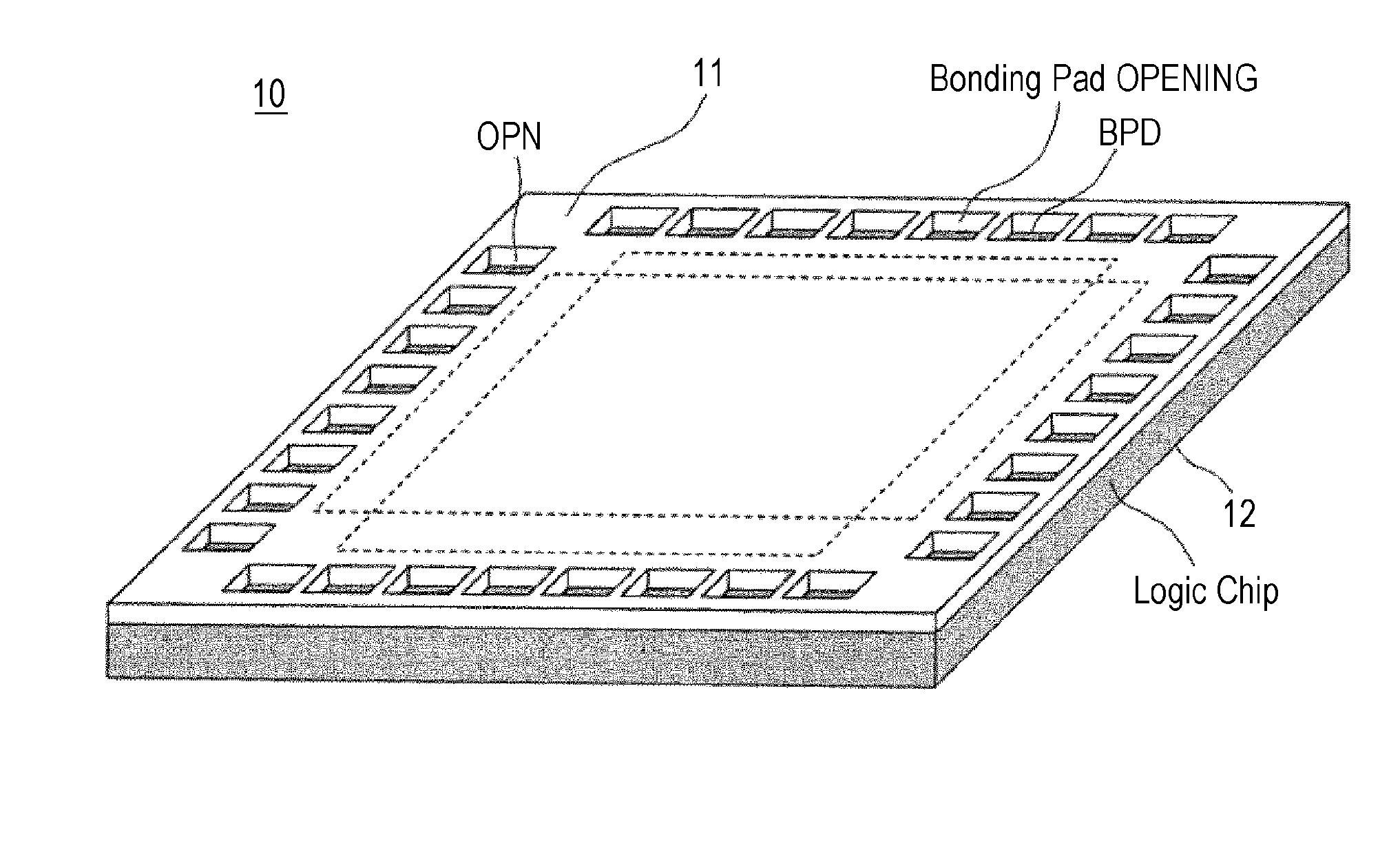

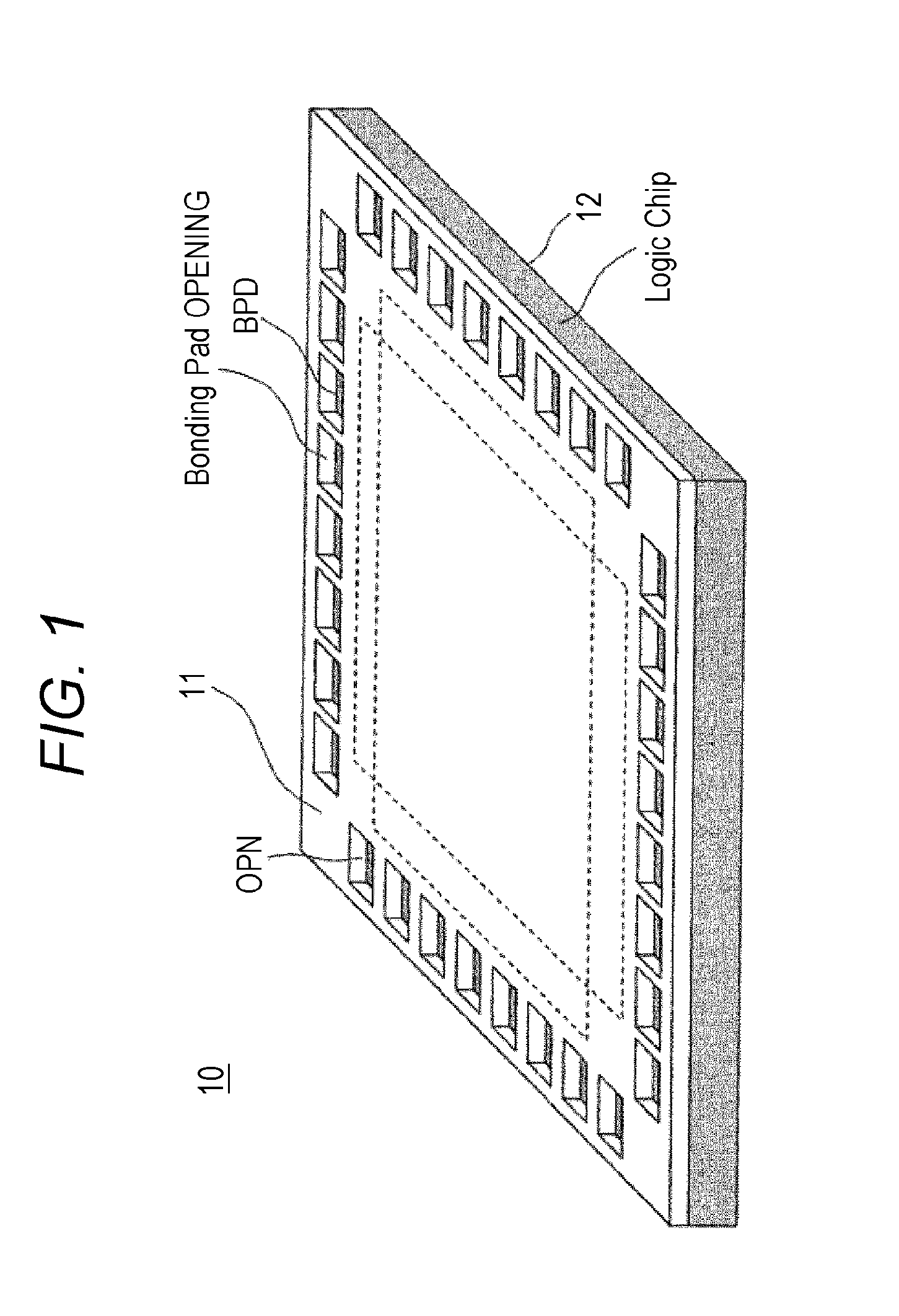

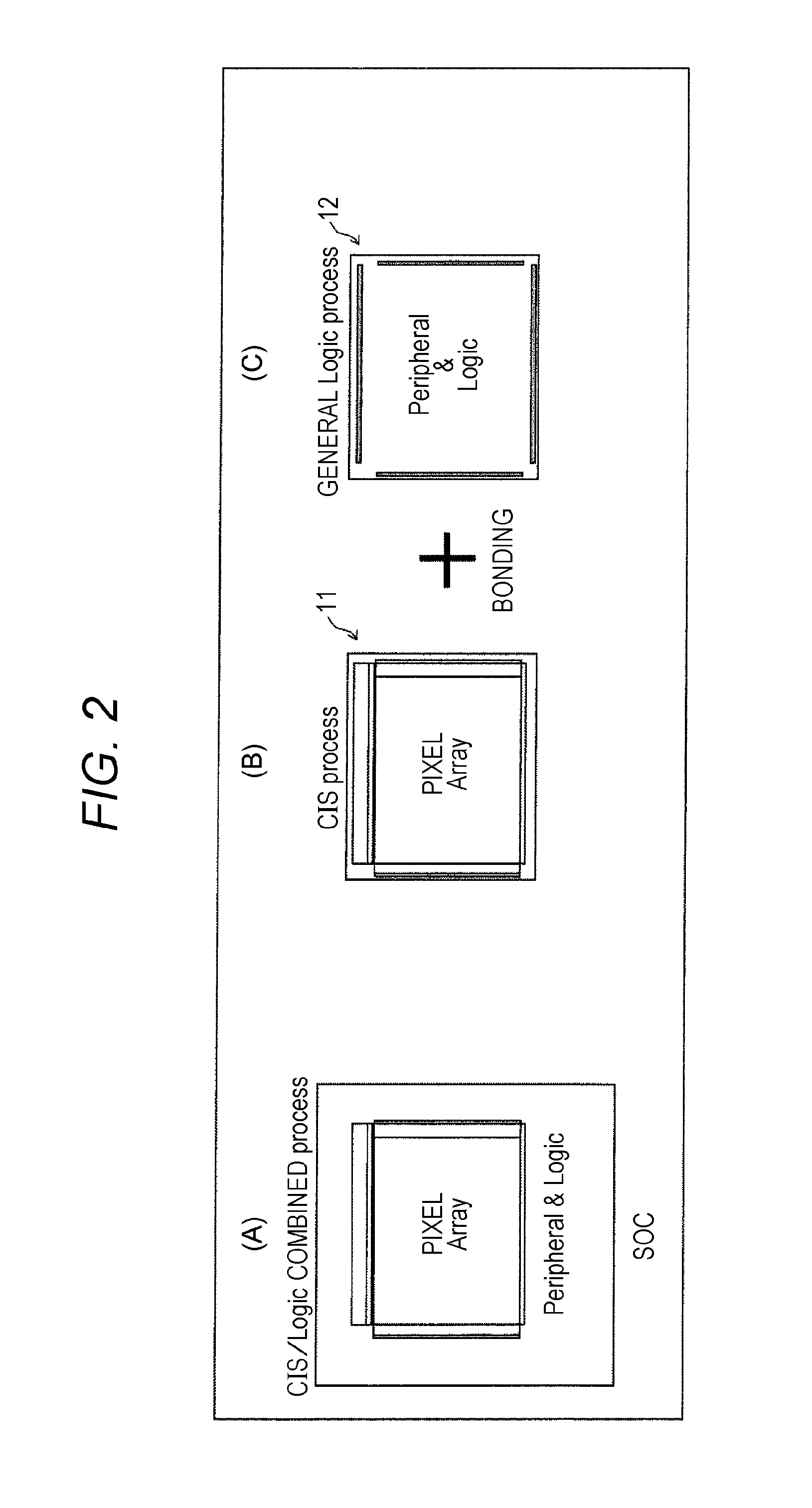

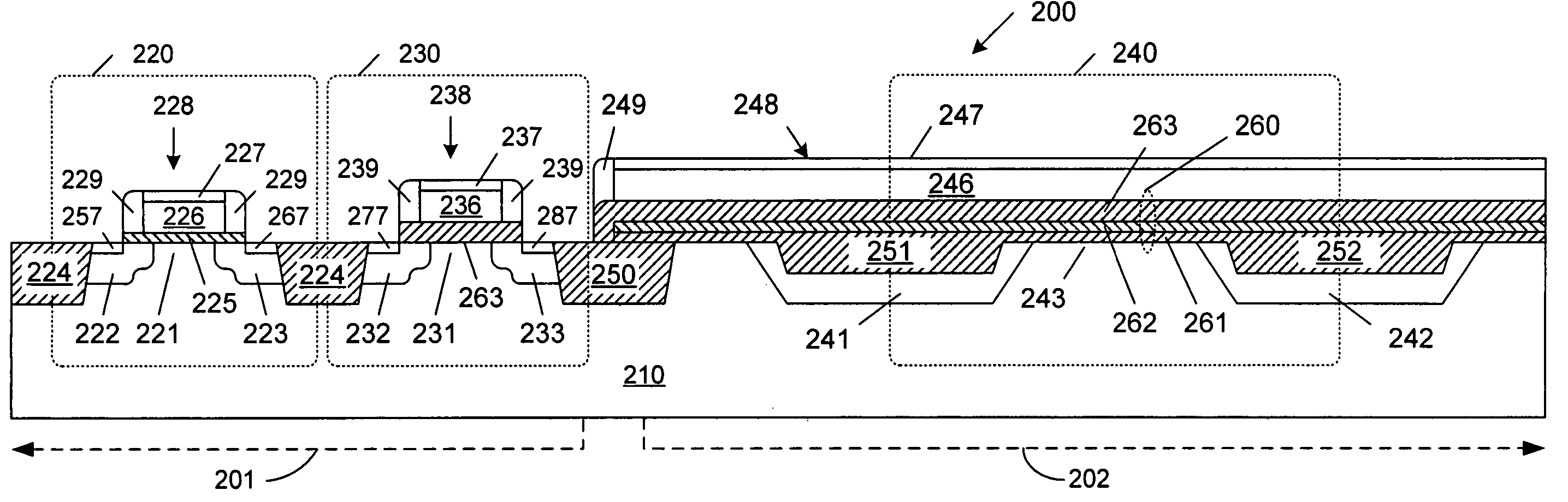

Semiconductor device, solid-state image sensor and camera system

InactiveUS20120293698A1Noise influencingLow costTelevision system detailsTelevision system scanning detailsPower semiconductor deviceHigh voltage transistors

The present invention relates to a semiconductor device, a solid-state image sensor and a camera system capable of reducing the influence of noise at a connection between chips without a special circuit for communication and reducing the cost as a result. The semiconductor device includes: a first chip 11; and a second chip 12, wherein the first chip 11 and the second chip 12 are bonded to have a stacked structure, the first chip 11 has a high-voltage transistor circuit mounted thereon, the second chip 12 has mounted thereon a low-voltage transistor circuit having lower breakdown voltage than the high-voltage transistor circuit, and wiring between the first chip and the second chip is connected through a via formed in the first chip.

Owner:SONY CORP

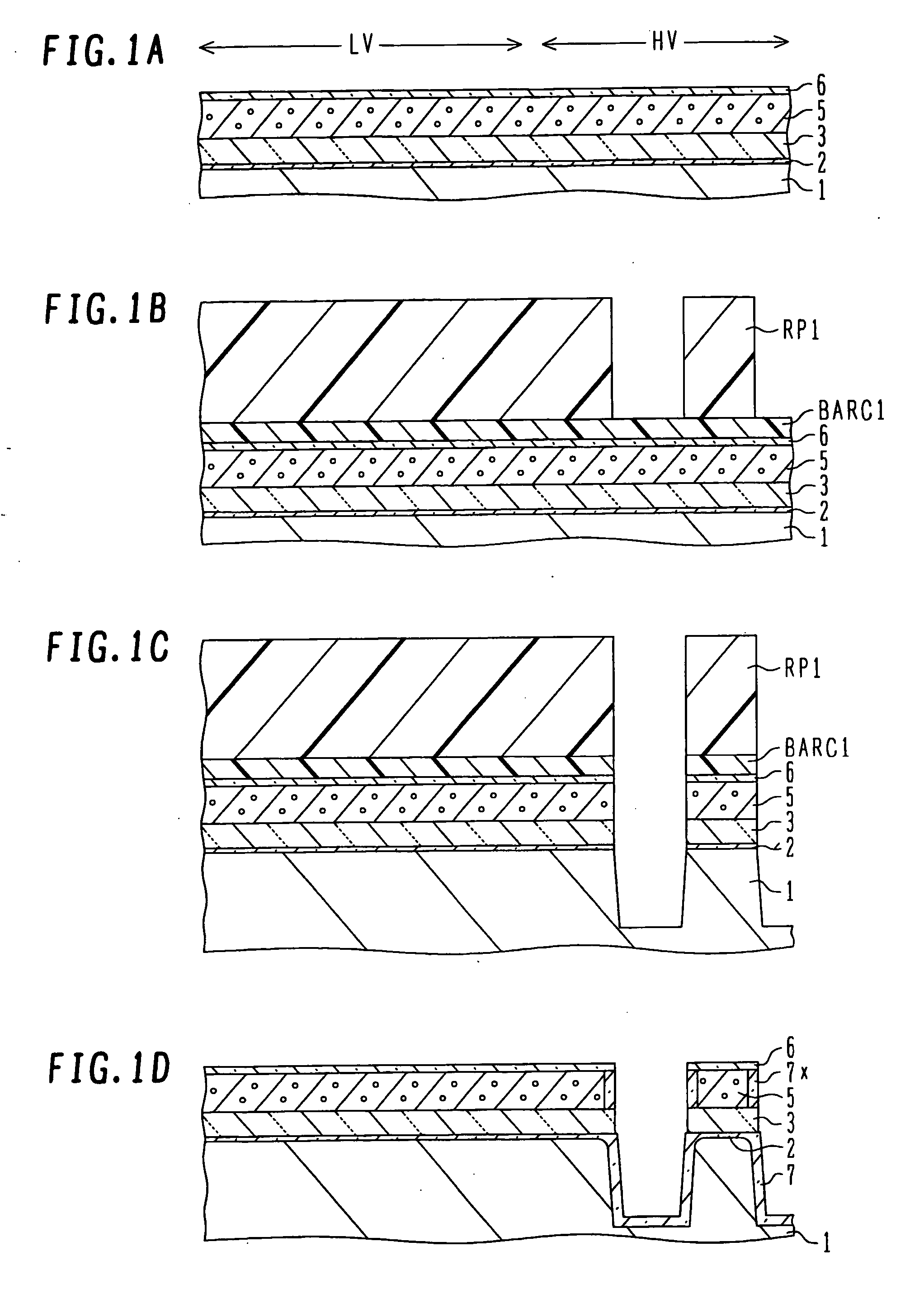

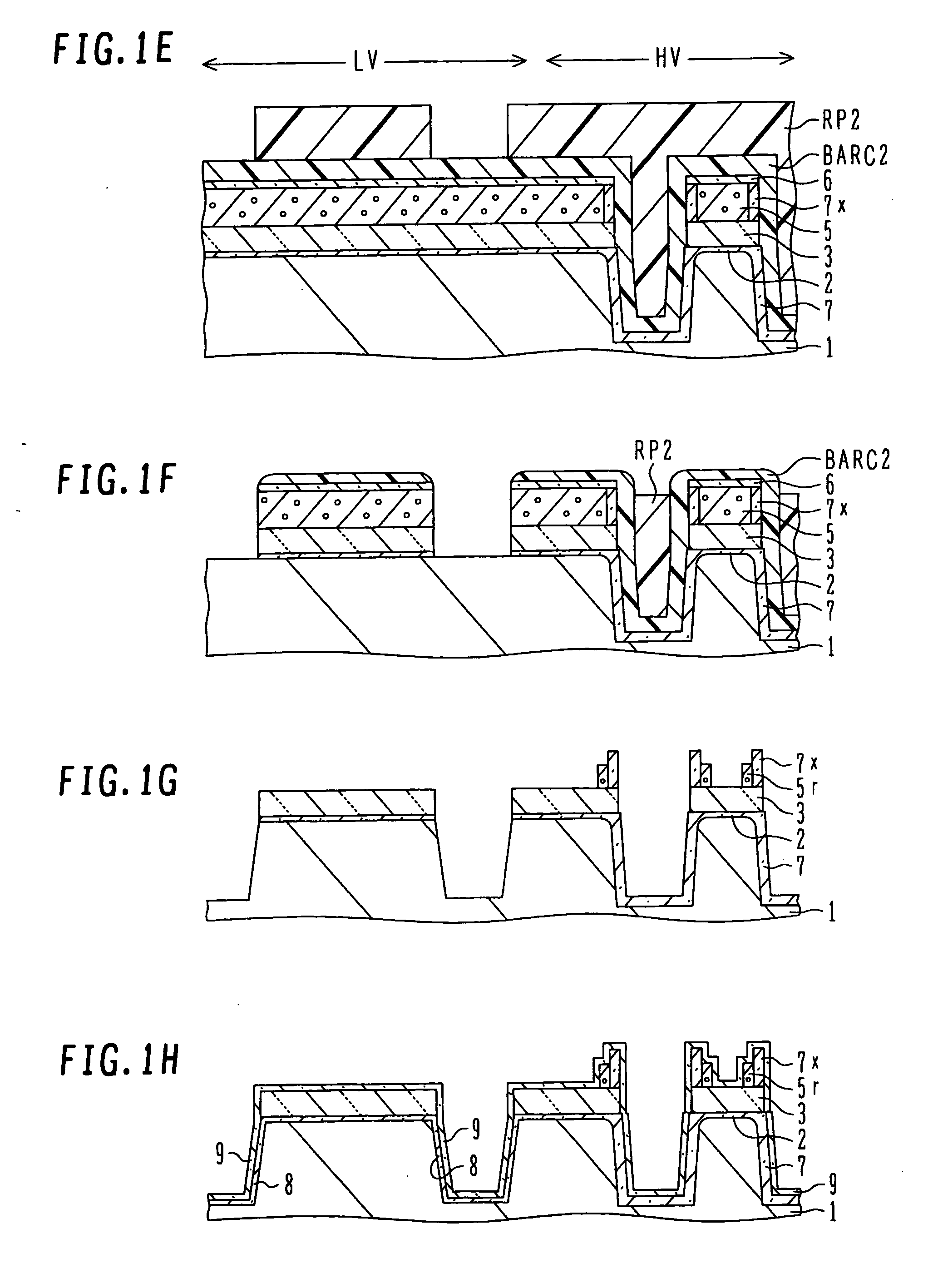

SONOS embedded memory with CVD dielectric

InactiveUS20050186741A1Faster rateRegion of becomes thinSolid-state devicesSemiconductor/solid-state device manufacturingCMOSBit line

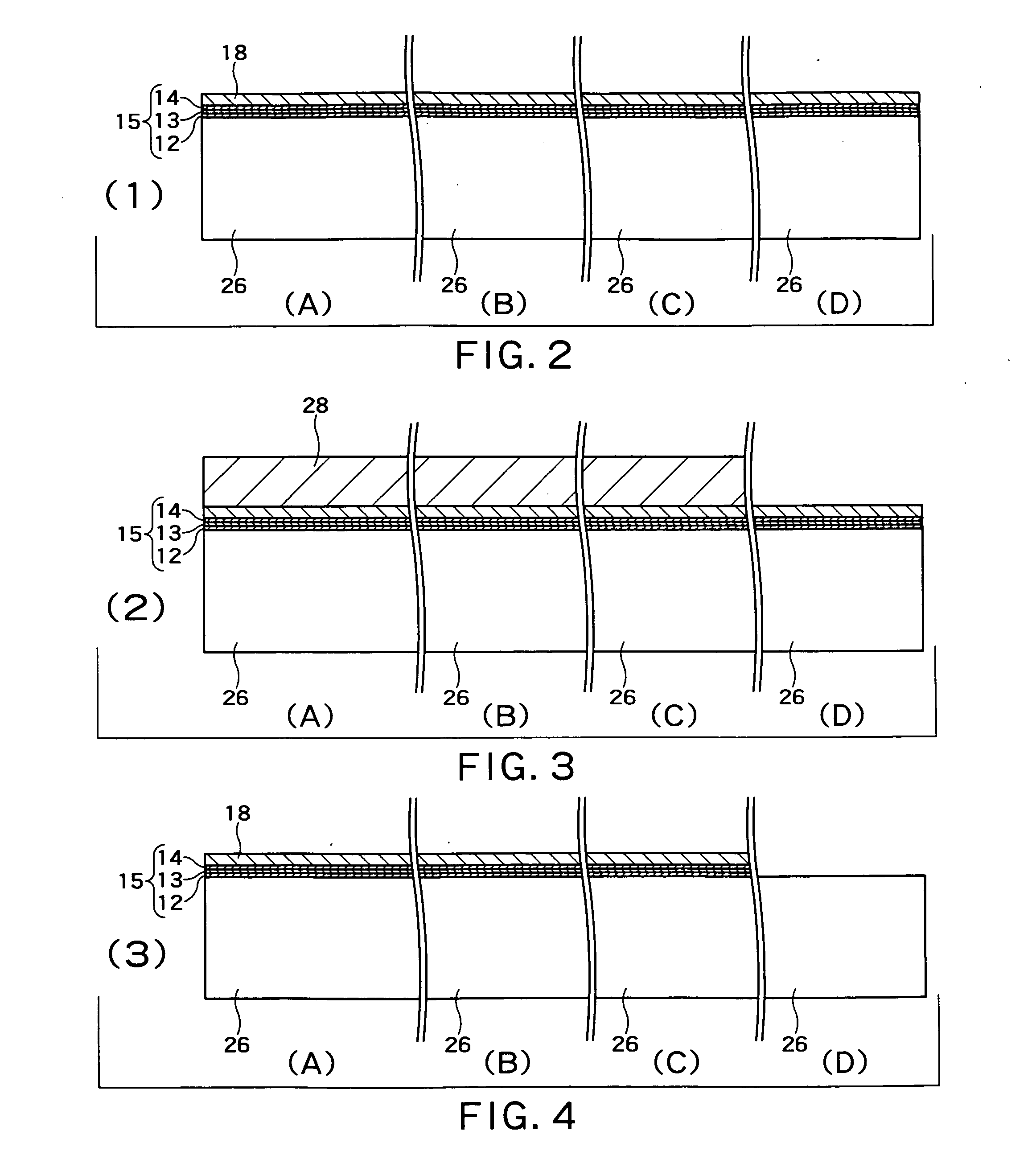

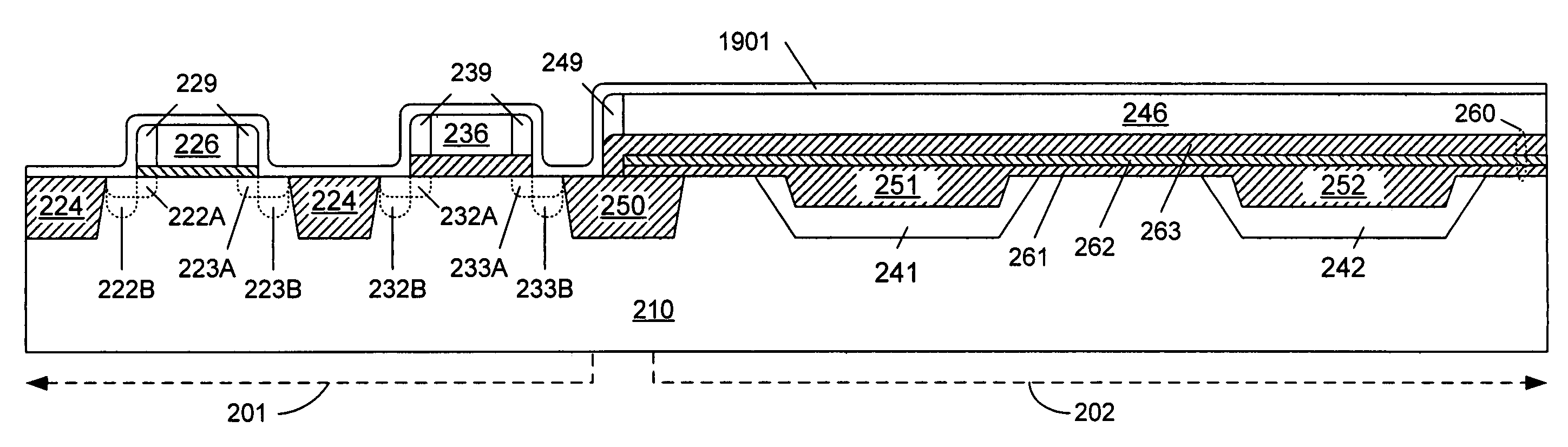

An embedded semiconductor memory is fabricated by: forming diffusion bit line regions in a semiconductor substrate; then thermally oxidizing the upper surface of the substrate, thereby forming a bottom oxide layer over the substrate and simultaneously forming bit line oxide regions over each of the diffusion bit line regions; and then forming an intermediate dielectric layer (e.g., silicon nitride), over the bottom oxide layer and the bit line oxide regions. CMOS well implants are then performed in a CMOS section of the device through the silicon nitride layer and bottom oxide layer. The silicon nitride layer and bottom oxide layer are then removed in the CMOS section, and a top dielectric layer, such as a high-temperature oxide or a high-k dielectric, is deposited. The top dielectric layer completes a memory stack of the memory device, and forms a gate dielectric layer of a high voltage transistor in the CMOS section.

Owner:PS4 LUXCO SARL

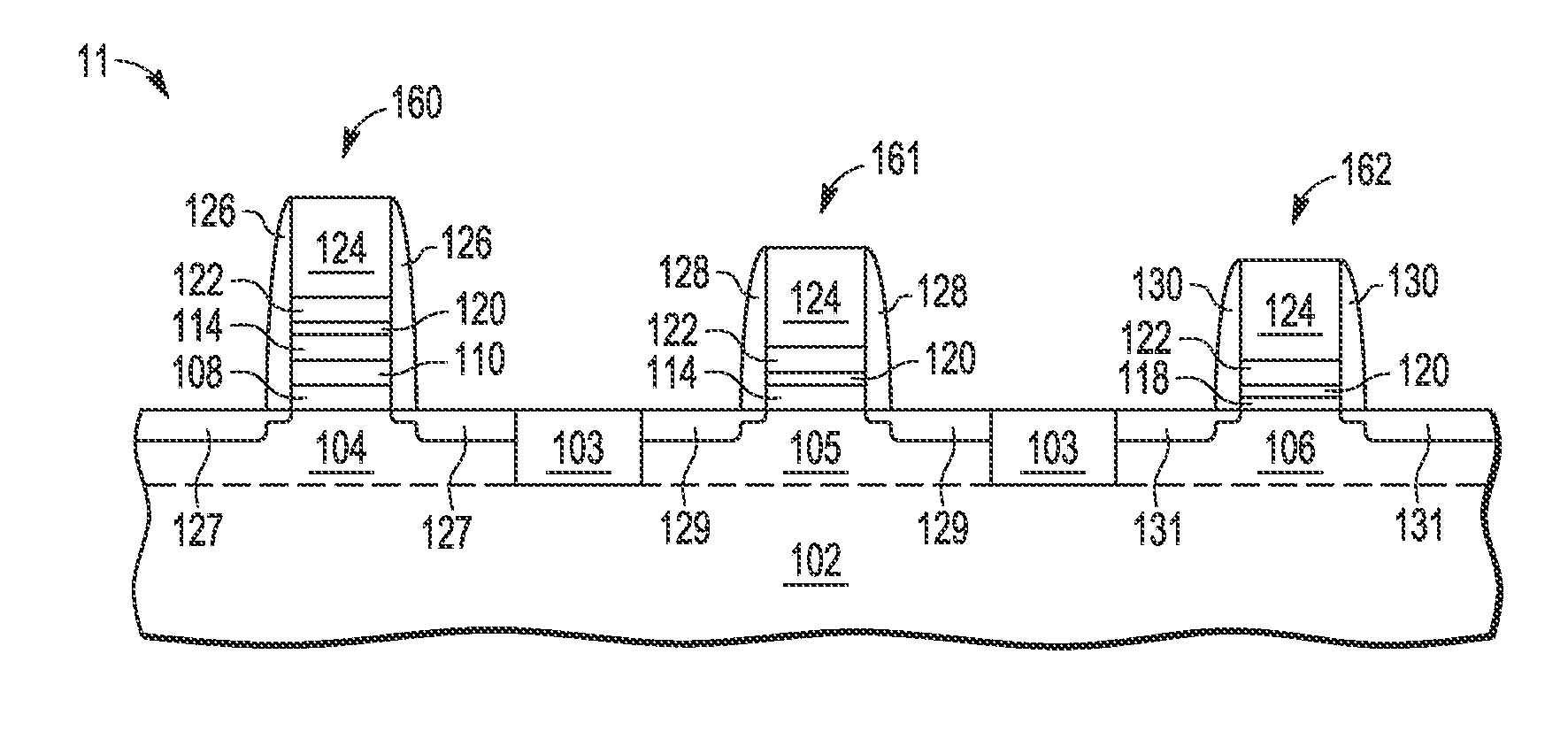

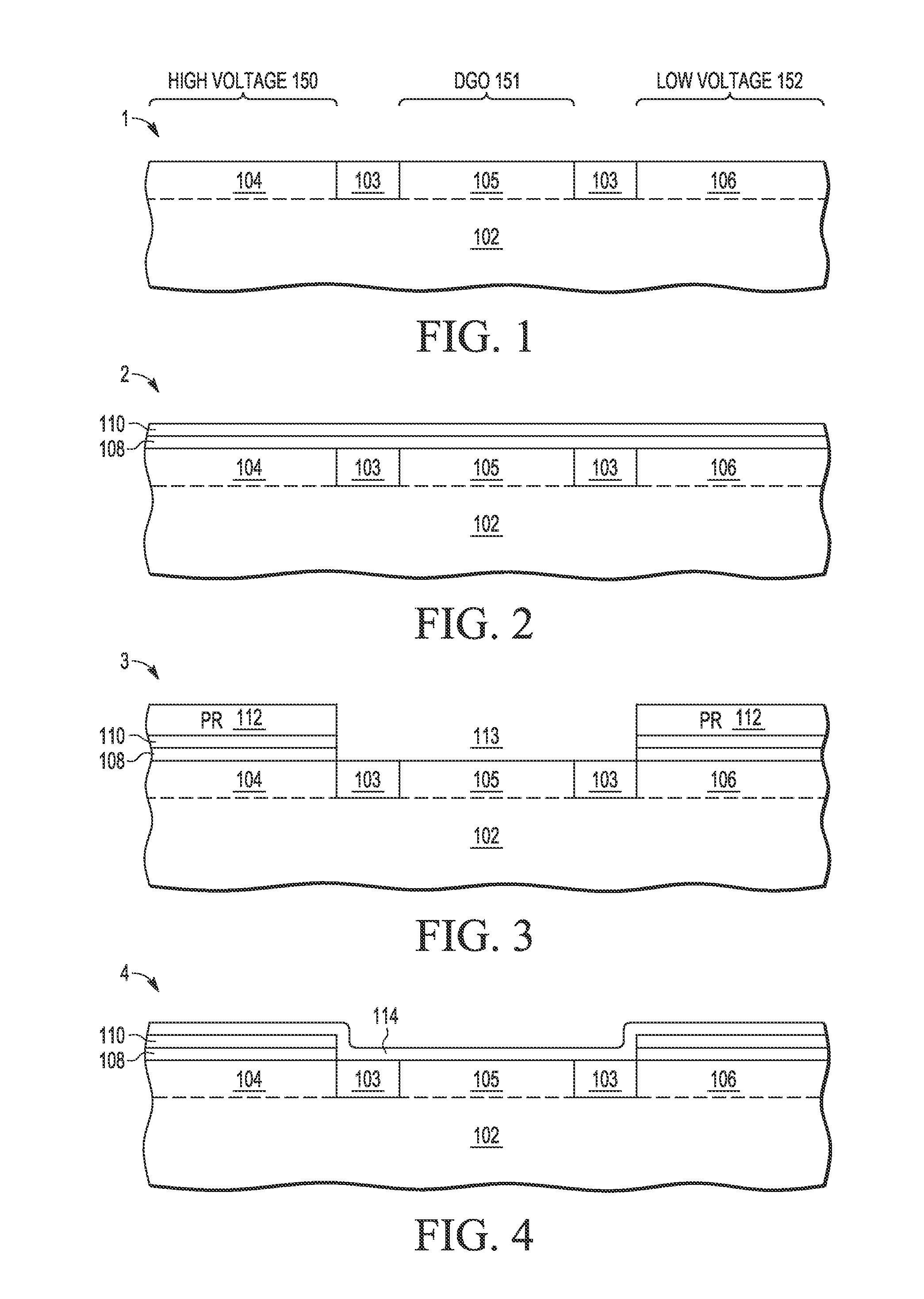

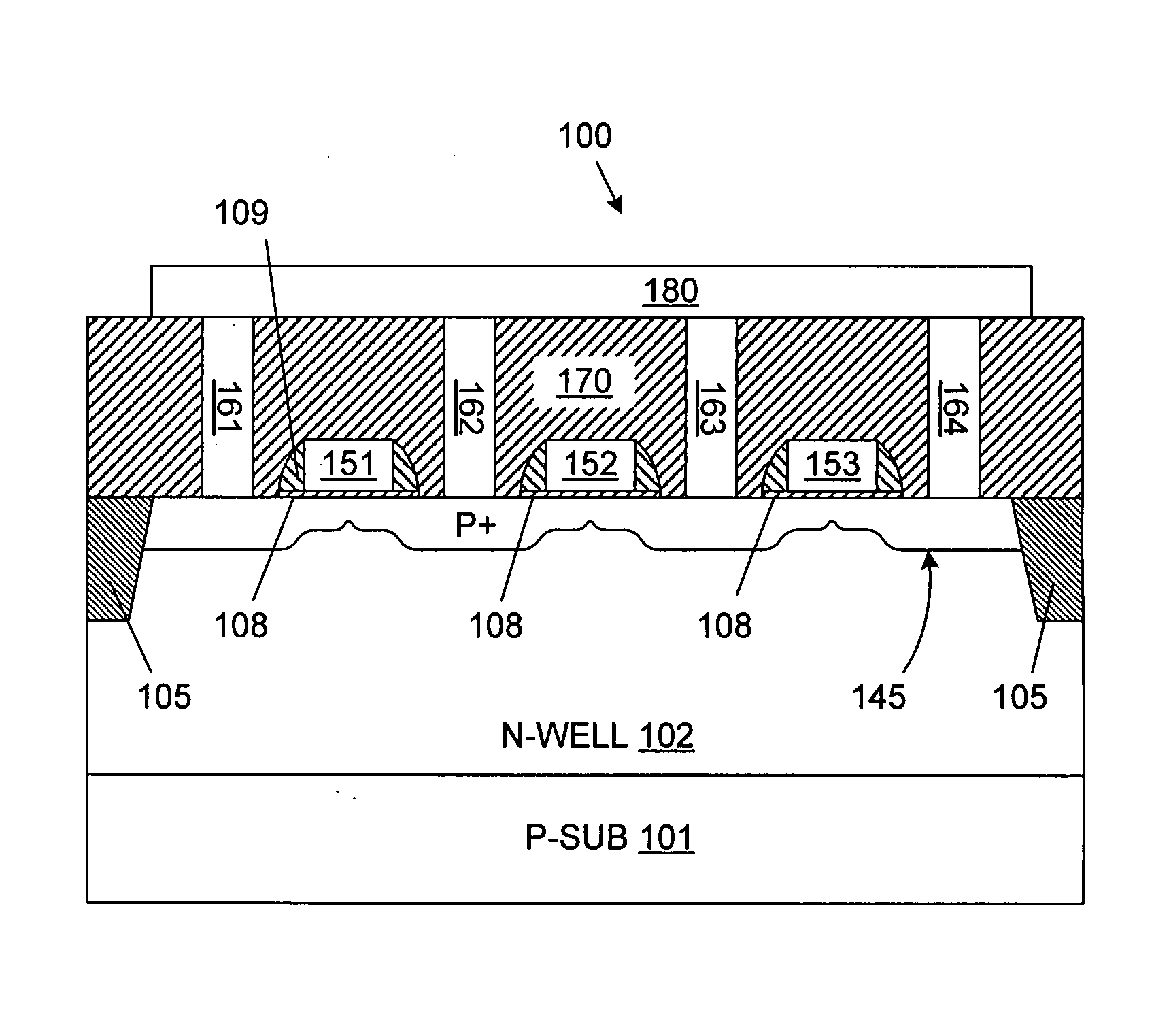

Method of Forming Different Voltage Devices with High-K Metal Gate

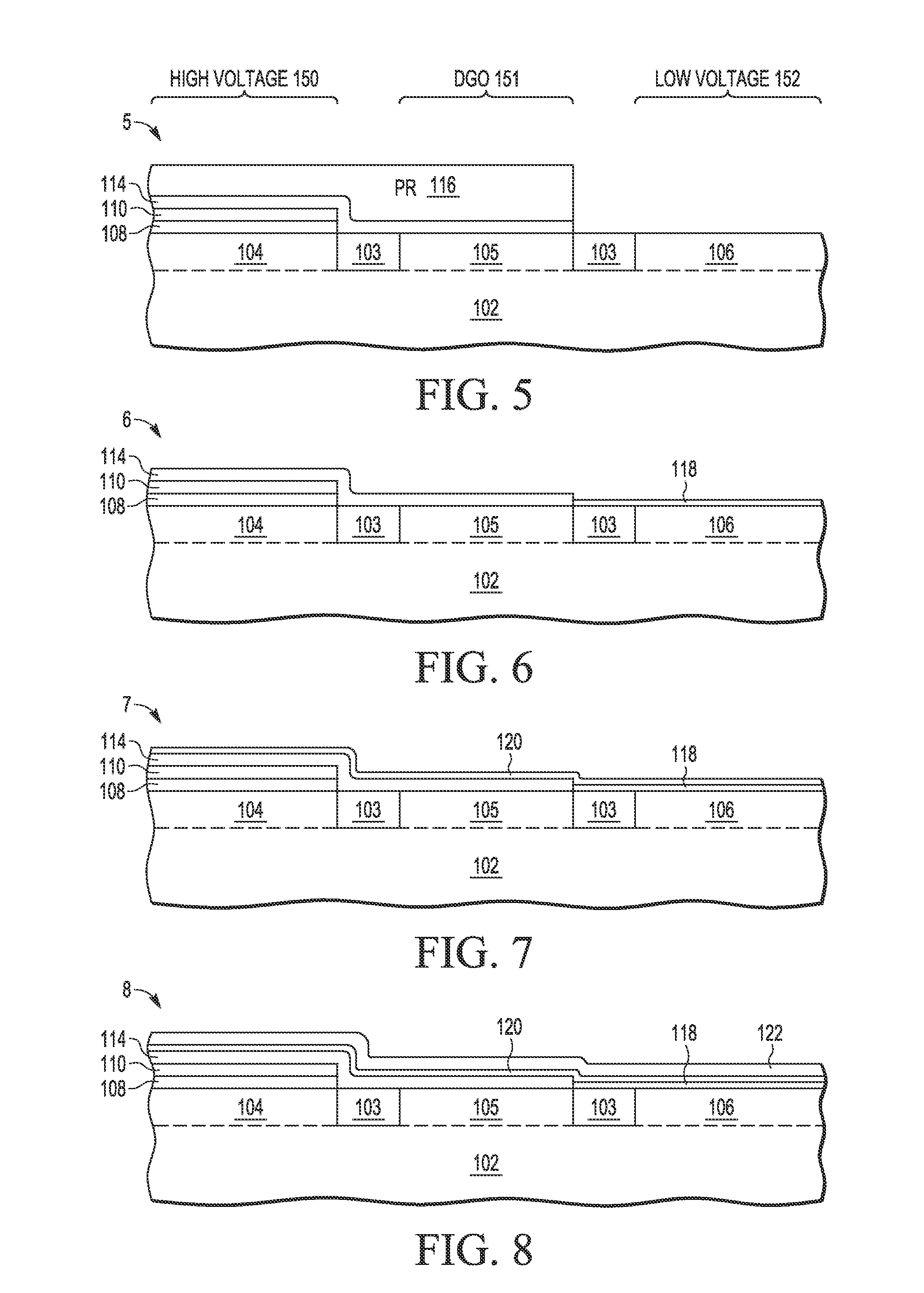

A method and apparatus are described for integrating high voltage (HV) transistor devices and medium voltage or dual gate oxide (DGO) transistor devices with low voltage (LV) core transistor devices on a single substrate, where each high voltage transistor device (160) includes a metal gate (124), an upper high-k gate dielectric layer (120), a middle gate dielectric layer (114) formed with a relatively lower high-k dual gate oxide layer, and a lower high voltage gate dielectric stack (108, 110) formed with one or more low-k gate oxide layers (22), where each DGO transistor device (161) includes a metal gate (124), an upper high-k gate dielectric layer (120), and a middle gate dielectric layer (114) formed with a relatively lower high-k dual gate oxide layer, and where each core transistor device (162) includes a metal gate (124), an upper high-k gate dielectric layer (120), and a base oxide layer (118) formed with one or more low-k gate oxide layers.

Owner:VLSI TECH LLC

Method of fabricating a high-voltage transistor with a multi-layered extended drain structure

A method for fabricating a high-voltage transistor with an extended drain region includes forming an epitaxial layer on a substrate, the epitaxal layer and the substrate being of a first conductivity type; then etching the epitaxial layer to form a pair of spaced-apart trenches that define first and second sidewall portions of the epitaxial layer. A dielectric layer is formed that partially fills each of the trenches, covering the first and second sidewall portions. The remaining portions of the trenches are then filled with a conductive material to form first and second field plate members that are insulated from the substrate and the epitaxial layer. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used o interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:POWER INTEGRATIONS INC

Method of fabricating a high-voltage transistor with an extended drain structure

Owner:POWER INTEGRATIONS INC

Three-dimensional control-gate architecture for single poly EPROM memory devices fabricated in planar CMOS technology

ActiveUS20070166912A1Increasing ratio of controlLarge capacitanceSolid-state devicesRead-only memoriesCMOSCapacitance

A capacitor for a single-poly floating gate device is fabricated on a semiconductor substrate along with low and high voltage transistors. Each transistor has a gate width greater than or equal to a minimum gate width of the associated process. A dielectric layer is formed over the substrate, and a patterned polysilicon structure is formed over the dielectric layer. The patterned polysilicon structure includes one or more narrow polysilicon lines, each having a width less than the minimum gate width. The LDD implants for low and high voltage transistors of the same conductivity type are allowed to enter the substrate, using the patterned polysilicon structure as a mask. A thermal drive-in cycle results in a continuous diffusion region that merges under the narrow polysilicon lines. Contacts formed adjacent to the narrow polysilicon lines and a metal-1 trace connected to the contacts may increase the resulting capacitance.

Owner:TOWER SEMICONDUCTOR

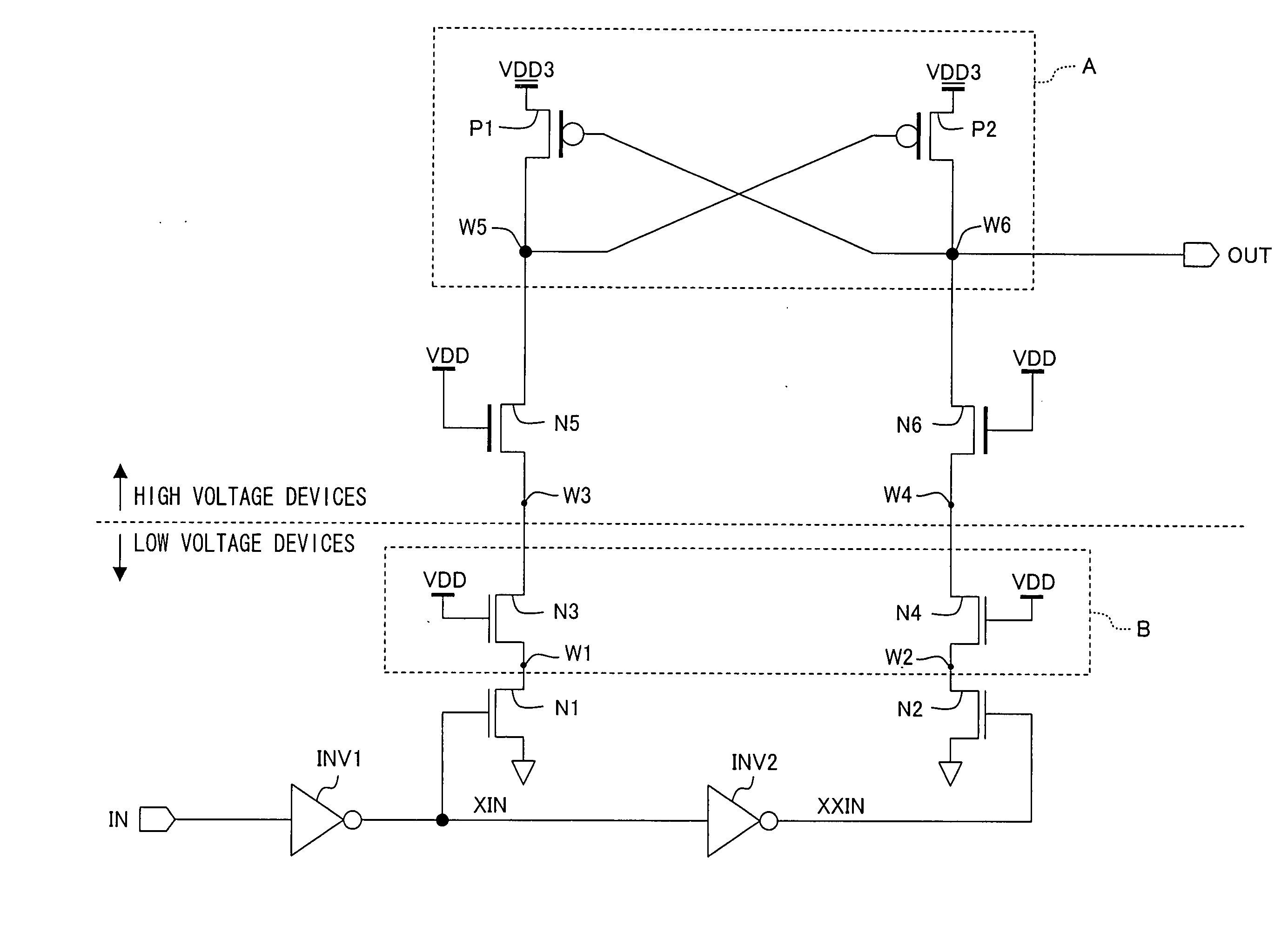

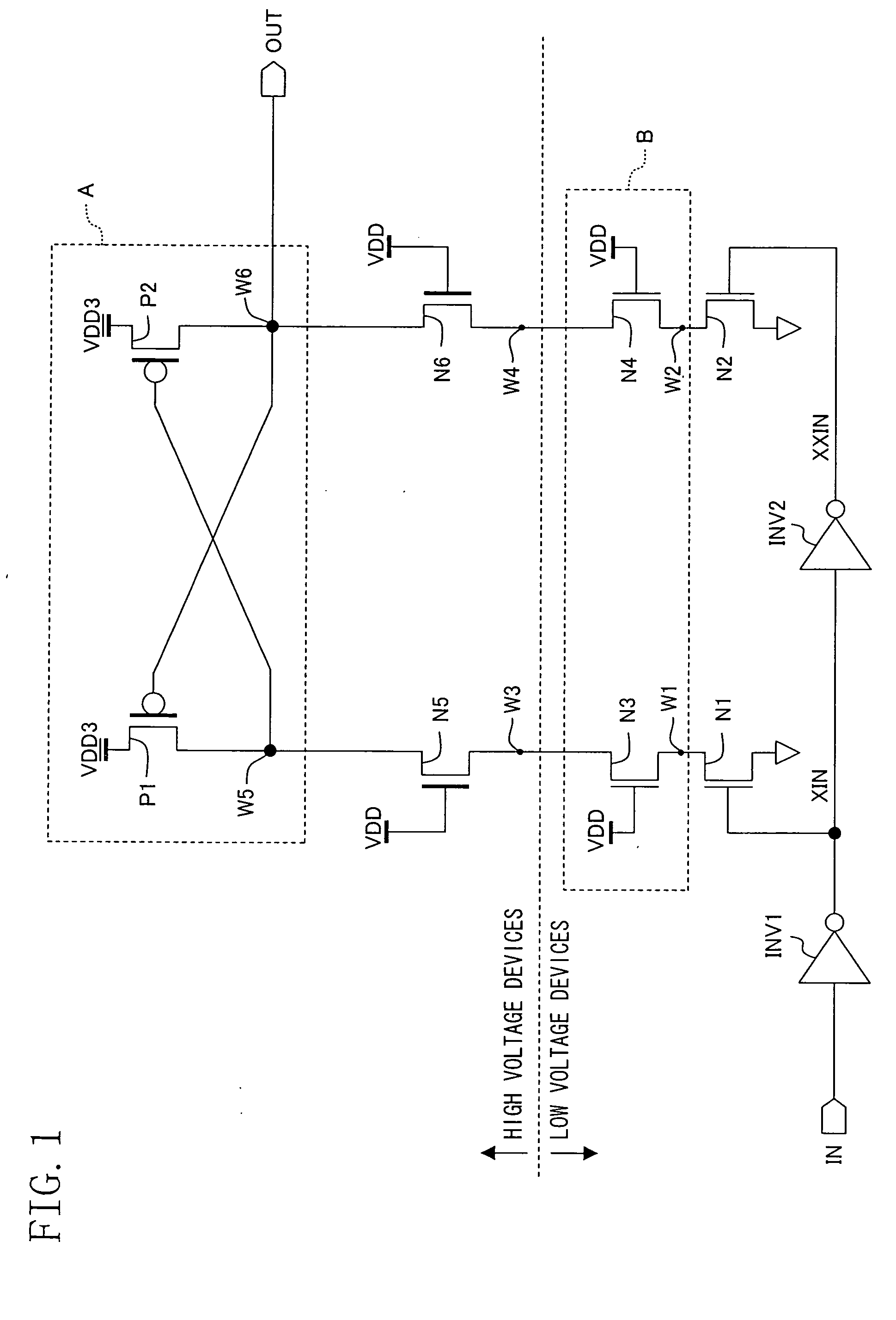

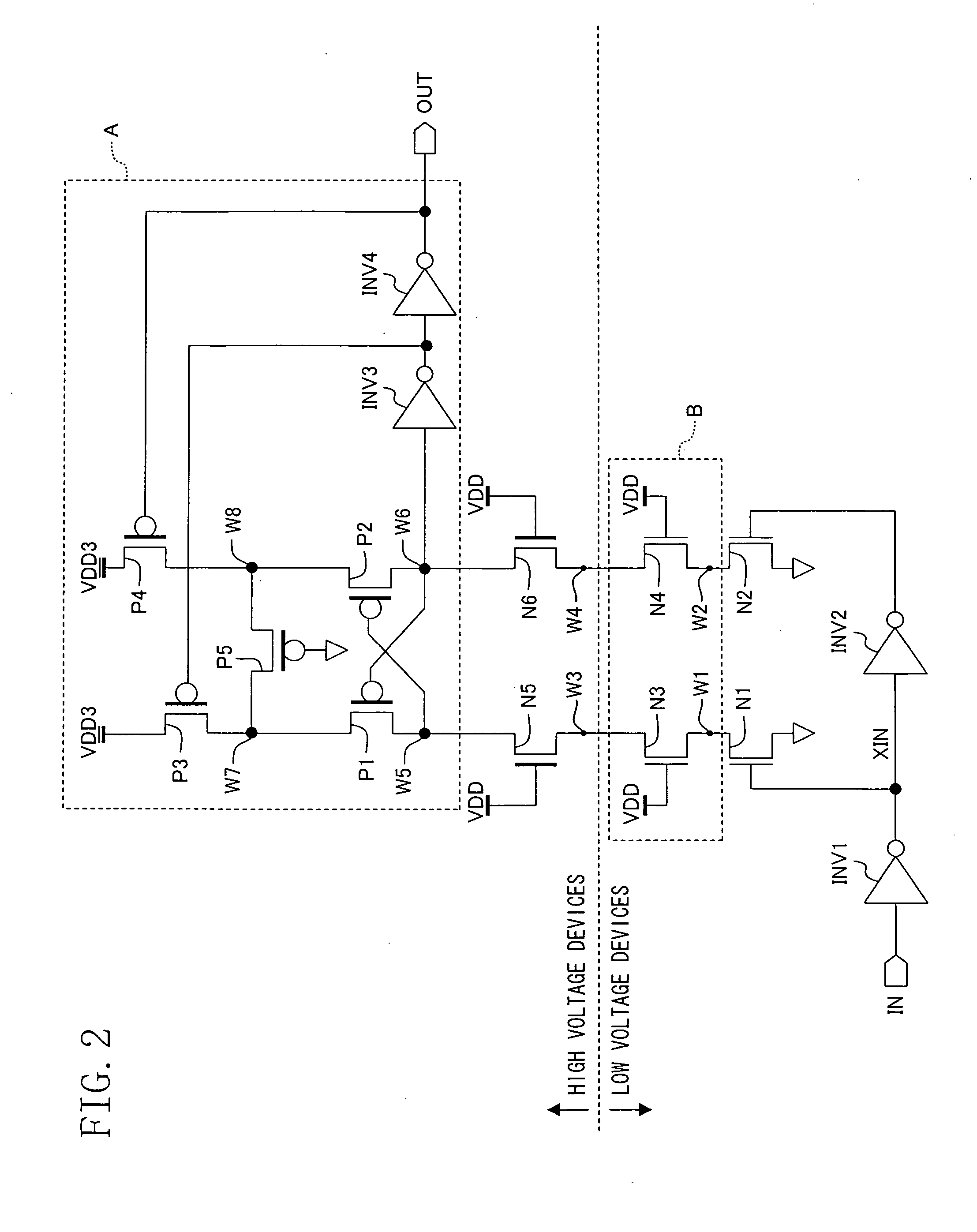

Level shift circuit

InactiveUS20050134355A1Avoid flowAvoid failurePulse automatic controlElectronic switchingReverse currentHigh voltage transistors

In a level shift circuit, the threshold voltage of N-type high-voltage transistors, to whose gates the voltage of a low-voltage supply VDD is applied, is set low. An input signal IN powered by the low-voltage supply VDD is input to the gate of an N-type transistor by way of an inverter. Therefore, even if the potentials at nodes W3 and W4 exceed the voltage of the low-voltage supply VDD, reverse current flow from the nodes W3 and W4 via parasitic diodes within the inverters into the low-voltage supply VDD is prevented. A protection circuit, composed of N-type transistor whose respective gates are fixed to the low-voltage supply VDD, is disposed between the two N-type high-voltage transistors N5, N6 and two N-type low-voltage transistors N1, N2 for receiving the complementary signals IN and XIN, thereby preventing the breakdown of those N-type complementary-signal-receiving transistors.

Owner:PANASONIC CORP

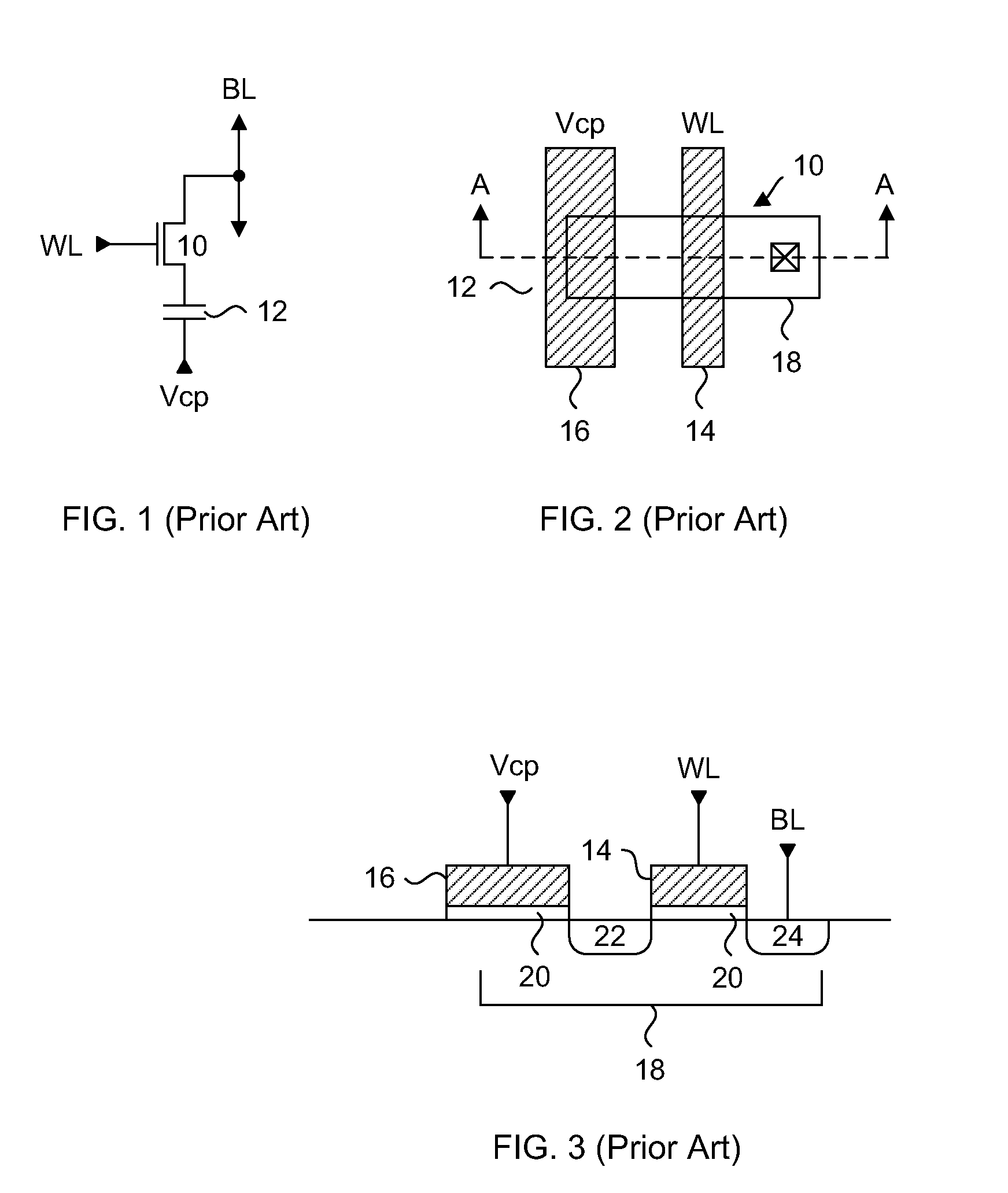

Low vt antifuse device

ActiveUS20090250726A1Semiconductor/solid-state device detailsSolid-state devicesHigh voltage transistorsProcess manufacturing

A one time programmable memory cell having an anti-fuse device with a low threshold voltage independent of core circuit process manufacturing technology is presented. A two transistor memory cell having a pass transistor and an anti-fuse device, or a single transistor memory cell having a dual thickness gate oxide, are formed in a high voltage well that is formed for high voltage transistors. The threshold voltage of the anti-fuse device differs from the threshold voltages of any transistor in the core circuits of the memory device, but has a gate oxide thickness that is the same as a transistor in the core circuits. The pass transistor has a threshold voltage that differs from the threshold voltages of any transistor in the core circuits, and has a gate oxide thickness that differs from any transistor in the core circuits. The threshold voltage of the anti-fuse device is lowered by omitting some or all of the threshold adjustment implants that is used for high voltage transistors fabricated in the I / O circuits.

Owner:SYNOPSYS INC

High voltage double diffused drain MOS transistor with medium operation voltage

InactiveUS20050227448A1Improve performanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricHigh voltage transistors

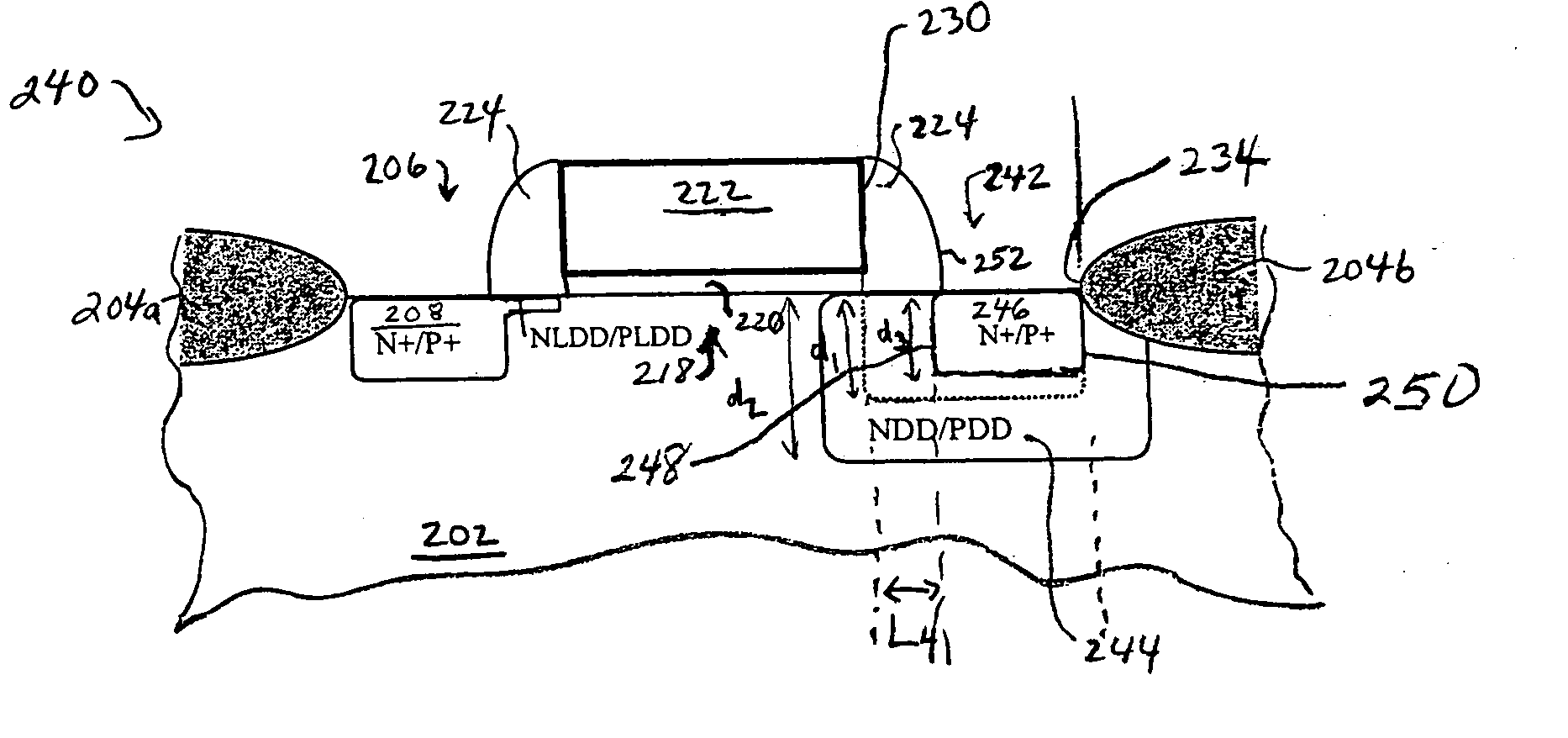

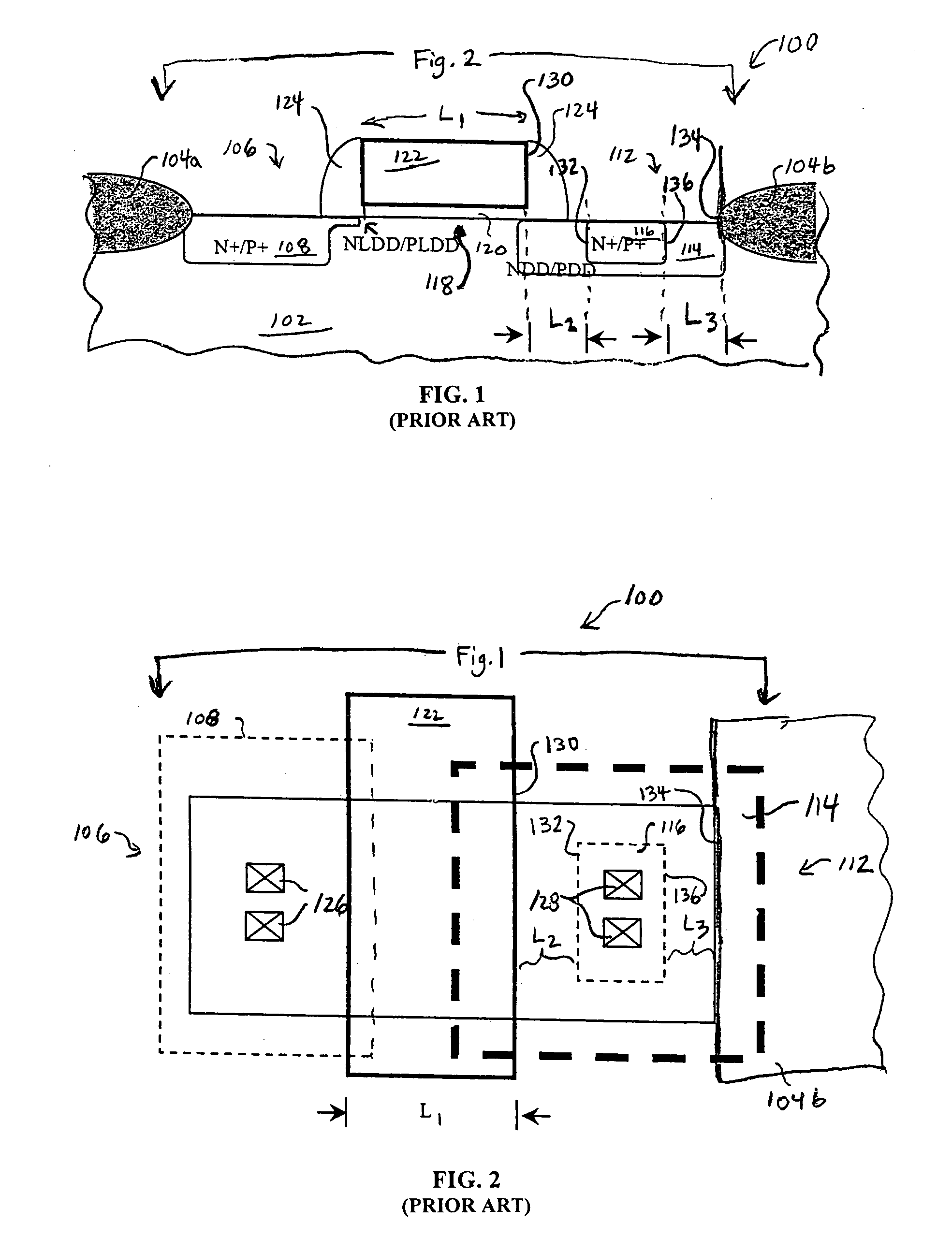

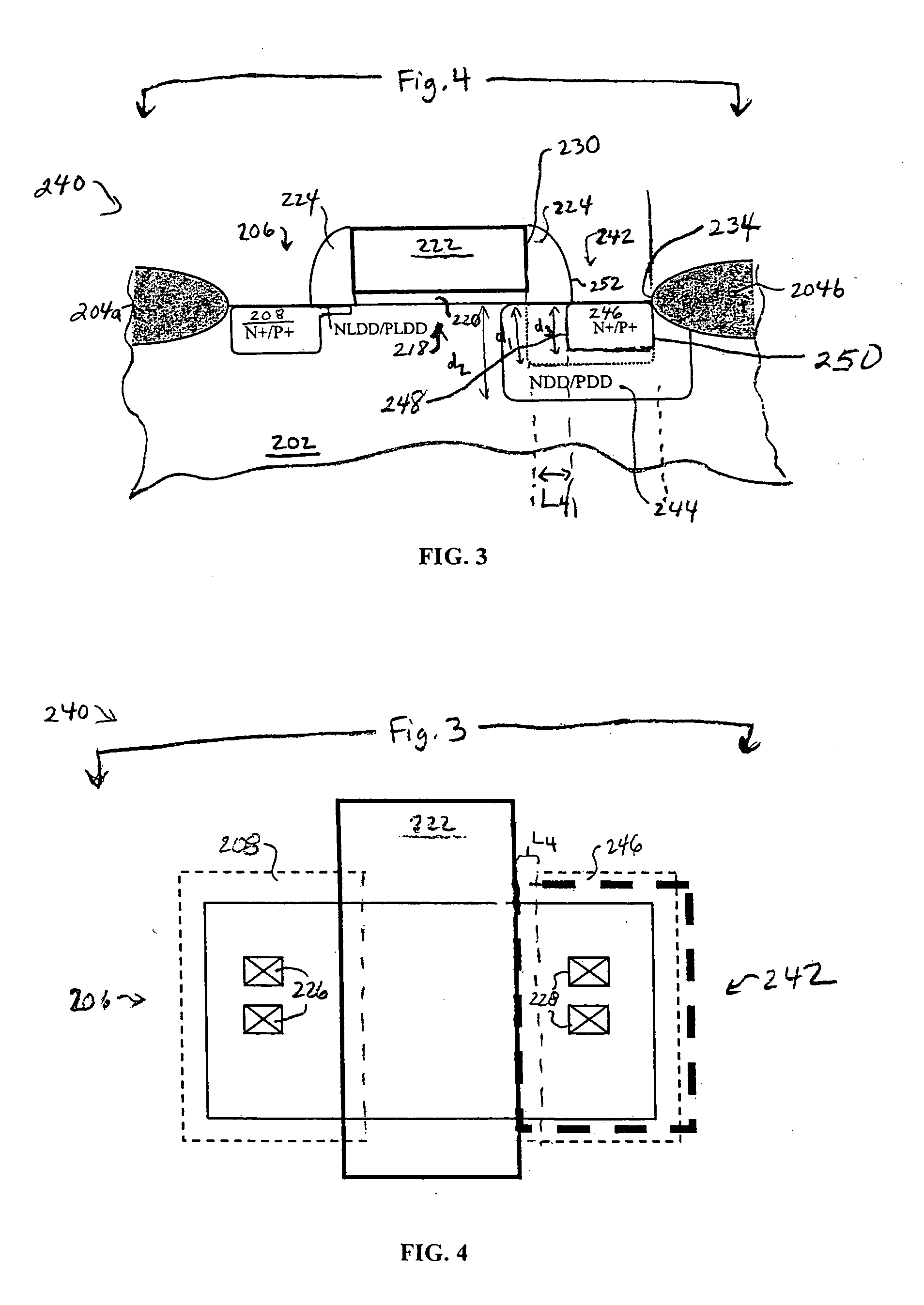

A method of fabricating a high voltage MOS transistor with a medium operation voltage on a semiconductor wafer. The transistor has a double diffused drain (DDD) and a medium operation voltage such as 6 to 10 volts, which is advantageous for applications having both low and higher operation transistor devices. The second diffusion region of the DDD is self-aligned to the spacer on the sidewalls of the gate and gate dielectric, so that the transistor size may be decreased.

Owner:TAIWAN SEMICON MFG CO LTD

SONOS embedded memory with CVD dielectric

InactiveUS7390718B2Faster rateSolid-state devicesSemiconductor/solid-state device manufacturingBit lineCMOS

An embedded semiconductor memory is fabricated by: forming diffusion bit line regions in a semiconductor substrate; then thermally oxidizing the upper surface of the substrate, thereby forming a bottom oxide layer over the substrate and simultaneously forming bit line oxide regions over each of the diffusion bit line regions; and then forming an intermediate dielectric layer (e.g., silicon nitride), over the bottom oxide layer and the bit line oxide regions. CMOS well implants are then performed in a CMOS section of the device through the silicon nitride layer and bottom oxide layer. The silicon nitride layer and bottom oxide layer are then removed in the CMOS section, and a top dielectric layer, such as a high-temperature oxide or a high-k dielectric, is deposited. The top dielectric layer completes a memory stack of the memory device, and forms a gate dielectric layer of a high voltage transistor in the CMOS section.

Owner:PS4 LUXCO SARL

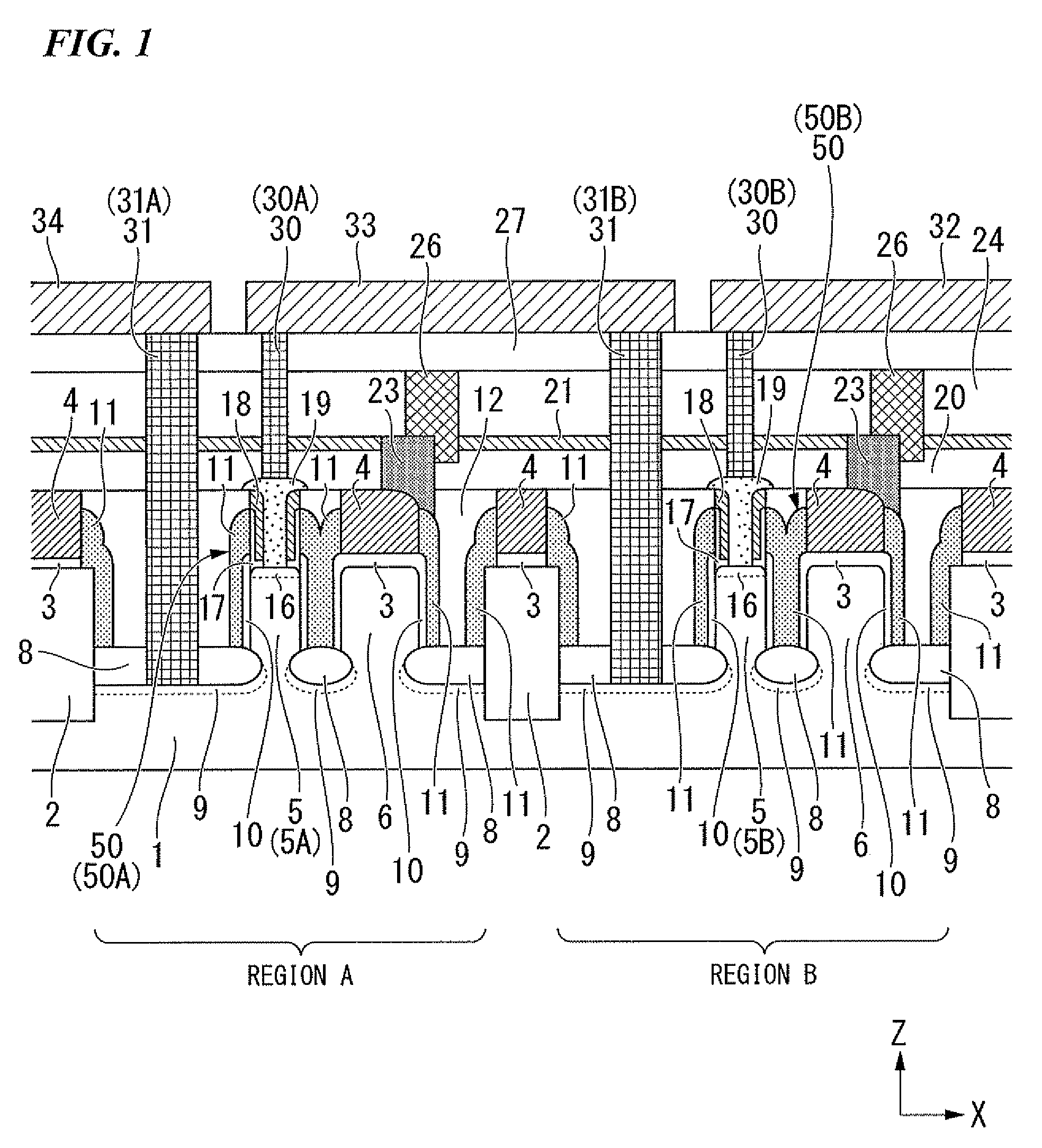

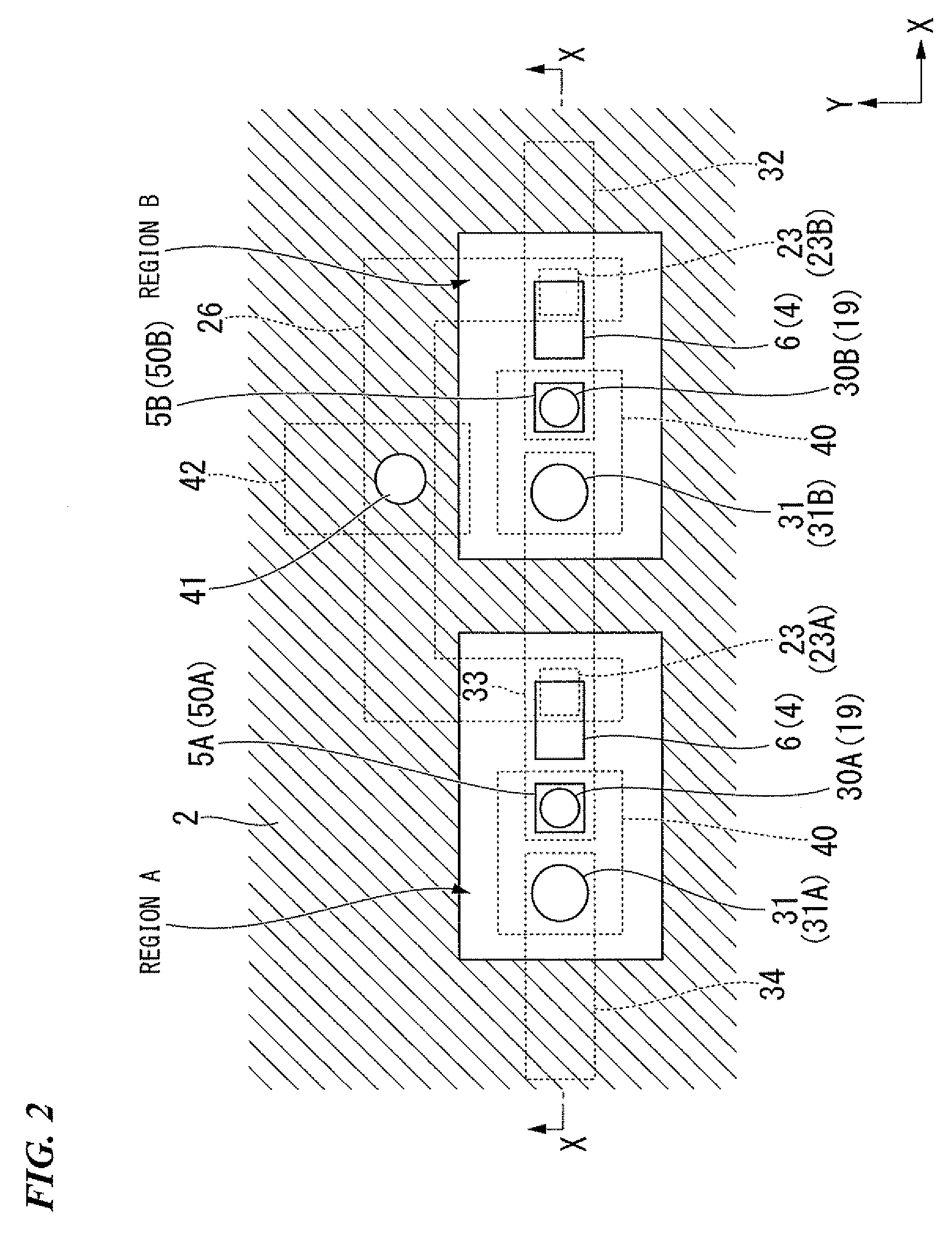

Semiconductor device and method of forming the same as well as data processing system including the semiconductor device

ActiveUS20090085088A1Increase the driving voltageSolid-state devicesSemiconductor/solid-state device manufacturingData processing systemHigh voltage transistors

A semiconductor device includes low voltage and high voltage transistors over a substrate. The low voltage transistor is configured by at least one unit transistor. The high voltage transistor is configured by a greater number of the unit transistors than the at least one unit transistor that configures the low voltage transistor. Each of the unit transistors may include a vertically extending portion of semiconductor providing a channel region and having a uniform height, a gate insulating film extending along a side surface of the vertically extending portion of semiconductor, a gate electrode separated by the gate insulating film from the vertically extending portion of semiconductor, and upper and lower diffusion regions being respectively disposed near the top and bottom of the vertically extending portion of semiconductor. The greater number of the unit transistors are connected in series to each other and have gate electrodes eclectically connected to each other.

Owner:NVIDIA CORP

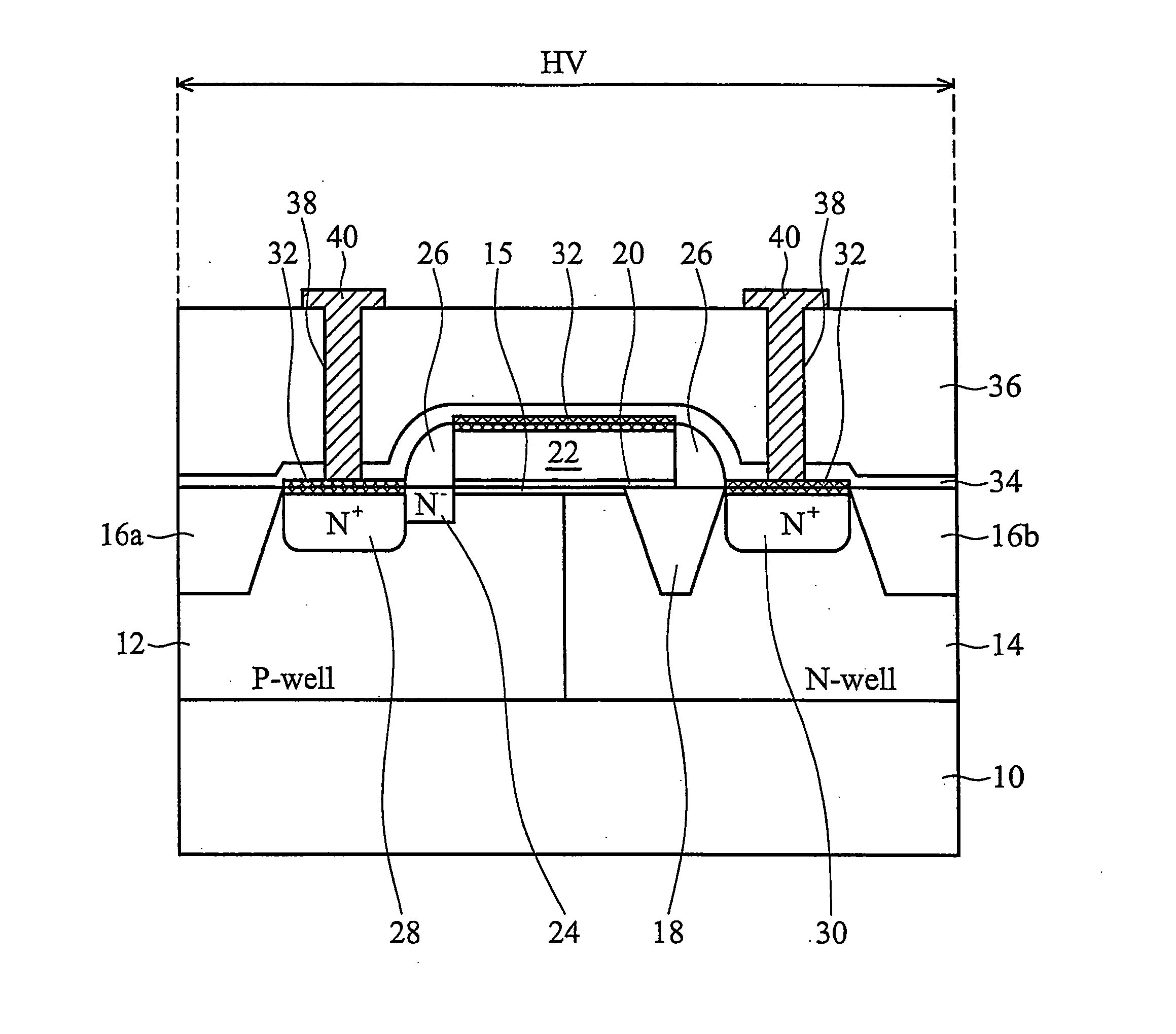

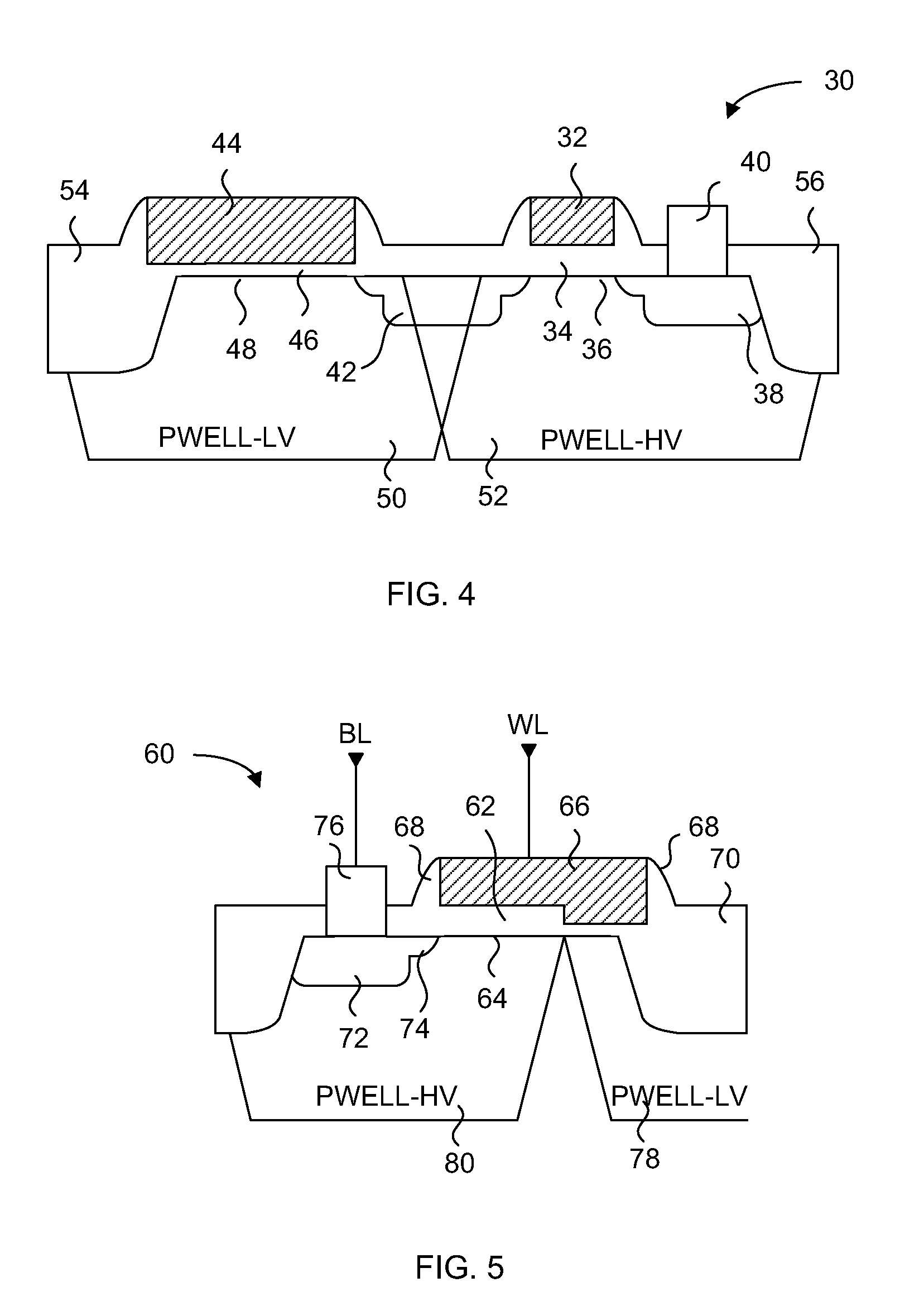

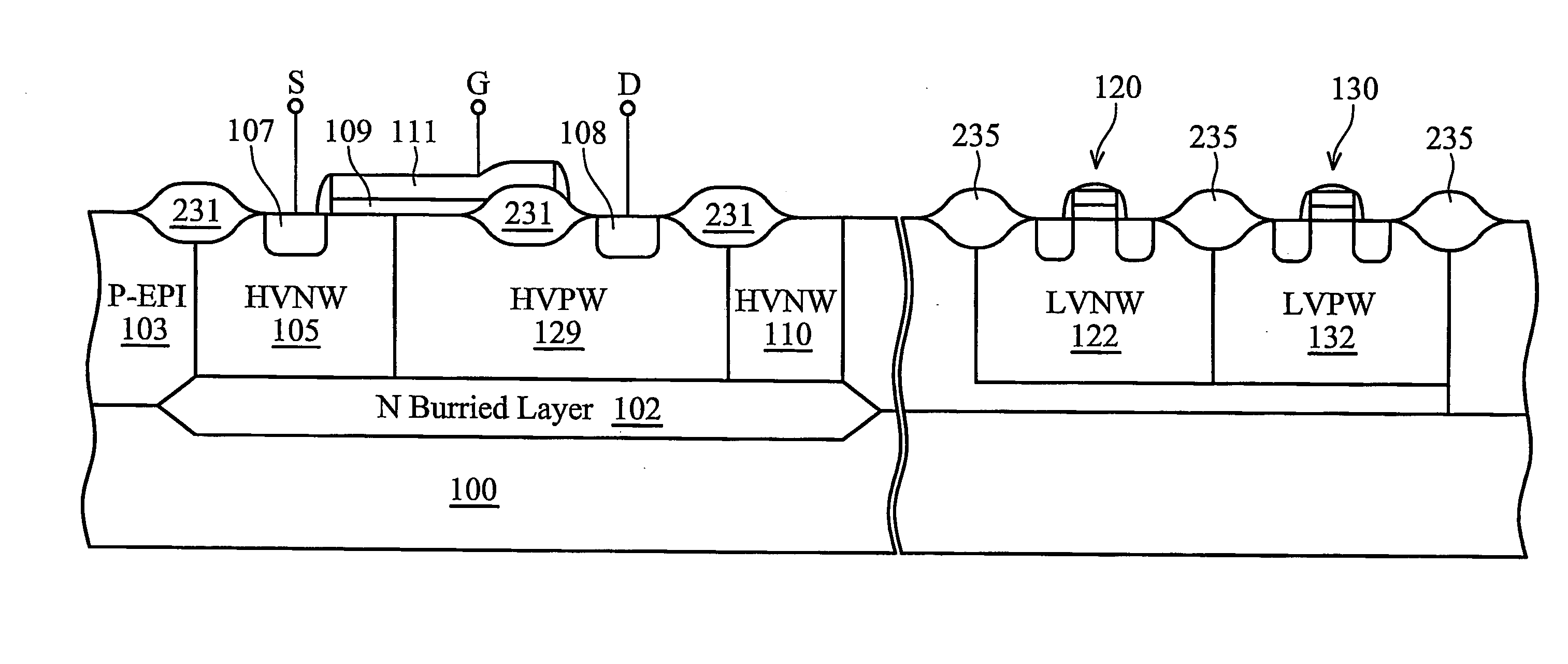

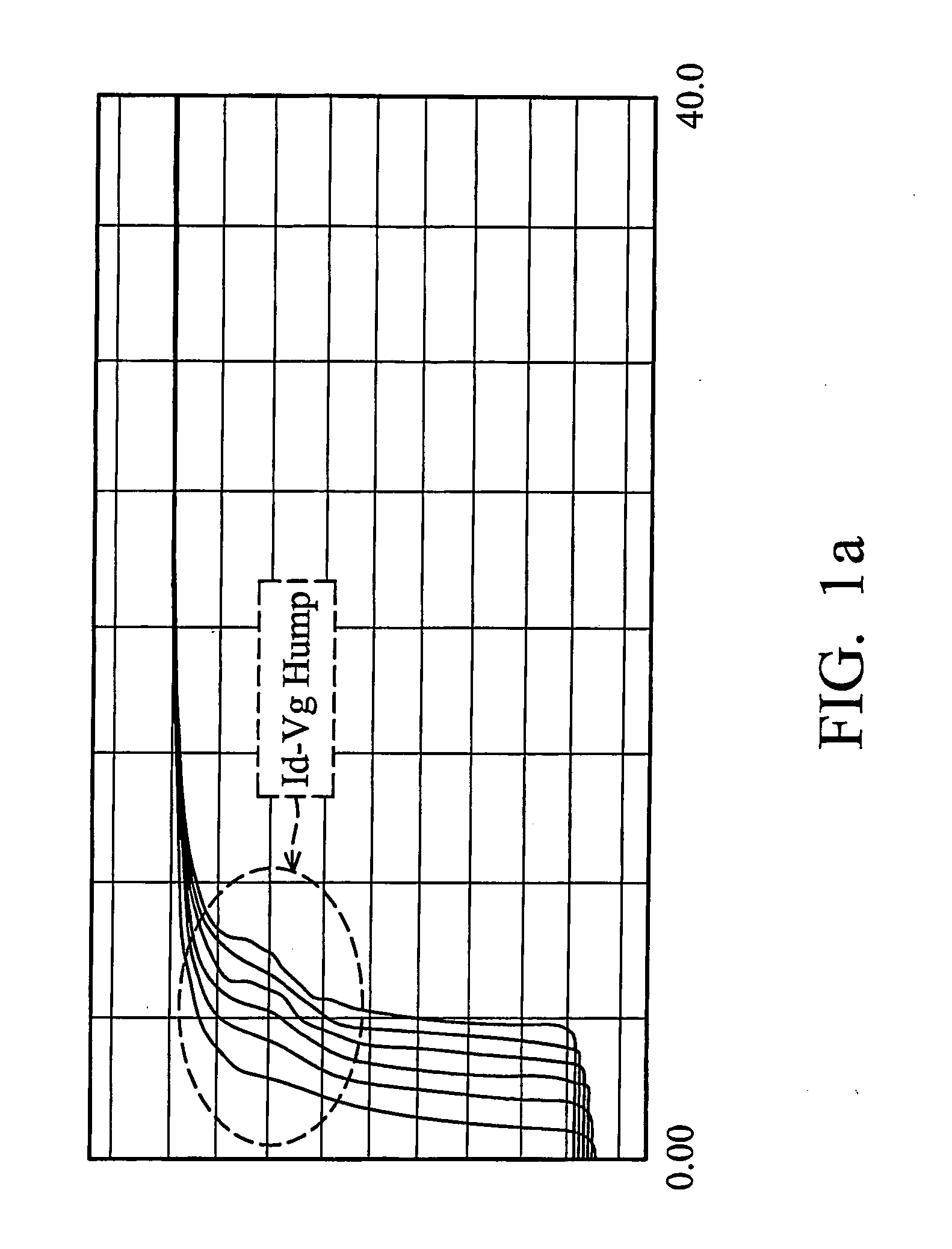

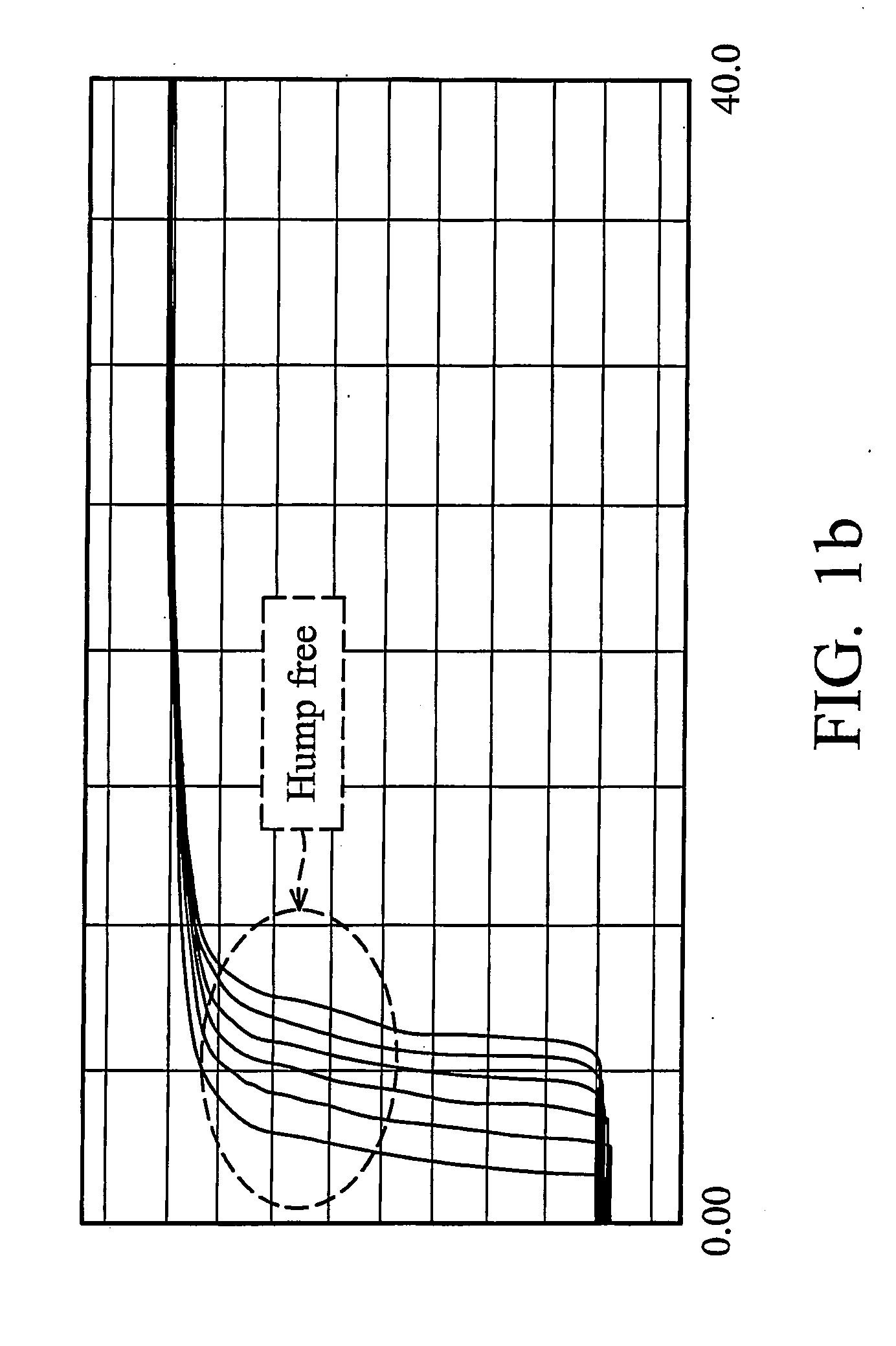

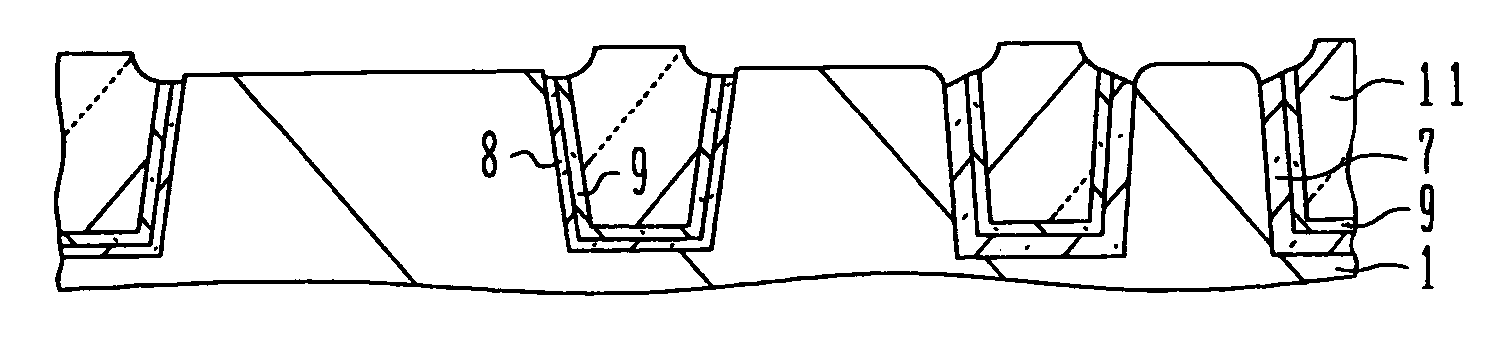

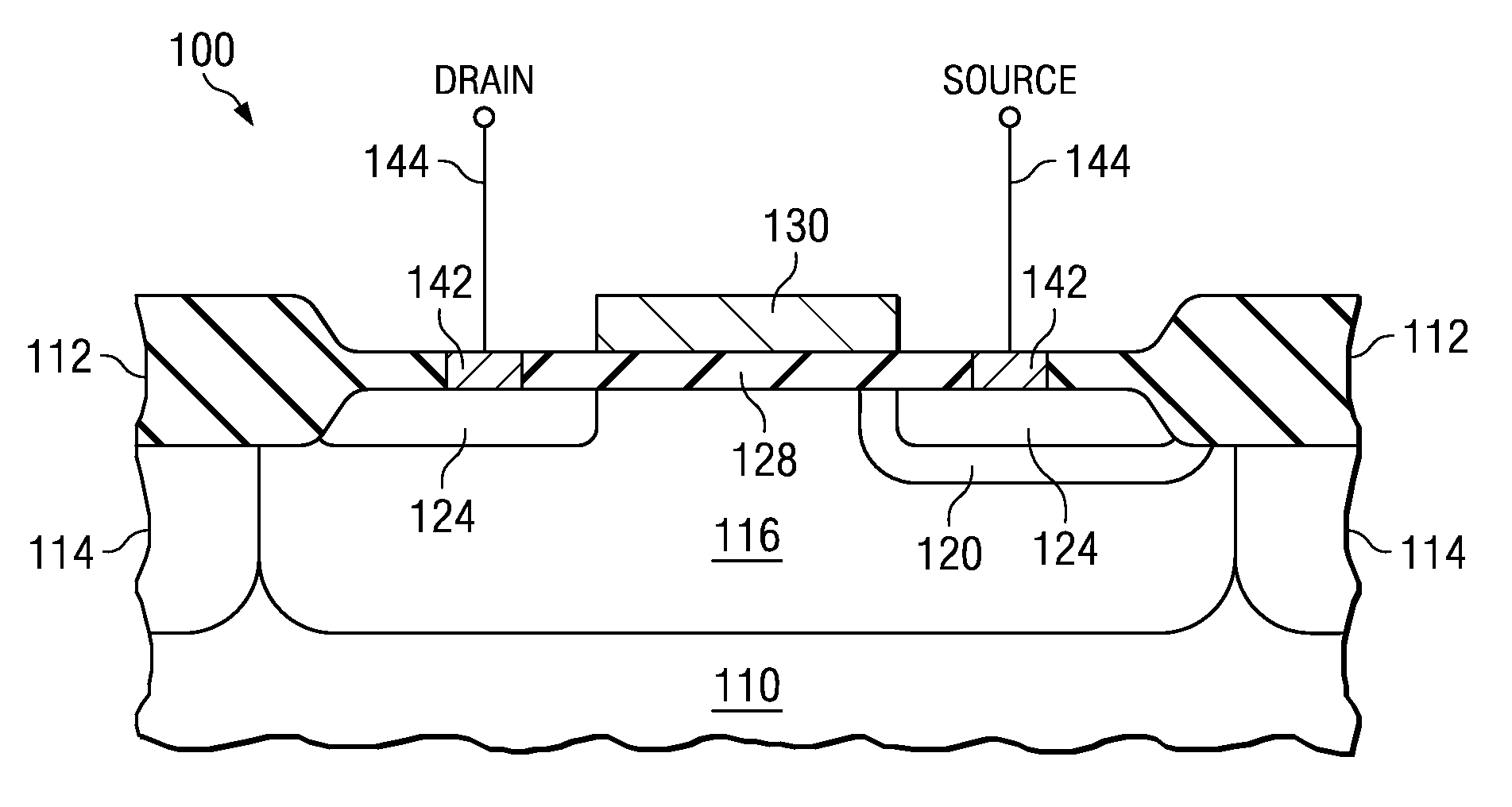

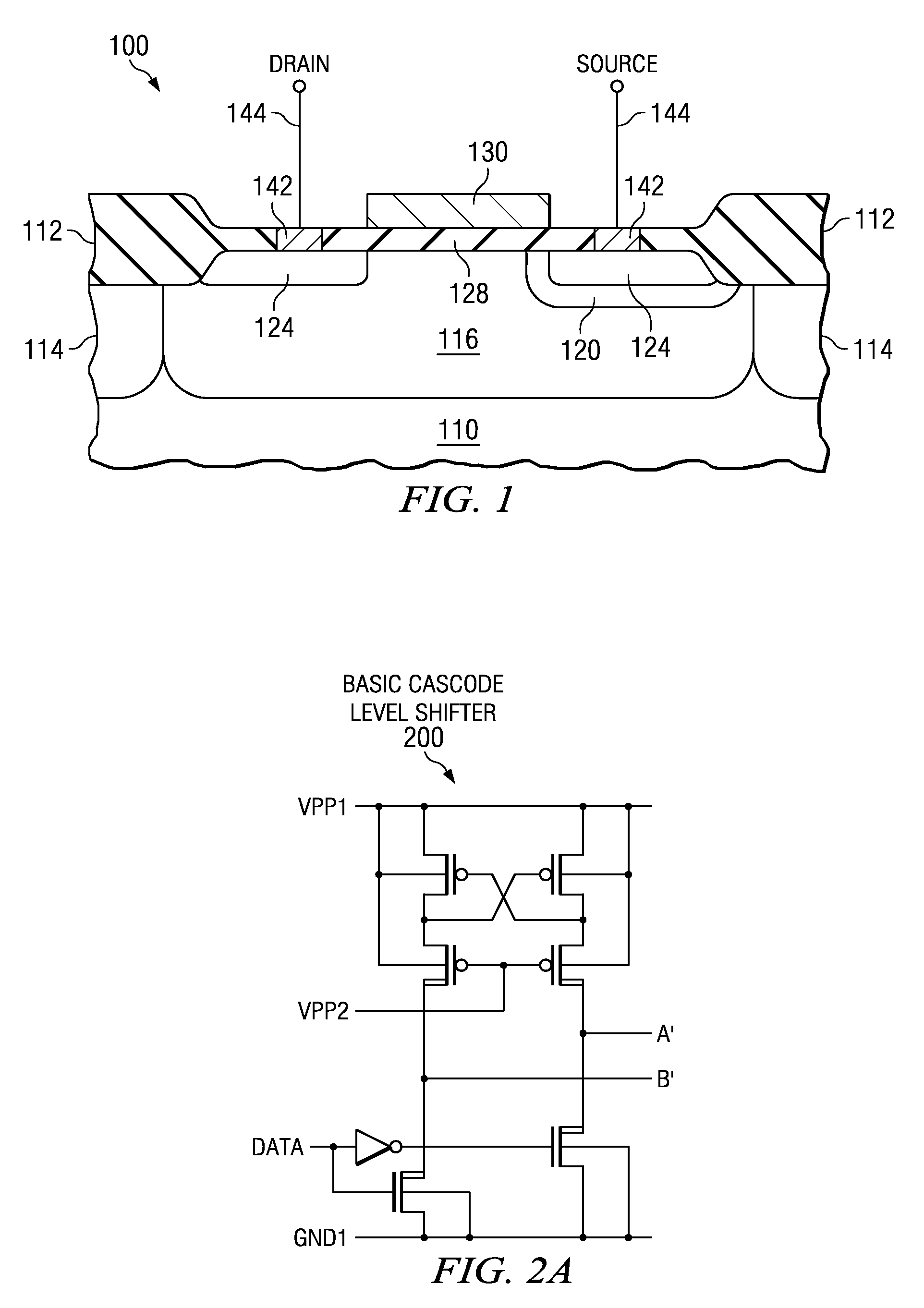

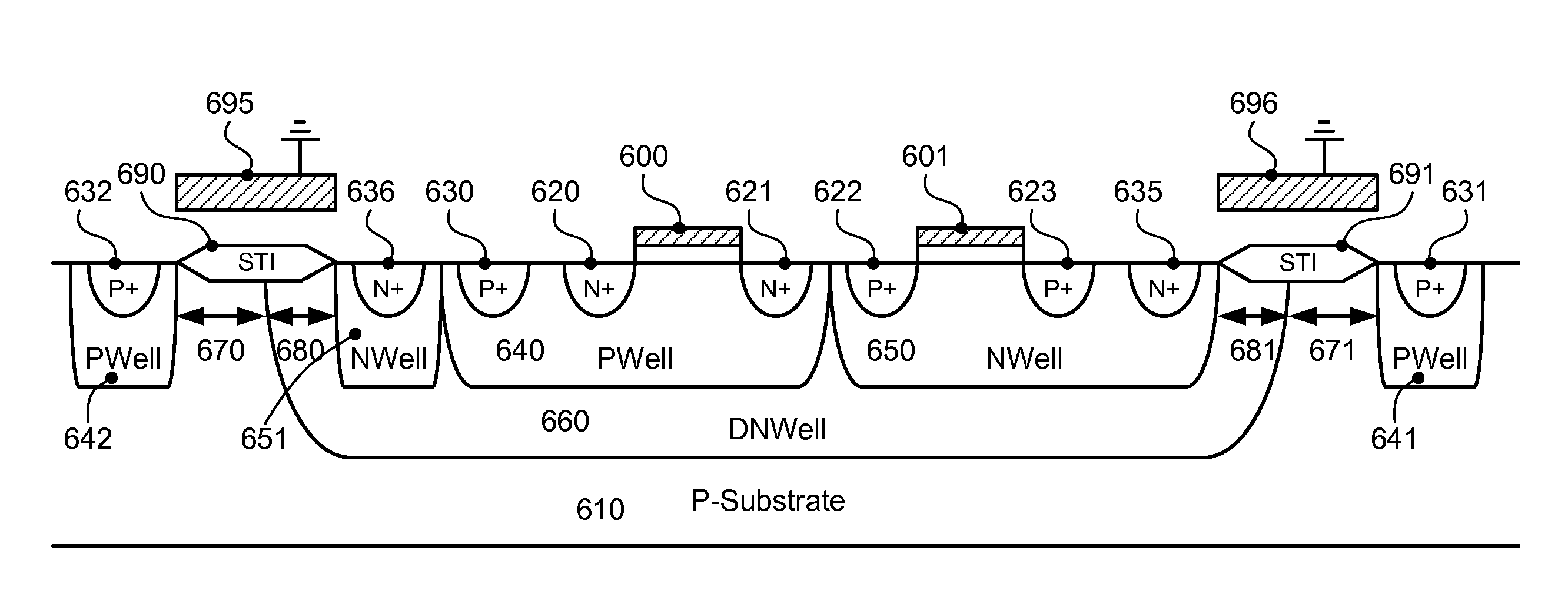

Method and apparatus for a semiconductor device having low and high voltage transistors

ActiveUS20060006462A1Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsEngineering

Method and apparatus for a semiconductor device including high voltage MOS transistors is described. A substrate is provided with a low voltage and a high voltage region separated one from the other. Isolation regions containing an insulator are formed including at least one formed within one of said wells within the high voltage region. The angle of the transition from the active areas to the isolation regions in the high voltage device region is greater than a predetermined angle, in some embodiments it is greater than 40 degrees from vertical. In some embodiments the isolation regions are formed using shallow trench isolation techniques. In alternative embodiments the isolation regions are formed using field oxide formed by local oxidation of silicon techniques.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device with nanoclusters

Owner:TAIWAN SEMICON MFG CO LTD

High-voltage vertical transistor with a multi-gradient drain doping profile

InactiveUS20050133858A1Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsSubject matter

A high-voltage transistor includes first and second trenches that define a mesa in a semiconductor substrate. First and second field plate members are respectively disposed in the first and second trenches, with each of the first and second field plate members being separated from the mesa by a dielectric layer. The mesa includes a plurality of sections, each section having a substantially constant doping concentration gradient, the gradient of one section being at least 10% greater than the gradient of another section. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:POWER INTEGRATIONS INC

High-voltage transistor fabrication with trench etching technique

ActiveUS20060261407A1Improve abilitiesReduce heat dissipationTransistorThyristorEtchingSemiconductor materials

A lateral high-voltage depletion-mode device structure in which fingers of semiconductor material are interdigitated with trench gates. Since the effective channel area is proportional to the depth of the trenches, a large amount of active channel area can be achieved for a given surface area.

Owner:BOURNS INC

Semiconductor device and its manufacture method

InactiveUS20060220144A1Improve reliabilityOperating voltageSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialHigh voltage transistors

A semiconductor device includes: a semiconductor substrate; and STIs formed in the semiconductor substrate and defining a high voltage transistor area and a low voltage transistor area, the STIs including: a first STI with a first liner including a thermal oxide film and not including a nitride film and surrounding at least a portion of the high voltage transistor area; and a second STI with a second liner of a lamination of a thermal oxide film and a nitride film and surrounding the low voltage transistor area.

Owner:FUJITSU LTD

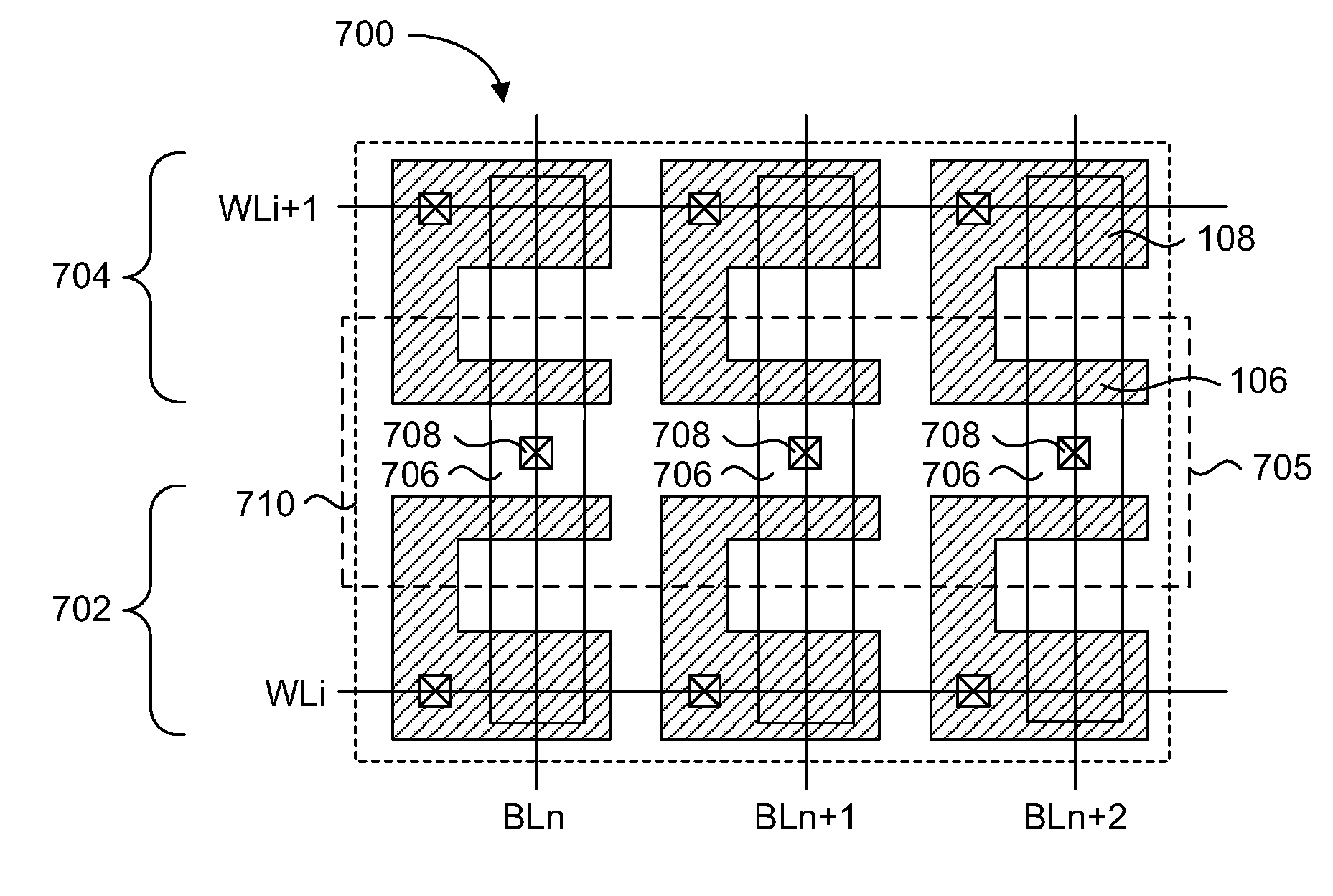

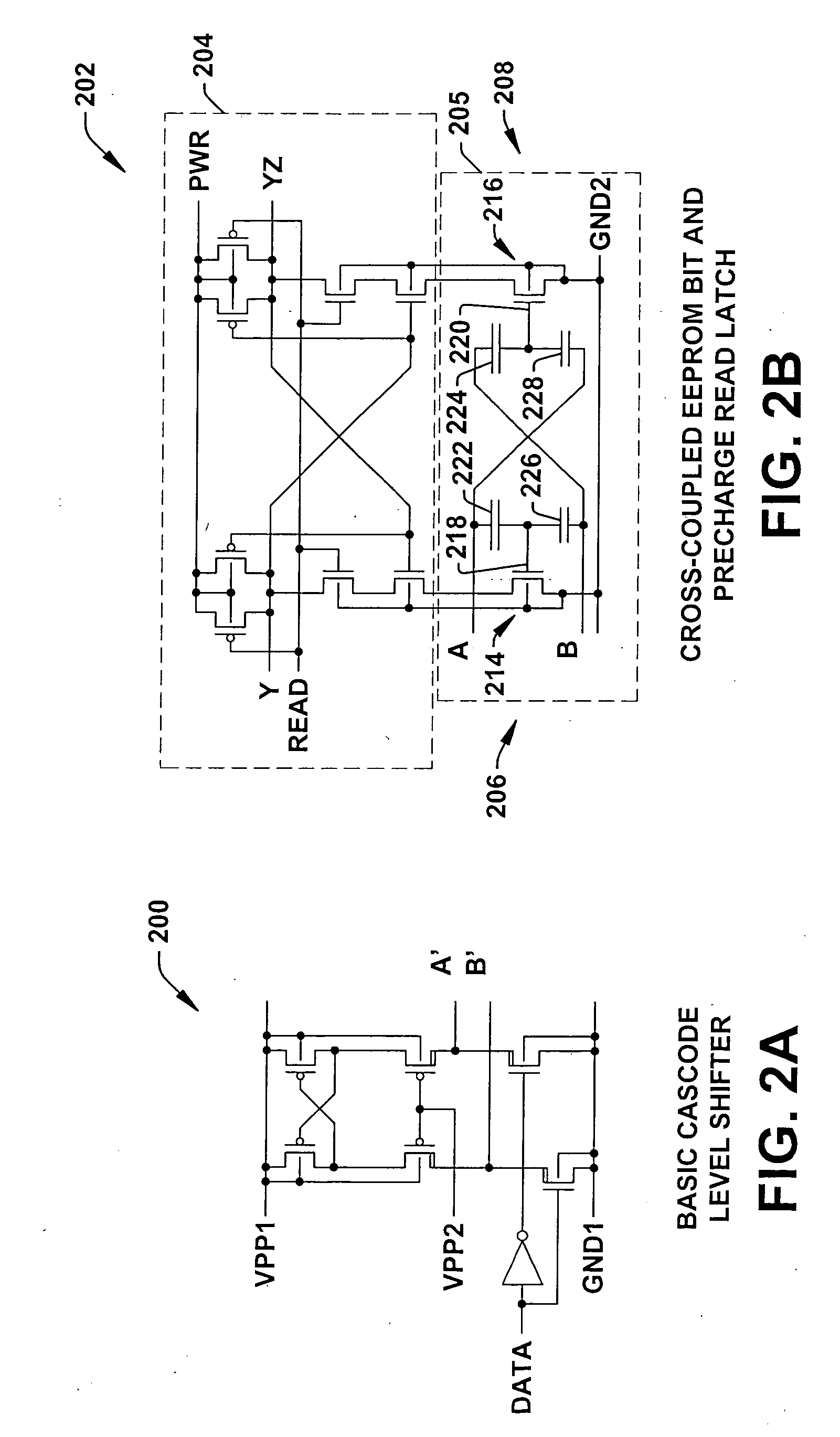

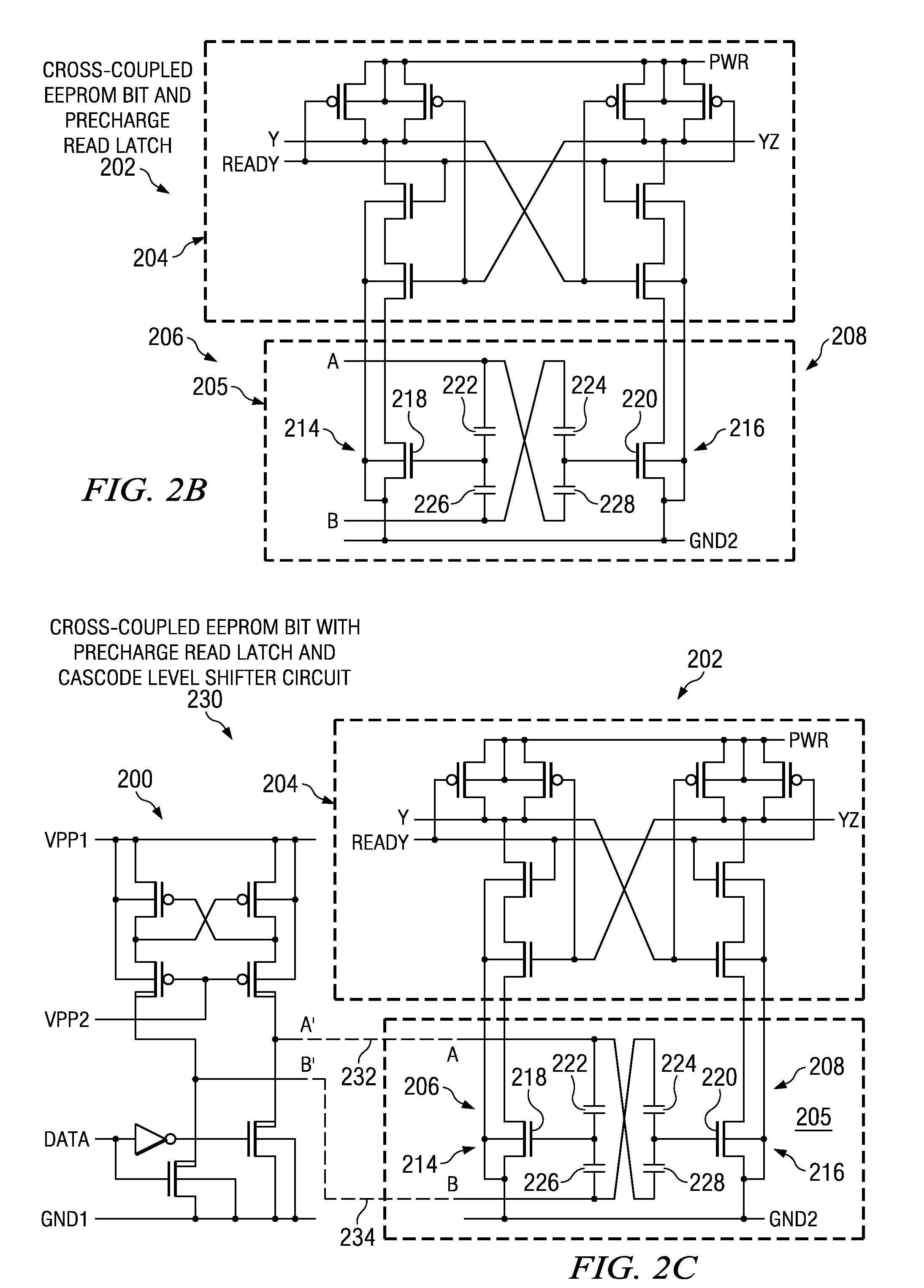

Embedded EEPROM array techniques for higher density

ActiveUS20070064494A1Simple structureWafer Area ReductionSolid-state devicesRead-only memoriesHigh densityHigh voltage transistors

An array structure of single-level poly NMOS EEPROM memory cells and method of operating the array is discussed implemented in a higher density embedded EEPROM layout that eliminates the use of high voltage transistors from the array core region. If they are utilized, the high voltage transistors are moved to row and column drivers in the periphery region to increase array density with little or no added process complexity to allow economic implementation of larger embedded SLP EEPROM arrays. During program or erase operations of the array, the method provides a programming voltage for the selected memory cells of the array, and a half-write (e.g., mid-level) voltage to the remaining unselected memory cells to avoid disturbing the unselected memory cells of the array.

Owner:TEXAS INSTR INC

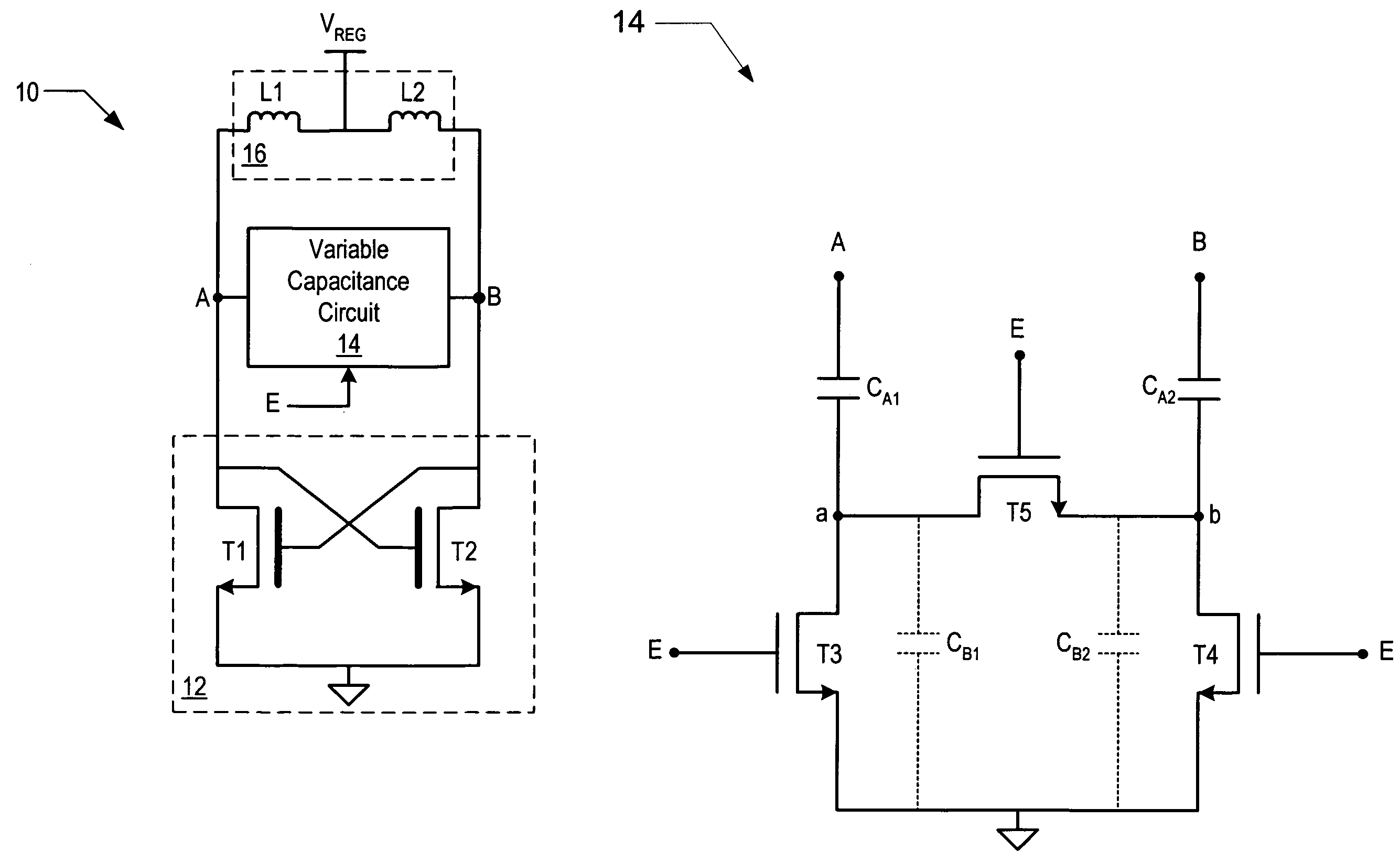

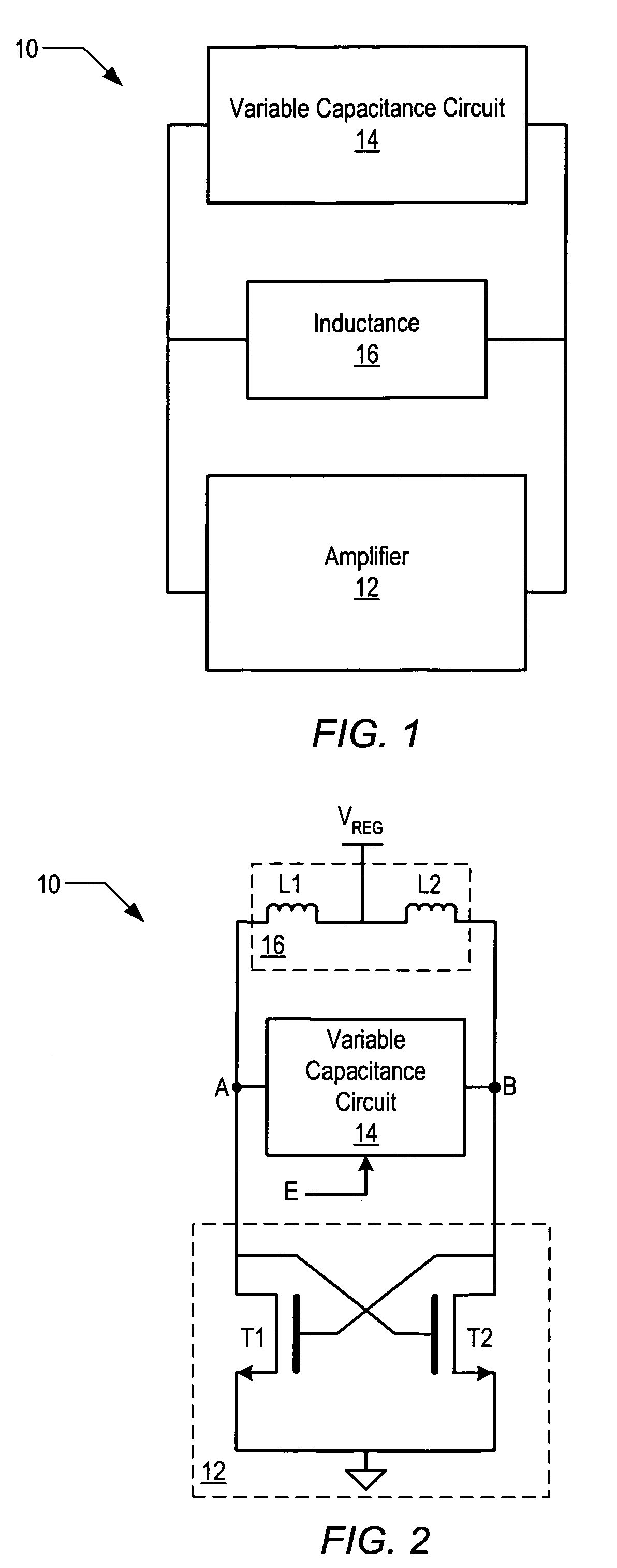

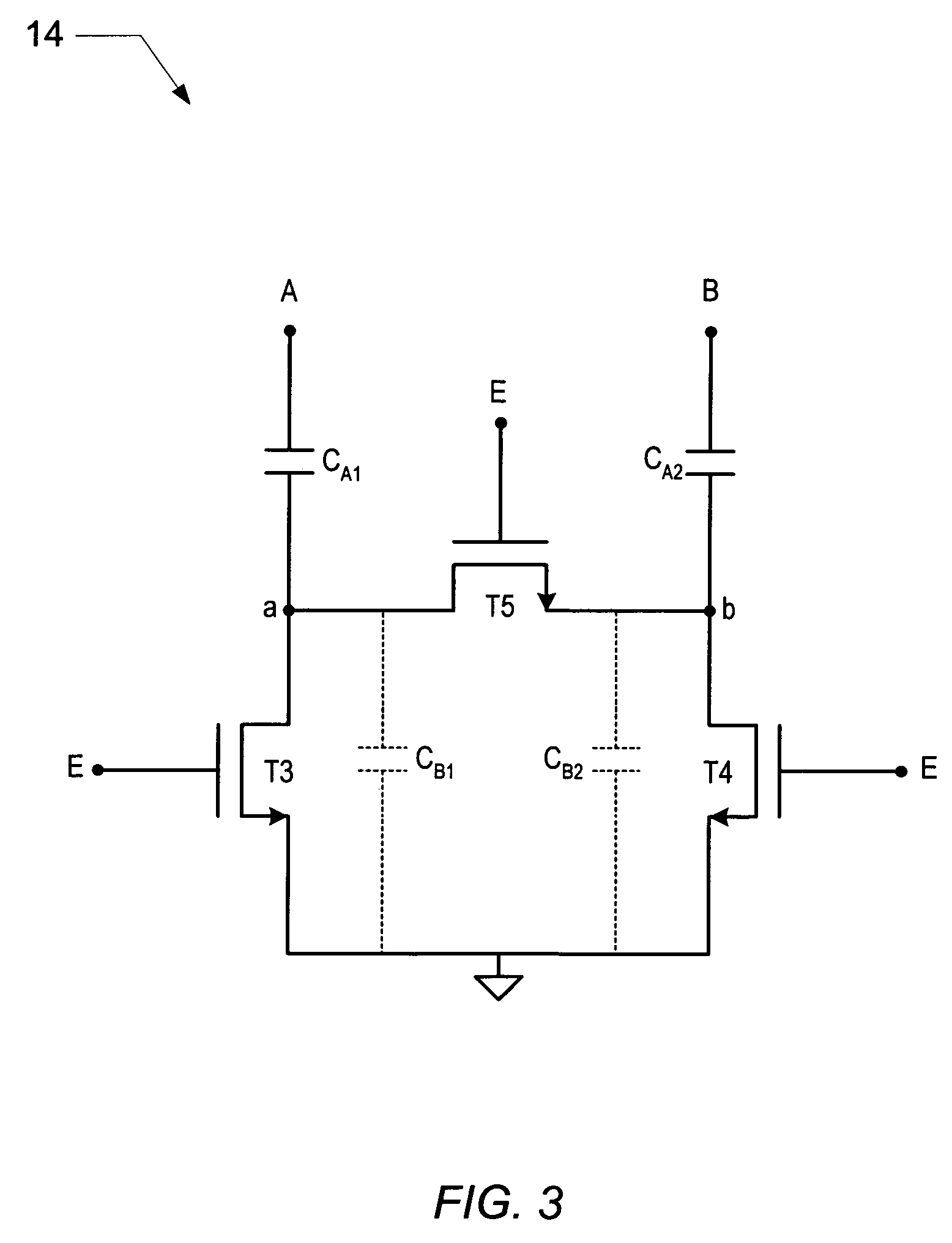

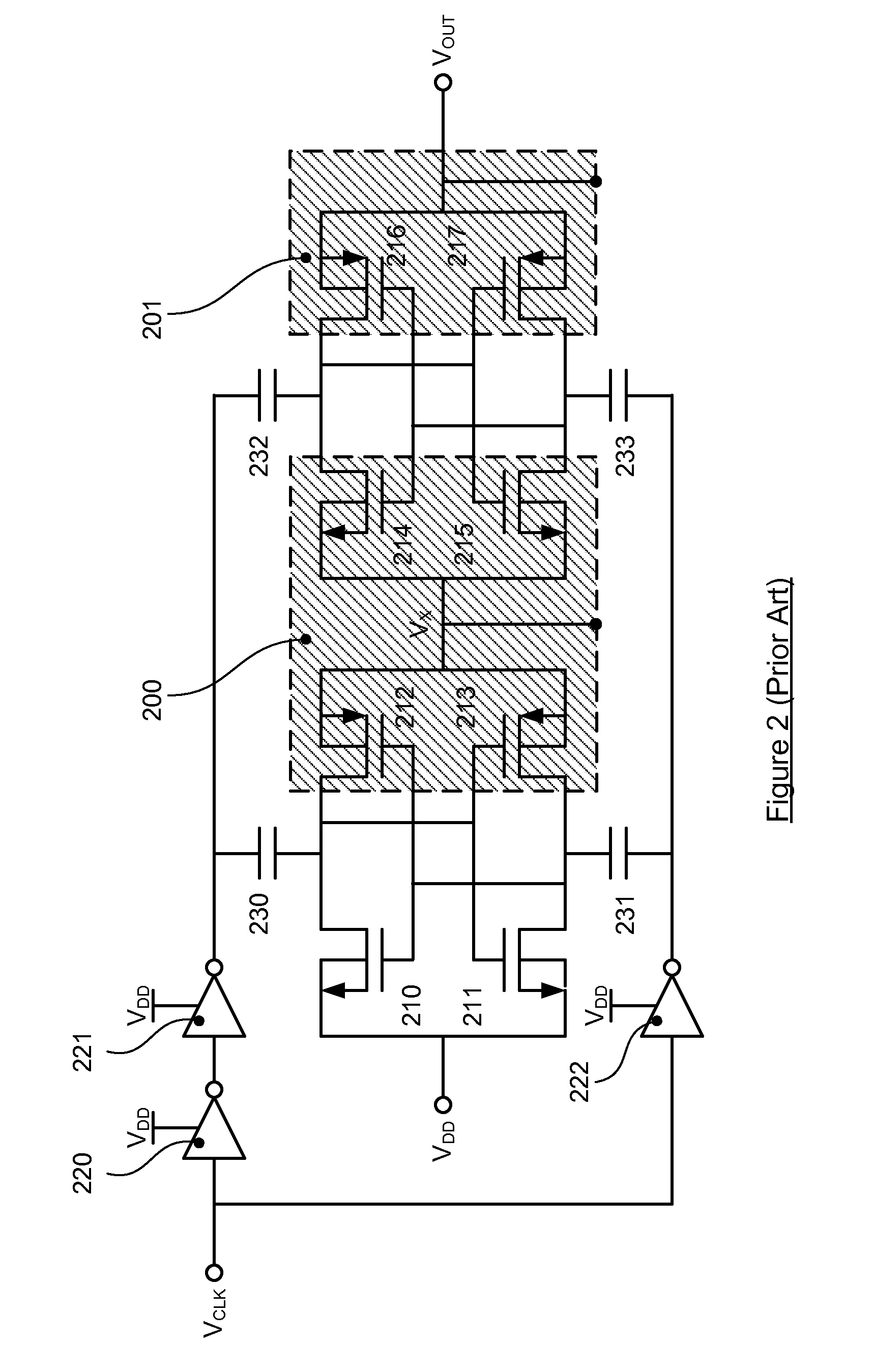

Controlled oscillator

ActiveUS7230504B1Angle modulation by variable impedenceAngle modulation detailsCapacitanceAudio power amplifier

A controlled oscillator circuit includes an amplifier including a first transistor coupled between a first node and a reference node, and a second transistor coupled between a second node and the reference node. The gate of first transistor and the gate of the second transistor may be cross-coupled. The oscillator may also include one or more variable capacitance circuits coupled between the first node and the second node, each including a first capacitor coupled between the first node and a third node, and a second capacitor coupled between the second node and a fourth node. Each variable capacitance circuit may also include a third, a fourth and a fifth transistor interconnected to selectively couple the first and second capacitors to the reference node. The third, fourth and fifth transistors may be low voltage transistors and the first and the second transistors may be high voltage transistors.

Owner:SILICON LAB INC

Embedded EEPROM array techniques for higher density

ActiveUS7471570B2Eliminate useIncrease array densityRead-only memoriesDigital storageHigh densityArray data structure

An array structure of single-level poly NMOS EEPROM memory cells and method of operating the array is discussed implemented in a higher density embedded EEPROM layout that eliminates the use of high voltage transistors from the array core region. If they are utilized, the high voltage transistors are moved to row and column drivers in the periphery region to increase array density with little or no added process complexity to allow economic implementation of larger embedded SLP EEPROM arrays. During program or erase operations of the array, the method provides a programming voltage for the selected memory cells of the array, and a half-write (e.g., mid-level) voltage to the remaining unselected memory cells to avoid disturbing the unselected memory cells of the array.

Owner:TEXAS INSTR INC

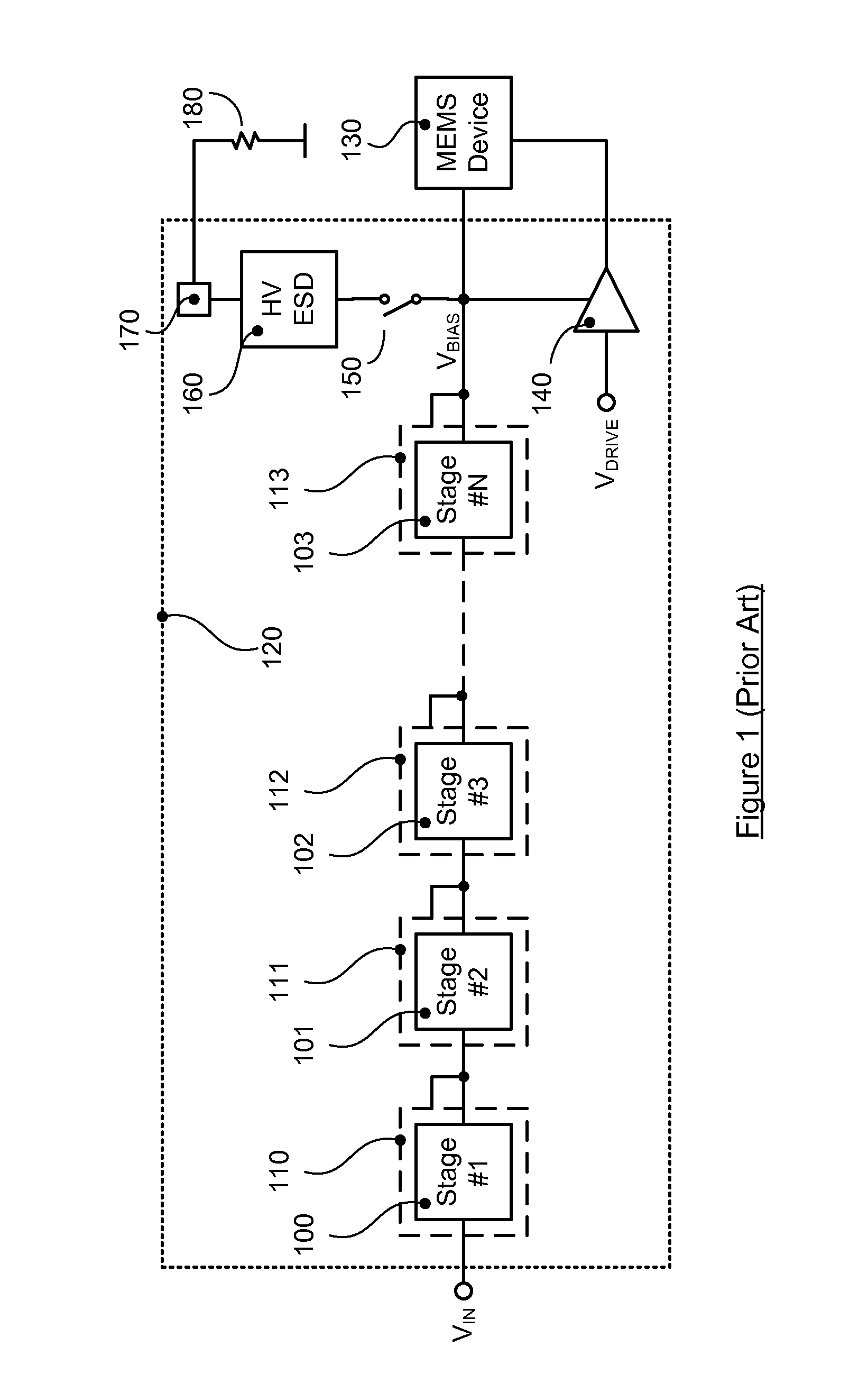

High-voltage MEMS apparatus and method

ActiveUS20120242400A1Reduce complexityReduce processing costsTransistorSemiconductor/solid-state device manufacturingHigh voltage transistorsEngineering

A high-voltage MEMS system compatible with low-voltage semiconductor process technology is disclosed. The system comprises a MEMS device coupled to a high-voltage bias generator employing an extended-voltage isolation residing in a semiconductor technology substrate. The system avoids the use of high-voltage transistors so that special high-voltage processing steps are not required of the semiconductor technology, thereby reducing process cost and complexity. MEMS testing capability is addressed with a self-test circuit allowing modulation of the bias voltage and current so that a need for external high-voltage connections and associated electro-static discharge protection circuitry are also avoided.

Owner:INVENSENSE

High-voltage transistor device having an interlayer dielectric etch stop layer for preventing leakage and improving breakdown voltage

ActiveUS7301185B2Prevent leakageImprove breakdown voltageTransistorSolid-state devicesDielectricHigh voltage transistors

A high-voltage transistor device with an interlayer dielectric (ILD) etch stop layer for use in a subsequent contact hole process is provided. The etch stop layer is a high-resistivity film having a resistivity greater than 10 ohm-cm, thus leakage is prevented and breakdown voltage is improved when driving a high voltage greater than 5V at the gate site. A method for fabricating the high-voltage device is compatible with current low-voltage device processes and middle-voltage device processes.

Owner:TAIWAN SEMICON MFG CO LTD

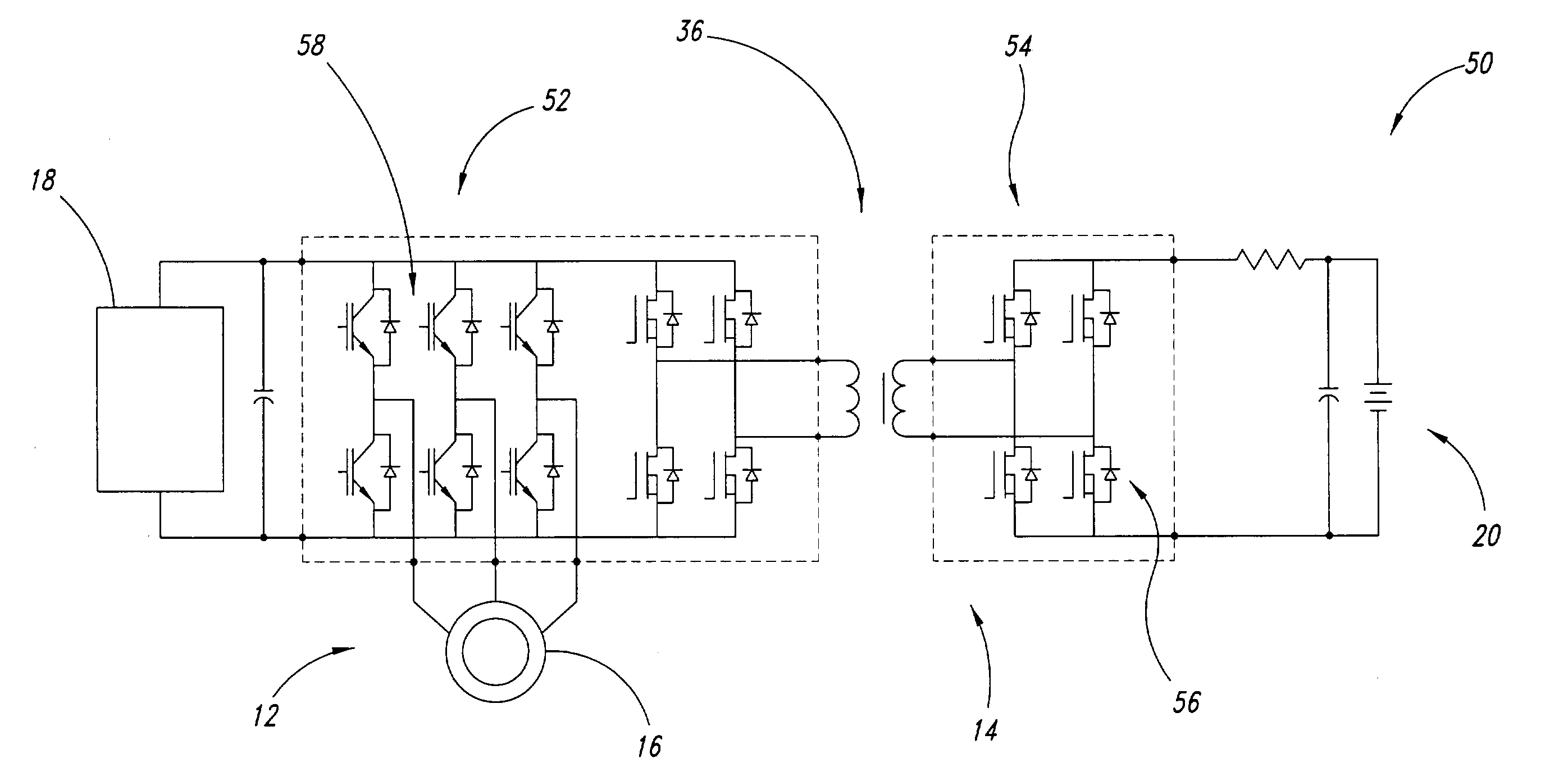

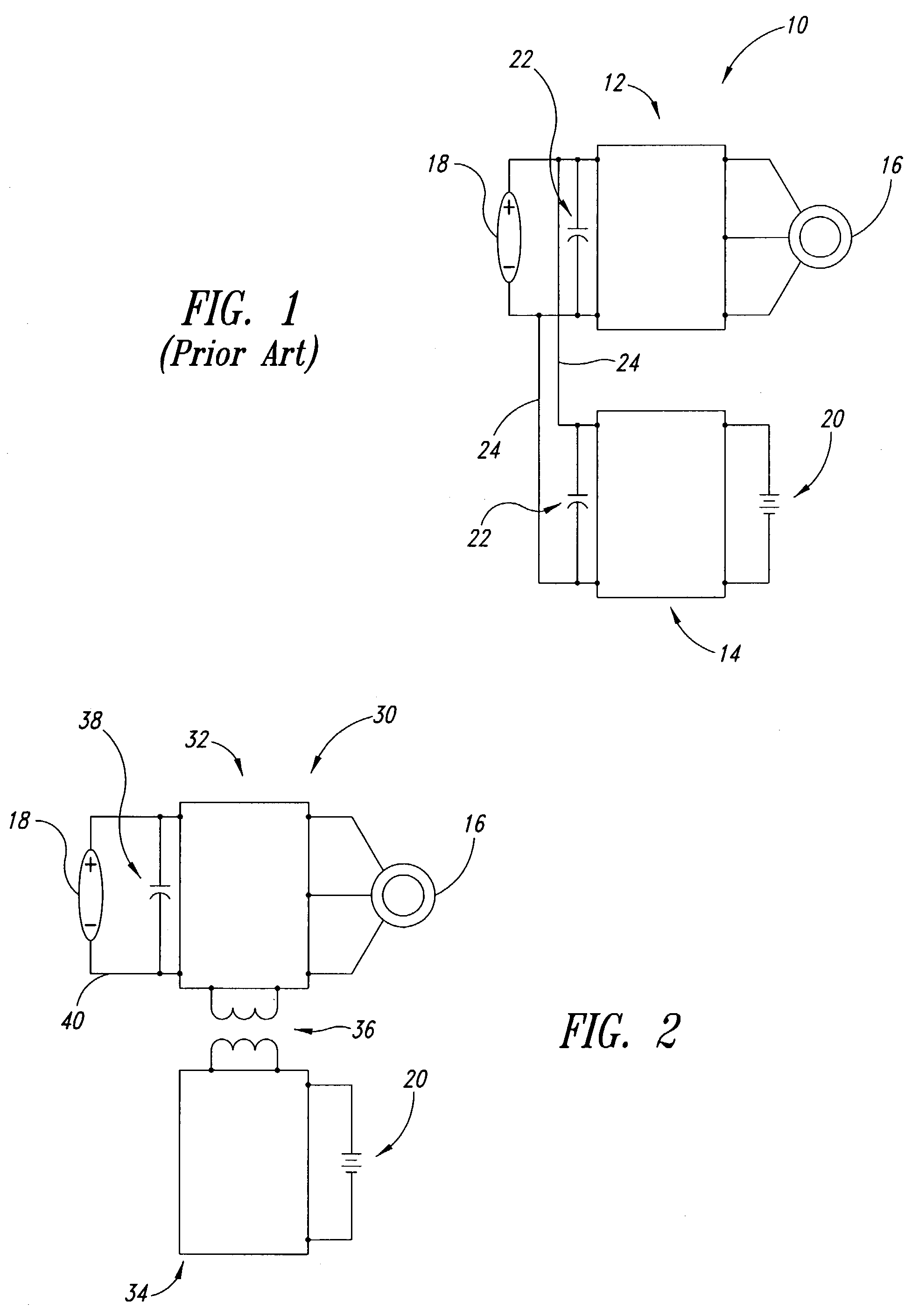

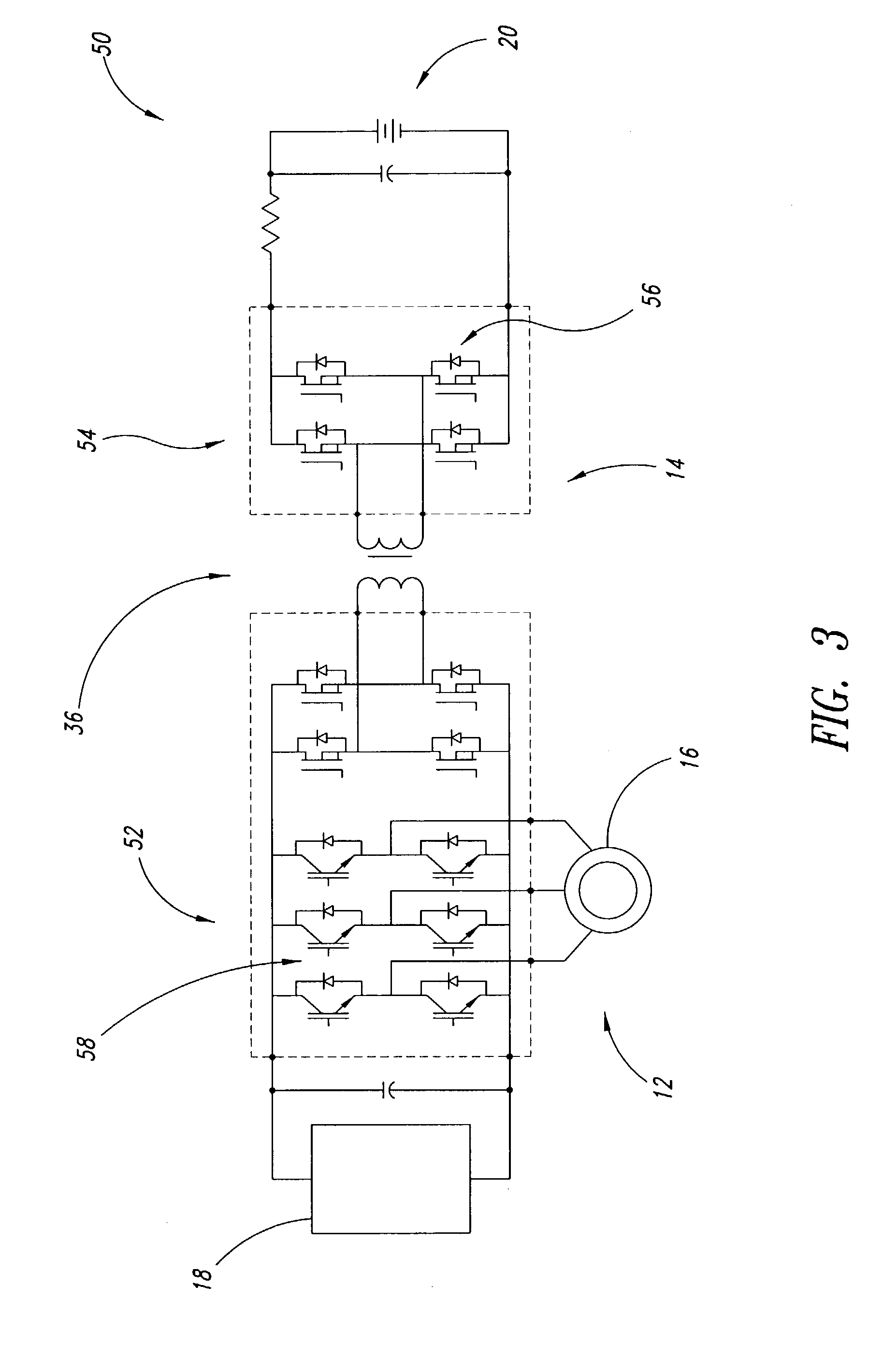

Integrated traction inverter module and DC/DC converter

InactiveUS7012822B2Simple, compact, and inexpensive TIM DC/DCAc-dc conversion without reversalDc-dc conversionDc currentHigh voltage transistors

Integrated power conversion systems and methods for use in an electric vehicle having an electric motor, a primary high-voltage energy source, and an auxiliary energy source including a traction inverter module operable for converting a DC current generated by the high-voltage energy source into an AC current capable of powering the electric motor, and a DC / DC converter operable to step-down a voltage of the high-voltage energy source or step-up a voltage of the auxiliary energy source, wherein the traction inverter module and the DC / DC converter may share one or more common components, such as a common high-voltage DC bus capacitor, a common DC bus bar, and / or a common high-voltage transistor.

Owner:VITESCO TECH USA LLC