Patents

Literature

753results about How to "Raise the threshold voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

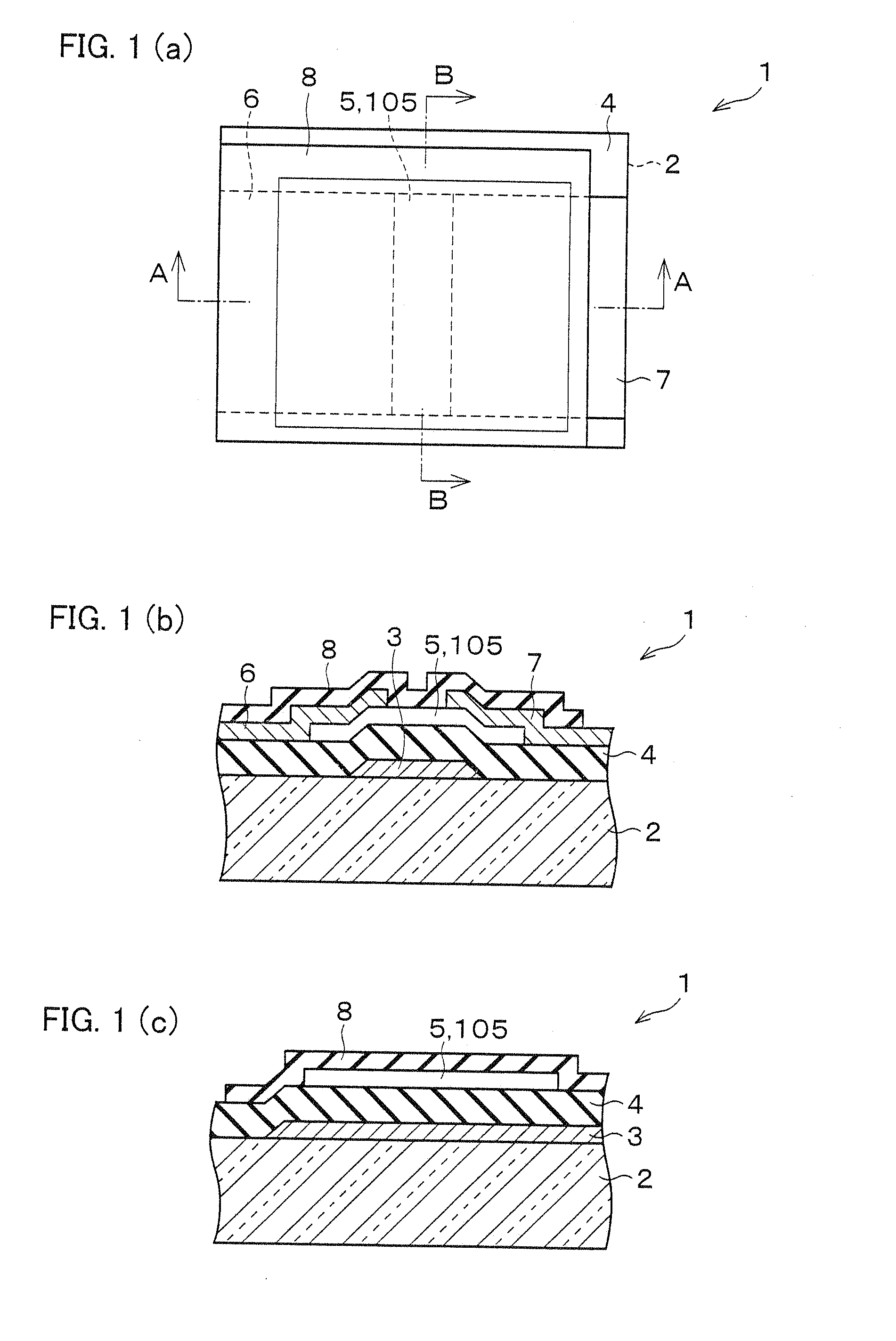

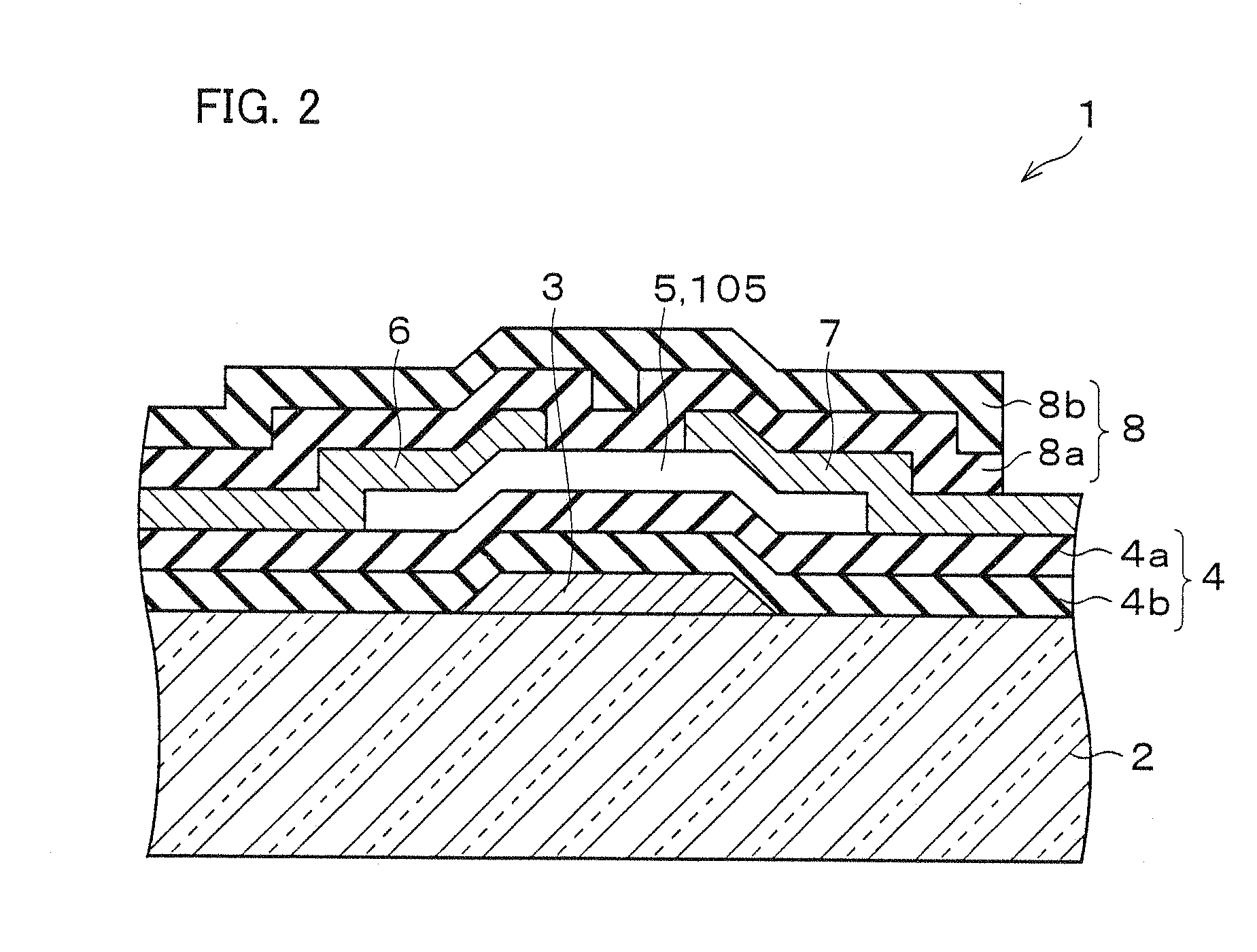

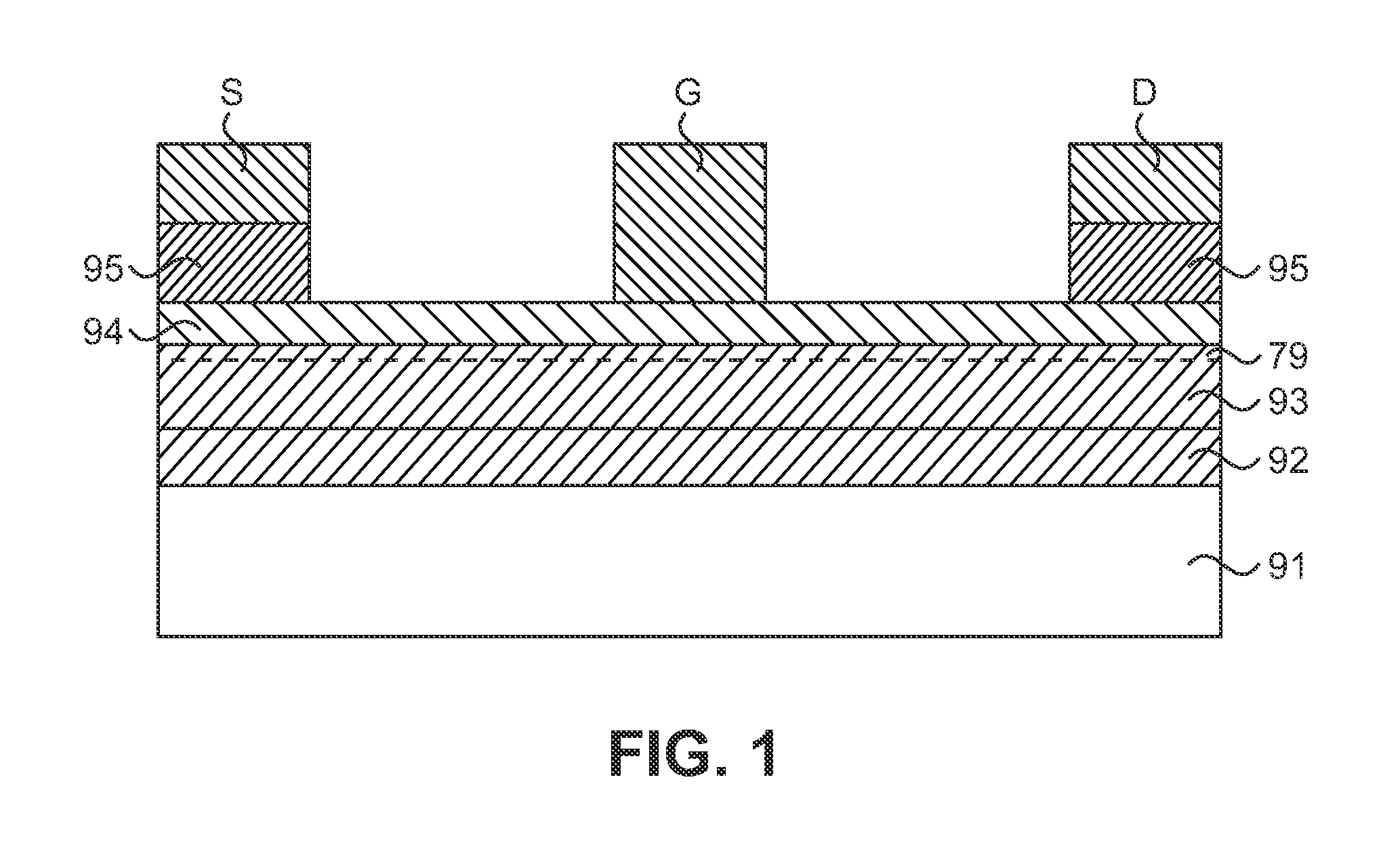

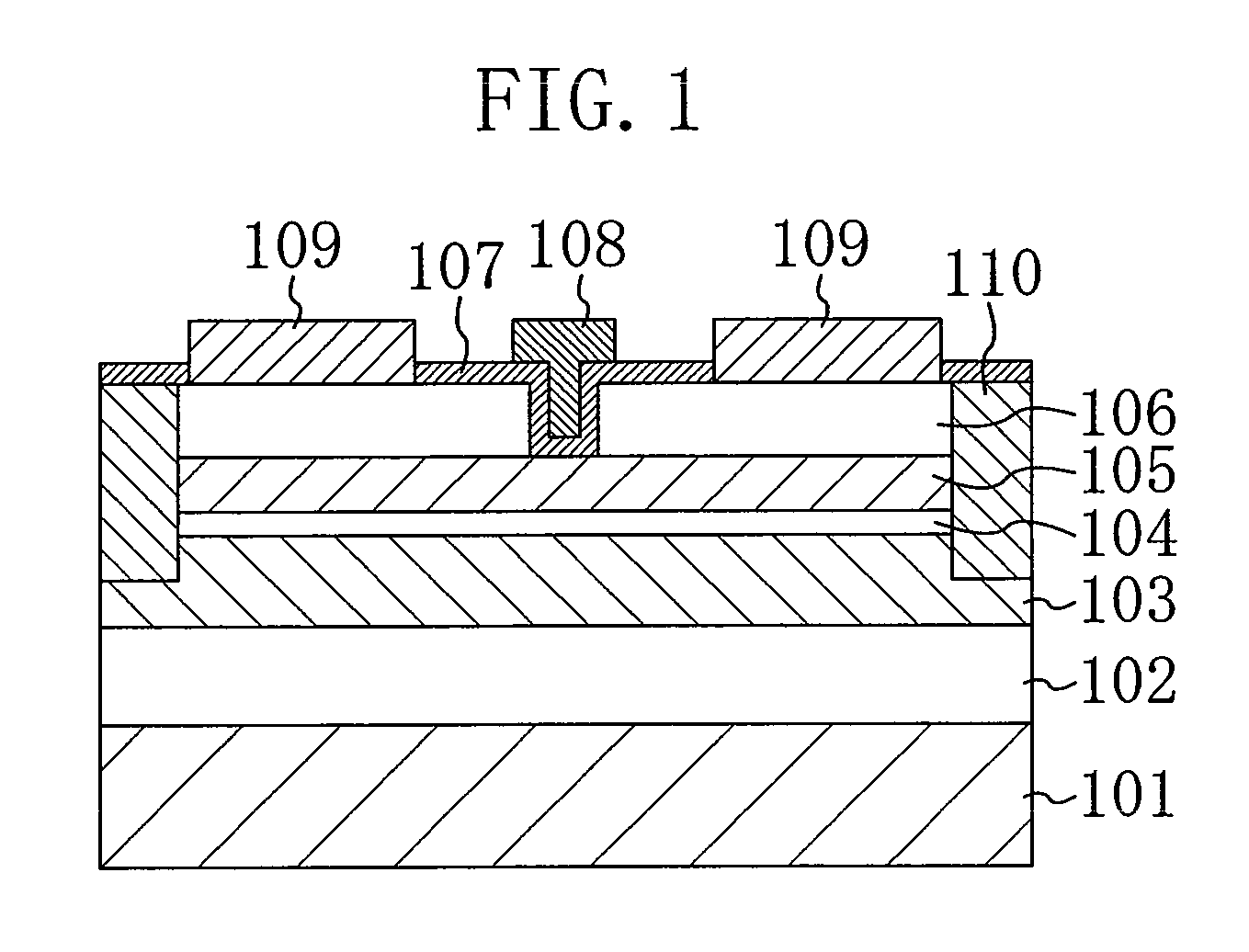

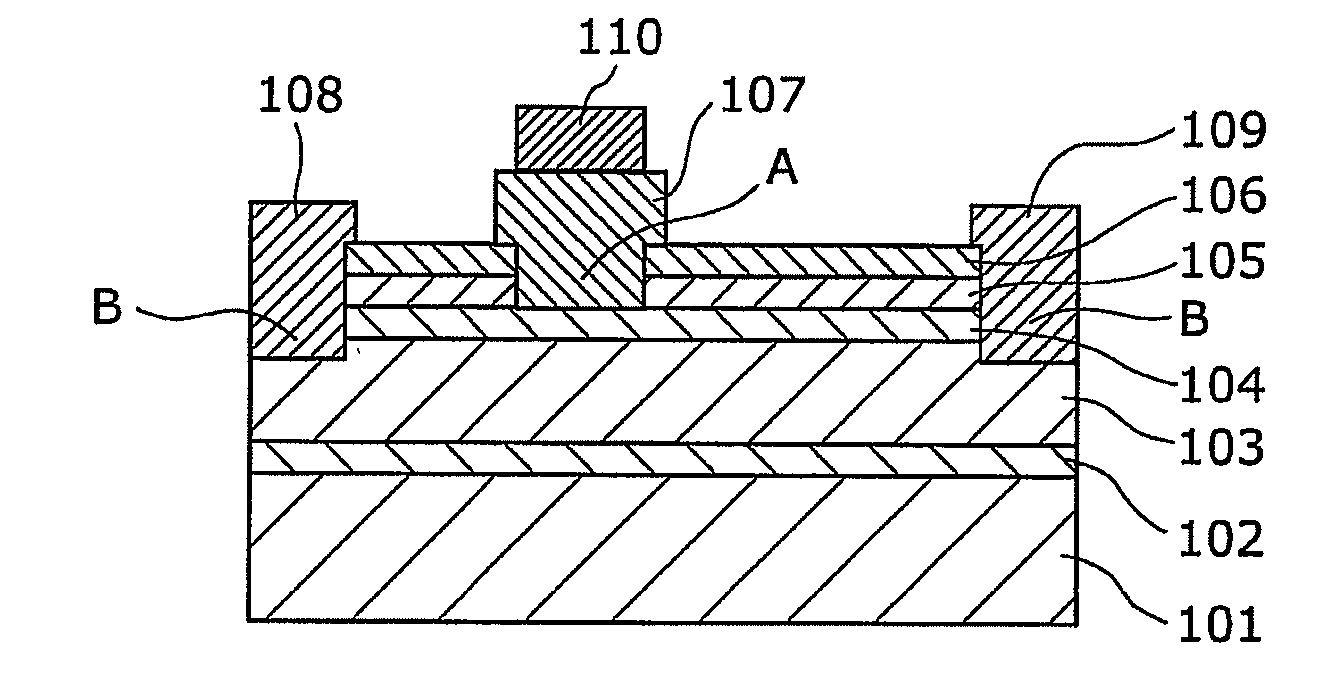

Semiconductor device, manufacturing method, and electronic device

ActiveUS20060244107A1Stabilize element propertyEasy to manufactureTransistorSemiconductor/solid-state device detailsSurface levelIntrinsic resistance

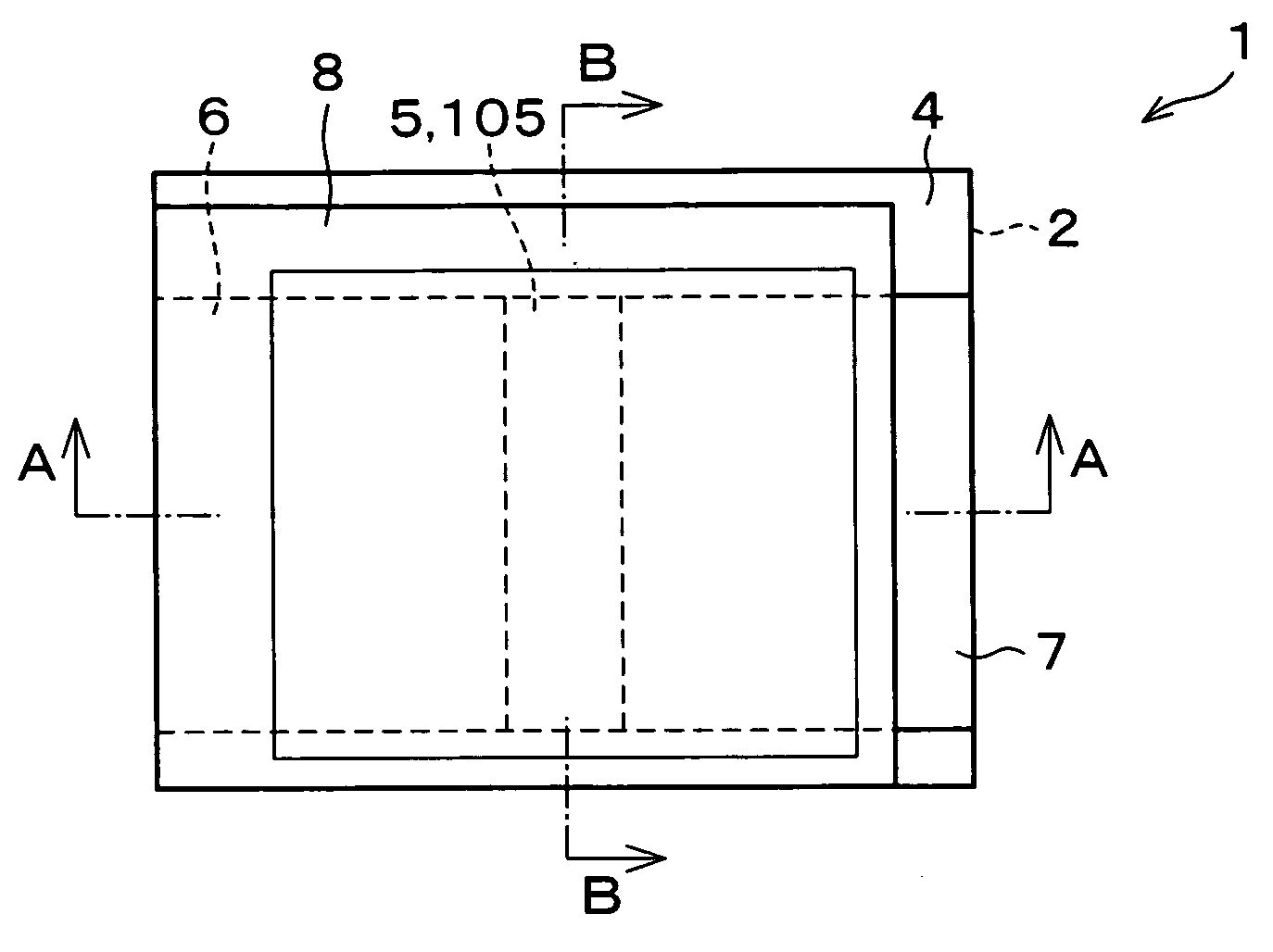

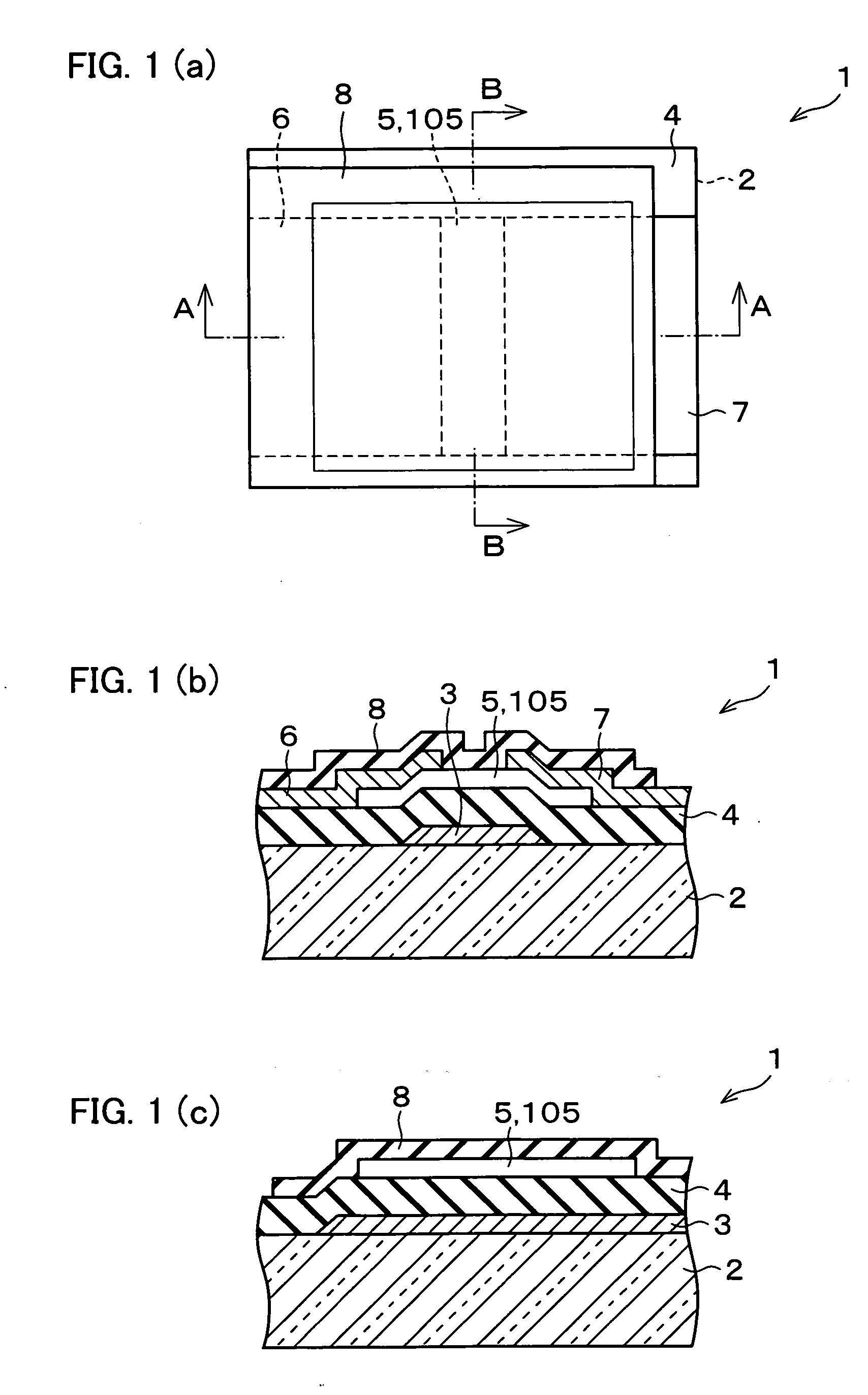

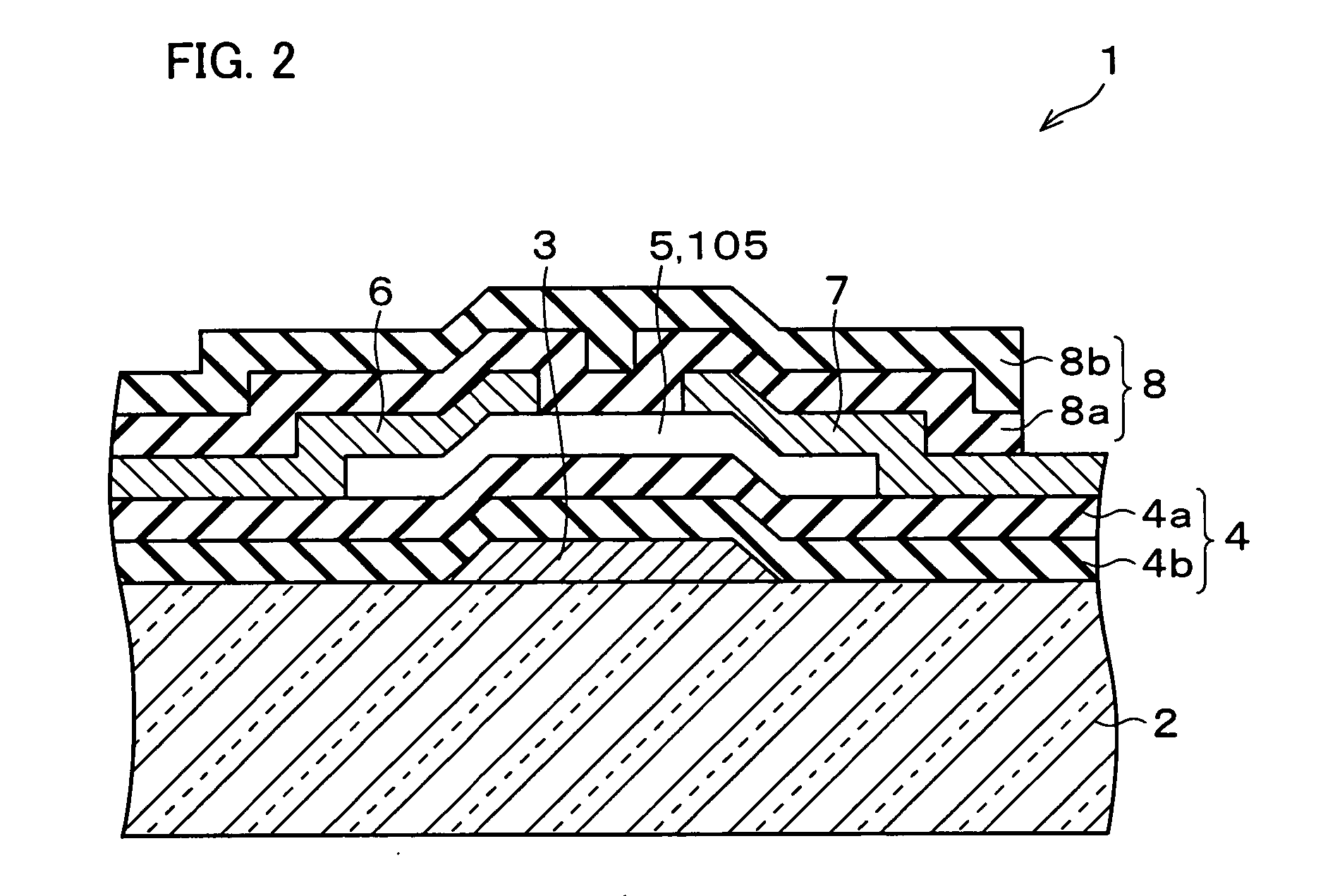

In a thin film transistor (1), a gate insulating layer (4) is formed on a gate electrode (3) formed on an insulating substrate (2). Formed on the gate insulating layer (4) is a semiconductor layer (5). Formed on the semiconductor layer (5) are a source electrode (6) and a drain electrode (7). A protective layer (8) covers them, so that the semiconductor layer (5) is blocked from an atmosphere. The semiconductor layer (5) (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. The protective layer (8) thus formed causes decrease of a surface level of the semiconductor layer (5). This eliminates a depletion layer spreading therewithin. Accordingly, the ZnO becomes an n-type semiconductor indicating an intrinsic resistance, with the result that too many free electrons are generated. However, the added element works on the ZnO as an accepter impurity, so that the free electrons are reduced. This decreases a gate voltage required for removal of the free electrons, so that the threshold voltage of the thin film transistor (1) becomes on the order of 0V. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

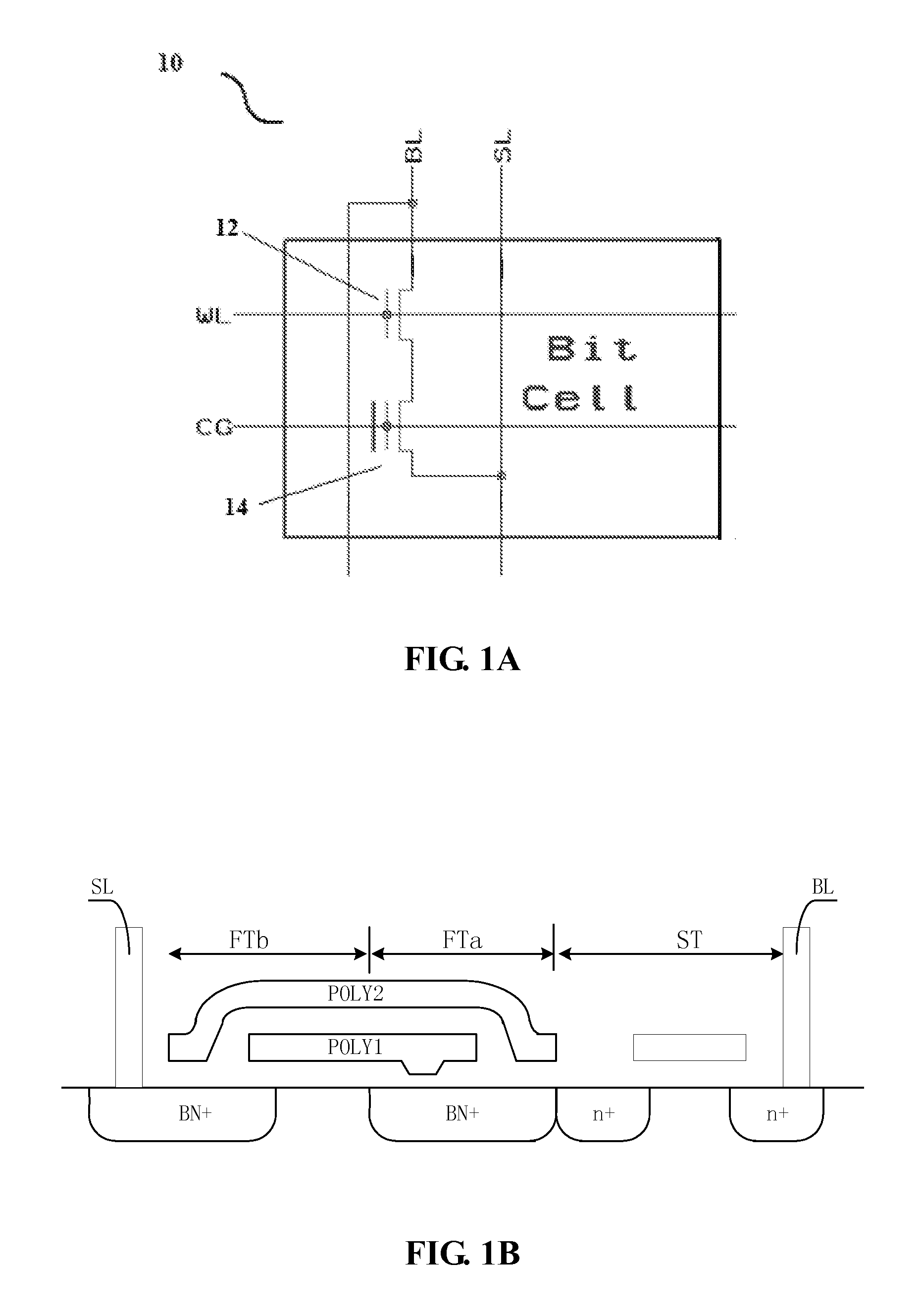

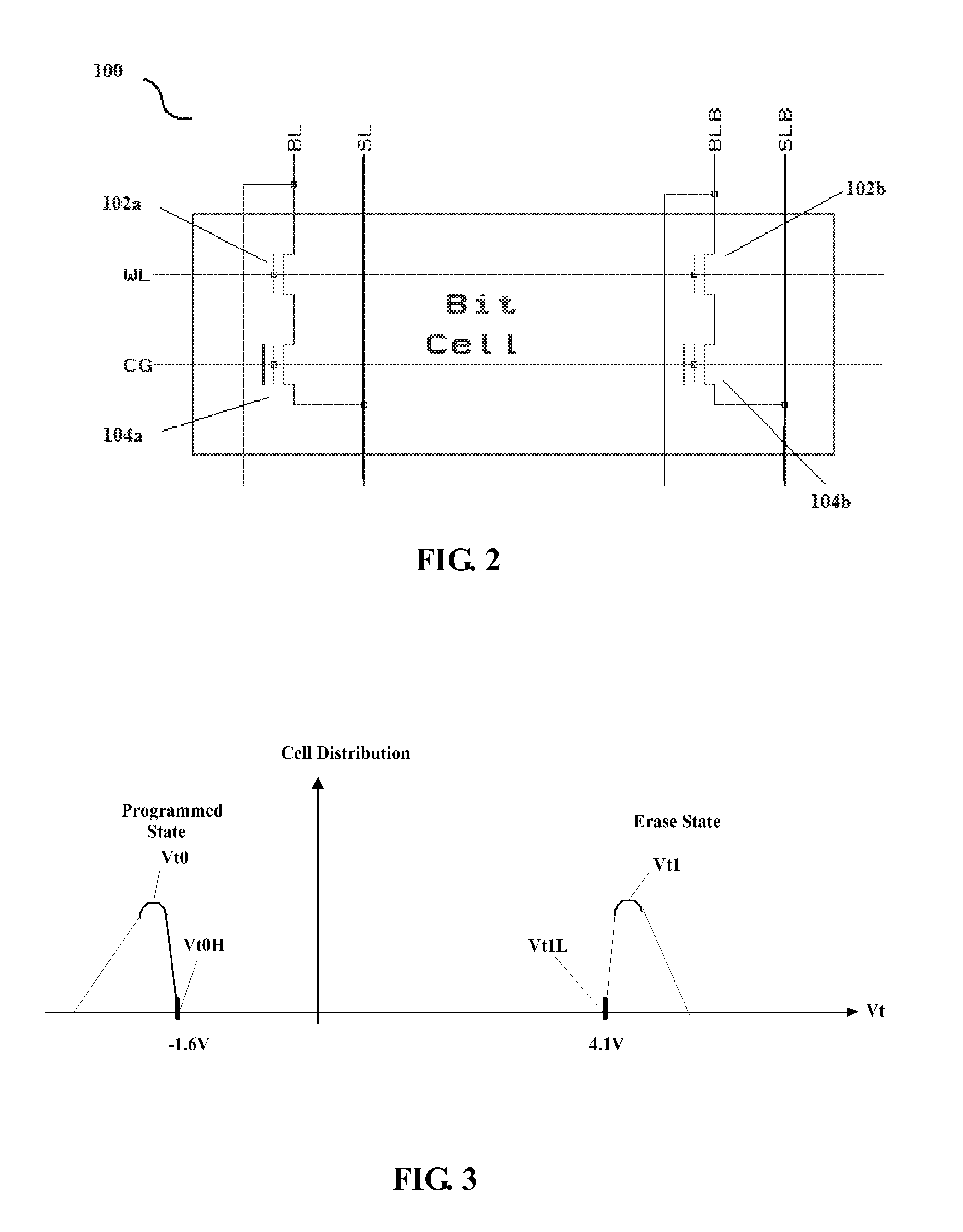

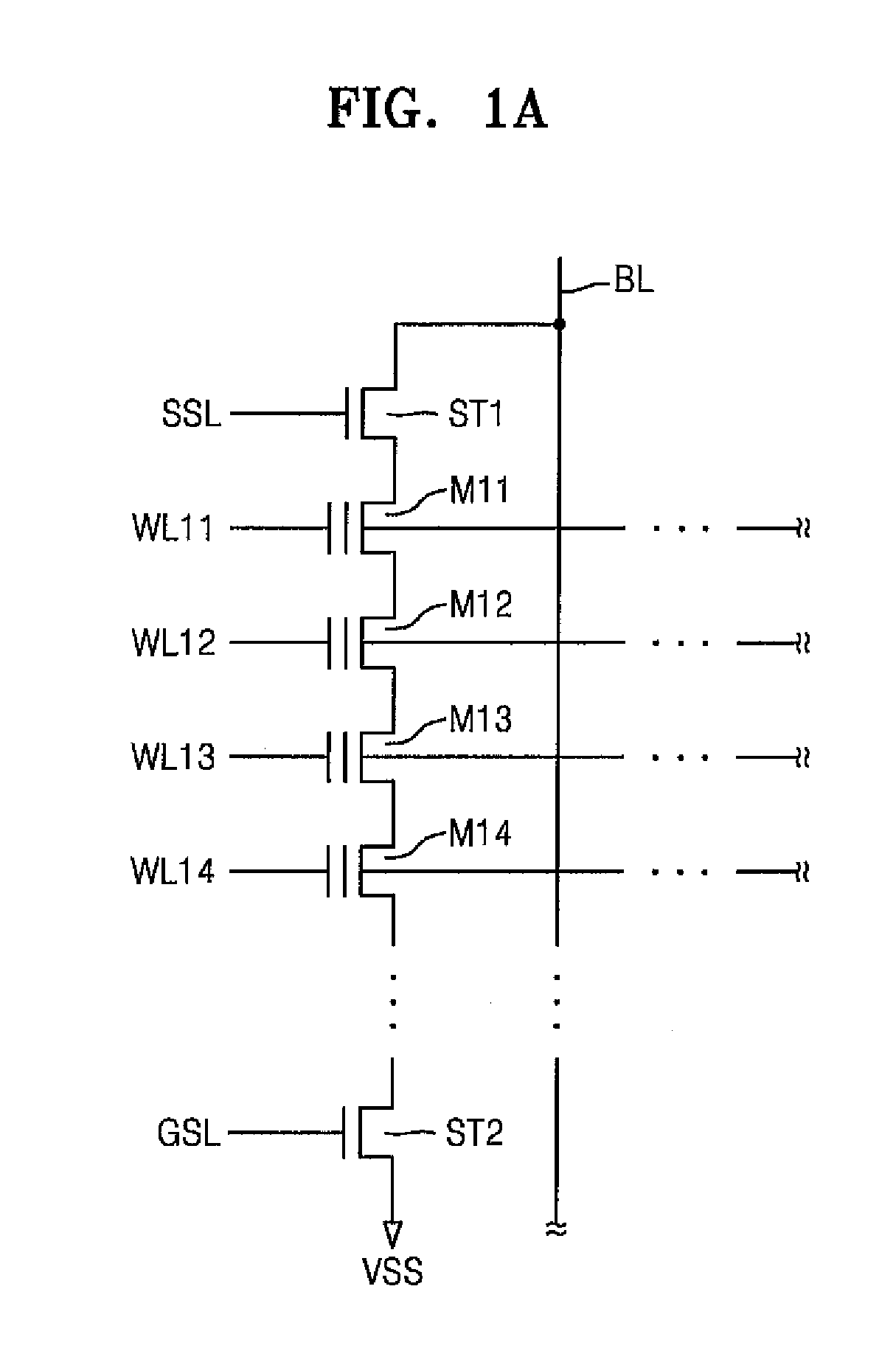

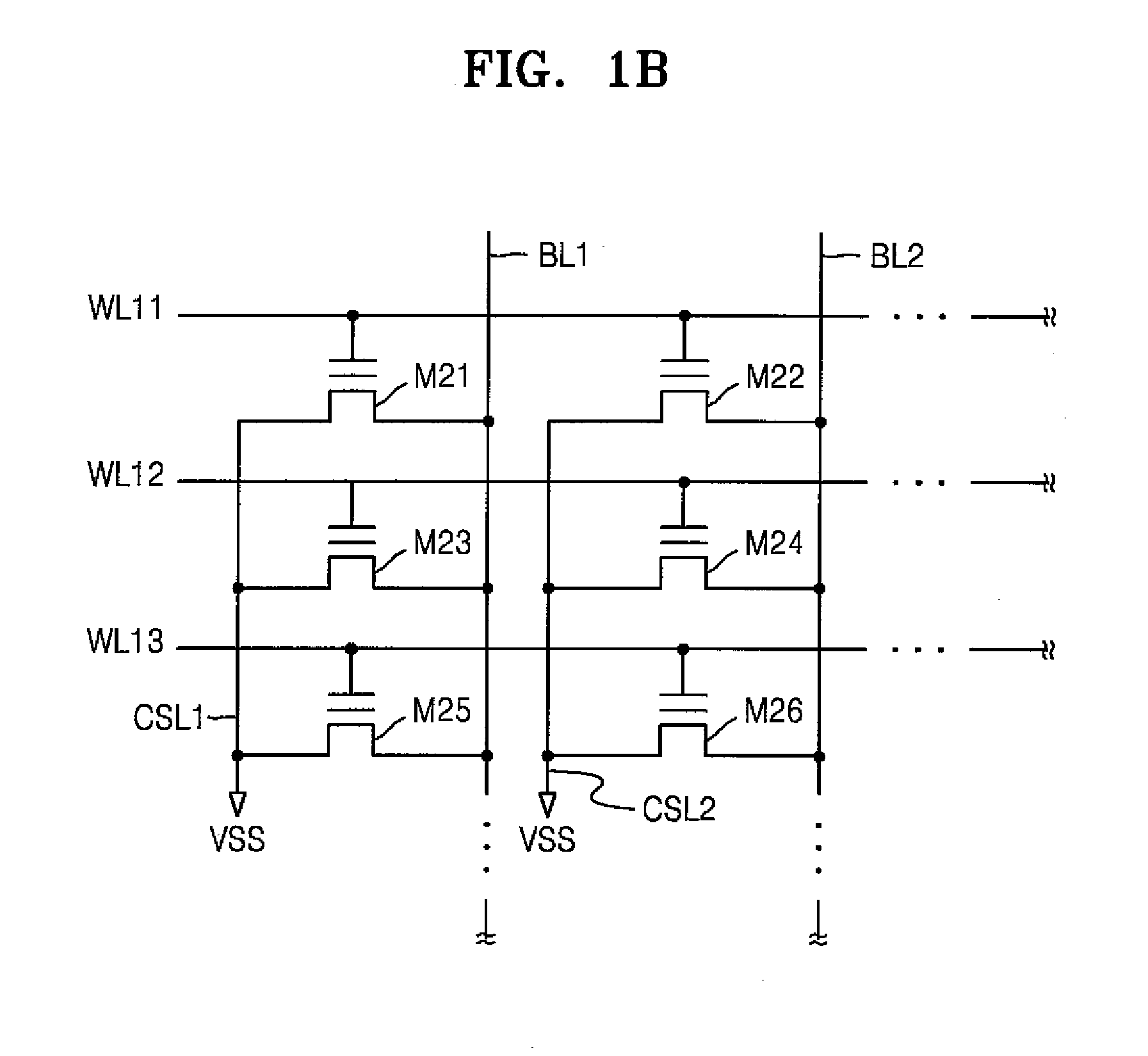

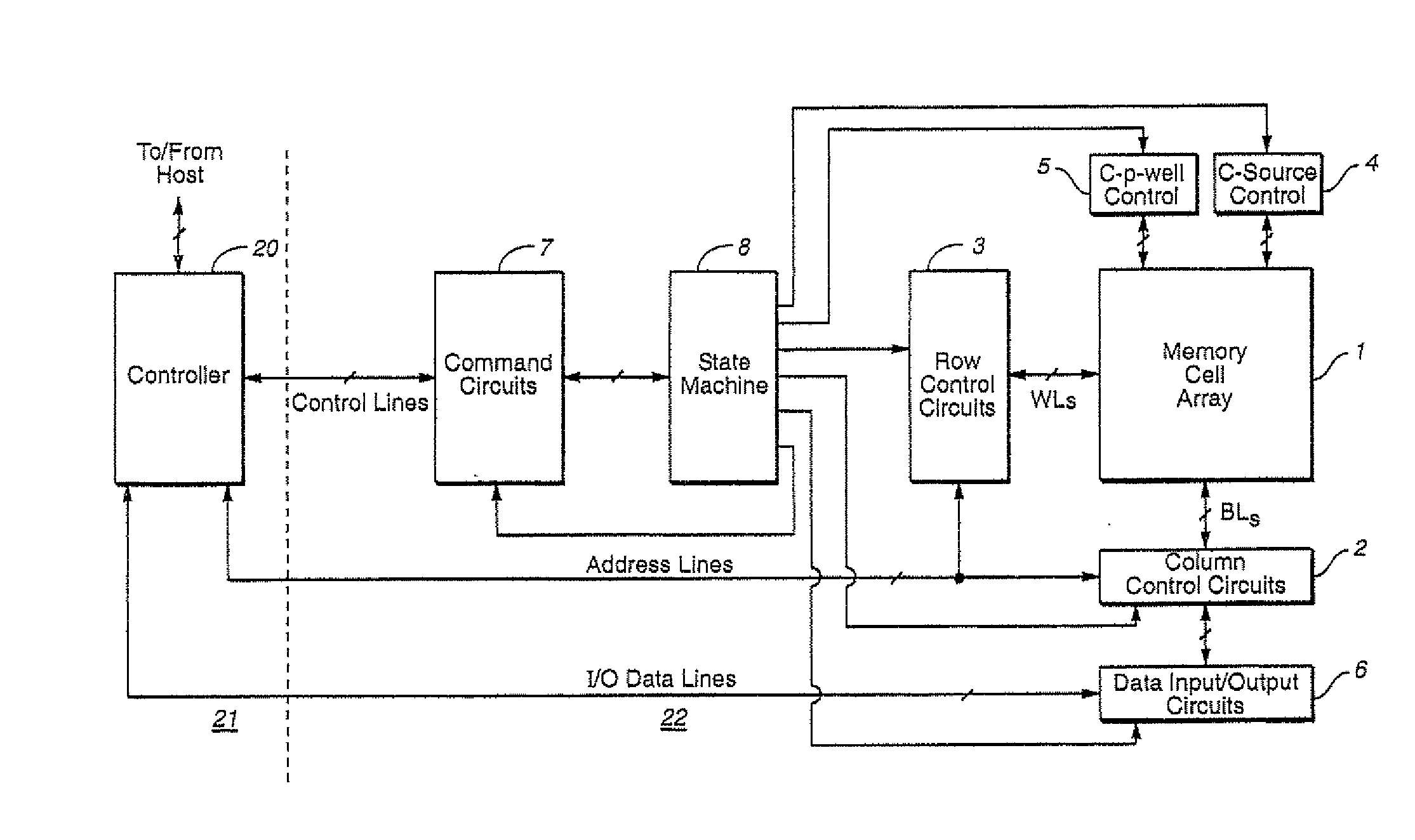

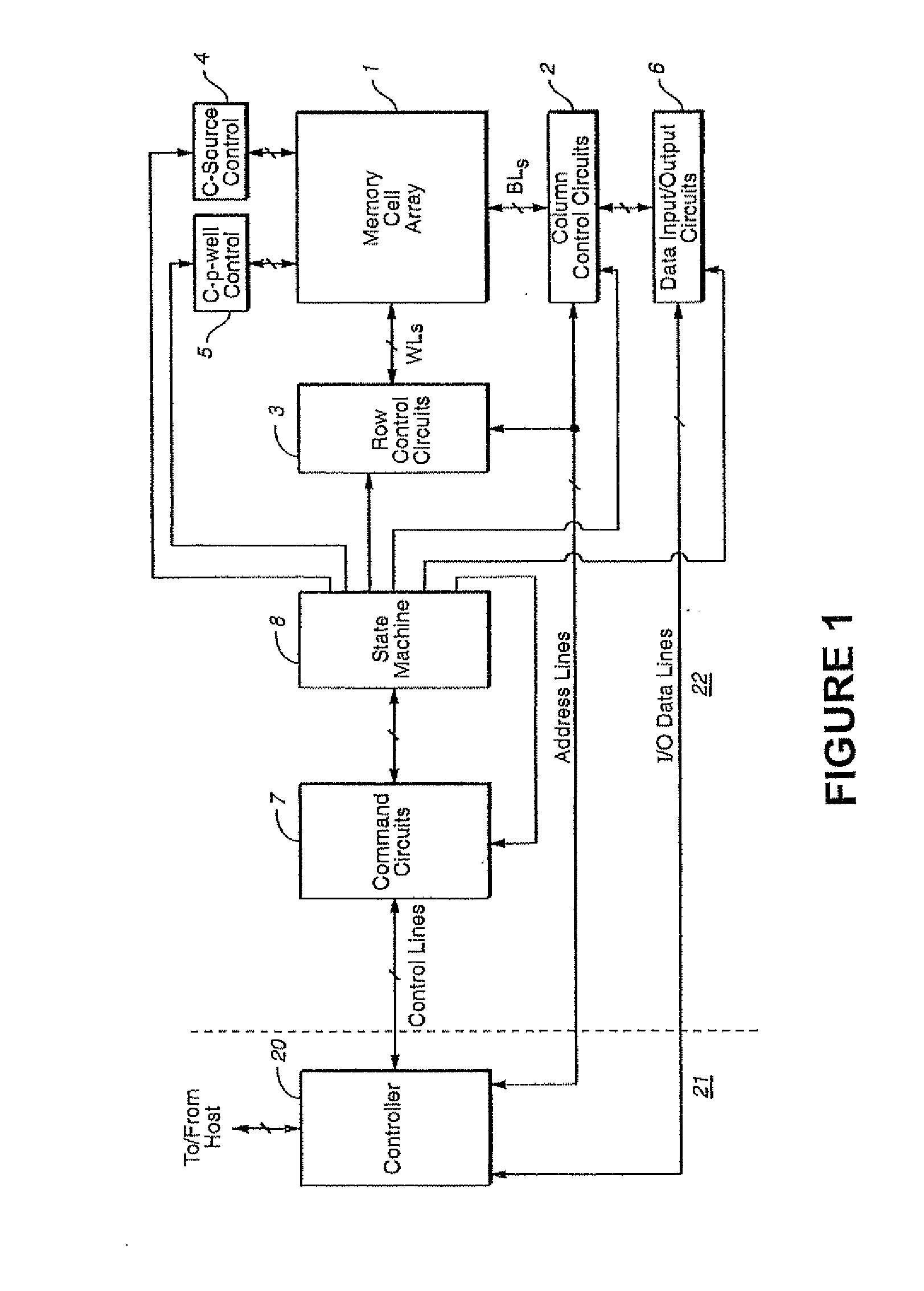

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

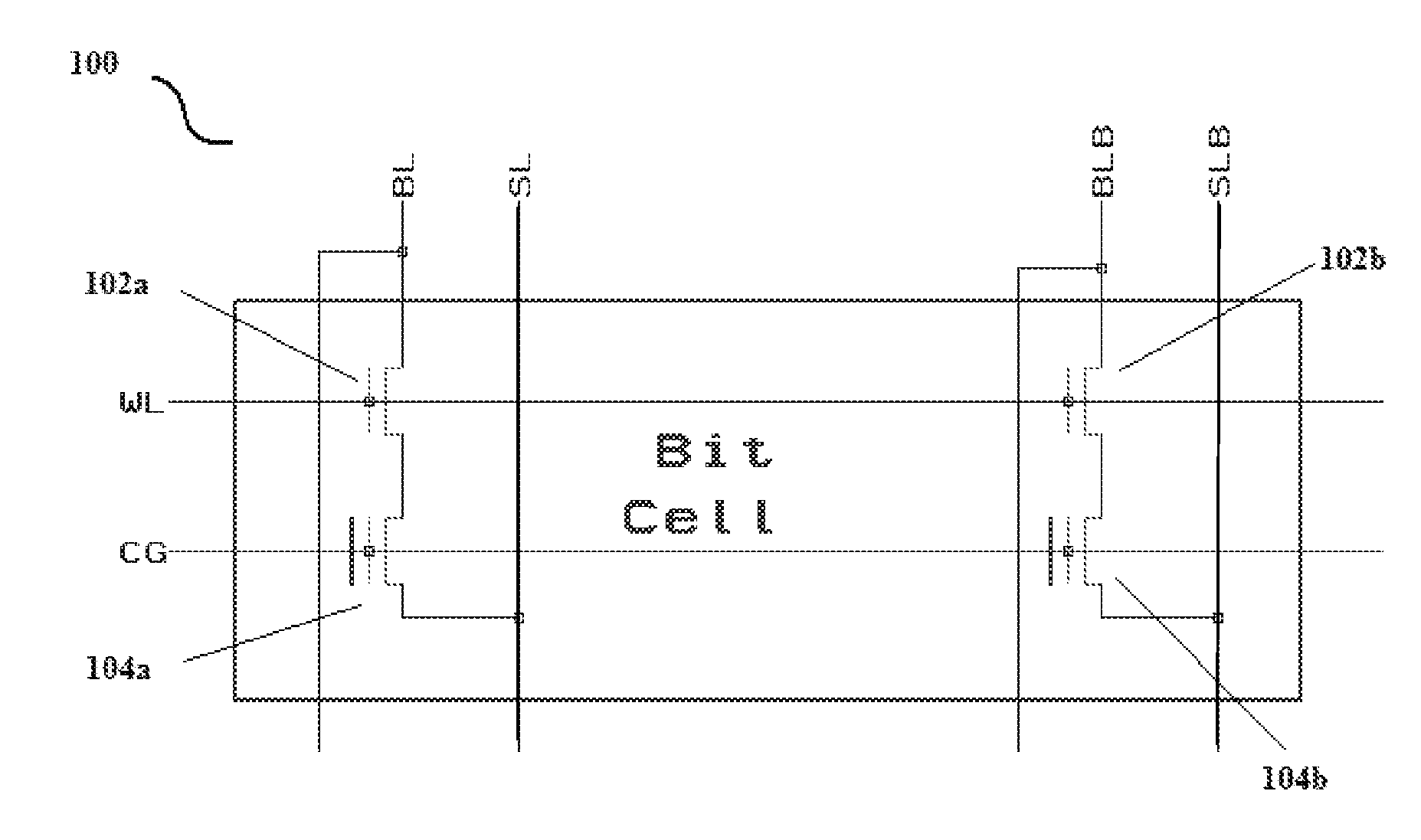

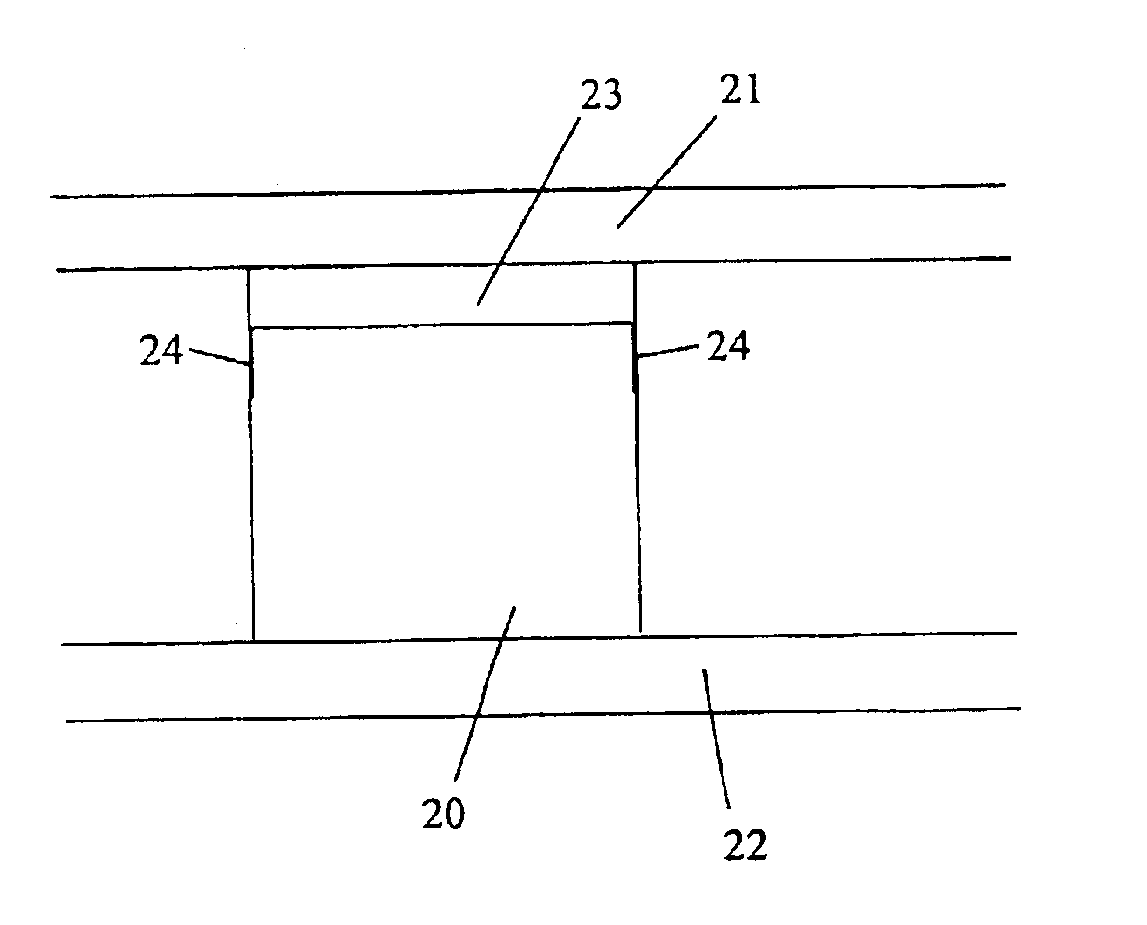

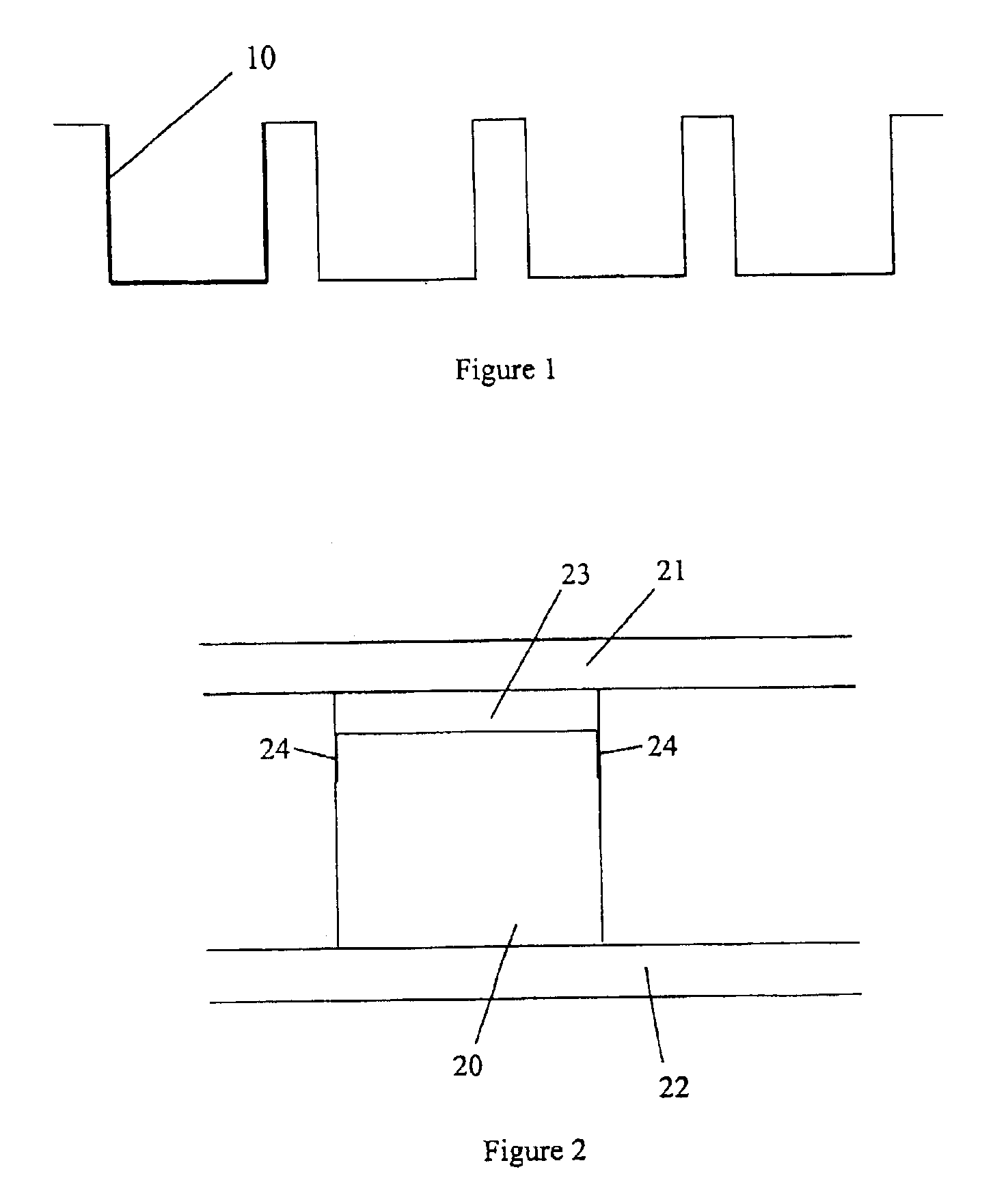

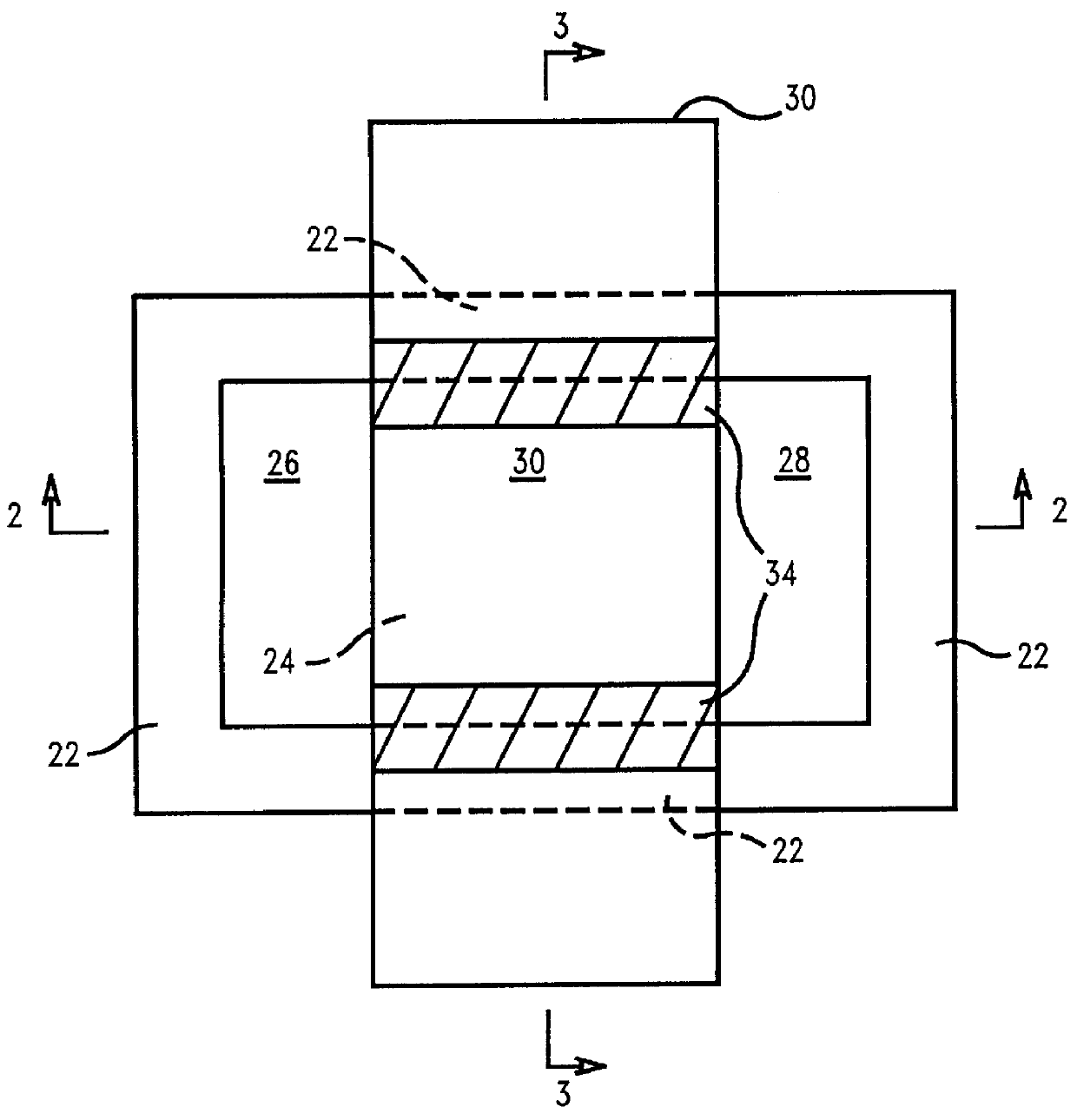

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

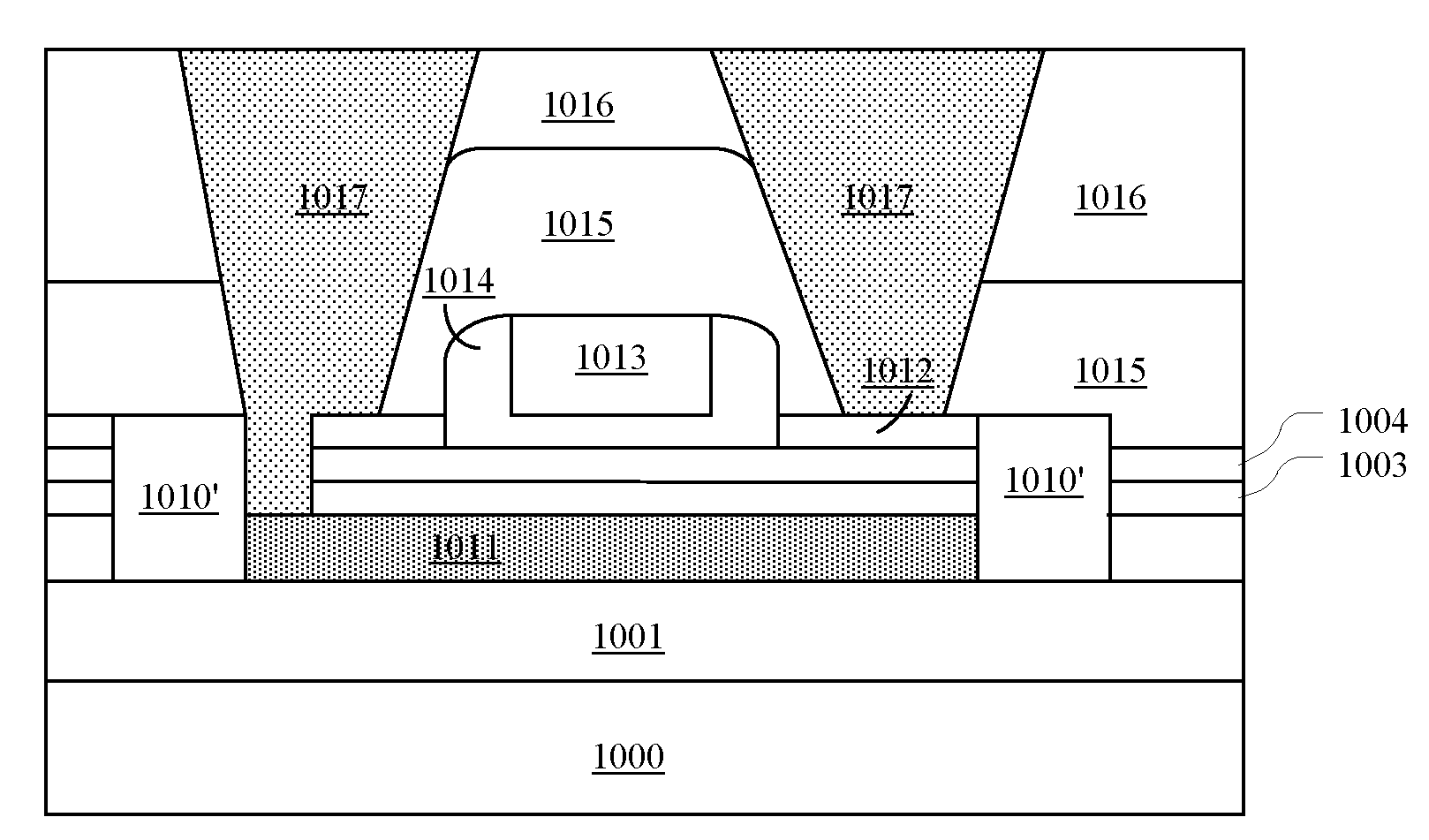

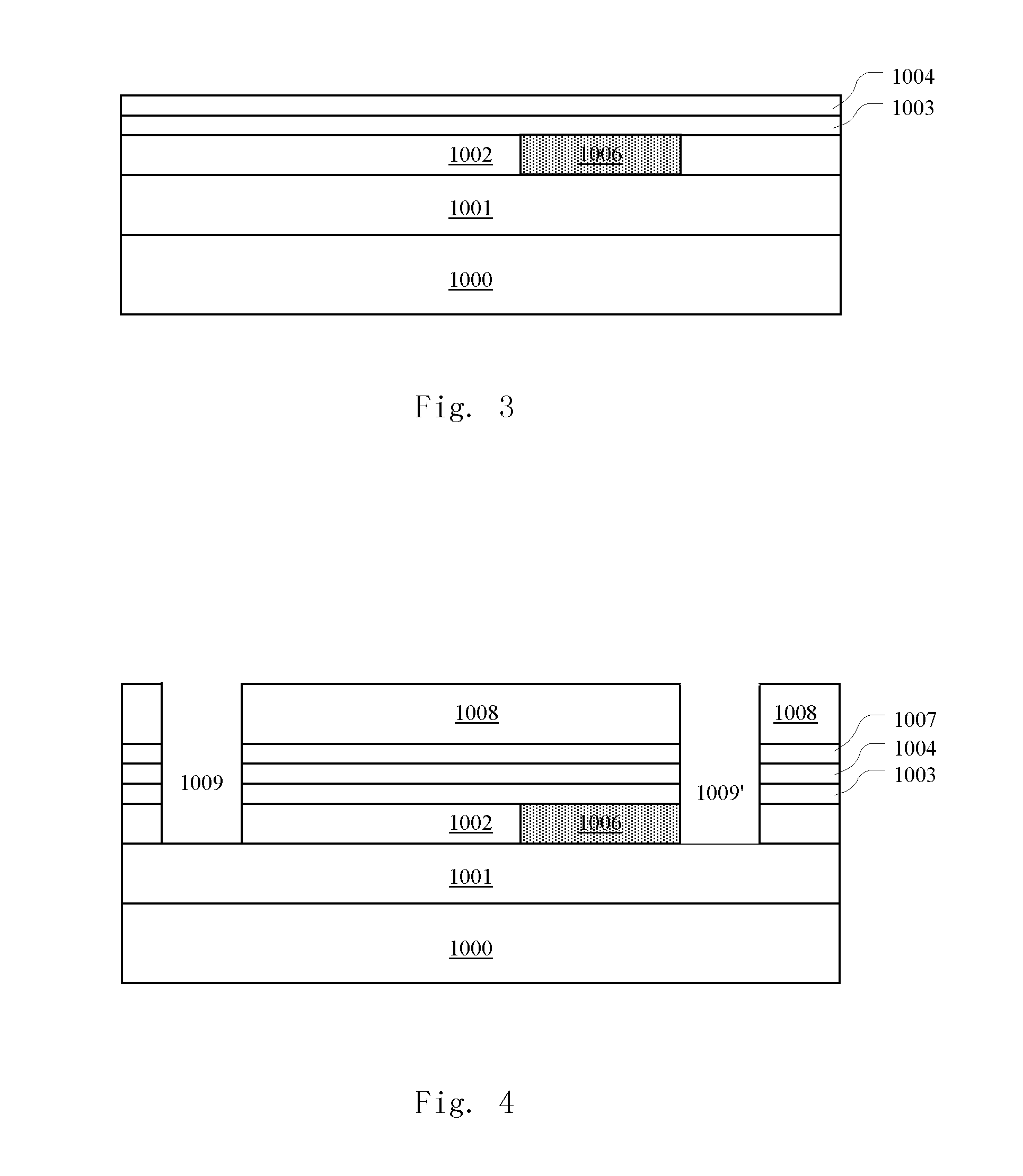

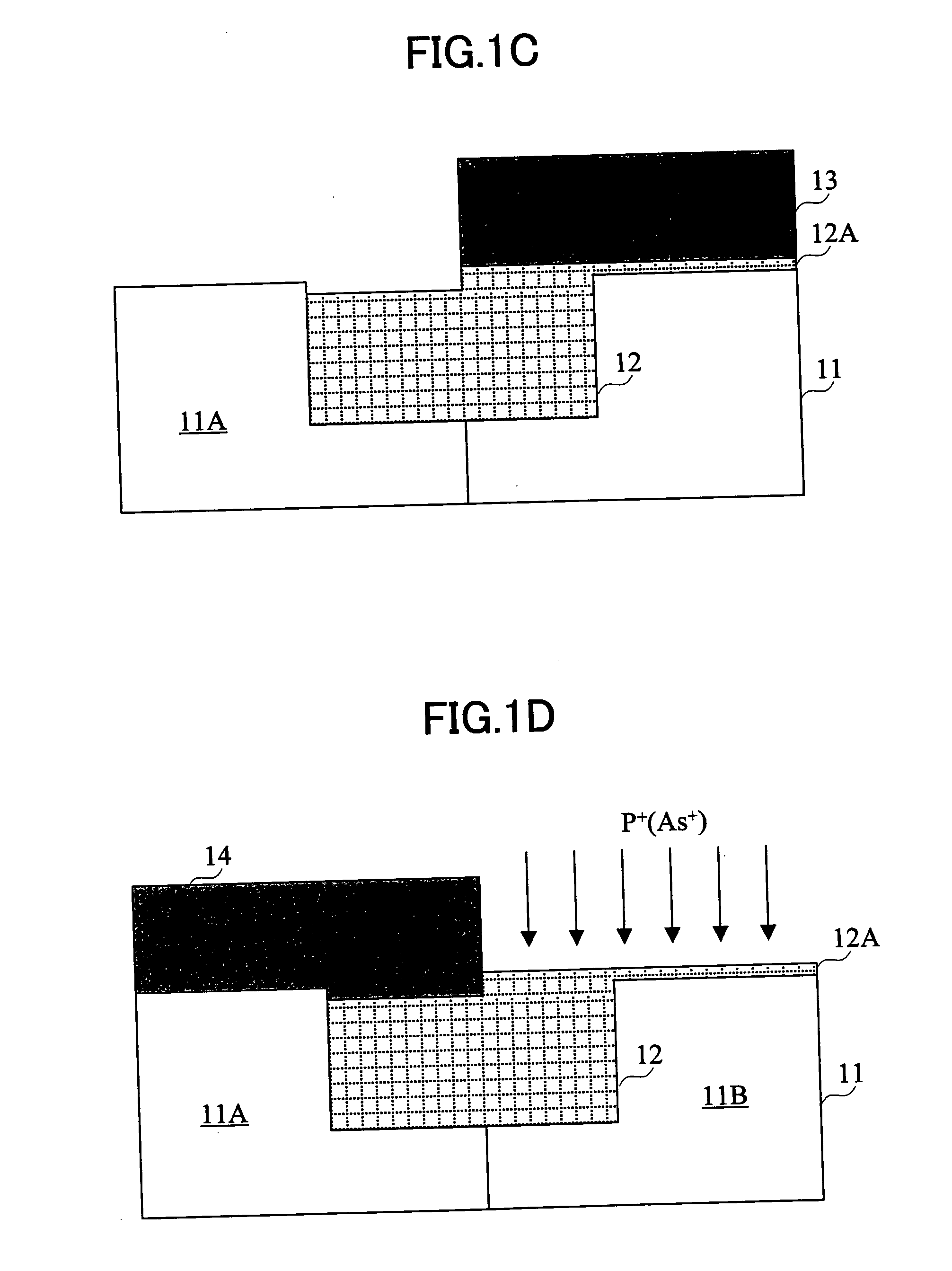

Semiconductor structure and method for manufacturing the same

ActiveUS20120104495A1Simple manufacturing processHighly integratedTransistorSolid-state devicesSemiconductor structureEngineering

The present application discloses a semiconductor structure and a method for manufacturing the same. The semiconductor structure according to the present invention adjusts a threshold voltage with a common contact, which has a portion outside the source or drain region extending to the back-gate region and provides an electrical contact of the source or drain region and the back-gate region, which leads to a simple manufacturing process, an increased integration level and a lowered manufacture cost. Moreover, the asymmetric design of the back-gate structure further increases the threshold voltage and improves the performance of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

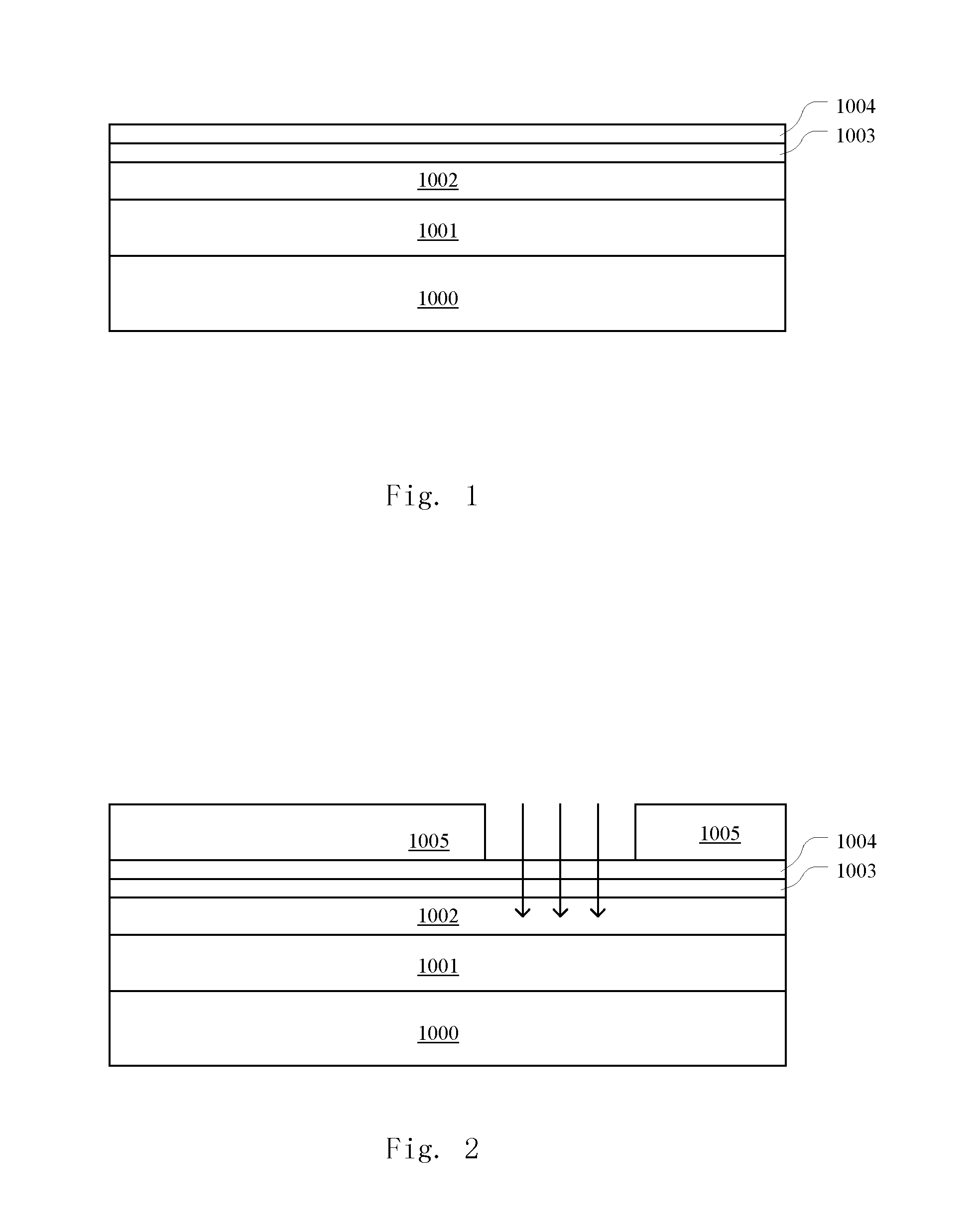

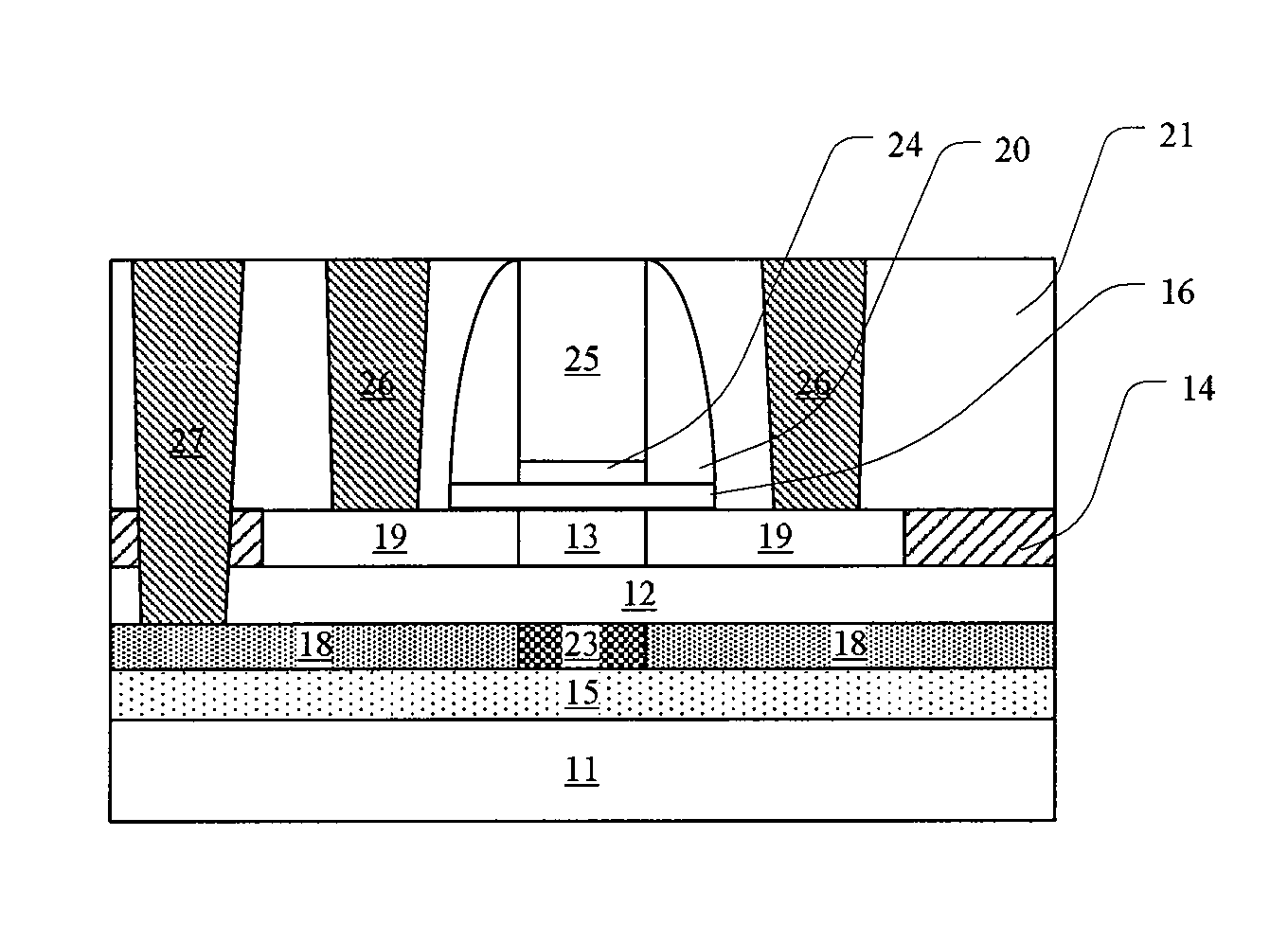

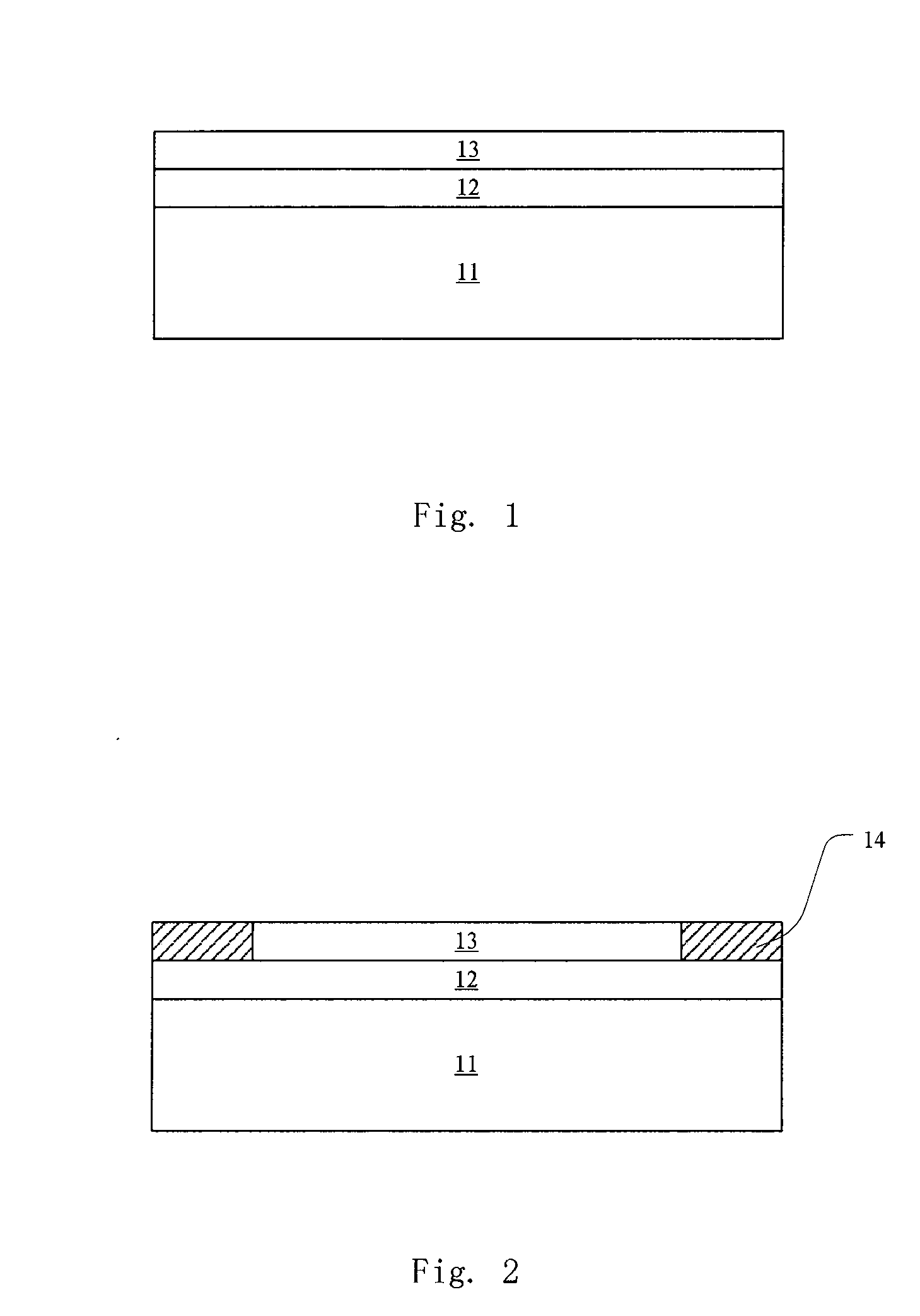

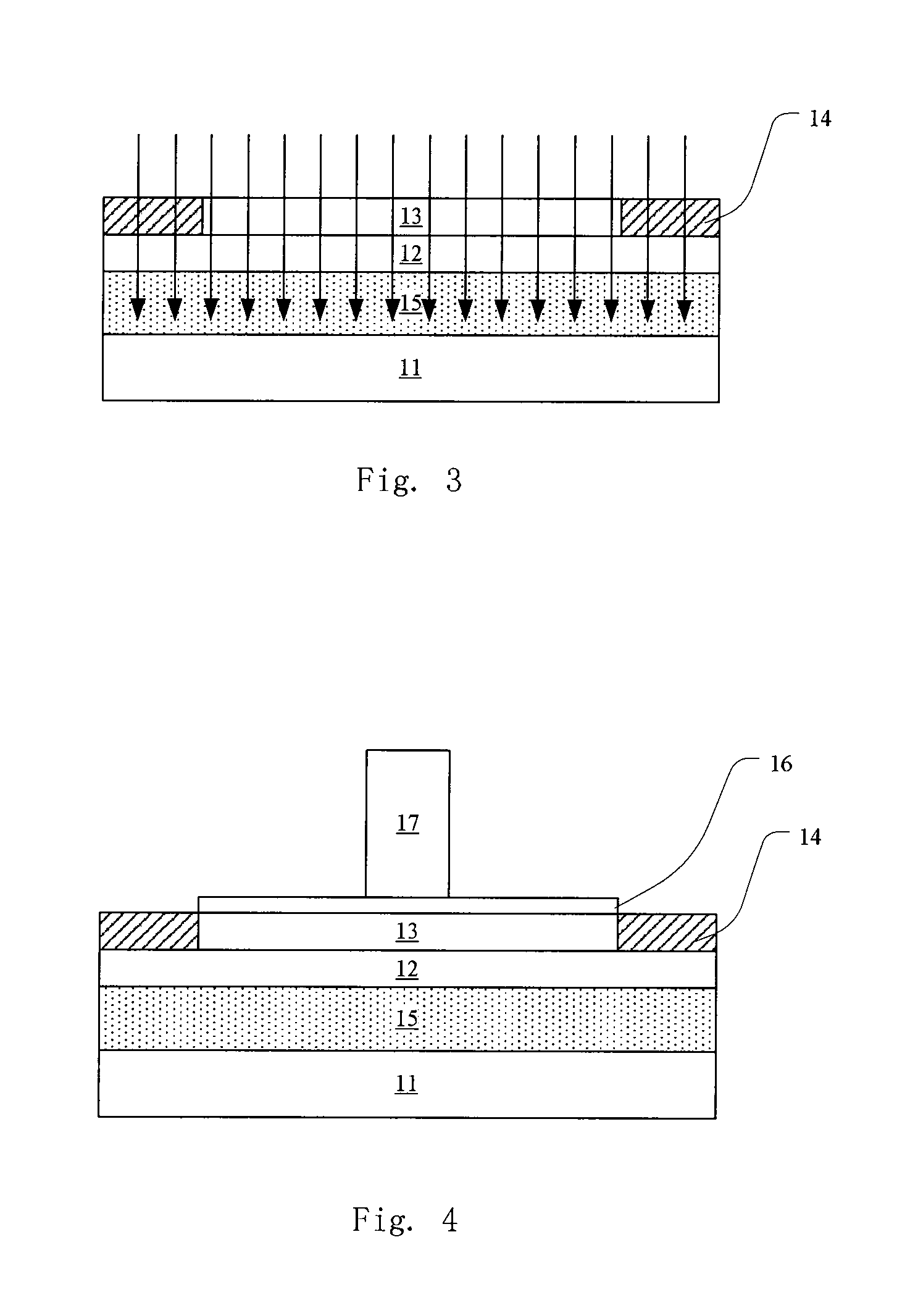

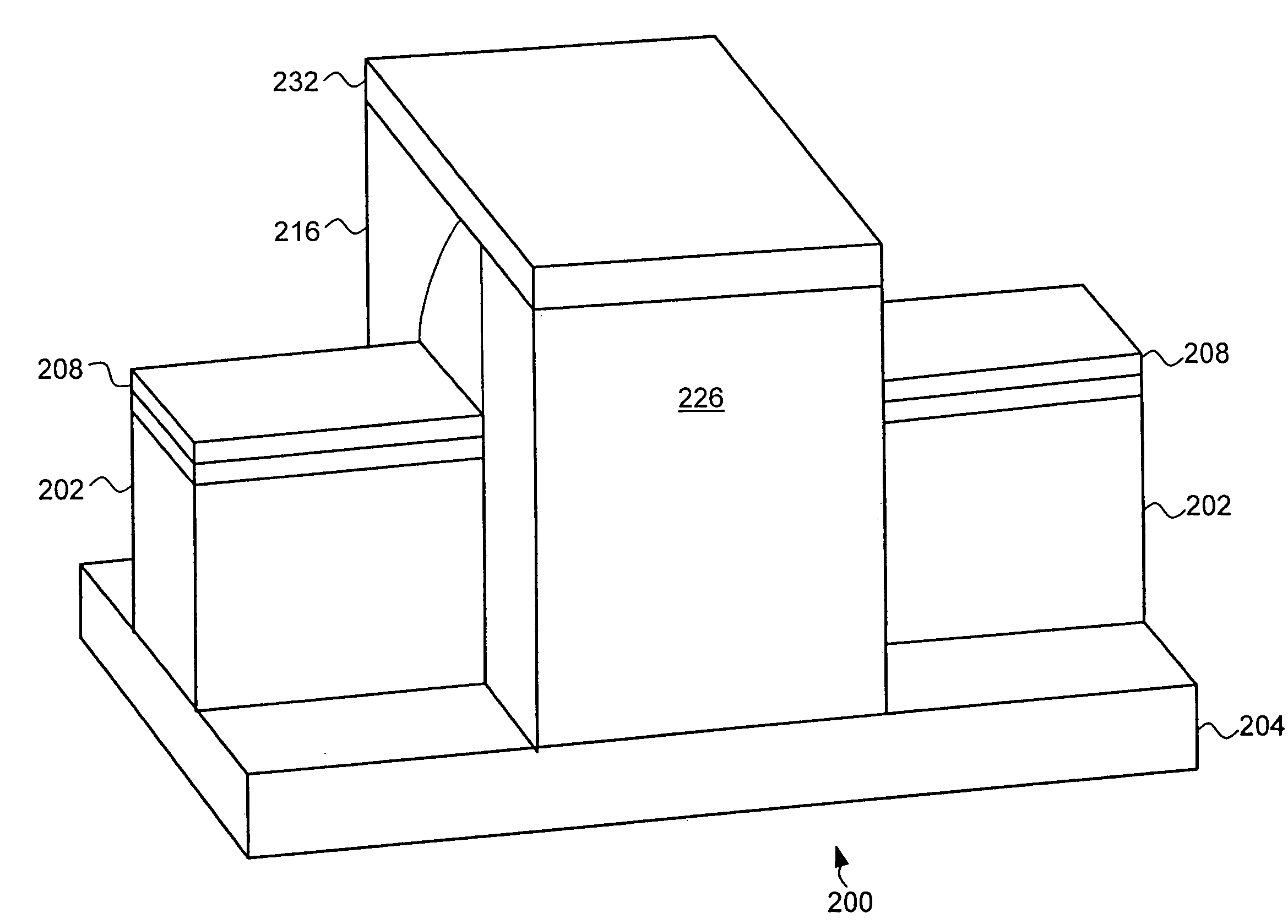

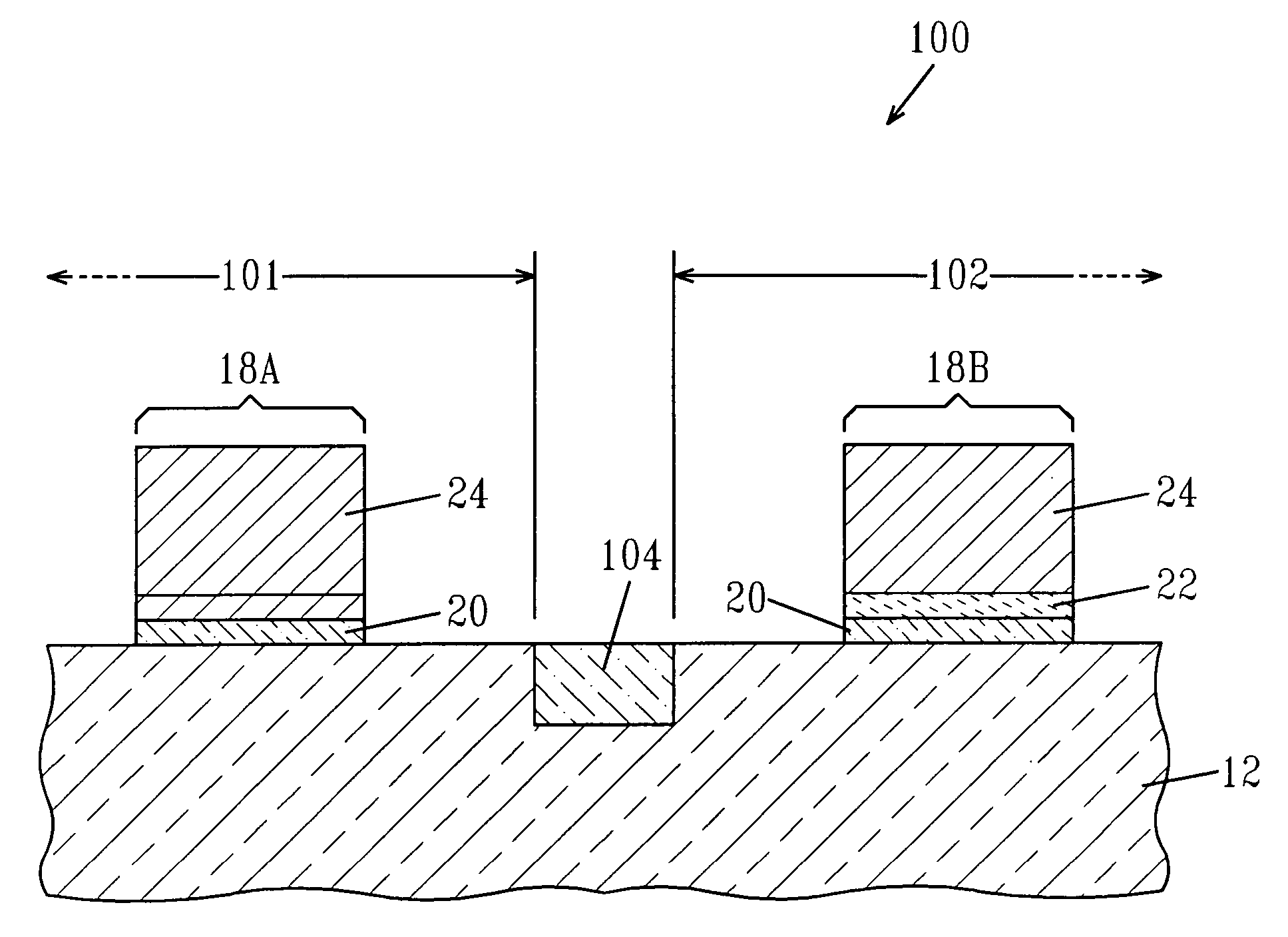

Mosfet and method for manufacturing the same

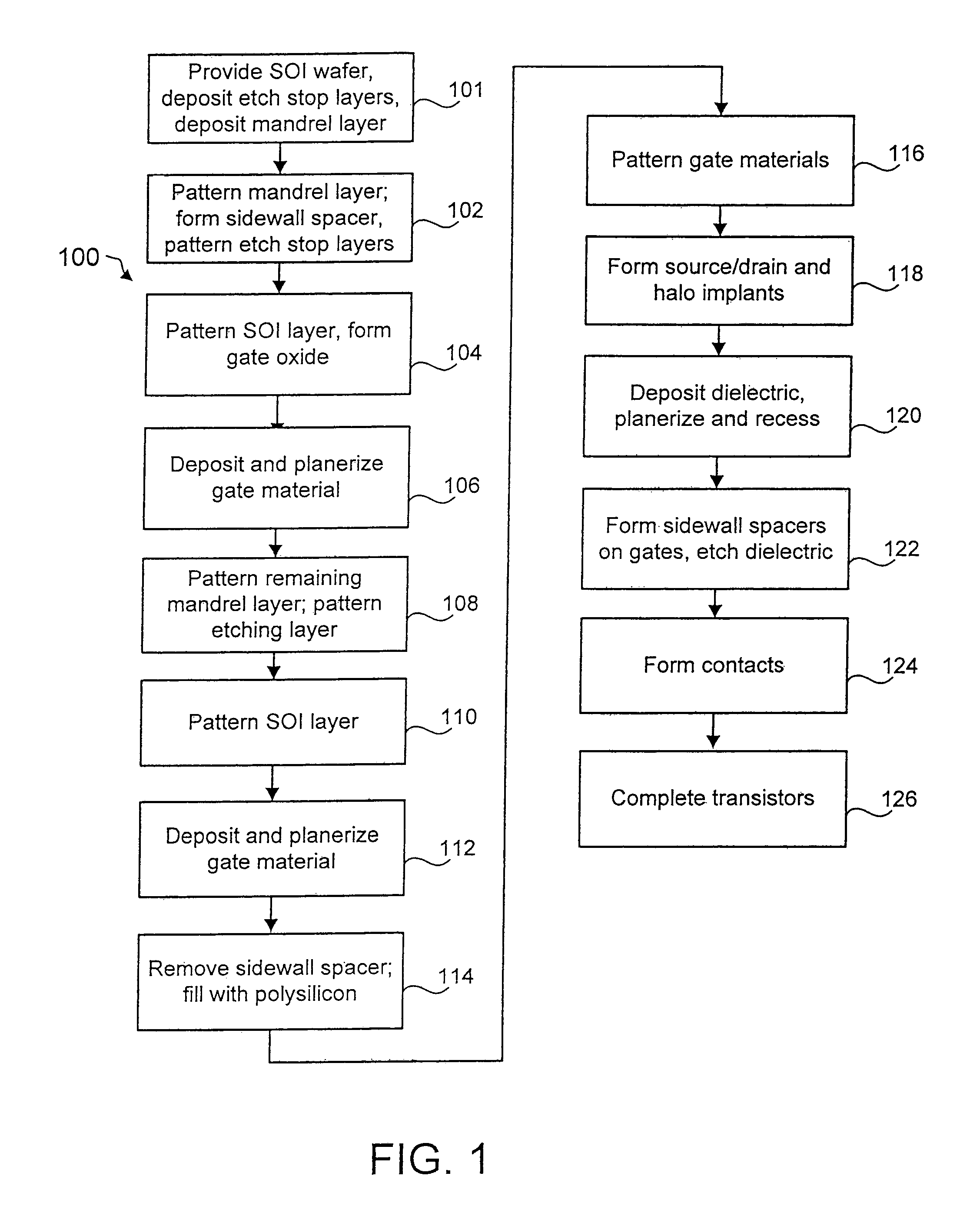

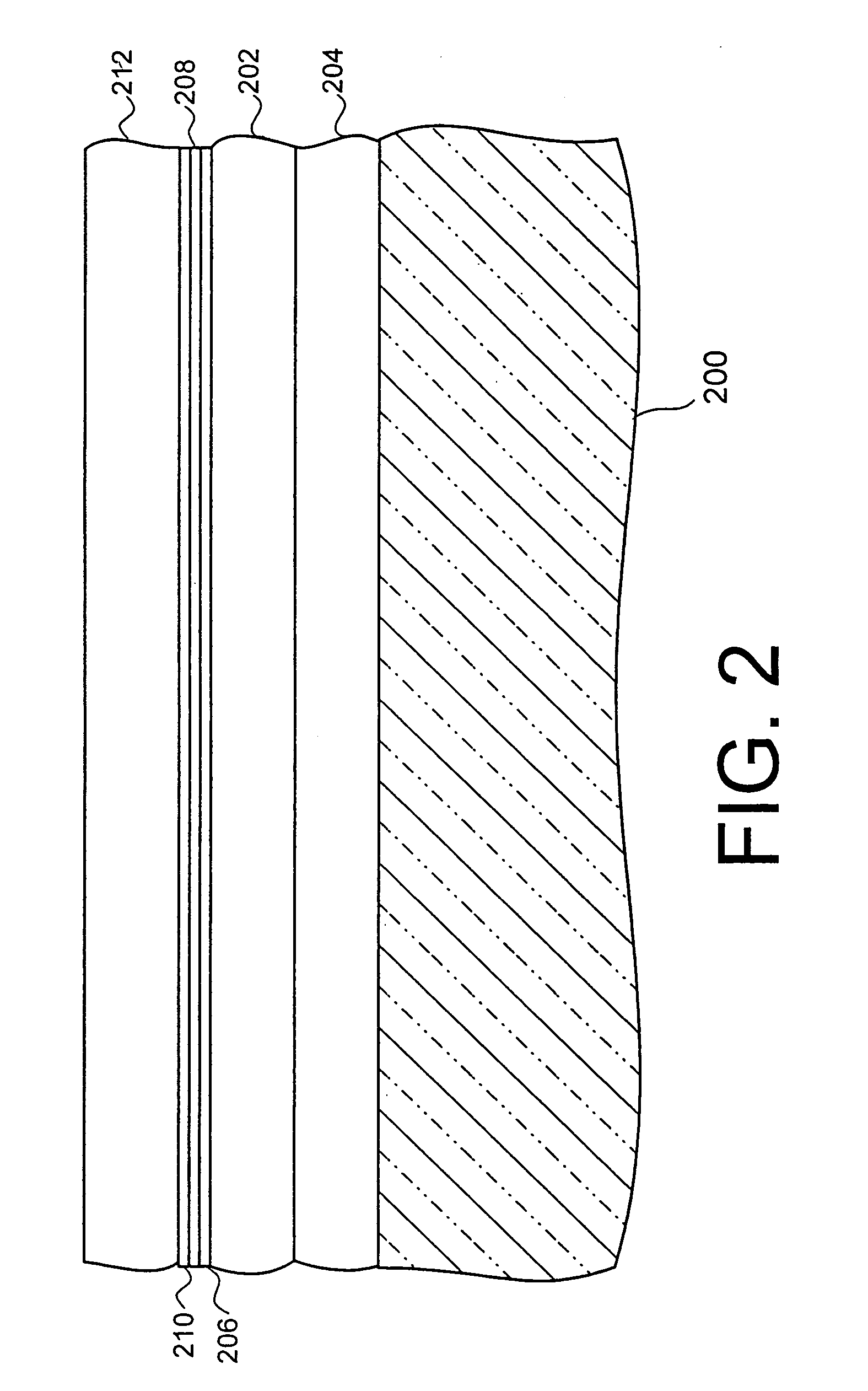

ActiveUS20130099315A1Adjustment of threshold voltageRaise the threshold voltageTransistorSolid-state devicesMOSFETWafering

The present disclosure discloses a MOSFET and a method for manufacturing the same, wherein the MOSFET comprises: an SOI wafer which comprises a semiconductor substrate, a buried insulating layer, and a semiconductor layer, the buried insulating layer being on the semiconductor substrate, and the semiconductor layer being on the buried insulating layer; a gate stack on the semiconductor layer; a source region and a drain region, which are in the semiconductor layer and on opposite sides of the gate stack; and a channel region, which is in the semiconductor layer and sandwiched by the source region and the drain region, wherein the MOSFET further comprises a back gate, the back gate being located in the semiconductor substrate and having a first doped region in a lower portion of the back gate and a second doped region in an upper portion of the back gate. The MOSFET can adjust the threshold voltage by changing the doping type and doping concentration of the anti-doped region.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

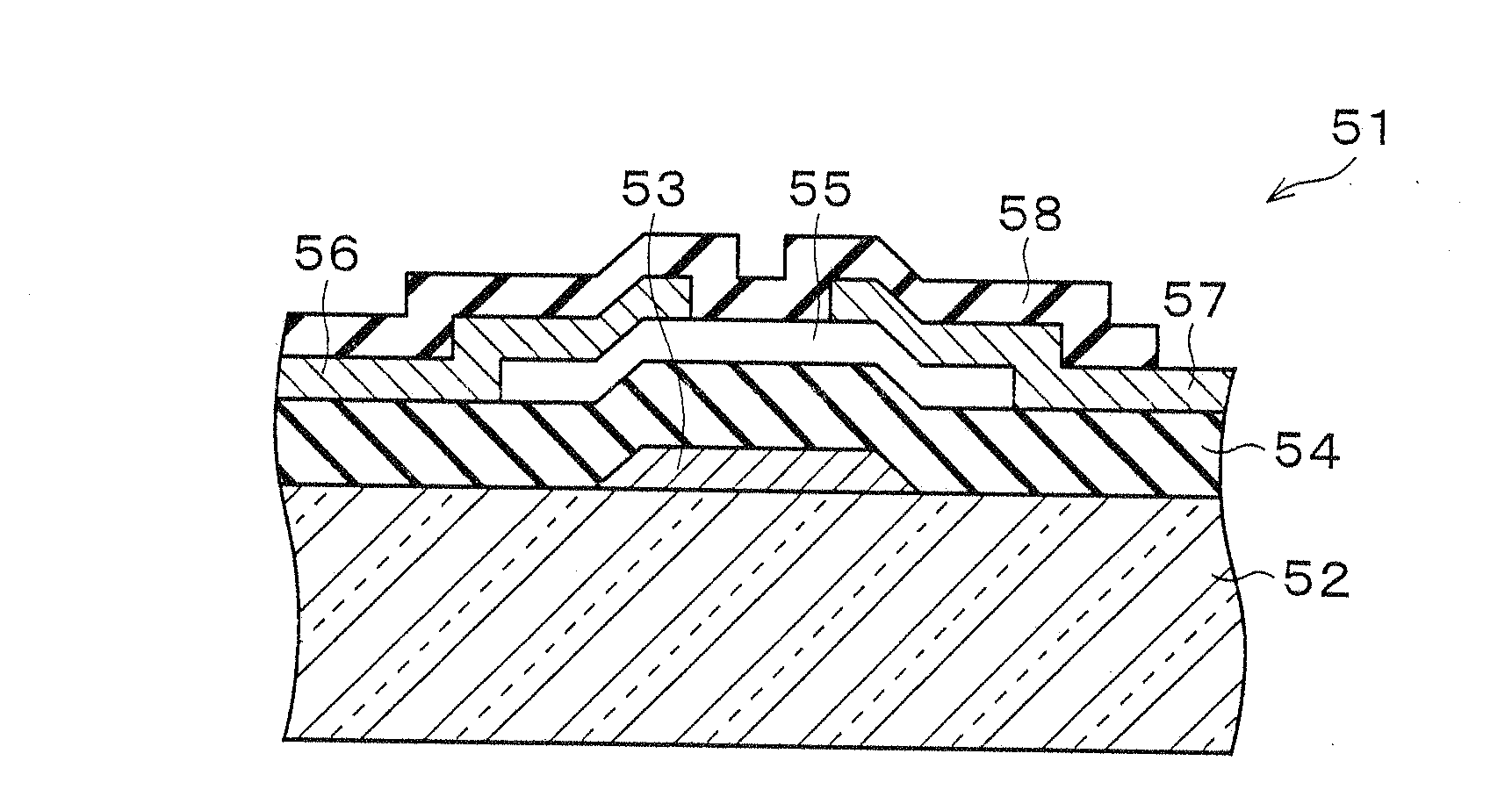

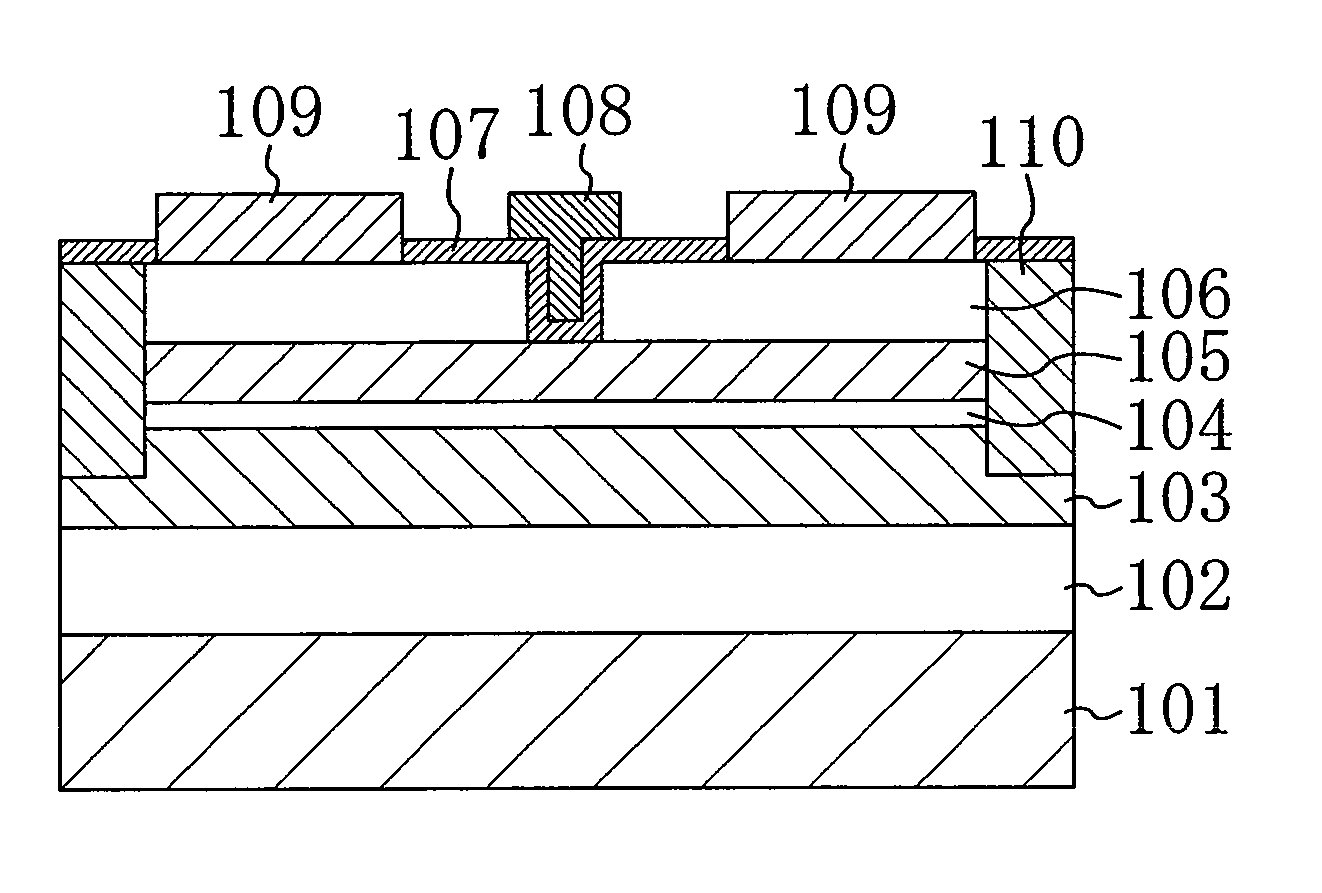

Semiconductor device, manufacturing method thereof, and electronic device

InactiveUS20110175090A1Low costFree electronTransistorSemiconductor/solid-state device manufacturingSemiconductor packageProtection layer

In a thin film transistor, a gate insulating layer is formed on a gate electrode formed on an insulating substrate. Formed on the gate insulating layer is a semiconductor layer. Formed on the semiconductor layer are a source electrode and a drain electrode. A protective layer covers them, so that the semiconductor layer is blocked from an atmosphere. The semiconductor layer (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

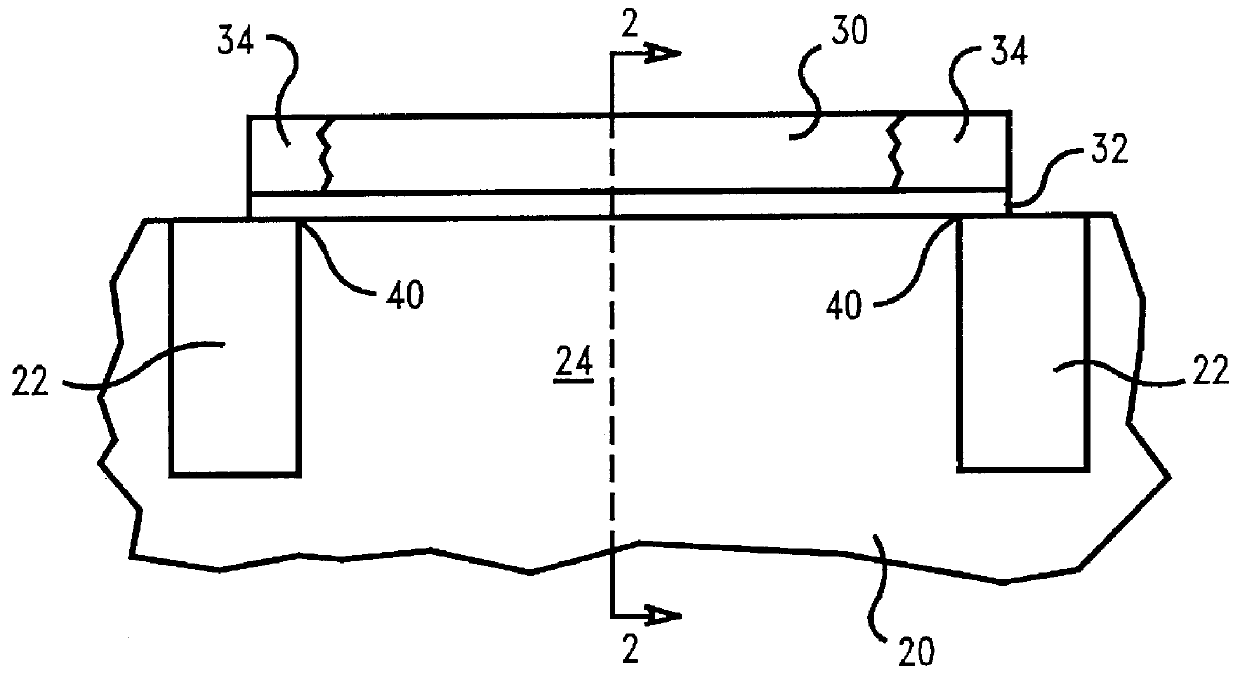

Double gated transistor and method of fabrication

InactiveUS7288445B2High densityImprove performanceTransistorSemiconductor/solid-state device manufacturingNon symmetricLow voltage cmos

Owner:GLOBALFOUNDRIES INC

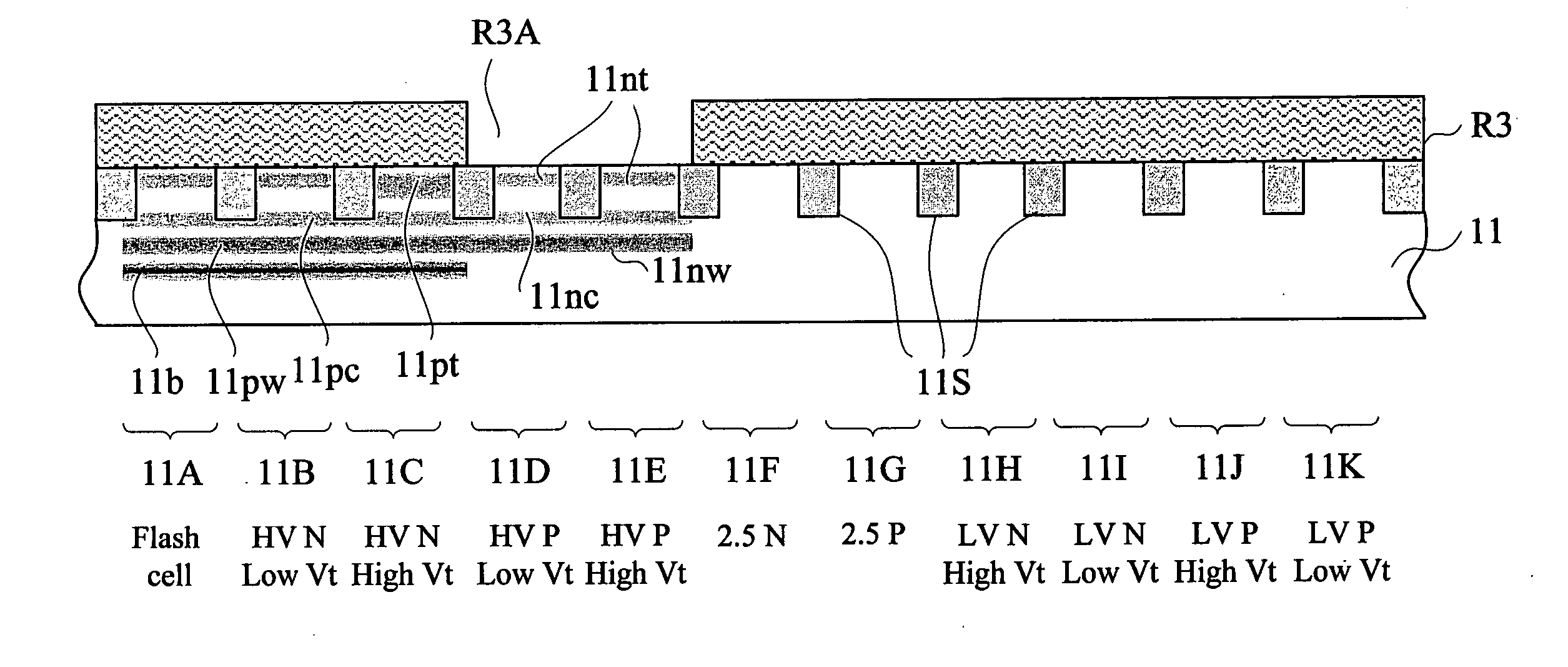

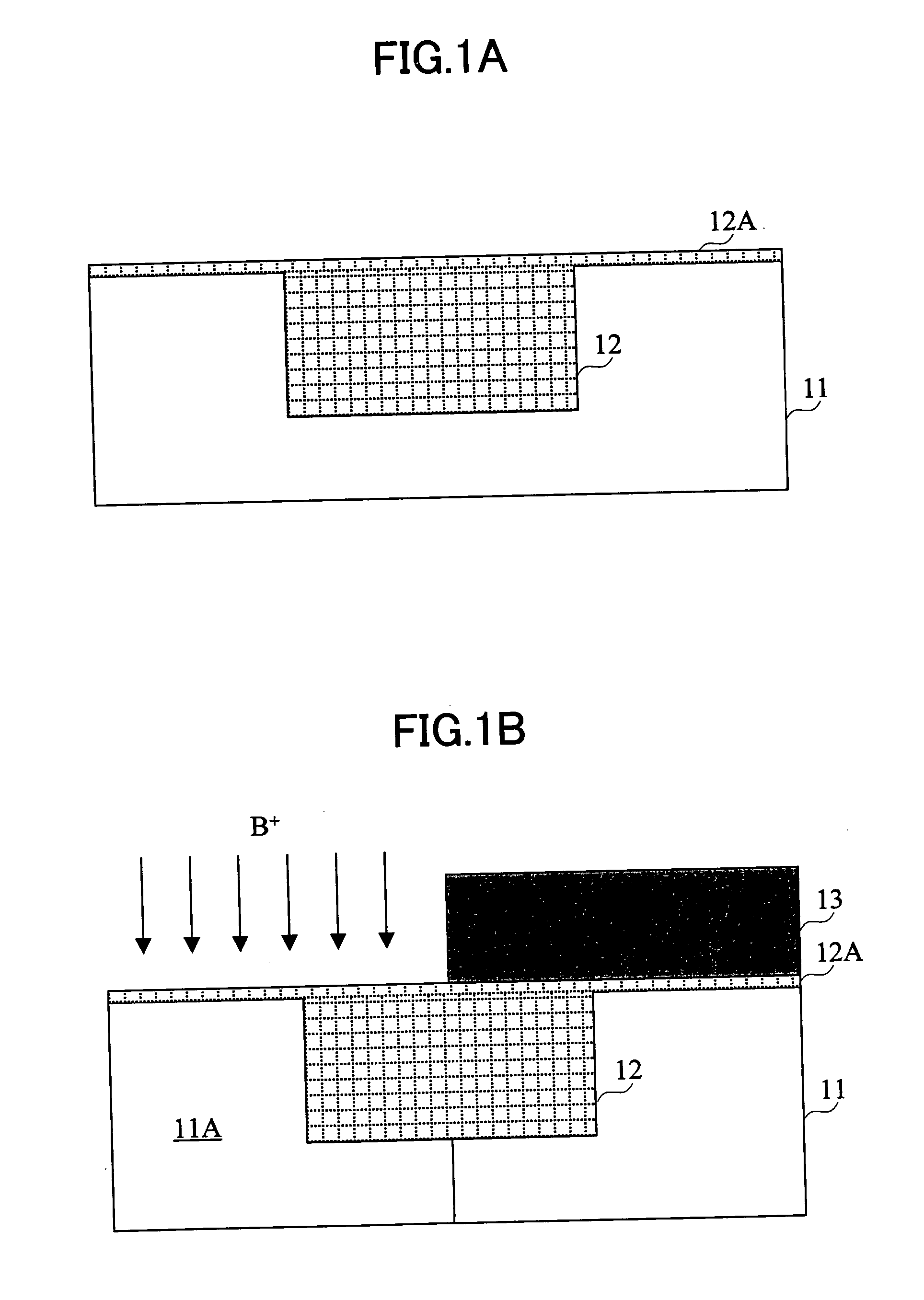

Semiconductor integrated circuit device having improved punch-through resistance and production method thereof, semiconductor integrated circuit device including a low-voltage transistor and a high-voltage transistor

InactiveUS20050280075A1Increase resistanceRaise the threshold voltageTransistorSolid-state devicesHigh voltage transistorsHigh pressure

An integrated circuit device comprises a memory cell well formed with a flash memory device, first and second well of opposite conductivity types for formation of high voltage transistors, and third and fourth wells of opposite conductivity types for low voltage transistors, wherein at least one of the fist and second wells and at least one of the third and fourth wells have an impurity distribution profile steeper than the memory cell well.

Owner:FUJITSU SEMICON LTD

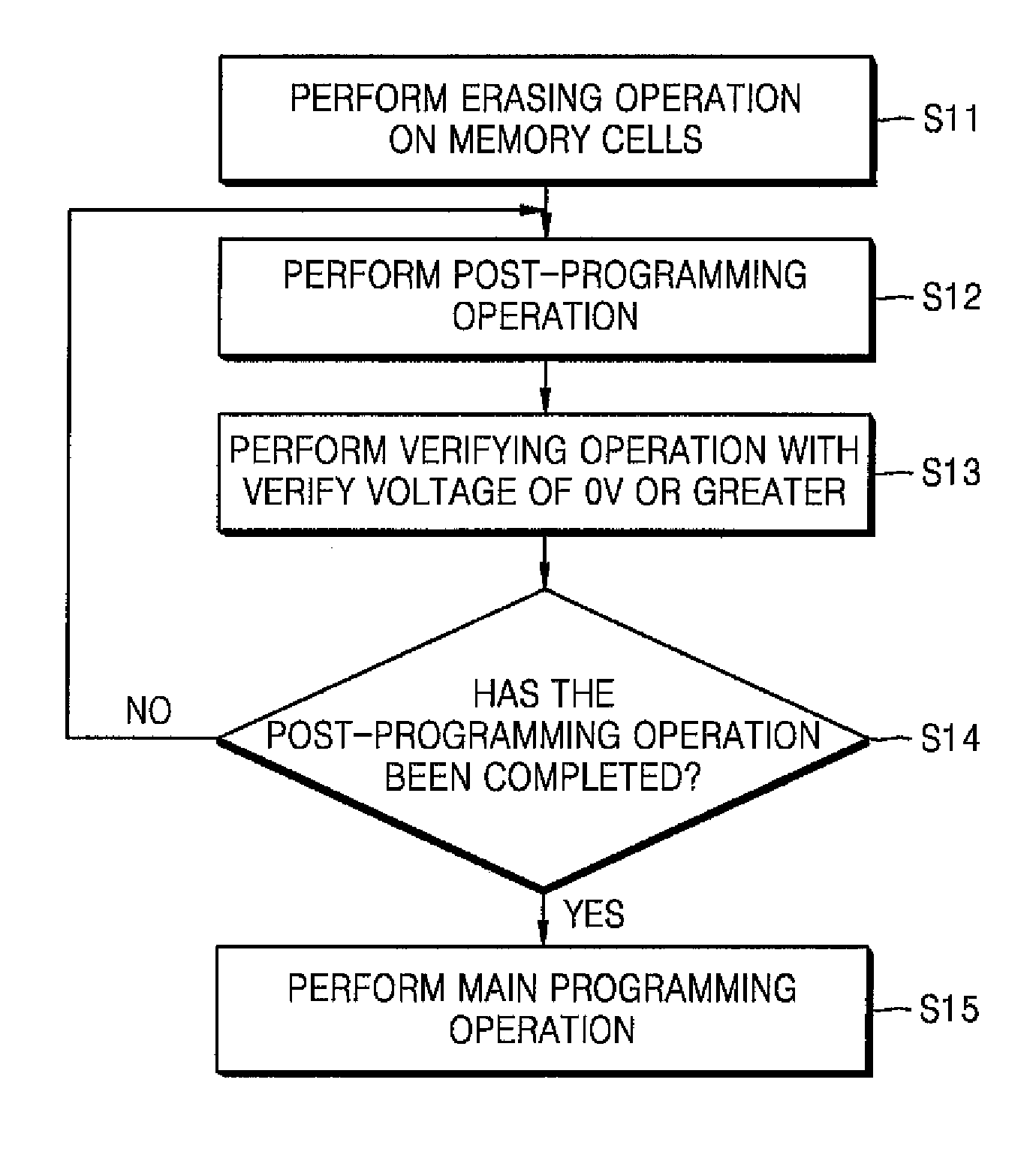

Flash memory device with reduced coupling effect among cells and method of driving the same

ActiveUS20080225599A1Improve reliabilityMinimize coupling effectRead-only memoriesDigital storageComputer scienceThreshold voltage

Embodiments of the invention provide a flash memory device that can improve the reliability of a reading operation by minimizing a variation in the threshold voltage distribution that occurs due to coupling between cells, and a method of driving the flash memory device. In an embodiment of the invention, the method of driving the flash memory includes: performing an erasing operation on memory cells; after the performing the erasing operation, performing a post-programming operation to control a threshold voltage of the memory cells; and after performing the post-programming operation, performing a main programming operation on the memory cells, wherein the performing of the post-programming operation comprises increasing the threshold voltage of the memory cells in an erased state, thereby reducing a difference in the threshold voltage between the memory cells in the erased state and the memory cells in the programmed state.

Owner:SAMSUNG ELECTRONICS CO LTD

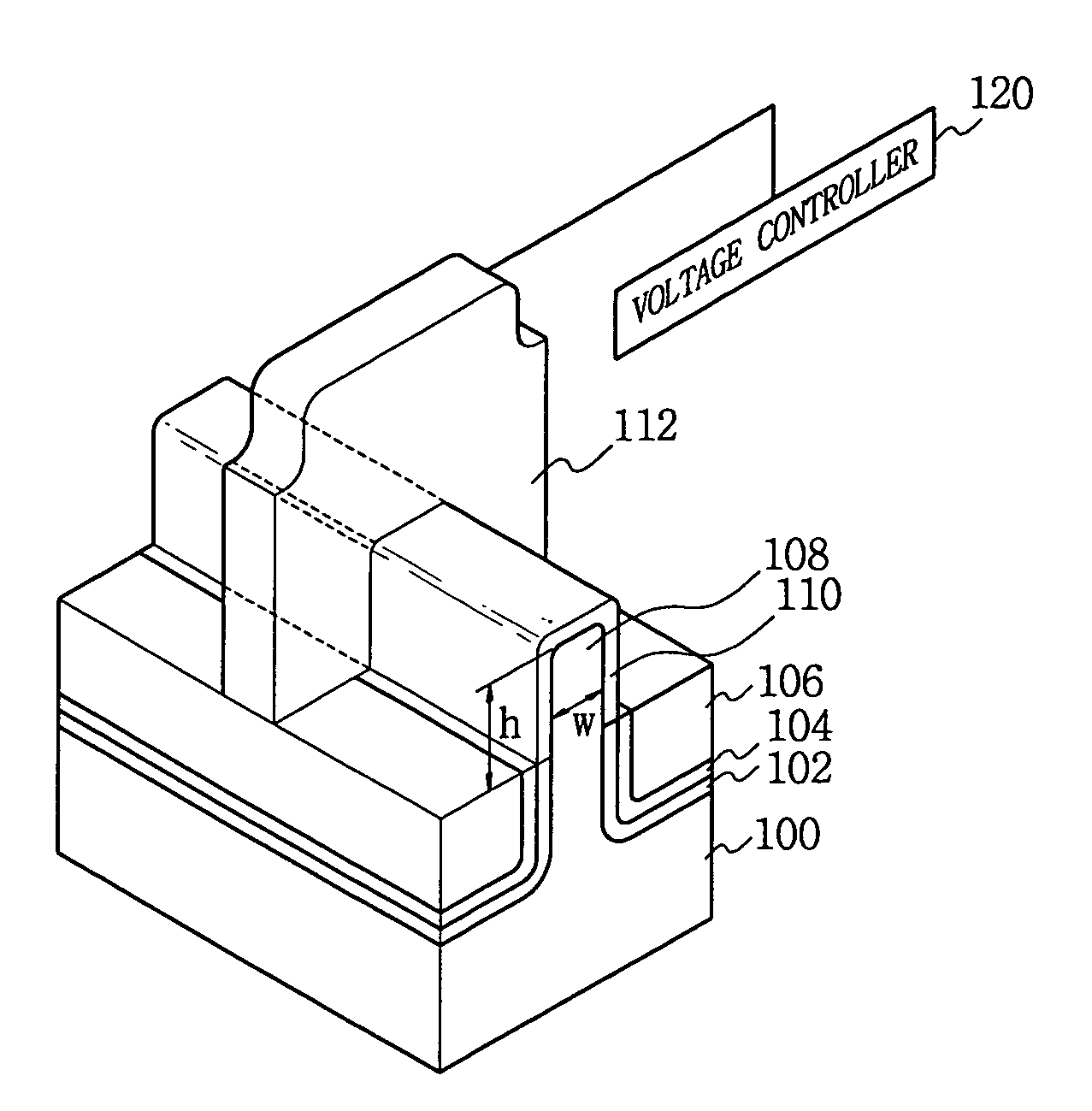

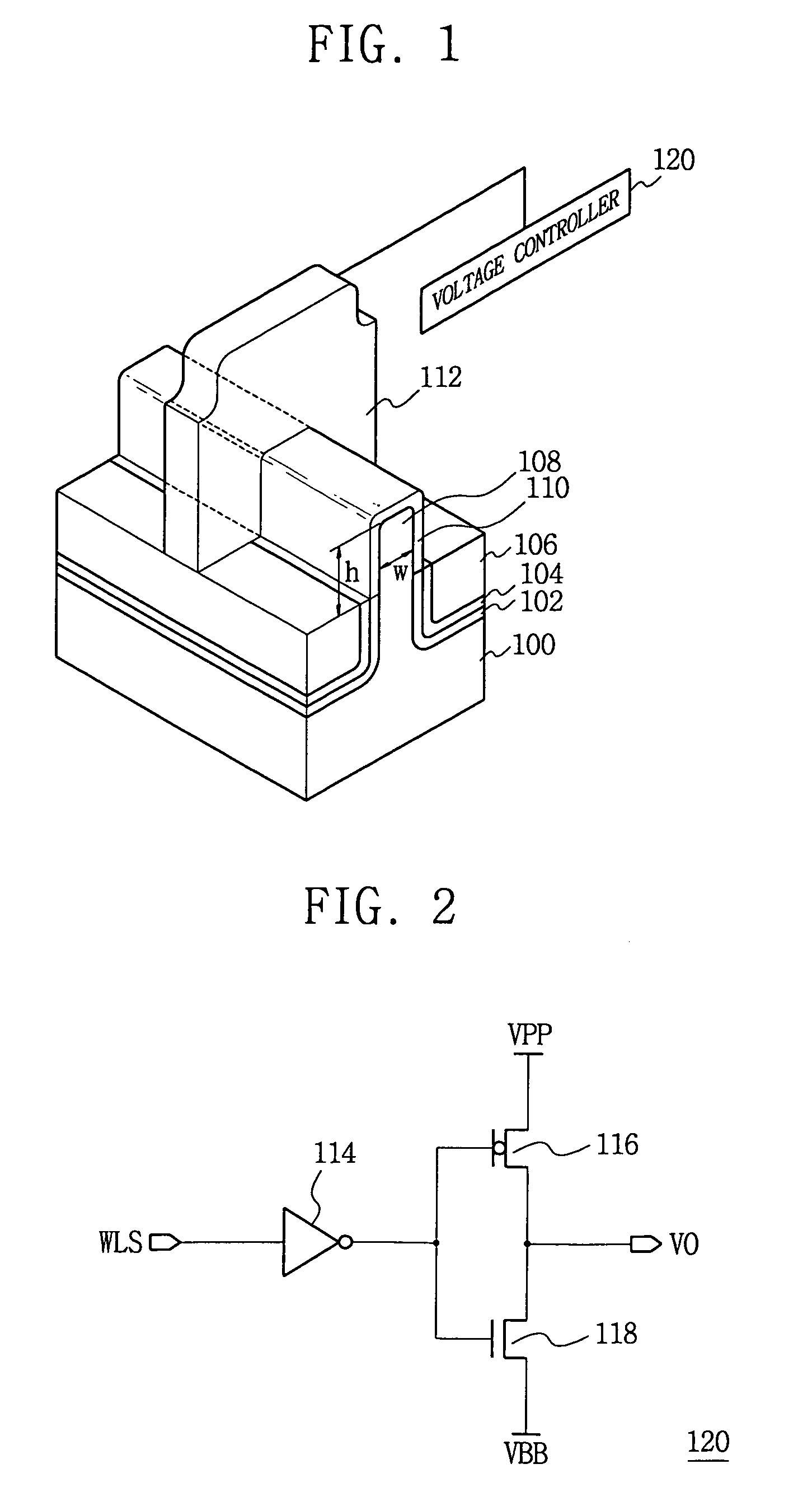

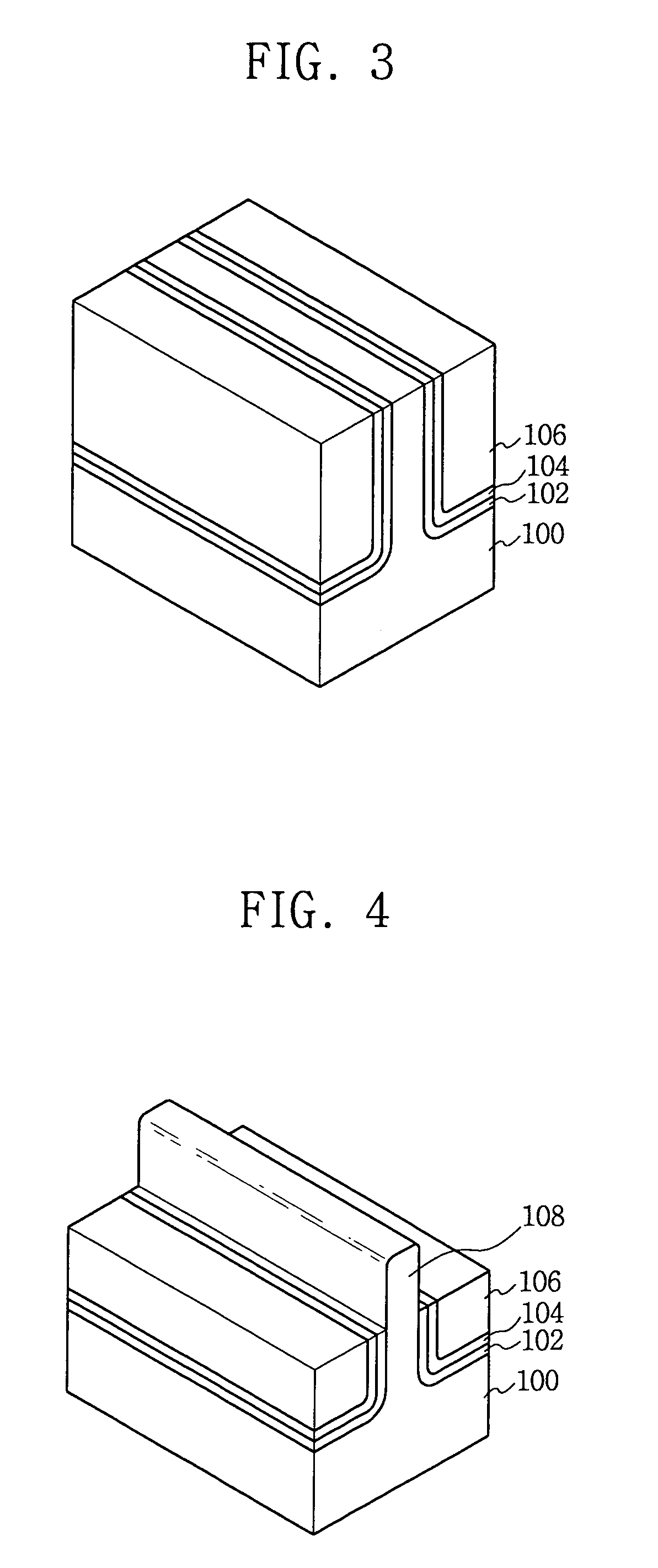

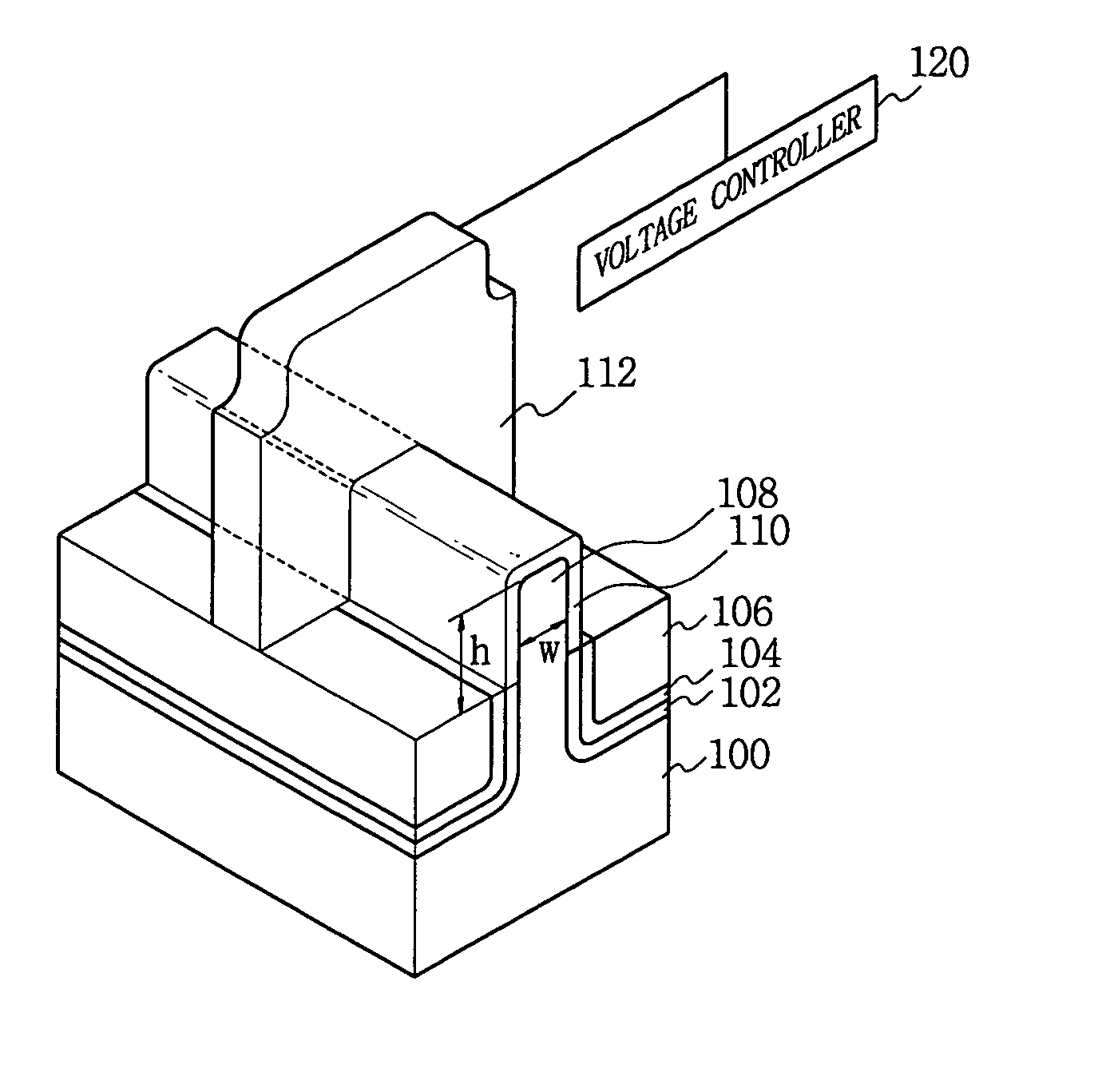

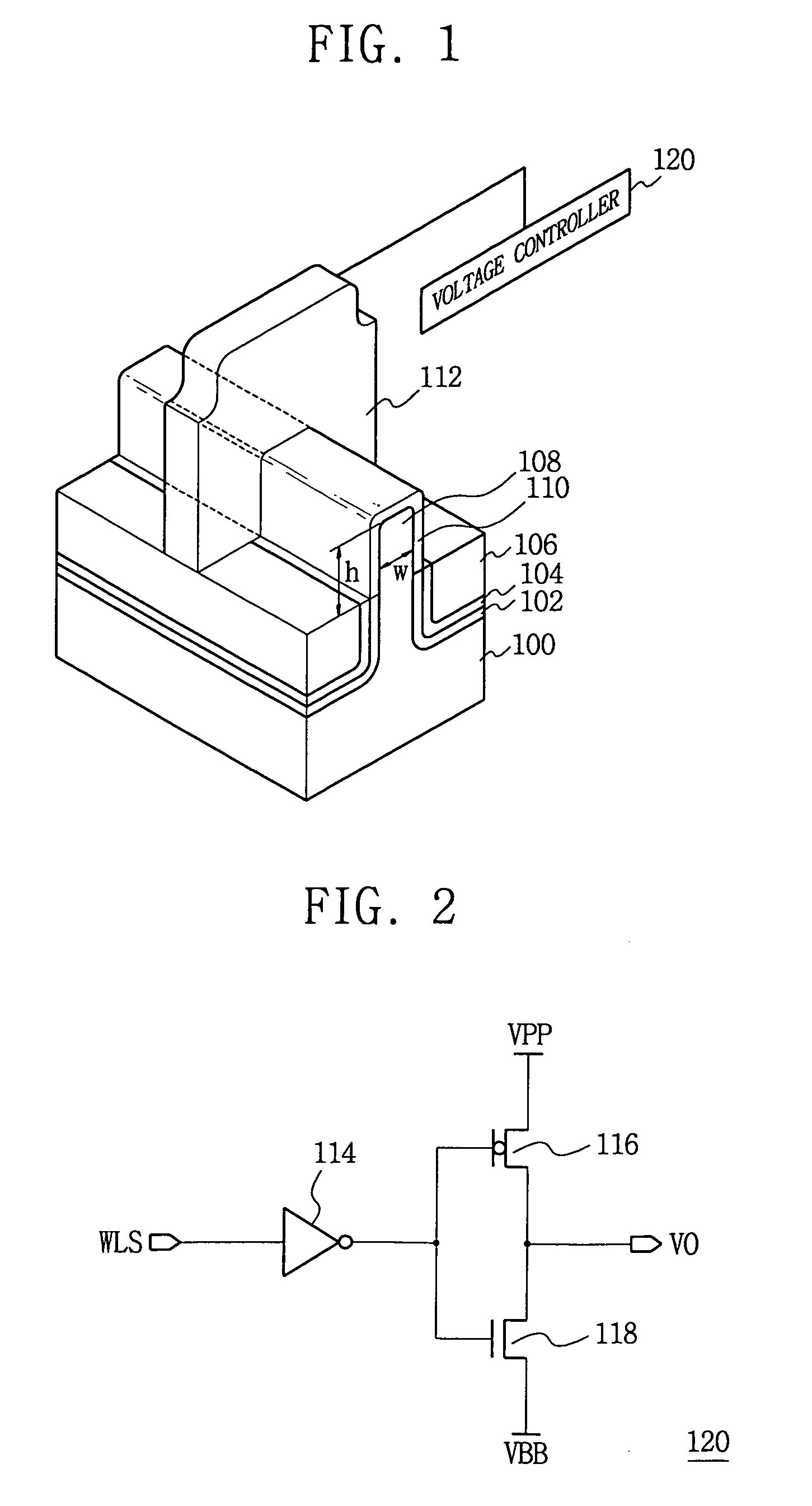

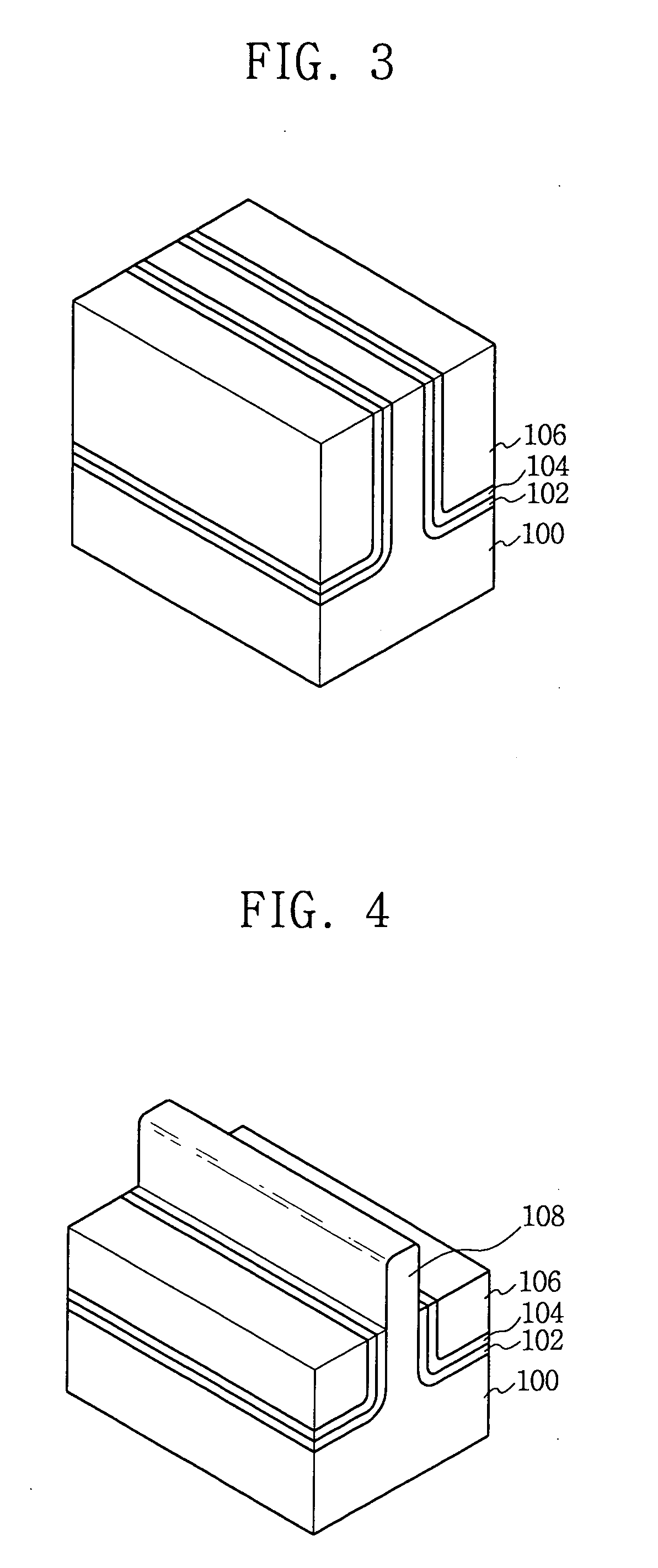

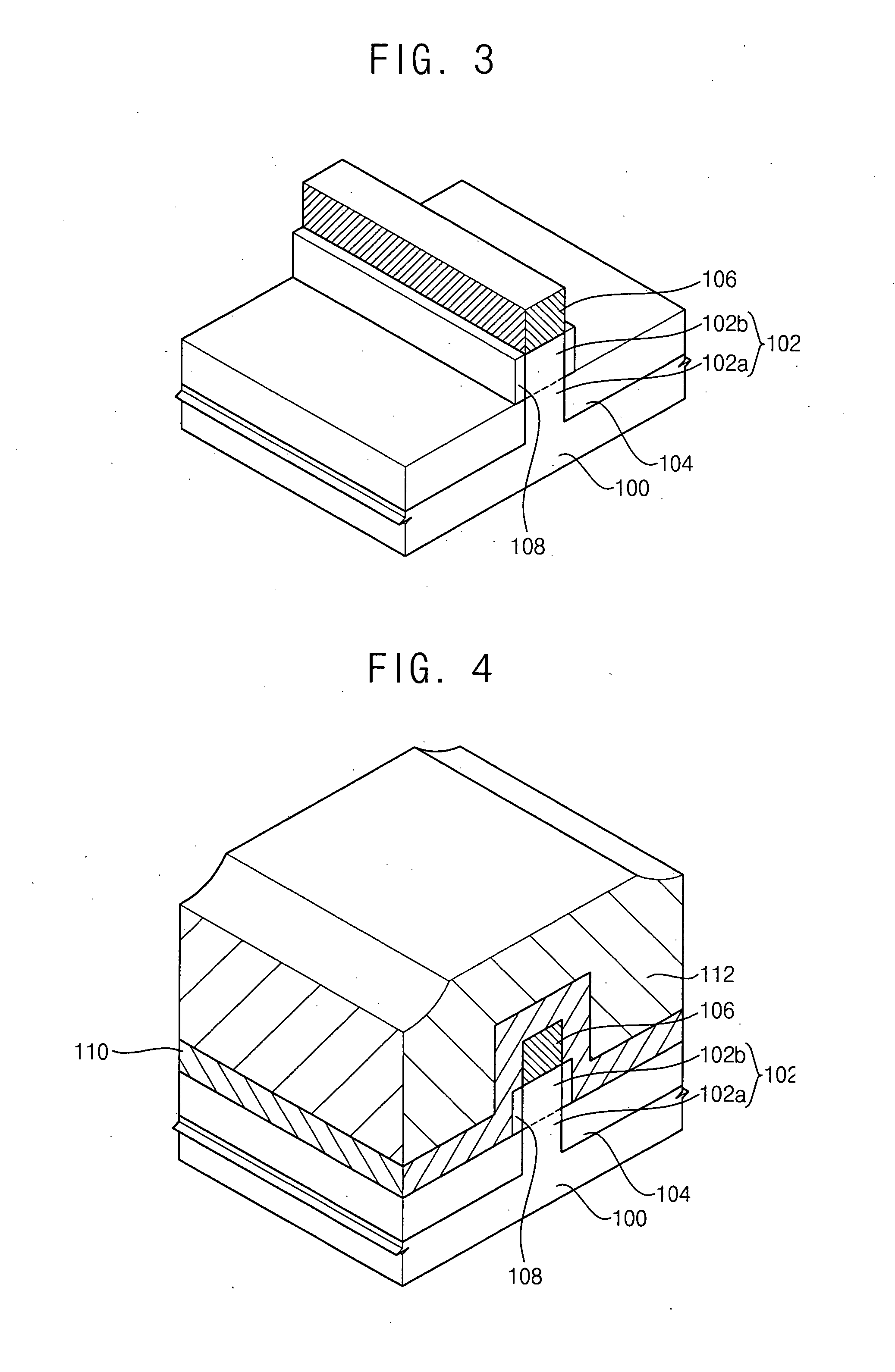

Fin FET structure

ActiveUS7317230B2Reducing and preventing leakage currentReduced Junction Leakage CurrentTransistorSolid-state devicesInsulation layerEngineering

A fin FET structure employs a negative word line scheme. A gate electrode of a fin FET employs an electrode doped with n+ impurity, and a channel doping for a control of threshold voltage is not executed, or the channel doping is executed by a low density, thereby remarkably improving characteristics of the fin FET. A semiconductor substrate is formed in a first conductive type, and a fin active region of a first conductive type is projected from an upper surface of the semiconductor substrate and is connected to the semiconductor substrate. An insulation layer is formed on the semiconductor substrate, and a gate insulation layer is formed in upper part and sidewall of the fin active region. A gate electrode is formed on the insulation layer and the gate insulation layer. Source and drain are formed in the fin active region of both sides of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

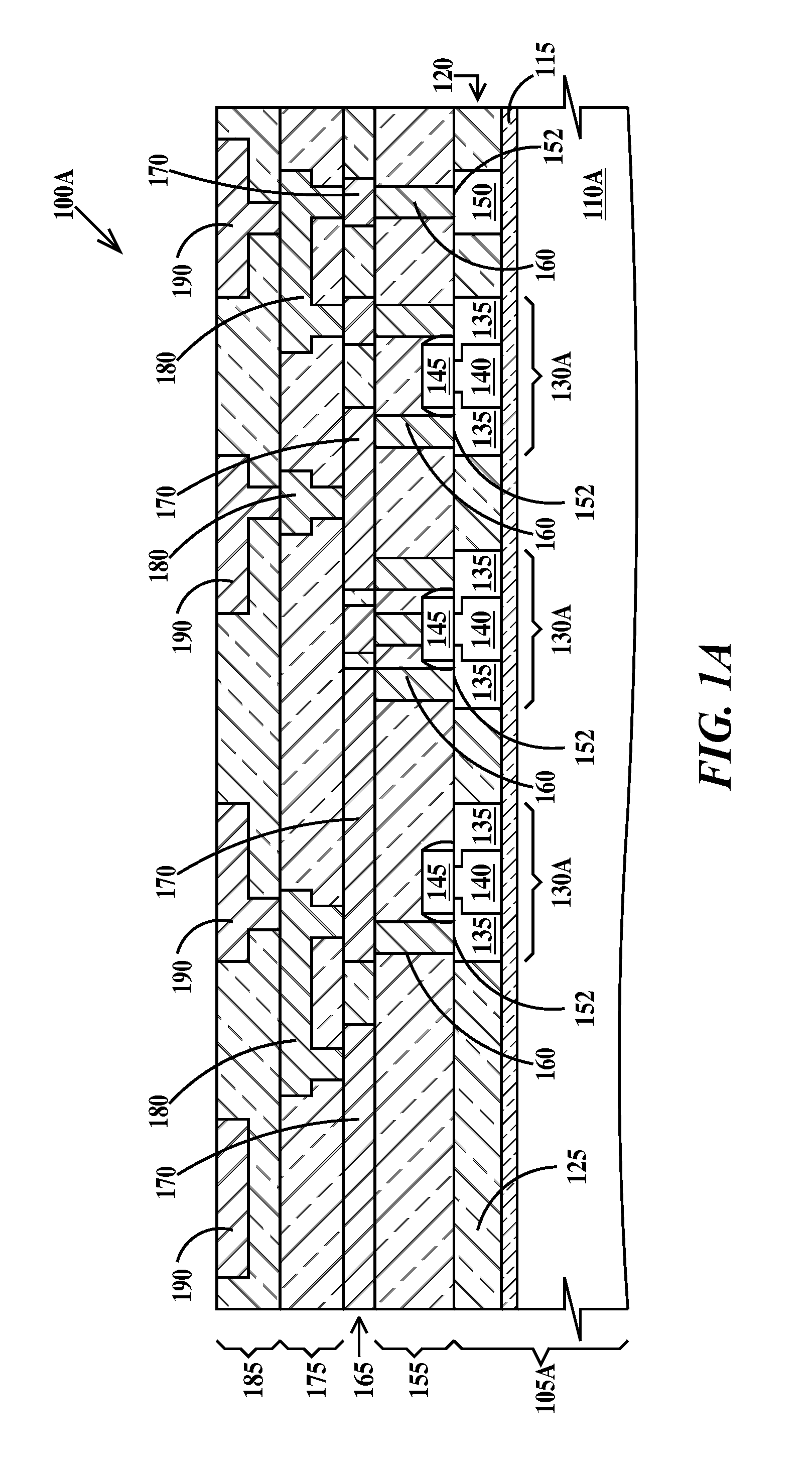

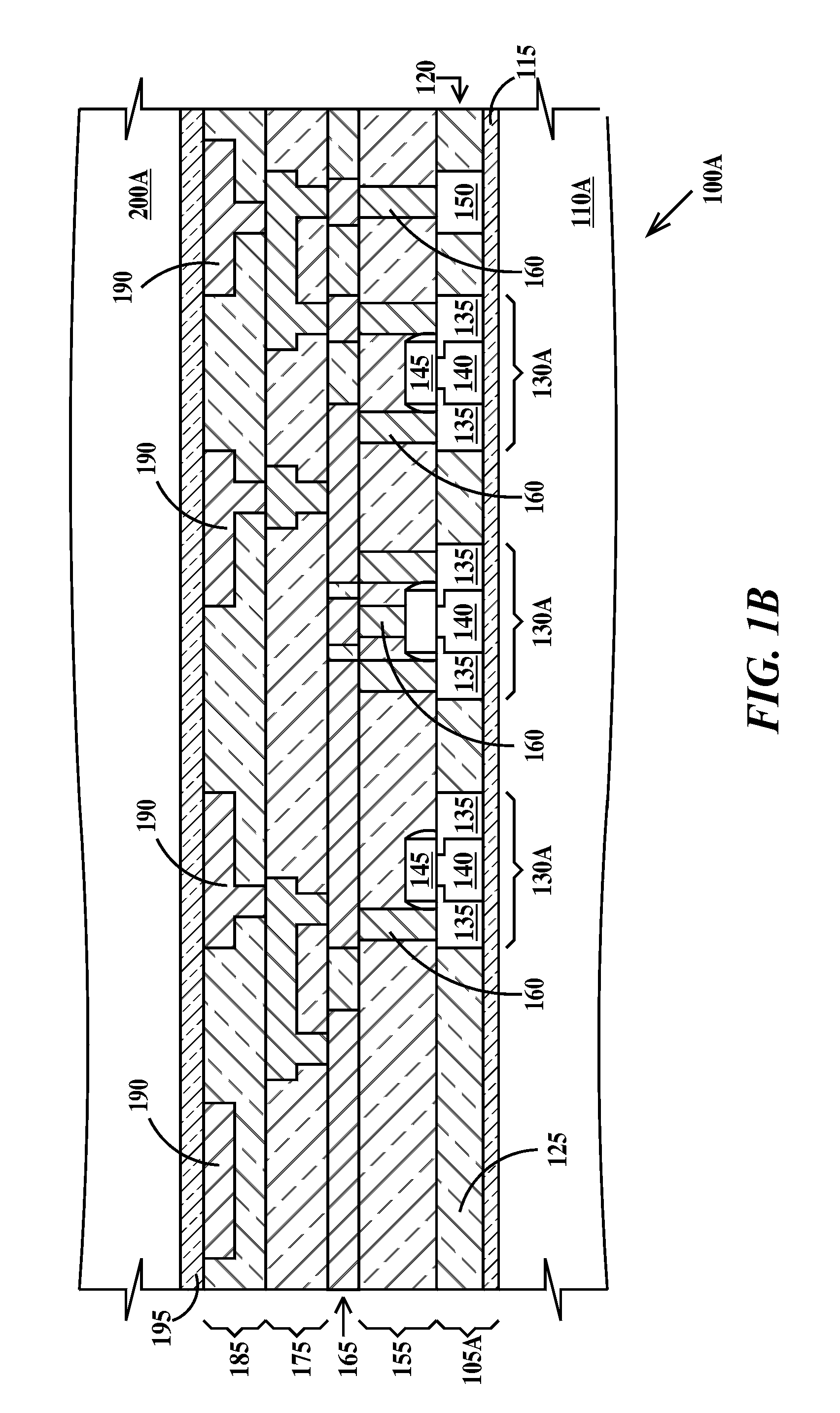

Double-sided integrated circuit chips

ActiveUS20070267723A1Raise the threshold voltageSemiconductor/solid-state device detailsSolid-state devicesBuried oxideIntegrated circuit

A semiconductor structure and method of fabricating the structure. The method includes removing the backside silicon from two silicon-on-insulator wafers having devices fabricated therein and bonding them back to back utilizing the buried oxide layers. Contacts are then formed in the upper wafer to devices in the lower wafer and wiring levels are formed on the upper wafer. The lower wafer may include wiring levels. The lower wafer may include landing pads for the contacts. Contacts to the silicon layer of the lower wafer may be silicided.

Owner:GLOBALFOUNDRIES US INC

Method Of Improving Programming Precision In Flash Memory

ActiveUS20080181000A1Raise the threshold voltageSignificant disturbanceRead-only memoriesDigital storageFlash memory

Data are stored in cells of a flash memory by assigning a first portion of the data to be stored in a first cell and a second portion of the data to be stored in one or more second cells. The first cell is programmed to store the first portion in accordance with the second portion. The second cell(s) is / are programmed to store the second portion. At least a portion of the programming of the first cell is effected before any of the programming of the second cell(s).

Owner:WESTERN DIGITAL ISRAEL LTD

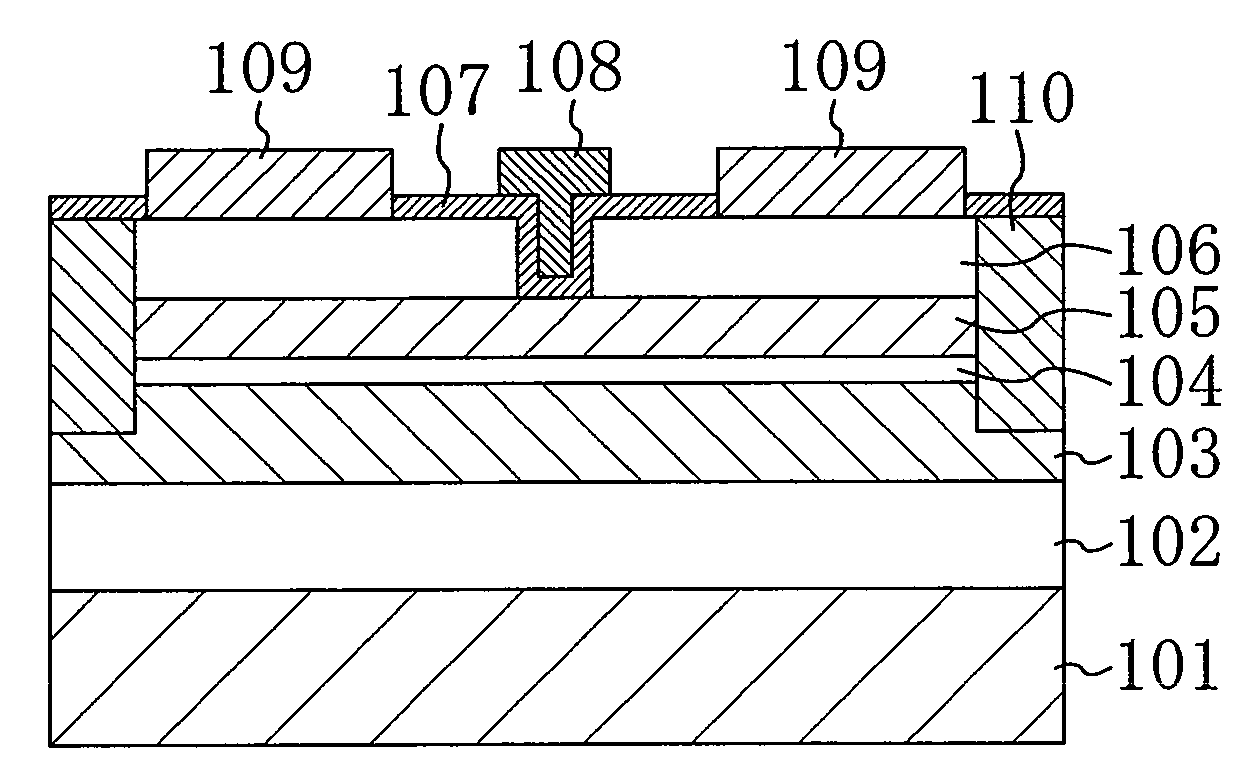

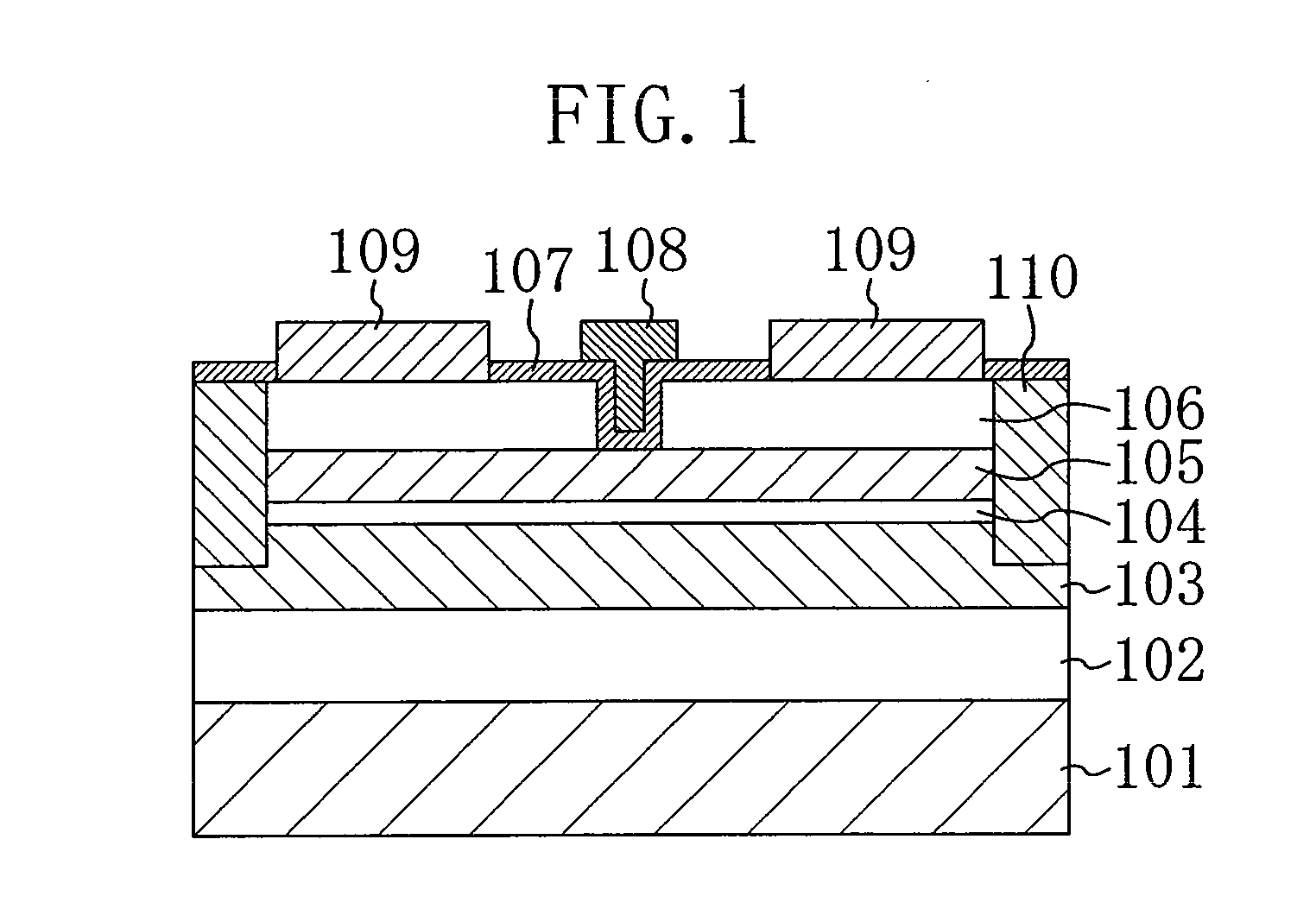

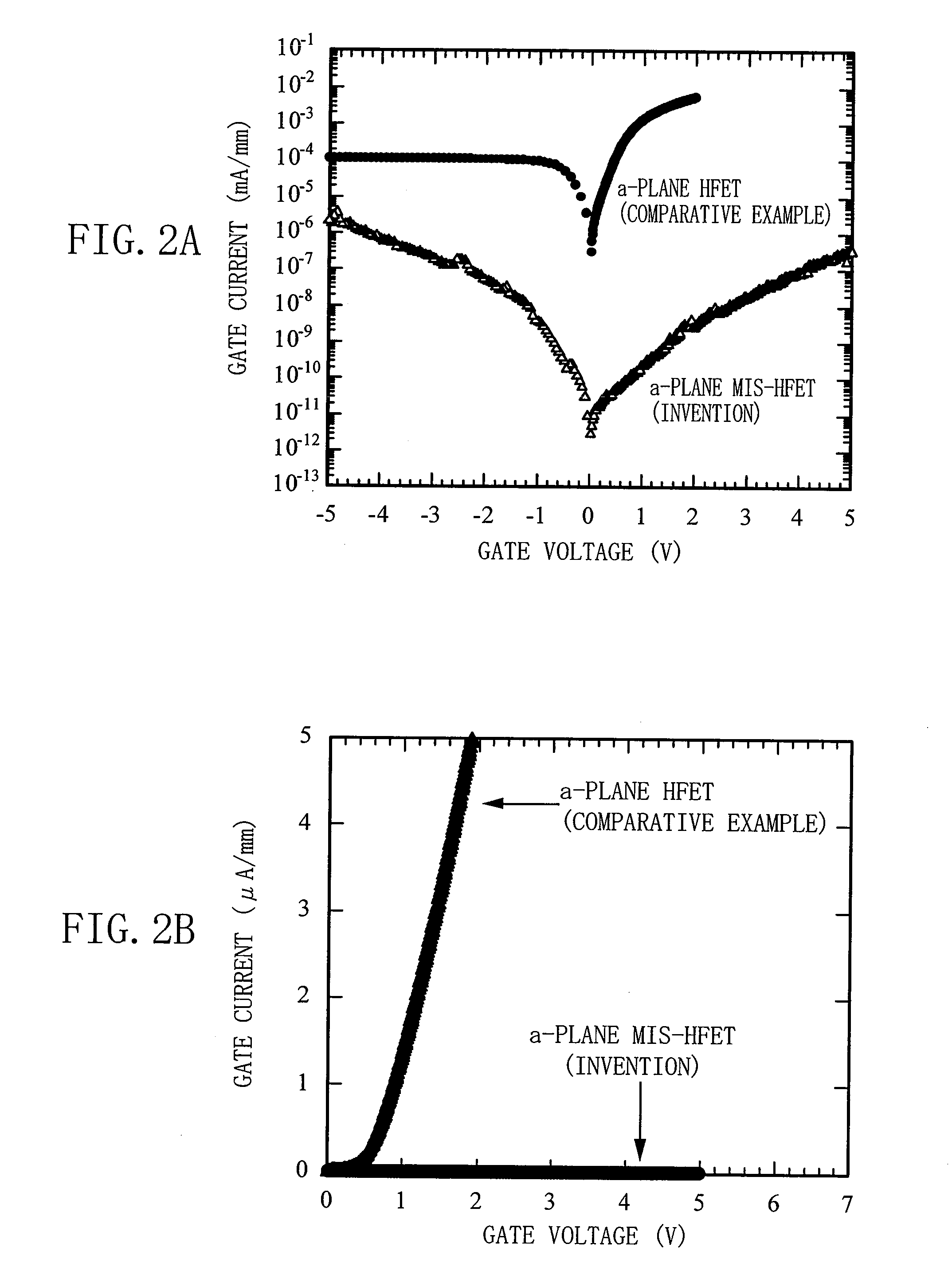

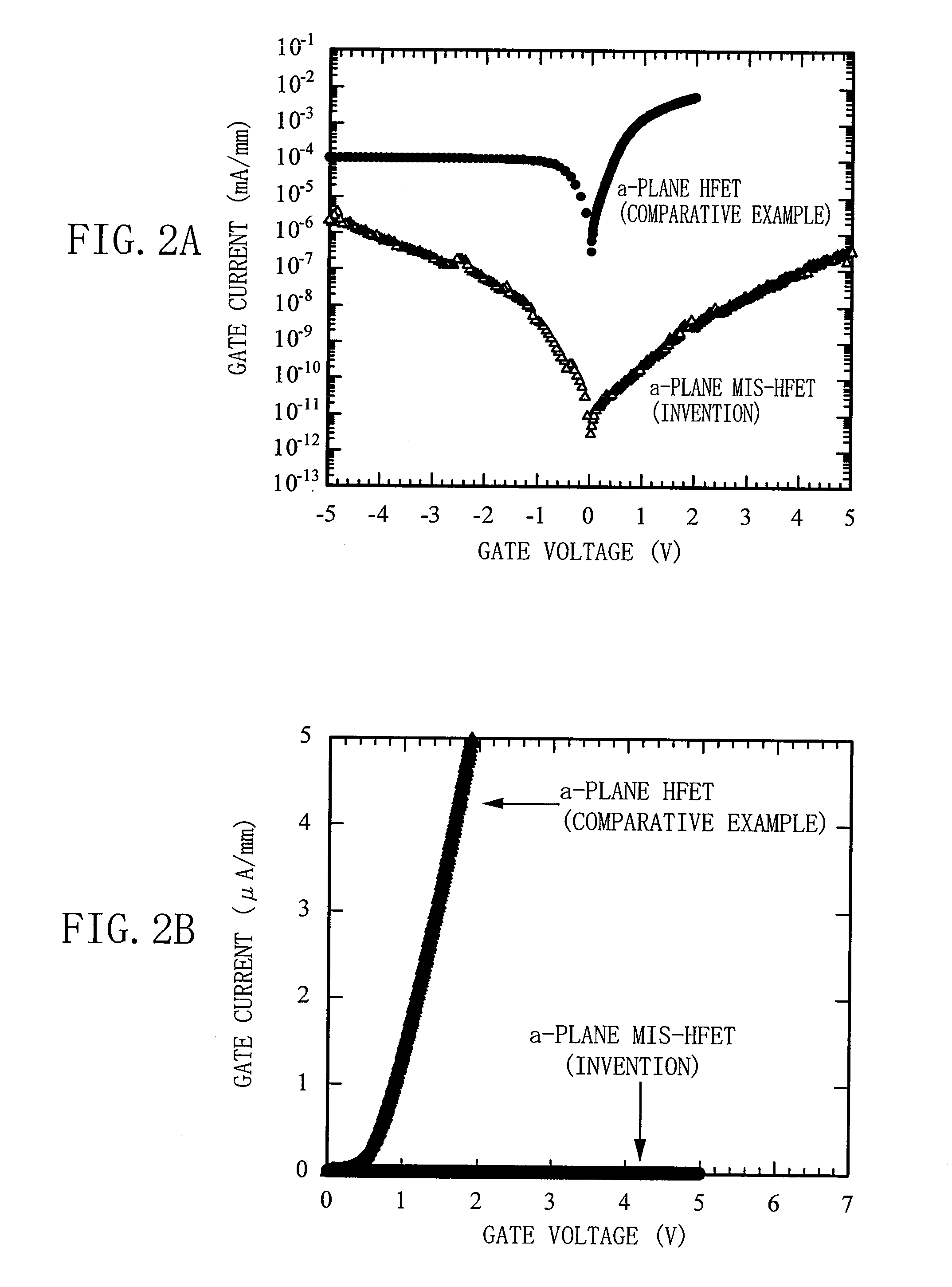

Field effect transistor

ActiveUS20080258243A1Suppress generationReduced series resistanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringField effect

A field effect transistor includes: a first nitride semiconductor layer having a plane perpendicular to a (0001) plane or a plane tilted with respect to the (0001) plane as a main surface; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider bandgap than the first nitride semiconductor layer; a third nitride semiconductor layer formed on the second nitride semiconductor layer; and a source electrode and a drain electrode formed so as to contact at least a part of the second nitride semiconductor layer or the third nitride semiconductor layer. A recess that exposes a part of the second nitride semiconductor layer is formed between the source electrode and the drain electrode in the third nitride semiconductor layer. A gate electrode is formed in the recess and an insulating film is formed between the third nitride semiconductor layer and the gate electrode.

Owner:PANASONIC CORP

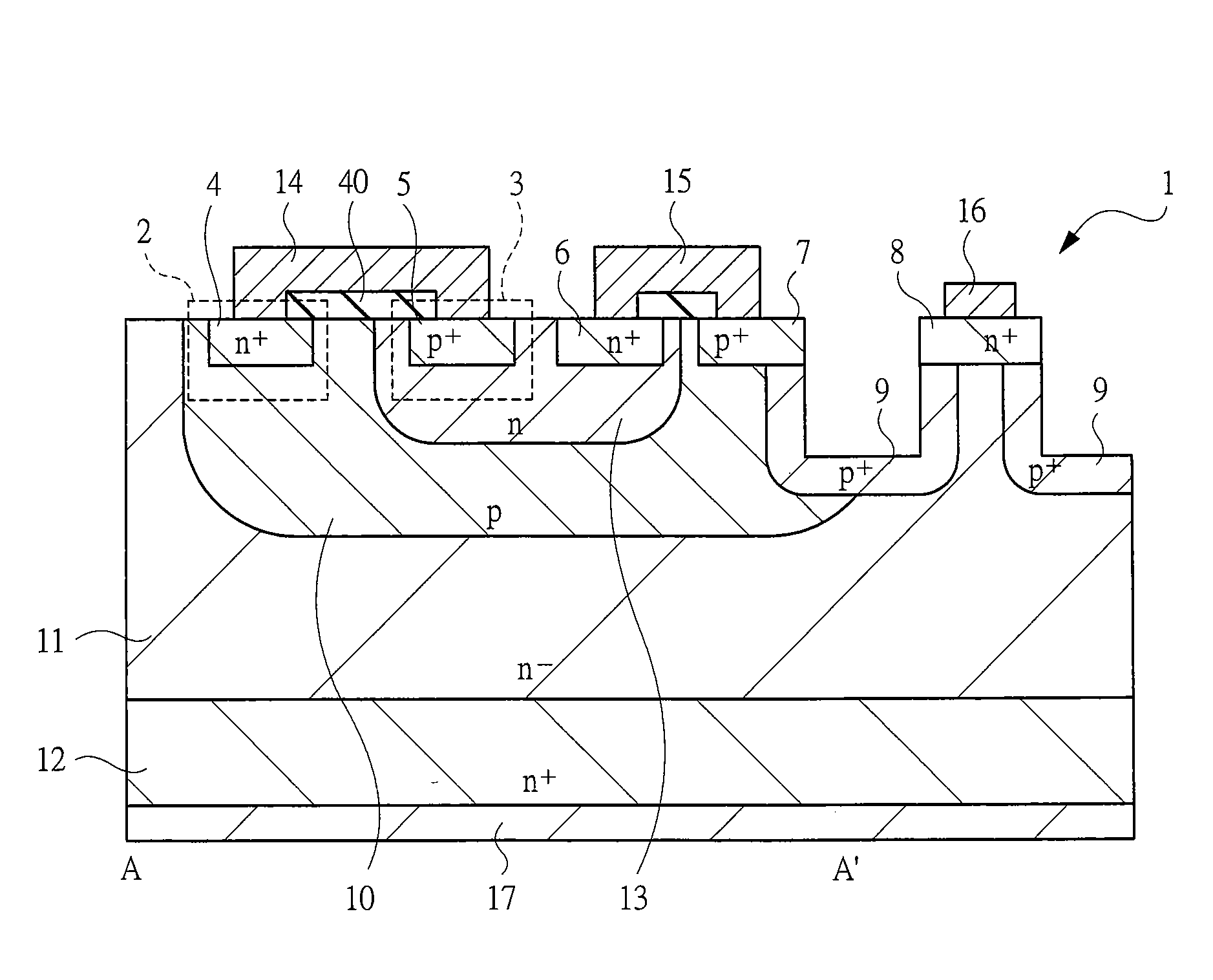

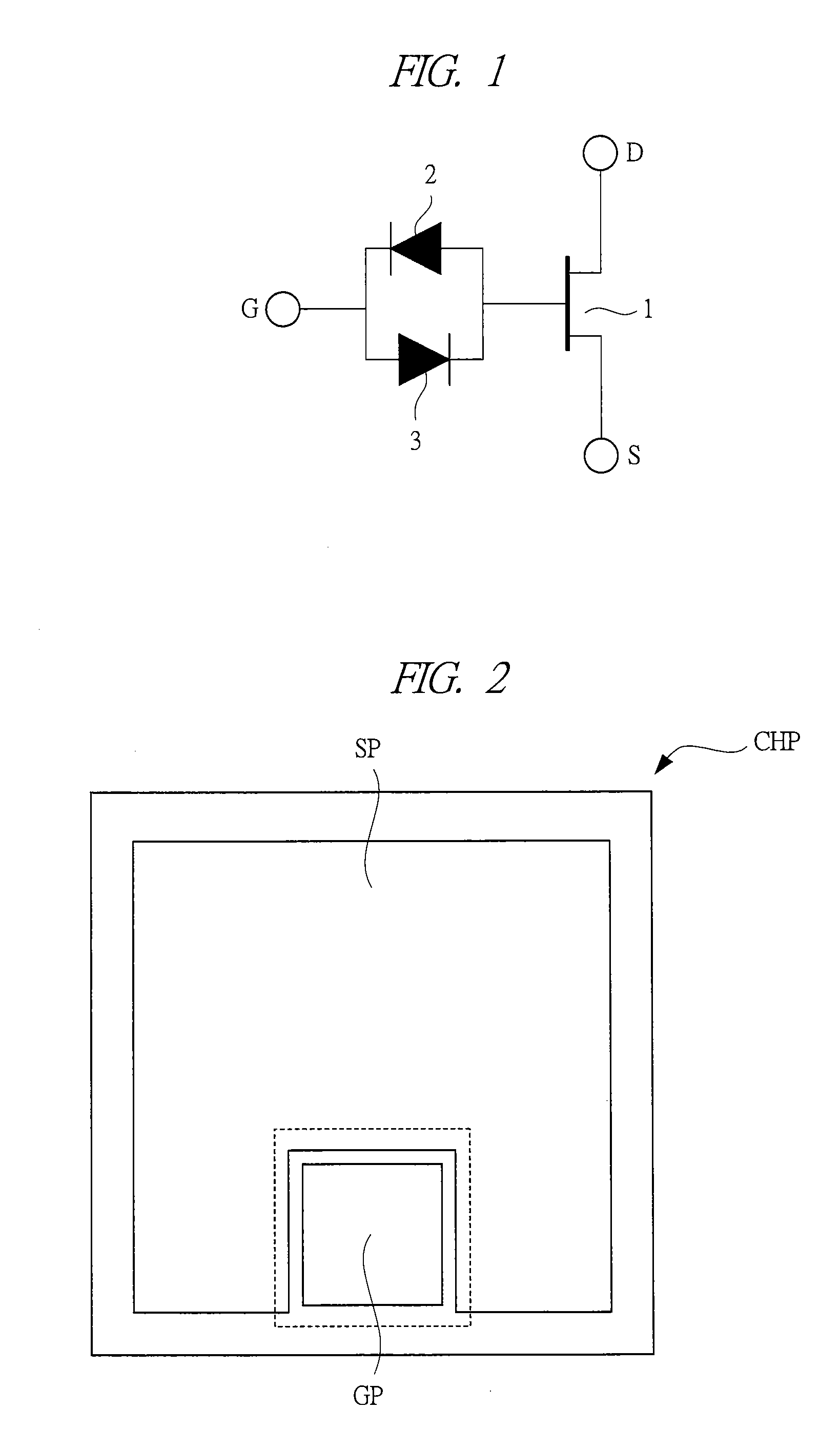

Semiconductor device with large blocking voltage

InactiveUS20090014719A1Large noise marginRaise the threshold voltageTransistorSolid-state devicesNoise marginSemiconductor

A junction FET having a large gate noise margin is provided. The junction FET comprises an n− layer forming a drift region of the junction FET formed over a main surface of an n+ substrate made of silicon carbide, a p+ layer forming a gate region formed in contact with the n− layer forming the drift region and a gate electrode provided in an upper layer of the n+ substrate. The junction FET further incorporates pn diodes formed over the main surface of the n+ substrate and electrically connecting the p+ layer forming the gate region and the gate electrode.

Owner:RENESAS ELECTRONICS CORP

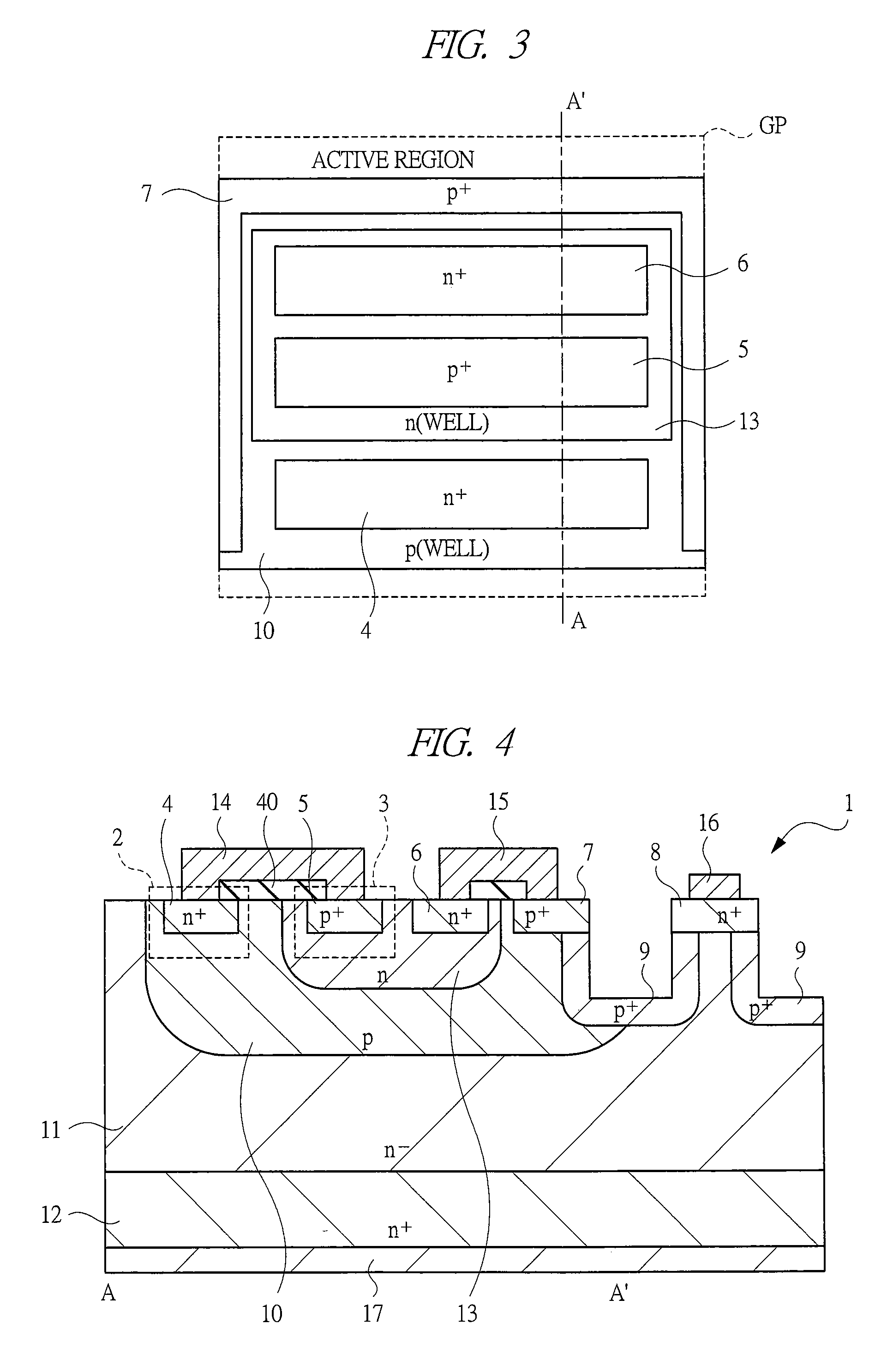

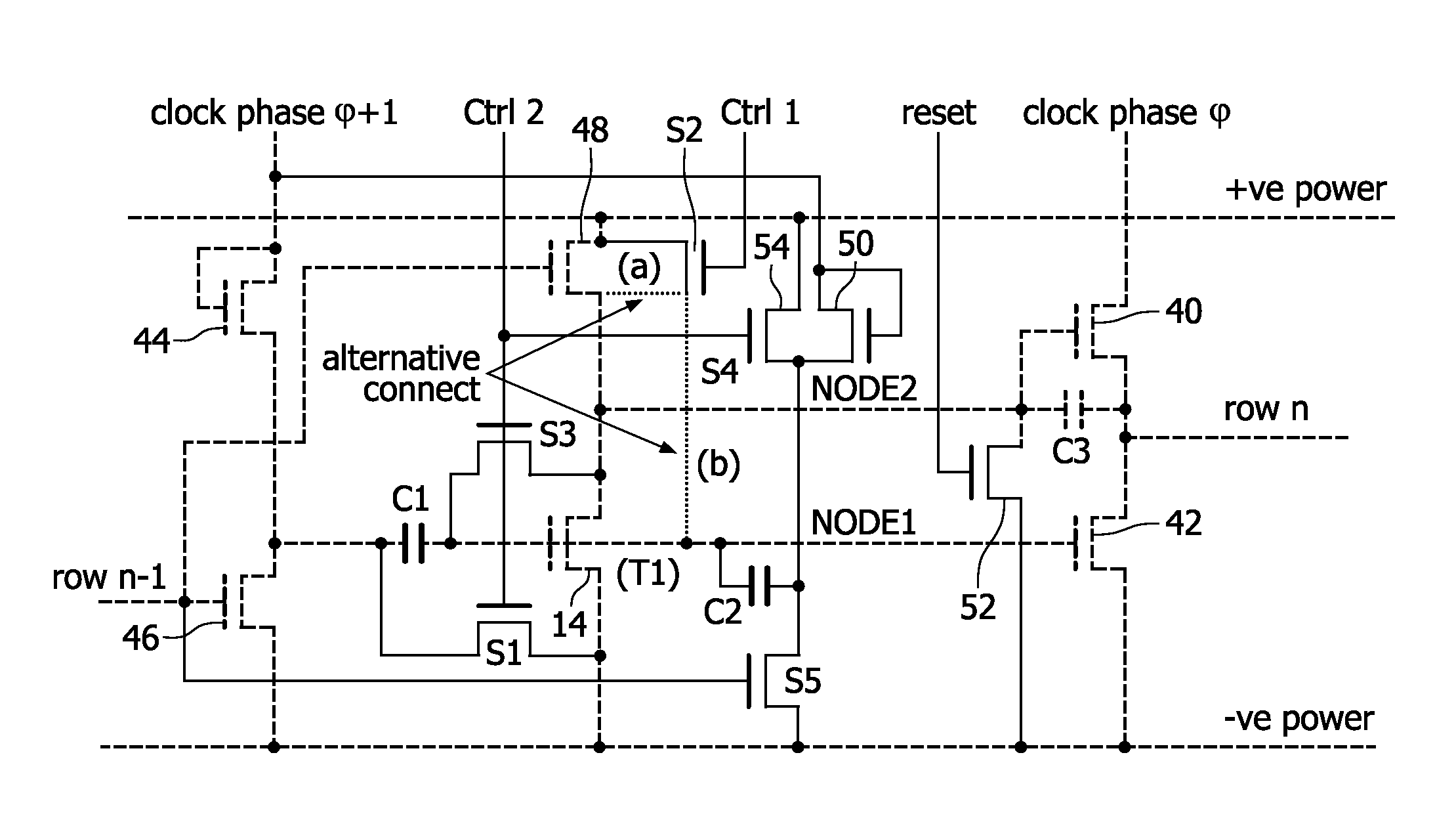

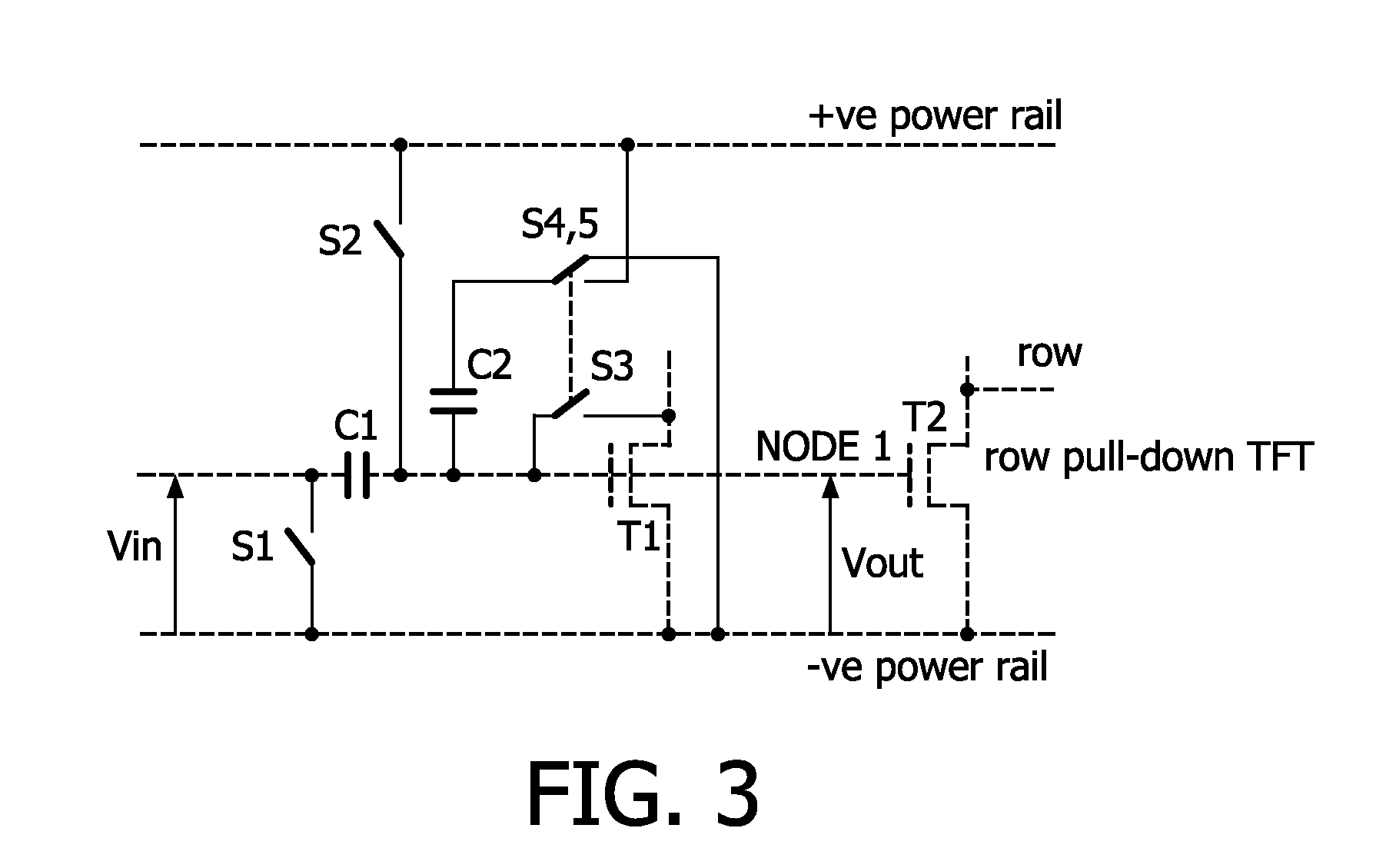

Shift register circuit having threshold voltage compensation

InactiveUS20100188385A1Raise the threshold voltageCathode-ray tube indicatorsDigital storageShift registerLow voltage

A shift register circuit comprises a plurality of stages, each stage being for providing an output signal to an output load and comprising a pull up transistor for pulling the output signal up to a high voltage rail and a pull down transistor for pulling the output signal down to a low voltage rail. Each stage comprises a circuit for sampling the threshold voltage of at least one of the pull up and pull down transistors and for adding the sampled threshold voltage to a control voltage offset, to provide a threshold-voltage-compensated signal for controlling the gate of the at least one of the pull up and pull down transistors. This provides threshold voltage sampling, in particular for the thin film transistor whose threshold voltage drift must be compensated (for example the pull-down thin film transistor).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

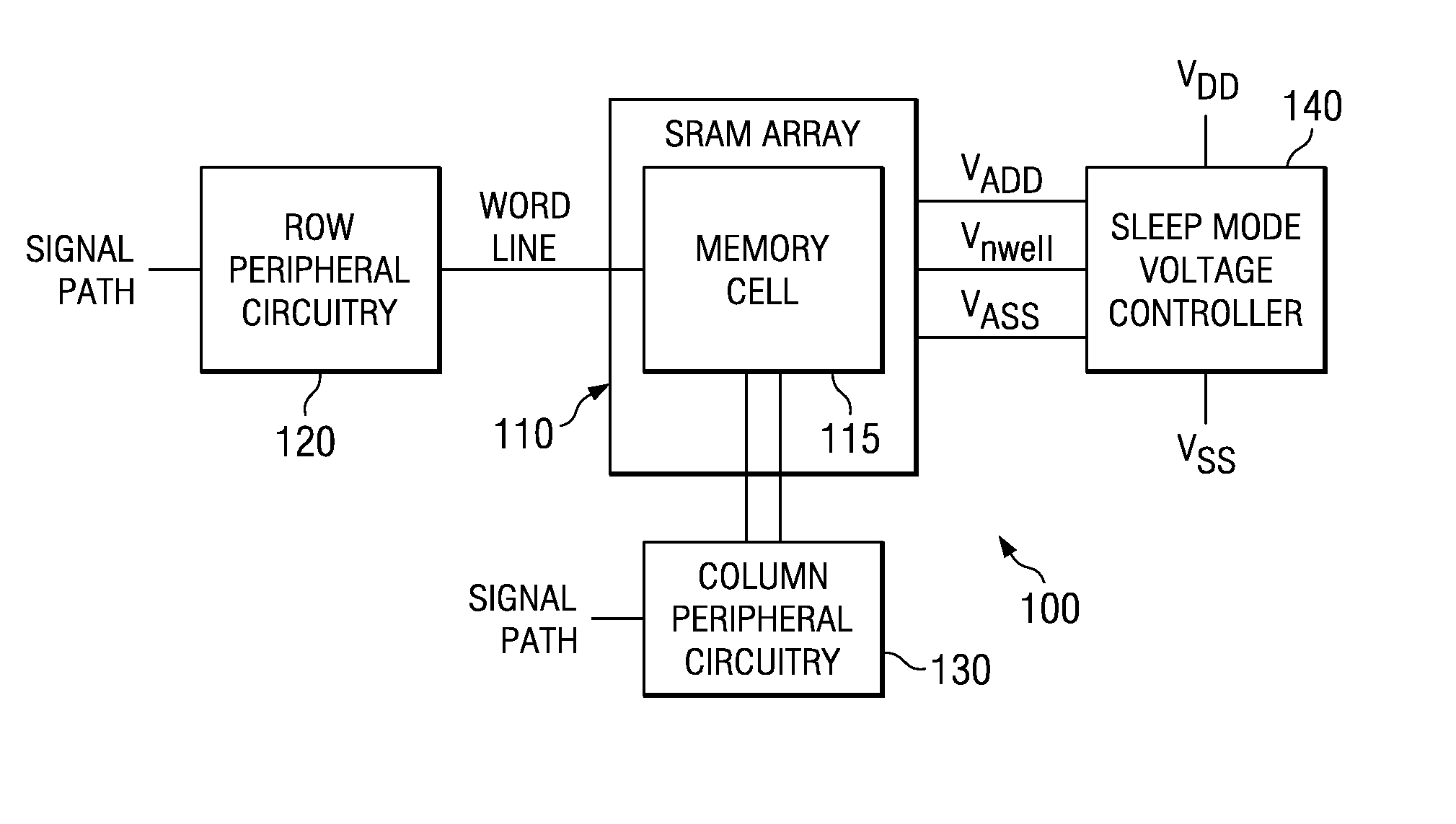

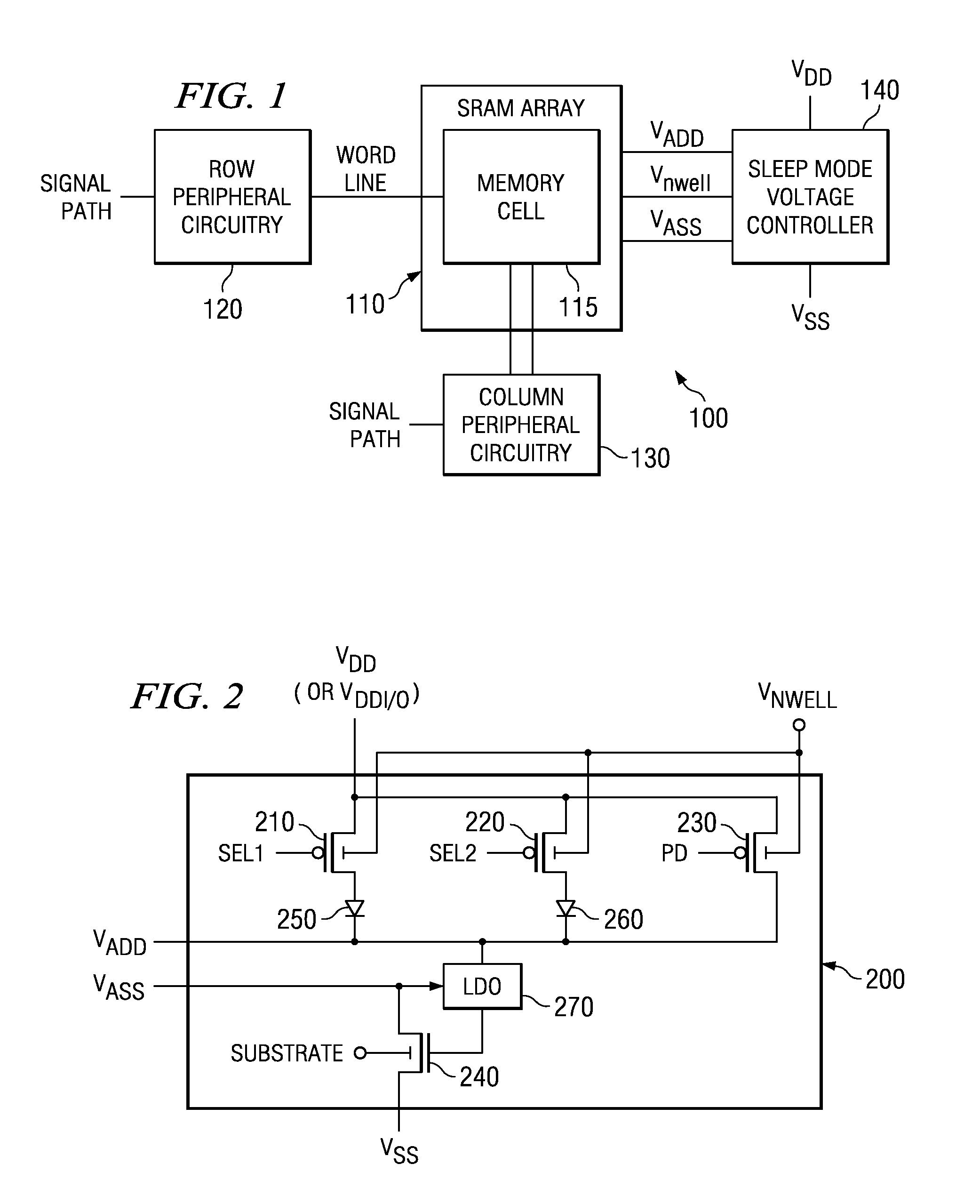

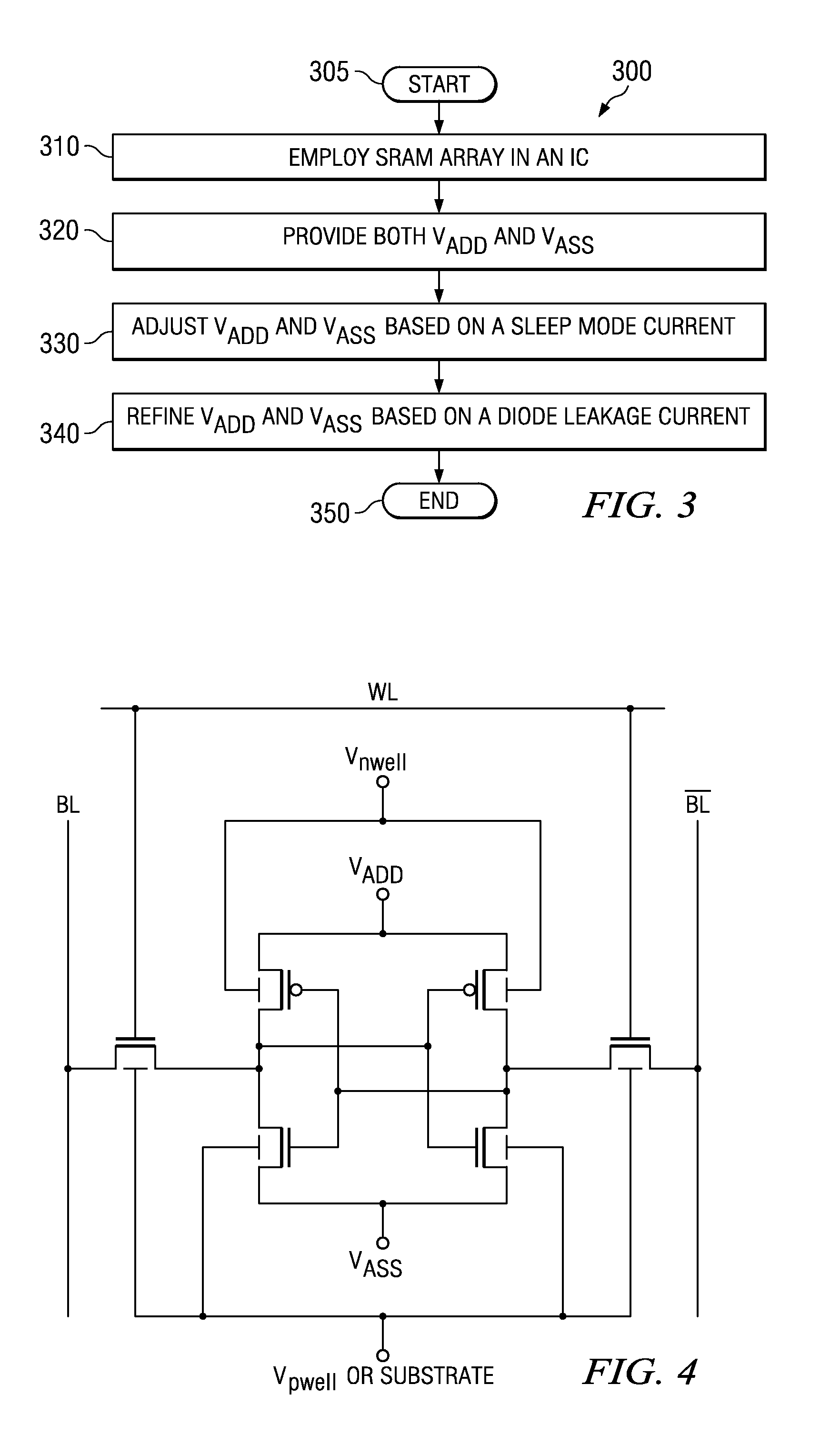

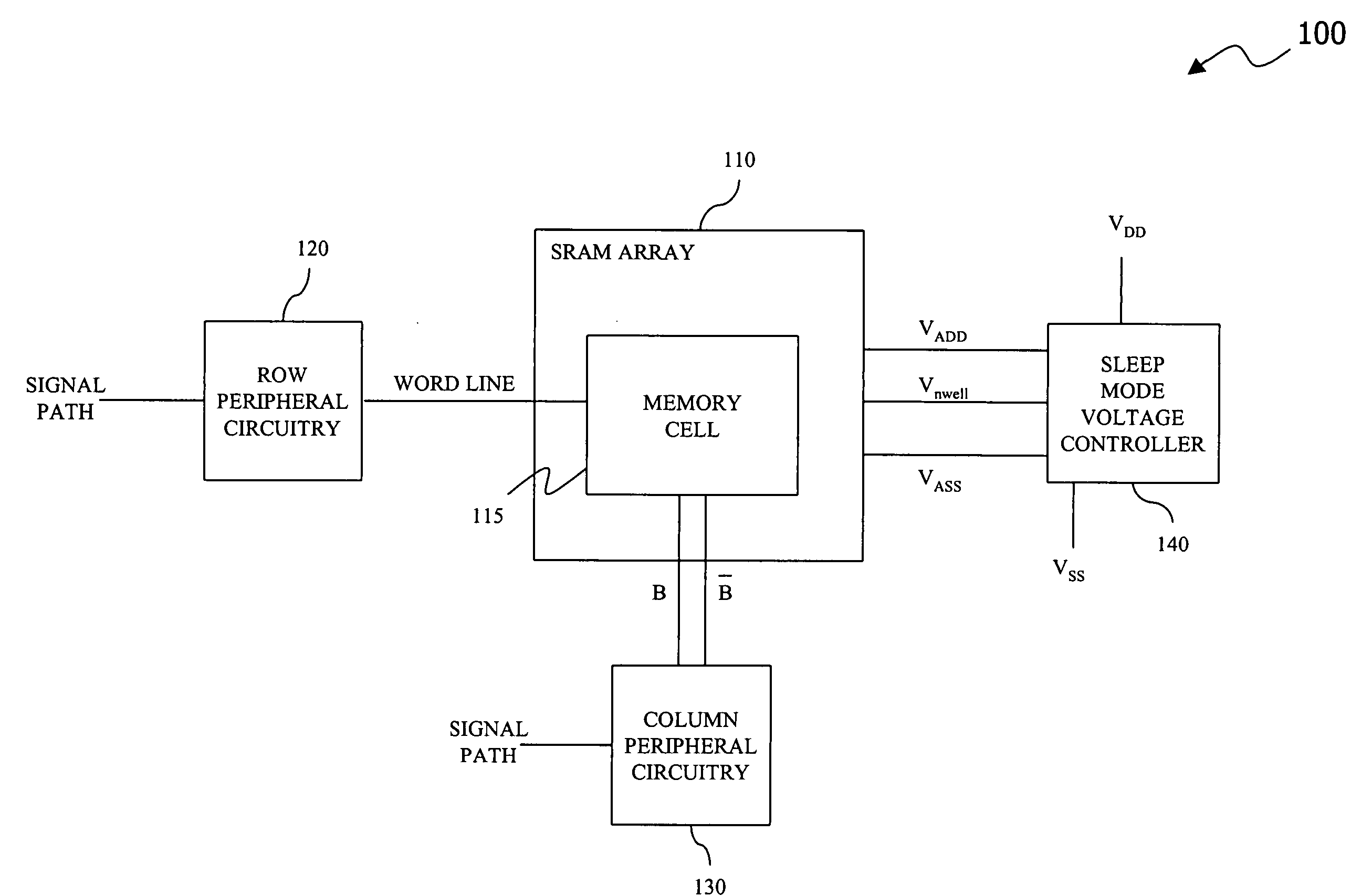

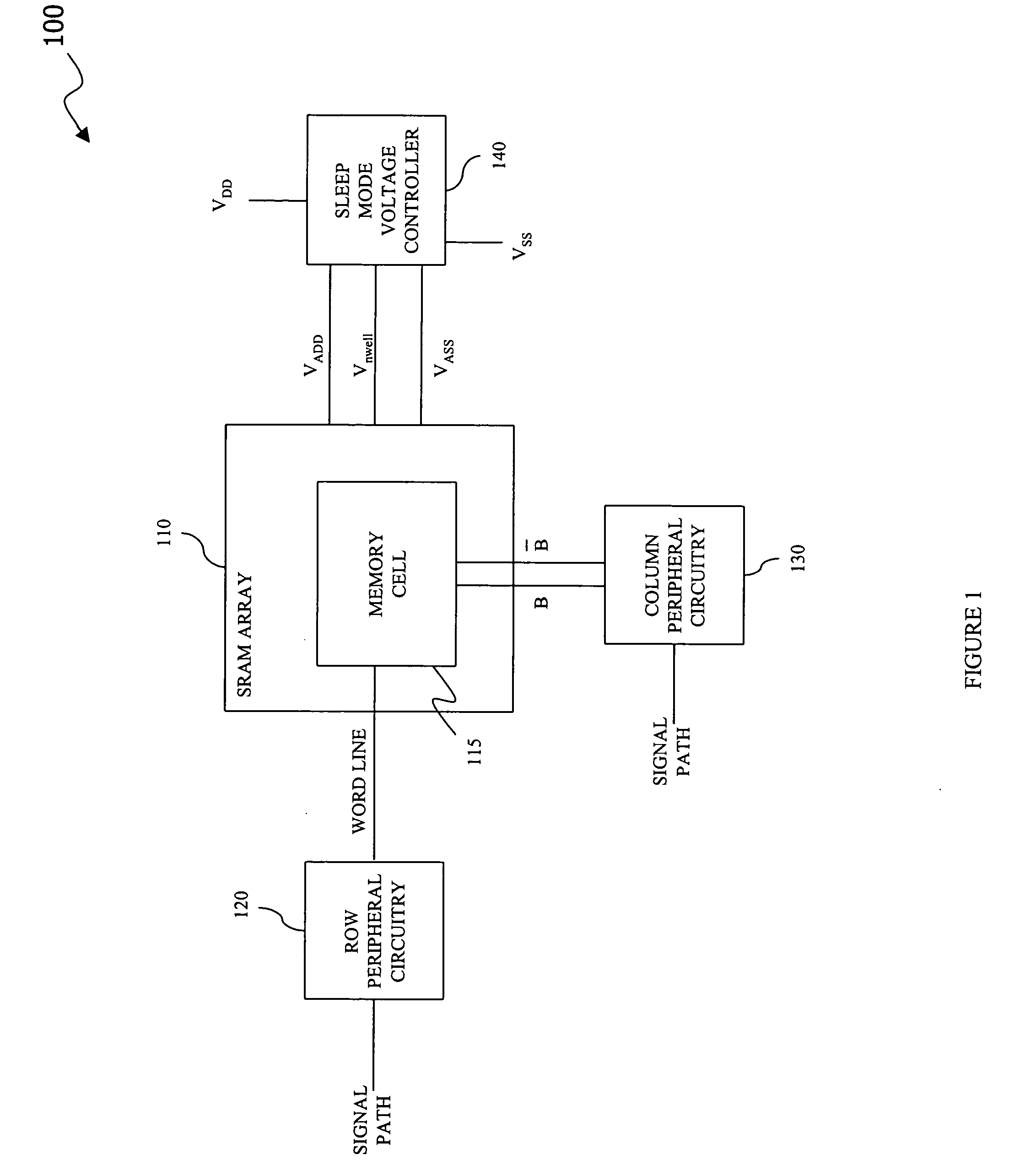

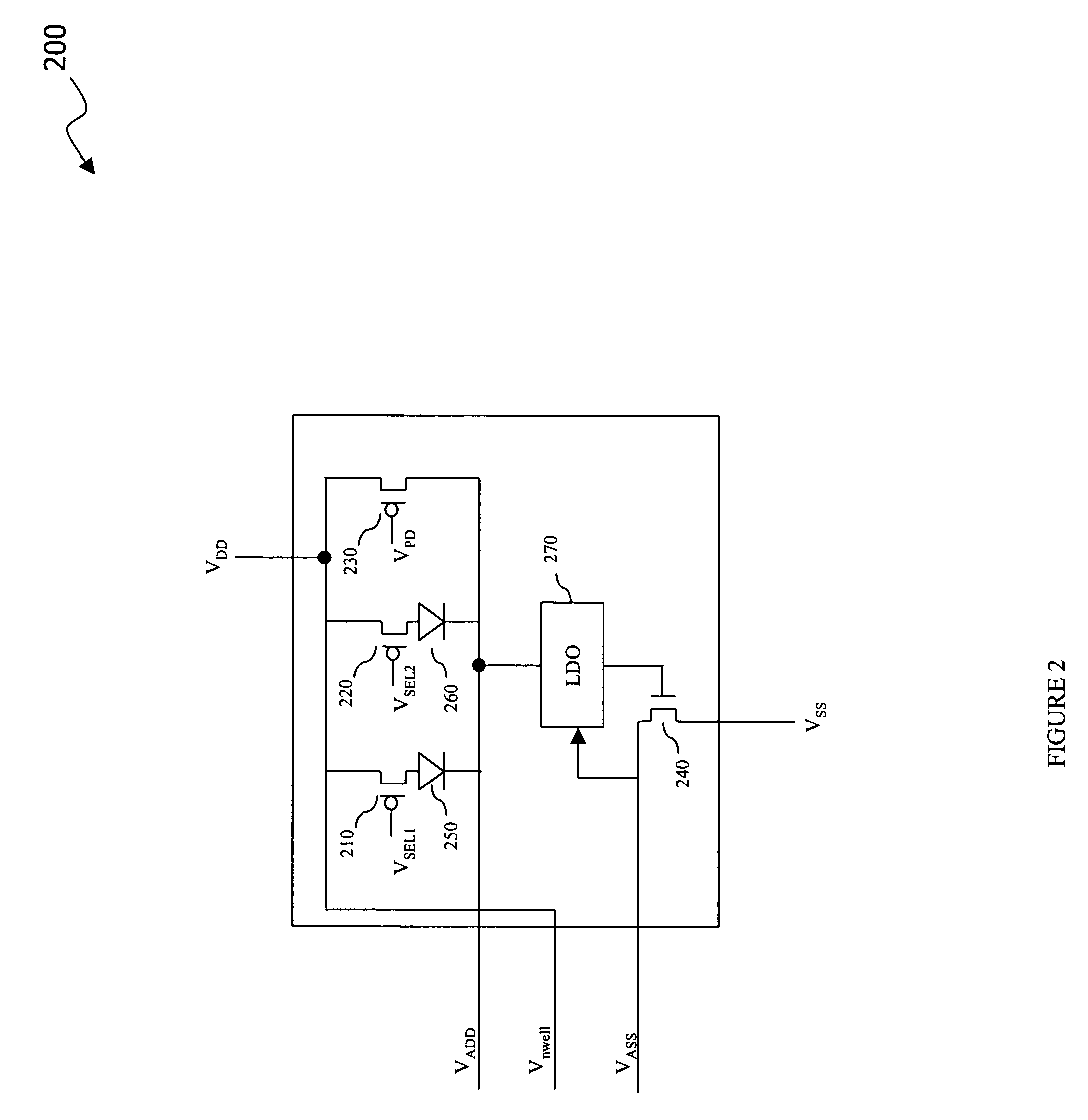

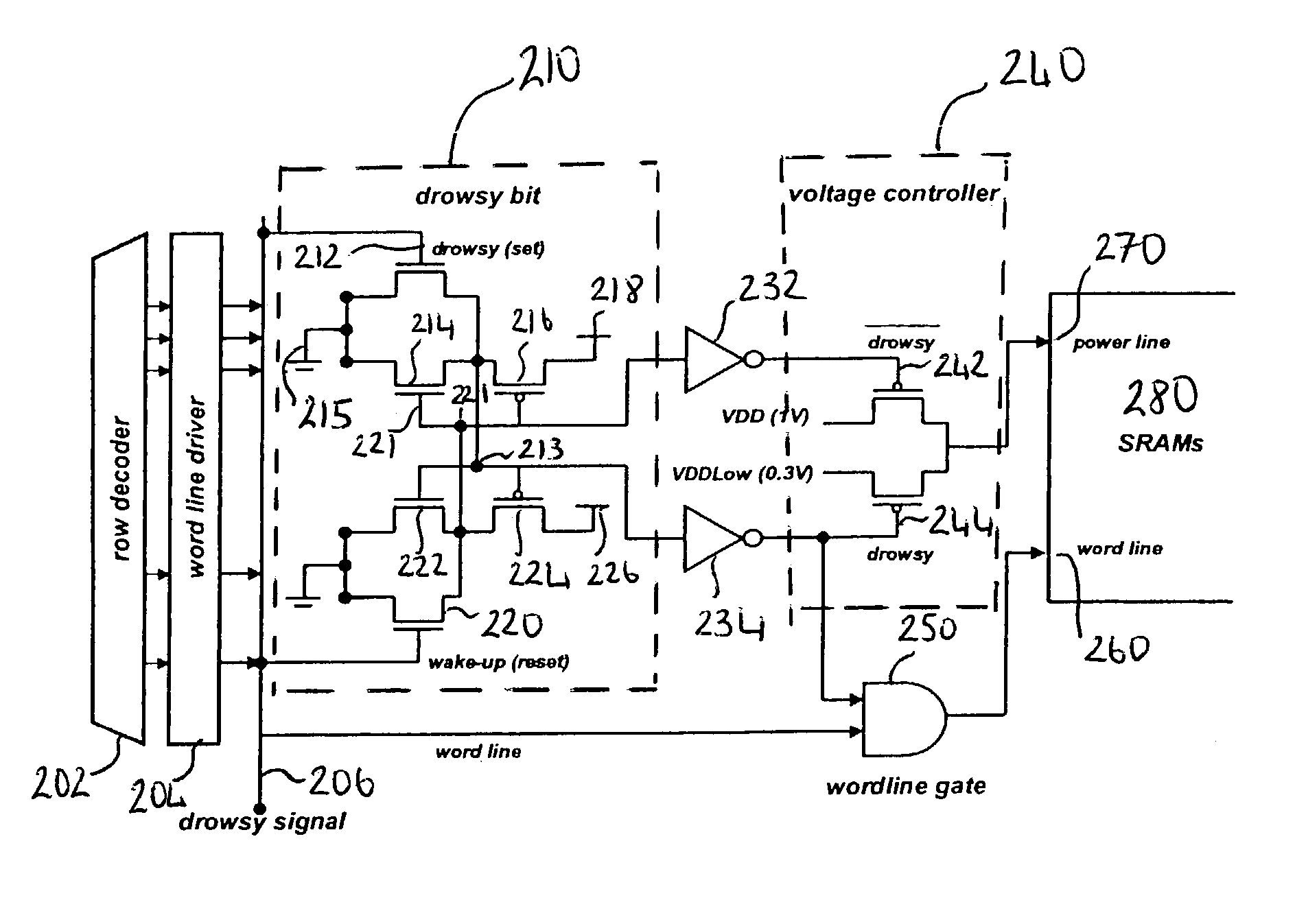

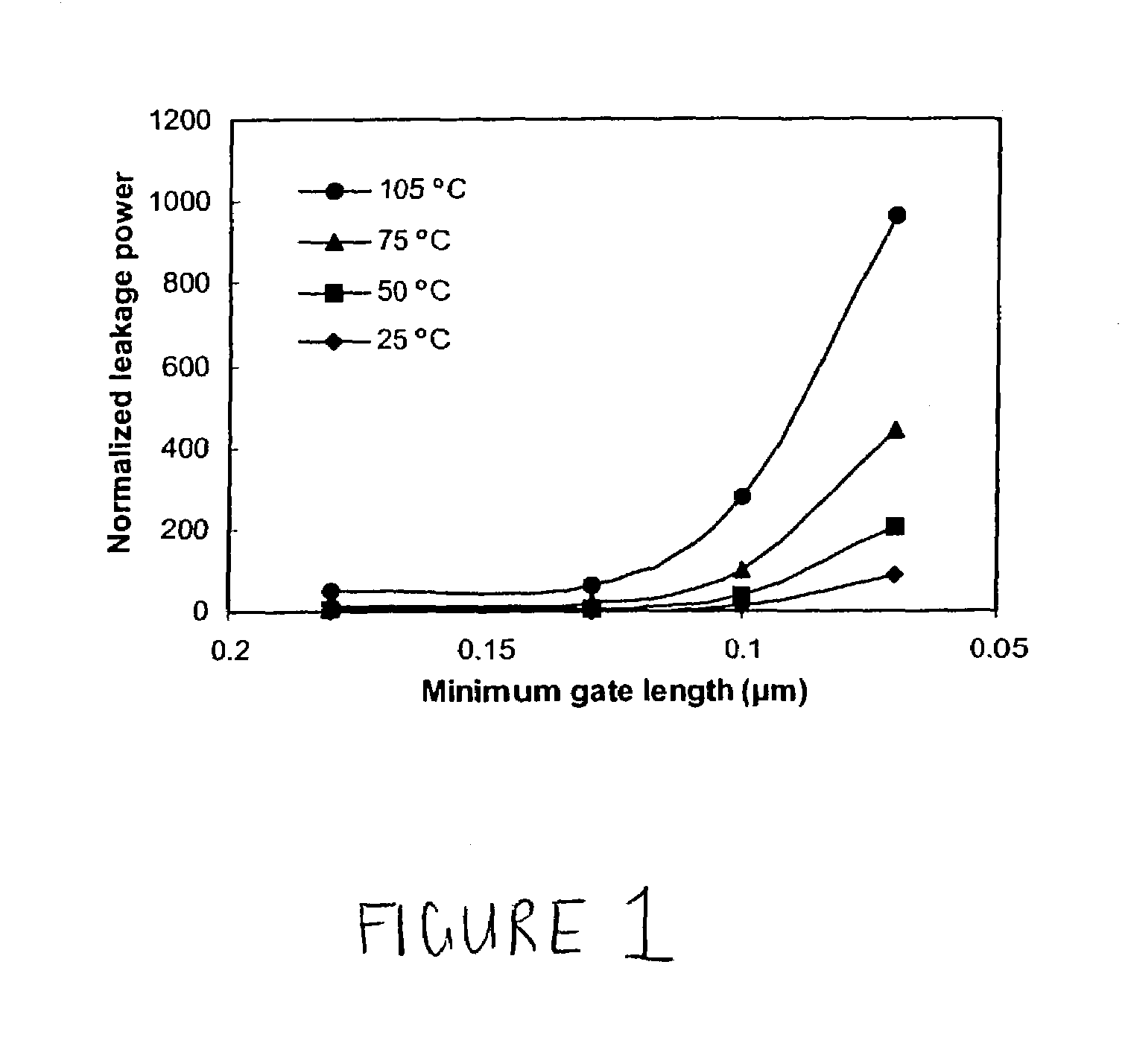

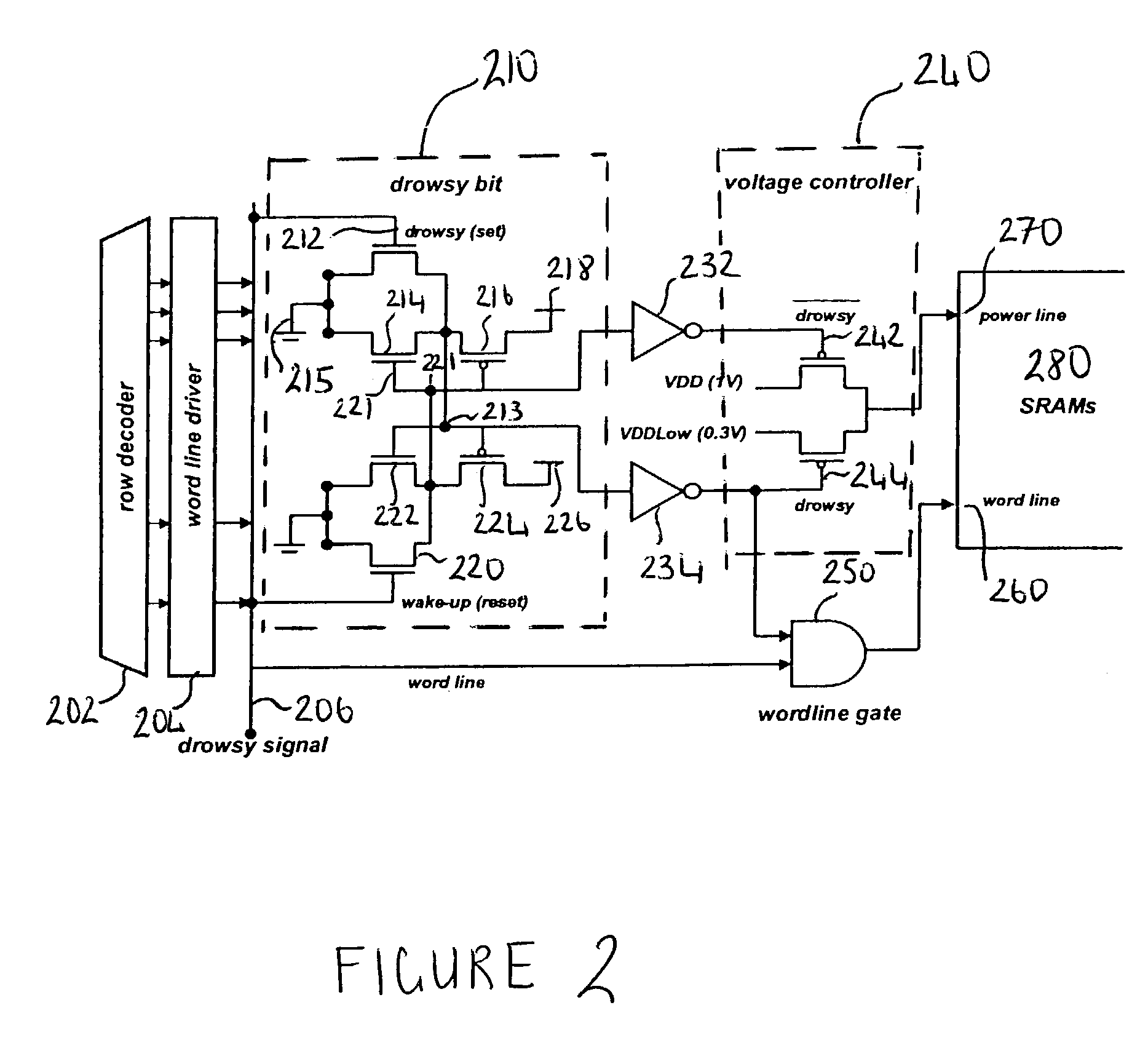

SRAM device and a method of operating the same to reduce leakage current during a sleep mode

An SRAM device and a method of operating an SRAM device. In one embodiment, the SRAM device includes (1) an SRAM array coupled to row peripheral circuitry by a word line and coupled to column peripheral circuitry by bit lines and (2) a sleep mode voltage controller configured to provide both an array high supply voltage VADD that is lower than a high operating voltage VDD and an array low supply voltage VASS that is higher than a low operating voltage VSS to the SRAM array during a sleep mode.

Owner:TEXAS INSTR INC

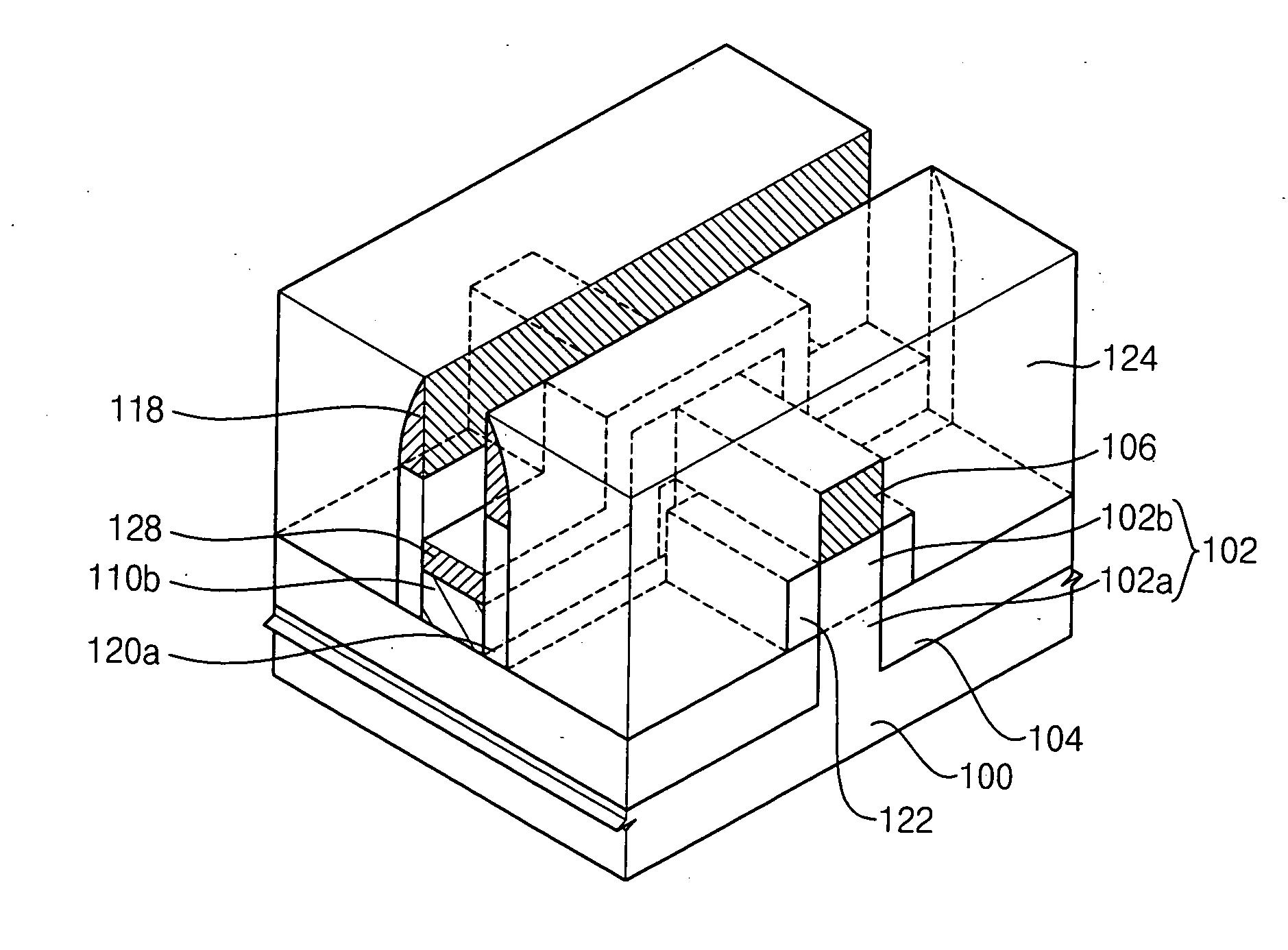

Fin fet structure

ActiveUS20050173768A1Reducing and preventing leakage currentReduced Junction Leakage CurrentTransistorSolid-state devicesInsulation layerEngineering

A fin FET structure employs a negative word line scheme. A gate electrode of a fin FET employs an electrode doped with n+ impurity, and a channel doping for a control of threshold voltage is not executed, or the channel doping is executed by a low density, thereby remarkably improving characteristics of the fin FET. A semiconductor substrate is formed in a first conductive type, and a fin active region of a first conductive type is projected from an upper surface of the semiconductor substrate and is connected to the semiconductor substrate. An insulation layer is formed on the semiconductor substrate, and a gate insulation layer is formed in upper part and sidewall of the fin active region. A gate electrode is formed on the insulation layer and the gate insulation layer. Source and drain are formed in the fin active region of both sides of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

SRAM device and a method of operating the same to reduce leakage current during a sleep mode

ActiveUS20050128789A1Reducing subthreshold current leakageIncreasing diode gate leakageDigital storageBit lineHemt circuits

An SRAM device and a method of operating an SRAM device. In one embodiment, the SRAM device includes (1) an SRAM array coupled to row peripheral circuitry by a word line and coupled to column peripheral circuitry by bit lines and (2) a sleep mode voltage controller configured to provide both an array high supply voltage VADD that is lower than a high operating voltage VDD and an array low supply voltage VASS that is higher than a low operating voltage VSS to the SRAM array during a sleep mode.

Owner:TEXAS INSTR INC

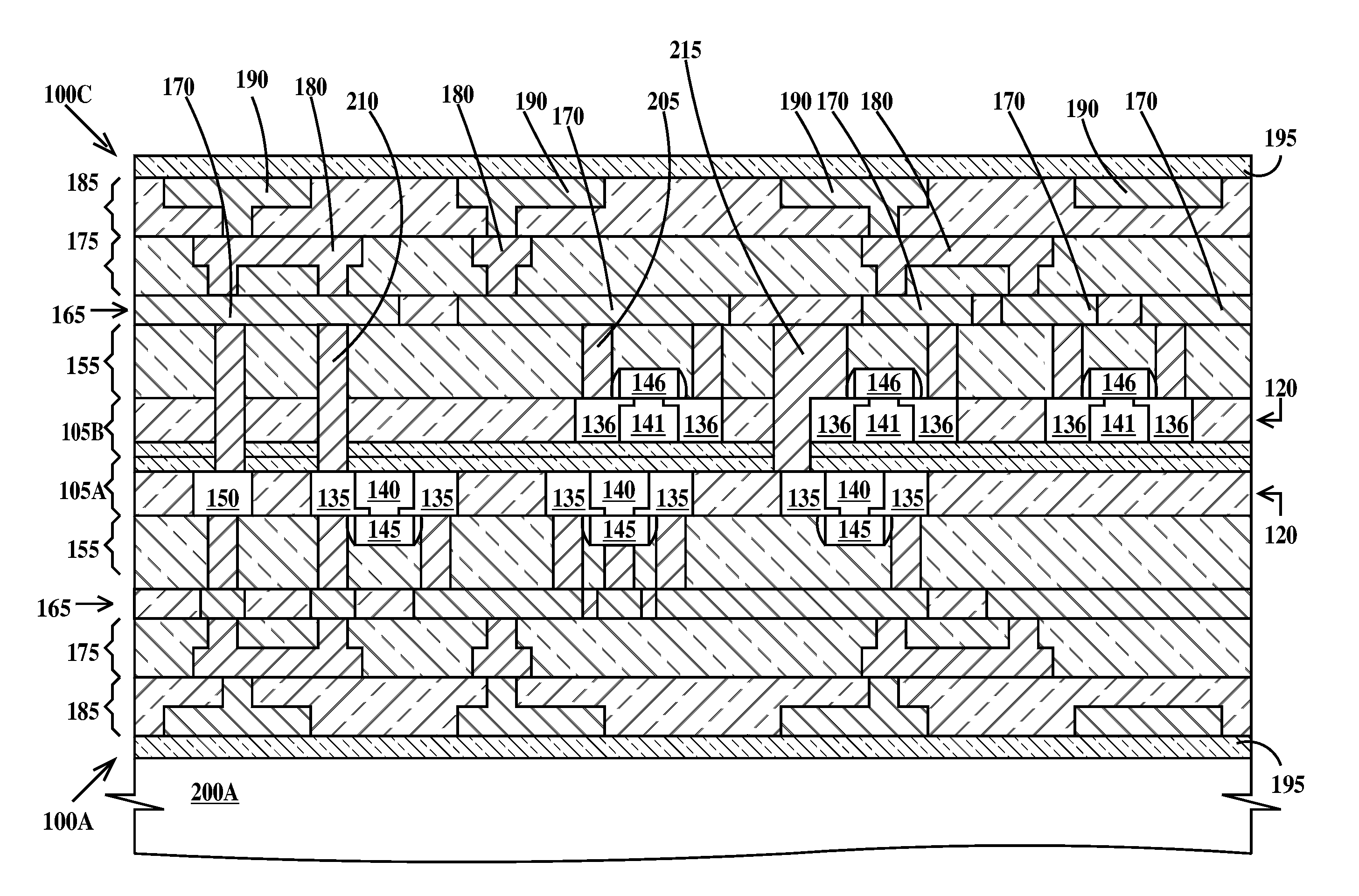

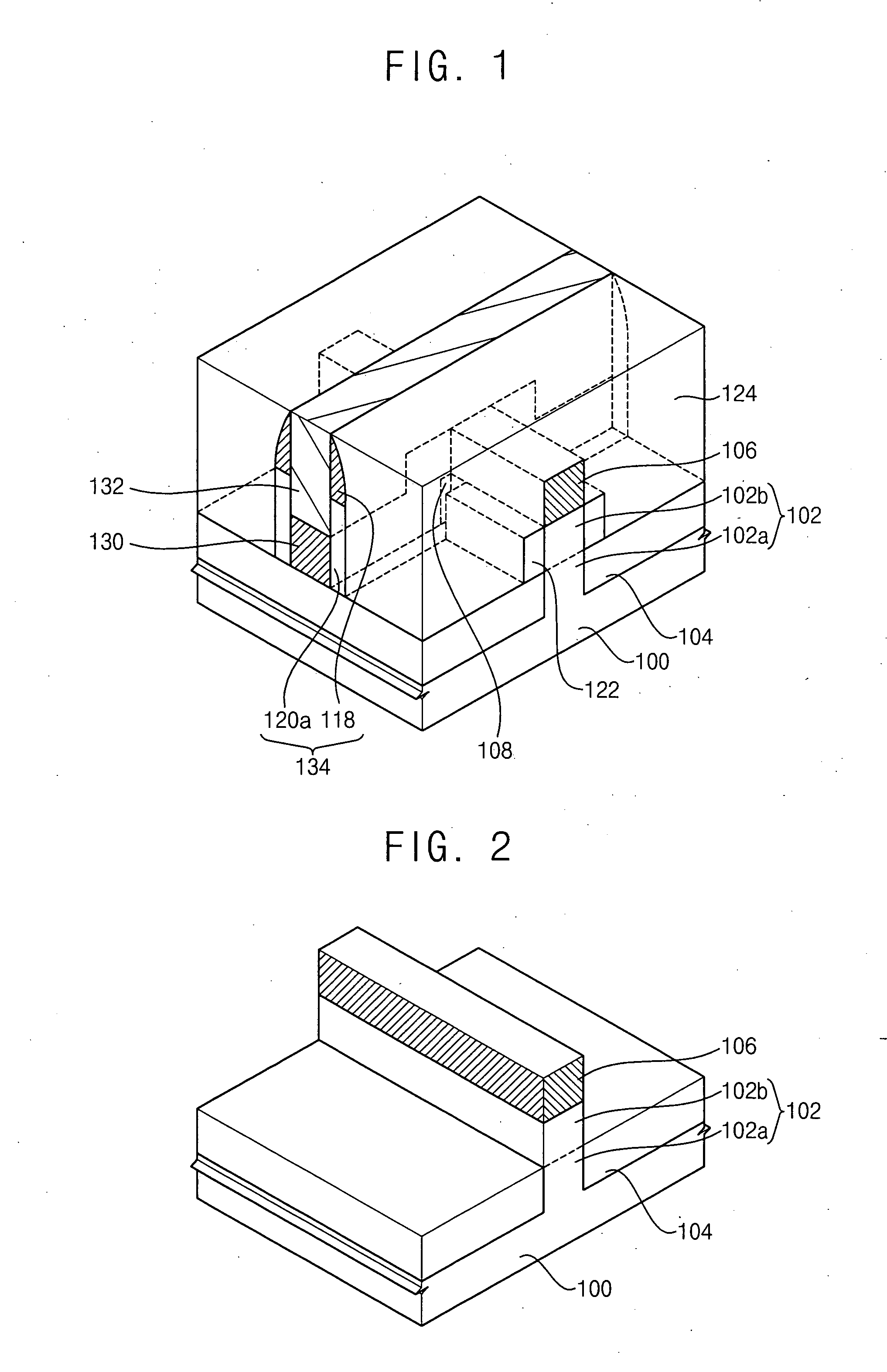

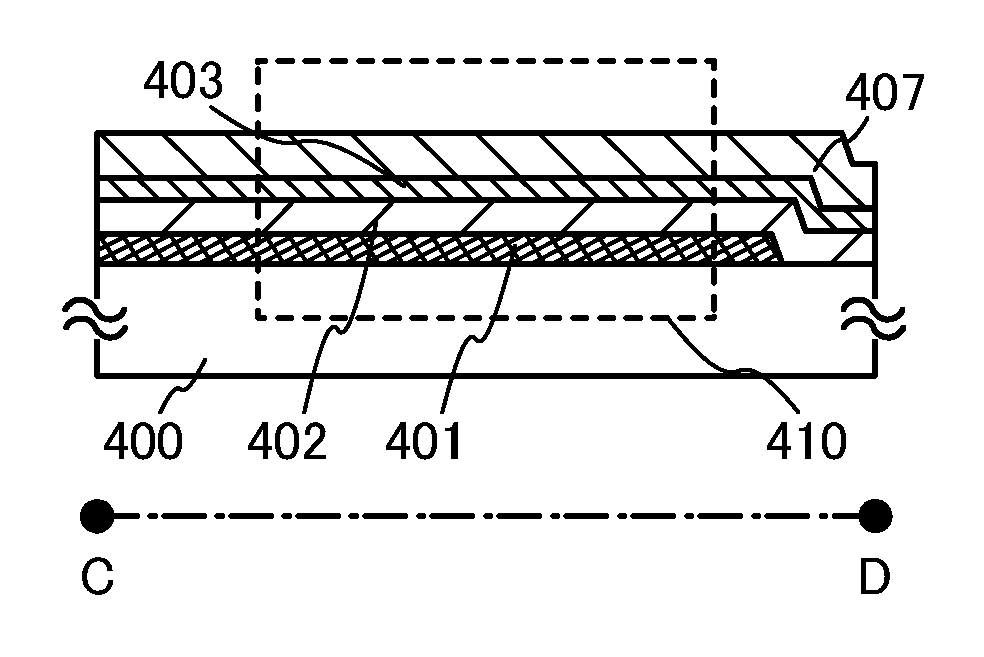

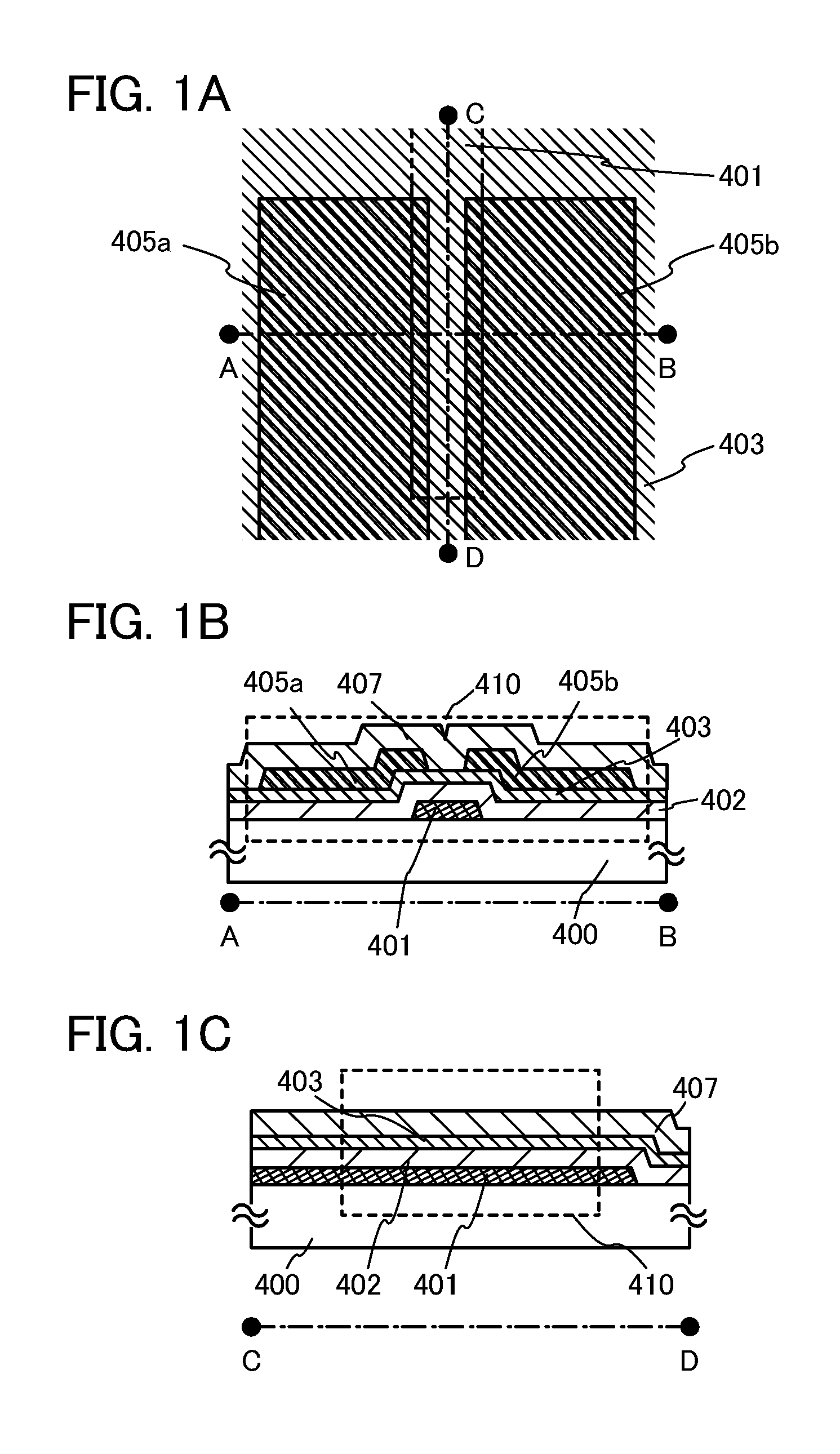

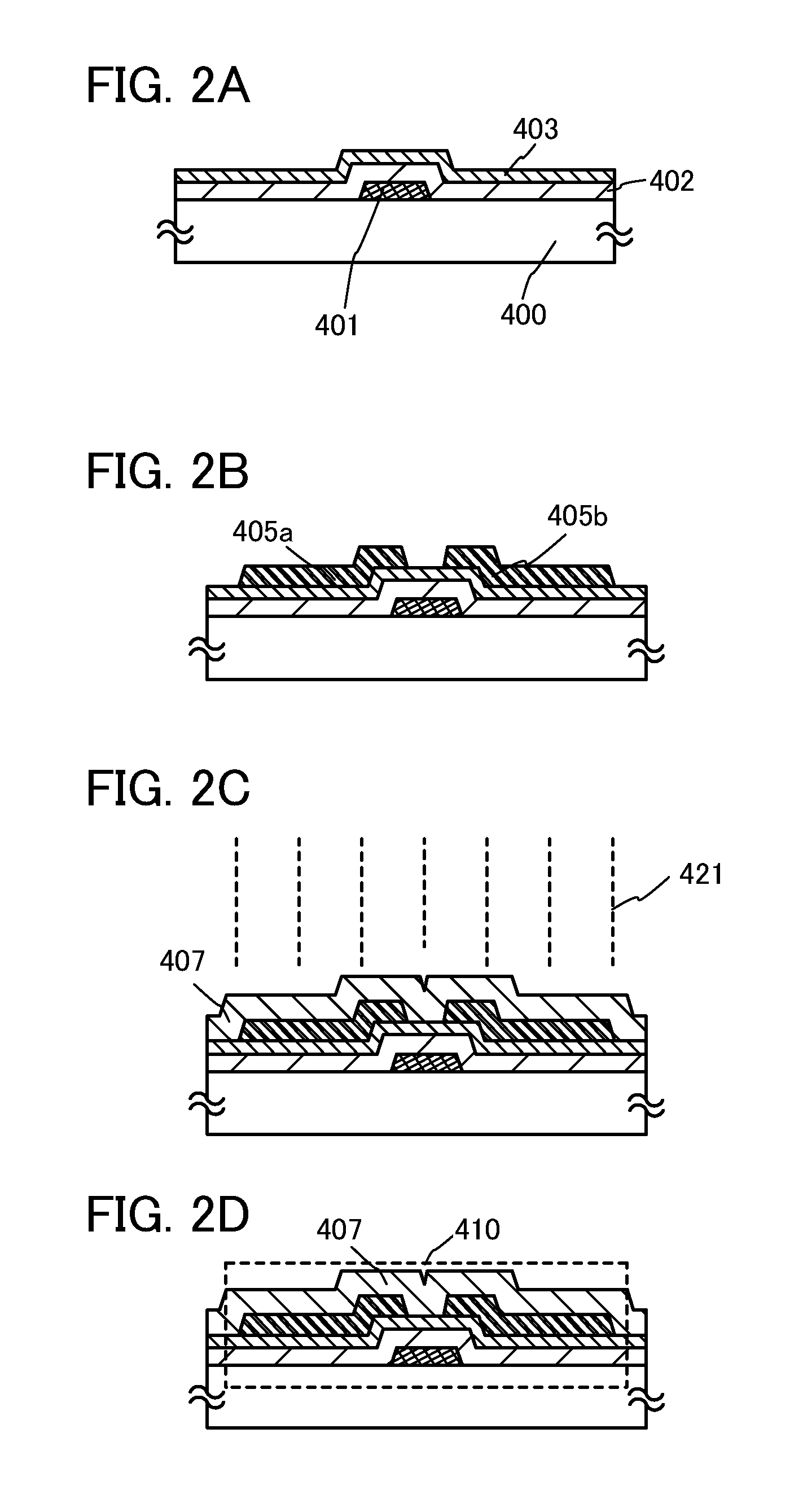

Fin type field effect transistors and methods of manufacturing the same

ActiveUS20060189058A1Threshold voltage can be more readily controlledRaise the threshold voltageTransistorSolid-state devicesOptoelectronicsField-effect transistor

A fin type field effect transistor includes a semiconductor substrate, an active fin, a first hard mask layer pattern, a gate insulation layer pattern, a first conductive layer pattern, and source / drain regions. The active fin includes a semiconductor material and is formed on the substrate and extends in a direction away from a major surface of the substrate. The first hard mask layer pattern is formed on a distal surface of the active fin from the substrate. The gate insulation layer is formed on a sidewall portion of the active fin. The first conductive layer pattern includes a metal silicide and is formed on surfaces of the substrate and the gate insulation layer pattern, and on a sidewall of the first hard mask pattern. The source / drain regions are formed in the active fin on opposite sides of the first conductive layer pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

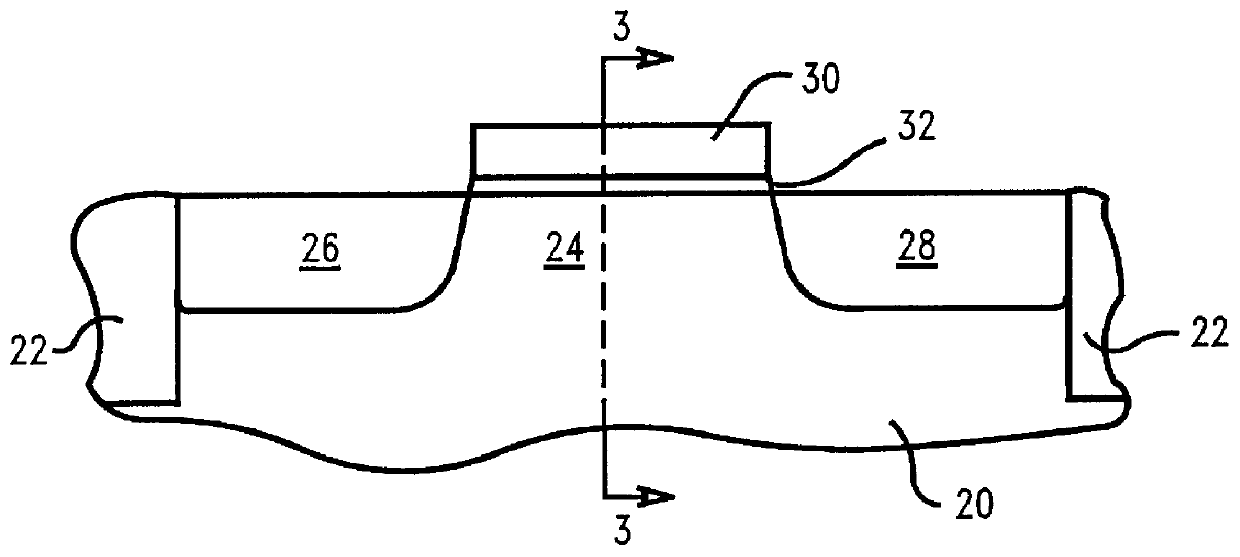

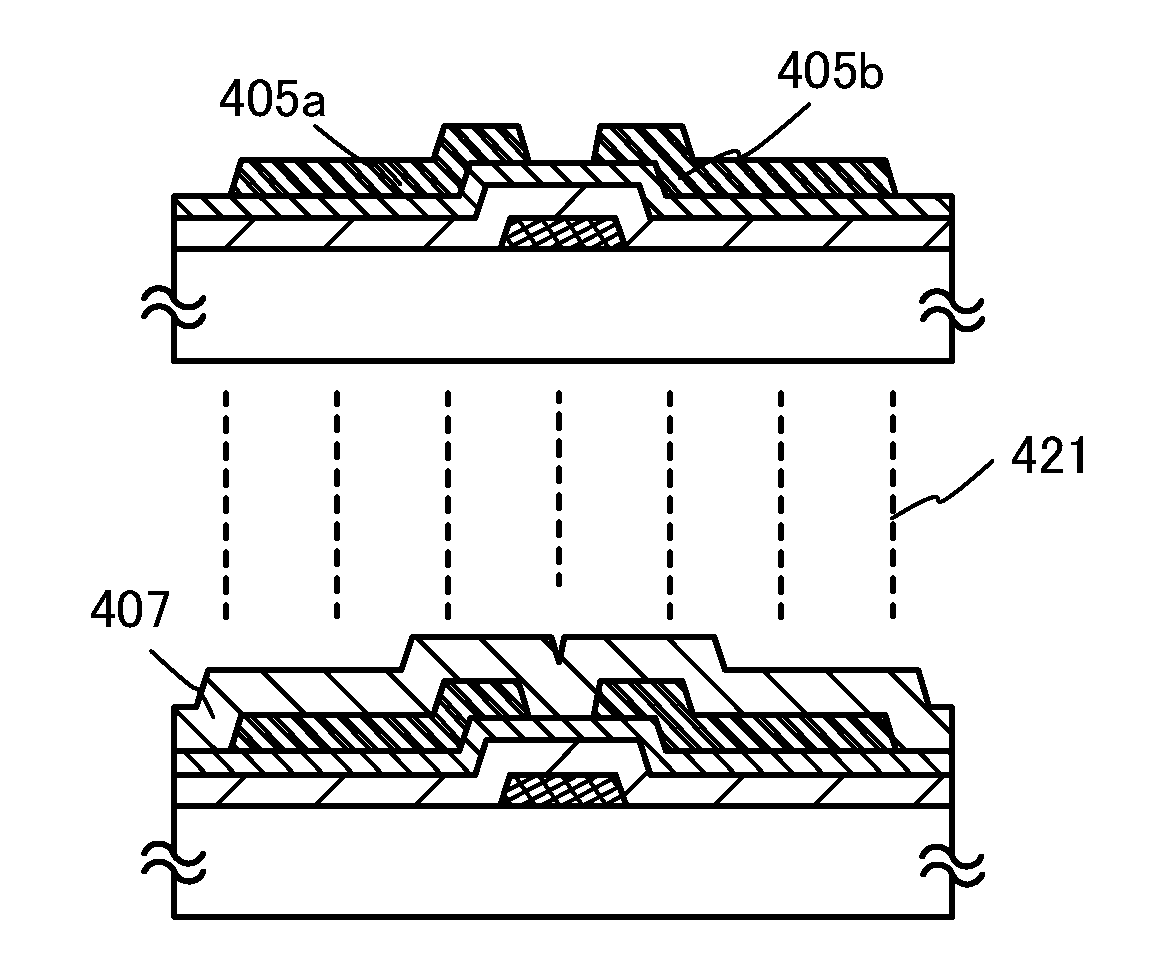

Method of manufacturing semiconductor device

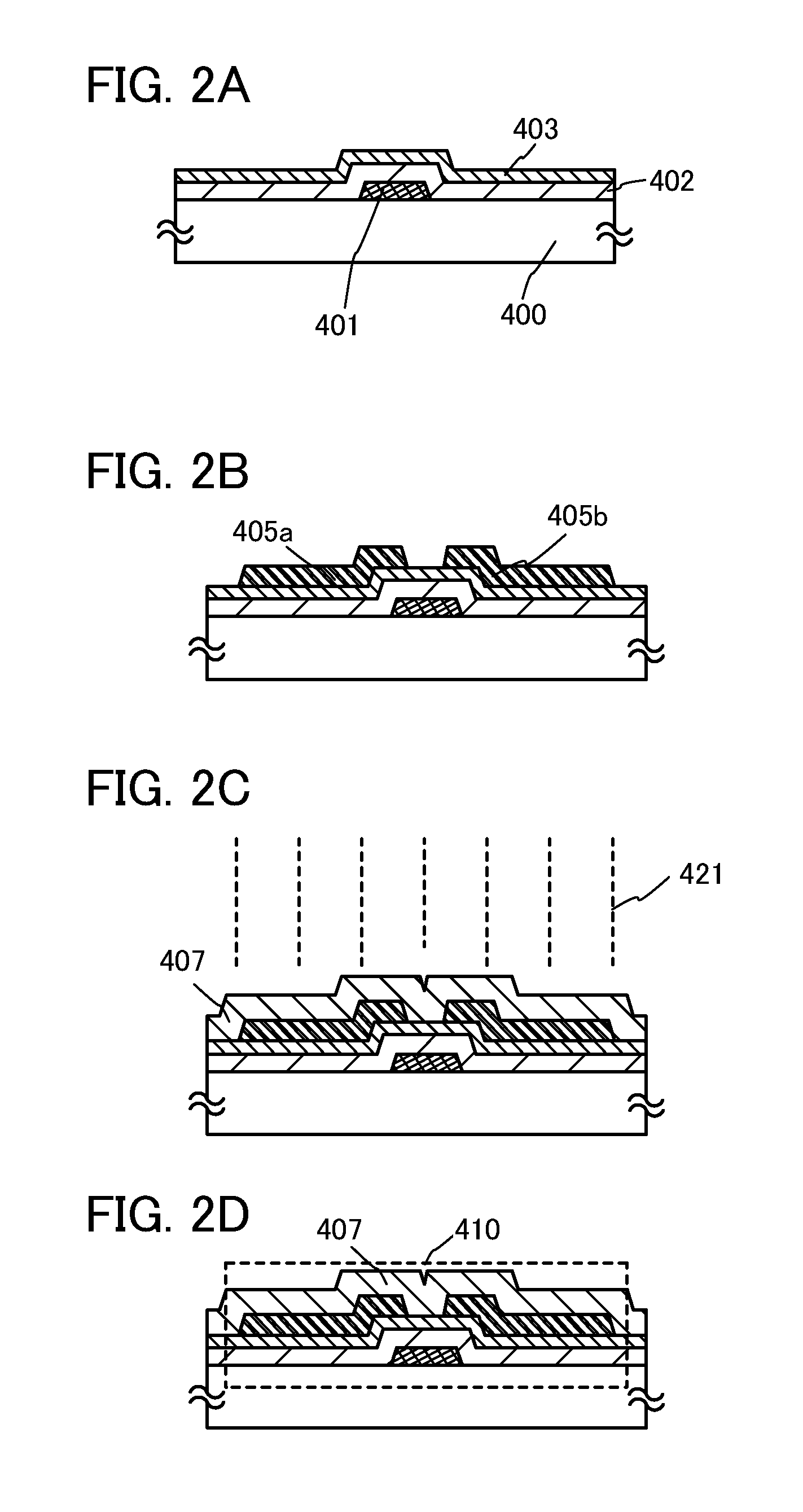

ActiveUS20120231580A1Increasing oxide thicknessLess fluctuationSolid-state devicesSemiconductor/solid-state device manufacturingBias temperature stressSemiconductor

In a manufacturing process of a transistor including an oxide semiconductor film, oxygen doping treatment is performed on the oxide semiconductor film, and then heat treatment is performed on the oxide semiconductor film and an aluminum oxide film provided over the oxide semiconductor film. Consequently, an oxide semiconductor film which includes a region containing more oxygen than a stoichiometric composition is formed. The transistor formed using the oxide semiconductor film can have high reliability because the amount of change in the threshold voltage of the transistor by a bias-temperature stress test (BT test) is reduced.

Owner:SEMICON ENERGY LAB CO LTD

Nitrogen-containing field effect transistor gate stack containing a threshold voltage control layer formed via deposition of a metal oxide

InactiveUS7242055B2Avoid interactionReduce capacitanceTransistorSemiconductor/solid-state device detailsGate dielectricControl layer

A semiconductor structure is provided that includes a Vt stabilization layer between a gate dielectric and a gate electrode. The Vt stabilization layer is capable of stabilizing the structure's threshold voltage and flatband voltage to a targeted value and comprises a nitrided metal oxide, or a nitrogen-free metal oxide, with the proviso that when the Vt stabilization layer comprises a nitrogen-free metal oxide, at least one of the semiconductor substrate or the gate dielectric includes nitrogen. The present invention also provides a method of fabricating such a structure.

Owner:GLOBALFOUNDRIES INC

Data processor memory circuit

ActiveUS7055007B2Reduce leakageRaise the threshold voltageMemory architecture accessing/allocationEnergy efficient ICTMemory circuitsComputer science

A memory circuit for use in a data processing circuit is described, in which memory cells have at least two states, each state being determined by both a first voltage level corresponding to a first supply line and a second voltage level corresponding to a second supply line. The memory circuit comprises a readable state in which information stored in a memory cell is readable and an unreadable state in which information stored in said memory cell is reliably retained but unreadable. Changing the first voltage level but keeping the second voltage level substantially constant effects a transition between the readable state and the unreadable state. In use, the static power consumption of the memory cell in the unreadable state is less than static power consumption of the memory cell in the readable state.

Owner:ARM LTD +1

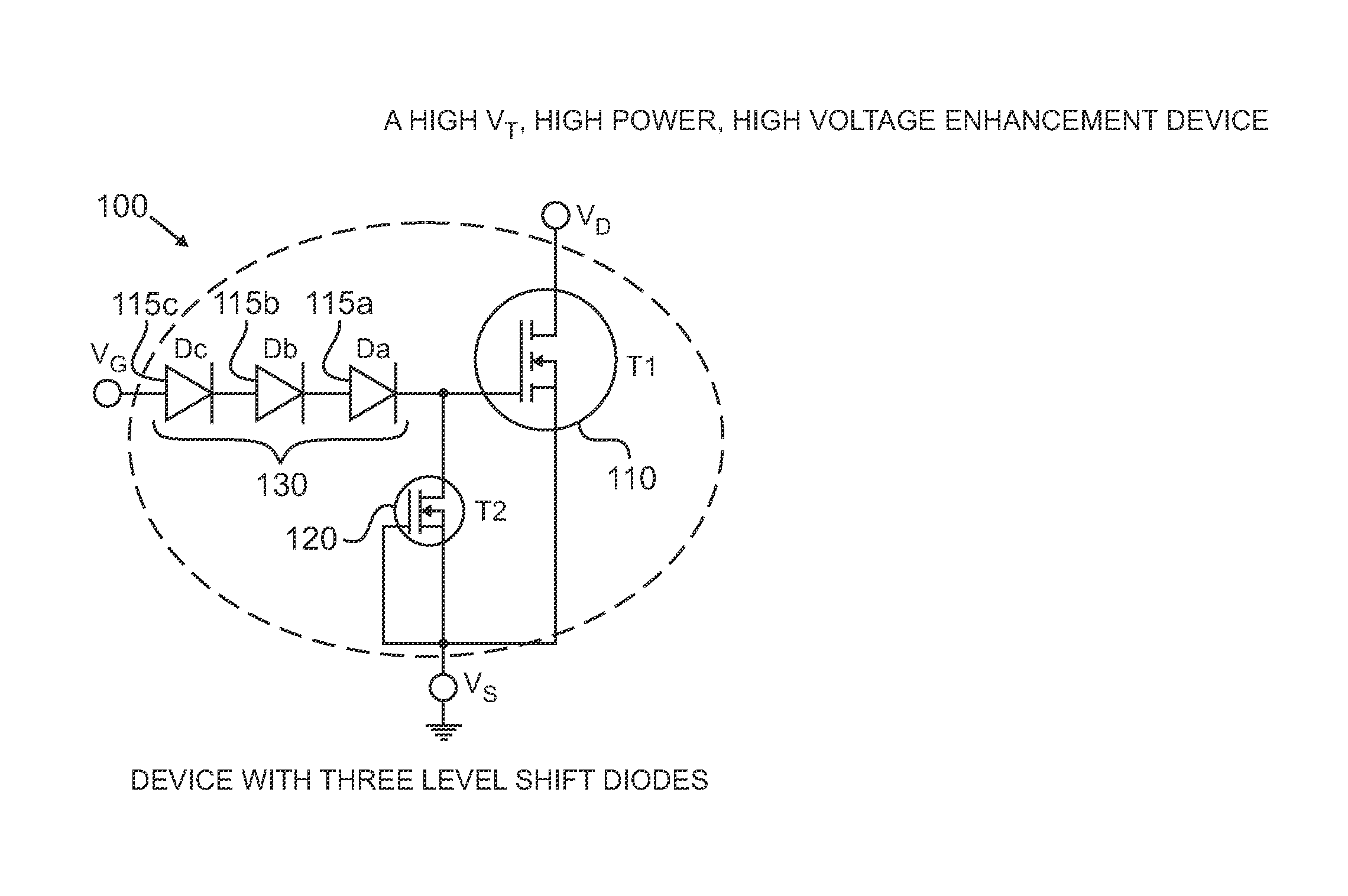

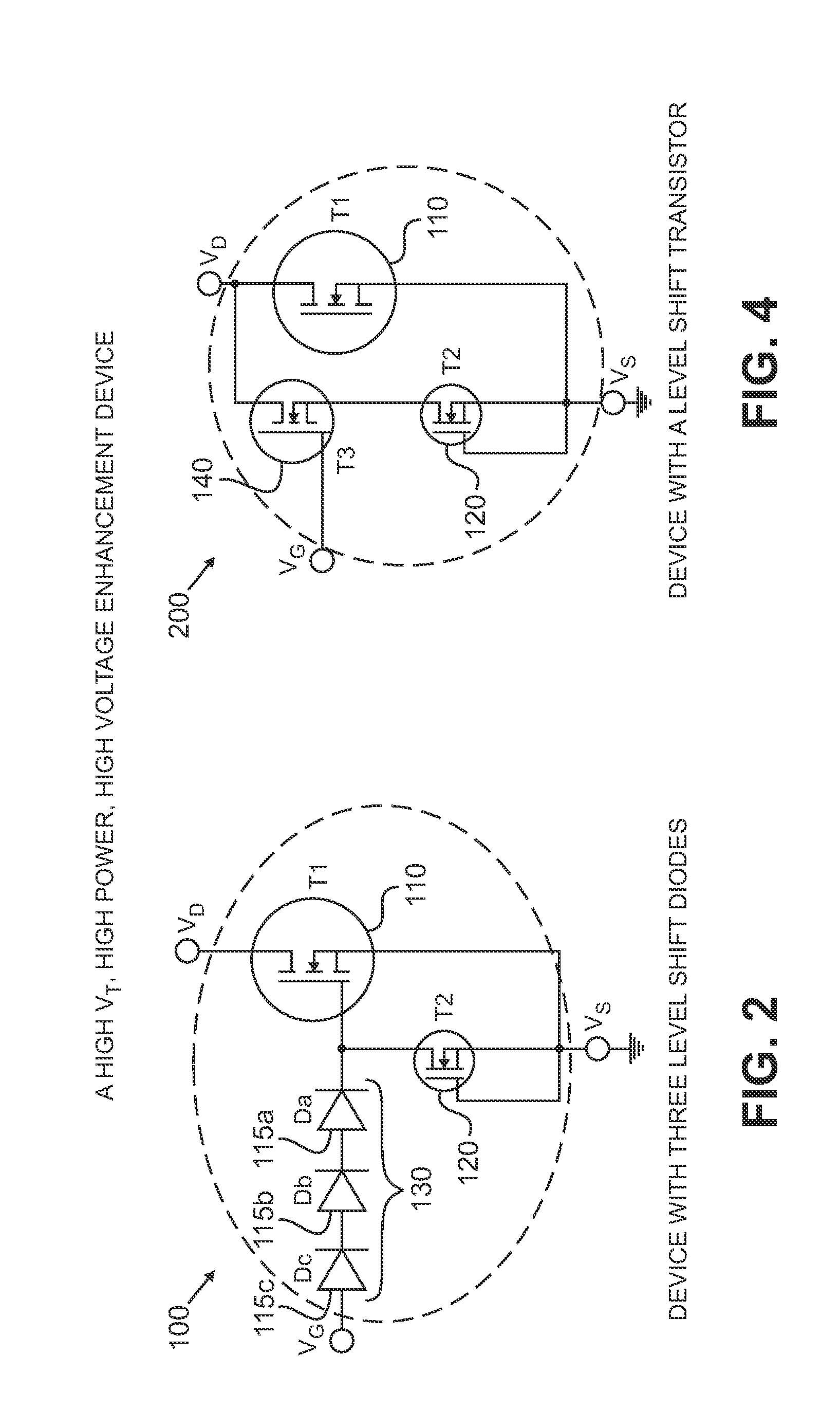

Enhancement-mode hfet circuit arrangement having high power and a high threshold voltage

ActiveUS20110309372A1Raise the threshold voltageTransistorSolid-state devicesLoad resistanceHemt circuits

A circuit includes input drain, source and gate nodes. The circuit also includes a group III nitride enhancement-mode HFET having a source, drain and gate and a voltage shifter having a first terminal connected to the gate of the enhancement mode HFET at a common junction. The circuit also includes a load resistive element connected to the common junction. The drain of the enhancement-mode HFET serves as the input drain node, the source of the enhancement-mode HFET serves as the input source node and a second terminal of the voltage shifter serves as the input gate node.

Owner:POWER INTEGRATIONS INC

Field effect transistor

ActiveUS7956383B2Suppress generationInhibition formationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

A field effect transistor includes: a first nitride semiconductor layer having a plane perpendicular to a (0001) plane or a plane tilted with respect to the (0001) plane as a main surface; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider bandgap than the first nitride semiconductor layer; a third nitride semiconductor layer formed on the second nitride semiconductor layer; and a source electrode and a drain electrode formed so as to contact at least a part of the second nitride semiconductor layer or the third nitride semiconductor layer. A recess that exposes a part of the second nitride semiconductor layer is formed between the source electrode and the drain electrode in the third nitride semiconductor layer. A gate electrode is formed in the recess and an insulating film is formed between the third nitride semiconductor layer and the gate electrode.

Owner:PANASONIC CORP

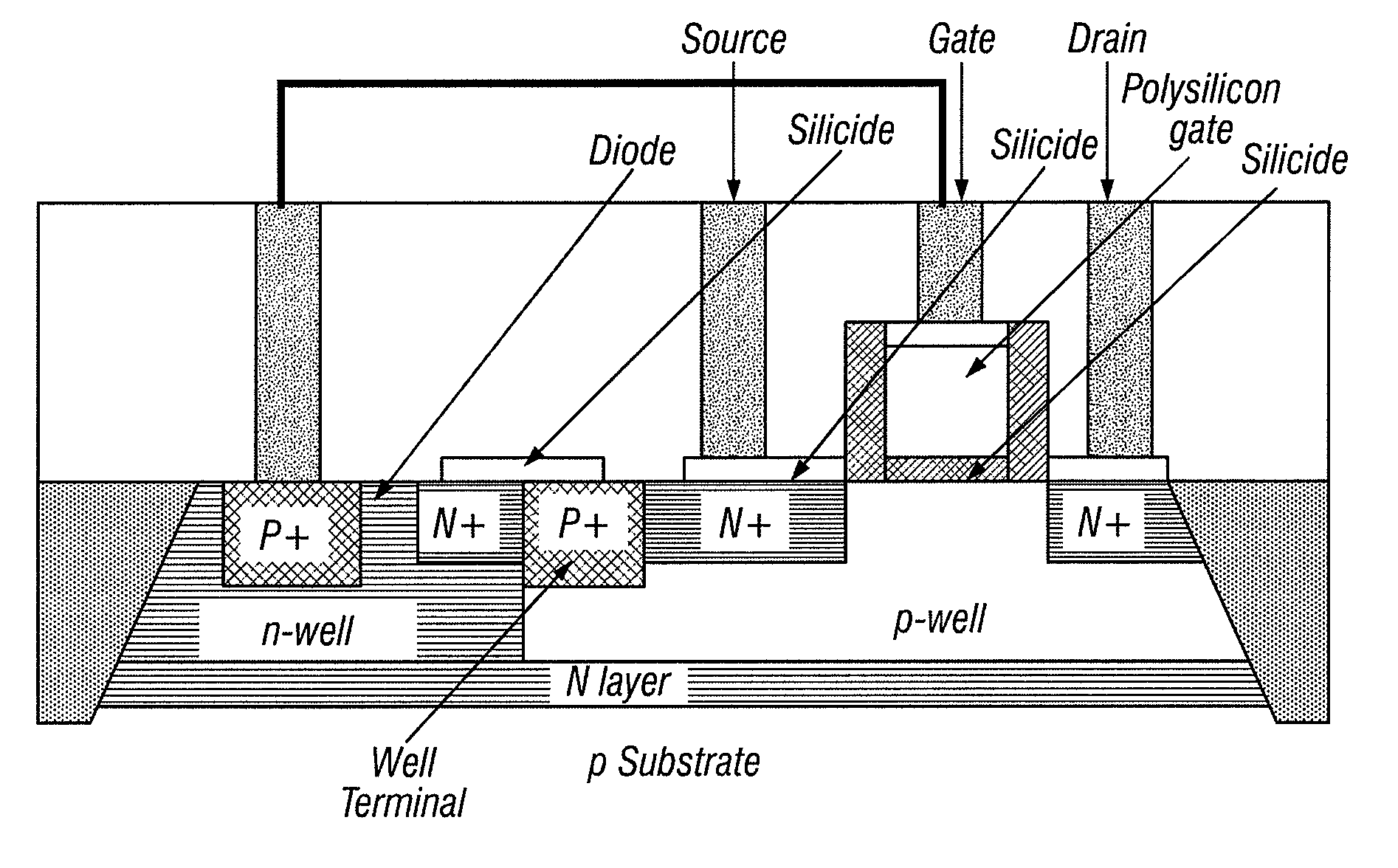

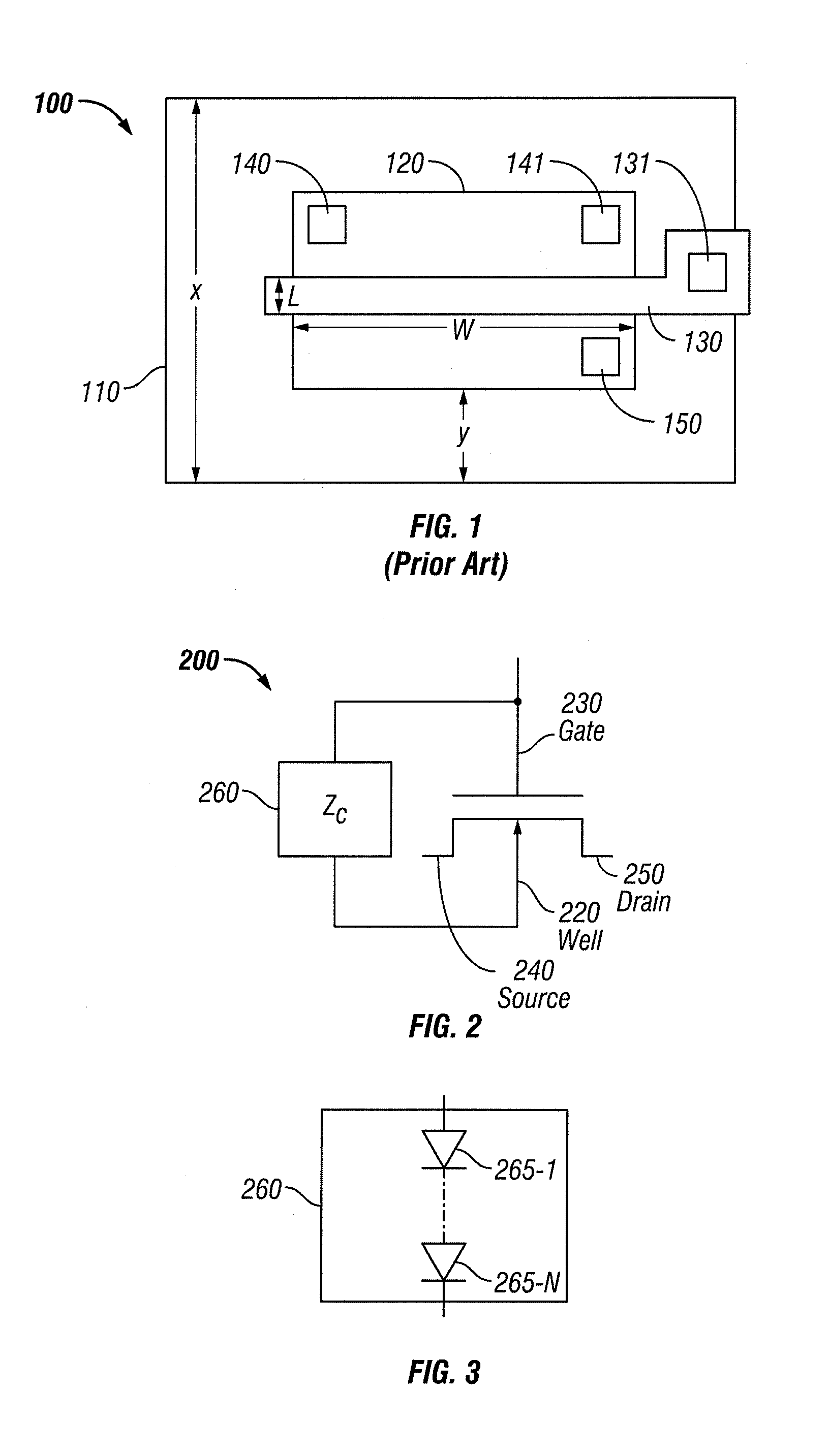

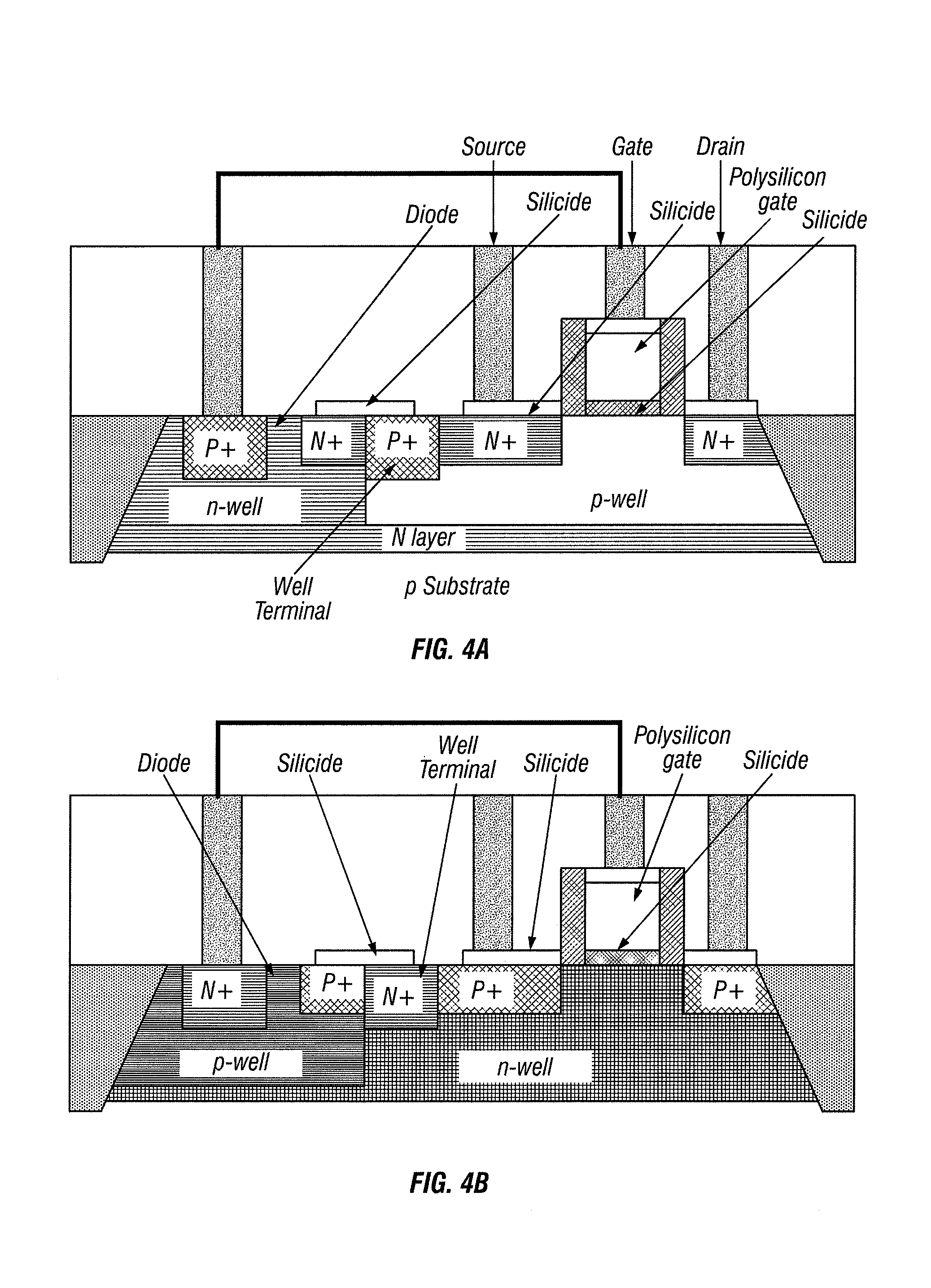

Apparatus and method for improving drive-strength and leakage of deep submicron MOS transistors

InactiveUS7683433B2Increase drive strengthReduce leakage currentTransistorInput/output impedence modificationCMOSEngineering

An apparatus and method of manufacture for metal-oxide semiconductor (MOS) transistors is disclosed. Devices in accordance with the invention are operable at voltages below 2V. The devices are area efficient, have improved drive strength, and have reduced leakage current. A dynamic threshold voltage control scheme comprised of a forward biased diode in parallel with a capacitor is used, implemented without changing the existing MOS technology process. This scheme controls the threshold voltage of each transistor. In the OFF state, the magnitude of the threshold voltage of the transistor increases, keeping the transistor leakage to a minimum. In the ON state, the magnitude of the threshold voltage decreases, resulting in increased drive strength. The invention is particularly useful in MOS technology for both bulk and silicon on insulator (SOI) CMOS. The use of reverse biasing of the well, in conjunction with the above construct to further decrease leakage in a MOS transistor, is also shown.

Owner:SEMI SOLUTIONS LLC

Field effect transistor and method of manufacturing the same

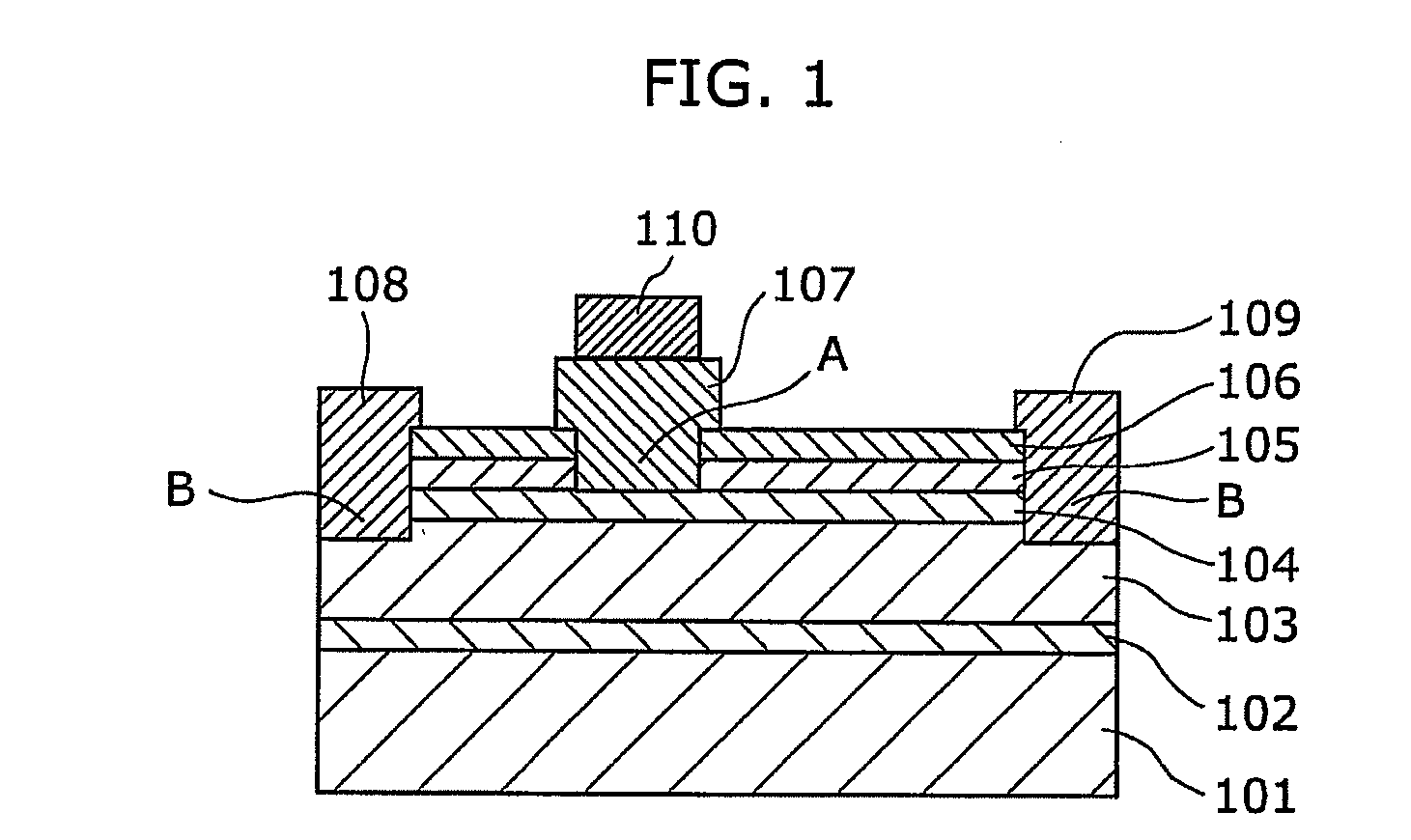

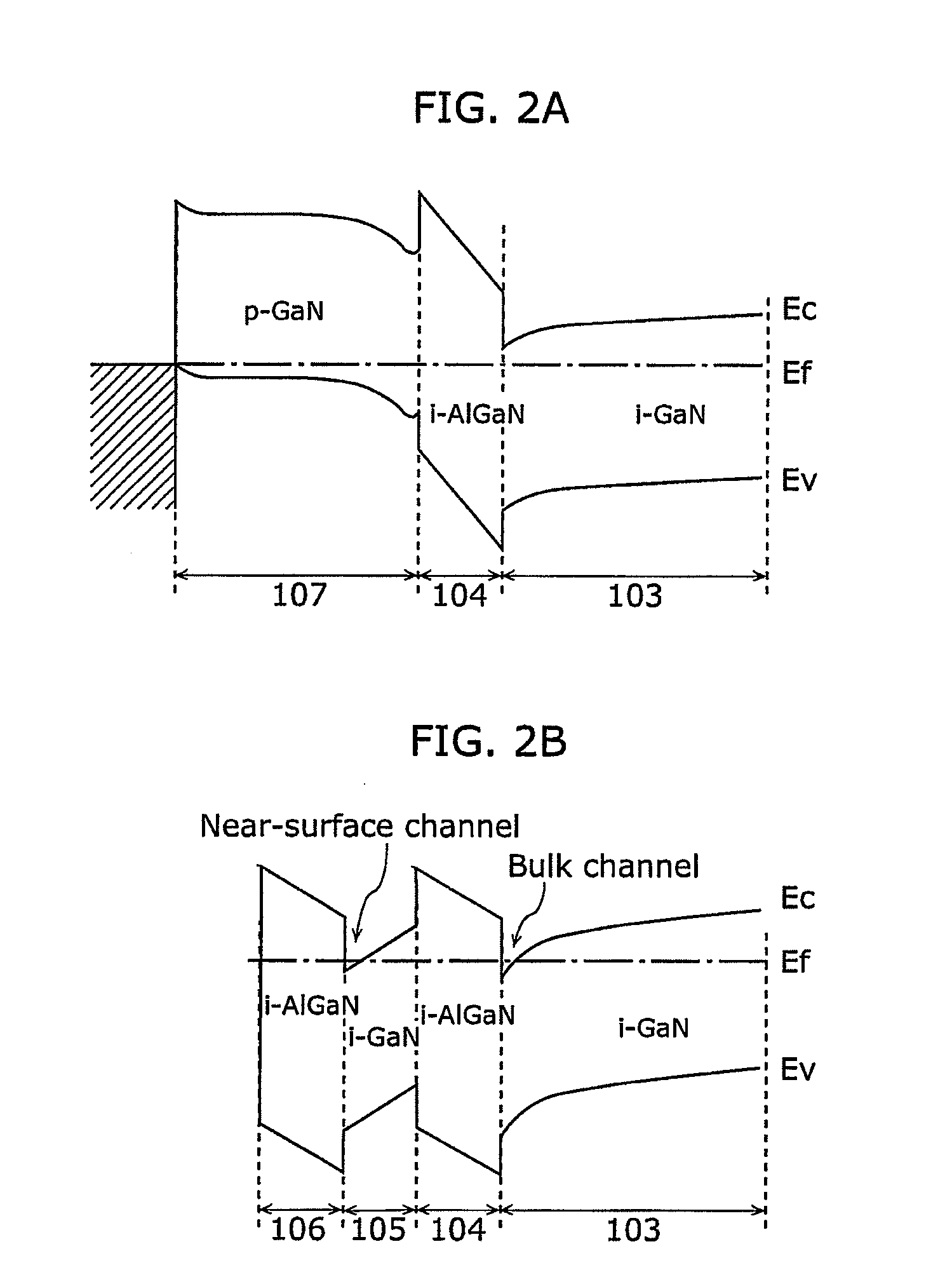

ActiveUS20110227093A1Raise the threshold voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionField-effect transistor

The present invention has an object to provide an FET and a method of manufacturing the FET that are capable of increasing the threshold voltage as well as decreasing the on-resistance. The FET of the present invention includes a first undoped GaN layer; a first undoped AlGaN layer formed on the first undoped GaN layer, having a band gap energy greater than that of the first undoped GaN layer; a second undoped GaN layer formed on the first undoped AlGaN layer; a second undoped AlGaN layer formed on the second undoped GaN layer, having a band gap energy greater than that of the second undoped GaN layer; a p-type GaN layer formed in the recess of the second undoped AlGaN layer; a gate electrode formed on the p-type GaN layer; and a source electrode and a drain electrode which are formed in both lateral regions of the gate electrode, wherein a channel is formed at the heterojunction interface between the first undoped GaN layer and the first undoped AlGaN layer.

Owner:PANASONIC CORP

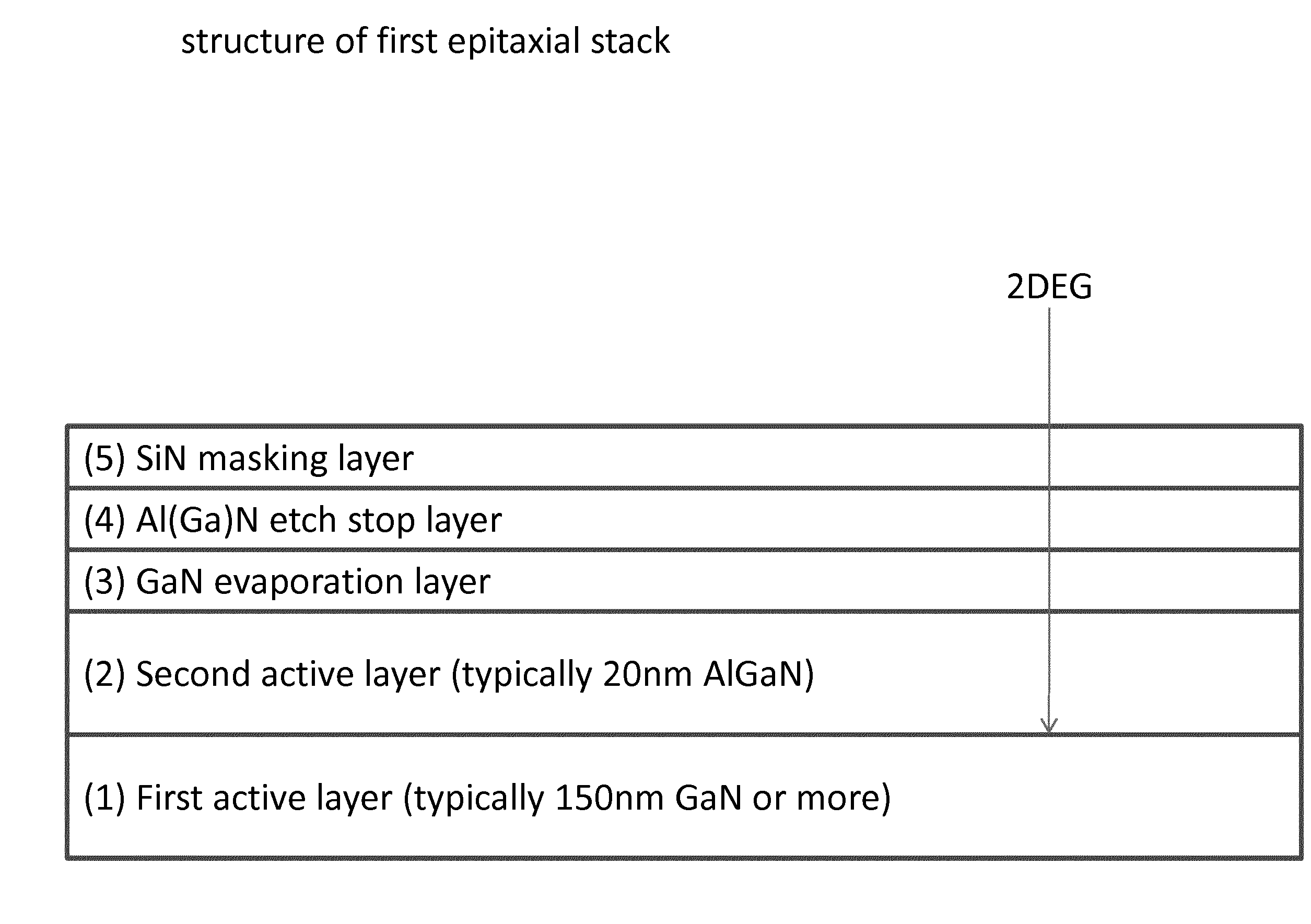

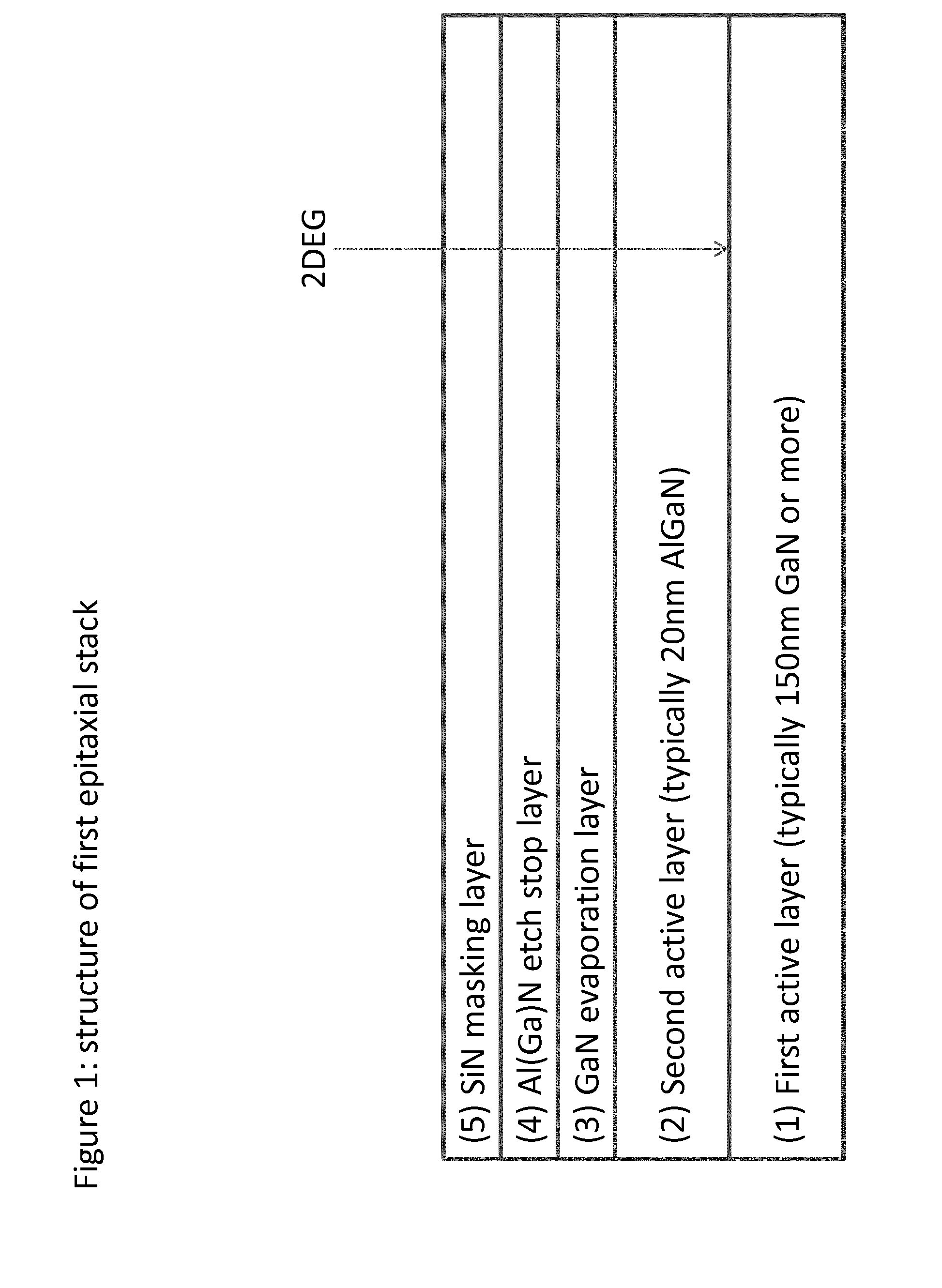

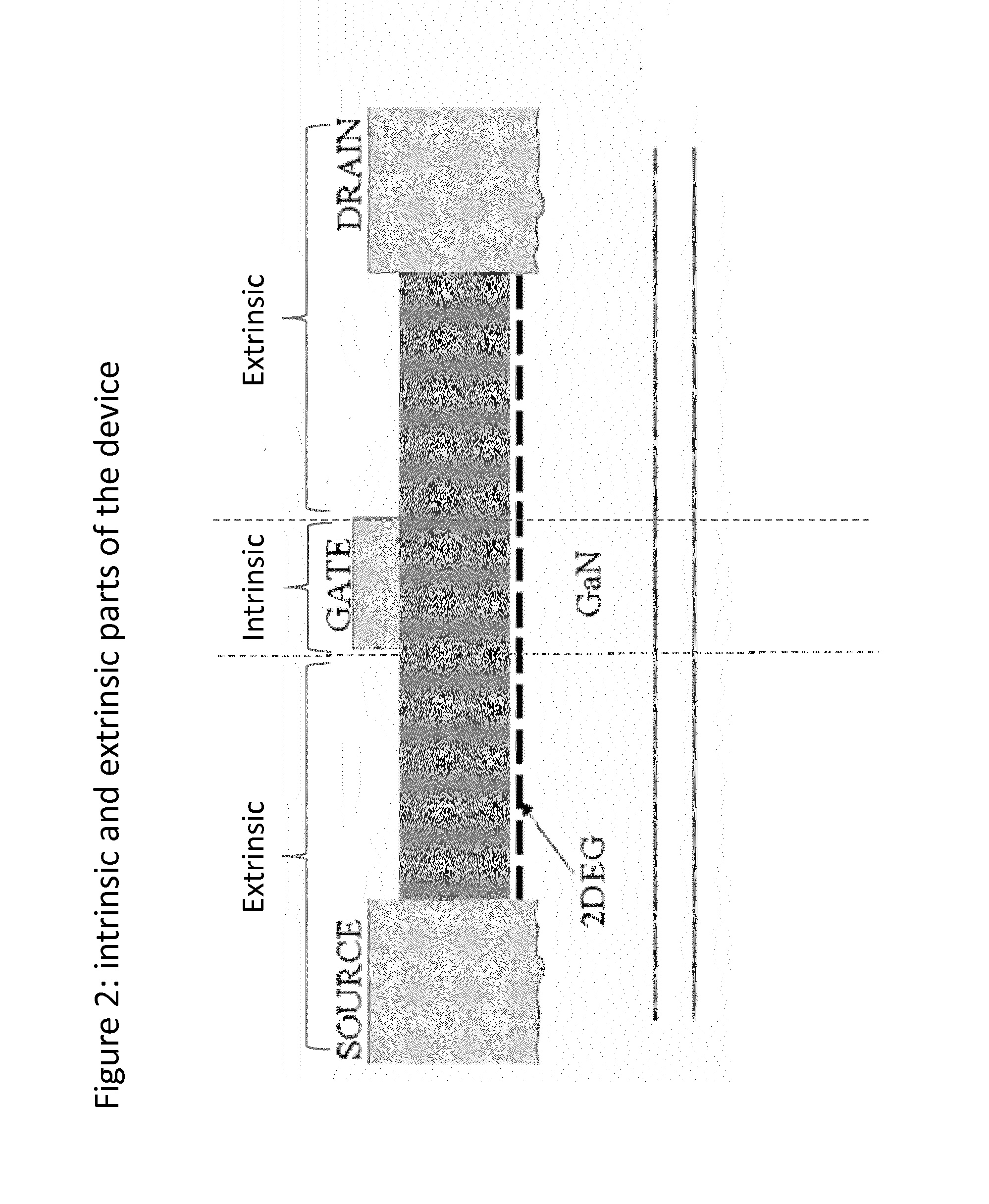

Method for Growing III-V Epitaxial Layers and Semiconductor Structure

ActiveUS20140159119A1Without jeopardizing functionality and advantageGood ohmic contactSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structurePower switching

Disclosed are methods of growing III-V epitaxial layers on a substrate, a semiconductor structure comprising a substrate, a device comprising such a semiconductor structure, and an electronic circuit. Group III-nitride devices, such as, for example, high-electron-mobility transistors, may include a two-dimensional electron gas (2DEG) between two active layers. For example, the 2DEG may be between a GaN layer and a AlGaN layer. These transistors may work in depletion-mode operation, which means the channel has to be depleted to turn the transistor off. For certain applications, such as, for example, power switching or integrated logic, negative polarity gate supply is undesired. Transistors may then work in enhancement mode (E-mode).

Owner:EPIGAN NV

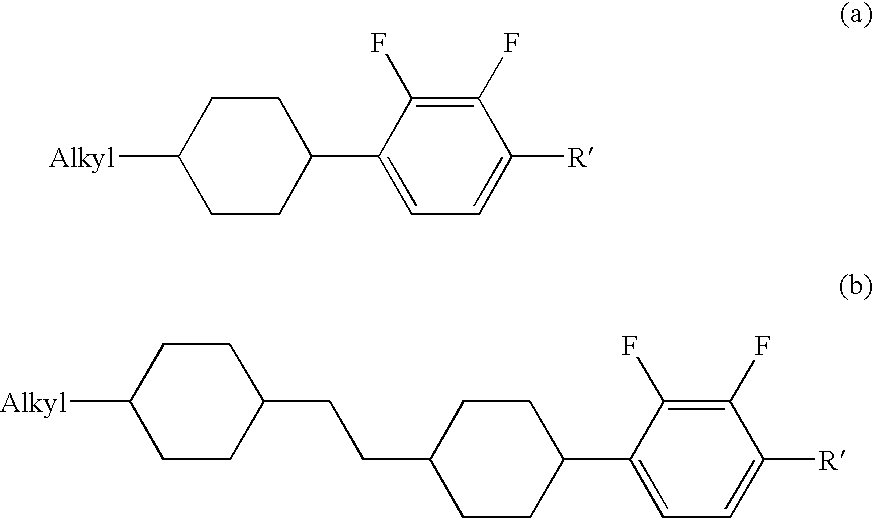

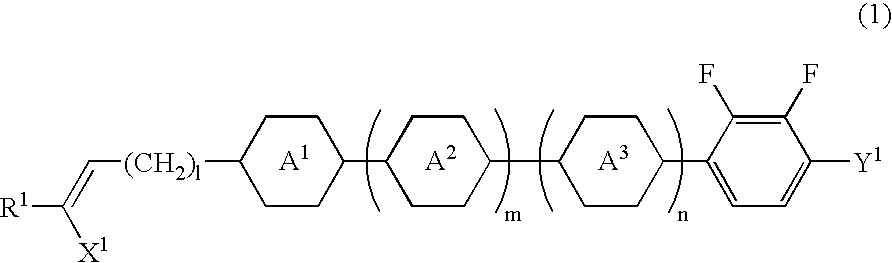

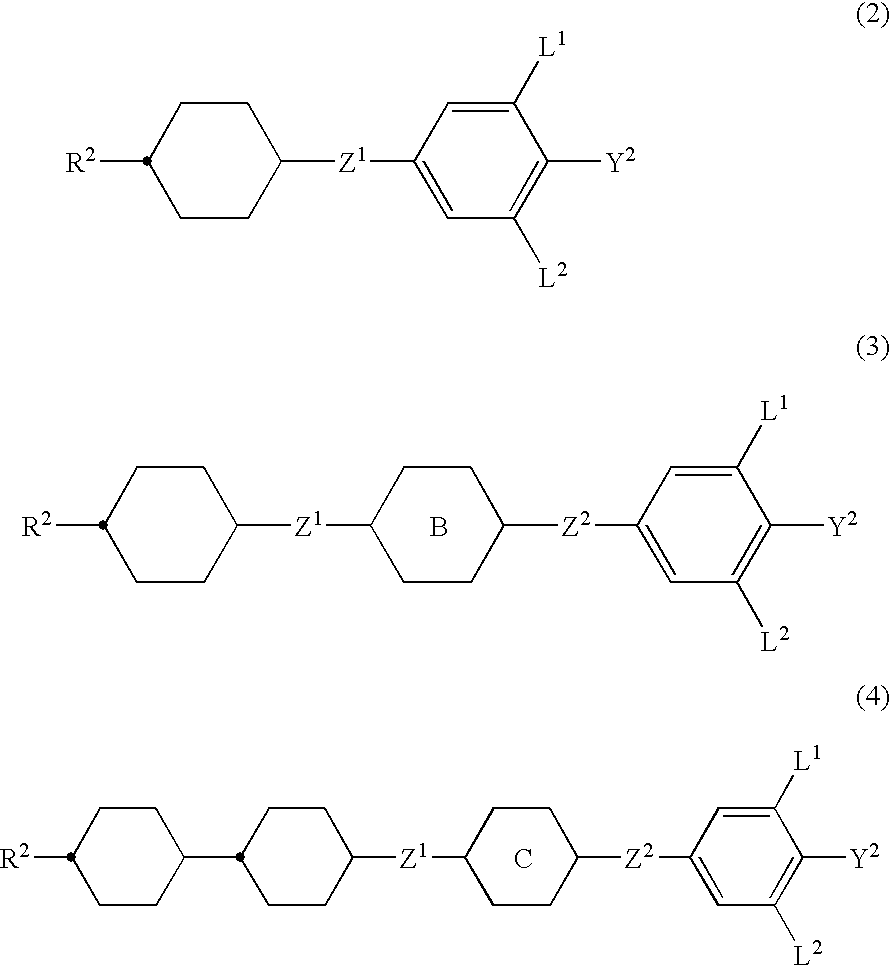

Alkenyl compound having a negative Deltaepsilon value, liquid crystal composition, and liquid crystal display device

InactiveUS6692657B1Low viscosityImprove solubilityLiquid crystal compositionsSilicon organic compoundsCrystallographySolubility

Liquid crystalline compounds having a large negative Delta∈ low viscosity, a large K33 / K11 value, a small Delta∈ / Delta⊥ and mutually excellent solubility even at low temperature, compositions containing at least one of the compounds and liquid crystal display devices containing such a liquid crystal compositions are disclosed.

Owner:JNC CORP

Methods of surface modification for improving electrophoretic display performance

InactiveUS6870662B2Improve surface propertiesIncrease contrastSludge treatmentStatic indicating devicesImaging qualityDisplay device

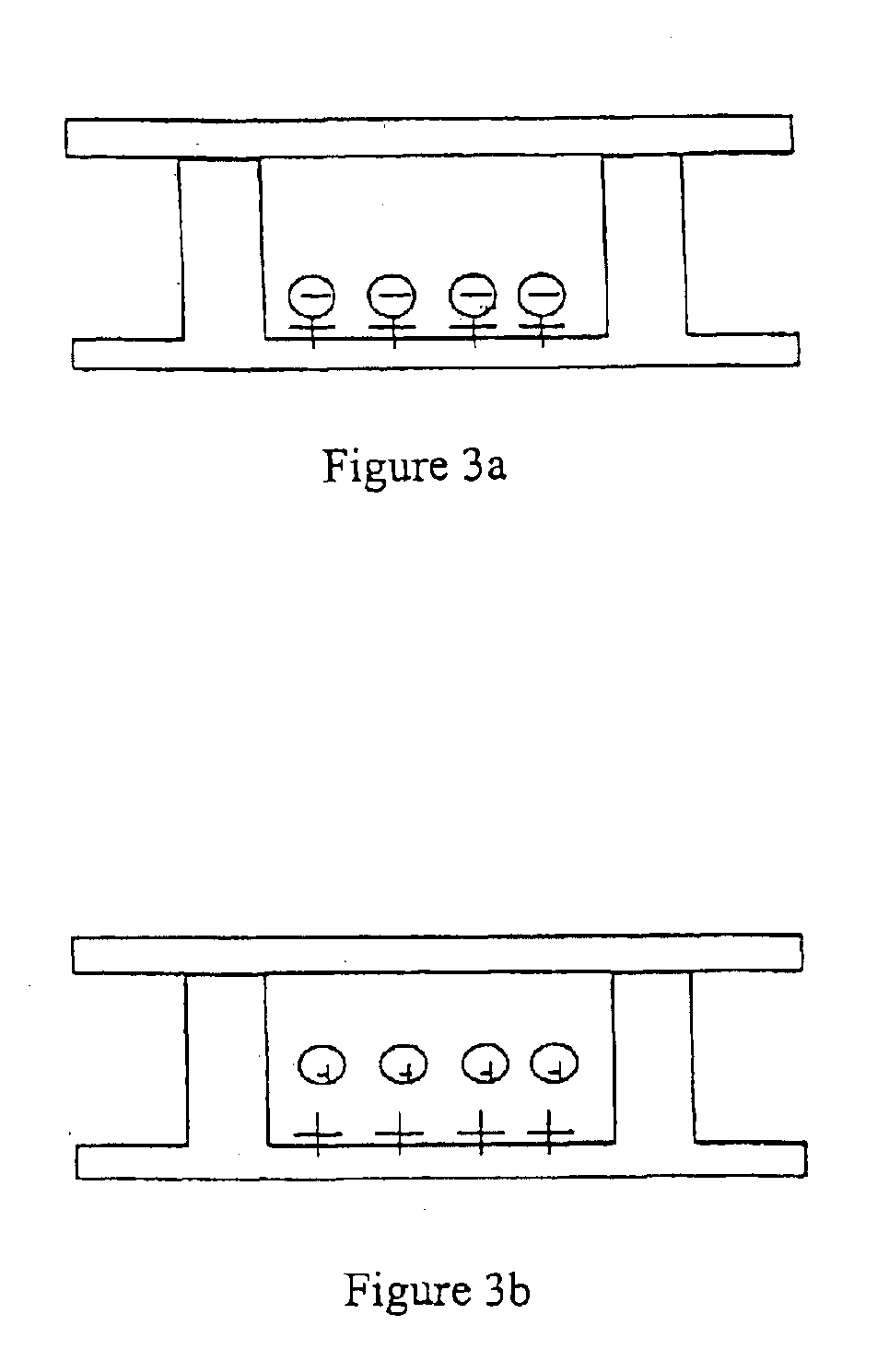

The present invention is directed to methods for improving the performance of an electrophoretic display by modifying the display cell surface. More specifically, the methods are directed to modification of the microcup surface after the microcups are released from the mold. The microcups which have undergone any of the treatment methods of the invention show significant improvement in their surface properties, such as chemical functionality, surface roughness, surface tension, morphology, surface charge, surface reflectivity, surface conductivity and optical properties, particularly optical density in the visible light region. An electrophoretic display formed from the treated microcups has many advantages. For example, the display shows a higher contrast ratio, lower electro-optic response time, lower driving voltage, longer shelf life, higher imageincreasing bistability and higher threshold voltage. In addition, it exhibits an improved image quality by reducing undesirable scum formation or irreversible particle deposition on the microcup surface.

Owner:E INK CALIFORNIA

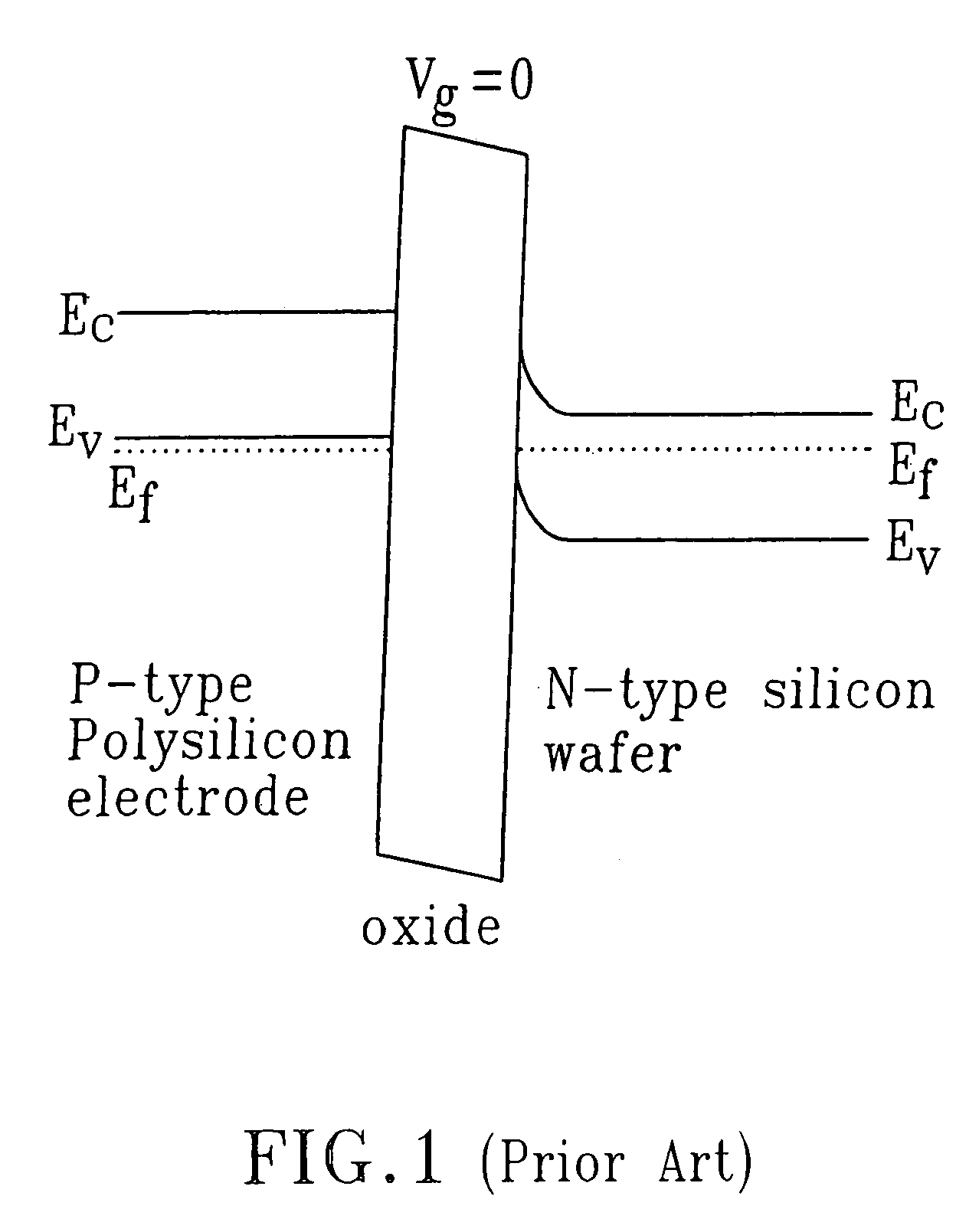

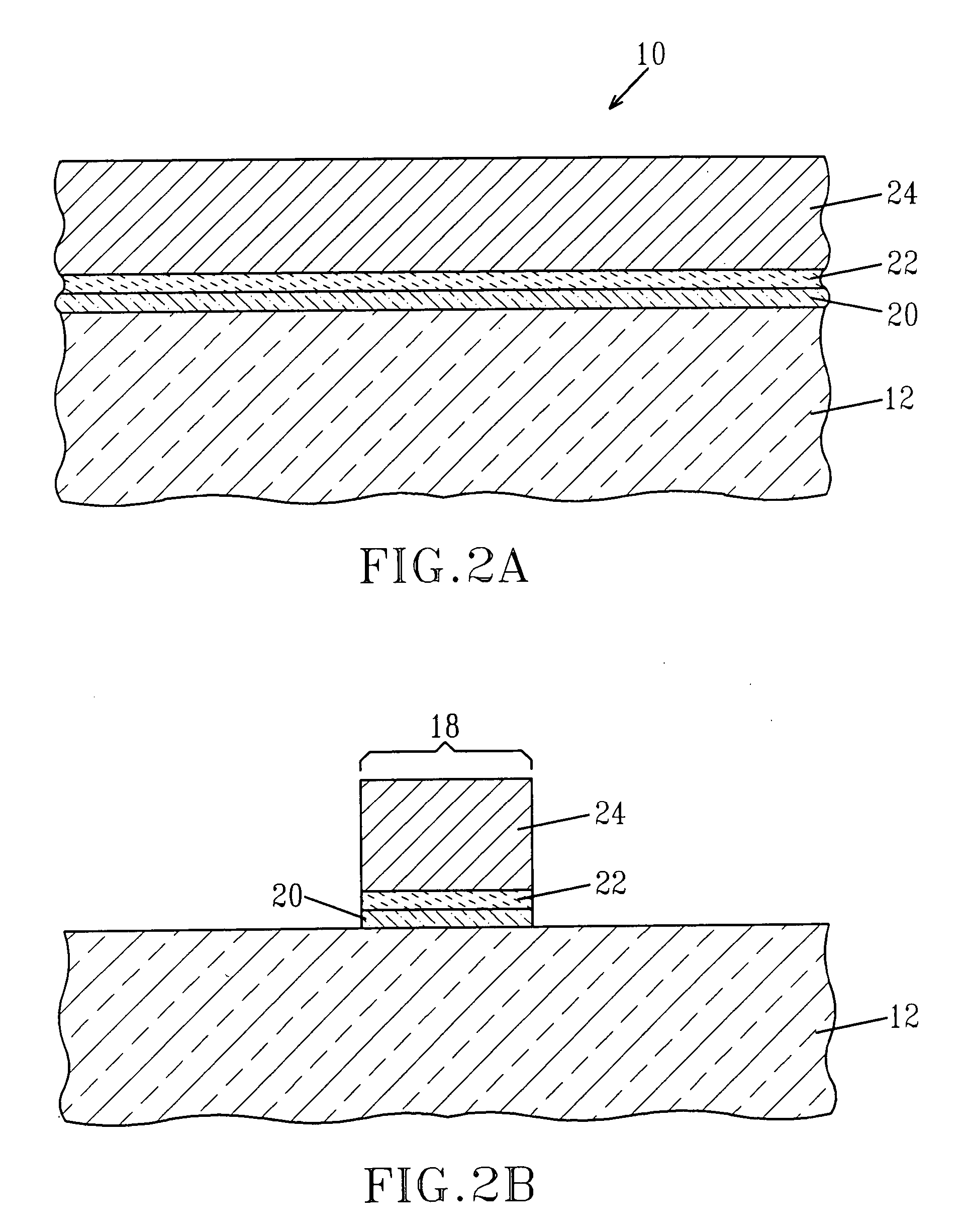

Method of making a depleted poly-silicon edged MOSFET structure

InactiveUS6100143AReduce complexityRaise the threshold voltageTransistorSemiconductor/solid-state device manufacturingMOSFETDielectric

A field effect transistor with reduced corner device problems comprises source and drain regions formed in a substrate, a channel region between the source and drain regions, isolation regions in the substrate adjacent the source, channel and drain regions; and a gate having a gate dopant over the channel region and separated therefrom by a gate dielectric. The isolation regions define corner regions of the channel along interfaces between the channel and isolation regions. The gate includes regions depleted of the gate dopant and overlapping at least the channel region and the isolation regions, such that voltage thresholds of the channel corner regions beneath depleted portions of the gate conductor layer are increased compared to regions of the channel between the corner regions. The field effect transistor with reduced dopant concentration on the MOSFET gate "corner" has an improved edge voltage tolerance. The structure has improved edge dielectric breakdown and lower MOSFET gate-induced drain leakage (GIDL). This structure is intended for analog applications, mixed voltage tolerant circuits and electrostatic (ESD) networks.

Owner:IBM CORP

Method of manufacturing semiconductor device

ActiveUS8828794B2Stable electrical characteristicsImprove reliabilityTransistorSolid-state devicesBias temperature stressSemiconductor

In a manufacturing process of a transistor including an oxide semiconductor film, oxygen doping treatment is performed on the oxide semiconductor film, and then heat treatment is performed on the oxide semiconductor film and an aluminum oxide film provided over the oxide semiconductor film. Consequently, an oxide semiconductor film which includes a region containing more oxygen than a stoichiometric composition is formed. The transistor formed using the oxide semiconductor film can have high reliability because the amount of change in the threshold voltage of the transistor by a bias-temperature stress test (BT test) is reduced.

Owner:SEMICON ENERGY LAB CO LTD