Patents

Literature

53results about How to "Reduced Junction Leakage Current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

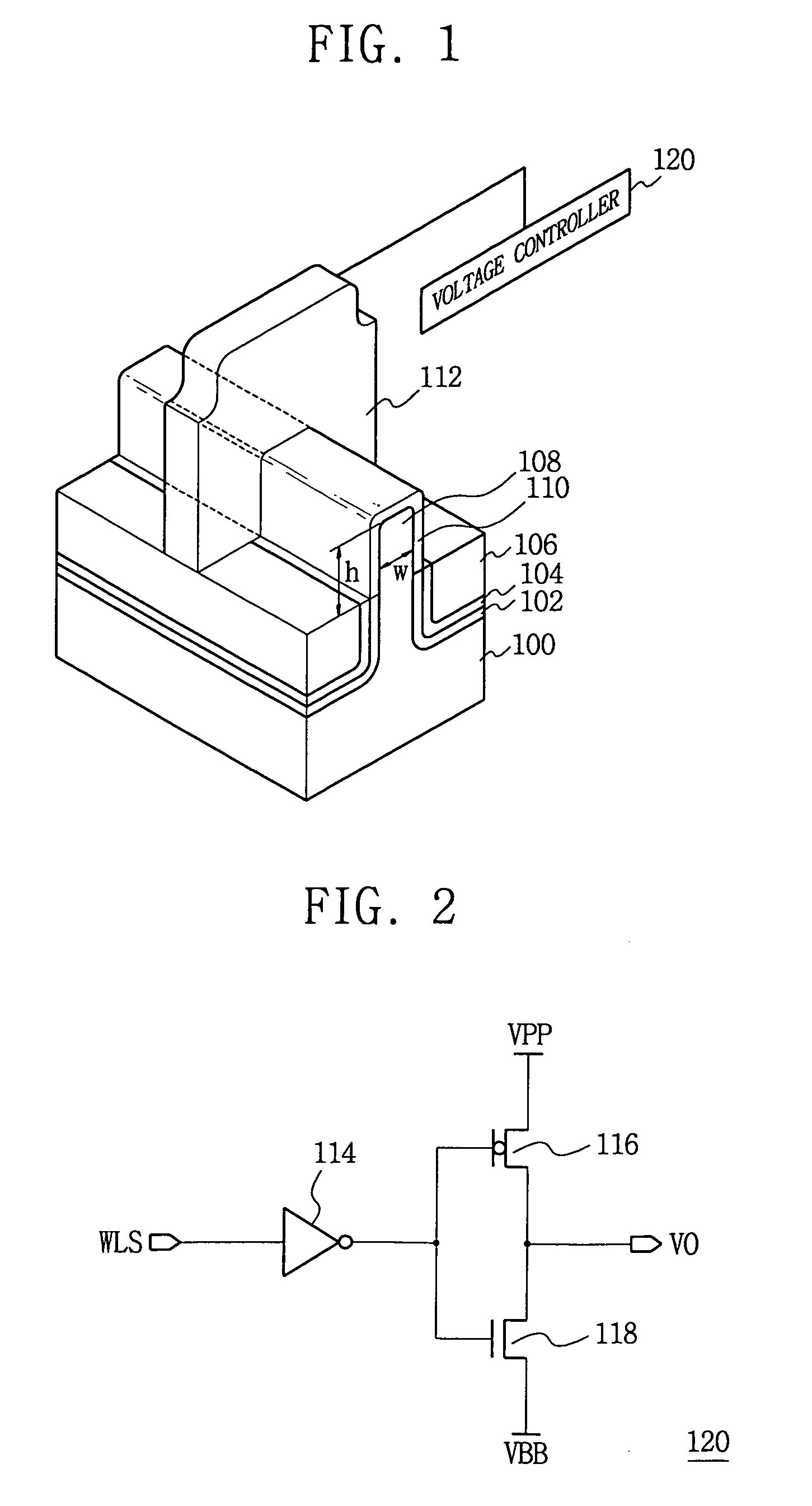

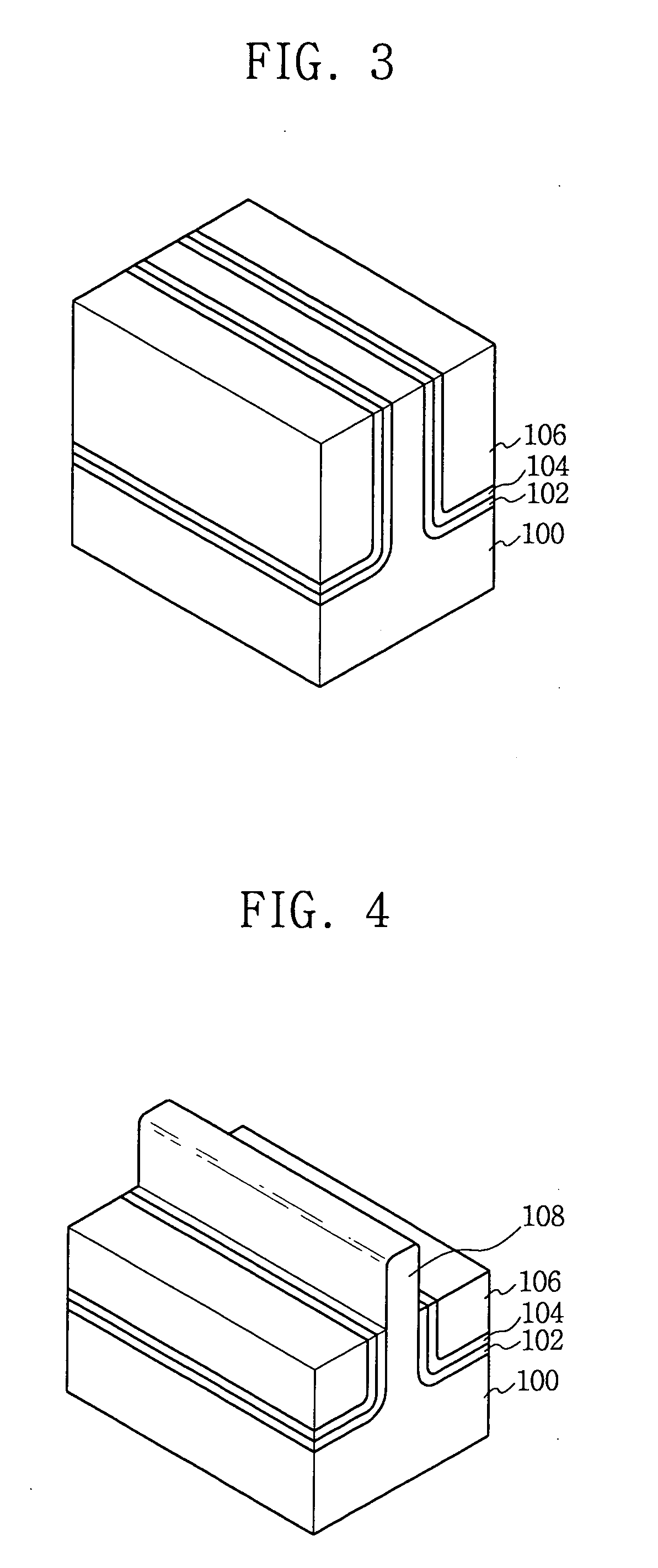

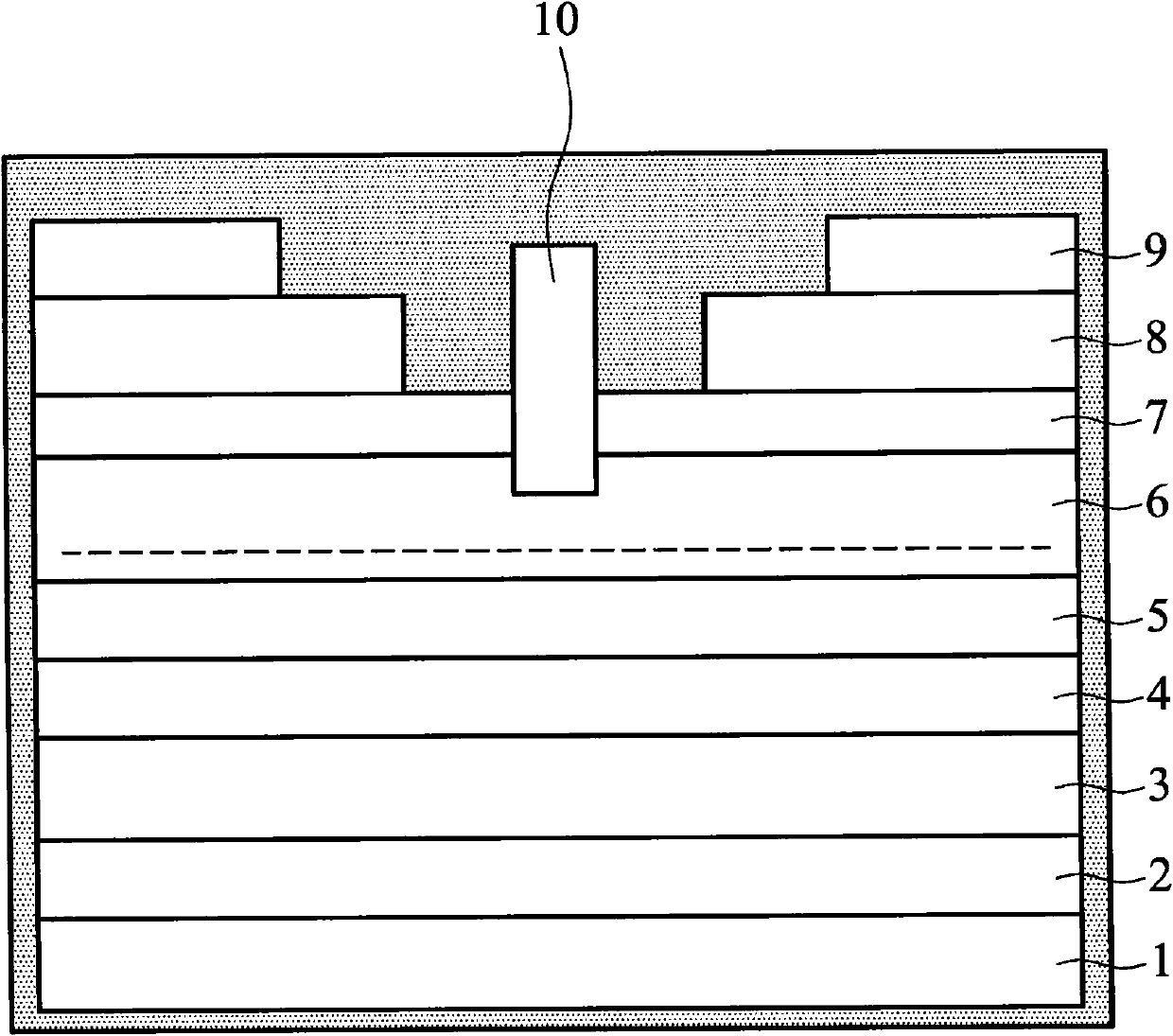

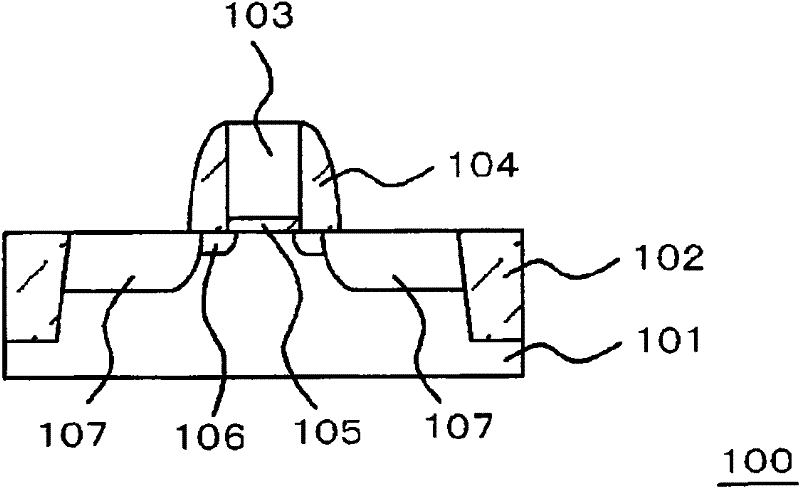

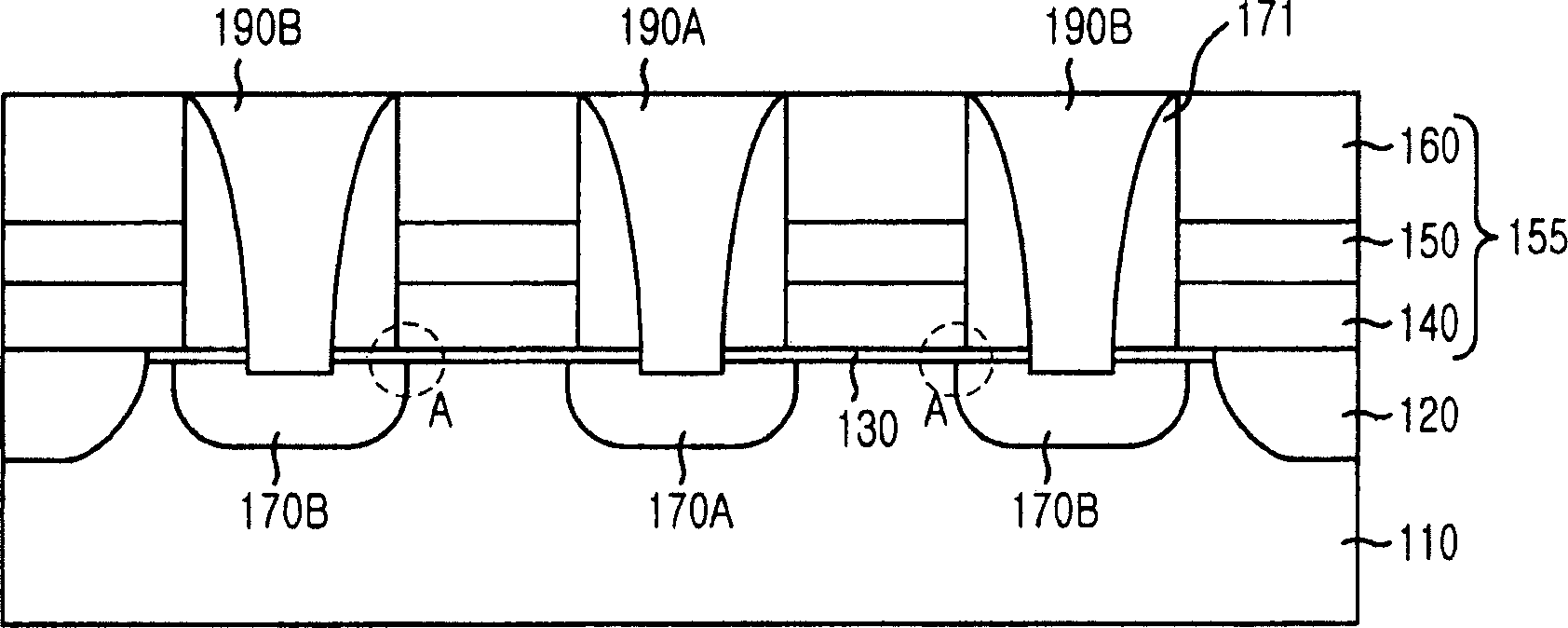

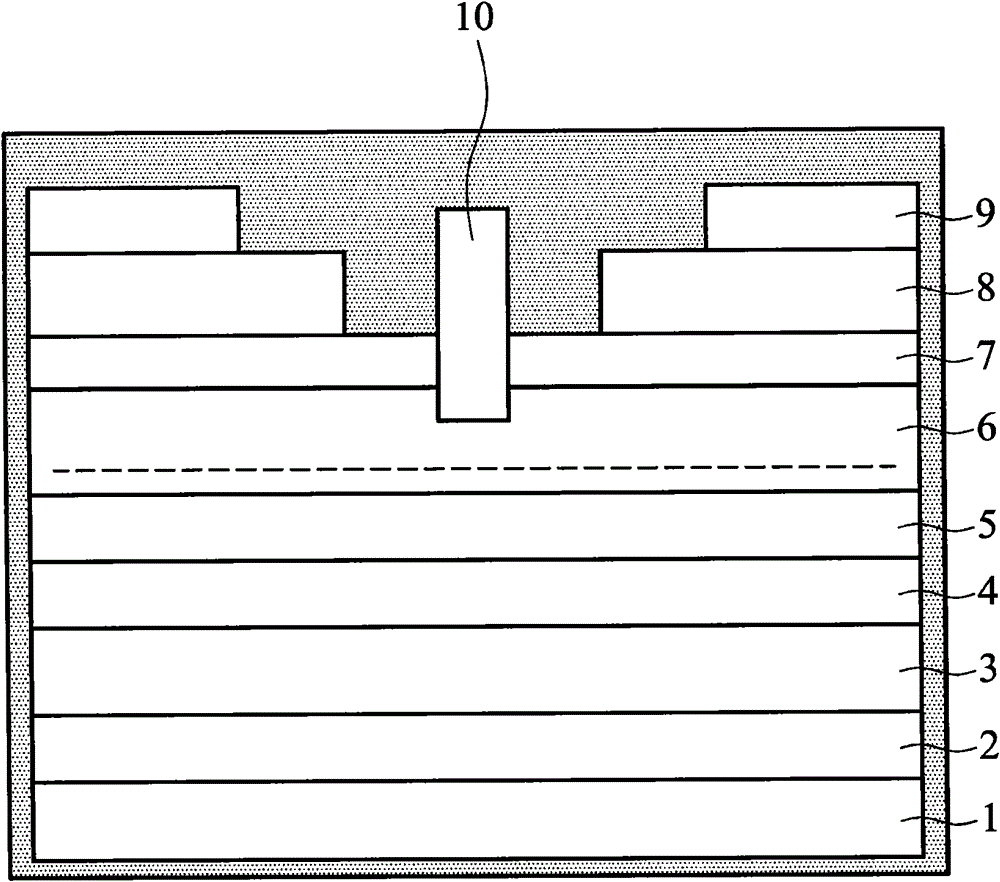

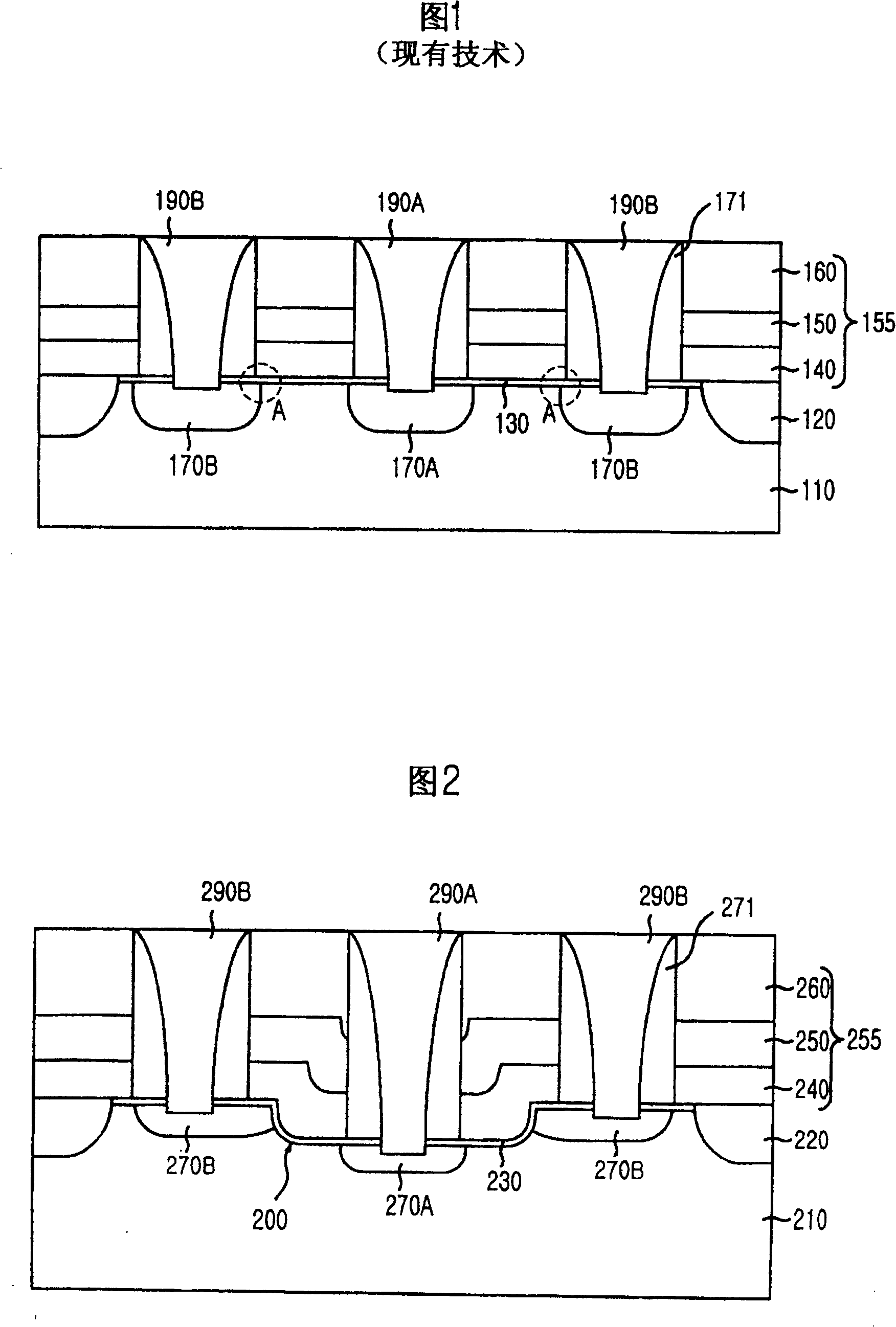

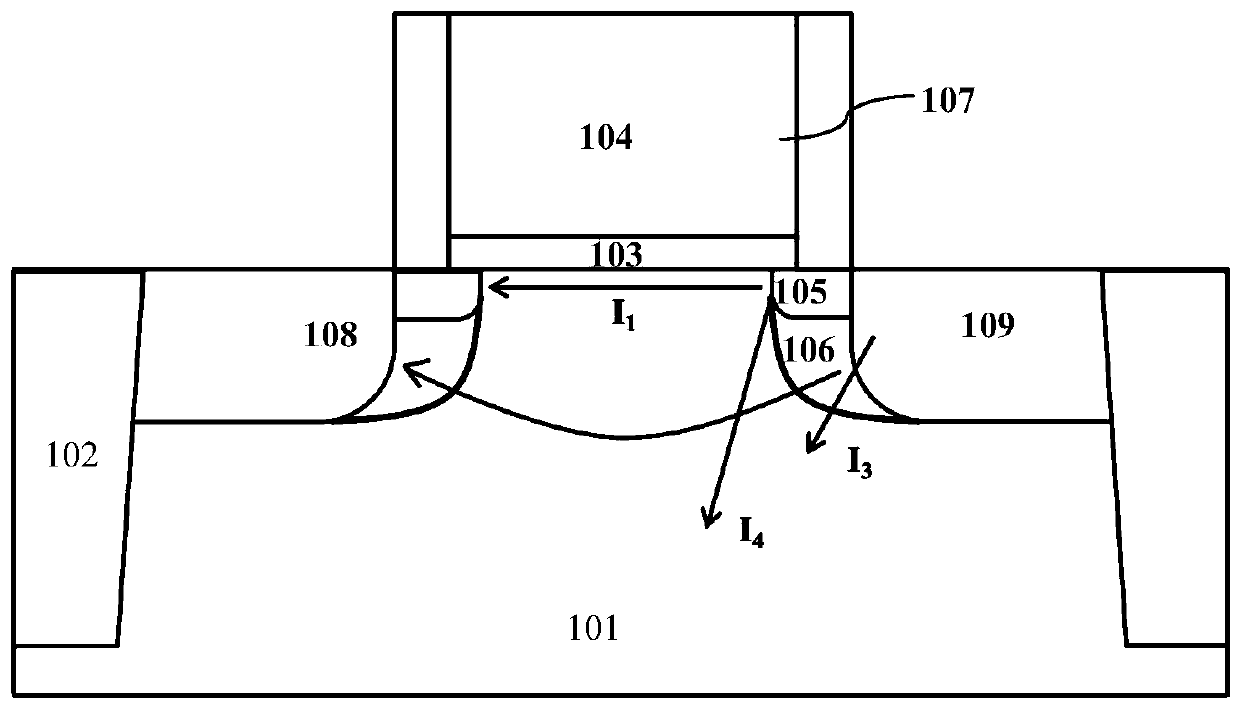

Fin FET structure

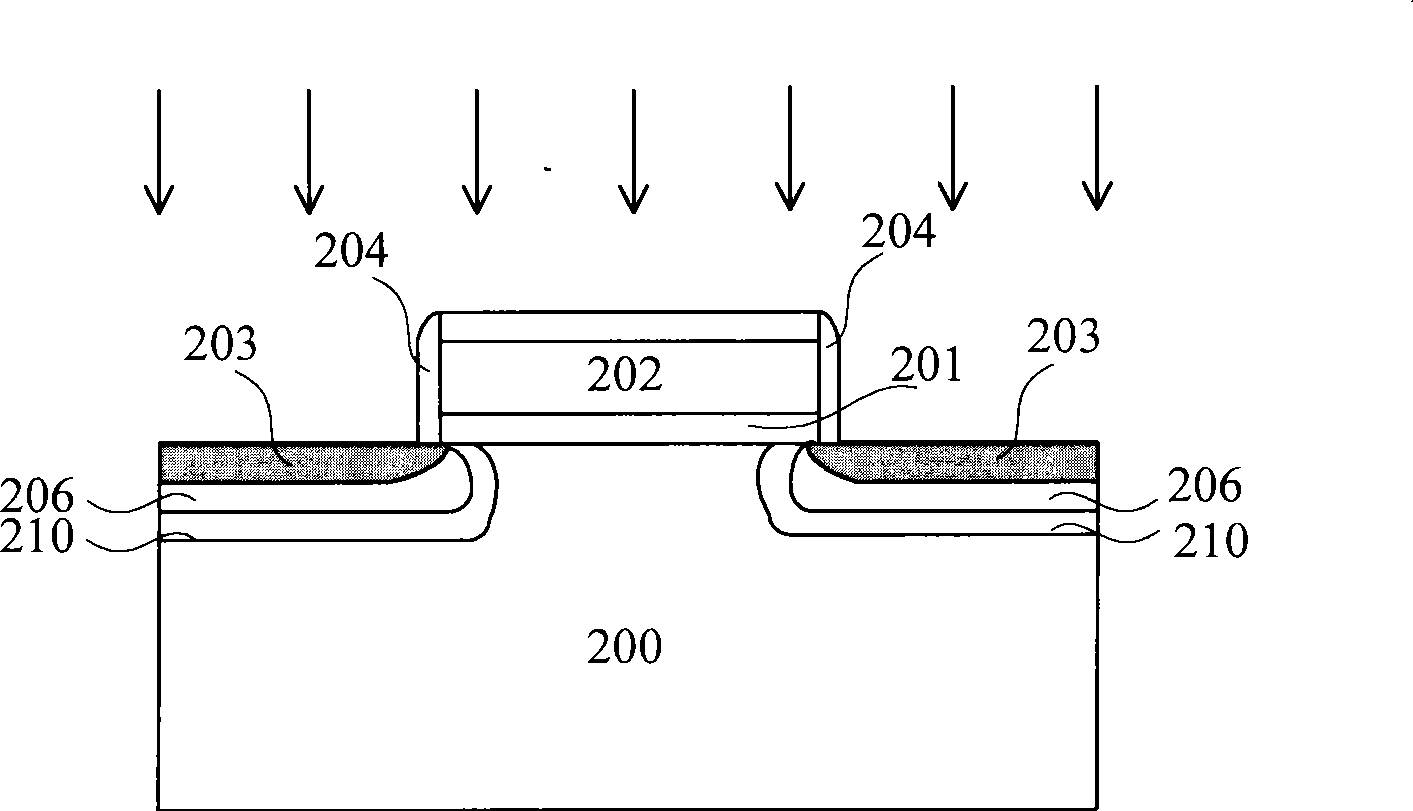

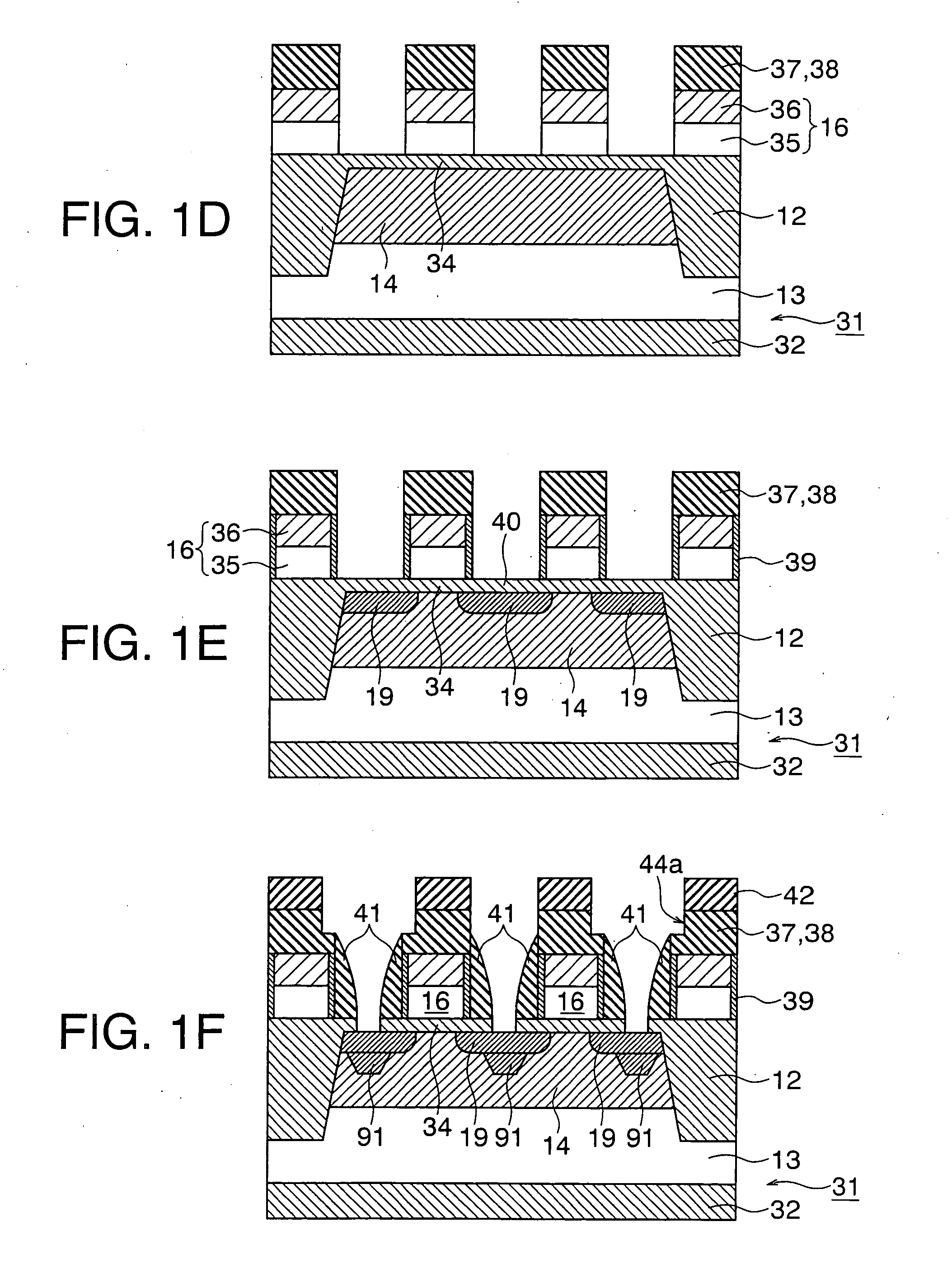

ActiveUS7317230B2Reducing and preventing leakage currentReduced Junction Leakage CurrentTransistorSolid-state devicesInsulation layerEngineering

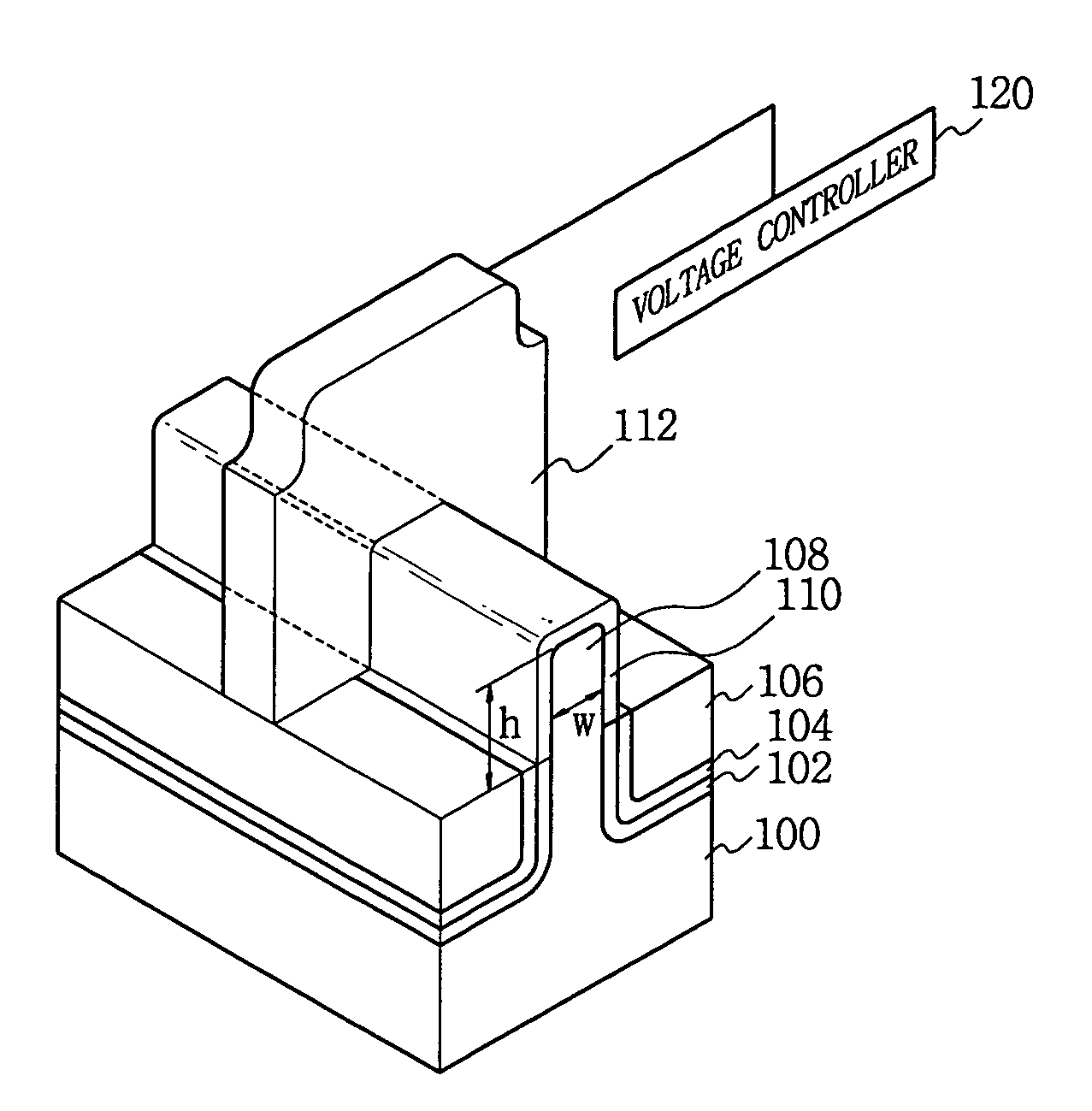

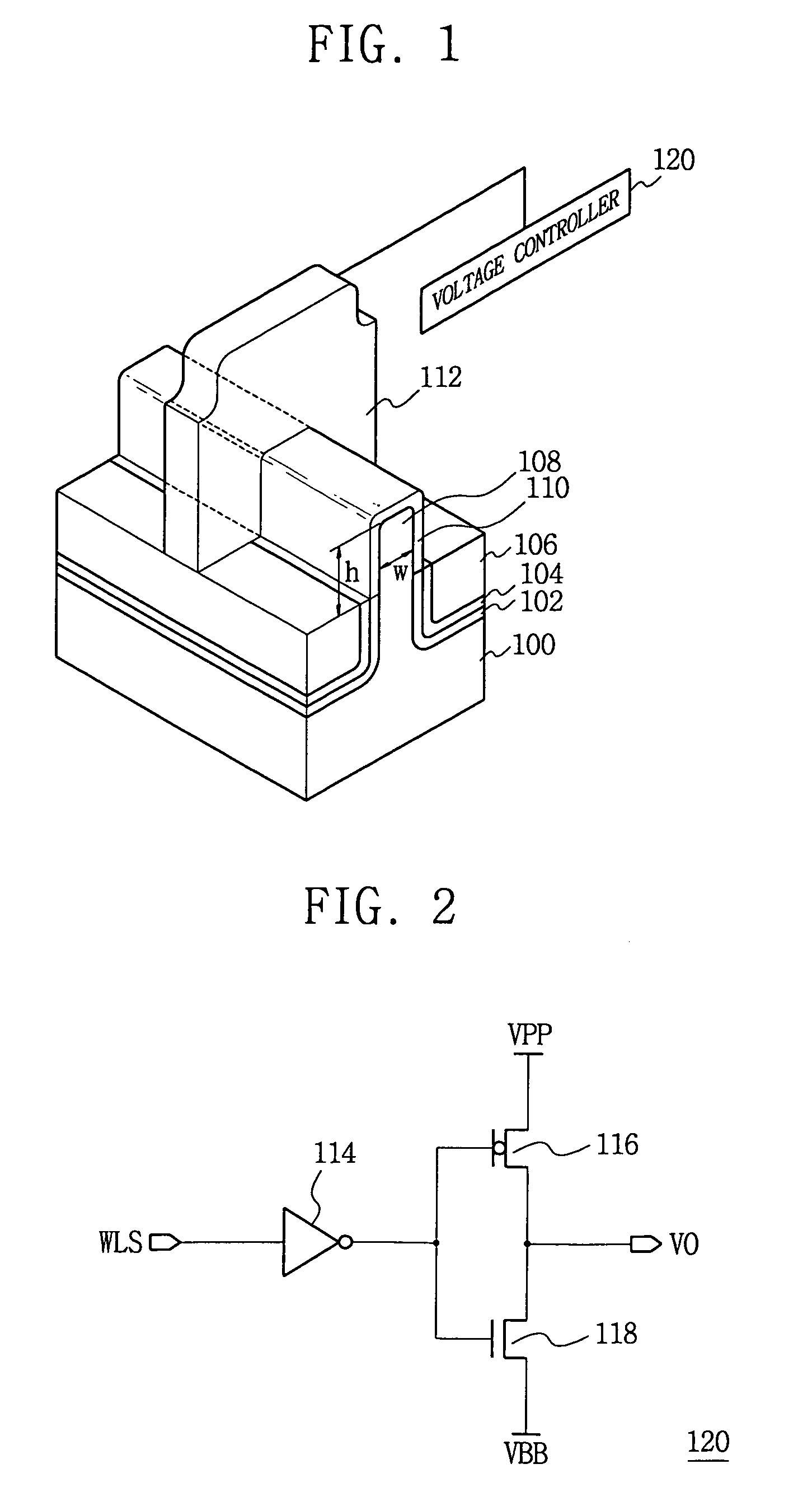

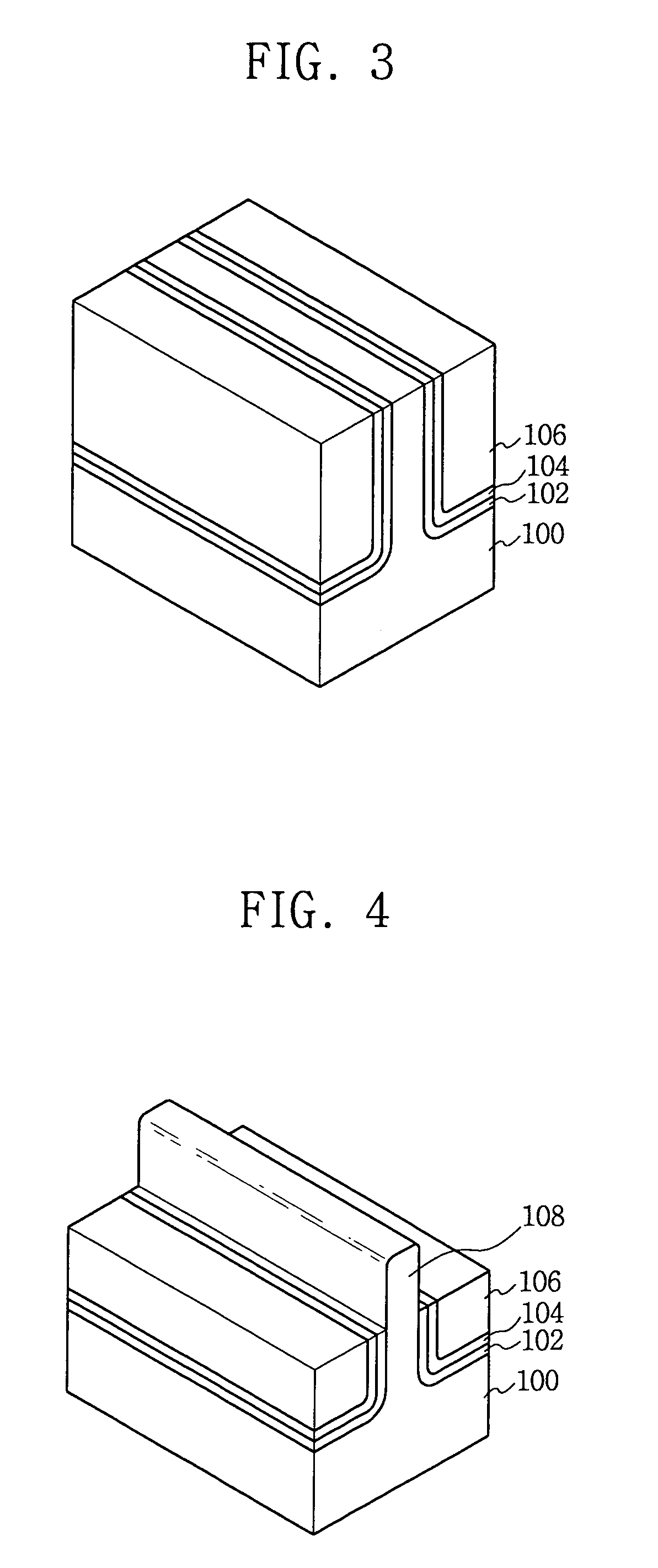

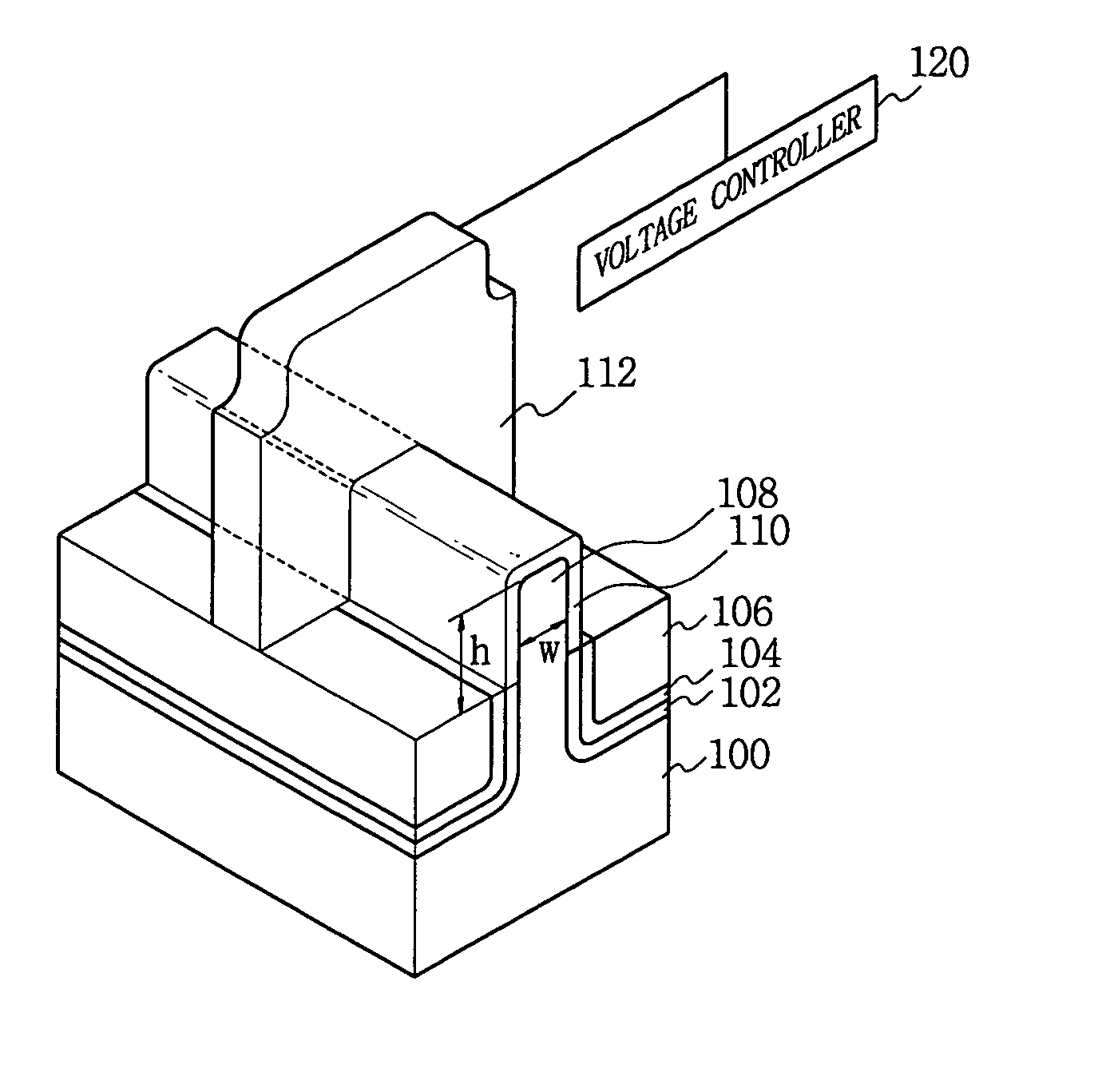

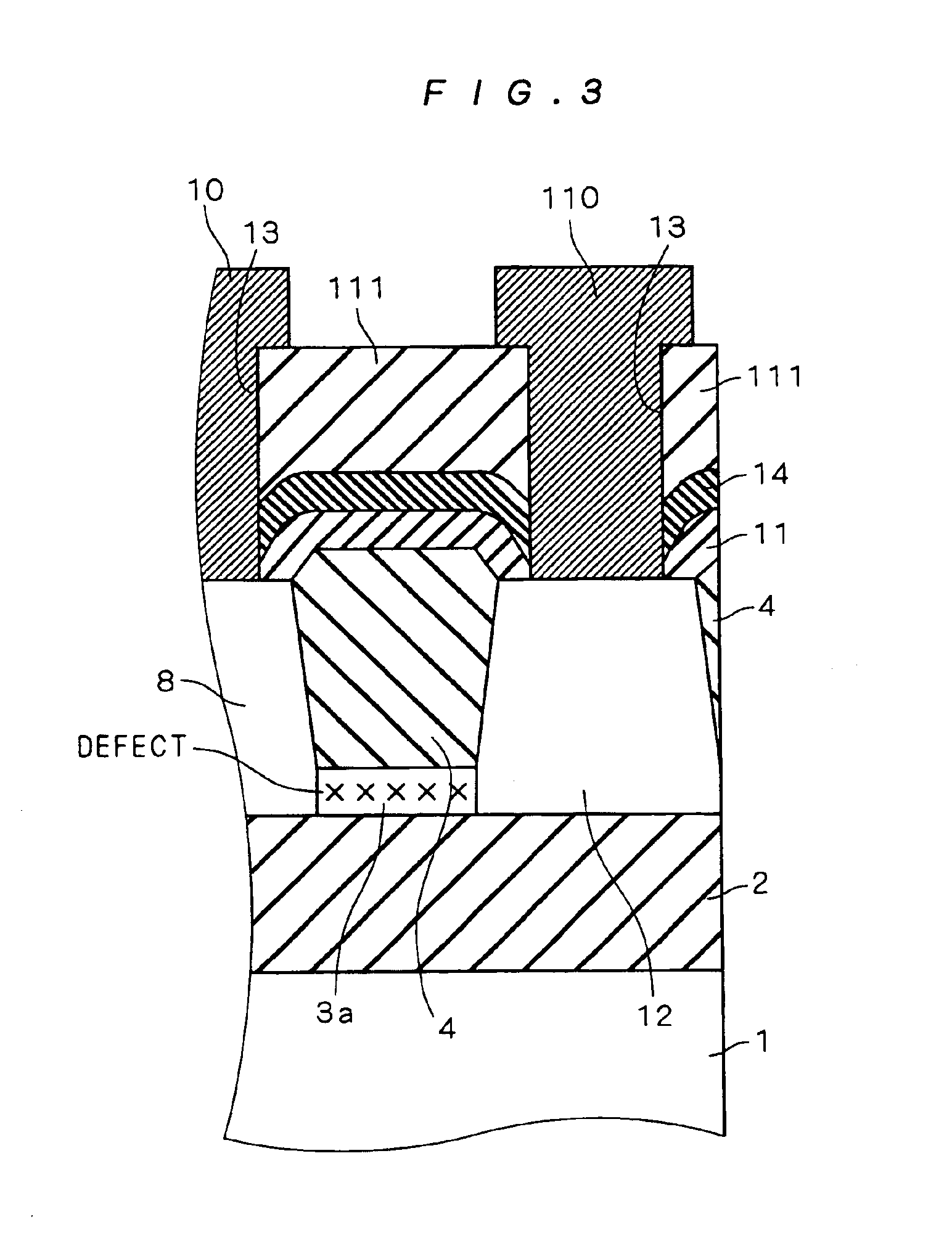

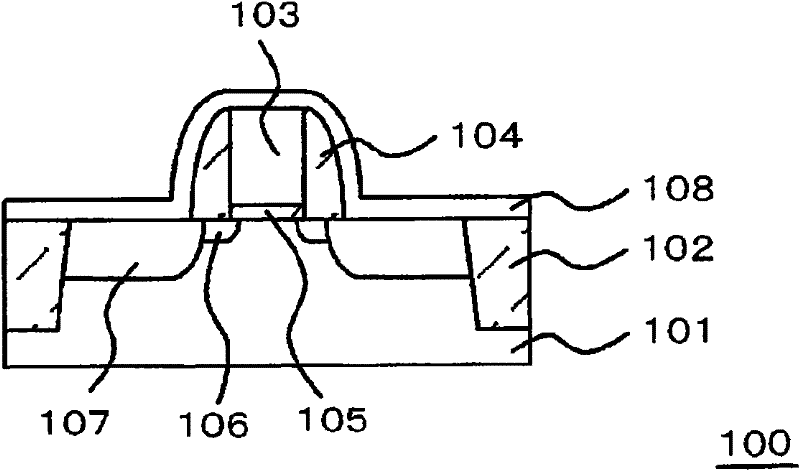

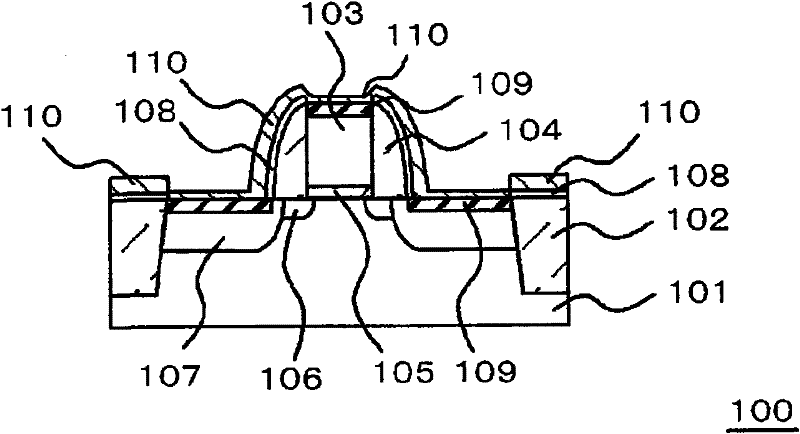

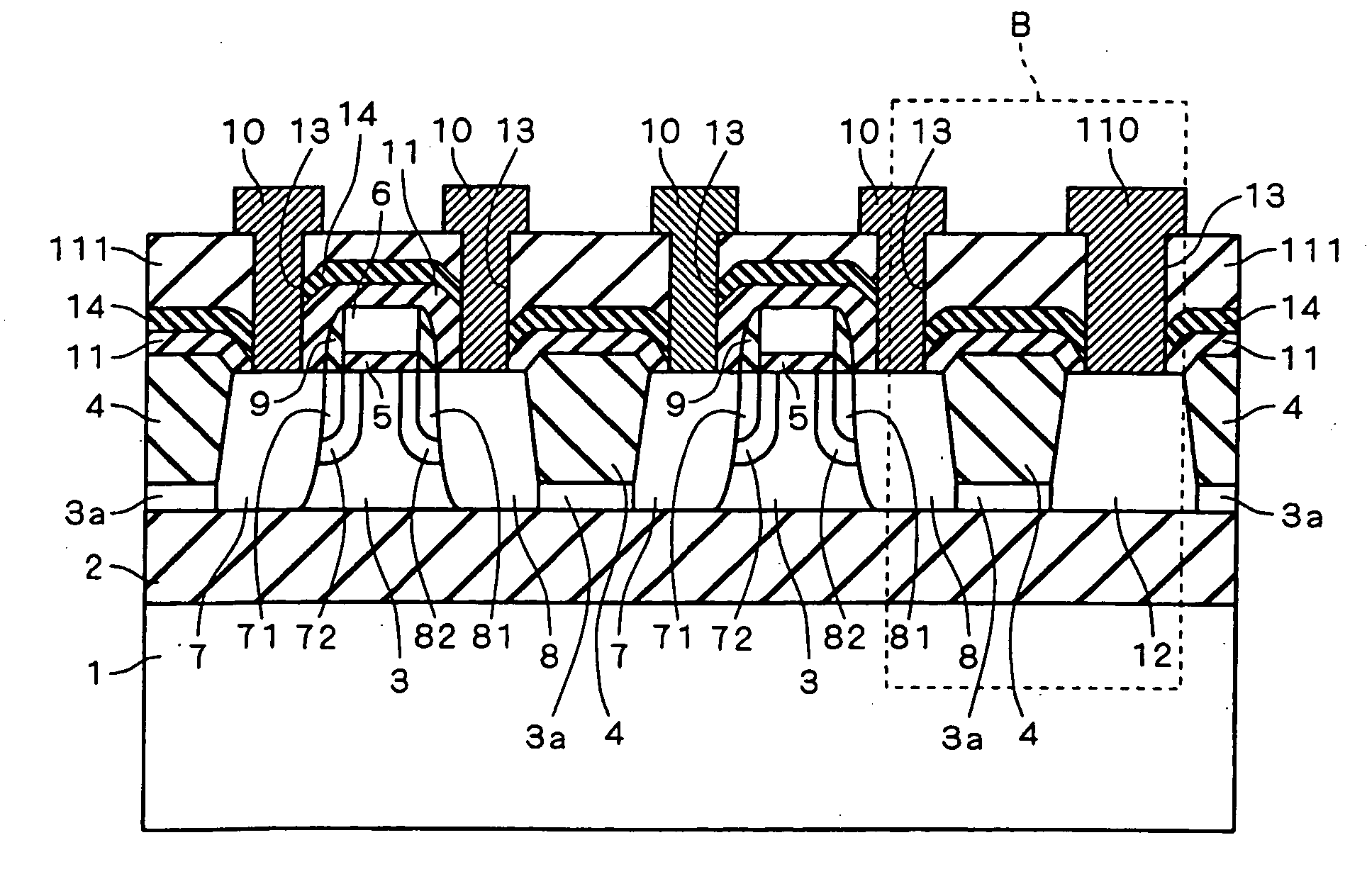

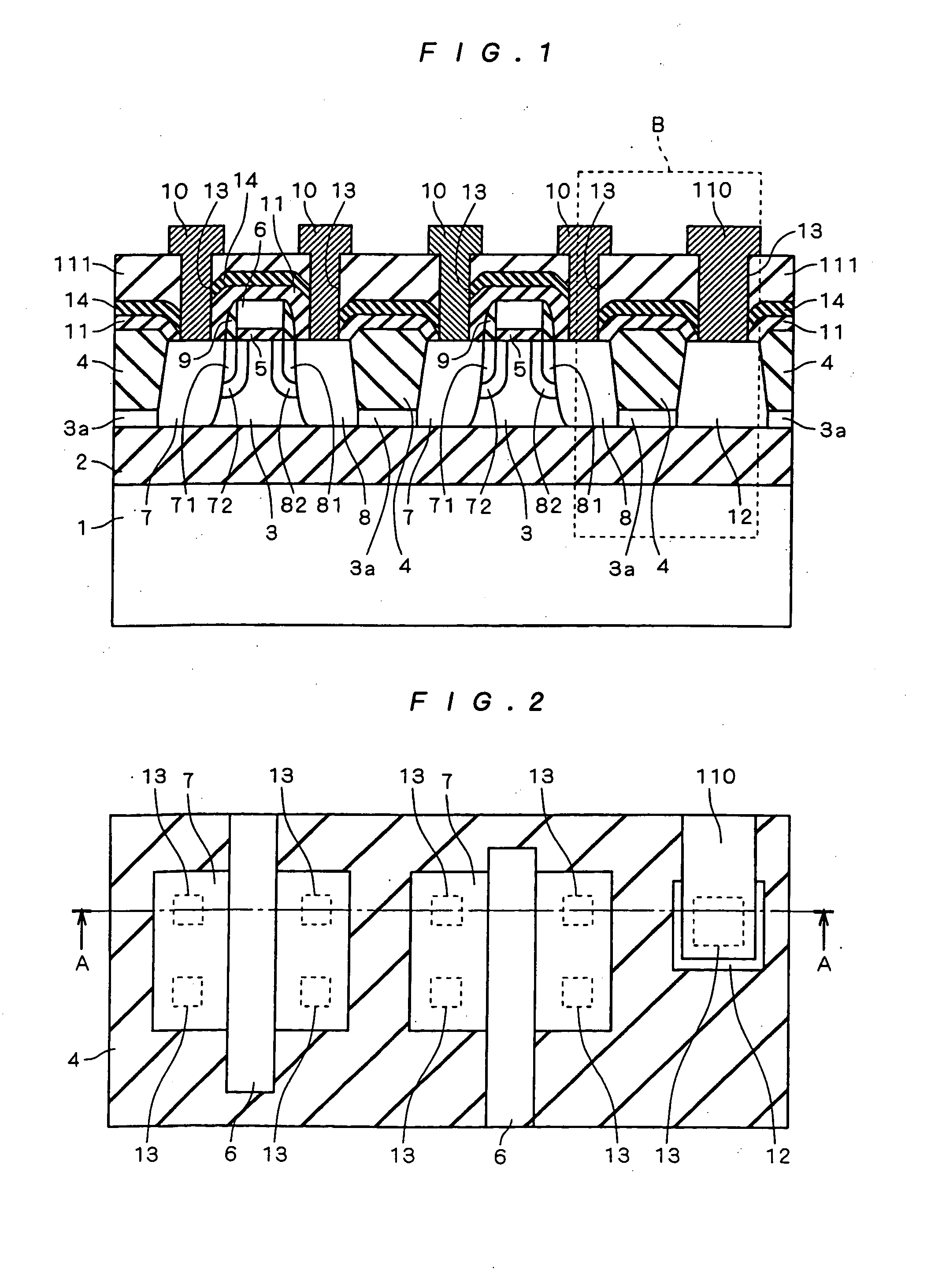

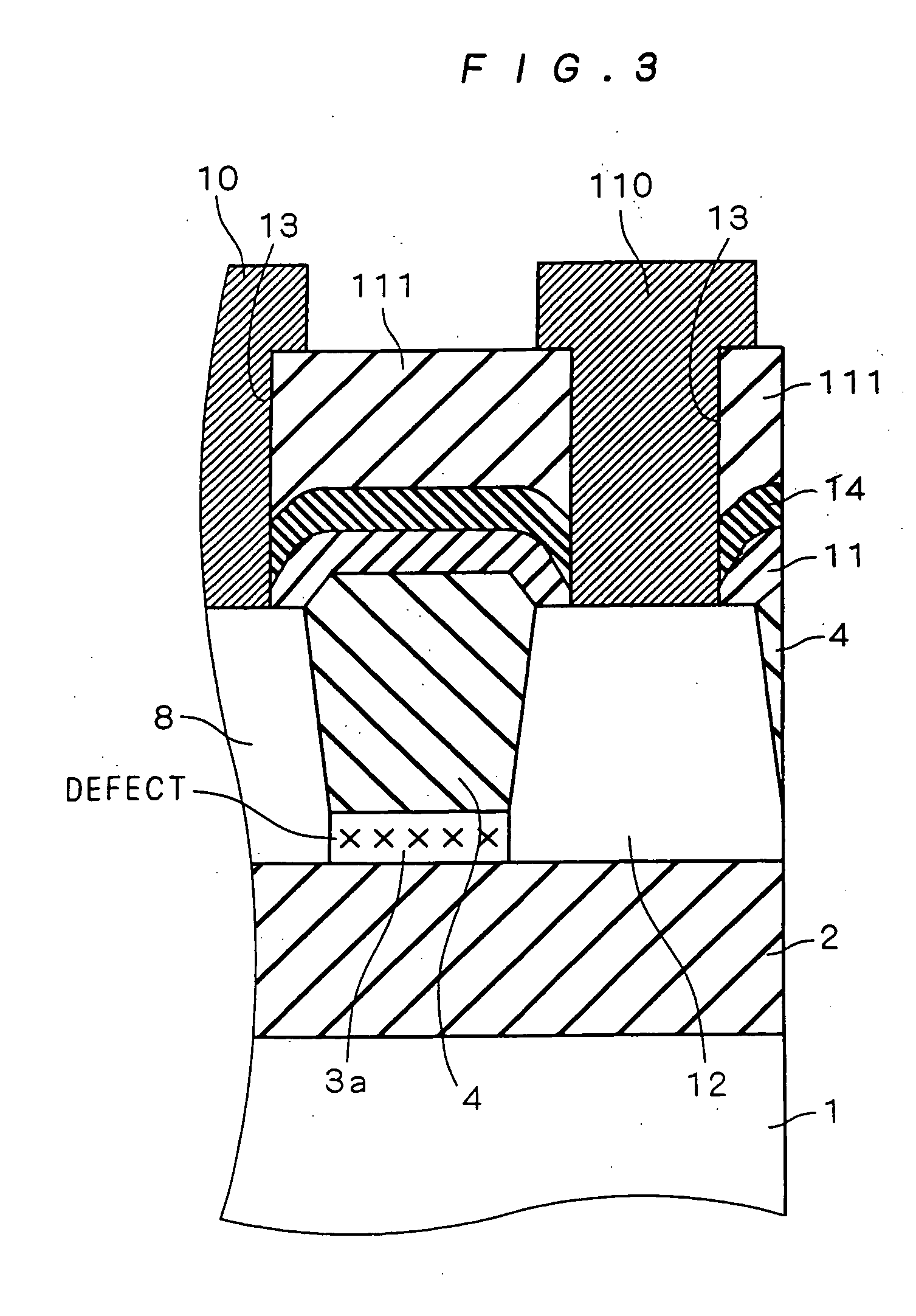

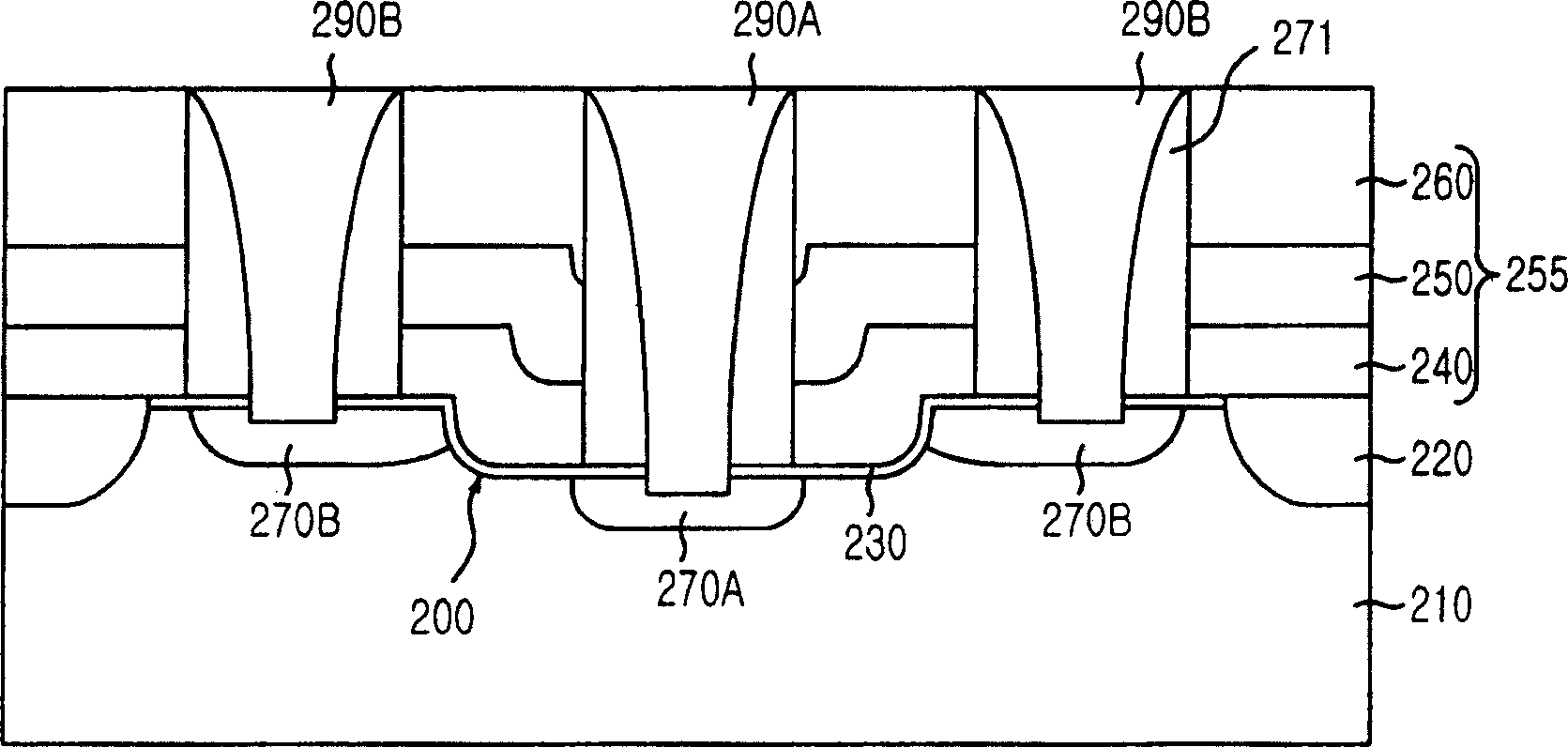

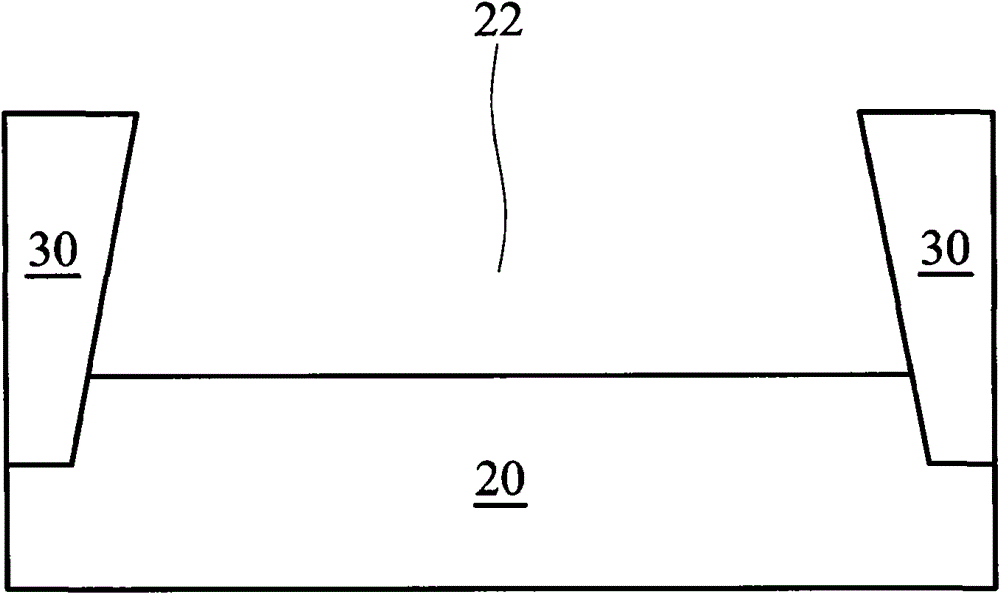

A fin FET structure employs a negative word line scheme. A gate electrode of a fin FET employs an electrode doped with n+ impurity, and a channel doping for a control of threshold voltage is not executed, or the channel doping is executed by a low density, thereby remarkably improving characteristics of the fin FET. A semiconductor substrate is formed in a first conductive type, and a fin active region of a first conductive type is projected from an upper surface of the semiconductor substrate and is connected to the semiconductor substrate. An insulation layer is formed on the semiconductor substrate, and a gate insulation layer is formed in upper part and sidewall of the fin active region. A gate electrode is formed on the insulation layer and the gate insulation layer. Source and drain are formed in the fin active region of both sides of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

Fin fet structure

ActiveUS20050173768A1Reducing and preventing leakage currentReduced Junction Leakage CurrentTransistorSolid-state devicesInsulation layerEngineering

A fin FET structure employs a negative word line scheme. A gate electrode of a fin FET employs an electrode doped with n+ impurity, and a channel doping for a control of threshold voltage is not executed, or the channel doping is executed by a low density, thereby remarkably improving characteristics of the fin FET. A semiconductor substrate is formed in a first conductive type, and a fin active region of a first conductive type is projected from an upper surface of the semiconductor substrate and is connected to the semiconductor substrate. An insulation layer is formed on the semiconductor substrate, and a gate insulation layer is formed in upper part and sidewall of the fin active region. A gate electrode is formed on the insulation layer and the gate insulation layer. Source and drain are formed in the fin active region of both sides of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

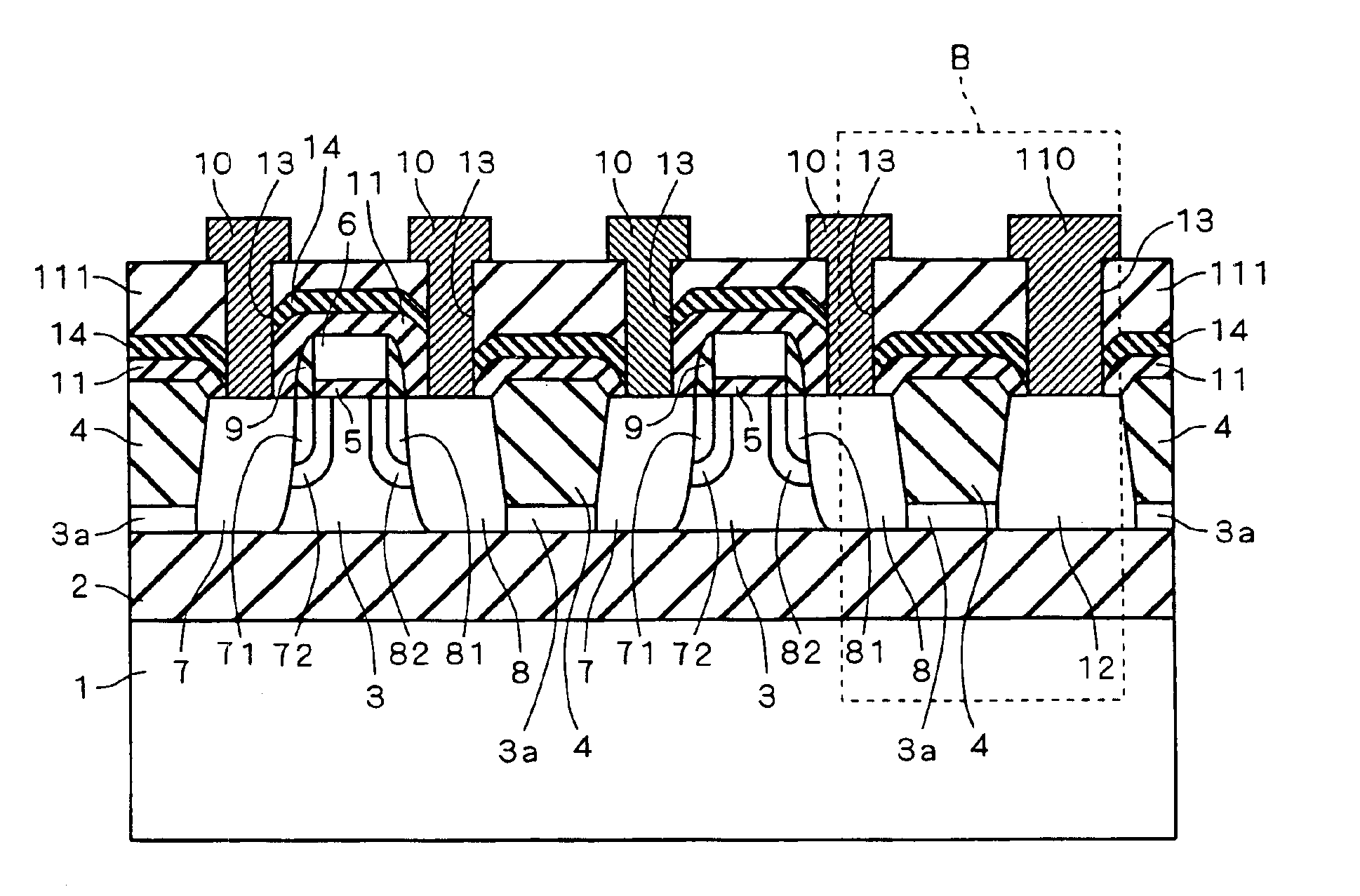

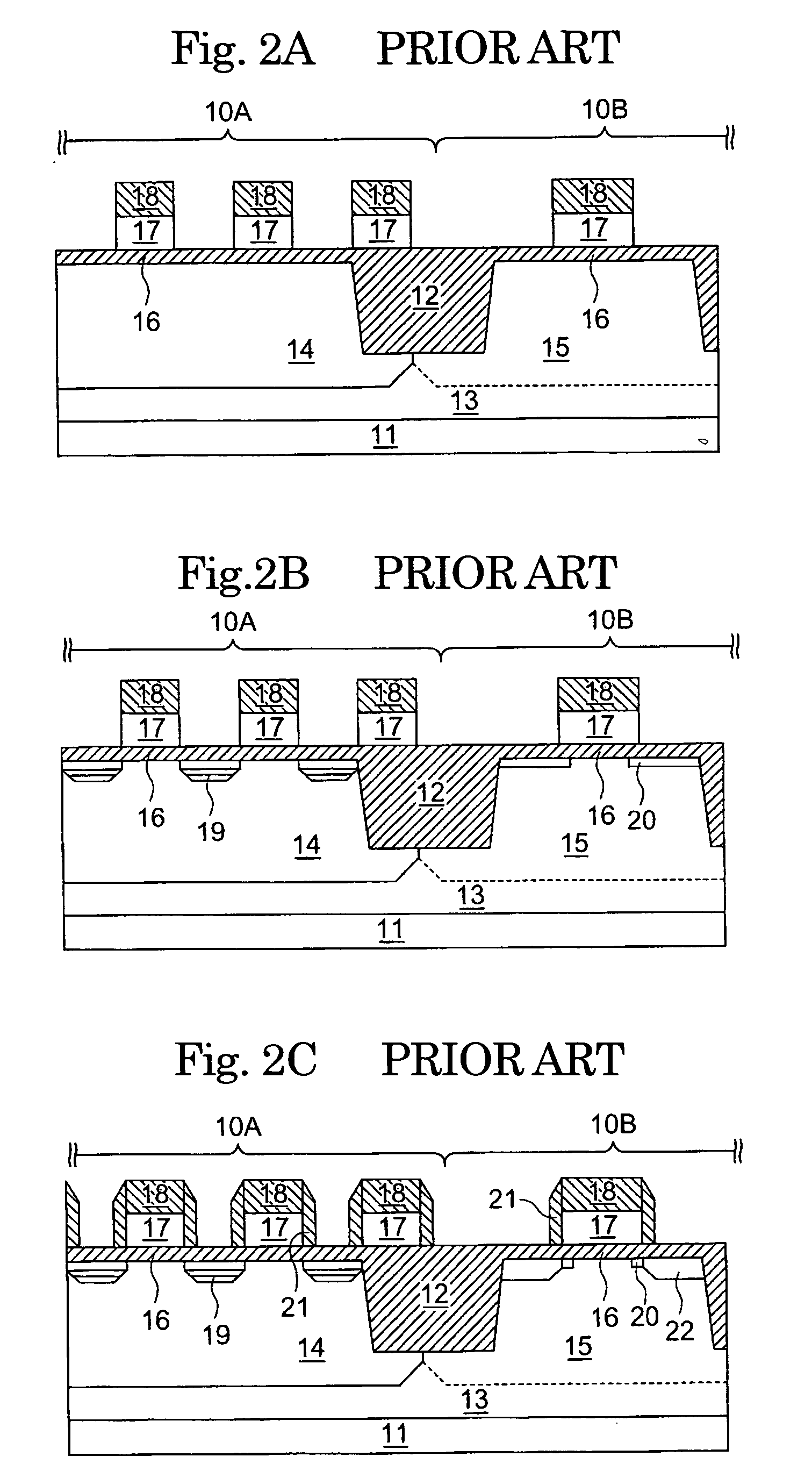

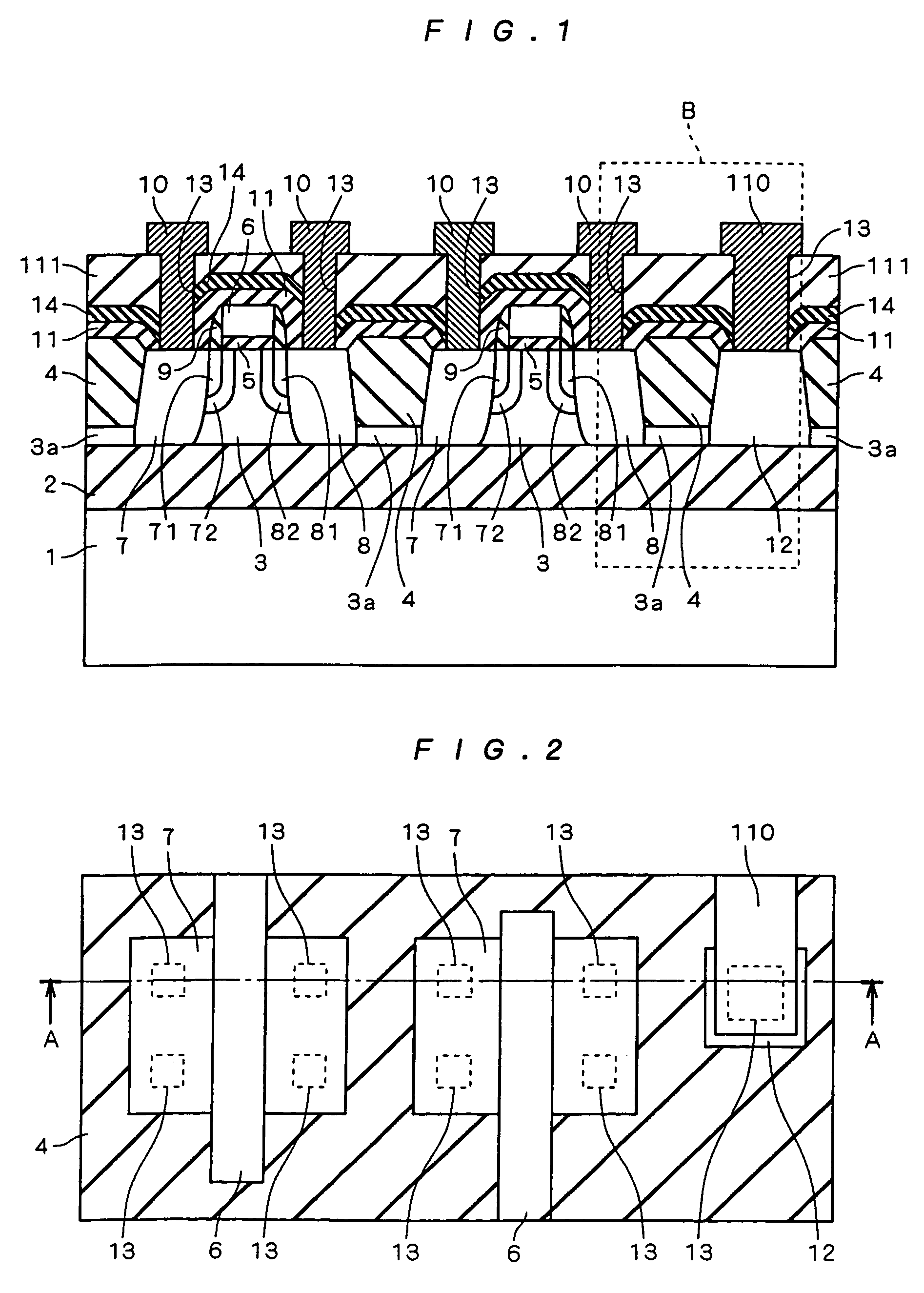

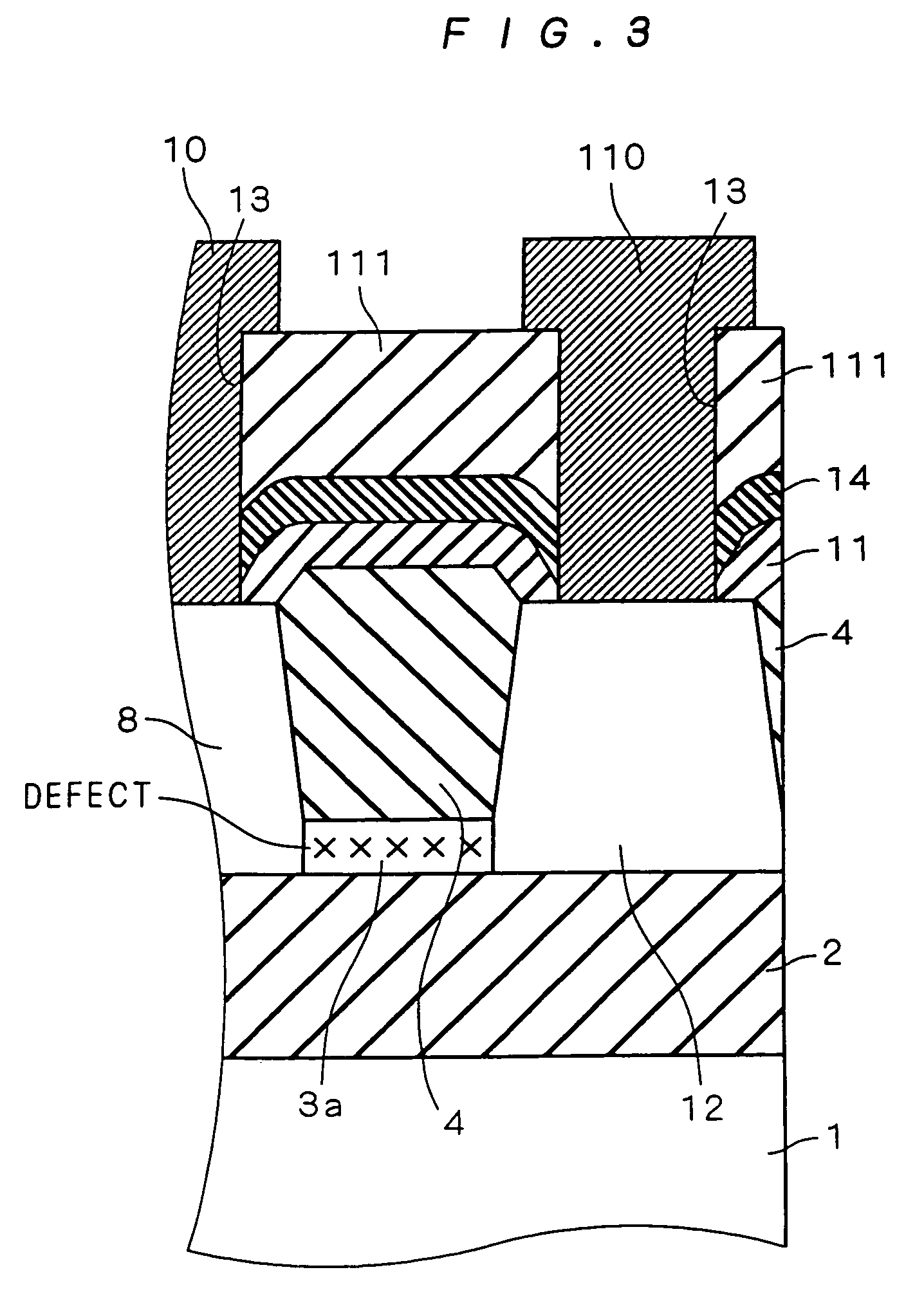

Semiconductor device and method of manufacturing the same

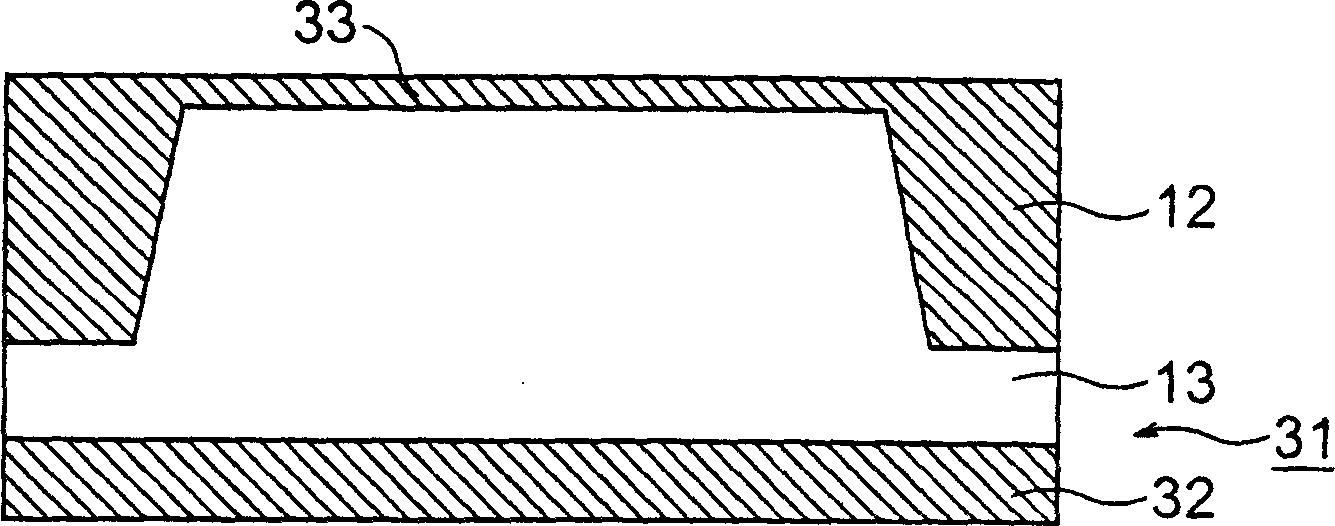

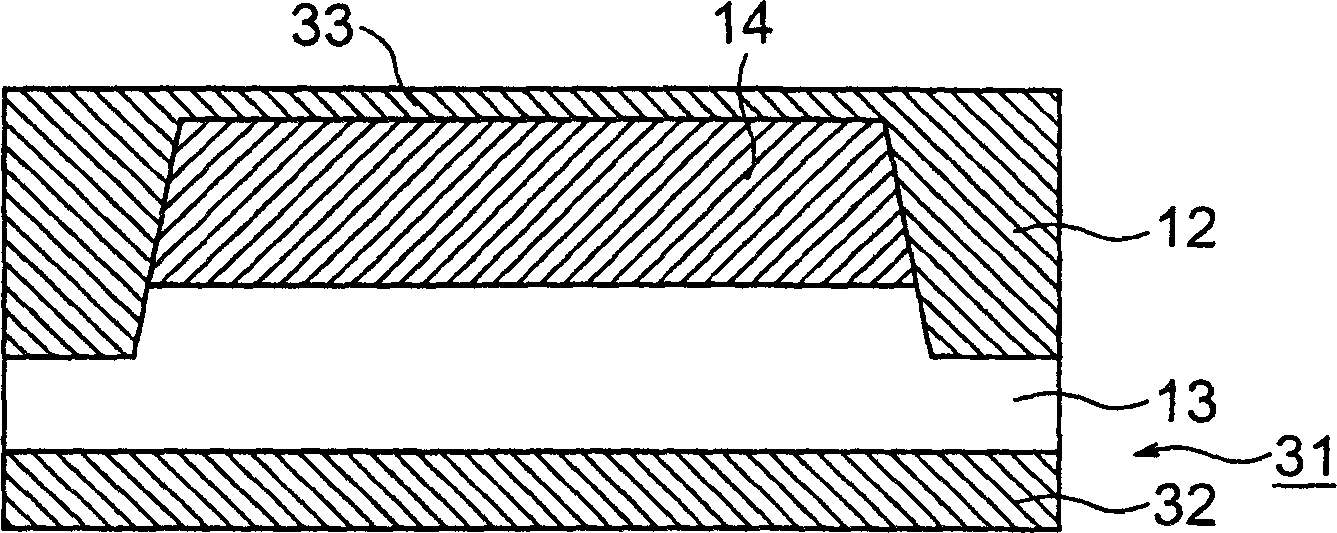

InactiveUS6933565B2Improve reliabilityIncrease breakdown voltageTransistorSemiconductor/solid-state device detailsFloating body effectSilicon nitride

A silicon nitride film is formed between interlayer insulating films covering an upper surface of an element formed on a surface of a semiconductor layer. With this structure, a semiconductor device comprising an isolation insulating film of PTI structure, which suppresses a floating-body effect and improves isolation performance and breakdown voltage, and a method of manufacturing the semiconductor device can be obtained.

Owner:RENESAS ELECTRONICS CORP

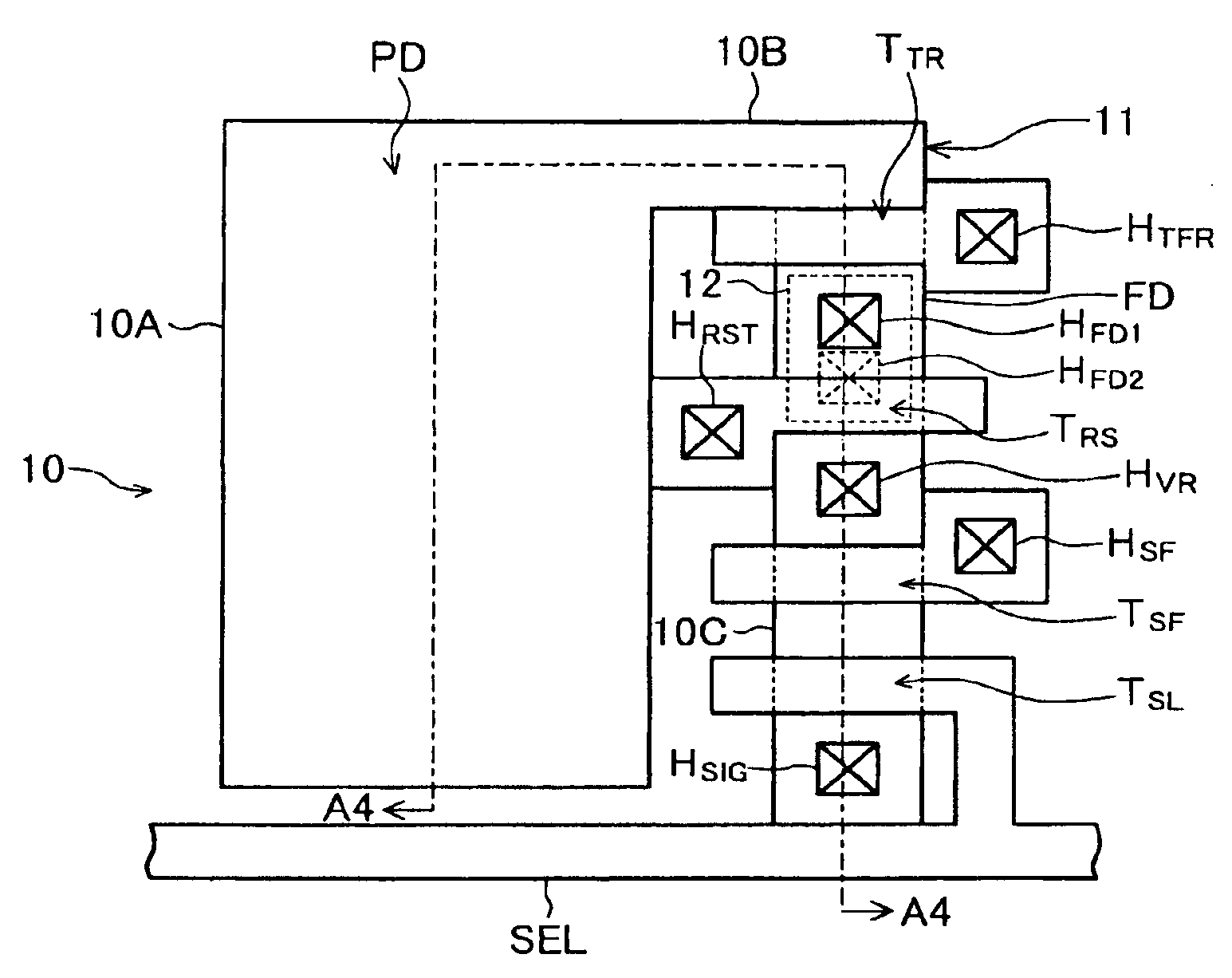

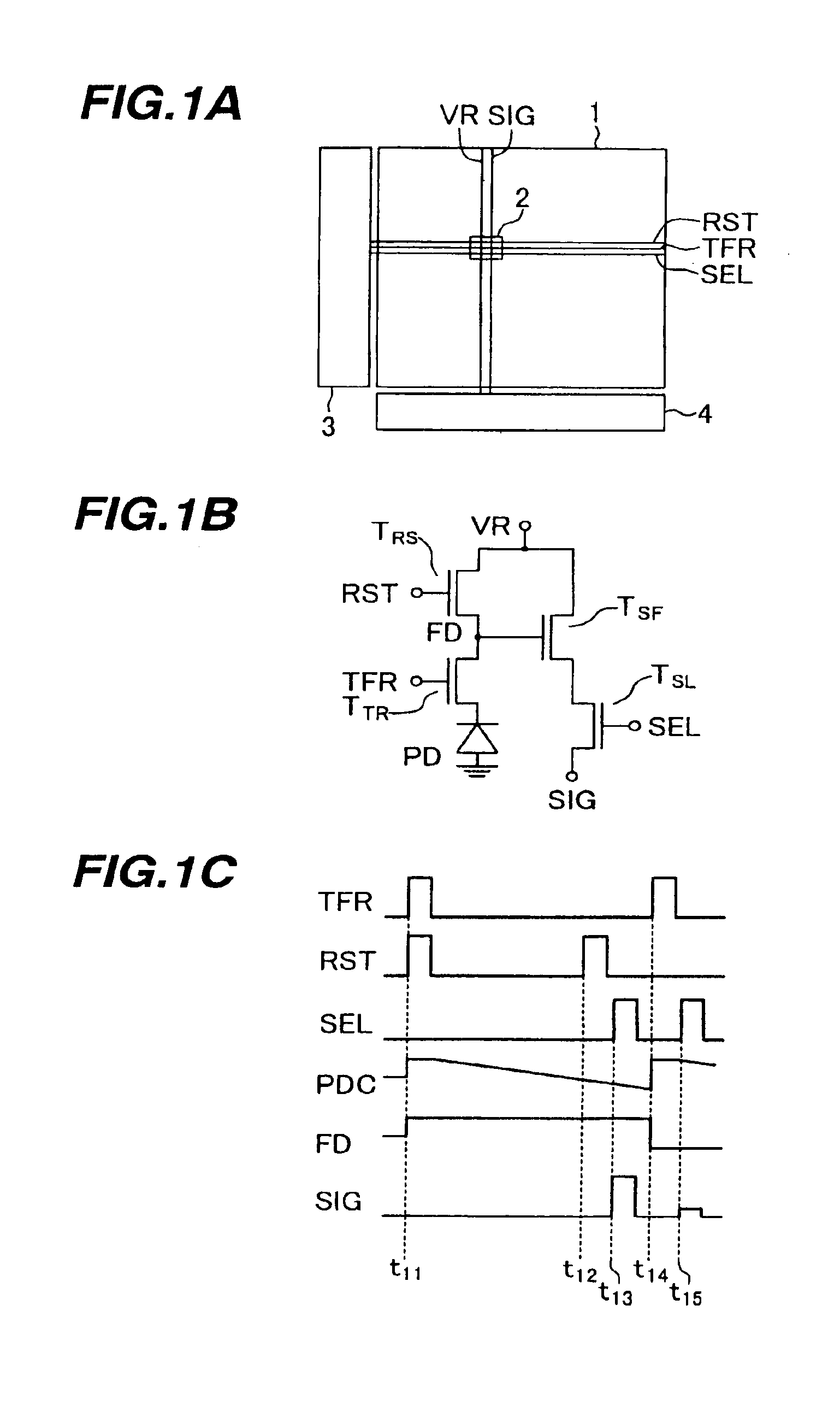

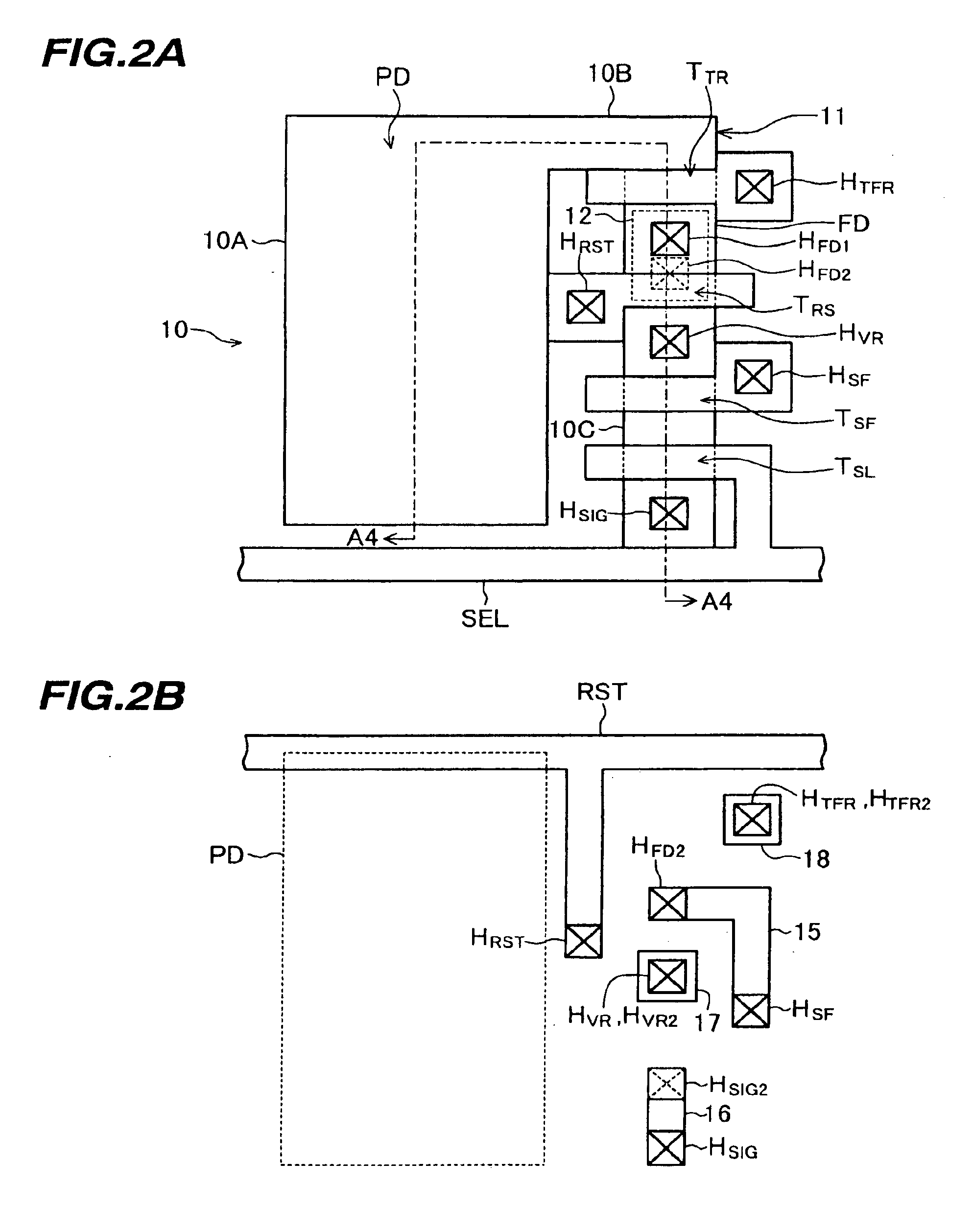

Semiconductor device for reading signal from photodiode via transistors

ActiveUS6930299B2Increase the area ratioReduced Junction Leakage CurrentTelevision system detailsTelevision system scanning detailsEngineeringPhotodiode

Pixels are disposed on a semiconductor substrate in a matrix shape. Each pixel includes a photodiode, a reset transistor, a source follower transistor and a select transistor. An active region in which the photodiode and transistors are disposed includes a first area in which the photodiode is disposed and a second area having an are elongated in a first direction. Each of the gate electrodes of the reset transistor, source follower transistor and select transistor crosses the area, elongated in the first direction, of the second area. An intra-pixel wiring line interconnects the drain region of the reset transistor and the gate electrode of the source follower transistor.

Owner:FUJITSU SEMICON LTD

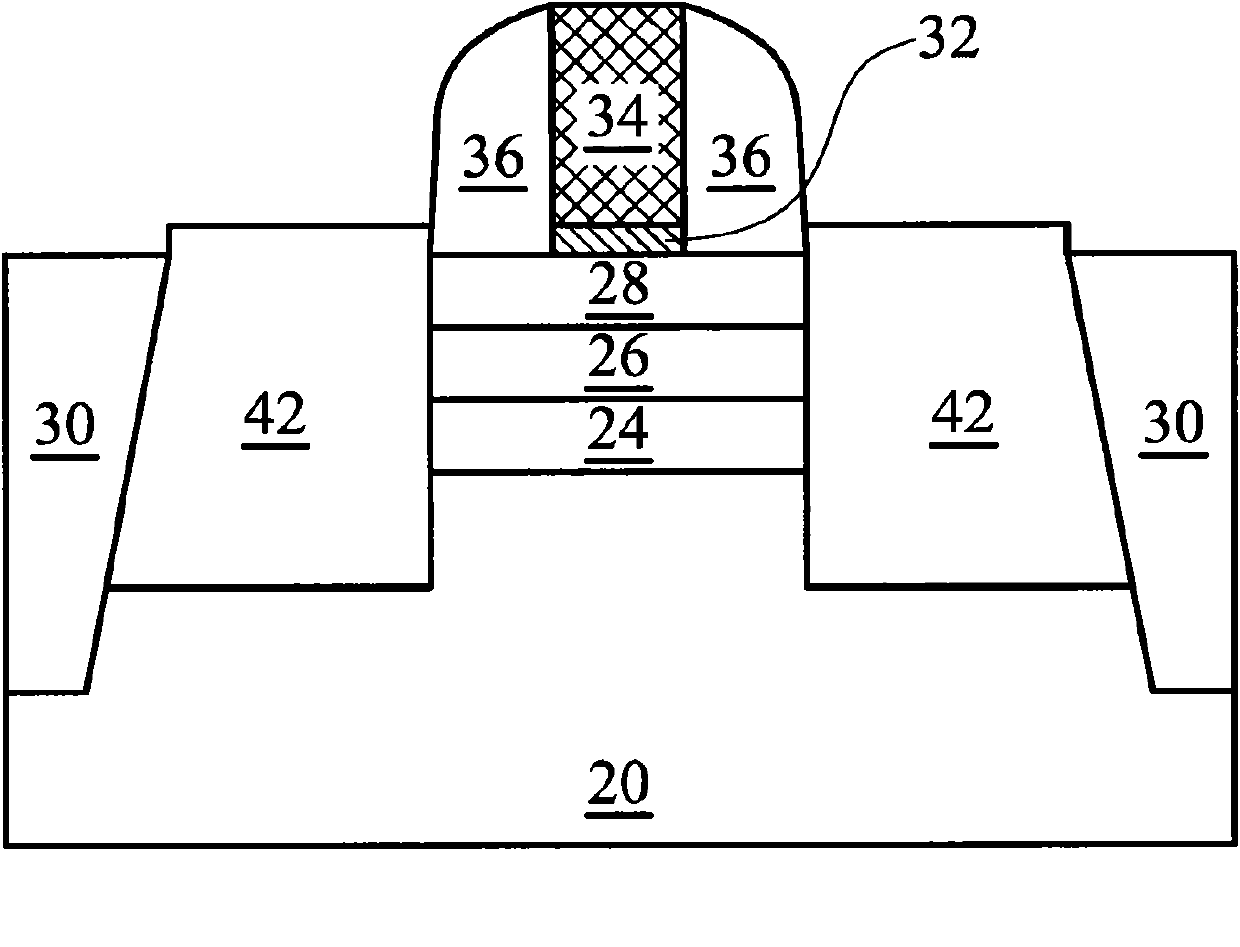

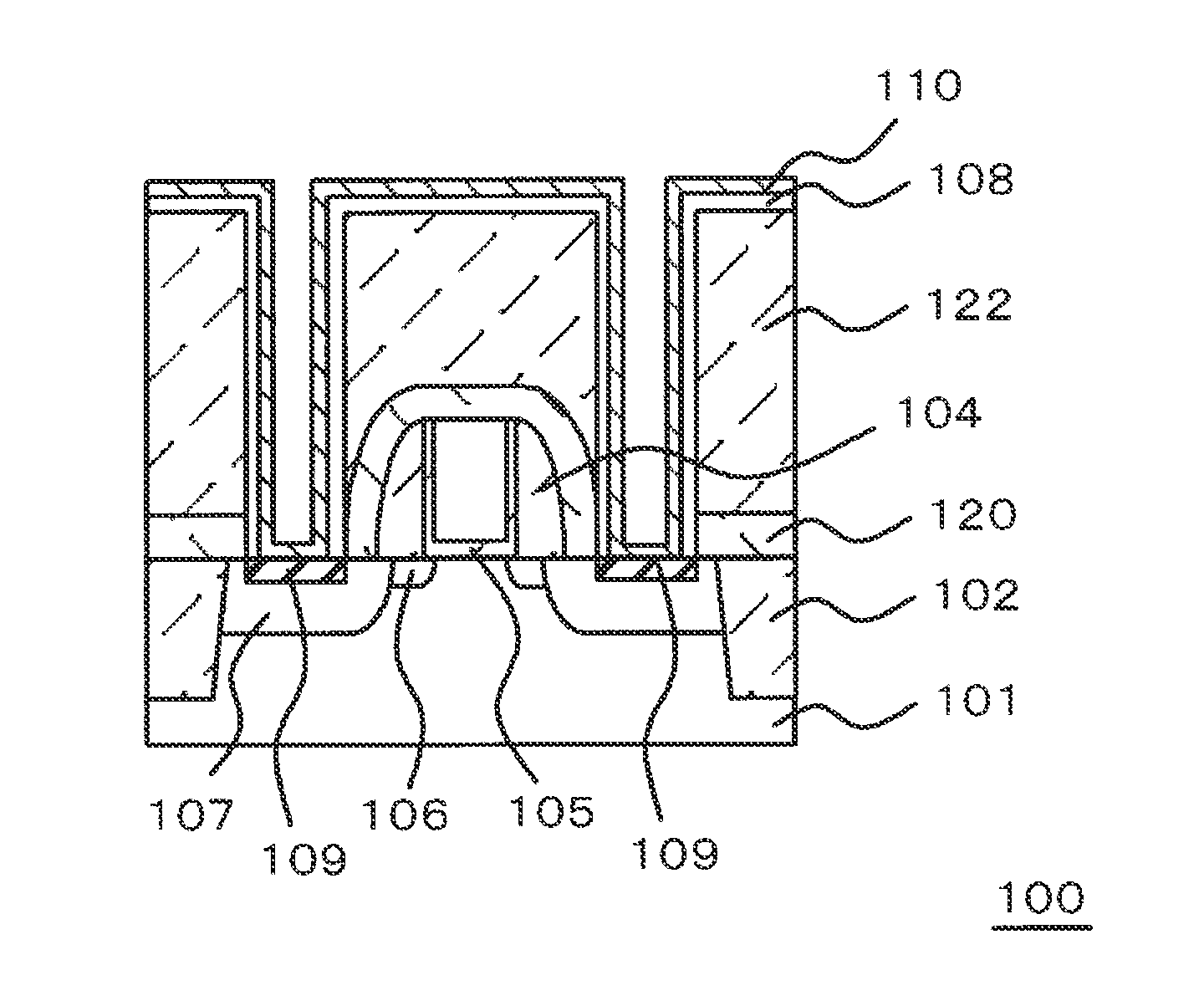

Integrated circuit structure

ActiveCN101908543ALower resistanceImprove drive currentTransistorSemiconductor/solid-state device manufacturingDriving currentSemiconductor materials

An integrated circuit structure includes a substrate, and a channel over the substrate. The channel includes a first III-V compound semiconductor material formed of group III and group V elements. A gate structure is over the channel. A source / drain region is adjacent the channel and includes a group-IV region formed of a doped group-IV semiconductor material selected from the group consisting essentially of silicon, germanium, and combinations thereof. By re-growing silicon / germanium source / drain regions, the existing silicidation technique can be used to reduce the source / drain resistance and to improve drive currents of the resulting transistors. Buffer layers have the effect of smoothening the lattice constant transition between the channel of the transistor and the source / drain regions, resulting in a reduced defect density and reduced junction leakage currents.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor structure forming method

ActiveCN106373924AReduced Junction Leakage CurrentReduce the overall heightTransistorSolid-state devicesSemiconductor structureDielectric layer

The invention discloses a semiconductor structure forming method. The method comprises steps: a substrate is provided, wherein the substrate comprises a first area and a second area, surfaces of the first area and the second area of the substrate are provided with pseudo gate structures respectively, and the pseudo gate structure comprises a pseudo gate layer and an initial mask layer located on the surface of the pseudo gate layer; a first stress layer is formed in the substrate at two sides of the pseudo gate structure in the first area; a first deep injection process is adopted to dope ions of a first type in the first stress layer and in the partial substrate at the bottom part of the first stress layer; after the first deep injection process, the thickness of the initial mask layer is thinned, and a first mask layer is formed; a second source-drain area is formed in the substrate at two sides of the pseudo gate structure in the second area; and after the first mask layer and the second source-drain area are formed, a dielectric layer is formed on the surface of the substrate, the dielectric layer covers the side wall surface of the pseudo gate structure, and the surface of the dielectric layer is flush with the top surface of the first mask layer. The performance of the formed semiconductor structure is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

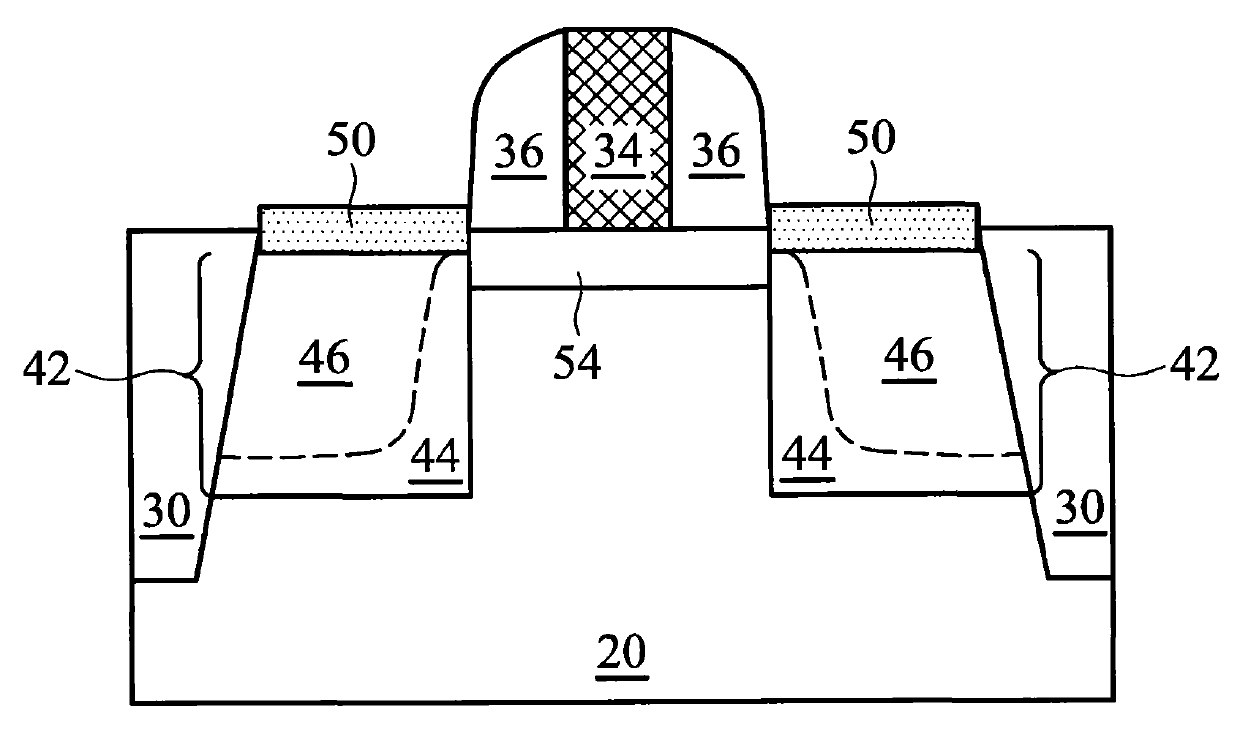

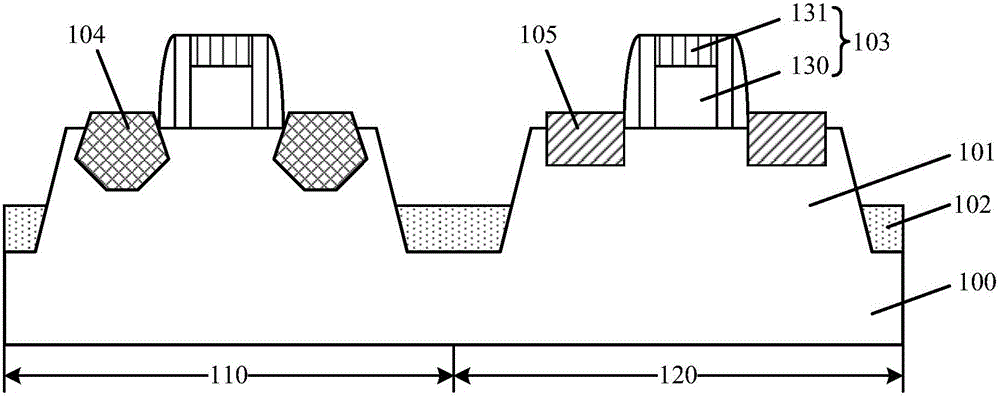

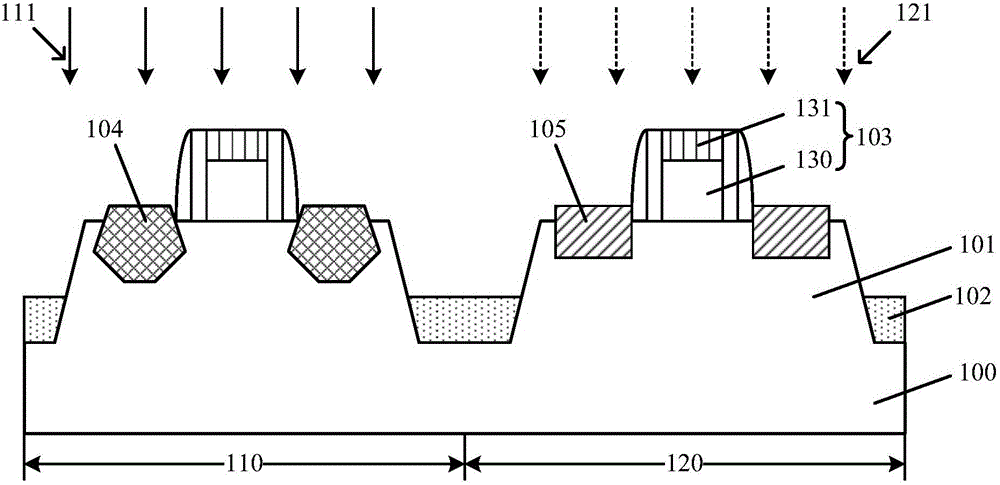

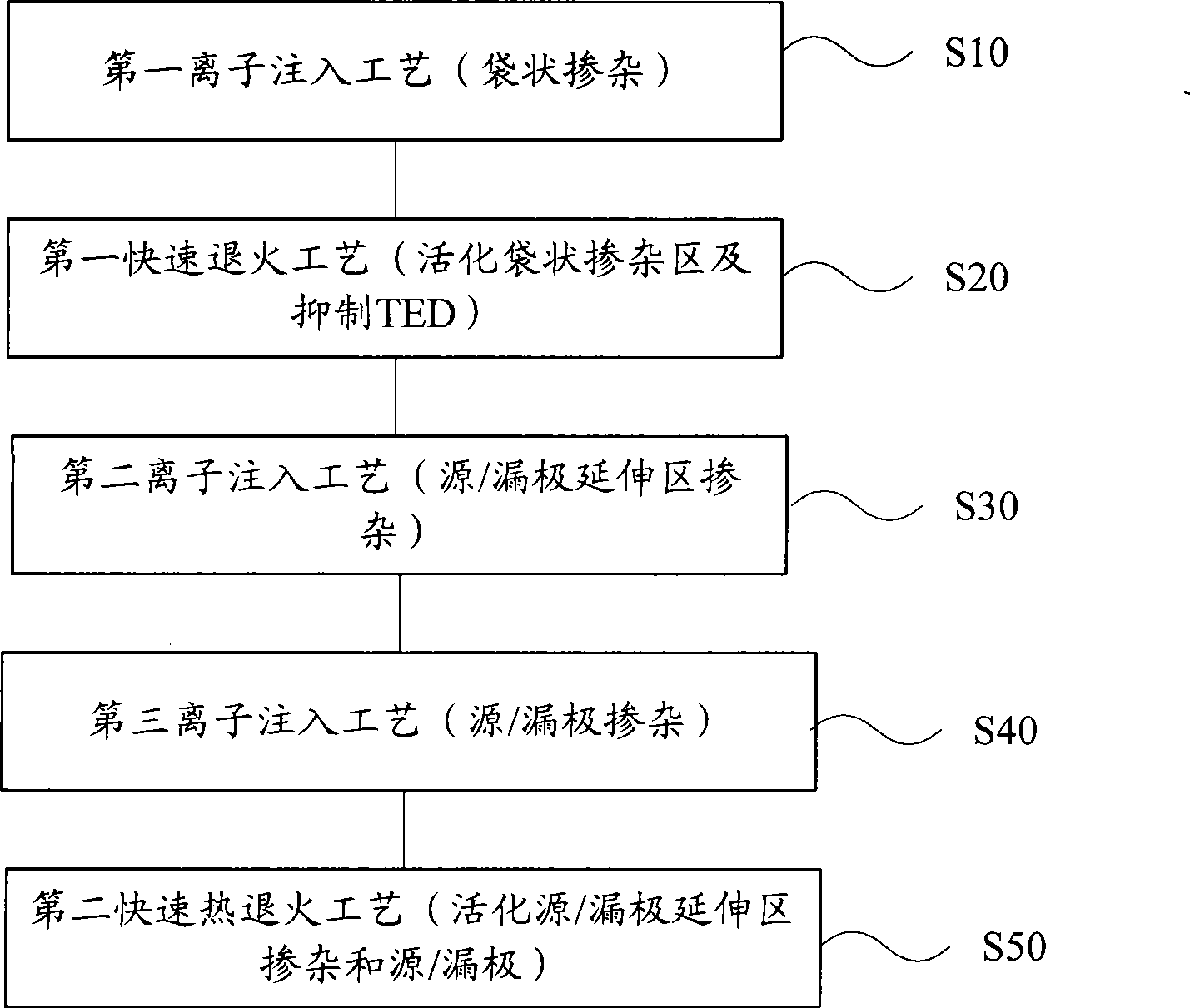

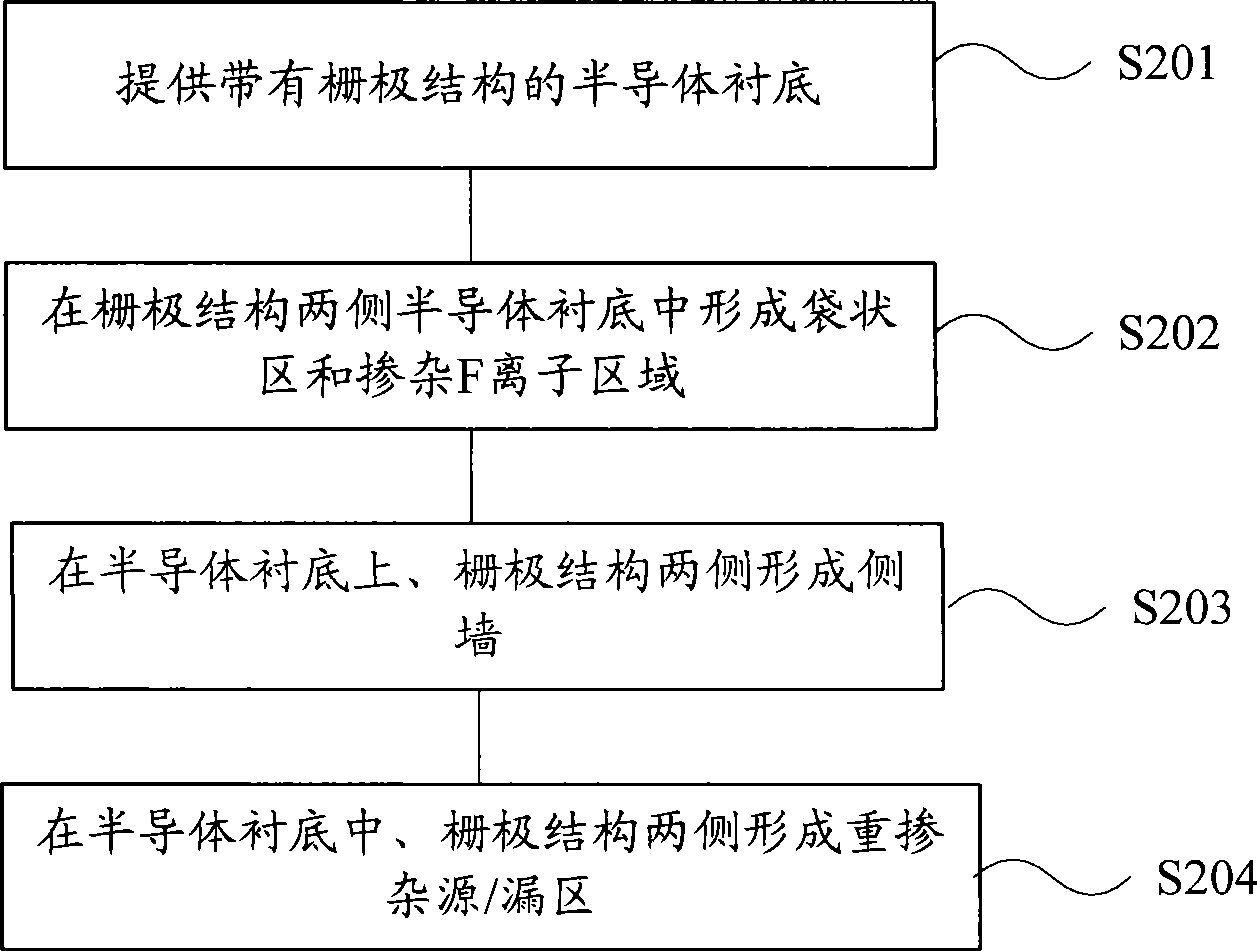

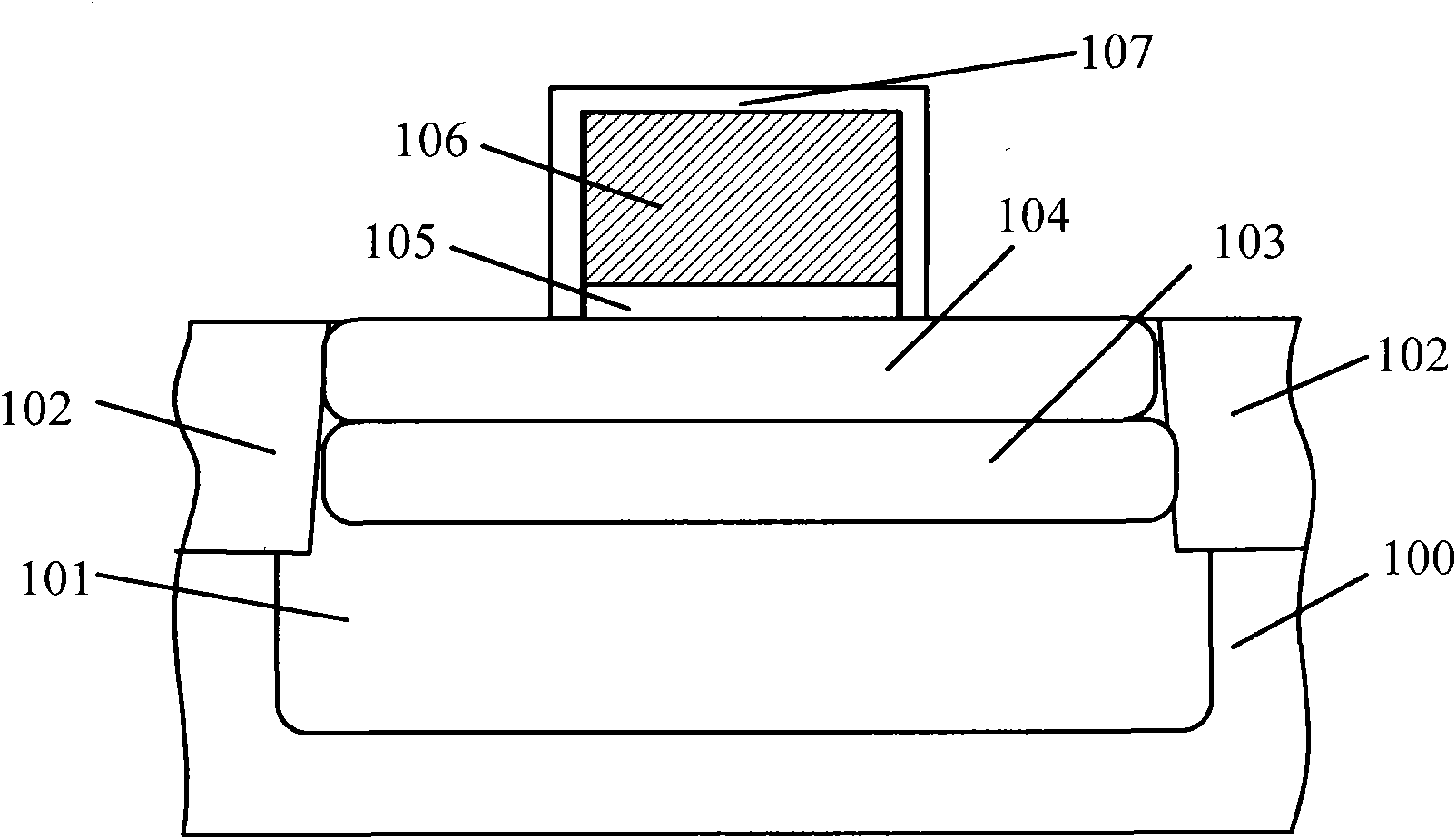

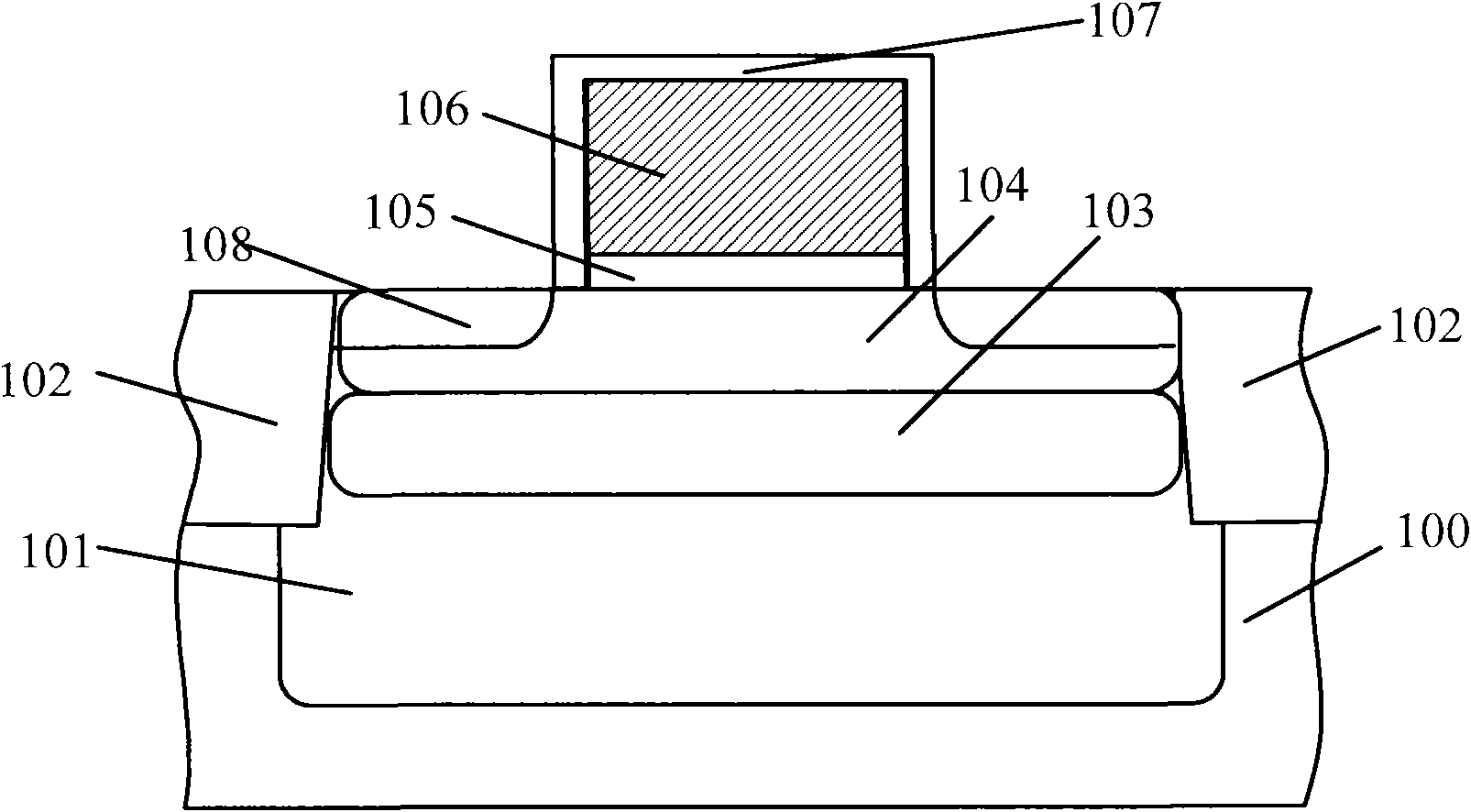

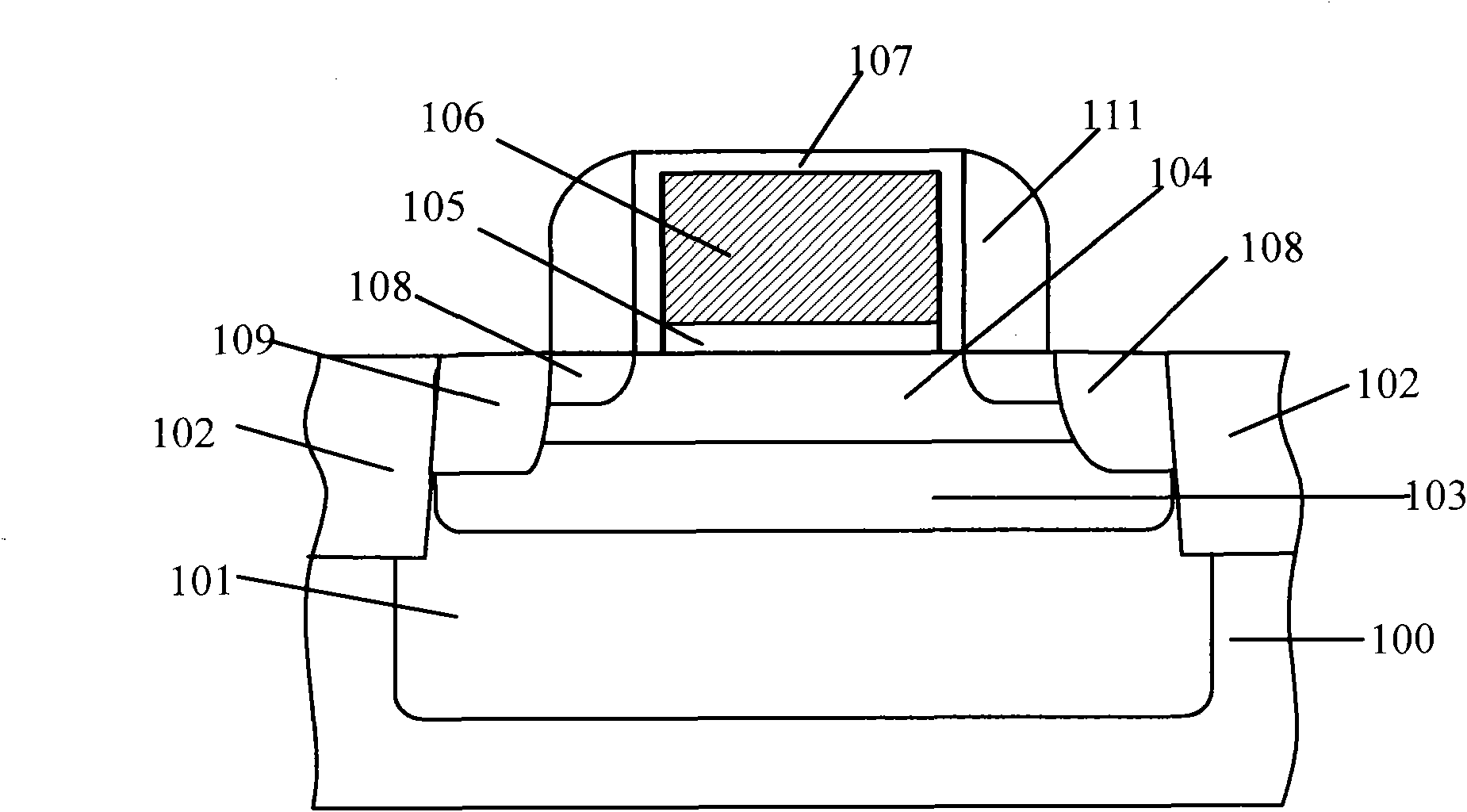

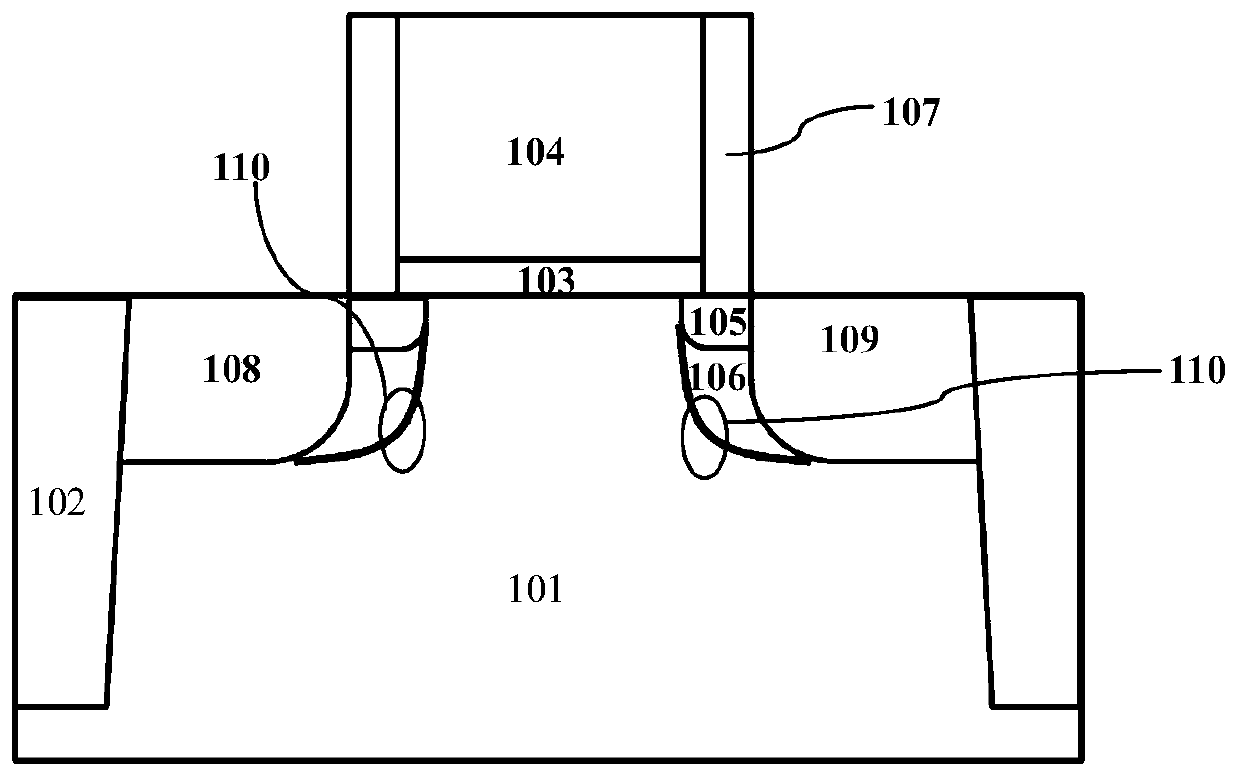

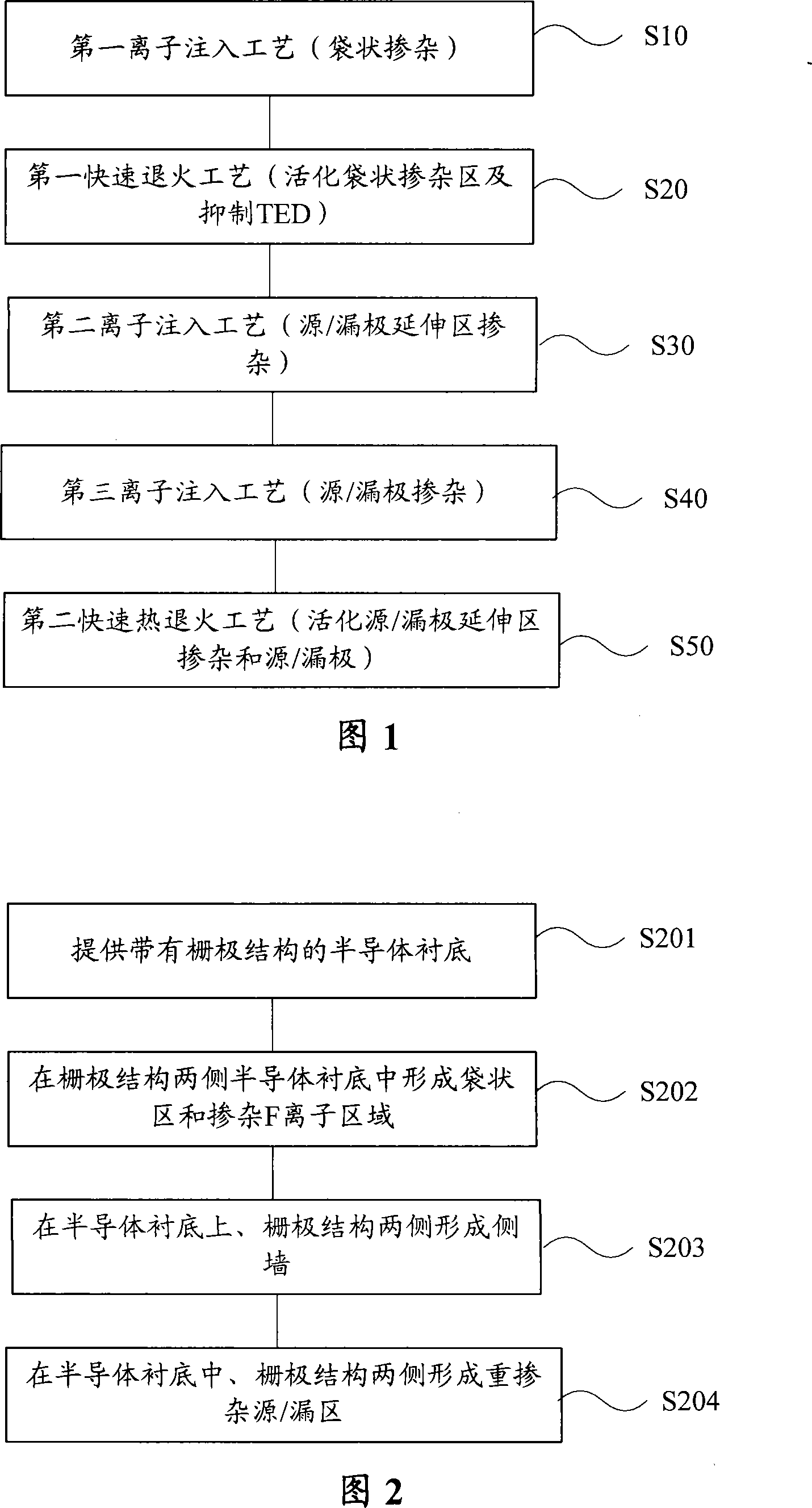

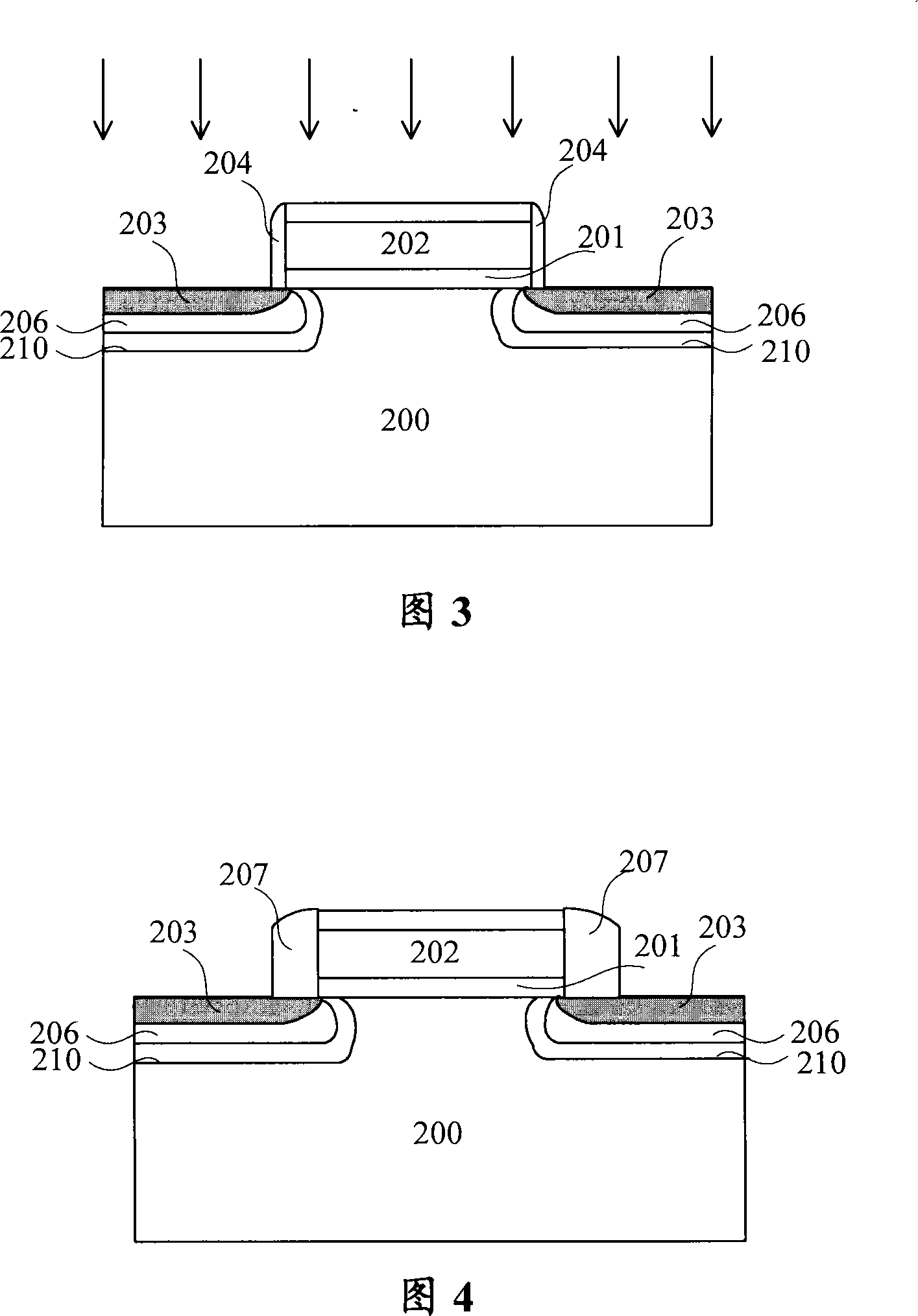

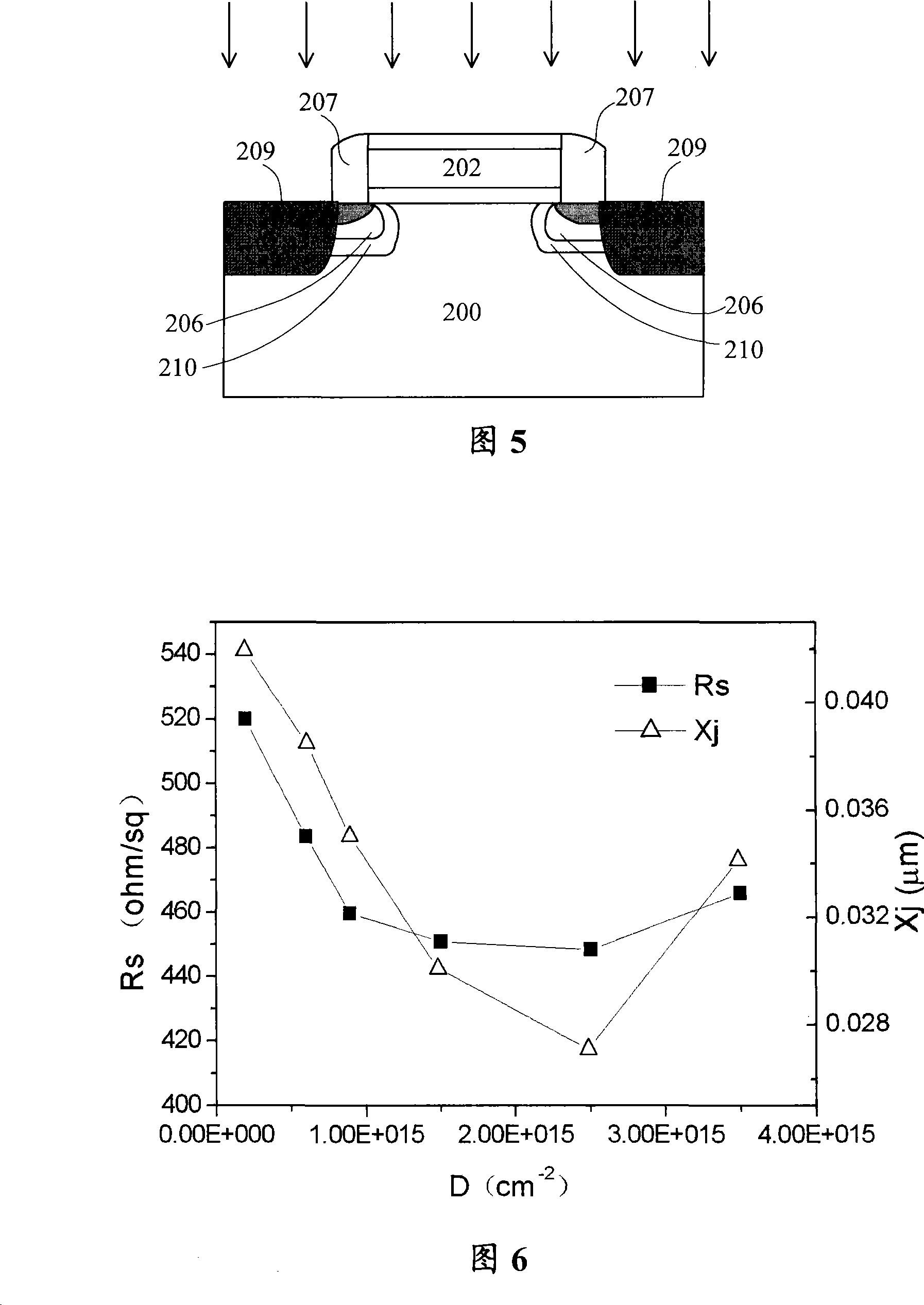

MOS transistor and forming method thereof

ActiveCN101459082AImprove performanceReduce junction depthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorJunction depth

An MOS transistor comprises low doped source / drain extended regions in a semiconductor substrate and on two sides of a grid structure, sidewalls located on the semiconductor substrate on two sides of the grid structure, heavily doped source / drain regions located in the semiconductor and on two sides of the grid structure, and pocket regions and F-ion doped regions respectively located in the semiconductor substrate and on two sides of the grid structure, wherein the F-ion doped regions are located around the pocket regions. The invention further provides a method of forming the MOS transistors. By forming the F-ion doped regions around the pocket regions of the MOS transistor, transient enhanced diffusion effect of ions from the pocket regions into the semiconductor substrate can be prevented, thereby reducing junction depth, decreasing junction current leakage, and improving the performance of the MOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for manufacturing a semiconductor device

InactiveUS20050164438A1Reduce acceleration energy for implantationReduce harmTransistorSolid-state devicesDopantBiomedical engineering

A method for manufacturing a MOS transistors in a semiconductor device includes the step of implanting a dopant in a channel layer or source / drain regions by using a multi-step implantation and an associated multi-step heat treatment, wherein the multi-step implantation includes a number of steps of implantation each for implanting the dopant at a dosage lower than 1×1013 / cm2. The total dosage of the multi-step implantation ranges between 1×1013 / cm2 and 3×1013 / cm2.

Owner:ELPIDA MEMORY INC

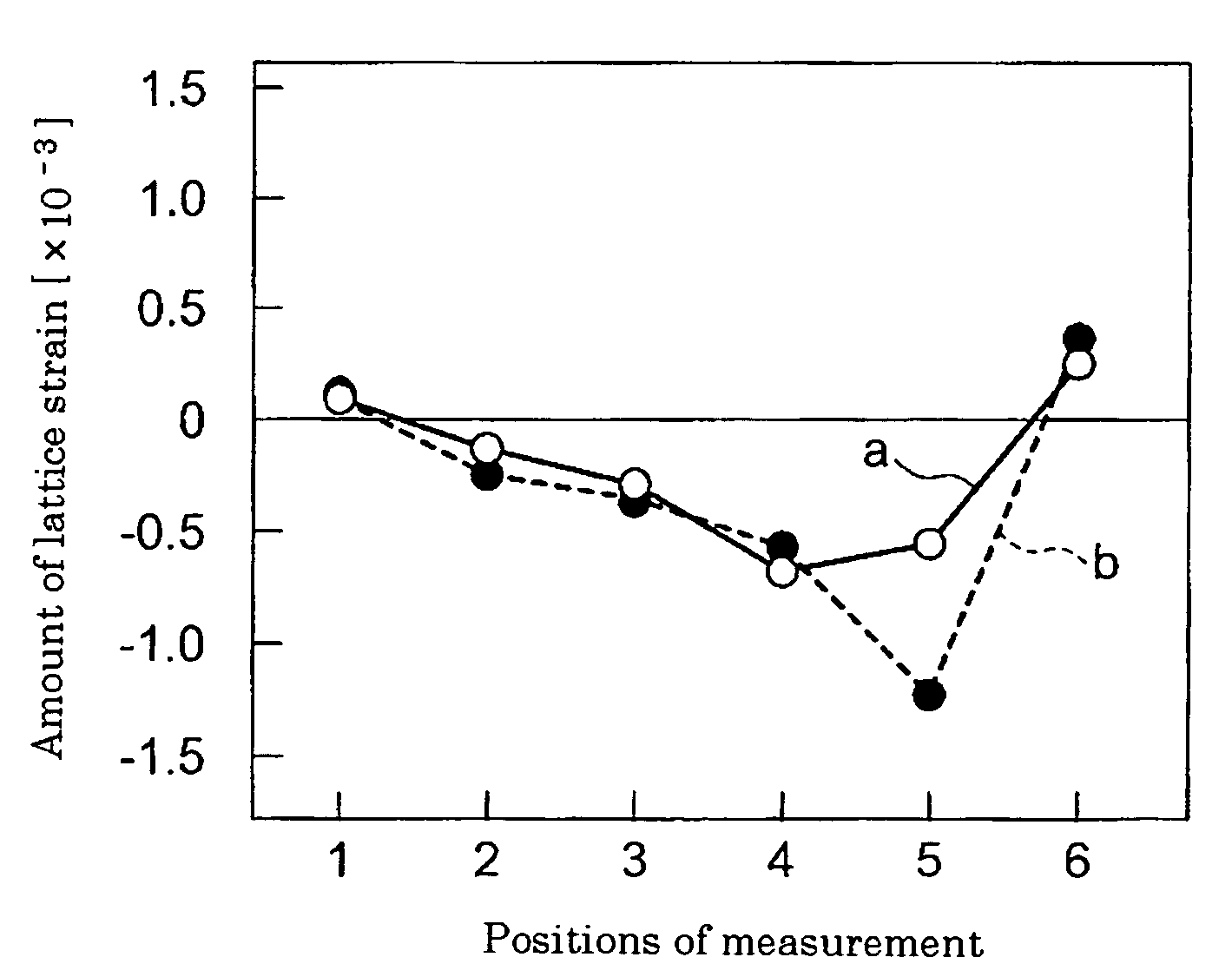

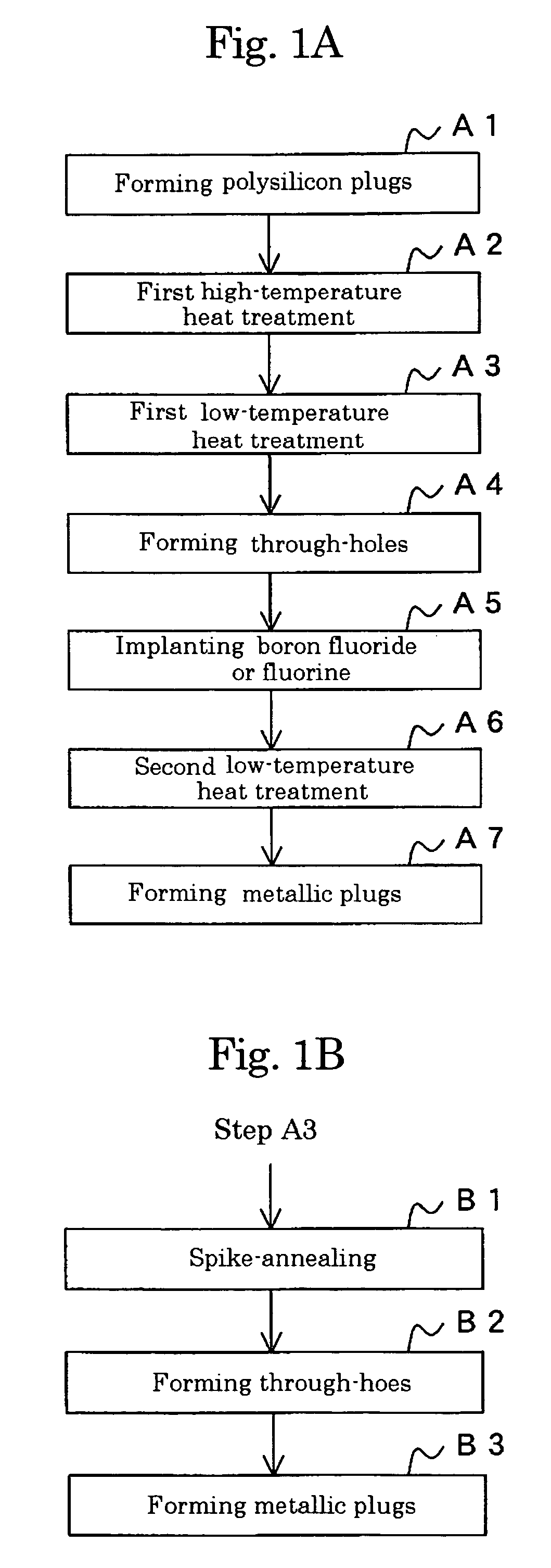

Method for manufacturing a semiconductor device having polysilicon plugs

InactiveUS20050282335A1Reduce contact resistanceSuppress leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringFluoride

A method for manufacturing a DRAM device on a silicon substrate includes: forming cell transistors in a memory cell area and other transistors in a peripheral circuit area; forming polysilicon plugs connected to diffused regions of the cell transistors and metallic plugs connected to diffused regions of the other transistors; heat treating at a temperature of 980 to 1,020 degrees C.; heat treating at a temperature of 700 to 850 degrees C.; implanting fluorine or boron fluoride into the diffused regions of the other transistors; and heat treating at a temperature of 500 to 850 degrees C.

Owner:LONGITUDE SEMICON S A R L

Method of manufacturing semiconductor device

InactiveCN102208348APrevents change in sheet resistanceReduced Junction Leakage CurrentSolid-state devicesSemiconductor/solid-state device manufacturingCompound (substance)Silicon

The invention relates to a method of manufacturing semiconductor device. The method comprises forming a metal film over silicon regions and insulating films; performing a first heat treatment under an oxygen atmosphere containing oxygen as a main ingredient, to form a first silicide film in the silicon region by reacting the metal film and the silicon region, and to simultaneously form a metal oxide by oxidizing the entire surface of the metal film from the surface side thereof; and selectively removing the metal oxide and the unreacted metal film using a chemical.

Owner:RENESAS ELECTRONICS CORP

Method for manufacturing a semiconductor device

InactiveUS20050164448A1Reduced Junction Leakage CurrentImproved data retention capabilityTransistorSolid-state devicesDopantSemiconductor memory

A method for forming a semiconductor memory device includes the steps of: implanting a dopant in a semiconductor substrate; heat treating the semiconductor substrate in an oxidizing ambient to diffuse the dopant for forming diffused regions in the semiconductor substrate; and forming memory cells each including a MOS transistor having the diffused regions as source / drain regions.

Owner:RAMBUS INC

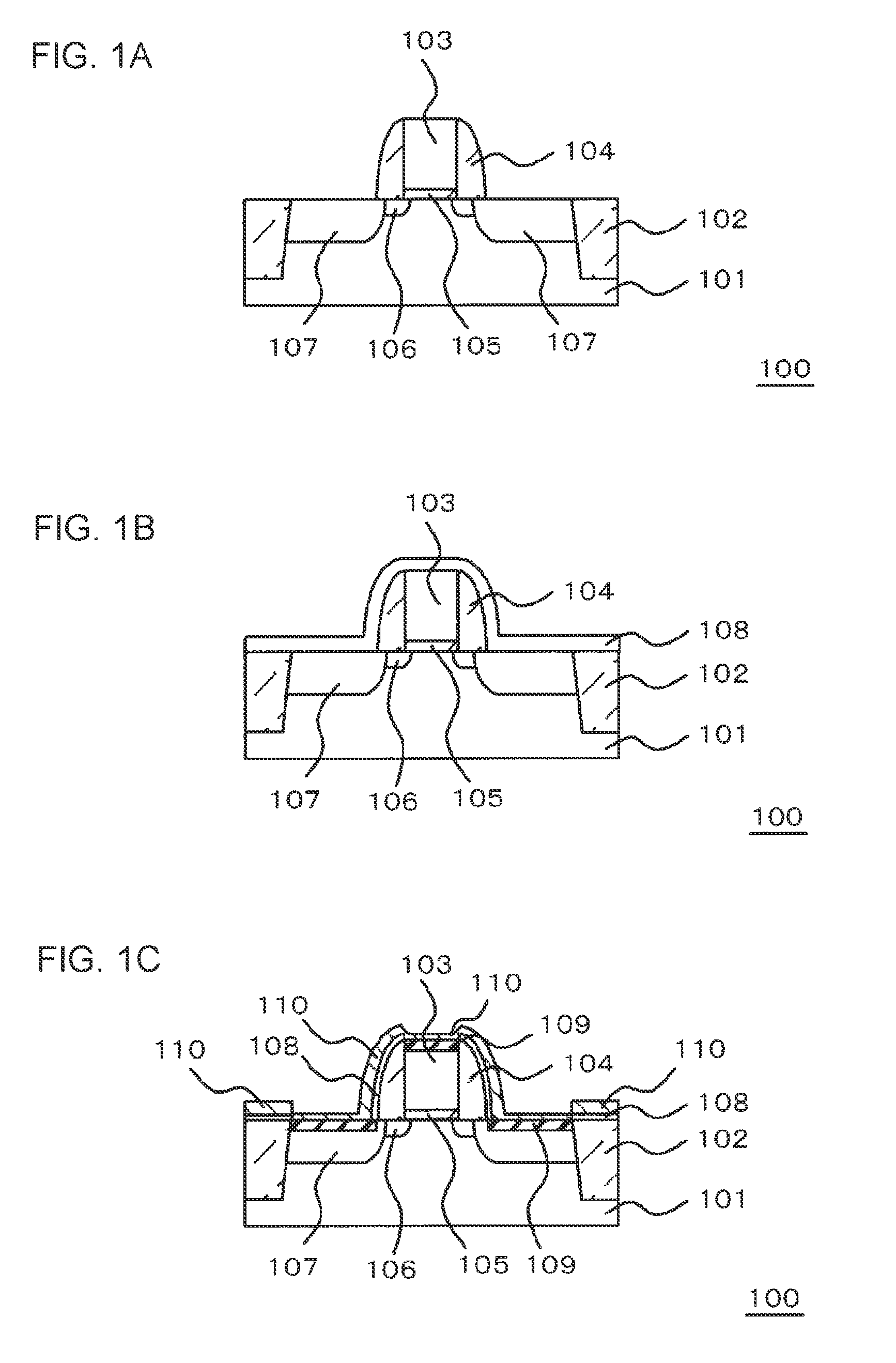

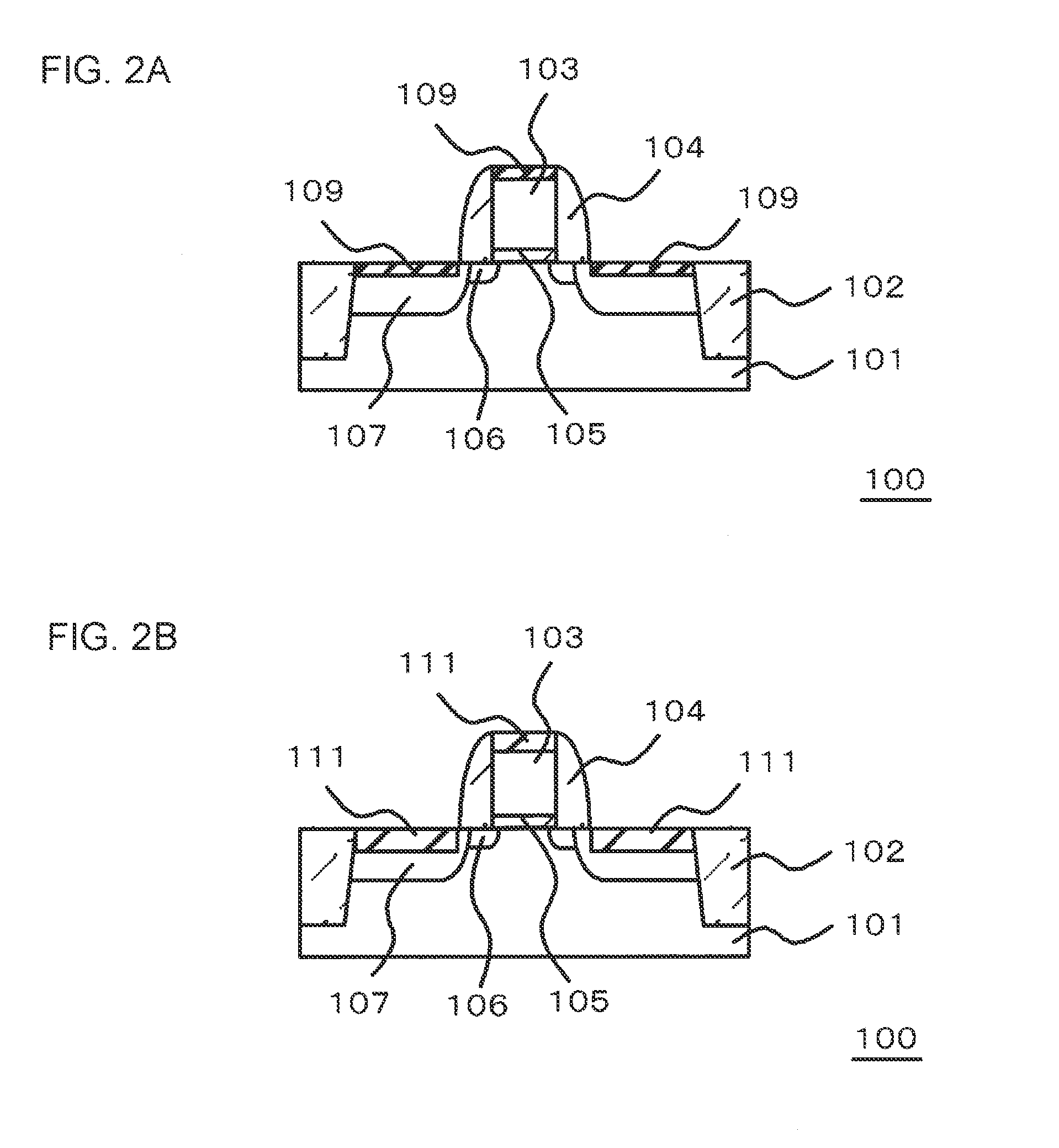

MOS transistor and manufacturing method thereof

ActiveCN102468167AIncrease resistancePrevent channelingSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceIon implantation

The invention provides an MOS transistor and a manufacturing method thereof. The manufacturing method comprises the following steps: providing a semiconductor substrate; carrying out non-crystallization ion implantation on the semiconductor substrate, and forming a non-crystallization region in the semiconductor substrate; carrying out threshold voltage injection on the semiconductor substrate, and forming a threshold voltage injection region on the non-crystallization region; forming a gate structure at a semiconductor substrate surface above the threshold voltage injection region; forming a source / drain region in the semiconductor substrate at two sides of the gate structure. According to the MOS transistor and the manufacturing method in the invention, junction capacitance of the MOS transistor is reduced, a response speed of the MOS transistor is raised, and leakage current of the MOS transistor is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

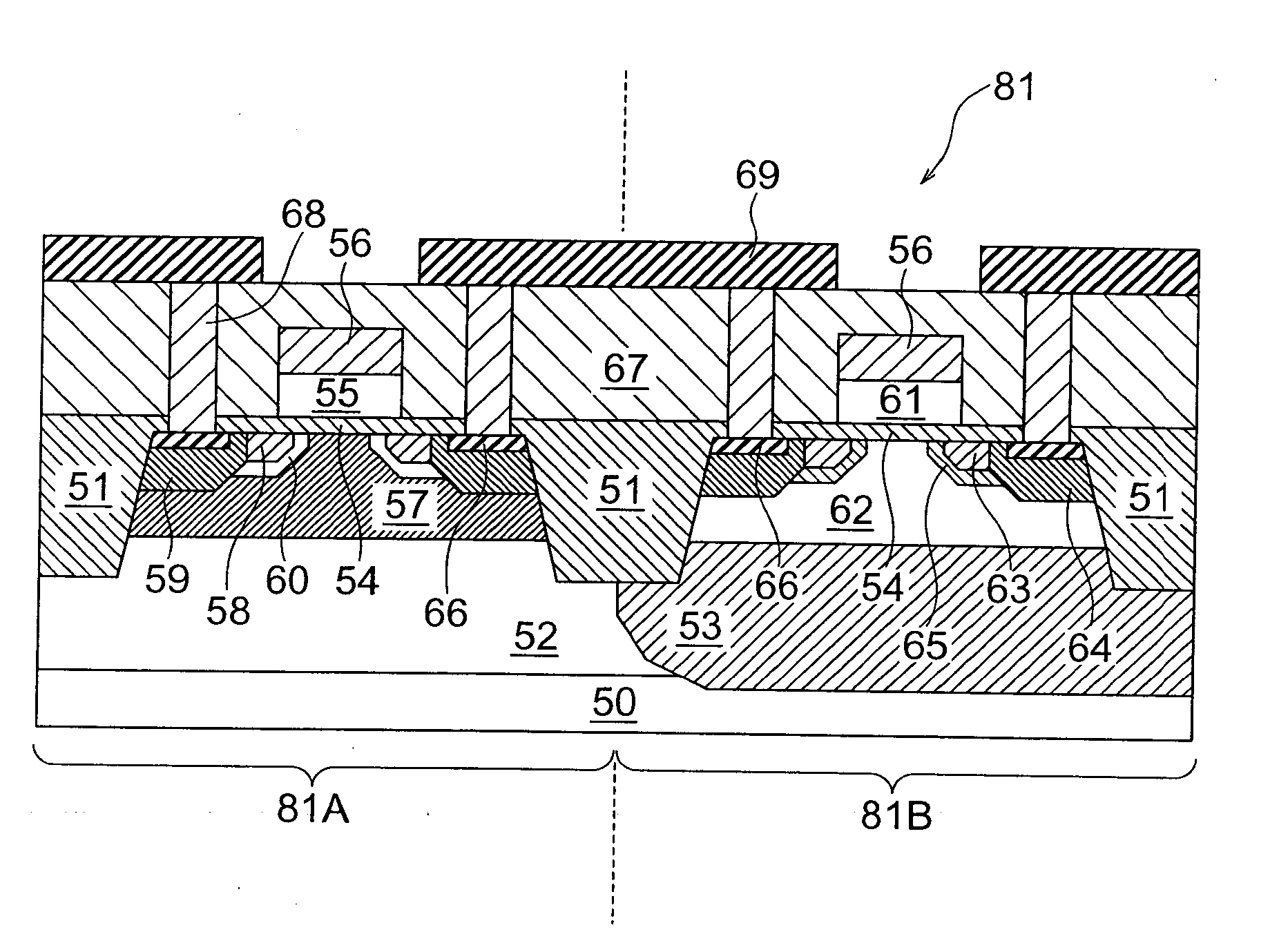

Semiconductor device and method of manufacturing the same

InactiveUS20050253219A1Reduced life-timeReduced Junction Leakage CurrentTransistorSemiconductor/solid-state device detailsFloating body effectDevice material

A silicon nitride film is formed between interlayer insulating films covering an upper surface of an element formed on a surface of a semiconductor layer. With this structure, a semiconductor device comprising an isolation insulating film of PTI structure, which suppresses a floating-body effect and improves isolation performance and breakdown voltage, and a method of manufacturing the semiconductor device can be obtained.

Owner:RENESAS ELECTRONICS CORP

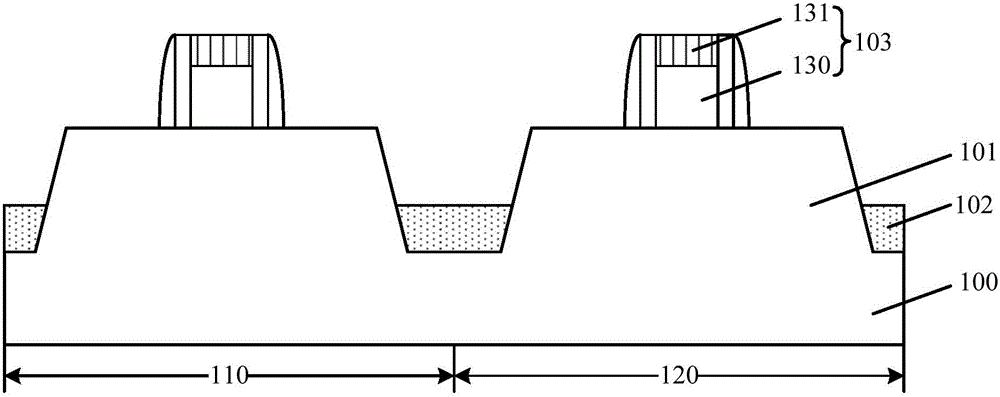

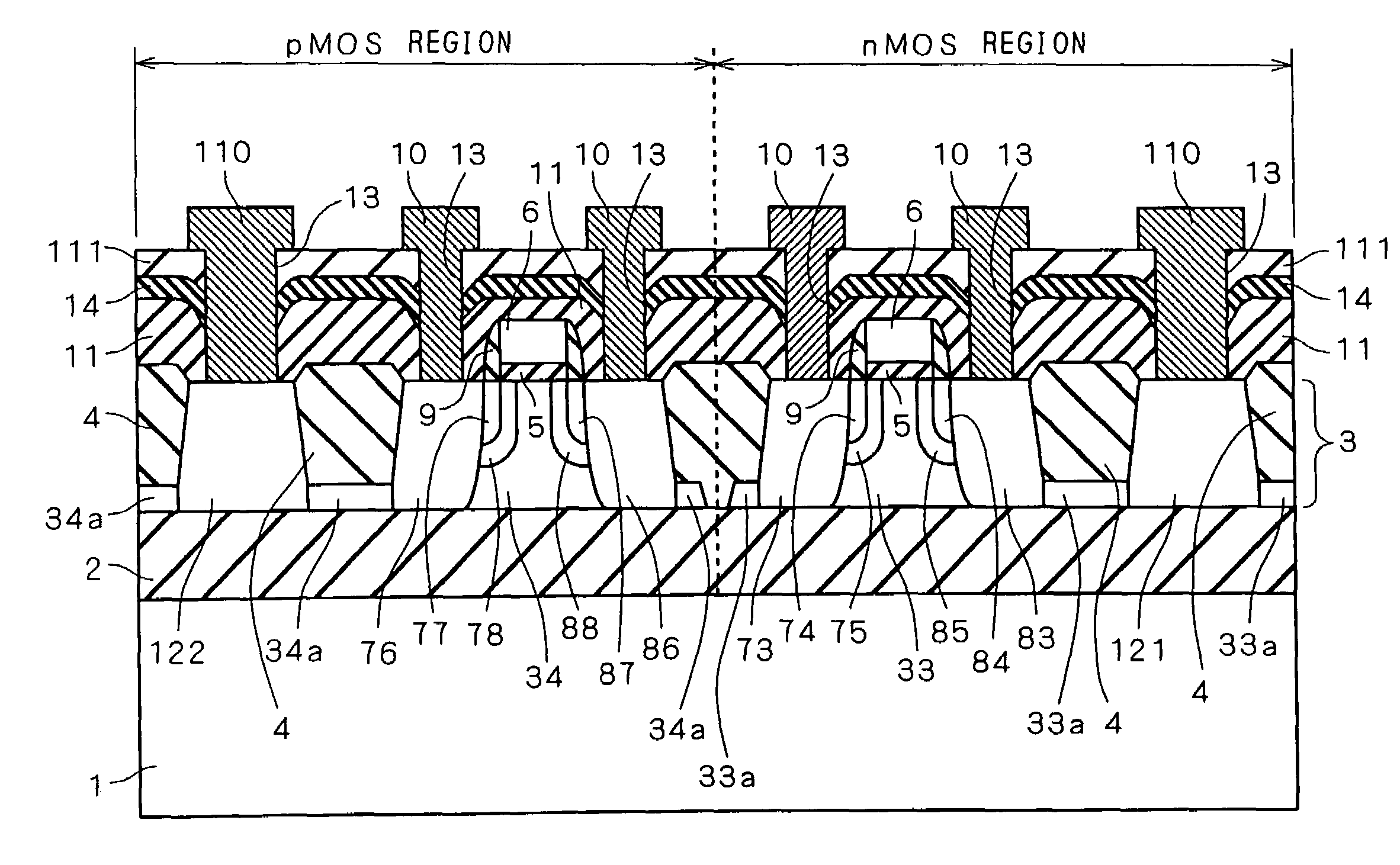

Semiconductor device and forming method thereof

ActiveCN106548983AImproved Junction Leakage CurrentReduced Junction Leakage CurrentSemiconductor/solid-state device manufacturingJunction leakageElectric properties

The invention discloses a semiconductor device and a forming method thereof. The forming method of the semiconductor device comprises the steps as follows: a first ion implantation process is carried out on a substrate in a PMOS peripheral region at two sides of a first gate structure and a first graded junction region is formed at the lower part of a first peripheral source-drain region; a second ion implantation process is carried out on the first peripheral source-drain region and a first core drain-source region, and a first contact resistance region is formed on the surface of the first peripheral source-drain region and the surface of the first core drain-source region; a third ion implantation process is carried out on the substrate in an NMOS peripheral region at two sides of a third gate structure and a second graded junction region is formed at the lower part of a second peripheral source-drain region; and a fourth ion implantation process is carried out on a second peripheral source-drain region and a second core drain-source region, and a second contact resistance region is formed on the surface of the second peripheral source-drain region and the second core drain-source region. According to the semiconductor device, the problem of a short channel effect of a core device is solved while junction leakage current of an input / output device is reduced, thereby improving the electric property of the formed semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

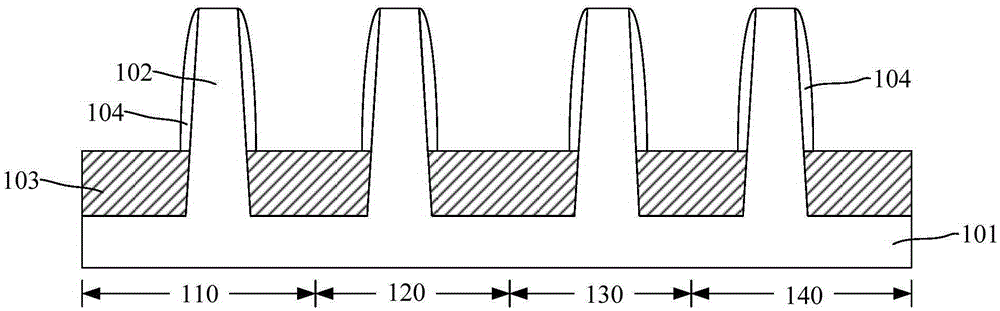

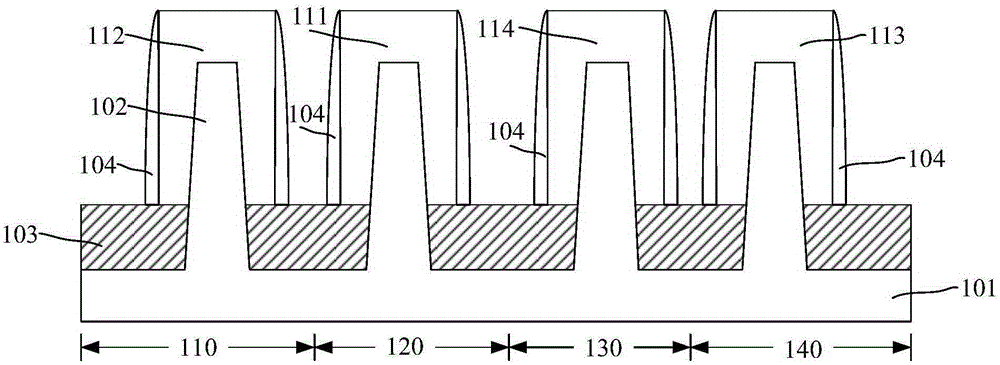

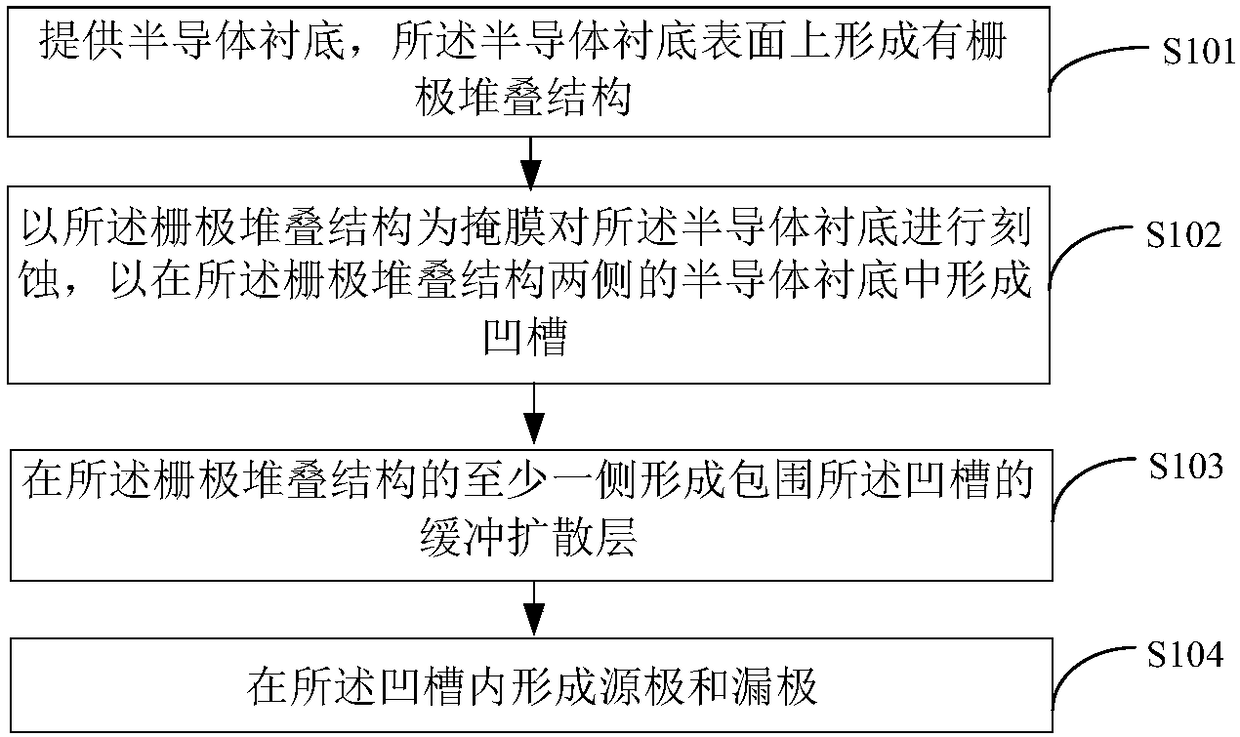

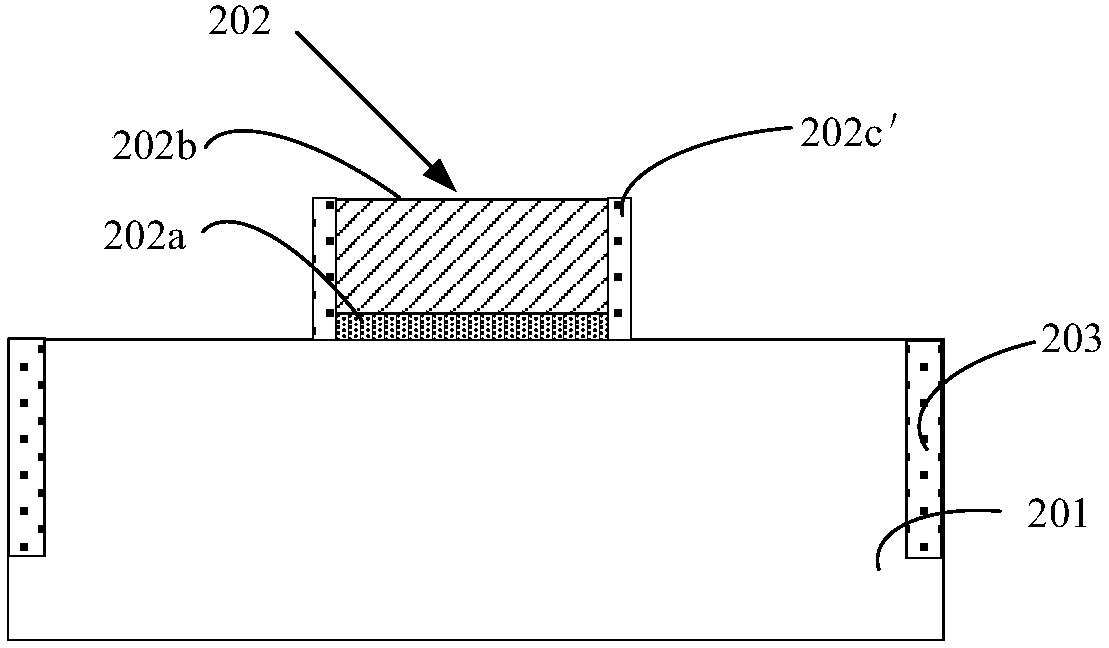

Manufacturing method of semiconductor device

ActiveCN109087859AEvenly distributedAvoid lateral spreadSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention provides a manufacturing method of a semiconductor device. The method includes the following steps: providing a semiconductor substrate, and forming a gate stacking structure on the surface of the semiconductor substrate; etching the semiconductor substrate by using the gate stacking structure as a mask so as to form grooves in the semiconductor substrate on the two sides of the gatestacking structure; forming buffer diffusion layers surrounding the corresponding grooves on at least one side of the gate stacking structure; and forming a source electrode and a drain electrode inthe grooves. According to the method of the invention, the buffer diffusion layers are formed before forming the source electrode and the drain electrode, diffusion of impurities in the buffer diffusion layers drives diffusion of impurities in the source electrode and drain electrode regions in a subsequent annealing process, and so the distribution of the impurities in the source electrode and the drain electrode regions more uniform, the electric field distribution of PN junctions of the source electrode and the drain electrode regions is reduced, lateral diffusion of the impurities can be avoided, lateral short channel effect is controlled, the junction capacitance and the junction leakage current of the source electrode and the drain electrode regions are reduced, and the yield rate and performance of the semiconductor device are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

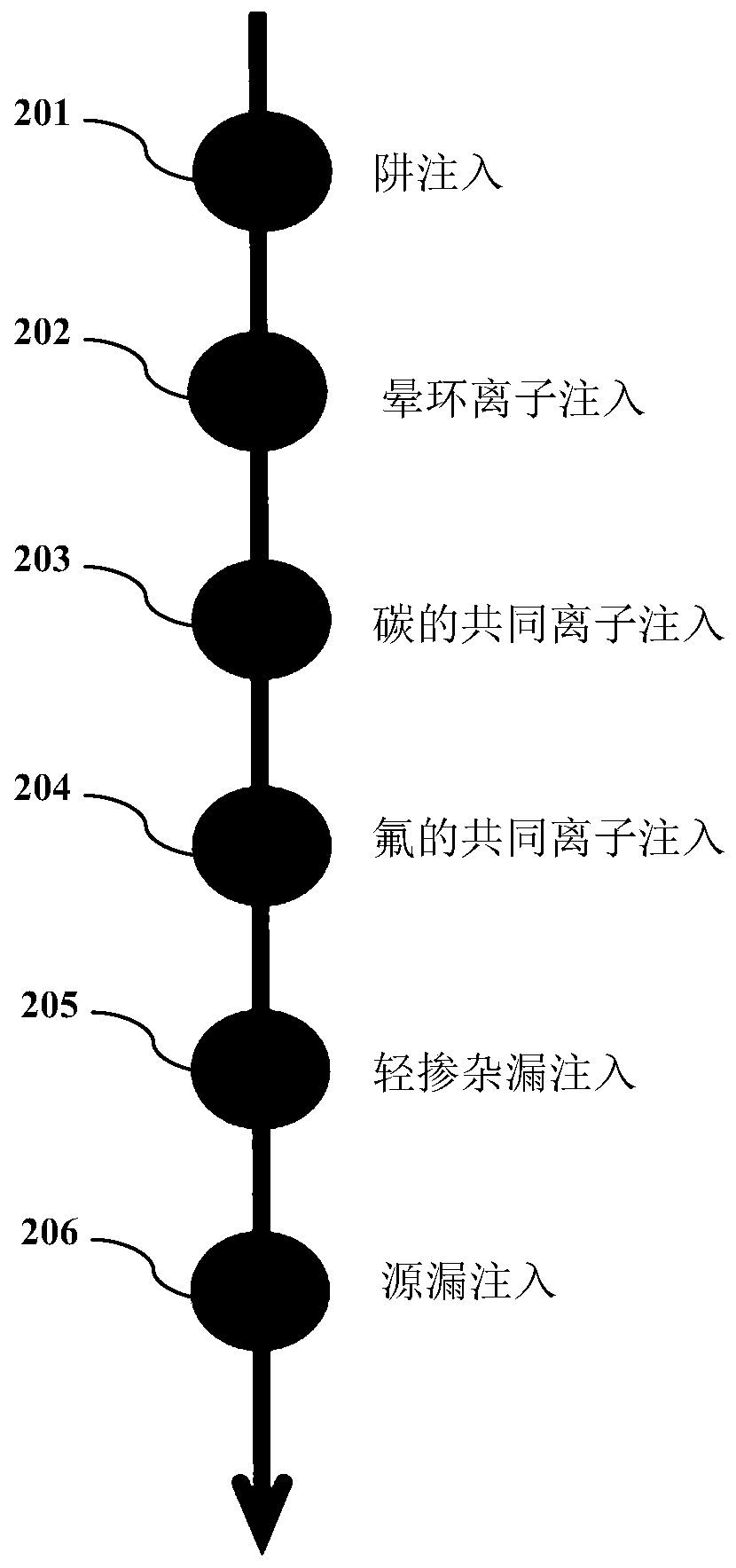

Transistor forming method

ActiveCN102800593AReducing Diffusion EffectsReduce concentrationTransistorSemiconductor/solid-state device manufacturingCapacitanceDrain current

The invention provides a transistor forming method. The transistor forming method comprises the following steps of: providing a substrate; forming a well region in the substrate; forming a gate structure on the surface of the substrate, wherein the gate structure comprises a gate oxide layer and a gate positioned on the surface of the gate oxide layer; forming a source region and a drain region which are positioned in the substrate on the two sides of the gate structure; and after forming the source region and the drain region, doping first ions in the substrate to adjust a threshold voltage. The first ions for adjusting the threshold voltage are injected after the formation of the source region and the drain region, so that the influence on the diffusion of the first ions caused by a heat treatment process before injecting the first ions is reduced; most of the first ions are distributed close to the surface of the substrate; the concentration of the first ions diffused in the substrate is reduced; the junction capacitance between the source region / drain region and the substrate is reduced; the junction drain current is reduced; the operation speed of a device is increased; and the performance of the device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

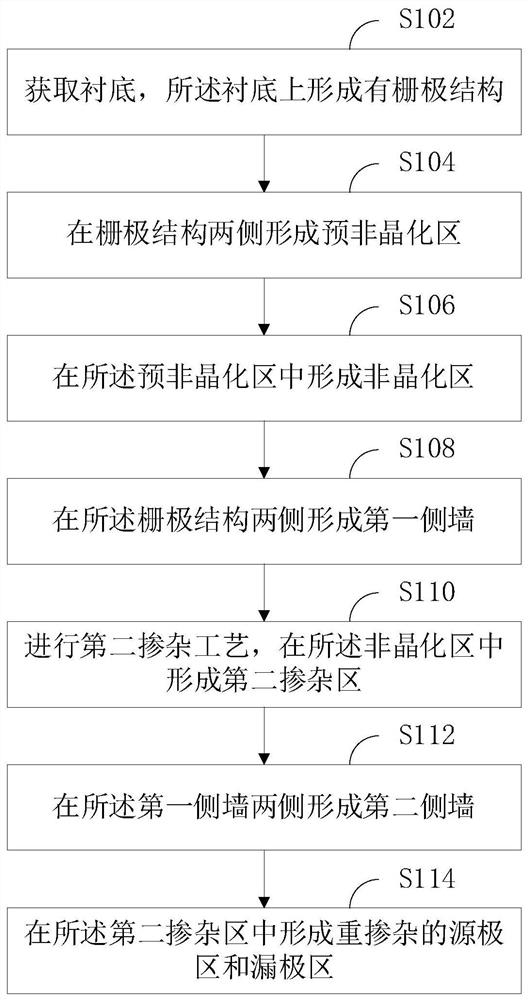

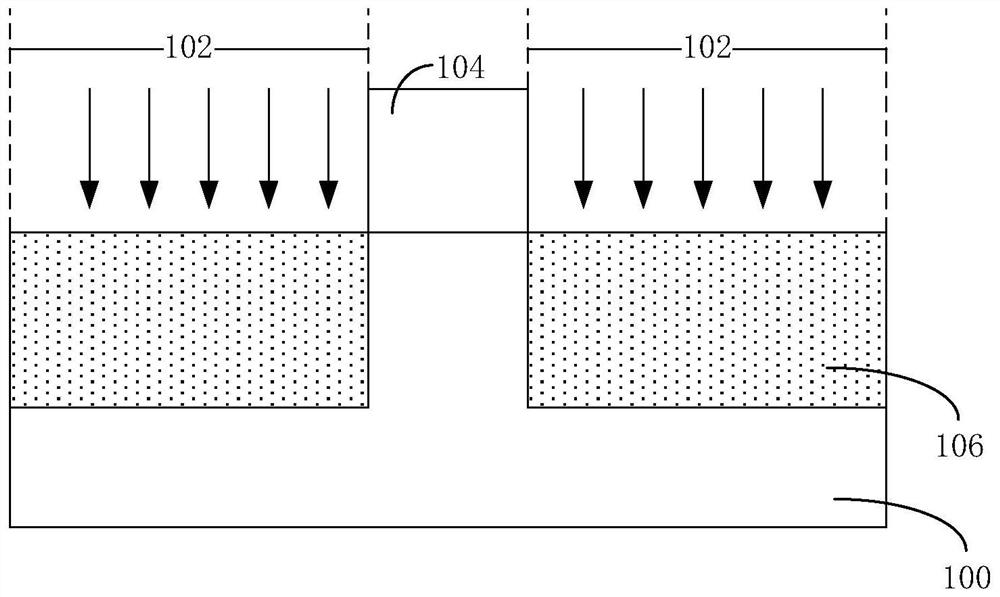

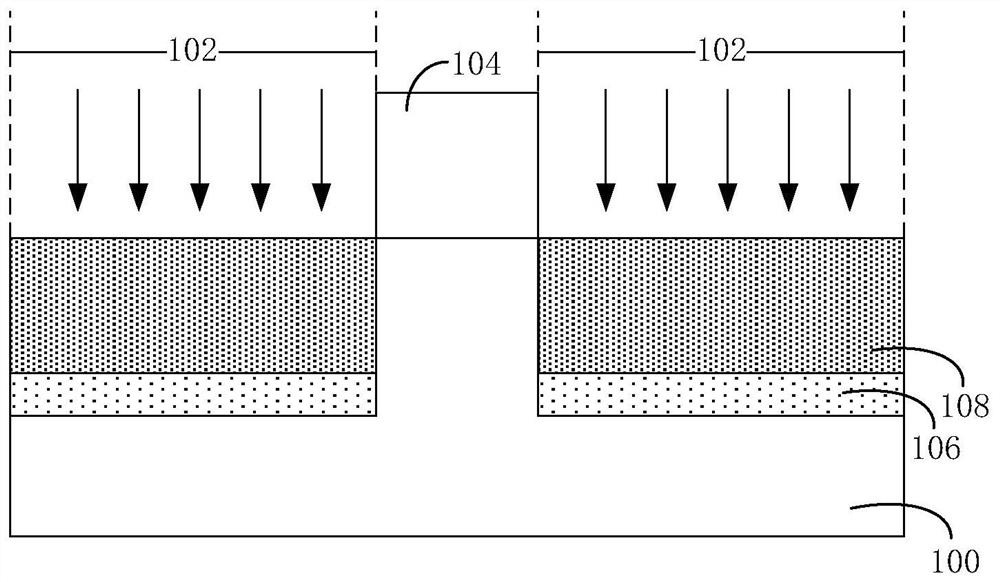

Preparation method of semiconductor device

PendingCN114121659AInhibition of lateral diffusionLongitudinal diffusion inhibitionTransistorSemiconductor/solid-state device manufacturingJunction leakageDevice material

The invention relates to a preparation method of a semiconductor device, and the method comprises the steps: obtaining a substrate, and forming a gate structure on the substrate; first ion implantation is carried out on the substrate, and pre-amorphization regions are formed on the two sides of the gate structure; second ion implantation is carried out on the pre-amorphization area, and an amorphization area is formed in the pre-amorphization area; forming first side walls on two sides of the gate structure; performing a second doping process, and forming a second doped region in the non-crystallization region; second side walls are formed on the two sides of the first side walls; and forming a heavily doped source region and a heavily doped drain region in the second doped region. Transverse diffusion and longitudinal diffusion of doped ions in the second doped region are inhibited, and the effective distance between the heavily doped drain region and the edge of the drain region is increased, so that the junction leakage current is reduced.

Owner:CHANGXIN MEMORY TECH INC

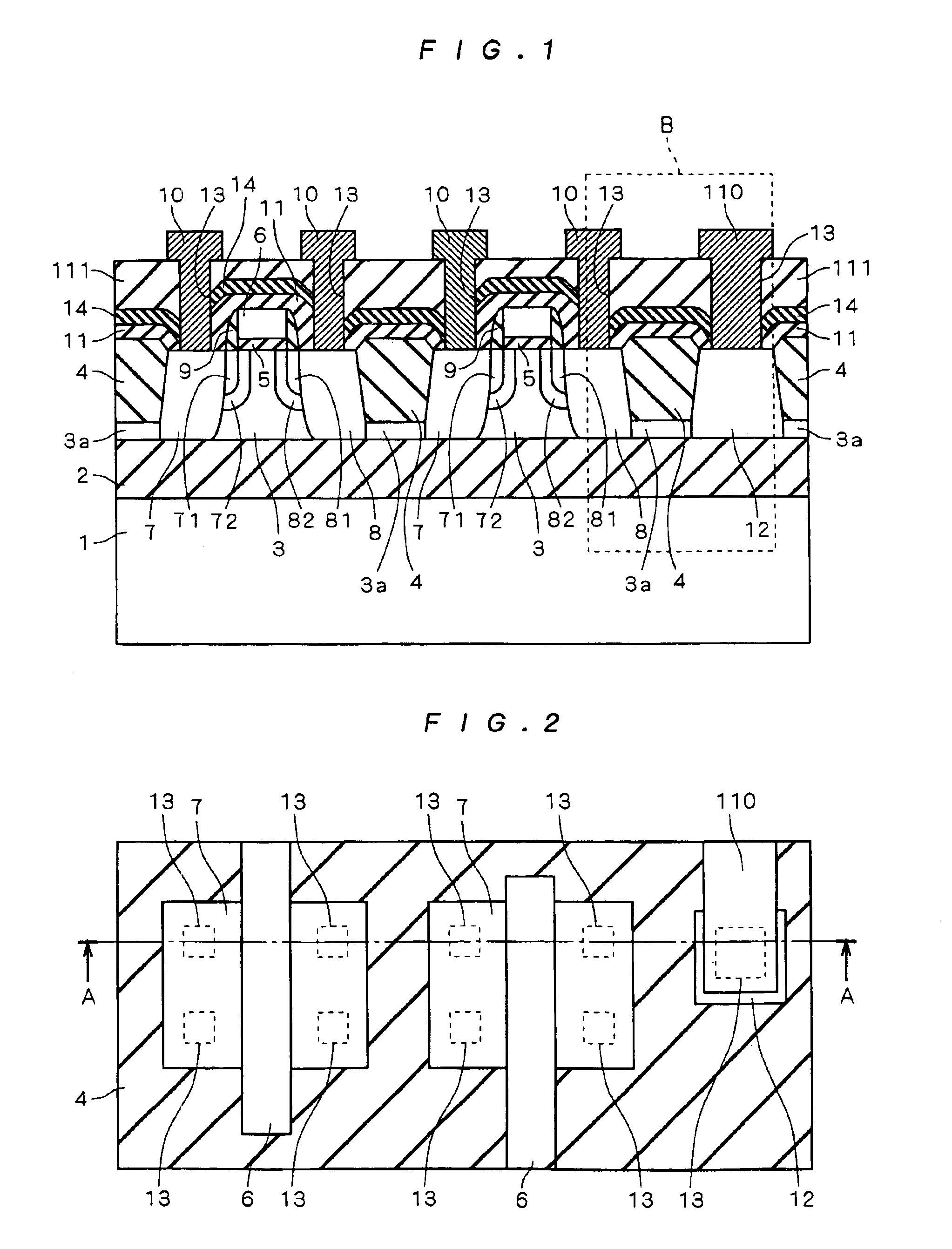

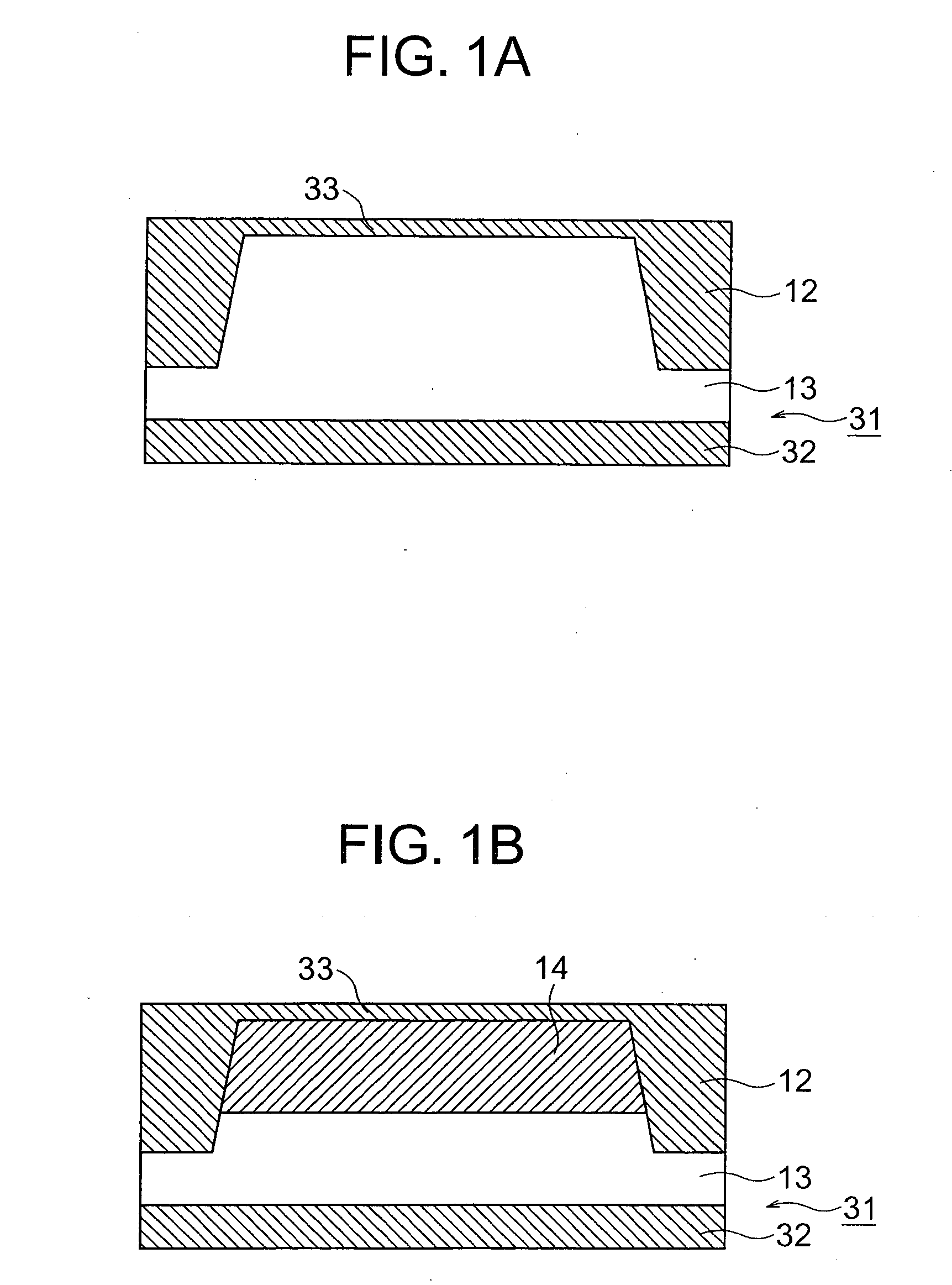

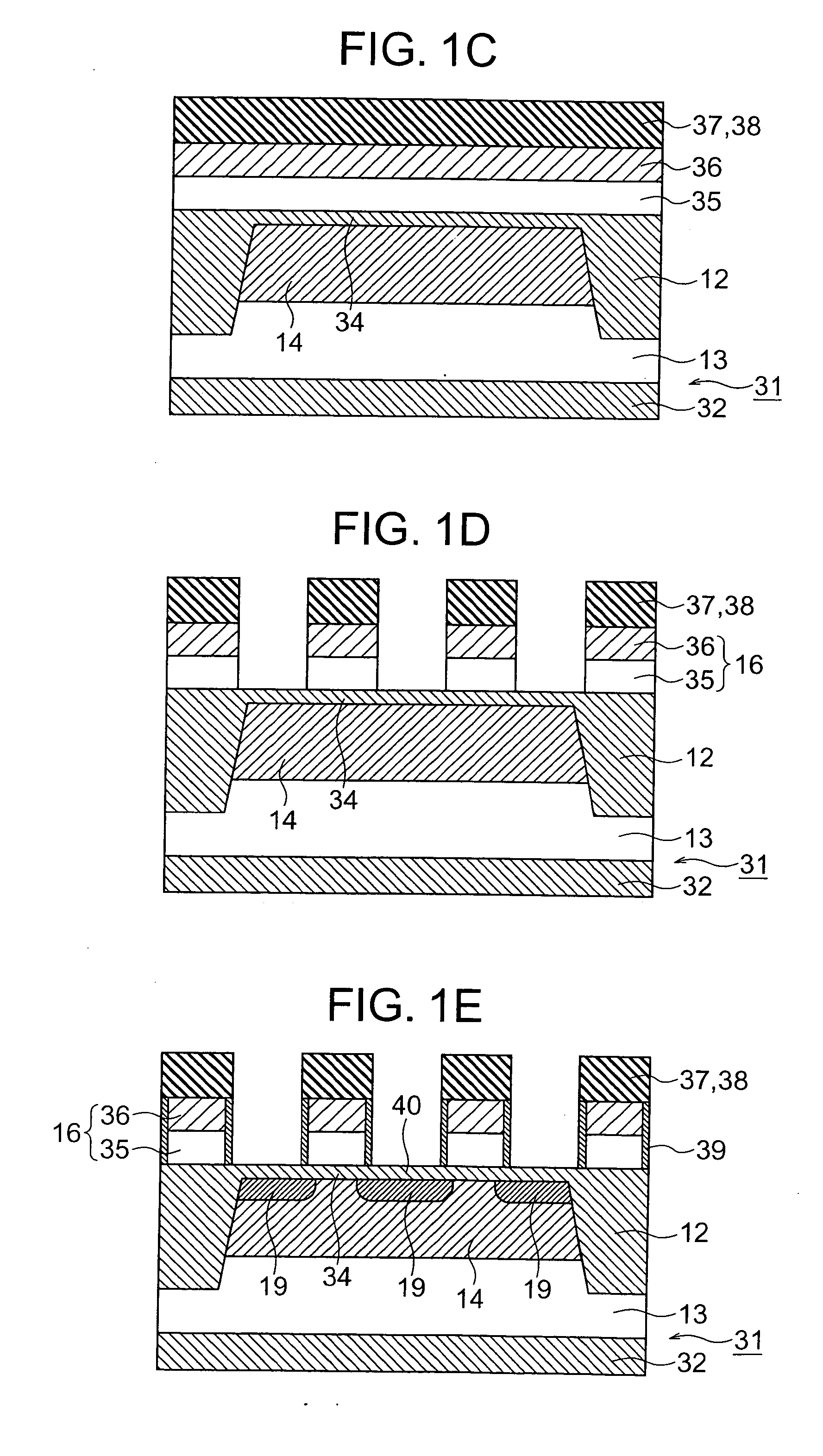

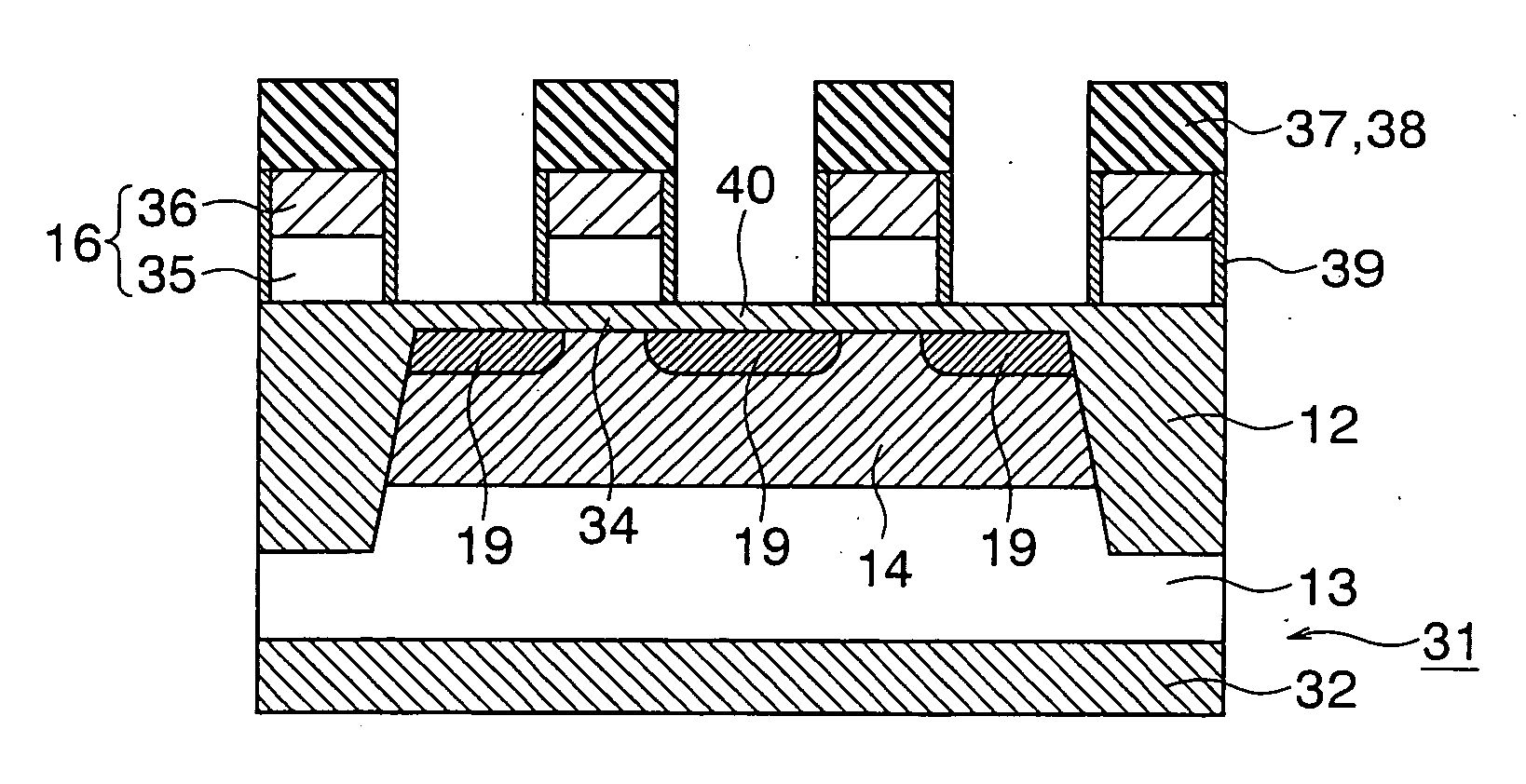

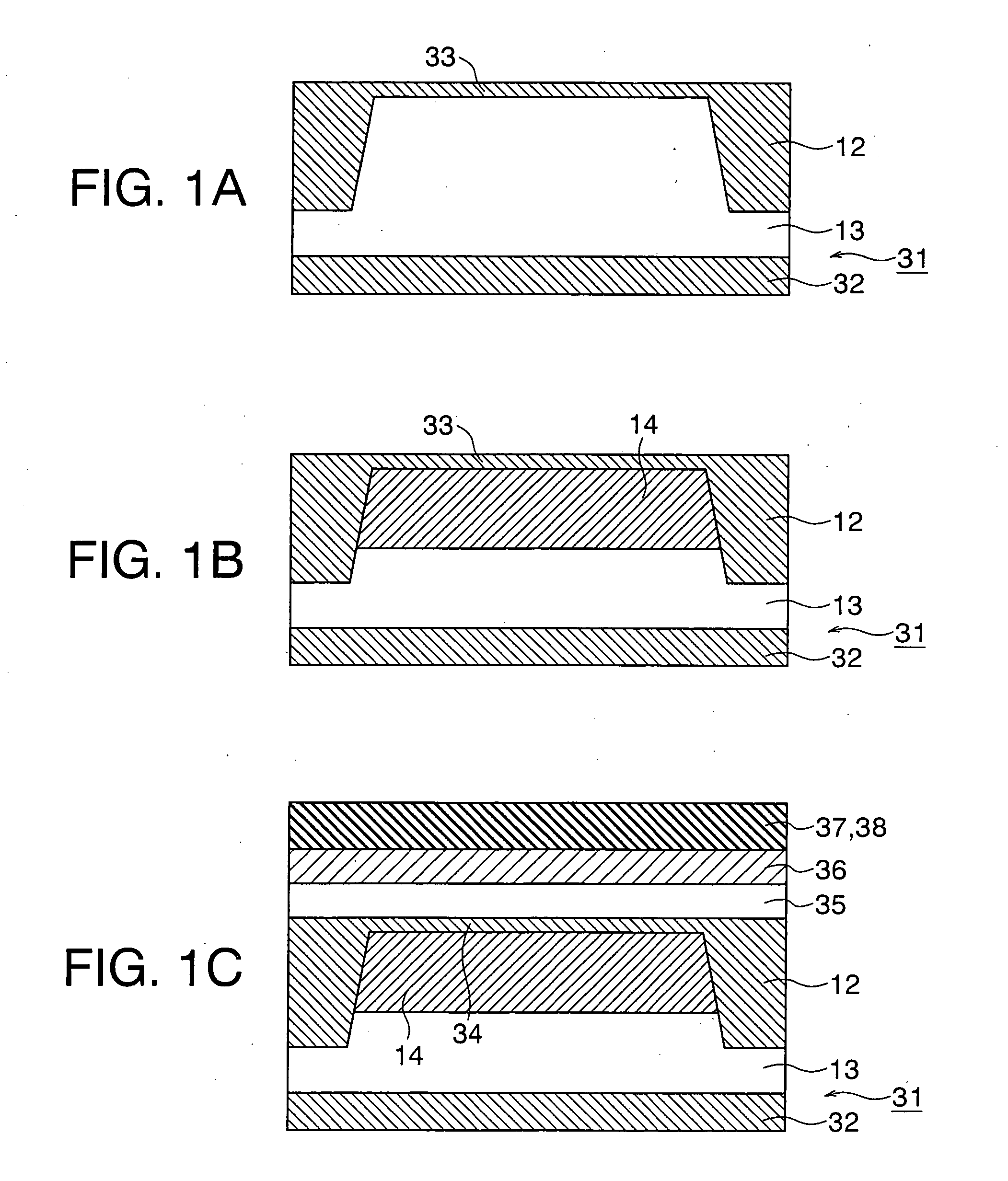

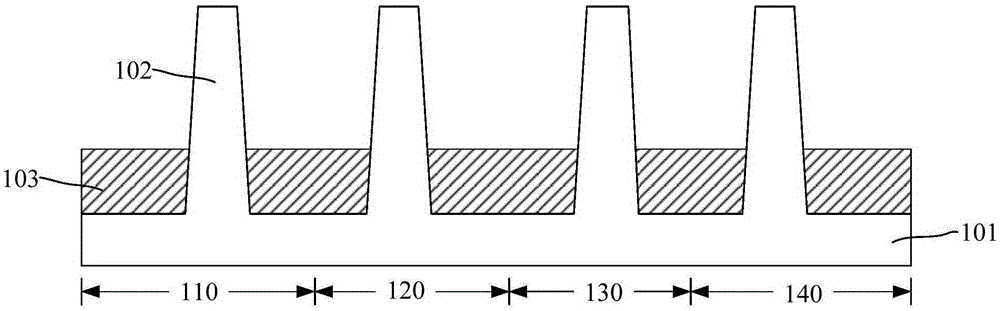

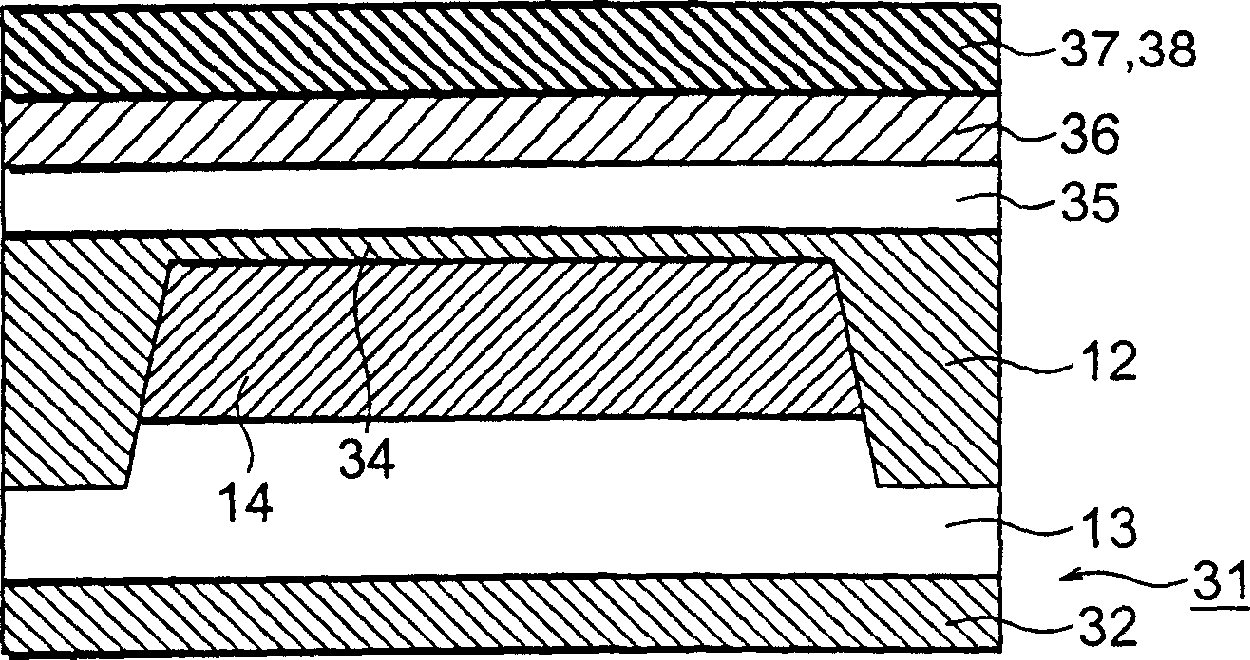

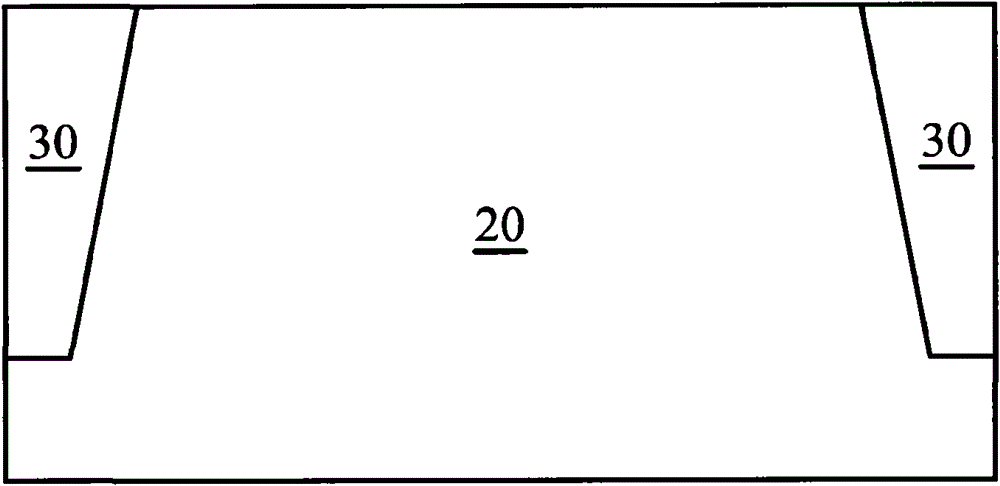

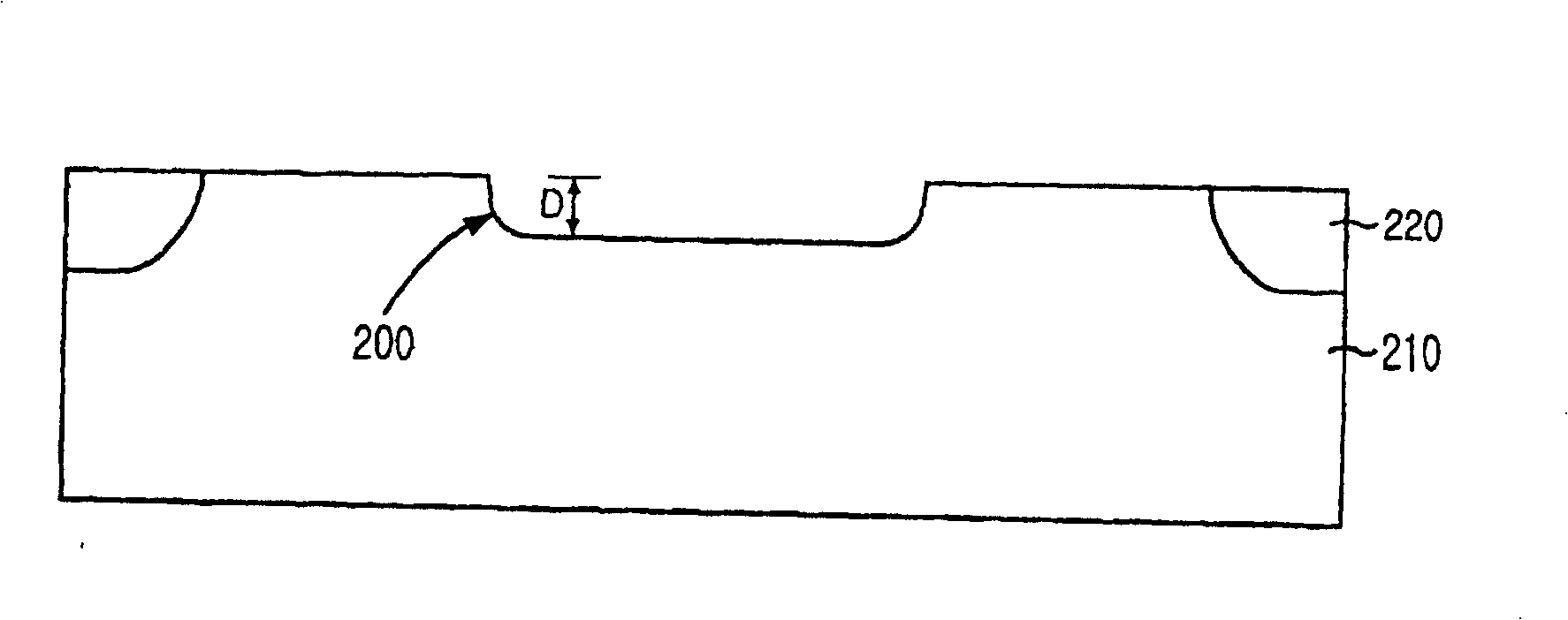

Memory device and method for fabricating the same

InactiveCN1728387AReduced Junction Leakage CurrentData retention time is longTransistorSolid-state devicesBit lineCell region

Disclosed are a memory device and a method for fabricating the same. The memory device includes: a substrate provided with a trench; a bit line contact junction formed beneath the trench; a plurality of storage node contact junctions formed outside the trench; and a plurality of gate structures each being formed on the substrate disposed between the bit line contact junction and one of the storage node contact junctions. Each sidewall of the trench becomes a part of the individual channels and thus, channel lengths of the transistors in the cell region become elongated. Accordingly, the storage node contact junctions have a decreased level of leakage currents, thereby increasing data retention time.

Owner:SK HYNIX INC

Method for manufacturing a semiconductor device

InactiveCN1649113AReduce standby currentImprove data retention characteristicsTransistorSolid-state devicesDopantBiomedical engineering

A method for manufacturing a MOS transistors in a semiconductor device includes the step of implanting a dopant in a channel layer or source / drain regions by using a multi-step implantation and an associated multi-step heat treatment, wherein the multi-step implantation includes a number of steps of implantation each for implanting the dopant at a dosage lower than 1x1013 / cm2. The total dosage of the multi-step implantation ranges between 1x1013 / cm2 and 3x1013 / cm2.

Owner:ELPIDA MEMORY INC

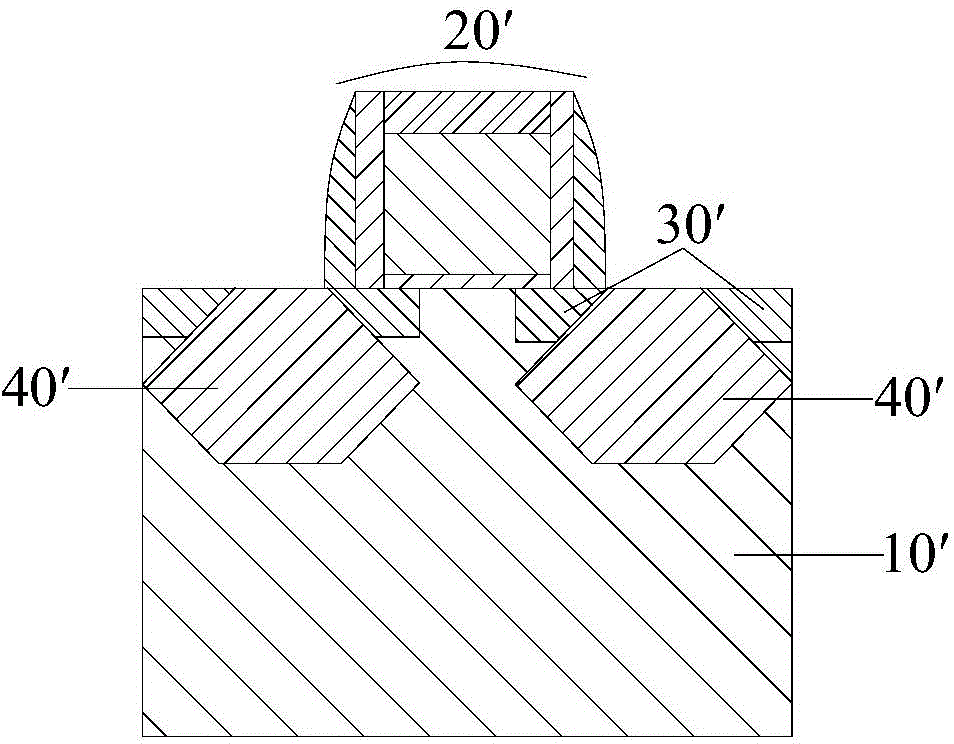

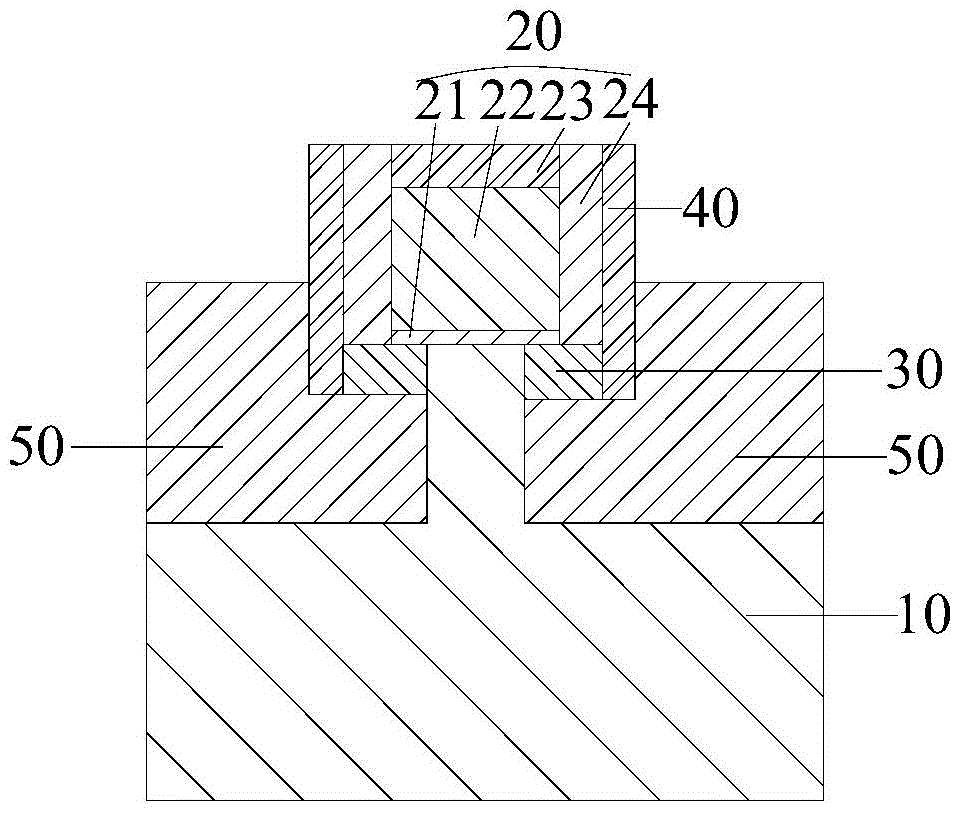

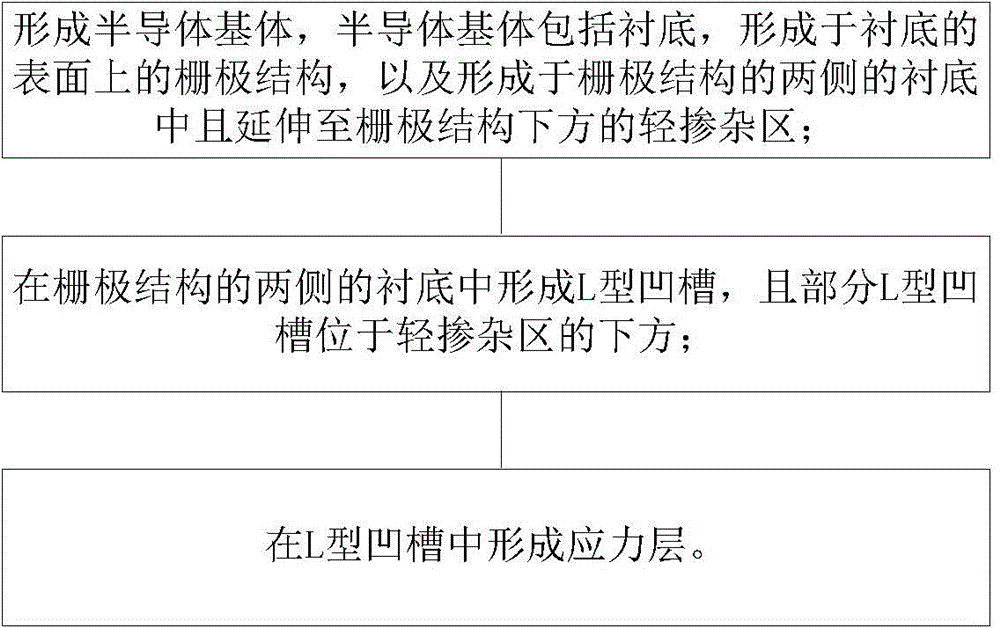

Semiconductor device and manufacturing method thereof

InactiveCN105762185AAvoid Junction Leakage CurrentReduce stressSemiconductor/solid-state device manufacturingSemiconductor devicesJunction leakageEngineering

The invention discloses a semiconductor device and a manufacturing method thereof. The semiconductor device comprises a substrate; a gate structure disposed on the surface of the substrate; a lightly doped region arranged in the substrate on the two sides of the gate structure and extending to be below the gate structure; an L-shaped groove and a stress layer in the L-shaped groove. The L-shaped groove is arranged in the substrate on the two sides of the gate structure. One part of the stress layer is arranged below the lightly doped region. The stress layer below the lightly doped region is of a cuboid structure. In this way, the formation of a tip structure between the stress layer and the substrate is avoided, so that the junction leakage current caused by the tip structure is avoided. Meanwhile, below a conductive channel, the stress layer of the cuboid structure is away from the conductive channel compared with a sigma-type stress layer. Therefore, the stress below the conductive channel is reduced, and the junction leakage current is further reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device and method of manufacturing the same

InactiveUS7393731B2Reduced life-timeReduced Junction Leakage CurrentTransistorSemiconductor/solid-state device detailsFloating body effectEngineering

A silicon nitride film is formed between interlayer insulating films covering an upper surface of an element formed on a surface of a semiconductor layer. With this structure, a semiconductor device comprising an isolation insulating film of PTI structure, which suppresses a floating-body effect and improves isolation performance and breakdown voltage, and a method of manufacturing the semiconductor device can be obtained.

Owner:RENESAS ELECTRONICS CORP

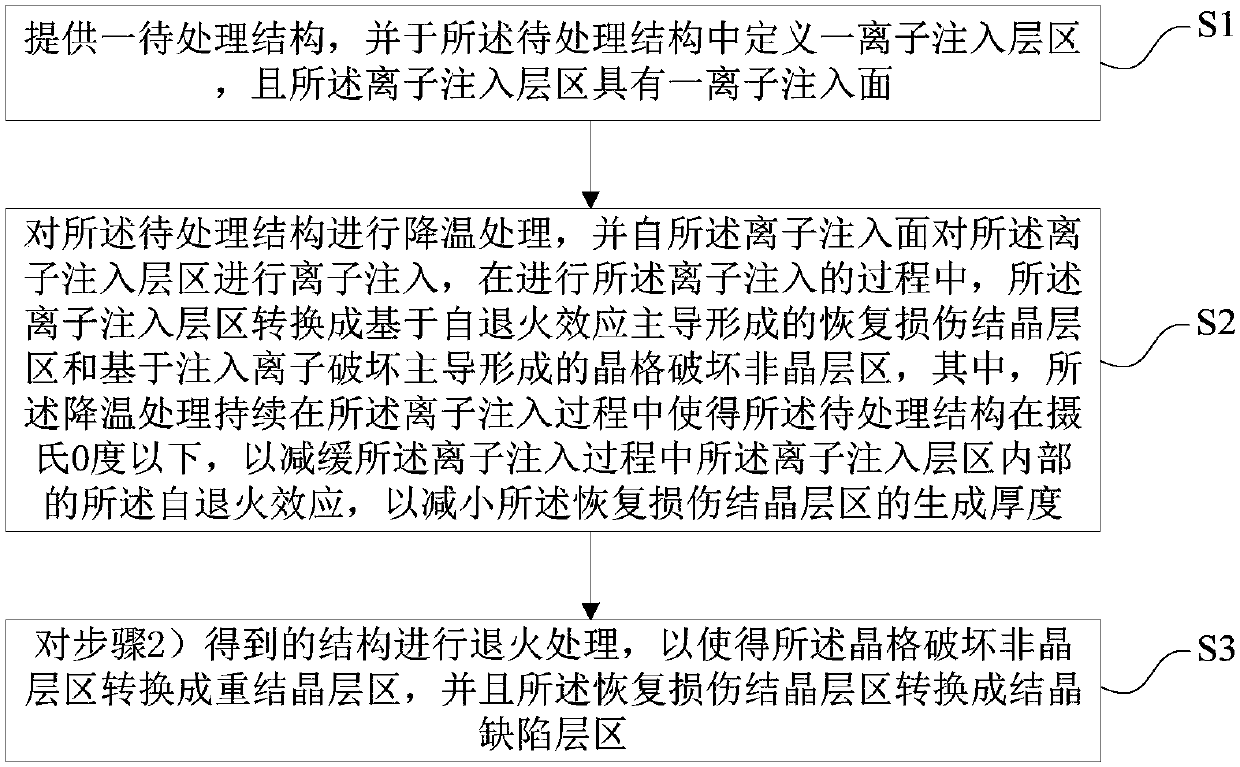

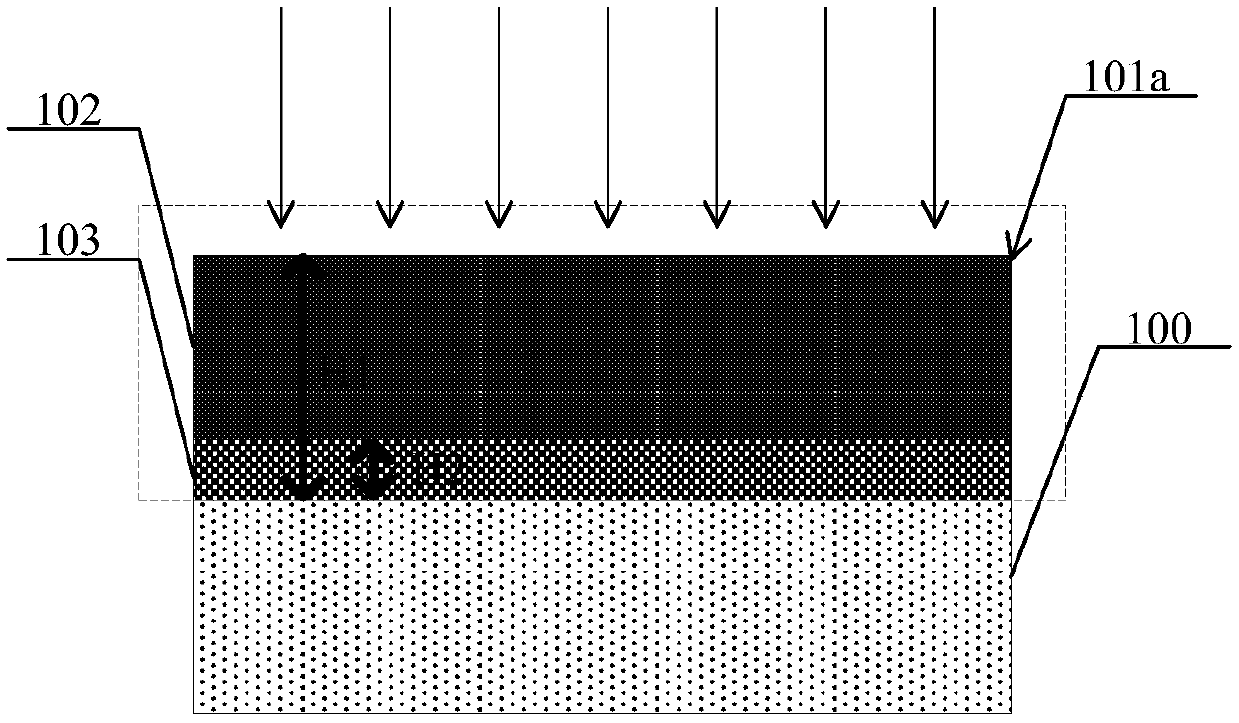

Semiconductor structure, preparation method of transistor structure and semiconductor processing device

PendingCN110534516AReduce thicknessReduce power consumptionTransistorSemiconductor/solid-state device manufacturingJunction leakageSemiconductor structure

The invention discloses a semiconductor structure based on low-temperature ion implantation, transistor preparation and a semiconductor processing device. The method comprises the steps of: providinga to-be-processed structure, and defining an ion implantation layer region with an ion implantation surface; cooling the to-be-processed structure, performing ion implantation from the ion implantation surface, wherein in the ion implantation process, an ion implantation layer area is converted into a recovery damage crystallization layer area and a lattice damage amorphous layer area, the self-annealing effect in the ion implantation layer area is relieved through cooling treatment, and the size of the recovery damage crystallization layer area is reduced; and performing annealing treatment,converting the lattice damage amorphous layer area into a recrystallization layer area, and converting the recovery damage crystallization layer area into a crystallization defect layer area. The to-be-processed structure is cooled in the ion implantation process, ion implantation is carried out under the low-temperature condition, and the self-annealing effect in the ion implantation process is relieved, so that the EOR defect after annealing is reduced, the junction leakage current is reduced, and the power consumption of an electronic device is reduced.

Owner:CHANGXIN MEMORY TECH INC

integrated circuit structure

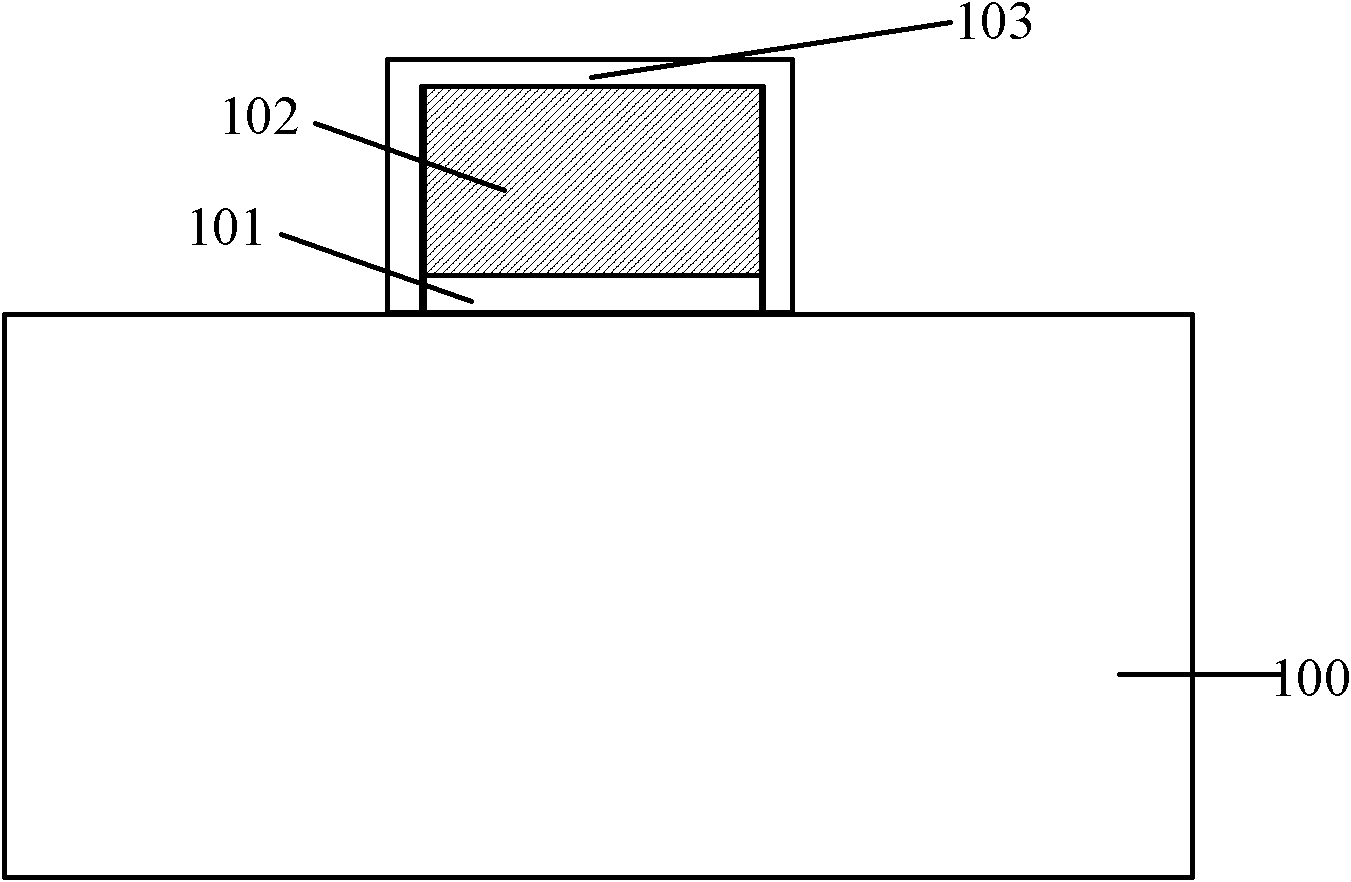

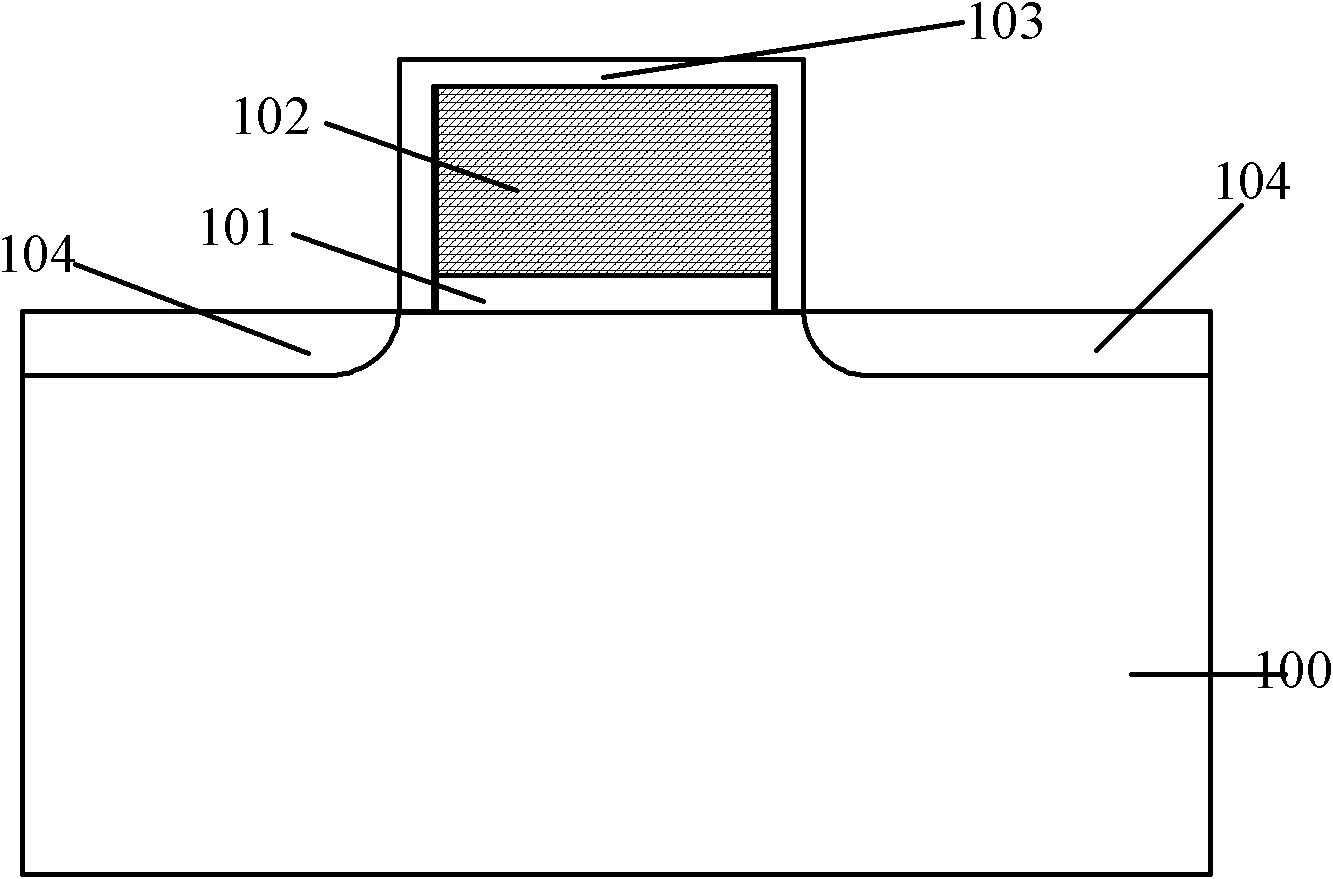

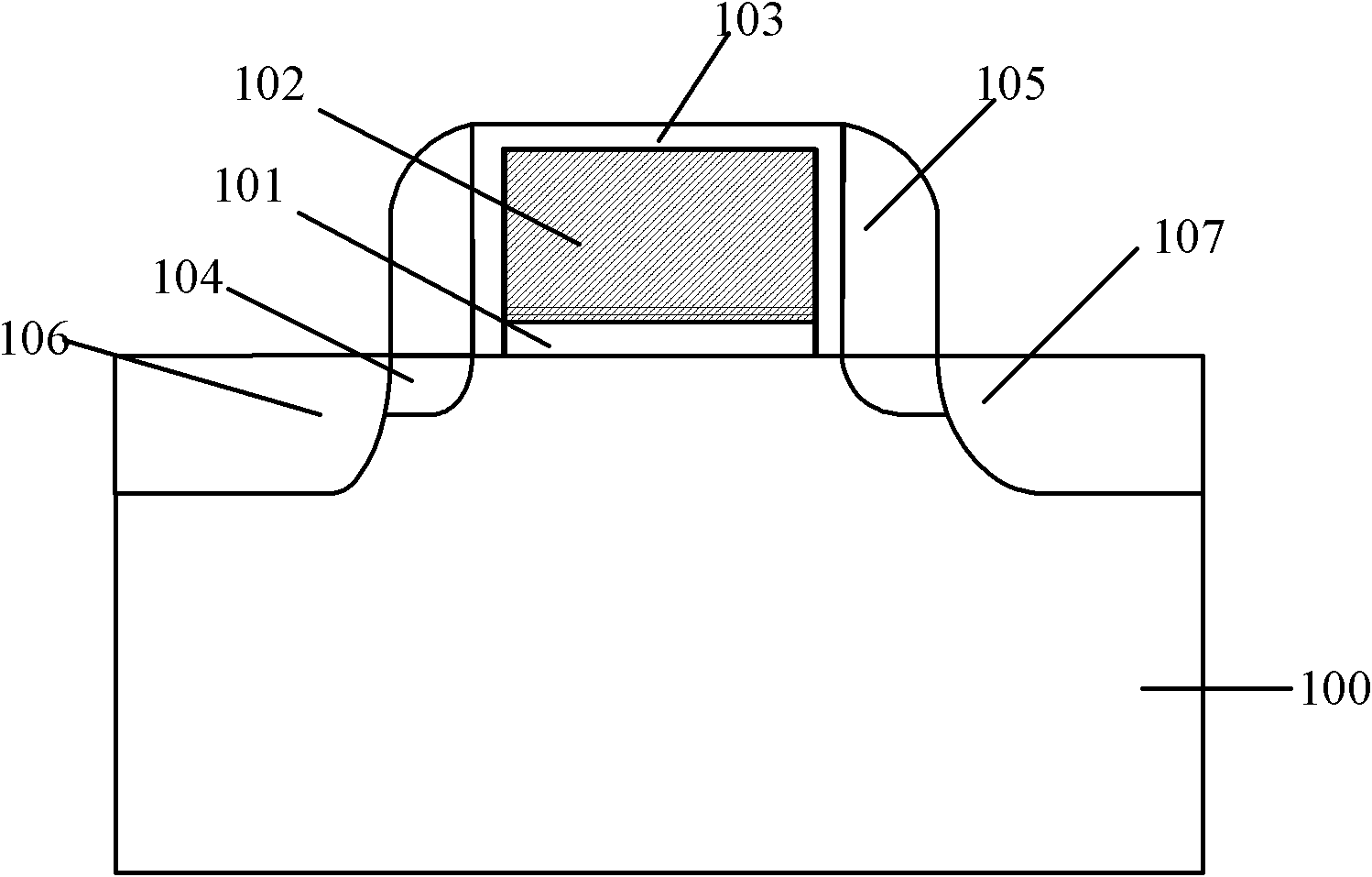

ActiveCN101908543BLower resistanceImprove drive currentTransistorSemiconductor/solid-state device manufacturingDriving currentJunction leakage

The present invention provides integrated circuit structures. The above-mentioned integrated circuit structure includes a base and a channel on the base. The channel includes a first group III-V compound semiconductor material composed of group III elements and group V elements. A gate structure is disposed on the channel. A source / drain region adjoins the channel, and the source / drain region includes a Group IV region selected from a group consisting essentially of silicon, germanium, and combinations thereof. By regrowing Si / Ge source / drain regions, existing silicidation techniques can be used to reduce source / drain resistance and improve final transistor drive current. The buffer layer has the effect of moderating the lattice constant transition between the channel and source / drain regions of the transistor, thus resulting in a reduced defect density and reduced junction leakage.

Owner:TAIWAN SEMICON MFG CO LTD

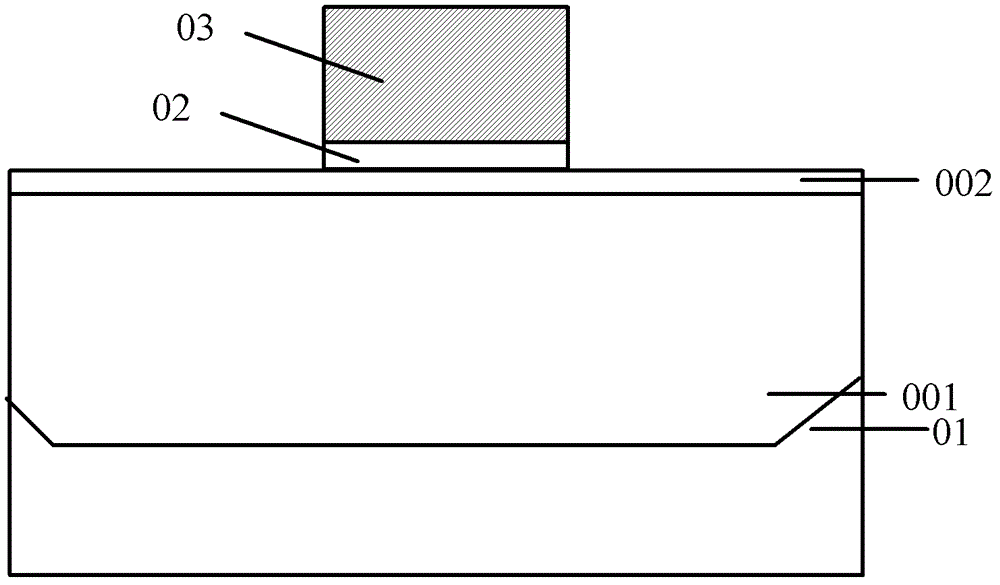

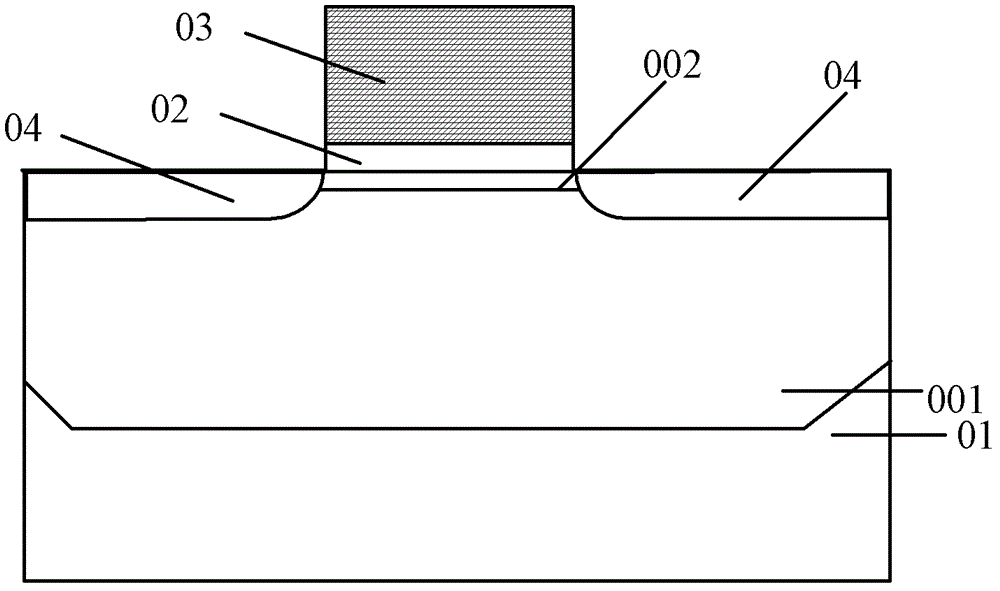

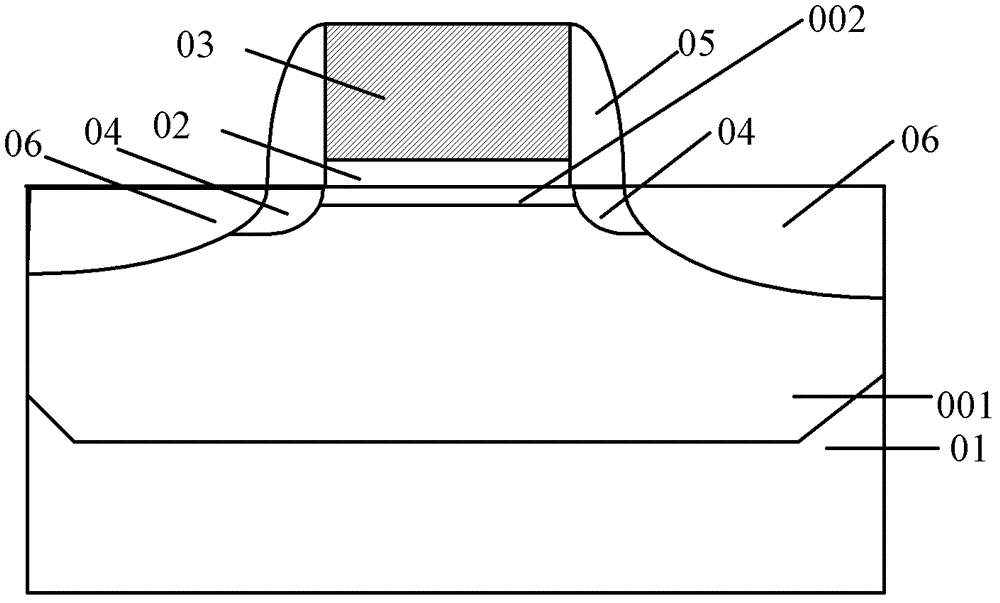

Transistor and manufacturing method for same

ActiveCN102479707BAvoid lateral spreadImprove short channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringActive layer

The invention provides a transistor and a manufacturing method for the same. The method includes the steps: providing a semiconductor substrate with a formed active layer; forming buried layers spaced from the active layer on the surface of the semiconductor substrate on two sides of the active layer; forming first epitaxial layers flush with the active layer on the surfaces of the buried layers and in the space between each buried layer and the active layer; forming grooves exposed out of the semiconductor substrate in the first epitaxial layers, wherein the grooves are positioned among the buried layers and the active layer; forming buried side walls in the grooves, wherein the thickness of each buried side wall is smaller than the depth of each groove; forming second epitaxial layers on the surfaces of the buried side walls, the active layer and the first epitaxial layers; forming gate structures on the surfaces of the second epitaxial layers above the active layer; and forming a source region and a drain region in the second epitaxial layer and the first epitaxial layer on two sides of each gate structure, wherein the source region and the drain region are positioned on two sides of an isolating side wall. By the aid of the method, the short-channel effect and the performance of the transistor are improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Memory device and method for fabricating the same

InactiveCN100438036CReduced Junction Leakage CurrentData retention time is longTransistorSolid-state devicesBit lineCell region

Disclosed are a memory device and a method for fabricating the same. The memory device includes: a substrate provided with a trench; a bit line contact junction formed beneath the trench; a plurality of storage node contact junctions formed outside the trench; and a plurality of gate structures each being formed on the substrate disposed between the bit line contact junction and one of the storage node contact junctions. Each sidewall of the trench becomes a part of the individual channels and thus, channel lengths of the transistors in the cell region become elongated. Accordingly, the storage node contact junctions have a decreased level of leakage currents, thereby increasing data retention time.

Owner:SK HYNIX INC

Method of manufacturing semiconductor device

InactiveUS8435862B2Avoid abnormal growthAvoid formingSolid-state devicesSemiconductor/solid-state device manufacturingAdditive ingredientSemiconductor

The method of manufacturing a semiconductor device comprises forming a metal film over silicon regions and insulating films; performing a first heat treatment under an oxygen atmosphere containing oxygen as a main ingredient, to form a first silicide film in the silicon region by reacting the metal film and the silicon region, and to simultaneously form a metal oxide by oxidizing the entire surface of the metal film from the surface side thereof; and selectively removing the metal oxide and the unreacted metal film using a chemical.

Owner:RENESAS ELECTRONICS CORP

P-type FET and manufacturing method thereof

ActiveCN111463285AAchieve independent regulationIncrease contact areaSemiconductor/solid-state device manufacturingSemiconductor devicesJunction leakageEngineering

The invention discloses a P-type FET. A halo injection region comprises first halo injection sub-regions capable of independently adjusting sub-threshold leakage current and second halo injection sub-regions capable of independently adjusting drain terminal junction leakage current; the junction depth of the first halo injection sub-regions is larger than that of the lightly doped drain regions but smaller than that of the drain regions, the first halo injection sub-regions transversely extend into the channel regions outside the side surfaces of the corresponding lightly doped drain regions,and the first halo injection sub-regions wrap the bottom surfaces and the side surfaces of the lightly doped drain regions; the junction depth of the second halo injection sub-regions is larger than that of the first halo injection regions, the second halo injection sub-regions are located on the inner sides of the side faces of the lightly doped drain regions and located at the bottoms of the lightly doped drain regions, and the second halo injection sub-regions wrap the side faces, located at the bottoms of the lightly doped drain regions, of the corresponding source regions or drain regions. The invention further discloses a manufacturing method of the P-type FET. According to the invention, sub-threshold leakage current and junction leakage current of the device can be reduced at the same time, and extremely low electric leakage is realized.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Semiconductor device and method of forming the same

ActiveCN106548983BImproved Junction Leakage CurrentReduced Junction Leakage CurrentSemiconductor/solid-state device manufacturingJunction leakageDevice material

The invention discloses a semiconductor device and a forming method thereof. The forming method of the semiconductor device comprises the steps as follows: a first ion implantation process is carried out on a substrate in a PMOS peripheral region at two sides of a first gate structure and a first graded junction region is formed at the lower part of a first peripheral source-drain region; a second ion implantation process is carried out on the first peripheral source-drain region and a first core drain-source region, and a first contact resistance region is formed on the surface of the first peripheral source-drain region and the surface of the first core drain-source region; a third ion implantation process is carried out on the substrate in an NMOS peripheral region at two sides of a third gate structure and a second graded junction region is formed at the lower part of a second peripheral source-drain region; and a fourth ion implantation process is carried out on a second peripheral source-drain region and a second core drain-source region, and a second contact resistance region is formed on the surface of the second peripheral source-drain region and the second core drain-source region. According to the semiconductor device, the problem of a short channel effect of a core device is solved while junction leakage current of an input / output device is reduced, thereby improving the electric property of the formed semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

MOS transistor and forming method thereof

ActiveCN101459082BImprove performanceReduce junction depthSemiconductor/solid-state device manufacturingSemiconductor devicesCondensed matter physicsSemiconductor

An MOS transistor comprises low doped source / drain extended regions in a semiconductor substrate and on two sides of a grid structure, sidewalls located on the semiconductor substrate on two sides of the grid structure, heavily doped source / drain regions located in the semiconductor and on two sides of the grid structure, and pocket regions and F-ion doped regions respectively located in the semiconductor substrate and on two sides of the grid structure, wherein the F-ion doped regions are located around the pocket regions. The invention further provides a method of forming the MOS transistors. By forming the F-ion doped regions around the pocket regions of the MOS transistor, transient enhanced diffusion effect of ions from the pocket regions into the semiconductor substrate can be prevented, thereby reducing junction depth, decreasing junction current leakage, and improving the performance of the MOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

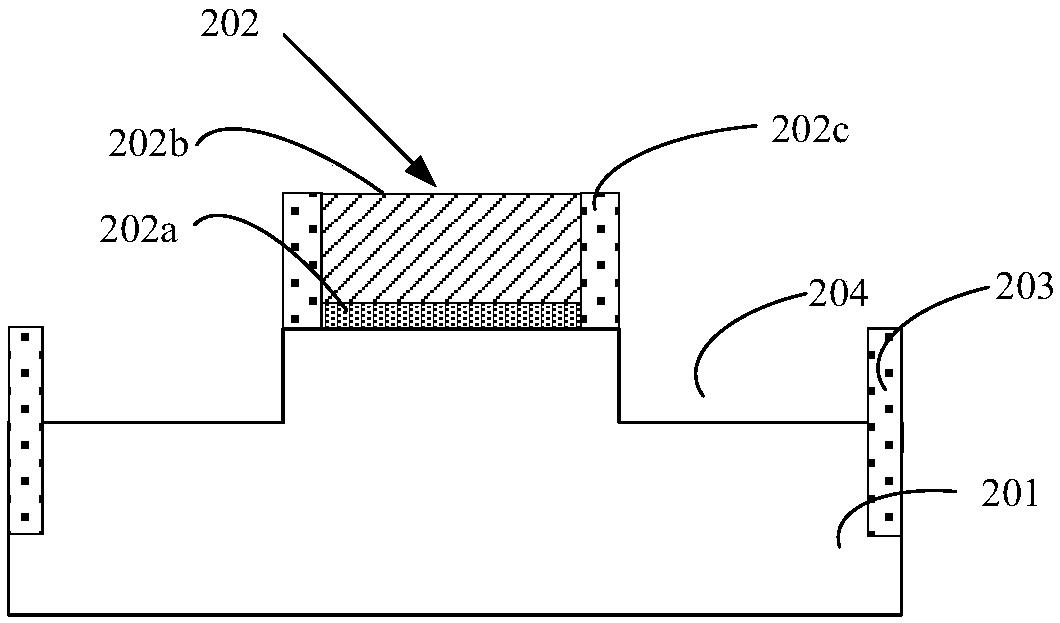

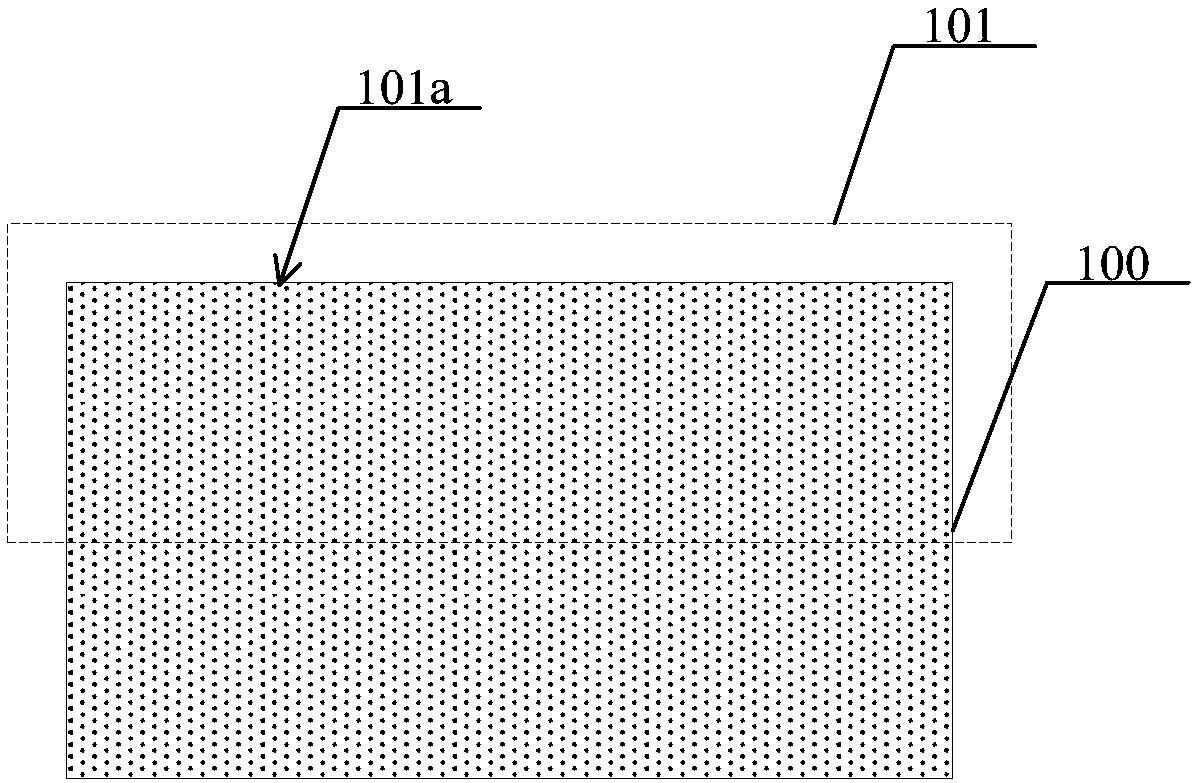

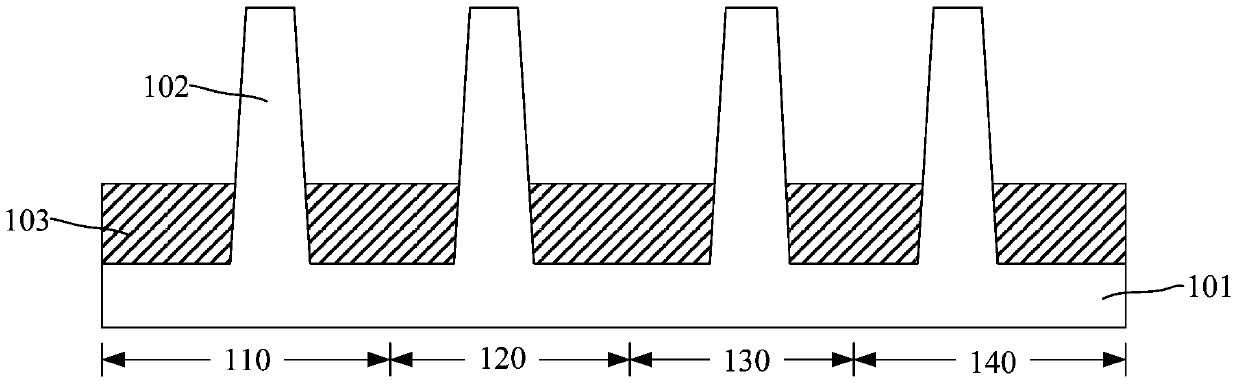

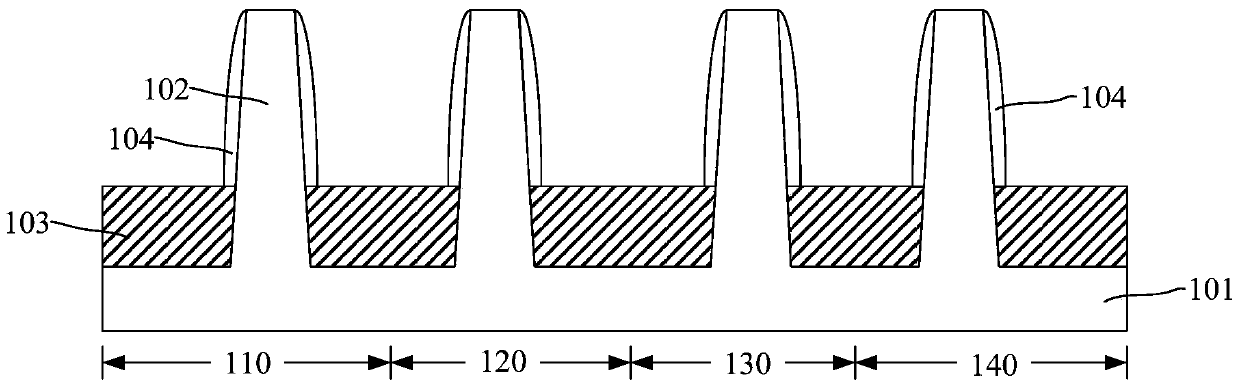

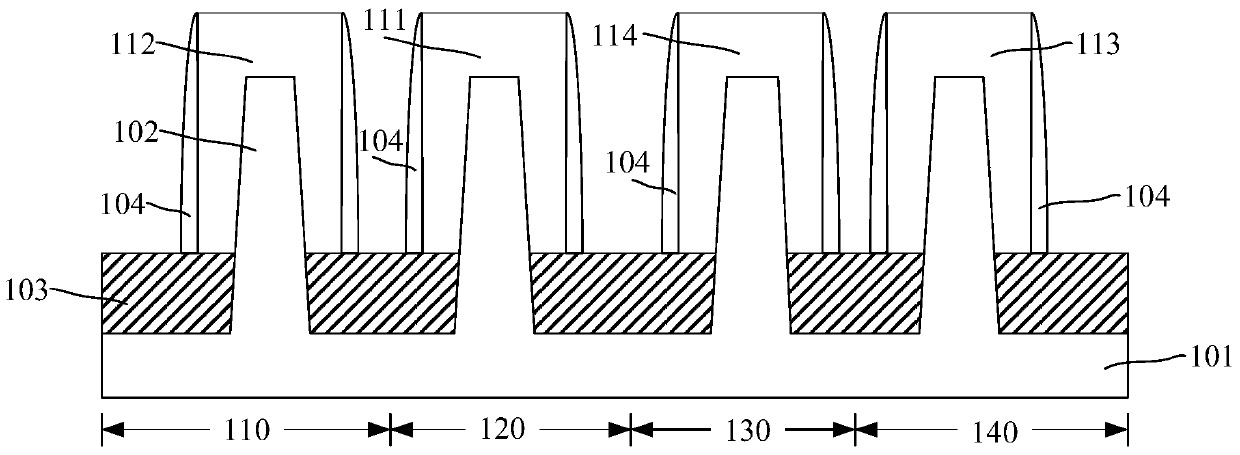

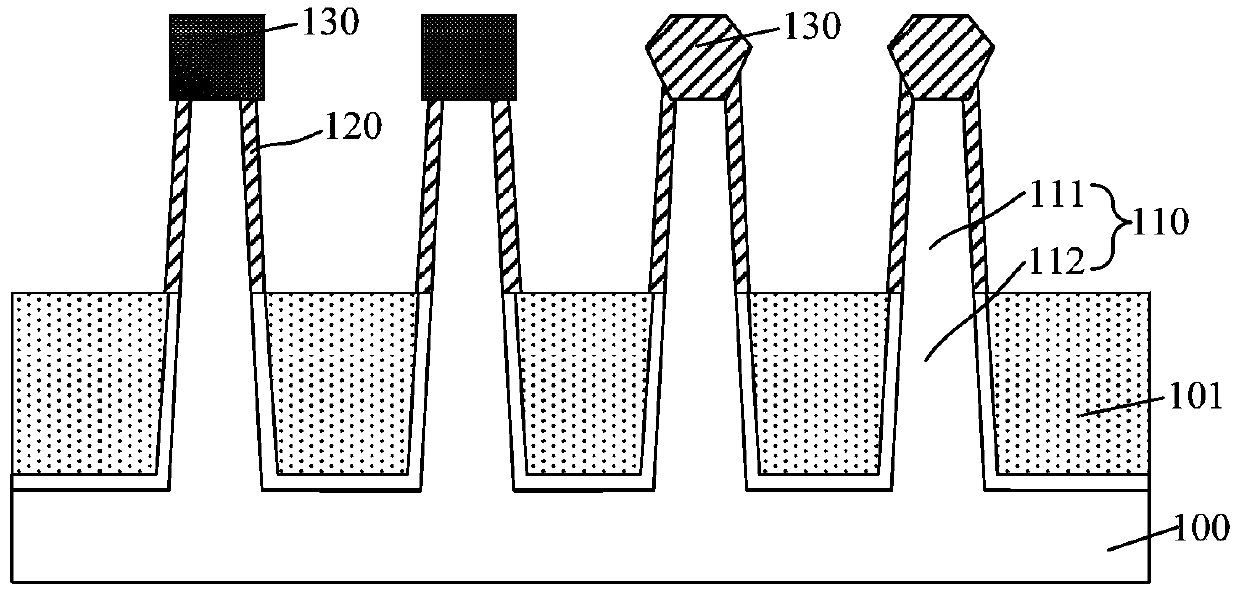

Semiconductor structure and manufacturing method thereof

ActiveCN107437533BDecrease the concentration gradientReduced Junction Leakage CurrentTransistorSolid-state devicesJunction leakageSemiconductor structure

The invention relates to a semiconductor structure and a manufacturing method thereof. The method comprises the steps of providing a base, wherein the base comprises a first depth region, a second depth region and a third depth region; forming a buffer doping ion region in the base of the second depth region; removing a part of the base of the second depth region and the third depth region to form a substrate and fin parts protruding out of the substrate; forming an isolation structures with thickness equal to the depth of the second depth region on the substrate, wherein the fin part exposed out of the isolation structure is a fin part first region, and a part which is not exposed is a fin part second region; forming a punchthrough-prevention doping ion region with an ion type same as that of the buffer doping ion region in the fin part second region, wherein the ion concentration of the punchthrough-prevention doping ion region is larger than that of the buffer doping ion region; forming a grid structure bridging the fin parts; and forming a source-drain doping region in the fin part first region at two sides of the grid structure. The ion concentration of the punchthrough-prevention doping ion region is between that of the source-drain doping region and that of the buffer doping ion region, and thus, the junction leak current between the source-drain doping region and the substrate is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1