MOS transistor and forming method thereof

A MOS transistor and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of increasing the thermal budget of semiconductor devices, unfavorable ultra-small devices, increasing process costs, etc., to reduce junction leakage current, Effect of suppressing diffusion effect and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

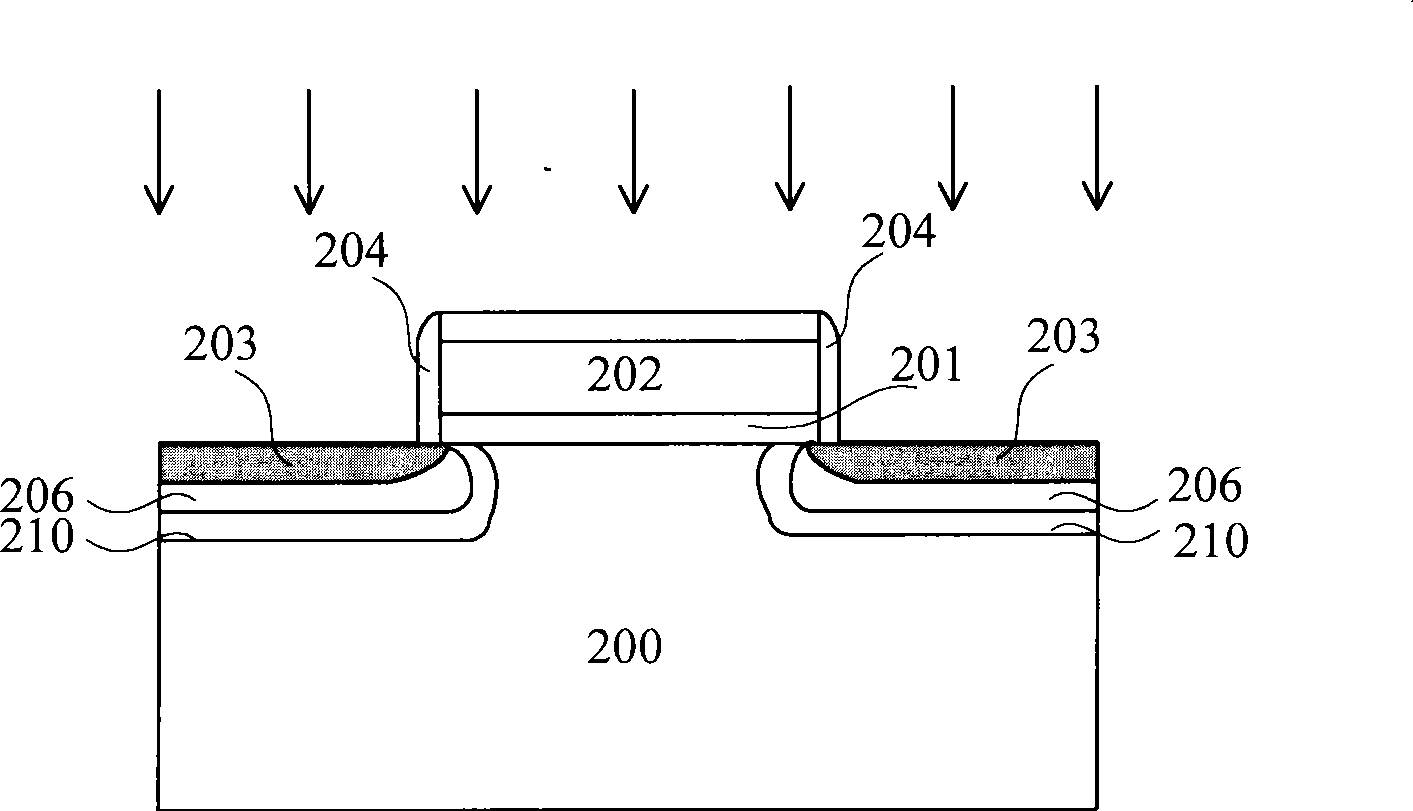

[0034] The present invention provides a MOS transistor, by doping F ions around the pocket region of the MOS transistor to form a F ion doped region, suppressing the transient enhanced diffusion effect of doping ions in the pocket region, and reducing the junction leakage of the MOS transistor current, improving the performance of MOS transistors.

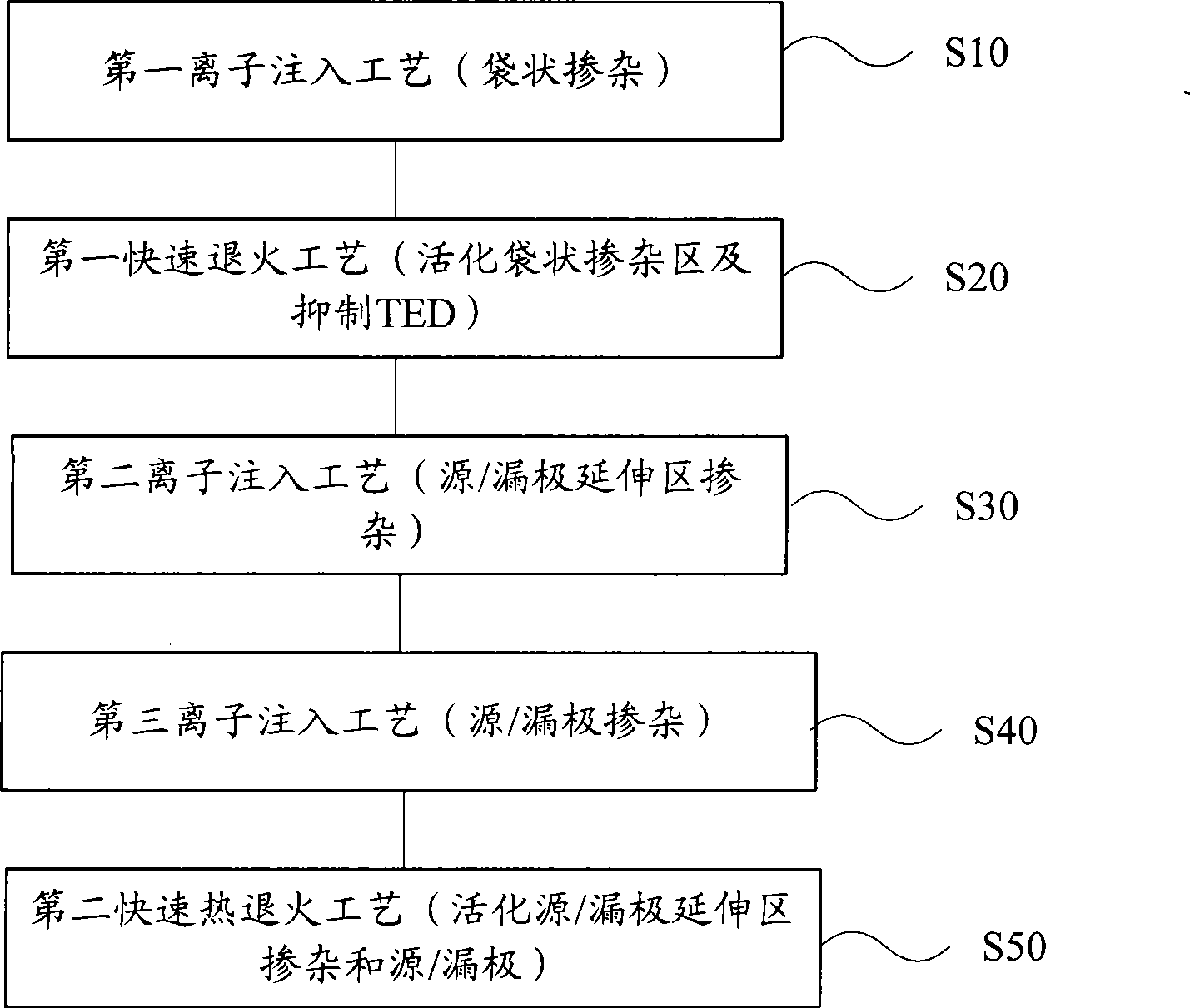

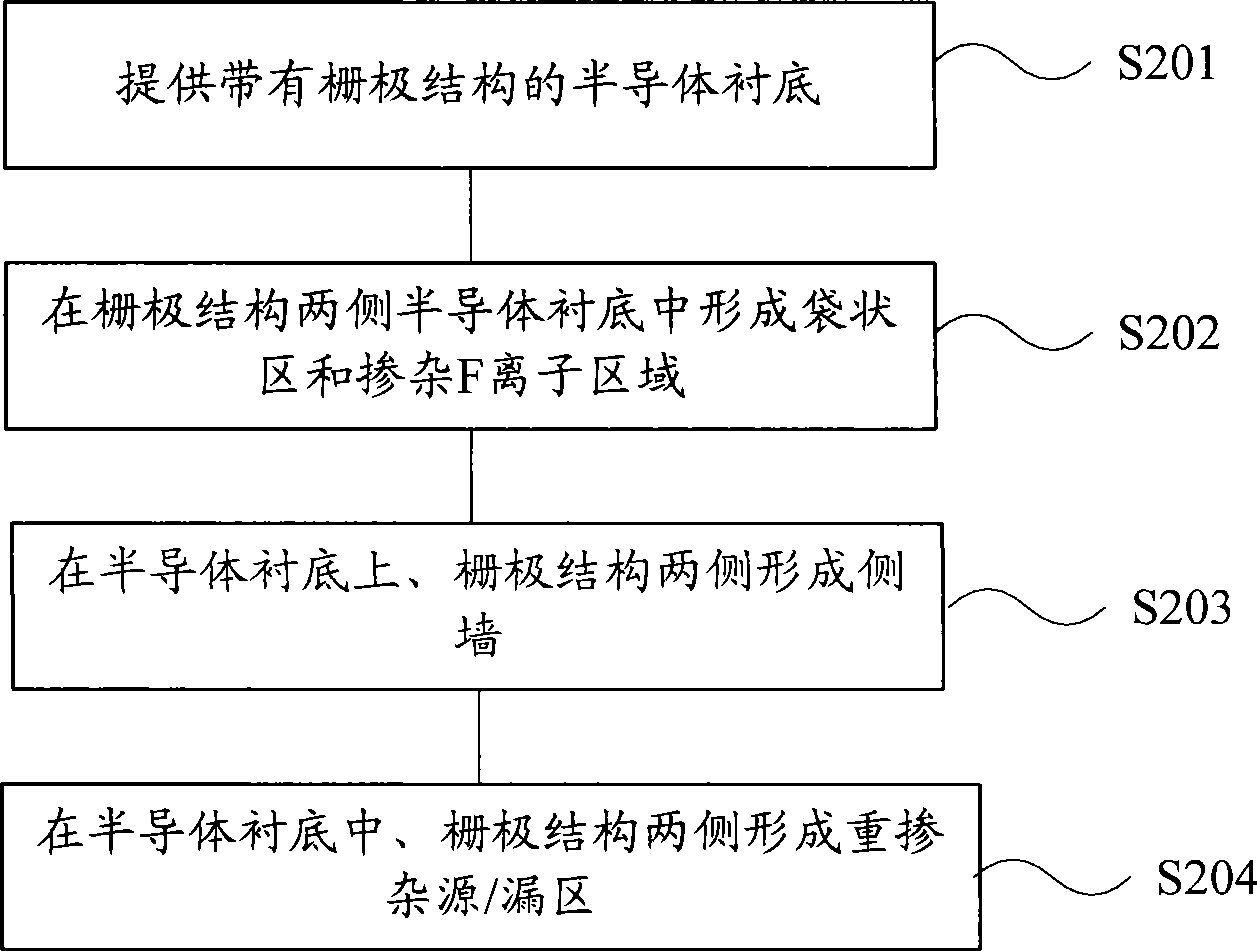

[0035] refer to figure 2 It is a schematic flow chart of a specific embodiment of forming a MOS transistor in the present invention, including the following steps: performing step S201, providing a semiconductor substrate with a gate structure; performing step S202, forming pockets in the semiconductor substrate on both sides of the gate structure Shaped region and doped F ion region, the doped F ion region is located around the pocket region; step S203 is performed to form sidewalls on the semiconductor substrates on both sides of the gate structure; step S204 is performed to form sidewalls on both sides of the gate structure A ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More