Patents

Literature

612 results about "Programming process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Programming Process. The procress of creating a program consists the following stages: The process goes in cycles. You start with a design, and try to write code to implement that design. As you write the code you may come across problems that send you back to the design stage. Once you have code written you try to compile it.

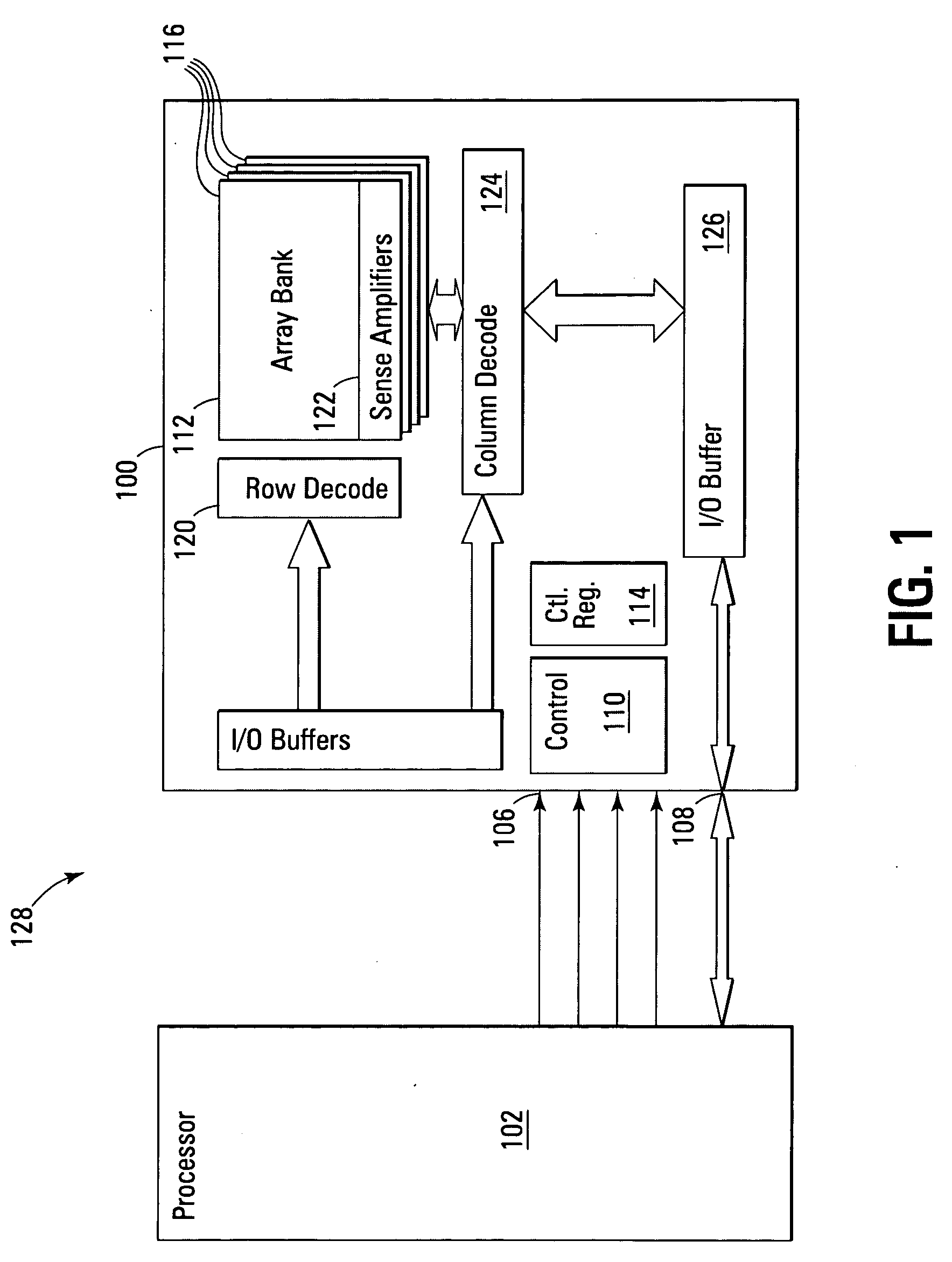

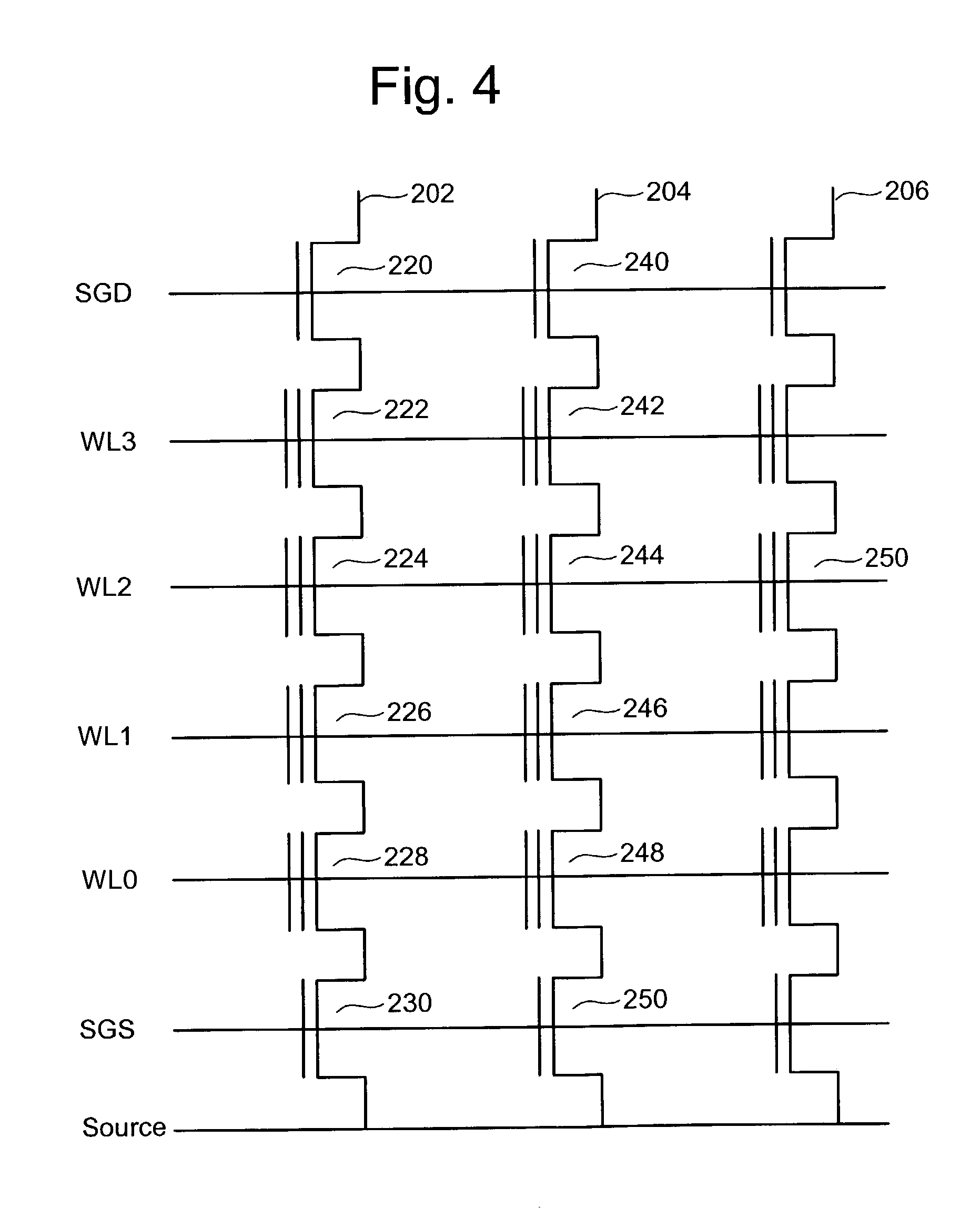

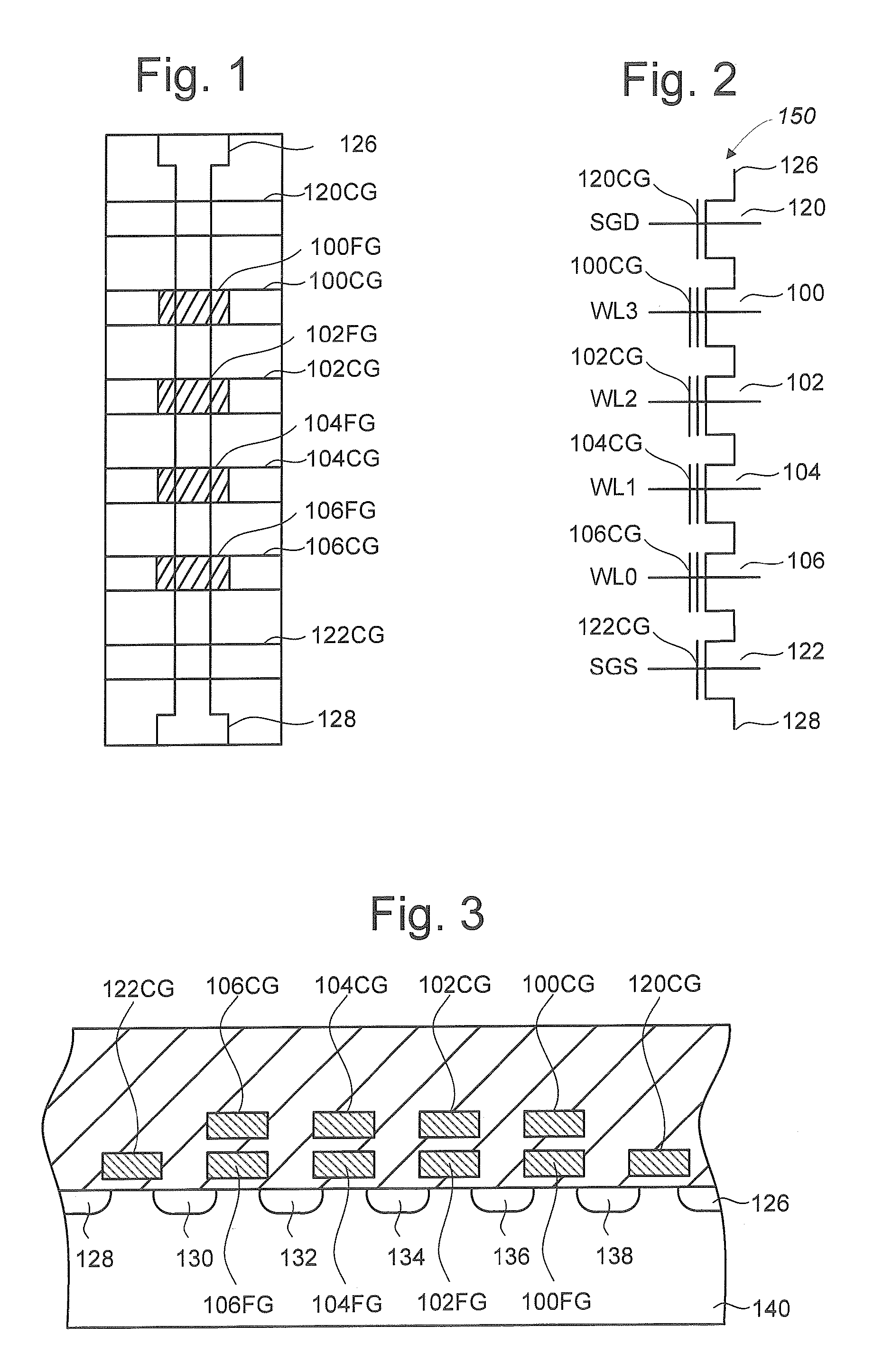

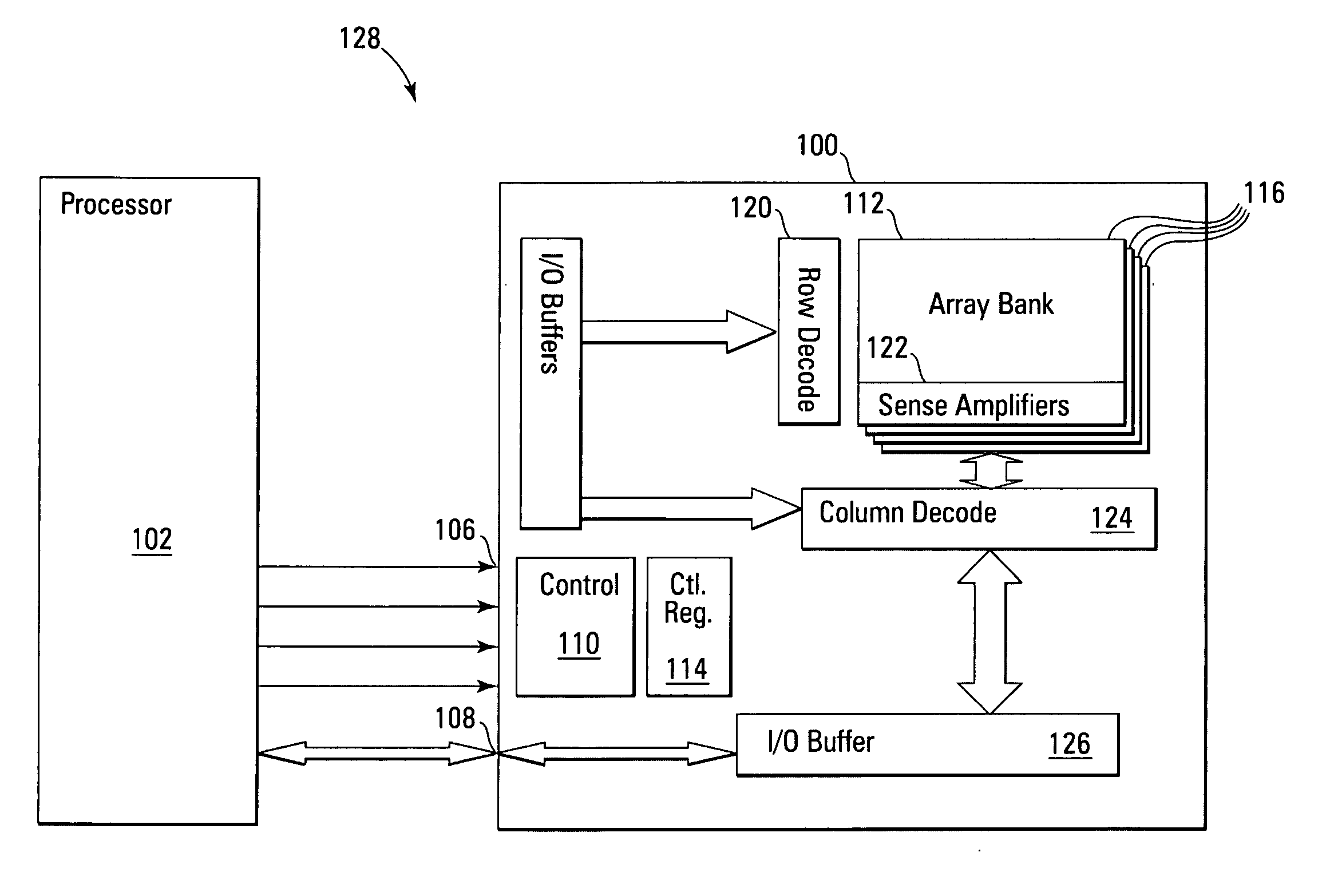

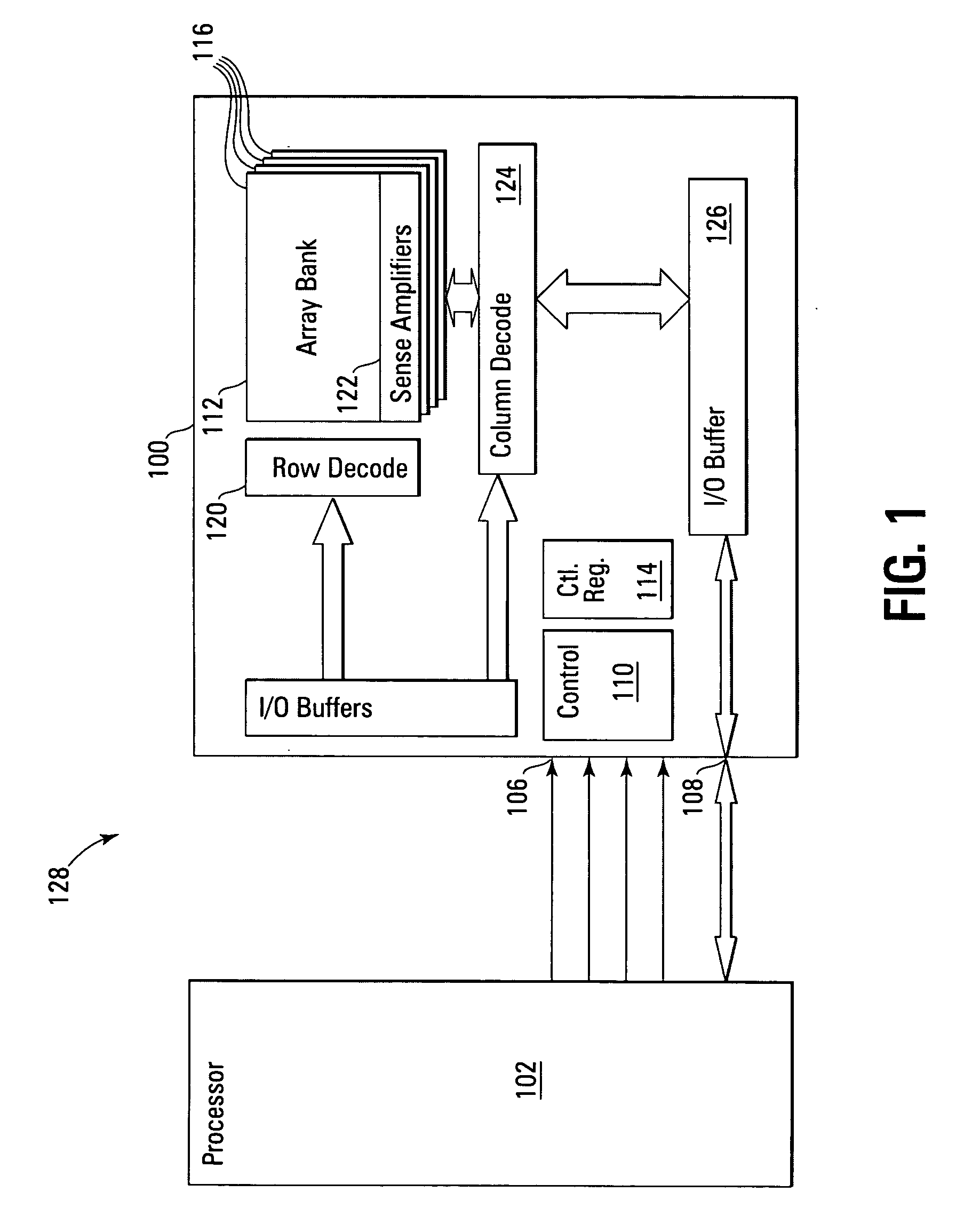

Source side self boosting technique for non-volatile memory

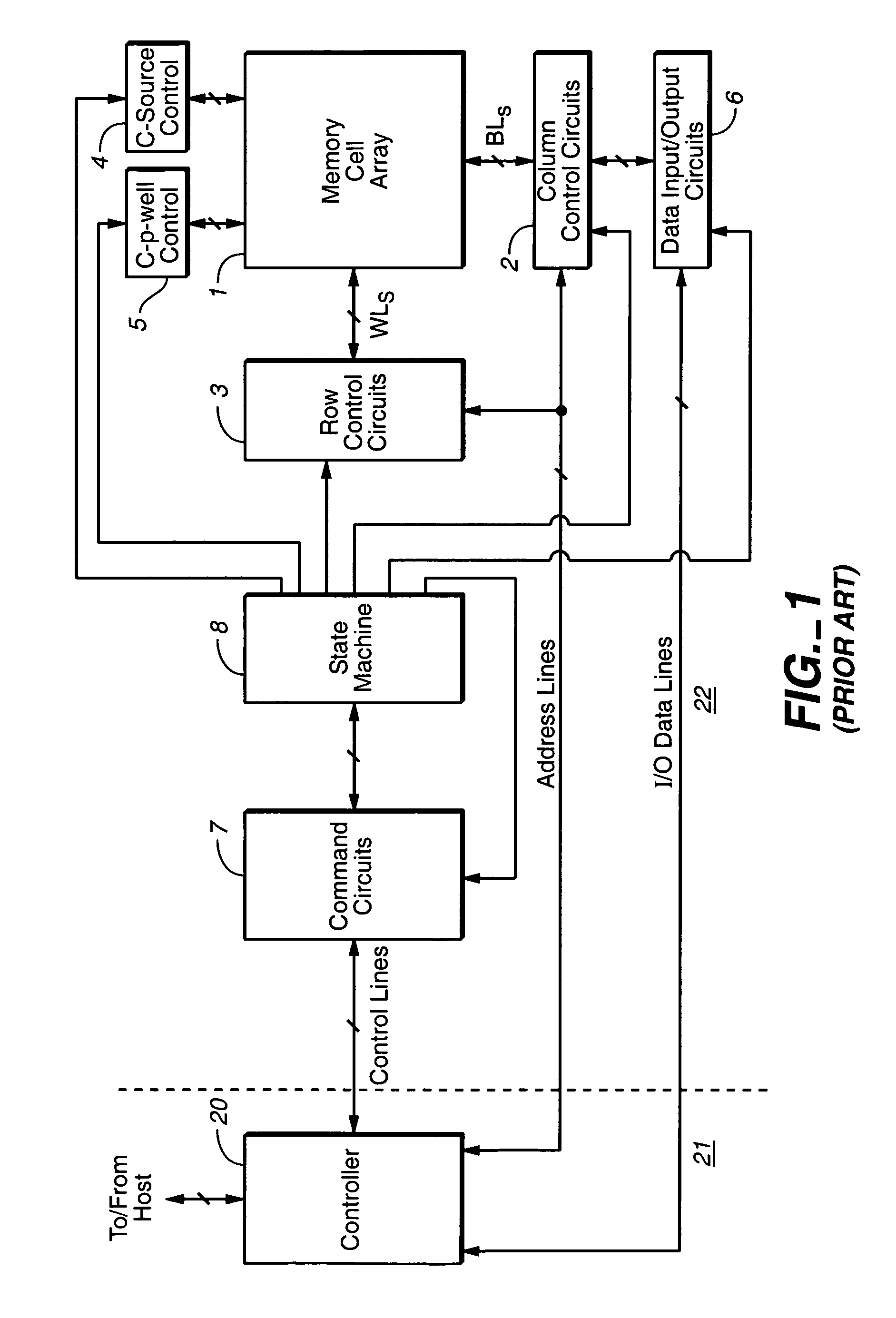

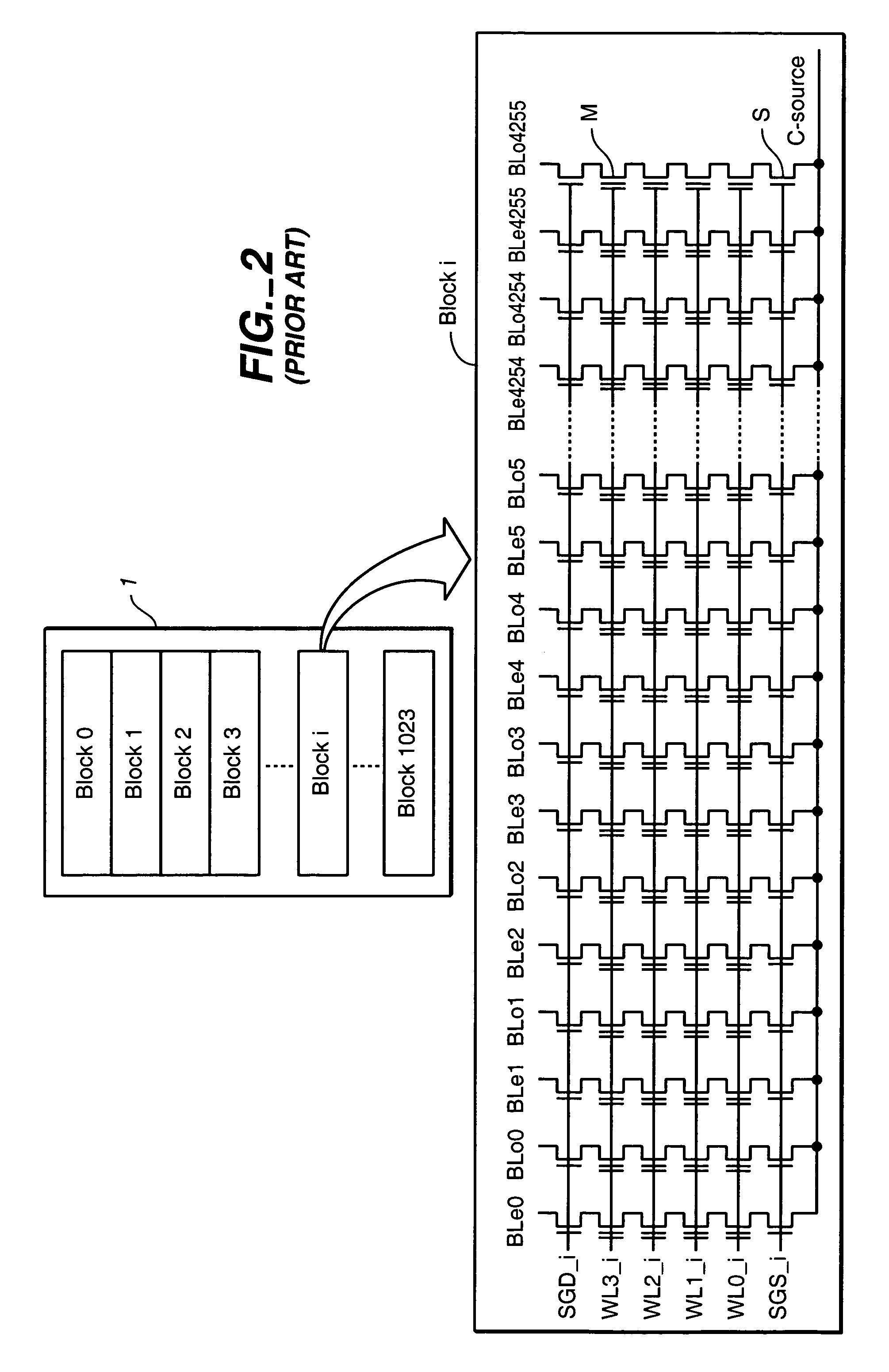

InactiveUS6859397B2Improve performanceMinimize program disturbRead-only memoriesDigital storagePre-chargeProgramming process

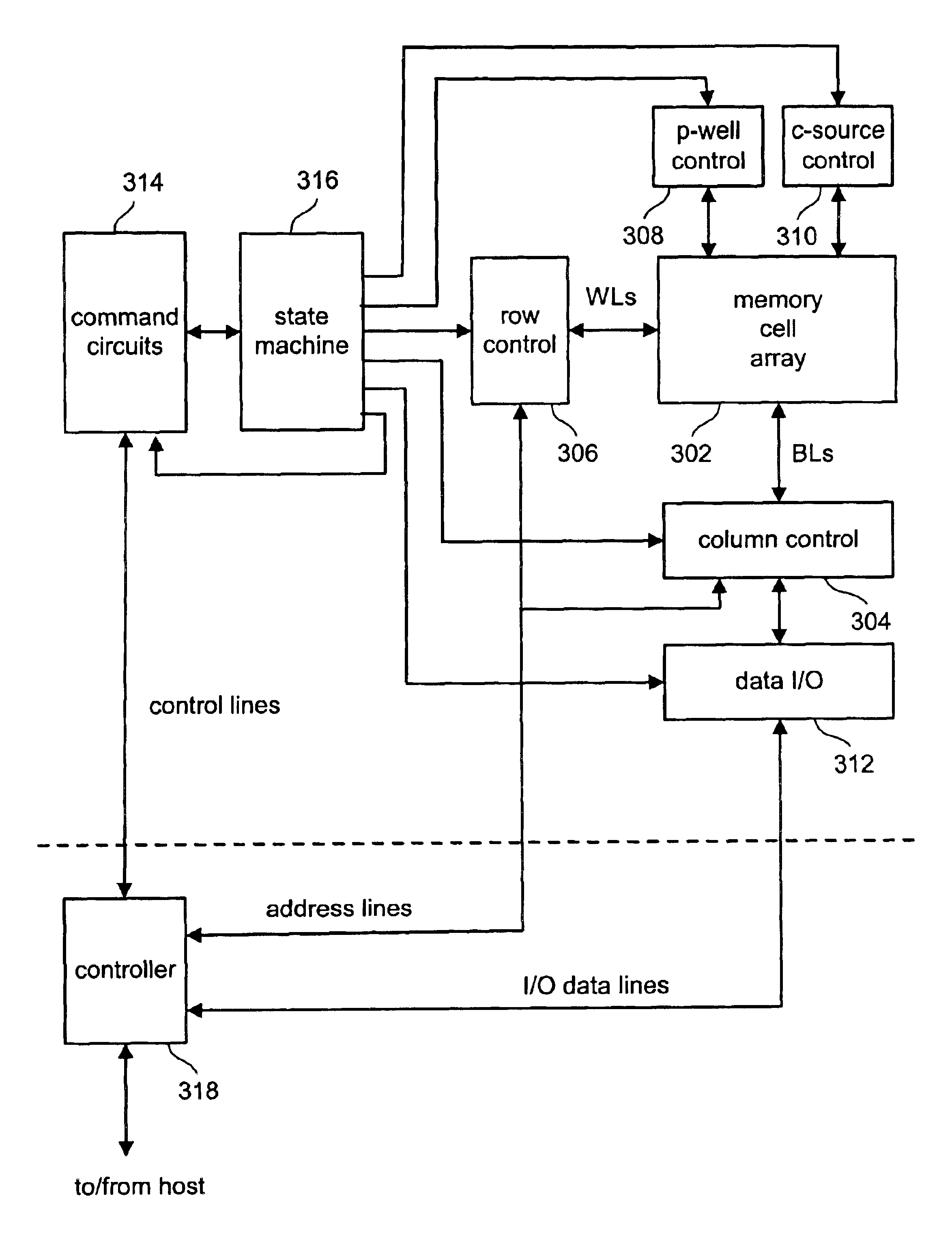

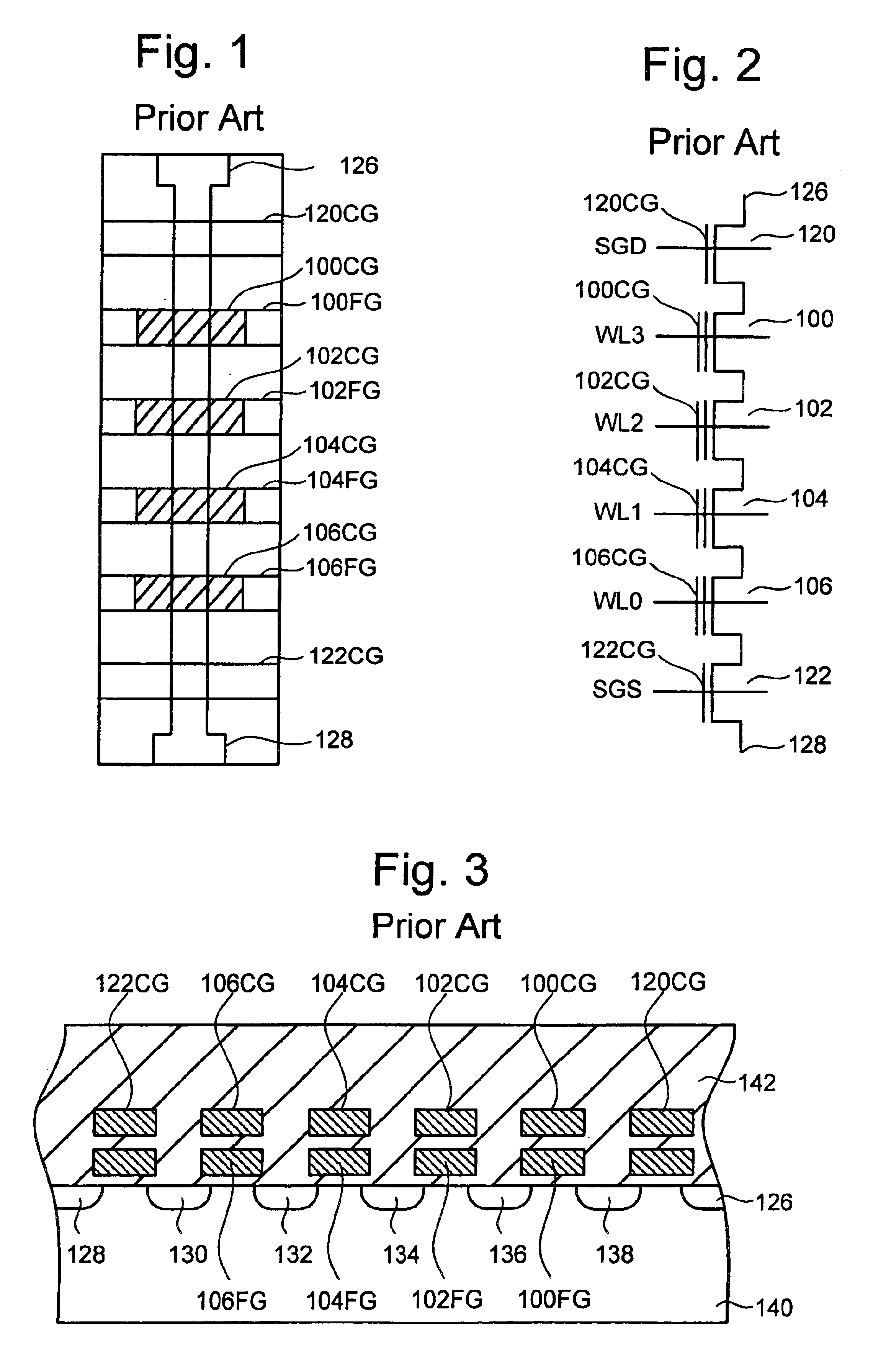

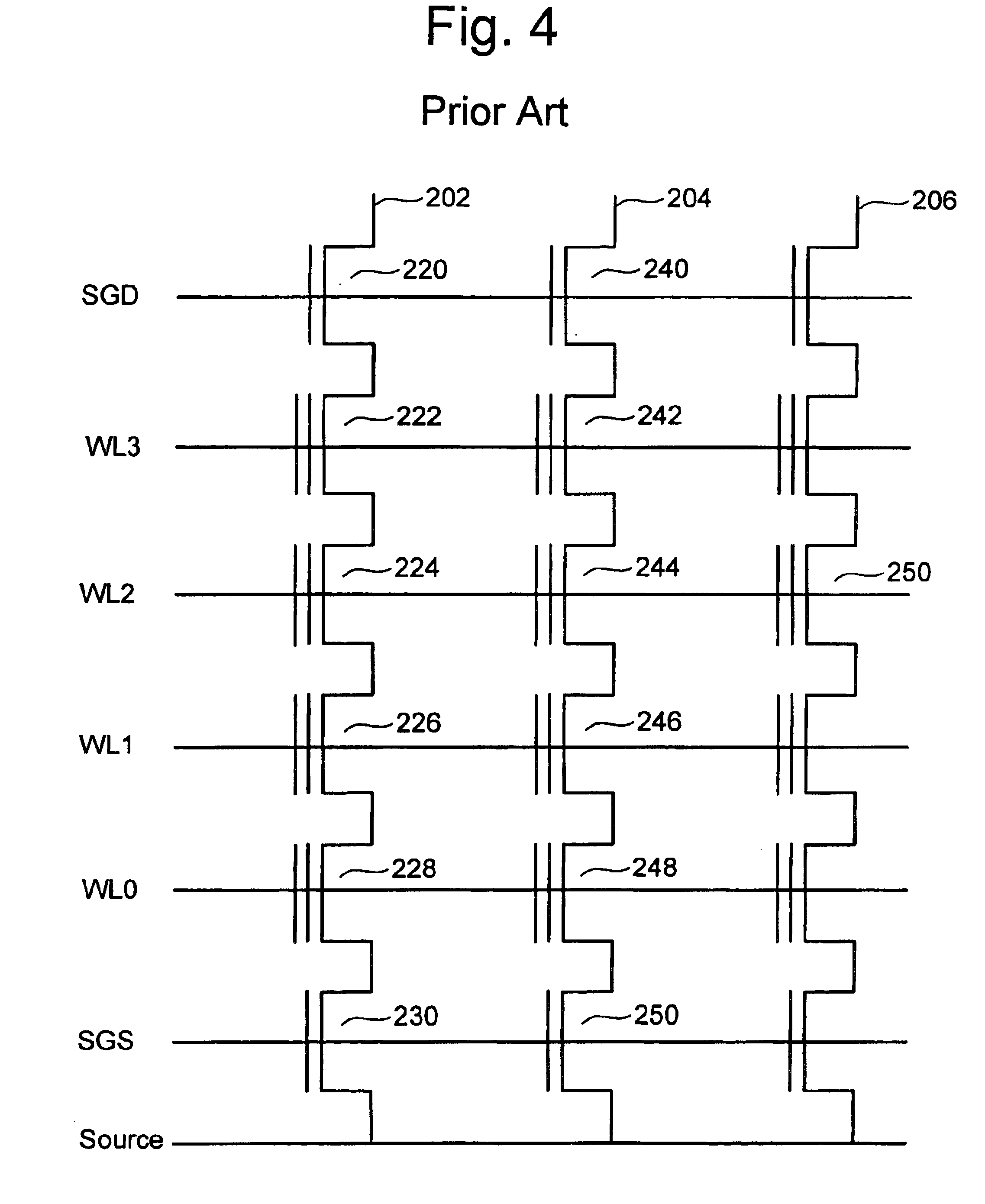

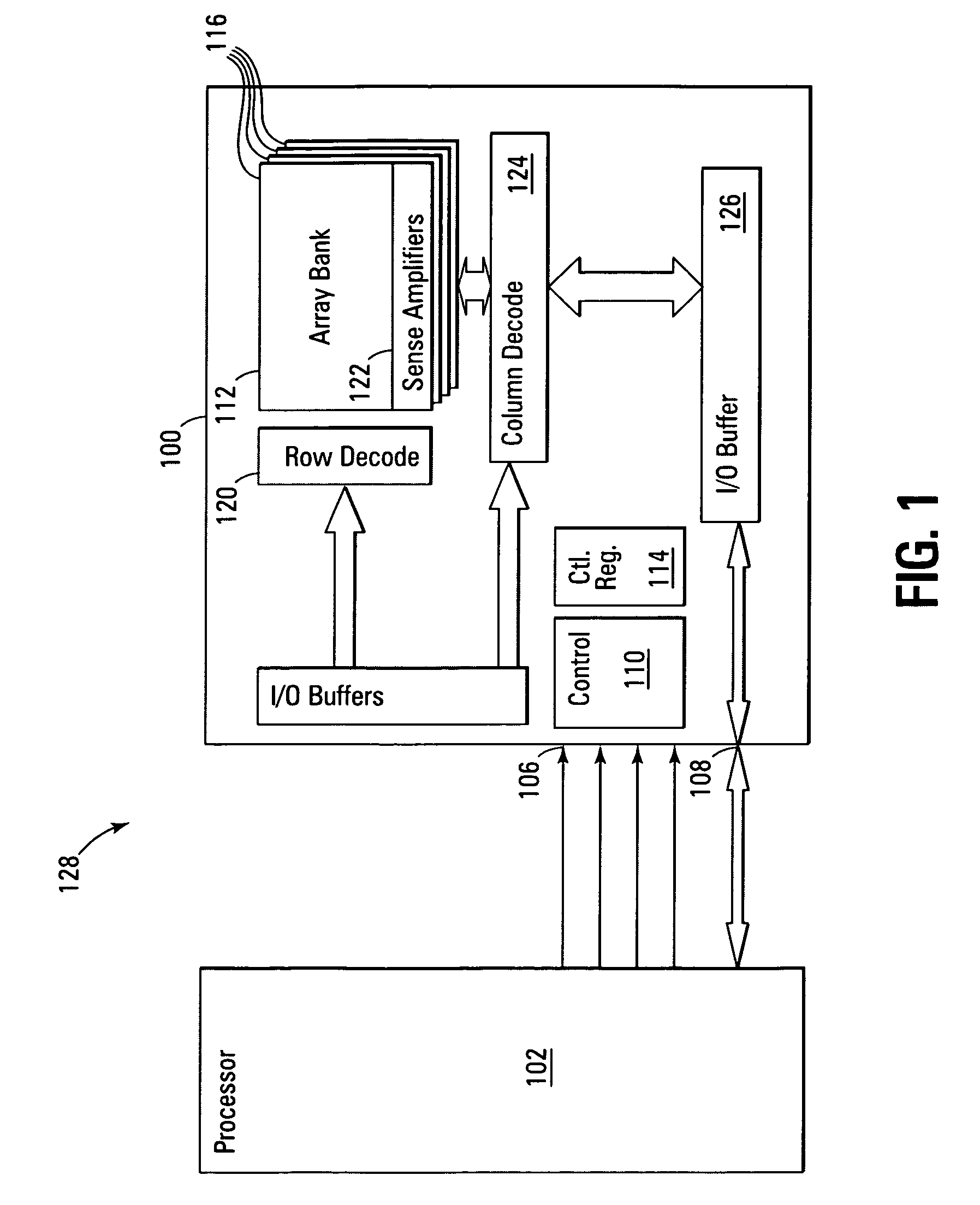

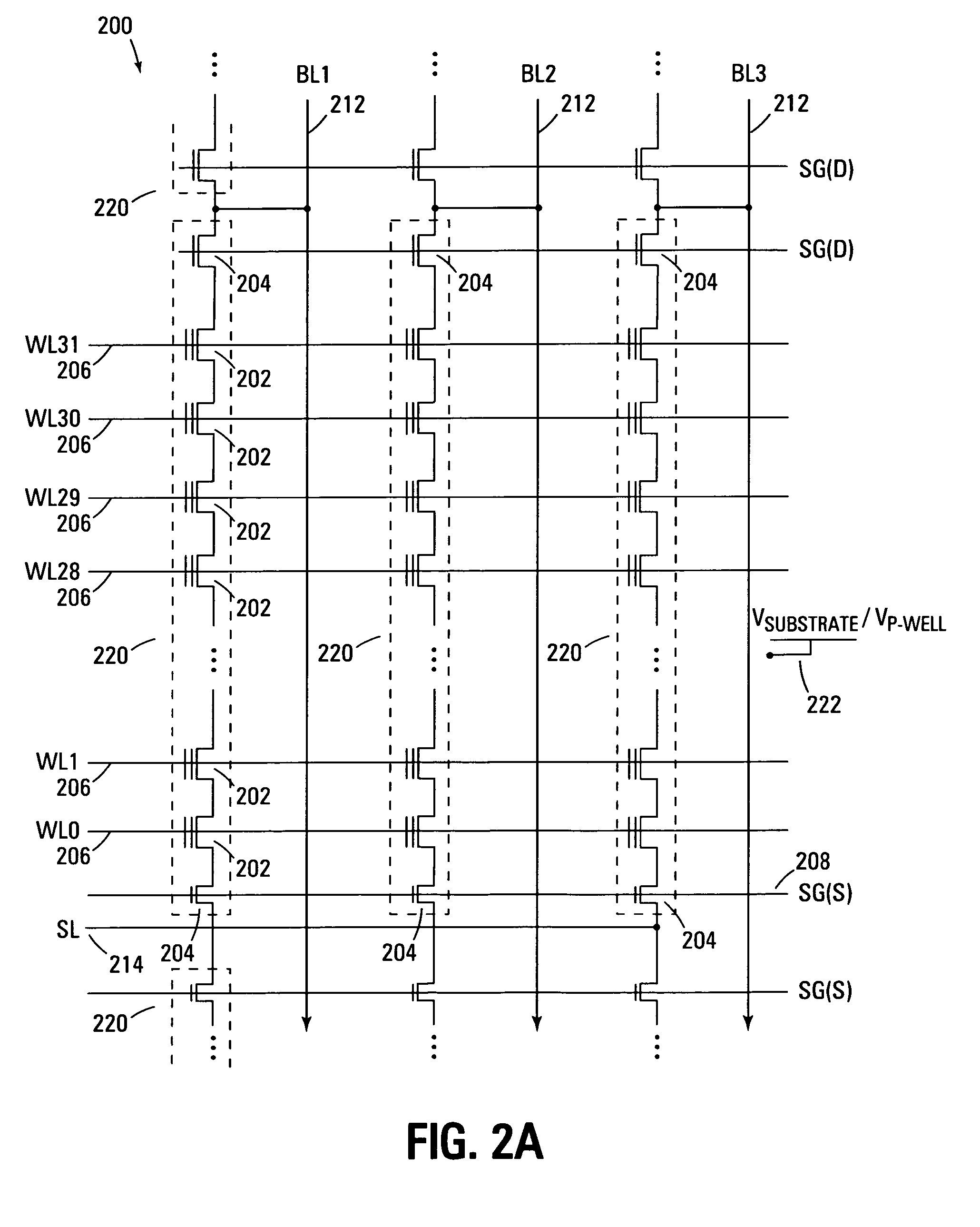

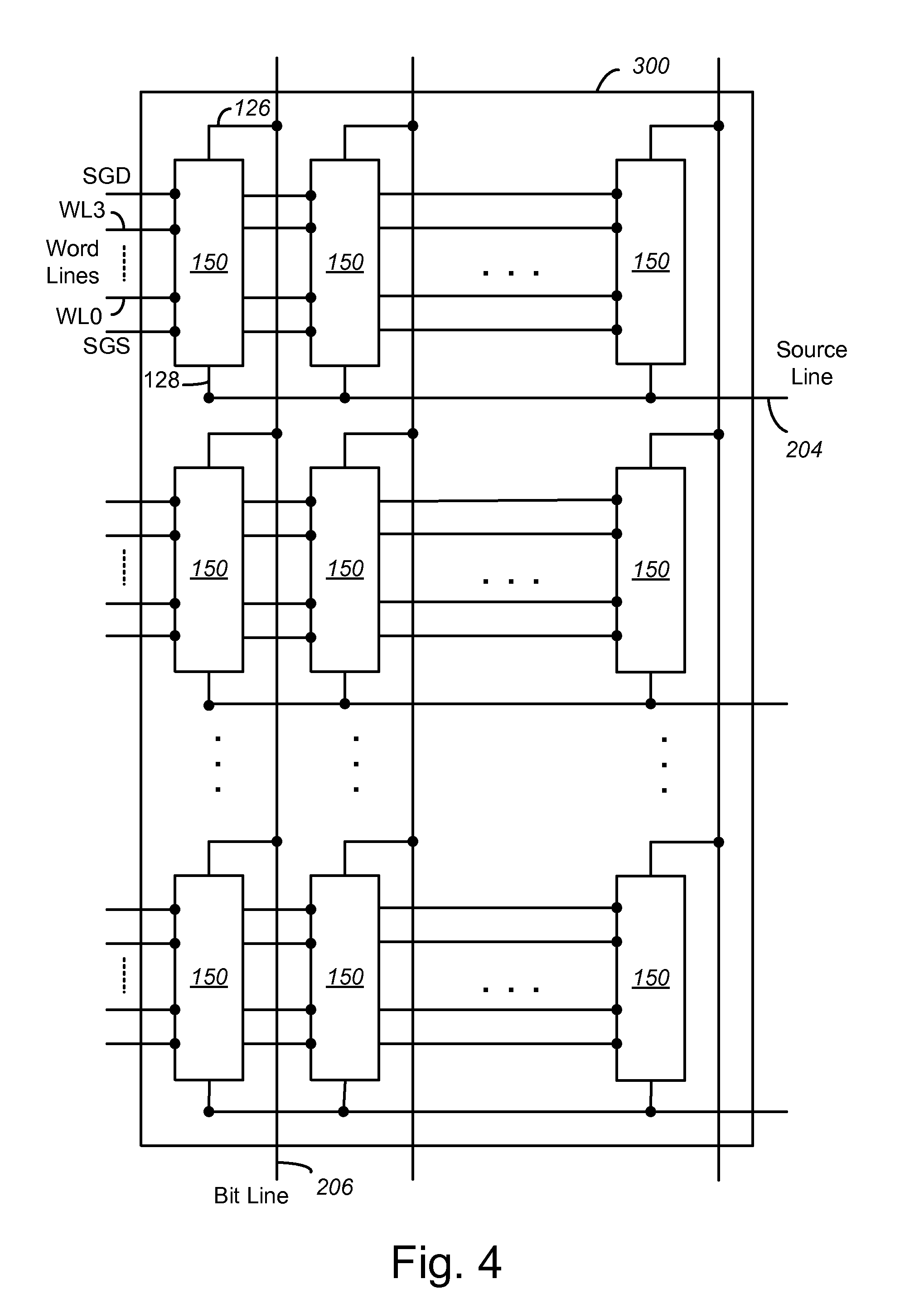

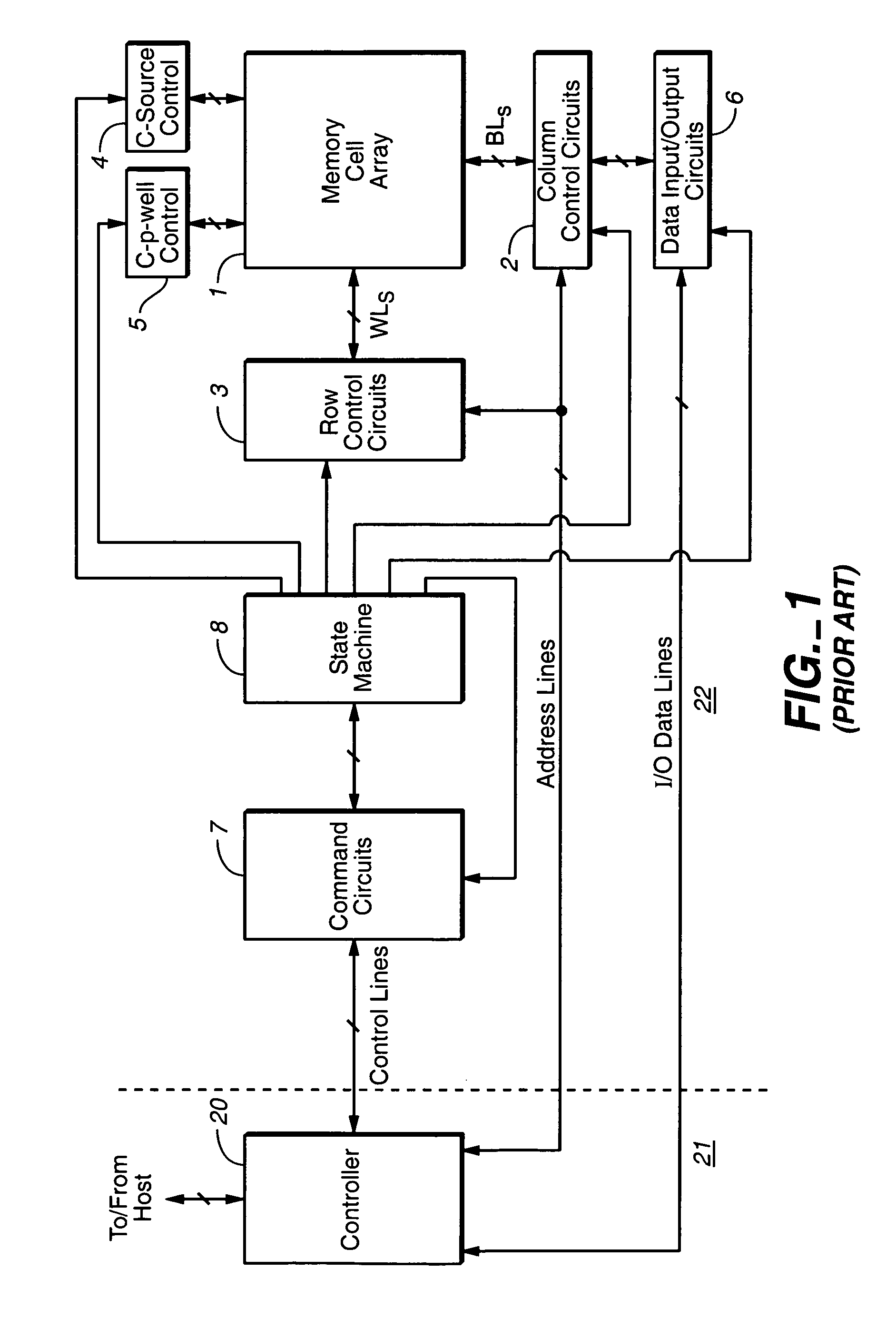

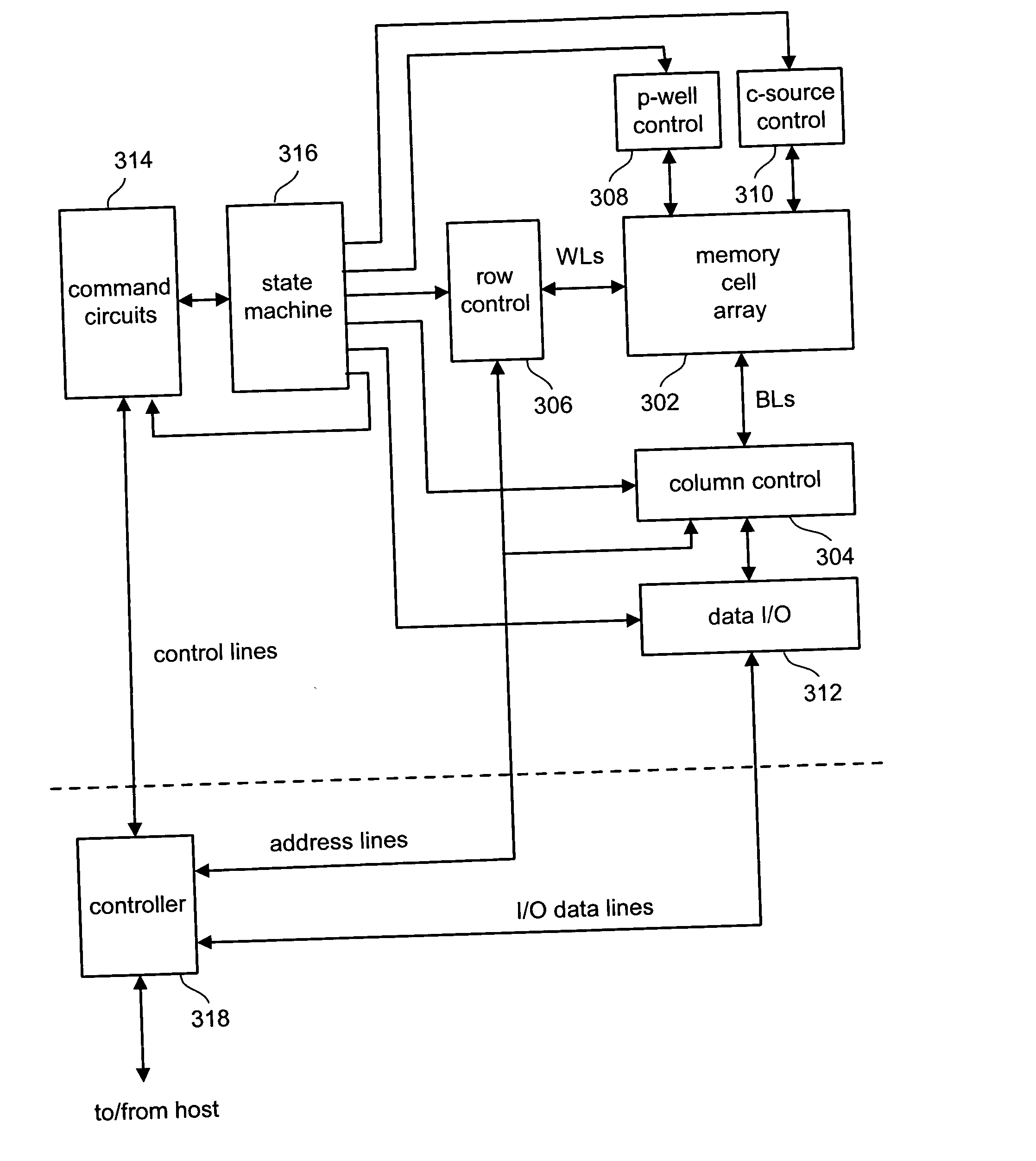

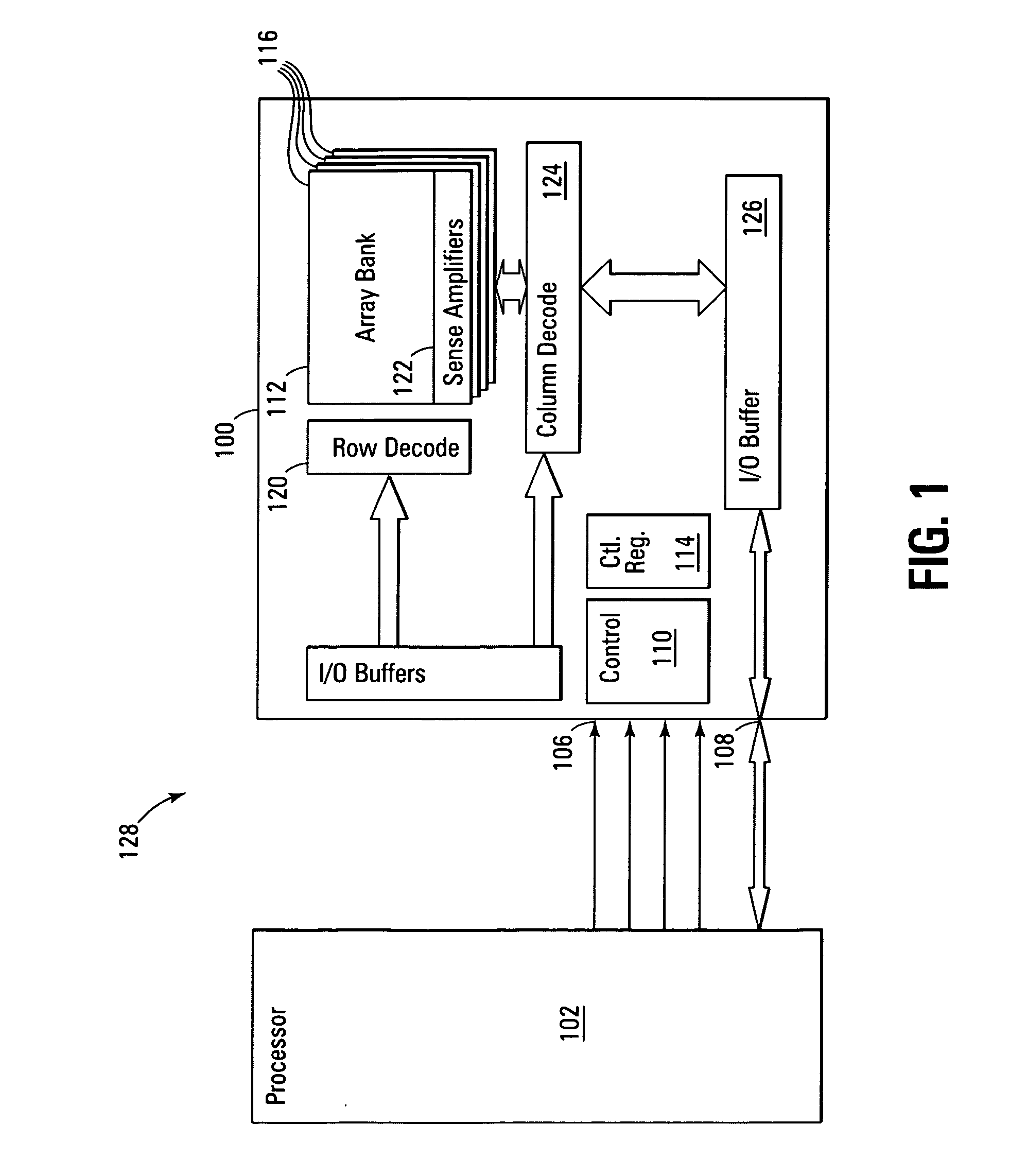

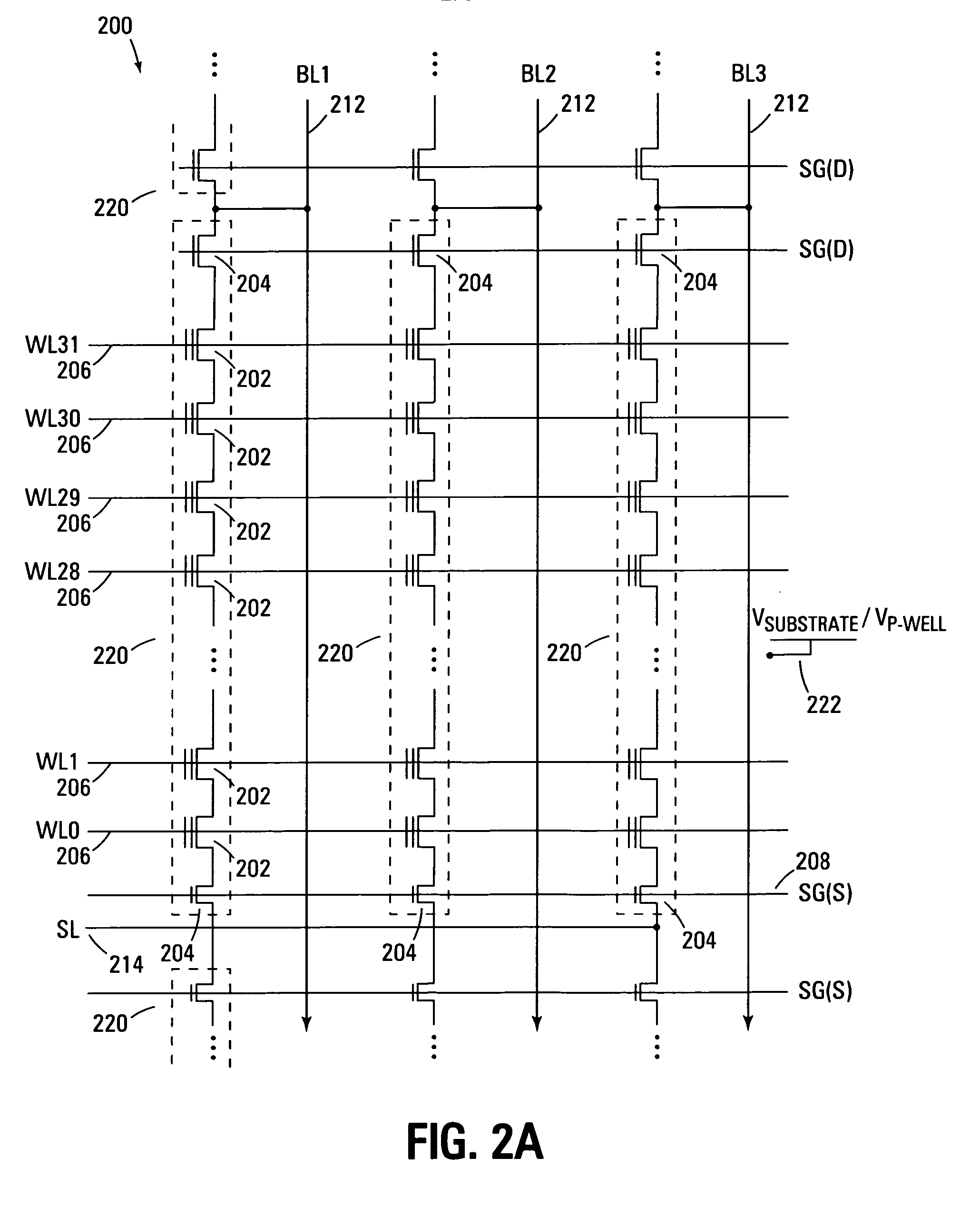

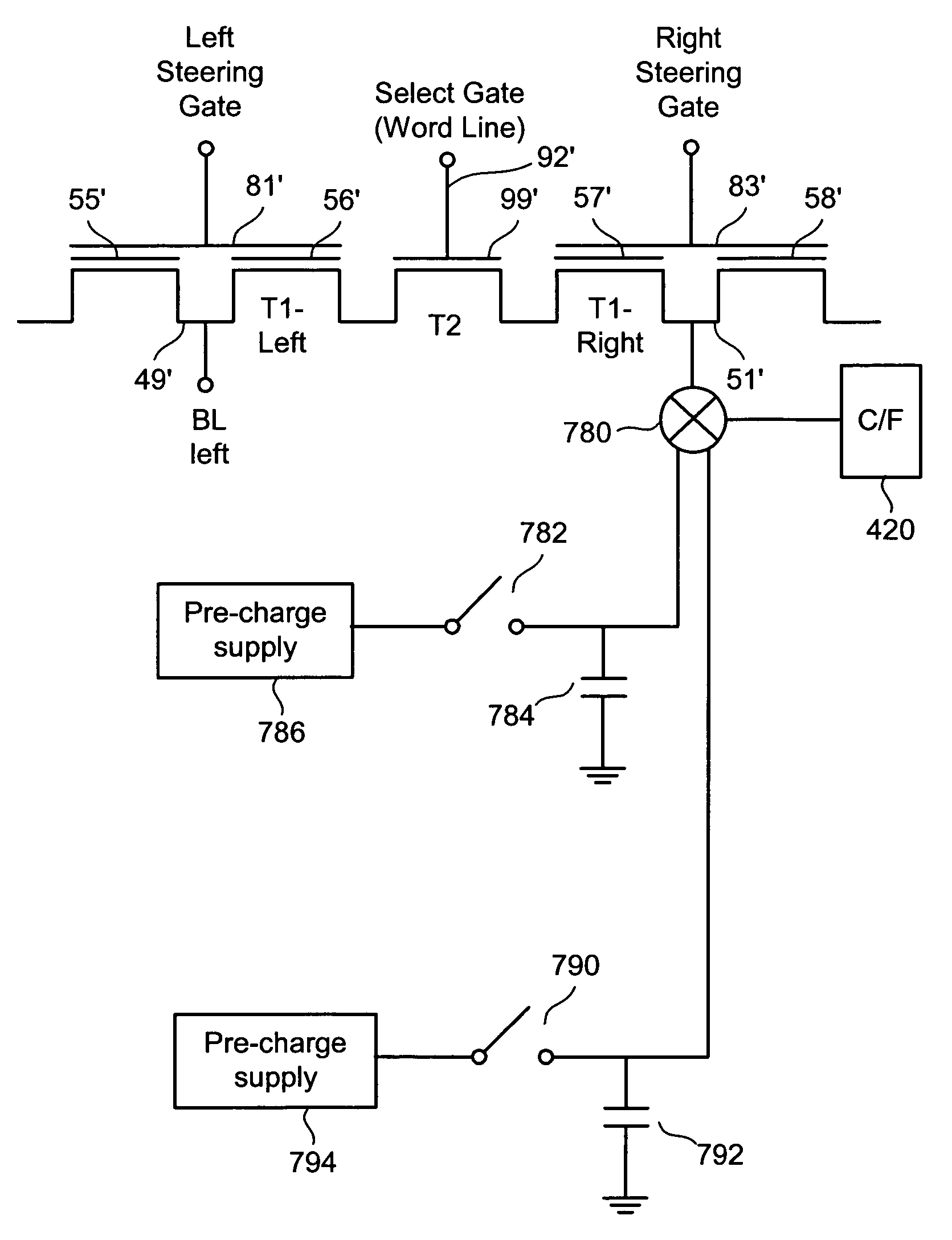

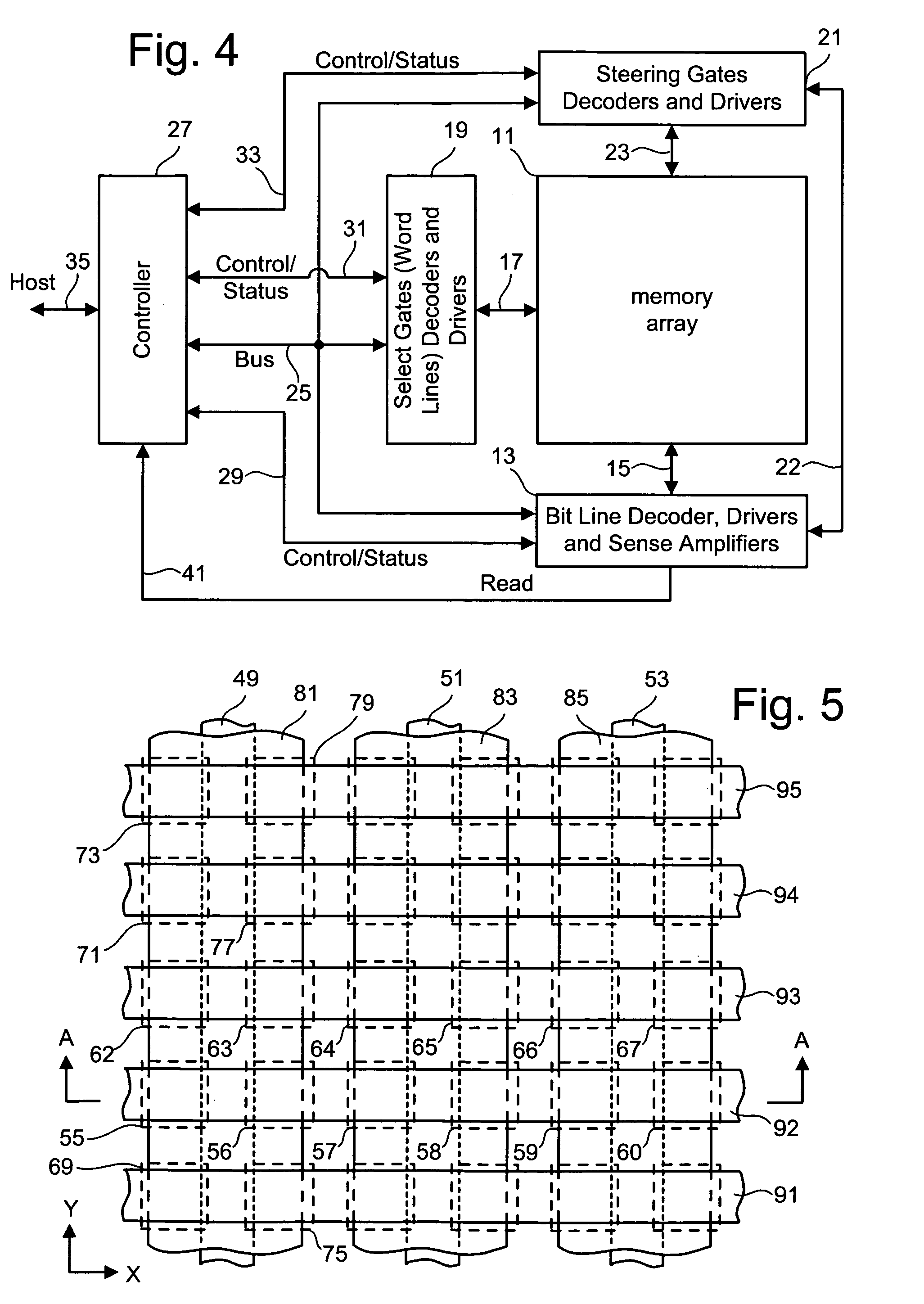

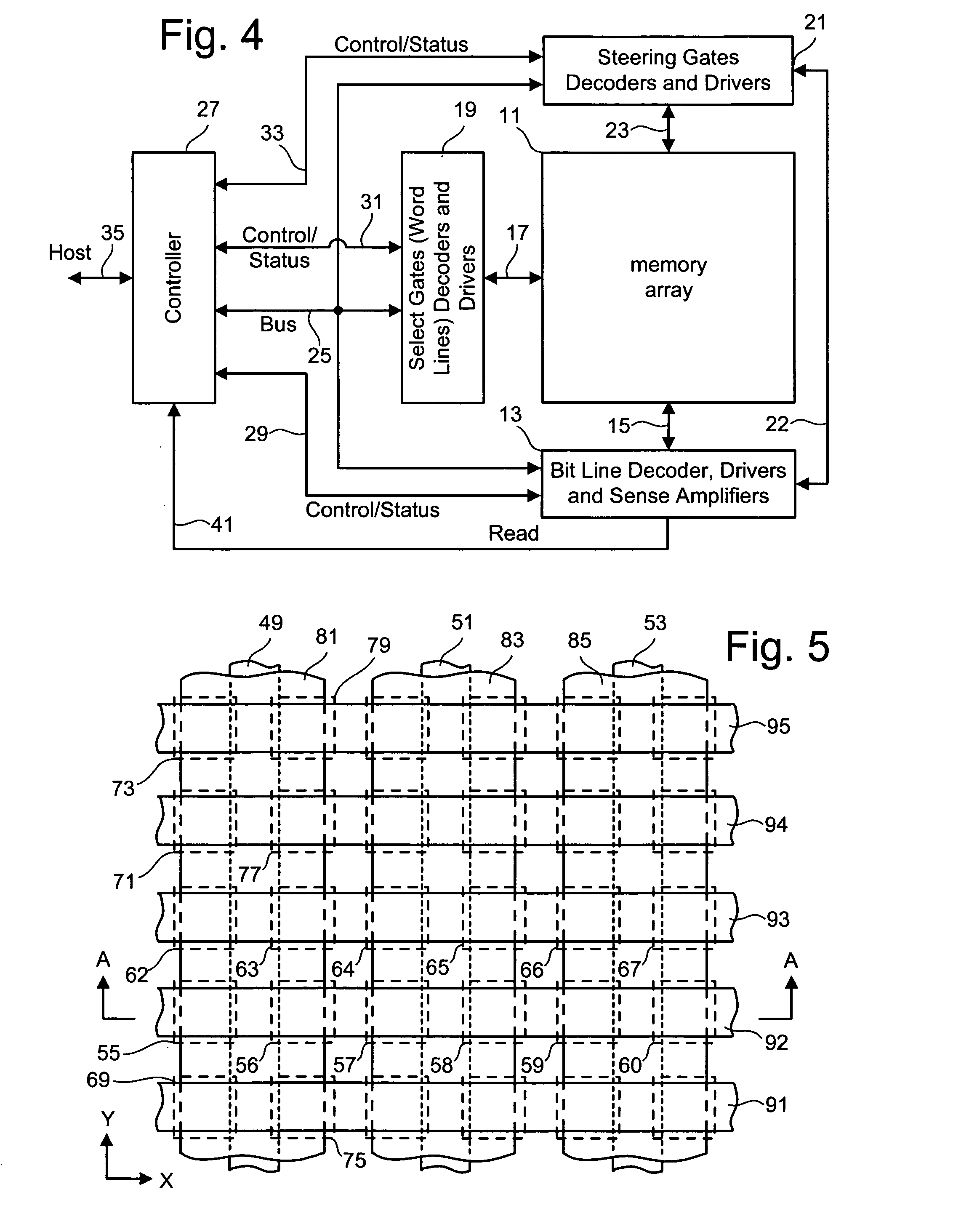

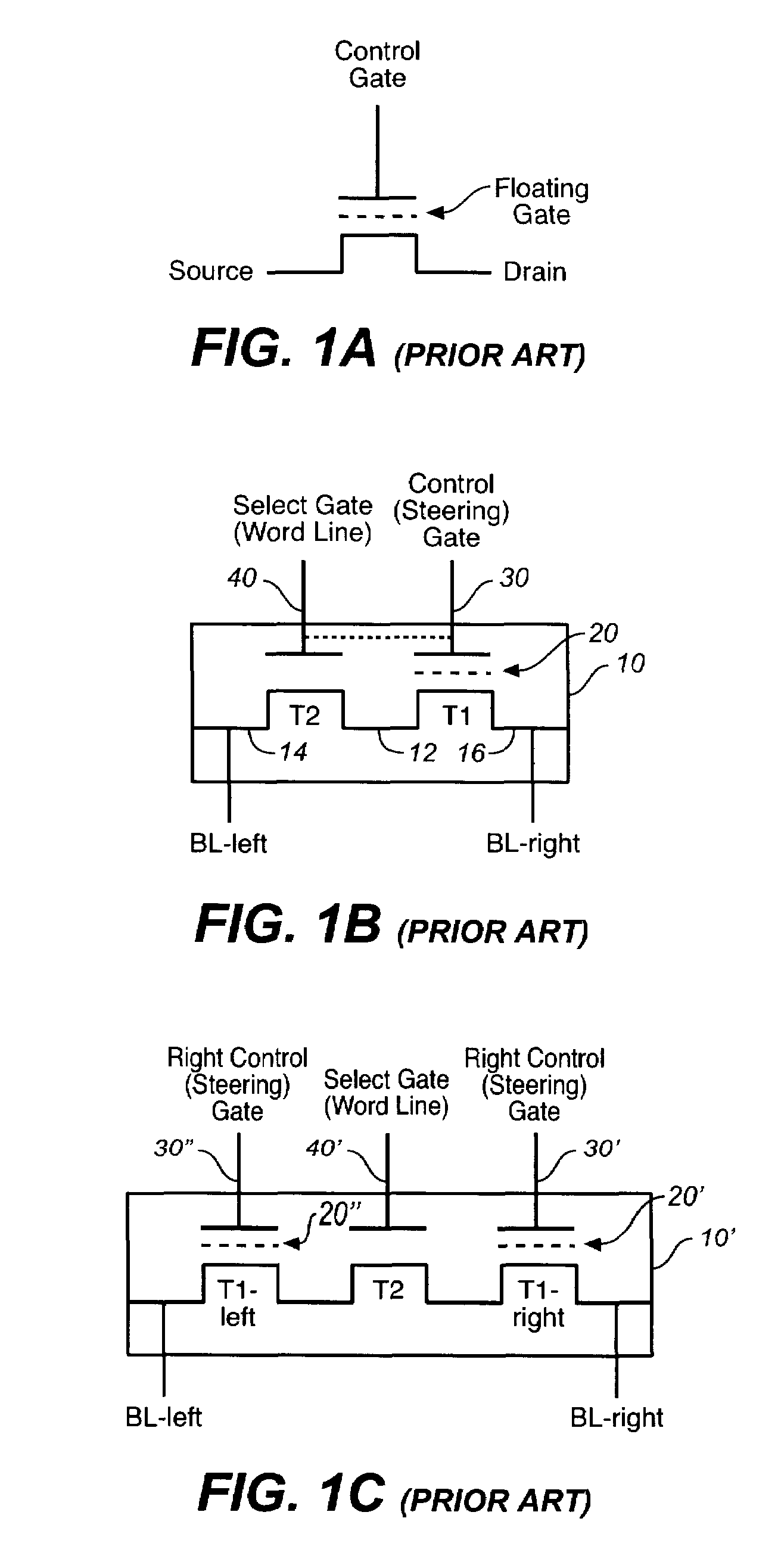

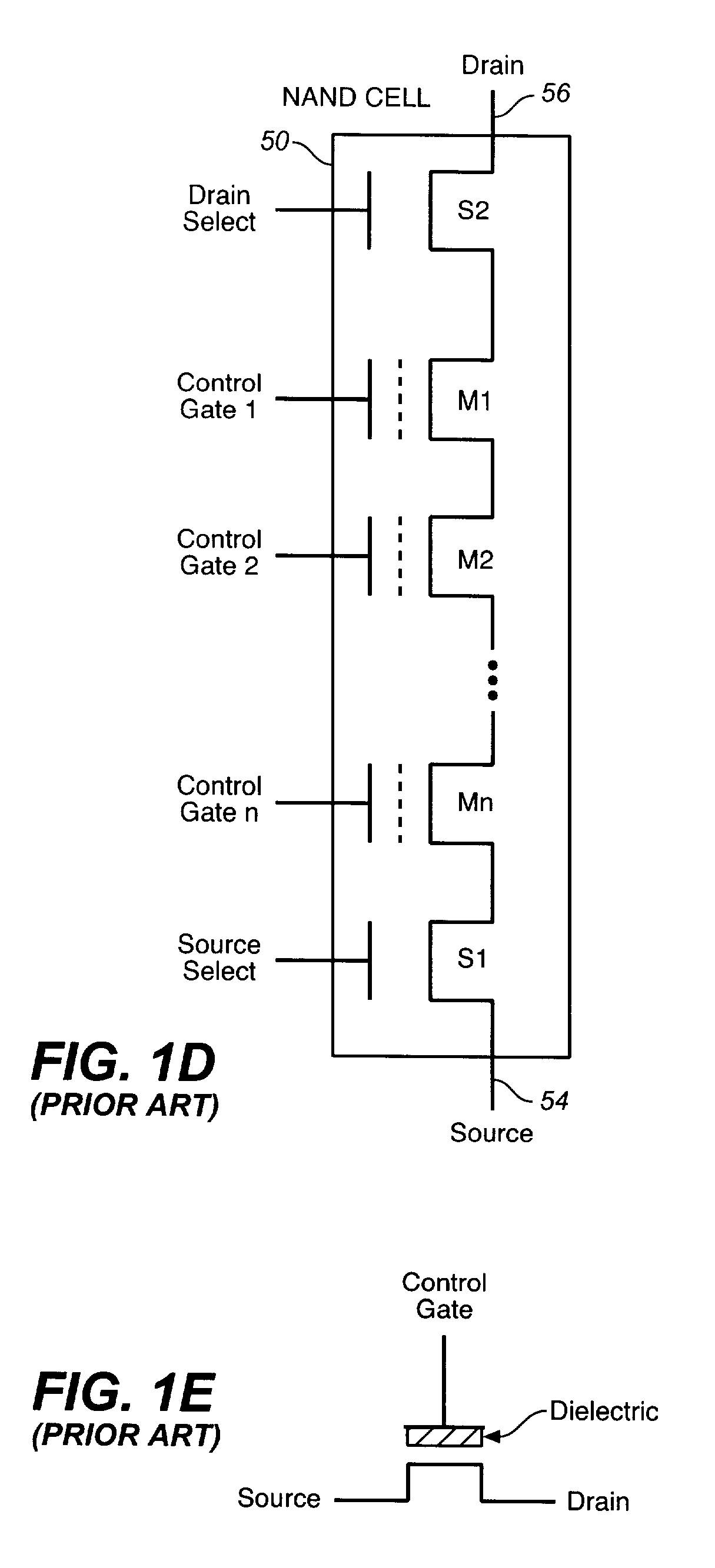

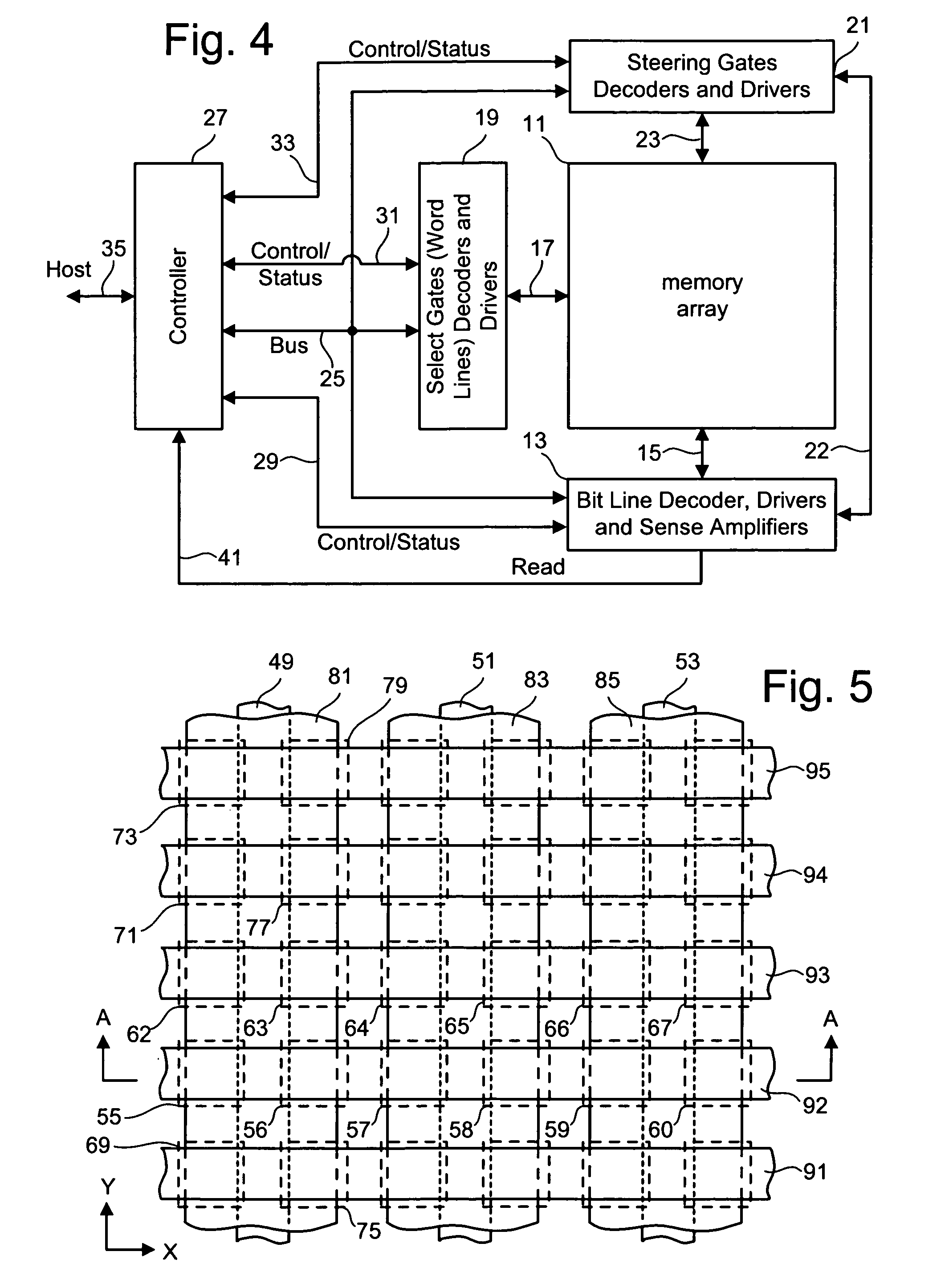

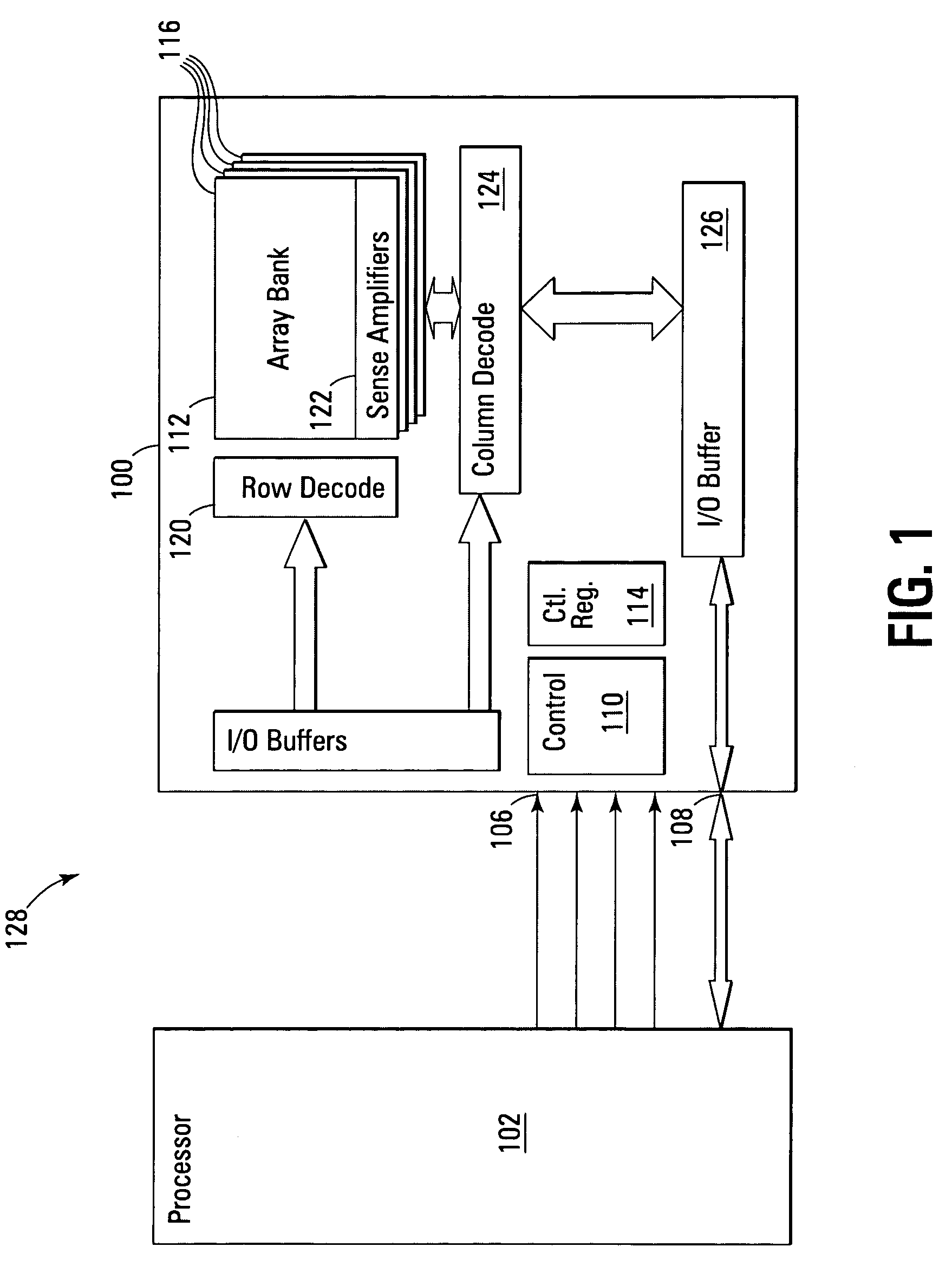

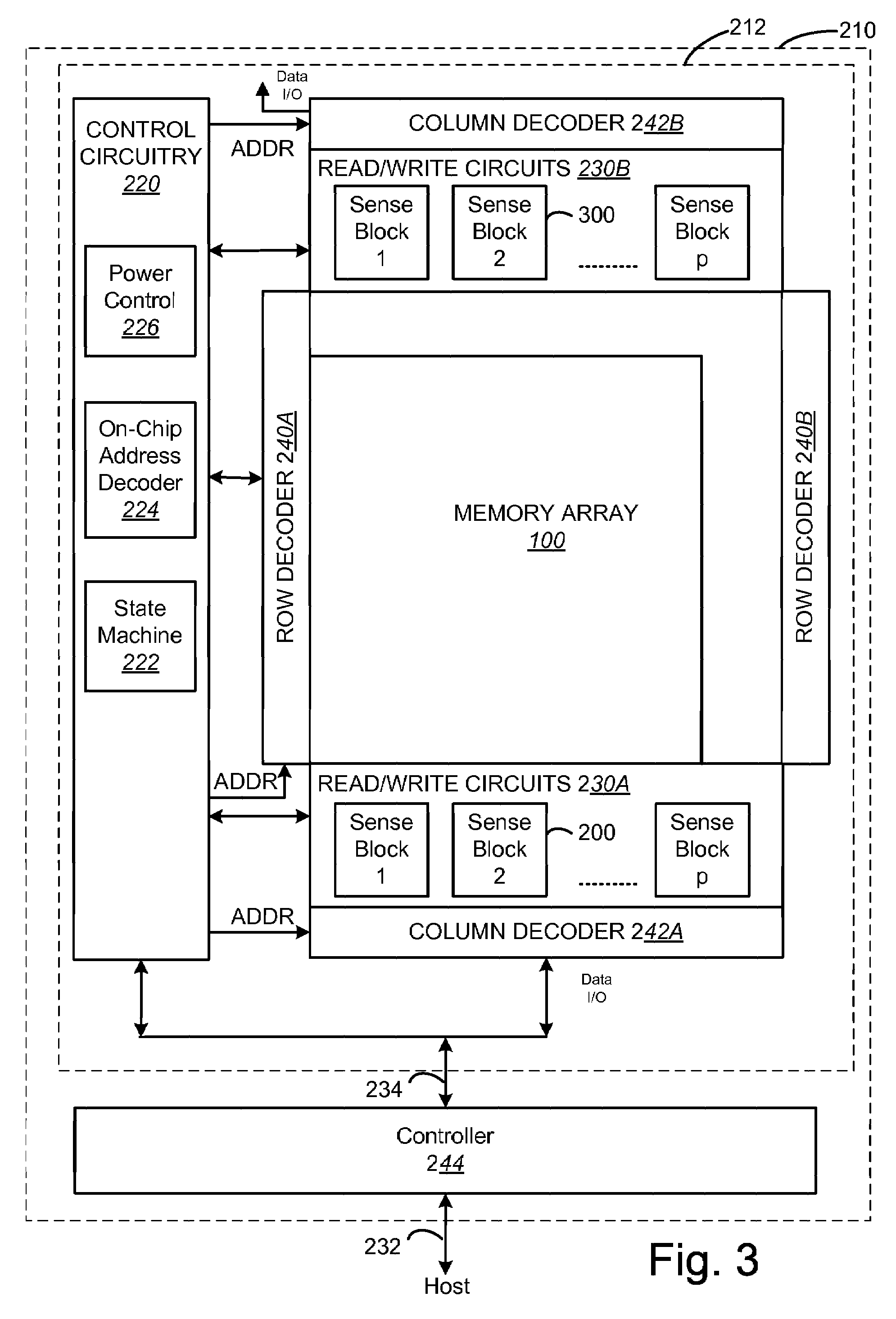

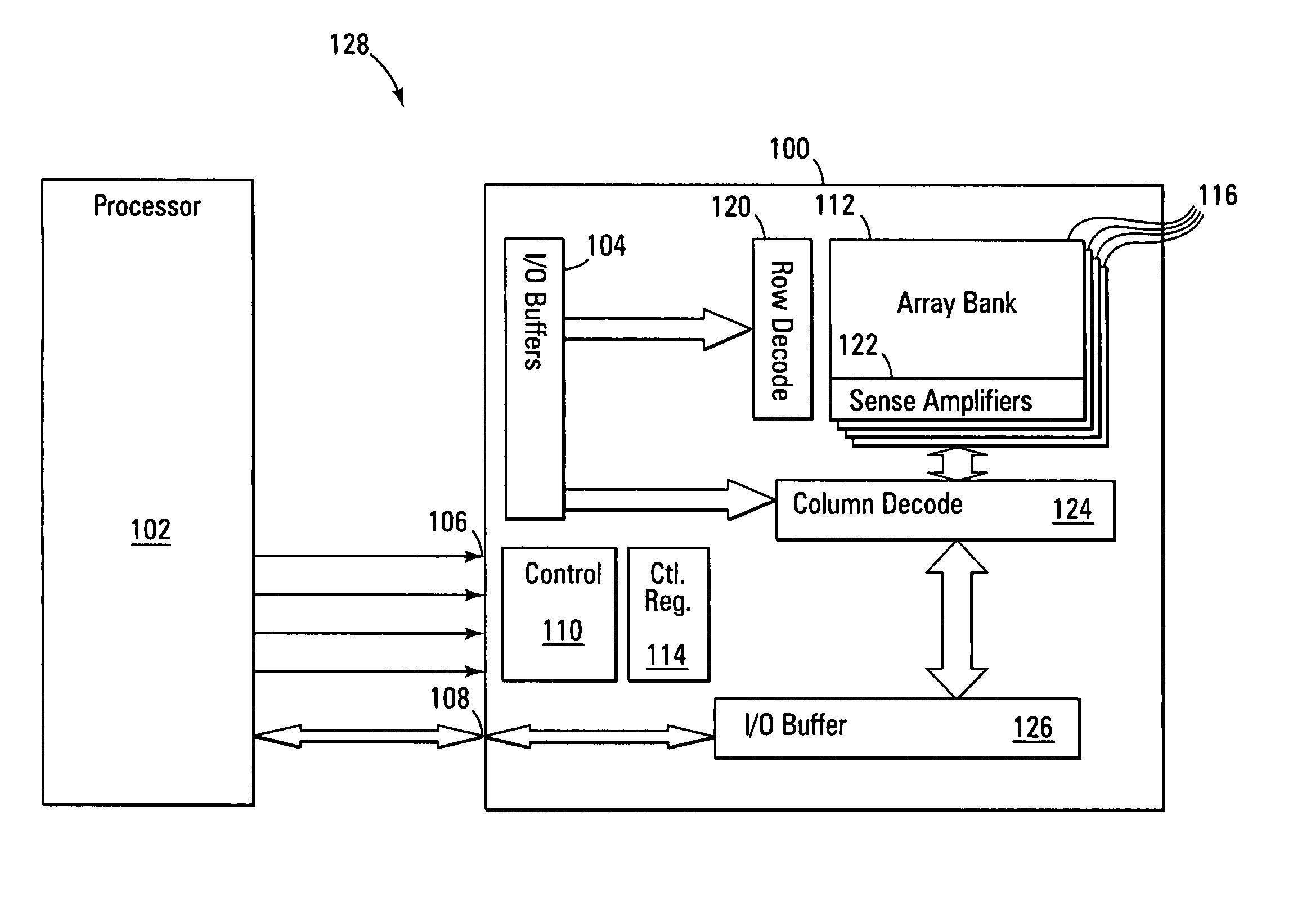

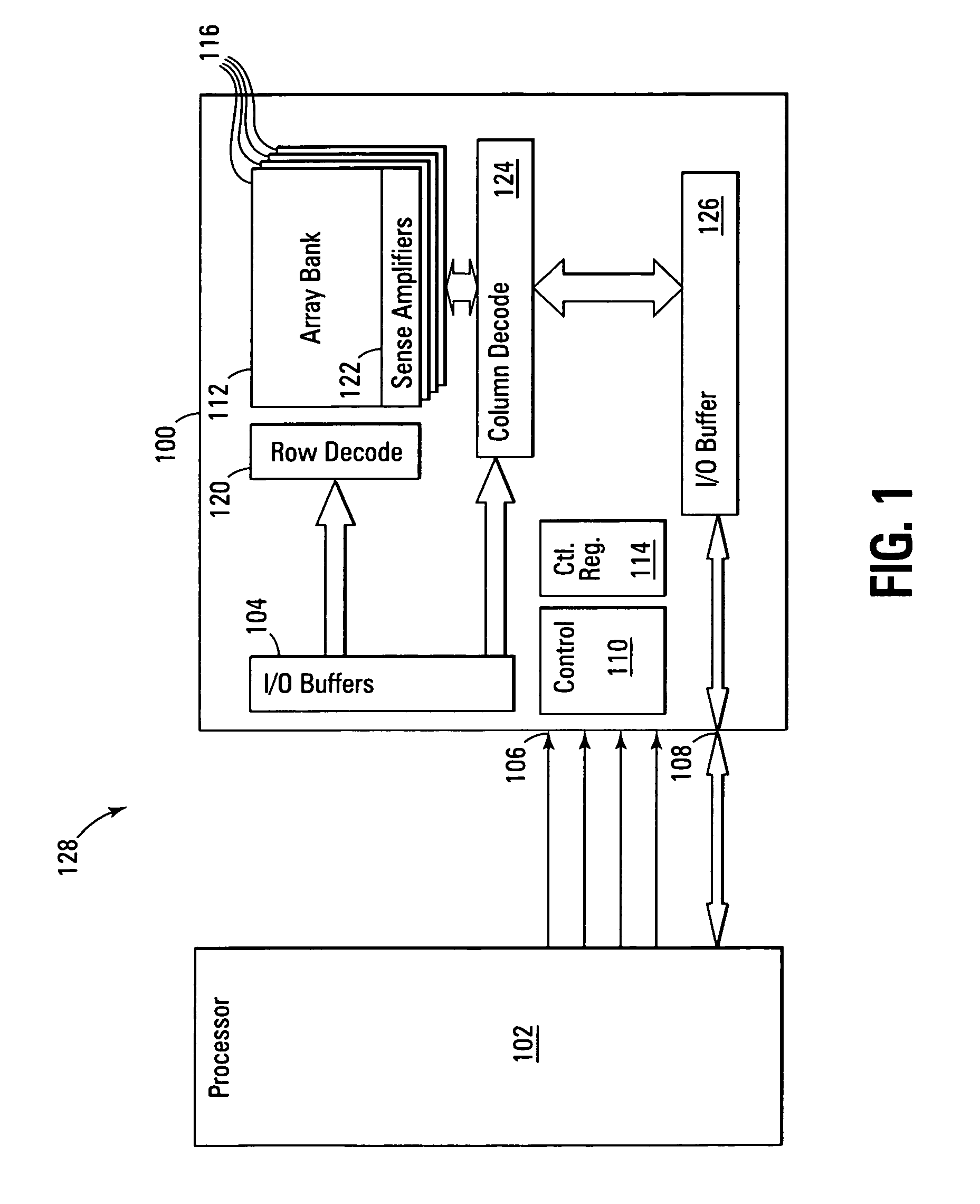

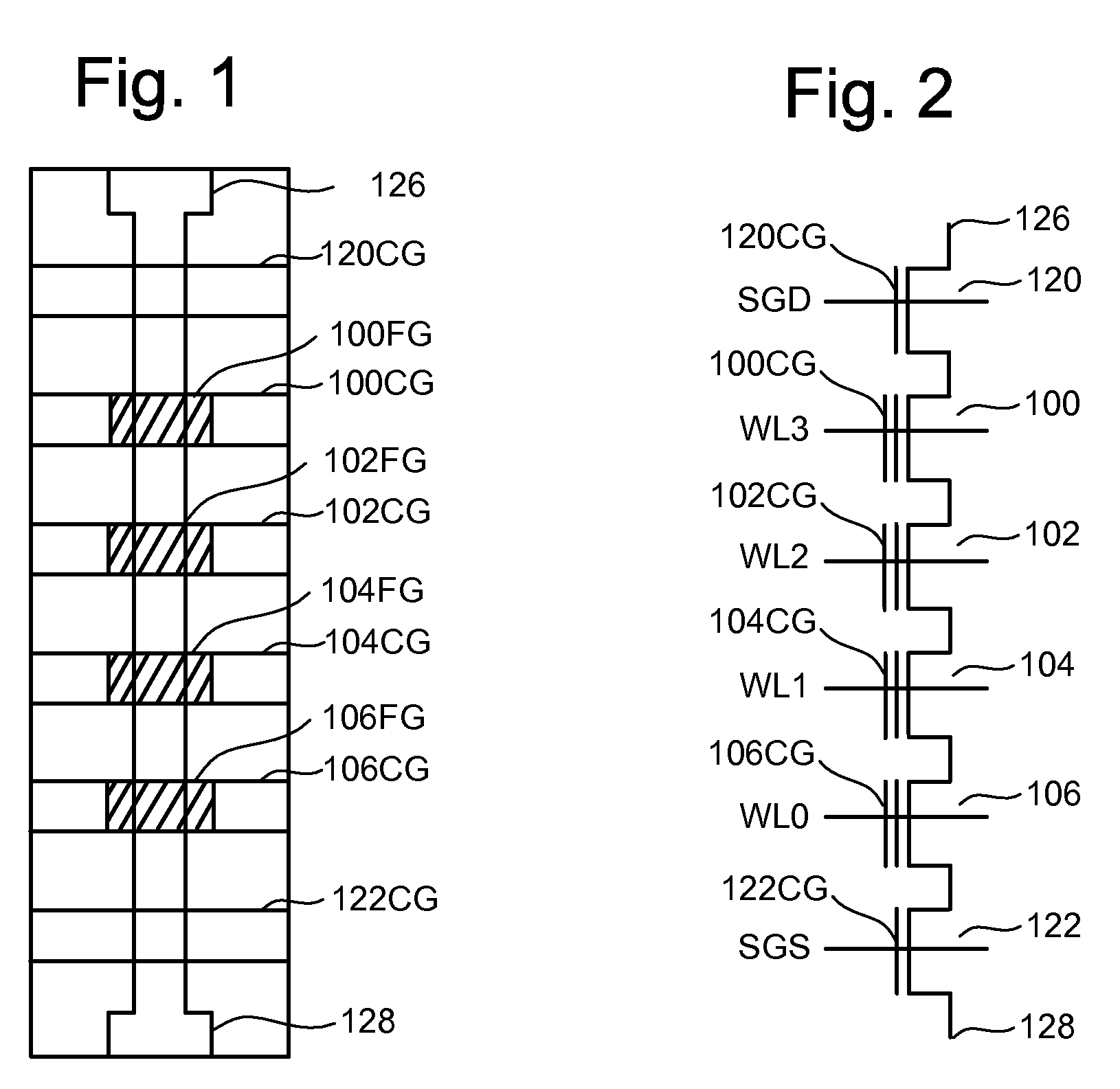

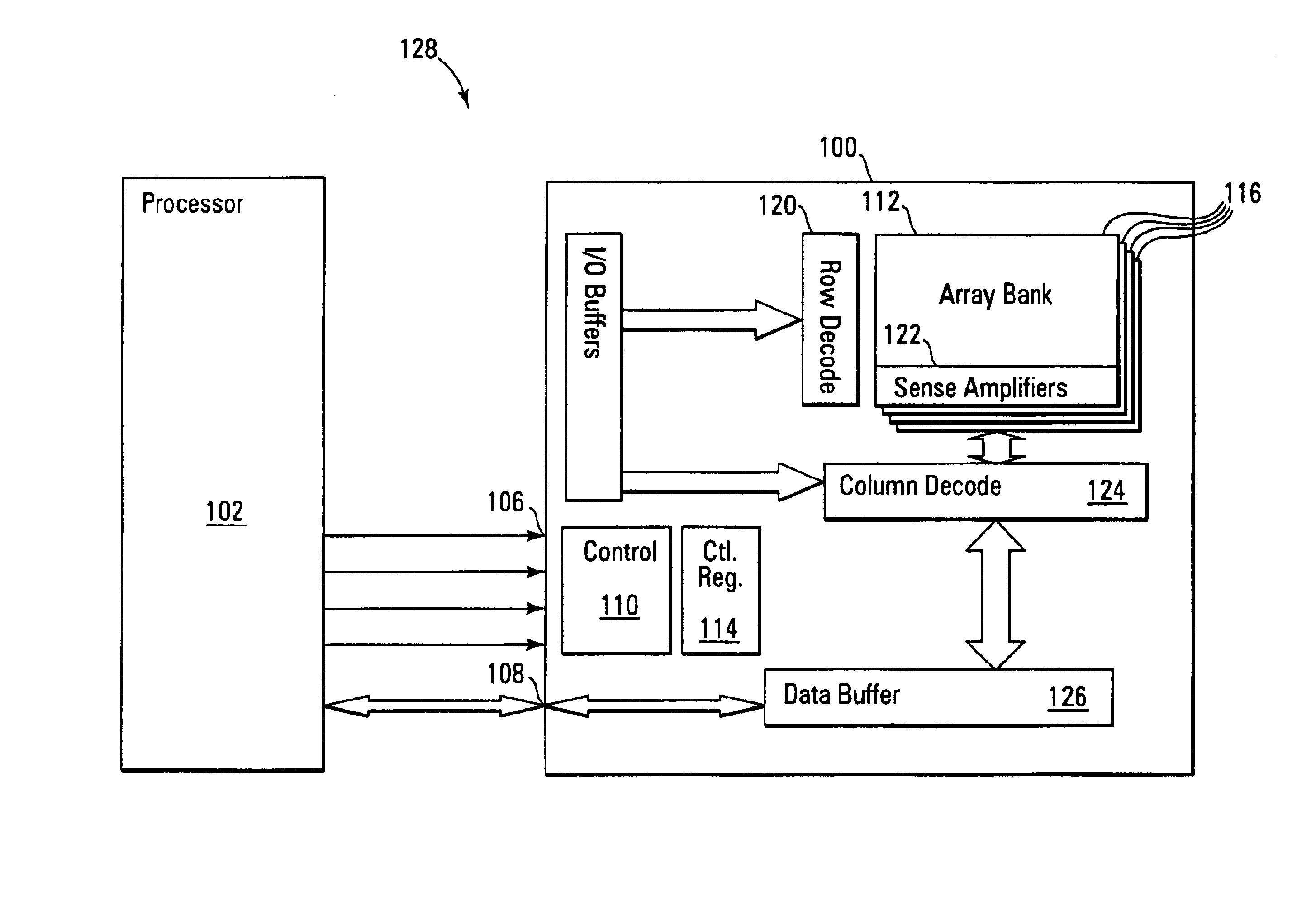

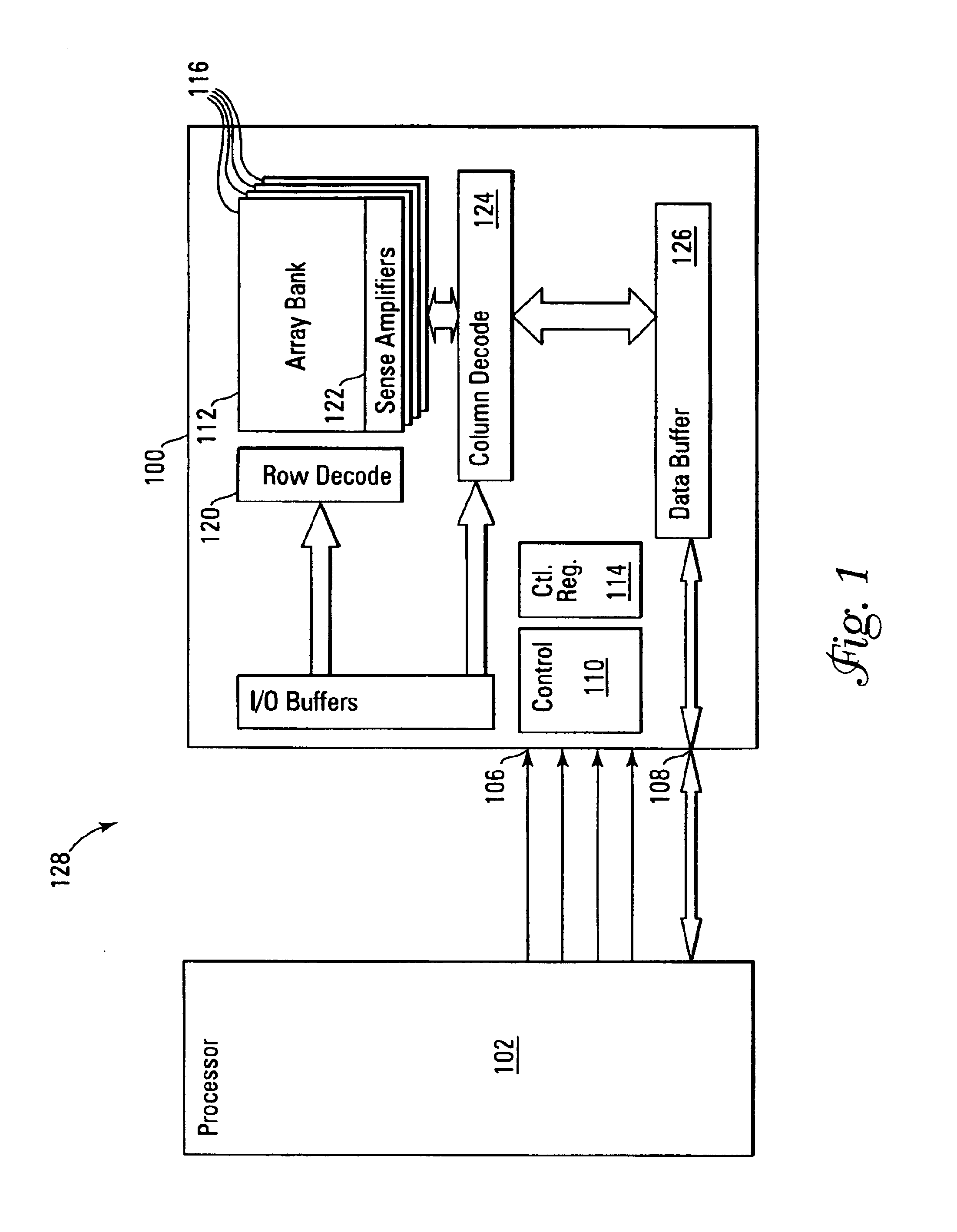

A non-volatile semiconductor memory system (or other type of memory system) is programmed in a manner that avoids program disturb. In one embodiment that includes a flash memory system using a NAND architecture, program disturb is avoided by increasing the channel potential of the source side of the NAND string during the programming process. One exemplar implementation includes applying a voltage (e.g. Vdd) to the source contact and turning on the source side select transistor for the NAND sting corresponding to the cell being inhibited. Another implementation includes applying a pre-charging voltage to the unselected word lines of the NAND string corresponding to the cell being inhibited prior to applying the program voltage.

Owner:SANDISK TECH LLC

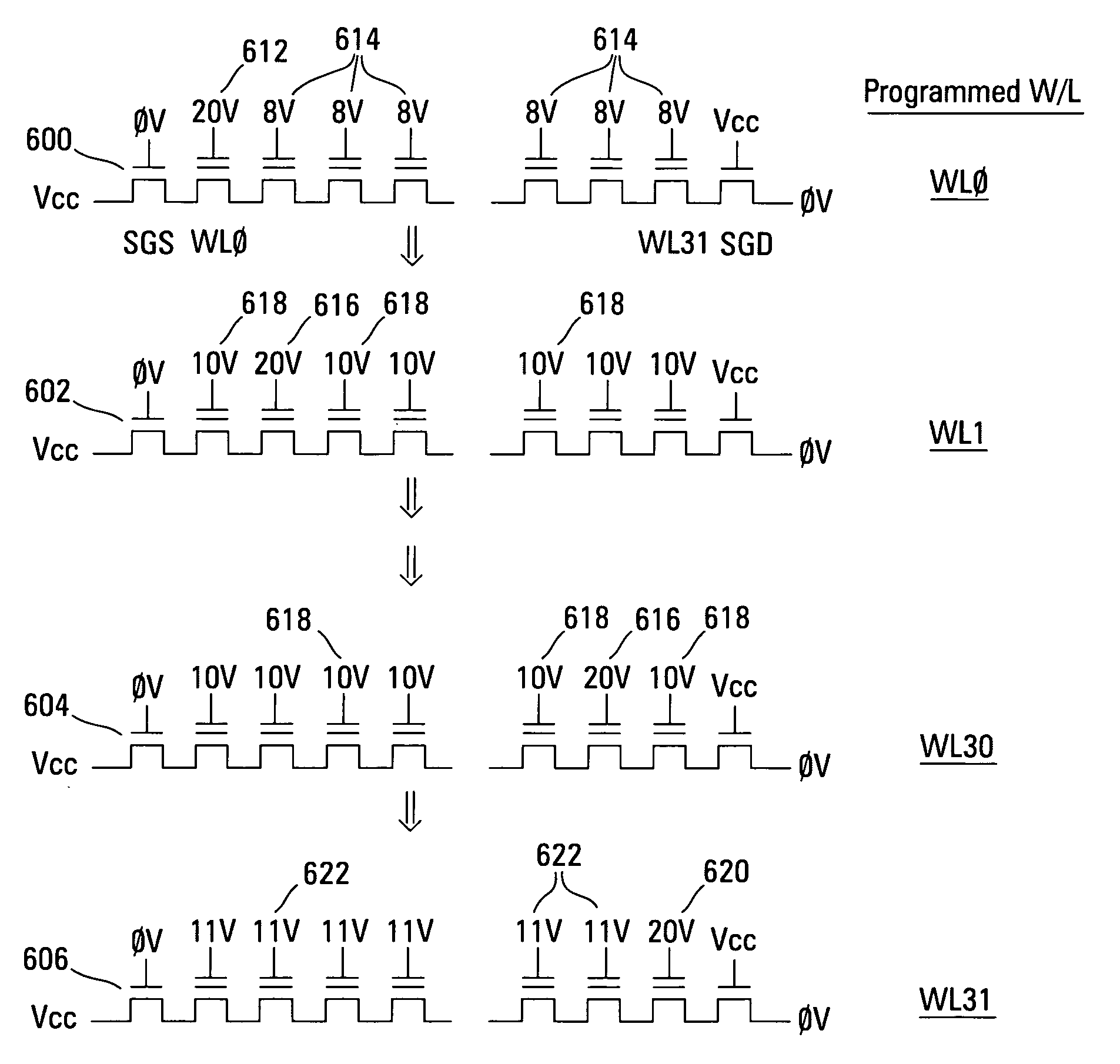

Programming method to reduce gate coupling interference for non-volatile memory

Owner:MICRON TECH INC

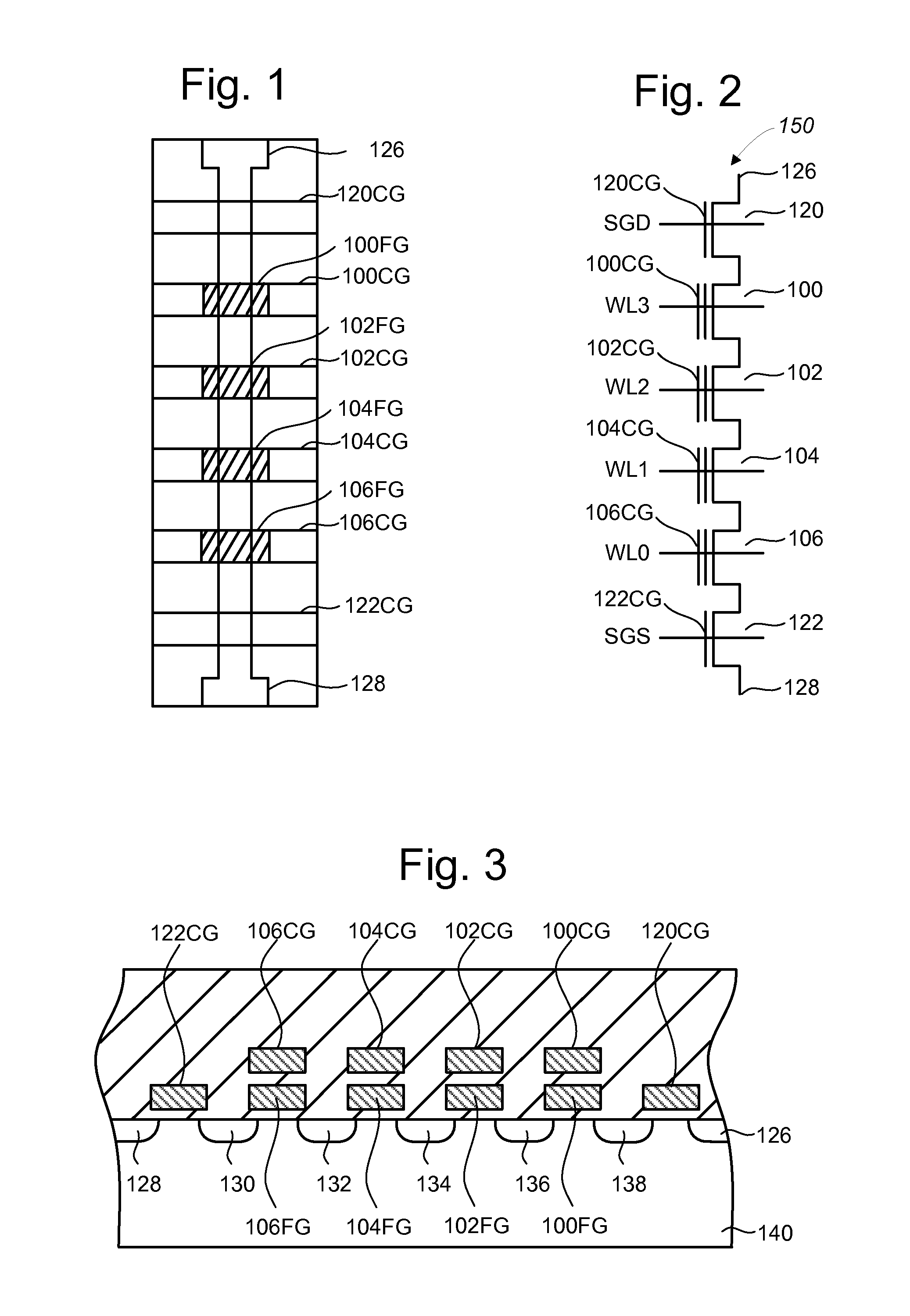

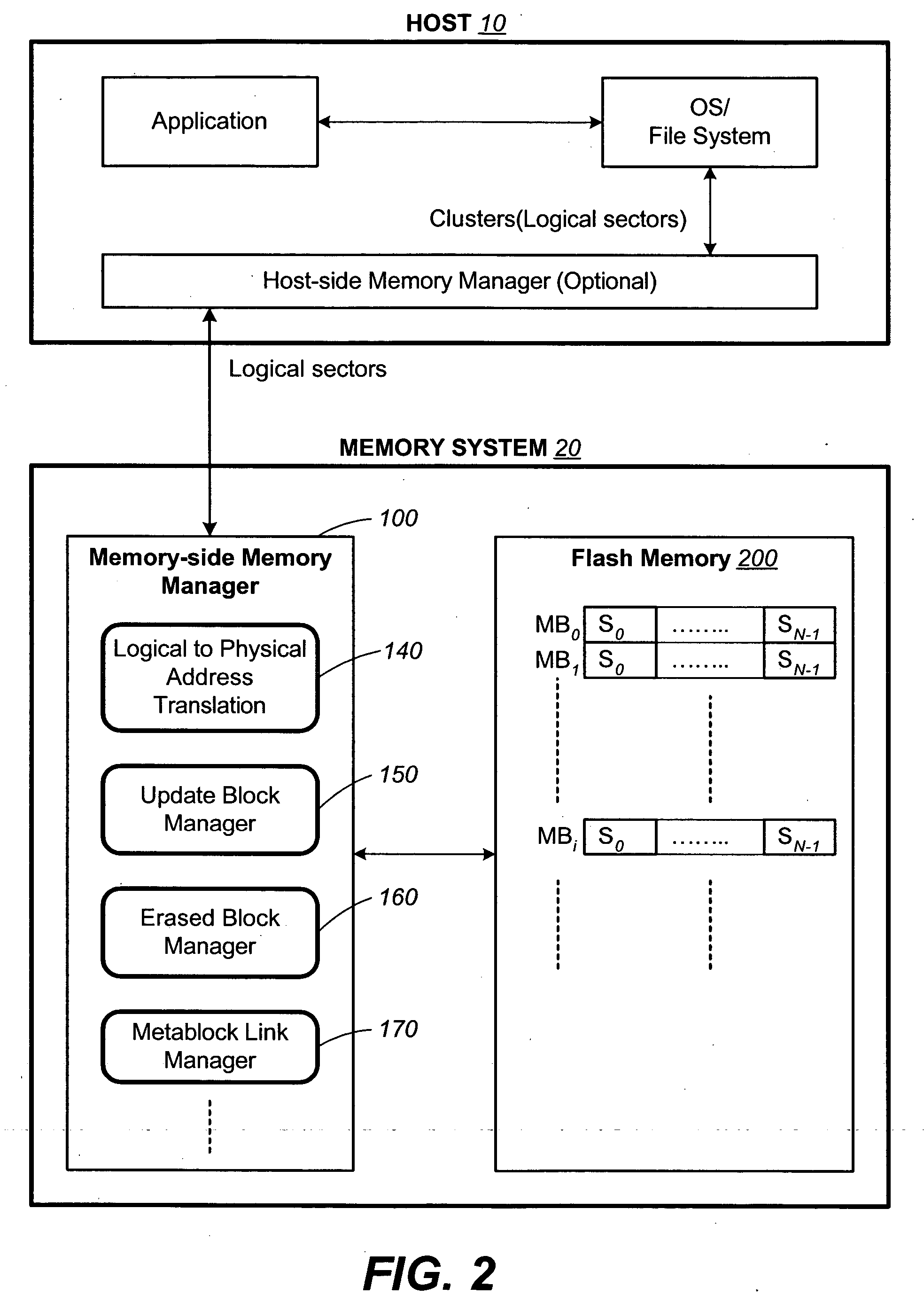

Compensating for coupling during programming

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

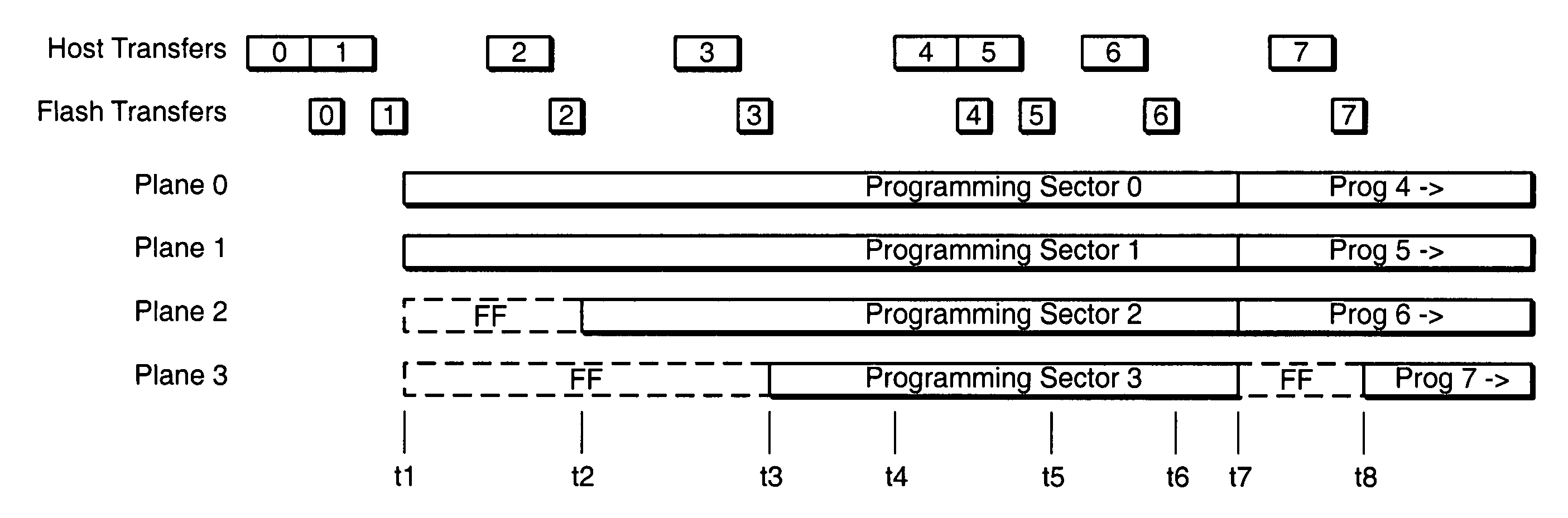

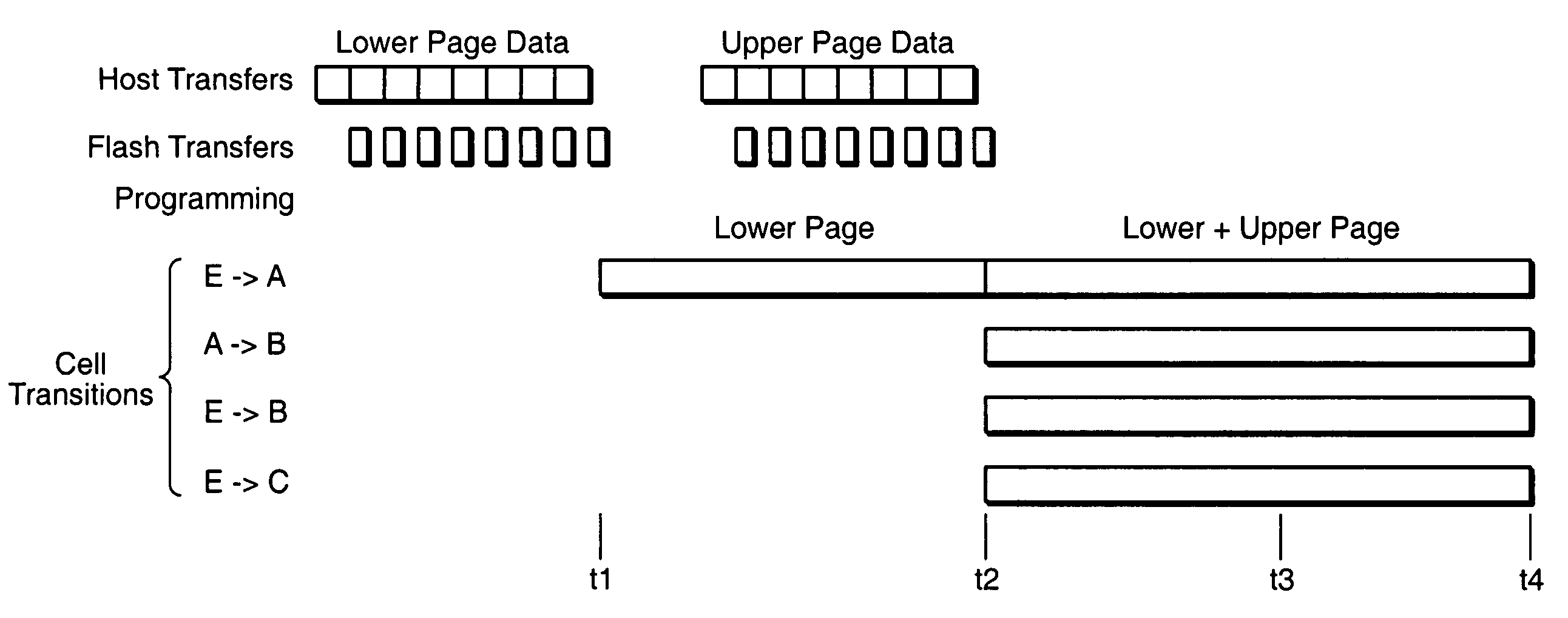

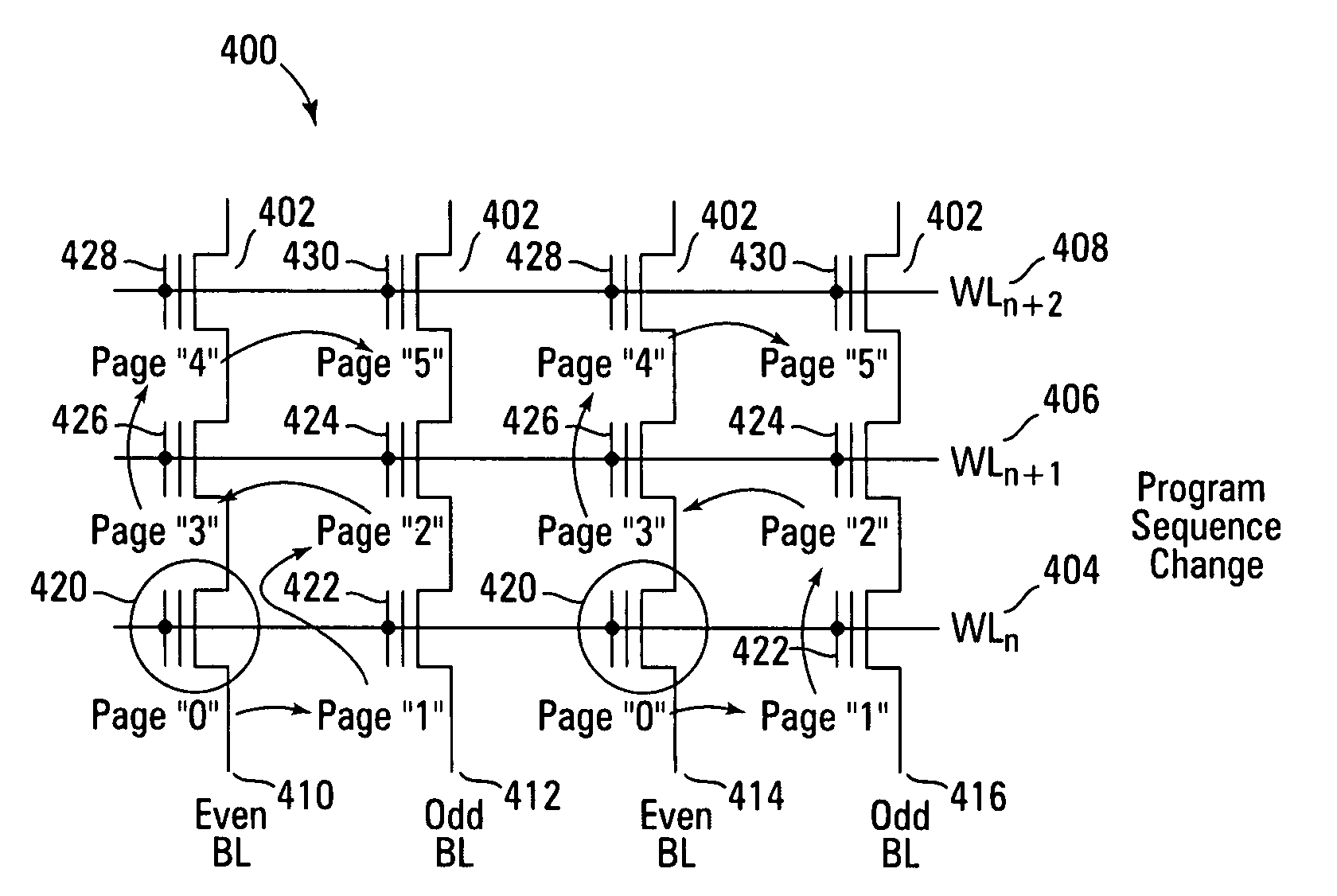

Pipelined programming of non-volatile memories using early data

ActiveUS20060126390A1Improve performanceRead-only memoriesDigital storageFull dataProgramming process

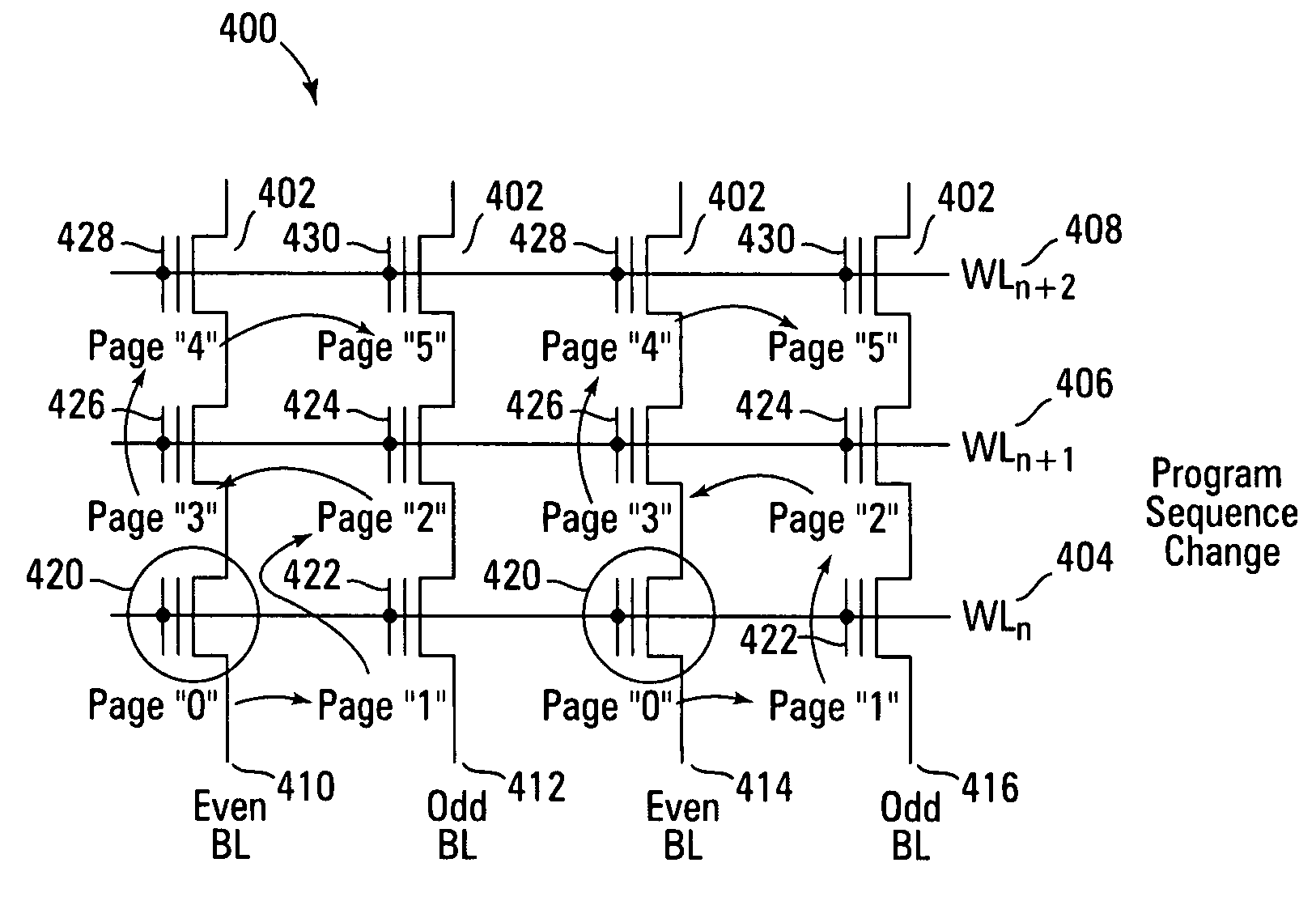

The present invention presents techniques whereby a memory system interrupts a programming process and restarts it including additional data. More specifically, when a memory system programs data into a group of cells together as programming unit, programming can begin with less than the full data content which the group can hold. In one embodiment, the present invention allows overlapped programming of upper and lower data pages, where once the memory begins programming the lower logical data page, if data is received for the upper page assigned to the same physical page, programming is interrupted and recommenced with the concurrent programming of both the upper and the loser pages. In a complimentary embodiment, when a page contains multiple sectors of data, programming of the physical page can begin when one or more, but less than all, of the sectors forming the corresponding logical page have been received, stopped and restarted to include additional sectors of the page.

Owner:SANDISK TECH LLC

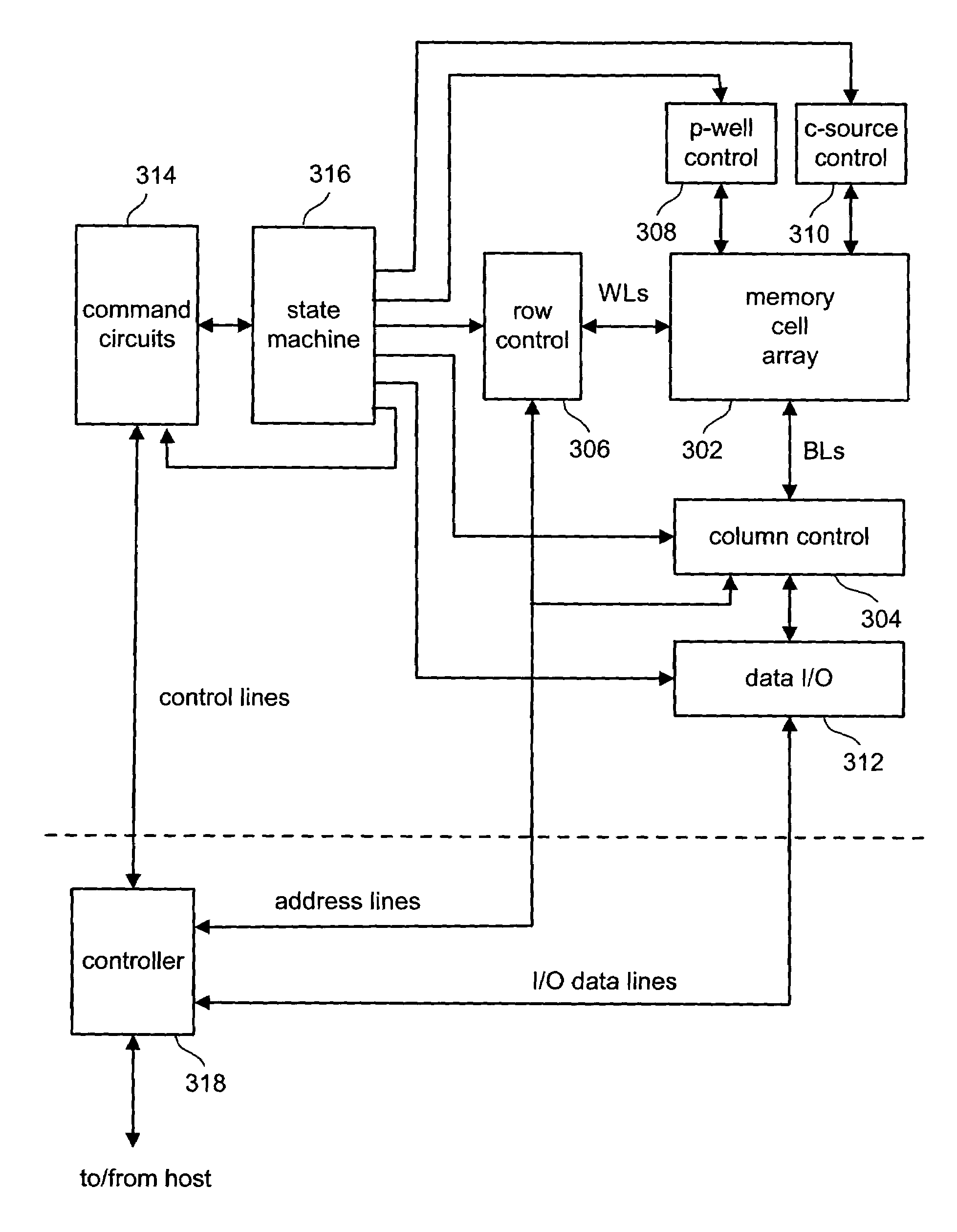

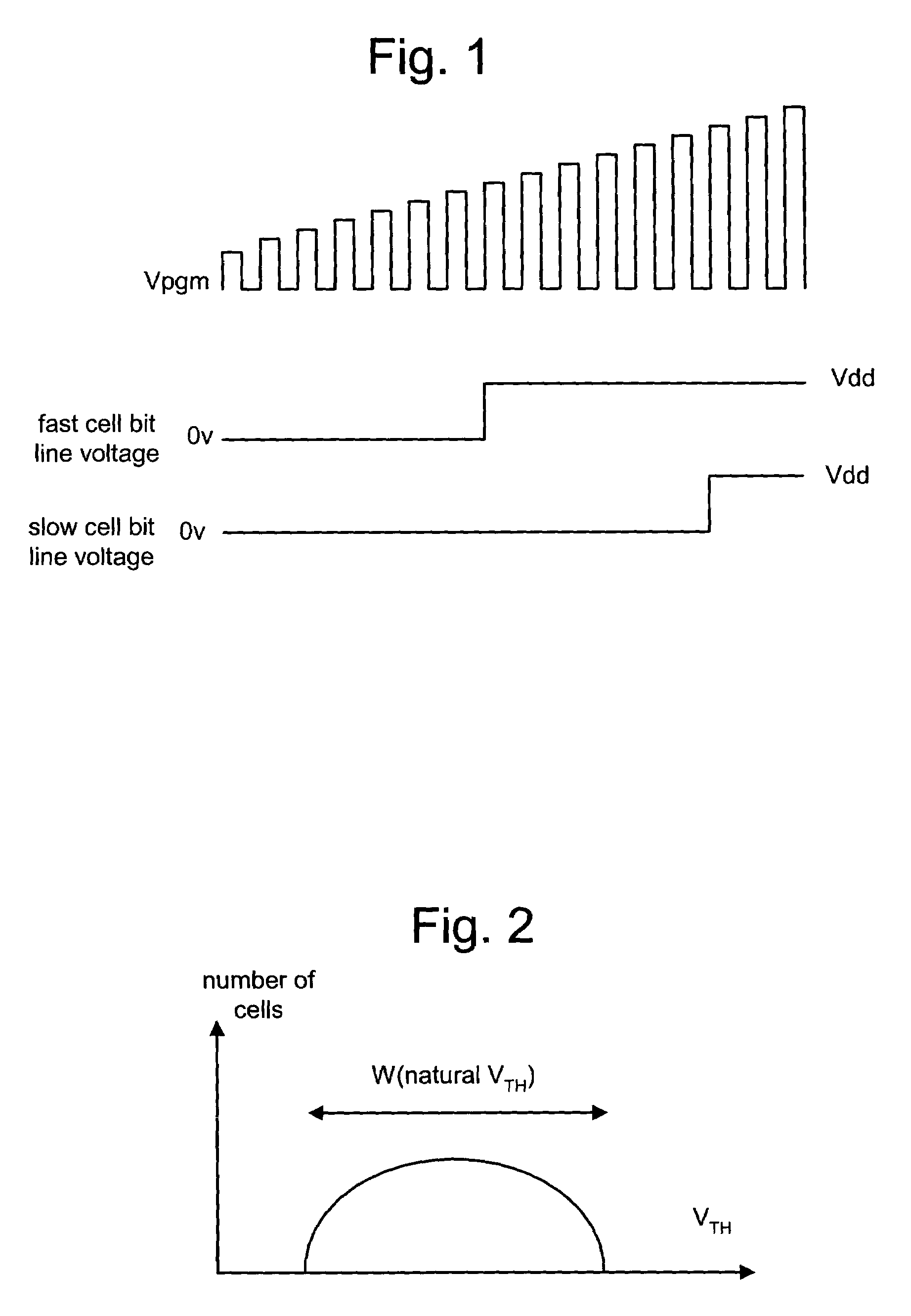

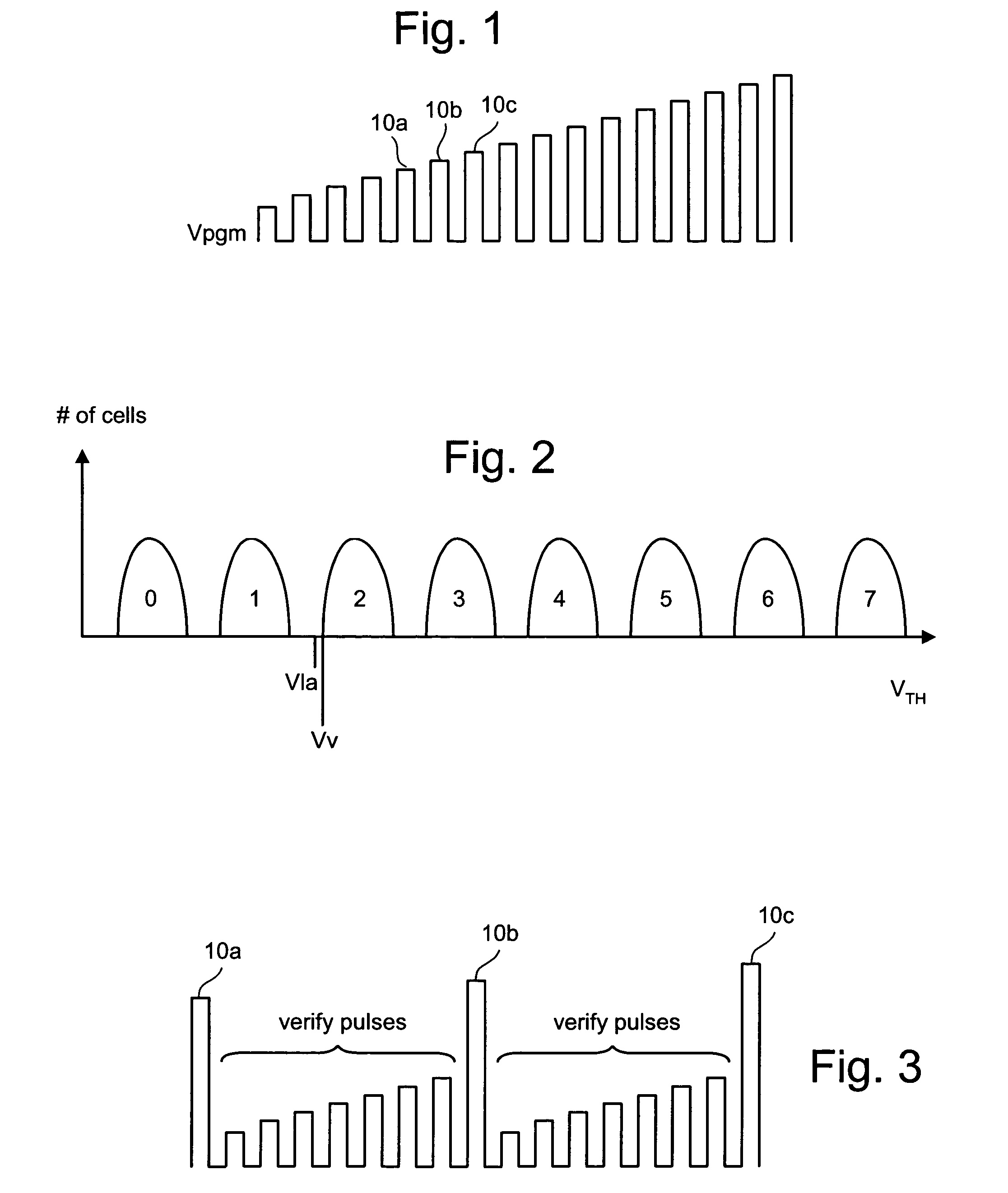

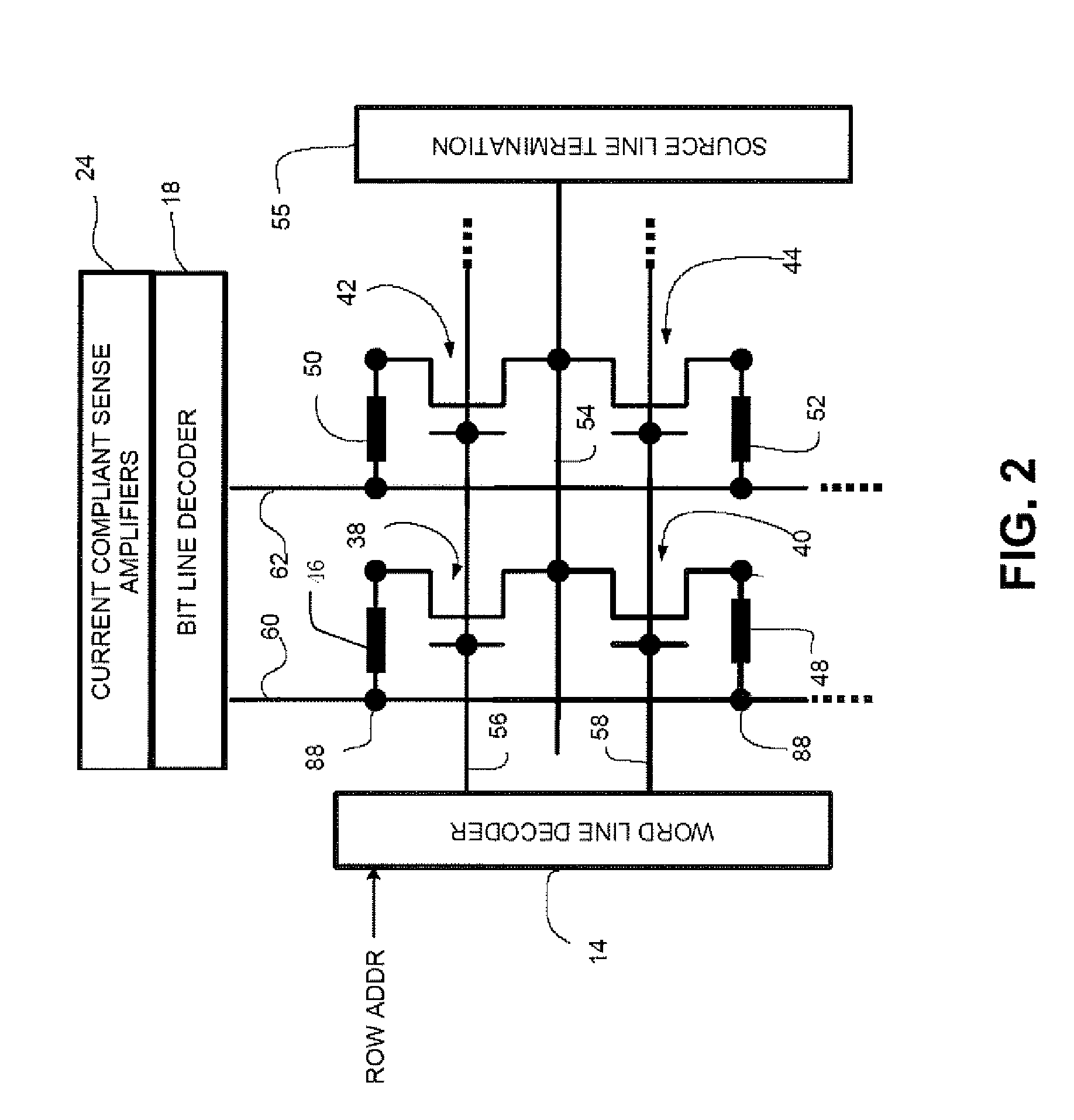

Behavior based programming of non-volatile memory

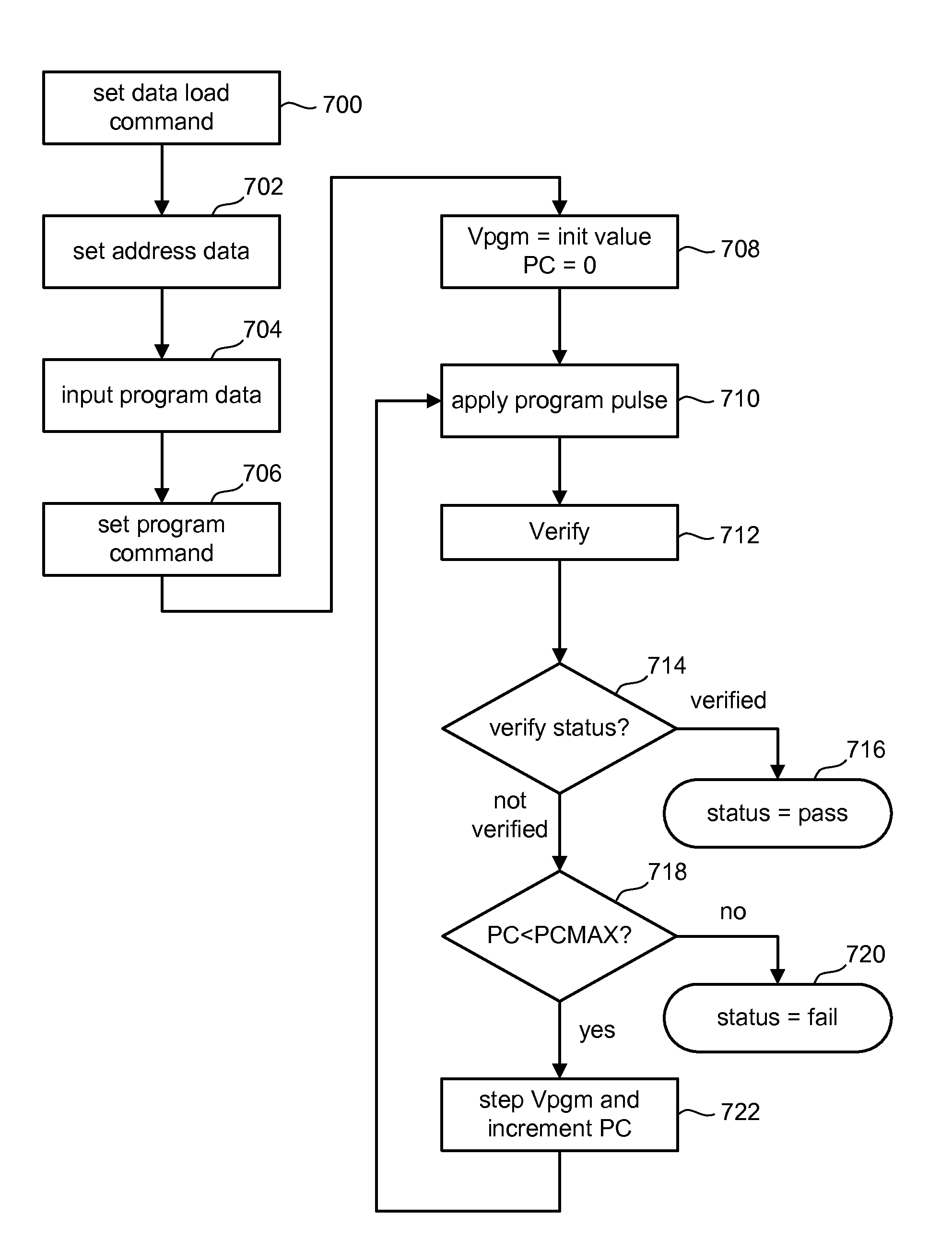

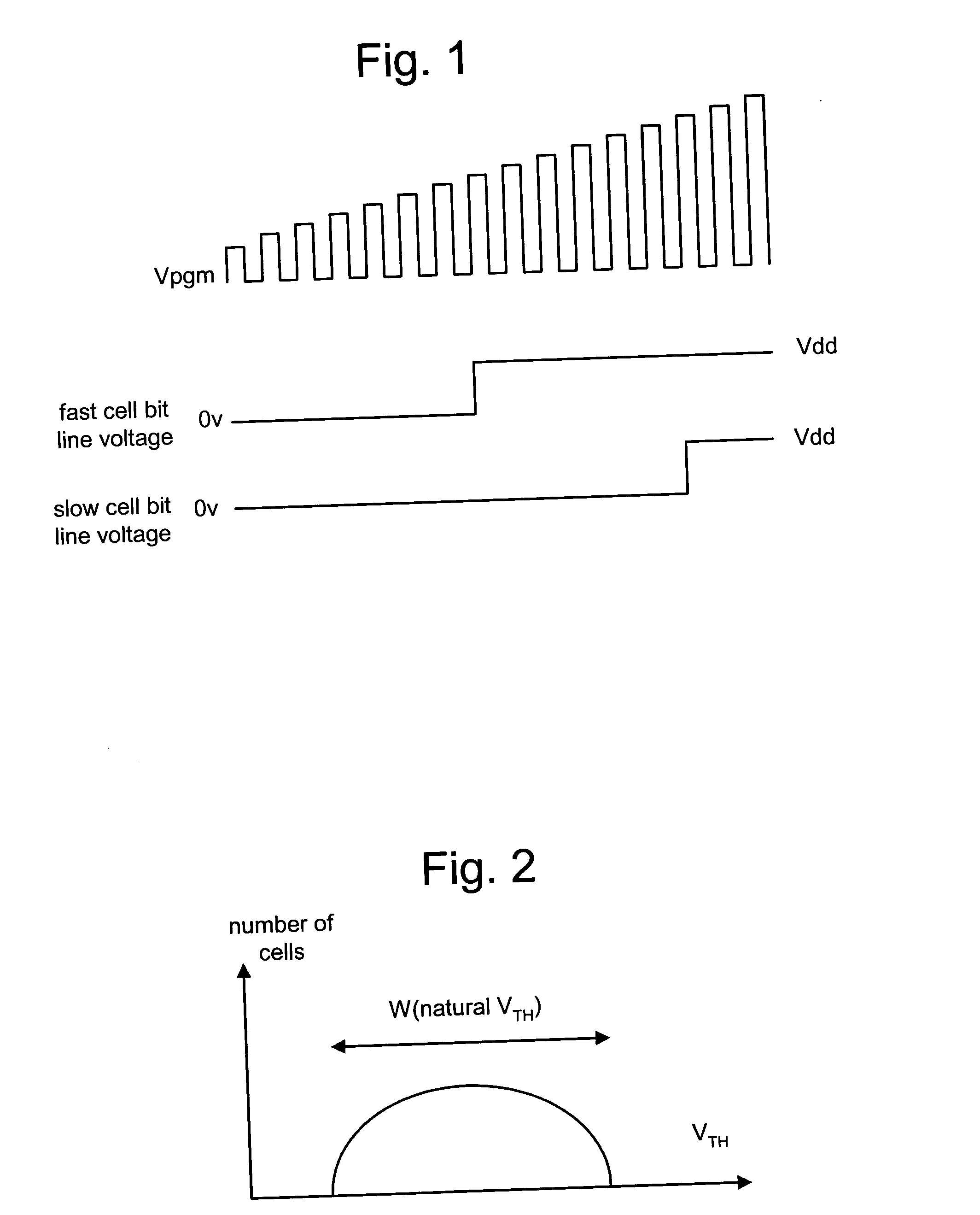

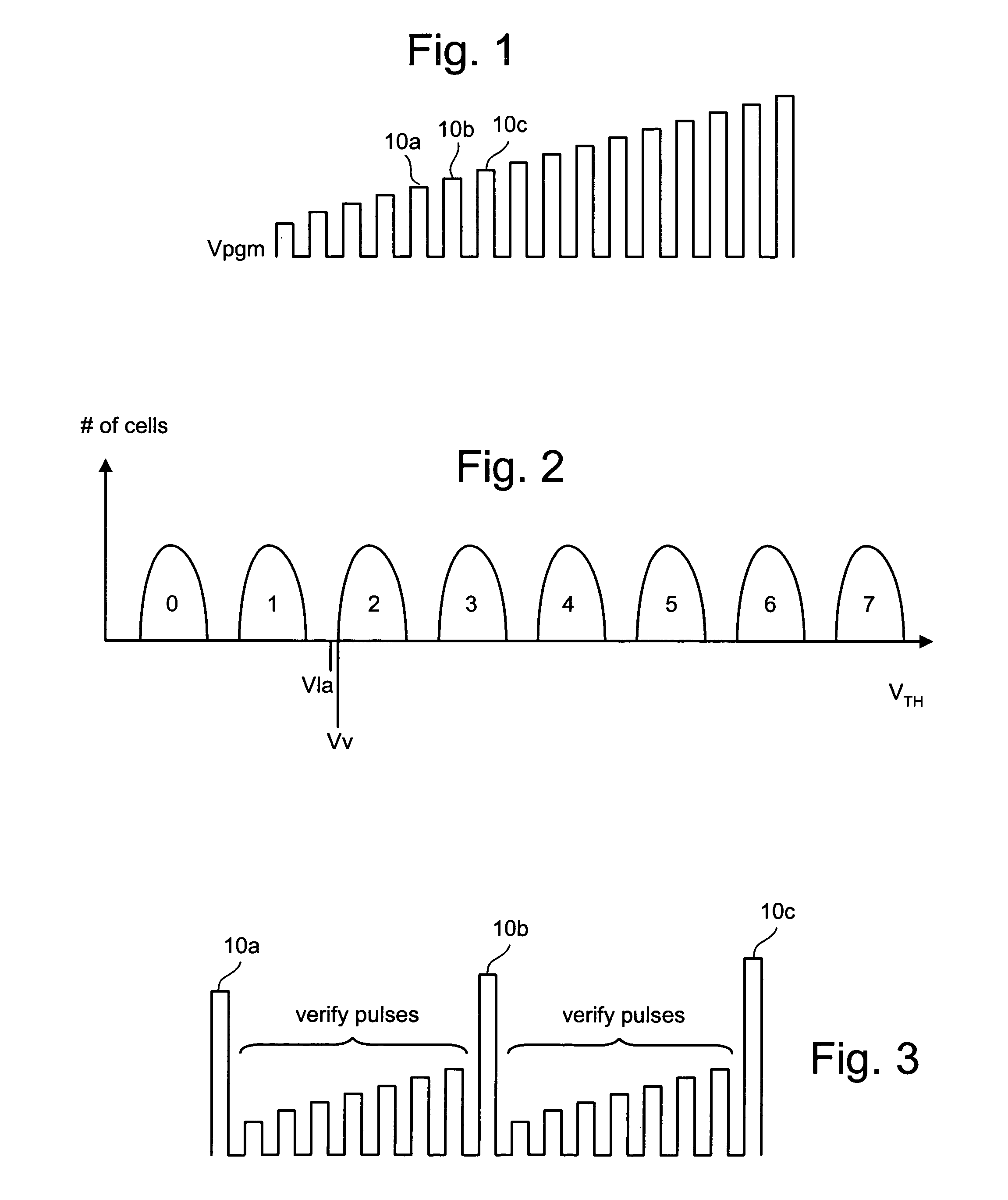

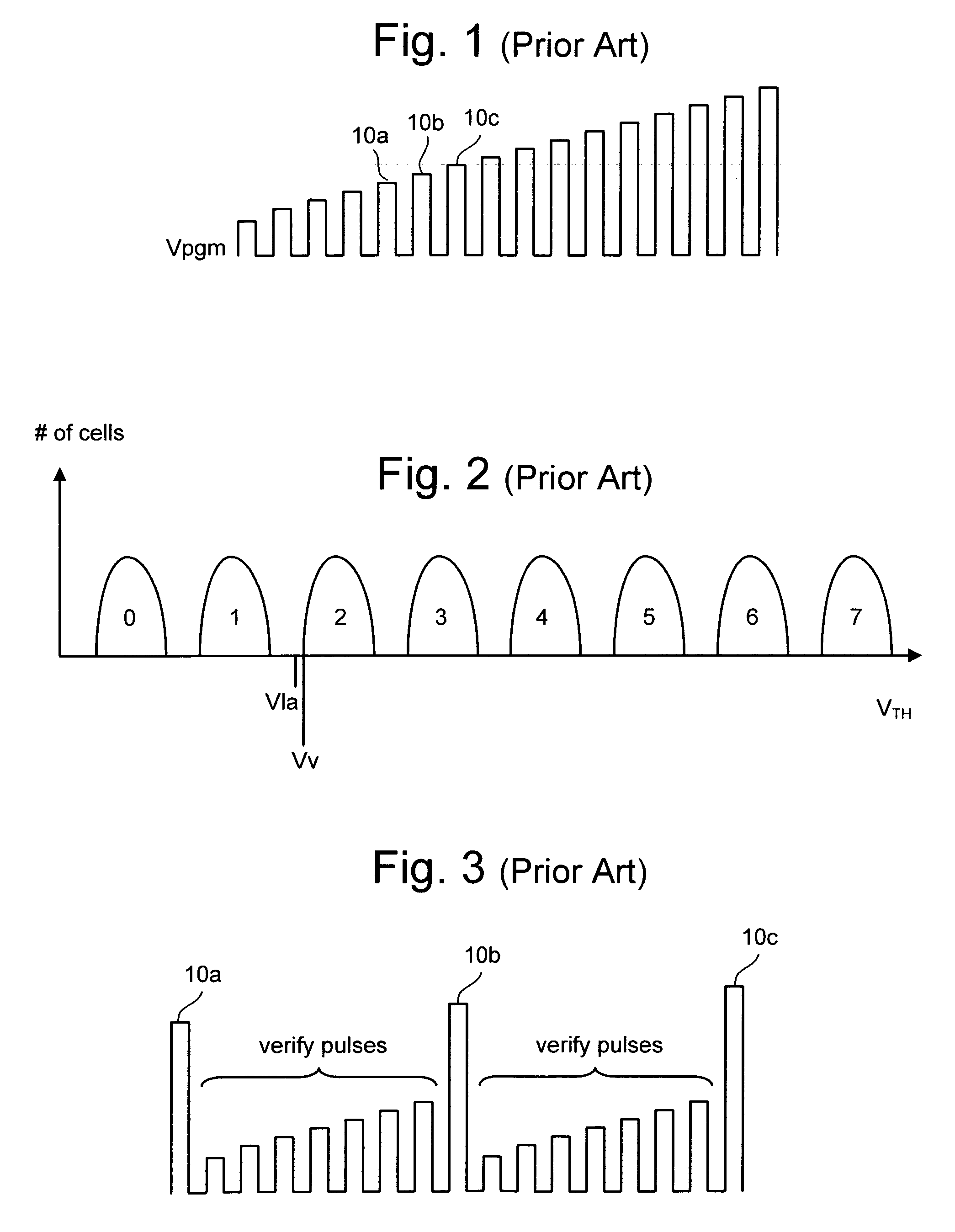

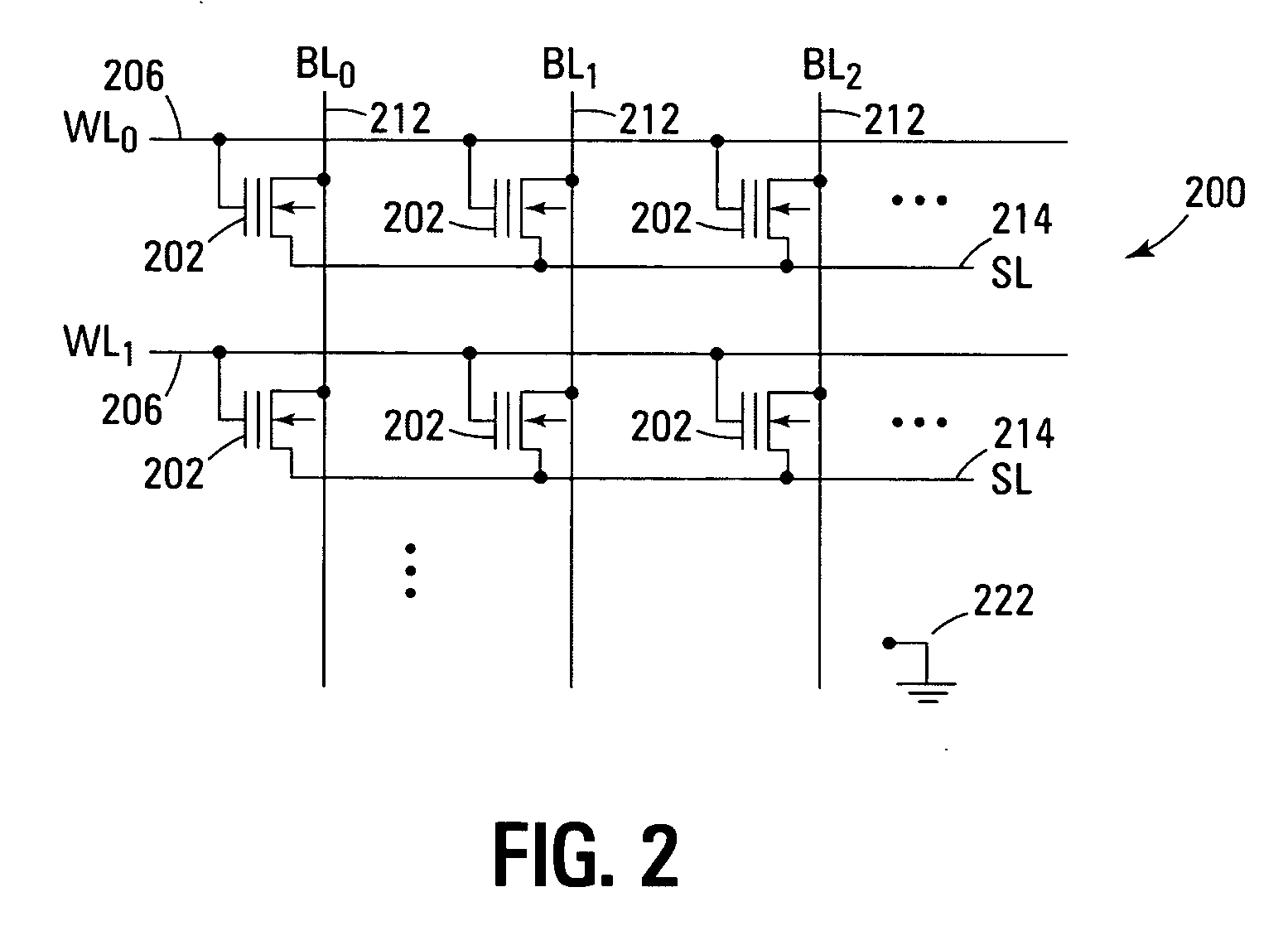

ActiveUS20050083735A1Speed up the processTransistorSolid-state devicesBit lineComputer architecture

The process for programming a set of memory cells is improved by adapting the programming process based on behavior of the memory cells. For example, a set of program pulses is applied to the word line for a set of flash memory cells. A determination is made as to which memory cells are easier to program and which memory cells are harder to program. Bit line voltages (or other parameters) can be adjusted based on the determination of which memory cells are easier to program and which memory cells are harder to program. The programming process will then continue with the adjusted bit line voltages (or other parameters).

Owner:KIOXIA CORP +1

Pipelined programming of non-volatile memories using early data

Owner:SANDISK TECH LLC

Behavior based programming of non-volatile memory

The process for programming a set of memory cells is improved by adapting the programming process based on behavior of the memory cells. For example, a set of program pulses is applied to the word line for a set of flash memory cells. A determination is made as to which memory cells are easier to program and which memory cells are harder to program. Bit line voltages (or other parameters) can be adjusted based on the determination of which memory cells are easier to program and which memory cells are harder to program. The programming process will then continue with the adjusted bit line voltages (or other parameters).

Owner:KIOXIA CORP +1

Programming method to reduce gate coupling interference for non-volatile memory

ActiveUS20070189073A1Reduce the impactReduce impactRead-only memoriesDigital storageGoal programmingEngineering

A non-volatile memory device and programming process is described that compensates for coupling effects on threshold gate voltages of adjacent floating gate or non-conductive floating node memory cells by adjusting the threshold voltage level programmed in view of the data being programmed on a following programming cycle into adjacent memory cells, so that the coupling effect results in the desired target threshold voltages for the cells. In one embodiment of the present invention, memory cell coupling is compensated for by adjusting programming level of one or more memory cells of a first page a memory array to a higher or lower threshold verify target voltage given the data / programming level to be written to directly adjacent memory cells of a second page, so that coupling between the directly adjacent memory cells of the first and second pages brings the memory cells of first page to their final target programming level.

Owner:MICRON TECH INC

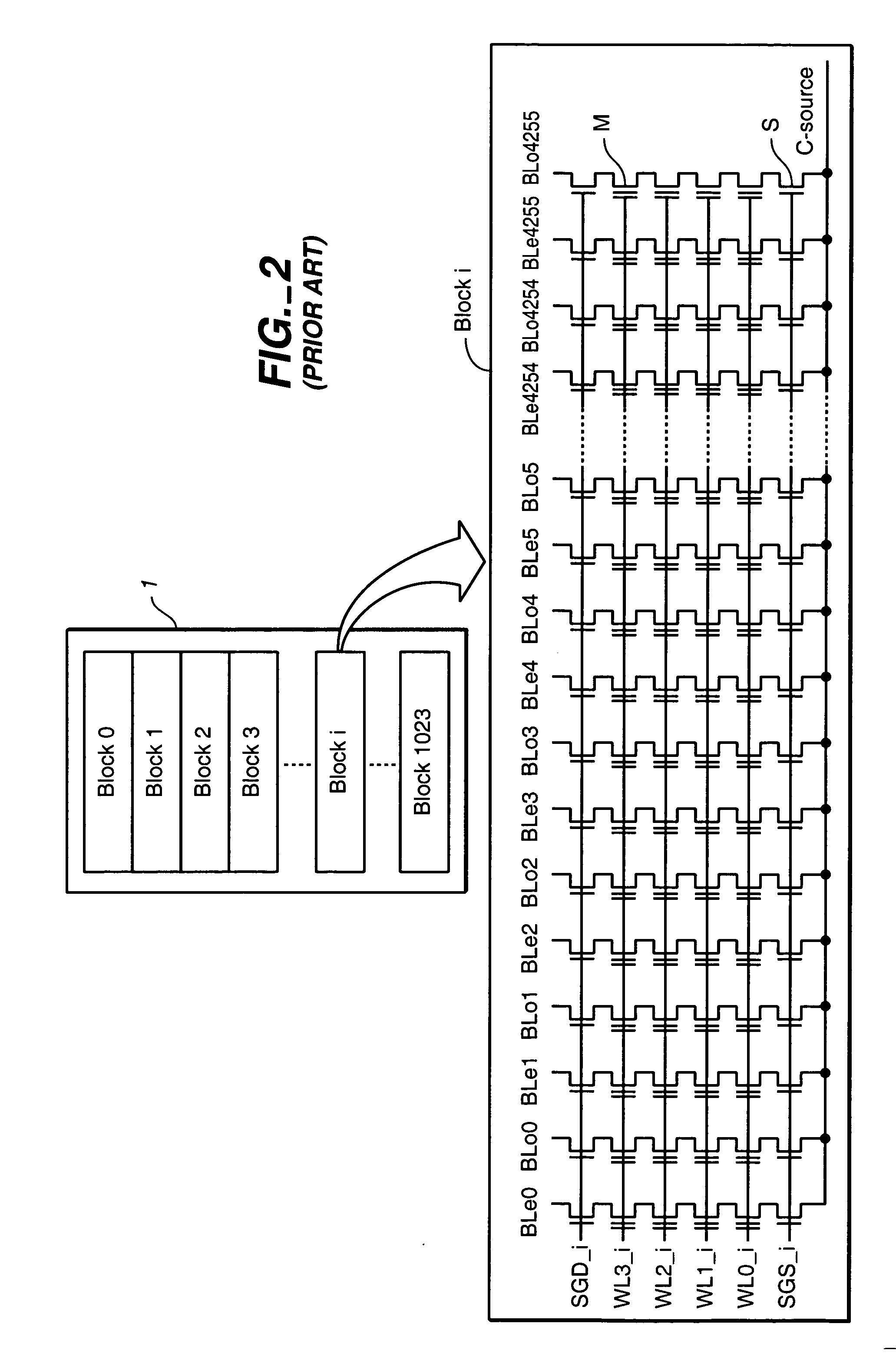

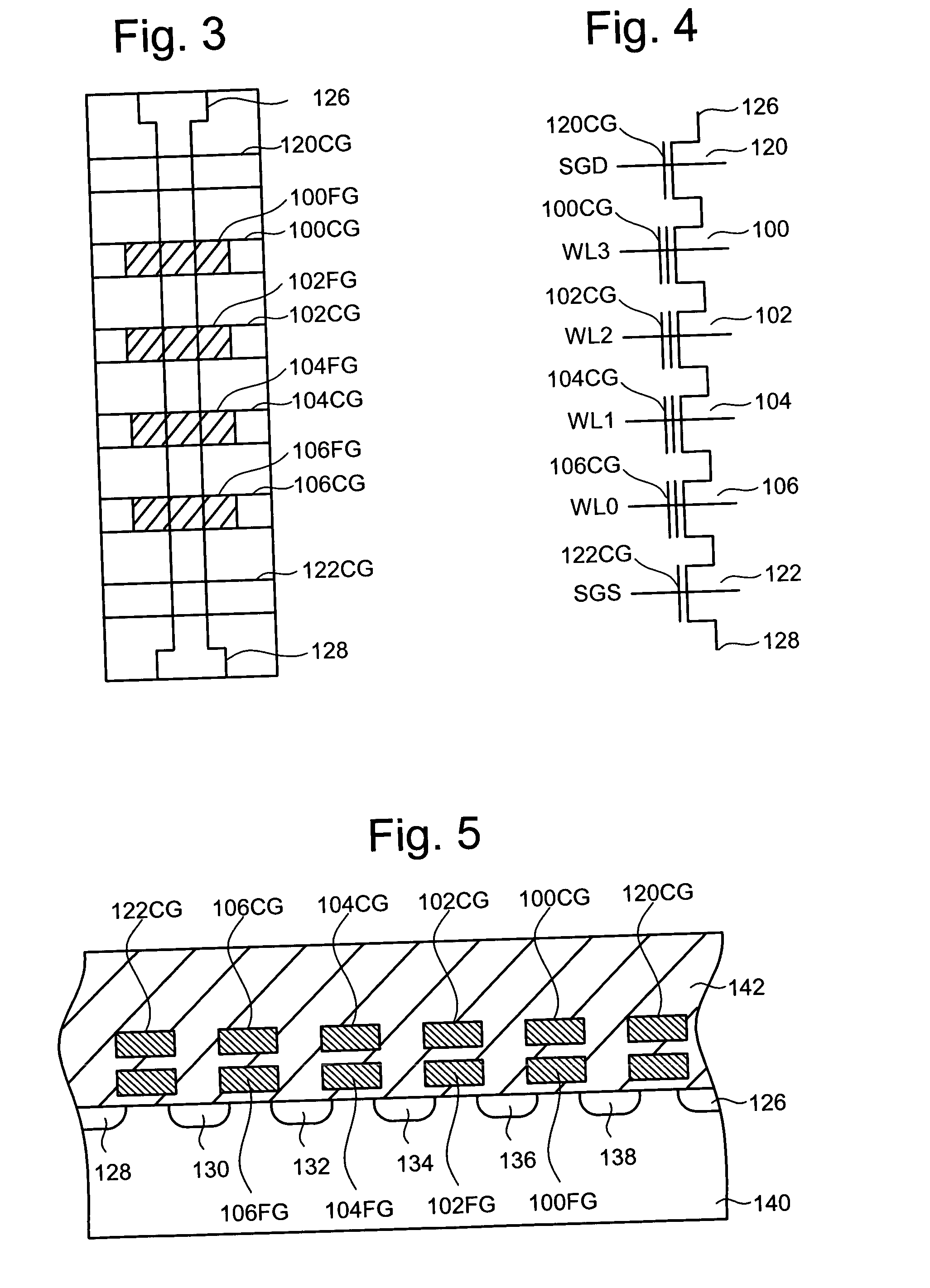

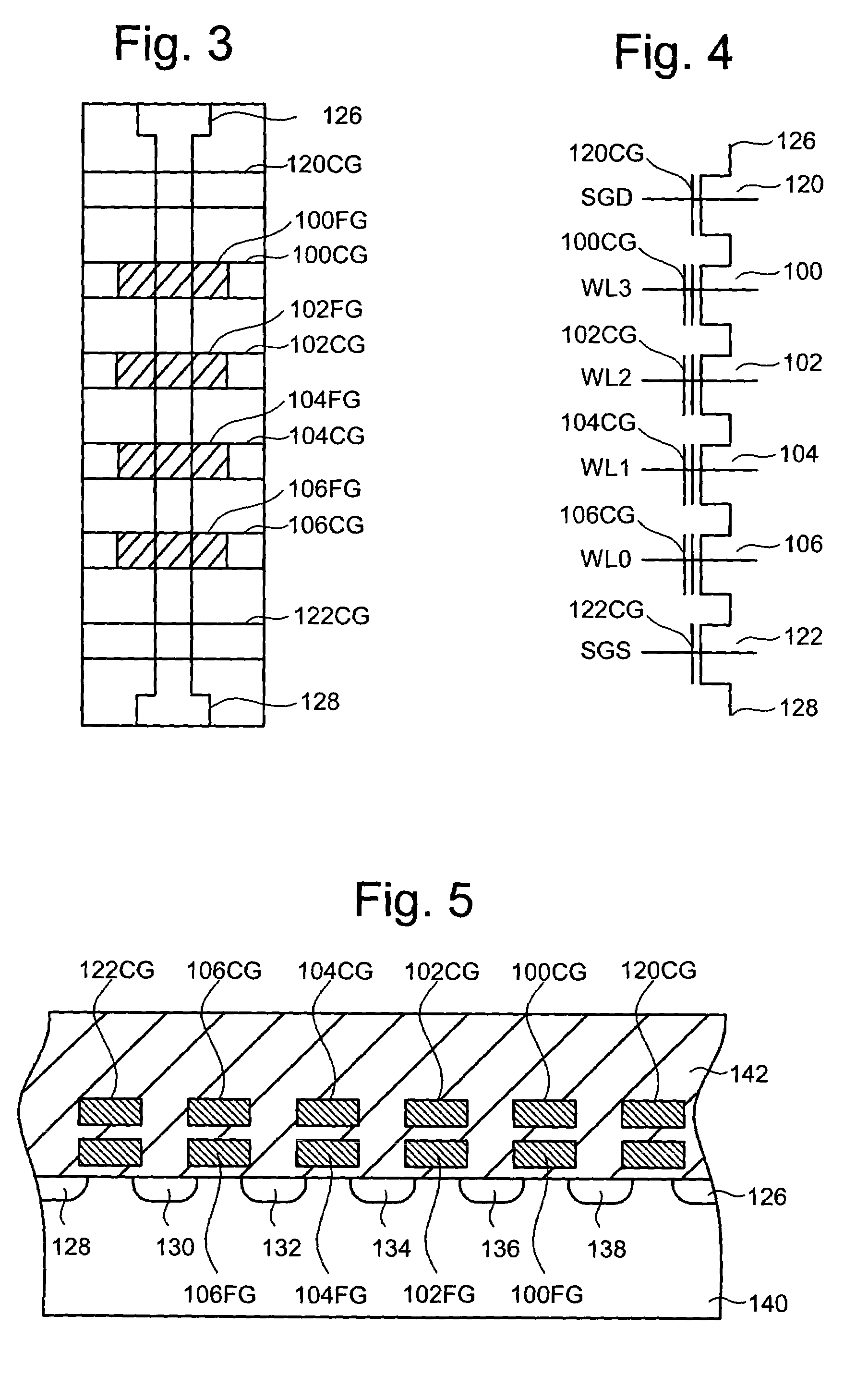

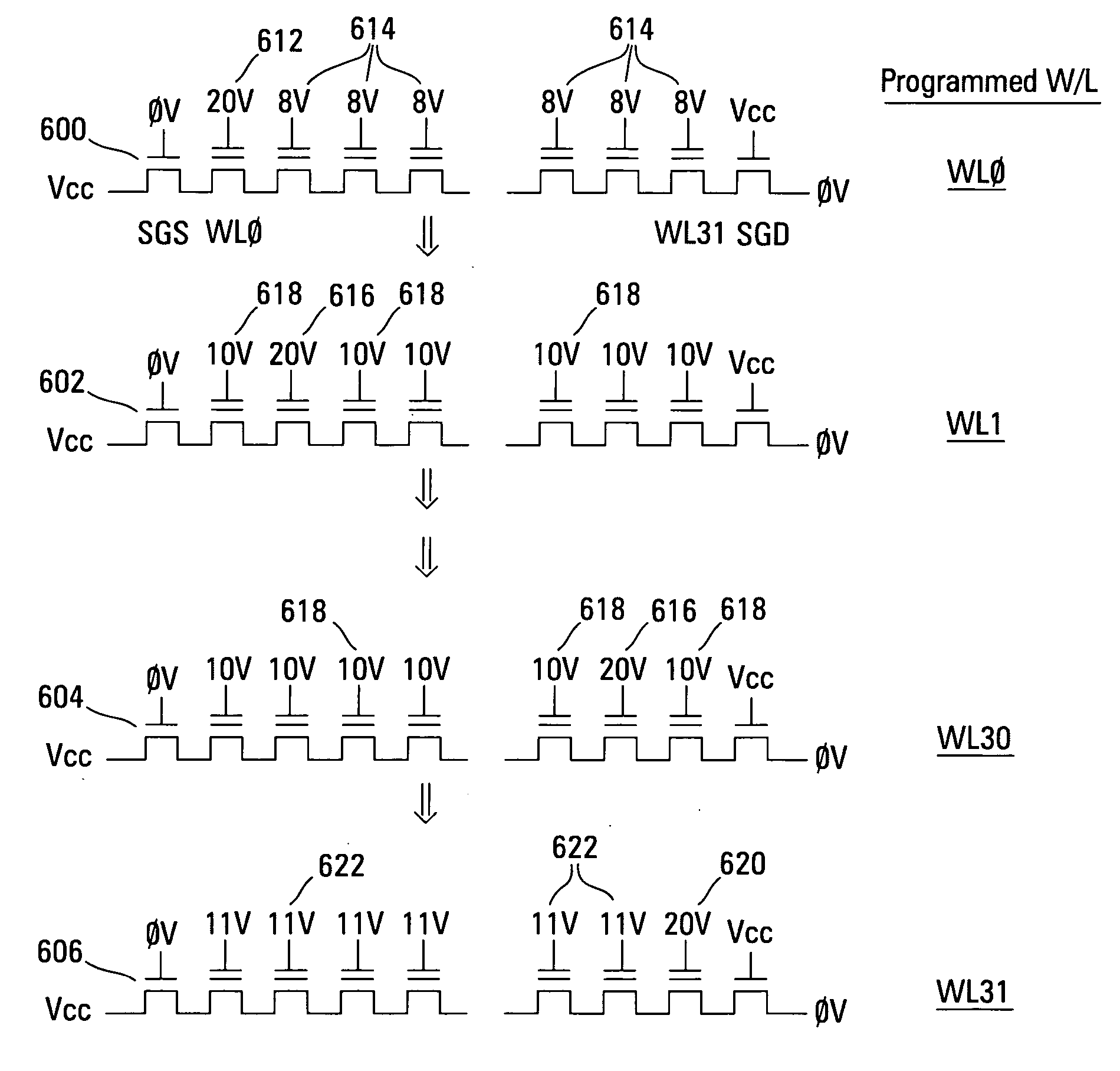

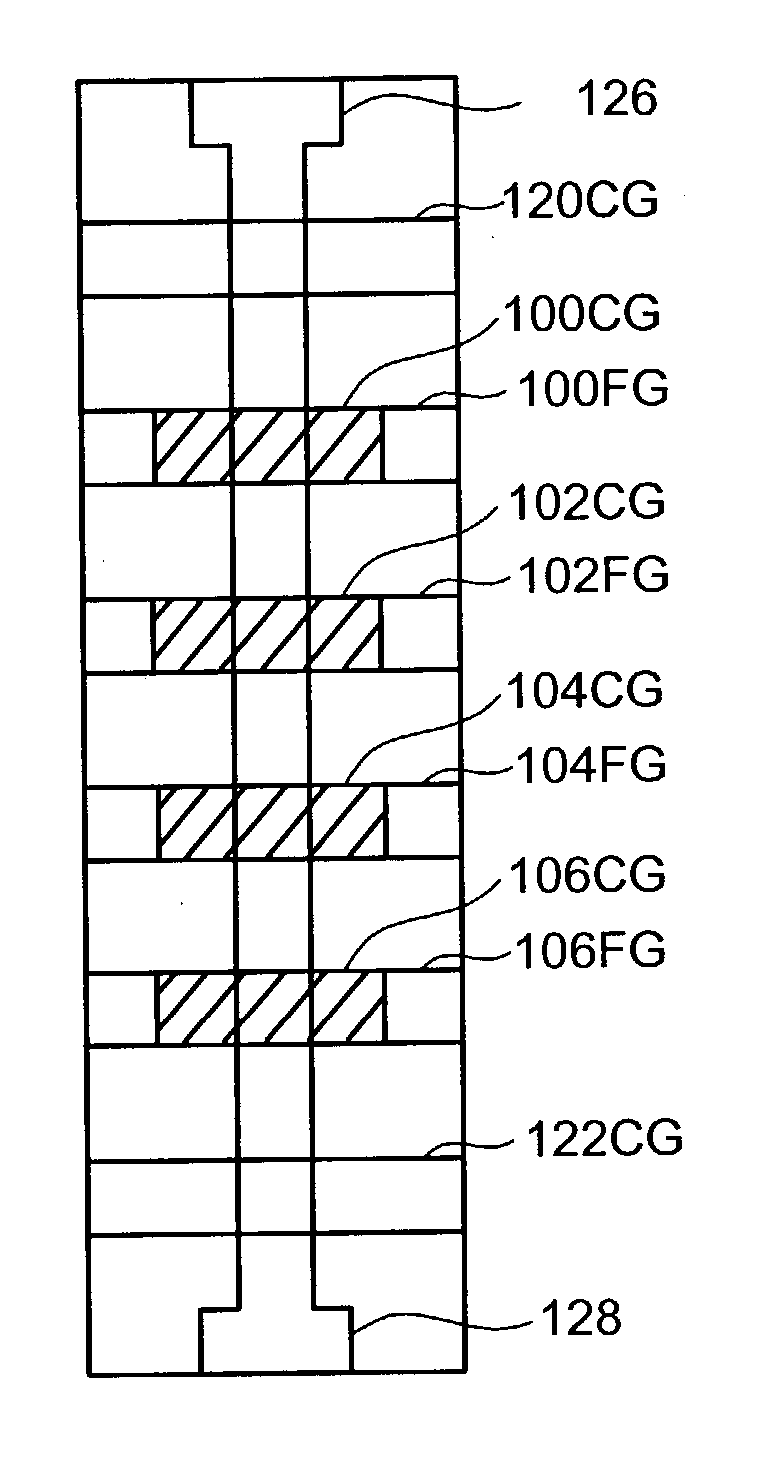

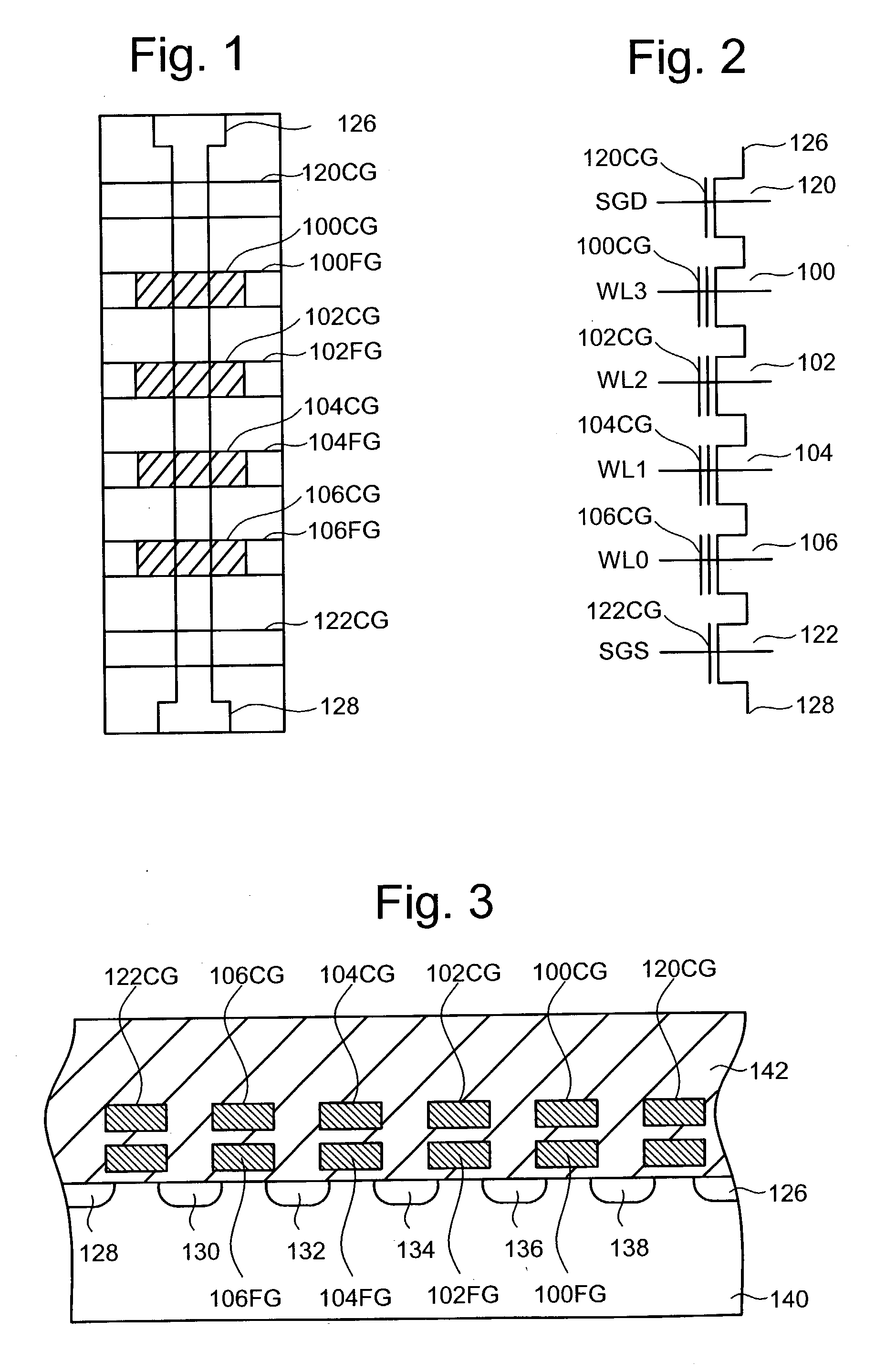

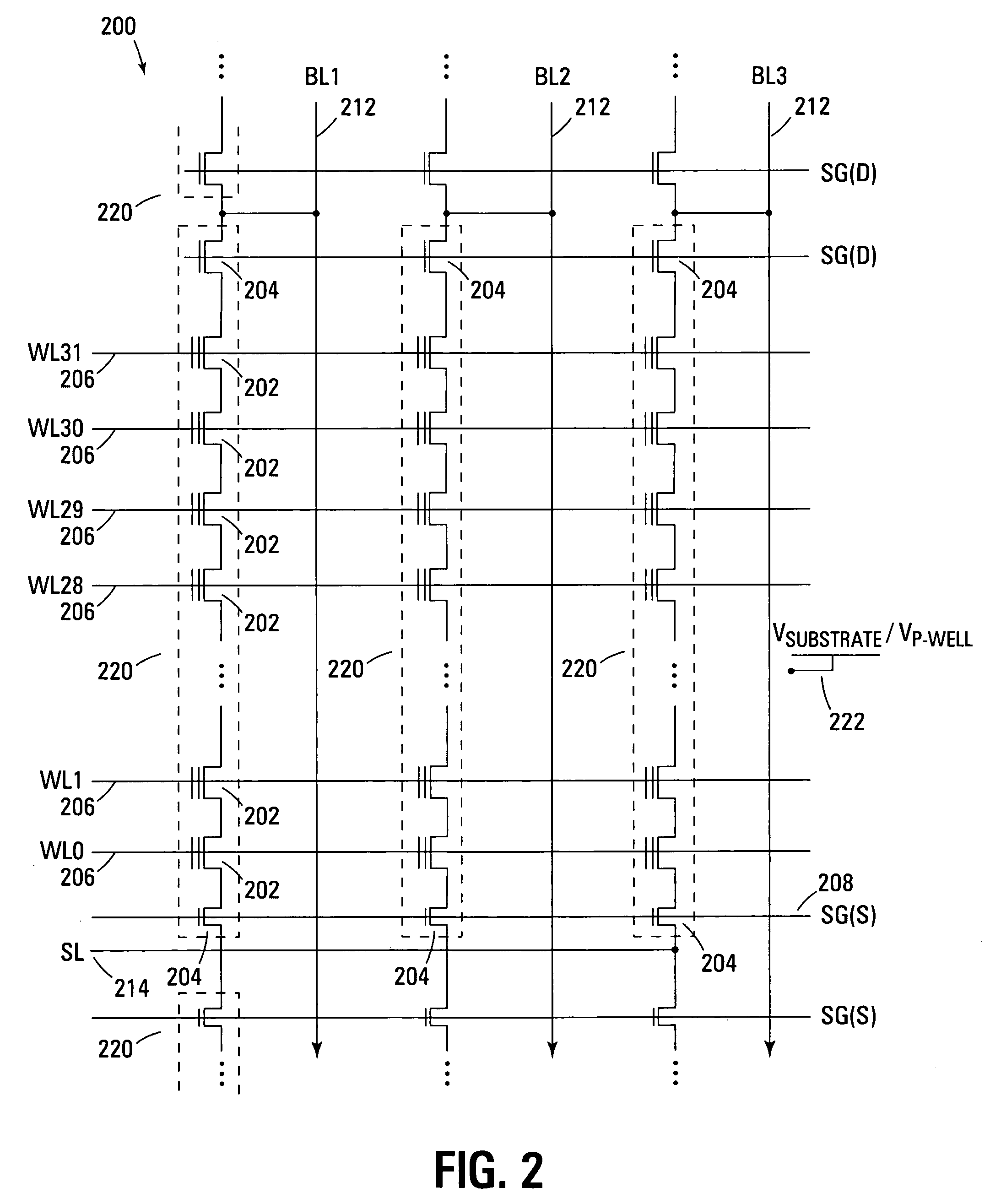

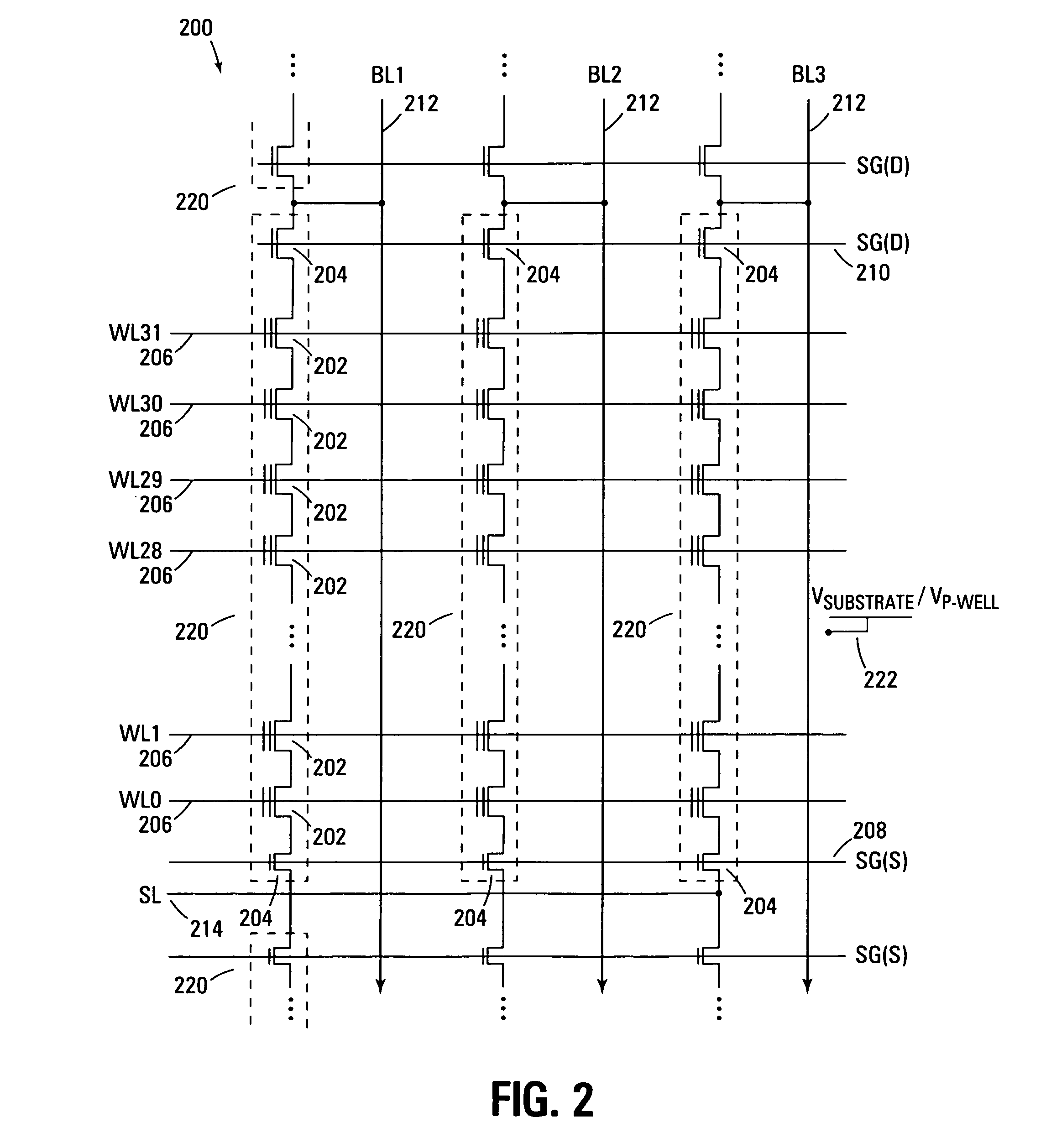

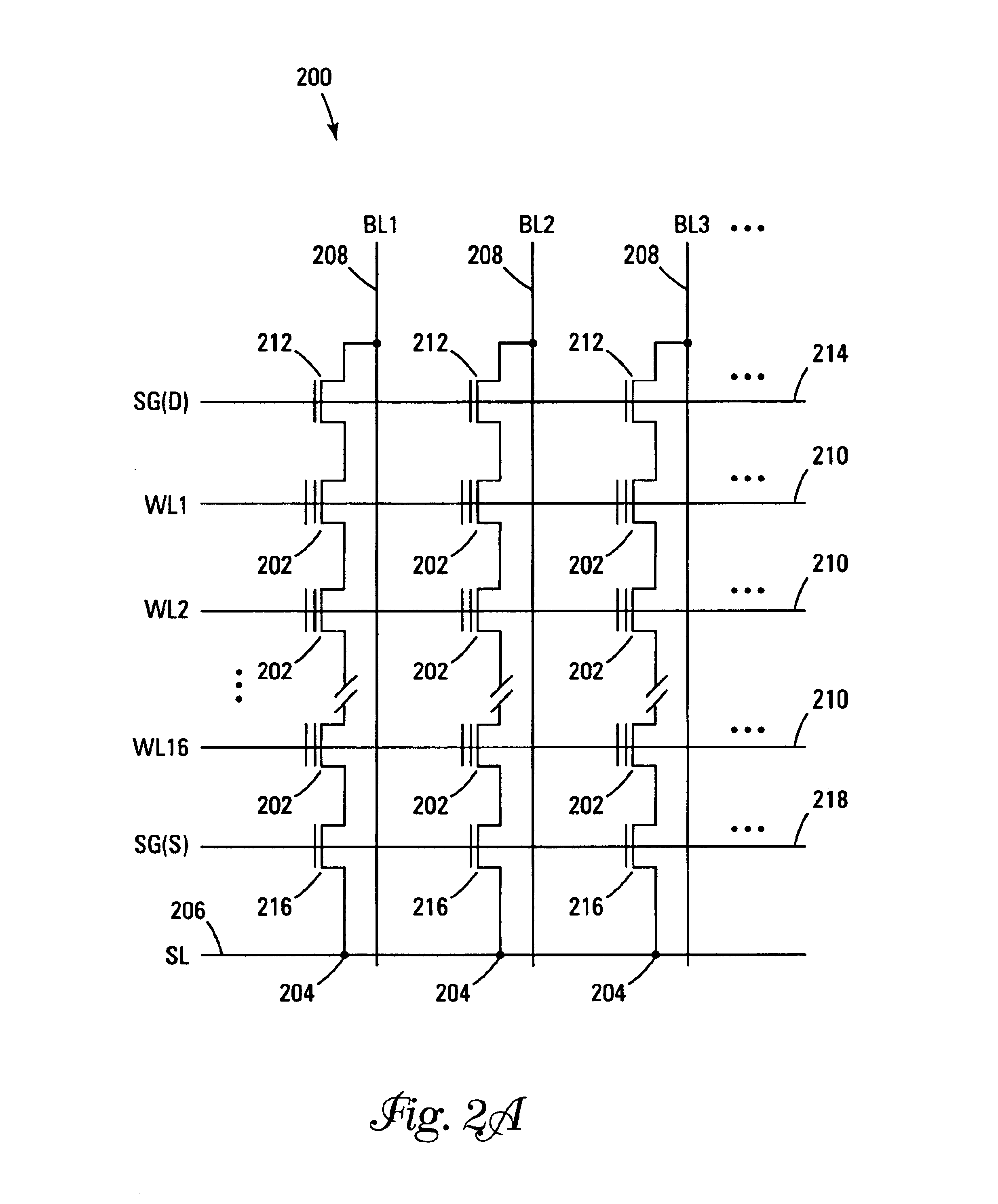

Programming method for NAND EEPROM

A NAND architecture non-volatile memory device and programming process is described that programs the various cells of strings of non-volatile memory cells by the application of differing word line pass voltages (Vpass) to the unselected word lines of the memory cell string or array during an programming cycle. In one embodiment of the present invention, the differing word line pass voltages (Vpass) are utilized depending on the placement of the memory cell in the NAND memory cell string. In another embodiment of the present invention, the differing word line pass voltages (Vpass) are utilized to compensate for faster and slower programming word lines / memory cells.

Owner:MICRON TECH INC

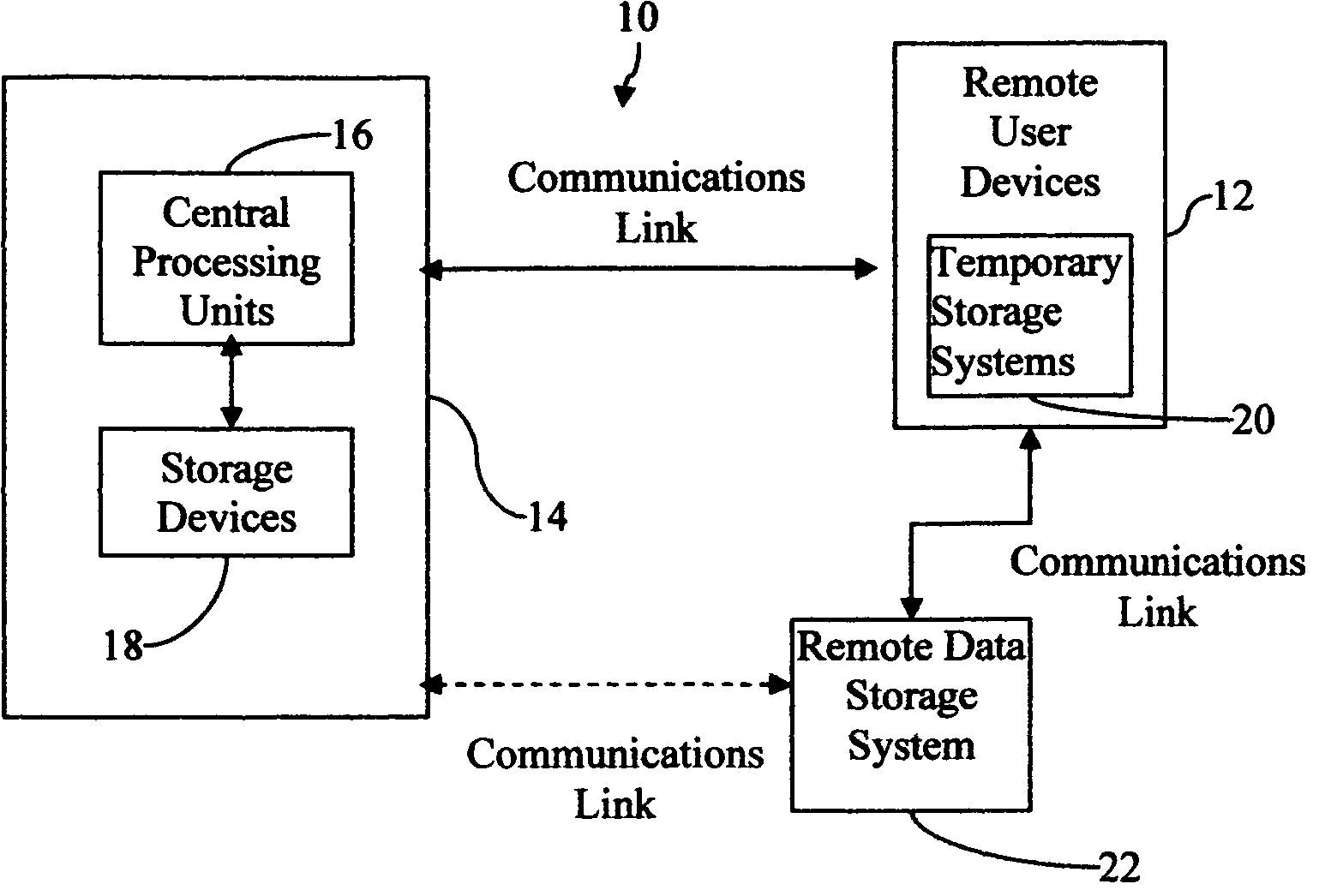

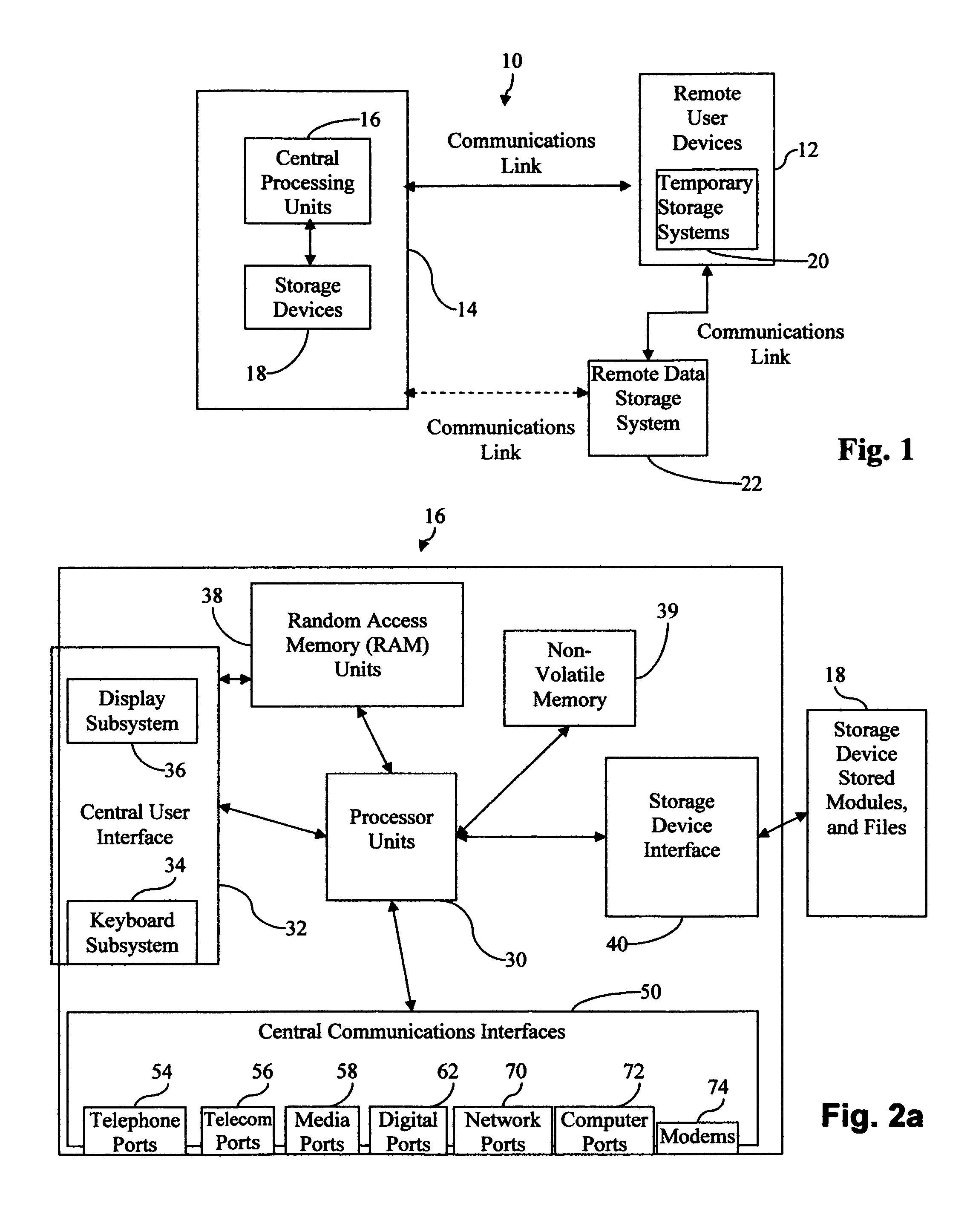

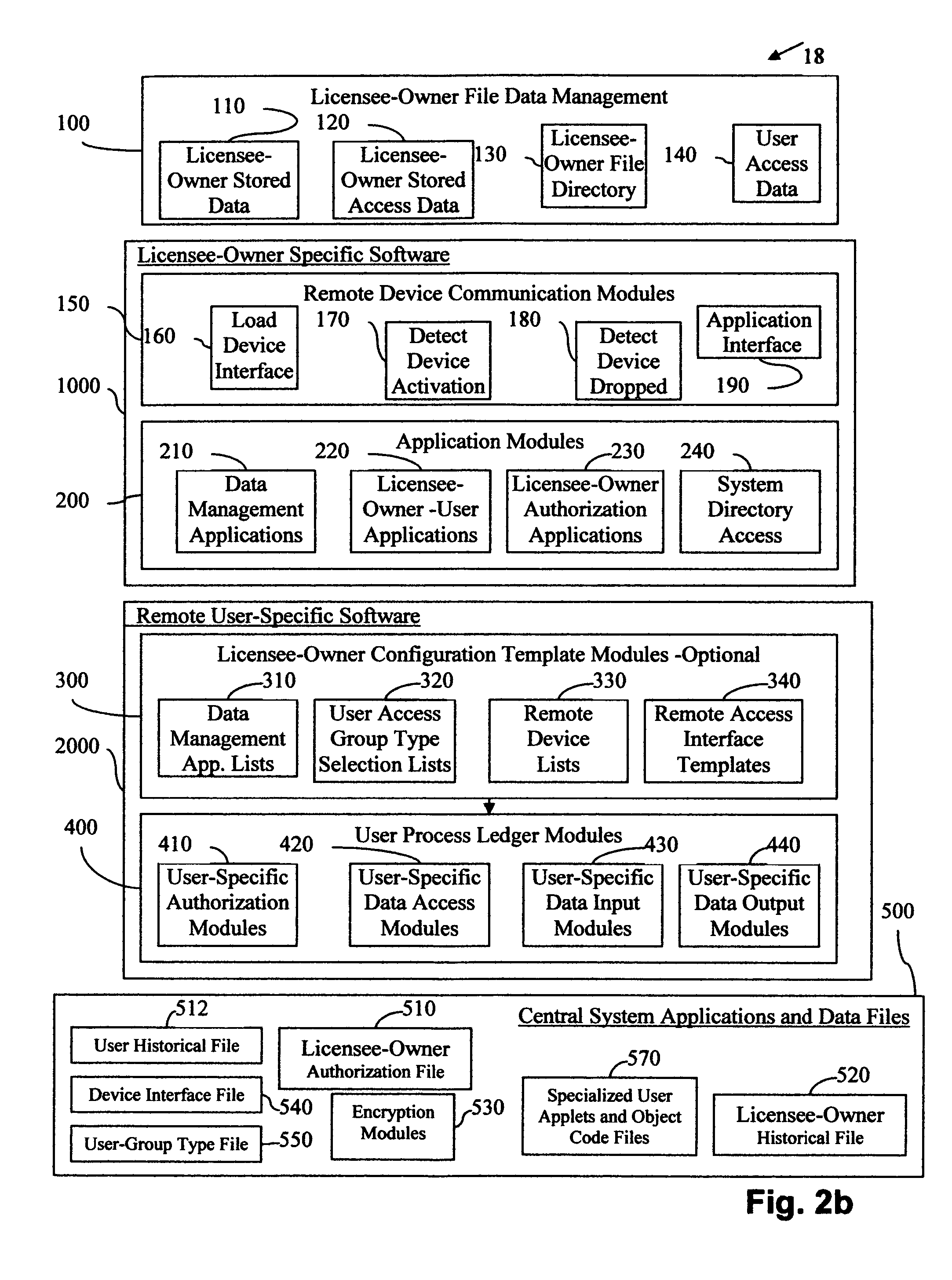

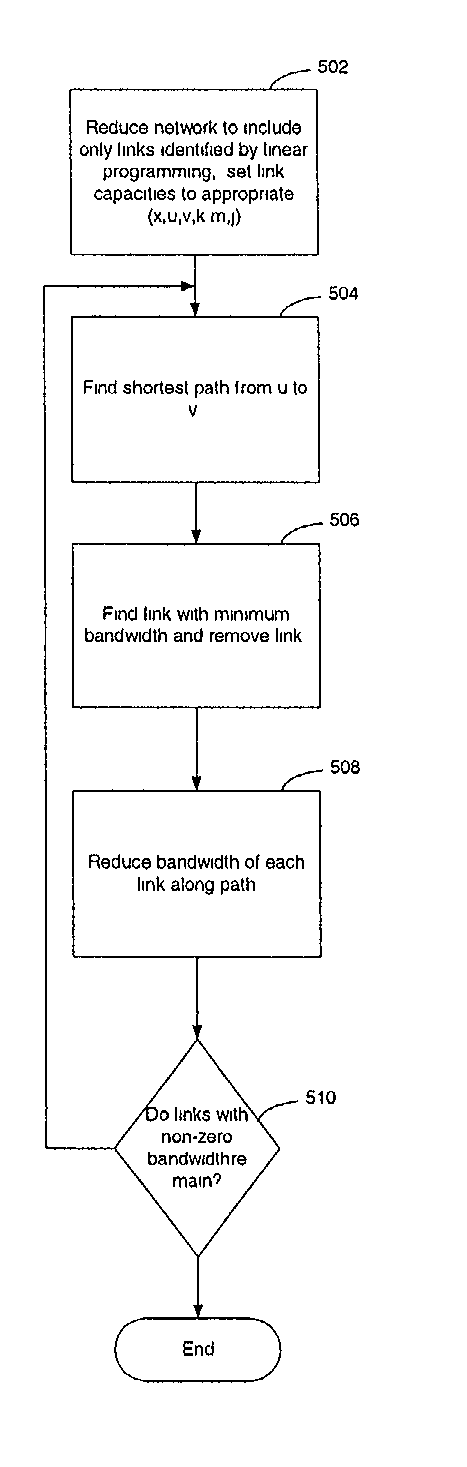

Central work-product management system for coordinated collaboration with remote users

InactiveUS7761591B2Easy accessFinanceMultiple digital computer combinationsService product managementMulti protocol

Client-specified methods, systems and computer program product with multi-protocol access for data input requests designed around a client's business application. It does this by interfacing IVR / telephony programming of multiple communication device protocols to separate data source input protocol programming, including remoting programming. Data input is by selected IVR / telephony responses designed around the needs of the individual client through selection process within a variety of configuration templates. The templates are designed to interface with the business applications through programming procedures for data entry specific to each application's protocol. The advantage, templates reduce user / client's interface with the business applications resulting in minimal time and knowledge of each applications data requirements, and limits each user's access to the system to specific data input. System response for data output is limited to the requested input for error reduction.

Owner:GRAHAM JEAN A

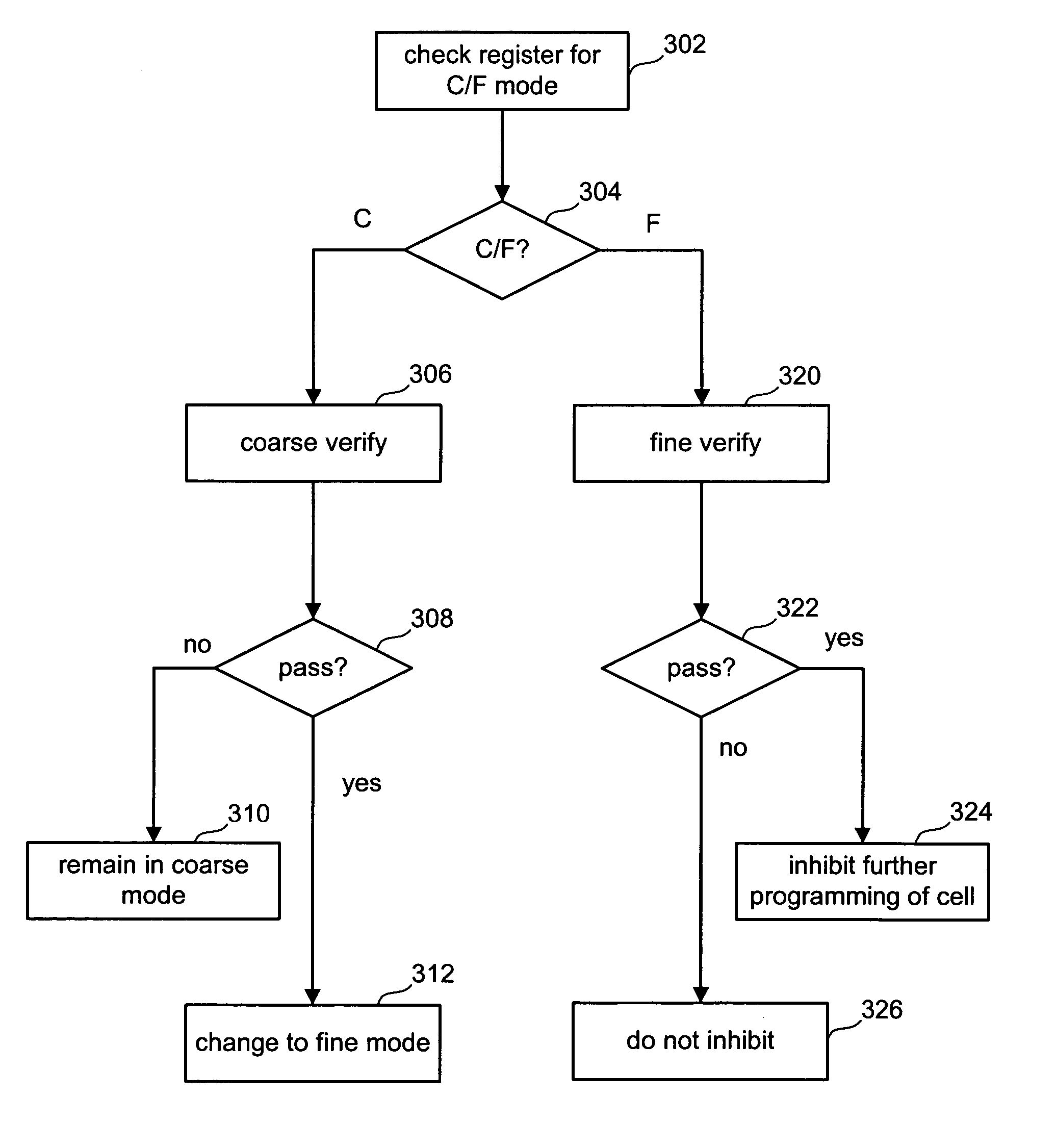

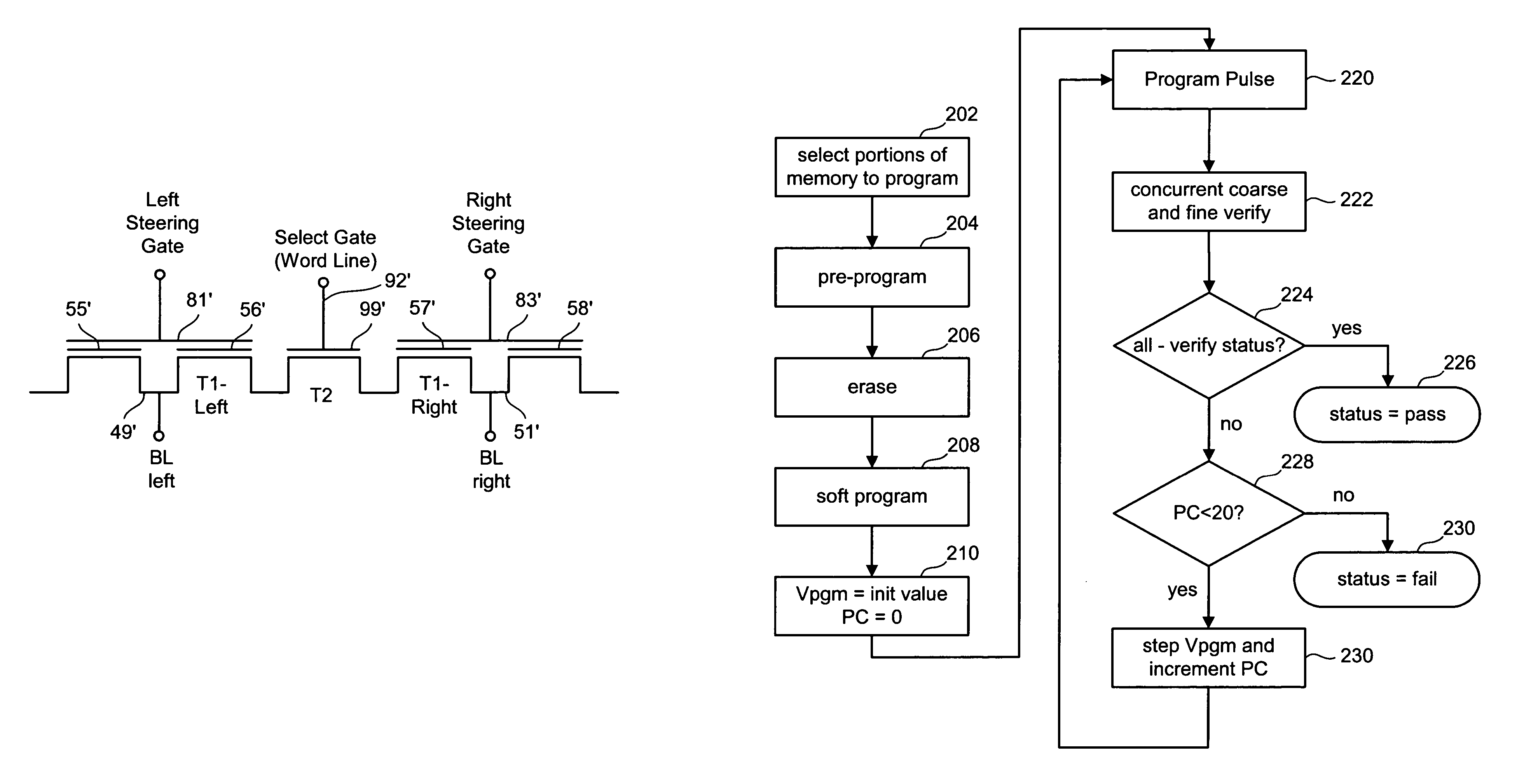

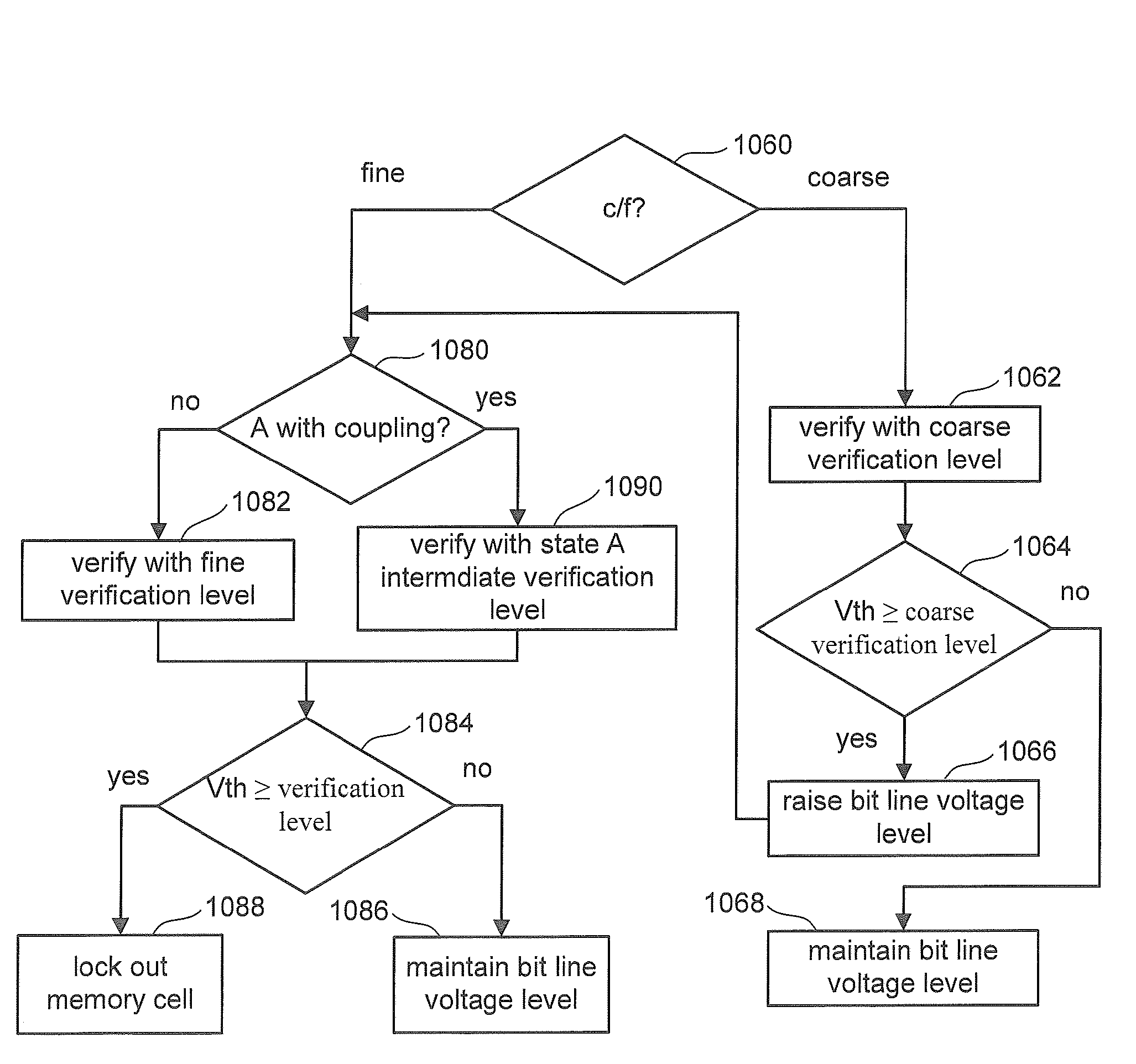

Charge packet metering for coarse/fine programming of non-volatile memory

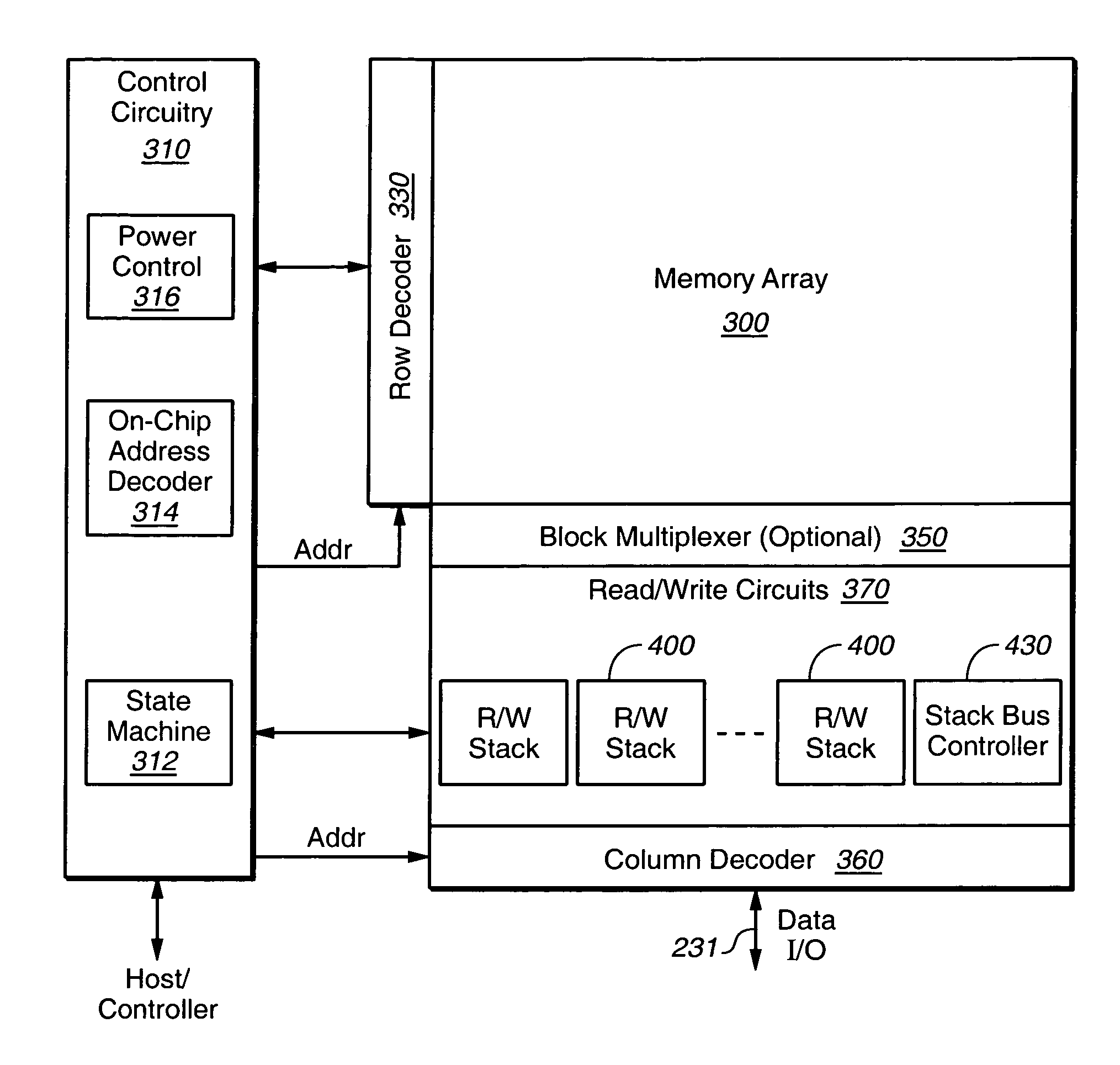

A non-volatile memory device is programmed by first performing a coarse programming process and subsequently performing a fine programming process. The coarse / fine programming methodology is enhanced by using an efficient verification scheme that allows some non-volatile memory cells to be verified for the coarse programming process while other non-volatile memory cells are verified for the fine programming process. The fine programming process can be accomplished using current sinking, charge packet metering or other suitable means.

Owner:SANDISK TECH LLC

Non-volatile memory and method with phased program failure handling

InactiveUS20050166087A1Improve efficiencyReduce overheadMemory architecture accessing/allocationMemory adressing/allocation/relocationError processingTime critical

In a memory with block management system, program failure in a block during a time-critical memory operation is handled by continuing the programming operation in a breakout block. Later, at a less critical time, the data recorded in the failed block prior to the interruption is transferred to another block, which could also be the breakout block. The failed block can then be discarded. In this way, when a defective block is encountered during programming, it can be handled without loss of data and without exceeding a specified time limit by having to transfer the stored data in the defective block on the spot. This error handling is especially critical for a garbage collection operation so that the entire operation need not be repeated on a fresh block during a critical time. Subsequently, at an opportune time, the data from the defective block can be salvaged by relocation to another block.

Owner:SANDISK TECH LLC

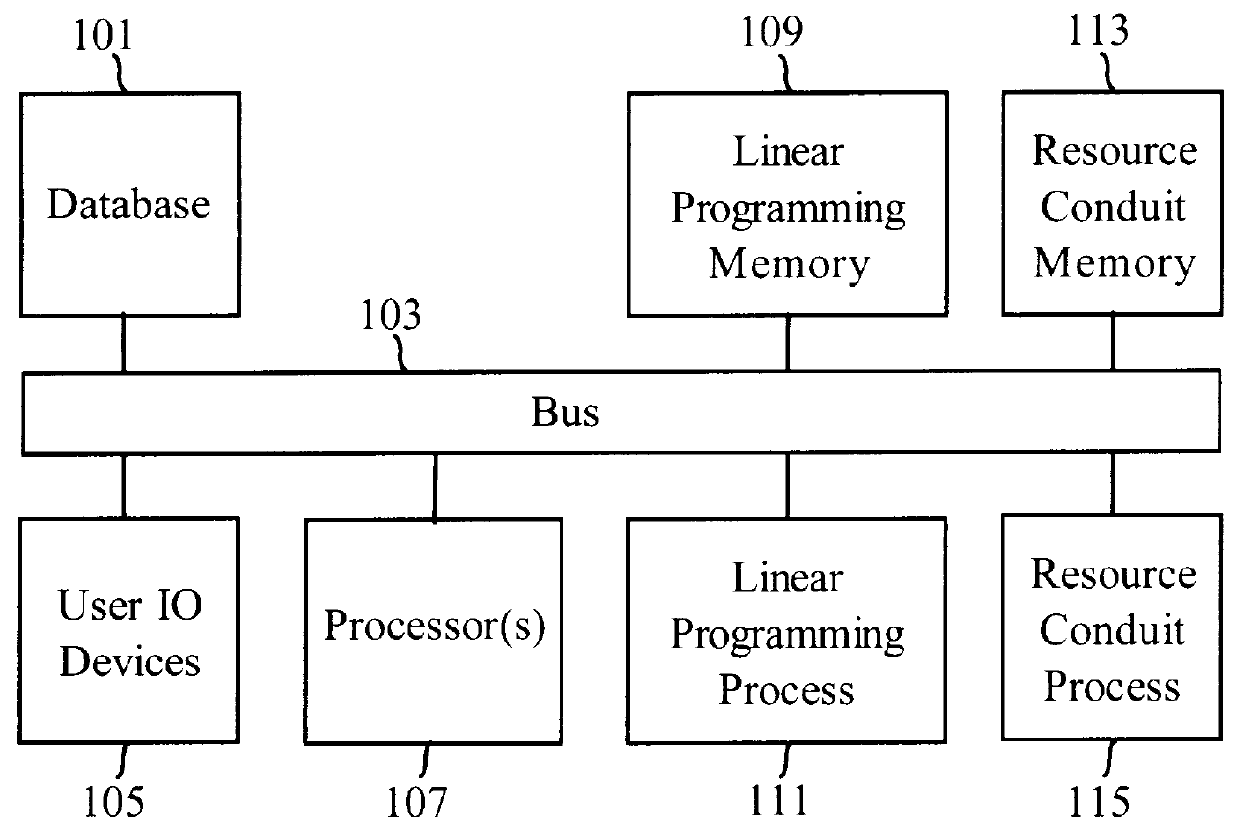

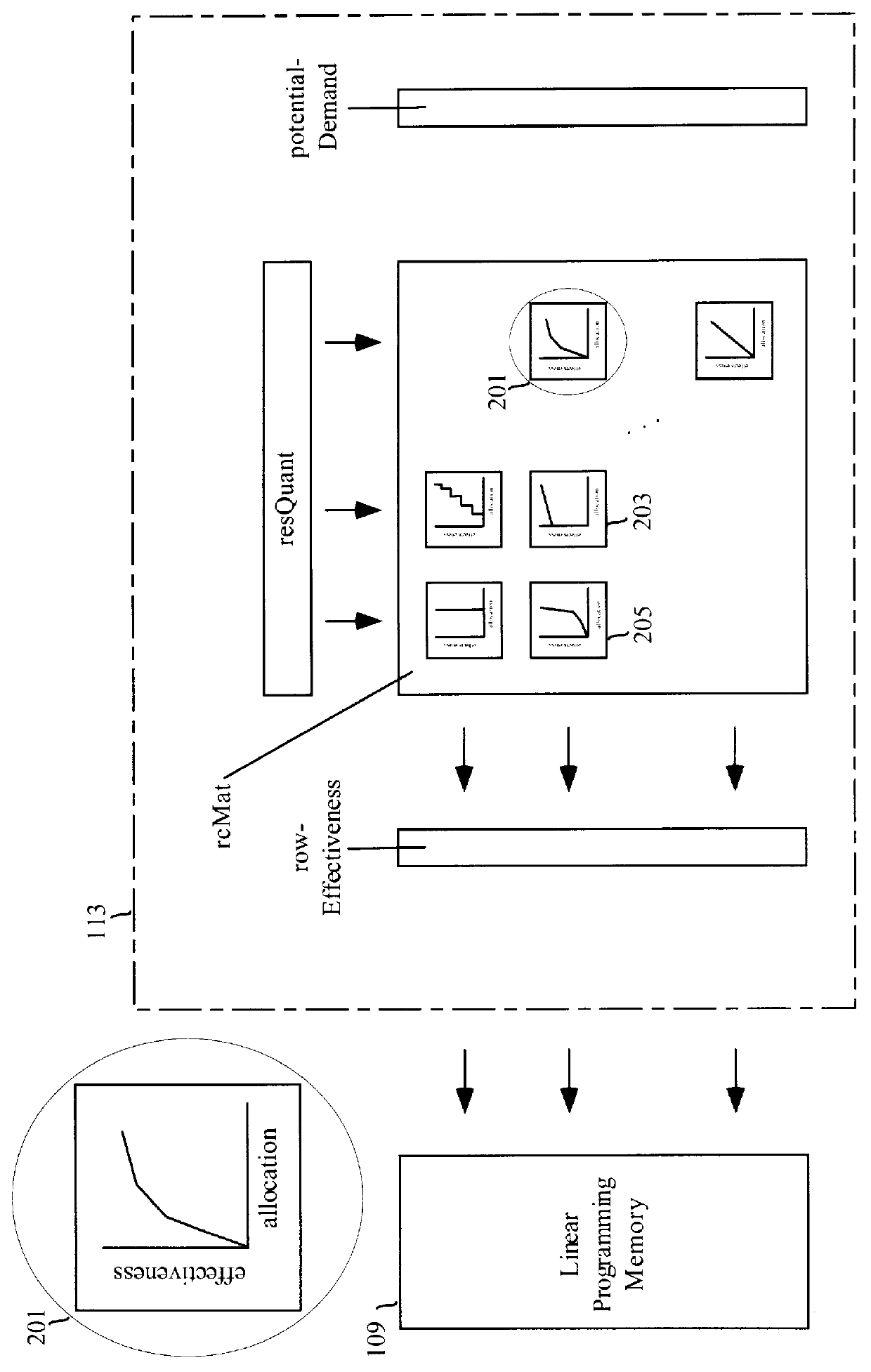

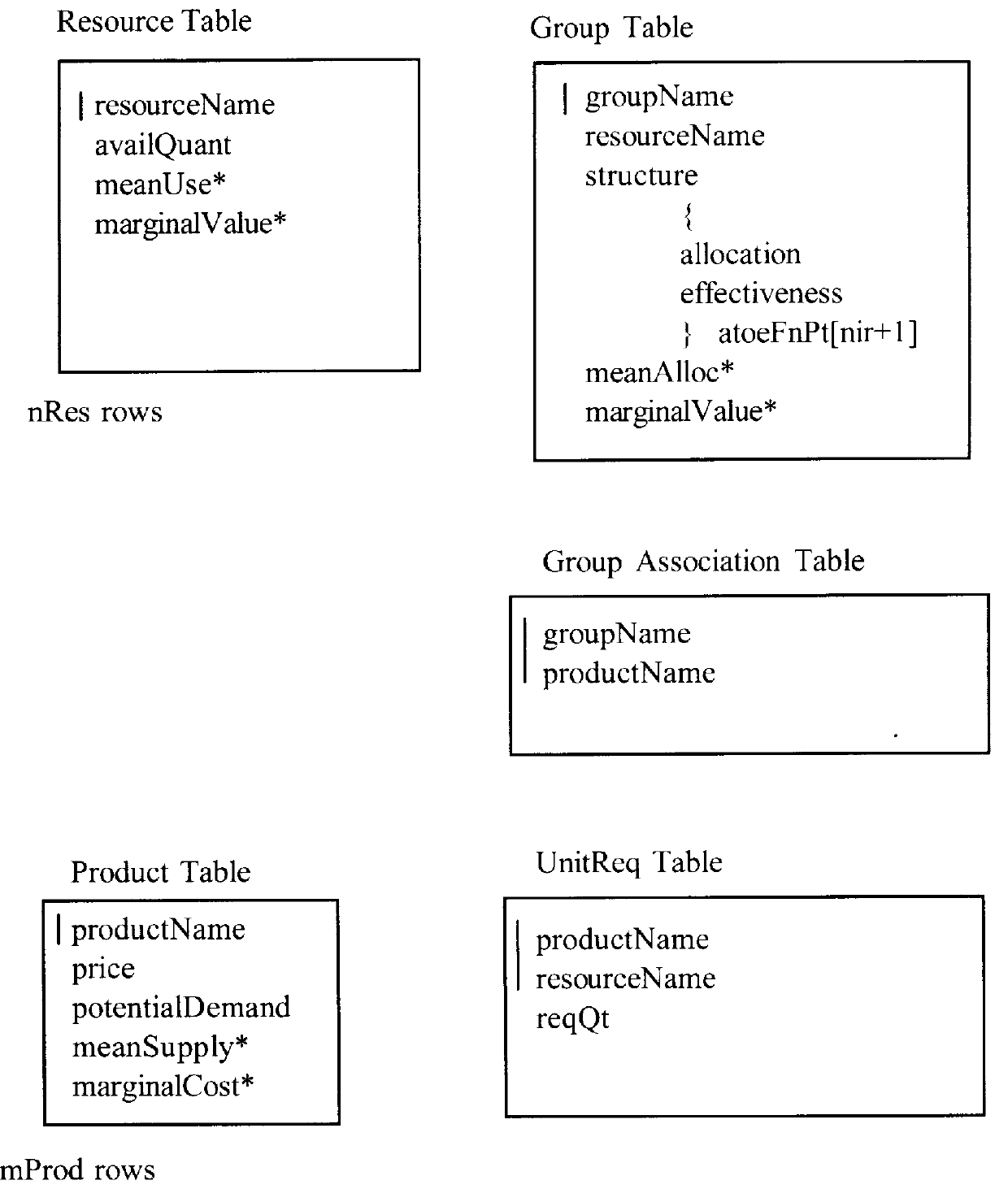

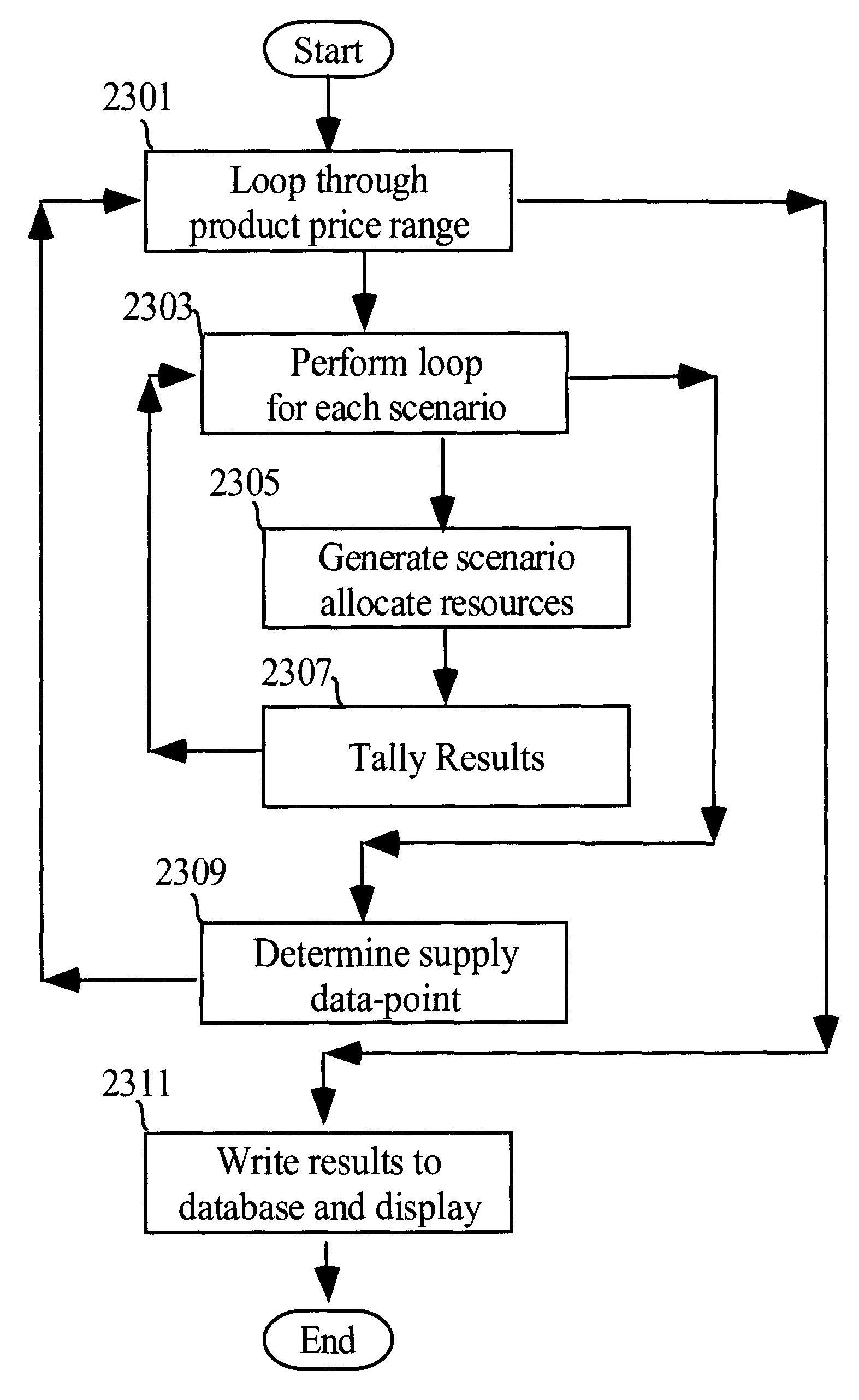

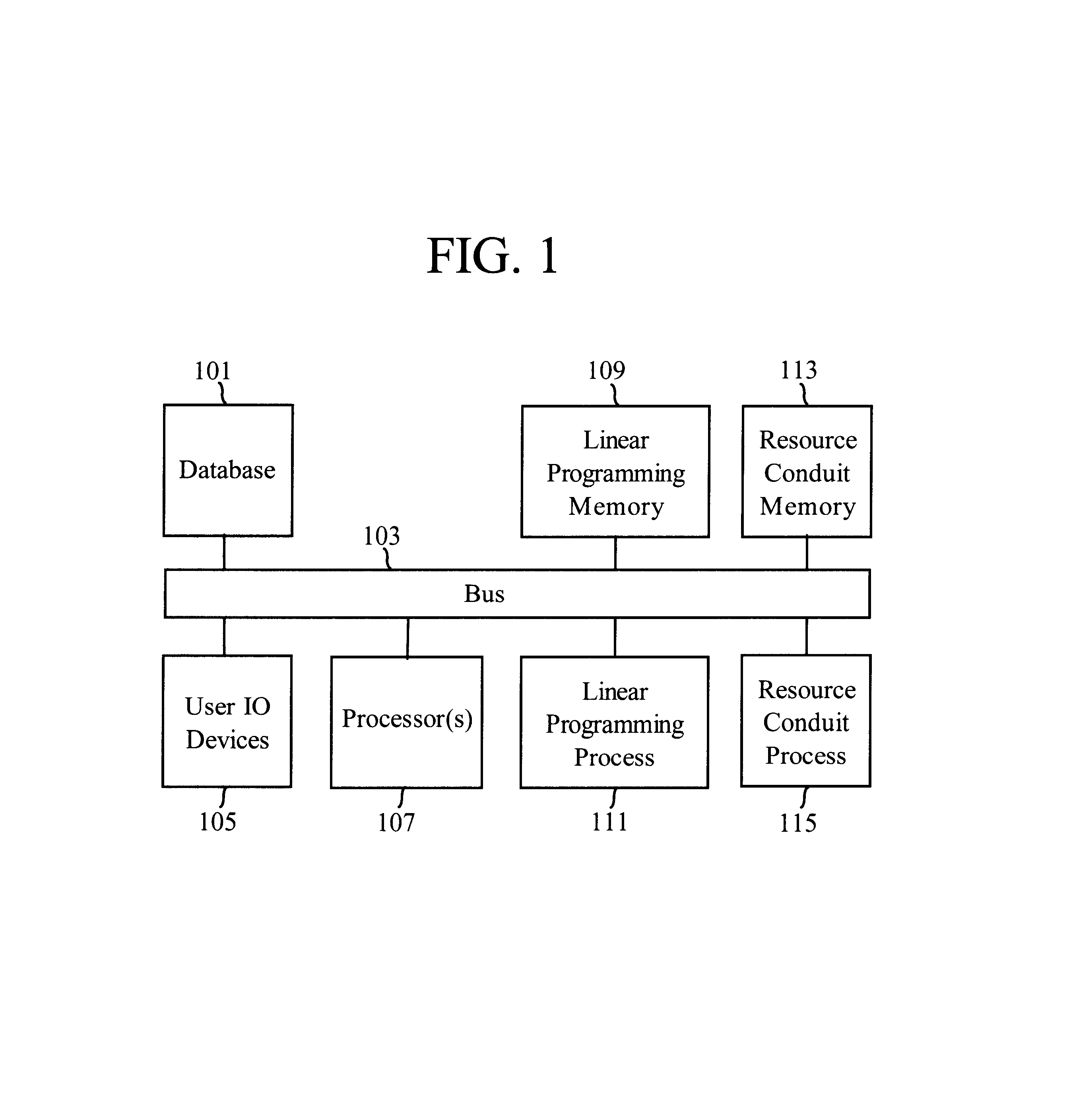

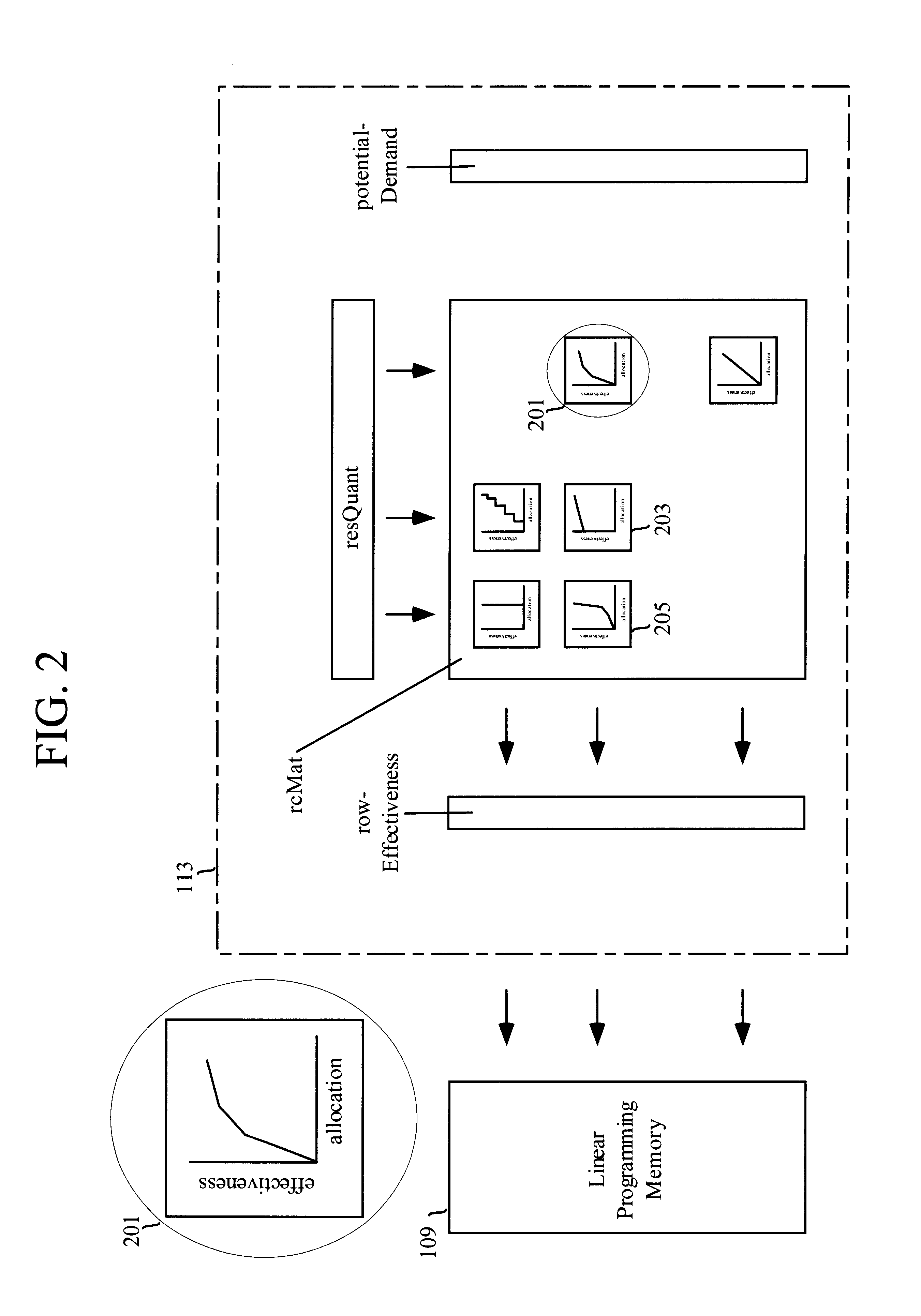

Method and apparatus for allocating, costing, and pricing organizational resources

This invention is a means both to allocate all types of resources for commercial, governmental, or non-profit organizations and to price such resources. A linear programming process makes fulfillment allocations used to produce product units. A Resource-conduit process governs the linear programming process, uses two-sided shadow prices, and makes aperture allocations to allow Potential-demand to become Realized-demand. A strict opportunity cost perspective is employed, and the cost of buyable resources is deemed to be the opportunity cost of tying up cash. Resource available quantities, product resource requirements, and Potential-demand as a statistical distribution are specified in a database. The invention reads the database, performs optimization, and then writes allocation directives to the database. Also determined and written to the database are resource marginal (incremental) values and product marginal costs. The database can be viewed and edited through the invention's Graphical User Interface. Monte Carlo simulation, along with generation of supply and demand schedules, is included to facilitate analysis, explore "what if," and interact with the user to develop product offering, product pricing, and resource allocation strategies and tactics.

Owner:JAMESON JOEL

Variable current sinking for coarse/fine programming of non-volatile memory

A non-volatile memory device is programmed by first performing a coarse programming process and subsequently performing a fine programming process. The coarse / fine programming methodology is enhanced by using an efficient verification scheme that allows some non-volatile memory cells to be verified for the coarse programming process while other non-volatile memory cells are verified for the fine programming process. The fine programming process can be accomplished using current sinking, charge packet metering or other suitable means.

Owner:SANDISK TECH LLC

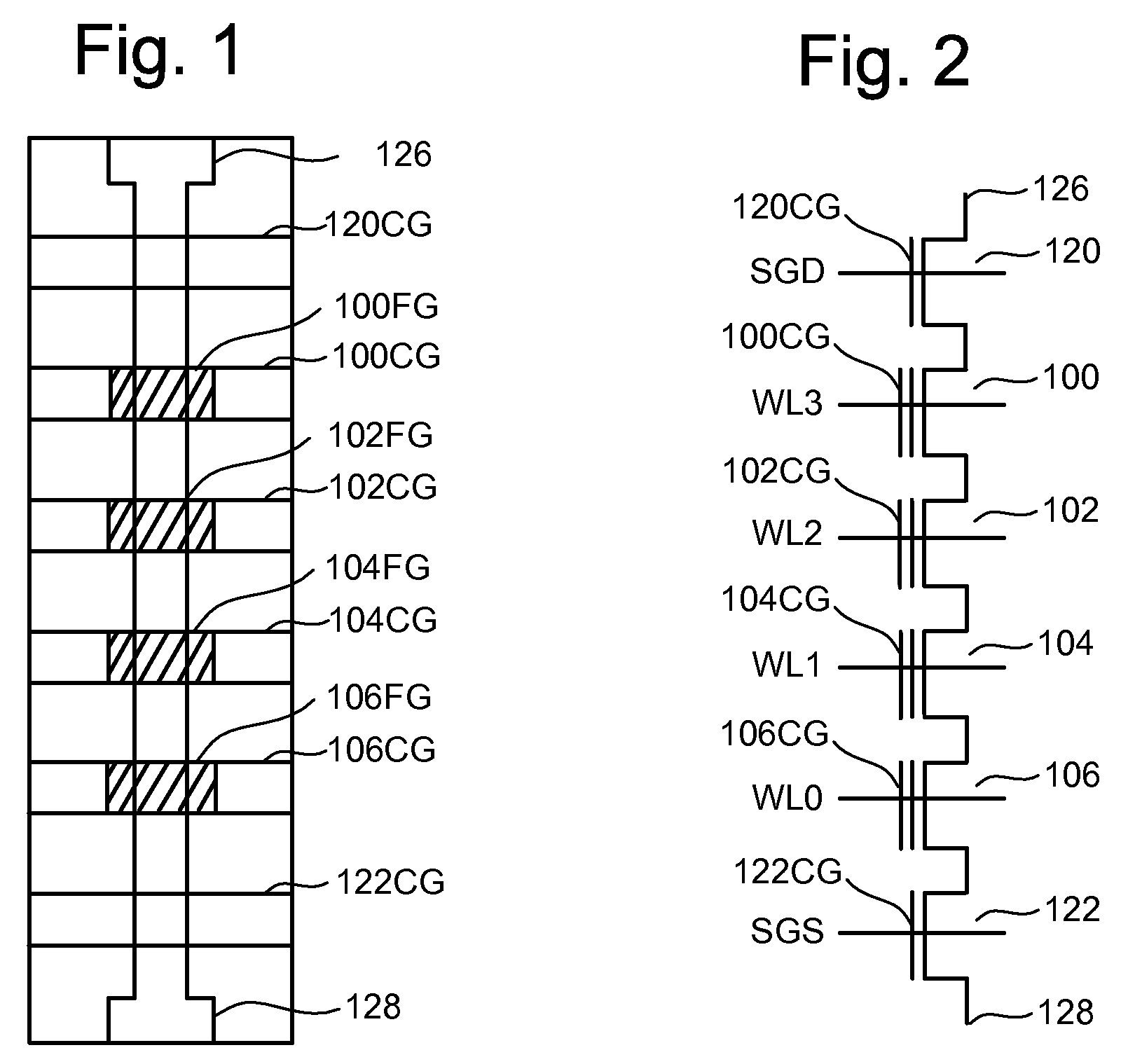

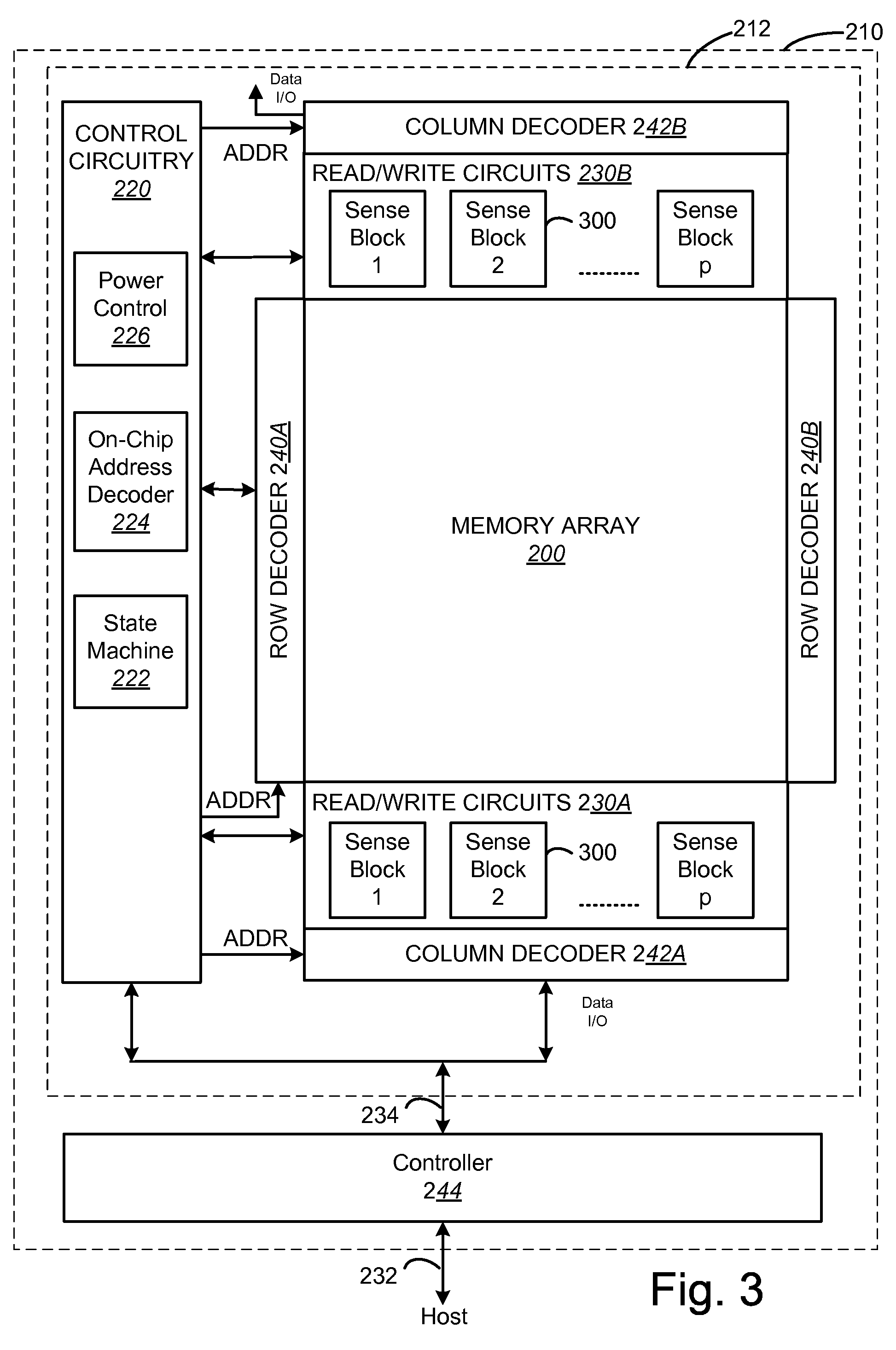

Use of data latches in multi-phase programming of non-volatile memories

A non-volatile memory device includes circuitry for governing a multi-phase programming process in a non-volatile memory. The exemplary embodiment uses a quick pass write technique where a single programming pass is used, but the biasing of the selected memory cells is altered to slow programming as the memory cells approach their target values by raising the voltage level of the channels of the selected memory cells. A principle aspect of the present invention introduces a latch associated with the read / write circuitry connectable to each selected memory cell along a corresponding bit line for the storage of the result of the verify at this lower level.

Owner:SANDISK TECH LLC

Efficient verification for coarse/fine programming of non-volatile memory

A non-volatile memory device is programmed by first performing a coarse programming process and subsequently performing a fine programming process. The coarse / fine programming methodology is enhanced by using an efficient verification scheme that allows some non-volatile memory cells to be verified for the coarse programming process while other non-volatile memory cells are verified for the fine programming process. The fine programming process can be accomplished using current sinking, charge packet metering or other suitable means.

Owner:SANDISK TECH LLC

Self boosting technique

A non-volatile semiconductor memory system (or other type of memory system) is programmed in a manner that avoids program disturb. In one embodiment that includes a flash memory system using a NAND architecture, program disturb is avoided by increasing the channel potential of the source side of the NAND string during the programming process. One exemplar implementation includes applying a voltage (e.g. Vdd) to the source contact and turning on the source side select transistor for the NAND sting corresponding to the cell being inhibited. Another implementation includes applying a pre-charging voltage to the unselected word lines of the NAND string corresponding to the cell being inhibited prior to applying the program voltage.

Owner:SANDISK TECH LLC

Programming method for NAND EEPROM

Owner:MICRON TECH INC

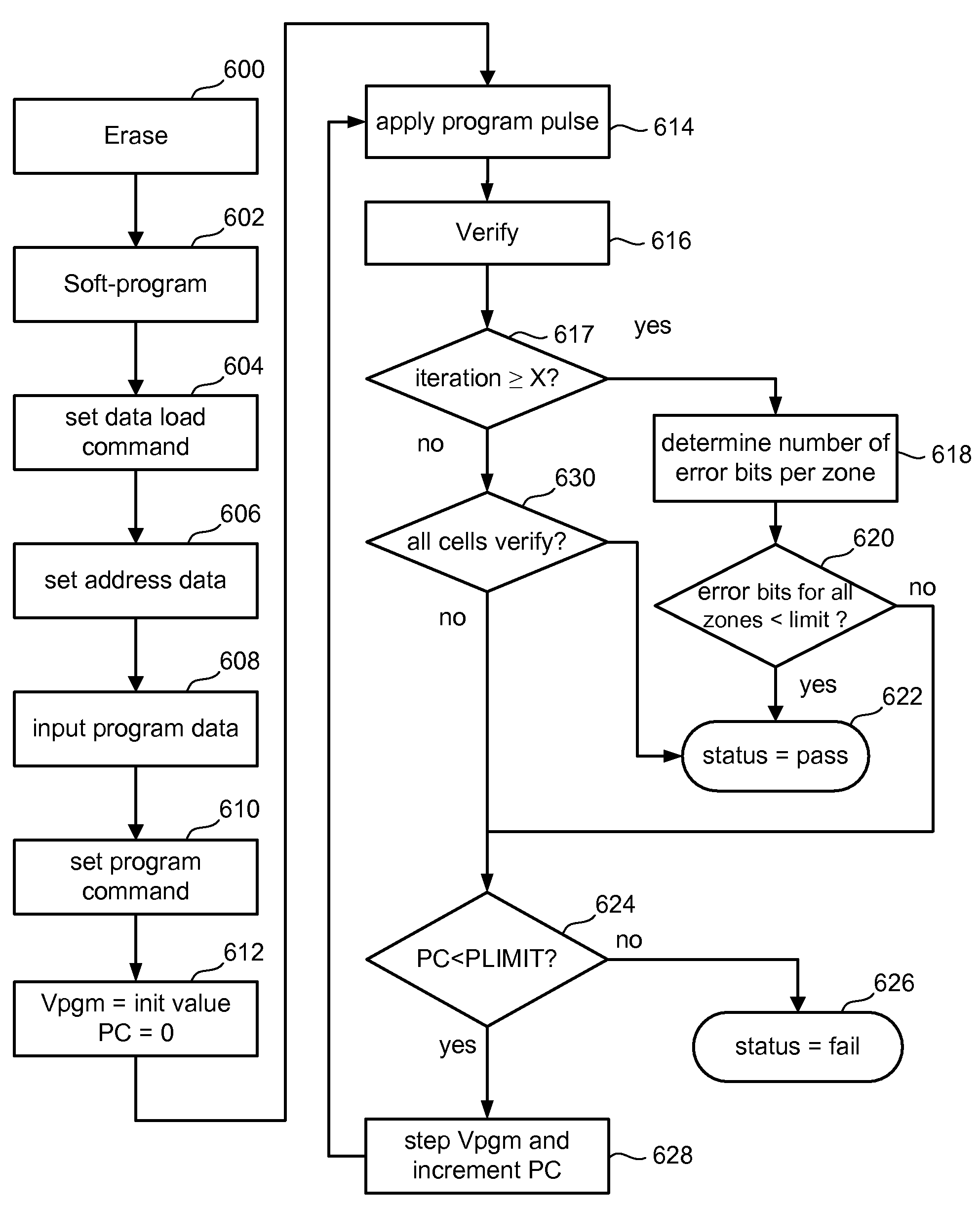

Apparatus with segemented bitscan for verification of programming

ActiveUS20080127104A1Bit errorError can not be correctedError detection/correctionRead-only memoriesProgramming languageProgramming process

A set non-volatile storage elements are subjected to a programming process in order to store a set of data. During the programming process, one or more verification operations are performed to determine whether the non-volatile storage elements have reached their target condition to store the appropriate data. Decisions about whether to continue programming or whether the programming is successful are made based on whether overlapping groups of the non-volatile storage elements have less than a threshold number of non-volatile storage elements that are not properly programmed.

Owner:SANDISK TECH LLC

Programming method to reduce word line to word line breakdown for NAND flash

ActiveUS20070236990A1Reduce line voltageDecreases likelihood of breakdown and punchSolid-state devicesRead-only memoriesProgramming processComputer science

A NAND architecture non-volatile memory device and programming process is described that programs the various cells of strings of non-volatile memory cells by the application of differing word line pass voltages (Vpass) to the unselected word lines adjacent to the selected word line and memory cell being programmed in order to reduce voltage differences between the word lines of the memory cell string or array during a programming cycle. This allows the word line to word line voltage differential to be reduced and thus decreases the likelihood of breakdown or punch through of the insulator materials placed between the adjacent word lines.

Owner:MICRON TECH INC

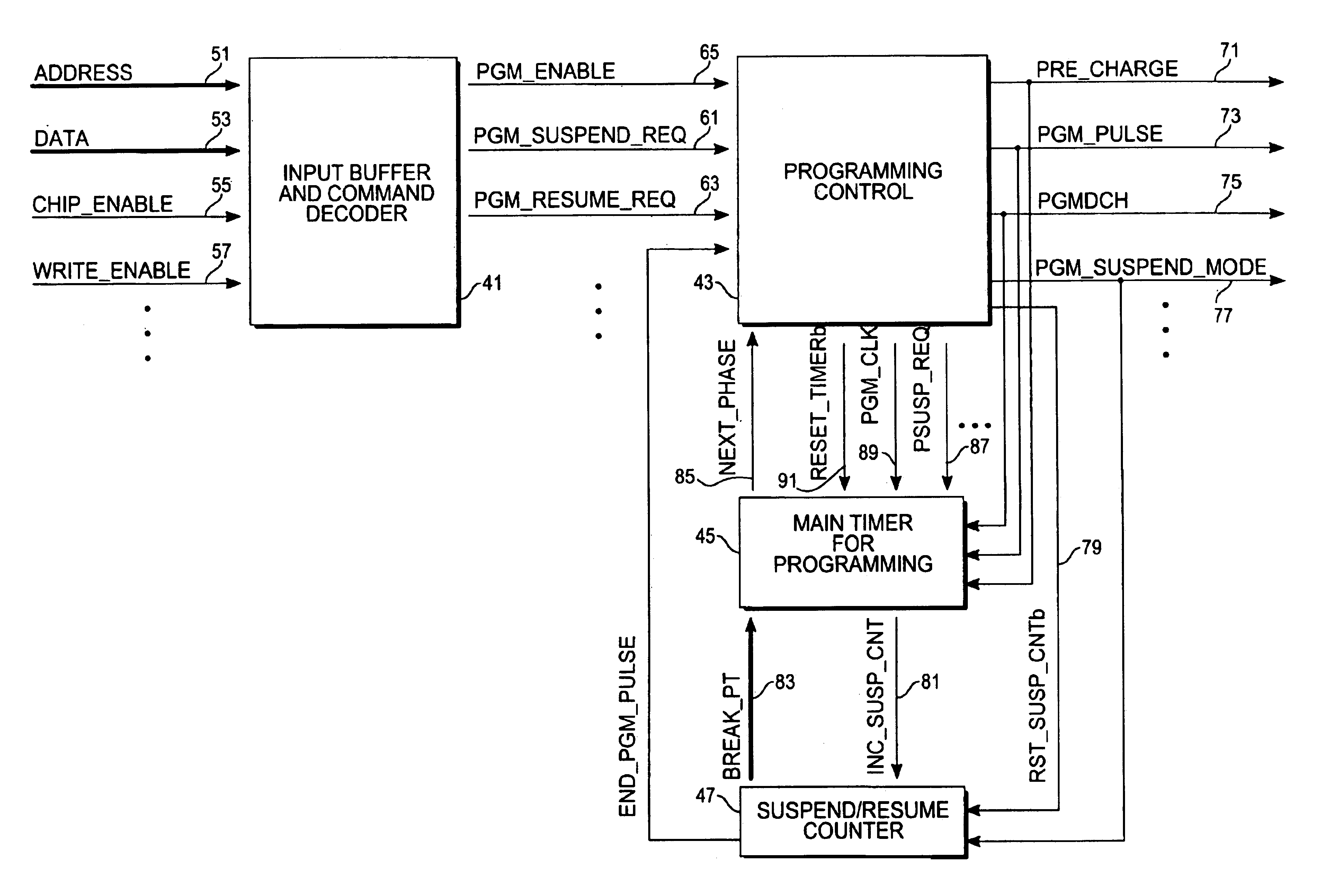

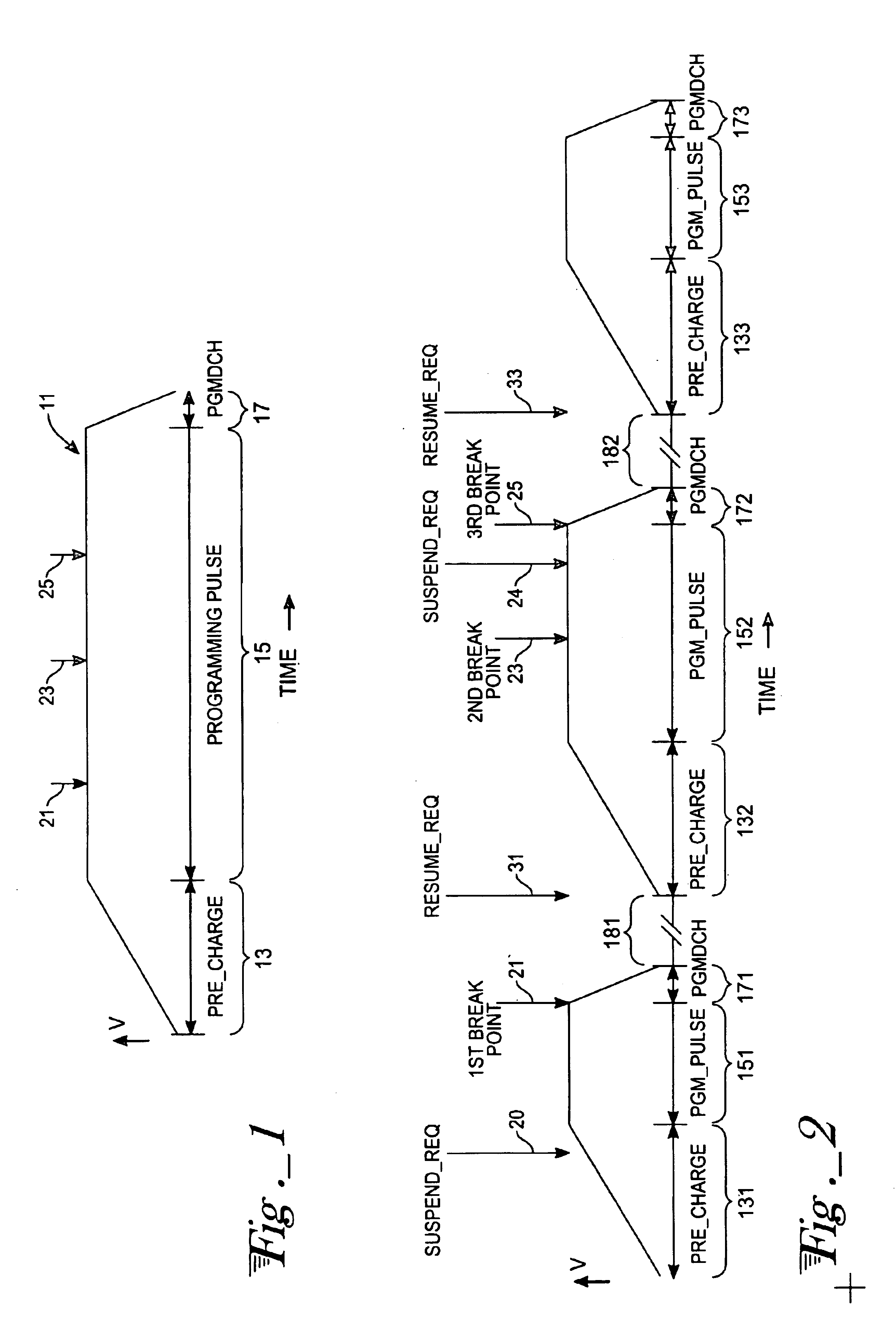

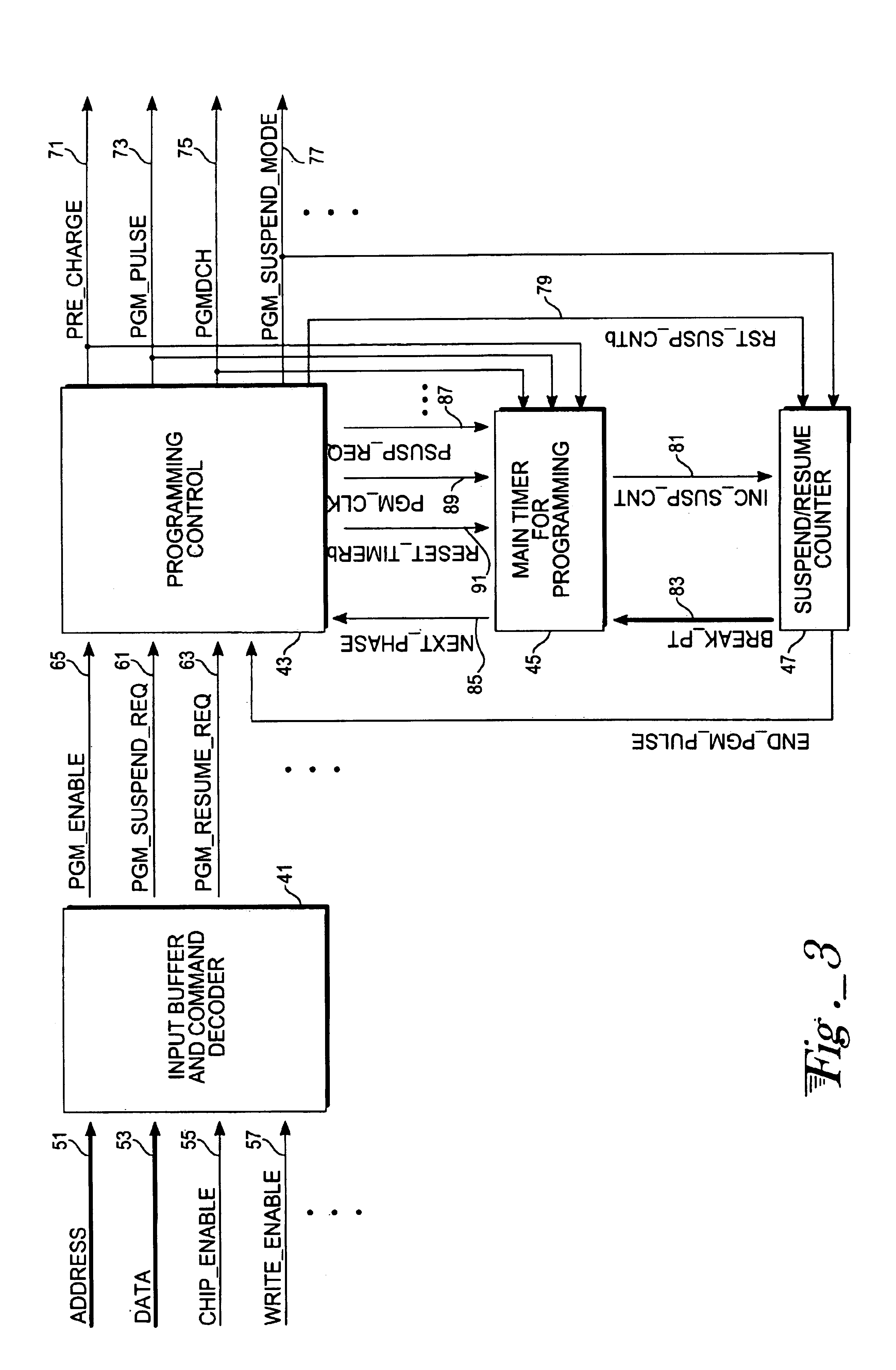

Suspend-resume programming method for flash memory

In a non-volatile memory, a programming cycle consists of the following phases: high voltage charging up, programming pulse, and discharge. The actual programming process only takes place in the programming pulse phase. Several break points are defined relative to elapsed time and introduced in the programming pulse phase. Upon receiving a suspend request, the programming operation will advance to the next break point, then discharge the high programming voltage and go to a suspend state. A separate counter is used to monitor the break points so that elapsed non-programming time can be deducted from the total programming pulse time when the programming operation is resumed. By doing so, the device can handle frequent suspend and resume requests. Since the total time duration in the programming pulse phase is equal for the programming operation with and without suspend and resume requests, the programming proceeds efficiently to completion.

Owner:ATMEL CORP

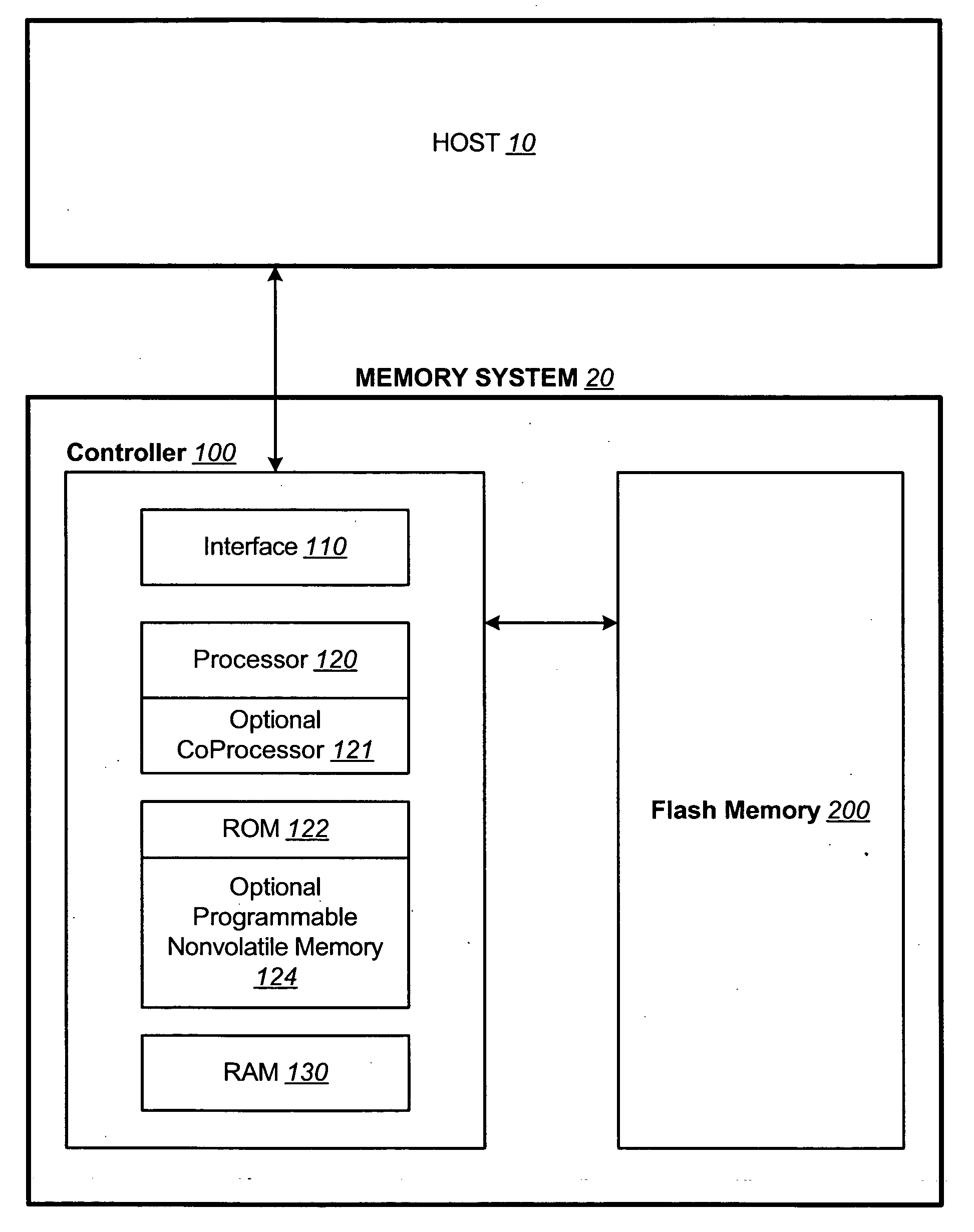

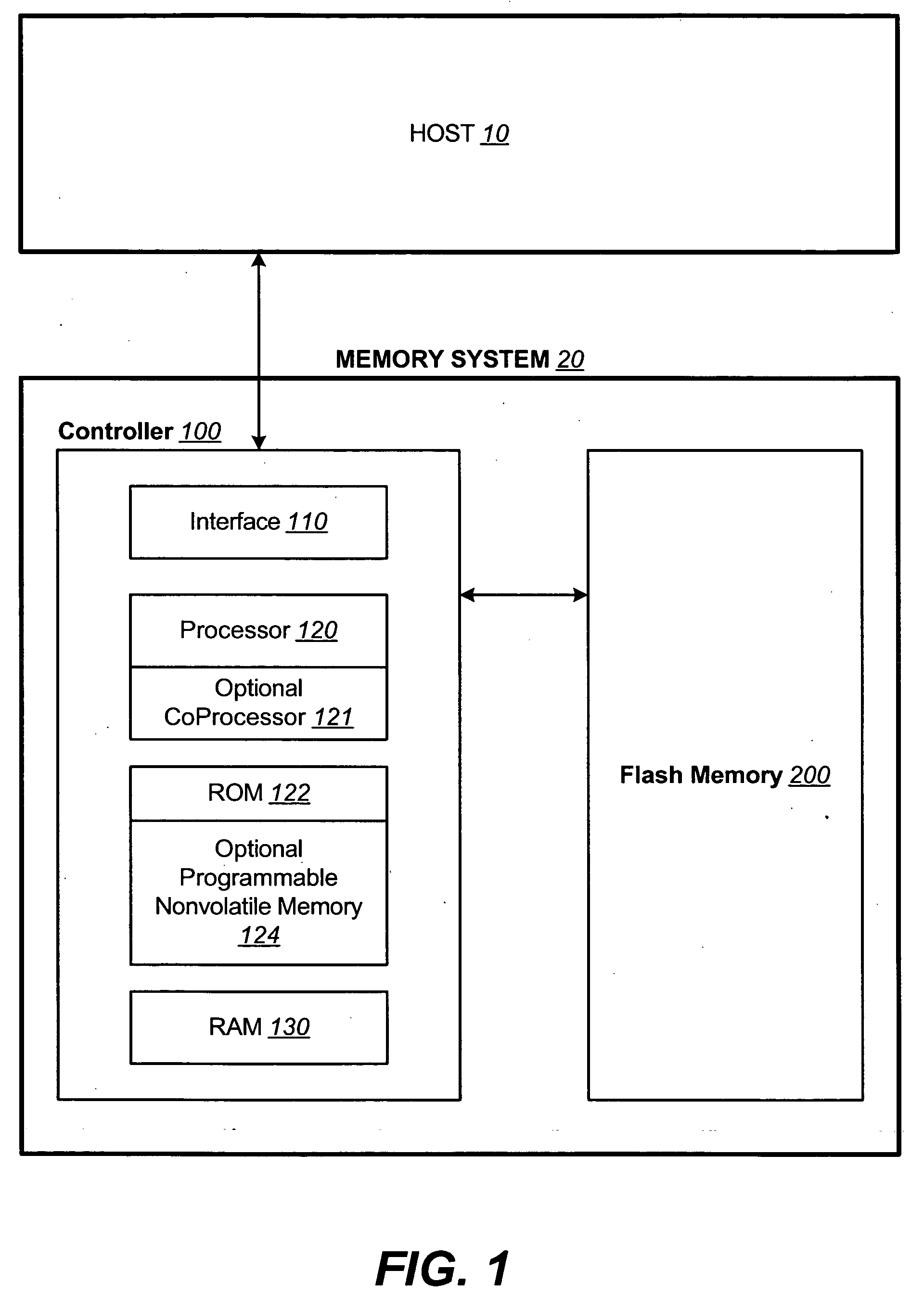

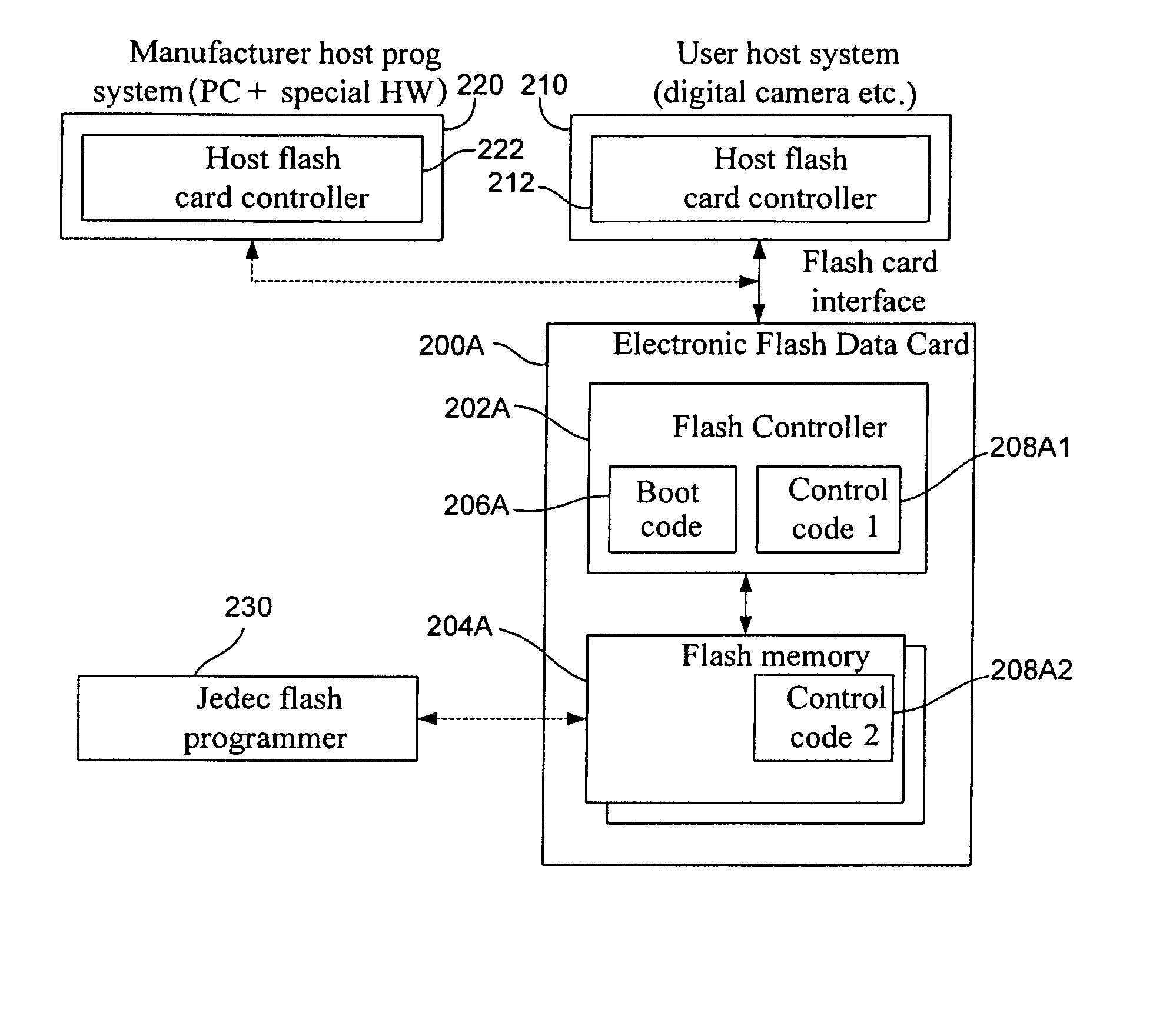

Flash memory controller controlling various flash memory cells

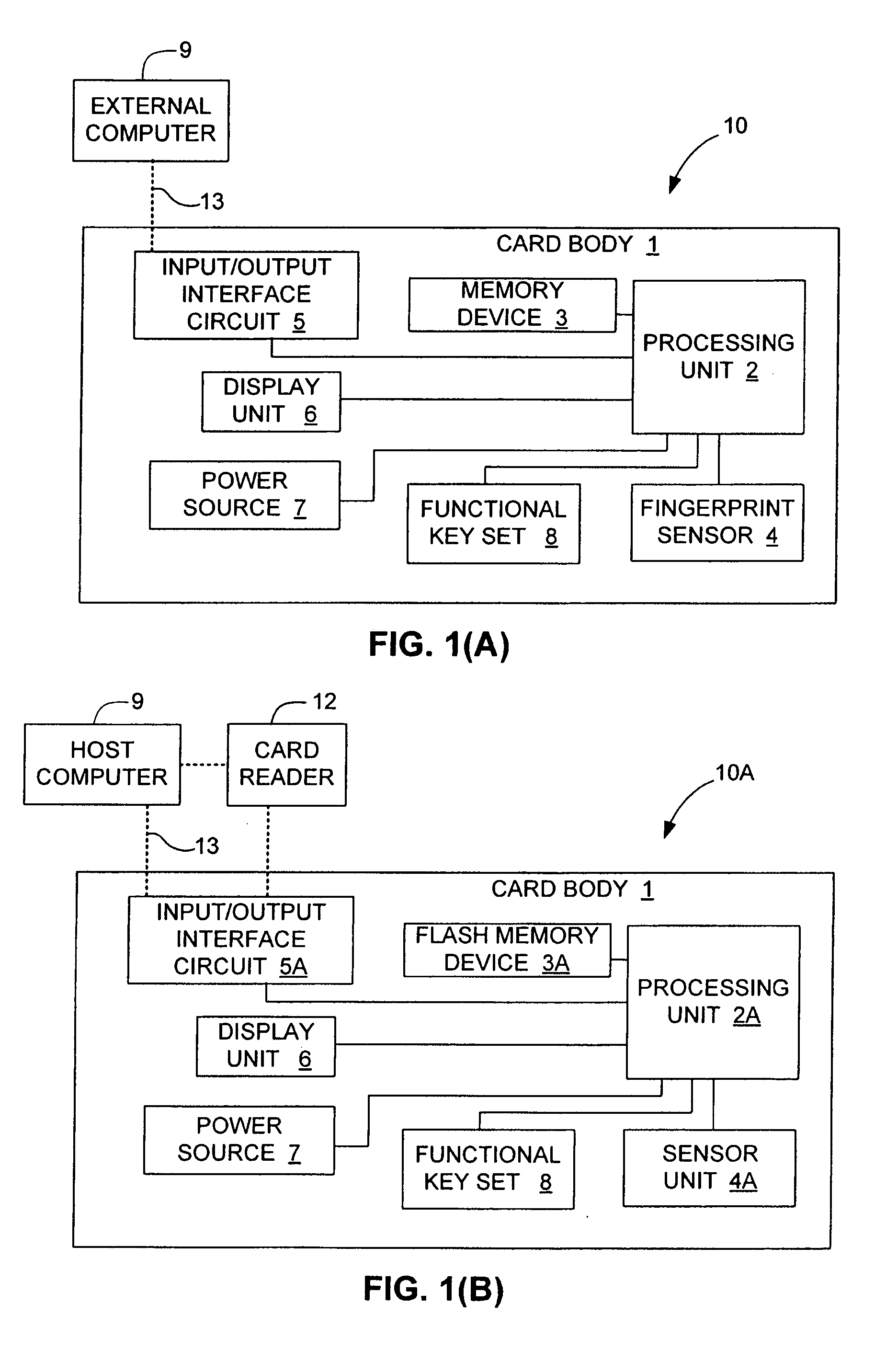

InactiveUS20080086631A1Easy to updateSoftware engineeringMemory adressing/allocation/relocationSingle flashRandom access memory

An electronic data flash card is accessible by a host system, and includes a flash memory controller and at least one flash memory device coupled to the flash controller. The boot code and control code for the flash memory system (flash card) are stored in the flash memory device during a programming procedure. The flash controller transfers the boot code and control code to a volatile main memory (e.g., random access memory or RAM) at start up or reset making a RAM-based memory system. Boot code and control code are selectively overwritten during a code updating operation. A single flash controller thus supports multiple brands and types of flash memory to eliminate stocking issues.

Owner:SUPER TALENT TECH CORP

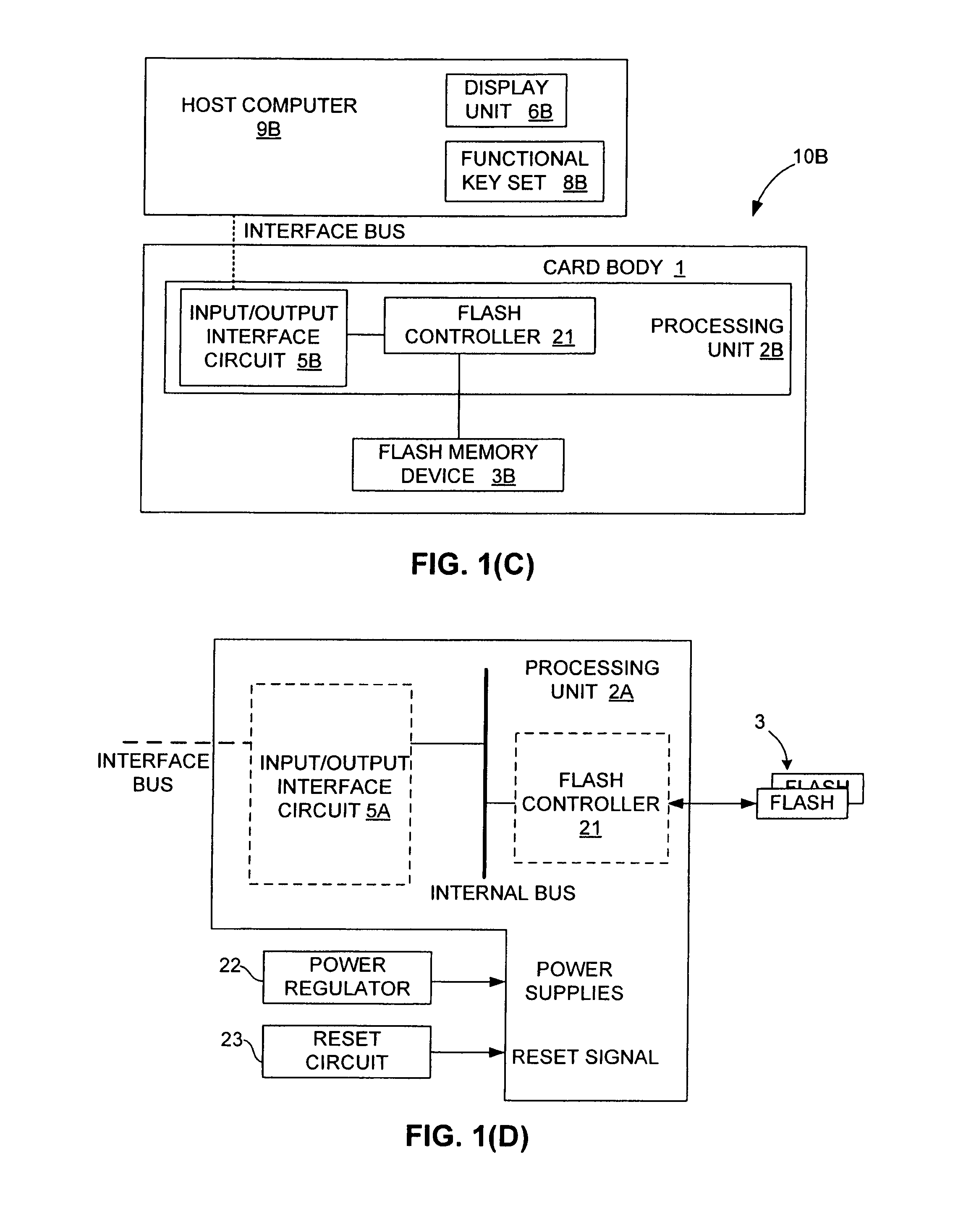

Linear program-based technique for placing FRR TE tunnels with bandwidth guarantee

ActiveUS6978394B1Reduce complexityError preventionTransmission systemsProgramming processSimplex algorithm

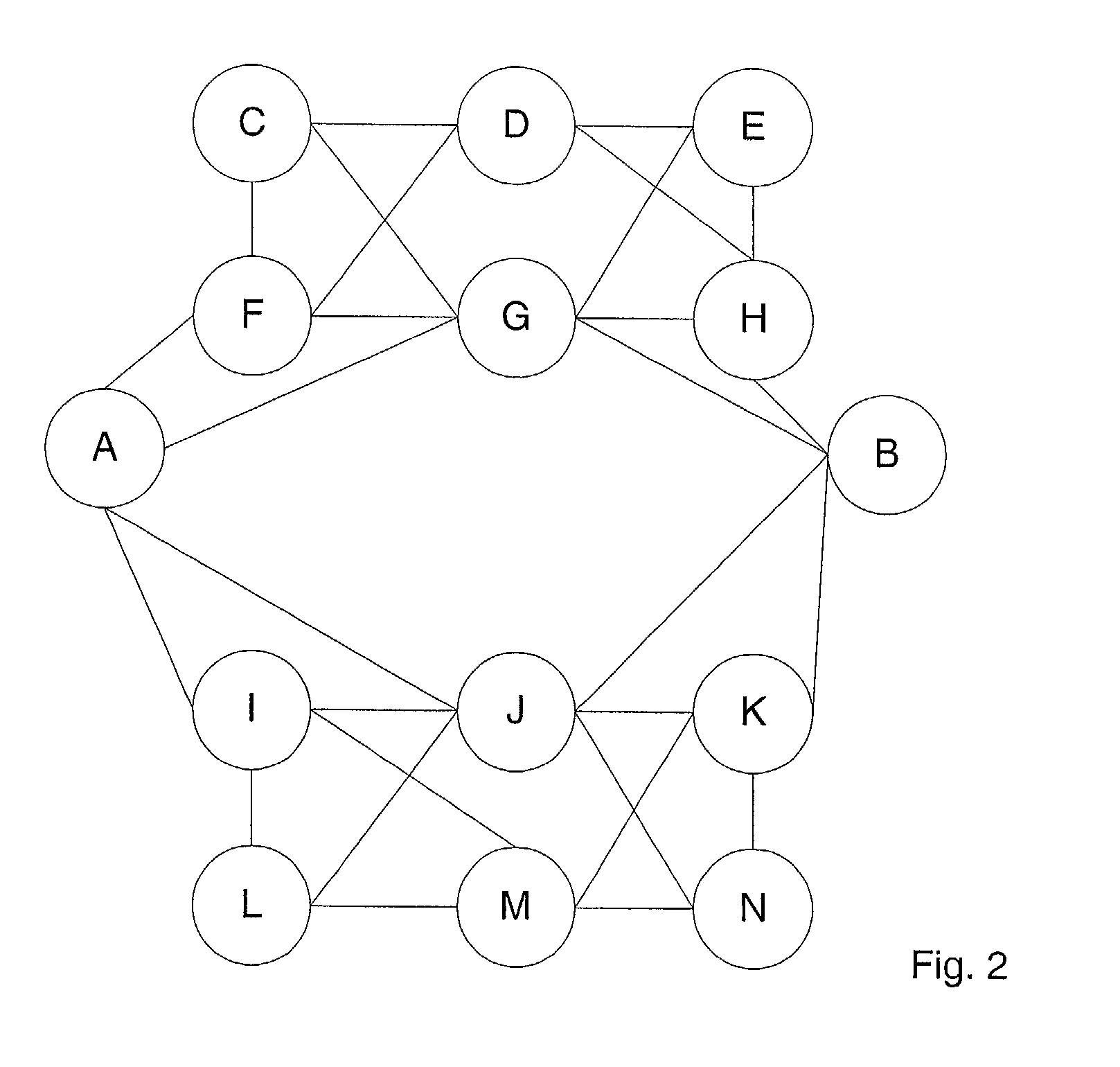

Load balancing enables the use of linear programming techniques to reduce the complexity of computing backup tunnel placement for guaranteed bandwidth protection. The ability to load balance among multiple backup tunnels transforms the placement problem into one that may be characterized as a series of linear constraints usable as input to a linear programming procedure such as the simplex method. Each node may compute its own backup tunnels and signal the tunnels to its neighbors with zero bandwidth to allow implicit sharing of backup bandwidth.

Owner:CISCO TECH INC

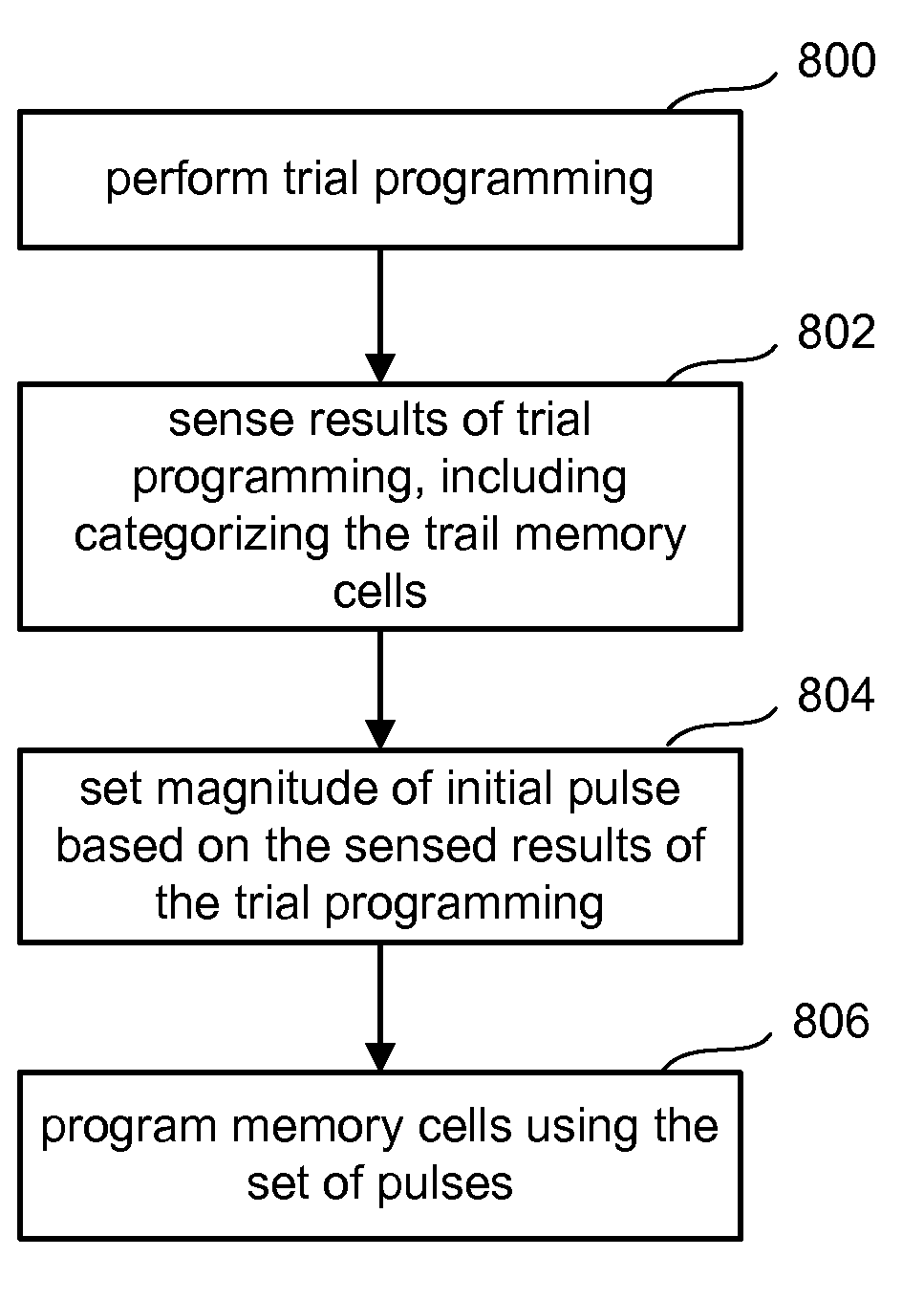

Non-volatile storage system with initial programming voltage based on trial

A trial programming process is performed for a first set of one or more non-volatile storage elements to test usage of the non-volatile storage system. Based on this trial programming, a programming signal is calibrated by adjusting its initial magnitude. The calibrated programming signal is then used to program a second set of non-volatile storage elements (which may or may not include the first set).

Owner:SANDISK TECH LLC

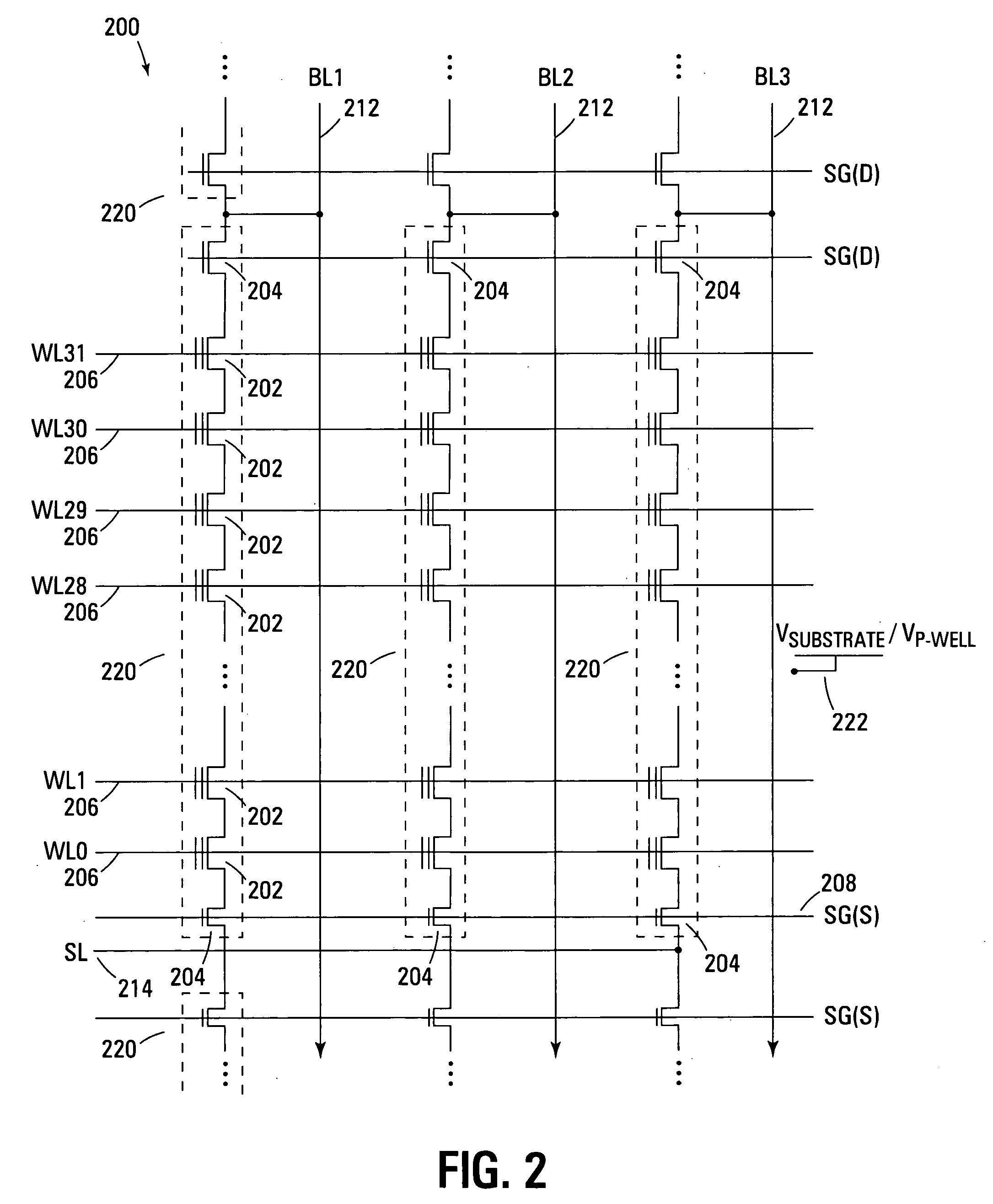

Boosted substrate/tub programming for flash memories

InactiveUS6977842B2Uniform natureBoosted tub” programmingRead-only memoriesDigital storageBit lineCharge carrier

A boosted substrate tub / substrate floating gate memory cell programming process is described that applies a voltage to the substrate or substrate “tub” of a NAND Flash memory array to precharge a channel of carriers within the floating gate memory cells prior to applying a high gate programming voltage to the gate of the selected floating gate memory cells and coupling a program or program-inhibit voltage to program the selected floating gate memory cell(s) as desired. The use of a boosted tub programming approach avoids the requirement that the bitline and / or source line circuit design of the NAND Flash array be able to withstand or carry high voltages during programming of a floating gate memory cells and allows reuse of the block erase high voltage circuits connected to the substrate tub. This allows the NAND Flash memory array to be designed with smaller circuit designs and / or smaller circuit feature elements.

Owner:MICRON TECH INC

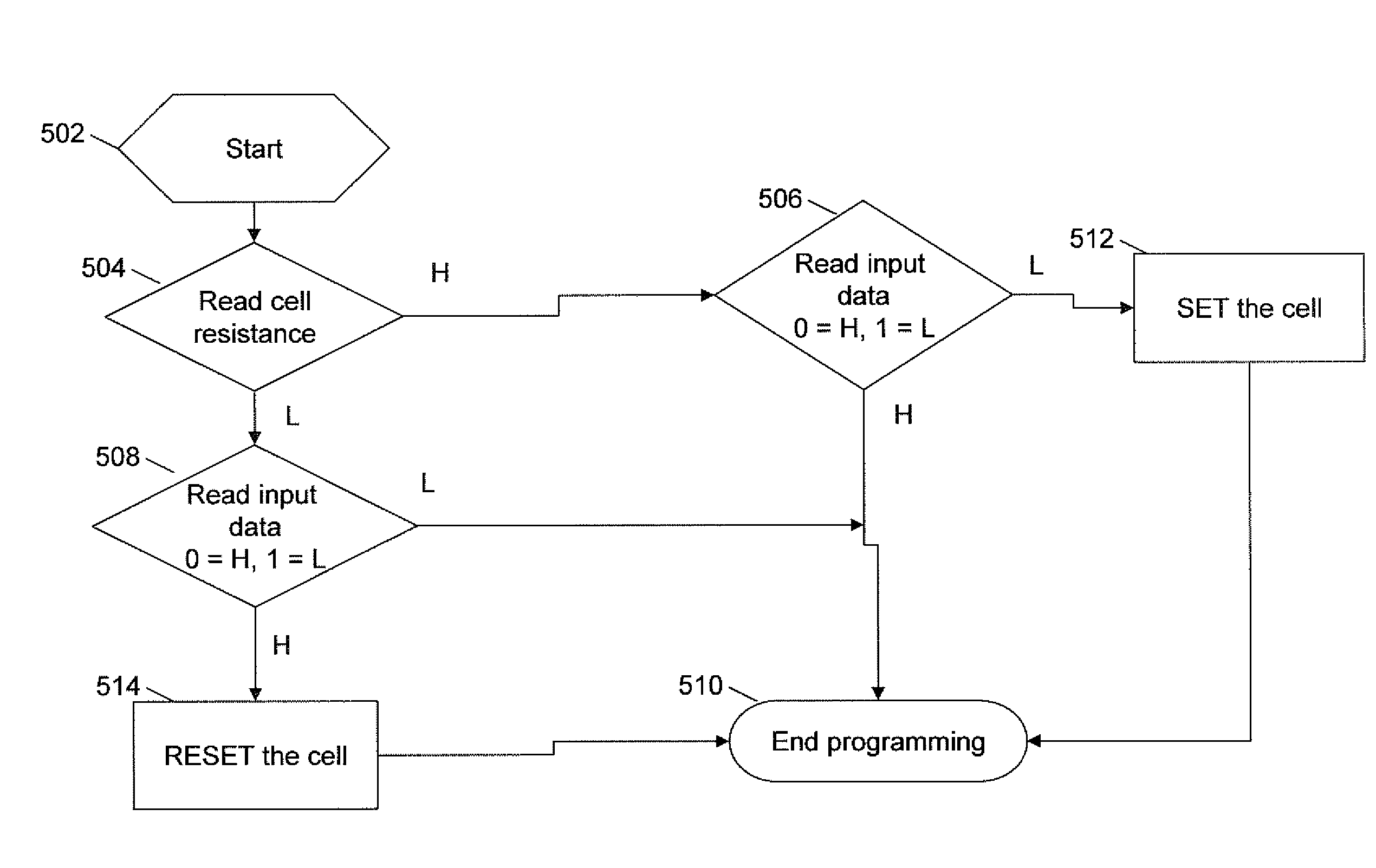

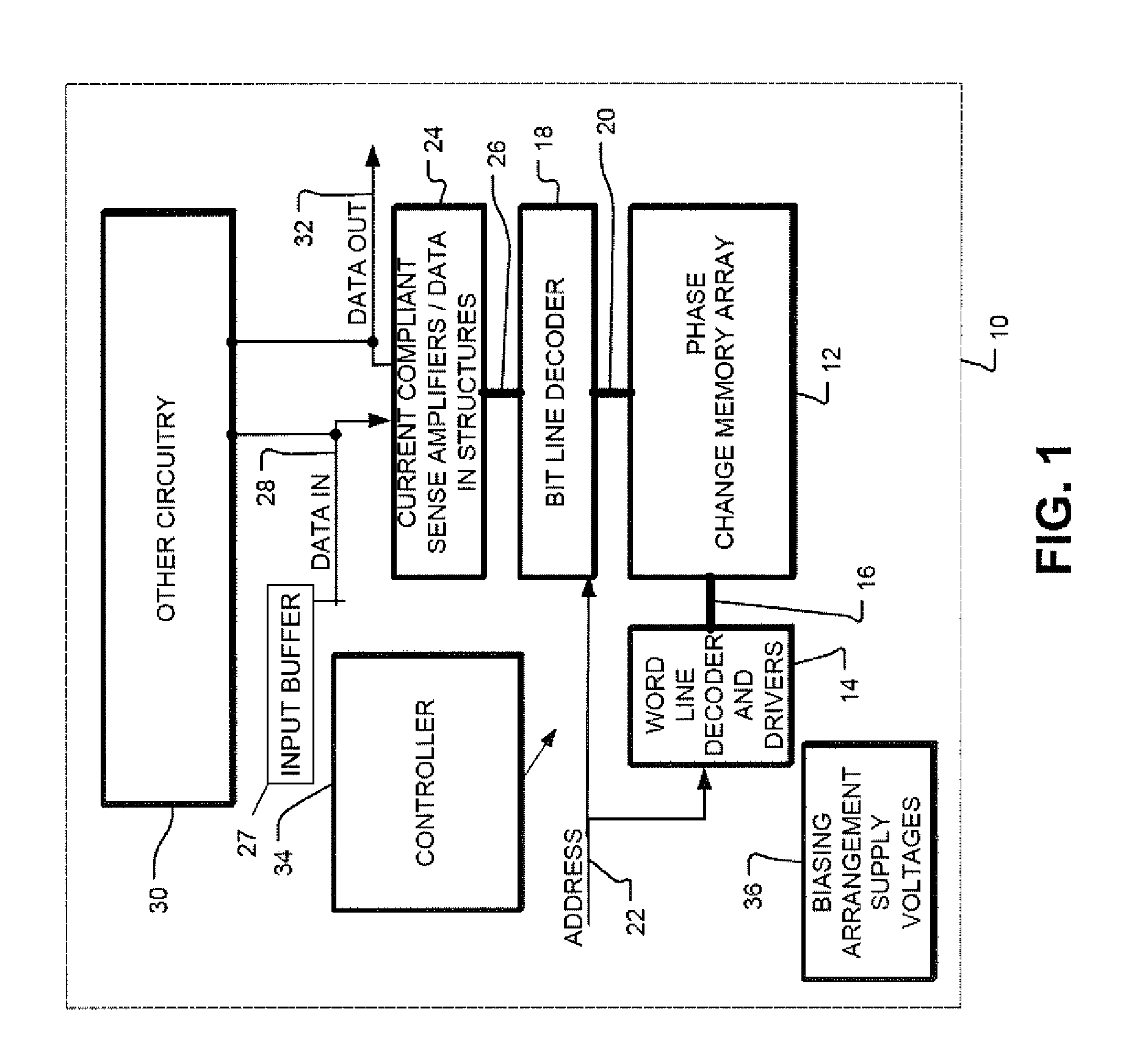

Method, Apparatus and Computer Program Product for Stepped Reset Programming Process on Programmable Resistive Memory Cell

ActiveUS20080165572A1High voltageHigh resistanceRead-only memoriesDigital storageBit linePhase-change memory

A method, system and computer program product for resetting a phase change memory cell having a memory cell threshold voltage is disclosed. The method includes reading a resistance of the memory cell. If the resistance is larger than a chosen resistance, the resetting of the memory cell ends. Otherwise, the method proceeds by applying a voltage, larger than the memory cell threshold voltage, to the bit line, and applying a voltage VWL, larger than the access device threshold voltage, to the word line. The resistance of the memory cell is again read. If the resistance is larger than the chosen resistance, the resetting of the memory cell ends. Otherwise, the method proceeds by applying a voltage, larger than the memory cell threshold voltage, to the bit line, increasing voltage VWL by a voltage ΔV and applying the increased voltage VWL to the word line.

Owner:MACRONIX INT CO LTD

Methods and apparatus for allocating, costing, and pricing organizational resources

This invention is a means both to allocate all types of resources for commercial, governmental, or non-profit organizations and to price such resources. A linear programming process makes fulfillment allocations used to produce product units. A Resource-conduit process governs the linear programming process, uses two-sided shadow prices, and makes aperture allocations to allow Potential-demand to become Realized-demand. A strict opportunity cost perspective is employed, and the cost of buyable resources is deemed to be the opportunity cost of tying up cash. Resource available quantities, product resource requirements, and Potential-demand as a statistical distribution are specified in a database. The invention reads the database, performs optimization, and then writes allocation directives to the database. Also determined and written to the database are resource marginal (incremental) values and product marginal costs. The database can be viewed and edited through the invention's Graphical User Interface. Monte Carlo simulation, along with generation of supply and demand schedules, is included to facilitate analysis, explore “what if,” and interact with the user to develop product offering, product pricing, and resource allocation strategies and tactics.

Owner:JAMESON JOEL

System that compensates for coupling based on sensing a neighbor using coupling

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

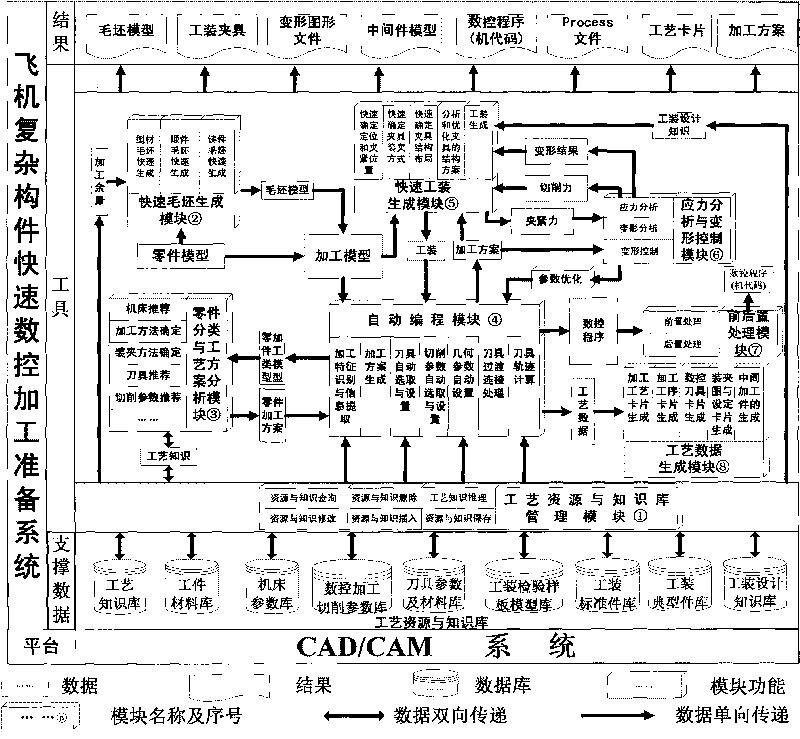

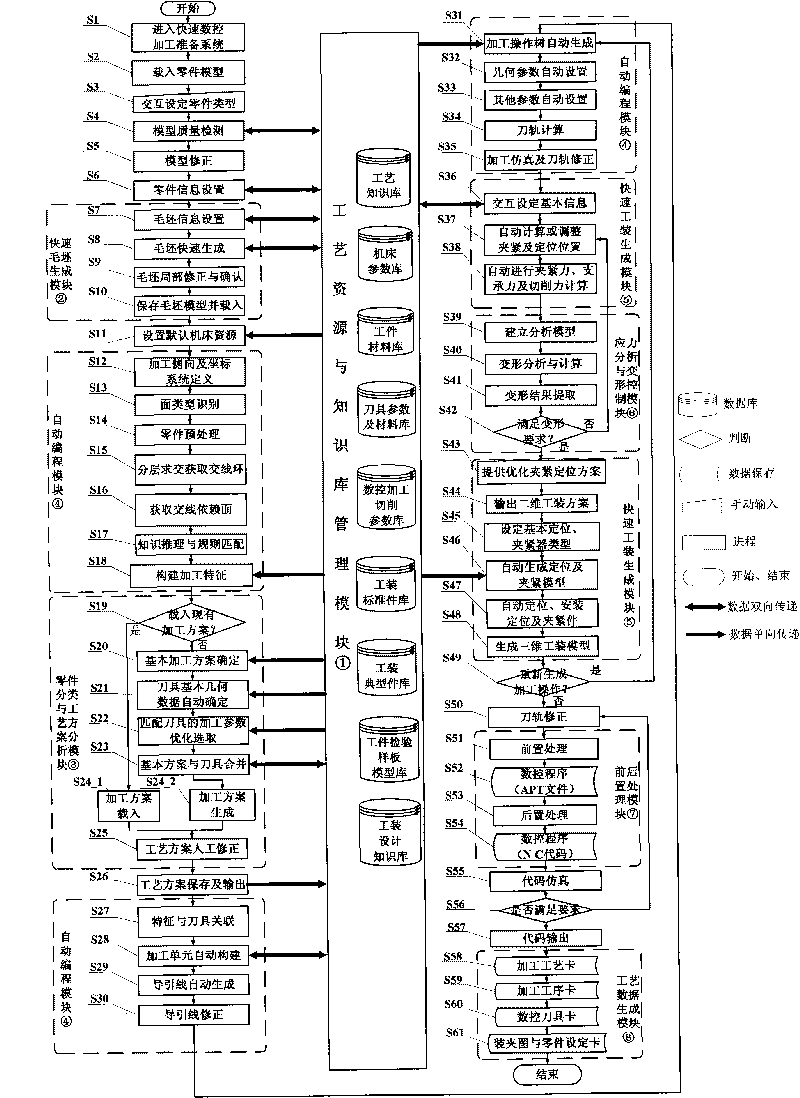

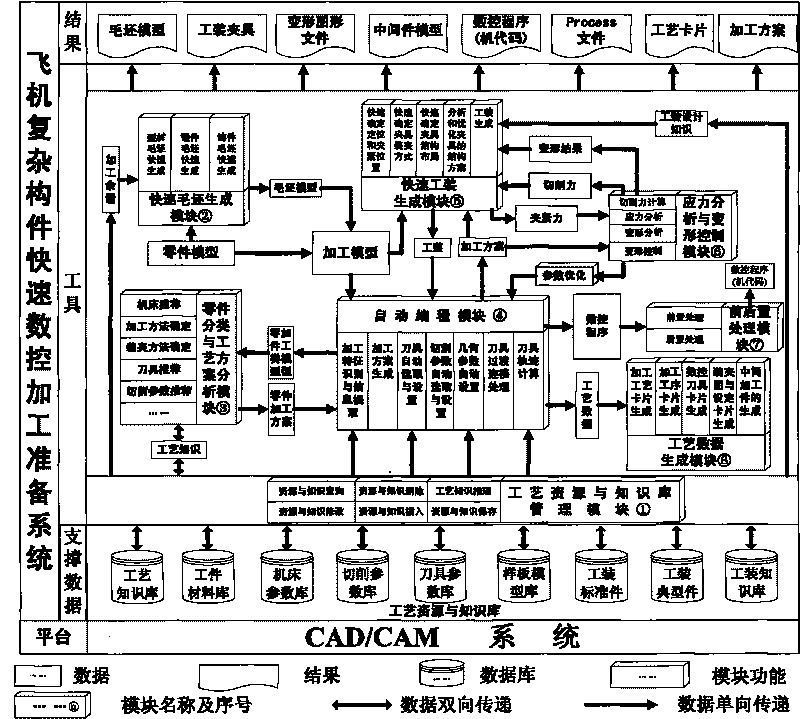

Preparation system of quick numerical control machining of complex parts of airplane and method

InactiveCN101763068ASolve problems such as unreasonable designIncrease specializationProgramme controlComputer controlNumerical controlProcess module

The invention discloses a preparation system of quick numerical control machining of complex parts of an airplane and a method. The system takes the existing CAD / CAM system as a platform, and comprises a technology resource and knowledge base management module, a quick blank generation module, a part classification and technical scheme analysis module, an automatic programming module, a quick tool generation module, a strain analysis and deformation control module, a front and rear process module and a technology data generation module. The system is built on the basis of a three-dimensional numeric part model, systematically and exactly embodies a specialized flow path for supporting the numerical control machining technology preparing and the programming of the complex parts of the airplane, can greatly reduce man-machine interaction operation required by preparing technology and programming, effectively solves the problems of the unstable programmed procedure and the unreasonable scheme design of the machining technology caused by the lack of the experience of process operators, and the like, can effectively control the deformation quantity during and after machining the parts, can obviously improve the efficiency and the quality of the numerical control machining preparing and the programming, and improves the professional level and the intelligence level of the CAD / CAM system.

Owner:SHENYANG AIRCRAFT CORP +1

Program method with optimized voltage level for flash memory

ActiveUS20060285396A1Faster programming operationExact matchRead-only memoriesDigital storageProgramming processNon-volatile memory

A non-volatile memory device and programming process is described that increases the programming voltage of successive programming cycles in relation to the percentage of the data bits that failed programming verification during the previous programming cycle and were not correctly programmed into the memory array. This allows for a faster on average program operation and a more accurate match of the subsequent increase in the programming voltage to the non-volatile memory device, the specific region or row being programmed and any changes due to device wear. In one embodiment of the present invention the manufacturing process / design and / or specific memory device is characterized by generating a failed bit percentage to programming voltage increase profile to set the desired programming voltage delta / increase. In another embodiment of the present invention, methods and apparatus are related for the programming of data into non-volatile memory devices and, in particular, NAND and NOR architecture Flash memory.

Owner:MICRON TECH INC