Patents

Literature

58 results about "Single flash" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

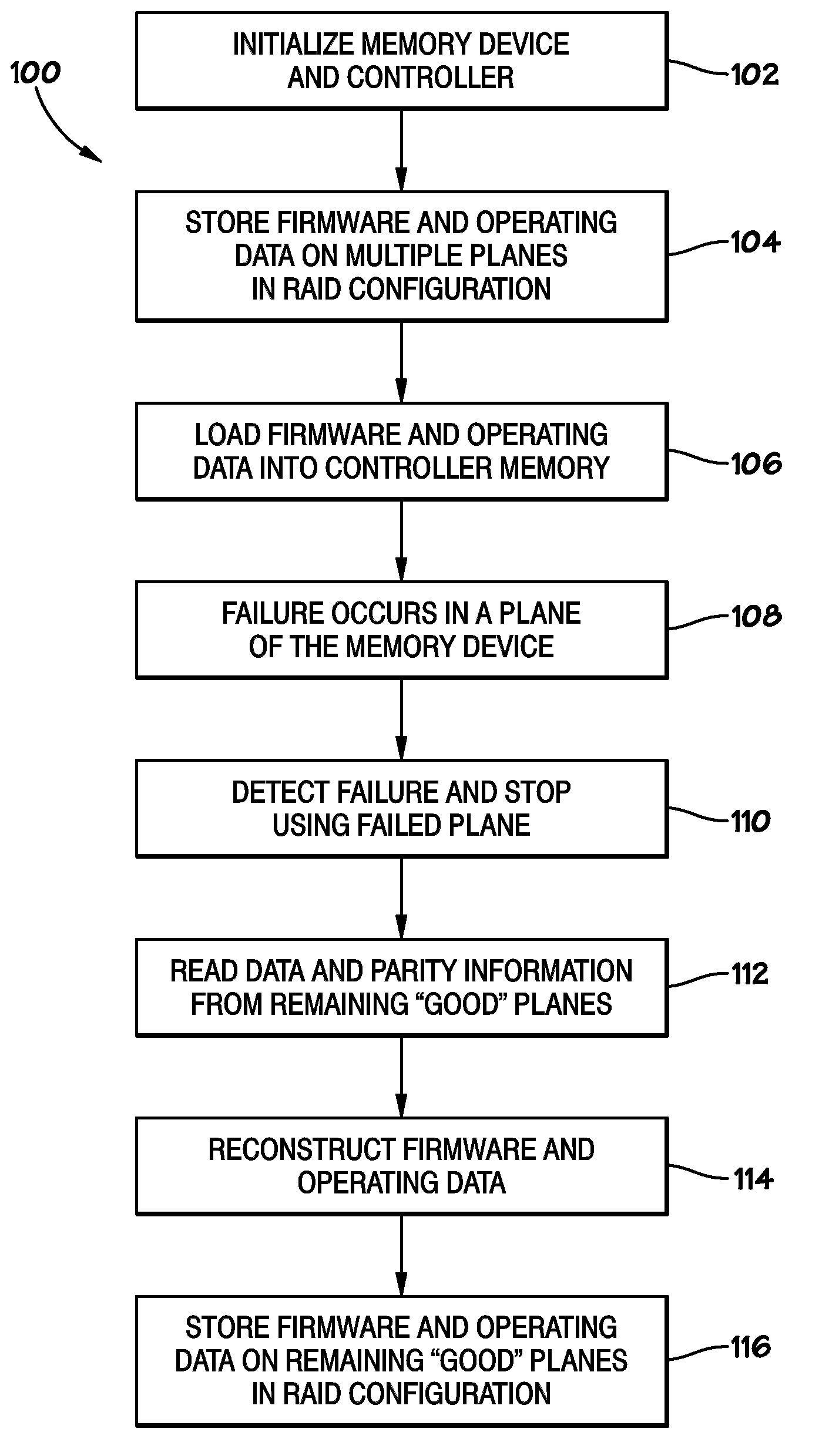

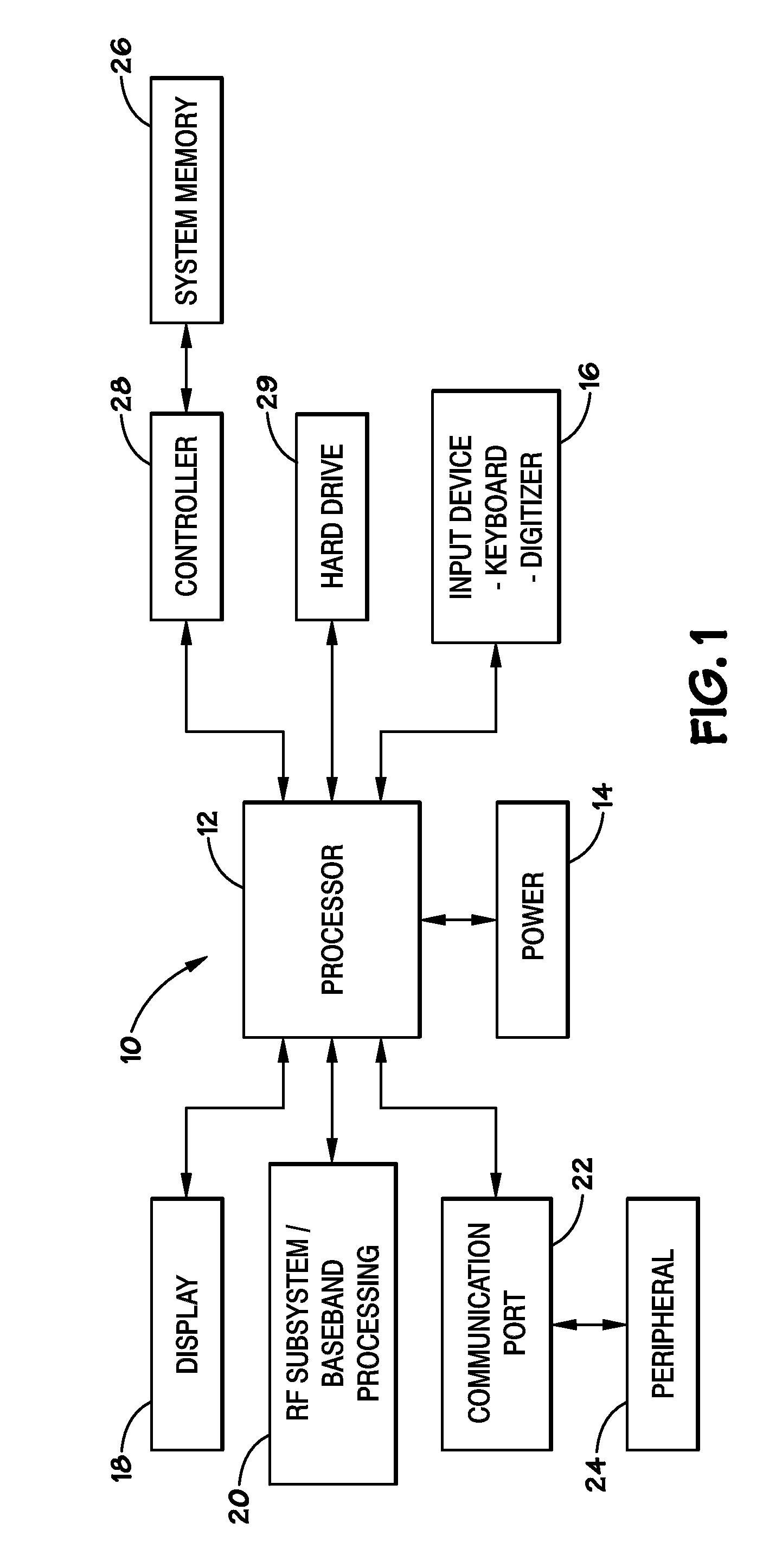

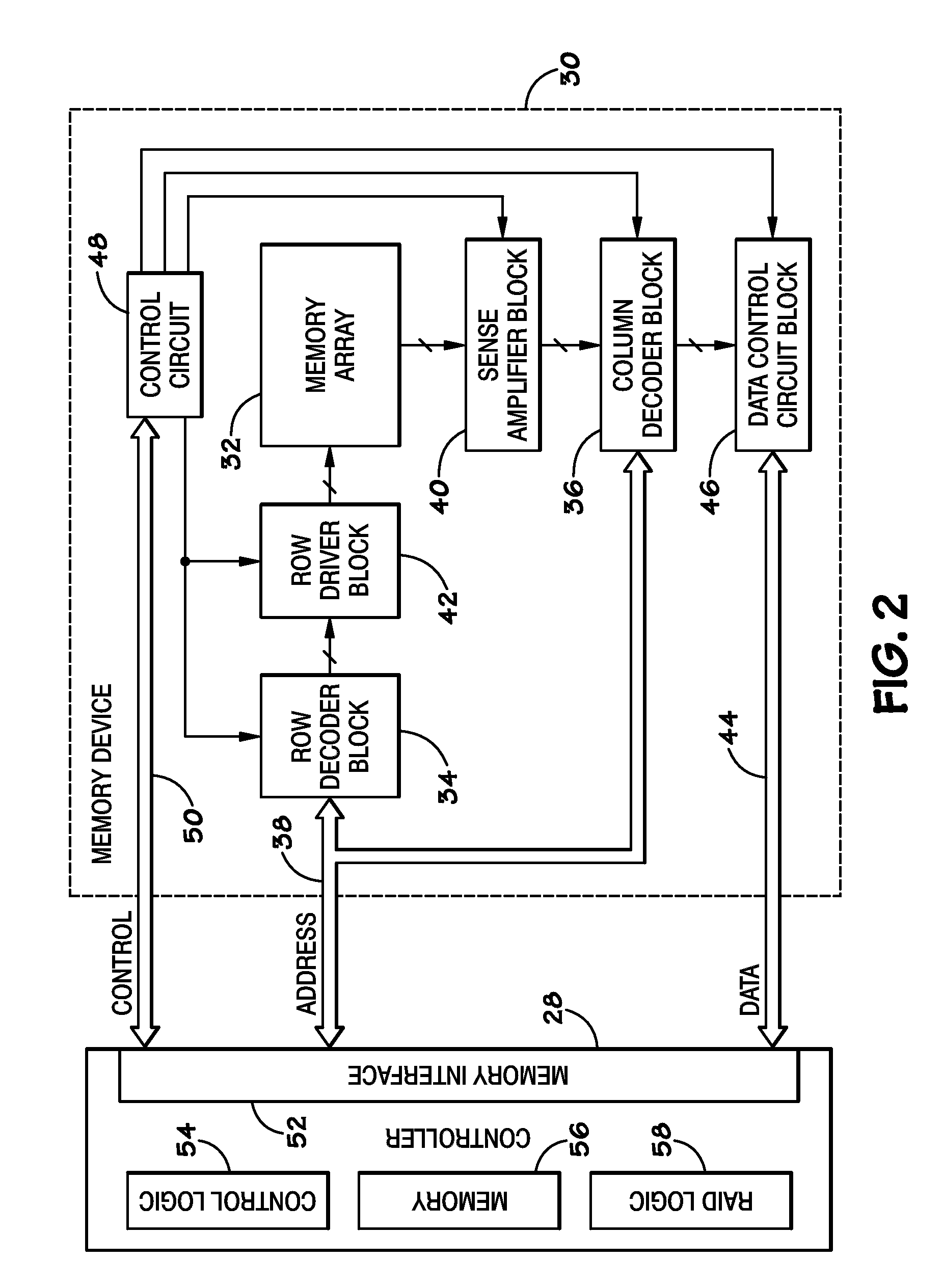

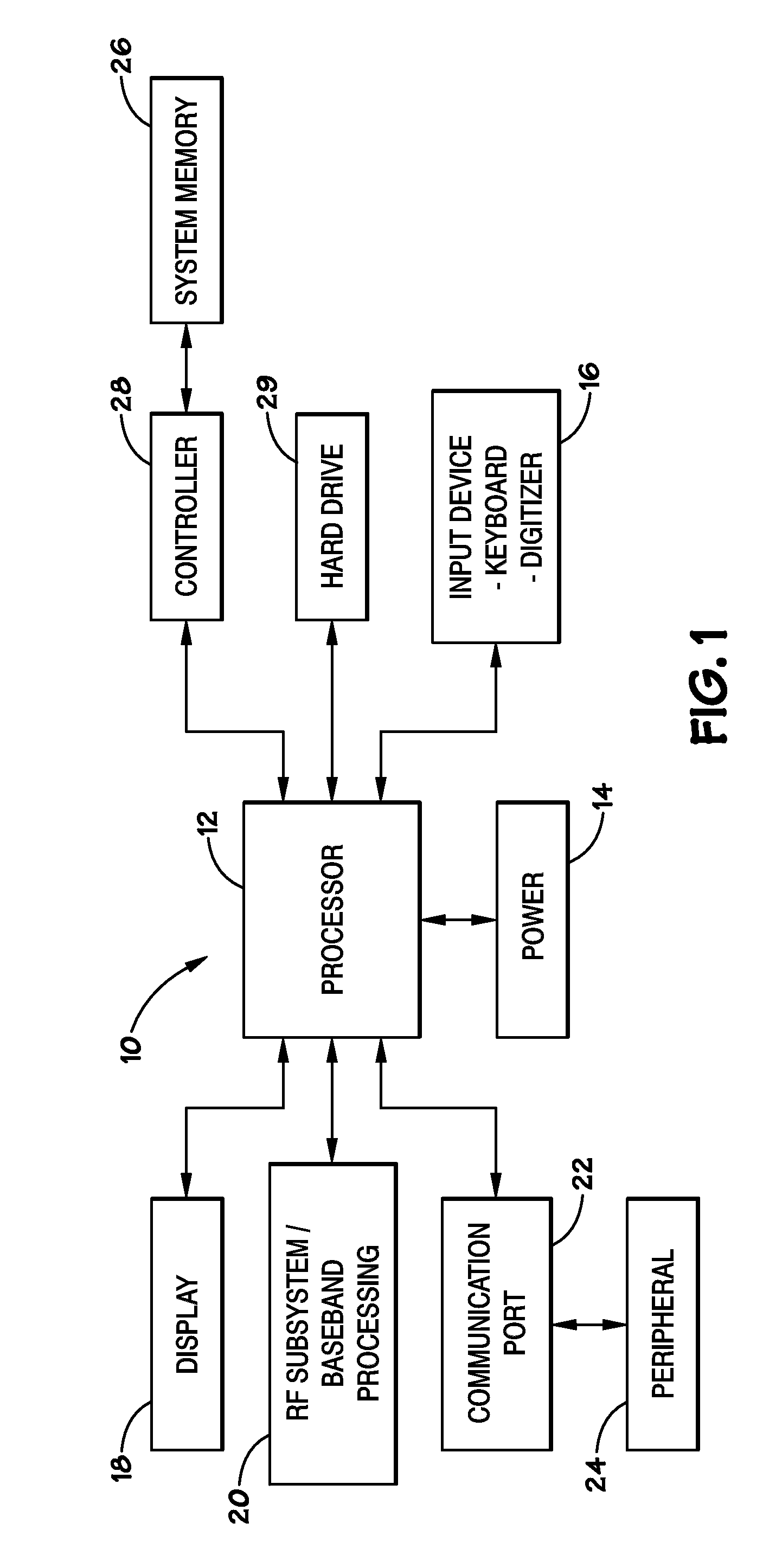

Systems and Methods for Storing and Recovering Controller Data in Non-Volatile Memory Devices

Systems and methods are disclosed for storing the firmware and other data of a flash memory controller, such as using a RAID configuration across multiple flash memory devices or portions of a single memory device. In various embodiments, the firmware and other data used by a controller, and error correction information, such as parity information for RAID configuration, may be stored across multiple flash memory devices, multiple planes of a multi-plane flash memory device, or across multiple blocks or pages of a single flash memory device. The controller may detect the failure of a memory device or a portion thereof, and reconstruct the firmware and / or other data from the other memory devices or portions thereof.

Owner:MICRON TECH INC

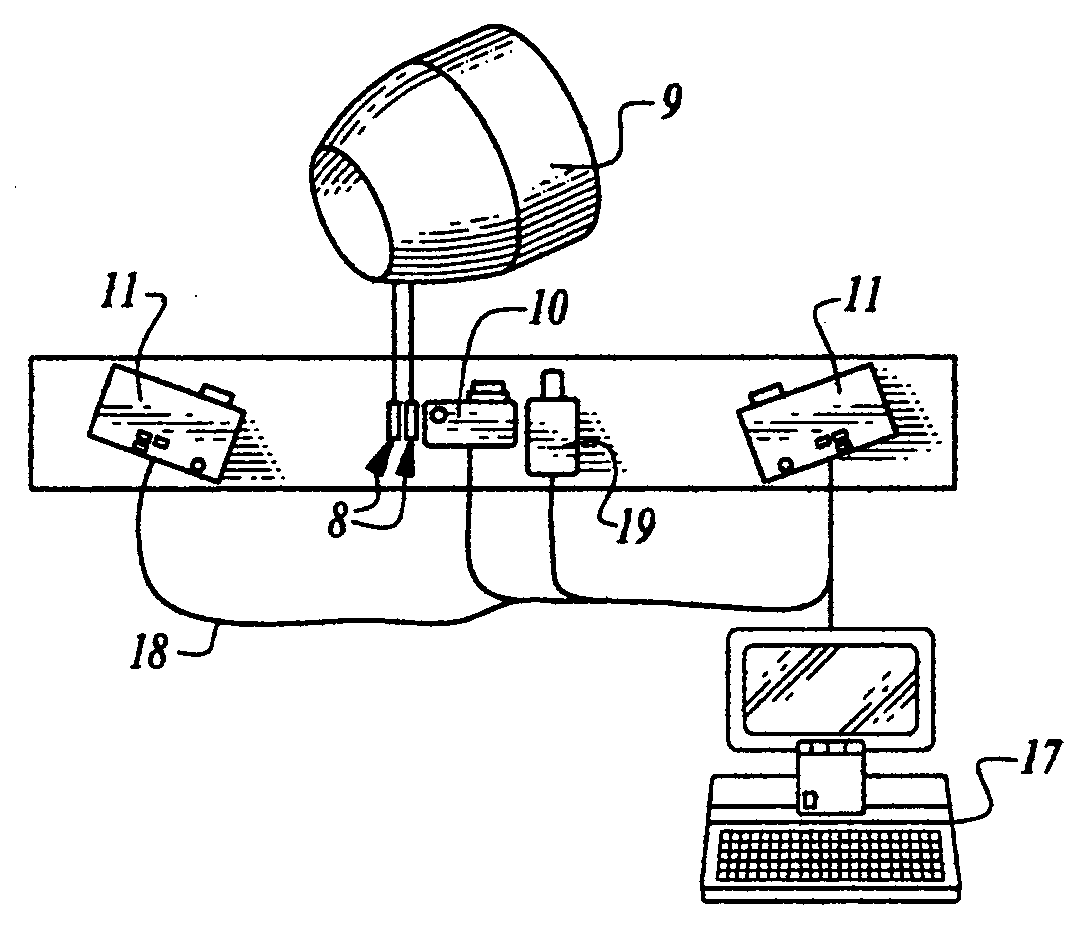

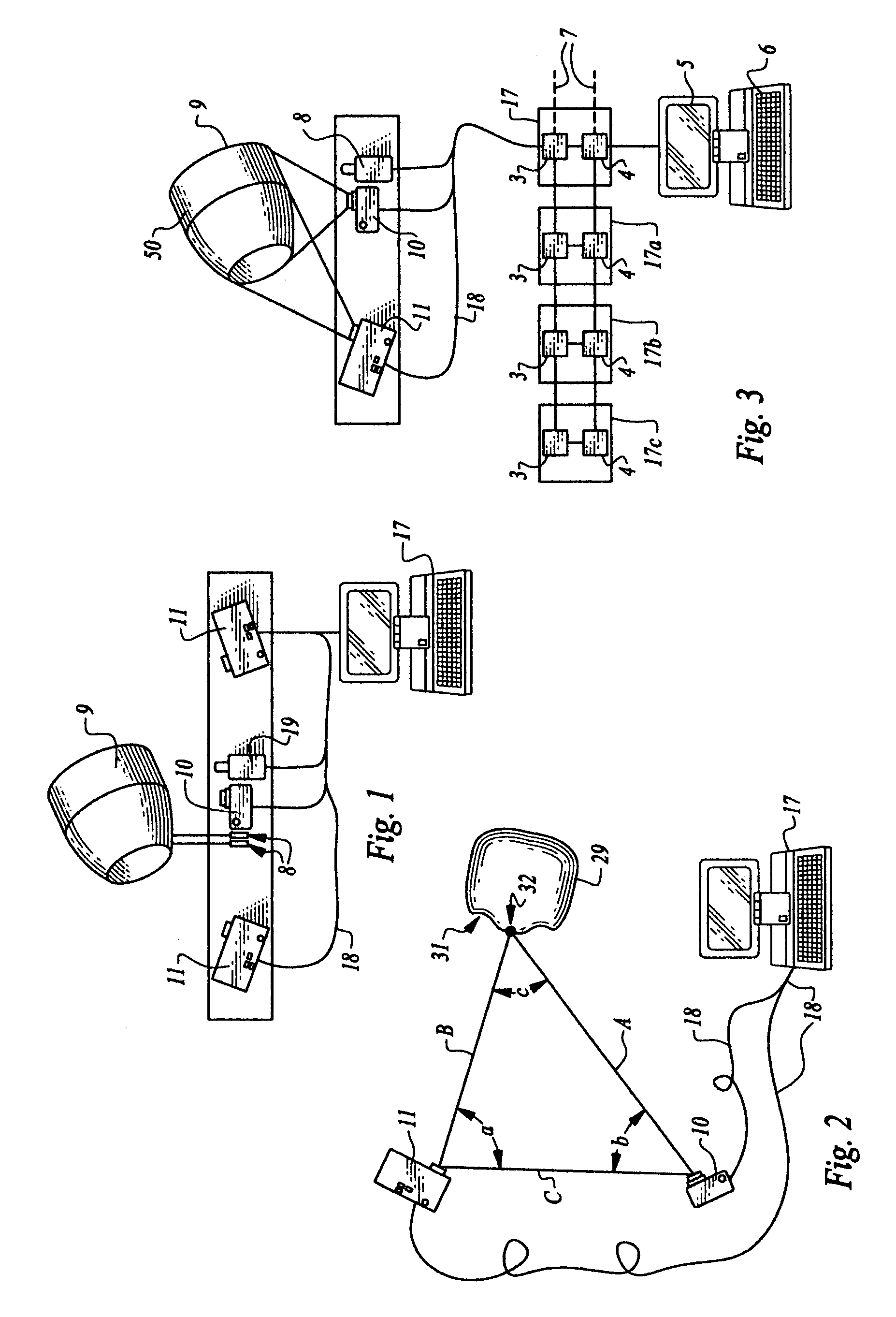

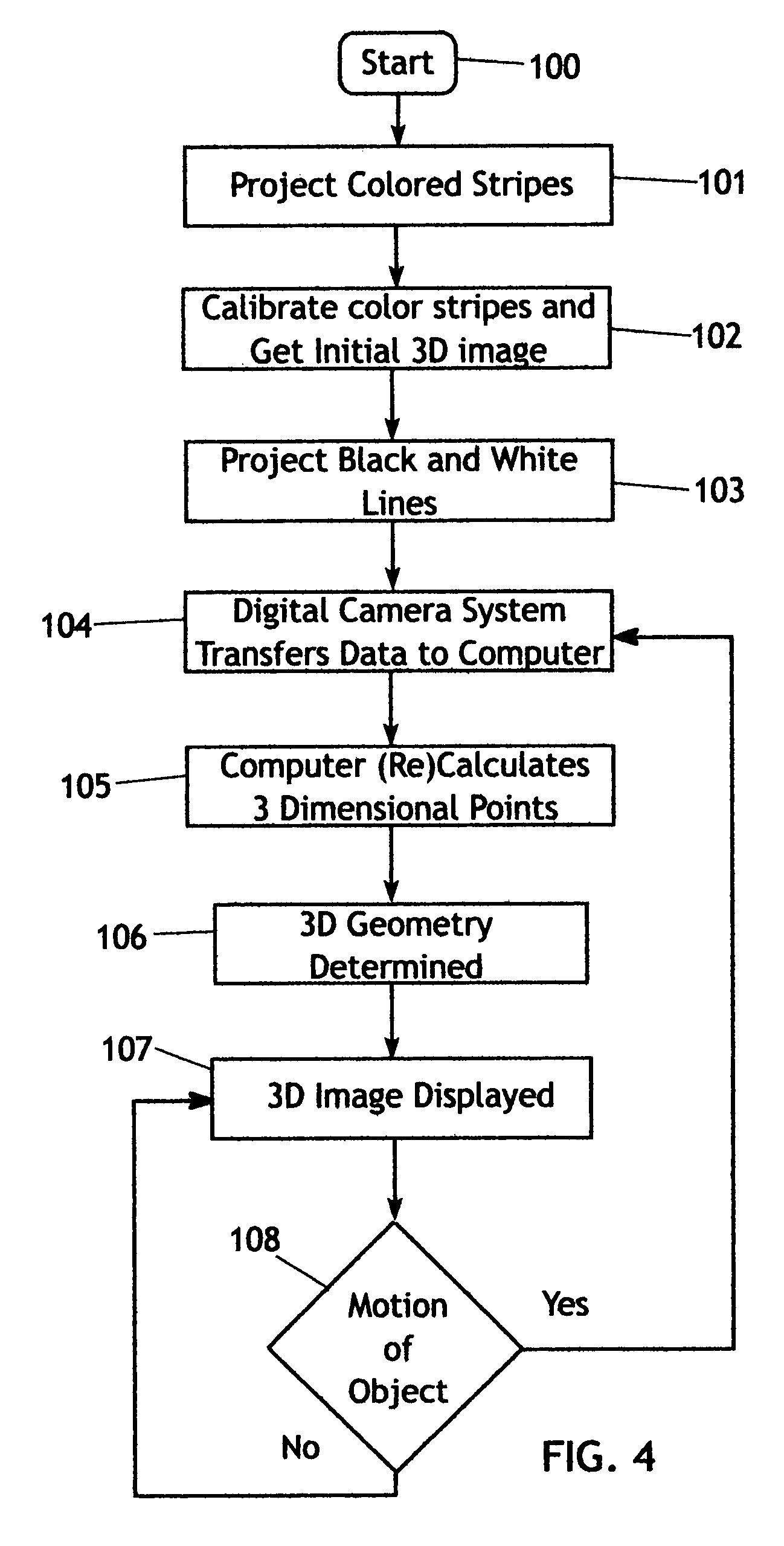

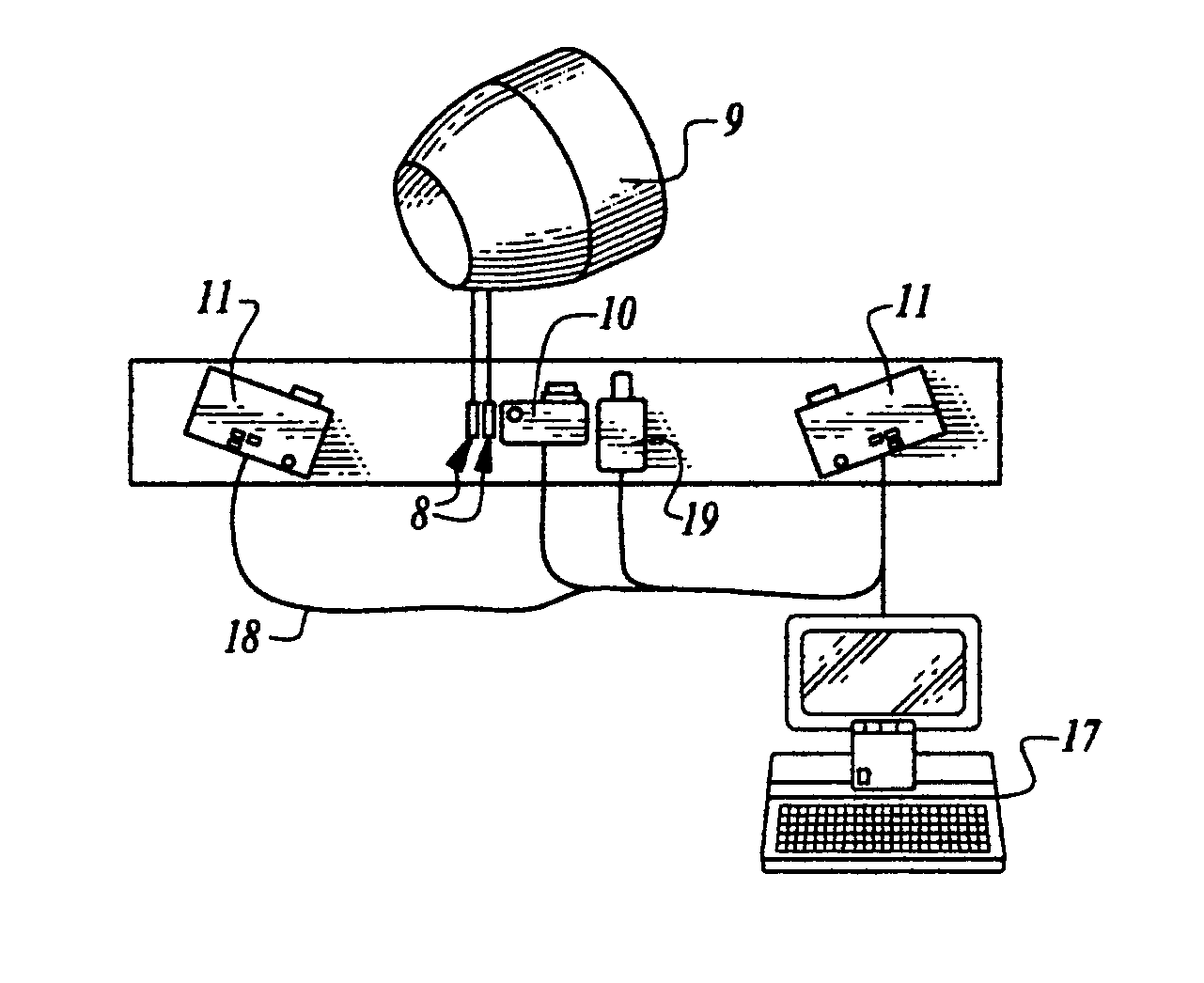

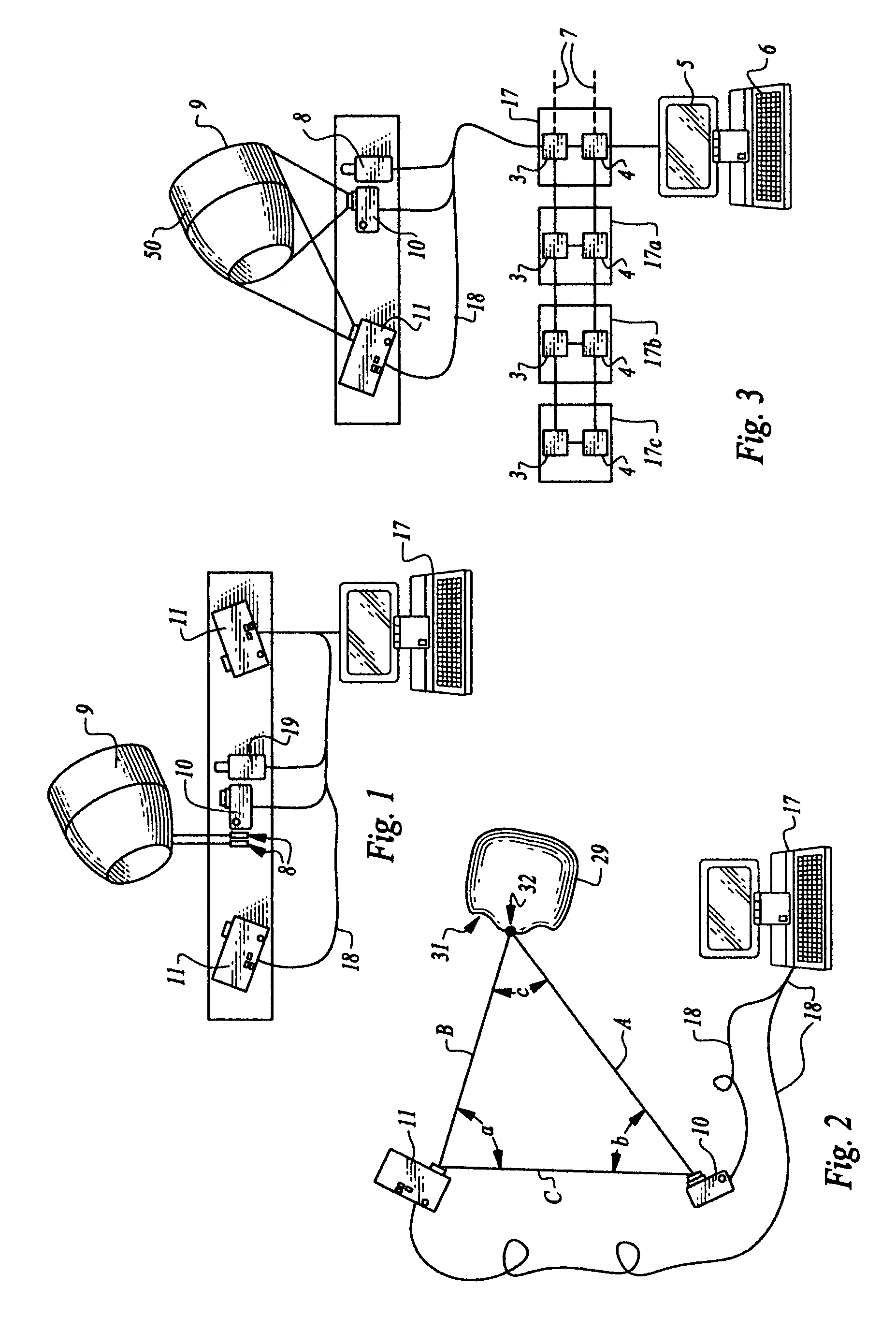

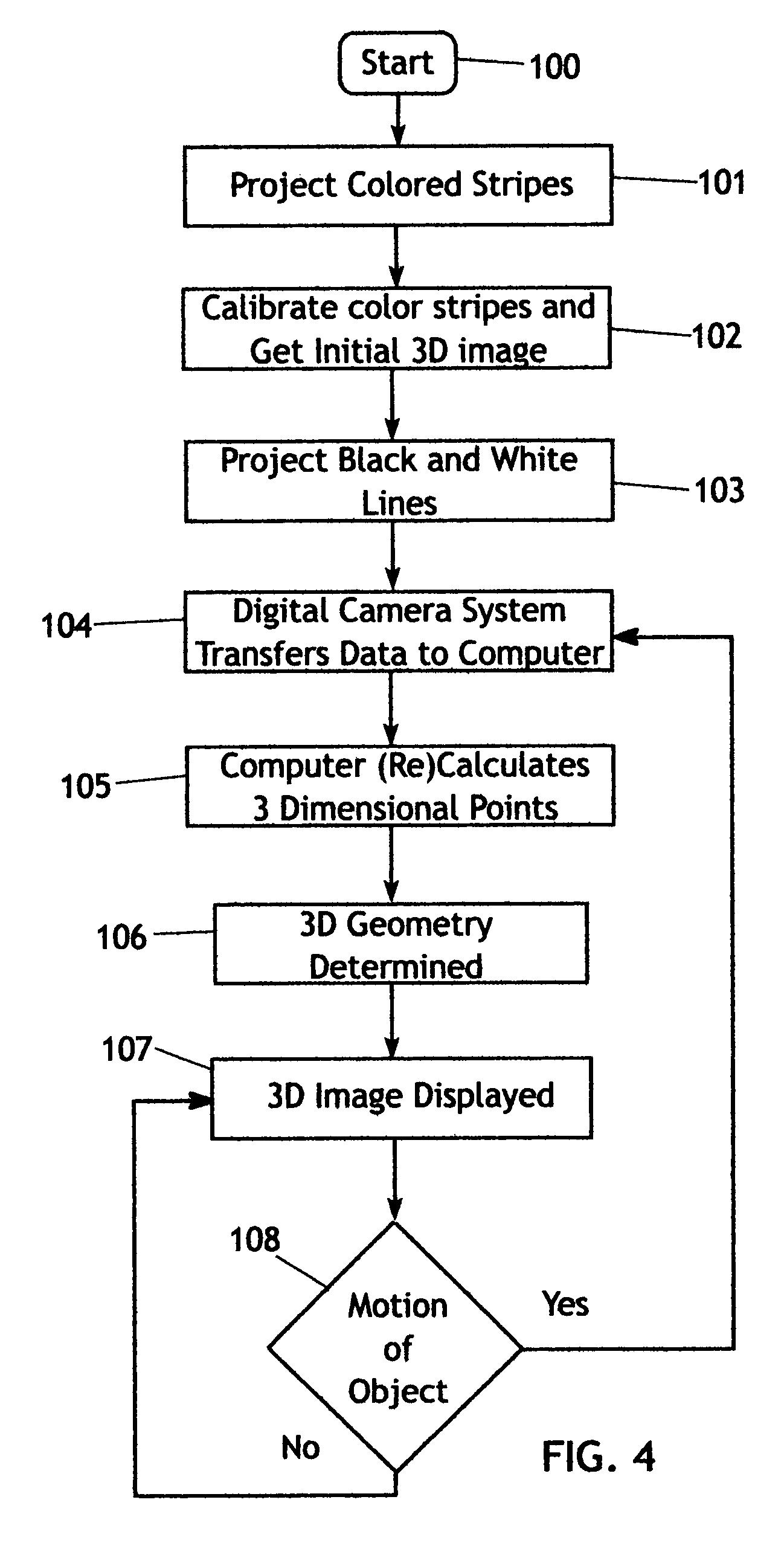

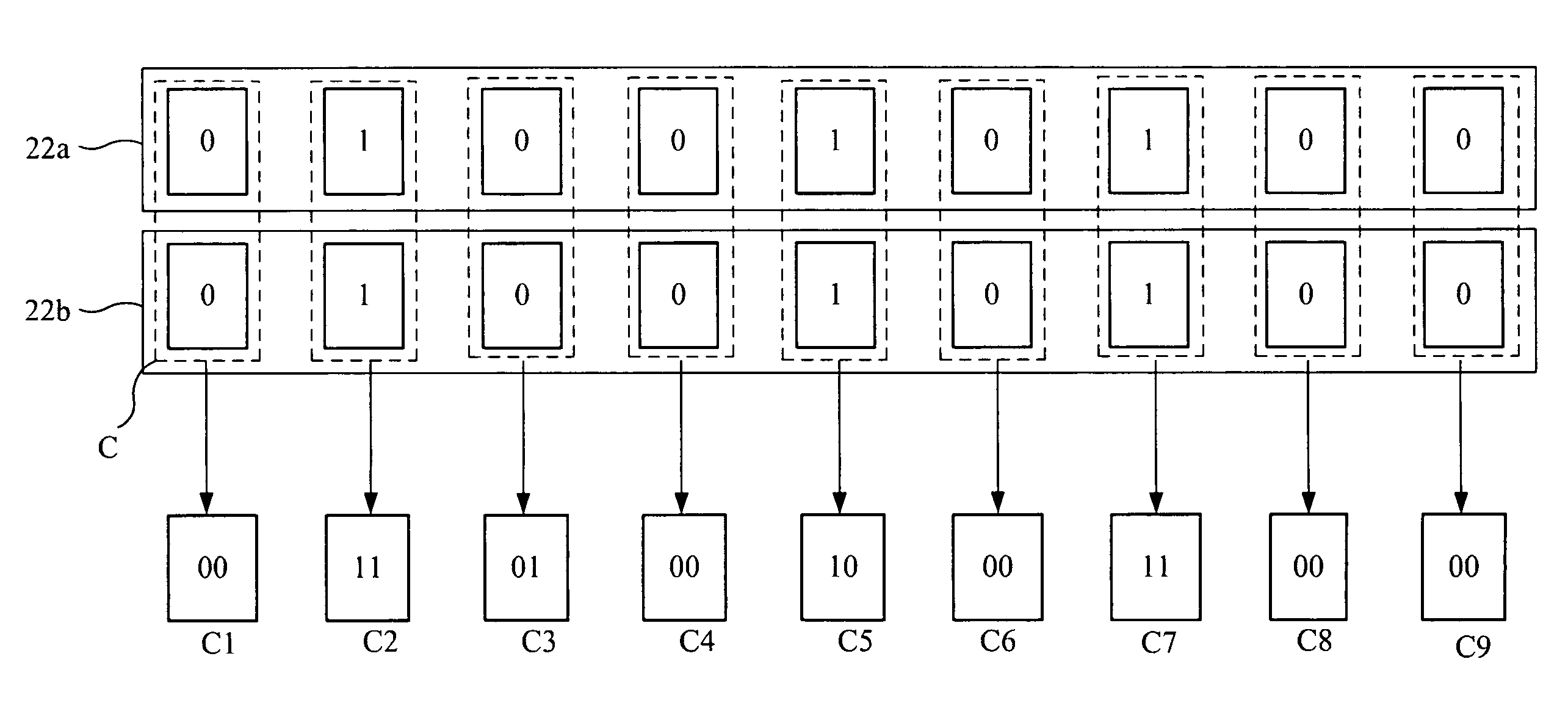

Method and apparatus for dynamic space-time imaging system

InactiveUS20070299338A1Fast enough to eliminateNo blurringImage analysisMaterial analysis by optical meansSingle flashJet aeroplane

A method for creating a 3 D map of the surface contours of an object includes projecting a variety of patterns onto the object, and imaging the patterns as they fall on the object to encode the topographic features of the object. In one embodiment a three dimensional image is taken in a single flash to avoid blurring due to motion of the object. Thereafter a secondary pattern is projected to detect changes in the initial image. The images are processed in a computer program in a manner such that a complete 3D map of the surface of the object is obtained in digital form. Reiteration of the method can detect motional variation such as a breathing human, flexure of a complex mechanical structure, or a stress-strain testing of an airplane, vehicle, beam, bridge, or other structure.

Owner:4D IMAGING +1

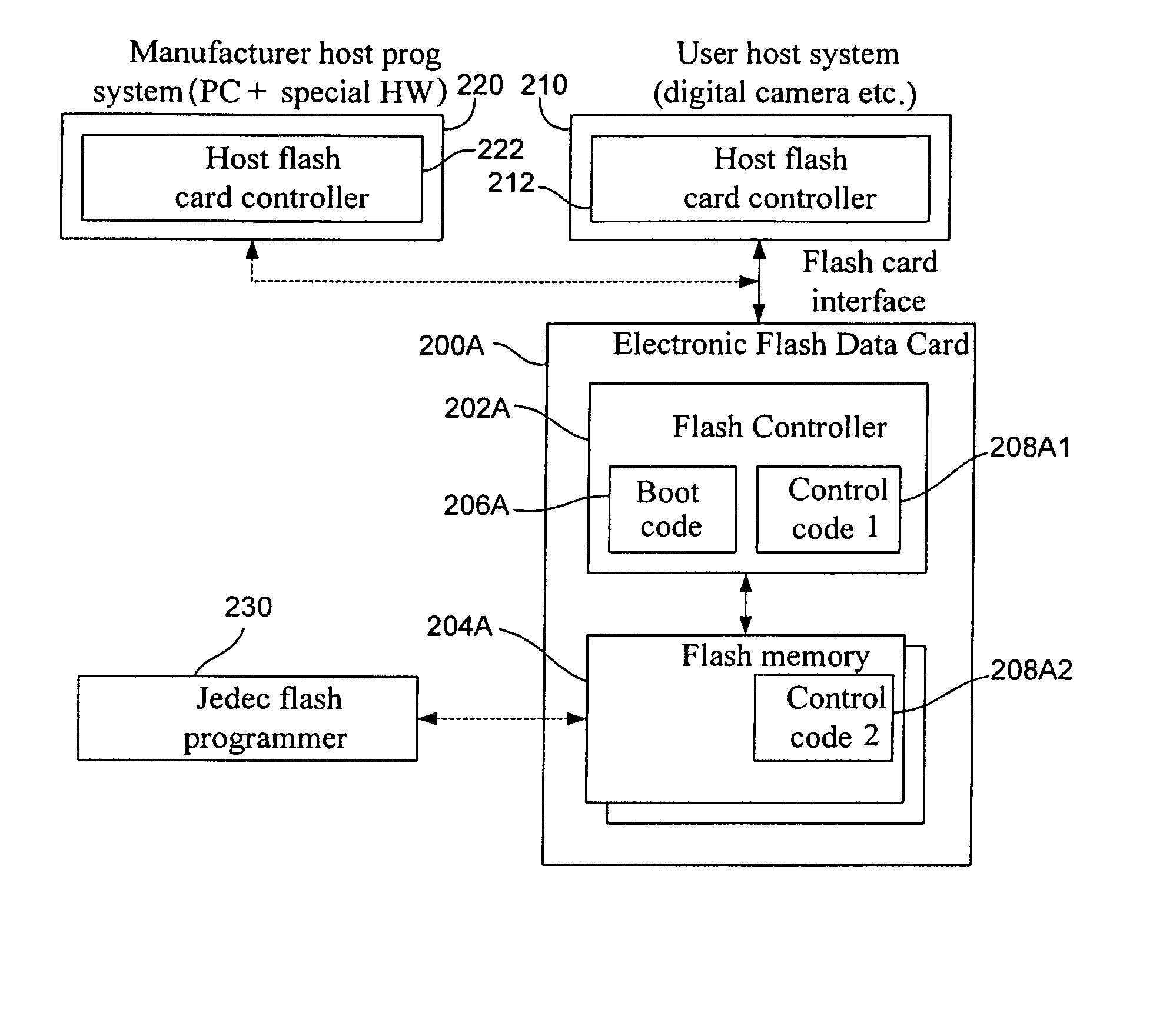

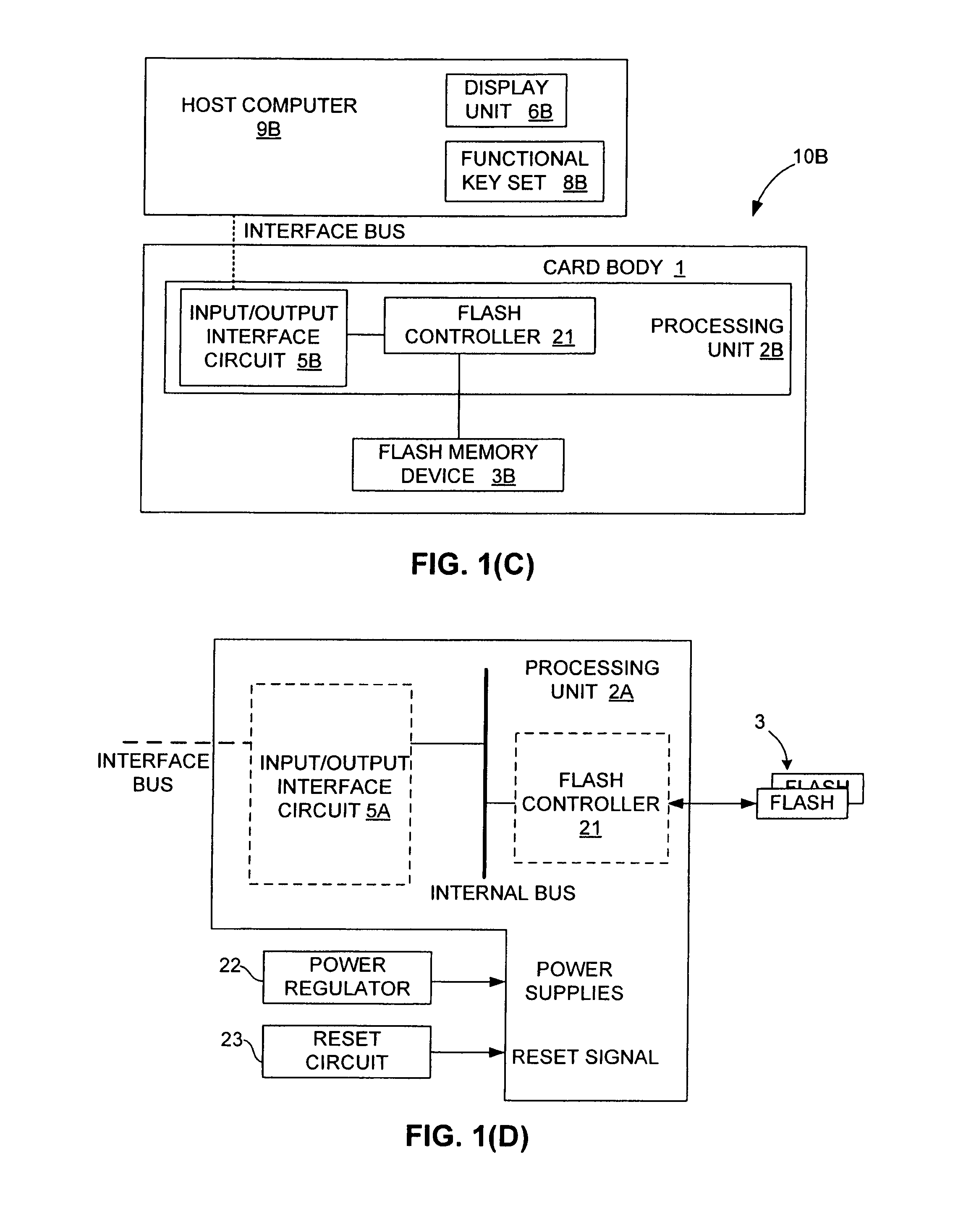

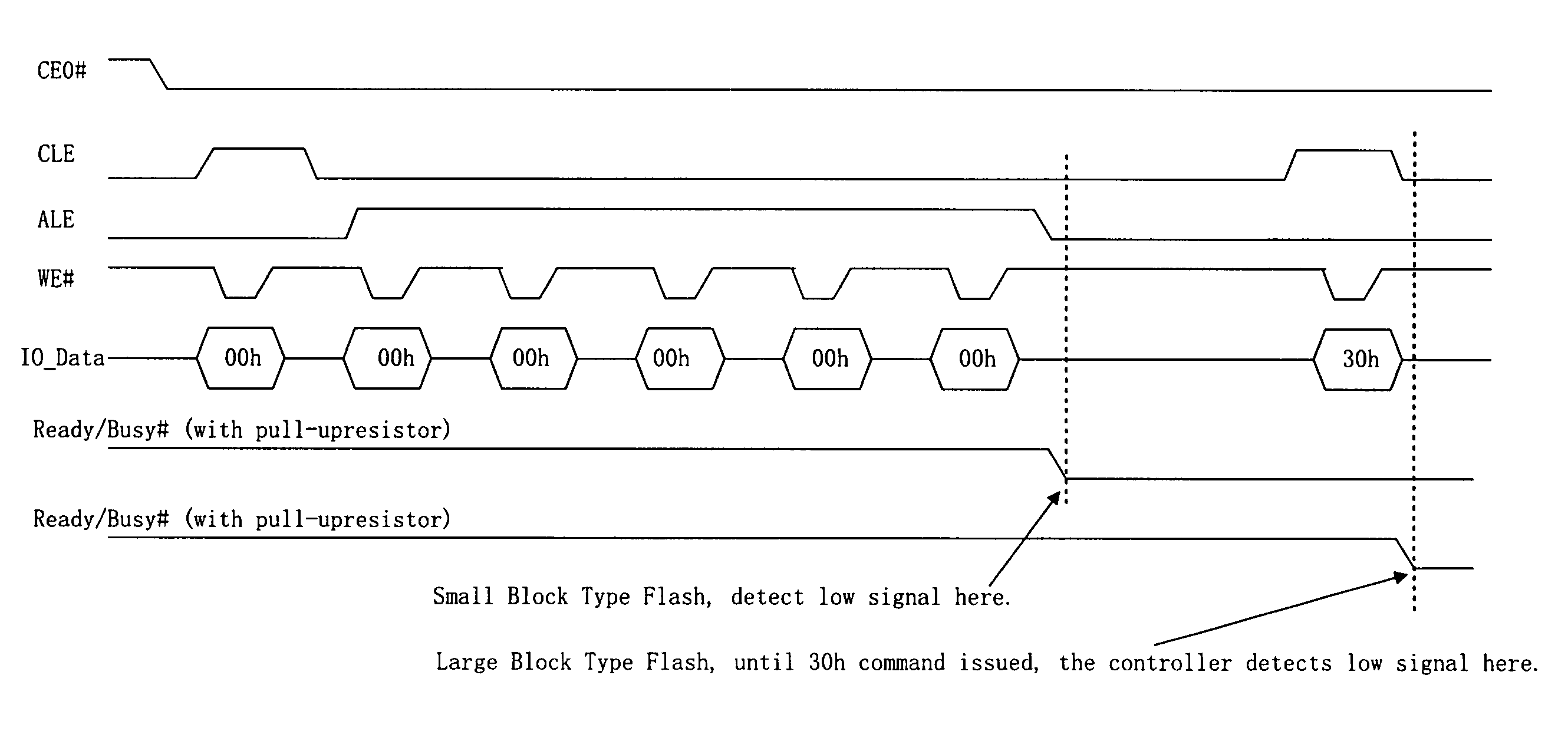

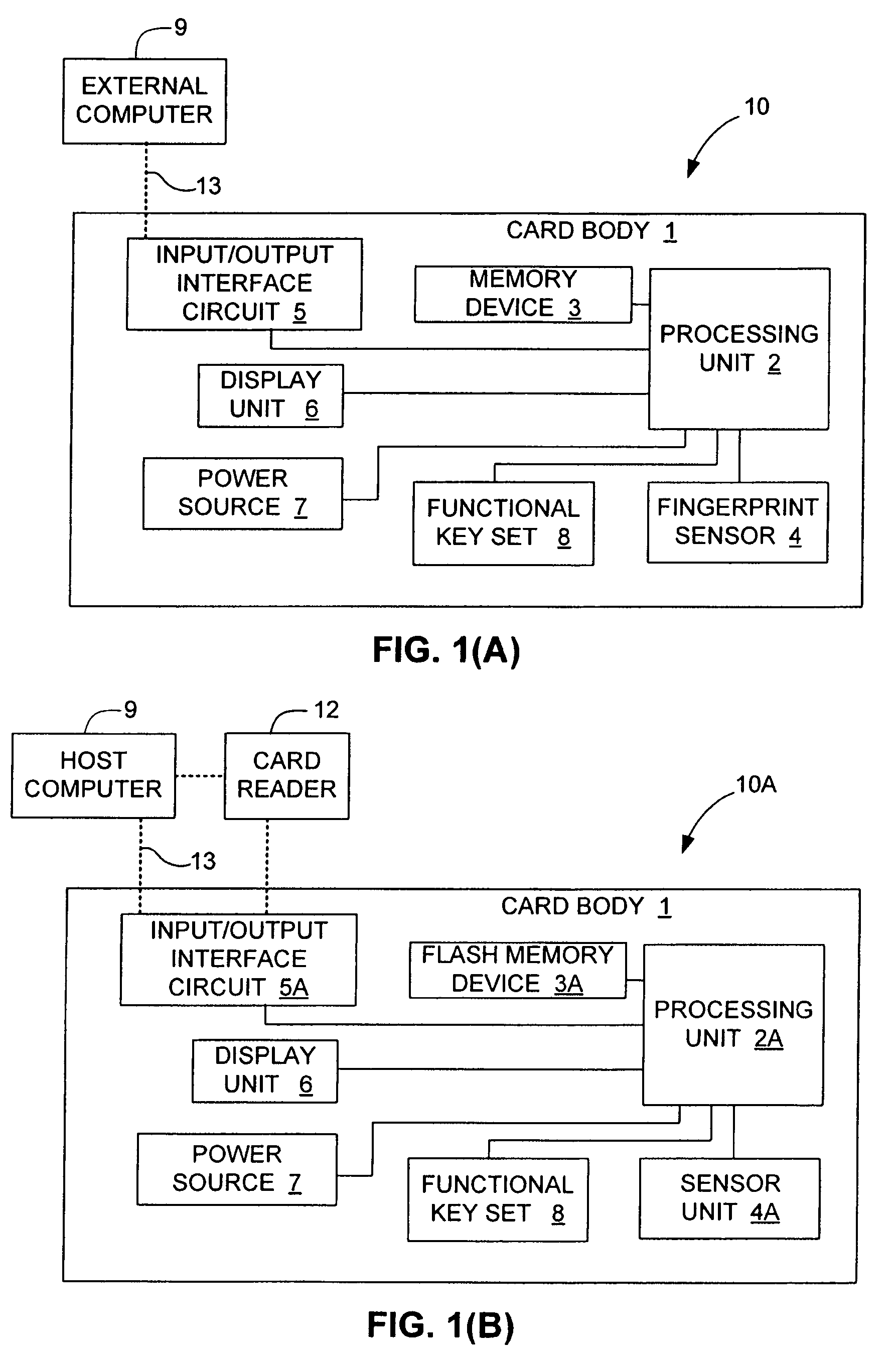

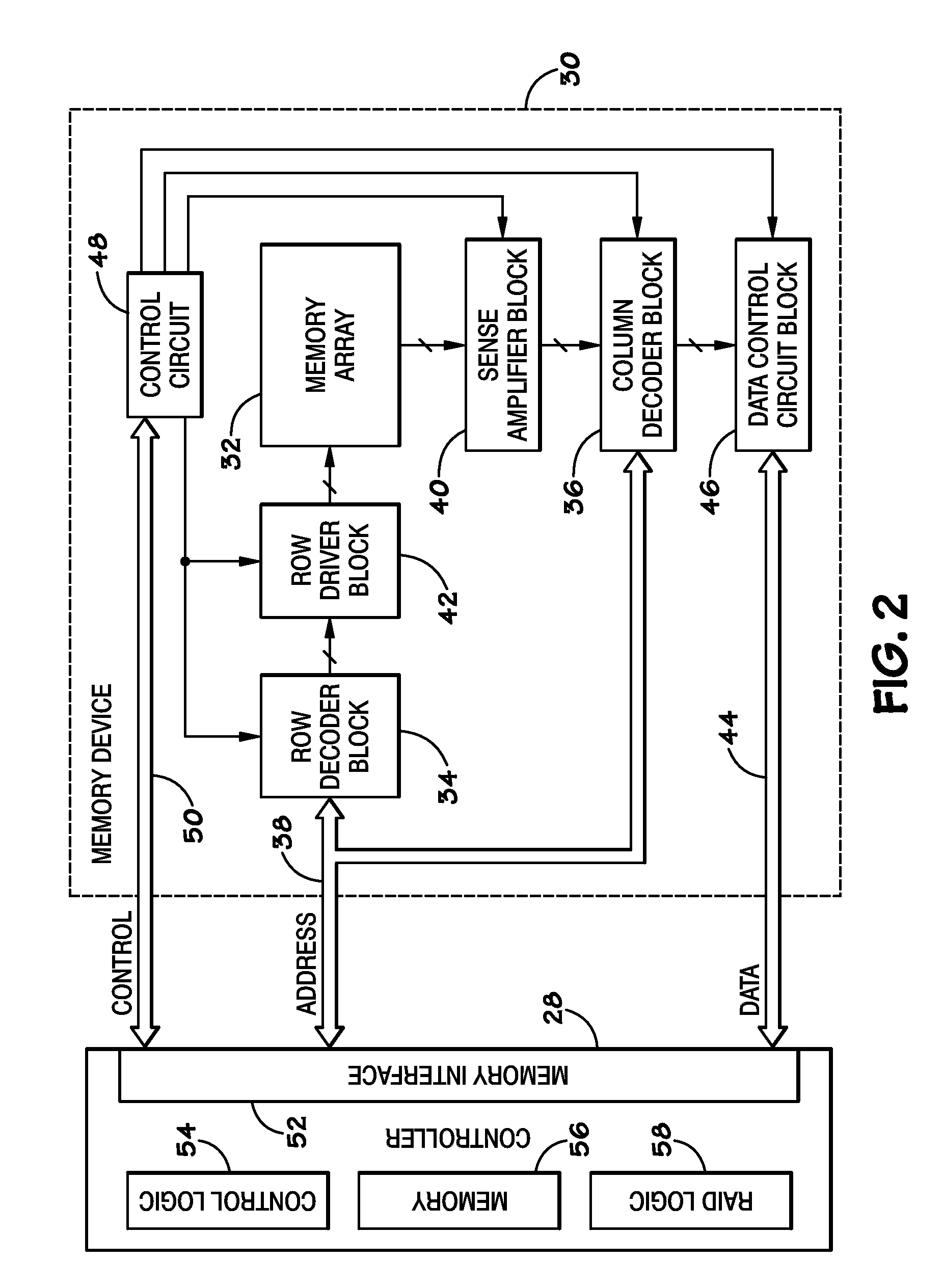

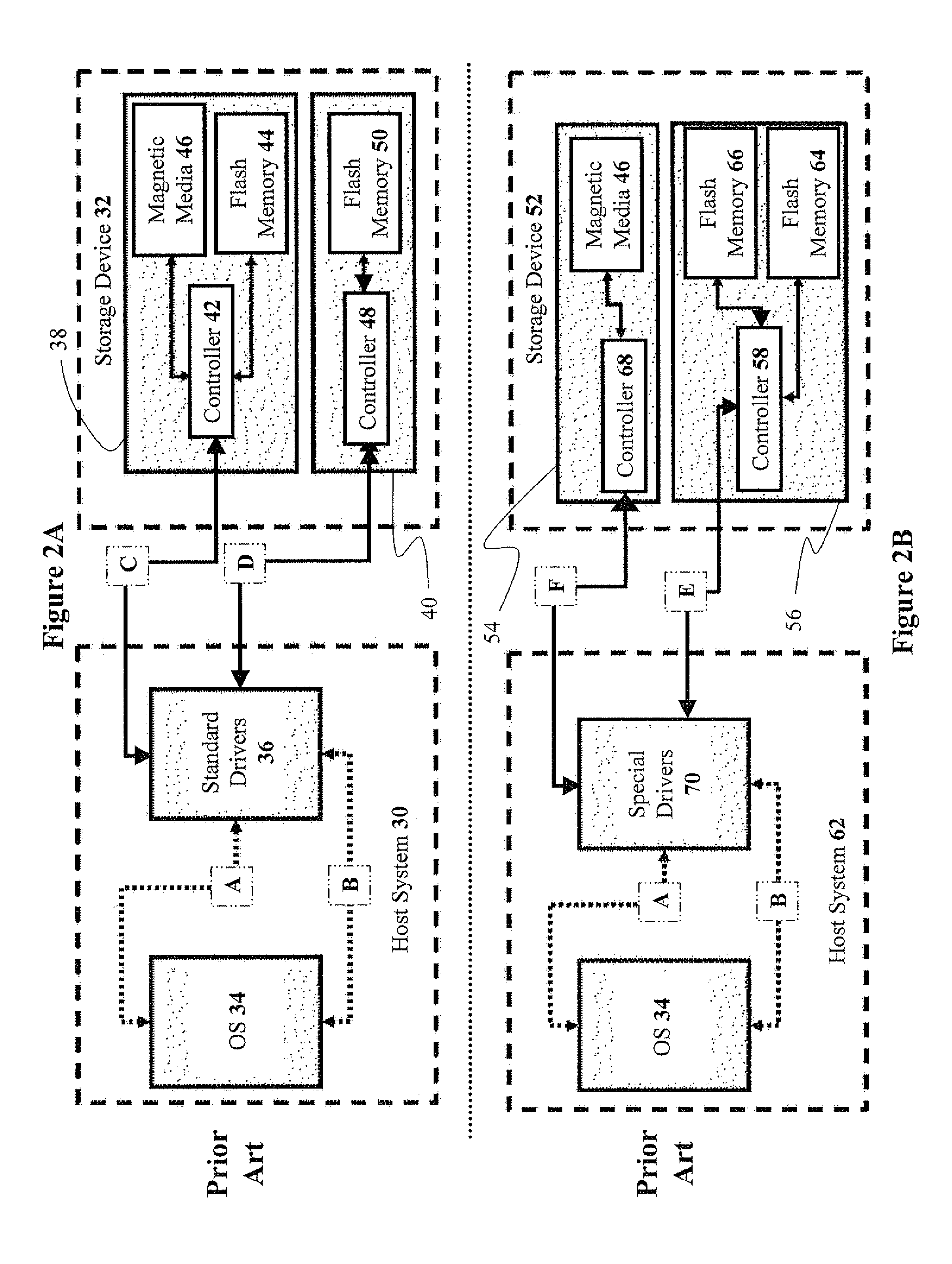

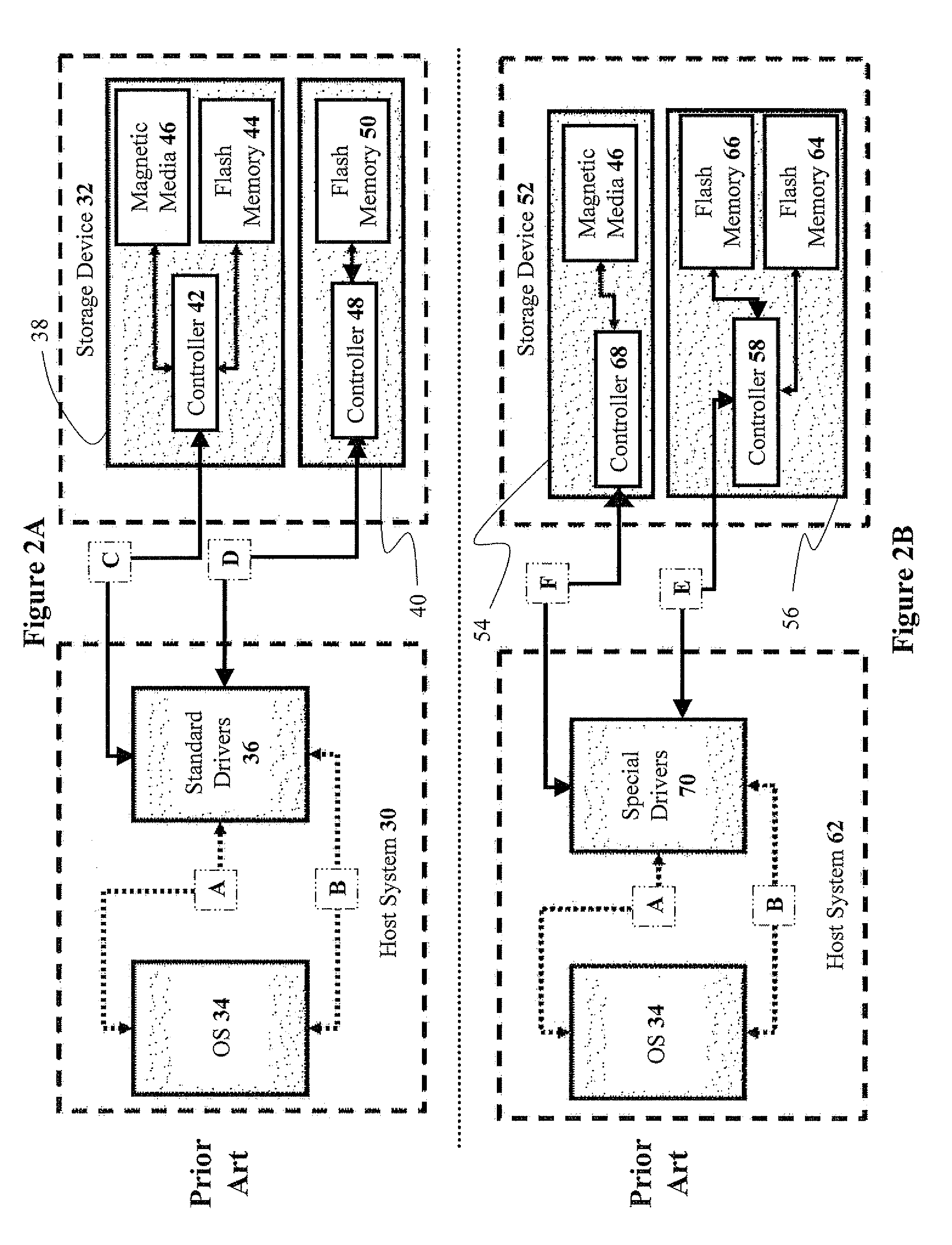

Flash memory controller controlling various flash memory cells

InactiveUS20080086631A1Easy to updateSoftware engineeringMemory adressing/allocation/relocationSingle flashRandom access memory

An electronic data flash card is accessible by a host system, and includes a flash memory controller and at least one flash memory device coupled to the flash controller. The boot code and control code for the flash memory system (flash card) are stored in the flash memory device during a programming procedure. The flash controller transfers the boot code and control code to a volatile main memory (e.g., random access memory or RAM) at start up or reset making a RAM-based memory system. Boot code and control code are selectively overwritten during a code updating operation. A single flash controller thus supports multiple brands and types of flash memory to eliminate stocking issues.

Owner:SUPER TALENT TECH CORP

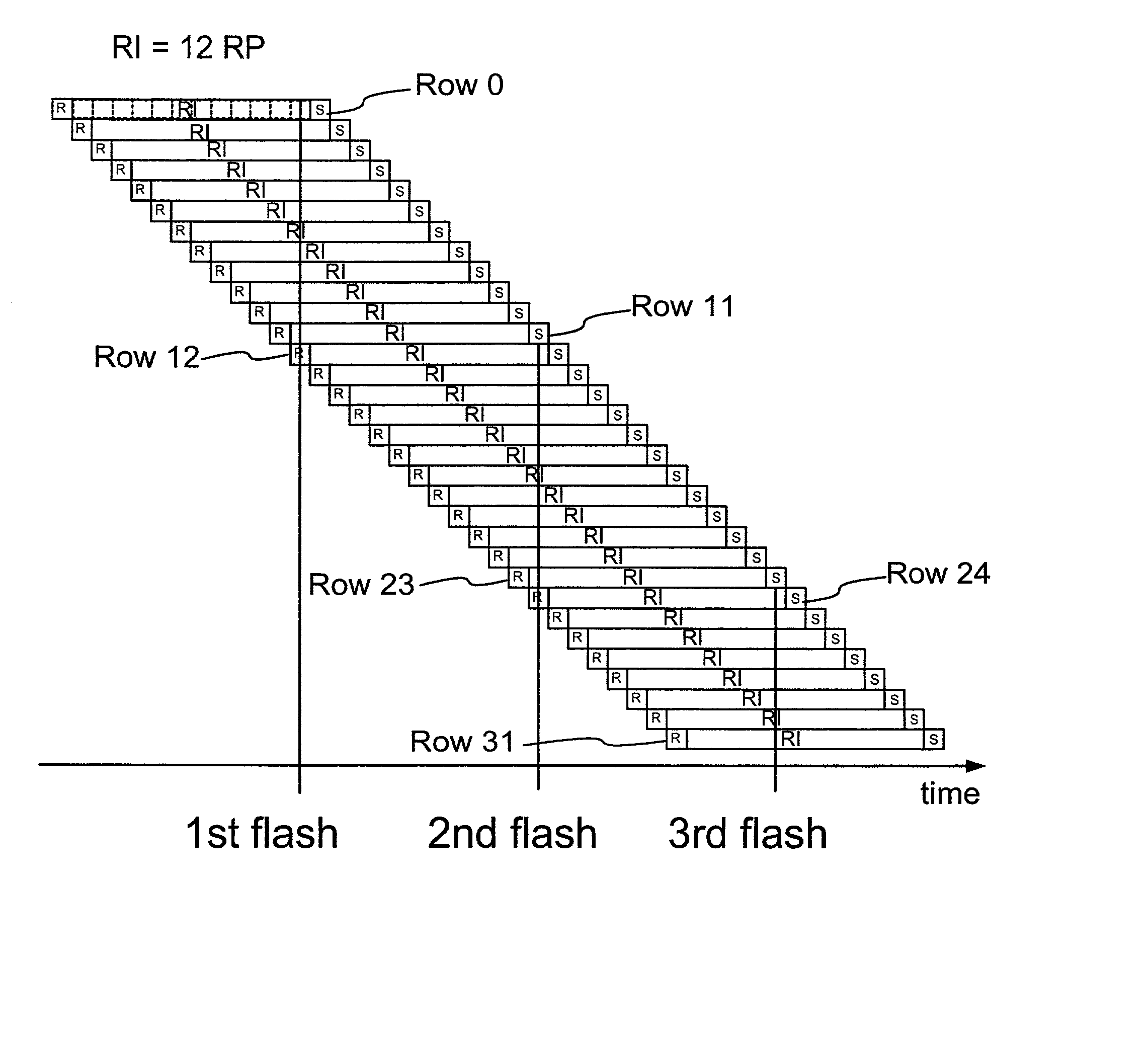

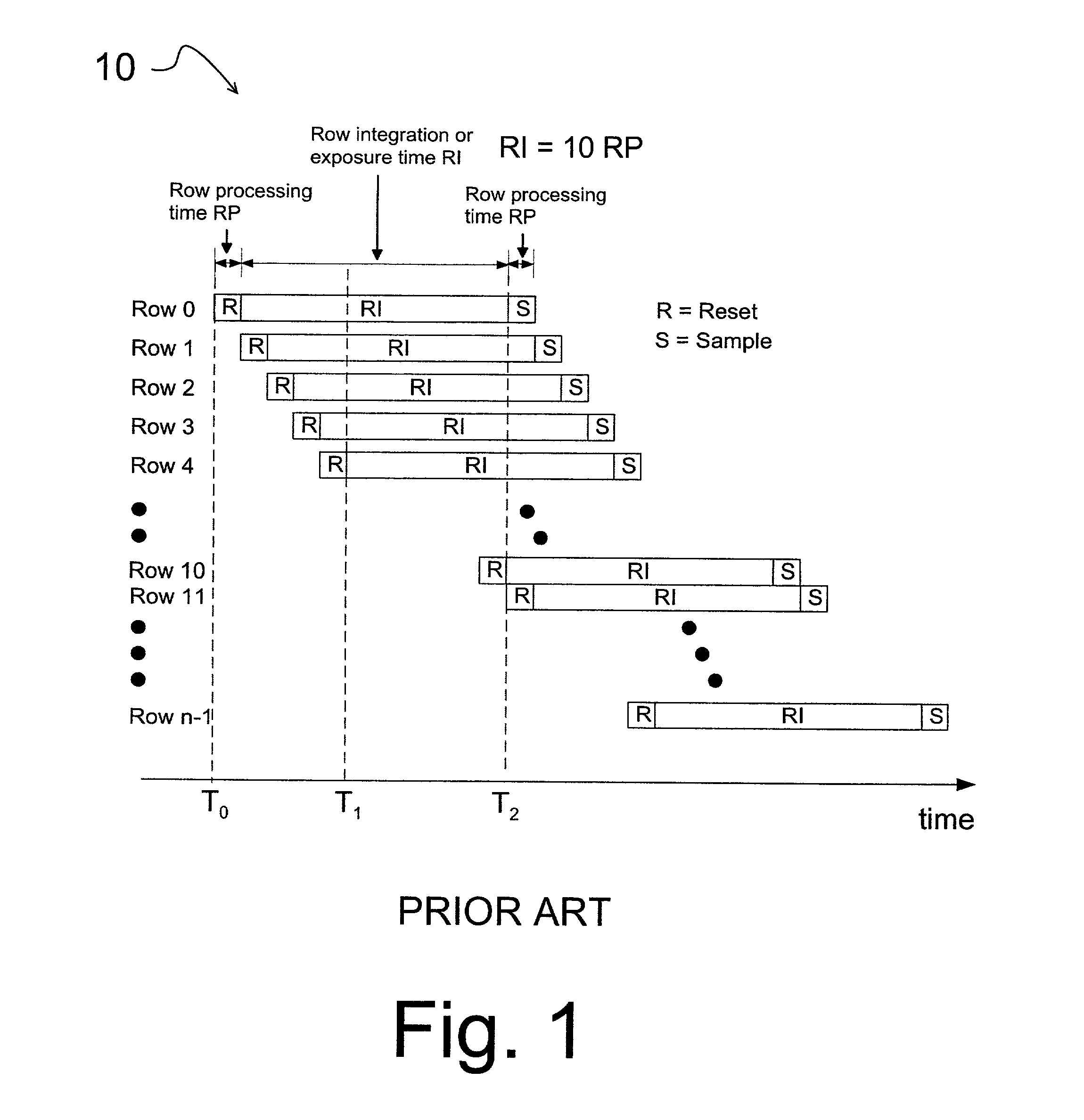

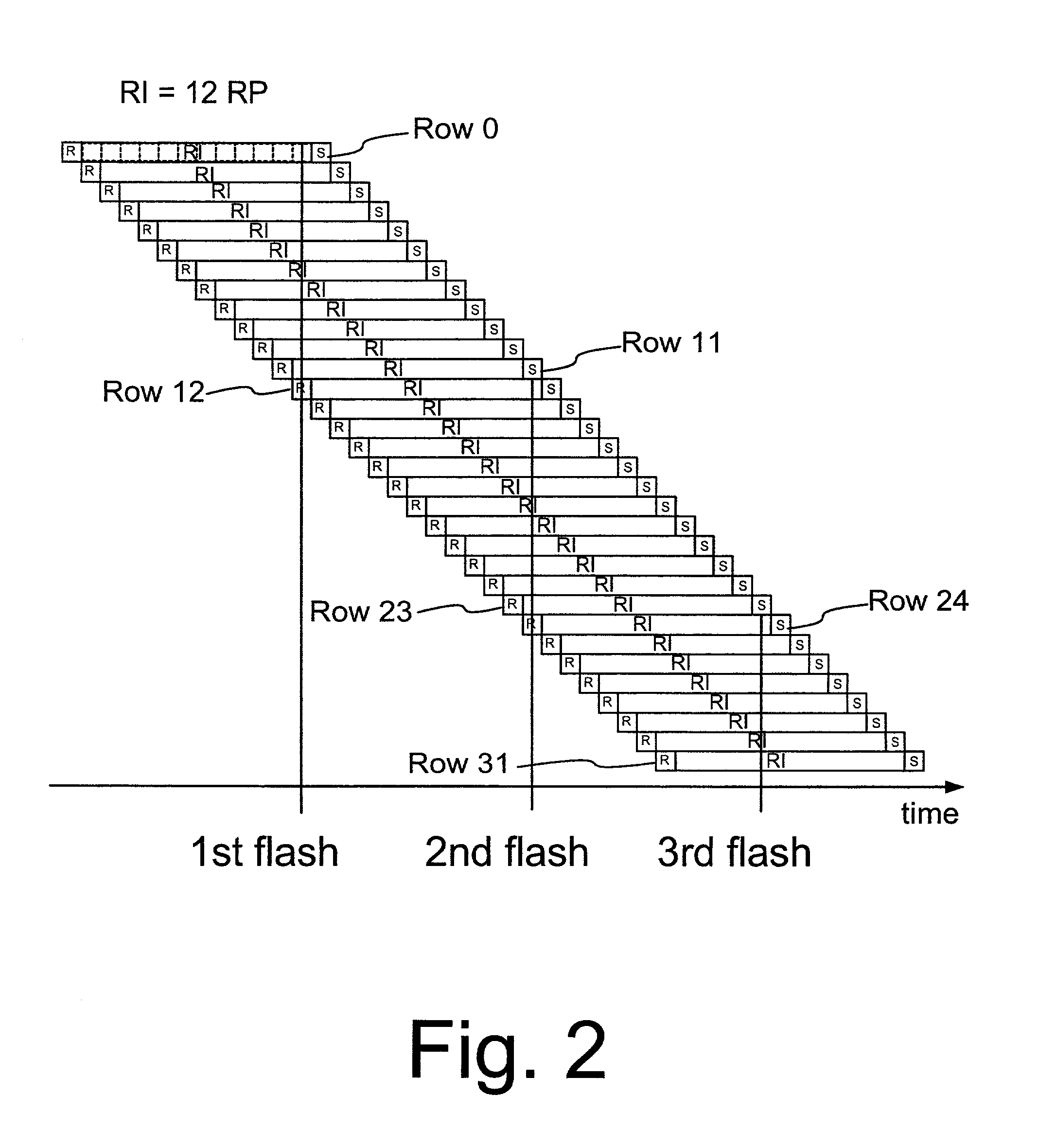

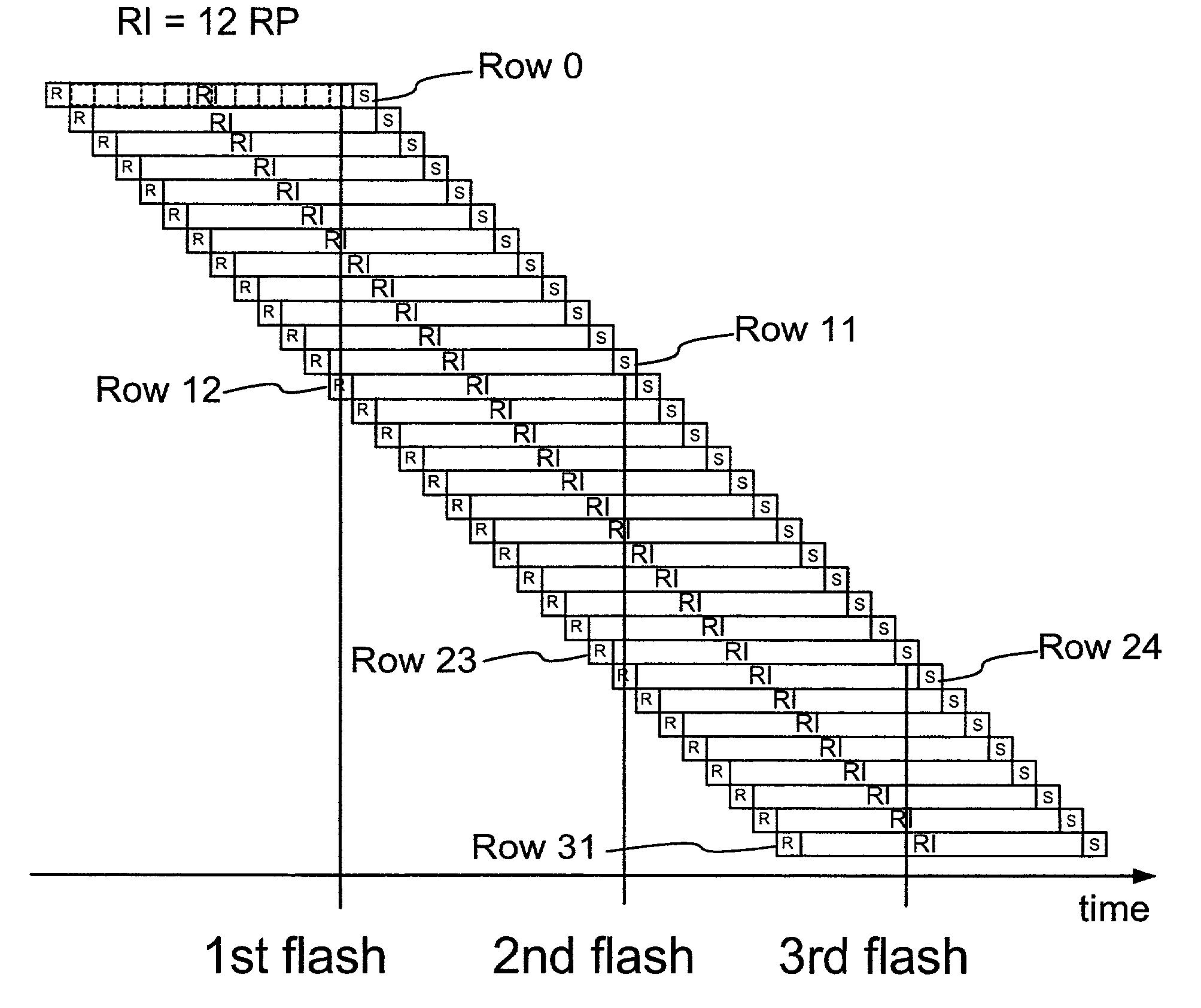

Control of a flash unit in a digital camera

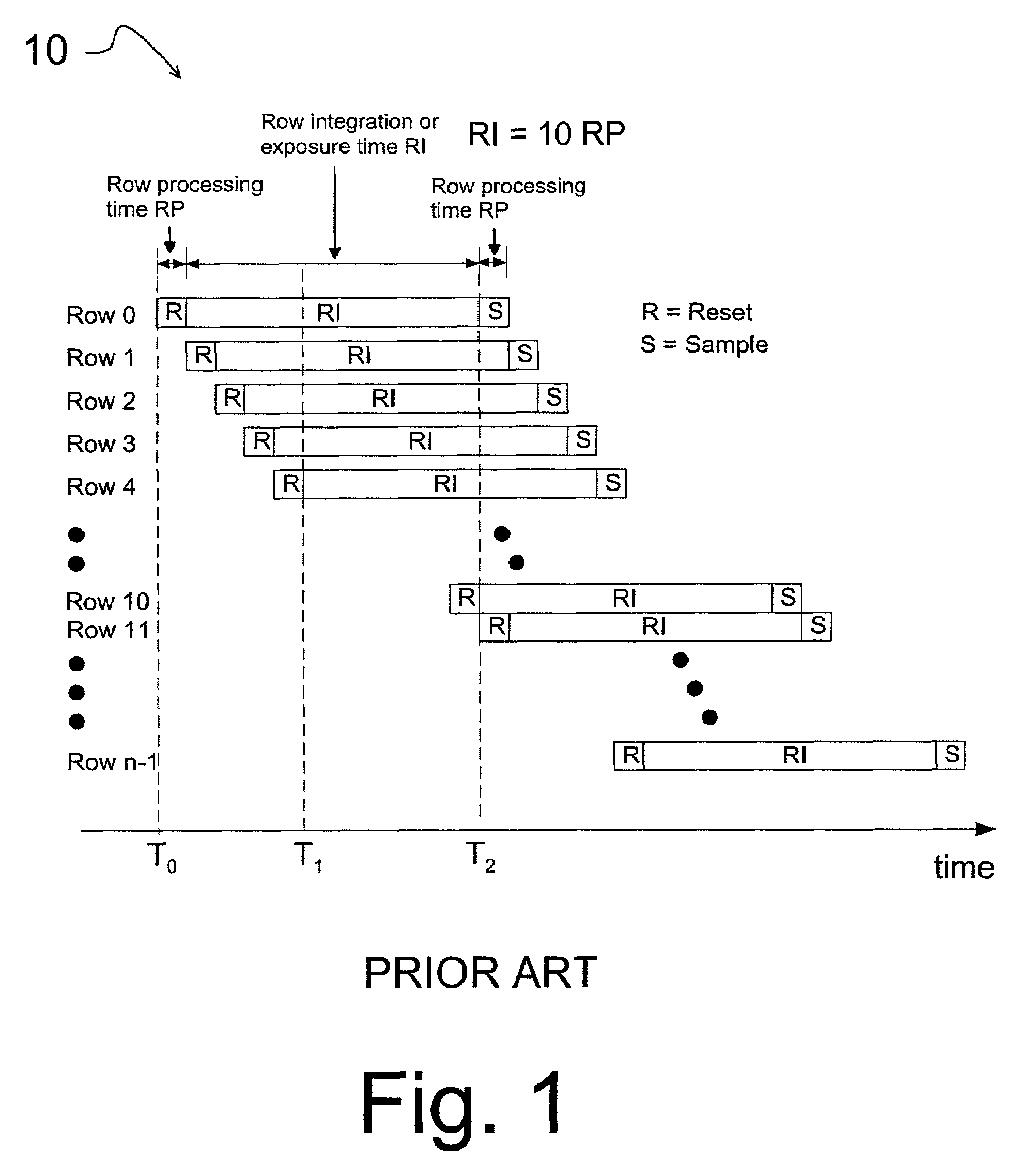

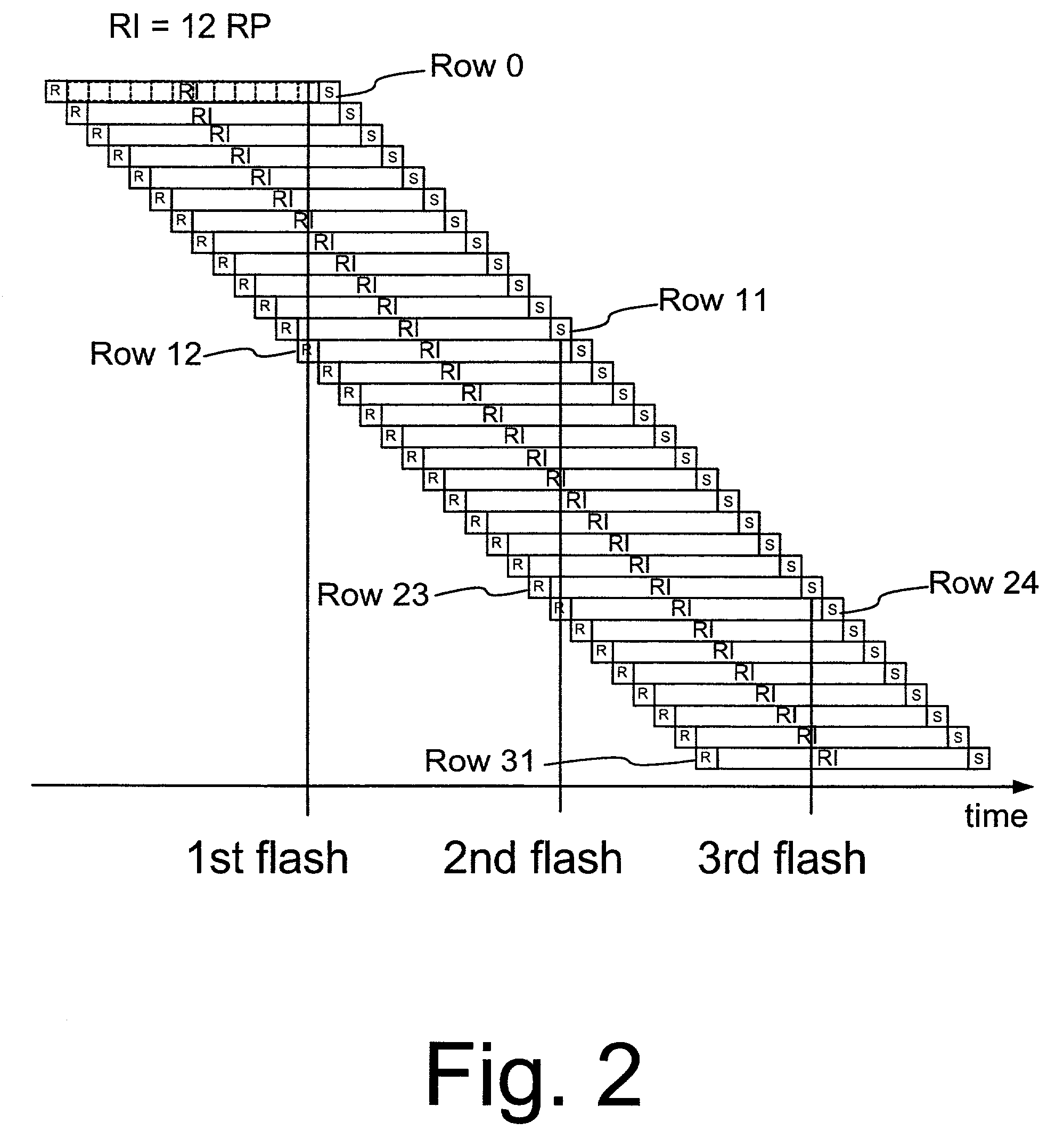

ActiveUS20030007088A1Television system detailsTelevision system scanning detailsSingle flashElectronic shutter

The invention is based on a method for controlling a flashlight in connection with a digital image sensor without a mechanical shutter, wherein the exposure of the image sensor is performed in sub-areas, such as pixel rows or columns, or in another order, by using a rolling electronic shutter or the like. Thus, the exposure of said sub-areas of the image sensor takes place at least partly at different times. According to the invention, during the time of exposure of one image, i.e. substantially all the sub-areas of the image sensor, several discrete, successive flashes of the flashlight are used to achieve even exposure of the image area, which the flashes are timed in such a way that each single flash is triggered at a point of time which is common to the integration or exposure time of as many successive sub-areas of the image sensor as possible. According to the invention, the successive light flashes are also timed in such a way that one and only one flash of the flashlight occurs during the integration or exposure time of each single sub-area. By the present invention, the significant advantage is attained that the invention minimizes the number of light flashes required for one image while it also secures that each sub-area of the sensor to be exposed at a different time is illuminated as evenly as possible.

Owner:NOKIA TECHNOLOGLES OY

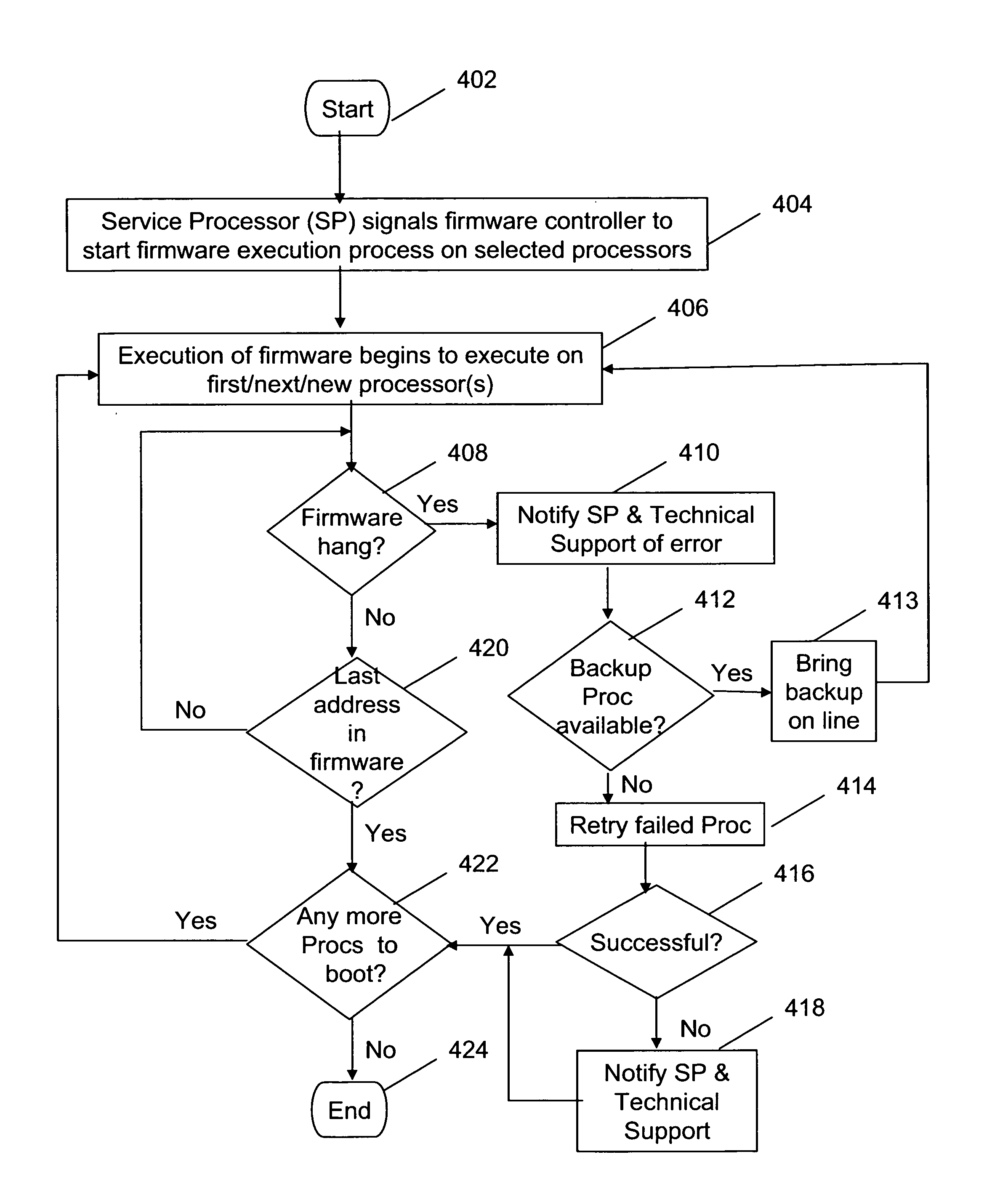

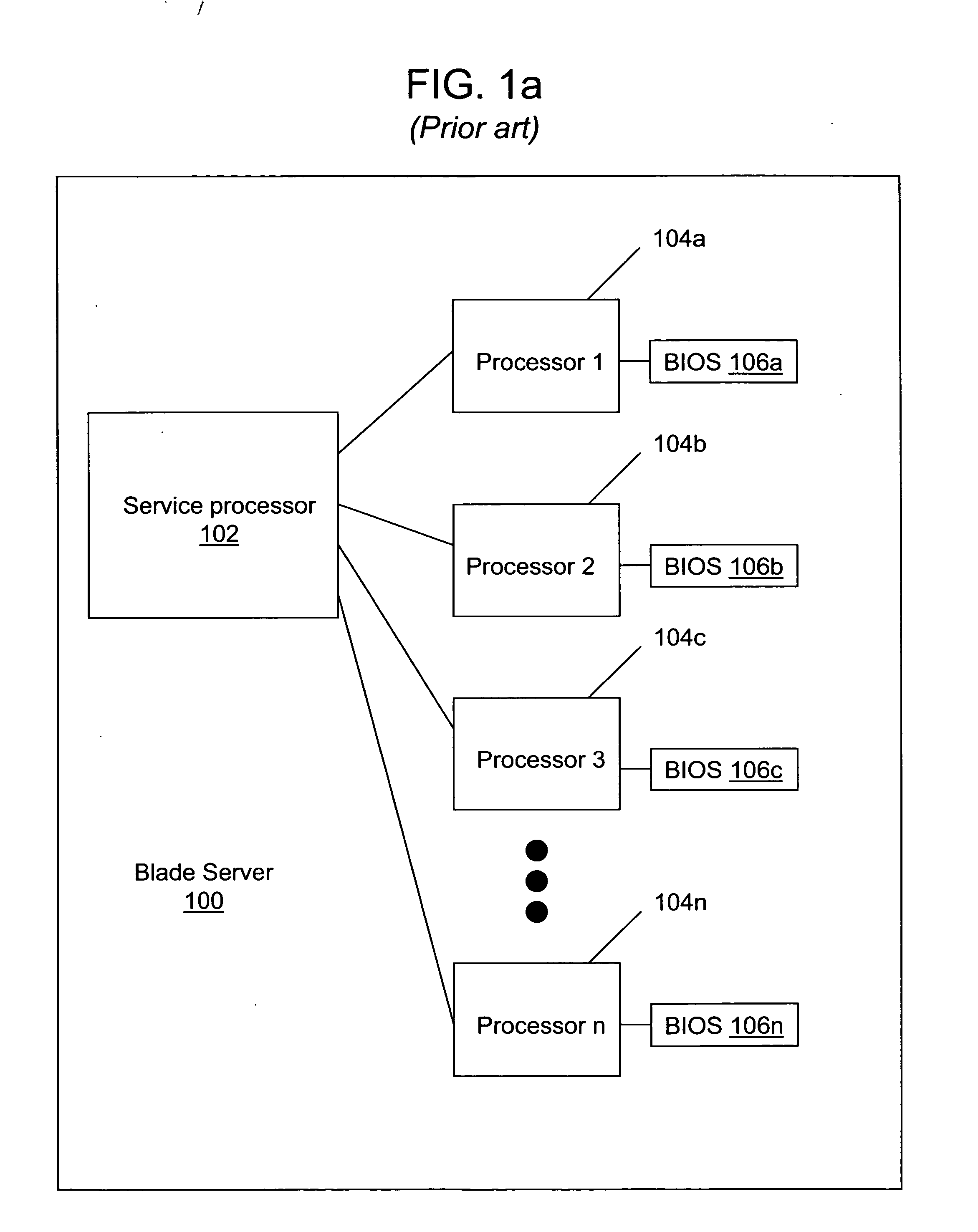

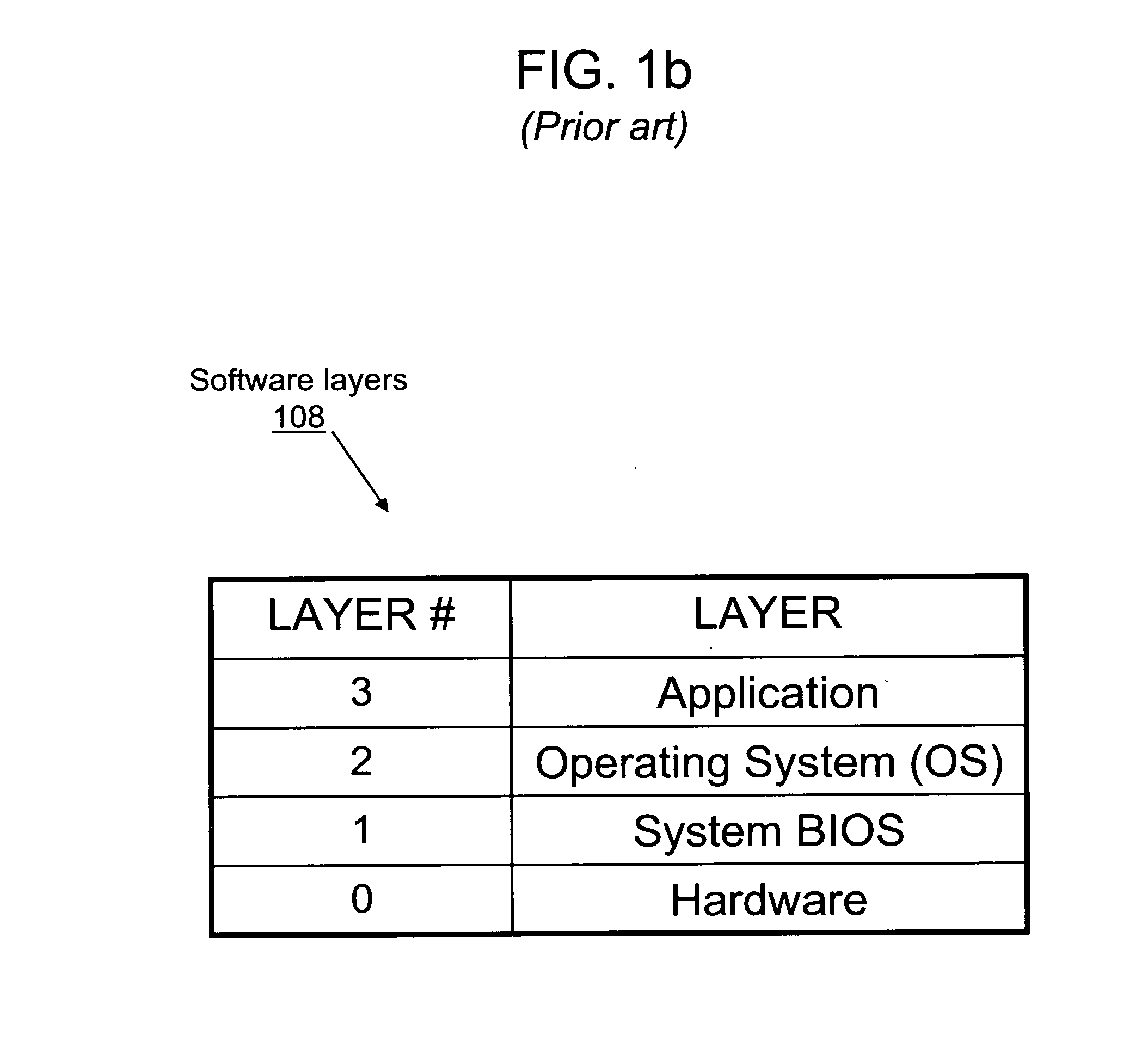

Booting multiple processors with a single flash ROM

A method, apparatus and computer-usable medium are presented for loading firmware onto multiple processors. A firmware controller is coupled to multiple processors and a firmware memory. A service processor, by controlling the operation of the firmware controller, selects one or more of the multiple processors. Under the control of the service processor, the firmware controller sends firmware from the firmware memory to each of the selected processors, either sequentially or simultaneously. If one of the selected processors fails to fully execute the firmware from the firmware memory, the firmware controller notifies the service processor of that failure as well as the particular memory address in the firmware where the failure occurred.

Owner:GERHARDT DIANA R

Flash memory controller controlling various flash memory cells

InactiveUS7676640B2Easy to updateSoftware engineeringDigital computer detailsSingle flashStatic random-access memory

Owner:SUPER TALENT TECH CORP

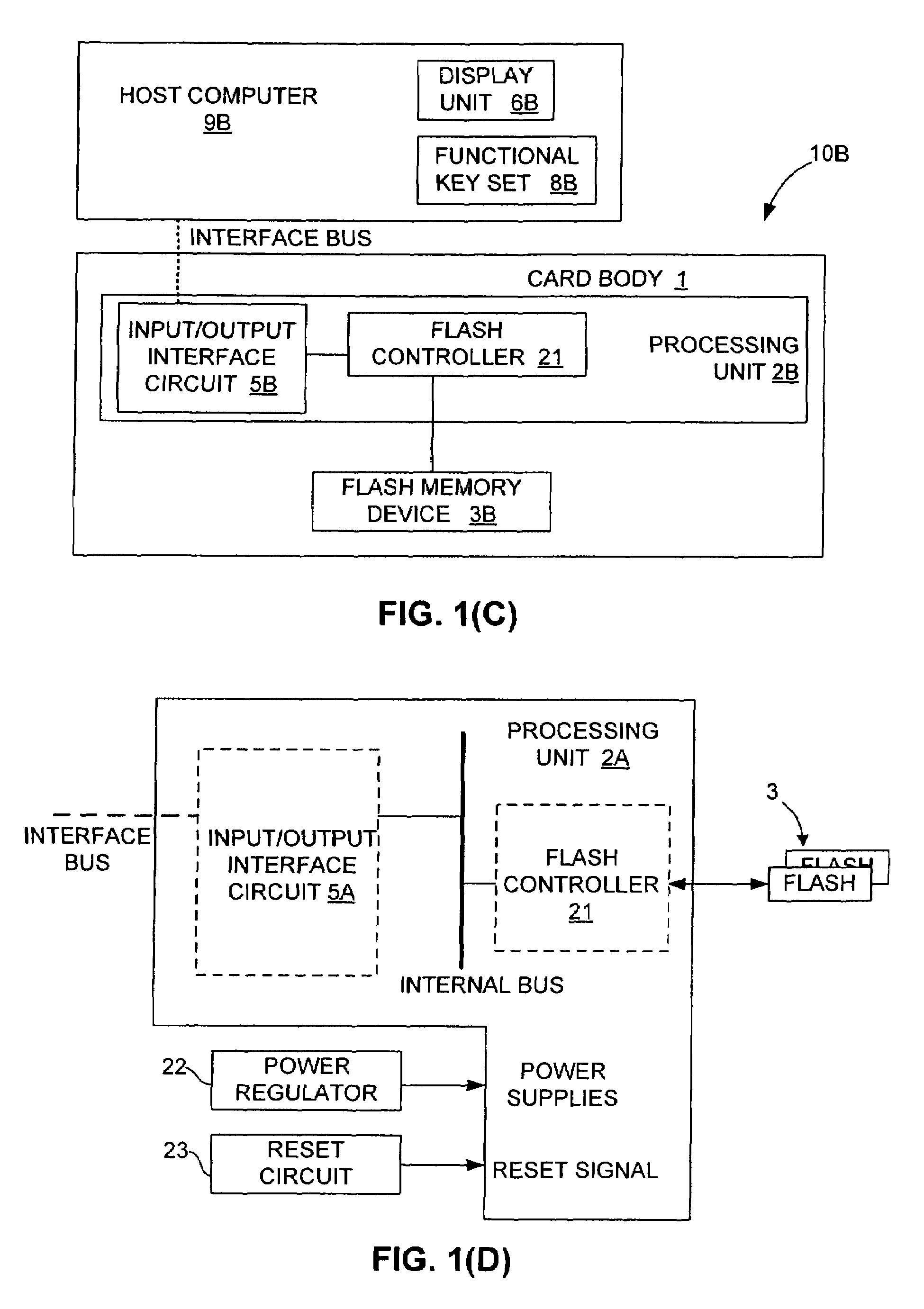

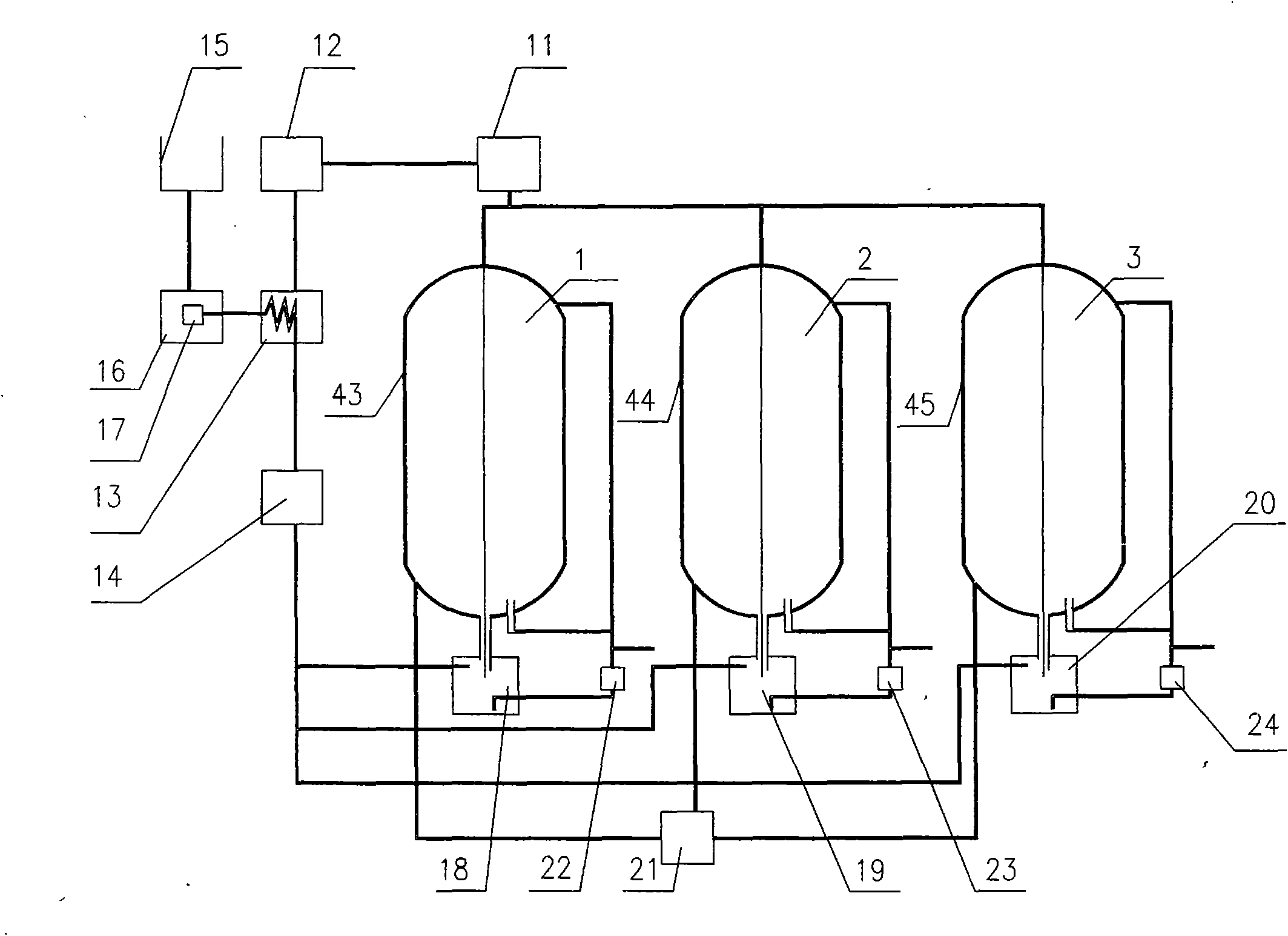

Method of preparing taurine

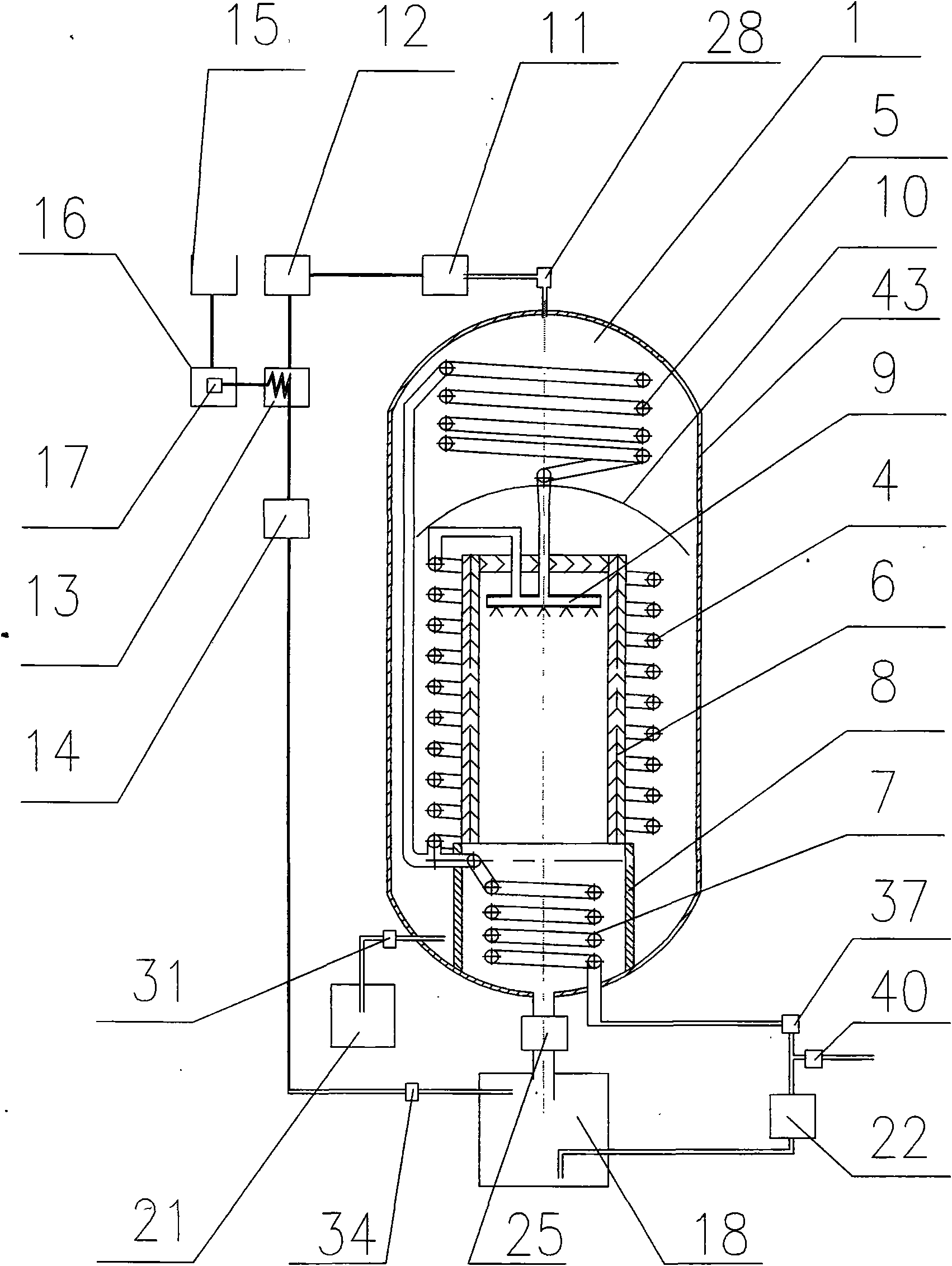

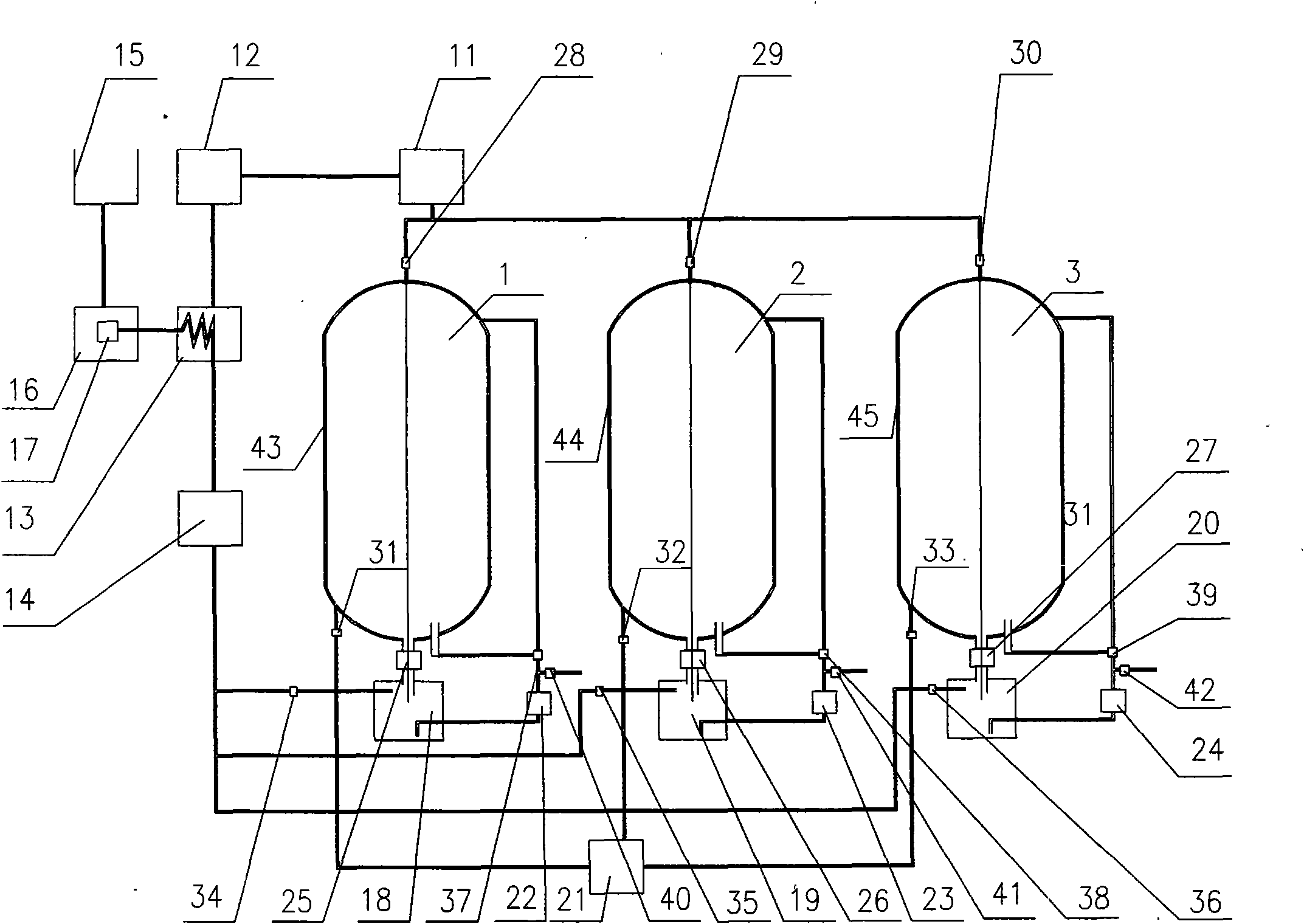

The invention relates to method for preparing taurine, comprising the following steps: (1) reacting epoxy ethane with sodium sulfite under 0.05 to 0.1MPa, with pH value of 6.5 to 7.5 and at temperature between 75 and 85 DEG C to obtain hydroxyethyl sodium sulfonate; (2) carrying out ammonolysis reaction on the hydroxyethyl sodium sulfonate and liquid ammonia under 14 to 21MPa and at temperature between 160 and 280 DEG C to obtain ammonolysis solution containing sodium taurate; (3) introducing the ammonolysis solution into a single flash evaporator for primary flash evaporating at a temperature between 160 and 200 DEG C and under 1.3 to 2.0MPa; introducing the flash evaporated liquid into a secondary flash evaporating and falling film evaporator, using the primary flash vapor as a heating medium to carry out flash evaporating and falling film evaporating on the primary flash evaporated liquid in the secondary flash evaporating and falling film evaporator at a temperature between 110 and 140 DEG C and at 0.1 to 0.6MPa; evaporating and concentrating the flash evaporated liquid subjected to secondary flash evaporating and falling film evaporating with flash vapor and steam as heating media in a multi-effect flash evaporating and falling film evaporator; and (4) neutralizing the sodium taurate by sulphuric acid to obtain the taurine. The method for preparing the taurine has the advantages of short time, high yield and low cost, and is easy for industrialized production. In addition, by primary flash evaporating and secondary flash evaporating processes, almost all the ammonia and 40% to 60% of water in the flash evaporated liquid can be removed, thus having double effects of removing ammonia and condensing.

Owner:王代龙 +1

Systems and methods for storing and recovering controller data in non-volatile memory devices

Owner:MICRON TECH INC

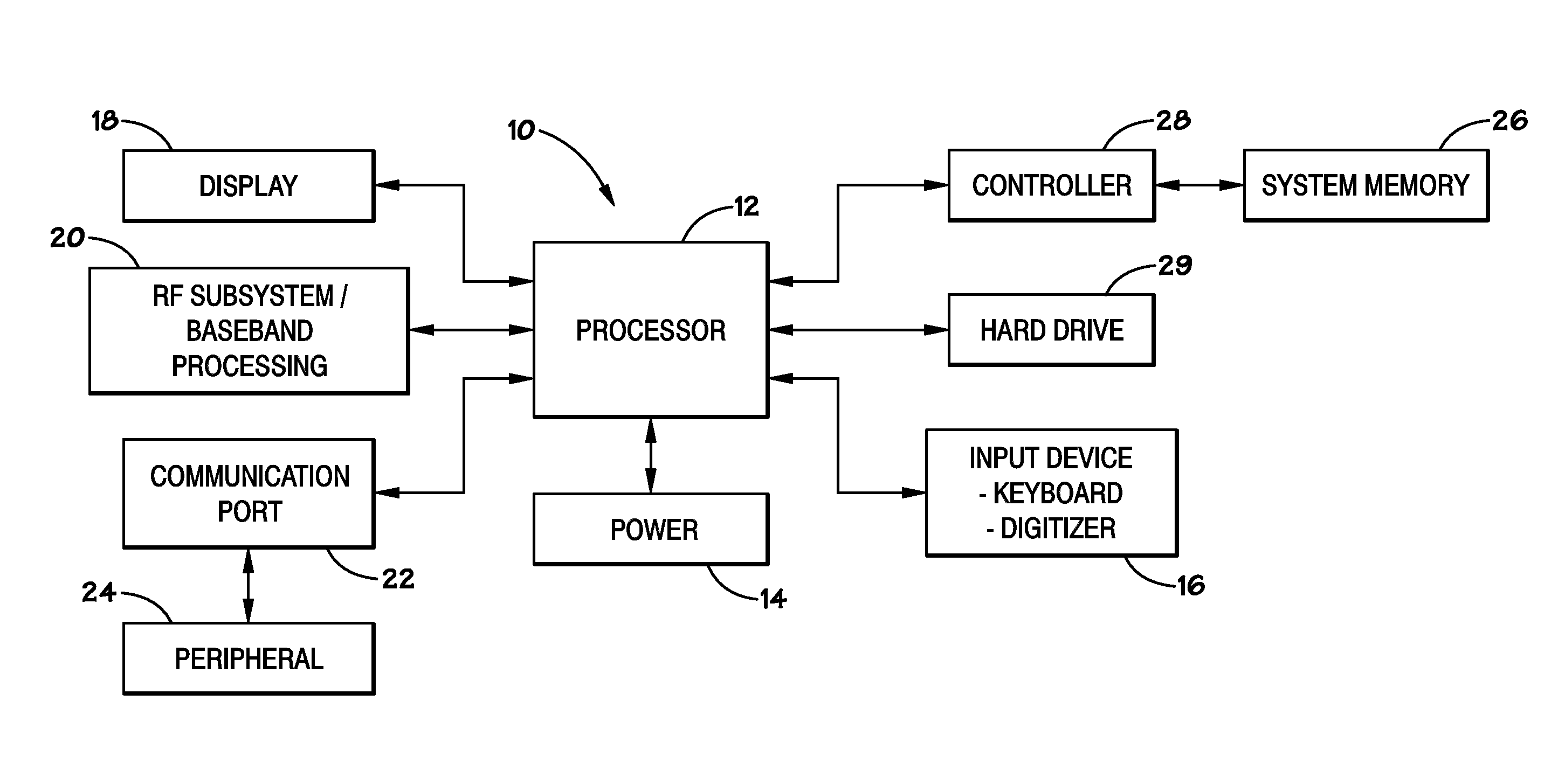

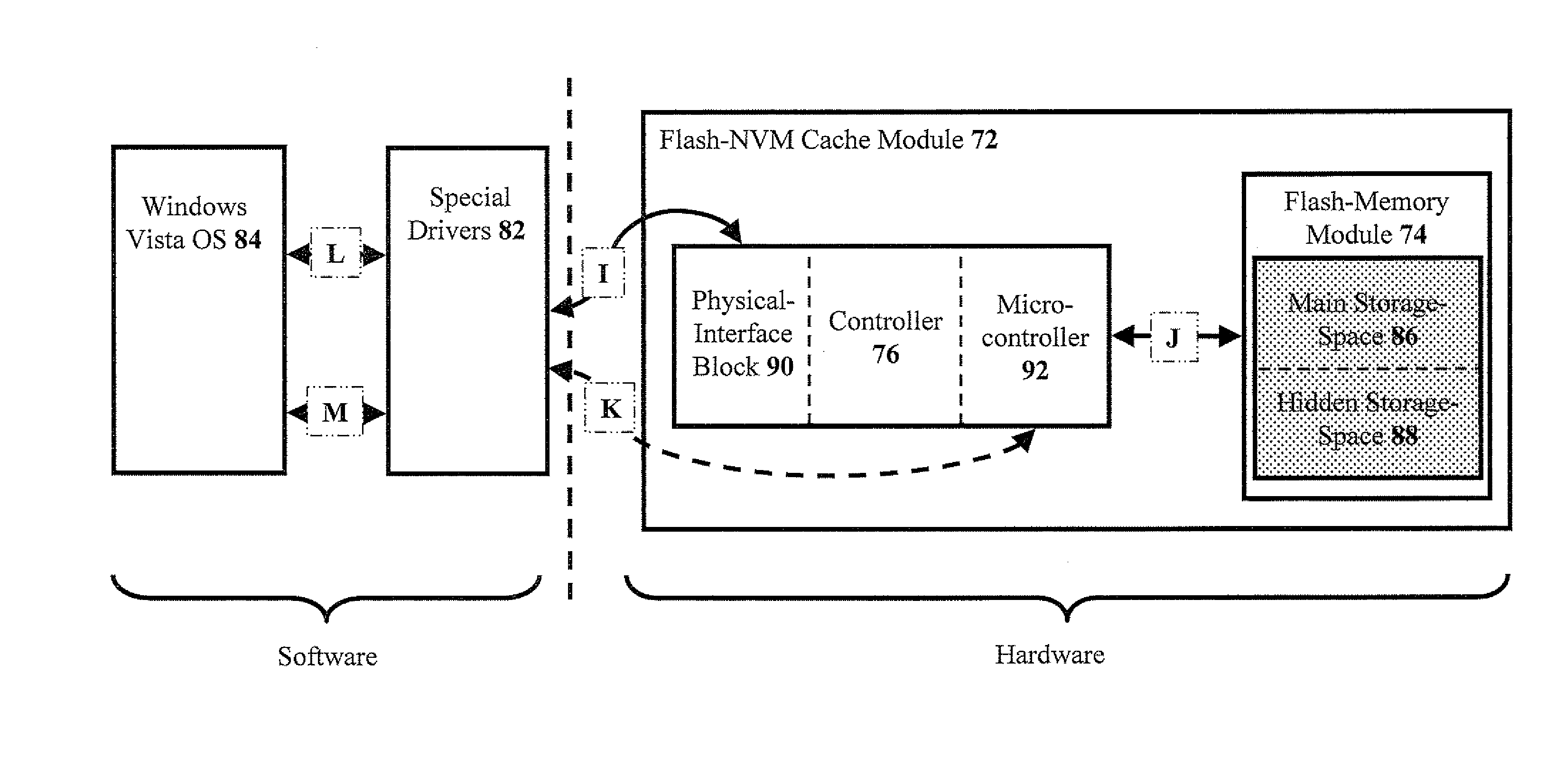

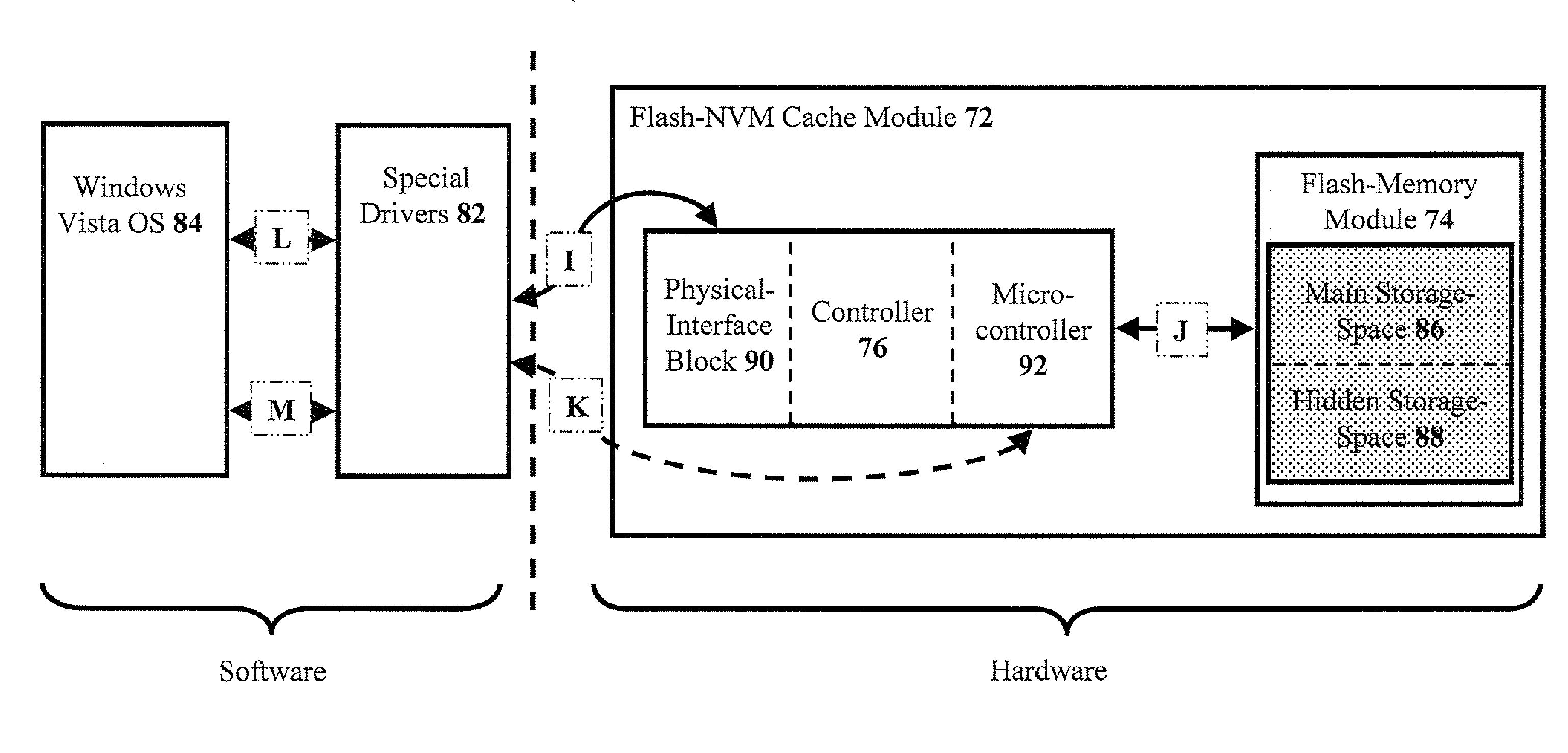

Methods For Supporting Readydrive And Readyboost Accelerators In A Single Flash-Memory Storage Device

InactiveUS20080172519A1Improve performanceLess timeMemory architecture accessing/allocationMemory adressing/allocation/relocationSingle flashOperational system

Methods for enhancing the performance of a host system including the steps of: providing an operating system, running on the host system, that supports a ReadyDrive and ReadyBoost accelerator; and providing a flash-memory storage device, which supports both the accelerators, having a single flash-memory module. Preferably, the method further includes the steps of: monitoring a frequency of write commands by the host system to the device; and upon the frequency exceeding a predefined threshold, suspending operations of the accelerators until the frequency is below the threshold. A repartitioning method for changing a storage-space ratio between a ReadyDrive and ReadyBoost storage-space including the steps of: copying data from the ReadyDrive storage-space in a flash-memory storage device; temporarily storing the data in an HDD; followed by partitioning the flash-memory device to a desired storage-space ratio between the ReadyDrive and ReadyBoost storage-space; and restoring the data from the HDD into the flash-memory device.

Owner:SANDISK IL

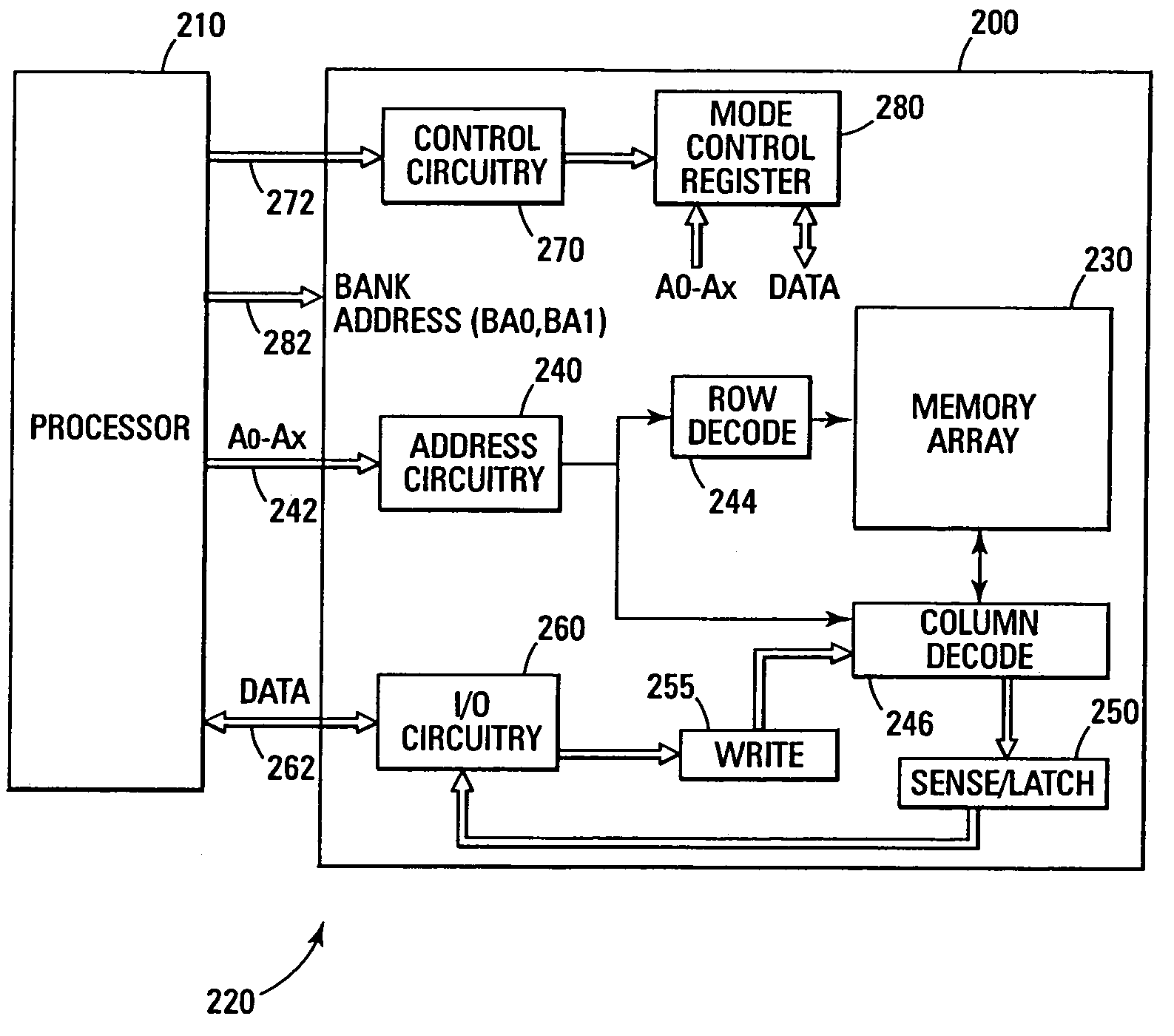

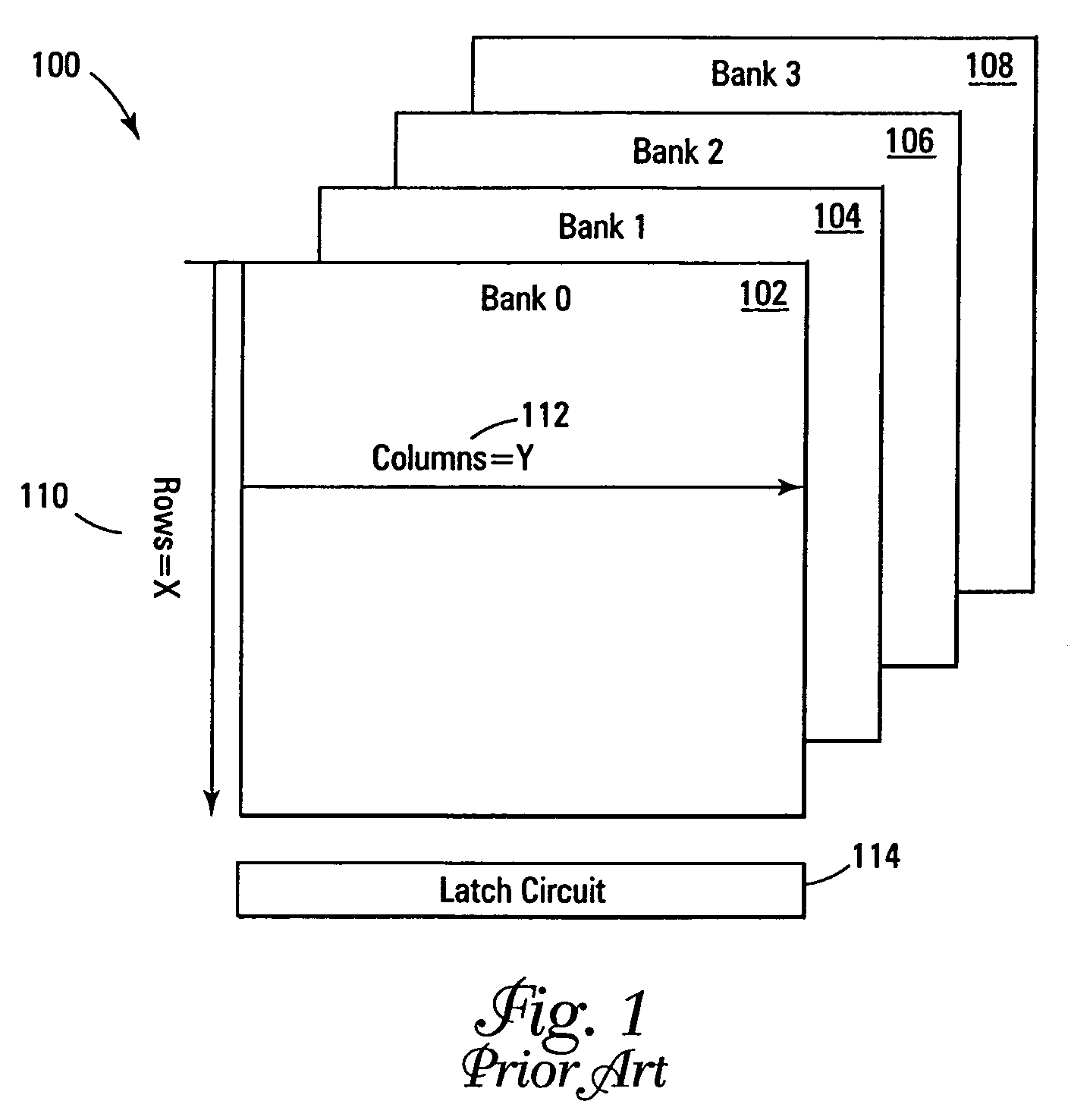

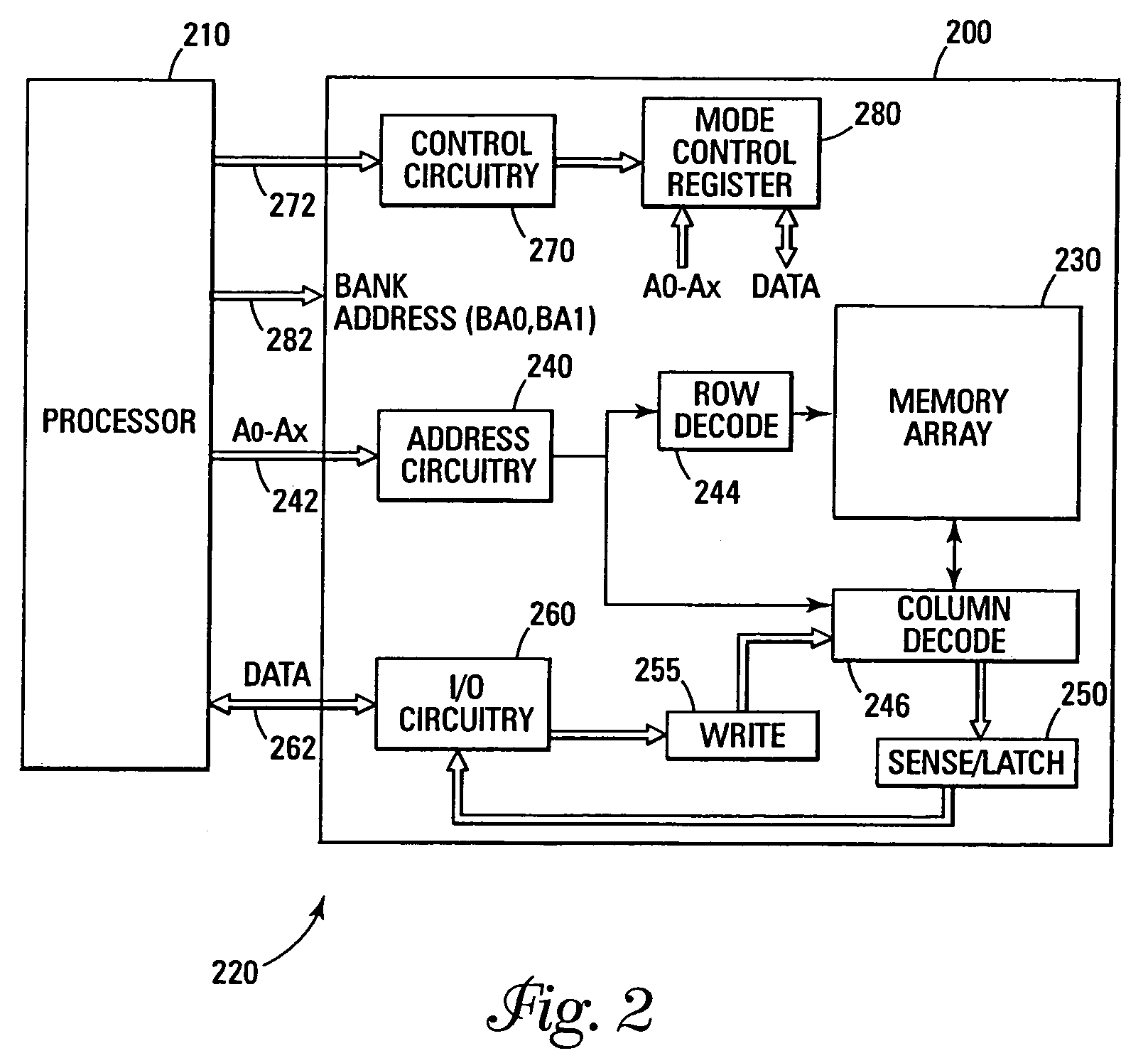

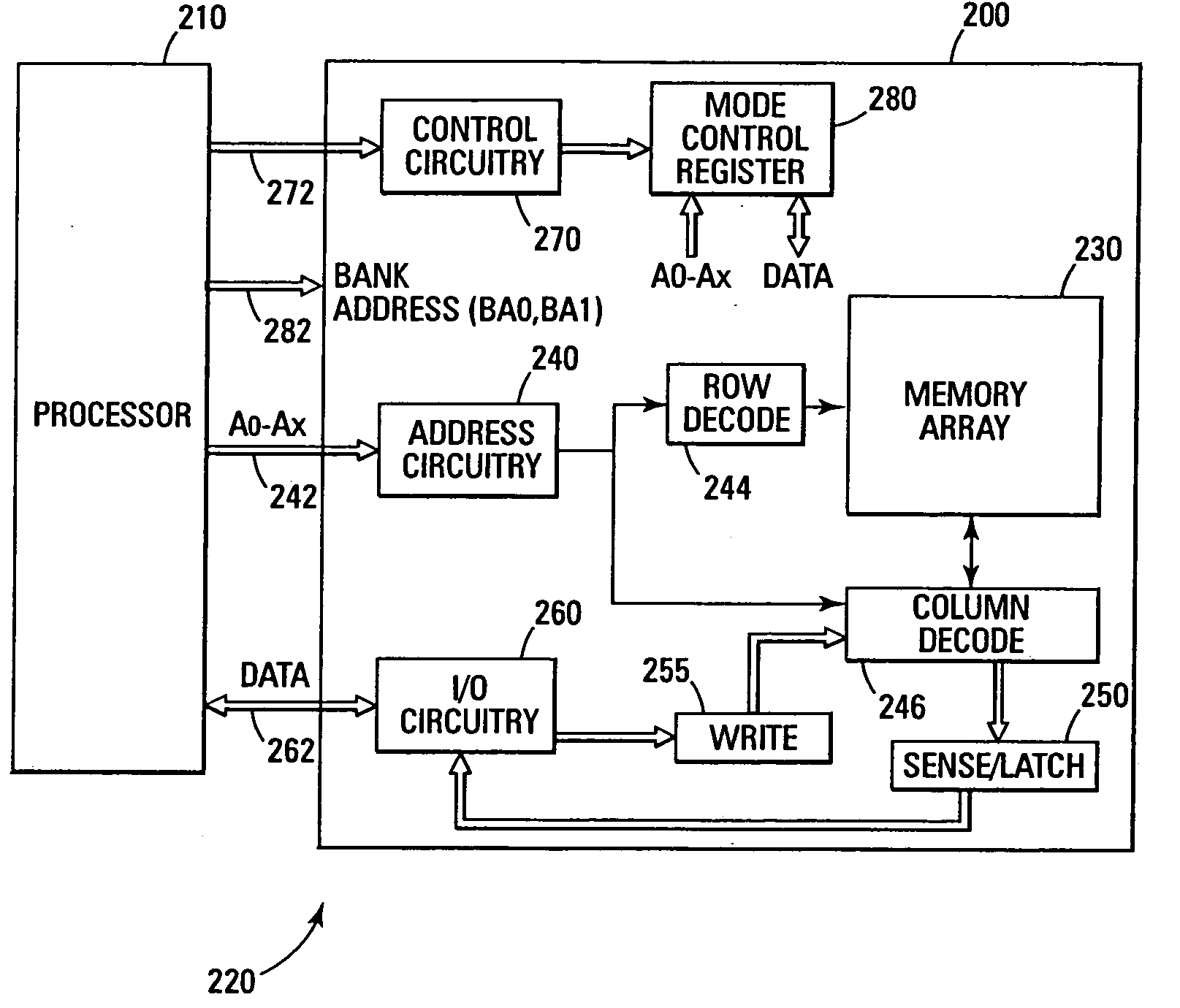

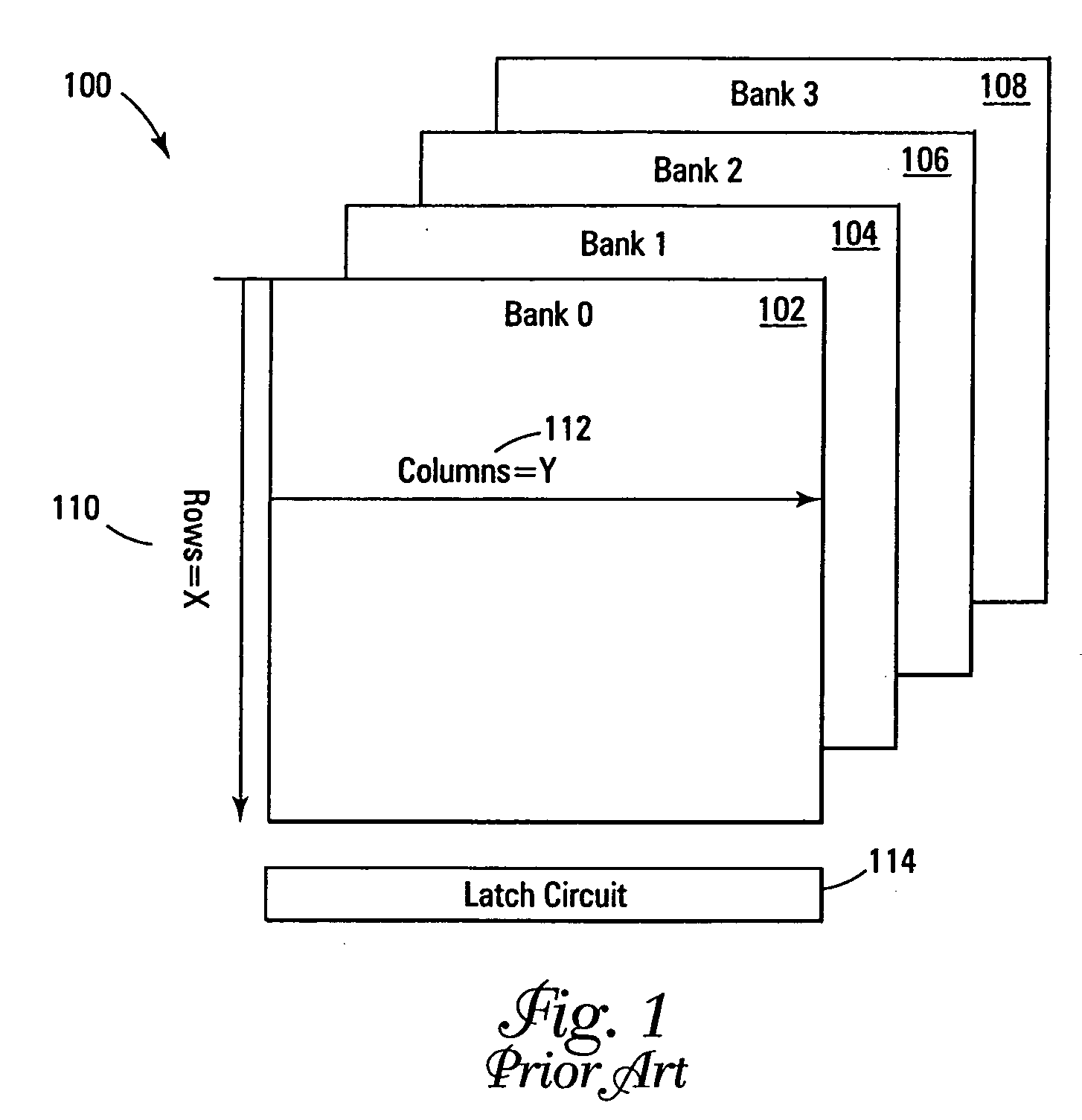

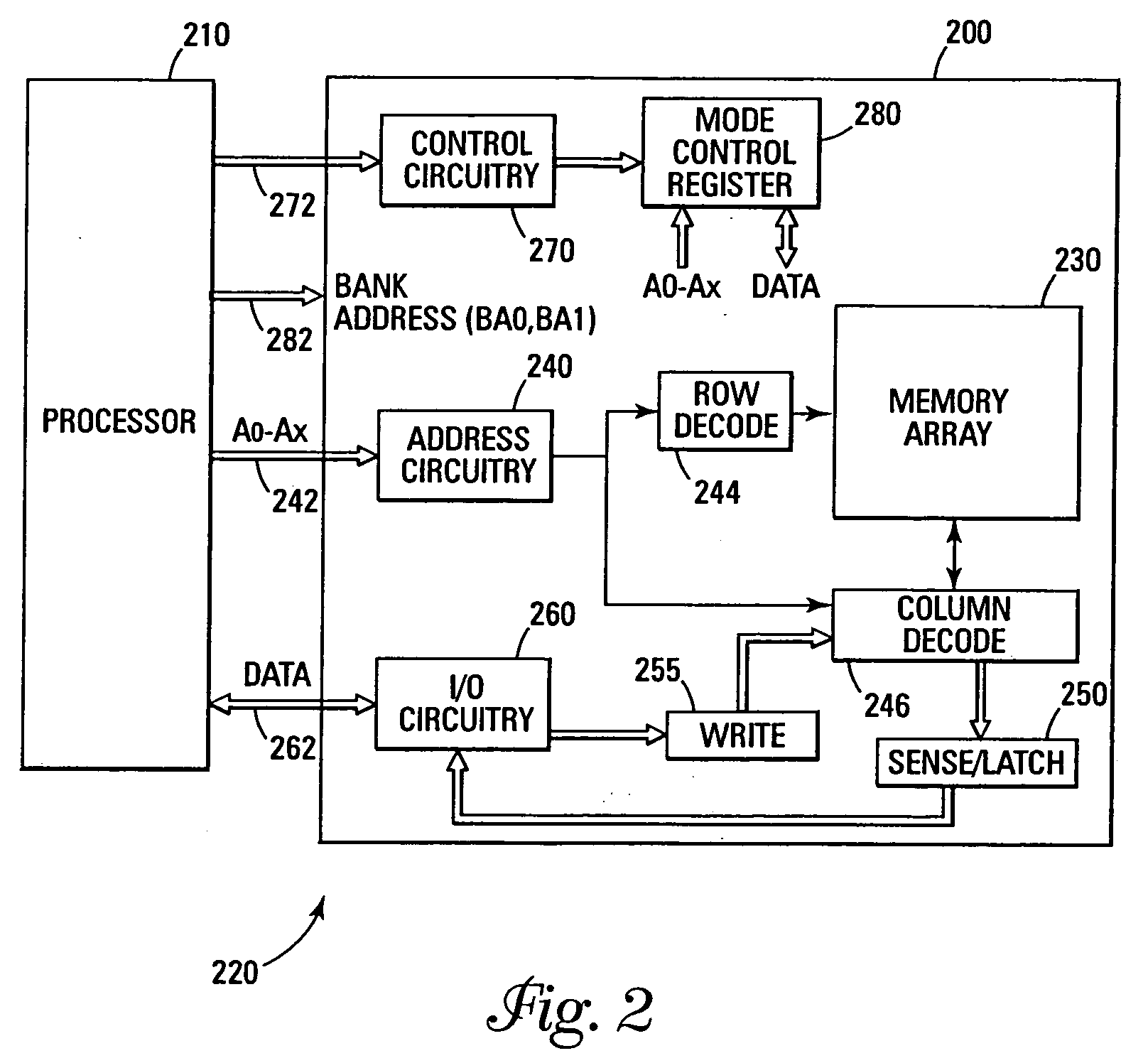

Mode selection in a flash memory device

A single flash memory device has selectable read modes for either a segment mode or a page mode. The desired mode is selected by writing a control word to a mode control register. Selecting the segment mode causes the device to output selected memory segments. Selecting the page mode causes the device to output selected memory pages.

Owner:ROUND ROCK RES LLC

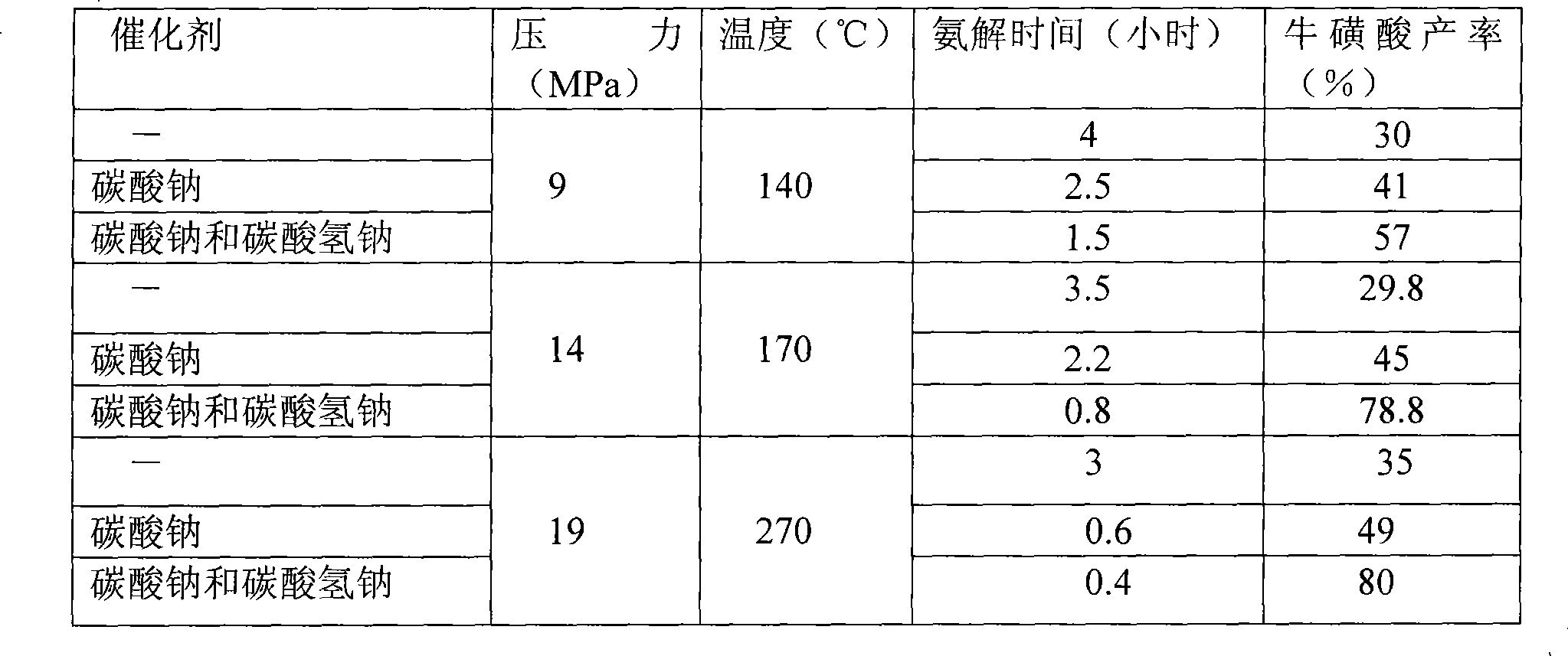

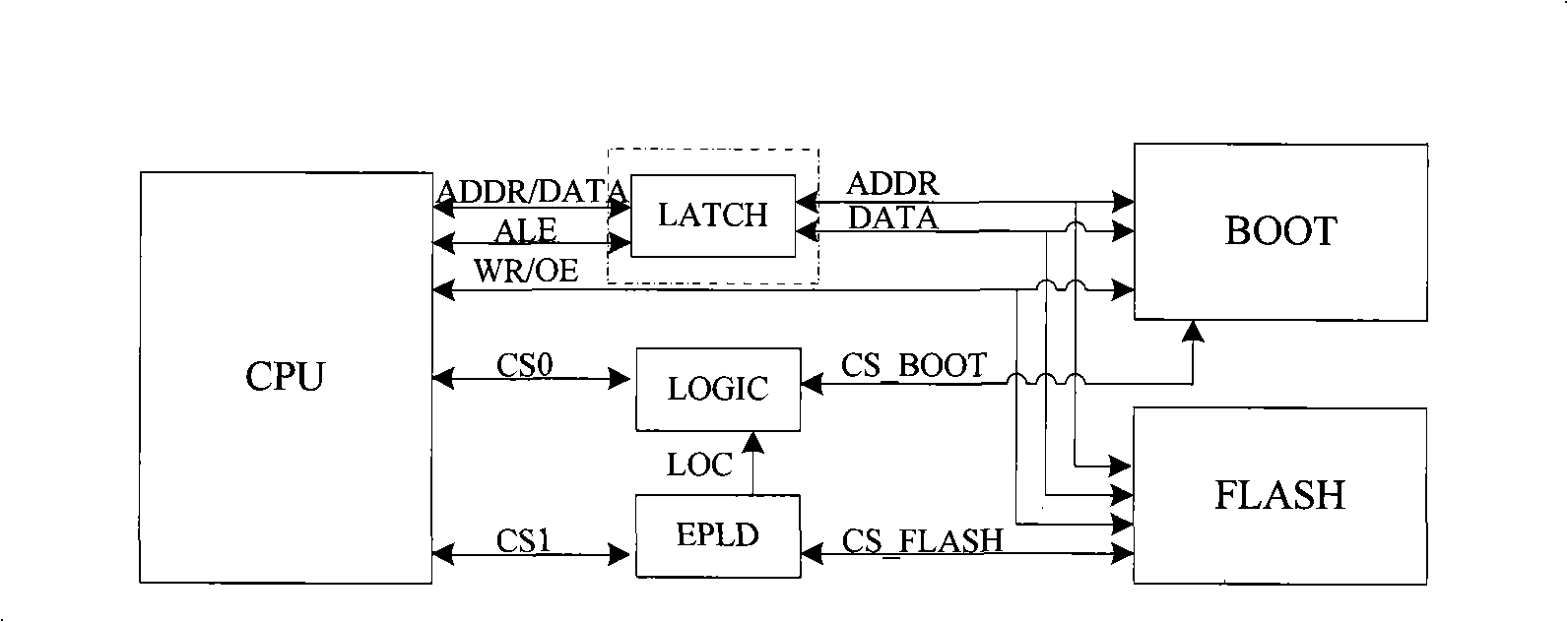

Method and apparatus for starting CPU by BOOT

InactiveCN101329632ASimple hardware structureSimple structureProgram loading/initiatingHardware structureSingle flash

The invention provides a method and a device for starting a CPU by using BOOT, which are used in the fields of telecom and communication. A single FLASH storage medium is adopted in a BOOT start device in the invention; FLASH is divided into at least two BOOT start areas according to different address spaces; when one BOOT start area can not start the CPU normally, other BOOT start areas are adopted to restart the CPU. The method and the device solve the problem that single BOOT can not provide enough guarantees for the accidents in the communication filed, such as the interruption of power supply, etc., and for the reliability of long-distance update, thus increasing long-distance operability and update reliability; in addition, the double BOOT device has simple hardware structure and is also applicable to small single board modules with a strict requirement for the size of space.

Owner:梁英

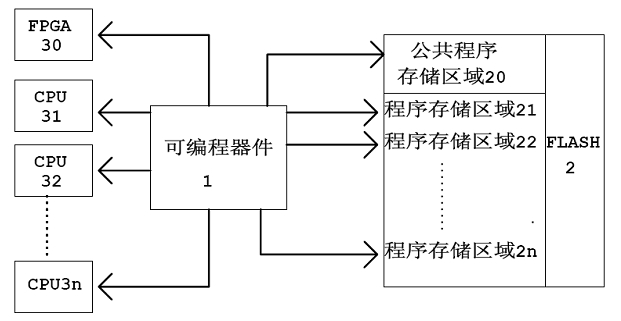

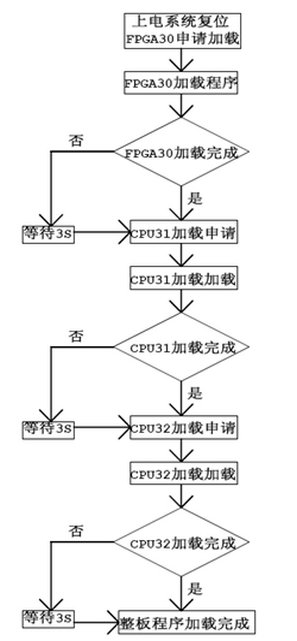

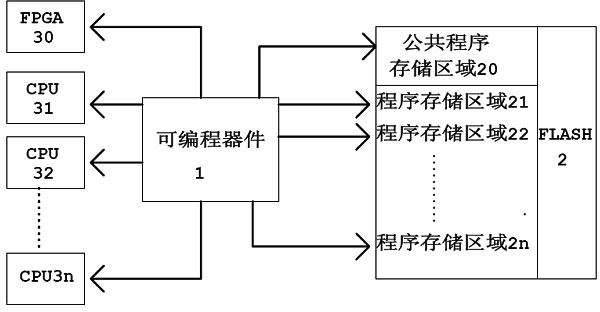

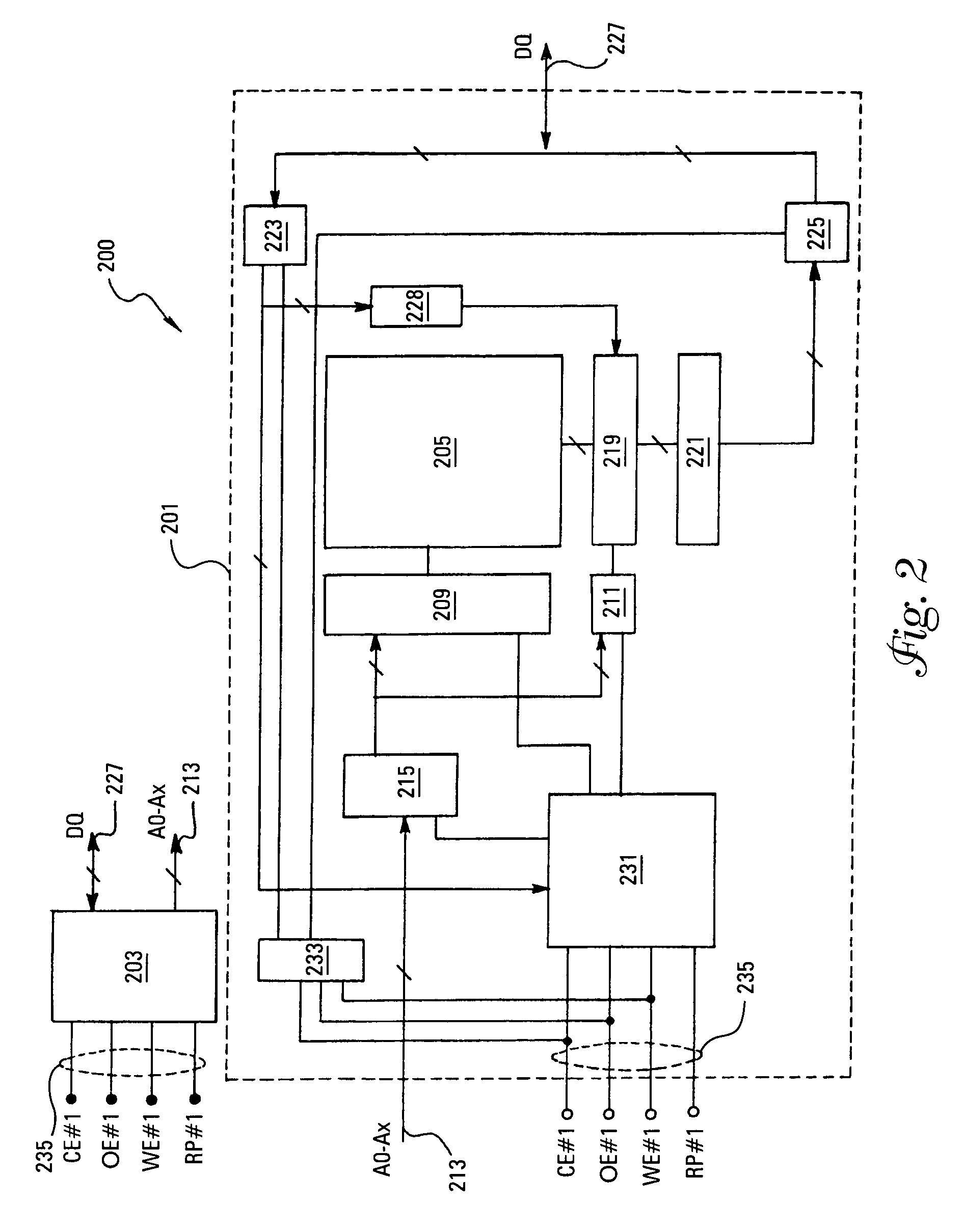

Module for starting multiple user programs by single Flash

InactiveCN102662718AEasy to writeReduce in quantityMultiple digital computer combinationsProgram loading/initiatingSingle flashProgrammable read-only memory

The invention discloses a module for starting multiple user programs by a single Flash. The module is characterized by comprising one programmable device and one FLASH chip connected with the programmable device, wherein multiple user program storage regions and one public program storage region are divided in the FLASH chip, each user program storage region stores one corresponding user program, and the public program storage region stores one corresponding EEPROM (Electrically Erasable Programmable Read-Only Memory) program; the programmable device can accept the access of multiple CPUs (Central Processing Units) and one FPGA (Field Programmable Gate Array) in parallel, thereby realizing that the public program storage region in the FLASH chip corresponds to the FPGA, and each user program storage region respectively corresponds to one CPU; and a bus switching module is designed in the programmable device, and the bus switching module can orderly transmit the user programs in the user program storage regions of the FLASH chip to the corresponding CPUs and transmit the EEPROM program to the corresponding FPGA.

Owner:TIANJIN EMBEDTEC

Systems For Supporting Readydrive And Readyboost Accelerators In A Single Flash-Memory Storage Device

InactiveUS20080172518A1Less timeReduce consumptionMemory architecture accessing/allocationMemory adressing/allocation/relocationSingle flashMemory module

The present invention discloses a flash-memory storage device for implementing both ReadyBoost and ReadyDrive Windows PC accelerators, the device including: a single flash-memory module adapted to be configured as a ReadyBoost accelerator and as a ReadyDrive accelerator; and a controller for controlling the flash-memory module. Preferably, the device further includes: a mechanism for wear-leveling the flash-memory module. Preferably, the device further includes: a mechanism for repartitioning the flash-memory module. Most preferably, the mechanism is configured to erase the flash-memory module. A flash-memory storage device including: a flash-memory module having at least one partition, wherein at least one partition is adapted to be alternatively reversibly configured as a ReadyBoost accelerator and as a ReadyDrive accelerator; and a controller for controlling the flash-memory module. Preferably, the device further includes: a mechanism for wear-leveling the flash-memory module.

Owner:SANDISK IL LTD

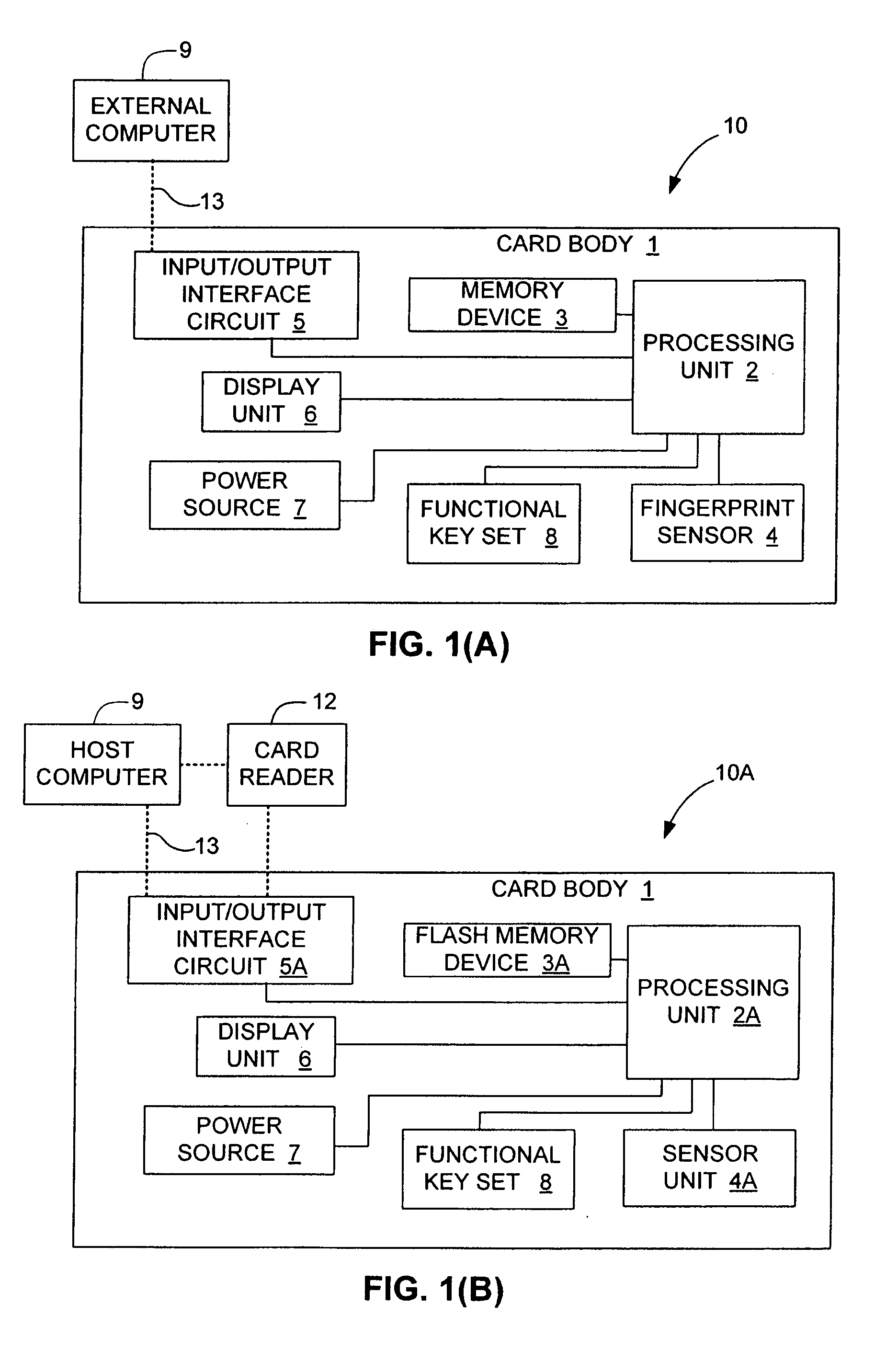

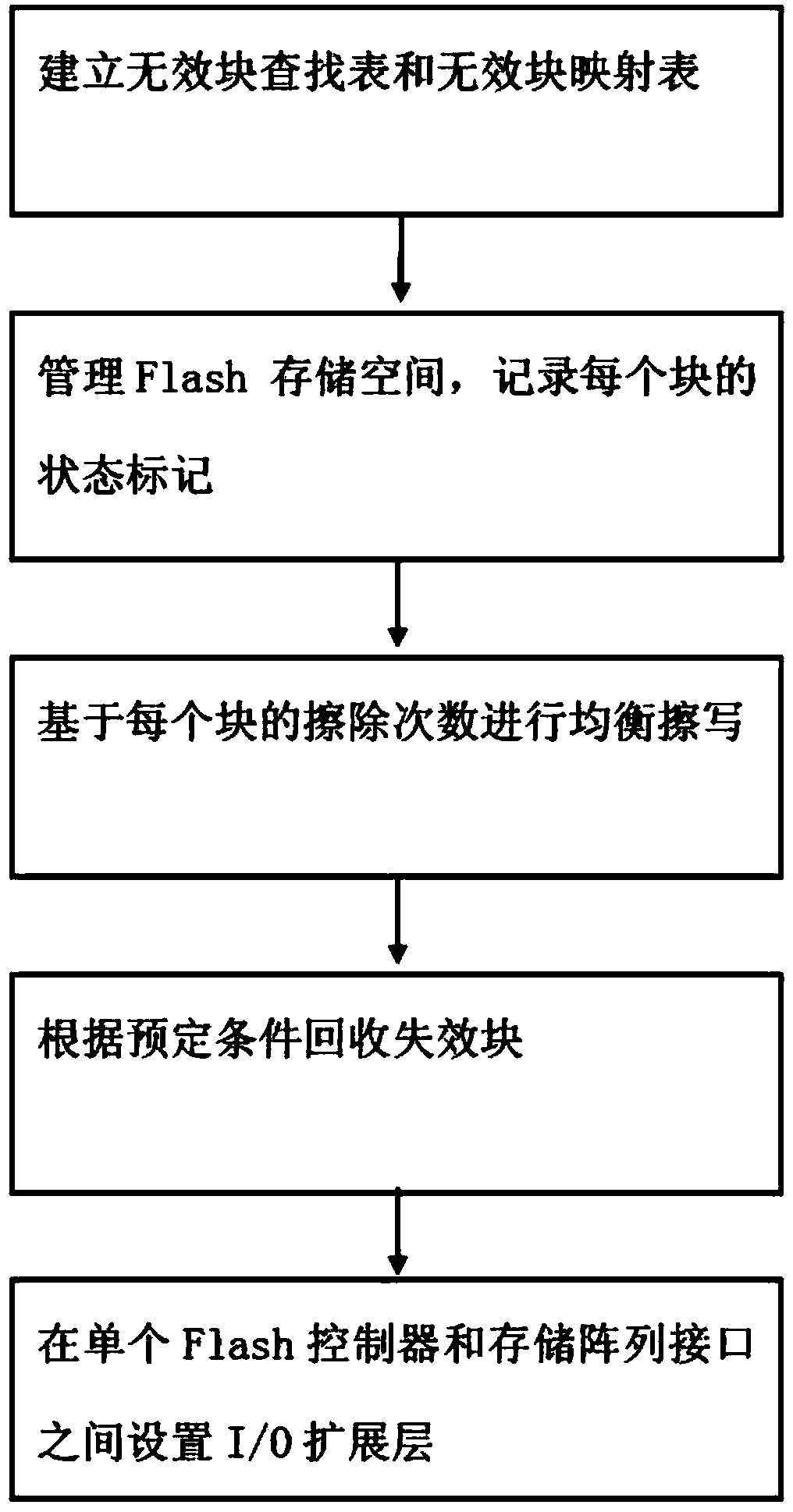

Data access method of electronic equipment

ActiveCN104063186AGuaranteed Erase and Write BalanceExtended service lifeInput/output to record carriersMemory adressing/allocation/relocationSingle flashAccess method

The invention provides a data access method of electronic equipment, and the data access method is used for reading, writing and erasing data in a Flash memory of embedded equipment. The method comprises the following steps: establishing an invalid block look-up table and an invalid block mapping table, managing a Flash memory space, recording the state mark of each block, performing balanced erasing based on the erasing frequency of each block, recovering invalid blocks according to preset conditions, arranging an I / O (Input / Output) expansion layer between a single Flash controller and a memory array interface, and reading and writing multiple pieces of Flash. The data access method can be used for improving data storage management in an embedded system and further improving the storage efficiency and reliability.

Owner:CHENGDU WANWEI TUXIN INFORMATION TECH

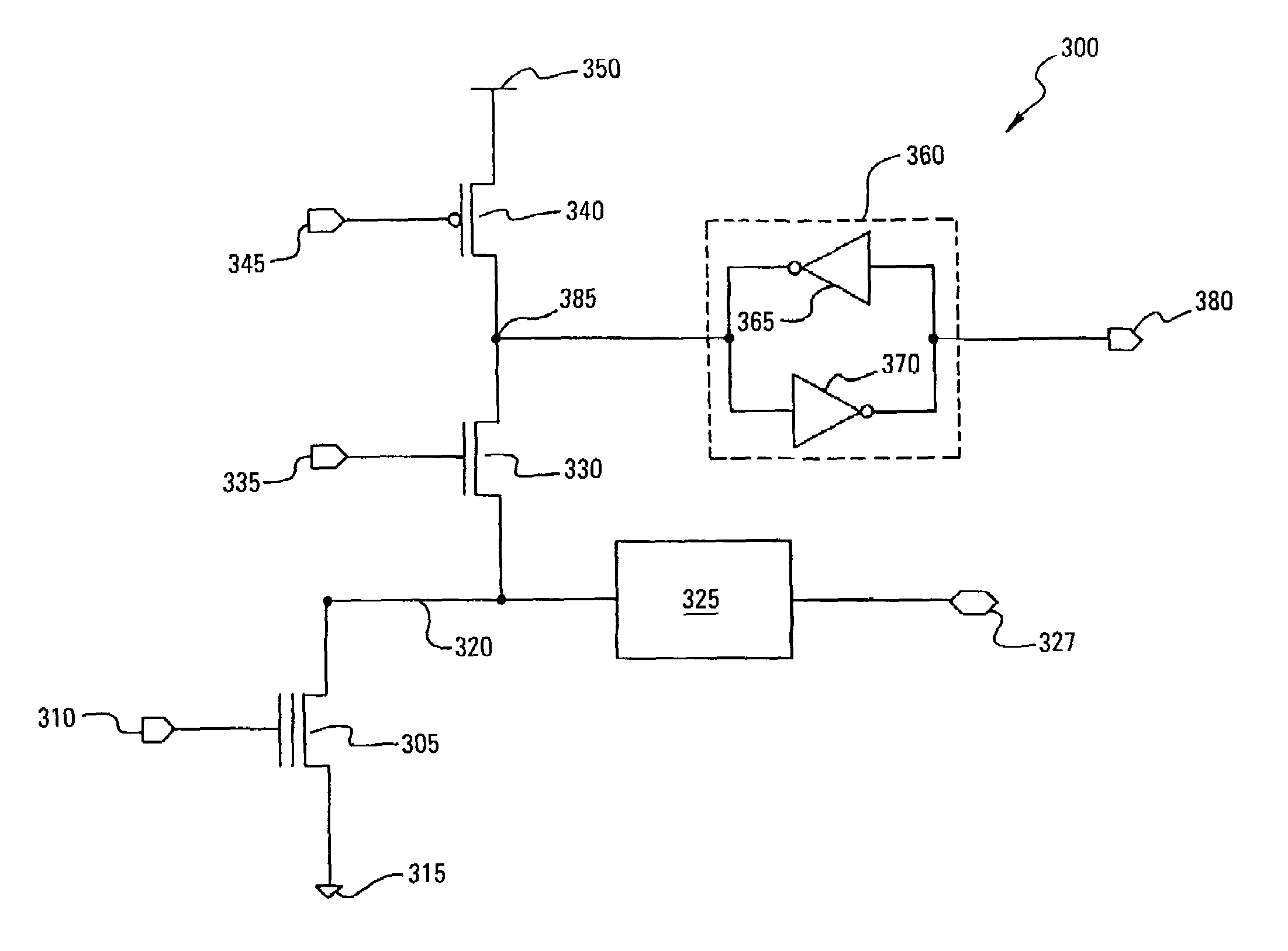

Flash cell fuse circuit

InactiveUS7002828B2Easy to useEasy to manufactureRead-only memoriesDigital storageSingle flashComputer architecture

Fuse circuits based on a single flash cell or floating-gate memory cell are adapted for use in memory devices, particularly in low-voltage, flash memory applications. The fuse circuits include a floating-gate memory cell for storing a data value and a fuse latch to hold and transfer the data value of the floating-gate memory cell at power-up or upon request. A latch driver circuit can write data values to the fuse latch without affecting the data value stored in the floating-gate memory cell. The fuse circuits can further utilize the same structure, pitch, bit-line organization and word-line organization as the memory device's memory array. As the fuse circuits can utilize the same structure and organization, the data value of the fuse circuit can be programmed, erased and read using the same data path as the regular memory array.

Owner:MICRON TECH INC

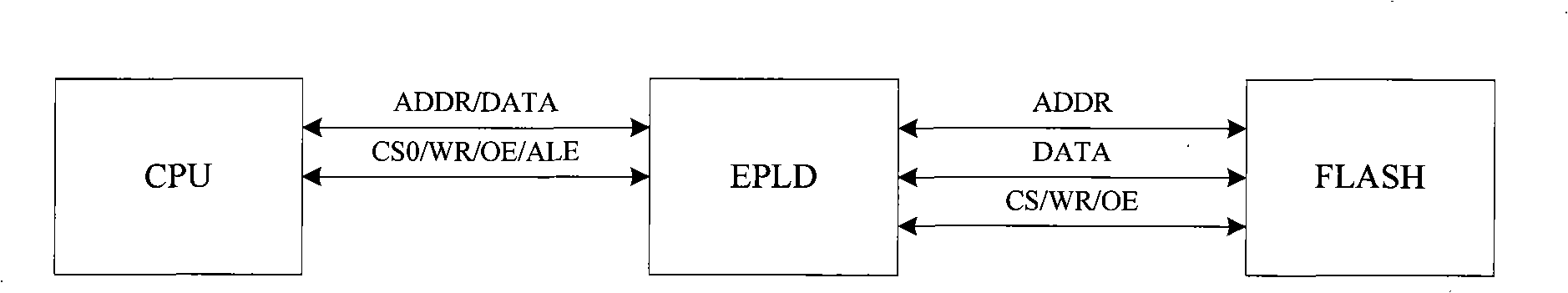

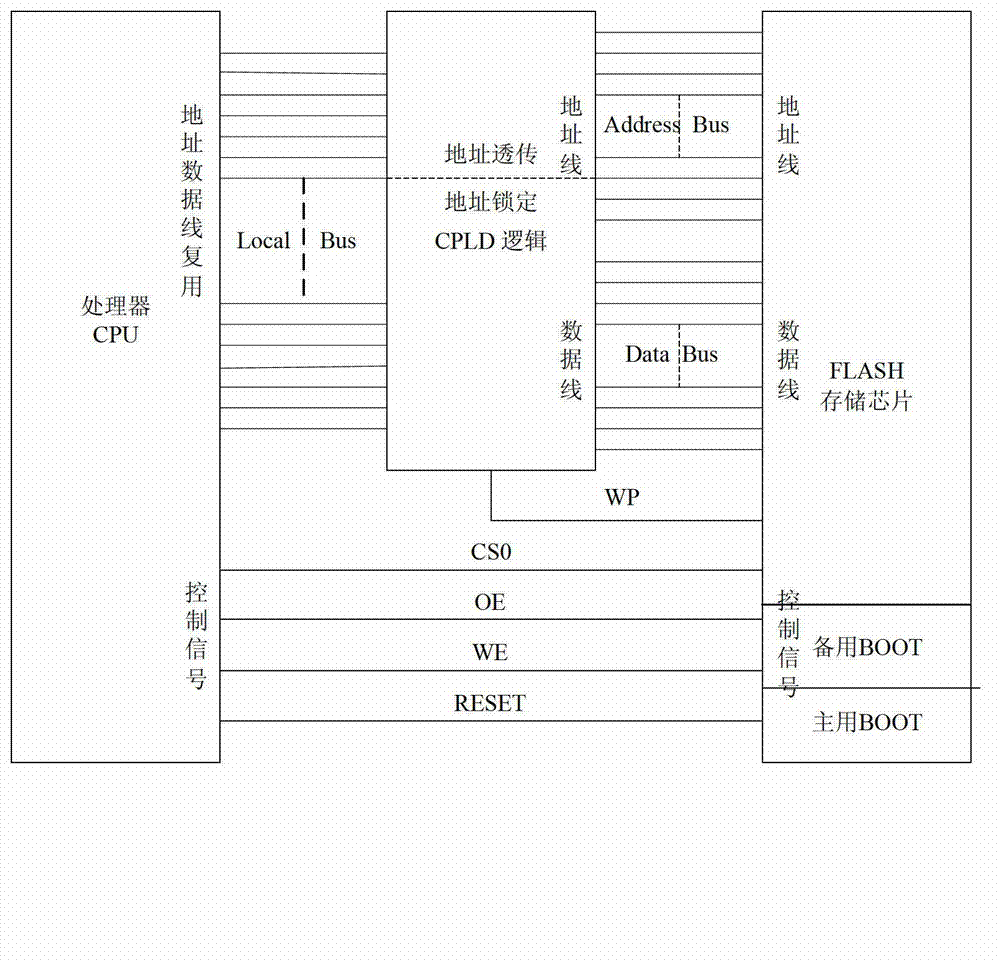

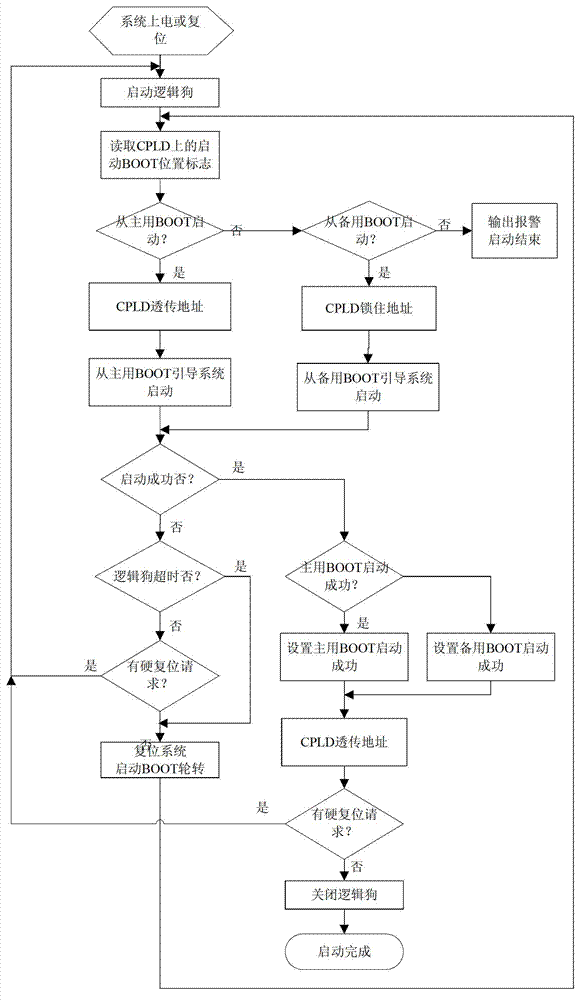

Double-booting method based on single FLASH storage chip

InactiveCN103116511AImprove reliabilityLow costProgram loading/initiatingSingle flashProcessor register

The invention discloses a double-booting method based on a single FLASH storage chip. The double-booting method based on the single FLASH storage chip includes the following steps: a master BOOT and a backup BOOT are respectively stored on different positions of the storage chip, and an address wire of a central processing unit (CPU) is connected with an address wire of the storage chip through a complex programmable logic device (CPLD) logic module; a successful booting marker register is arranged on the CPLD logic module, and a corresponding setting is carried out by the successful booting marker register according to whether booting of the master BOOT or the backup BOOT is successful; round robin of the master BOOT and the backup BOOT is carried out by the CPLD logic module according to the state of the successful booting marker register, if booting is carried out by the master BOOT, address information of the CPU is transferred to the storage chip, and system booting is guided from the master BOOT; if booting is carried out by the backup BOOT, the corresponding address wire is locked according to the position of a backup BOOT program in a storer, and the system booting is guided from the backup BOOT. According to the double-booting method based on the single FLASH storage chip, a double-booting function is achieved by adopting only one storage chip, and the problems that a double-FLASH is high in cost, large in size and high in system energy consumption are solved.

Owner:FENGHUO COMM SCI & TECH CO LTD

Control of a flash unit in a digital camera

ActiveUS7129983B2Quality improvementMinimize the numberTelevision system detailsTelevision system scanning detailsSingle flashElectronic shutter

The invention is based on a method for controlling a flash unit in connection with a digital image sensor without a mechanical shutter, wherein the exposure of the image sensor is performed in sub-areas, such as pixel rows or columns, or in another order, by using a rolling electronic shutter or the like. Thus, the exposure of said sub-areas of the image sensor takes place at least partly at different times. According to the invention, during the time of exposure of one image, i.e. substantially all the sub-areas of the image sensor, several discrete, successive flashes of the flash unit are used to achieve even exposure of the image area, which the flashes are timed in such a way that each single flash is triggered at a point of time which is common to the integration or exposure time of as many successive sub-areas of the image sensor as possible. According to the invention, the successive light flashes are also timed in such a way that one and only one flash of the flash unit occurs during the integration or exposure time of each single sub-area. By the present invention, the significant advantage is attained that the invention minimizes the number of light flashes required for one image while it also secures that each sub-area of the sensor to be exposed at a different time is illuminated as evenly as possible.

Owner:NOKIA TECHNOLOGLES OY

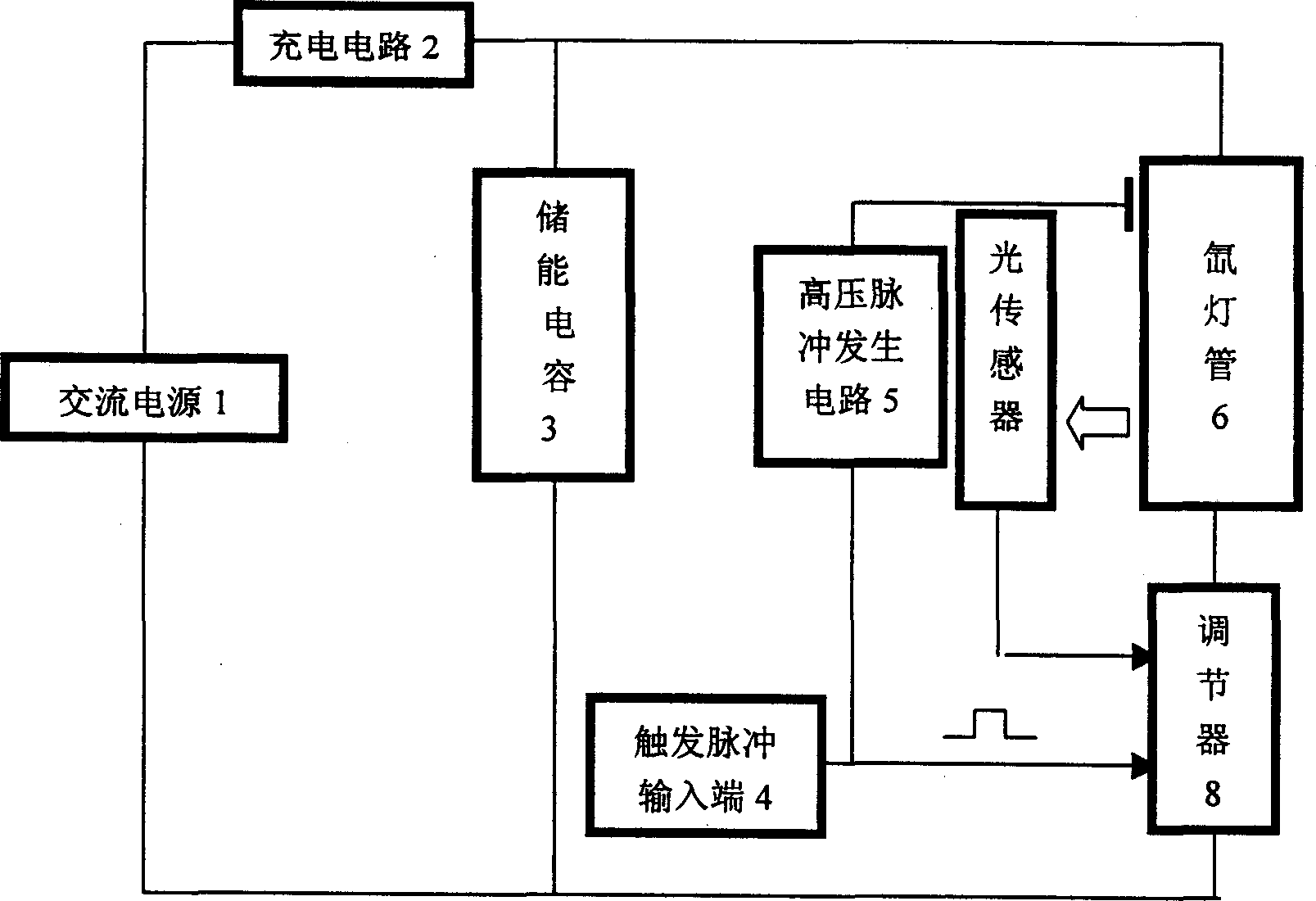

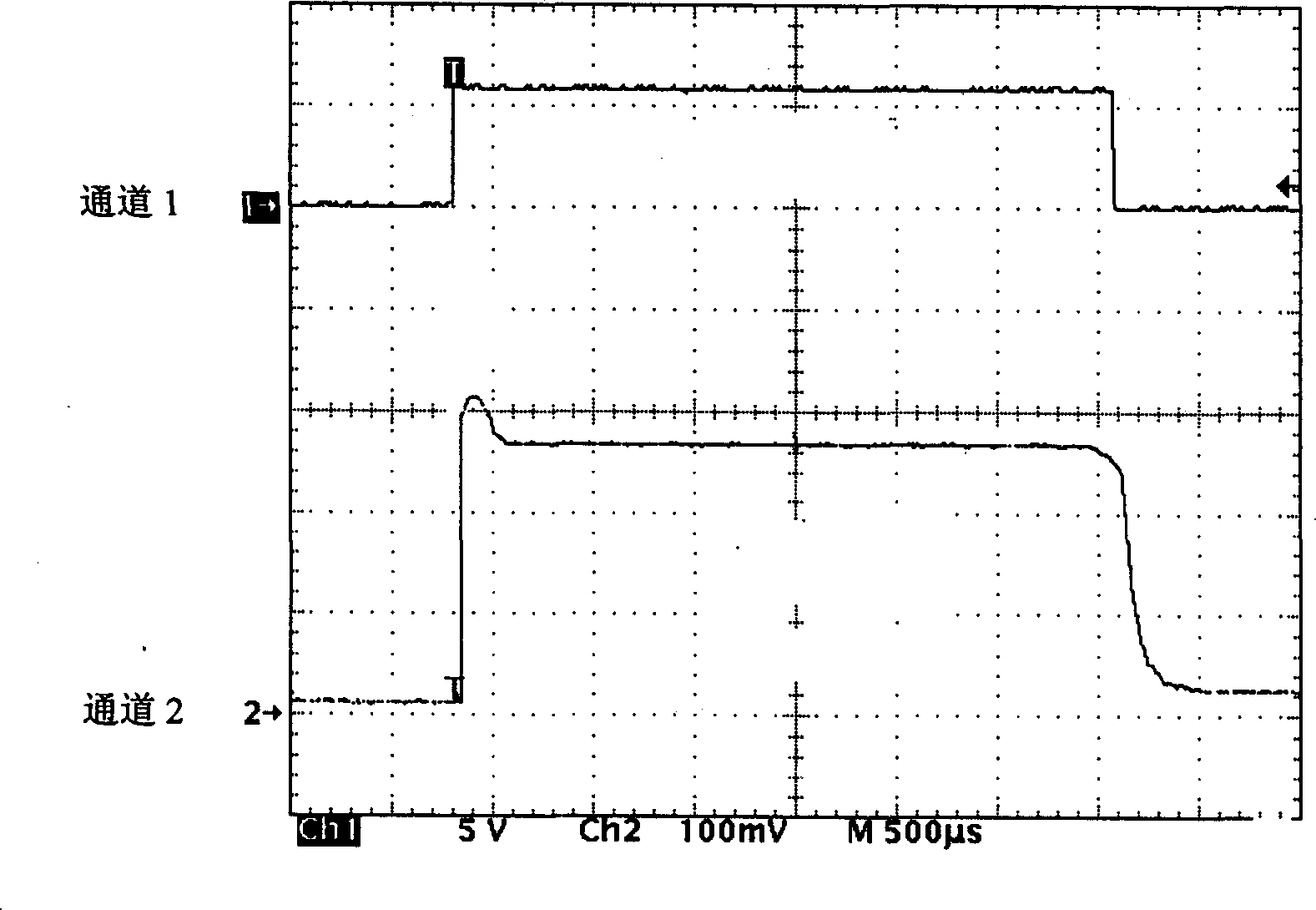

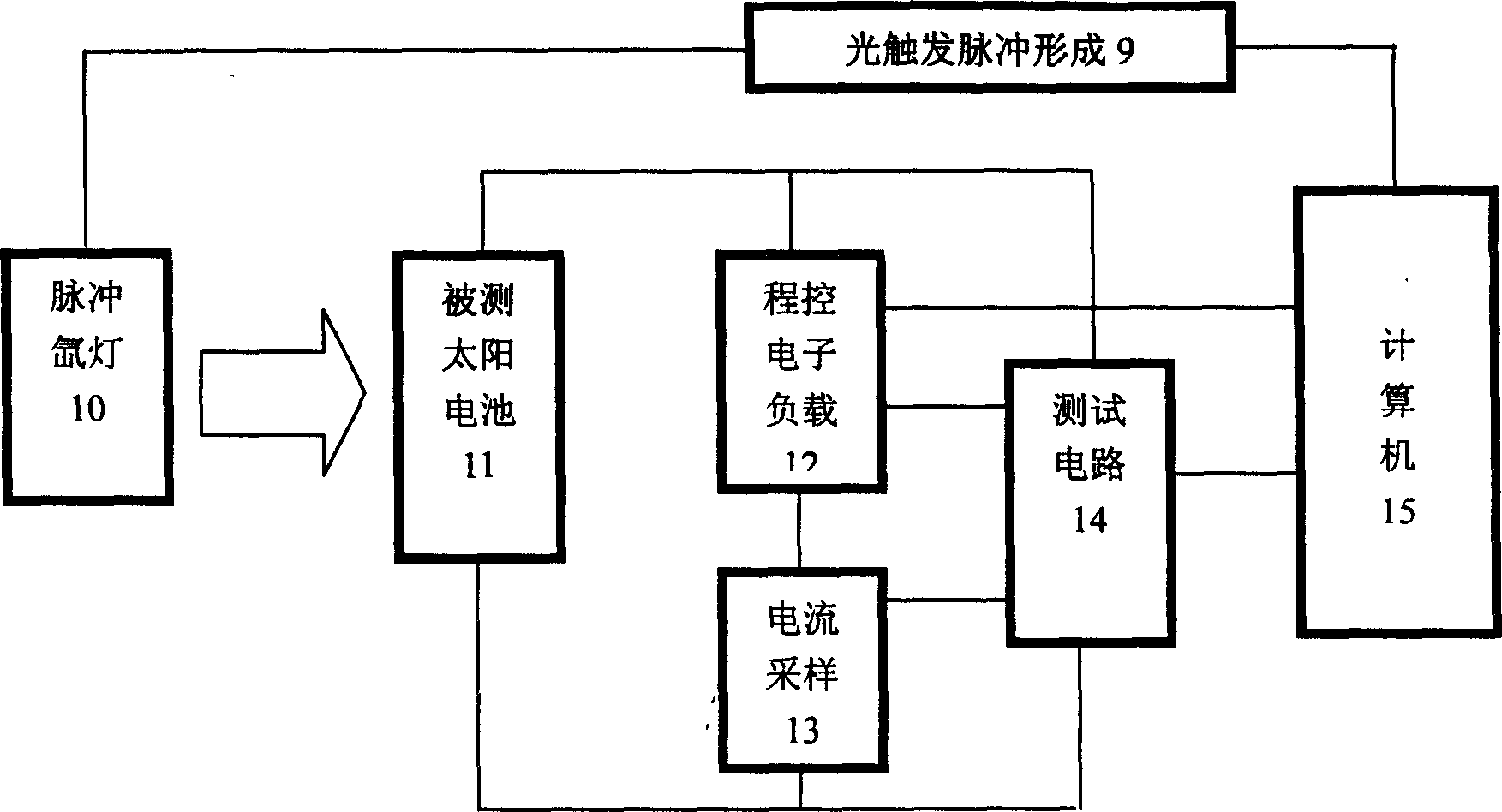

Constant pulsed light xenon lamp solar cell testing method

InactiveCN1456899AQuick testSimple structurePhotovoltaic monitoringPhotovoltaic energy generationSingle flashAutomatic control

A testing method utilizes light feedback and automatic control technique to modify camera used flash light or similar ones to be impulse xenon lamp with constant light strength in addition to conventional program-controlled electron load, testing circuit and computer. The light impulse with several milliseconds of constant light strength can be obtained at each flash of the light source and I-V curve data collection of solar energy battery can be finished by computer-controlled testing circuit within the period of single flash and to finalize test of solar battery electric parameter in several seconds. The method also can be used to test solar battery component as well as can be utilized to manufacture the testing device for both of one-body solar battery and solar battery component.

Owner:XI AN JIAOTONG UNIV

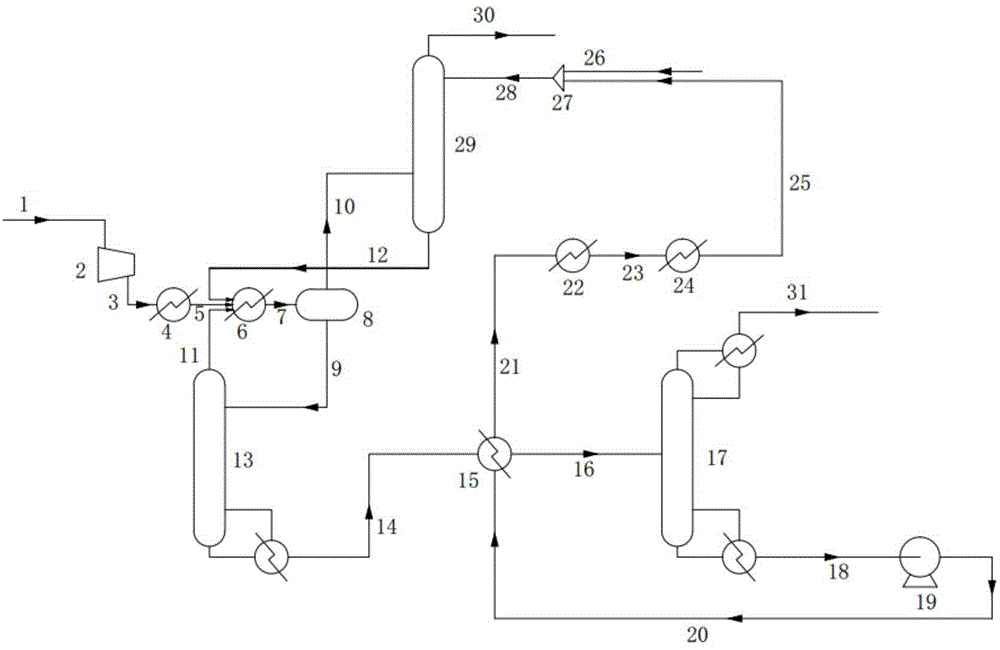

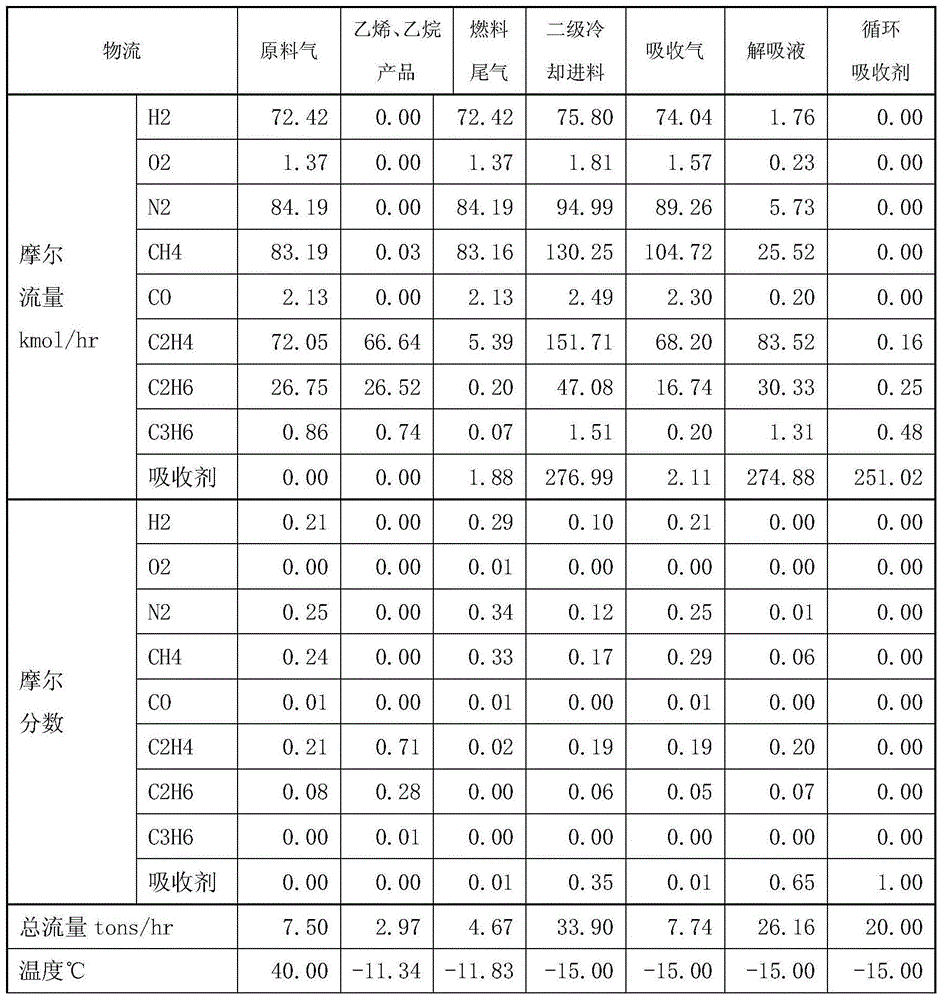

Three-tower device and method for recycling ethylene and ethane from dry gas through oil absorption

InactiveCN104892340AAdaptableAbsorption is flexibleDistillation purification/separationEthylene productionSingle flashGas phase

The invention relates to a three-tower device and method for recycling ethylene and ethane from dry gas through oil absorption. The method comprises the following steps: pressurizing and cooling the dry gas through a compressor, mixing the dry gas with rich liquid from an absorption tower and desorbed gas from a desorption tower, enabling the mixture to enter a heat exchanger for cooling so as to enable the temperature of the mixture to reach absorbent temperature; enabling the mixture to enter a flash drum for single flash, and enabling a gas phase used as a gas phase feeding material of the absorption tower to enter from the tower bottom; enabling a liquid phase used as a feeding material of the desorption tower to enter from the tower top; refining products at the bottom of the desorption tower through a rectifying tower so as to obtain the products of ethylene and ethane; enabling the products at the bottom of the rectifying tower to be supplemented and cooled, and then returned to the rectifying tower top to be used as an absorbent. An intercondenser is arranged in the absorption tower, so that heat generated can be absorbed timely. According to the invention, the contents of methane and other light components are adjusted through the desorption tower, the content of the methane is 0.05% lower than that of the ethylene and polymer grade ethylene can be obtained directly from an ethylene tower. The method provided by the invention is suitable for separating and recycling C2 component from catalytic cracking dry gas and has the high potential of replacing a deep-cooling method.

Owner:TIANJIN UNIV

Mode selection in a flash memory device

A single flash memory device has selectable read modes for either a segment mode or a page mode. The desired mode is selected by writing a control word to a mode control register. Selecting the segment mode causes the device to output selected memory segments. Selecting the page mode causes the device to output selected memory pages.

Owner:ROUND ROCK RES LLC

Device for desalinating seawater through normal-temperature distillation

InactiveCN102030385AMeet needsReduce manufacturing costGeneral water supply conservationSeawater treatmentSingle flashDistillation

The invention discloses a device for desalinating seawater through normal-temperature distillation, which belongs to a device for desalinating seawater or saline-alkali water by using a desalination method, and comprises a generator, a precipitating and filtering pond, a pretreatment tank, a vapor compressor, a vacuum pump, a seawater preheater, a seawater heater, a submersible pump, a seawater circulation tank, a canned motor pump and a desalination tank. The device disclosed by the invention is characterized in that the device is not provided with a fan. A seawater / freshwater isolator is internally provided with an evaporator, so that the evaporation mode of the device is changed from a single flash evaporation mode into two evaporation modes, namely, a flash evaporation mode and a membrane evaporation mode, the seawater subjected to two times of temperature reduction enters into an evaporator tube to carry out the third temperature reduction, and then enters into a condenser tube to absorb the heats emitted from liquefied vapors outside the condenser tube, which not only saves the cooling water, but also recovers the heats. In the invention, the produced large and medium-sized devices are multi-tank desalination devices which are composite units respectively formed by connecting single tanks in parallel, and the large and medium-sized desalination devices are quick in manufacturing speed and convenient for transportation; and the manufacturing cost of the desalination device is reduced, the energy consumption of the device is reduced, the economic benefit of the device is high, and the concentrated seawater does not pollute the environment.

Owner:张世严

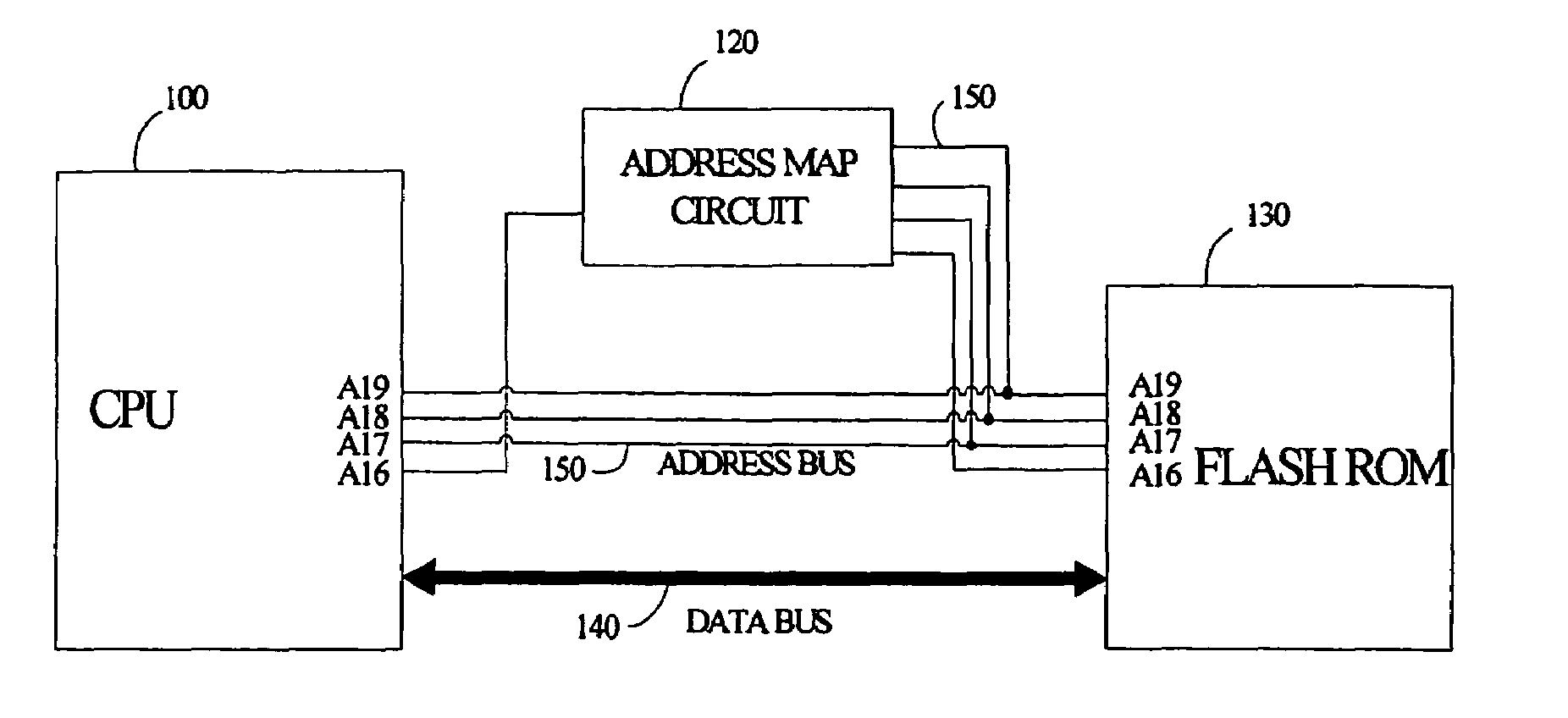

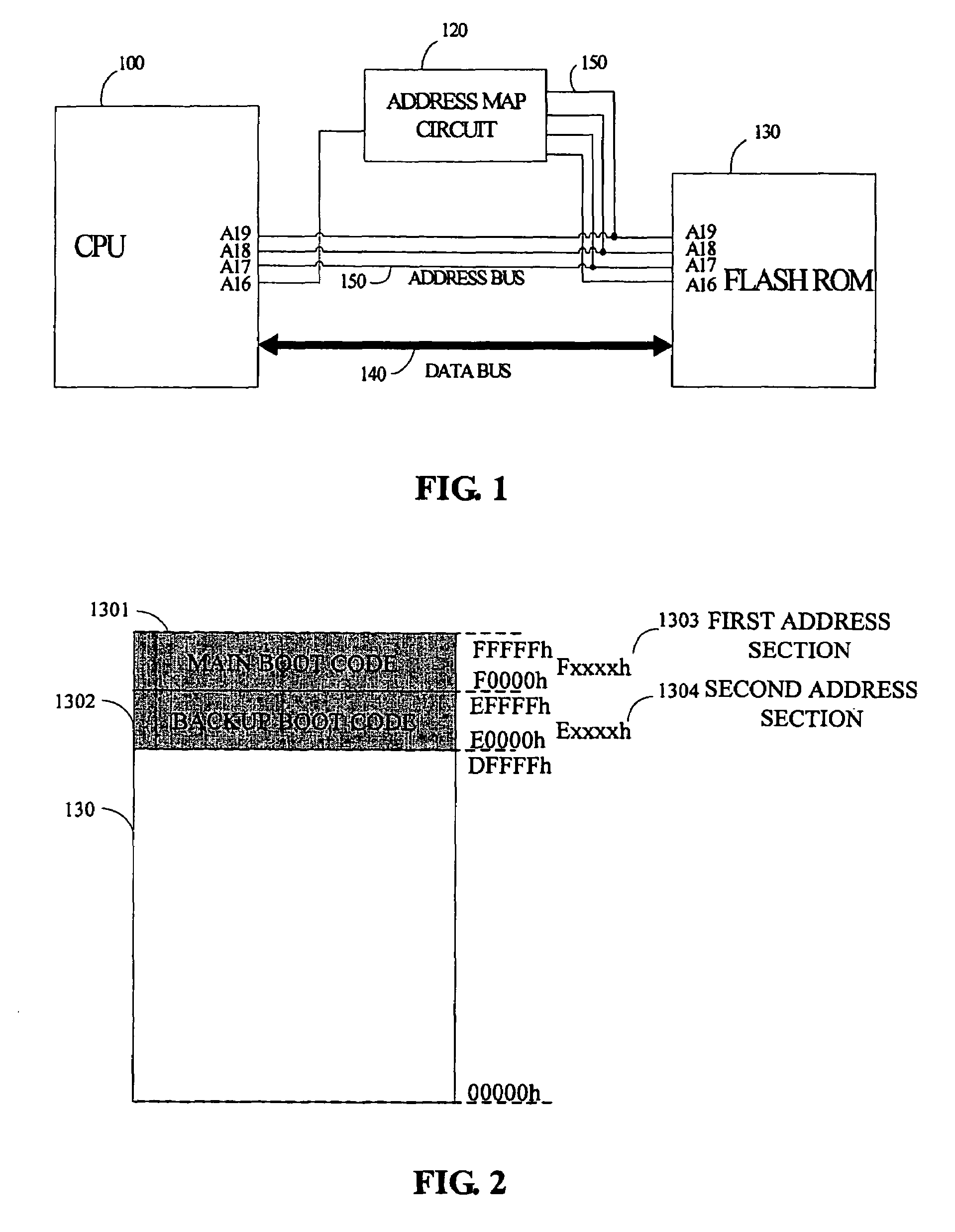

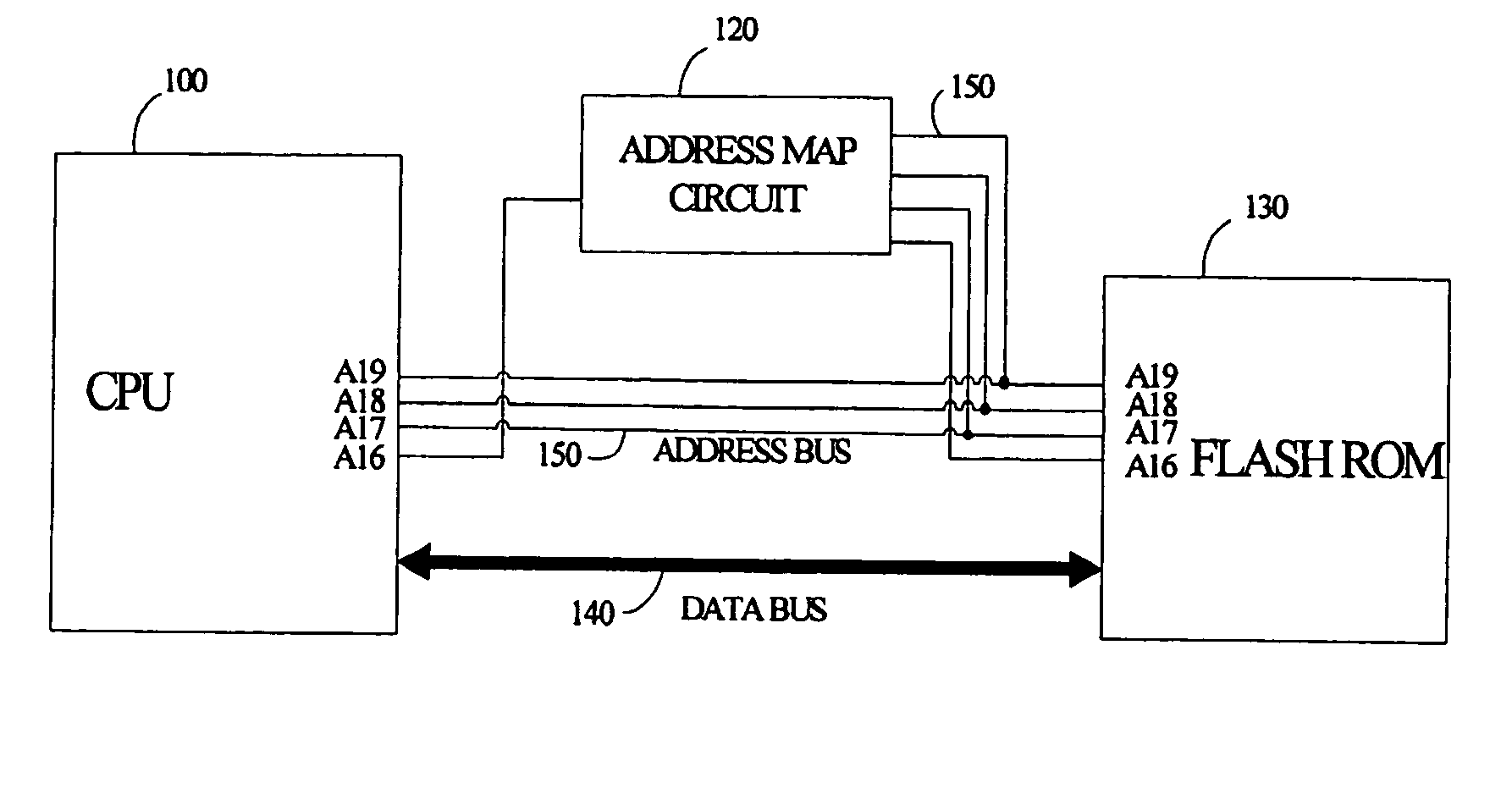

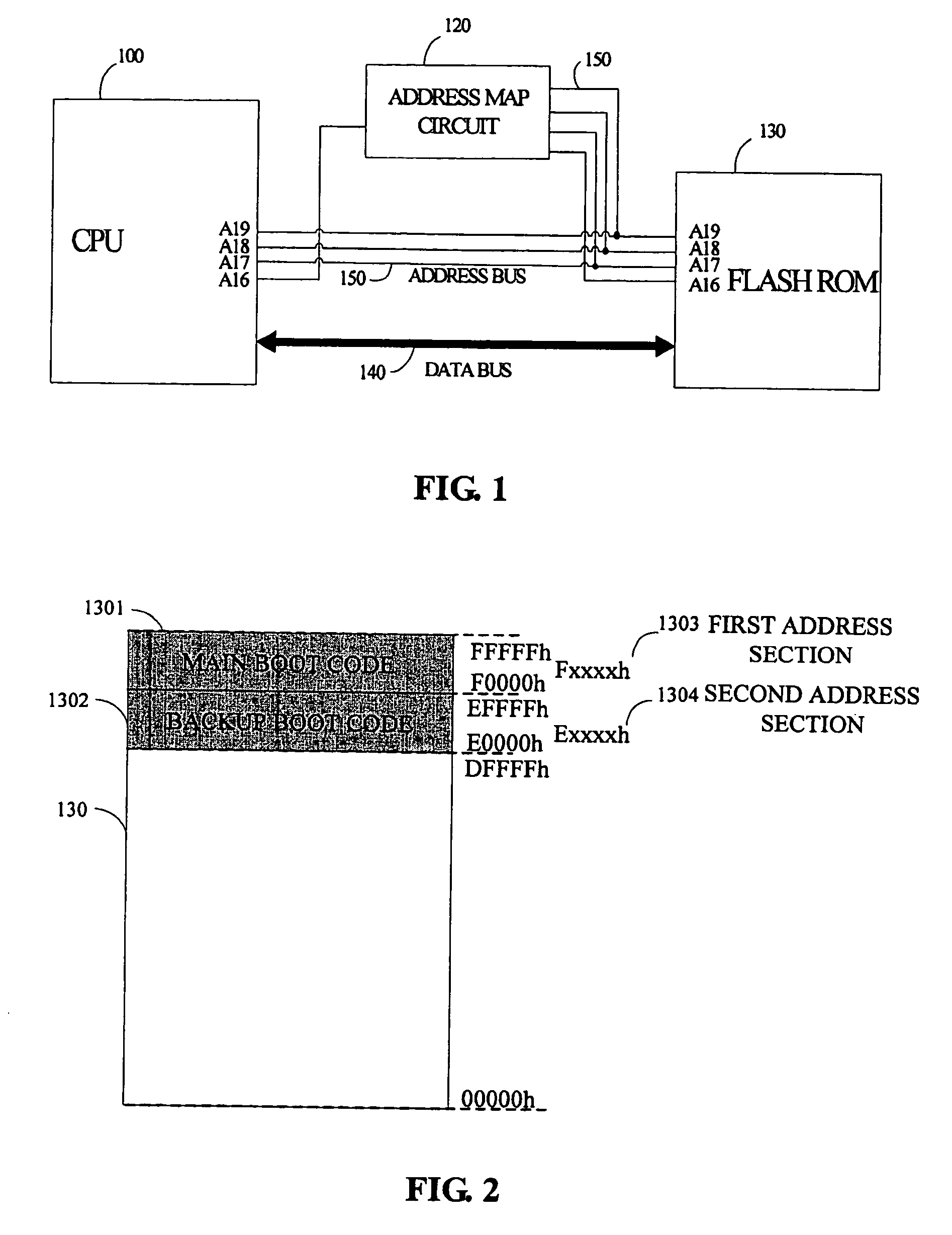

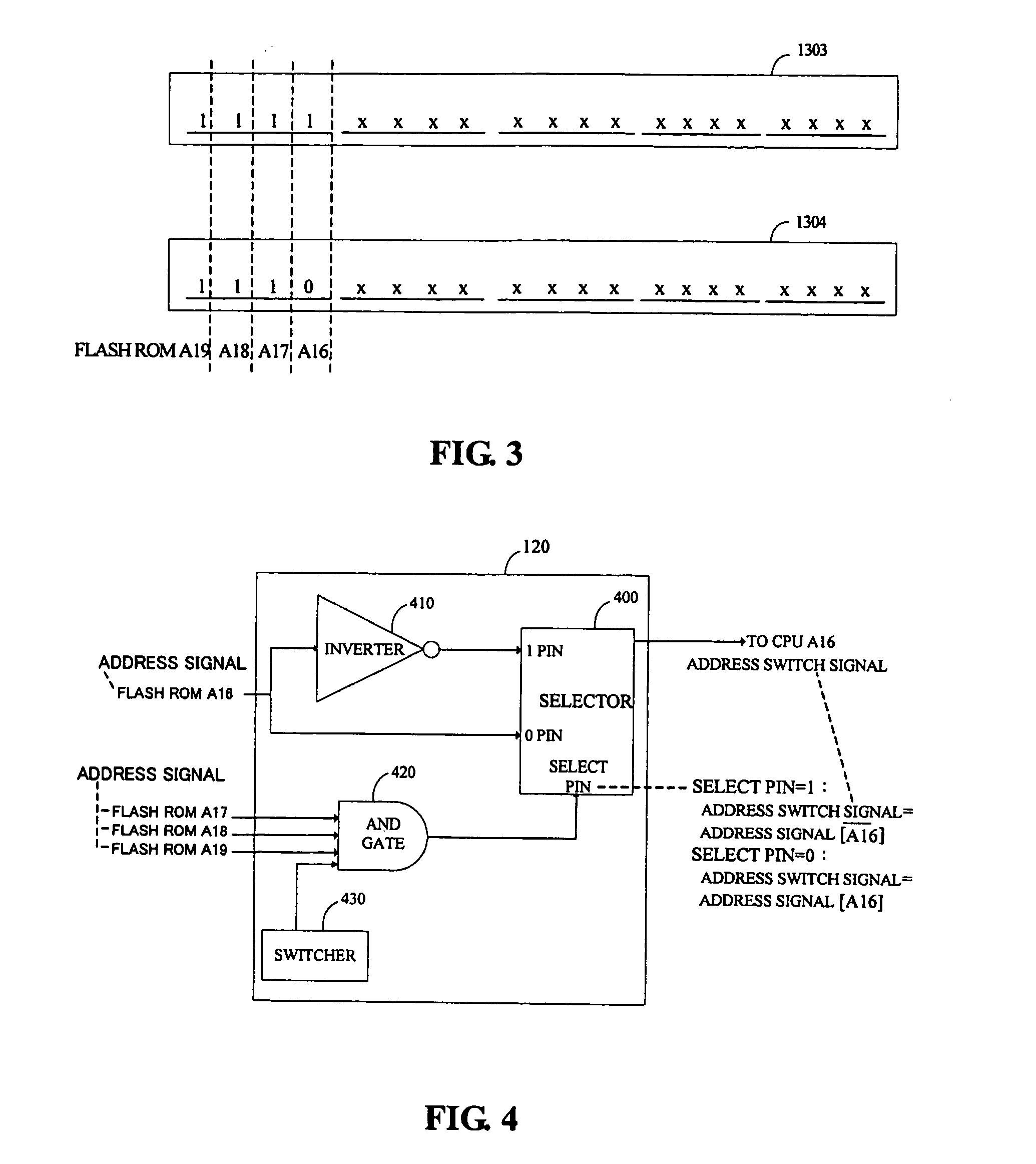

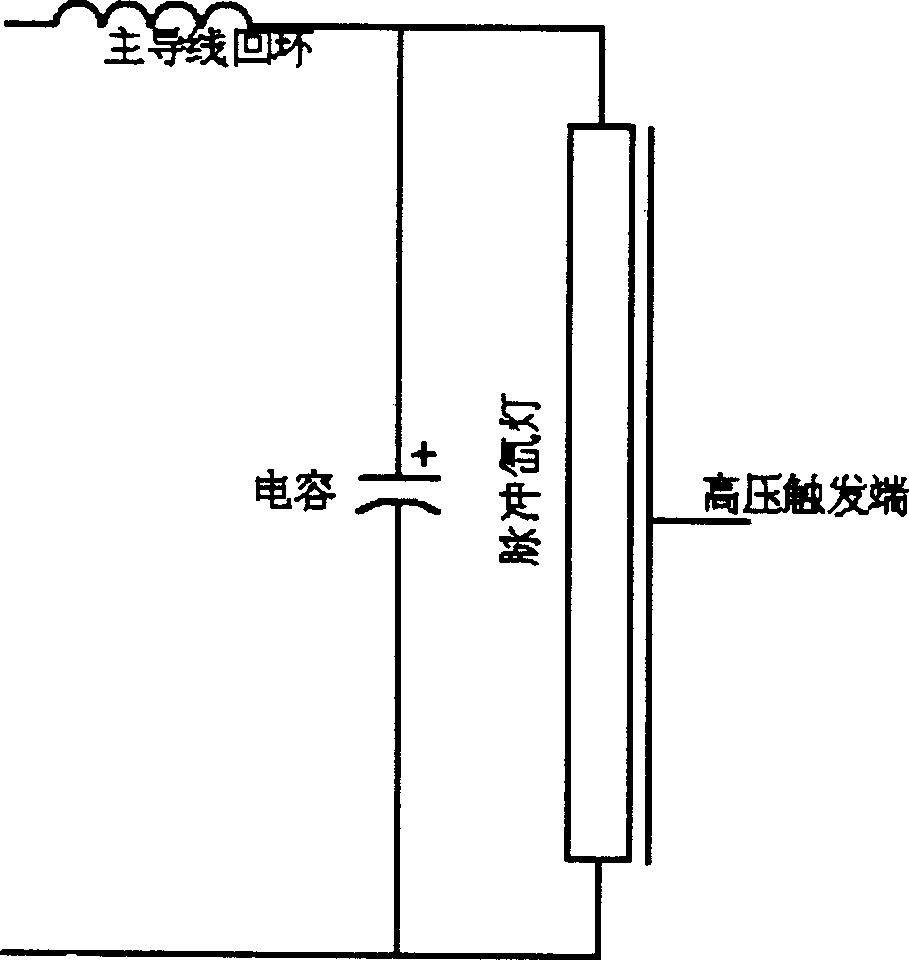

System and method for automatic booting based on single flash ROM

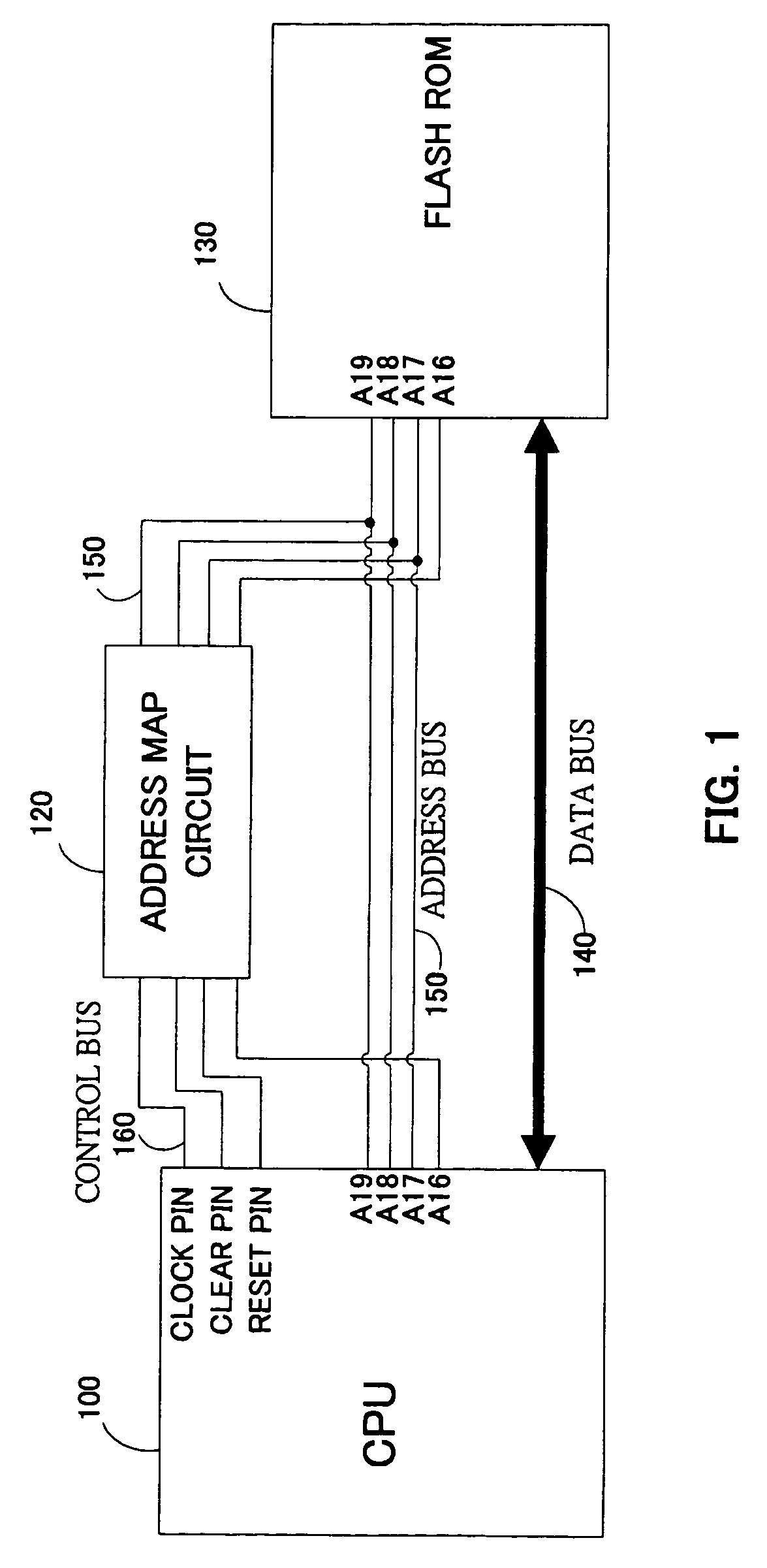

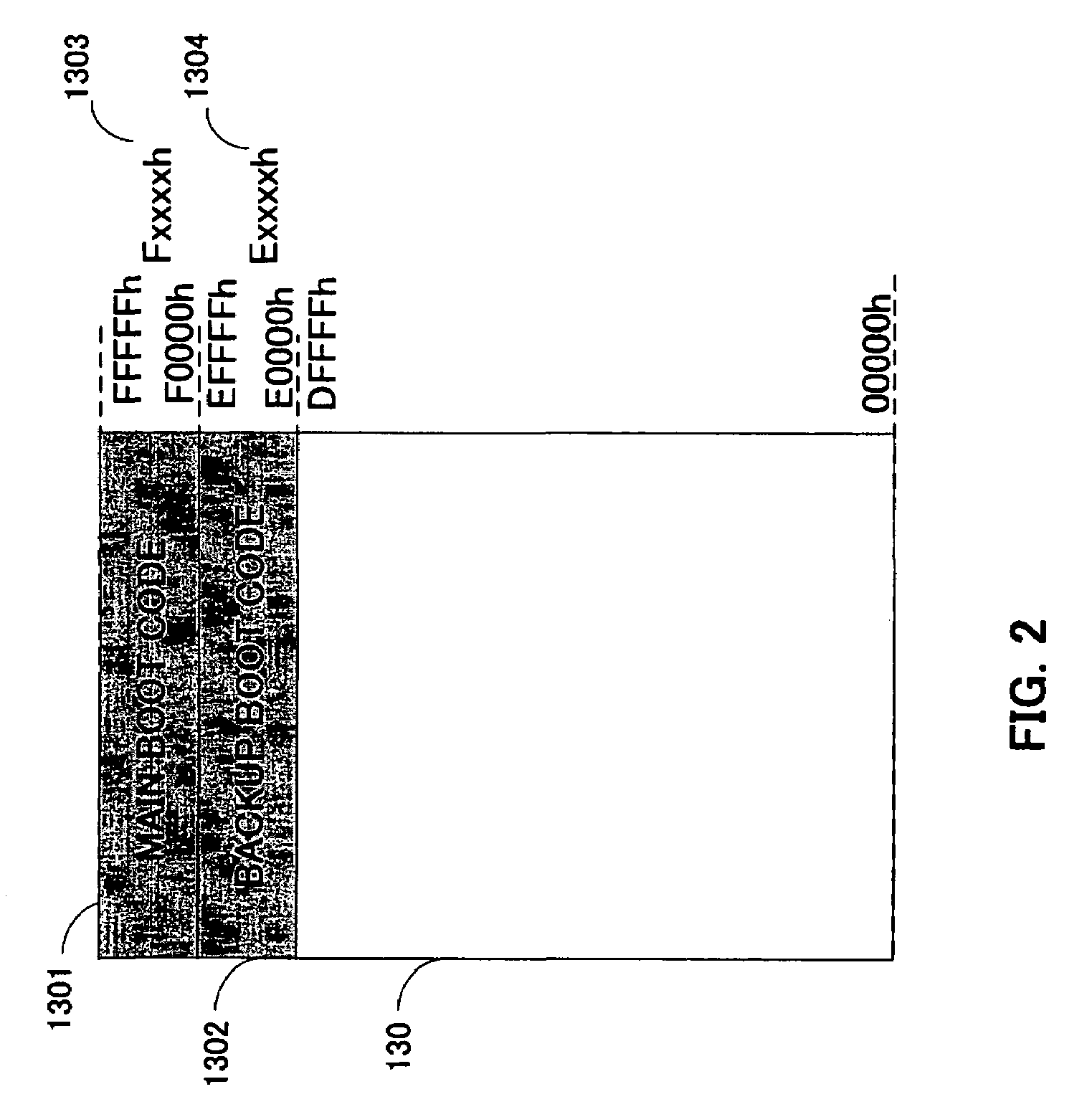

InactiveUS7219221B2Inexpensively allowReliable automatic booting of a computerRead-only memoriesDigital computer detailsSingle flashAddress decoder

A system and method for automatic booting based on a single flash ROM includes a flash ROM (130) and an address map circuit (120). The flash ROM is stored with a main boot code (1301) in a first address section (1303) and with a backup boot code (1302) in a second address section (1304). The address map circuit connects to a CPU (100) and the flash ROM, and includes a counter (1202) and an address decoder (1201). A related method includes the steps of: (a) a computer being powered on; (b) a CPU of the computer retrieving the main boot code and checking whether the main boot code is corrupted; and (c) the CPU retrieving the backup boot code if the main boot code is checked as corrupted.

Owner:HON HAI PRECISION IND CO LTD

Method and apparatus for dynamic space-time imaging system

InactiveUS7961912B2Fast enough to eliminateNo blurringImage analysisMaterial analysis by optical meansSingle flash3d image

A method for creating a 3D map of the surface contours of an object includes projecting a variety of patterns onto the object, and imaging the patterns as they fall on the object to encode the topographic features of the object. In one embodiment a three dimensional image is taken in a single flash to avoid blurring due to motion of the object. Thereafter a secondary pattern is projected to detect changes in the initial image. The images are processed in a computer program in a manner such that a complete 3D map of the surface of the object is obtained in digital form. Reiteration of the method can detect motional variation such as a breathing human, flexure of a complex mechanical structure, or a stress-strain testing of an airplane, vehicle, beam, bridge, or other structure.

Owner:4D IMAGING +1

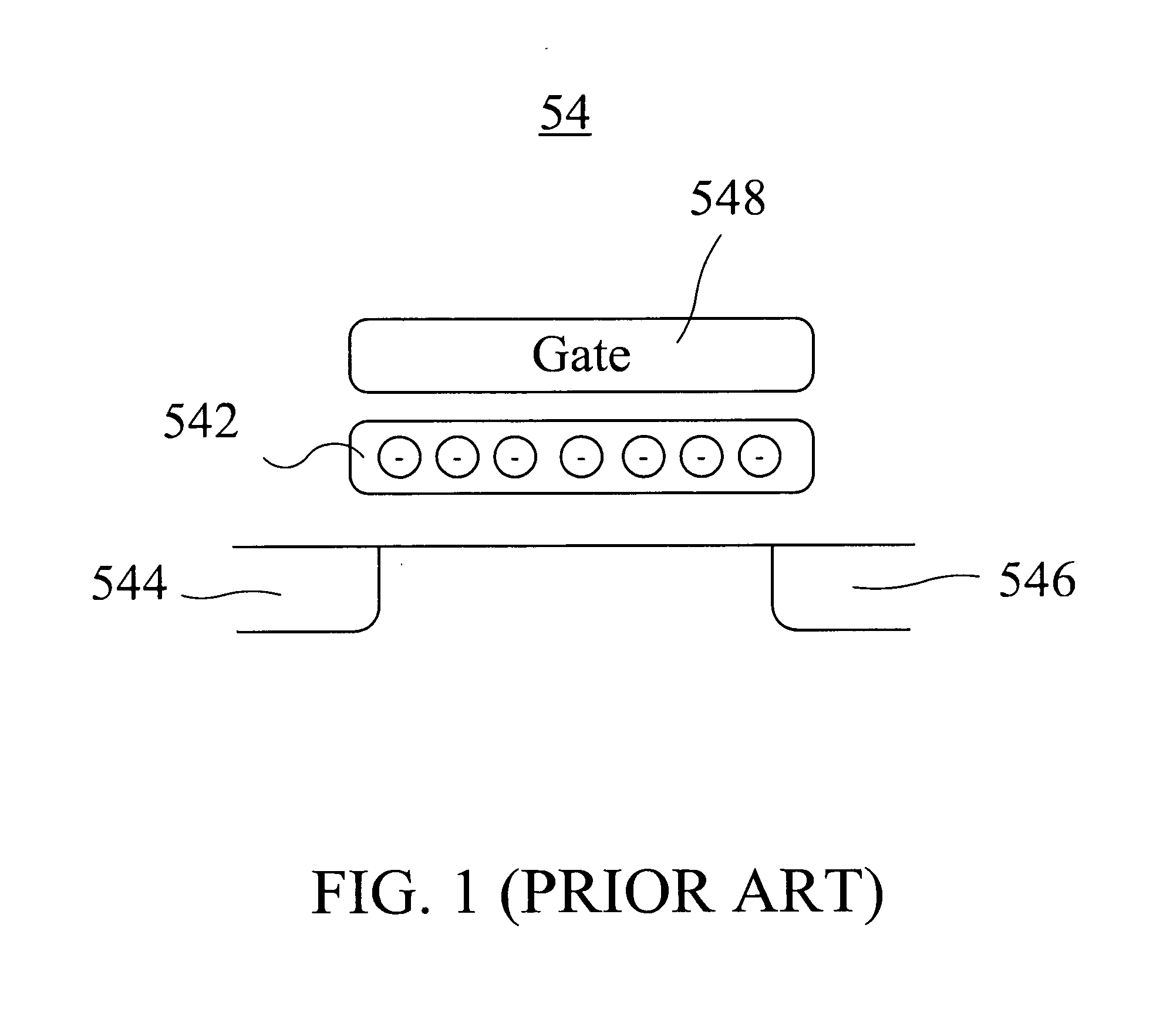

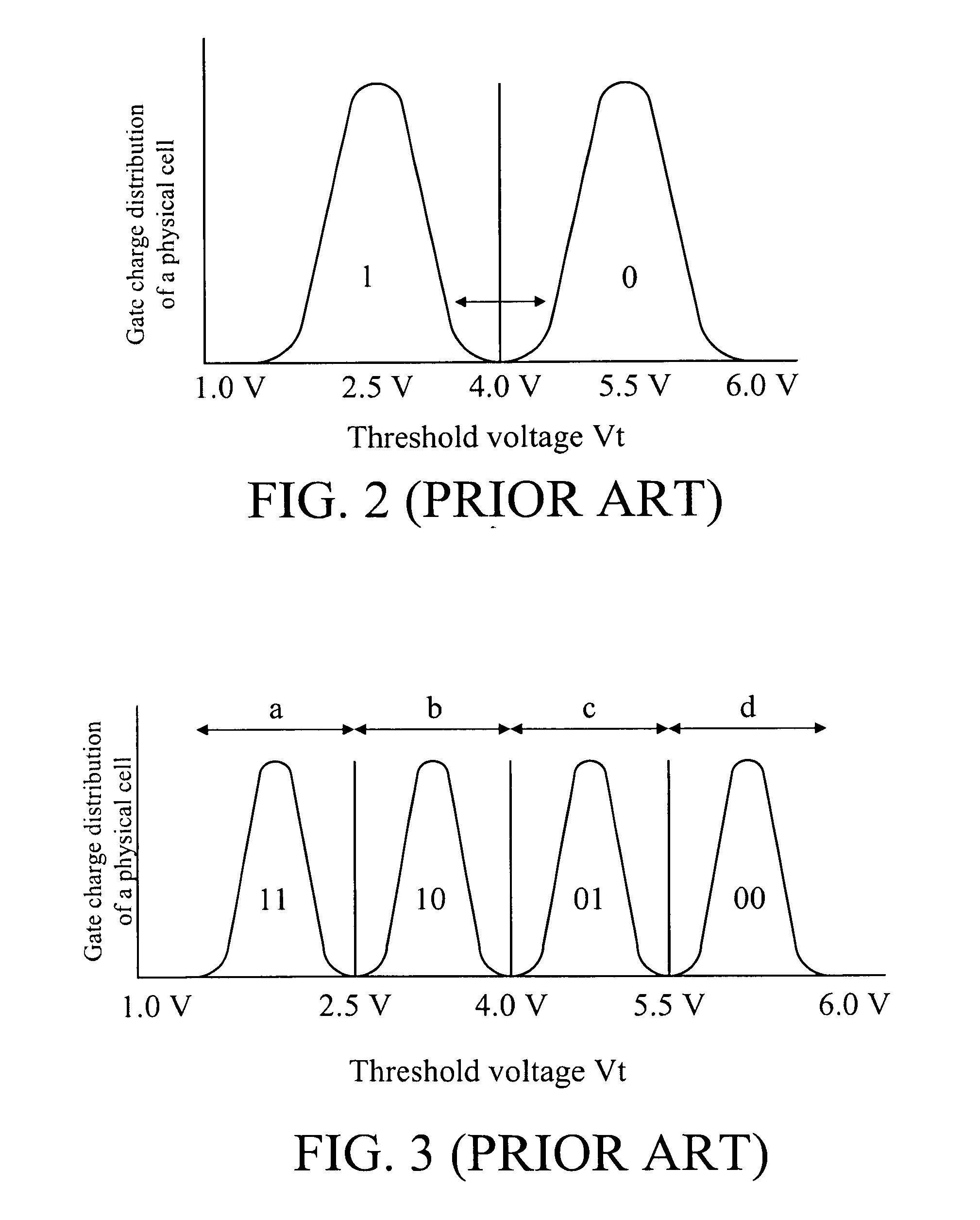

Storage device using a multi-level flash memory as a single flash memory and method for the same

InactiveUS20100049904A1Low costMemory adressing/allocation/relocationRead-only memoriesSingle flashMulti-level cell

A storage device includes a multi-level cell flash memory having a plurality of physical memory cells, a read controller, and a write controller. The physical memory cells form a first page and a second page. The write controller in response to a first request is used for writing first data into the first page, duplicating the first data as a second data and writing the second data into the second page. The read controller is used for adjusting the stored data value complying with a desired storing value. Each physical memory cell comprises four threshold voltage ranges indicative of two-bit logical values. The two-bit data is assigned as a first logical value accordingly in response to a two-bit data corresponding to a first and second threshold voltage ranges in a first physical memory cell. The two-bit data is assigned as a second logical value accordingly in response to a two-bit data corresponding to a third and fourth threshold voltage ranges in a second physical memory cell.

Owner:GENESYS LOGIC INC

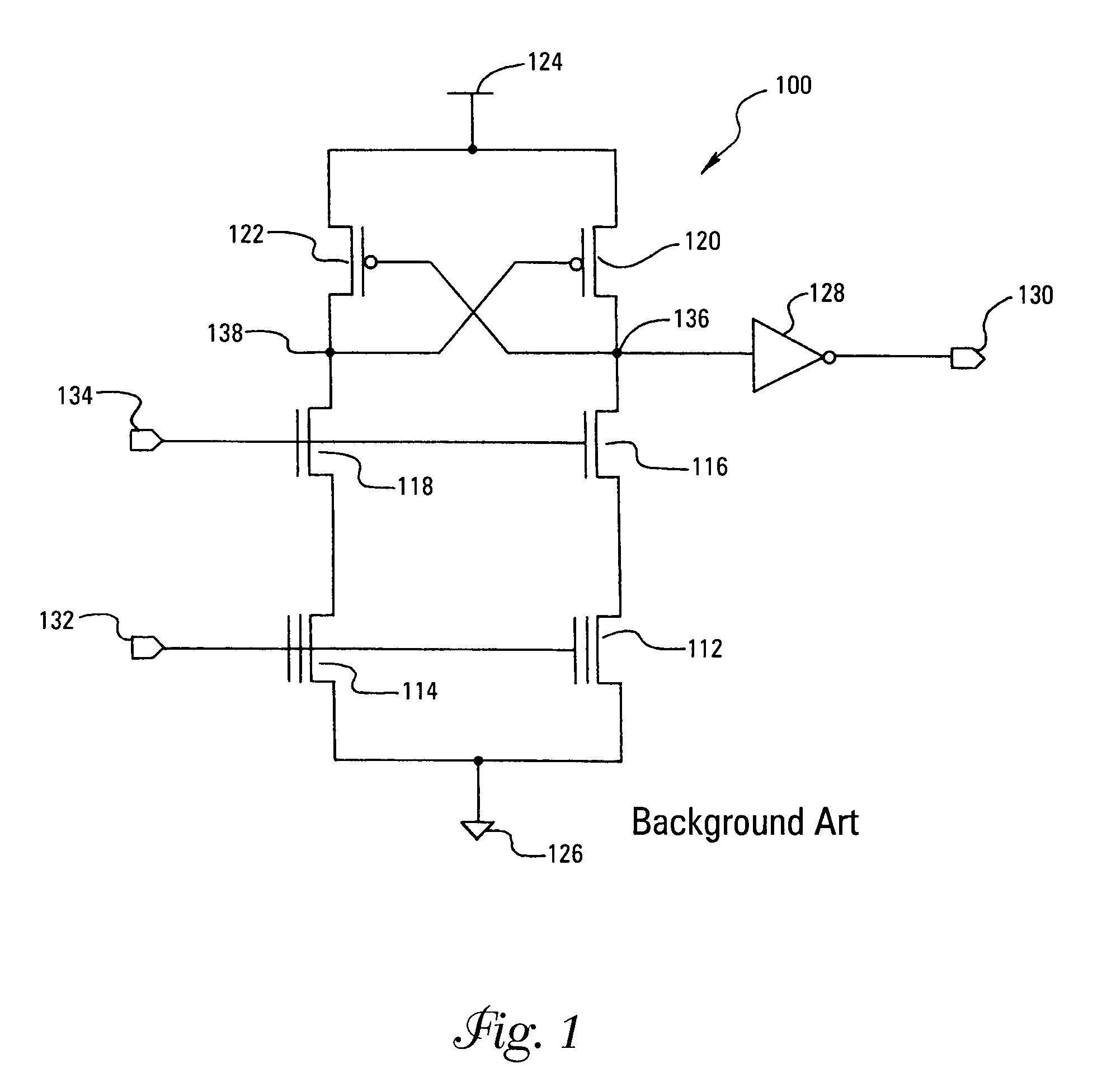

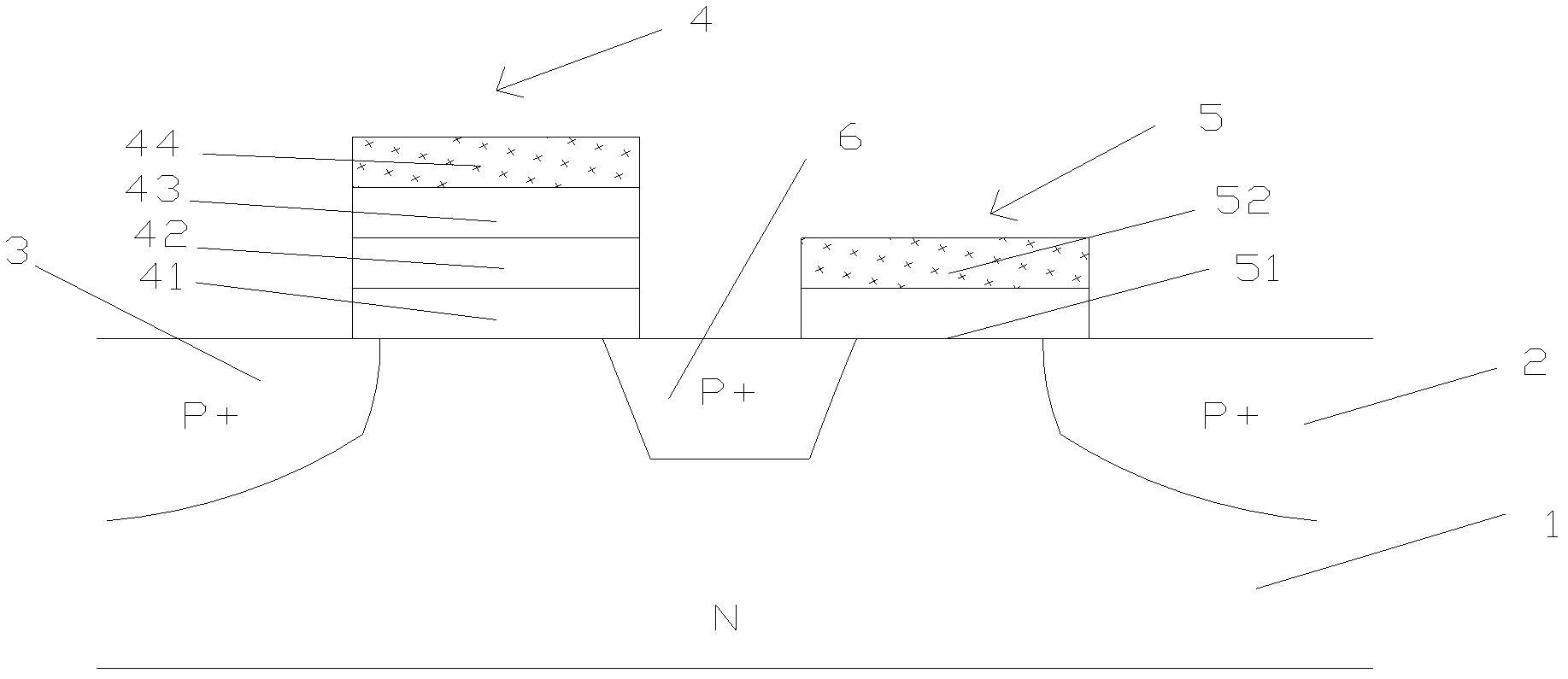

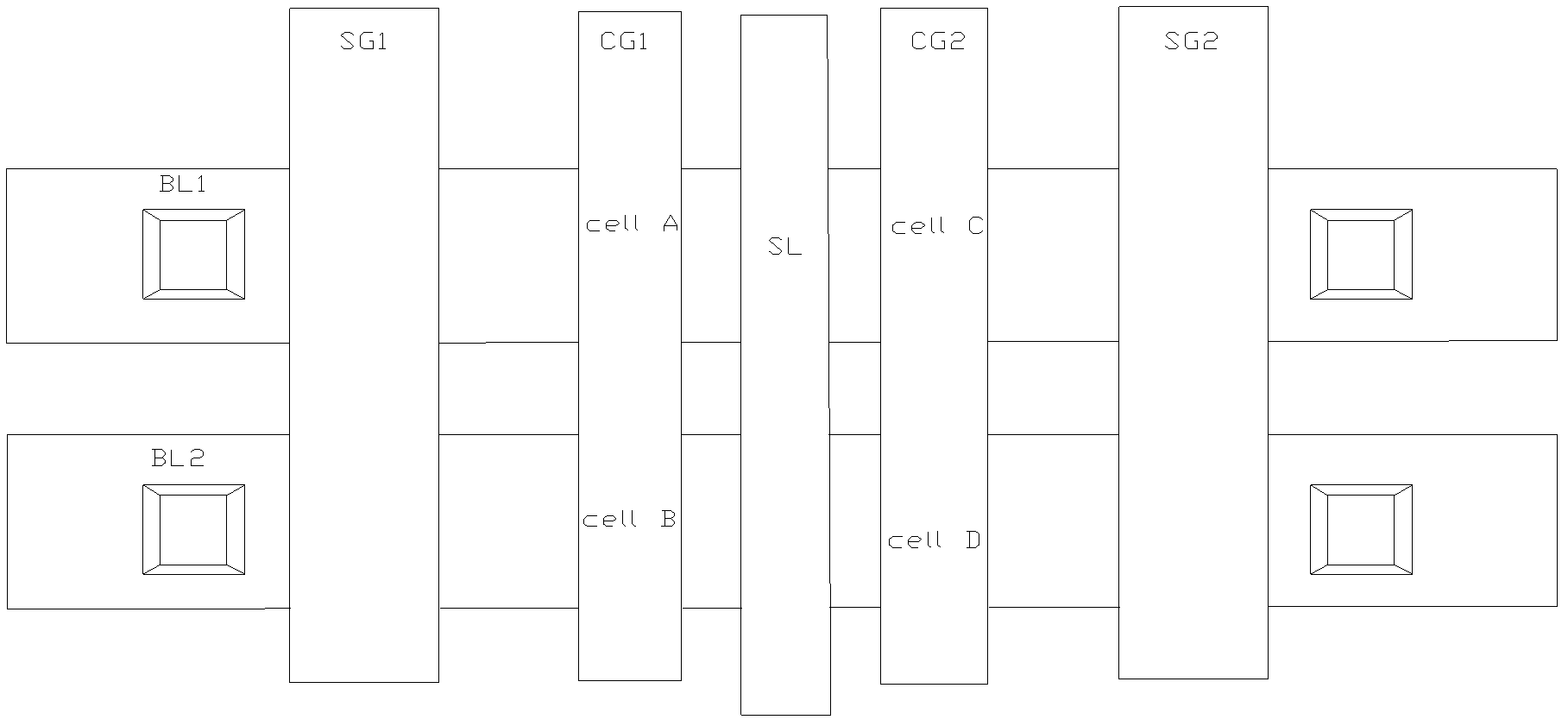

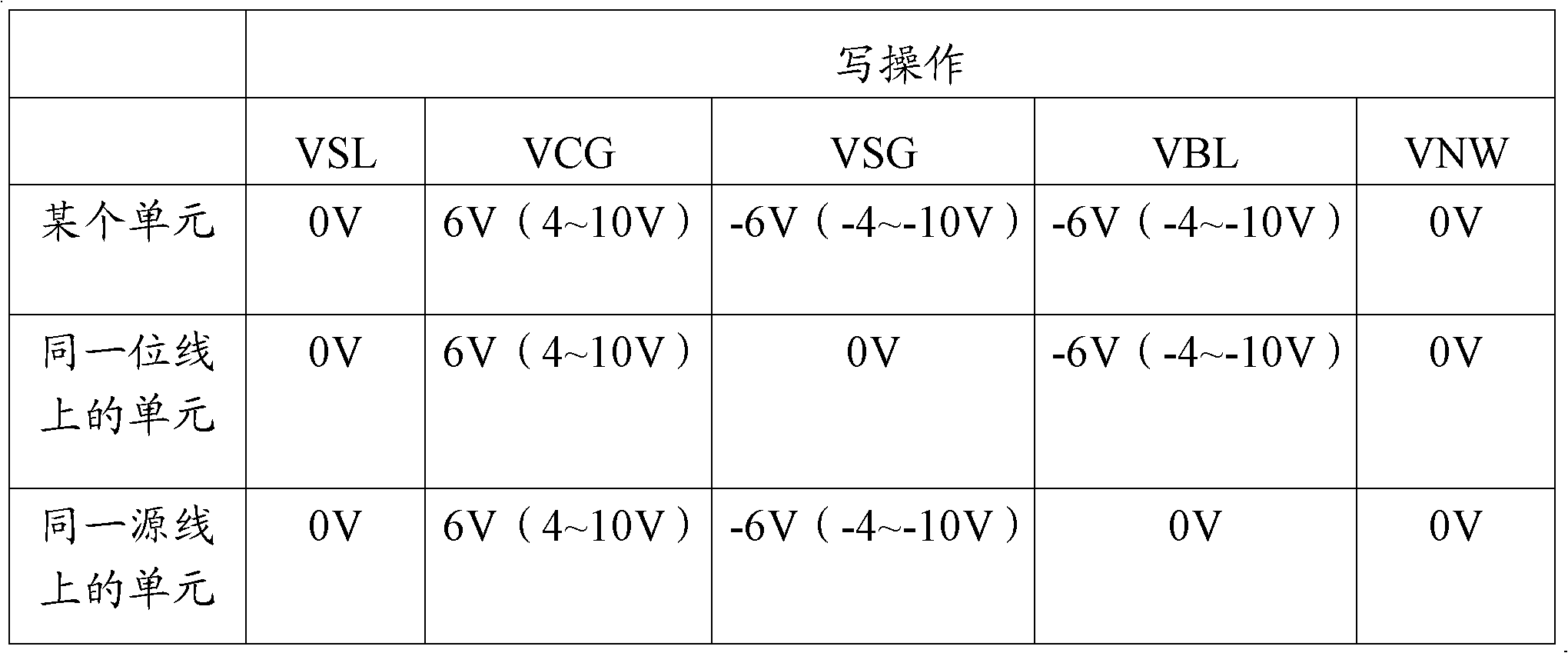

Novel SONOS (Silicon Oxide Nitride Oxide Semiconductor) flash memory unit structure of double transistor and operation method thereof

ActiveCN102324429APrecision Erase OperationThere is no problem of over-erasingSolid-state devicesRead-only memoriesCMOSSingle flash

The invention relates to a novel SONOS (Silicon Oxide Nitride Oxide Semiconductor) flash memory unit structure of a double transistor and an operation method thereof. The SONOS flash memory unit structure of the double transistor comprises an SONOS memory transistor and a memory unit selectron, wherein a selecting grid of the memory unit selectron is used as a selecting end; a drain region close to one side of the grid of the memory unit selectron is a bit line end while a source region close to one side of the SONOS memory transistor is used as a source line end; and a control grid of the SONOS memory transistor is a control end. The operation method of the SONOS memory unit of the double transistor comprises the steps of selecting the unit in reading and writing operation by using the bit line end and the selecting end and selecting the unit in erasing operation by using the control end. The novel SONOS flash memory unit structure of the double transistor, provided by the invention, is completely compatible with a standard CMOS logic process; and the over-erasing shortcoming of a single flash memory transistor memory unit are overcome.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

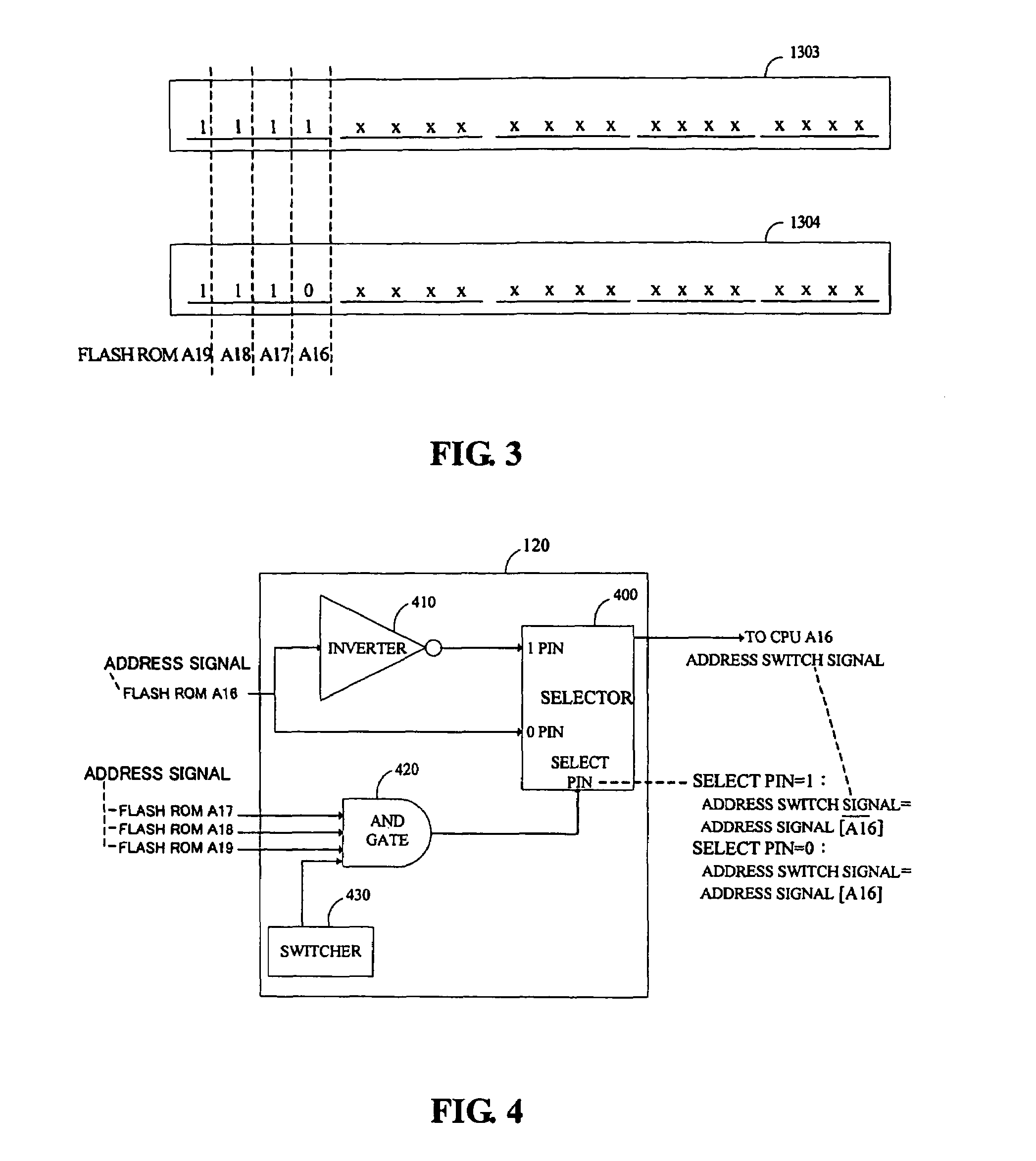

System and method for manual fail-safe bootstrap based on a single flash ROM

A system for manual fail-safe bootstrap based on a single flash Read-Only Memory (ROM) includes a flash ROM (130) and an address map circuit (120). The flash ROM stores a main boot code (1301) in a first address section (1303) thereof, and a backup boot code (1302) in a second address section (1304) thereof. The address map circuit connects to a Central Processing Unit (CPU) (100) and the flash ROM, and includes a selector (400), an inverter (410), an AND gate (420) and a switcher (430). A related method for manual fail-safe bootstrap based on a single flash ROM is also provided.

Owner:HON HAI PRECISION IND CO LTD

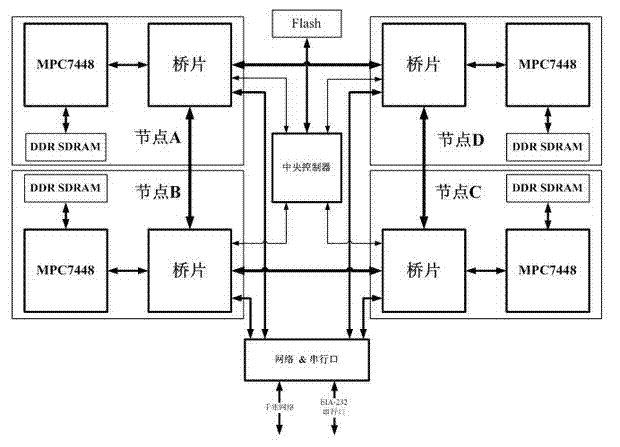

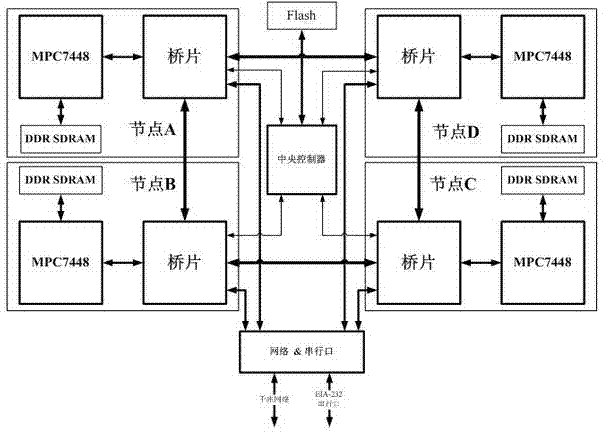

System for configuring multi-processor in single Flash in embedded manner

InactiveCN102521200ASolve problems with complex traditional structuresReduce manufacturing costDigital computer detailsElectric digital data processingSingle flashAuto-configuration

The invention relates to the technical field of configuring a processor in an embedded manner, in particular to a system for configuring a multi-processor in single Flash in an embedded manner. The system comprises a central processing unit, four processor nodes and a Flash memory, wherein the central processing unit is both connected with the four processor nodes and the Flash memory; each processor node comprises an MPC (Multimedia Personal Computer) 7448 processor, a bridge sheet and a double data rate synchronous dynamic random-access memory DDRSDRAM, wherein the DDRSDRAM is connected with the processor, the processor is connected with the bridge sheet and the bridge sheet is connected with the central processing unit; bridge sheets of each two processor nodes are connected through a PCI-X (Peripheral Components Interconnect) bus, and the four processor nodes and four PCI-X buses are connected circularly. According to the invention, the problem of complex traditional structure is solved, the production cost is reduced greatly, and the system provided by the invention has a simple structure, small size and relatively low production cost; furthermore, automatic configuration can be performed according to processor demands and a high-speed serial bus is provided.

Owner:SICHUAN SDRISING INFORMATION TECH

Method for on-line burning large-capacity or multiple FLASH files by DSP

InactiveCN101499014AEliminate human errorReduce labor intensityProgram loading/initiatingSingle flashPaging

A method for writing large capacity or a plurality of FLASHs is provided. Being characterized in that the method comprising the following steps: firstly determining whether the capacity of a single FLASH chip DSP is greater than the contents of the volume; if the DSP chip is greater than the contents of the volume, then to their page, so that each page is less than the capacity of the contents of the volume of DSP chip; Secondly, the use of the conditions of pre-compiled manner programmer to be the source of all the above-mentioned file name and destination address; Third, the preparation of a batch GEL FLASH programmer script control procedures; Finally, GEL load and run a batch script to set the DSP to carry out the conditions of the cycle, compile, link, load and run the operation until the last one burned into the FLASH source file after the termination of the cycle. Invented the use of this script programmer completely replace the page in the process of manual intervention, you can eliminate manual errors, reduce labor intensity and improve production efficiency, the product can not break the technical bottlenecks in production and to reduce labor costs.

Owner:PANDA ELECTRONICS GROUP +2

System and method for manual fail-safe bootstrap based on a single flash ROM

A system for manual fail-safe bootstrap based on a single flash Read-Only Memory (ROM) includes a flash ROM (130) and an address map circuit (120). The flash ROM stores a main boot code (1301) in a first address section (1303) thereof, and a backup boot code (1302) in a second address section (1304) thereof. The address map circuit connects to a Central Processing Unit (CPU) (100) and the flash ROM, and includes a selector (400), an inverter (410), an AND gate (420) and a switcher (430). A related method for manual fail-safe bootstrap based on a single flash ROM is also provided.

Owner:HON HAI PRECISION IND CO LTD

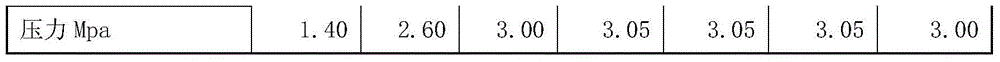

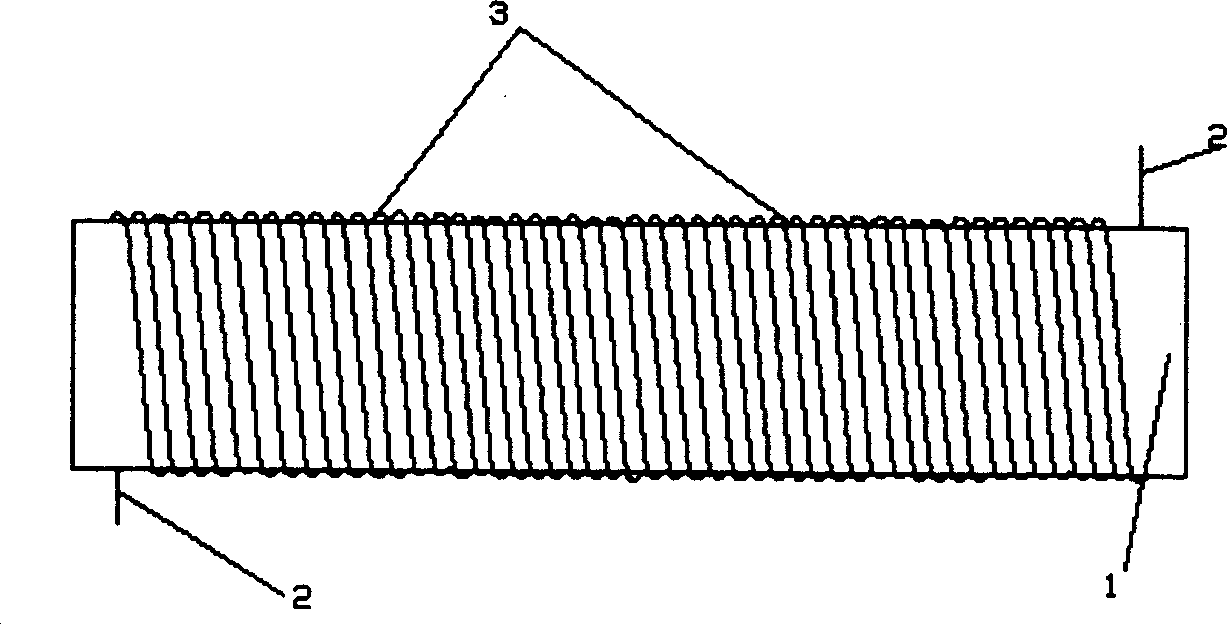

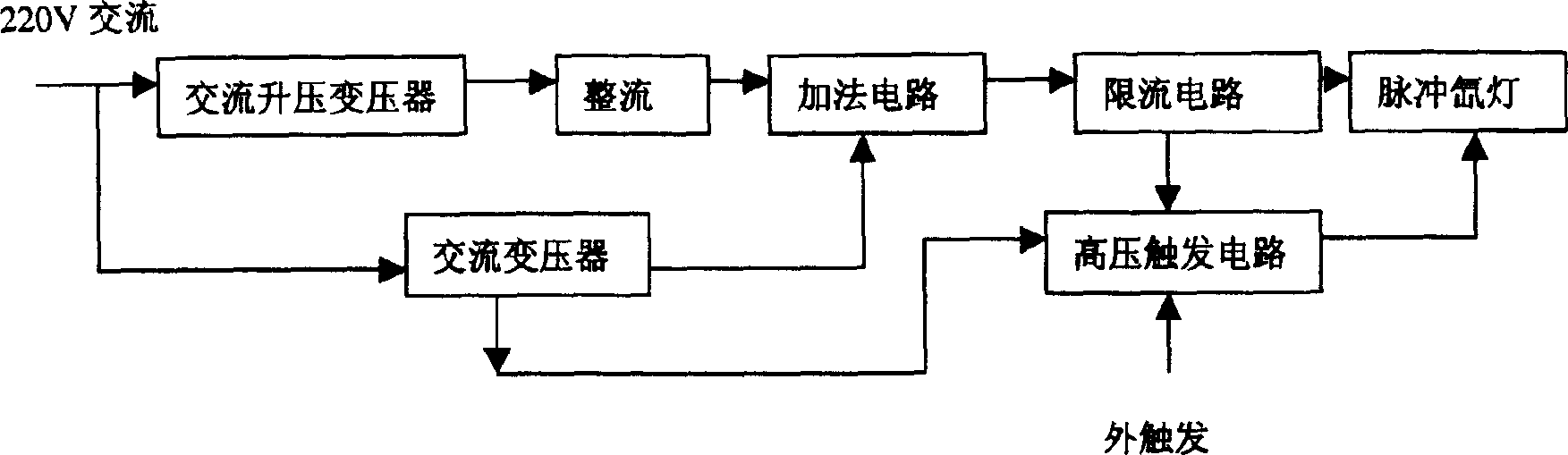

Single flash testing instrument of film solar battery assembly

InactiveCN1538187AMeet slow response requirementsMeet the test requirementsPhotovoltaic monitoringElectric lighting sourcesSingle flashCapacitance

A single flash tester of film solar cell module is disclosed. Its analog light source is the parallelly connected two pulse xenon lamps connected to main power supply. Each pulse xenon lamp is connected to a large-current preburning circuit isolated to the main power supply by diode. A coil at the output of main power supply is serially connected to a capacitor parallelly connected with pulse xenon lamps. A scanning voltage is used to scan the module to be tested in decrement mode beginning from its open-circuit voltage. Its advantage is no influence of the capacitance to result.

Owner:SHANGHAI JIAO TONG UNIV