Patents

Literature

93273results about How to "Reduce consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

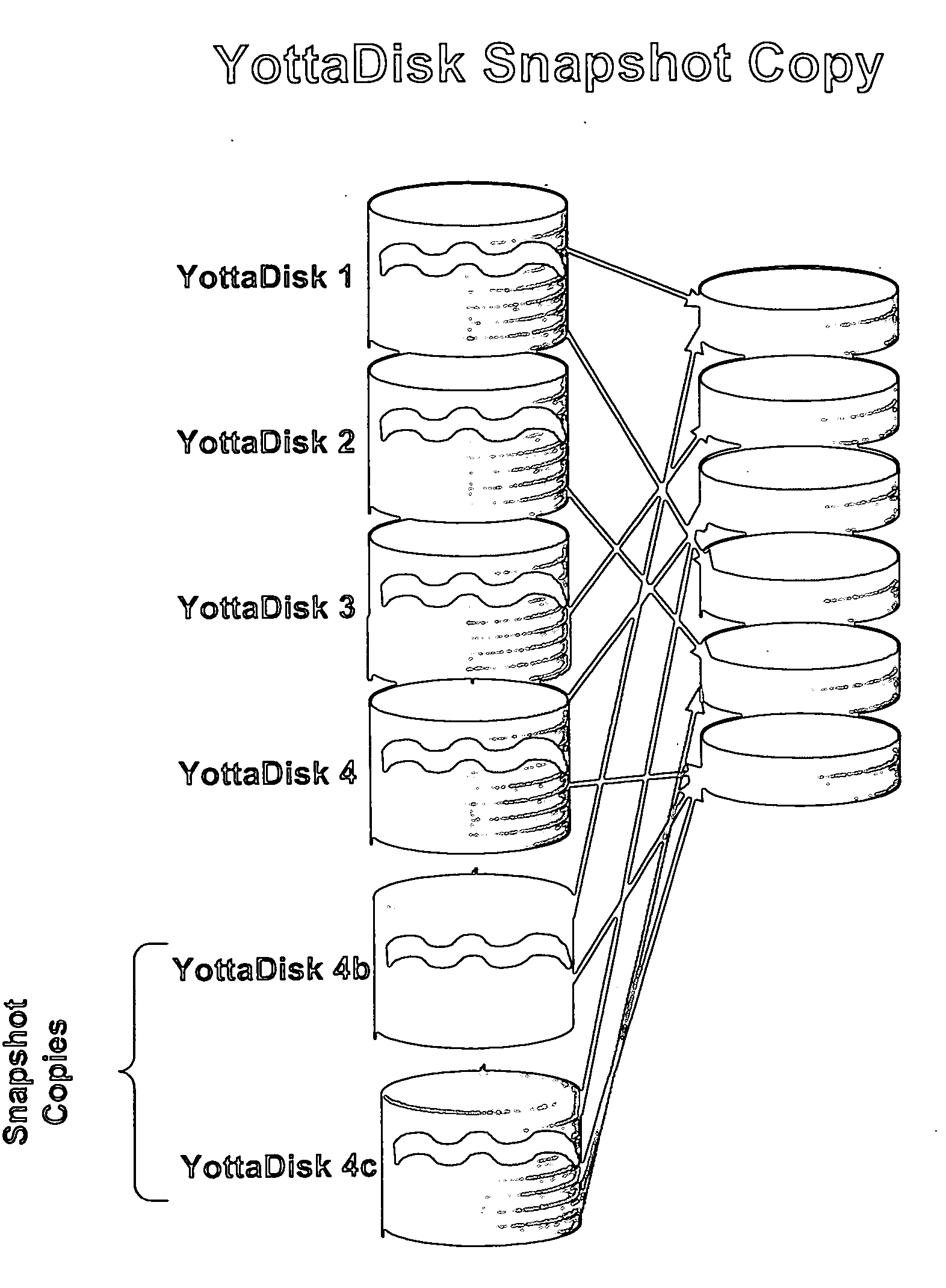

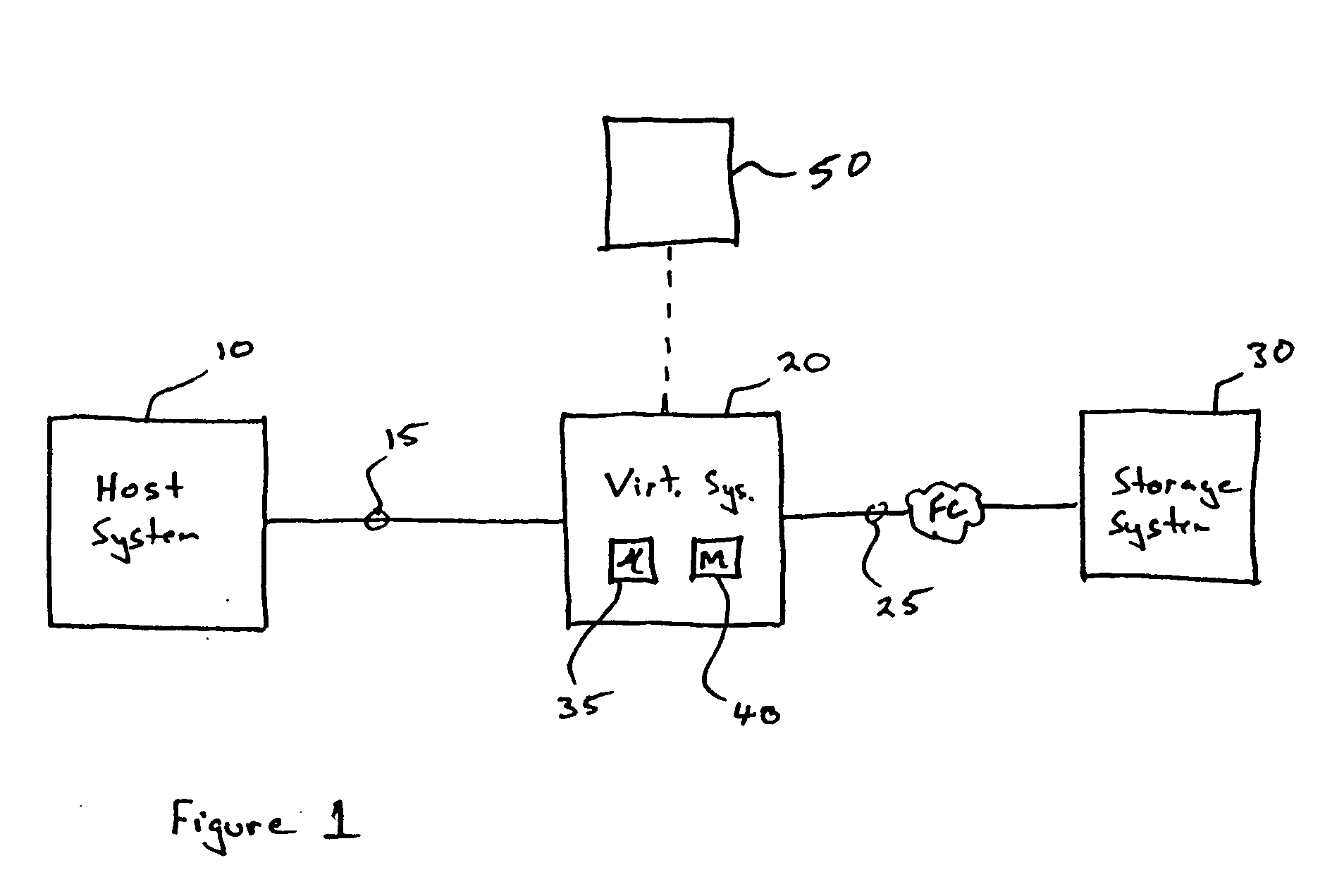

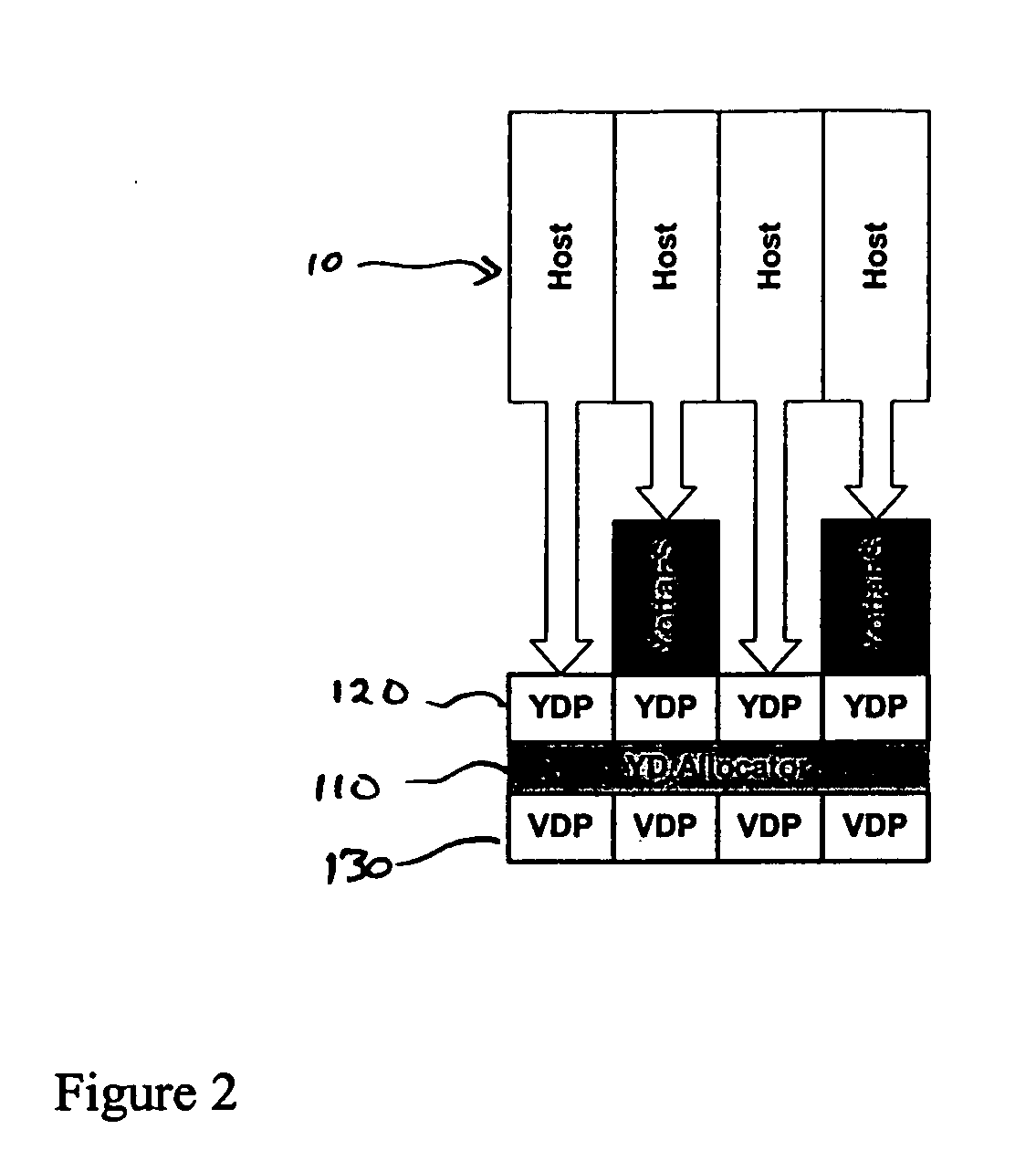

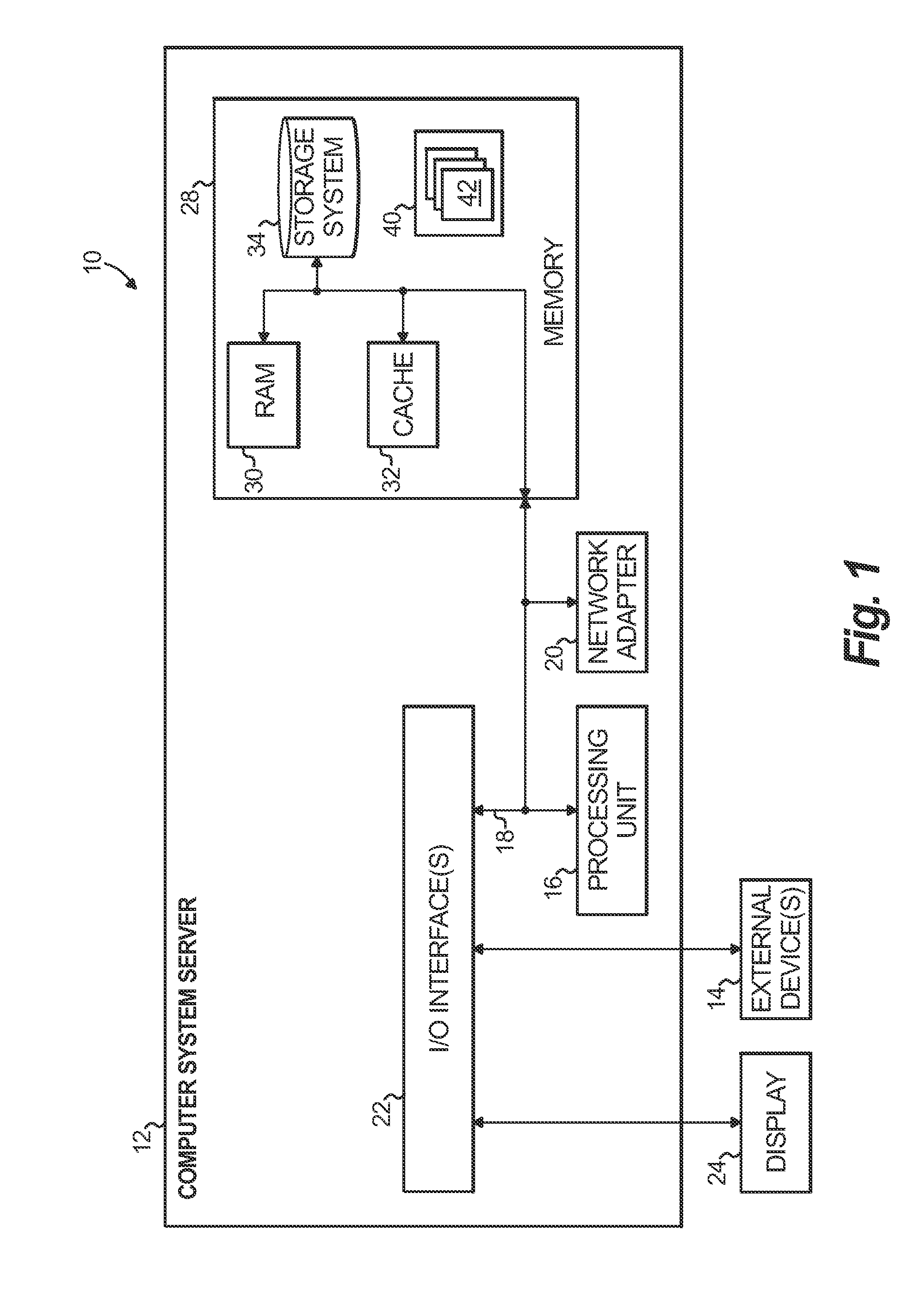

Storage virtualization system and methods

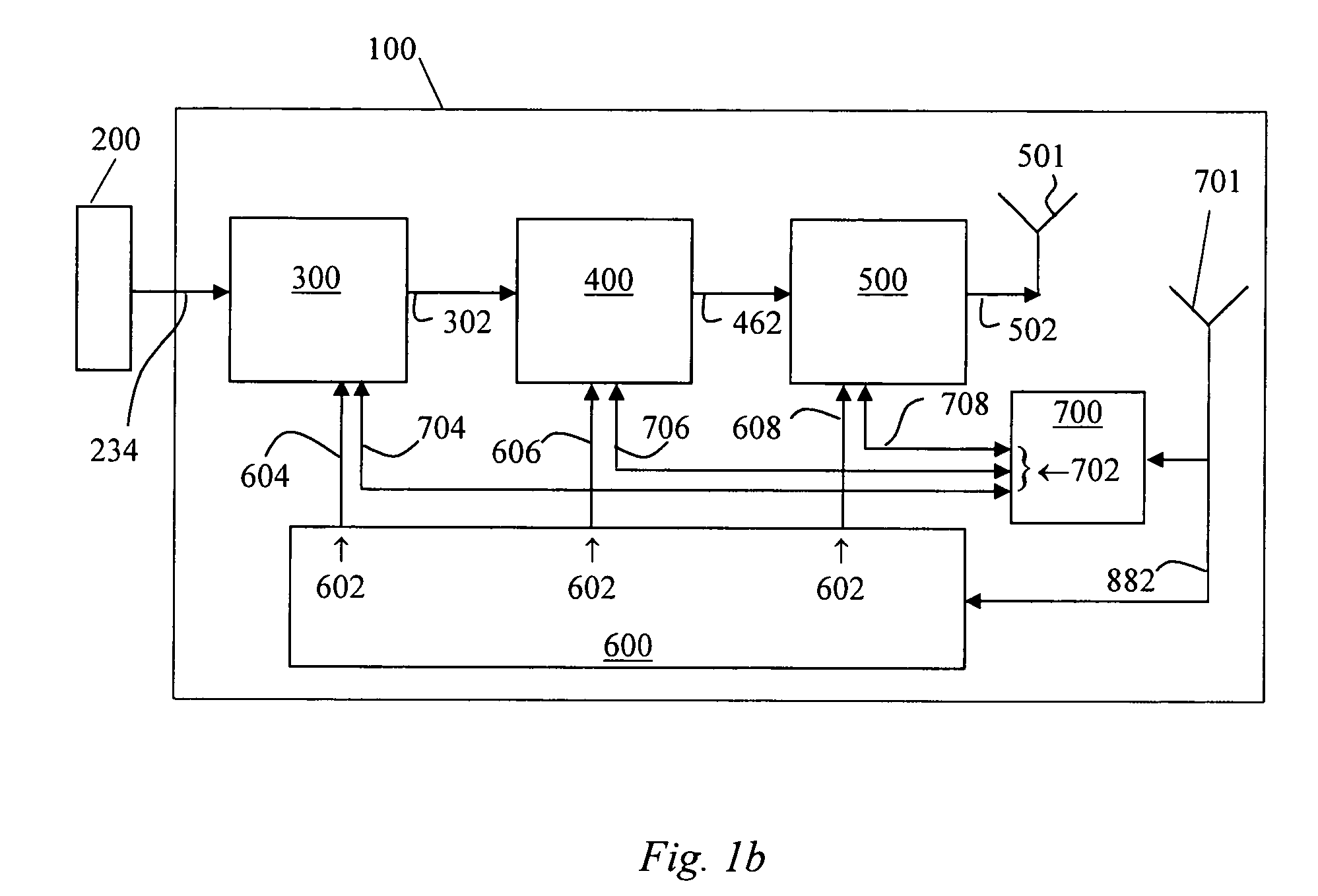

InactiveUS20050125593A1Reduce consumptionWithout impactInput/output to record carriersMemory adressing/allocation/relocationRAIDIslanding

Storage virtualization systems and methods that allow customers to manage storage as a utility rather than as islands of storage which are independent of each other. A demand mapped virtual disk image of up to an arbitrarily large size is presented to a host system. The virtualization system allocates physical storage from a storage pool dynamically in response to host I / O requests, e.g., SCSI I / O requests, allowing for the amortization of storage resources-through a disk subsystem while maintaining coherency amongst I / O RAID traffic. In one embodiment, the virtualization functionality is implemented in a controller device, such as a controller card residing in a switch device or other network device, coupled to a storage system on a storage area network (SAN). The resulting virtual disk image that is observed by the host computer is larger than the amount of physical storage actually consumed.

Owner:EMC IP HLDG CO LLC

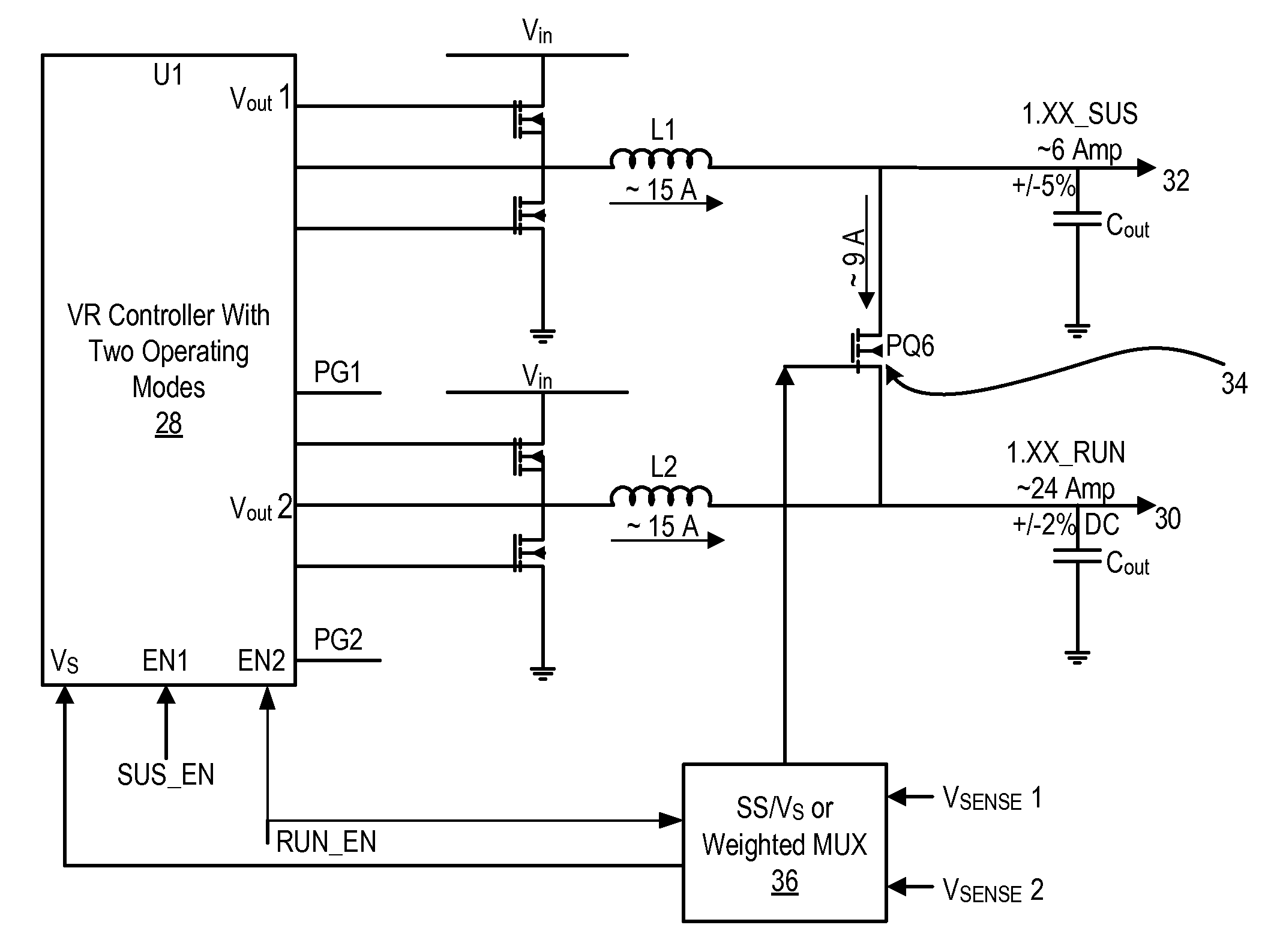

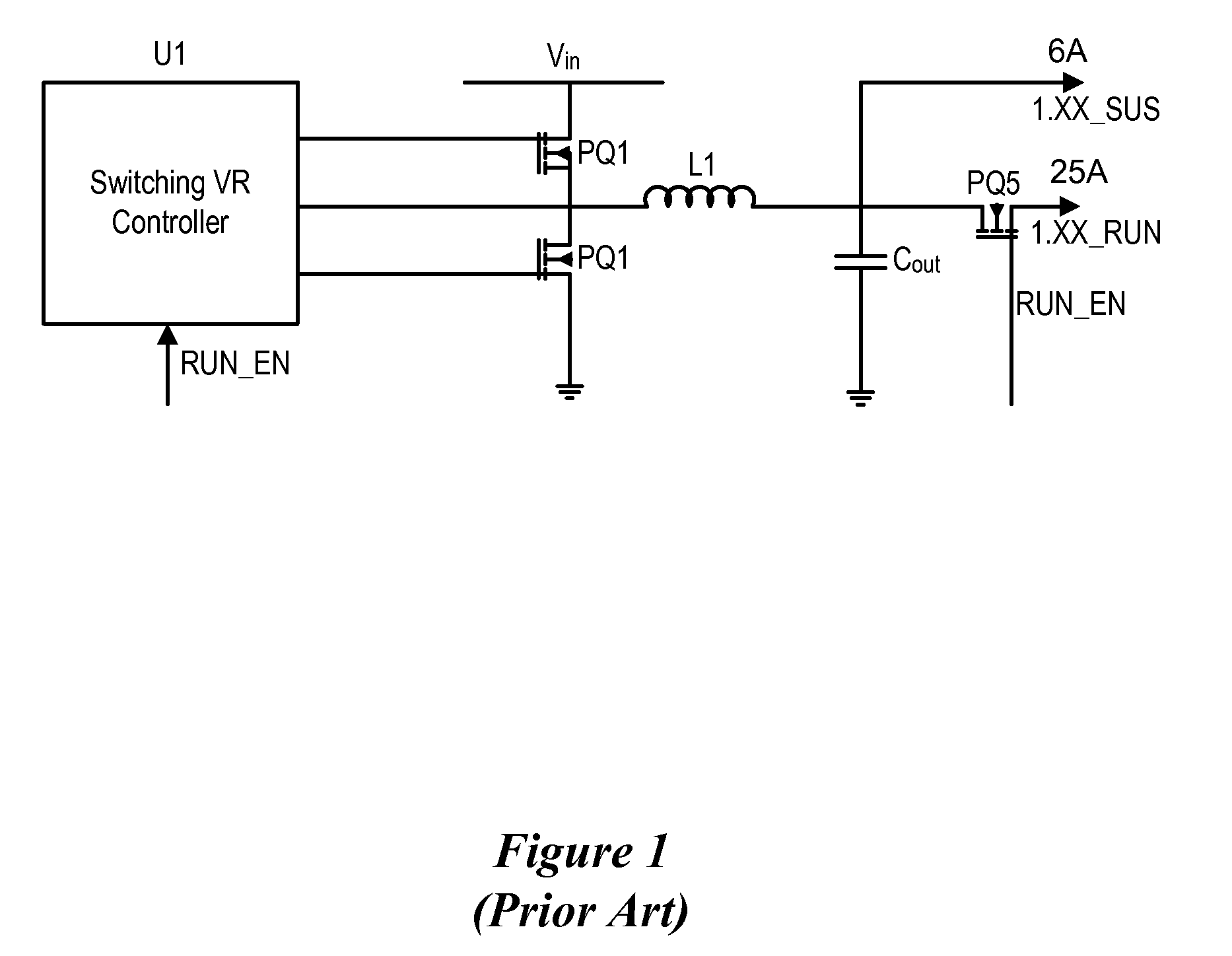

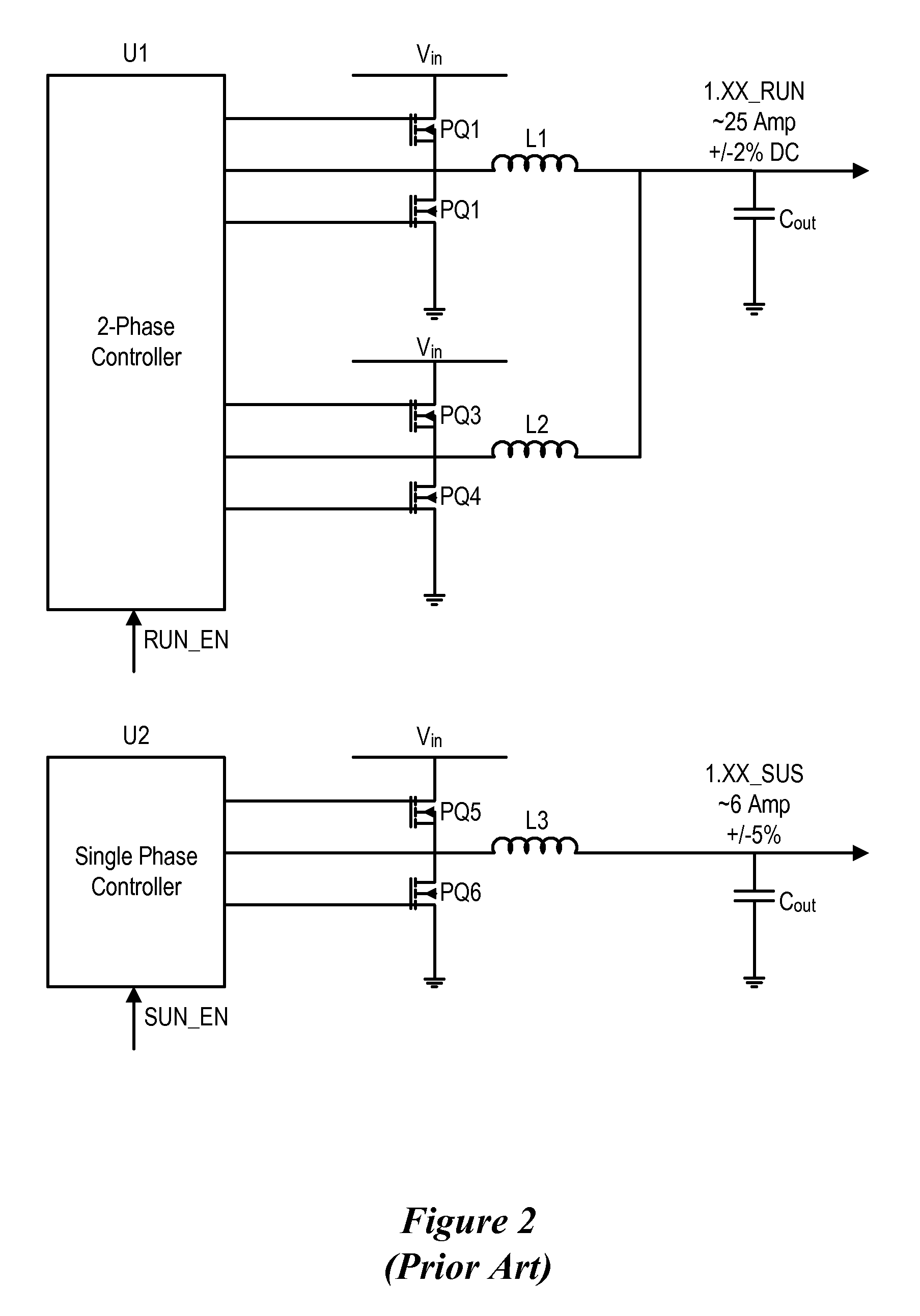

System and method for powering an information handling system in multiple power states

ActiveUS8063619B2Reduce disadvantagesReduce problemsElectric signal transmission systemsDc network circuit arrangementsMOSFETVoltage regulation

Power is supplied to an information handling system chipset with a single voltage regulator having dual phases. A first phase of the voltage regulator provides power to a low power state power rail in an independent mode to support a low power state, such as a suspend or hibernate state. A second phase of the voltage regulator provides power to a run power state power rail in combination with the first phase by activation of a switch, such as a MOSFET load switch, that connects the low power state power rail and the run power state power rail. Voltage sensed from both power rails is applied to control voltage output so that the run power state power rail is maintained within more precise constraints than the low power state power rail.

Owner:DELL PROD LP

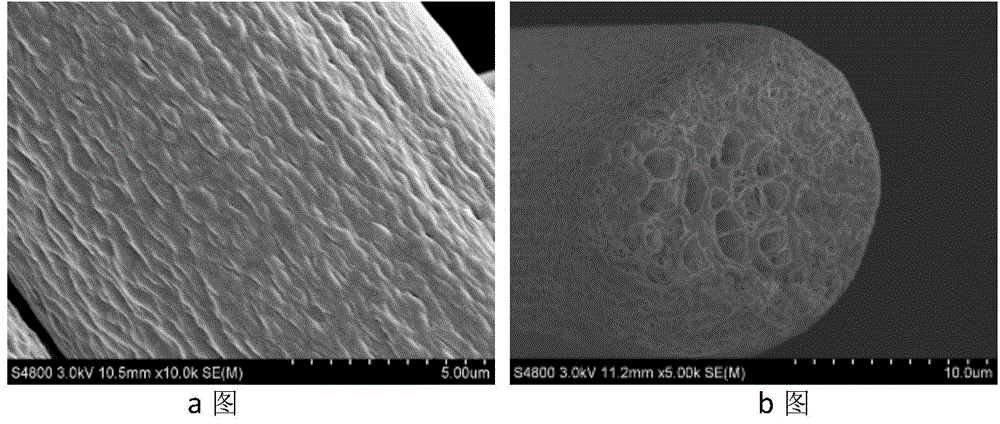

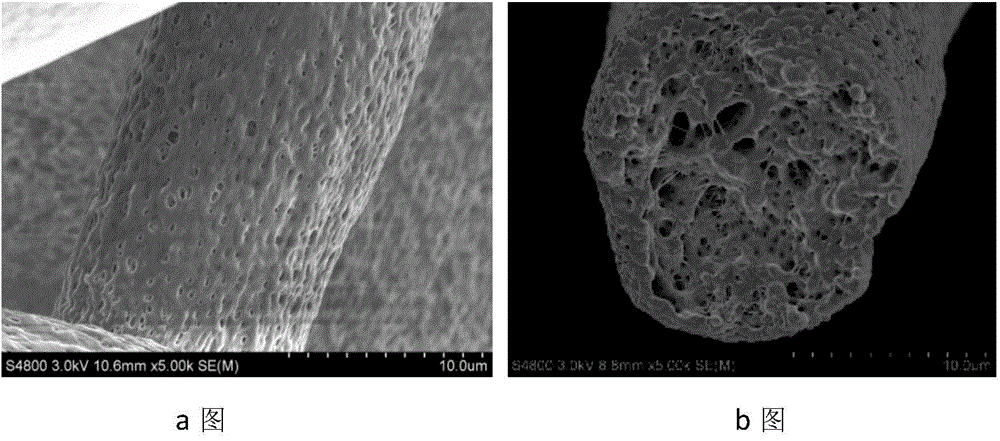

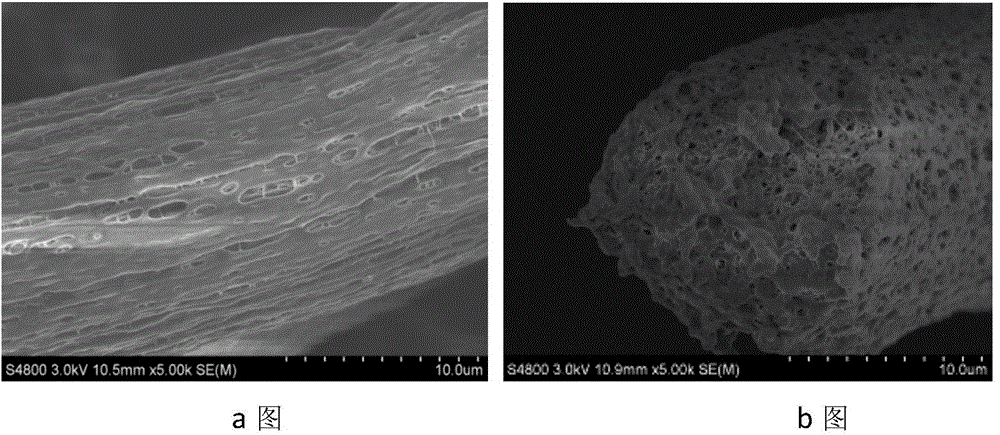

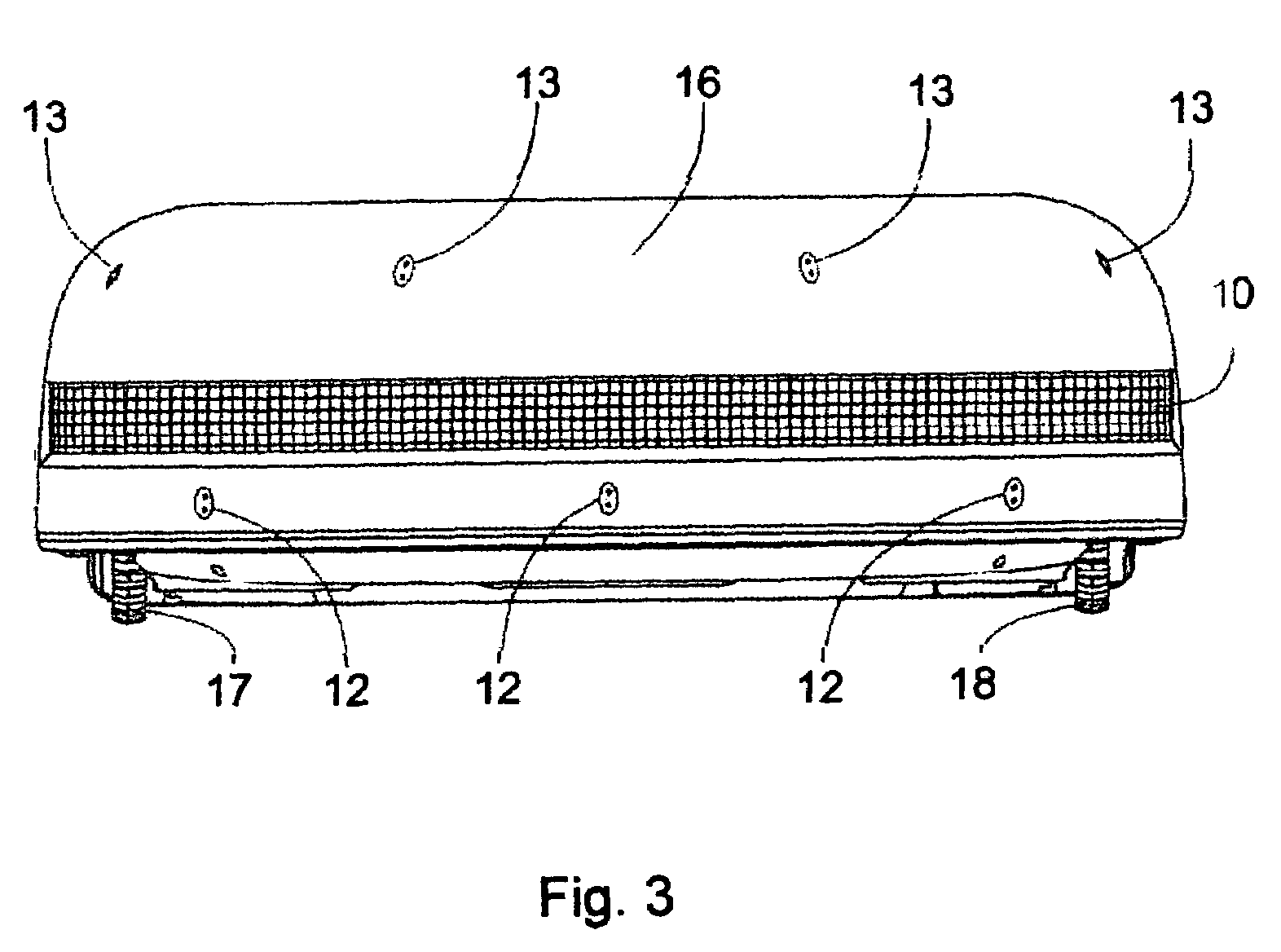

Preparation method of porous fiber non-woven fabric

ActiveCN103981635AReduce melt viscosityReduce degradationFilament forming substance formingMelt spinning methodsDiluentNonwoven fabric

The invention relates to a preparation method of a porous fiber non-woven fabric. The aim of the preparation method is to improve the product performance of the conventional non-woven fabric, so that the non-woven fabric meets the requirements on high-precision and high-performance filter. The technical scheme is that the preparation method of the porous fiber non-woven fabric comprises the following steps in sequence: (1) uniformly mixing a polymer and a diluent to obtain a blend with 10 to 60 percent of polymer; (2) melting and extruding the blend in the step (1) by adopting a screw extruder granulator, and directly cooling and granulating in air; (3) producing master batches in the step (2) by melt-down equipment to obtain a primary non-woven fabric; (4) extracting to remove the diluent from the primary non-woven fabric in the step (3), performing pore-forming on fibers in the non-woven fabric, and drying to obtain the porous fiber non-wave fabric; (5) recovering mixed waste liquid of the diluent and an extraction agent for reuse.

Owner:浙江省轻工业品质量检验研究院

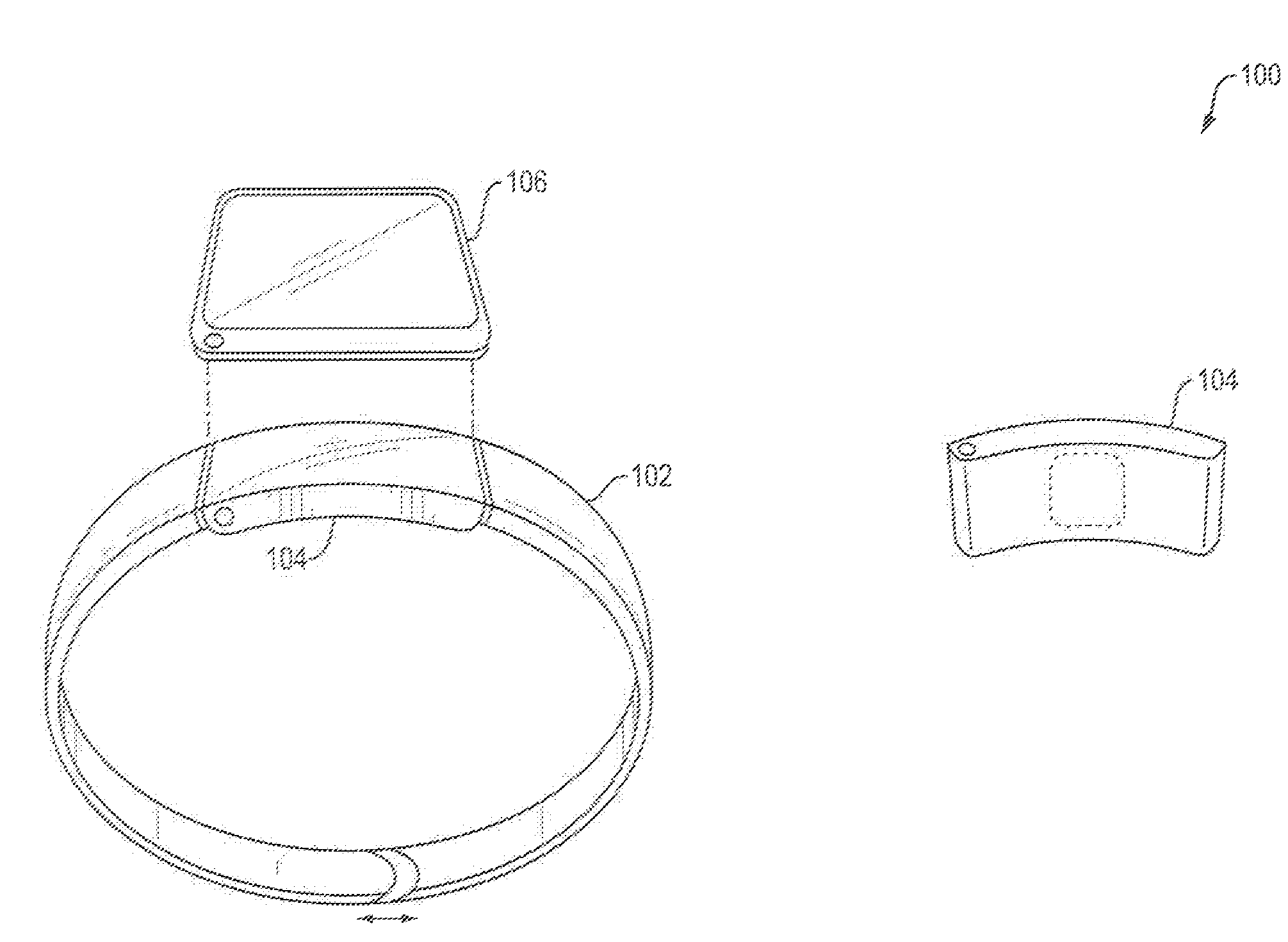

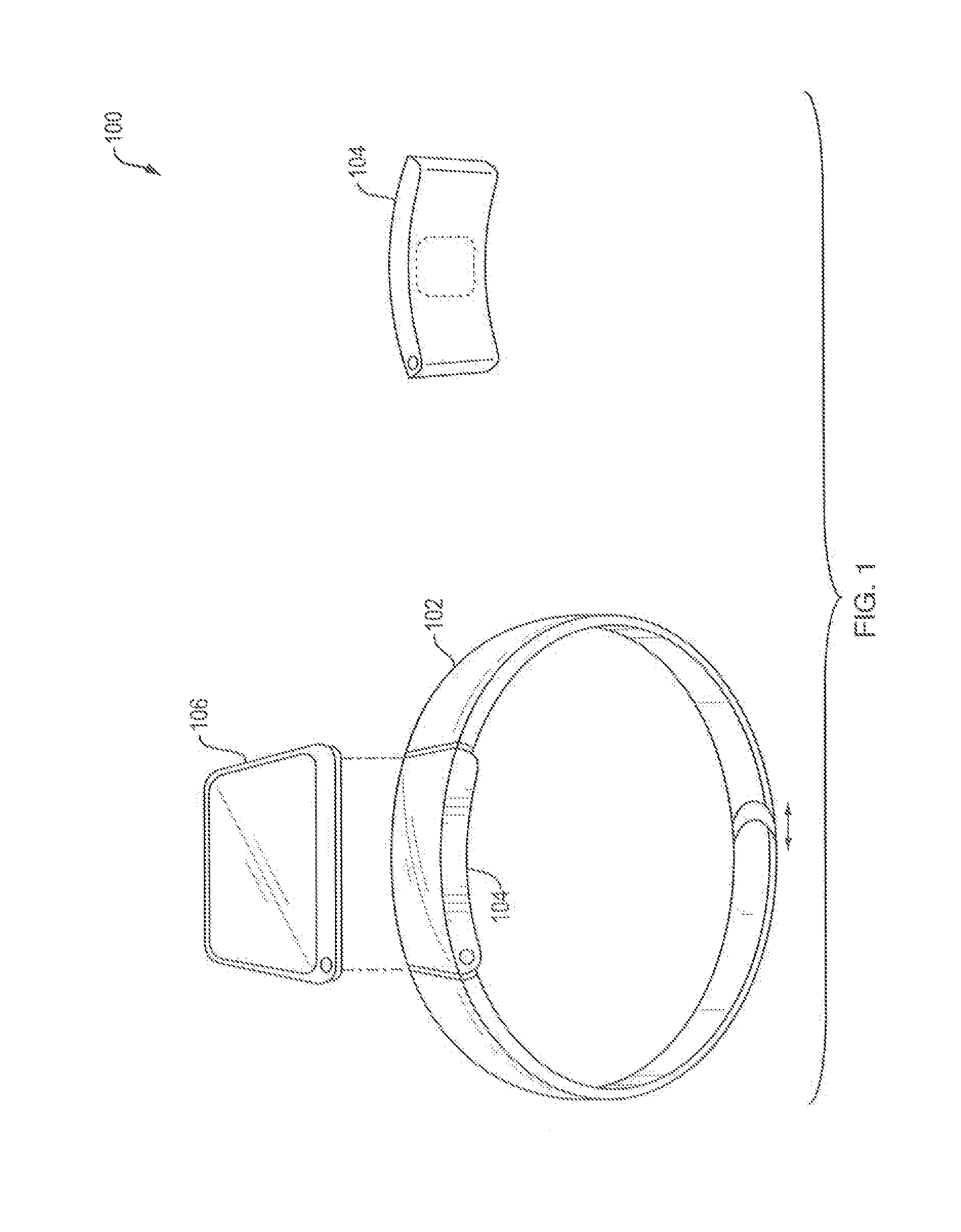

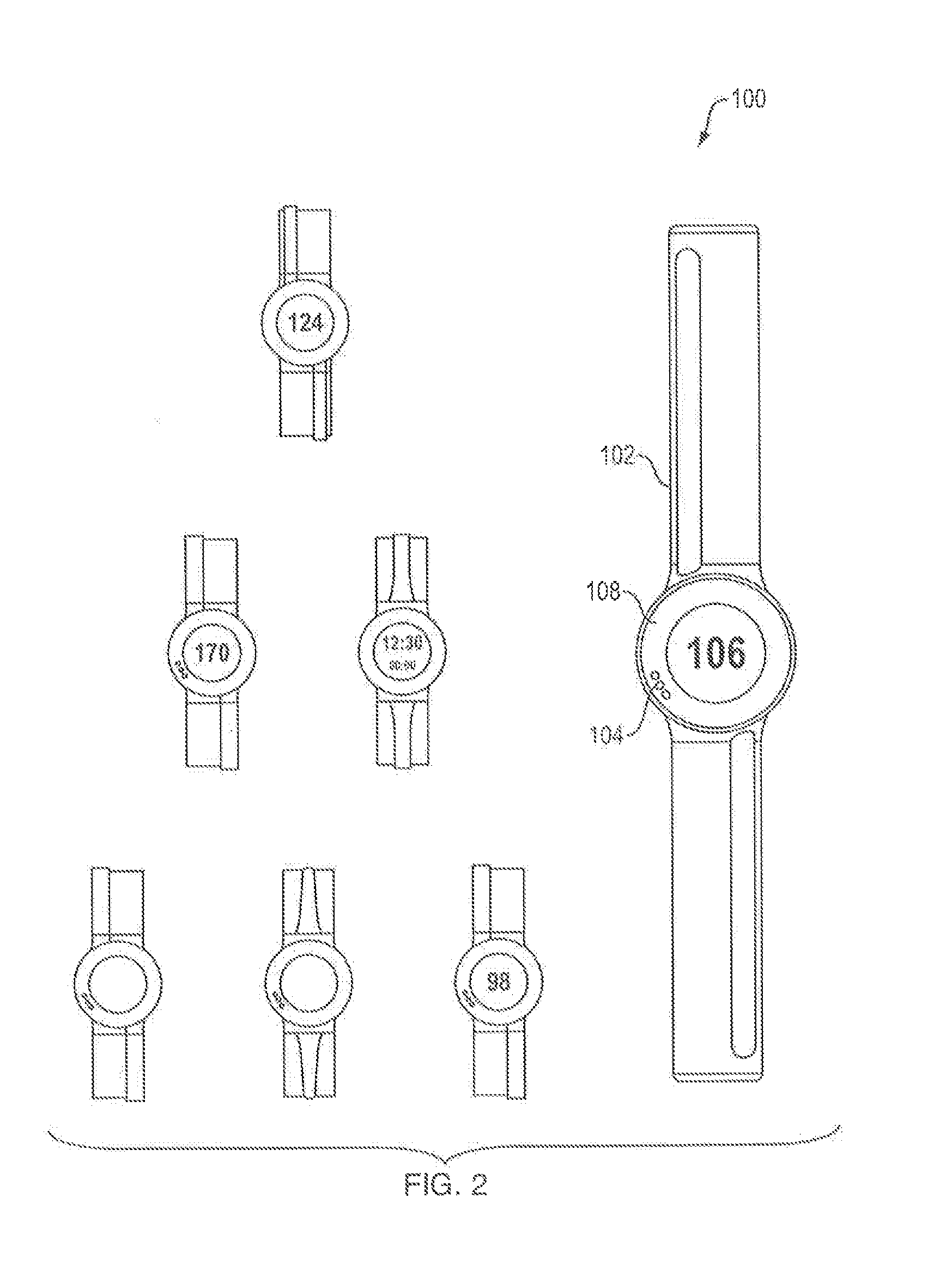

Systems, devices and methods for continuous heart rate monitoring and interpretation

InactiveUS20140073486A1Reduce consumptionPhysical therapies and activitiesMechanical/radiation/invasive therapiesPhysical ExertionsPhysical strength

Embodiments provide physiological measurement systems, devices and methods for continuous health and fitness monitoring. A lightweight wearable system is provided to collect various physiological data continuously from a wearer without the need for a chest strap. The system also enables monitoring of one or more physiological parameters in addition to heart rate including, but not limited to, body temperature, heart rate variability, motion, sleep, stress, fitness level, recovery level, effect of a workout routine on health, caloric expenditure. Embodiments also include computer-executable instructions that, when executed, enable automatic interpretation of one or more physiological parameters to assess the cardiovascular intensity experienced by a user (embodied in an intensity score or indicator) and the user's recovery after physical exertion (embodied in a recovery score). These indicators or scores may be displayed to assist a user in managing the user's health and exercise regimen.

Owner:WHOOP

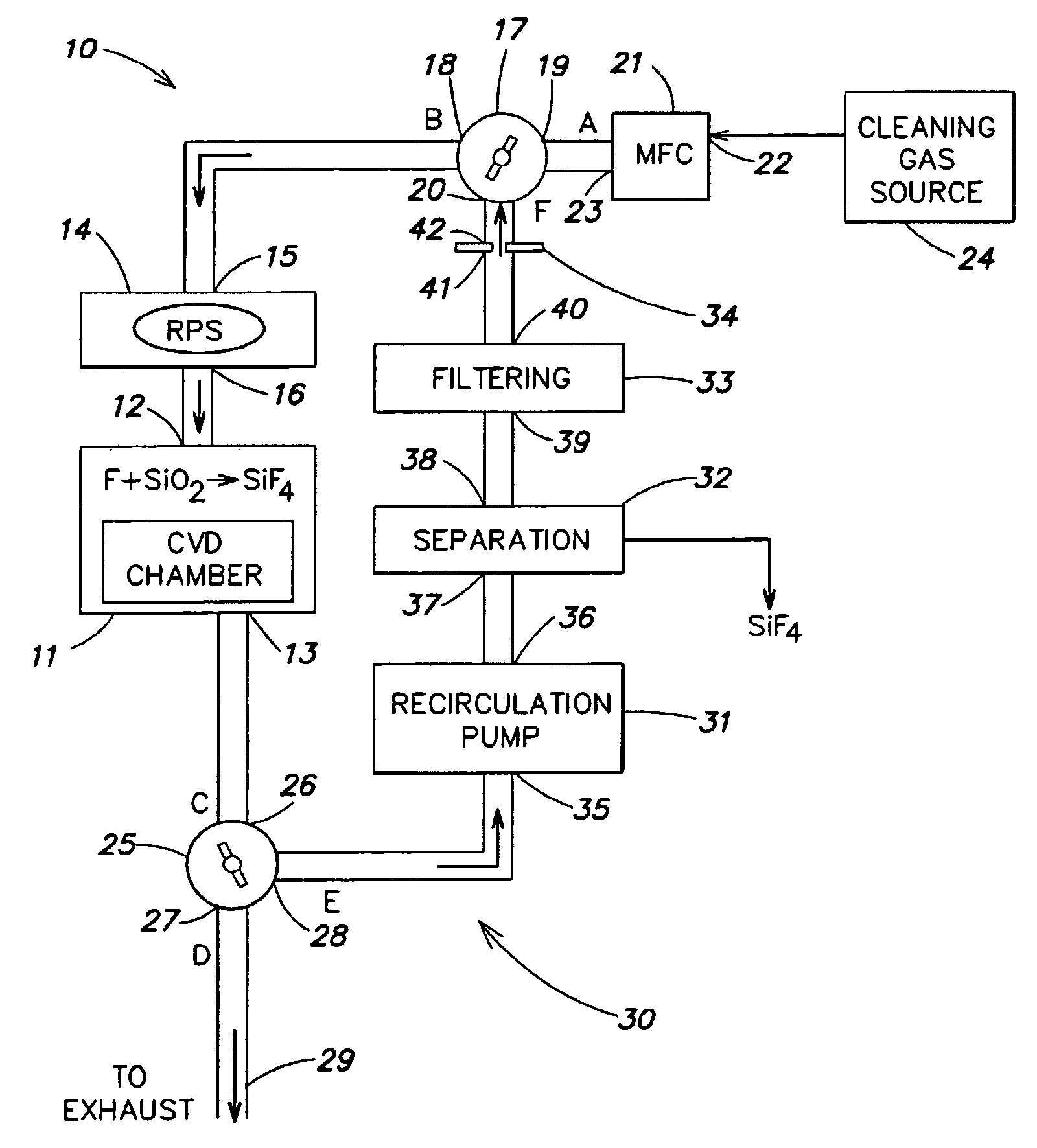

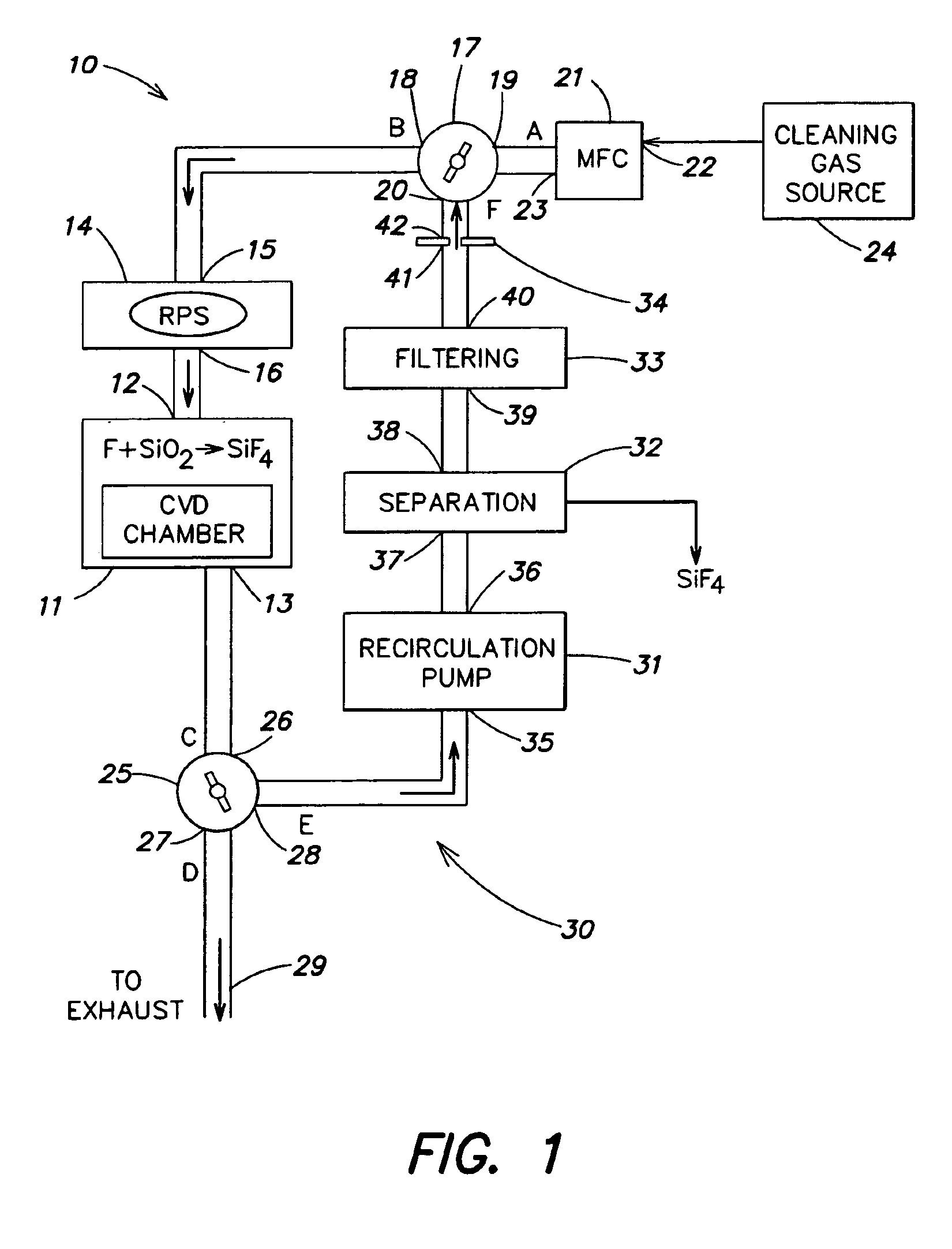

Semiconductor device fabrication chamber cleaning method and apparatus with recirculation of cleaning gas

InactiveUS6863019B2Low costReduce consumptionElectric discharge tubesElectrostatic cleaningNuclear engineeringProduct gas

A method of cleaning a semiconductor fabrication processing chamber involves recirculation of cleaning gas components. Consequently, input cleaning gas is utilized efficiently, and undesirable emissions are reduced. The method includes flowing a cleaning gas to an inlet of a processing chamber, and exposing surfaces of the processing chamber to the cleaning gas to clean the surfaces, thereby producing a reaction product. The method further includes removing an outlet gas including the reaction product from an outlet of the processing chamber, separating at least a portion of the reaction product from the outlet gas, and recirculating a portion of the outlet gas to the inlet of the processing chamber.

Owner:APPLIED MATERIALS INC

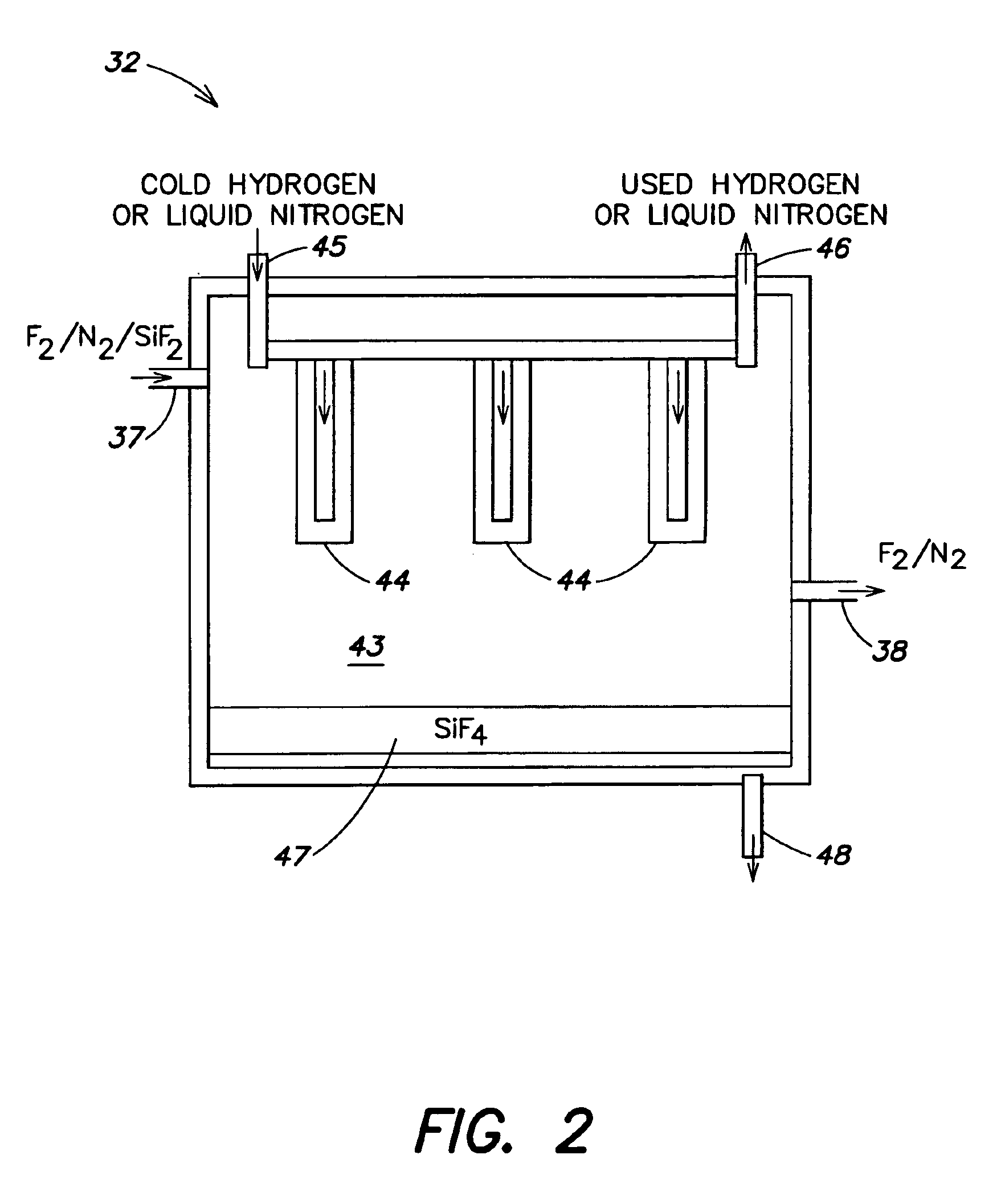

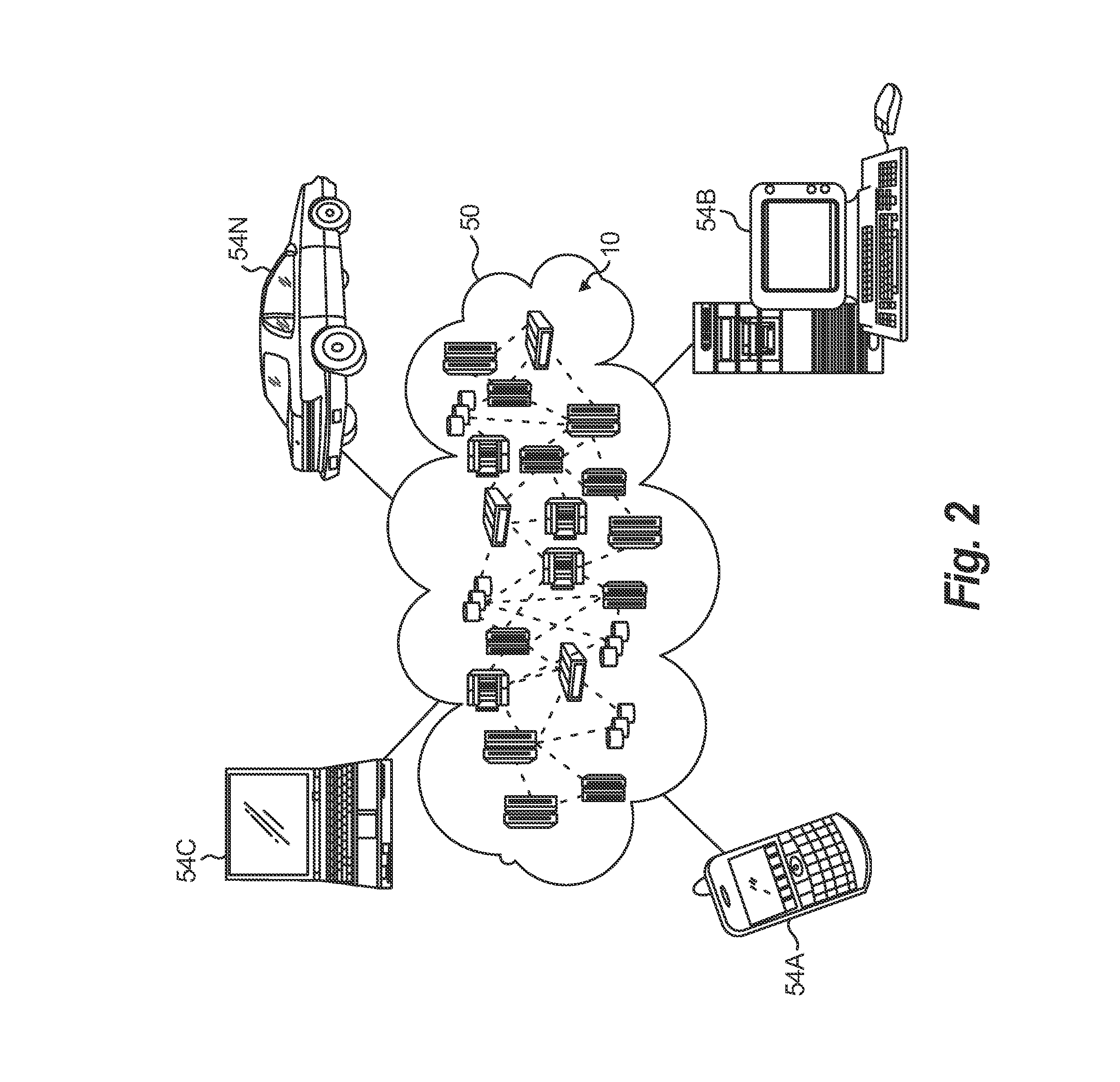

Method and Apparatus for Automated Migration of Data Among Storage Centers

InactiveUS20140173232A1Reduce data storage costsReduce deliveryInput/output to record carriersTransmissionData setData storing

A method for controlling the storage of data among multiple regional storage centers coupled through a network in a global storage system is provided. The method includes steps of: defining at least one dataset comprising at least a subset of the data stored in the global storage system; defining at least one ruleset for determining where to store the dataset; obtaining information regarding a demand for the dataset through one or more data requesting entities operating in the global storage system; and determining, as a function of the ruleset, information regarding a location for storing the dataset among regional storage centers having available resources that reduces the total distance traversed by the dataset in serving at least a given one of the data requesting entities and / or reduces the latency of delivery of the dataset to the given one of the data requesting entities.

Owner:IBM CORP

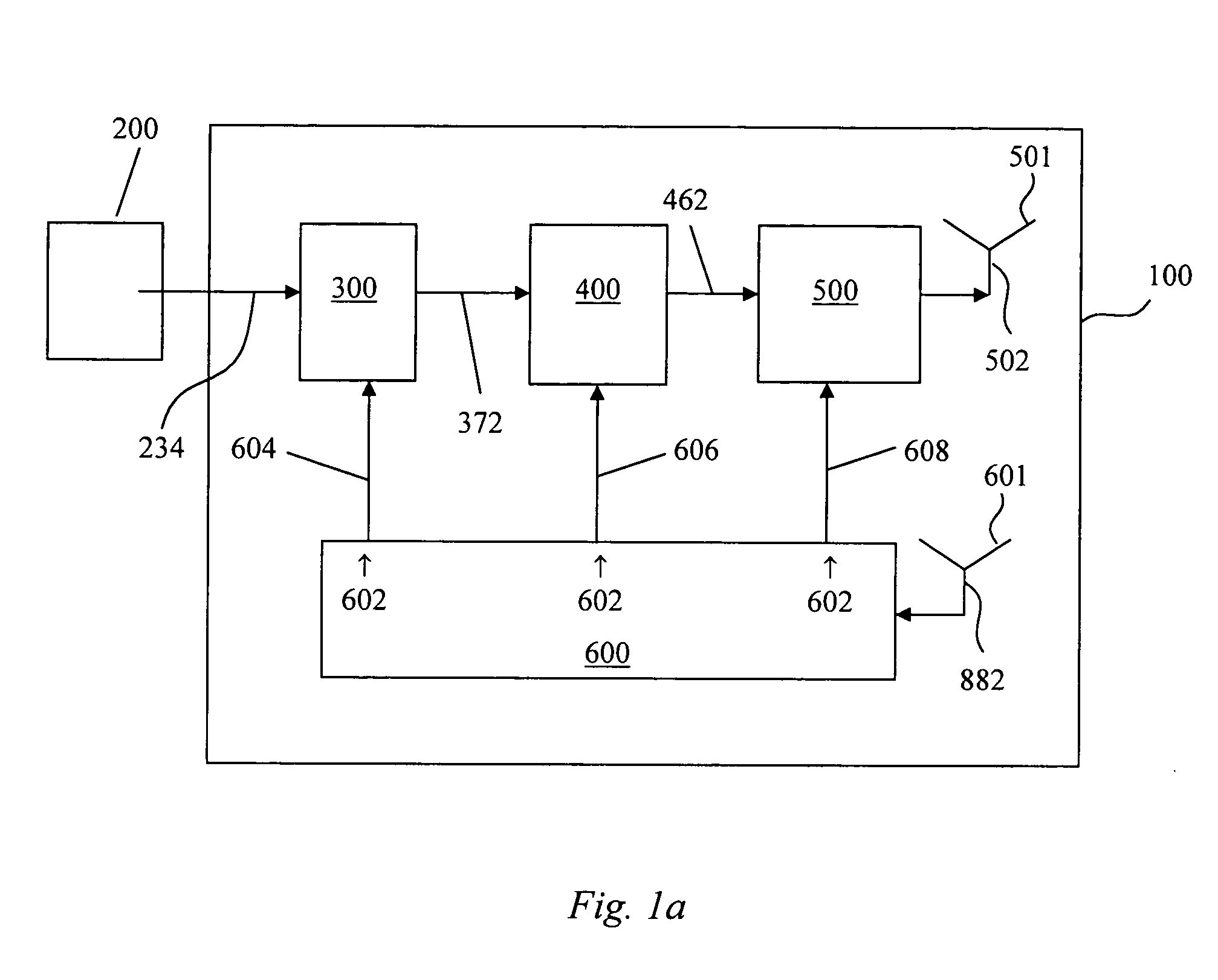

Embedded bio-sensor system

InactiveUS7125382B2Improve accuracyAccurate measurementTelemedicineEndoradiosondesGlucose sensorsConcentrations glucose

Provided is a bio-sensor system which utilizes radio frequency identification technology and which includes a remote transponder in wireless communication with an implantable passively-powered on-chip transponder. The bio-sensor system is specifically adapted to provide a substantially stable and precise sensor reference voltage to a sensor assembly that is included with the on-chip transponder. The remote transponder is also configured to remotely receive data representative of a physiological parameter of the patient as well as identification data and may enable readout of one or more of the physiological parameters that are measured, processed and transmitted by the on-chip transponder upon request by the remote transponder. The precision and stability of the sensor reference voltage is enhanced by the specific circuit architecture of the glucose sensor to allow for relatively accurate measurement of the physiological parameter such as measurement of glucose concentration by a glucose sensor without the use of a microprocessor.

Owner:JAMM TECH INC

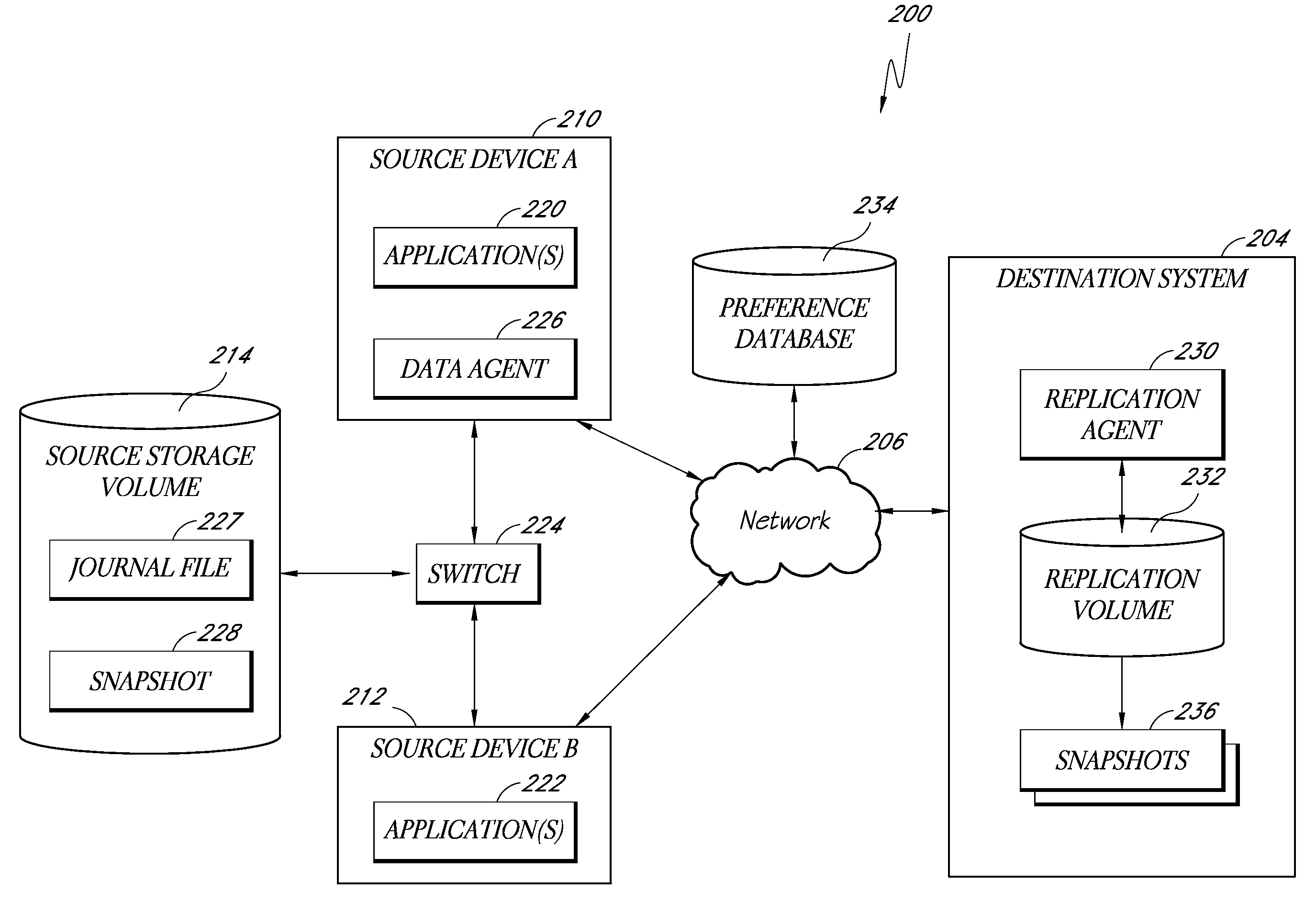

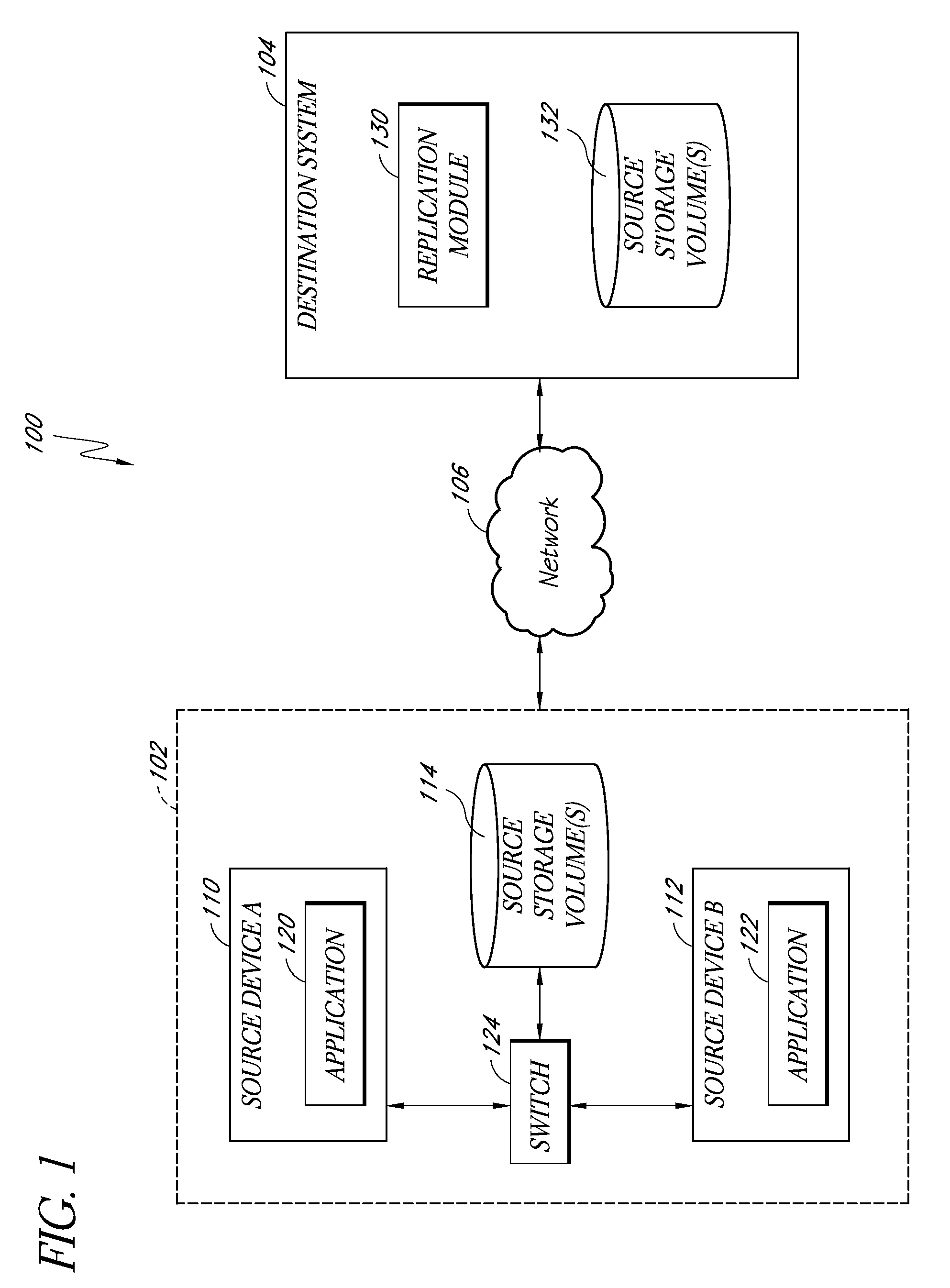

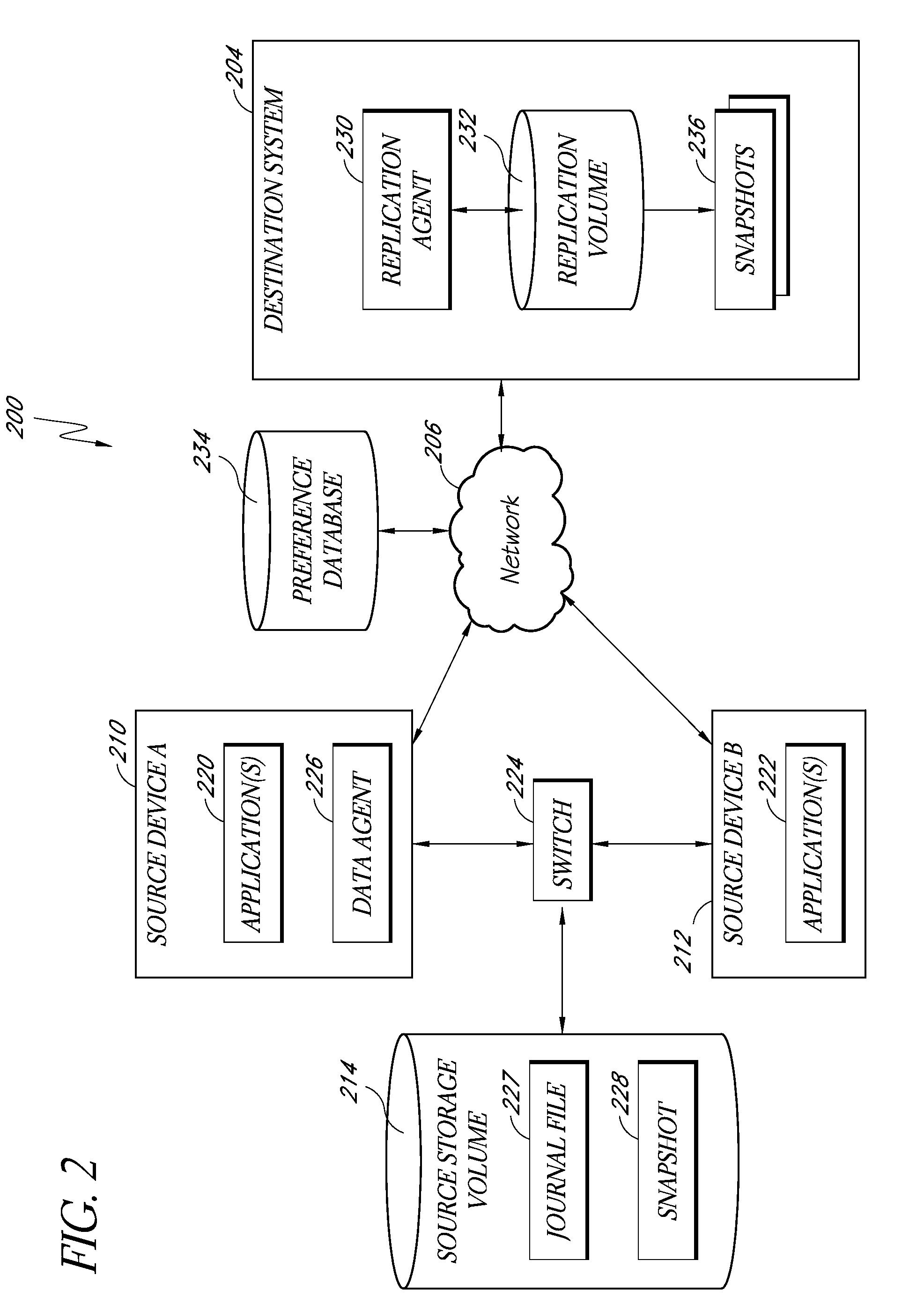

Systems and methods for performing discrete data replication

ActiveUS20100179941A1Reduce data volumeReduce consumptionDigital data information retrievalDigital data processing detailsBlock levelSource system

Systems and methods for performing intelligent replication of production data on a source storage device. In certain examples, a full backup of the production data is first performed and stored on a destination system. A journal module on the storage device (e.g., a shared storage device), or on at least one source system, tracks files on the storage device that change during a particular period of time. Following this period, a snapshot is taken of the production data. Upon mounting the snapshot, the replication system uses the journal information to identify modified files, conduct a block-level comparison of only the modified files with corresponding files on the destination system, and identify the particular data blocks that changed. The replication system then replicates only the changed blocks to the destination system. Certain systems further store information indicating a source system time of a known good state of the production data.

Owner:COMMVAULT SYST INC

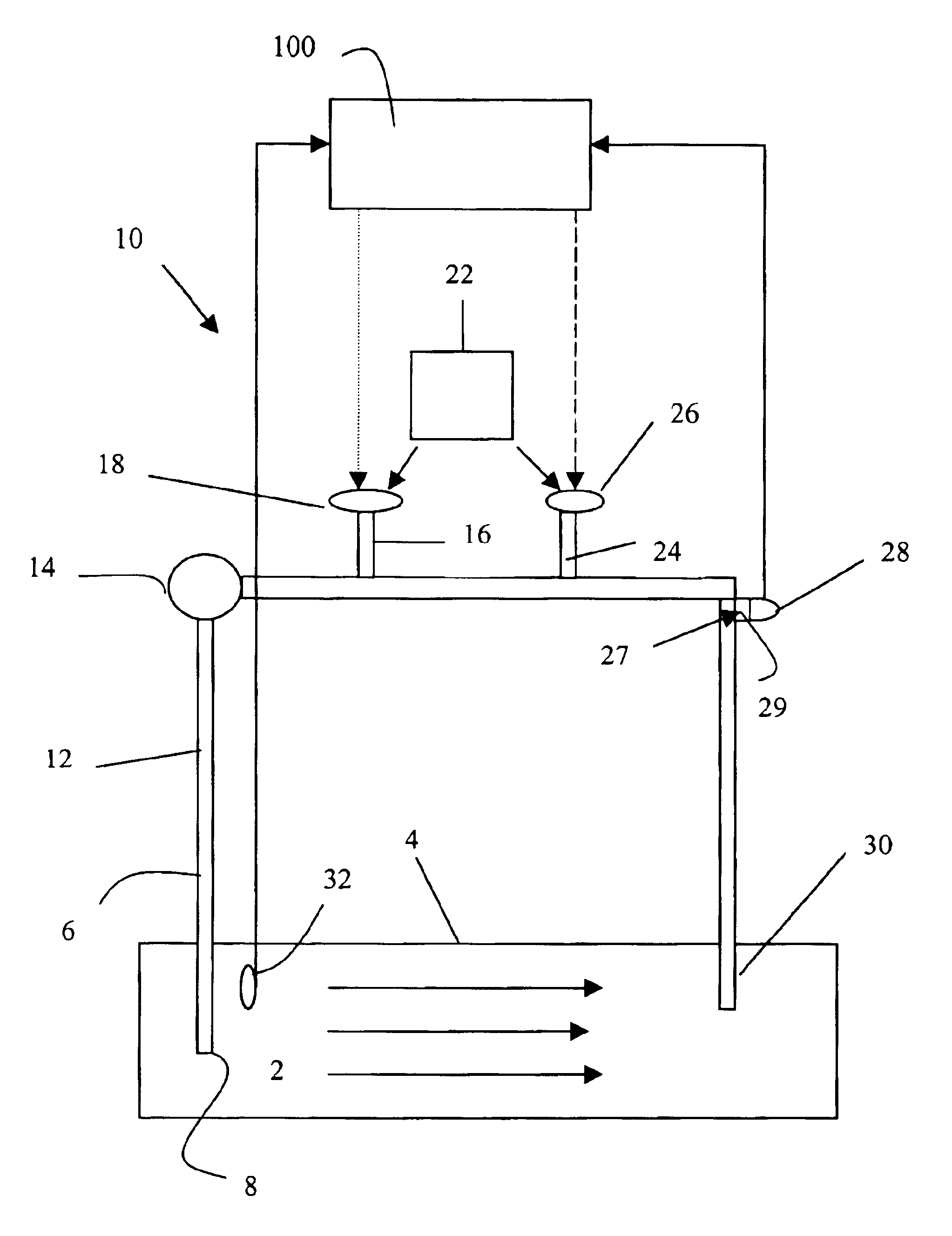

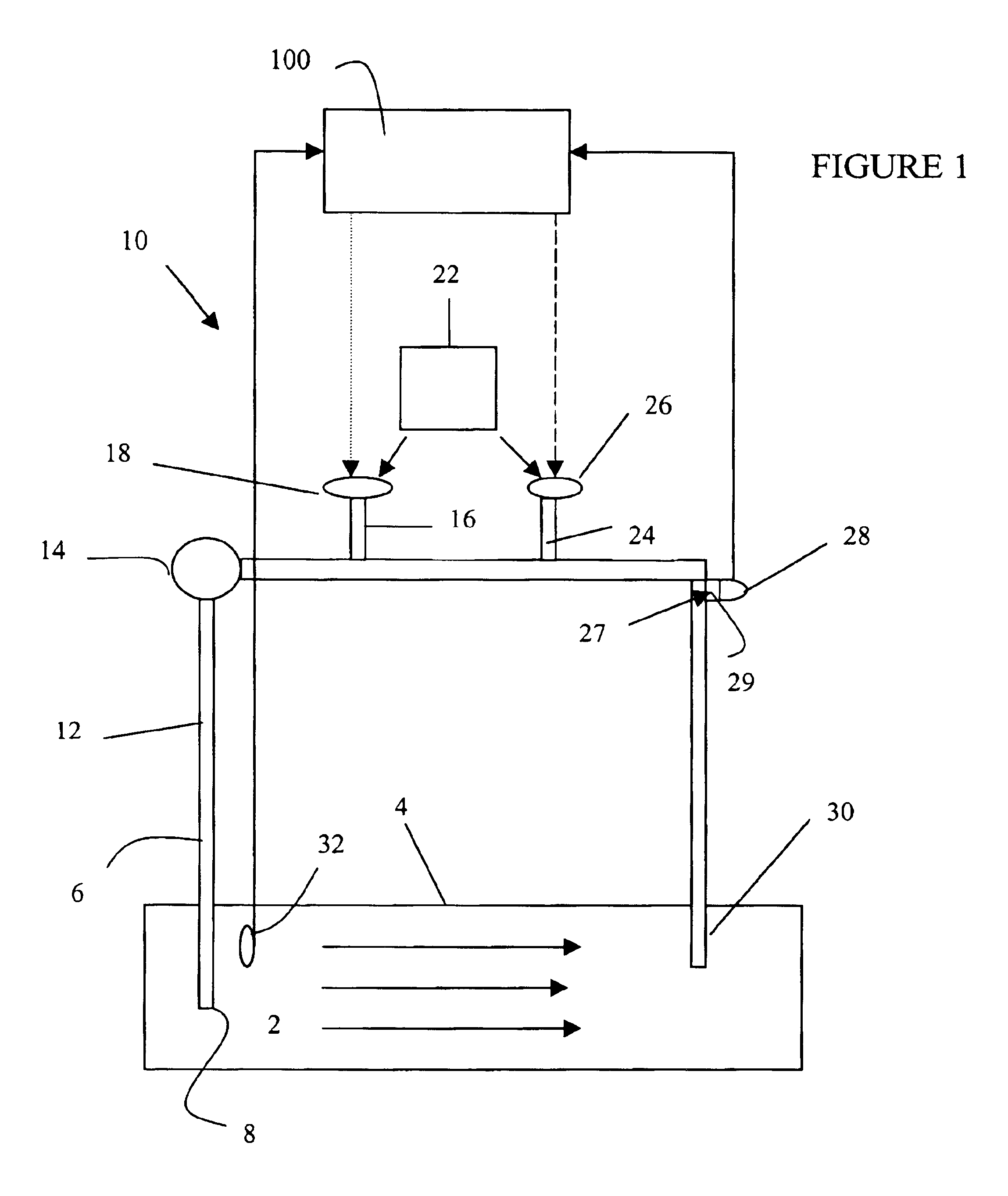

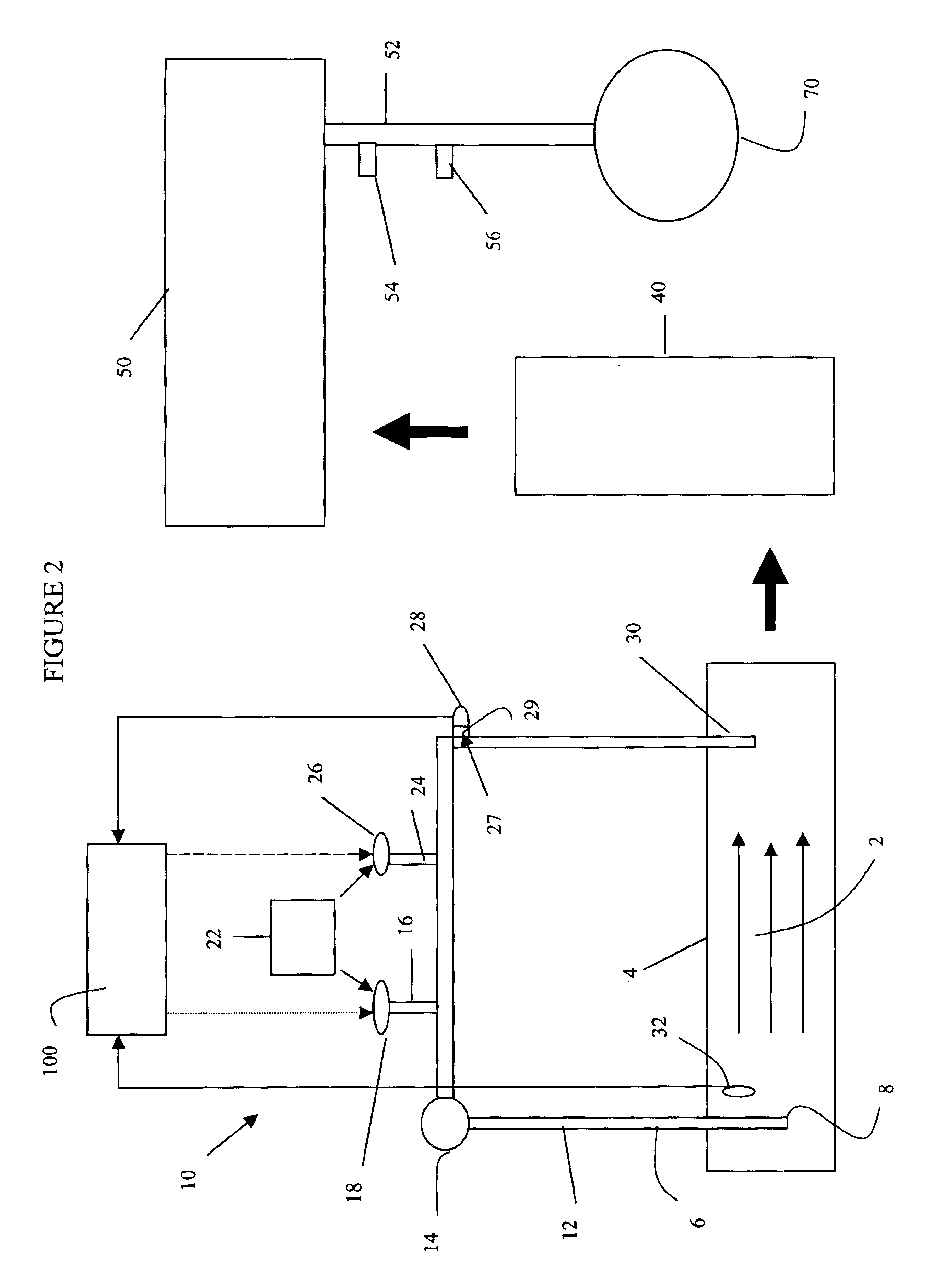

Methods and systems for improved dosing of a chemical treatment, such as chlorine dioxide, into a fluid stream, such as a wastewater stream

InactiveUS6949196B2Reduce consumptionQuantity minimizationWater treatment parameter controlOther chemical processesChemical treatmentChlorine dioxide

The invention is directed to methods, apparatuses, and systems for treatment of a liquid flow comprising addition of a chemical treatment at at least two locations along a side stream of a main flow of said liquid, in which the dosing by such additions is sufficient to treat the entire main flow upon return of the side stream to the main flow. Algorithms are utilized to control the additions at the locations of addition of chemical treatments. In a typical embodiment, one chemical addition is principally proportional to the flow rate of the liquid flow, and the other chemical addition is principally adjusted based on signals from a primary measuring device that measures a parameter in the flow after one or both chemical additions. The addition of chlorine dioxide as the chemical treatment, to disinfect wastewater, is discussed.

Owner:FKOS LLC +1

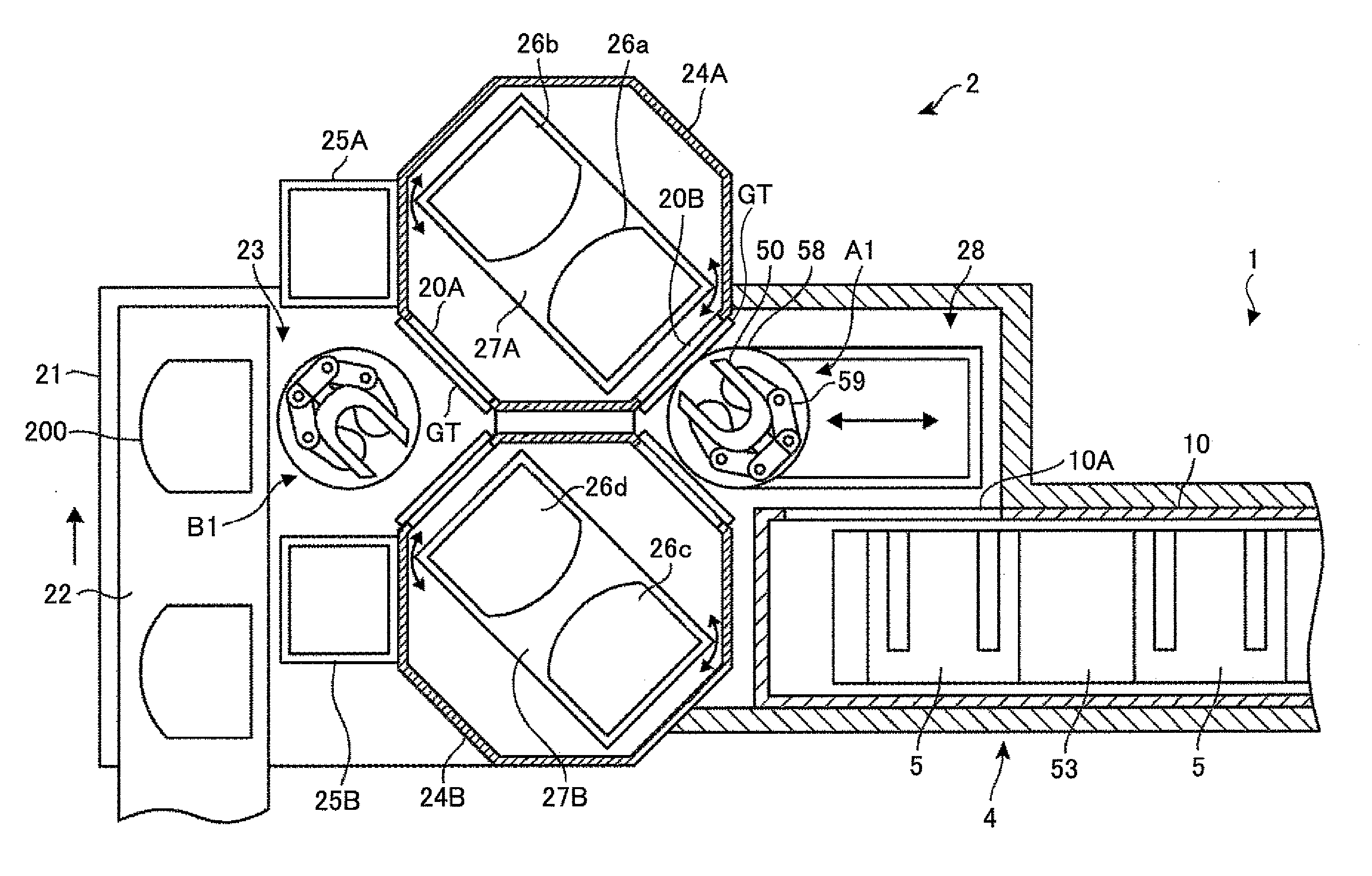

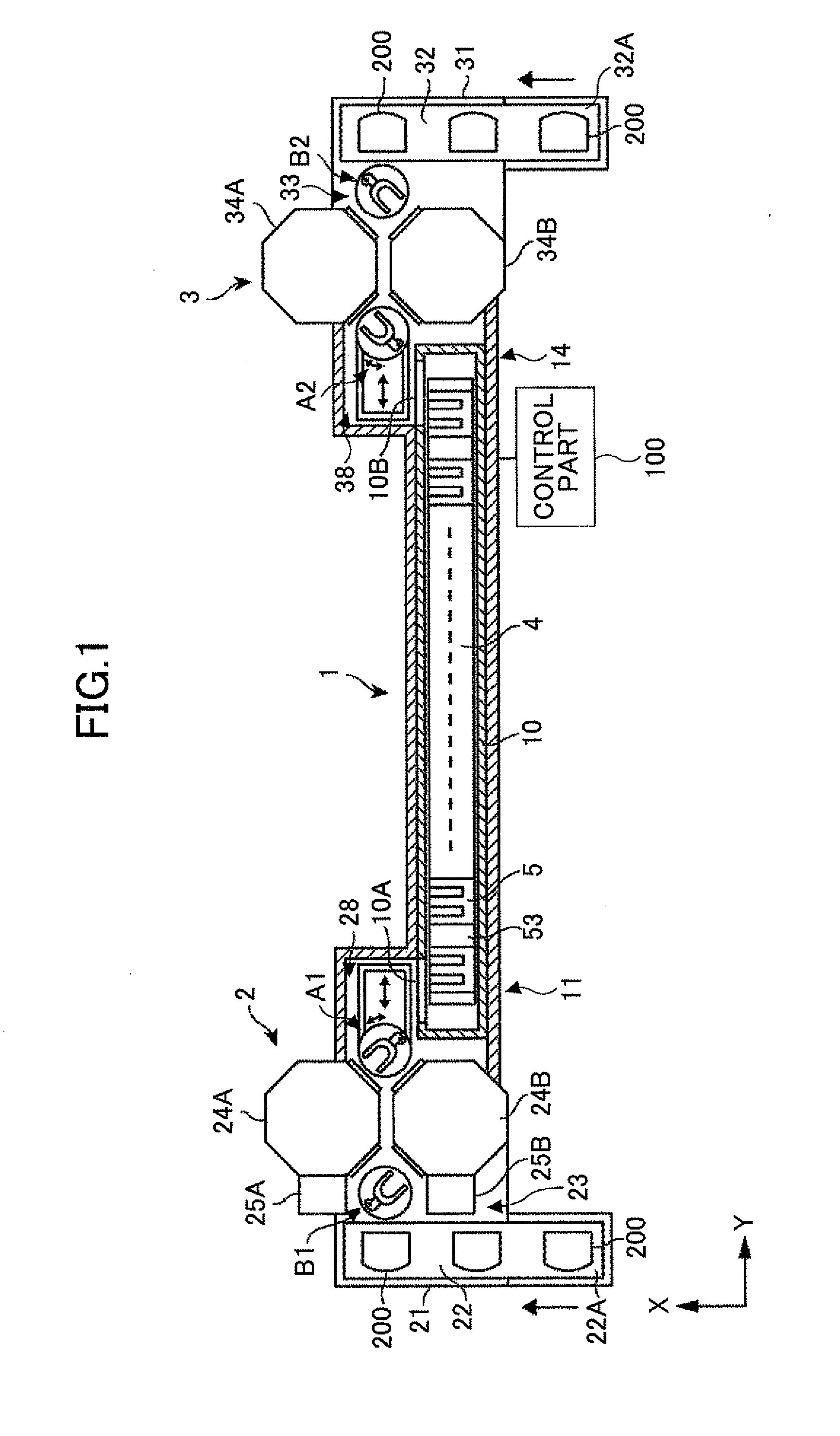

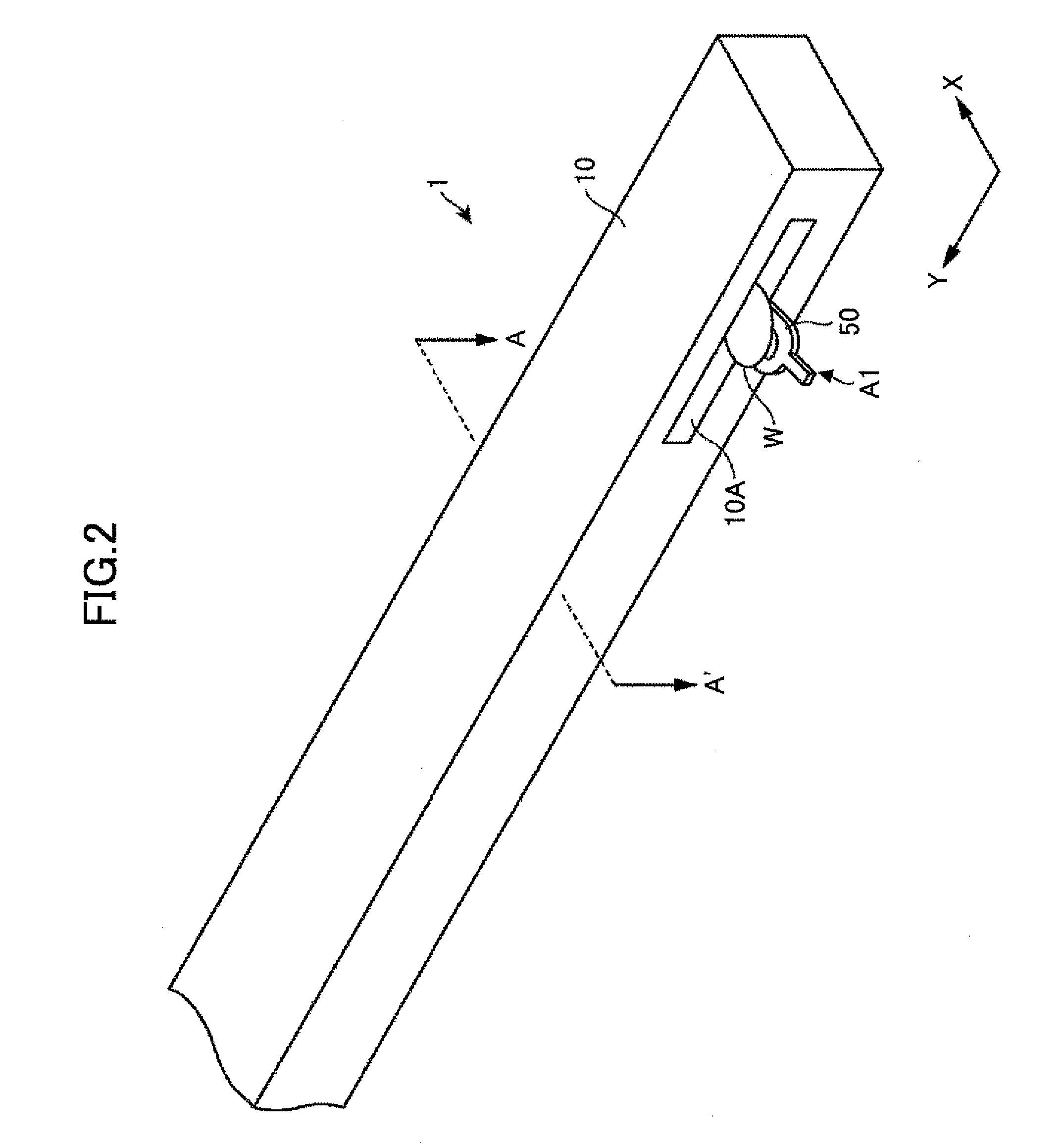

Film deposition device and substrate processing device

InactiveUS20110265725A1Improve throughputLow gas consumptionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingReactive gasGas supply

A film deposition device includes a substrate transporting device arranged in a vacuum chamber to include a circulatory transport path in which substrate mounting parts arranged in a row are transported in a circulatory manner, the circulatory transport path including a linear transport path in which the substrate mounting parts are transported linearly. A first reactive gas supplying part is arranged along a transporting direction in which the substrate mounting parts are transported in the linear transport path, to supply a first reactive gas to the substrate mounting parts. A second reactive gas supplying part is arranged alternately with the first reactive gas supplying part along the transporting direction, to supply a second reactive gas to the substrate mounting parts. A separation gas supplying part is arranged to supply a separation gas to a space between the first reactive gas supplying part and the second reactive gas supplying part.

Owner:TOKYO ELECTRON LTD

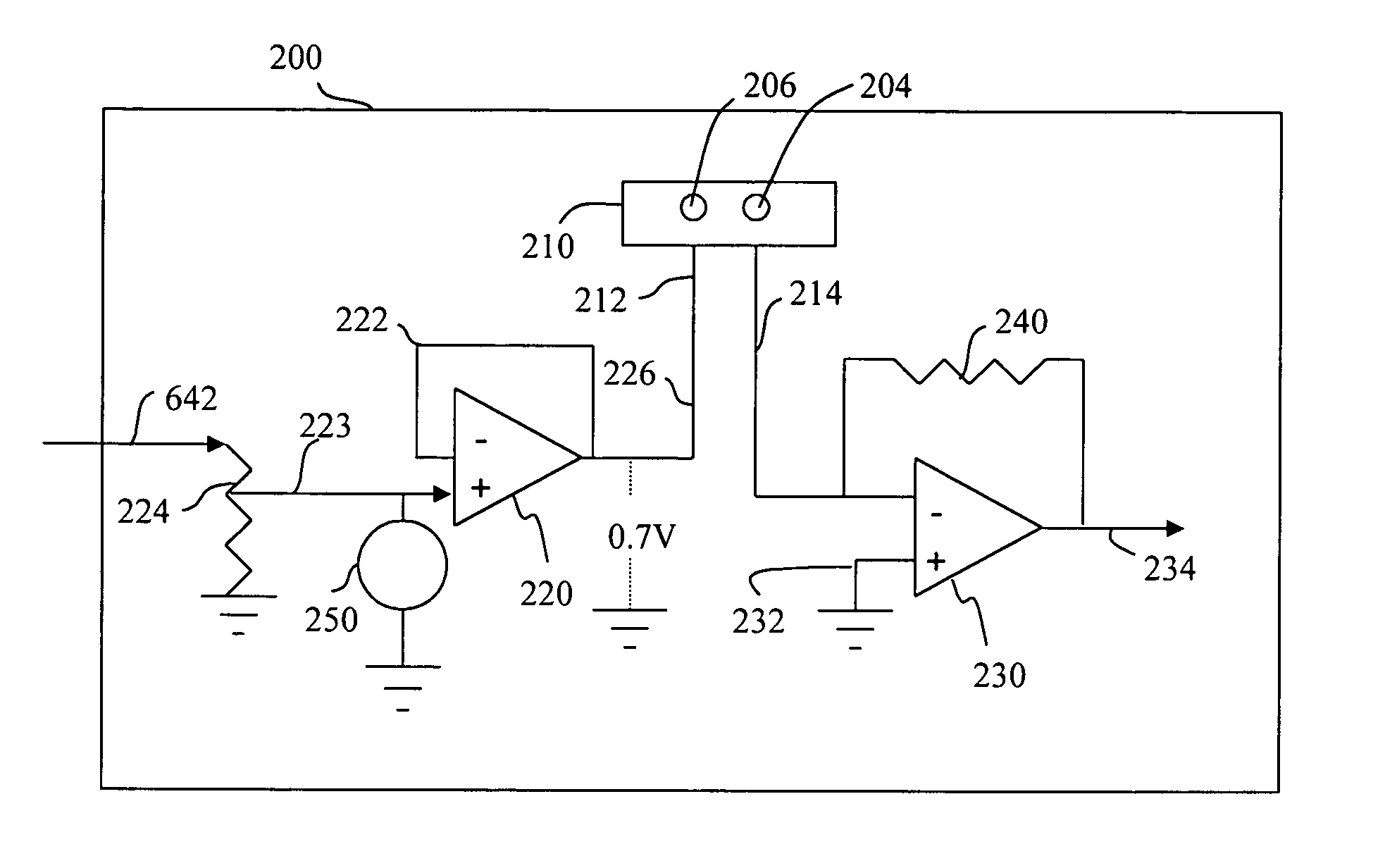

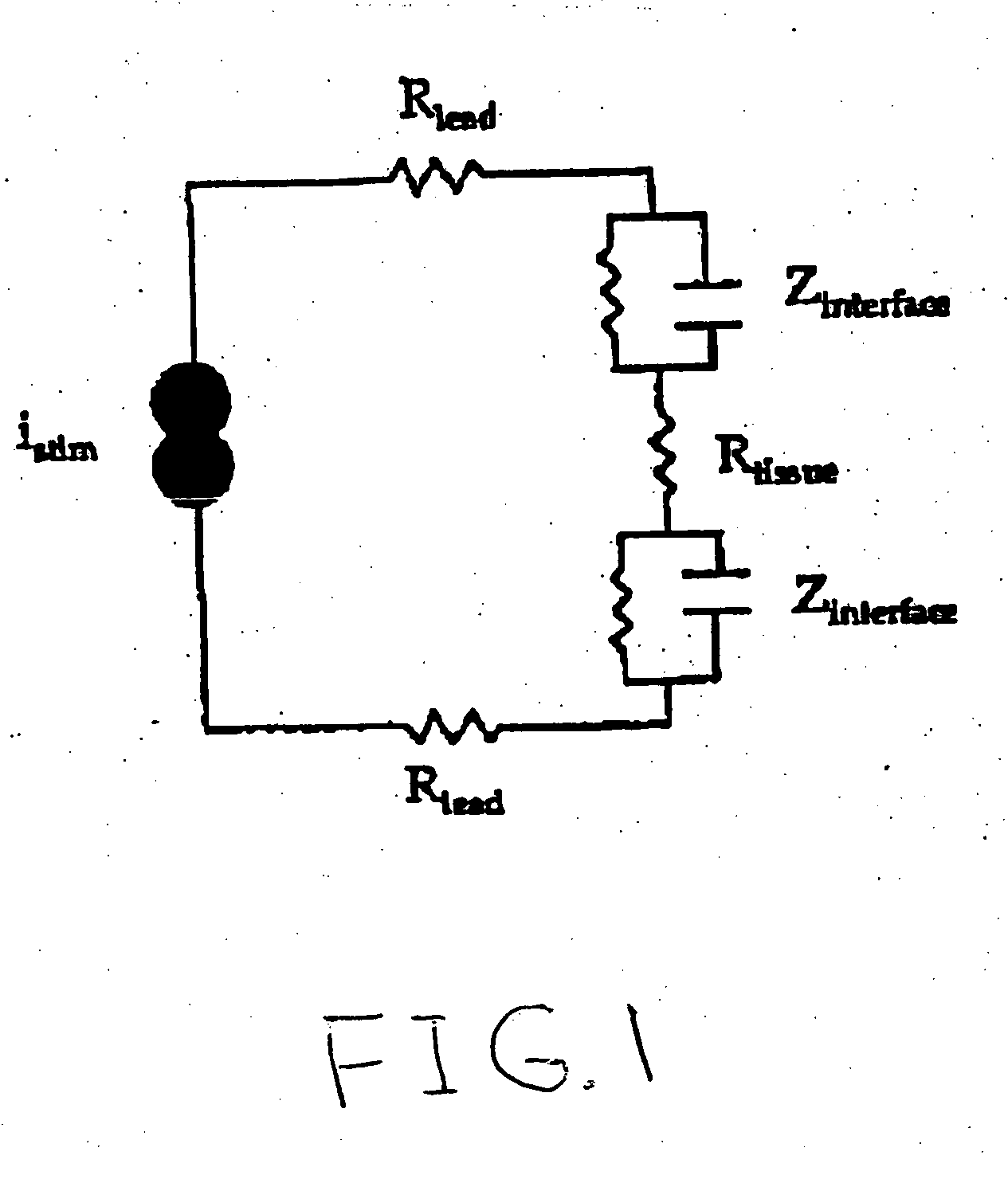

Transducer for embedded bio-sensor using body energy as a power source

InactiveUS20050261563A1Improve accuracyAccurate measurementTelemedicineEndoradiosondesMuscle tissueVoltage pulse

Provided is a bio-sensor system which utilizes radio frequency identification technology and which includes a remote transponder in wireless communication with an implantable on-chip transponder. A power supply collects alternating current voltage pulses from an electro-active polymer generator embedded in muscle tissue for generating power for the on-chip transponder. The power supply is specifically adapted to provide a stable and precise sensor reference voltage to a sensor assembly to enhance the accuracy of measurements of a physiological parameter of a patient. The remote transponder receives data representative of the physiological parameter such as glucose concentration levels. The data is processed and transmitted to the remote transponder by the on-chip transponder. The precision and stability of the sensor reference voltage is enhanced by the specific circuit architecture of a glucose sensor to allow for relatively accurate measurement of glucose concentration levels without the use of a microprocessor.

Owner:JAMM TECH INC

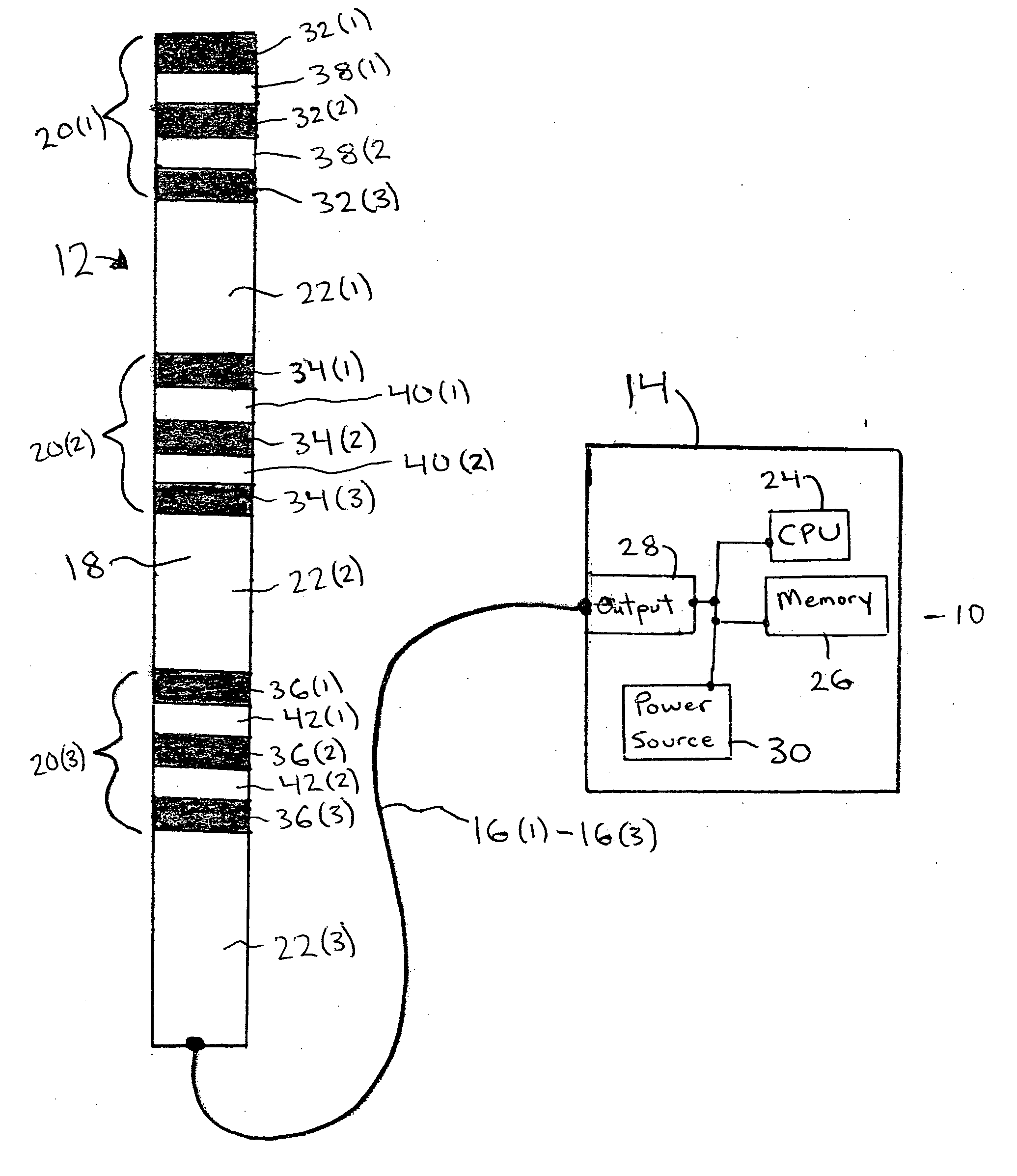

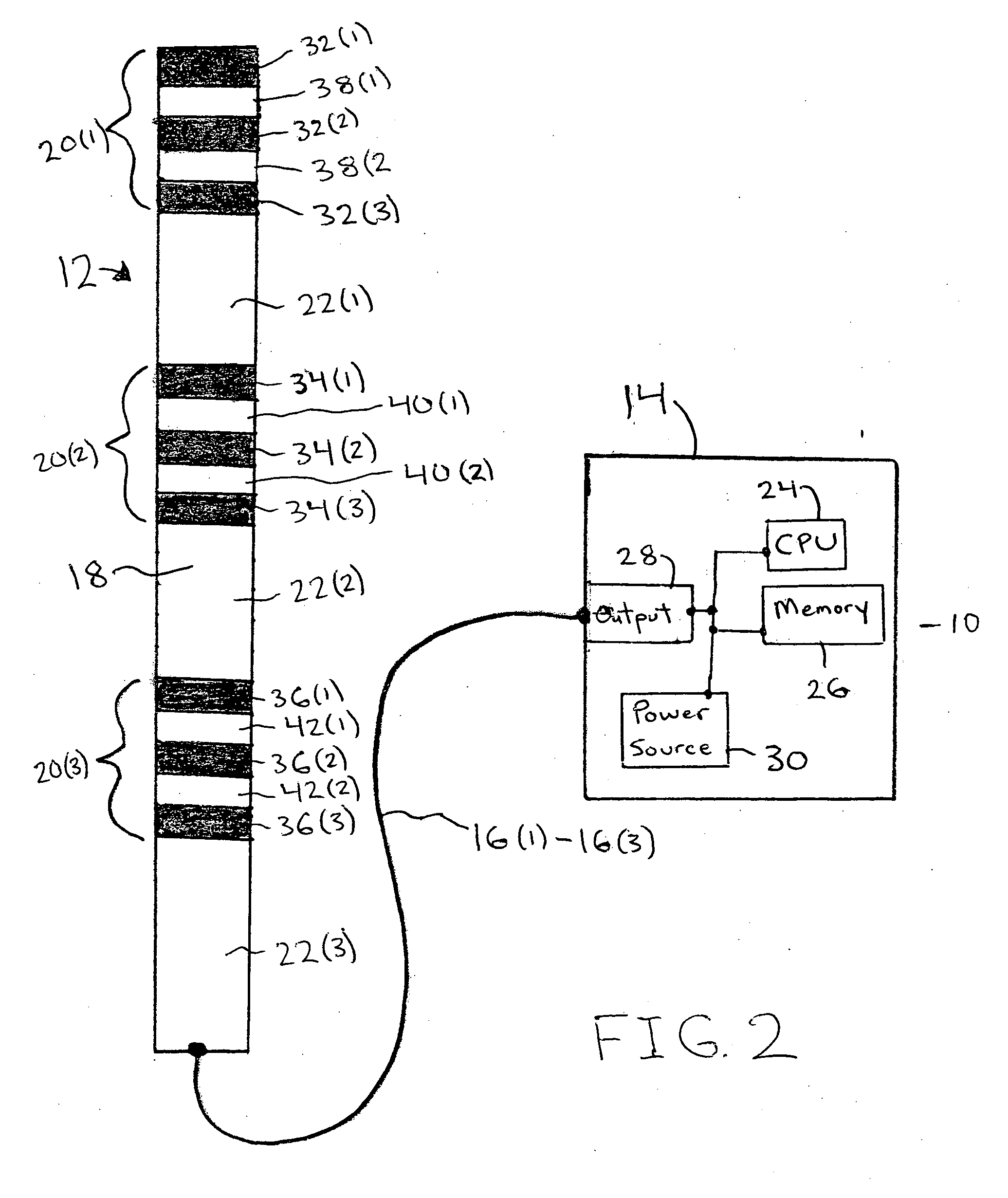

Electrode array for use in medical stimulation and methods thereof

InactiveUS20050038489A1Reduce power consumptionIncrease battery lifeSpinal electrodesExternal electrodesElectrode arrayBiomedical engineering

An electrode array for use in medical stimulation includes one or more electrodes along an array body and one or more leads. Each of the electrodes has one or more conductive sections and each of the conductive sections has an outer surface which is substantially exposed from the array body for coupling to tissue. At least one of the electrodes has at least one of: adjacent pairs of the conductive sections separated by an insulating section; the conductive section having at least one portion which is spaced in from other portions of the conductive section and which substantially extends all the way around or all along a length of the conductive section; at least one substantially non-planar end; and a substantially planar shape with a substantially non-linear outer edge. Each of the electrodes has at least one of the leads coupled to each of the conductive sections of the electrode.

Owner:CASE WESTERN RESERVE UNIV

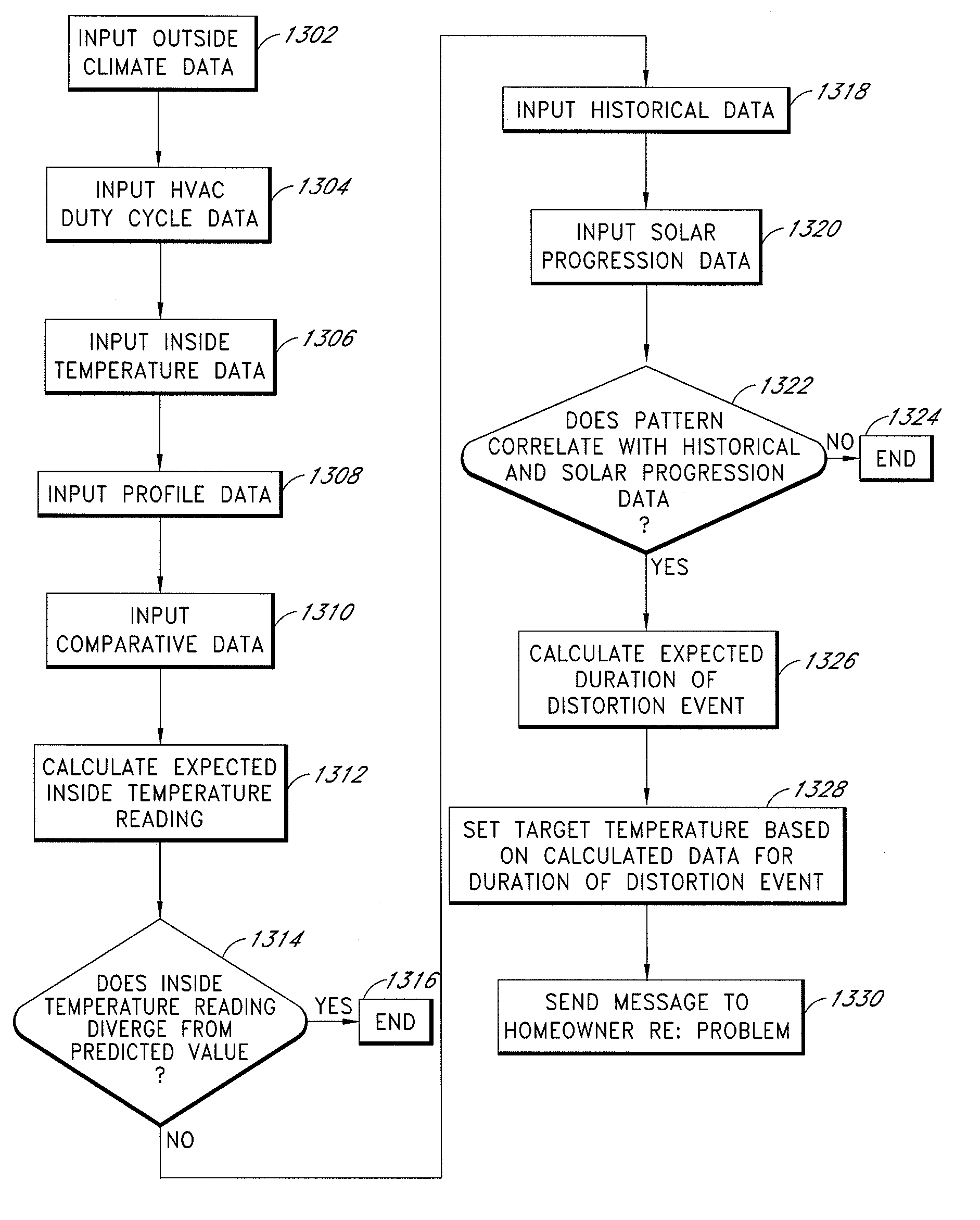

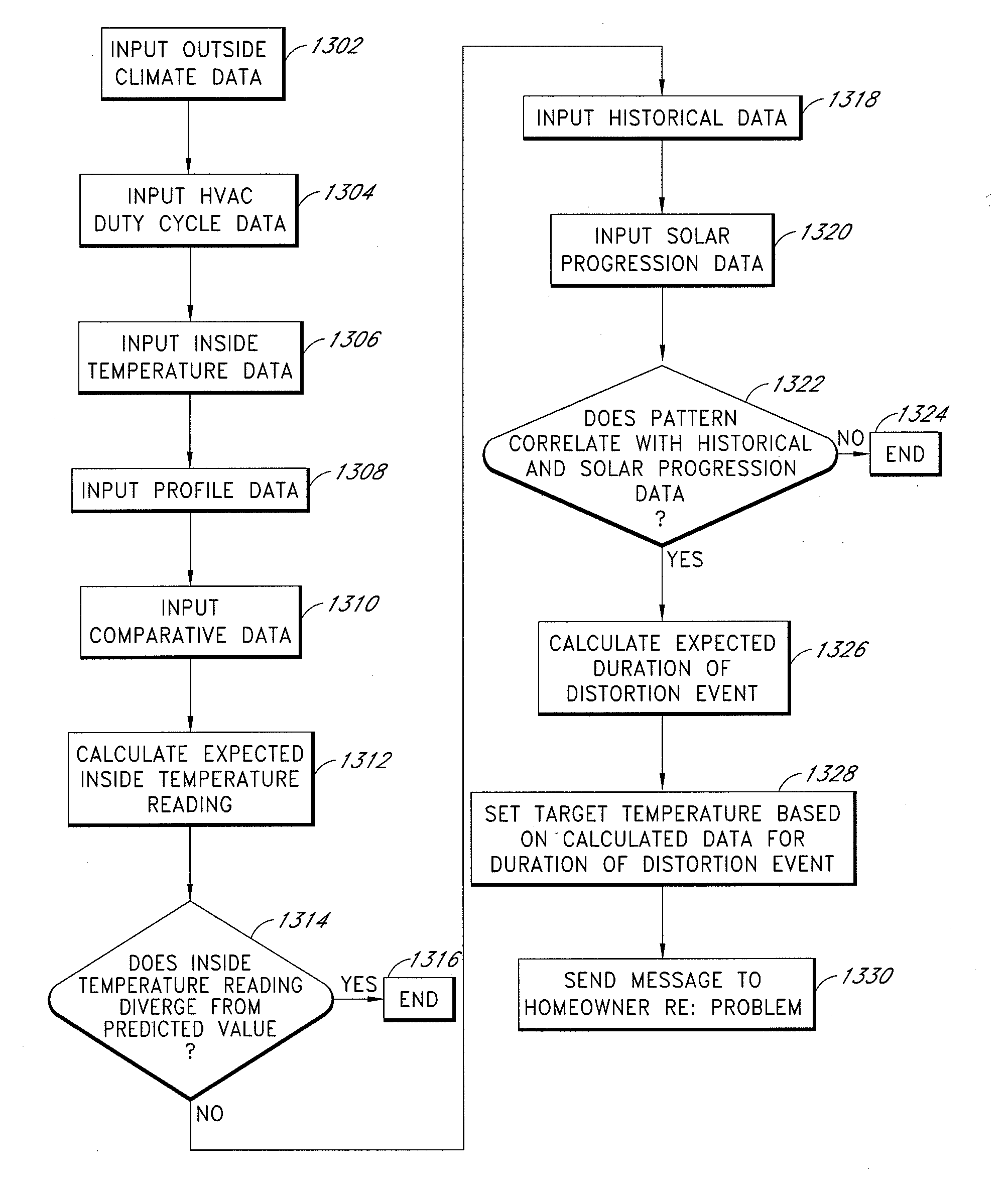

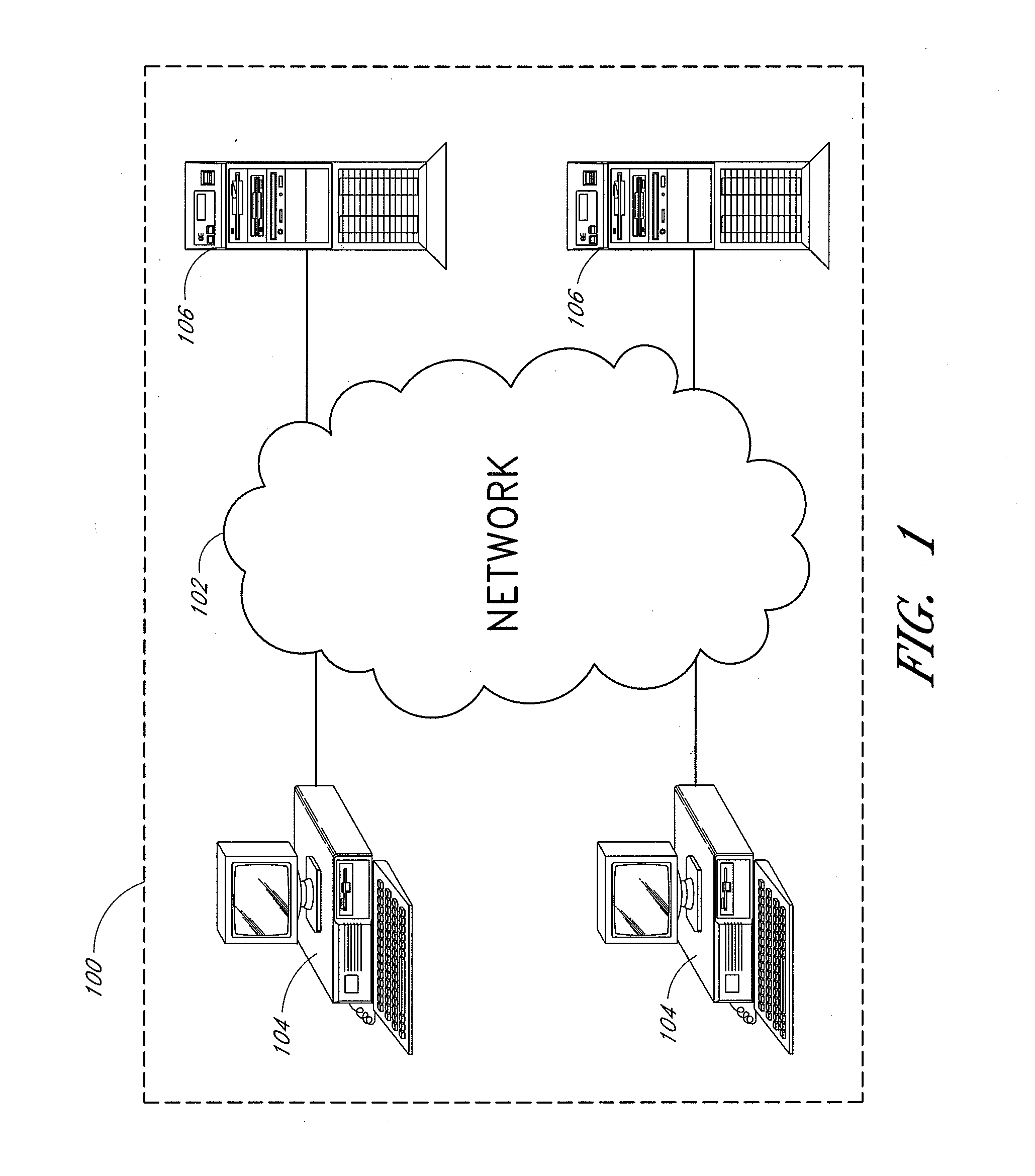

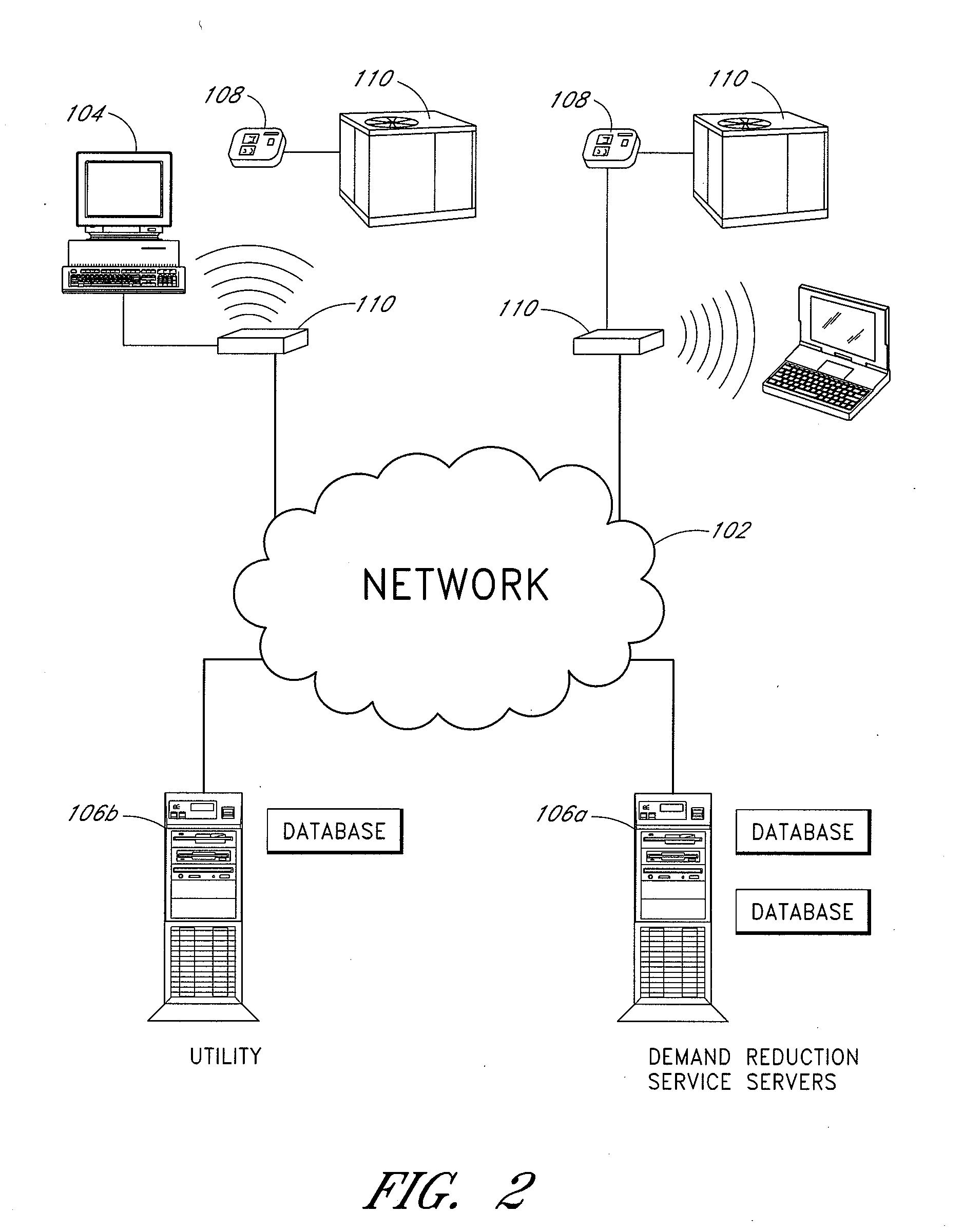

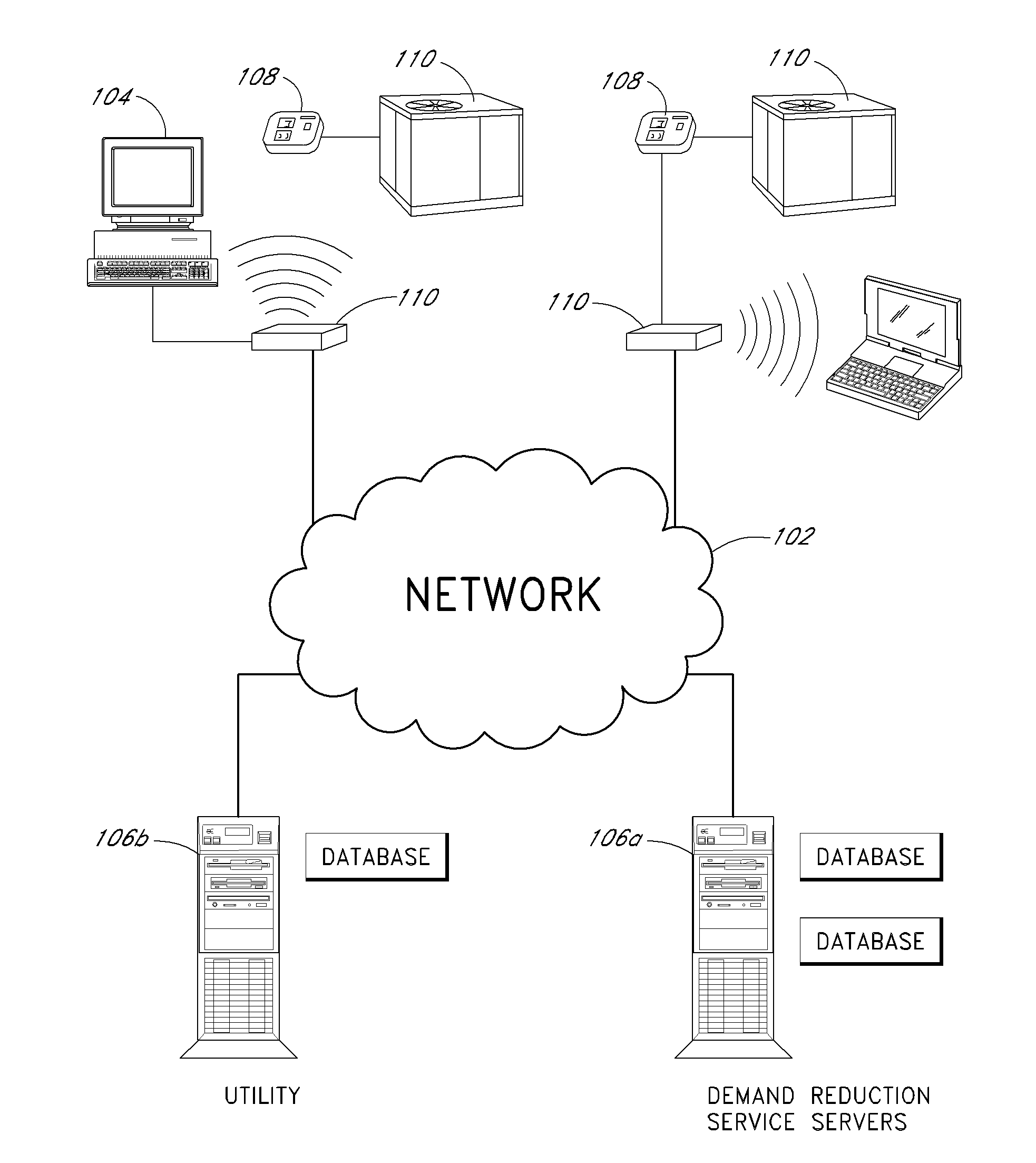

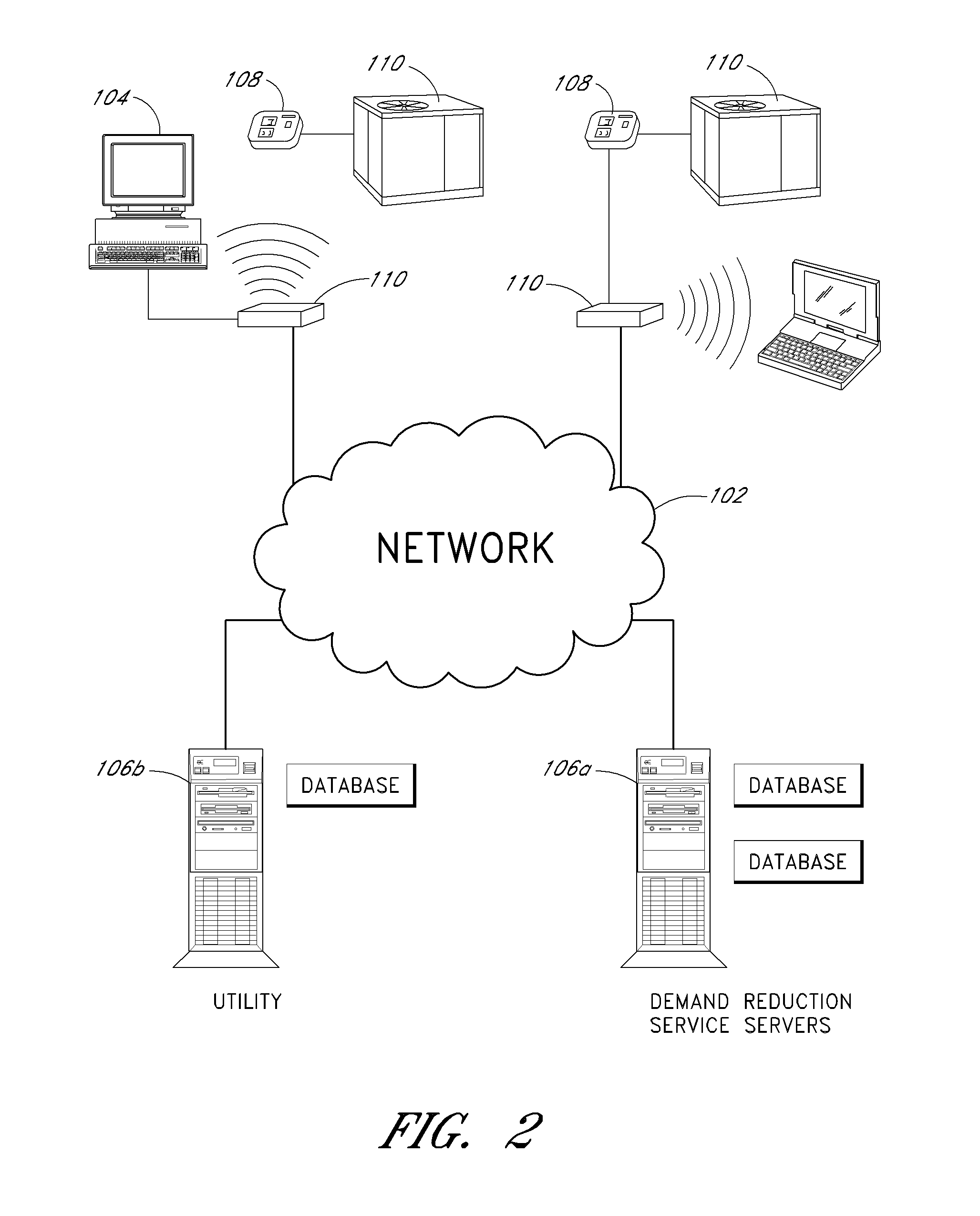

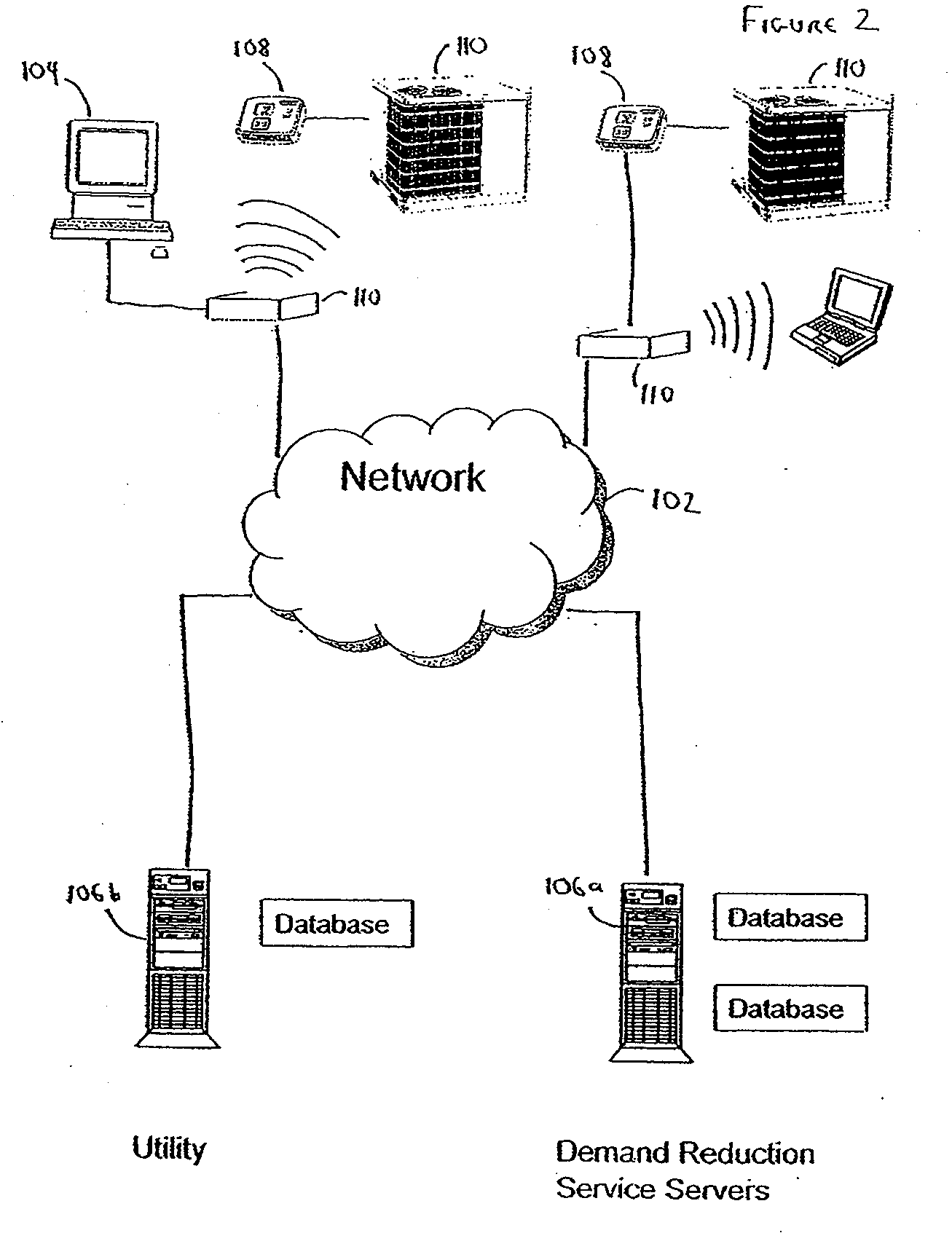

System and method for evaluating changes in the efficiency of an HVAC system

ActiveUS8019567B2Improve comfortReduce energy useTime indicationSpace heating and ventilationControl systemEngineering

The invention comprises systems and methods for evaluating changes in the operational efficiency of an HVAC system over time. The climate control system obtains temperature measurements from at least a first location conditioned by the climate system, and status of said HVAC system. One or more processors receives measurements of outside temperatures from at least one source other than said HVAC system and compares said temperature measurements from said first location with expected temperature measurements. The expected temperature measurements are based at least in part upon past temperature measurements.

Owner:ECOFACTOR

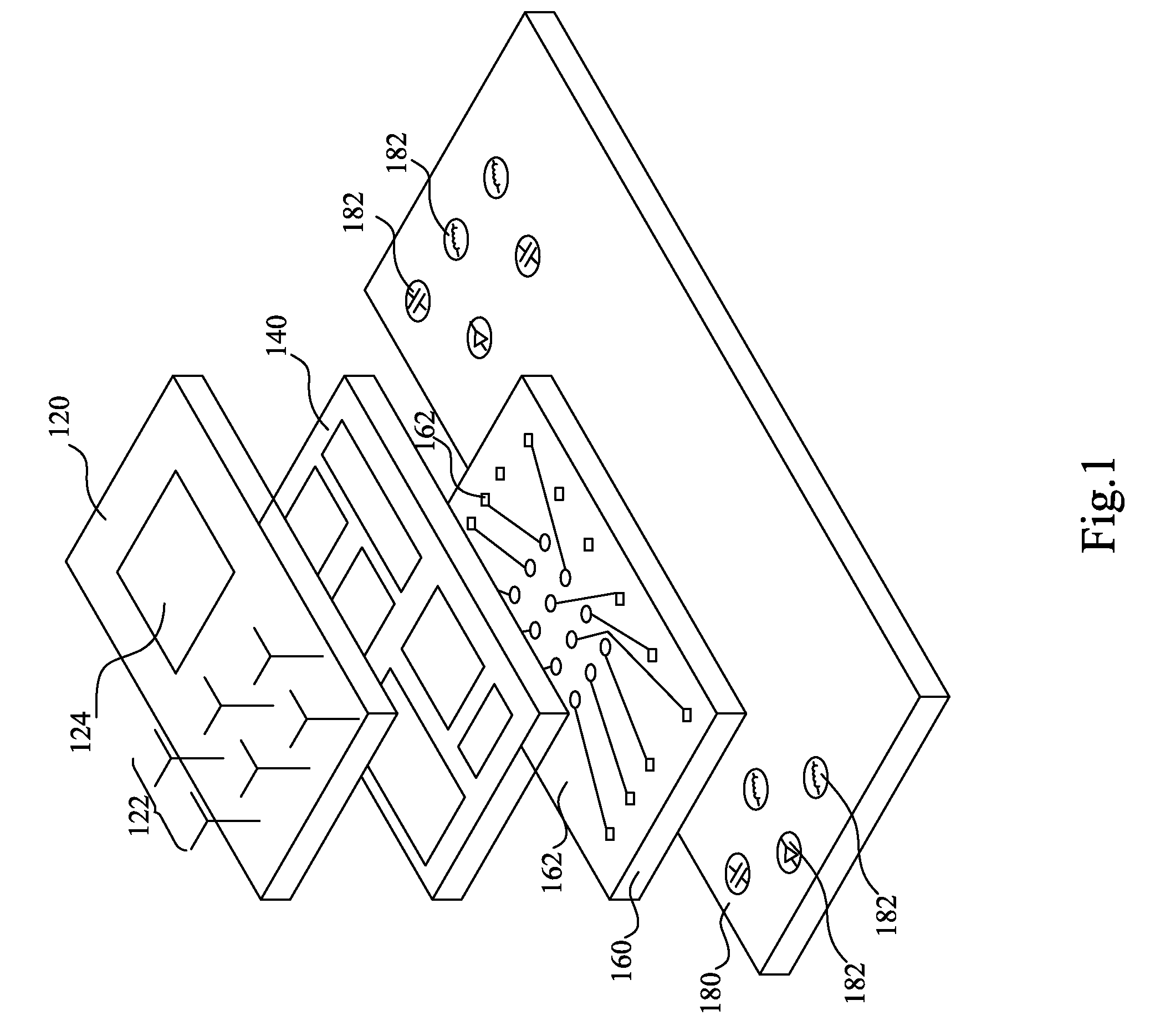

Methods and systems for the manufacture of layered three-dimensional forms

ActiveUS20050017394A1Lower potentialEasy to controlConfectionerySweetmeatsParticulatesBiological activation

New methods and systems for manufacturing a three-dimensional form, comprising steps of providing a plurality of particulates; contacting the particulates with an activation agent; contacting particulates having the activation agent with a binder material that is activatable by the activation agent; at least partially hardening the binder for forming a layer of the three-dimensional form; and repeating these steps to form the remainder of the three-dimensional form. Following sequential application of all required layers and binder material to make the form, the unbound particles are appropriately removed (and optionally re-used), to result in the desired three-dimensional form. The invention also contemplates a novel method for preparing a form, where unbound particulates free of binder material are re-claimed.

Owner:EXONE

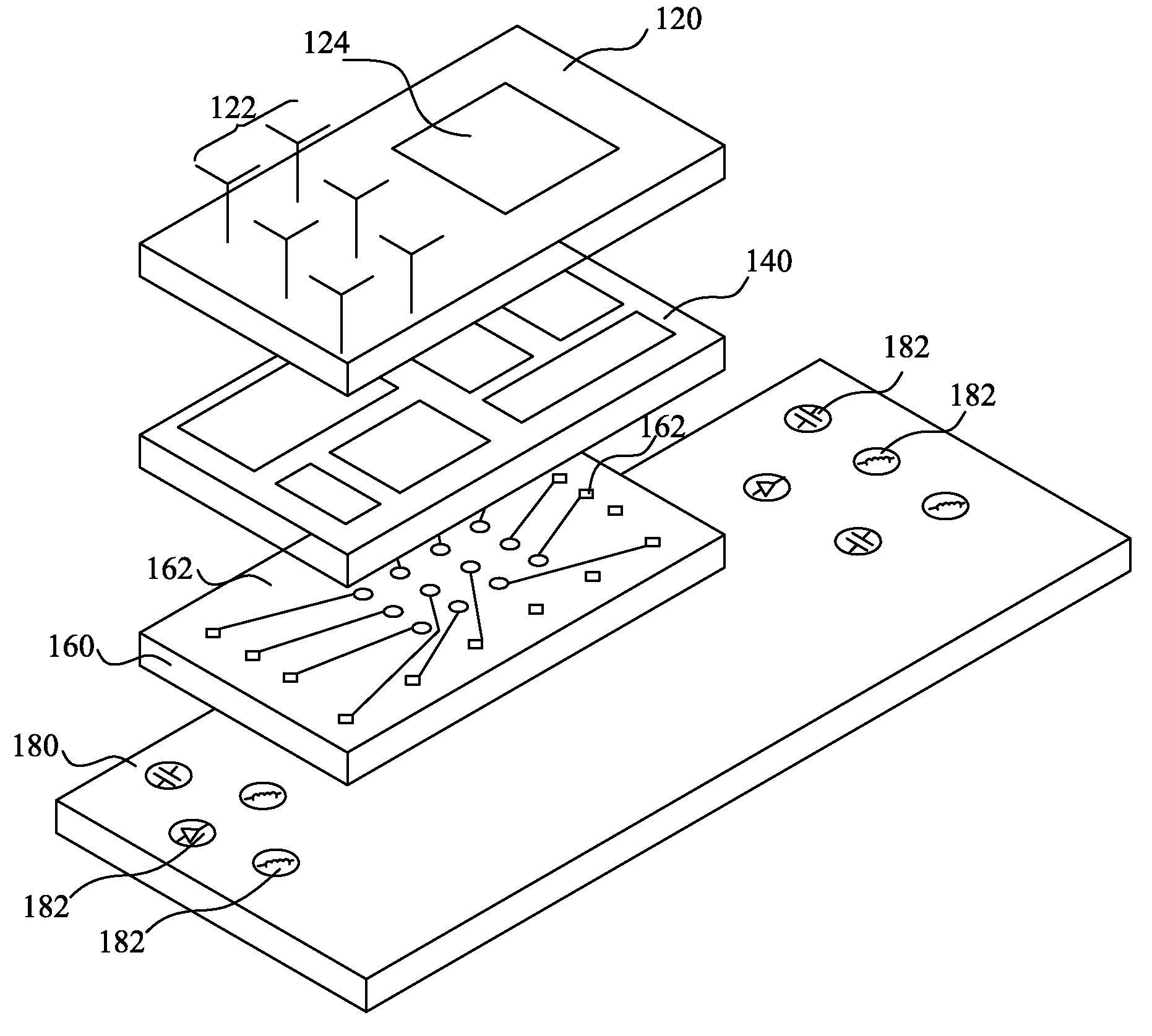

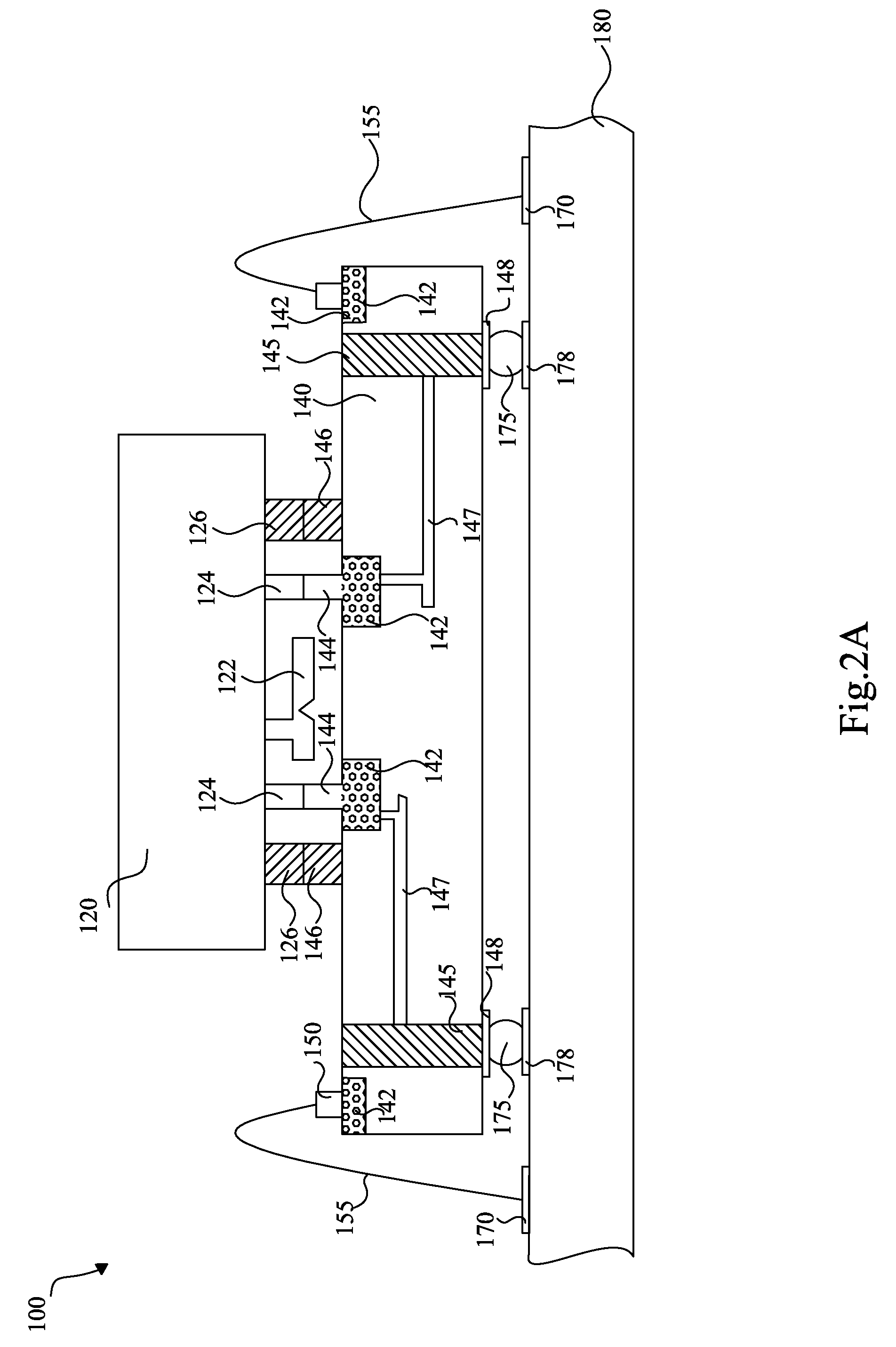

MEMS Packaging Including Integrated Circuit Dies

InactiveUS20090194829A1Highly integratedReduced package footprintSemiconductor/solid-state device detailsSolid-state devicesOn boardElectrical connection

MEMS packaging schemes having a system-on-package (SOP) configuration and a system-on-board (SOB) configuration are provided. The MEMS package comprises one or more MEMS dies, a cap section having one or more integrated circuit (IC) dies, and a packaging substrate or a printed circuit board (PCB) arranged in a stacking manner. Vertical connectors, such as through-silicon-vias (TSVs), are formed to provide short electrical connections between the various components. The MEMS packaging schemes enable higher integration density, reduced MEMS package footprints, reduced RC delays and power consumption.

Owner:TAIWAN SEMICON MFG CO LTD

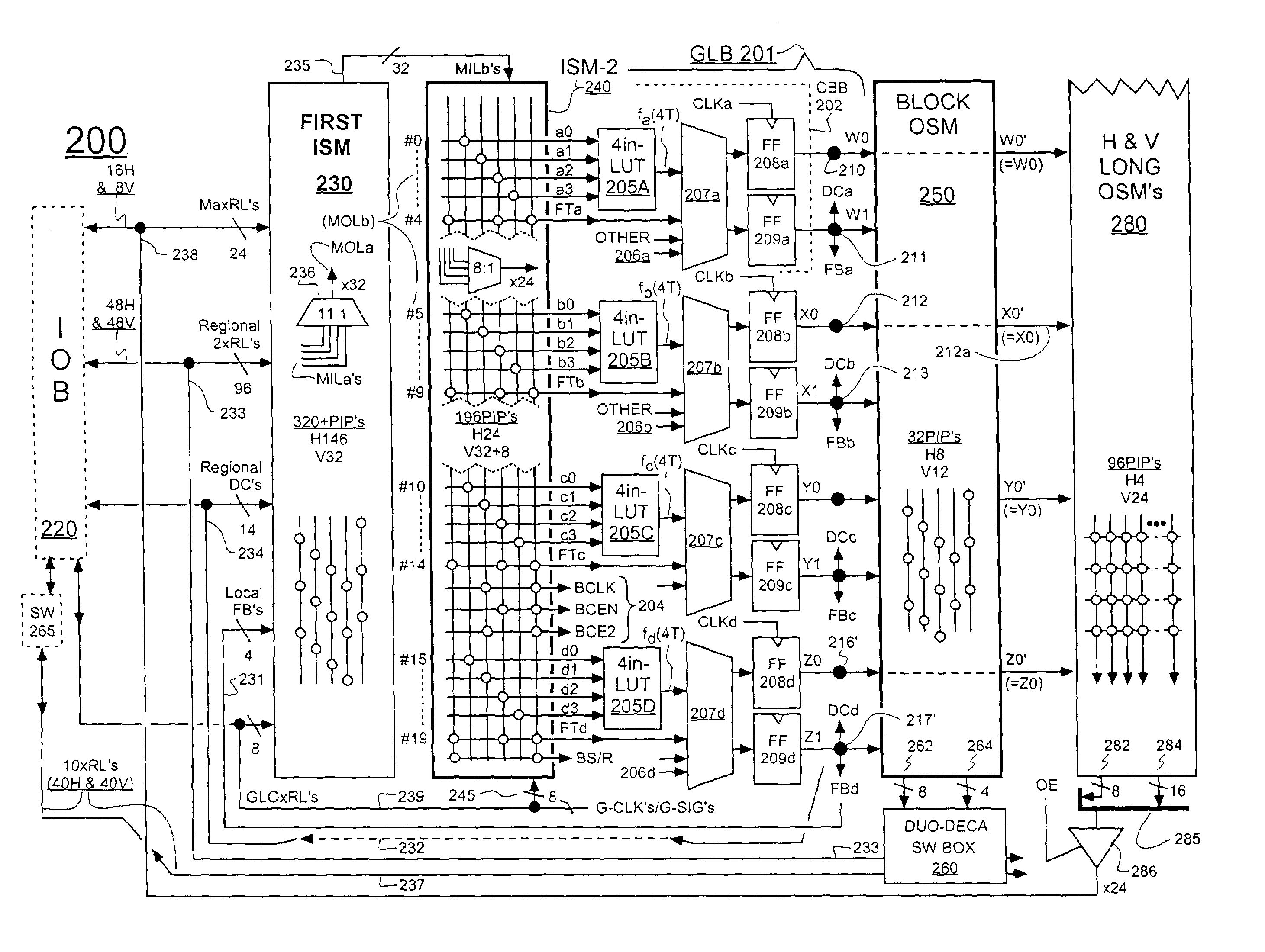

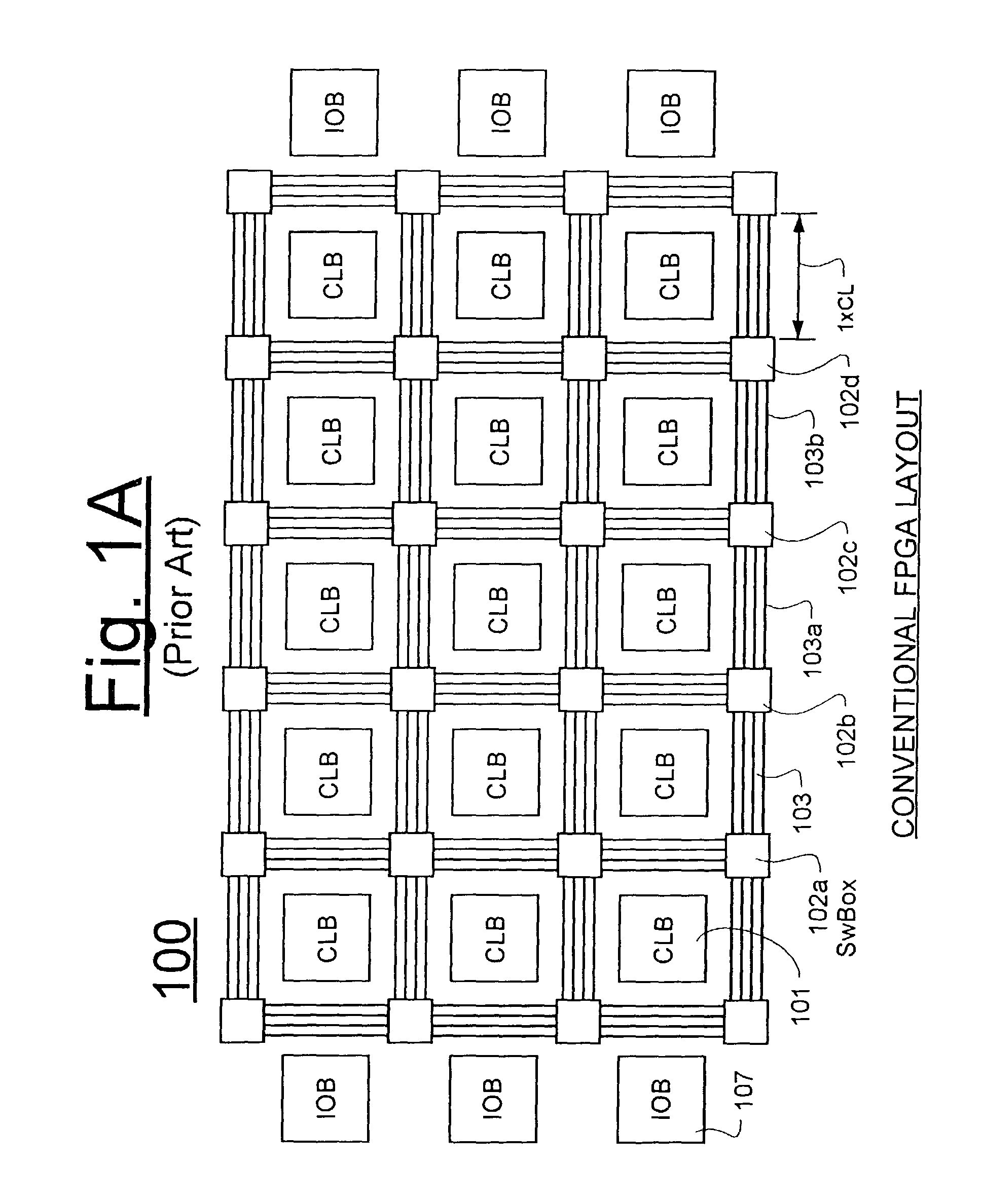

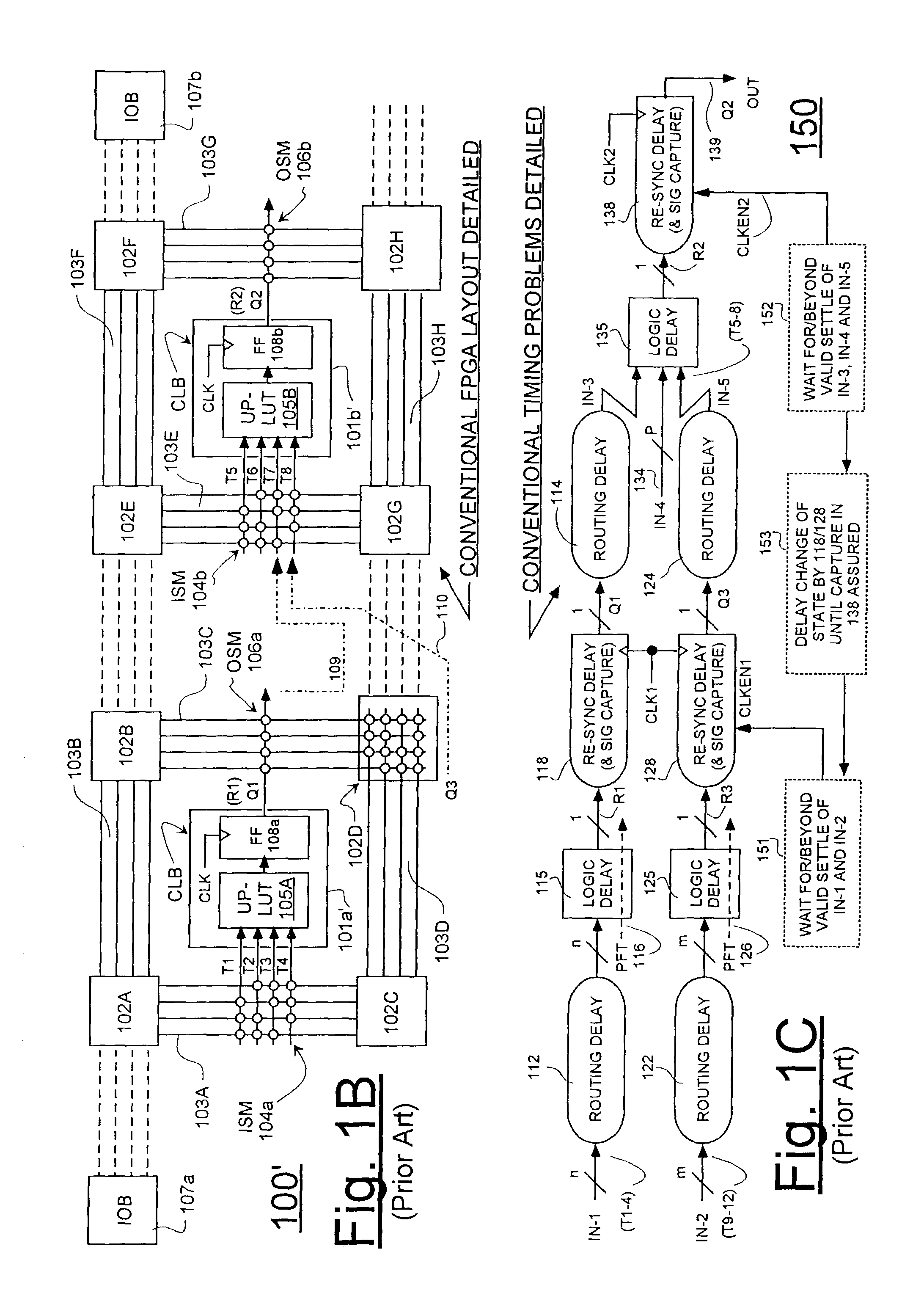

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

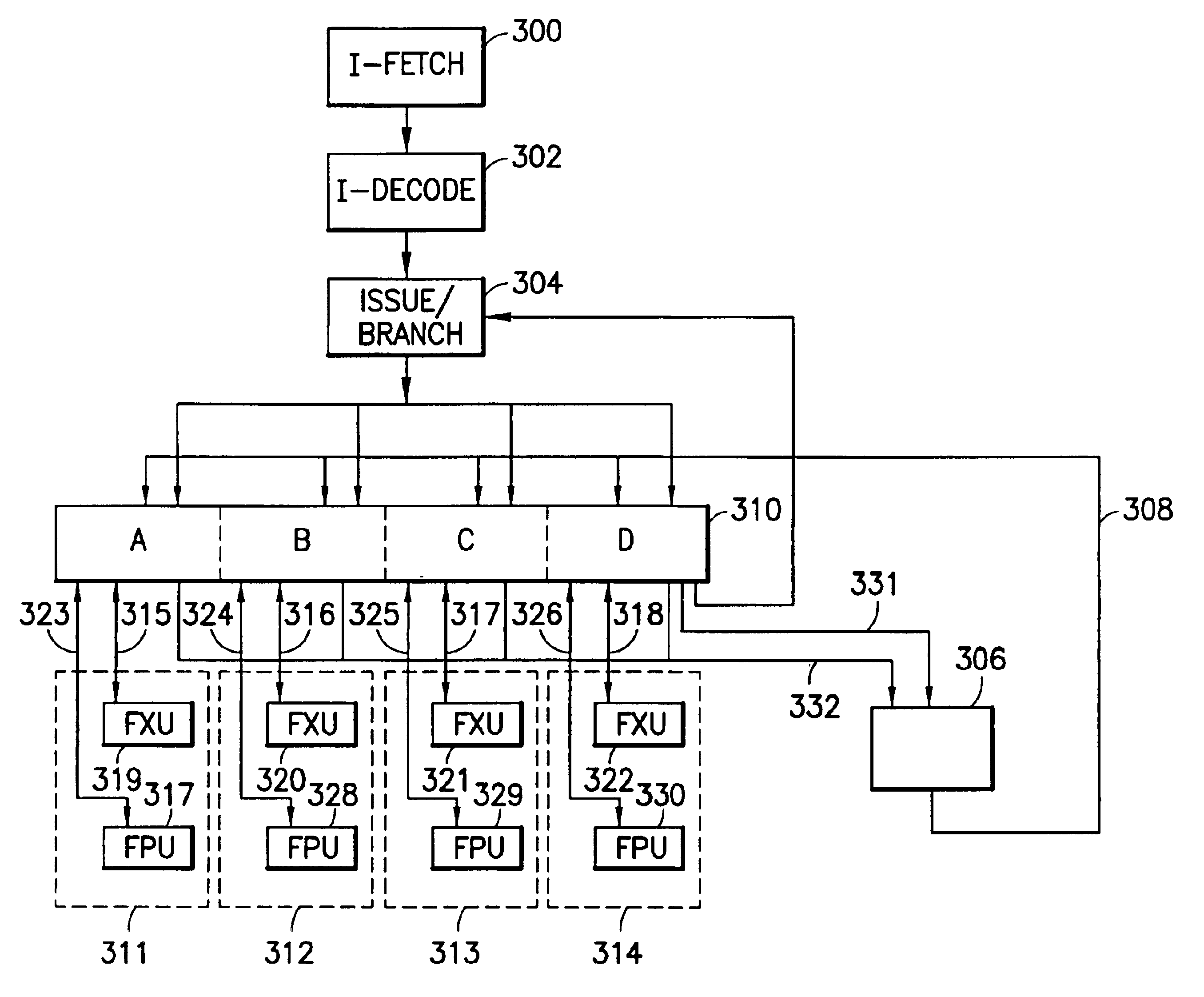

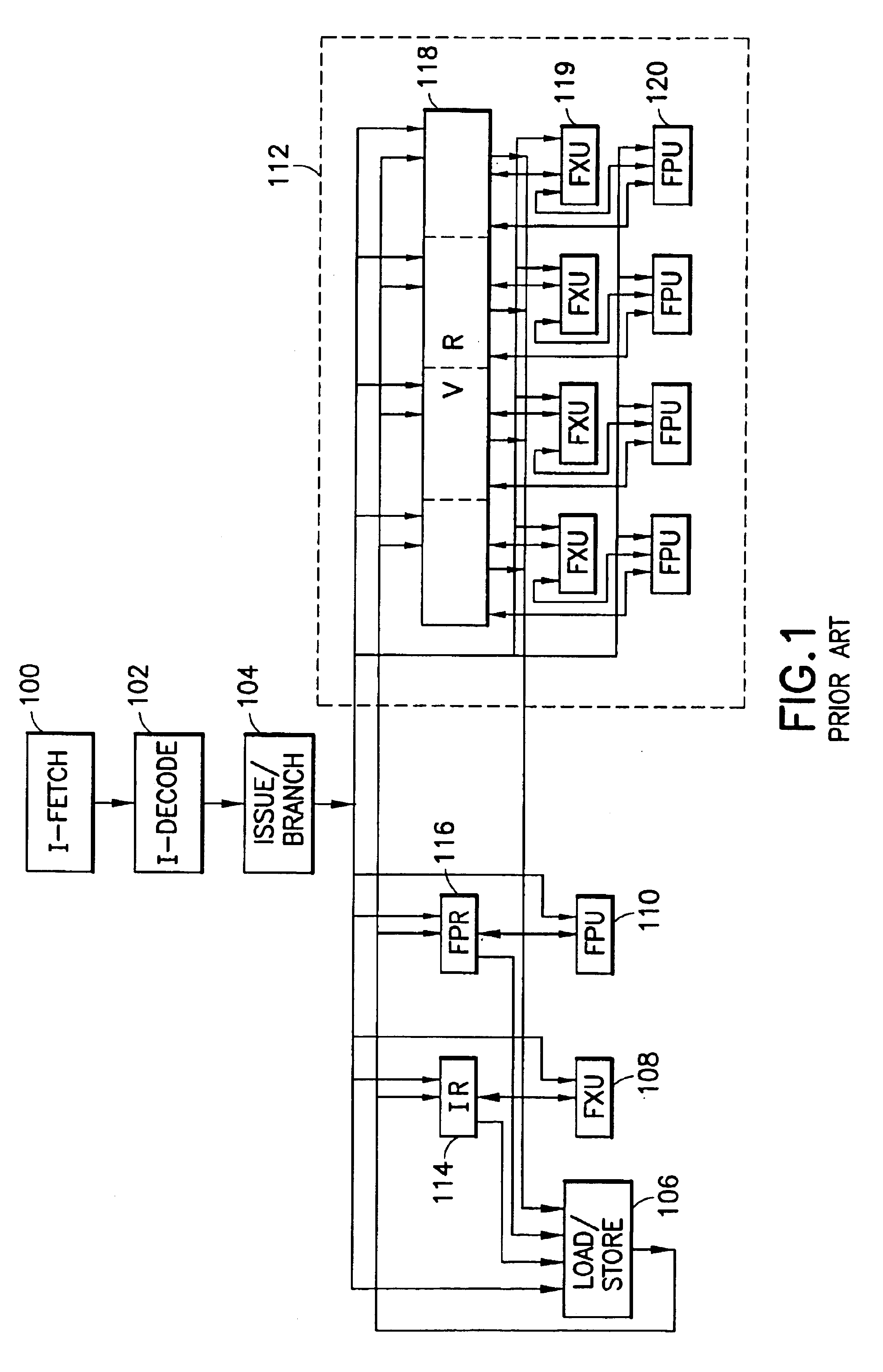

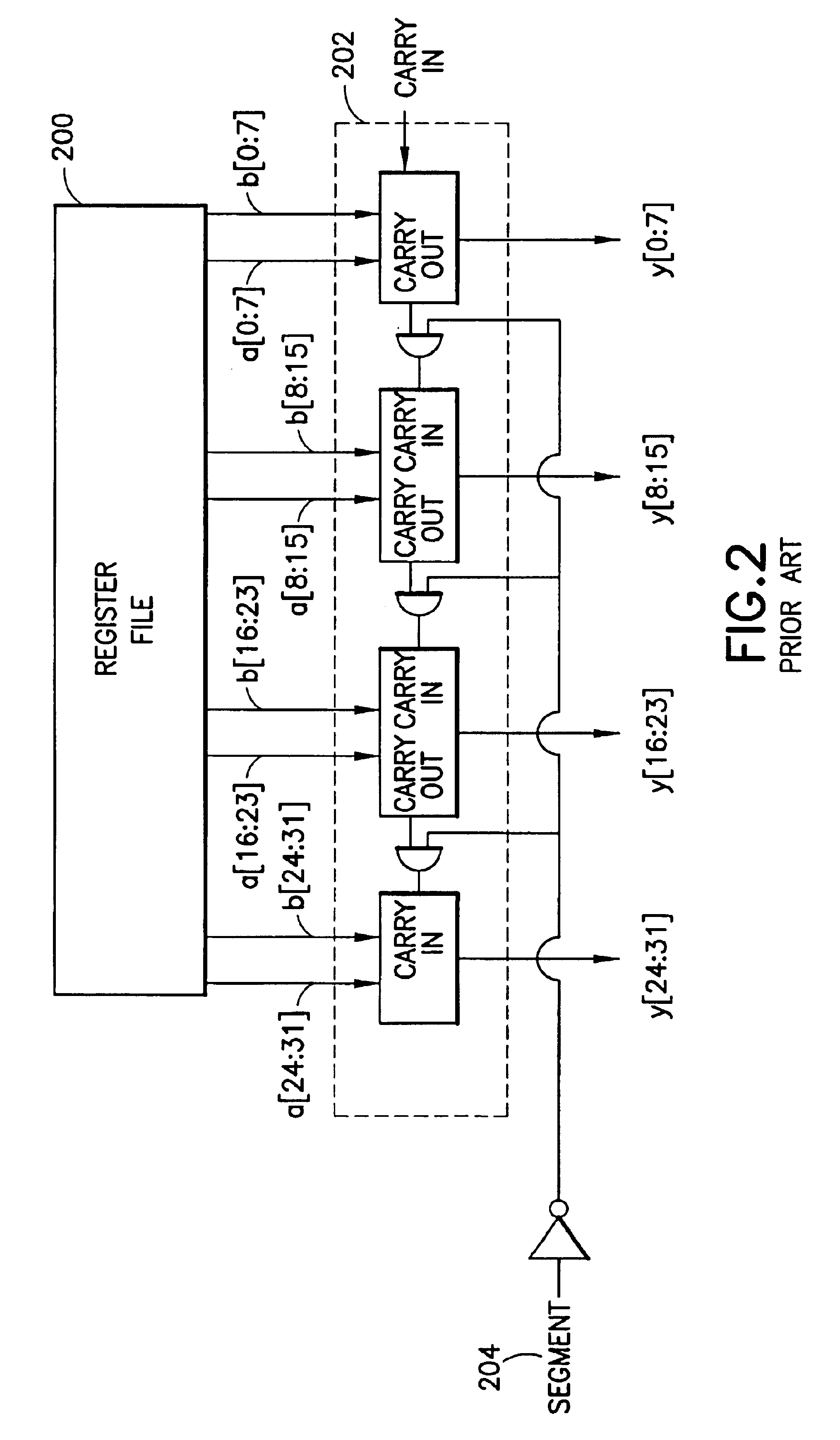

SIMD datapath coupled to scalar/vector/address/conditional data register file with selective subpath scalar processing mode

InactiveUS6839828B2Not compromise SIMD data processing performanceReduce consumptionRegister arrangementsDigital data processing detailsProcessor registerOperation mode

There is provided a processor designed to operate in a plurality of modes for processing vector and scalar instructions. Register files are each for storing scalar and vector data and address information. A parallel vector unit, coupled to the register files, includes functional units configurable to operate in a vector operation mode and a scalar operation mode. The vector unit includes an apparatus for tightly coupling the functional units to perform an operation specified by a current instruction. Under a vector operation mode, the vector unit performs, in parallel, a single vector operation on a plurality of data elements. The operations performed on the plurality of data elements are each performed by a different functional unit of the vector unit. Under a scalar operation mode, the vector unit performs a scalar operation on a data element received from the register files in a functional unit within the vector unit.

Owner:INTEL CORP

System and method for calculating the thermal mass of a building

ActiveUS7848900B2Improve comfortReduce energy useSpace heating and ventilationTemperatue controlControl systemHVAC control system

Owner:ECOFACTOR

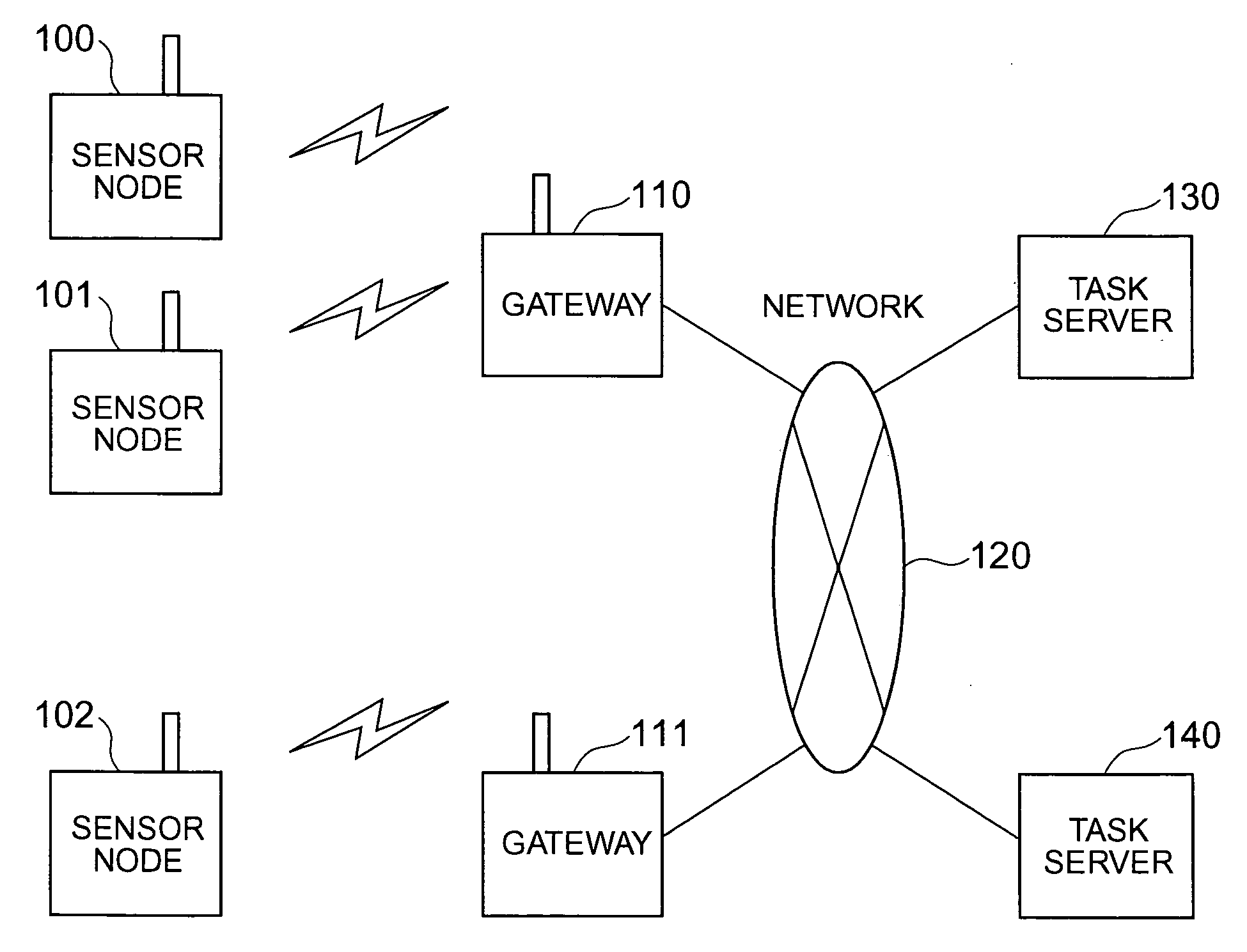

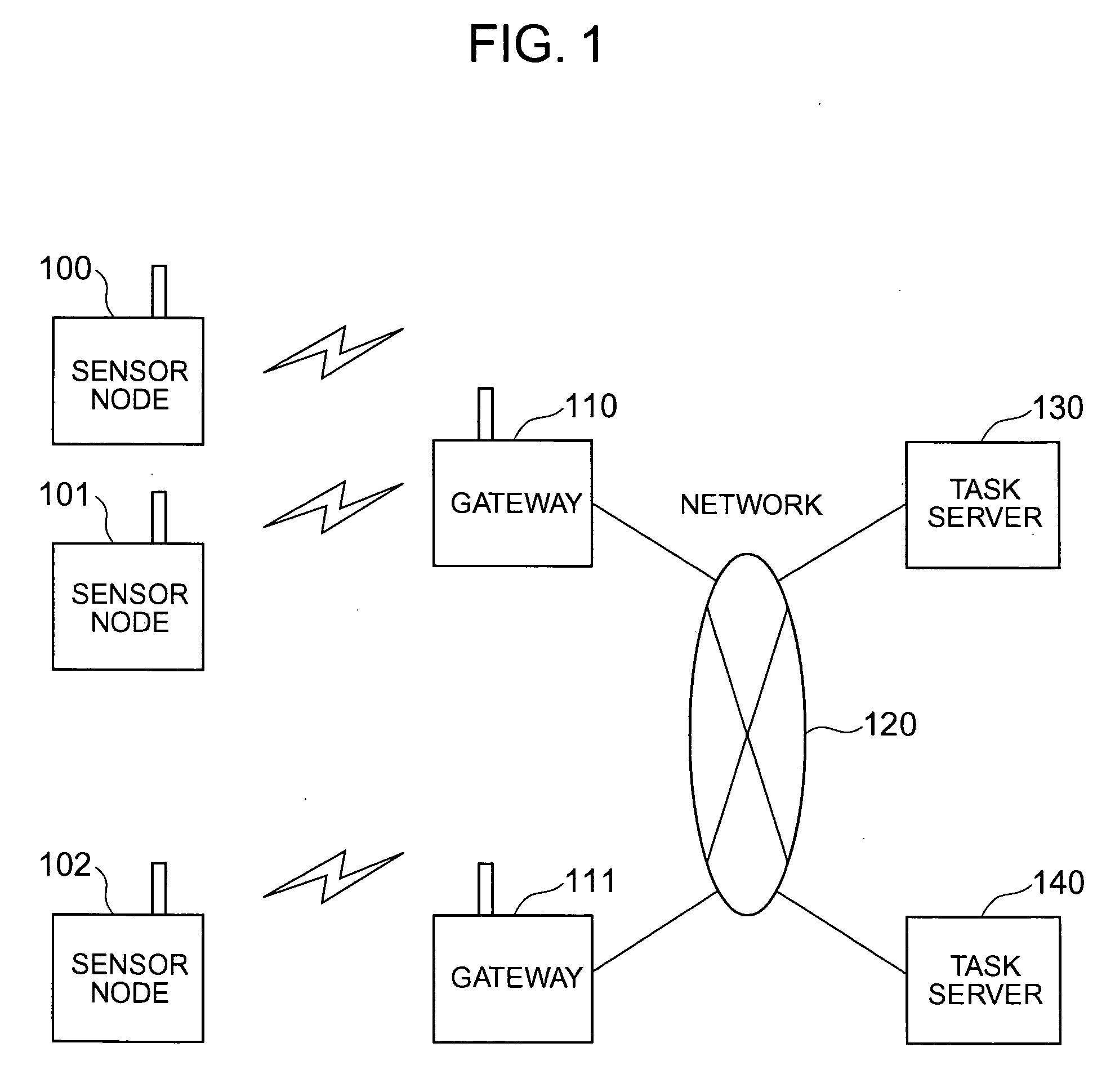

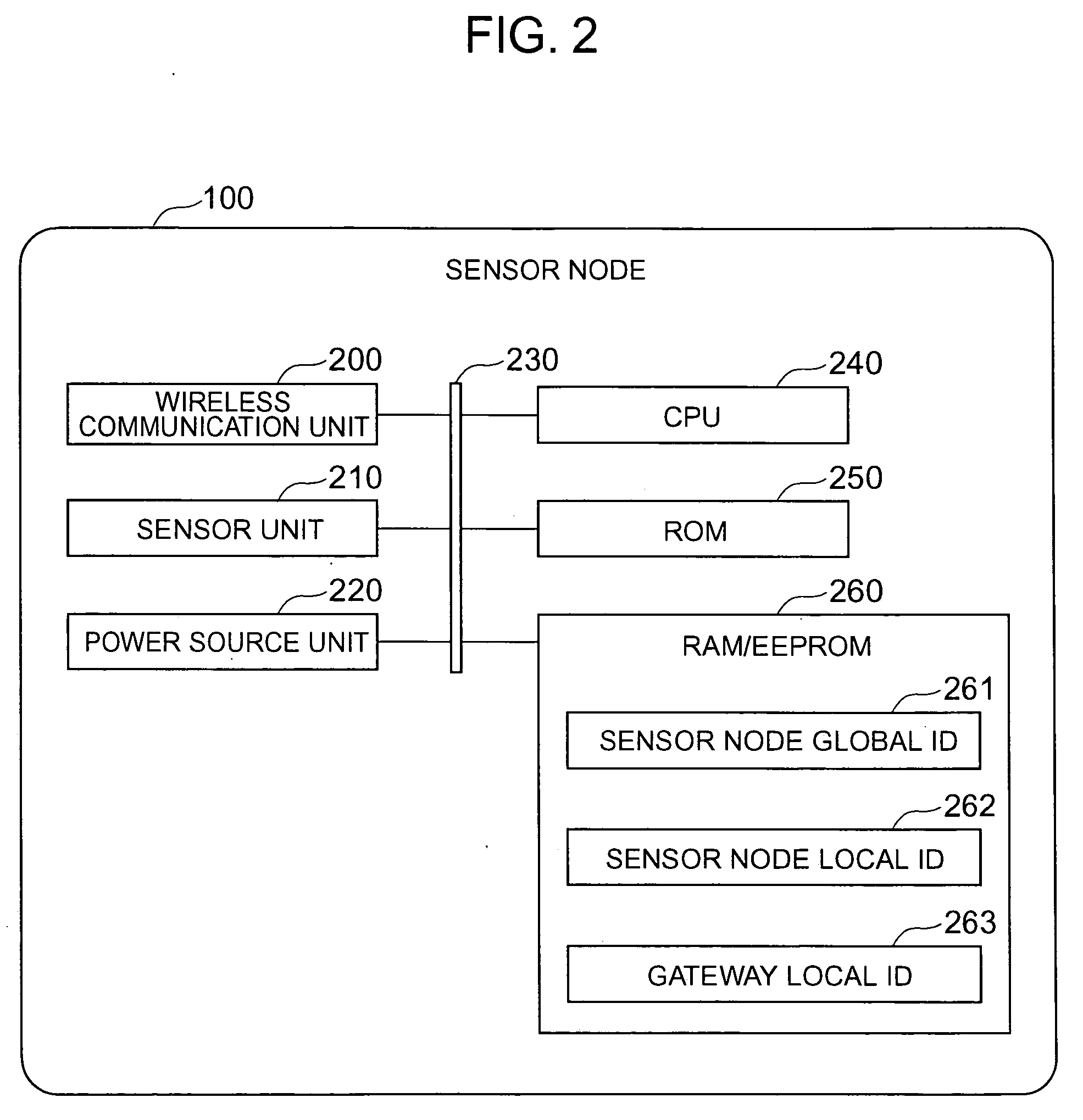

Sensor network management system

InactiveUS20060190458A1Easily lookIncrease freedomDigital data processing detailsActive radio relay systemsTrunkingNetwork management

An attribute value of a matter accompanied by a sensor is transmissibly accessible in a sensor node system constituted by wireless terminal computers having the sensor, the wireless communication base stations and server computers. The wireless terminal computer reports at the time of wireless communication an identification number of a wireless communication base station with which it communicates previously. A relay processing service is dynamically constituted so that when a wireless communication base station different from itself is reported, the wireless base station as the communication counter-part can transmissbly look up the wireless terminal computer from a host computer.

Owner:HITACHI LTD

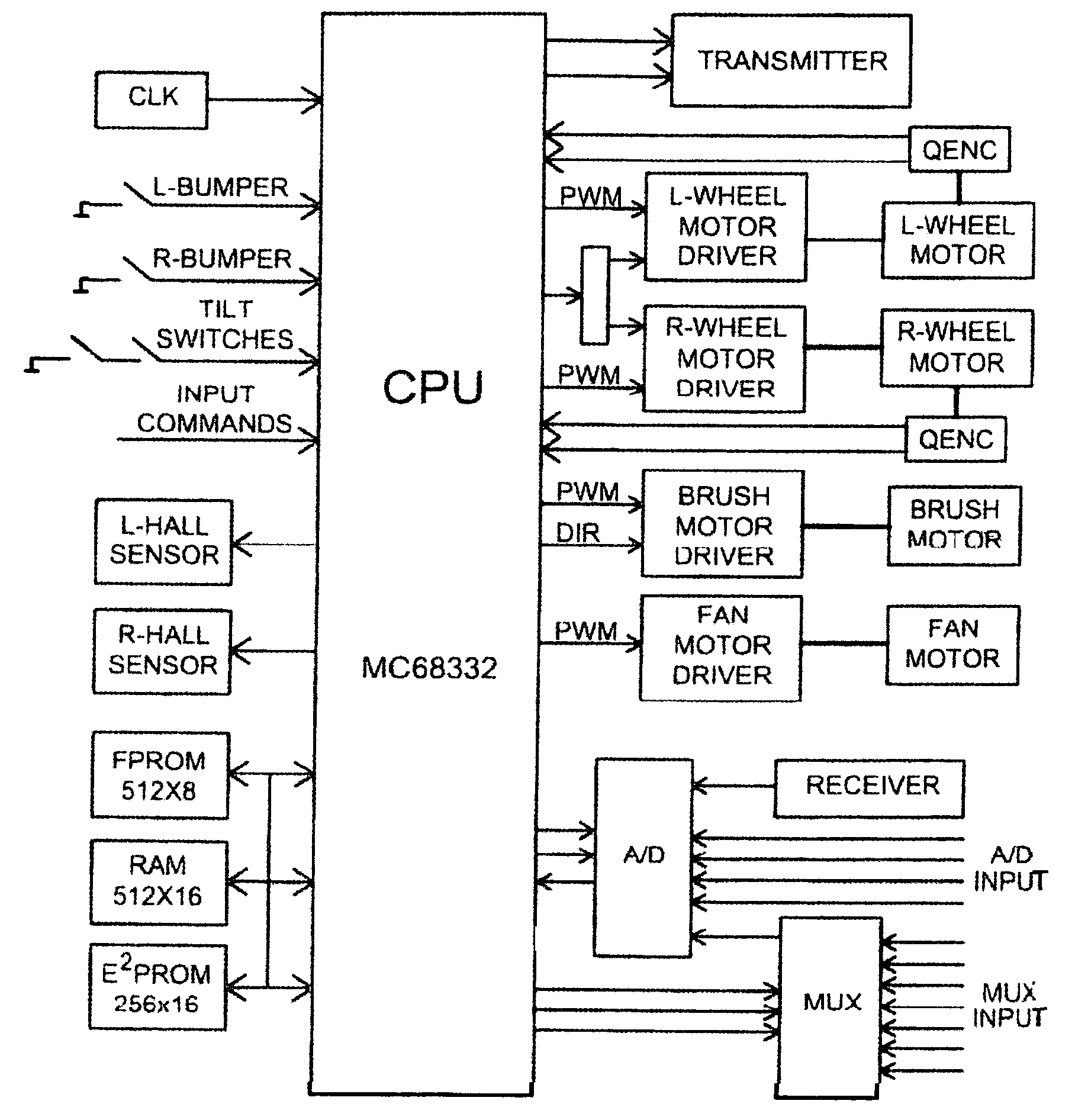

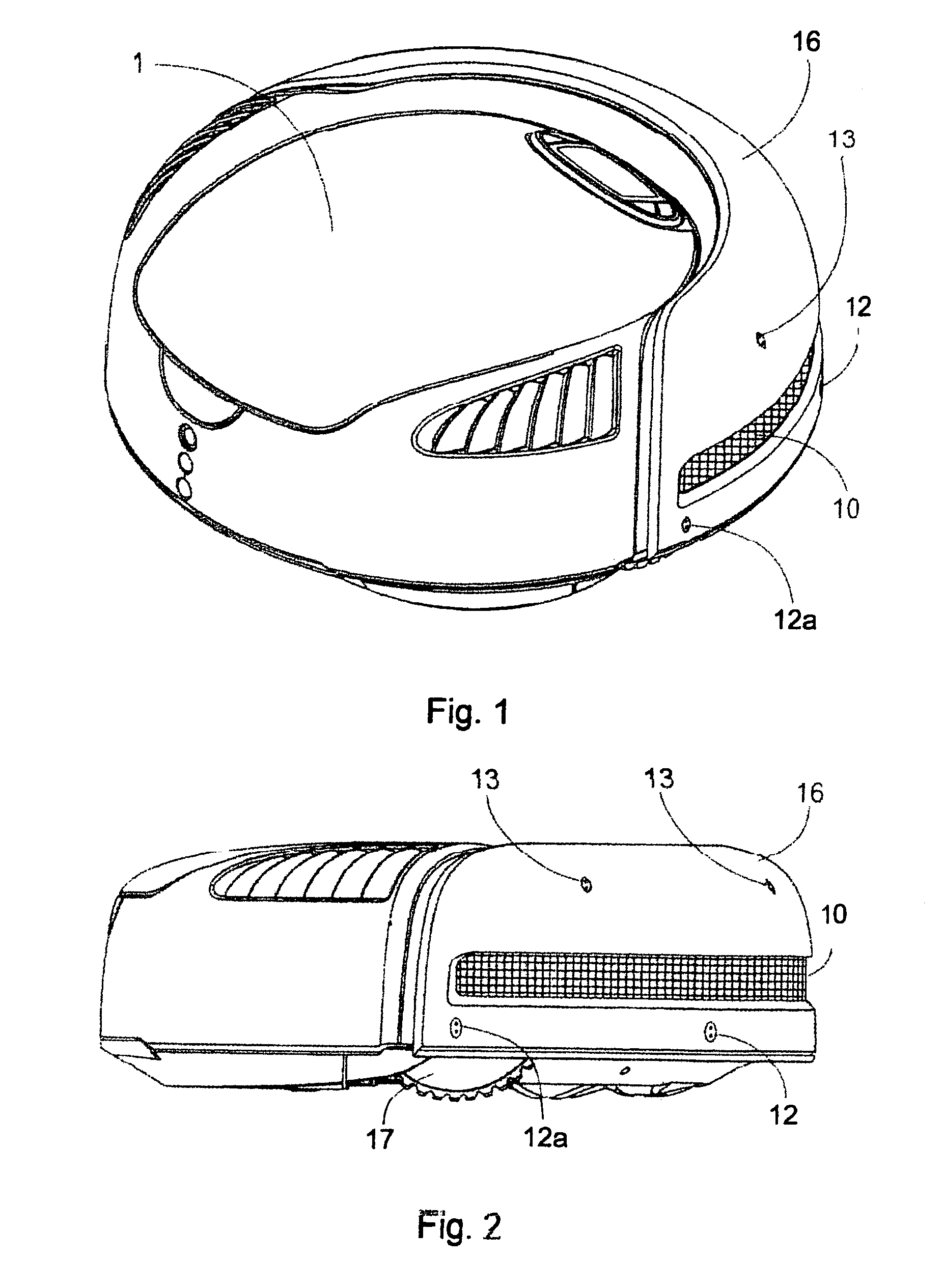

Efficient navigation of autonomous carriers

InactiveUS7206677B2Effective strategyMinimize energy consumptionSuction cleanersSpecial data processing applicationsComputation complexityEngineering

According to the invention, autonomous carriers or vehicles are efficiently navigated over a field of operation. The carriers are equipped to execute a selected procedure at more than one desired location on the field, and the navigation system of the invention directs the carrier to the location that is preferentially accessible to it, based on a defined criterion. After the carrier has executed the selected procedure at the location which is preferentially accessible to it, the navigation system directs the carrier to the location which is preferentially accessible to the carrier from the carrier's new position. This procedure is repeated until all the locations at which the procedure is to be executed have been reached. The task of determining a navigation route to a location that can be preferentially accessed is based on an efficient, structured search procedure of low computational complexity.

Owner:AB ELECTROLUX

System and method for evaluating changes in the efficiency of an HVAC system

ActiveUS20120065935A1Improve comfortReduce energy useMechanical apparatusSpace heating and ventilation safety systemsControl systemControl engineering

The invention comprises systems and methods for evaluating changes in the operational efficiency of an HVAC system over time. The climate control system obtains temperature measurements from at least a first location conditioned by the climate system, and status of said HVAC system. One or more processors receives measurements of outside temperatures from at least one source other than said HVAC system and compares said temperature measurements from said first location with expected temperature measurements. The expected temperature measurements are based at least in part upon past temperature measurements.

Owner:ECOFACTOR

System and method for evaluating changes in the efficiency of an HVAC system

ActiveUS20100070234A1Decrease energy useIncrease comfortTime indicationSpace heating and ventilationHVACTemperature measurement

The invention comprises systems and methods for evaluating changes in the operational efficiency of an HVAC system over time. The climate control system obtains temperature measurements from at least a first location conditioned by the climate system, and status of said HVAC system. One or more processors receives measurements of outside temperatures from at least one source other than said HVAC system and compares said temperature measurements from said first location with expected temperature measurements. The expected temperature measurements are based at least in part upon past temperature measurements.

Owner:ECOFACTOR

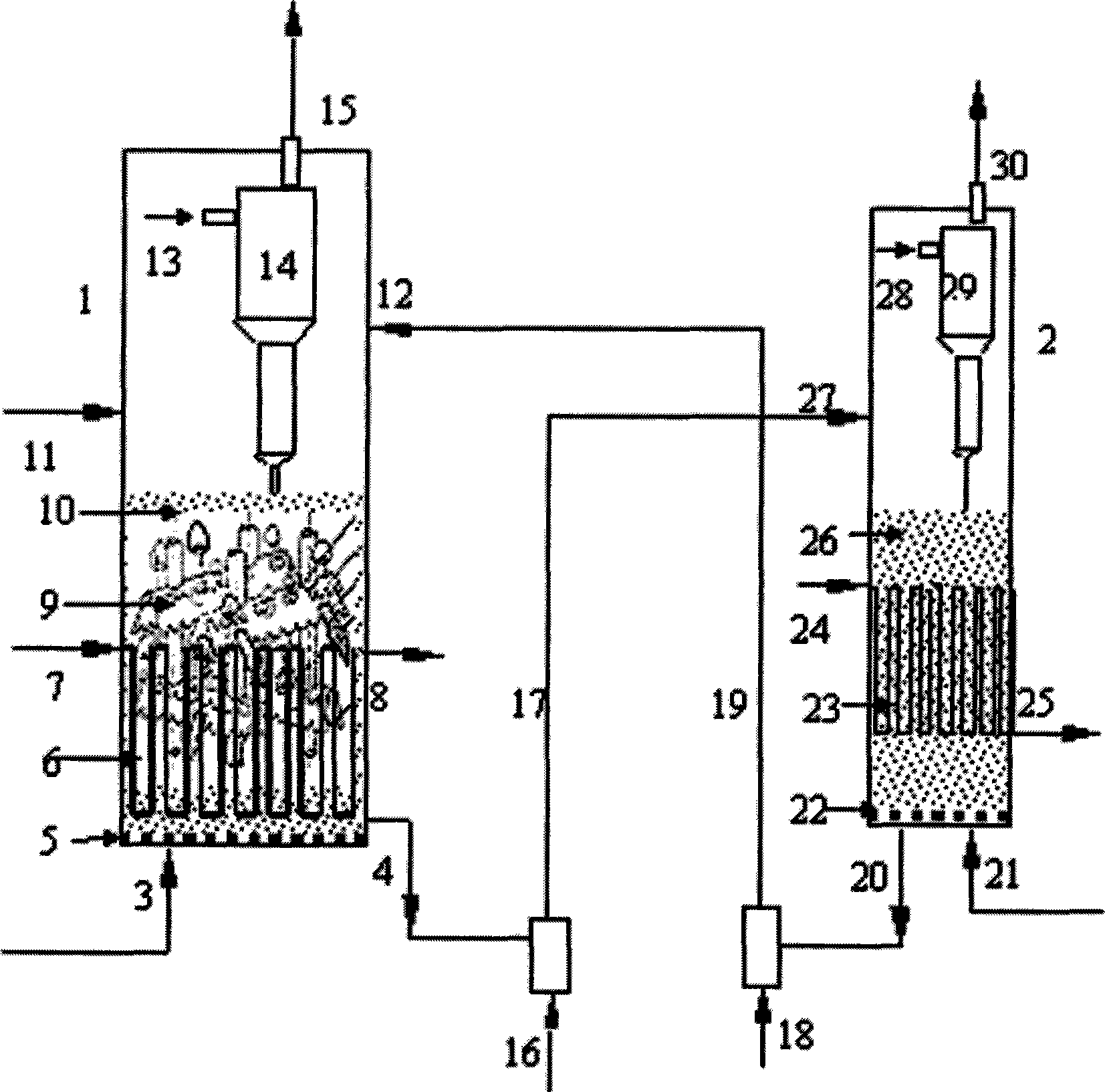

Continuous aromatization and catalyst regeneration device and method thereof

ActiveCN101244969ANo temperature fluctuationsDoes not affect aromatization reactionMolecular sieve catalystsCatalyst regeneration/reactivationFluidized bedAromatization

The invention discloses and belongs to the chemical equipment field, which more particularly relates to a C1-C2 hydrocarbon or methanol aromatization and catalyst regeneration fluidized bed device (comprising an aromatization fluidized bed, a catalyst continuous regeneration fluidized bed, a pipeline used for catalyst transportation and a solid transportation device which are arranged between the two fluidized beds), and an aromatization catalyst which is suitable for the fluidized bed operations and the operation methods of aromatization reaction, catalyst regeneration and the device. The device, the catalyst and the method are used for regulating the coking status of the catalyst in an aromatization reactor at any time, thus achieving the aim of transforming the C1-C2 hydrocarbon or the methanol continuously and efficiently and generating aromatics with high selectivity. The C1-C2 hydrocarbon or methanol aromatization and catalyst regeneration fluidized bed device of the invention with adjustable catalyst activity and selectivity can improve the purity and yield of the aromatics, can lead the aromatization reactor operates continuously without stopping at the same time, can improve the strength of aromatics production, and lower the operation cost of the catalyst regeneration when stopping and restarting the whole system.

Owner:TSINGHUA UNIV

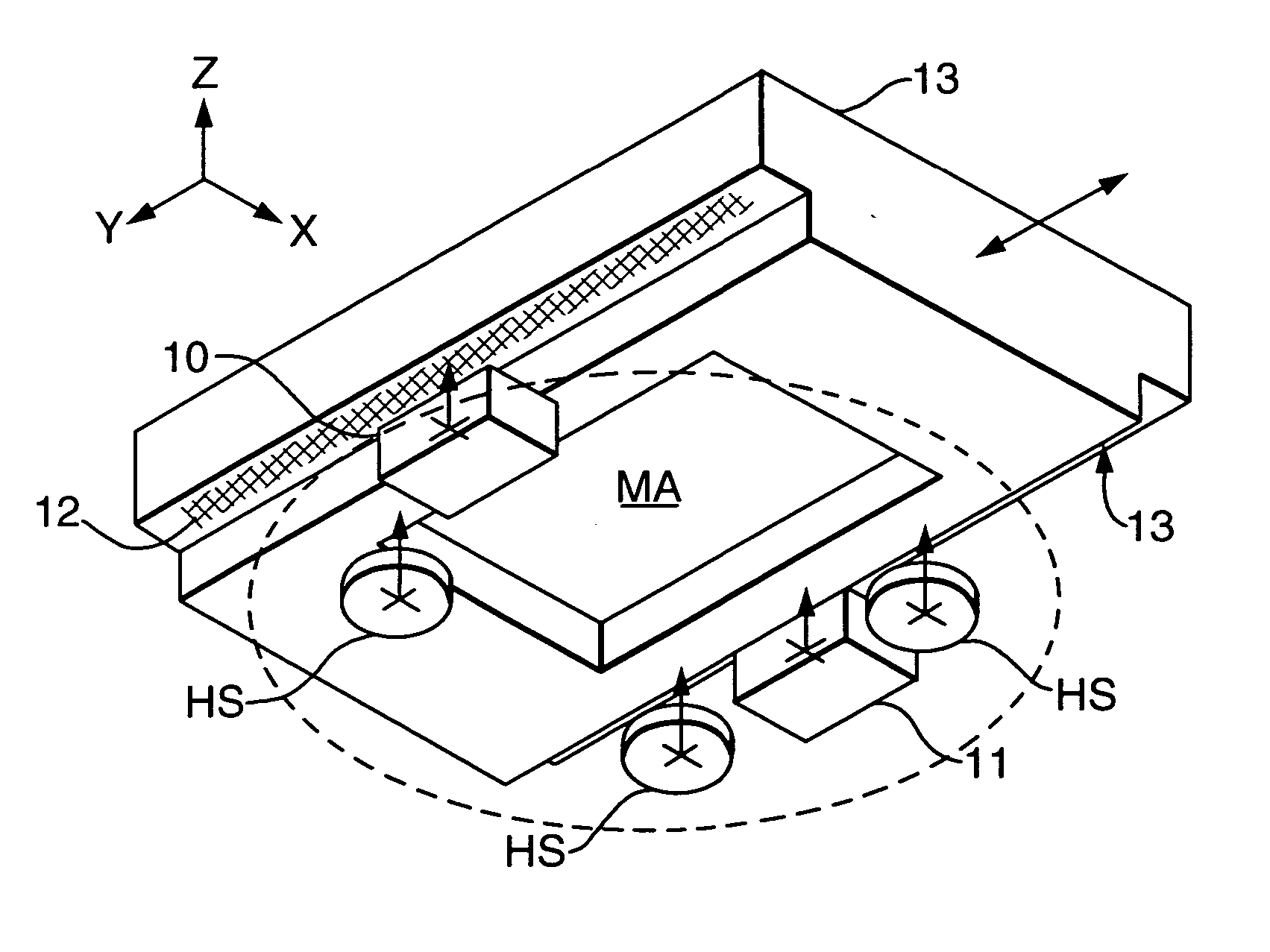

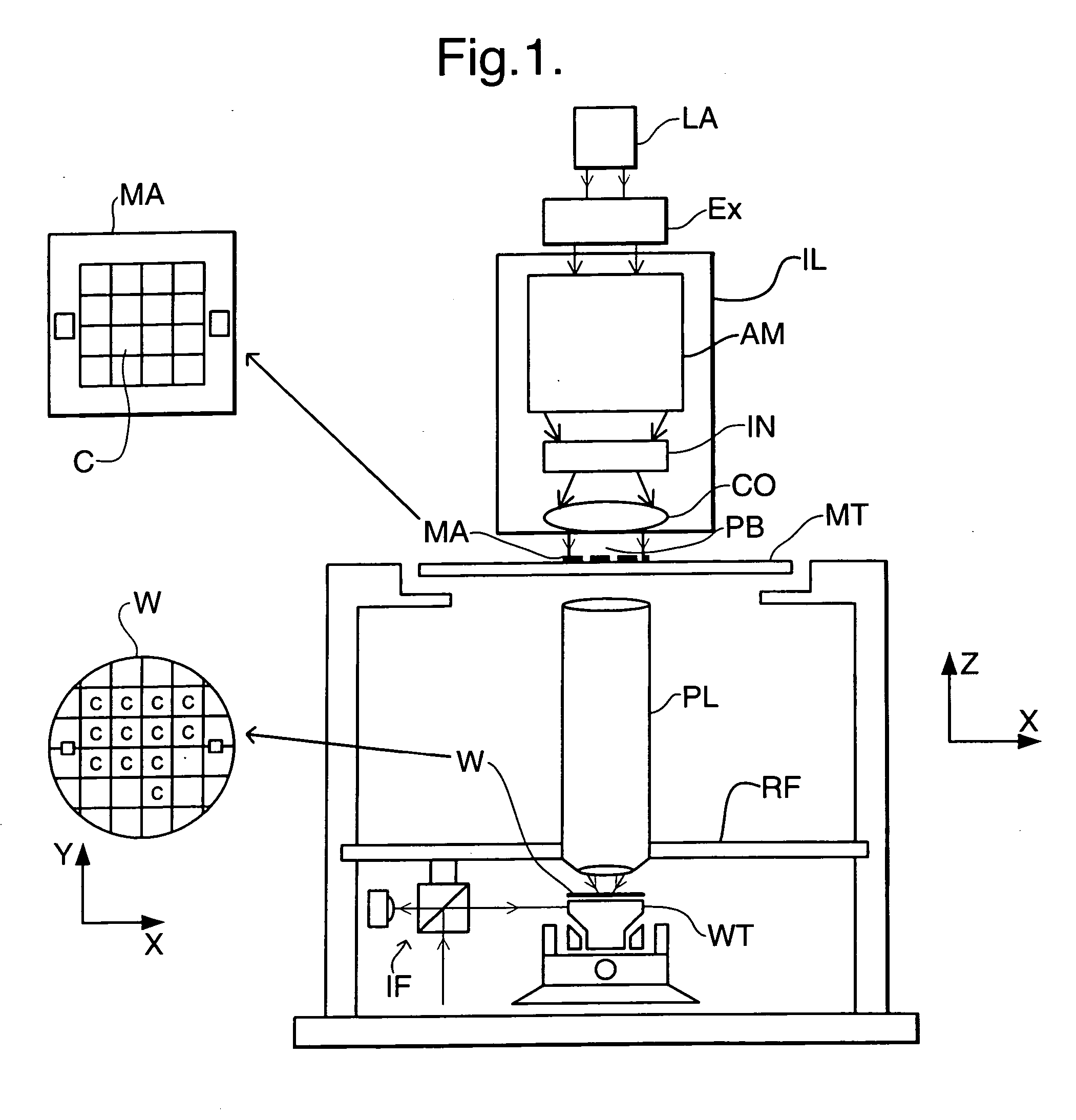

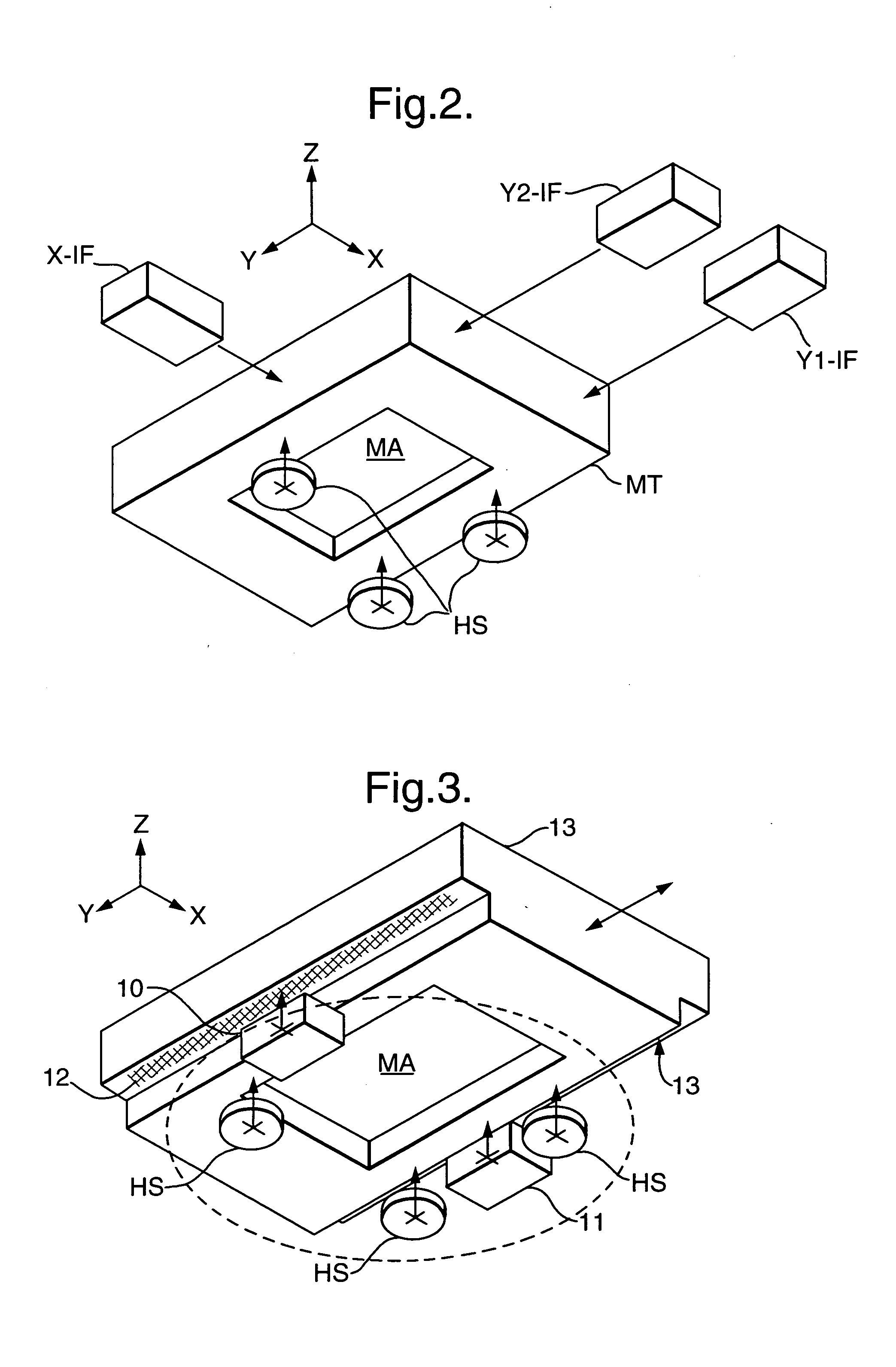

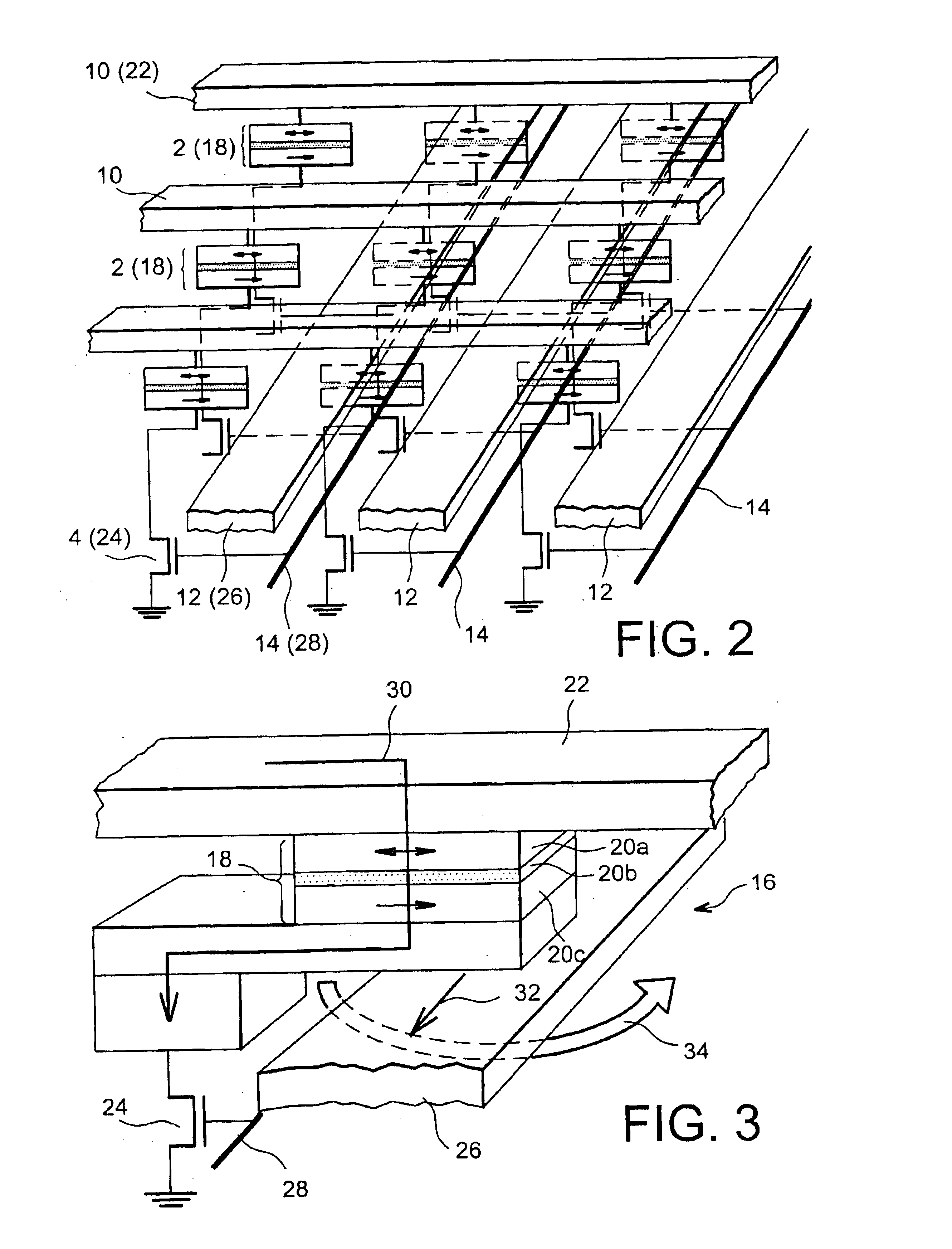

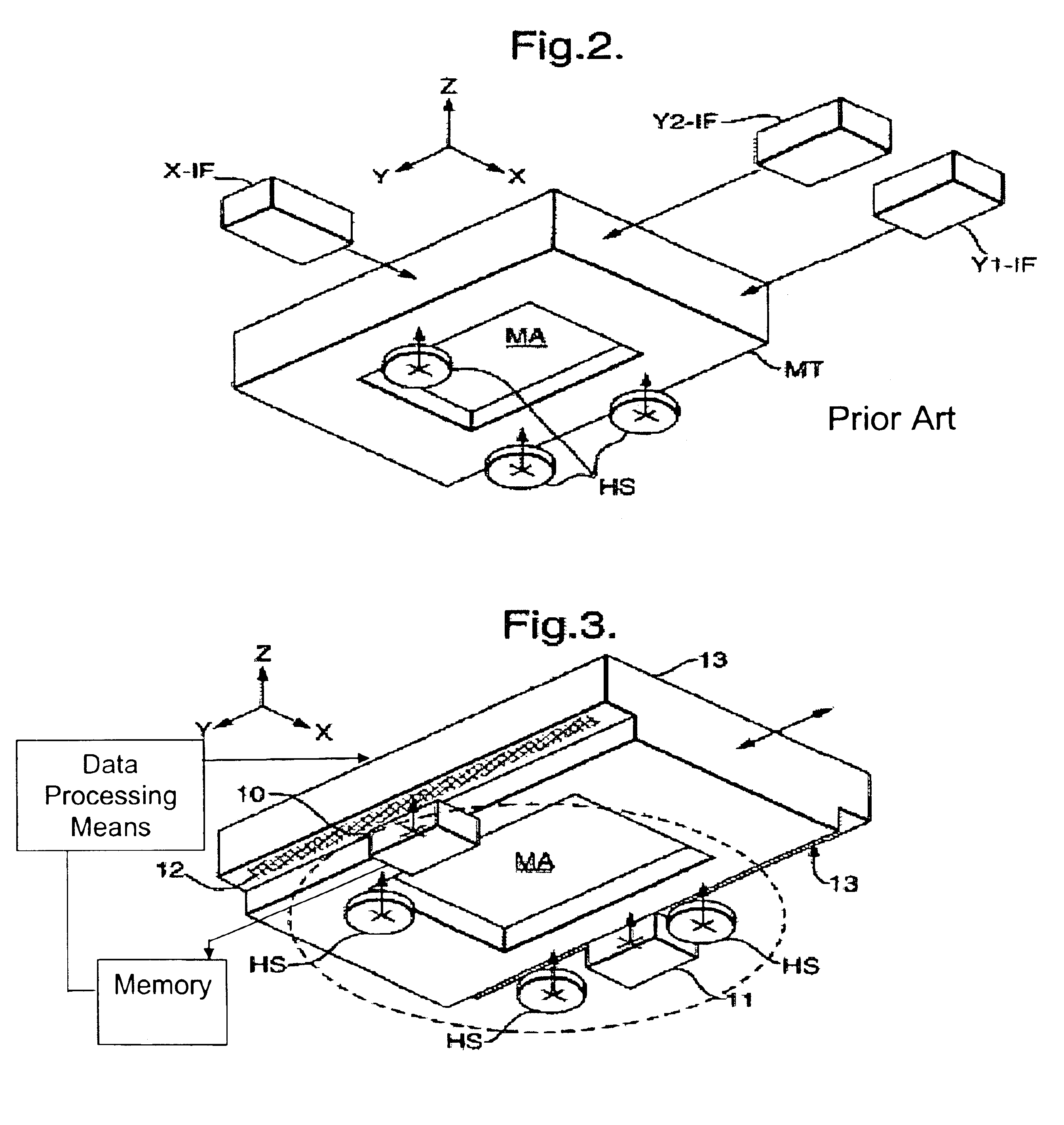

Lithographic apparatus, device manufacturing method and device manufacturing thereby

InactiveUS20040263846A1Improve stabilityReduce impactUsing optical meansPhotomechanical exposure apparatusCapacitanceGrating

The X, Y and Rx positions of a mask stage are measured using two optical encoder-reading heads measuring displacements of respective grid gratings mounted on the mask stage. The grid gratings are preferably provided on cut-away portions of the mask table so as to be coplanar with the pattern on the mask itself. Measurements of the table position in the other degrees of freedom can be measured with capacitative or optical height sensors.

Owner:ASML NETHERLANDS BV

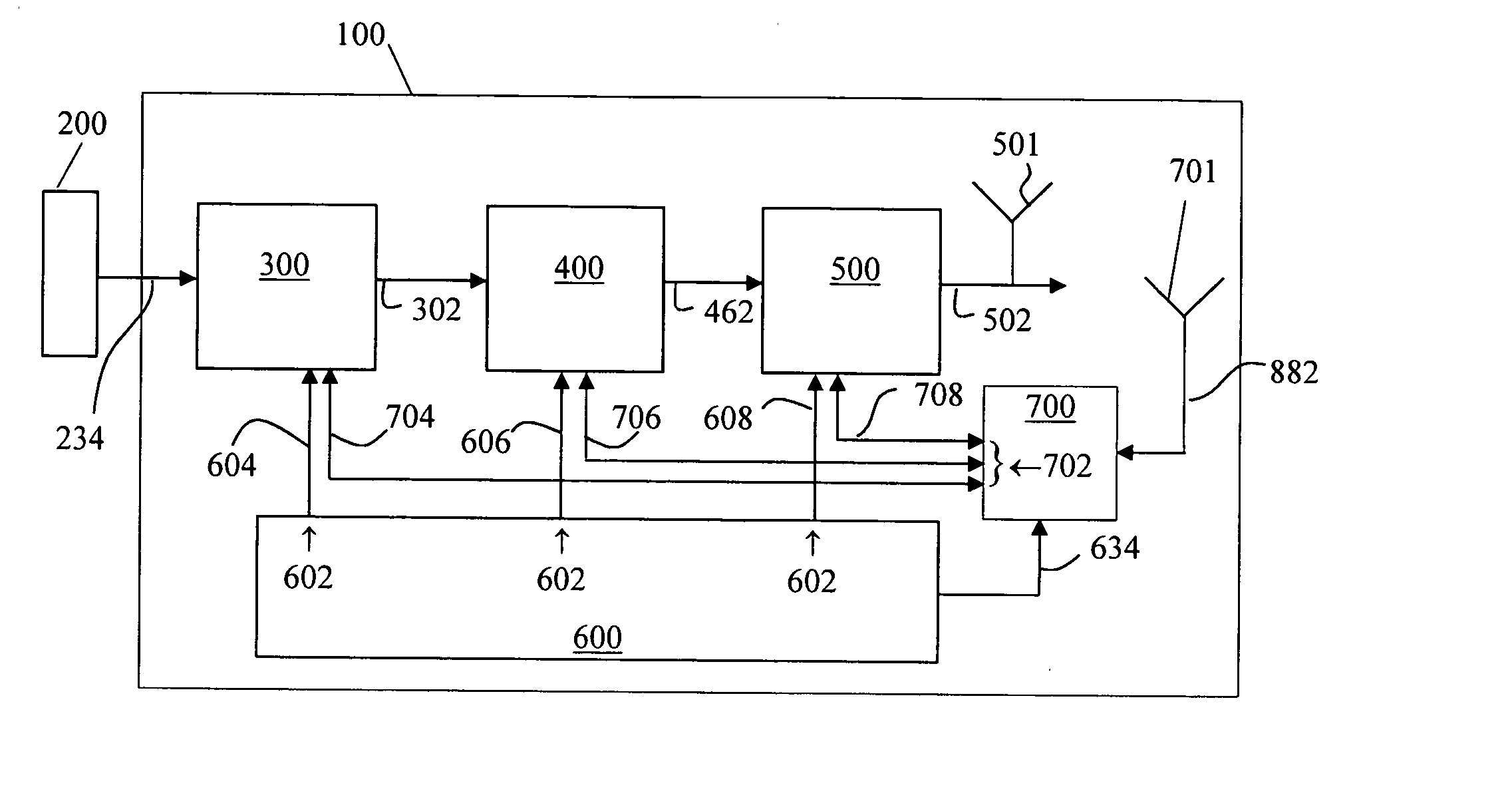

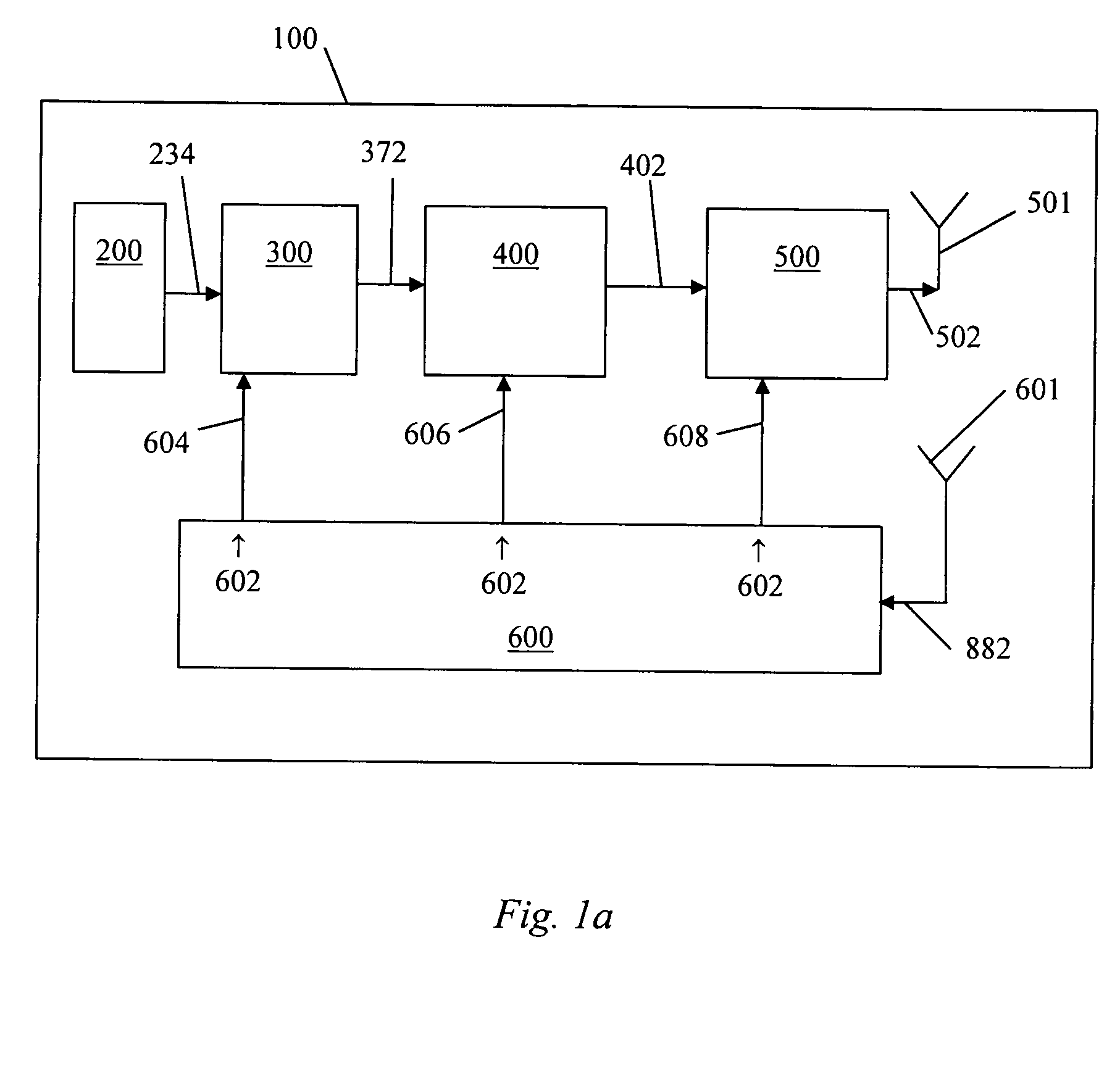

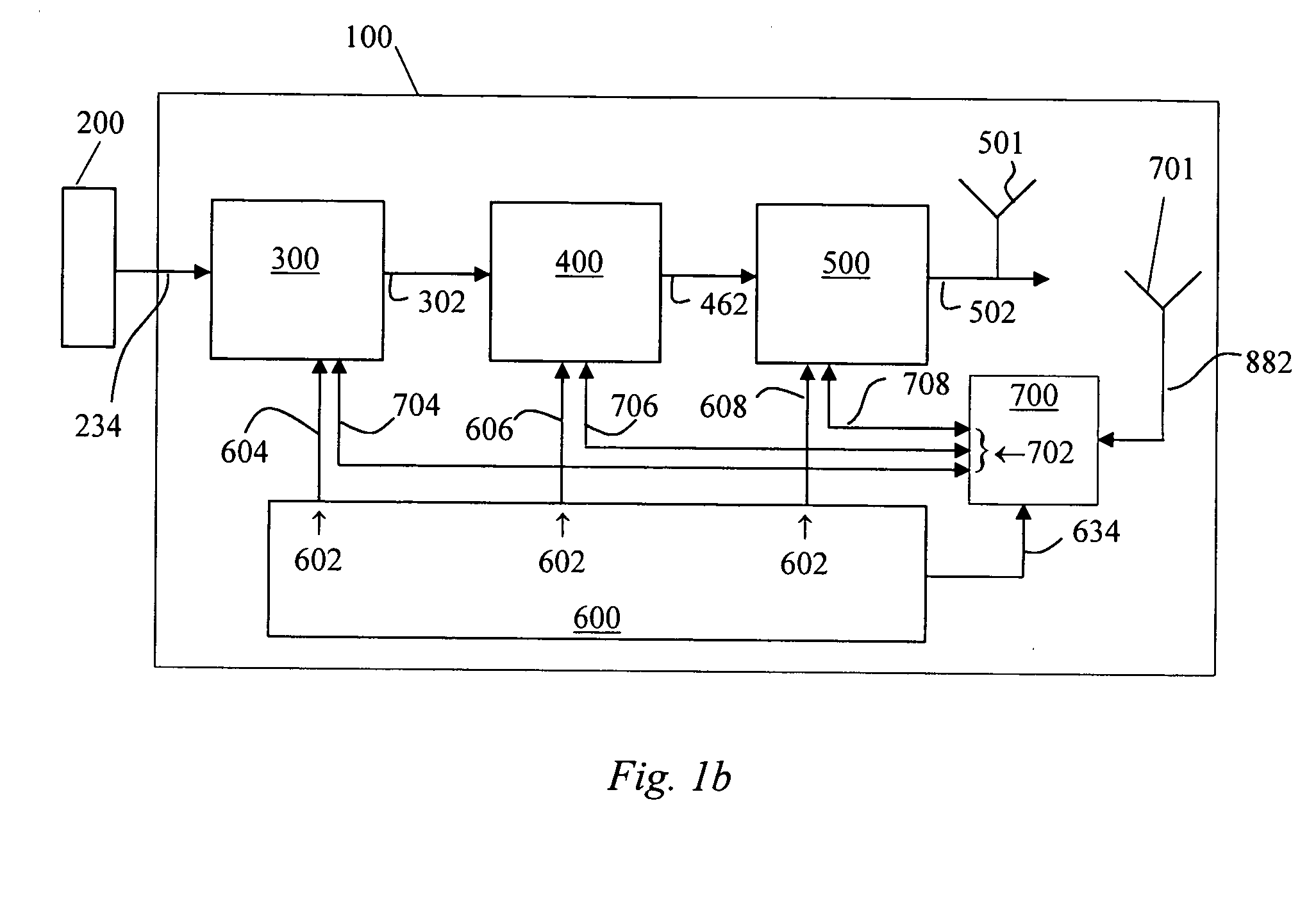

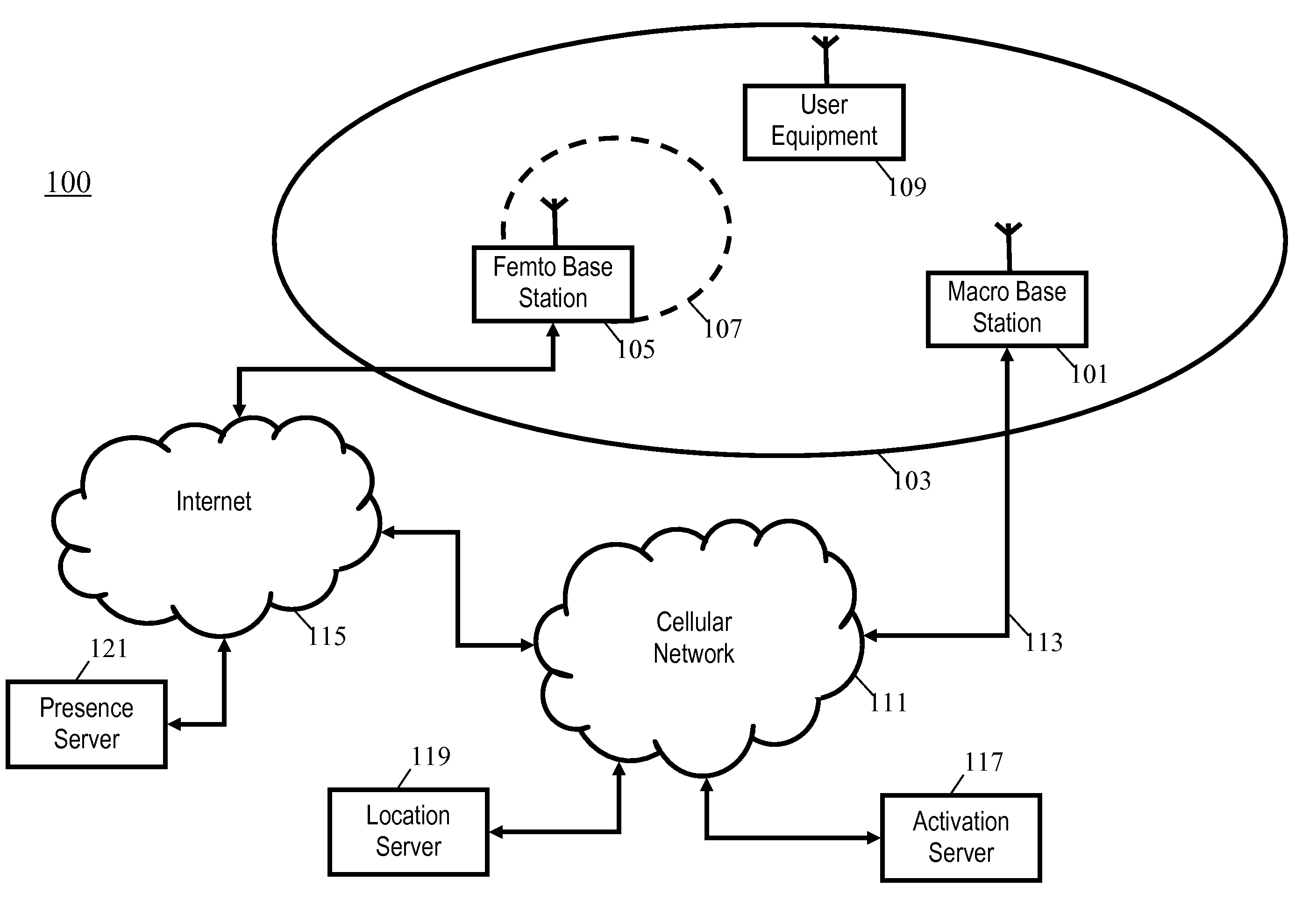

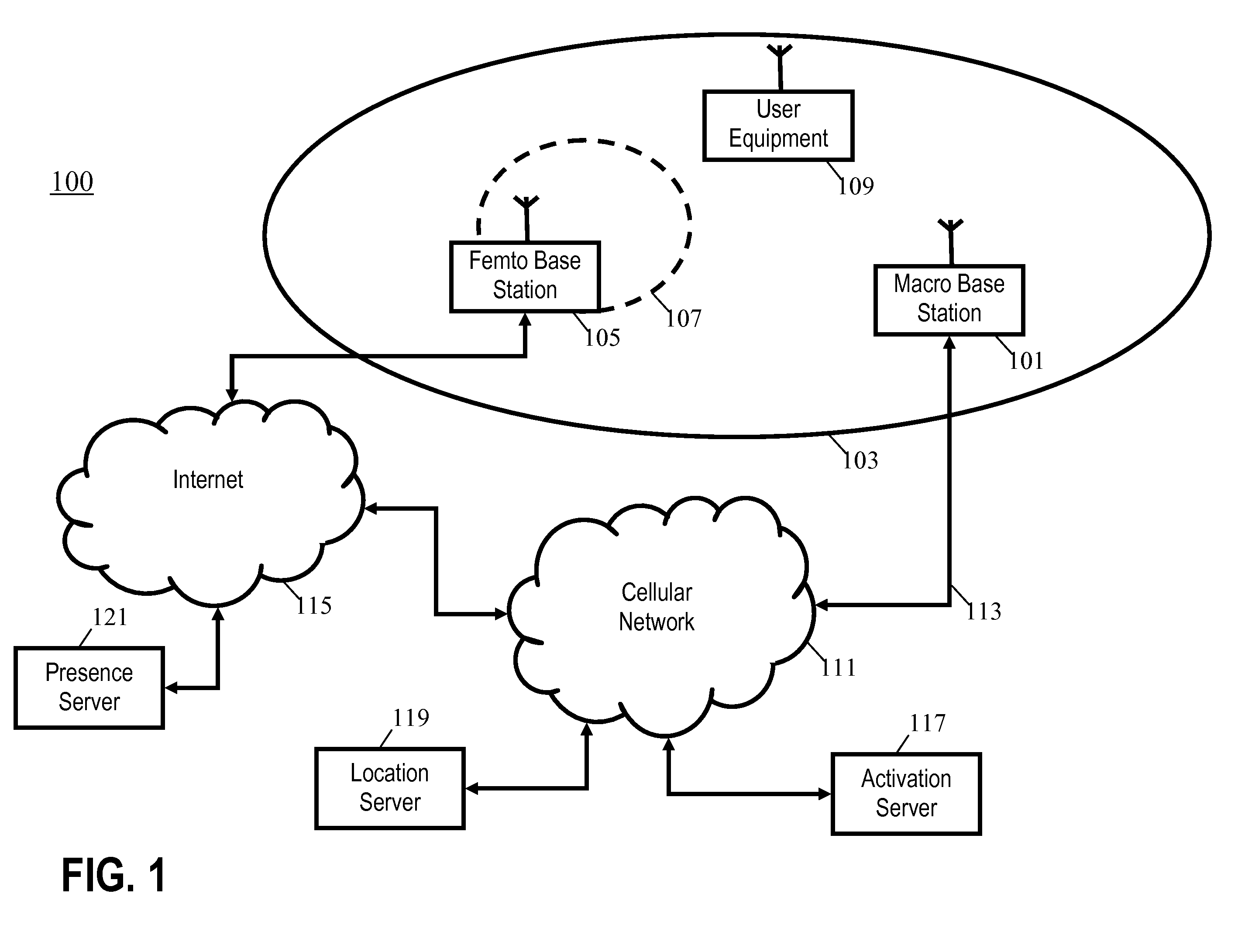

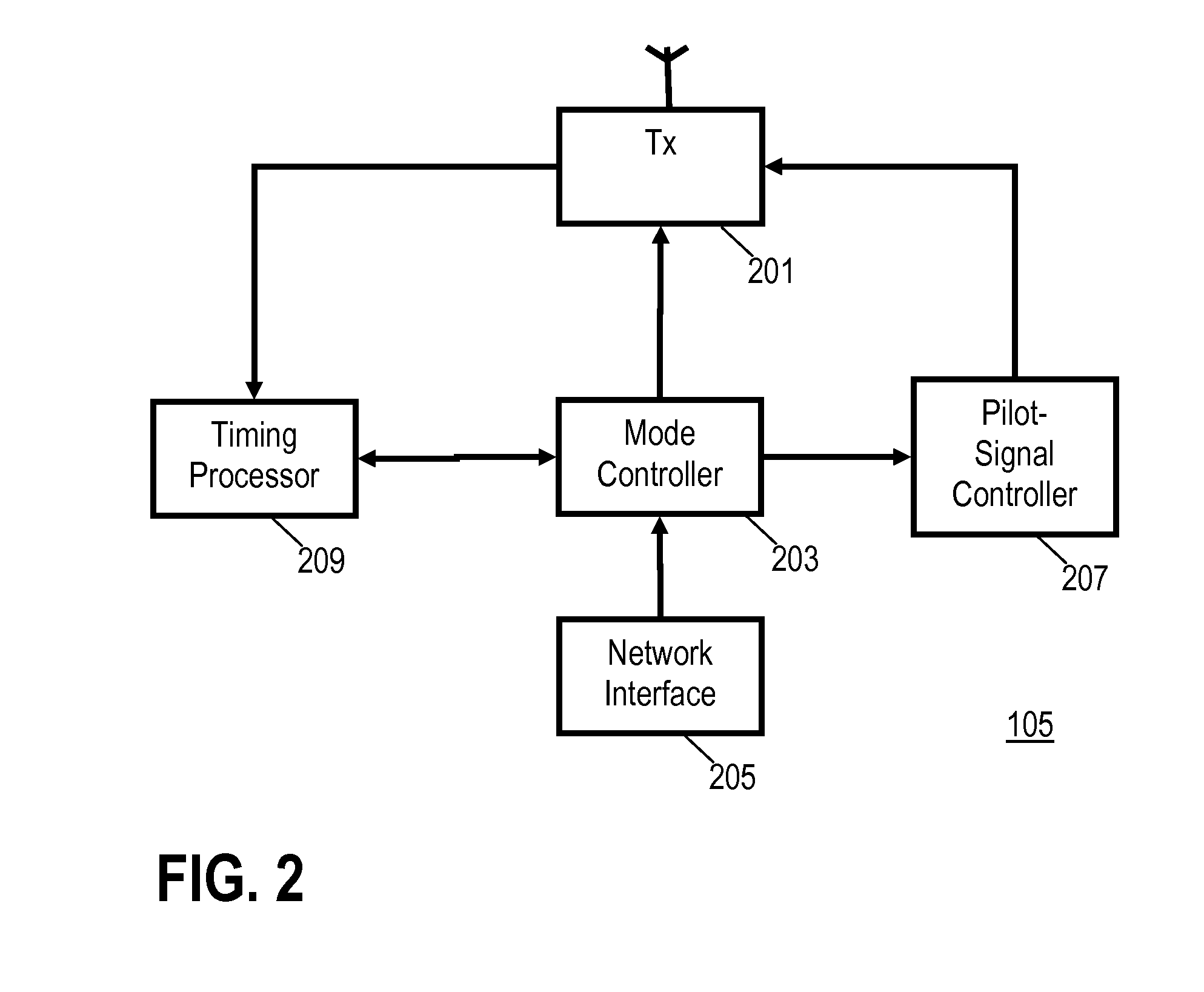

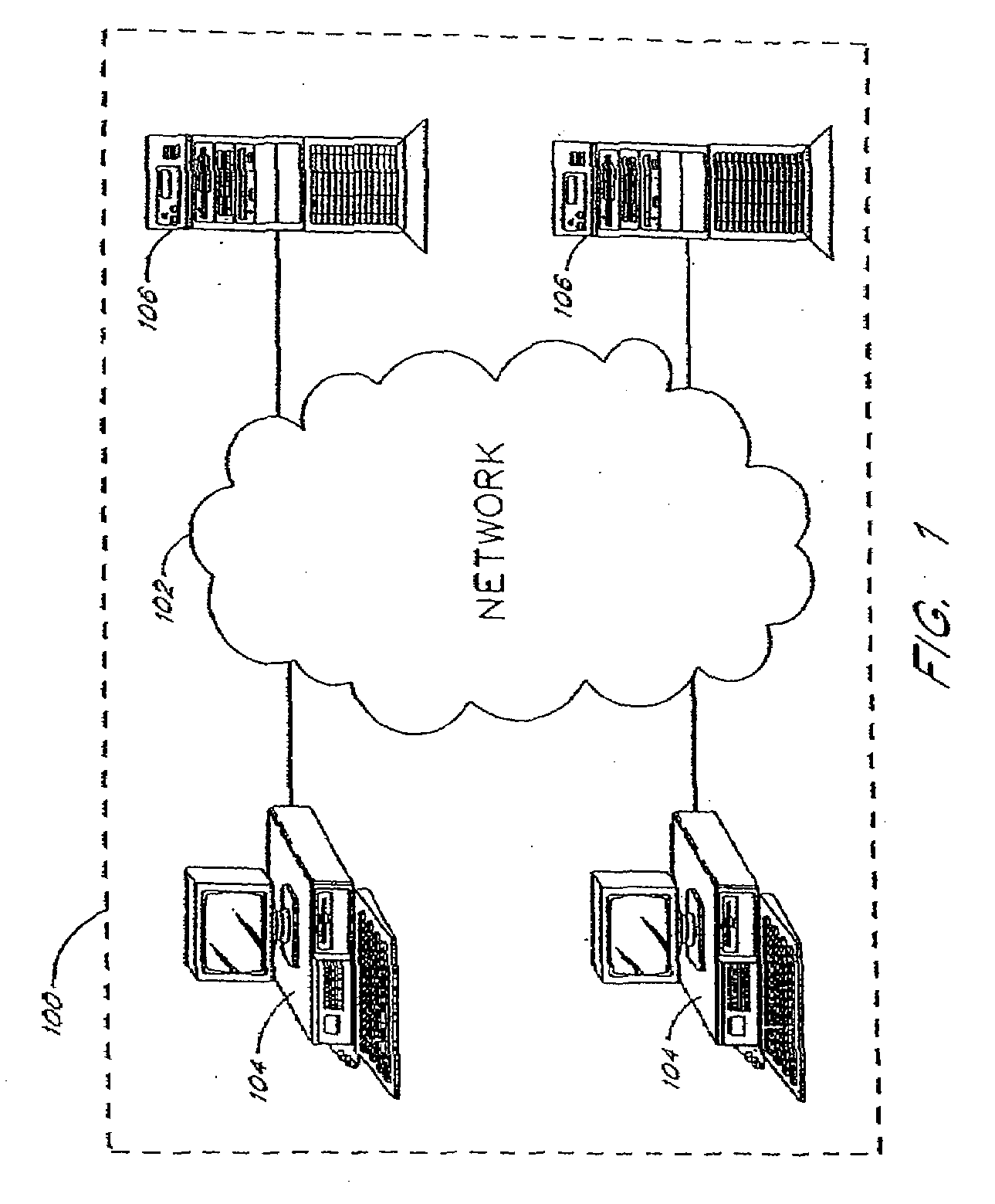

Presence-aware cellular communication system and method

InactiveUS20100056184A1Increase capacityReduce consumptionPower managementAssess restrictionAir interfaceCellular communication systems

A cellular communication system comprises a network supporting user equipment over an air interface, the network having a hierarchical cell arrangement with overlay cells and underlay cells. An underlay base station is associated with a subset of registered user equipment. An activation server switches the underlay base station between an inactive mode and an active mode in response to detecting that registered user equipment meets a location criterion. The underlay base station only supports user equipment when in the active mode, e.g., it may only transmit a pilot signal in this mode. Interference and power consumption may be substantially reduced by sending the base station into the inactive mode thereby resulting in increased capacity of the cellular communication system as a whole.

Owner:MOTOROLA MOBILITY LLC

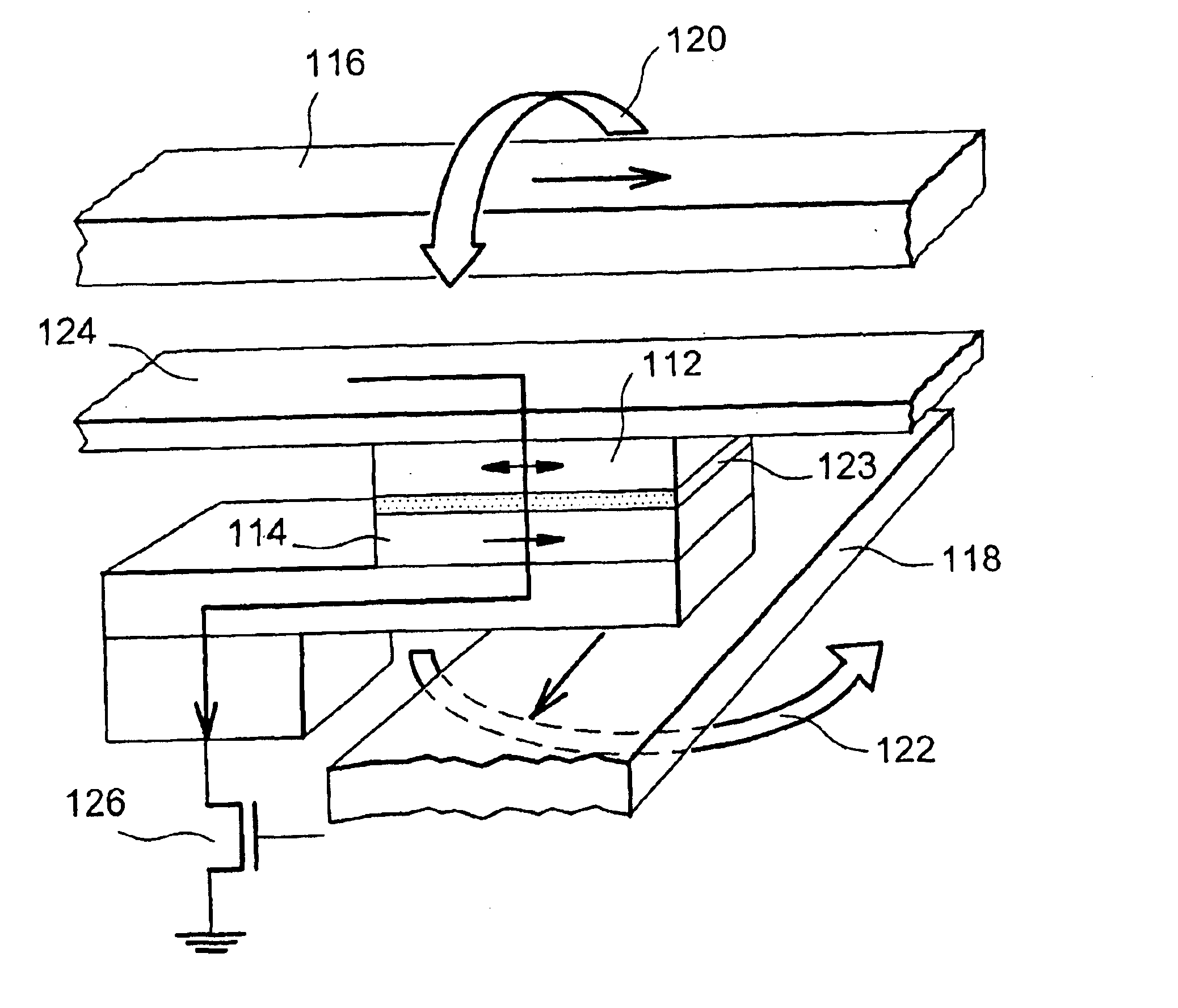

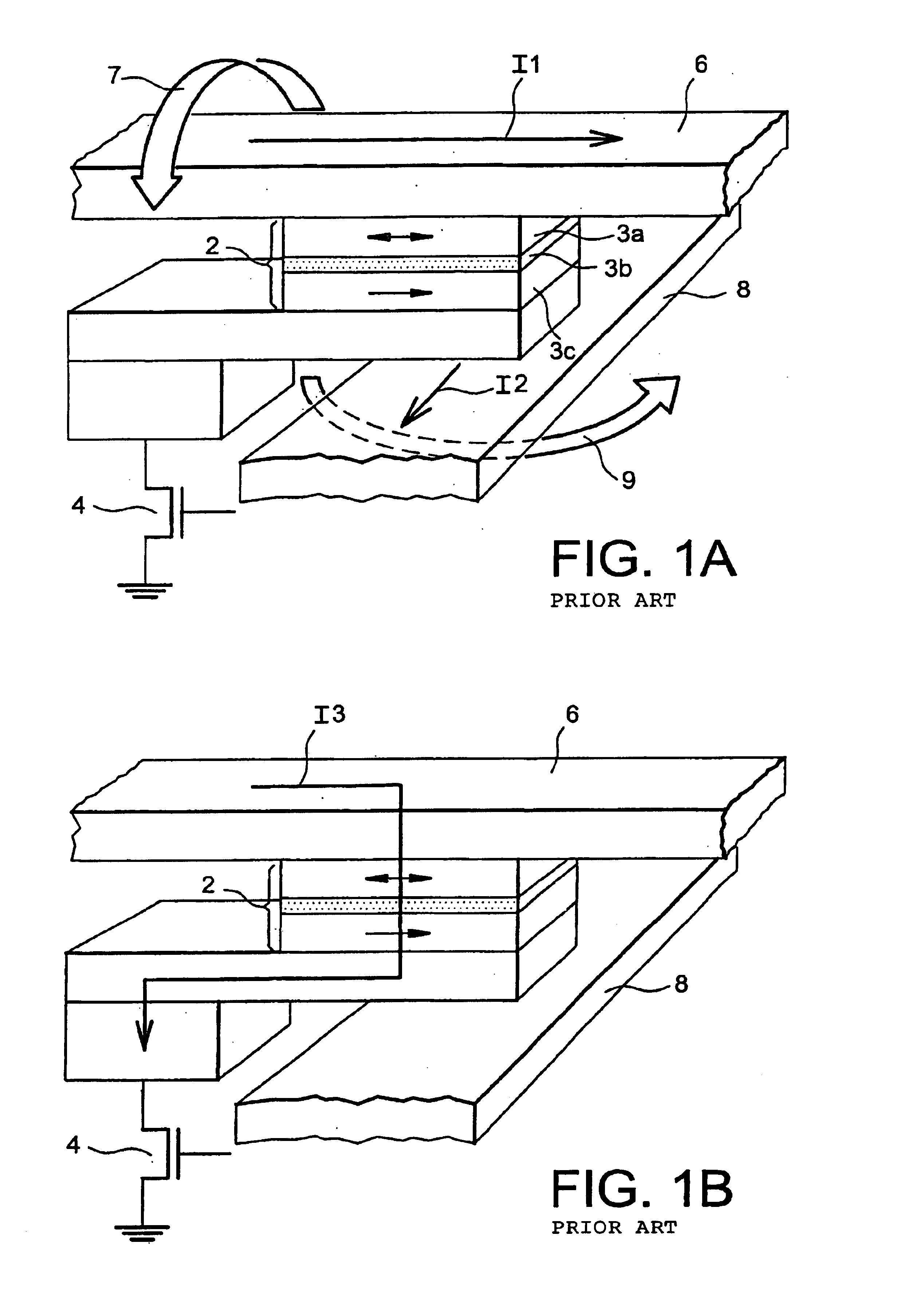

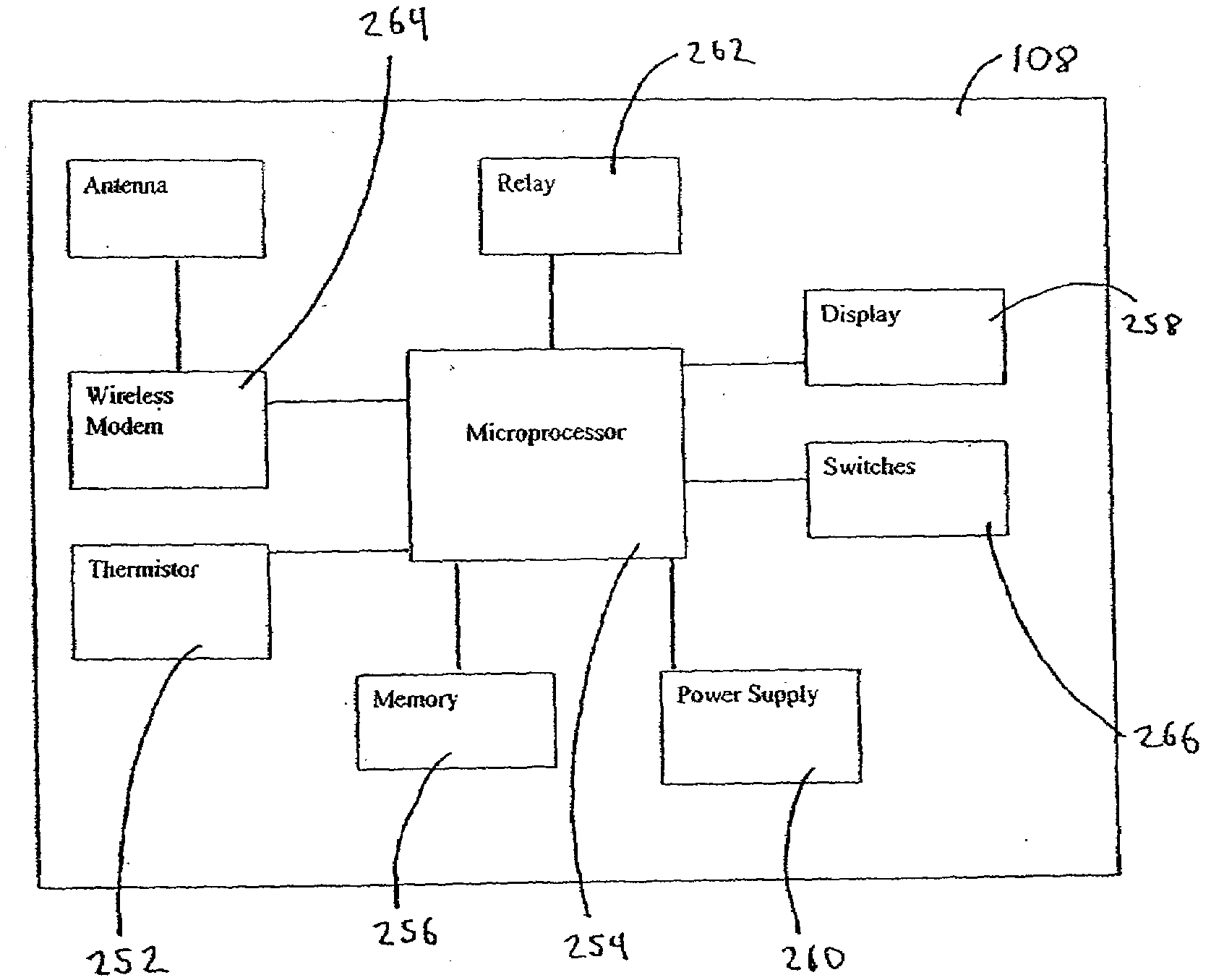

Magnetic tunnel junction magnetic device, memory and writing and reading methods using said device

InactiveUS6950335B2Good reproducibilityEliminate errorsNanomagnetismMagnetic-field-controlled resistorsMagnetizationSemiconductor

Magnetic tunnel junction magnetic device (16) for writing and reading uses a reference layer (20c) and a storage layer (20a) separated by a semiconductor or insulating layer (20b). The blocking temperature of the magnetisation of the storage layer is less than that of the reference layer. The storage layer is heated (22, 24) above the blocking temperature of its magnetisation. A magnetic field (34) is applied (26) to it orientating its magnetization with respect to that of the reference layer without modifying the orientation of the reference layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

System and method for calculating the thermal mass of a building

ActiveUS20100070084A1Improve comfortReduce energy useSpace heating and ventilationTemperatue controlControl systemEngineering

The invention comprises a system for calculating a value for the effective thermal mass of a building. The climate control system obtains temperature measurements from at least a first location conditioned by the climate system. One or more processors receive measurements of outside temperatures from at least one source other than the control system and compare the temperature measurements from the first location with expected temperature measurements. The expected temperature measurements are based at least in part upon past temperature measurements obtained by said HVAC control system and said outside temperature measurements. The processors then calculate one or more rates of change in temperature at said first location.

Owner:ECOFACTOR

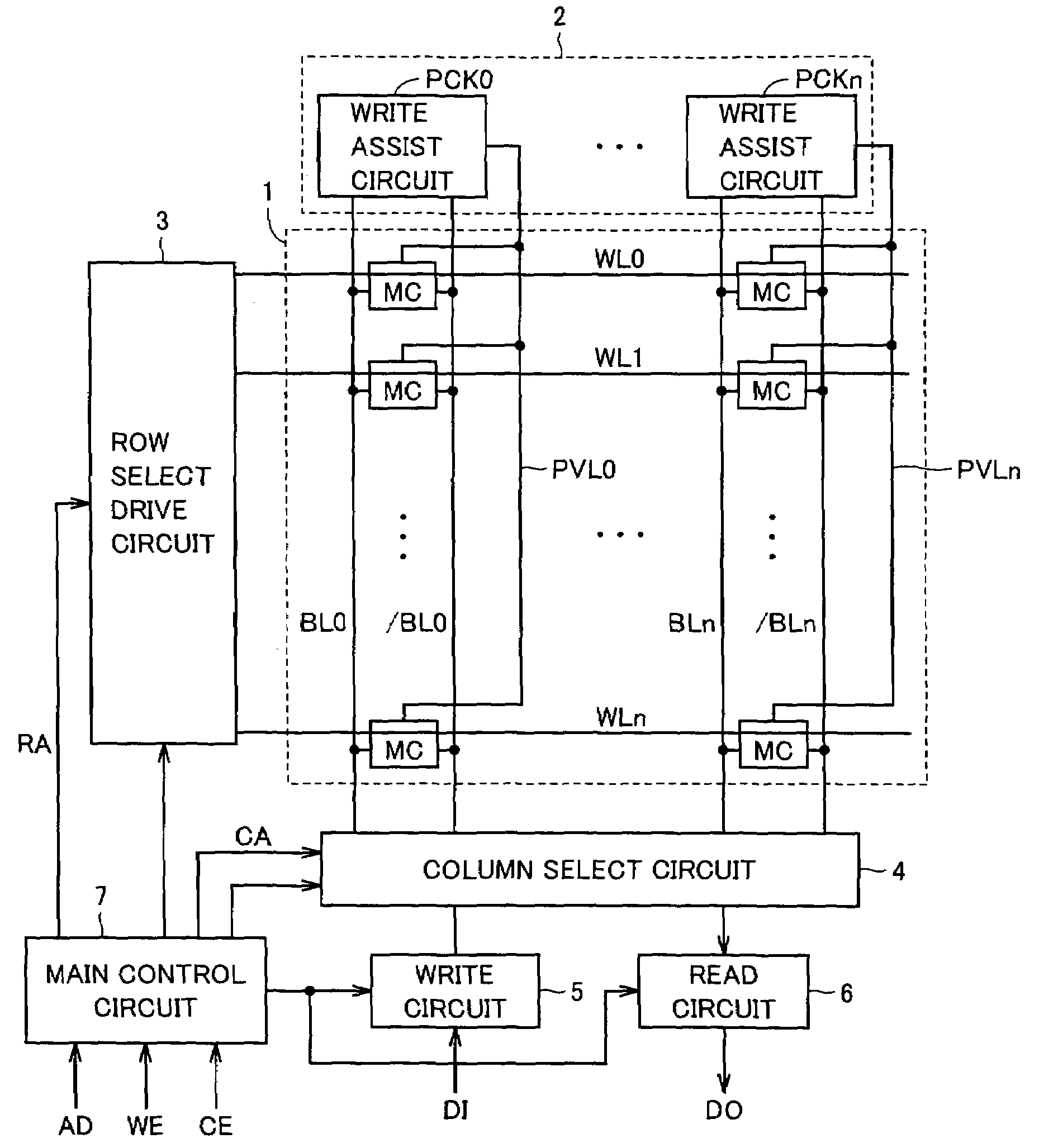

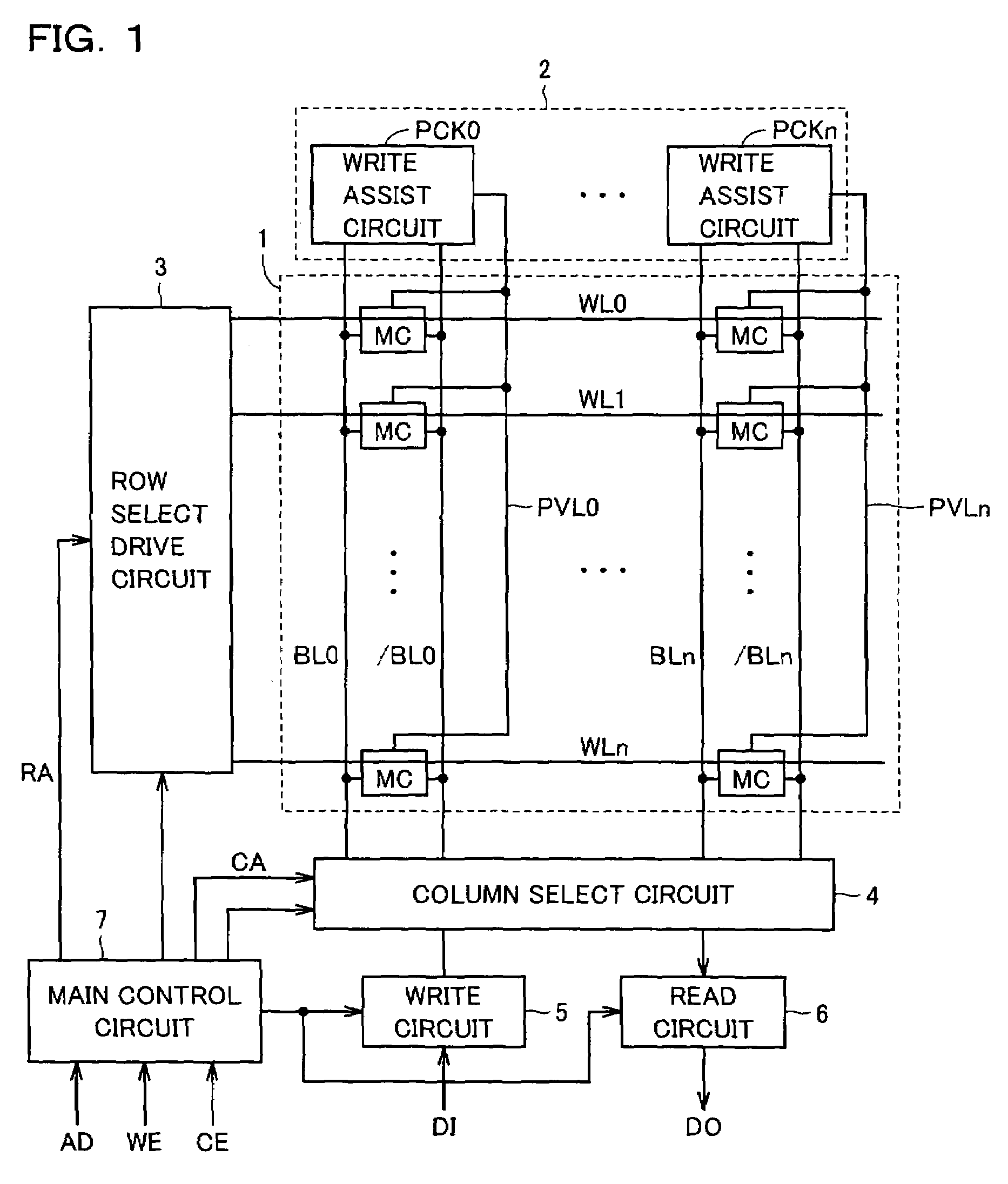

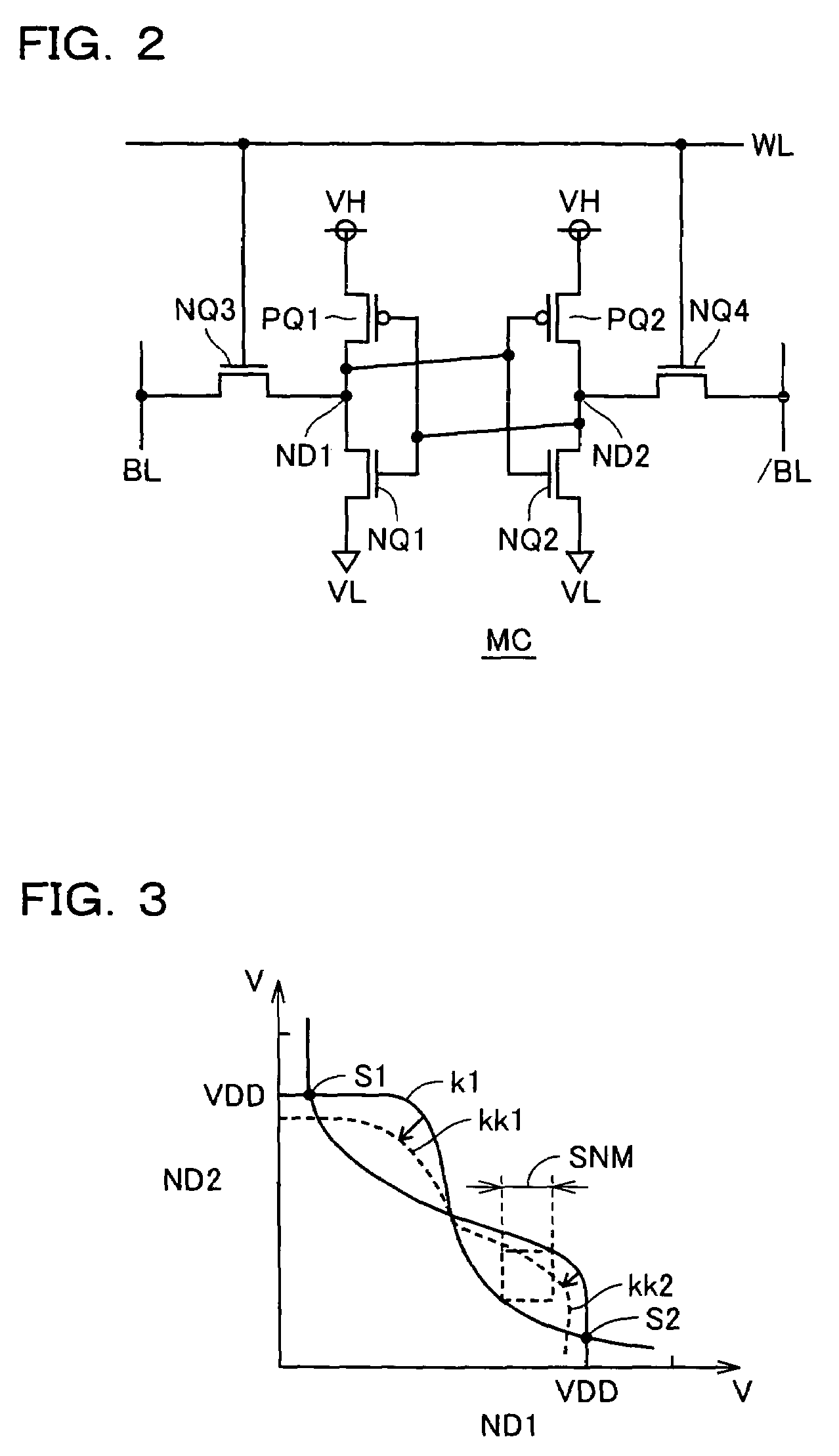

Semiconductor memory device

ActiveUS7502275B2Reduce consumptionLower performance requirementsDigital storageBit lineElectrical impedance

Cell power supply lines are arranged for memory cell columns, and adjust impedances or voltage levels of the cell power supply lines according to the voltage levels of bit lines in the corresponding columns, respectively. In the data write operation, the cell power supply line is forced into a floating state according to the bit line potential on a selected column and has the voltage level changed, and a latching capability of a selected memory cell is reduced to write data fast. Even with a low power supply voltage, a static semiconductor memory device that can stably perform write and read of data is implemented.

Owner:RENESAS ELECTRONICS CORP

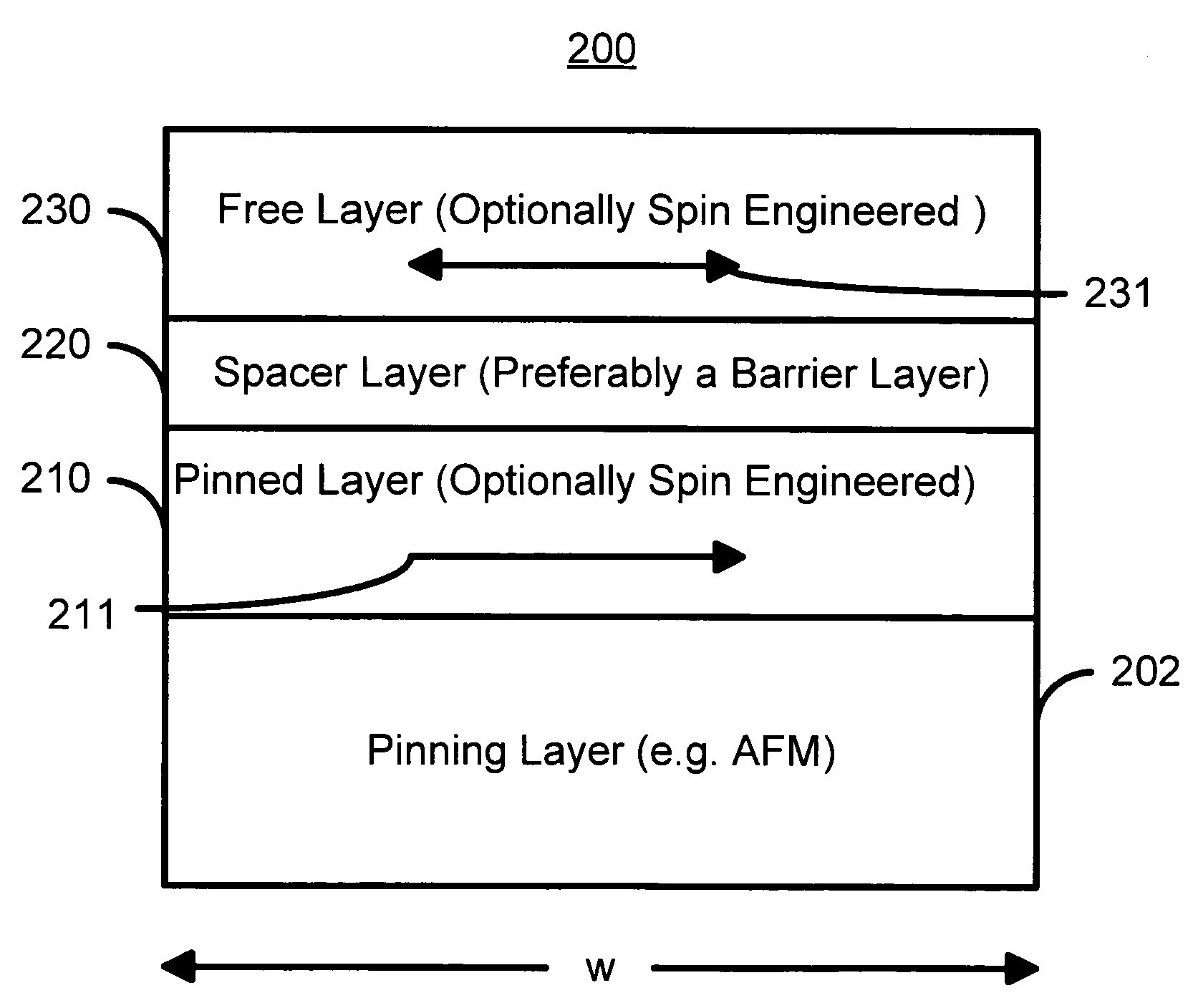

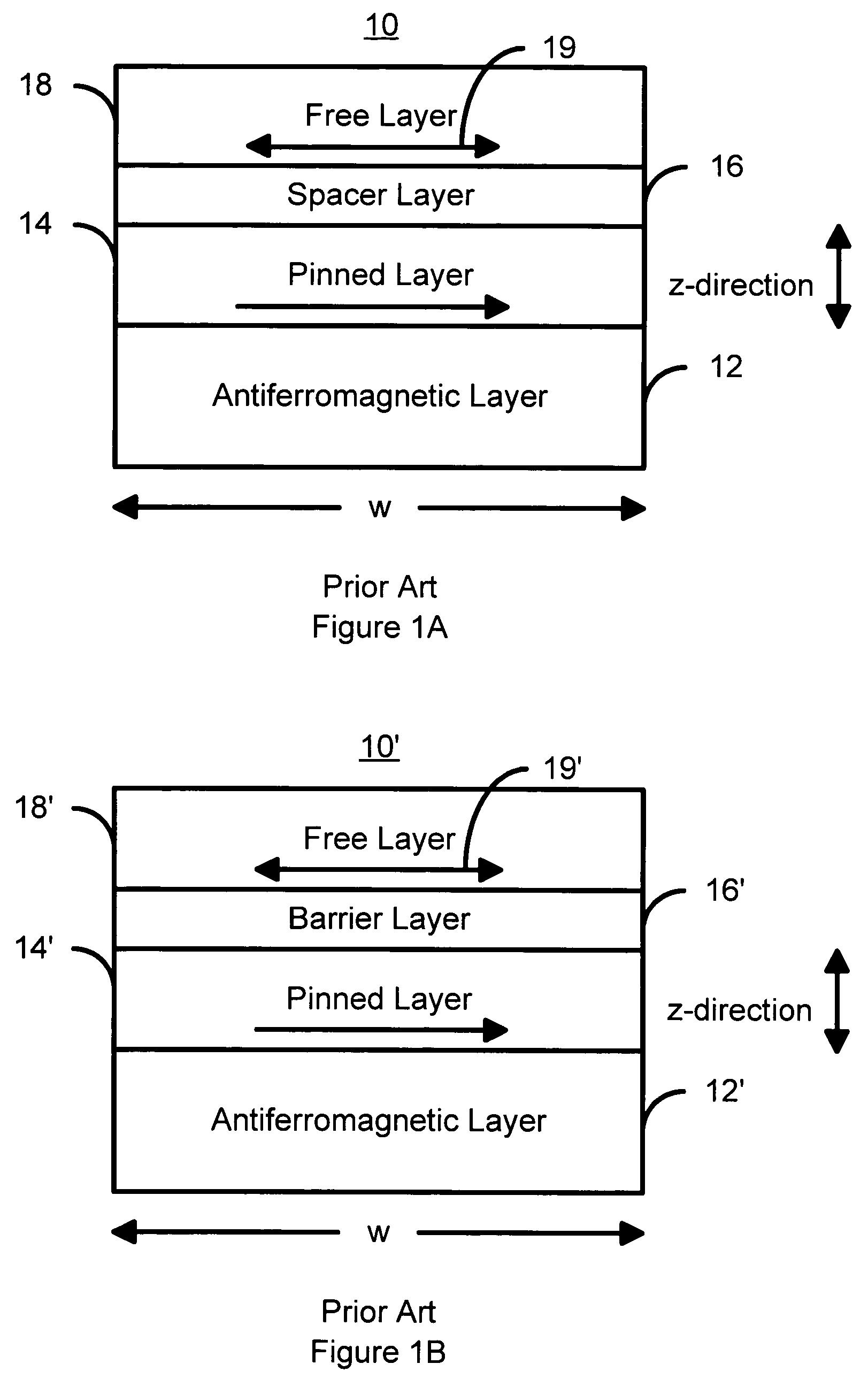

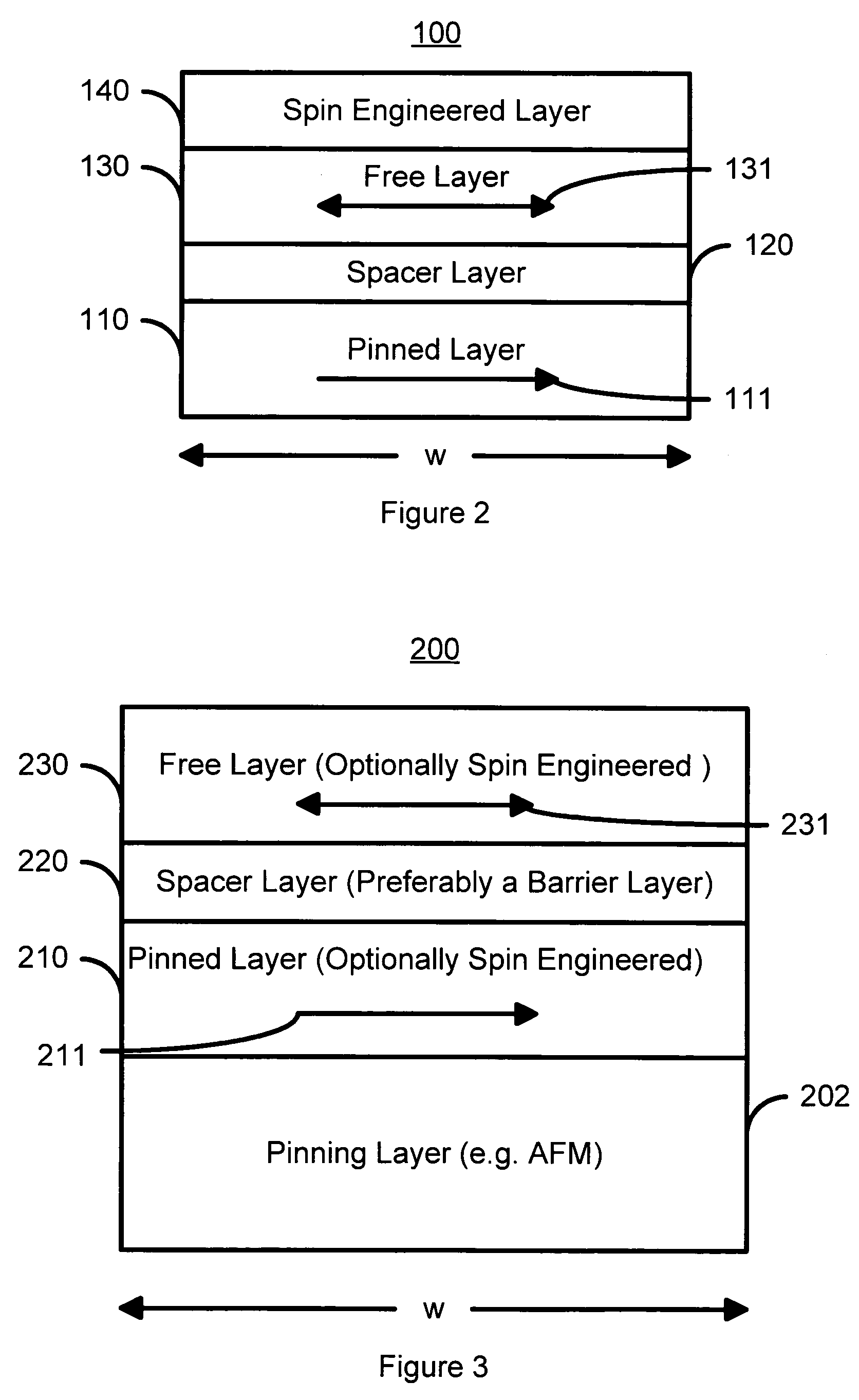

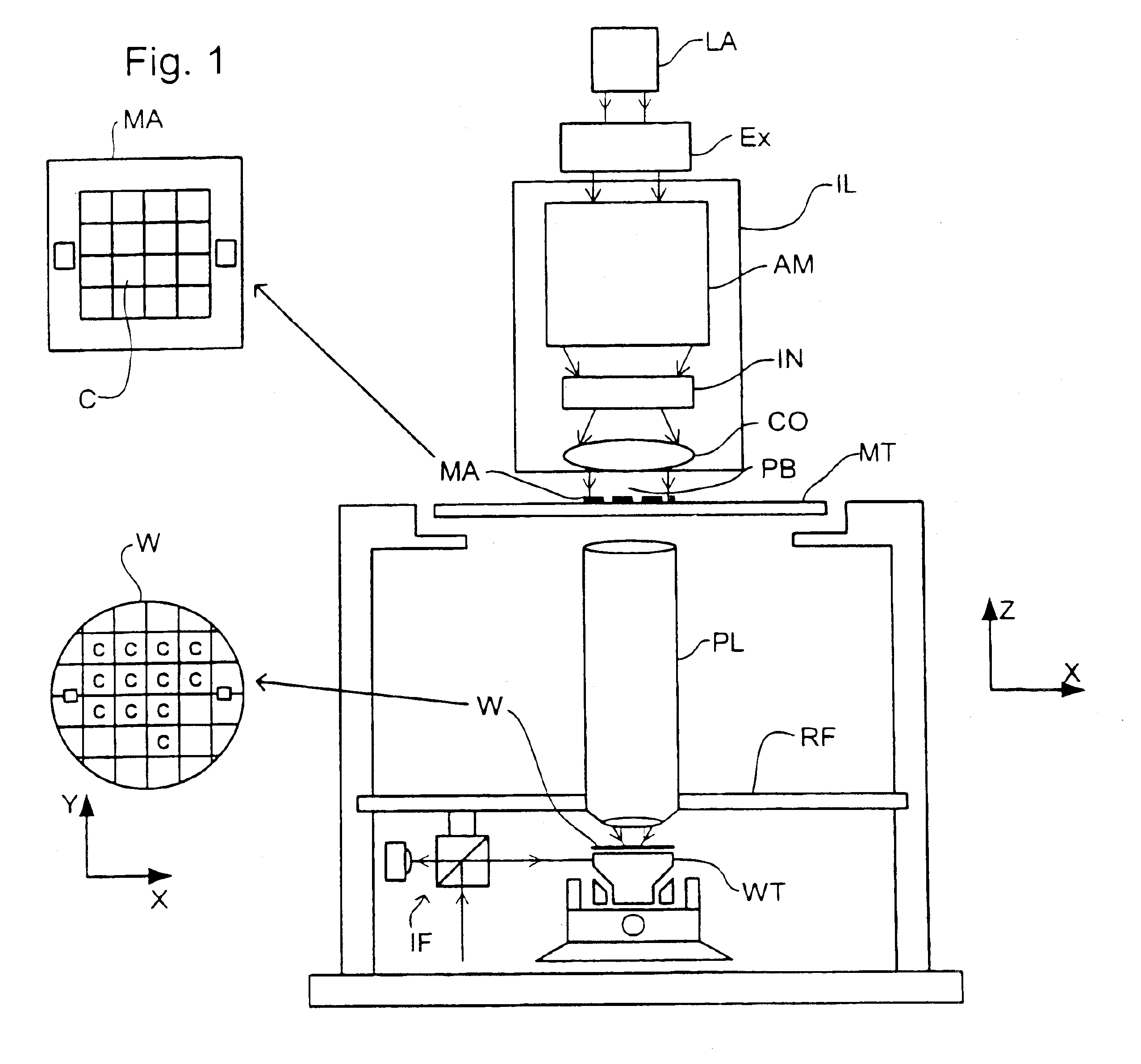

Magnetic elements with spin engineered insertion layers and MRAM devices using the magnetic elements

ActiveUS7369427B2Lower average currentReduce consumptionNanomagnetismGalvano-magnetic material selectionSpinsSpin transfer

A method and system include providing a pinned layer, a free layer, and a spacer layer between the pinned and free layers. The spacer layer is nonmagnetic. The magnetic element is configured to allow the free layer to be switched due to spin transfer when a write current is passed through the magnetic element. In one aspect, the method and system include providing a spin engineered layer adjacent to the free layer. The spin engineered layer is configured to more strongly scatter majority electrons than minority electrons. In another aspect, at least one of the pinned, free, and spacer layers is a spin engineered layer having an internal spin engineered layer configured to more strongly scatter majority electrons than minority electrons. In this aspect, the magnetic element may include another pinned layer and a barrier layer between the free and pinned layers.

Owner:SAMSUNG SEMICON

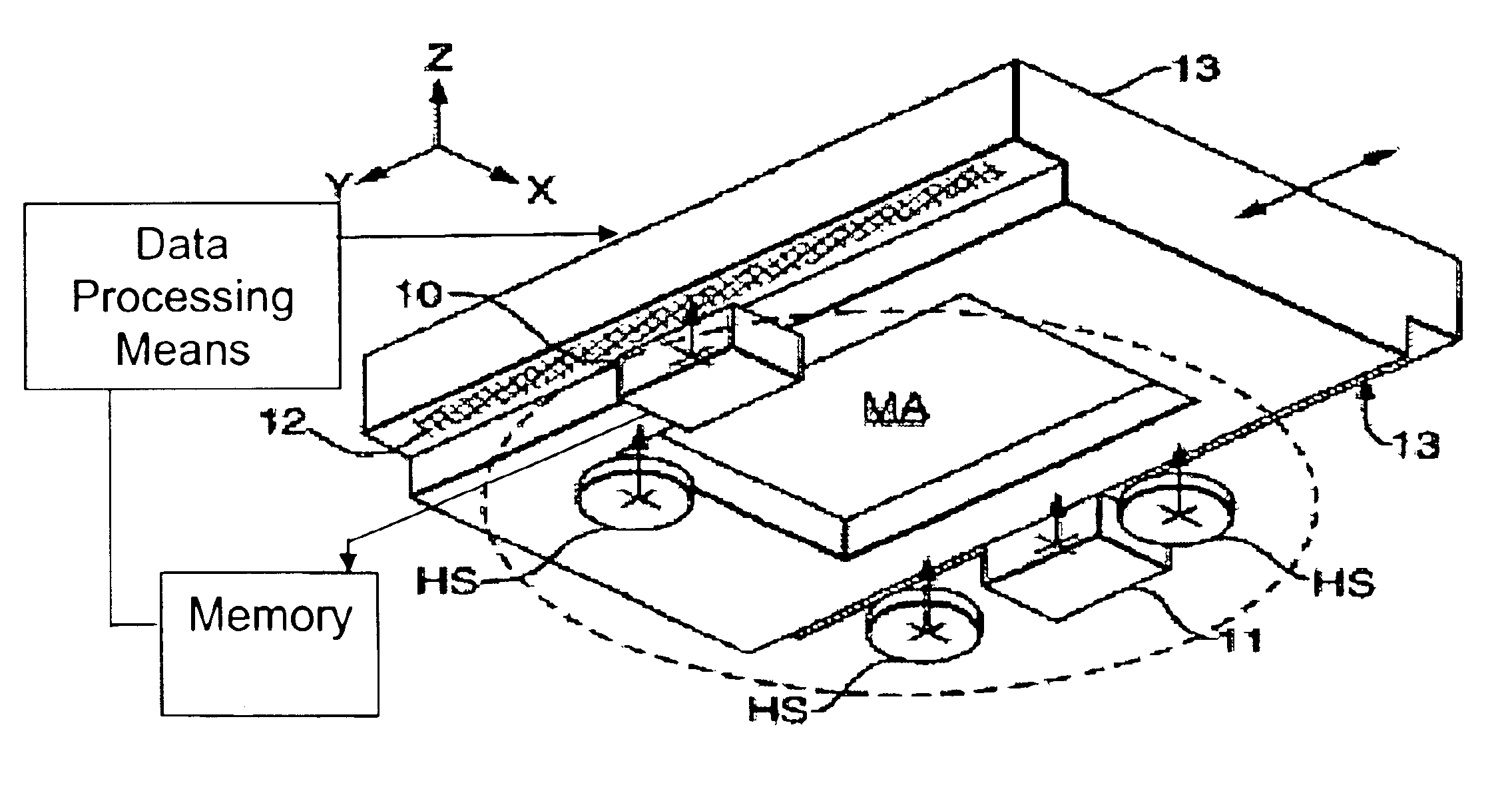

Lithographic apparatus, device manufacturing method, and device manufactured thereby

InactiveUS6819425B2Improve stabilityReduce impactInvestigating moving sheetsSemiconductor/solid-state device manufacturingCapacitanceGrating

The X, Y and Rx positions of a mask stage are measured using two optical encoder-reading heads measuring displacements of respective grid gratings mounted on the mask stage. The grid gratings are preferably provided on cut-away portions of the mask table so as to be co-planar with the pattern on the mask itself. Measurements of the table position in the other degrees of freedom can be measured with capacitative or optical height sensors.

Owner:ASML NETHERLANDS BV