Patents

Literature

1953 results about "Logic block" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, a logic block or configurable logic block (CLB) is a fundamental building block of field-programmable gate array (FPGA) technology. Logic blocks can be configured by the engineer to provide reconfigurable logic gates.

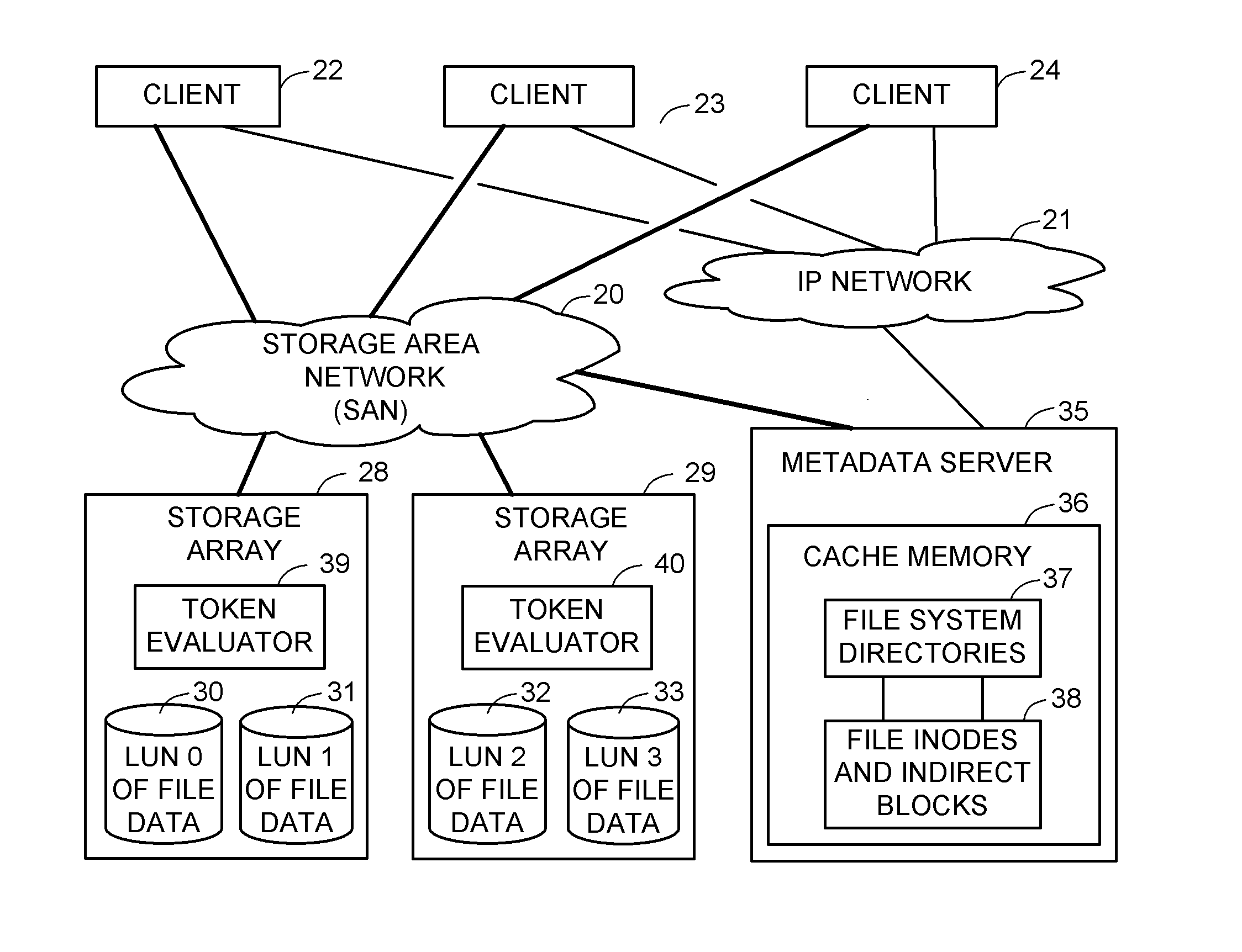

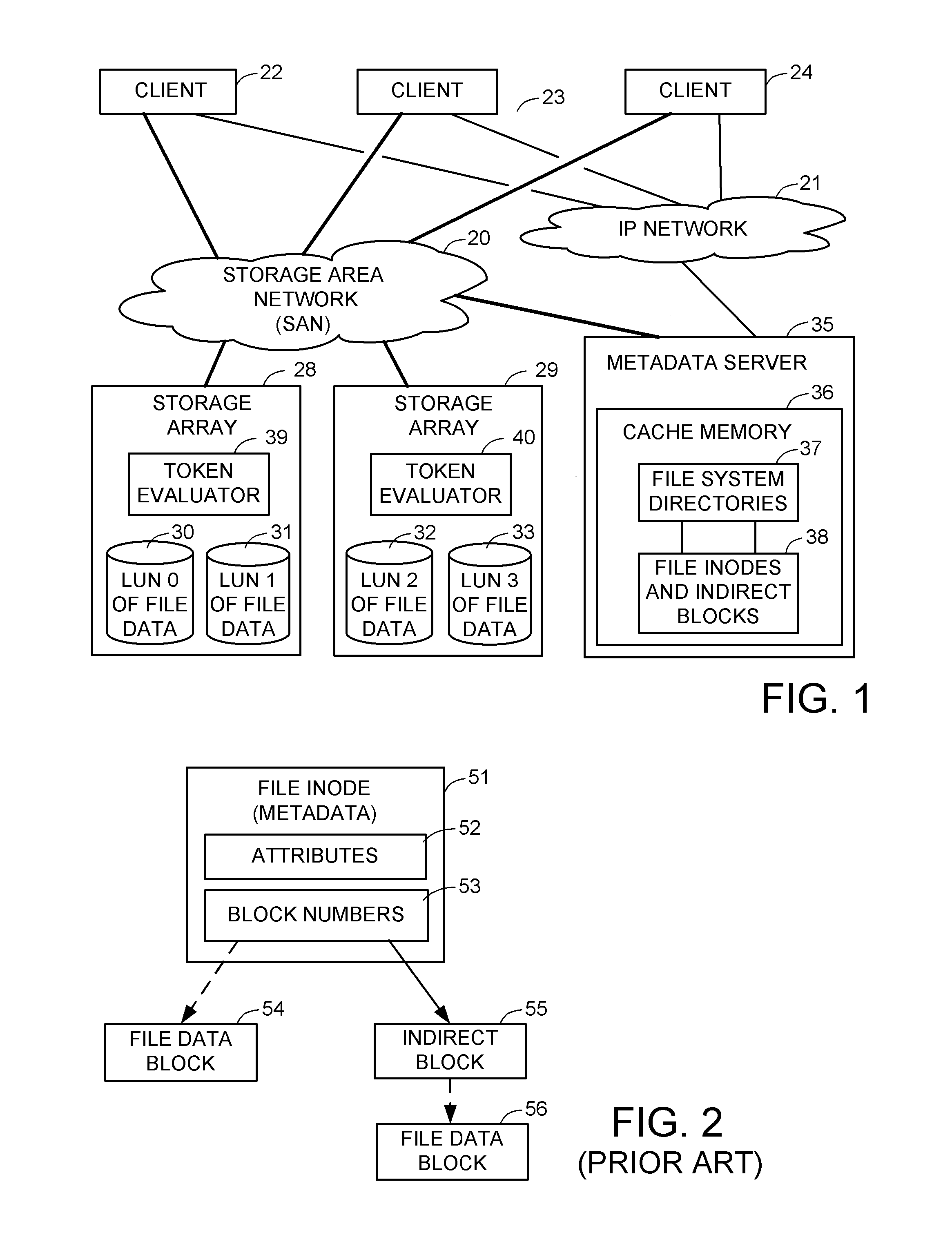

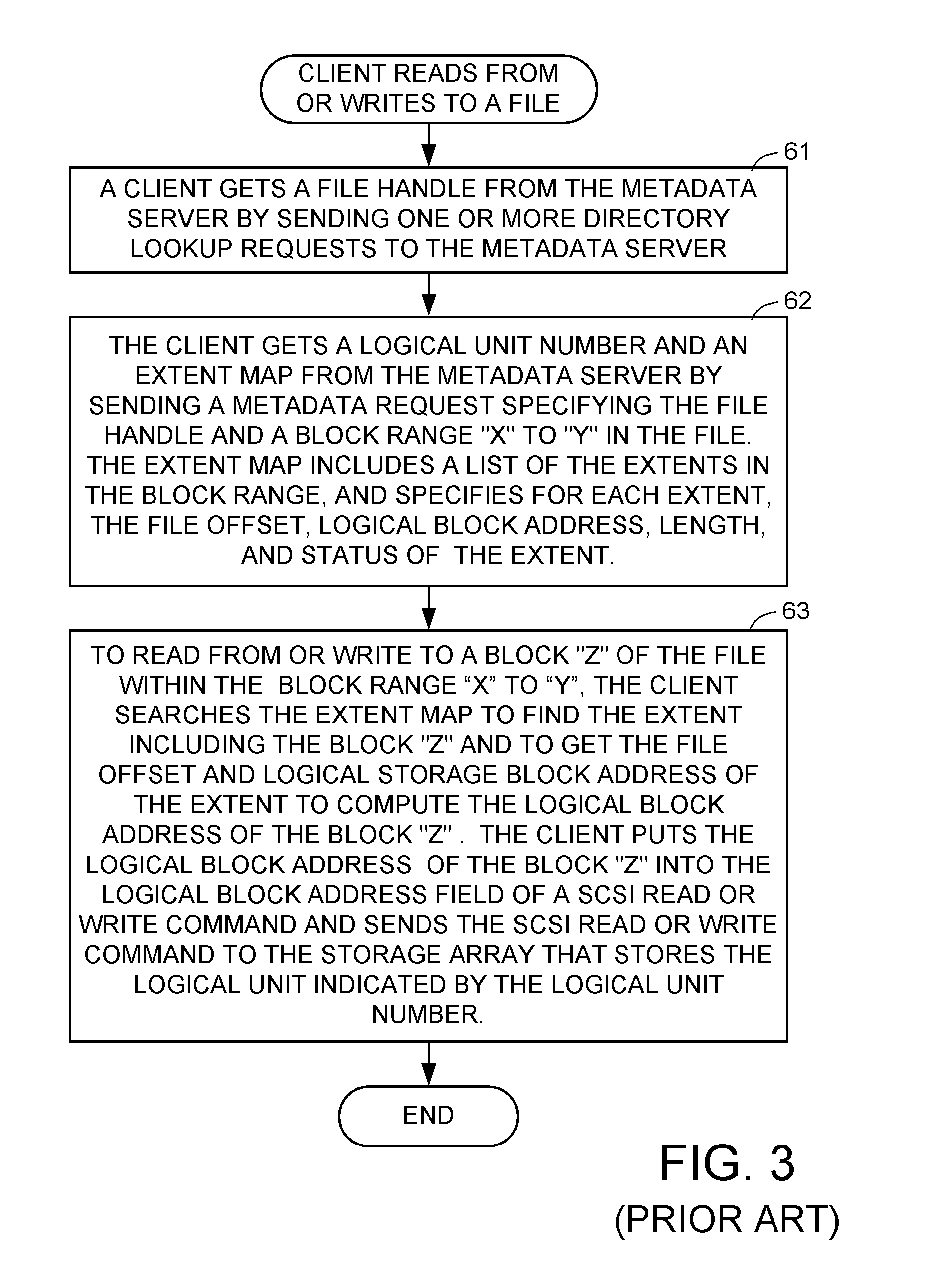

Access control to block storage devices for a shared disk based file system

ActiveUS8086585B1Improve securityChangeDigital data information retrievalDigital data processing detailsSCSILogical block addressing

For enhanced access control, a client includes a token in each read or write command sent to a block storage device. The block storage device evaluates the token to determine whether or not read or write access is permitted at a specified logical block address. For example, the token is included in the logical block address field of a SCSI read or write command. The client may compute the token as a function of the logical block address of a data block to be accessed, or a metadata server may include the token in each block address of each extent reported to the client in response to a metadata request. For enhanced security, the token also is a function of a client identifier, a logical unit number, and access rights of the client to a particular extent of file system data blocks.

Owner:EMC IP HLDG CO LLC

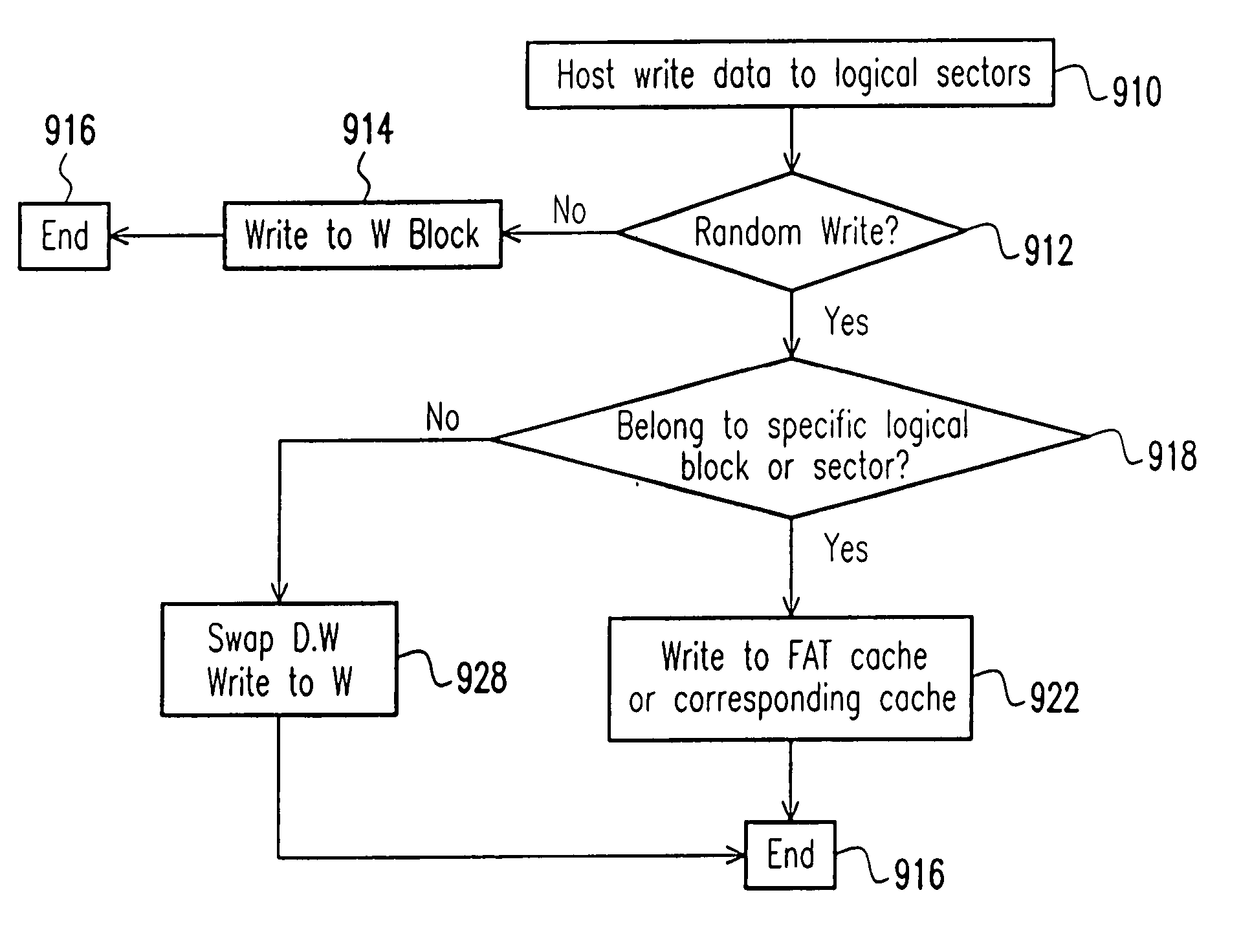

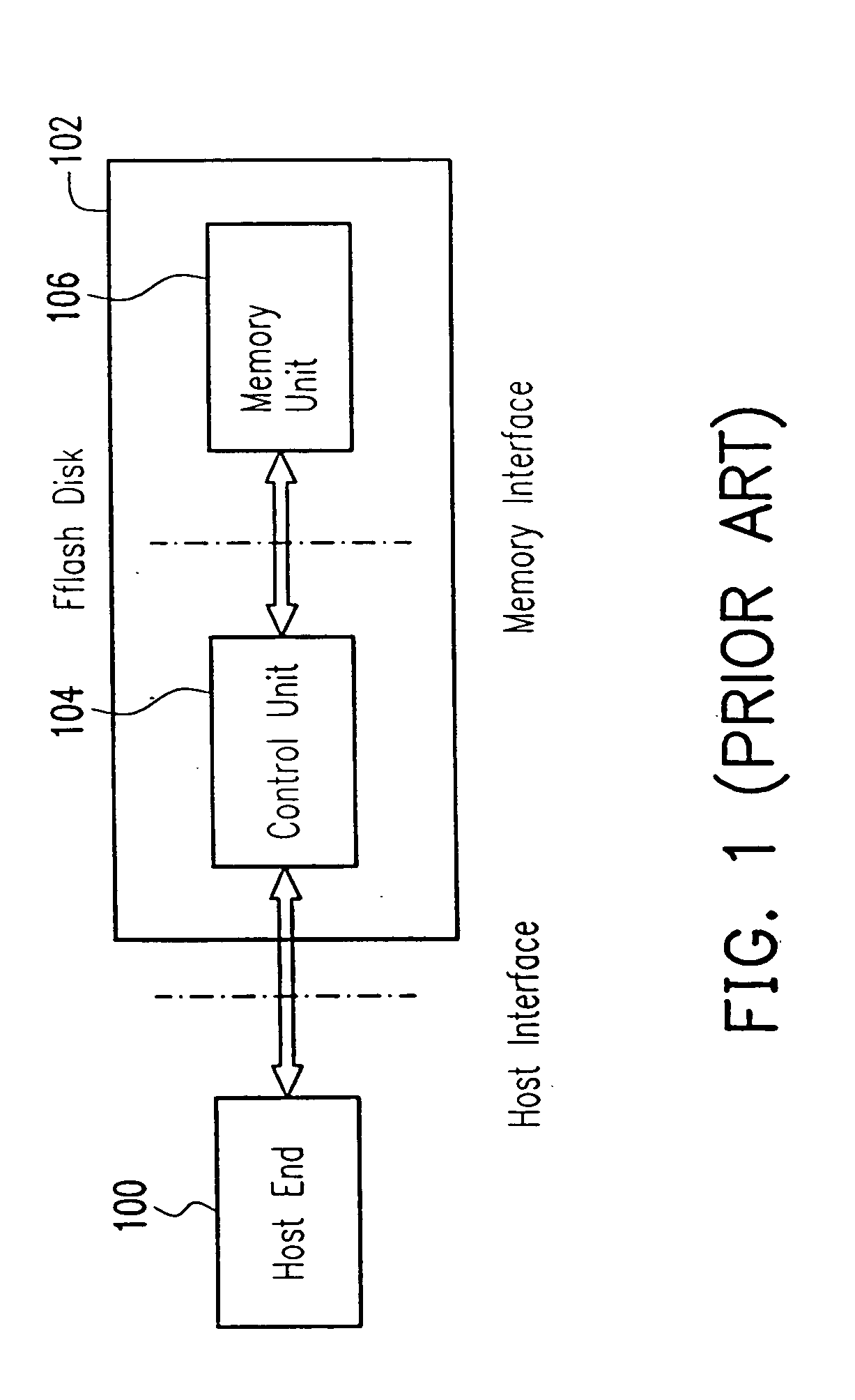

Nonvolatile memory unit with specific cache

InactiveUS20050015557A1Reduce frequencyAvoid actionMemory architecture accessing/allocationInput/output to record carriersOperating systemVolatile memory

The invention provides a method for organizing a writing operation to a nonvolatile memory. The method comprises setting a specific cache area, into which a specific data belonging to a specific group of logical blocks is to be written. It is determined whether or not the writing operation is a random write. If the writing operation is the random write, then the following steps are performed: determining whether or not the writing operation is to write a data that is belonging to the specific group of logical blocks; and writing the data into the specific cache area if the data is belonging to the specific group of logical blocks. As a result, a swap action between a data block and a writing block can be avoided during a random write operation. A storage structure in a nonvolatile memory device are organized to perform the forgoing writing operation.

Owner:SOLID STATE SYST

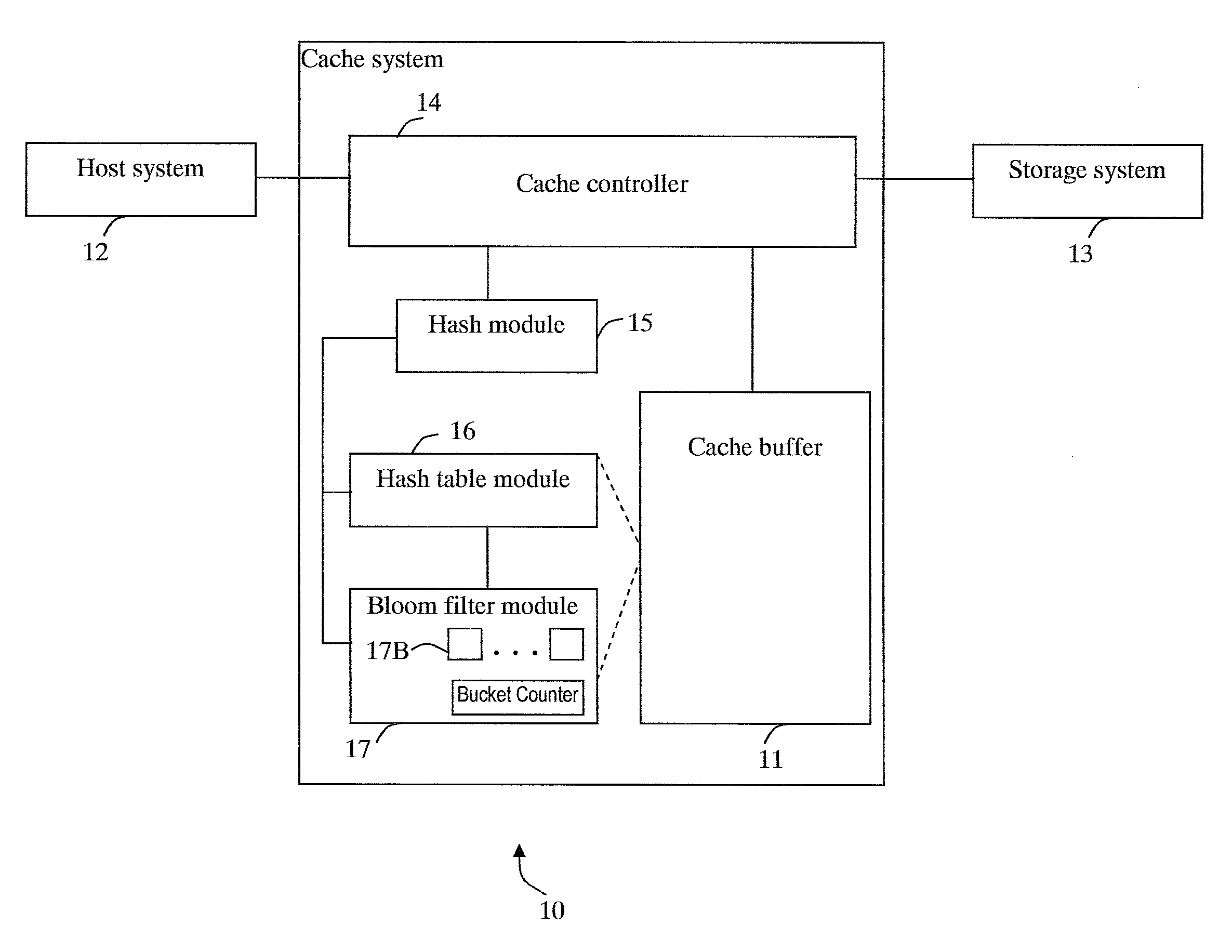

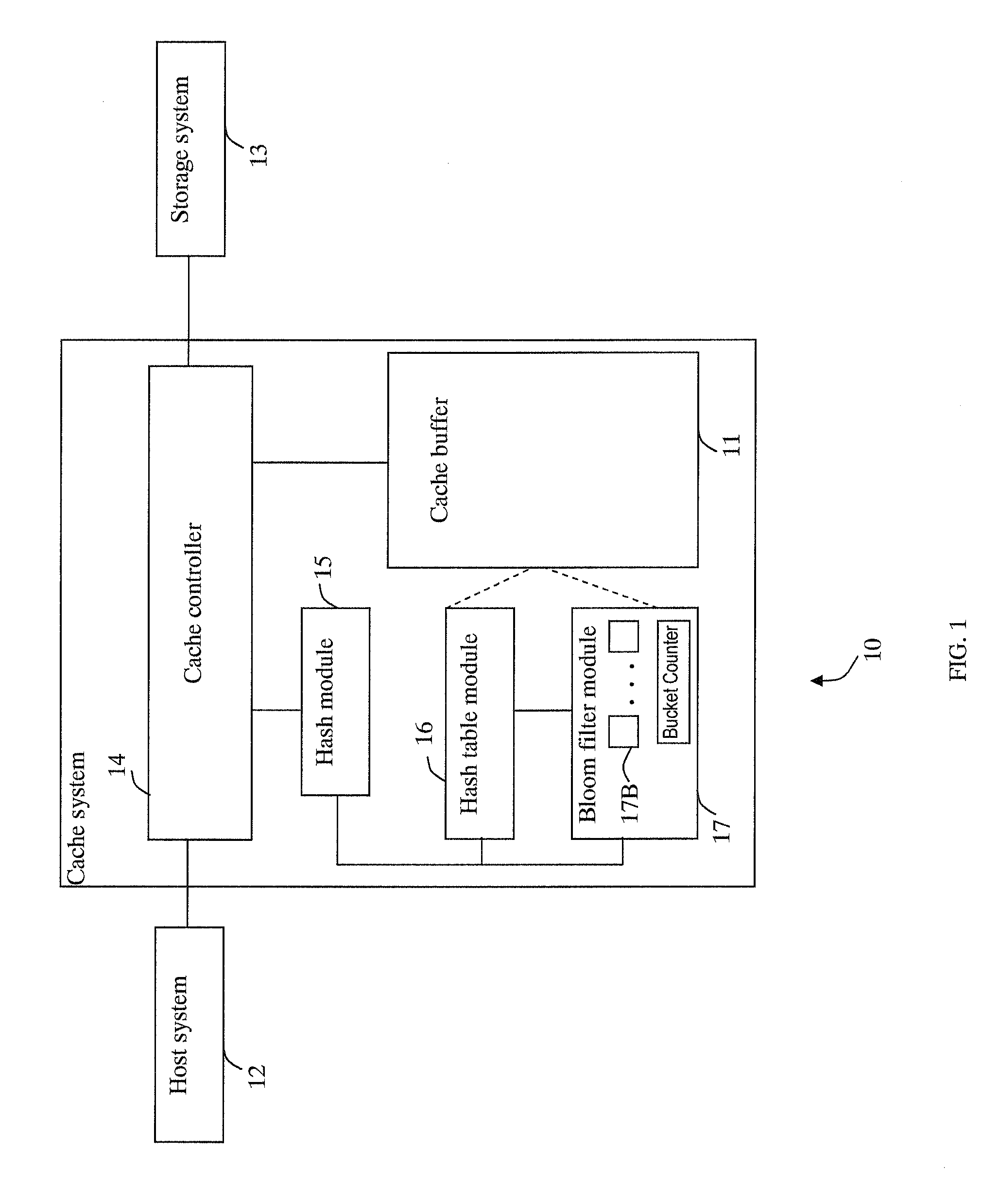

Cache system optimized for cache miss detection

ActiveUS20130326154A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingBloom filter

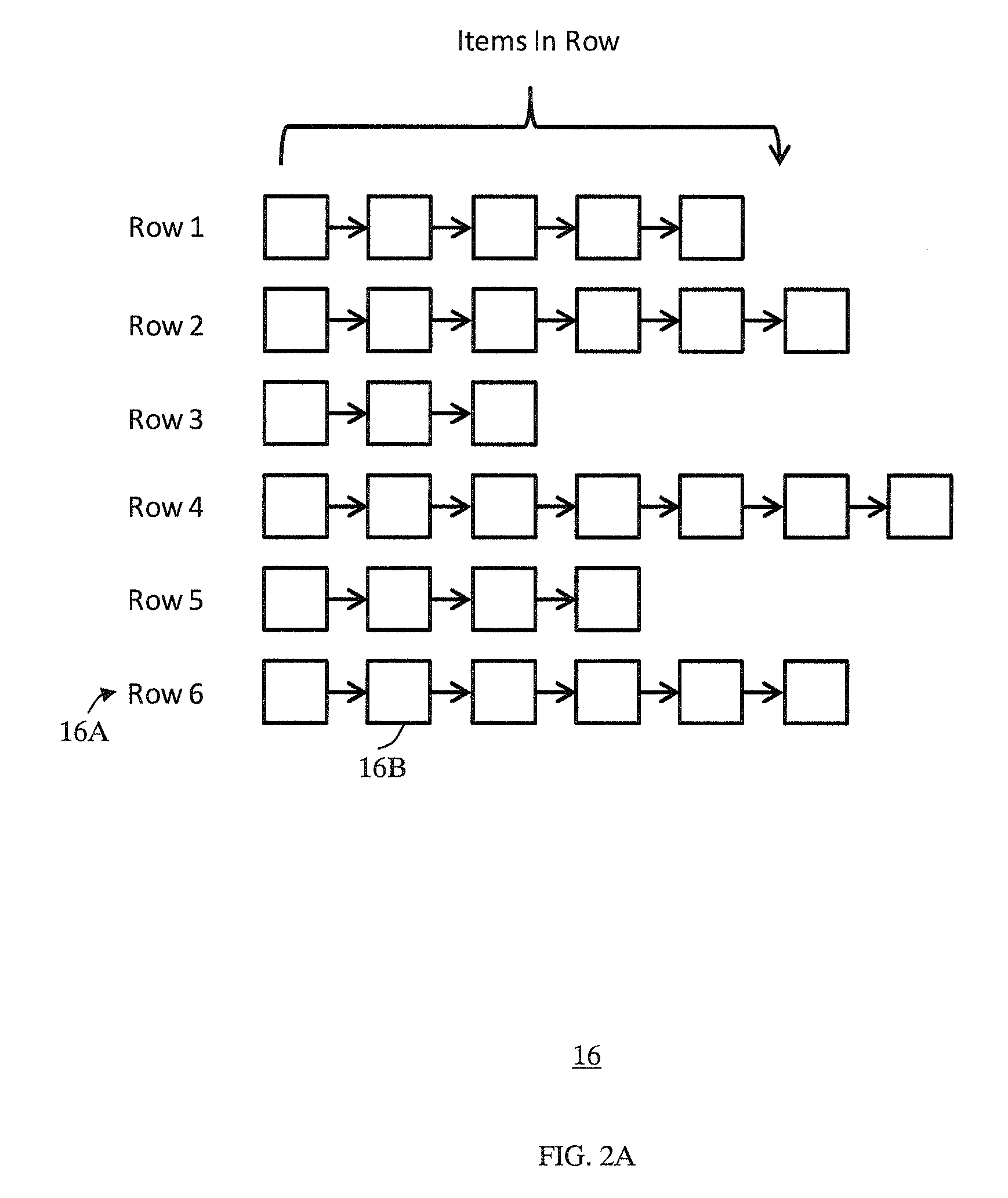

According to an embodiment of the invention, cache management comprises maintaining a cache comprising a hash table including rows of data items in the cache, wherein each row in the hash table is associated with a hash value representing a logical block address (LBA) of each data item in that row. Searching for a target data item in the cache includes calculating a hash value representing a LBA of the target data item, and using the hash value to index into a counting Bloom filter that indicates that the target data item is either not in the cache, indicating a cache miss, or that the target data item may be in the cache. If a cache miss is not indicated, using the hash value to select a row in the hash table, and indicating a cache miss if the target data item is not found in the selected row.

Owner:SAMSUNG ELECTRONICS CO LTD

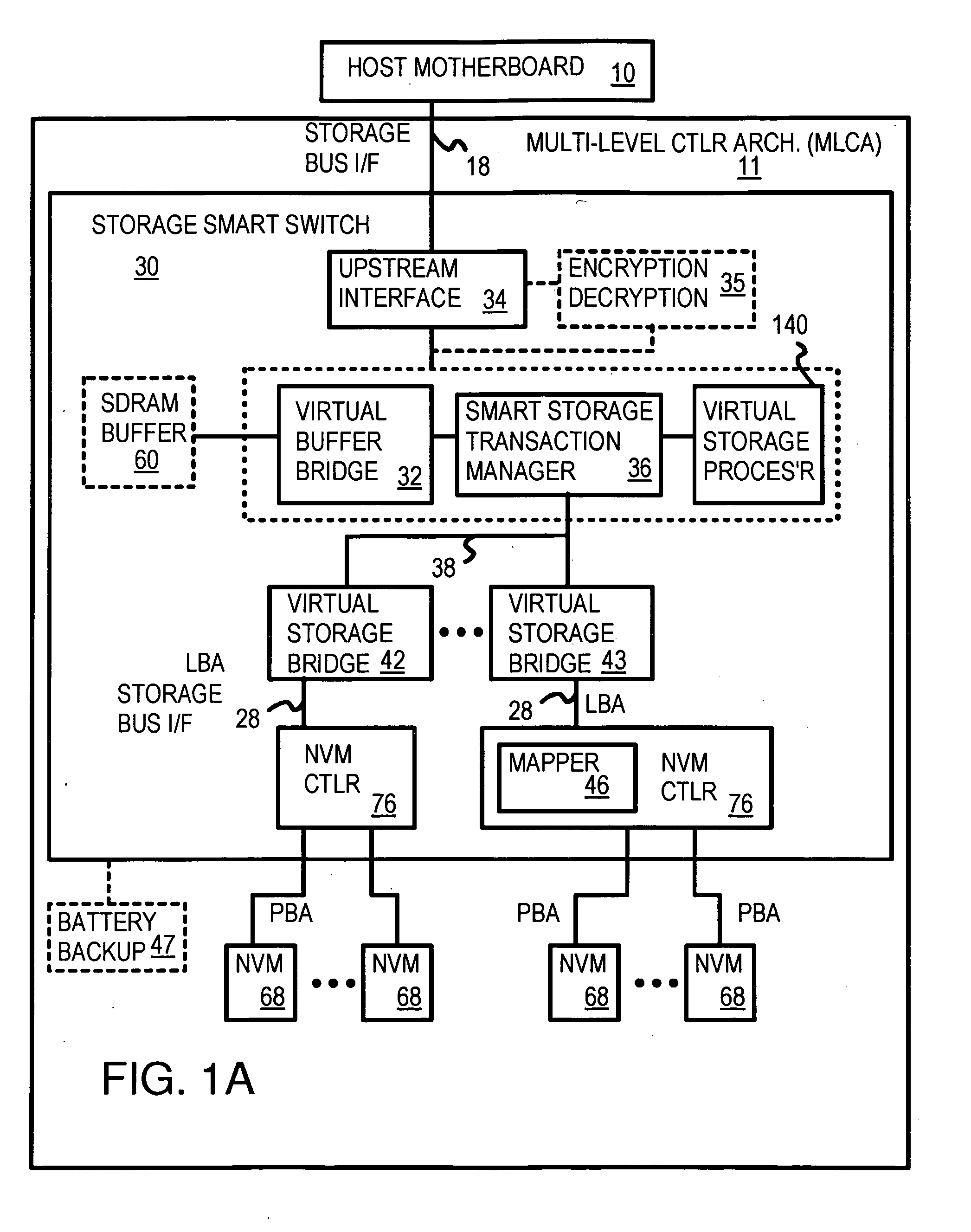

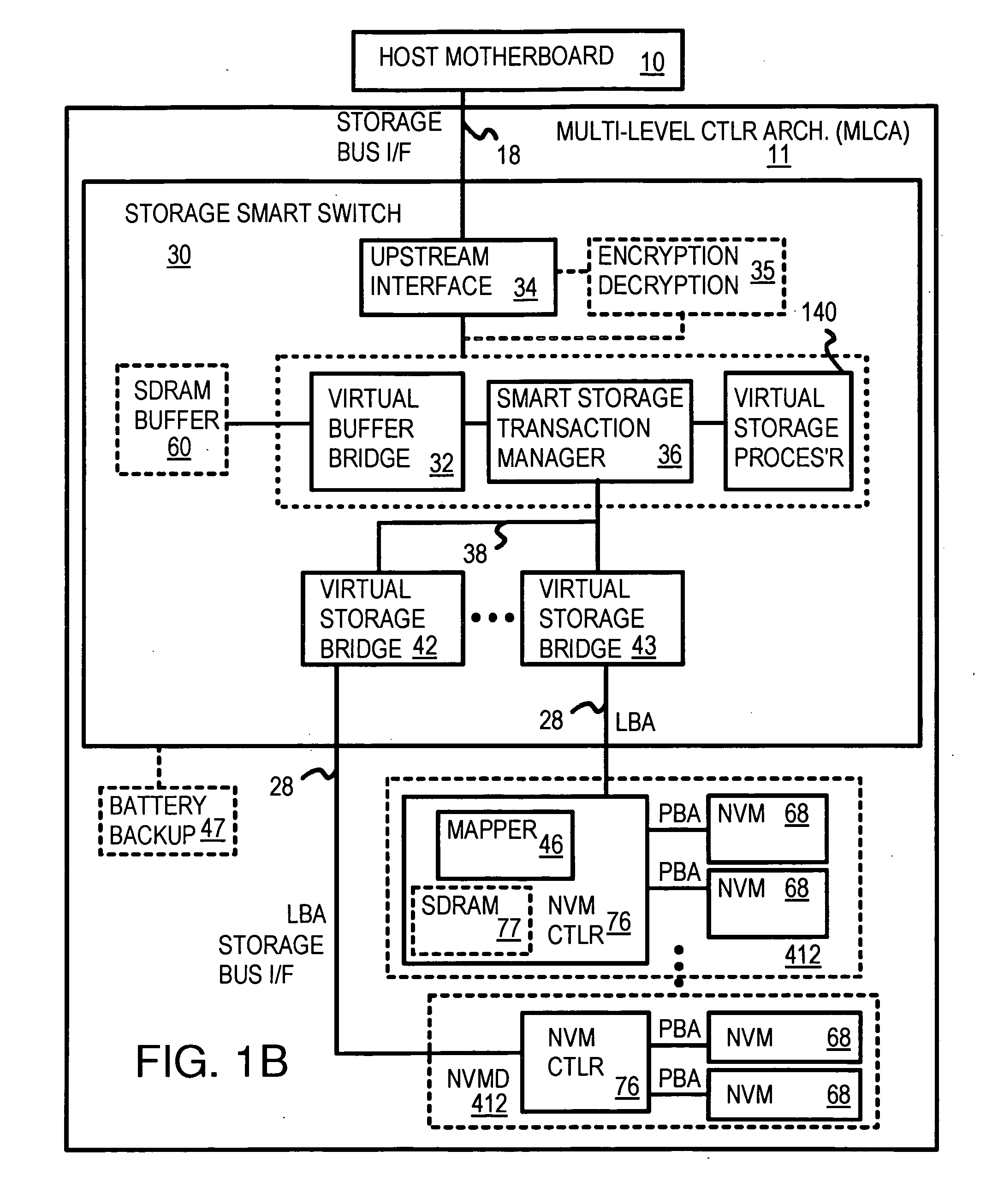

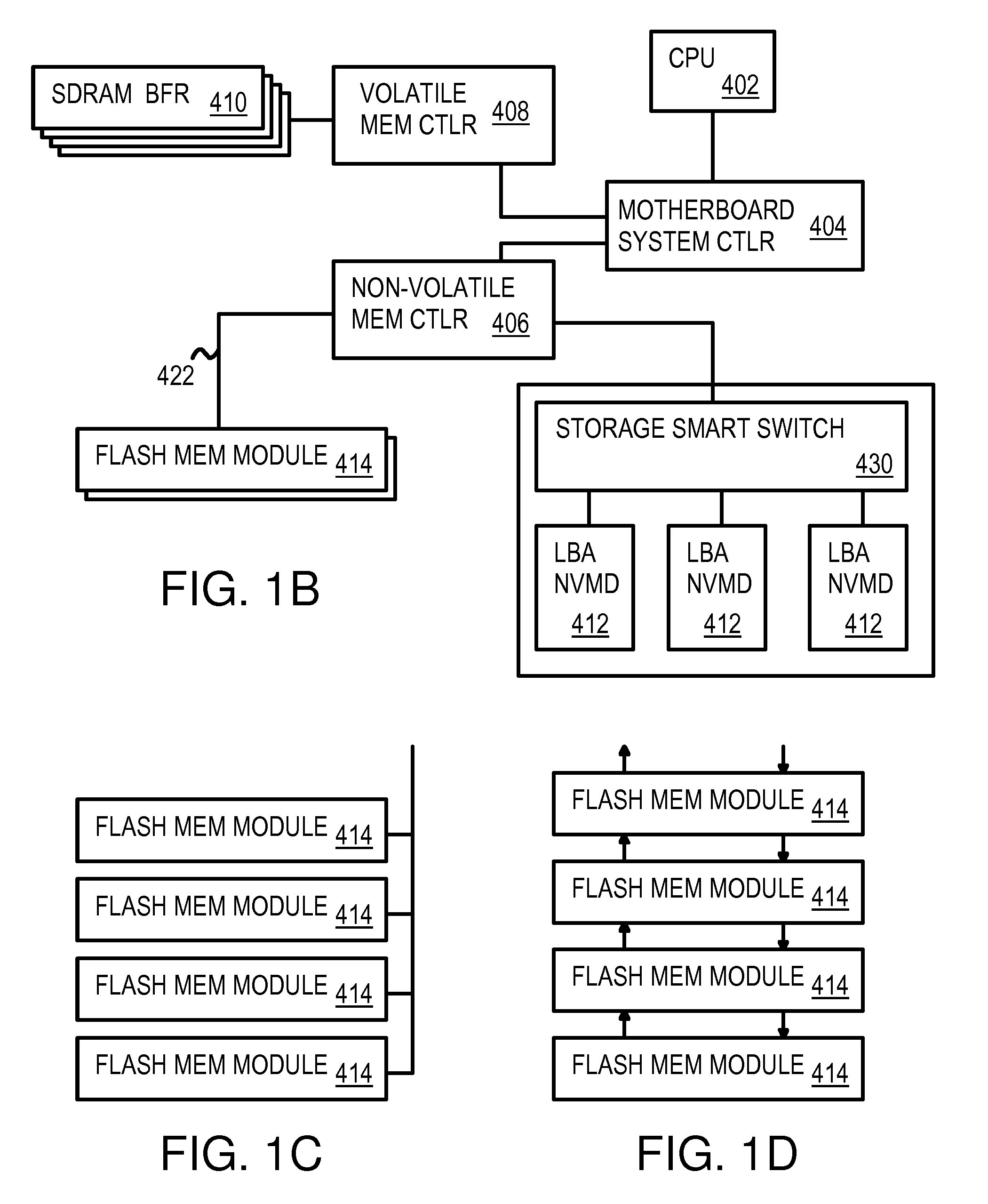

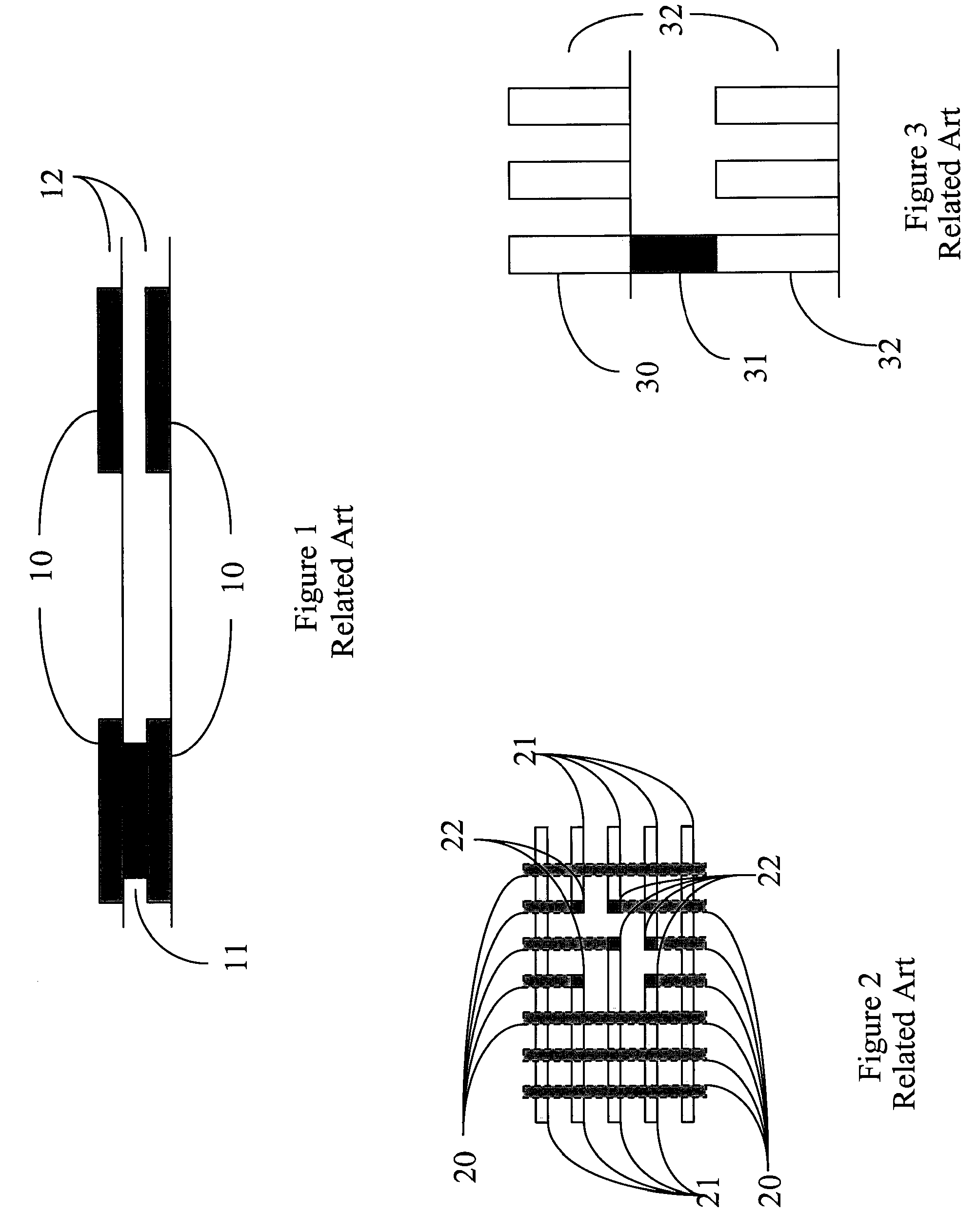

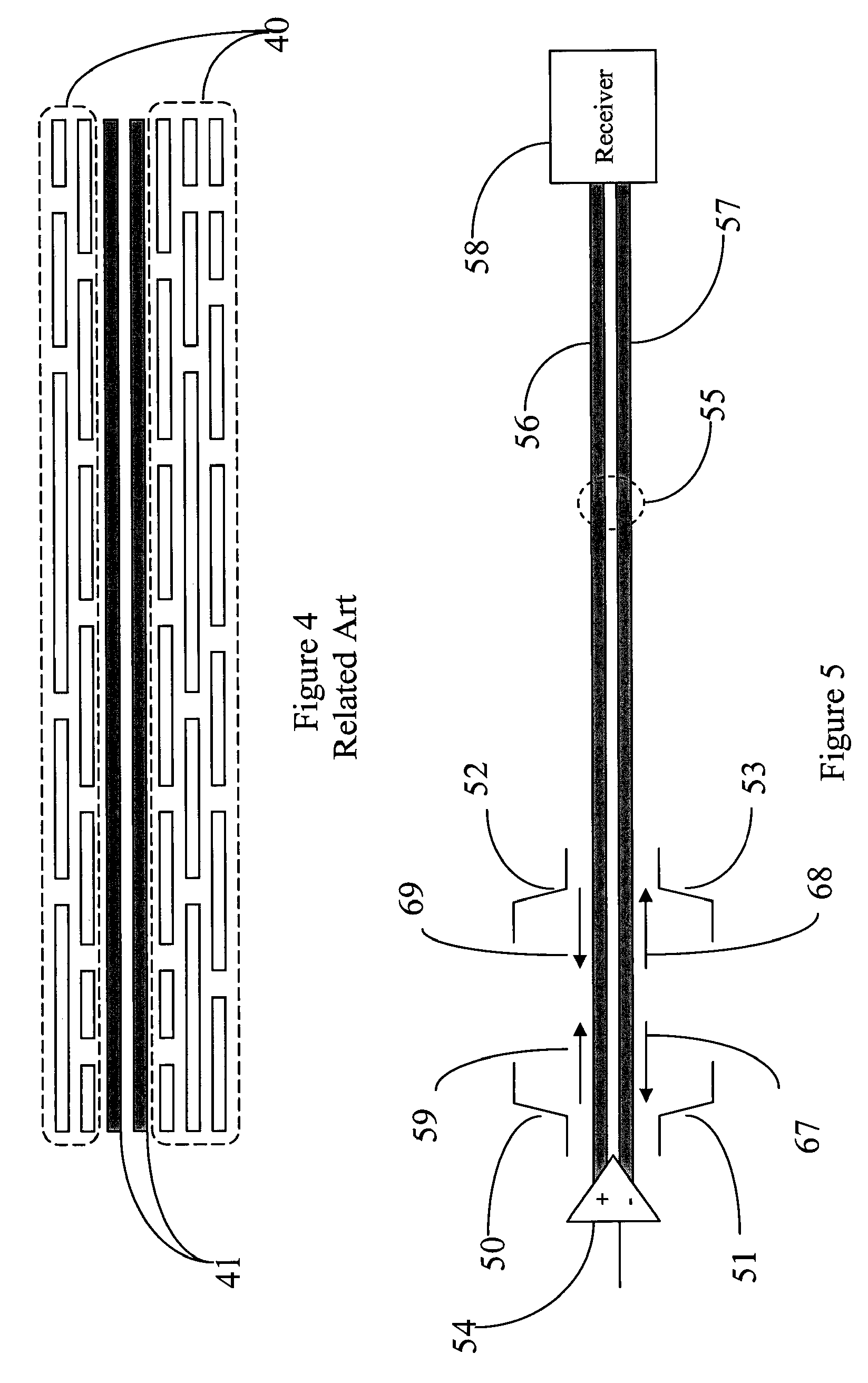

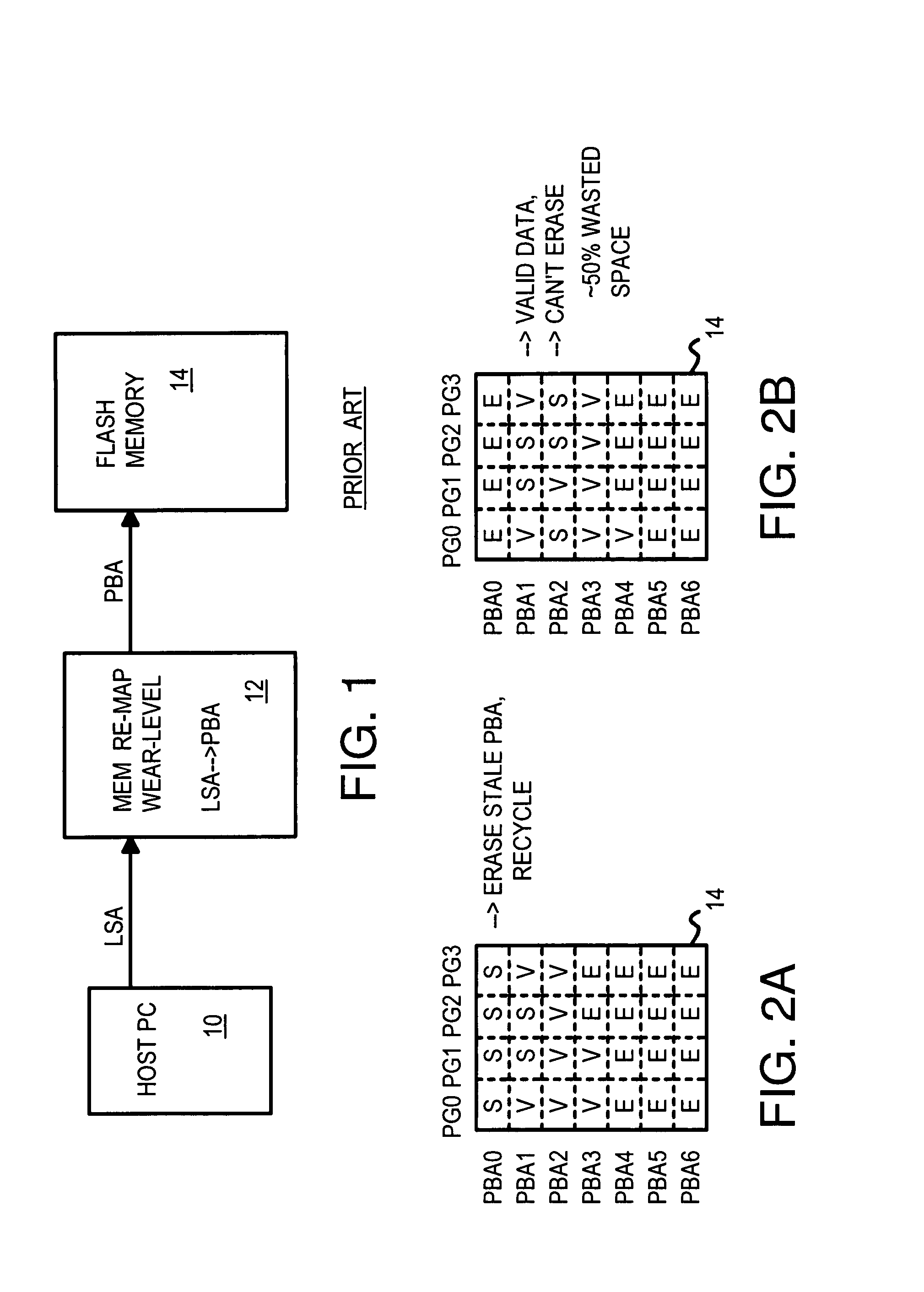

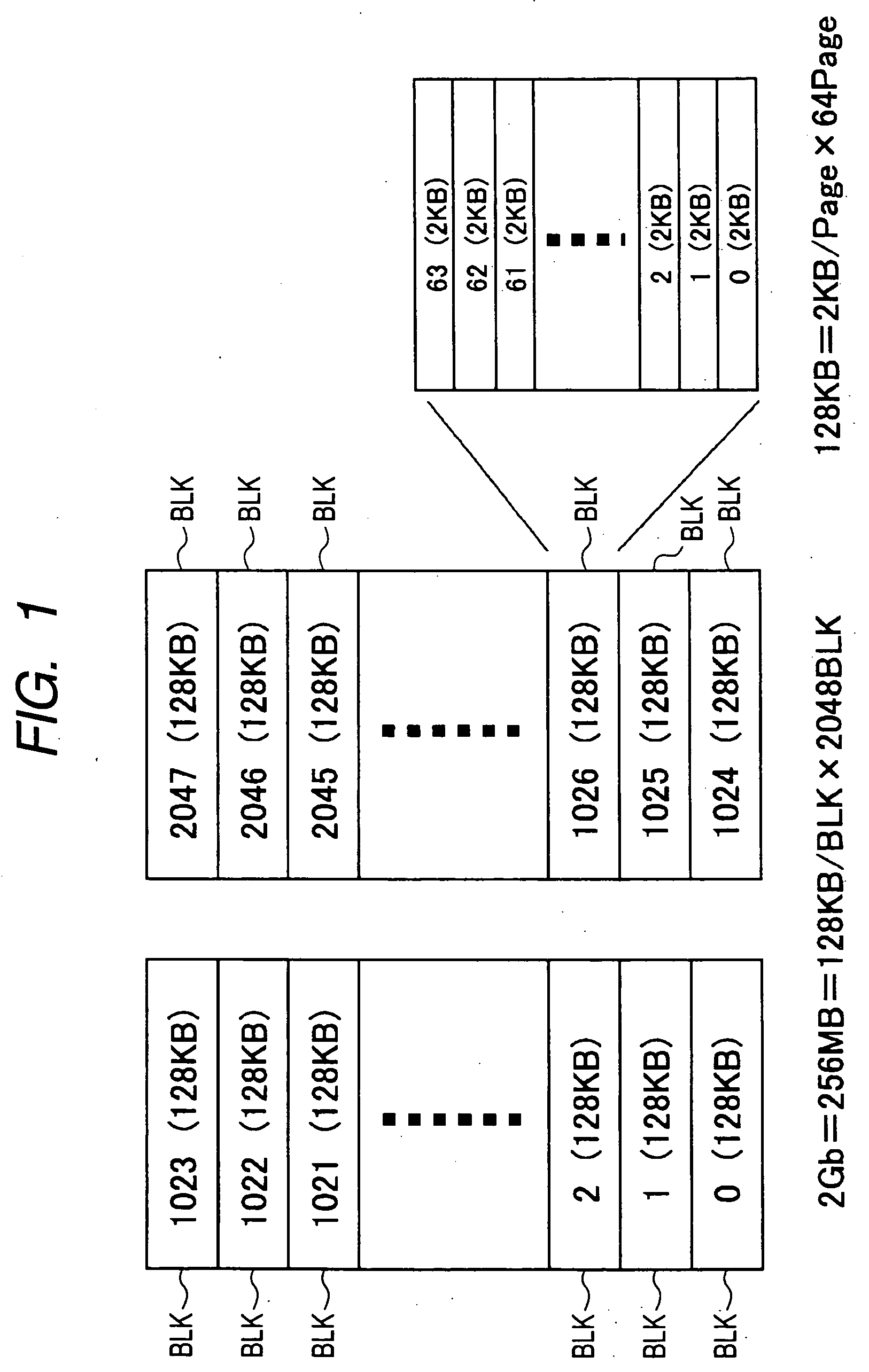

Multi-Level Striping and Truncation Channel-Equalization for Flash-Memory System

InactiveUS20090240873A1Memory architecture accessing/allocationError preventionLogical block addressingData access

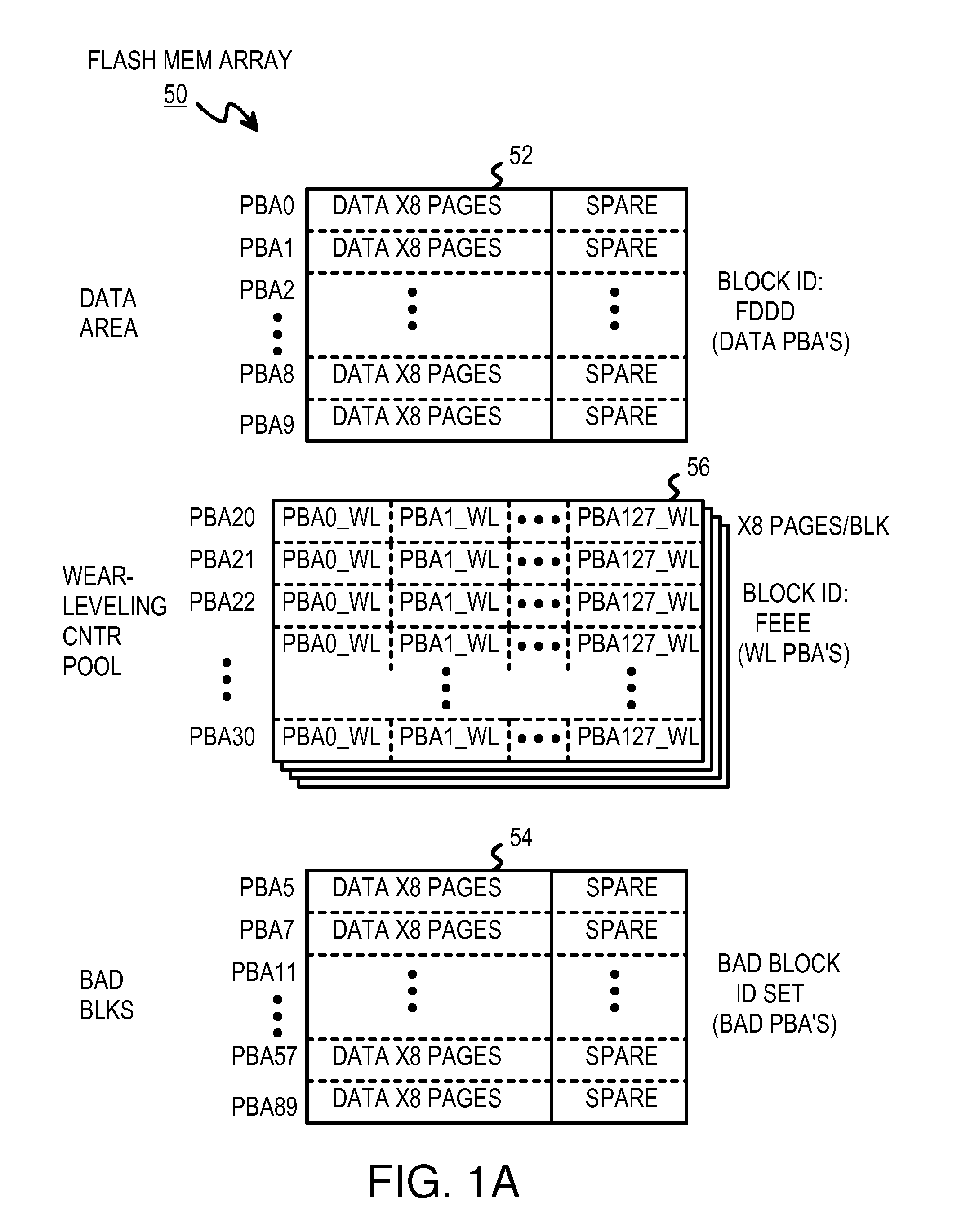

Truncation reduces the available striped data capacity of all flash channels to the capacity of the smallest flash channel. A solid-state disk (SSD) has a smart storage switch salvages flash storage removed from the striped data capacity by truncation. Extra storage beyond the striped data capacity is accessed as scattered data that is not striped. The size of the striped data capacity is reduced over time as more bad blocks appear. A first-level striping map stores striped and scattered capacities of all flash channels and maps scattered and striped data. Each flash channel has a Non-Volatile Memory Device (NVMD) with a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory in the NVMD. Wear-leveling and bad block remapping are preformed by each NVMD. Source and shadow flash blocks are recycled by the NVMD. Two levels of smart storage switches enable three-level controllers.

Owner:SUPER TALENT TECH CORP

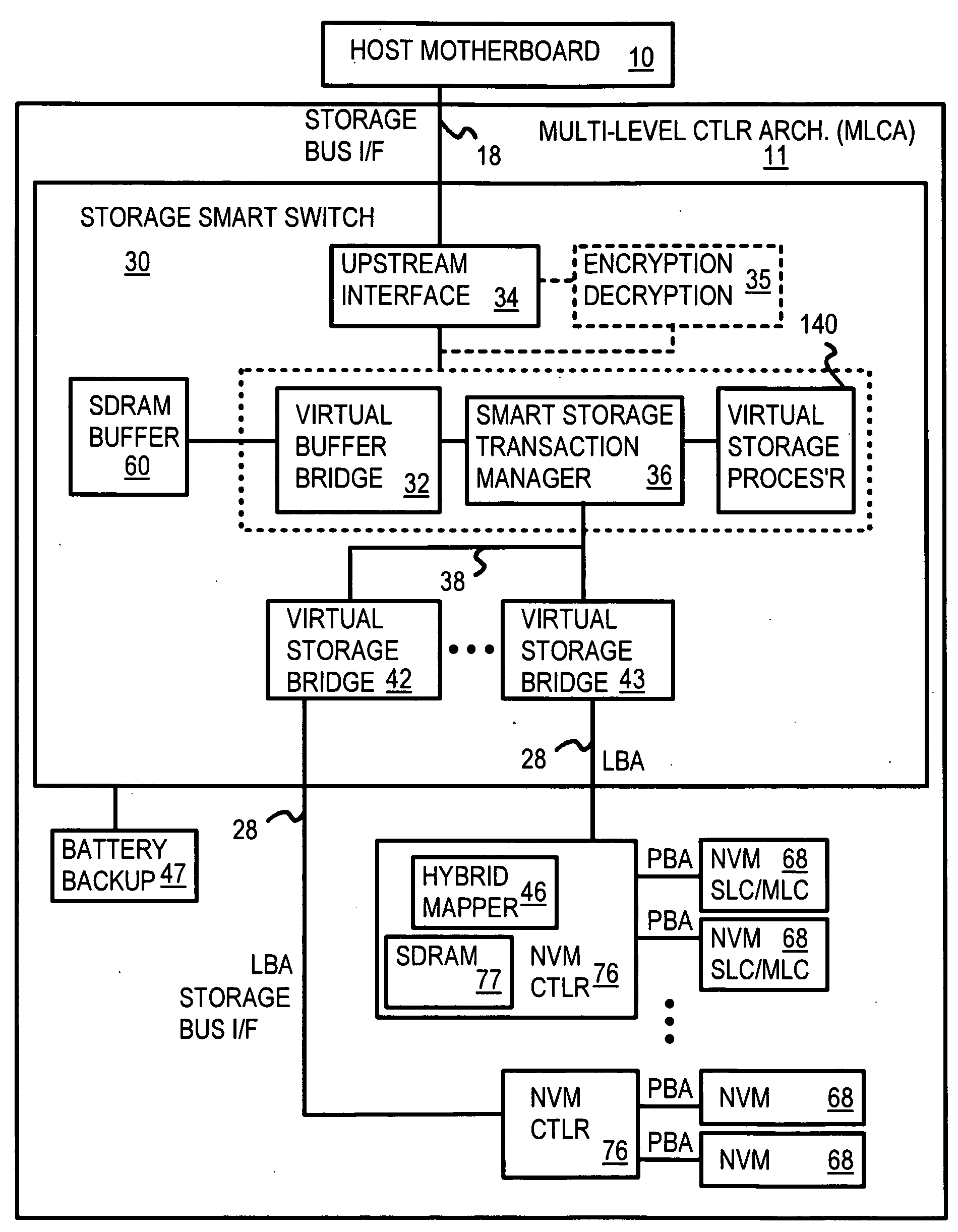

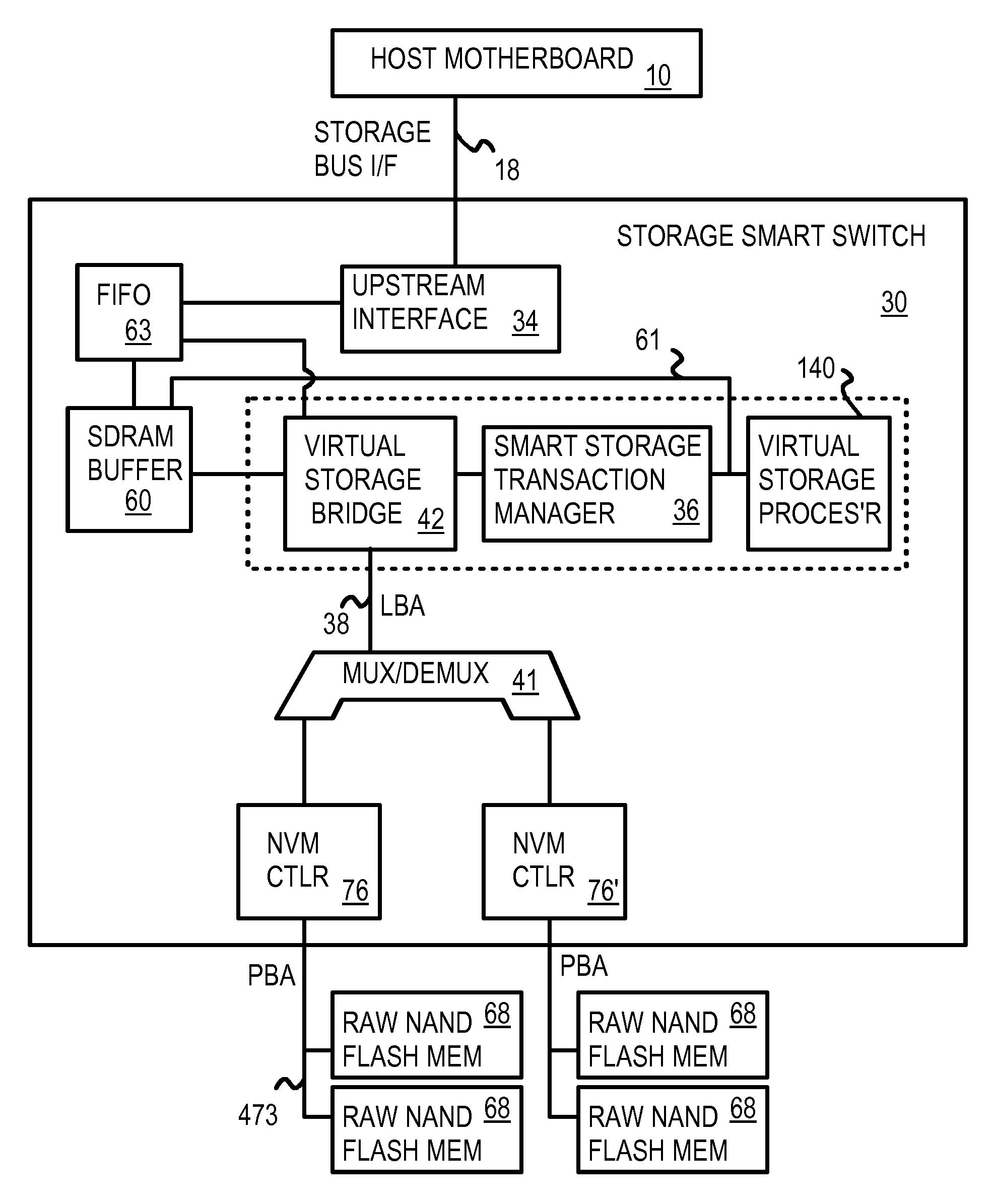

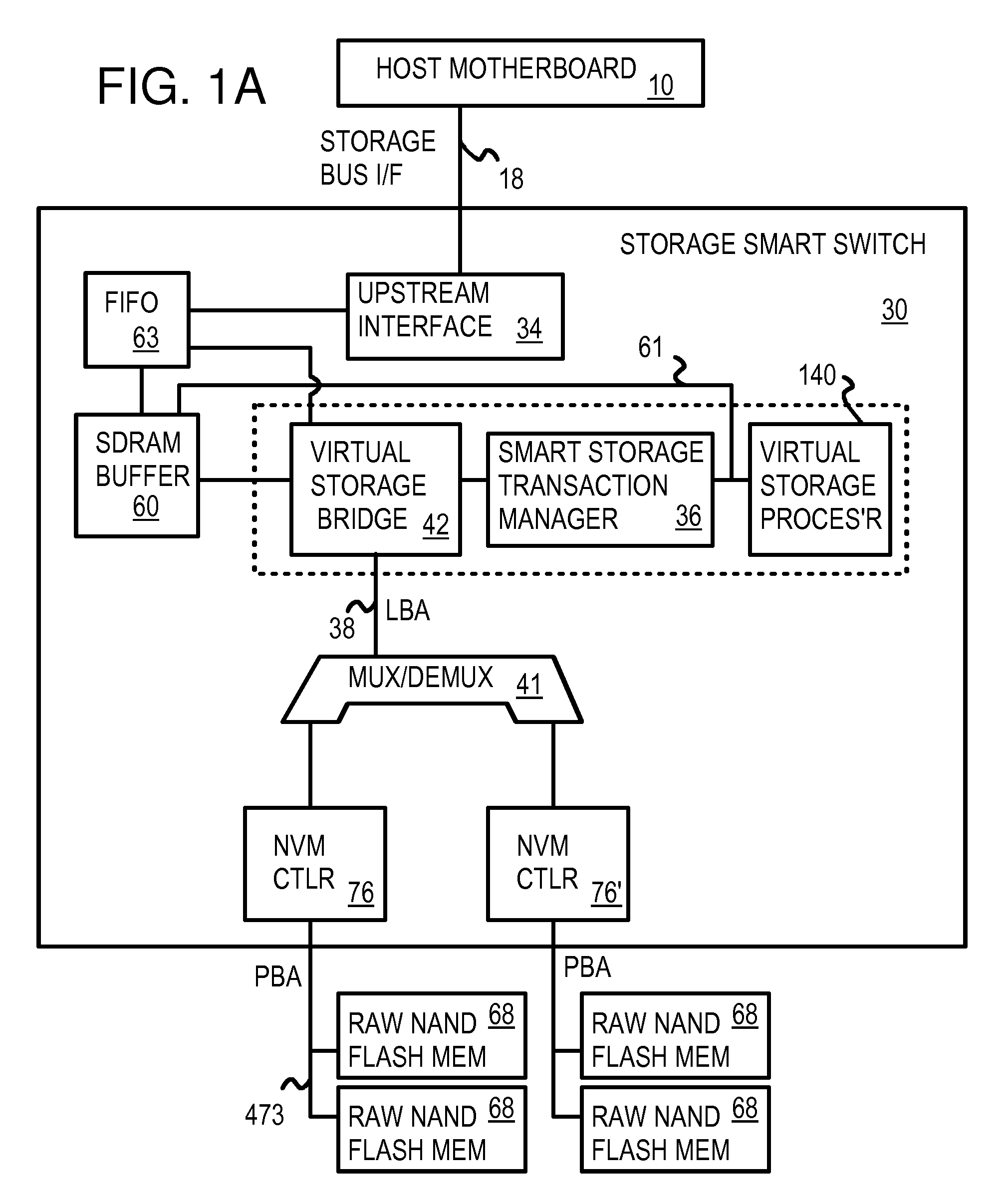

Multi-Level Controller with Smart Storage Transfer Manager for Interleaving Multiple Single-Chip Flash Memory Devices

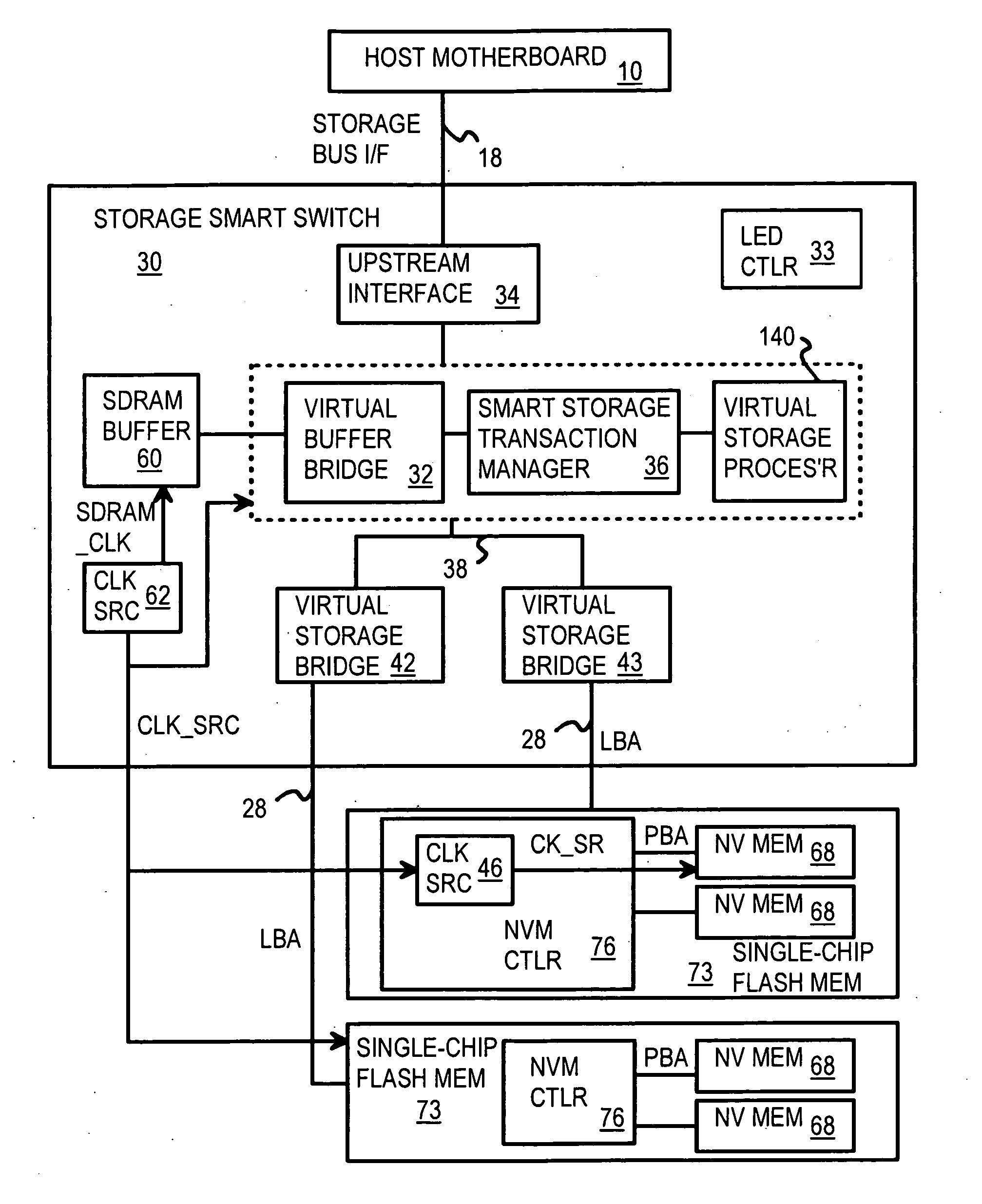

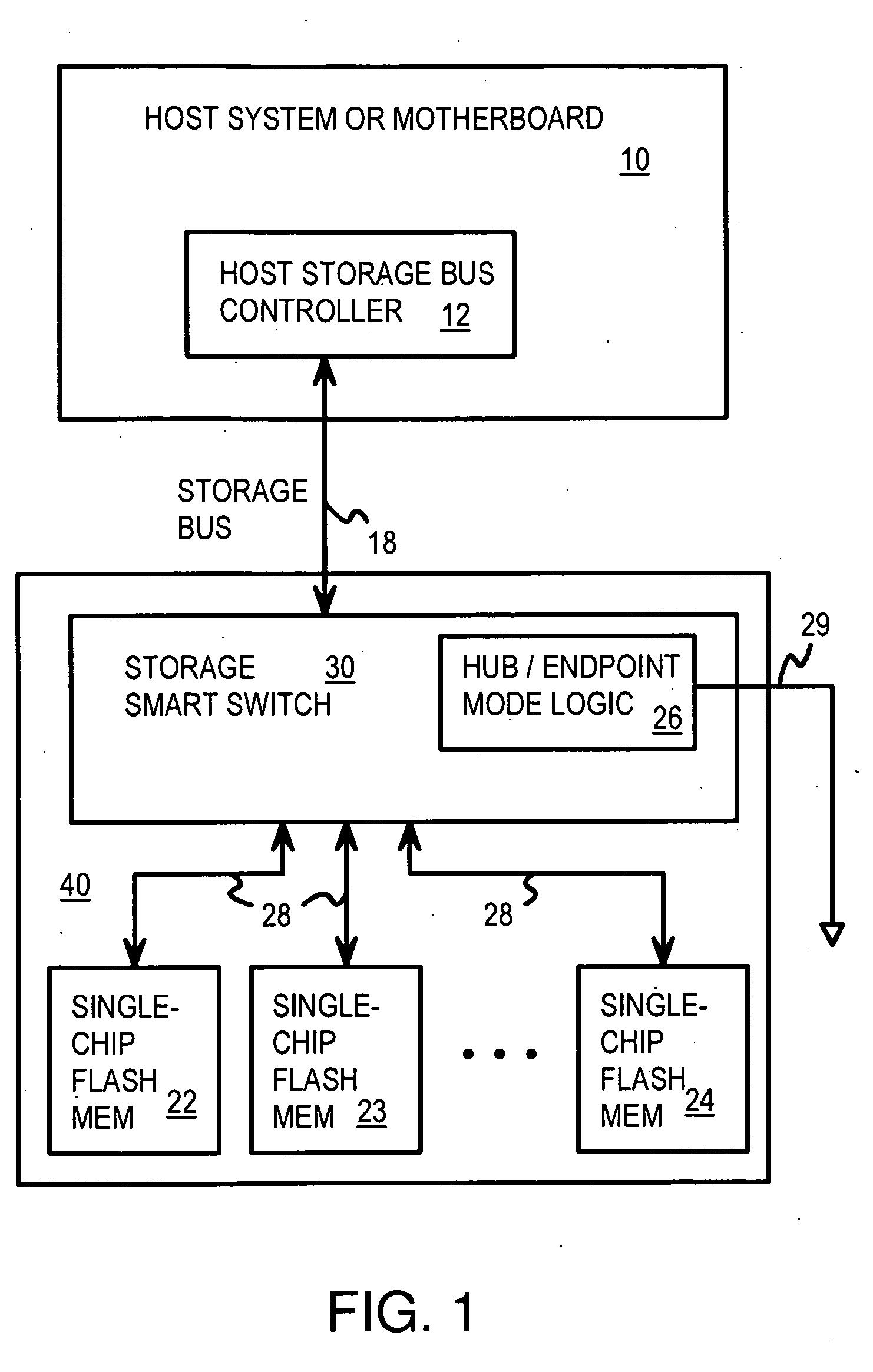

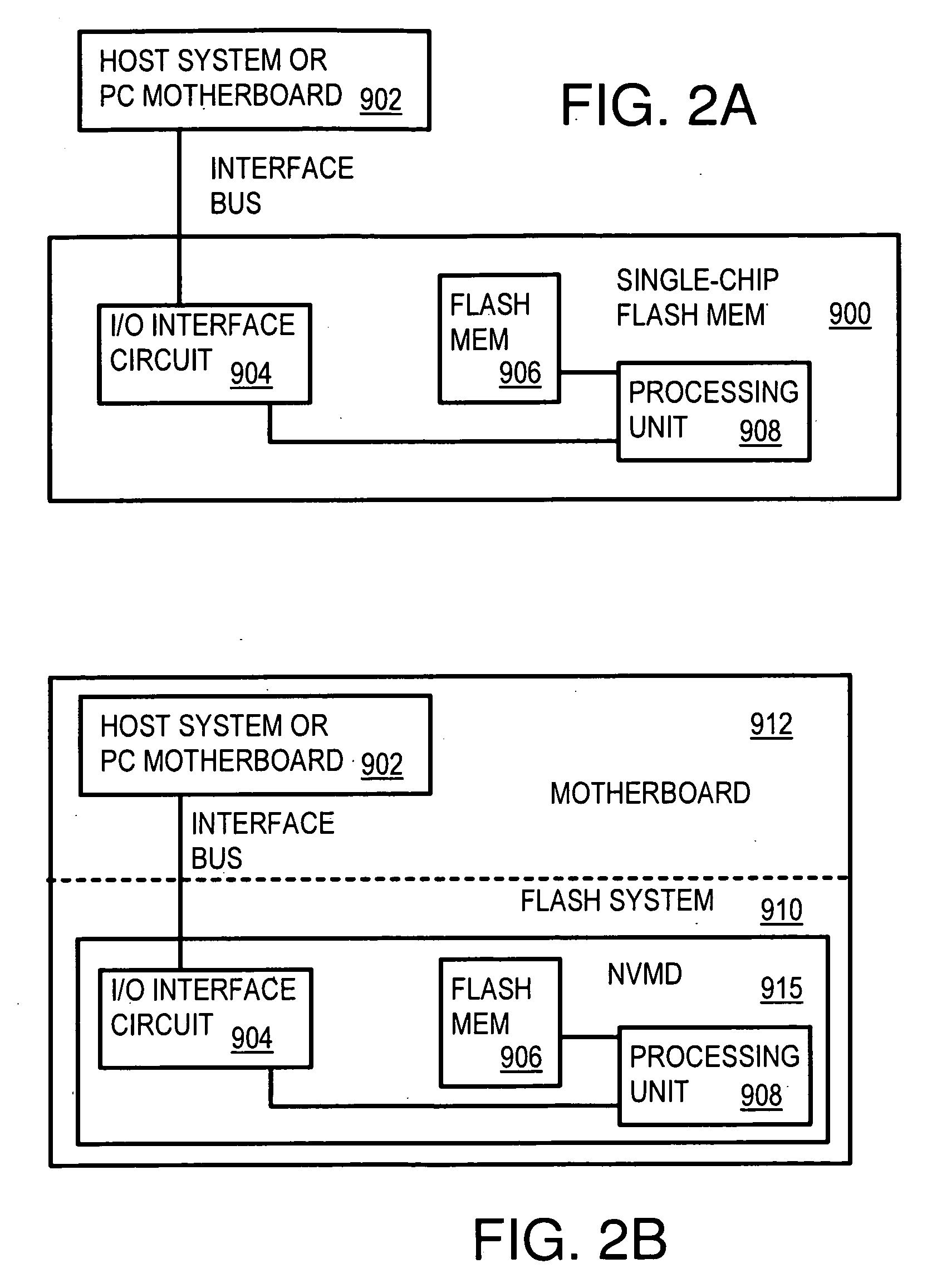

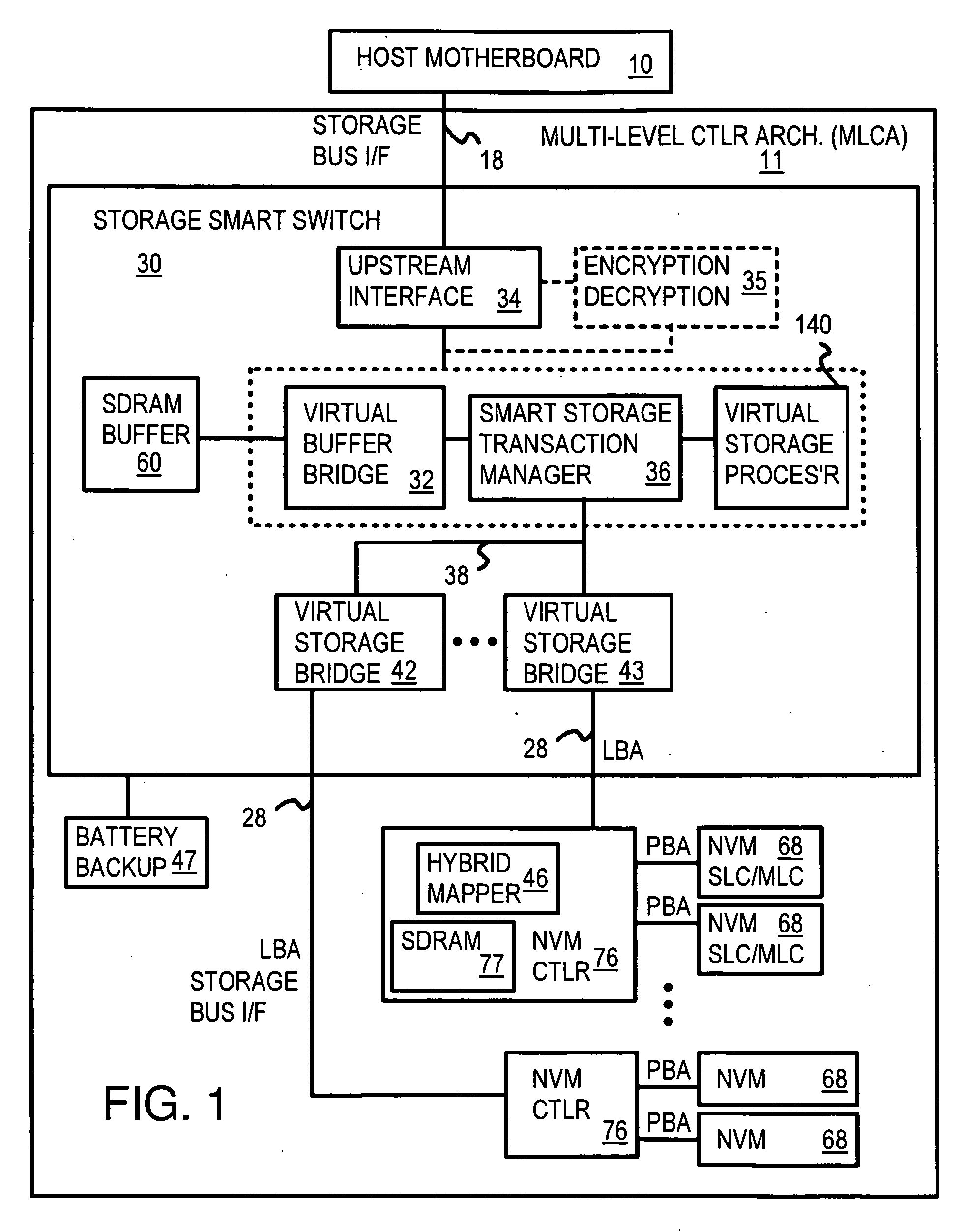

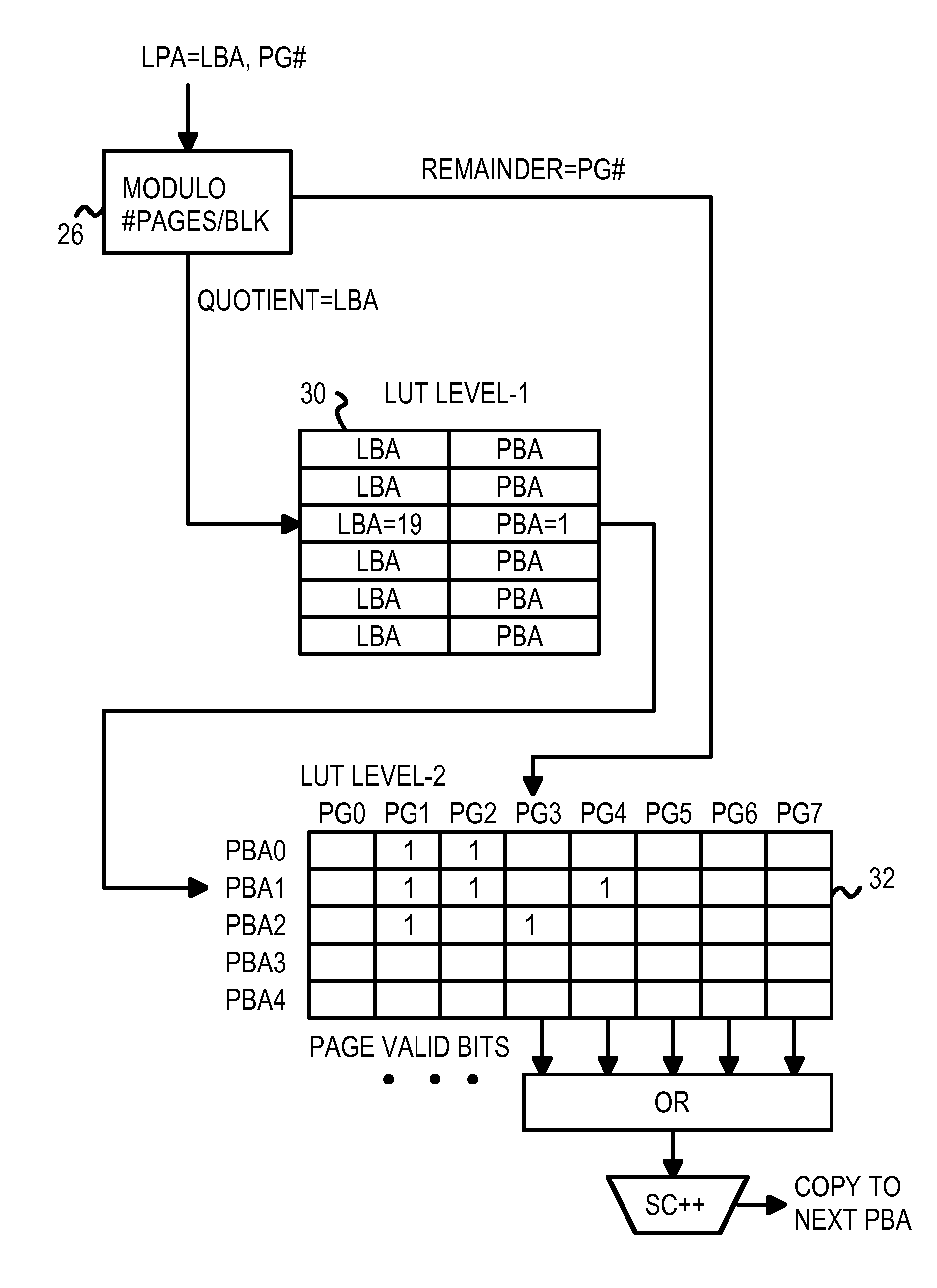

InactiveUS20080320214A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingSolid-state drive

A solid-state disk (SSD) has a smart storage switch with a smart storage transaction manager that re-orders host commands for accessing downstream single-chip flash-memory devices. Each single-chip flash-memory device has a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory blocks in the single-chip flash-memory device. Wear-leveling and bad block remapping are preformed by each single-chip flash-memory device, and at a higher level by a virtual storage processor in the smart storage switch. Virtual storage bridges between the smart storage transaction manager and the single-chip flash-memory devices bridge LBA transactions over LBA buses to the single-chip flash-memory devices. Data striping and interleaving among multiple channels of the single-chip flash-memory device is controlled at a high level by the smart storage transaction manager, while further interleaving and remapping may be performed within each single-chip flash-memory device.

Owner:SUPER TALENT TECH CORP

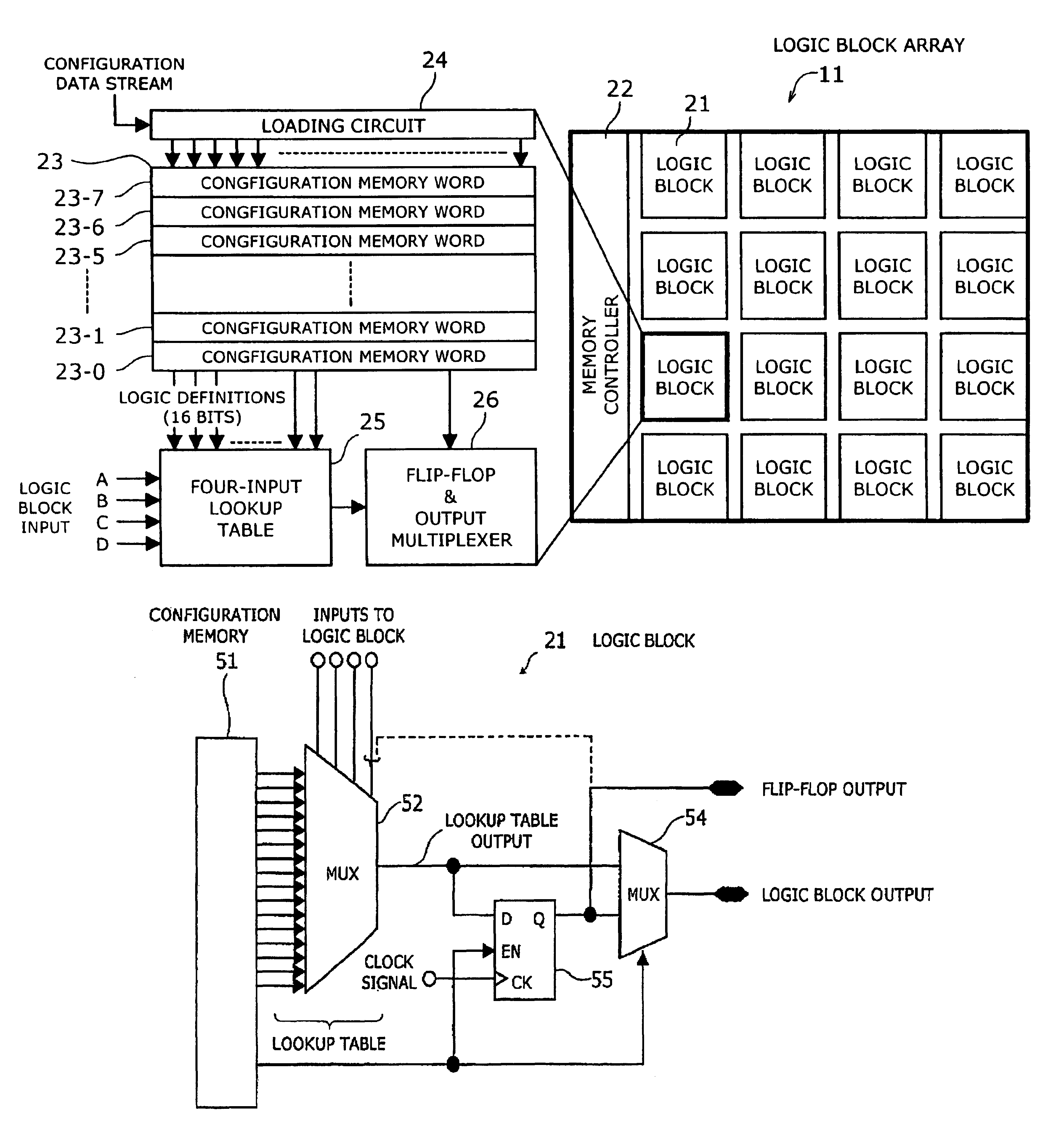

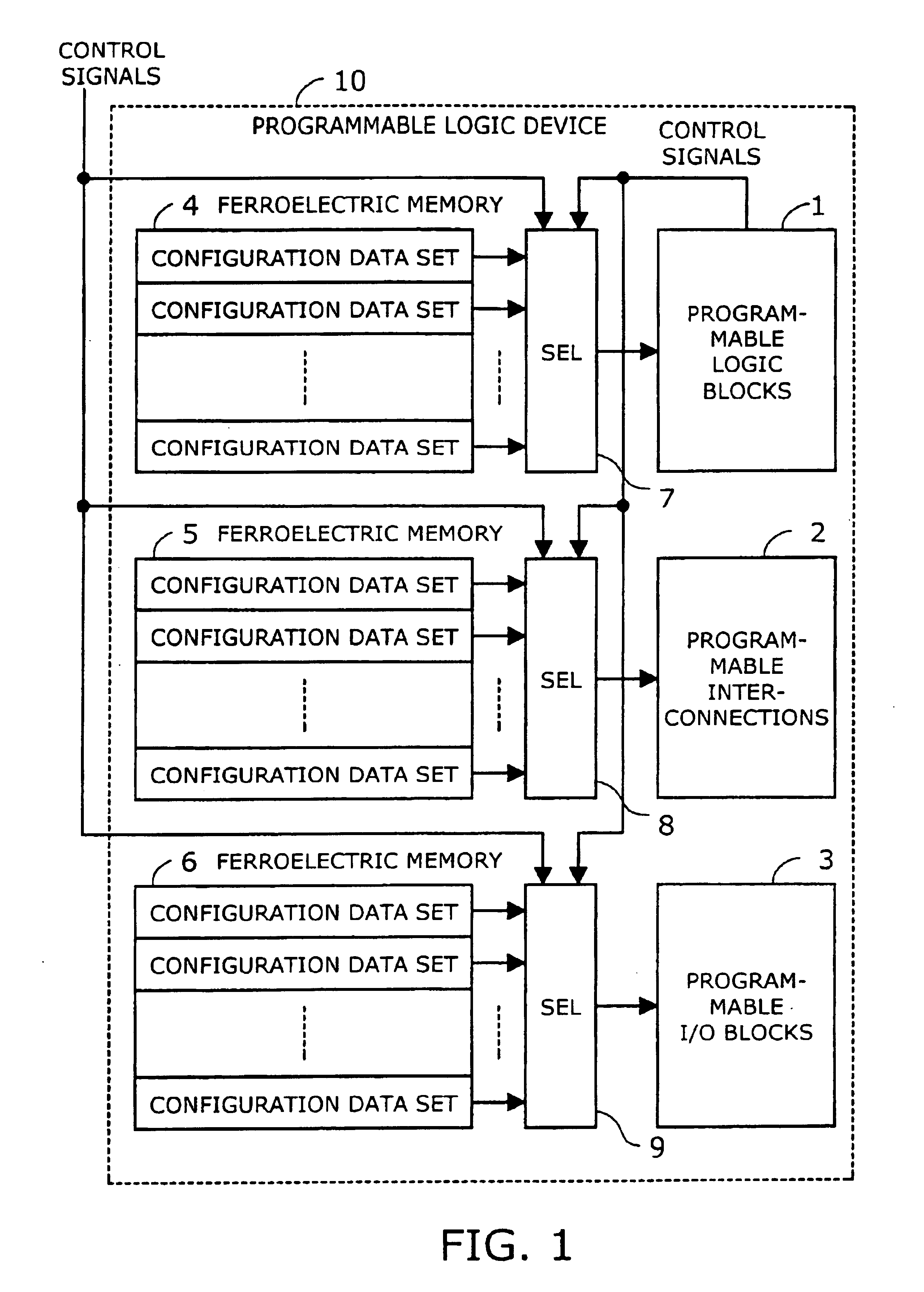

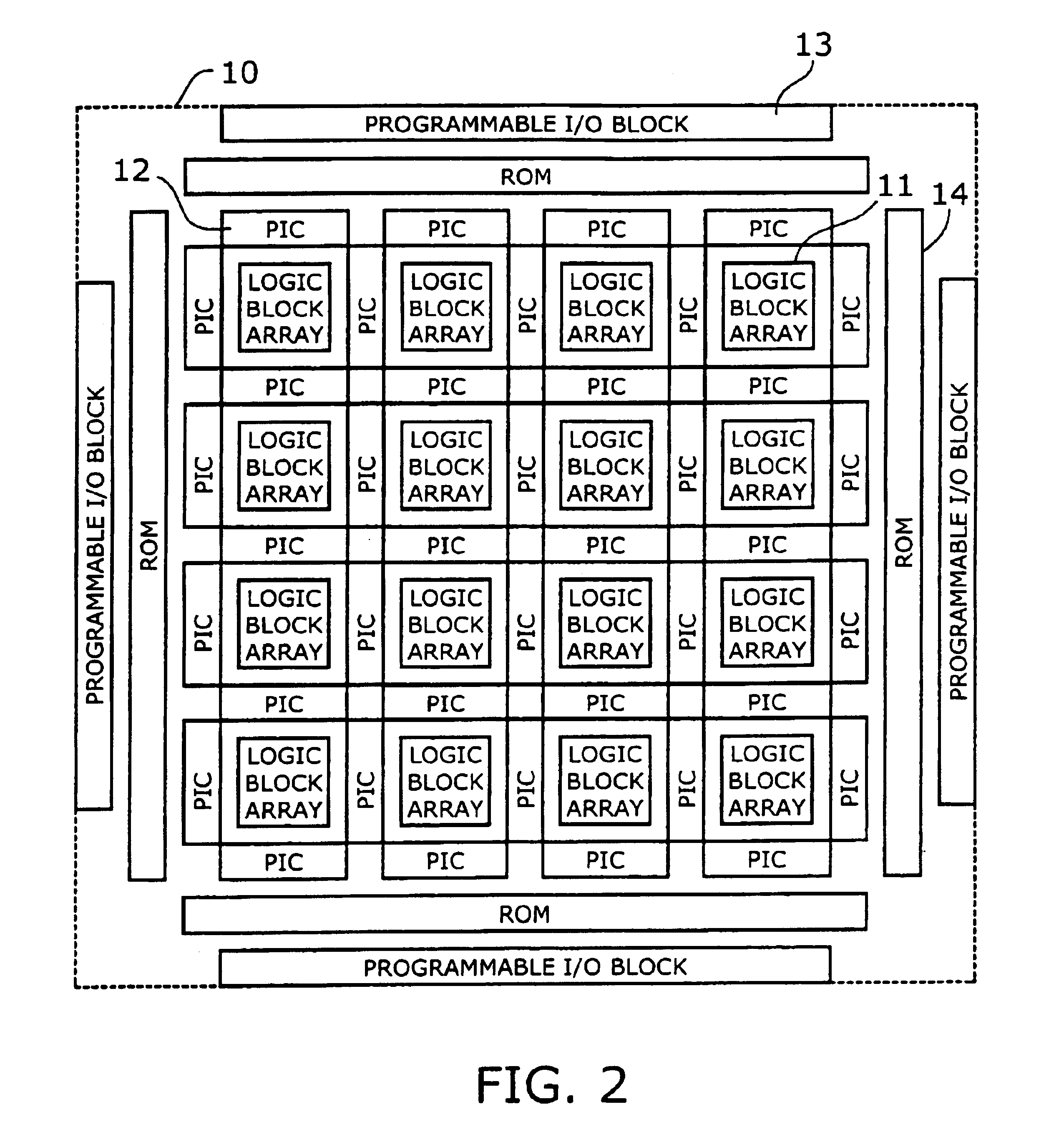

Programmable logic device with ferroelectric configuration memories

InactiveUS6924663B2Increase the effective amountEfficient architectureDigital storageInternal/peripheral component protectionElectricityData stream

A programmable logic device with ferroelectric configuration memories storing multiple configuration data sets. The device has programmable logic blocks, interconnections, and I / O blocks to provide desired logic functions. Those building blocks can be dynamically reconfigured by changing the selection of configuration data stored in the device's integral configuration memories. The configuration memories are divided into groups, so that they can be loaded concurrently with multiple configuration data streams. To protect the content of configuration memories from unauthorized access, the device employs an authentication mechanism that uses security IDs stored in the configuration memories. The device has a memory controller to provide an appropriate power supply sequence for ferroelectric memory cells to ensure the reliable data retention when the device is powered up or shut down.

Owner:FUJITSU SEMICON LTD

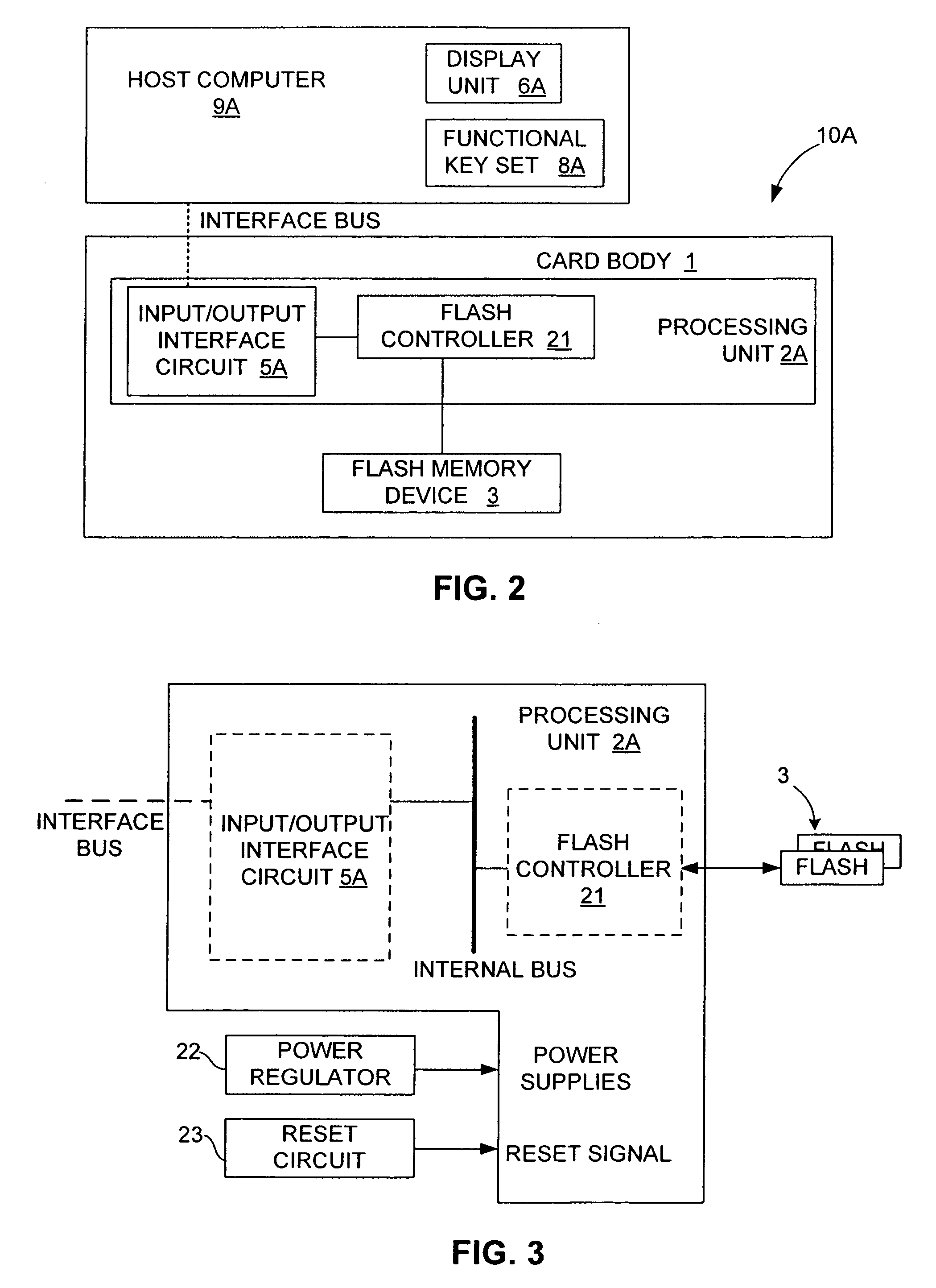

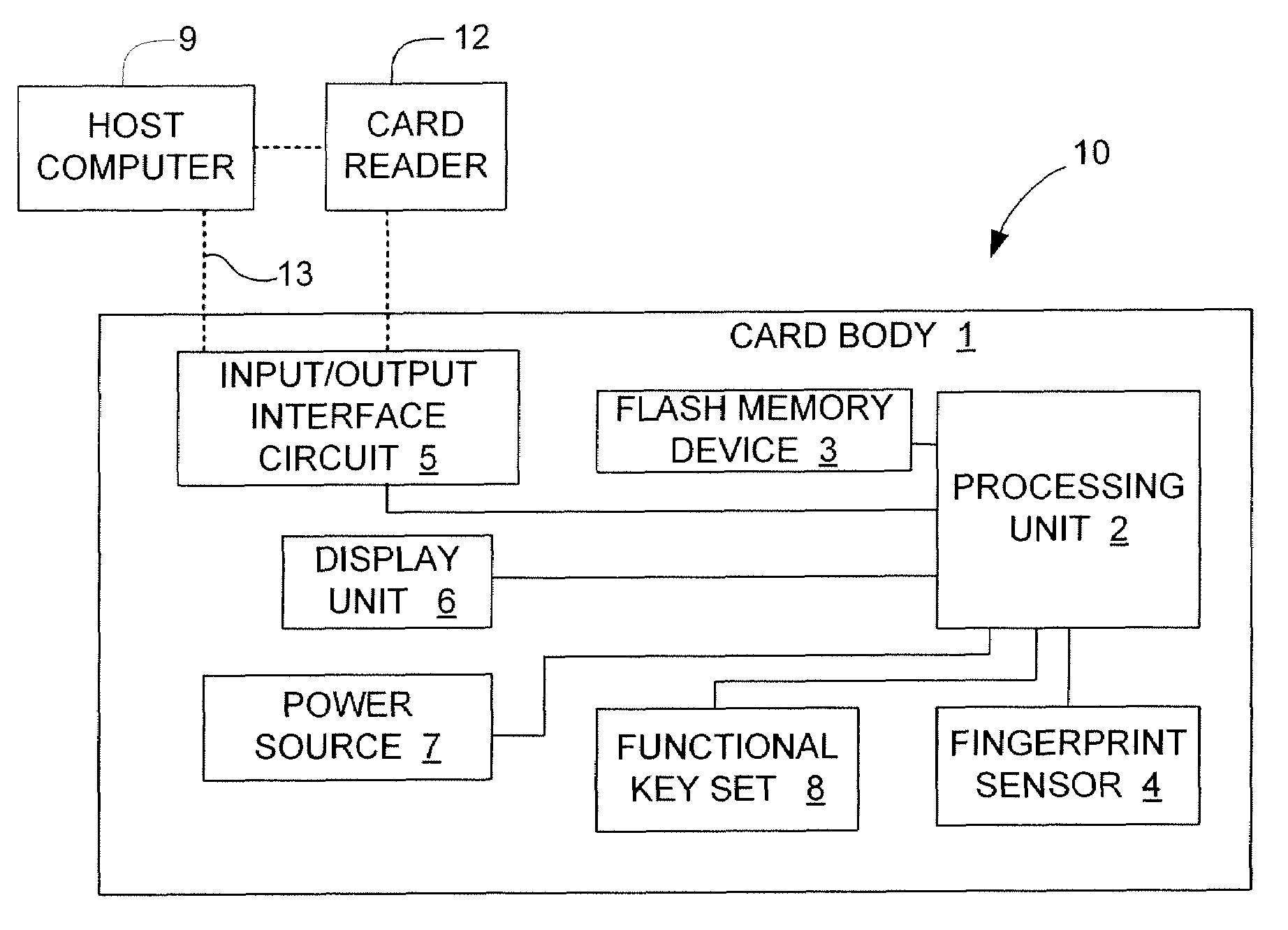

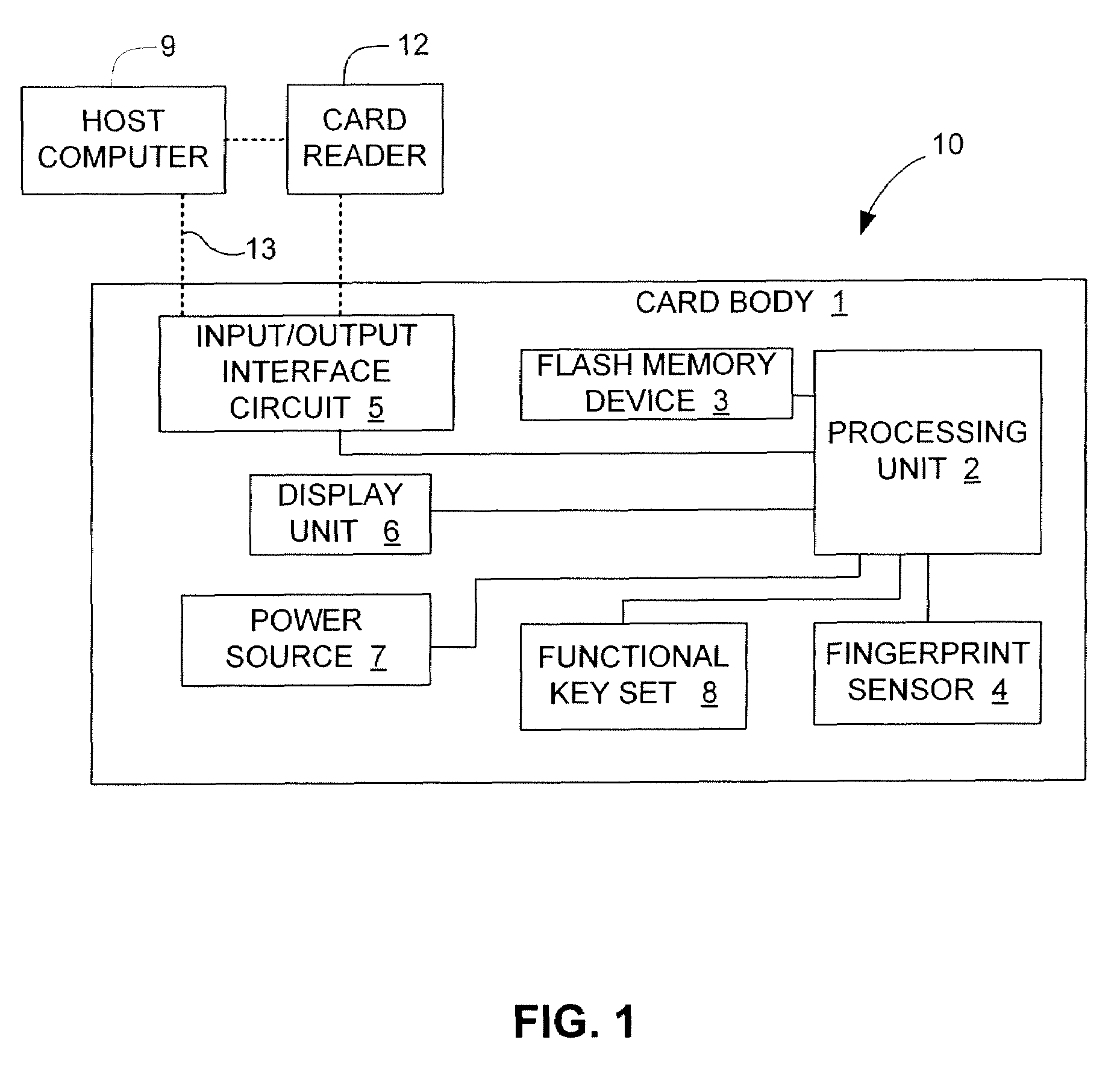

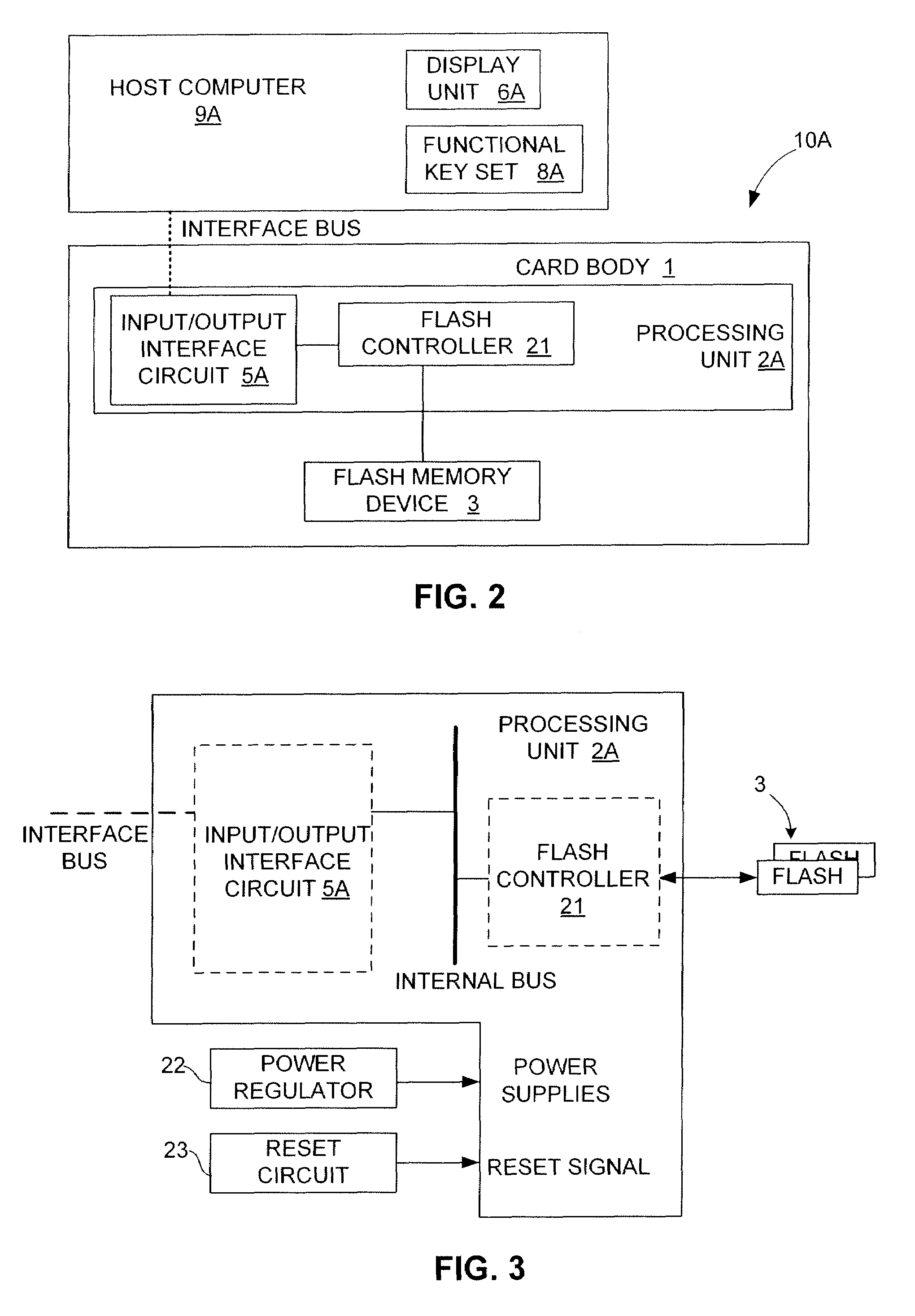

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

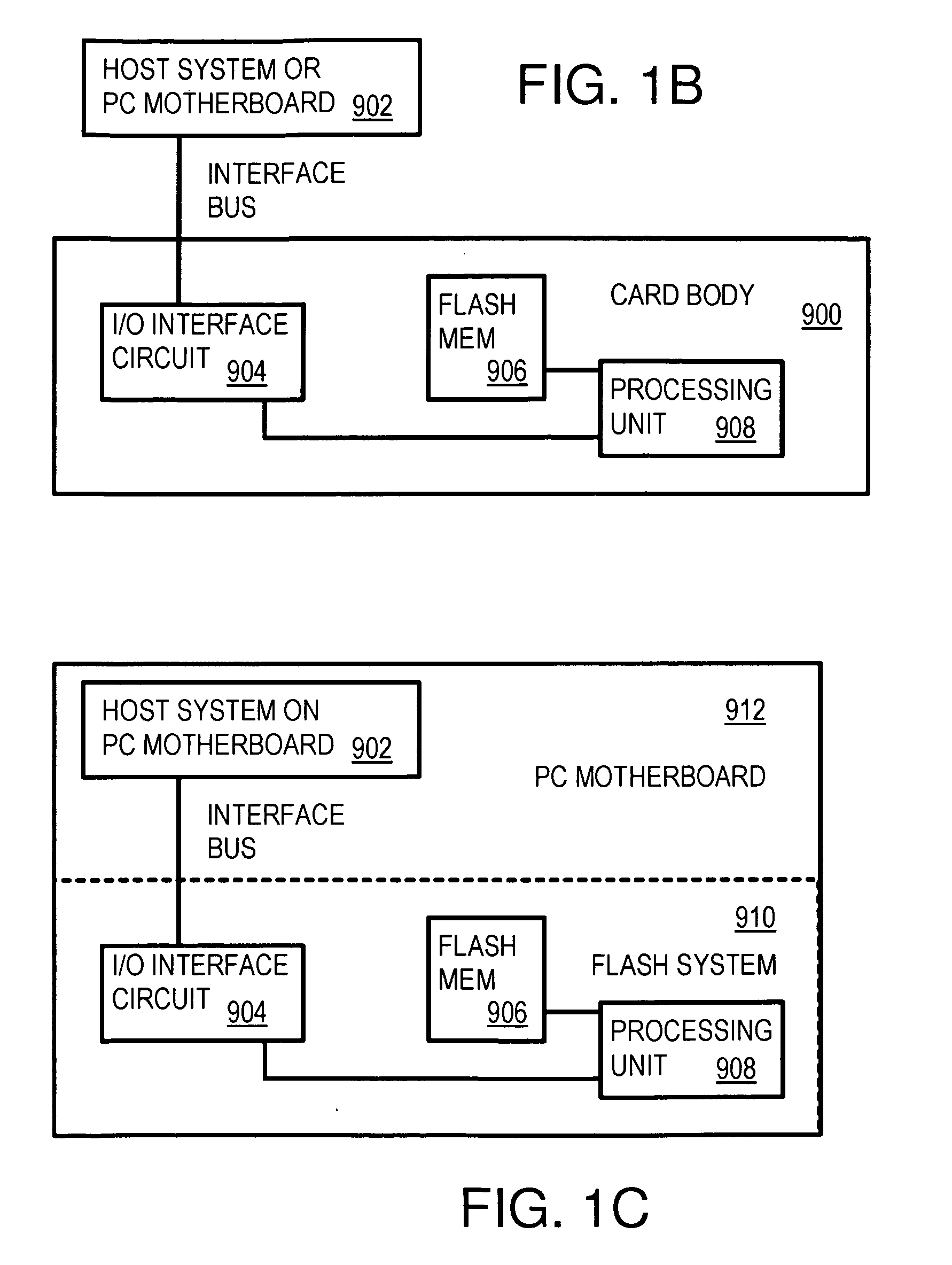

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

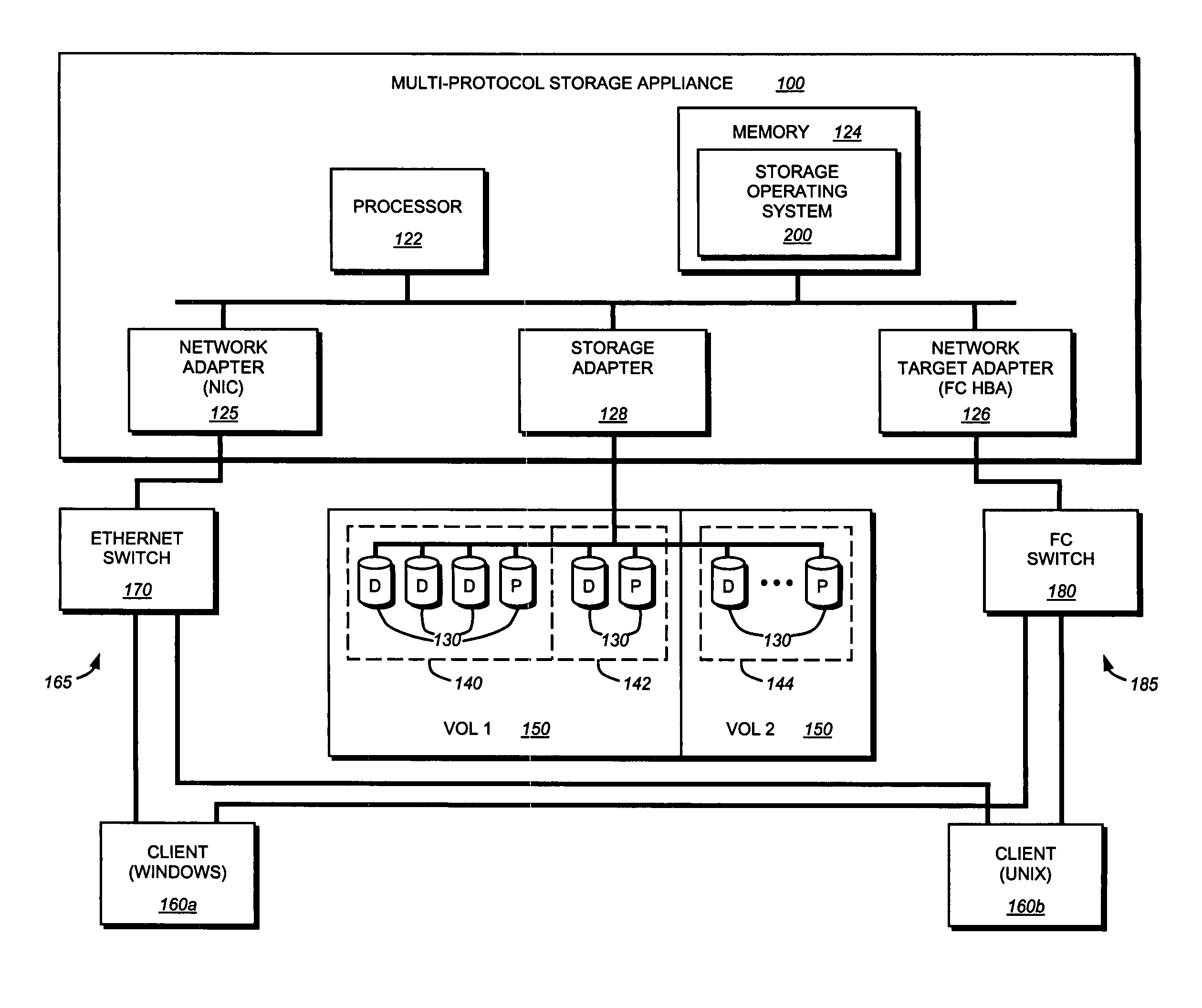

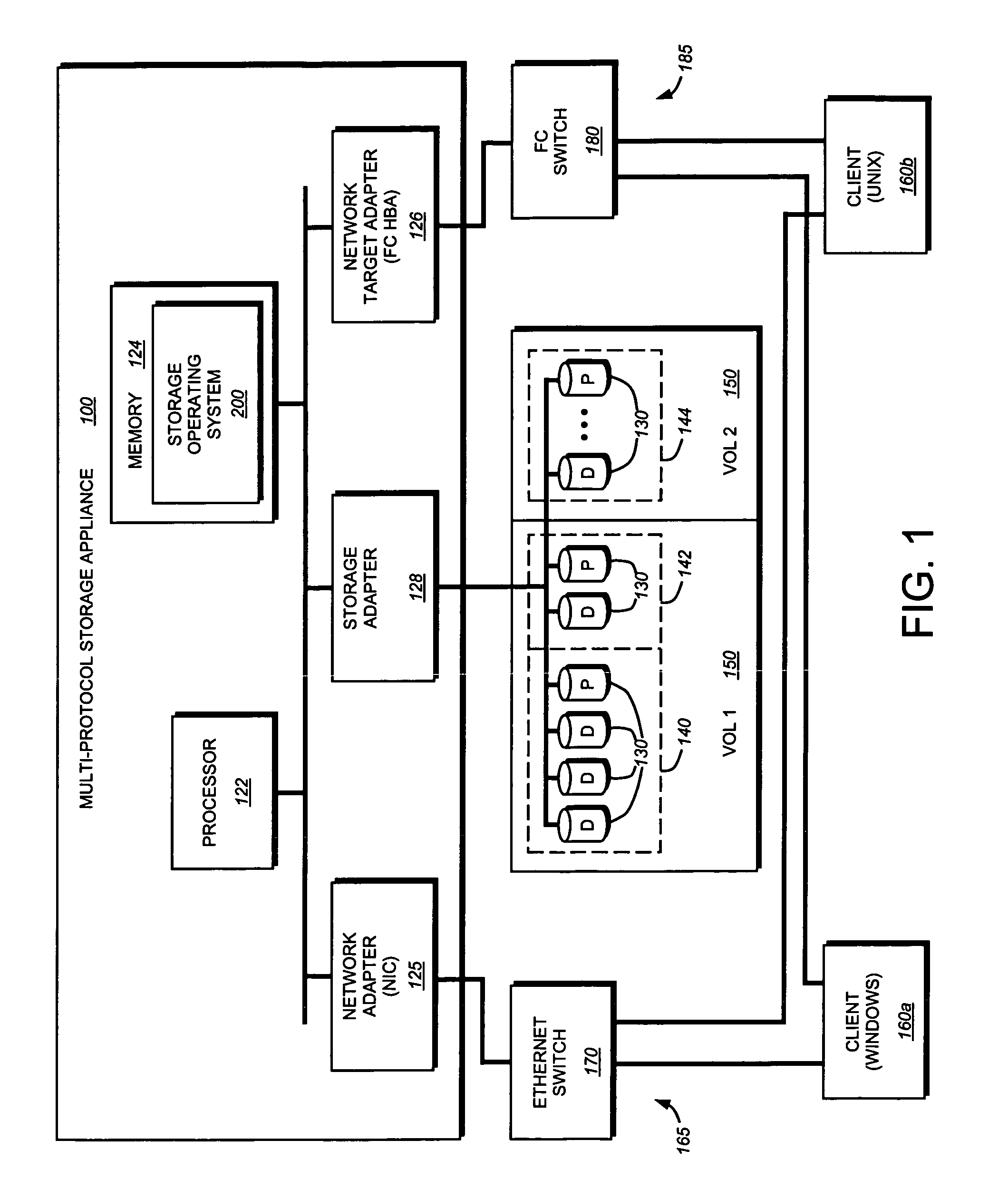

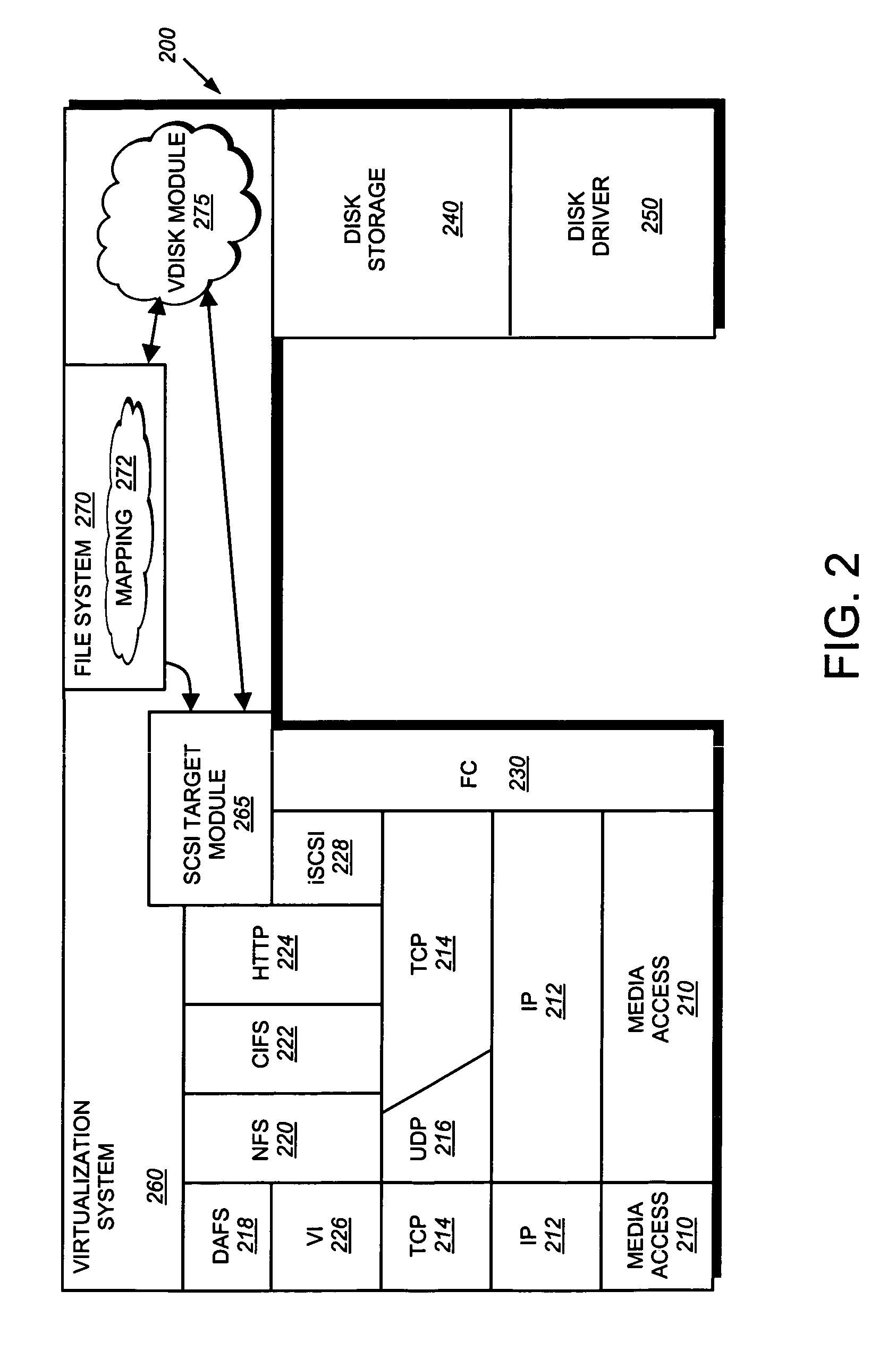

System and method for mapping file block numbers to logical block addresses

ActiveUS7437530B1Improve performanceRaise transfer toMultiple digital computer combinationsTransmissionOperational systemLogical block addressing

A system and method for mapping file block numbers (FBNs) to logical block addresses (LBAs) is provided. The system and method performs the mapping of FBNs to LBAs in a file system layer of a storage operating system, thereby enabling the use of clients in a storage environment that have not been modified to incorporate mapping tables. As a result, a client may send data access requests to the storage system utilizing FBNs and have the storage system perform the appropriate mapping to LBAs.

Owner:NETWORK APPLIANCE INC

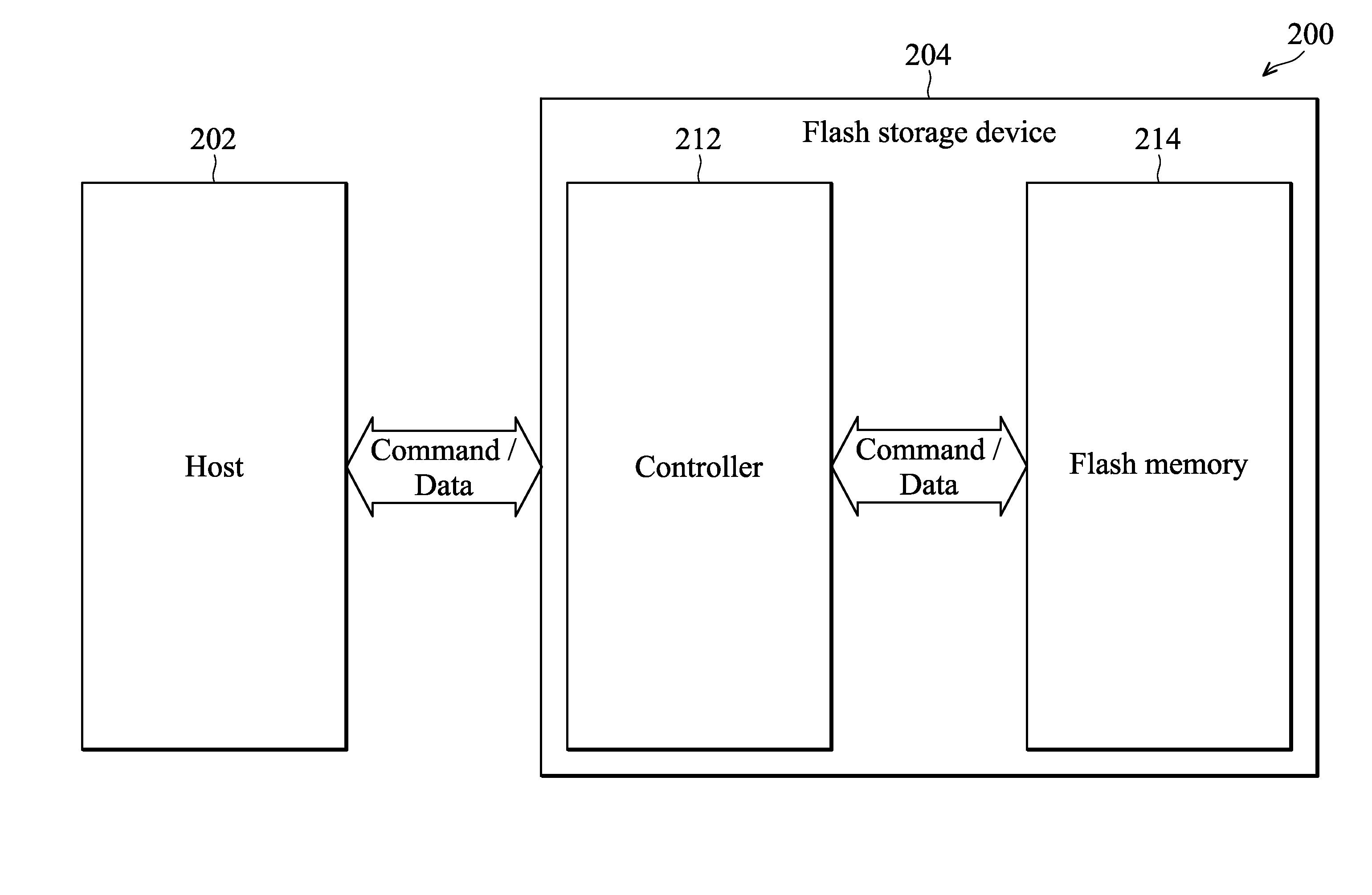

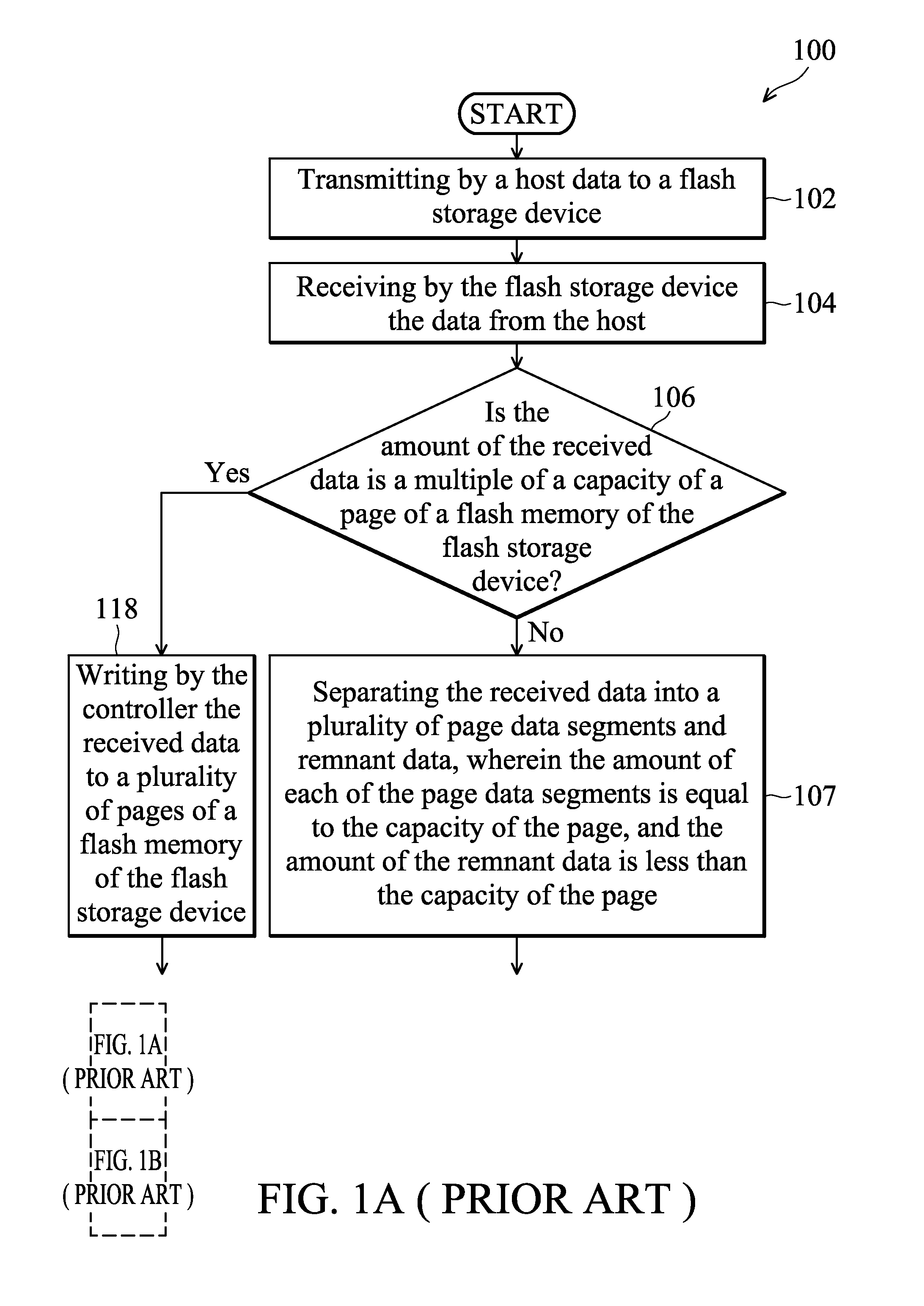

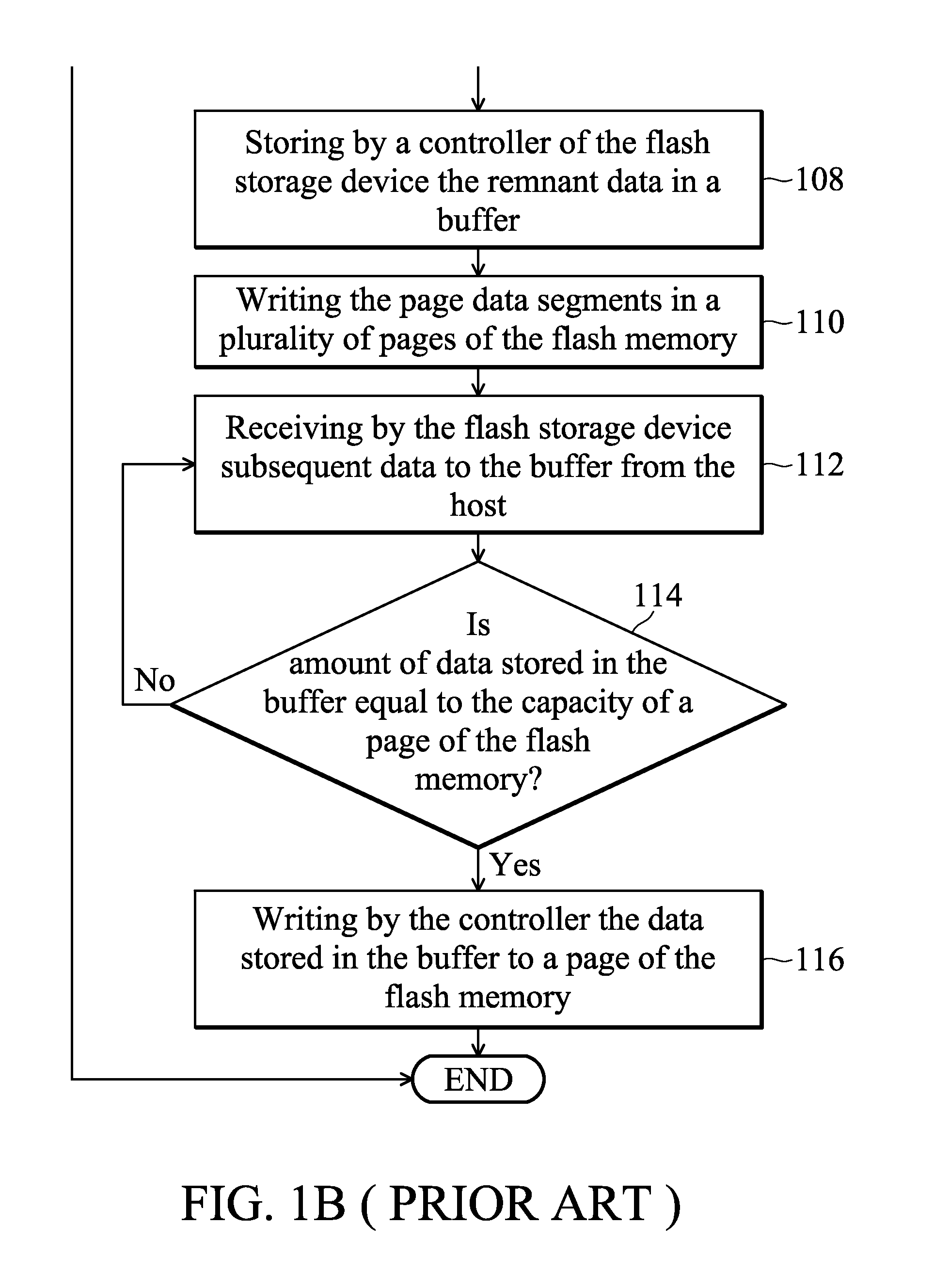

Flash storage device, data storage system, and data writing method

The invention provides a flash storage device. In one embodiment, the flash storage device comprises a flash memory and a controller. The flash memory comprises a plurality of storage units for data storage, wherein the total capacity of each of the storage units is equal to a storage unit capacity. When the flash storage device receives a read capacity command from a host, the controller determines the size of a logical block to be a specific multiple of the storage unit capacity, and sends information about the logical block size to the host in response to the read capacity command, wherein the specific multiple is a natural number. After the host receives the information from the flash storage device, the host retrieves the logical block size from the information, and sends only write data with an amount equal to a multiple of the logical block size to the flash storage device.

Owner:SILICON MOTION INC (TW)

Hybrid 2-Level Mapping Tables for Hybrid Block- and Page-Mode Flash-Memory System

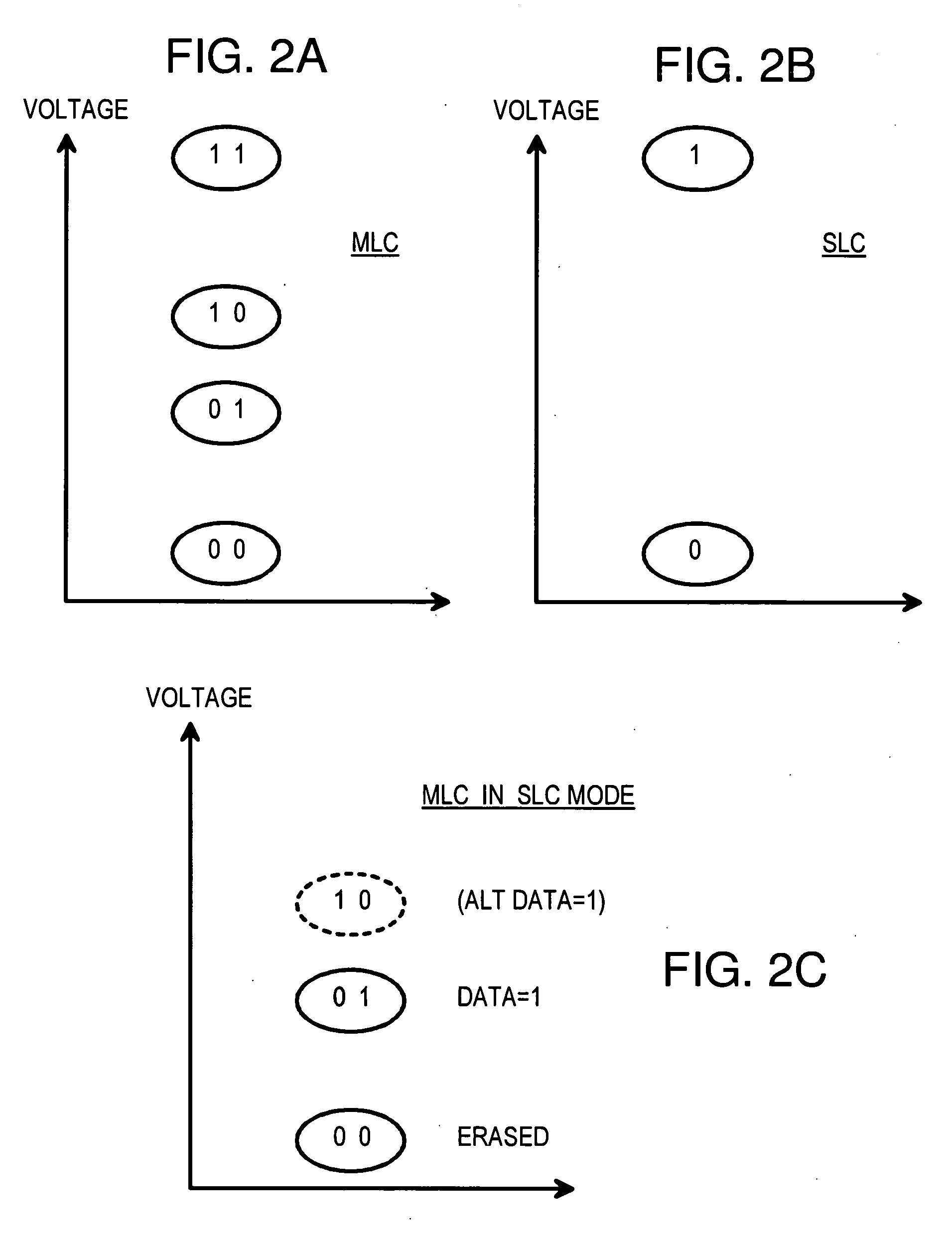

InactiveUS20090193184A1Memory architecture accessing/allocationMemory adressing/allocation/relocationVirtual fieldFrequency counter

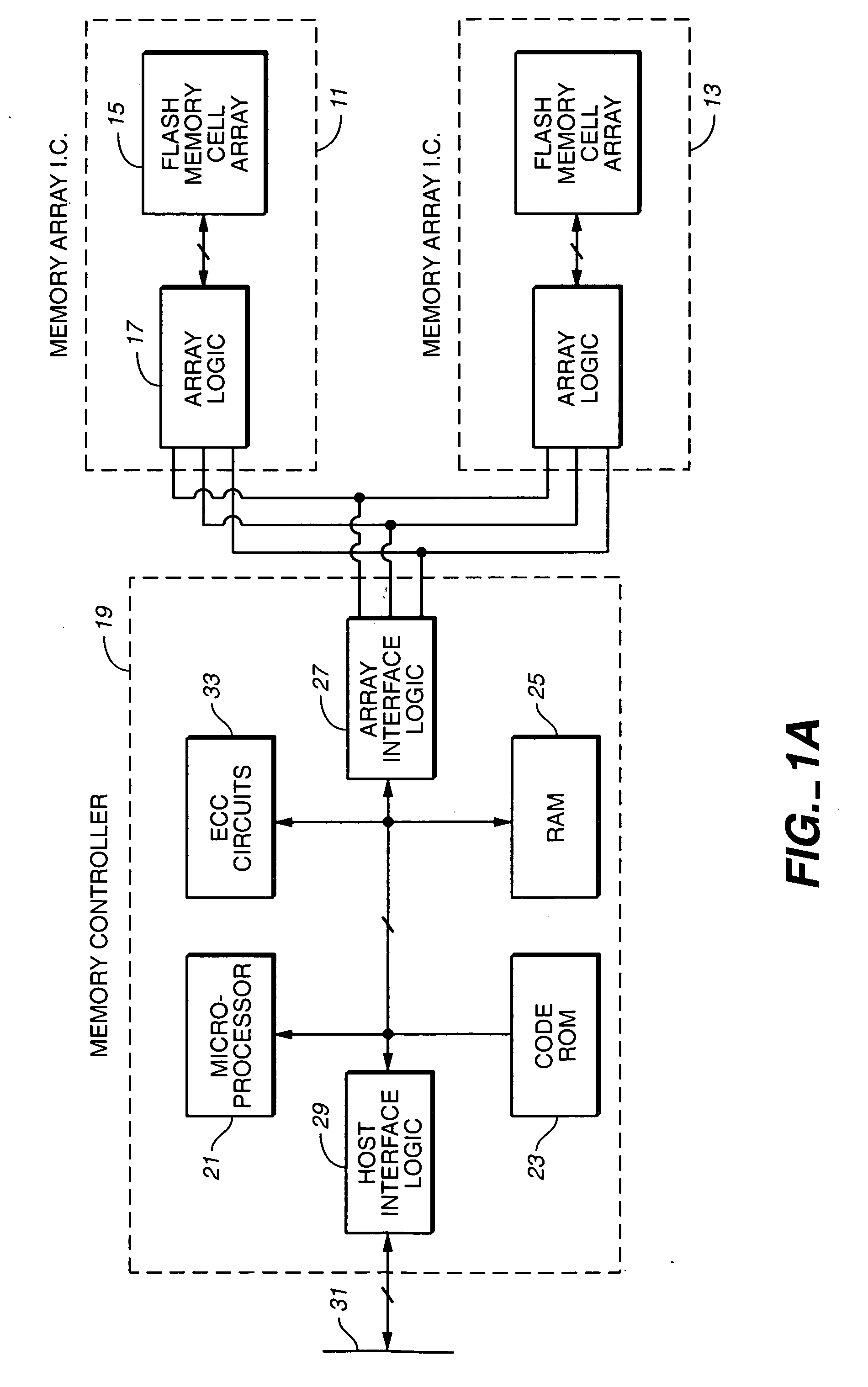

A hybrid solid-state disk (SSD) has multi-level-cell (MLC) or single-level-cell (SLC) flash memory, or both. SLC flash may be emulated by MLC that uses fewer cell states. A NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Most data is block-mapped and stored in MLC flash, but some critical or high-frequency data is page-mapped to reduce block-relocation copying. A hybrid mapping table has a first-level and a second level. Only the first level is used for block-mapped data, but both levels are used for page-mapped data. The first level contains a block-page bit that indicates if the data is block-mapped or page-mapped. A PBA field in the first-level table maps block-mapped data, while a virtual field points to the second-level table where the PBA and page number is stored for page-mapped data. Page-mapped data is identified by a frequency counter or sector count. SRAM space is reduced.

Owner:SUPER TALENT ELECTRONICS

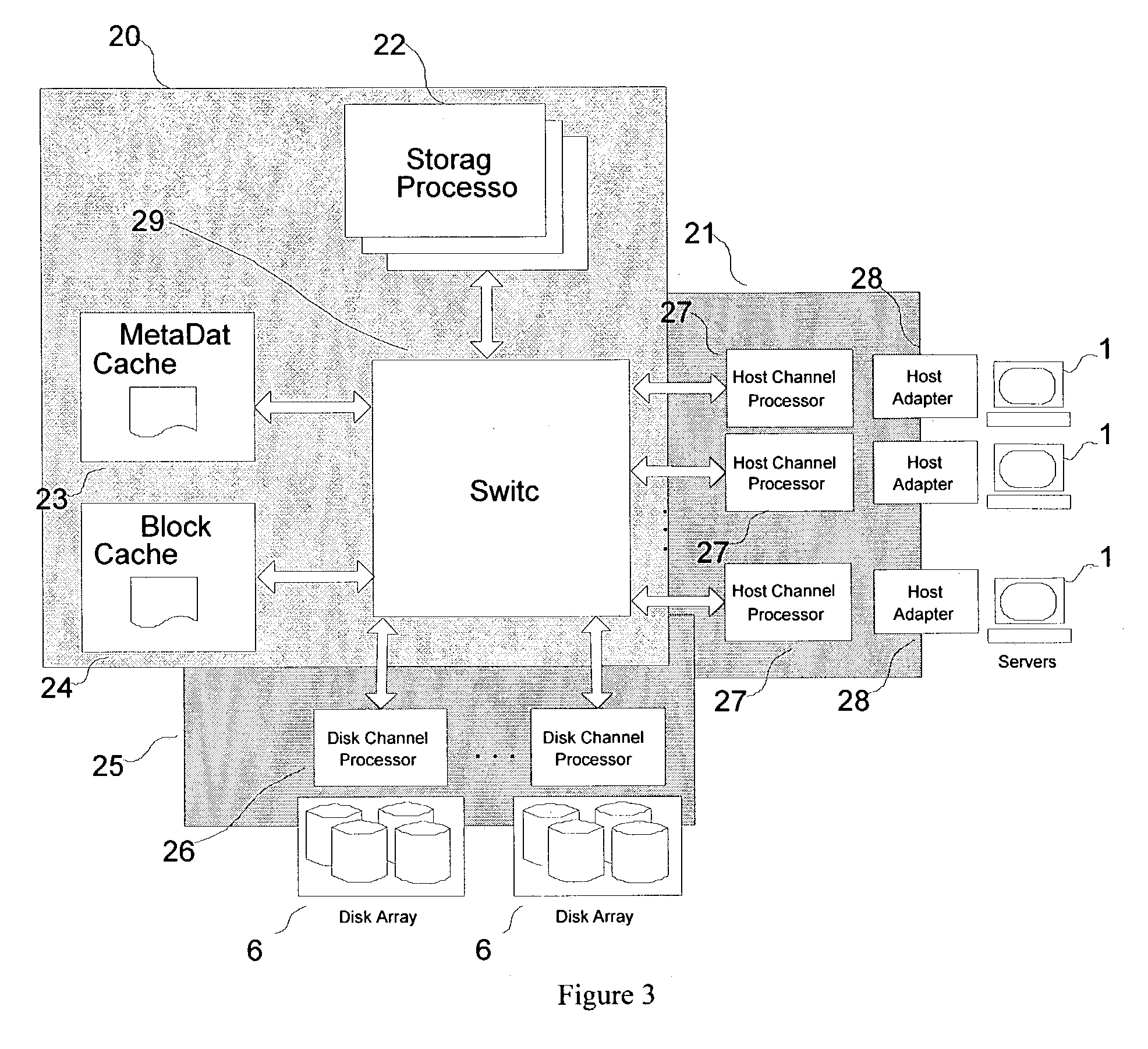

Method and apparatus for efficient scalable storage management

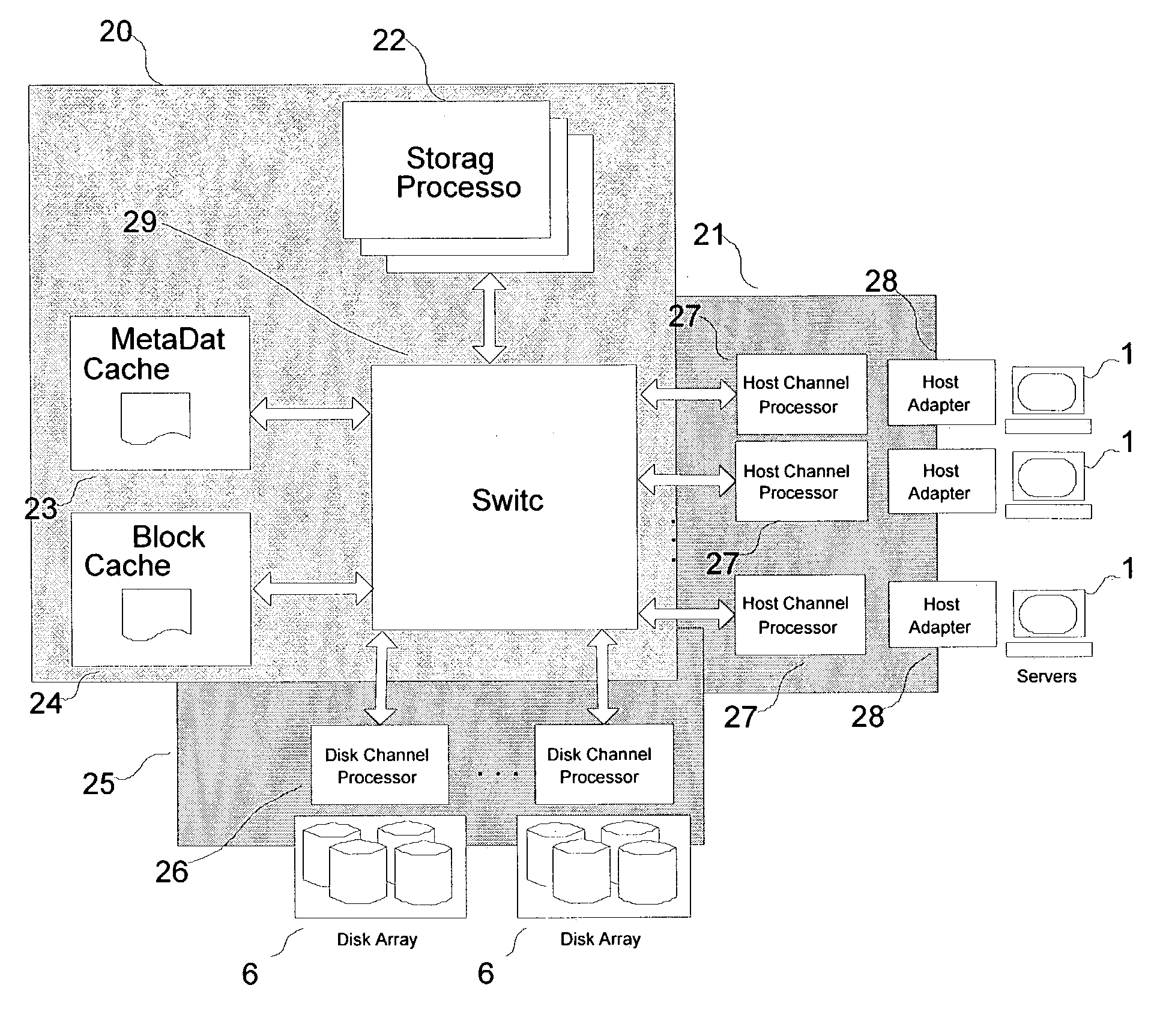

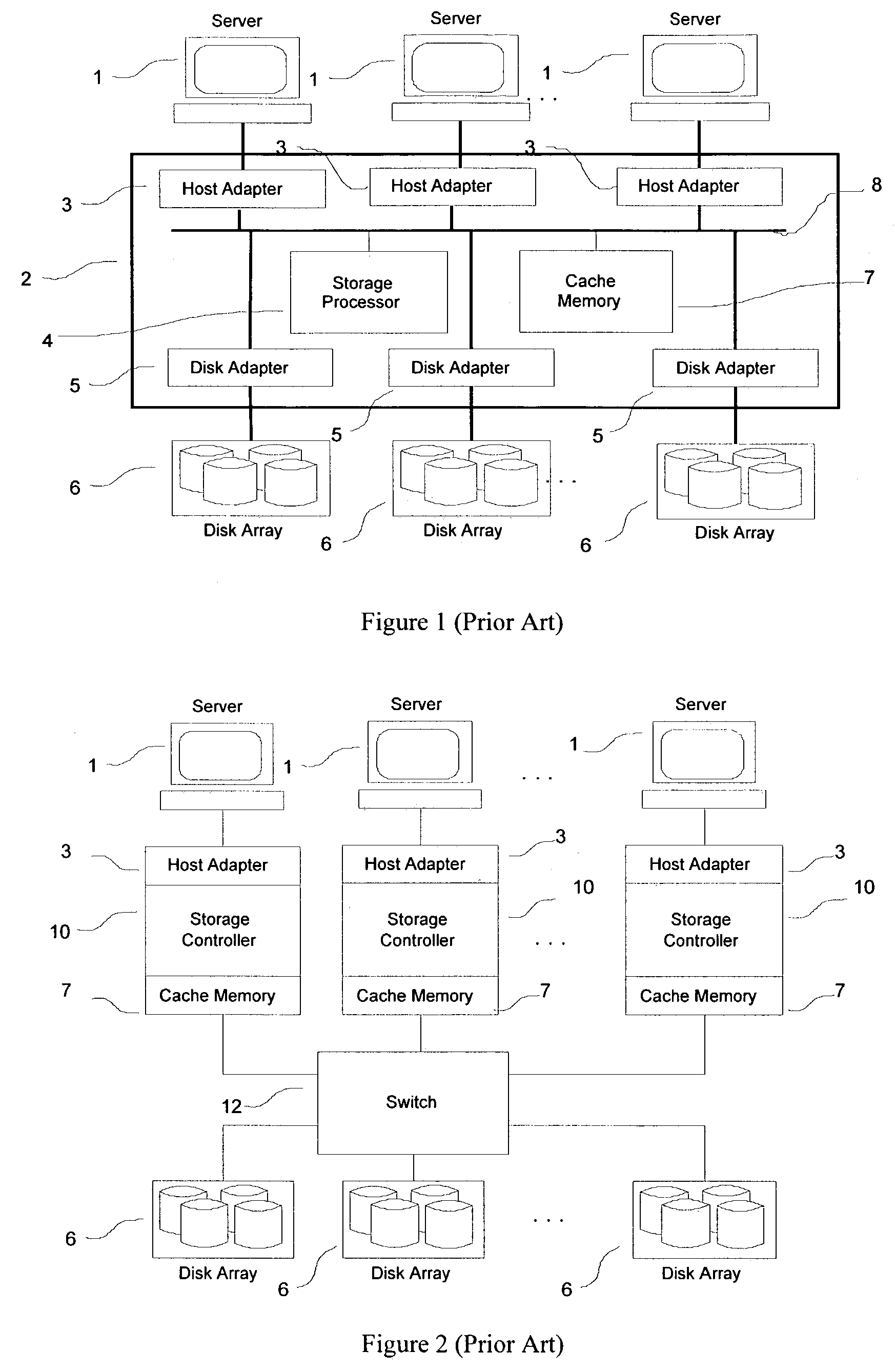

ActiveUS7181578B1Improve performanceSolve the lack of spaceMemory systemsInput/output processes for data processingHandling systemDatapath

A hybrid centralized and distributed processing system includes a switching device that connects a storage processor to one or more servers through a host channel processor. The switching device also connects the storage processor to one or more storage devices such as disk drive arrays, and to a metadata cache and a block data cache memory. The storage processor processes access request from one or more servers in the form of a logical volume or logical block address and accesses the metadata cache to determine the physical data address. The storage processor monitors the performance of the storage system and performs automatic tuning by reallocating the logical volume, load balancing, hot spot removal, and dynamic expansion of storage volume. The storage processor also provides fault-tolerant access and provides parallel high performance data paths for fail over. The storage processor also provides faster access by providing parallel data paths for, making local copies and providing remote data copies, and by selecting data from a storage device that retrieves the data the earliest.

Owner:COPAN SYST INC +1

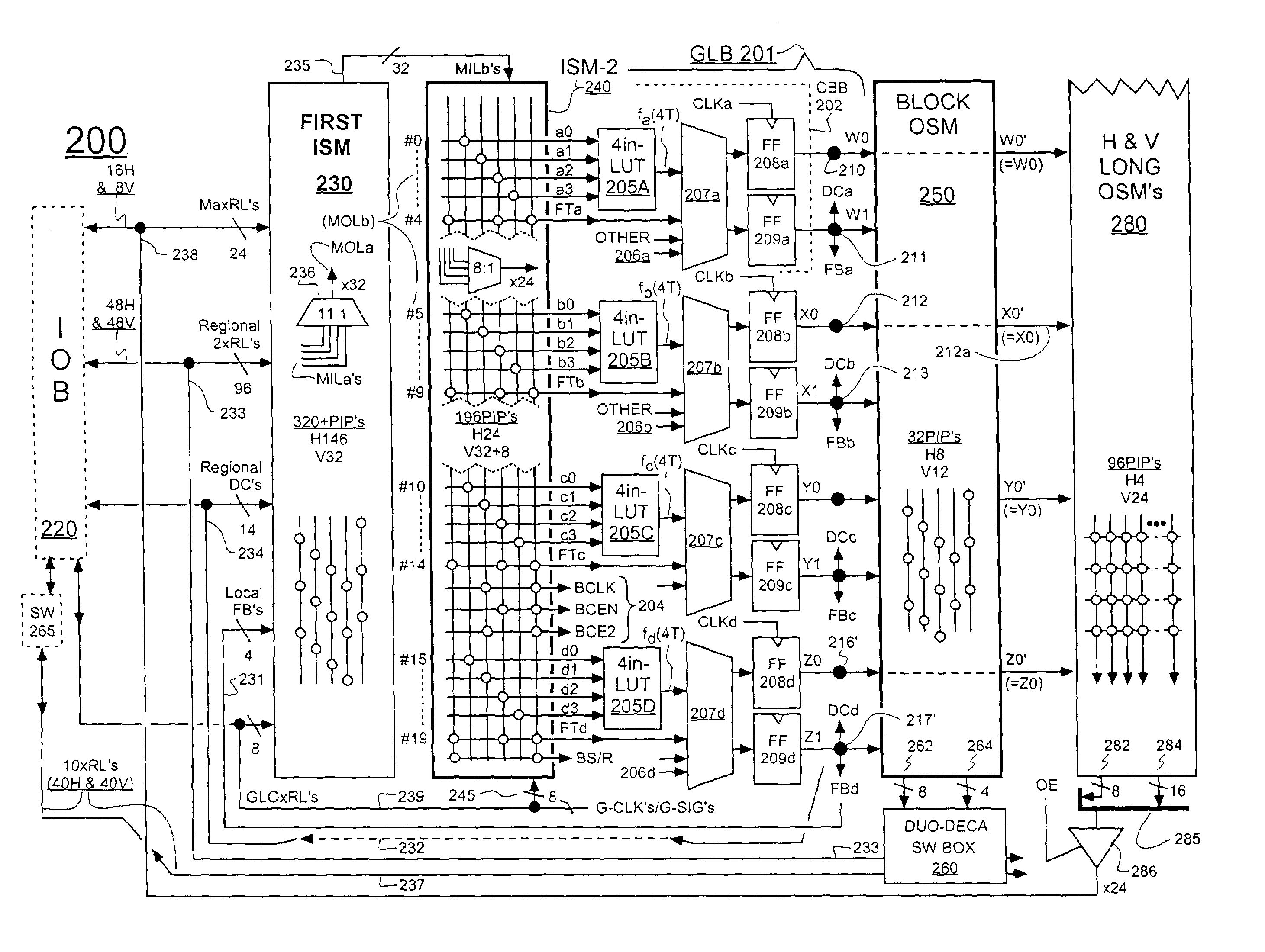

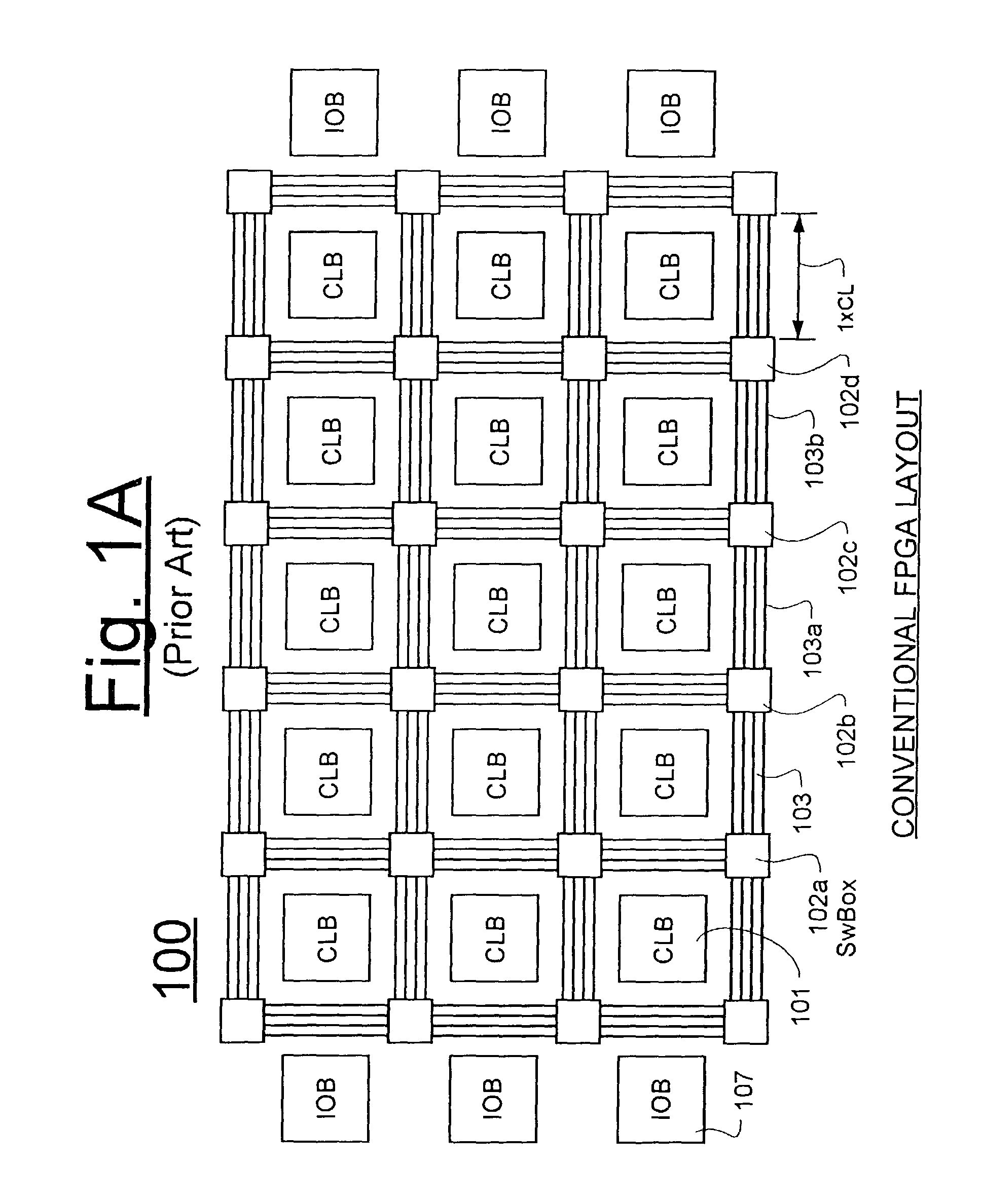

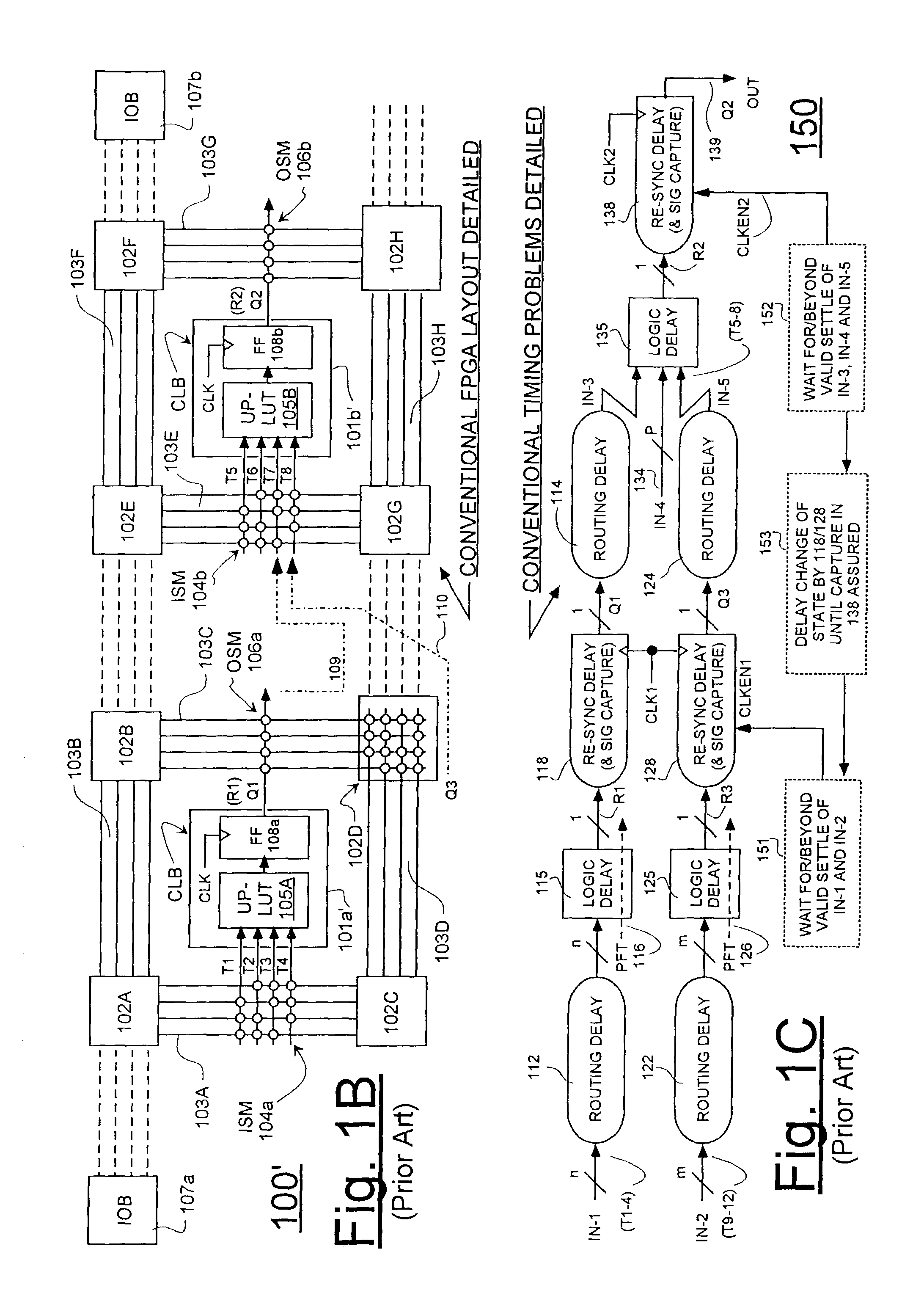

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

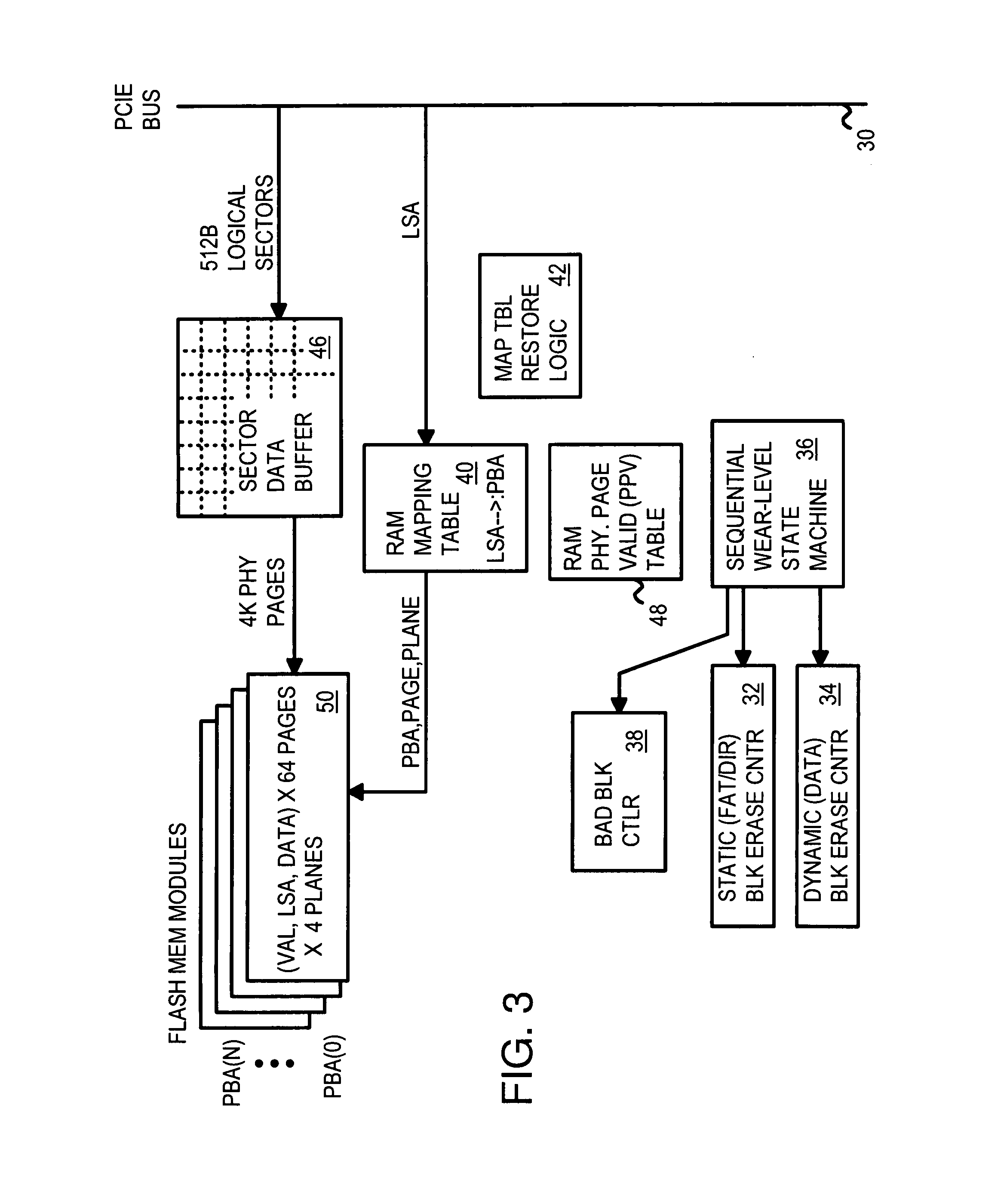

Command Queuing Smart Storage Transfer Manager for Striping Data to Raw-NAND Flash Modules

ActiveUS20090037652A1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingHost machine

A flash module has raw-NAND flash memory chips accessed over a physical-block address (PBA) bus by a NVM controller. The NVM controller is on the flash module or on a system board for a solid-state disk (SSD). The NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Data striping and interleaving among multiple channels of the flash modules is controlled at a high level by a smart storage transaction manager, while further interleaving and remapping within a channel may be performed by the NVM controllers. A SDRAM buffer is used by a smart storage switch to cache host data before writing to flash memory. A Q-R pointer table stores quotients and remainders of division of the host address. The remainder points to a location of the host data in the SDRAM. A command queue stores Q, R for host commands.

Owner:SUPER TALENT TECH CORP

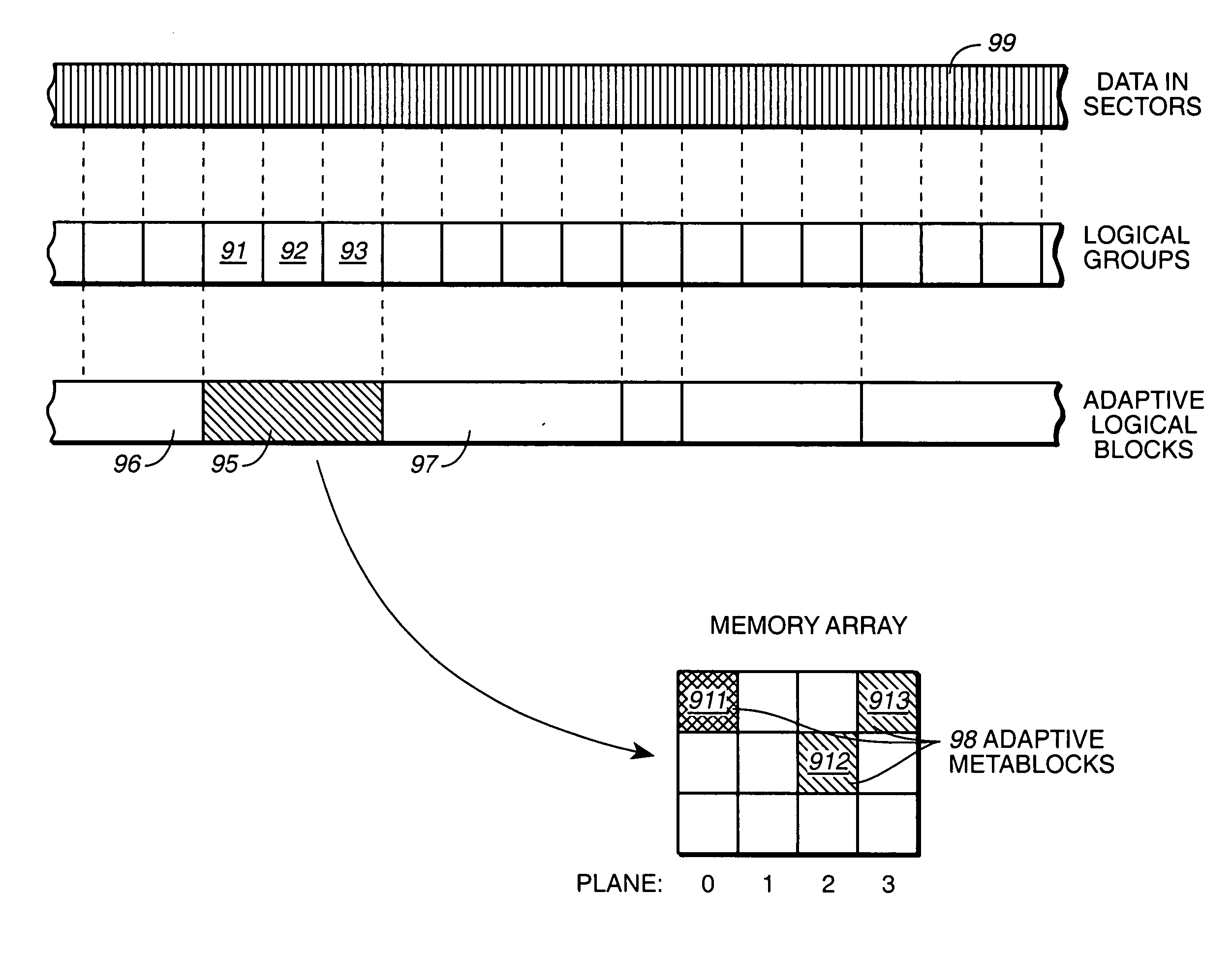

Adaptive metablocks

ActiveUS20050144357A1Reduce the impactEfficient updateMemory architecture accessing/allocationMemory adressing/allocation/relocationData selectionTheoretical computer science

In a memory system having multiple erase blocks in multiple planes, a selected number of erase blocks are programmed together as an adaptive metablock. The number of erase blocks in an adaptive metablock is chosen according to the data to be programmed. Logical address space is divided into logical groups, a logical group having the same size as one erase block. Adaptive logical blocks are formed from logical groups. One adaptive logical block is stored in one adaptive metablock.

Owner:SANDISK TECH LLC

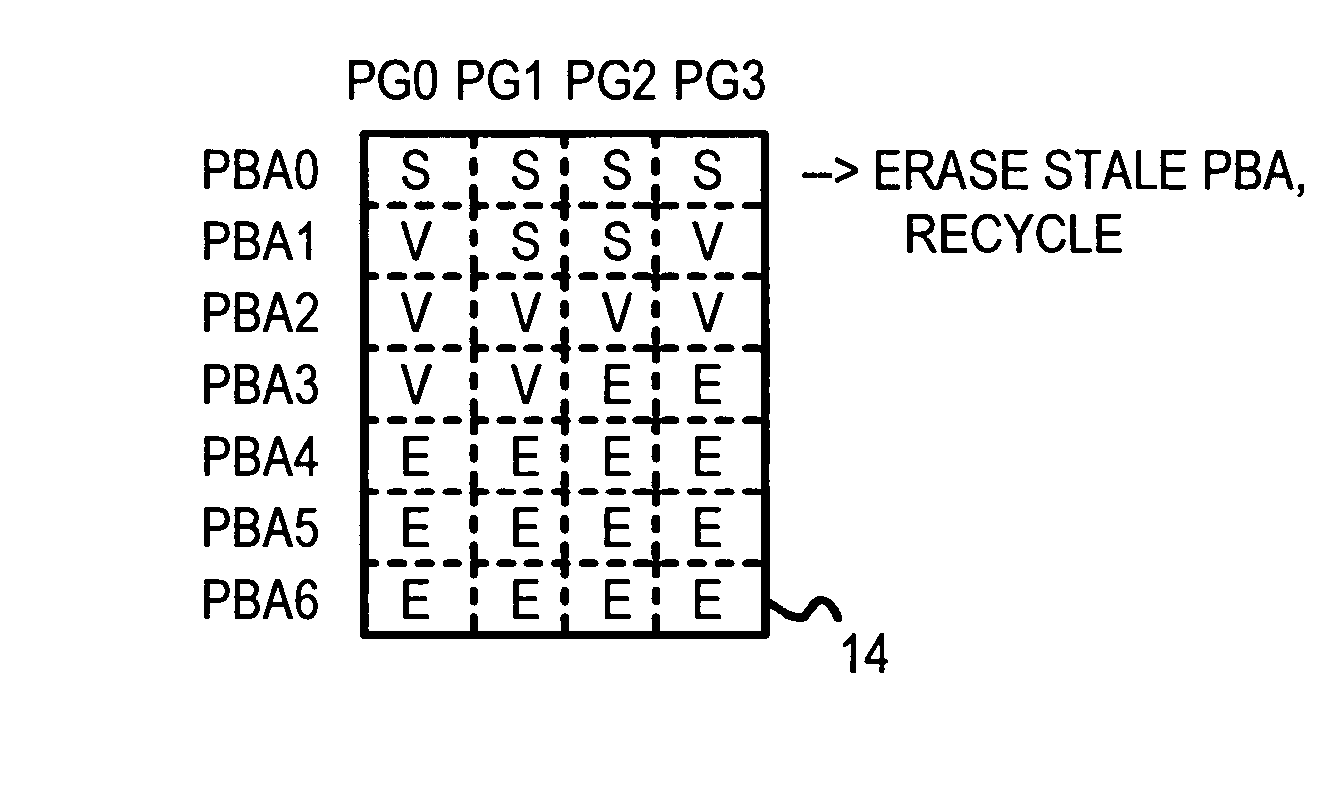

Two-Level RAM Lookup Table for Block and Page Allocation and Wear-Leveling in Limited-Write Flash-Memories

InactiveUS20070204128A1Memory architecture accessing/allocationRead-only memoriesRandom access memoryLogical block addressing

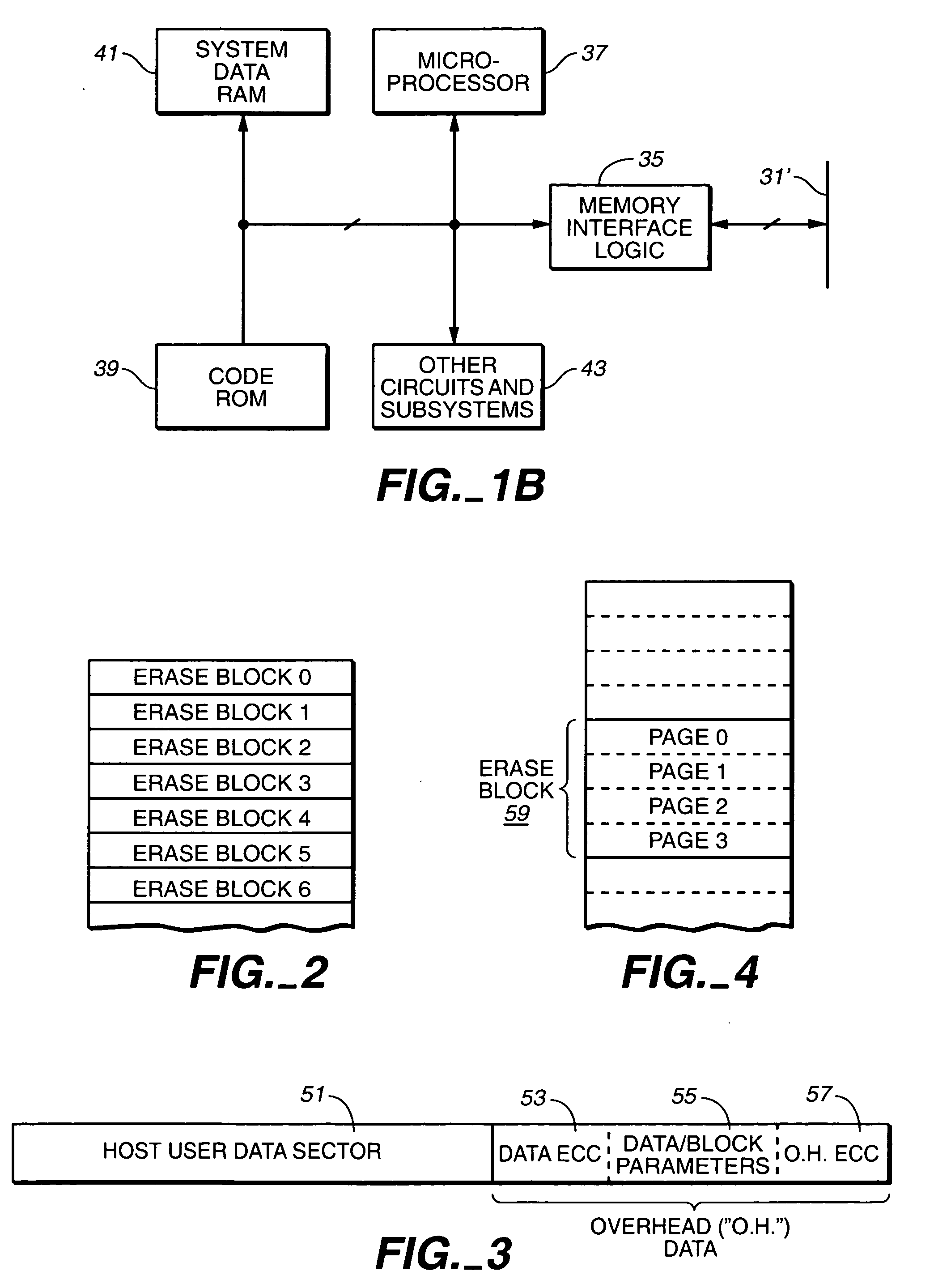

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

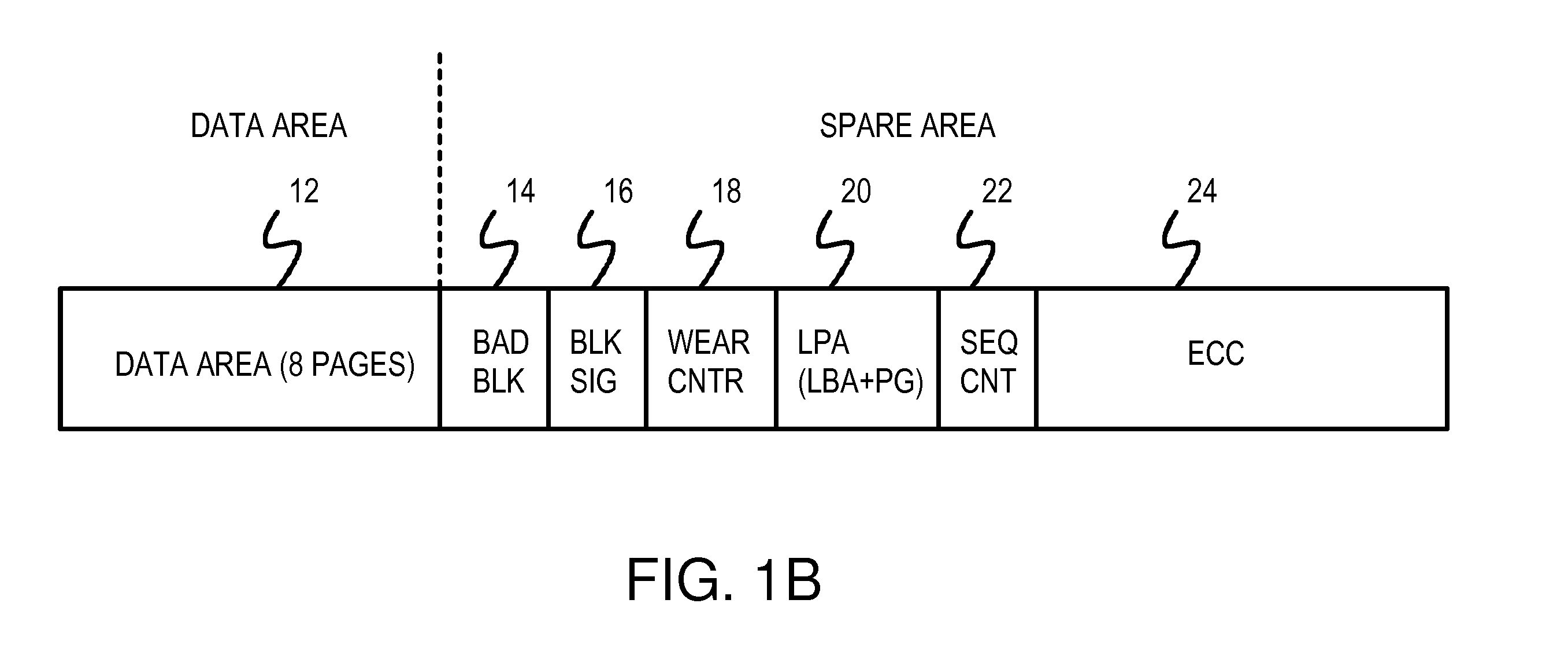

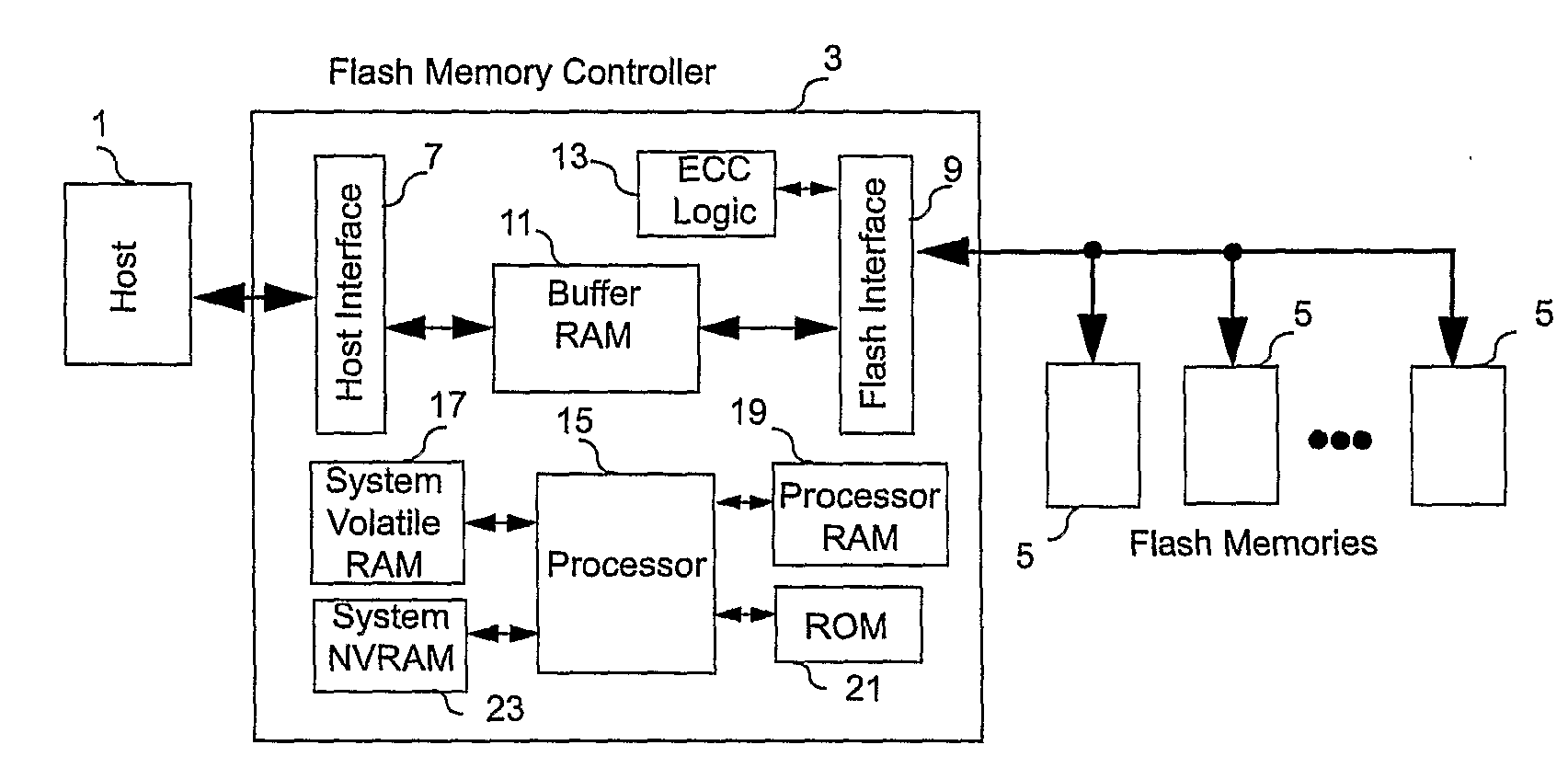

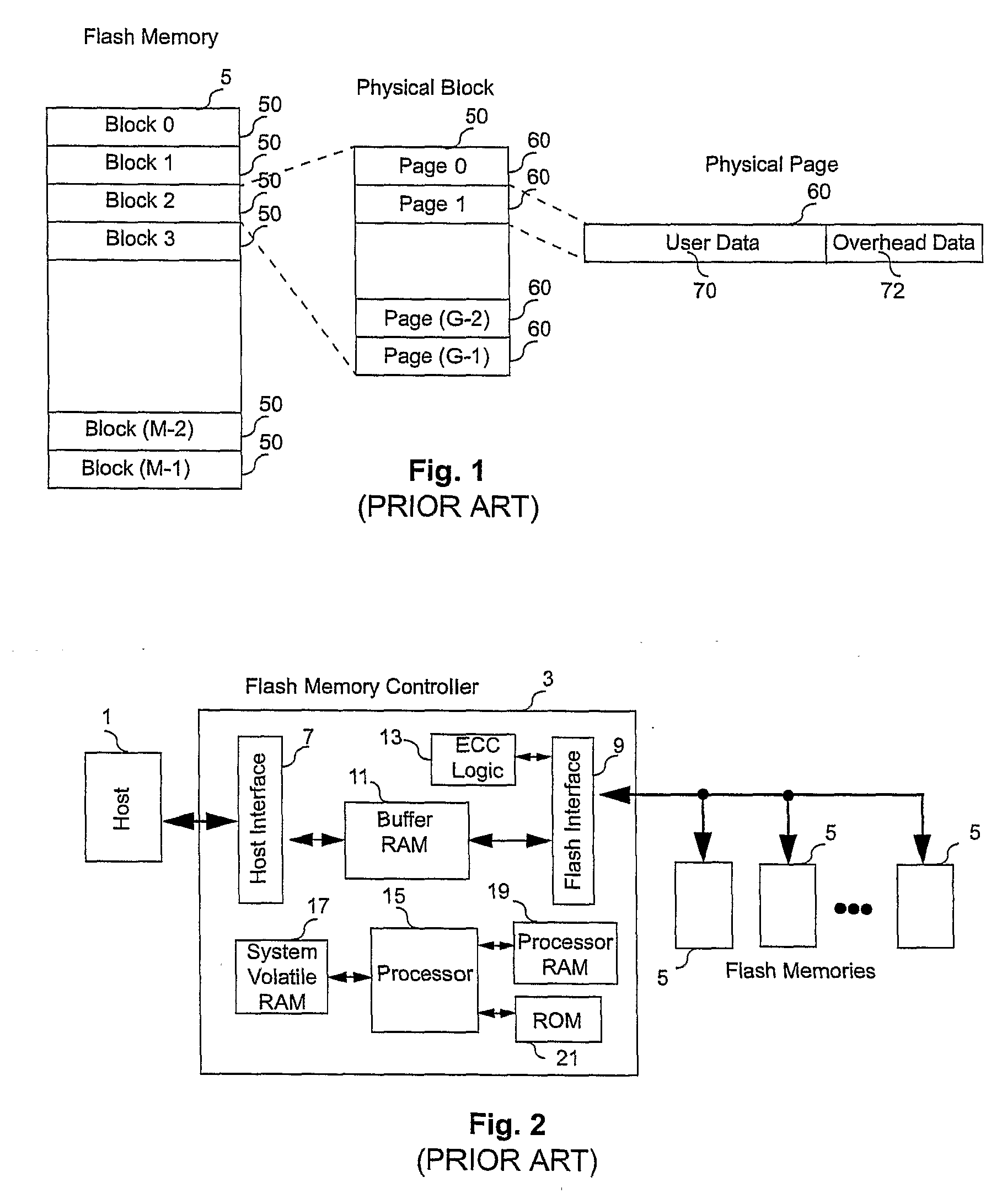

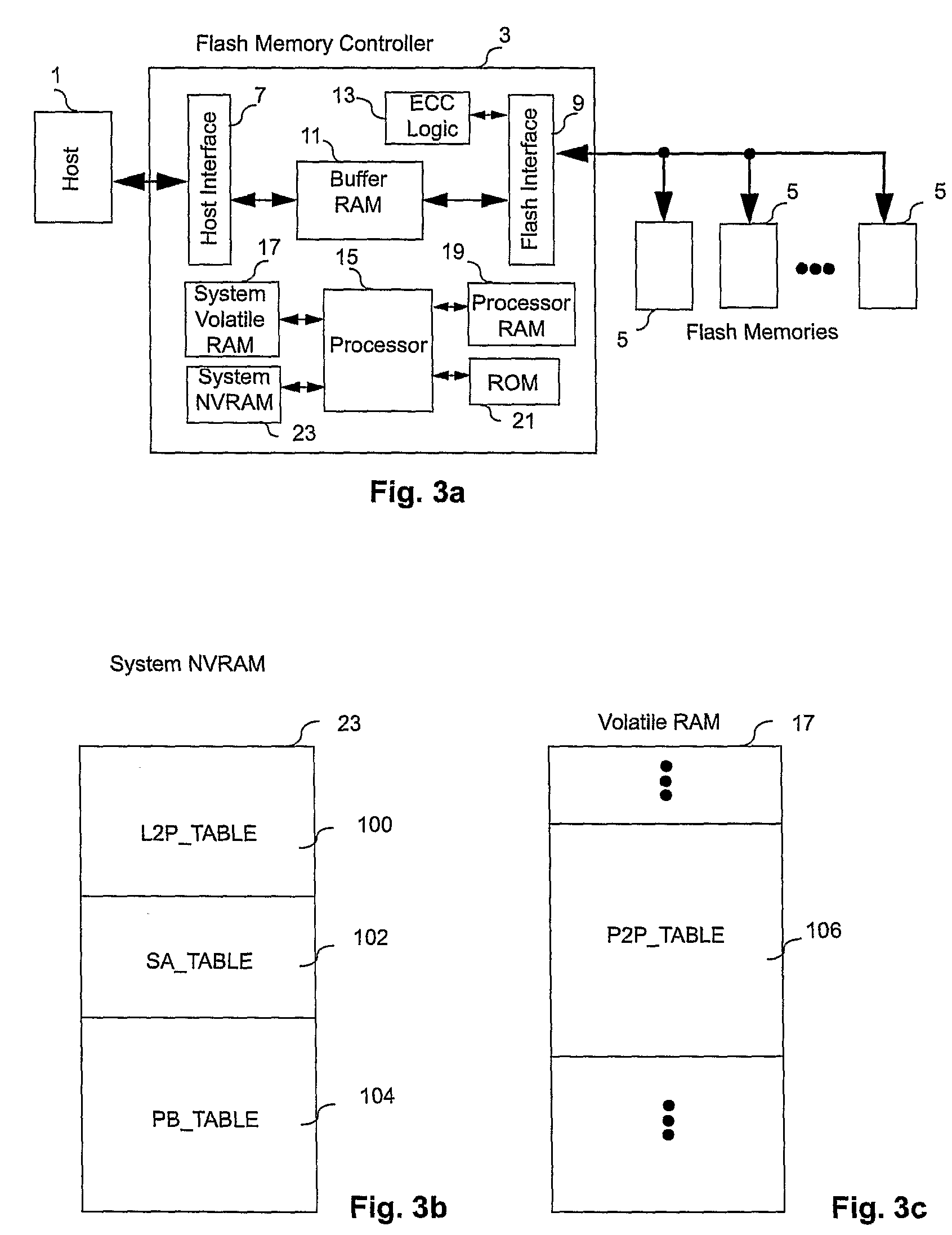

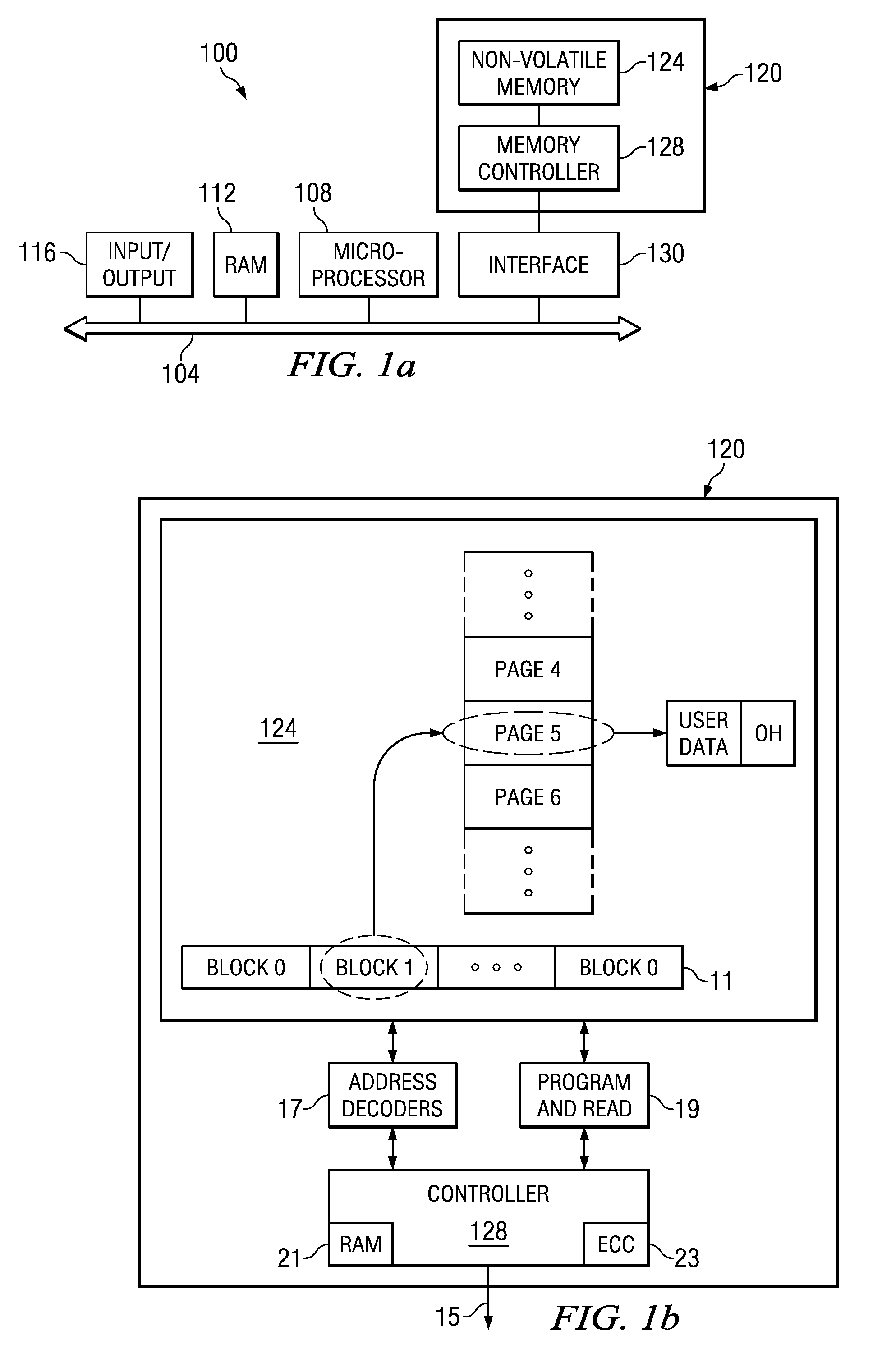

Controller for Non-Volatile Memories and Methods of Operating the Memory Controller

ActiveUS20080270680A1Improve system performanceReduce stepsMemory adressing/allocation/relocationRead-only memoriesMemory controllerByte

A non-volatile memory system (3) is proposed consisting of a first non-volatile flash memory (5) having a plurality of blocks, each block having a plurality of pages, each block being erasable and each page being programmable, and a second non-volatile random access memory (23) having a plurality of randomly accessible bytes. The second non-volatile memory (23) stores data for mapping logical blocks to physical blocks and status information of logical blocks. Each logical block has an associated physical page pointer stored in the second non-volatile memory (23) that identifies the next free physical page of the mapped physical block to be written. The page pointer is incremented after every page write to the physical block, allowing all physical pages to be fully utilized for page writes. Furthermore, a method of writing and reading data is disclosed whereby the most recently written physical page associated with a logical address is identifiable by the memory system without programming flags into superseded pages, or recording time stamp values in any physical page or block of the first non-volatile memory (5). Furthermore, a method is provided for a logical block to be mapped to two physical blocks instead of one to provide additional space for page writes, resulting in reduction in page copy operations, thereby increasing the performance of the system.

Owner:CHANG CHEE KENG

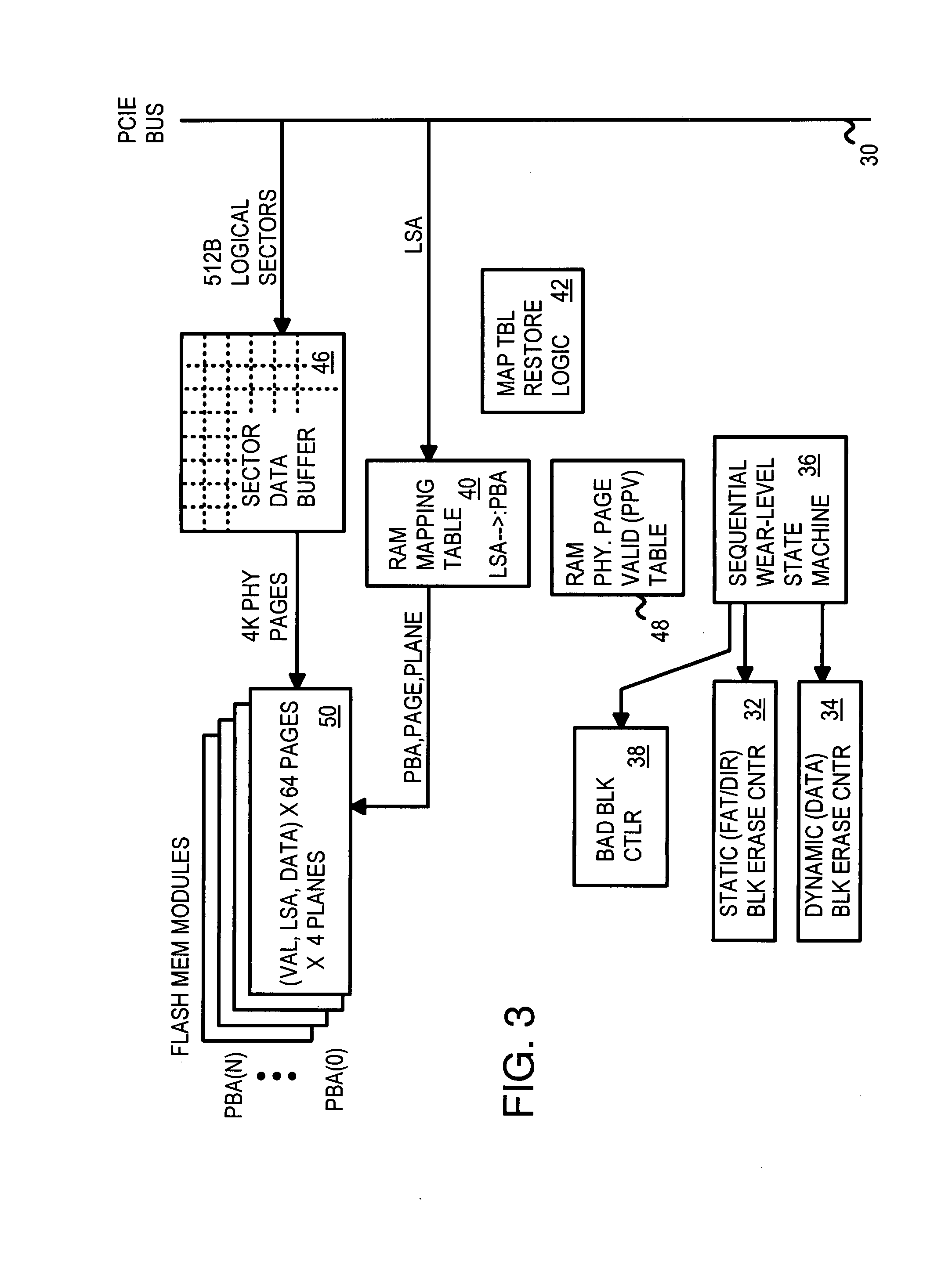

Flash Module with Plane-Interleaved Sequential Writes to Restricted-Write Flash Chips

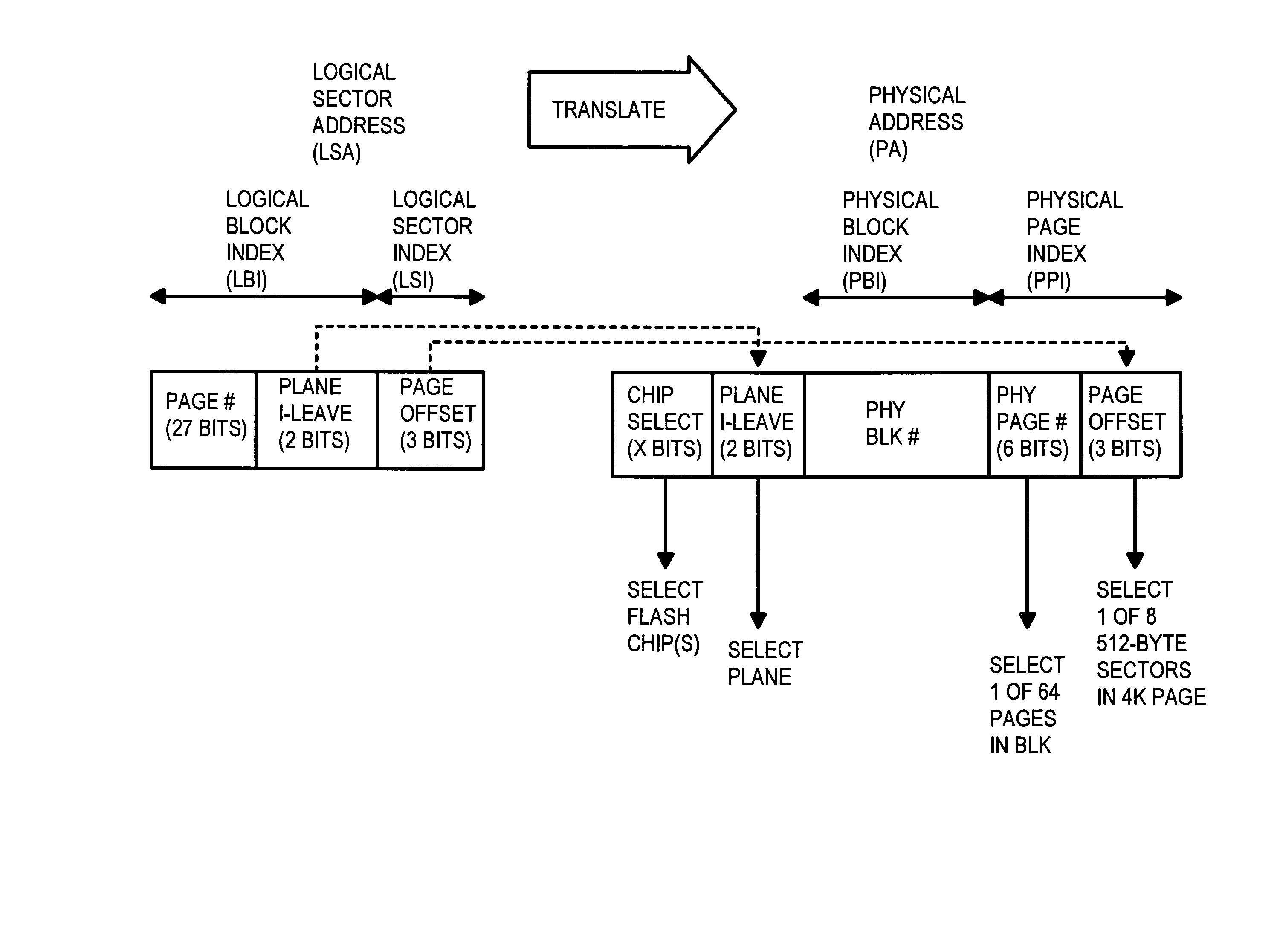

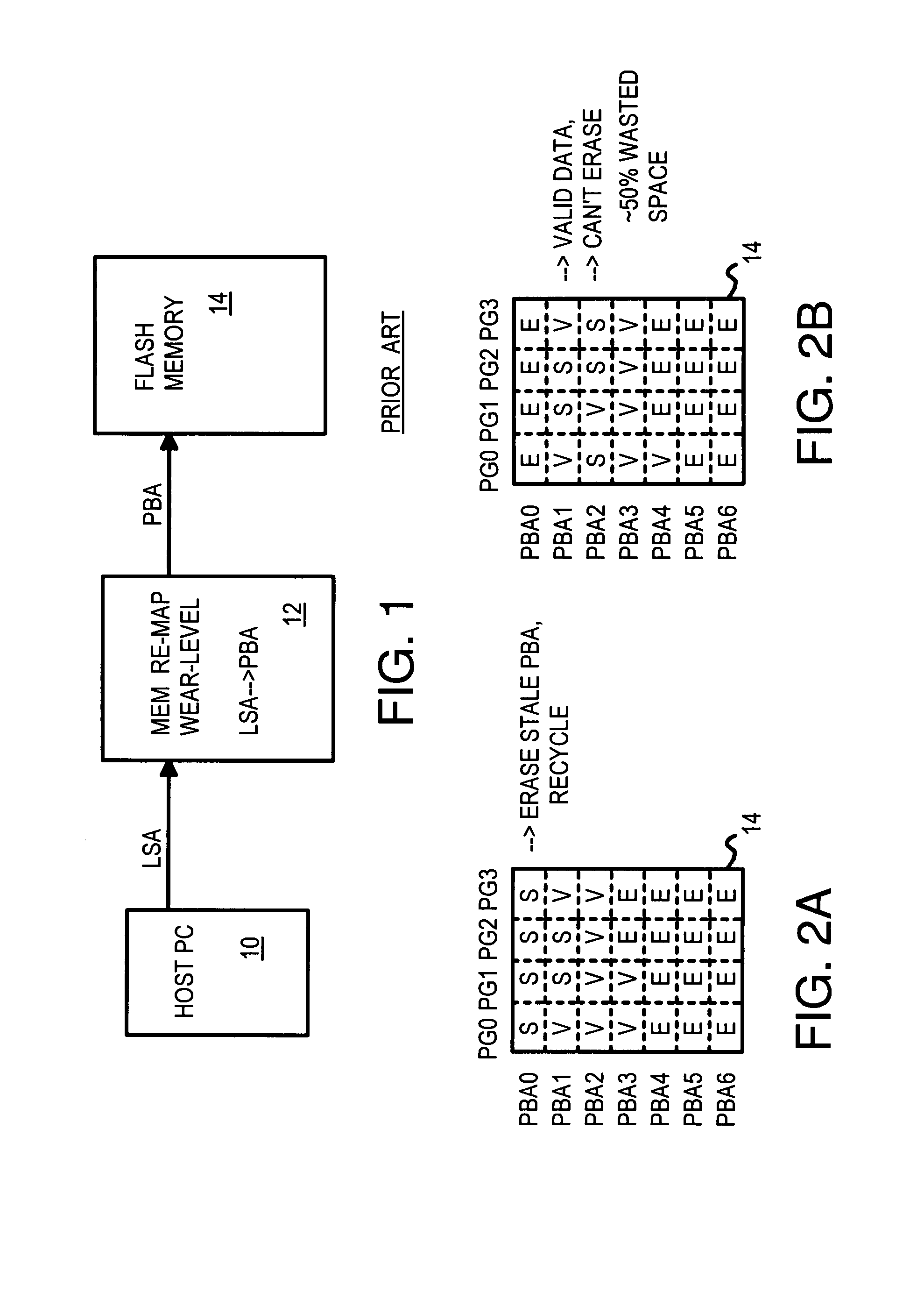

InactiveUS20080034153A1Memory architecture accessing/allocationRead-only memoriesFlash memory controllerBlock number

A flash memory controller on a PCIE bus controls flash-memory modules on a flash bus. The flash-memory modules are plane-interleaved using interleaved bits extracted from the lowest bits of the logical block index. These plane-interleave bits are split into a LSB and a MSB, with middle physical block bits between the LSB and MSB. A physical sequential address counter generates a physical block number by incrementing the plane-interleave bits before the middle physical block bits, and then relocating the MSB to above the middle physical block bits. This causes blocks to be accessed in a low-high sequence of 0, 1, 4096, 4097, 2, 3, 4098, 4099, etc. in the four planes of flash memory. A RAM physical page valid table tracks valid pages in the four planes, while a RAM mapping table stores the plane, block, and page addresses for logical sectors generated by the physical sequential address counter.

Owner:SUPER TALENT TECH CORP

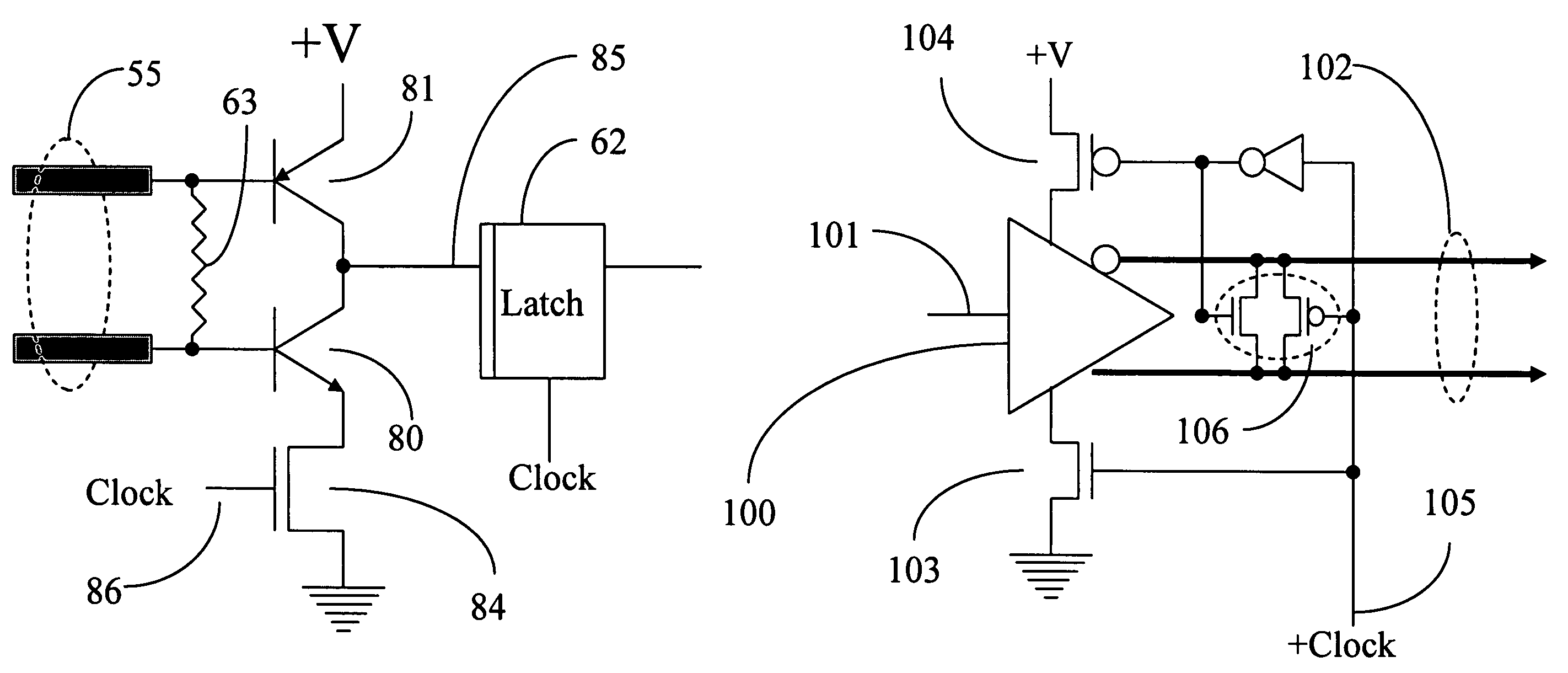

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

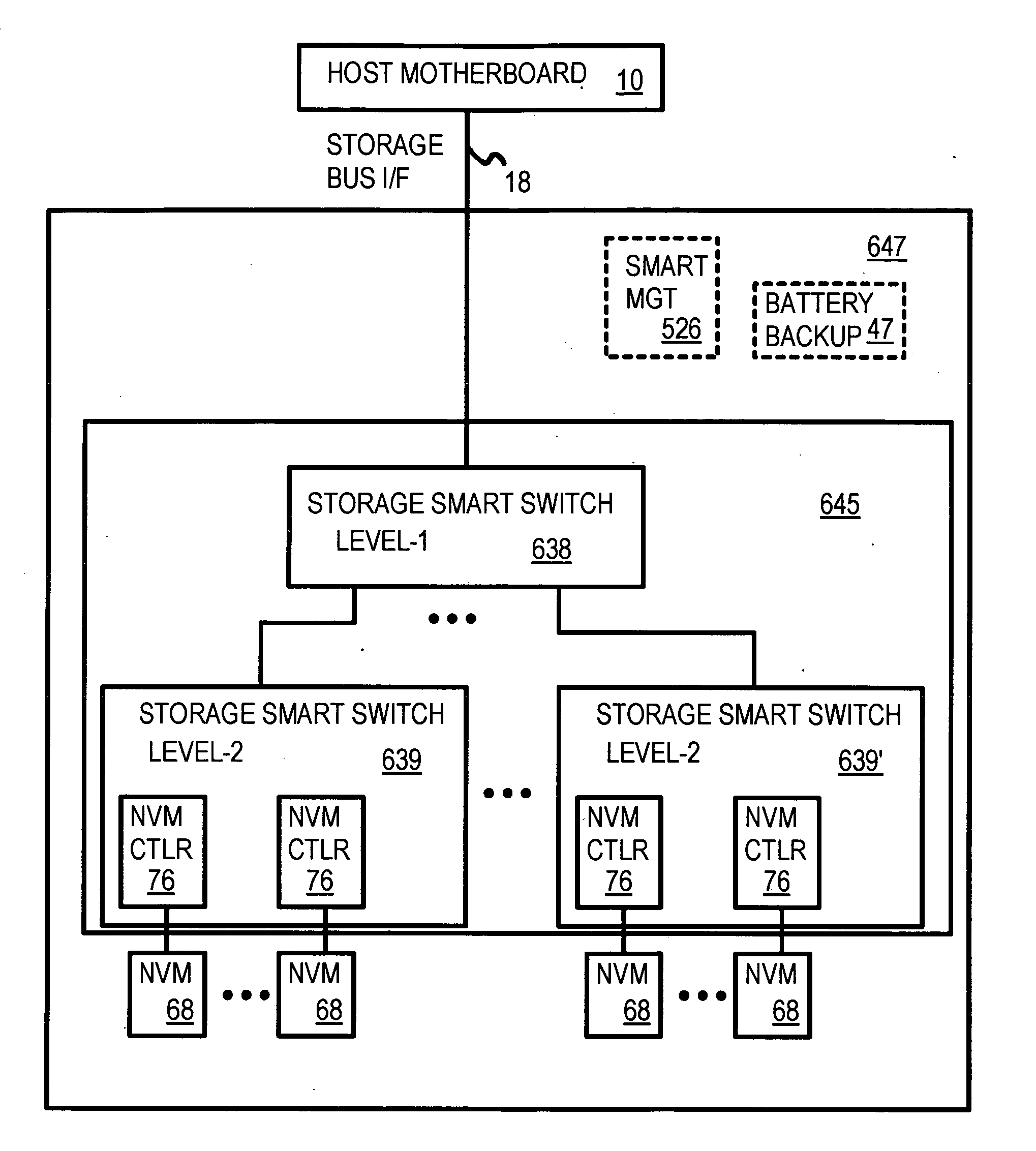

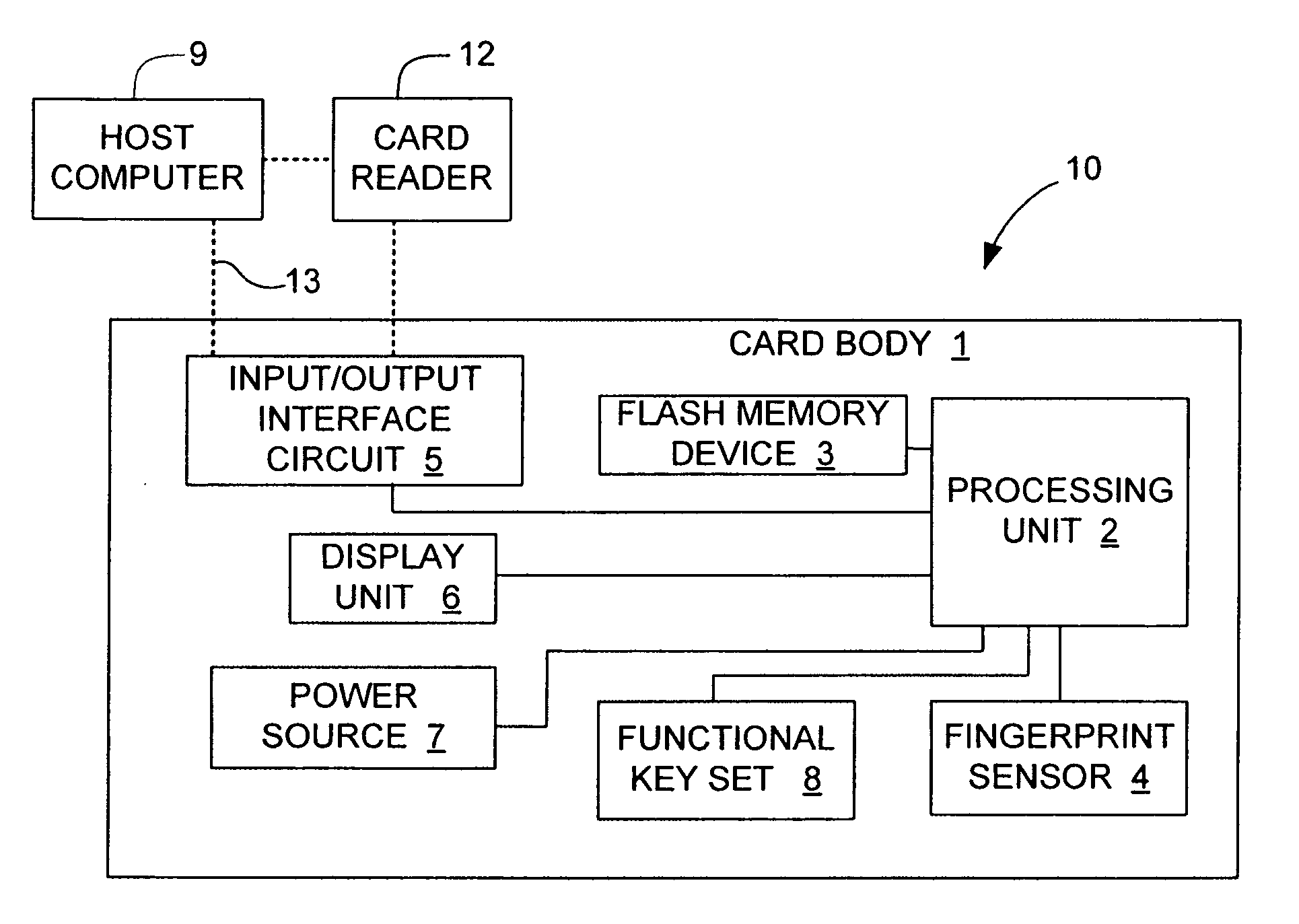

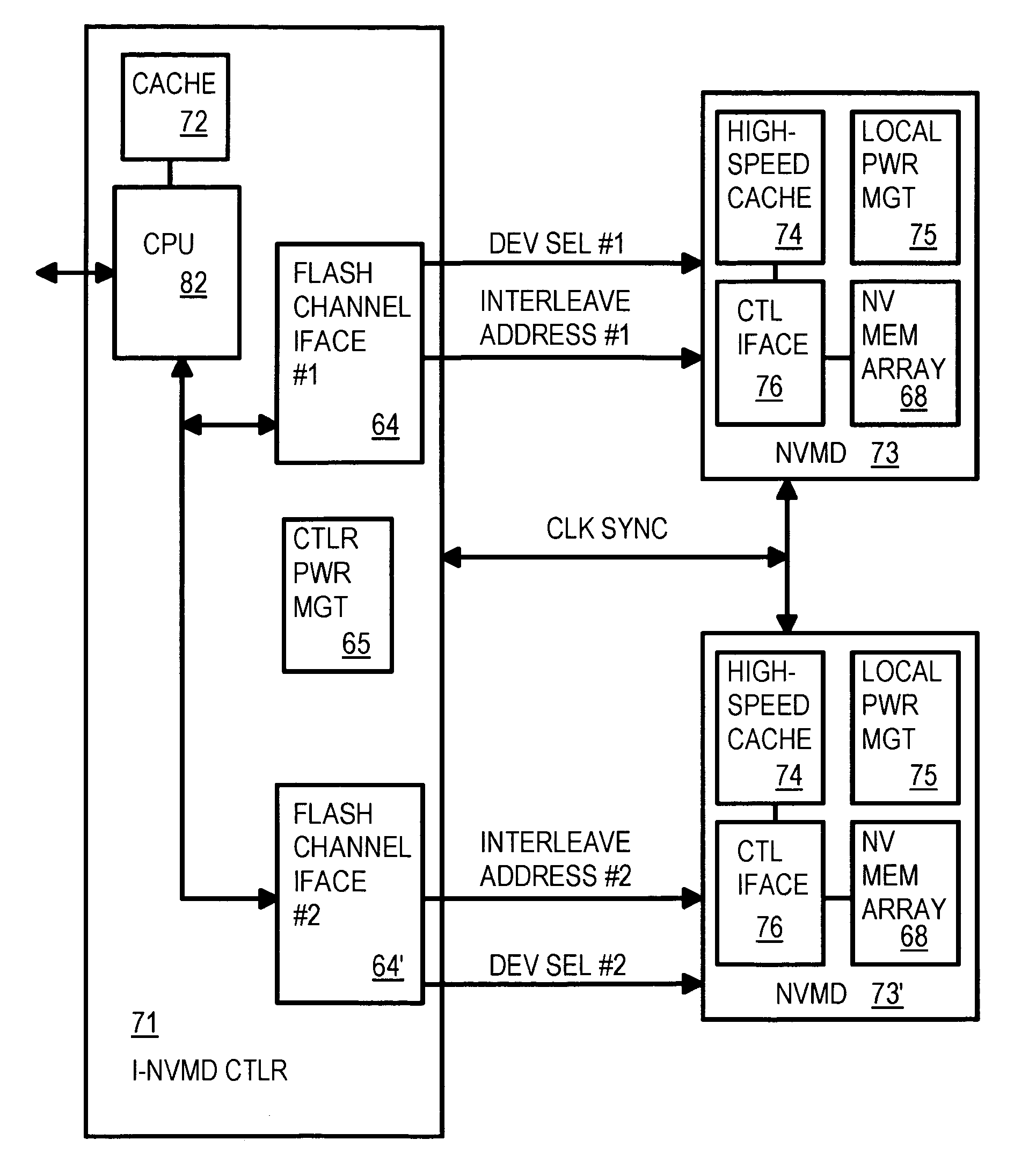

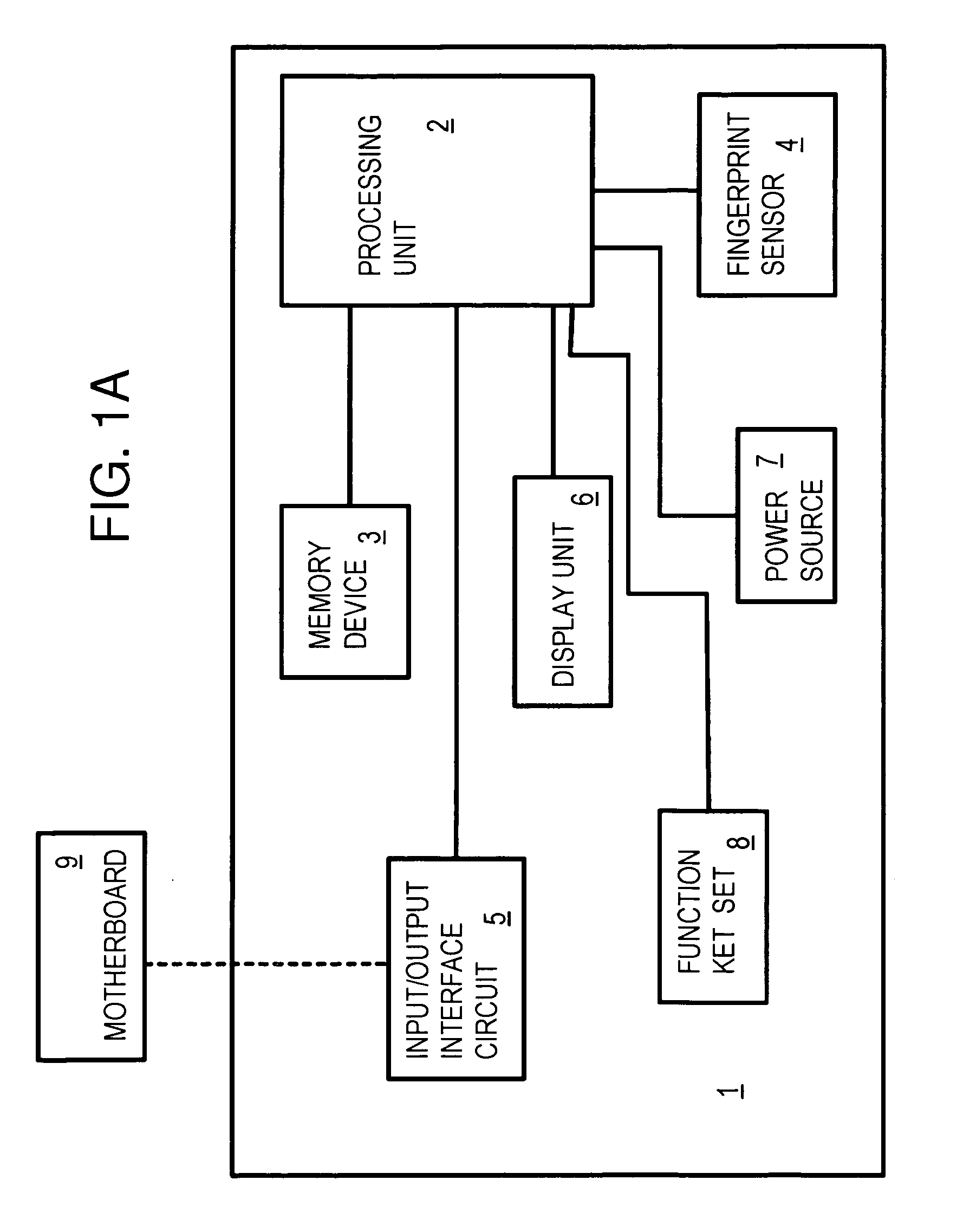

Intelligent Solid-State Non-Volatile Memory Device (NVMD) System With Multi-Level Caching of Multiple Channels

InactiveUS20080235443A1Memory architecture accessing/allocationEnergy efficient ICTPower controllerLogical block addressing

A flash memory system stores blocks of data in Non-Volatile Memory Devices (NVMD) that are addressed by a logical block address (LBA). The LBA is remapped for wear-leveling and bad-block relocation by the NVMD. The NVMD are interleaved in channels that are accessed by a NVMD controller. The NVMD controller has a controller cache that caches blocks stored in NVMD in that channel, while the NVMD also contain high-speed cache. The multiple levels of caching reduce access latency. Power is managed in multiple levels by a power controller in the NVMD controller that sets power policies for power managers inside the NVMD. Multiple NVMD controllers in the flash system may each controller many channels of NVMD. The flash system with NVMD may include a fingerprint reader for security.

Owner:SUPER TALENT TECH CORP

Multi-Channel Flash Module with Plane-Interleaved Sequential ECC Writes and Background Recycling to Restricted-Write Flash Chips

InactiveUS20080034154A1Memory architecture accessing/allocationRead-only memoriesInterleave sequenceBlock number

A RAM mapping table is restored from flash memory using plane, block, and page addresses generated by a physical sequential address counter. The RAM mapping table is restored following a plane-interleaved sequence generated by the physical sequential address counter using interleaved bits extracted from the lowest bits of the logical block index. These plane-interleave bits are split into a LSB and a MSB, with middle physical block bits between the LSB and MSB. The physical sequential address counter generates a physical block number by incrementing the plane-interleave bits before the middle physical block bits, and then relocating the MSB to above the middle physical block bits. This causes blocks to be accessed in a low-high sequence of 0, 1, 4096, 4097, 2, 3, 4098, 4099, etc. in the four planes of flash memory. Background recycling and ECC writes are also performed.

Owner:SUPER TALENT TECH CORP

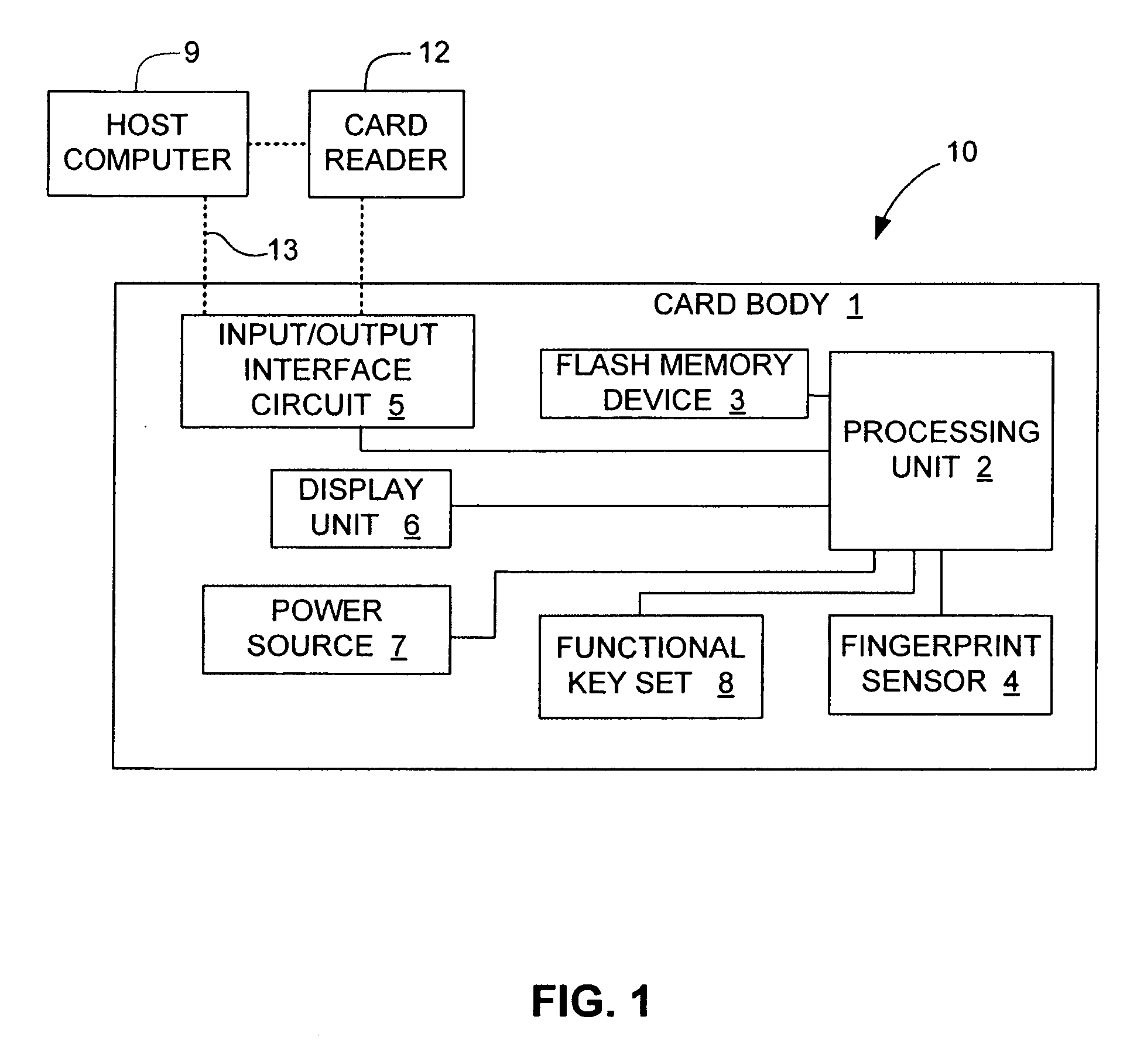

Managing Bad Blocks In Flash Memory For Electronic Data Flash Card

InactiveUS20070283428A1Reduce search timeAvoid congestionDigital data processing detailsUser identity/authority verificationLogical block addressingComputer access

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT TECH CORP

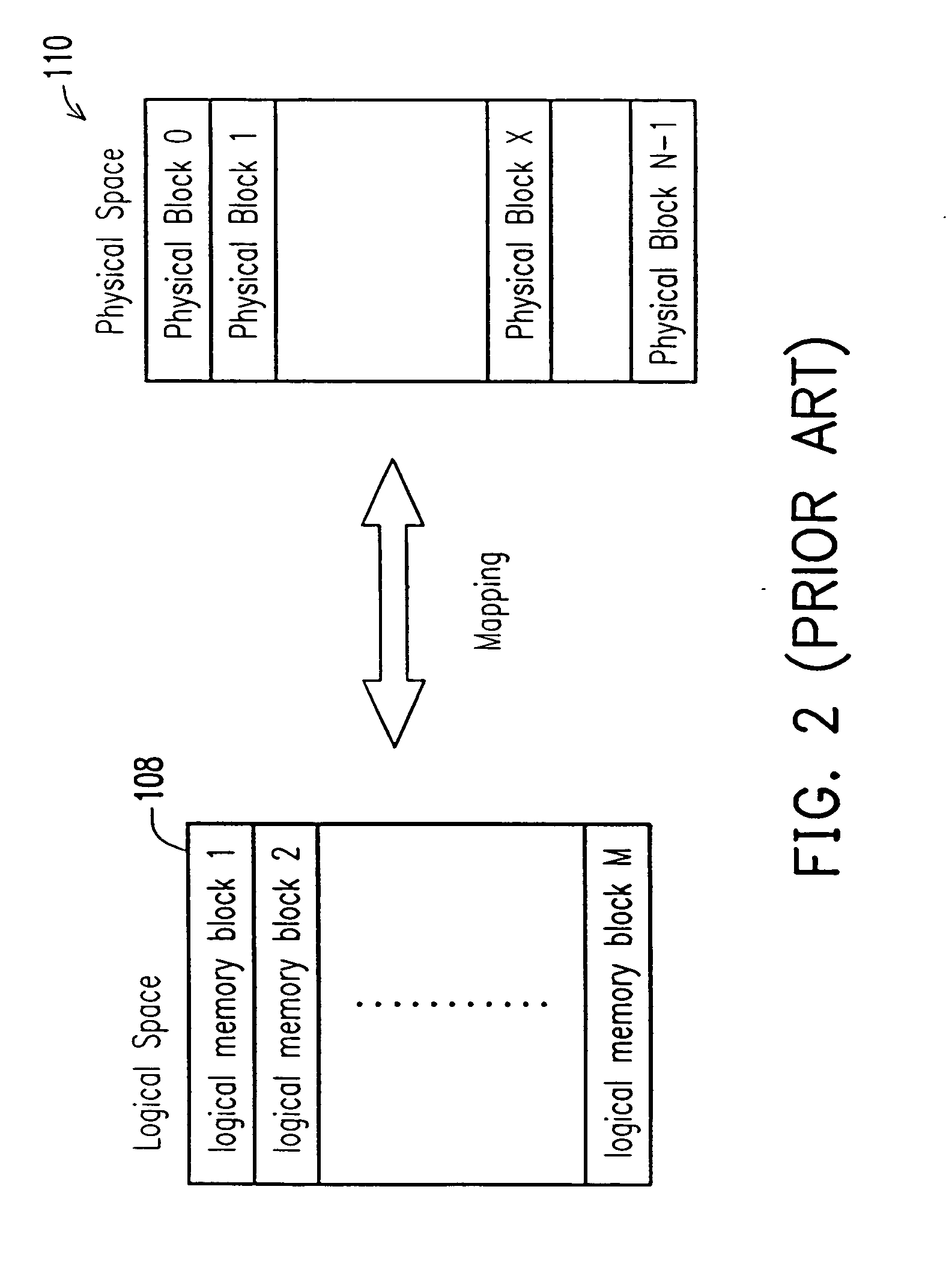

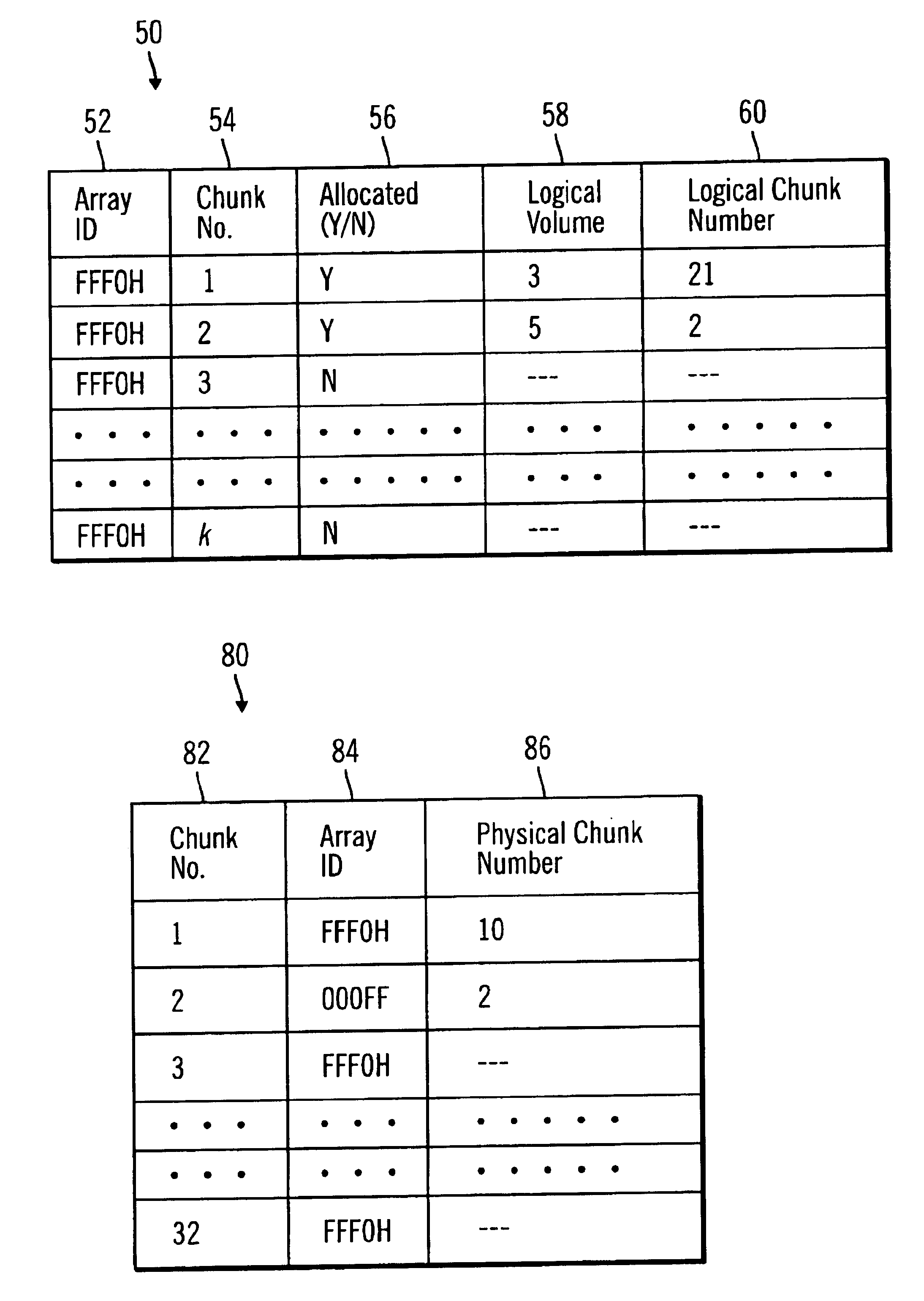

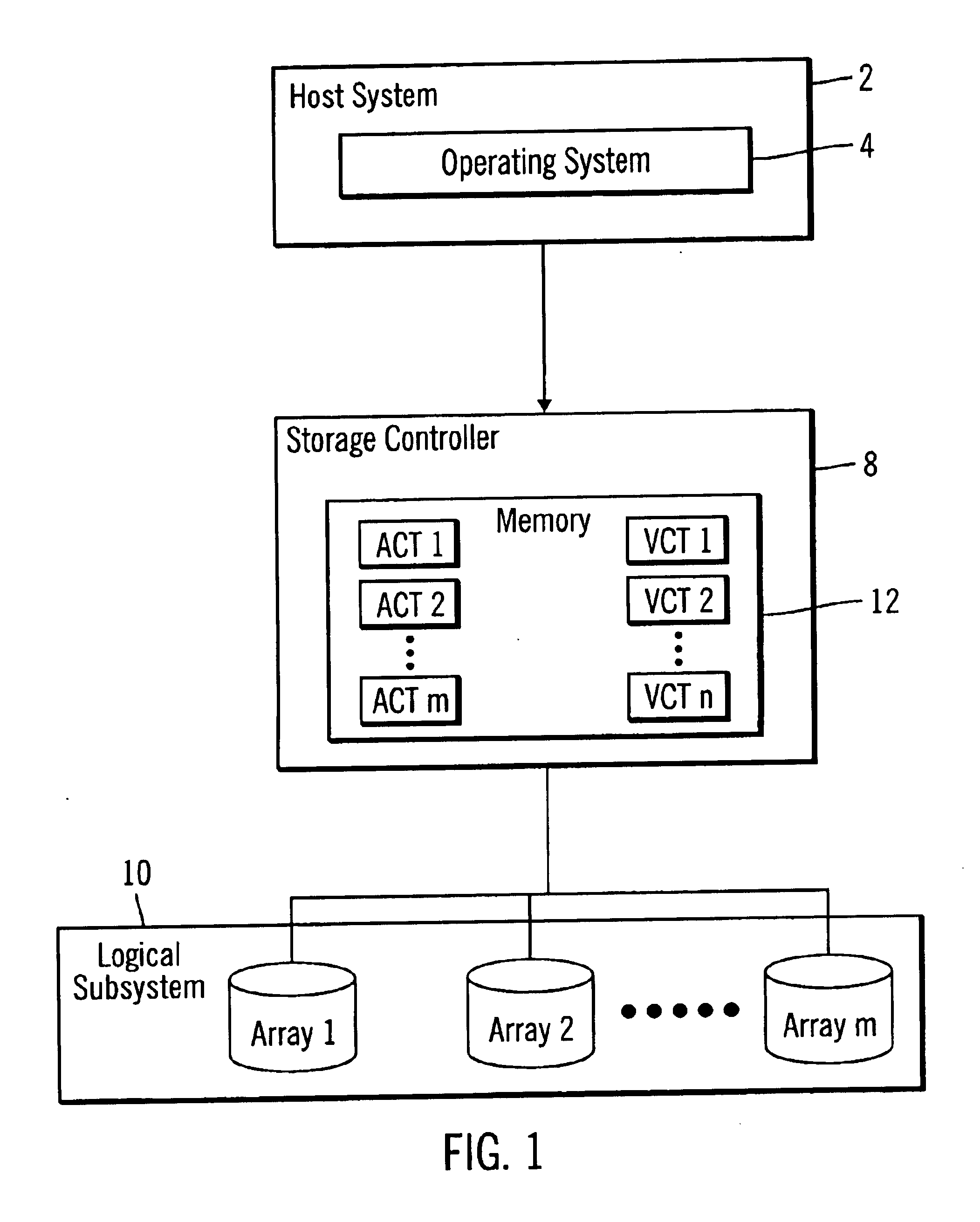

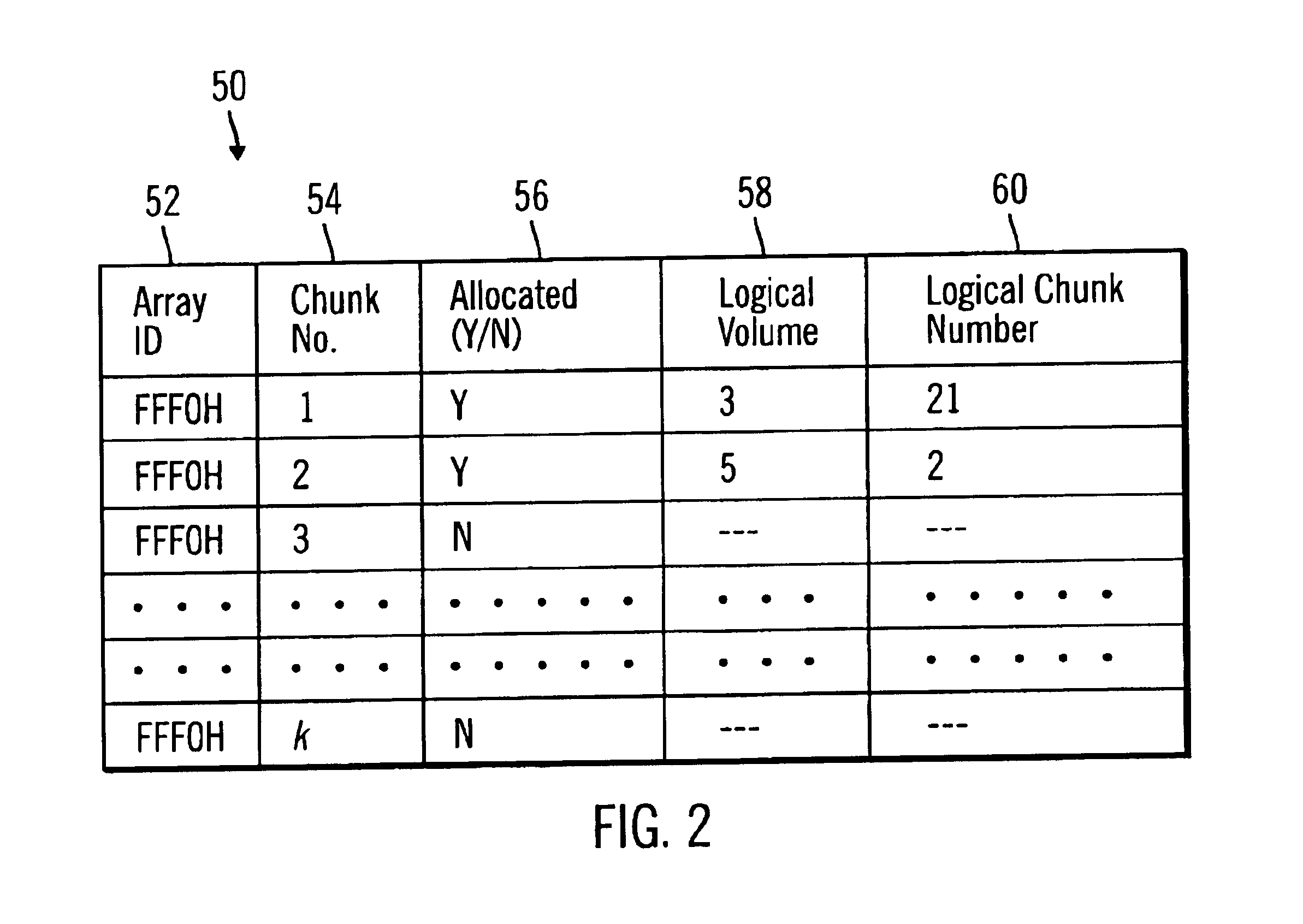

Method, system, program, and data structures for mapping logical blocks to physical blocks

InactiveUS6839827B1Increase in sizeAvoid performanceInput/output to record carriersMemory adressing/allocation/relocationArray data structureControl store

Disclosed is a method, system, program, and data structure for a storage controller to map logical blocks to physical storage blocks. The storage controller is in communication with at least one host system that views a logical storage space. The storage controller defines the logical storage space as a sequence of logical chunks, wherein each logical chunk comprises a plurality of logical blocks in the logical storage space. The storage controller further defines a physical storage space as a sequence of physical chunks, wherein each physical chunk comprises a plurality of physical blocks in the physical storage system. The storage controller associates each logical chunk in the sequence of logical chunks defining the logical storage space with one physical chunk in the physical storage system. Further, the contiguous logical chunks are capable of being associated with non-contiguous physical chunks.

Owner:IBM CORP

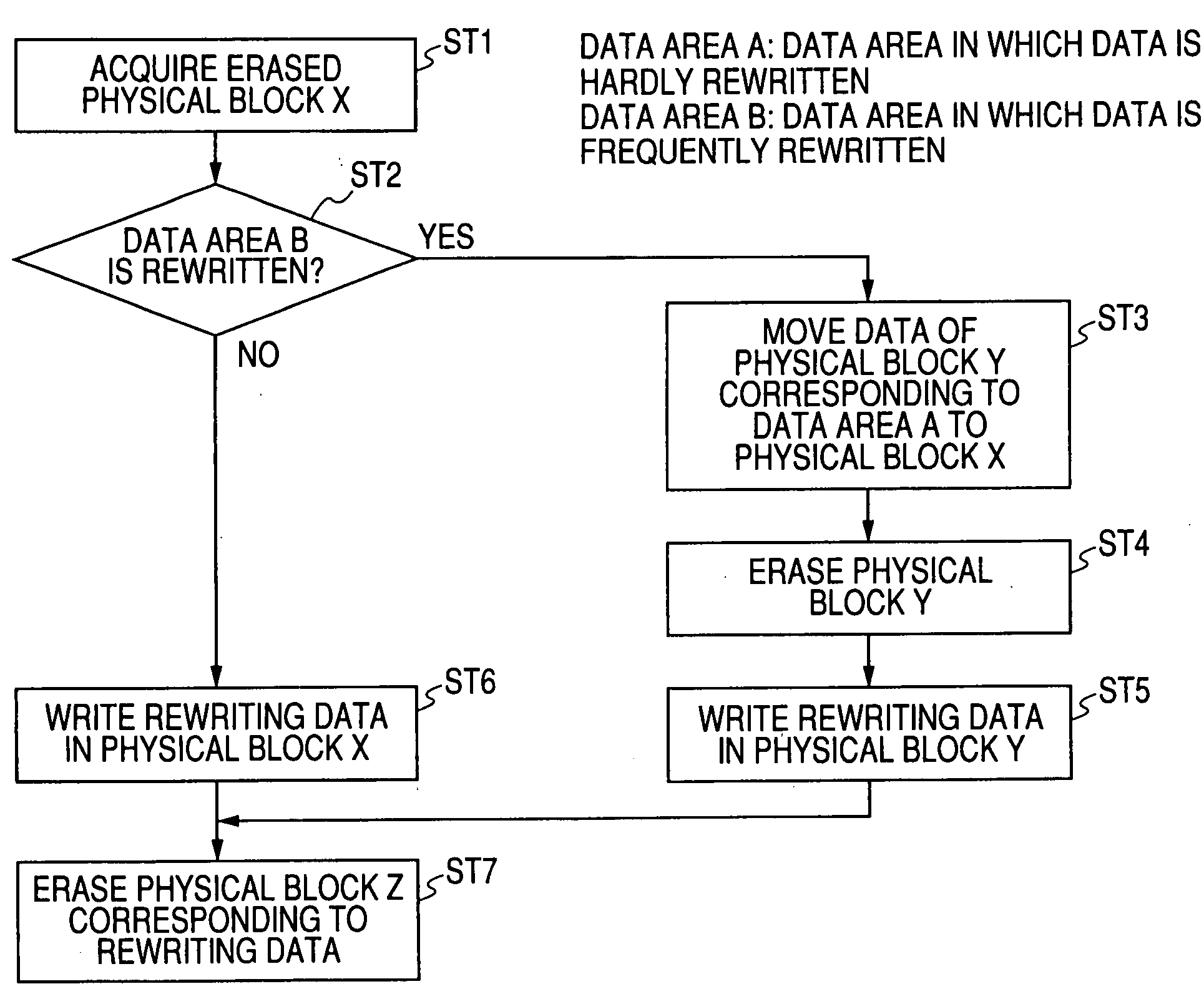

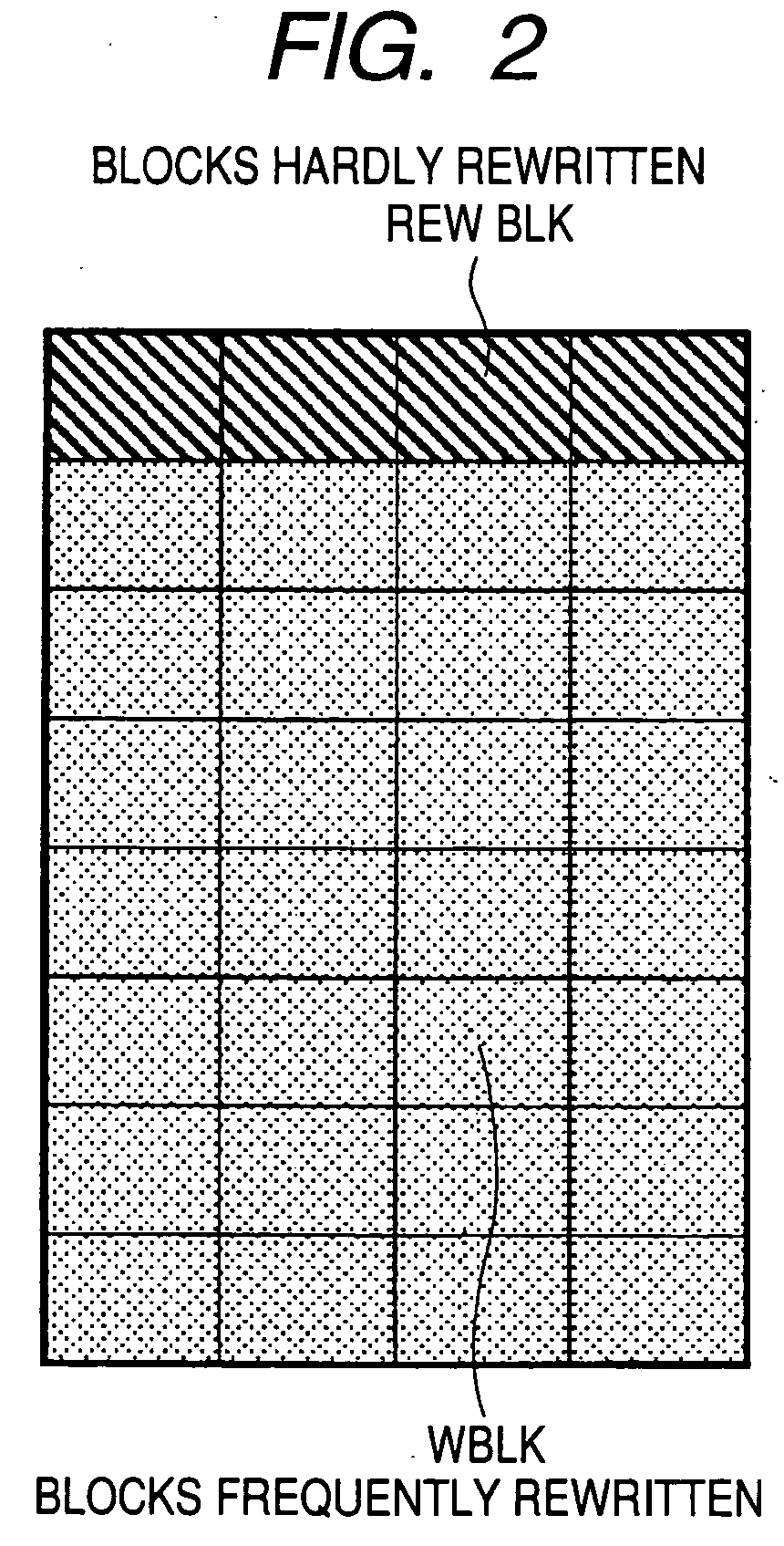

Memory system

ActiveUS20070103992A1Extend effective lifeEasy to controlMemory architecture accessing/allocationRead-only memoriesLogical block addressingSemiconductor storage devices

A memory system including a nonvolatile semiconductor storage device includes: a nonvolatile memory unit that includes a first data area in which data is frequently rewritten and a second data area in which data is hardly rewritten; and a control unit. The control unit sequentially selects logical block addresses in the second data area in which data is hardly rewritten and updates physical block addresses at new rewriting destinations in the first data area in which data is frequently rewritten to physical block addresses corresponding to the logical block addresses selected.

Owner:SONY CORP

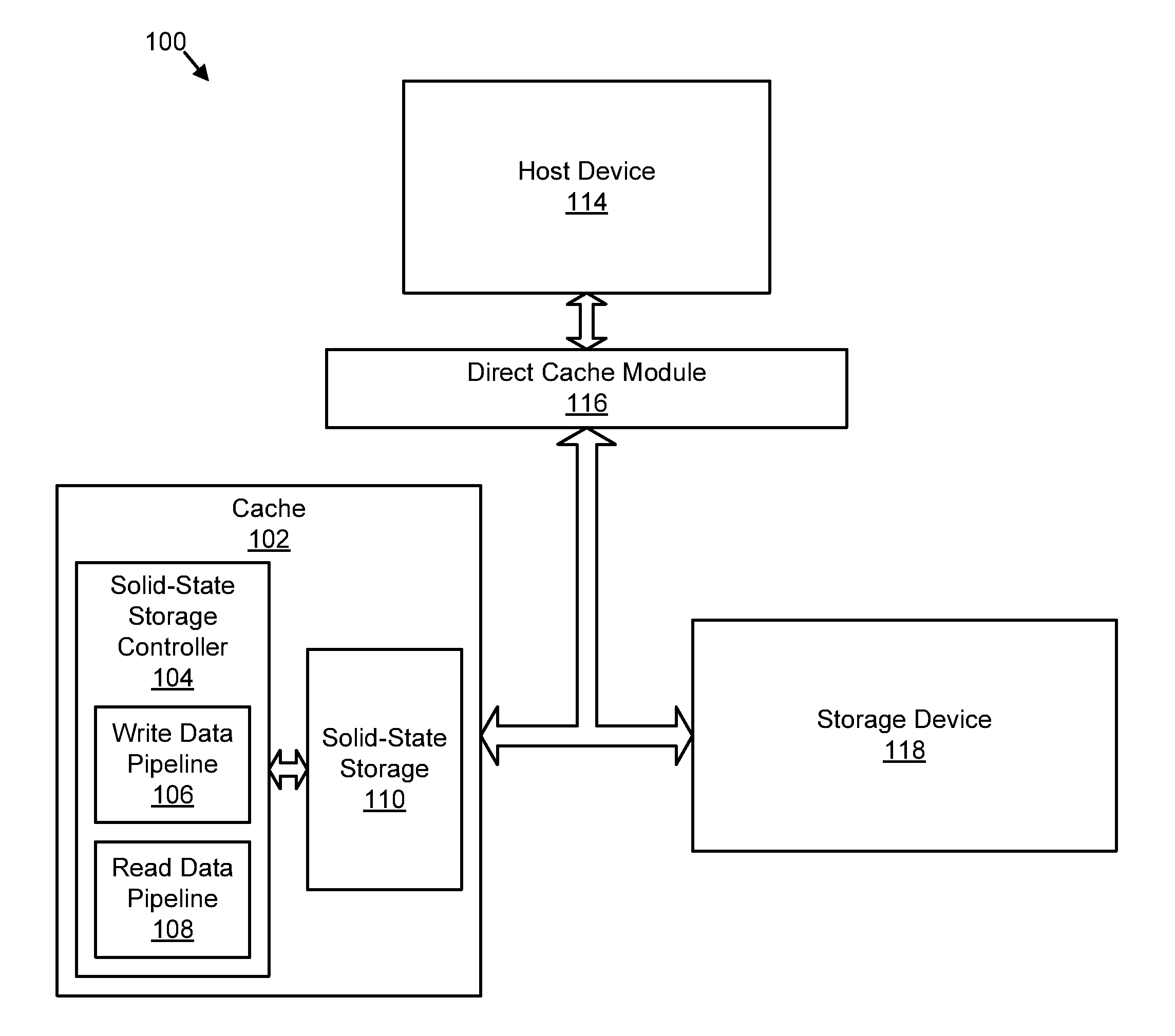

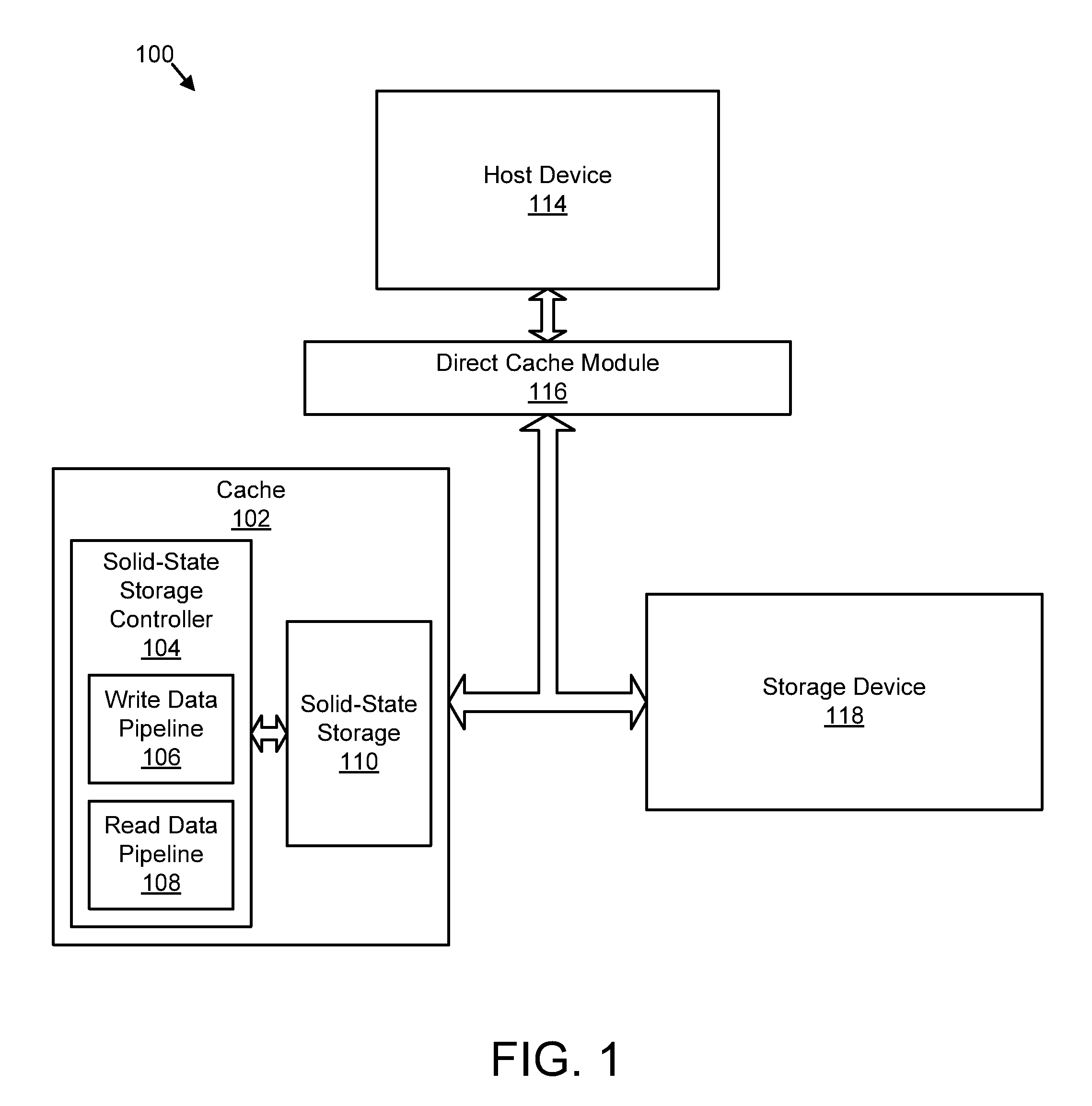

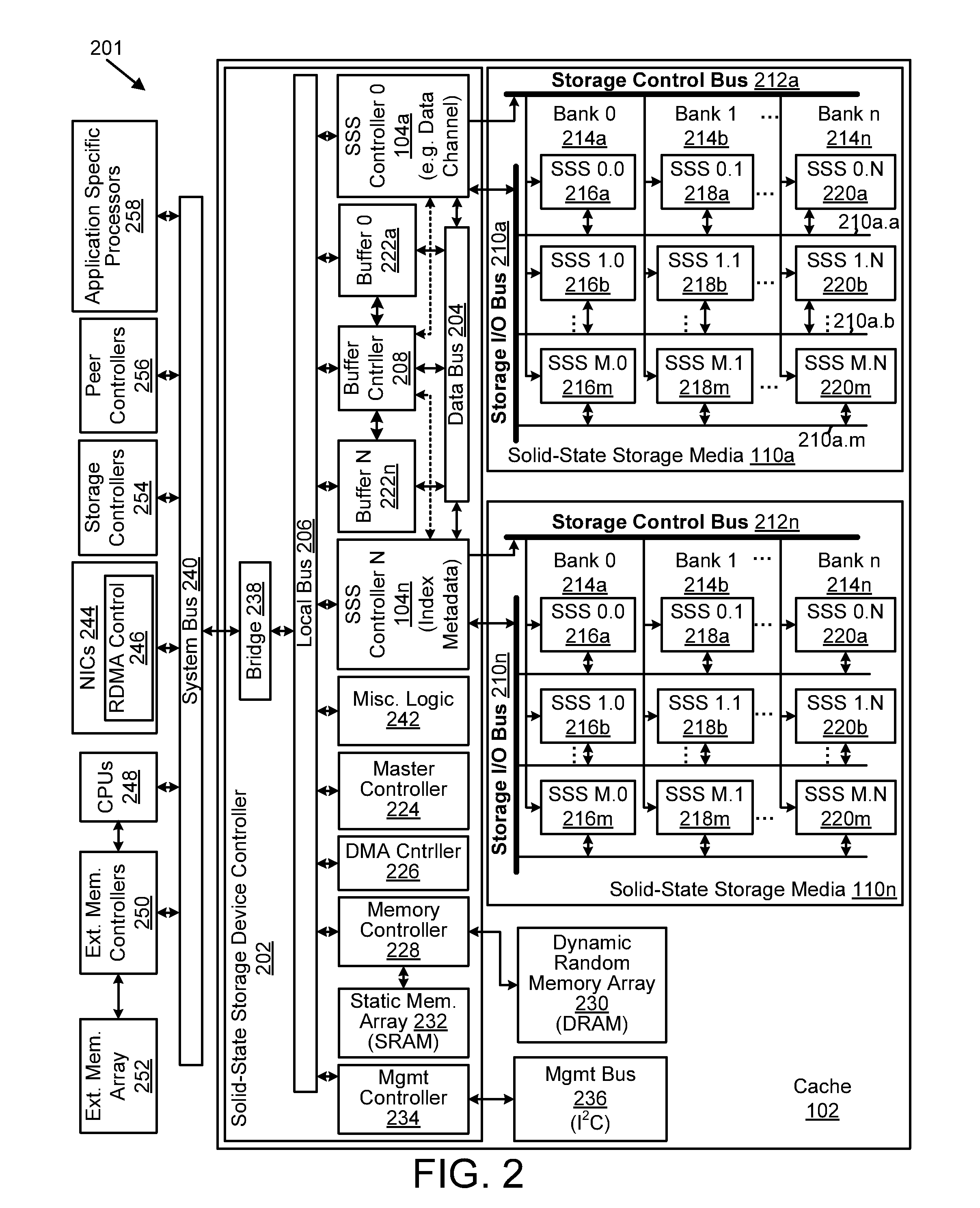

Apparatus, system, and method for caching data

ActiveUS20120210041A1Effective cachingMinimize cache collisionMemory architecture accessing/allocationServersSolid-state storageLogical block addressing

An apparatus, system, and method are disclosed for caching data. A storage request module detects an input / output (“I / O”) request for a storage device cached by solid-state storage media of a cache. A direct mapping module references a single mapping structure to determine that the cache comprises data of the I / O request. The single mapping structure maps each logical block address of the storage device directly to a logical block address of the cache. The single mapping structure maintains a fully associative relationship between logical block addresses of the storage device and physical storage addresses on the solid-state storage media. A cache fulfillment module satisfies the I / O request using the cache in response to the direct mapping module determining that the cache comprises at least one data block of the I / O request.

Owner:SANDISK TECH LLC

Range-based cache control system and method

InactiveUS6880043B1Memory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingControl system

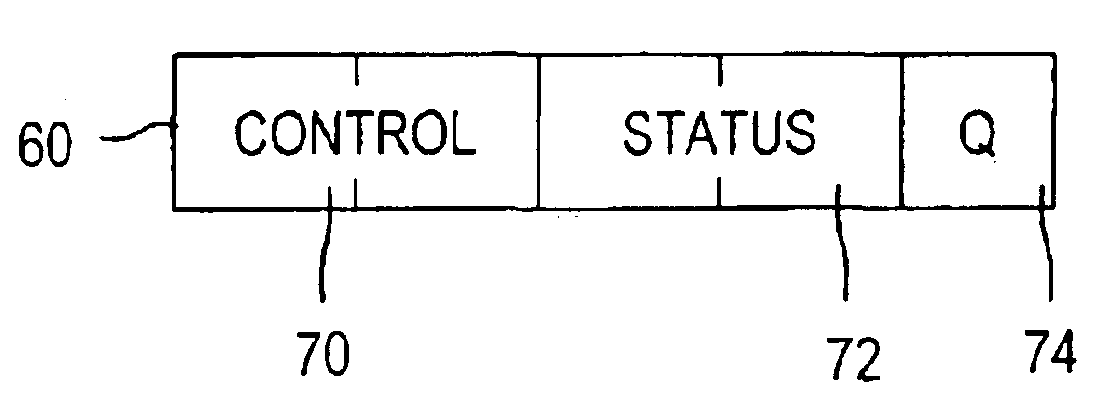

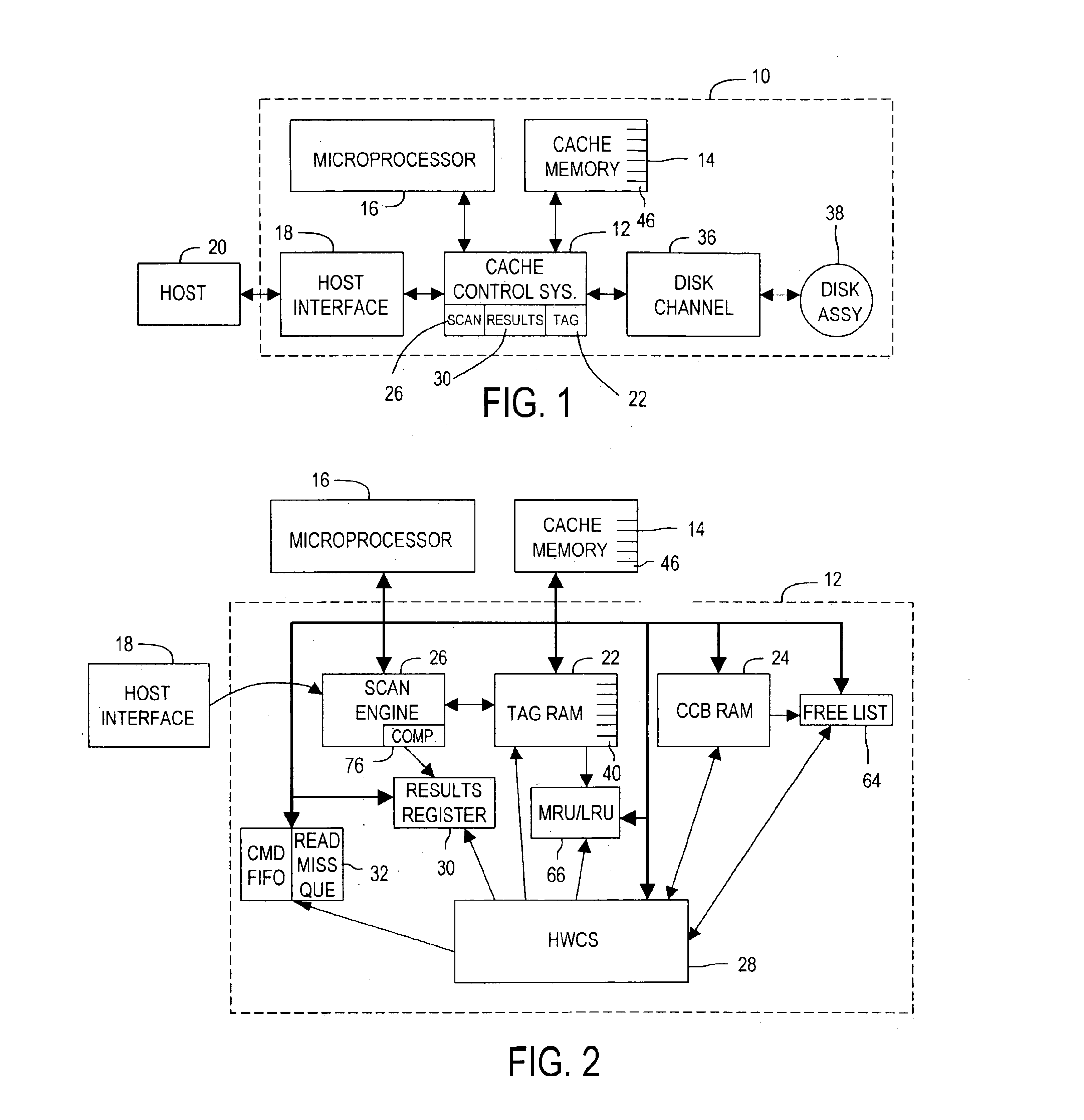

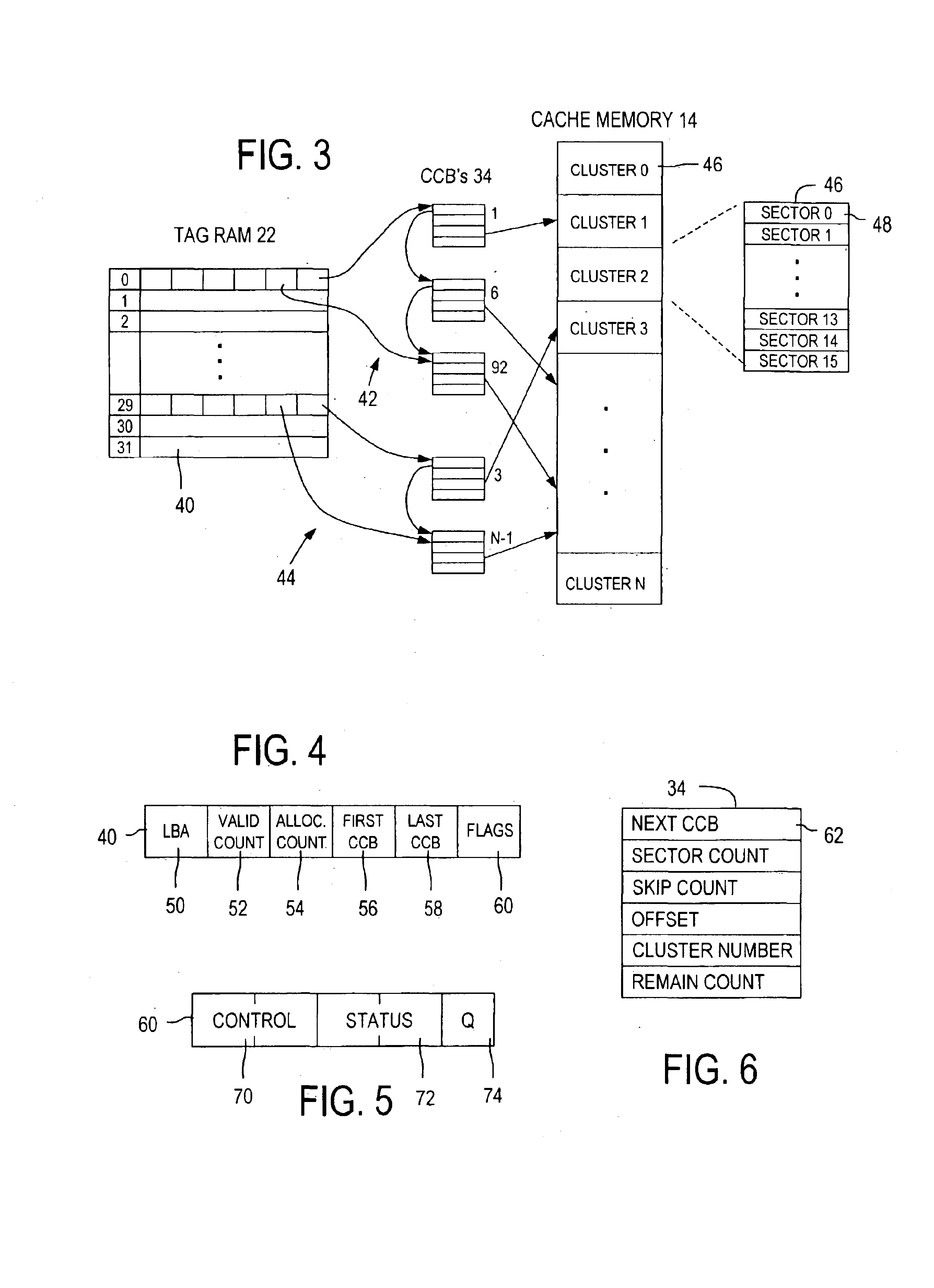

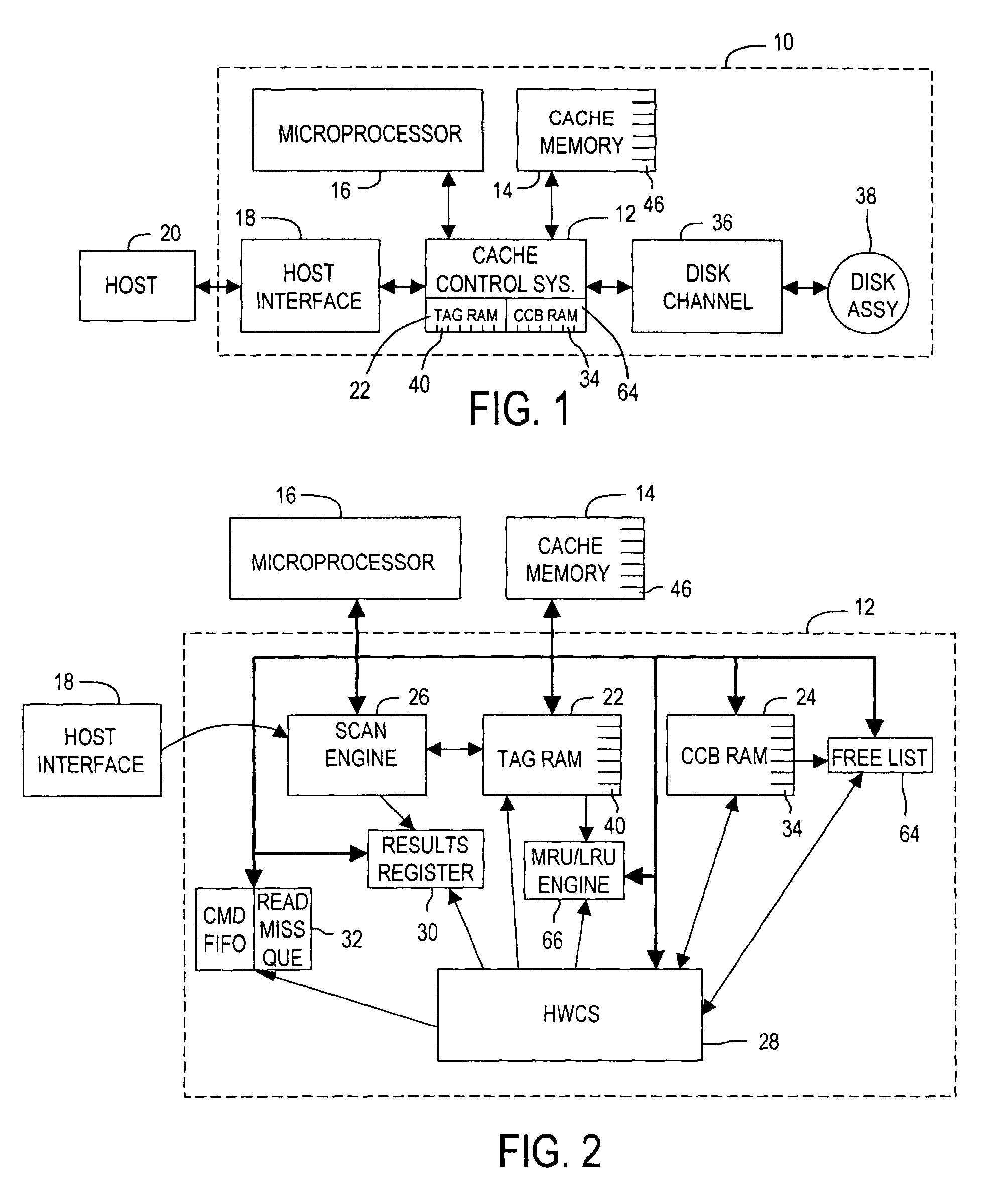

The present invention relates to disk drive having a cache control system that generates scan results that permit response to a host command using existing cached data having a logical block address (LBA) range that overlaps a host command LBA range. The cache control system forms variable length segments of memory clusters in a cache memory for caching disk data in contiguous LBA ranges. The cached LBA ranges are scanned for segments having LBA ranges overlapping with an LBA range of a host command. The cache control system is effective in exploiting any existing overlapping cache data.

Owner:WESTERN DIGITAL TECH INC

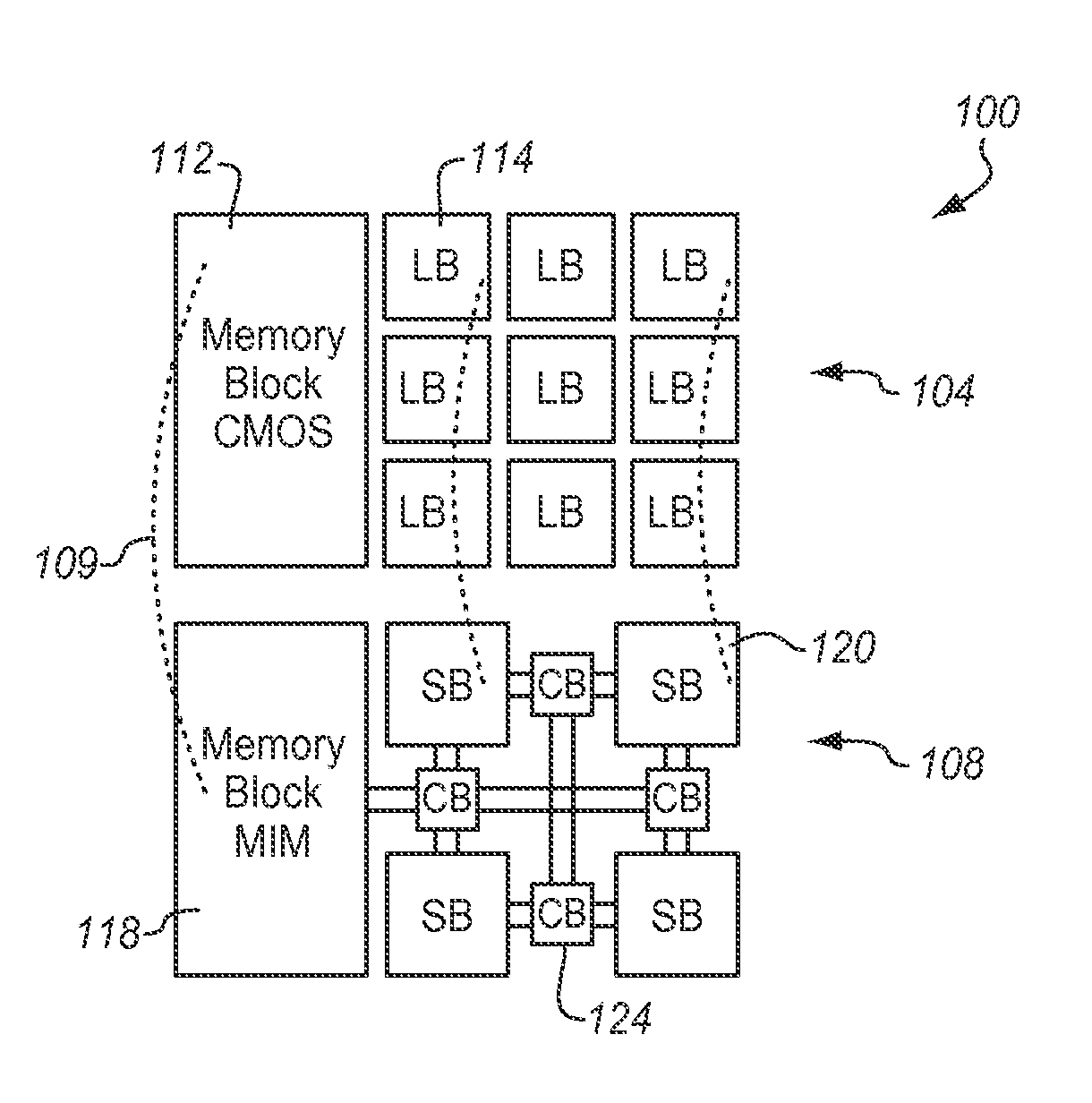

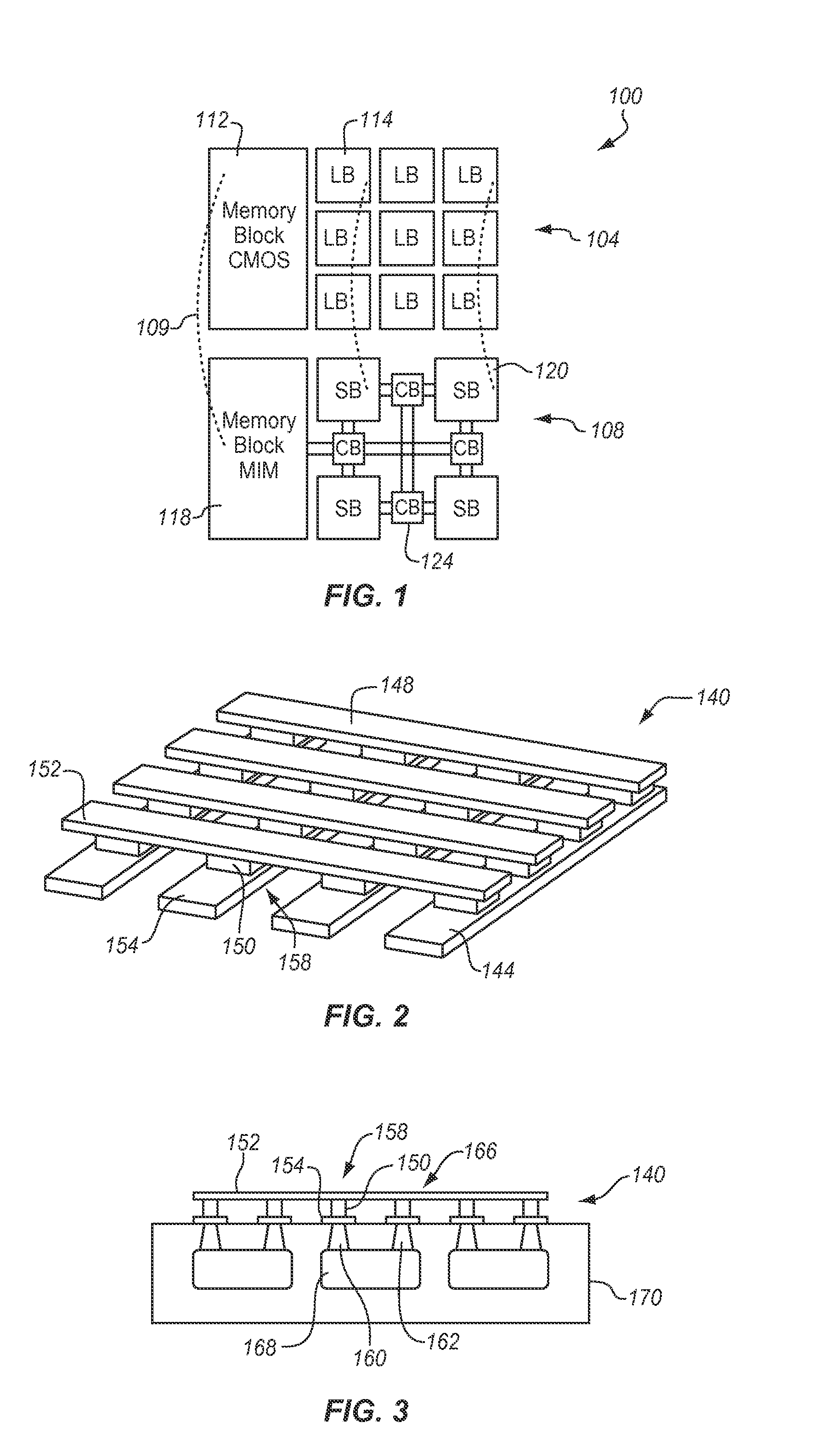

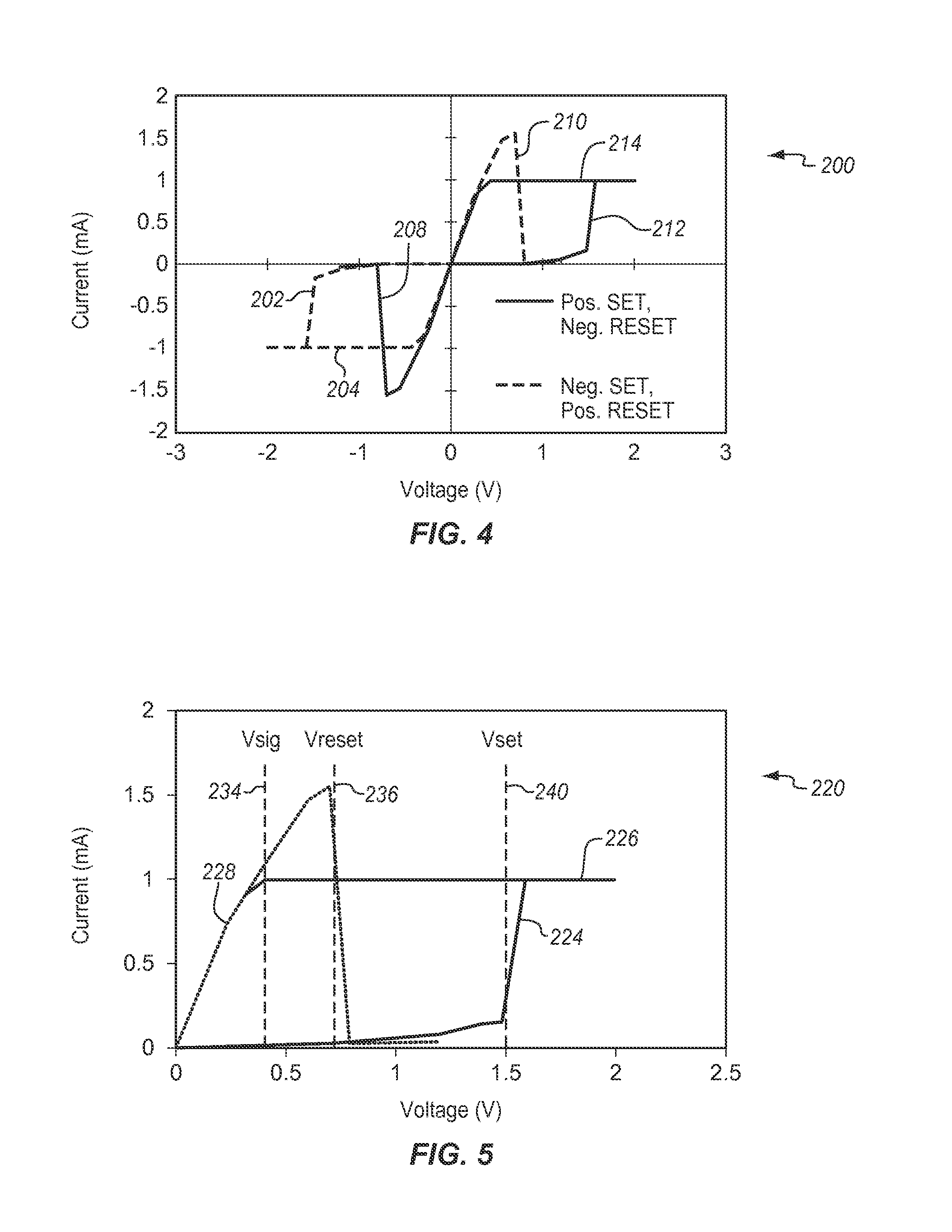

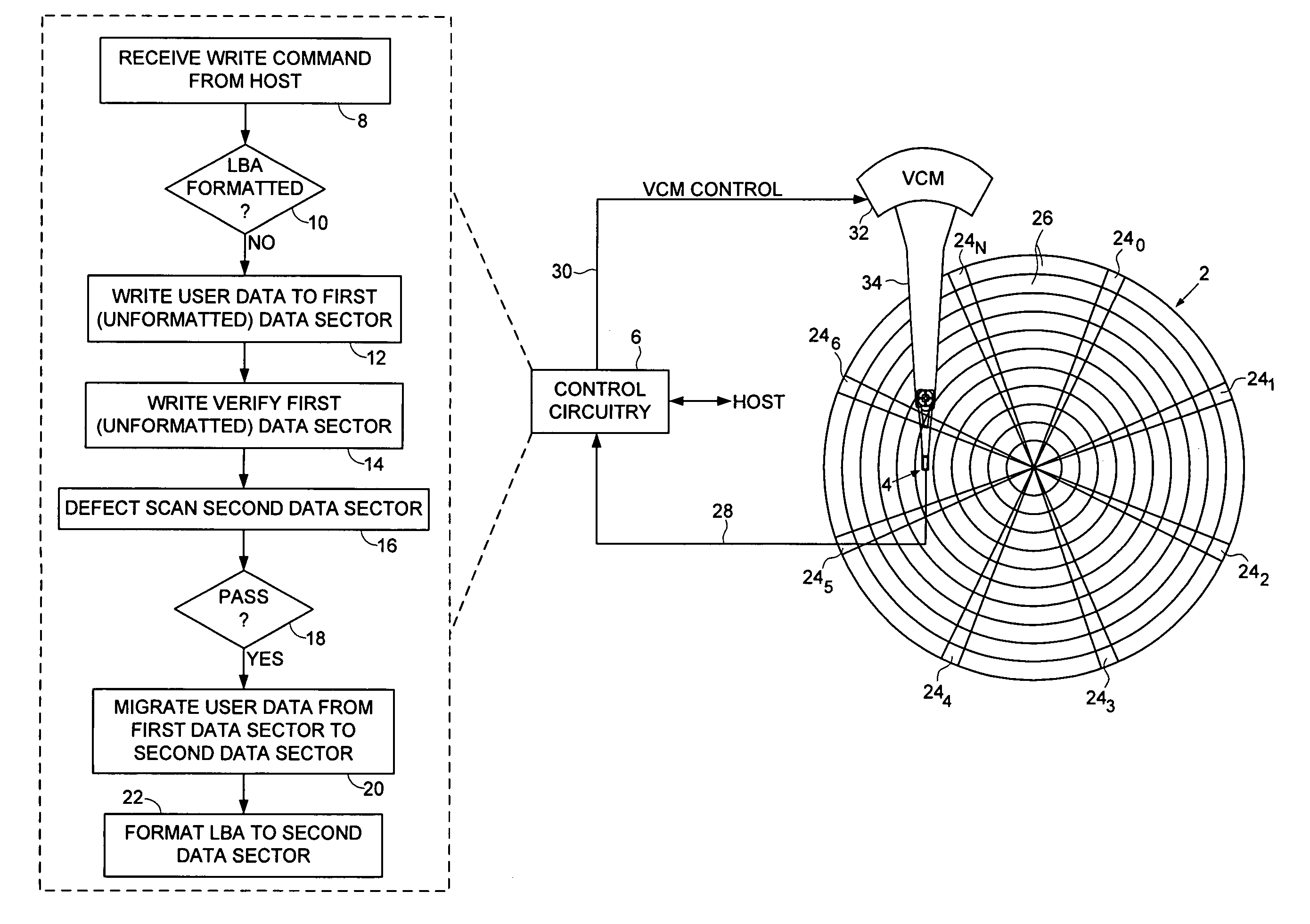

RE-PROGRAMMABLE ANTIFUSE FPGA UTILIZING RESISTIVE CeRAM ELEMENTS

ActiveUS20130285699A1Solid-state devicesRead-only memoriesElectrical resistance and conductanceResistive switching

A re-programmable antifuse field programmable gate array (FPGA) integrated circuit, the FPGA comprising: a plurality of CeRAM resistive switching elements forming a connection block, the switching elements capable of being switched from a conductive (ON) state to a non-conductive (OFF) state and back to a conductive (ON) state; a plurality of logic elements forming a logic block; and a programming circuit for turning the CeRAM switching elements OFF and ON to connect the logic elements to form the FPGA.

Owner:SYMETRIX MEMORY

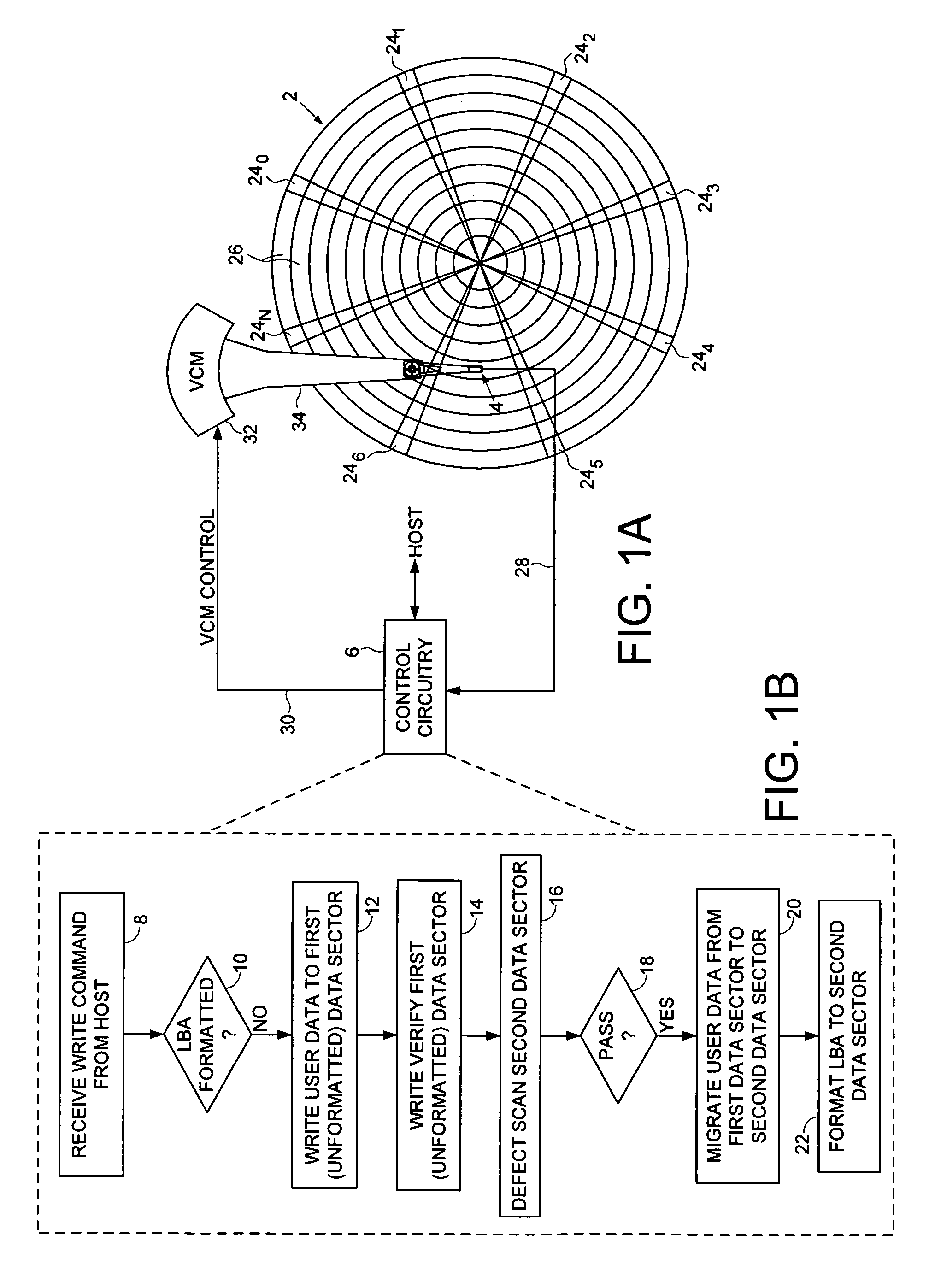

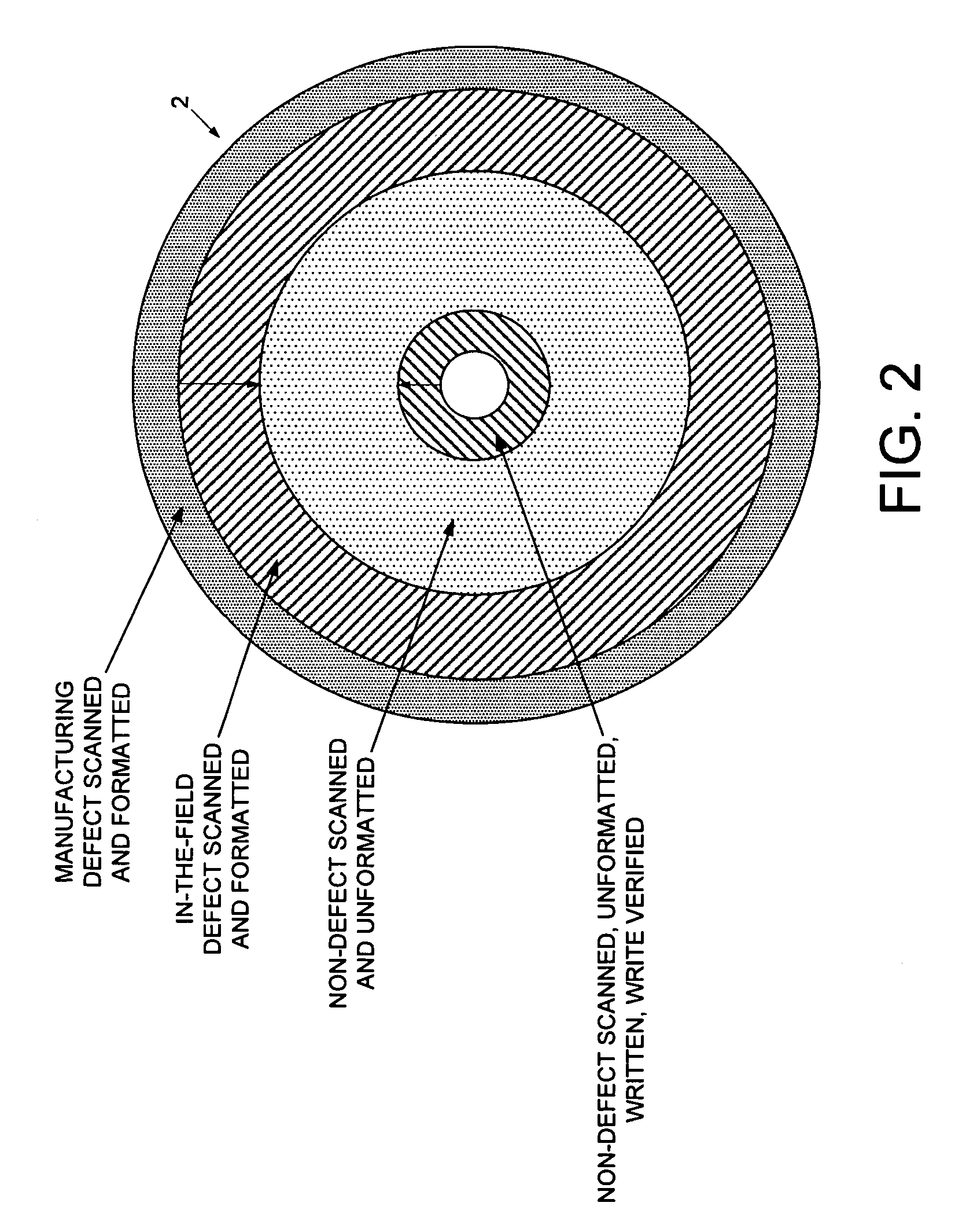

Disk drive write verifying unformatted data sectors

InactiveUS8004785B1Disc-shaped record carriersCopying/moving digital dataLogical block addressingPhysical address

Owner:WESTERN DIGITAL TECH INC

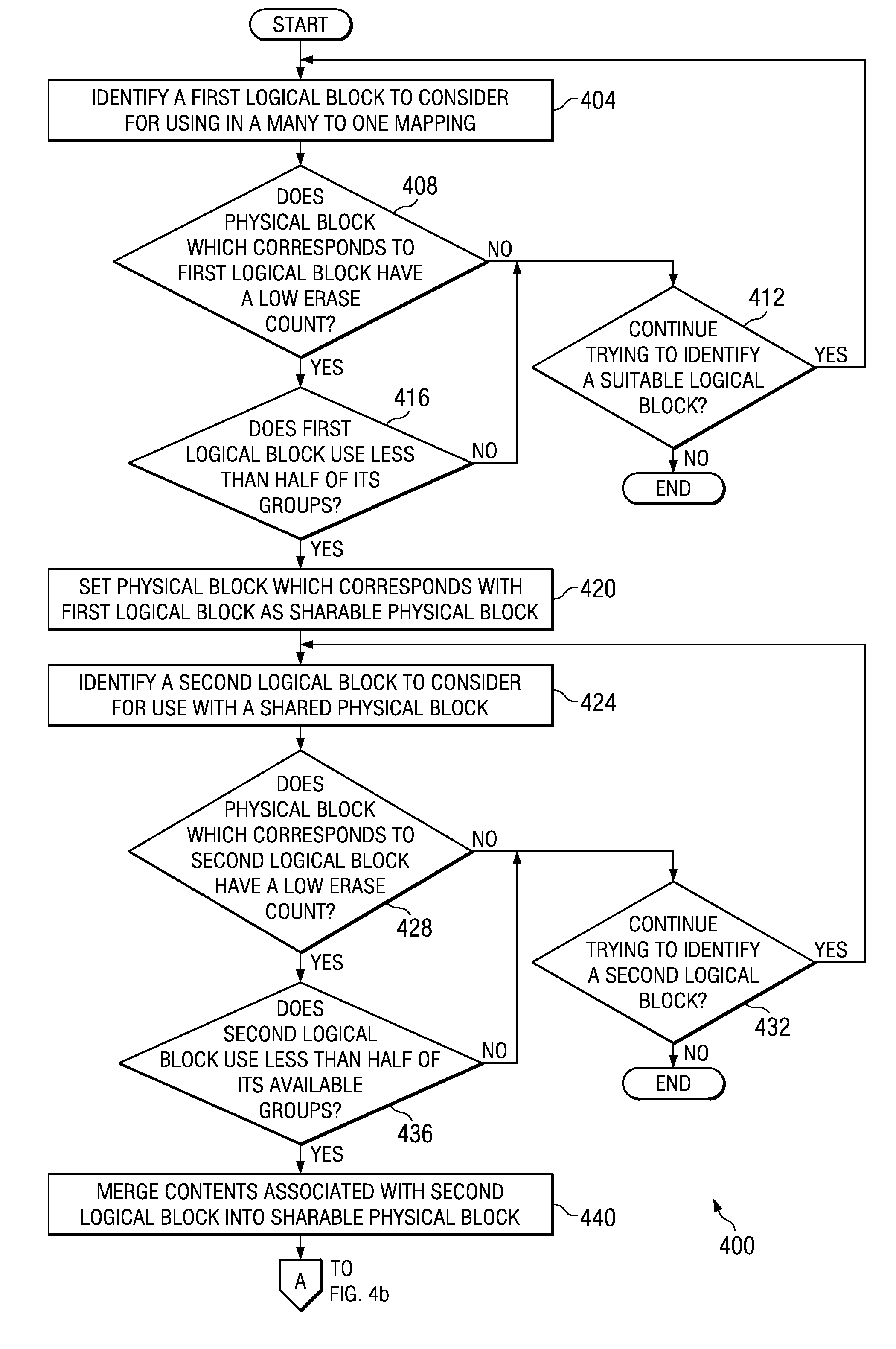

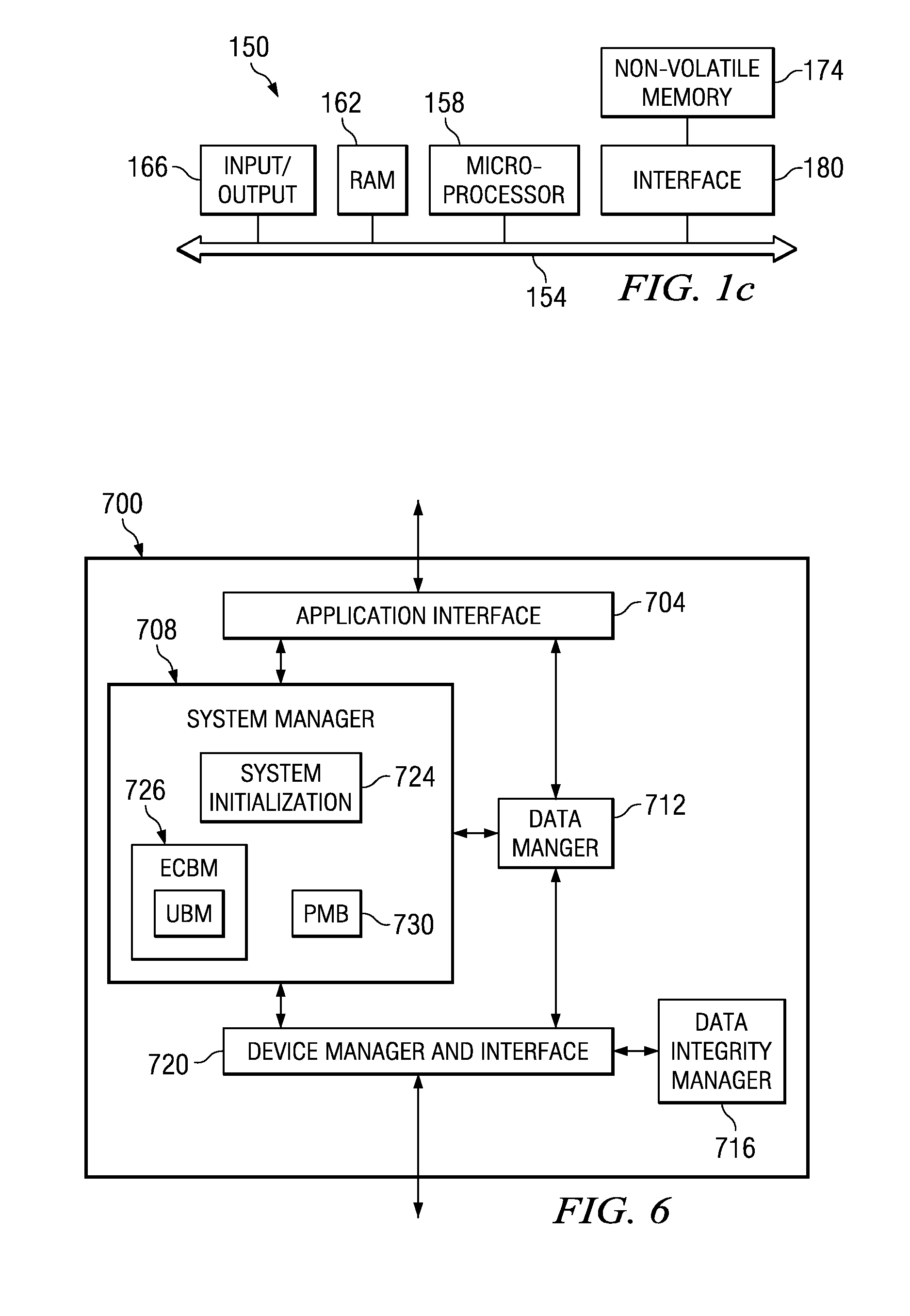

Hybrid Mapping Implementation Within a Non-Volatile Memory System

ActiveUS20070150694A1Extend system lifePerformanceMemory adressing/allocation/relocationStatic storageMemory systemsNon-volatile memory

Methods and apparatus for allow different mapping implementations, including a many-to-one logical to physical block mapping, to be used within a memory system are disclosed. According to one aspect of the present invention, a method for mapping a plurality of logical blocks to a physical block includes identifying a first logical block meets at least one criterion. The method also includes identifying a second logical block which is substantially complementary to the first logical block, and providing contents associated with the first logical block and contents associated with the second logical block to the physical block.

Owner:SANDISK TECH LLC

Cluster-based cache memory allocation

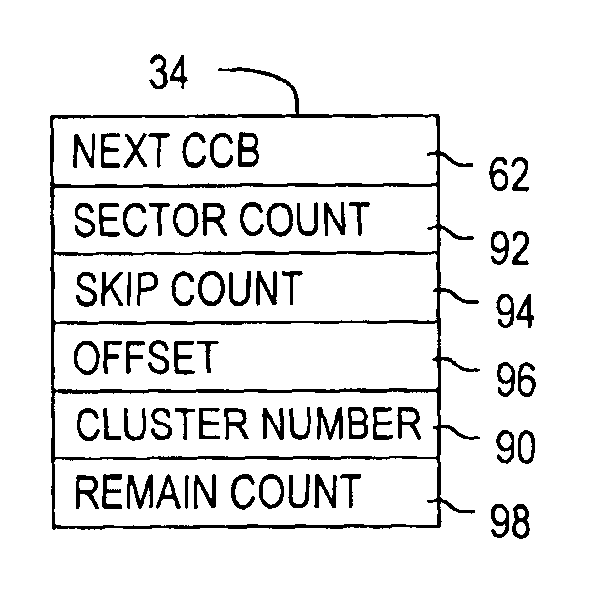

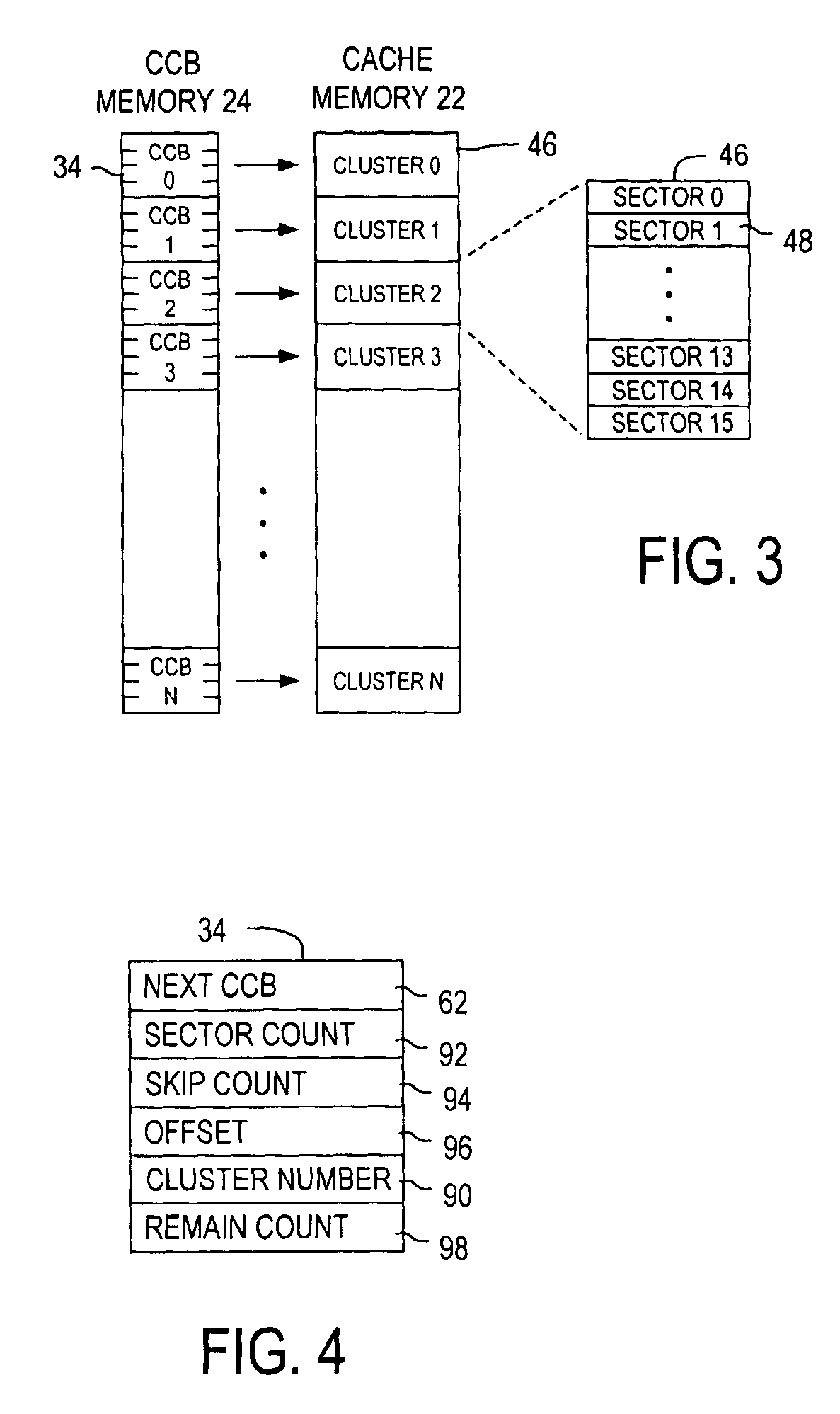

InactiveUS6996669B1Uniform sizeIncrease the lengthMemory architecture accessing/allocationMemory adressing/allocation/relocationLogical block addressingControl system

The present invention relates to a disk drive including a cache memory having a plurality of sequentially-ordered memory clusters for caching disk data stored in sectors (not shown) on disks of a disk assembly. The disk sectors are identified by logical block addresses (LBAs). A cache control system of the disk drive comprises a cluster control block memory, having a plurality of cluster control blocks (CCB), and a tag memory 22, having a plurality of tag records, that are embedded within the cache control system. Each CCB includes a cluster segment record with an entry for associating the CCB with a particular memory cluster and for forming variable length segments of the memory clusters without regard to the sequential order of the memory clusters. Each tag record assigns a segment to a continuous range of LBAs and defines the CCBs forming the segment. Each segment of the memory clusters is for caching data from a contiguous range of the logical block addresses. The cache control system efficiently exploits available memory clusters for responding to host commands.

Owner:WESTERN DIGITAL TECH INC

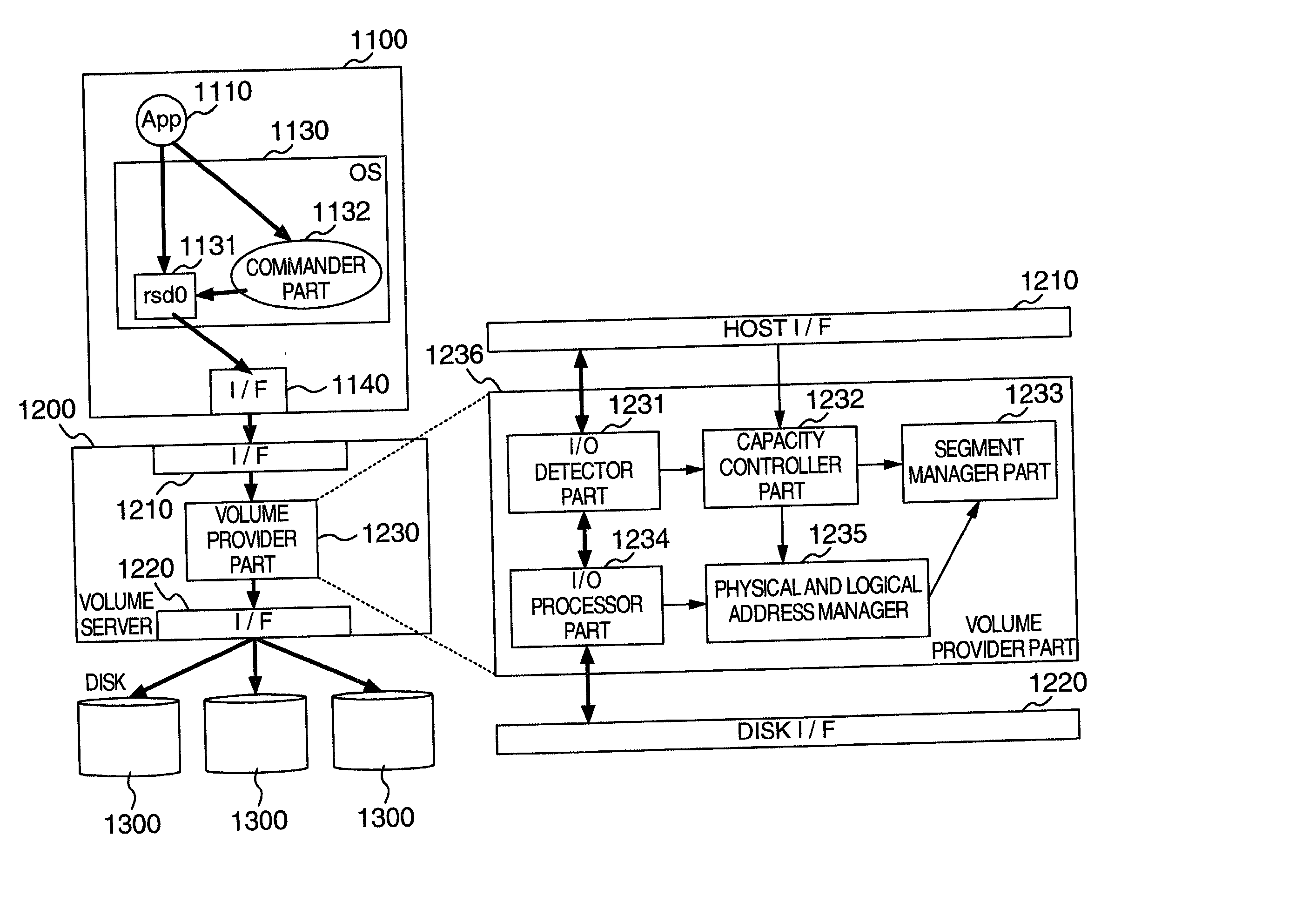

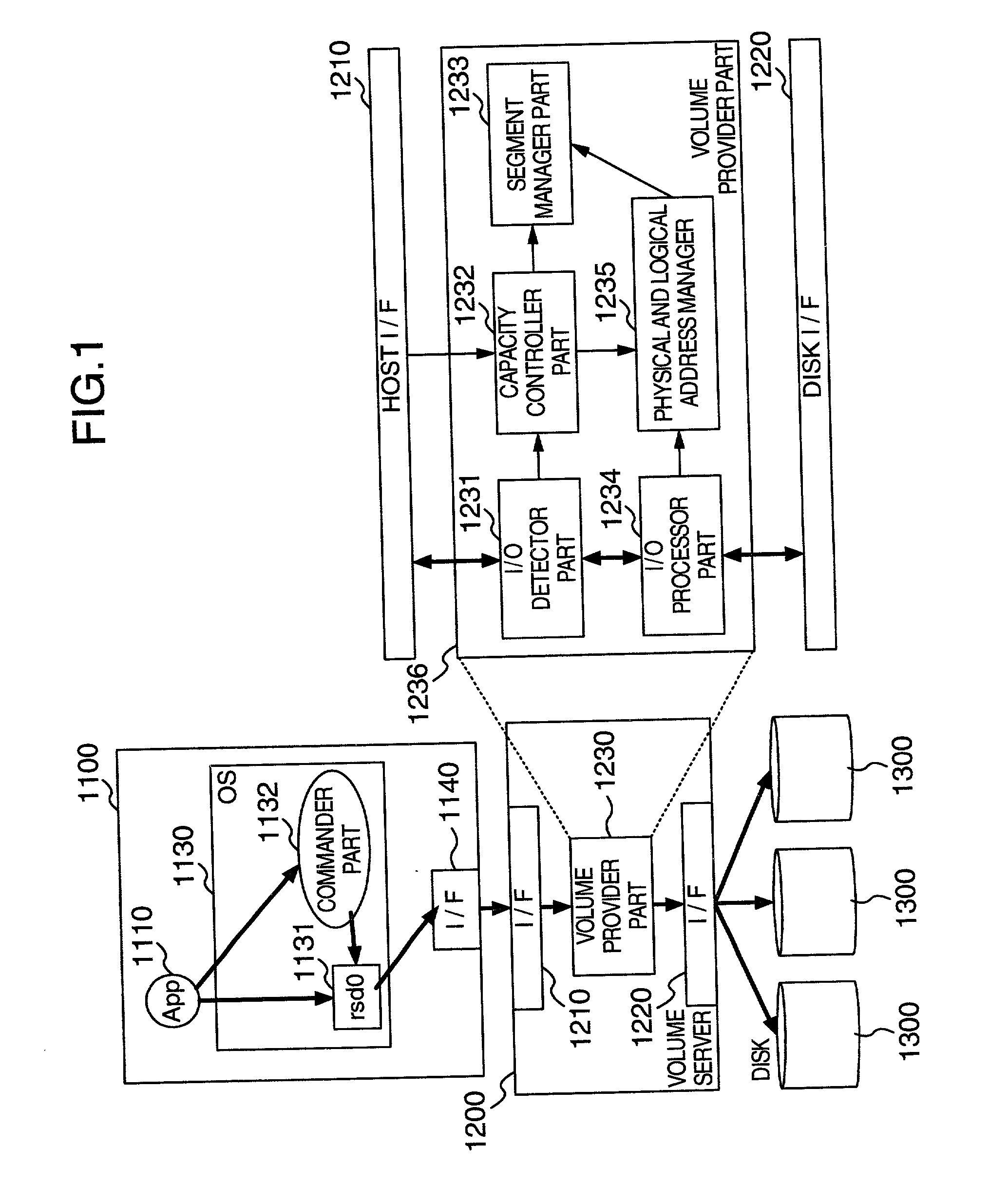

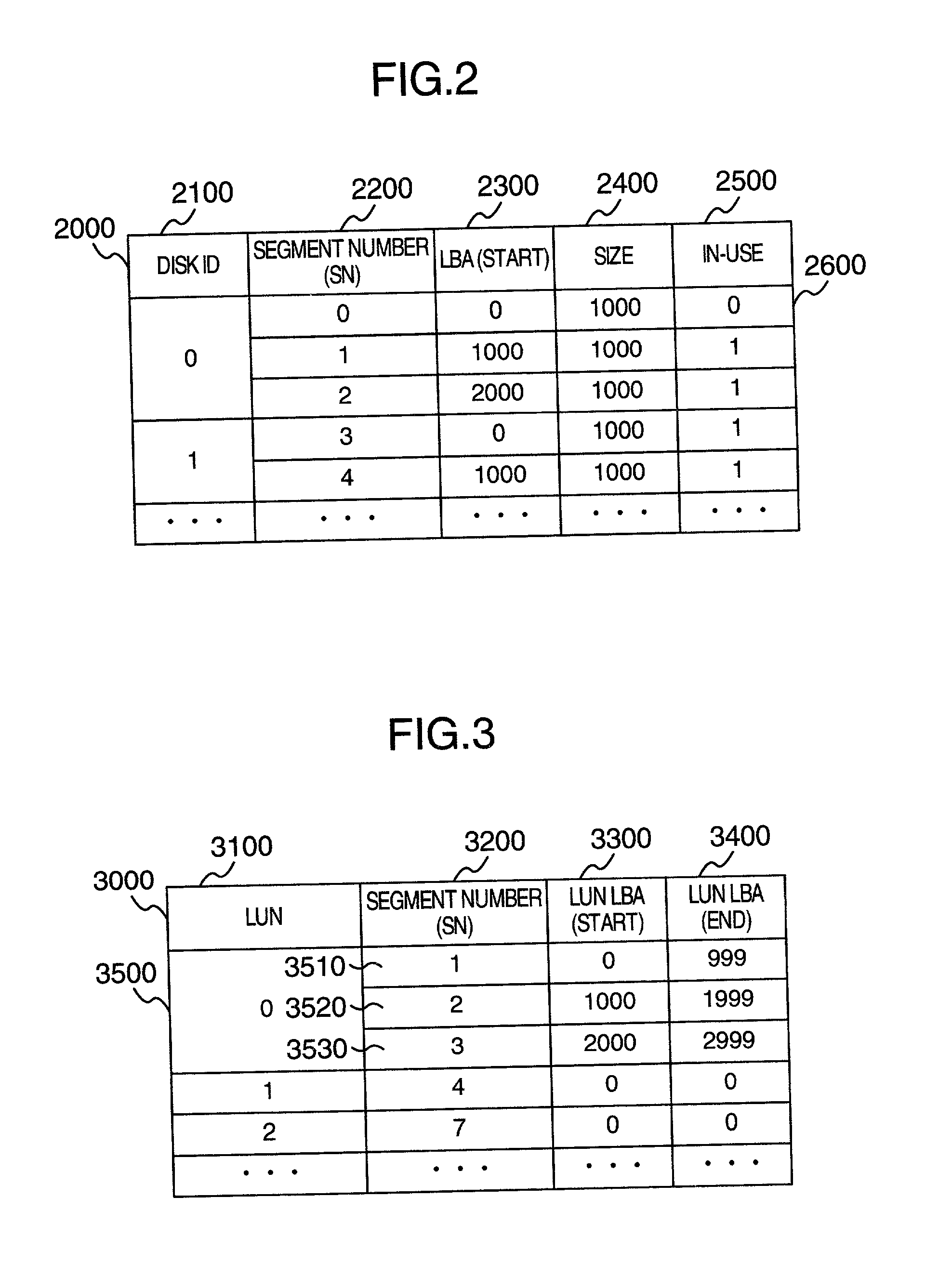

Automated on-line capacity expansion method for storage device

InactiveUS20030009619A1Input/output to record carriersMemory adressing/allocation/relocationLogical block addressingComputerized system

A volume provider unit in a computer system detects a logical block address of a read or write I / O accessing a logical volume of a storage device from a host. According to the logical block address fetched, a storage domain of the logical volume is dynamically expanded. Moreover, the storage domain of the logical volume is reduced or expanded according to an instruction of a logical volume capacity reduction or expansion from a host commander part to a volume server.

Owner:HITACHI LTD