Patents

Literature

1227 results about "Switch matrix" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

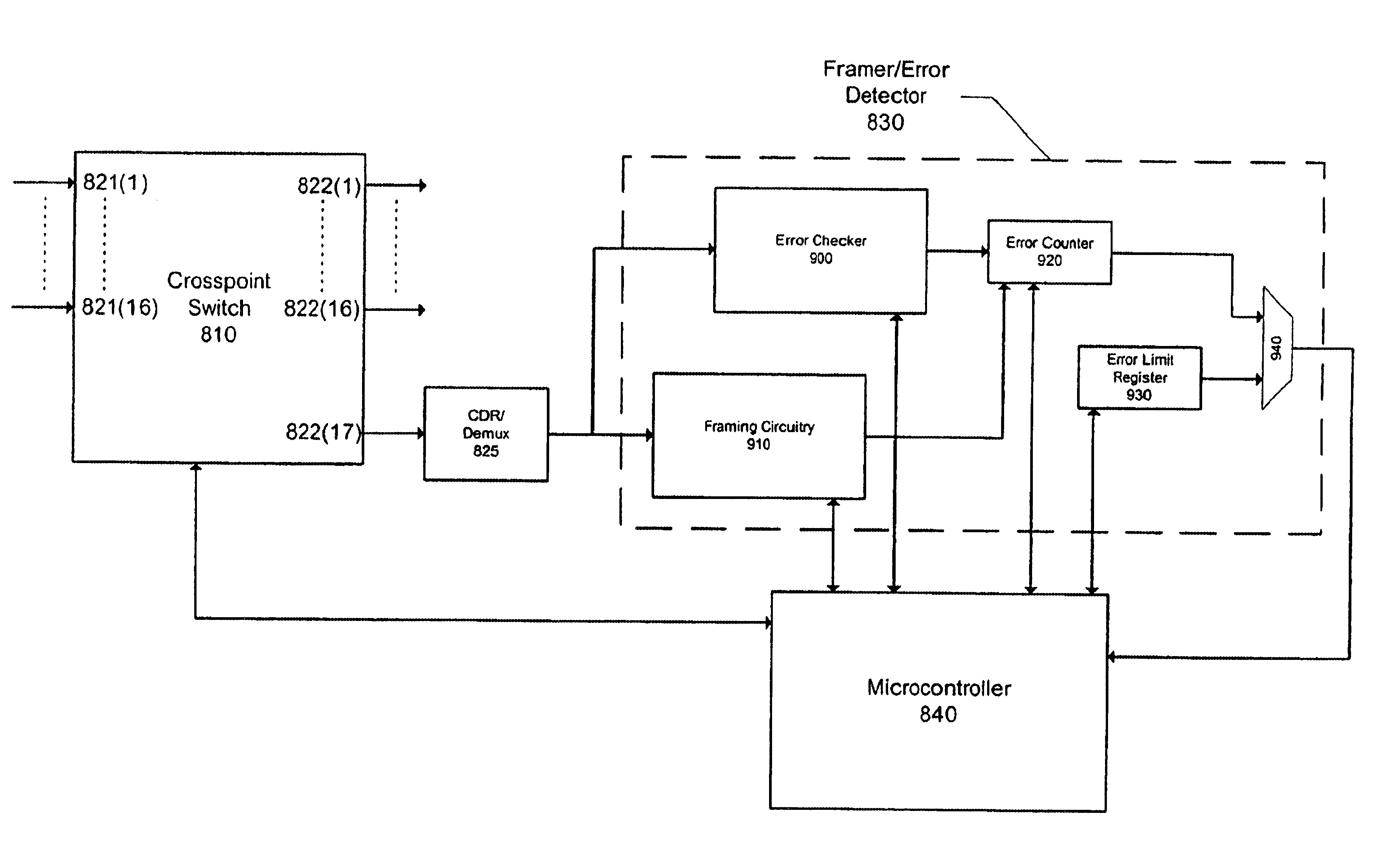

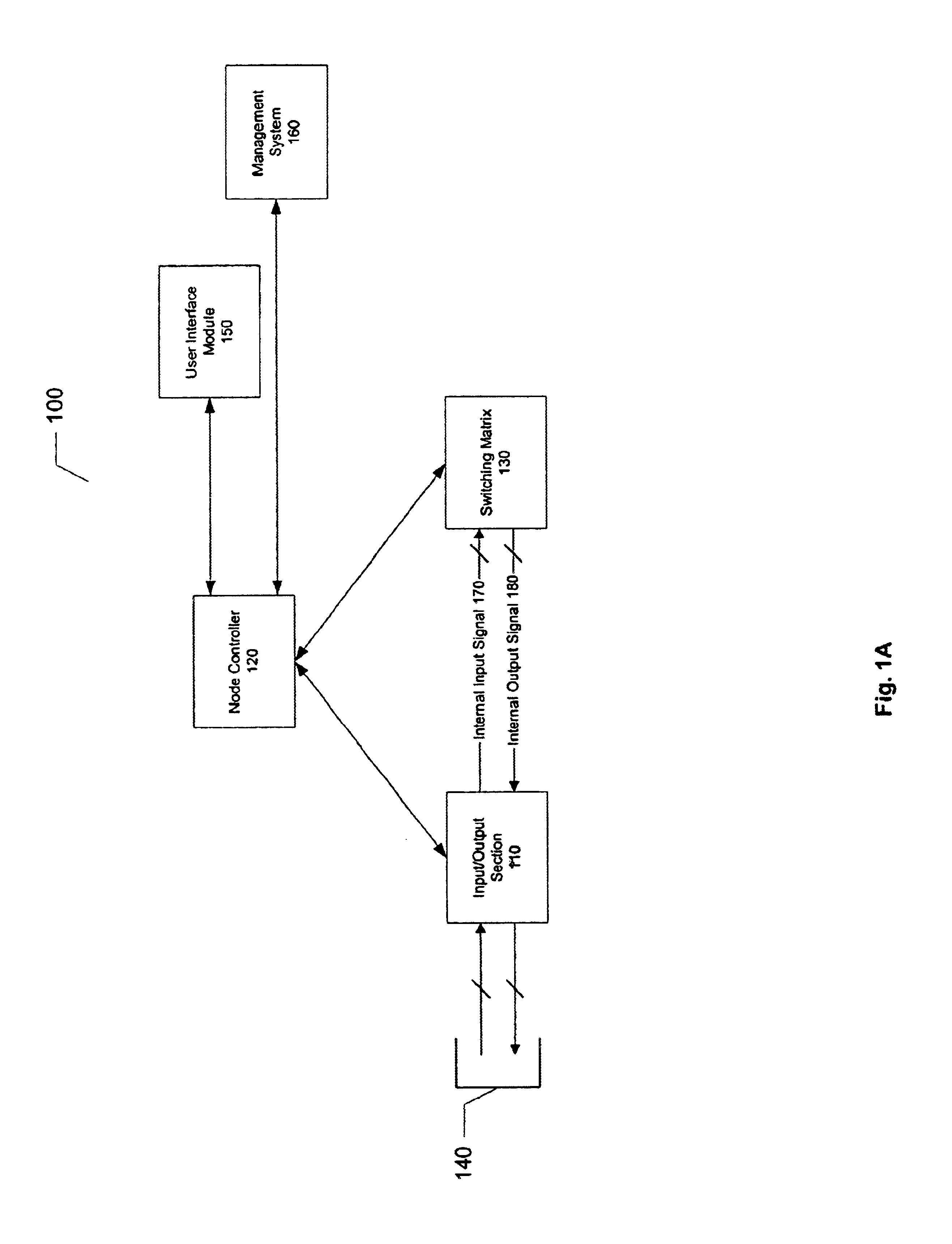

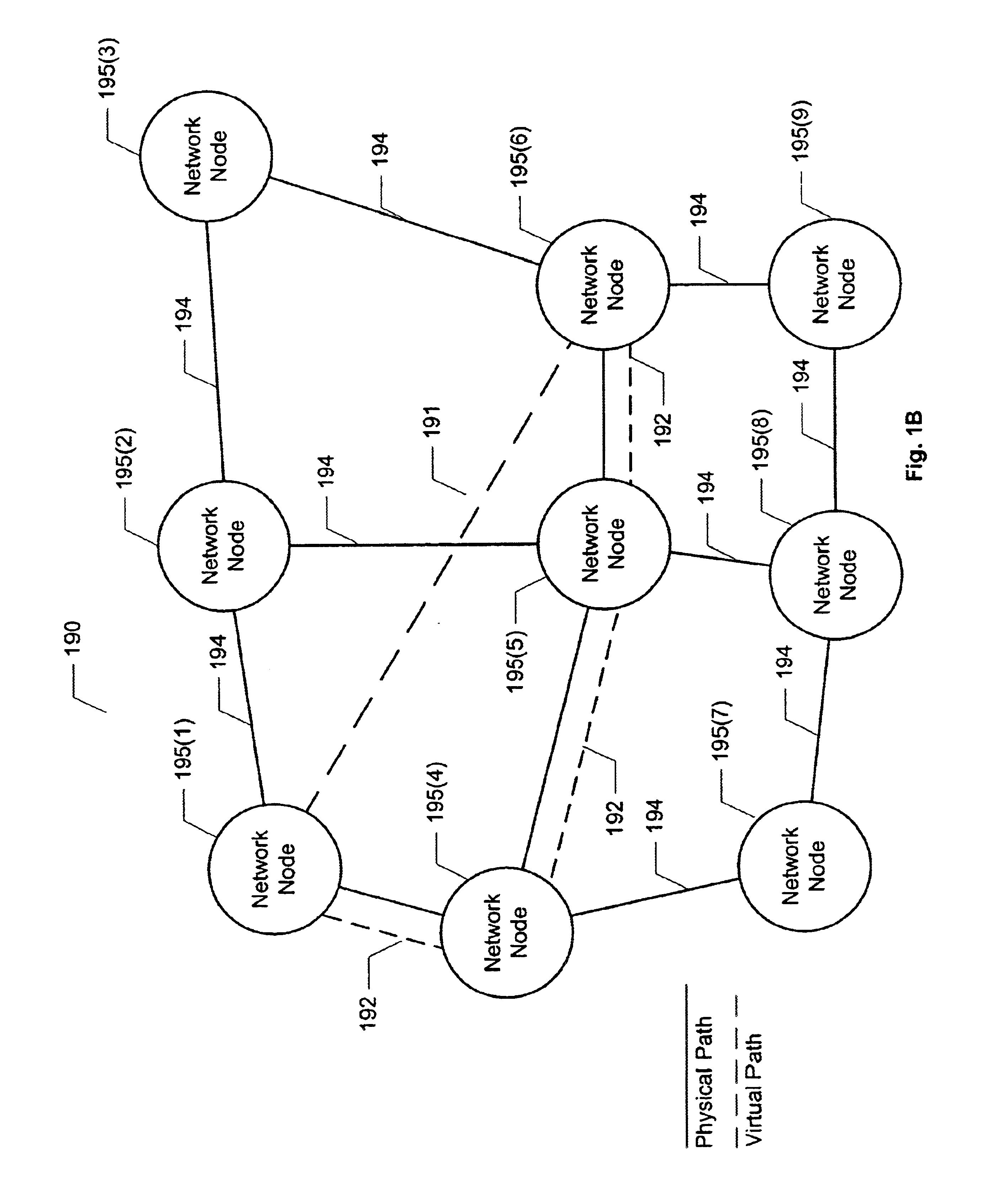

Method and apparatus for isolating faults in a switching matrix

A signal router is described. The signal router includes a switching matrix, an error detector and a controller. The switching matrix includes a first number of inputs and a second number of outputs, and is configured to receive an information stream. The error detector is coupled to one of the second number of outputs, and is configured to generate error information by virtue of being configured to detect errors in the information stream. Likewise, the controller is coupled to the switching matrix and error detector. The controller is configured to select one of the first number of inputs, receive error information from the error detector, and configure the switching matrix to couple the selected input to one of the outputs.

Owner:CISCO TECH INC

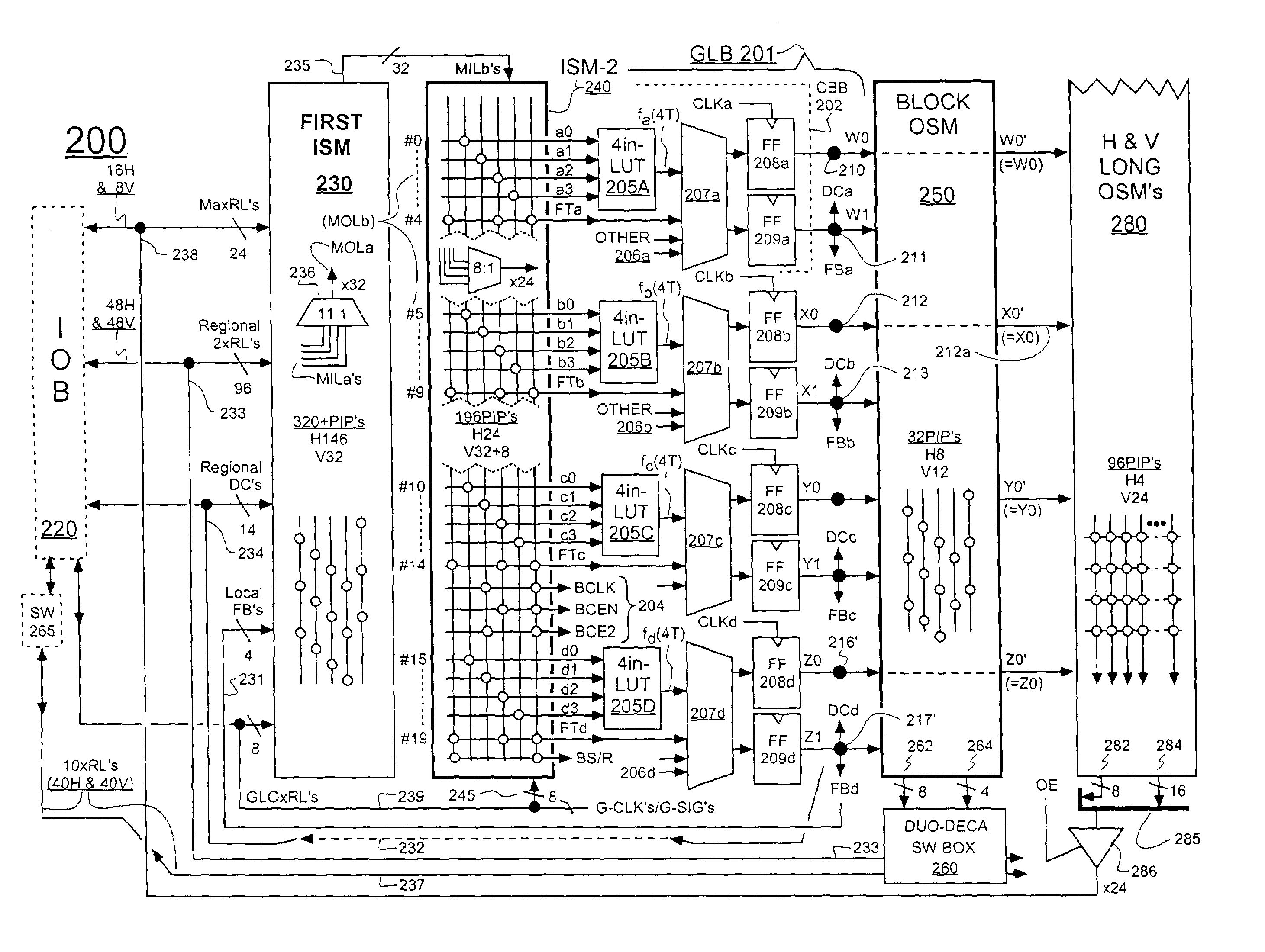

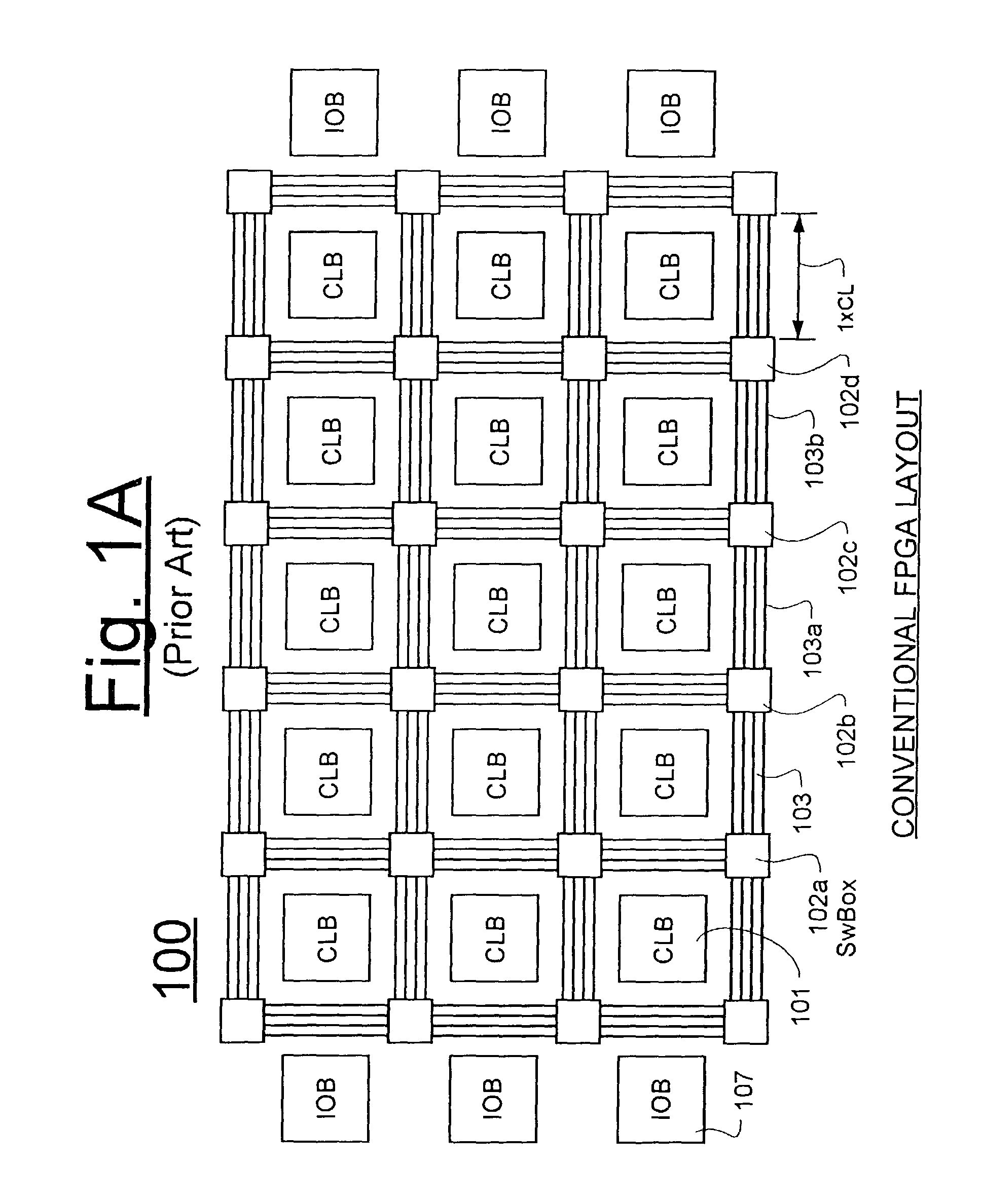

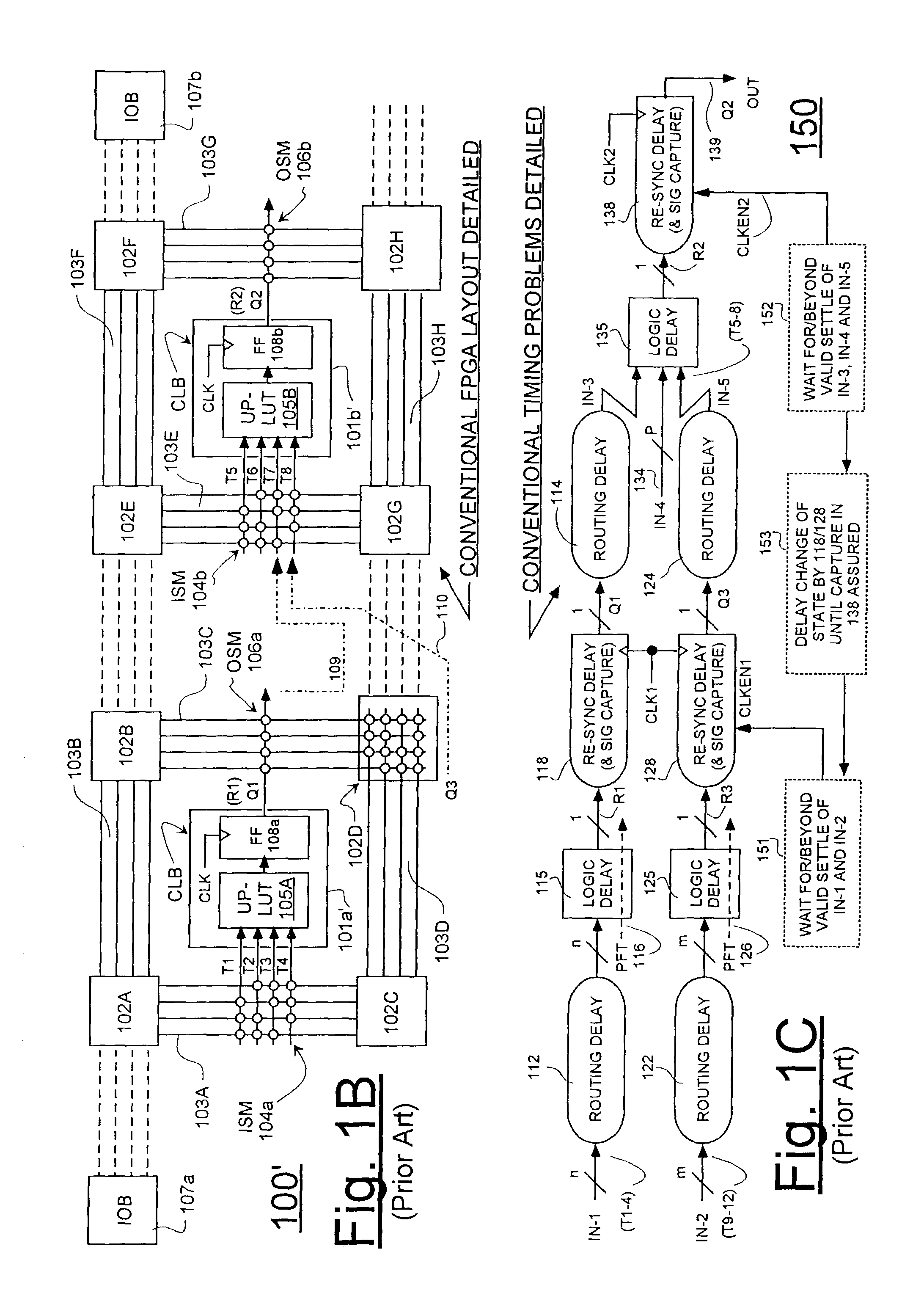

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

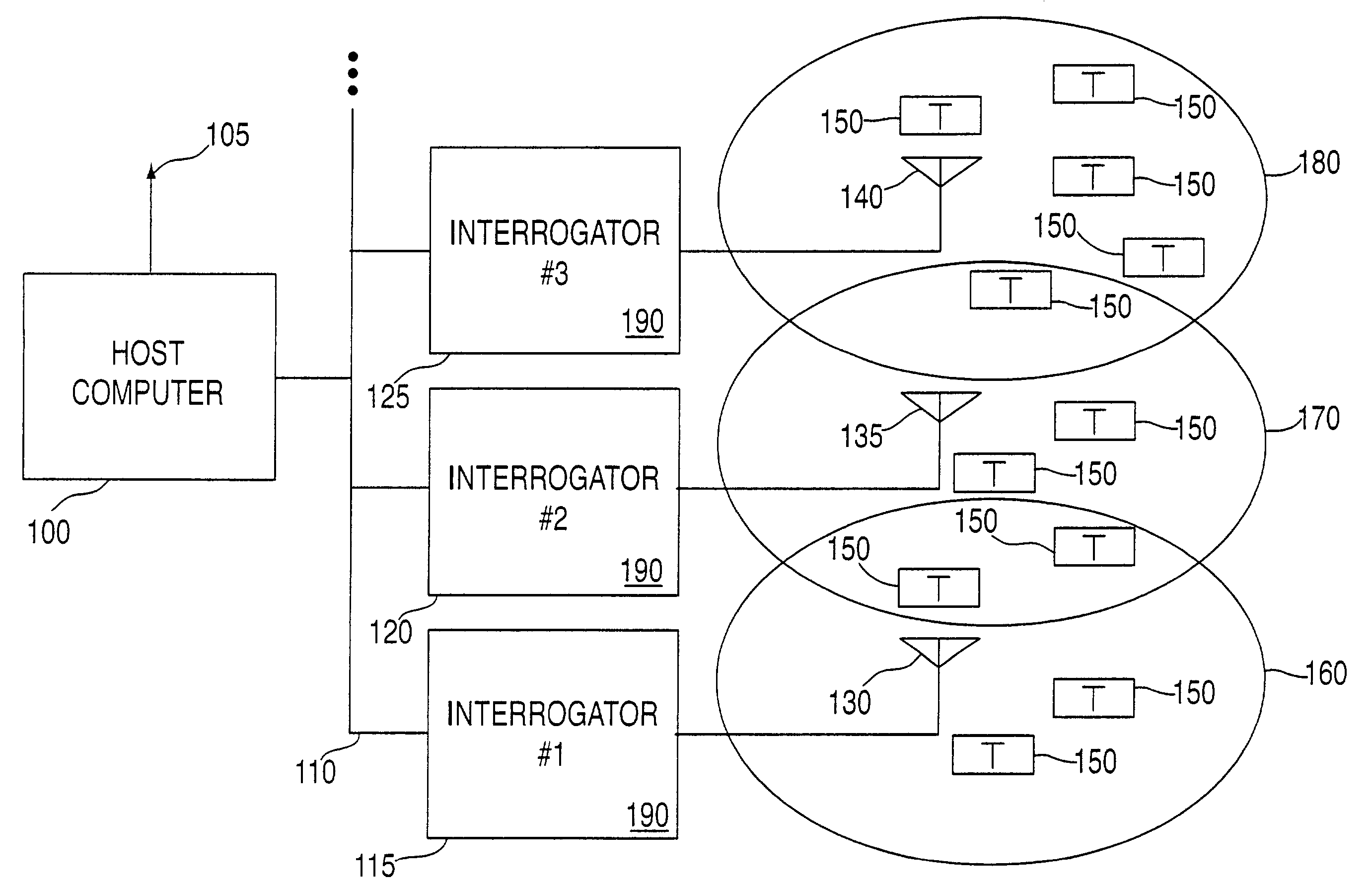

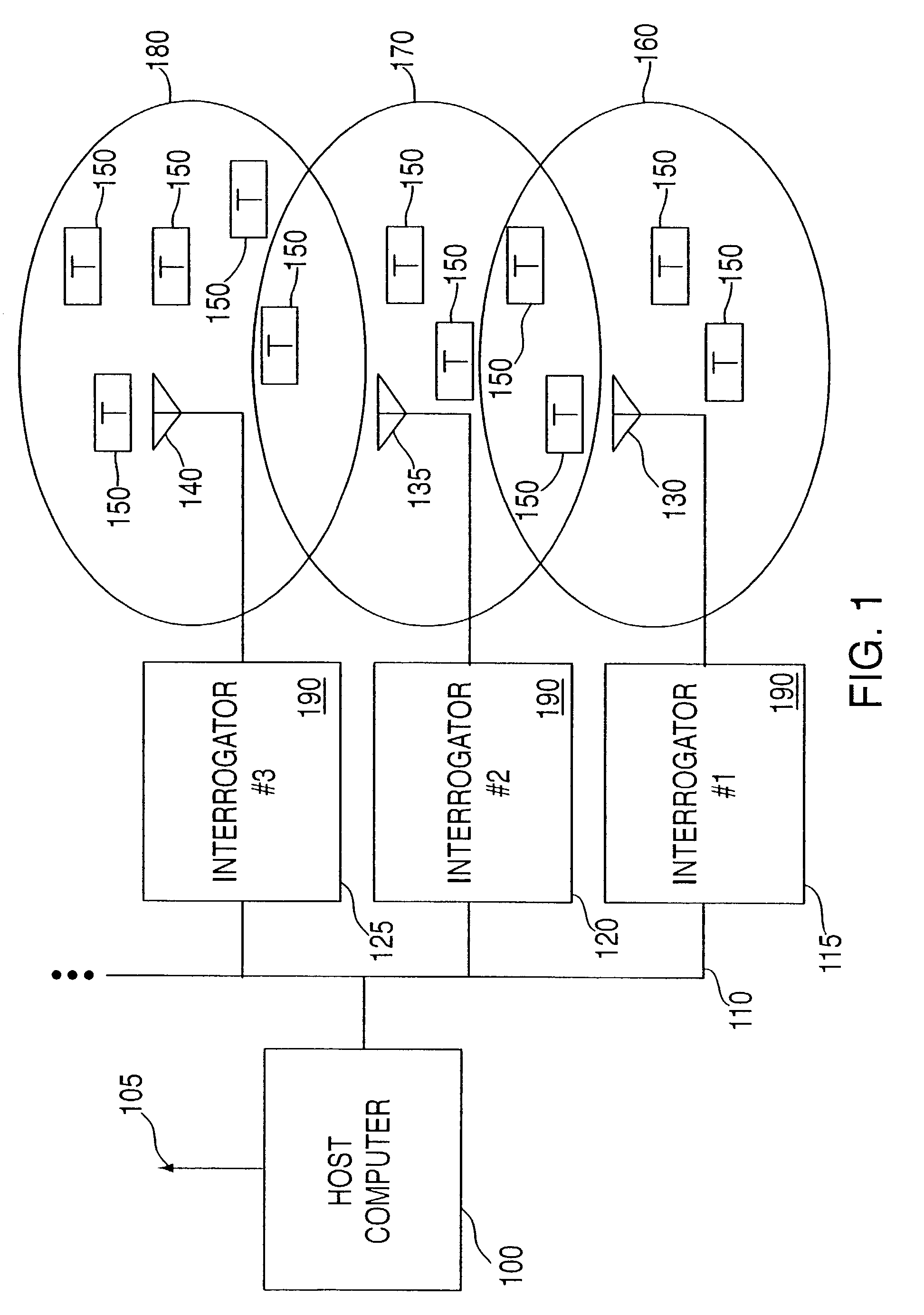

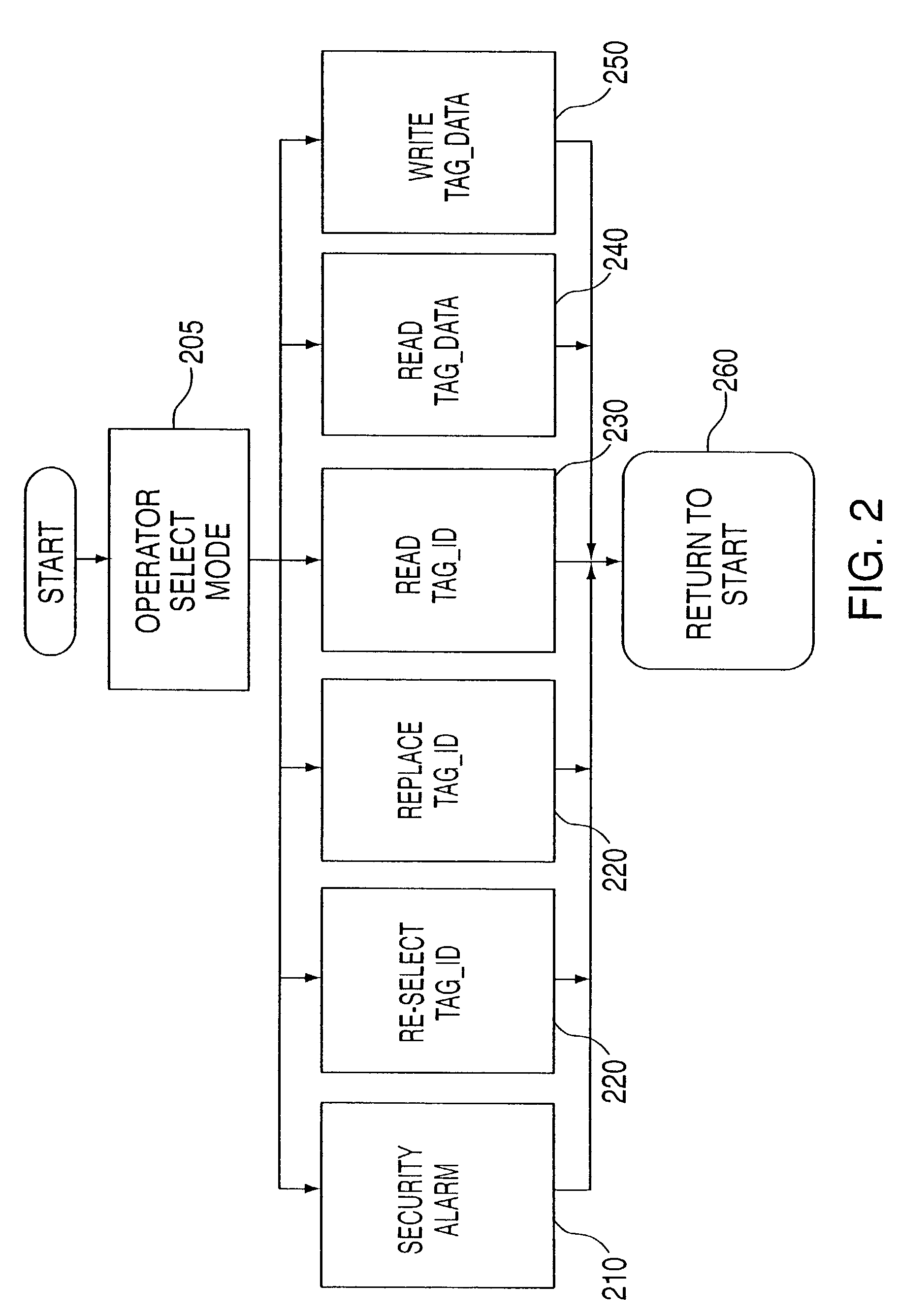

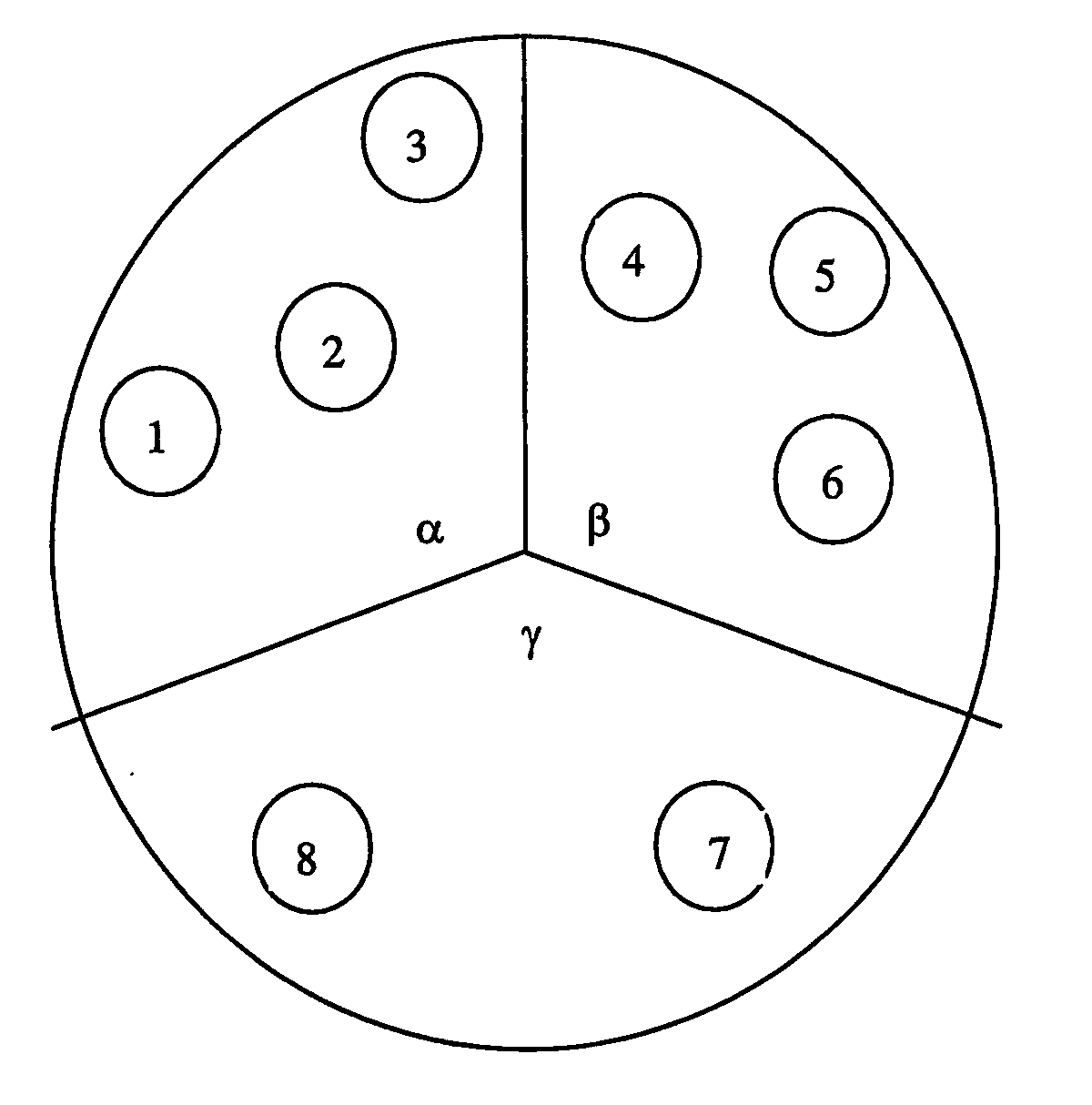

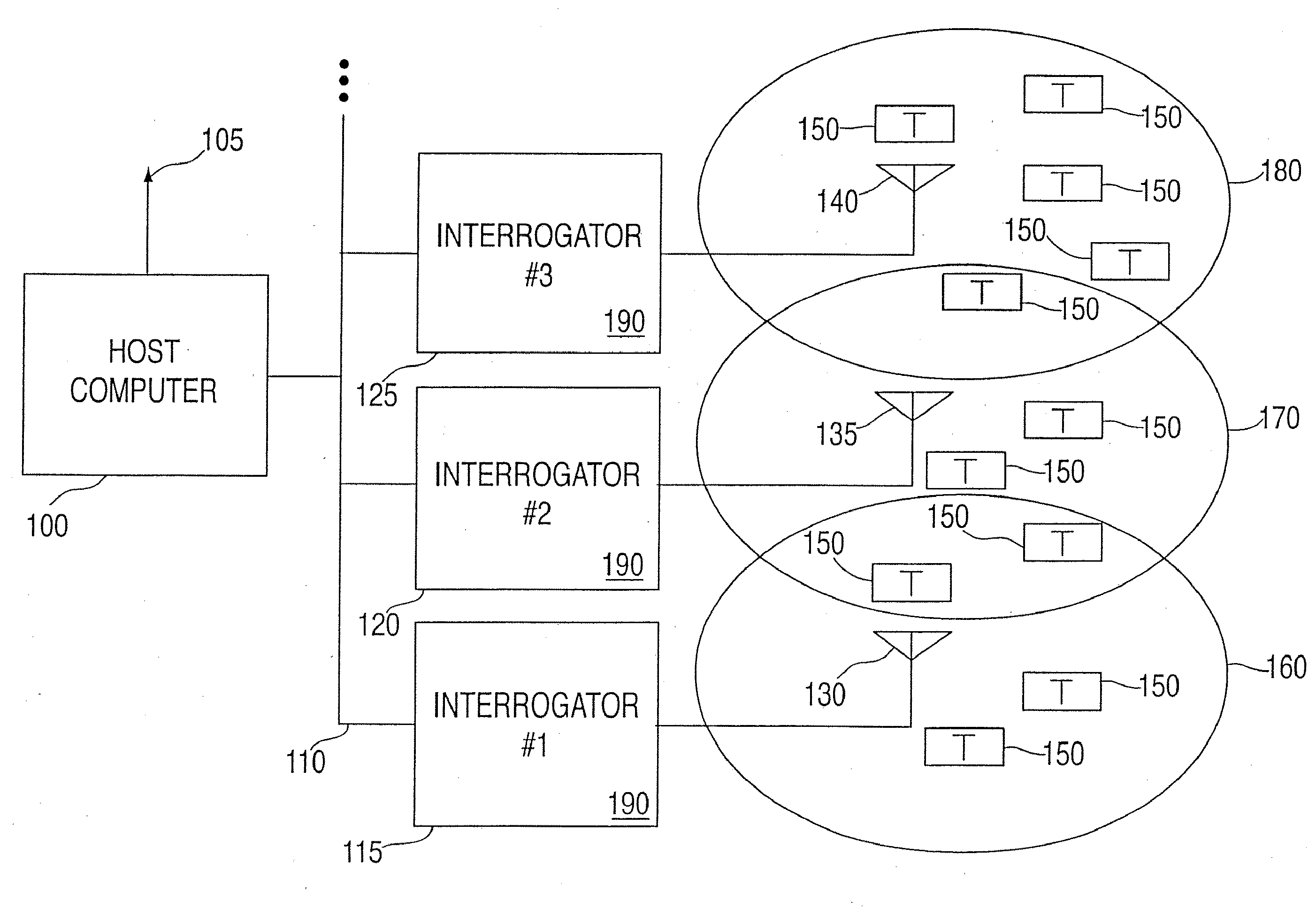

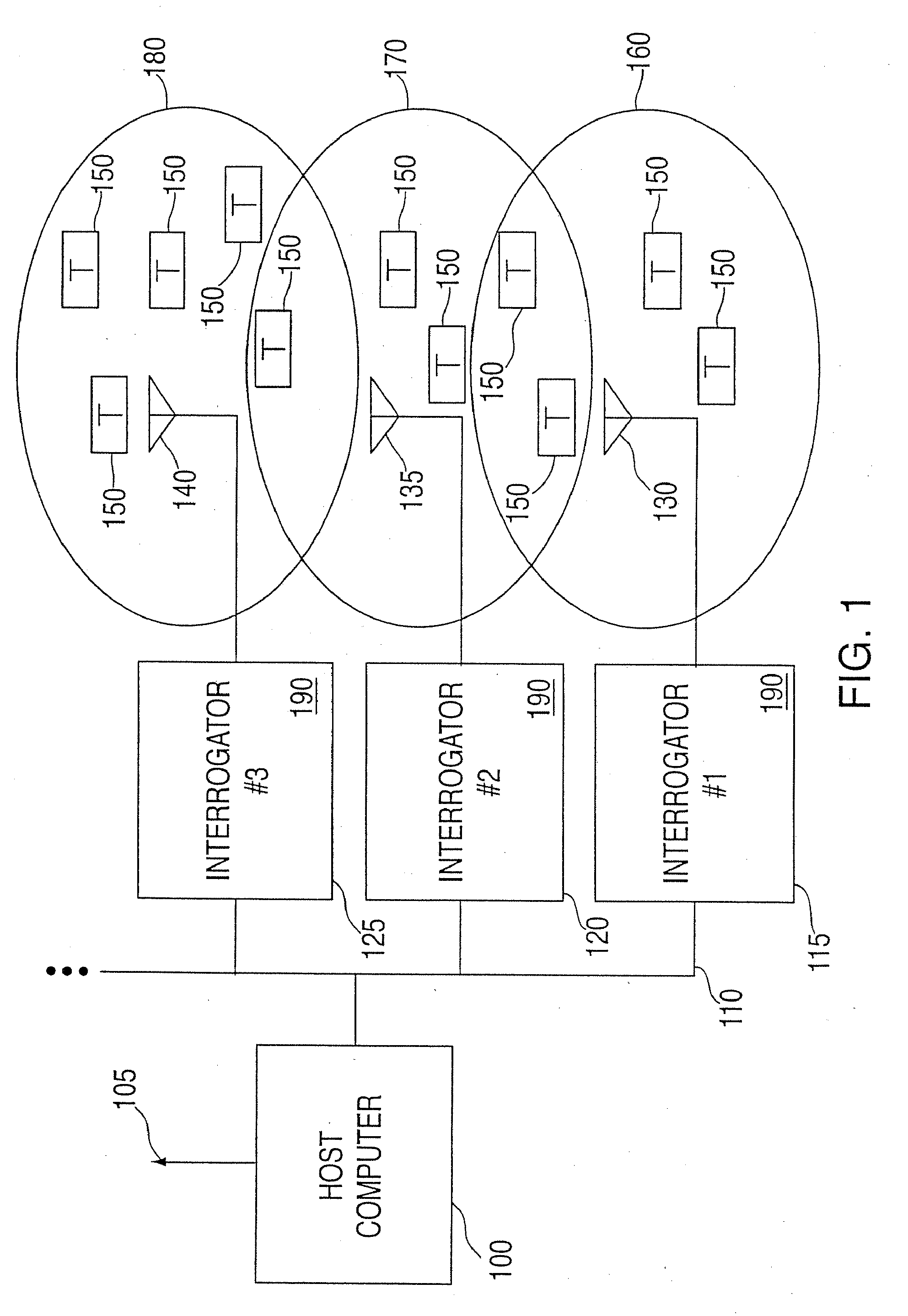

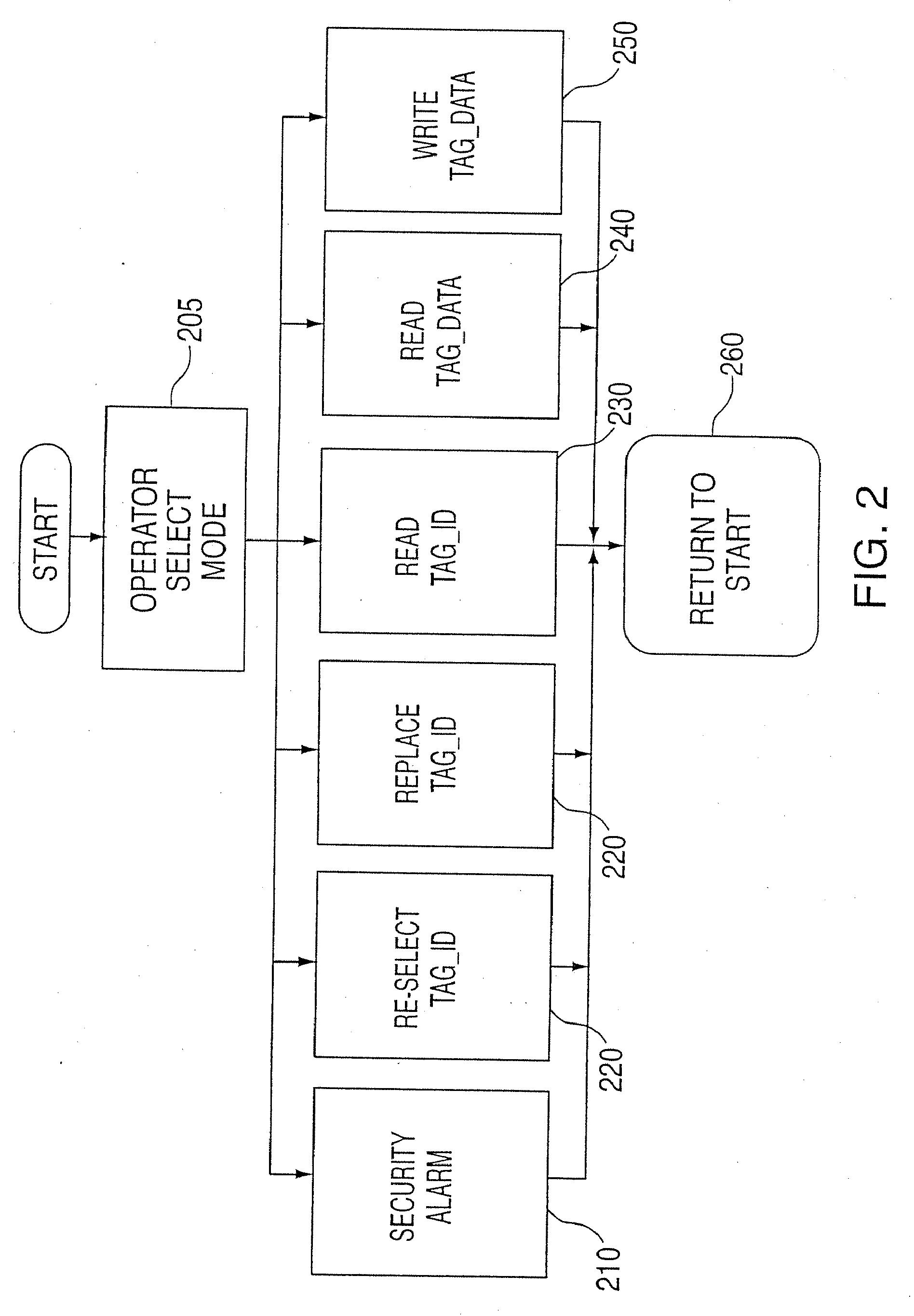

Method and system for communicating with and tracking RFID transponders

ActiveUS7253717B2Reduce the valueMemory record carrier reading problemsCo-operative working arrangementsNear neighborNumber generator

An RFID system and method for communicating between a host computer, one or more interrogators connected to the host computer, and a large body of transponders distributed within an area covered by the interrogators. Each transponder originally has a common identification code, and upon initialization by the host computer internally generates a unique identification code based upon an internally generated random number. The host, through the interrogators, reads each of the identification codes associated with each transponder by iteratively transmitting a read identification code command along with a controlled variable. Each transponder compares the received controlled variable to an internally generated random number, and selectively transmits its identification code based upon the outcome of this comparison. After the completion of each read identification code iteration, the host adjusts the controlled variable based upon the responses received in the previous iteration. Preferably, communications between the interrogators and the transponders are DSSS signals in TDMA format, and the transponders use the random number generator to assign a time slot for transmission of their response. Each interrogator includes an antenna system utilizing a switch matrix to connect multiple antennas having different polarizations, which ensures that all transponders within the range of the interrogator receive the signals from the interrogator. In a further aspect, the interrogators are arranged in groups, each group in nearest neighbor format, to reduce the time for reading the transponders and the emissions generated when more than one interrogator is active at the same time.

Owner:TERRESTRIAL COMMS LLC

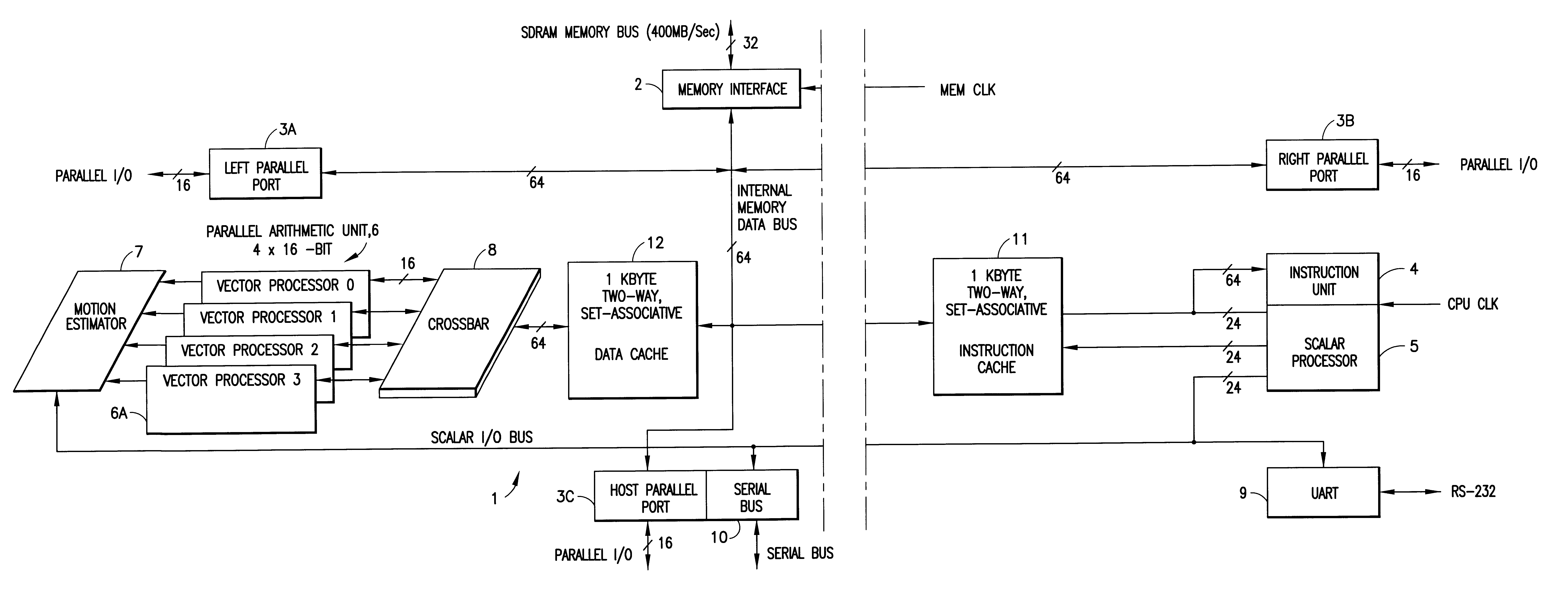

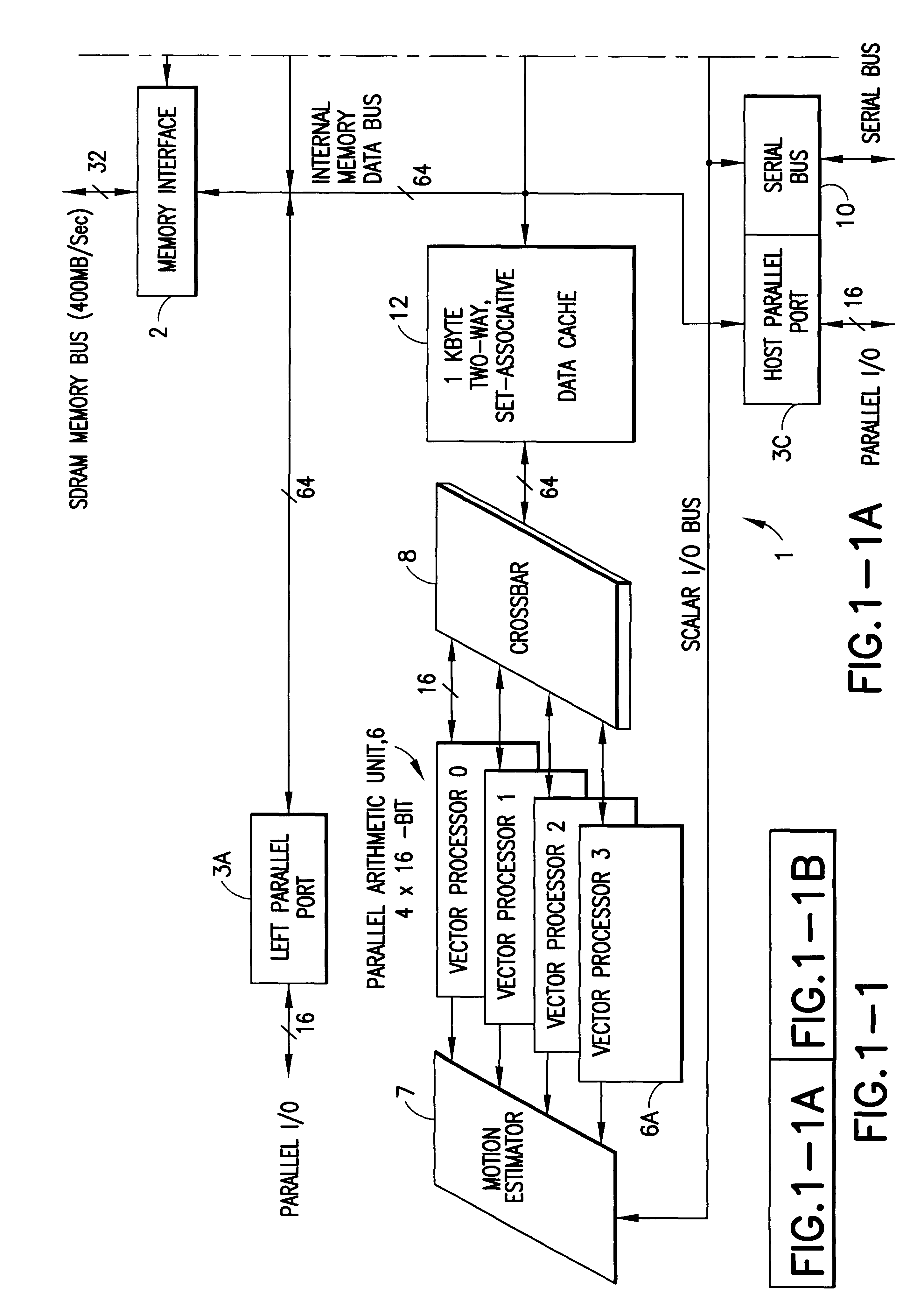

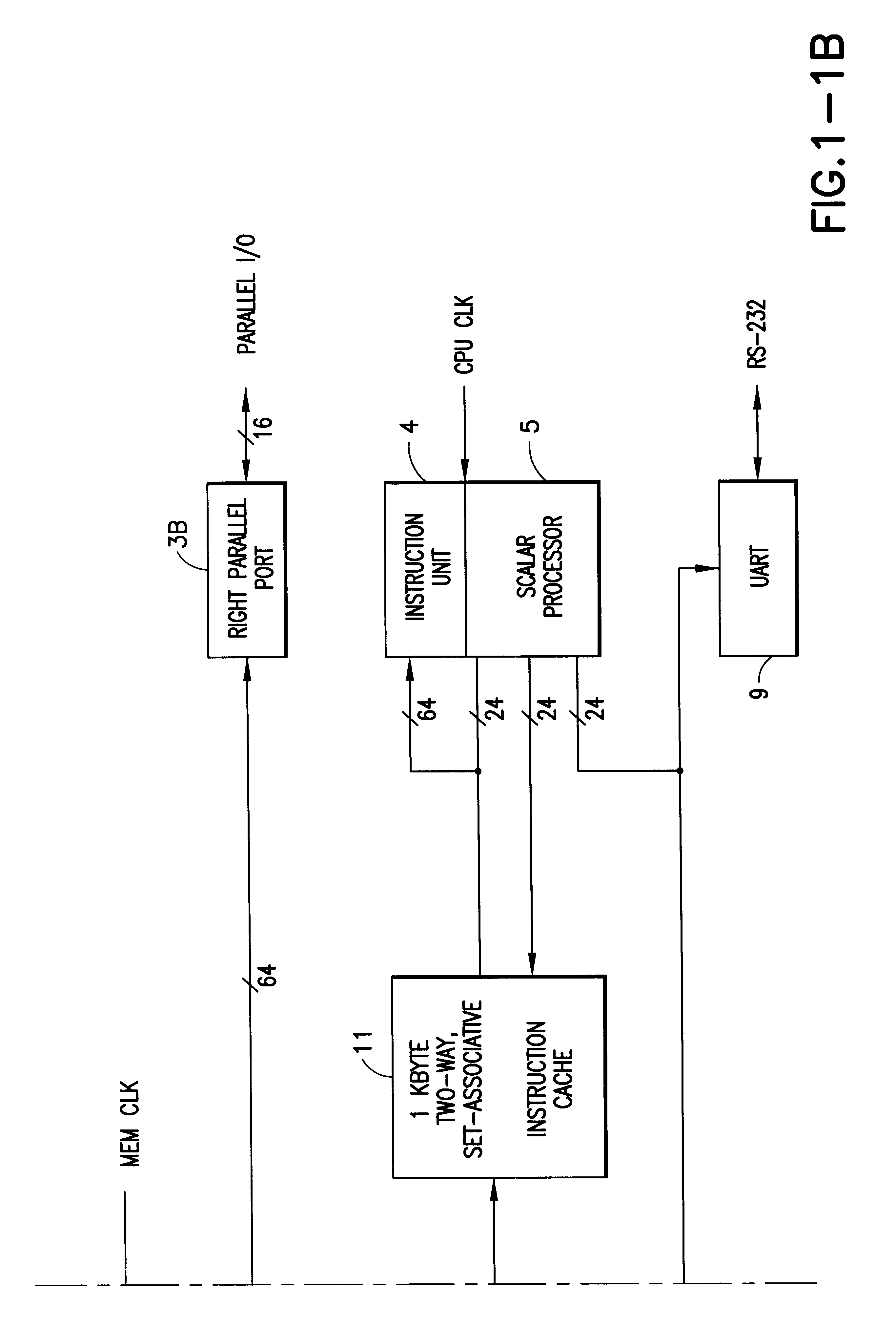

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

A digital data processor integrated circuit (1) includes a plurality of functionally identical first processor elements (6A) and a second processor element (5). The first processor elements are bidirectionally coupled to a first cache (12) via a crossbar switch matrix (8). The second processor element is coupled to a second cache (11). Each of the first cache and the second cache contain a two-way, set-associative cache memory that uses a least-recently-used (LRU) replacement algorithm and that operates with a use-as-fill mode to minimize a number of wait states said processor elements need experience before continuing execution after a cache-miss. An operation of each of the first processor elements and an operation of the second processor element are locked together during an execution of a single instruction read from the second cache. The instruction specifies, in a first portion that is coupled in common to each of the plurality of first processor elements, the operation of each of the plurality of first processor elements in parallel. A second portion of the instruction specifies the operation of the second processor element. Also included is a motion estimator (7) and an internal data bus coupling together a first parallel port (3A), a second parallel port (3B), a third parallel port (3C), an external memory interface (2), and a data input / output of the first cache and the second cache.

Owner:CUFER ASSET LTD LLC

Communications system and method

ActiveUS7313415B2Fine granularityReduce congestionSubstation equipmentTransmissionSignal routingCommunications system

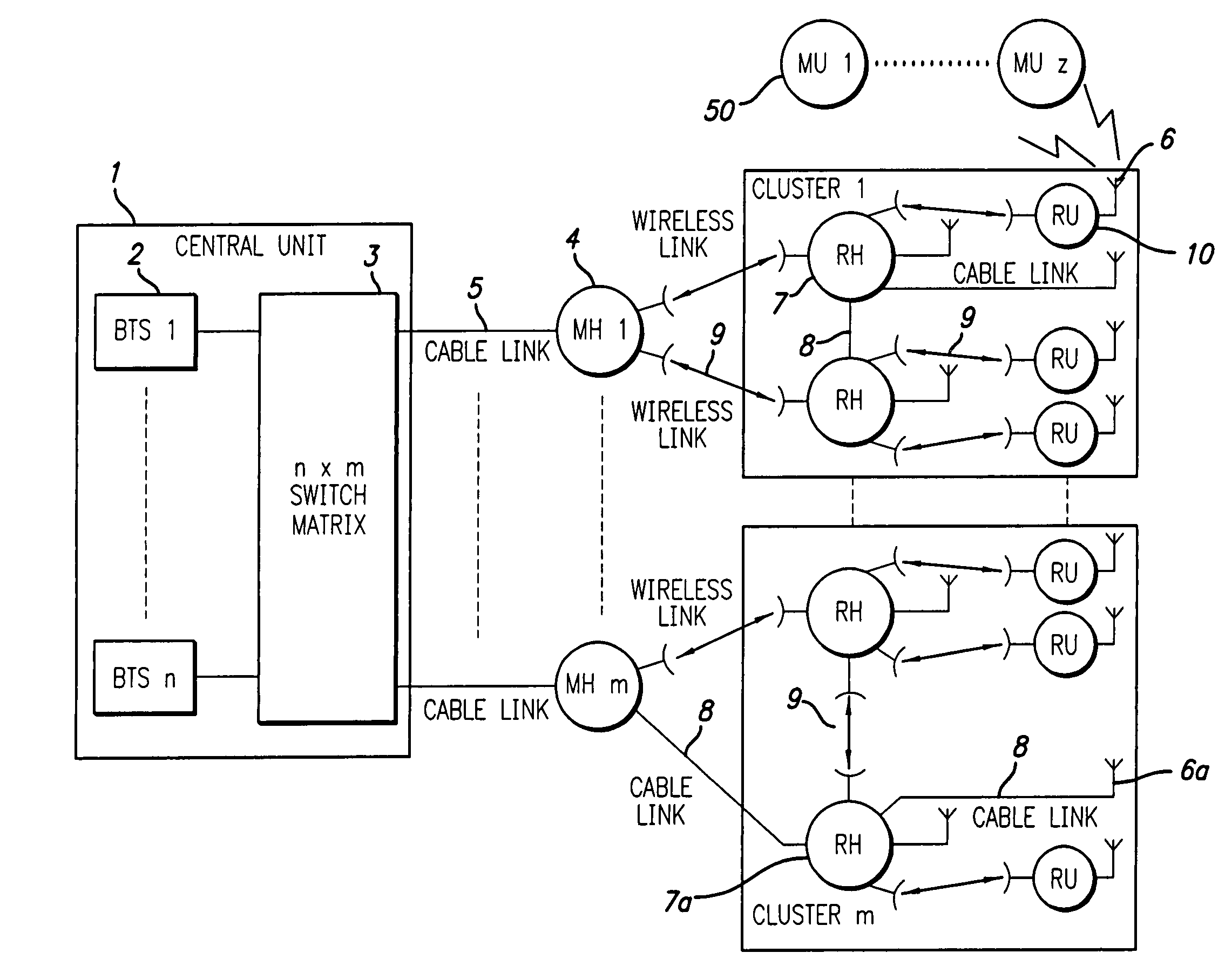

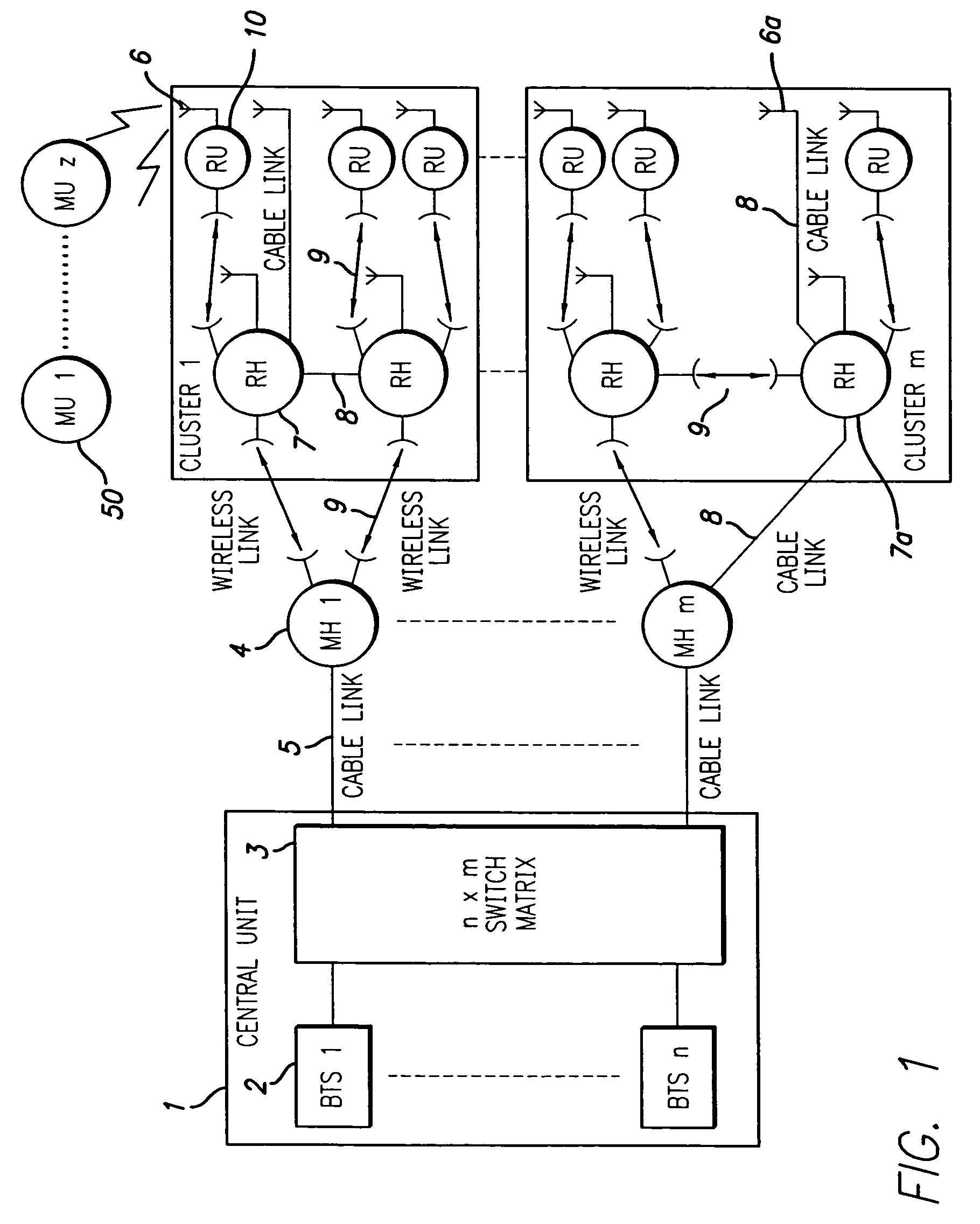

A signal distribution system for distributing signals, such as for outdoor wireless networks, comprises a number of remote hubs, each of which can direct wireless signals to a number of antennas. The antennas are used to provide wireless service to the service users, such as mobile units, within their geographic coverage area. The remote hubs are connected to main hubs, which are usually located centrally. Each main hub can support a number of remote hubs. The main hubs are connected to a number of base stations (again usually located centrally) in a flexible and re-configurable manner using a switch matrix. Some remote hubs may also include switched matrices for a further level of signal routing.

Owner:NEXTG NETWORKS INC

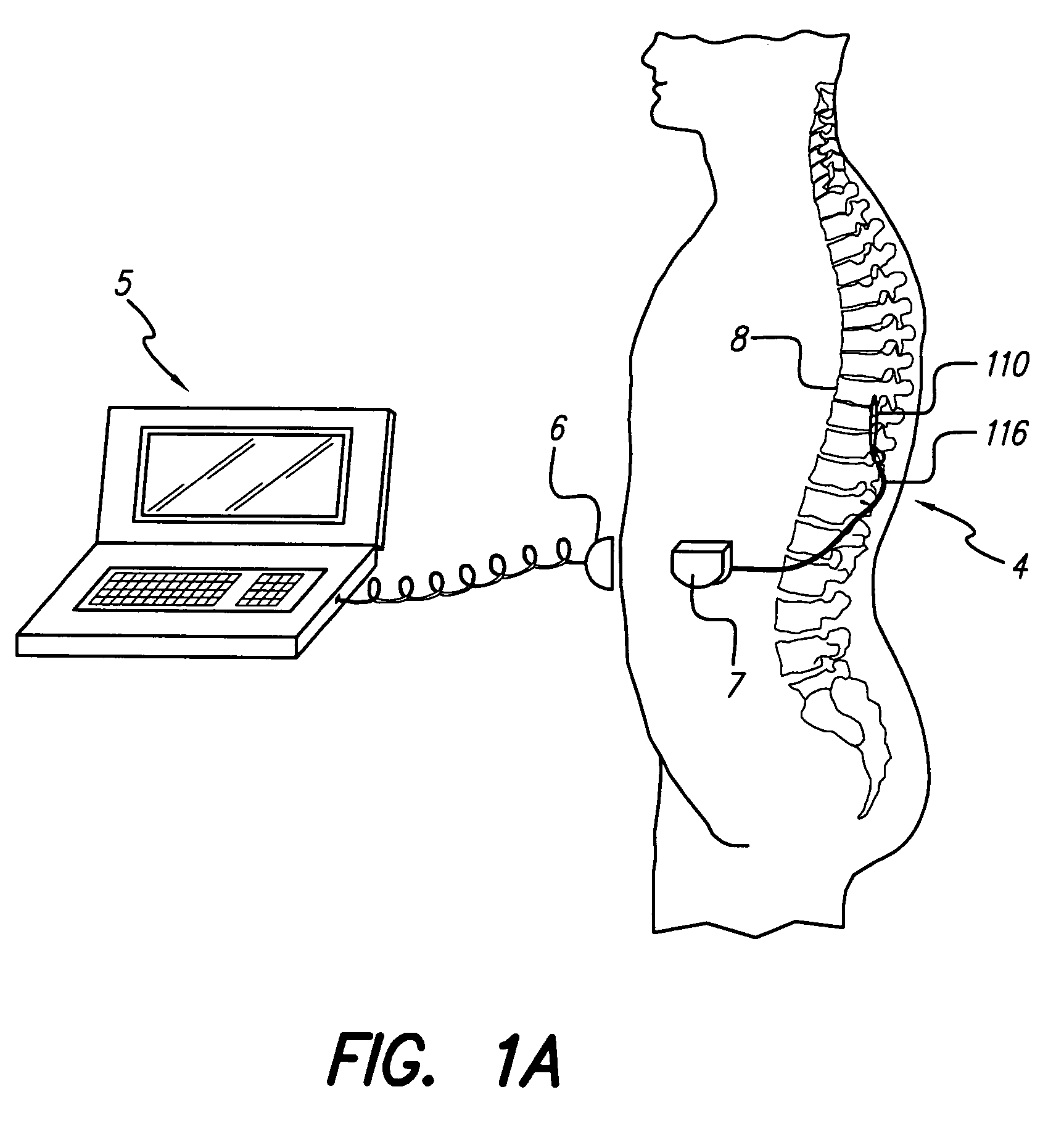

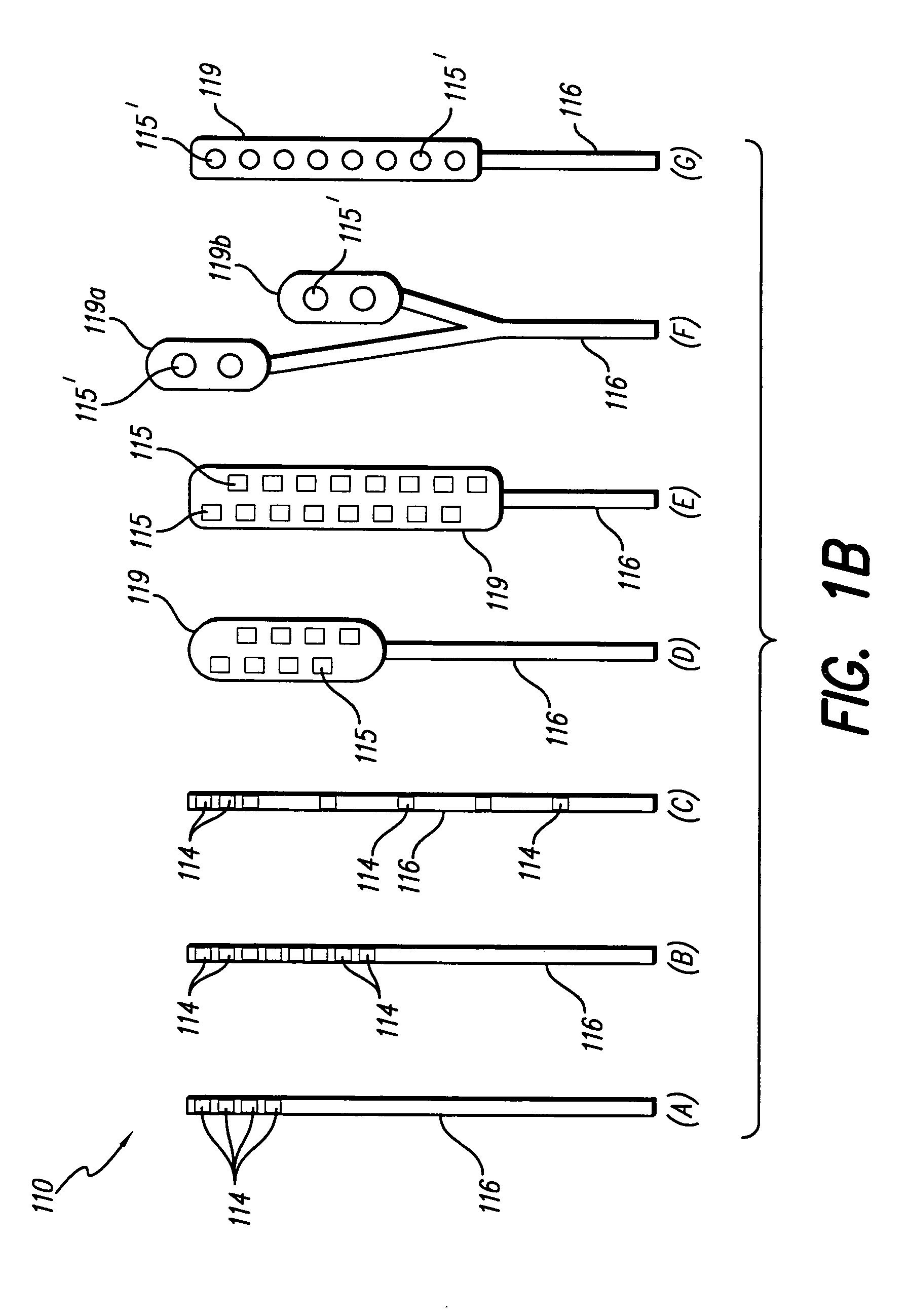

Switched-matrix output for multi-channel implantable stimulator

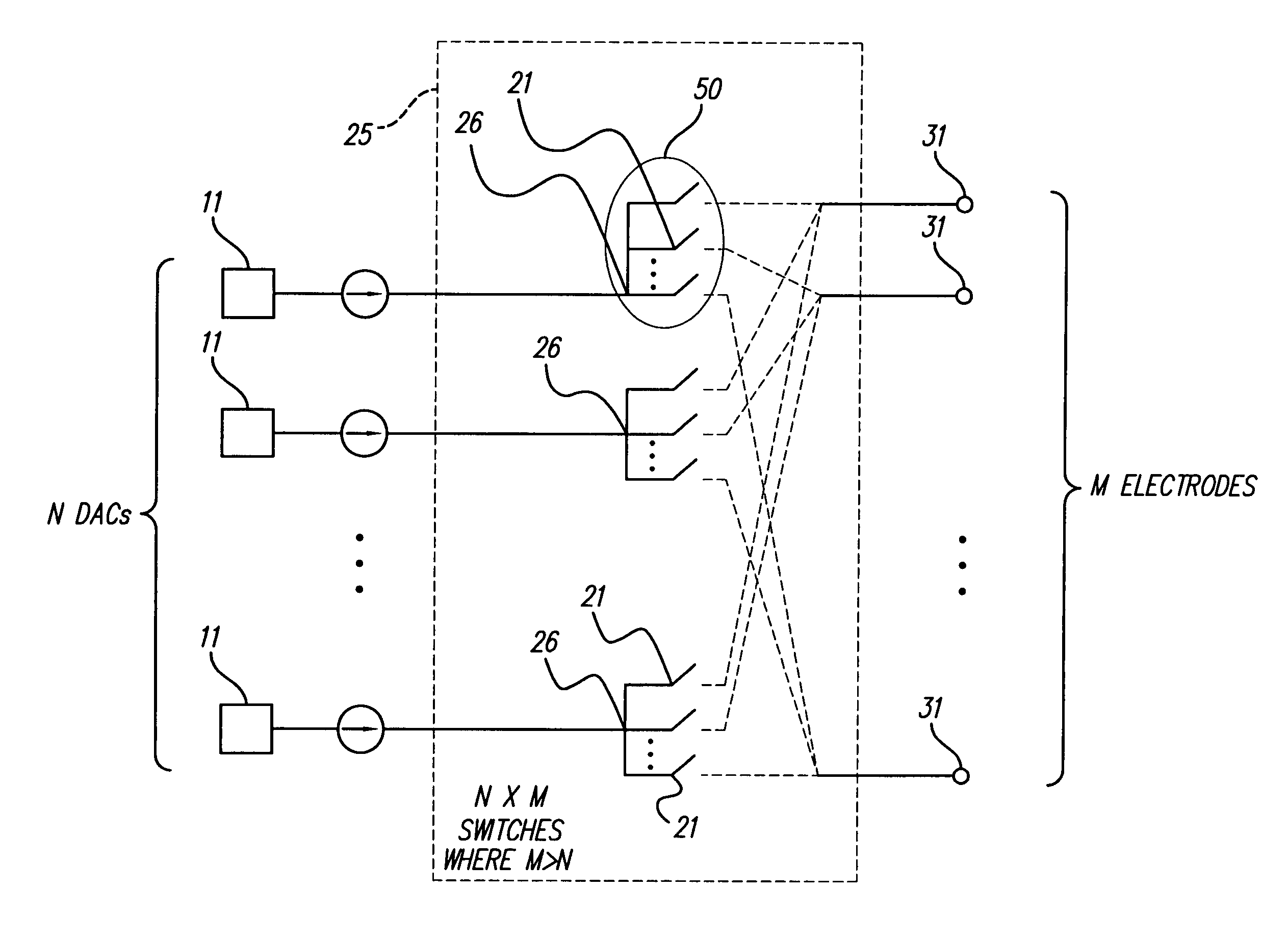

ActiveUS7127298B1Saving limited device spaceLimited spaceElectrotherapyDigital analog converterElectrode Contact

The invention is a switched-matrix output for a multi-channel stimulator. The switch-matrix output system uses groups of switches connectively placed between N number of digital-to-analog convertors (DACs) and M electrode contacts to permit fewer, space-consuming DACs to be used in an implantable stimulator, thereby saving internal stimulator space. One embodiment of the switched matrix output uses switches to activate only one active-electrode subset of M electrode contacts at any one time, so that the total number of DACs contained in the stimulator can be less than the M total number of electrode contacts.

Owner:BOSTON SCI NEUROMODULATION CORP

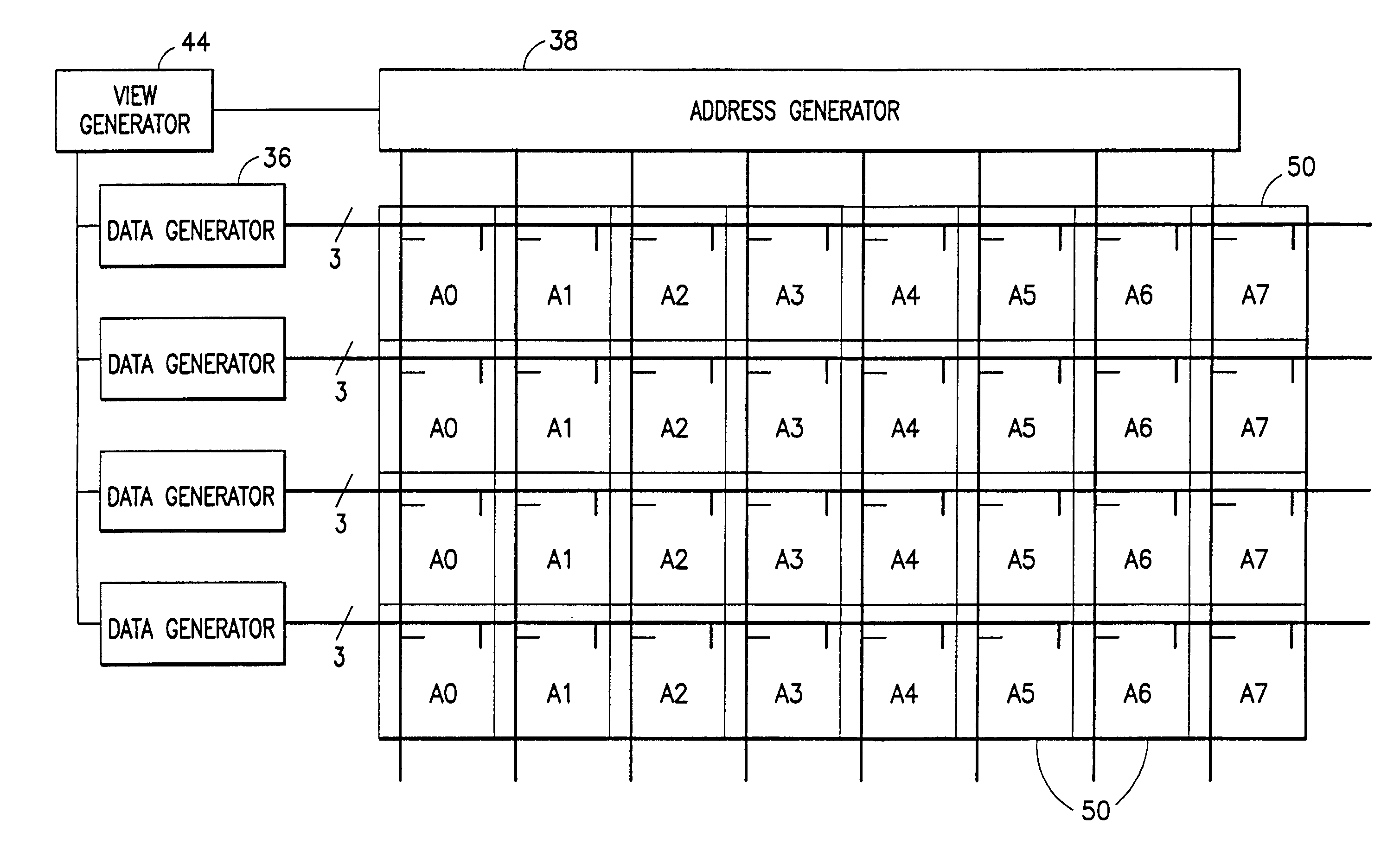

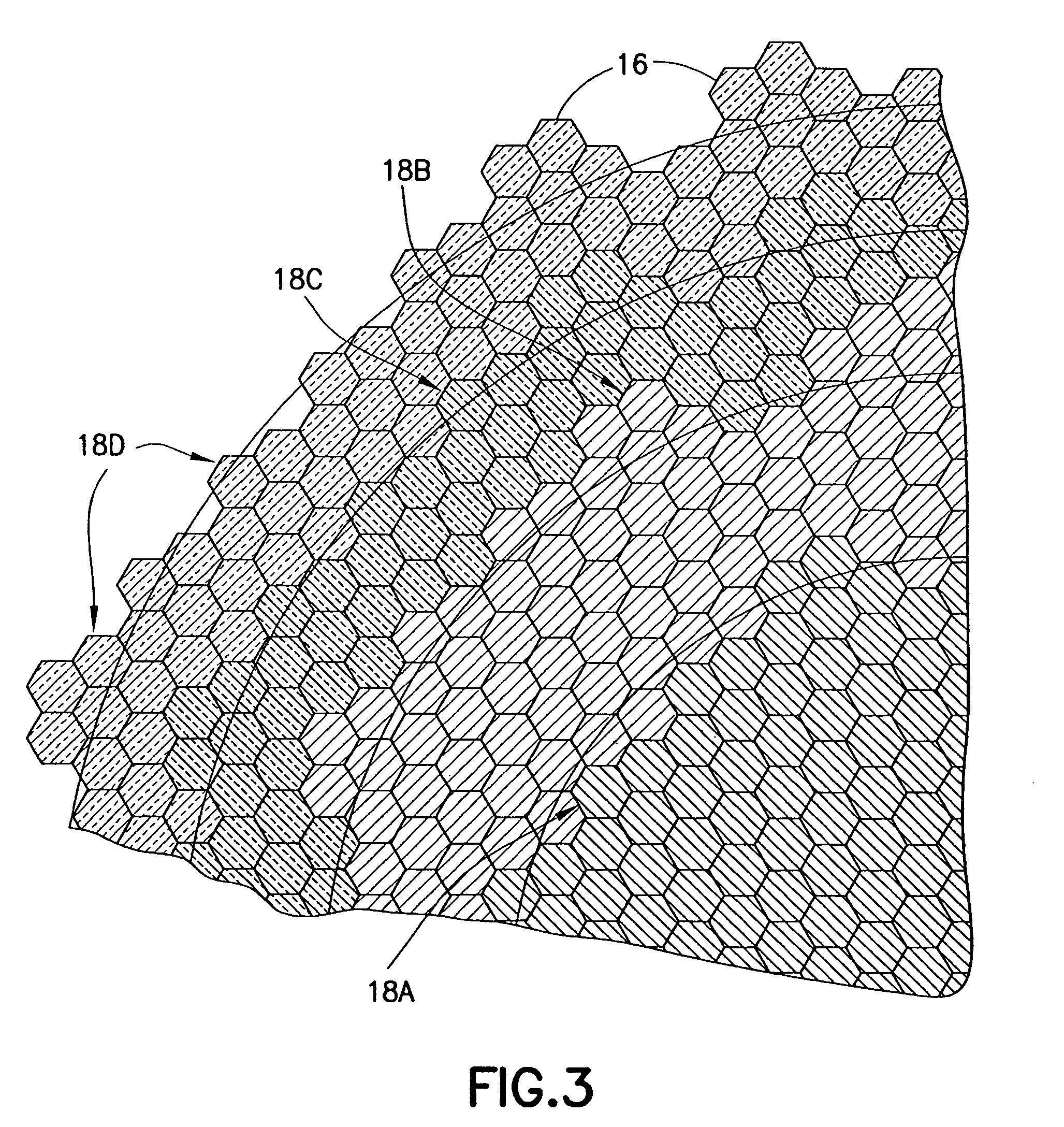

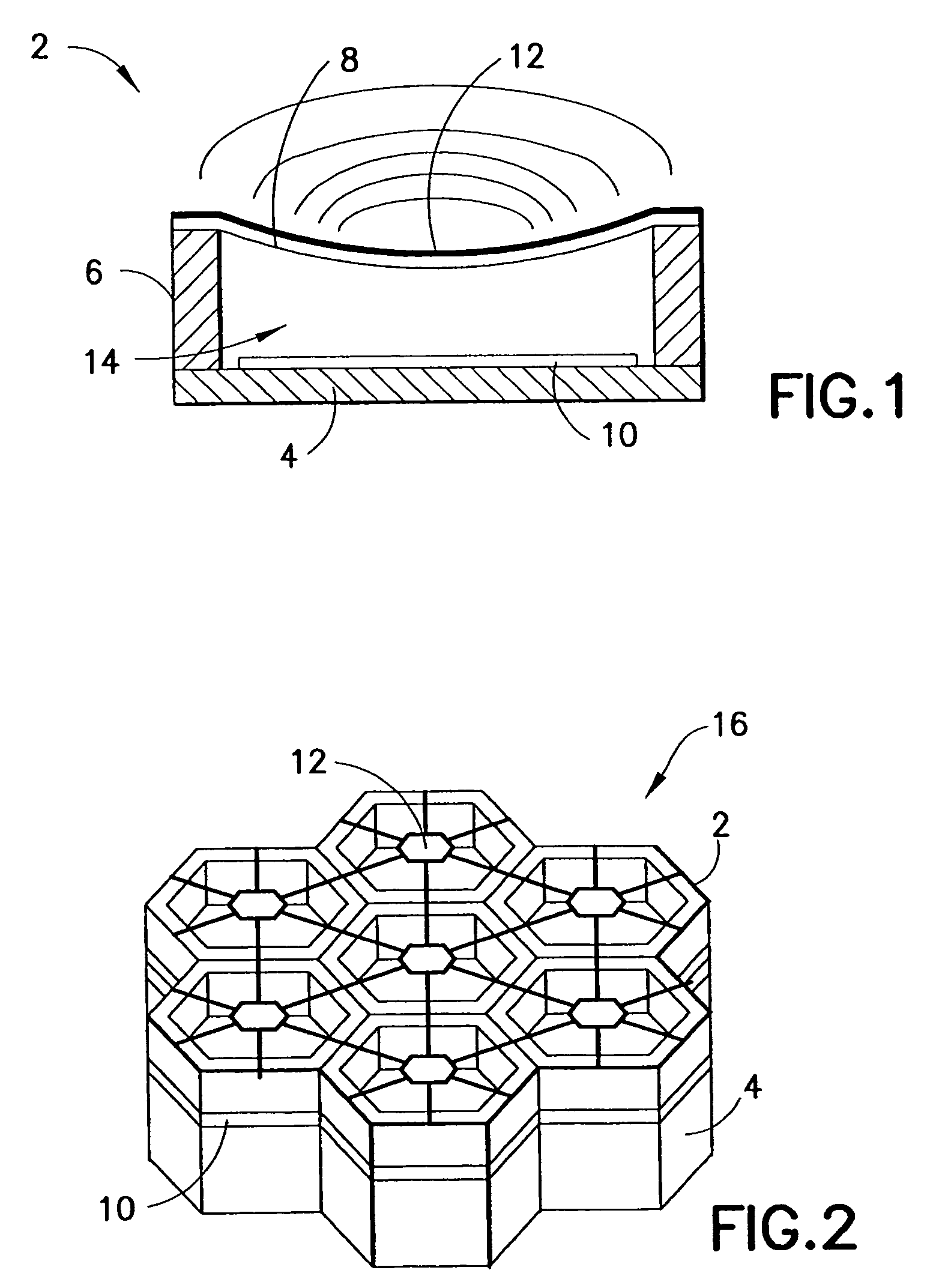

Method and apparatus for controlling scanning of mosaic sensor array

InactiveUS7313053B2Quick configurationMinimize powerUltrasonic/sonic/infrasonic diagnosticsWave based measurement systemsComputer hardwareSensor array

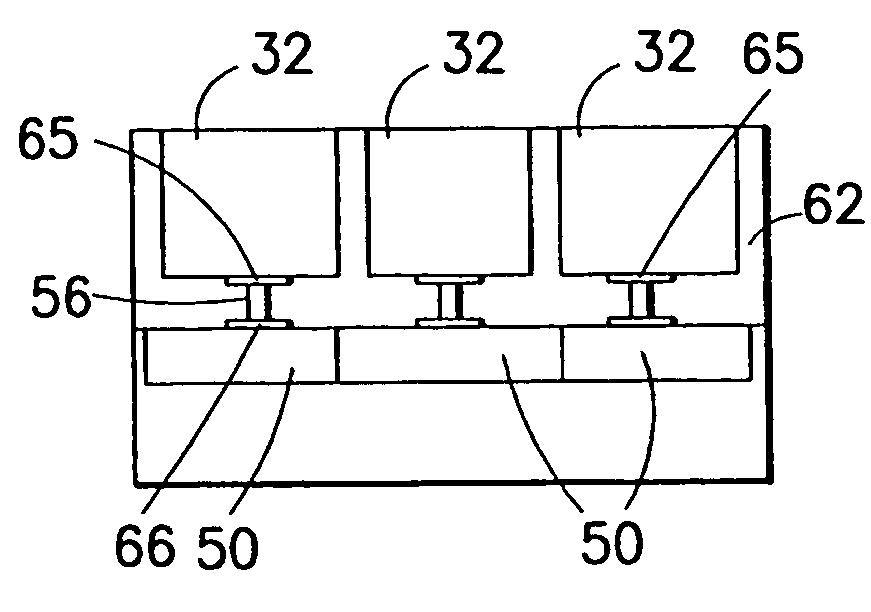

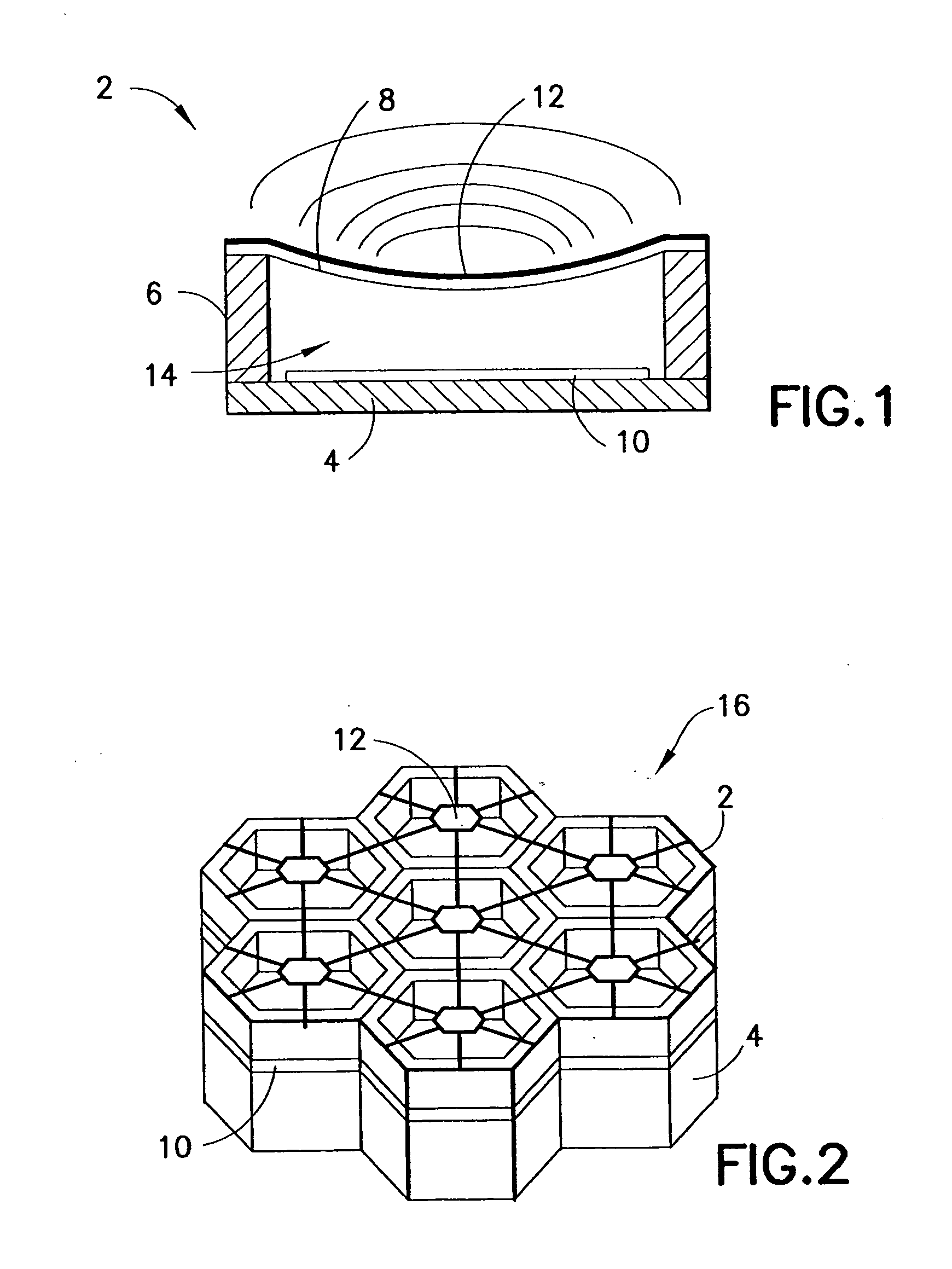

A scanning architecture that makes it possible to update only those ultrasonic transducer subelements of a mosaic transducer array that change from view to view. The configuration of the switch matrix is fully programmable. The switch matrix includes access switches that connect subelements to bus lines and matrix switches that connect subelements to subelements. Each subelement has a unit switch cell associated therewith, each unit switch cell comprising at least one access switch, at least one matrix switch, and addressing and control logic. Optionally, each unit switch cell also includes latches for storing the future switch states of the switches to be programmed. The switches themselves have memory for storing their current switch states.

Owner:GENERAL ELECTRIC CO

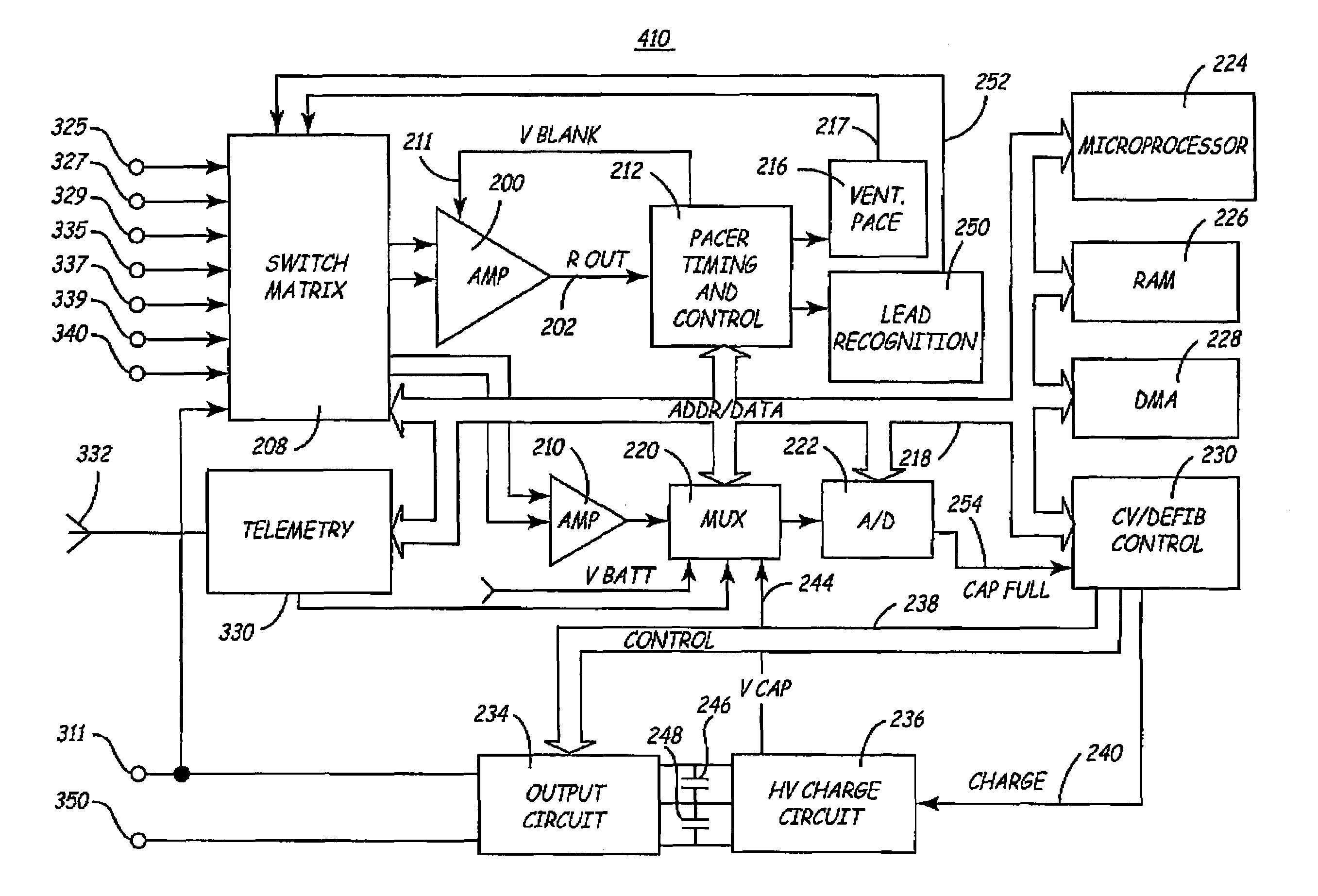

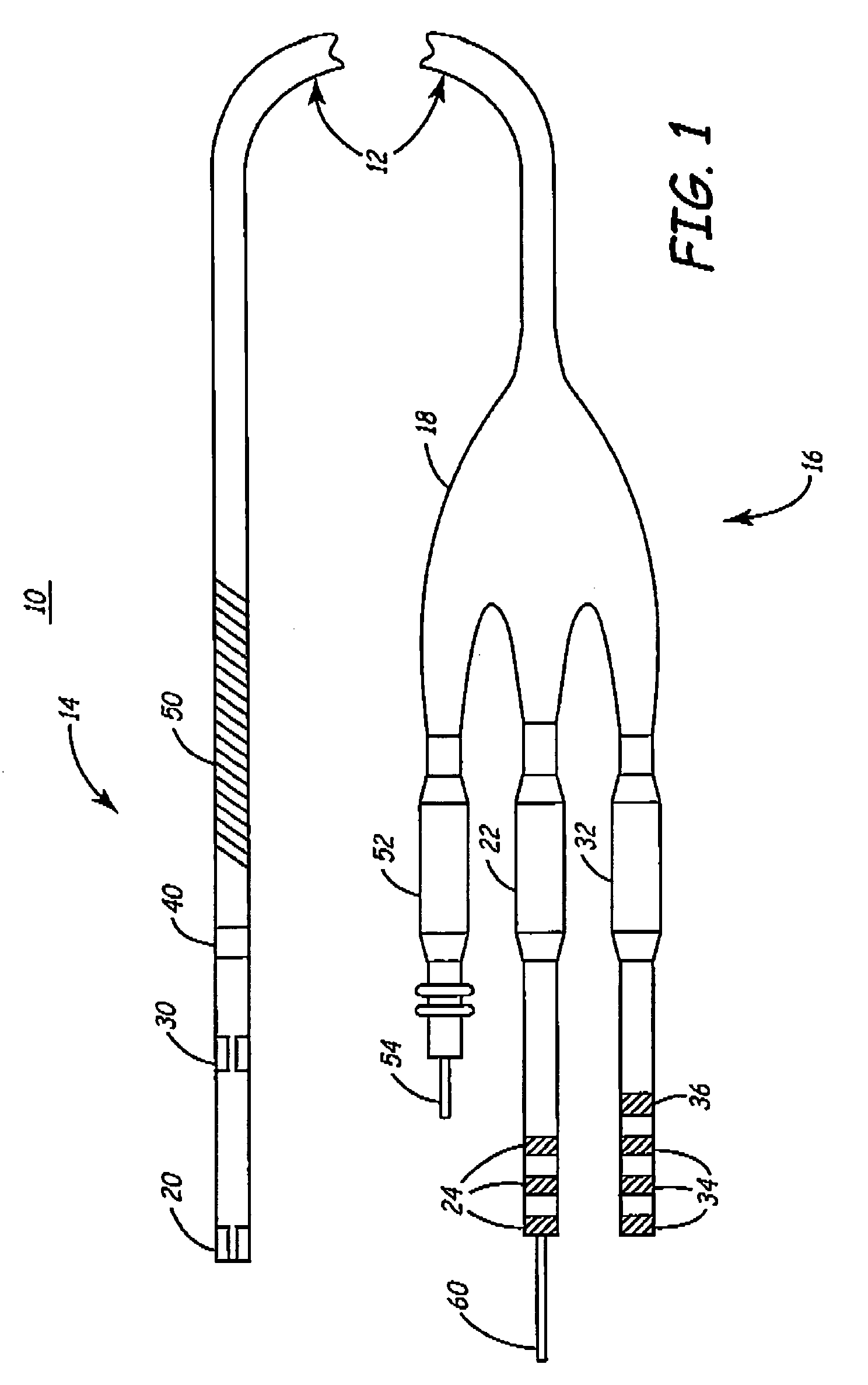

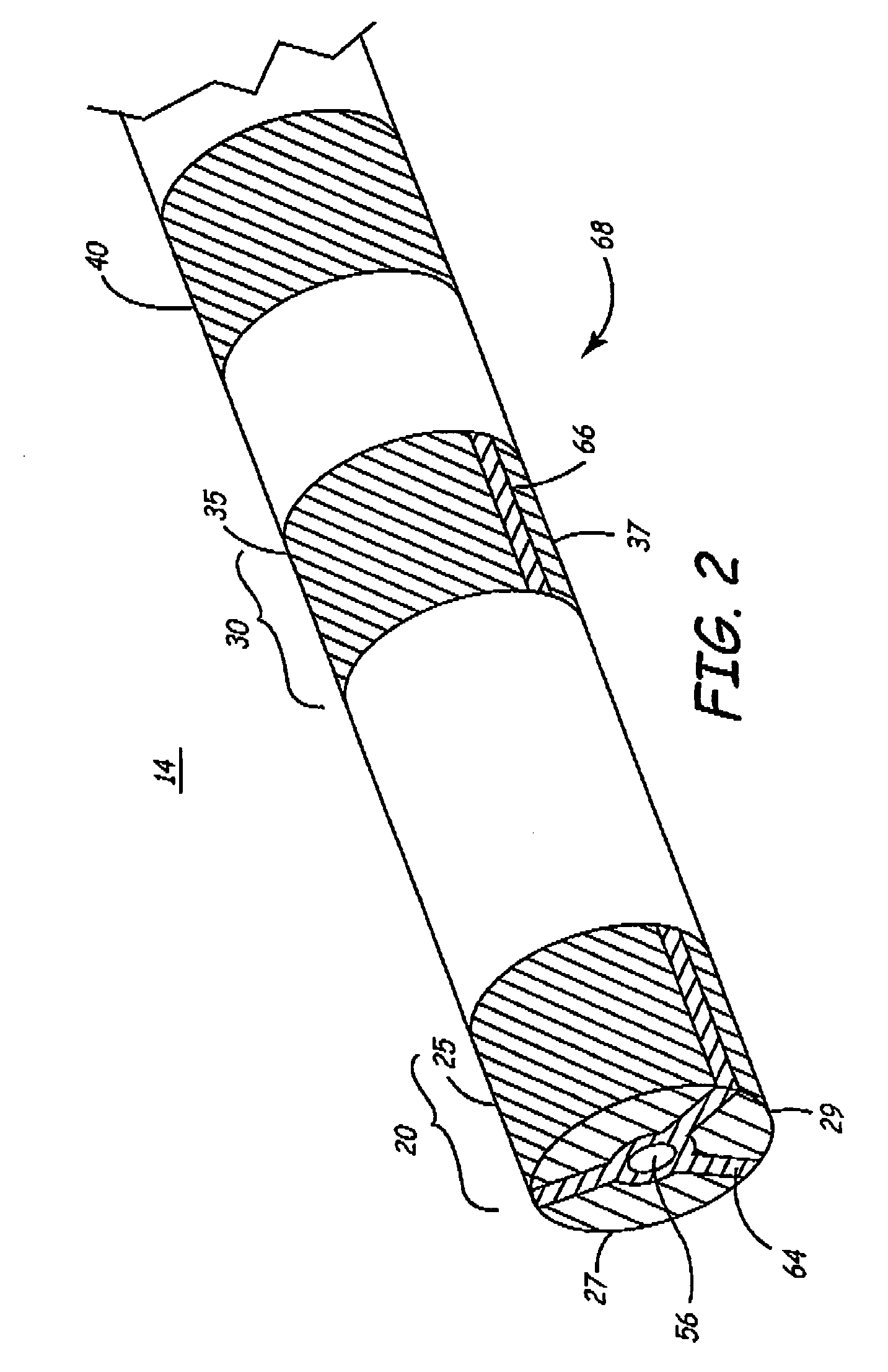

Method and apparatus for selecting an optimal electrode configuration of a medical electrical lead having a multiple electrode array

InactiveUS6978178B2ElectrocardiographyTransvascular endocardial electrodesElectrical conductorElectrode Contact

An electrical medical lead is provided having two or more electrodes, electrically insulated from each other and electrically coupled to individually insulated filars in a multi-filar coiled conductor. When the lead is used with a medical device equipped with a switch matrix, electrodes are selected individually or simultaneously to serve as an anode or cathode in any unipolar, bipolar or multi-polar configuration for delivering stimulation and / or sensing signals in excitable tissue. In one embodiment, a tip electrode array is expandable for improving electrode contact with targeted tissue and stabilizing lead position.

Owner:MEDTRONIC INC

Capacitive-inductive touch screen

InactiveUS20100328249A1Transmission systemsInput/output processes for data processingClosed loopTouchscreen

Owner:STMICROELECTRONICS ASIA PACIFIC PTE

Distributed cell balancing

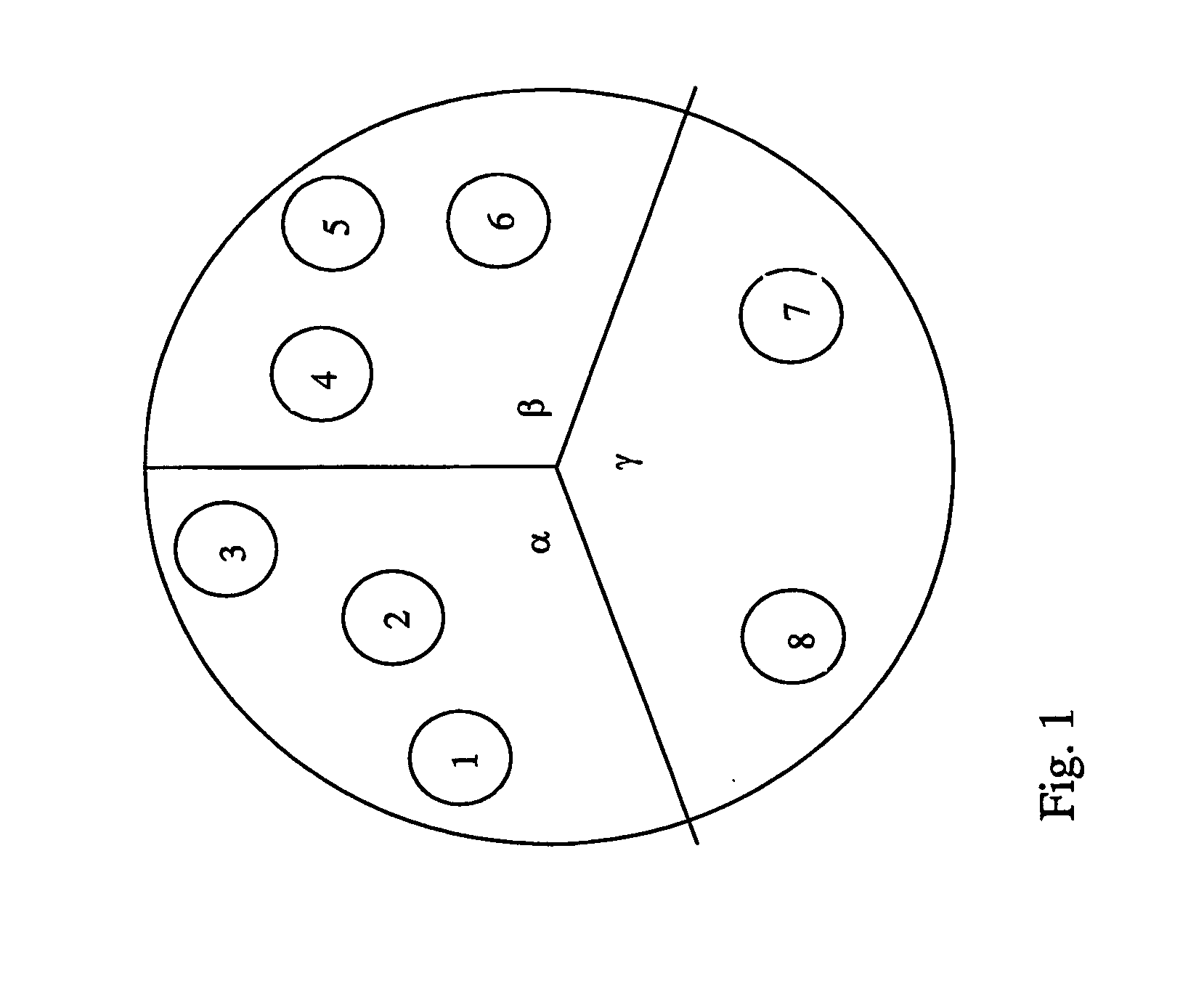

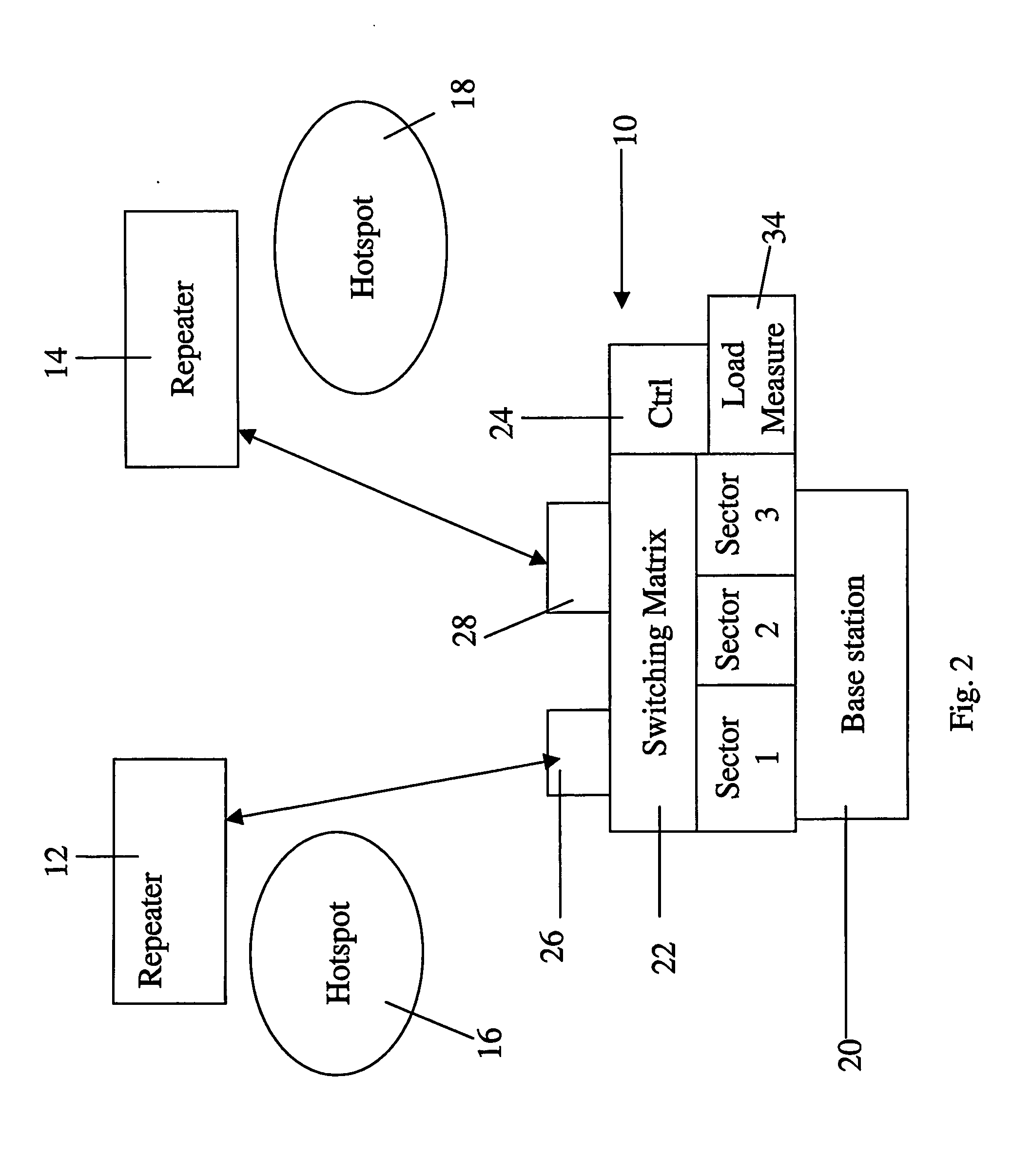

InactiveUS20070129071A1Avoid problemsEffective wayRadio/inductive link selection arrangementsWireless commuication servicesRepeaterDynamic equilibrium

A load balancing system for dynamic balancing of load between sectors of a sectored cellular base station, comprises a plurality of repeaters with local coverage in the sectors, and a switching matrix, for associating between the repeaters and the base station, and for allowing the repeaters to be switched between different sectors. If the system uses the base station assigned frequency band for communication with the repeaters then the system can be provided with minimal interference as an add-on to a legacy base station. An add-on may also be provided using microwave frequency and dedicated antennas.

Owner:CELLETRA

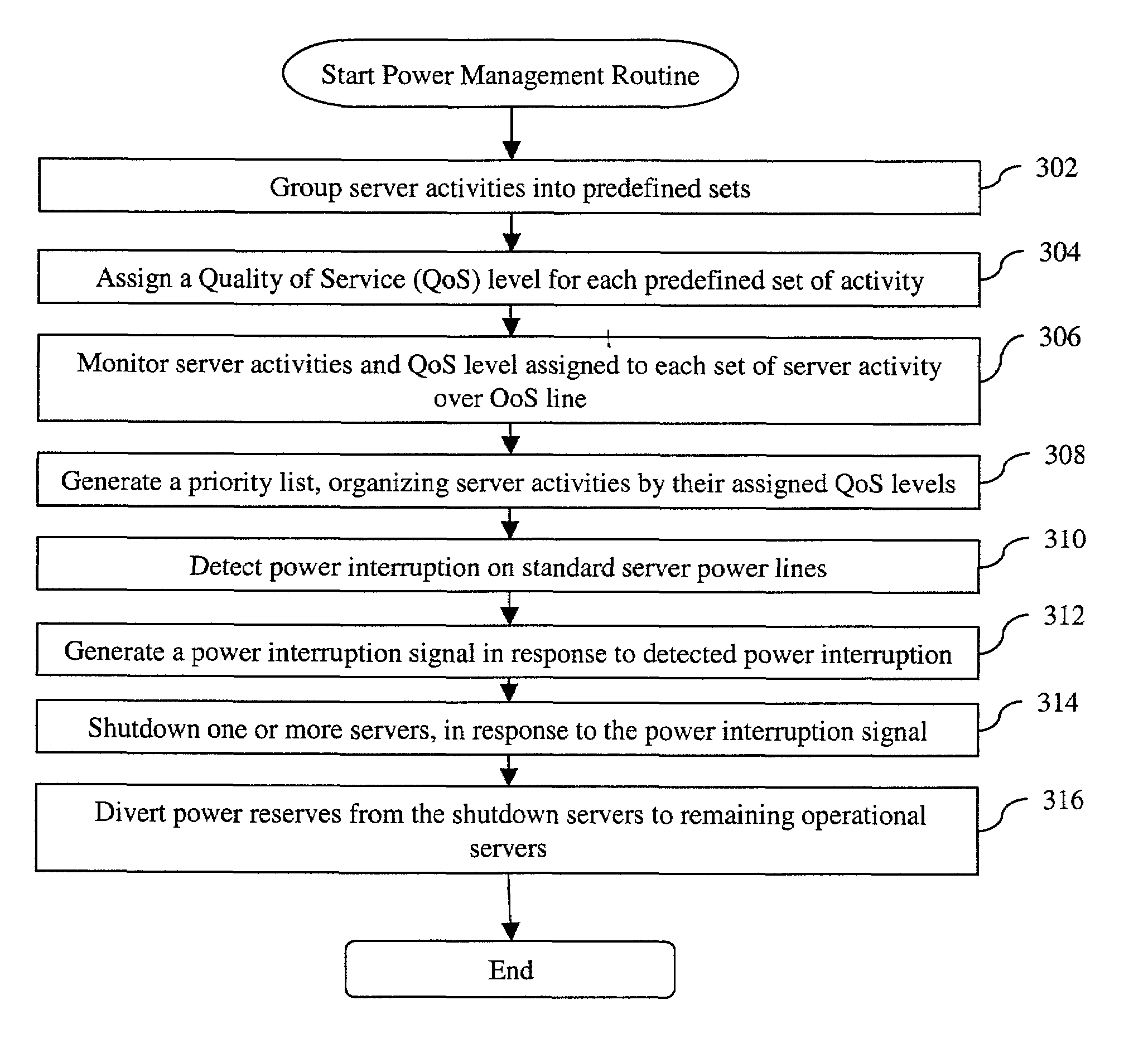

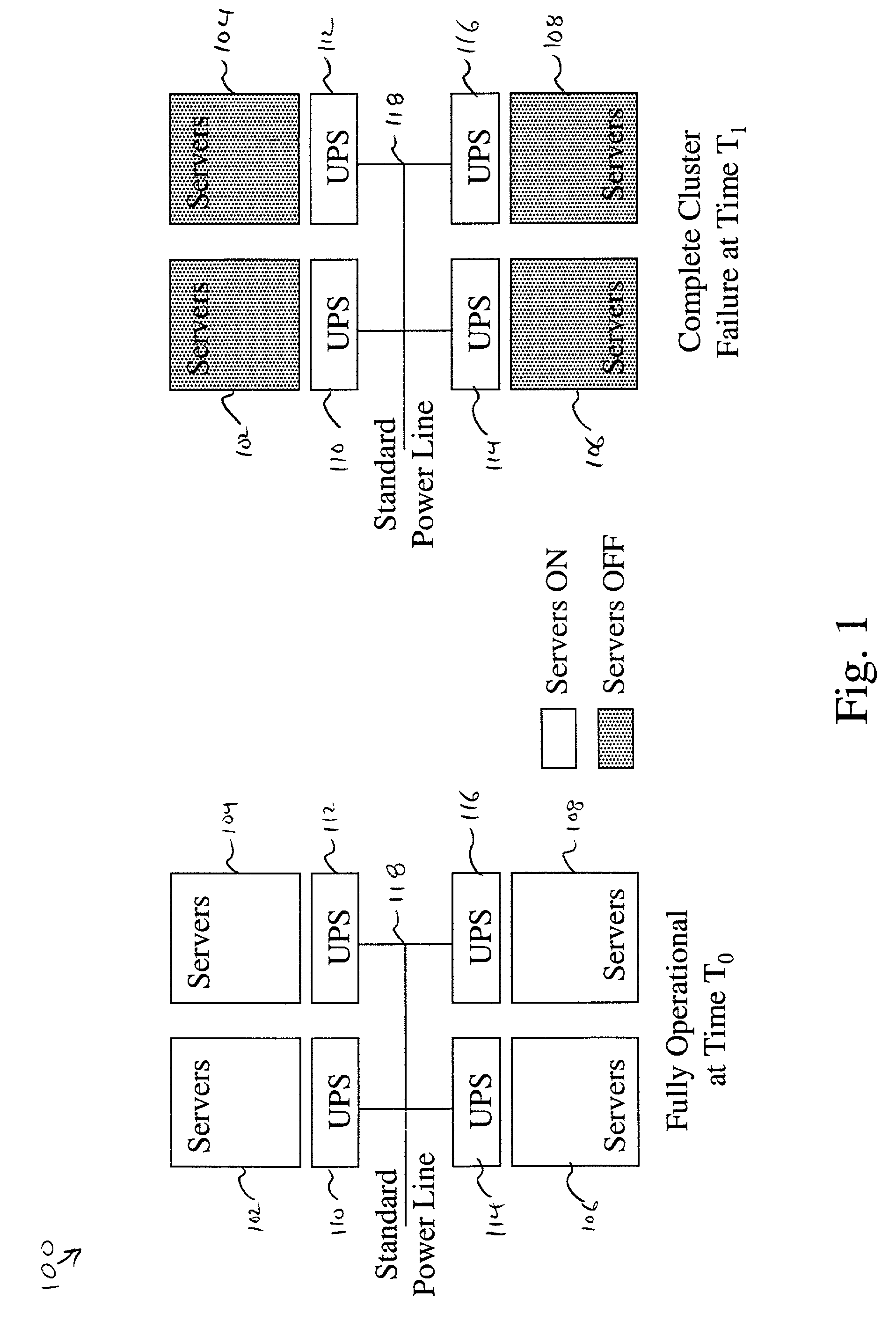

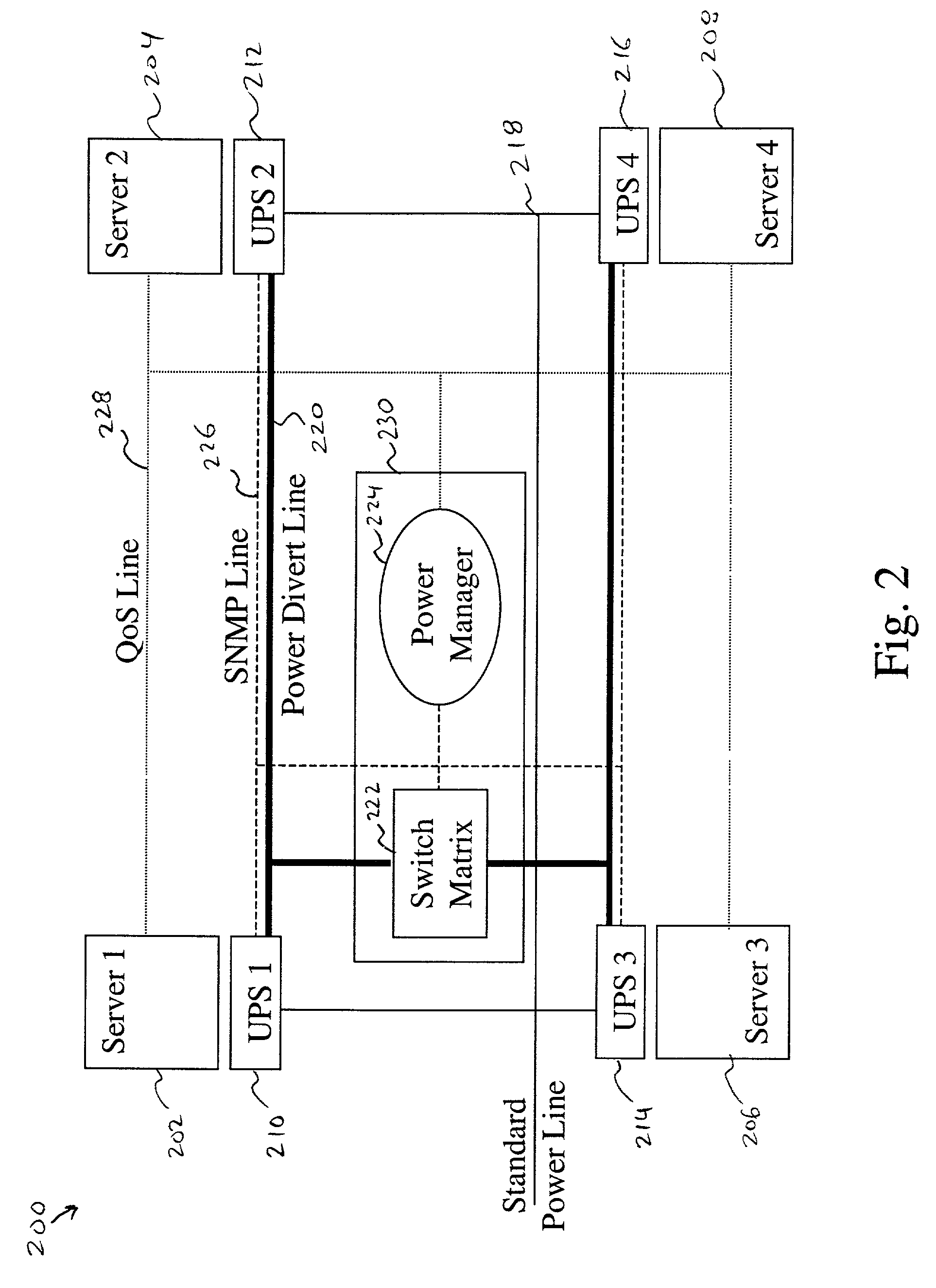

Method for diverting power reserves and shifting activities according to activity priorities in a server cluster in the event of a power interruption

InactiveUS6990593B2Volume/mass flow measurementMultiple digital computer combinationsQuality of serviceElectric power

A system and method for Quality of Service (QoS) based server cluster power management is disclosed. The method of the present invention includes: grouping activities within a server cluster into predefined sets; assigning a priority level to each set; identifying a server hosting a set of lower-priority activities within the cluster; receiving a power interruption signal; and diverting power reserves of the server to another server in the cluster, in response to the power interruption signal. The system of the present invention includes: servers, hosting a plurality of activity sets each having an associated QoS level; power reserves coupled to the servers; a switch matrix coupled to direct the power reserves between the servers; and a power manager, coupled to the switch matrix, for commanding the switch matrix to divert power from servers hosting low QoS activity sets to servers hosting high-priority activity sets, in response to a power interruption.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

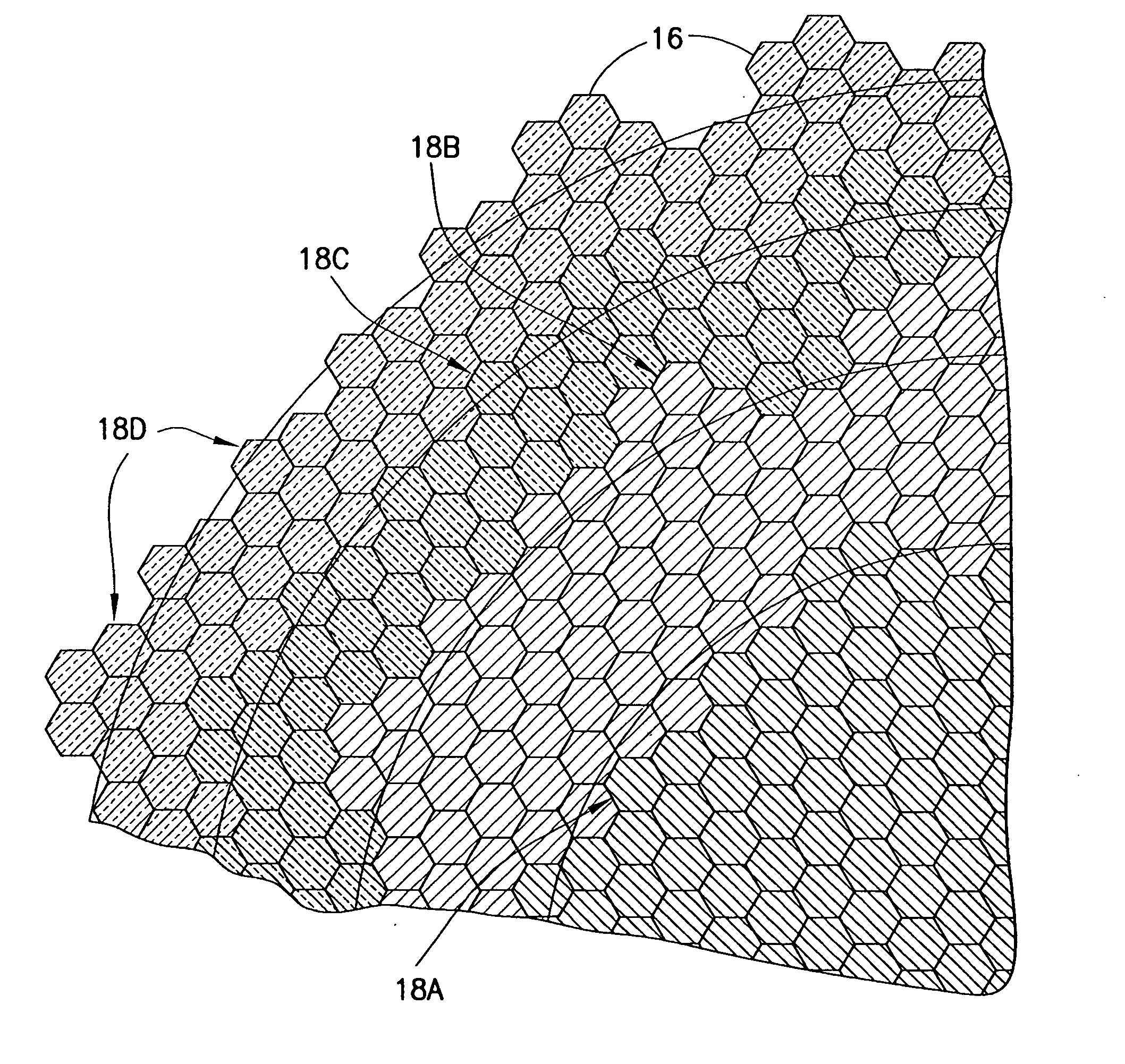

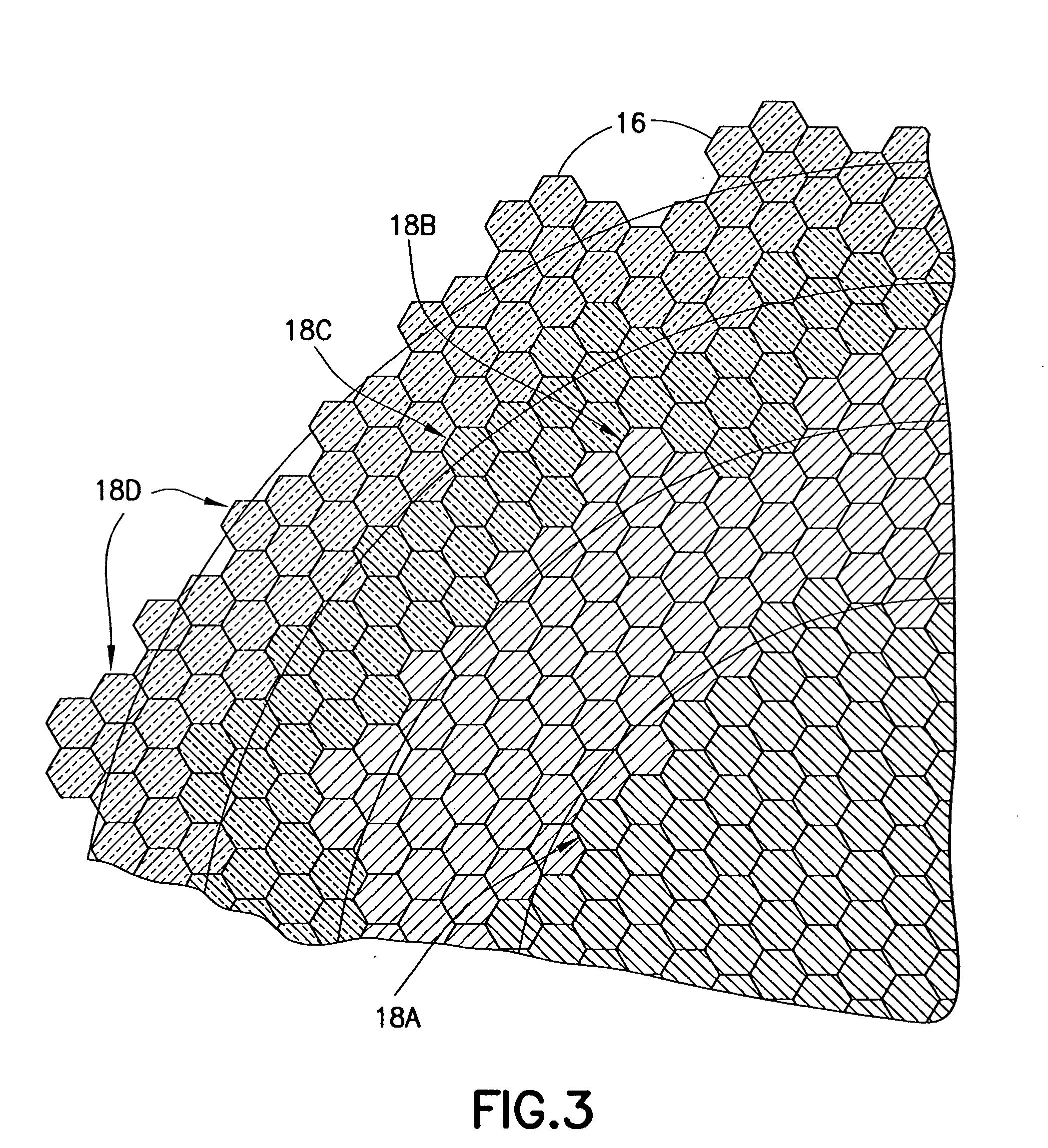

Method and apparatus for controlling scanning of mosaic sensor array

InactiveUS20050057284A1Quick configurationMinimize powerUltrasonic/sonic/infrasonic diagnosticsElectronic switchingSensor arrayUltrasonic sensor

A scanning architecture that makes it possible to update only those ultrasonic transducer subelements of a mosaic transducer array that change from view to view. The configuration of the switch matrix is fully programmable. The switch matrix includes access switches that connect subelements to bus lines and matrix switches that connect subelements to subelements. Each subelement has a unit switch cell associated therewith, each unit switch cell comprising at least one access switch, at least one matrix switch, and addressing and control logic. Optionally, each unit switch cell also includes latches for storing the future switch states of the switches to be programmed. The switches themselves have memory for storing their current switch states.

Owner:GENERAL ELECTRIC CO

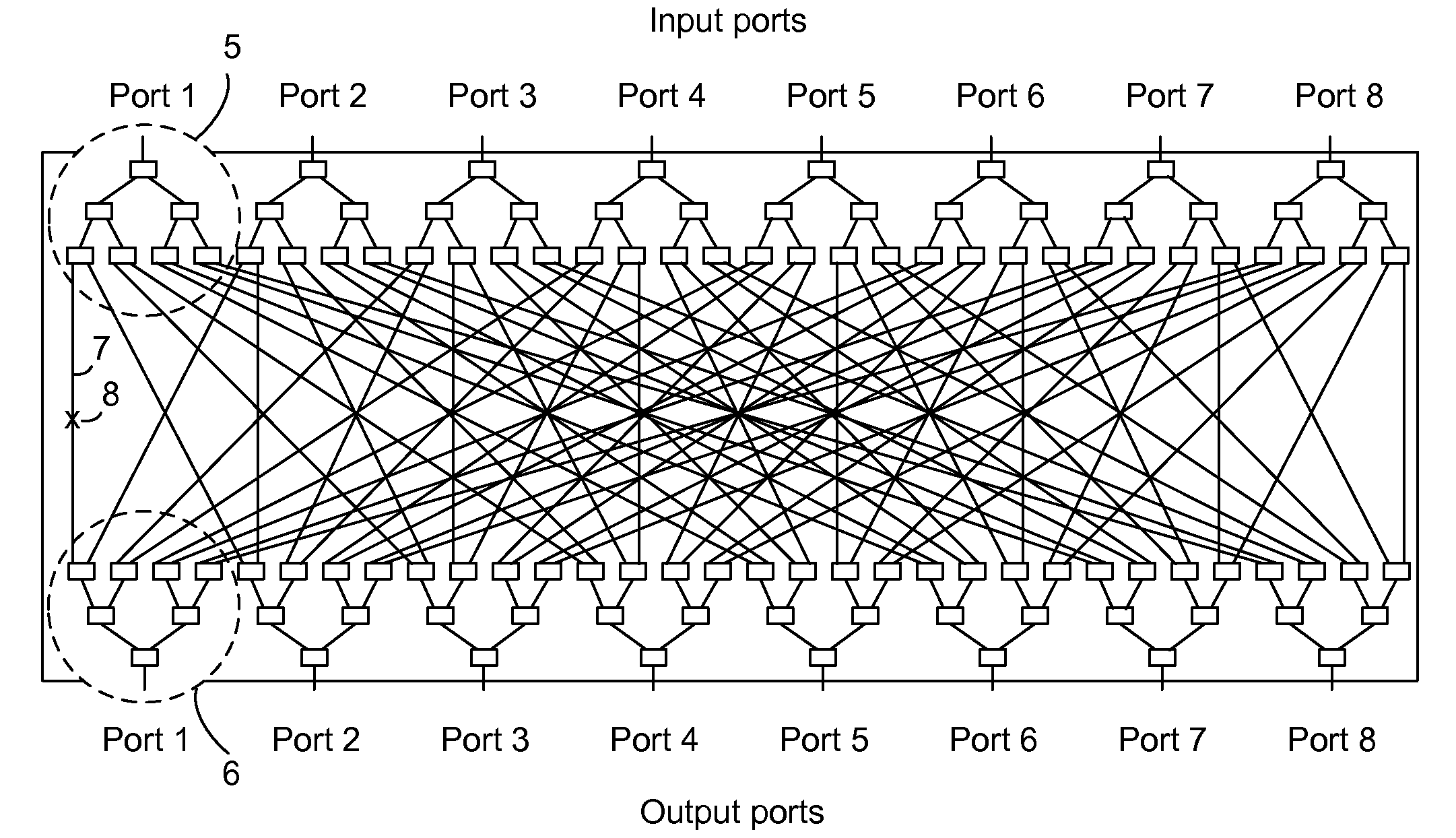

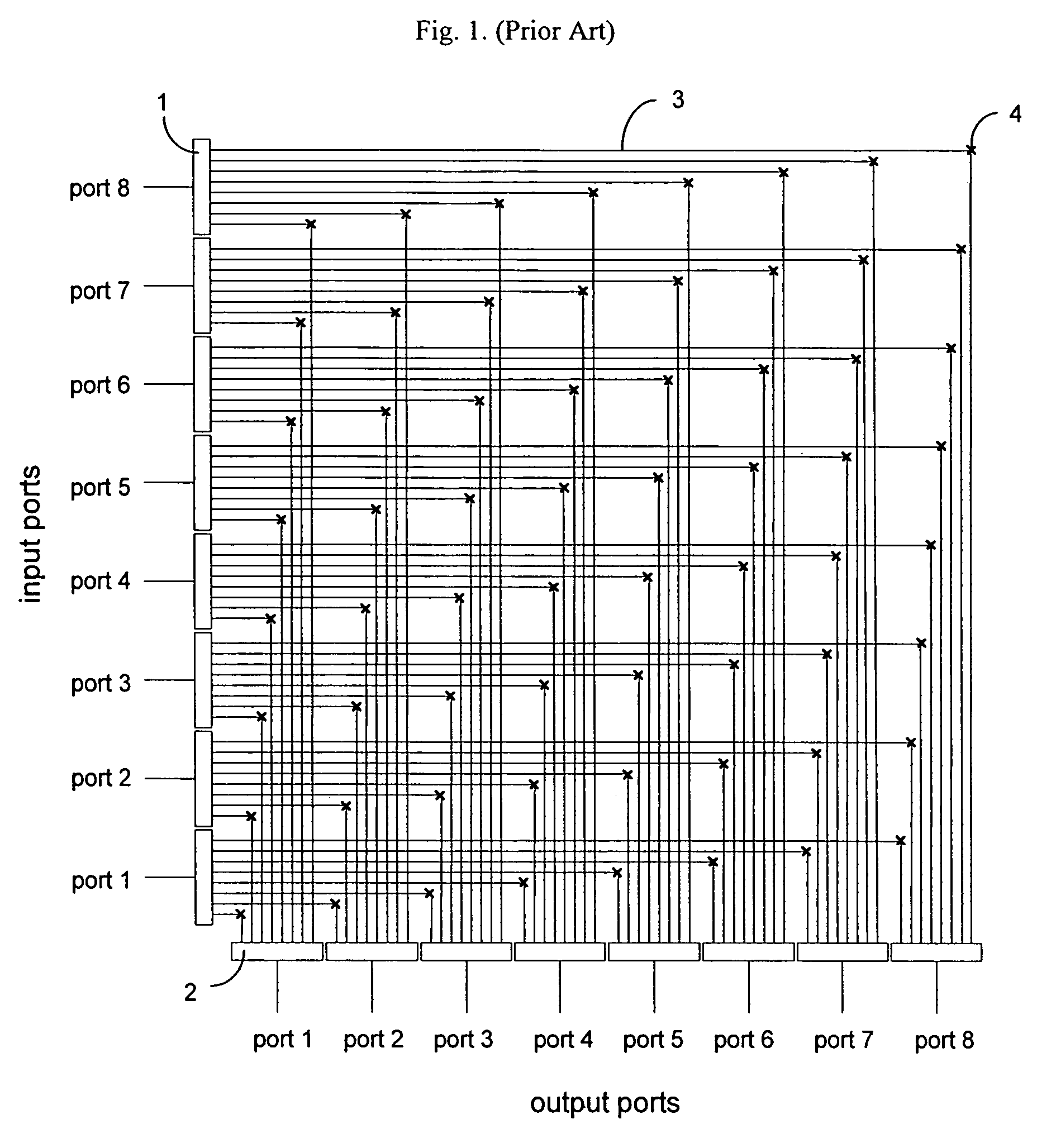

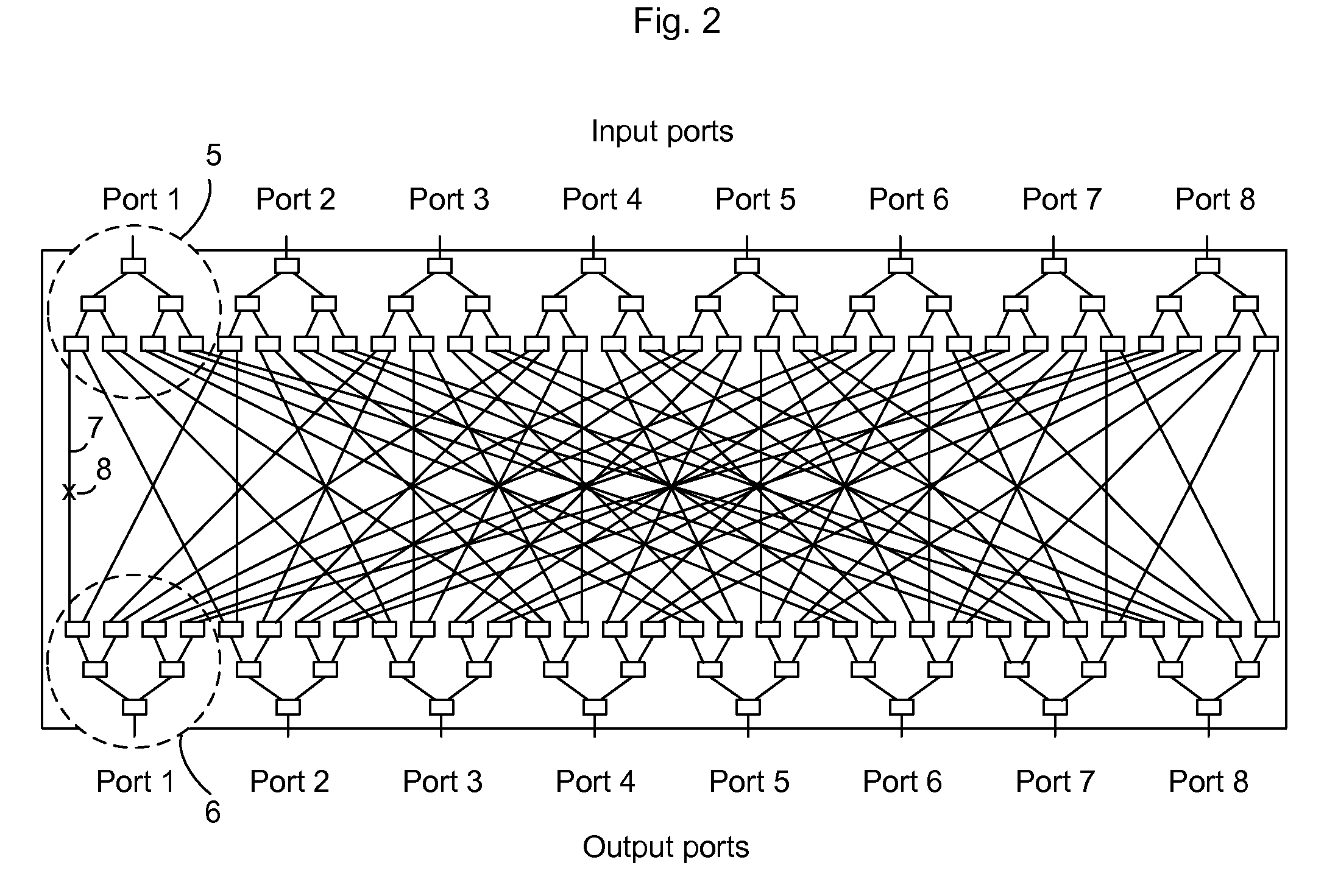

Distributed matrix switch

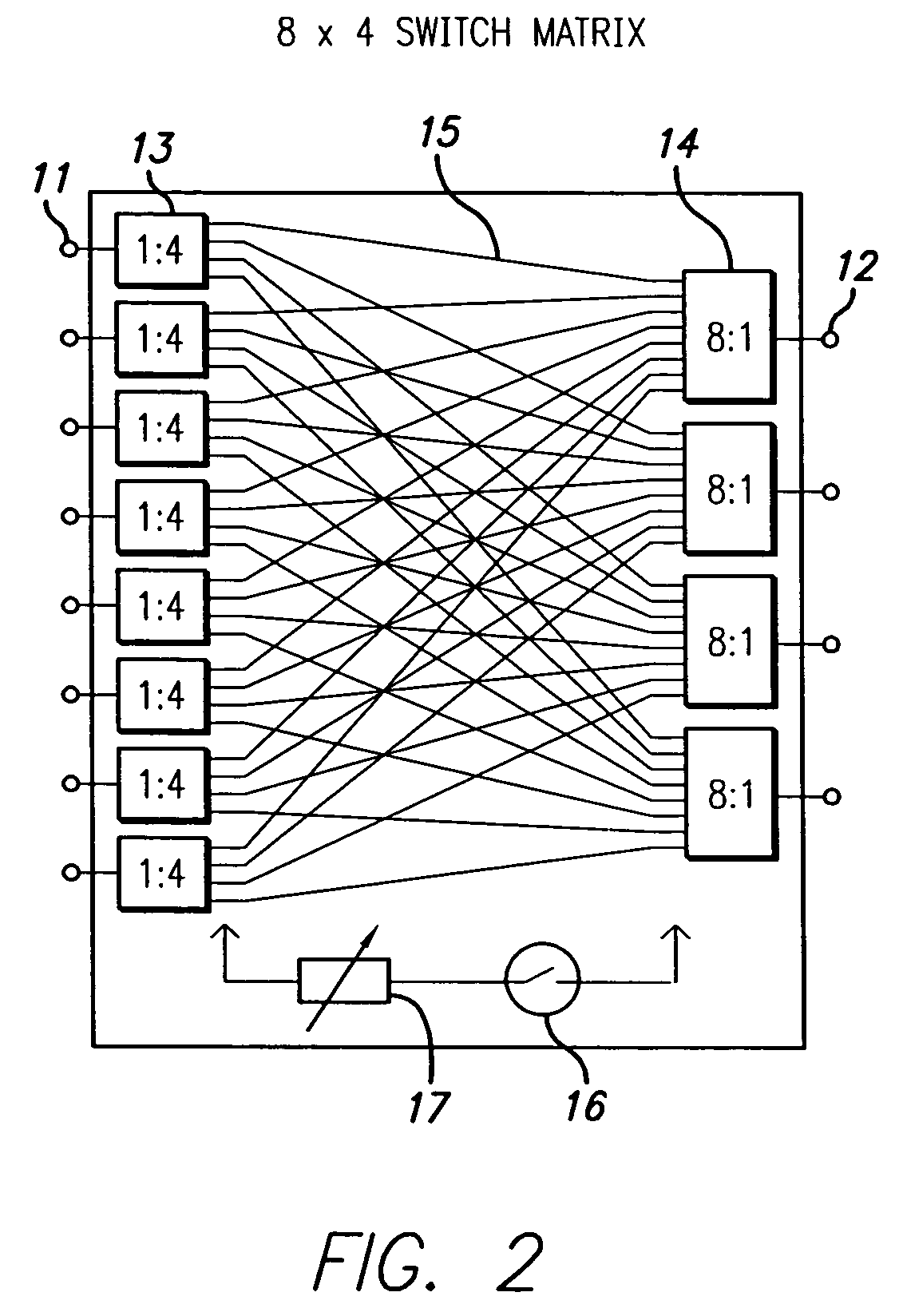

ActiveUS7205864B2Low costSmall sizeMultiplex system selection arrangementsCoupling devicesCross connectionEngineering

The present invention relates to an electrical space switch matrix having m input ports and n output ports, the switch matrix comprising (m.n) / (i.j) switch blocks, each having i input ports and j output ports, where i is less than m and j is less than n; and a plurality of input elements and a plurality of output elements, the plurality of input elements and plurality of output elements being arranged so as to connect the switch blocks to the input and output ports of the switch matrix. In an embodiment of the invention, the input and output elements can be power splitters and power combiners respectively and are arranged so as to include crossover connection paths therebetween, with the result that crossover of connection paths is distributed between the power dividing / combining function and the switching function.

Owner:NEXTG NETWORKS INC

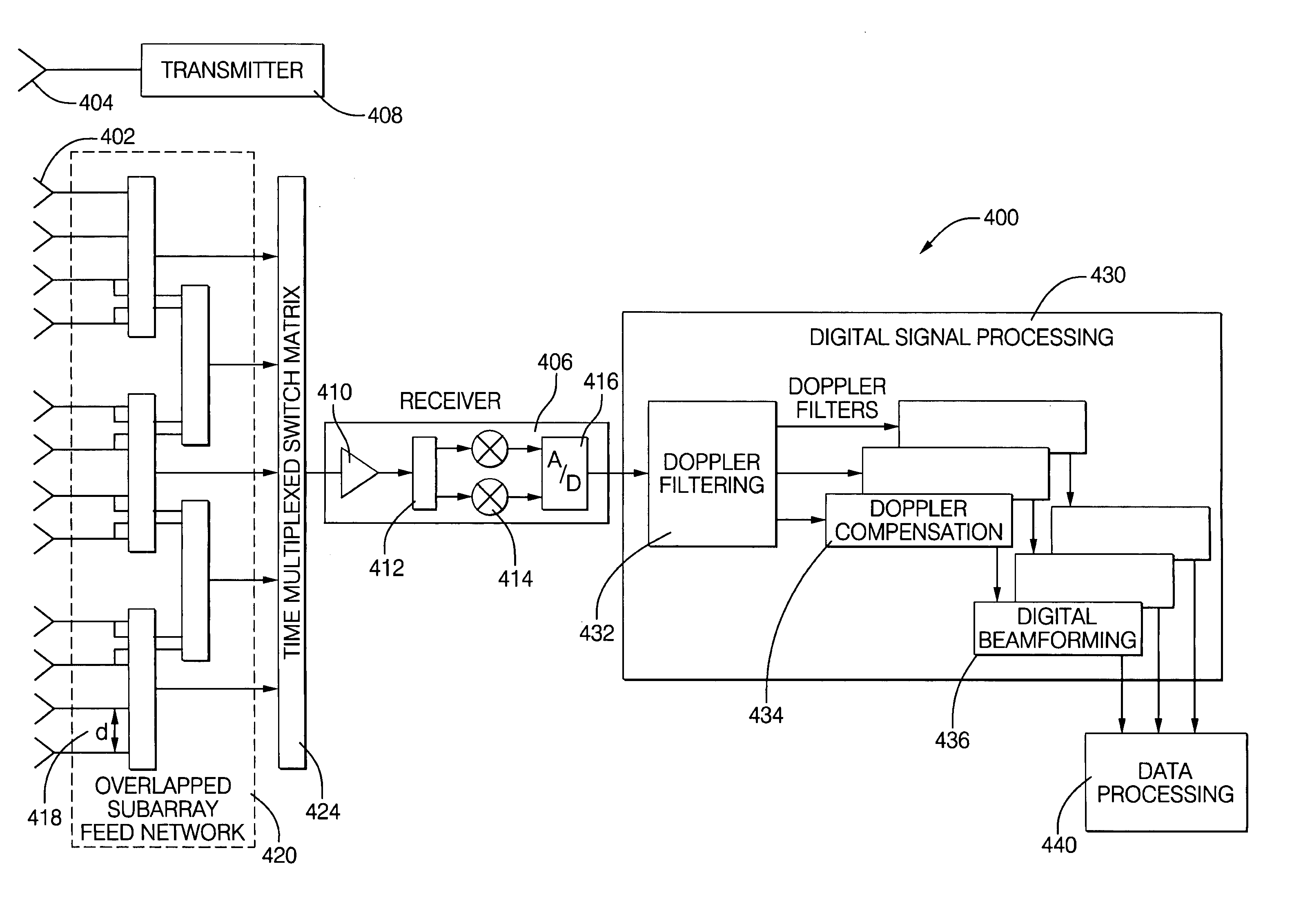

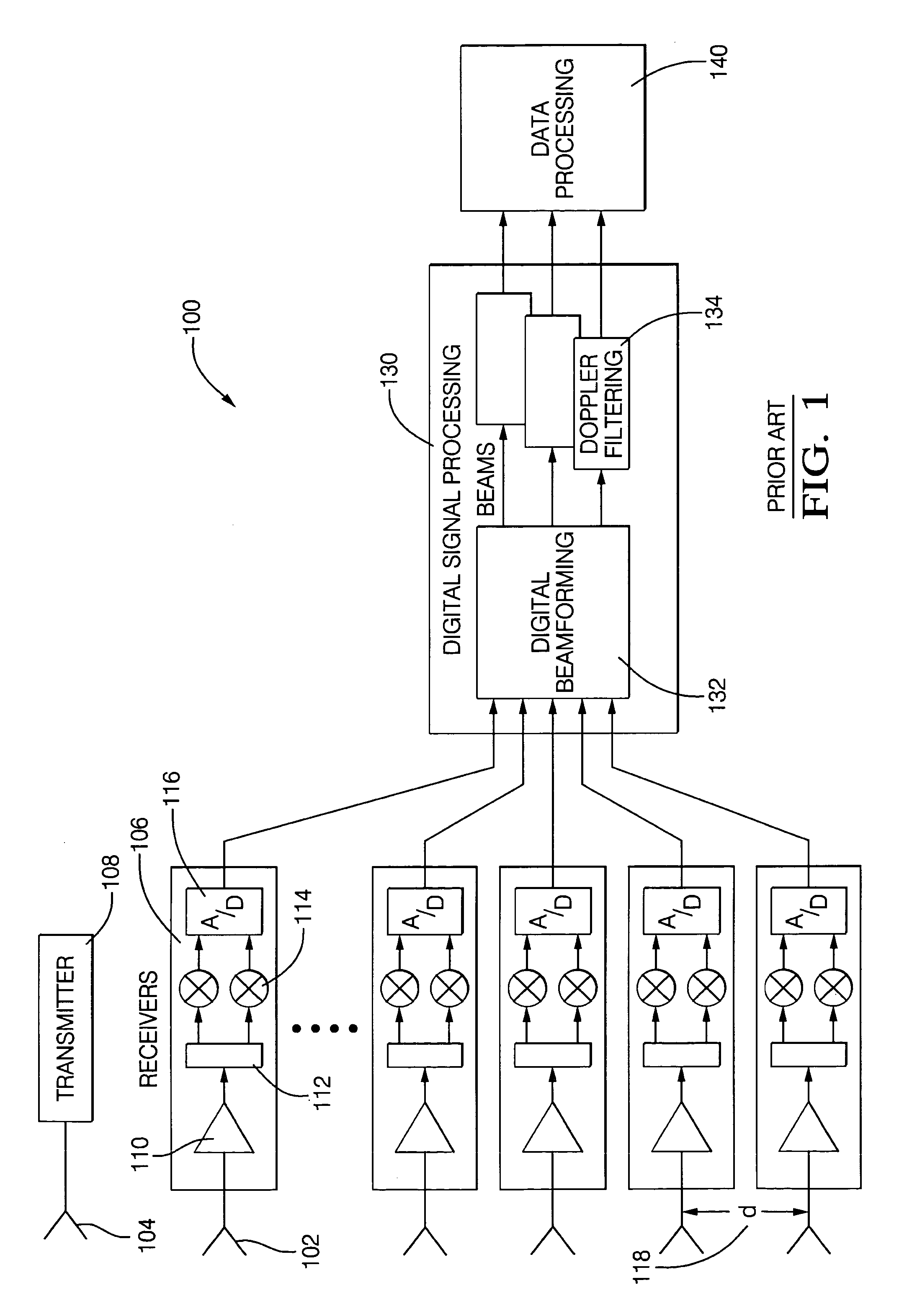

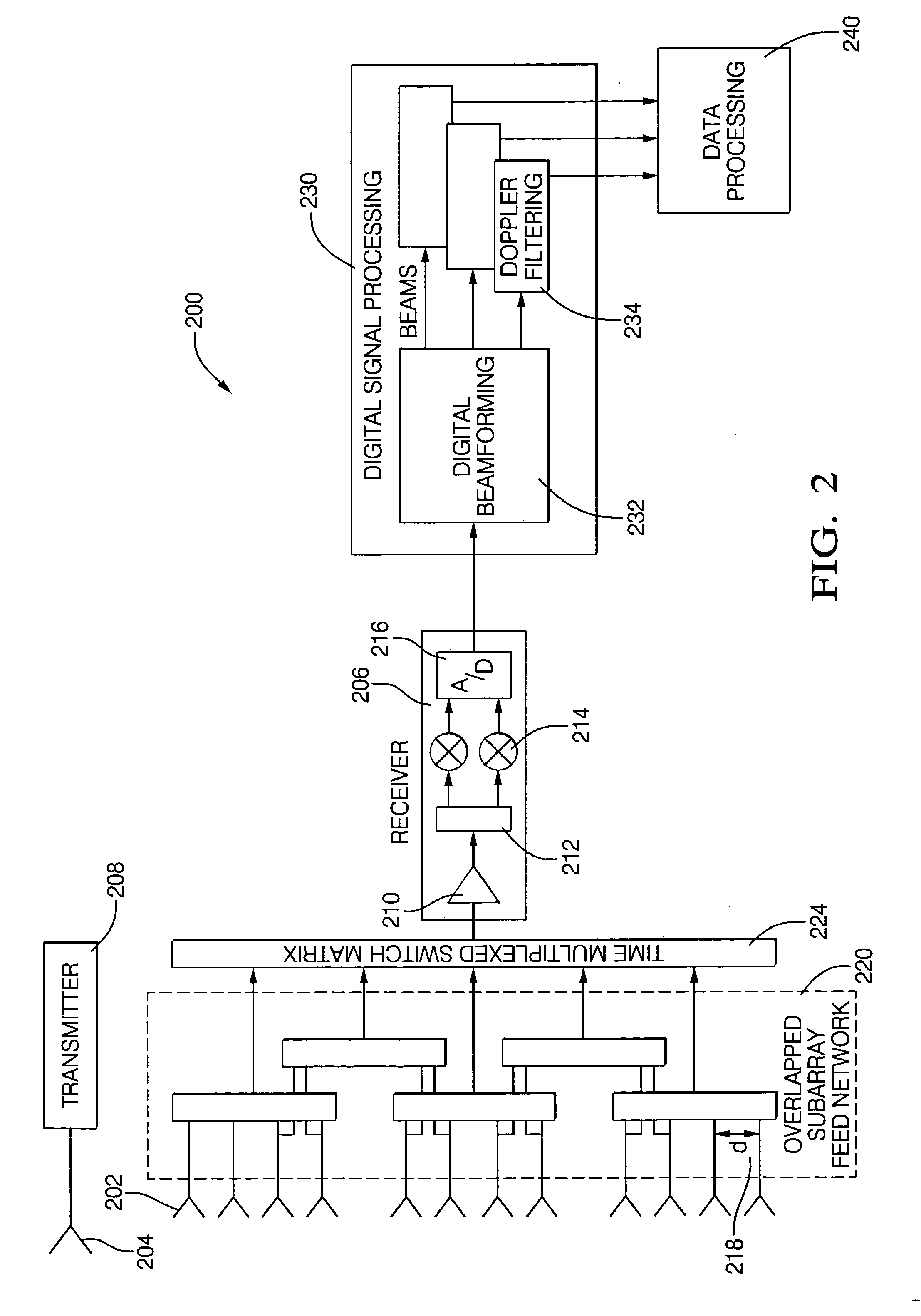

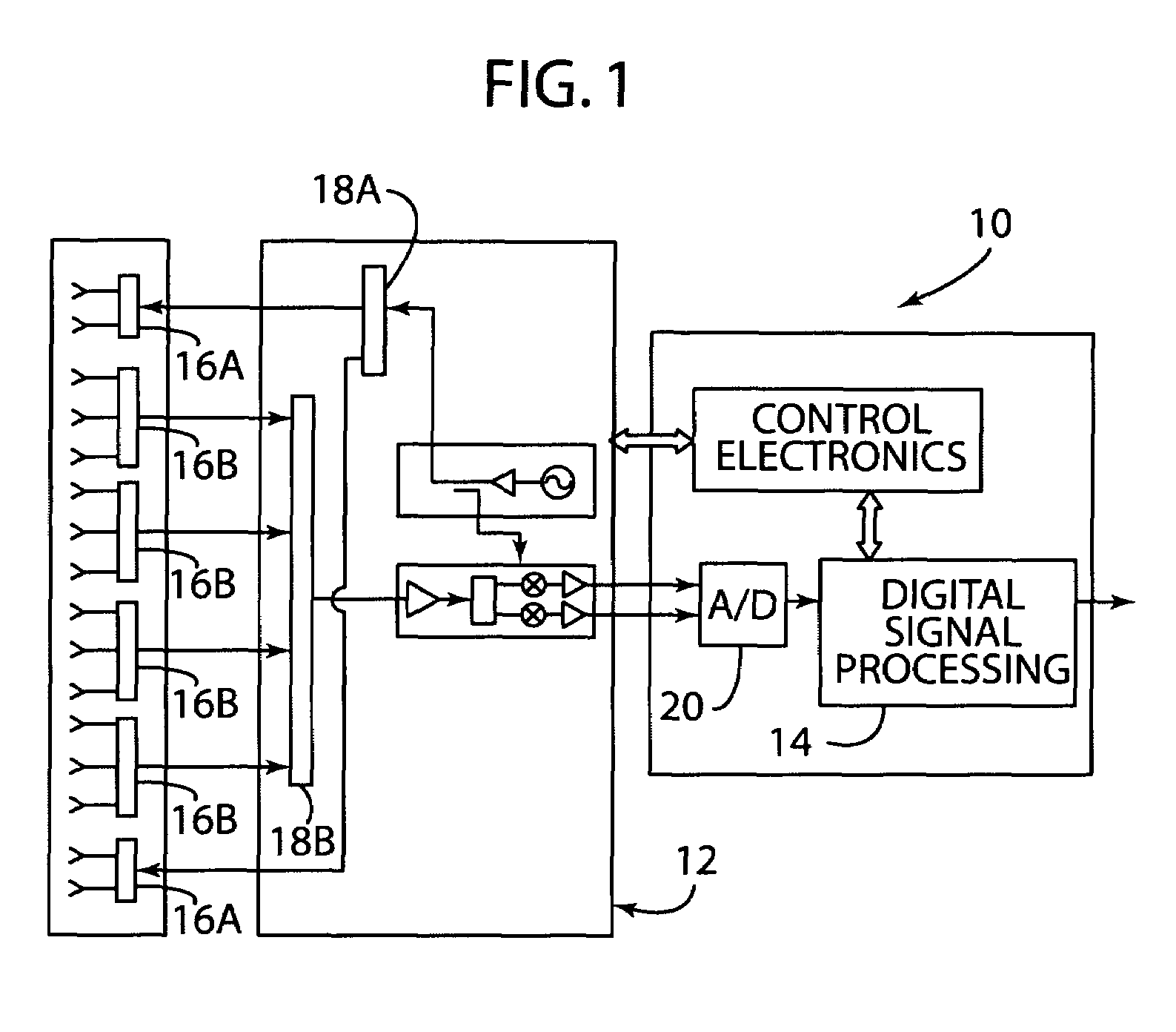

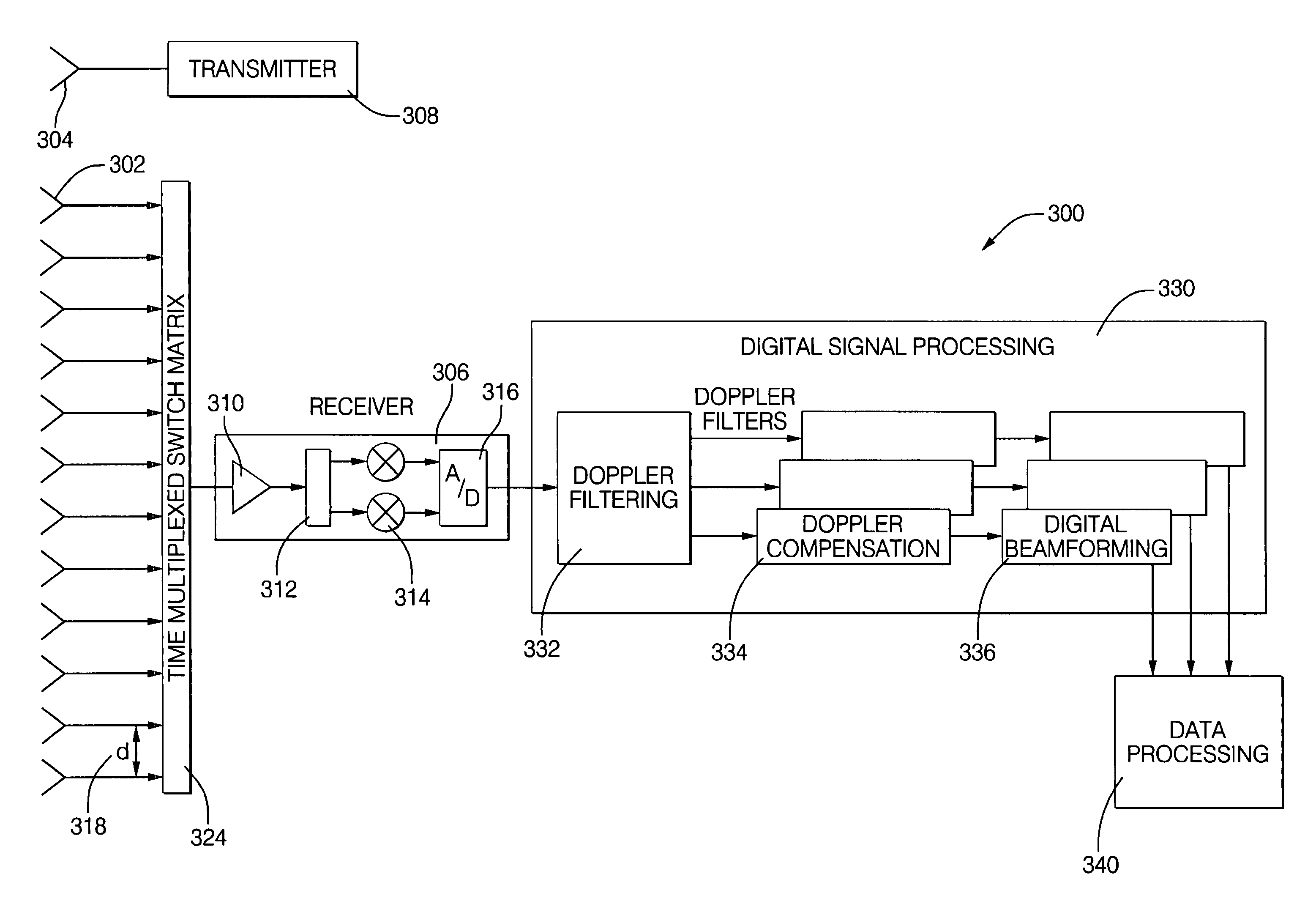

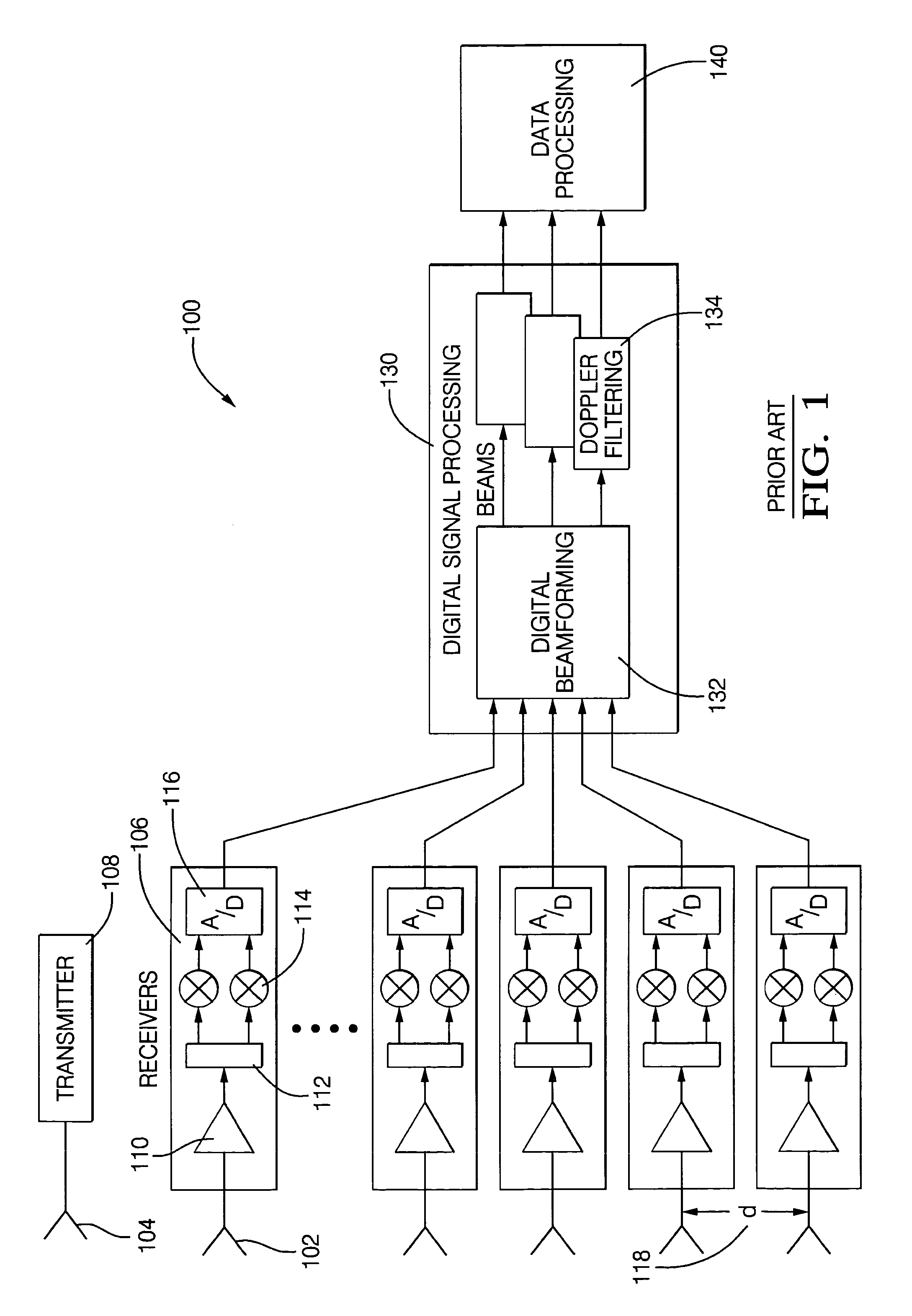

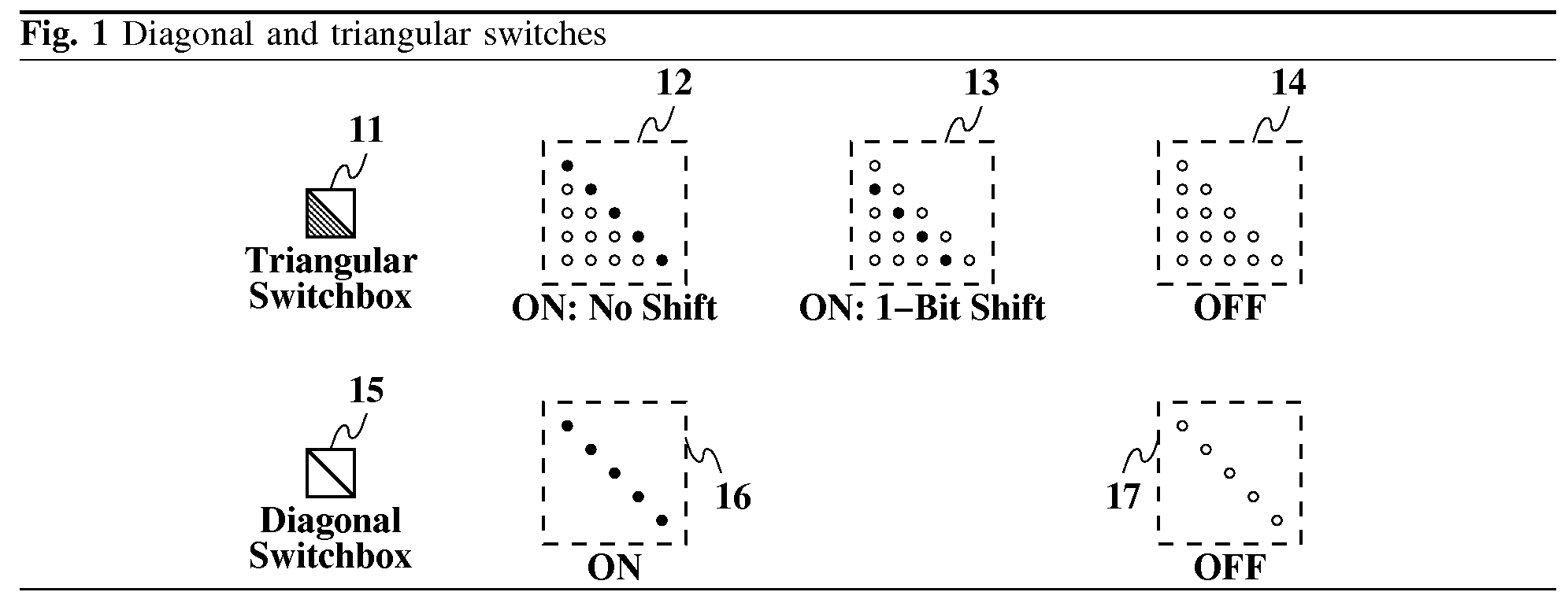

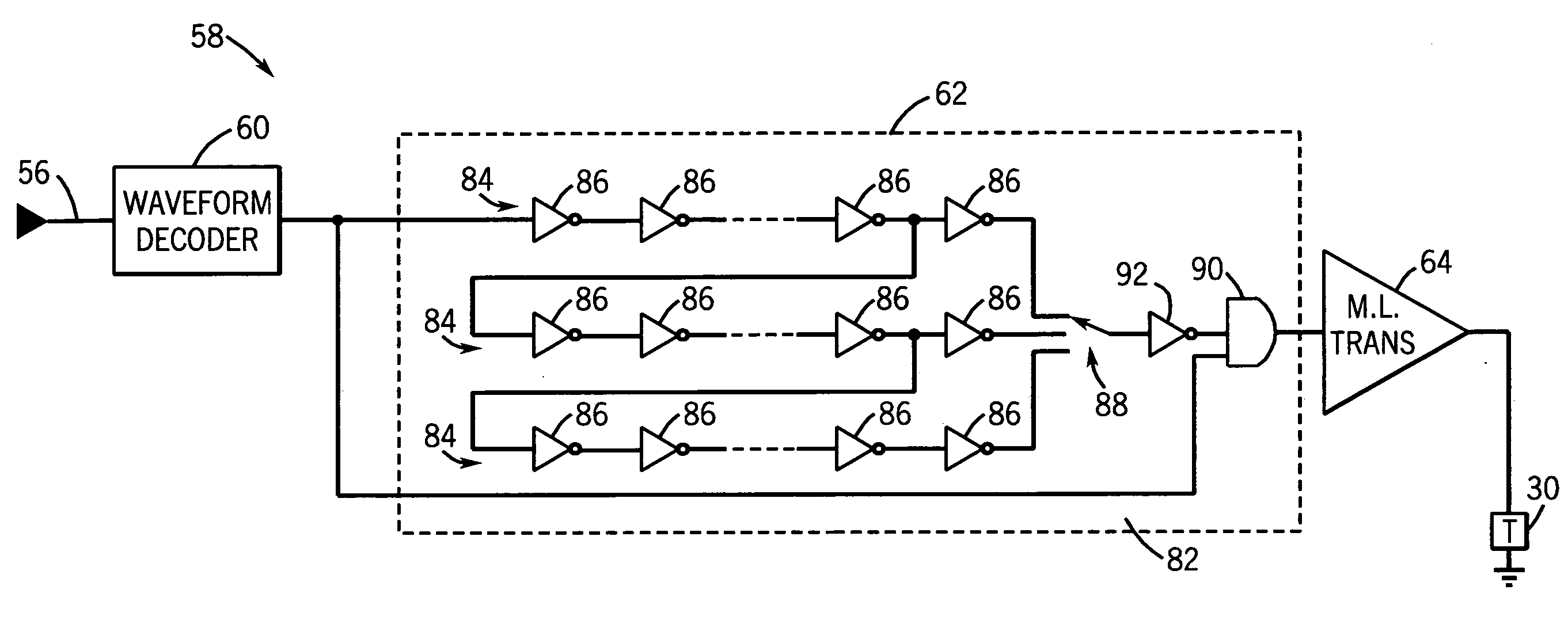

Digital beamforming for an electronically scanned radar system

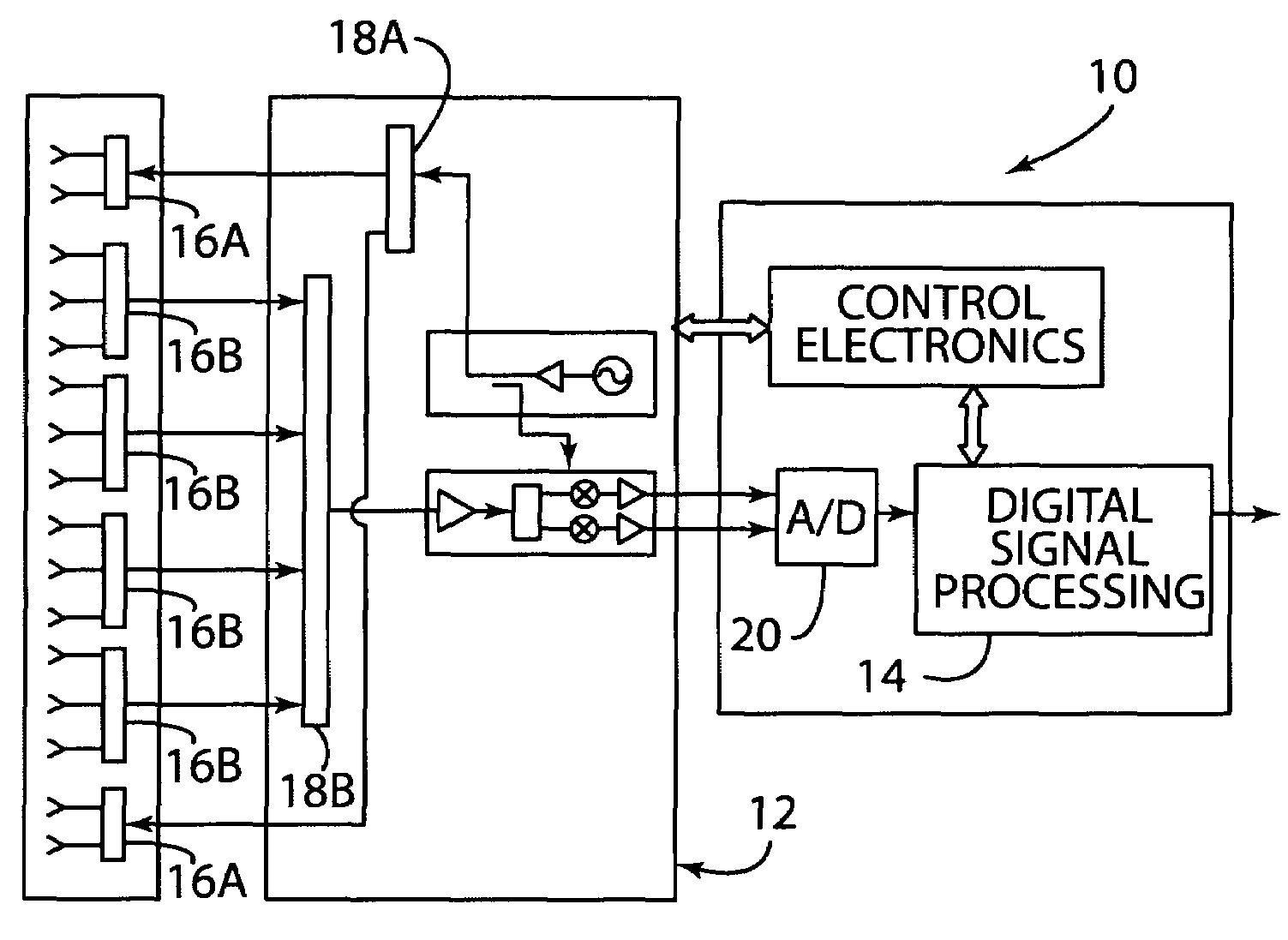

ActiveUS20070001897A1Improve performanceLow costParticular array feeding systemsRadio transmissionRadar systemsGrating lobe

Digital beamforming is provided for use with electronically scanned radar. In an aspect, the present invention provides enhanced sensitivity, wide angle or field of view (FOV) coverage with narrow beams, minimized number of receivers, reduced sidelobes, eliminated grating lobes and beam compensation for target motion. In an aspect, the present invention employs a uniform overlapped subarray feed network, a time multiplexed switch matrix, and a restructured digital signal processor. Antenna channels share a receiver, rather than maintain a dedicated receiver for each antenna element, as in conventional systems. In an aspect, Doppler / frequency filtering is performed on each antenna element or subarray output prior to digital beamforming. Further, Doppler compensation is employed following Doppler / frequency filtering, followed by digital beamforming.

Owner:APTIV TECH LTD

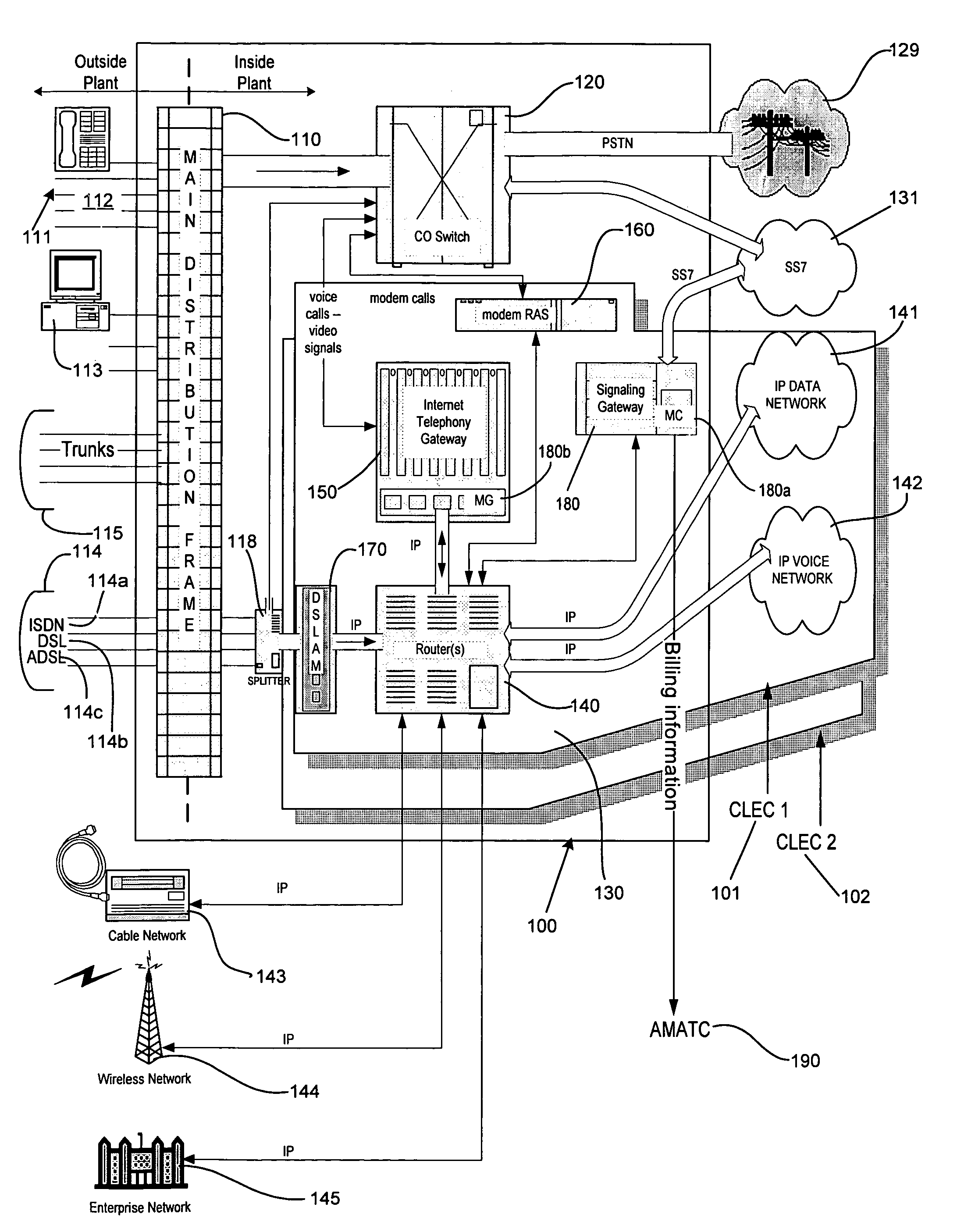

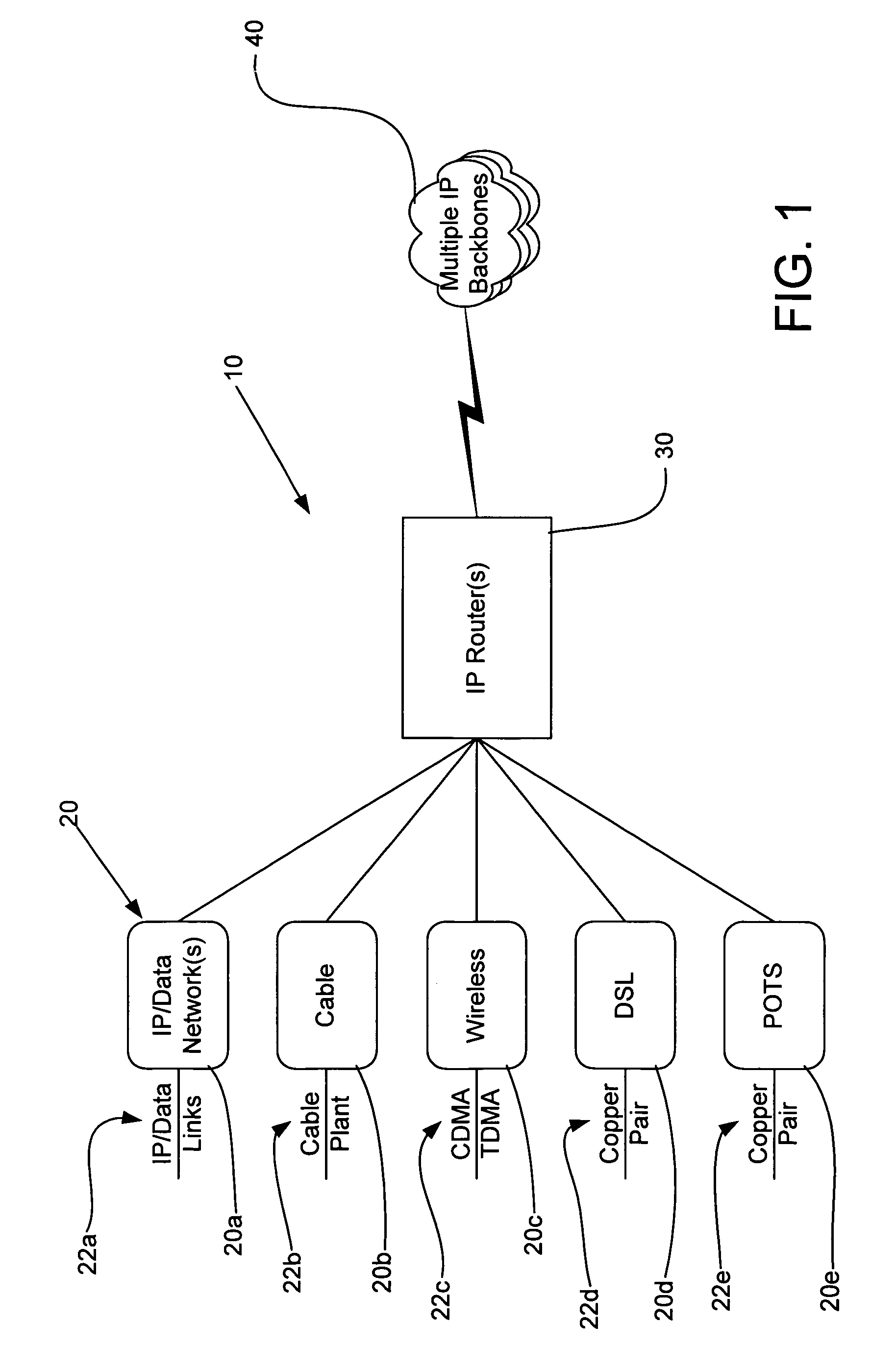

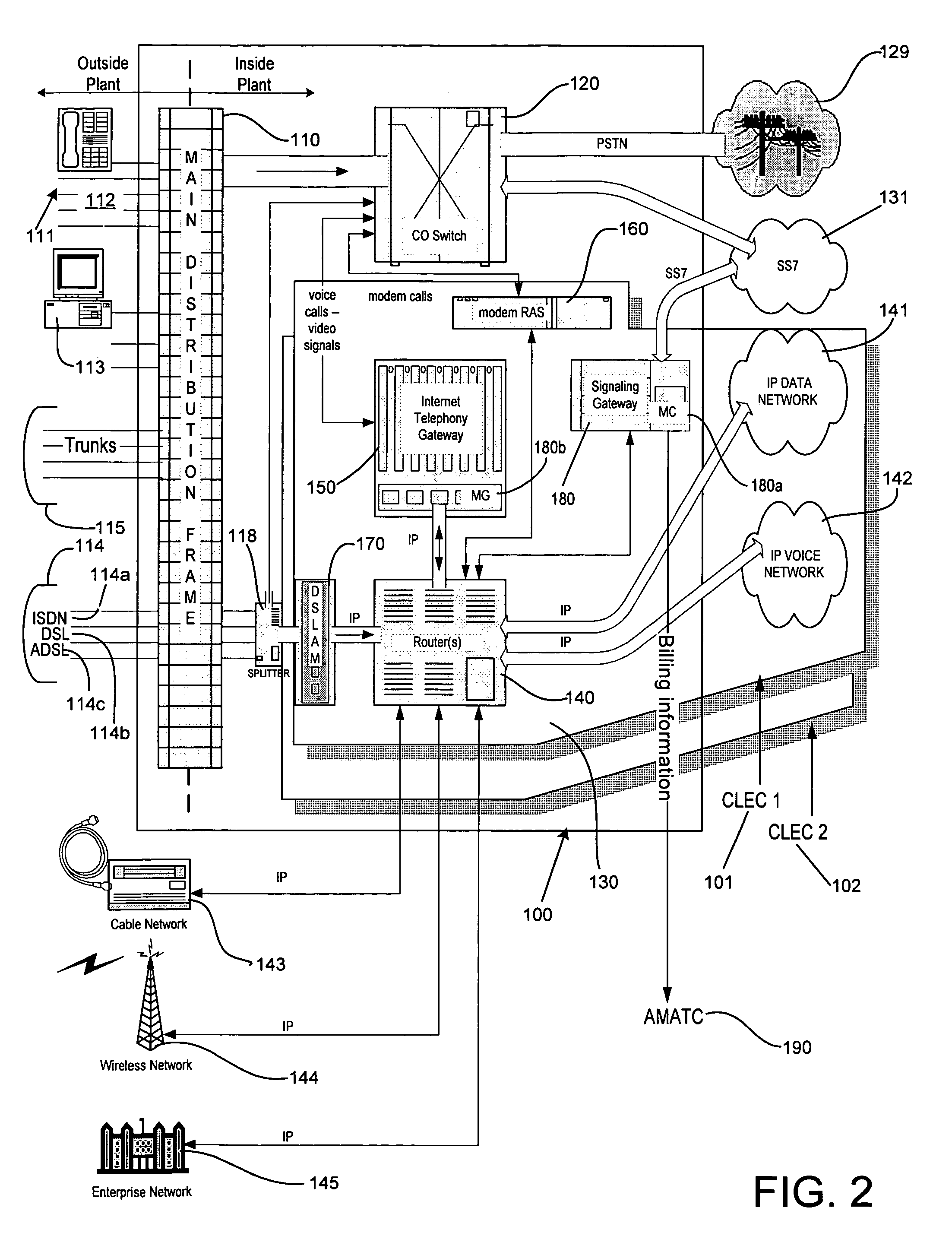

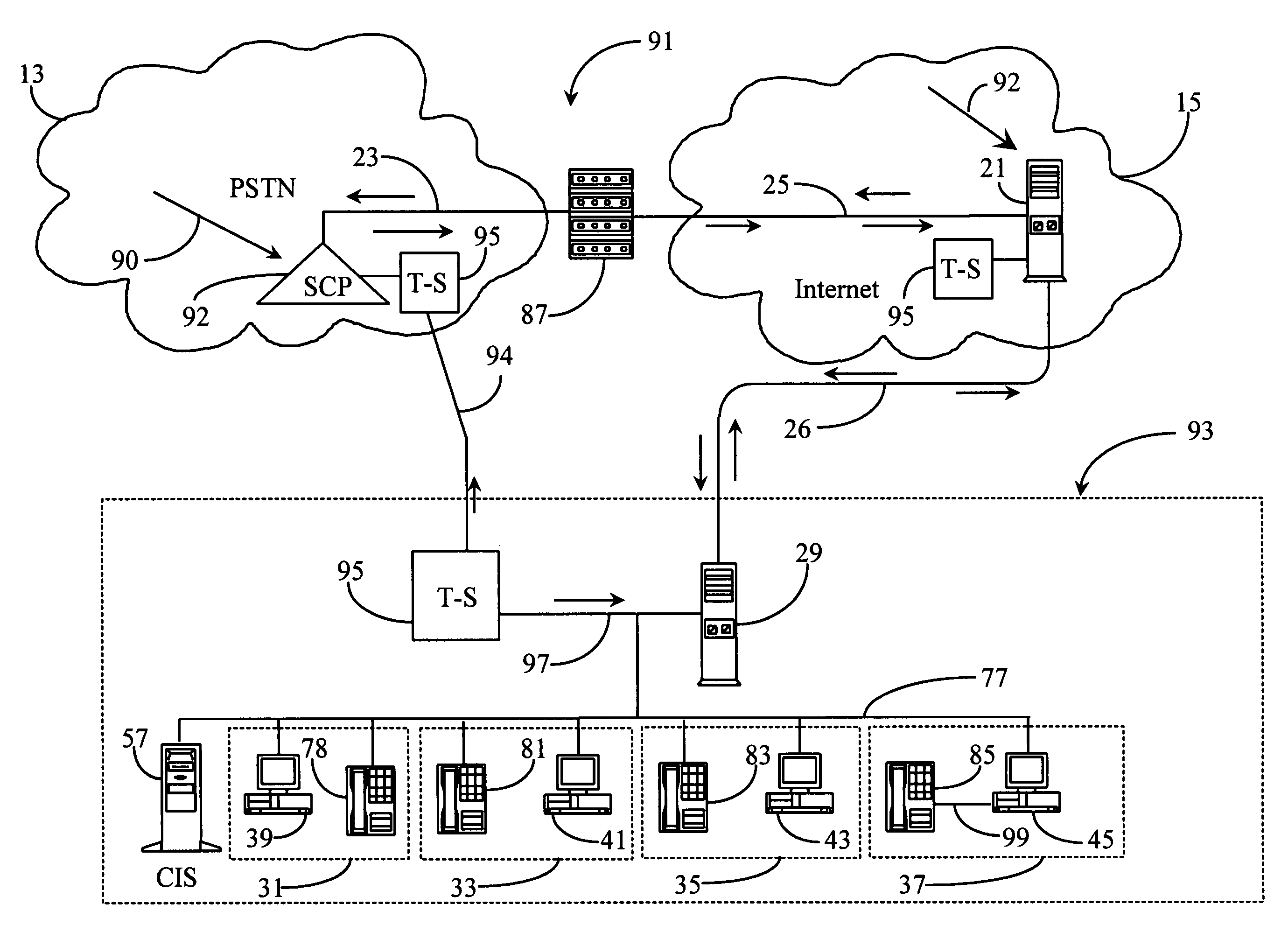

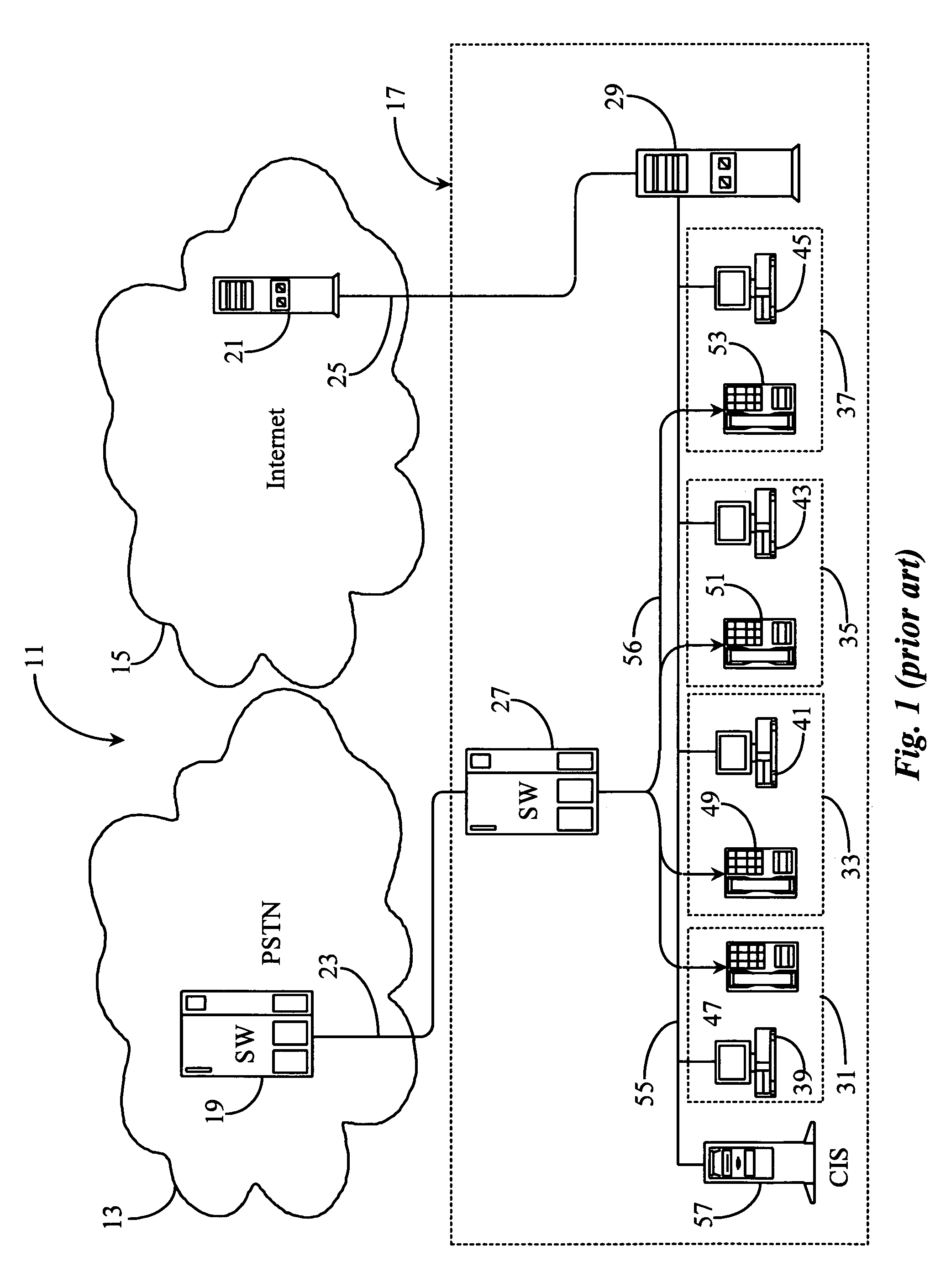

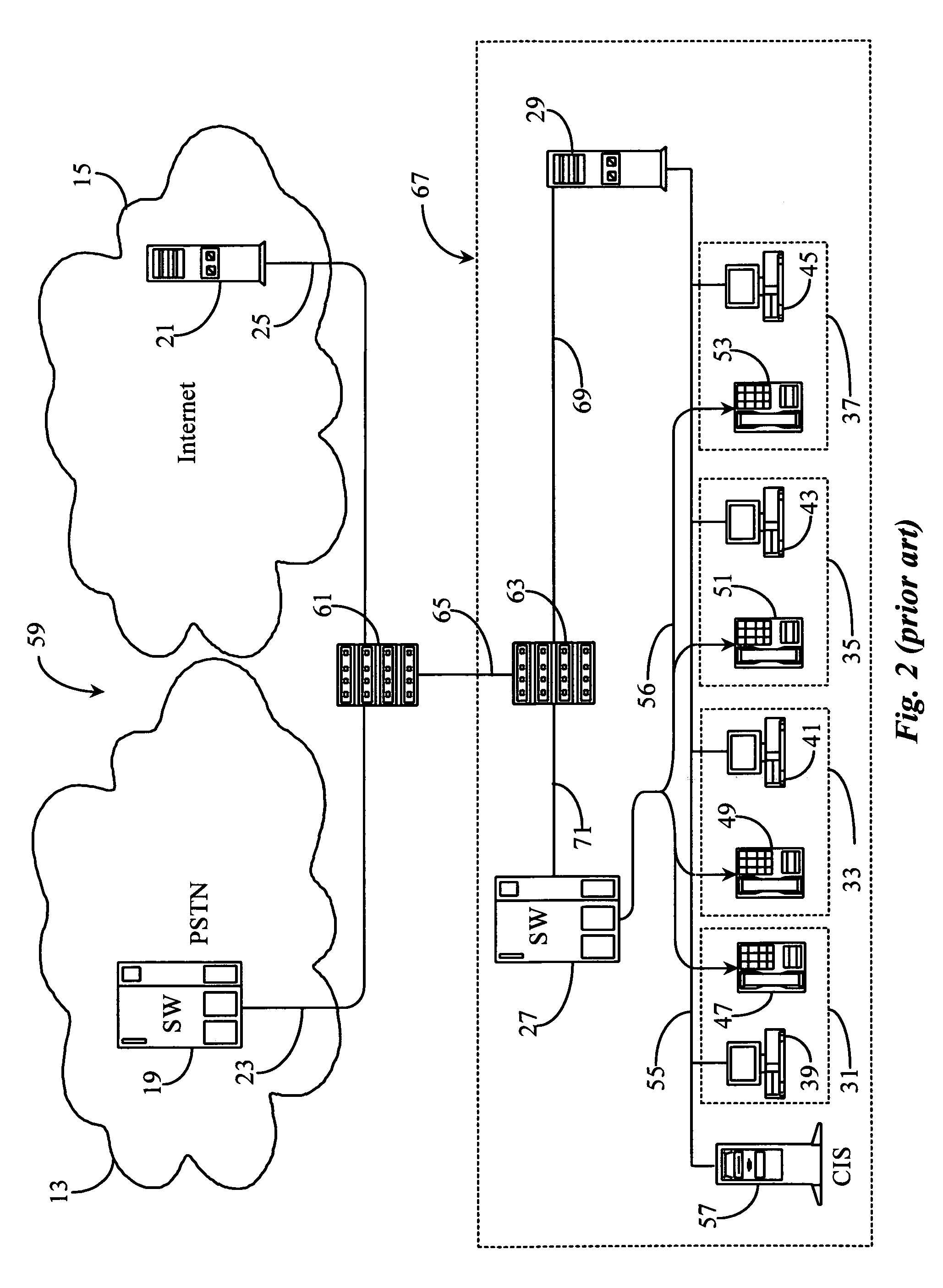

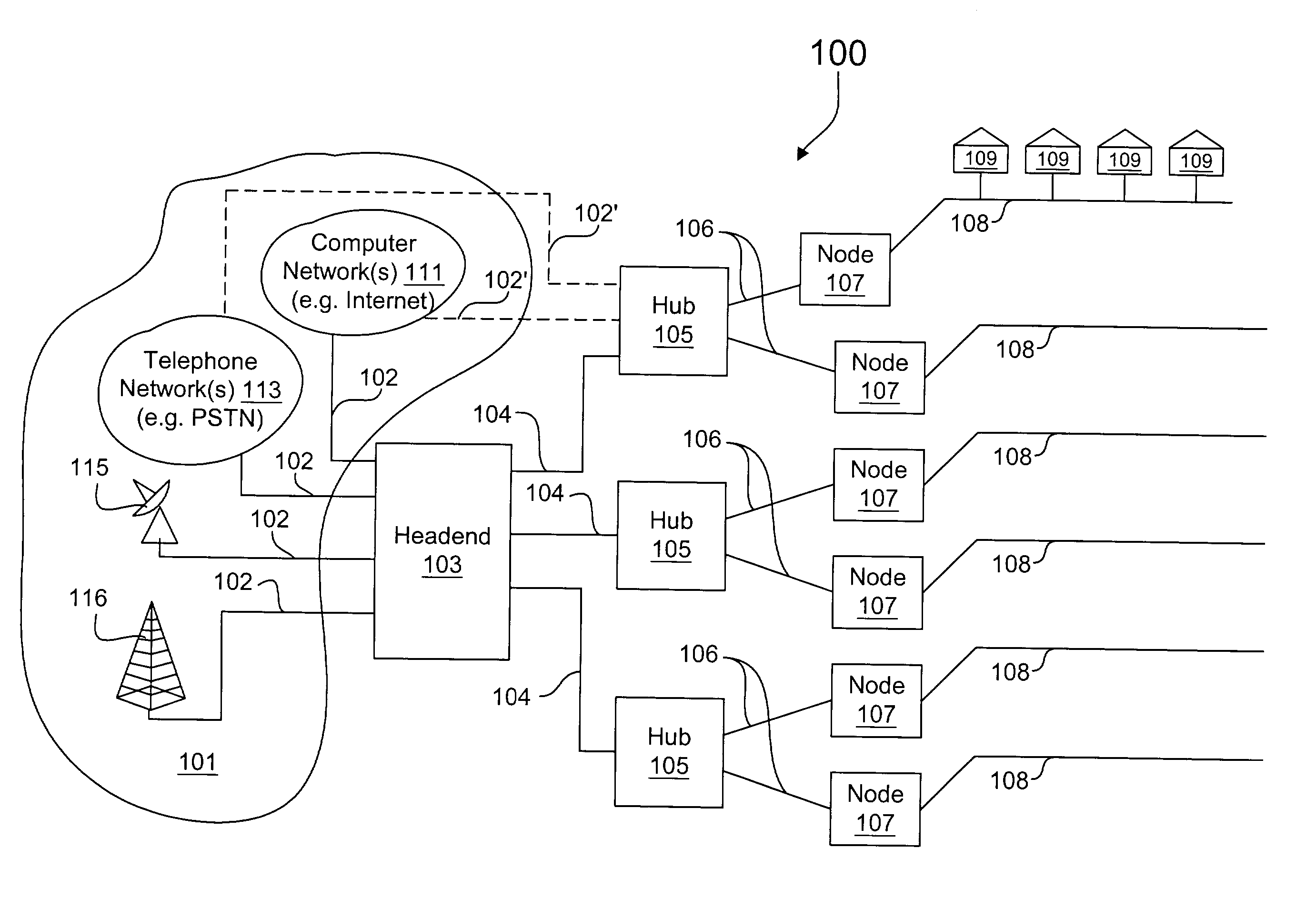

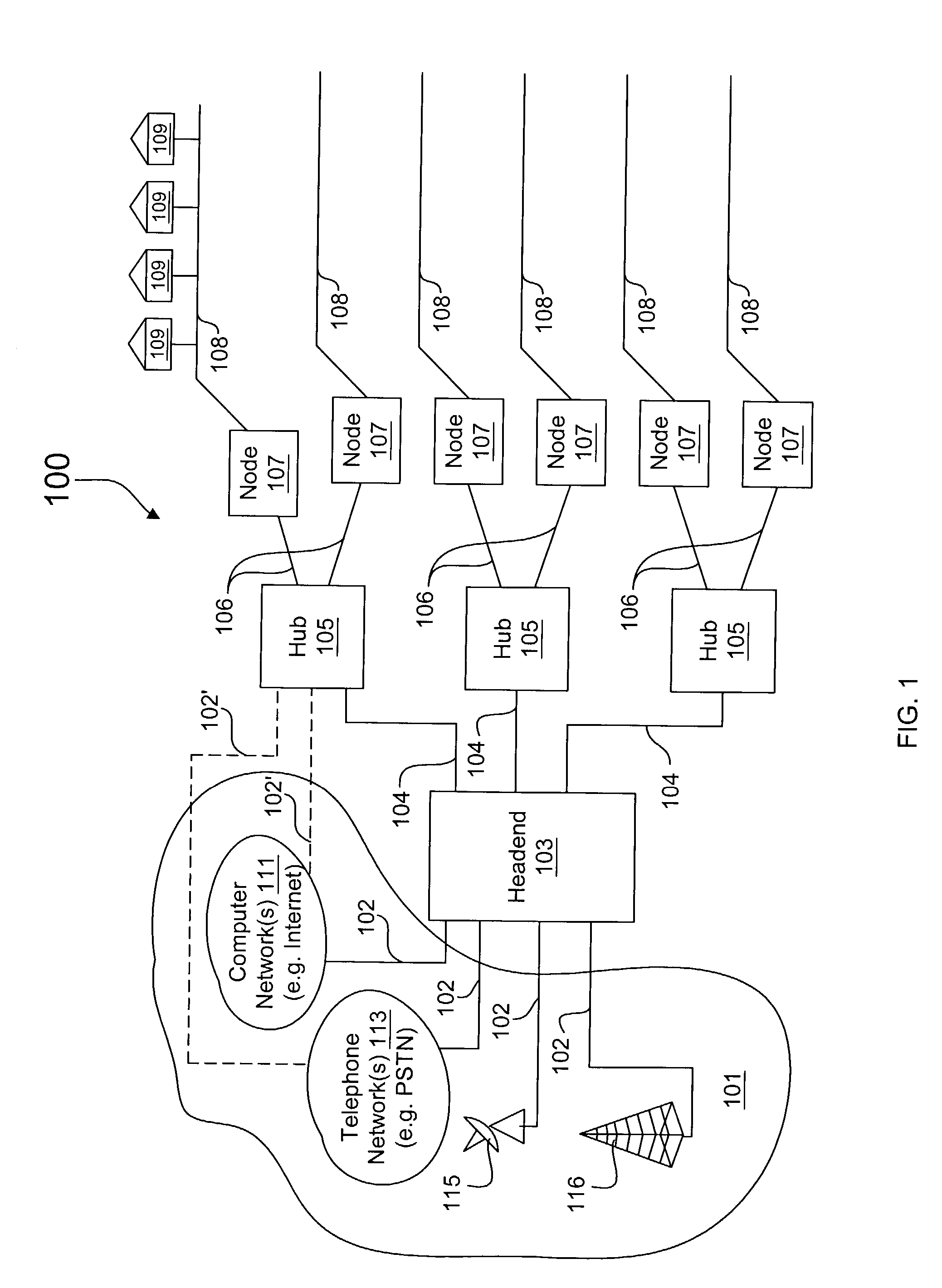

Architecture for a central office using IP technology

A telephony system and method having a switch for analog voice and data signals that is connected to a first network, and a router for routing Internet Protocol packets that is connected to a second network using Internet Protocol addressing. The telephony system and method also includes a telephony gateway that is connected to both the switch and the router for converting analog voice signals into Internet Protocol packets and for converting Internet Protocol packets into analog voice signals, the telephony gateway being connected, and a remote access server that is connected to both the switch and the router for converting analog data signals into Internet Protocol packets and for converting Internet Protocol packets into analog data signals. The switch may have a switch matrix capable of being connected to the Public Switched Telephone Network, a line rack with a plurality of line cards connected to the switch matrix, and a trunk rack with a plurality of trunk cards connected to the switch matrix. The switch matrix may also be connected to the telephony gateway and the remote access server.

Owner:UTSTARCOM INC

Integrated interface electronics for reconfigurable sensor array

ActiveUS7257051B2Ultrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesElectricitySensor array

Owner:GENERAL ELECTRIC CO

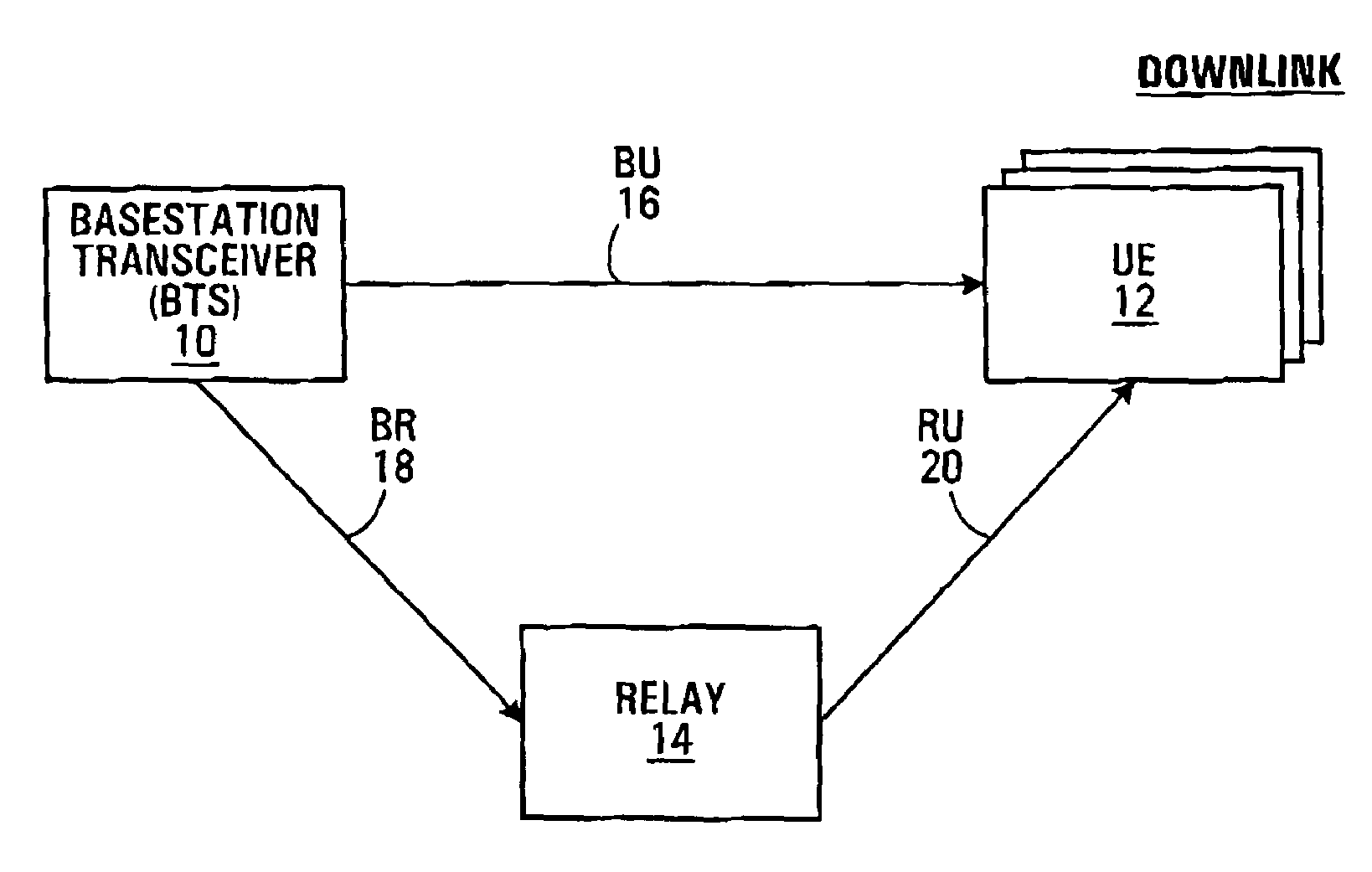

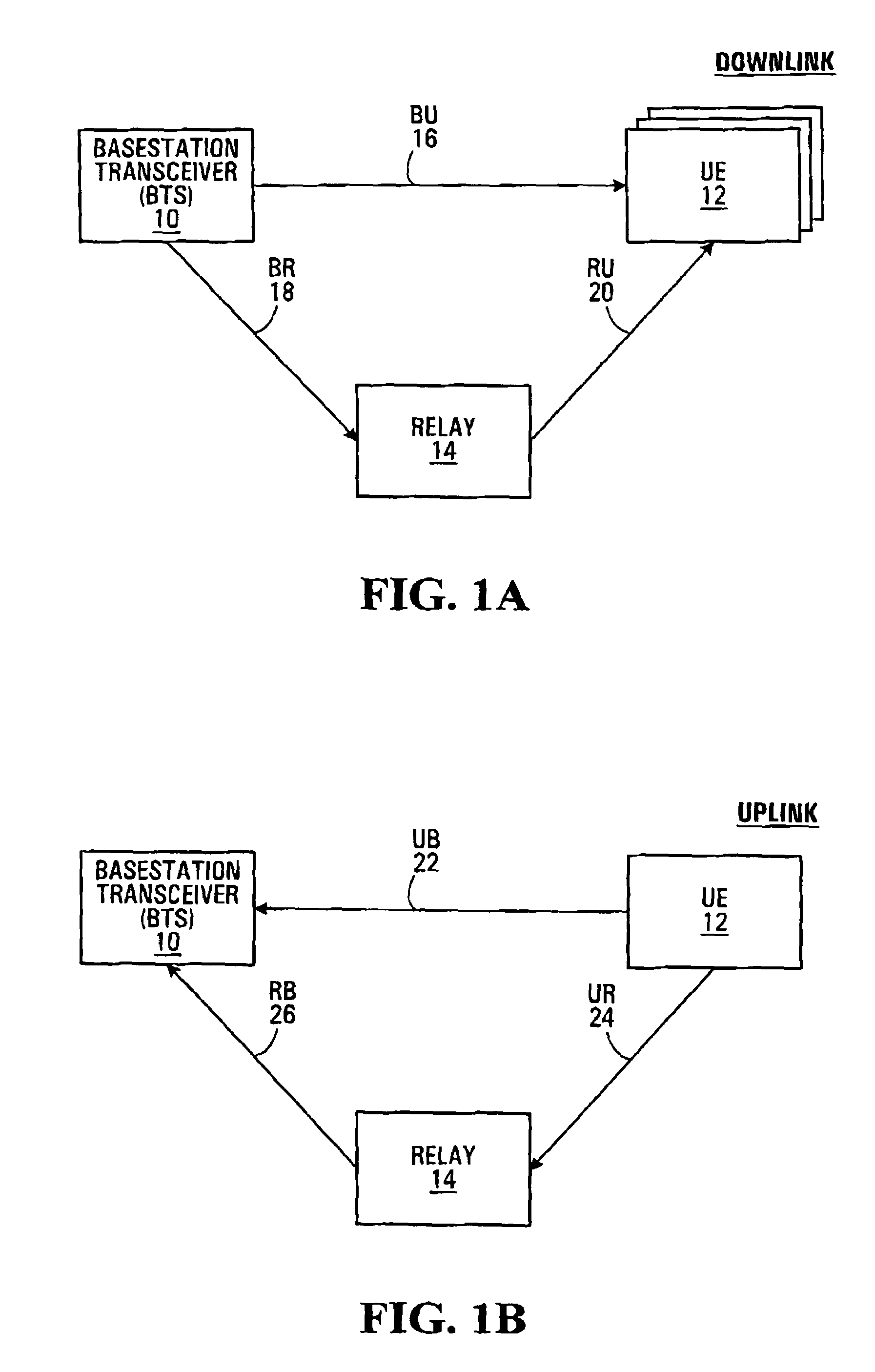

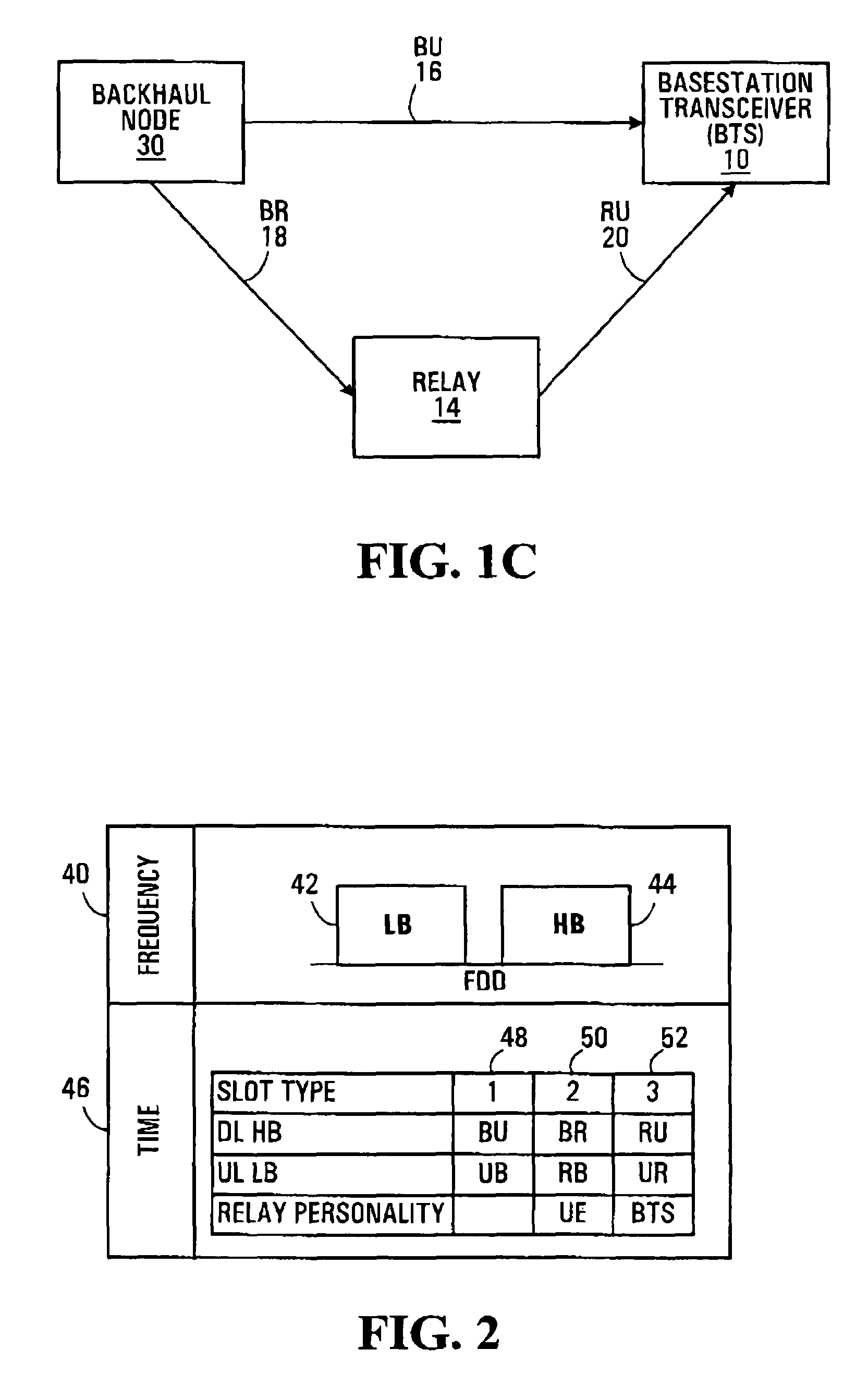

Method and apparatus for relaying a wireless signal

Systems and Methods are provided for relaying wireless signals bi-directionally between user equipment (UE) and base station transceivers (BTS). Various slot types are defined during which a relay node takes on the personality of either the UE or the BTS. In order to implement the relay node with a single transceiver chain, a first switching matrix is used to switch high band and low band RF bandpass filters between receive and transmit paths, and a second switching matrix is used to switch two frequency sources between the receive and transmit path. In this way, a single receive path can function both in the UE and BTS personality, as can the single transmit path.

Owner:MALIKIE INNOVATIONS LTD

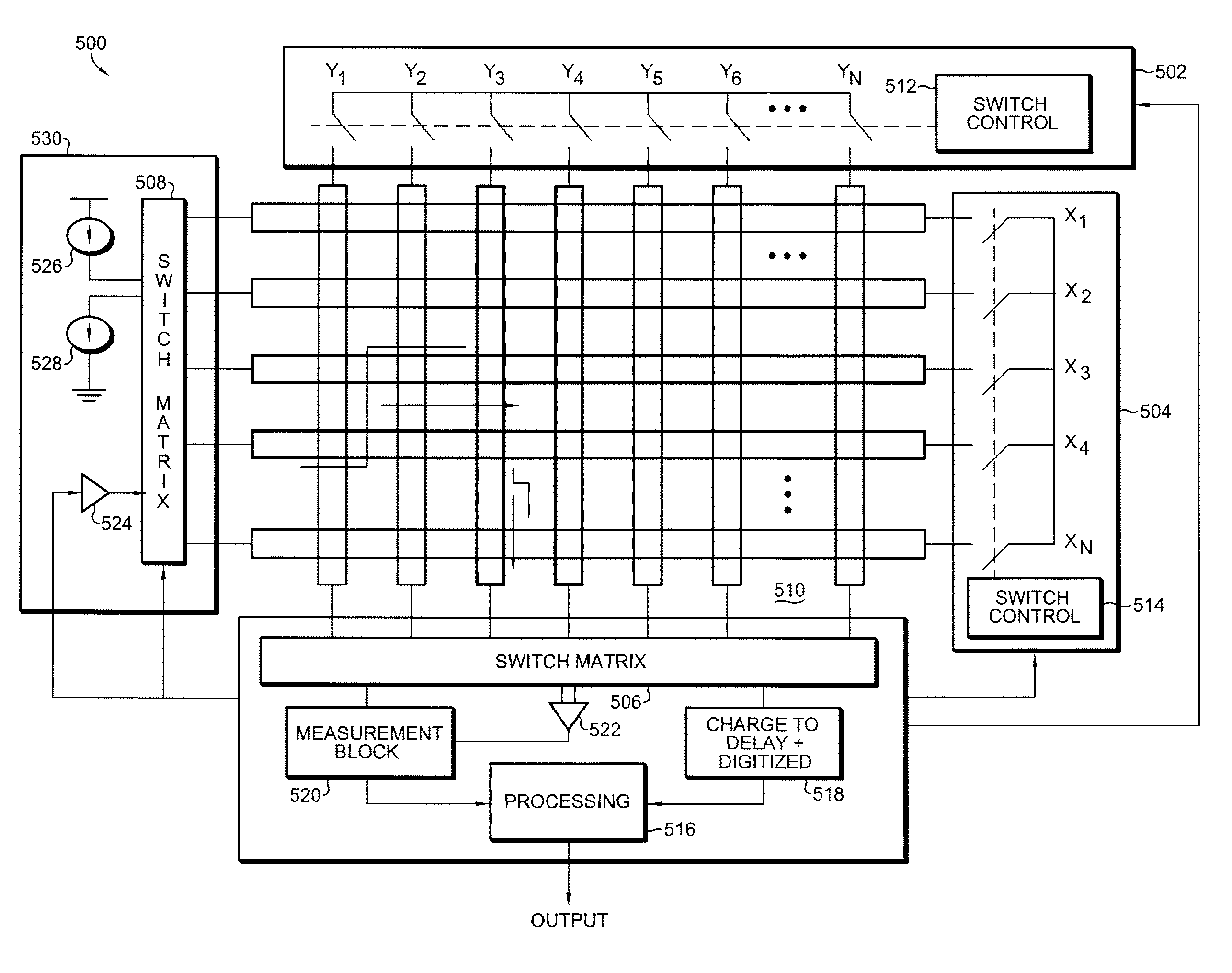

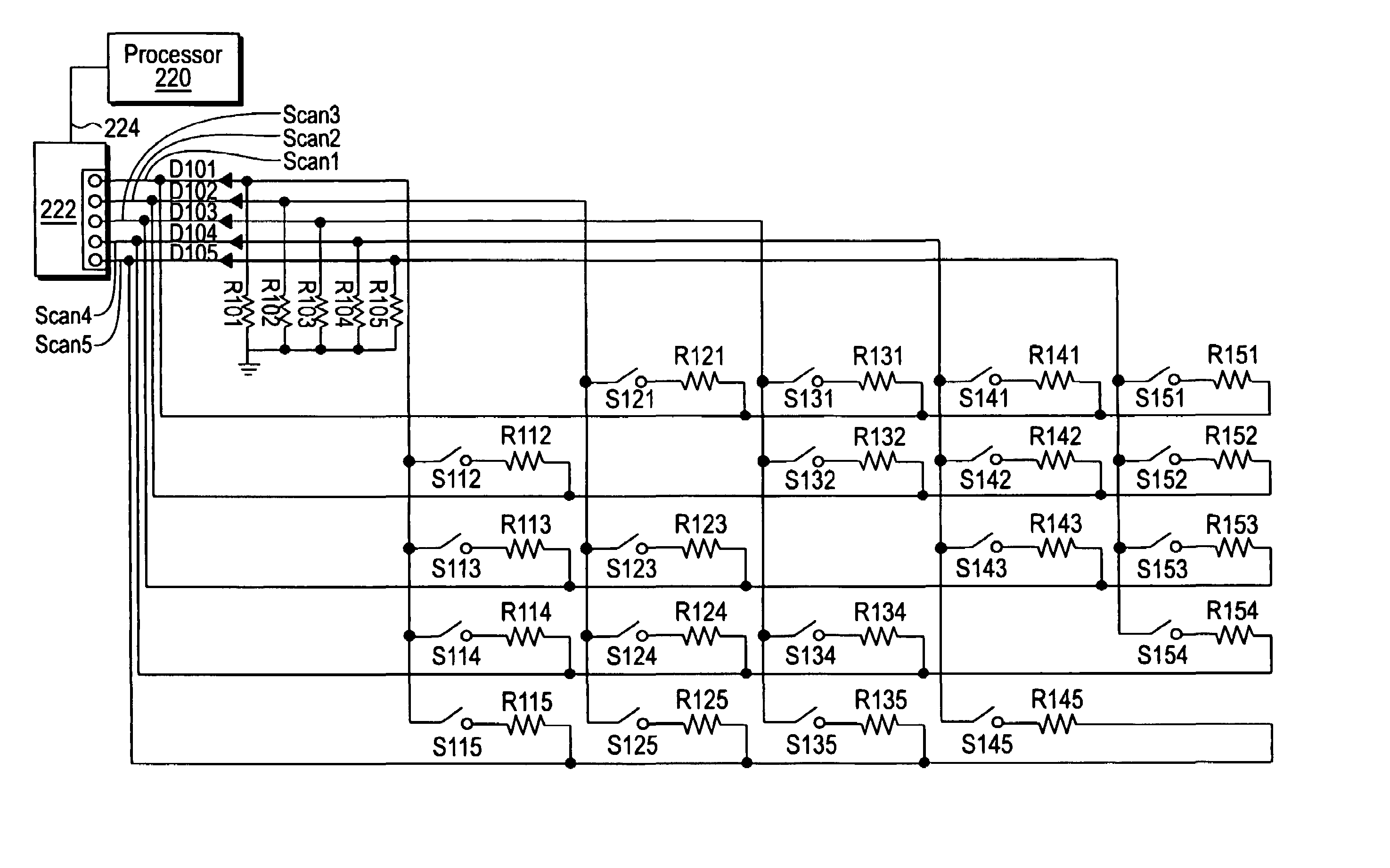

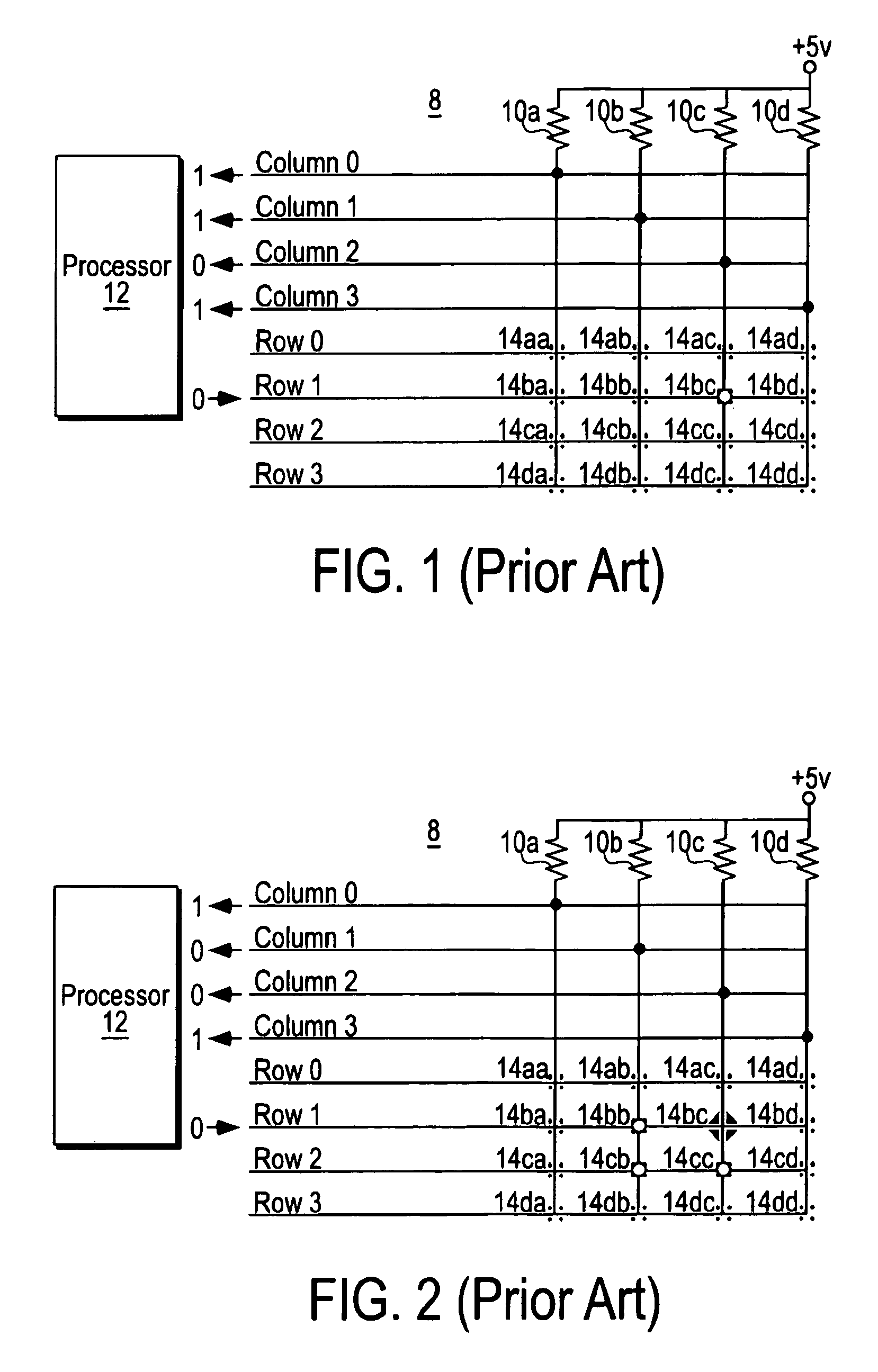

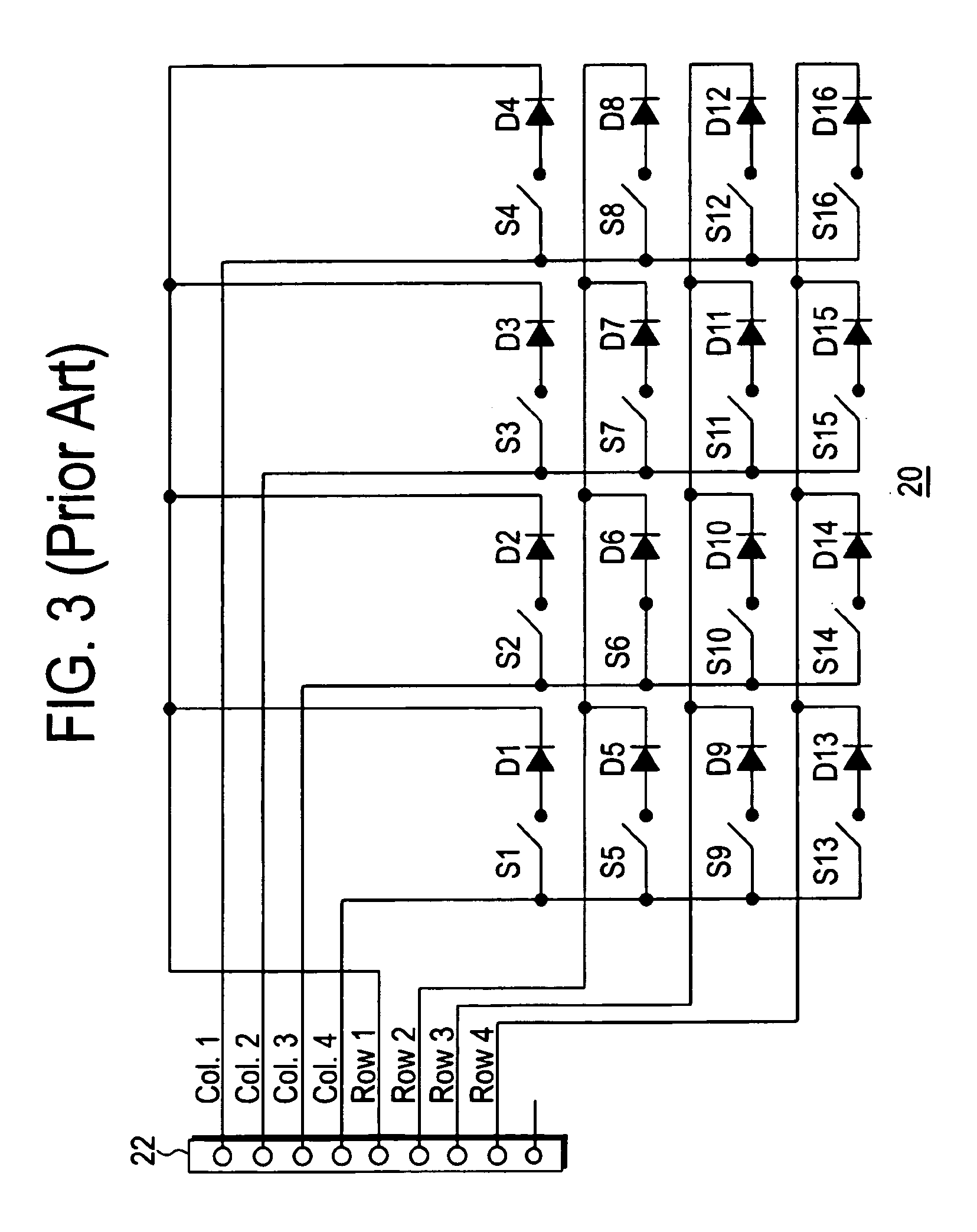

Circuit and method for a switch matrix and switch sensing

Aspects of a switch matrix circuit are provided. In accordance with a circuit aspect, a plurality of switches are organized in a row and column configuration. Coupled to the plurality of switches is a current sensing circuit. The current sensing circuit includes a transistor and at least one resistor per column of the plurality of switches. Current amplified by the transistor and converted by the at least one resistor in a column is sensed as a logic level indicative of a switch status within the column for a selected row. The current sensing arrangement may also be used in an embodiment utilizing bi-directional signal control to minimize the number of I / O lines required to scan the switch matrix. The bi-directional signal scanning may also be implemented in another embodiment that senses voltage levels to determine switch closures.

Owner:IMMERSION CORPORATION

Method and system for communicating with and tracking RFID transponders

InactiveUS20070075834A1Reduce the valueMemory record carrier reading problemsCo-operative working arrangementsNear neighborNumber generator

An RFID system and method for communicating between a host computer, one or more interrogators connected to the host computer, and a large body of transponders distributed within an area covered by the interrogators. Each transponder originally has a common identification code, and upon initialization by the host computer internally generates a unique identification code based upon an internally generated random number. The host, through the interrogators, reads each of the identification codes associated with each transponder by iteratively transmitting a read identification code command along with a controlled variable. Each transponder compares the received controlled variable to an internally generated random number, and selectively transmits its identification code based upon the outcome of this comparison. After the completion of each read identification code iteration, the host adjusts the controlled variable based upon the responses received in the previous iteration. Preferably, communications between the interrogators and the transponders are DSSS signals in TDMA format, and the transponders use the random number generator to assign a time slot for transmission of their response. Each interrogator includes an antenna system utilizing a switch matrix to connect multiple antennas having different polarizations, which ensures that all transponders within the range of the interrogator receive the signals from the interrogator. In a further aspect, the interrogators are arranged in groups, each group in nearest neighbor format, to reduce the time for reading the transponders and the emissions generated when more than one interrogator is active at the same time.

Owner:TERRESTRIAL COMMS LLC

Using XML expressed primitives for platform and system-independent call modeling

InactiveUS6985478B2Multiplex system selection arrangementsSpecial service for subscribersThird partyCall control

A system for providing third-party call control in a telecommunications environment is provided. The system comprises, a call-control mechanism for providing service logic and routing intelligence, a control application for providing service-logic description and command instruction for implementing third-party controlled call connections, a call-switching mechanism for providing an abstract state of switching matrix and for commutation of external and internal call legs and a commutation application for making and breaking call connections according to commands sent from the control application. The call-control mechanism, using the control application, sends primitive text commands to the call-switching mechanism, which utilizing the commutation application, receives, reads and implements the text commands containing all of the service logic and instructions required to successfully construct call connections and wherein the call-switching mechanism by virtue of the commutation application sends notification of success or failure regarding implementation of received commands back to the control application.

Owner:GENESYS TELECOMMUNICATIONS LABORATORIES INC

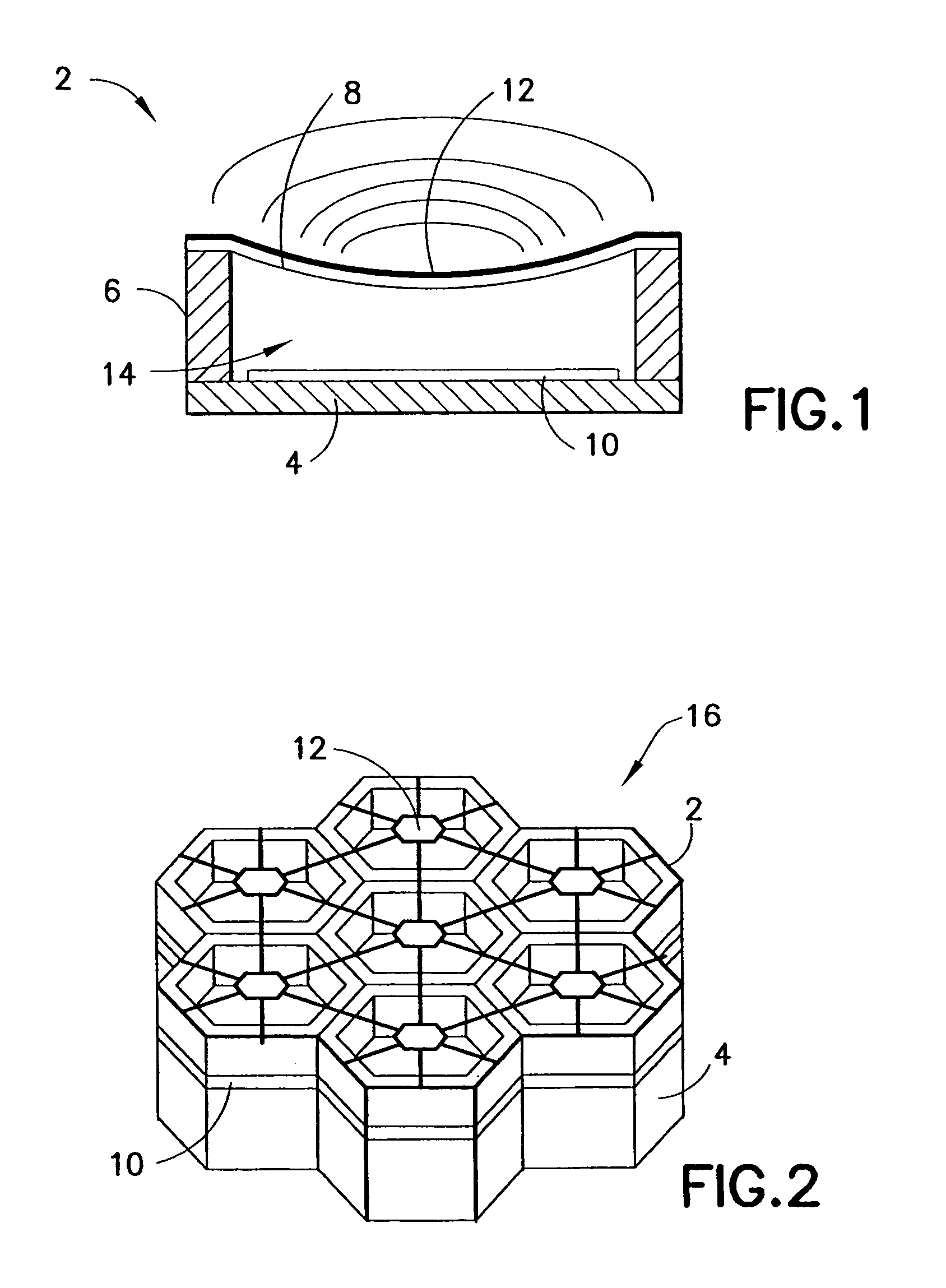

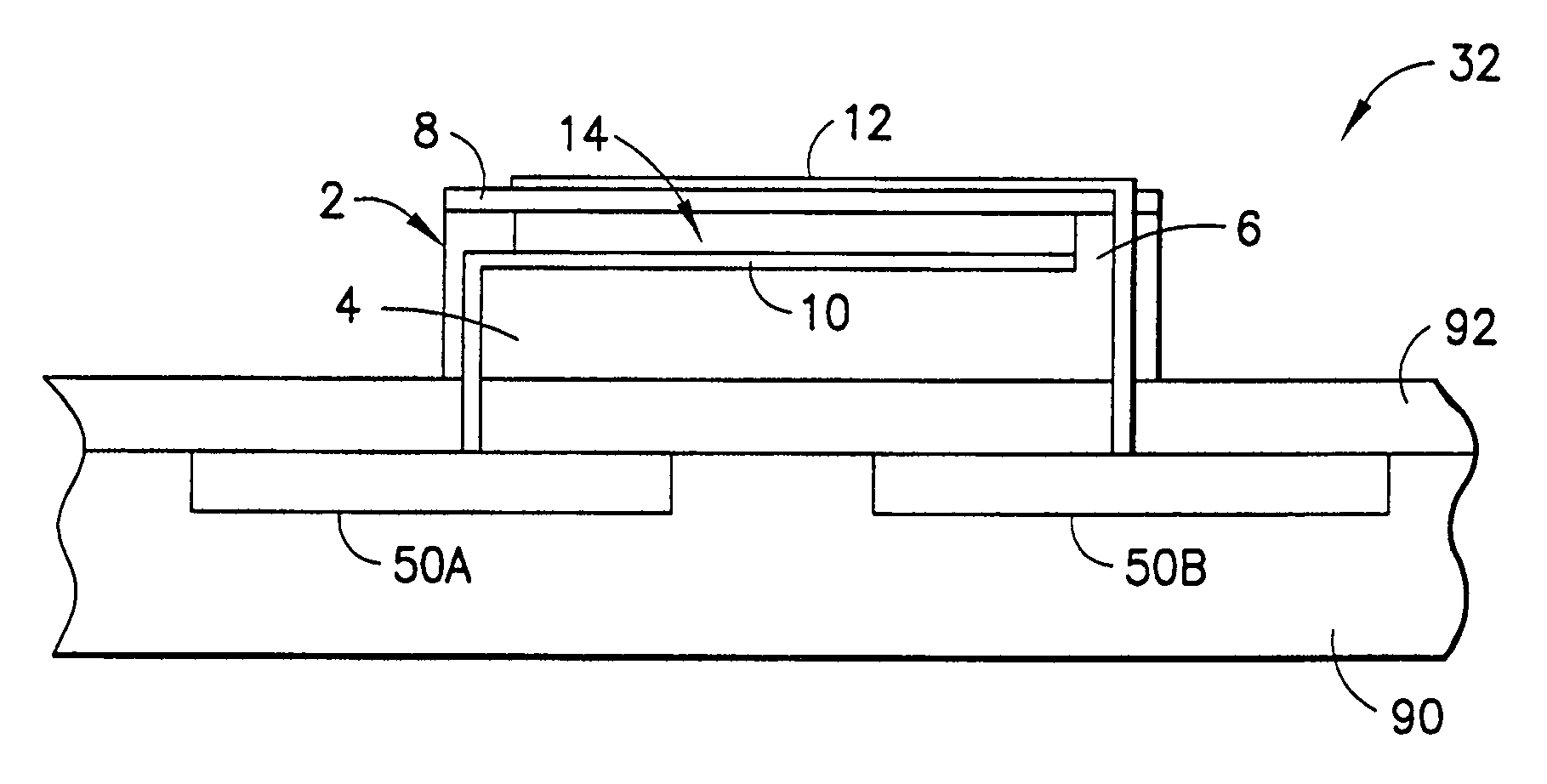

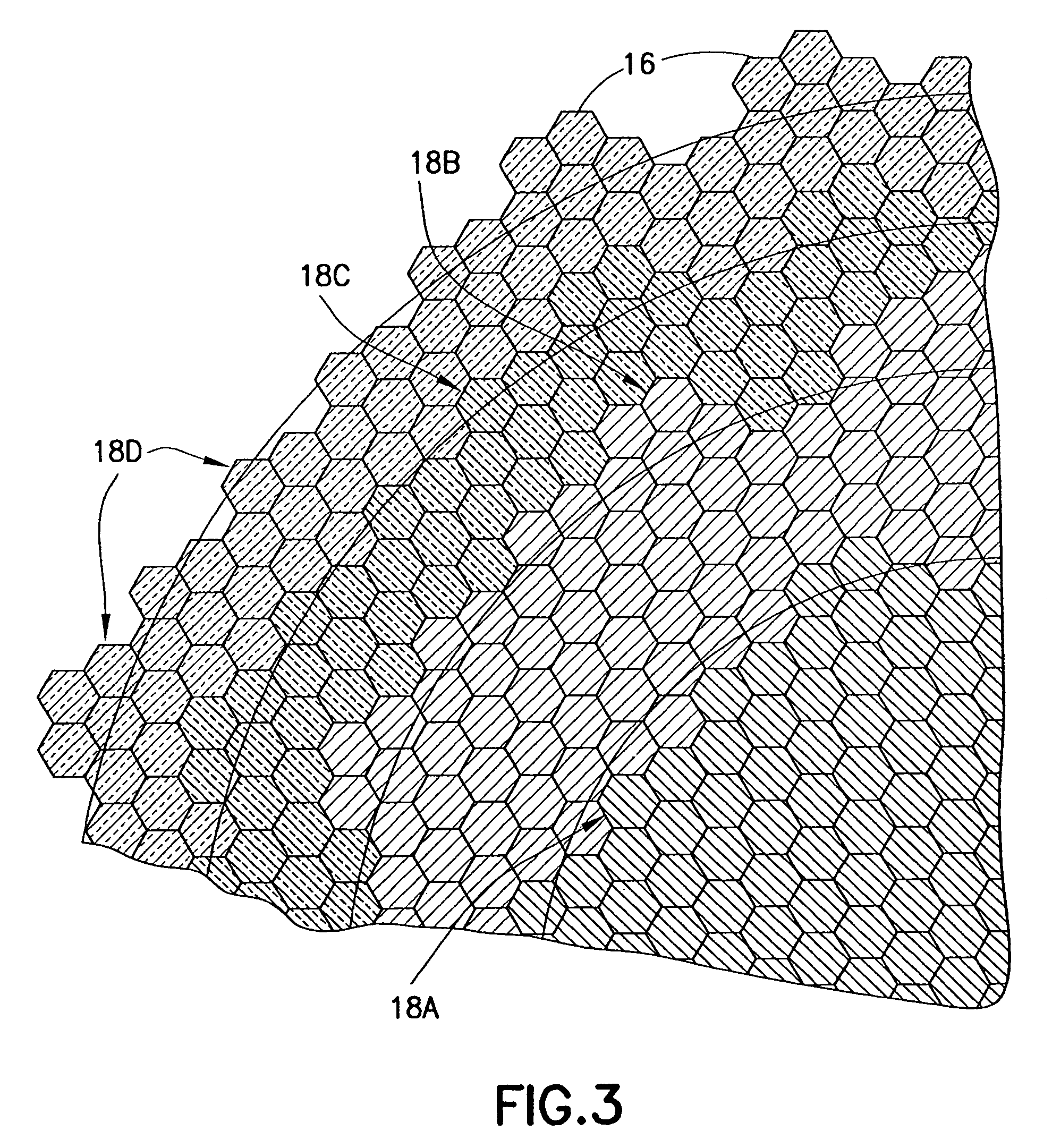

Integrated interface electronics for reconfigurable sensor array

ActiveUS20050094490A1Quickly reconfiguredUltrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesElectricitySensor array

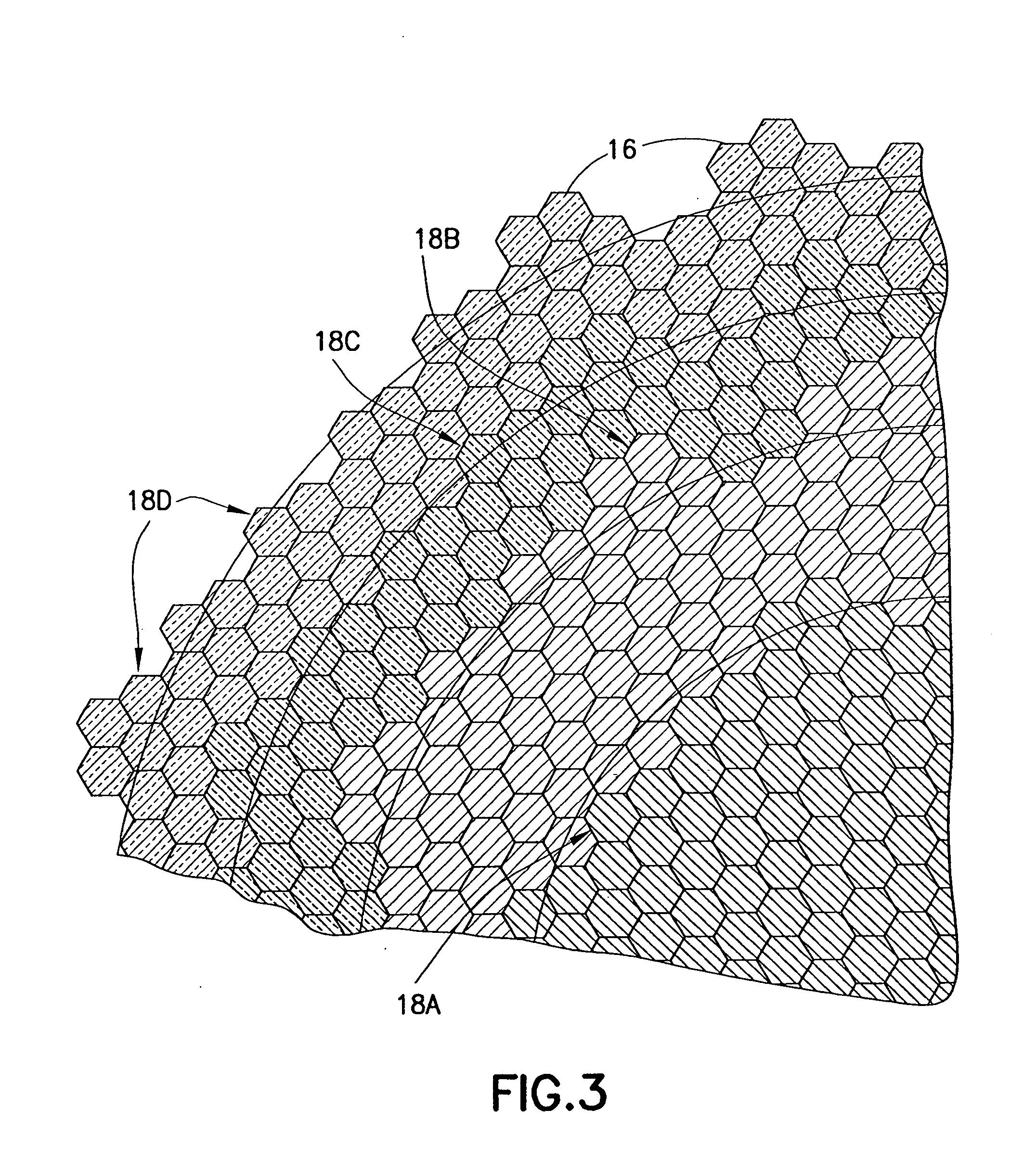

An integrated switch matrix for reconfiguring subelements of a mosaic sensor array to form elements. The configuration of the switch matrix is fully programmable. The switch matrix includes access switches that connect subelements to bus lines and matrix switches that connect subelements to subelements. Each subelement has a unit switch cell comprising at least one access switch, at least one matrix switch, a respective memory element for storing the future state of each switch, and a respective control circuit for each switch. The access and matrix switches are of a type having the ability to memorize control data representing the current switch state of the switch, which control data includes a data bit input to turn-on / off circuits incorporated in the control circuit. The sensor array and the switching matrix may be built in different strata of a co-integrated structure or they may be built on separate wafers that are electrically connected. If the sensors are arranged on a hexagonal grid, the unit switch cells may be arranged on either a hexagonal or rectangular grid.

Owner:GENERAL ELECTRIC CO

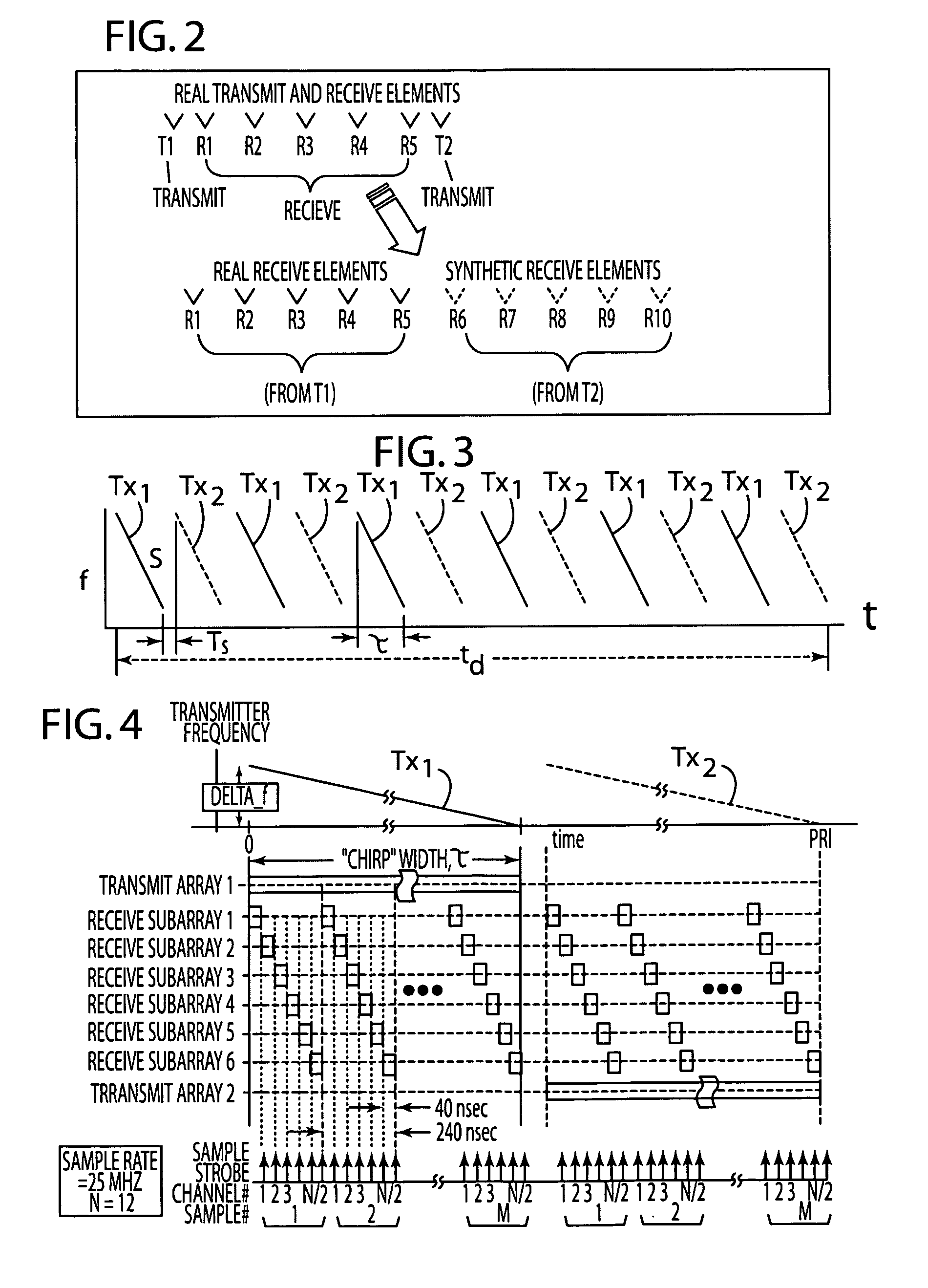

Radar system and method of digital beamforming

A radar system and method is provided, in which the radar system includes a first transmitting portion of antenna elements, a second transmitting portion of antenna elements, and a receiving portion of antenna elements, such that the receiving antenna elements form a plurality of subarrays that represent real and synthetic antenna elements. The radar system further includes a transceiving device having a switching matrix. At least first and second switching transmit antenna elements are configured and time-multiplexed, wherein a receive aperture of the receiving antenna elements is increased. A first signal transmitted is received by the real antenna elements and a second signal transmitted is received by the real antenna elements, and combined so that the signals received from the first switching transmit antenna element represents a signal received by the real receive antenna element, and the signal received from the second switching transmit antenna element represents a signal received by the synthetic receive antenna element.

Owner:APTIV TECH LTD

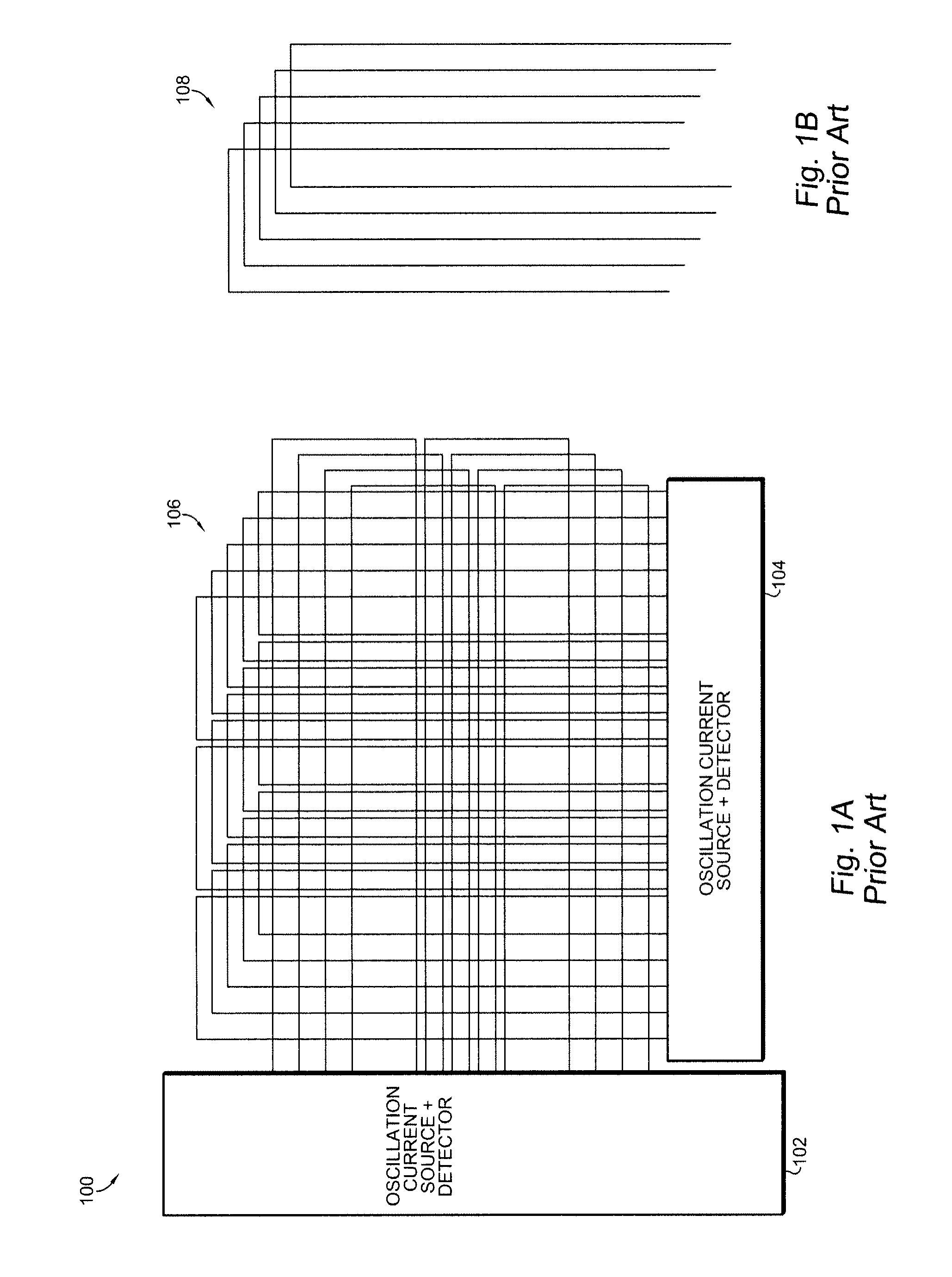

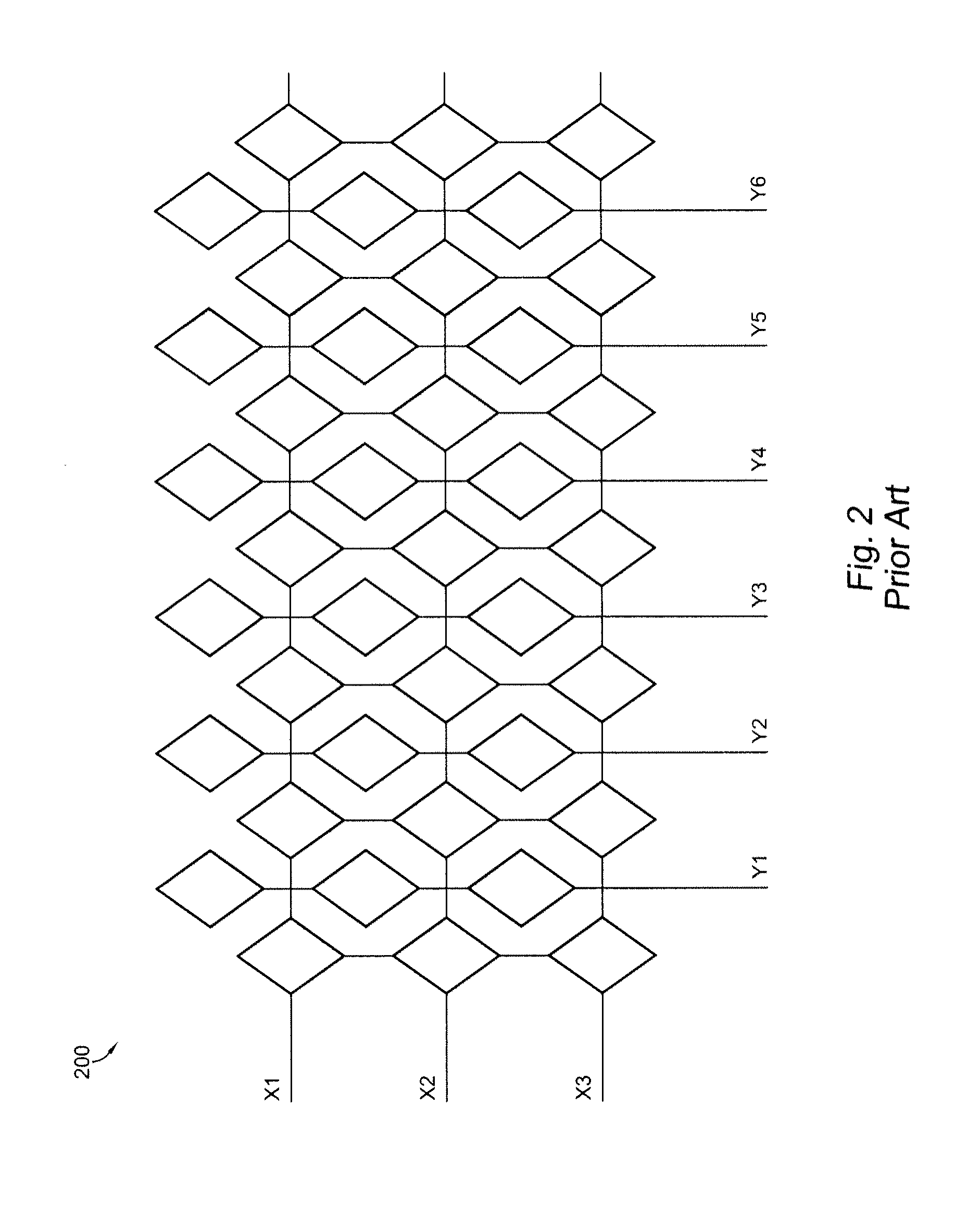

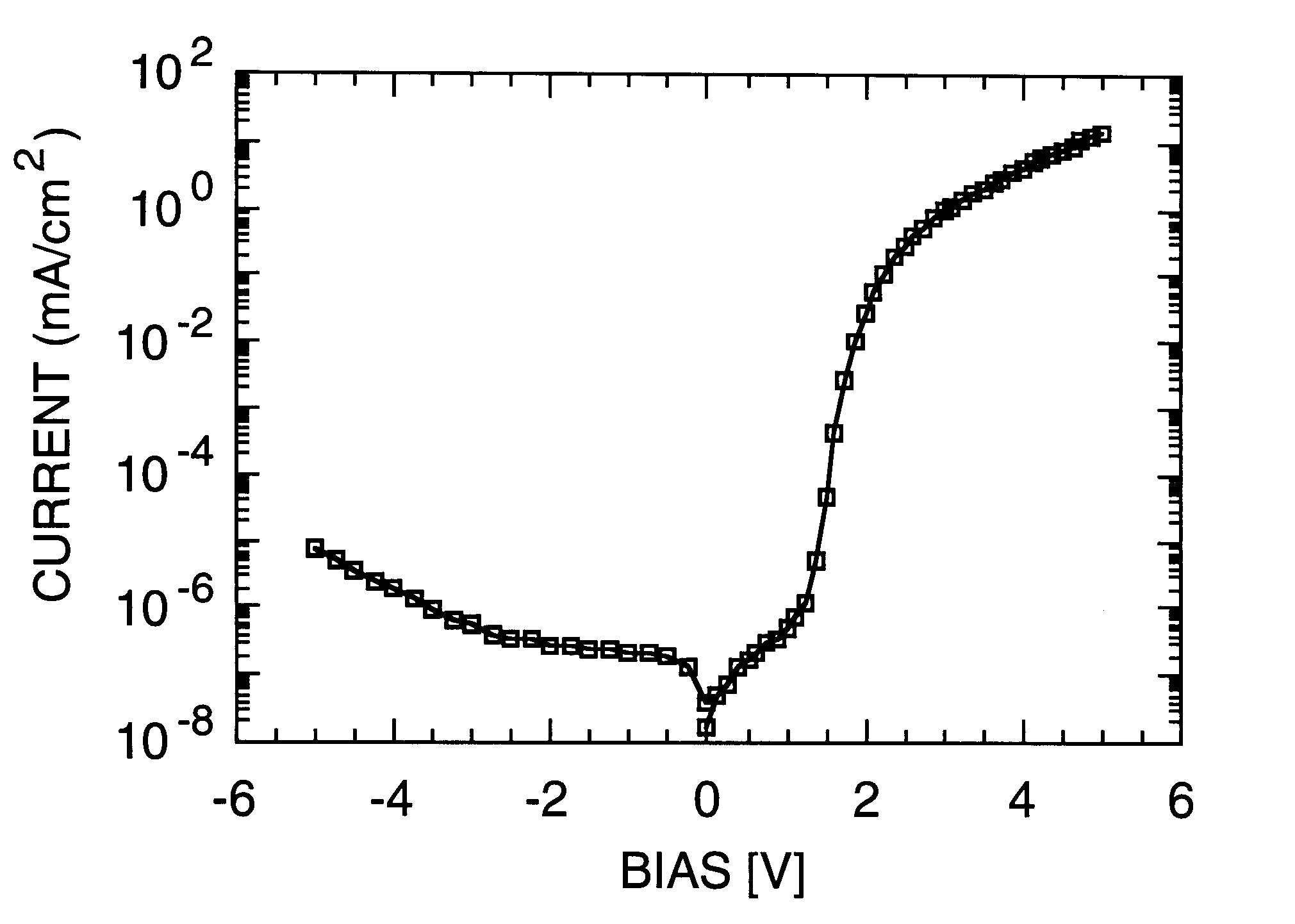

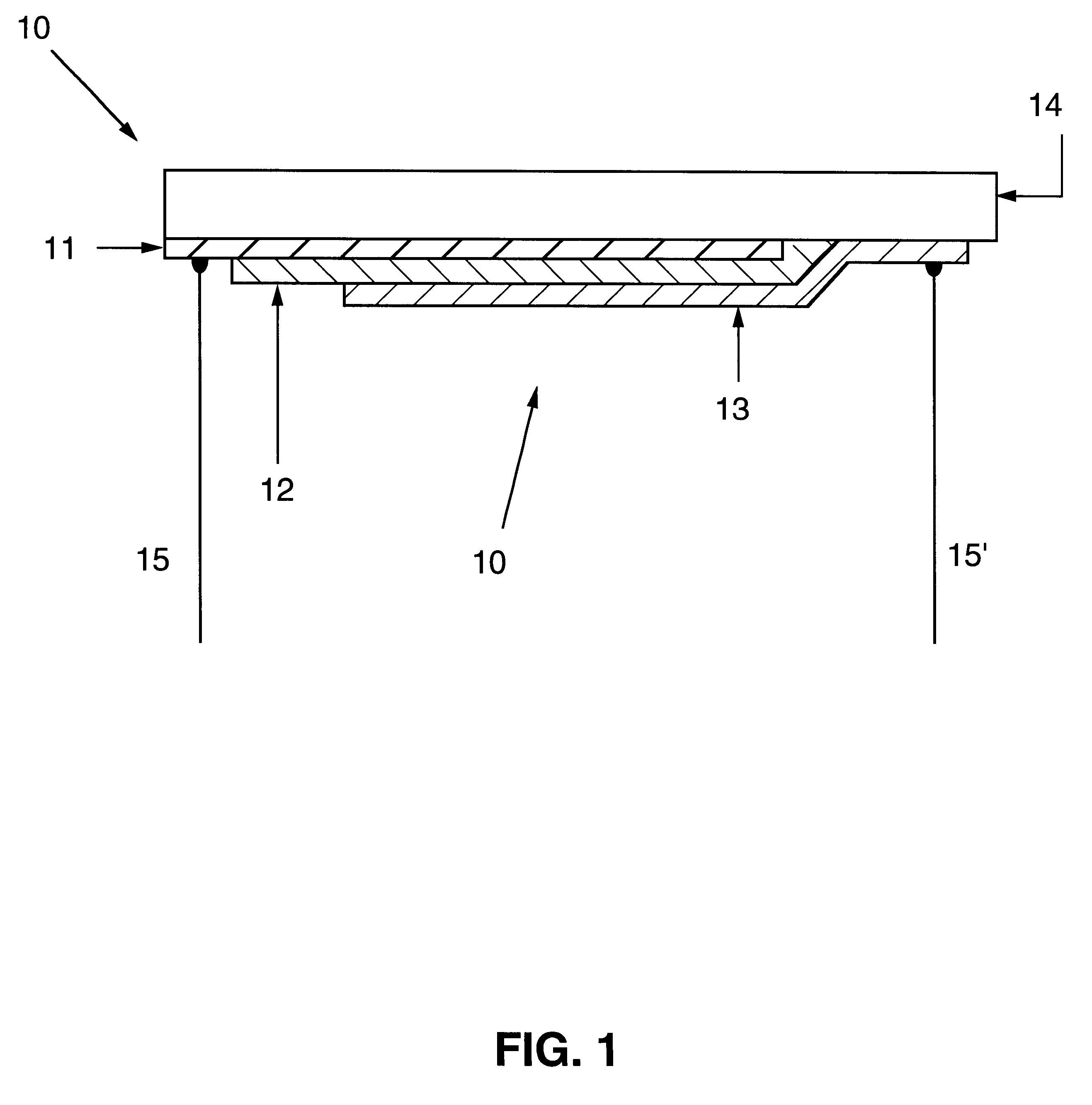

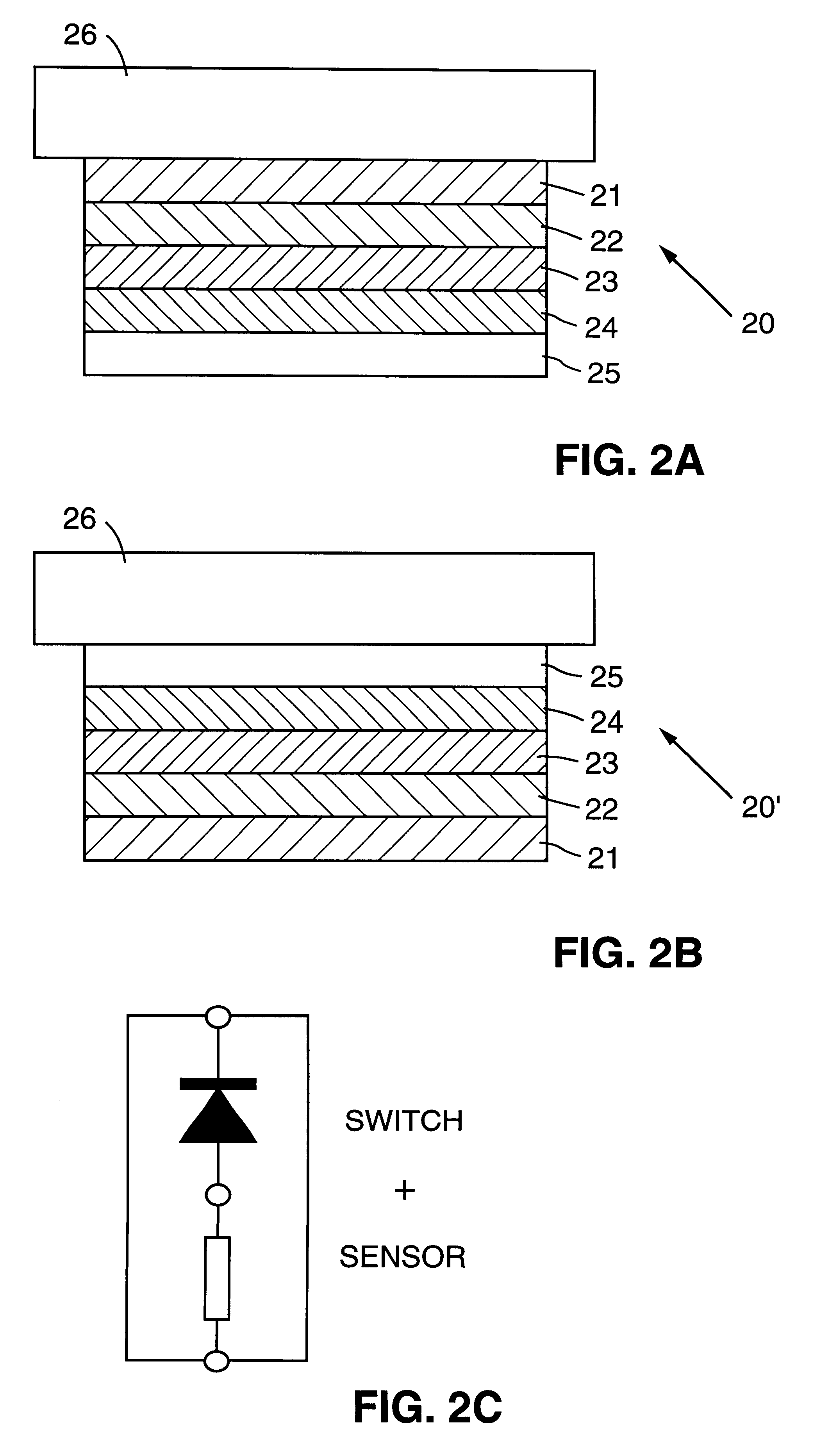

Column-row addressable electric microswitch arrays and sensor matrices employing them

The present invention relates generally to fabricating two-terminal electric microswitches comprising thin semiconductor films and using these microswitches to construct column-row (x-y) addressable microswitch matrices. These microswitches are two terminal devices through which electric current and electric potential (or their derivatives or integrals) can be switched on and off by the magnitude or the polarity of the external bias. The microswitches are made from semiconducting thin films in a electrode / semiconductor / electrode, thin film configuration. Column-row addressable electric microswitch matrices can be made in large areas, with high pixel density. Such matrices can be integrated with a sensor layer with electronic properties which vary in response to external physical conditions (such as photon radiation, temperature, pressure, magnetic field and so on), thereby forming a variety of detector matrices.

Owner:DUPONT DISPLAY +1

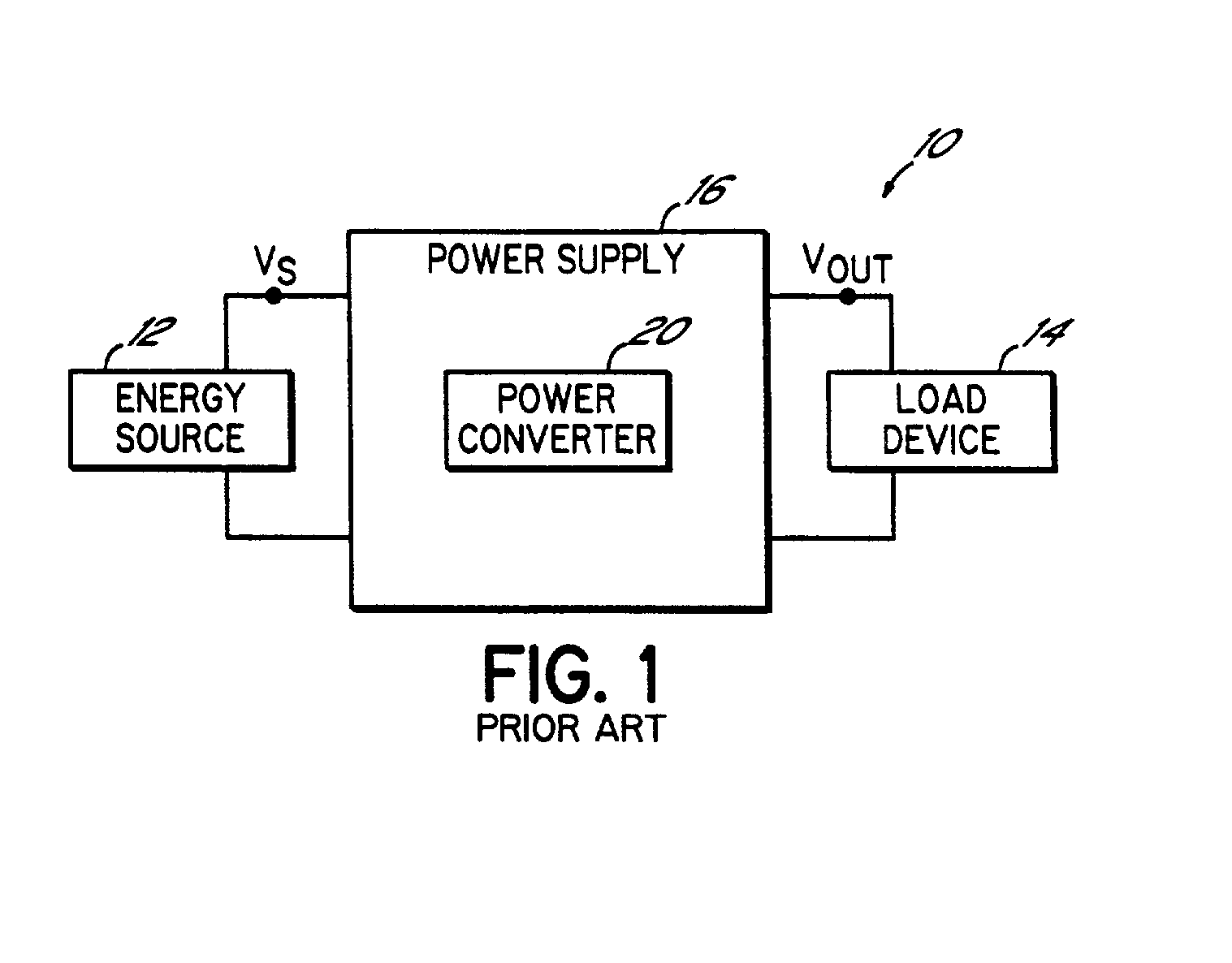

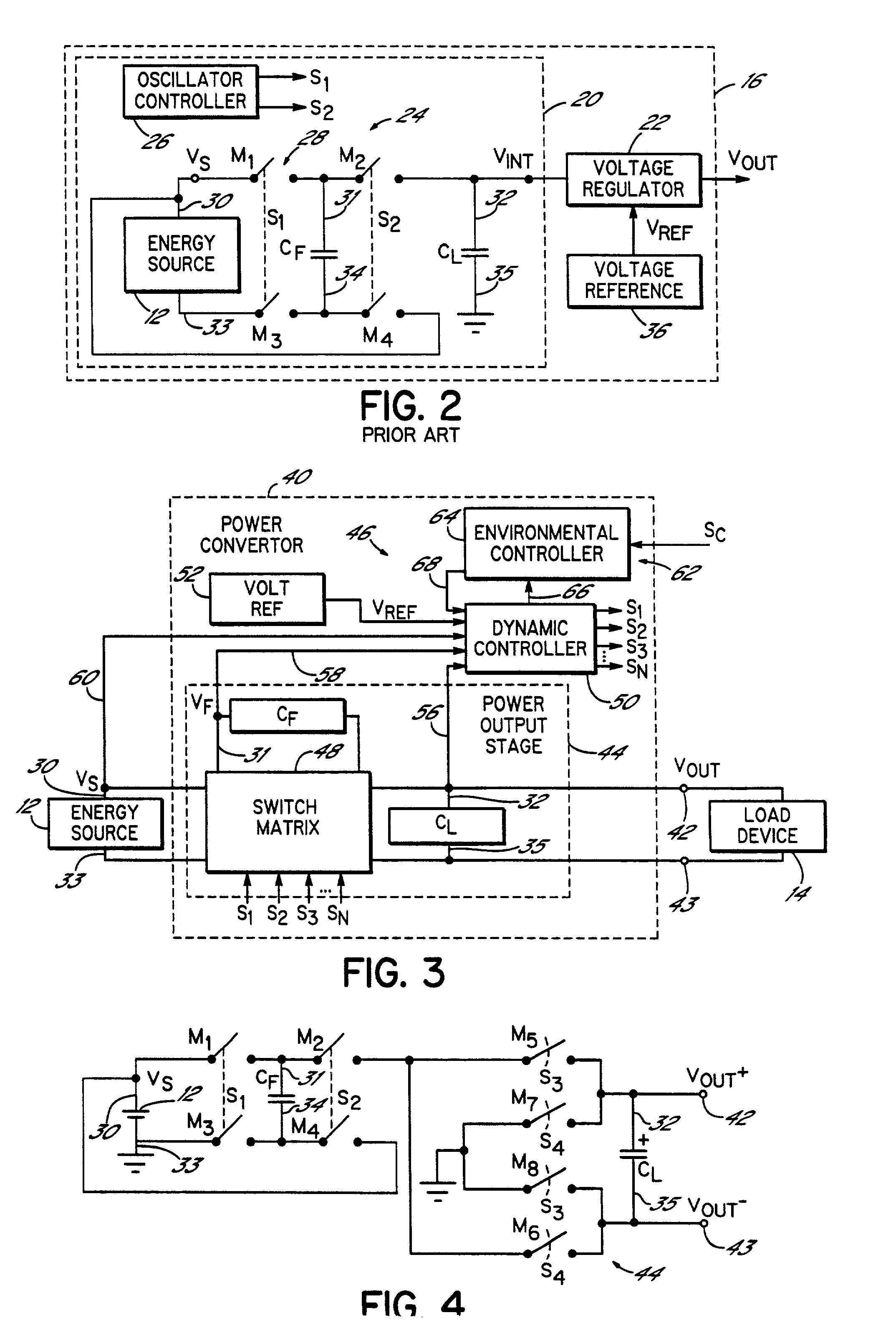

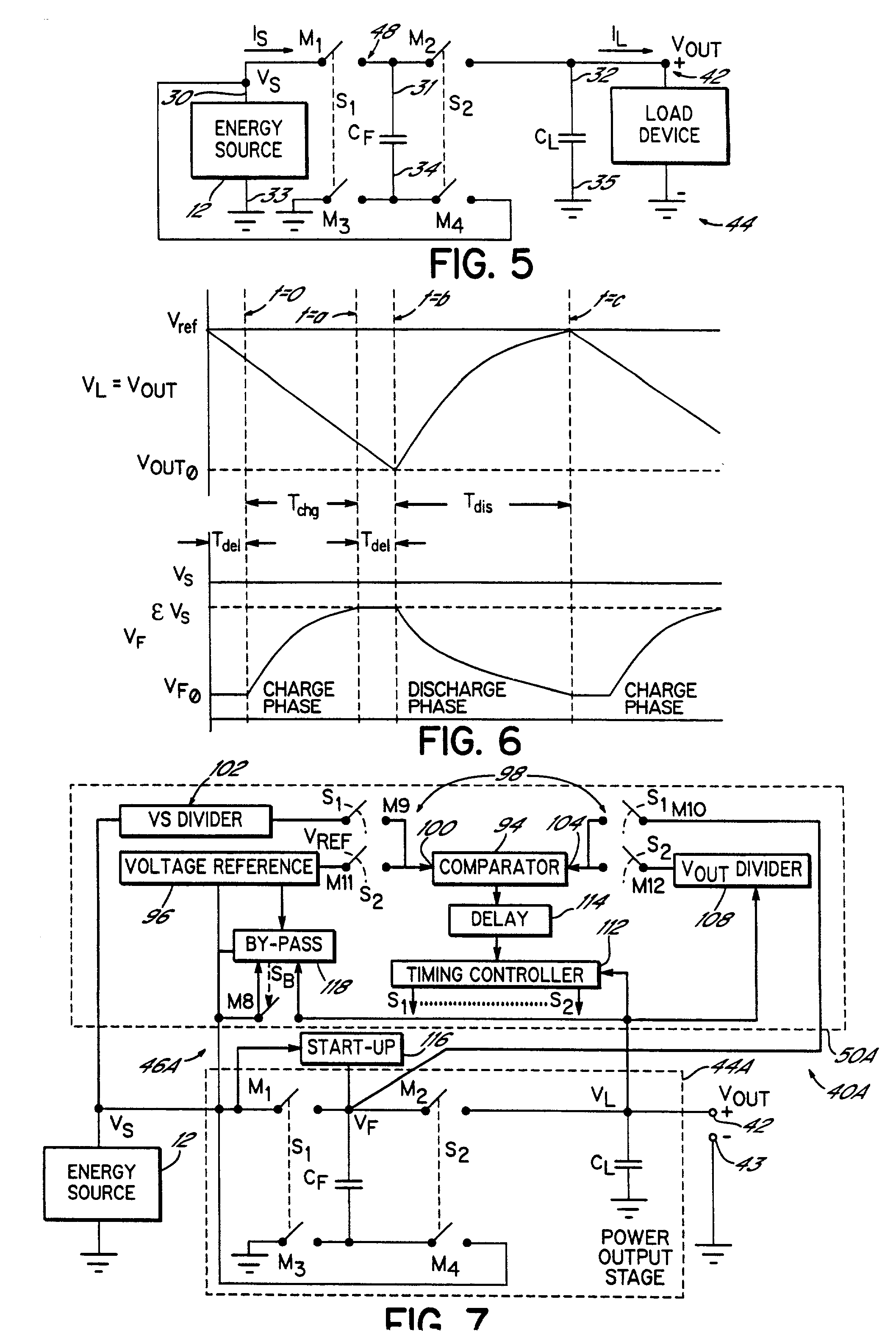

Progressive start-up circuit for activating a charge pump

InactiveUS20010033501A1Enhance battery service lifeHigh energyBatteries circuit arrangementsEfficient power electronics conversionClosed loopPower MOSFET

A charge pump power converter efficiently provides electrical power by dynamically controlling a switch matrix of the charge pump. Instead of open-loop oscillator-based control, a dynamic controller provides power upon demand by sensing the output voltage and changing the operating frequency of the charge pump in response. Moreover, this closed-loop dynamic control intrinsically voltage regulates the output voltage of the charge pump power converter without the inefficient addition of a step-down voltage regulator, downstream of the power converter. In addition, this closed-loop dynamic control allows for maintaining a desired output voltage even with variations in the input voltage. Also, the dynamic control accommodates the advantages of using ultra-capacitors in the charge pump. The power converter is capable of operating with a sub-one volt input voltage incorporating low-threshold, low on-resistance power MOSFET switches in the switch matrix of the charge pump. A progressive start-up circuit further allows the power converter to start from a discharged state even with a sub-one volt input voltage.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

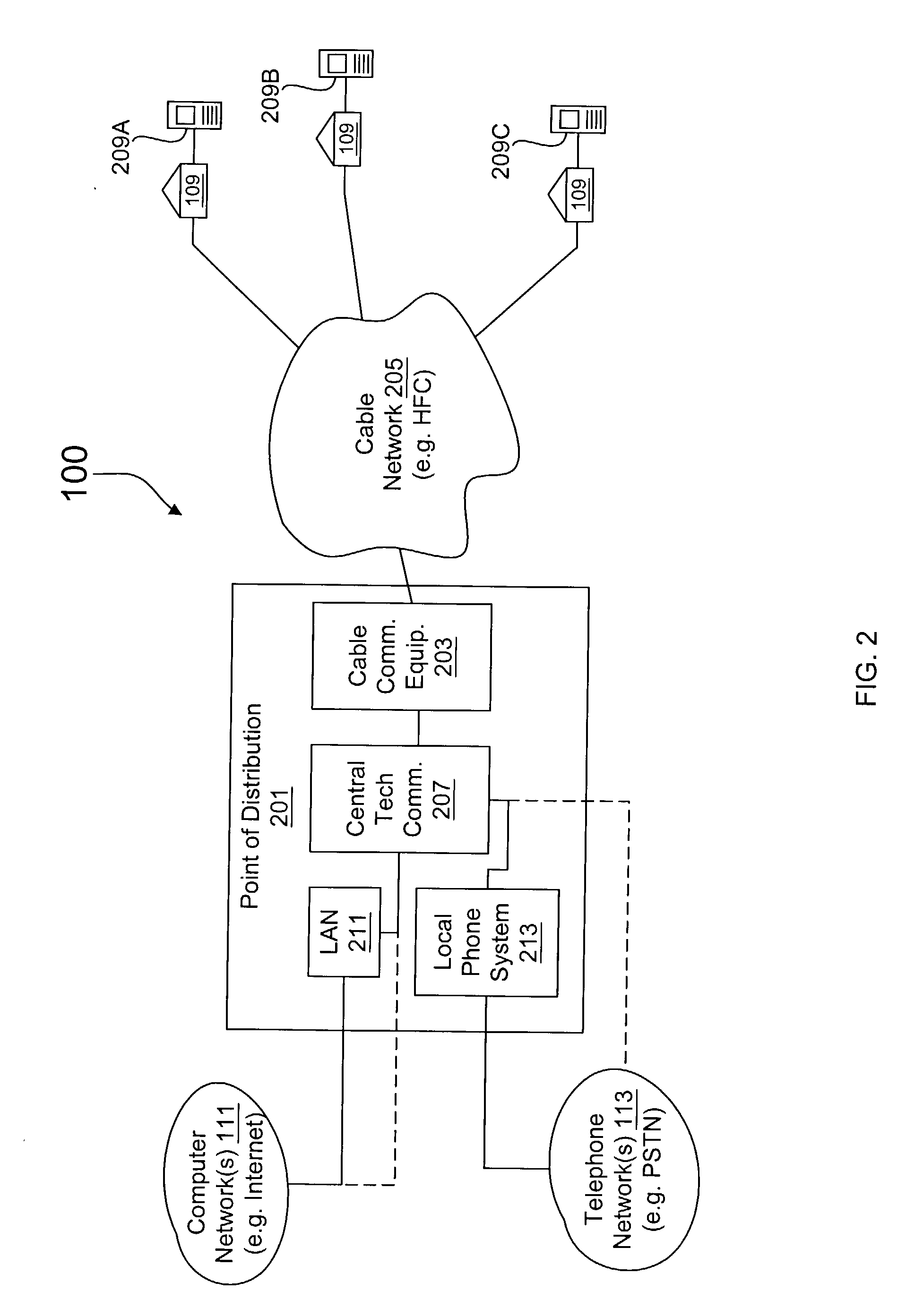

Field technician communicator

InactiveUS20030163831A1Data switching by path configurationTwo-way working systemsTelecommunications linkTransceiver

A hand-held cable communicator unit for technicians that enables voice and data communications across a cable network. The communicator includes a cable connector, a diplex filter, a transceiver circuit, an audio circuit and a control circuit. The transceiver circuit tunes to selected downstream and upstream channels signals. The audio circuit enables bidirectional voice communications using the selected channels signals via the cable network. The control circuit establishes a communication link and initiates and terminates communications. A communication system for field technicians of a cable network includes at least one communicator and a central communicator located at a point of distribution of the cable network. The central communicator includes transceivers, a switch matrix and a controller. Each central transceiver establishes a communication link with any linked communicator. The switch matrix forwards upstream and downstream communications between linked communicators. The controller performs functions to establish communication connections.

Owner:PANGRAC & ASSOCS DEVMENT

Digital beamforming for an electronically scanned radar system

ActiveUS7474262B2Improve performanceLow costParticular array feeding systemsRadio transmissionRadar systemsEngineering

Digital beamforming is provided for use with electronically scanned radar. In an aspect, the present invention provides enhanced sensitivity, wide angle or field of view (FOV) coverage with narrow beams, minimized number of receivers, reduced sidelobes, eliminated grating lobes and beam compensation for target motion. In an aspect, the present invention employs a uniform overlapped subarray feed network, a time multiplexed switch matrix, and a restructured digital signal processor. Antenna channels share a receiver, rather than maintain a dedicated receiver for each antenna element, as in conventional systems. In an aspect, Doppler / frequency filtering is performed on each antenna element or subarray output prior to digital beamforming. Further, Doppler compensation is employed following Doppler / frequency filtering, followed by digital beamforming.

Owner:APTIV TECH LTD

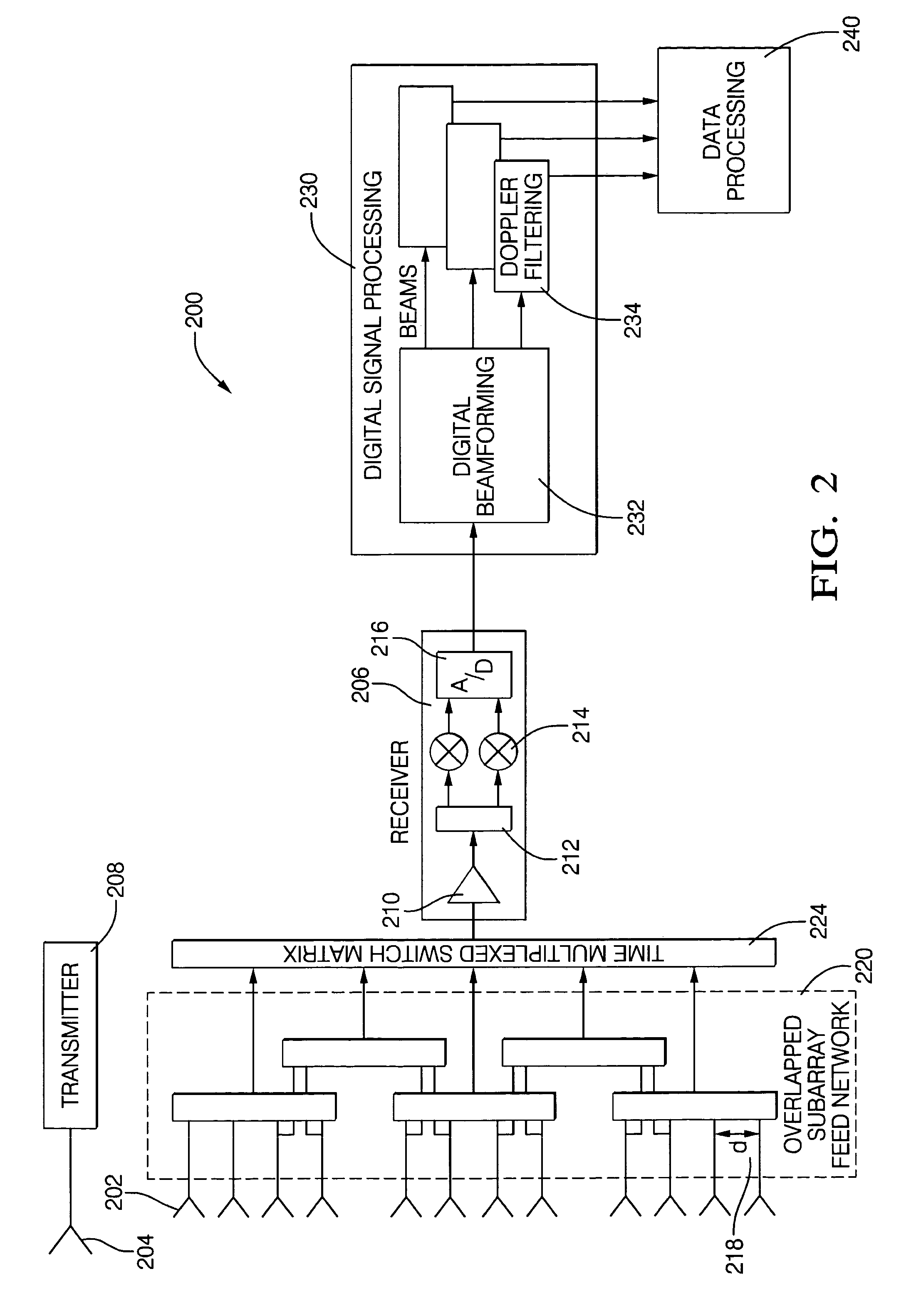

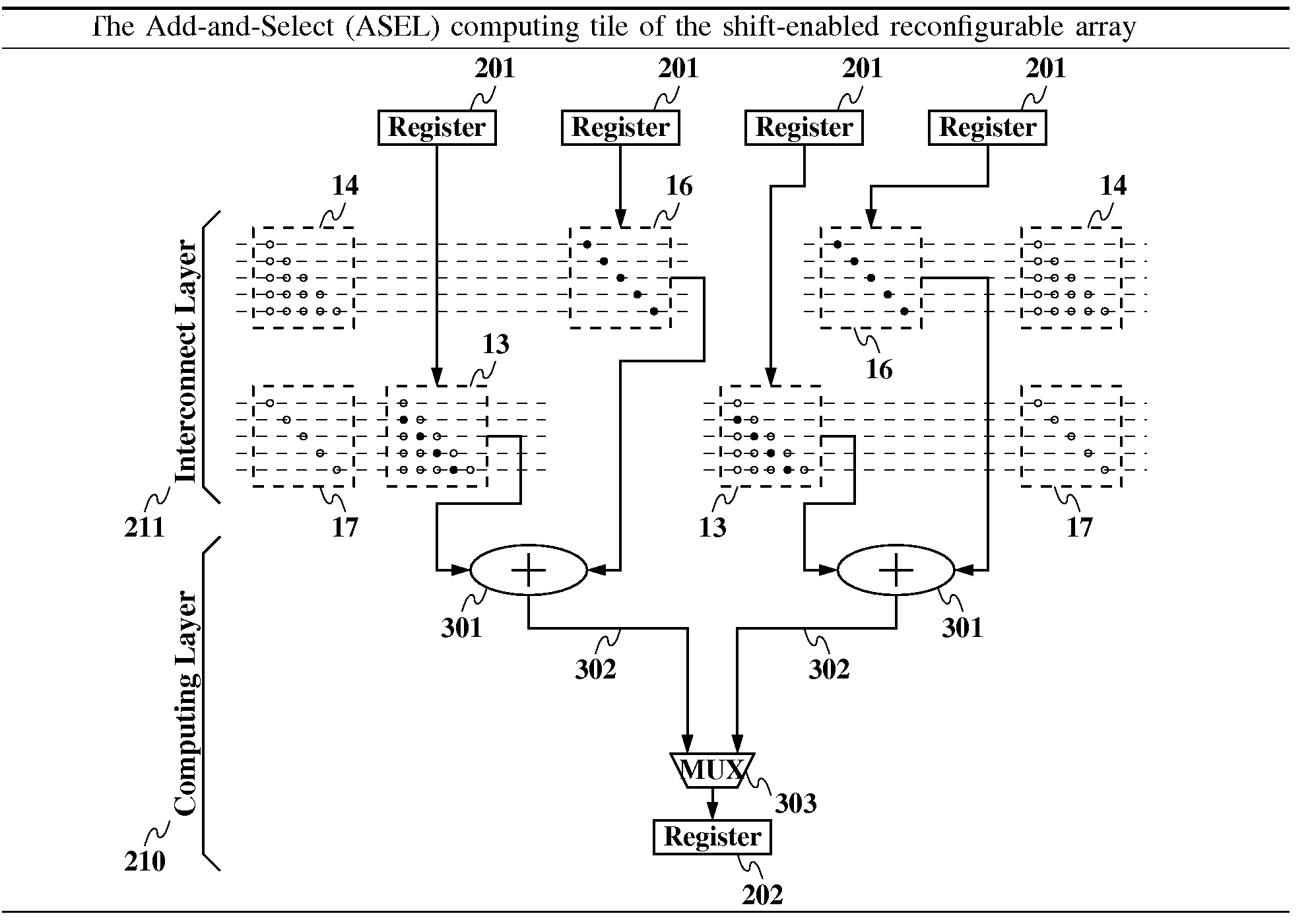

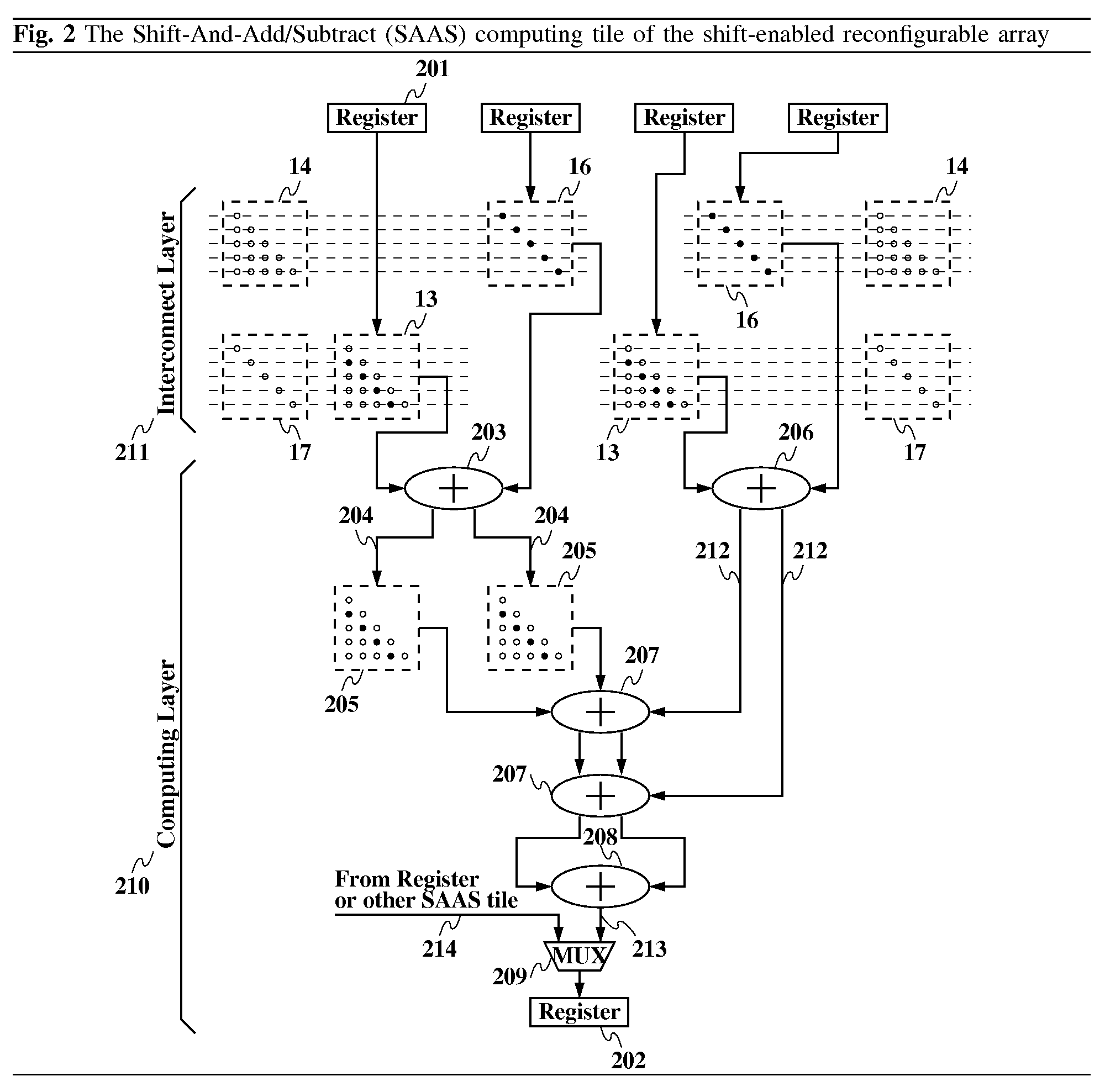

Shift-enabled reconfigurable device

A coarse-grain reconfigurable array that implements shift operations within its interconnection network is disclosed. The interconnection network of such a coarse-grain reconfigurable array contains partially or fully populated matrices of switches, where each such matrix of switches is obtained by merging a standard diagonal switch matrix with an array shift unit. The disclosed device provides better performance when the standard routing and shift functions are both required.

Owner:SIMA MIHAI +2

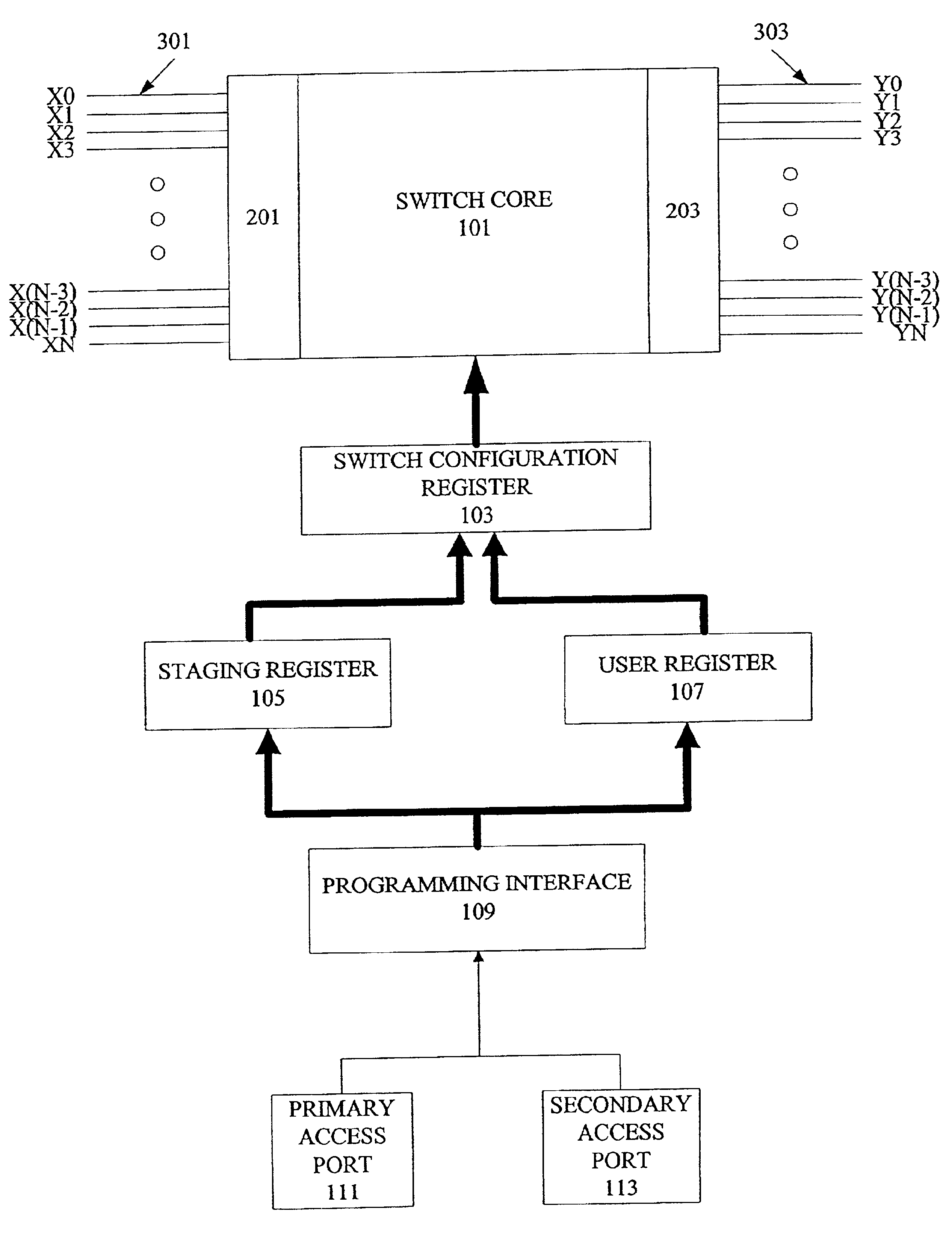

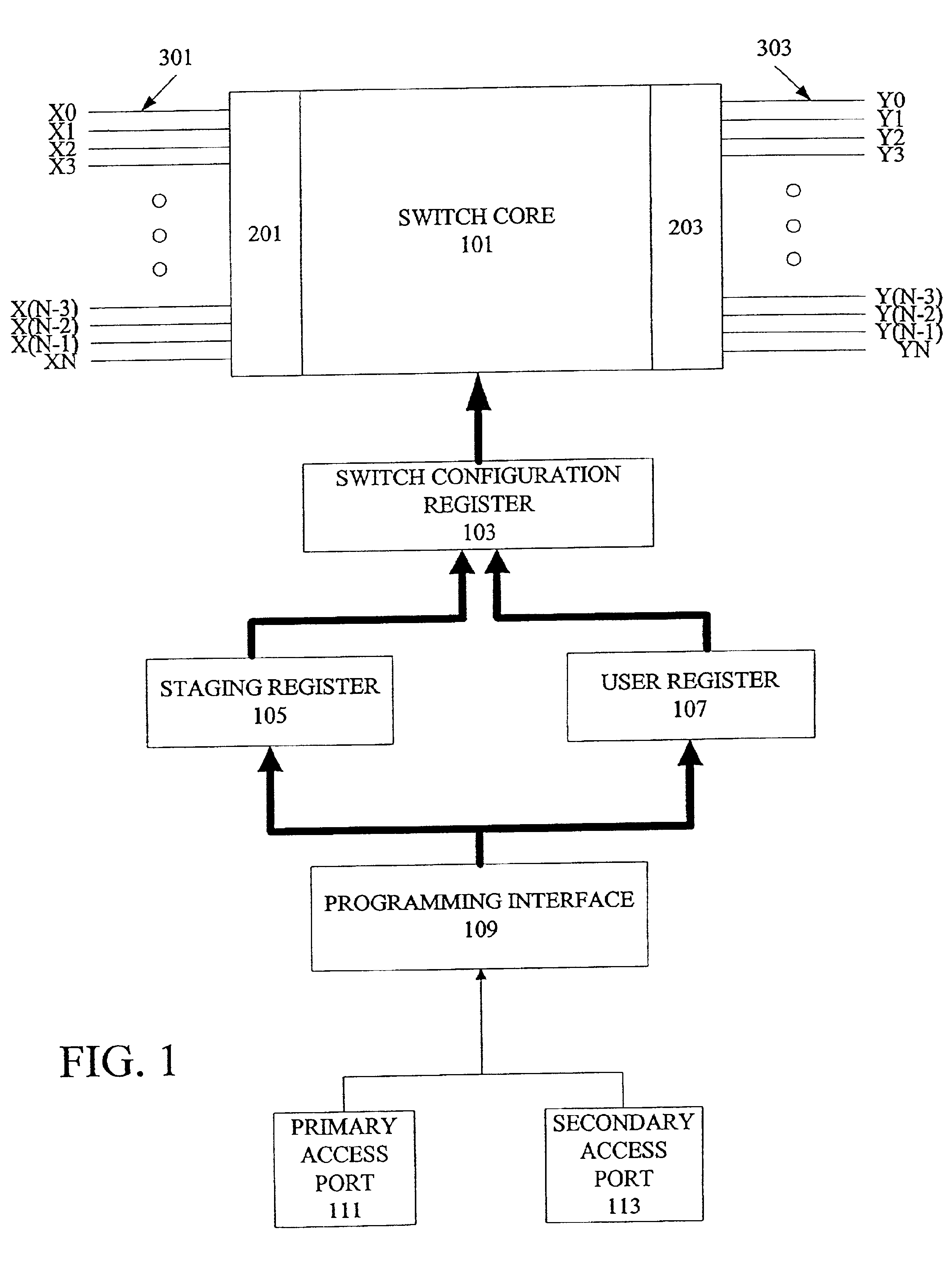

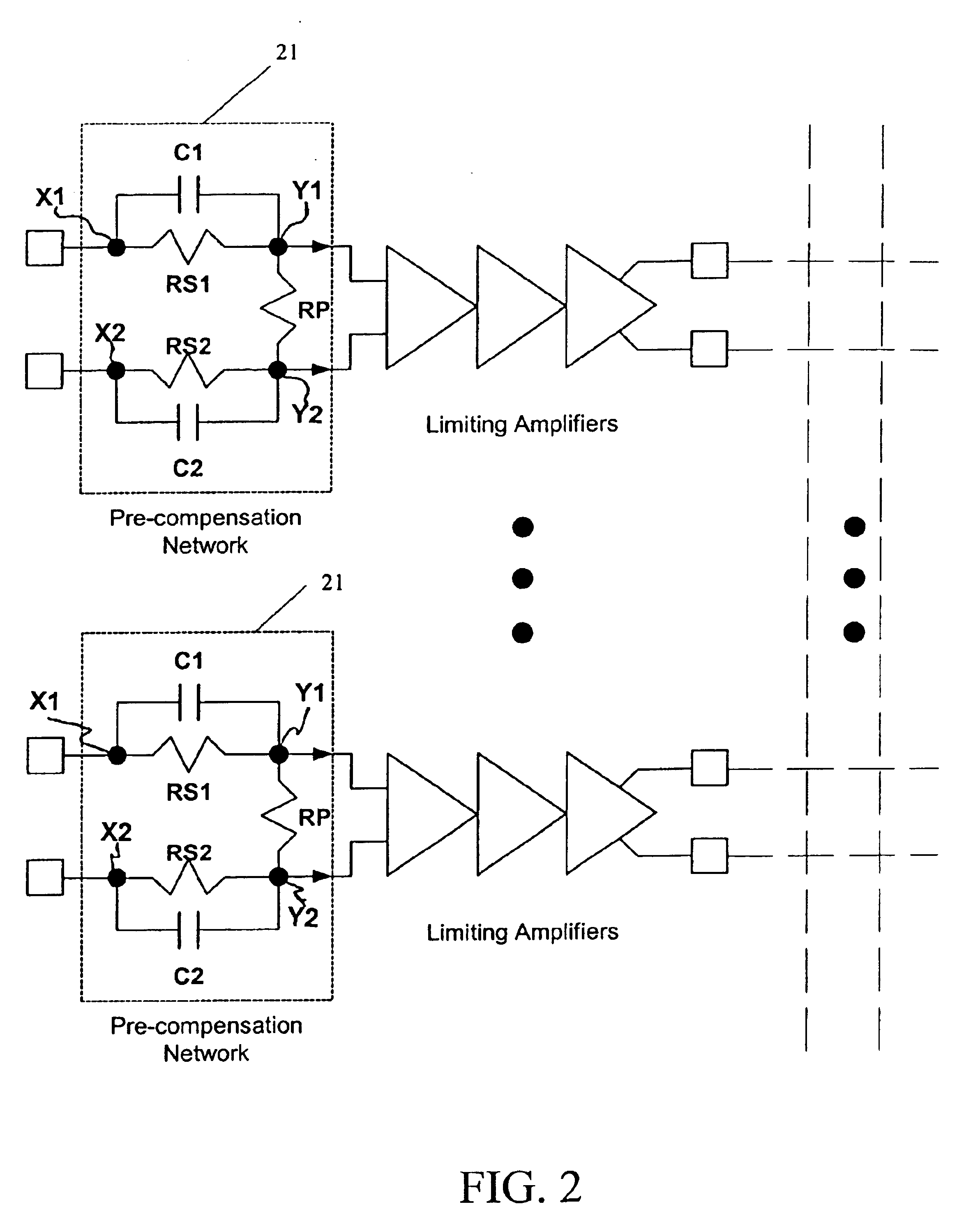

Crosspoint switch with switch matrix module

InactiveUS6946948B2Easy to appreciatePulse automatic controlSemiconductor/solid-state device detailsComputer moduleSwitch matrix

A crosspoint switch including a switch matrix modules and programming features. A switch matrix modules include input lines tied to inputs of the switch through precompensation networks. The programming features include user initialization states and reduced and grouping command configuration operations.

Owner:MICROSEMI STORAGE SOLUTIONS

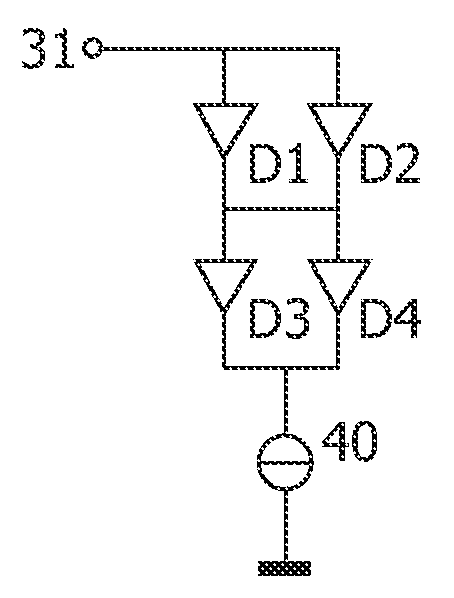

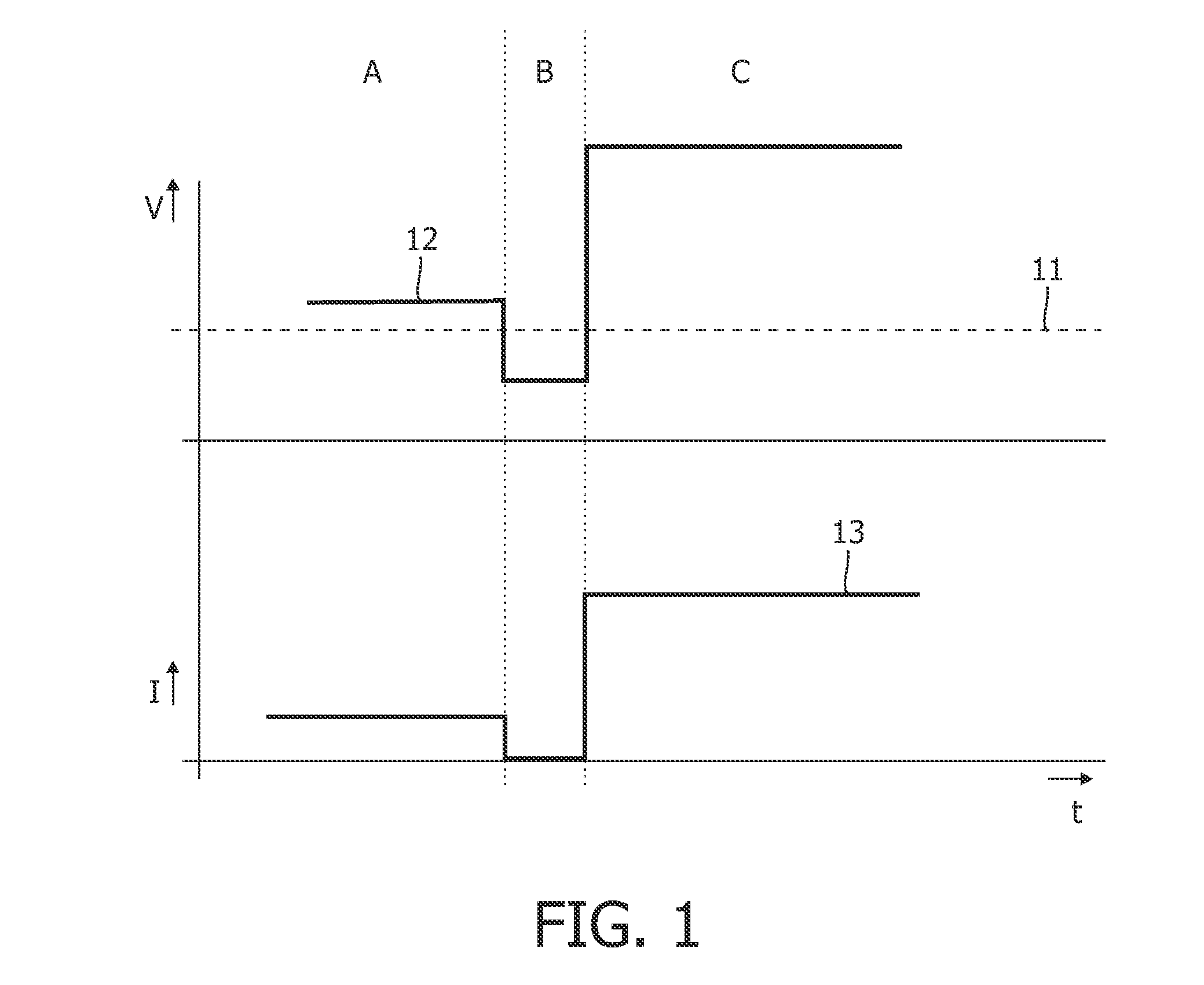

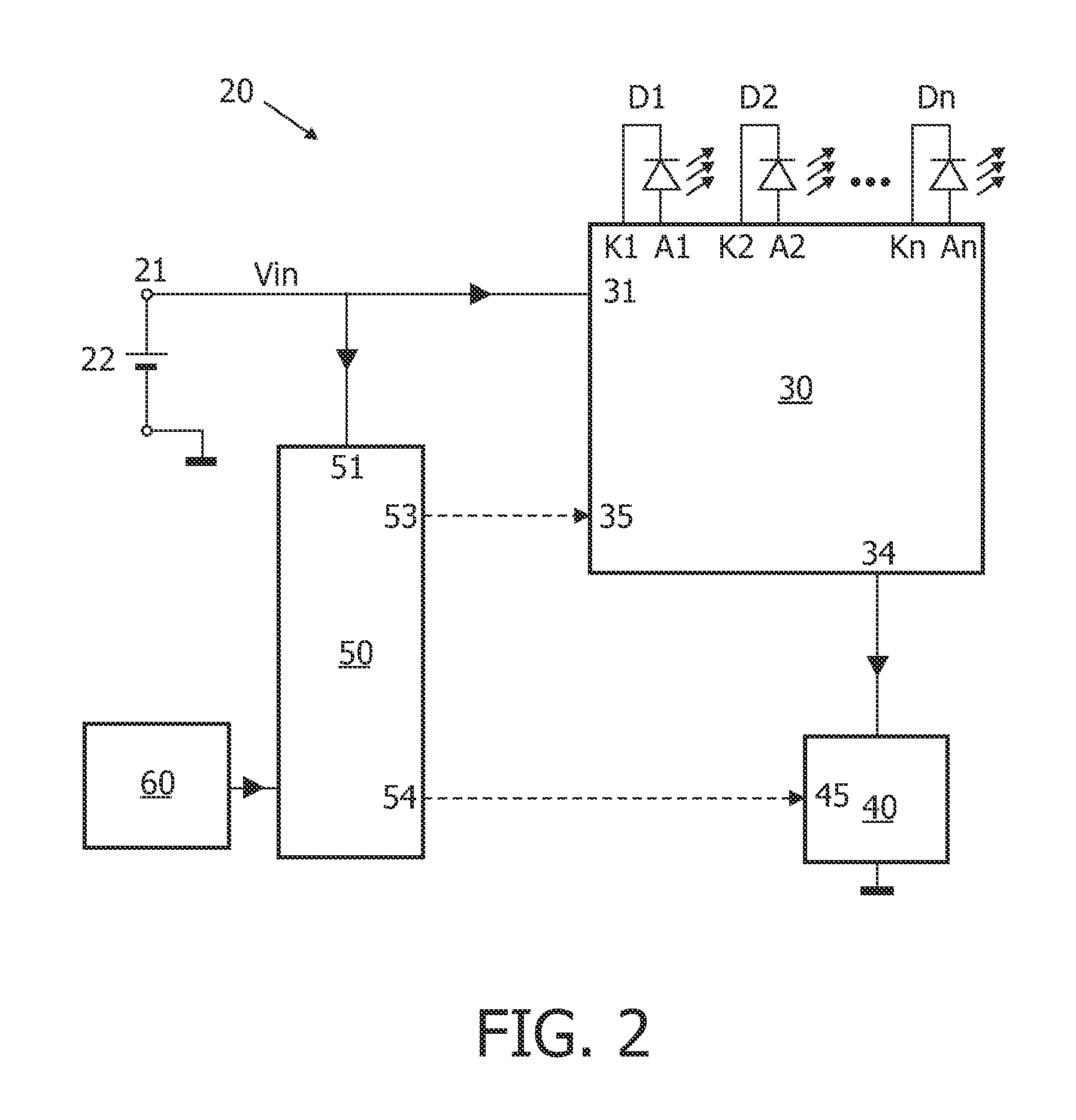

Illumination Device Comprising Multiple LEDs

InactiveUS20110133658A1Electrical apparatusElectroluminescent light sourcesEngineeringCurrent source

A light generating device (20) comprises: —an input for receiving a DC input voltage (Vin) of varying magnitude; —a controllable current source (40); —a switch matrix (30) comprising a plurality of controllable switches (S1-SN); —a plurality of n LEDs (D1, D2, . . . Dn) connected to output terminals of the switch matrix (30); —a controller (50) controlling said switches and controlling the current generated by the current source dependent on the momentary value of the DC input voltage (Vin). The controller is capable of operating in at least three different control states. In a first control state all LEDs are connected in parallel. In a second control state all LEDs are connected in series. In a third control state at least two of said LEDs are connected in parallel while also at least two of said LEDs are connected in series.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

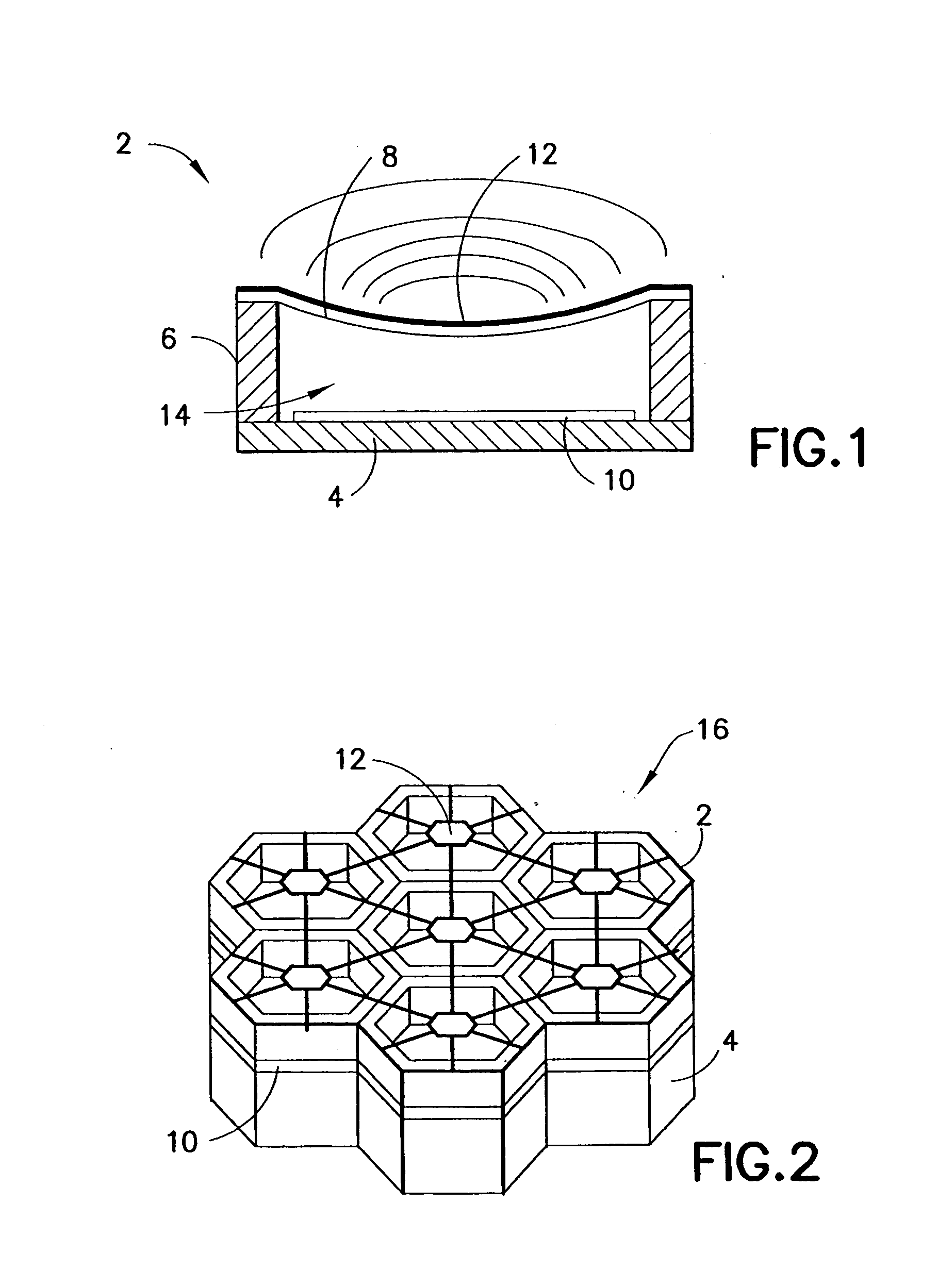

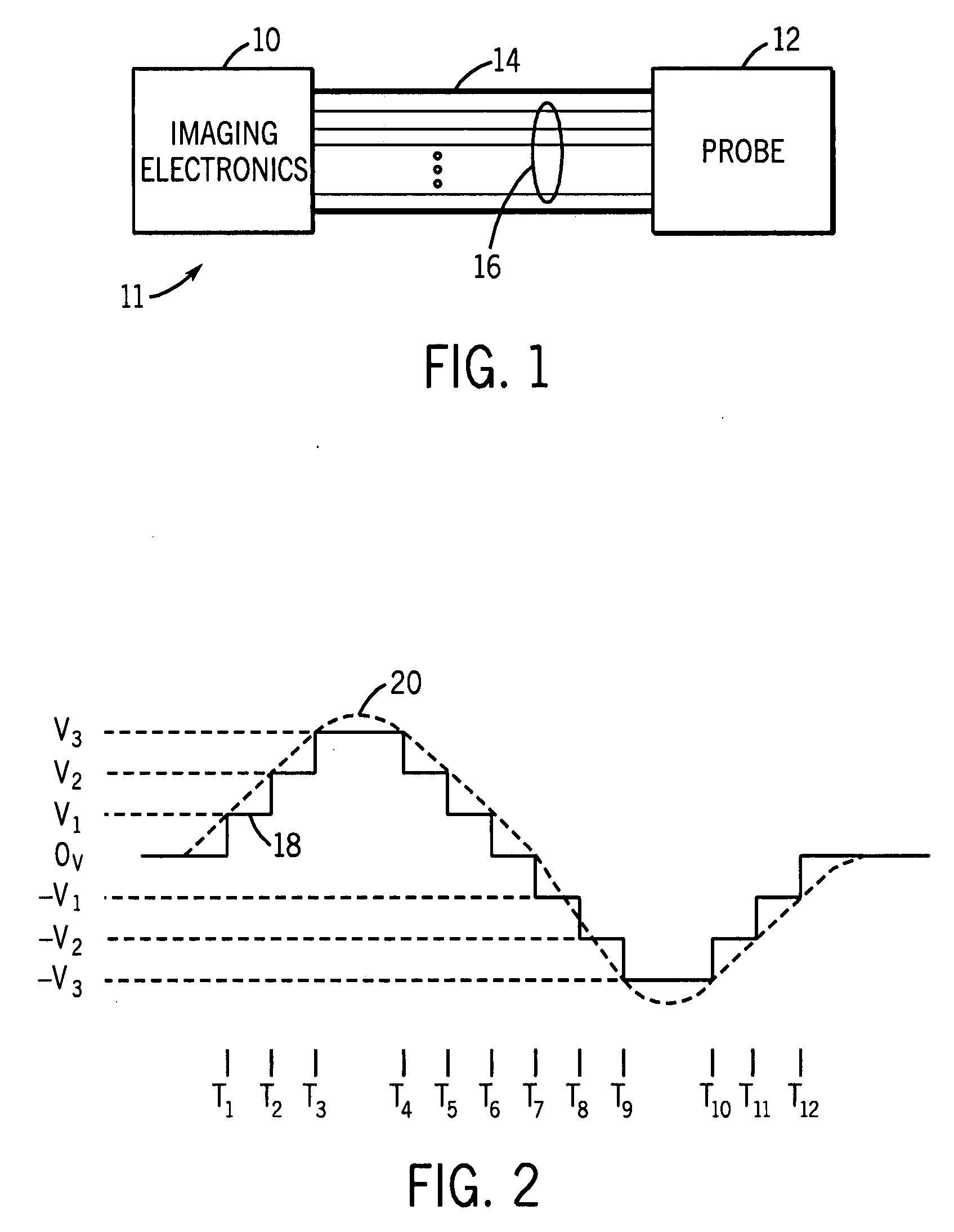

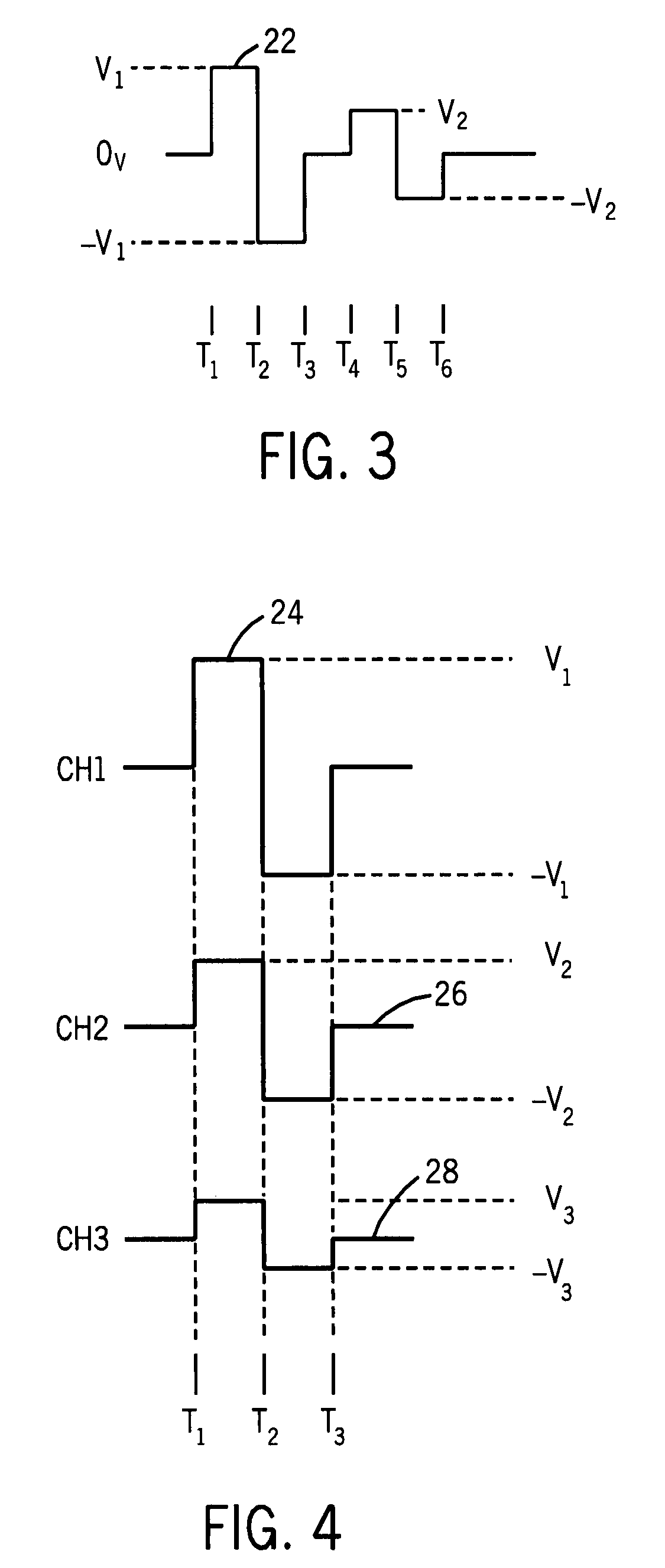

Reconfigurable array with multi-level transmitters

ActiveUS20080264171A1Minimal expenditure of powerSmall footprintUltrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesAcoustic energyEngineering

An imaging probe having multi-level transmitter cells. The imaging probe includes a plurality of acoustical sub-elements for transmitting and receiving acoustic energy for imaging. Each of the multi-level transmitter cells is arranged along a respective transmitter cell path between a switching matrix and one of the acoustical sub-elements. The multi-level transmitter cells in the probe are capable of producing signals having multiple voltage levels.

Owner:GENERAL ELECTRIC CO