Patents

Literature

236 results about "Reconfigurable array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

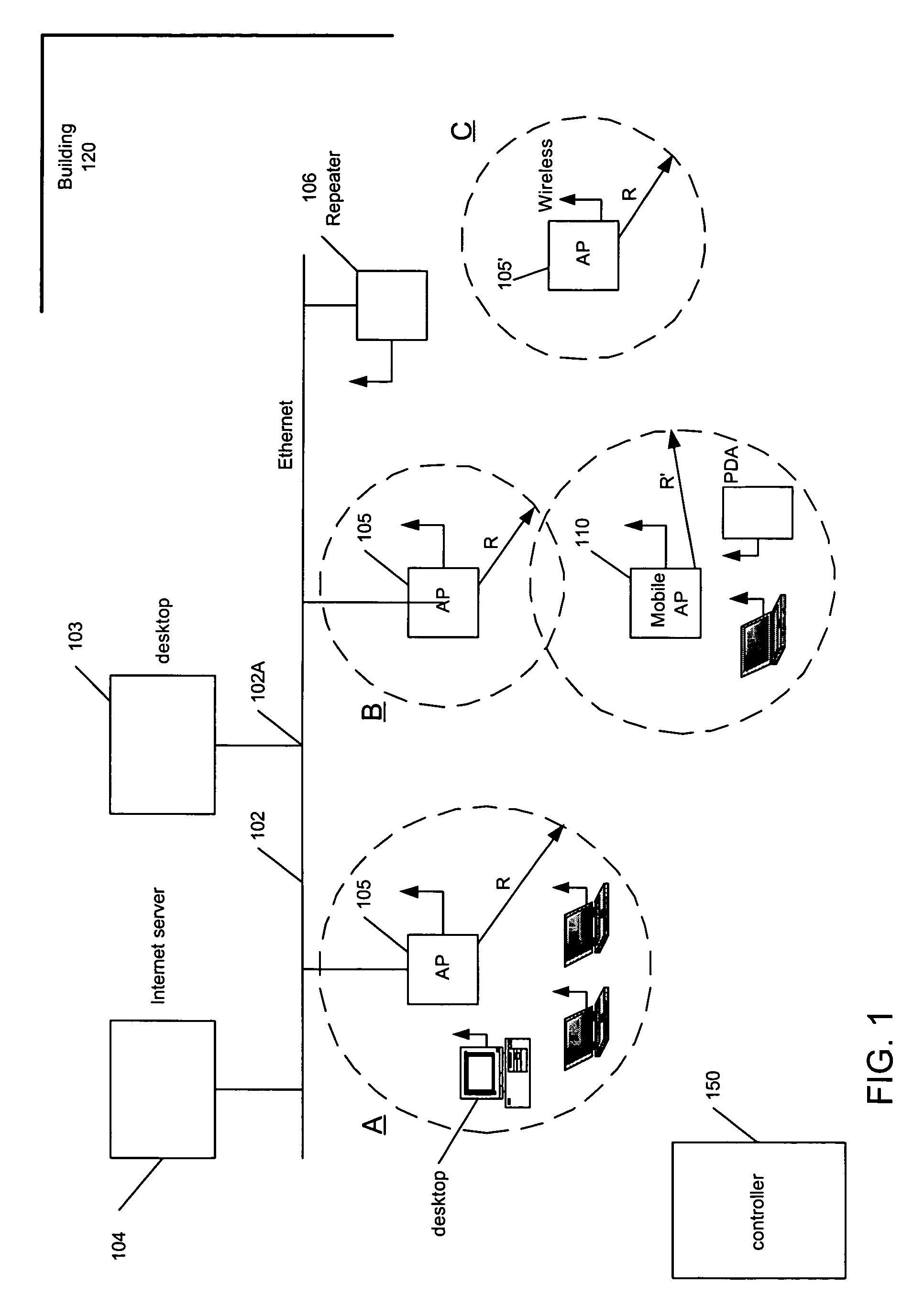

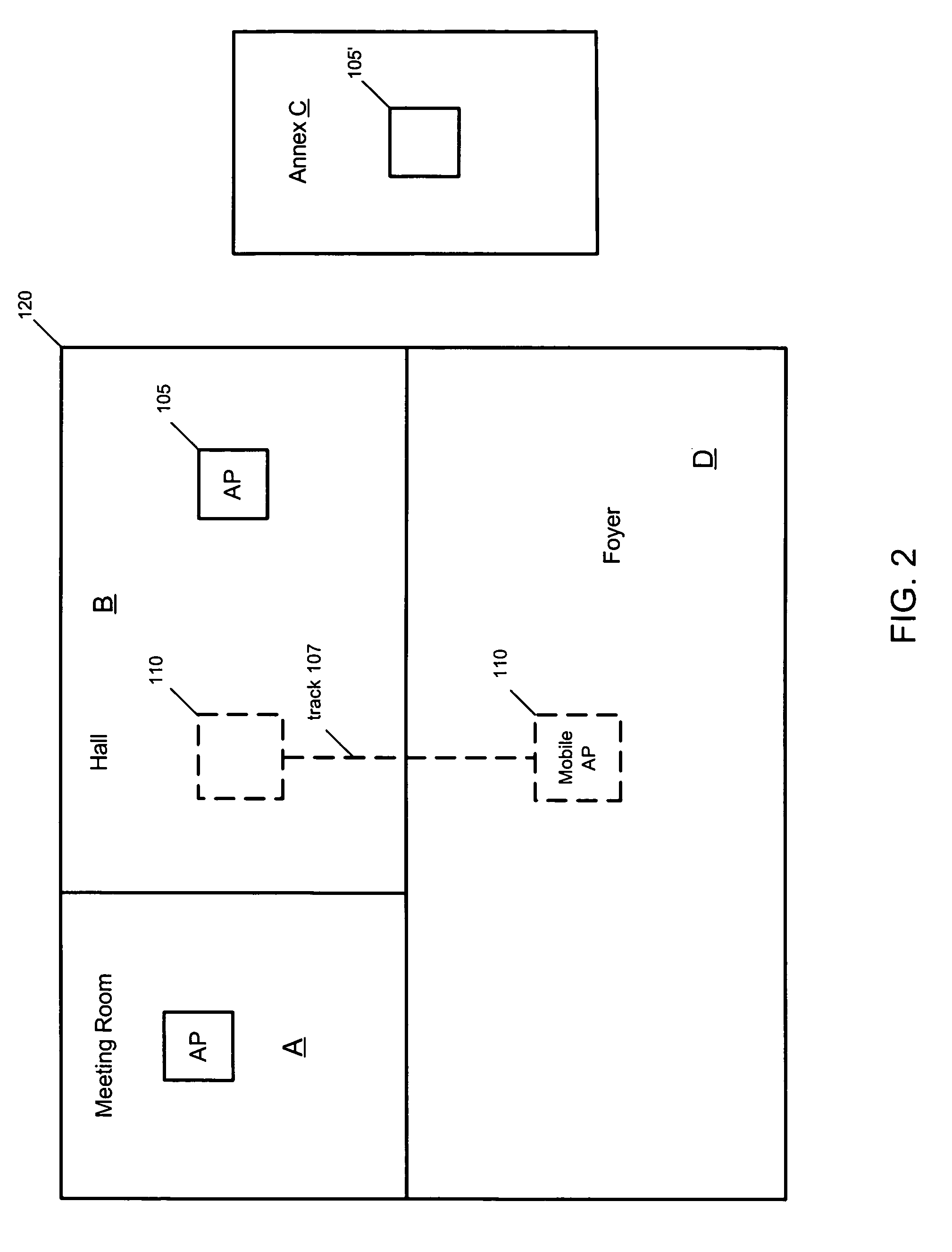

Reconfigureable arrays of wireless access points

ActiveUS20060002326A1Meet real-timeBroadcast with distributionNetwork topologiesQuality of serviceGeographic distribution

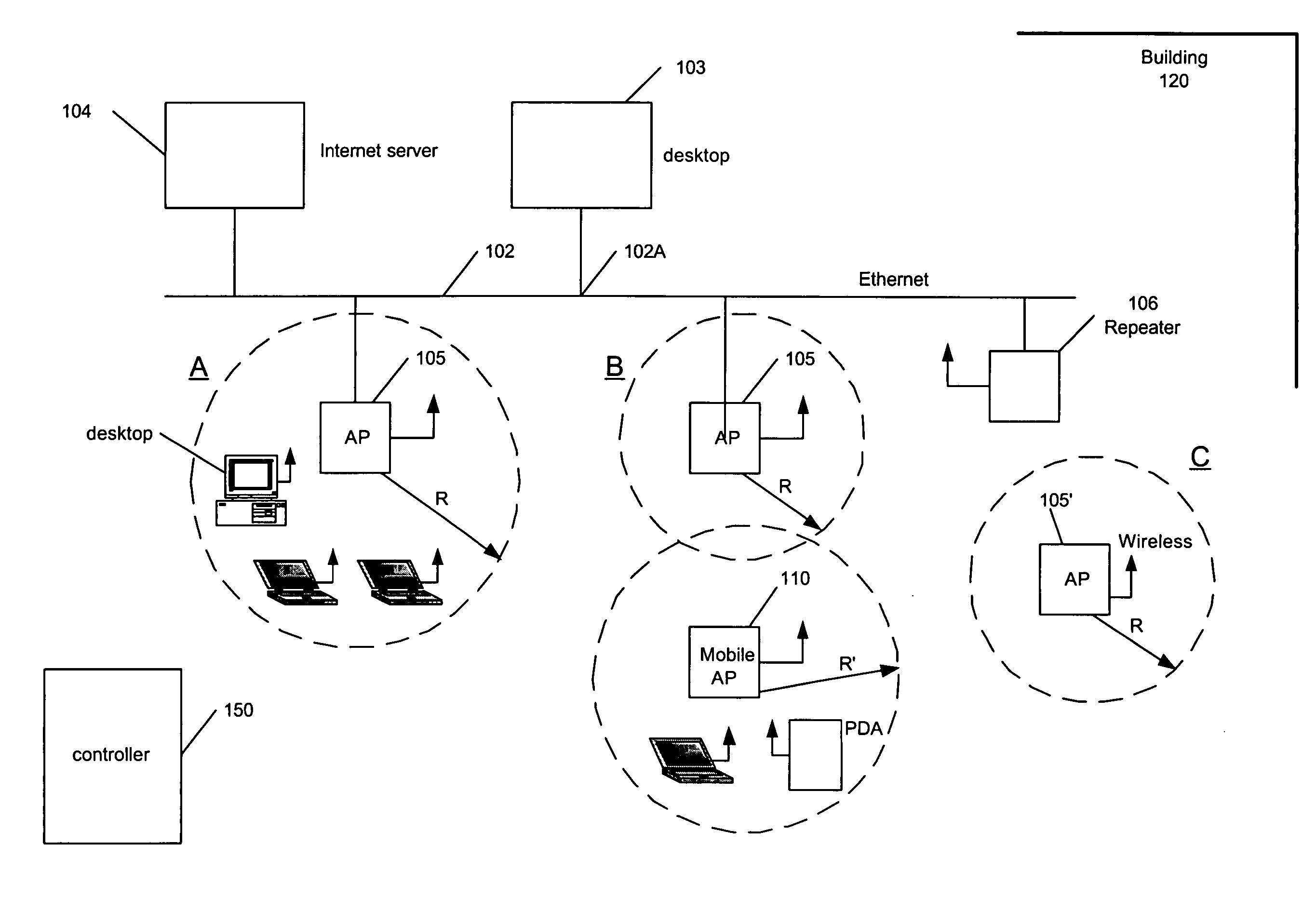

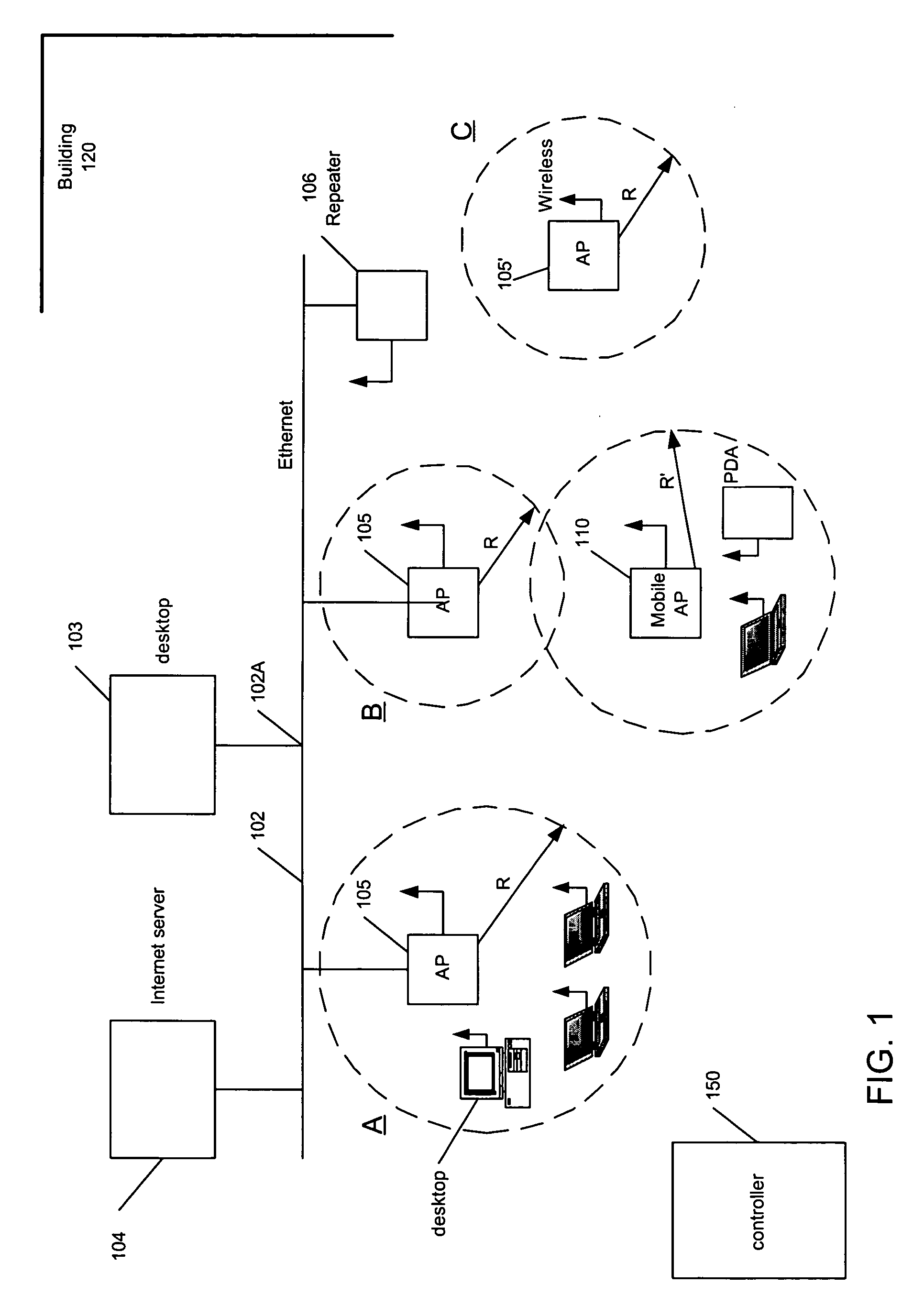

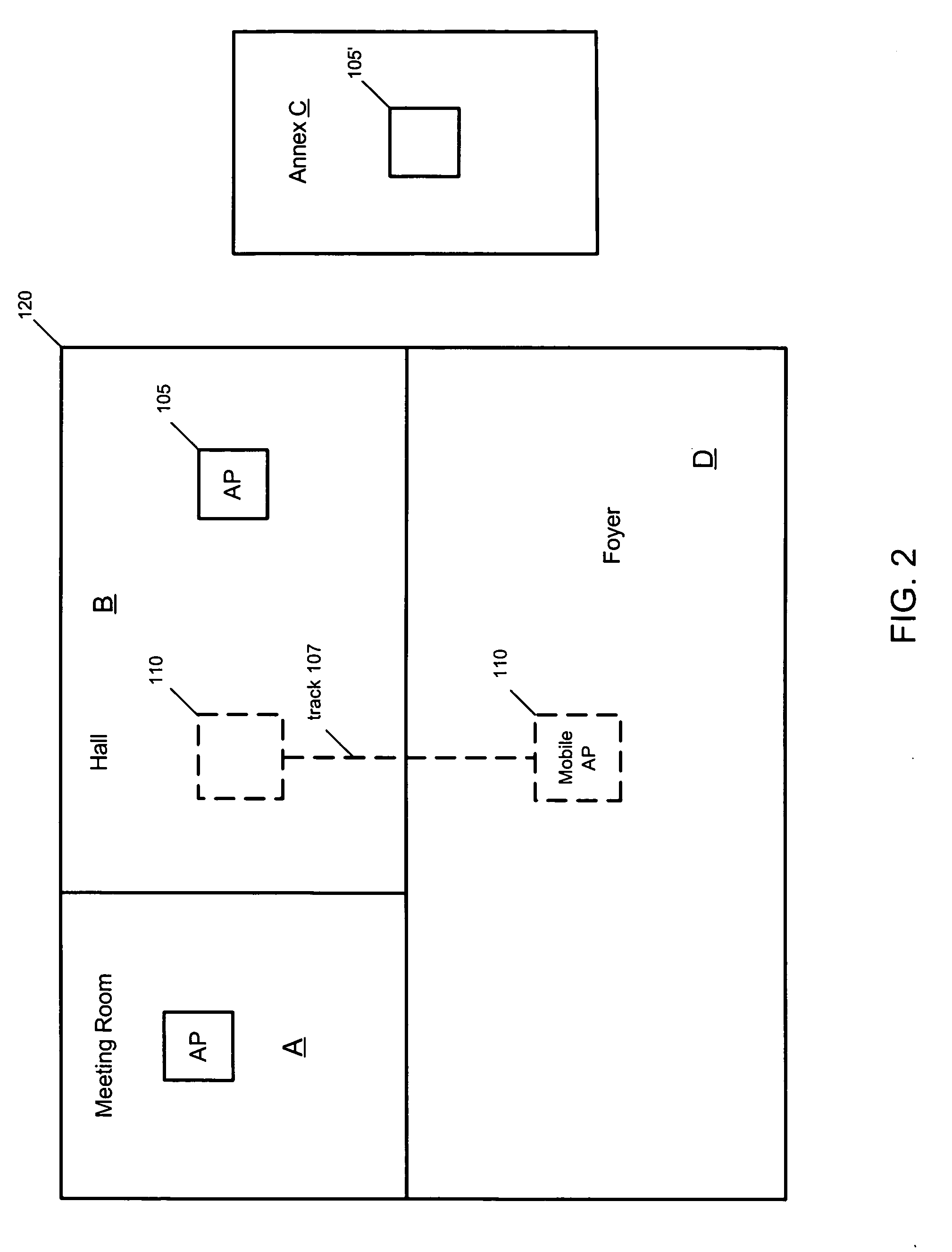

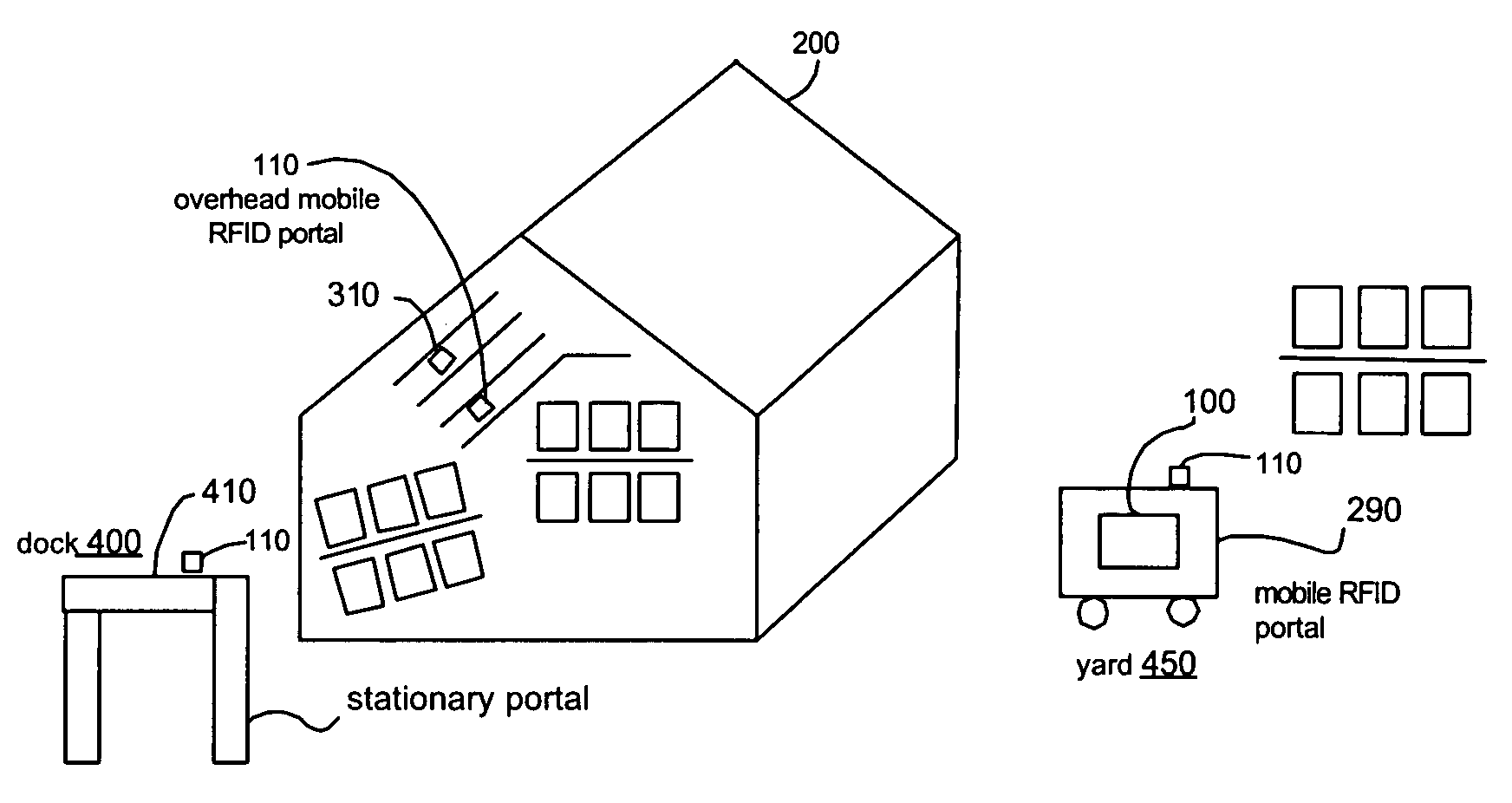

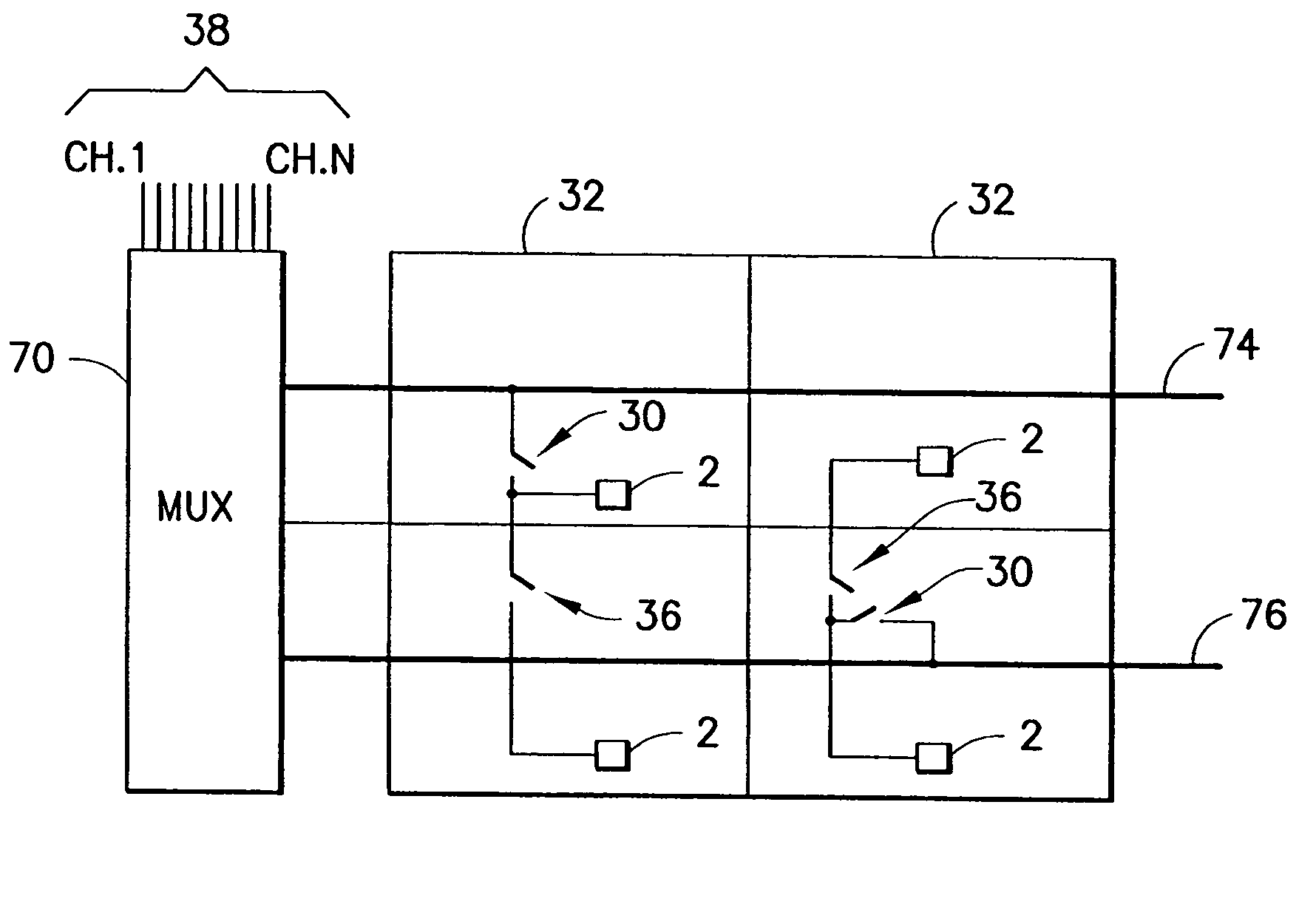

A wireless communications network includes a reconfigurable array of access points for linking wireless devices in an infrastructure mode. One or more of the access points are mobile. The mobile access points in the network can be repositioned to change the geographic distribution of the bandwidth coverage provided by the wireless network. The mobile access points may be repositioned to redistribute available network bandwidth heterogeneously according to the demand for bandwidth in local areas and to meet quality of service standards.

Owner:EXTREME NETWORKS INC

Reconfigureable arrays of wireless access points

ActiveUS7496070B2Meet real-timeBroadcast with distributionNetwork topologiesQuality of serviceWireless mesh network

A wireless communications network includes a reconfigurable array of access points for linking wireless devices in an infrastructure mode. One or more of the access points are mobile. The mobile access points in the network can be repositioned to change the geographic distribution of the bandwidth coverage provided by the wireless network. The mobile access points may be repositioned to redistribute available network bandwidth heterogeneously according to the demand for bandwidth in local areas and to meet quality of service standards.

Owner:EXTREME NETWORKS INC

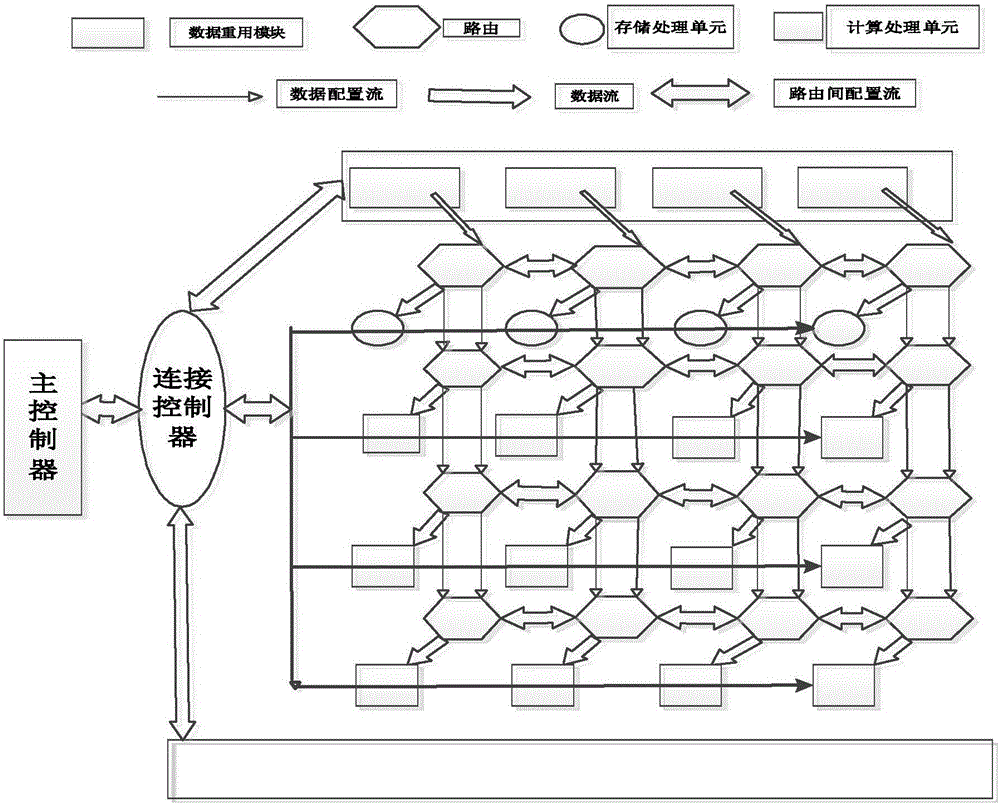

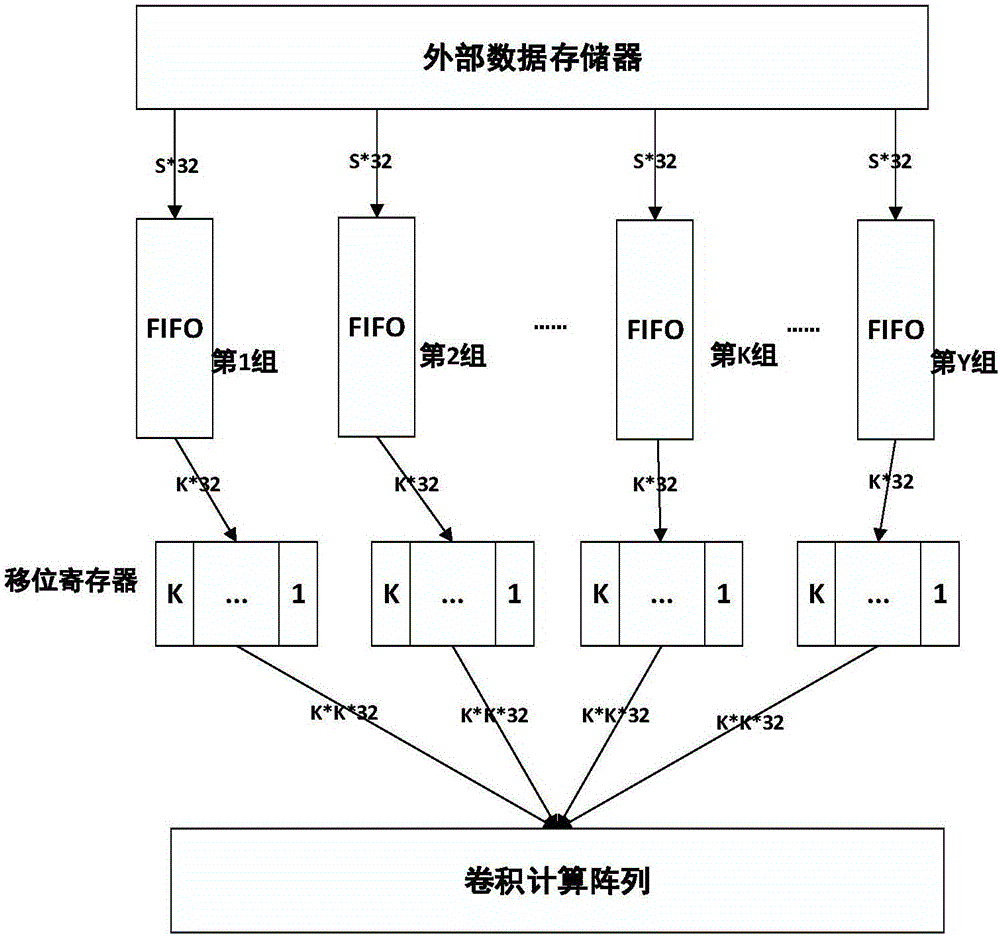

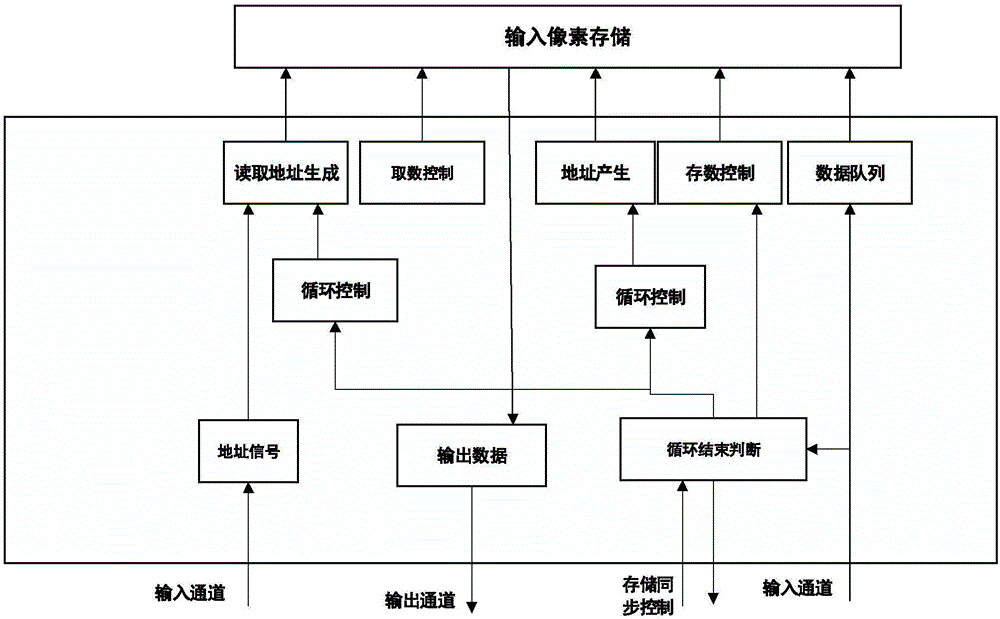

System for circular convolution calculation data reuse of convolutional neural network

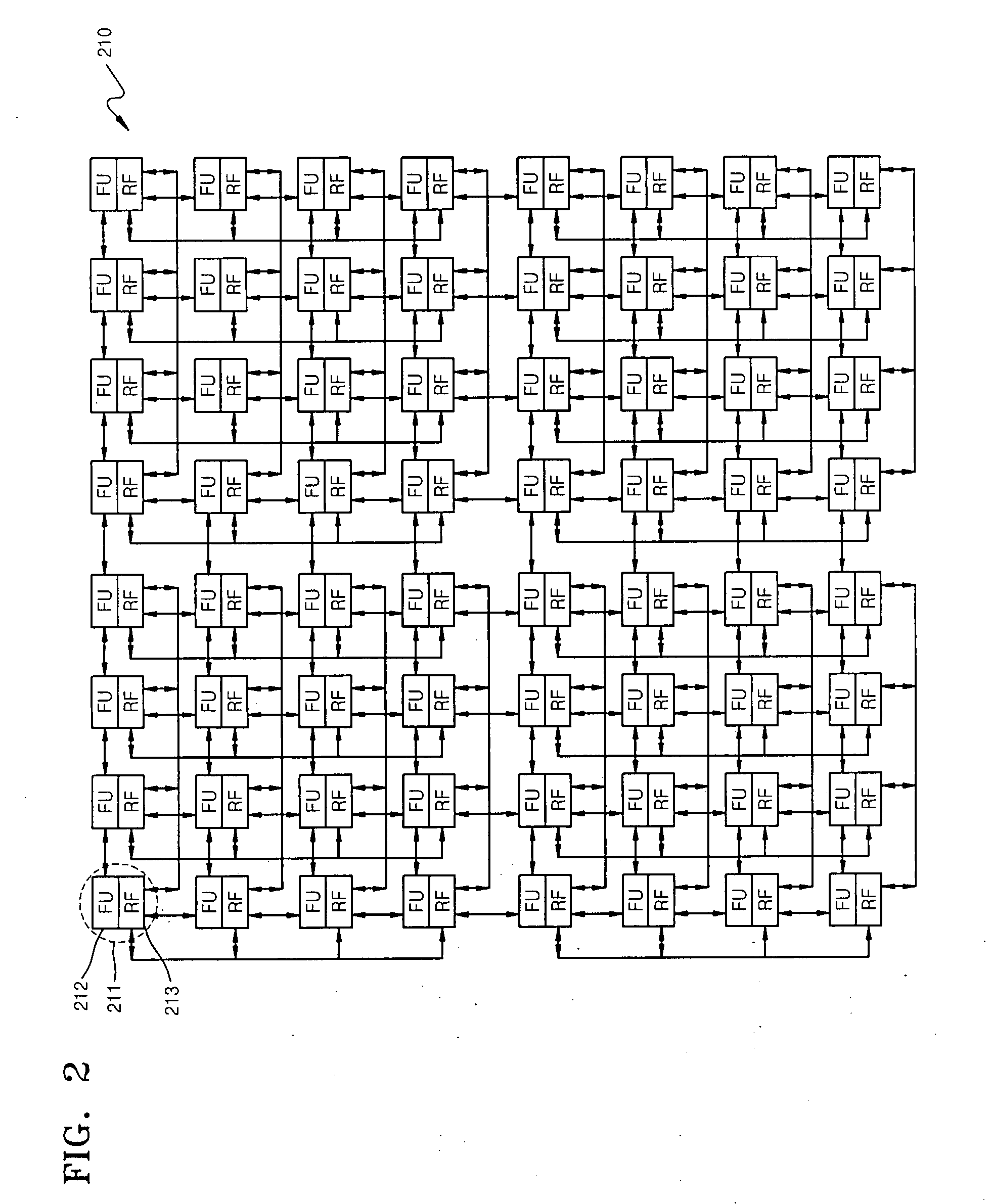

InactiveCN106250103ARegister arrangementsConcurrent instruction executionProcessor registerComputation process

The invention discloses a coarse-grained reconfigurable system-oriented convolution neural network loop convolution calculation data reuse system, including a main controller and a connection control module, an input data reuse module, a convolution loop operation processing array, and a data transmission Pathways in four parts. During the convolution cycle operation, the essence is to multiply multiple two-dimensional input data matrices with multiple two-dimensional weight matrices. Generally, these matrices are large in size, and the multiplication takes up most of the time of the entire convolution calculation. The present invention utilizes a coarse-grained reconfigurable array system to complete the convolution calculation process. After receiving the convolution operation request instruction, the register rotation method is used to fully explore the reusability of the input data in the convolution cycle calculation process, which improves the data utilization rate. It also reduces the bandwidth access pressure, and the designed array unit is configurable, and can complete convolution operations with different cyclic convolution scales and step sizes.

Owner:SOUTHEAST UNIV

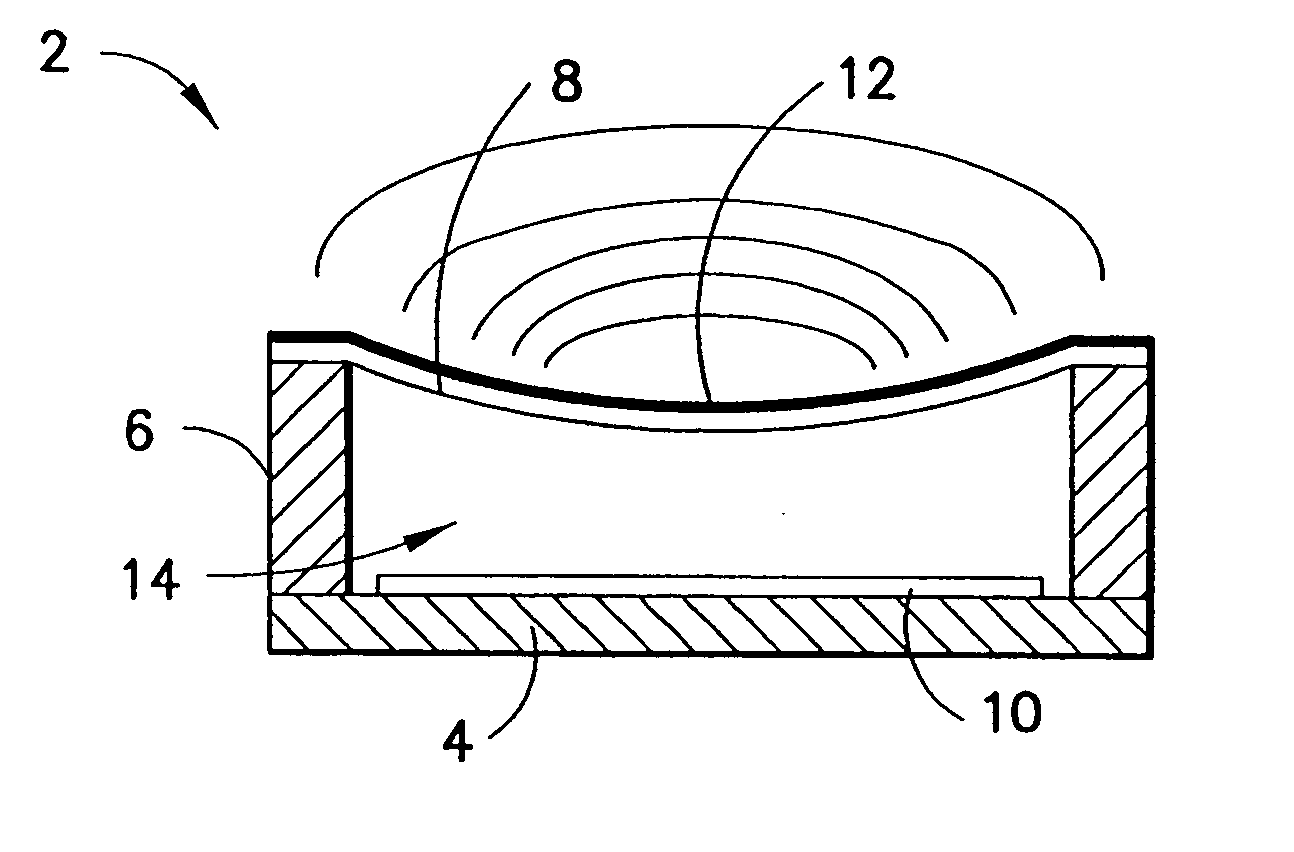

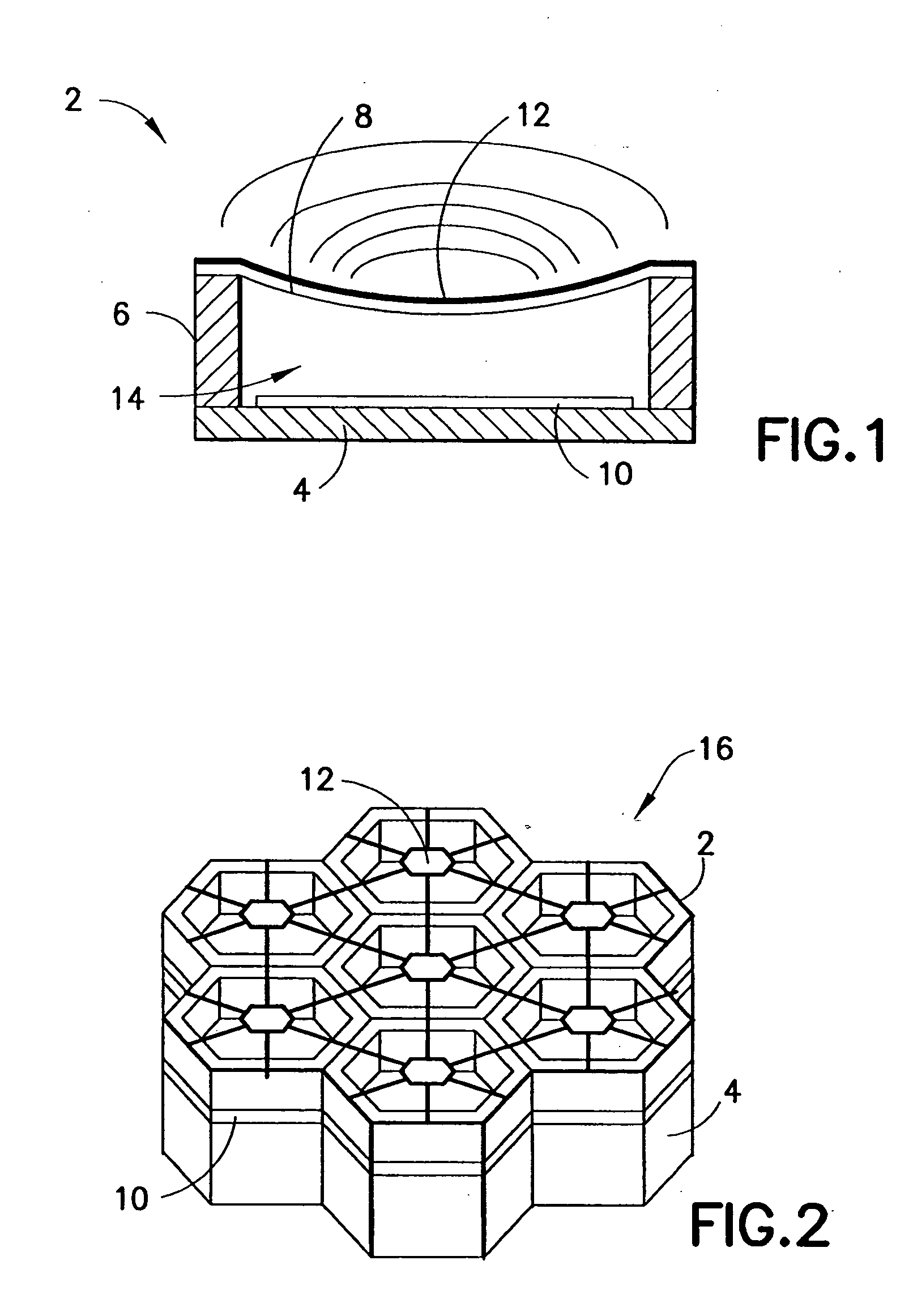

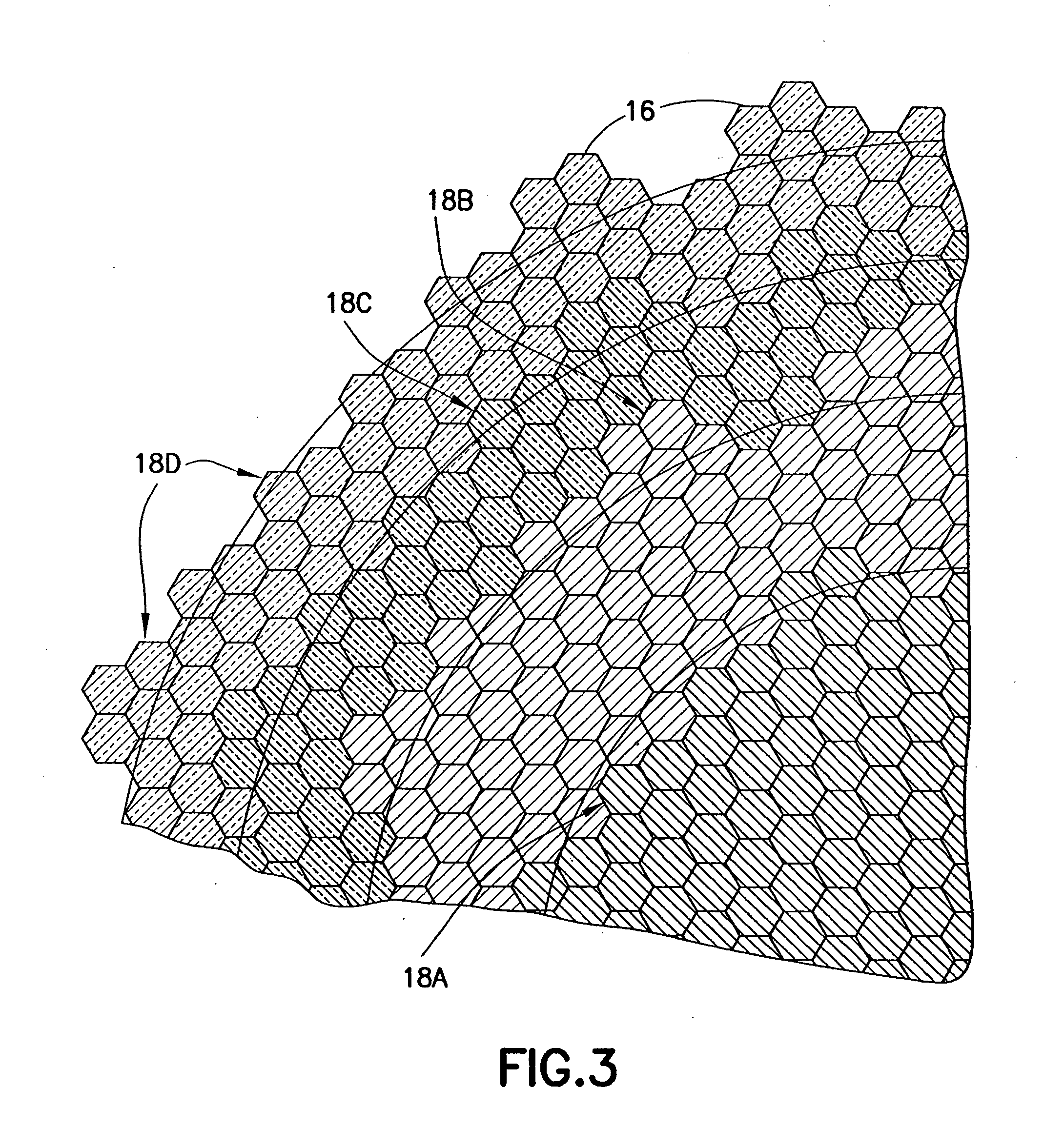

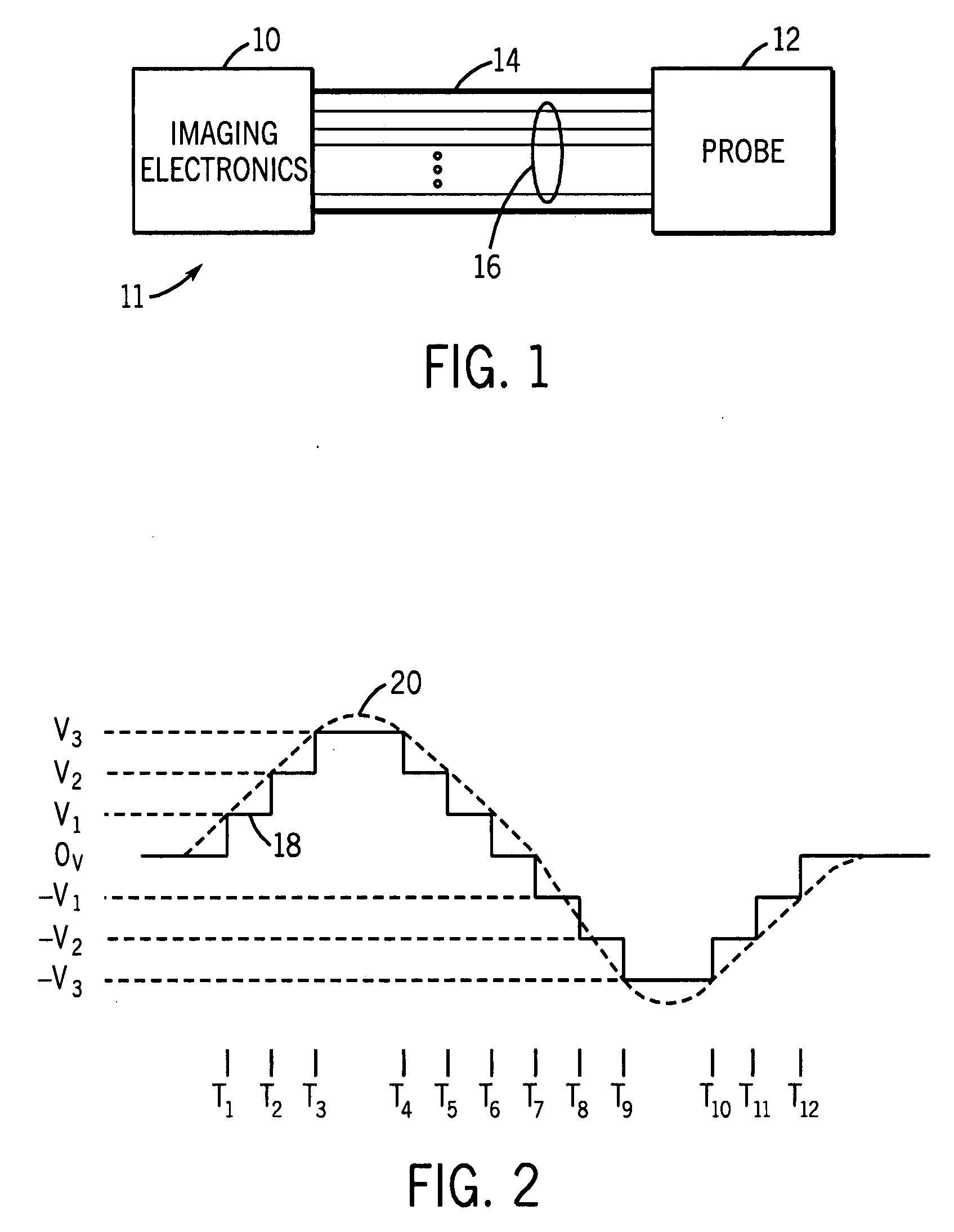

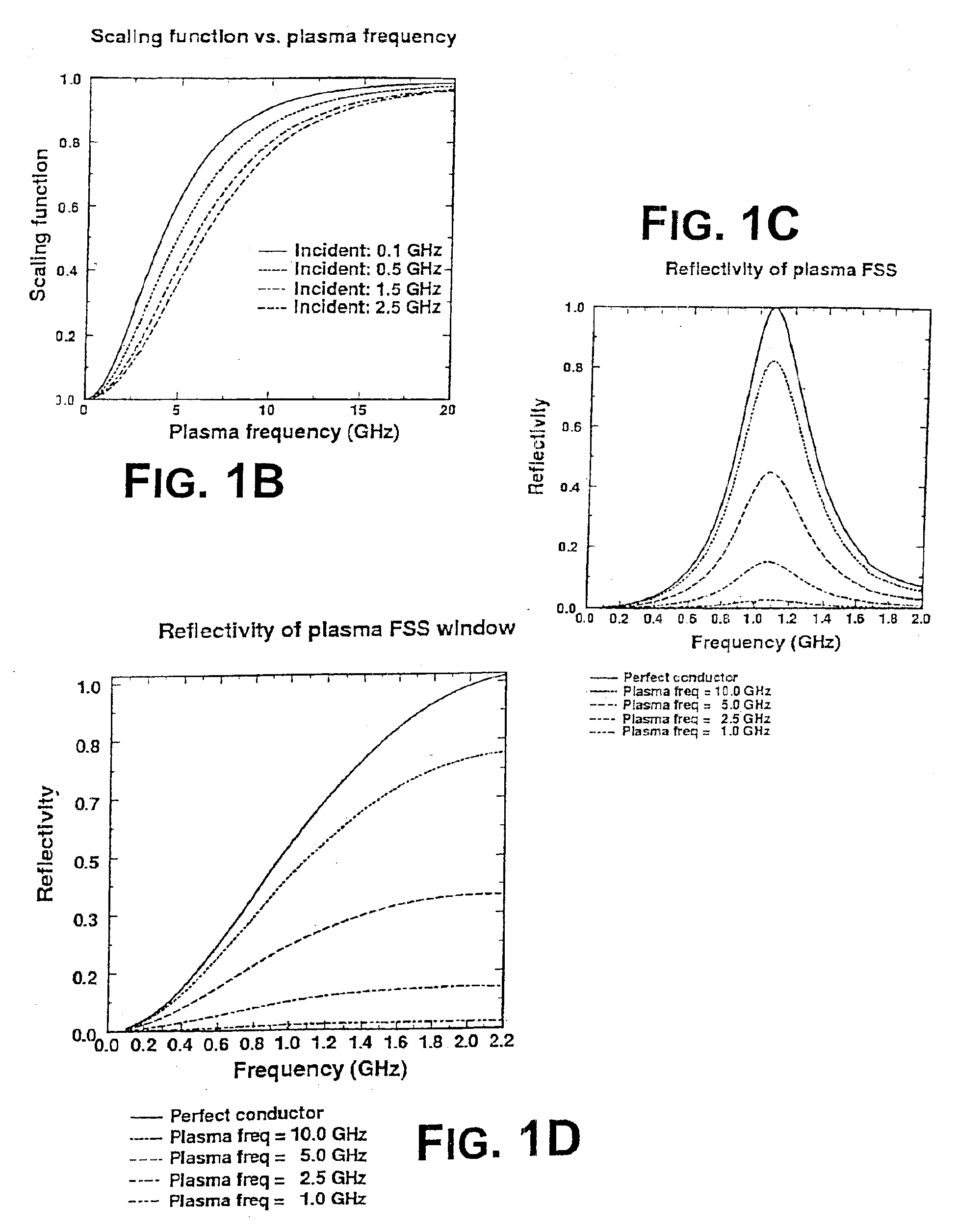

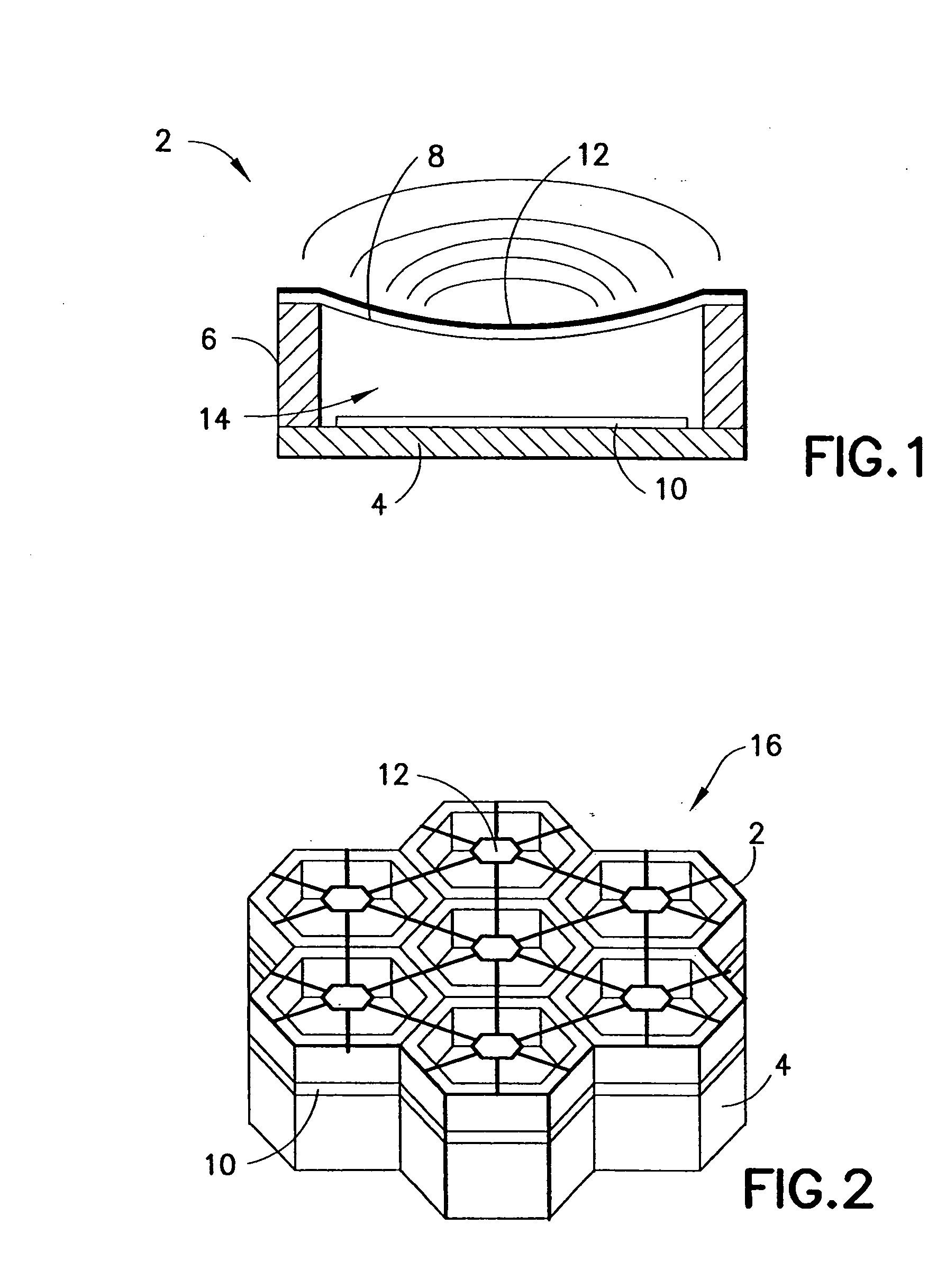

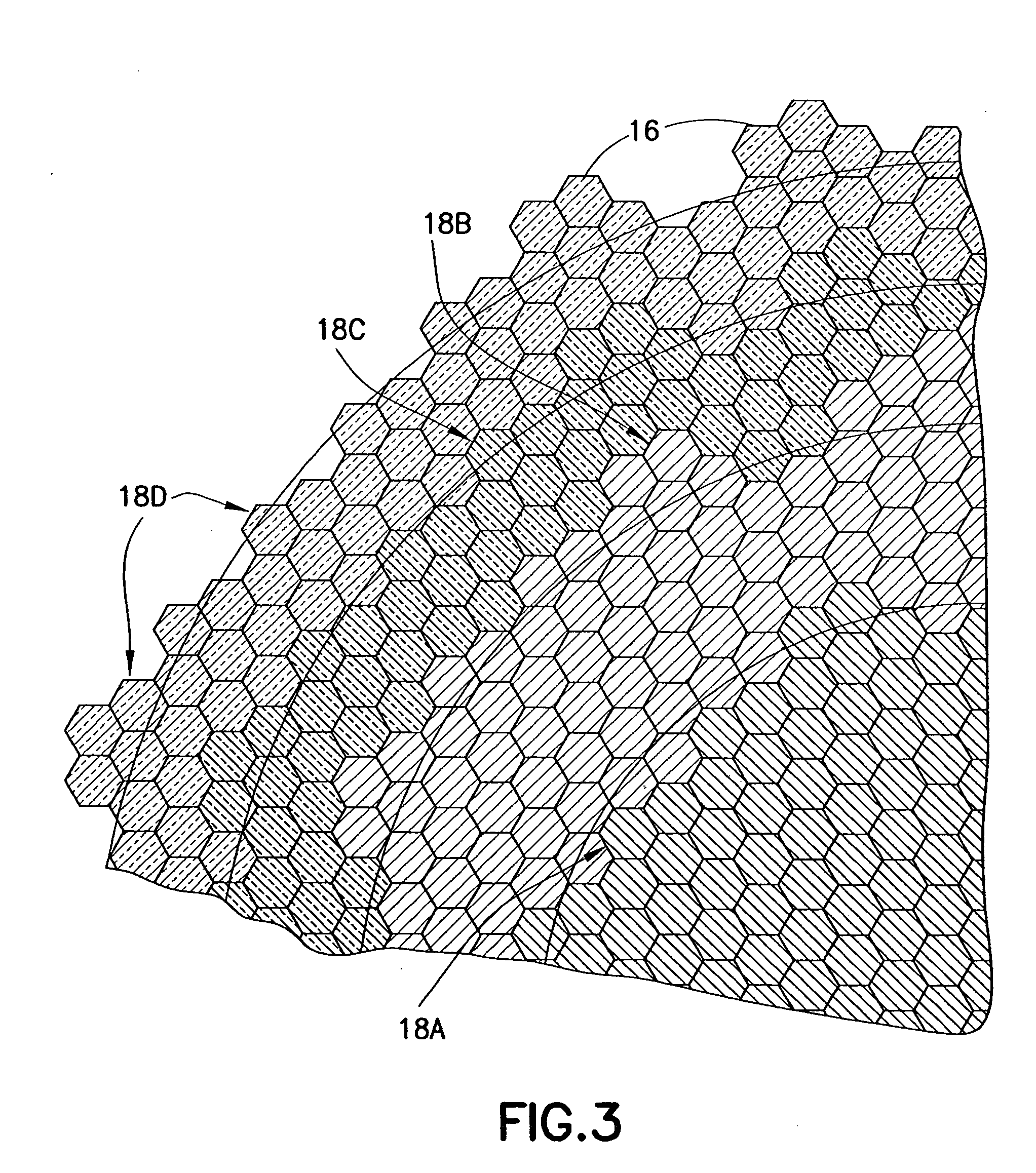

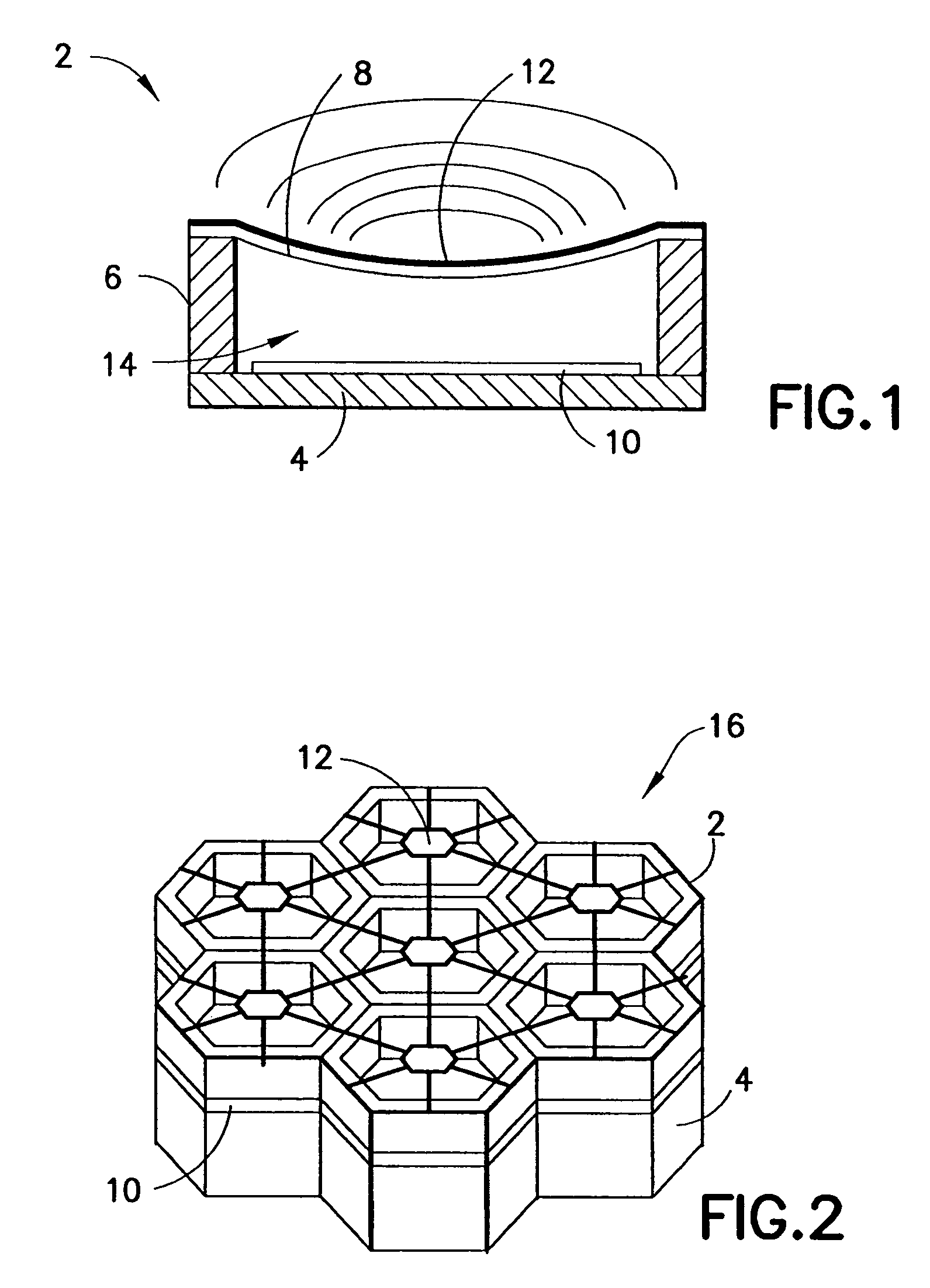

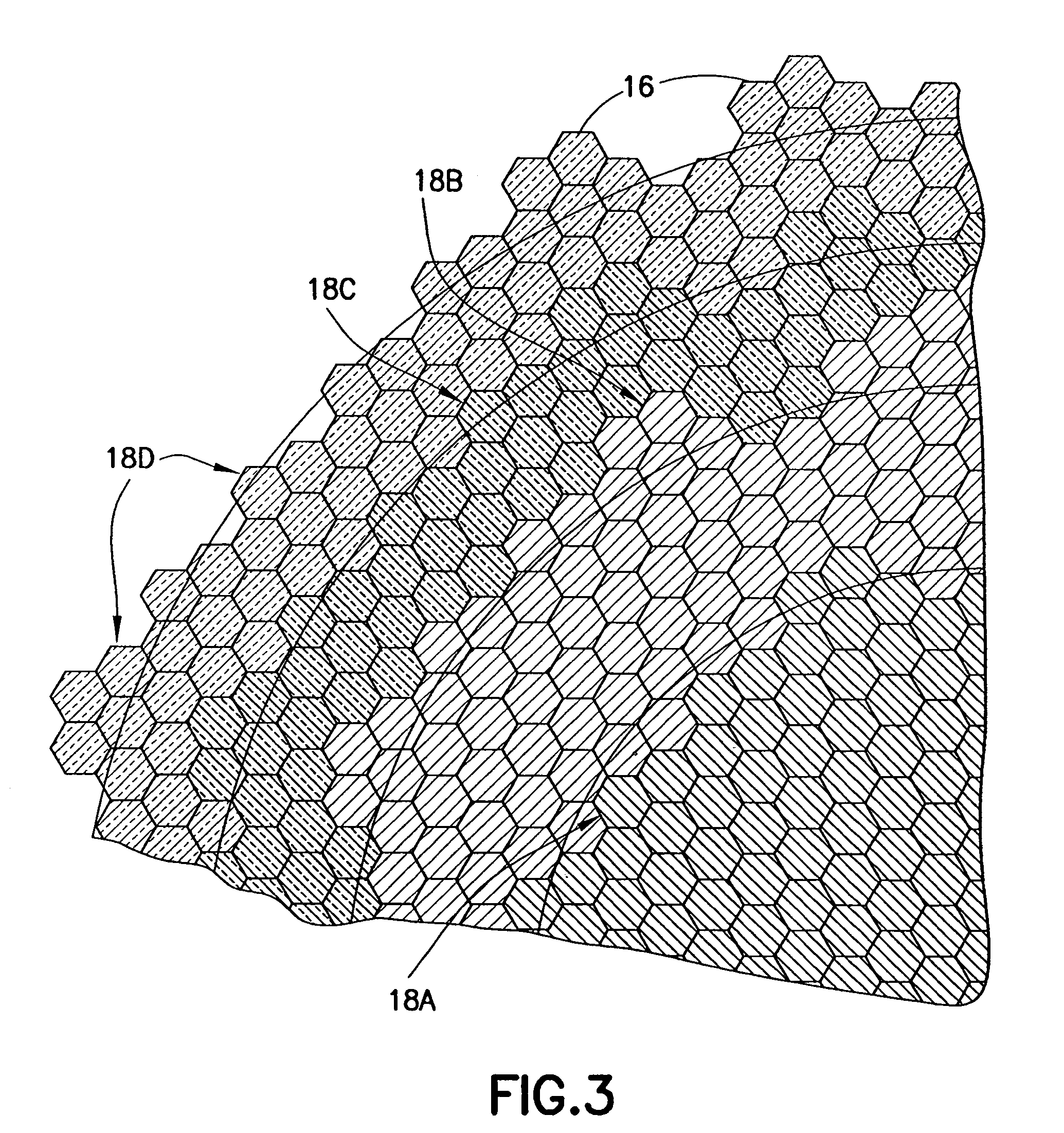

Optimized switching configurations for reconfigurable arrays of sensor elements

InactiveUS20050096546A1Minimize cost functionImage analysisPiezoelectric/electrostrictive transducersReconfigurabilitySonification

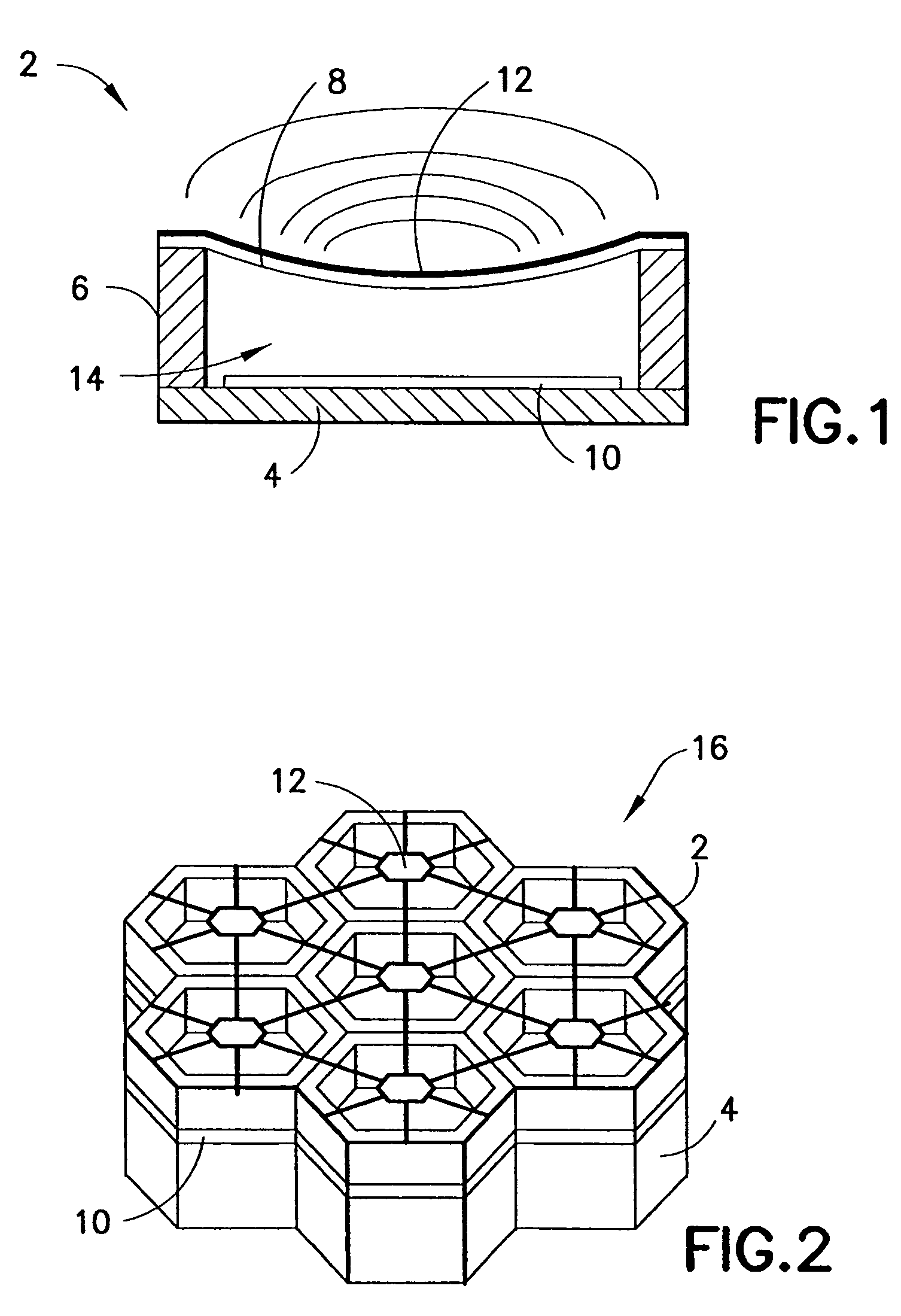

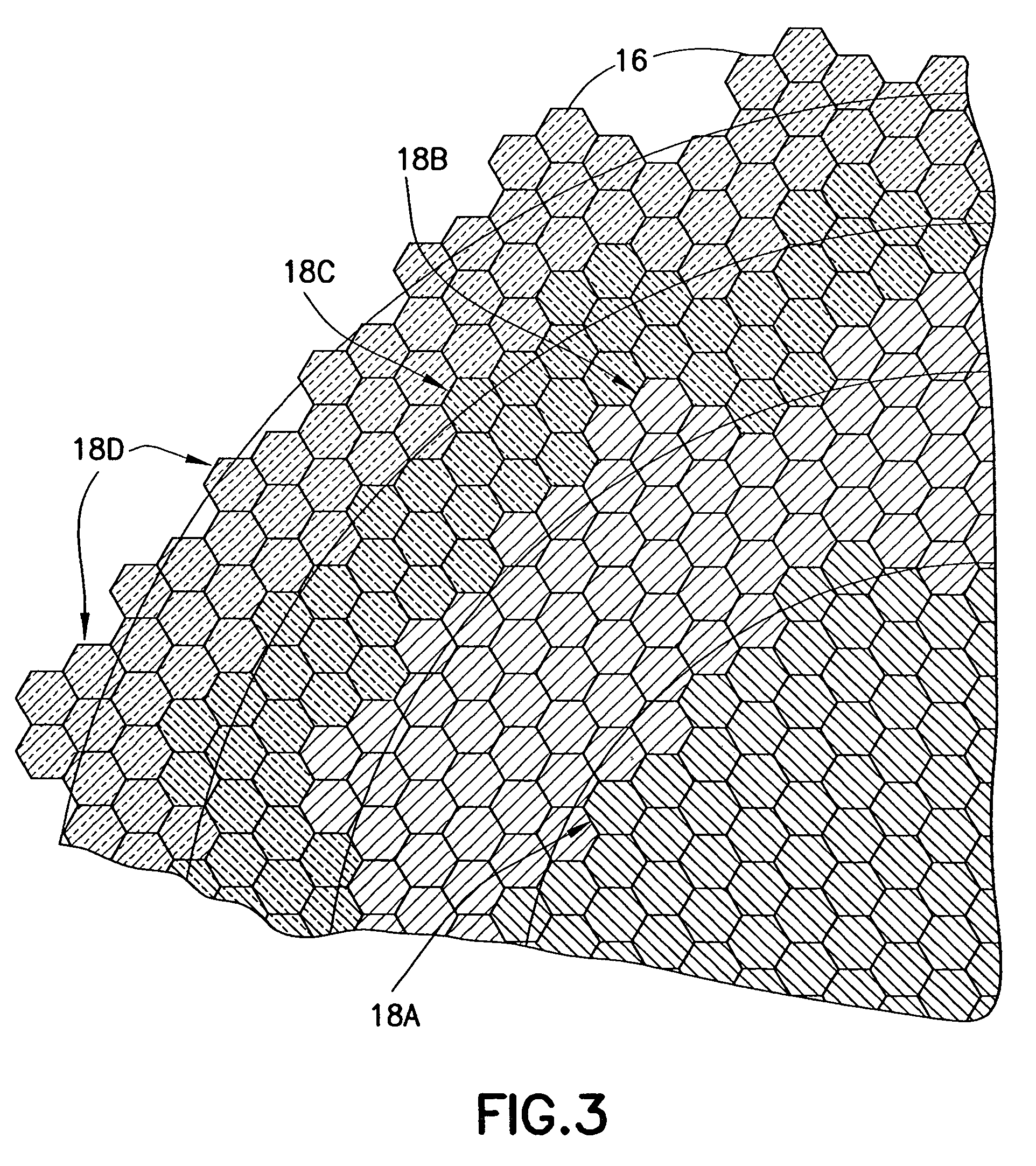

The reconfigurable ultrasound array disclosed herein is one that allows groups of subelements to be connected together dynamically so that the shape of the resulting element can be made to match the shape of the wave front. This can lead to improved performance and / or reduced channel count. Reconfigurability can be achieved using a switching network. A methodology and an algorithm are disclosed that allows the performance of this switching network to be improved by properly choosing the configuration of the switching network.

Owner:GENERAL ELECTRIC CO

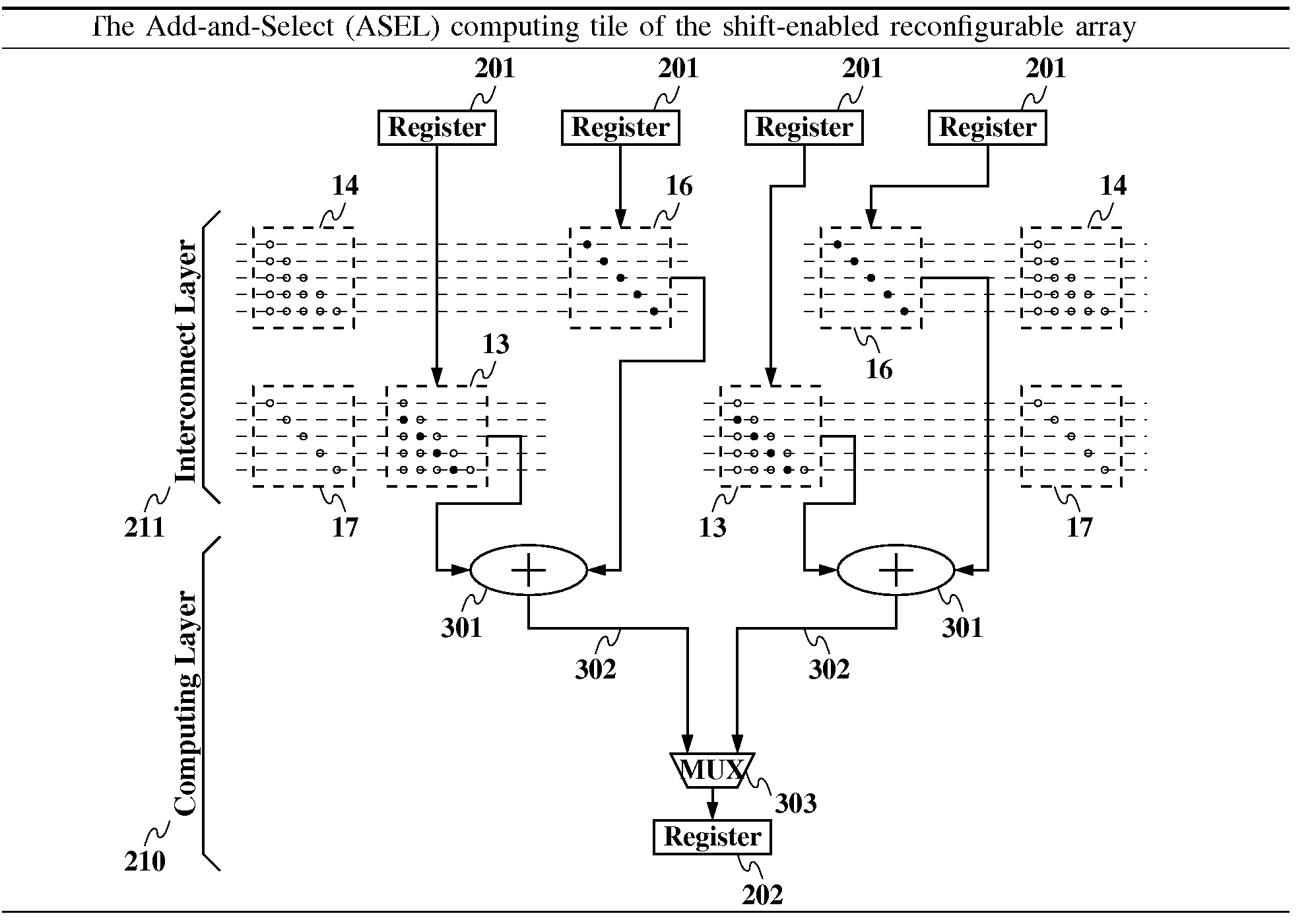

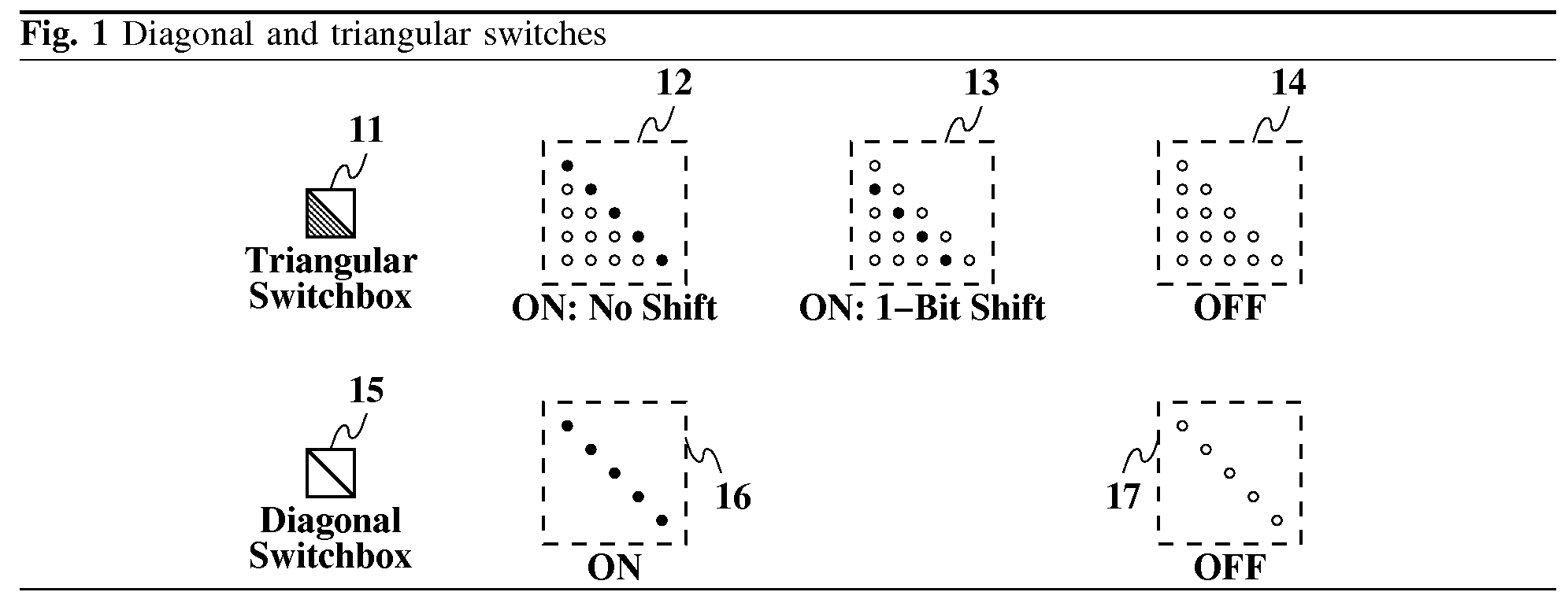

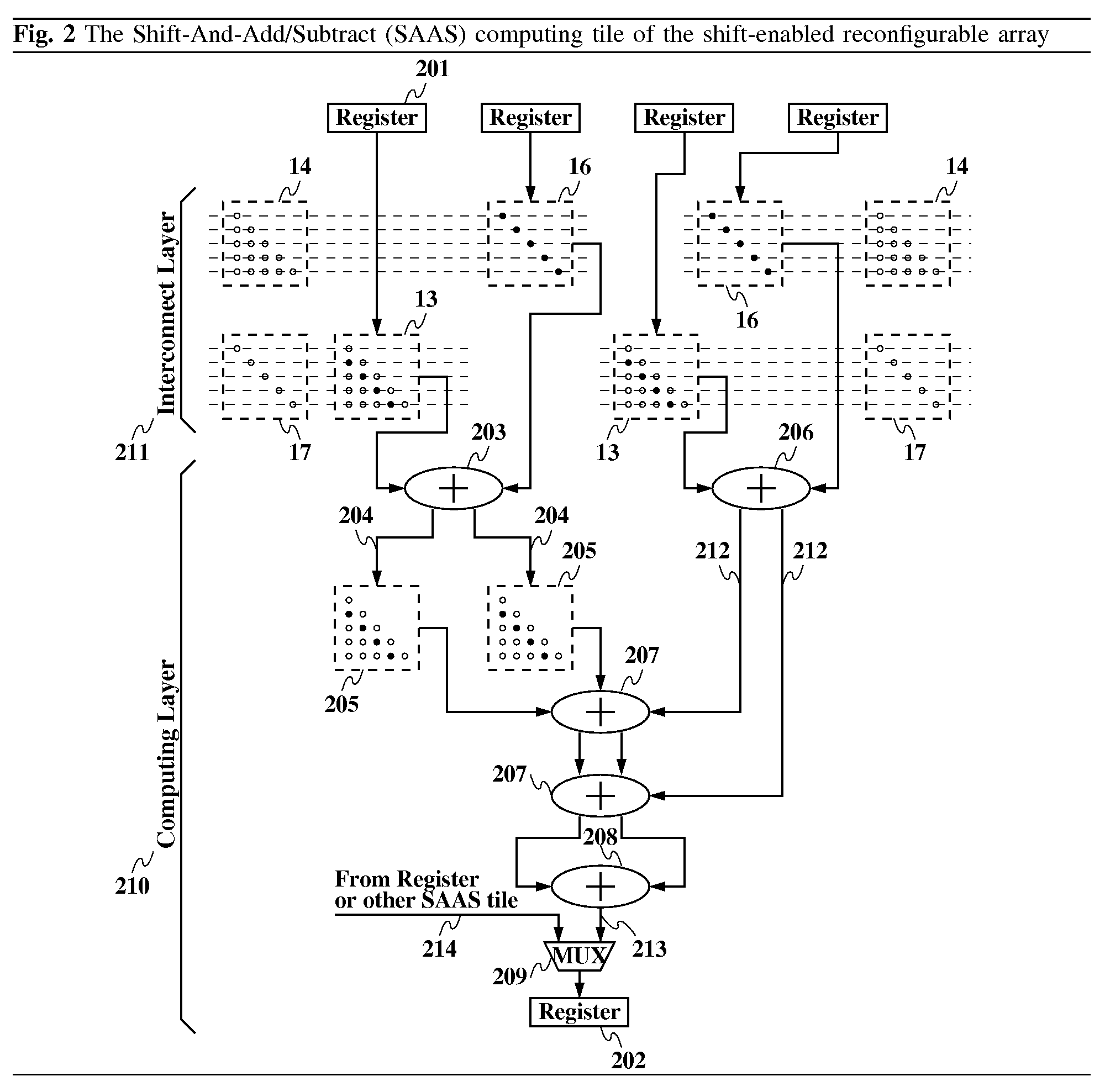

Shift-enabled reconfigurable device

A coarse-grain reconfigurable array that implements shift operations within its interconnection network is disclosed. The interconnection network of such a coarse-grain reconfigurable array contains partially or fully populated matrices of switches, where each such matrix of switches is obtained by merging a standard diagonal switch matrix with an array shift unit. The disclosed device provides better performance when the standard routing and shift functions are both required.

Owner:SIMA MIHAI +2

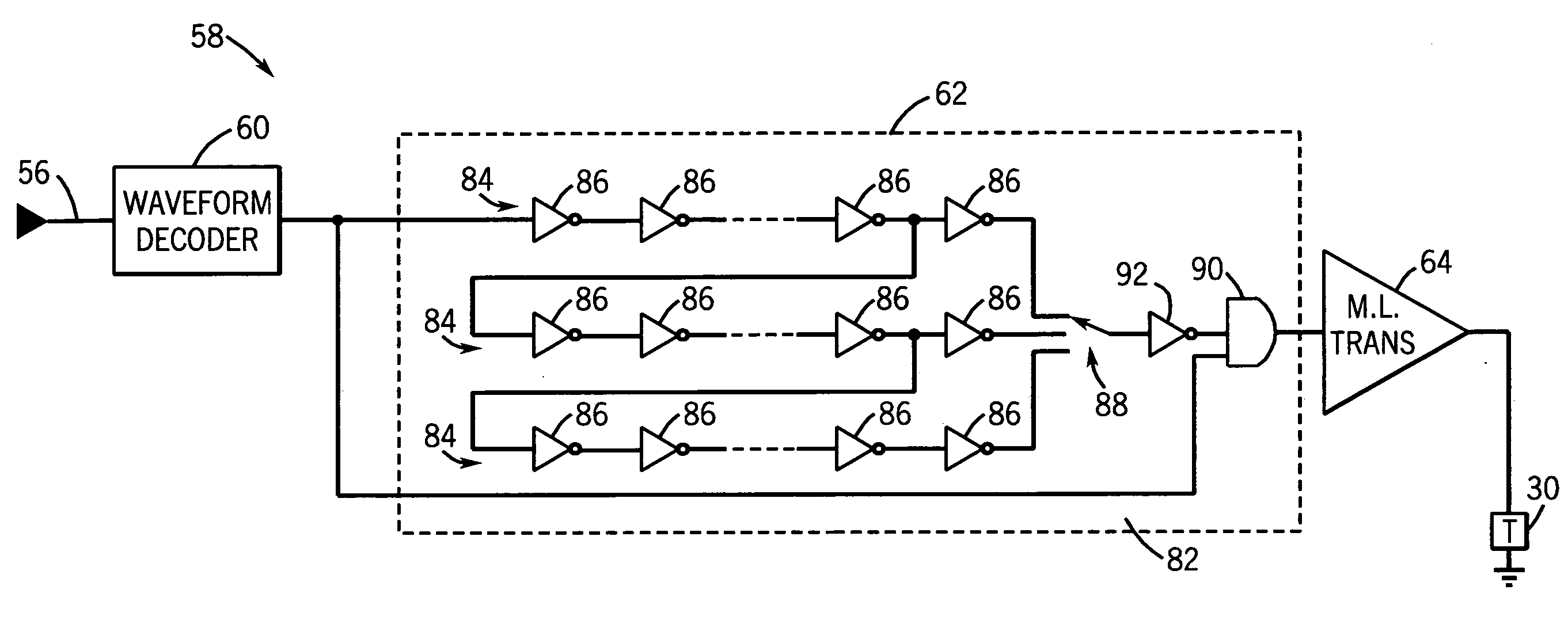

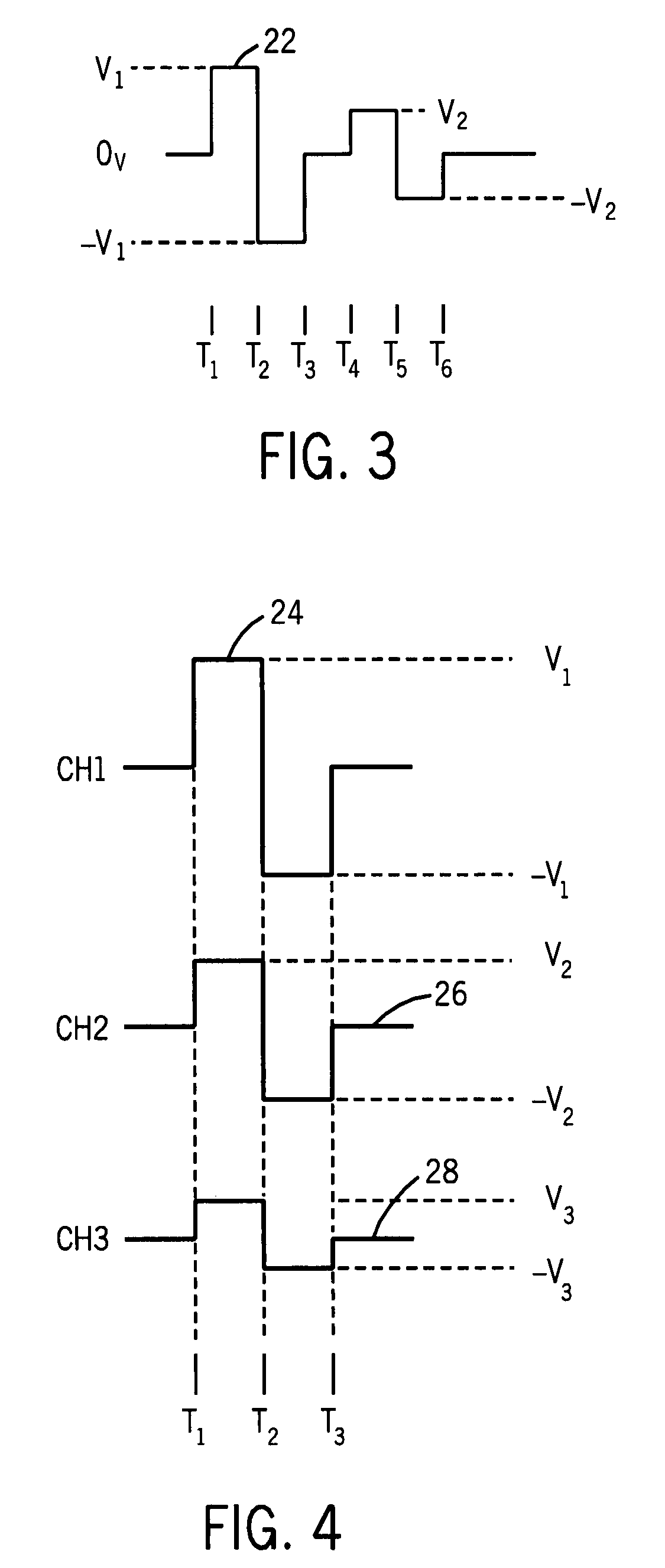

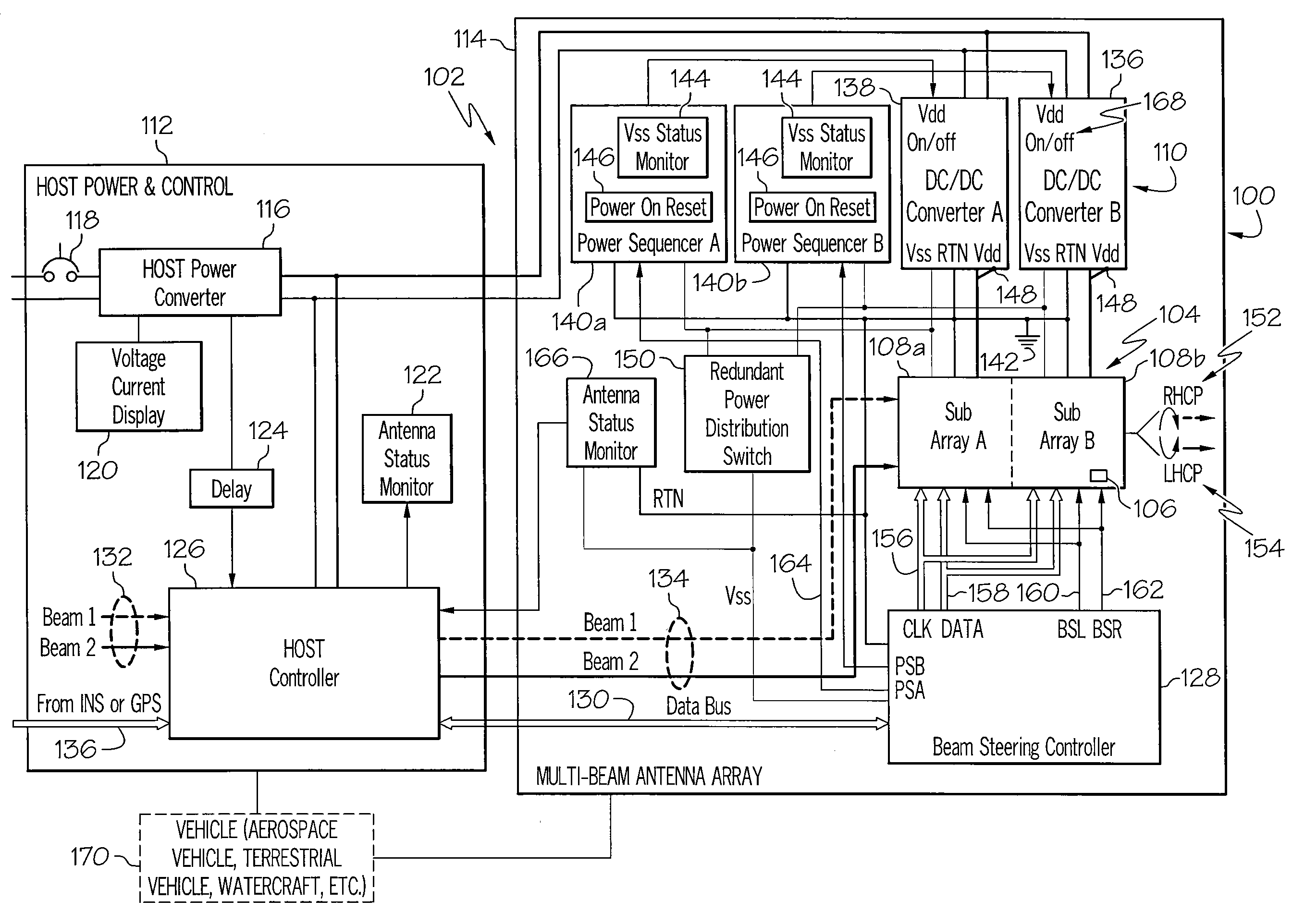

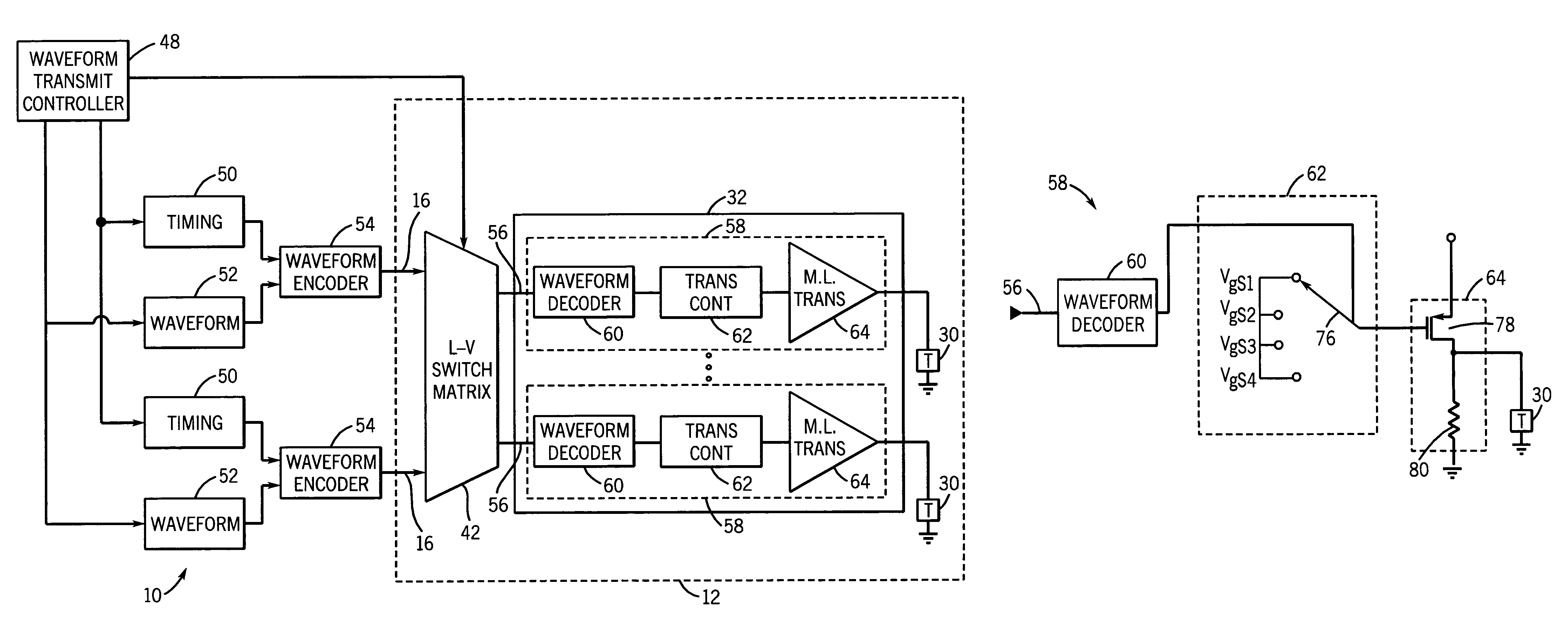

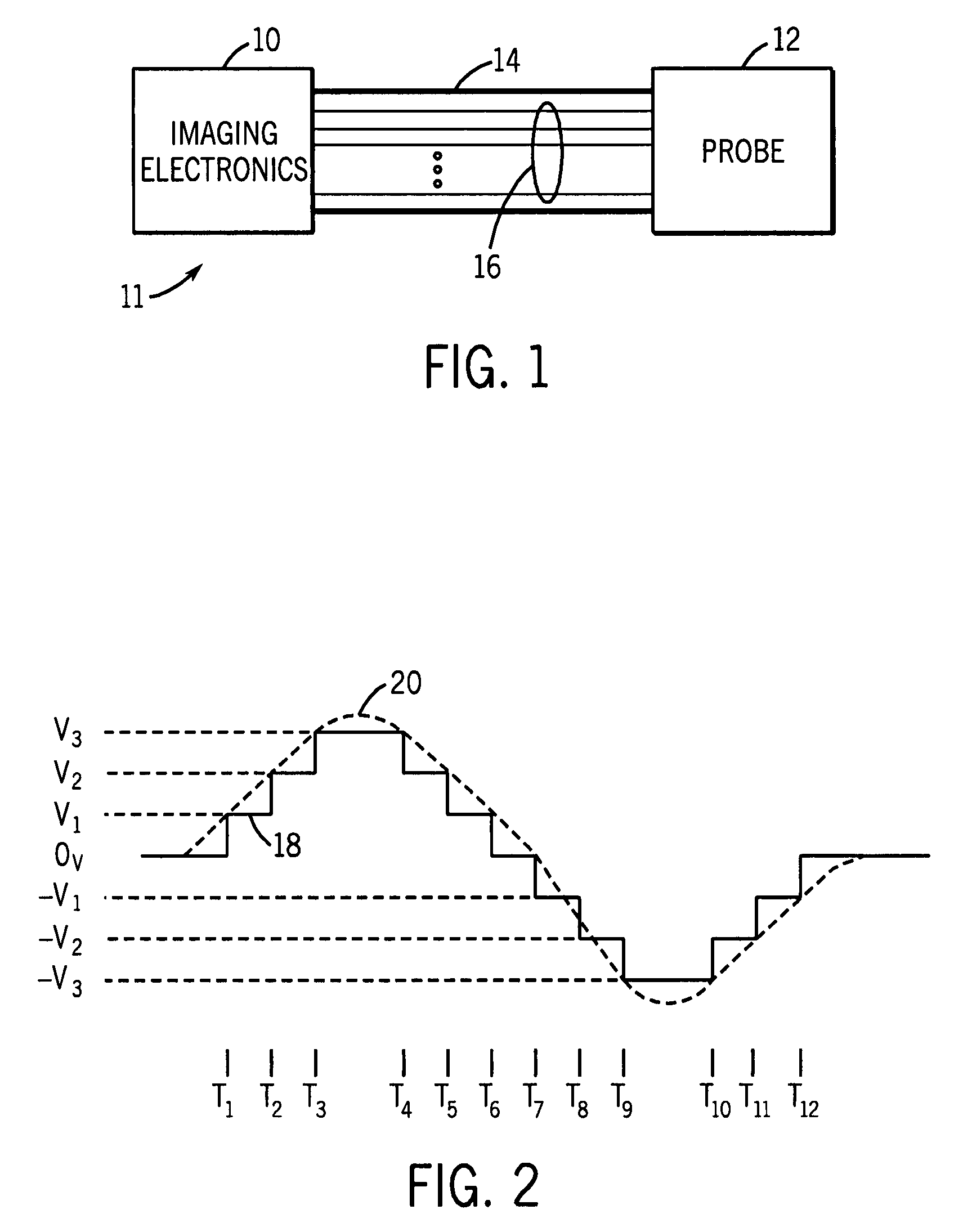

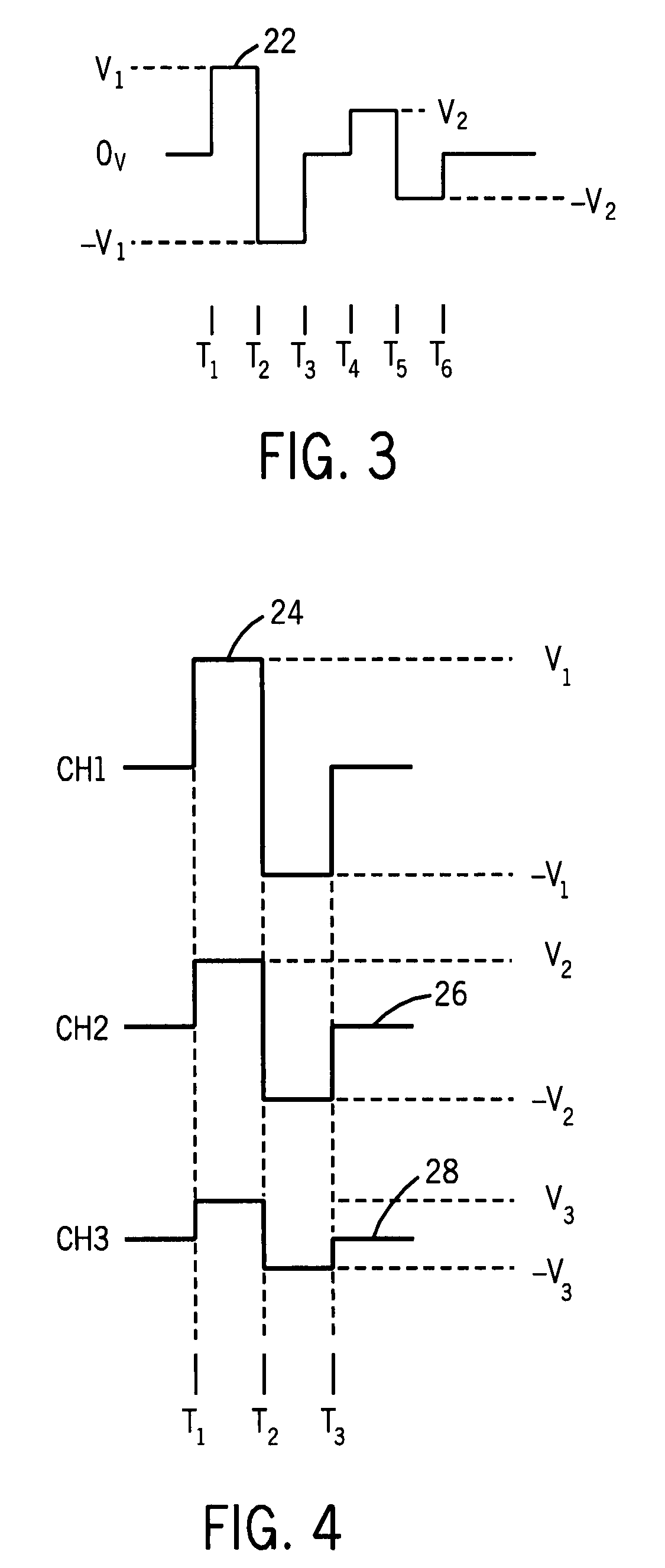

Reconfigurable array with multi-level transmitters

ActiveUS20080264171A1Minimal expenditure of powerSmall footprintUltrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesAcoustic energyEngineering

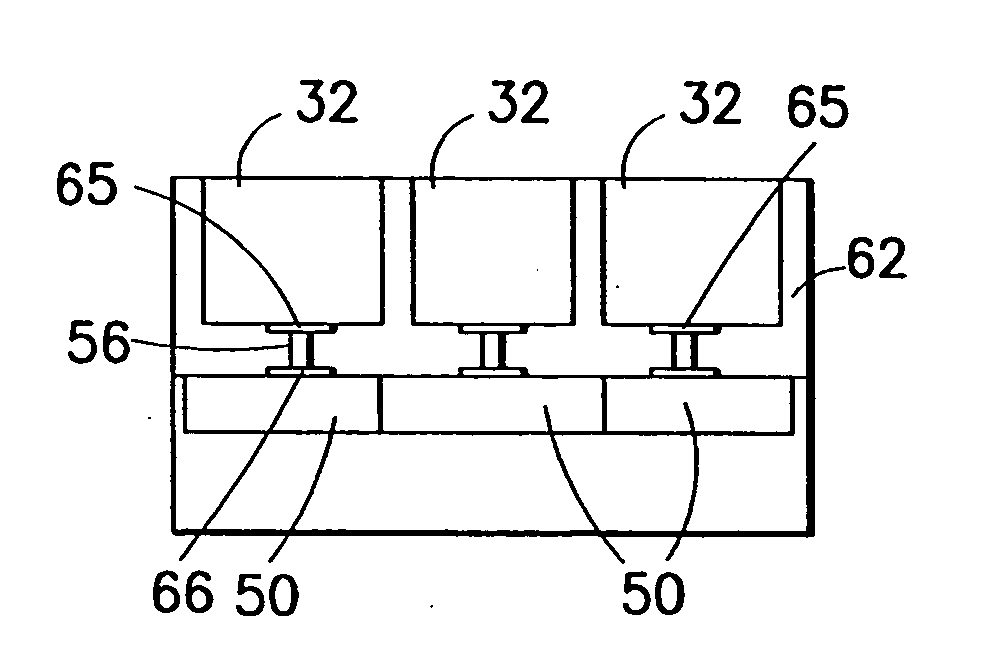

An imaging probe having multi-level transmitter cells. The imaging probe includes a plurality of acoustical sub-elements for transmitting and receiving acoustic energy for imaging. Each of the multi-level transmitter cells is arranged along a respective transmitter cell path between a switching matrix and one of the acoustical sub-elements. The multi-level transmitter cells in the probe are capable of producing signals having multiple voltage levels.

Owner:GENERAL ELECTRIC CO

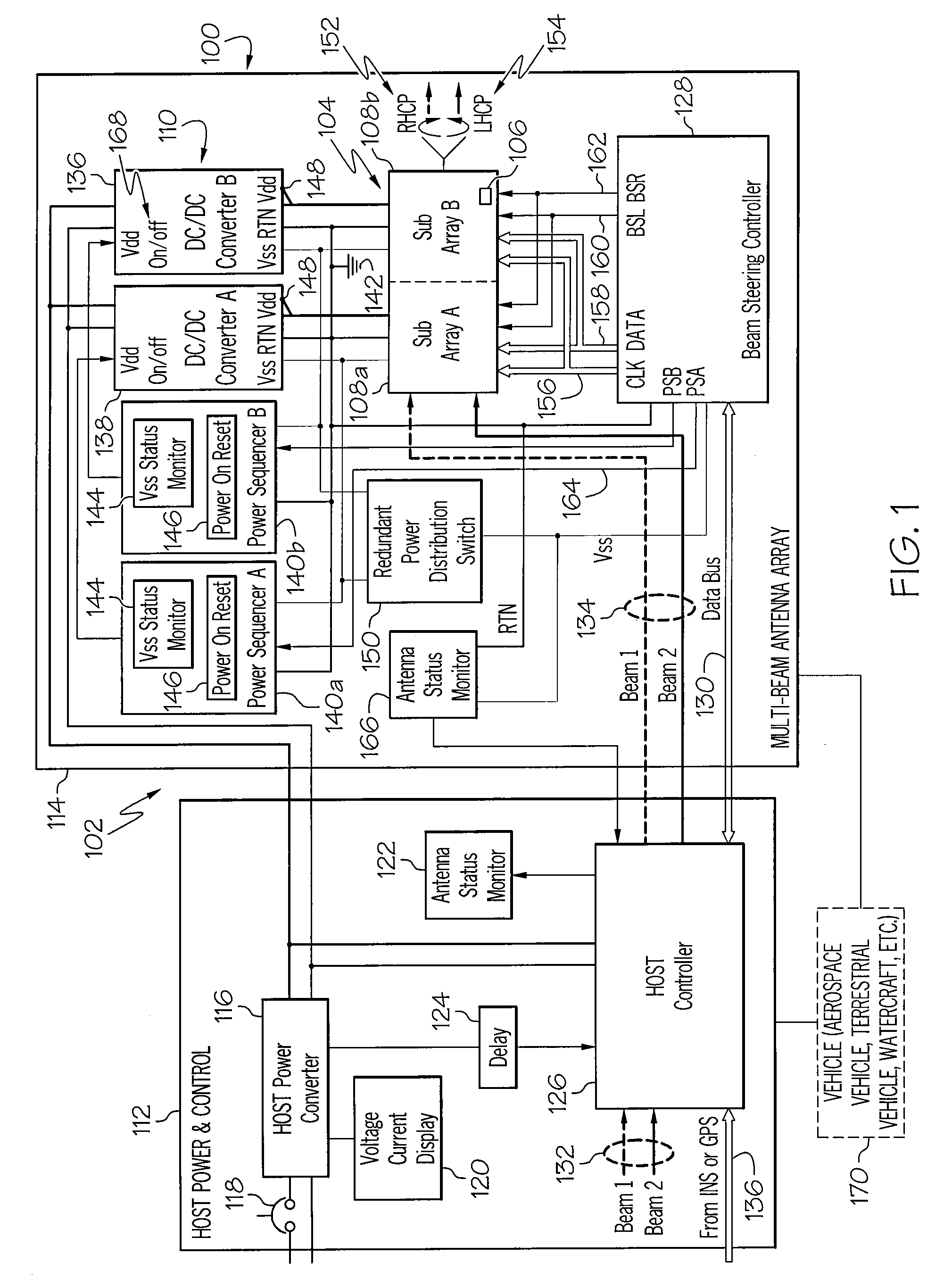

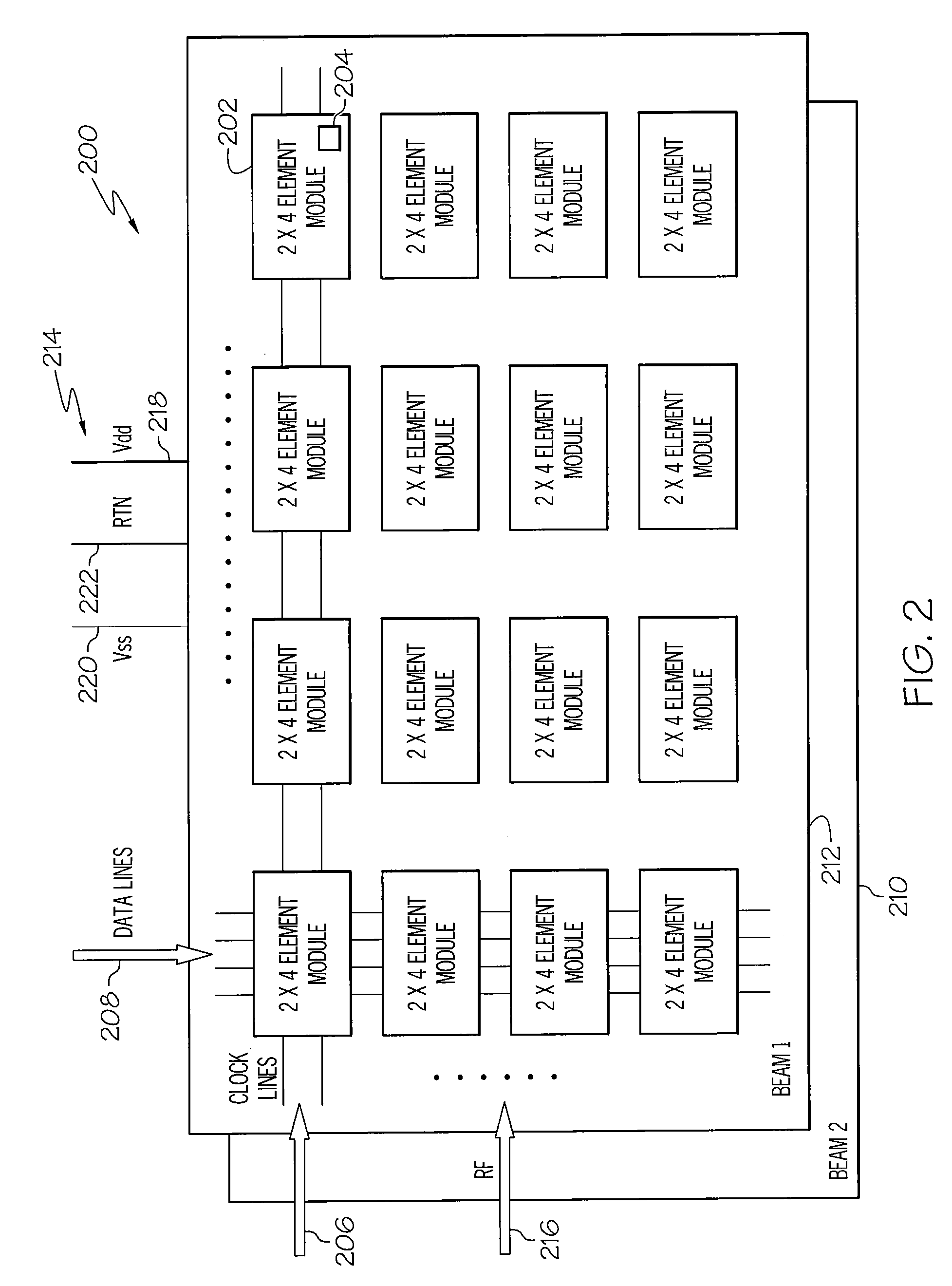

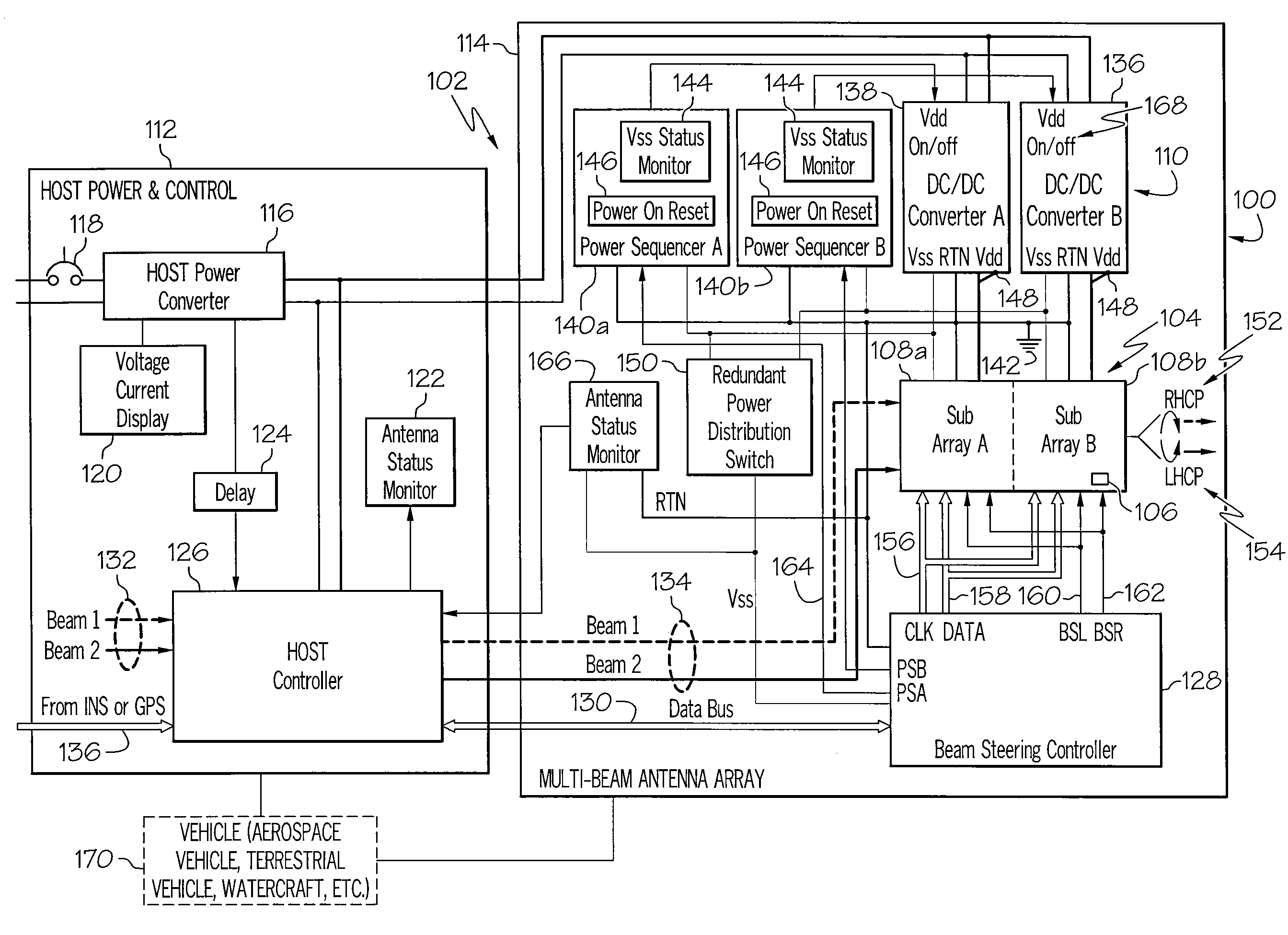

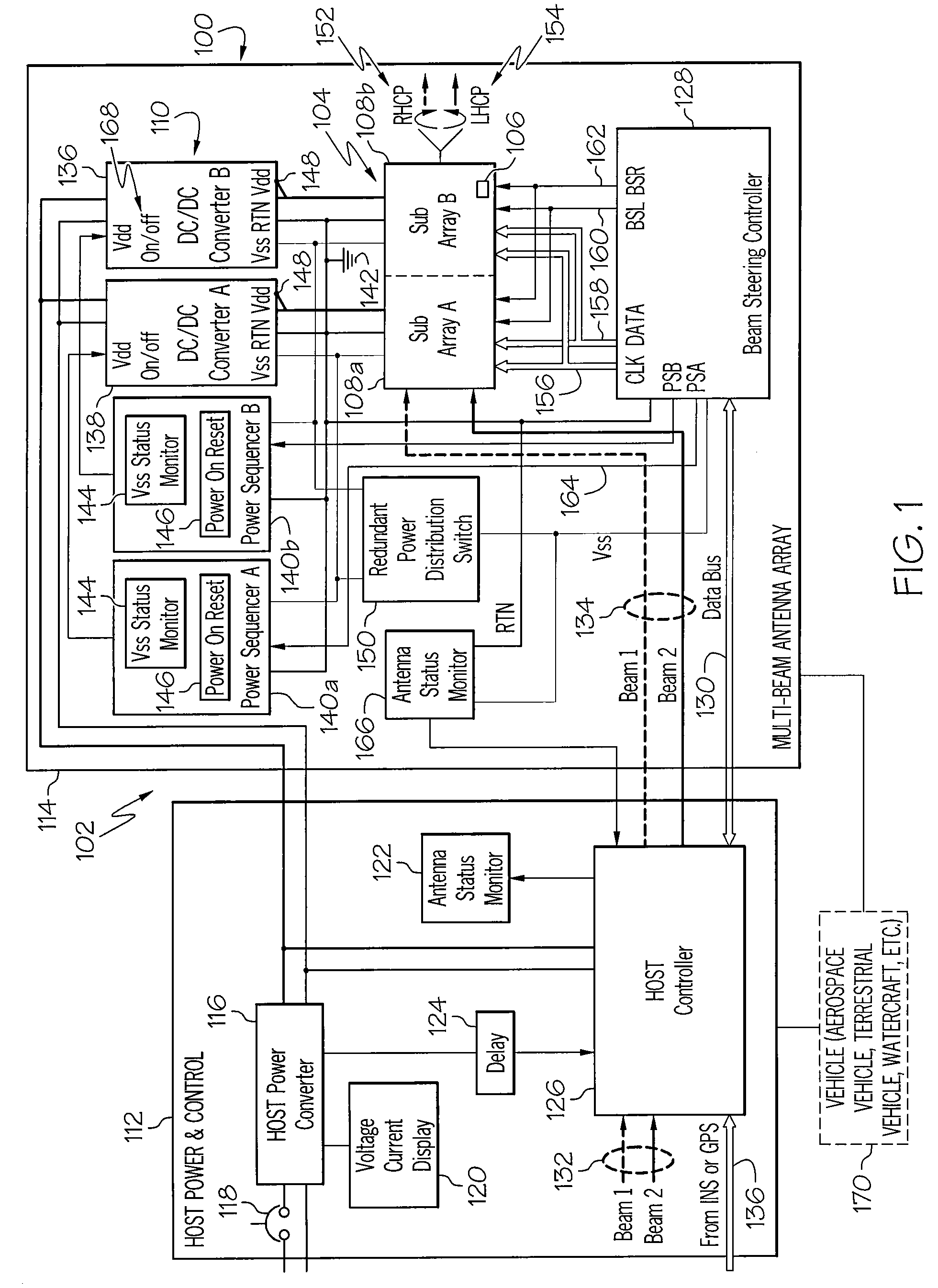

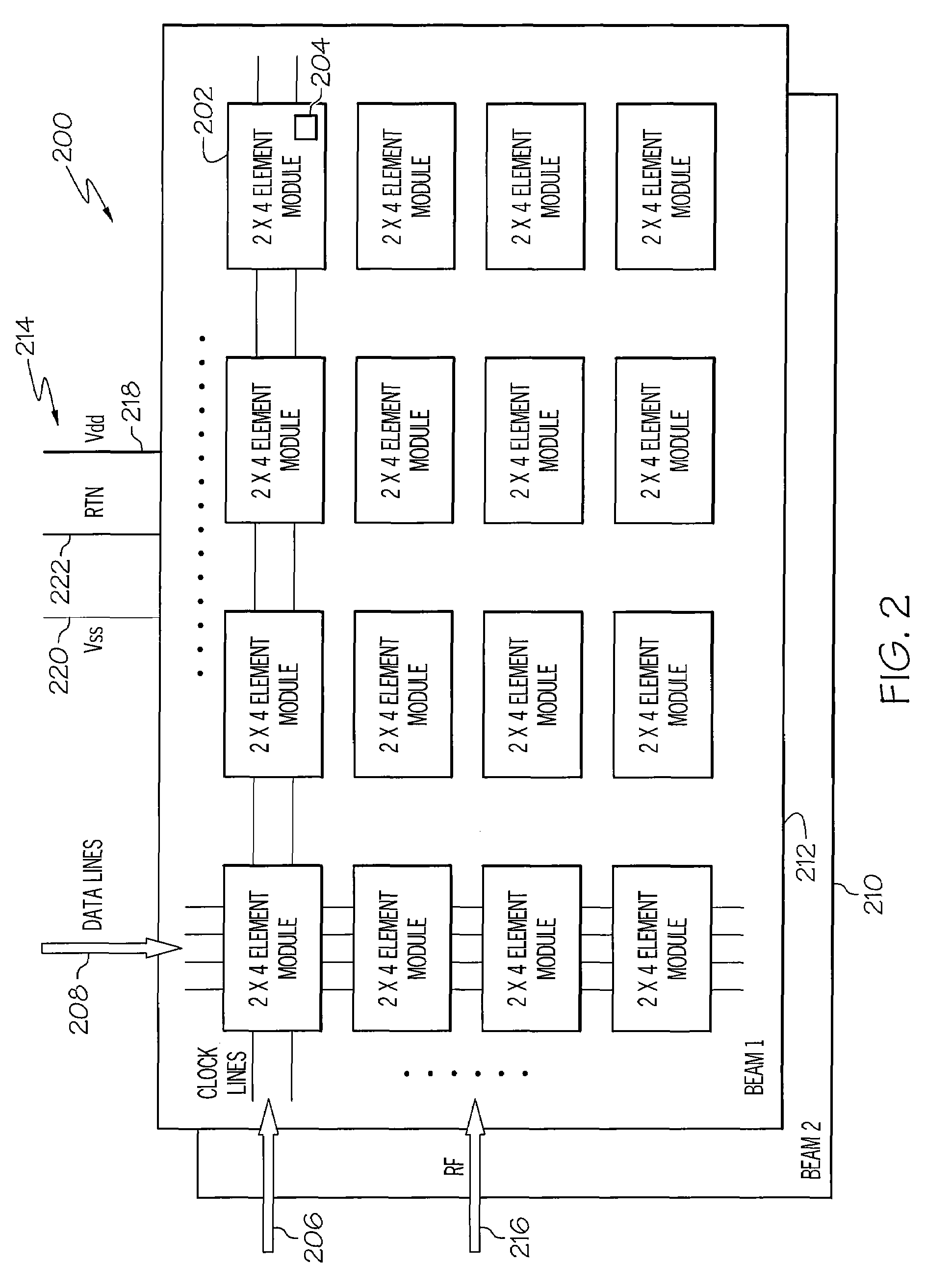

Antenna system including a power management and control system

ActiveUS20080268790A1Resonant long antennasIndividually energised antenna arraysControl systemBeam pattern

An antenna system may include a reconfigurable array antenna system including a plurality of elements each capable of radiating and receiving electromagnetic energy. The antenna system may also include an electronically reconfigurable power management and control system to selectively power each of the plurality of elements to generate a desired beam pattern.

Owner:THE BOEING CO

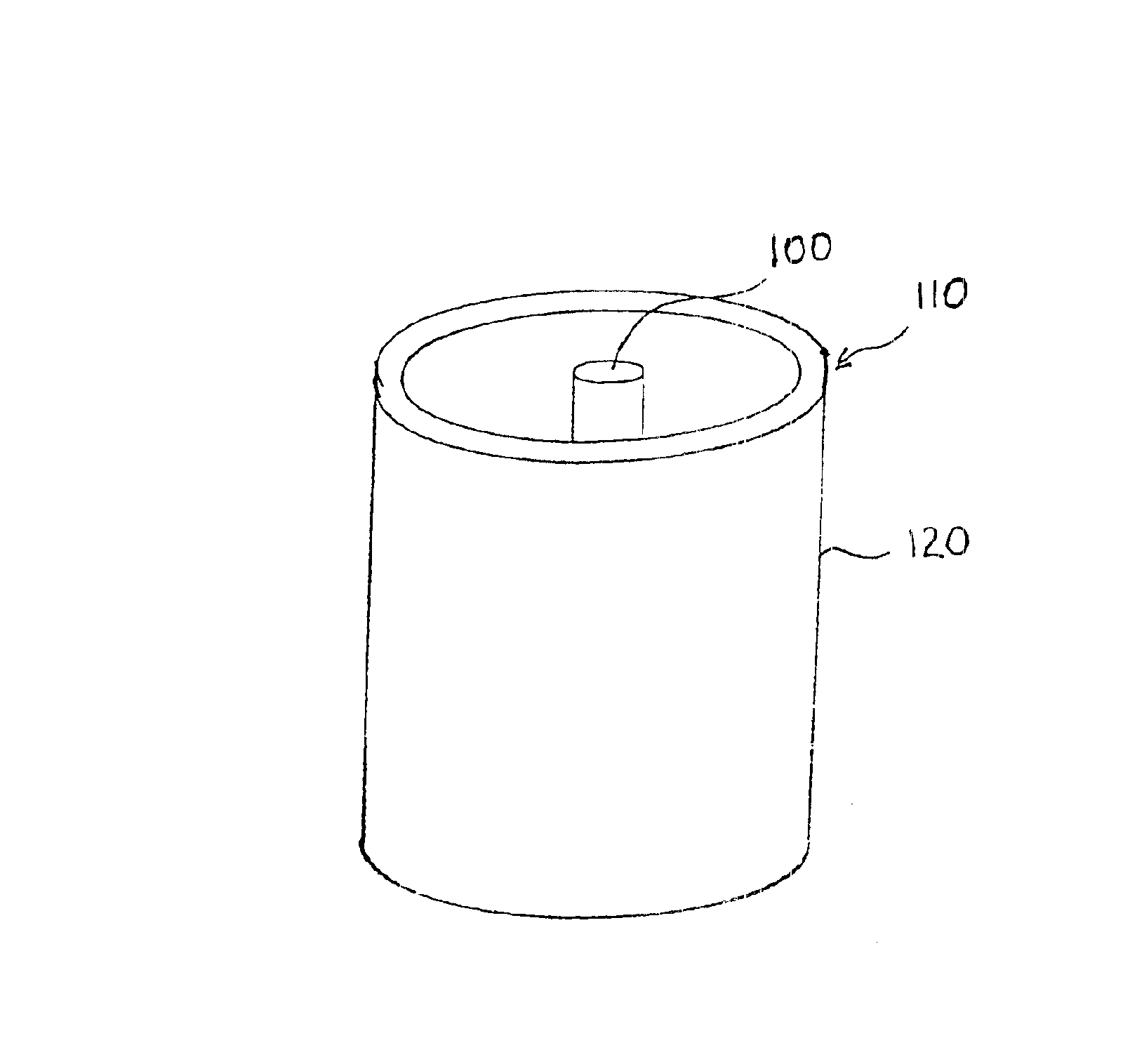

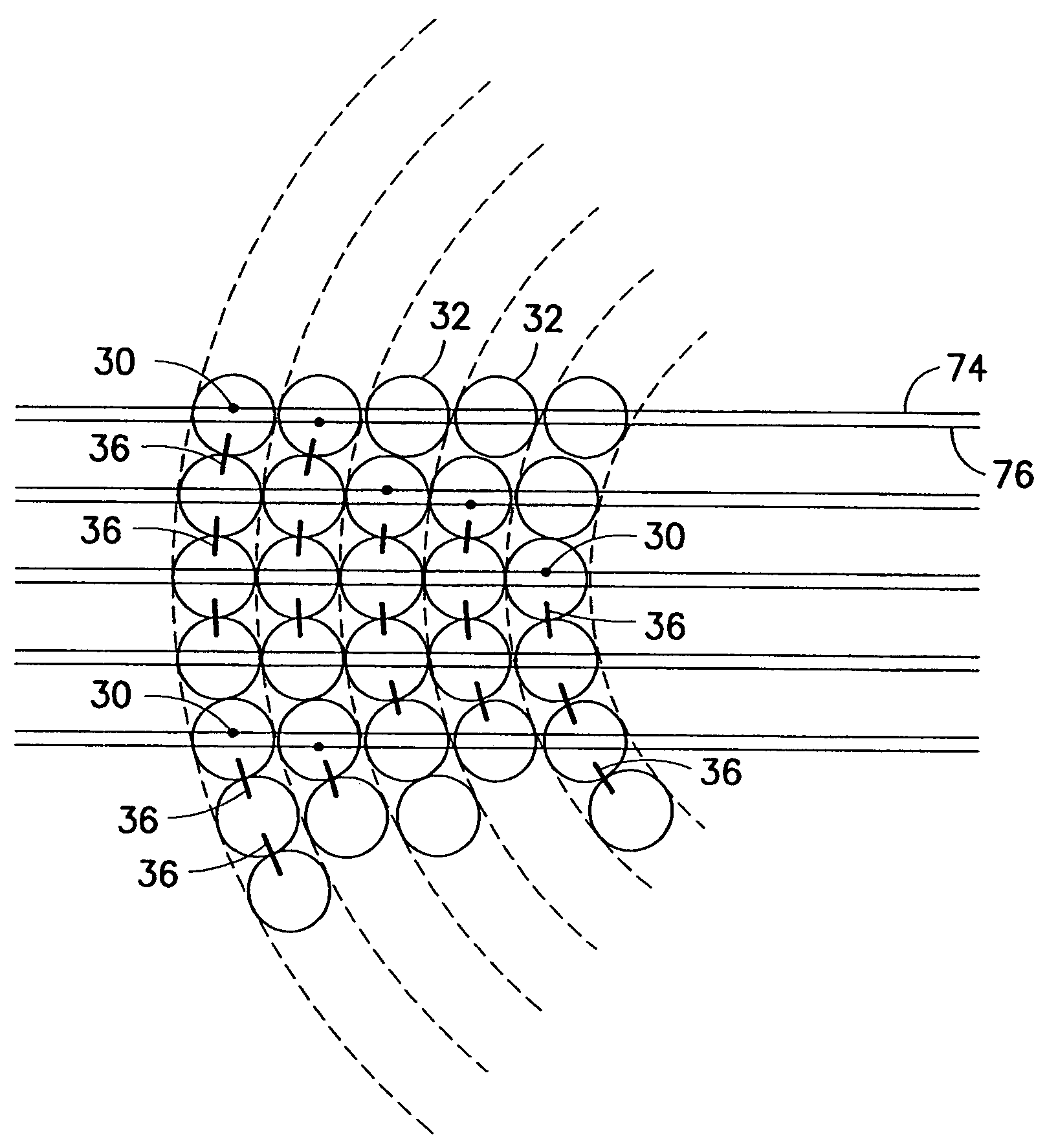

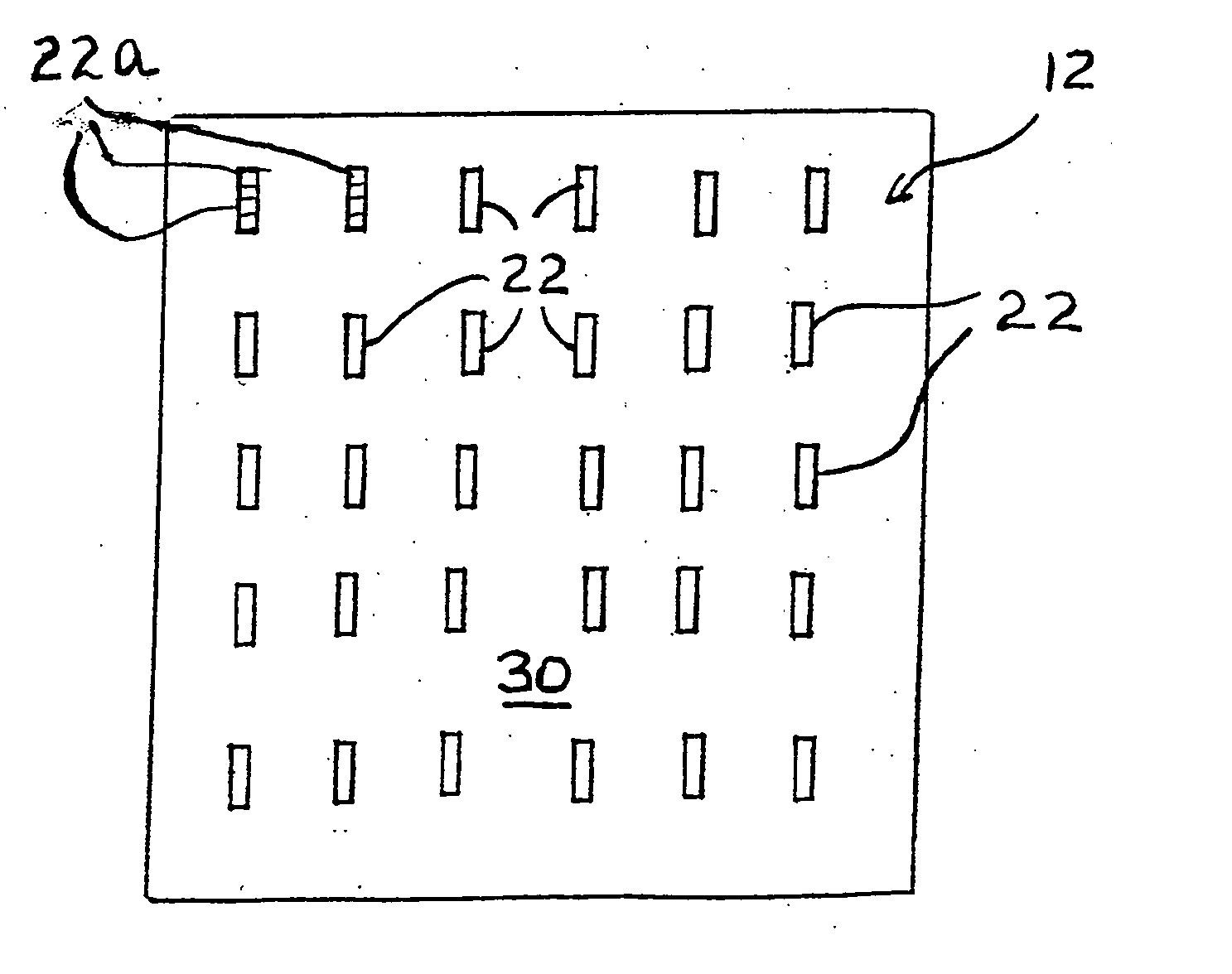

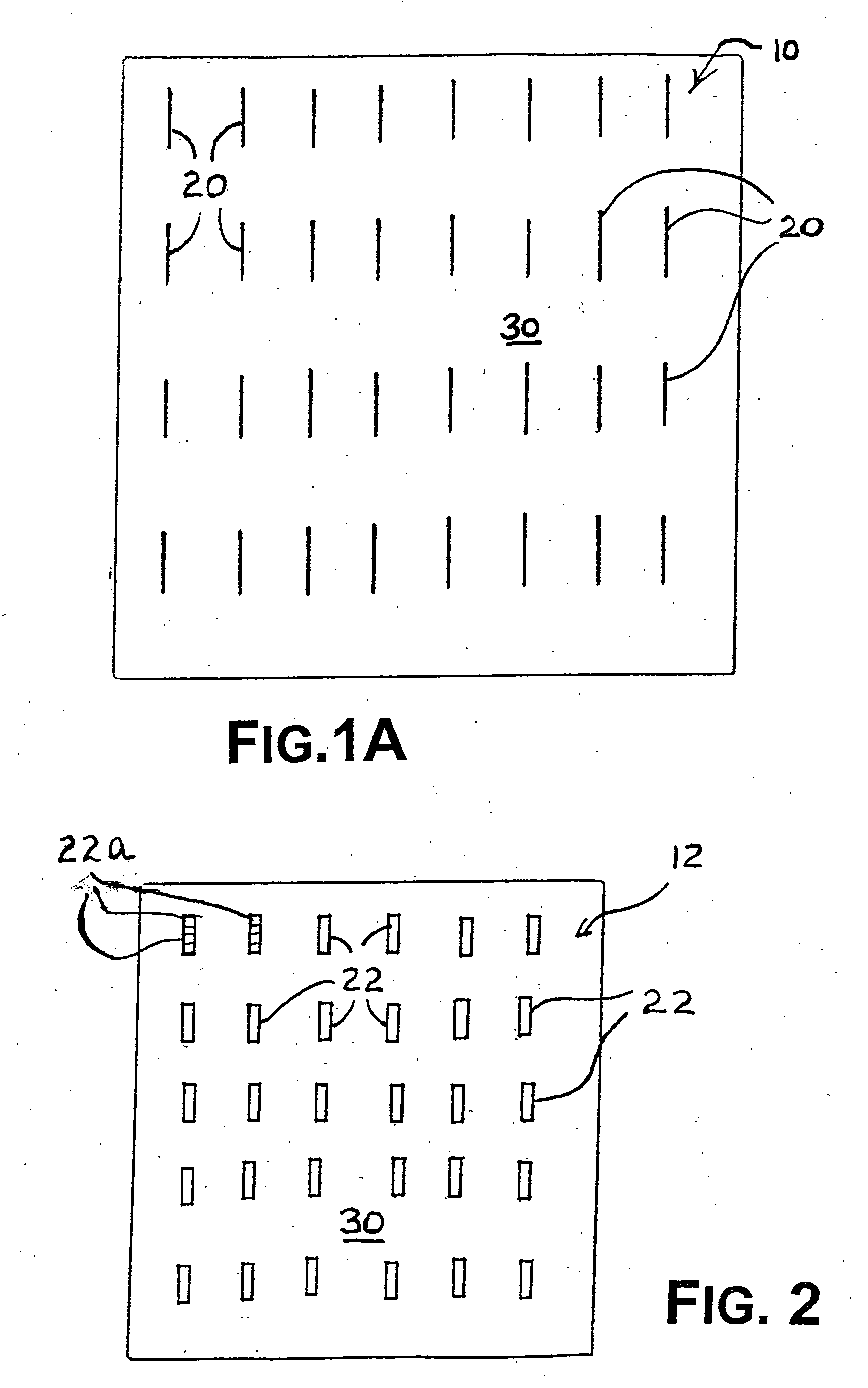

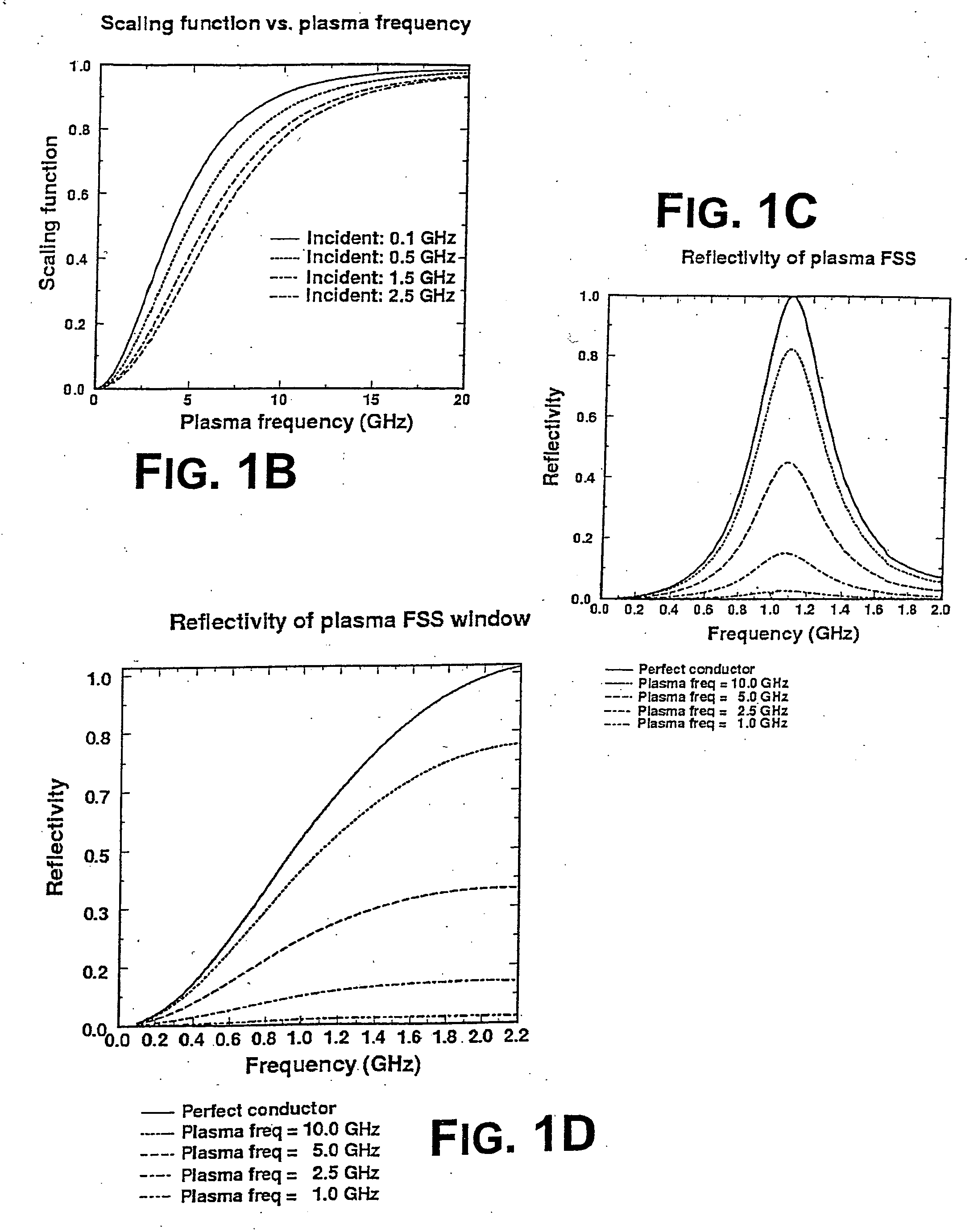

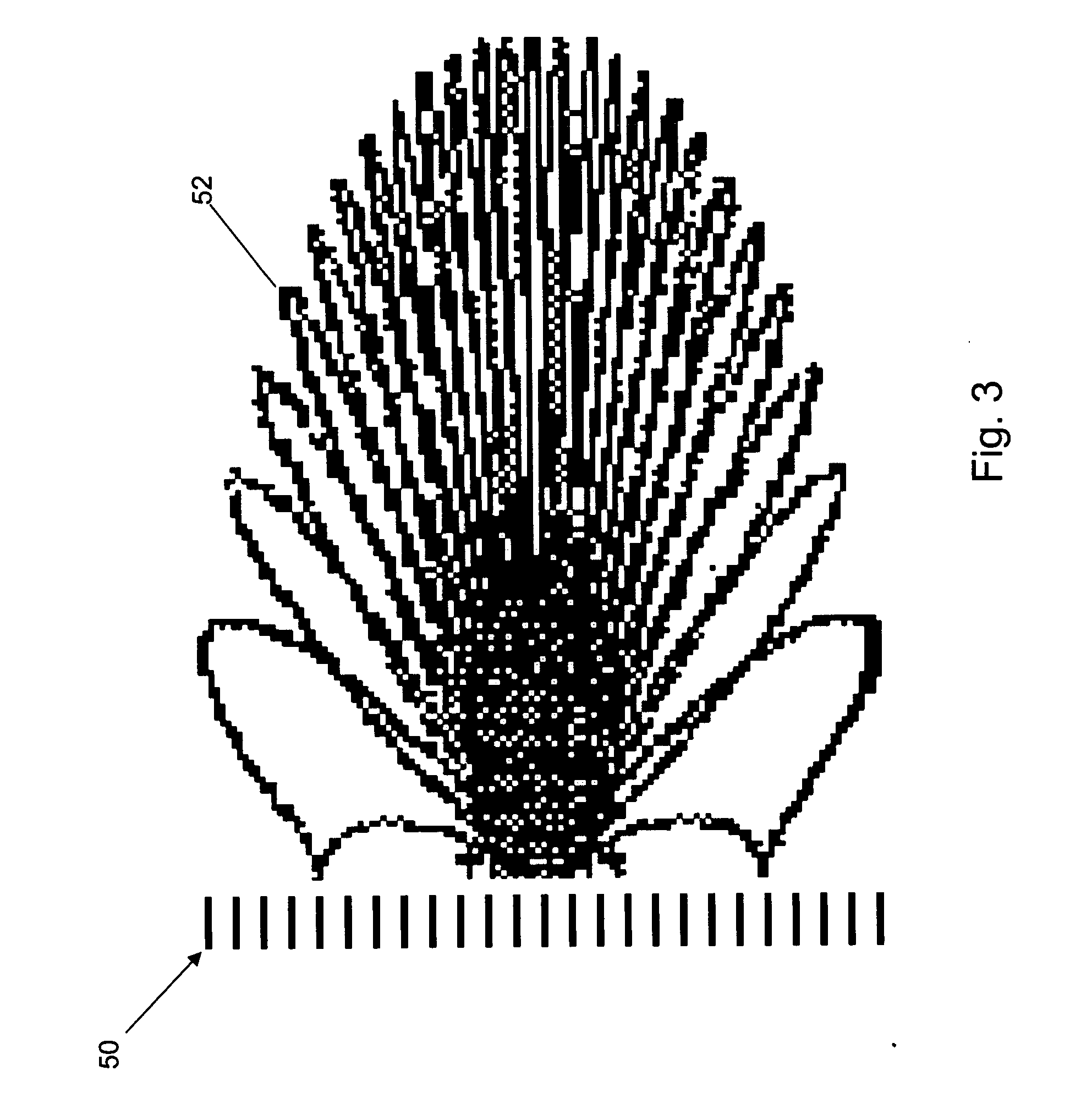

Configurable arrays for steerable antennas and wireless network incorporating the steerable antennas

InactiveUS6870517B1Improve data transfer performanceControl moreAntenna supports/mountingsRadiating elements structural formsReconfigurable antennaEngineering

An reconfigurable array of variable conductive elements is provided for reflecting, filtering and steering electromagnetic radiation across a wide range of frequencies. The reconfigurable array is combined with a transmitting antenna to make a steerable antenna. The reconfigurable array surrounds the transmitting antenna and reflects all transmissions except on selected radials where apertures in the reconfigurable array are formed for permitting transmission lobes. The reconfigurable arrays can be arranged in stacked layers to make transceiving multiband antennas. Communications networks using the steerable antennas nas and arrays are also disclosed.

Owner:ANDERSON THEODORE R

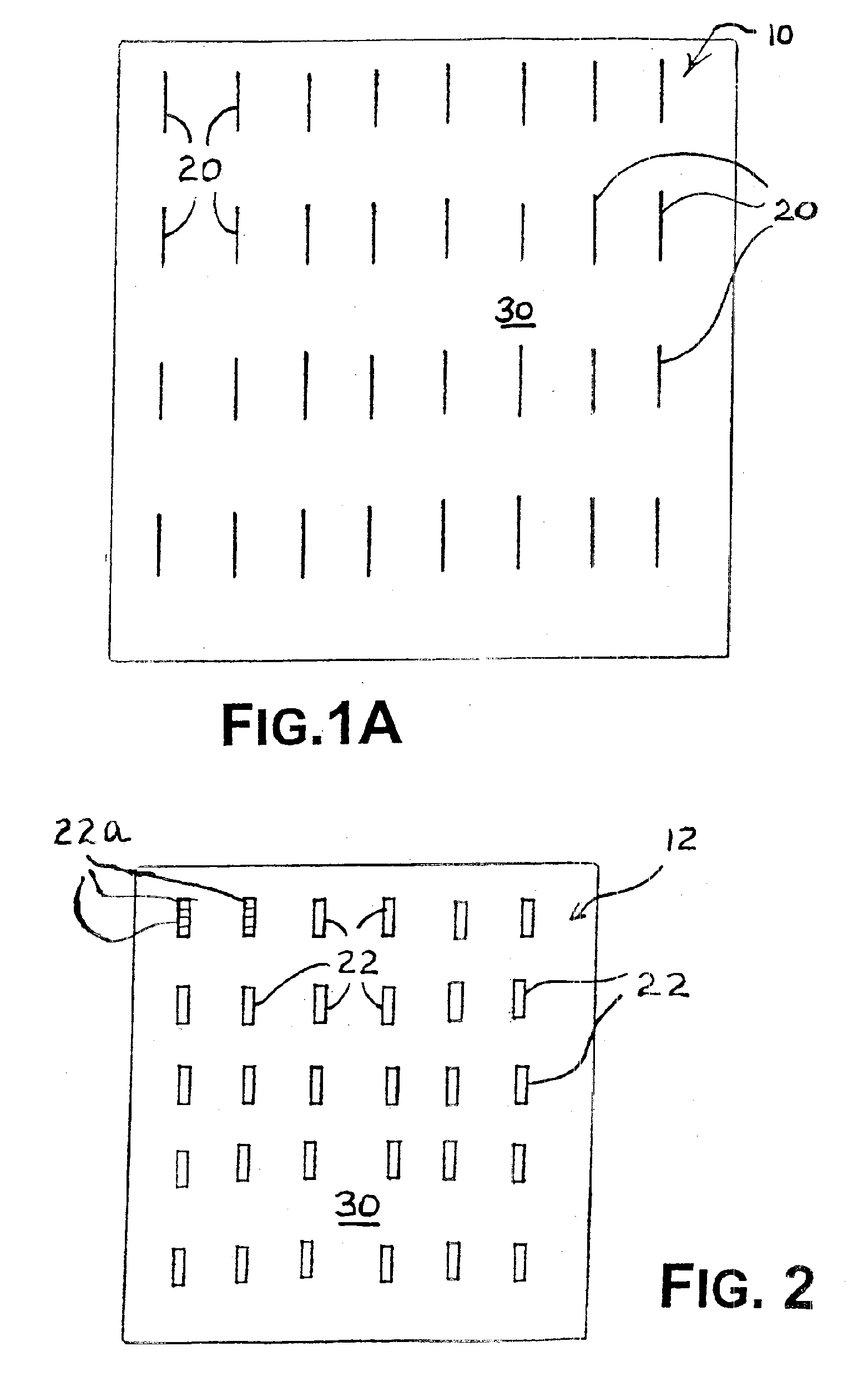

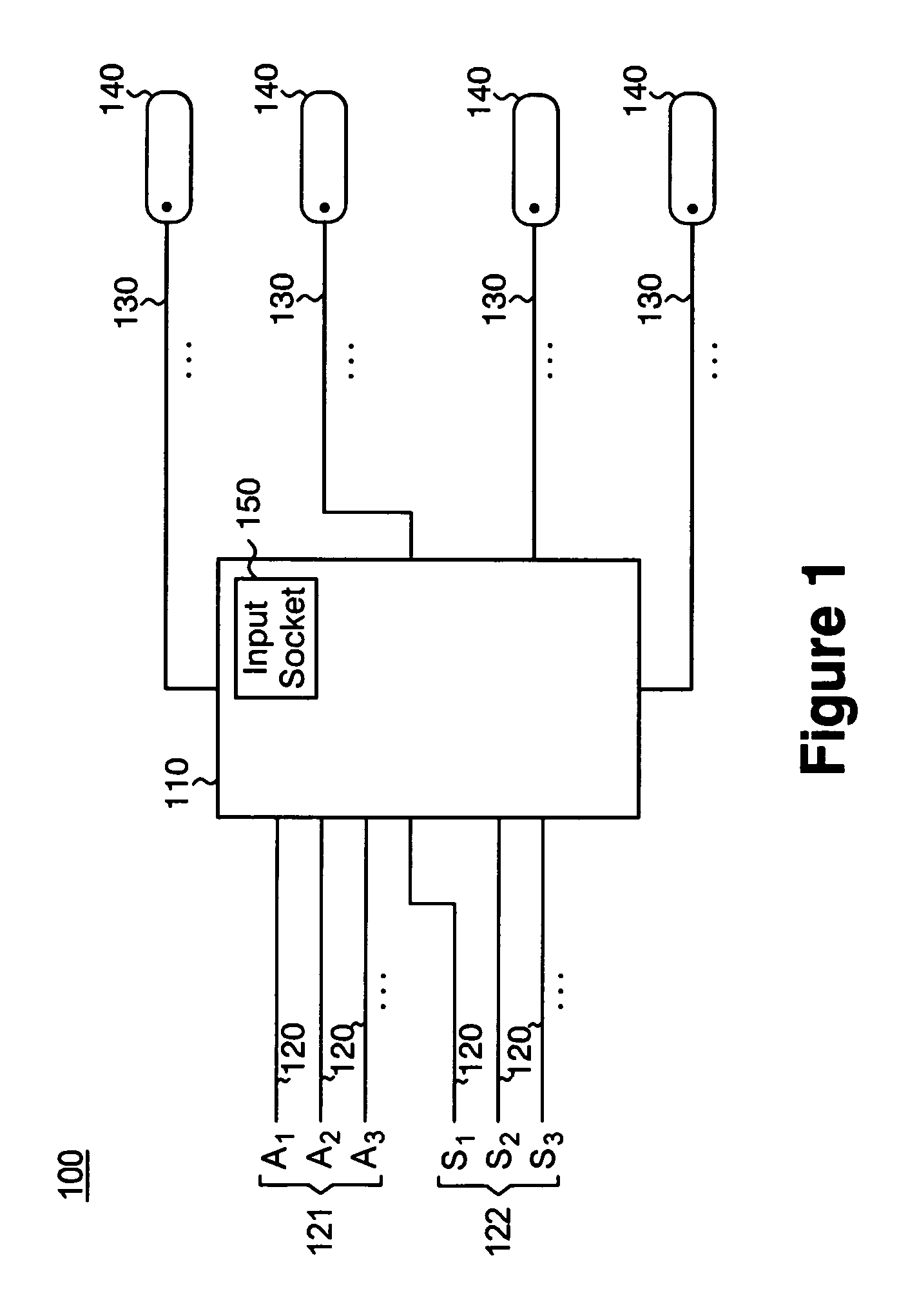

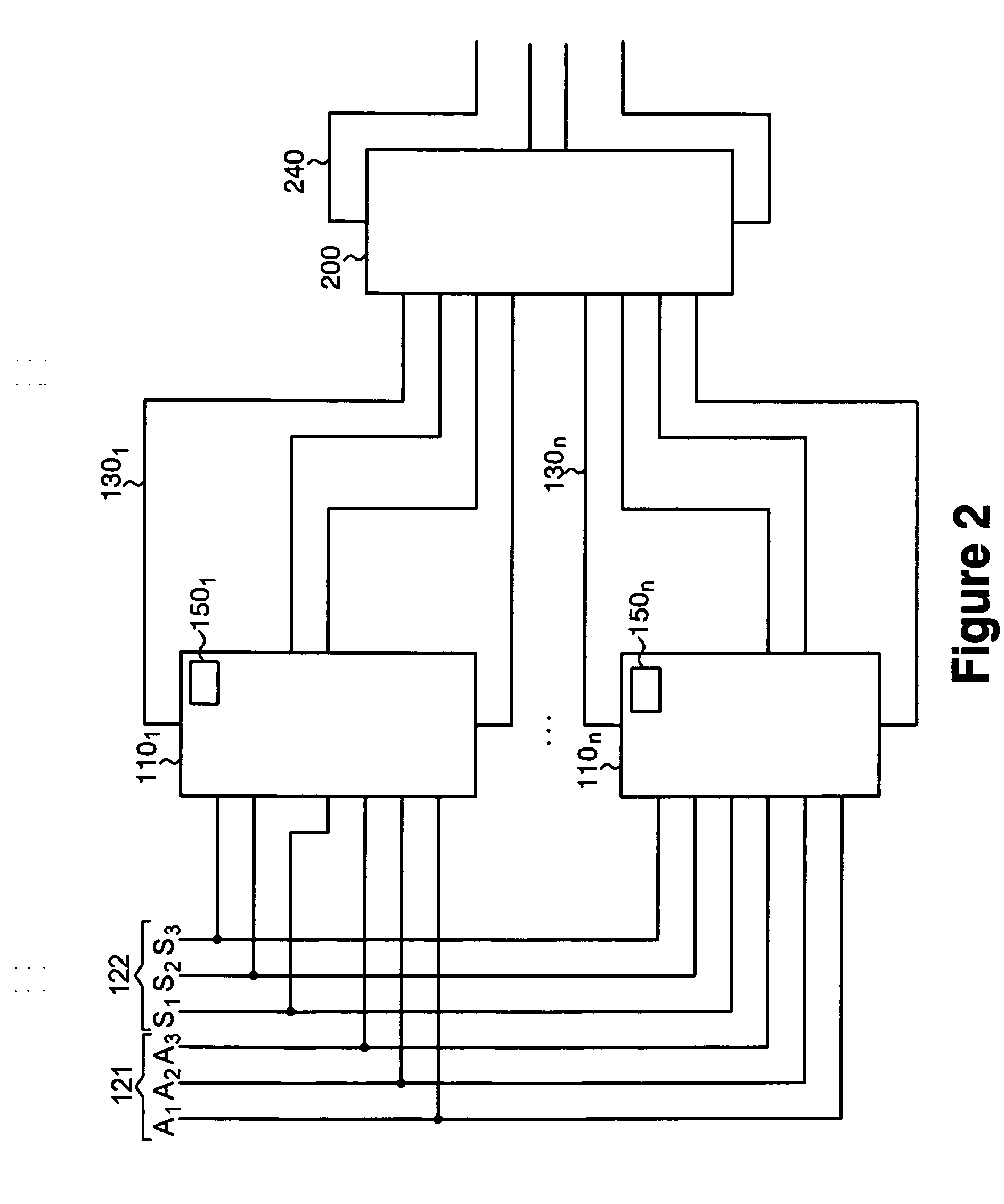

Switching circuitry for reconfigurable arrays of sensor elements

ActiveUS7280435B2Ultrasonic/sonic/infrasonic diagnosticsMaterial analysis using sonic/ultrasonic/infrasonic wavesSensor arrayUltrasonic sensor

A device comprising an array of sensors that are reconfigurable by means of a switching network. The sensors may be optical, thermal or pressure sensors or ultrasonic transducers. More specifically, the device comprises: a multiplicity of sensor elements; a plurality of bus lines; a set of access switches for selectively connecting a set of the sensor elements in a row to a bus line, one of the access switches being connected to a first sensor element; a multiplicity of sets of matrix switches, each of the sets of matrix switches selectively connecting a respective sensor element of the multiplicity of sensor elements to a respective set of adjacent sensor elements, one of the matrix switches being connected to the first sensor element and to a second sensor element that is not a member of the set of sensor elements; and control circuitry that controls the access switches and the matrix switches in accordance with a selected switching configuration such that the first sensor element is connected to the bus line via said one access switch, while at the same time the second sensor element is connected to said one access switch via said one matrix switch.

Owner:GENERAL ELECTRIC CO

Switching circuitry for reconfigurable arrays of sensor elements

ActiveUS20050169107A1Ultrasonic/sonic/infrasonic diagnosticsValve arrangementsSensor arrayUltrasonic sensor

A device comprising an array of sensors that are reconfigurable by means of a switching network. The sensors may be optical, thermal or pressure sensors or ultrasonic transducers. More specifically, the device comprises: a multiplicity of sensor elements; a plurality of bus lines; a set of access switches for selectively connecting a set of the sensor elements in a row to a bus line, one of the access switches being connected to a first sensor element; a multiplicity of sets of matrix switches, each of the sets of matrix switches selectively connecting a respective sensor element of the multiplicity of sensor elements to a respective set of adjacent sensor elements, one of the matrix switches being connected to the first sensor element and to a second sensor element that is not a member of the set of sensor elements; and control circuitry that controls the access switches and the matrix switches in accordance with a selected switching configuration such that the first sensor element is connected to the bus line via said one access switch, while at the same time the second sensor element is connected to said one access switch via said one matrix switch.

Owner:GENERAL ELECTRIC CO

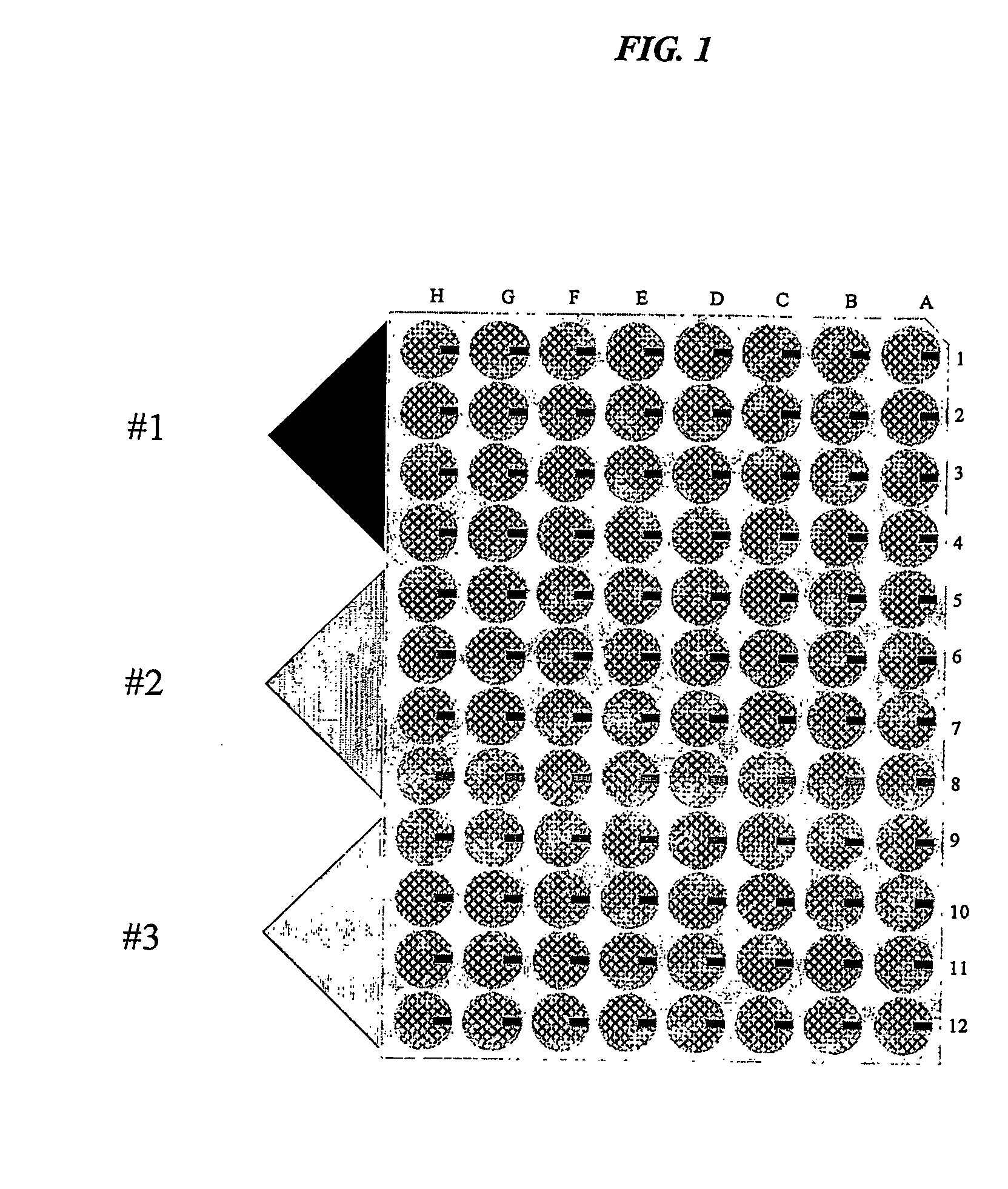

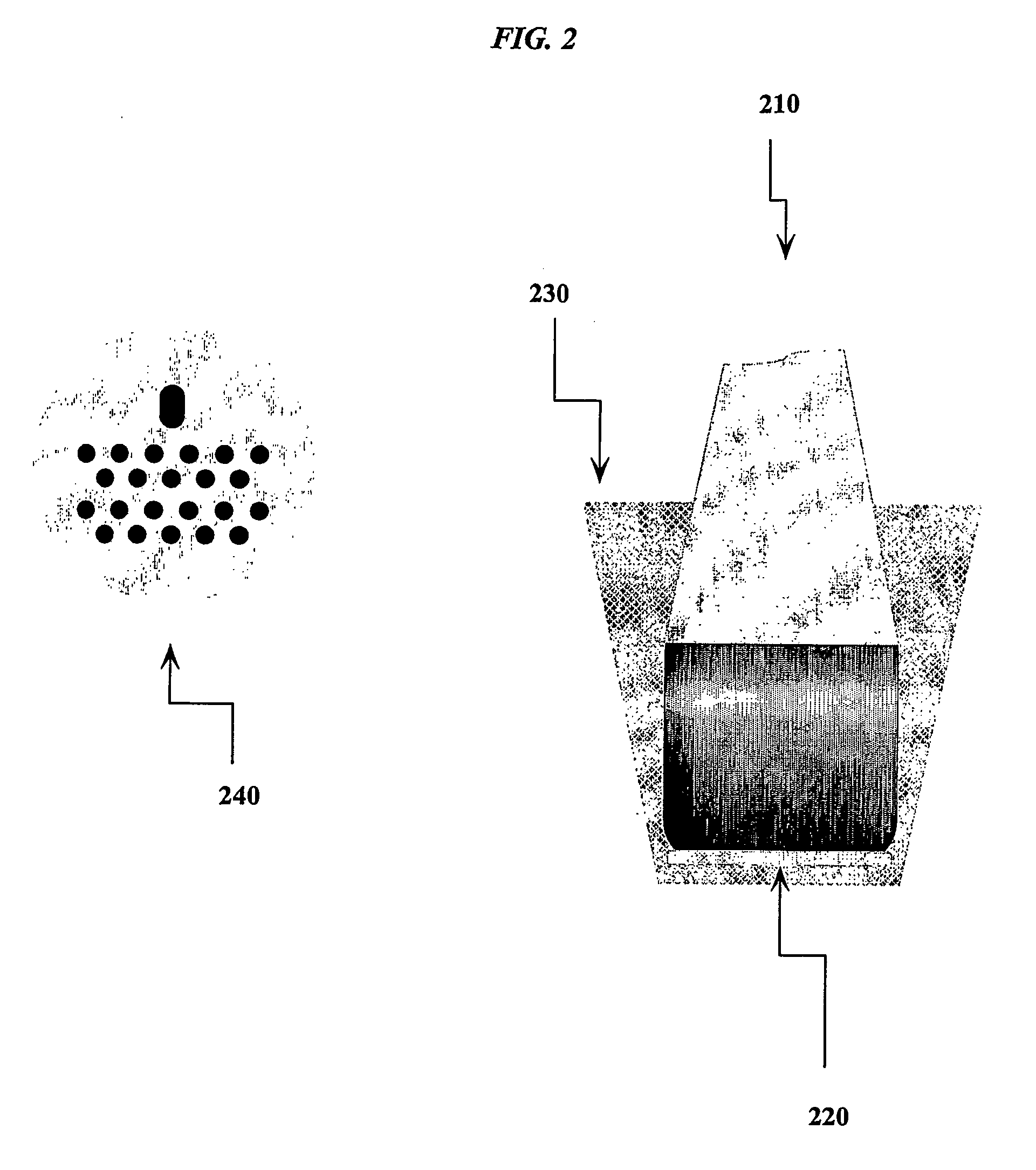

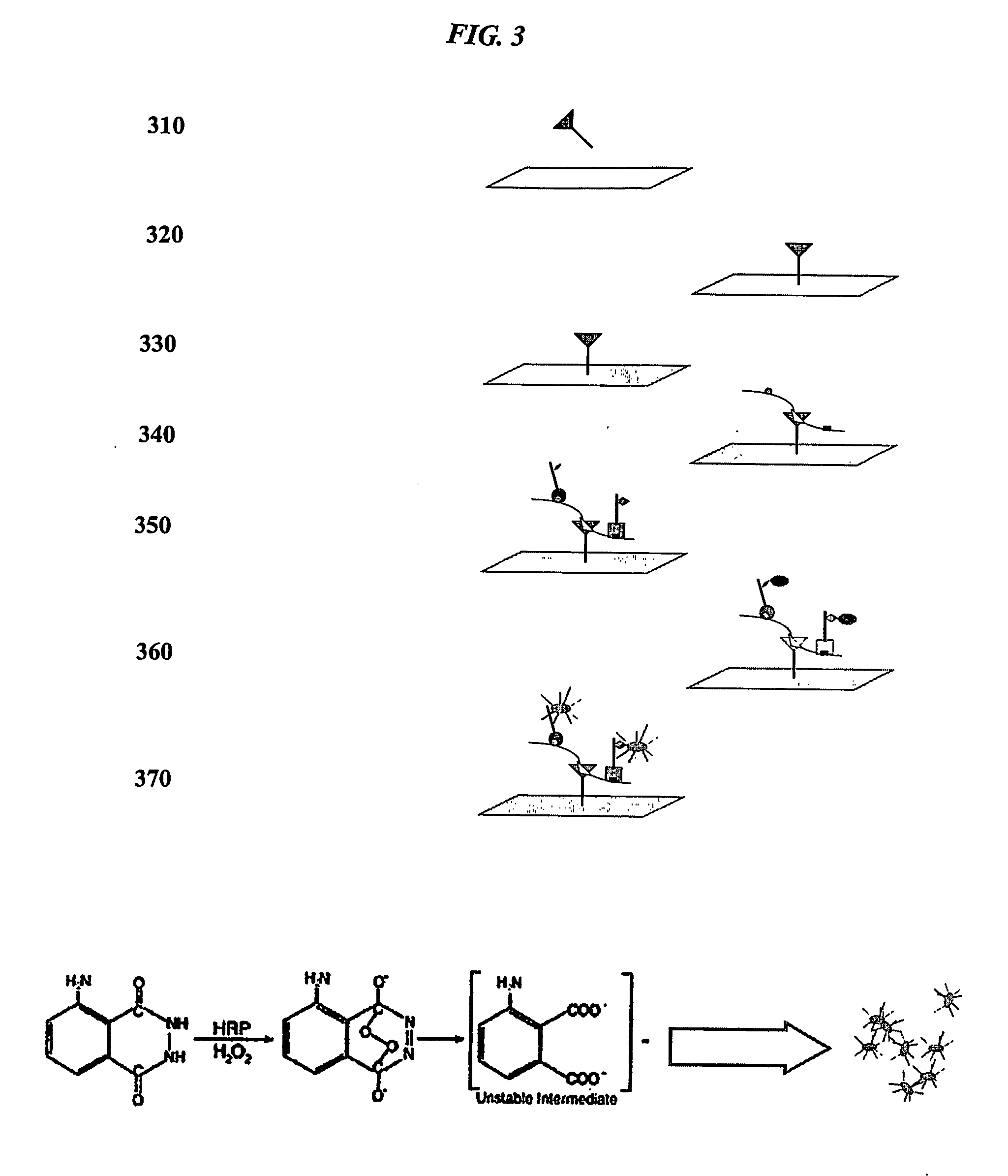

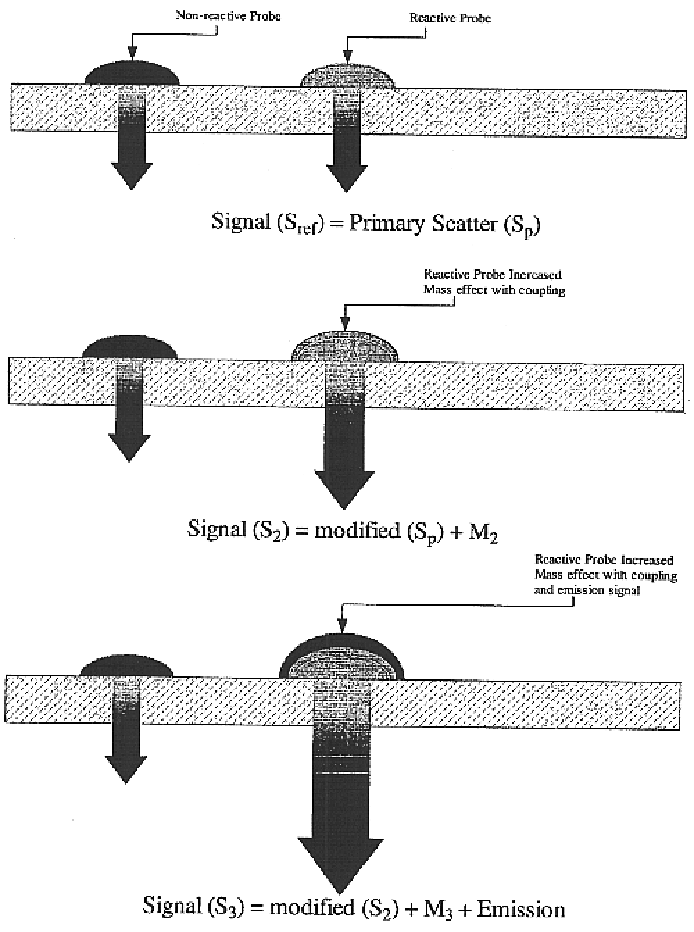

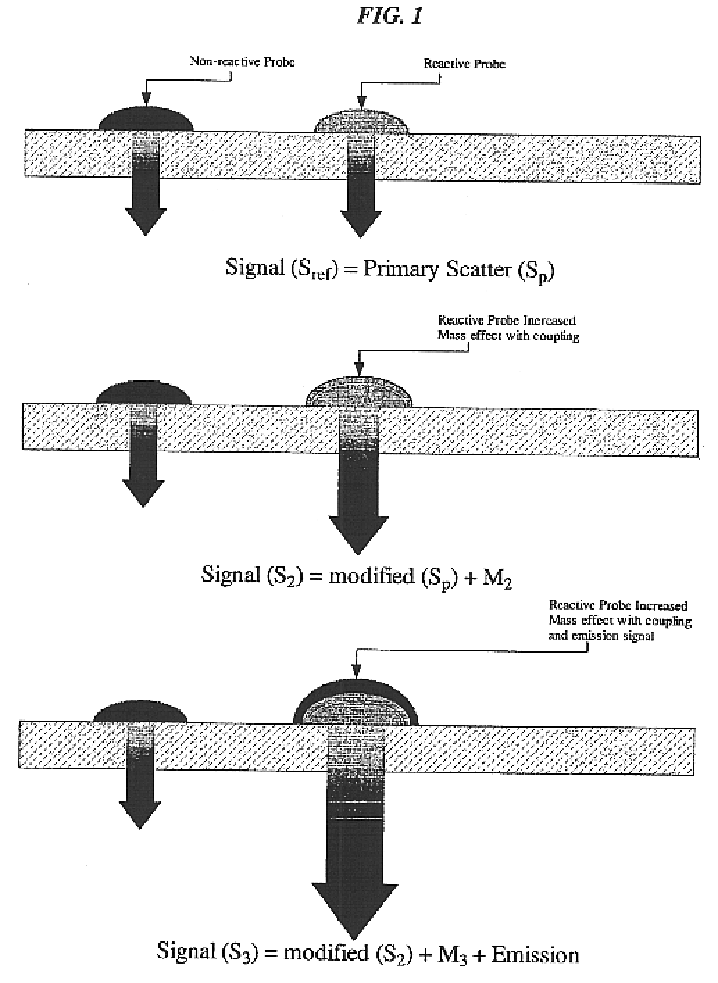

Translucent solid matrix assay device dor microarray analysis

InactiveUS20060211044A1Low production costImprove the level ofBioreactor/fermenter combinationsImage enhancementNitrocelluloseCellophane

The present invention concerns methods and compositions relating to translucent matrix arrays. In certain embodiments, the arrays are reconfigurable. Reconfigurable arrays may be produced using small linker molecules, such as aptamers or affibodies, which preferably bind to an IgG specific portion of antibodies. Such arrays may be used to detect any target that binds selectively or specifically to an IgG. Translucent matrix arrays may utilize cellophane, rayon or a translucent, colloidal form of nitrocellulose to coat the substrate. Other embodiments concern methods of data analysis and apparatus for analyte detection. Certain embodiments concern a total optical assay device (TOAD™), which may be used with GRABBER™ slides and / or FOOTPAD™ microtiter well assay devices.

Owner:PRITEST

Reconfigurable array with multi-level transmitters

ActiveUS7824335B2Ultrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesAcoustic energyEngineering

An imaging probe having multi-level transmitter cells. The imaging probe includes a plurality of acoustical sub-elements for transmitting and receiving acoustic energy for imaging. Each of the multi-level transmitter cells is arranged along a respective transmitter cell path between a switching matrix and one of the acoustical sub-elements. The multi-level transmitter cells in the probe are capable of producing signals having multiple voltage levels.

Owner:GENERAL ELECTRIC CO

Antenna system including a power management and control system

ActiveUS7570209B2Resonant long antennasIndividually energised antenna arraysControl systemBeam pattern

Owner:THE BOEING CO

Optimized switching configurations for reconfigurable arrays of sensor elements

InactiveUS7353056B2Minimize cost functionUltrasonic/sonic/infrasonic diagnosticsImage analysisReconfigurable antennaReconfigurability

Owner:GENERAL ELECTRIC CO

Translucent solid matrix assay device for microarray analysis

InactiveUS6861251B2Low production costImprove the level ofMaterial nanotechnologyBioreactor/fermenter combinationsColloidBiology

The present invention concerns methods and compositions relating to matrix arrays. In certain embodiments, the arrays are translucent. In other embodiments, the arrays are reconfigurable. In preferred embodiments, the arrays are translucent and reconfigurable. Reconfigurable arrays may be produced using small linker molecules, such as aptamers or affibodies, attached to the array substrate. Preferably, the small linker molecules bind to an IgG specific portion of antibodies. Such arrays may be used to detect any target that binds selectively or specifically to an IgG, allowing great flexibility of use. Translucent matrix arrays may utilize a translucent, colloidal form of nitrocellulose to coat the array substrate.

Owner:PRITEST

Configurable arrays for steerable antennas and wireless network incorporating the steerable antennas

ActiveUS20050057432A1More selective controlGuaranteed effective sizeAntenna supports/mountingsRadiating elements structural formsReconfigurable antennaEngineering

An reconfigurable array of variable conductive elements is provided for reflecting, filtering and steering electromagnetic radiation across a wide range of frequencies. The reconfigurable array is combined with a transmitting antenna to make a steerable antenna. The reconfigurable array surrounds the transmitting antenna and reflects all transmissions except on selected radials where apertures in the reconfigurable array are formed for permitting transmission lobes. The reconfigurable arrays can be arranged in stacked layers to make transceiving multiband antennas. Communications networks using the steerable antennas and arrays are also disclosed.

Owner:ANDERSON THEODORE R

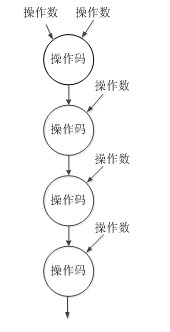

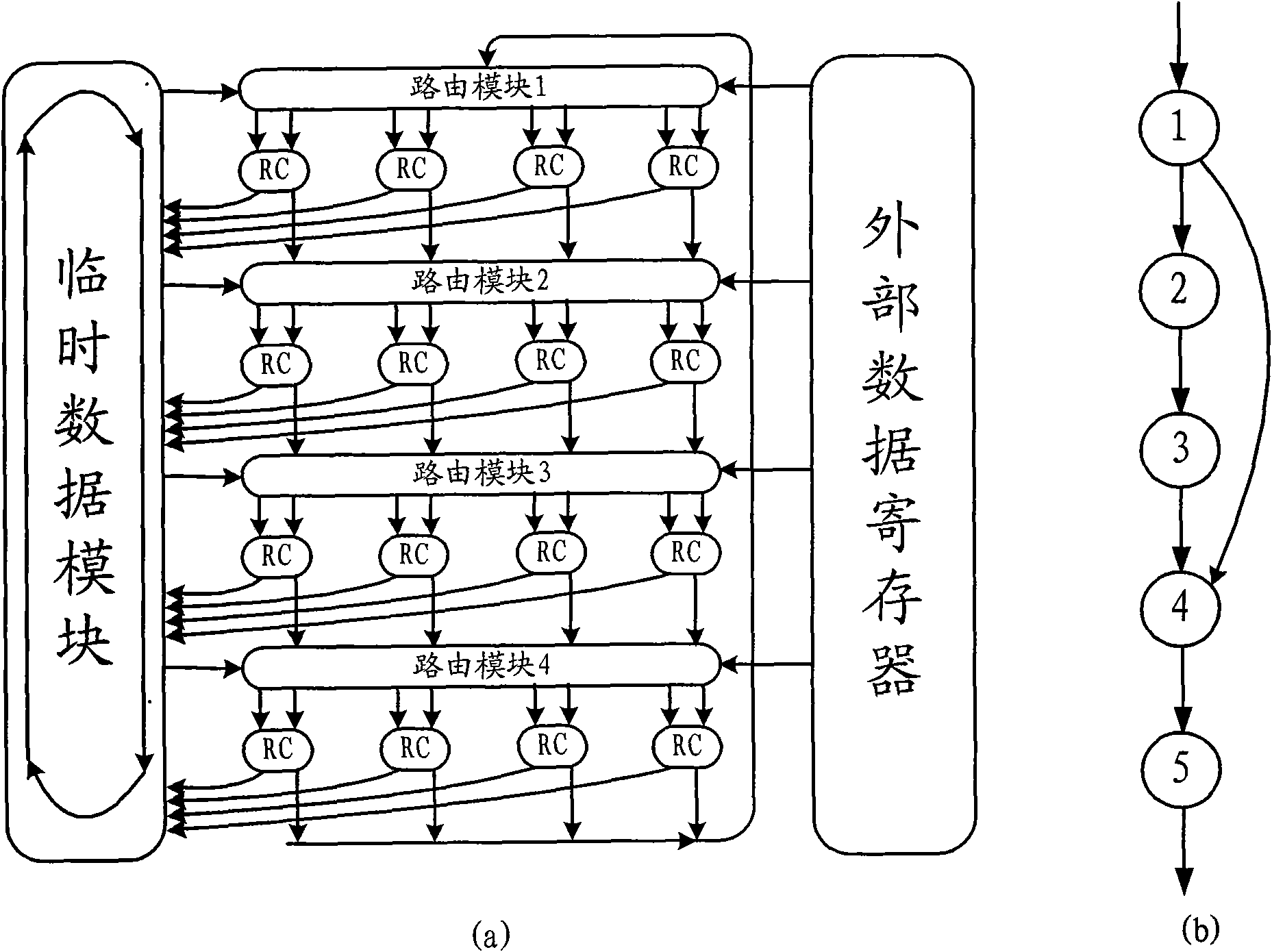

Configuration method applied to coarse-grained reconfigurable array

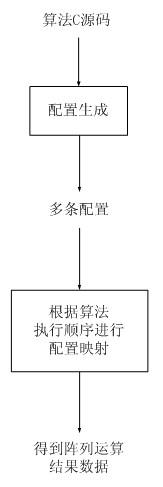

InactiveCN102508816AReduce the amount of informationReduce visitsProgram controlArchitecture with single central processing unitConfiguration generationEngineering

The invention discloses a configuration method applied to a coarse-grained reconfigurable array, which aims at a coarse-grained reconfigurable array with a certain scale, and comprises a configuration defining scheme taking data links as basic description objects, a corresponding configuration generating scheme and a corresponding configuration mapping scheme. The configuration defining scheme includes that a program corresponds to a plurality of configurations, each configuration corresponds to one data link, and each data link consists of a plurality of reconfigurable cells with data dependence relations. Compared with a traditional scheme taking RCs (reconfigurable cells) as basic description objects, the configuration defining scheme is capable of concealing interlinking information among the RCs and providing a larger configuration information compression space, thereby being beneficial to decrease of the total amount of configuration and time for switching configuration. Besides, the configuration of one description data link consists of a route, a functional configuration and one or more data configurations, the data configurations share one route and functional configuration information, and switching of one configuration includes one-time or multiple switching of the data configuration after one-time switching of the corresponding route and the functional configuration.

Owner:SOUTHEAST UNIV

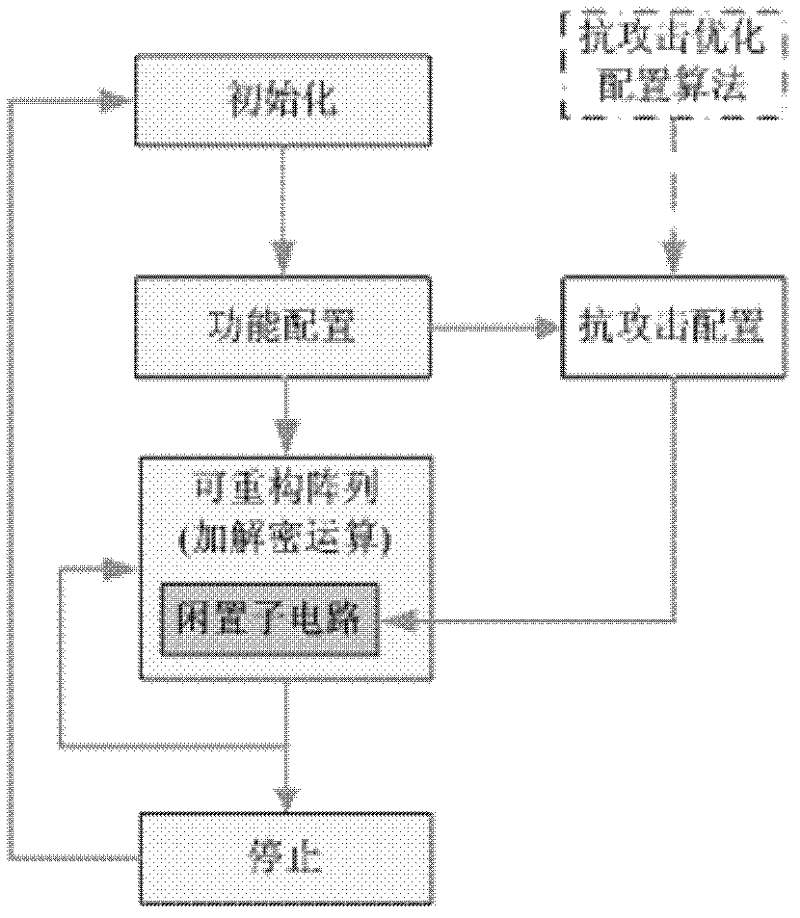

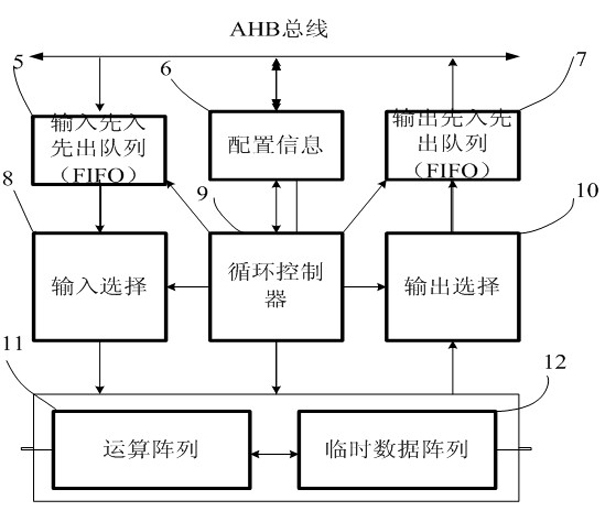

Reconfigurable cipher processor and anti-power consumption attach method

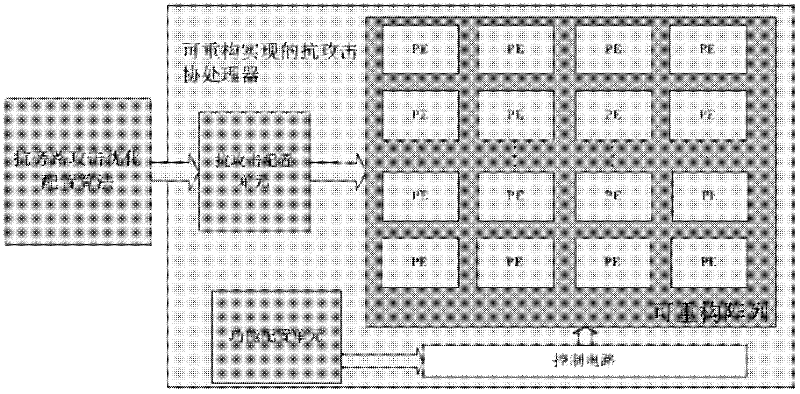

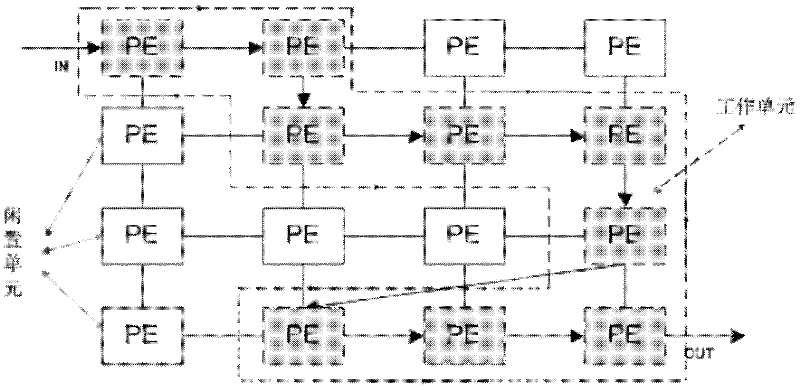

ActiveCN102509036AReduce overheadImprove resource utilizationDigital data authenticationExtensibilityResource utilization

The invention discloses a reconfigurable cipher processor. The reconfigurable cipher processor comprises a reconfigurable array, a control circuit, a functional configuration unit and an anti-attack configuration unit, wherein the functional configuration unit is used for configuring the reconfigurable array into an operating unit and an idle unit through the control circuit; and the anti-attack configuration unit is used for making the idle unit generate random power consumption. The invention also discloses an anti-power consumption attack method implemented by means of the reconfigurable cipher processor. The reconfigurable cipher processor has the characteristics of low circuit cost, high resource utilization rate, high flexibility, high anti-attack capability, applicability to various cipher algorithms, extensibility, upgradeability and the like, can be used in related fields of information security and computer system structures, and provides new solutions for designing cipher processor chips with high security, high flexibility and moderate areas.

Owner:SOUTHEAST UNIV

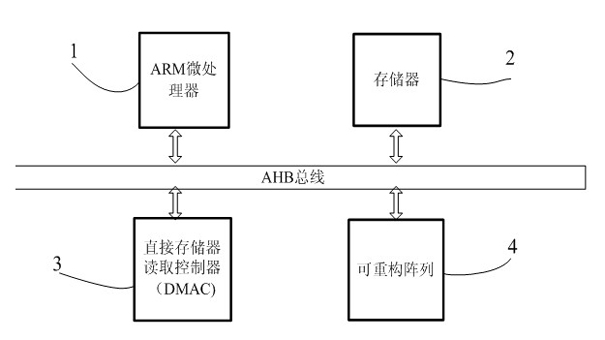

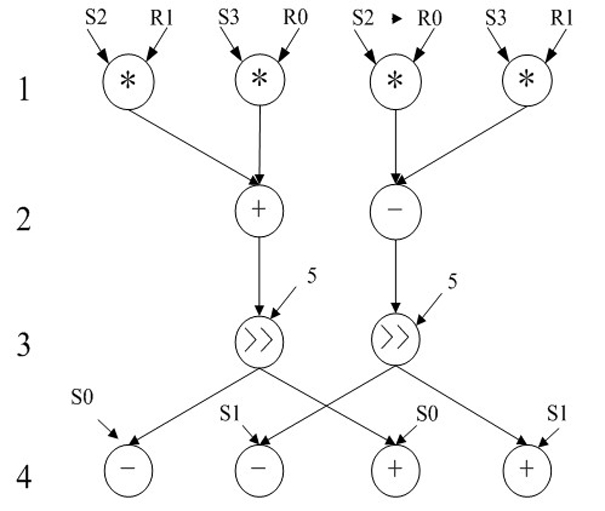

Fourier transform implementation method based on reconfigurable technology

InactiveCN102043761AImprove computing efficiencyIncrease flexibilityComplex mathematical operationsDirect memory accessFourier transform on finite groups

The invention relates to a Fourier transform implementation method based on a reconfigurable technology. In the method, aiming at the common point-based discrete Fourier transform algorithm, the point-based fast Fourier transform computing is decomposed into M exponent arithmetic processes, each exponent arithmetic is composed of N / 2 butterfly arithmetics, and each butterfly arithmetic utilizes one twiddle factor, wherein M is any positive integer, and N is the length of a sequence needing to be subject to Fourier transform, namely a corresponding value. The method can be applied to an embedded system which comprises a bus, an embedded microprocessor, a memory, a reconfigurable array and a direct memory access (DMA) controller, wherein the embedded microprocessor, the memory, the reconfigurable array and the DMA controller respectively communicate with the bus. By utilizing the method, the computing efficiency is improved.

Owner:SOUTHEAST UNIV

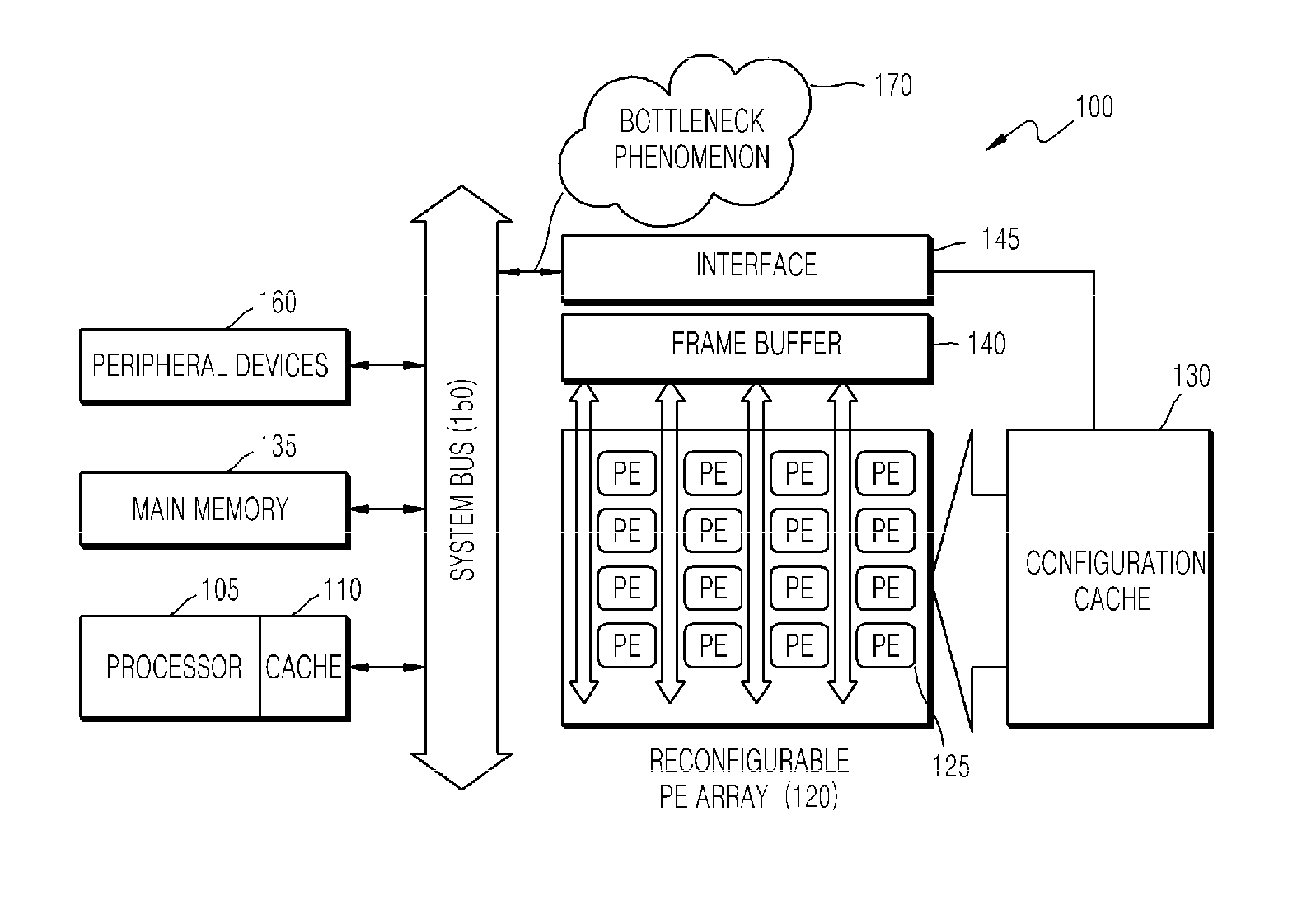

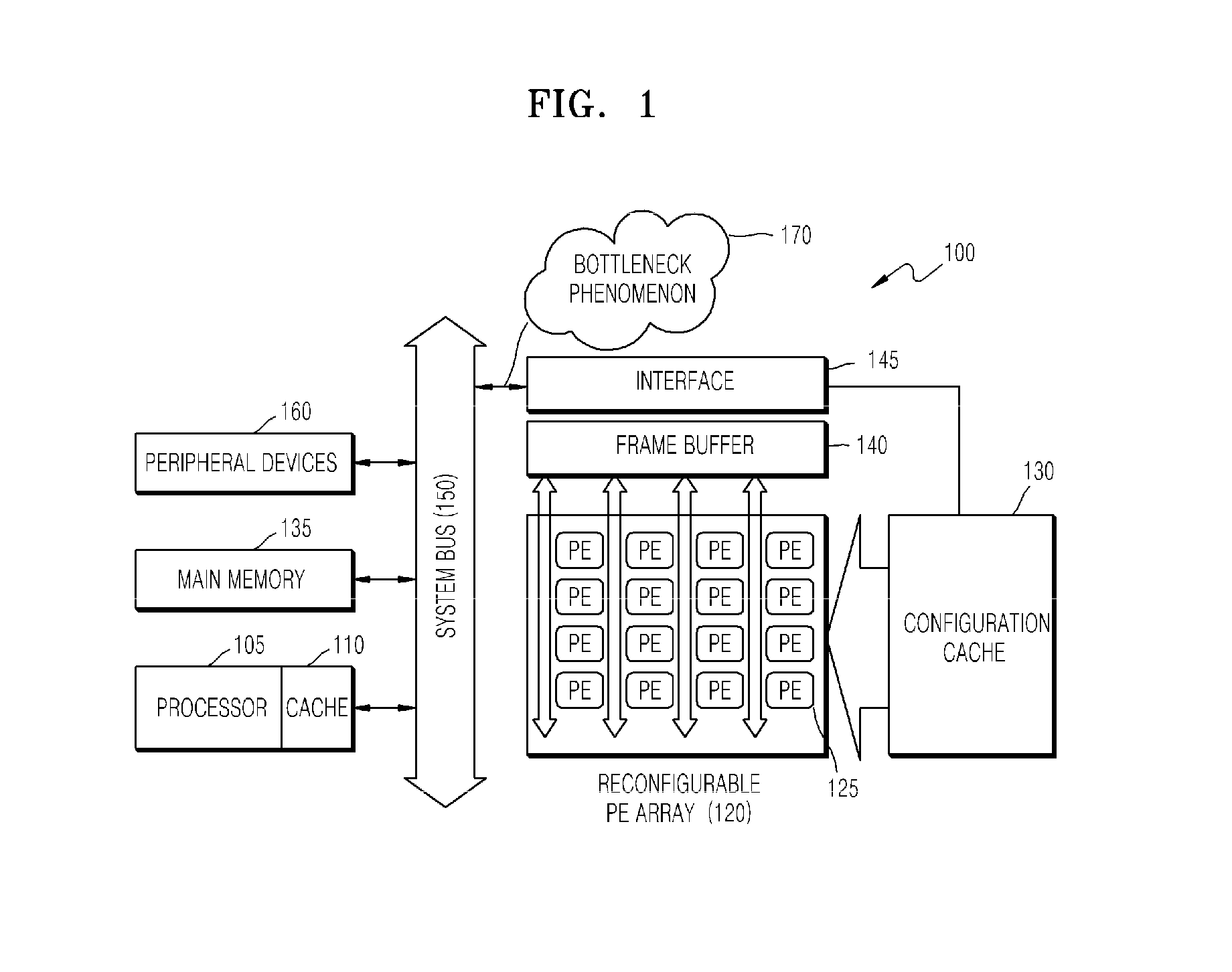

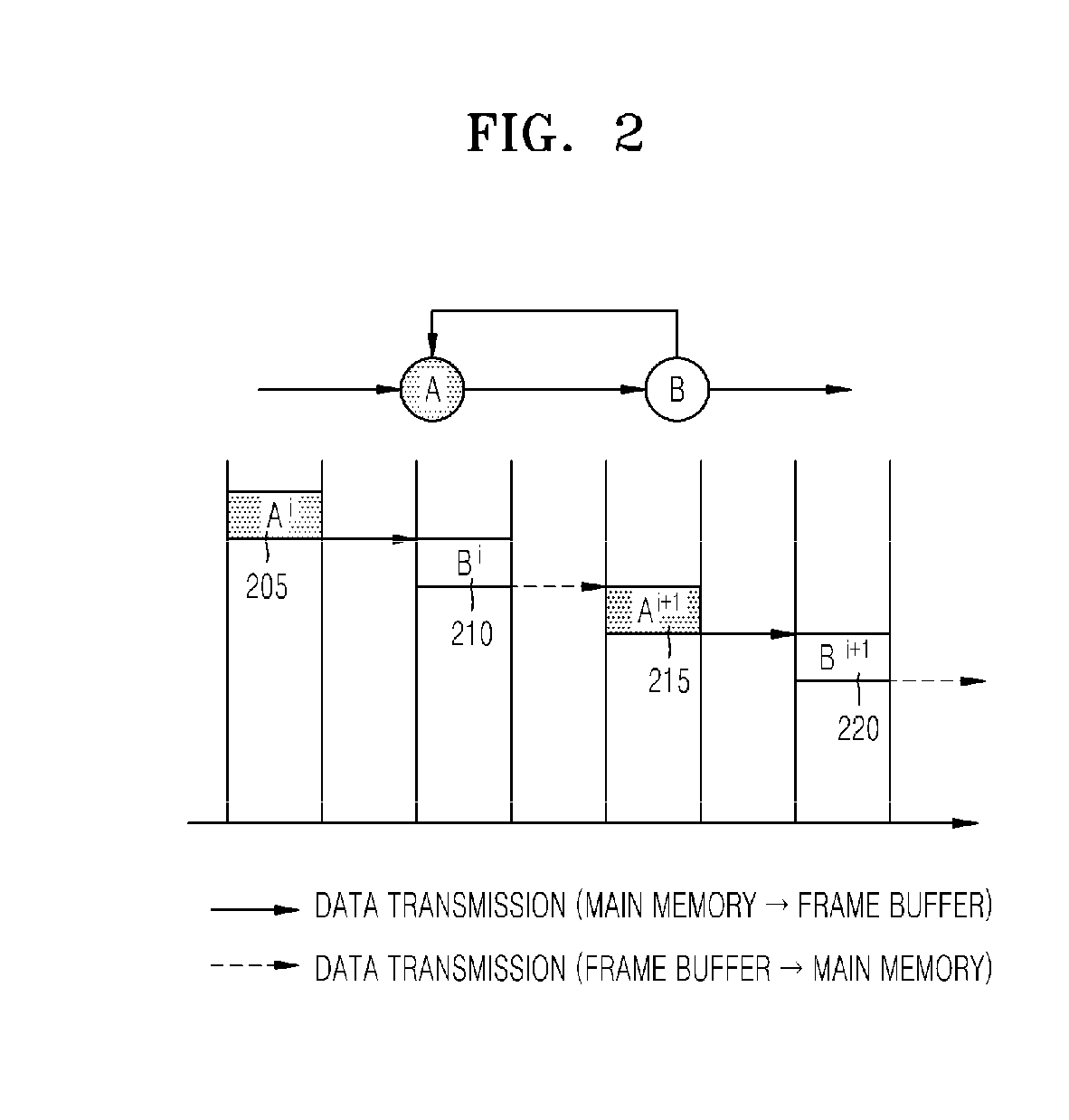

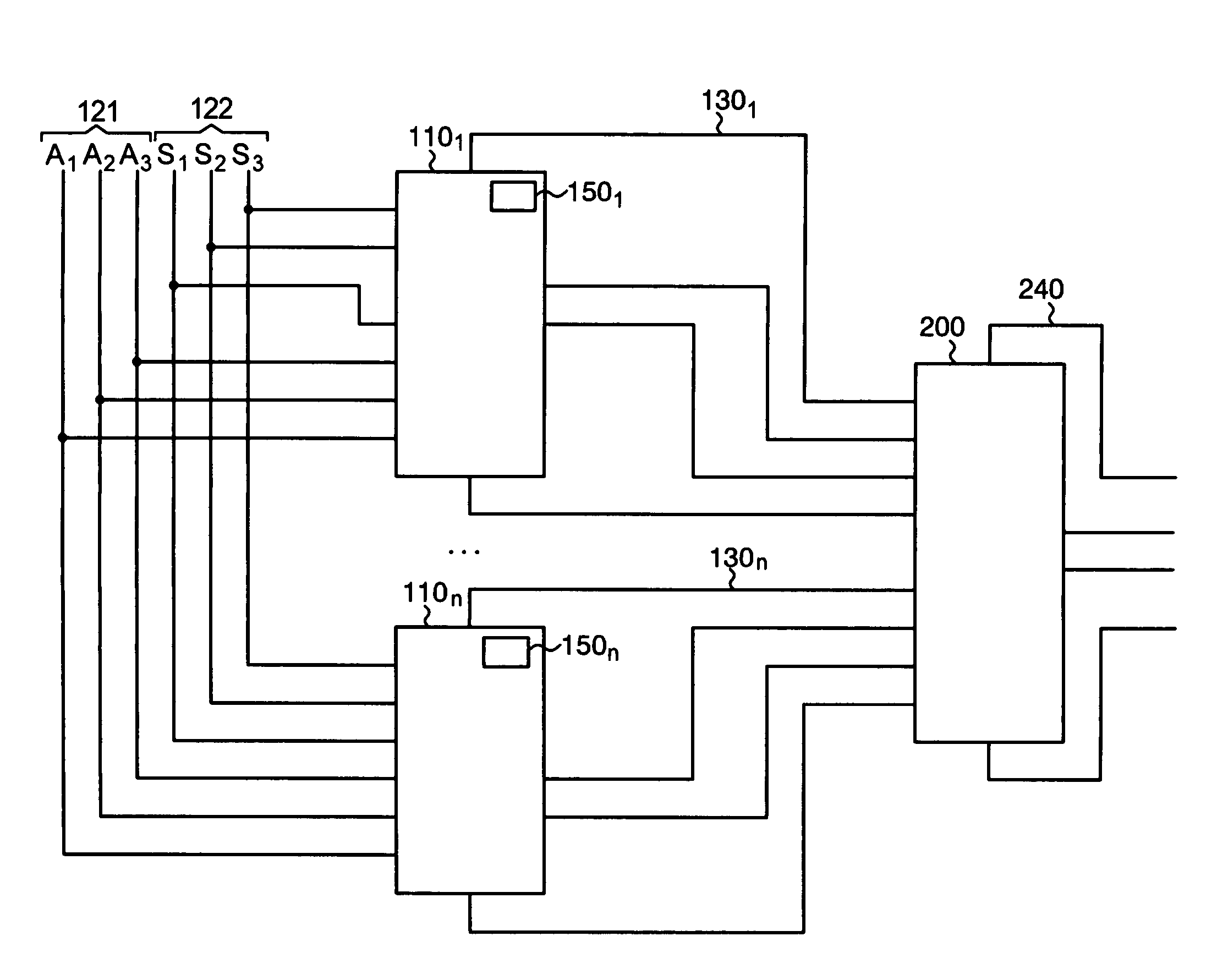

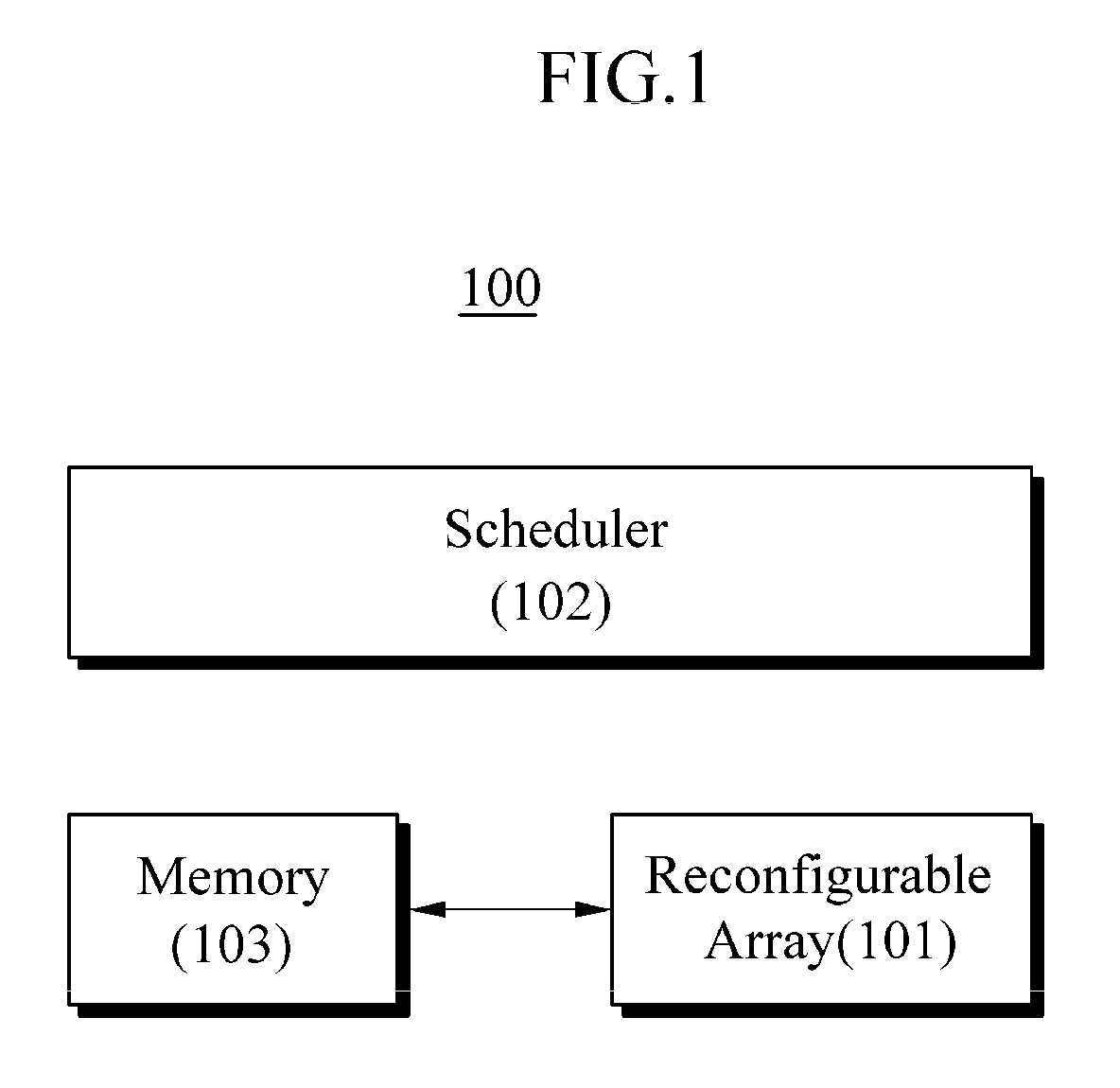

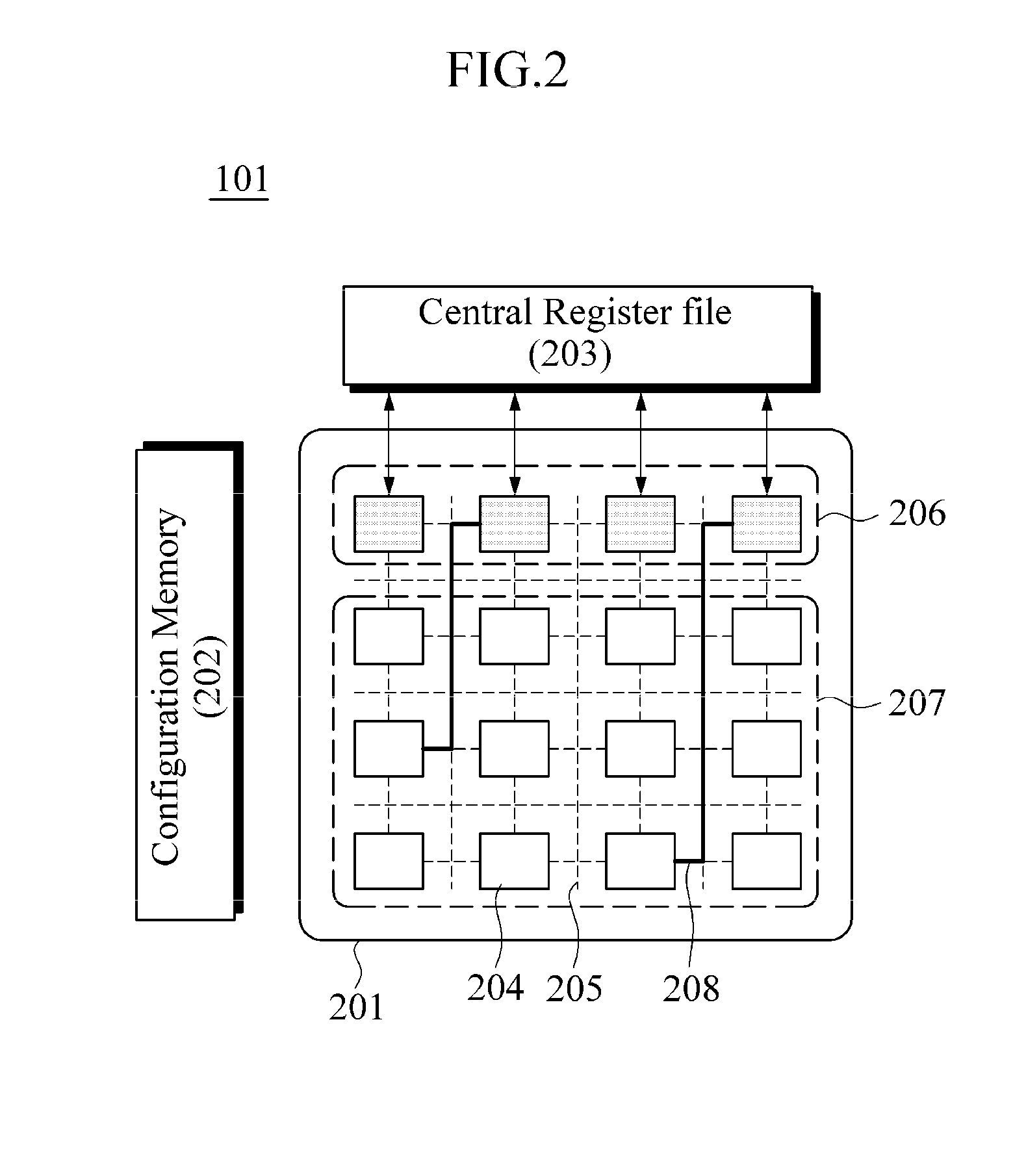

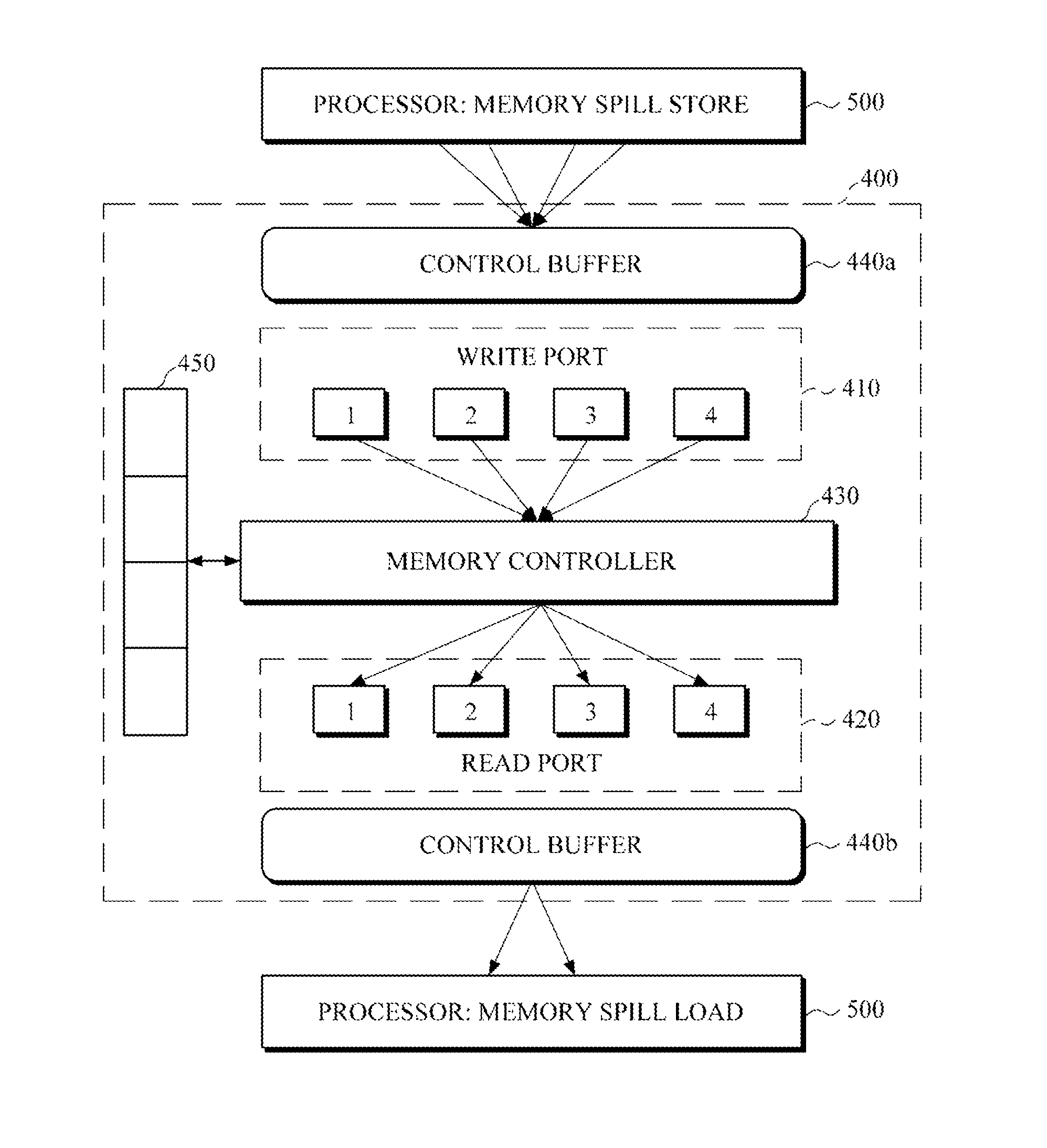

Memory-centered communication apparatus in a coarse grained reconfigurable array

ActiveUS20130024621A1Improve performanceReduce communication overheadMemory adressing/allocation/relocationDigital computer detailsTerm memoryProcessing element

The present invention relates to a coarse-grained reconfigurable array, comprising: at least one processor; a processing element array including a plurality of processing elements, and a configuration cache where commands being executed by the processing elements are saved; and a plurality of memory units forming a one-to-one mapping with the processor and the processing element array. The coarse-grained reconfigurable array further comprises a central memory performing data communications between the processor and the processing element array by switching the one-to-one mapping such that when the processor transfers data from / to a main memory to / from a frame buffer, a significant bottleneck phenomenon that may occur due to the limited bandwidth and latency of a system bus can be improved.

Owner:SEOUL NAT UNIV R&DB FOUND

Safety system based on reconfigurable array of logic gates

InactiveUS20070152709A1Eliminate needEasy to reconfigureProgramme controlSafety arrangmentsEngineeringLogic gate

An array of logic gates is configured to implement a predefined strategy for an emergency response system in a hardware-only runtime environment. The array of logic gates receives a plurality of input signals from a set of sensors and actuators located within an industrial processing system. Based upon the received plurality of input signals, the array of logic gates determines an emergency response using the predefined strategy. The array of logic gates implements the emergency response to control the industrial processing system based upon the predefined strategy. The array of logic gates can be reconfigured based upon a change in the predefined strategy.

Owner:HONEYWELL INT INC

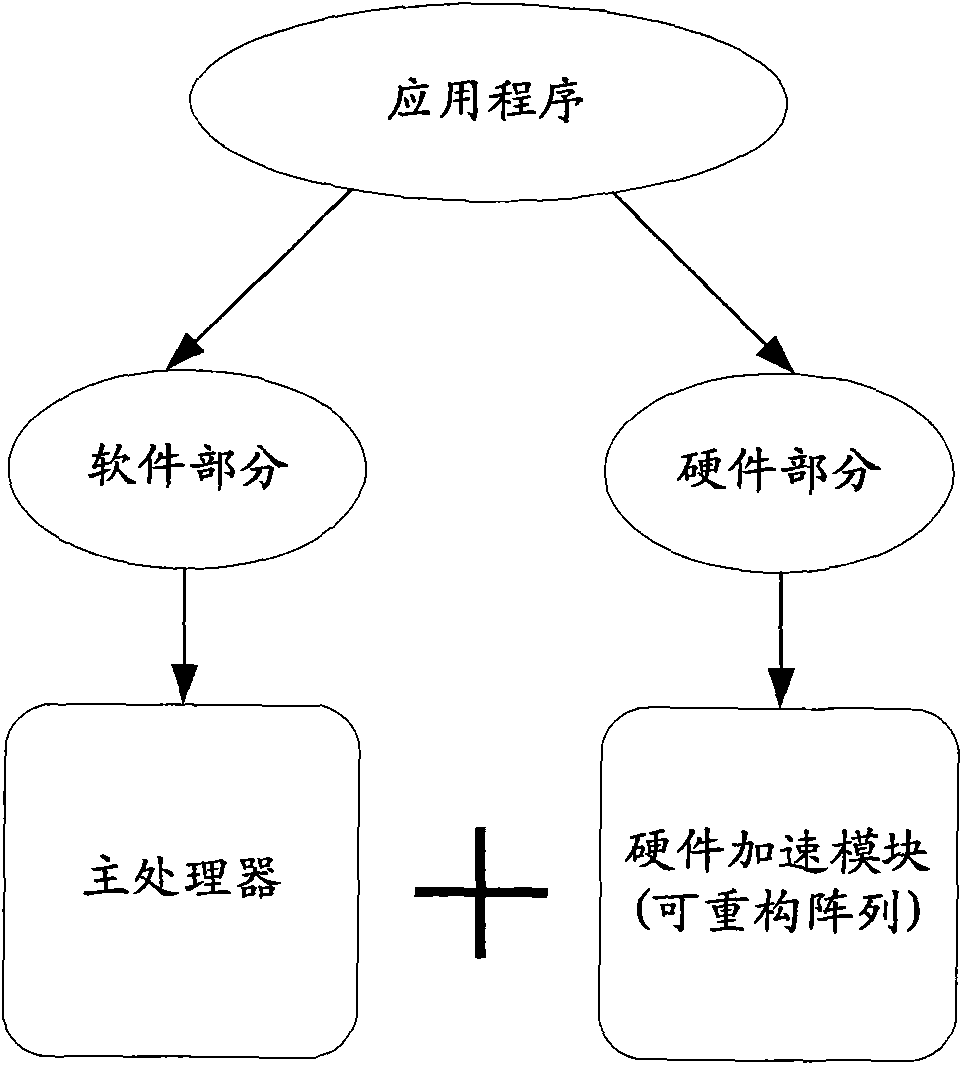

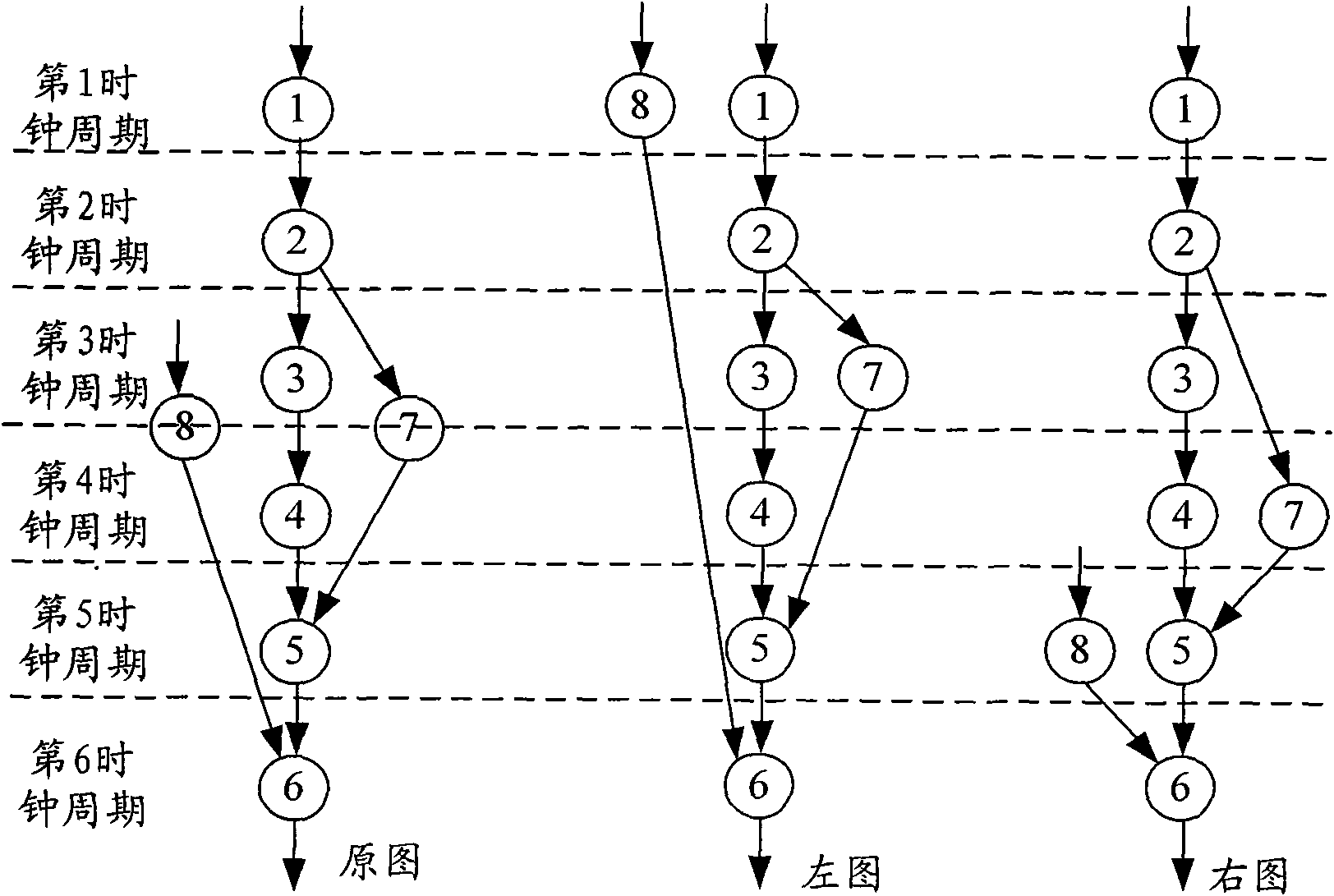

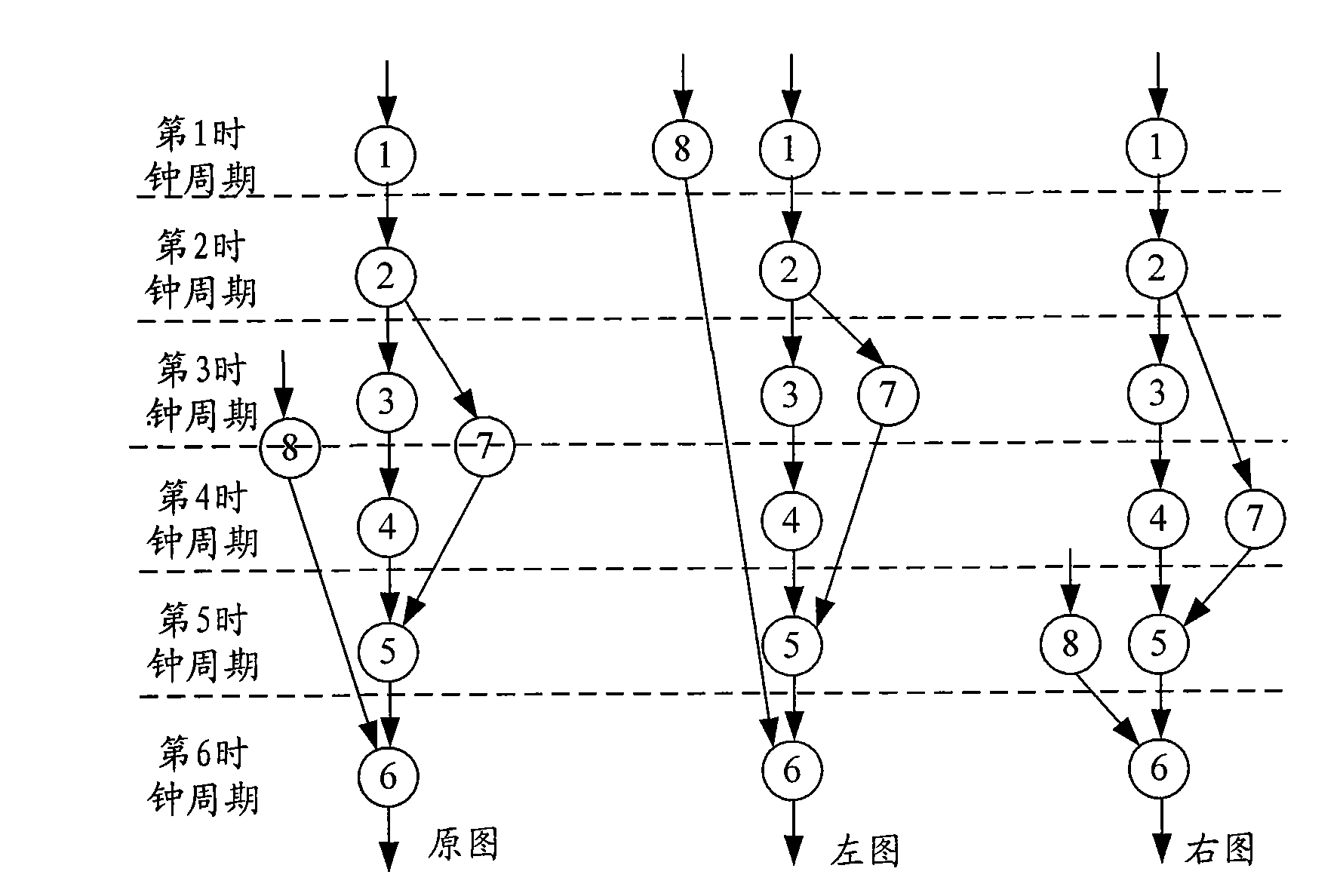

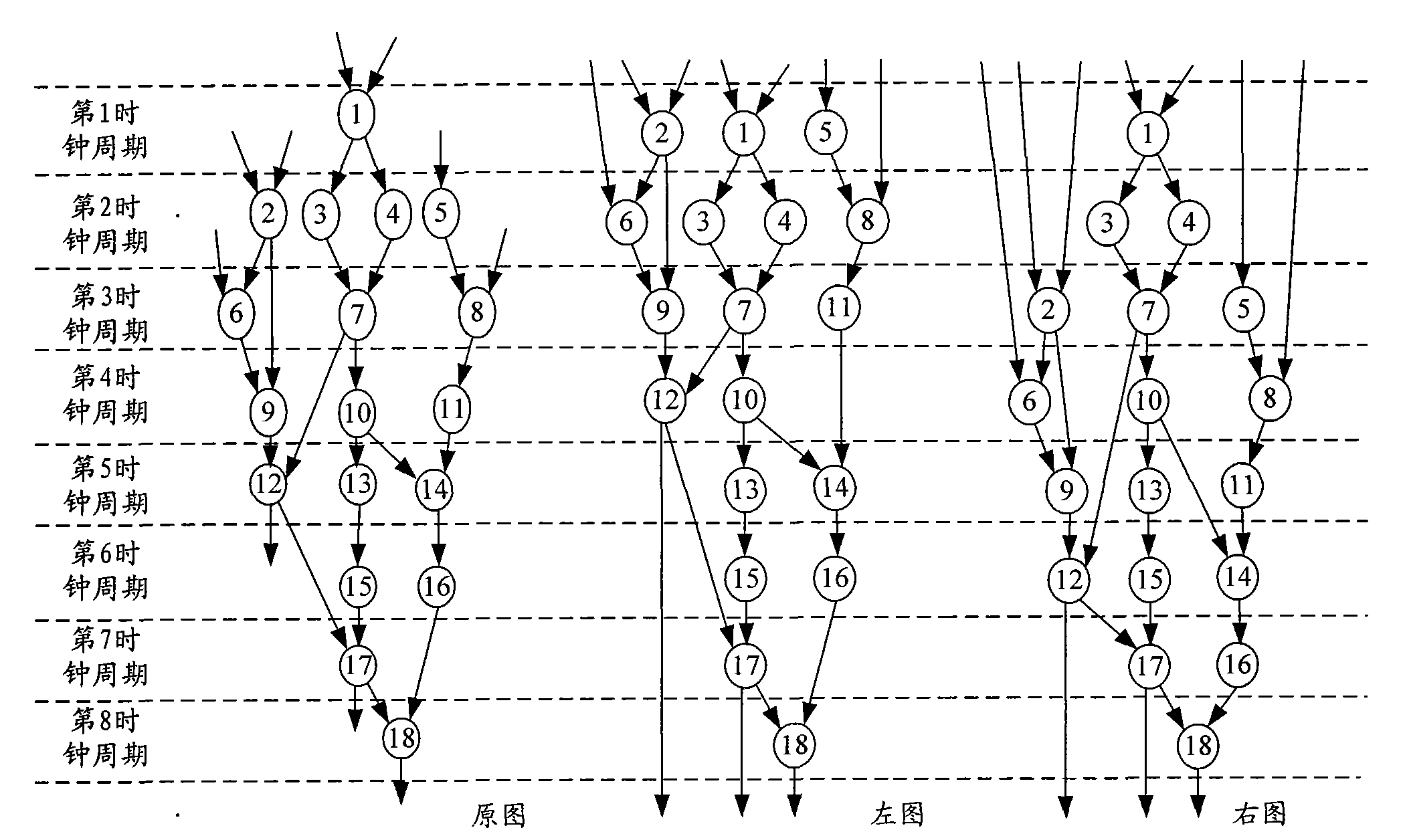

Realizing method of configuration information for generating cycle task and device thereof

InactiveCN101630275AShorten the timeImprove processing efficiencyResource allocationData streamCritical path method

The invention discloses a realizing method of configuration information for generating a cycle task and a device thereof, belonging to the field of an embedded system. When the scale of data stream is not larger than that of a reconfigurable array, the method comprises the following steps of: adjusting nodes of data stream currently executed by the reconfigurable array by means of arithmetic operators; according to the adjusting result of the arithmetic operators, obtaining the length of a key route, the free degree of the each node, and the clock period of the each node; according to the length of the key route and the columns of the reconfigurable array, setting up a matrix; when the data stream has unmapped nodes, according to the free degree of the unmapped nodes, the clock period of the unmapped nodes and a mapping rule, mapping the unmapped nodes into the matrix; and according to a mapping result, obtaining the configuration information of the cycle task on the reconfigurable array. The scheme only generates a set of configuration information of the reconfigurable array, reduces the time that transmits the configuration information to the reconfigurable array, and improves efficiency.

Owner:SHENZHEN PANGO MICROSYST CO LTD

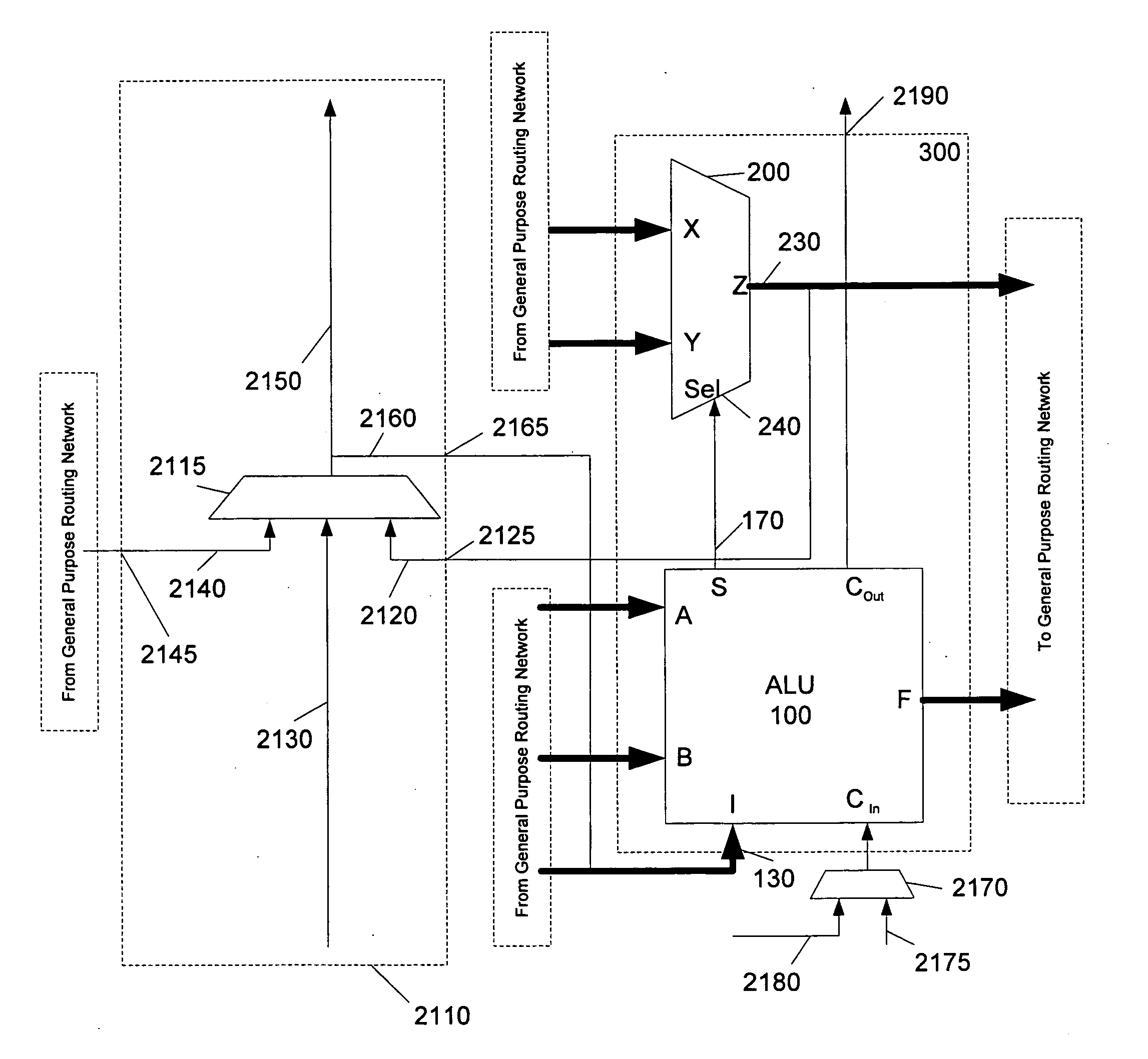

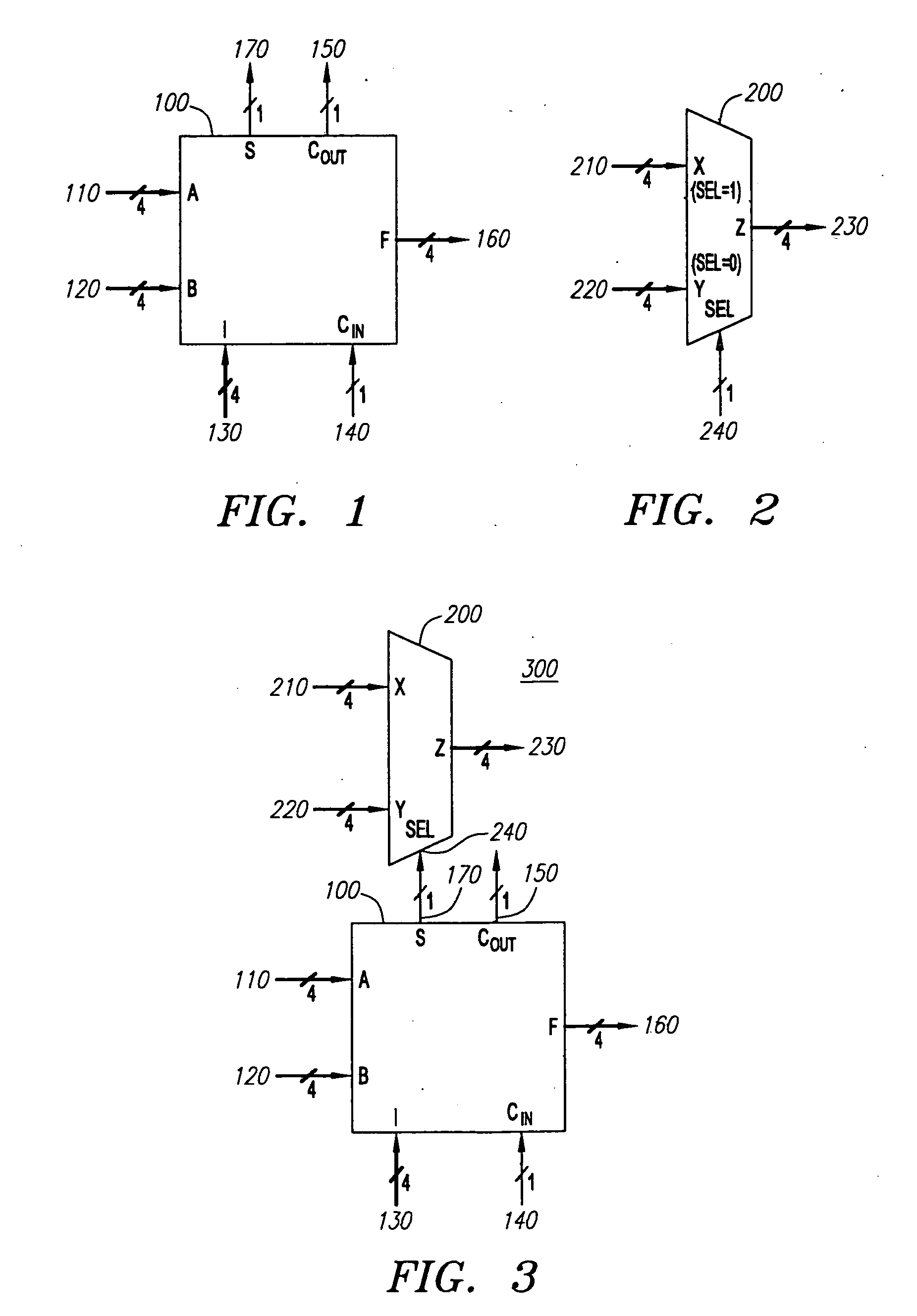

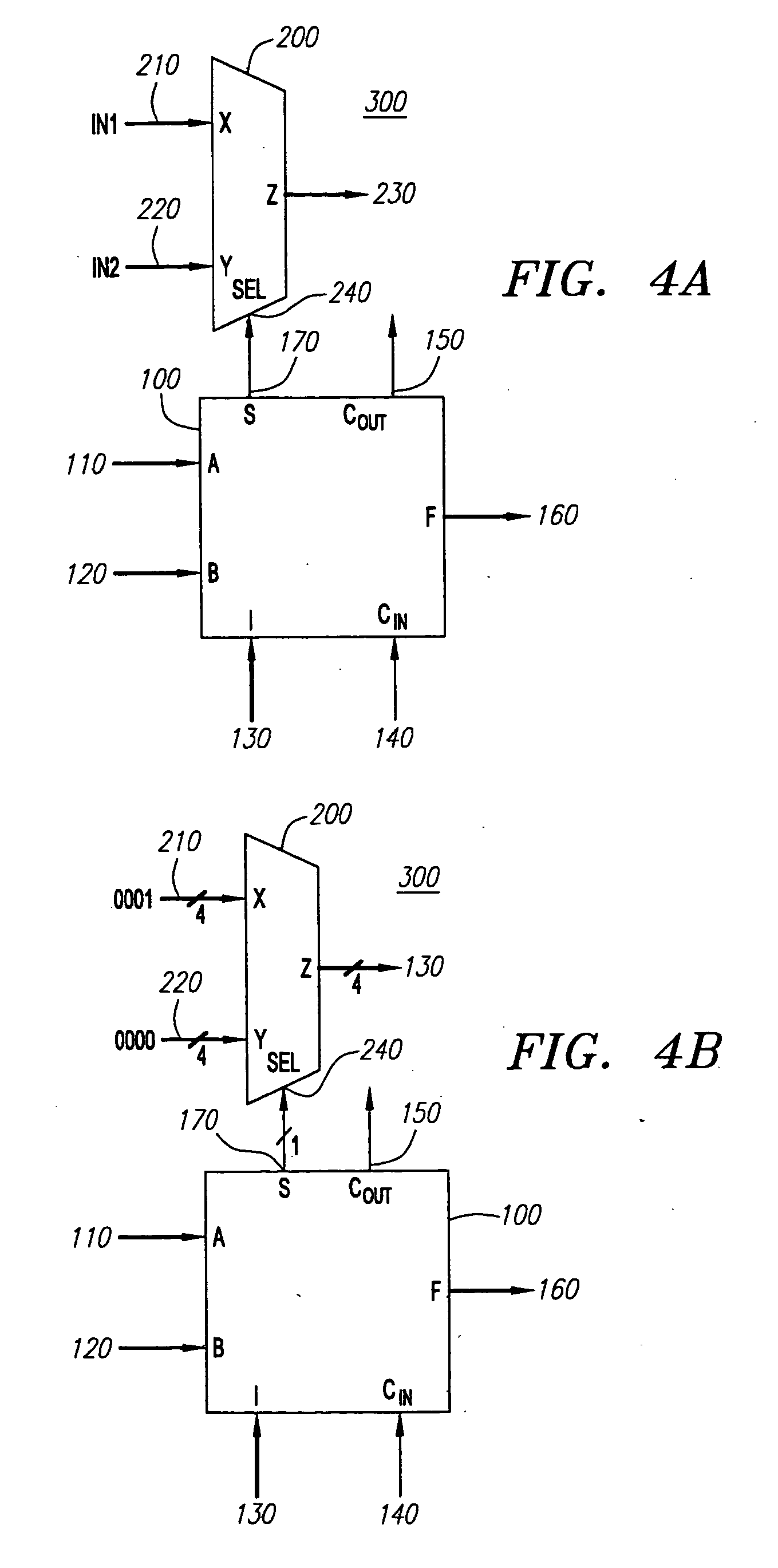

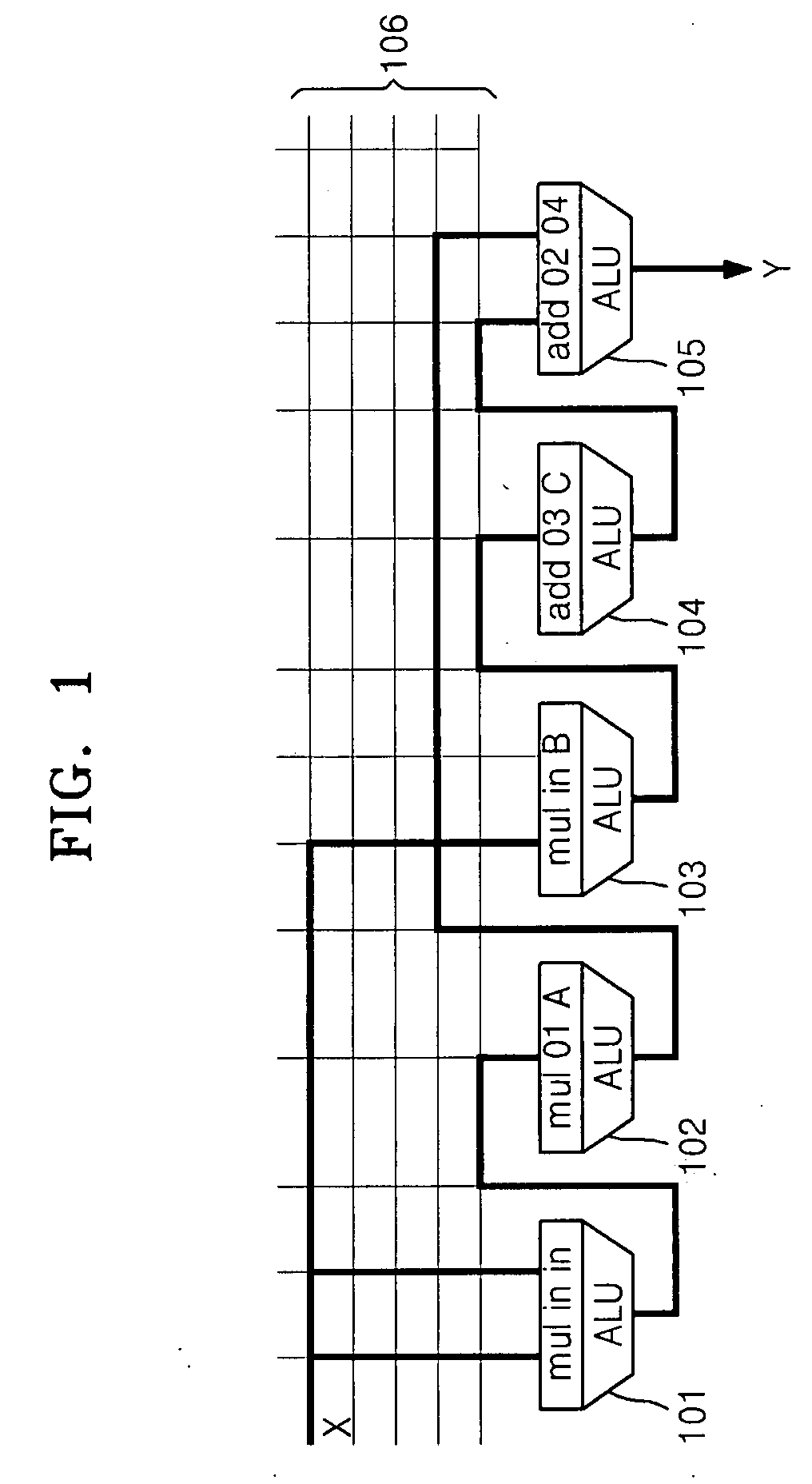

Loosely-biased heterogeneous reconfigurable arrays

InactiveUS20050257024A1Reduce the numberImprove performanceElectronic switchingProgram controlGeneral purposeMultiplexer

A heterogeneous array includes clusters of processing elements. The clusters include a combination of ALUs and multiplexers linked by direct connections and various general-purpose routing networks. The multiplexers are controlled by the ALUs in the same cluster, or alternatively by ALUs in other clusters, via a special purpose routing network. Components of applications configured onto the array are selectively implemented in either multiplexers or ALUs, as determined by the relative efficiency of implementing the component in one or the other type of processing element, and by the relative availability of the processing element types. Multiplexer control signals are generated from combinations of ALU status signals, and optionally routed to control multiplexers in different clusters.

Owner:PANASONIC CORP

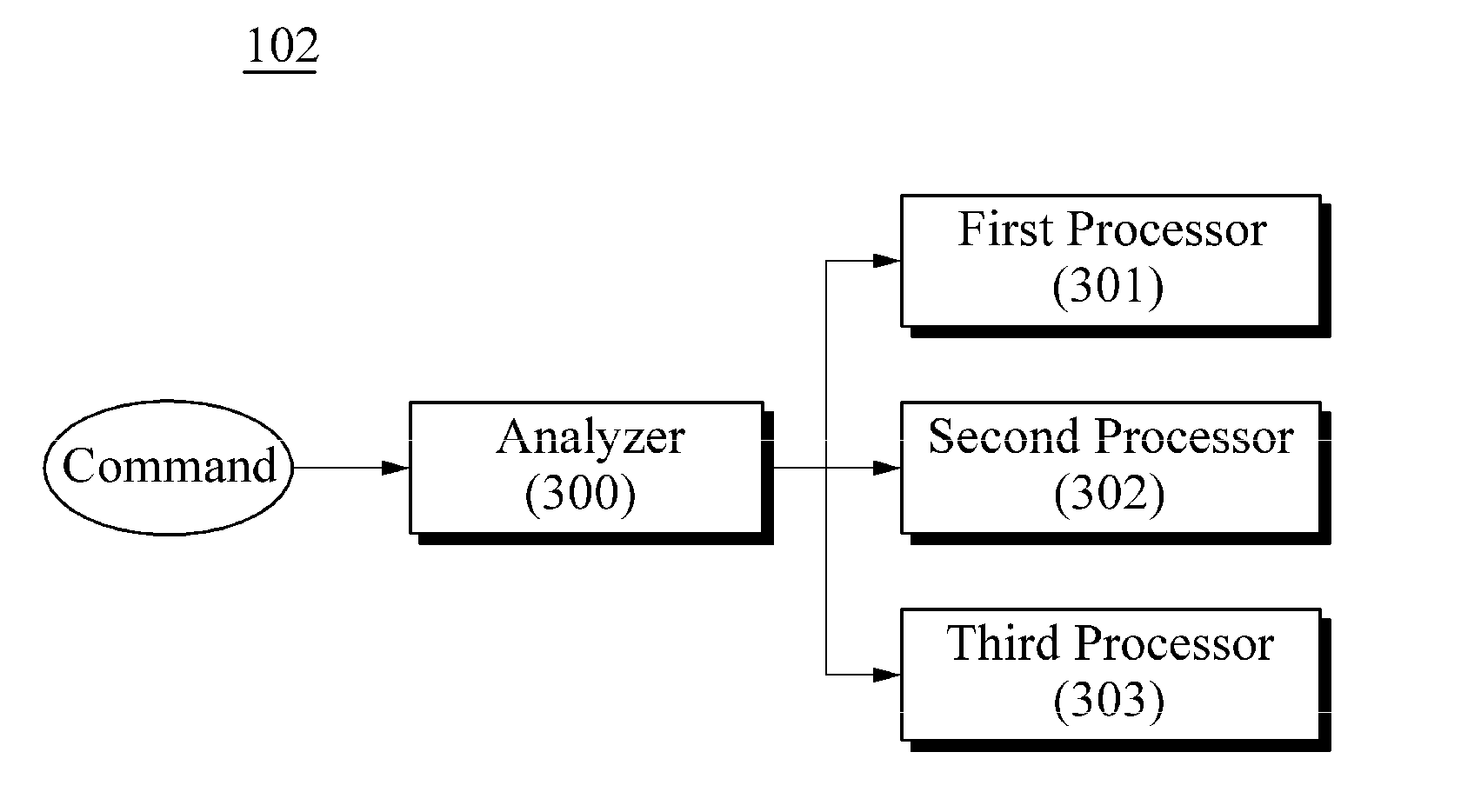

Scheduler of reconfigurable array, method of scheduling commands, and computing apparatus

InactiveUS20100199069A1Program control using stored programsProgram control using wired connectionsReconfigurable antennaOperating speed

A scheduler of a reconfigurable array, a method of scheduling commands, and a computing apparatus are provided. To perform a loop operation in a reconfigurable array, a recurrence node, a producer node, and a predecessor node are detected from a data flow graph of the loop operation such that resources are assigned to such nodes so as to increase the loop operating speed. Also, a dedicated path having a fixed delay may be added to the assigned resources.

Owner:SAMSUNG ELECTRONICS CO LTD

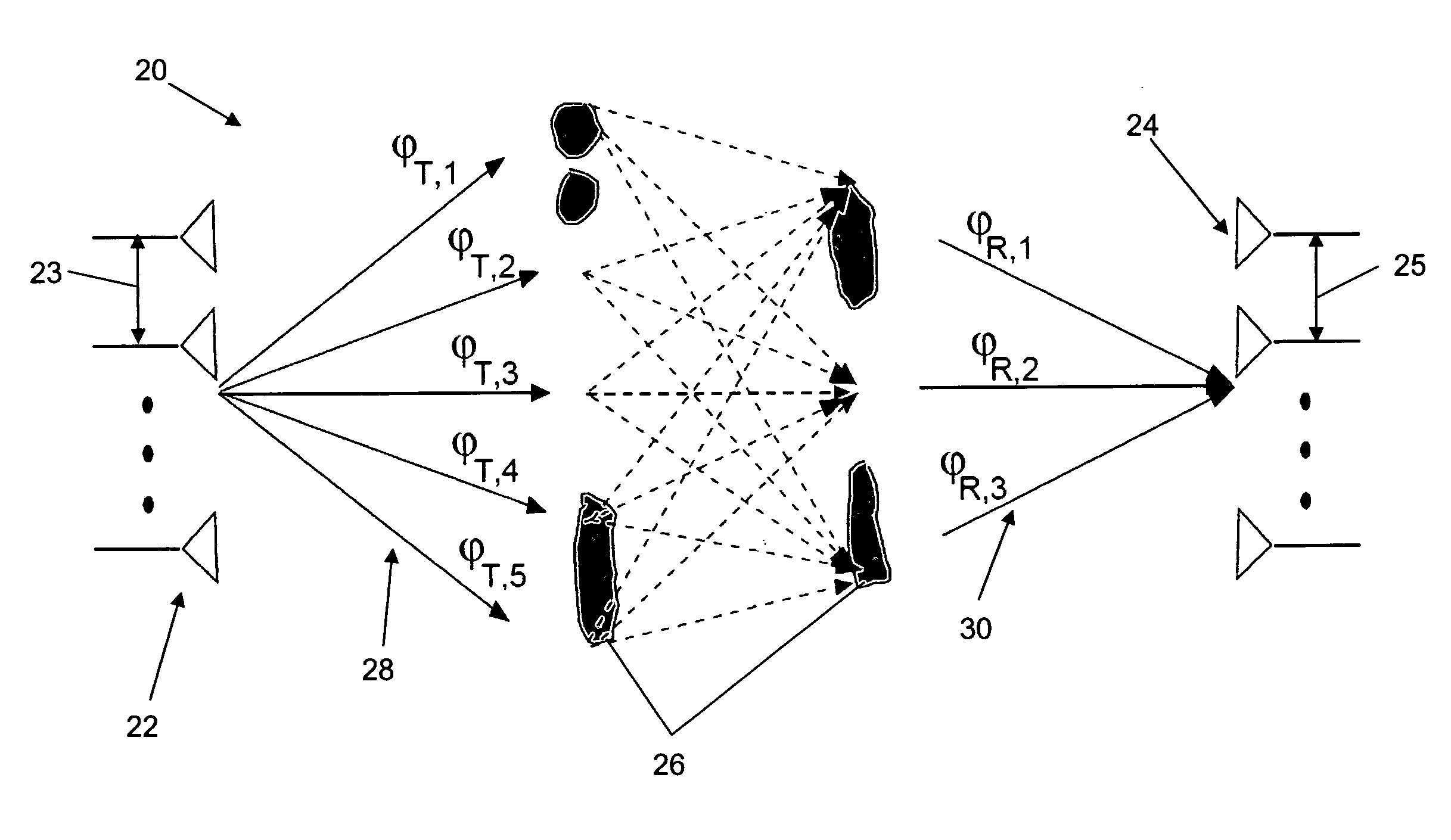

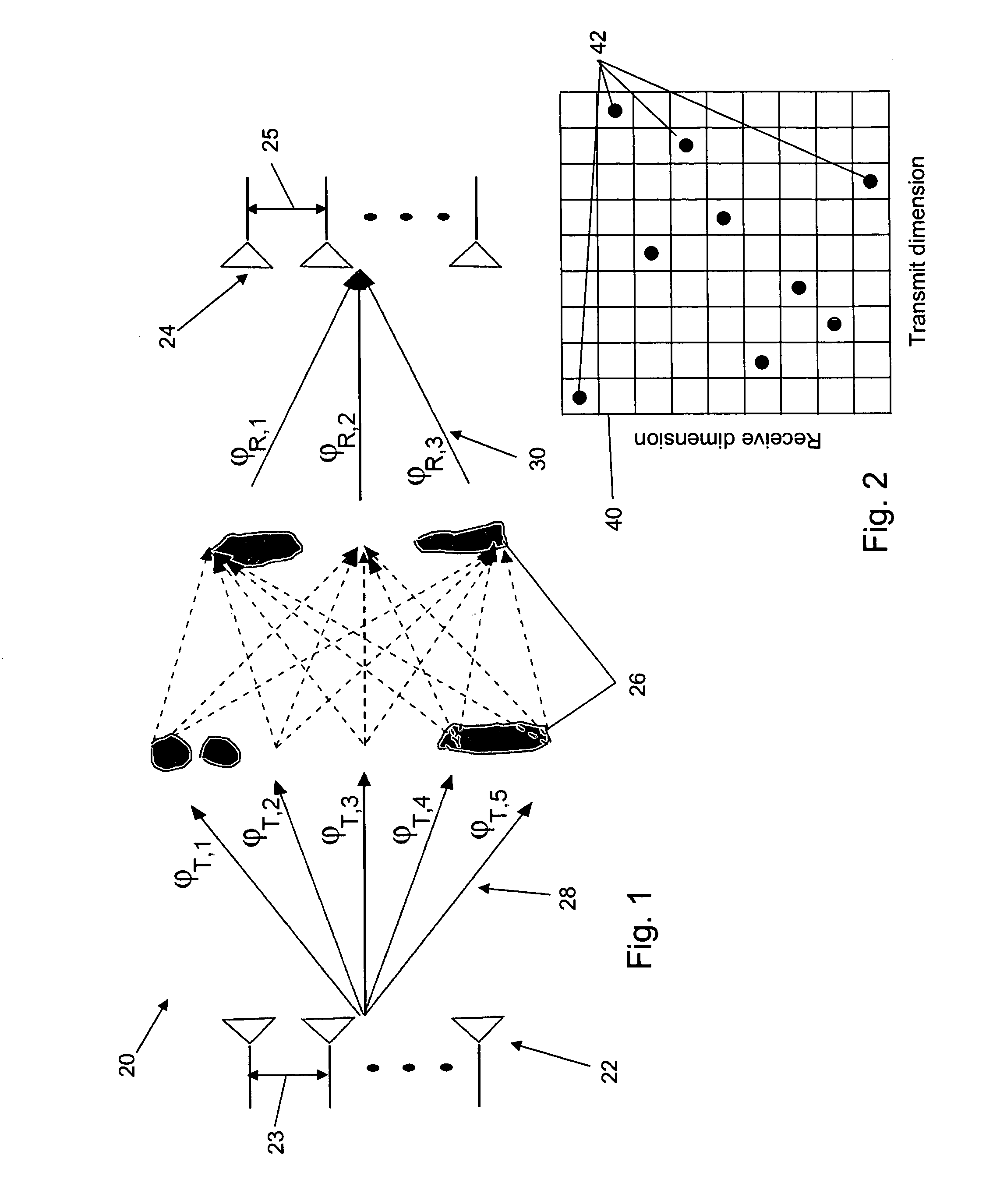

Method and system for improving performance in a sparse multi-path environment using reconfigurable arrays

ActiveUS20080009321A1Improve performanceIncrease capacitySubstation equipmentRadio transmissionReconfigurable antennaCommunications system

A wireless communication system supporting improved performance in a sparse multi-path environment is provided that uses spatially reconfigurable arrays. The system includes a first device and a second device. The first device includes a plurality of antennas and a processor operably coupled to the plurality of antennas. The plurality of antennas are adapted to transmit a first signal toward a the second device and to receive a second signal from the second device. The processor is configured to determine an antenna spacing between the plurality of antennas based on an estimated number of spatial degrees of freedom and an estimated operating signal-to-noise ratio. The second device includes a receiver adapted to receive the first signal from the first device, a transmitter adapted to transmit the second signal toward the first device, and a processor. The processor estimates the number of spatial degrees of freedom and the operating signal-to-noise ratio from the received first signal.

Owner:WISCONSIN ALUMNI RES FOUND

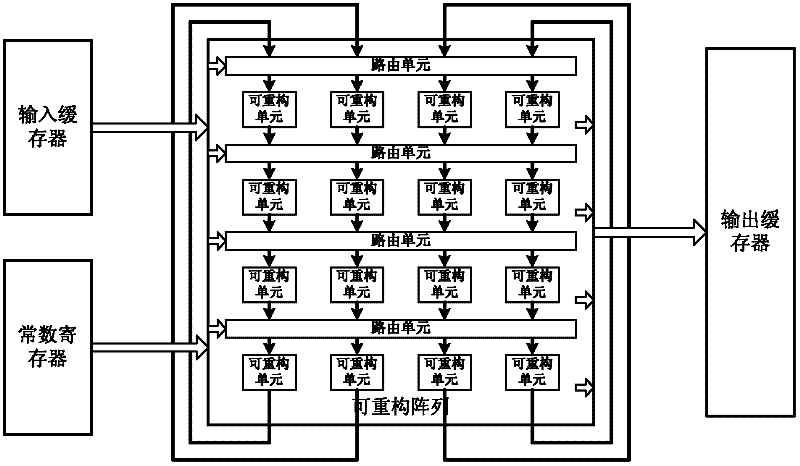

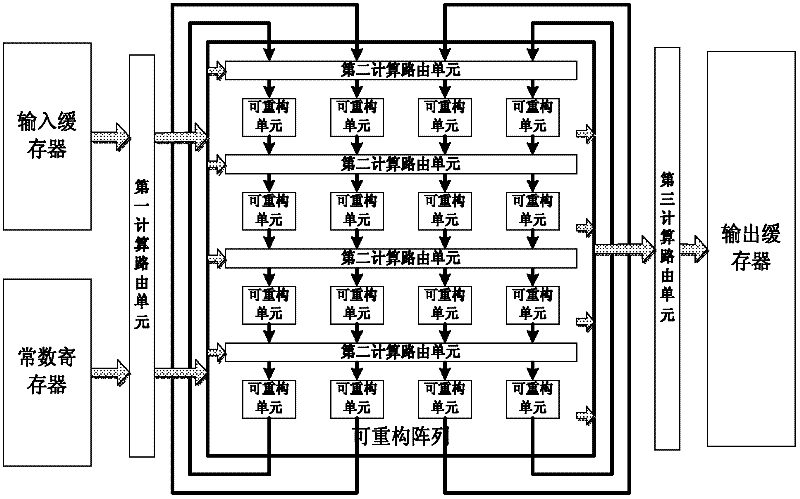

Dynamic reconfigurable processor

ActiveCN102541809AAvoid operational occupationAvoid occupyingArchitecture with single central processing unitExternal dataReconfigurable array

The invention provides a dynamic reconfigurable processor, which comprises an input buffer, a first calculation routing unit, a reconfigurable array, a plurality of second calculation routing unit, a third calculation routing unit and an output buffer, wherein the input buffer is used for buffering external data, and outputting the data to the first calculation routing unit; the first calculation routing unit is used for receiving the data of the input buffer, computing the data, and outputting computation result data to a reconfigurable array; the reconfigurable array is used for computing the input data, and outputting computation result data to the third calculation routing unit, and comprises a plurality of reconfigurable units for completing computing operation of the input data; the second calculation routing units are used for completing connection of data between the reconfigurable units and computing the data; the third calculation routing unit is used for receiving output data of the reconfigurable array, and computing the data; and the output buffer is used for receiving result data output by the third calculation routing unit, and outputting the data to an external device.

Owner:TSINGHUA UNIV

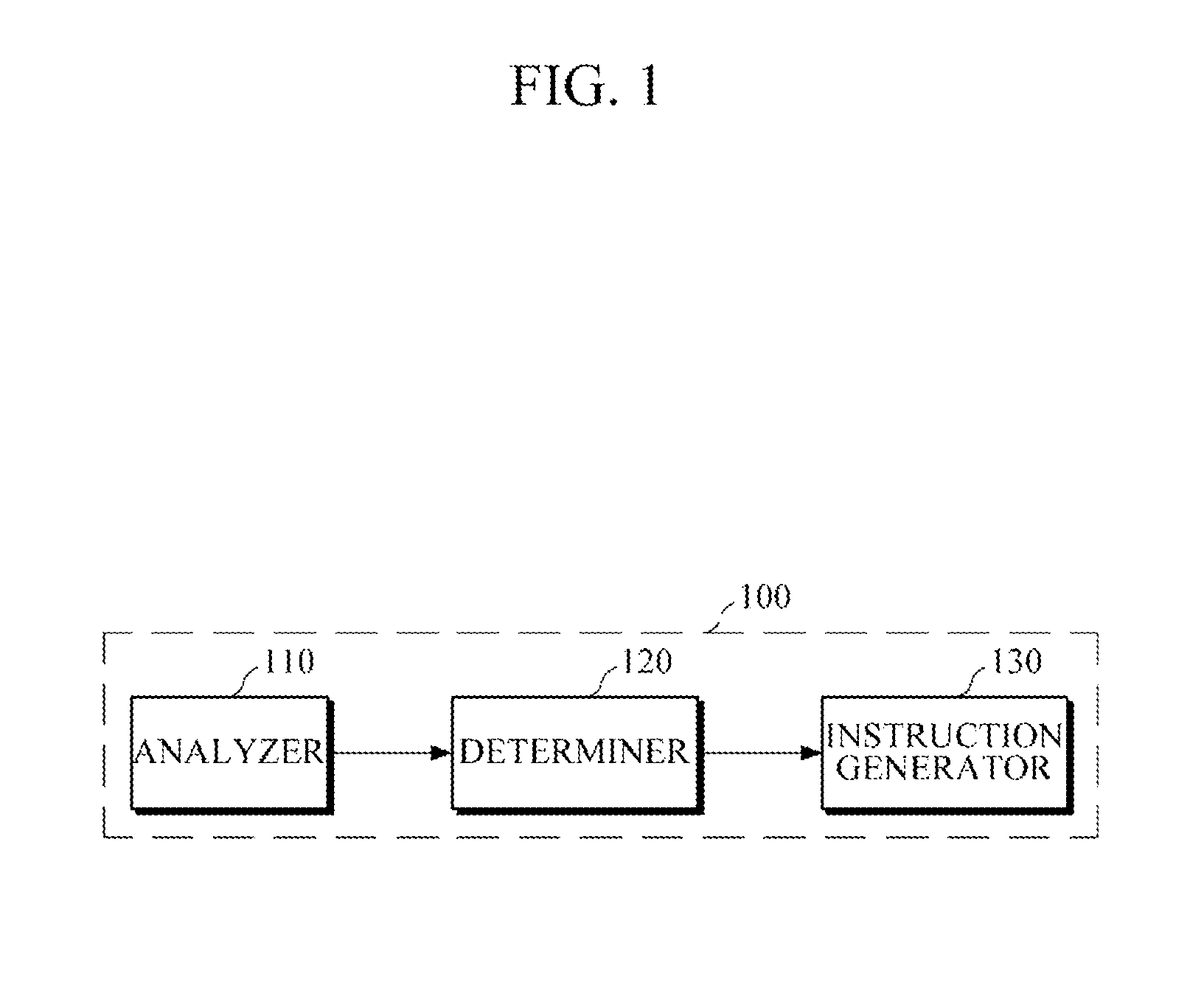

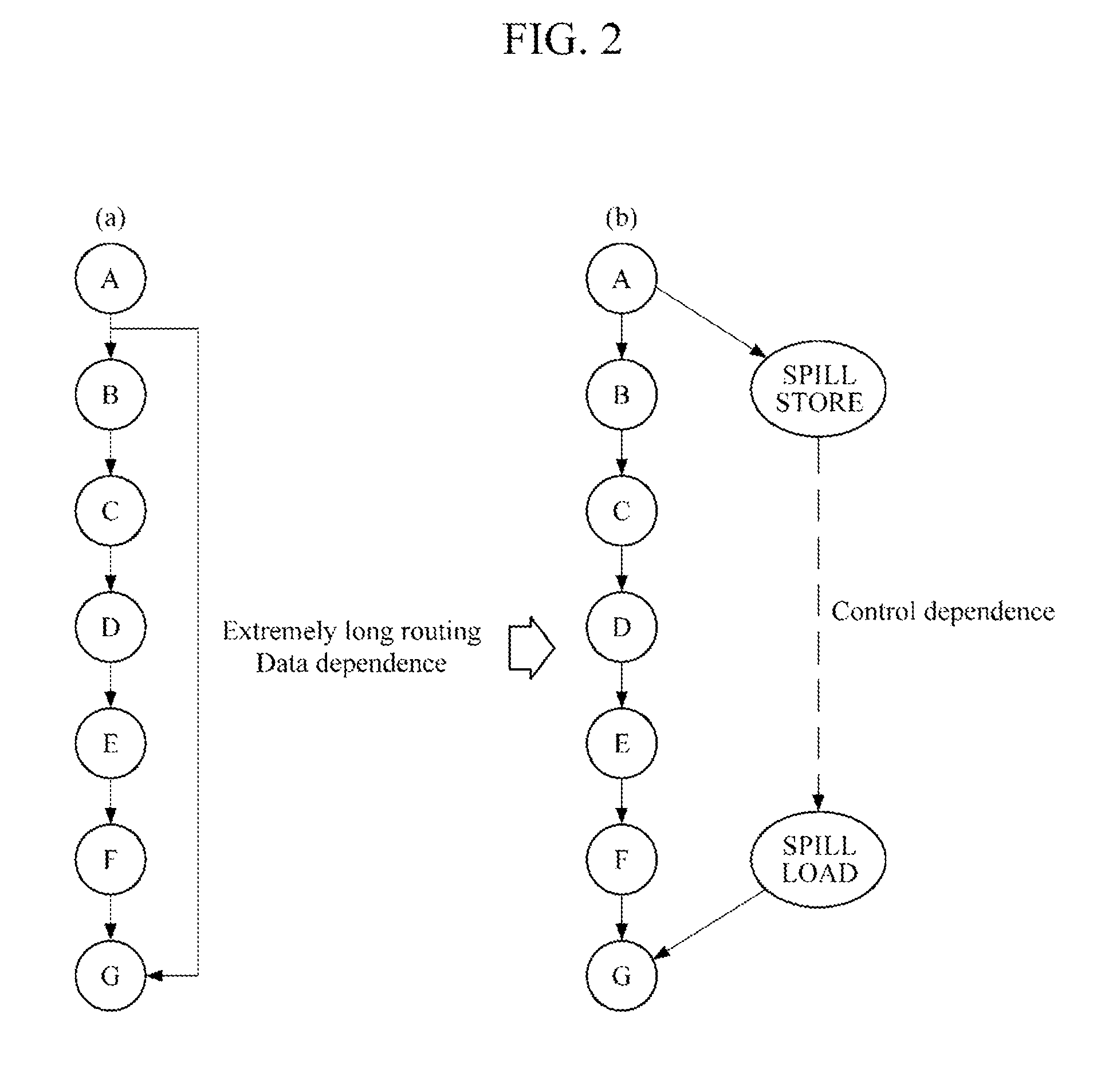

Memory apparatus for processing support of long routing in processor, and scheduling apparatus and method using the memory apparatus

InactiveUS20140317628A1Eliminate dependenciesInput/output to record carriersProgram initiation/switchingData streamProcess support

Provided are a scheduling apparatus and method for effective processing support of long routing in a coarse grain reconfigurable array (CGRA)-based processor. The scheduling apparatus includes: an analyzer configured to analyze a degree of skew in a data flow of a program; a determiner configured to determine whether operations in the data flow utilize a memory spill based on the analyzed degree of skew; and an instruction generator configured to eliminate dependency between the operations that are determined to utilize the memory spill, and to generate a memory spill instruction.

Owner:SAMSUNG ELECTRONICS CO LTD

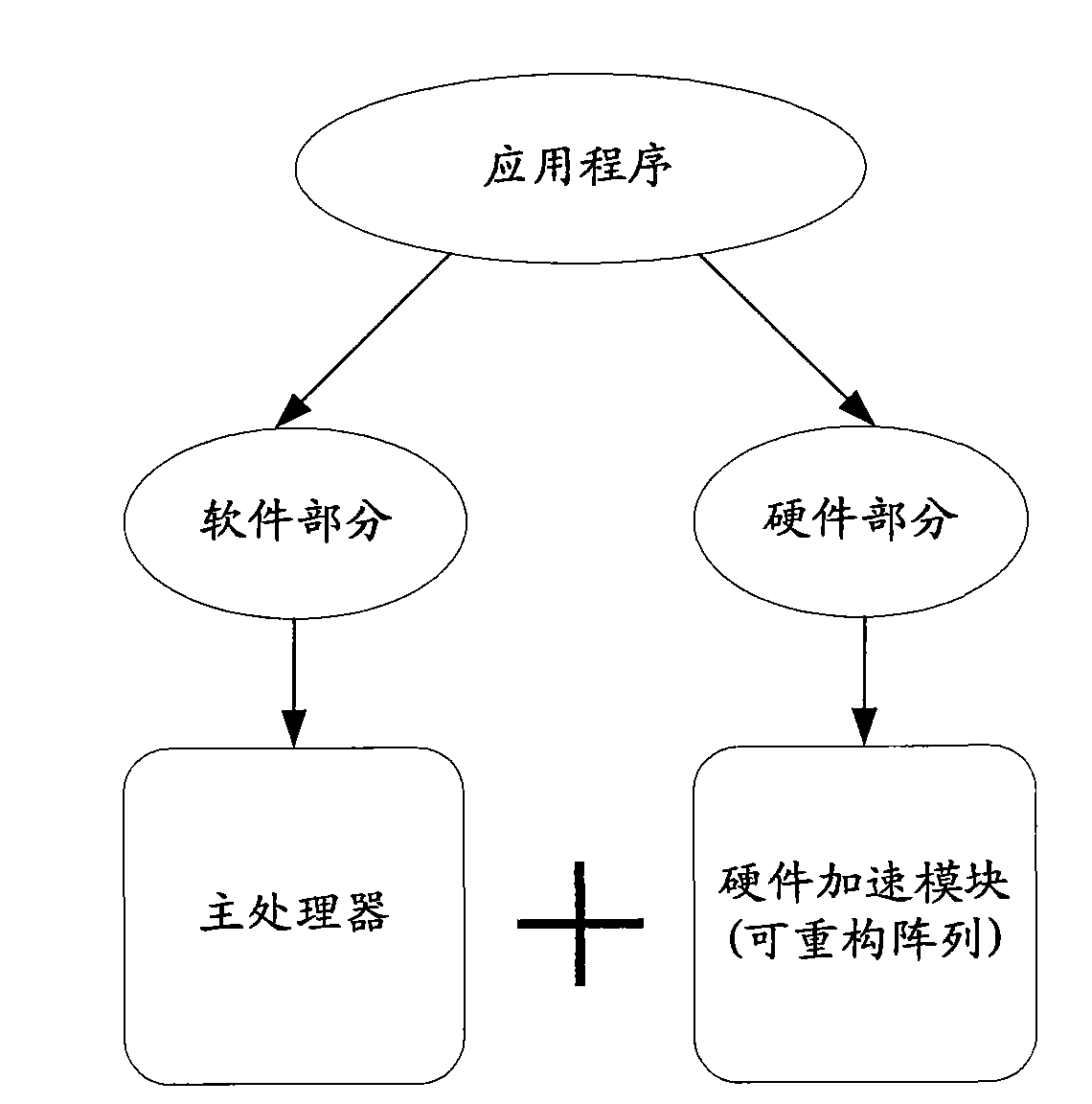

Method for dividing cycle task by means of software and hardware and device thereof

The invention discloses a method for dividing a cycle task by means of software and hardware and a device thereof, belonging to the field of an embedded system. When the number of nodes of data stream currently executed by a reconfigurable array is larger than the scale of the reconfigurable array, the method comprises the following steps: adjusting the nodes of the data stream currently executed by the reconfigurable array by means of arithmetic operators; according to the adjusting result of the arithmetic operators, obtaining the free degree of the input nodes; obtaining the output number of the input nodes; obtaining the input node with highest free degree and least output numbers according to the obtained free degree of the input nodes and the obtained output number of the input nodes; and dividing the obtained input nodes to a main processor. The method enlarges the scale of a cycle body which can be executed by a reconfigurable processor, plays the characteristic that the reconfigurable array is good at executing the cycle task, reduces the executing time of a whole application program, and meets the requirement in practical application.

Owner:SHENZHEN PANGO MICROSYST CO LTD

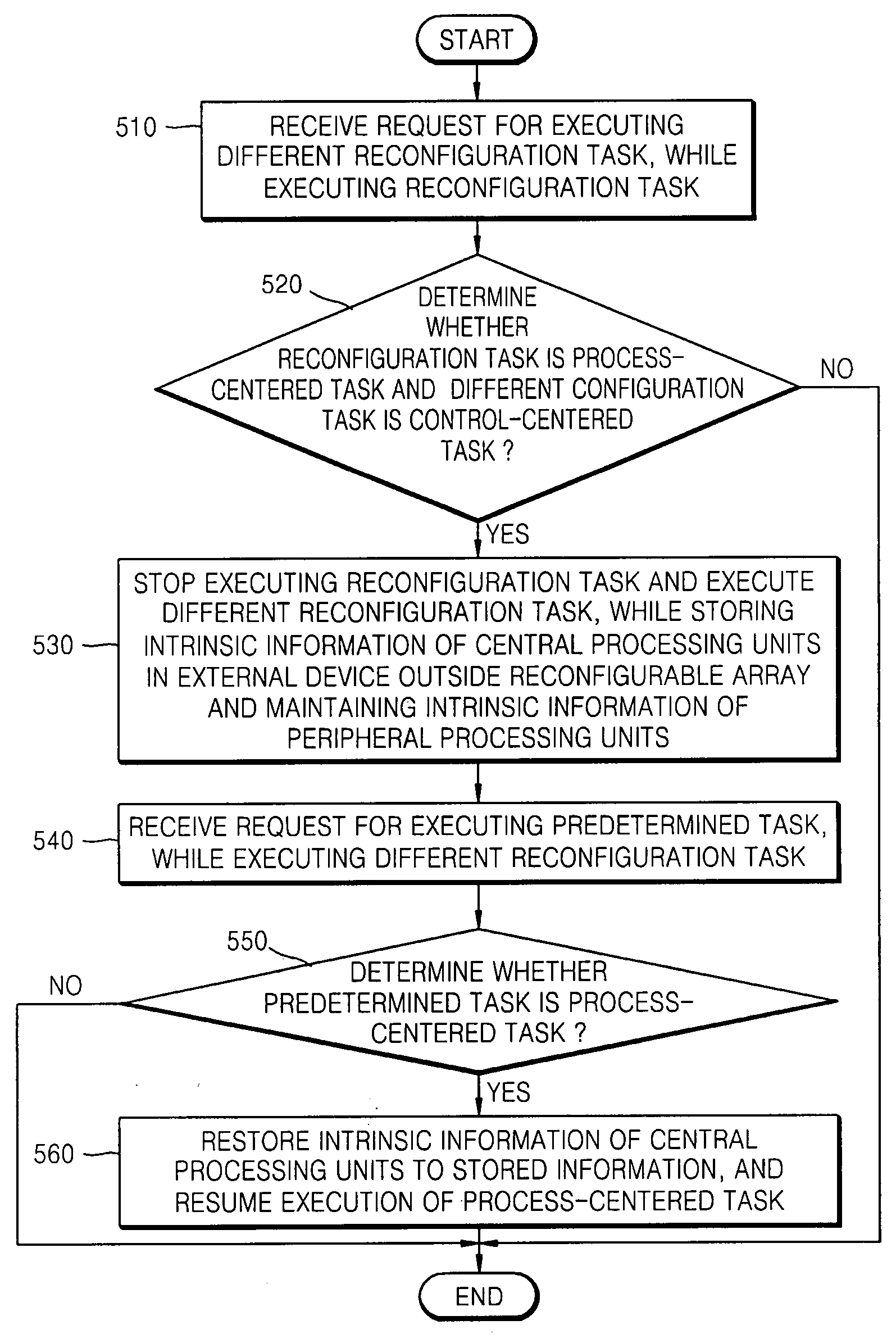

Multitasking method and apparatus for reconfigurable array

ActiveUS20070288930A1Quickly complete execution of multitaskingFast executionMultiprogramming arrangementsMemory systemsReconfigurable antennaReconfigurable array

Provided are a multitasking method and apparatus. By continuously maintaining the intrinsic information of each peripheral processing unit of when a process-centered task is stopped, when a reconfigurable array stops executing the process-centered task and executes a different process-centered task, by stopping executing a control-centered task and executing a reconfiguration task, only when the reconfigurable array receives an execution request of the reconfiguration task while the reconfigurable array is performing the control-centered task, or by causing a predetermined number of processing units to execute each of a plurality of reconfiguration tasks that are to be simultaneously executed by the reconfigurable array, wherein the predetermined number of processing units is set in consideration of an expected data processing amount required for the reconfiguration task, the reconfigurable array can more quickly complete execution of multitasking.

Owner:SAMSUNG ELECTRONICS CO LTD

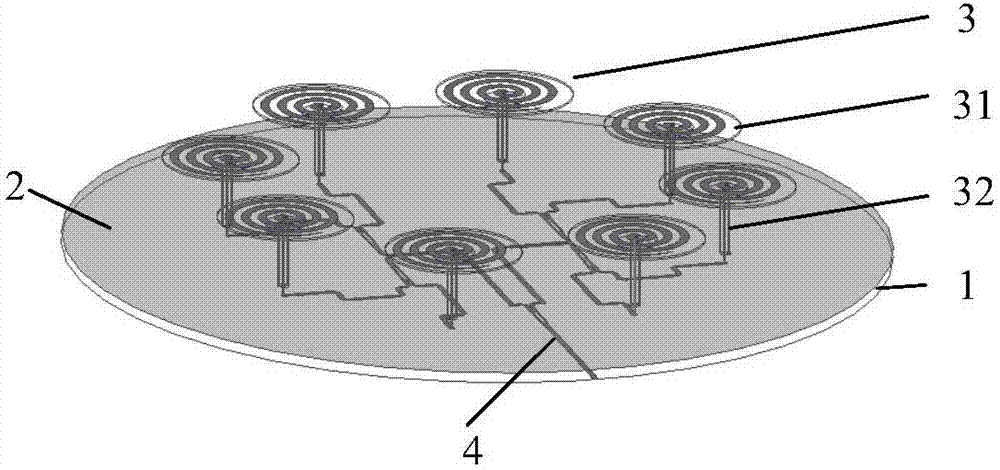

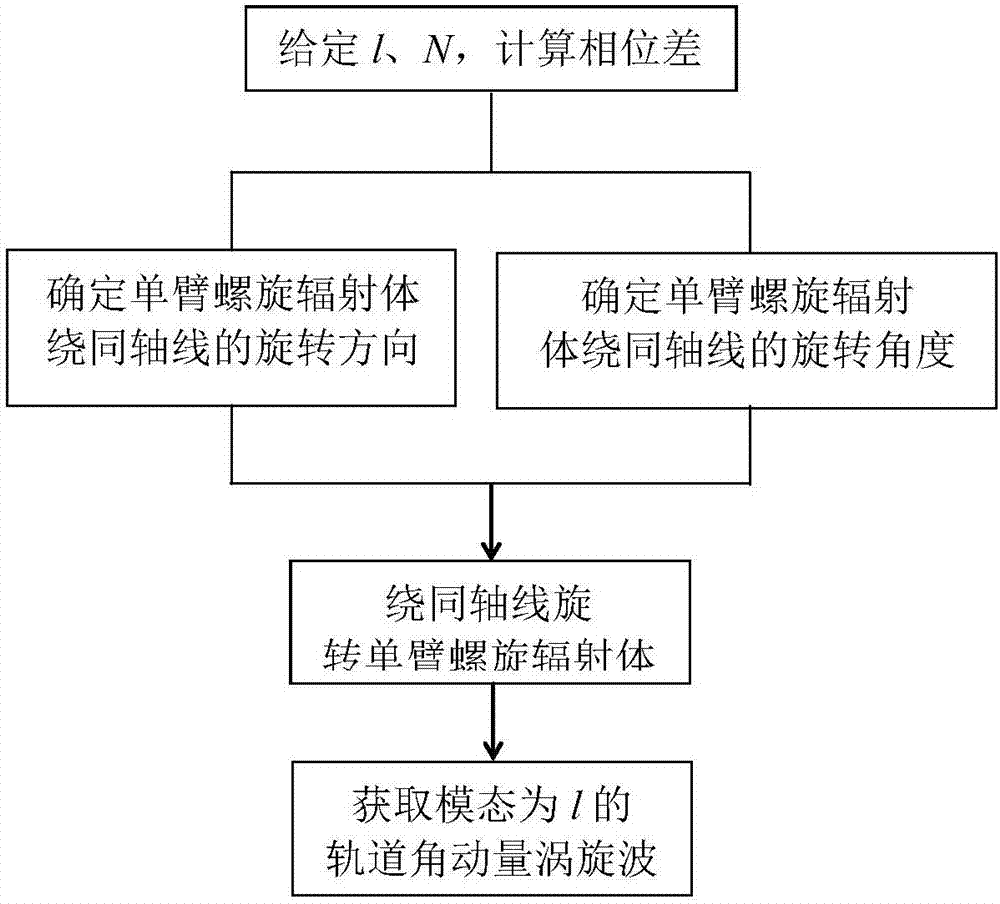

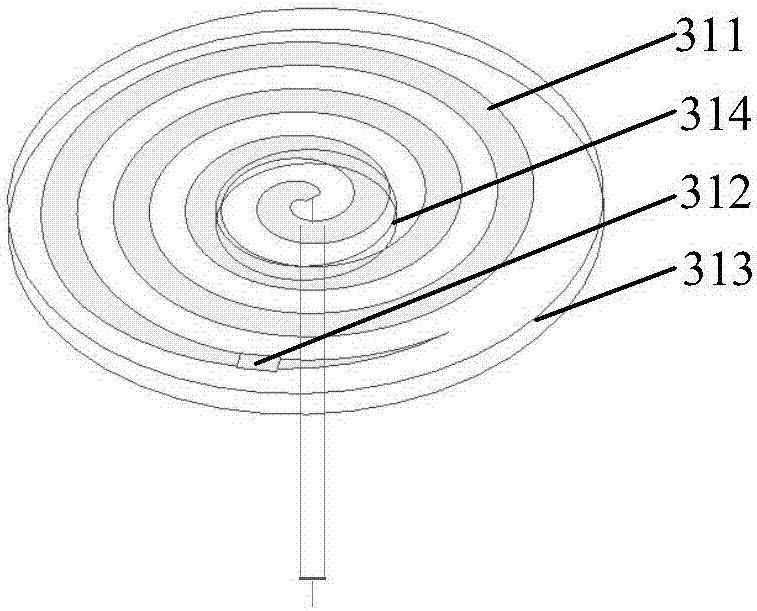

Device for generating multimodal orbital angular momentum of mechanical reconfigurable array antennas and method thereof

InactiveCN107331957AImplement reconfigurable featuresSimple structureRadiating elements structural formsDifferential interacting antenna combinationsCoaxial lineDielectric substrate

The invention provides a device for generating multimodal orbital angular momentum of mechanical reconfigurable array antennas and method thereof, and aims at realizing the mechanical reconfigurable characteristic of the generation device and generating the multimodal orbital angular momentum. The generation device comprises a feed network which is composed of a first dielectric substrate, a first metal ground plate and a microstrip power divider and array antennas formed by single-arm spiral antenna units which are arranged along a ring structure, wherein the single-arm spiral radiators can rotate around the lower coaxial line so as to realize the phase compensation characteristic of the multimodal orbital angular momentum. An electric signal is transmitted to each single-arm spiral radiator through the input end and all the output ends of the microstrip power divider and the coaxial line connected with all the output ends, and the single-arm spiral radiators rotate different angles along different directions to provide different amount of phase compensation to the electric signal to generate different modes of orbital angular momentum vortex beams so as to realize the mechanical reconfigurable characteristic. The device and the method can be used for information transmitting and receiving in the communication technology.

Owner:XIDIAN UNIV