Patents

Literature

41 results about "Arithmetic operators" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Numeric_std is a library package defined for VHDL. It provides arithmetic functions for vectors. Overrides of std_logic_vector are defined for signed and unsigned arithmetic. It defines numeric types and arithmetic functions for use with synthesis tools. Two numeric types are defined: UNSIGNED (represents UNSIGNED number in vector form) and SIGNED (represents a SIGNED number in vector form). The base element type is type STD_LOGIC. The leftmost bit is treated as the most significant bit. Signed vectors are represented in two's complement form. This package contains overloaded arithmetic operators on the SIGNED and UNSIGNED types. The package also contains useful type conversions functions.

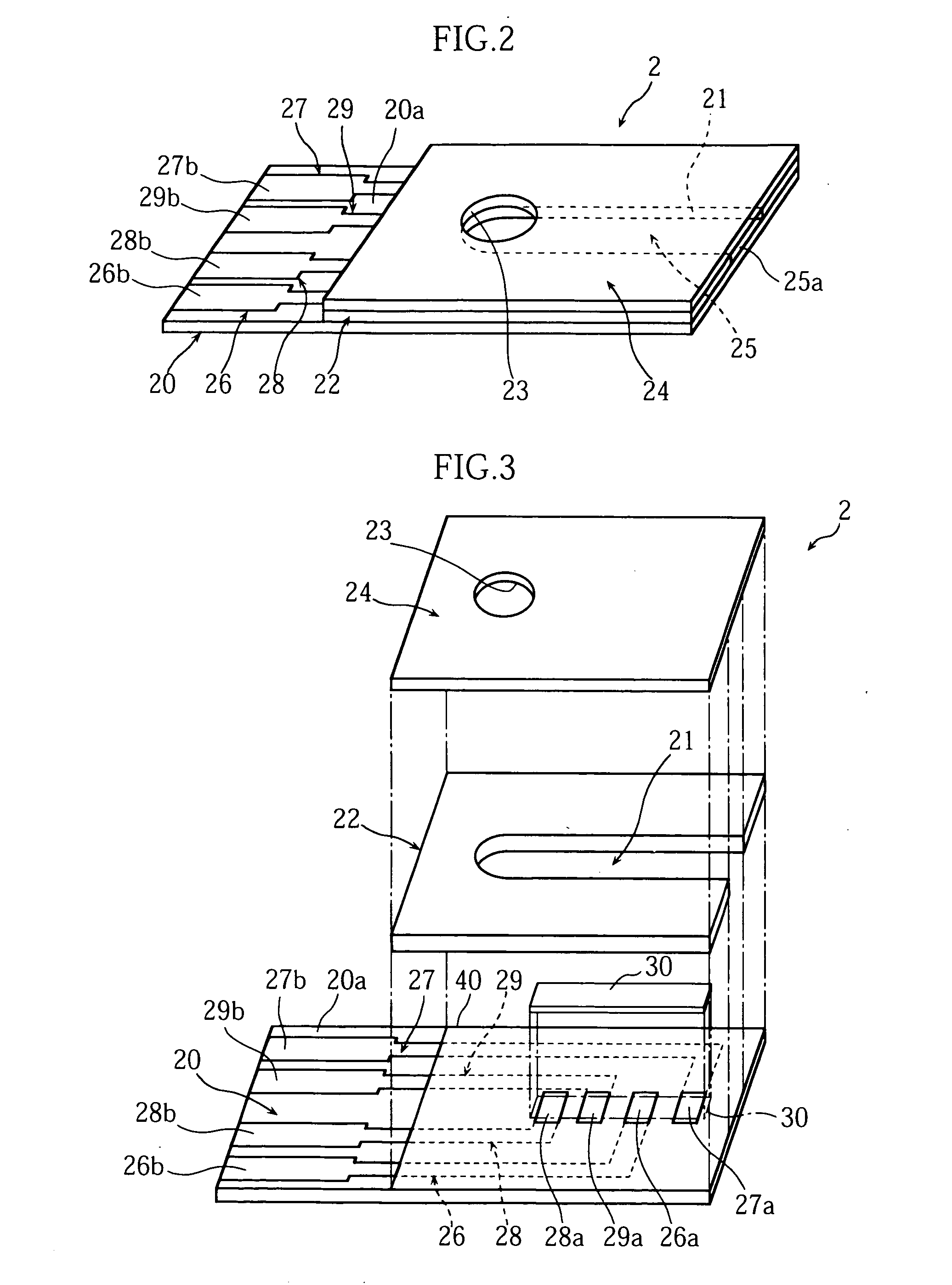

Microphone and sound amplification system

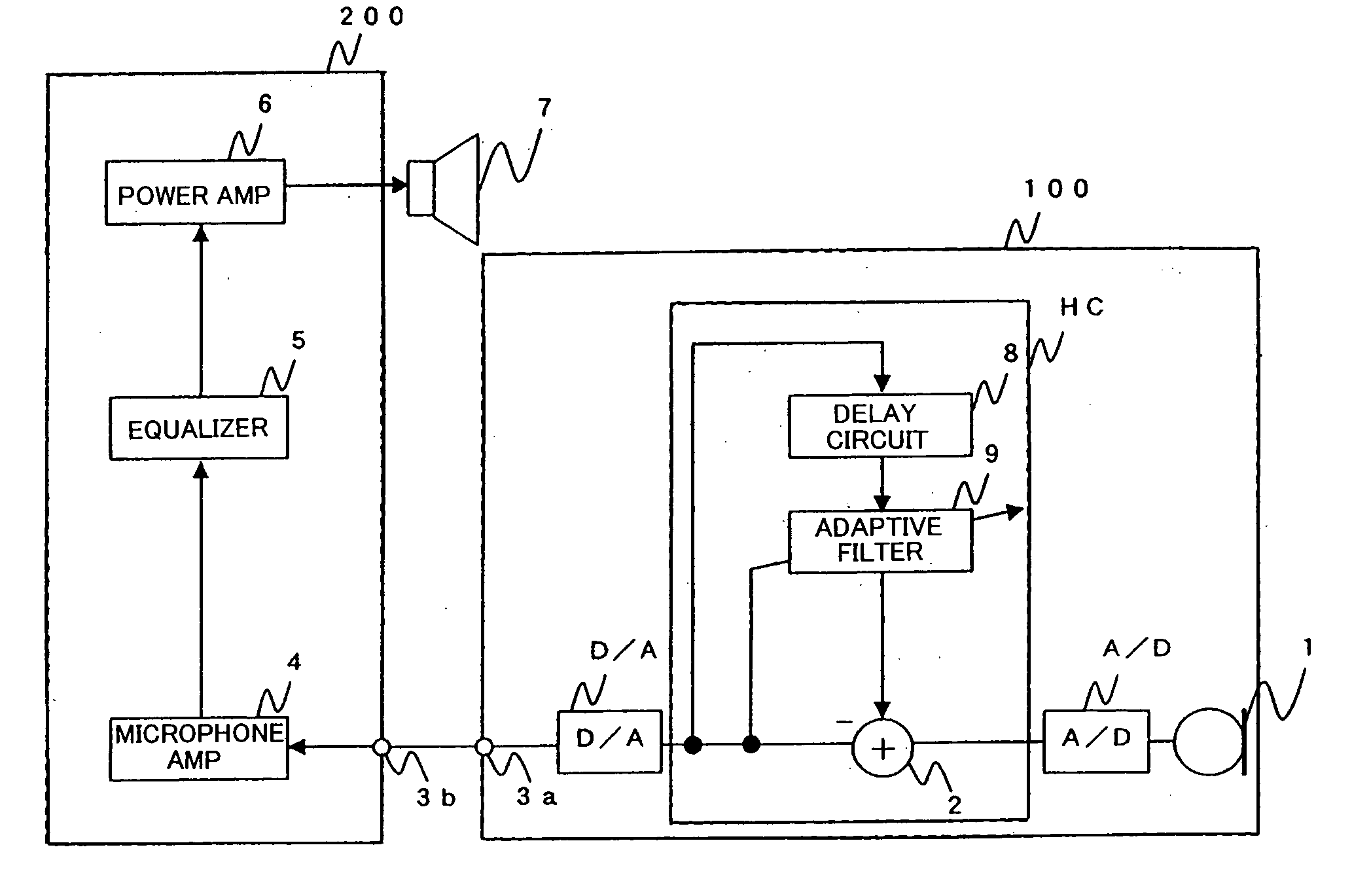

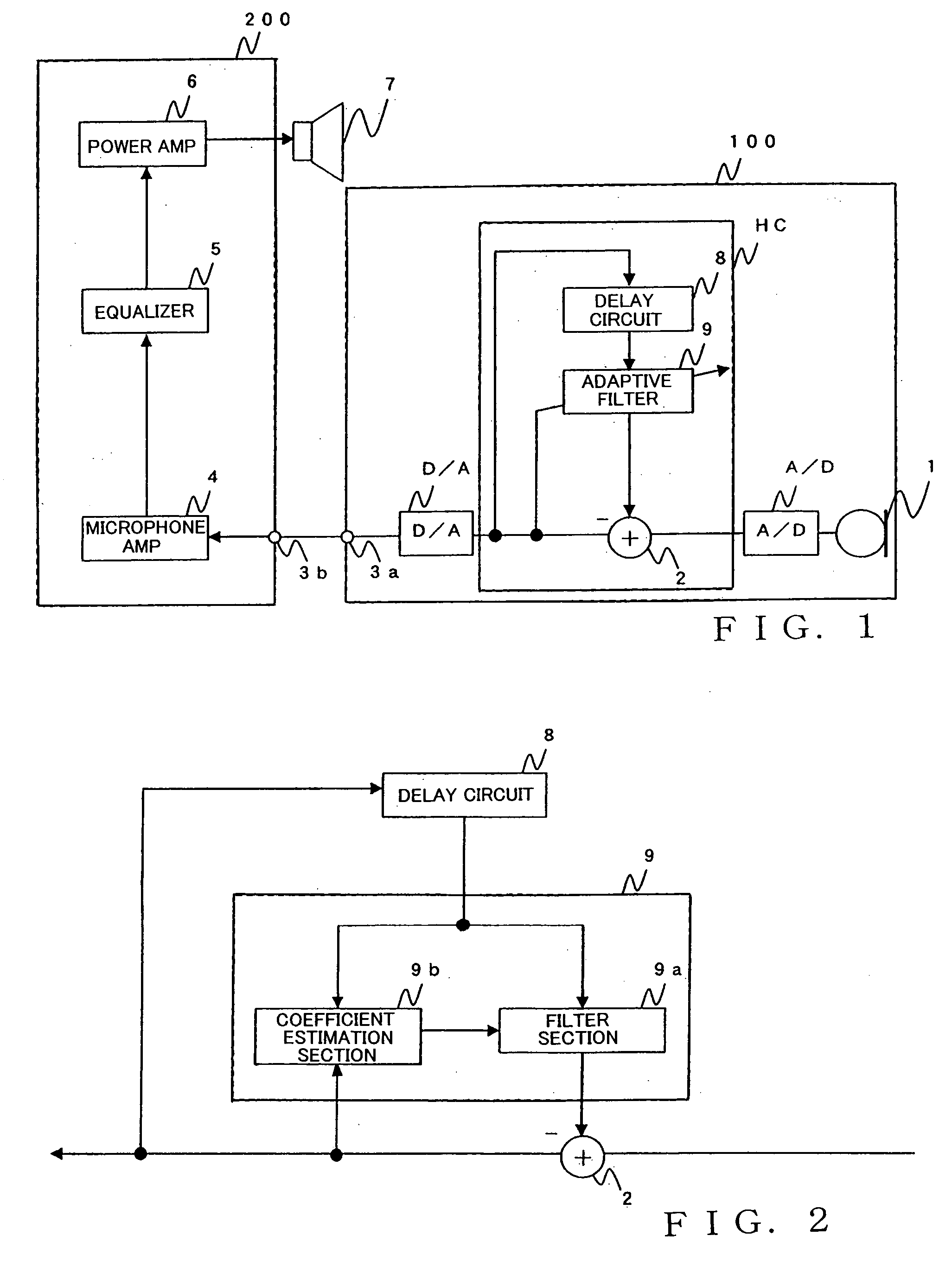

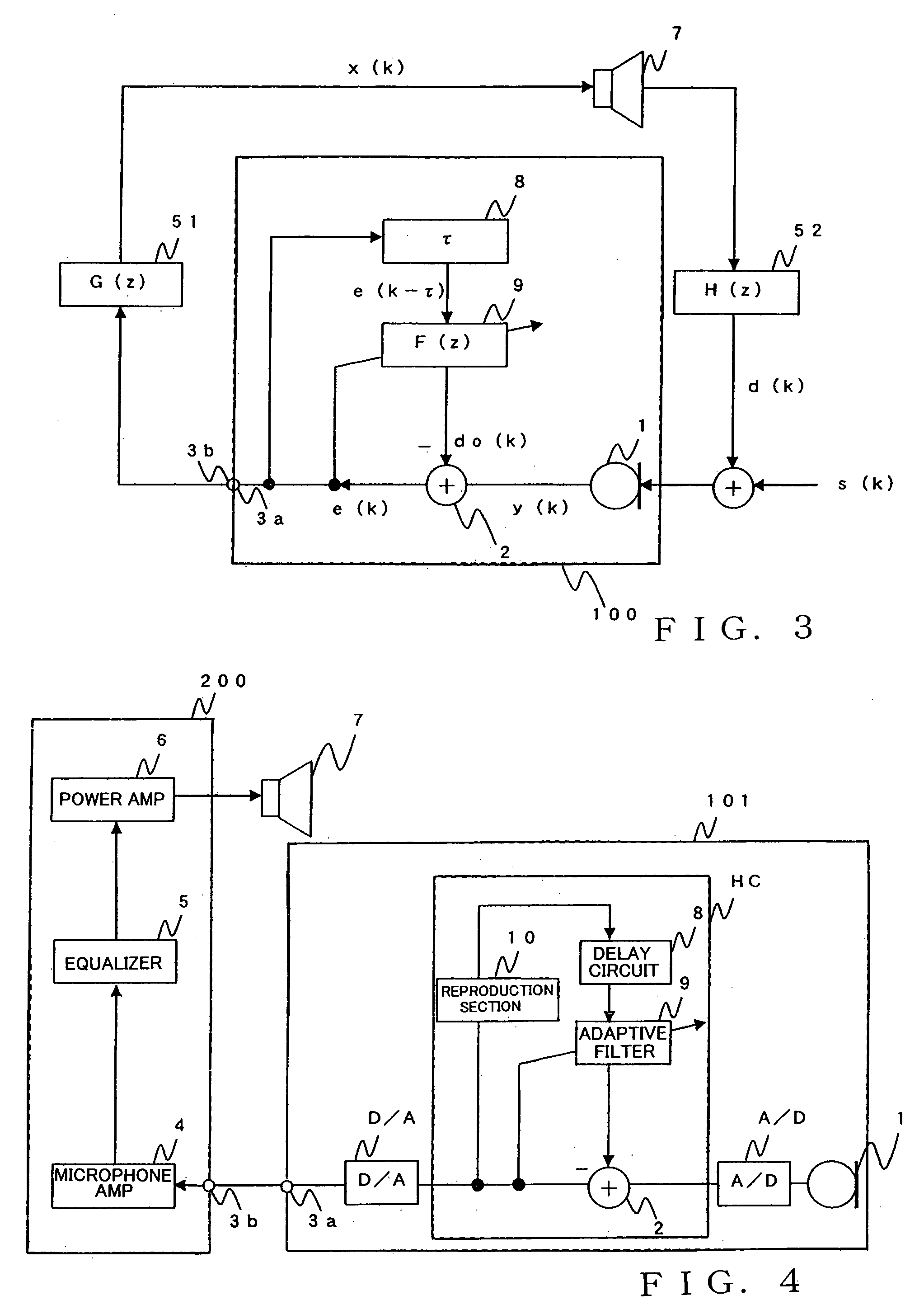

InactiveUS20060153400A1Reliably cancel howlingTransducer acoustic reaction preventionLine-transmissionAnalog feedbackAudio power amplifier

Microphone includes: a microphone element; a simulative feedback signal generation section that generates a simulative feedback signal simulating a feedback signal generated by a sound, produced via a speaker, returning the microphone element; and an arithmetic operator that subtracts the simulative feedback signal, generated by the simulative feedback signal generation section, from a sound signal collected by the microphone element, to thereby output the subtraction result as a residual signal. The residual signal output by the arithmetic operator is supplied to an amplifier device of the speaker as an output signal of the microphone. The simulative feedback signal generation section includes a delay circuit that delays the residual signal, output by the arithmetic operator, by a given time, and an adaptive filter that generates the simulative feedback signal by filtering a previous residual signal delayed by the delay circuit. The adaptive filter updates a filter coefficient on the basis of the previous residual signal delayed by the delay circuit and a current residual signal output by the arithmetic operator.

Owner:YAMAHA CORP

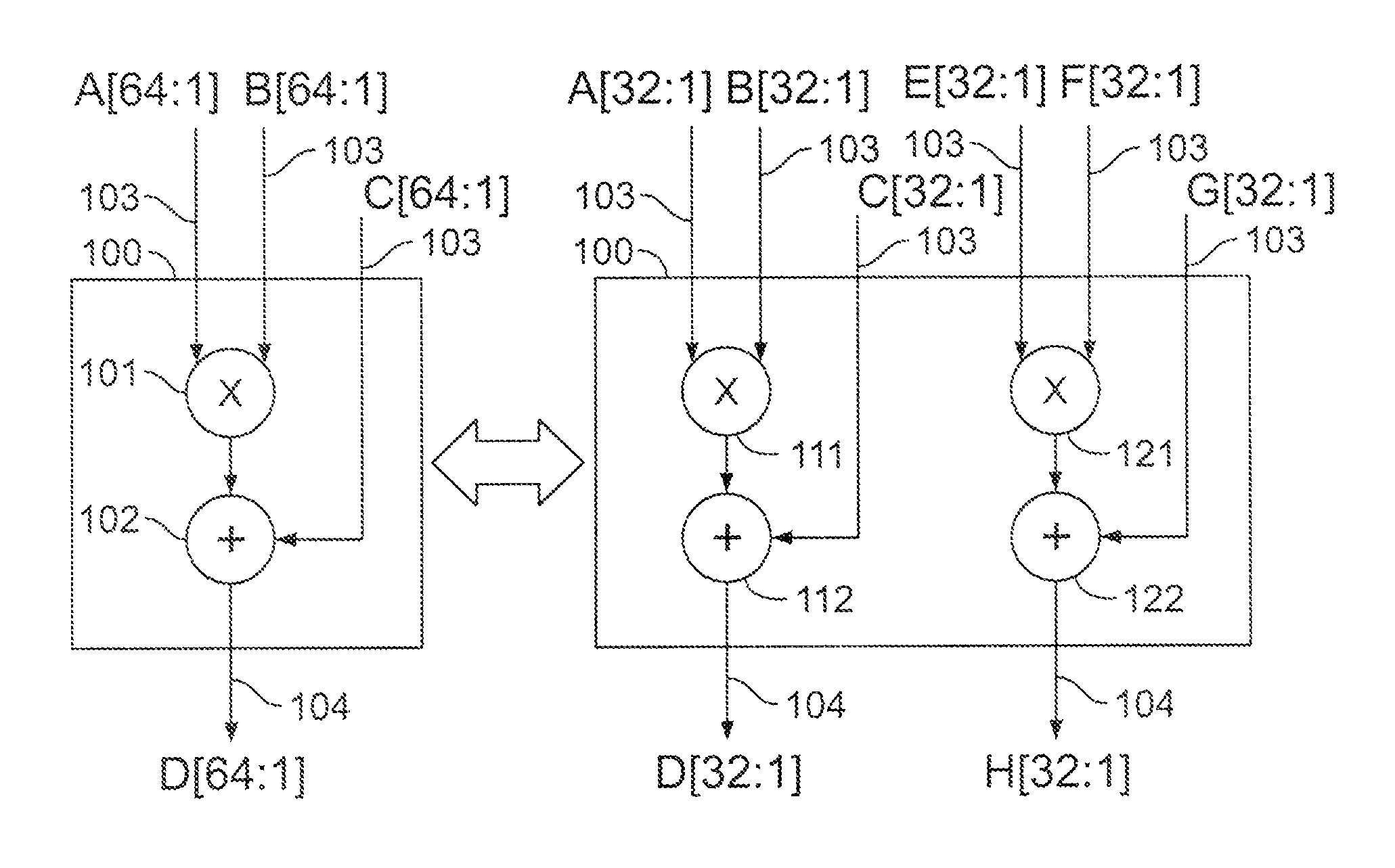

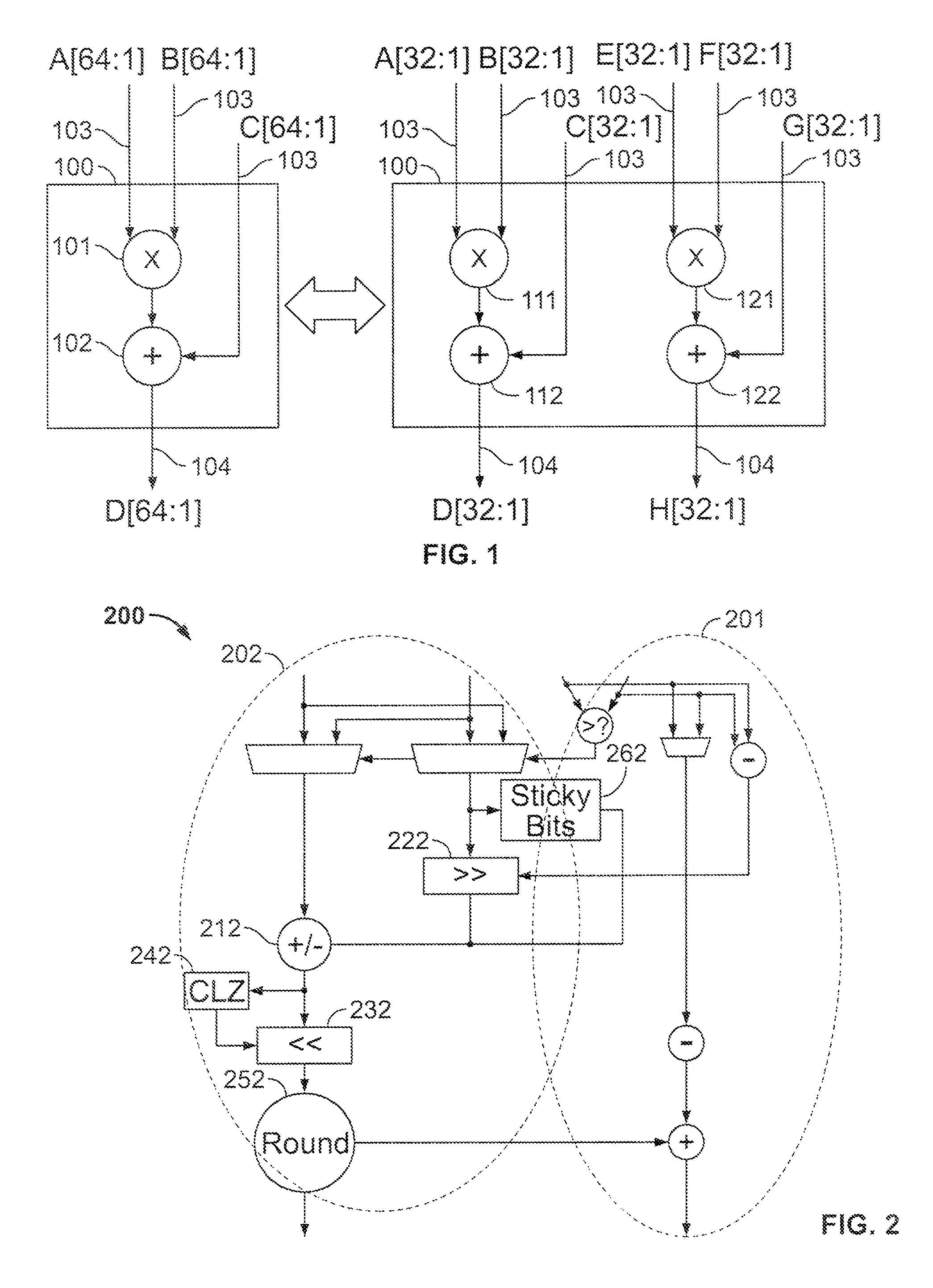

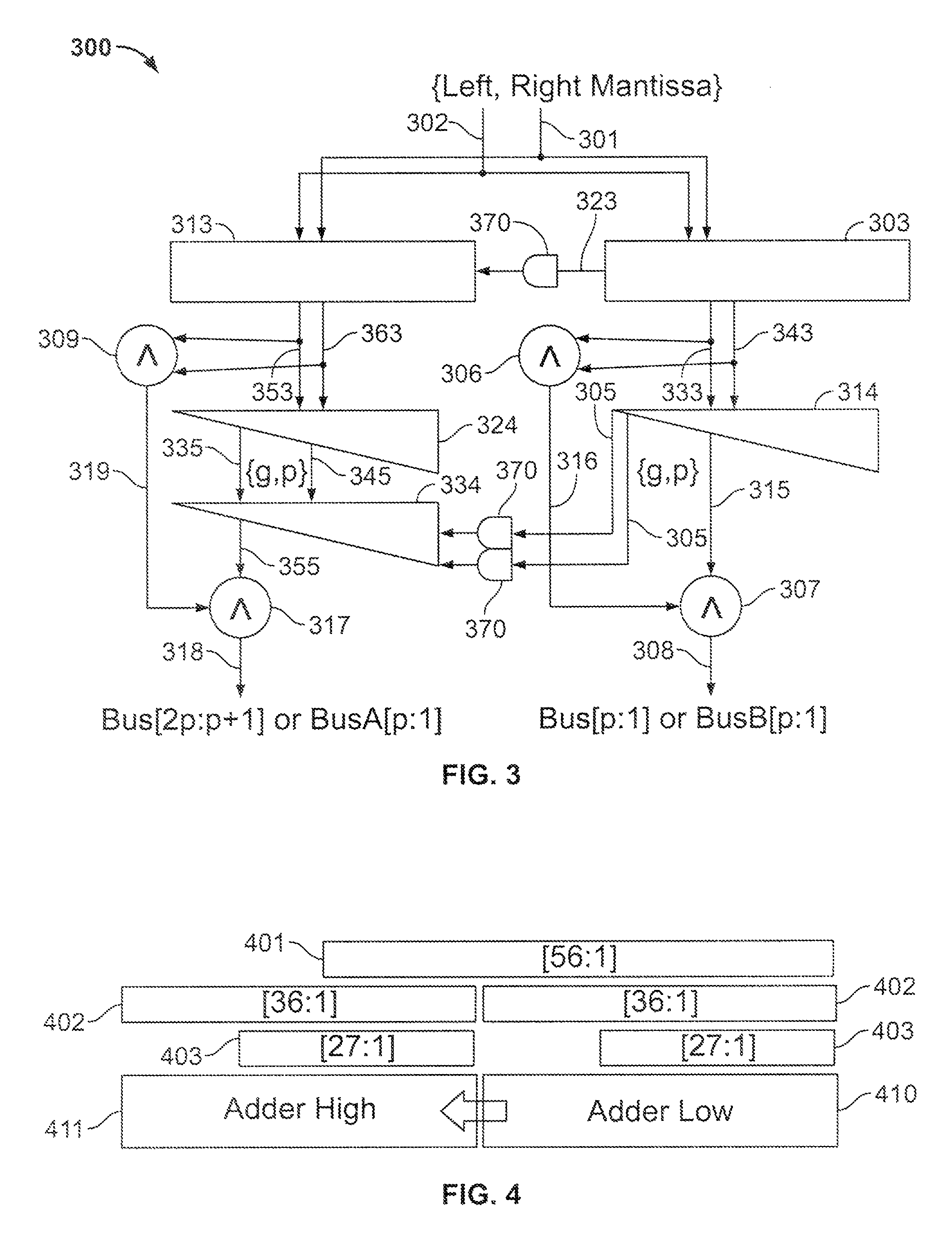

Multiple-precision processing block in a programmable integrated circuit device

A specialized processing block in a programmable integrated circuit device is configurable to perform floating-point arithmetic operations at selectable different precisions. The specialized processing block includes a plurality of different respective types of floating-point arithmetic operator structures. For each respective type of floating-point arithmetic operator structure, respective control circuitry for partitions the respective type of floating-point arithmetic operator structure to select between a first precision for which the respective type of floating-point arithmetic operator structure is not partitioned, and at least a second precision, less than the first precision, for which the respective type of floating-point arithmetic operator structure is partitioned into at least two smaller ones of the respective type of floating-point arithmetic operator structure.

Owner:ALTERA CORP

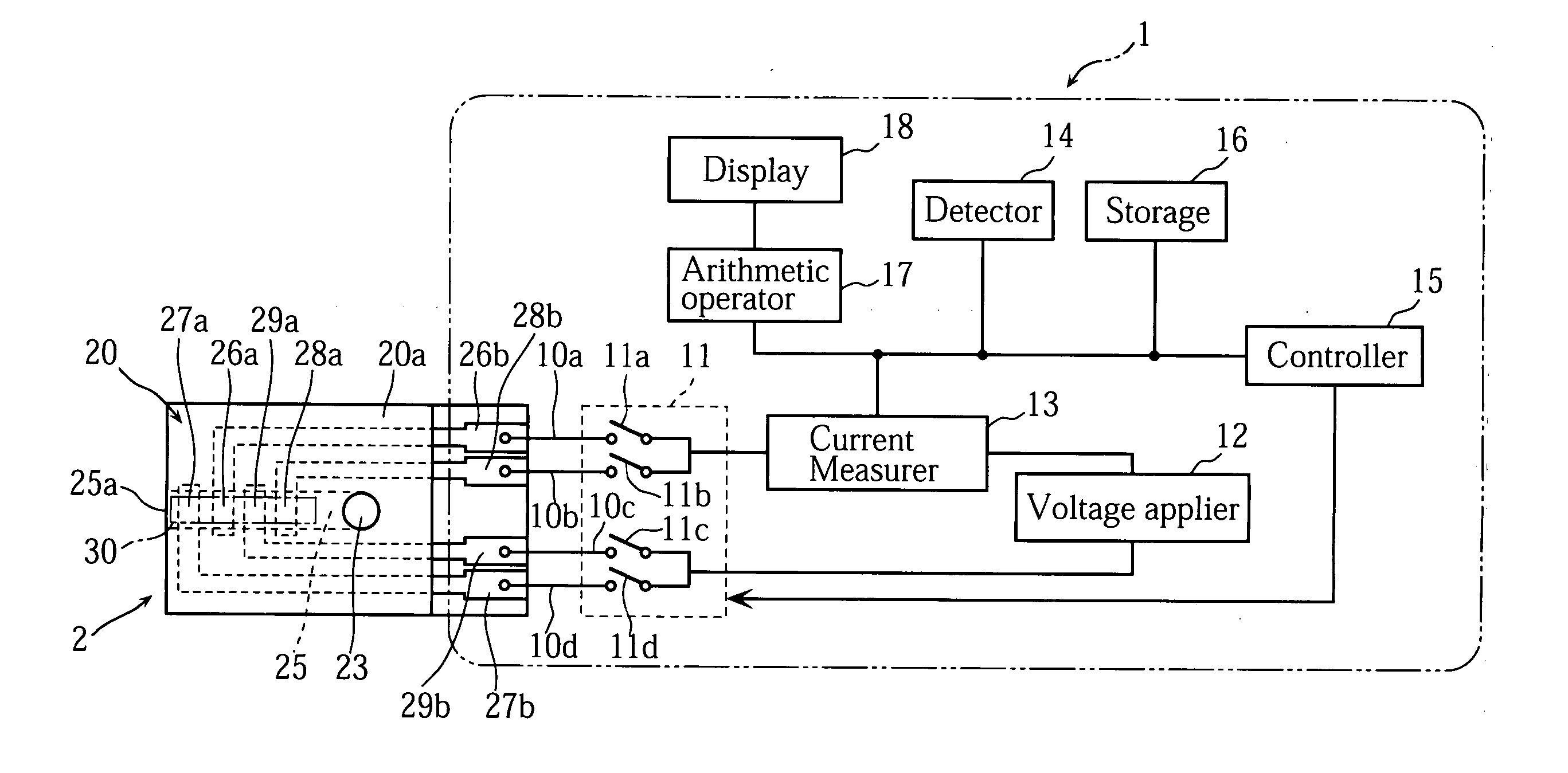

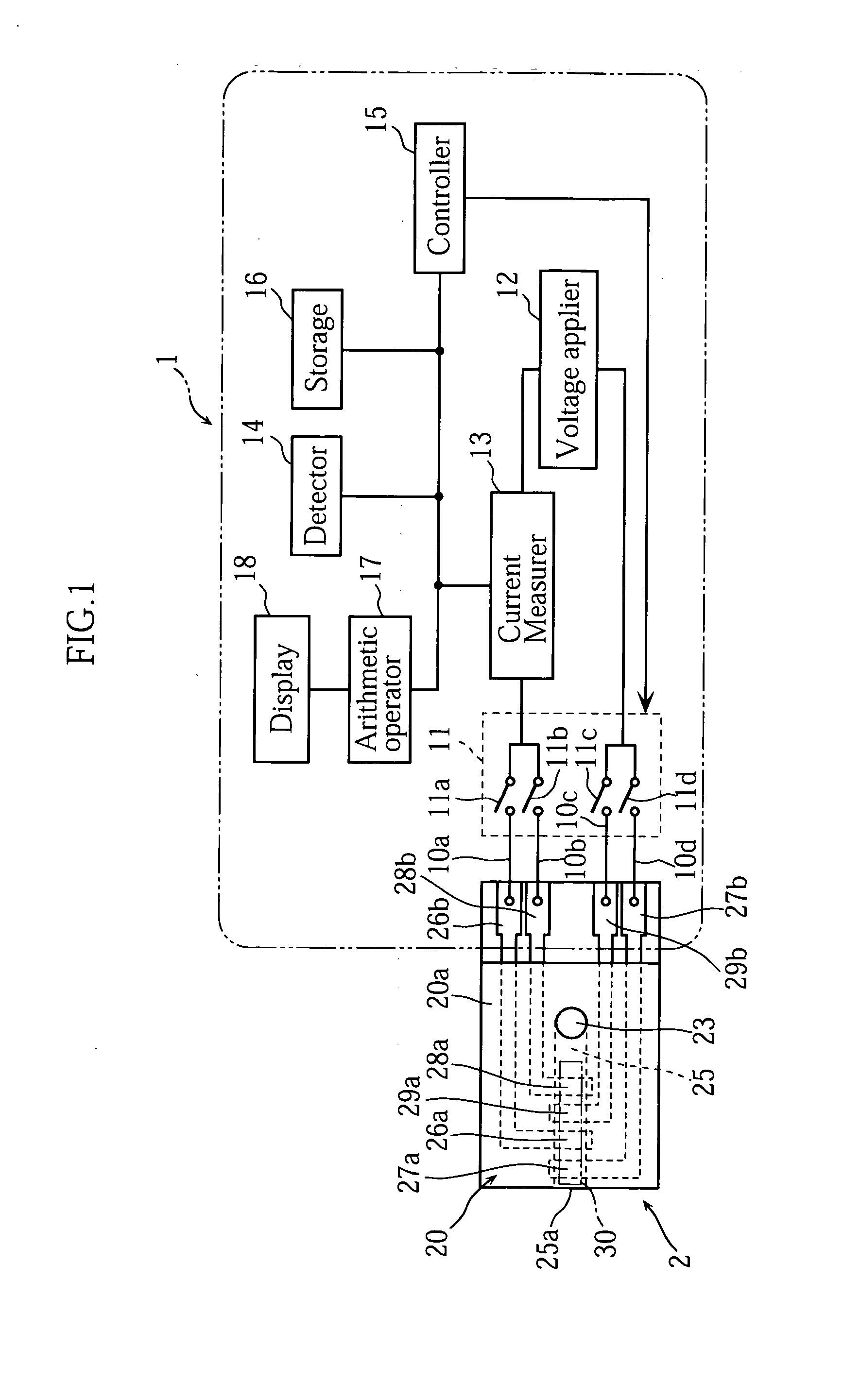

Sample analyzing method and sample analyzing device

ActiveUS20060224658A1Without sacrificing accuracy of analysisImprove accuracyMicrobiological testing/measurementVolume/mass flow measurementReaction fieldEngineering

This invention relates to a technique for analyzing a sample. A sample analyzer (1) provided by the invention includes: a voltage applier (12) for applying a voltage to a reaction field which includes a sample; a response measurer (13) for measurement of a response to the voltage applied to the reaction field; a selector (11) for selecting a first voltage application state for measurement of a first response for use in calculation necessary for analyzing the sample or a second voltage application state for measurement of a second response for use in determining whether or not the reaction field has been supplied with a target amount of the sample; an arithmetic operator (17) for calculation necessary for analyzing the sample based on the first response; a determiner (17) for determination, based on the second response, on whether or not the reaction field has been supplied with the target amount of sample; and a controller (15) which makes the selector select the second voltage application state after making the selector select the first voltage application state.

Owner:ARKRAY INC

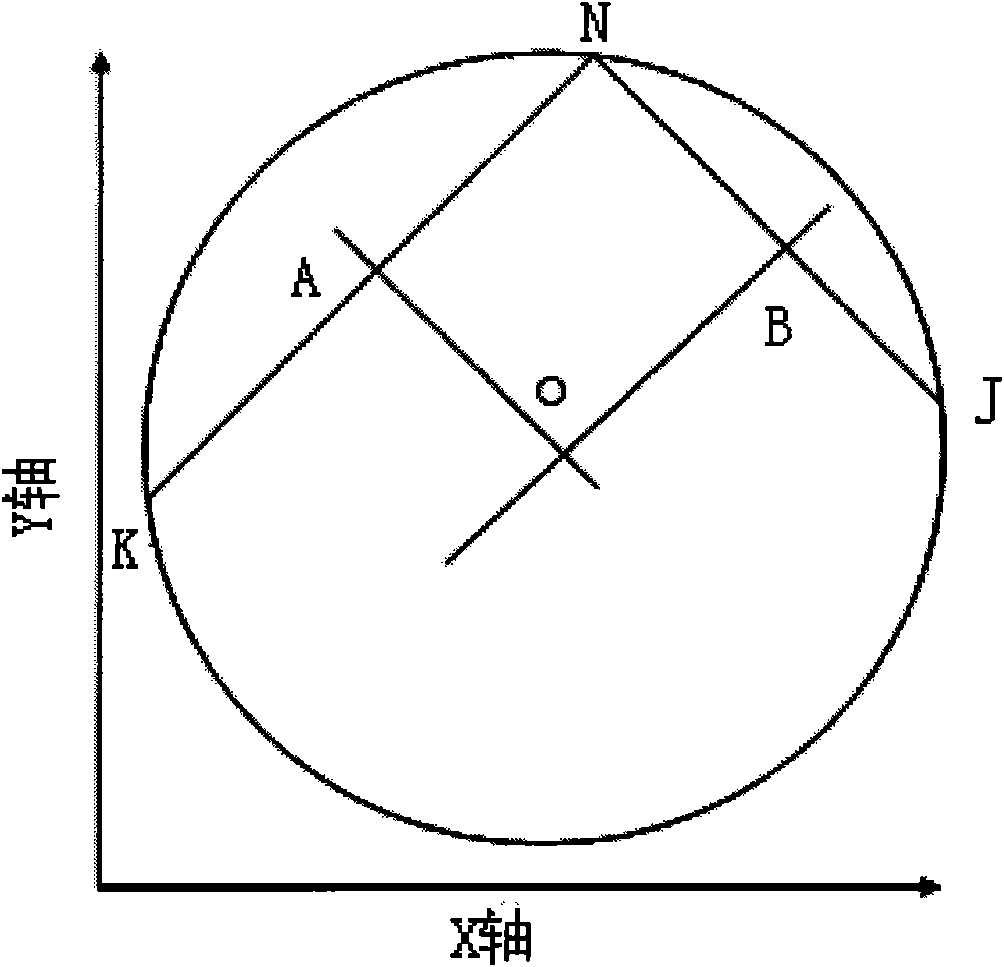

Method for quickly positioning circular mark in PCB visual detection

ActiveCN102034101AFast operationHigh precision requirementsCharacter and pattern recognitionHough transformErrors and residuals

The invention discloses a round sub-pixel detection algorithm based on point Hough transform and Legendre moments, and provides a method for quickly positioning a circular mark in polymerase chain reaction (PCR) visual detection. The method comprises the following steps of: performing edge detection and Hough transform to acquire a circular mark pixel-level reference value by using a Canny arithmetic operator; filtering off noise points in edge points by using the circular mark pixel-level reference value; analyzing a sub-pixel edge positioning method based on Legendre orthogonal moments, and an error; evaluating sub-pixels of the edge points from which the noise points are filtered off by using the Legendre orthogonal moments and an error method; and finally fitting the edge points by a fast least square method to acquire accurate circle center positioning parameter and radius parameter of a round. By the method, the characteristic of high speed of point Hough transform operation is kept; and the method has the characteristics of high positioning accuracy, high noise resistance, accuracy, high speed and robustness and meets the requirements of high accuracy and real-time property in the PCB visual detection.

Owner:GUANGDONG UNIV OF TECH

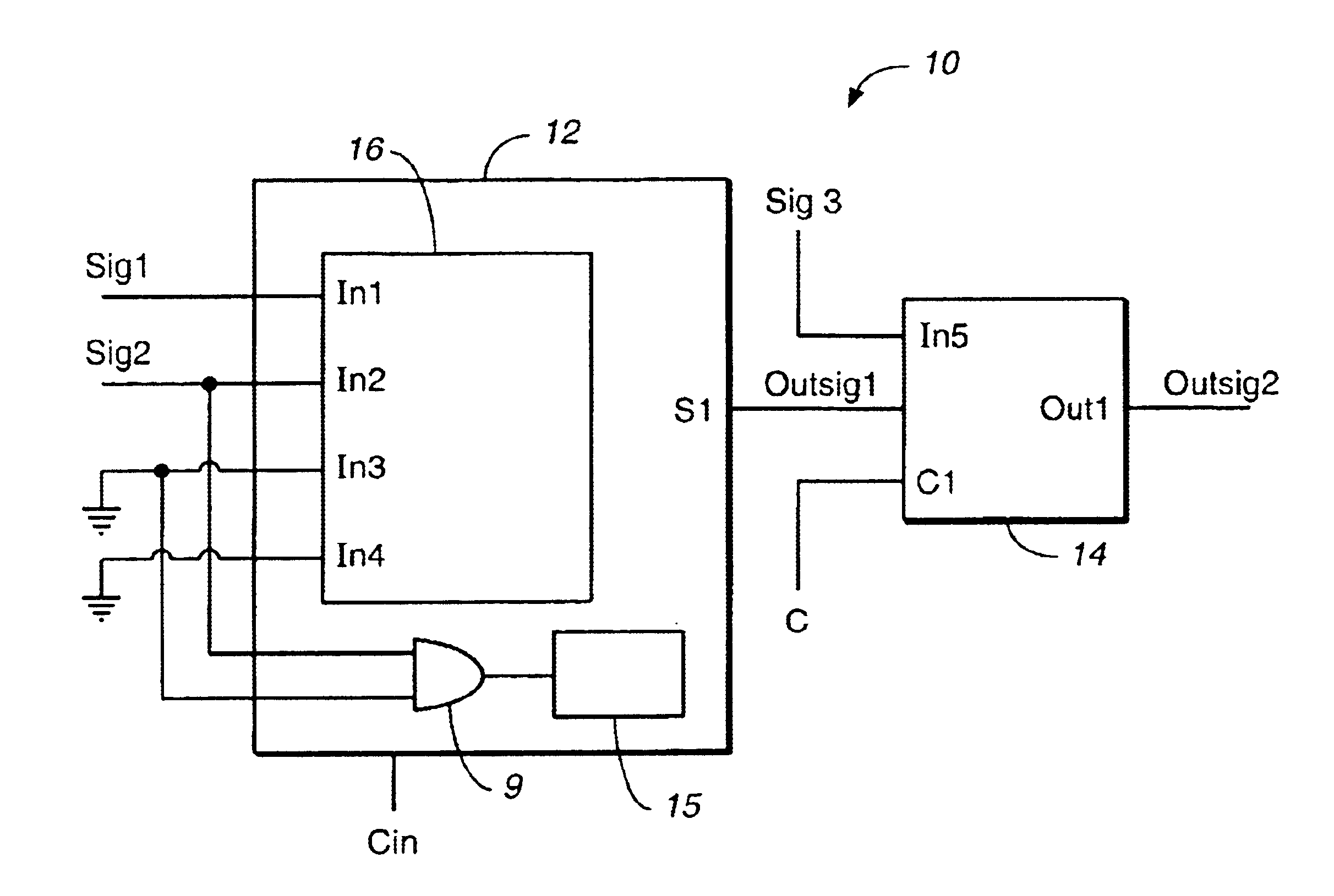

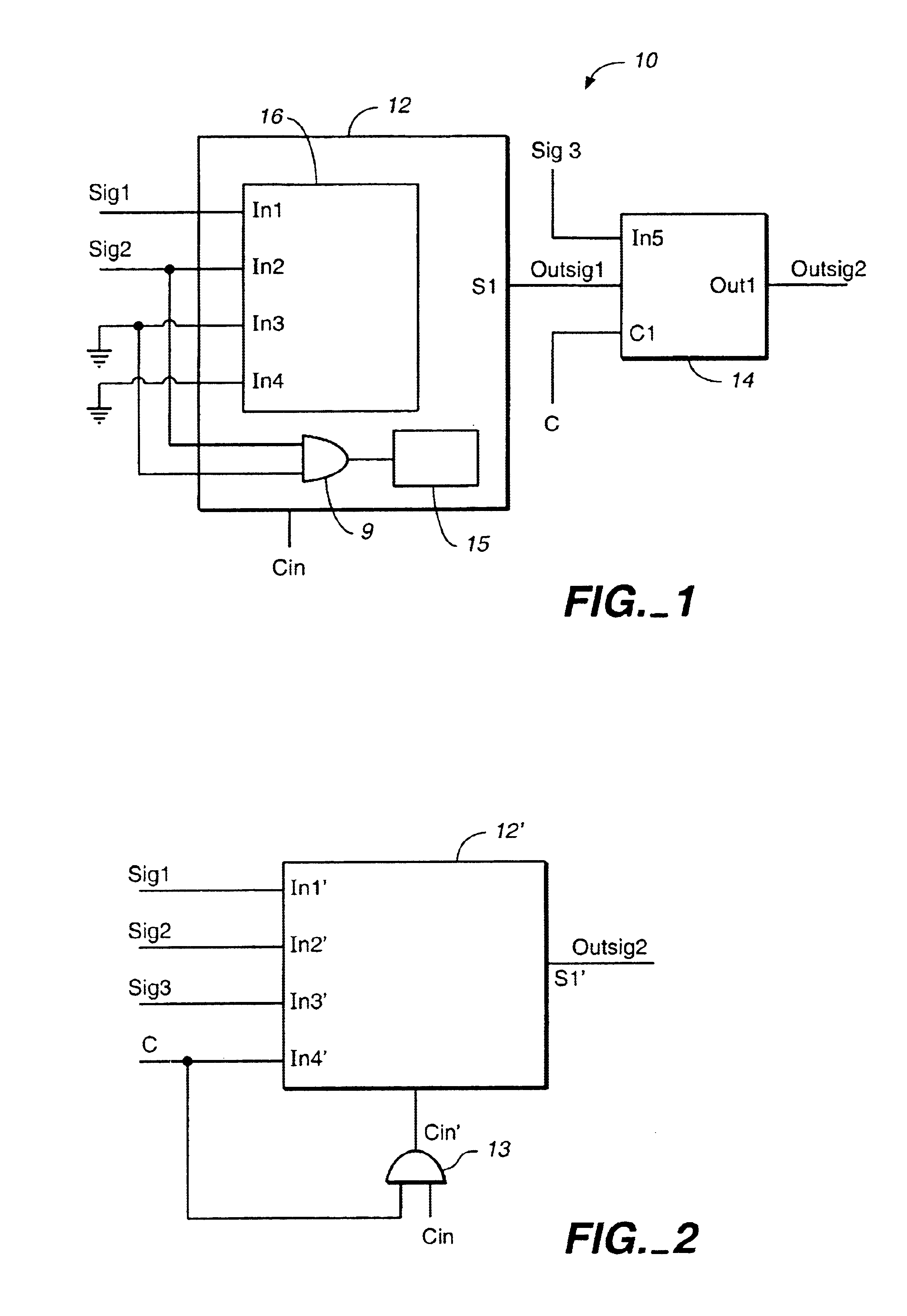

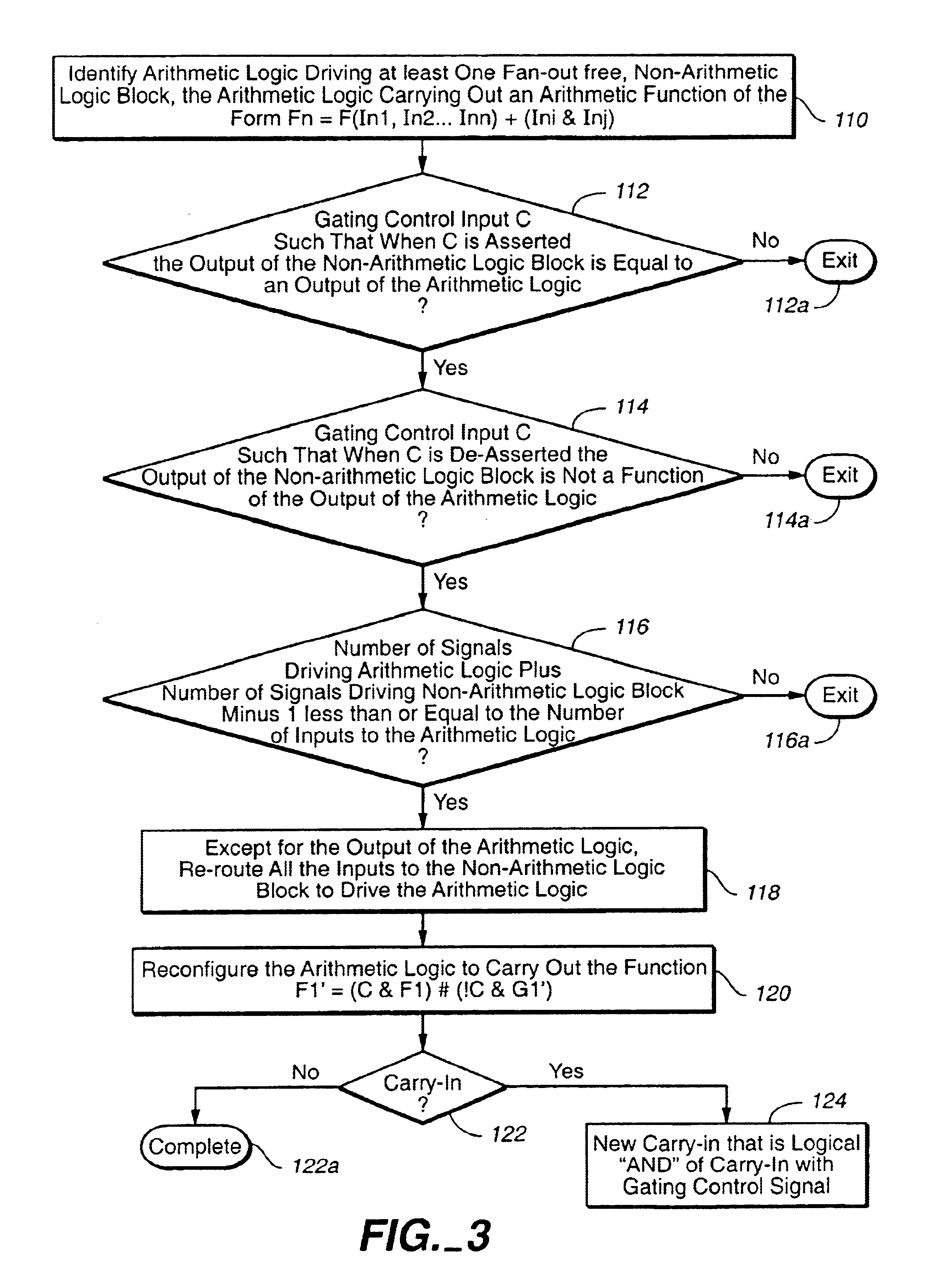

Automated implementation of non-arithmetic operators in an arithmetic logic cell

InactiveUS6873181B1Special data processing applicationsLogic circuits using elementary logic circuit componentsProgramming languageArithmetic logic unit

Disclosed is a method of freeing up a non-arithmetic logic block by configuring an LE driving the non-arithmetic logic block to carry out the non-arithmetic logic function of the non-arithmetic logic block. Appropriately configured LEs are identified and the LEs are reconfigured to incorporate or “push back” the non-arithmetic logic into the LE, thus advantageously freeing up the non-arithmetic logic block and allowing it to be used for logic functions driven by other LEs.

Owner:ALTERA CORP

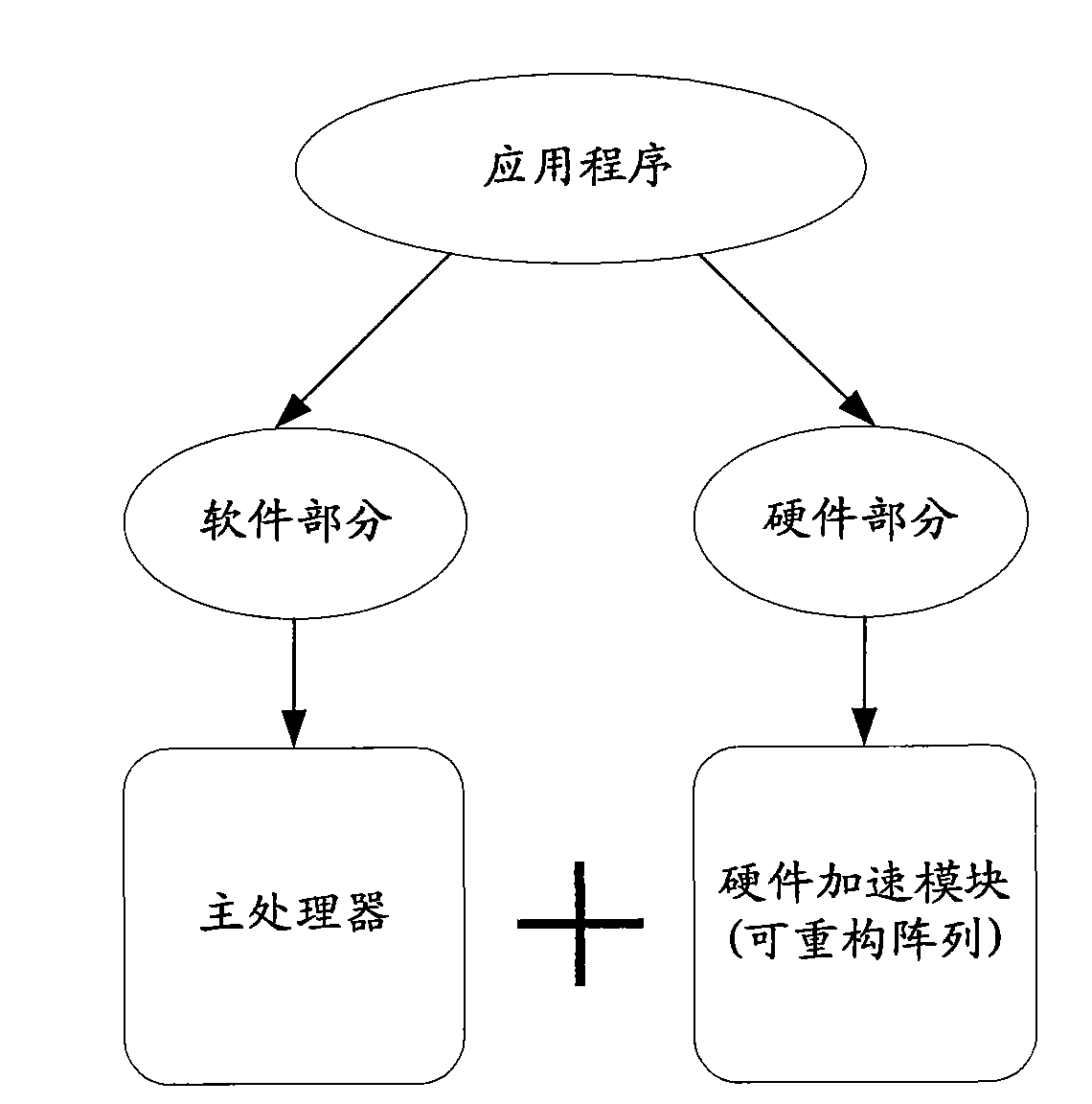

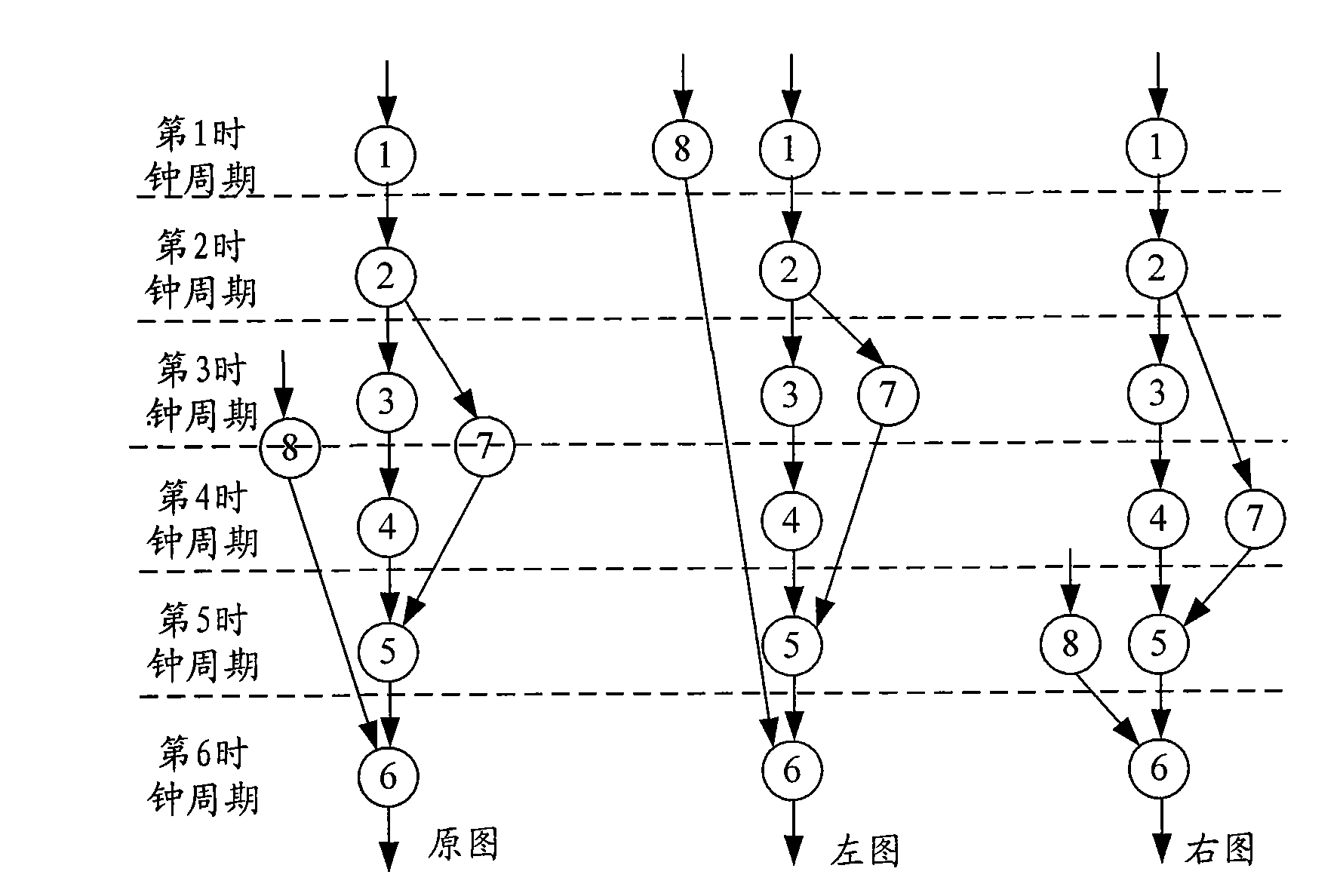

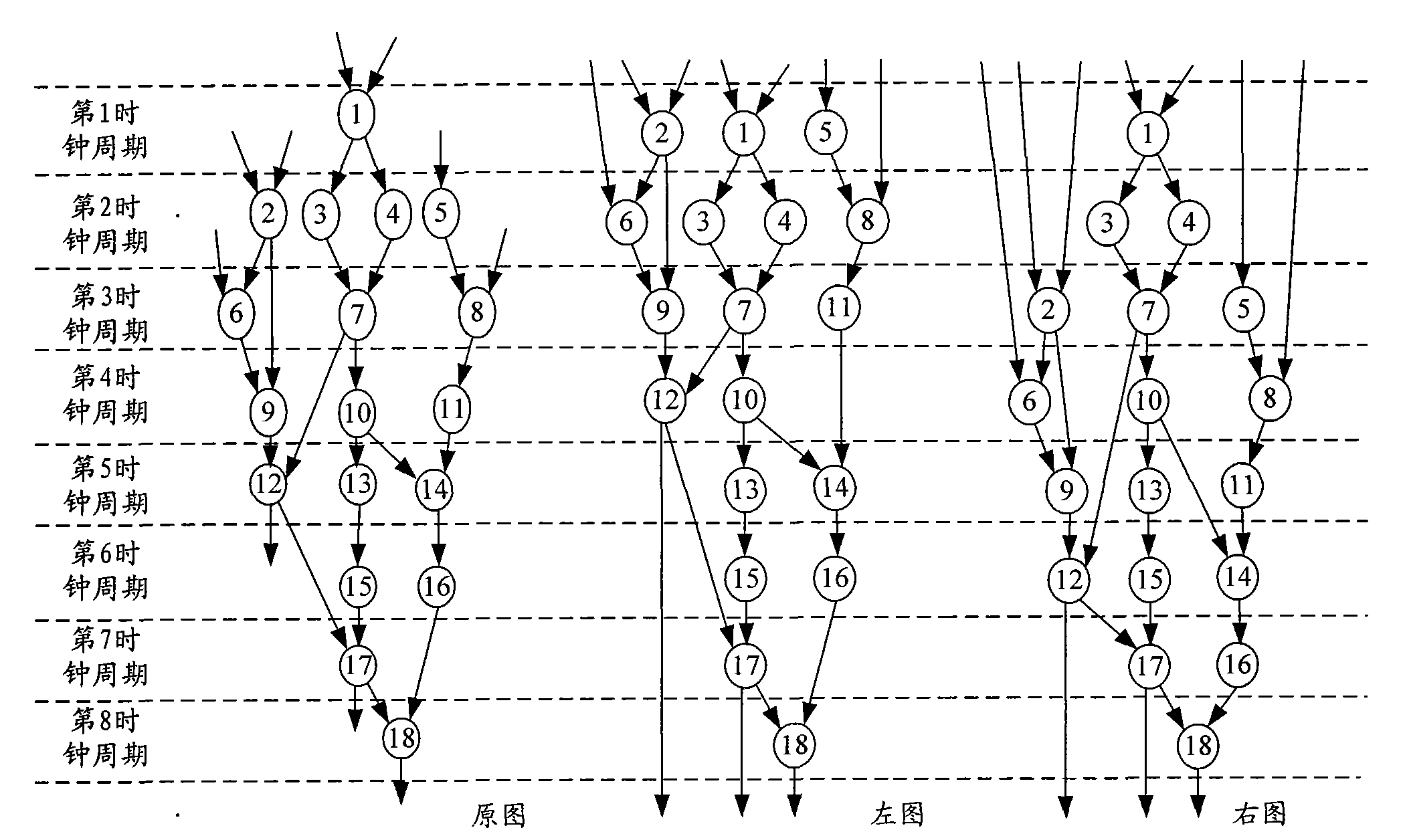

Method for dividing cycle task by means of software and hardware and device thereof

The invention discloses a method for dividing a cycle task by means of software and hardware and a device thereof, belonging to the field of an embedded system. When the number of nodes of data stream currently executed by a reconfigurable array is larger than the scale of the reconfigurable array, the method comprises the following steps: adjusting the nodes of the data stream currently executed by the reconfigurable array by means of arithmetic operators; according to the adjusting result of the arithmetic operators, obtaining the free degree of the input nodes; obtaining the output number of the input nodes; obtaining the input node with highest free degree and least output numbers according to the obtained free degree of the input nodes and the obtained output number of the input nodes; and dividing the obtained input nodes to a main processor. The method enlarges the scale of a cycle body which can be executed by a reconfigurable processor, plays the characteristic that the reconfigurable array is good at executing the cycle task, reduces the executing time of a whole application program, and meets the requirement in practical application.

Owner:SHENZHEN PANGO MICROSYST CO LTD

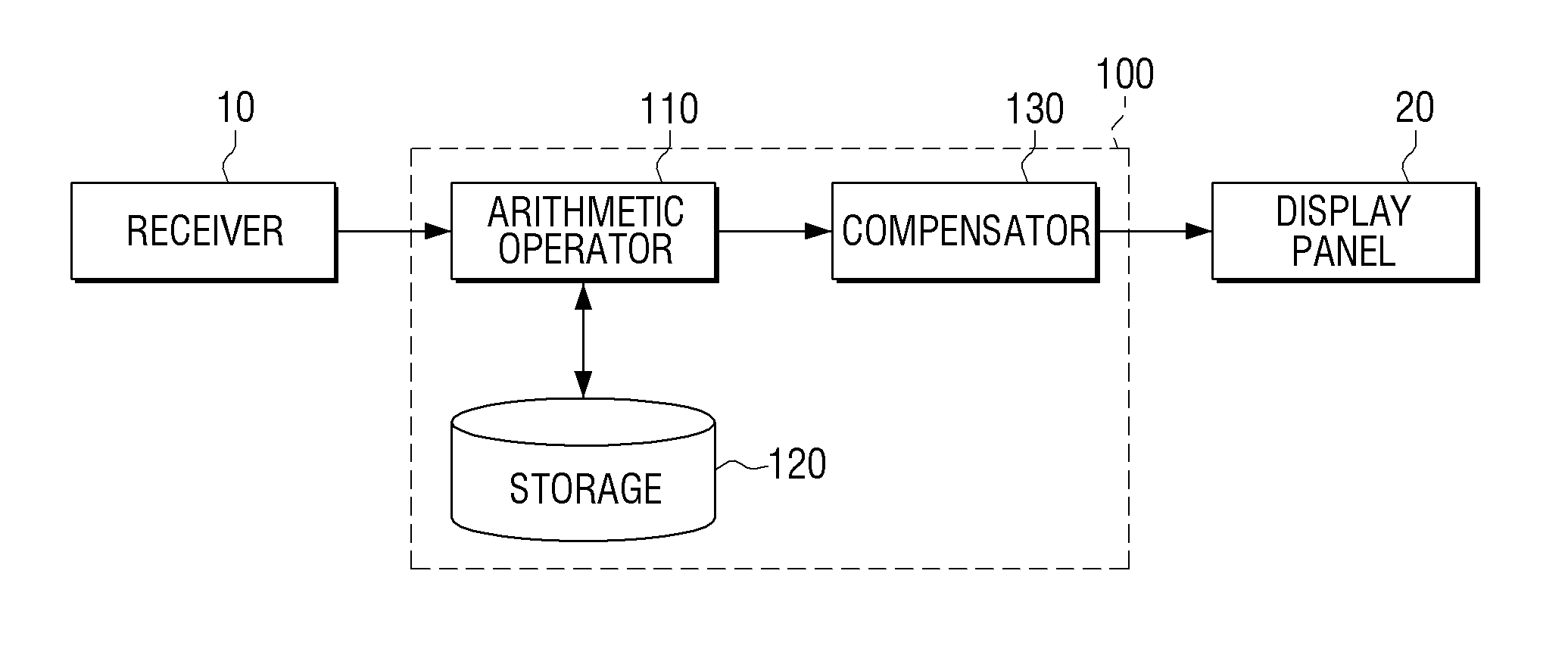

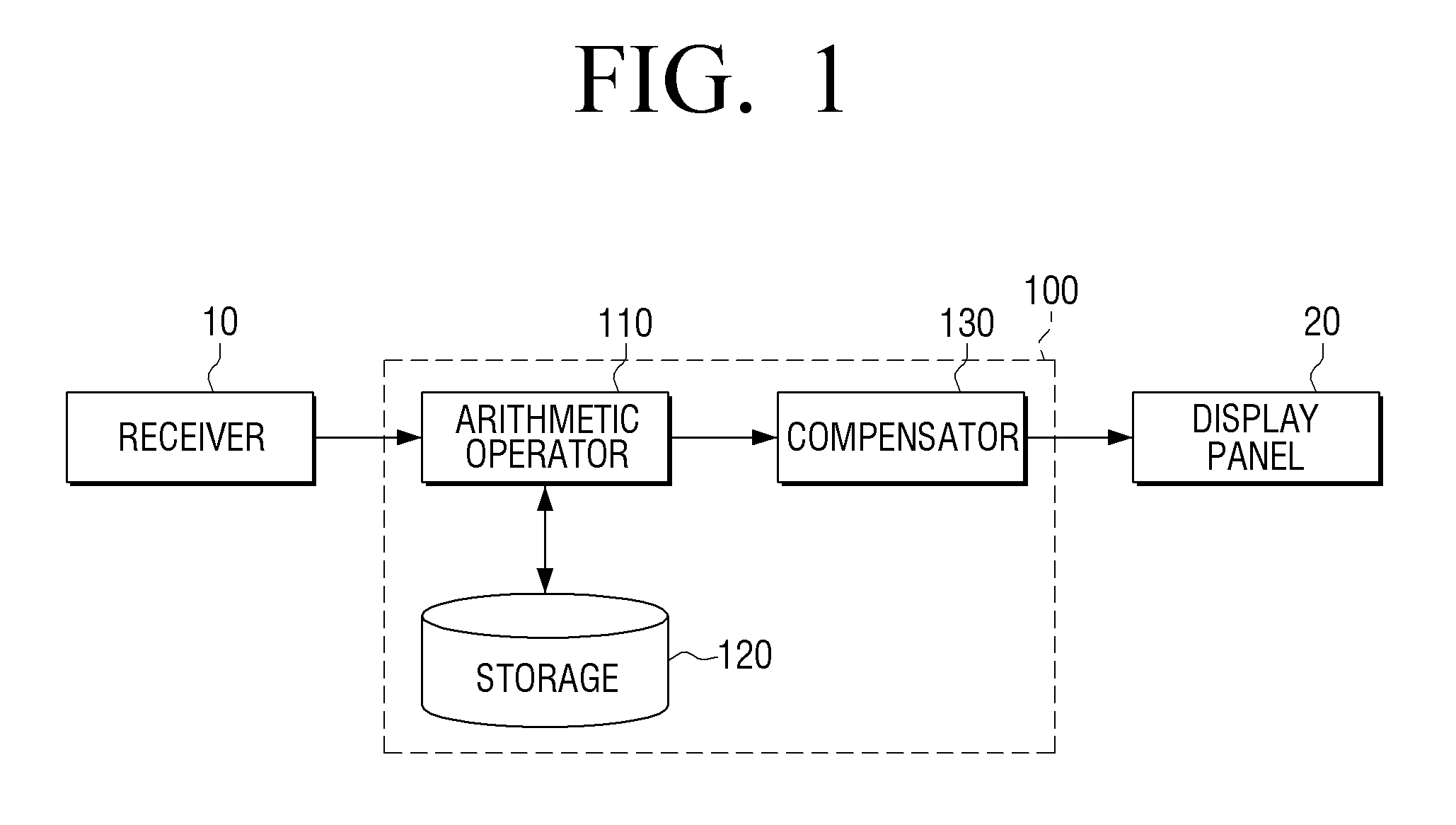

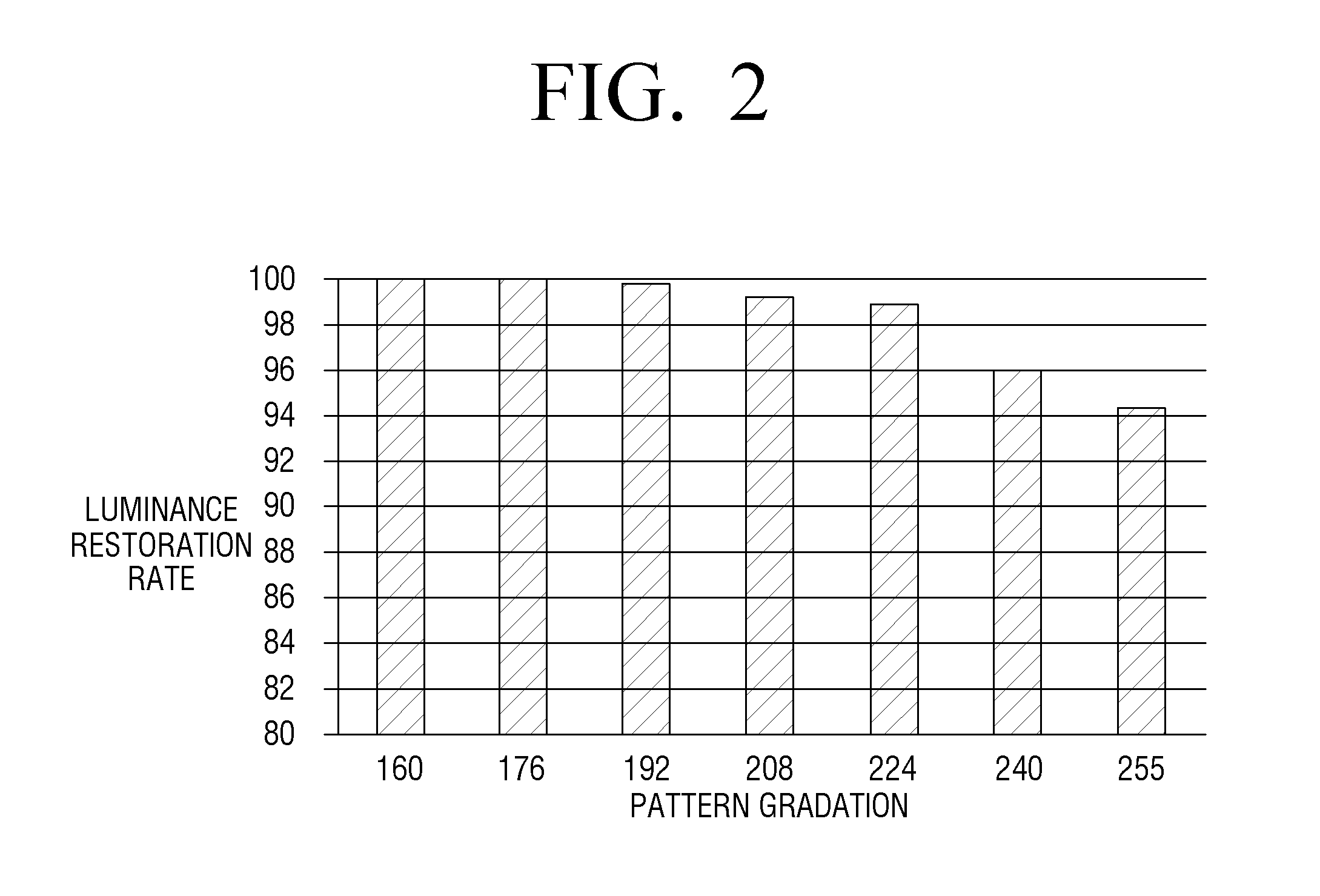

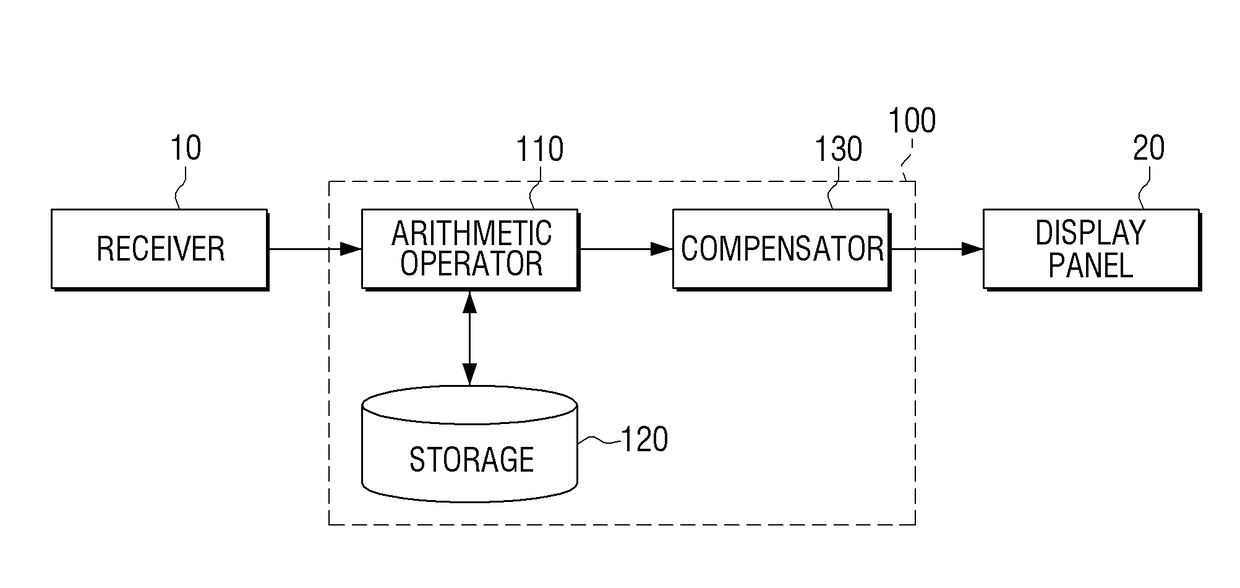

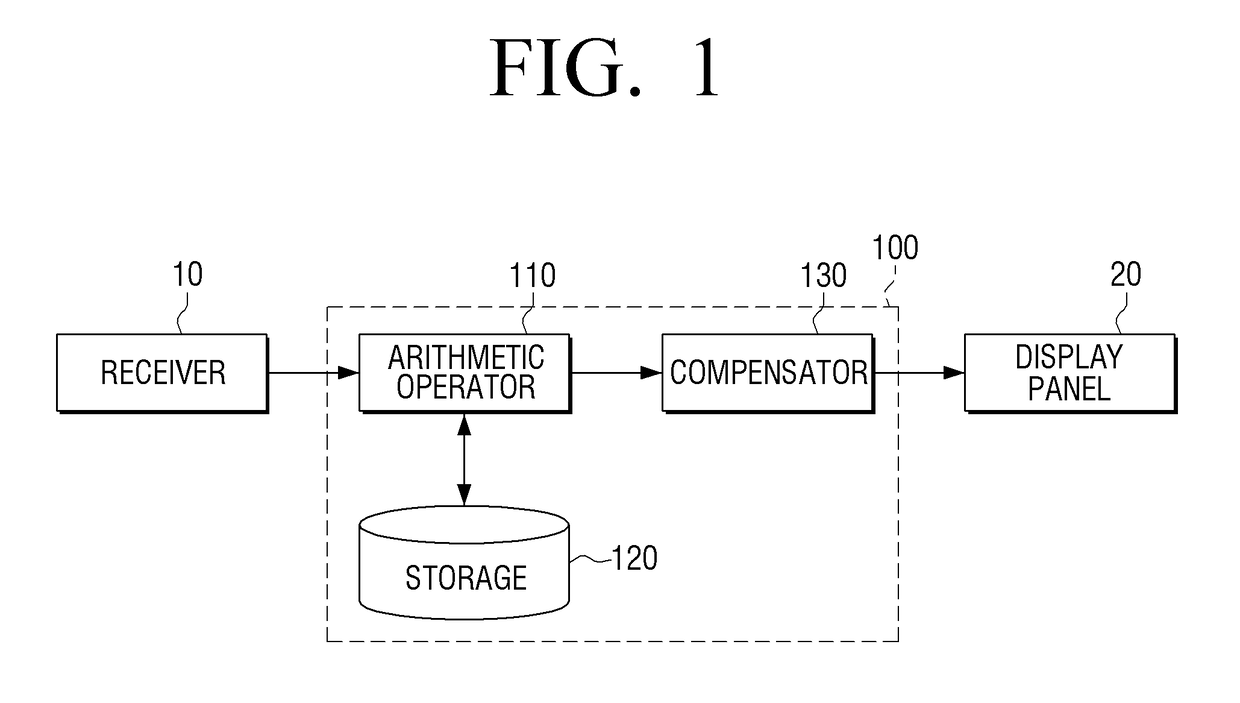

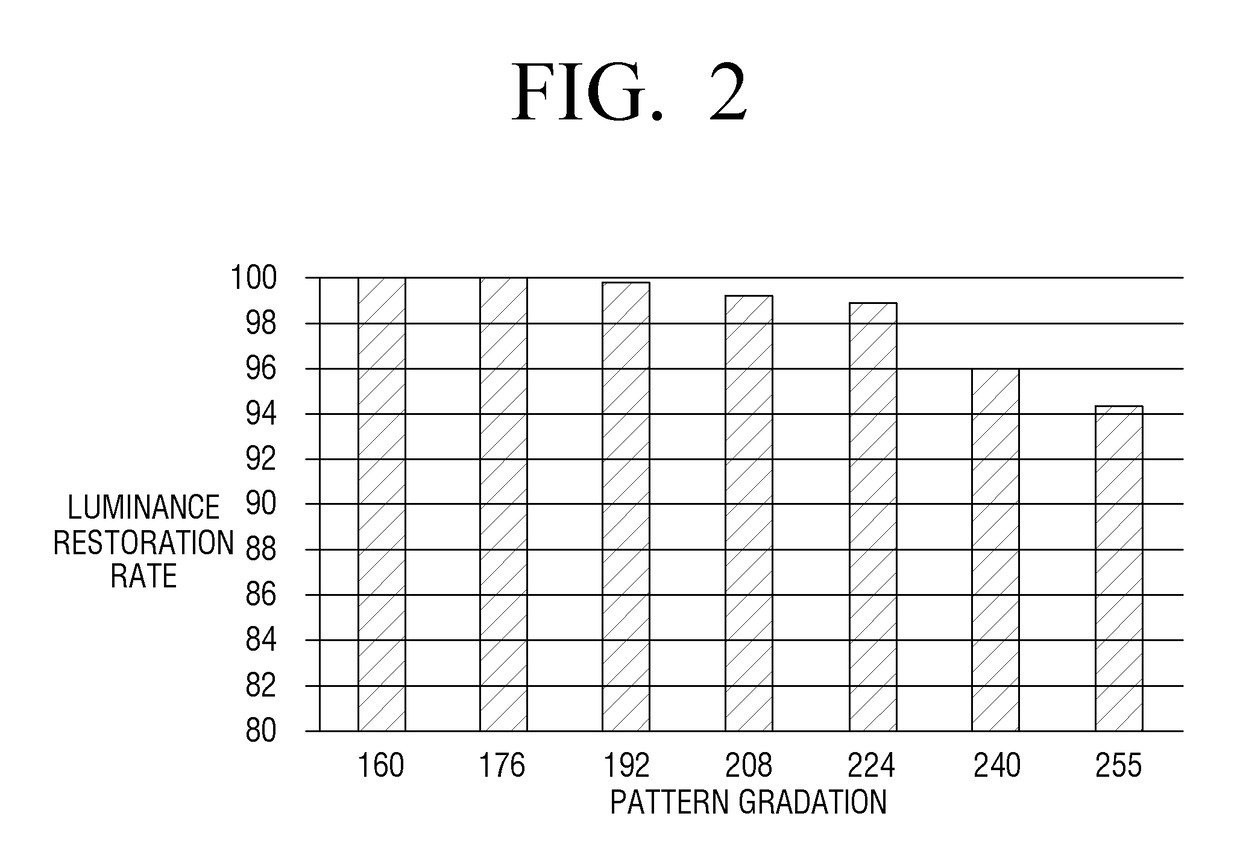

Display device and method thereof

ActiveUS20150103108A1Extend your lifeImprove efficiencyCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceAfterimage

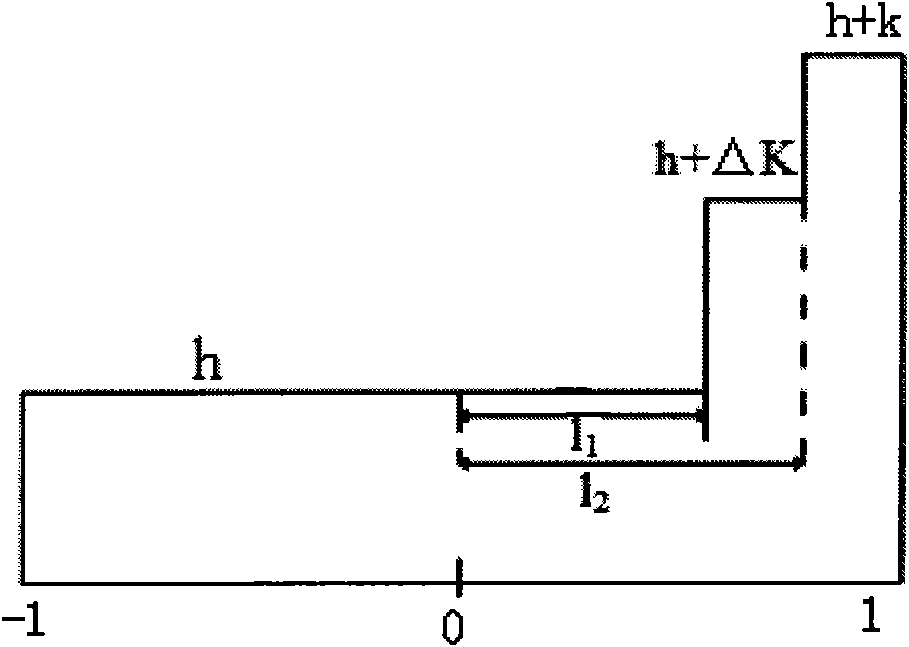

A display apparatus includes: a display panel configured to display an image frame; an arithmetic operator configured to divide the image frame into blocks, calculate a pixel gradation value of the pixel blocks, and accumulate the calculated pixel gradation values; and a compensator configured to locally reduce a luminance of a corresponding pixel block, of which a respective accumulated pixel gradation value exceeds a threshold value of among the plurality of pixel blocks, and to compensate for a luminance difference between the corresponding pixel block, for which the luminance has been reduced, and surrounding pixel blocks. Accordingly, it is possible to effectively remove an afterimage.

Owner:SAMSUNG ELECTRONICS CO LTD

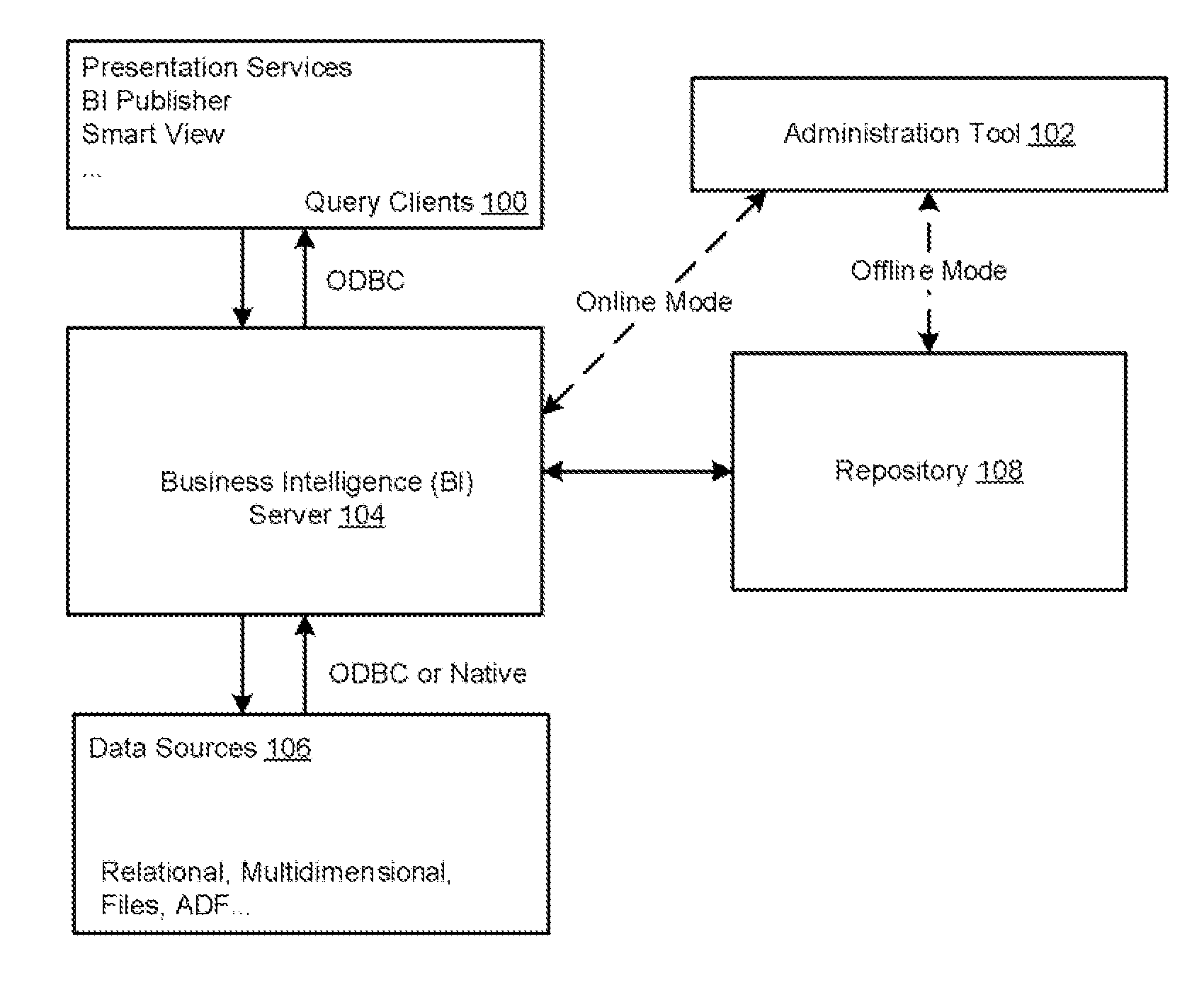

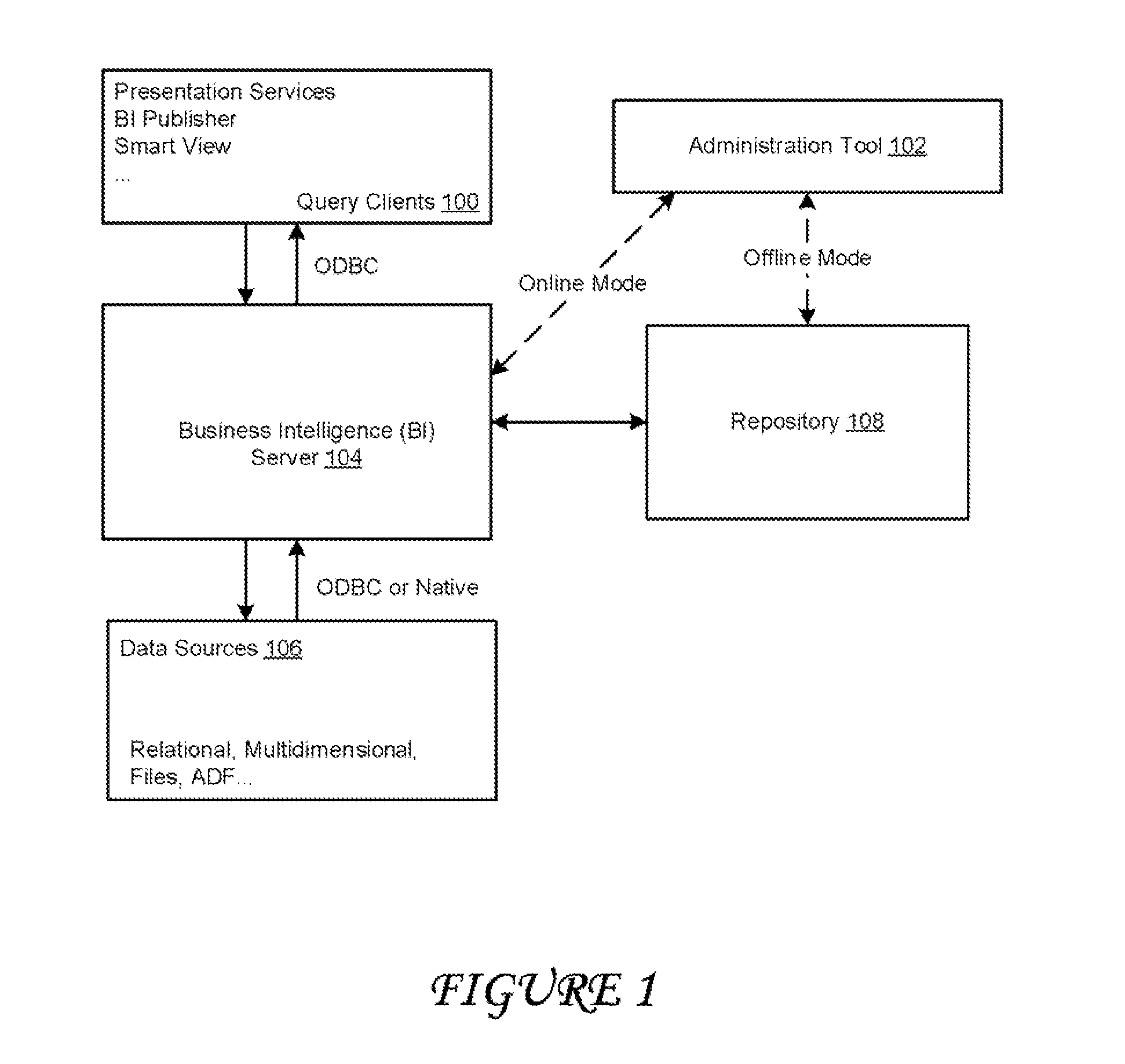

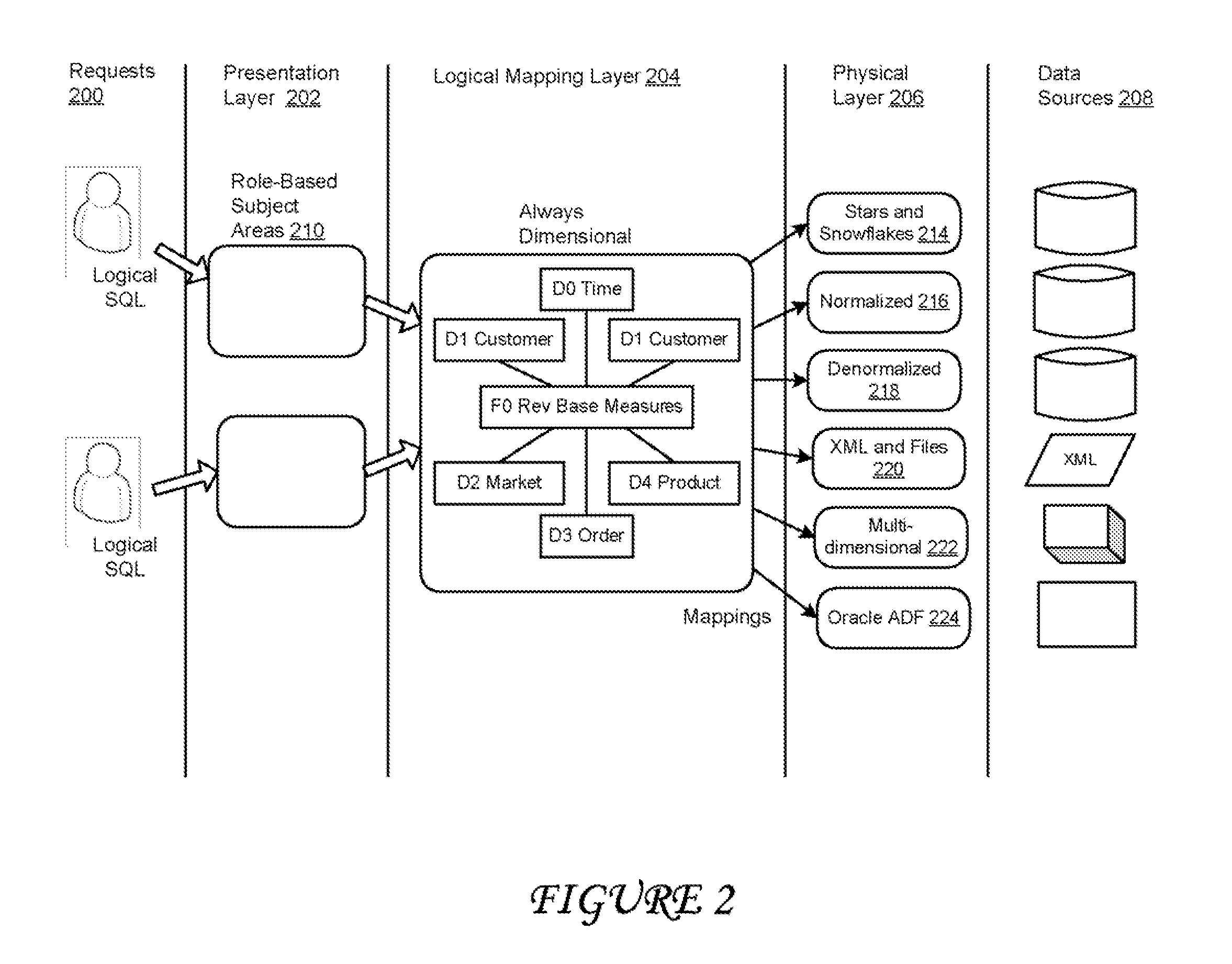

Systems and methods for providing custom or calculated data members in queries of a business intelligence server

ActiveUS20110295870A1Digital data information retrievalDigital data processing detailsData sourceBusiness intelligence

A business intelligence (BI) server and repository are described which support a set of customized and / or calculated data members. In accordance with an embodiment, the BI server maintains a connection to a plurality of data sources which may store a set of dimension members. The data source can be relational, file storage based, multidimensional and other types. In accordance with an embodiment, the BI server can accept queries from the user that contain calculated members as a parameter. The calculated member is defined by an expression including multiple dimension members and one or more arithmetic operators. The BI server can parse and validate the query and rewrite the query for the data source. After the query is rewritten and optimized, it is executed against the data source and a set of results is received.

Owner:ORACLE INT CORP

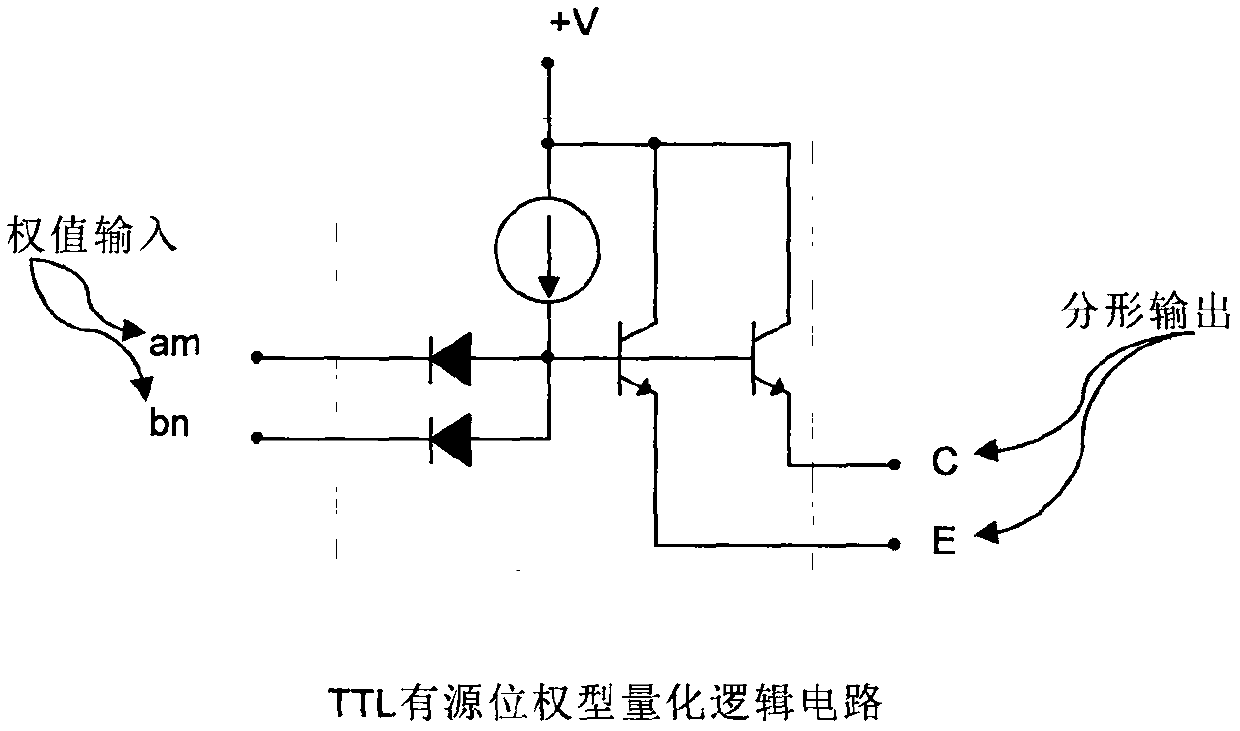

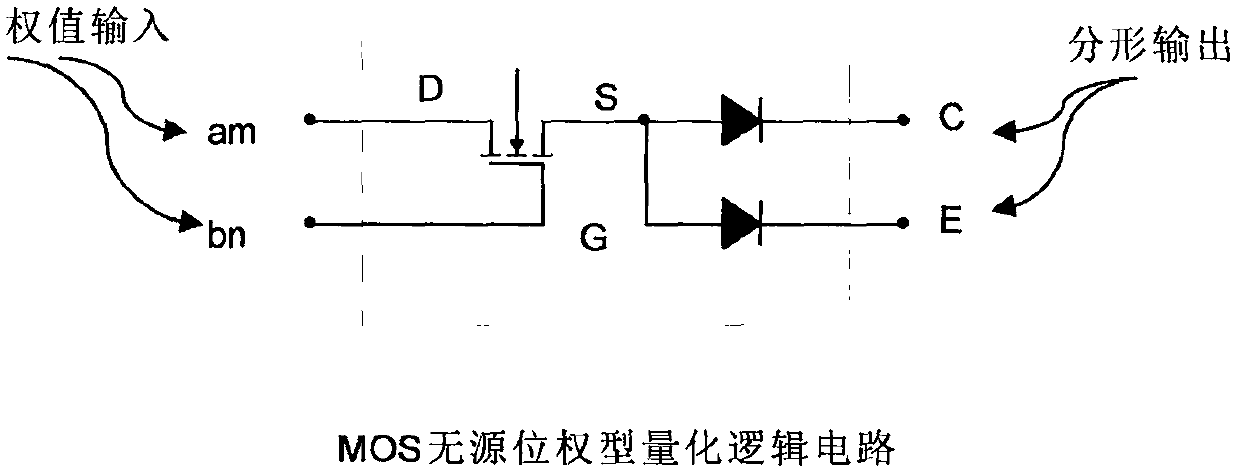

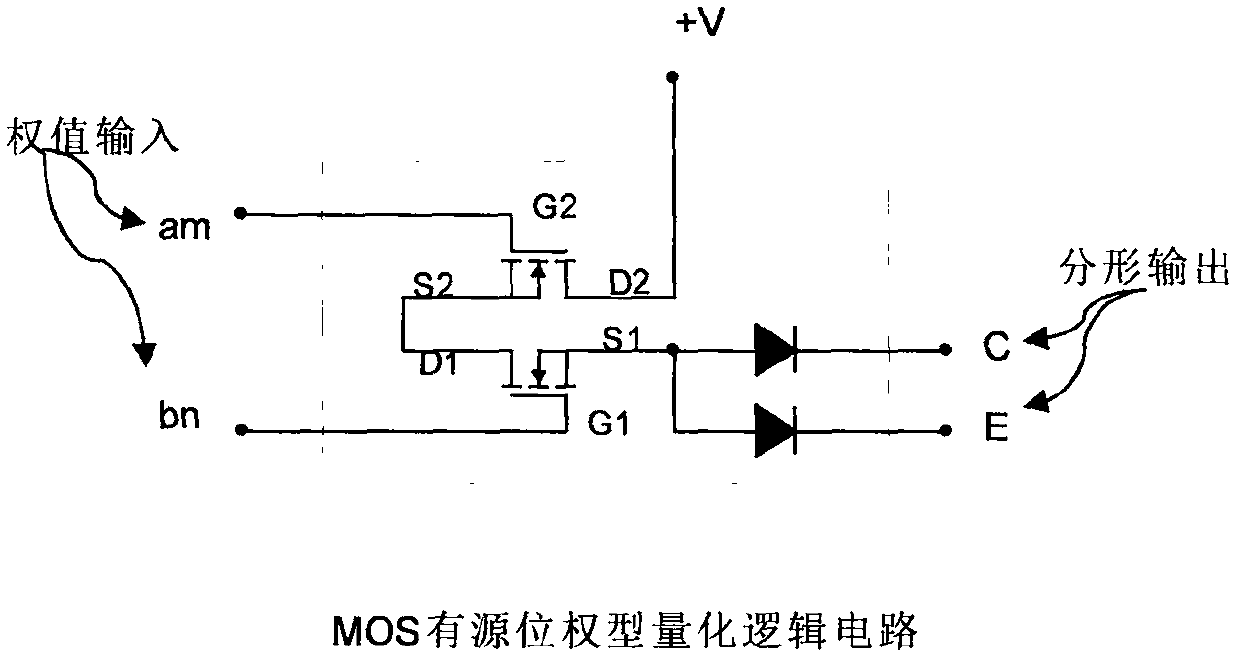

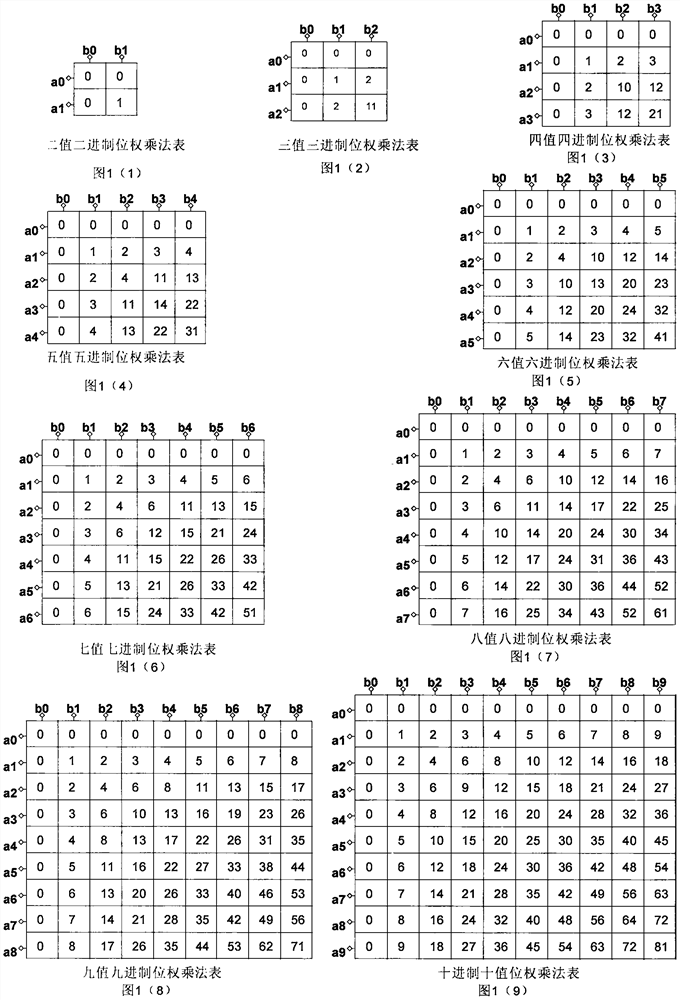

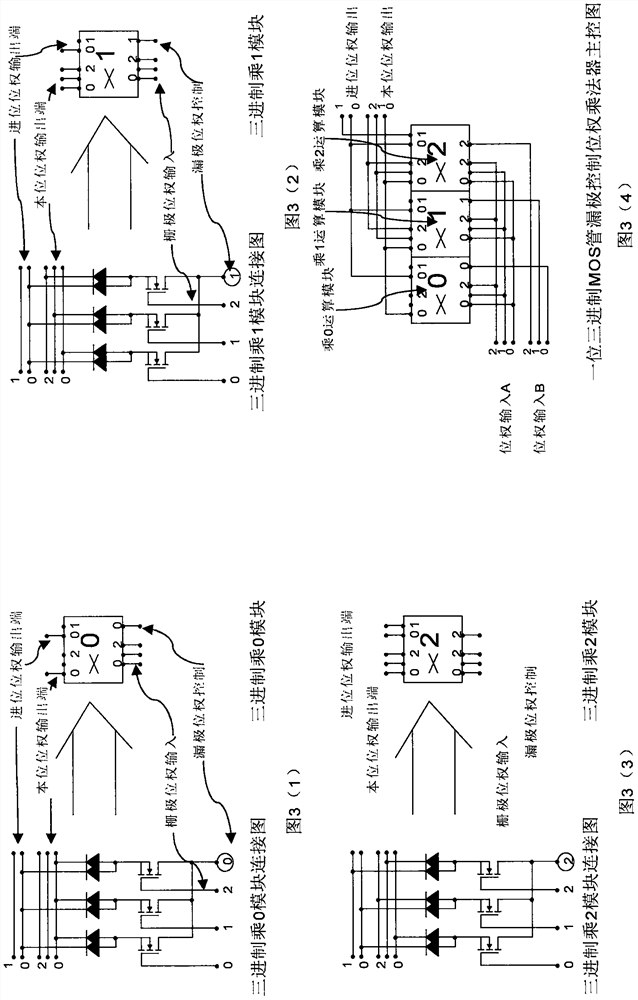

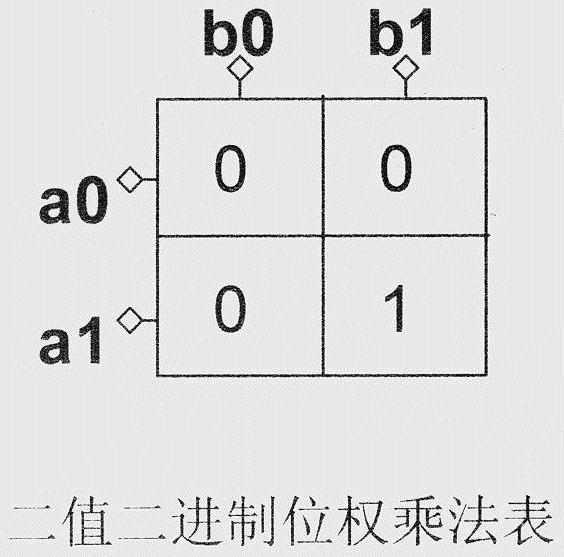

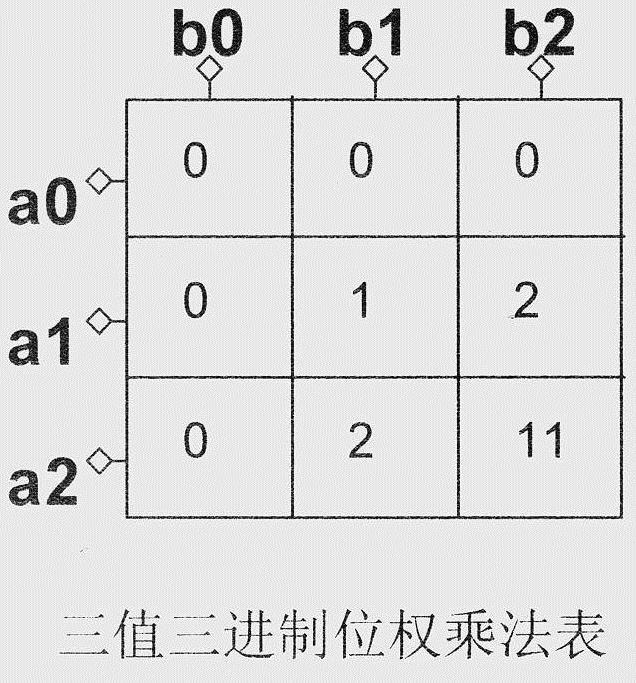

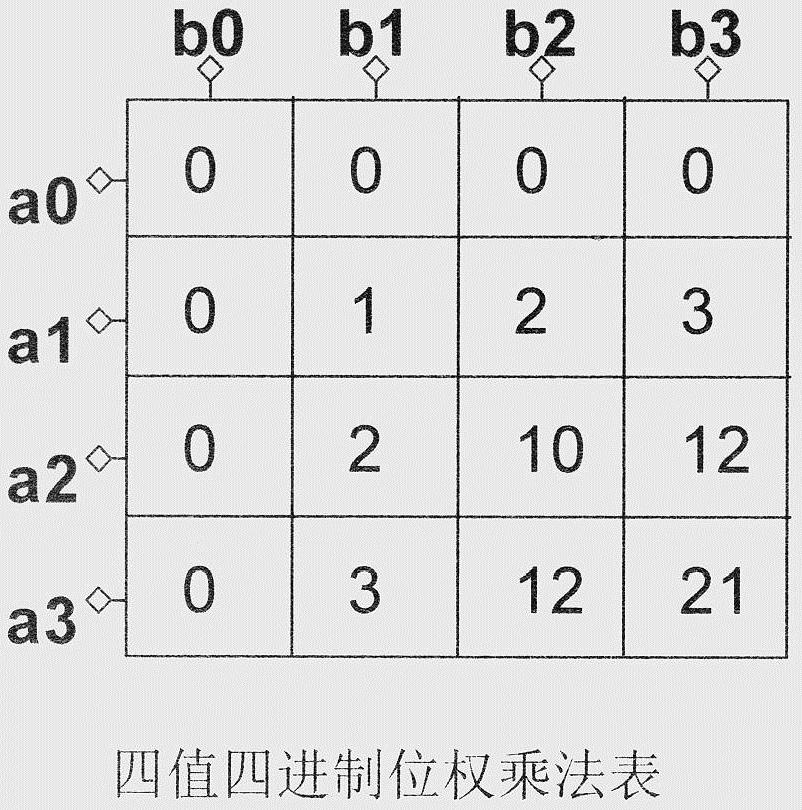

A multi-system arithmetic operator of quantization logic which assigns a fractal integration unit circuit

PendingCN109725877AEffective hardware supportSolve multivalued operationsLogic circuits characterised by logic functionComputation using denominational number representationArithmetic ErrorEngineering

The quantification logic circuit is composed of two parts Includes an Input operation part and Output fractal isolation portion; the input operation part comprises at least two input terminals for complete logic operation; the output part is provided with two output terminals, the two output terminals are isolated from each other, each output terminal also has an isolation capability with the next-stage connection part, the two output terminals are in fractal isolation, and the isolation of the output terminals and the next-stage connection part is in order to realize unidirectional transmission and three-state blocking. The quantization logic circuit is an implementation circuit of a multi-system arithmetic unit.

Owner:胡五生

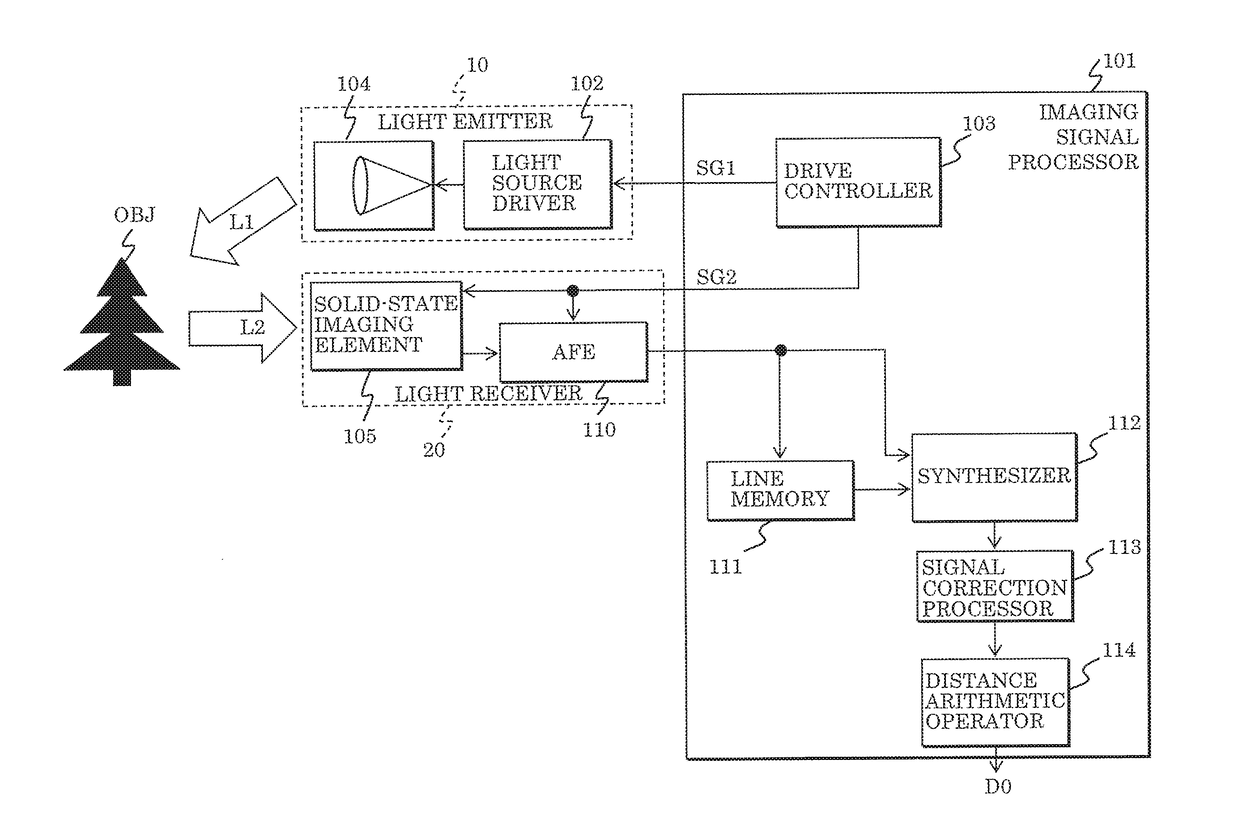

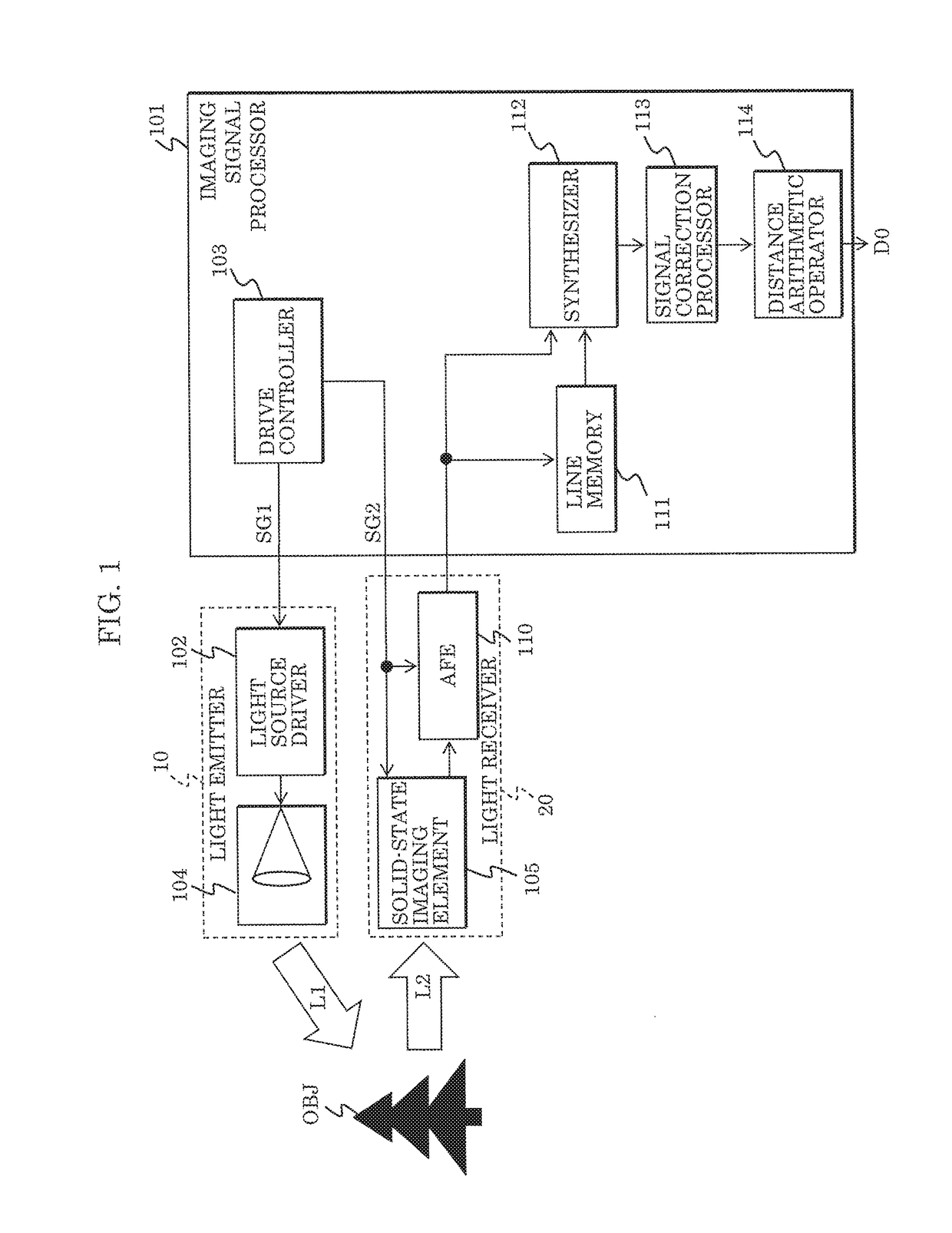

Distance measuring device and distance image synthesizing method

ActiveUS20180120423A1Improved pixel sensitivityHigh sensitivityOptical rangefindersElectromagnetic wave reradiationObject basedSaturation level

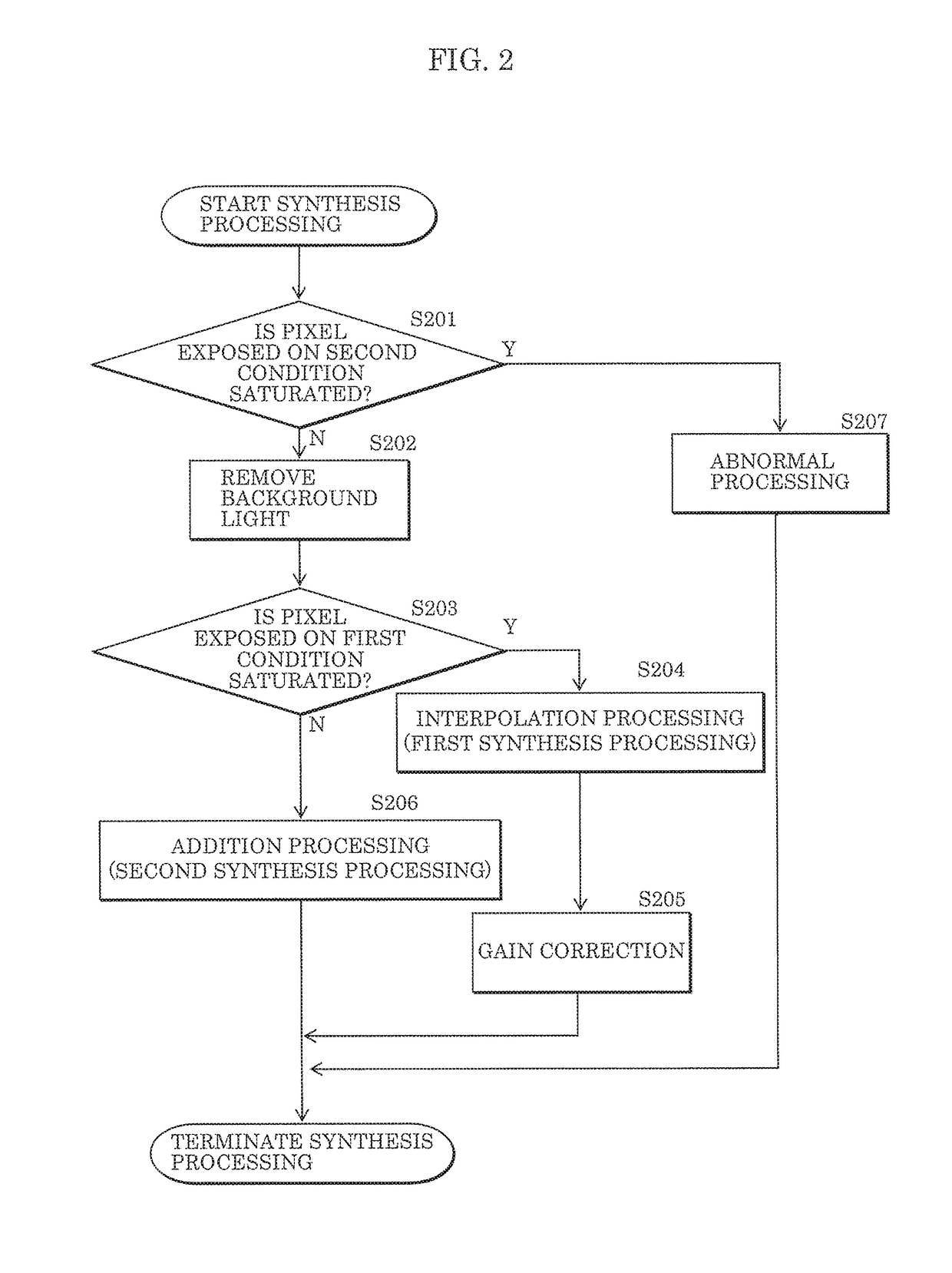

A distance measuring device includes: a light emitter which emits light from a light source to a target object; a light receiver which receives reflected light in a group of pixels two-dimensionally disposed, the reflection light being generated through reflection of the light emitted from the light emitter on the target object; a synthesizer which generates a synthesized signal by synthesizing pixel signals read from pixels exposed at different exposure intervals to generate a synthesized signal; and a distance arithmetic operator which calculates a value of distance to the target object based on the synthesized signal and the difference in time between emission and reception of the light. The synthesizer generates the synthesized signal by the first synthesis processing when a pixel signal of a pixel exposed at a first exposure interval has a signal level higher than a predetermined saturation level, and generates the synthesized signal by second synthesis processing the pixel signal of the pixel exposed at the first exposure interval has a signal level lower than the predetermined saturation level.

Owner:NUVOTON TECH CORP JAPAN

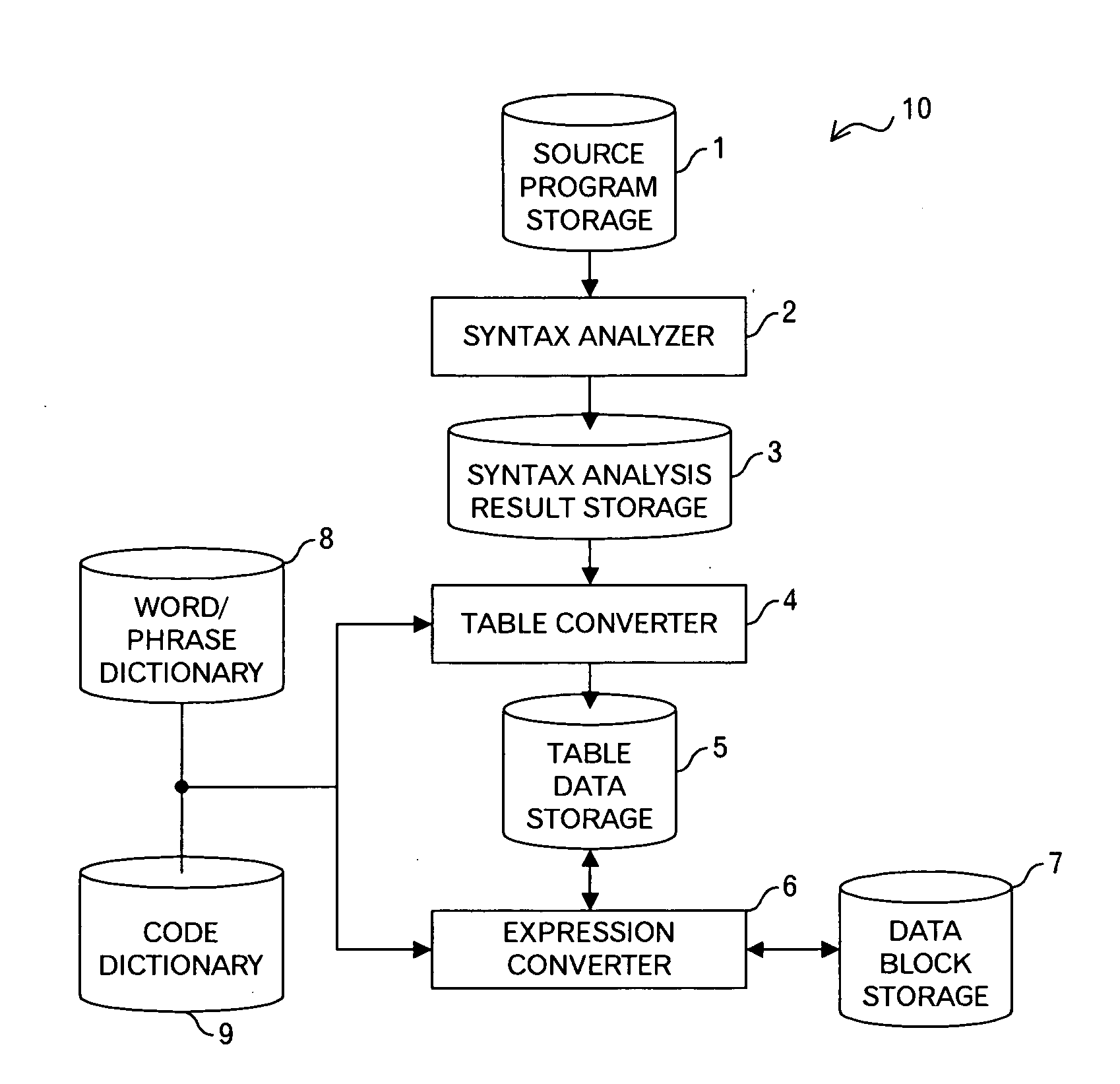

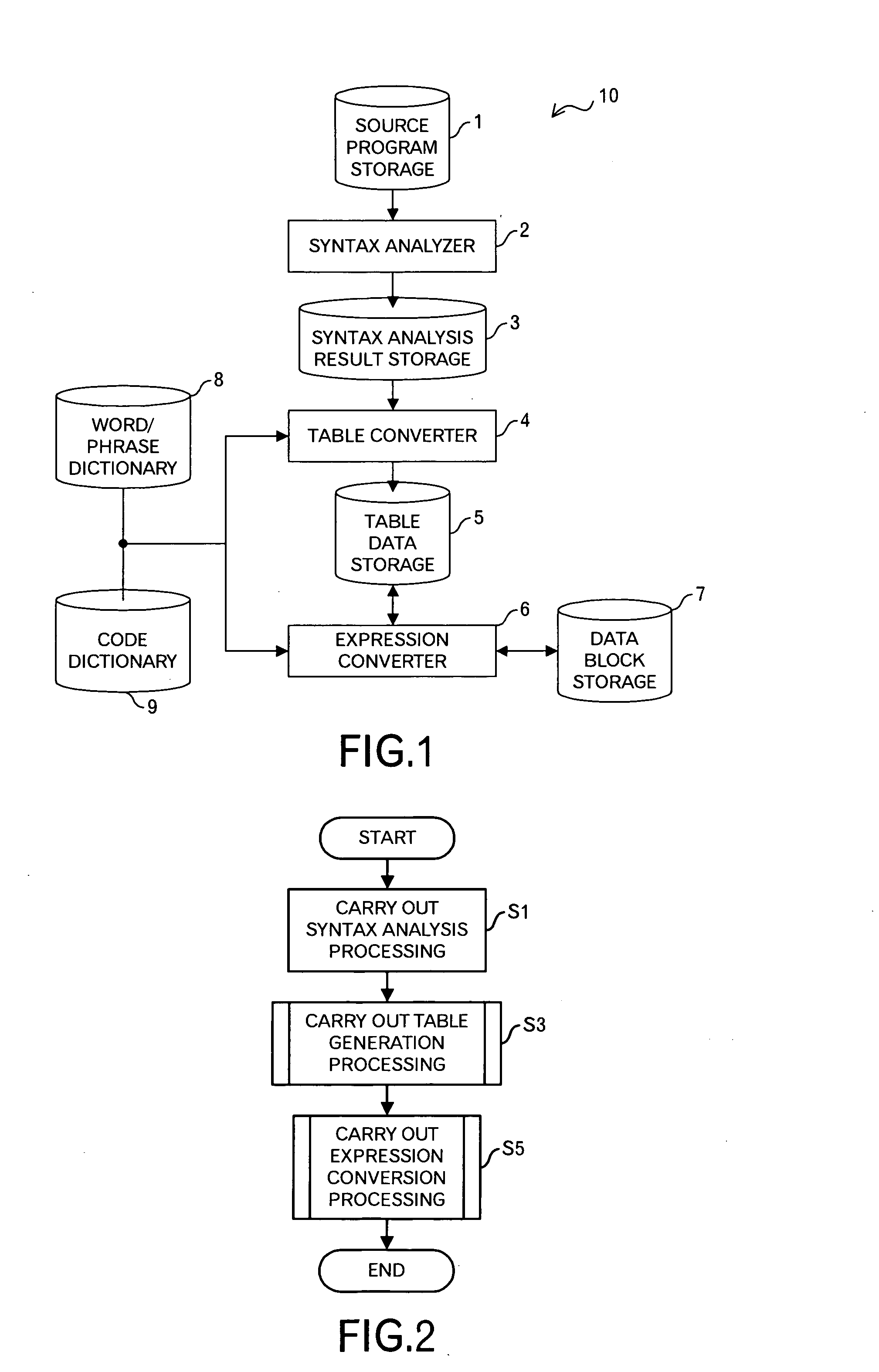

Method and apparatus for generating specification data

InactiveUS20060107253A1Easy to understandRequirement analysisSpecific program execution arrangementsData storingArithmetic computation

When a source program written in Java or the like and using methods of BigDecimal class, a priority conforming to a predetermined arithmetic rule is identified for an arithmetic operational method included in an arithmetic operation statement, and the arithmetic operational method and the identified priority are registered into a storage device. Then, in a case where it is judged based on data stored in the storage device that a plurality of arithmetic operational methods are included in an arithmetic operational statement, and an arithmetic operational method with low priority is defined as an instance of an arithmetic operational method with high priority, following processing is carried out to generate specification data, that is, the arithmetic operational method with low priority and an instance and argument of the arithmetic operational method with low priority are converted into a first subexpression using an arithmetic operational sign in accordance with a predetermined rule. Then, parentheses representing that the arithmetic operation are carried out with priority is added to the first subexpression. In addition, the arithmetic operational method with high priority and an argument of the arithmetic operational method with high priority are converted into a second subexpression using an arithmetic operational sign in accordance with the predetermined rule. Finally, the second subexpression is linked with the first subexpression.

Owner:FUJITSU LTD

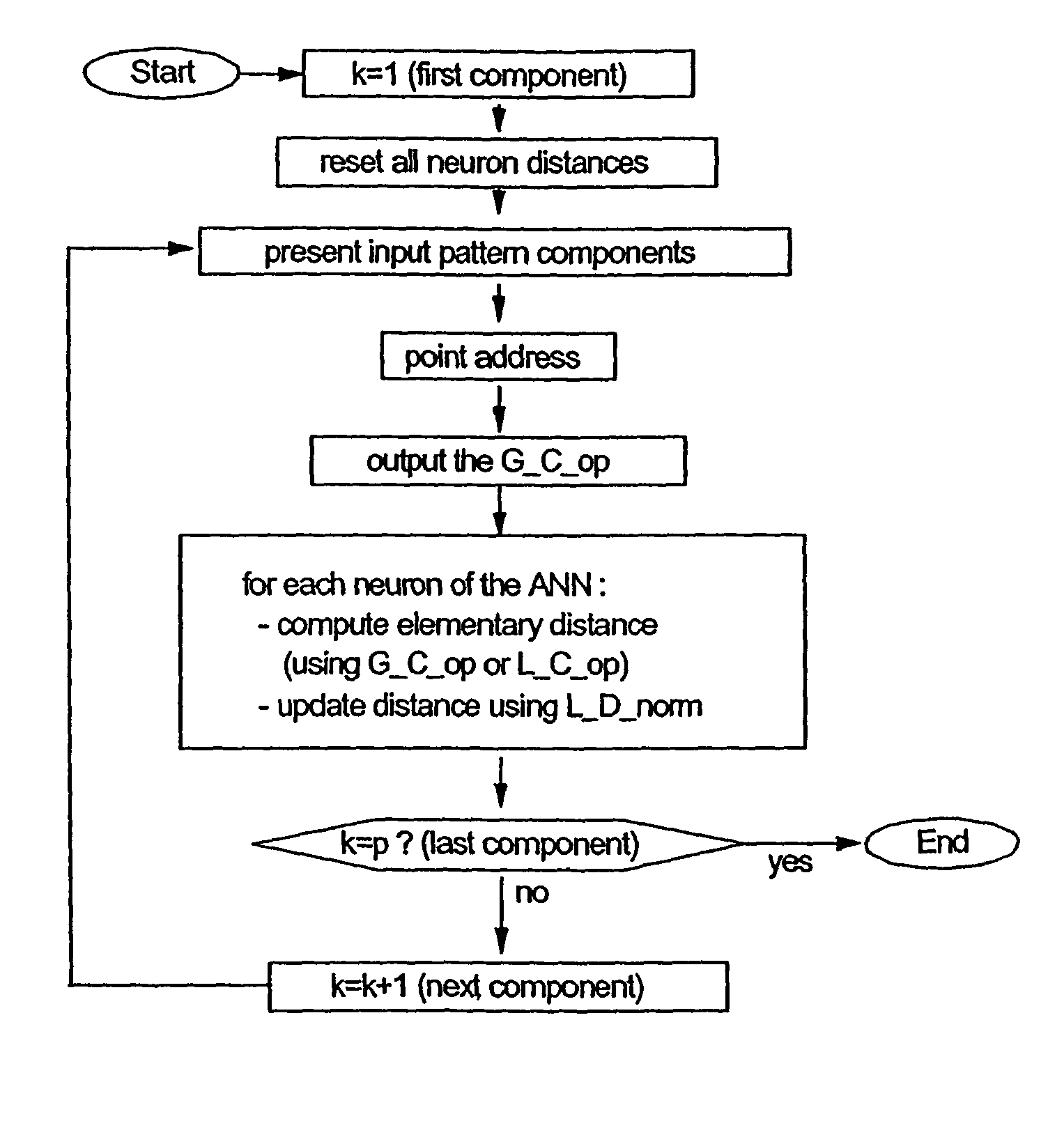

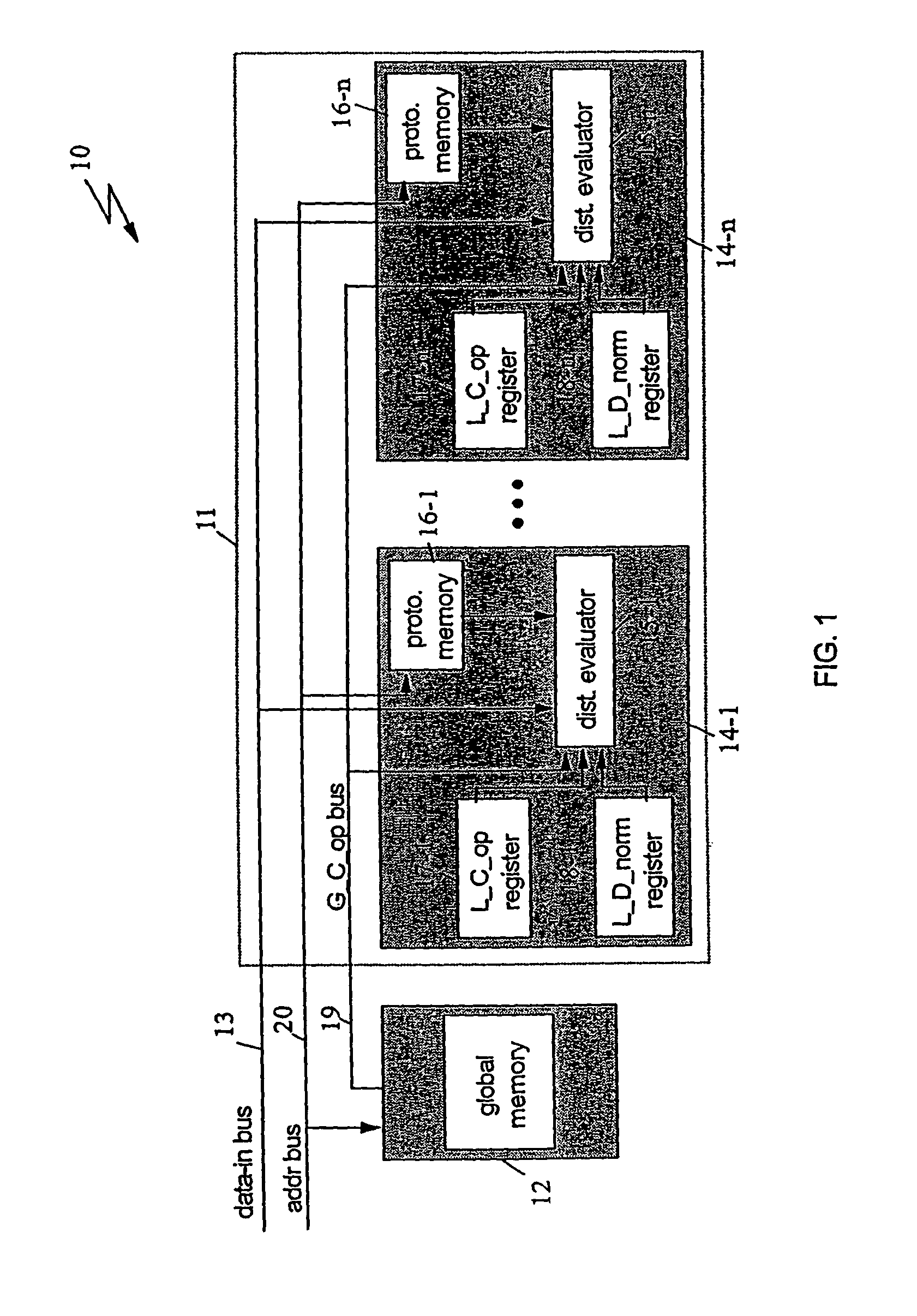

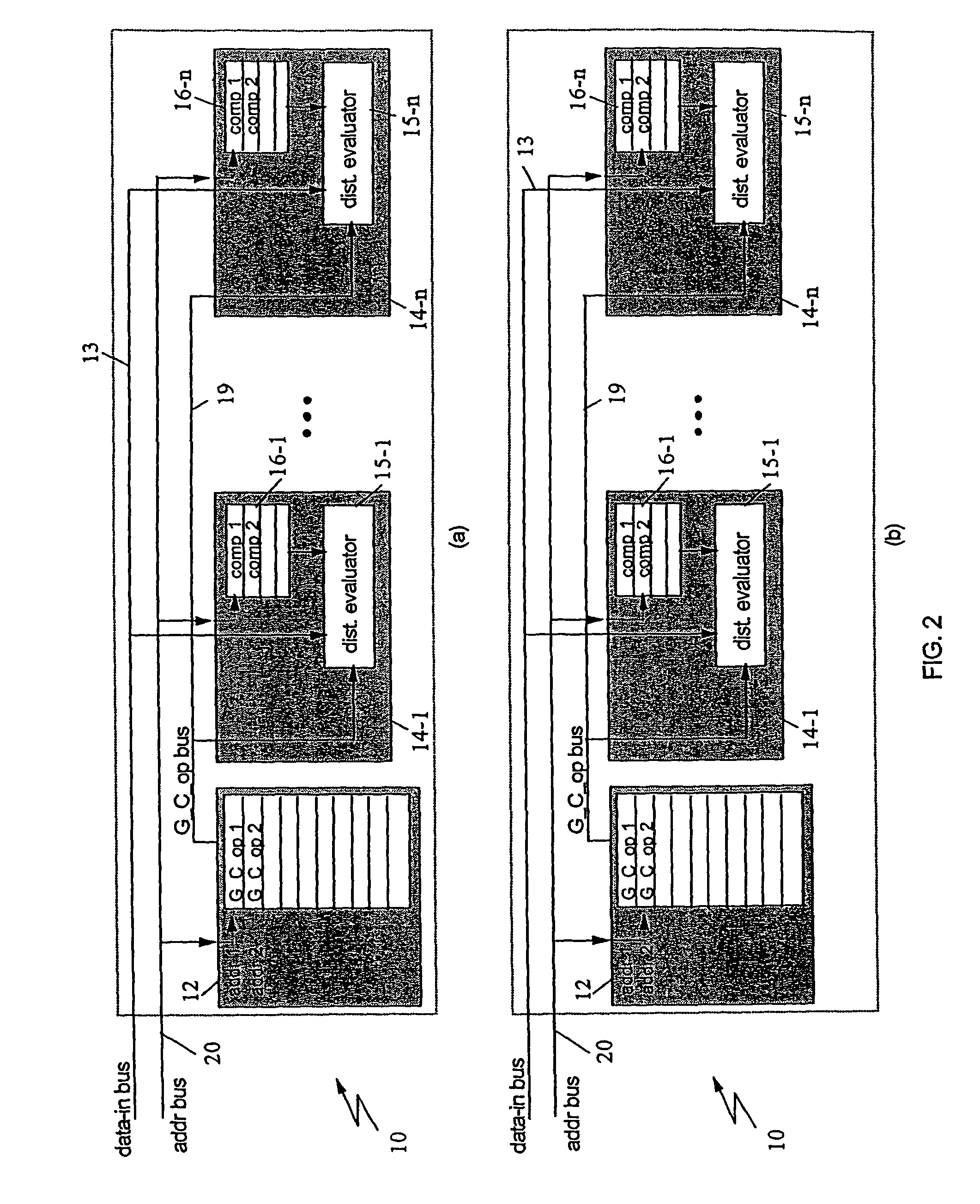

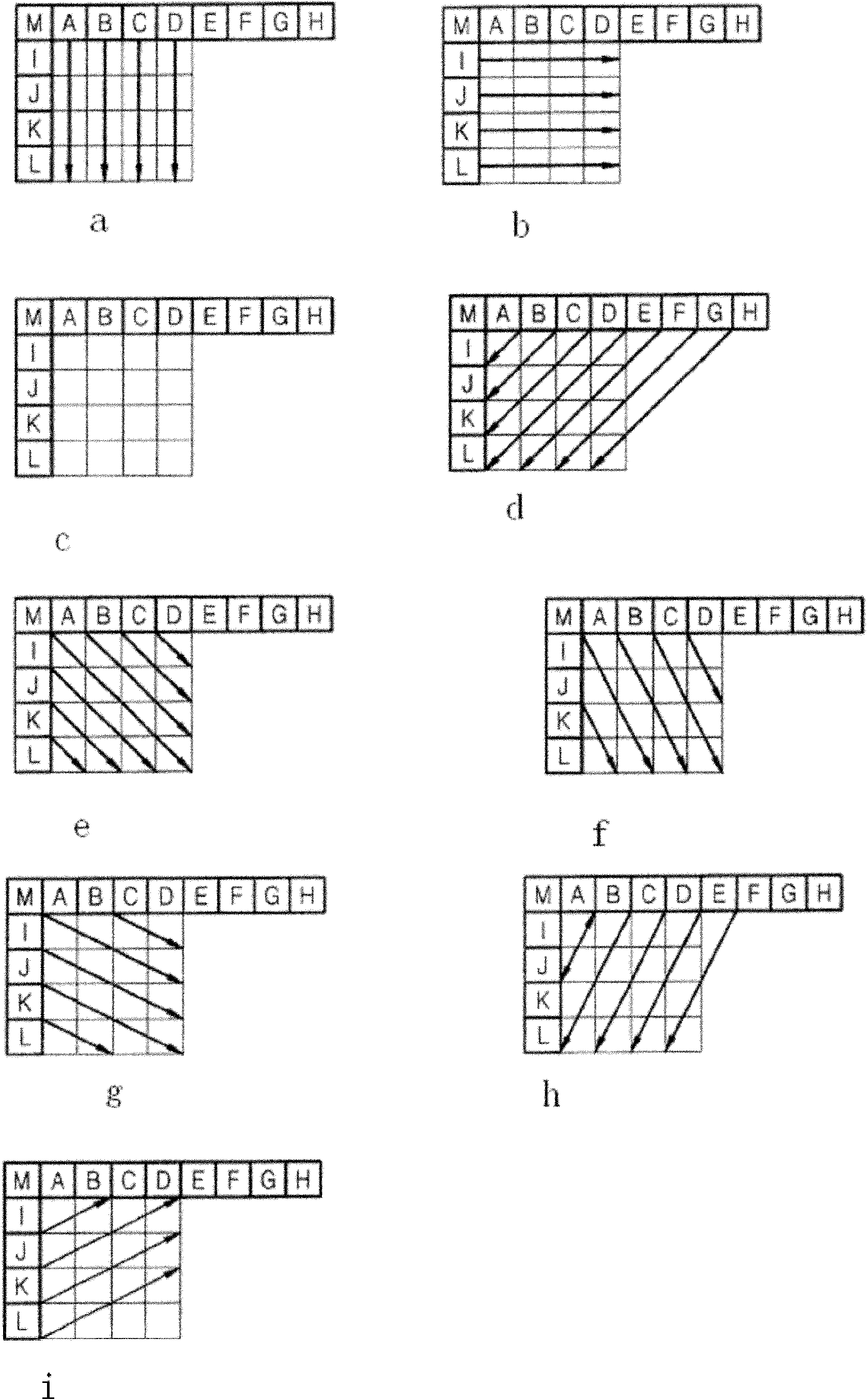

Method and circuits for associating a complex operator to each component of an input pattern presented to an artificial neural network

InactiveUS8027942B2Save spaceReduce component countDigital computer detailsCharacter and pattern recognitionTheoretical computer scienceSpace mapping

The method and circuits of the present invention aim to associate a complex component operator (CC_op) to each component of an input pattern presented to an input space mapping algorithm based artificial neural network (ANN) during the distance evaluation process. A complex operator consists in the description of a function and a set of parameters attached thereto. The function is a mathematical entity (either a logic operator e.g. match(Ai,Bi), abs(Ai−Bi), . . . or an arithmetic operator, e.g. >, <, . . . ) or a set of software instructions possibly with a condition. In a first embodiment, the ANN is provided with a global memory, common for all the neurons of the ANN, that stores all the CC_ops. In another embodiment, the set of CC_ops is stored in the prototype memory of the neuron, so that the global memory is no longer physically necessary. According to the present invention, a component of a stored prototype may now designate objects of different nature. In addition, either implementation significantly reduces the number of components that are required in the neurons, therefore saving room when the ANN is integrated in a silicon chip.

Owner:IBM CORP

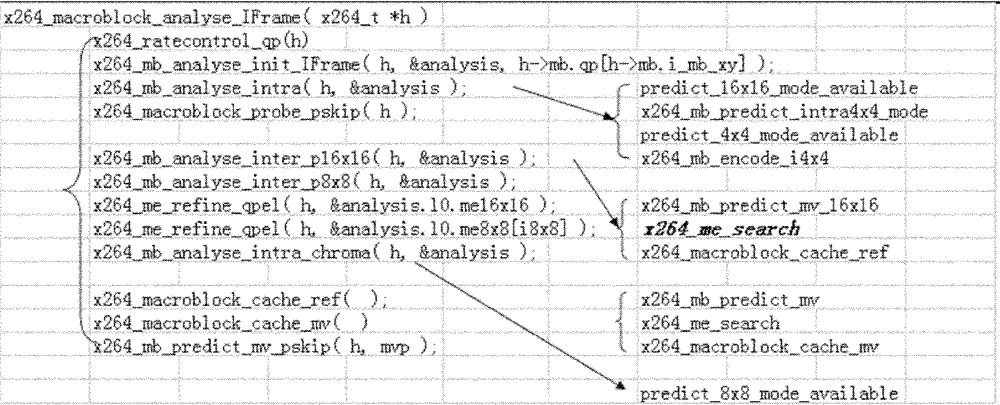

Intra-frame sub-block predictor circuit for video encoder and method for implementing same

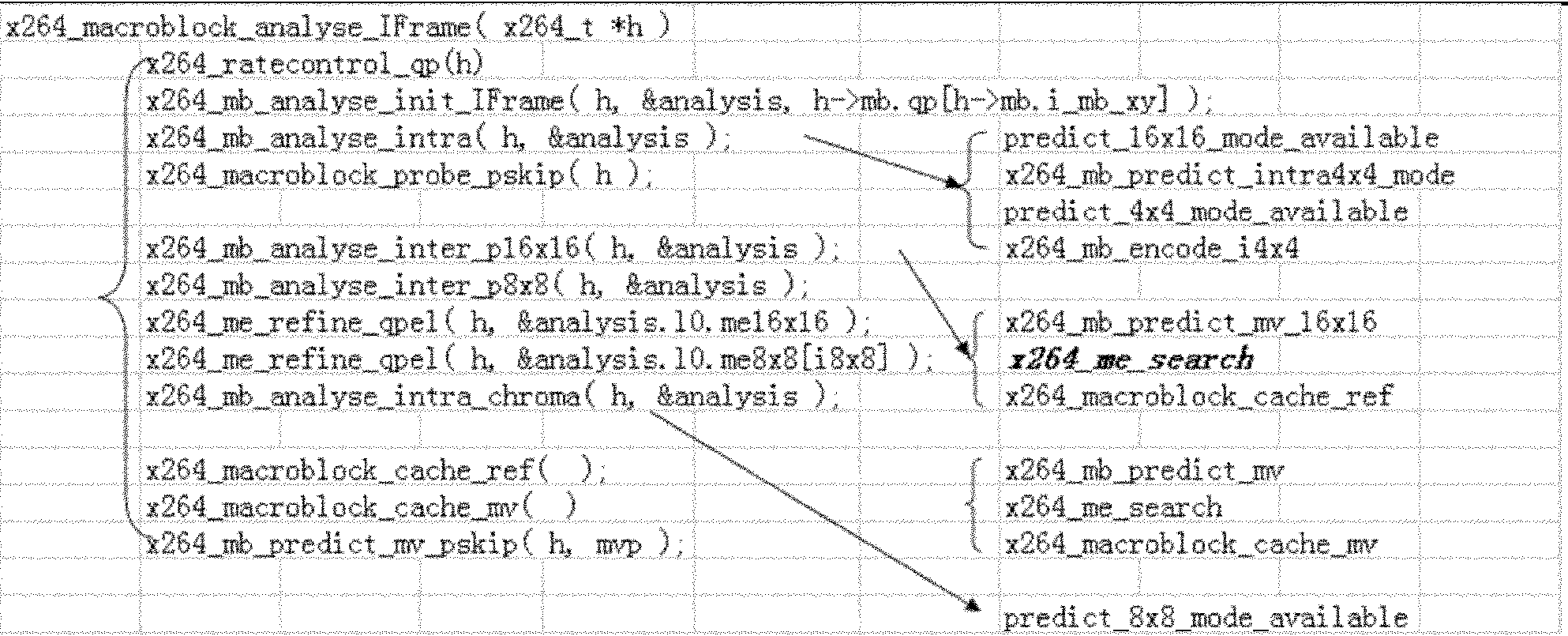

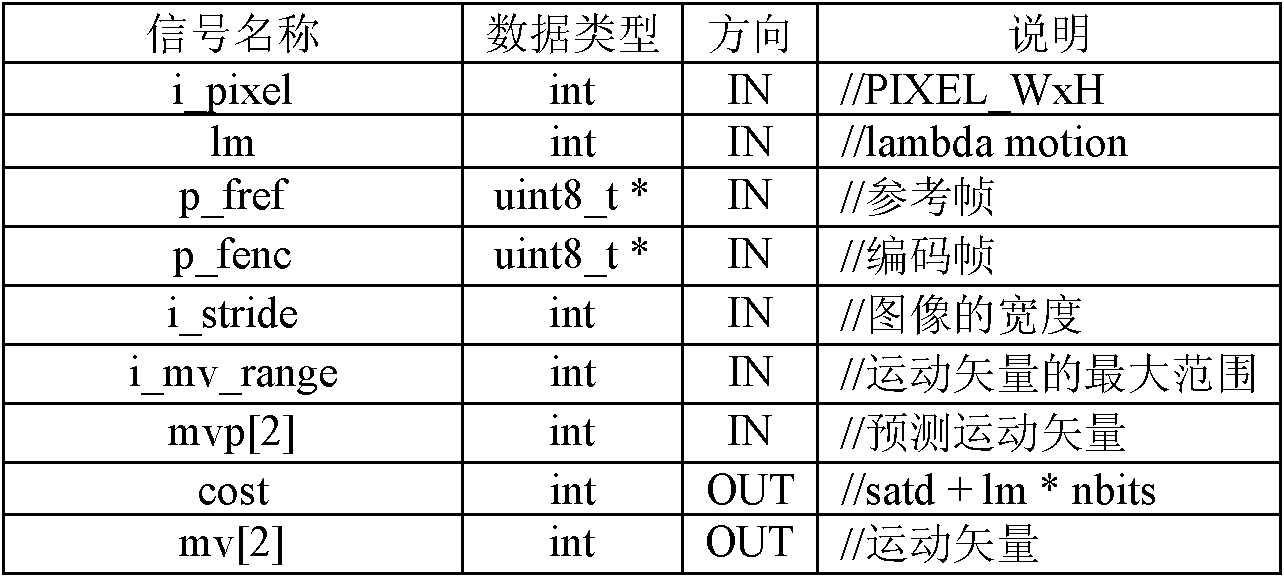

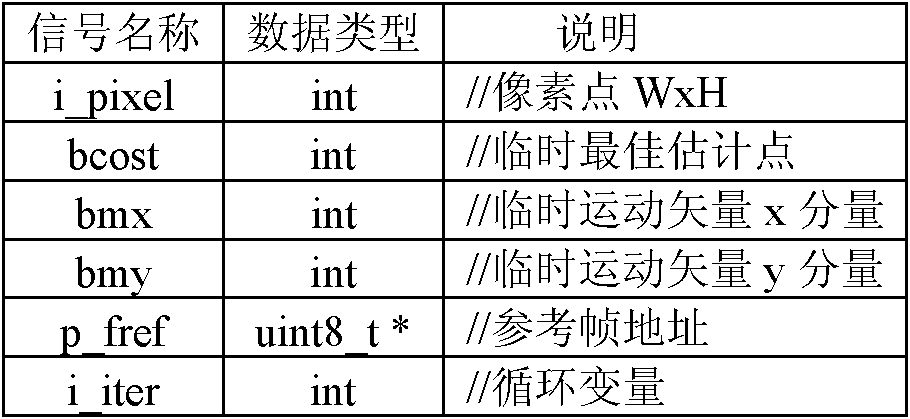

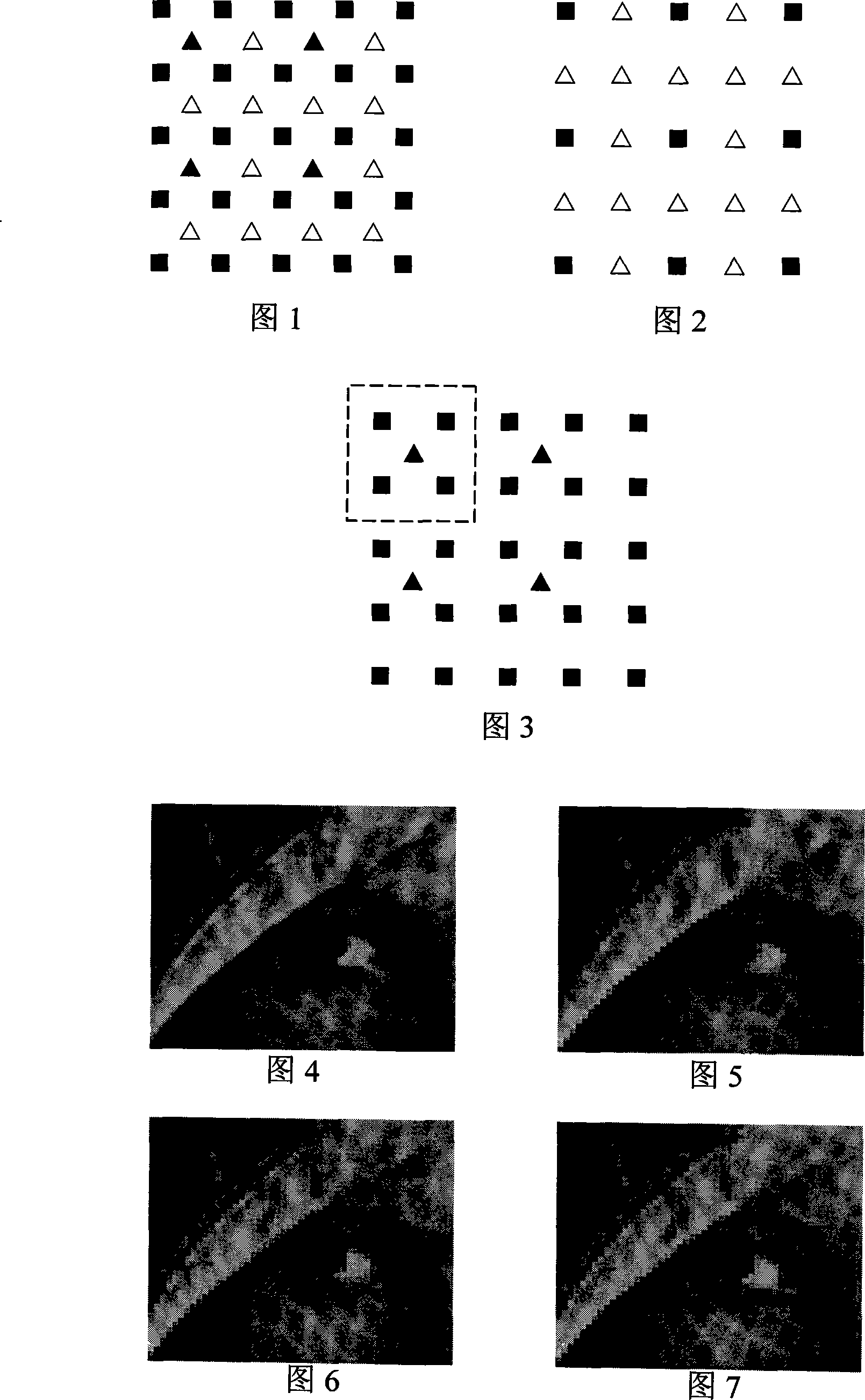

InactiveCN102075763AImprove design efficiencyBalance areaTelevision systemsDigital video signal modificationVideo encodingTheoretical computer science

The invention discloses a method for implementing an intra-frame sub-block predictor circuit for a video encoder. The method comprises the following steps of: mapping each encoding functional block of the intra-frame sub-block predictor circuit of the video encoder which is described by a high-level program language algorithm into hardware logic description consisting of arithmetic operator units; and generating a hardware integrated circuit of the intra-frame sub-block predictor circuit by the hardware logic description consisting of the arithmetic operator units. The invention also discloses the intra-frame sub-block predictor circuit of the video encoder, which comprises a calculation encoding functional block for calculating predicted values, a selection encoding functional block for selecting the optimum predicted value from the predicted values and a residual calculation encoding functional block for acquiring the sum of corresponding residual calculation matrix element absolute values according to the optimum predicted value. By the circuit and the method, the efficiency of hardware design is improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

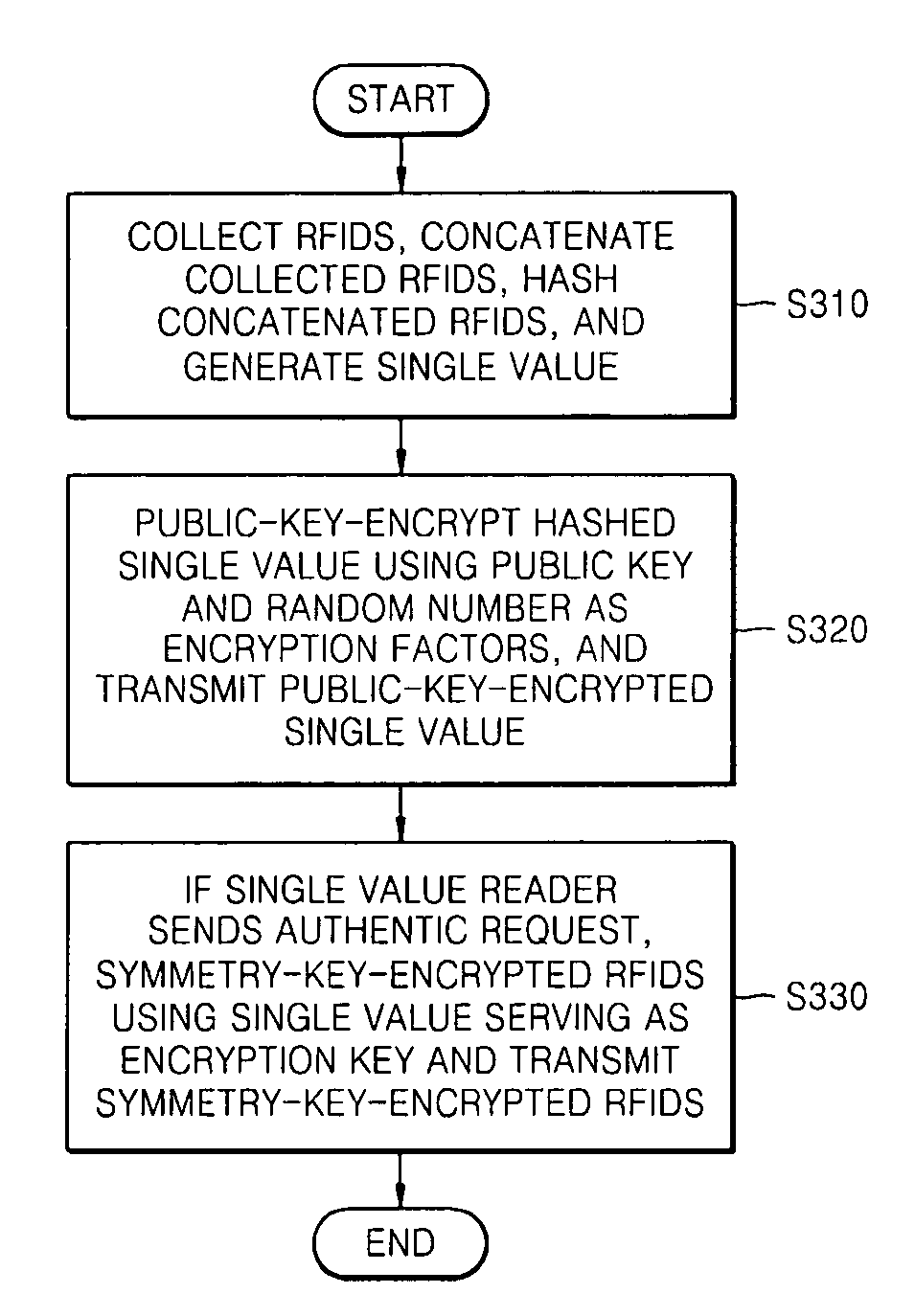

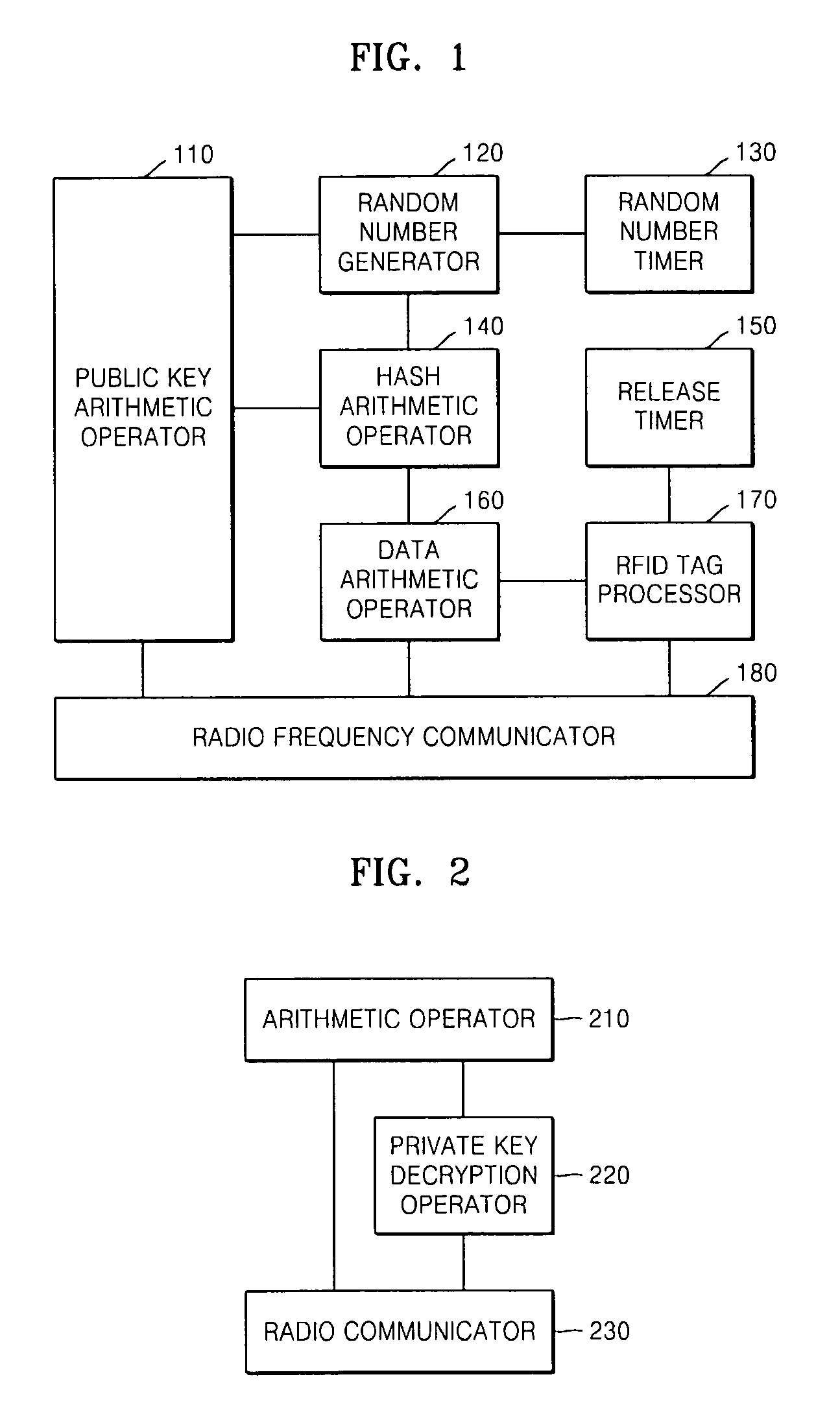

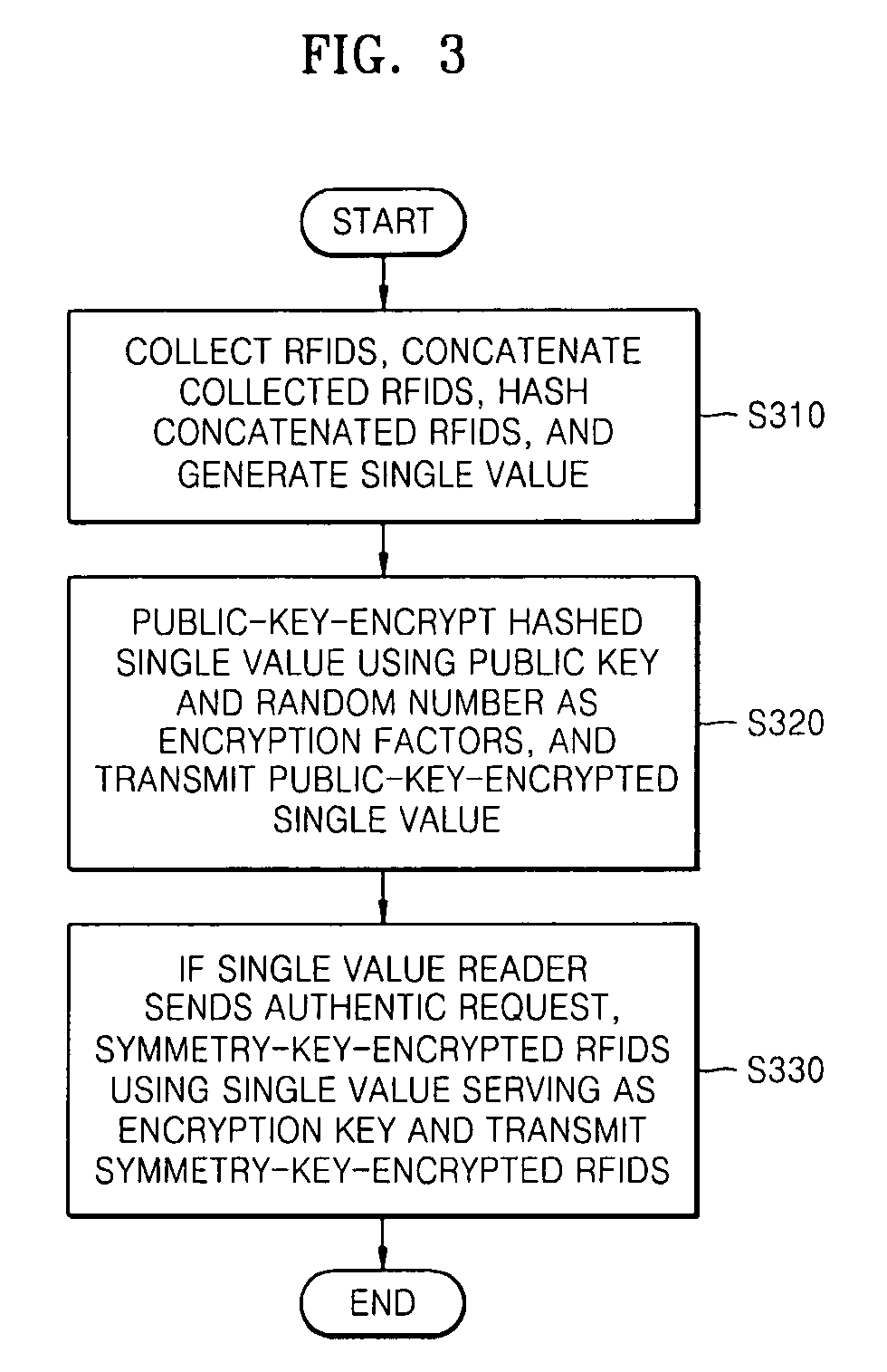

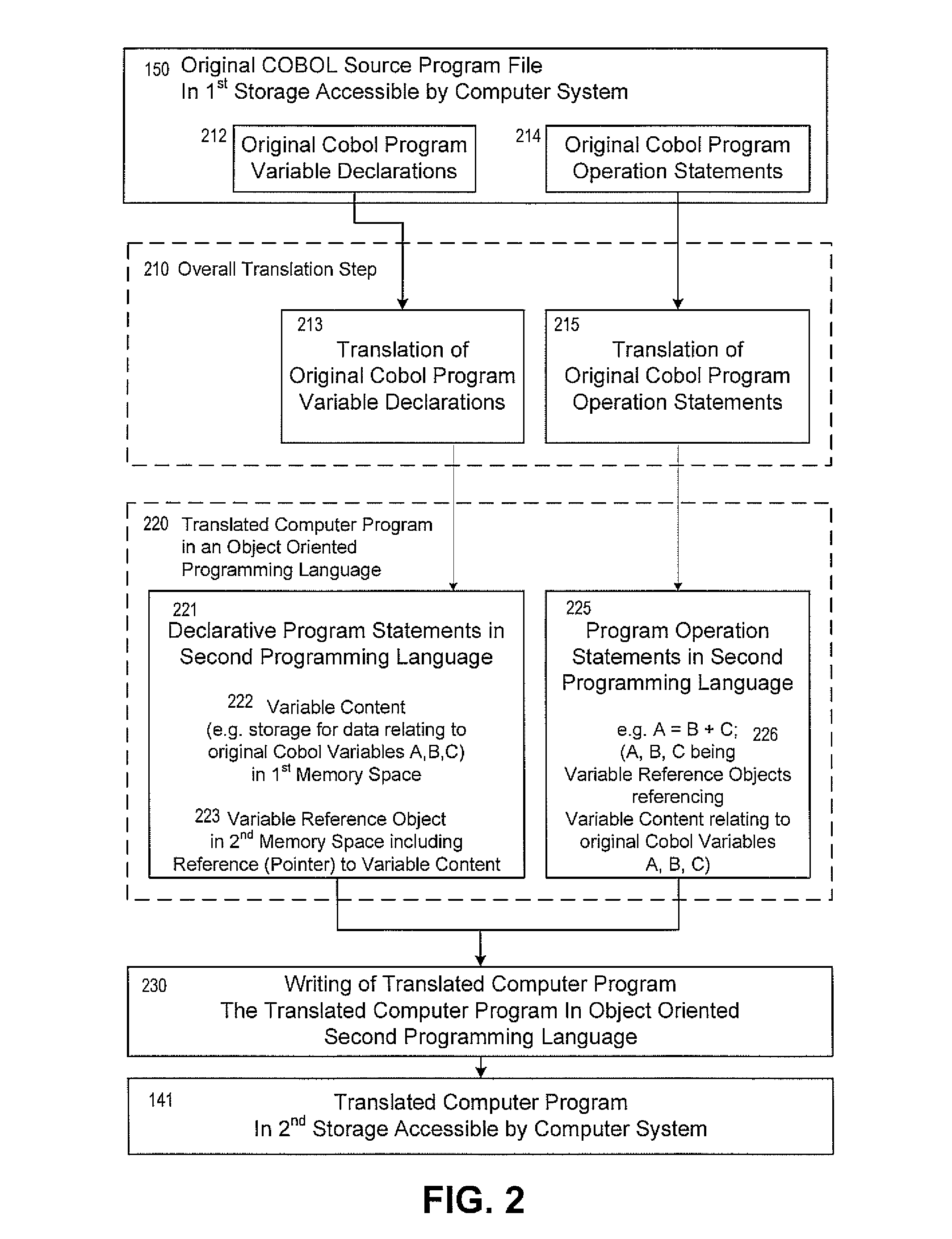

Apparatus and method for unifying multiple radio frequency identifications

InactiveUS7649440B2Privacy protectionCo-operative working arrangementsSecret communicationComputer hardwareCiphertext

An apparatus and method for unifying multiple radio frequency identifications (RFIDs) are provided. The apparatus includes: a data arithmetic operator collecting RFIDs, storing the collected RFIDs, and repeatedly performing the collection and storage when a time out event occurs; a hash arithmetic operator concatenating the RFIDs, hashing the concatenated RFIDs, and outputting a hashed single value; a random number generator generating a random number used as an encryption factor to public-key-encrypt the single value; an RFID tag processor controlling locking / unlocking of the RFID tags; a public key arithmetic operator public-key-encrypting the single value using a predetermined public key and the random number as encryption factors and outputting a cipher text; and a radio frequency communicator converting the cipher text into a radio signal and sending the radio signal to a radio section. Information transmitted to a radio section is a cipher text obtained by public-key-encrypting the single value. Therefore, the number of the RFID tags belonging to a user is not exposed to an eavesdropper, thereby protecting user's privacy.

Owner:ELECTRONICS & TELECOMM RES INST

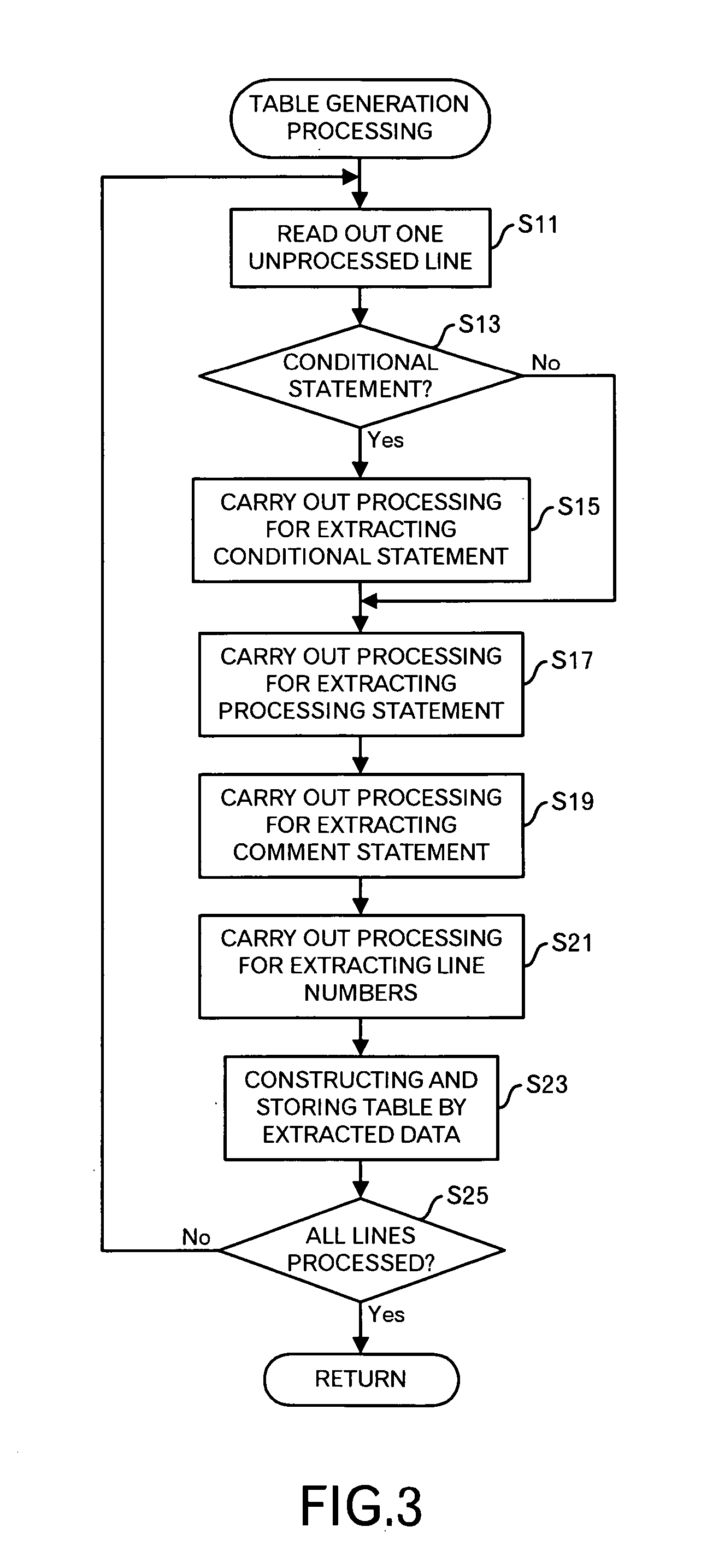

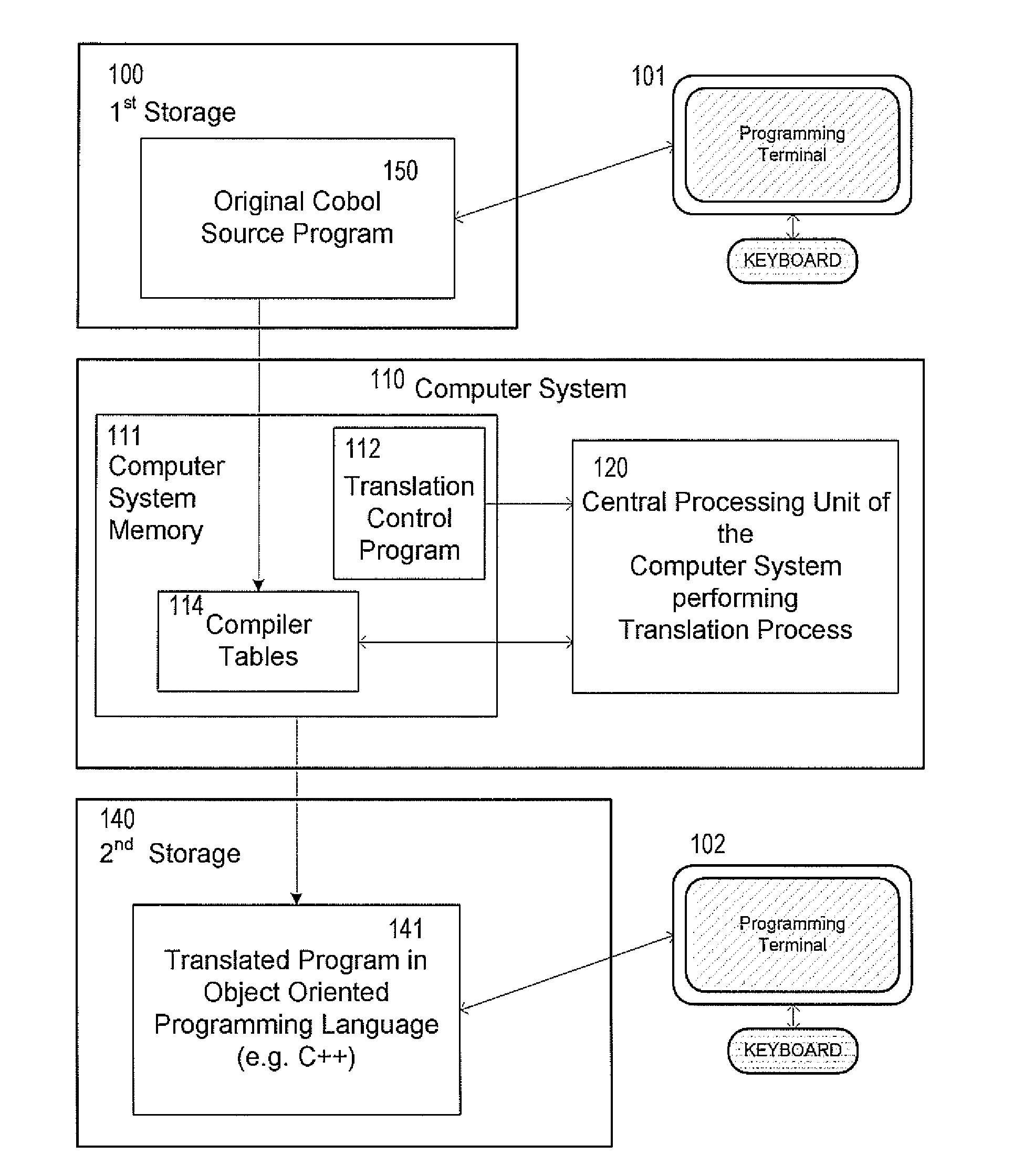

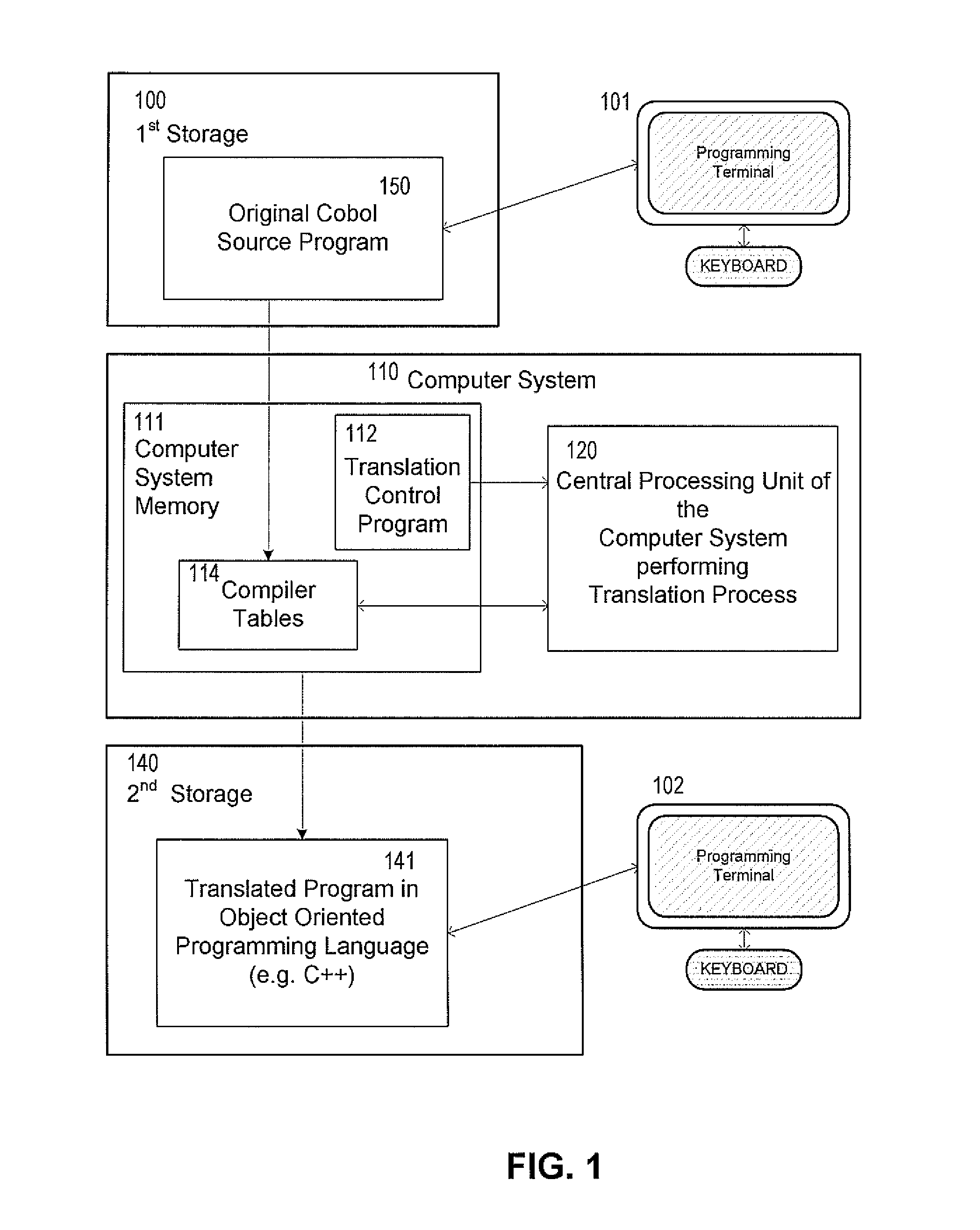

Method for translating a cobol source program into readable and maintainable program code in an object oriented second programming language

ActiveUS9182962B2Easily readableEasily understandableProgramming languages/paradigmsSpecific program execution arrangementsCode readabilityHuman language

A method is disclosed for translating by a computer system of a COBOL computer program into a translated computer program in a readable and maintainable syntax in an object oriented programming language. The translated program including variable names equivalent to the original COBOL variable names and with attributes described in COBOL syntax. The translating method further providing for memory allocation in the translated computer program for storage of “COBOL” variables compatible with that of the original COBOL program; a description of program flow that is readable, and utilizing arithmetic operators to describe operations between COBOL variables. Also disclosed is a special object oriented run-time library for creating and performing operations between COBOL numeric objects, including maintaining storage of variable content in the original COBOL format, and for enabling readability of the translated source code by allowing arguments for variable type descriptions to be expressed in COBOL syntax.

Owner:BULL HN INFORMATION SYST INC

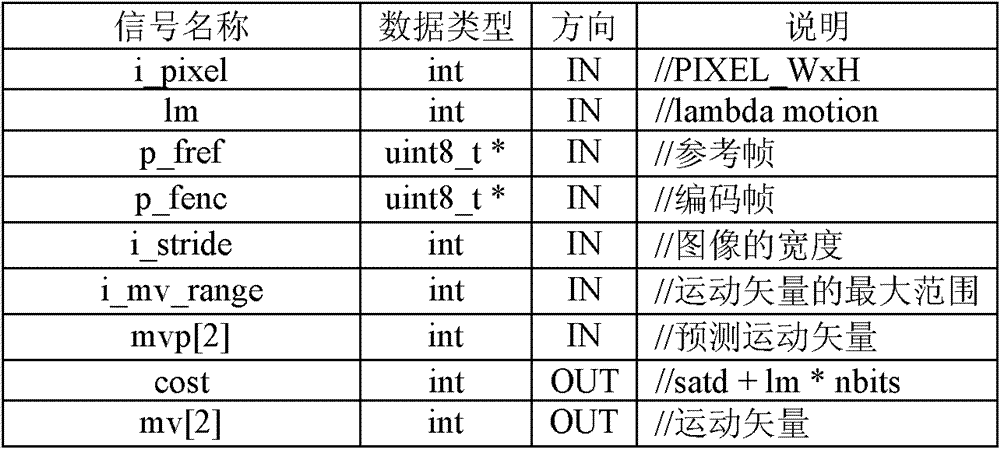

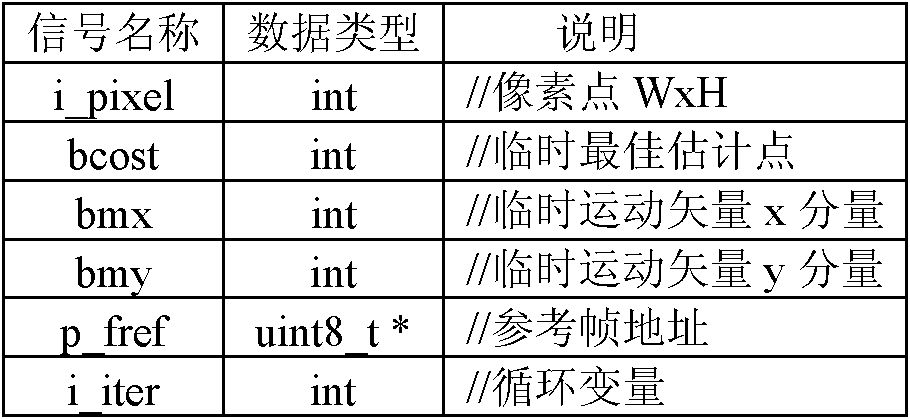

Inter-frame predictor circuit for video encoder and method for implementing same

InactiveCN102075762ADesign fasterTelevision systemsDigital video signal modificationComputer architectureVideo encoding

The invention discloses a method for implementing an inter-frame predictor for a video encoder. The method comprises the following steps of: mapping each functional block of the inter-frame predictor of the video encoder which is described by a high-level program language algorithm into hardware logic description consisting of arithmetic operator units; and generating a hardware integrated circuit of the inter-frame predictor by the hardware logic description consisting of the arithmetic operator units. By the method, the speed for implementing the integrated circuit of the inter-frame predictor can be increased. The invention also discloses the inter-frame predictor acquired by the method.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

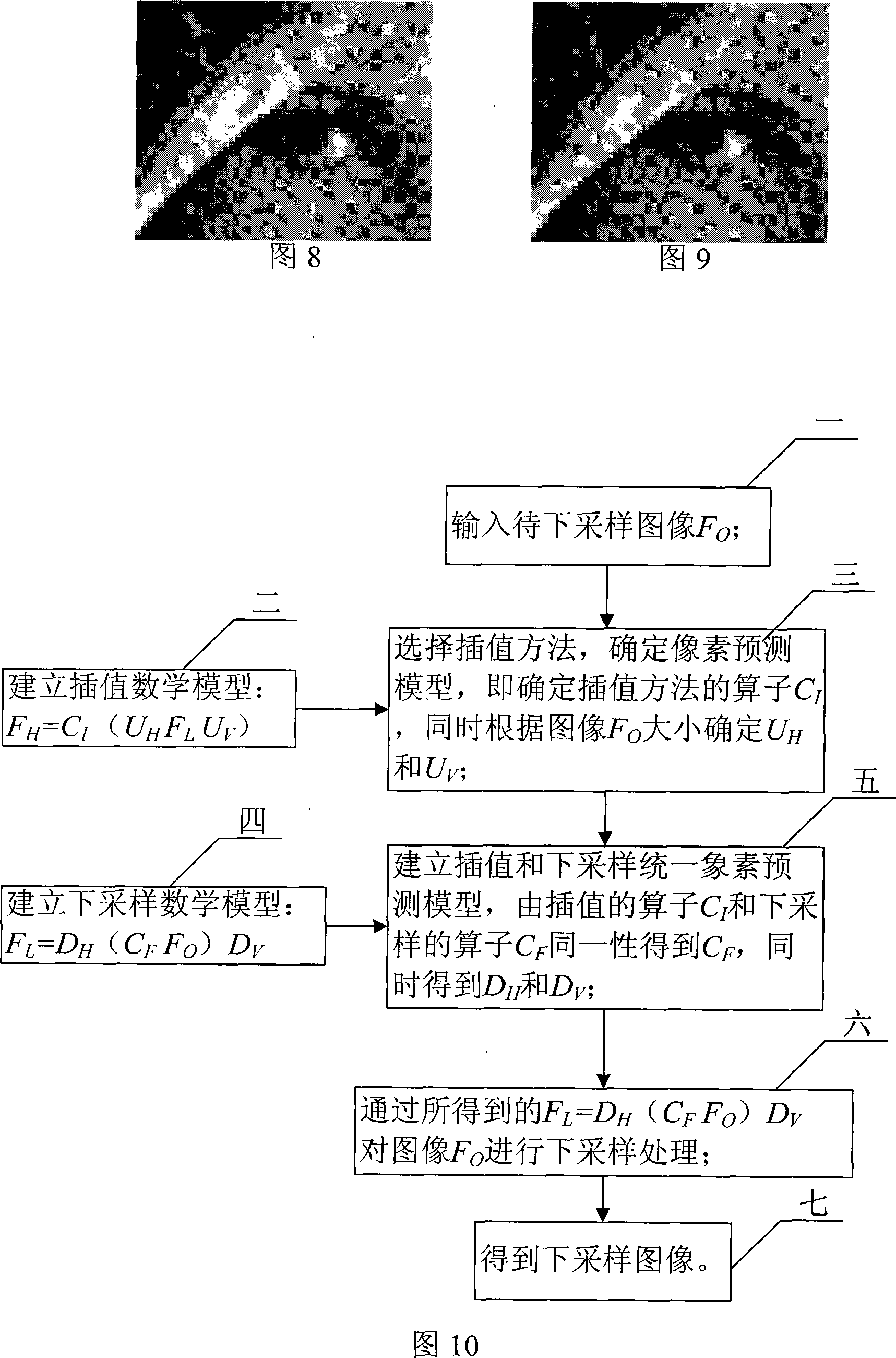

Method for processing image by using the mathematical model established based down sampling and interpolation

InactiveCN101188669ASmall amount of calculationProtection edgeTelevision system detailsPulse modulation television signal transmissionImaging processingMathematical model

The invention discloses an image processing method for establishing a mathematical model based on down sampling and interpolation, relates to an image processing method, and solves the prior problem that the image maintains a small amount of information after the down sampling. The invention adopts the steps that firstly, an image FO to be down-sampled is input; next, an interpolation mathematical model, namely, FH is equal to CI (U<H>F<L>U<V>) is established, and then an interpolation method is selected, a predictive model is determined, the arithmetic operator CI of the interpolation method is determined, and simultaneously UH and UV are determined according to the size of the image FO; and then a down sampling mathematical model, namely, FL is equal to DH (CF) DV is established; a predictive model with uniform image element of the interpolation and the down sampling is established, CF is obtained through the identity of the arithmetic operator the CI of the interpolation and the arithmetic operator the CF of the down sampling, and simultaneously the DH and the DV are obtained; finally, the down sampling processing to the image FO is performed through the obtained the FL being equal to the DH (CF) DV; the down sampling is obtained. The invention can be applied to the low code rate compression of images and videos, therefore reducing the amount of calculation of compression algorithm, quickening the processing speed and reducing the time delay, and also obviously improving the quality of restored images.

Owner:HARBIN INST OF TECH

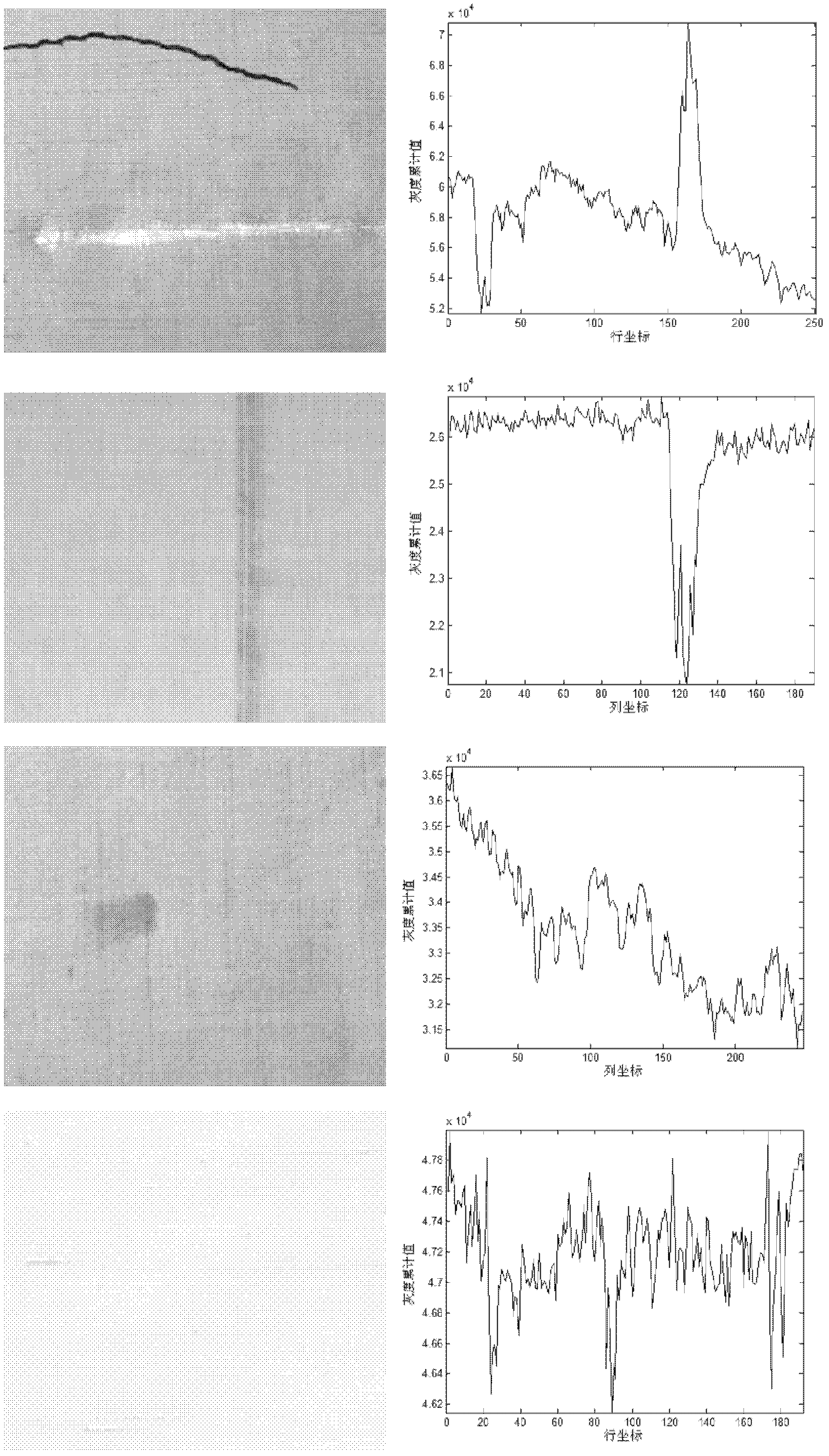

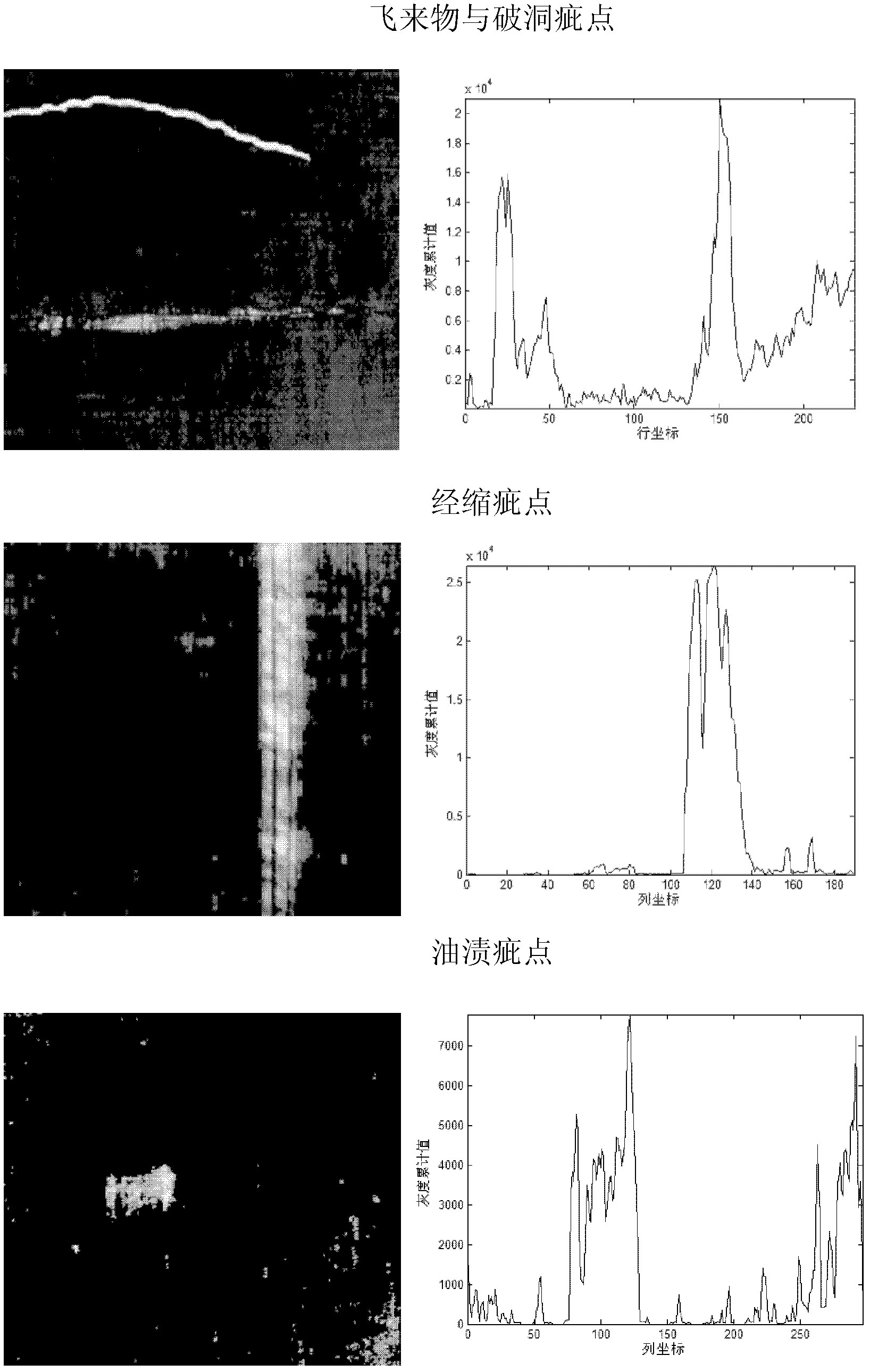

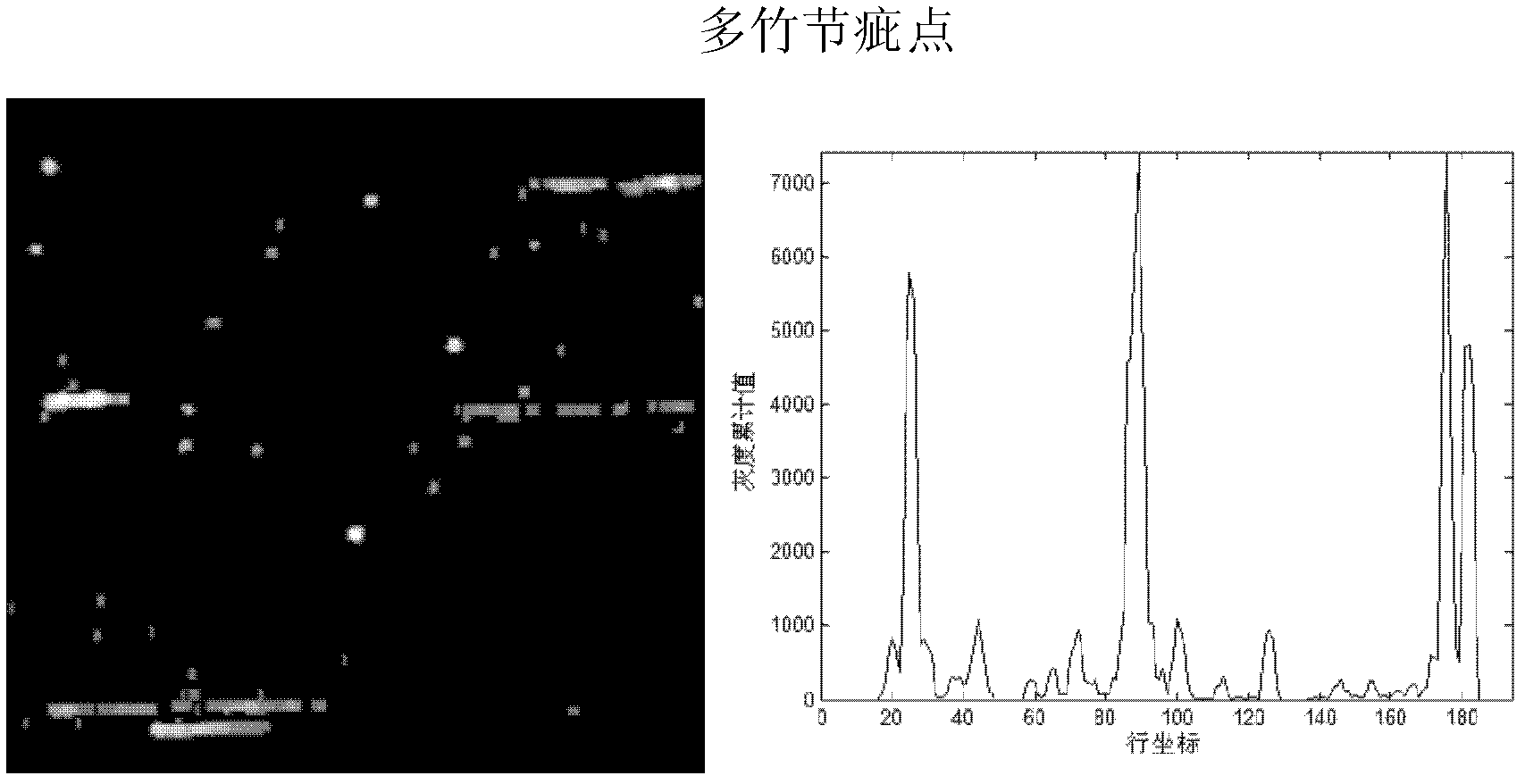

Dual-simplified pulse coupled neural network-based grey cloth defect division method

InactiveCN102592266ASolve problems that are difficult to synchronize calculationsGuaranteed real-timeImage enhancementComputation complexityDigital image

The invention discloses a dual-simplified pulse coupled neural network-based grey cloth defect division method, which comprises the following steps of: firstly, acquiring a digital image of grey cloth with the size of M*N by using a camera, and transmitting the digital image to an image cache; secondly, performing defect characteristic extraction calculation on the digital image in the image cache by adopting a local binary pattern arithmetic operator to eliminate the influence of illumination non-uniformity, a texture background and noise interference and highlight a defect area, and simultaneously compressing the calculated image into one-(n*n)th of the original image; thirdly, performing iteration calculation for high and low luminance grey cloth defect division on a processing result image by adopting a dual source pulse coupled neural network (DSPCNN); and finally, judging whether iteration is performed to set iteration times t or not, and performing merging calculation on a DSPCNN processing result to obtain a grey cloth defect division result diagram S. By the method, the problems of many regulation parameters, high calculation complexity and non-adaptability of the conventional grey cloth defect division technology are solved, and the real-time performance, consistence and accuracy of grey cloth defect detection are improved.

Owner:XI'AN POLYTECHNIC UNIVERSITY

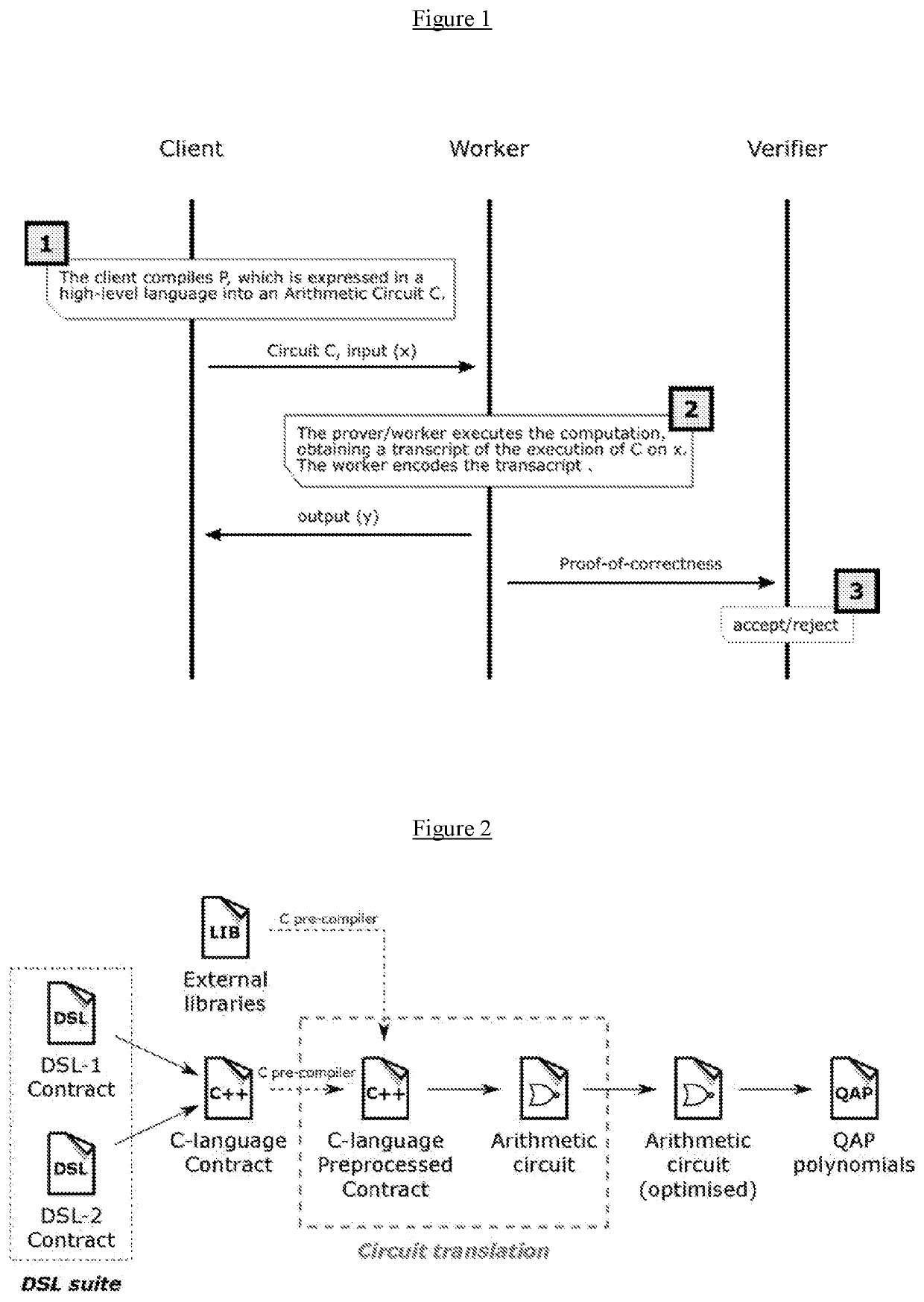

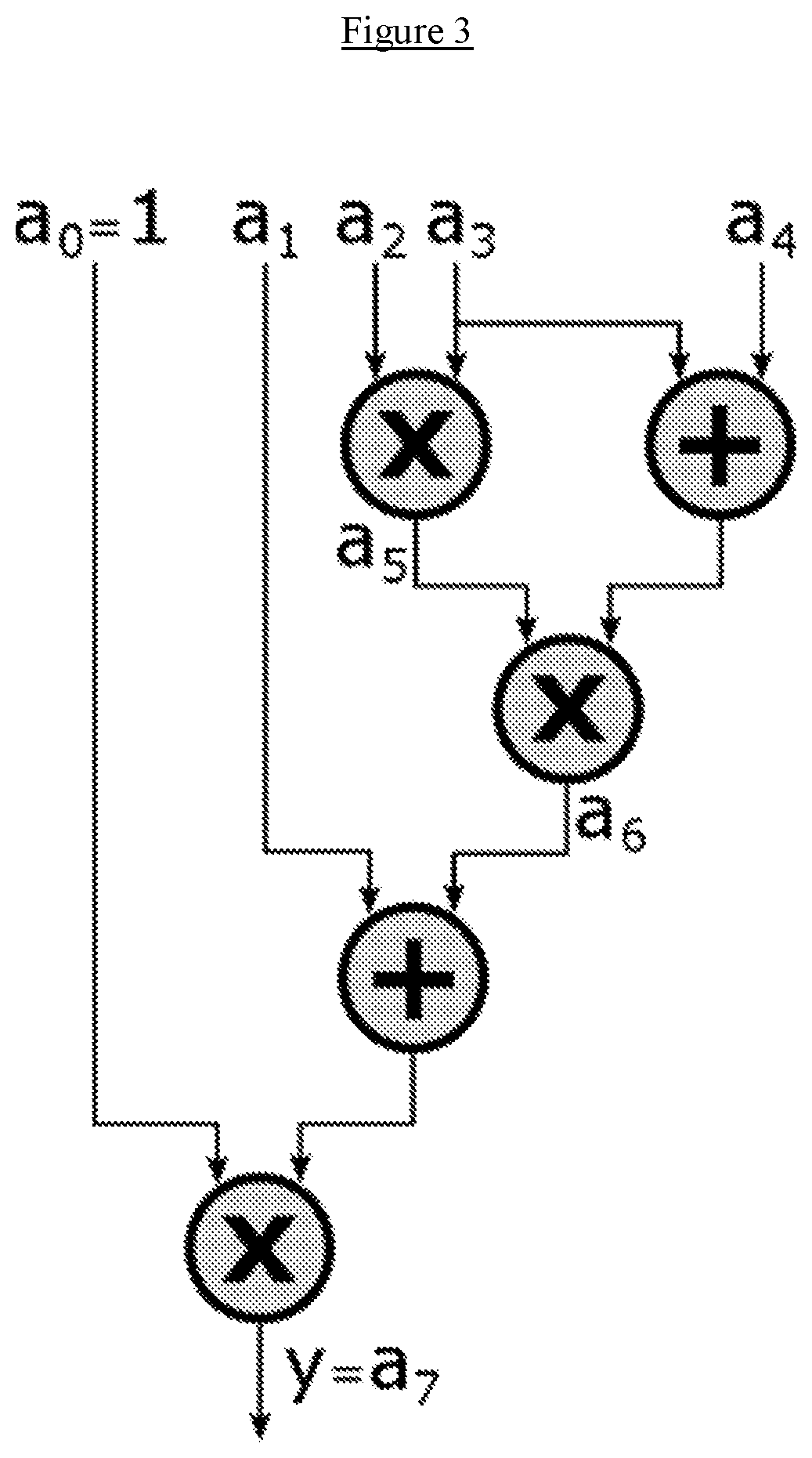

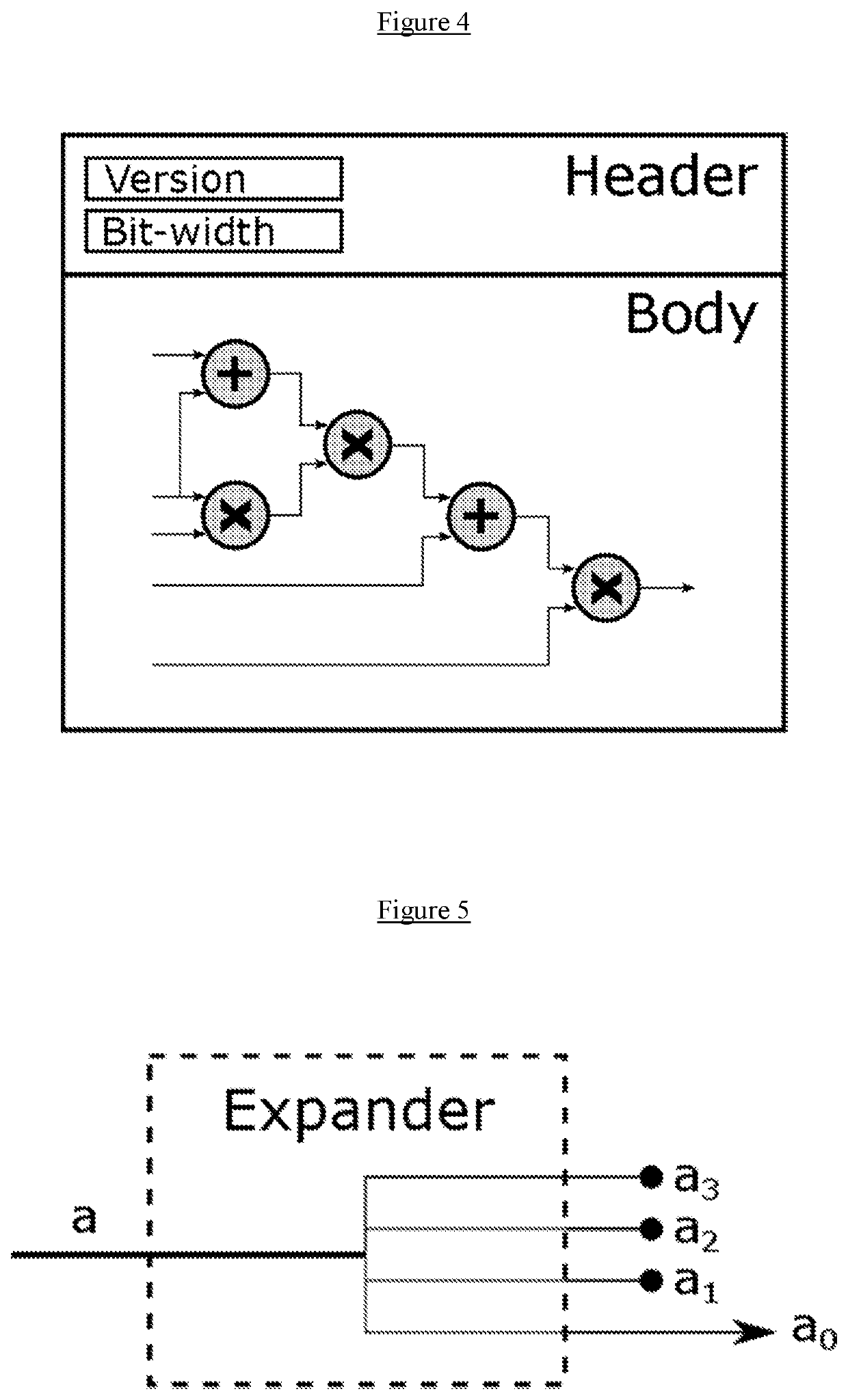

Arithmetic enhancement of c-like smart contracts for verifiable computation

ActiveUS20200348916A1Public key for secure communicationDatabase distribution/replicationComputer hardwareBit line

The invention provides systems and methods for converting high level source code into an arithmetic circuit which represents the functionality expressed in the source code. The invention comprises a translation / interpretation component for performing this conversion. In a preferred embodiment, the source code is a smart contract such as those used in relation to a blockchain platform. The invention could be used in relation to the Bitcoin network, for example. A method in accordance with an embodiment comprises the steps of: processing a portion of high level source code (e.g. a smart contract) to generate an arithmetic circuit. The arithmetic circuit comprises one or more arithmetic gates arranged to represent at least some of the functionality expressed in the source code. The processing involves evaluating one or more constants provided in the source code to produce one or more expressions that include Boolean and / or arithmetic operators. The arithmetic circuit comprises n-bit wires connected to arithmetic gates; it can be used to provide a hardware and / or software circuit. The arithmetic circuit can be used to generate a quadratic program which can be executed upon a processor.

Owner:NCHAIN LICENSING AG

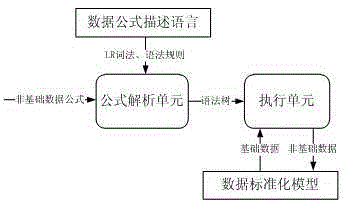

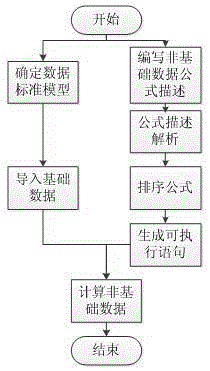

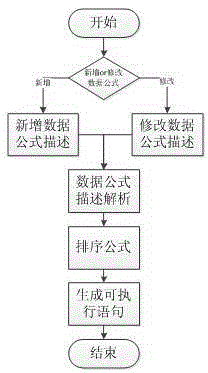

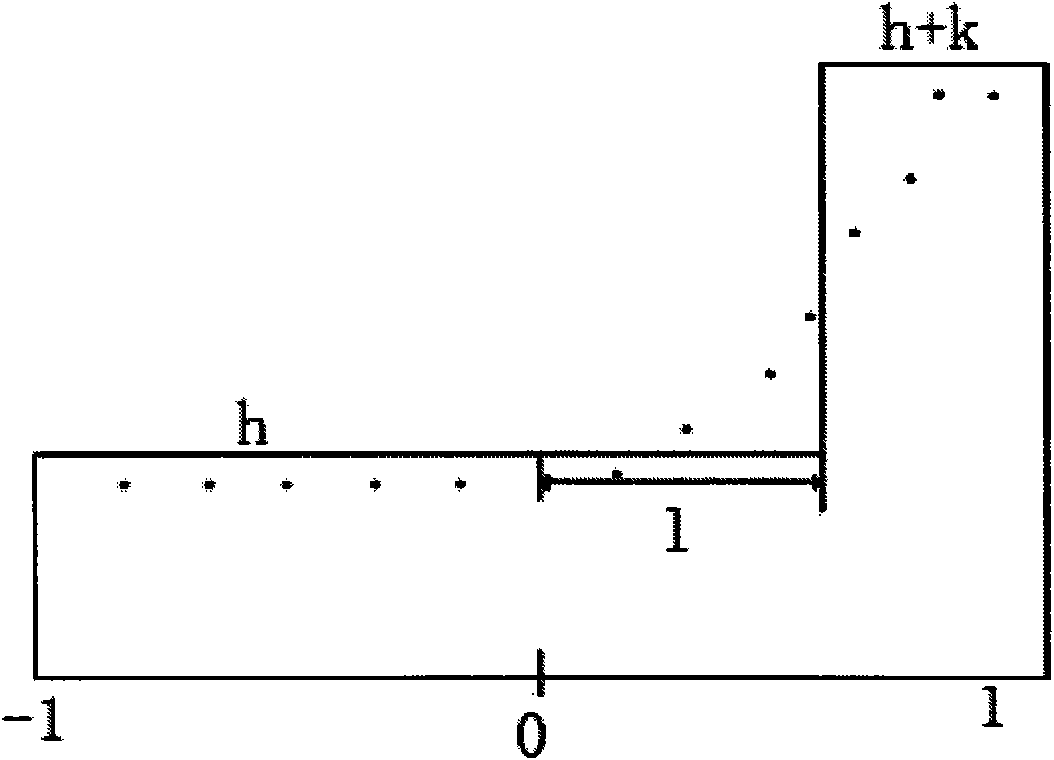

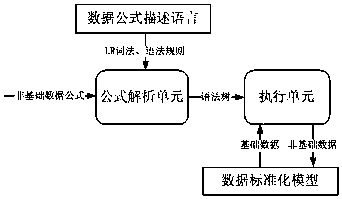

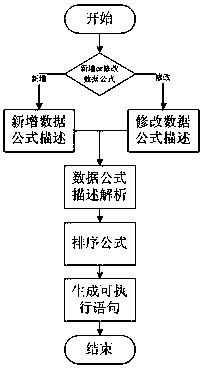

Formula analysis based complicated index set calculation method and system

ActiveCN105404608AFully automatedSolve inefficiencyComplex mathematical operationsData setData mining

Embodiments of the invention propose a formula analysis based complicated index set calculation method and system. The calculation method comprises: determining parameters of a data standardization model, wherein the parameters include a dimension, a measurement value and a derivative value of data in a data set; determining basic data in the data set; determining non-basic data in the data set and representing the non-basic data by arithmetic of at least one or more sub-data; representing each non-basic datum as a tree structure, wherein end points of the tree structure are arithmetic operators for generating the non-basic data, and branches of the tree structure are sub-data for generating the non-basic data; sorting formulae corresponding to all the generated non-basic data to ensure that formulae corresponding to the sub-data cited by the non-basic data are arranged before formulae corresponding to the non-basic data; then generating executable statements according to the sorted formulae; and importing the basic data and then executing the executable statements in sequence.

Owner:CHINACCS INFORMATION IND

Method for quickly positioning circular mark in PCB visual detection

ActiveCN102034101BFast operationHigh precision requirementsCharacter and pattern recognitionHough transformErrors and residuals

The invention discloses a round sub-pixel detection algorithm based on point Hough transform and Legendre moments, and provides a method for quickly positioning a circular mark in polymerase chain reaction (PCR) visual detection. The method comprises the following steps of: performing edge detection and Hough transform to acquire a circular mark pixel-level reference value by using a Canny arithmetic operator; filtering off noise points in edge points by using the circular mark pixel-level reference value; analyzing a sub-pixel edge positioning method based on Legendre orthogonal moments, and an error; evaluating sub-pixels of the edge points from which the noise points are filtered off by using the Legendre orthogonal moments and an error method; and finally fitting the edge points by a fast least square method to acquire accurate circle center positioning parameter and radius parameter of a round. By the method, the characteristic of high speed of point Hough transform operation is kept; and the method has the characteristics of high positioning accuracy, high noise resistance, accuracy, high speed and robustness and meets the requirements of high accuracy and real-time property in the PCB visual detection.

Owner:GUANGDONG UNIV OF TECH

Display device and method thereof

ActiveUS9613563B2Inhibit deteriorationResolution problemStatic indicating devicesDisplay deviceAfterimage

A display apparatus includes: a display panel configured to display an image frame; an arithmetic operator configured to divide the image frame into blocks, calculate a pixel gradation value of the pixel blocks, and accumulate the calculated pixel gradation values; and a compensator configured to locally reduce a luminance of a corresponding pixel block, of which a respective accumulated pixel gradation value exceeds a threshold value of among the plurality of pixel blocks, and to compensate for a luminance difference between the corresponding pixel block, for which the luminance has been reduced, and surrounding pixel blocks. Accordingly, it is possible to effectively remove an afterimage.

Owner:SAMSUNG ELECTRONICS CO LTD

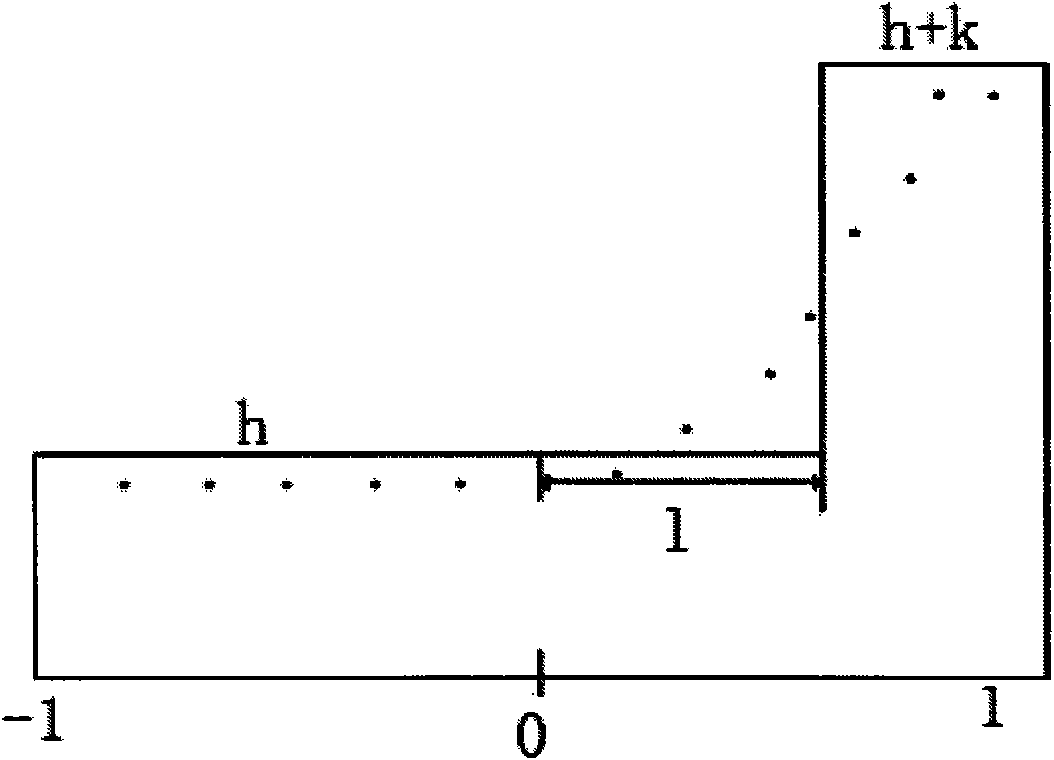

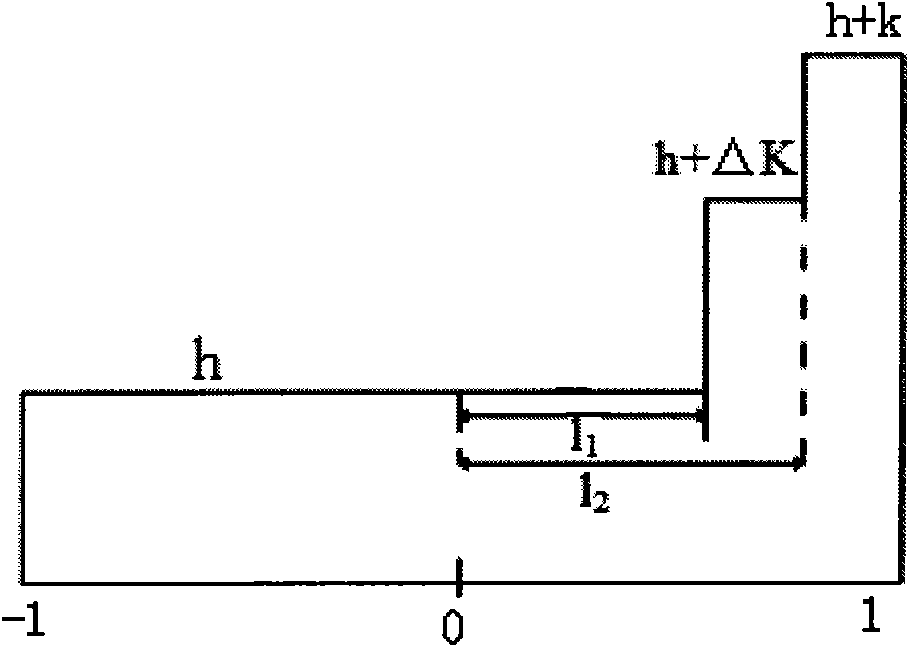

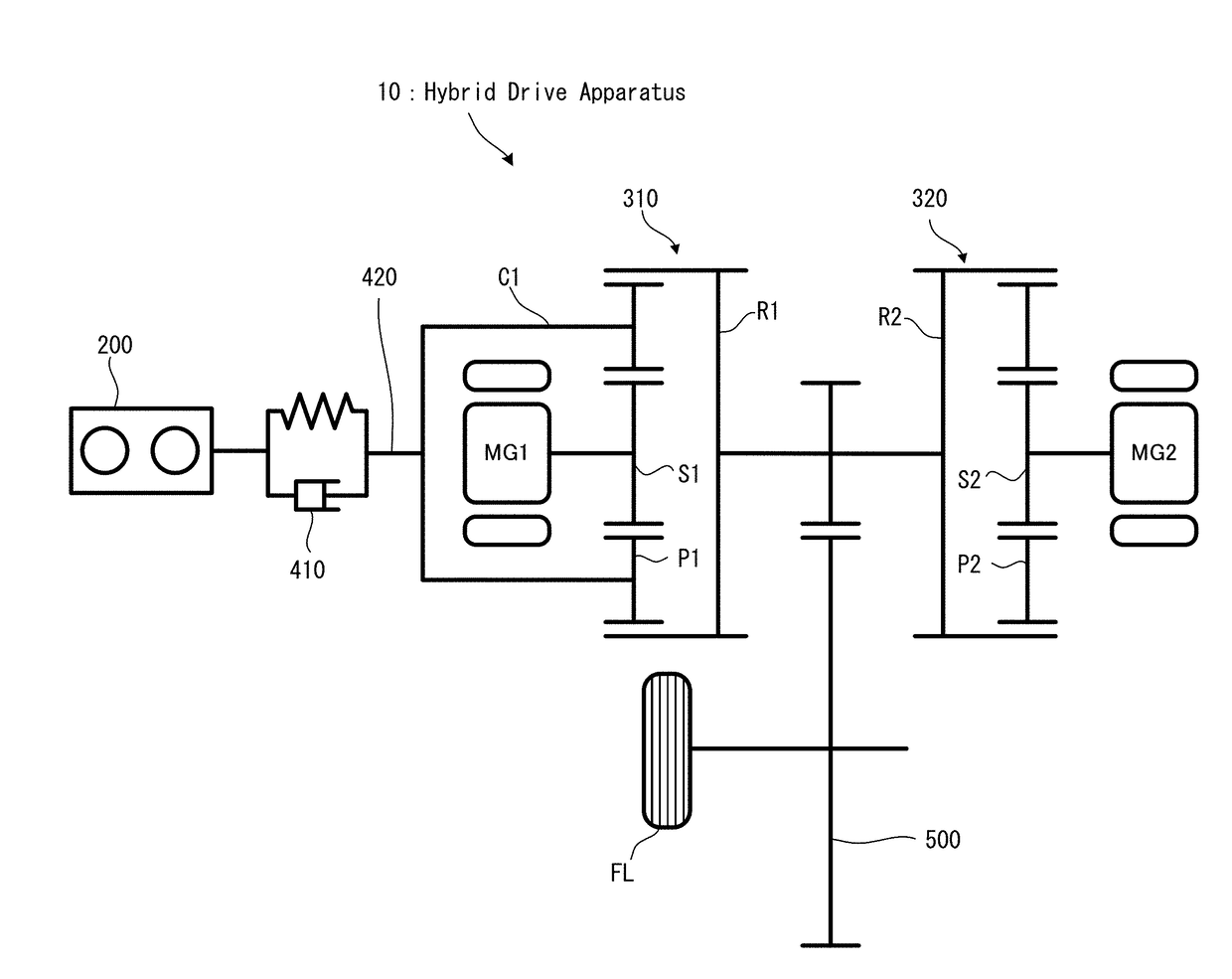

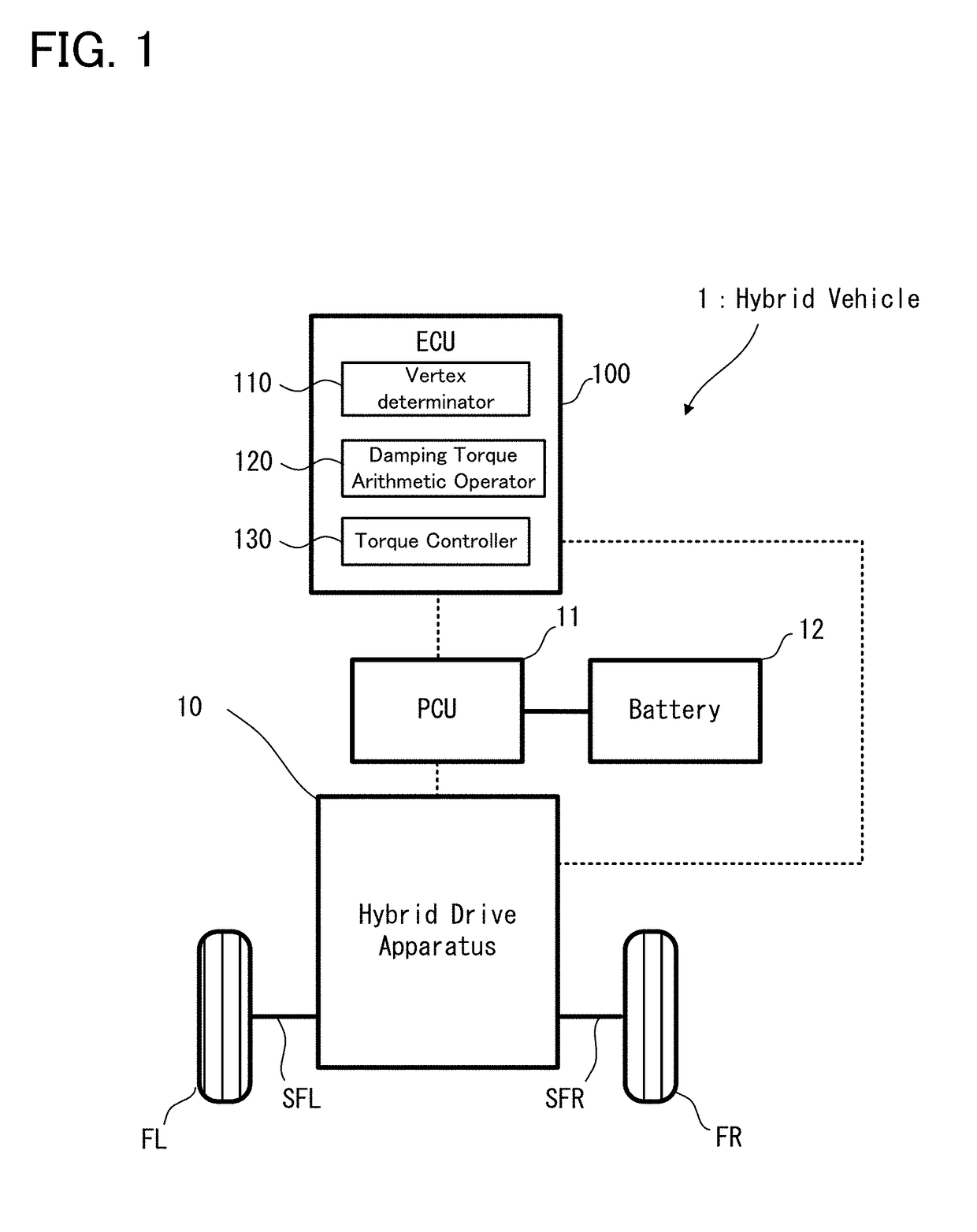

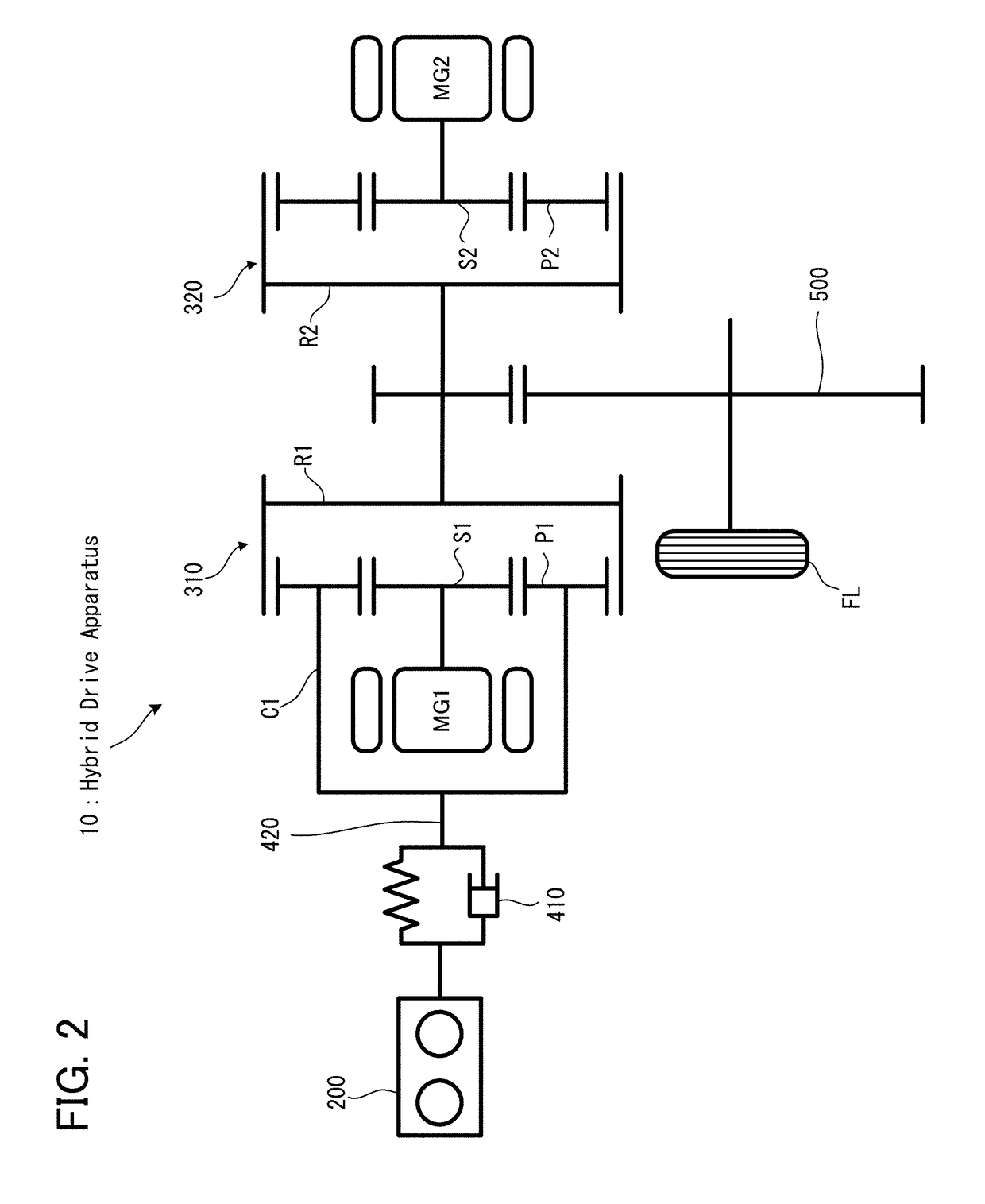

Control apparatus for hybrid vehicle

ActiveUS20180229711A1Influence of torque fluctuationAccurate valueHybrid vehiclesPropulsion using engine-driven generatorsControl theoryHybrid vehicle

A control apparatus for a hybrid vehicle is configured to control the hybrid vehicle. The control apparatus is provided with: an arithmetic operator configured to arithmetically operate a pulsation compensating torque for compensating a pulsation component; an arithmetic operation controller configured to control the arithmetic operator (i) to arithmetically operate the pulsation compensating torque in a first cycle in a period that does not include a vertex portion in which the pulsation compensating torque is locally maximal or locally minimal and (ii) to arithmetically operate the pulsation compensating torque in a second cycle, a length of which is shorter than that of the first cycle, in a period that includes the vertex portion; and a torque controller configured to control the electric motor to output a torque including the pulsation compensating torque arithmetically operated by the arithmetic operator.

Owner:TOYOTA JIDOSHA KK

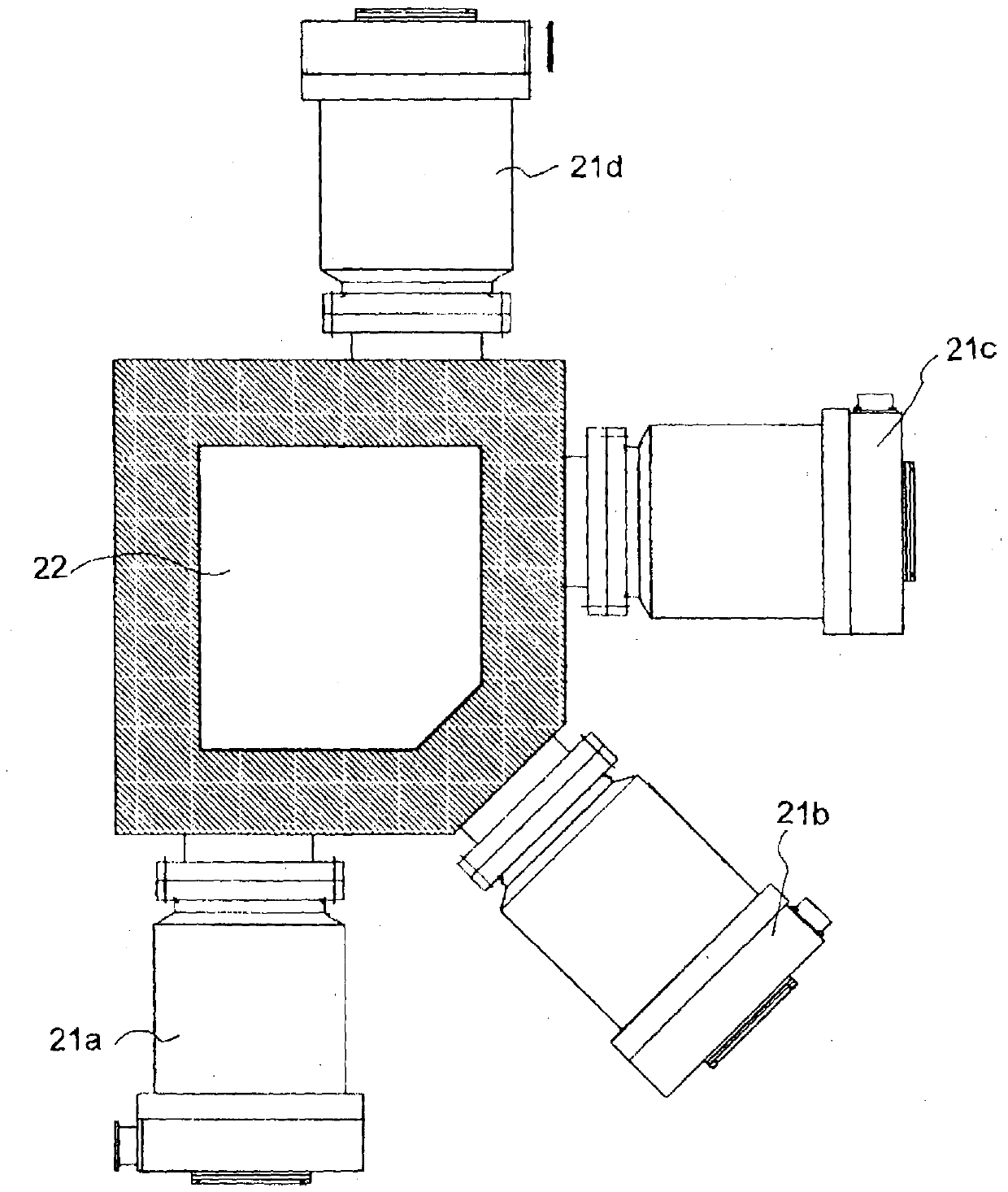

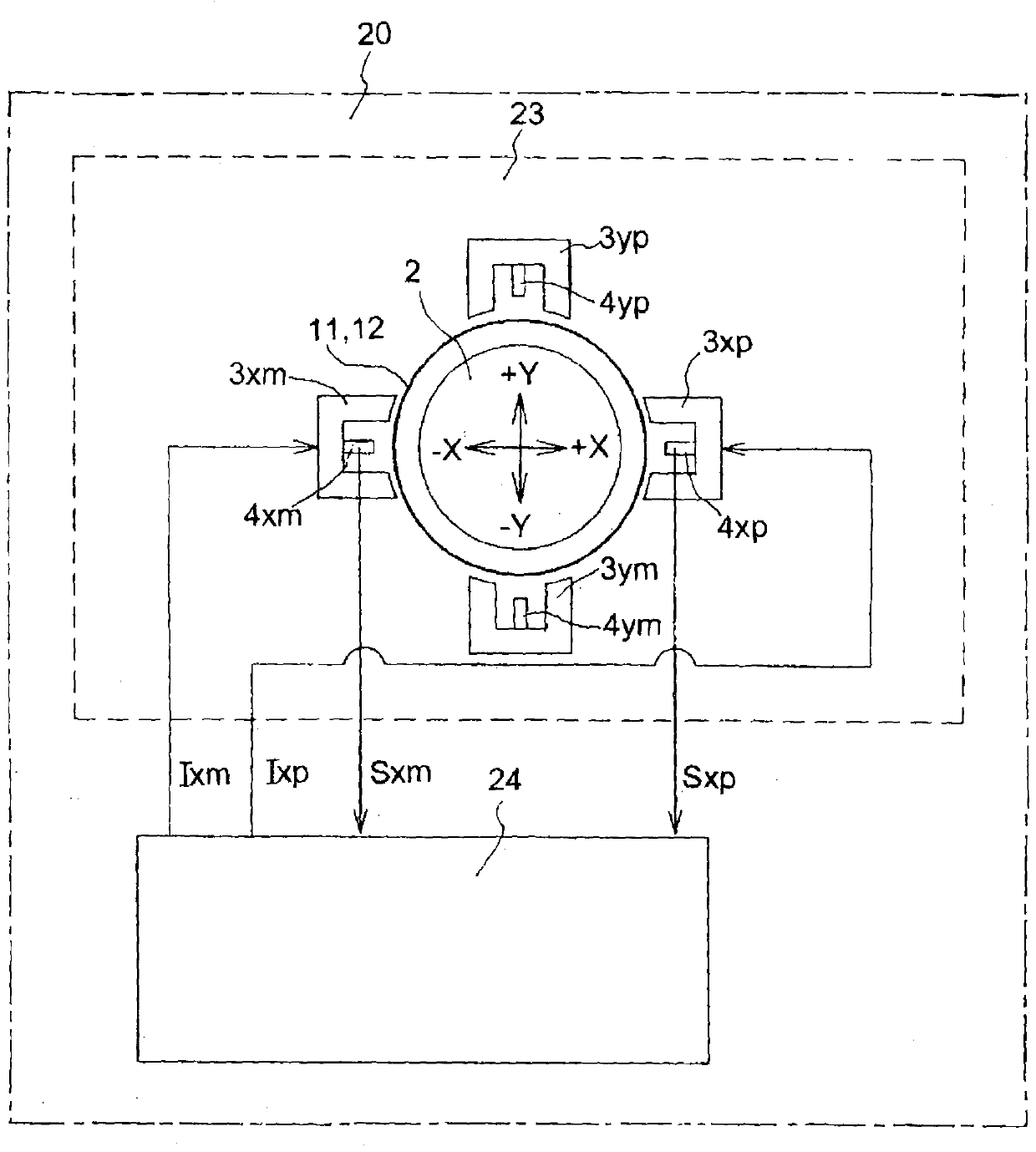

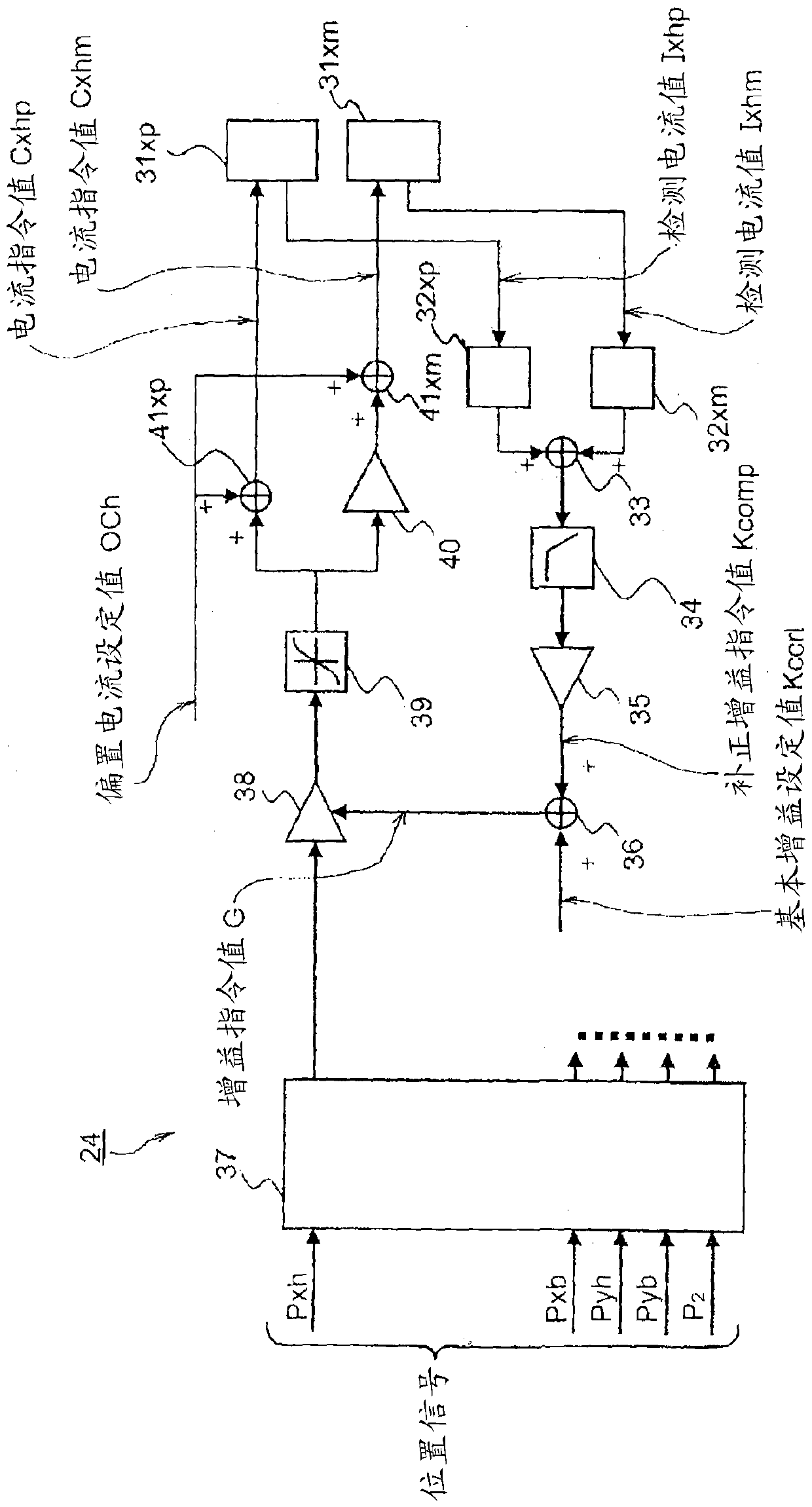

Magnetic bearing unit, and vacuum pump

ActiveCN105723107BReduce vibrationReduce memory capacityPump componentsShaftsMagnetic bearingAudio power amplifier

Provided is a magnetic bearing device which allows easy initial adjustment and allows optimal bearing control to be performed by a simple algorithm without increasing a memory capacity of a controller. A pair of square multipliers and an adder acquire respective steady-state current values of a pair of electromagnets which attract a rotor shaft of a magnetic bearing not shown in opposite radial directions, square the respective steady-state current values, and add up the respective squared steady-state current values. Then, to optimally change respective currents in the electromagnets in accordance with a mounting posture of the magnetic bearing, a correction coefficient arithmetic operator calculates a correction gain instruction value acting on the electromagnets from the steady-state current values squared / added up. Then, a gain instruction value obtained by adding the correction gain instruction value to a fundamental gain of a control circuit for the electromagnets is input to a gain amplifier. The gain amplifier generates a corrected current instruction value on the basis of the gain instruction value and optimally controls the magnetic bearing.

Owner:EDWARDS JAPAN

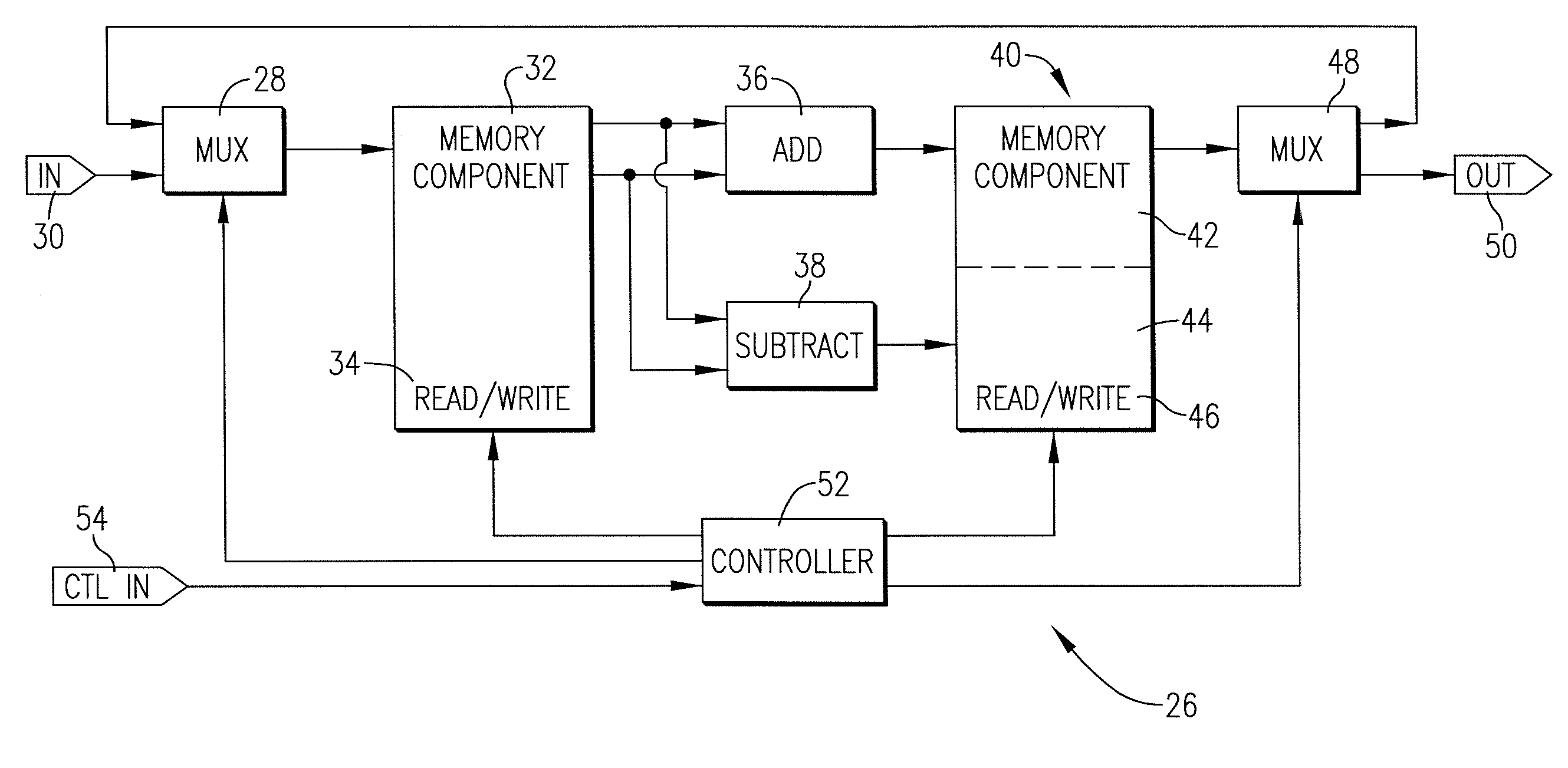

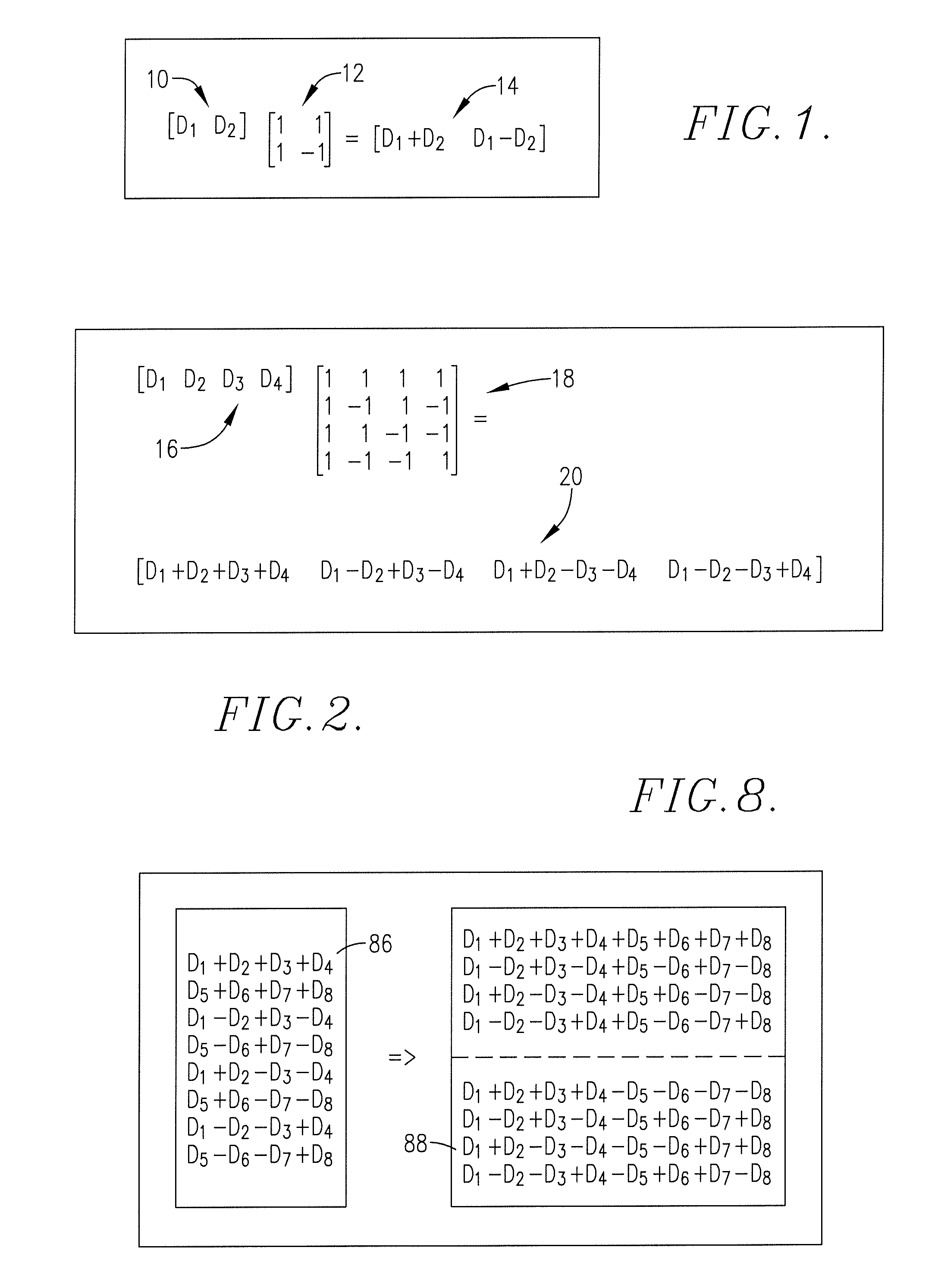

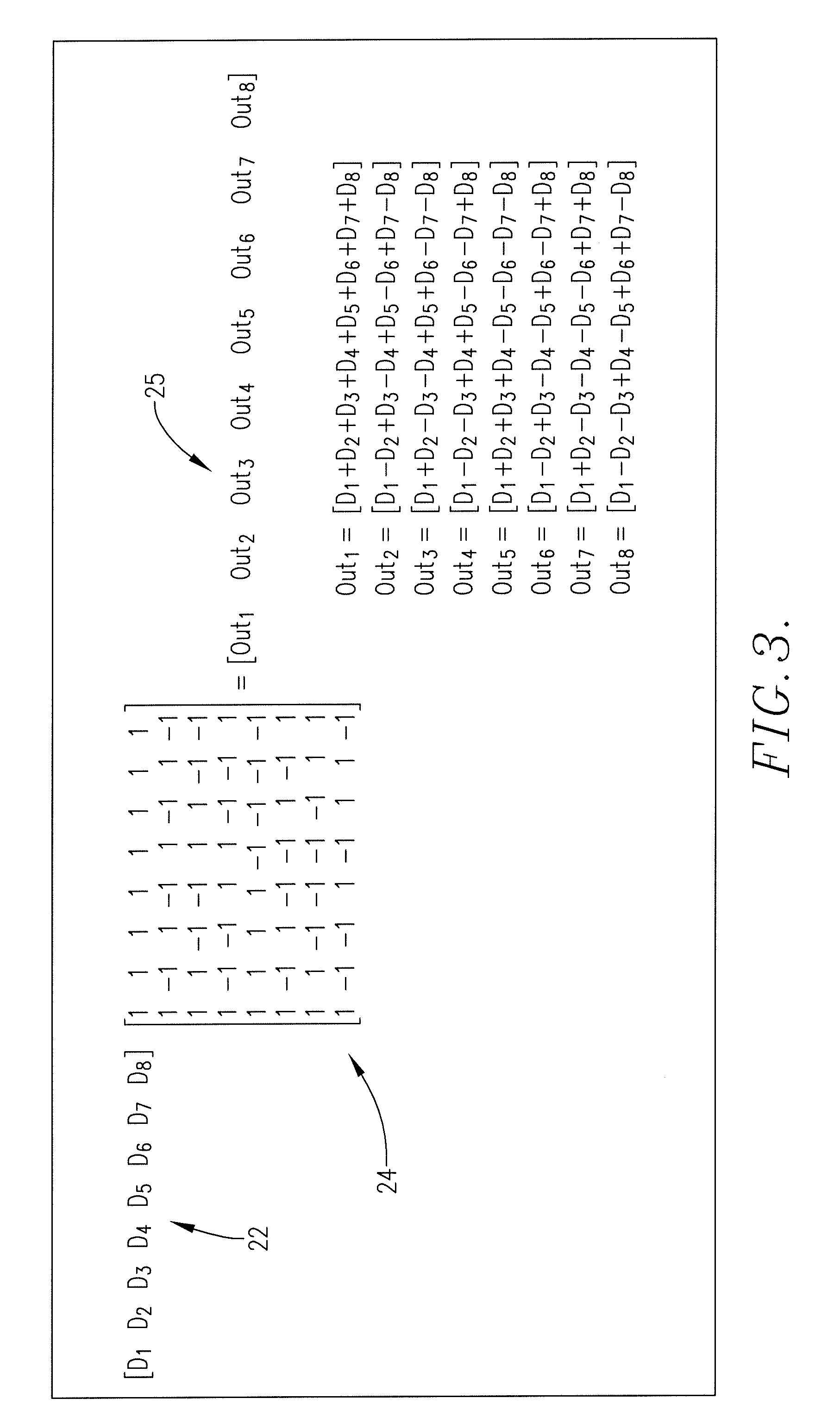

System and method for performing an optimized discrete walsh transform

InactiveUS20080109507A1Reduce settingsComputation using non-contact making devicesSpecial data processing applicationsData valueComputer science

A circuit (26) performs a discrete Walsh transform using a reduced set of arithmetic operators. The circuit (26) comprises a first memory component (32), an adder (36), a subtractor (38), a second memory component (40), and a controller (52). In each of a plurality of stages, the controller (52) enables the first memory component (32) to communicate each of a plurality of pairs of values stored therein to the adder (36) and to the subtractor (38). The controller (52) enables the second memory component (40) to store each of a plurality of results from the adder (36) and the subtractor (38) and to communicate the stored results to the first memory component (32) for use in a subsequent stage. In the subsequent stage, the controller (52) enables the first memory component (32) to communicate to the adder (36) and to the subtractor (38) a plurality of new pairs of data values consisting first of the add results from the previous stage in the order they were generated and then the subtract results in the order they were generated.

Owner:L 3 COMM CORP

Inter-frame predictor circuit for video encoder and method for implementing same

InactiveCN102075762BDesign fasterTelevision systemsDigital video signal modificationComputer architectureVideo encoding

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

A method and system for calculating complex index sets based on formula analysis

Embodiments of the invention propose a formula analysis based complicated index set calculation method and system. The calculation method comprises: determining parameters of a data standardization model, wherein the parameters include a dimension, a measurement value and a derivative value of data in a data set; determining basic data in the data set; determining non-basic data in the data set and representing the non-basic data by arithmetic of at least one or more sub-data; representing each non-basic datum as a tree structure, wherein end points of the tree structure are arithmetic operators for generating the non-basic data, and branches of the tree structure are sub-data for generating the non-basic data; sorting formulae corresponding to all the generated non-basic data to ensure that formulae corresponding to the sub-data cited by the non-basic data are arranged before formulae corresponding to the non-basic data; then generating executable statements according to the sorted formulae; and importing the basic data and then executing the executable statements in sequence.

Owner:CHINACCS INFORMATION IND

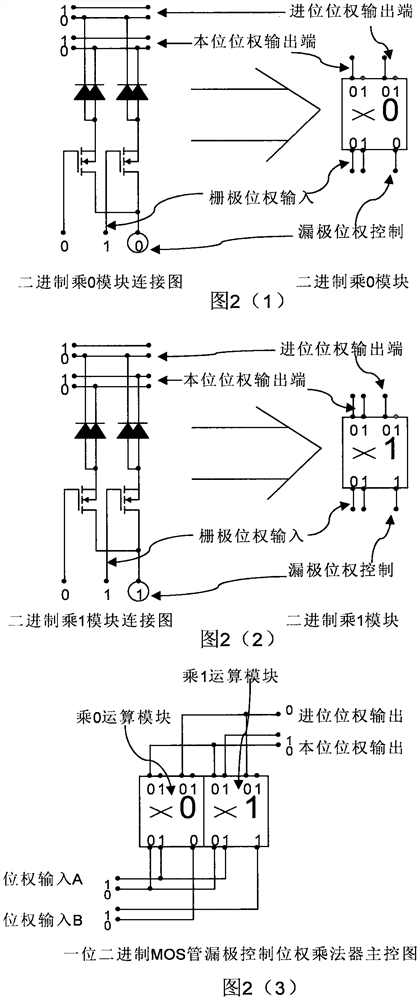

MOS transistor drain electrode control transmission type multi-system and decimal bit weight multiplier

The invention discloses a one-bit multi-valued digital multiplier (MOS transistor drain control transmission type multi-system and decimal bit weight multiplier) composed of MOS transistors. The one-bit multi-valued digital multiplier is composed of multiple-valued multiplication modules in different forms. The multi-valued multiplication module is provided with a 0 multiplying module, a 1 multiplying module, a 2 multiplying module,..., and an N multiplying module; the module is formed by combining and connecting arithmetic units which are connected in different modes. The unit is formed by permutation and combination of units according to the claim 3 of the patent application 20171111971. X 'a multi-system arithmetic operator of quantitative logic assignment fractal integrated unit circuit '. Drain electrodes of MOS tubes of all units are connected together to serve as a control end and are connected with a numerical value end of one set of bit weight input, grid electrodes of all theunits in the module serve as another set of bit weight data input end, and the formed module is called a leakage control multiplication operation module. The module outputs are divided into two groups, one group is standard output, and the carry systems of the selected circuits are different.

Owner:胡五生

MOS transistor array type multi-system and decimal bit weight multiplier

PendingCN111610952AEffective hardware supportSolve multivalued operationsDigital data processing detailsTransistor arrayBinary multiplier

Owner:胡五生

Analog to digital converter including differential vco

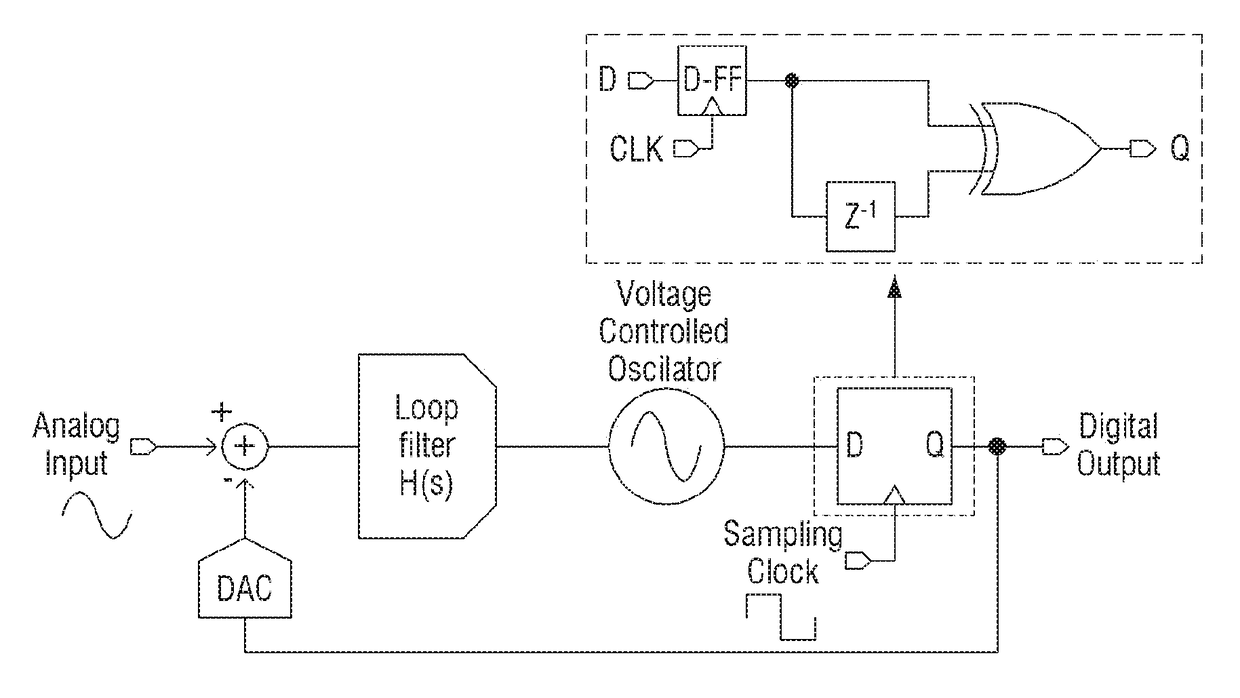

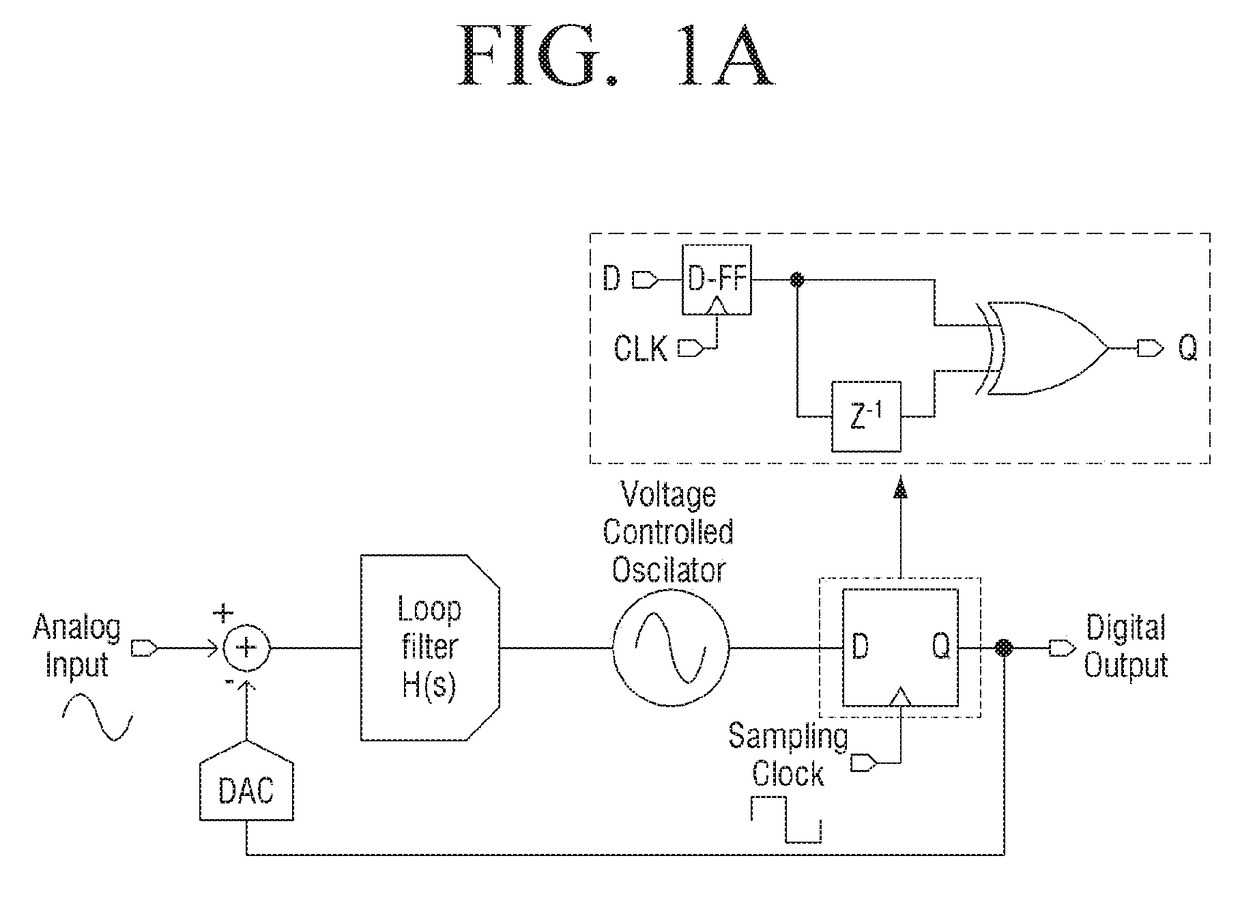

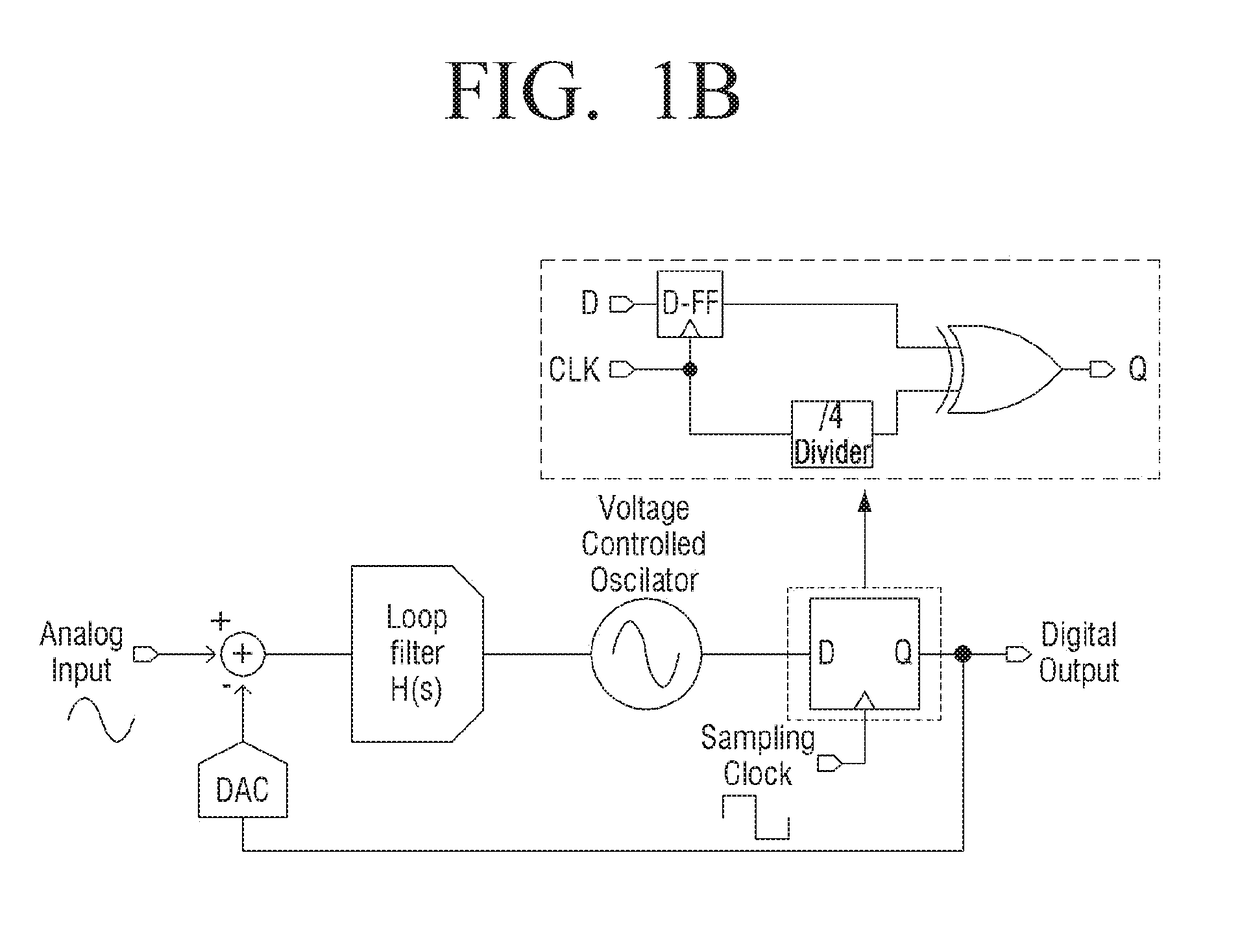

ActiveUS20170272094A1Increase rangeAdvantageous in area and power consumption and yieldExclusive-OR circuitsAnalogue conversionPhase detectorLoop filter

An analog to digital converter is provided. The analog to digital converter includes: an arithmetic operator combining an analog input signal with a feedback signal; a loop filter filtering an output signal of the arithmetic operator; a quantizer quantizing an output signal of the loop filter to output a digital signal; and a feedback converting the digital signal to output a feedback signal, in which the quantizer includes: a plurality of VCOs each receiving a positive output signal and a negative output signal of the loop filter and outputting VCO signals; a plurality of samplers receiving the VCO signals output from the plurality of VCOs, respectively and outputting sampled signals; and a phase detector detecting a phase difference in the sampled signals output from the plurality of samplers, respectively, to detect a phase difference in two VCO signals output from the plurality of VCOs, respectively.

Owner:IUCF HYU (IND UNIV COOP FOUND HANYANG UNIV)