Patents

Literature

2018 results about "Binary multiplier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

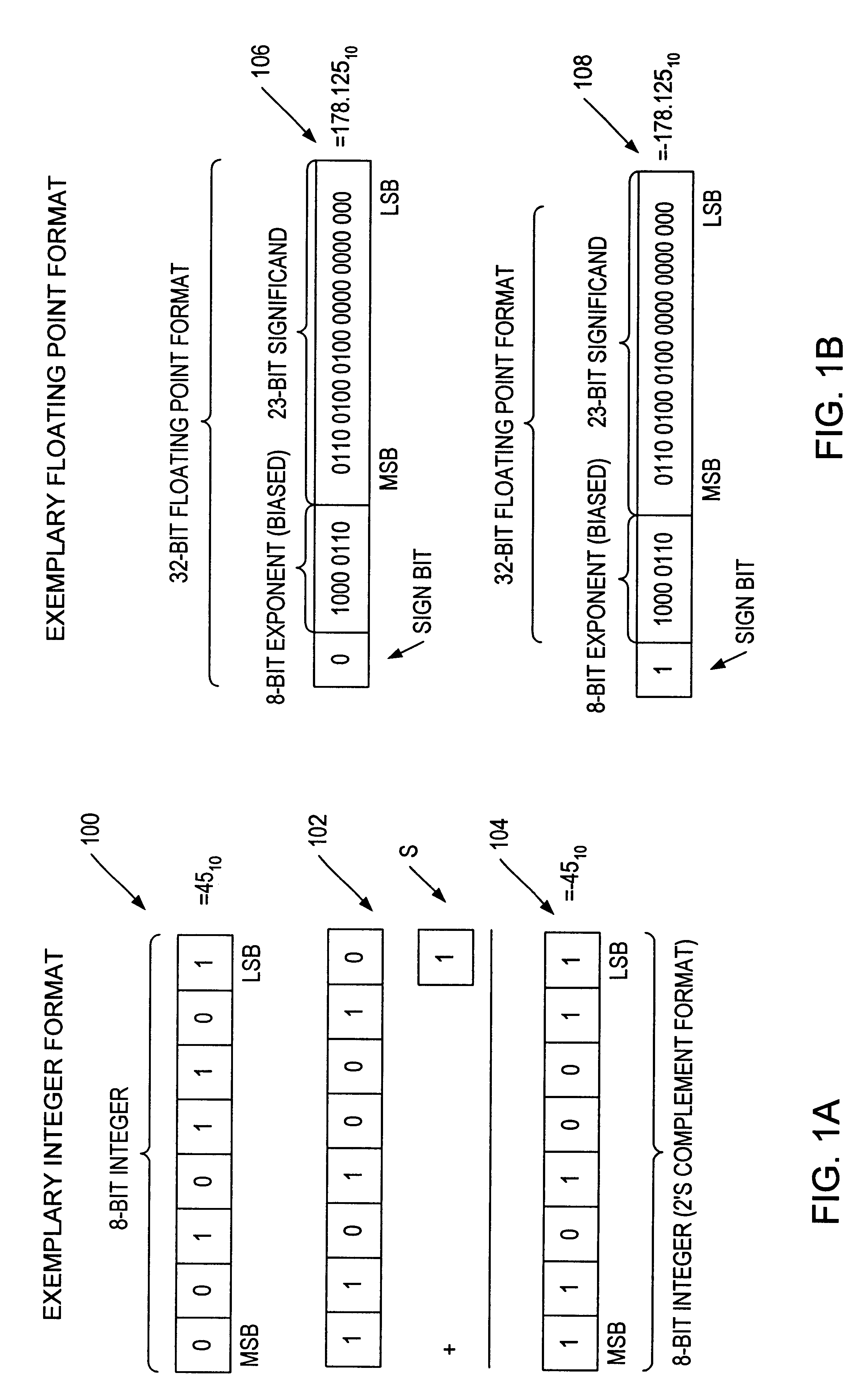

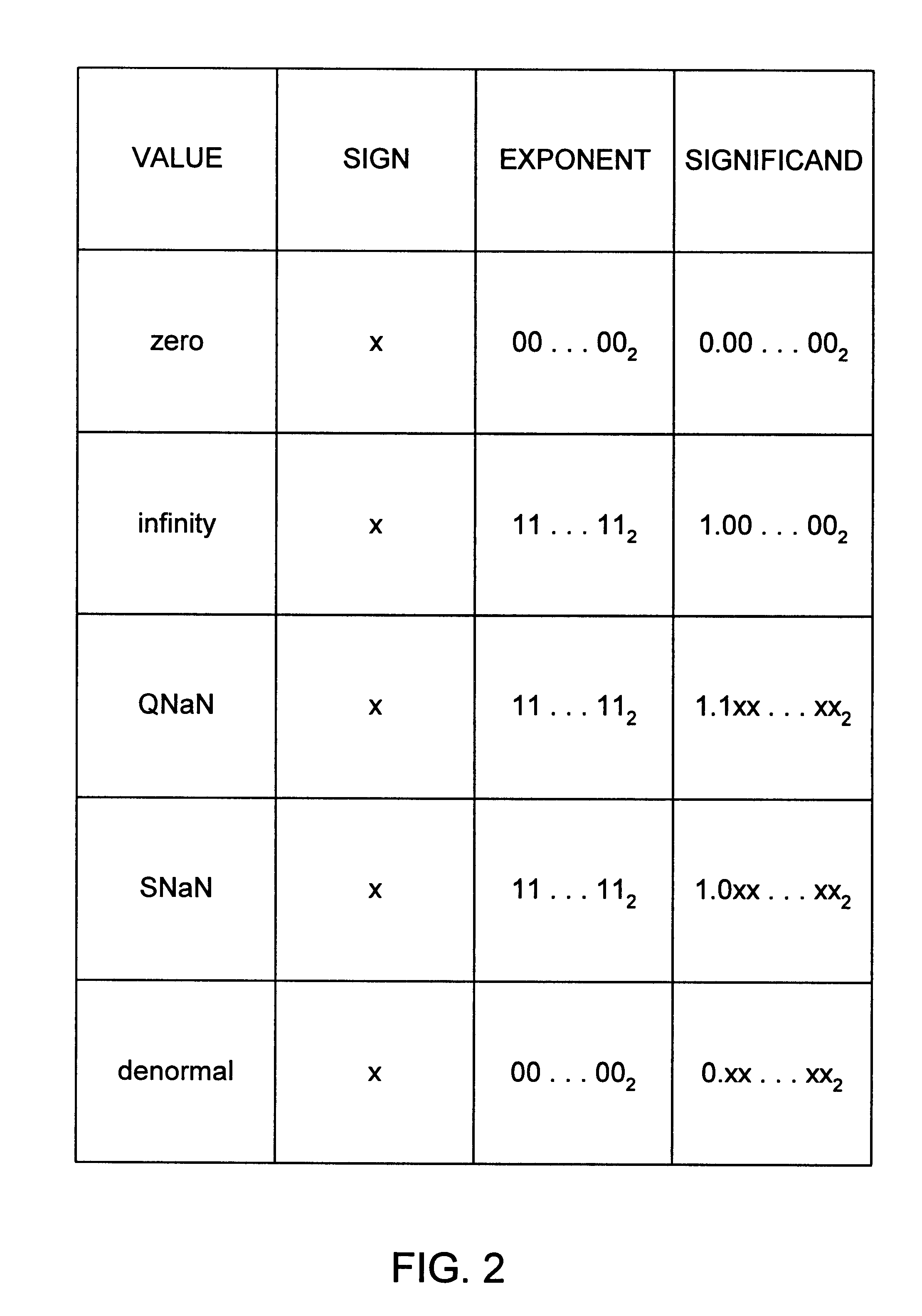

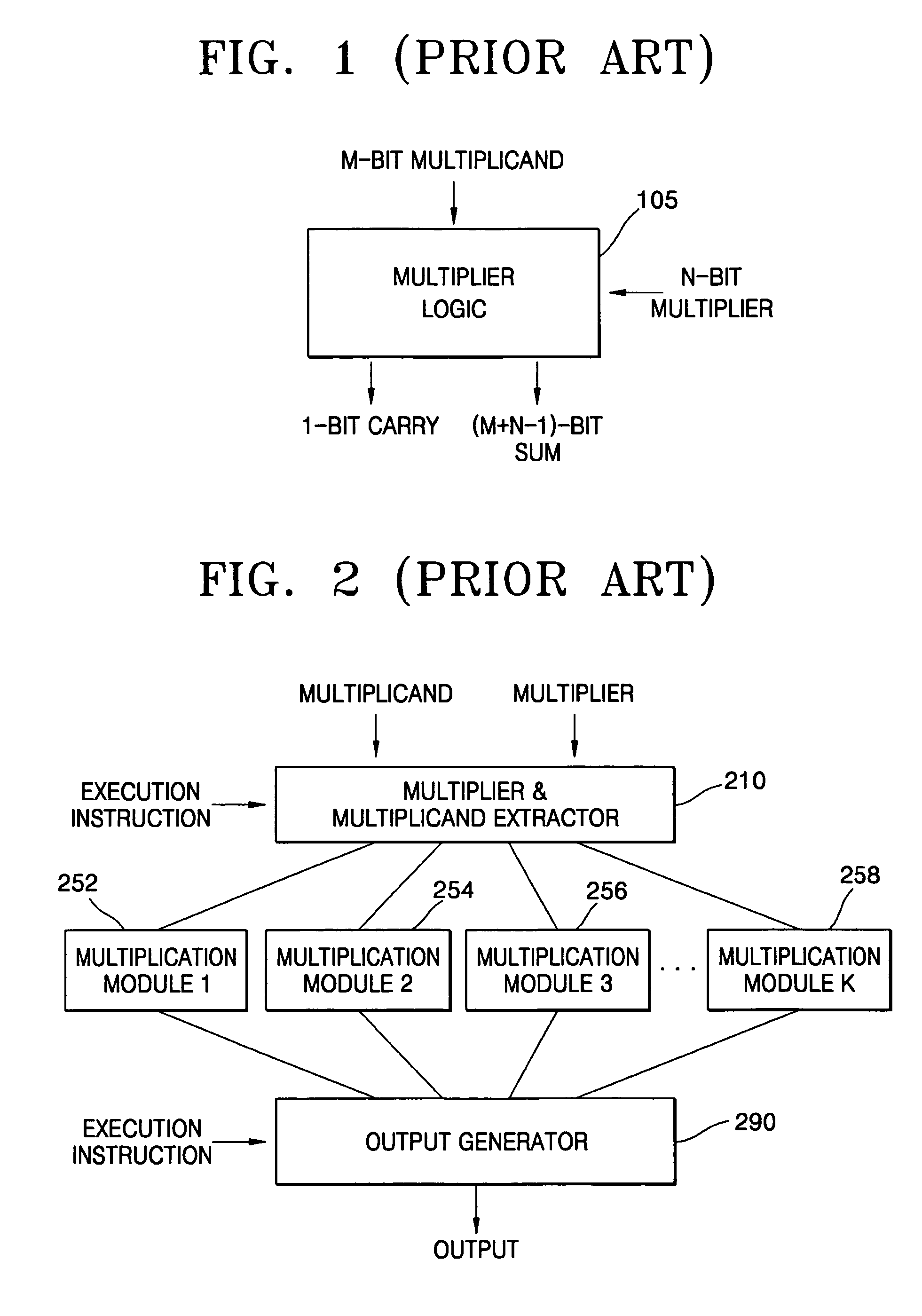

A binary multiplier is an electronic circuit used in digital electronics, such as a computer, to multiply two binary numbers. It is built using binary adders. A variety of computer arithmetic techniques can be used to implement a digital multiplier. Most techniques involve computing a set of partial products, and then summing the partial products together. This process is similar to the method taught to primary schoolchildren for conducting long multiplication on base-10 integers, but has been modified here for application to a base-2 (binary) numeral system.

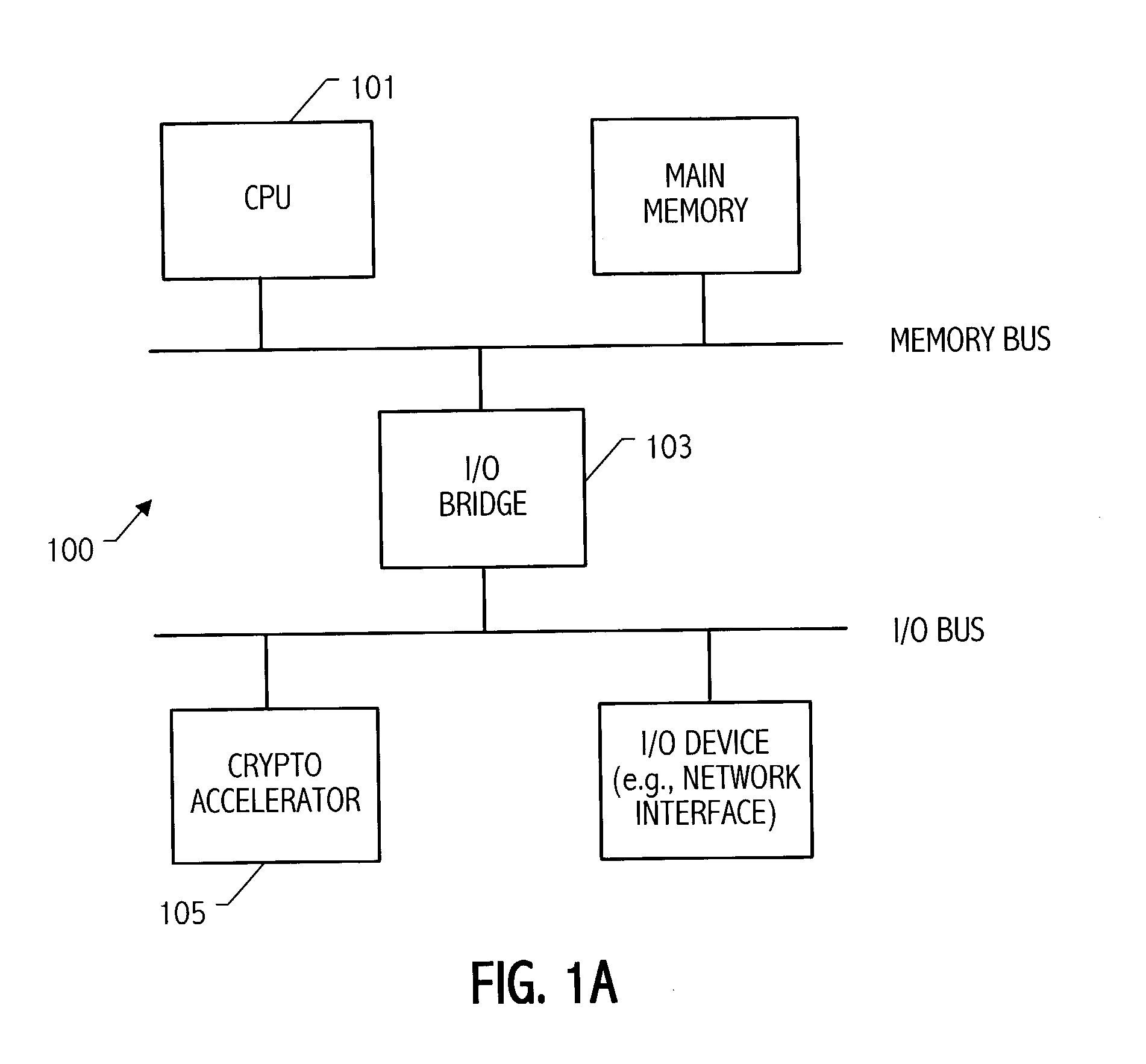

Shared FP and SIMD 3D multiplier

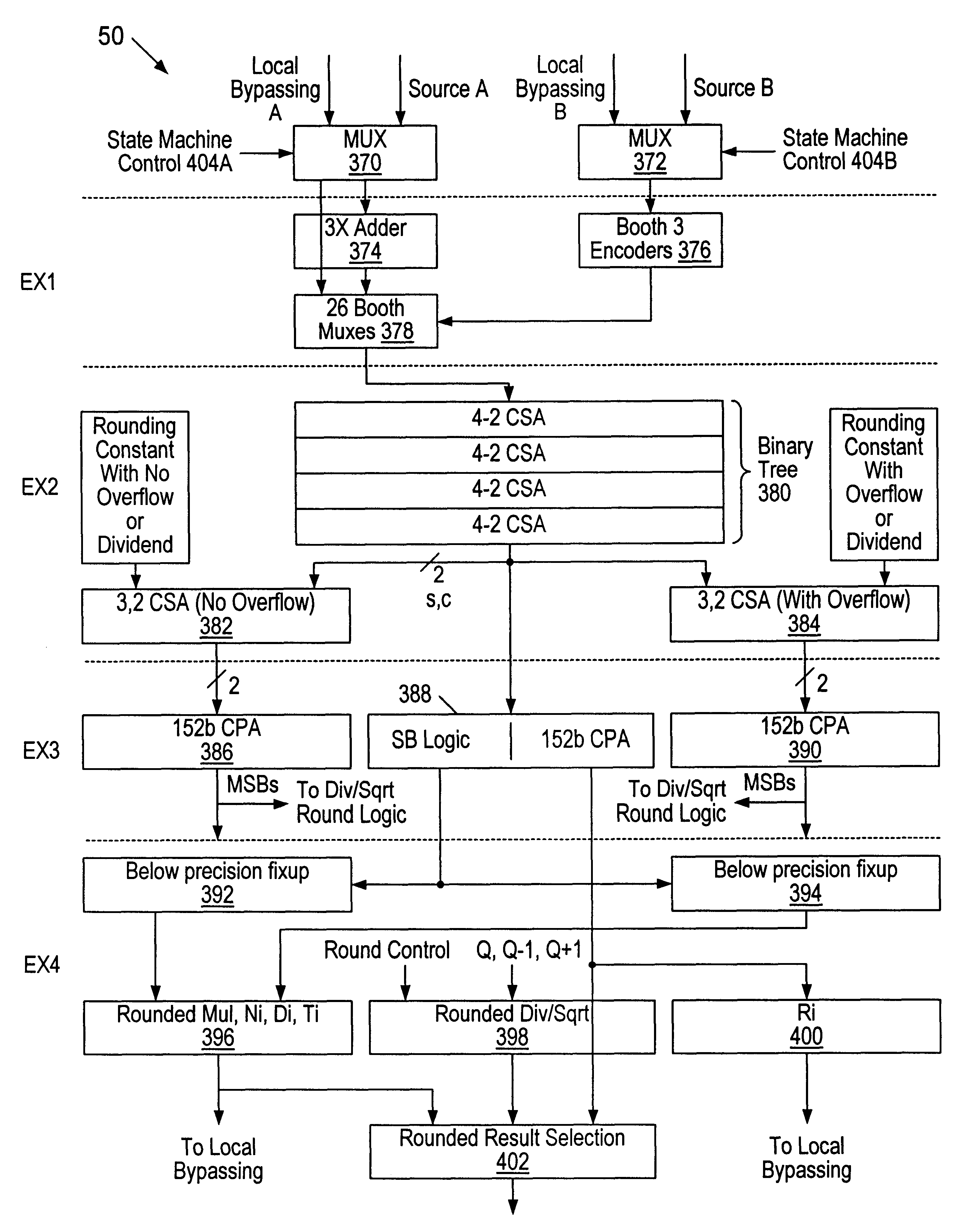

InactiveUS6490607B1Computations using contact-making devicesRuntime instruction translationComputerized systemTheoretical computer science

A multiplier configured to perform multiplication of both scalar floating point values (XxY) and packed floating point values (i.e., X1xY1 and X2xY2). In addition, the multiplier may be configured to calculate XxY-Z. The multiplier comprises selection logic for selecting source operands, a partial product generator, an adder tree, and two or more adders configured to sum the results from the adder tree to achieve a final result. The multiplier may also be configured to perform iterative multiplication operations to implement such arithmetical operations such as division and square root. The multiplier may be configured to generate two versions of the final result, one assuming there is an overflow, and another assuming there is not an overflow. A computer system and method for performing multiplication are also disclosed.

Owner:ADVANCED SILICON TECH

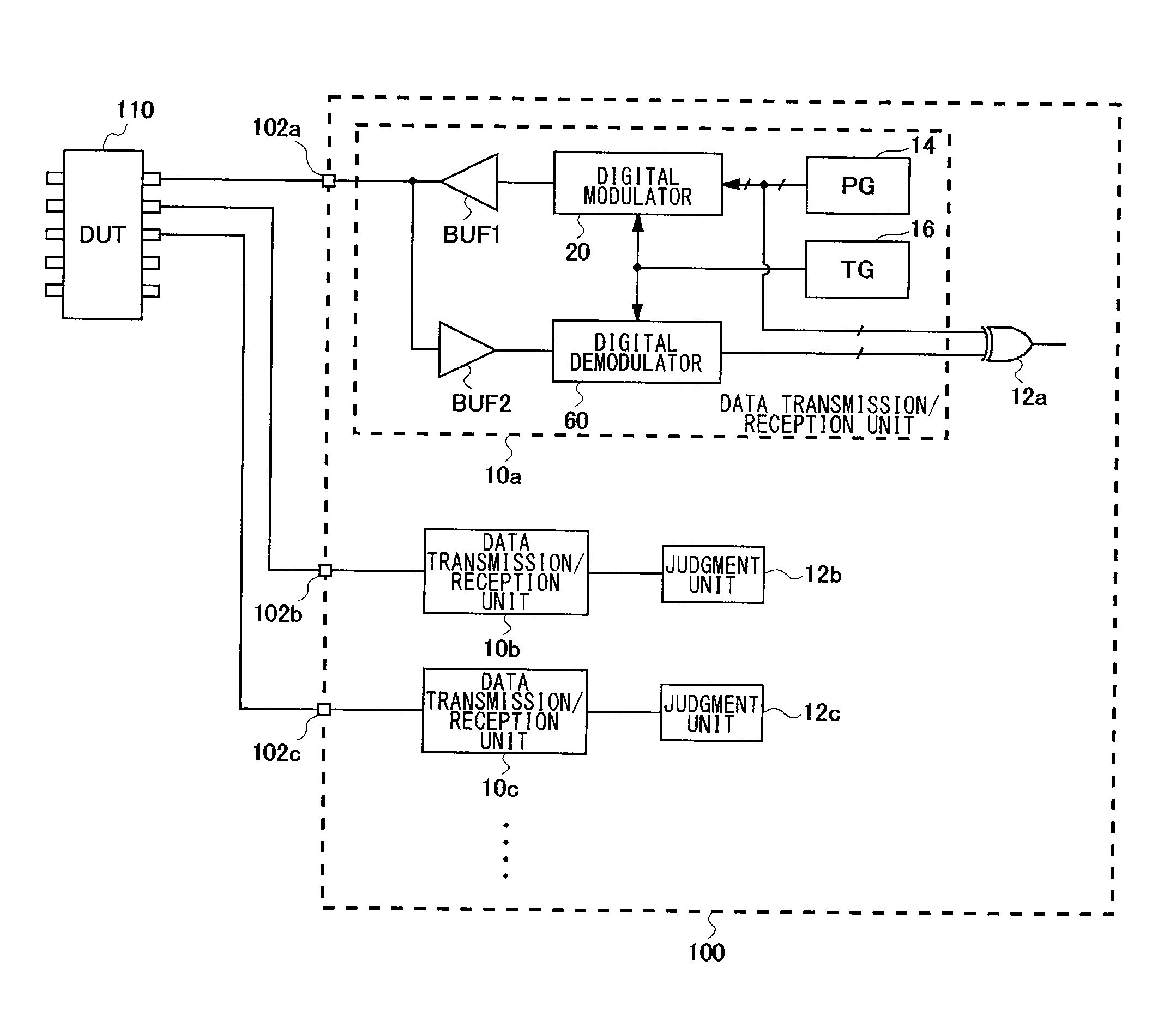

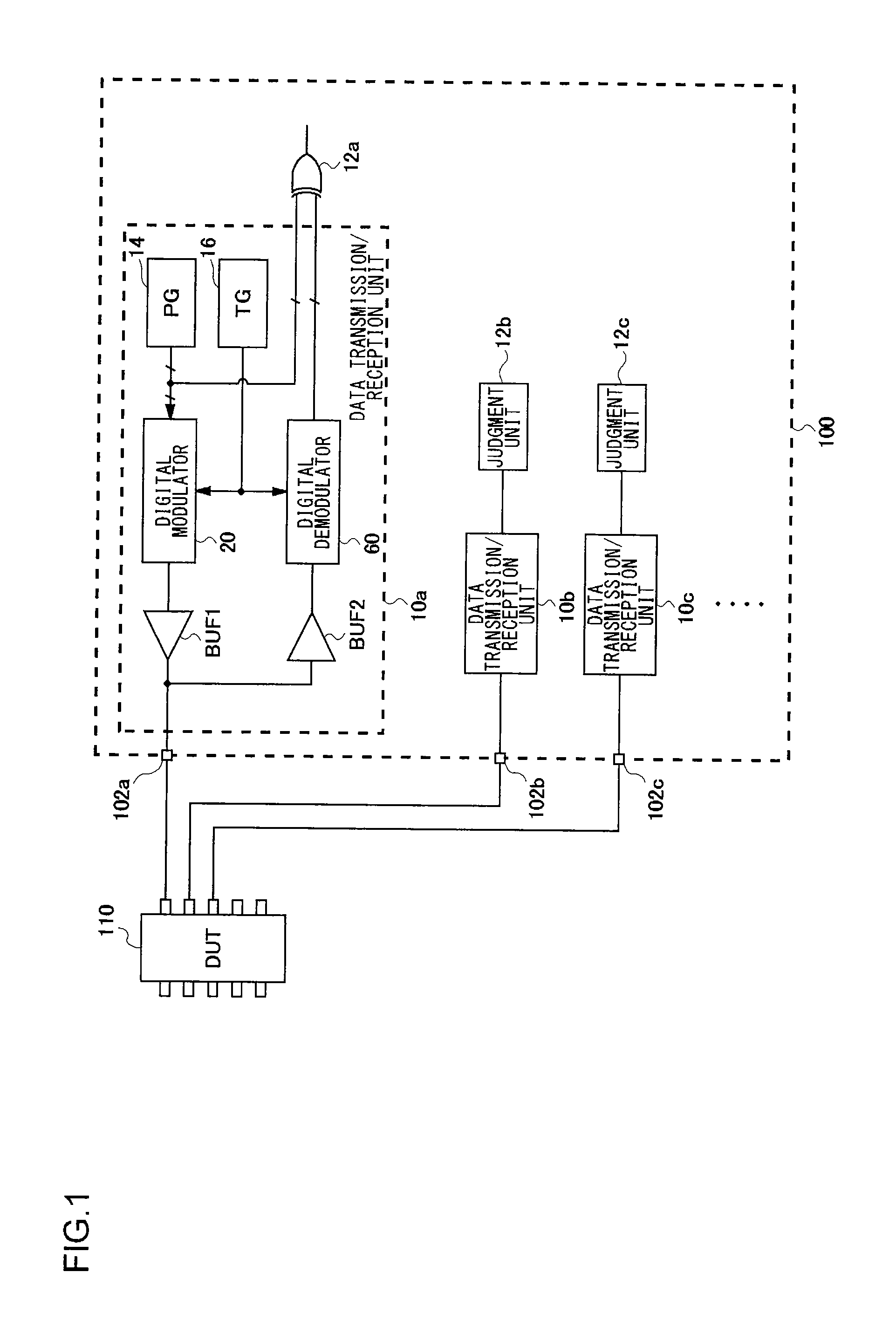

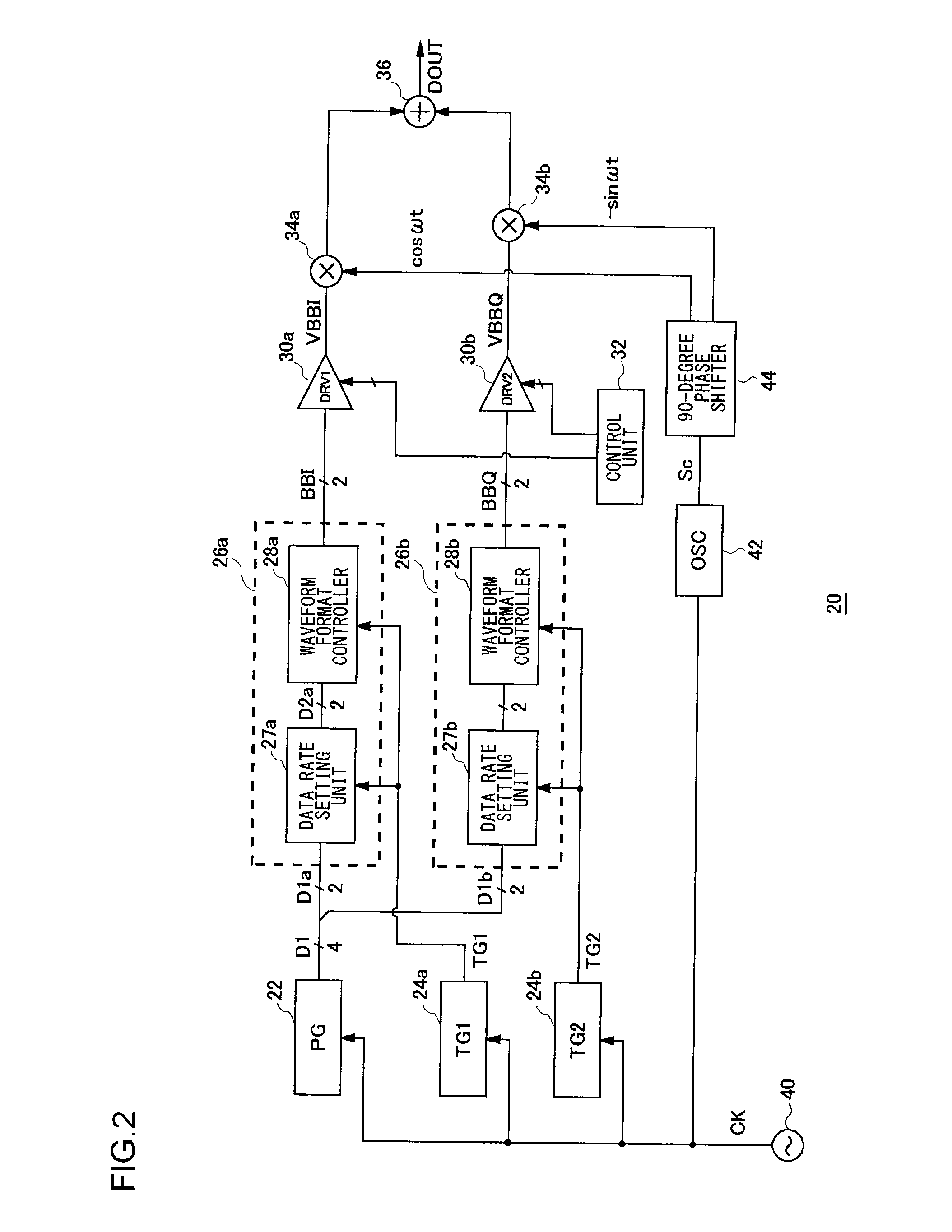

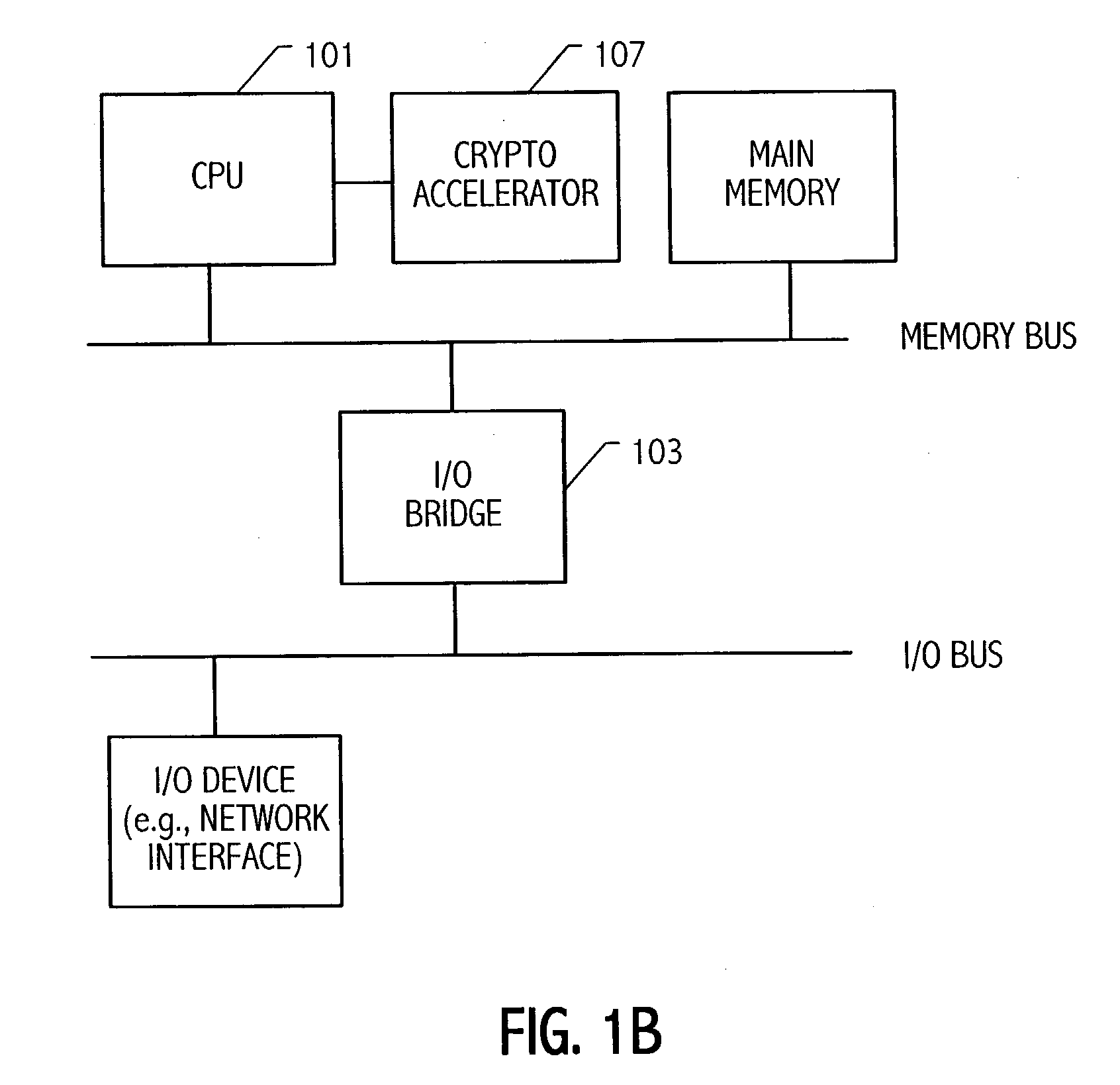

Test apparatus for digital modulated signal

ActiveUS20100321127A1Reduce circuit sizeCalibrating non-linear distortionElectrical testingAngle modulationBinary multiplierCarrier signal

A test apparatus includes digital modulators provided in increments of multiple channels. A baseband signal generator performs retiming of data input as a modulation signal for the in-phase (quadrature) component, using a timing signal the timing of which can be adjusted, thereby generating a baseband signal. A driver generates a multi-value digital signal having a level that corresponds to the baseband signal output from the baseband signal generator. A multiplier amplitude-modulates a carrier signal with the multi-value digital signal. An adder sums the output signals of the multipliers.

Owner:ADVANTEST CORP

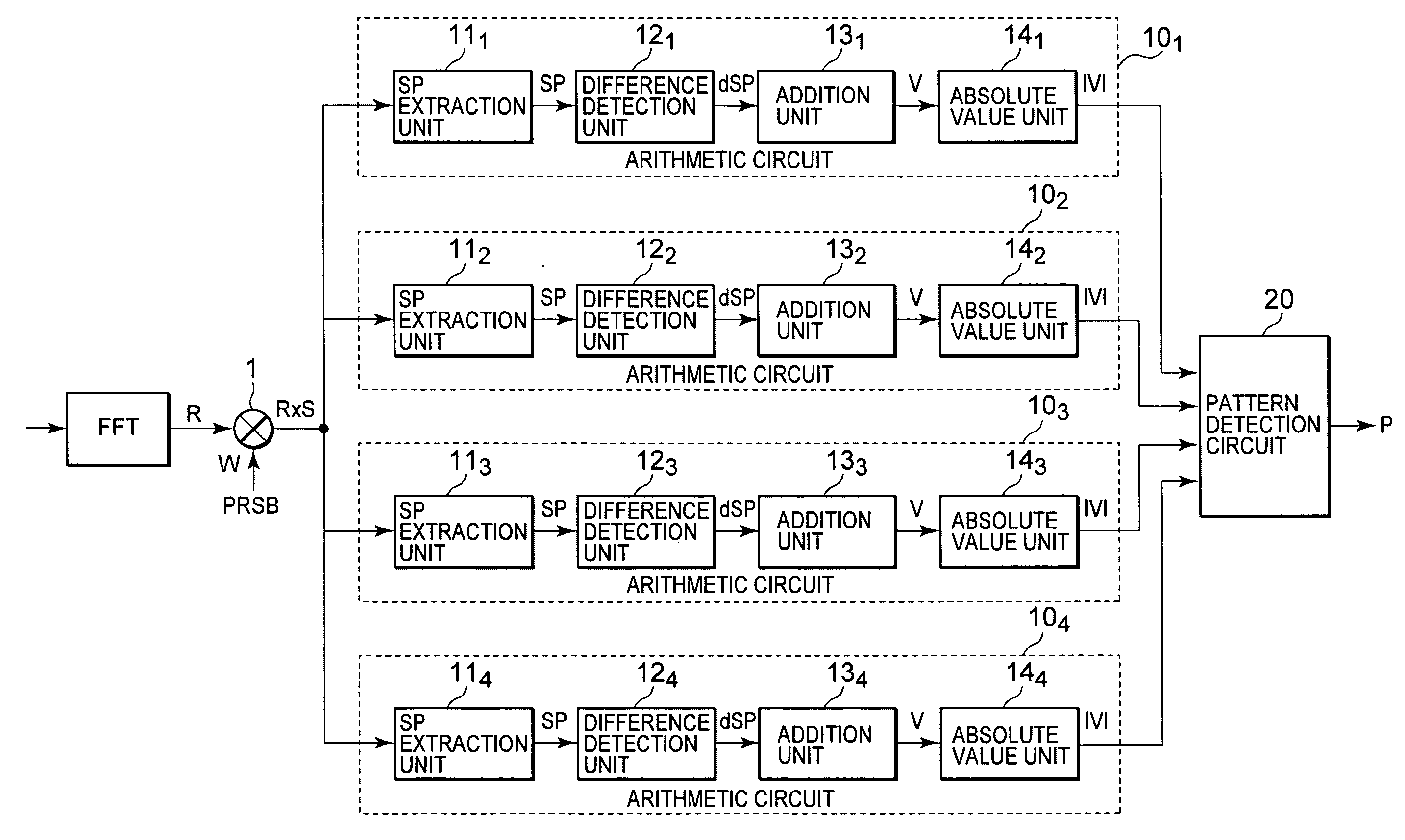

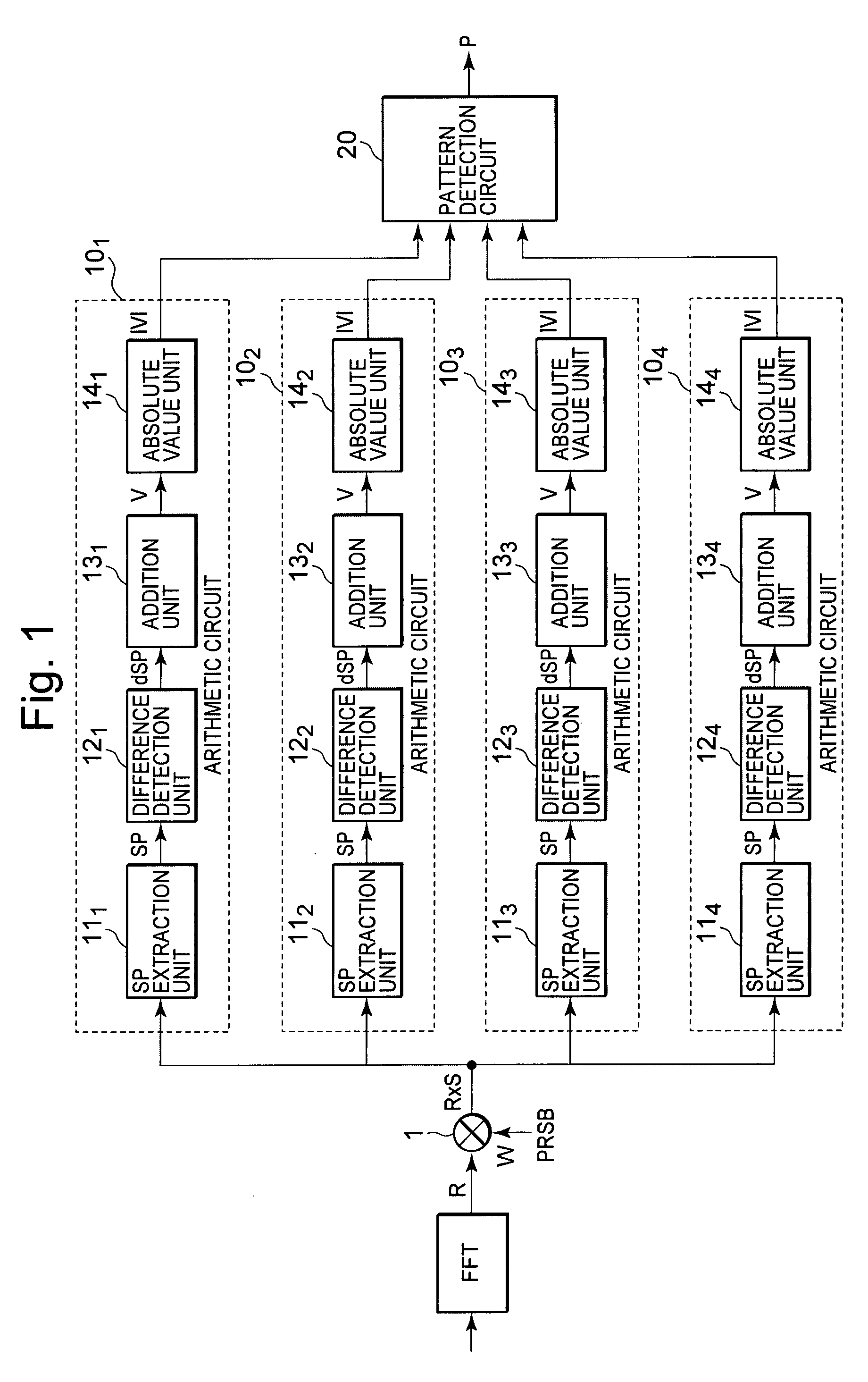

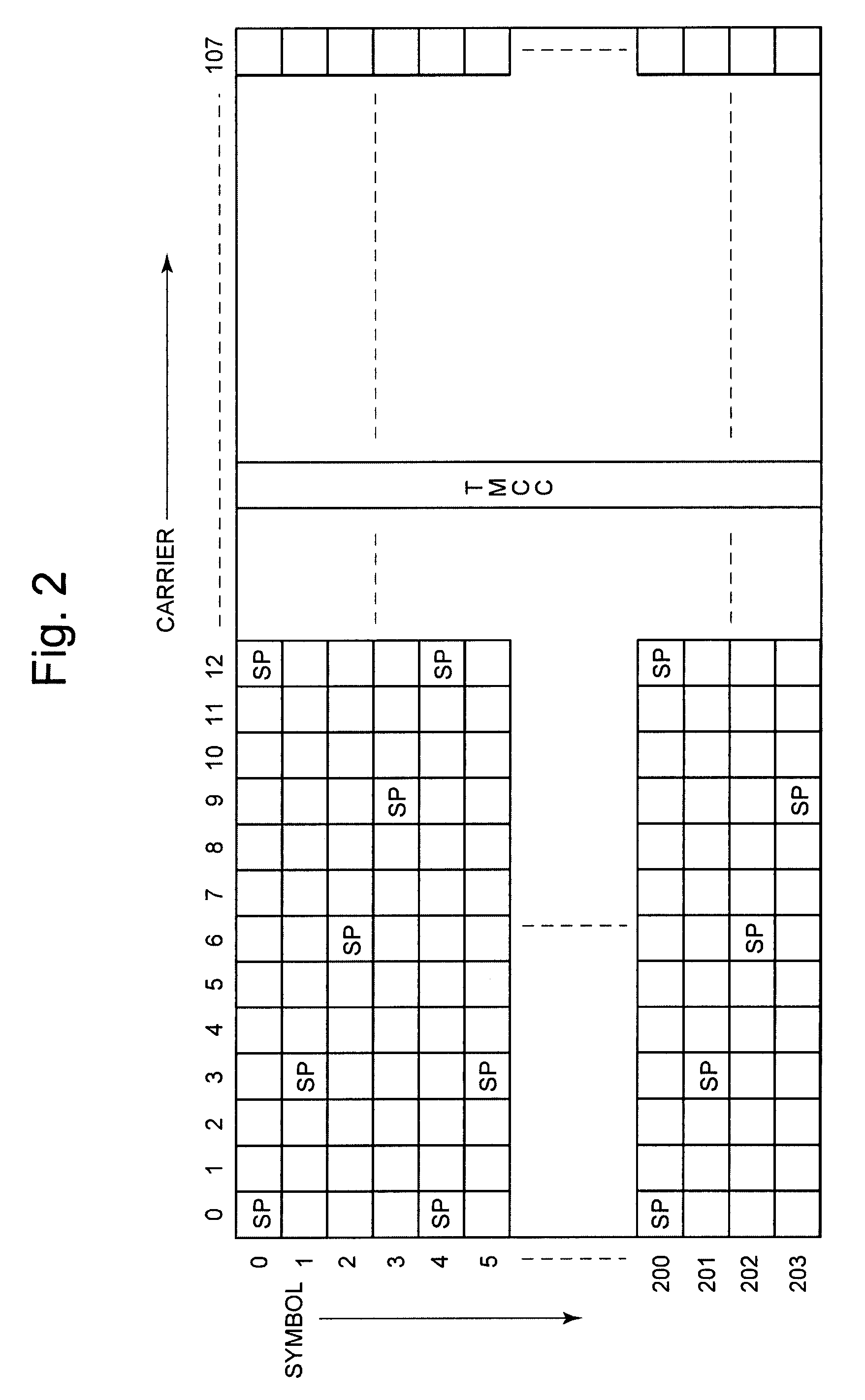

Scattered pilot location detector

ActiveUS20080095255A1Polarisation/directional diversityTransmission path divisionBinary multiplierPhase difference

The present invention provides a scattered pilot (SP) location detector capable of detecting patterns of SP symbols promptly without using a TMCC signal. The SP location detector comprises a multiplier which multiplies received signals generated by demodulating OFDM modulation signals in which pilot symbols are dispersively disposed in accordance with four types of patterns and which are transmitted periodically, by a pseudo-random number bit sequence, four arithmetic circuits which are respectively provided corresponding to the four types of patterns and which respectively extract pilot symbols corresponding to respective patterns from results of multiplication by the multiplier and calculate sums of phase differences between the extracted pilot symbols, followed by outputting absolute values thereof, and a pattern detection circuit which detects the corresponding arithmetic circuit maximum in the calculated absolute value from within the four arithmetic circuits.

Owner:LAPIS SEMICON CO LTD

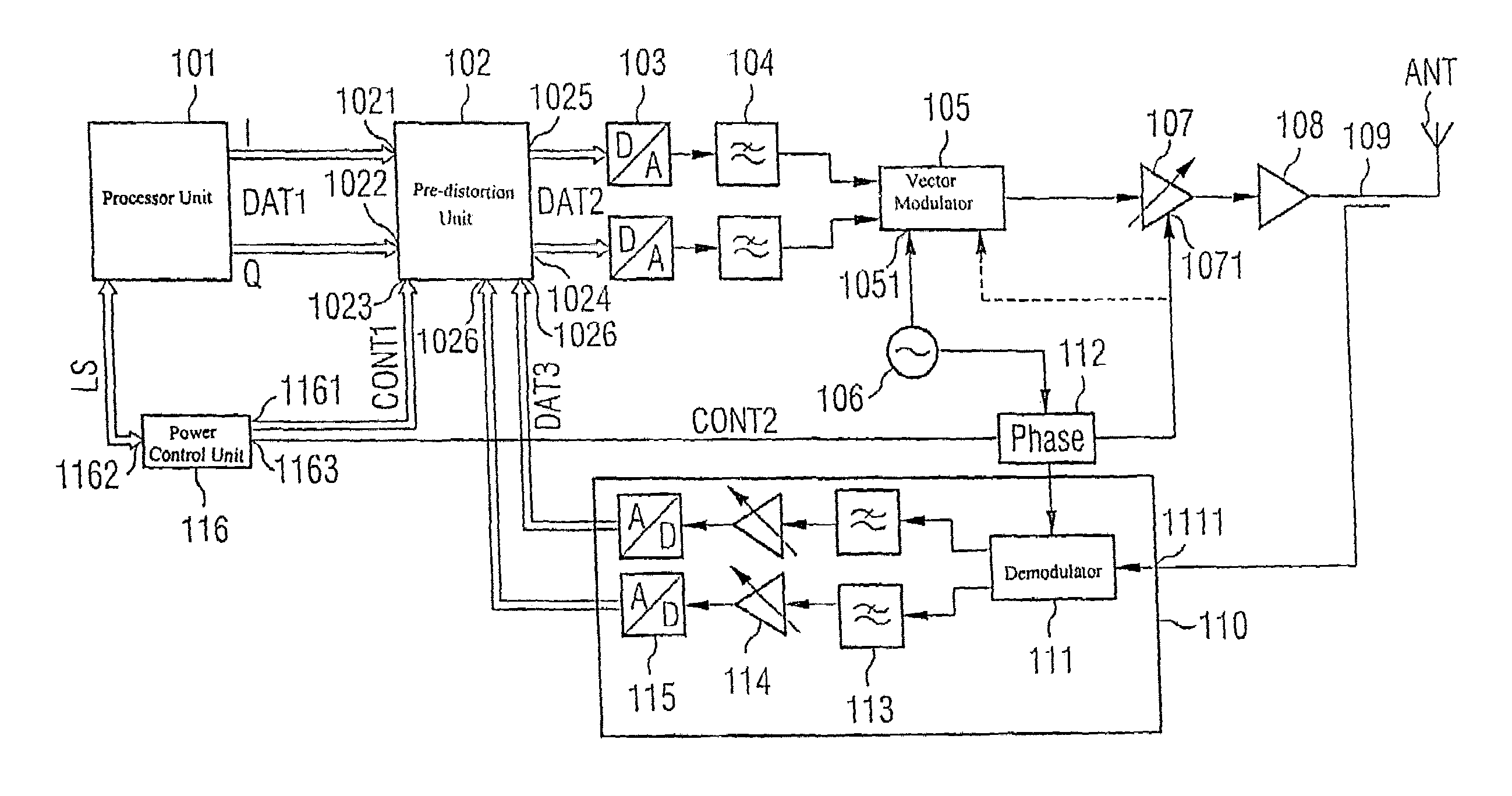

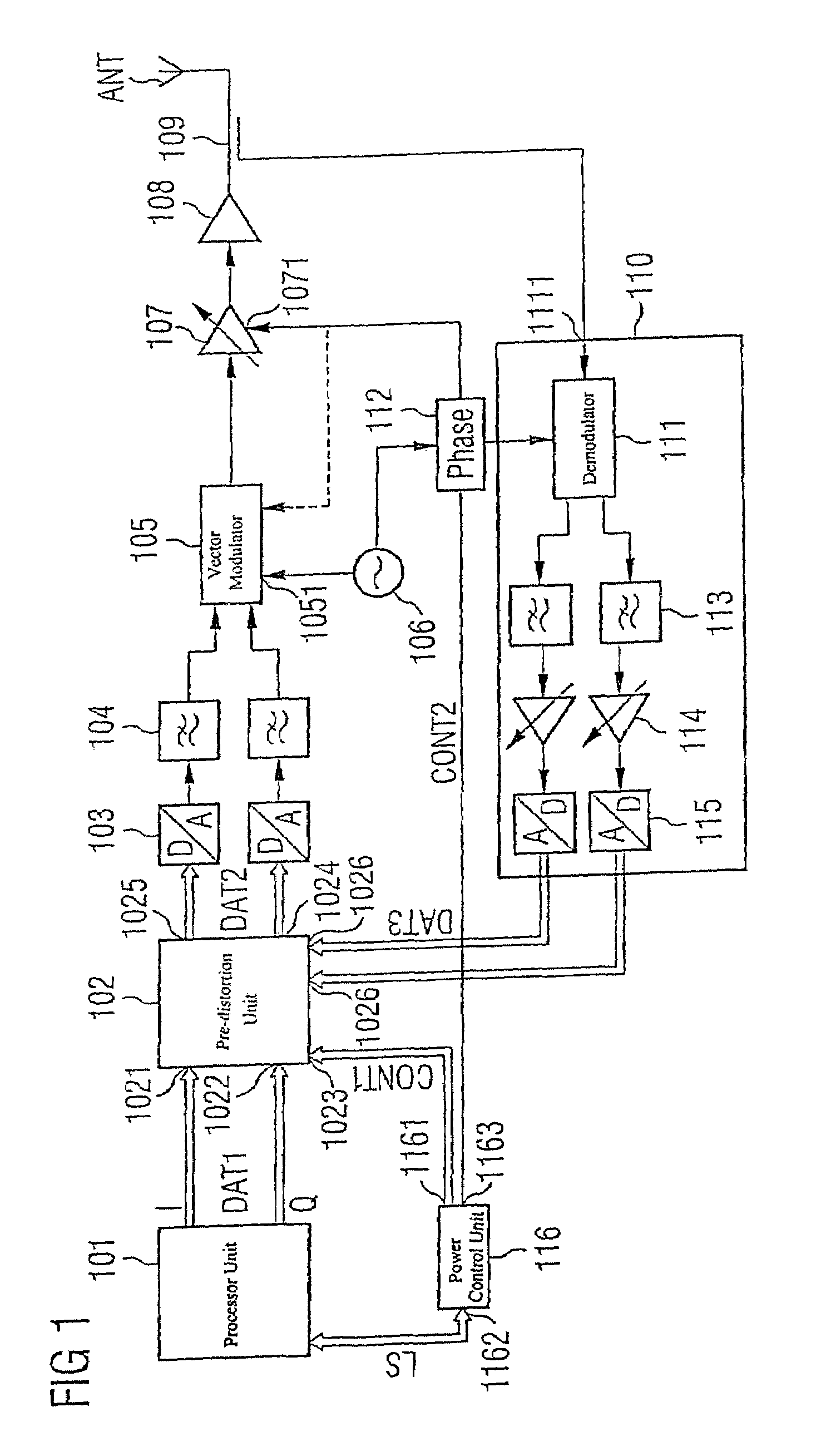

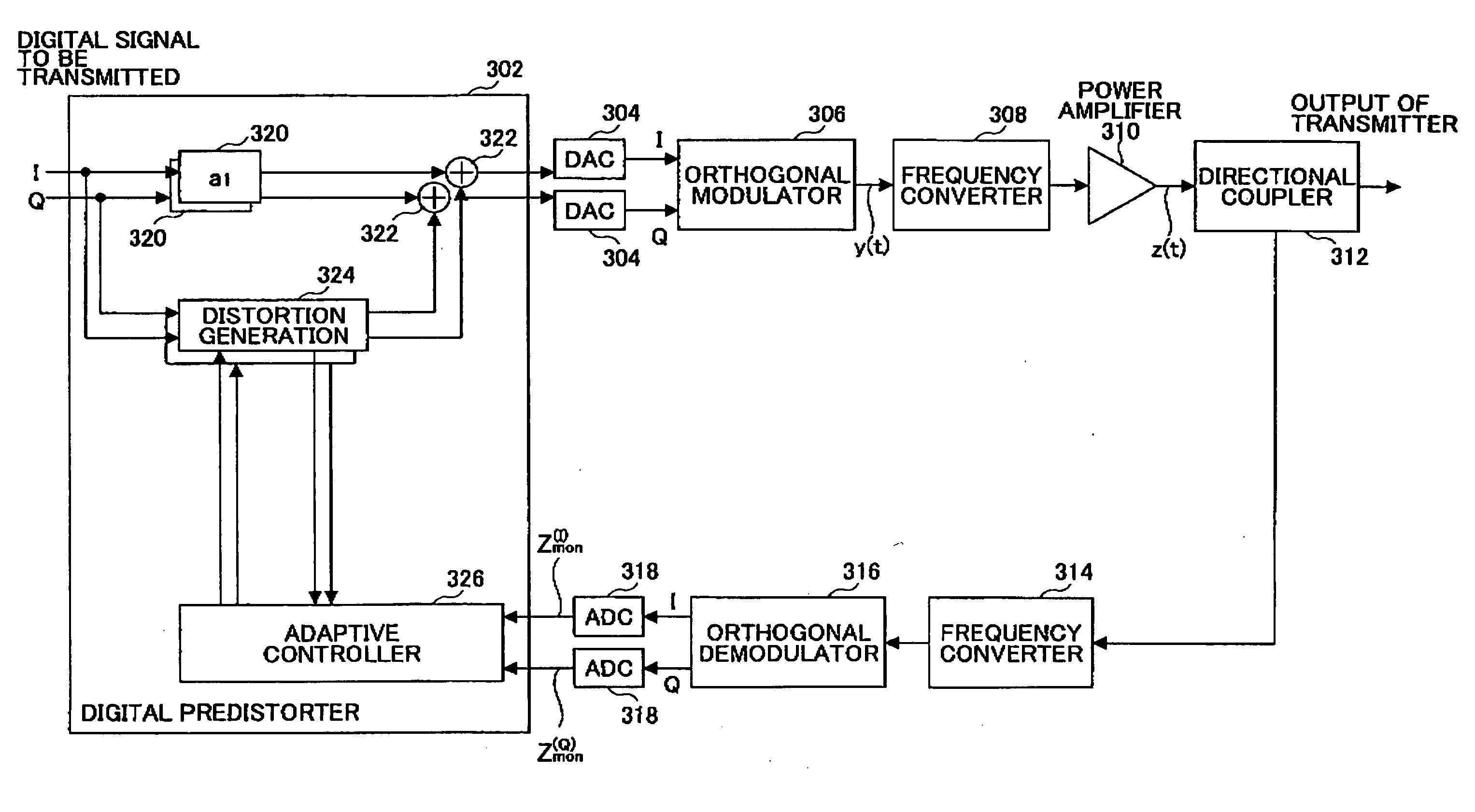

Transmission device with adaptive digital predistortion, transceiver with transmission device, and method for operating a transmission device

InactiveUS7372918B2Increase output powerGood linearityAmplifier modifications to reduce non-linear distortionGain controlBinary multiplierAudio power amplifier

The invention provides a transmission device having adaptive digital predistortion, which has a transmission path and a feedback path. The transmission path contains a predistortion unit which takes a derived control signal (LS) and baseband signals applied to the input side as a basis for calculating the address of a predistortion coefficient (KOEFF1) stored in a memory and logically combines this predistortion coefficient with the applied baseband signals in a complex multiplication unit. The use of complex coefficients and of the complex multipliers allows compensation both for AM / AM distortion and for AM / PM distortion in an amplifier device connected downstream of the predistortion unit. Usefully, the feedback path of the transmission device with digital adaptive predistortion can also be implemented using the reception device in a transceiver.

Owner:INFINEON TECH AG

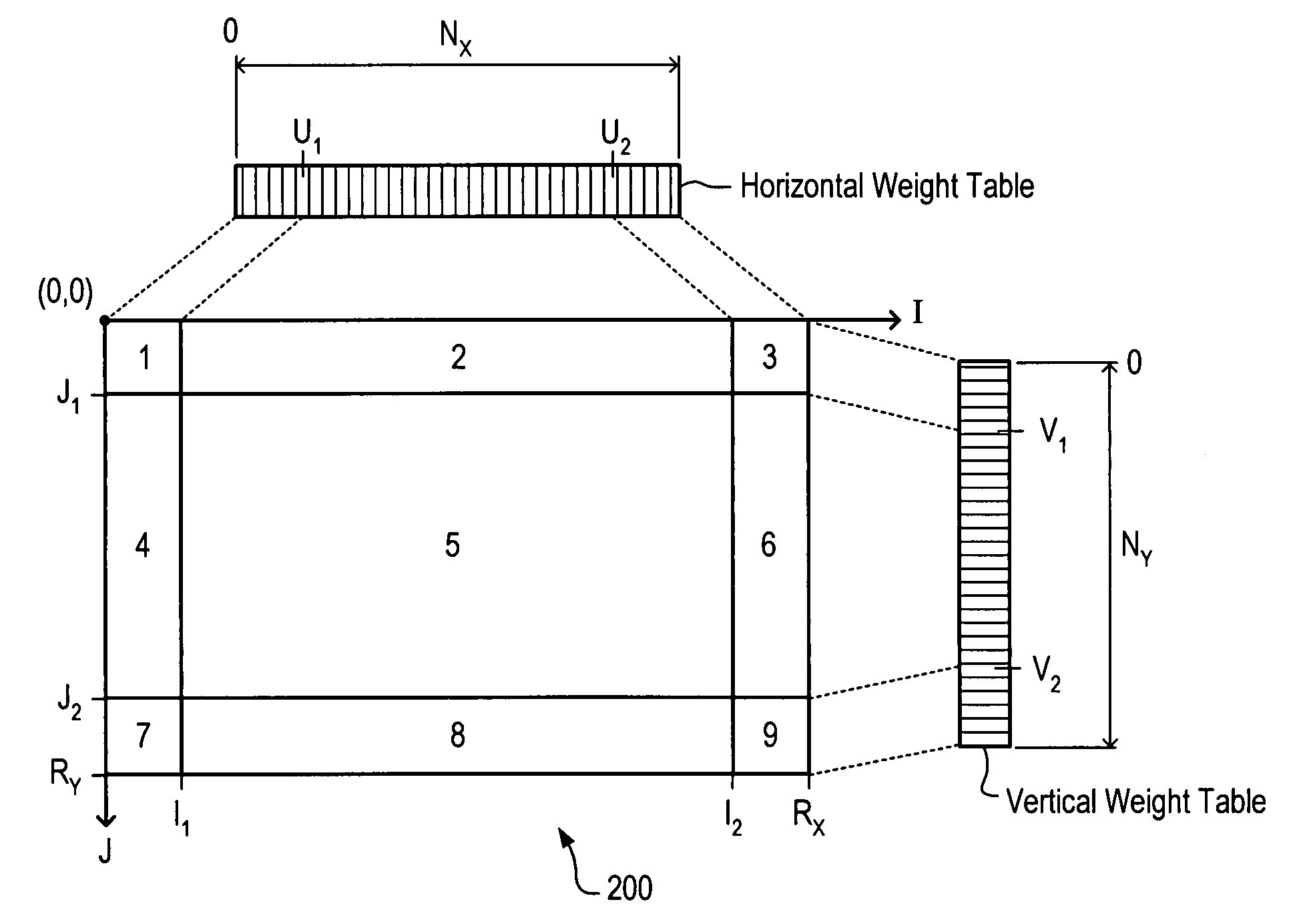

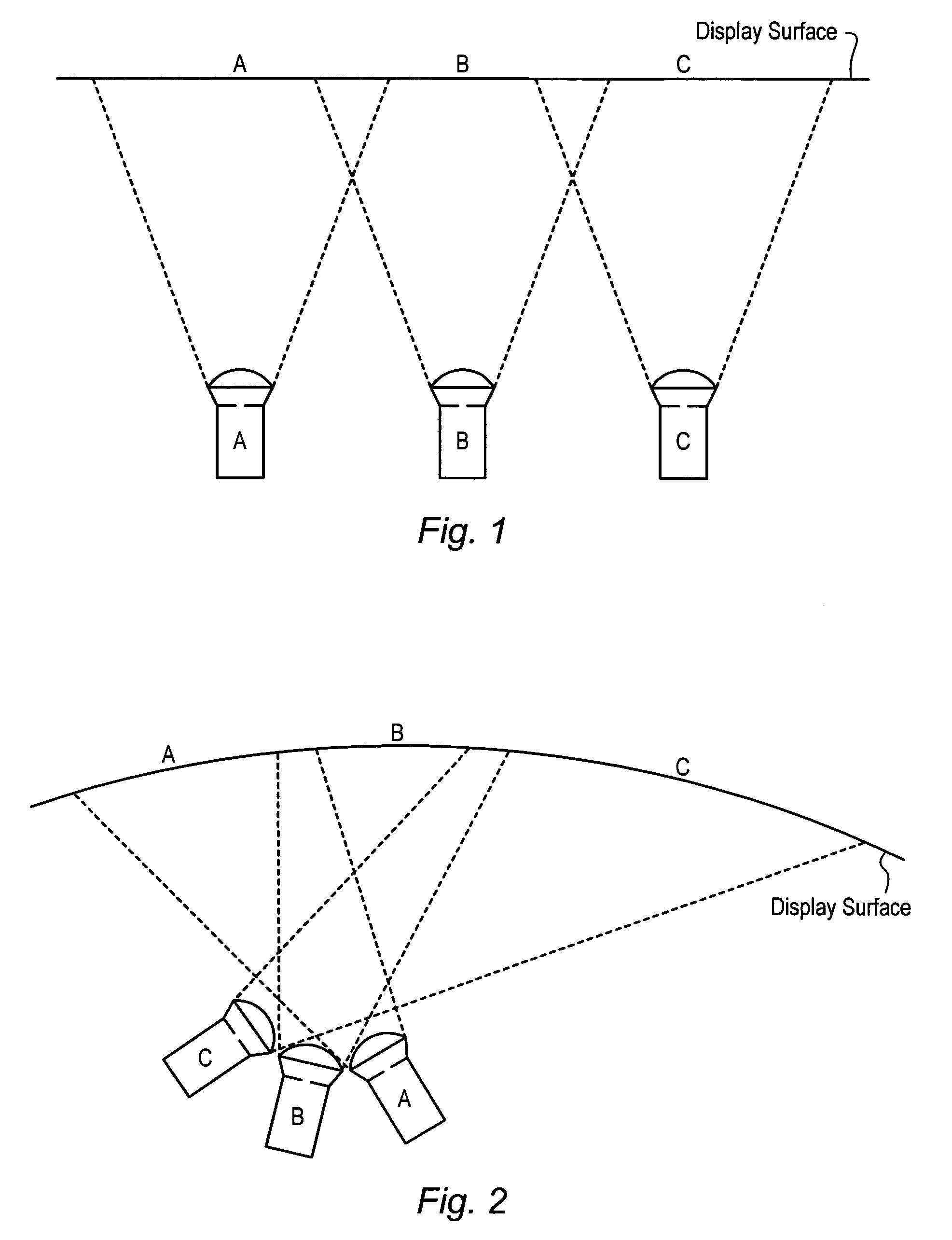

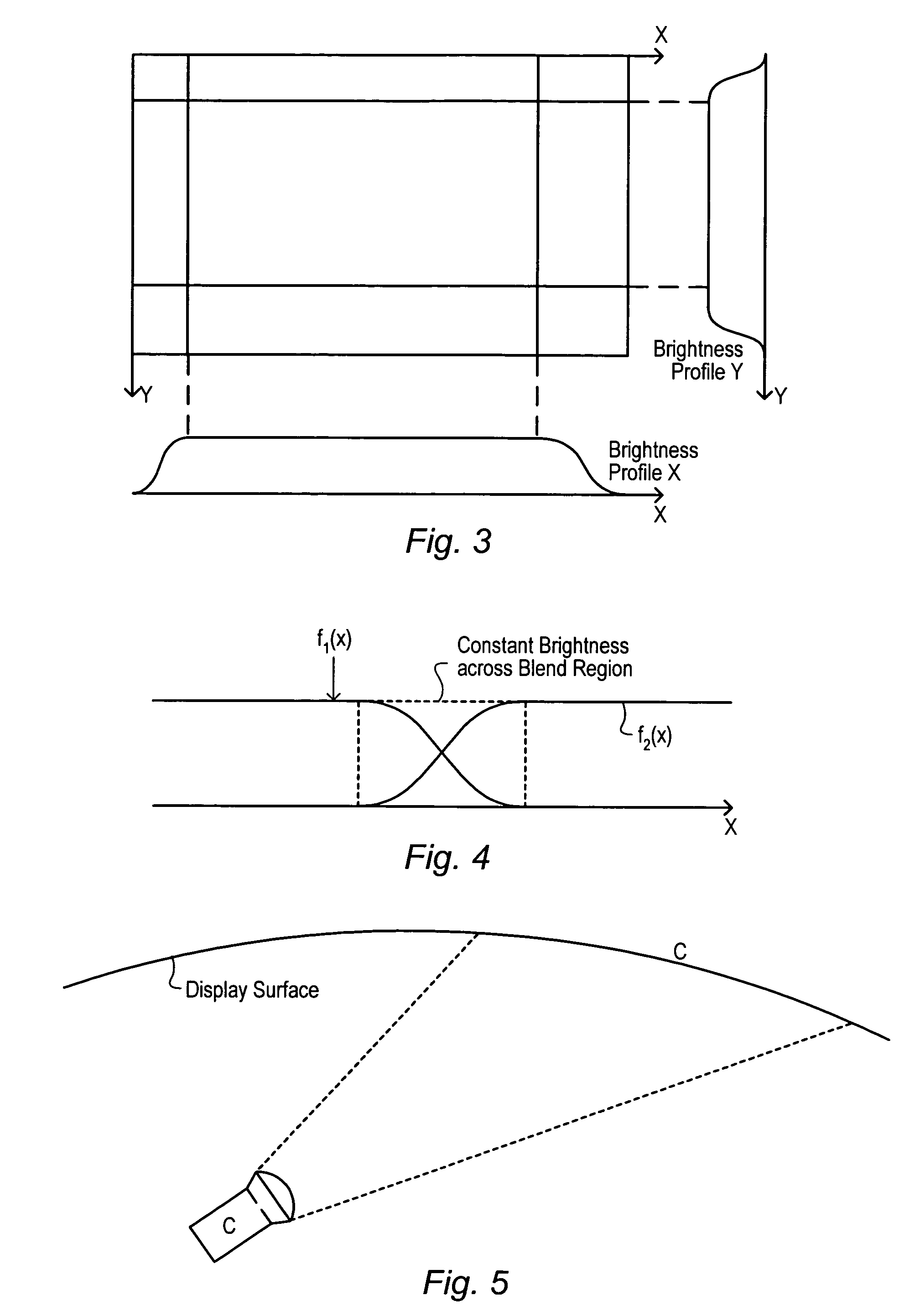

Computing blending functions for the tiling of overlapped video projectors

ActiveUS7292207B1Intensity PreciseColor television detailsCathode-ray tube indicatorsBinary multiplierComputer vision

A system for correcting the intensities of pixels supplied to a projector. An image generated by the projector has a number of regions formed by the overlapping of the image with one or more other images generated by one or more other projectors. The system includes: a first unit configured to generate a horizontal scaling value; a second unit configured to generate a vertical scaling value; a first multiplier configured to multiply the horizontal scaling value and the vertical scaling value to obtain a scaling coefficient, and a set of one or more additional multipliers configured to multiply components of an input pixel by the scaling coefficient to determine components for an output pixel. The first unit and second unit compute their respective scaling values in a way that allows for regions whose boundaries non-aligned in the vertical direction.

Owner:ORACLE INT CORP

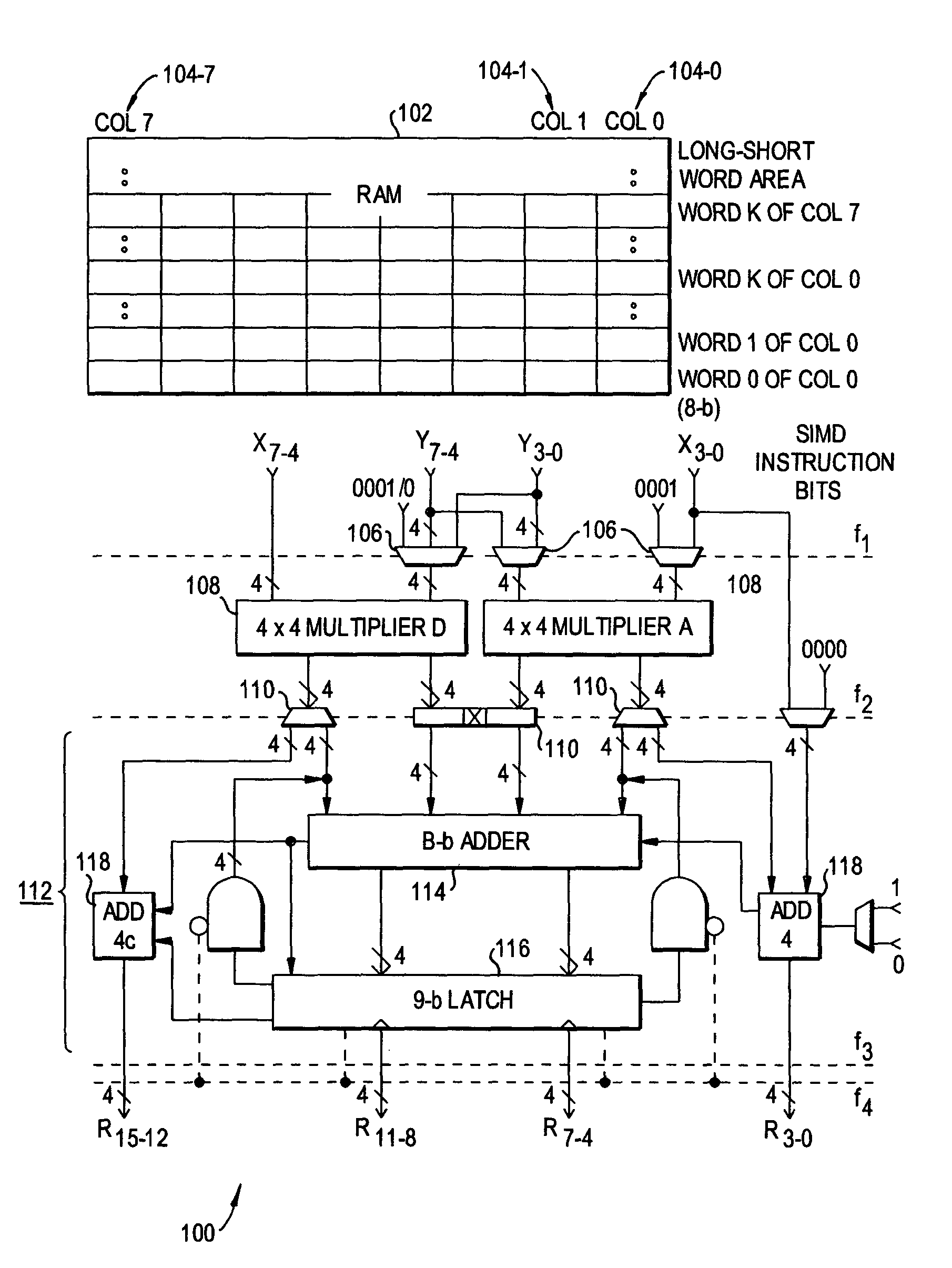

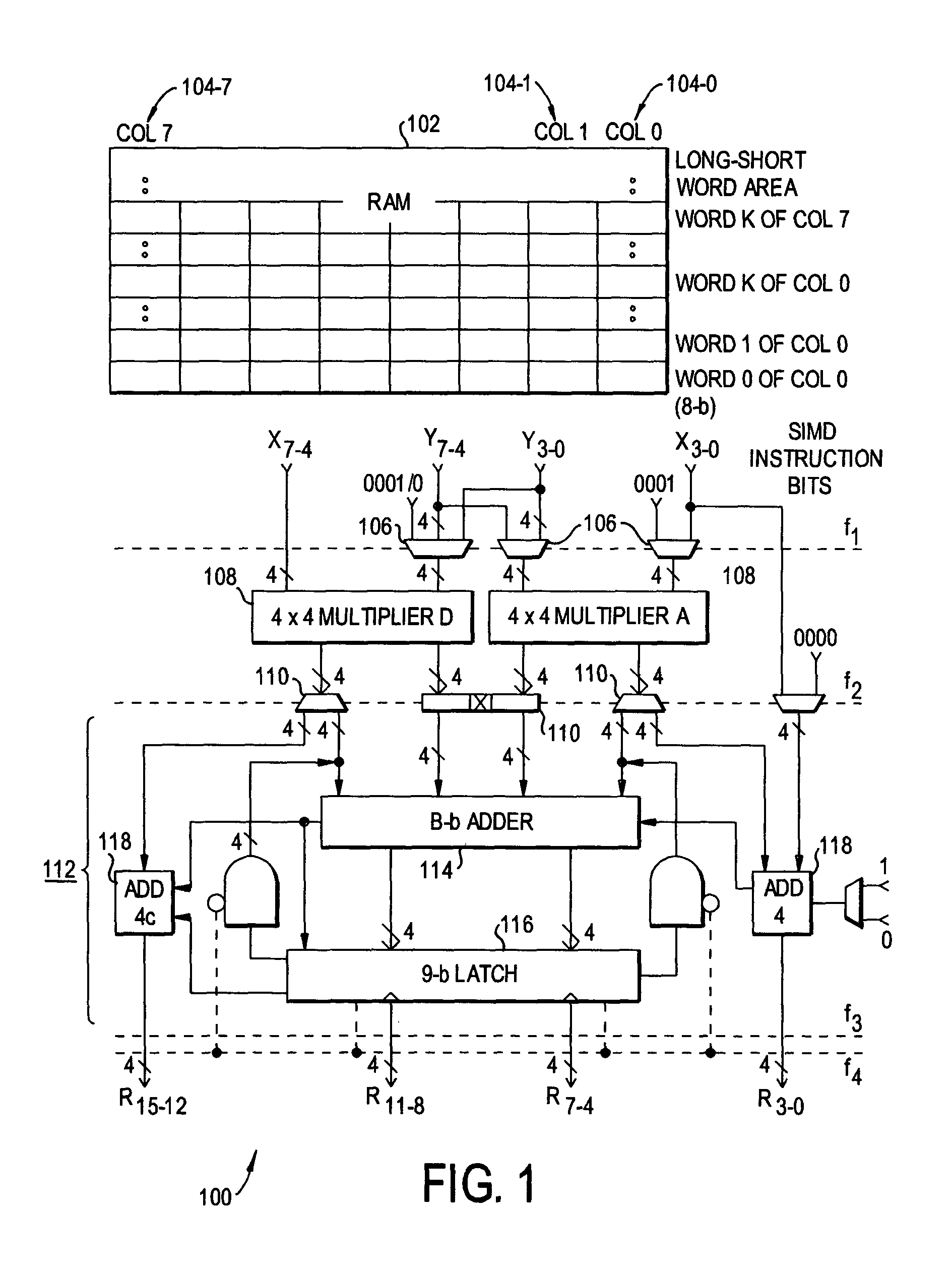

Multiplier-based processor-in-memory architectures for image and graphics processing

InactiveUS7167890B2Efficiently reconfiguredNegligible amountComputation using non-contact making devicesImage memory managementGraphicsComputational science

A Procesor-In-Memory (PIM) includes a digital accelerator for image and graphics processing. The digital accelerator is based on an ALU having multipliers for processing combinations of bits smaller than those in the input data (e.g., 4×4 adders if the input data are 8-bit numbers). The ALU implements various arithmetic algorithms for addition, multiplication, and other operations. A secondary processing logic includes adders in series and parallel to permit vector operations as well as operations on longer scalars. A self-repairing ALU is also disclosed.

Owner:UNIVERSITY OF ROCHESTER +2

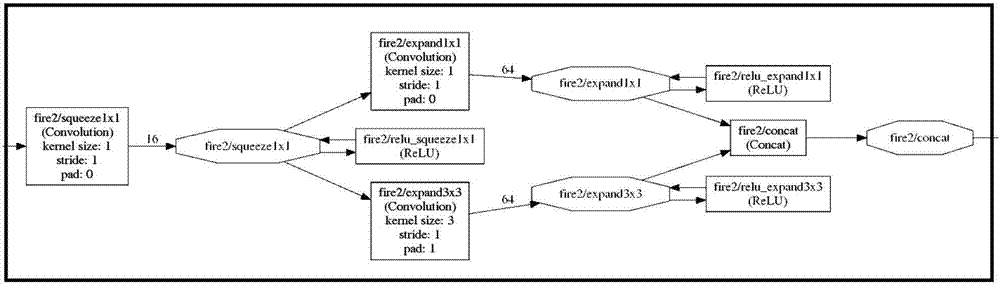

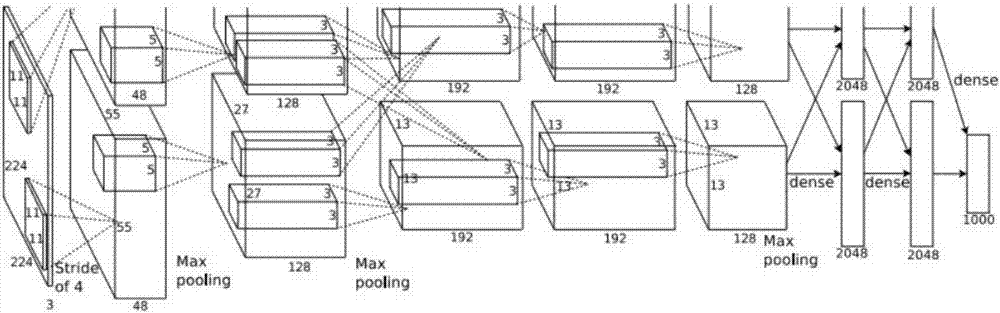

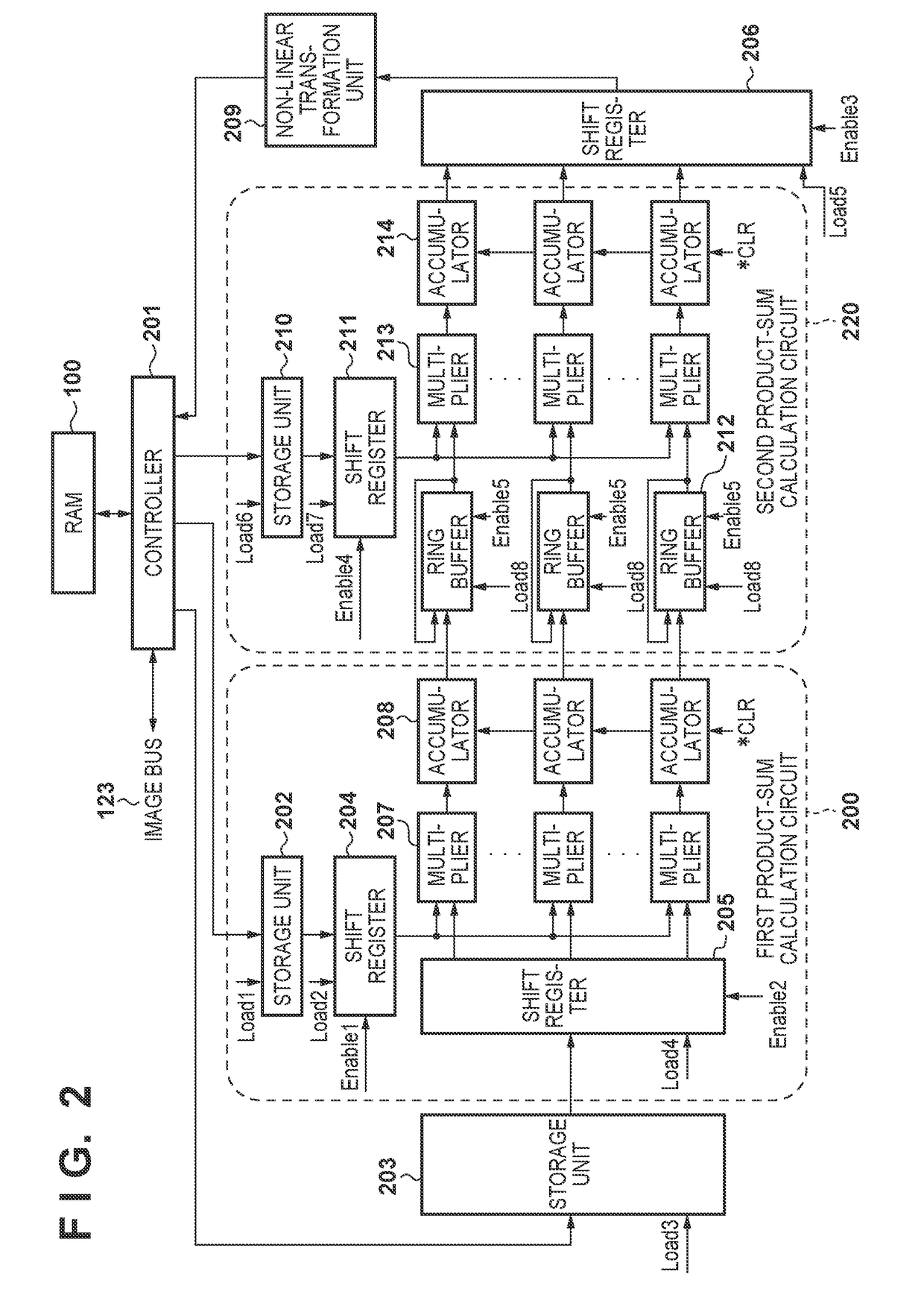

Compressed convolutional neural network-oriented parallel convolution operation method and apparatus

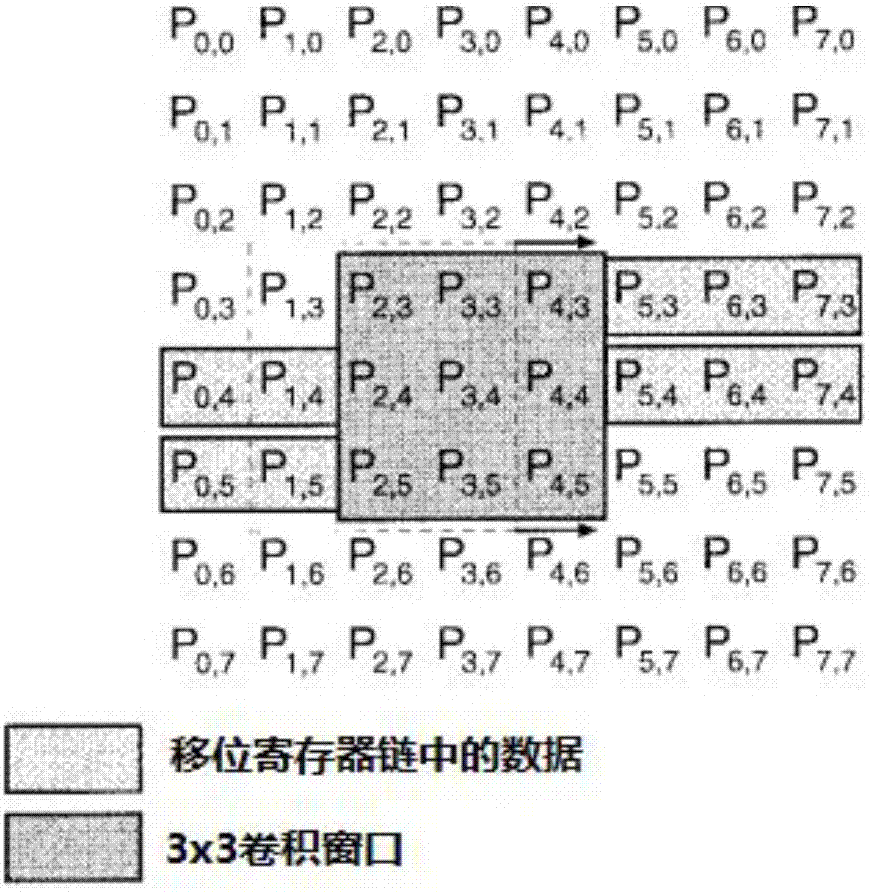

ActiveCN106951395AReduce duplicate readsIncrease profitNeural architecturesComplex mathematical operationsShift registerData stream

The invention provides a compressed convolutional neural network-oriented parallel convolution operation method and apparatus. The method comprises the steps of determining an adopted operation mode according to input control signal convolution data shift chain length selection, accumulated offset enabling and convolution calculation enabling; and by adopting two serial shift register chains, inputting convolution data, convolution parameters and channel offset, and performing 3X3 and 1X1 convolution operation at the same time for a same input convolution data stream. According to the method, a multiplier, an accumulator, a parameter register and an offset register are added only based on original serial shift register chain-based 3X3 convolution operation; the realization method is simple; the executive efficiency is high; and the convolution operation in a compressed neural network algorithm can be effectively accelerated. According to the apparatus, a plurality of characteristic graphs can be output at the same time through simple hardware unit expansion and copying; and the apparatus has the advantages of low power consumption, high function unit utilization rate and high processing speed.

Owner:国交金流供应链科技(上海)有限公司 +1

Method and apparatus for achieving higher frequencies of exactly rounded results

InactiveUS6134574ARuntime instruction translationComputation using non-contact making devicesBinary multiplierOperand

Owner:GLOBALFOUNDRIES INC

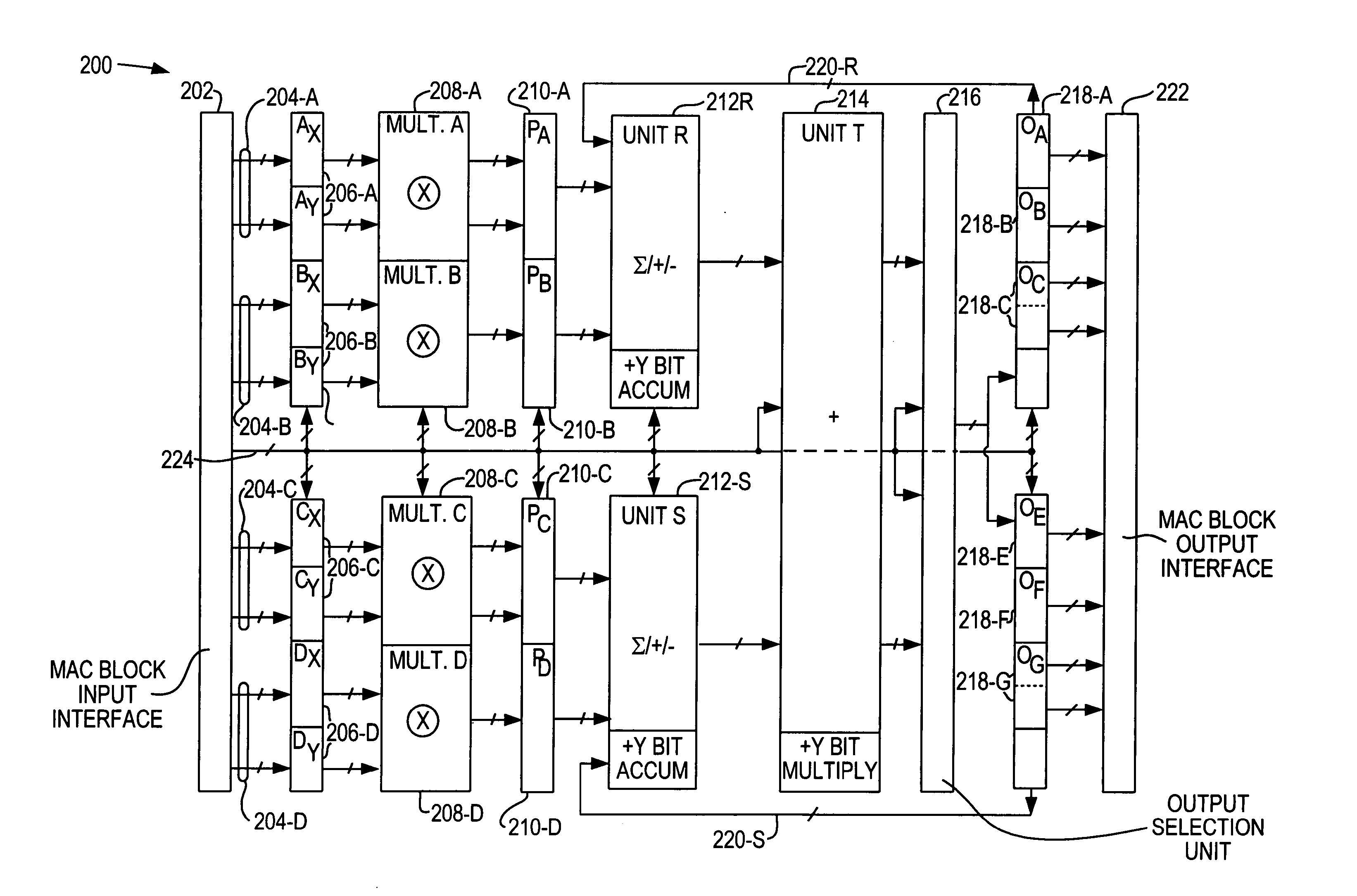

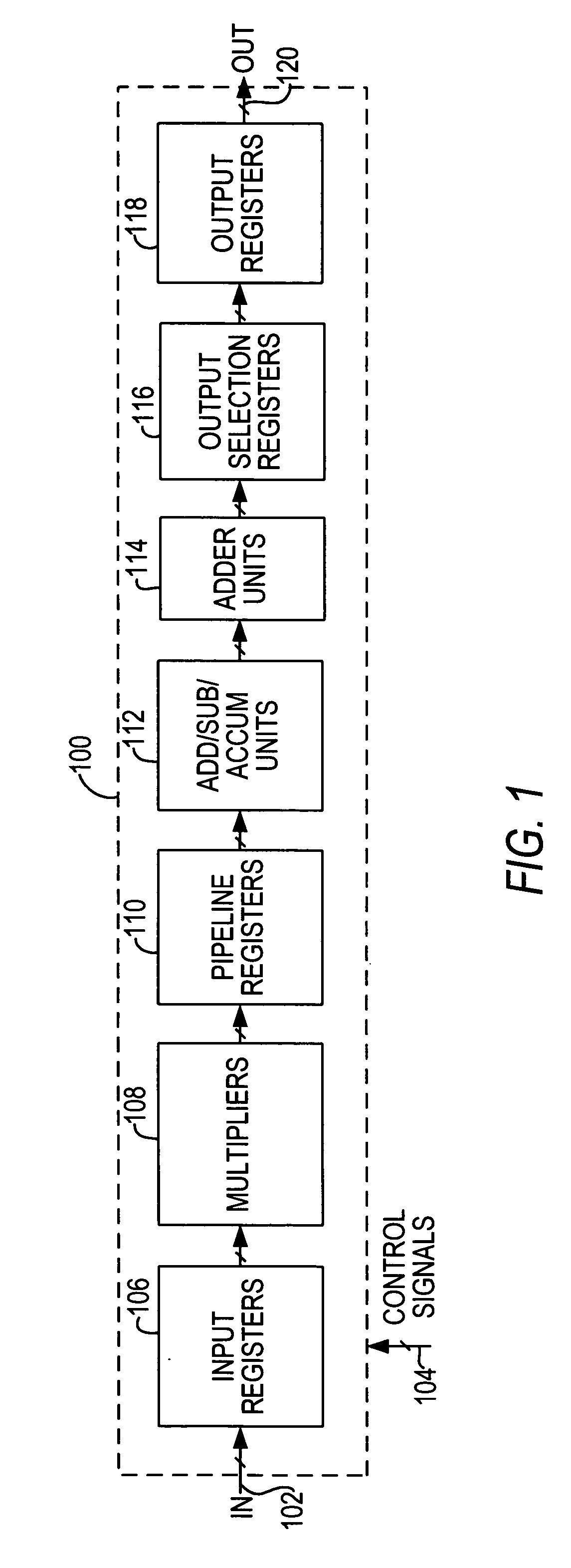

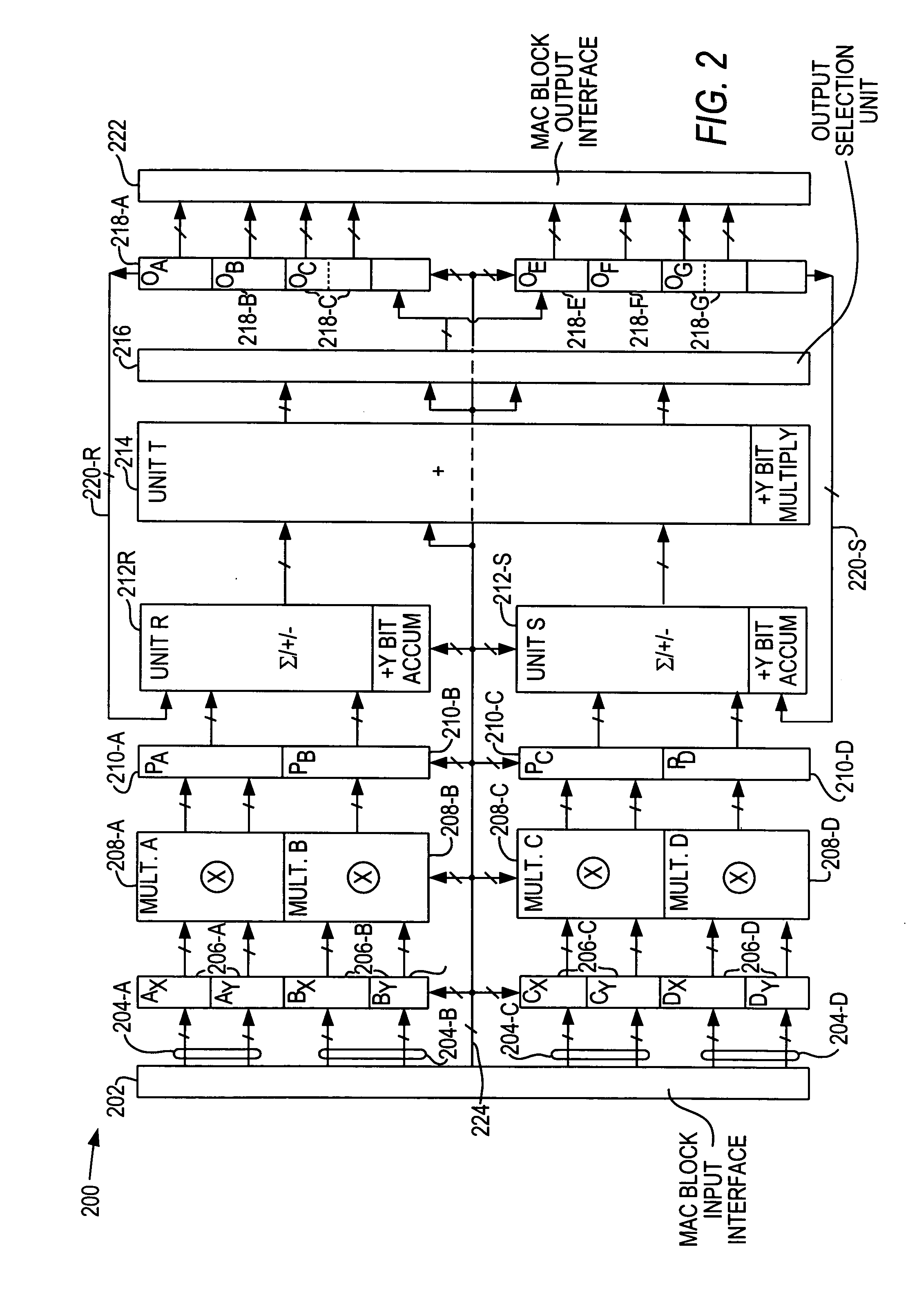

Saturation and rounding in multiply-accumulate blocks

ActiveUS20050187999A1Provide capabilityEasy to useComputation using non-contact making devicesRoundingBinary multiplier

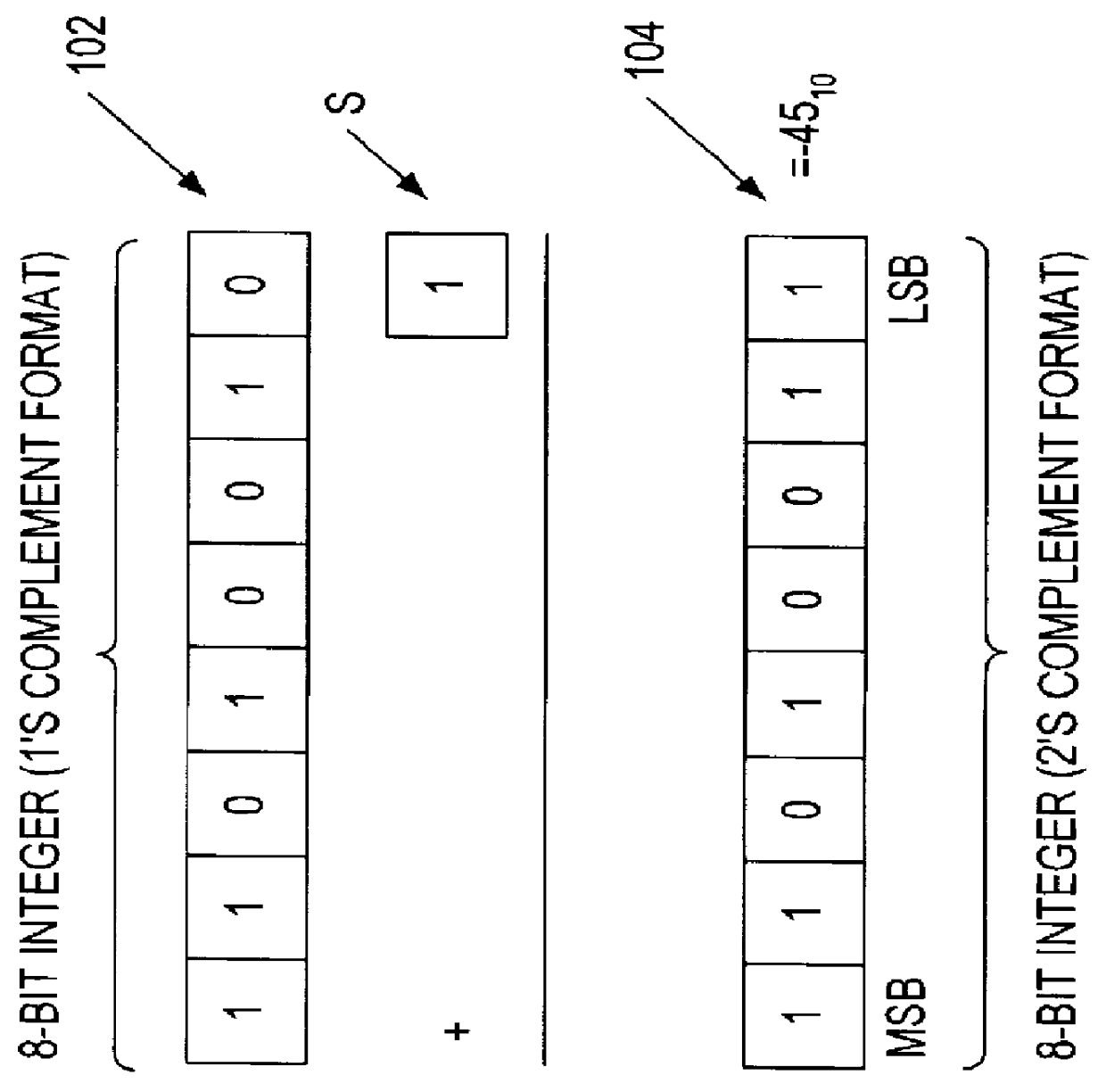

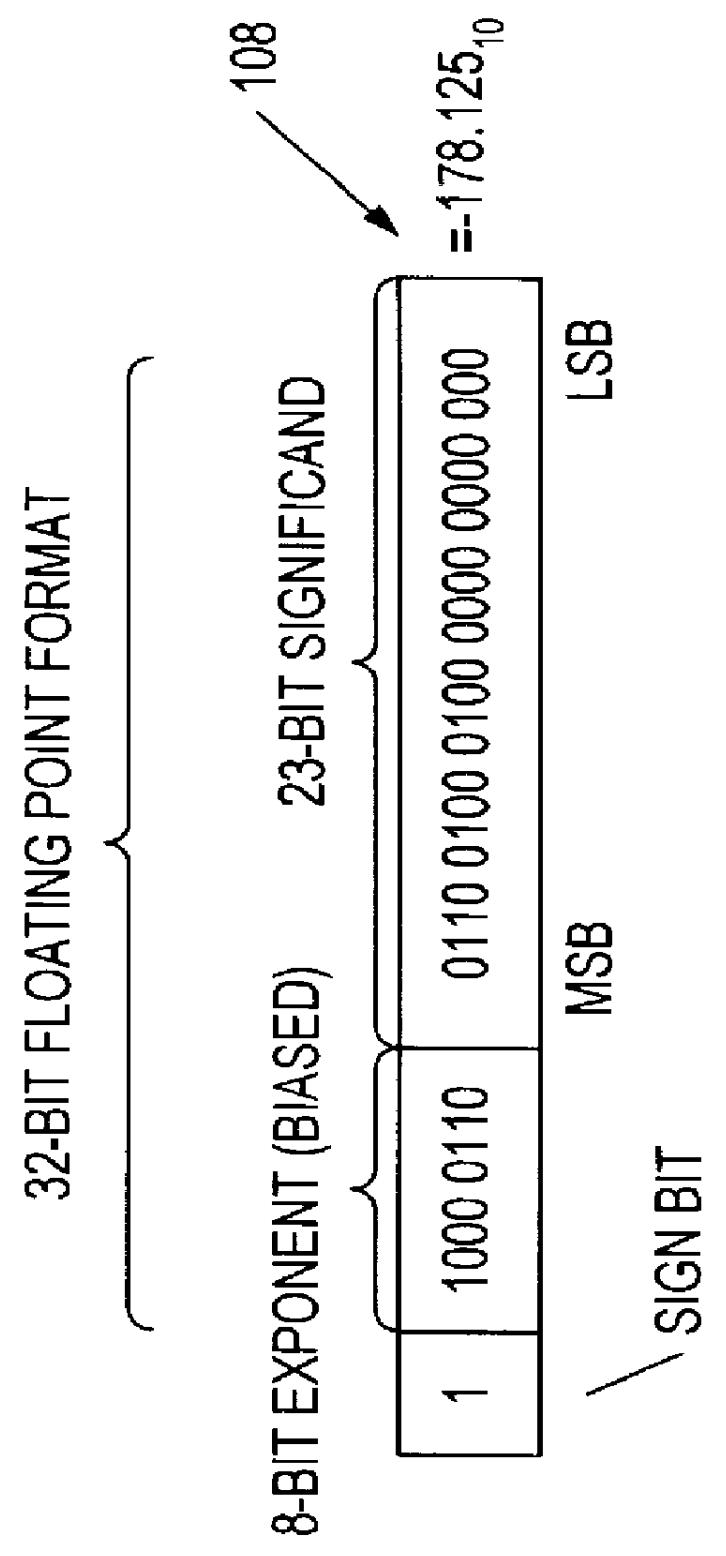

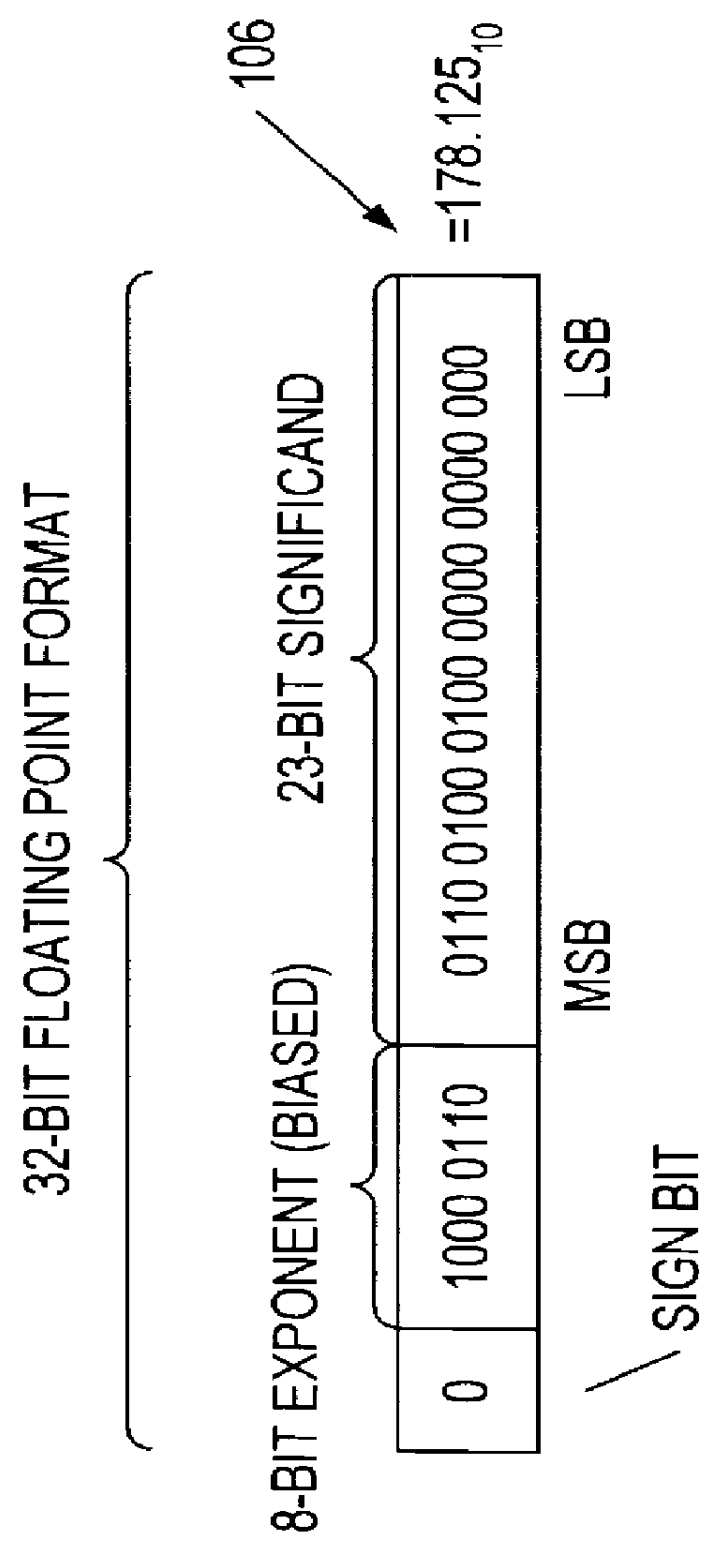

Saturation and rounding capabilities are implemented in MAC blocks to provide rounded and saturated outputs of multipliers and of add-subtract-accumulate circuitrs implemented using DSP. These features support any suitable format of value representation, including the x.15 format. Circuitry within the multipliers and the add-subtract-accumulate circuits implement the rounding and saturation features of the present invention.

Owner:TAHOE RES LTD

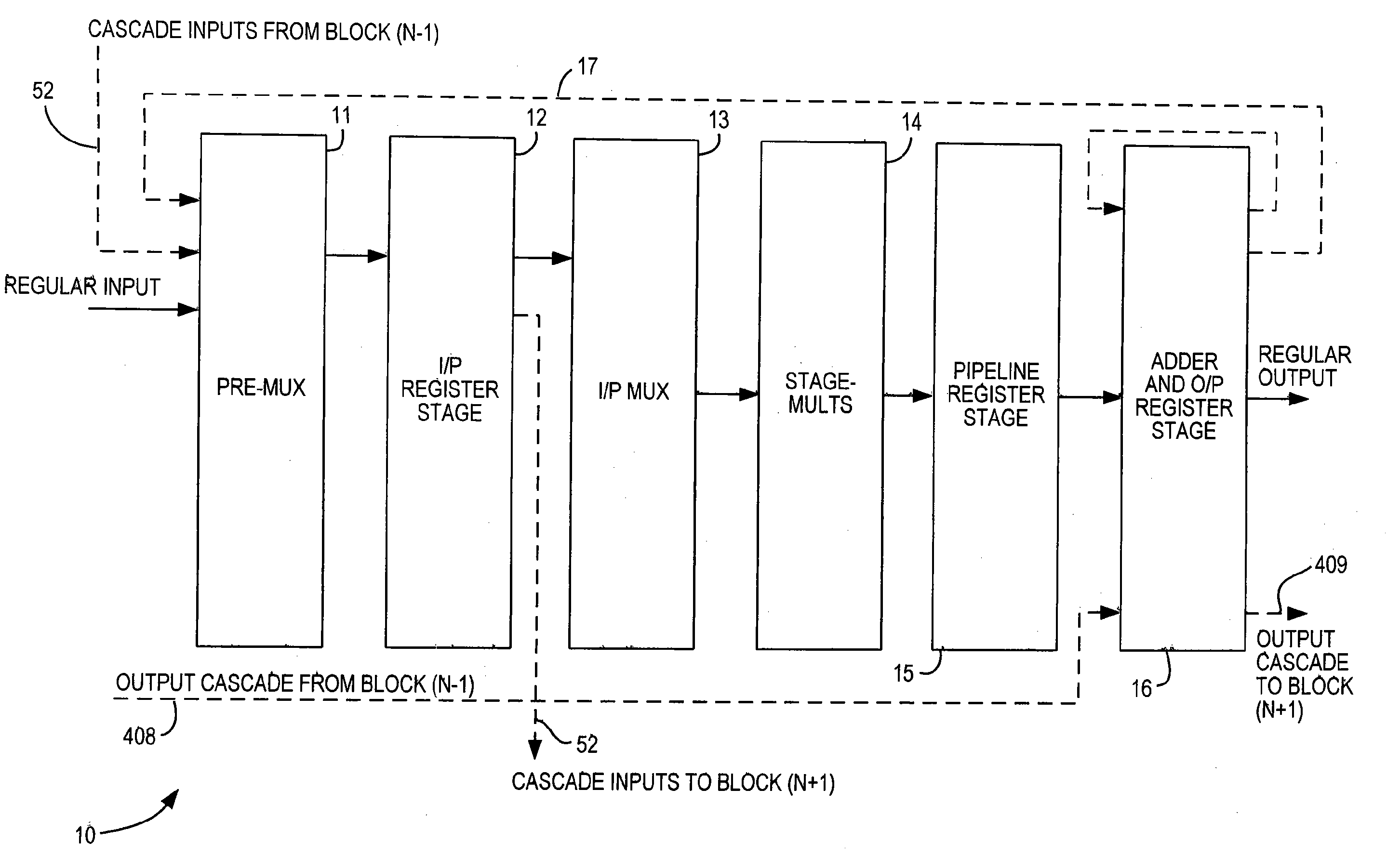

Specialized processing block for programmable logic device

ActiveUS20070185952A1Reduce areaImprove efficiencyDigital computer detailsLogic circuitsDigital signal processingBinary multiplier

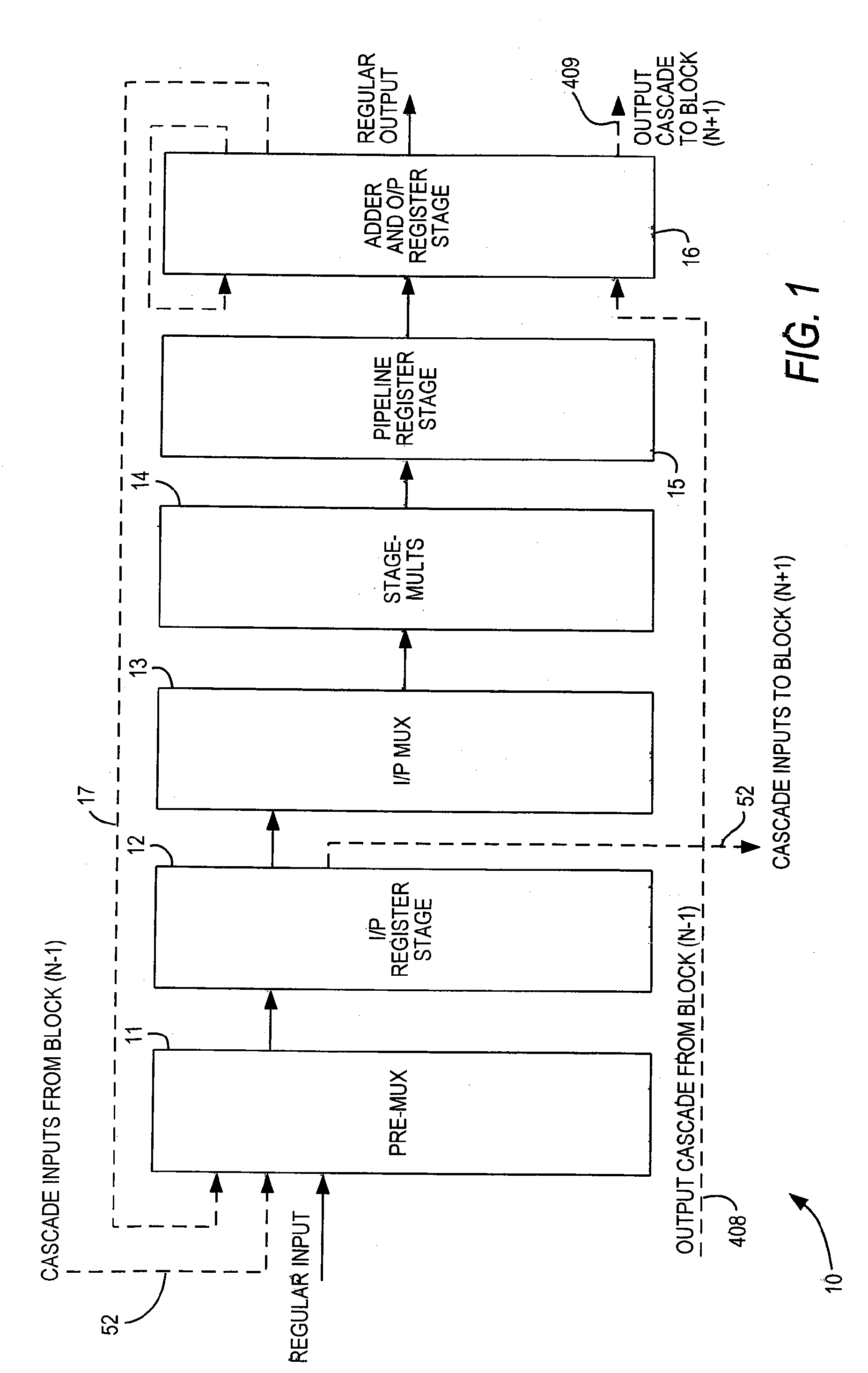

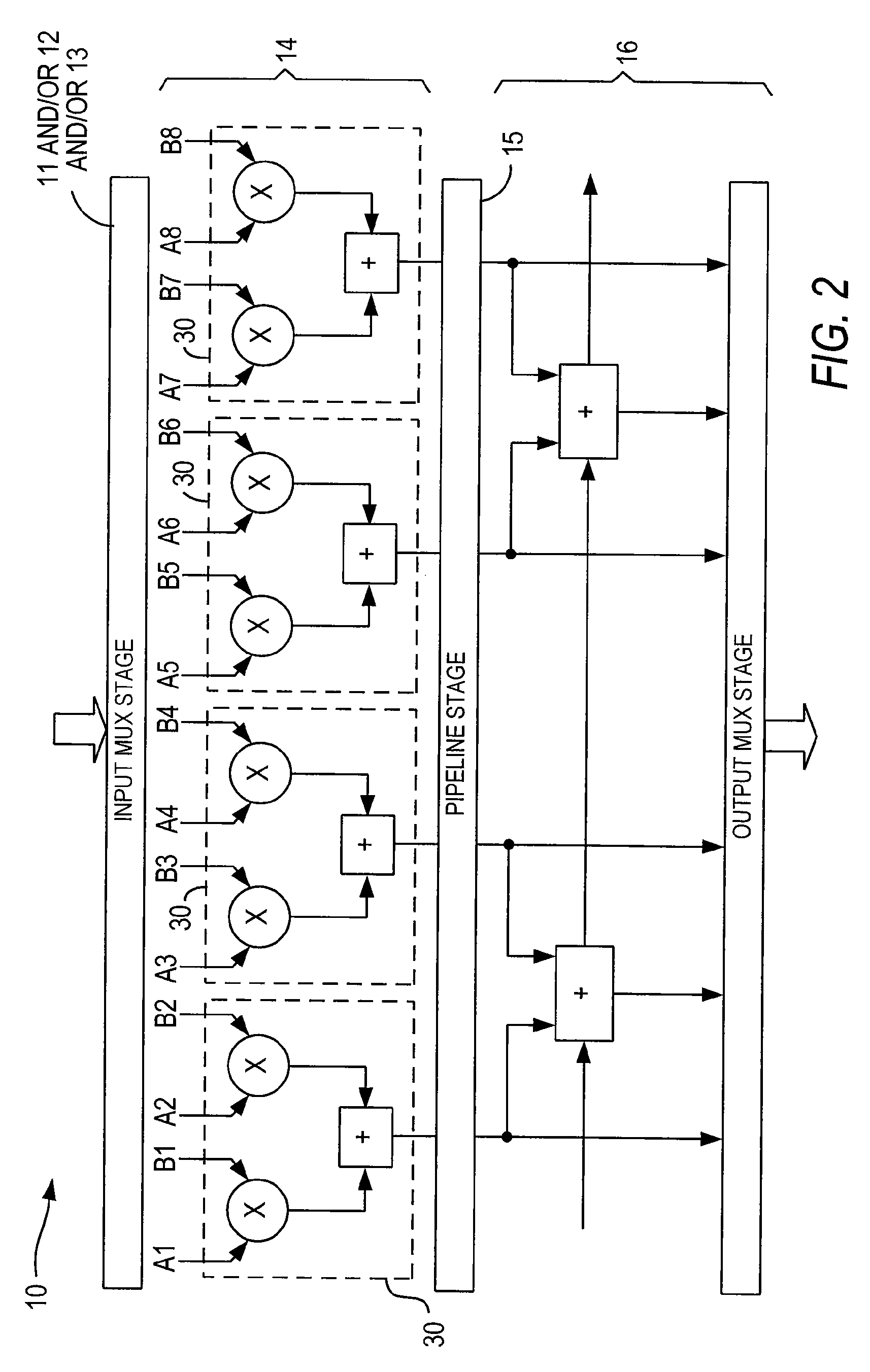

A specialized processing block for a programmable logic device incorporates a fundamental processing unit that performs a sum of two multiplications, adding the partial products of both multiplications without computing the individual multiplications. Such fundamental processing units consume less area than conventional separate multipliers and adders. The specialized processing block further has input and output stages, as well as a loopback function, to allow the block to be configured for various digital signal processing operations.

Owner:TAHOE RES LTD

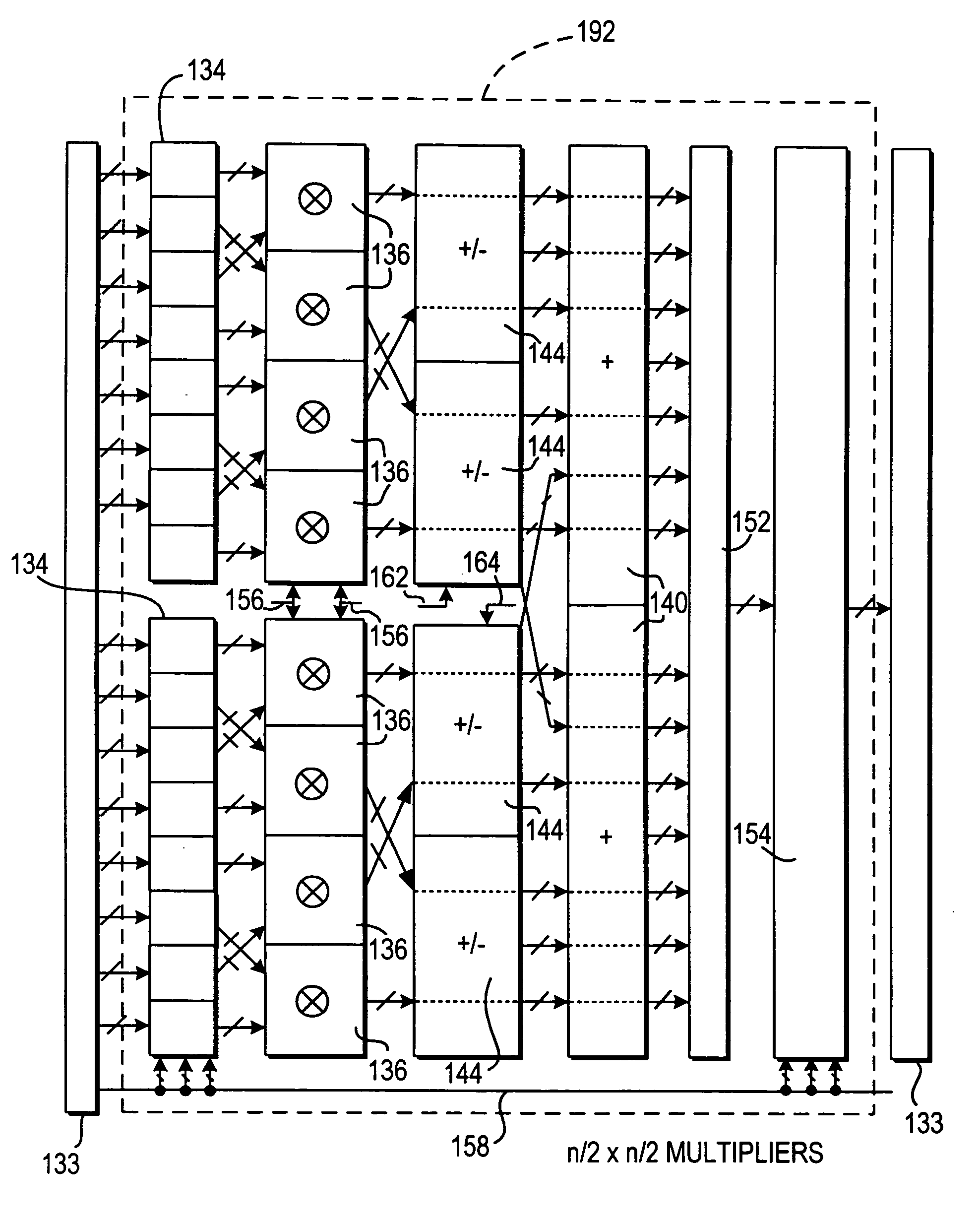

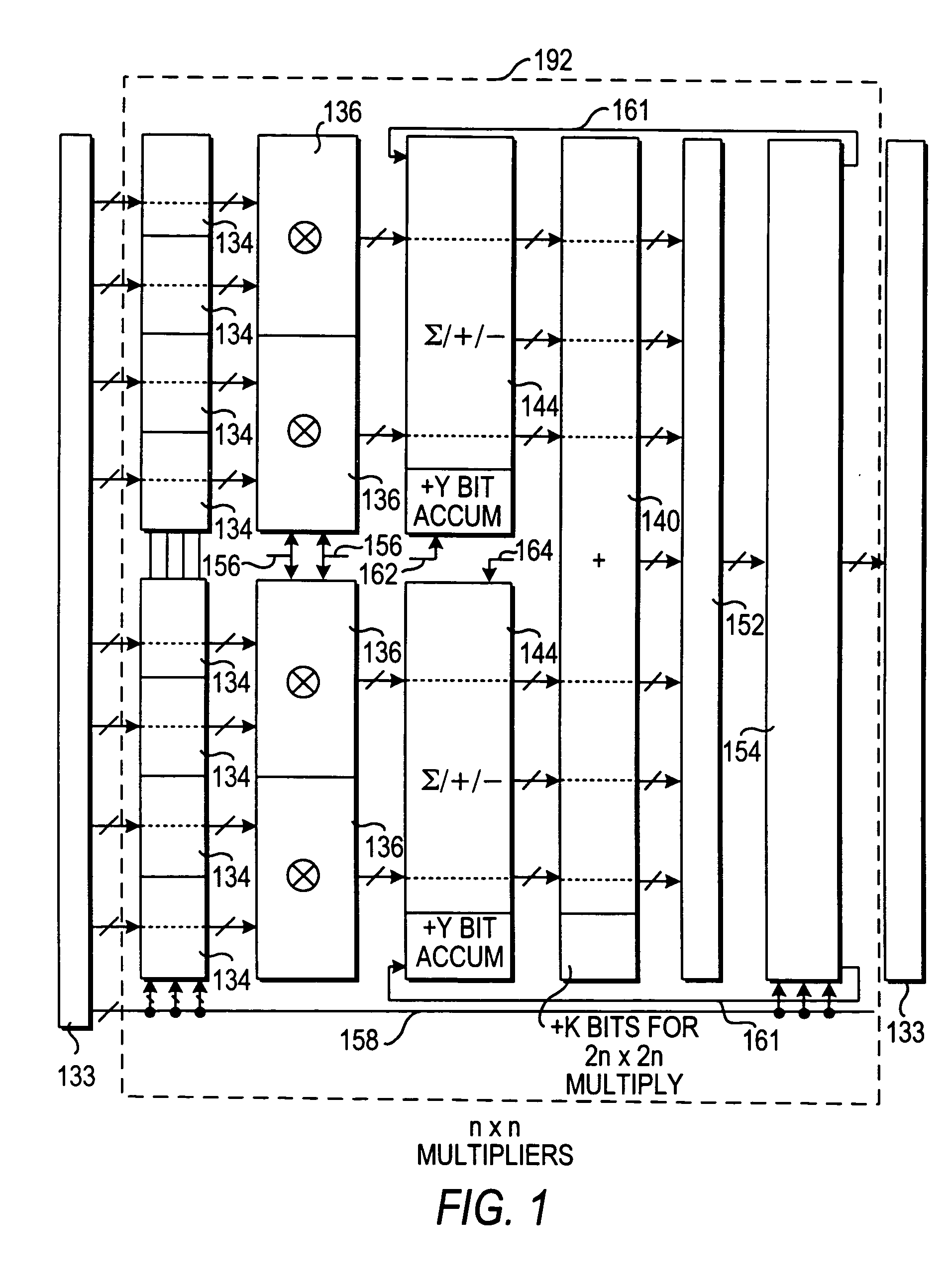

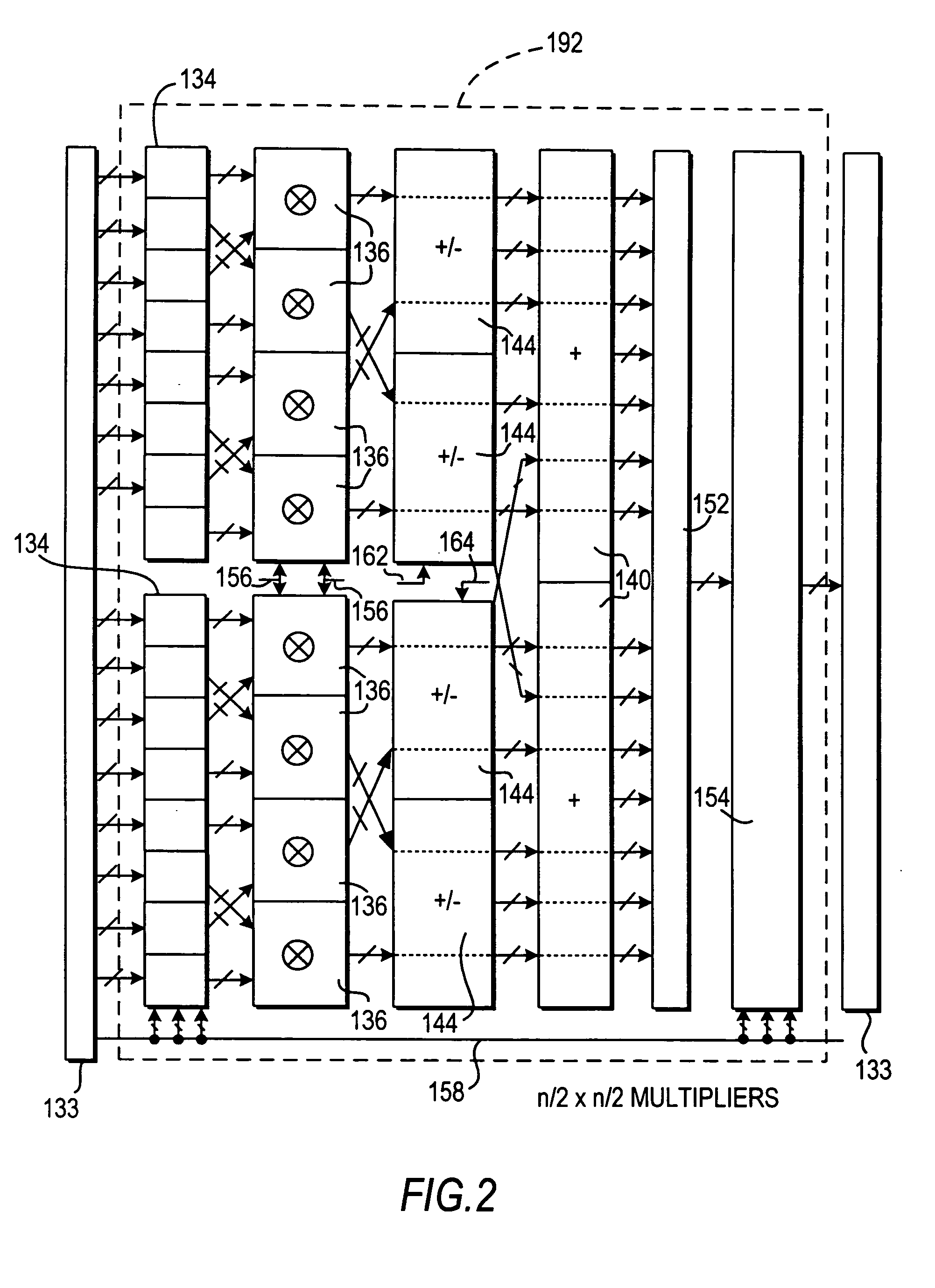

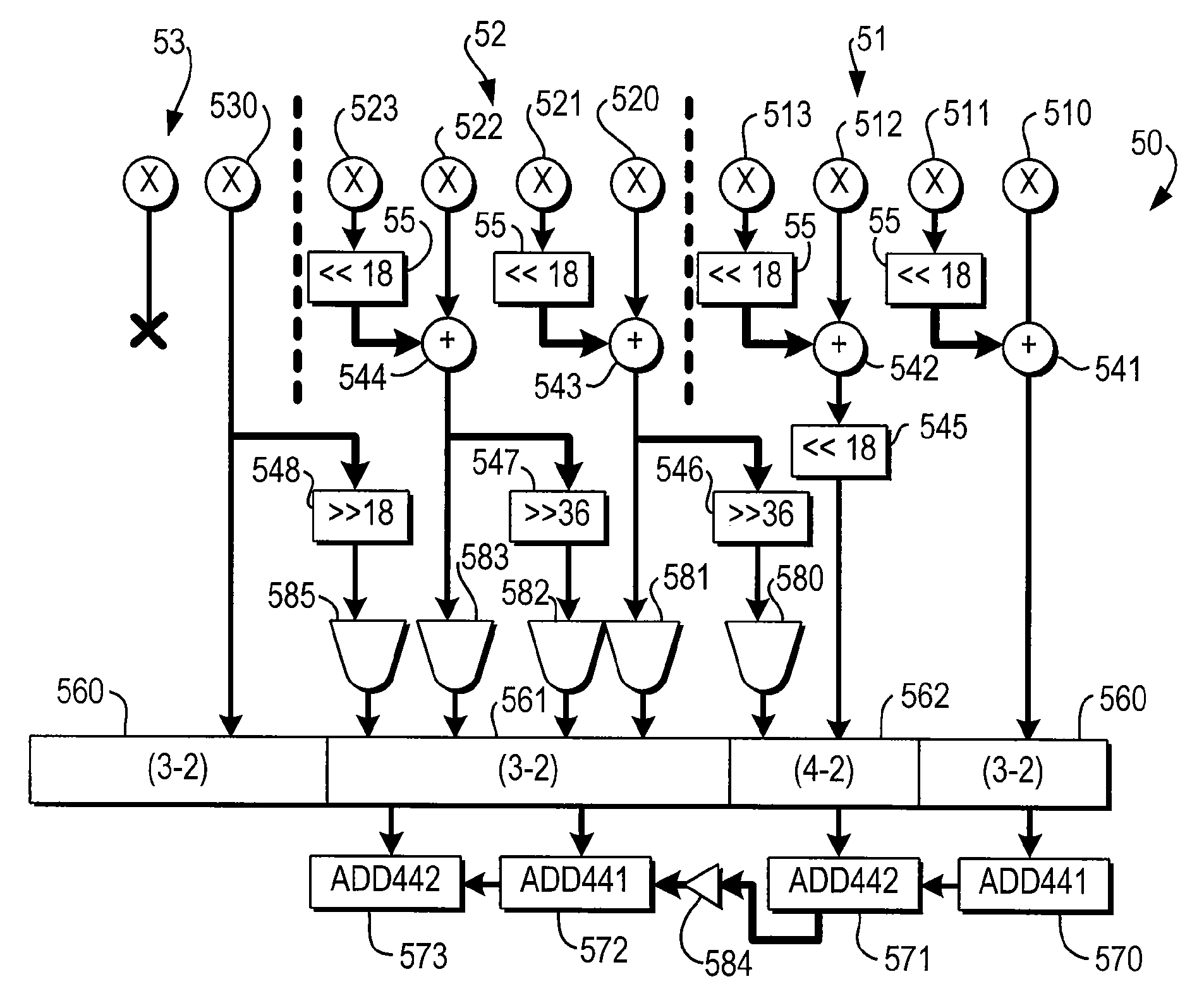

Large multiplier for programmable logic device

ActiveUS20080133627A1Improve performanceReducing and eliminating relianceComputation using non-contact making devicesComputer programmed simultaneously with data introductionBinary multiplierProgrammable logic device

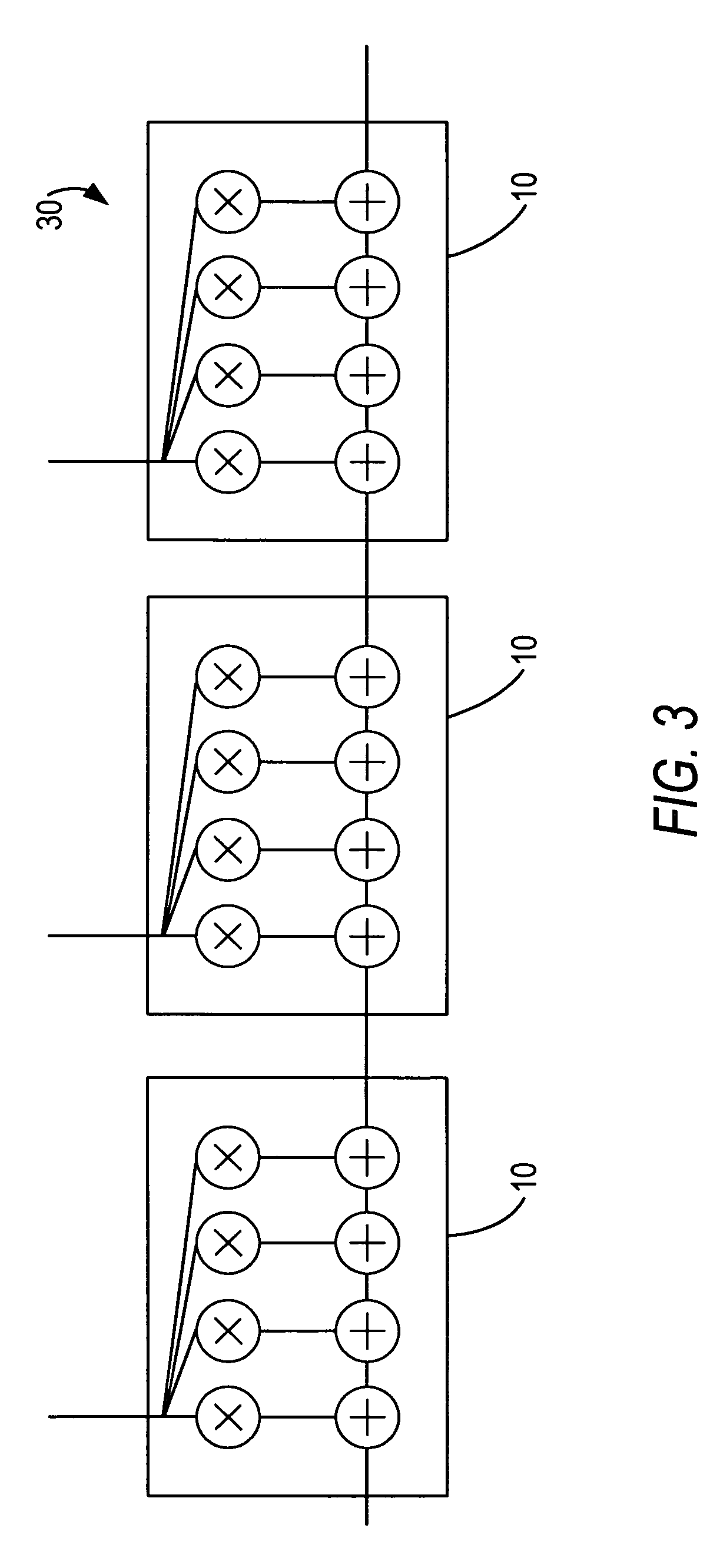

A plurality of specialized processing blocks in a programmable logic device, including multipliers and circuitry for adding results of those multipliers, can be configured as a larger multiplier by adding to the specialized processing blocks selectable circuitry for shifting multiplier results before adding. In one embodiment, this allows all but the final addition to take place in specialized processing blocks, with the final addition occurring in programmable logic. In another embodiment, additional compression and adding circuitry allows even the final addition to occur in the specialized processing blocks.

Owner:ALTERA CORP

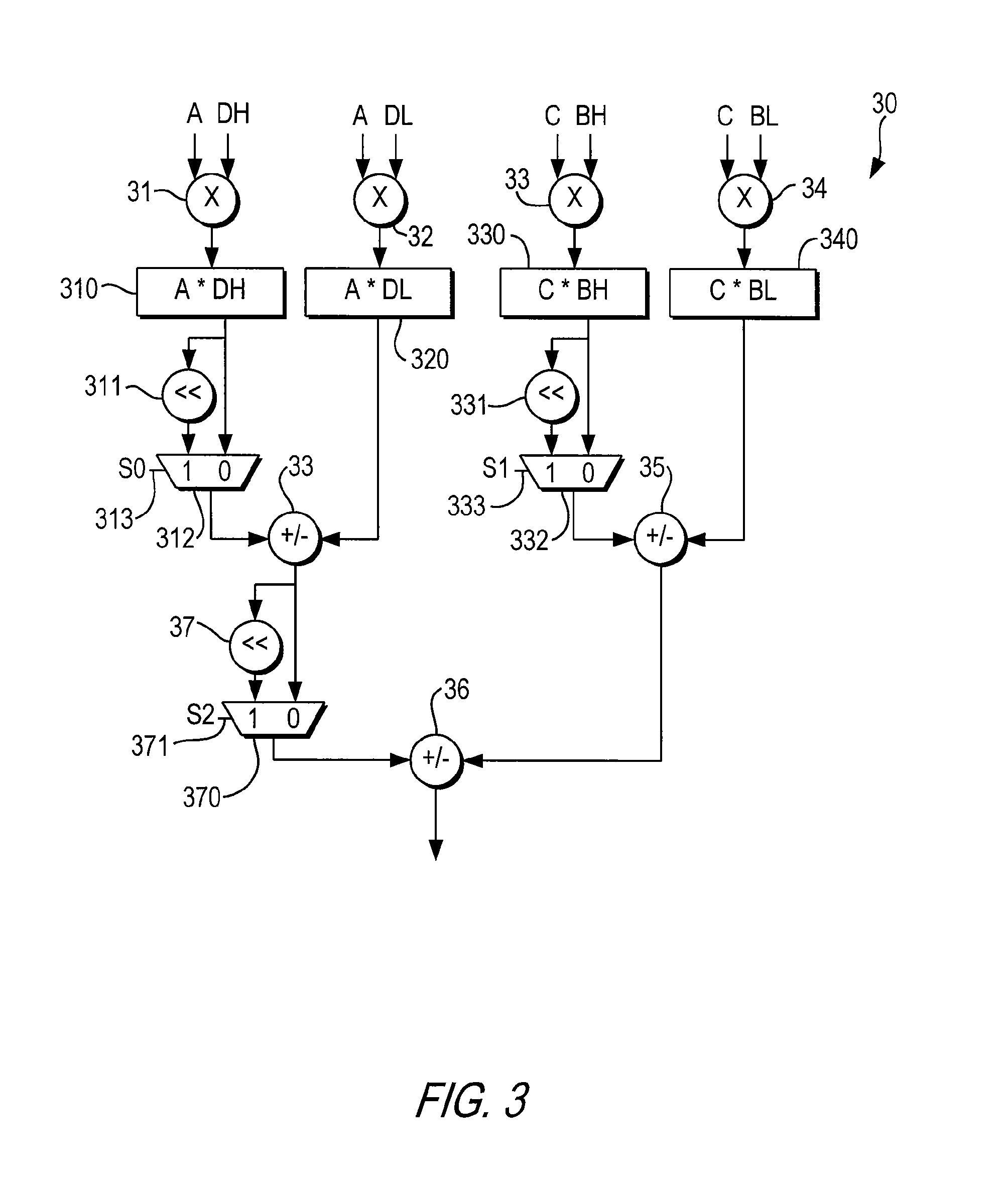

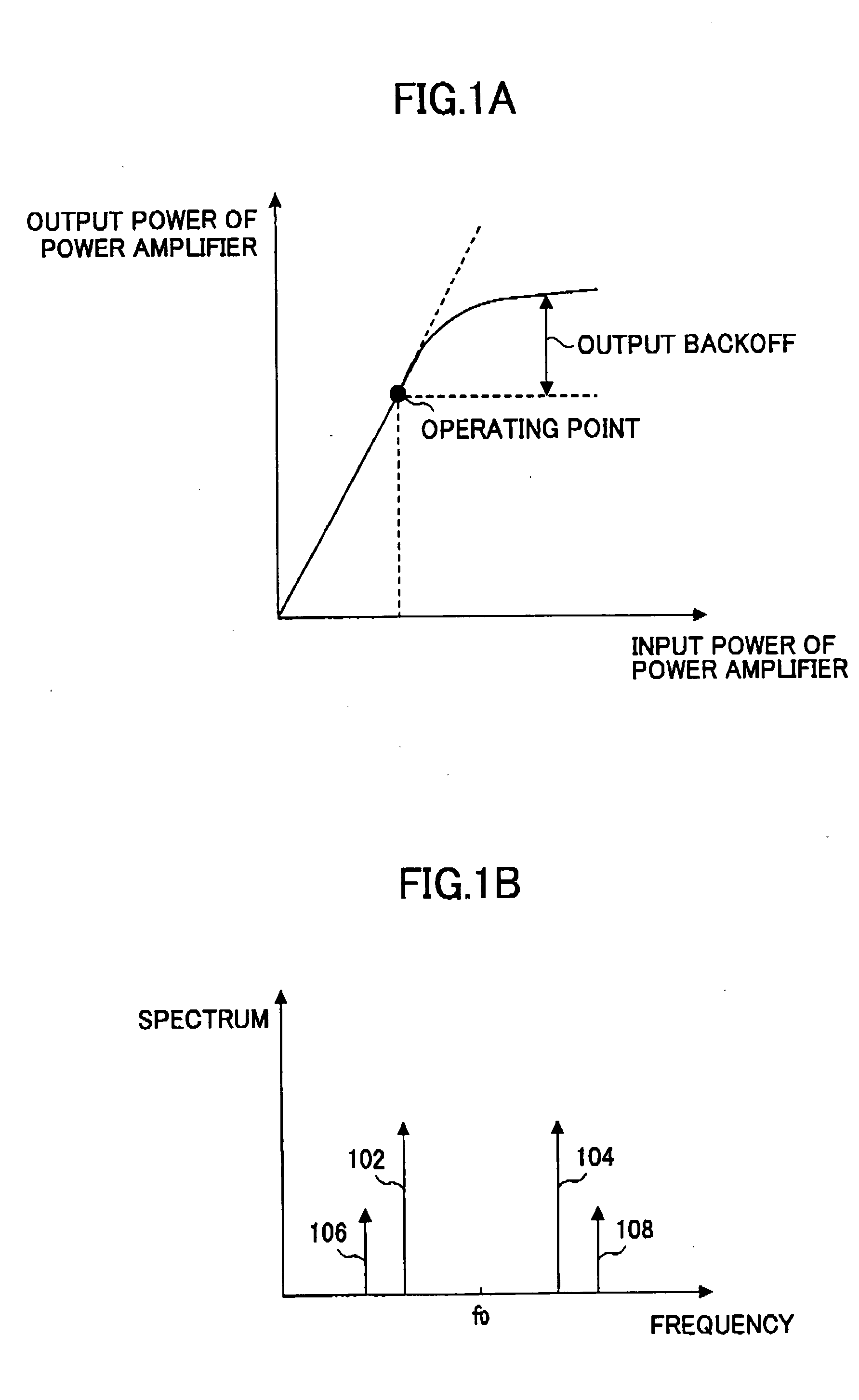

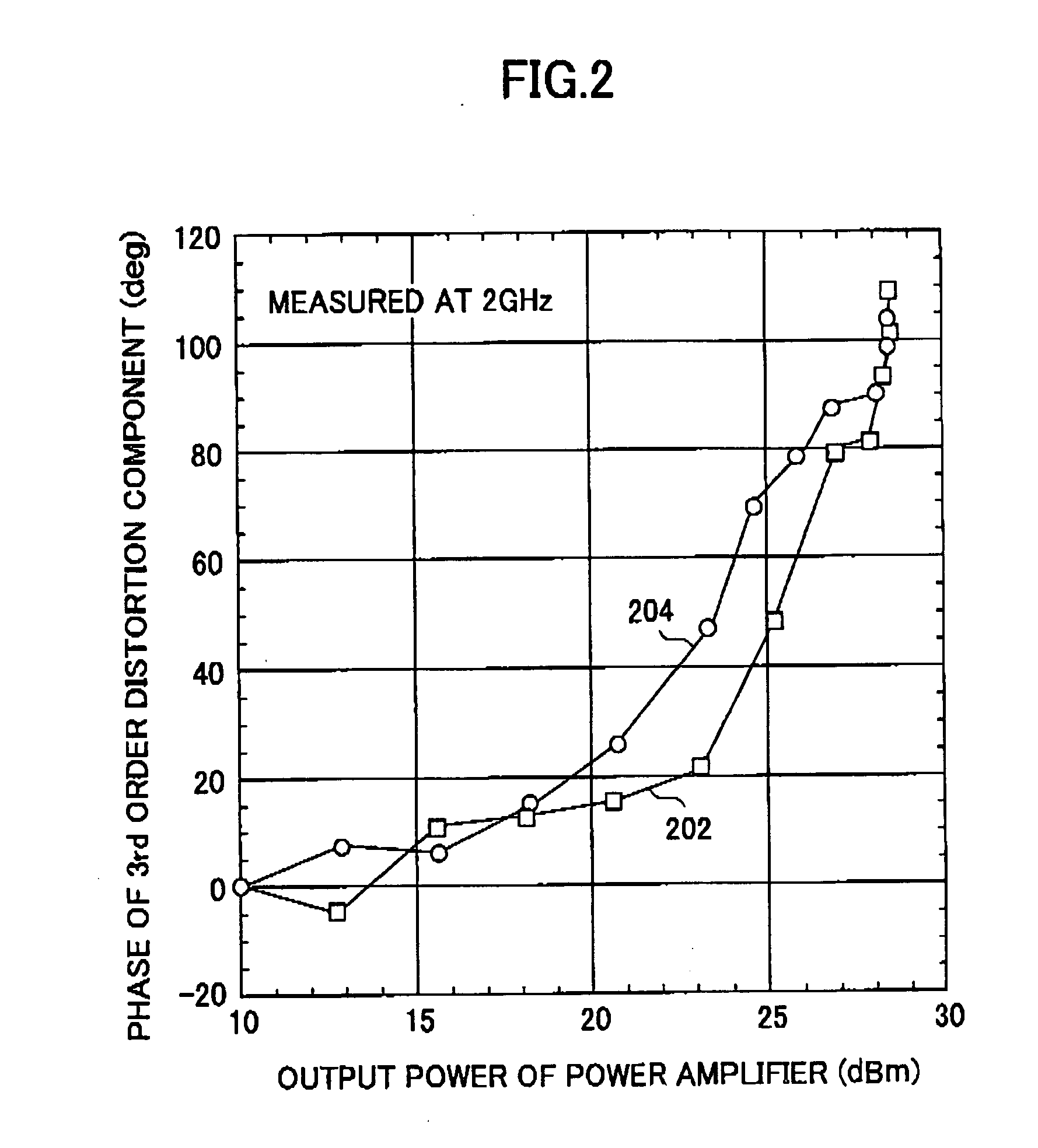

Digital predistorter using power series model

InactiveUS20050180527A1Highly precise nonlinear distortion compensationEfficiently cancel the distortion generatedAmplifier modifications to reduce non-linear distortionEnergy recovery in ventilation and heatingSelf adaptiveAdaptive control

A digital predistorter compensates for nonlinear distortion of a power amplifier using a power series model. The digital predistorter includes a distortion generating unit configured to introduce a nonlinear distortion component of a prescribed order into a digital input signal supplied to the digital predistorter. The distortion generating unit has a multiplier configured to raise the digital input signal to a power consistent with the prescribed order of the nonlinear distortion component, and a finite impulse response filter connected in series with the multiplier. The digital predistorter also includes an adaptive controller configured to receive a reference signal and adaptively adjust the tap coefficient of the finite impulse response filter so as to bring the reference signal to a desired level.

Owner:NTT DOCOMO INC

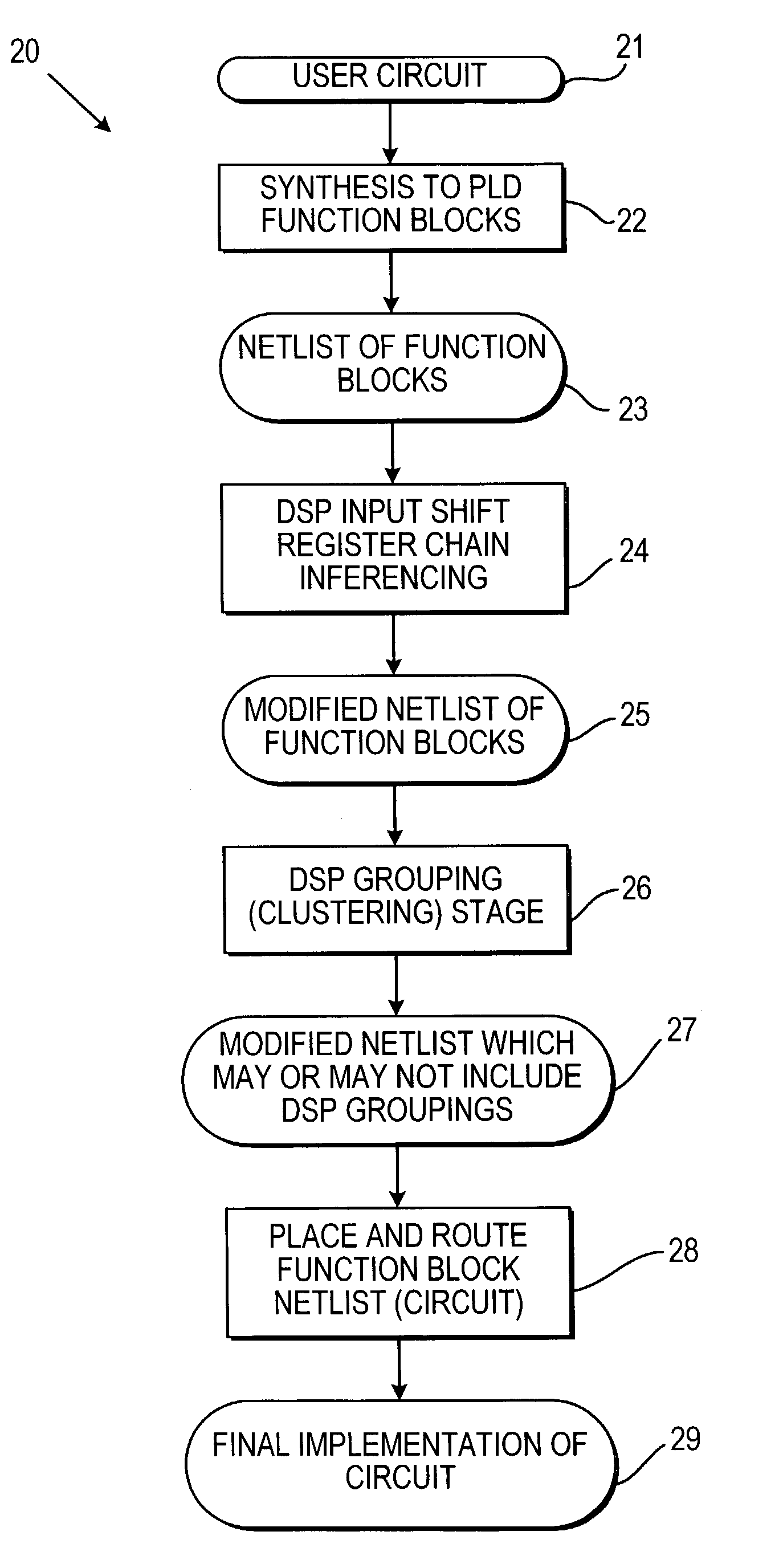

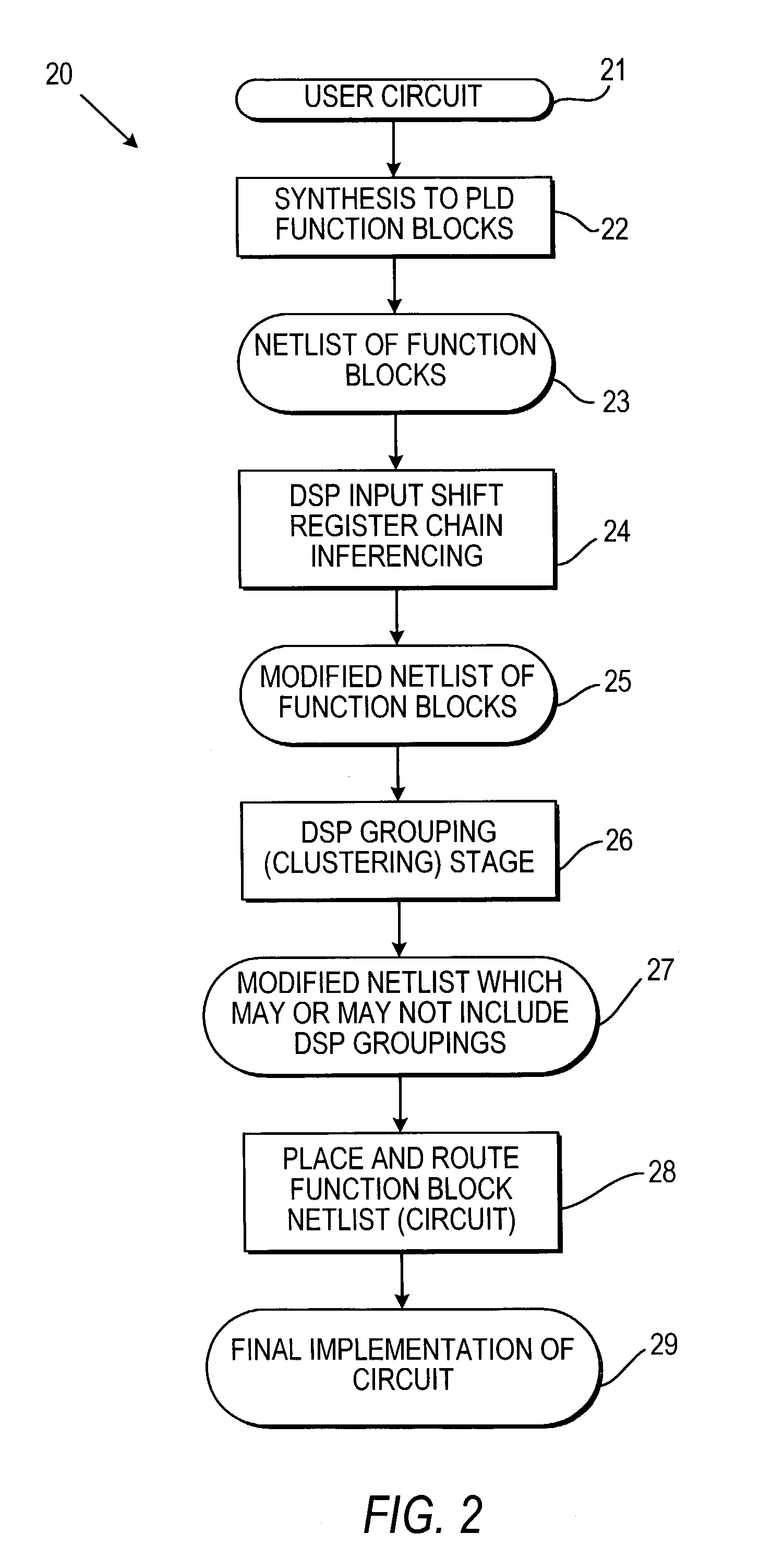

Method for programming programmable logic device with blocks that perform multiplication and other arithmetic functions

InactiveUS6971083B1CAD circuit designSpecial data processing applicationsGeneral purposeBinary multiplier

A programming method efficiently programs programmable logic devices of the type having specialized multiplier blocks that include multipliers and other arithmetic function elements. Such blocks can be used to perform certain multiplication and multiplication-related functions more efficiently than general-purpose programmable logic. In order to efficiently program devices having such specialized multiplier blocks, so that they are used to their full potential and so that the maximum number of multiplier-related functions can be accommodated on a single programmable logic device, the programming method pre-processes the netlist of function blocks in a user's programmable logic design, grouping multiplication and multiplication-related functions efficiently. The method takes into account limitations imposed by the structure of the specialized multiplier blocks, in addition to location constraints imposed by the user and location constraints dictated by the need for certain functions be carried out near where certain other functions are carried out.

Owner:ALTERA CORP

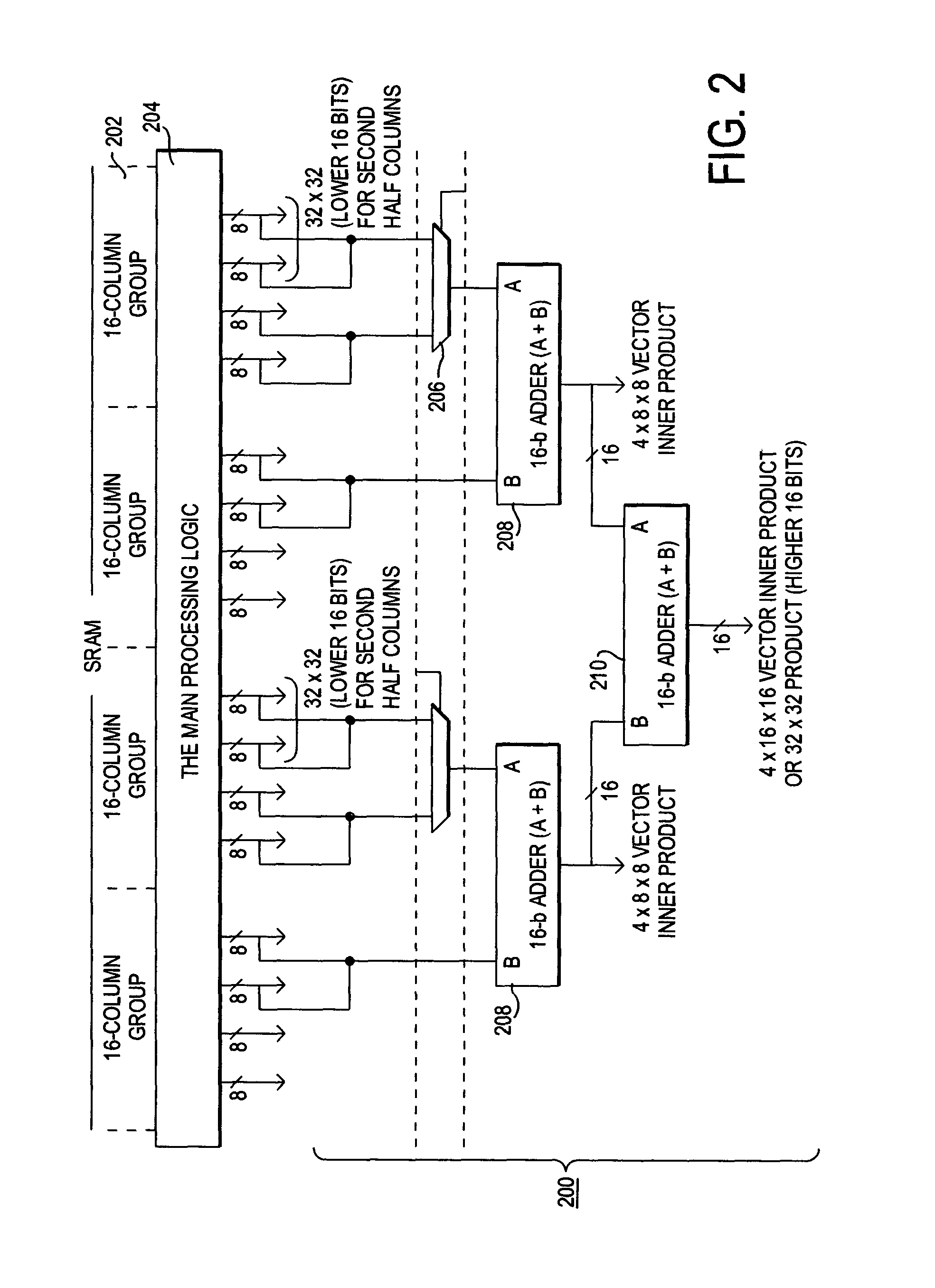

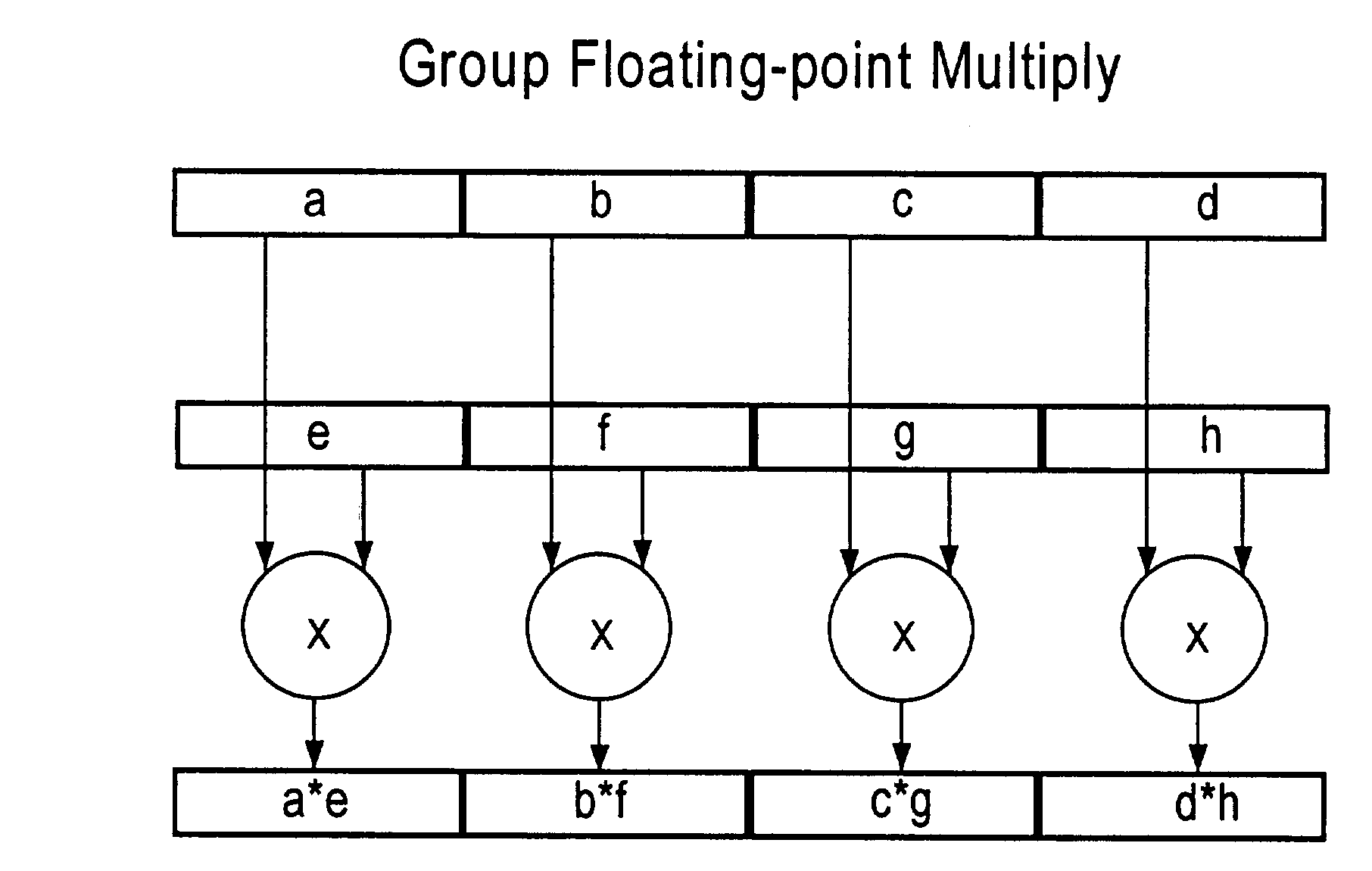

Multiplier array processing system with enhanced utilization at lower precision

InactiveUS7509366B2Increase profitSolve high precisionEnergy efficient ICTInstruction analysisBinary multiplierOperand

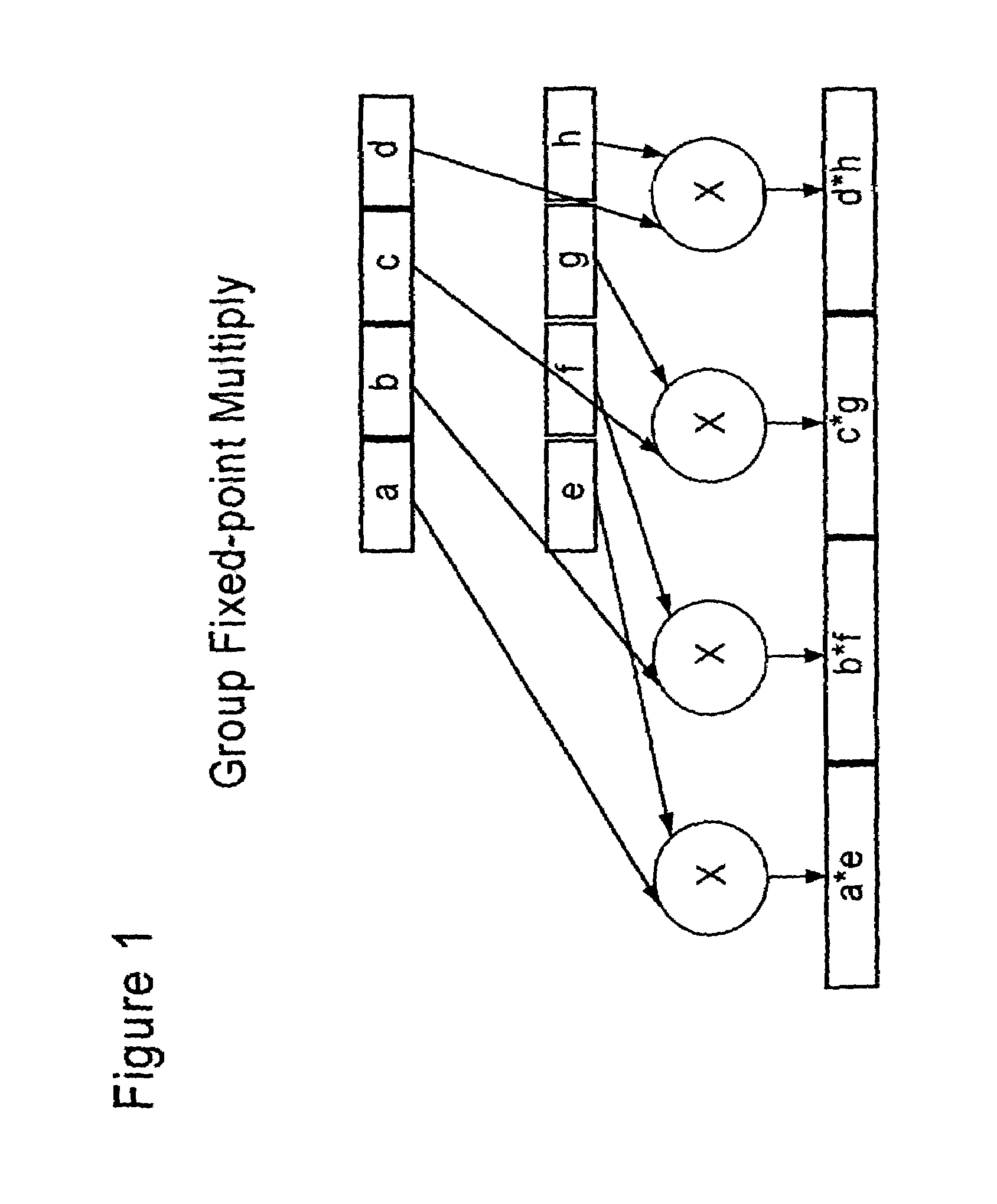

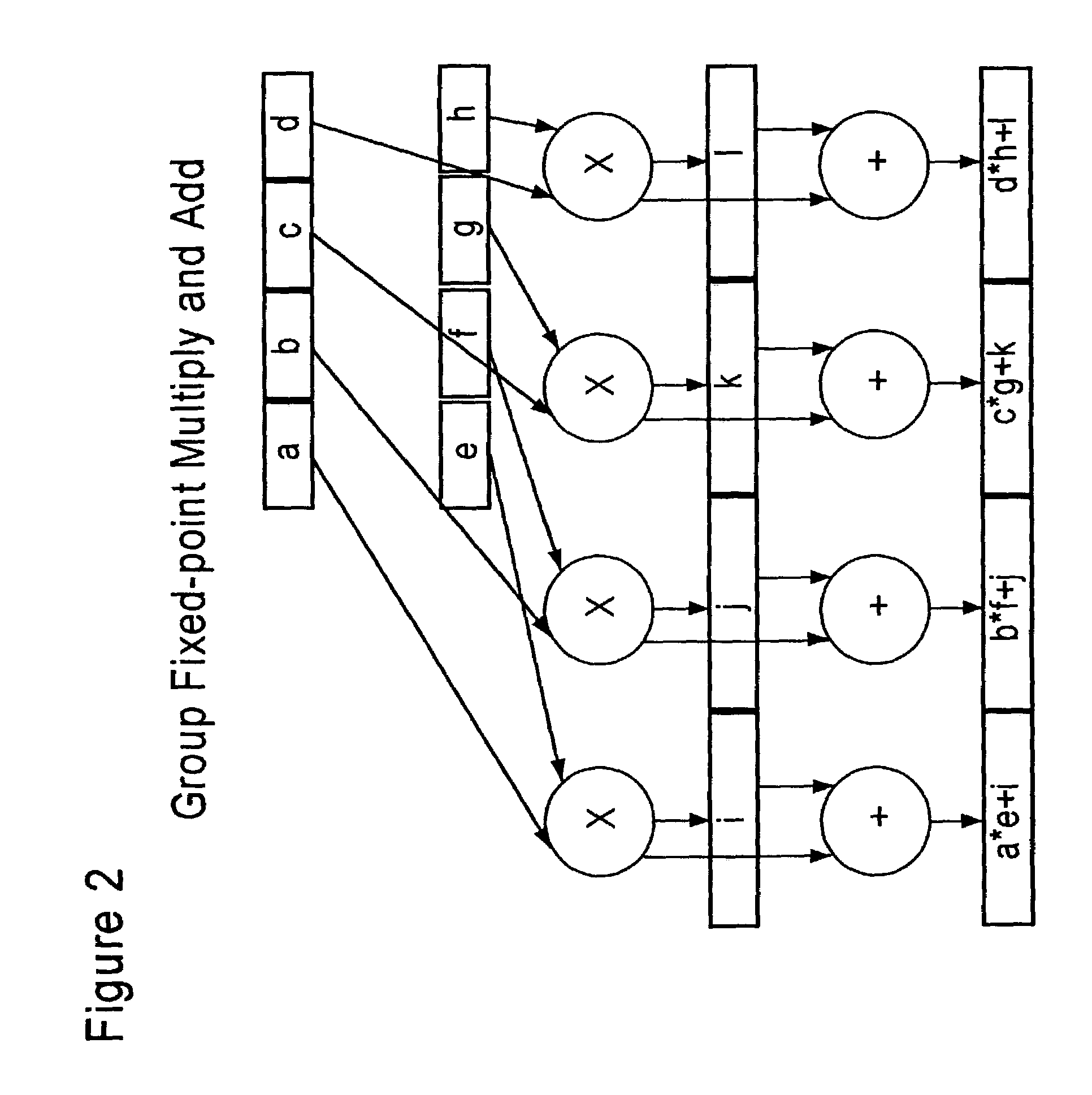

A multiplier array processing system which improves the utilization of the multiplier and adder array for lower-precision arithmetic is described. New instructions are defined which provide for the deployment of additional multiply and add operations as a result of a single instruction, and for the deployment of greater multiply and add operands as the symbol size is decreased.

Owner:MICROUNITY

Linear phase robust carrier recovery for QAM modems

InactiveUS6904098B1Large loop bandwidthLower latencyDc level restoring means or bias distort correctionAutomatic frequency control detailsQam modulationBlind equalization

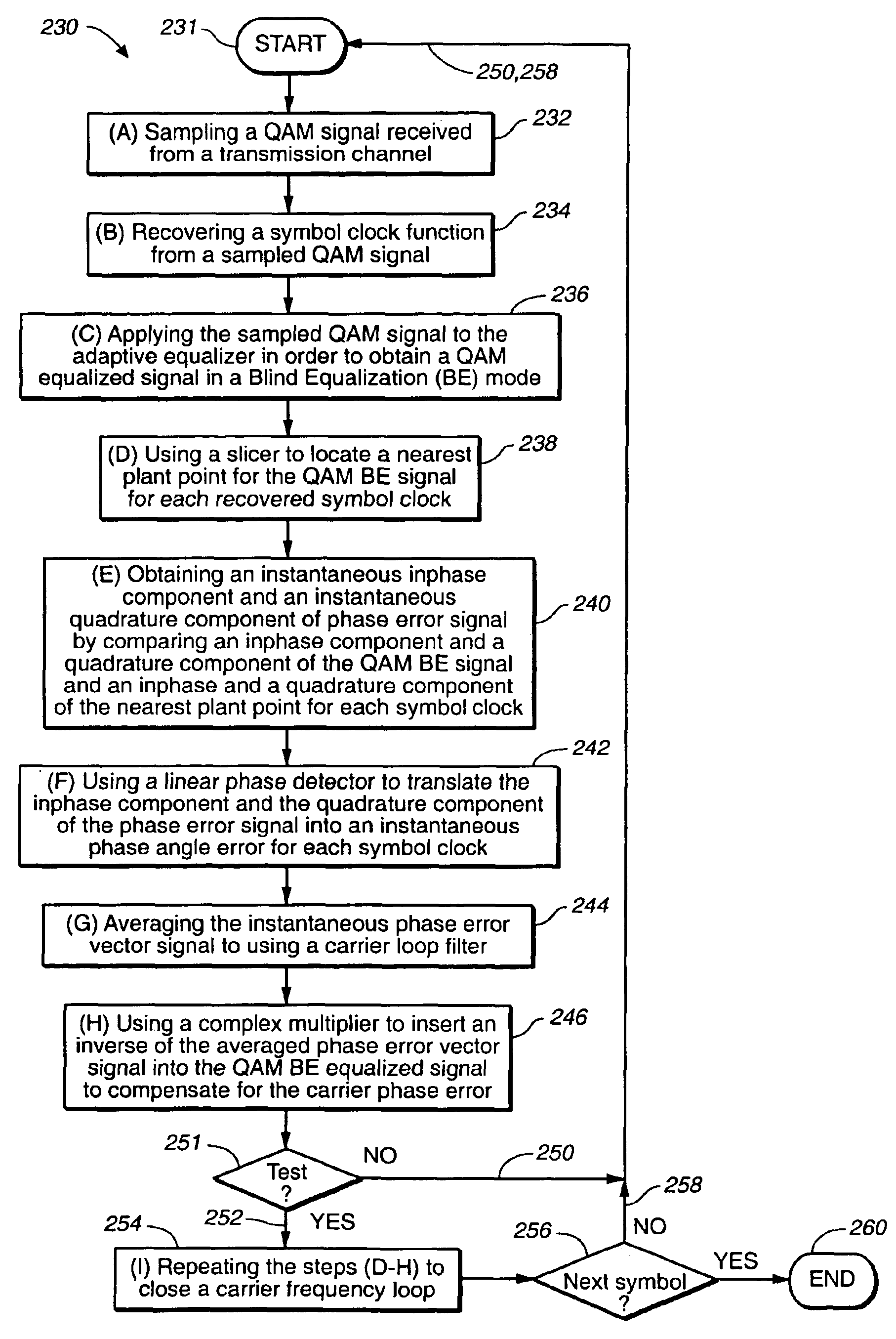

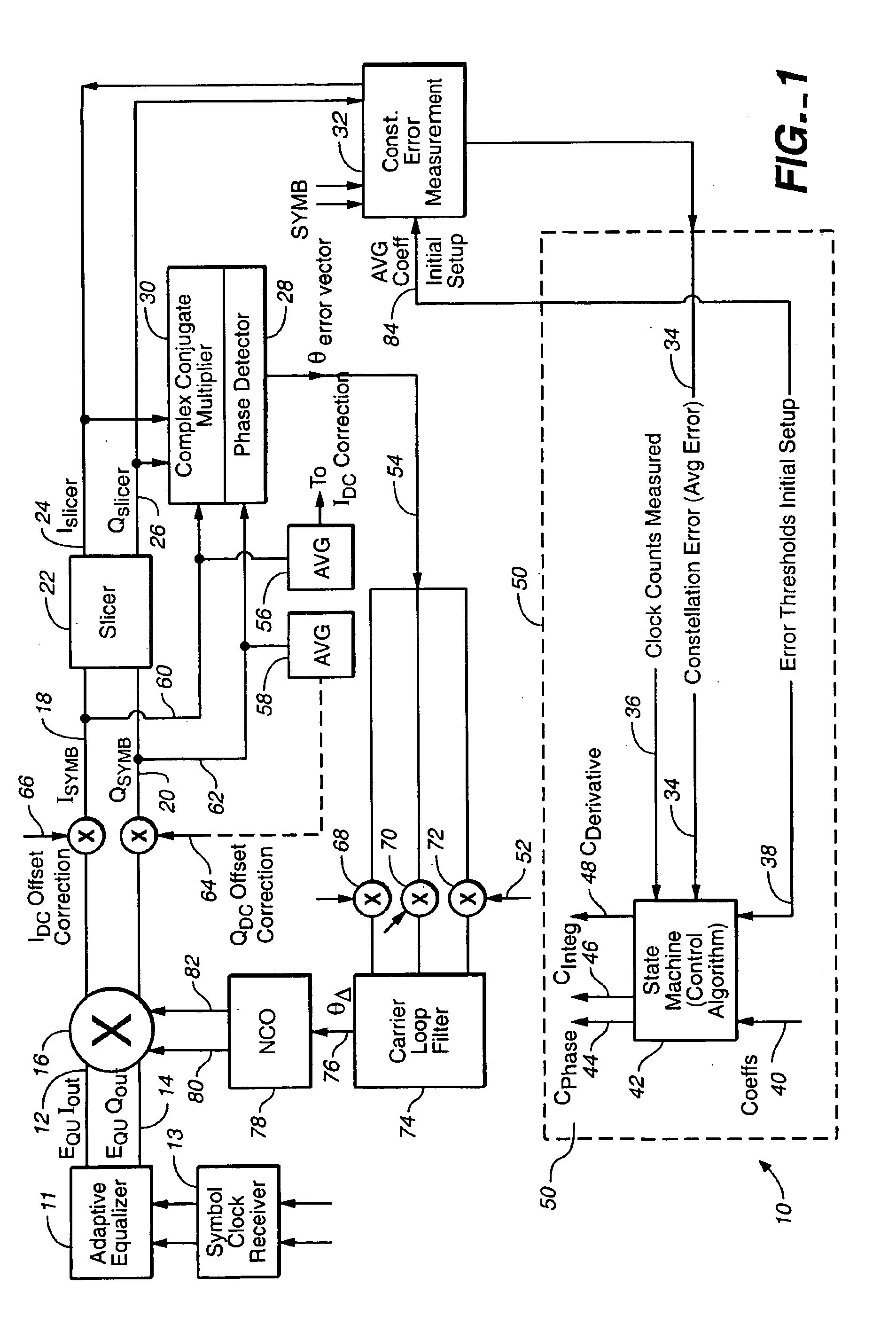

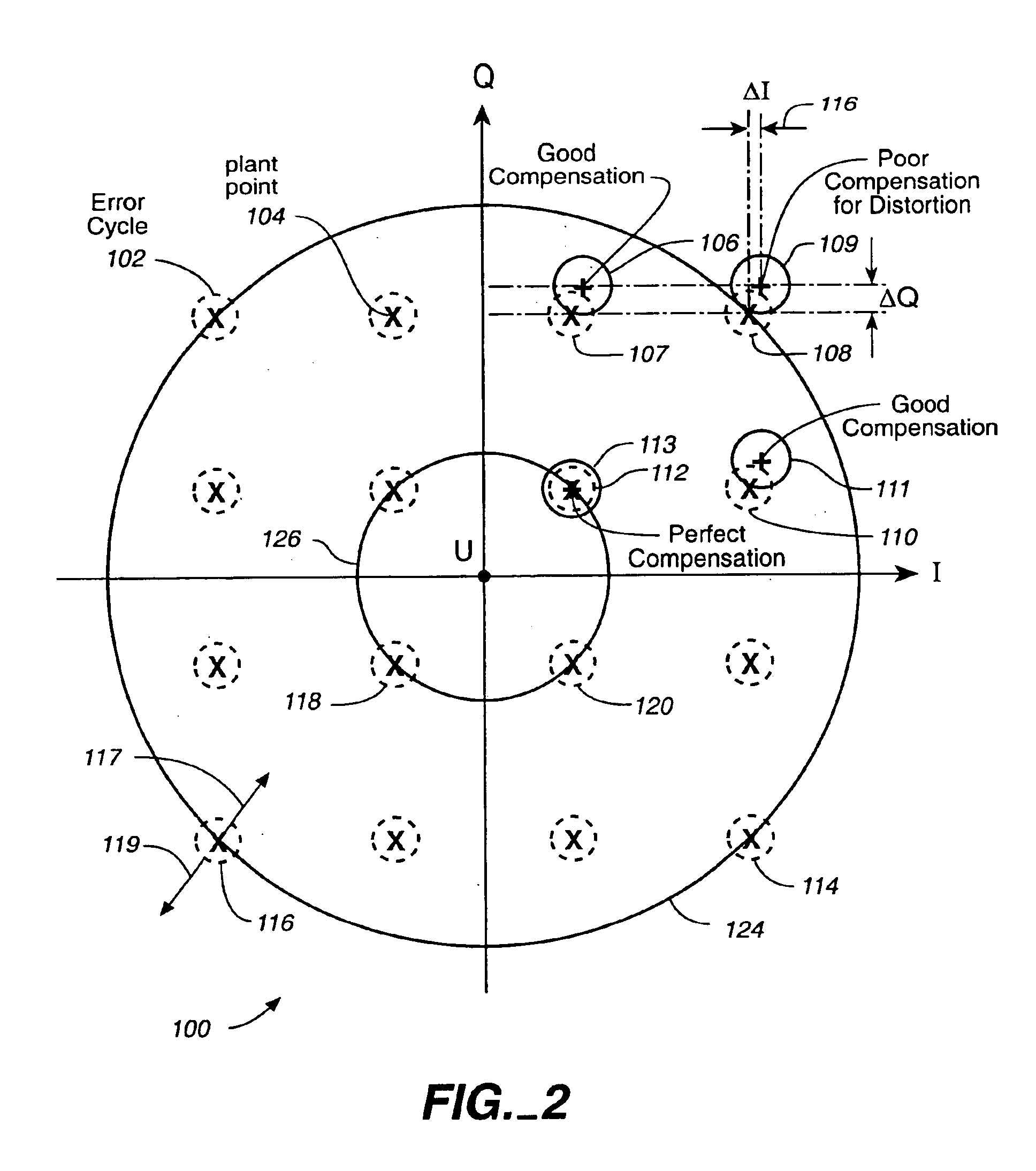

In a QAM demodulator including an adaptive equalizer, a method of carrier tracking comprising the following steps is disclosed: (A) sampling a QAM signal received from a transmission channel; (B) recovering a symbol clock function from the sampled QAM signal; (C) applying the sampled QAM signal to the adaptive equalizer in order to obtain a QAM equalized signal in a Blind Equalization (BE) mode; (D) using a slicer to locate a nearest plant point for the QAM Blind equalized signal for each recovered symbol clock; (E) using a complex conjugate multiplier to obtain an instantaneous inphase component and an instantaneous quadrature component of a phase angle error signal; (F) using a linear phase detector to obtain an instantaneous phase angle error for each symbol clock; (G) averaging the instantaneous phase angle error signal by using a carrier loop filter; (H) using a complex multiplier to insert an inverse of the averaged phase angle error signal into the QAM Blind equalized signal to compensate for the carrier phase angle error; and (I) repeating the steps (D-H) to close a carrier frequency loop.

Owner:REMEC BROADBAND WIRELESS NETWORKS LLC

Approximate bit-loading for data transmission over frequency-selective channels

InactiveUS7599390B2Multiplex system selection arrangementsTime-division multiplexFrequency spectrumBinary multiplier

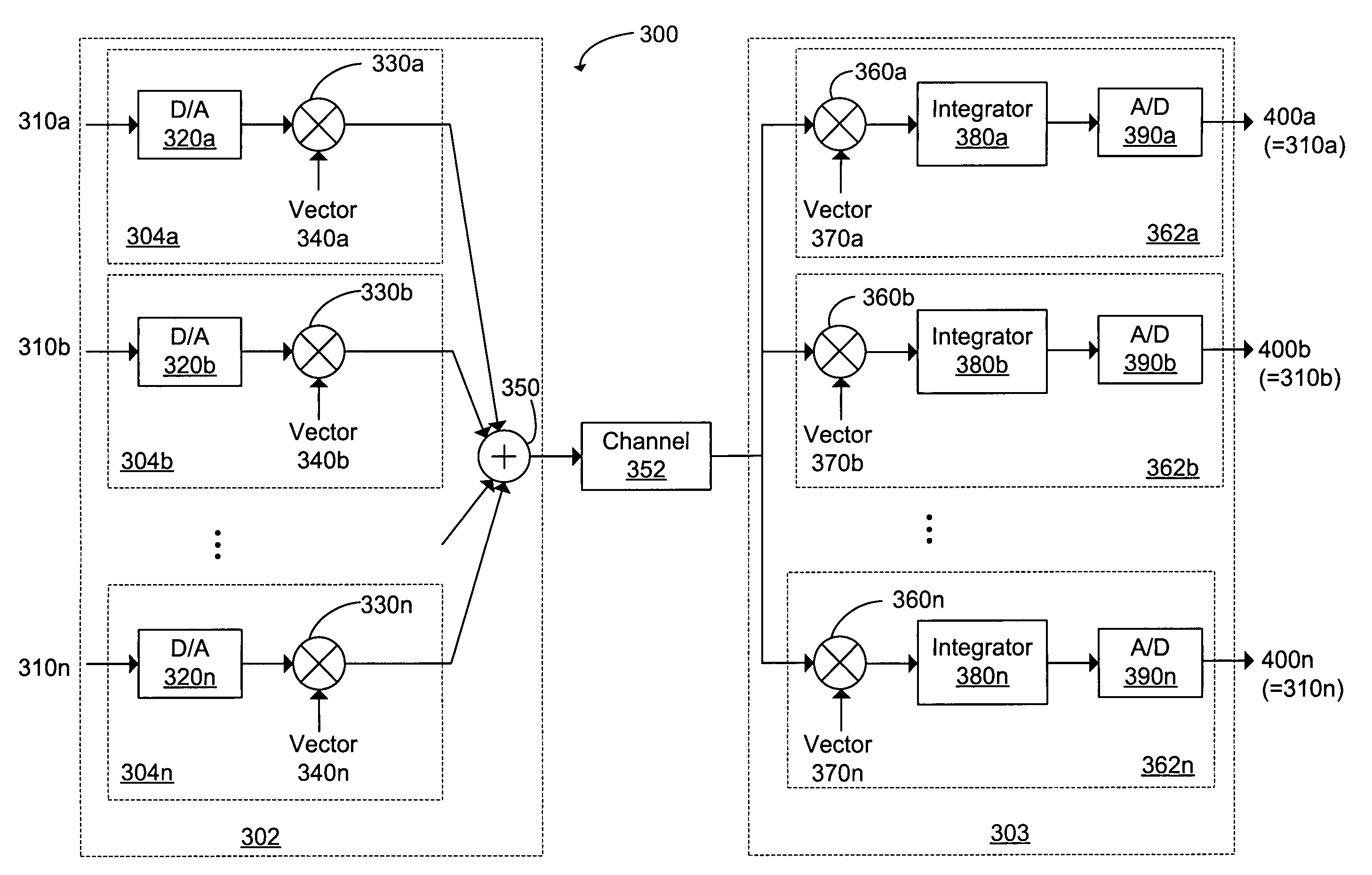

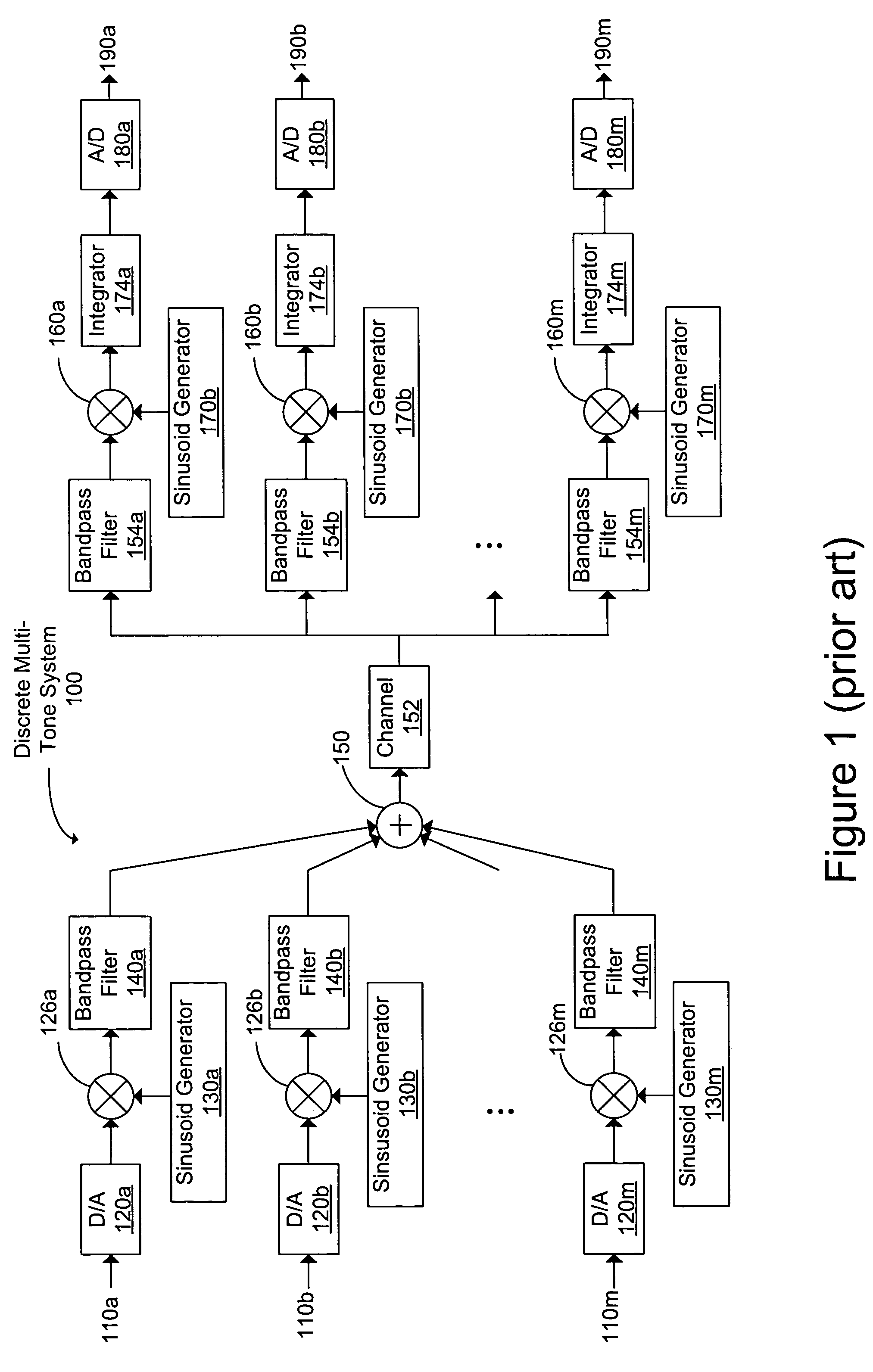

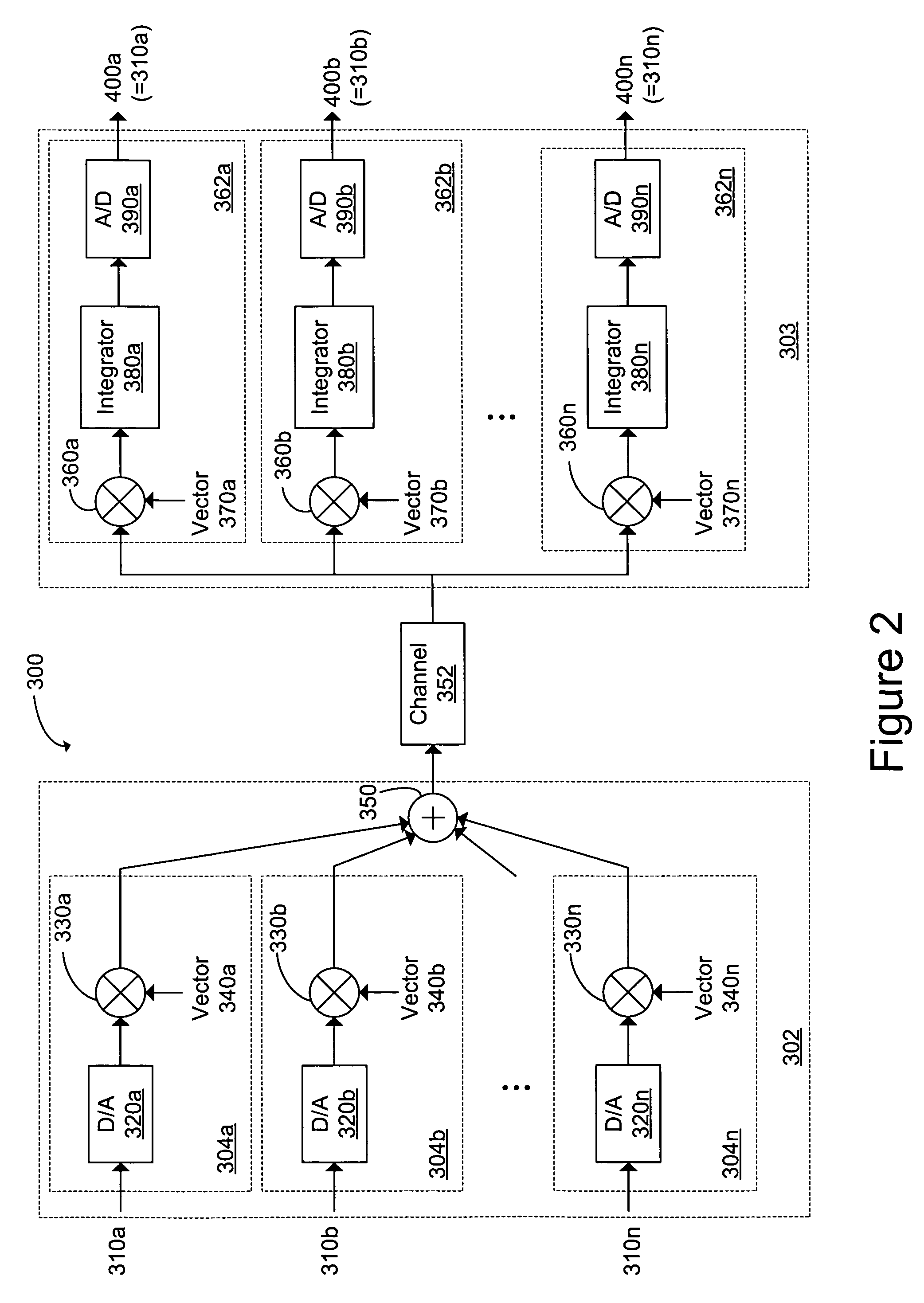

A high-speed communications system utilizes approximate bit-loading during data transmission in a channel. In one embodiment, a plurality of parallel data preparation circuits in a data transmission circuit receive respective subsets of a data stream, each of the respective subsets of the data stream having a data rate that is less than a data rate of the data stream. Converters in the data preparation circuits convert the respective subsets of the data stream into respective analog signals. Multipliers in the data preparation circuits multiply the respective analog signals by respective vectors to produce respective sub-channel signals. At least a frequency band in the spectrum corresponding to one of the respective sub-channel signals partially overlaps at least a frequency band for at least one other of the respective sub-channel signals. The respective sub-channel signals are combined prior to transmission.

Owner:RAMBUS INC

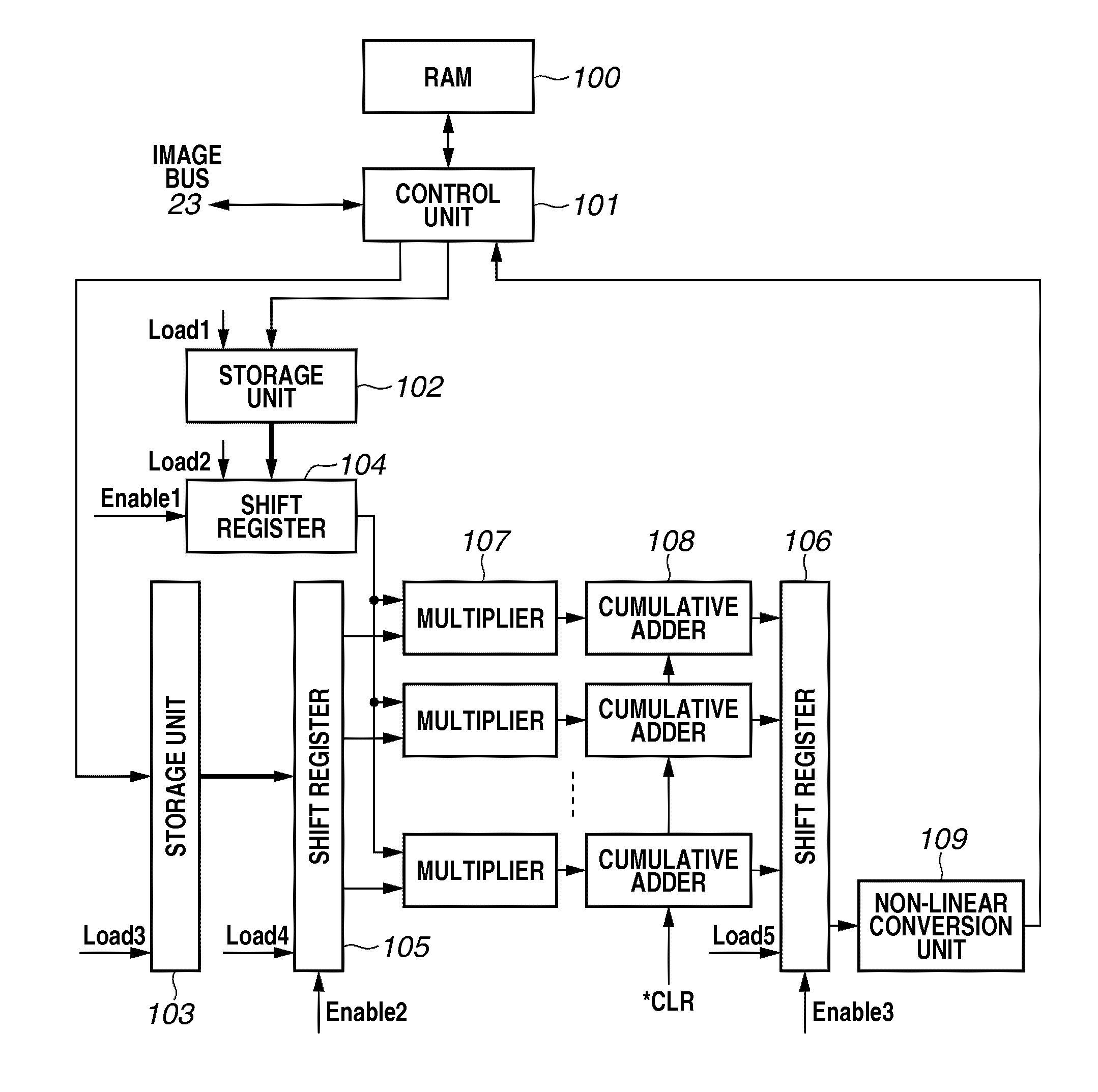

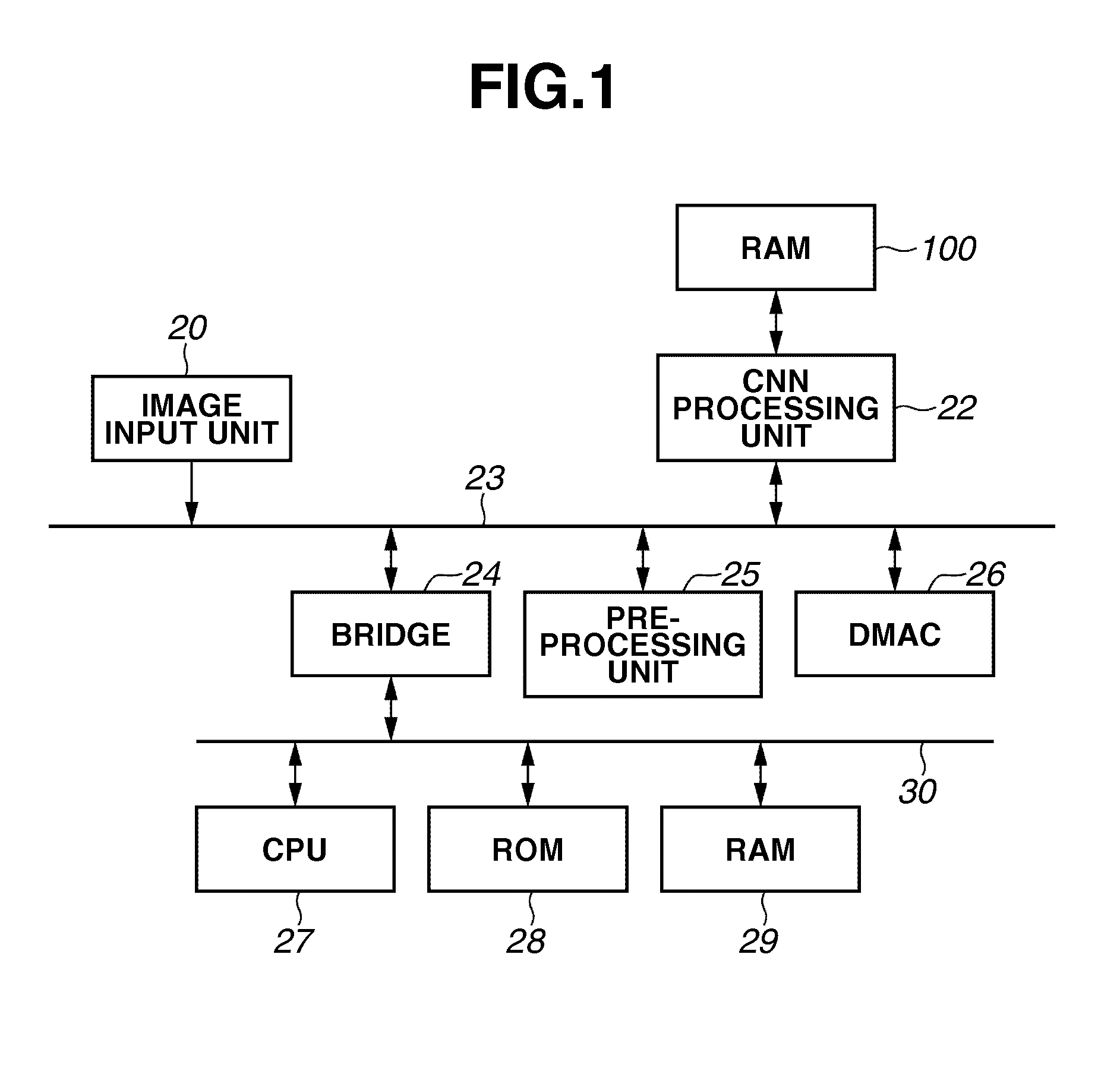

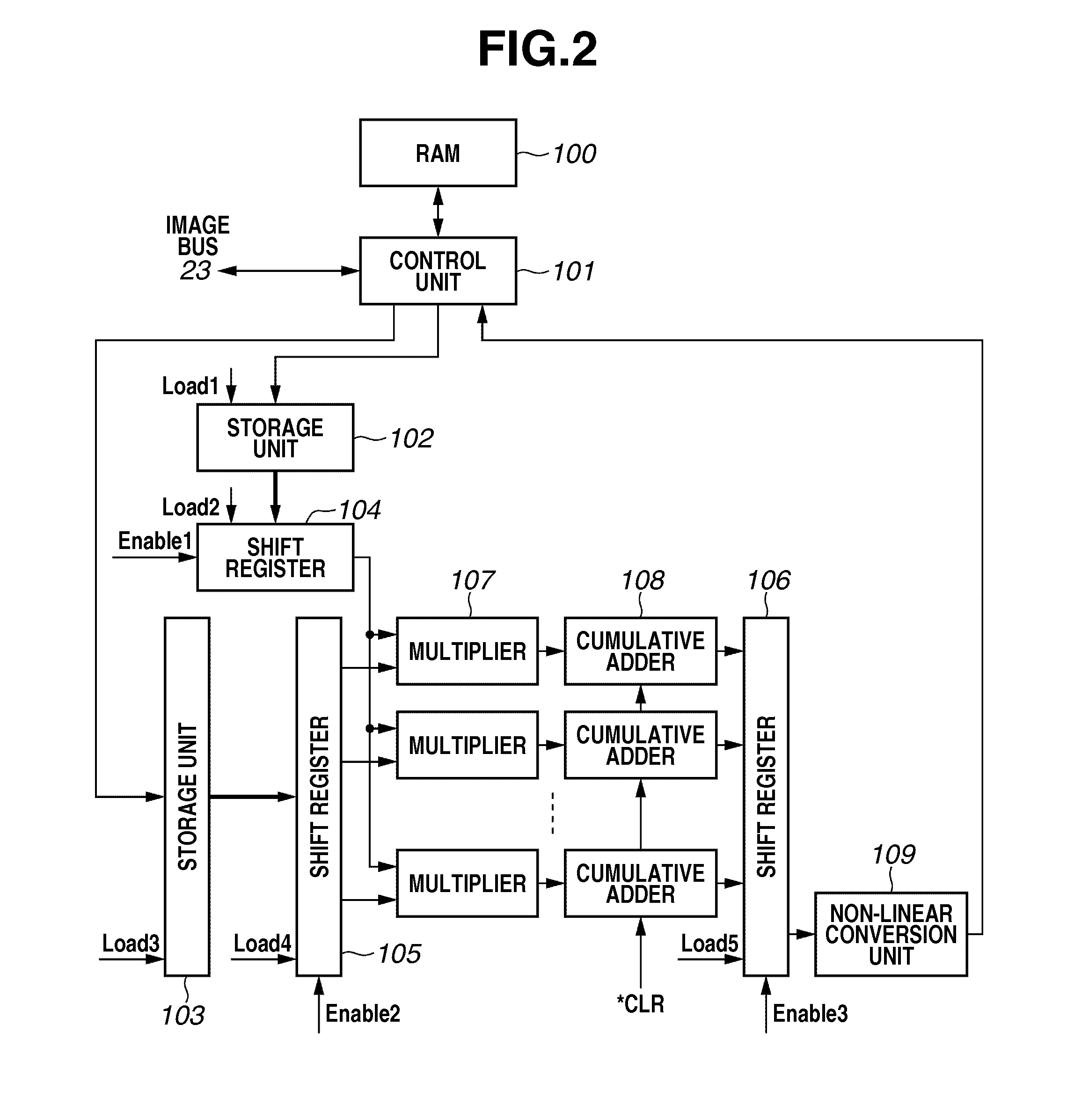

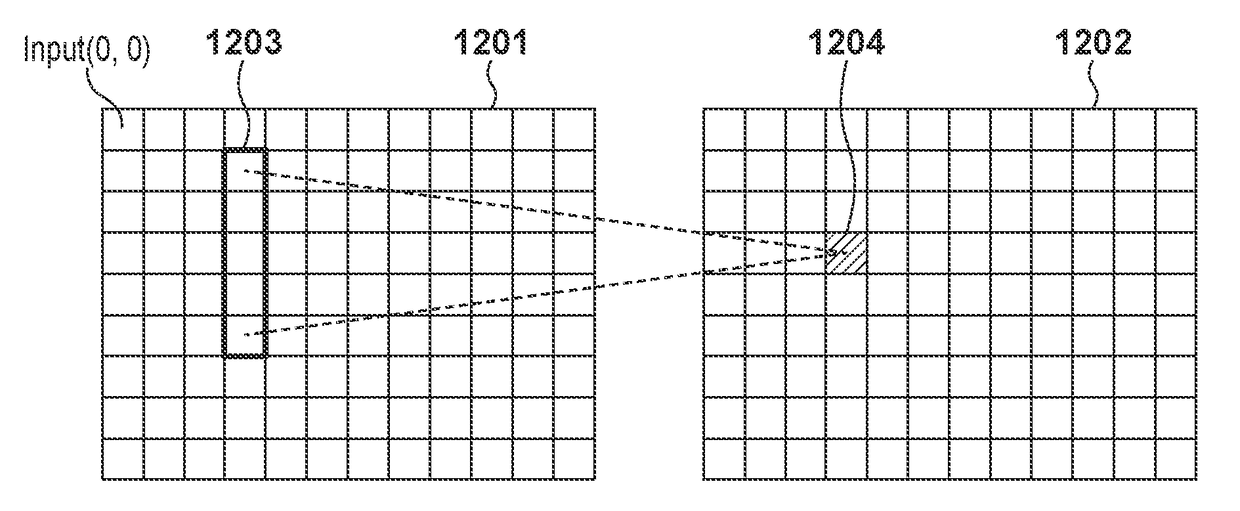

Convolution operation circuit and object recognition apparatus

InactiveUS20110239032A1Increase speedSimple configurationCharacter and pattern recognitionImage data processing detailsShift registerComputer architecture

In a convolution operation circuit, a first and a second shift registers provide data to a first and a second inputs of a plurality of multipliers, a first and a second storage units store data to be supplied to the first and the second shift registers, a plurality of cumulative adders accumulate output from the plurality of multipliers, a third storage unit latches output from the plurality of cumulative adders at predetermined timing, a fourth storage unit stores data to be stored in the first and the second storage units and data output from the third storage unit, and a control unit sets data stored in the first and the second storage units to the first and the second shift registers at predetermined timing, causes the first and the second shift registers to perform shift operations in synchronization with an operation of the cumulative adder.

Owner:CANON KK

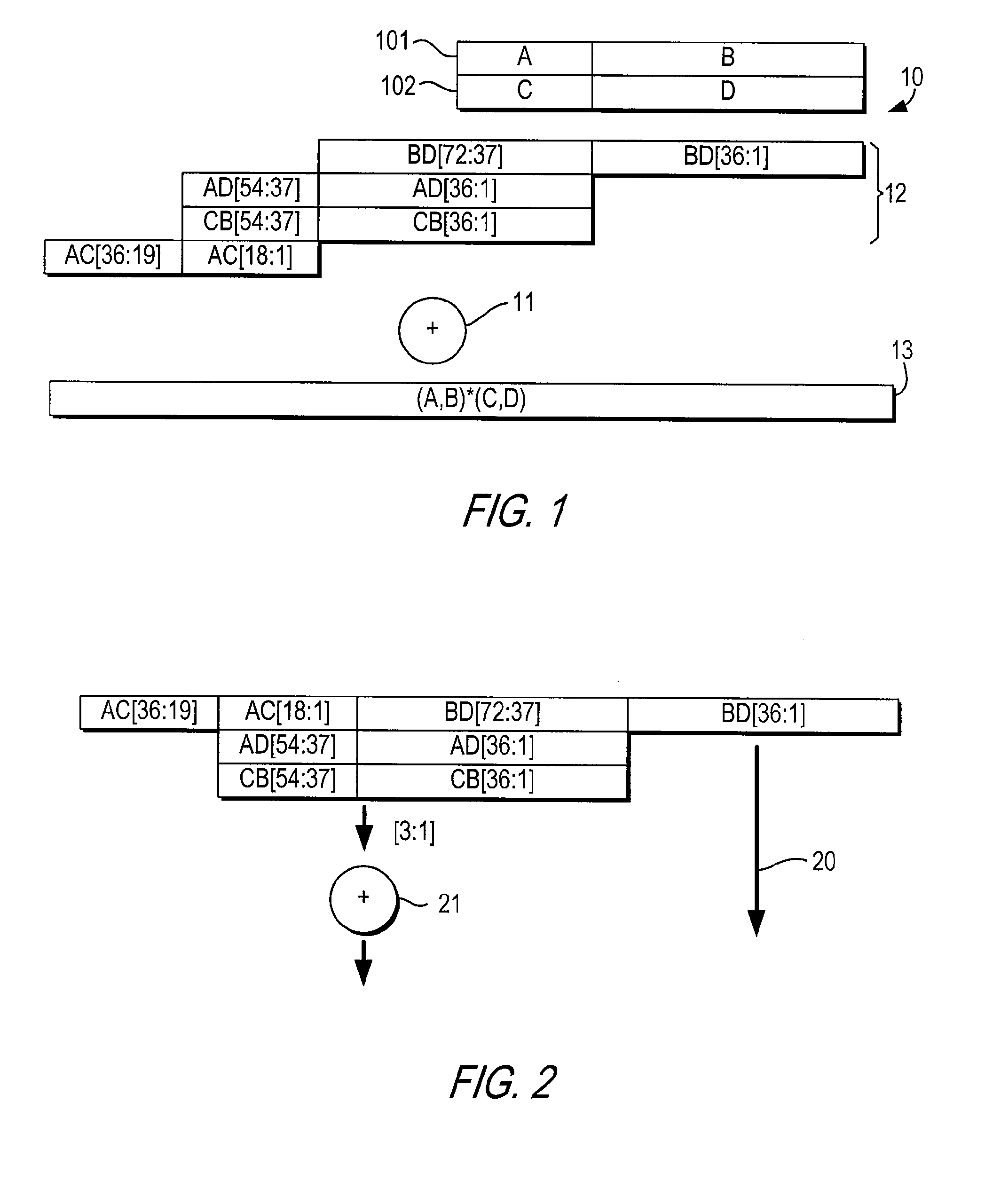

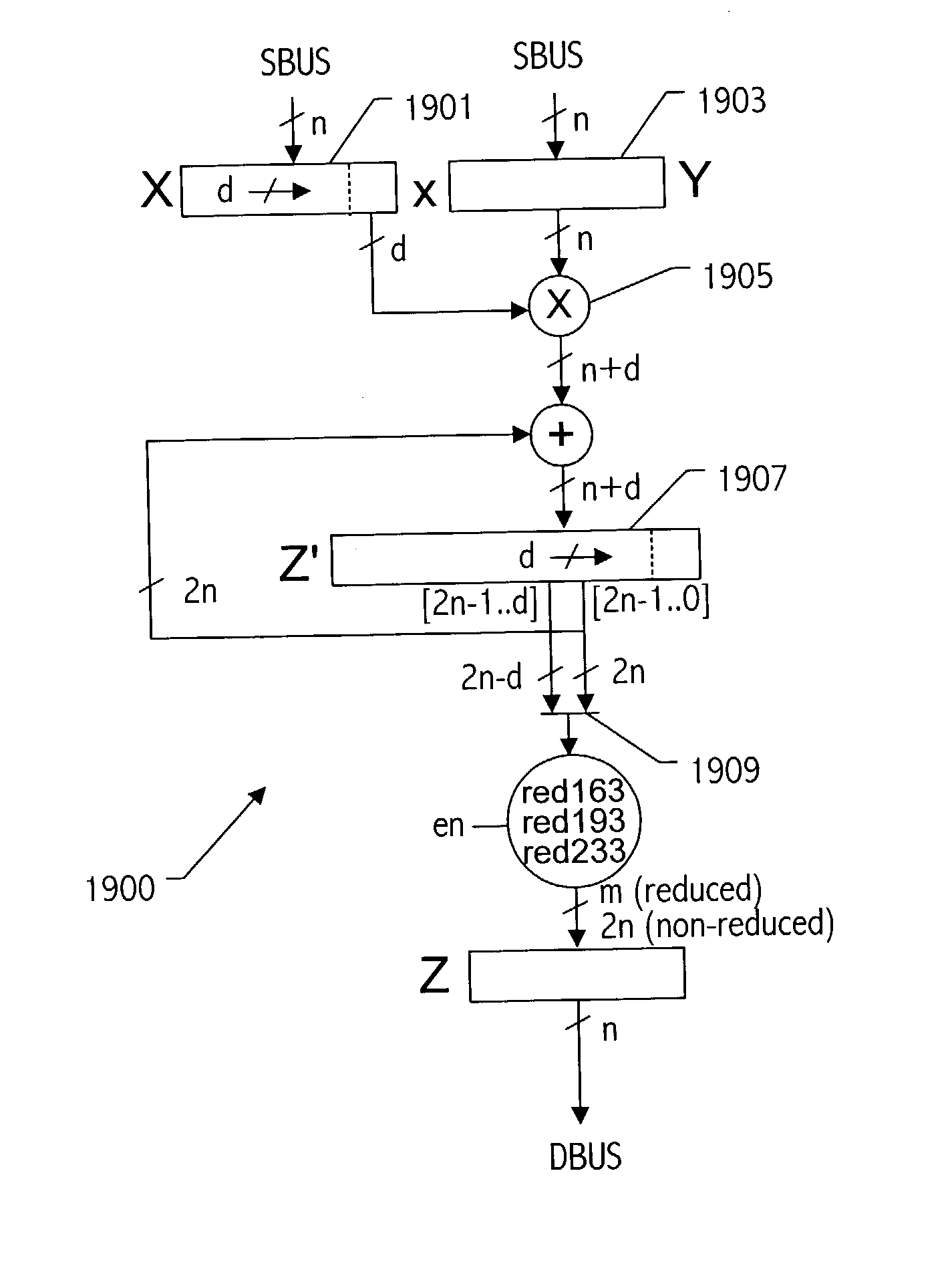

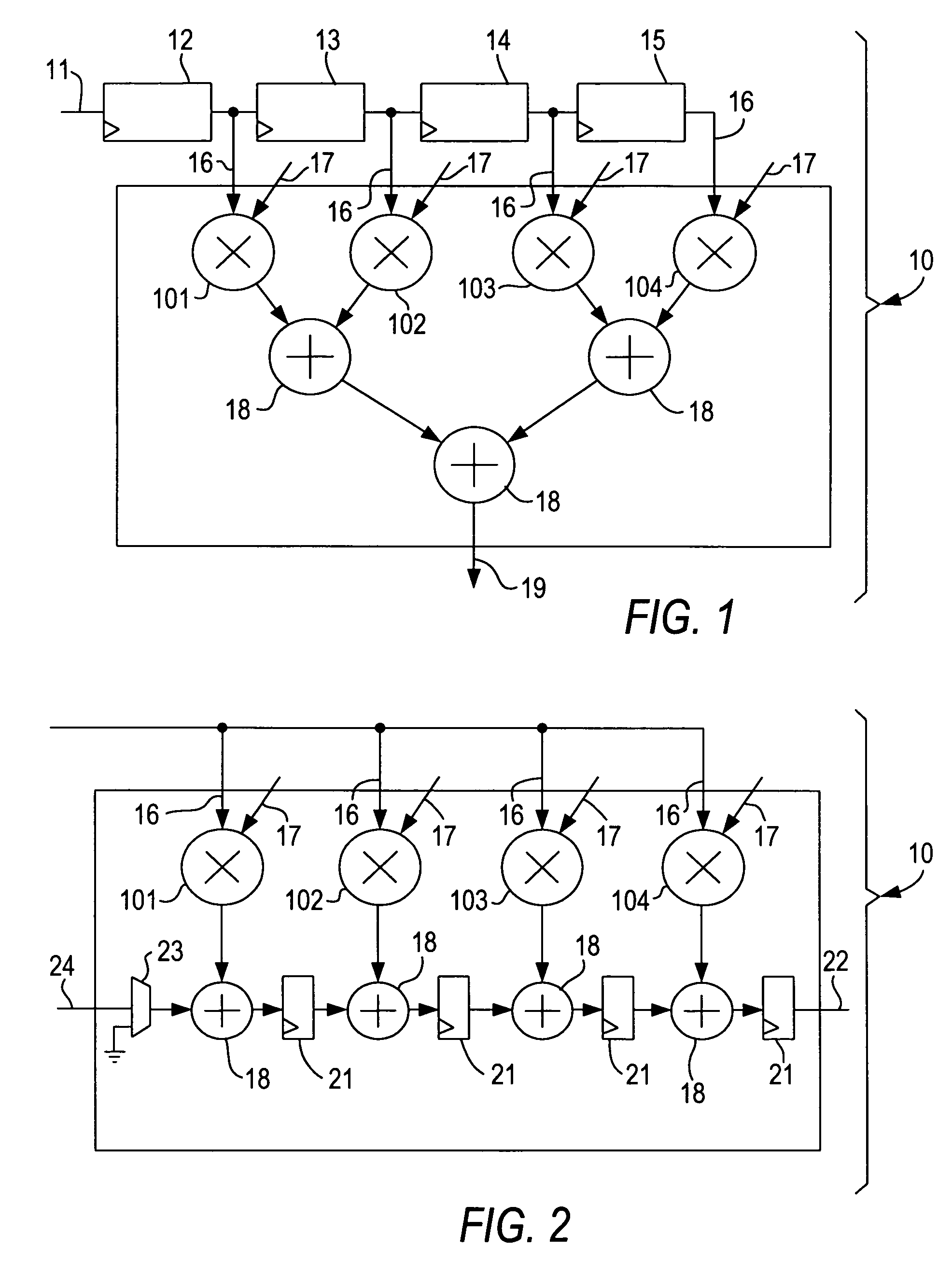

Generic implementations of ellipitic curve cryptography using partial reduction

ActiveUS20030208518A1Digital computer detailsComputations using residue arithmeticBinary multiplierOperand

A reduction operation is utilized in an arithmetic operation on two binary polynomials X(t) and Y(t) over GF(2), where an irreducible polynomial Mm(t)=t<m>+am-1t<m-1>+am-2t<m-2>+ . . . +a1t+a0, where the coefficients as are equal to either 1 or 0, and m is a field degree. The reduction operation includes partially reducing a result of the arithmetic operation on the two binary polynomials to produce a congruent polynomial of degree less than a chosen integer n, with m<=n. The partial reduction includes using a polynomial M'=(Mm(t)-t<m>)*t<n-m>, or a polynomial M''=Mm(t)*t<n-m >as part of reducing the result to the degree less than n and greater than or equal to m. The integer n can be the data path width of an arithmetic unit performing the arithmetic operation, a multiple of a digit size of a multiplier performing the arithmetic operation, a word size of a storage location, such as a register, or a maximum operand size of a functional unit in which the arithmetic operation is performed.

Owner:ORACLE INT CORP

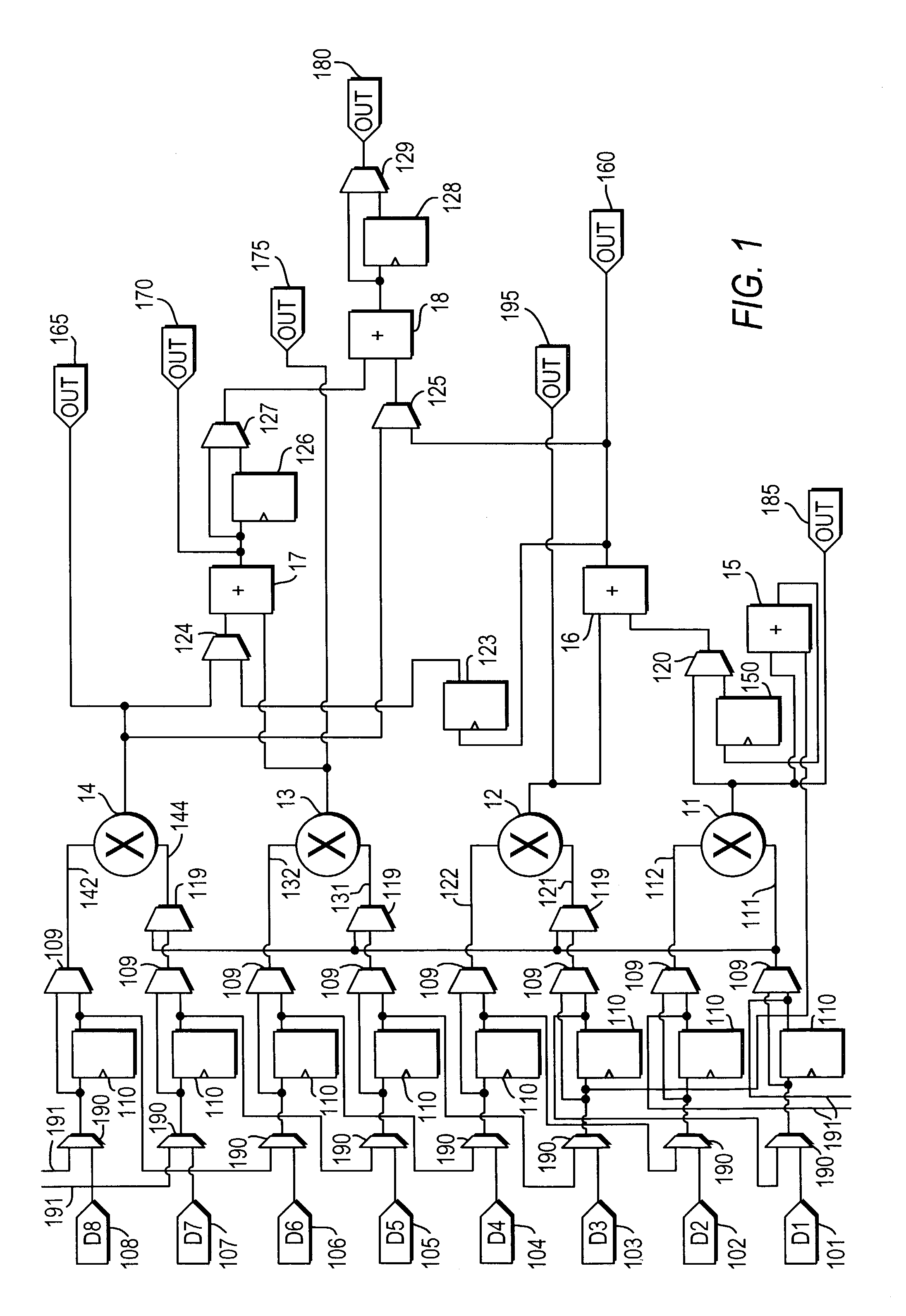

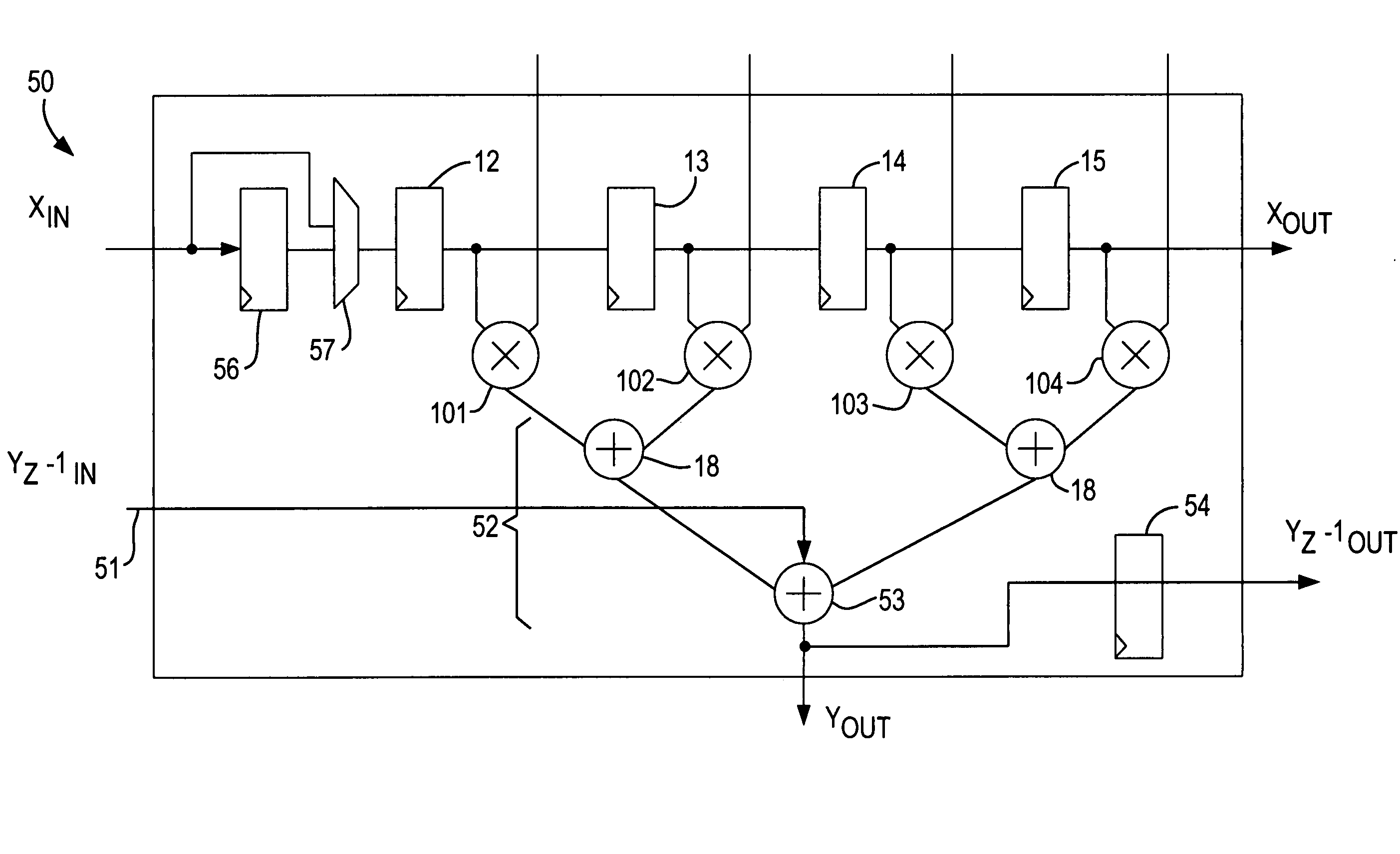

Programmable logic device with specialized multiplier blocks

InactiveUS7590676B1Good flexibilityDigital technique networkDigital data processing detailsFinite impulse responseBinary multiplier

A specialized multiplier block in a programmable logic device incorporates multipliers and adders, and is configurable as one or more types of finite impulse response (FIR) filter including a Direct Form II FIR filter. The specialized multiplier block further includes input and output registers to allow chaining of Direct Form II FIR filters into longer Direct Form II FIR filters. An output accumulator also allows the specialized multiplier block to operate as a time-division multiplexed FIR filter, performing several filtering operations during each clock cycle of the programmable logic device.

Owner:ALTERA CORP

Floating point multiplier/accumulator with reduced latency and method thereof

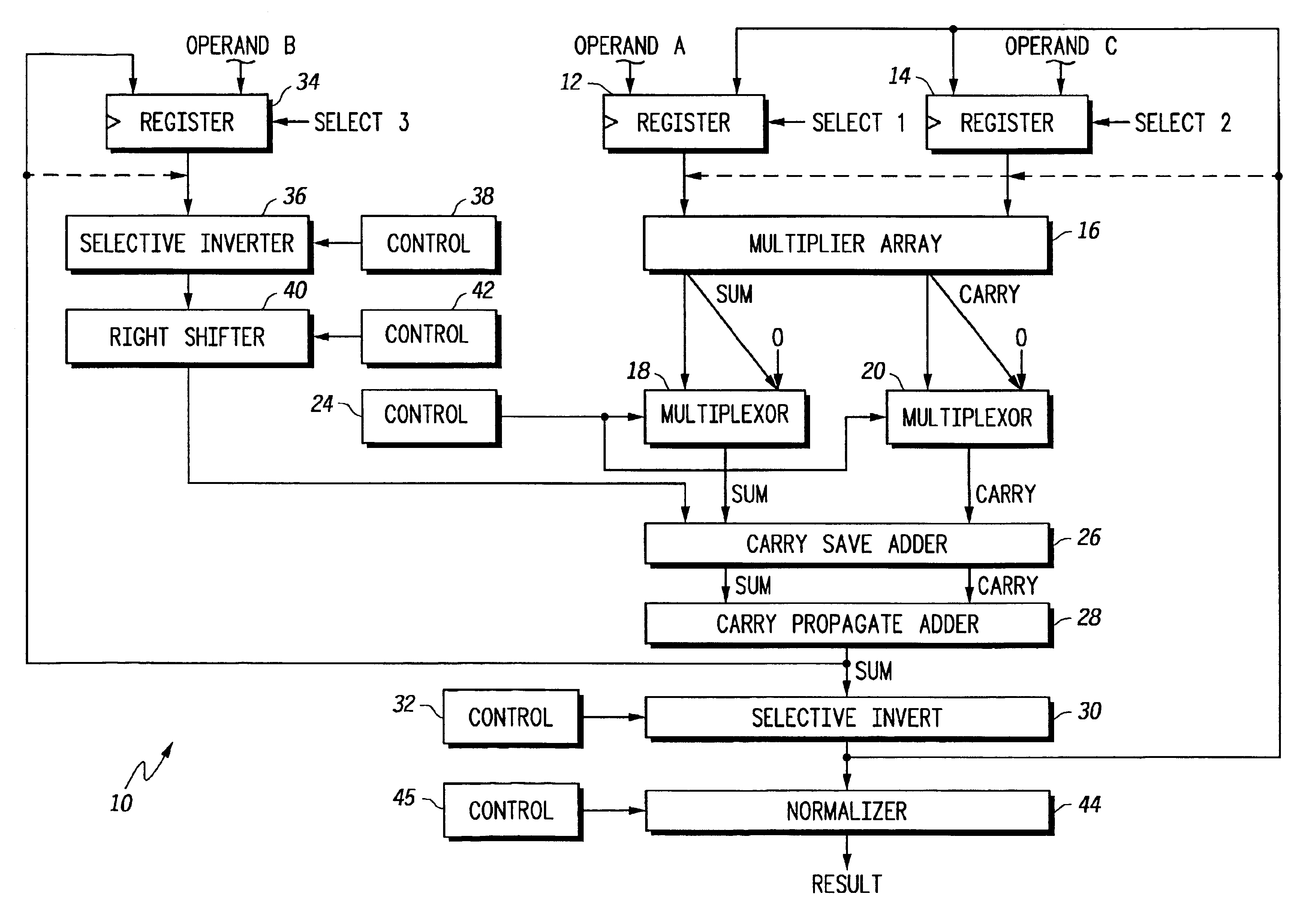

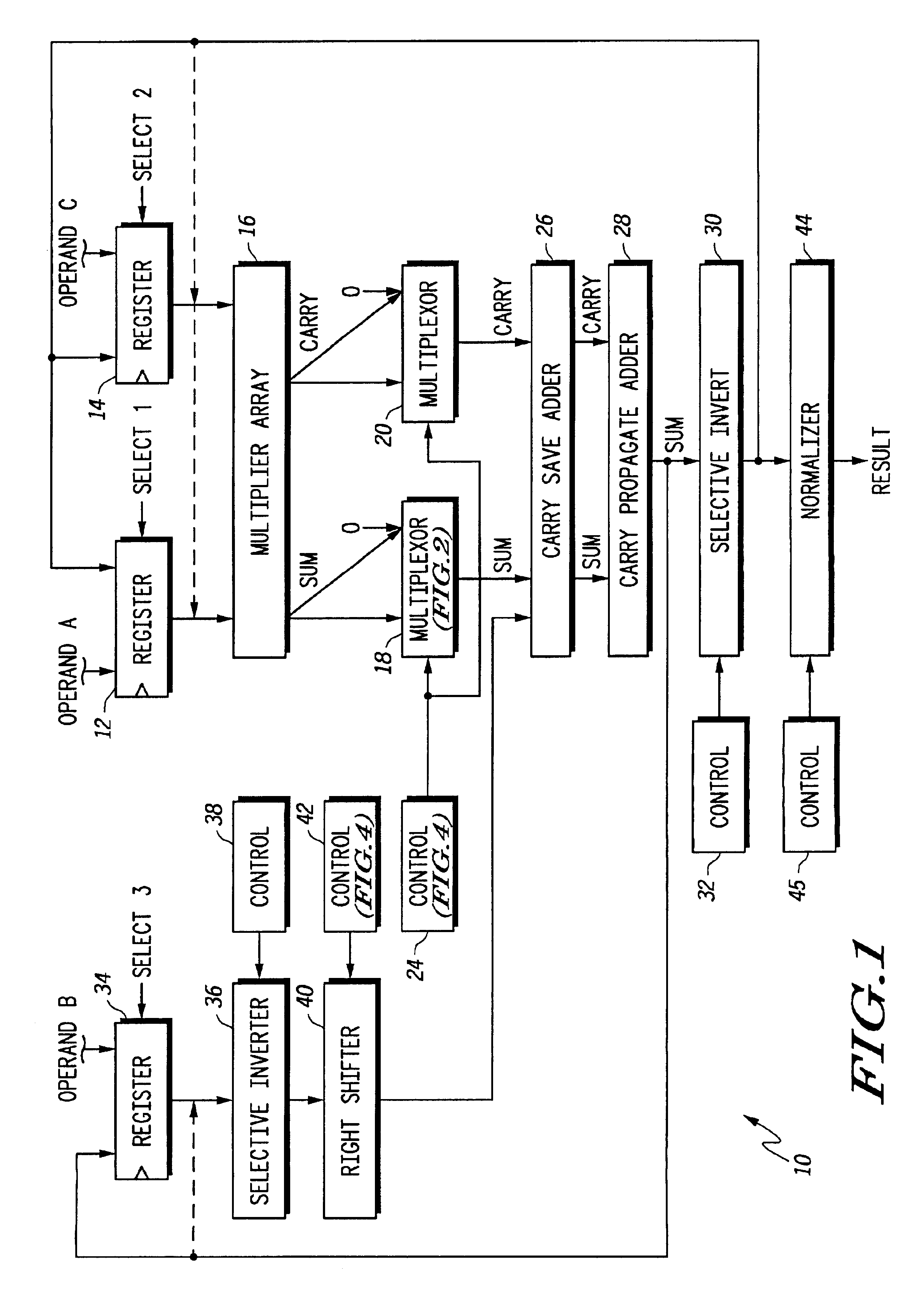

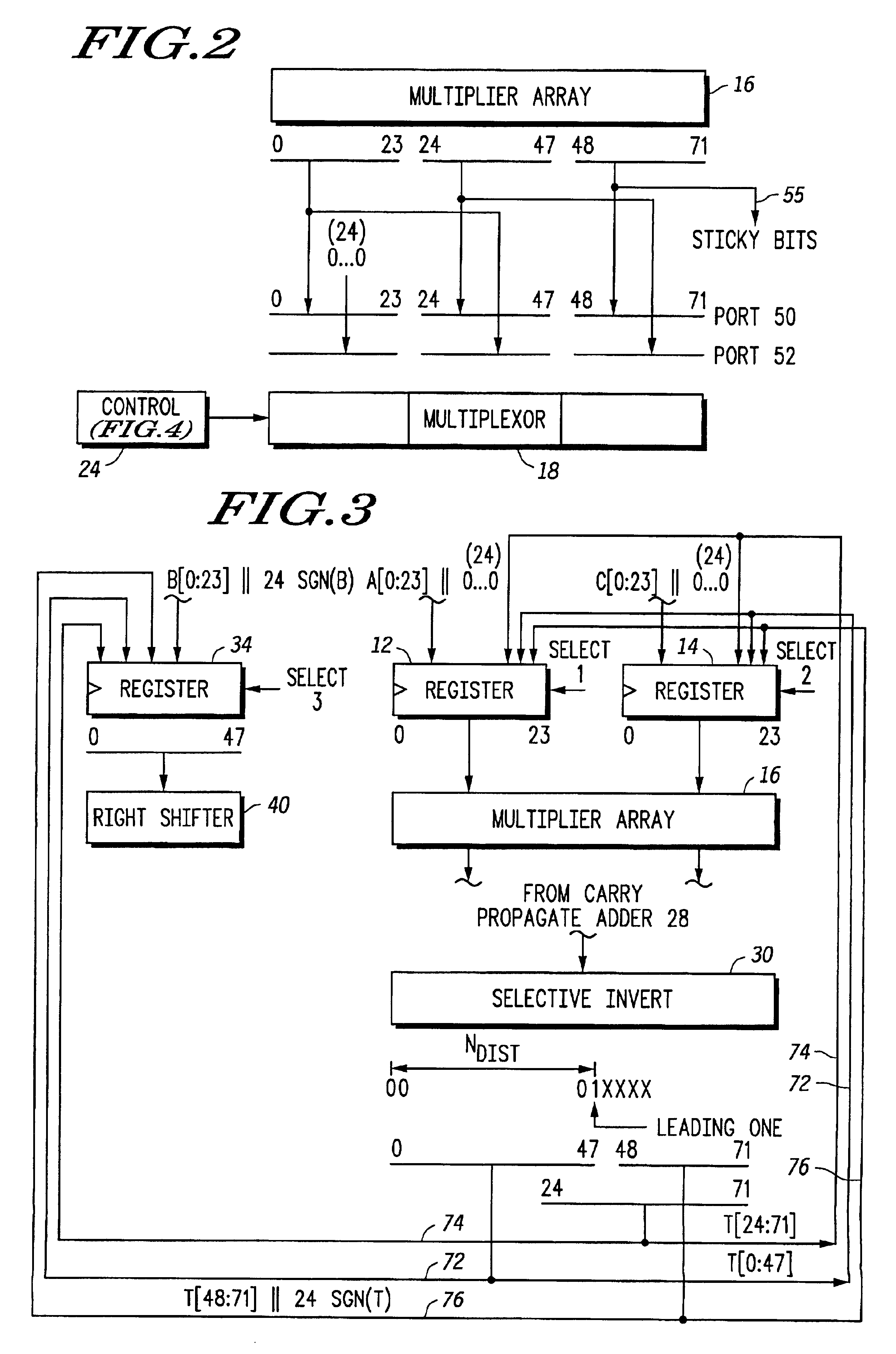

A circuit (10) for multiplying two floating point operands (A and C) while adding or subtracting a third floating point operand (B) removes latency associated with normalization and rounding from a critical speed path for dependent calculations. An intermediate representation of a product and a third operand are selectively shifted to facilitate use of prior unnormalized dependent resultants. Logic circuitry (24, 42) implements a truth table for determining when and how much shifting should be made to intermediate values based upon a resultant of a previous calculation, upon exponents of current operands and an exponent of a previous resultant operand. Normalization and rounding may be subsequently implemented, but at a time when a new cycle operation is not dependent on such operations even if data dependencies exist.

Owner:NORTH STAR INNOVATIONS

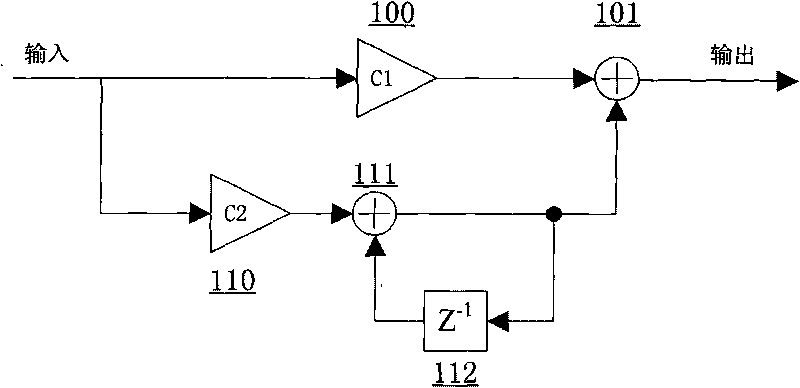

Flexible accumulator in digital signal processing circuitry

InactiveUS20050187997A1Computation using denominational number representationDigital signal processingBinary multiplier

A multiplier-accumulator (MAC) block can be programmed to operate in one or more modes. When the MAC block implements at least one multiply-and-accumulate operation, the accumulator value can be zeroed without introducing clock latency or initialized in one clock cycle. To zero the accumulator value, the most significant bits (MSBs) of data representing zero can be input to the MAC block and sent directly to the add-subtract-accumulate unit. Alternatively, dedicated configuration bits can be set to clear the contents of a pipeline register for input to the add-subtract-accumulate unit. The least significant bits (LSBs) can be tied to ground and sent along the feedback path. To initialize the accumulator value, the MSBs of the initialization value can be input to the MAC block and sent directly to the add-subtract-accumulate unit. The LSBs can be sent to another multiplier that performs a multiply-by-one operation before being sent to the add-subtract-accumulate unit.

Owner:ALTERA CORP

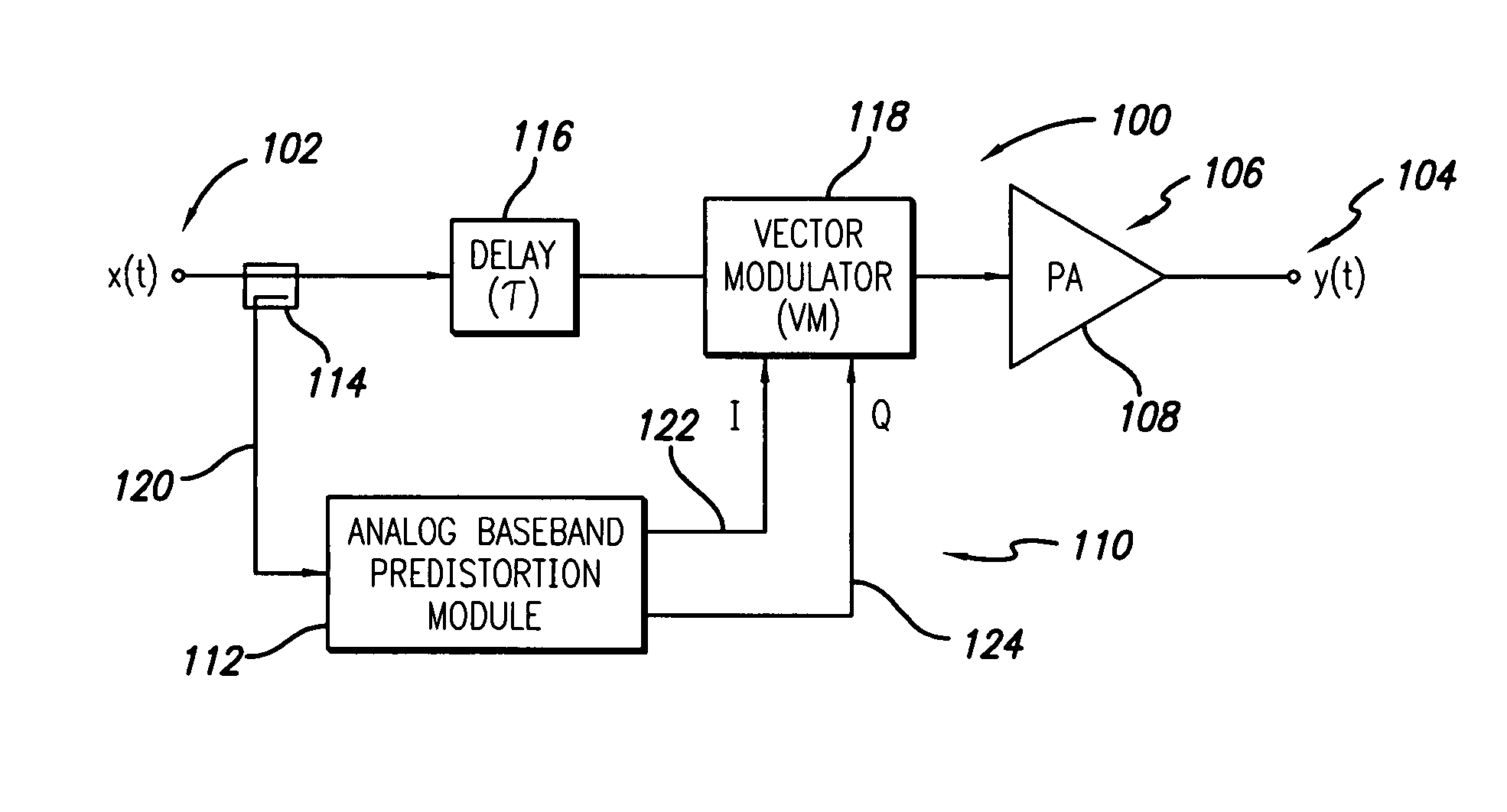

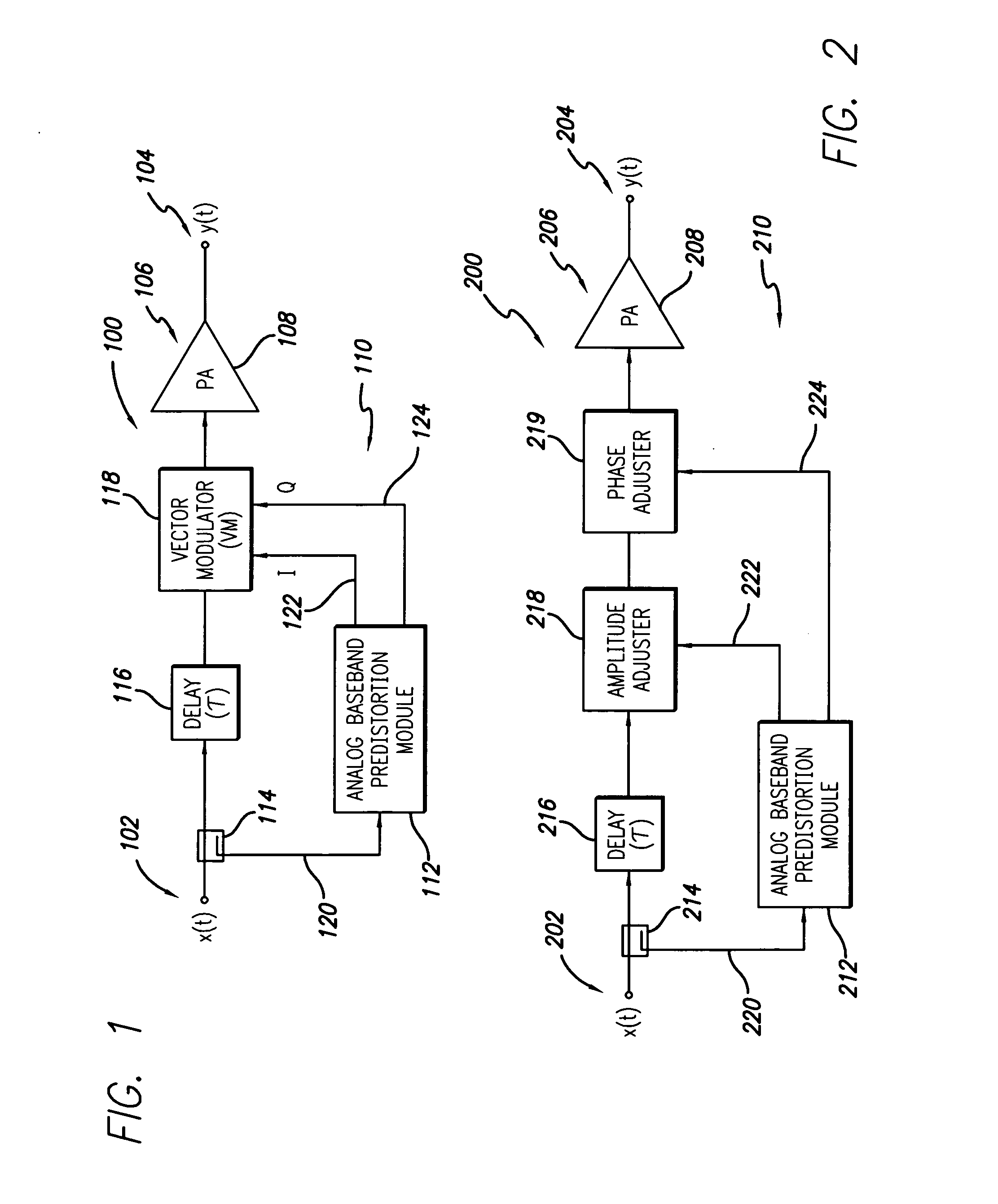

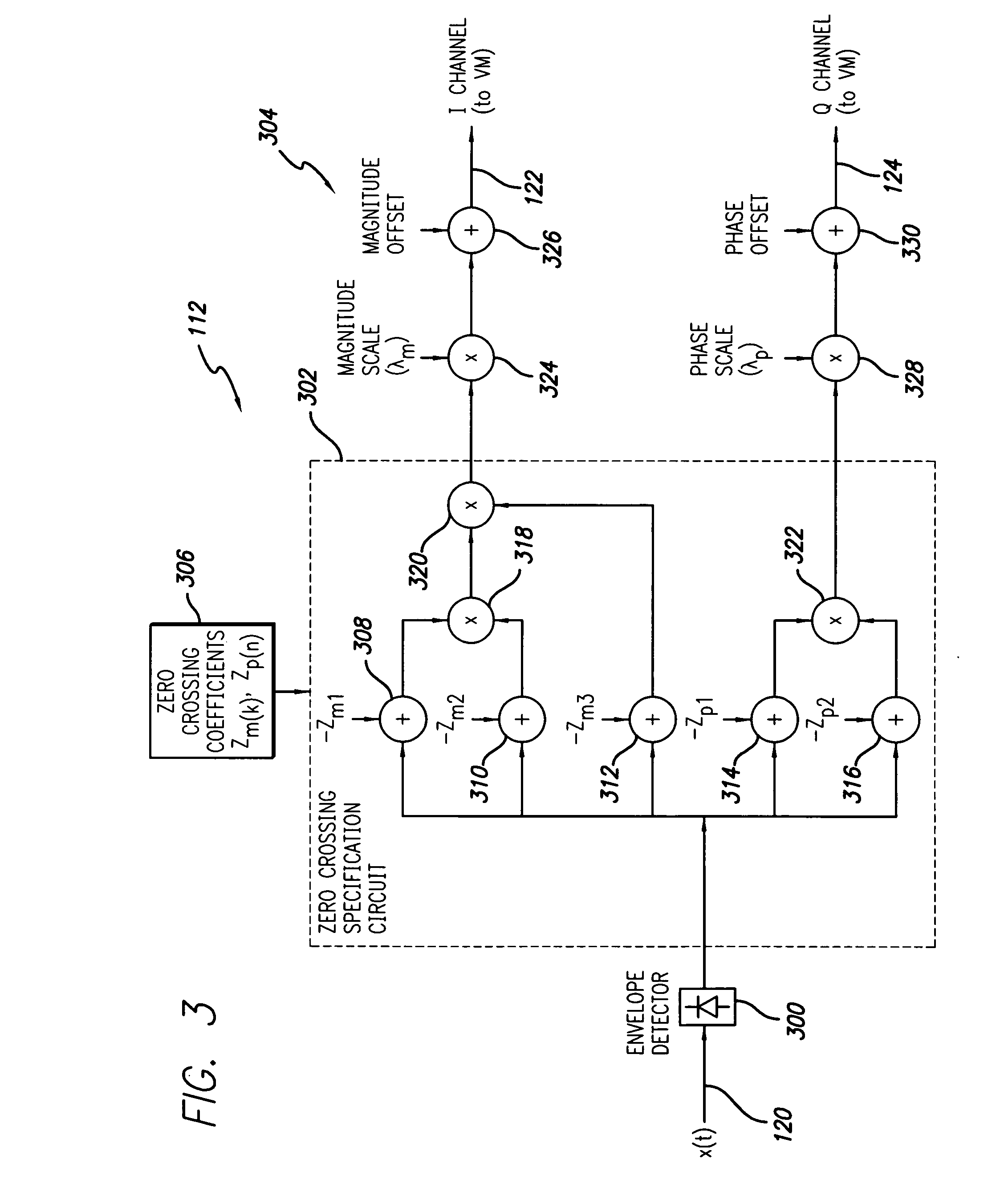

RF power amplifier system employing an analog predistortion module using zero crossings

ActiveUS20060217083A1Correct nonlinearityAmplifier modifications to reduce noise influenceAmplifier modifications to reduce temperature/voltage variationPhase correctionAudio power amplifier

An RF amplifier system employing an analog predistortion module is disclosed. The disclosed analog predistortion module is based on zero crossings of the gain error curves (AM-AM and AM-PM curves minus DC). The hardware structure uses the product of first-order functions avoiding the need for large differential swings in the coefficients to shape the lower part of the gain curves. The higher-order nonlinear functions are preferably derived from a single envelope detector. An equal number of multipliers are preferably used in each path when the order of the magnitude and phase corrections are equal or differ by one, thus reducing delay mismatches between the magnitude and phase correction signals.

Owner:INTEL CORP

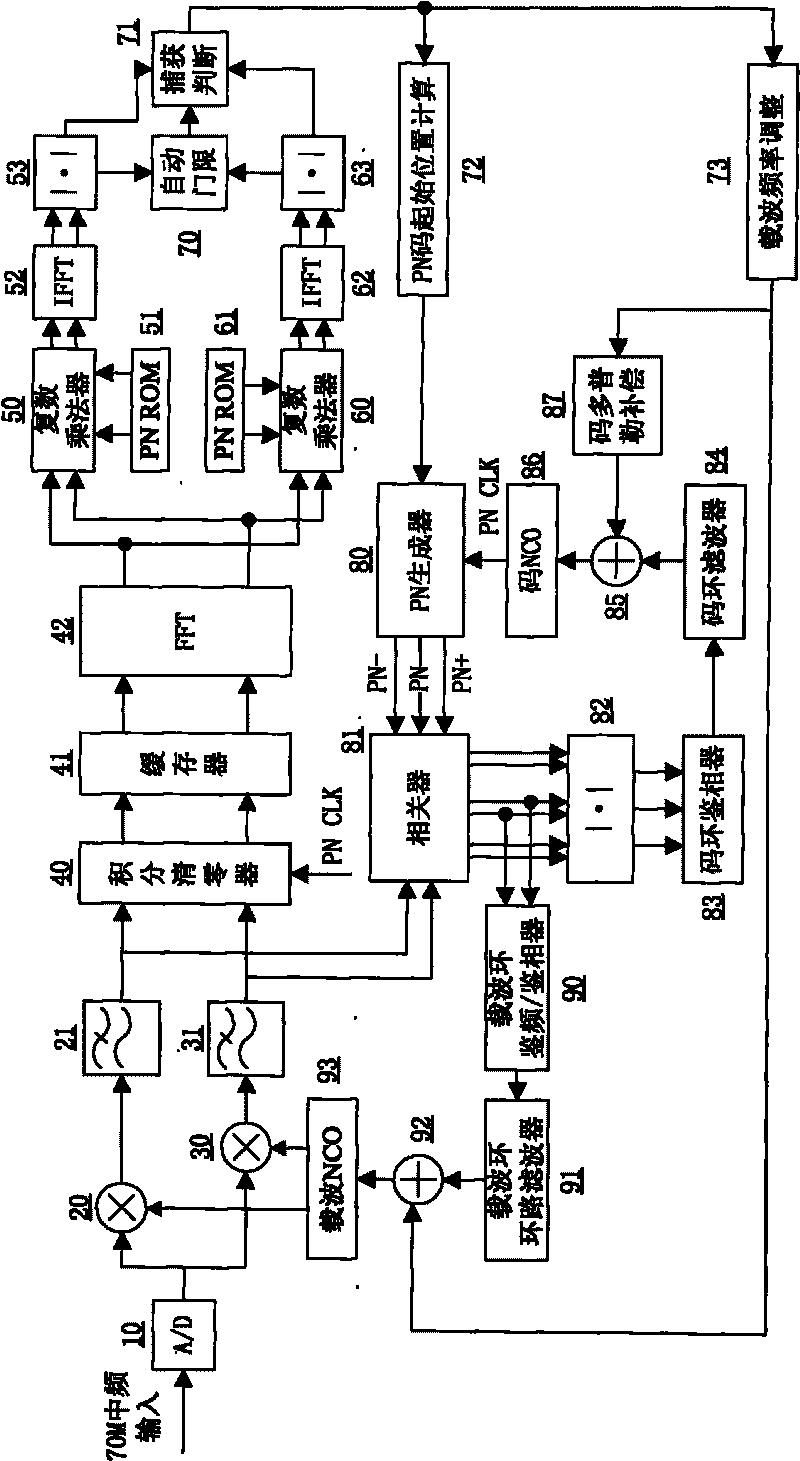

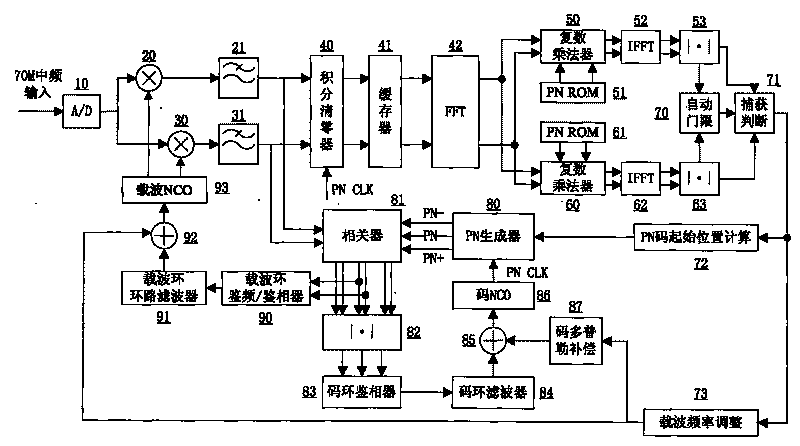

Intermediate frequency direct sequence spread spectrum receiver for satellite ranging

InactiveCN101726746AReduce resource consumptionFast captureSatellite radio beaconingDiscriminatorLow-pass filter

The invention relates to an intermediate frequency direct sequence spread spectrum receiver for satellite ranging, which consists of 37 parts of a front-end A / D, an FFT module, a local PN code generator, a correlator, an automatic threshold calculation module and the like. The connection relationship is as follows: the output of the front-end A / D and the output of a carrier tracking loop NCO are respectively connected to an in-phase branch multiplier and an orthogonal branch multiplier, the input of the front-end A / D and the input of the carrier tracking loop NCO enter into an in-phase branch FIR low-pass filter and an orthogonal branch FIR low-pass filter, consequently, on the one hand, the output is sent to an integral zero clearing device, then the output which is sent to the FFT module, a branch 1 local PN code memory ROM and a branch 2 local PN code memory ROM enters into a branch 1 complex multiplier and a branch 2 complex multiplier, the output is sent to a branch 1 root mean square module and a branch 2 root mean square module, the output is sent to the threshold calculation module and a capturing and judging module for carrying out code catching; and on the other hand, the output is sent to the correlator and the local PN code generator for carrying out code tracking. The output of the correlator is simultaneously sent into a frequency discriminator / phase discriminator of the carrier tracking loop and then enters into a loop filter of the carrier tracking loop, and the output of the loop filter of the carrier tracking loop enters into the carrier tracking loop NCO for carrying out carrier tracking.

Owner:BEIHANG UNIV

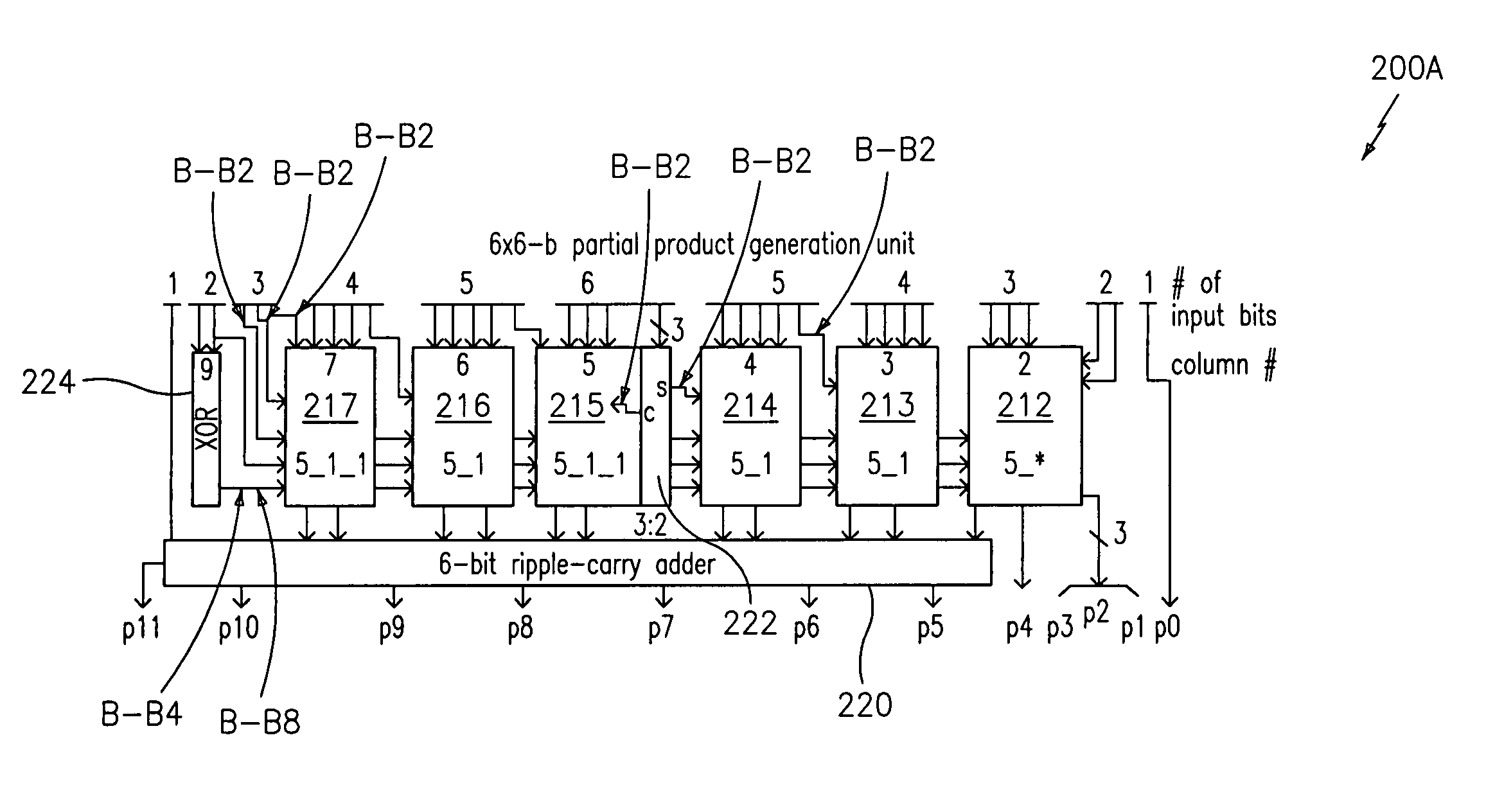

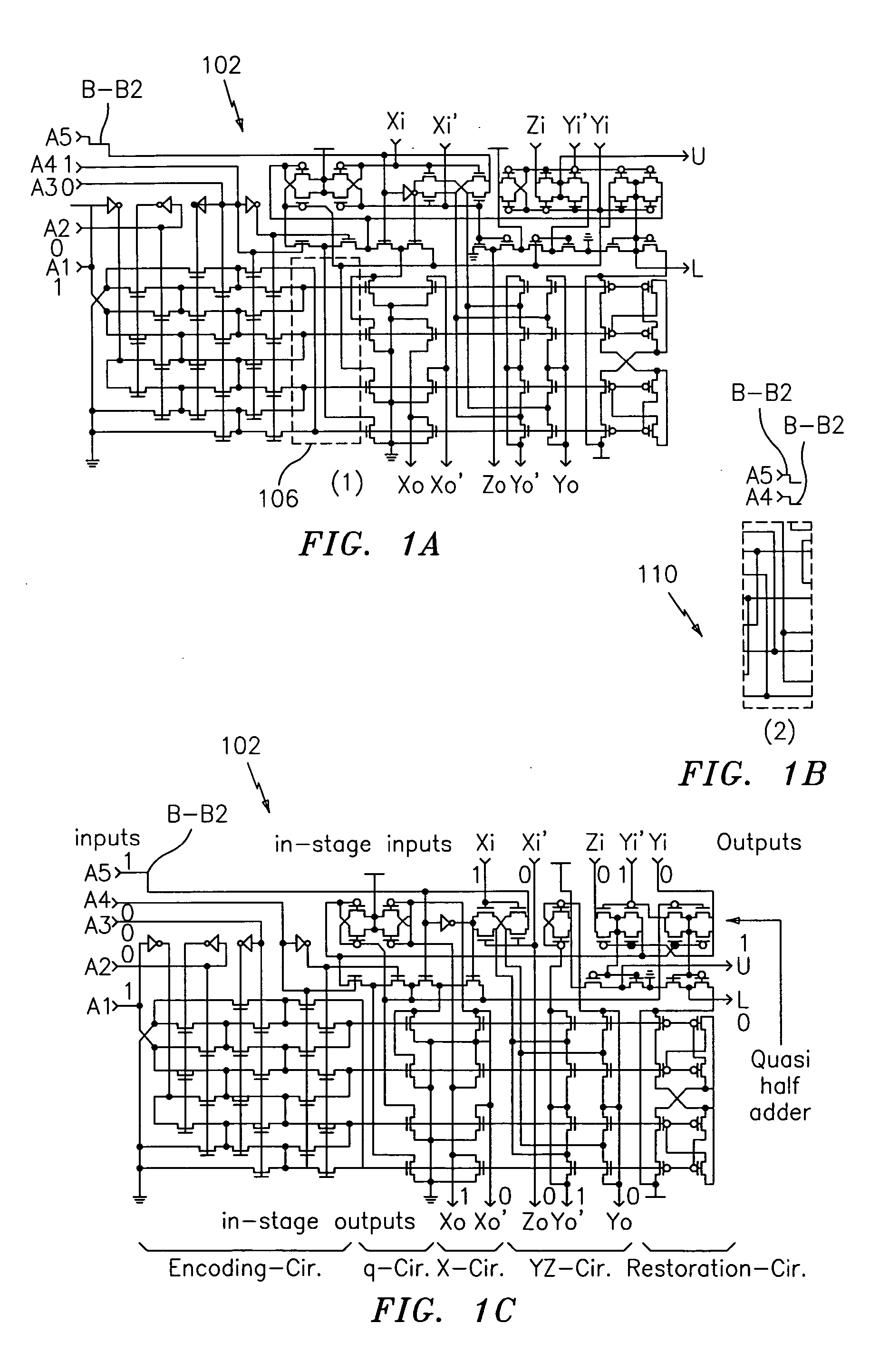

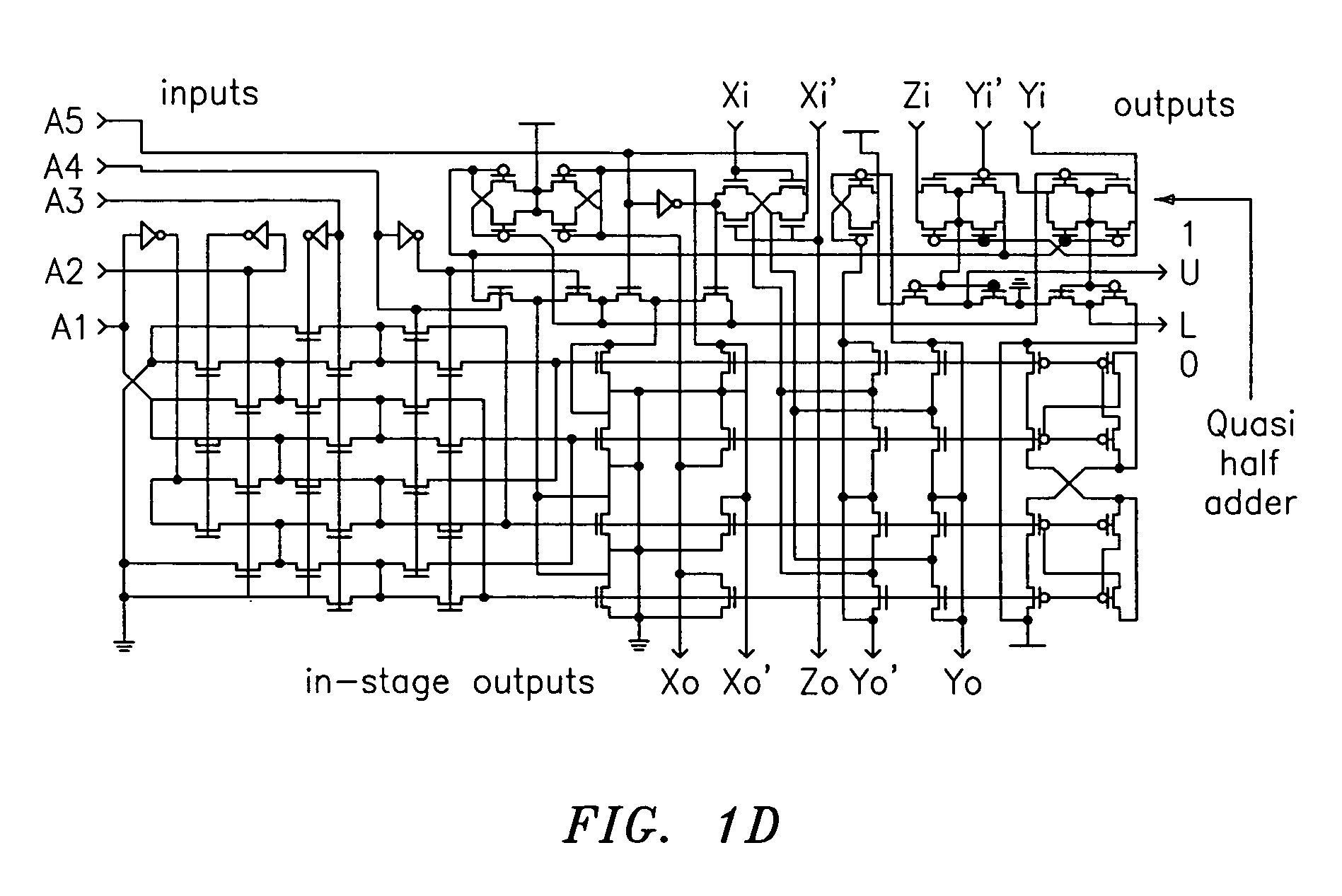

Library of low-cost low-power and high-performance multipliers

InactiveUS20060020655A1Highly complexity-effectiveMinimal costComputation using non-contact making devicesNumber-of-one countersBinary multiplierParallel computing

Disclosed is an apparatus and method for producing a library of low-cost, low-power multipliers which are easy to build, have self testing capabilities, and are regular. The multipliers multiply a first word having N bits by a second word having M bits and include a plurality of smaller multipliers each including a single array of borrow parallel counters for receiving a trisected input and processing at least part of a trisected input according to a predetermined formula, an x:2 (where x=3, 2) counter which may be coupled with at least one borrow parallel counter to form a synthesized borrow parallel counter, and an adder coupled to an output of at least one of the borrow parallel counters, the adder for summing the output of the at least one borrow parallel adder. Each of the smaller multipliers receives a trisected input and an adder for receiving and summing the outputs of the smaller multipliers.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

Floating-point multiply-add unit using cascade design

InactiveUS20140188966A1Incur areaIncur overheadComputation using denominational number representationBinary multiplierFloating point

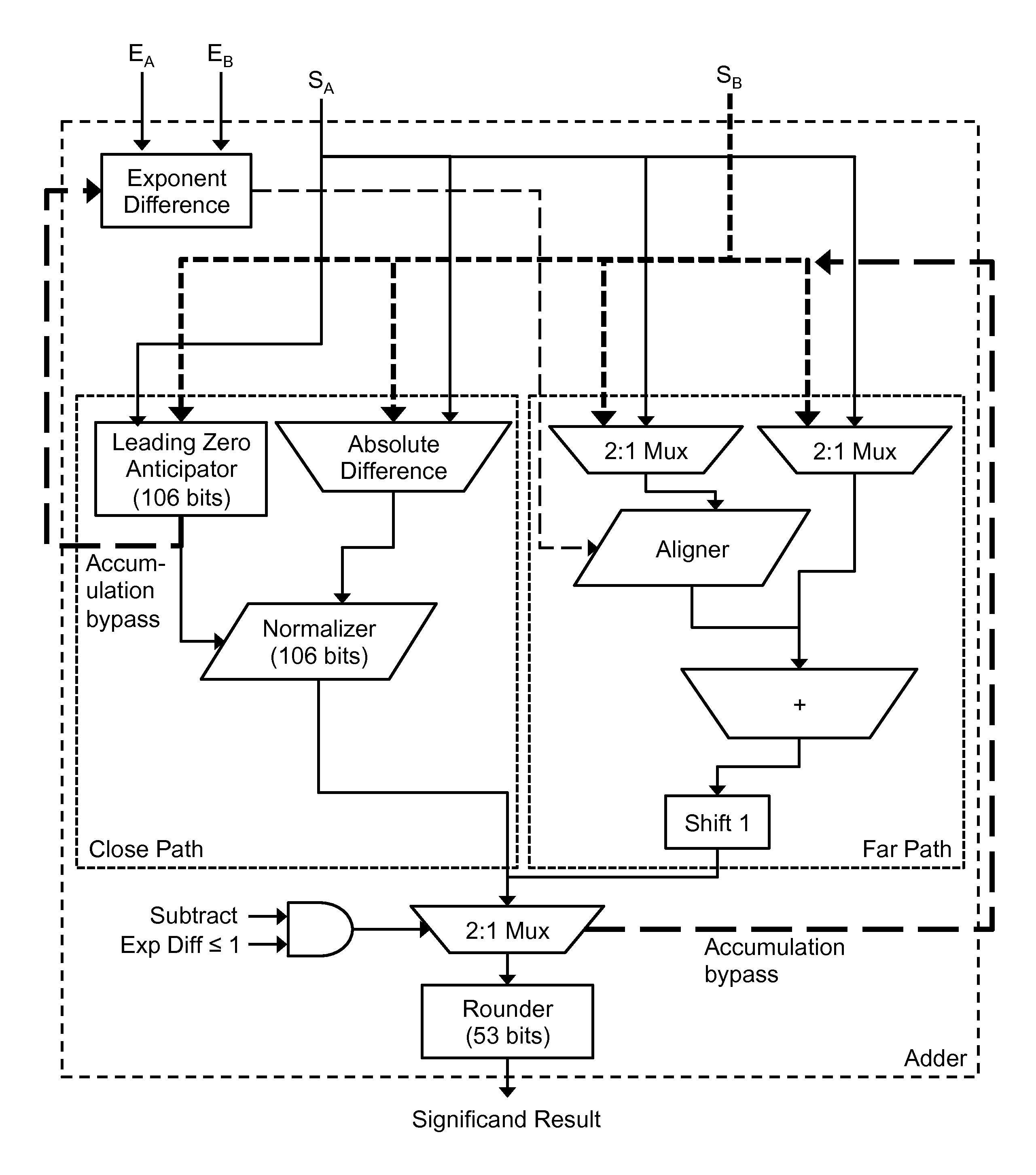

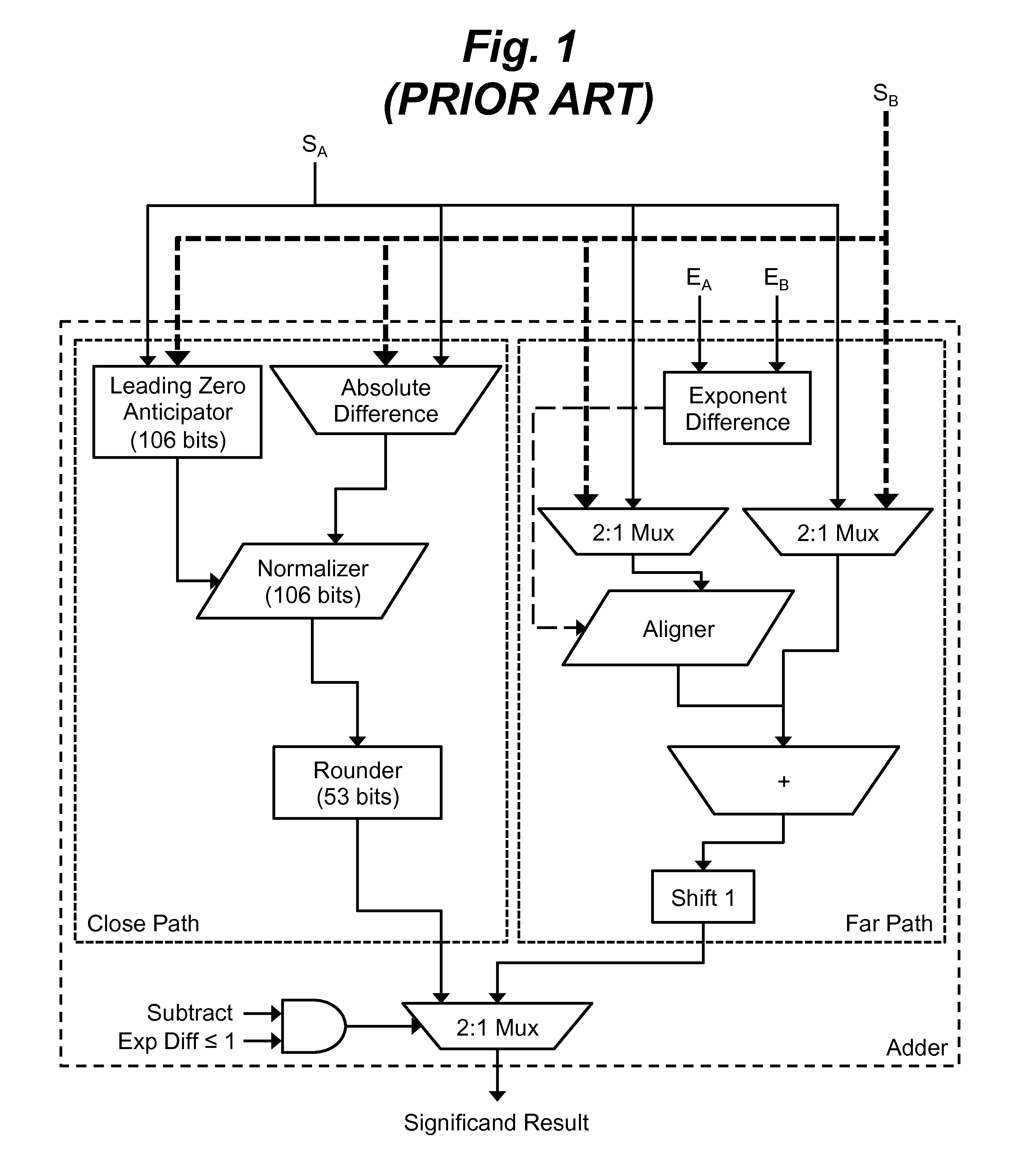

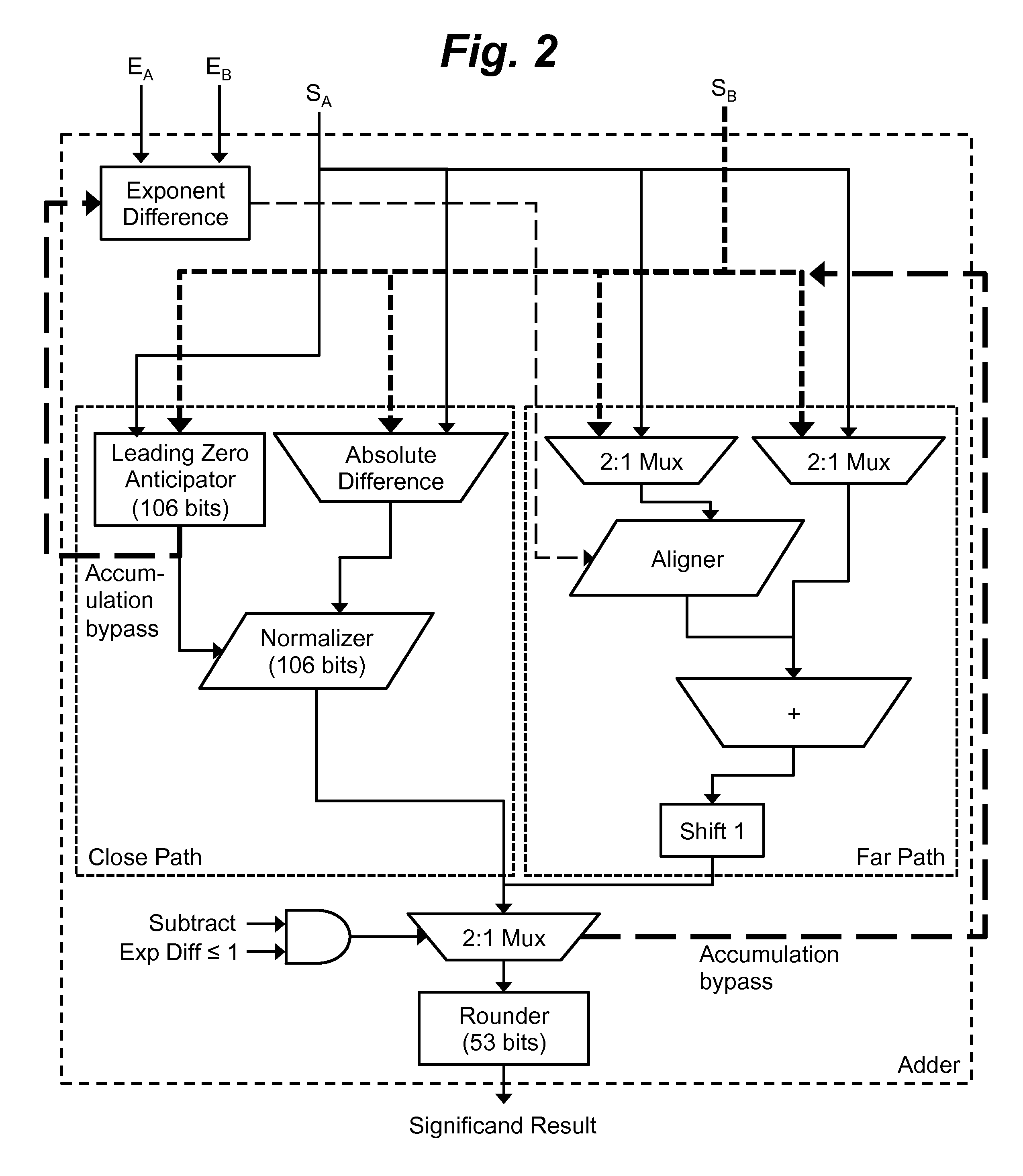

A floating-point fused multiply-add (FMA) unit embodied in an integrated circuit includes a multiplier circuit cascaded with an adder circuit to produce a result A*C+B. To decrease latency, the FMA includes accumulation bypass circuits forwarding an unrounded result of the adder to inputs of the close path and the far path circuits of the adder, and forwarding an exponent result in carry save format to an input of the exponent difference circuit. Also included in the FMA is a multiply-add bypass circuit forwarding the unrounded result to the inputs of the multiplier circuit. The adder circuit includes an exponent difference circuit implemented in parallel with the multiplier circuit; a close path circuit implemented after the exponent difference circuit; and a far path circuit implemented after the exponent difference circuit.

Owner:BOARD OF TRUSTEES OF TEH LELAND STANFORD JUNIOR UNIV THE

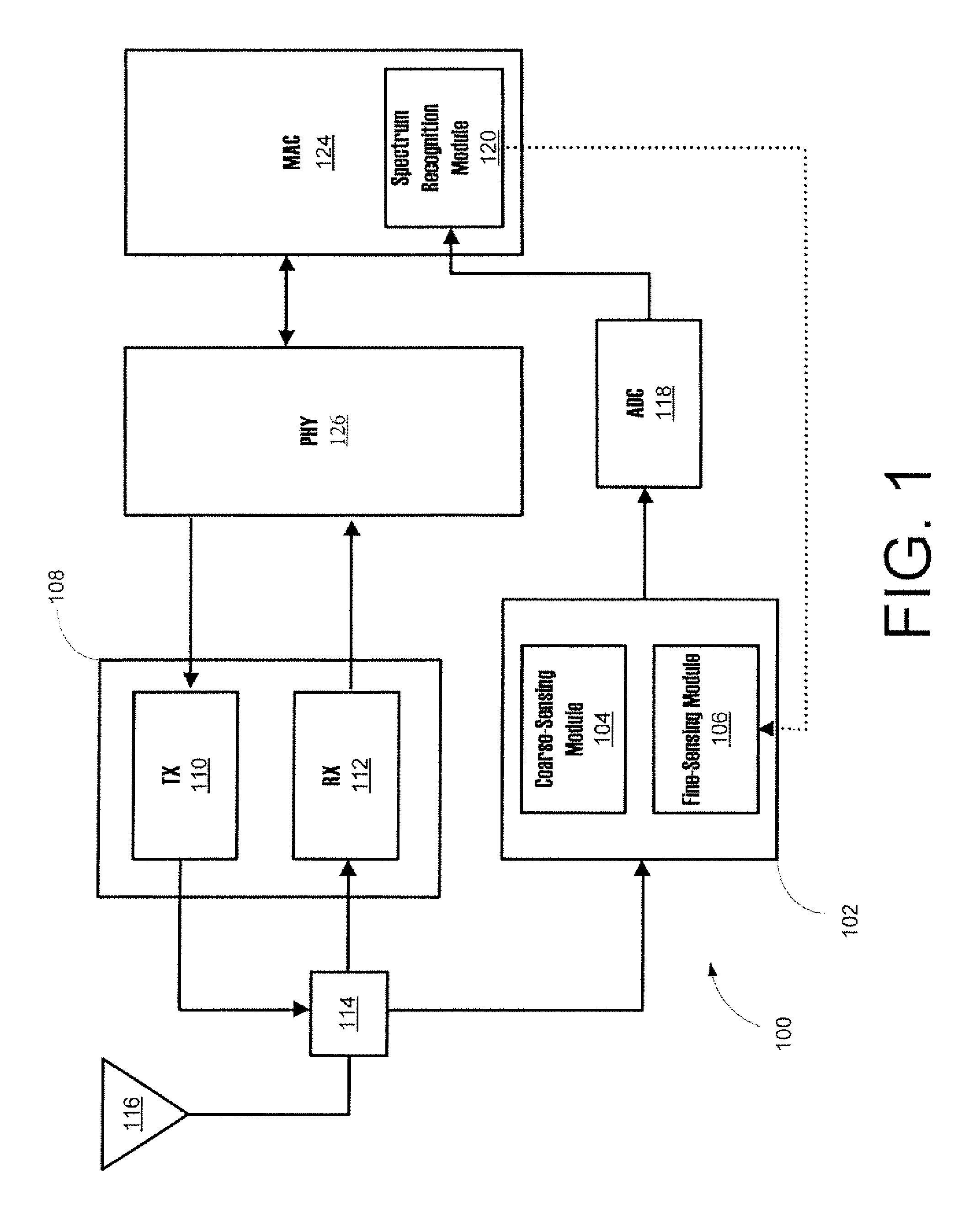

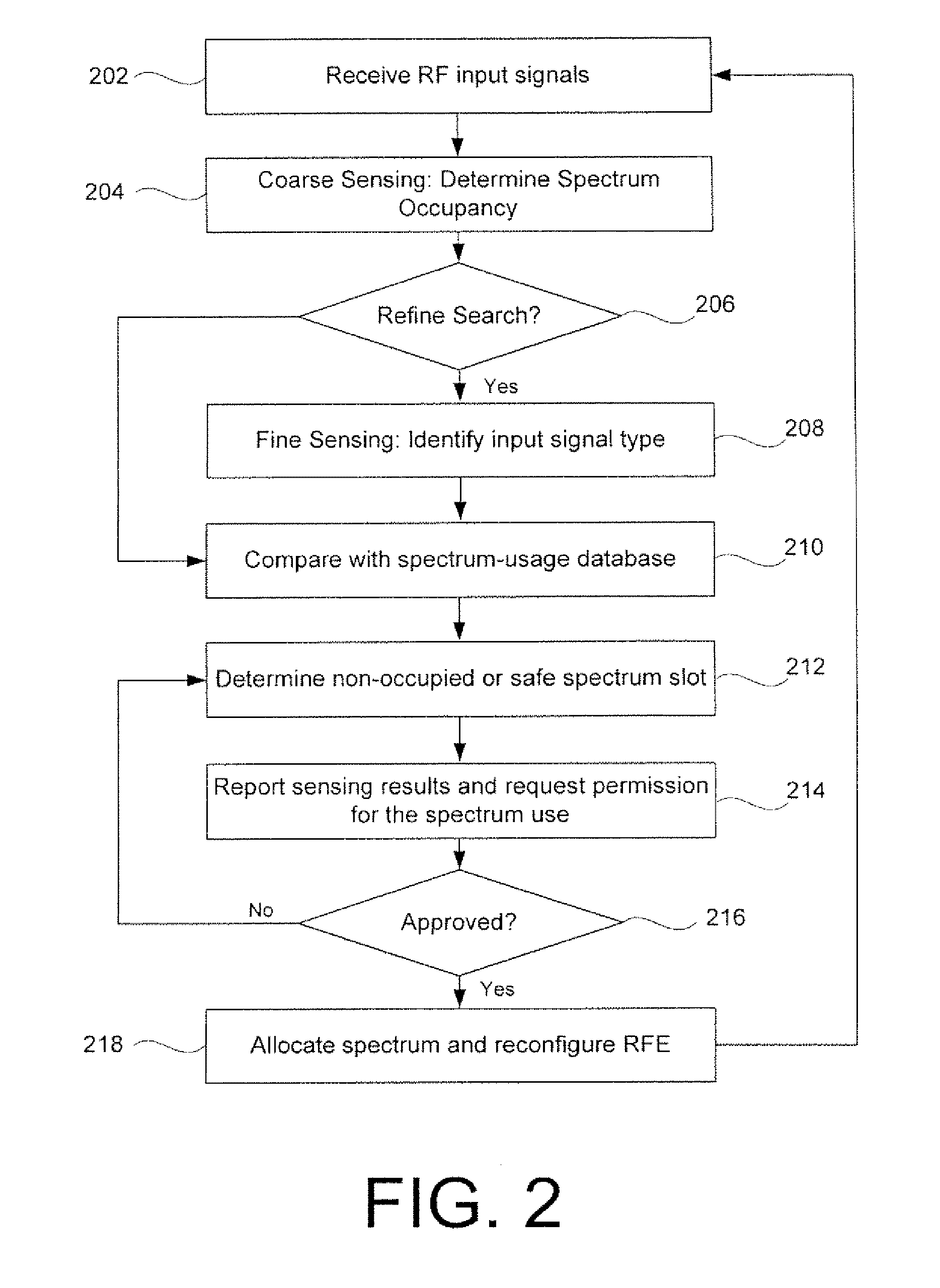

Systems, Methods, and Apparatuses for Coarse-Sensing Modules

InactiveUS20070091720A1Spectral/fourier analysisModulated carrier system with waveletsIntegratorFrequency spectrum

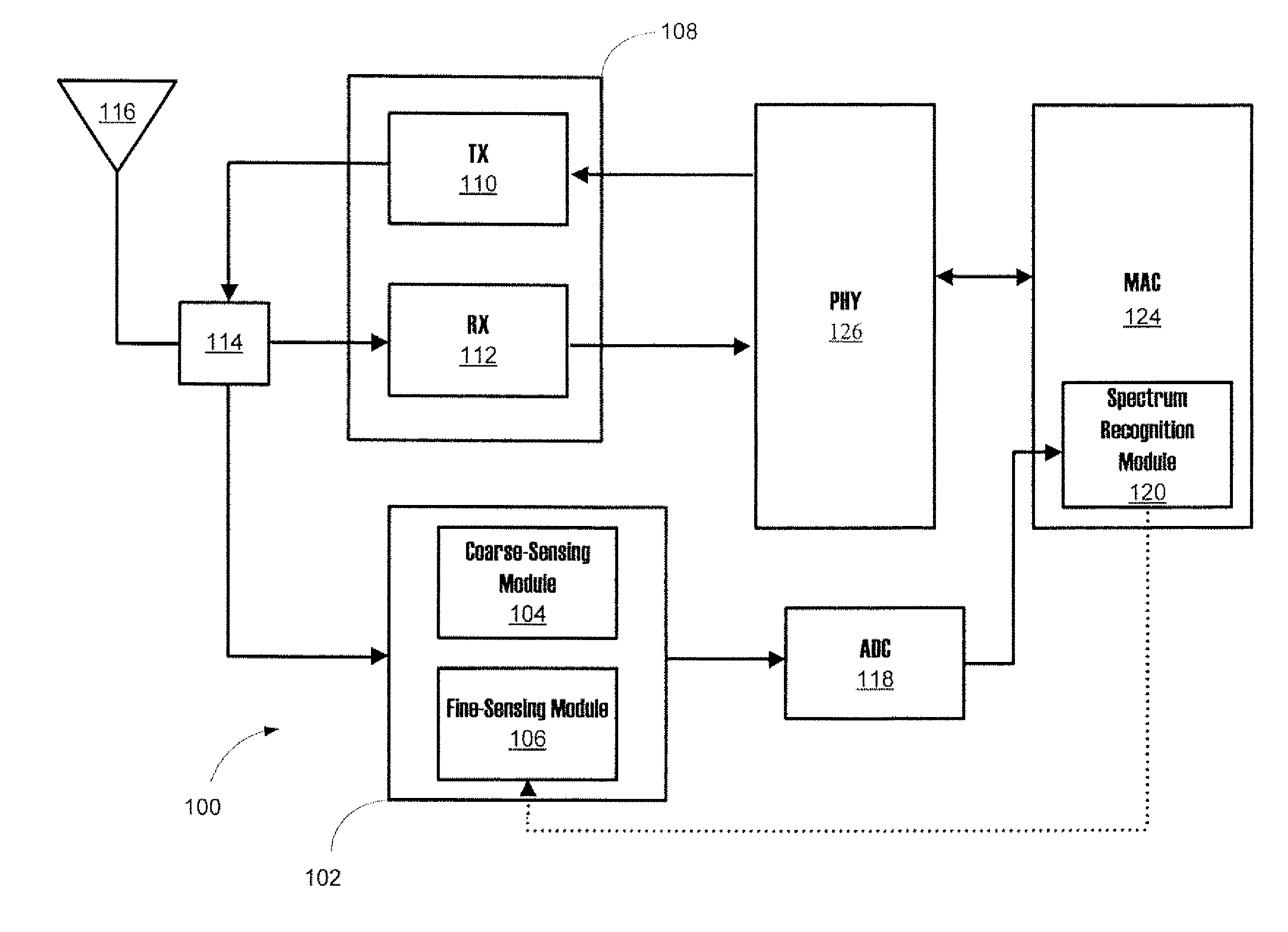

Systems, methods, and apparatuses are provided for coarse-sensing modules that are operative for providing initial determinations of spectrum occupancy. The coarse-sensing modules may include a wavelet waveform generator providing a plurality of wavelet pulses, and a multiplier that combines the wavelet pulses with an input signal to form a correlation signal. The coarse sensing modules may further include an integrator that receives the generated correlation signal from the multiplier, where the integrator determines correlation values from integrating the correlation signal, and a spectrum recognition module in communication with the integrator that determines an available spectrum segment based at least in part on the correlation values. In addition, the spectrum recognition module may determine an available spectrum segment by utilizing information from a spectrum usage database, where the spectrum usage database includes information associated with one or more known signal types.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

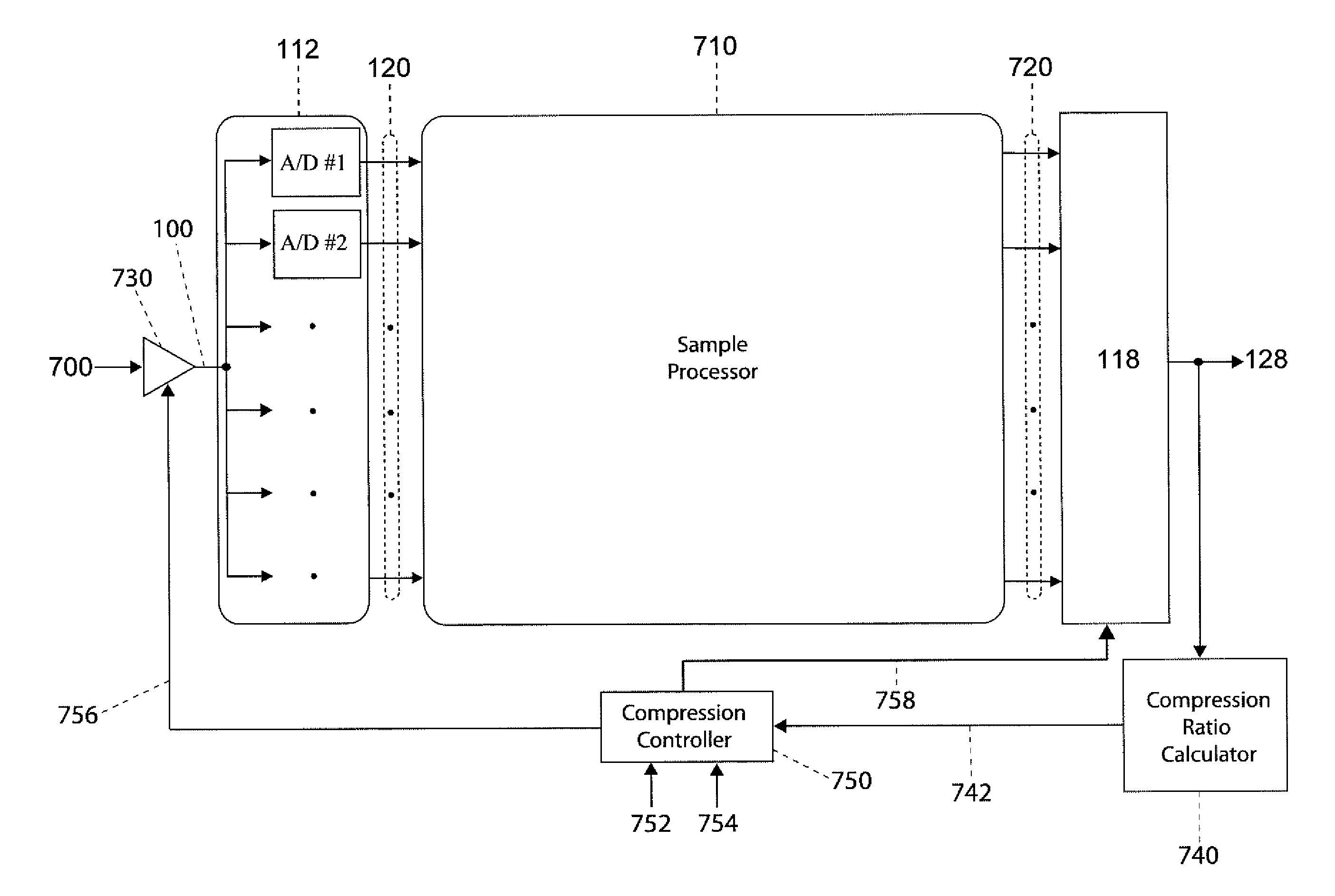

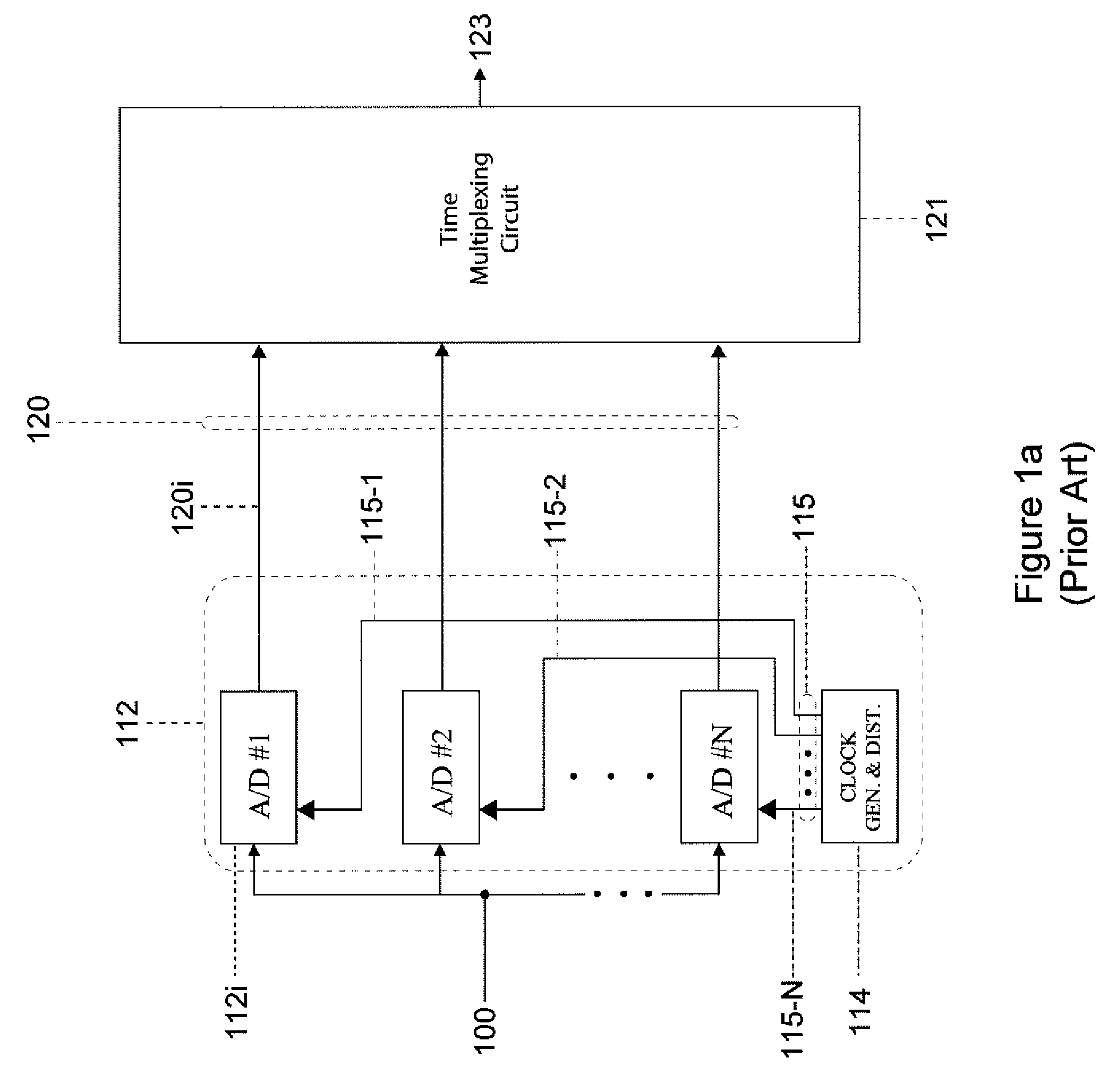

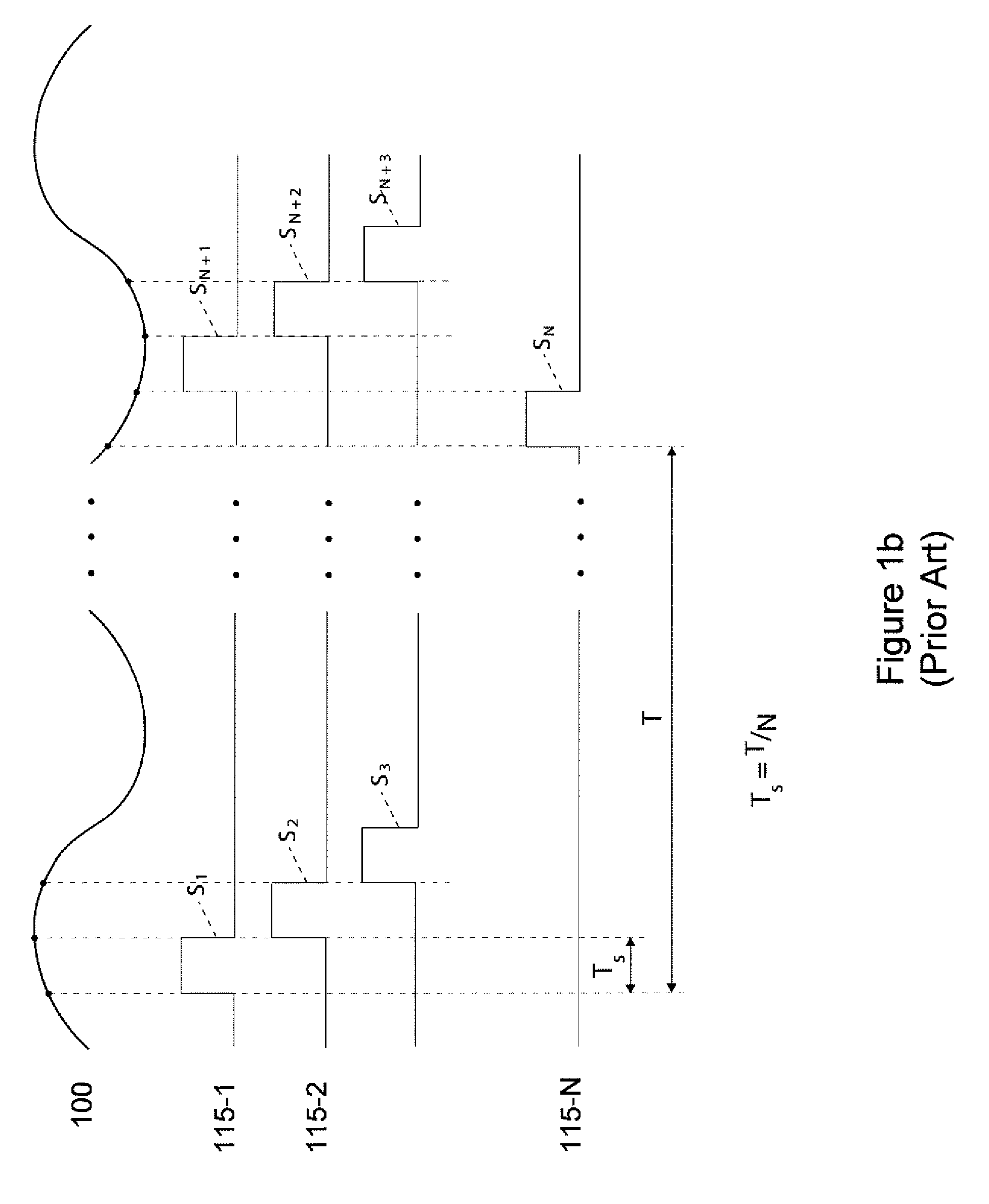

Enhanced Time-Interleaved A/D Conversion Using Compression

InactiveUS20080018502A1Increase the compression ratioDegrade signal qualityAnalogue/digital conversionBinary multiplierAnalog signal

Compression of signal samples output from a parallel, time-interleaved analog to digital converter (TIADC) for a baseband signal, includes calculating first or higher order differences of consecutive signal samples followed by lossless or lossy encoding of the difference samples to produce compressed samples. Compression of a TIADC output signal with a nonzero center frequency, includes calculating sums or differences of pairs of signal samples separated by an appropriate number of sampling intervals followed by lossless or lossy encoding. The sums or differences of the signal samples have lower magnitudes than the original samples, allowing more efficient compression. Lossy compression alternatives produce compressed data with a fixed bit rate or with a fixed quality in the decompressed samples. Alternatives for lossy compression include attenuating the analog signal before sampling by the TIADC, applying bit shifters or multipliers after sampling to reduce the magnitudes of the signal samples, and lossy encoding.

Owner:ALTERA CORP

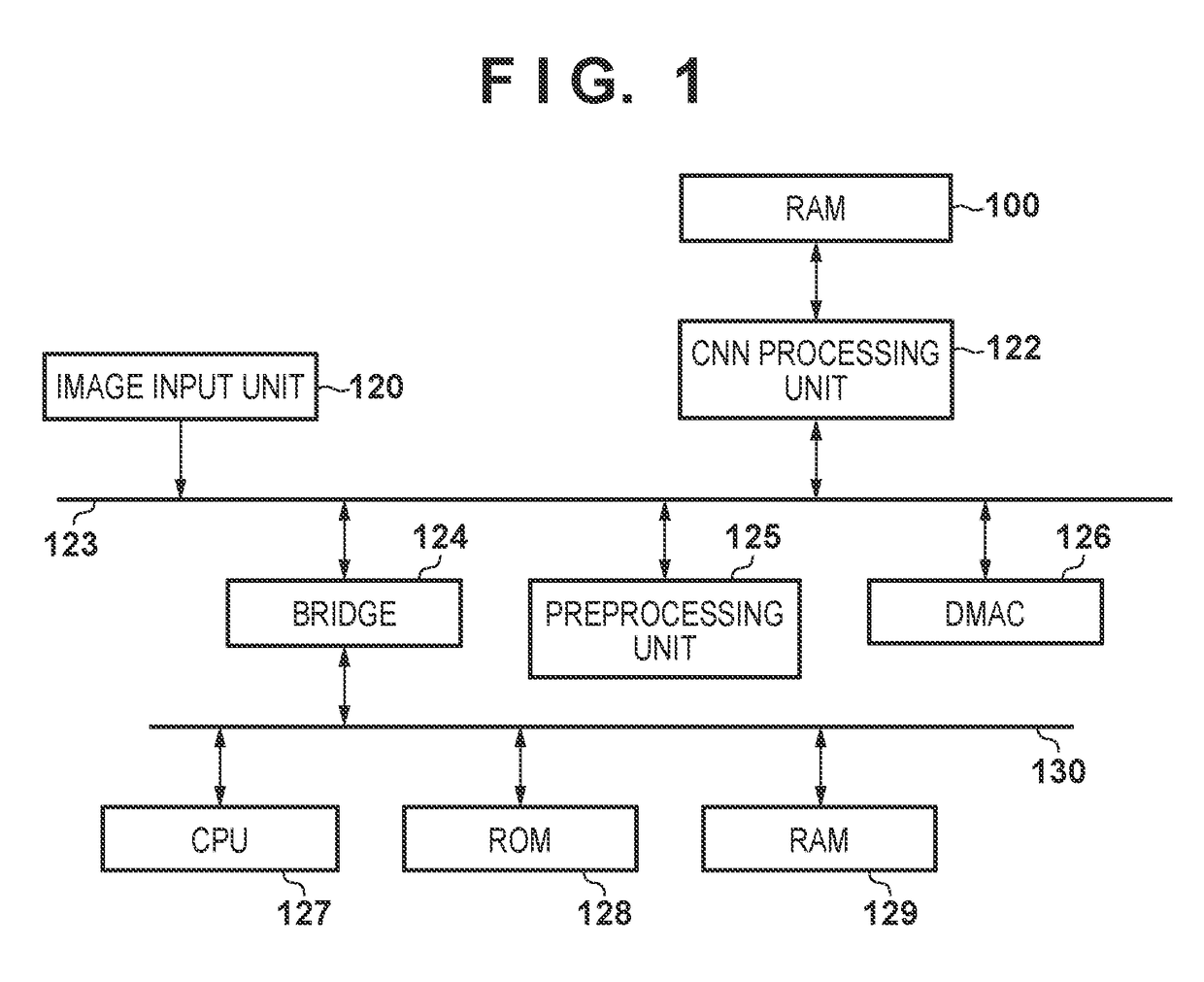

Convolution operation apparatus

ActiveUS20170116495A1Character and pattern recognitionNeural learning methodsBinary multiplierData mining

There is provided with a convolution operation apparatus. A first product-sum calculator includes a plurality of first multipliers, a plurality of first accumulators, a first data supplier which supplies first data to the plurality of first multipliers, and a second data supplier which supplies a plurality of second data to the plurality of first multipliers. A second product-sum calculator includes a plurality of second multipliers, a plurality of second accumulators, a third data supplier which supplies third data to the plurality of second multipliers, and a fourth data supplier which receives and holds an output from each of the plurality of first accumulators and supply the outputs as fourth data to a corresponding one of the plurality of second multipliers.

Owner:CANON KK

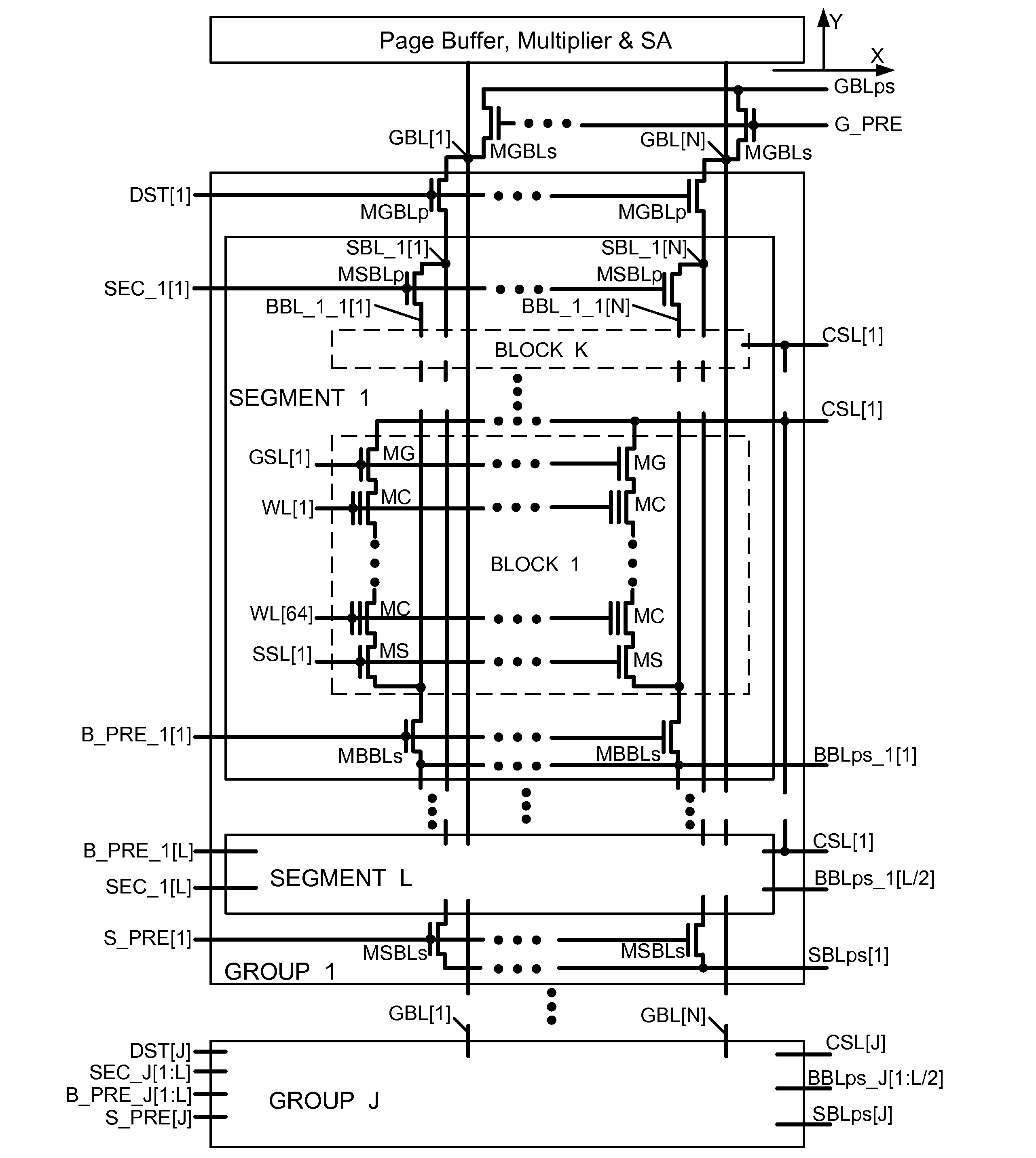

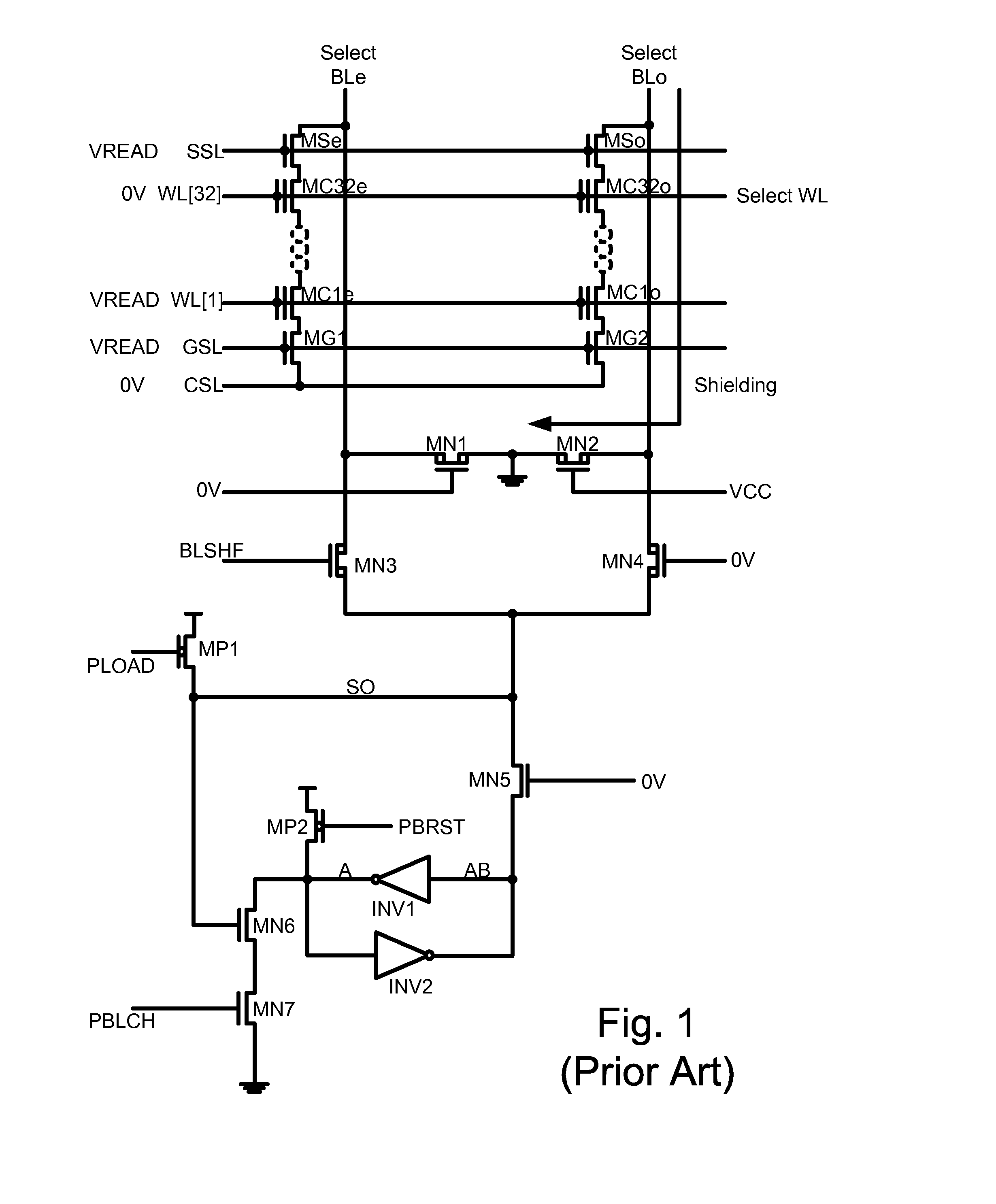

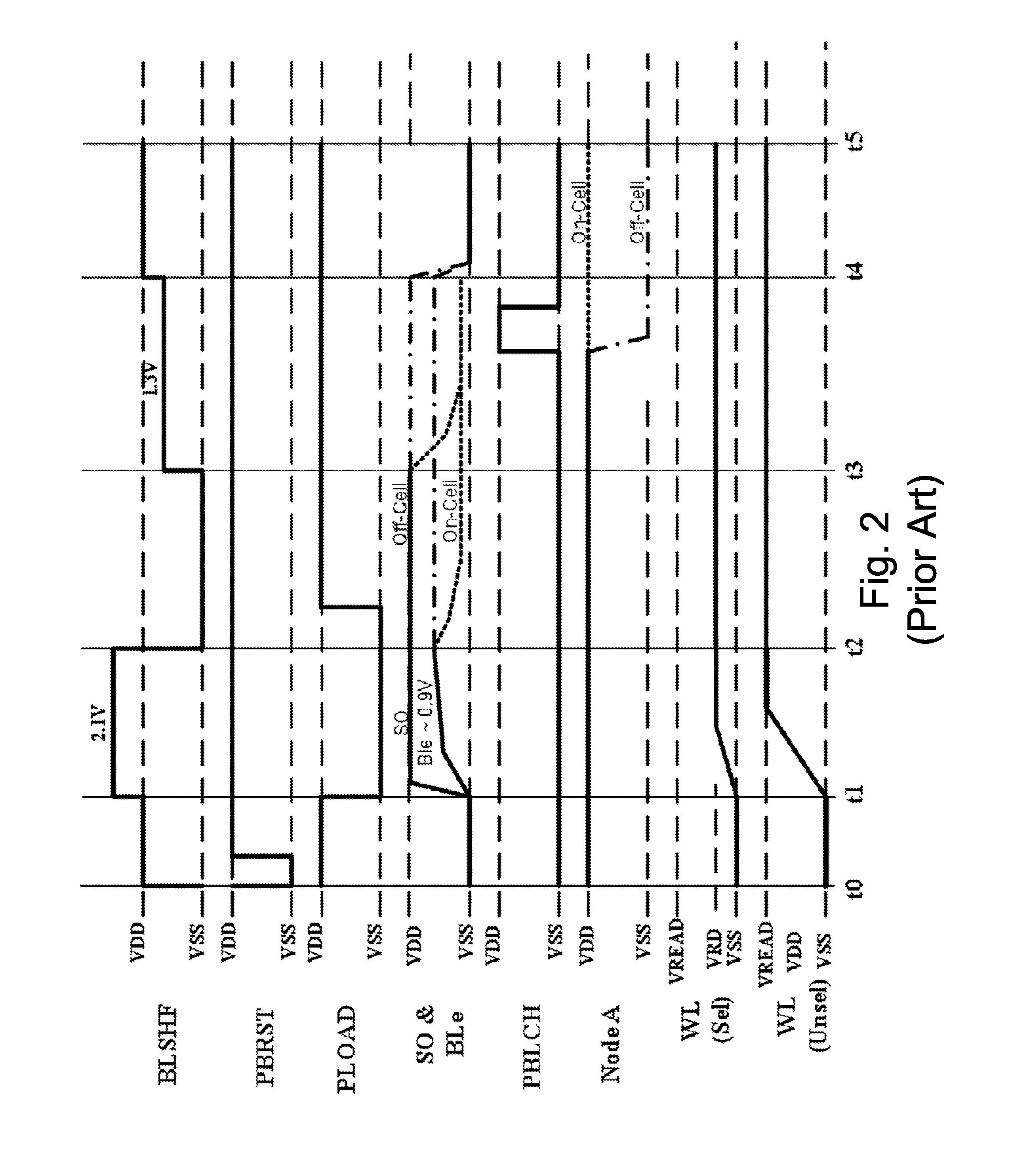

Novel NAND array architecture for multiple simutaneous program and read

ActiveUS20150003151A1Small sizeIncrease speedRead-only memoriesDigital storageCapacitanceBinary multiplier

This invention discloses a HiNAND array scheme with multiple-level of bit lines (BLs) including metal3 global bit lines (GBLs), divided metal2 Segment bit lines (SBLs), and divided metal1 block bit lines (BBLs) laid out in parallel to each other respectively for a plurality of NAND Strings. All other source lines or power lines connected to bottoms of corresponding String capacitances of GBLs, SBLs, and BBLs are associated with metal0 line laid out perpendicular to those BLs. Under the HiNAND array scheme, conventional one-WL Read and Program-Verify operations are replaced by multiple-WL and All-BL Read and Program-Verify operations executed with charge capacitance of SBLs being reduced to 1 / 10- 1 / 20 of capacitance of GBLs to achieve DRAM-like faster operation, less operation stress, and lower power consumption. A preferred set of program biased voltages on the selected WL and remaining non-selected WLs associated with a Multiplier and a DRAM-like charge-sharing Latch Sensing Amplifier is proposed.

Owner:APLUS FLASH TECH

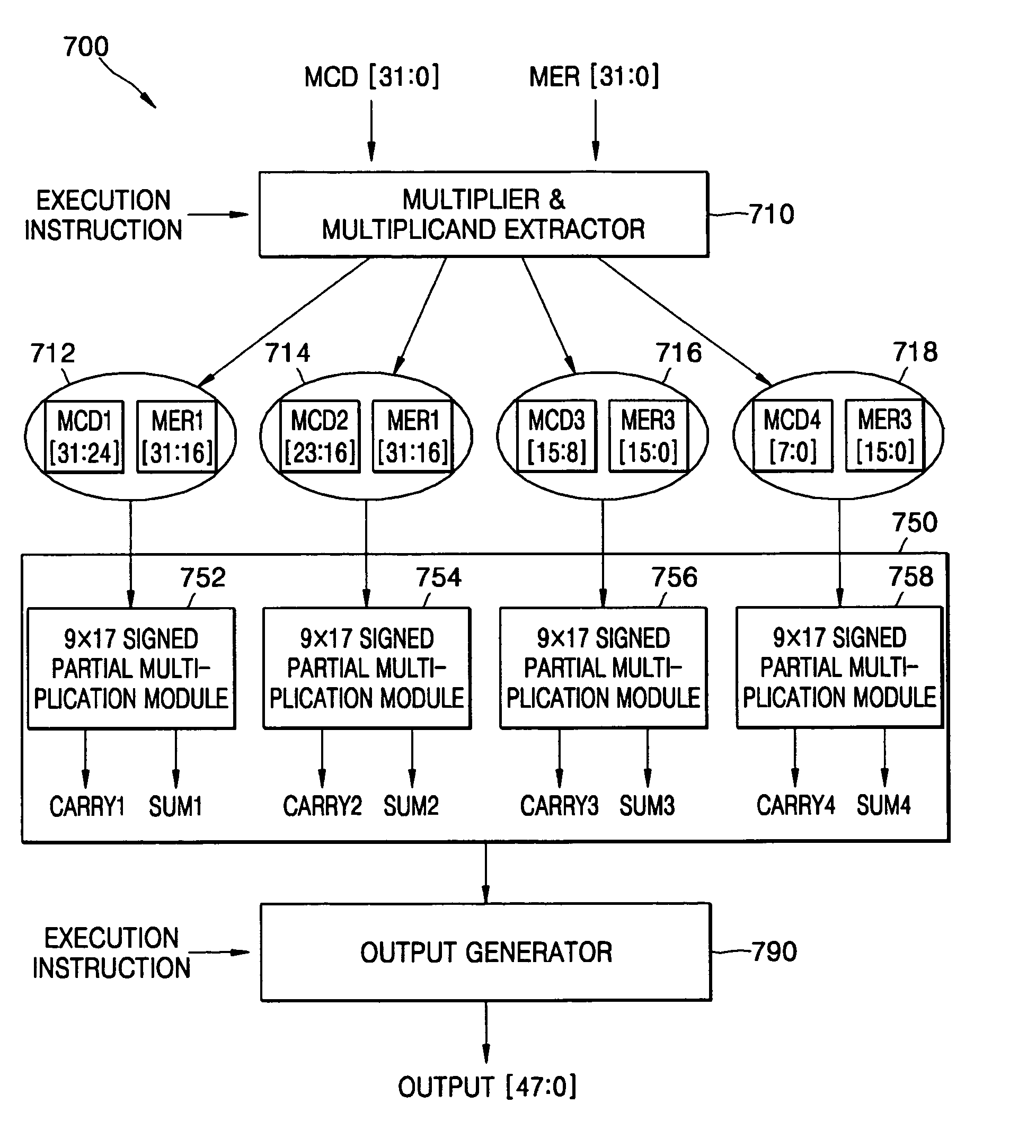

Apparatus and method of multiplication using a plurality of identical partial multiplication modules

InactiveUS7769797B2Reduce hardware sizeMinimize power consumptionComputation using non-contact making devicesBinary multiplierParallel computing

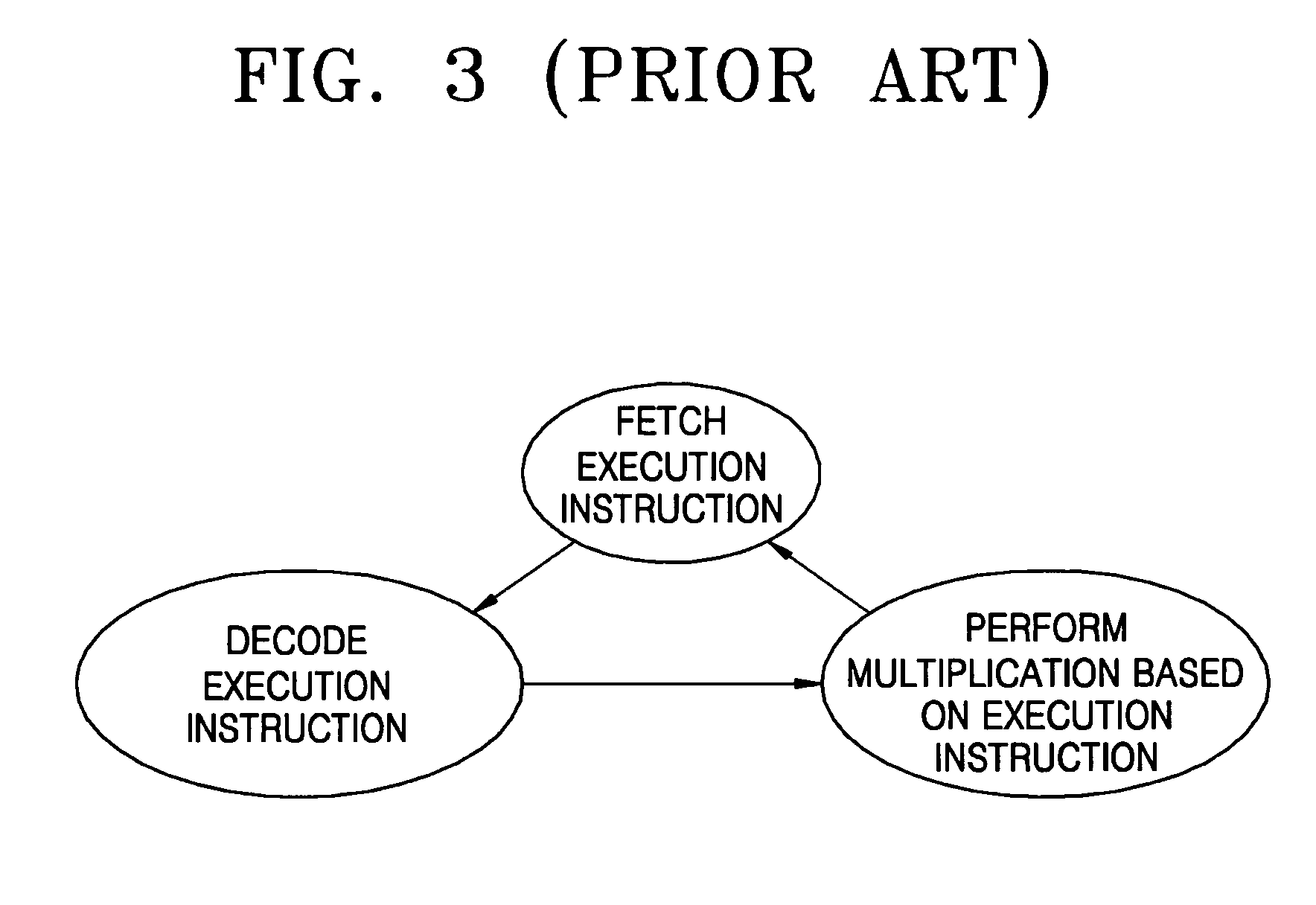

A multiplication apparatus including a multiplier and multiplicand extractor for dividing the multiplicand into partial multiplicands and dividing the multiplier into partial multipliers, and for generating partial input pairs by combining the partial multiplicands with the partial multipliers, and a multiplication executor including identical partial multiplication modules for receiving the partial input pairs and outputting partial carries and partial products. The apparatus further includes an output generator for combining the partial carries with the partial products according to the execution instruction to generate a final output. For simple multiplications, each of the partial multiplication modules can pass data to and from an adjacent partial multiplication module to calculate the partial carry and the partial product, and pass bits exceeding its own multiplication coverage.

Owner:S PRINTING SOLUTION CO LTD