Patents

Literature

4075results about "Digital technique network" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

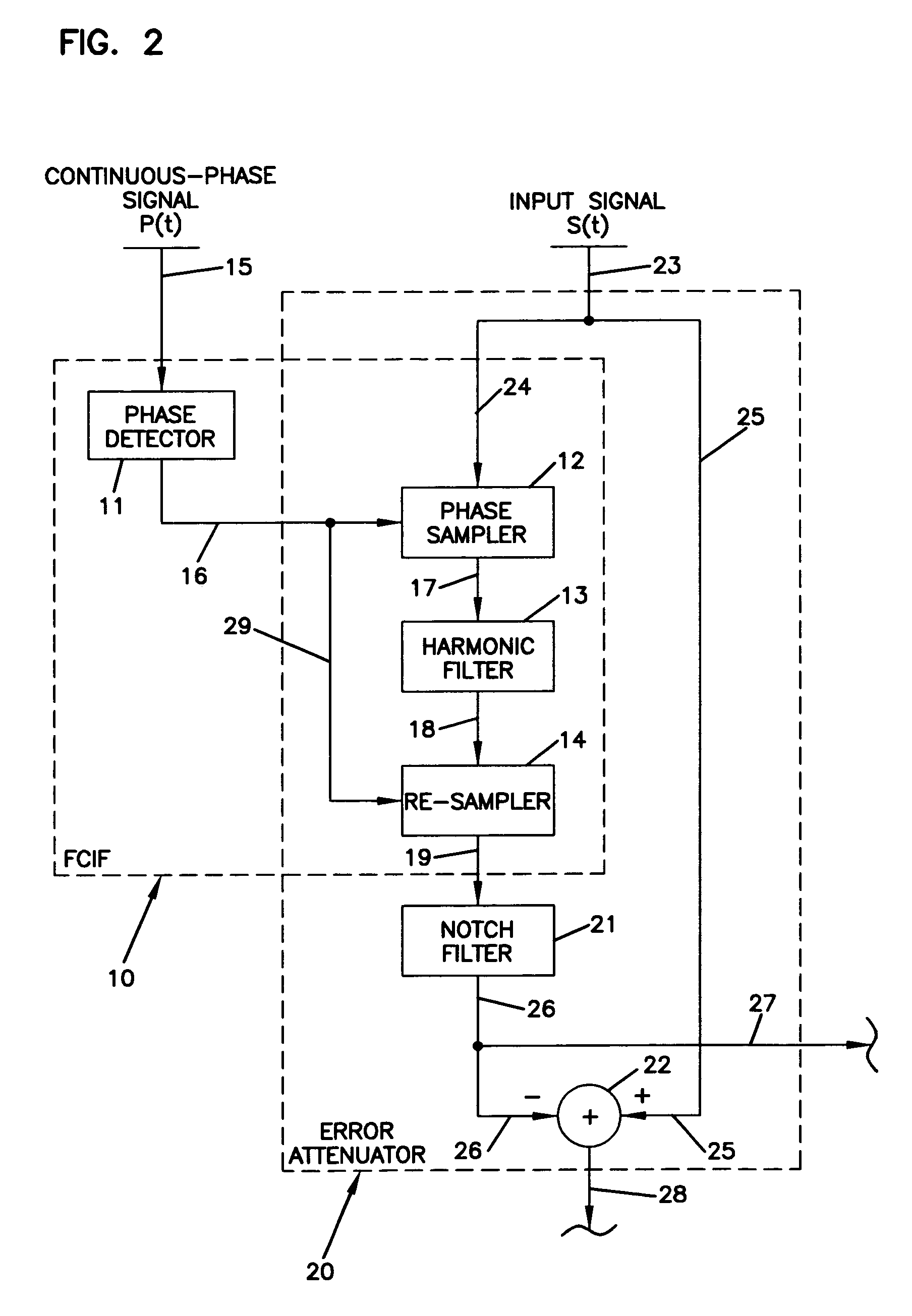

Mitigating interference in a signal

InactiveUS7626542B2Improve performanceLower requirementAdaptive networkDigital technique networkEngineeringNon orthogonal

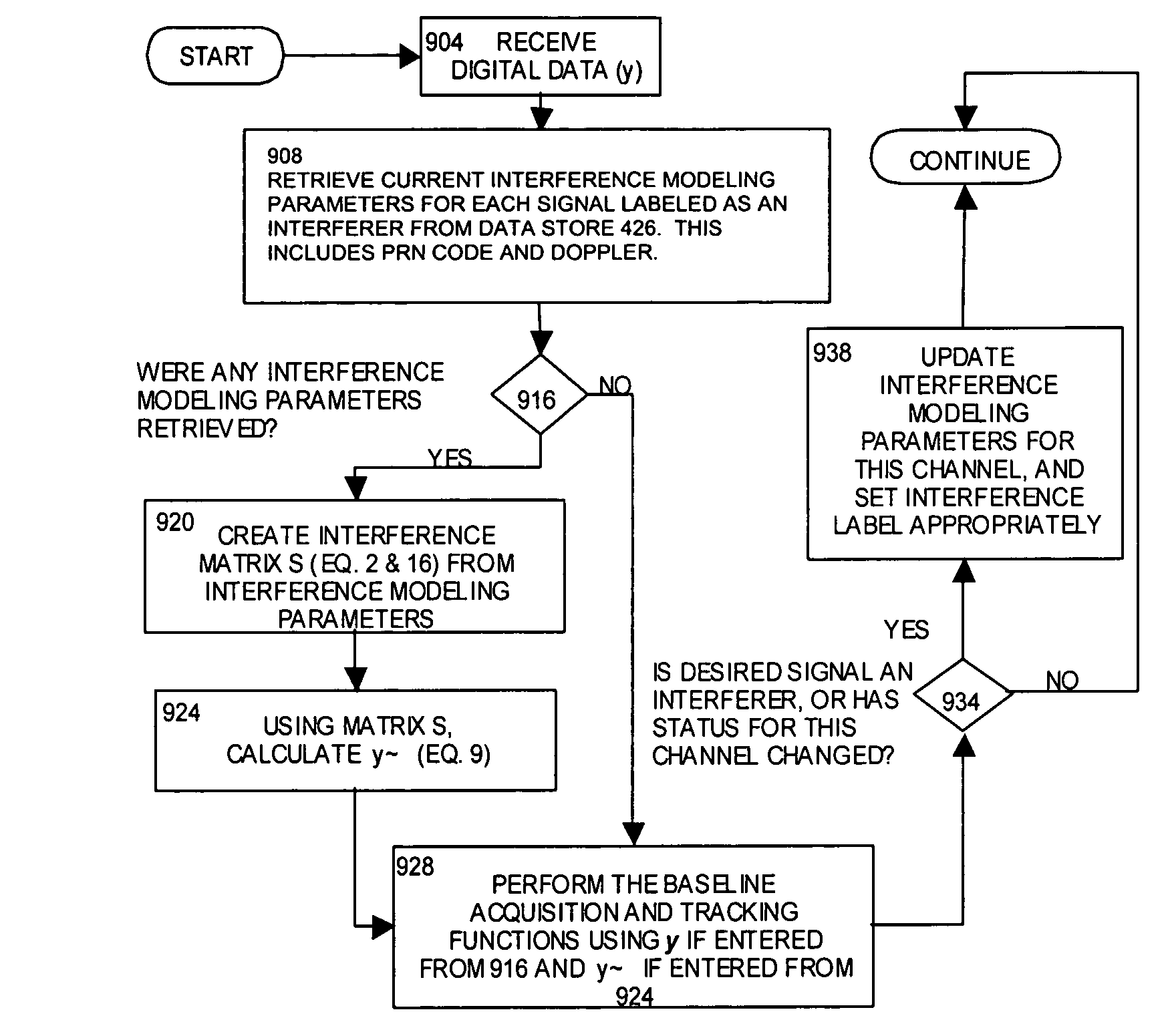

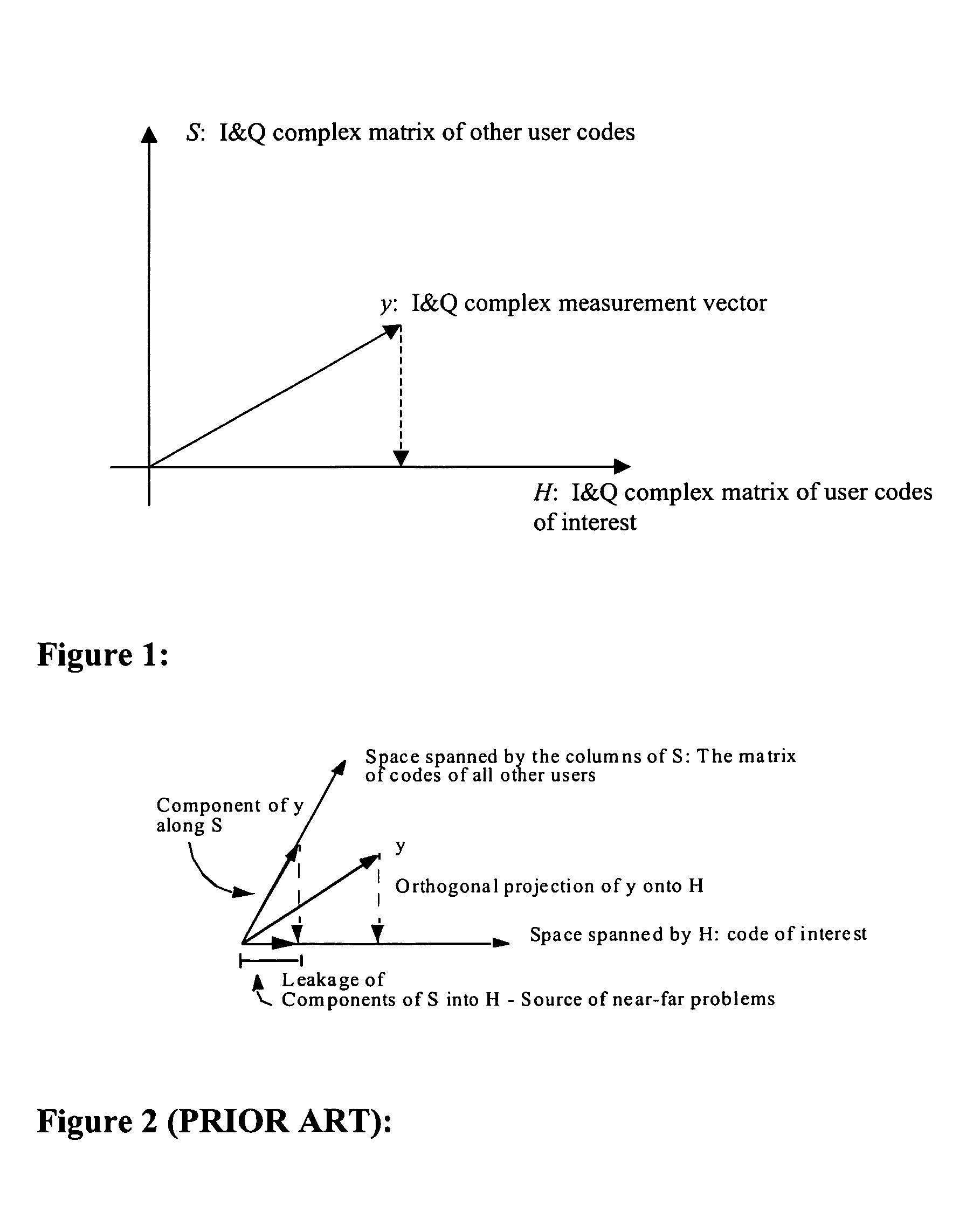

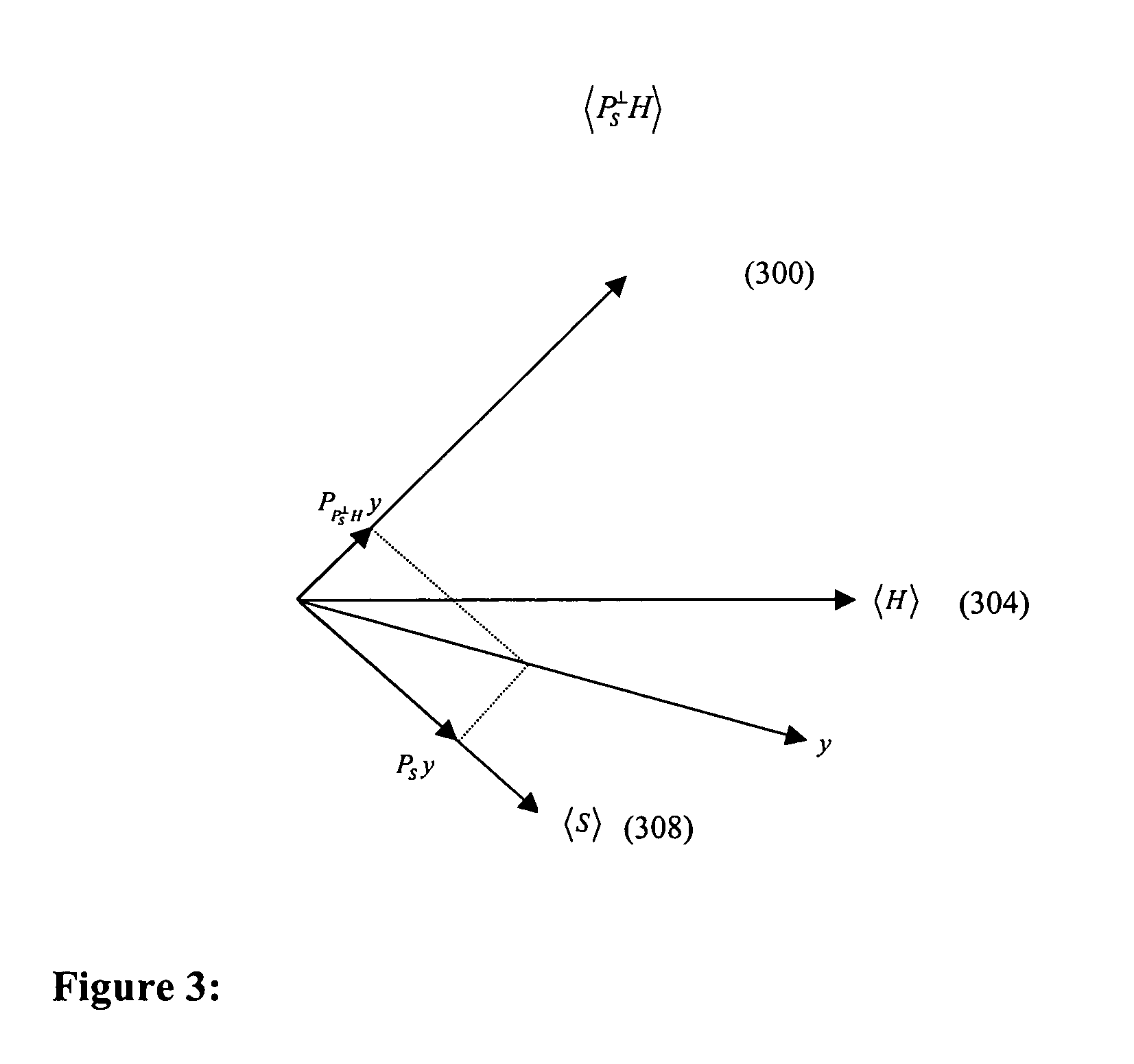

A method and receiver are disclosed for mitigating or substantially canceling signal interference between signals detected at the receiver. Once a presumed interfering signal(s) is acquired, parameters are determined that allow the interferer(s) to be modeled. The phase invariance of the process eliminates the need to acquire the interferer's phase. An orthogonal projection (for projecting onto a detection subspace which is orthogonal to a subspace spanned by the interferer(s)) is applied to the composite of all signals (y) for thereby projecting y onto the detection subspace. The interference subspace is non-orthogonal to a representation of desired (but interfered) signal of the composite signals. With the receiver properly equipped to perform this projection operation, interfering signals, multipath, multipath-like, and structured jamming signals can be effectively diminished.

Owner:DATA FUSION CORP

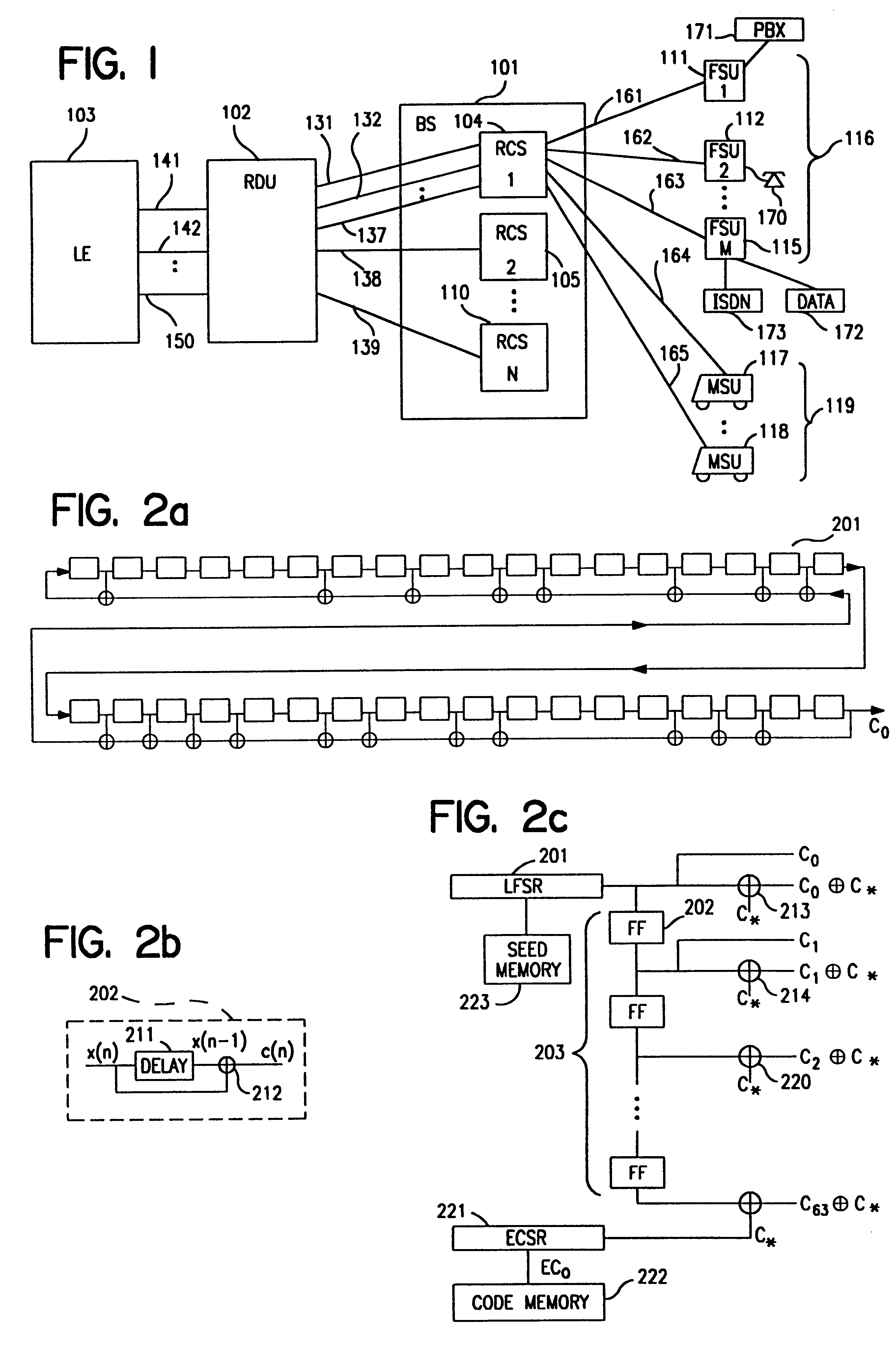

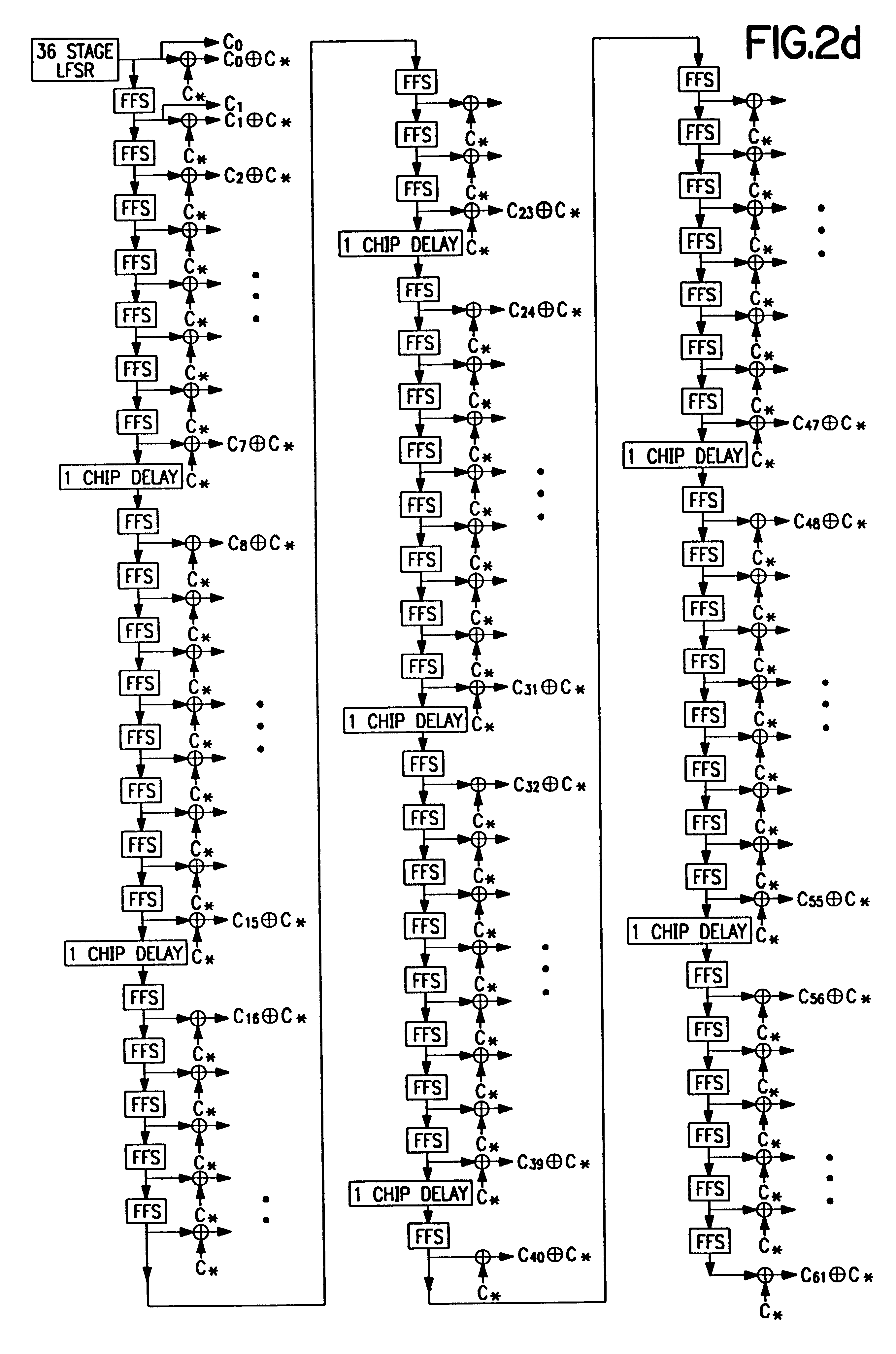

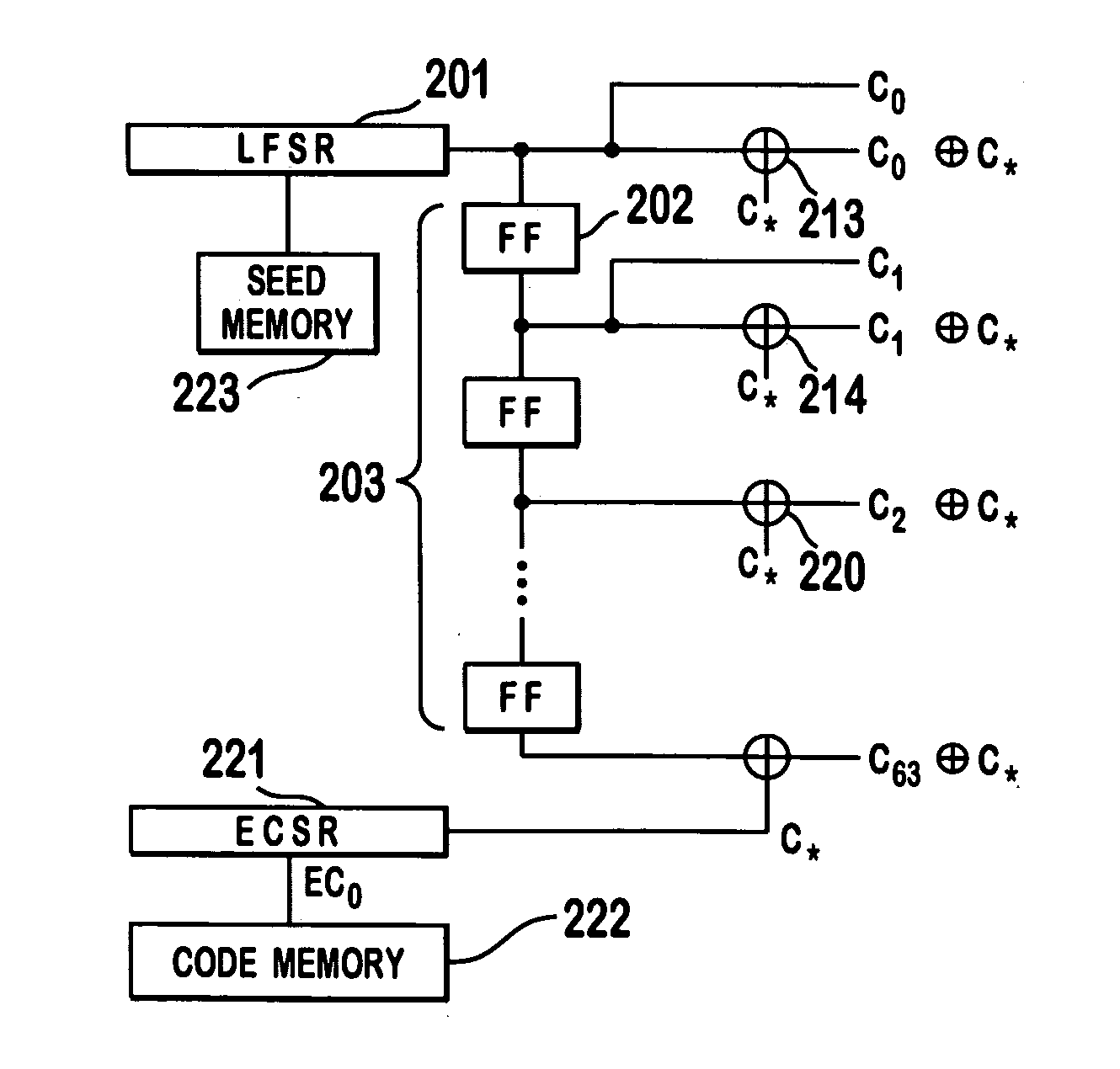

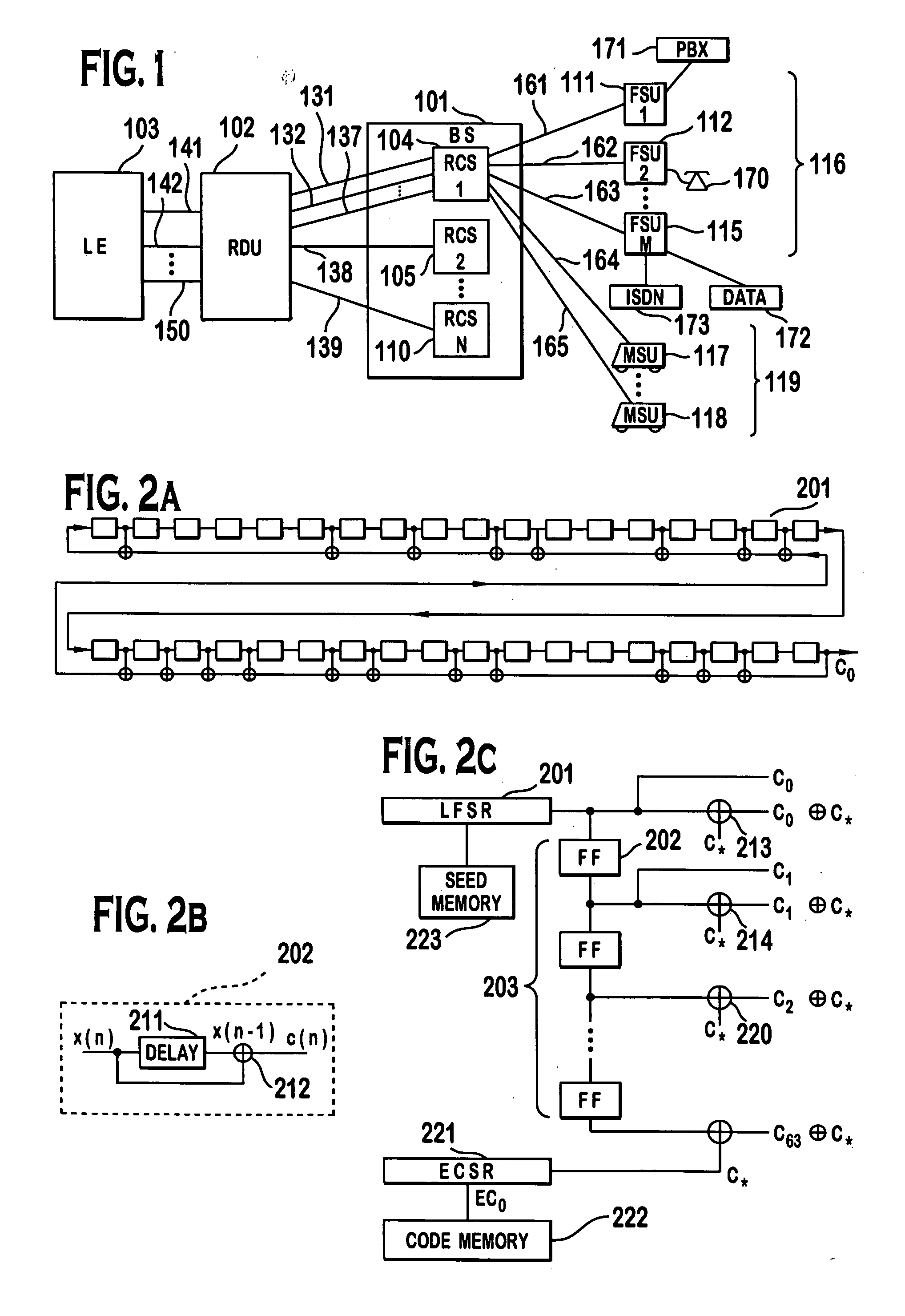

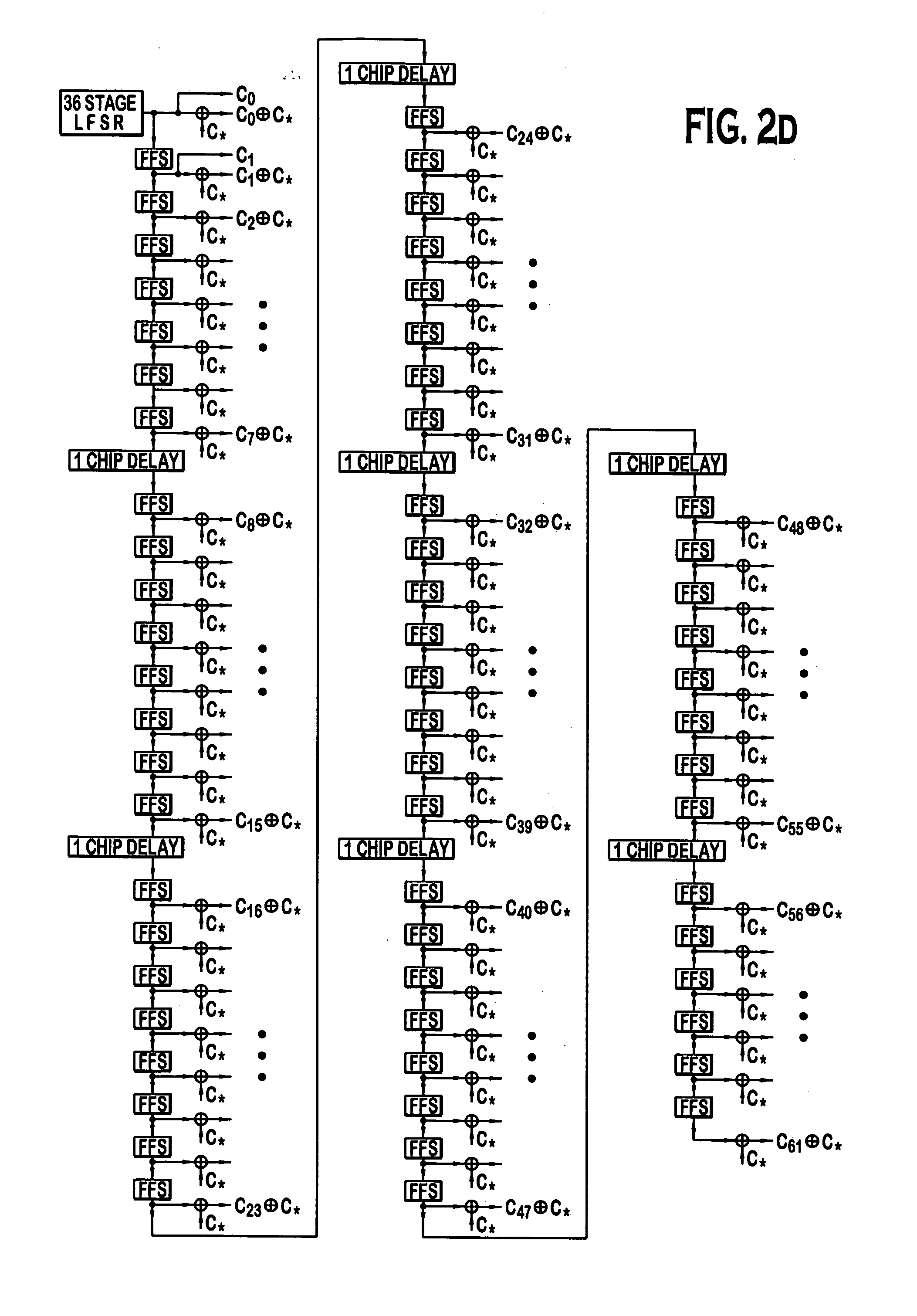

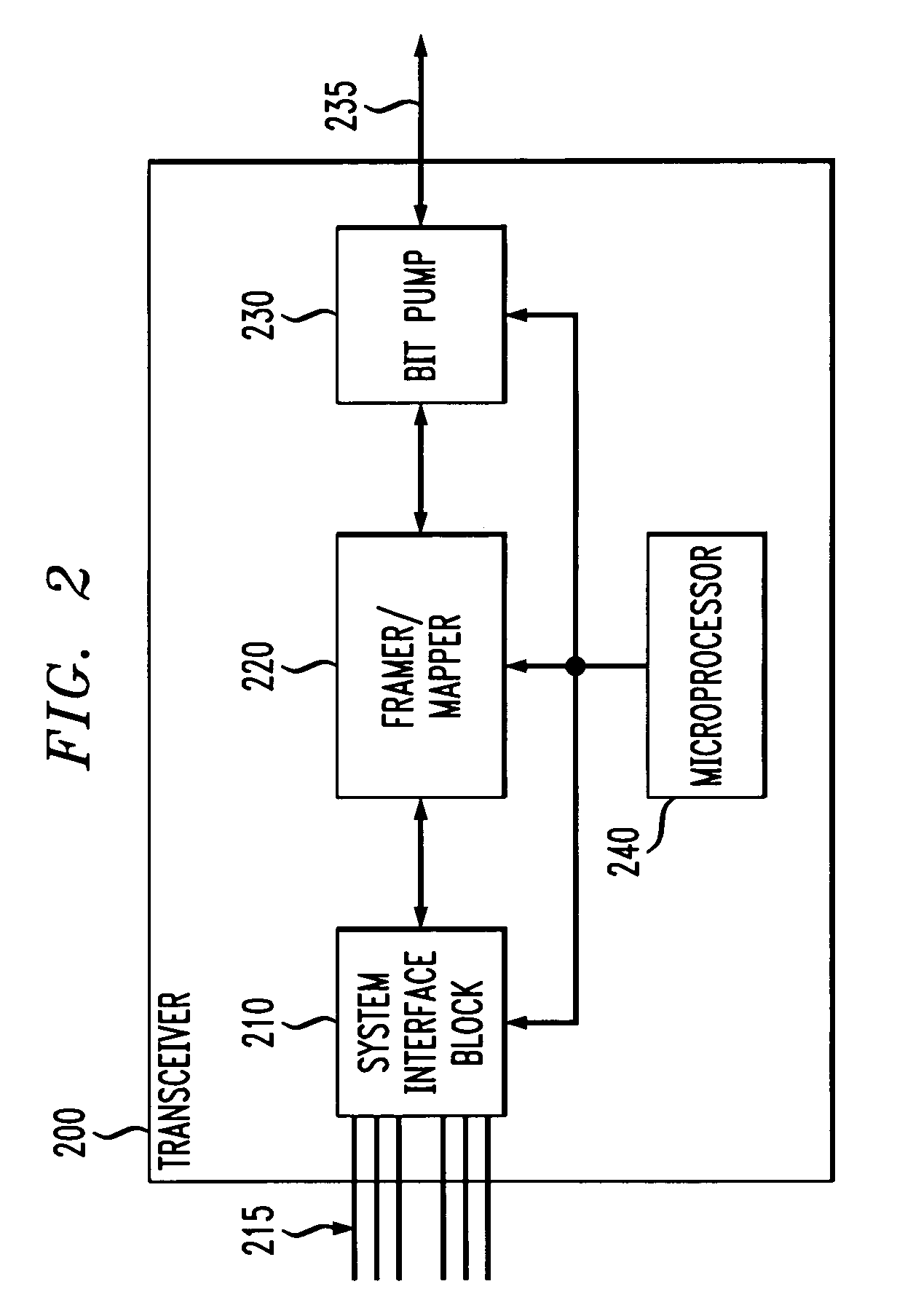

Code sequence generator in a CDMA modem

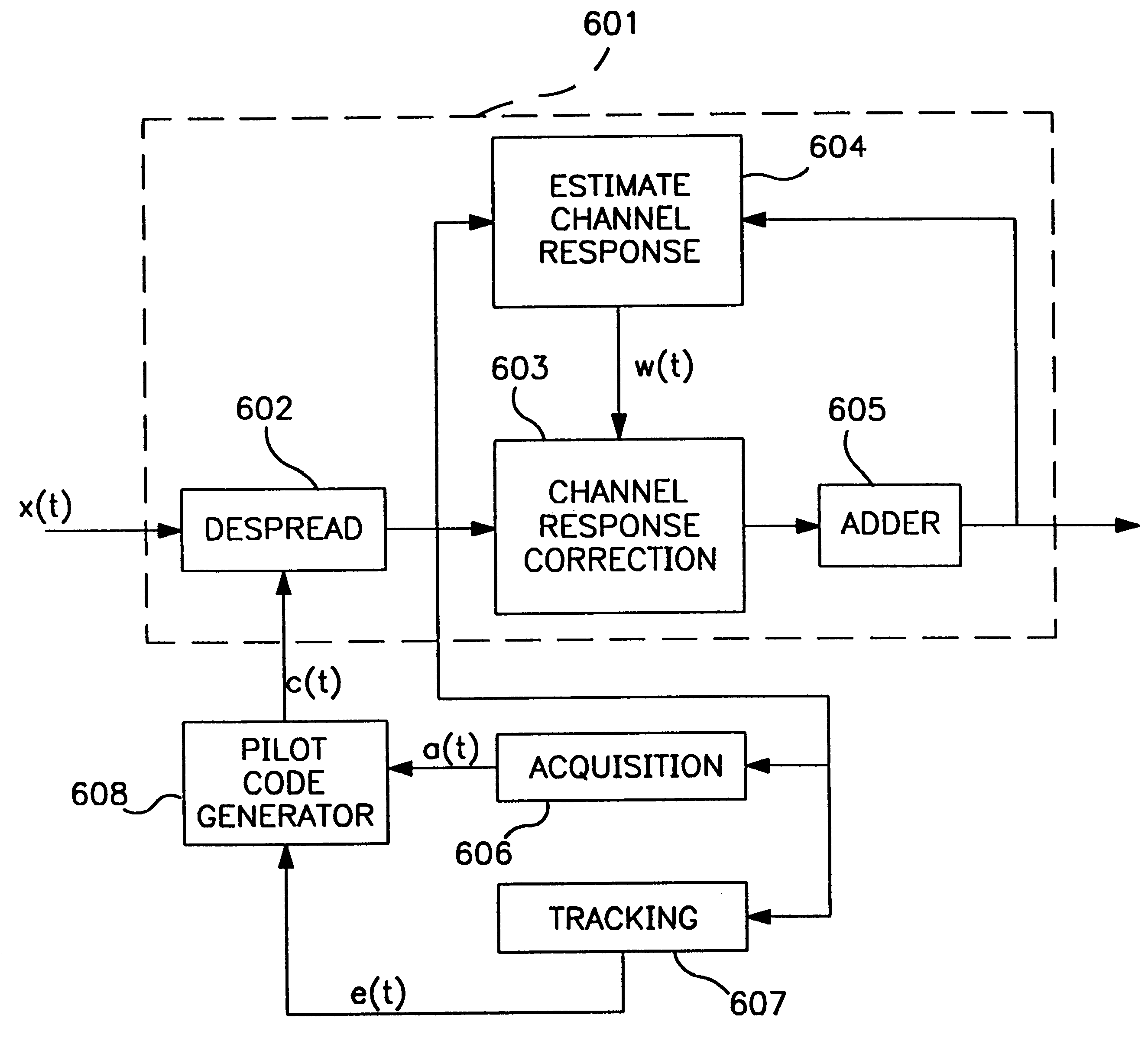

A CDMA modem includes a modem transmitter having: a code generator which provides an associated pilot code signal and which generates a plurality of message code signals: a spreading circuit which produces a spread-spectrum message signal by combining each of the information signals with a respective one of the message code signals; and a global pilot code generator that provides a global pilot code signal to which the message code signals are synchronized. The CDMA modem also includes a modem receiver having an associated pilot code generator and a group of associated pilot code correlators for correlating code-phase delayed versions of the associated pilot signal with a receive CDM signal to produce a despread associated pilot signal. The code phase of the associated pilot signal is changed responsive to an acquisition signal value until a pilot signal is received. The associated pilot code tracking logic adjusts the associated pilot code signal in phase responsive to the acquisition signal so that the signal power level of the despread associated pilot code signal is maximized. Finally, the CDMA modem receiver includes a group of message signal acquisition circuits, each including a plurality of receive message signal correlators which correlate respective local received message code signal to the CDM signal to produce a respective despread received message signal.

Owner:INTERDIGITAL TECH CORP

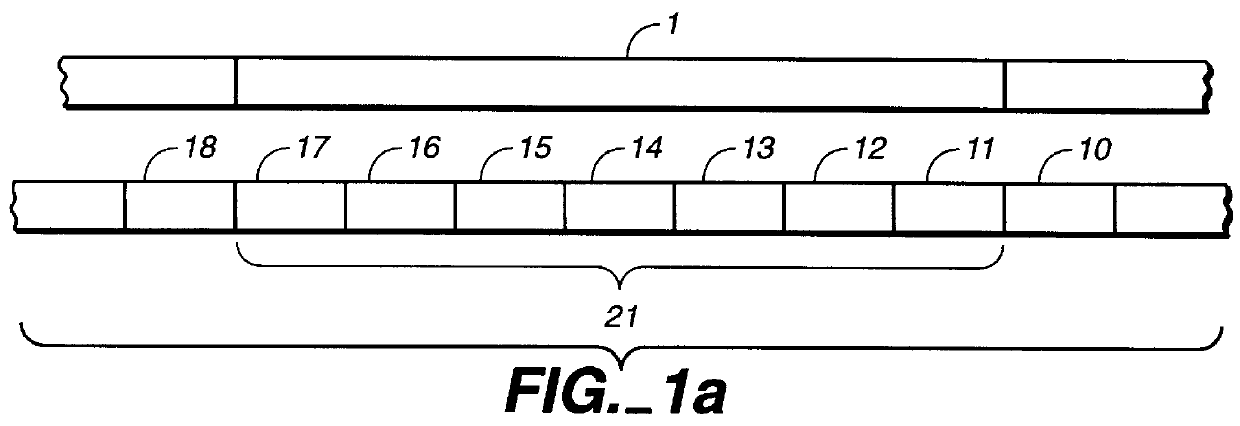

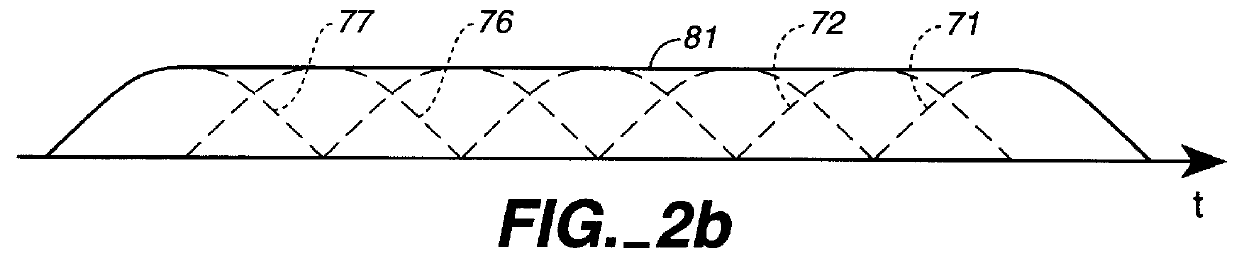

Frame-based audio coding with video/audio data synchronization by dynamic audio frame alignment

InactiveUS6124895AQuality improvementPicture reproducers using cathode ray tubesCode conversionUltrasound attenuationData synchronization

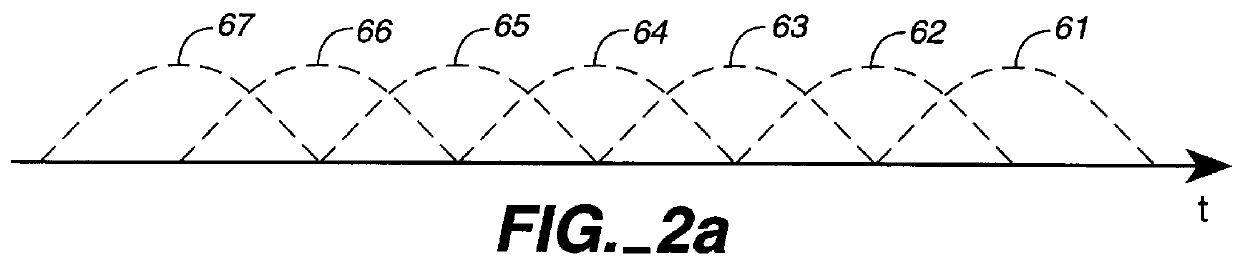

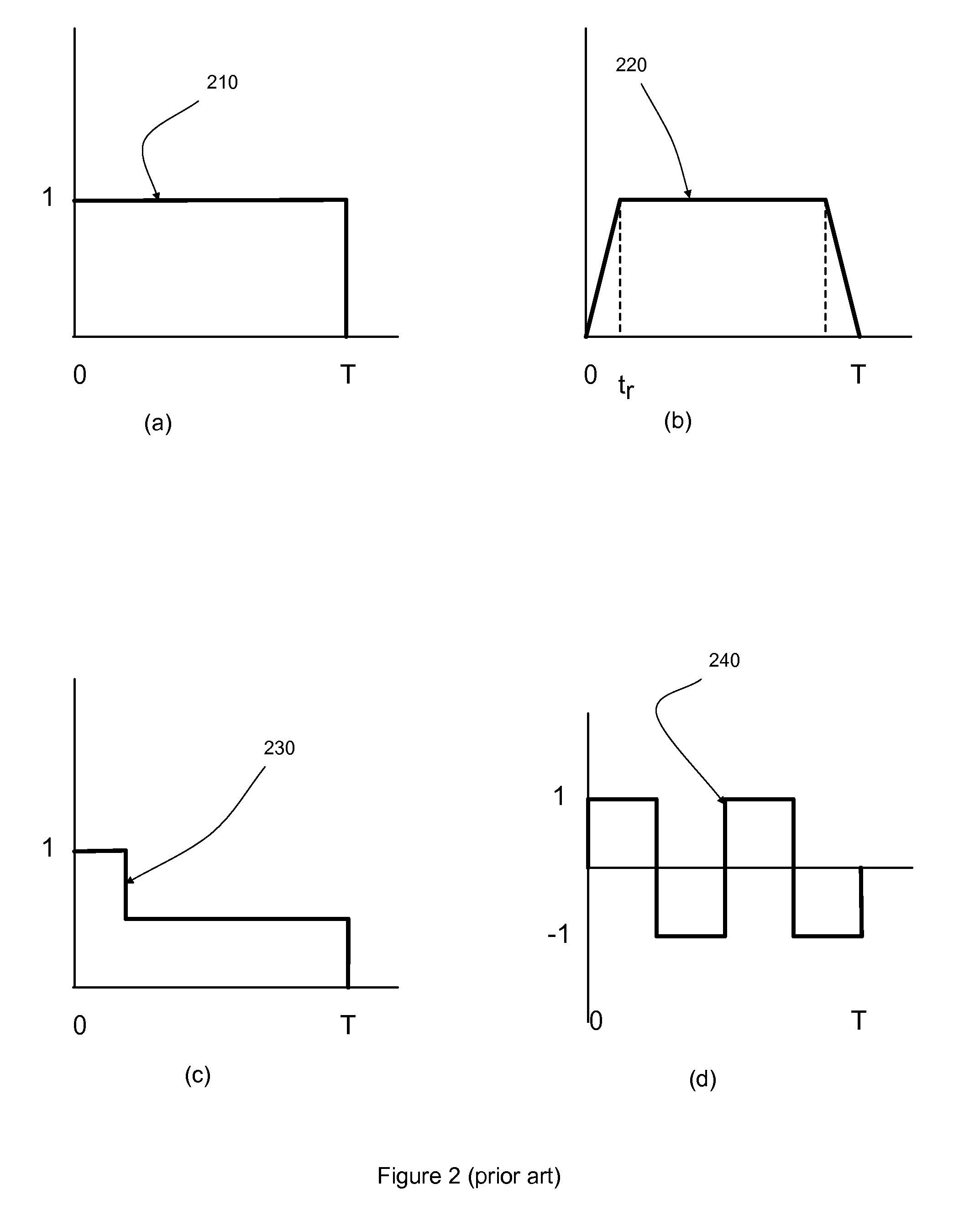

Several audio signal processing techniques may be used in various combinations to improve the quality of audio represented by an information stream formed by splice editing two or more other information streams. The techniques are particularly useful in applications that bundle audio information with video information. In one technique, gain-control words conveyed with the audio information stream are used to interpolate playback sound levels across a splice. In another technique, special filterbanks or forms of TDAC transforms are used to suppress aliasing artifacts on either side of a splice. In yet another technique, special filterbanks or crossfade window functions are used to optimize the attenuation of spectral splatter created at a splice. In a further technique, audio sample rates are converted according to frame lengths and rates to allow audio information to be bundled with, for example, video information. In yet a further technique, audio blocks are dynamically aligned so that proper synchronization can be maintained across a splice. An example for 48 kHz audio with NTSC video is discussed.

Owner:DOLBY LAB LICENSING CORP

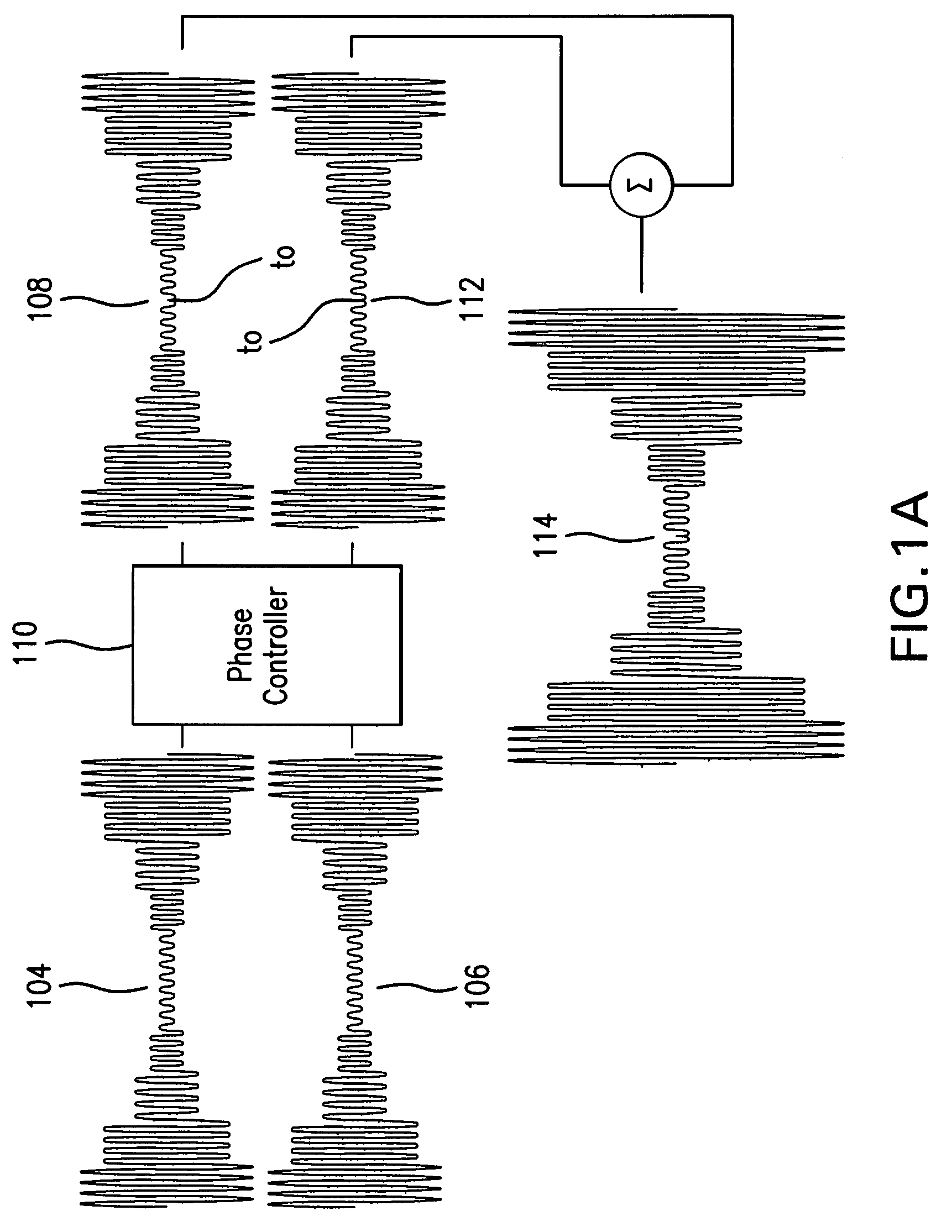

System for using rapid acquisition spreading codes for spread-spectrum communications

InactiveUS20050265430A1Increase profitEnergy efficient ICTRadio transmission for post communicationCode division multiple accessCarrier signal

A system for rapidly acquiring a spreading code, used in a code division multiple access (CDMA) system, comprises a generator for generating a first long code and a second long code, with each long code having a length of N chips. The first long code is different from the second long code. A transmitter transmits the first long code and the second long code at a first phase angle and at a second phase angle, respectively, on a carrier signal over a communications channel using radio waves. The first long code and the second long code may be transmitted at an in-phase (I) angle and at a quadrature-phase (Q) angle, respectively, on the carrier signal. From the communications channel, an I acquisition circuit and a Q acquisition circuit may acquire, in parallel, the first long code and the second long code from the I angle and the Q angle, respectively, of the carrier signal by searching, in parallel, N / 2 chips of the first long code and the second long code.

Owner:INTERDIGITAL TECH CORP

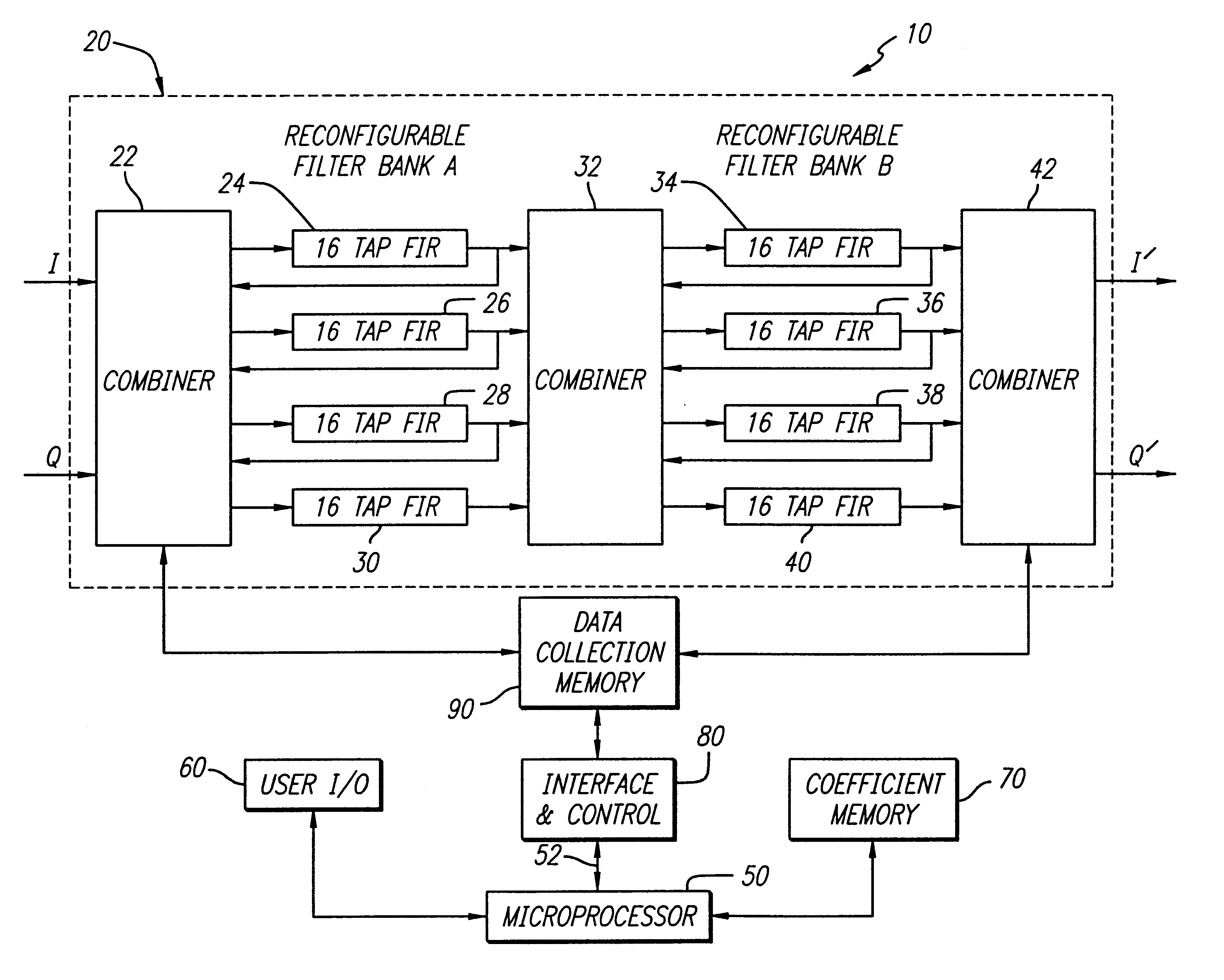

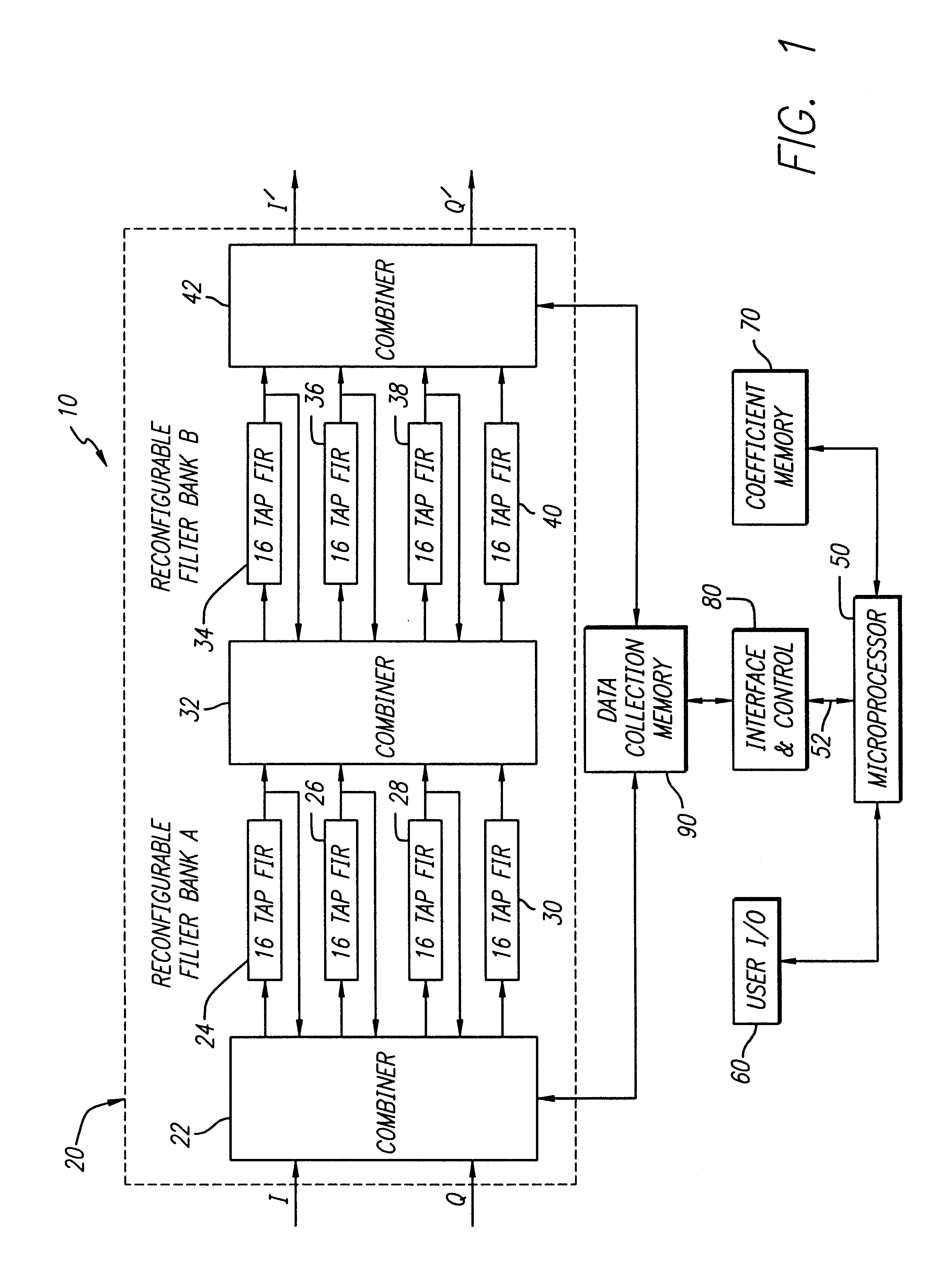

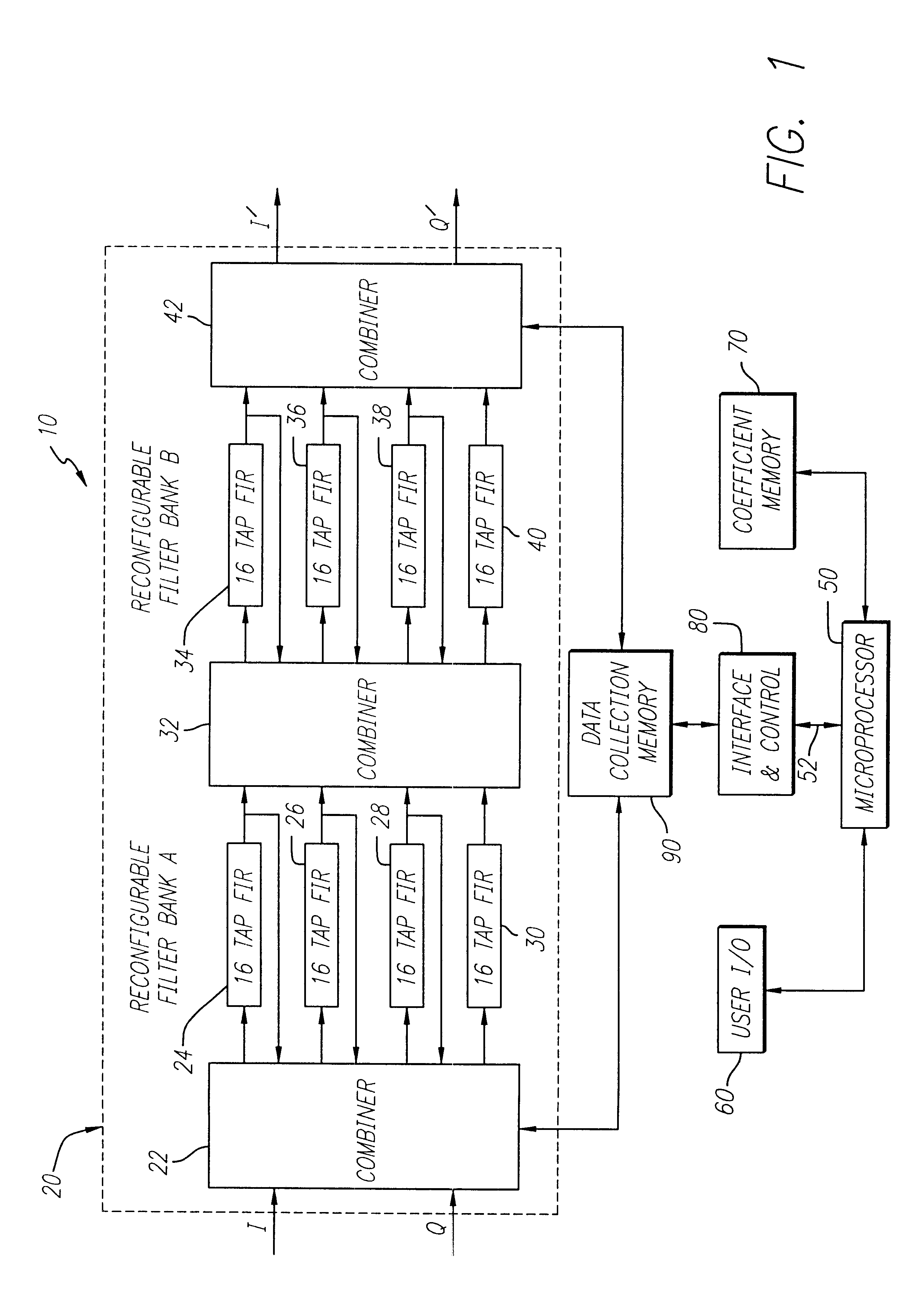

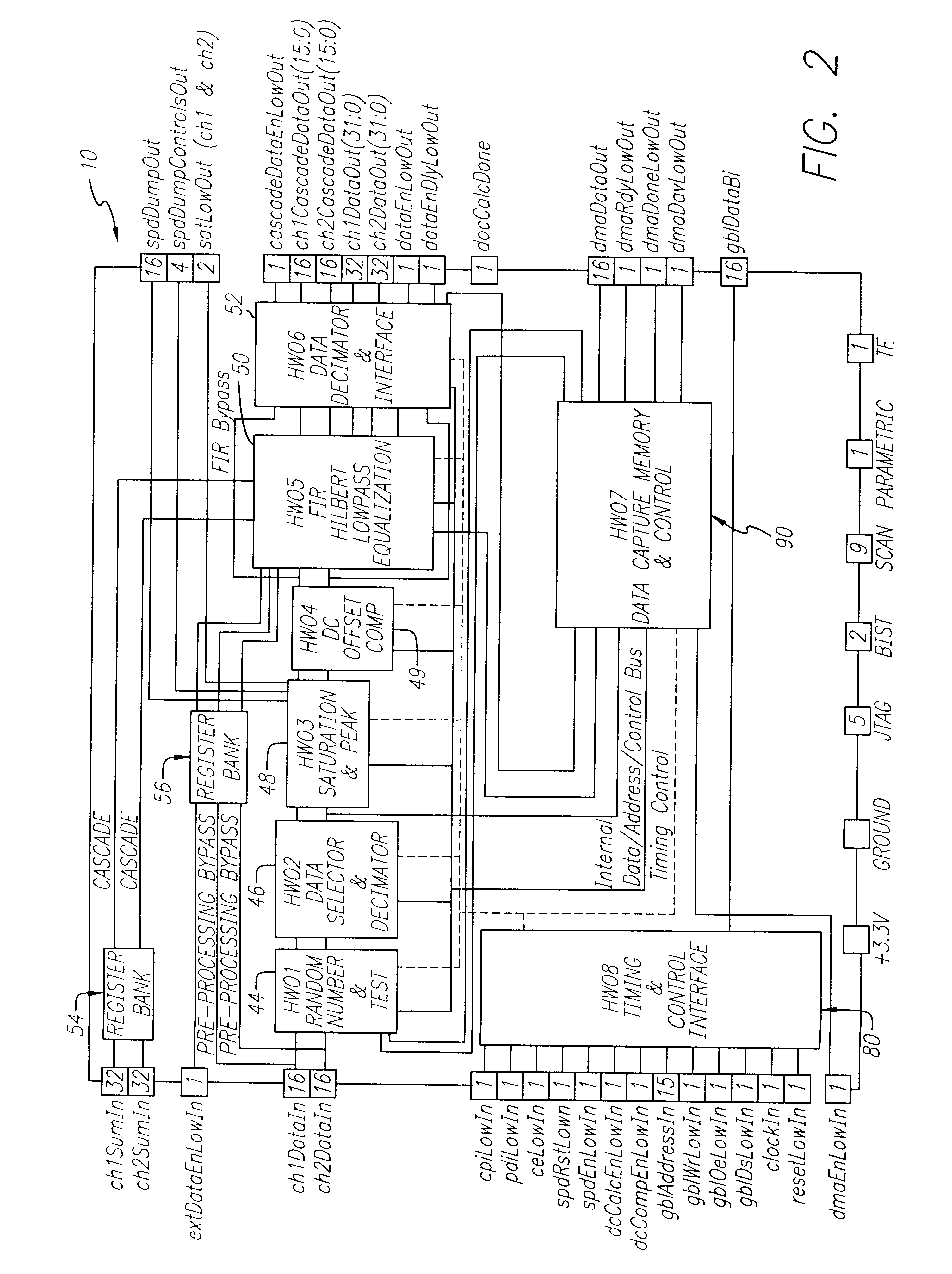

Equalization system using general purpose filter architecture

InactiveUS6411253B1Television system detailsDigital technique networkFinite impulse responseGeneral purpose

An equalization system and method. In a most general sense, the inventive equalization system includes first and second filters for filtering an in-phase component of a received signal in accordance with first and second sets of coefficients, respectively. The system includes third and fourth filters for filtering a quadrature component of the input signal in accordance with third and fourth sets of coefficients, respectively. The outputs of the first and third filters are subtracted to provide an equalized in-phase output signal and the outputs of the second and fourth filters are added to provide an equalized quadrature output signal. In the illustrative embodiment the filters are finite impulse response filters and the coefficients are provided by a microprocessor. In accordance with the present teachings, the filters are implemented in a general purpose filter. The delay elements of the filters are calculated in accordance with a mean square error algorithm. Accordingly, the coefficients are the product of the correlation between inputs to the delay elements and a cross correlation between the inputs and a set of values representative of a desired response.

Owner:RAYTHEON CO

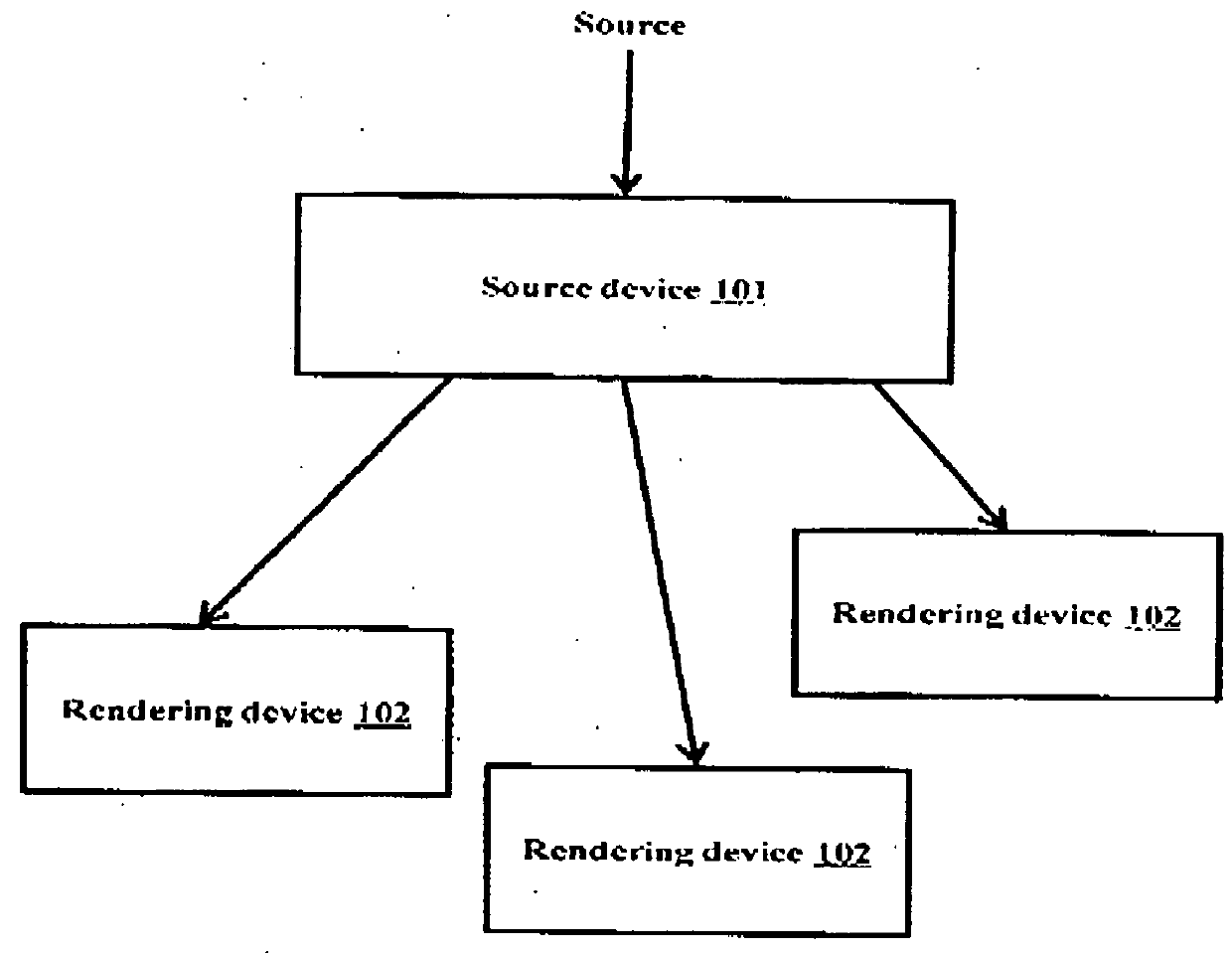

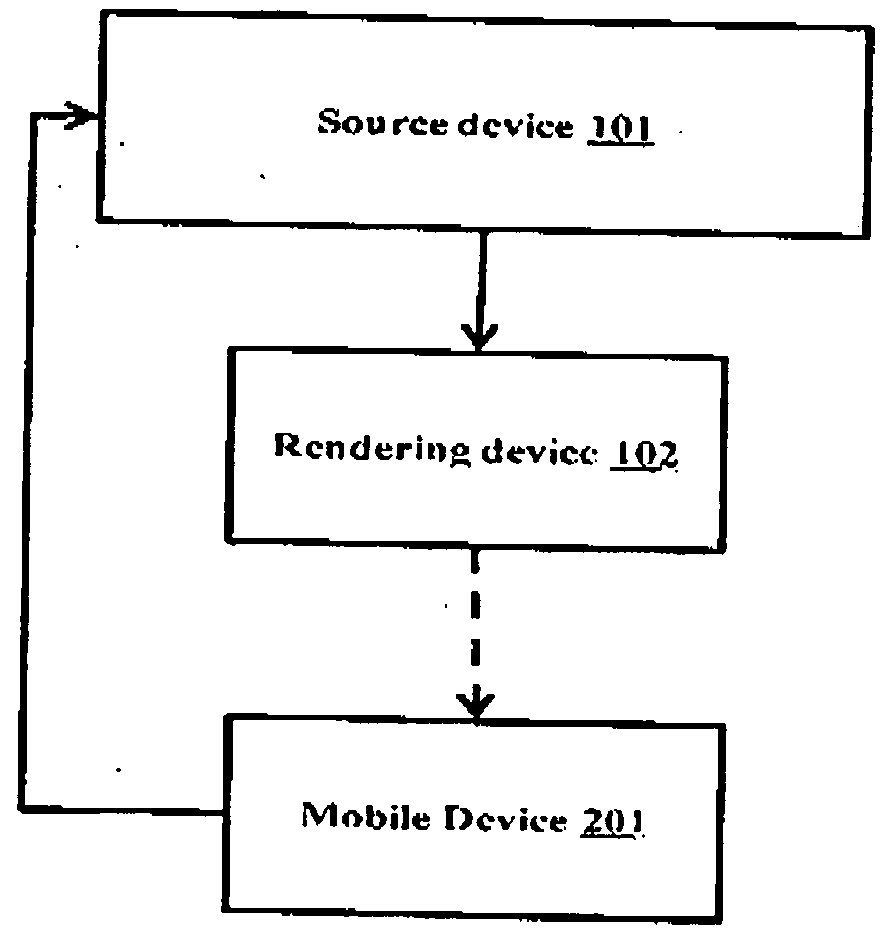

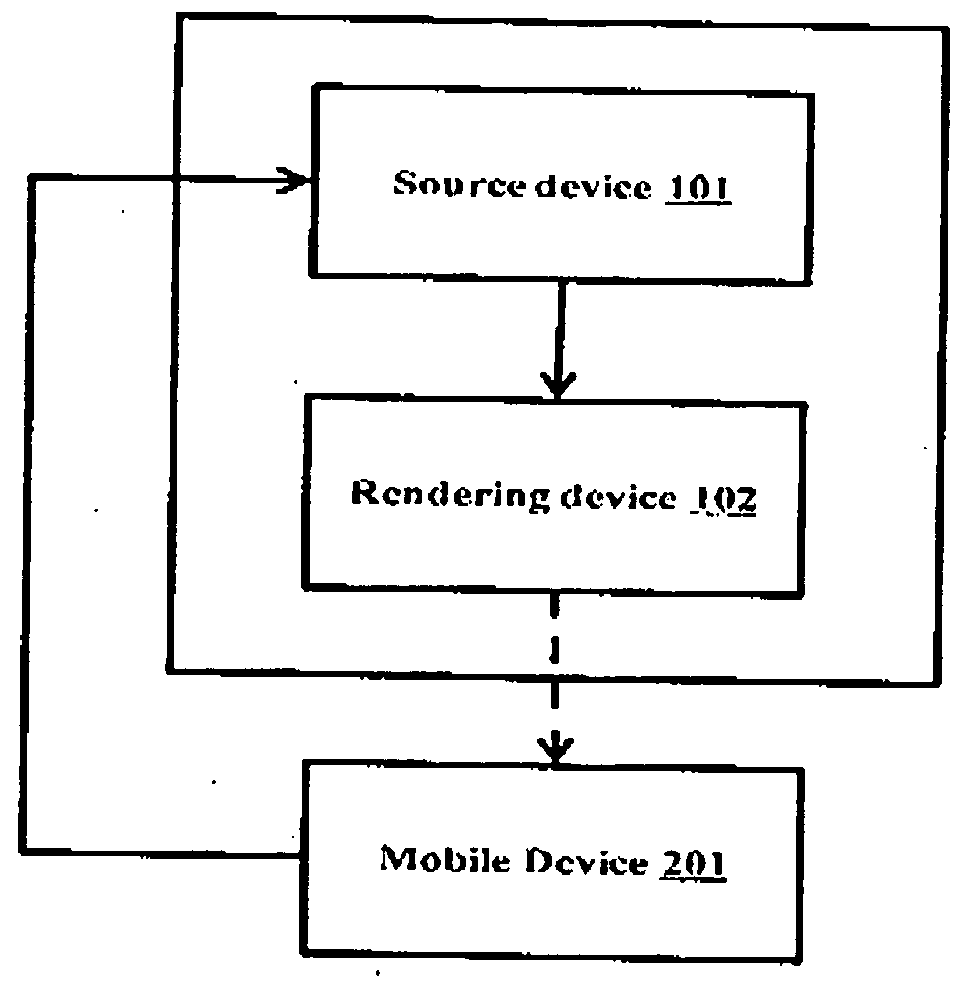

Enhancing audio using a mobile device

ActiveUS20160035337A1Gain controlVolume compression/expansion in untuned/low-frequency amplifiersNoise levelSound quality

Embodiments disclosed herein enable detection and improvement of the quality of the audio signal using a mobile device by determining the loss in the audio signal and enhancing audio by streaming the remainder portion of audio. Embodiments disclosed herein enable an improvement in the sound quality rendered by rendering devices by emitting an test audio signal from the source device, measuring the test audio signal using microphones, detecting variation in the frequency response, loudness and timing characteristics using impulse responses and correcting for them. Embodiments disclosed herein also compensate for the noise in the acoustic space by determining the reverberation and ambient noise levels and their frequency characteristics and changing the digital filters and volumes of the source signal to compensate for the varying noise levels.

Owner:CAAVO INC

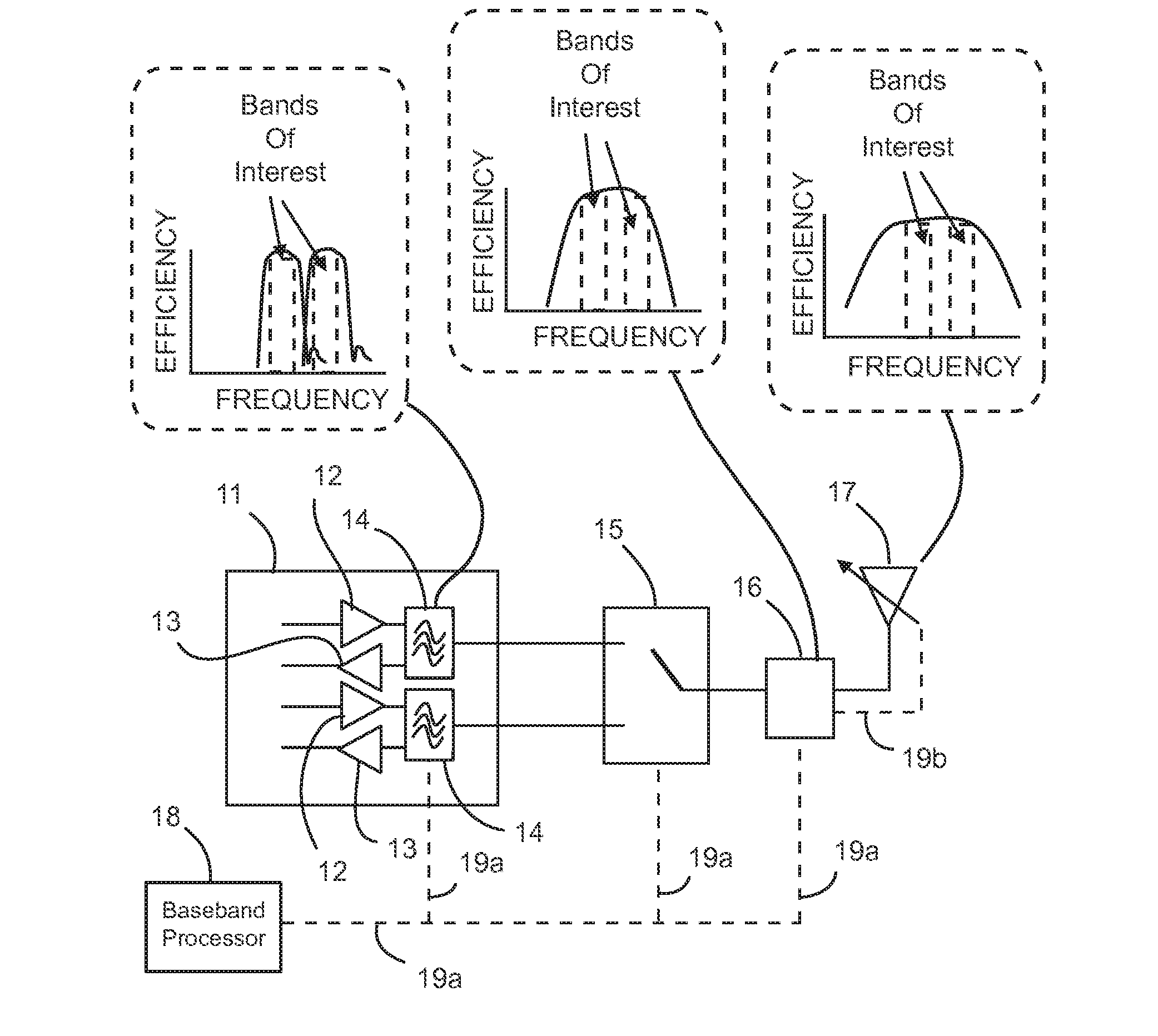

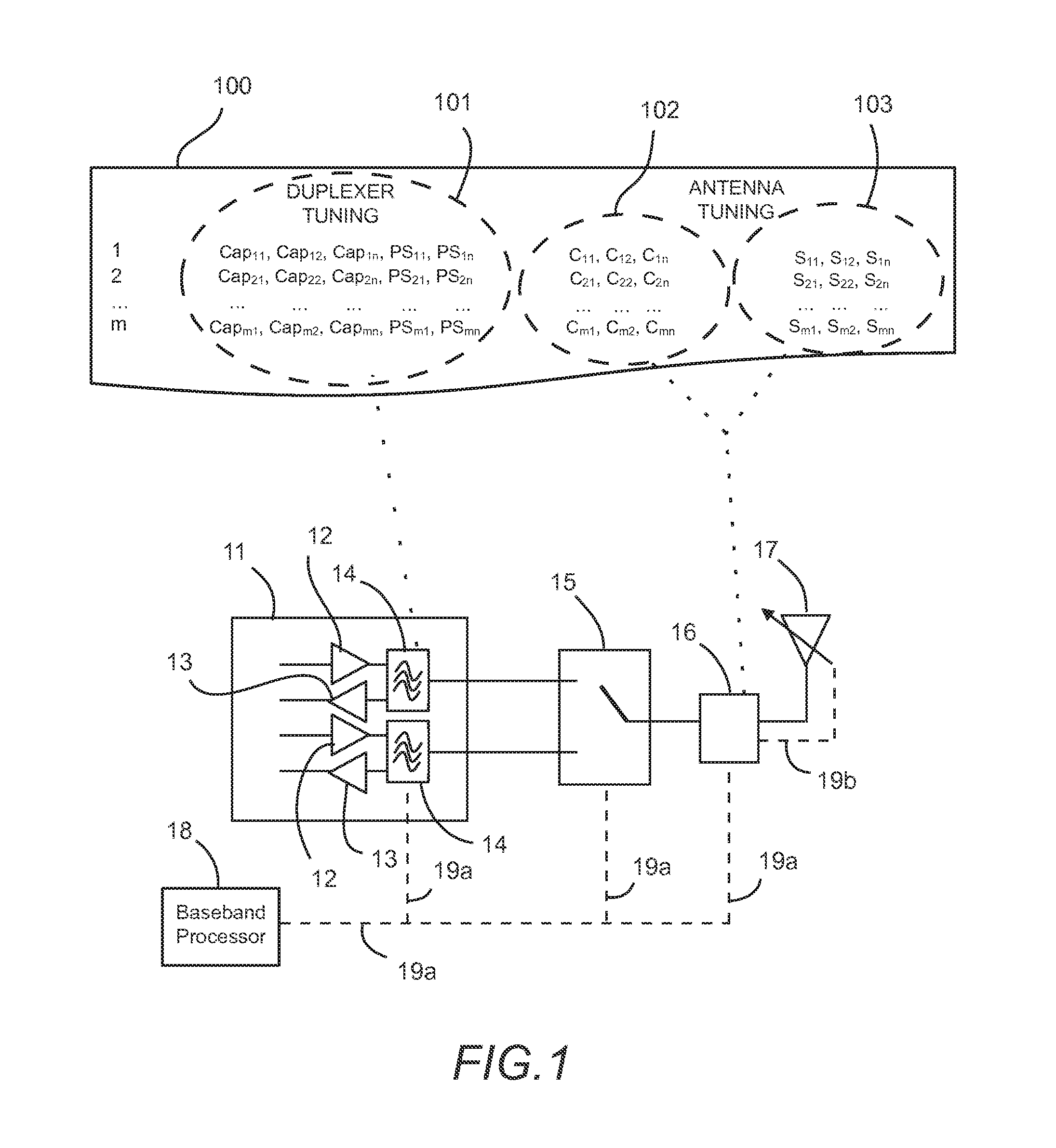

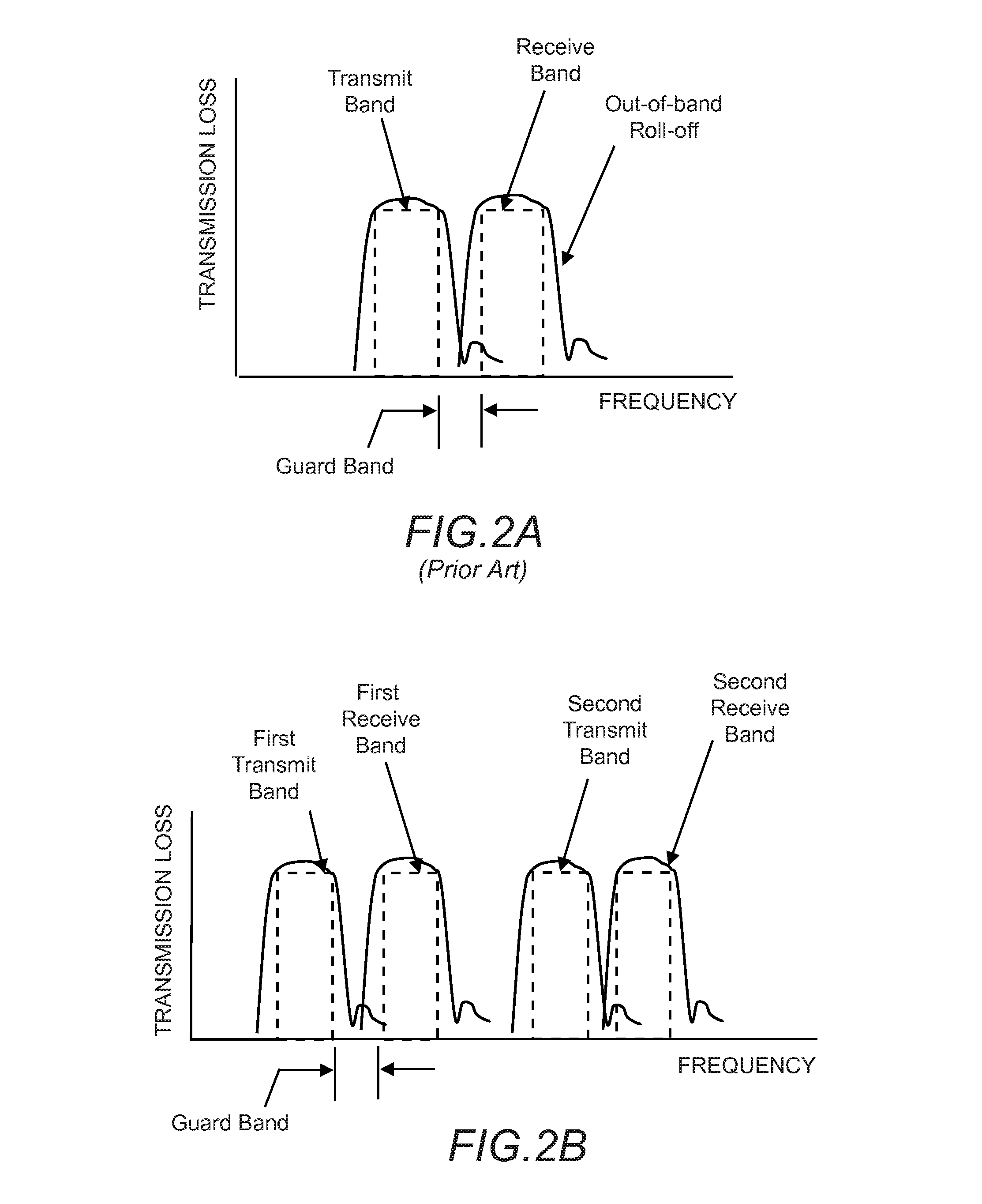

Tunable duplexing circuit

ActiveUS20150303892A1Improve performanceImprove out-of-band rejection performanceMultiple-port networksDigital technique networkRF front endTransceiver

A tunable duplexer circuit is described, wherein the frequency response as well as bandwidth and transmission loss characteristics can be dynamically altered, providing improved performance for transceiver front-end applications. The rate of roll-off of the frequency response can be adjusted to improve performance when used in duplexer applications. A method is described where the duplexer circuit characteristics are optimized in conjunction with a specific antenna frequency response to provide additional out-of-band rejection in a communication system. Dynamic optimization of both the duplexer circuit and an active antenna system is described to provide improved out-of-band rejection when implemented in RF front-end circuits of communication systems. Other features and embodiments are described in the following detailed descriptions.

Owner:KYOCERA AVX COMPONENTS (SAN DIEGO) INC

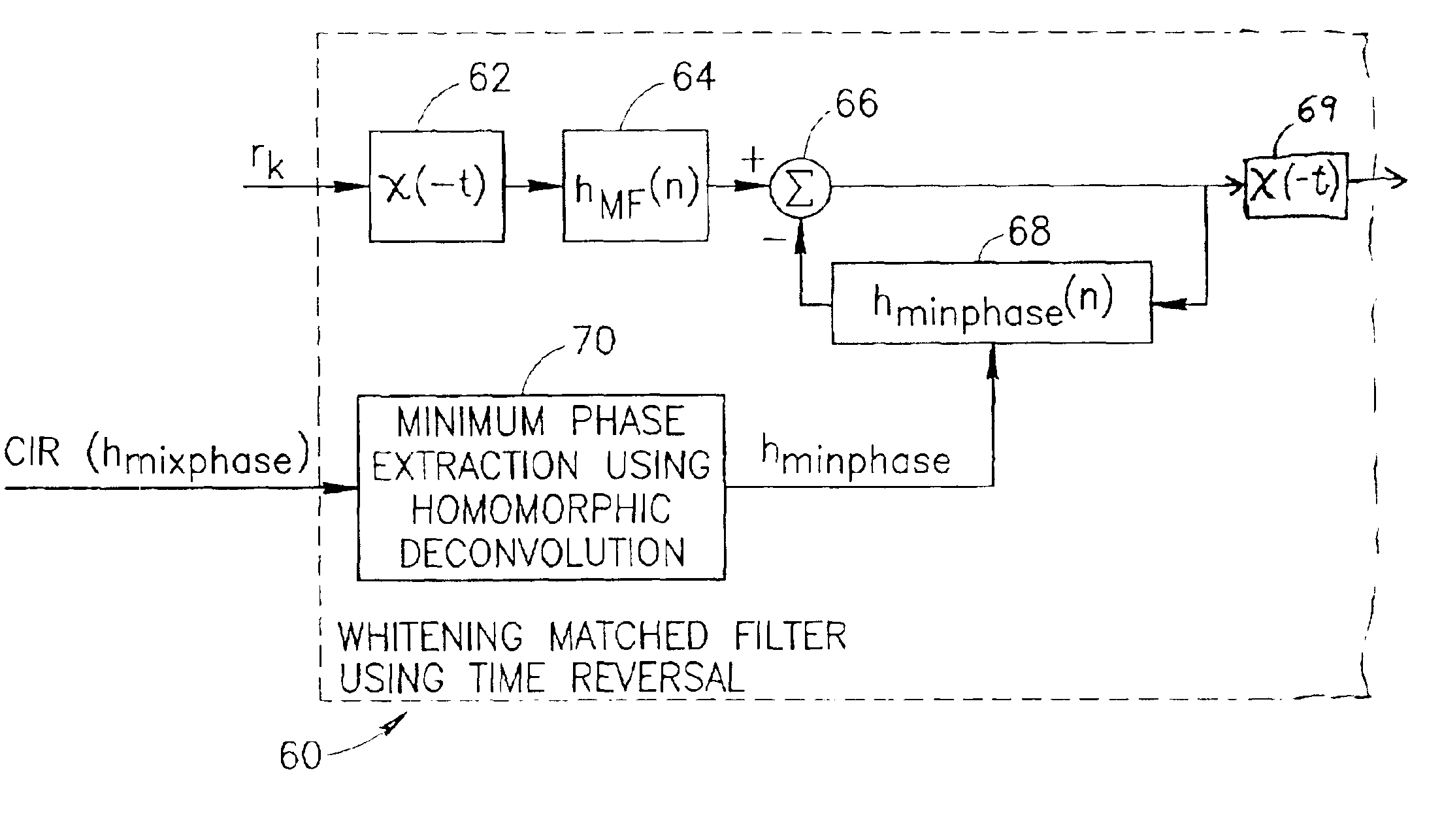

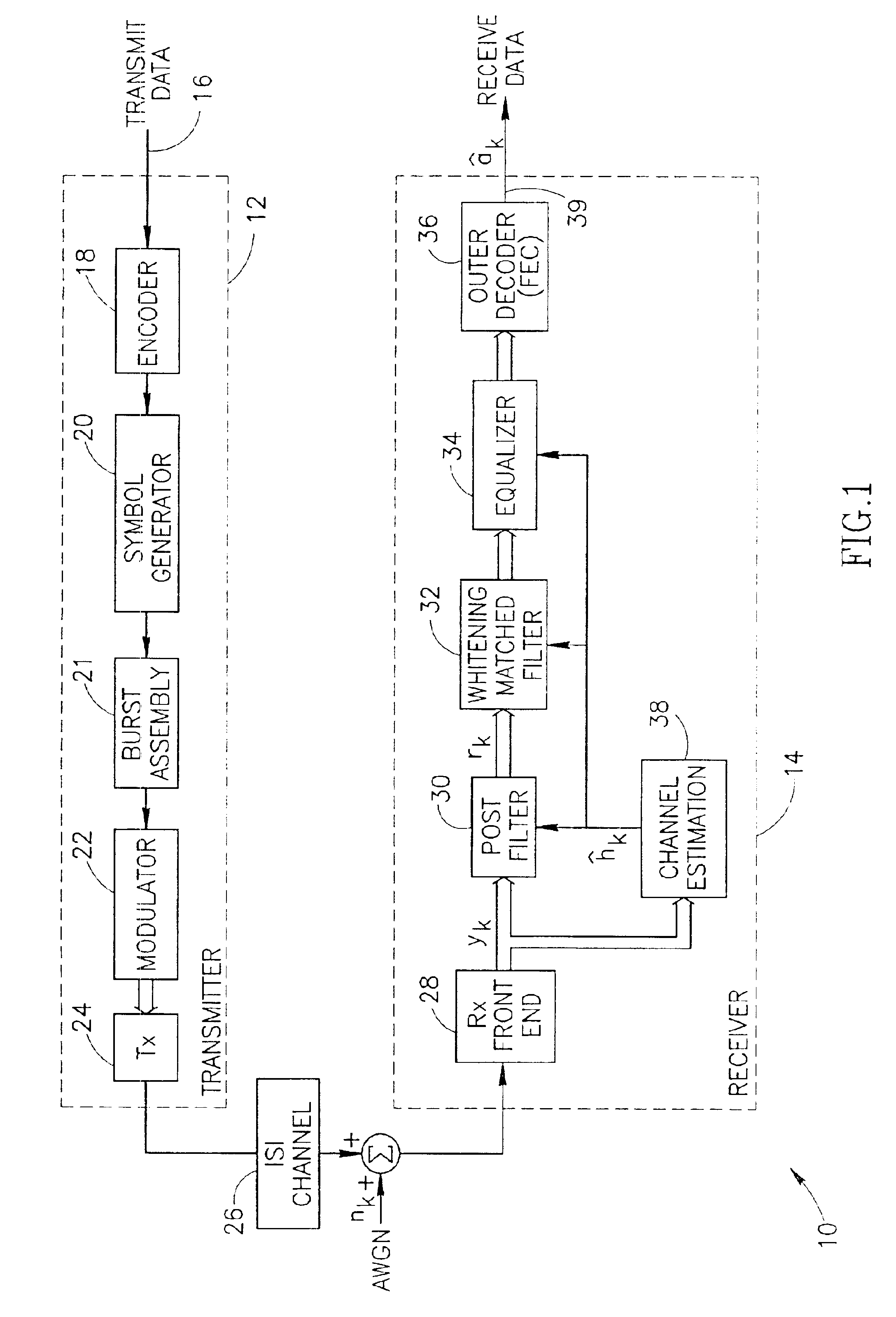

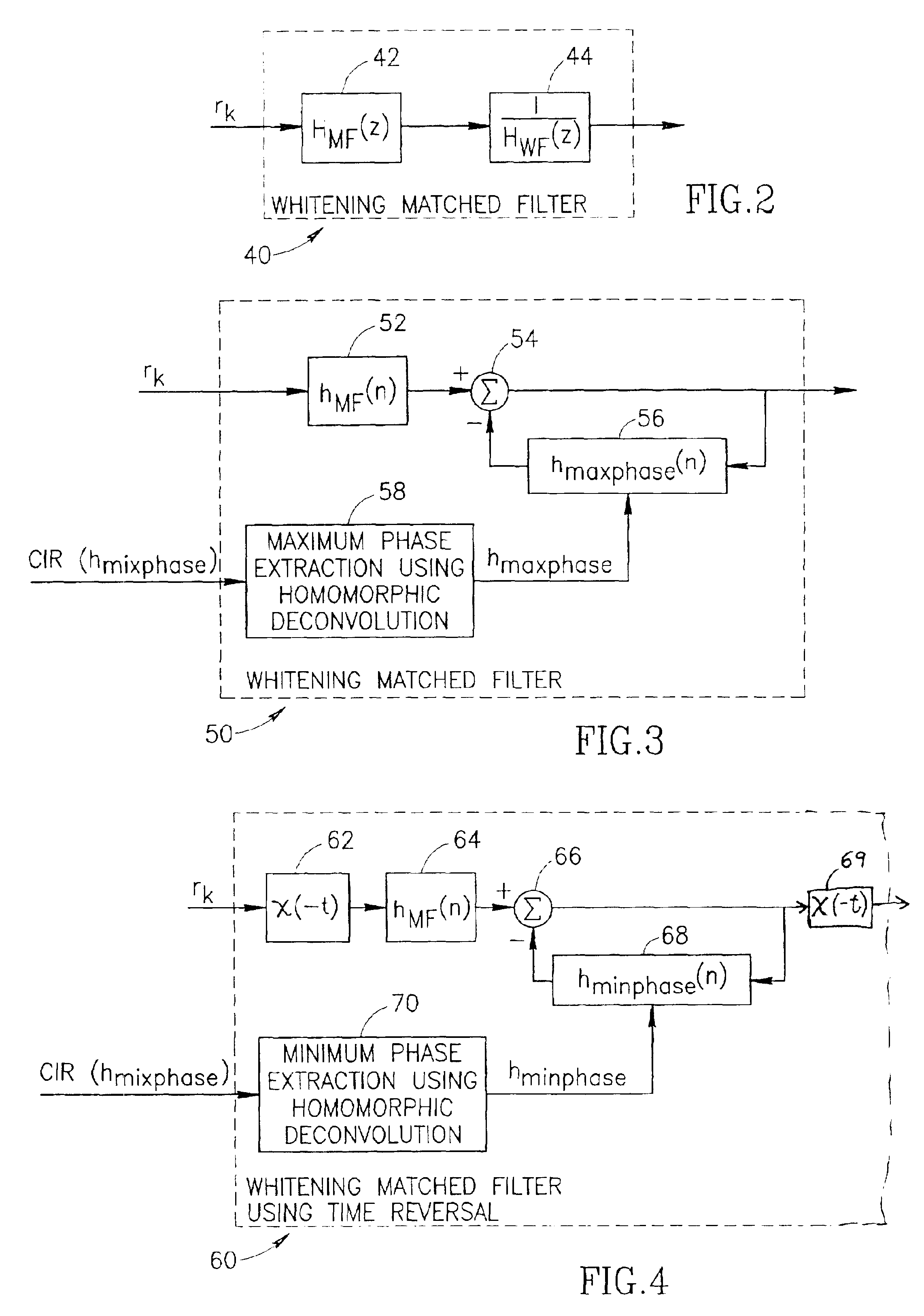

Whitening matched filter for use in a communications receiver

InactiveUS6862326B1Improve performanceMultiple-port networksDigital technique networkIir filteringChannel impulse response

A novel and useful whitening matched filter (WMF) for use in a communications receiver. The WMF is constructed by cascading a matched filter and a noise-whitening filter. The response of the matched filter is derived from the time reversed complex conjugate of the channel impulse response. The whitening filter is derived by extracting the minimum phase portion of the mixed phase channel impulse response using homomorphic deconvolution. The whitening filter is implemented using either an FIR or IIR filter adapted to process the data received before and after the training sequence using a minimum phase system in a direction in time opposite to that of the direction of corresponding data sample processing performed by the equalizer.

Owner:COMSYS COMM & SIGNAL PROC

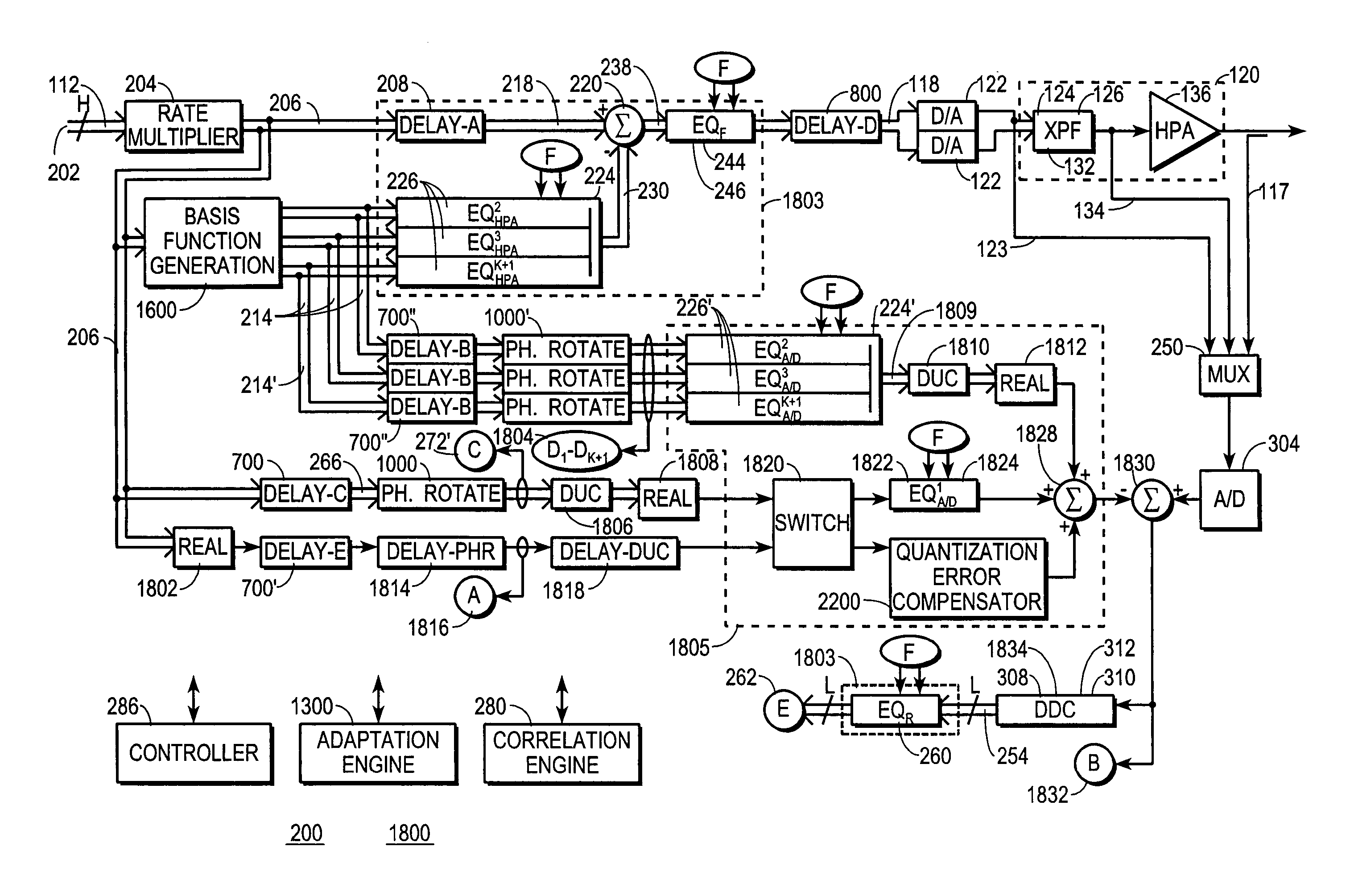

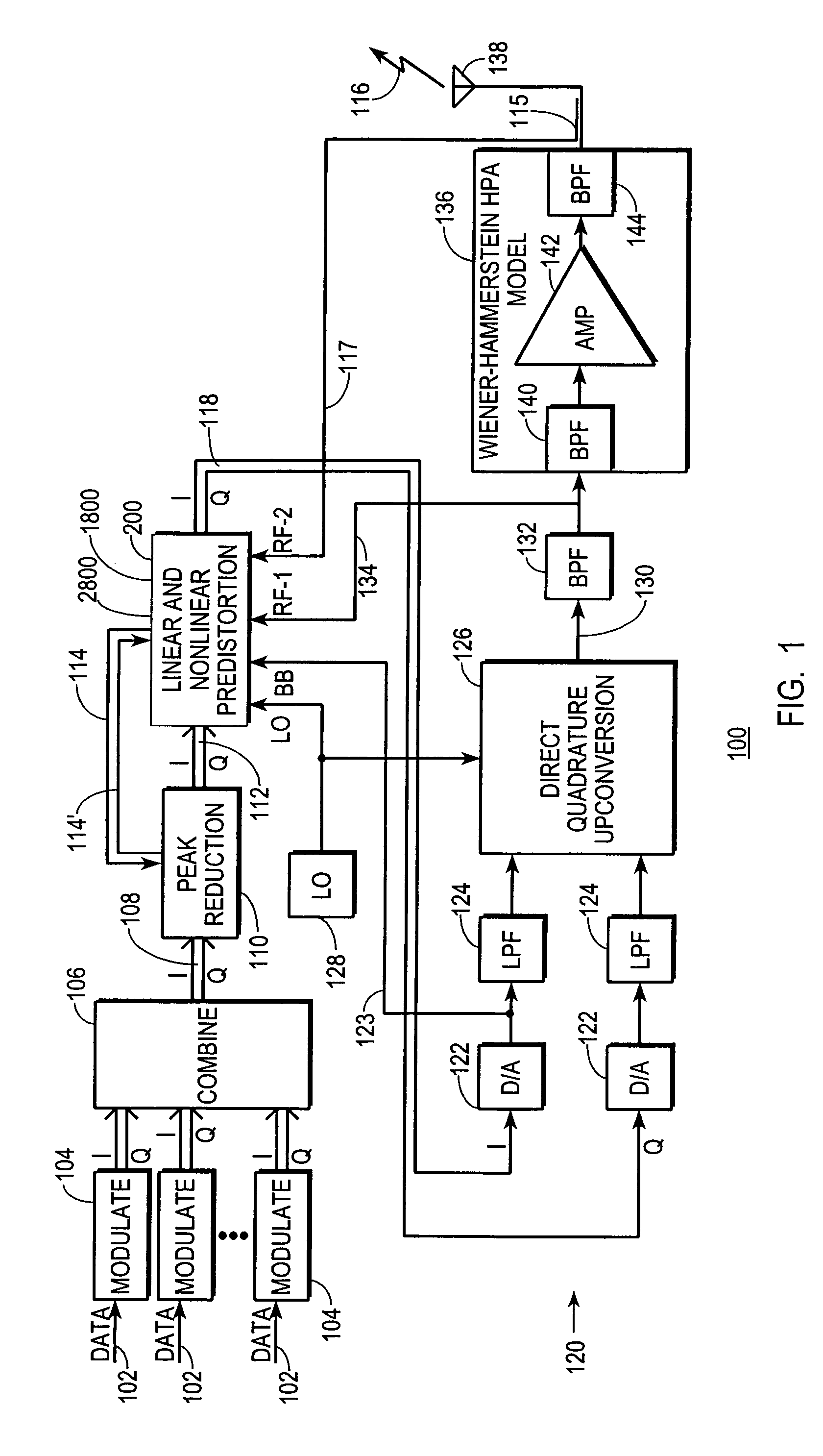

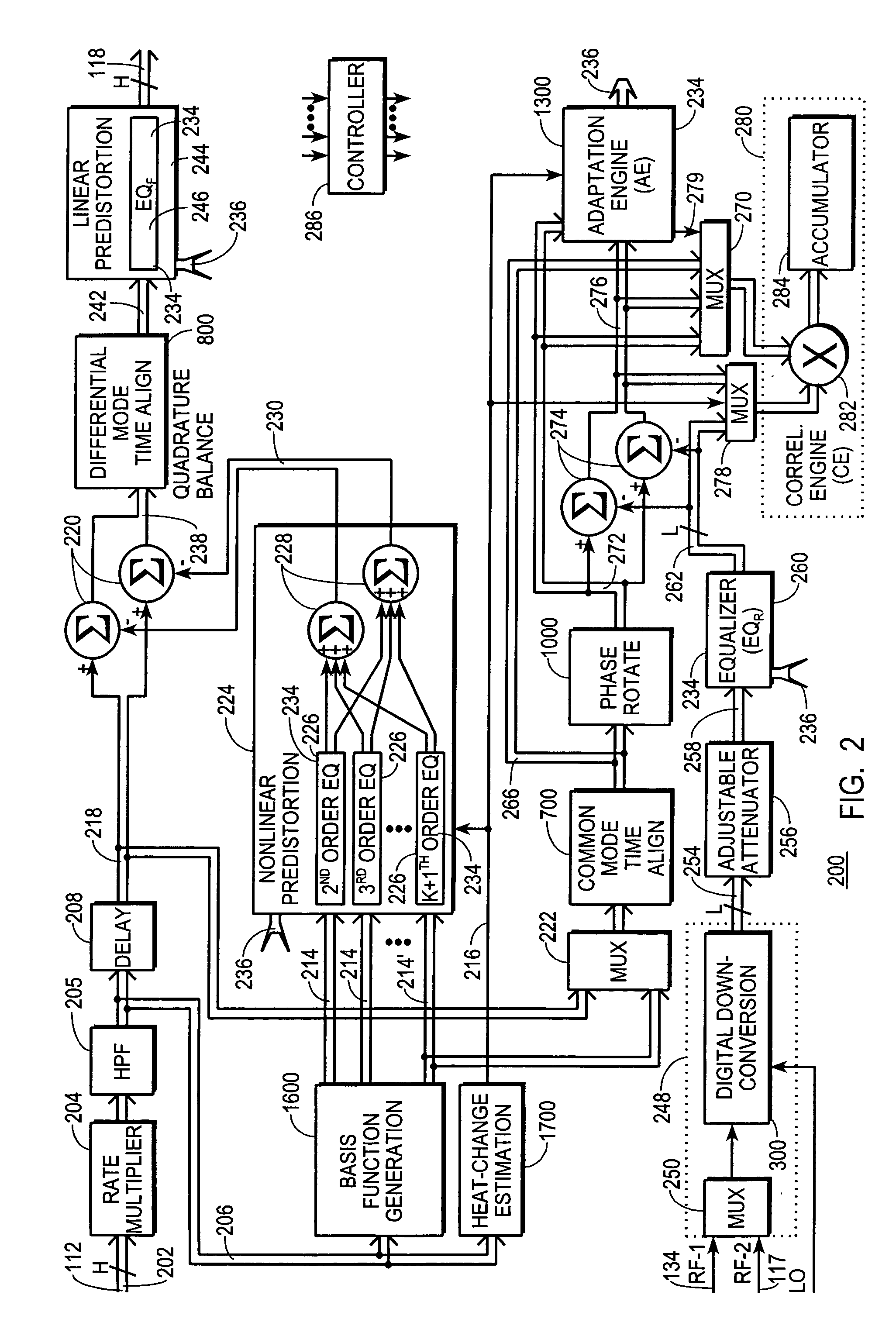

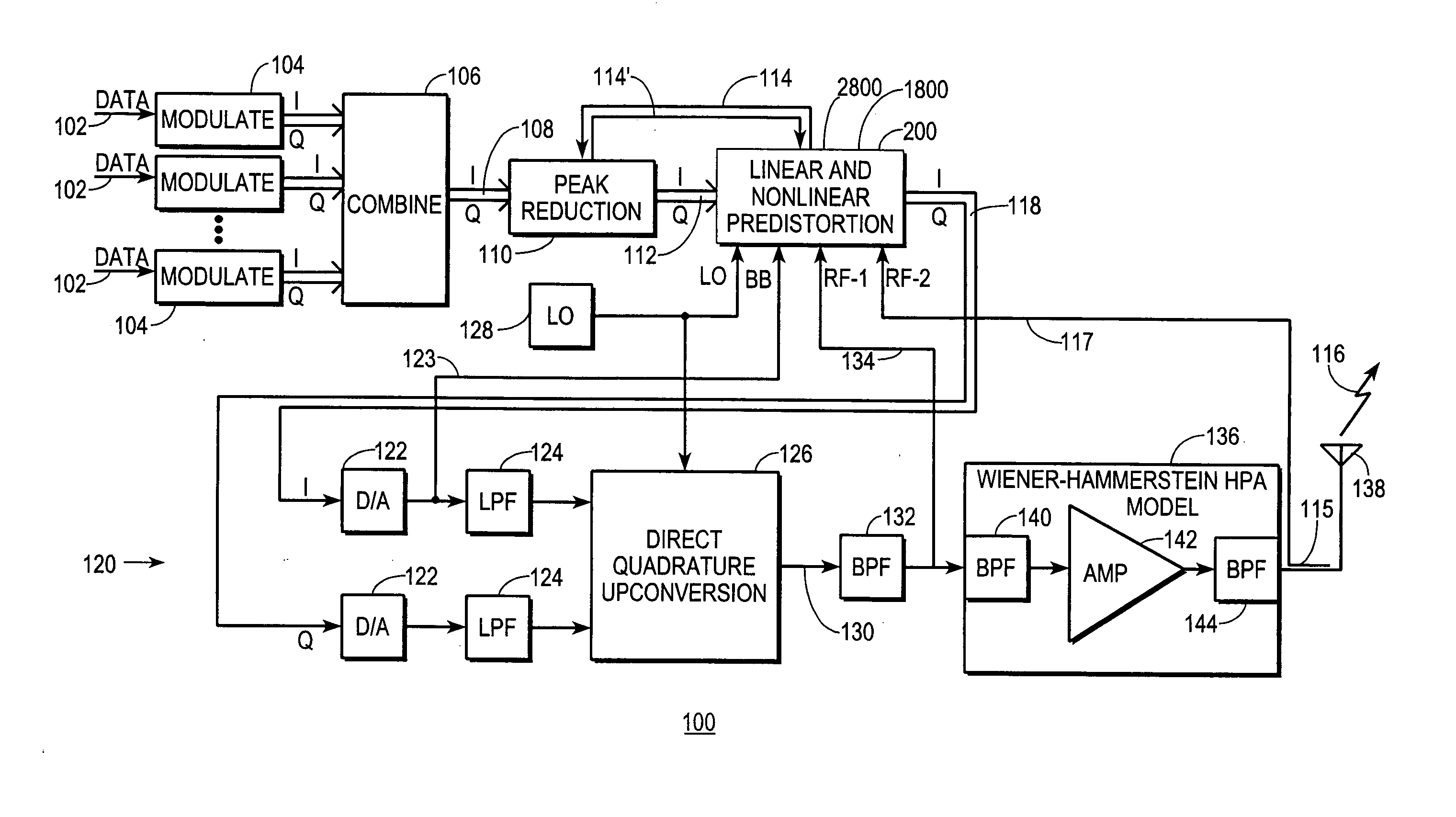

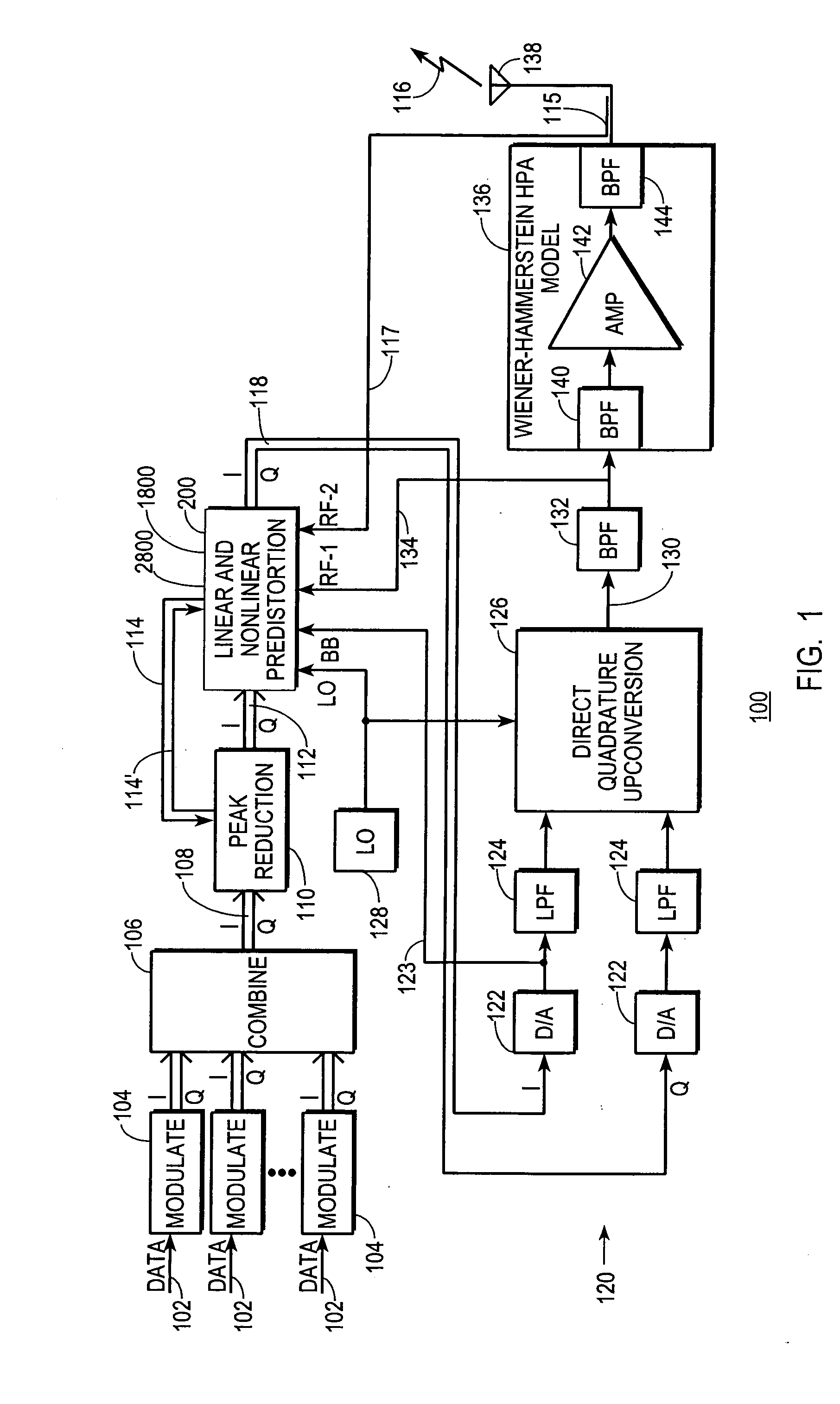

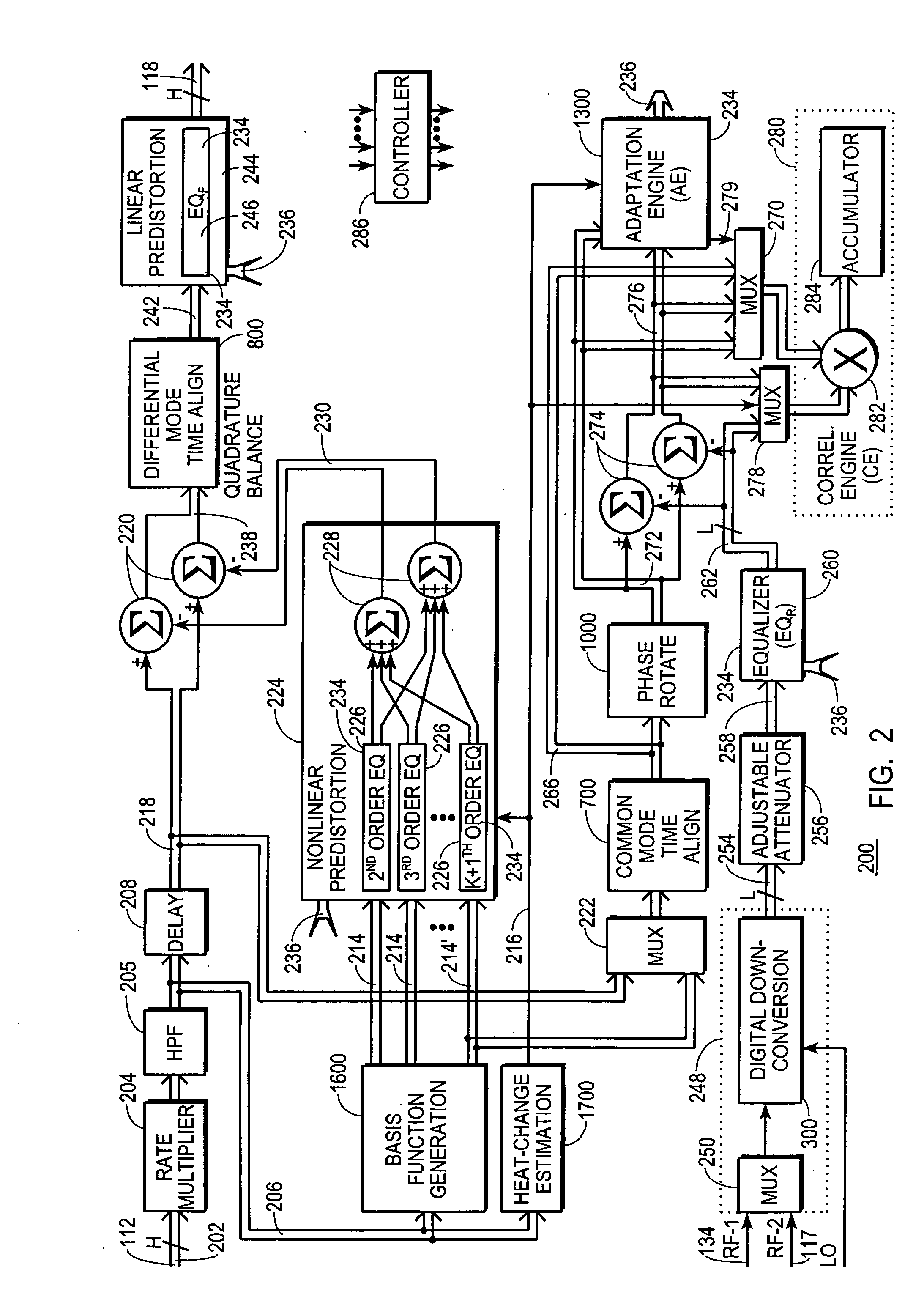

Transmitter predistortion circuit and method therefor

InactiveUS7469491B2Compensation DistortionMultiple-port networksPower amplifiersNonlinear distortionData stream

A digital communications transmitter (100) includes a digital linear-and-nonlinear predistortion section (200, 1800, 2800) to compensate for linear and nonlinear distortion introduced by transmitter-analog components (120). A direct-digital-downconversion section (300) generates a complex digital return-data stream (254) from the analog components (120) without introducing quadrature imbalance. A relatively low resolution exhibited by the return-data stream (254) is effectively increased through arithmetic processing. Distortion introduced by an analog-to-digital converter (304) may be compensated using a variety of adaptive techniques. Linear distortion is compensated using adaptive techniques with an equalizer (246) positioned in the forward-data stream (112). Nonlinear distortion is then compensated using adaptive techniques with a plurality of equalizers (226) that filter a plurality of orthogonal, higher-ordered-basis functions (214) generated from the forward-data stream (112). The filtered-basis functions are combined together and subtracted from the forward-data stream (112).

Owner:CRESTCOM INC

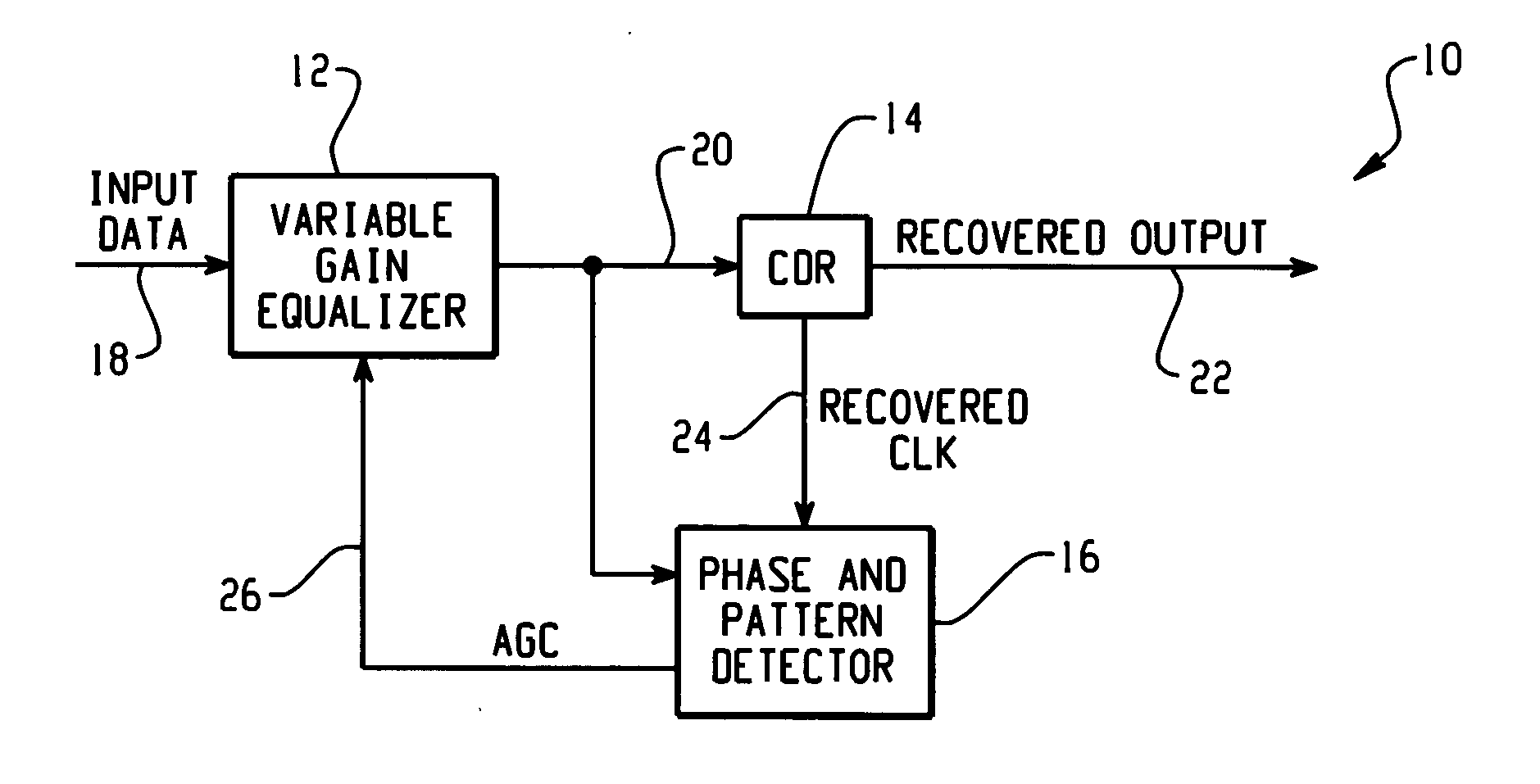

Precision adaptive equalizer

InactiveUS20050047500A1Multiple-port networksAdaptive networkDetector circuitsAutomatic gain control

In accordance with the teachings described herein, systems and methods are provided for a precision adaptive equalizer. A variable gain equalizer may be used to apply a variable gain to an input signal to generate an equalized output signal. A phase and pattern detector circuit may be coupled in a feedback loop with the variable gain equalizer. The phase and pattern detector circuit may be used to identify a high frequency data pattern in the equalized output signal and compare the high frequency data pattern with a clock signal to detect a high frequency phase error. The phase and pattern detector circuit may be further operable to generate an automatic gain control signal as a function of the high frequency phase error, the automatic gain control signal being fed back to the variable gain equalizer to control the variable gain applied to the input signal.

Owner:SEMTECH CANADA

Method and system for statistical filters and design of statistical filters

InactiveUS7184938B1Less dataLess signalDigital variable displayNoise figure or signal-to-noise ratio measurementFrequency spectrumFilter system

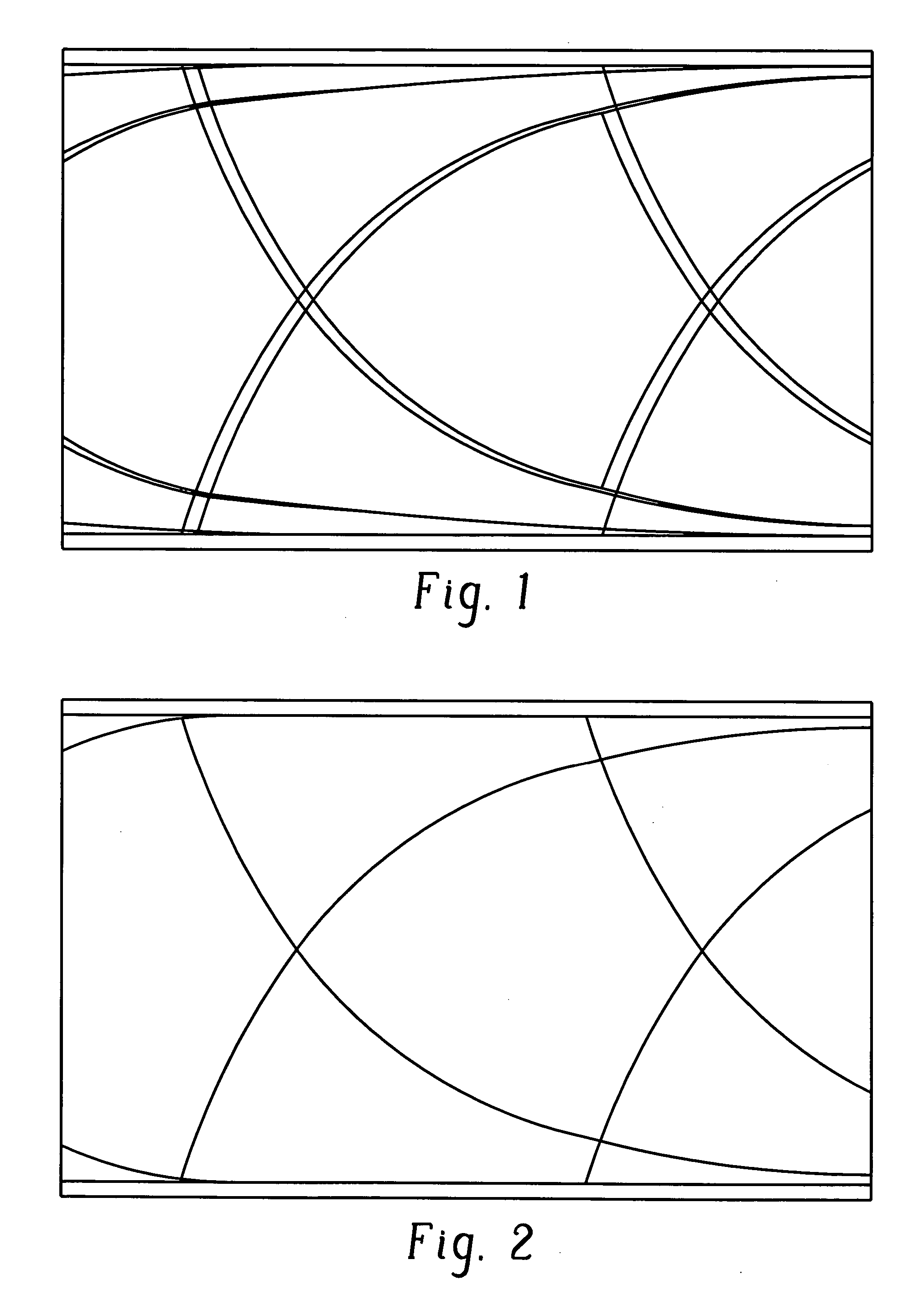

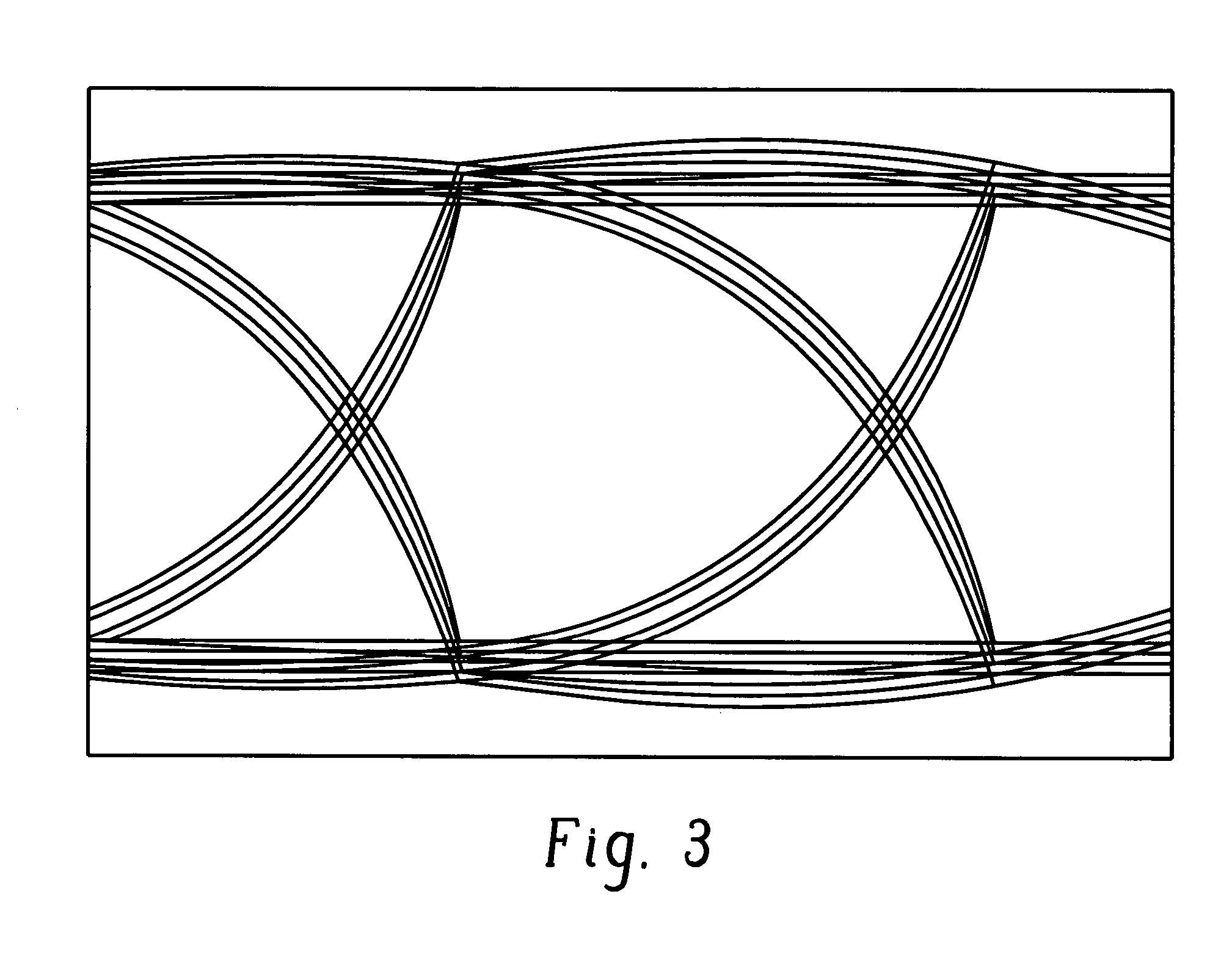

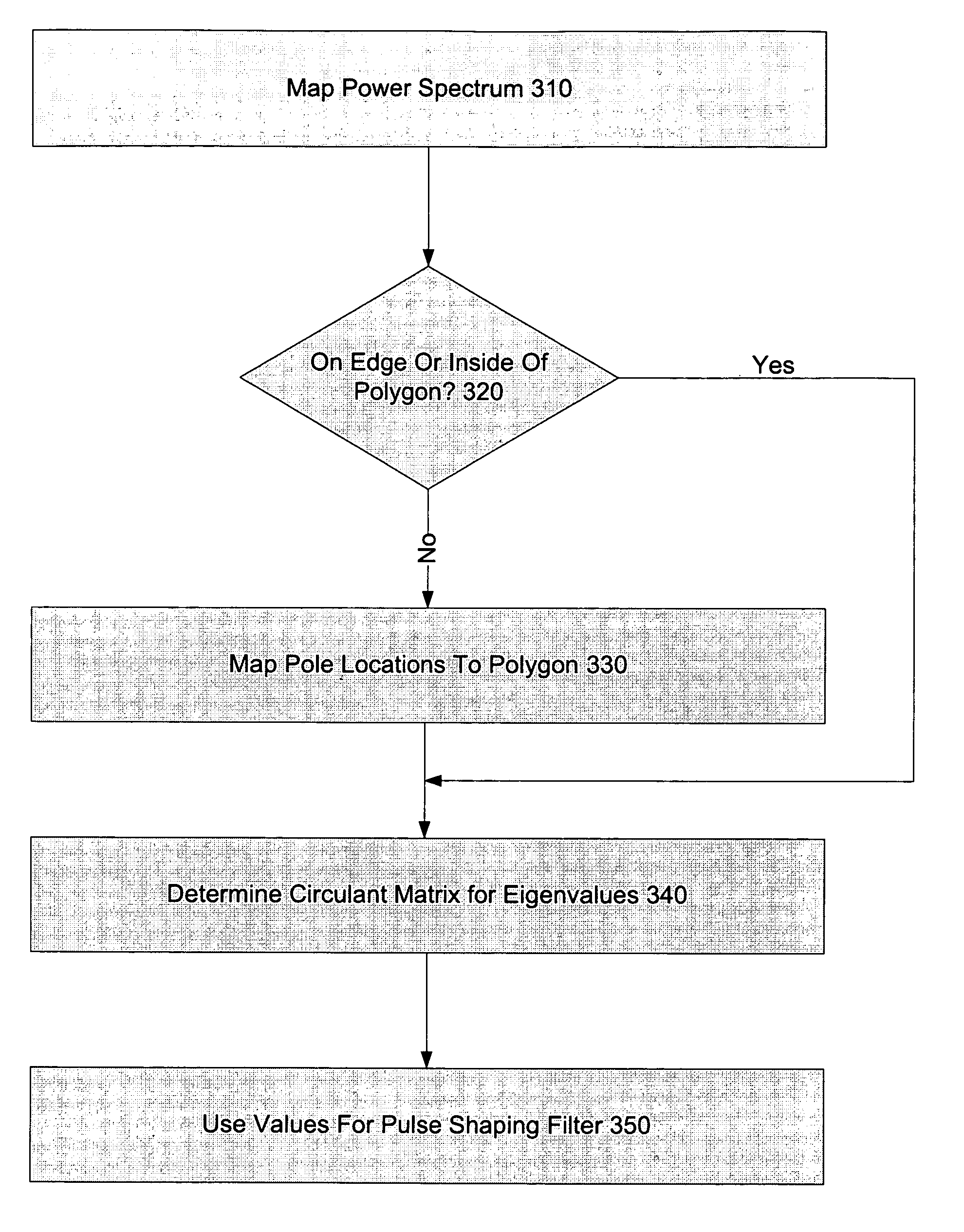

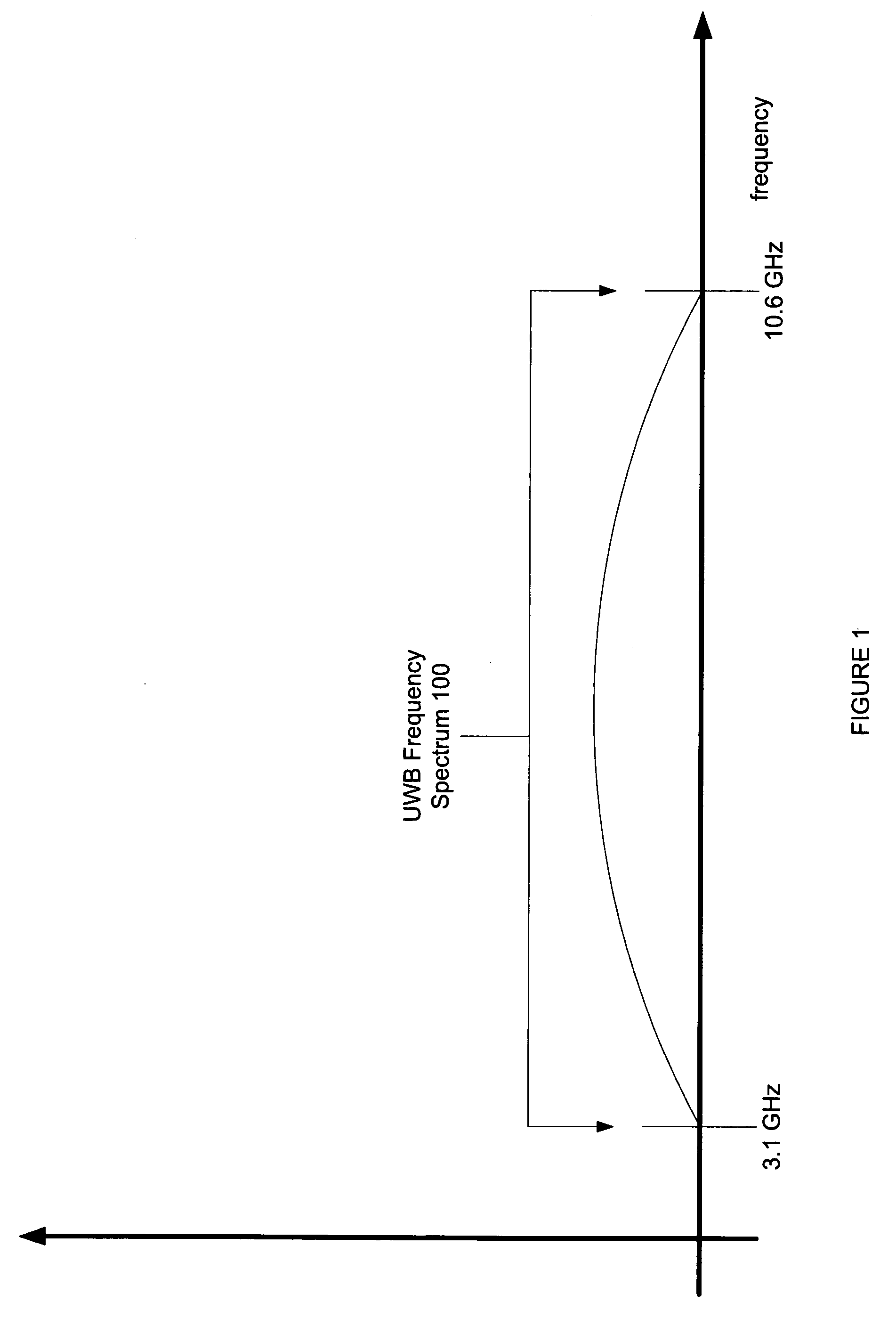

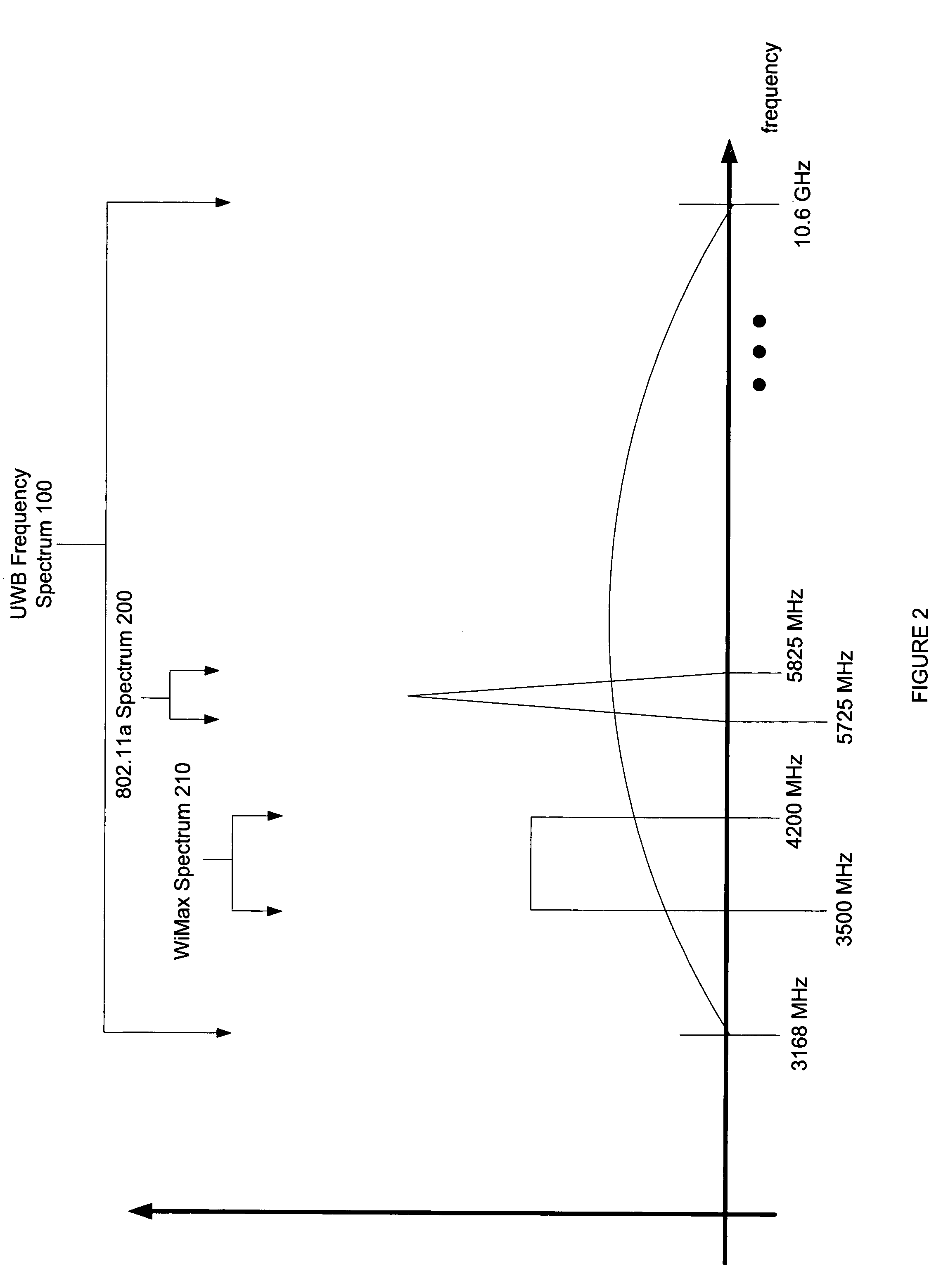

Systems and methods for the design or implementation of statistical filters for use in the spectral shaping of transmissions are disclosed. A desired power spectrum may be mapped to find pole locations that approximate the desired spectrum. These pole locations may then be mapped to the edge or inside of an equilateral polygon lying inside a unit circle, the equilateral polygon having the same number of sides as the order of the statistical filter desired and one vertex mapped to unity, to yield a set of eigenvalues. These eigenvalues may be the eigenvalues of a stochastic matrix the elements of which may be the Markov transition probabilities for use in a statistical filter designed to achieve the desired power spectrum. Use of a statistical filter employing these Markov transition values may be utilized to shape UWB or other signals to achieve the desired power spectrum.

Owner:ALEREON

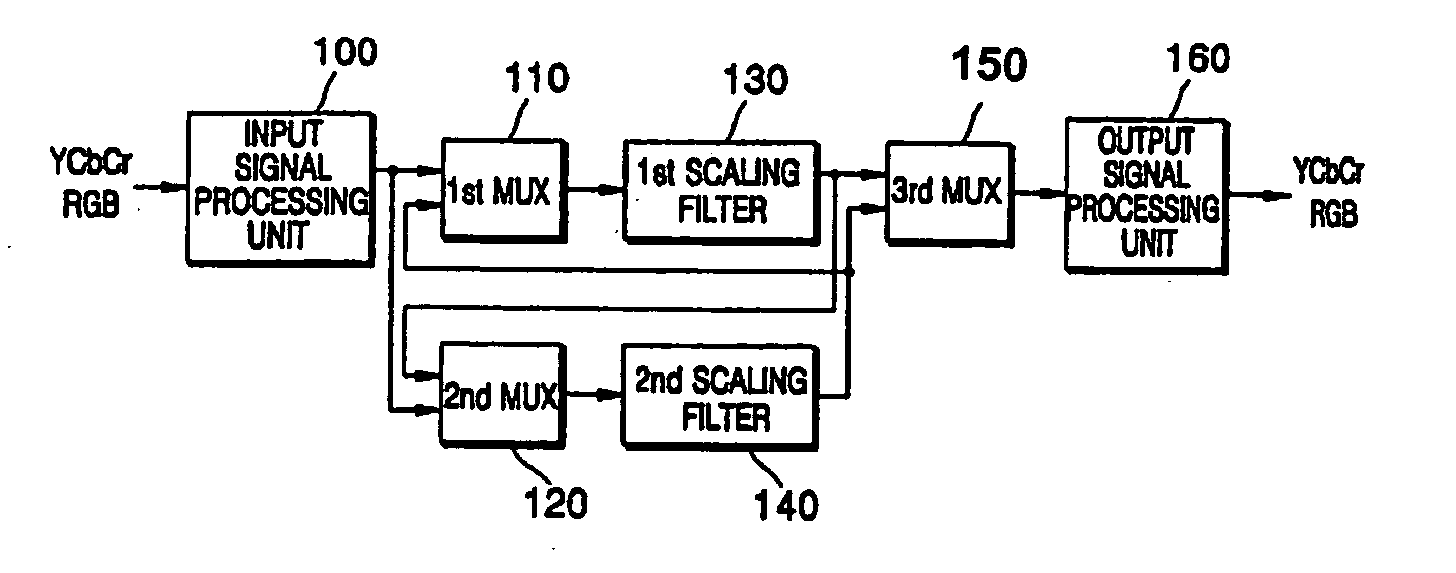

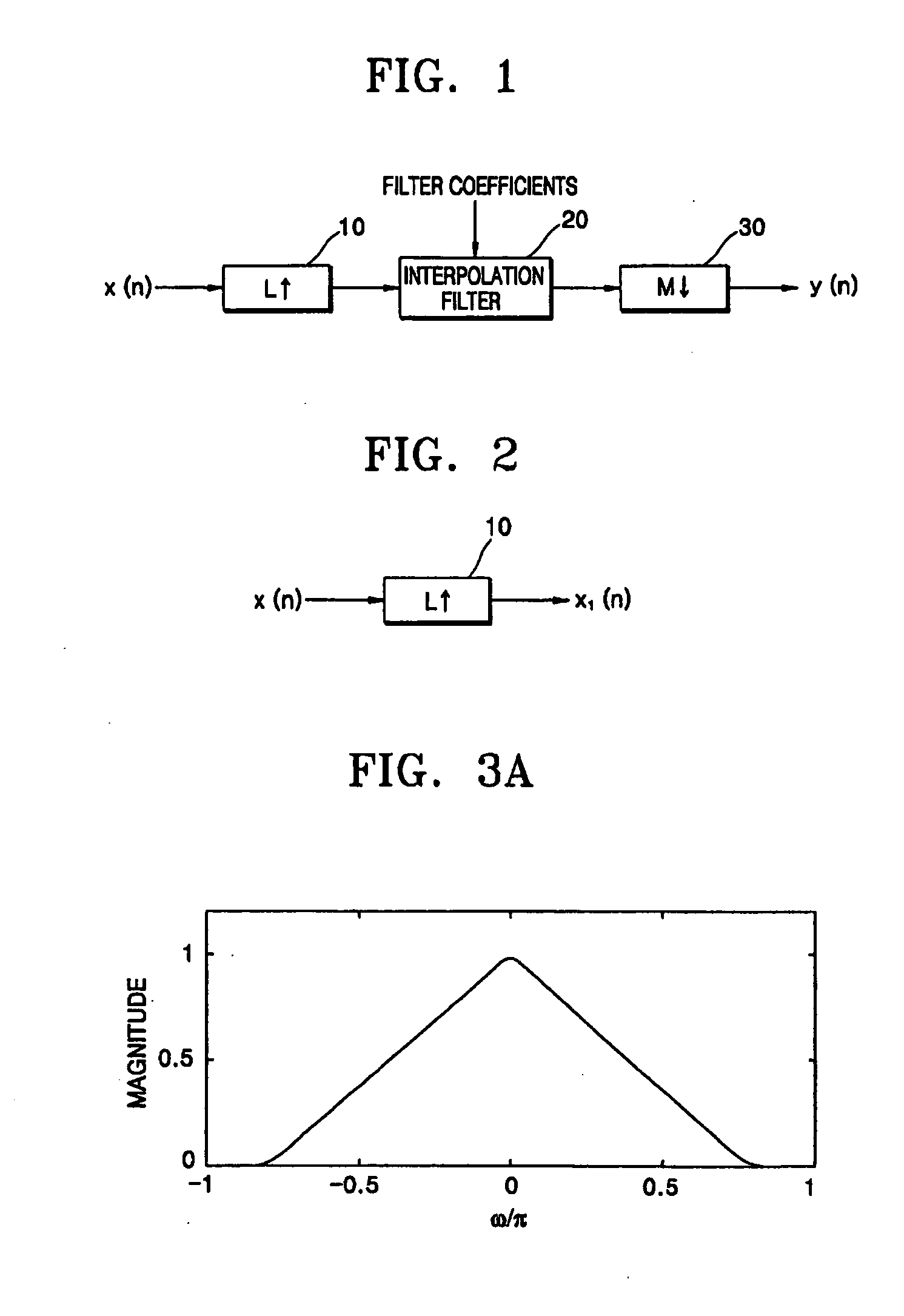

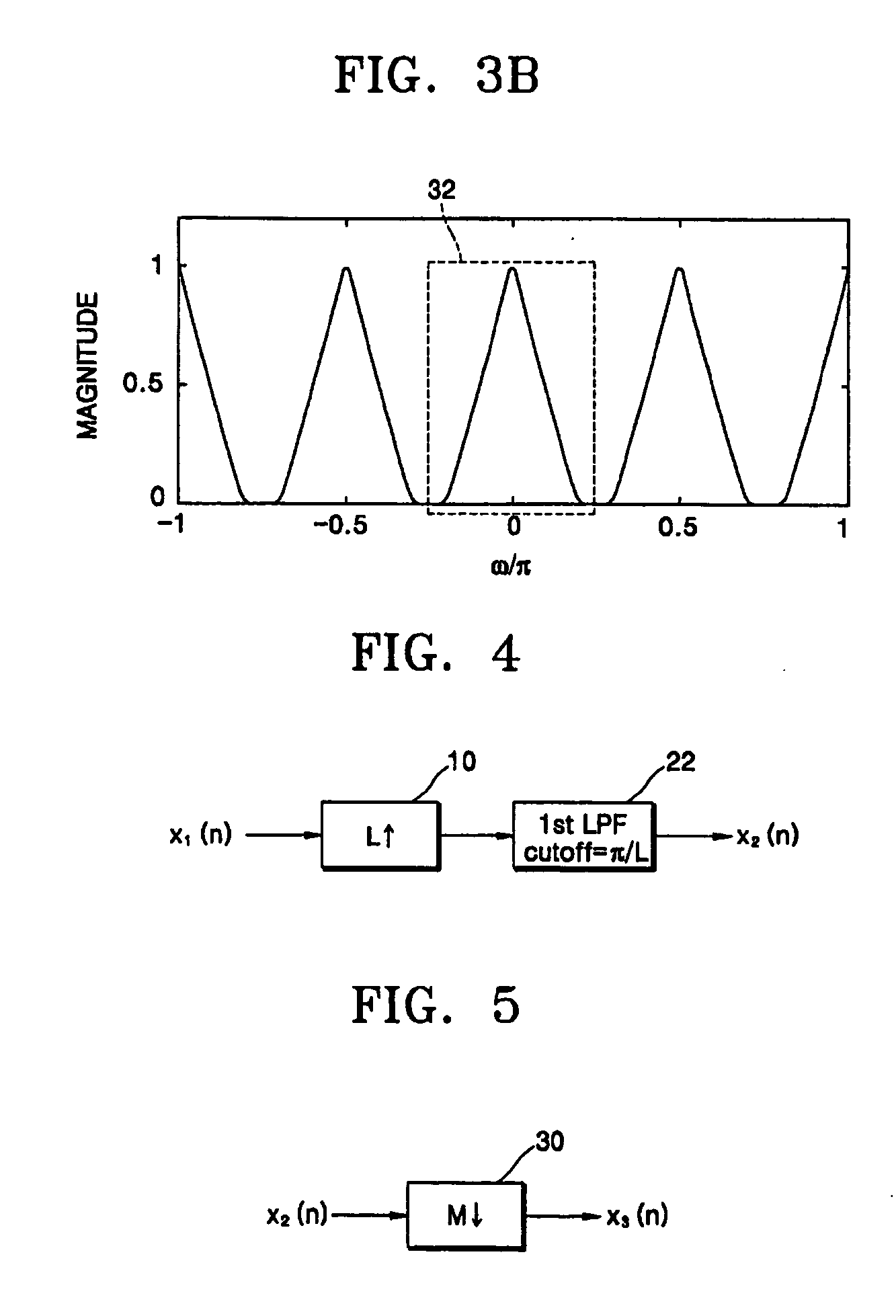

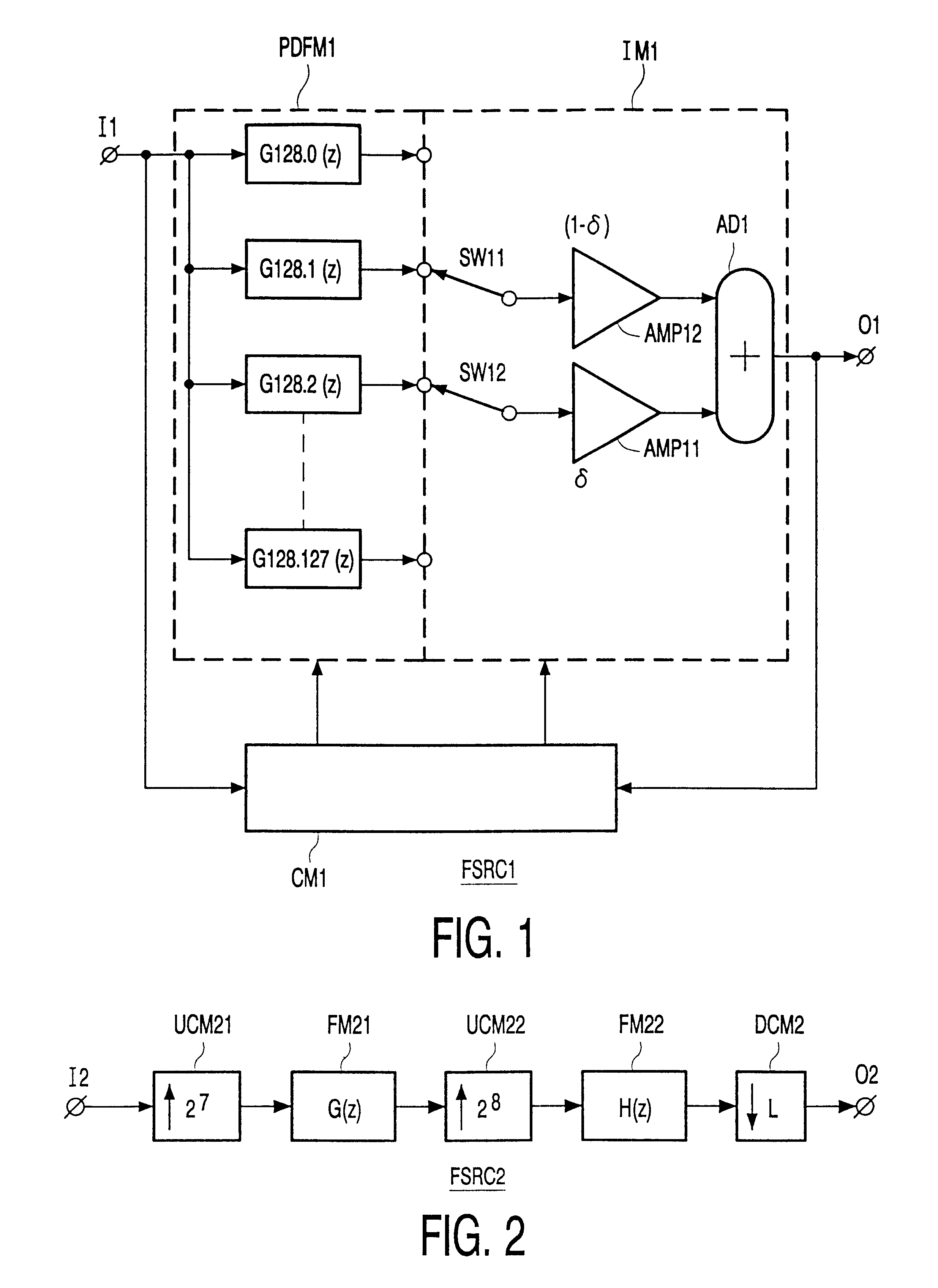

Method of converting resolution of video signals and apparatus using the same

ActiveUS20050134731A1Television system detailsGeometric image transformationImage resolutionGaussian function

A method converts a resolution of video signals, the method including: calculating up-sampling and down-sampling ratios based on a resolution of an input video signal and a desired resolution of an output video signal; calculating a number of filter tabs by multiplying the up-sampling and down-sampling ratios by a number of side lobes; calculating first filter coefficients of a same number of the filter tabs by multiplying a window function by a sinc function; calculating final filter coefficients by subtracting a result of a multiplication of a Gaussian function by a window function from the first filter coefficients, and then normalizing the final filter coefficients; and performing filtering in vertical and horizontal directions based on the final filter coefficients by modifying a sampling rate of an input video signal depending on the up-sampling and down-sampling ratios, to obtain clear video images.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitter predistortion circuit and method therefor

InactiveUS20050163252A1Easy to optimizeCompensation DistortionMultiple-port networksPower amplifiersNonlinear distortionData stream

A digital communications transmitter (100) includes a digital linear-and-nonlinear predistortion section (200, 1800, 2800) to compensate for linear and nonlinear distortion introduced by transmitter-analog components (120). A direct-digital-downconversion section (300) generates a complex digital return-data stream (254) from the analog components (120) without introducing quadrature imbalance. A relatively low resolution exhibited by the return-data stream (254) is effectively increased through arithmetic processing. Distortion introduced by an analog-to-digital converter (304) may be compensated using a variety of adaptive techniques. Linear distortion is compensated using adaptive techniques with an equalizer (246) positioned in the forward-data stream (112). Nonlinear distortion is then compensated using adaptive techniques with a plurality of equalizers (226) that filter a plurality of orthogonal, higher-ordered-basis functions (214) generated from the forward-data stream (112). The filtered-basis functions are combined together and subtracted from the forward-data stream (112).

Owner:CRESTCOM INC

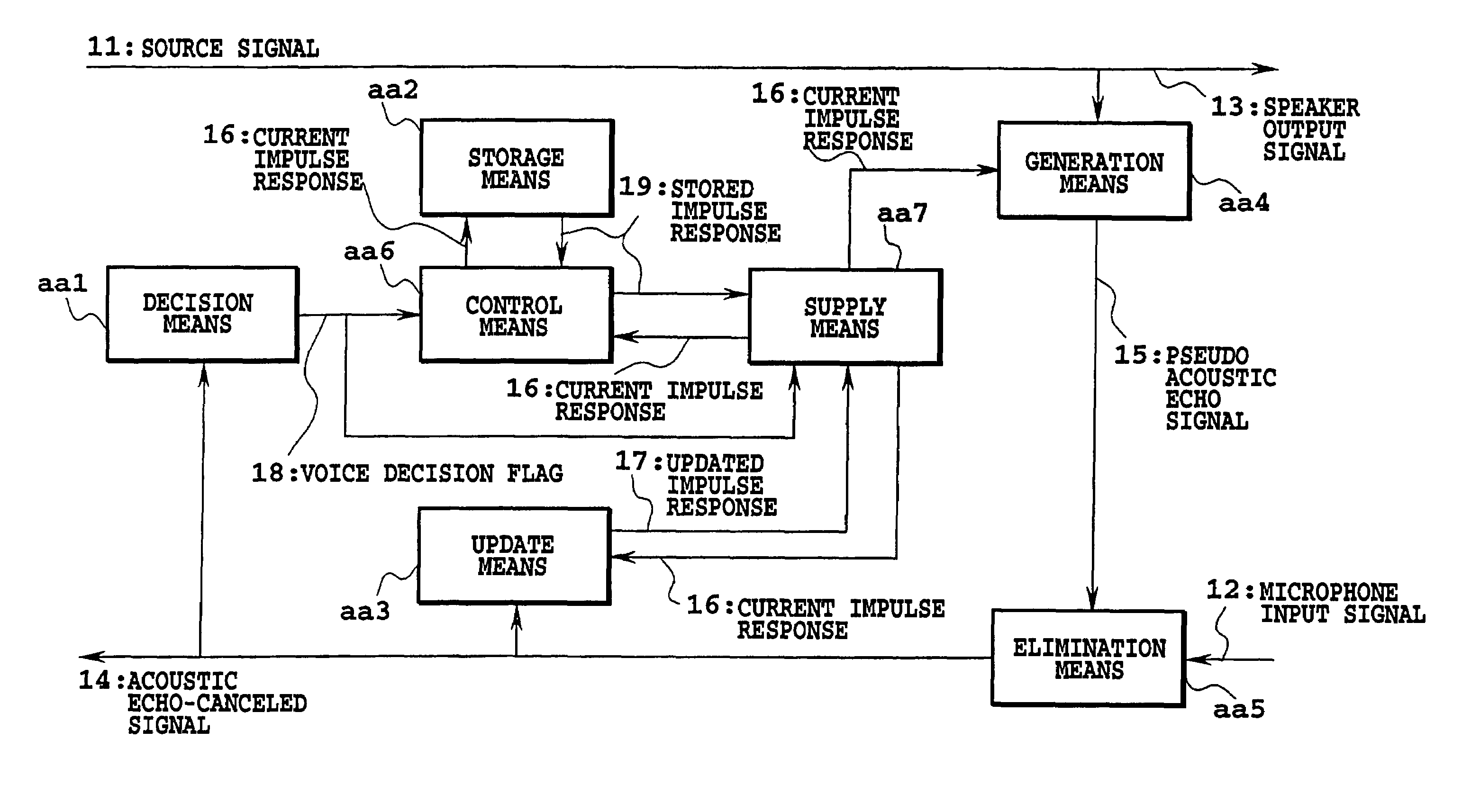

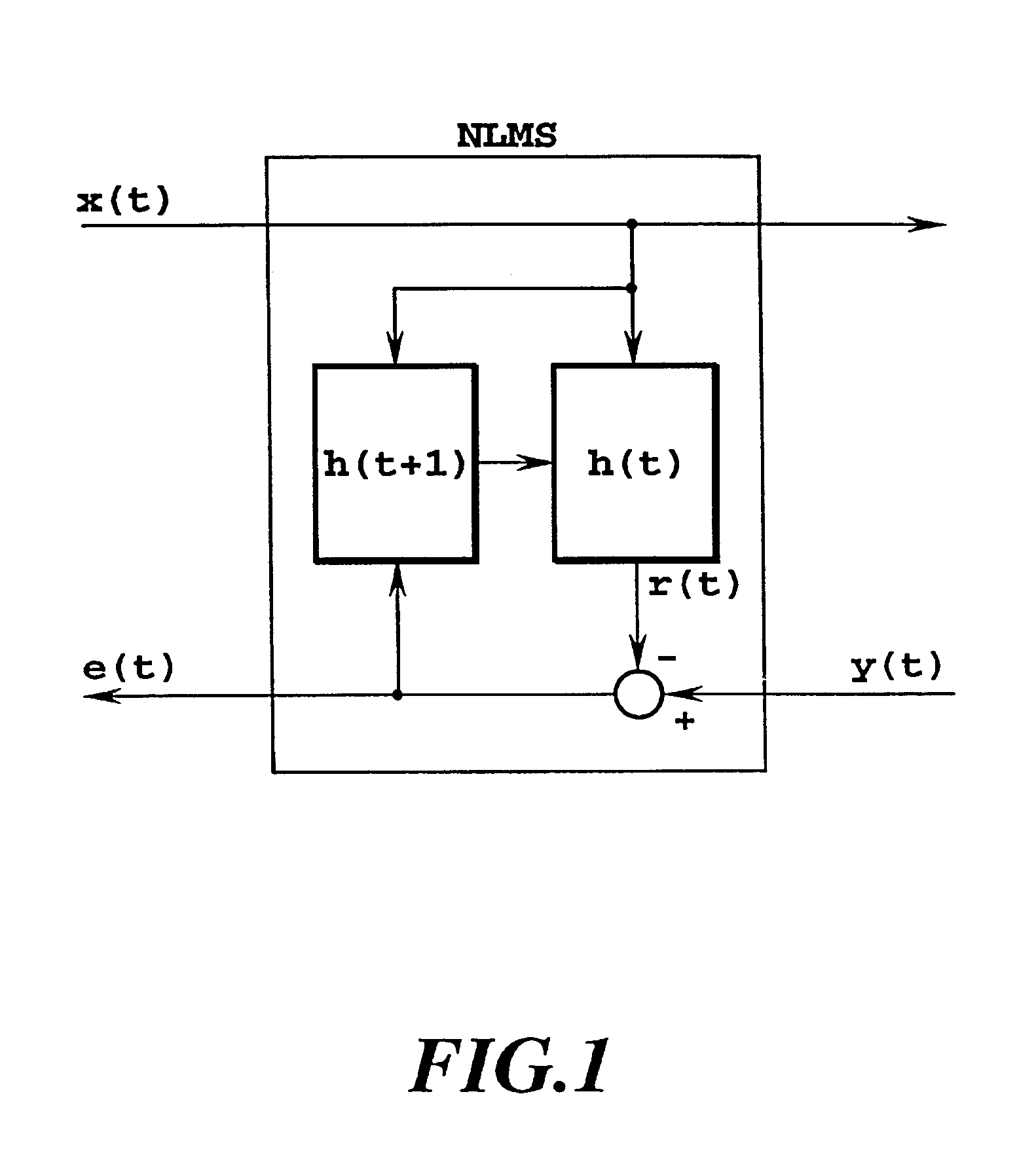

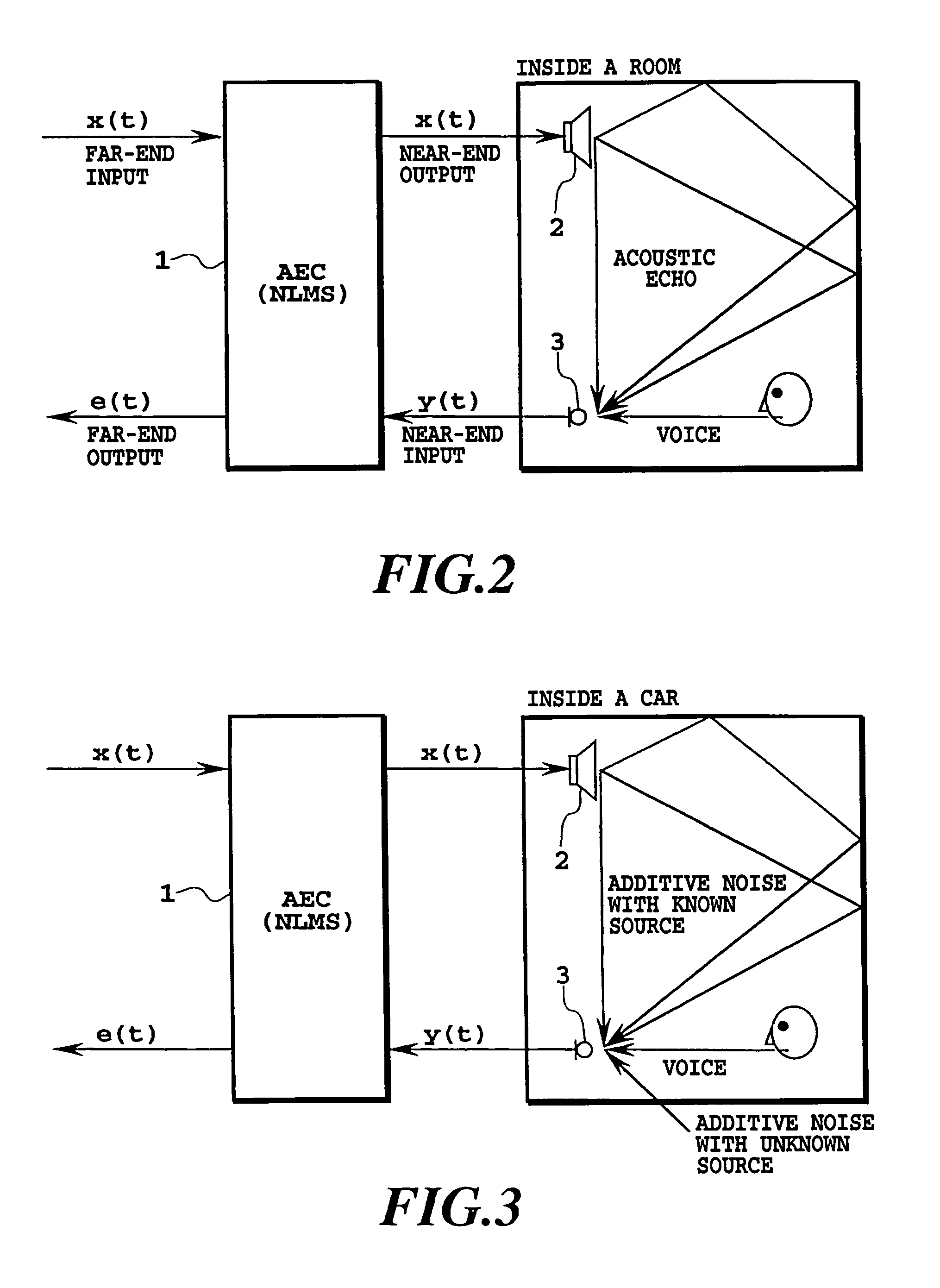

Speech processing method and apparatus for improving speech quality and speech recognition performance

InactiveUS7440891B1Remove additive noiseImprove abilitiesTwo-way loud-speaking telephone systemsDigital technique networkSpeech recognition performanceSpeech sound

A speech processing apparatus which, in the process of performing echo canceling by using a pseudo acoustic echo signal, continuously uses an impulse response used for the previous frame as an impulse response to generate the pseudo acoustic echo signal when a voice is contained in the microphone input signal, and which uses a newly updated impulse response when a voice is not contained in the microphone input signal.

Owner:ASAHI KASEI KK

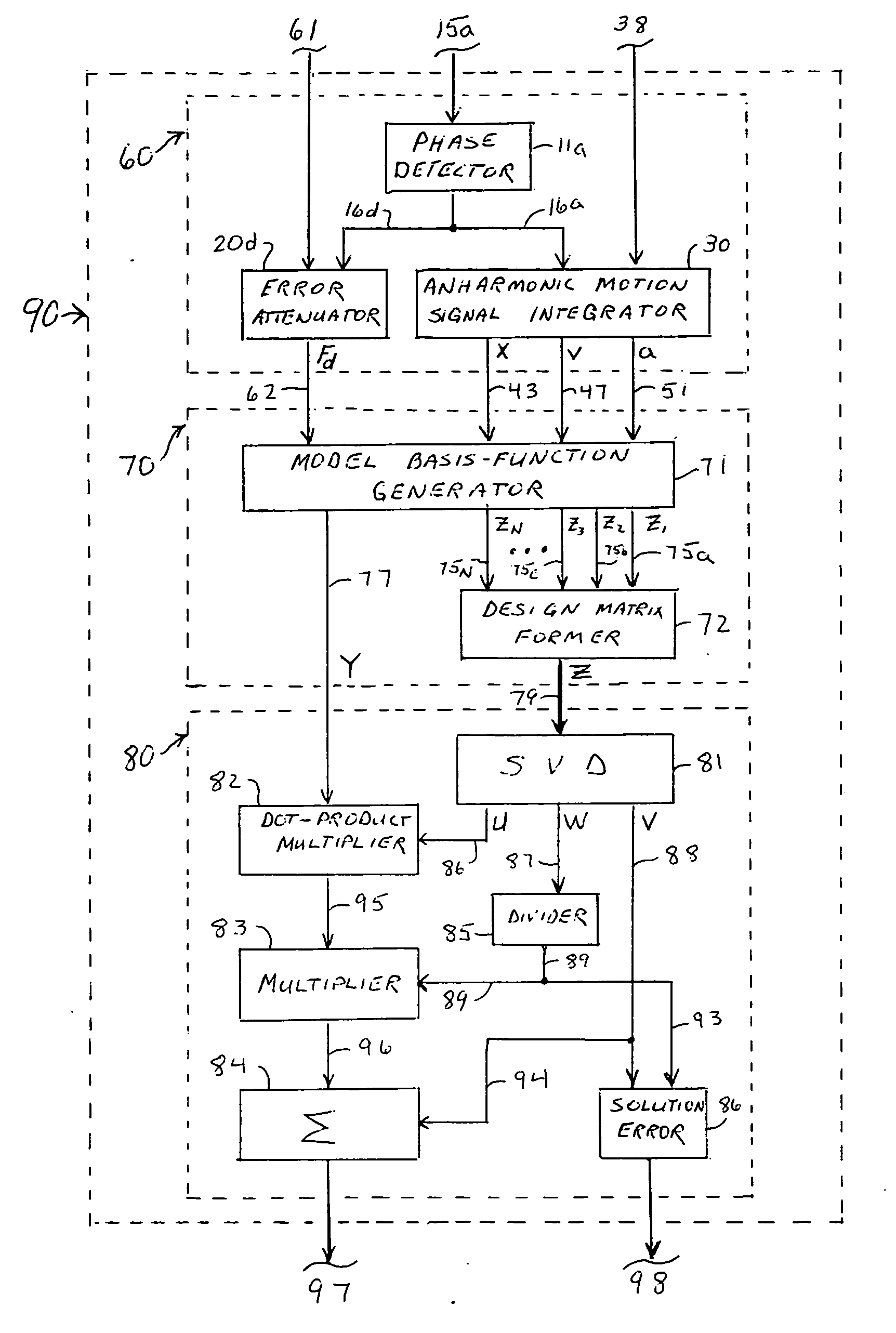

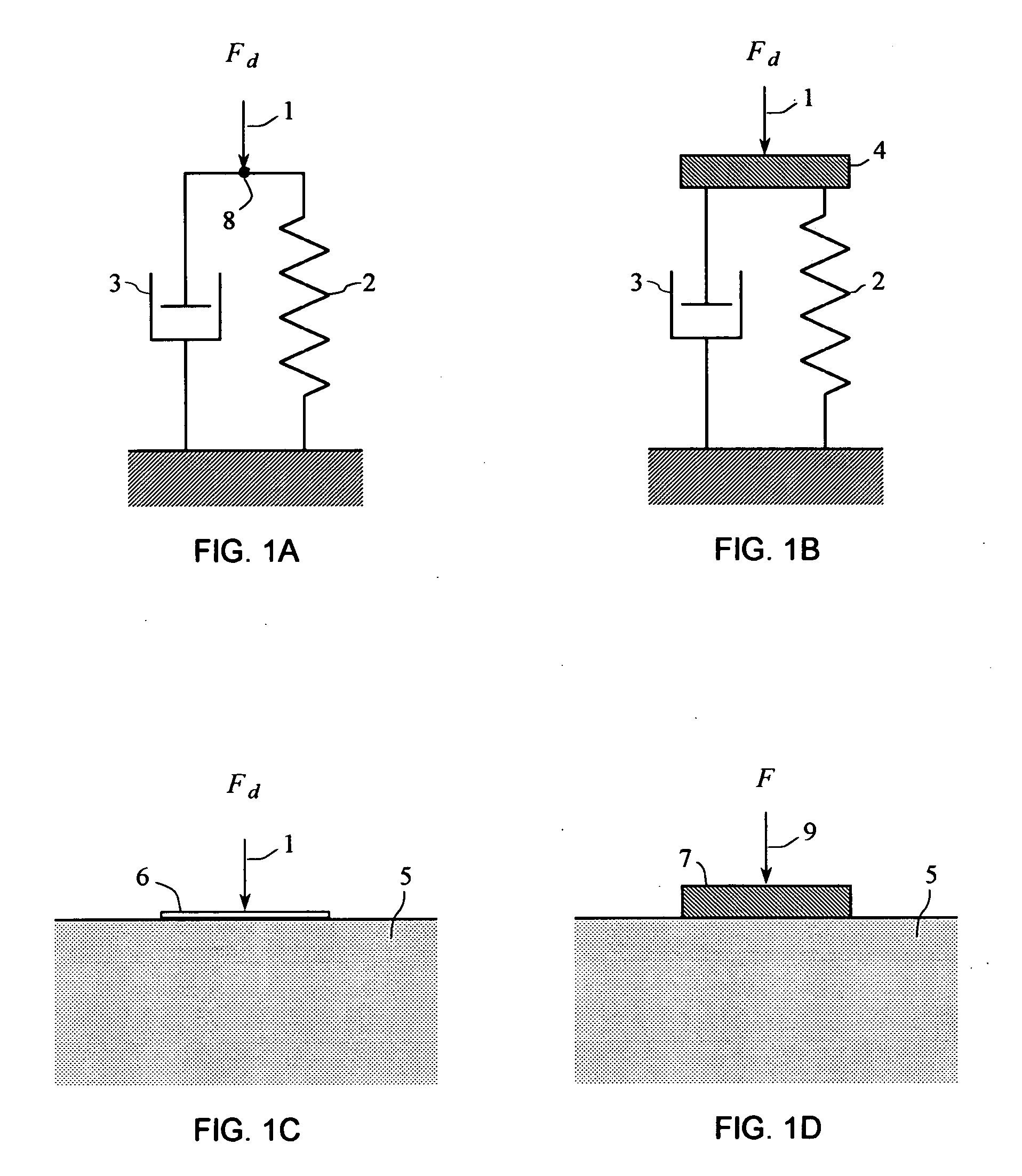

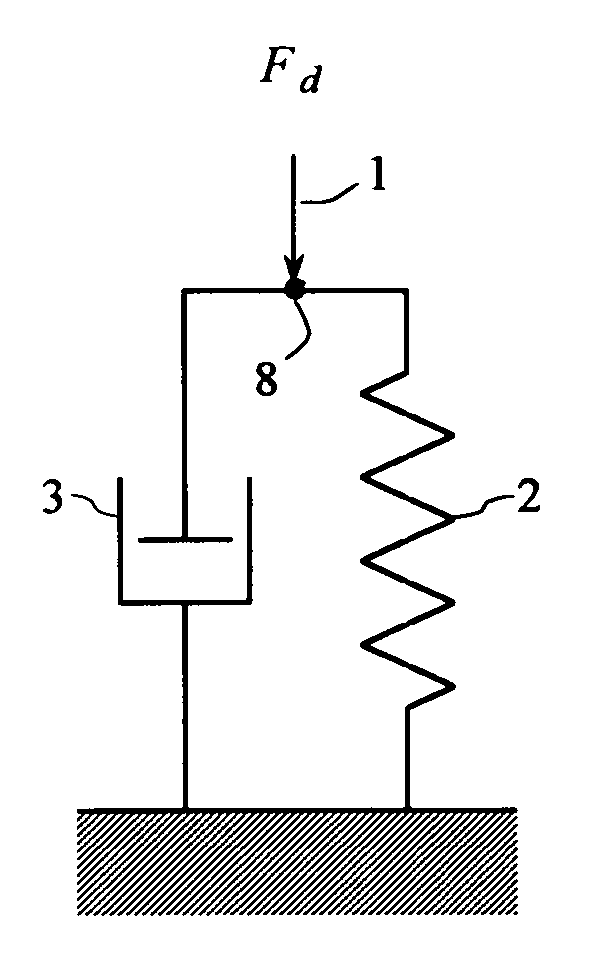

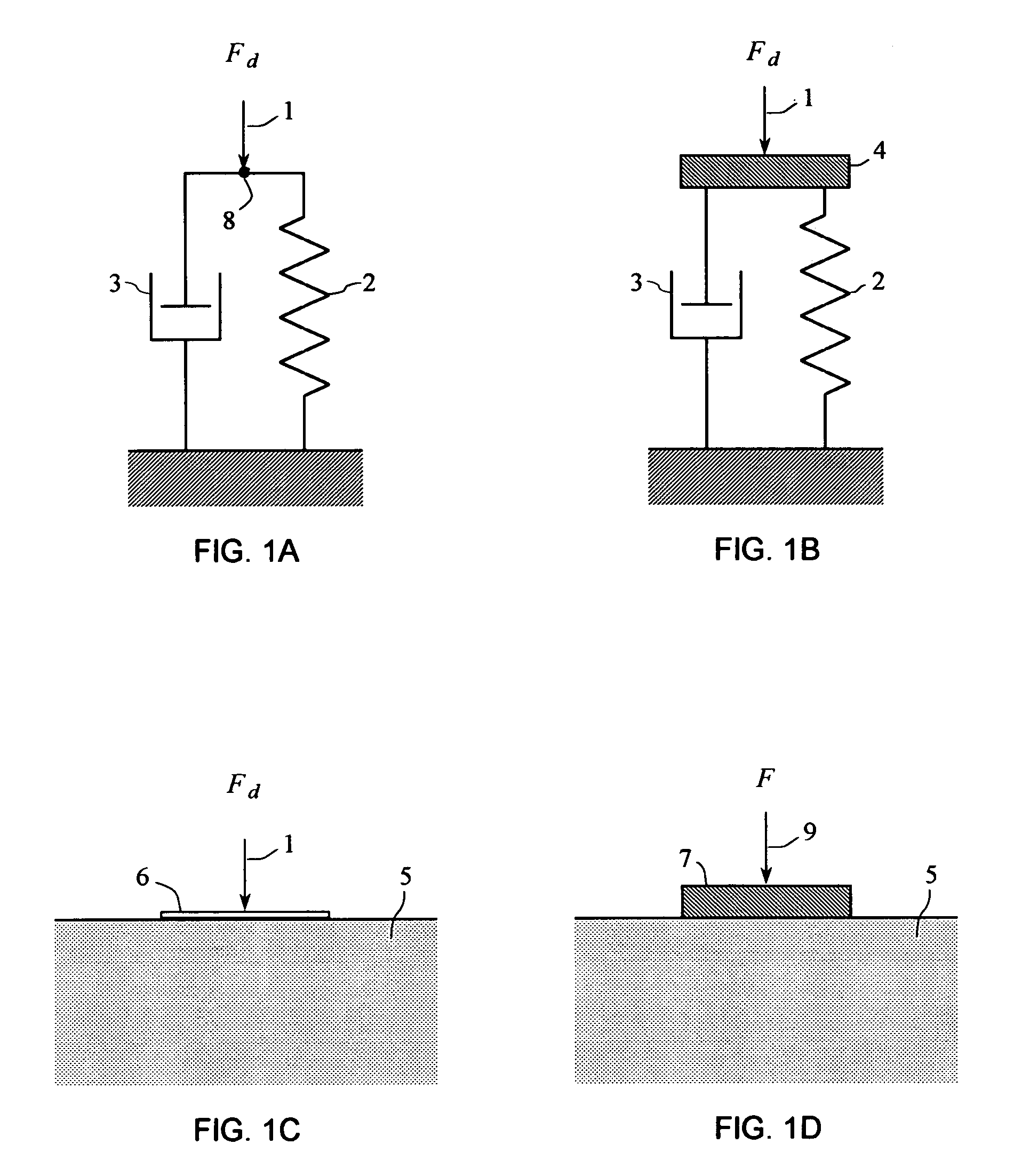

Systems and methods to determine elastic properties of materials

InactiveUS20050267695A1Elastic properties can be determinedInherent in massVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesTime domainHarmonic

The present invention provides systems and methods to use a measured driving-point response of a nonlinear material to determine one or more elastic properties of the material. The present invention takes advantage of the full information represented by the transient component, the steady-state component, the anharmonic components, and the nonlinear response components of a measured driving-point response of a real nonlinear material, without limitation in the use of large-amplitude forces. The elastic properties are determined by forming and solving a time-domain system of linear equations representing a differential equation model of the driving-point motions of the material. Based on a single, short duration, large-amplitude driving point measurement, both linear and nonlinear properties can be determined; both large-amplitude and near-zero amplitude properties can be determined; and elastic-wave speed and elastic moduli and their variation with depth can be determined. The present invention also provides a system and a method to filter an input signal to either attenuate or preserve each of one or more selected harmonic components that are harmonics of a phase reference signal.

Owner:GERMAN PETER THOMAS

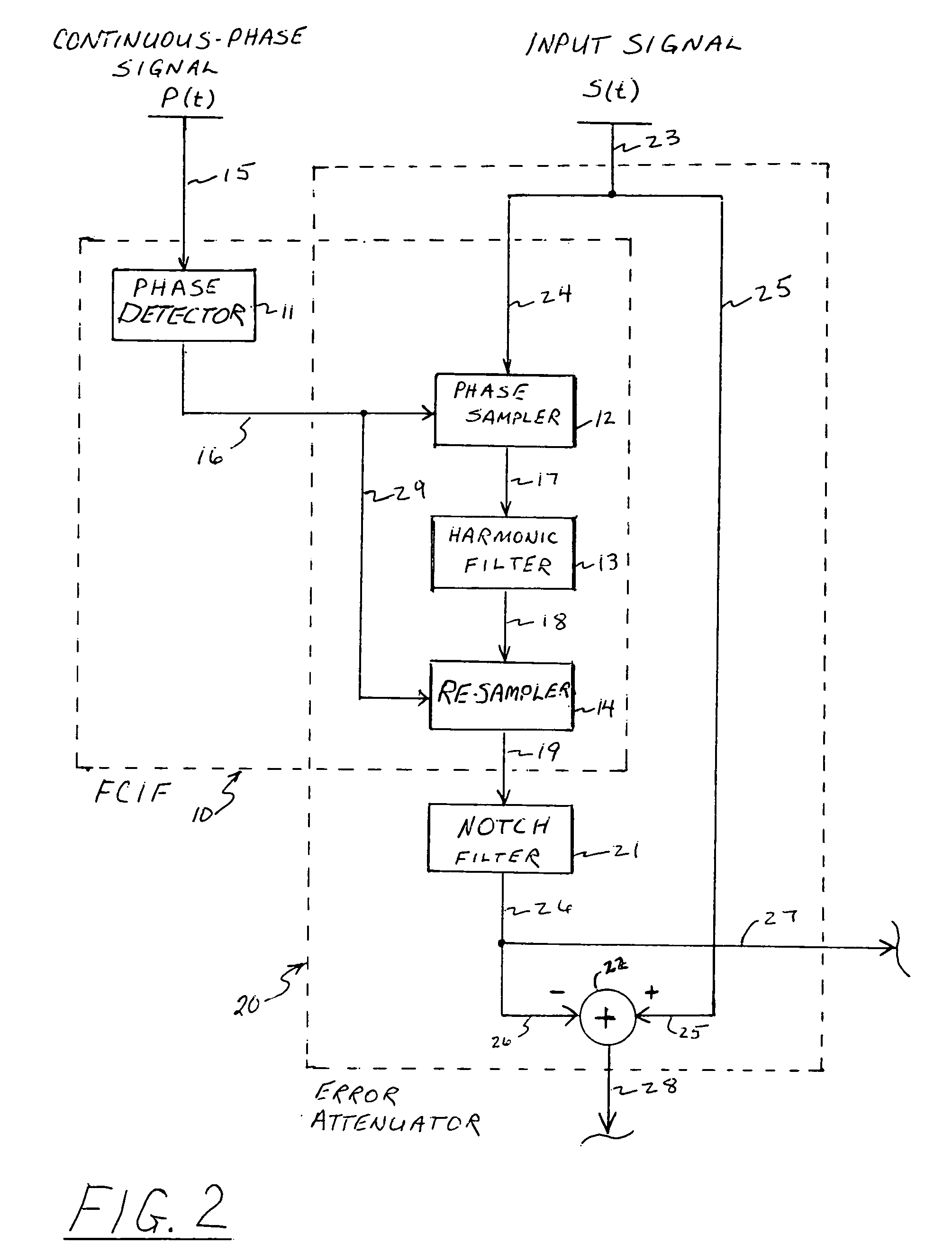

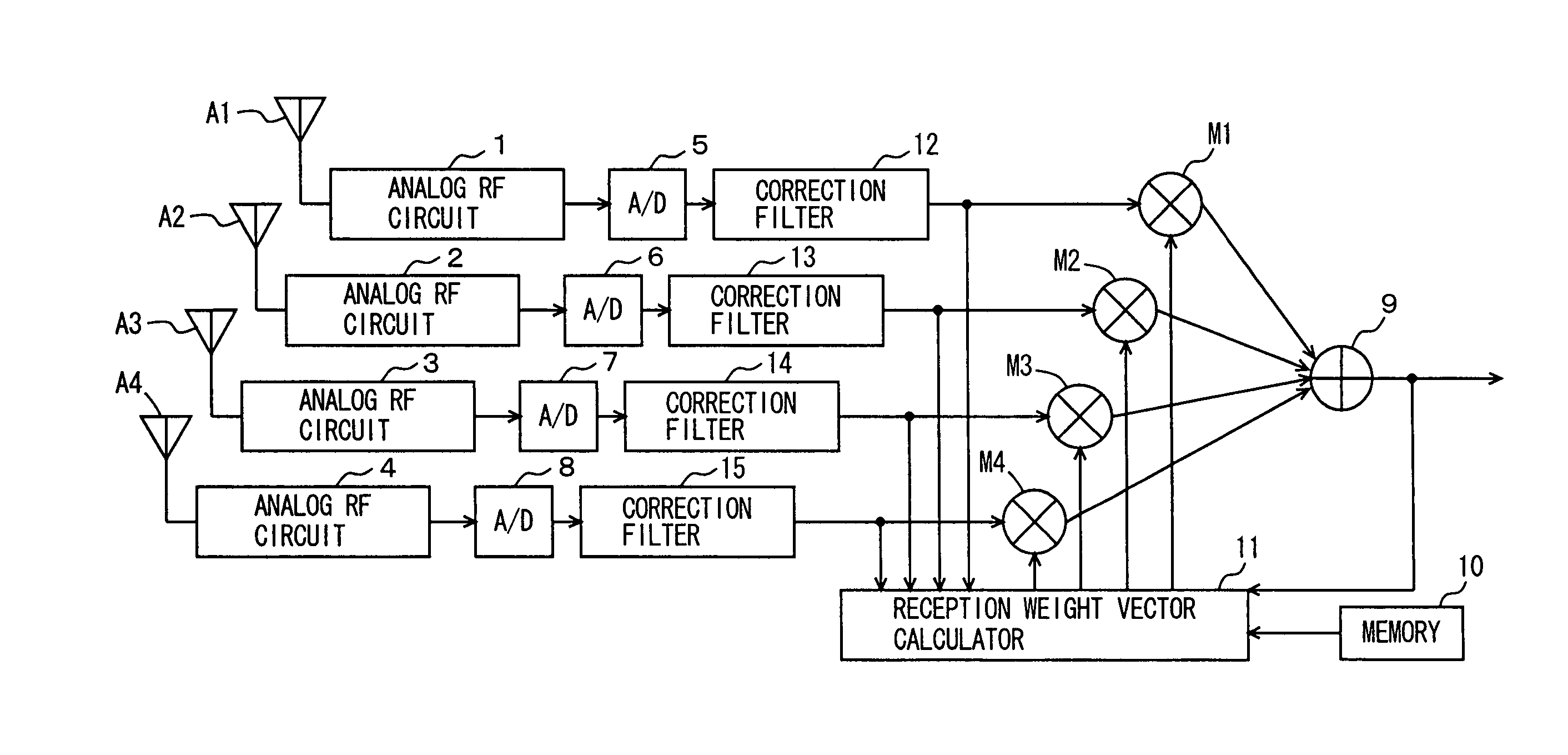

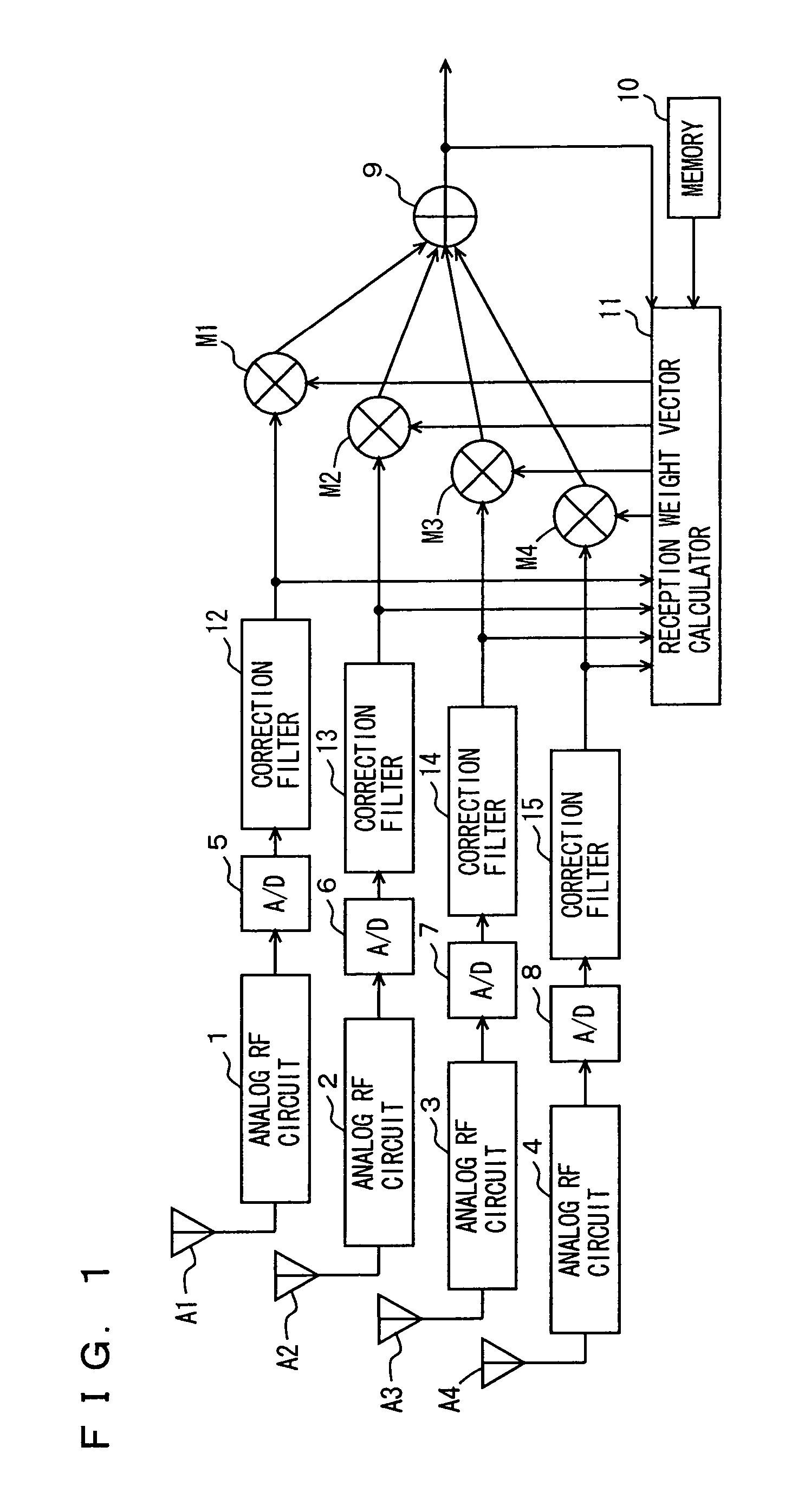

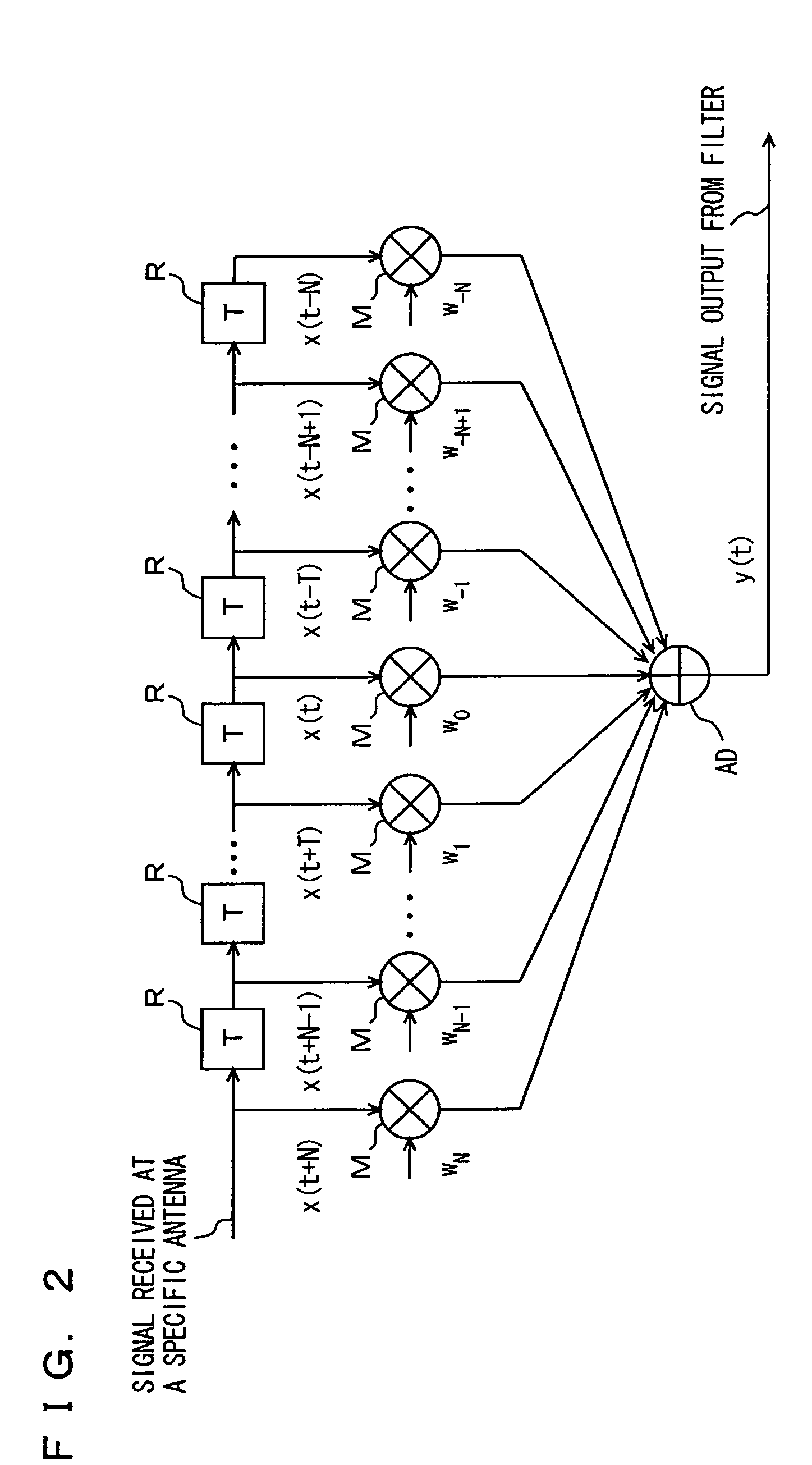

Radio apparatus, method for receiving its signal, method for measuring its filter coefficient, and program for measuring its filter coefficient

InactiveUS7110795B2Accurately determineError minimizationSpatial transmit diversityDigital technique networkRadio equipmentEngineering

Corresponding to antennas analog RF circuits are provided and their outputs are converted by A / D converters to digital signals. Subsequent thereto and preceding an adaptive array processing, correction filters are arranged. Each correction filter has a filter coefficient for compensating for a difference between a characteristic of an analog RF circuit corresponding thereto and an ideal circuit characteristic. Thus an error of a characteristic between the analog RF circuits can be compensated for. The series of operations are implemented by software.

Owner:GK BRIDGE 1

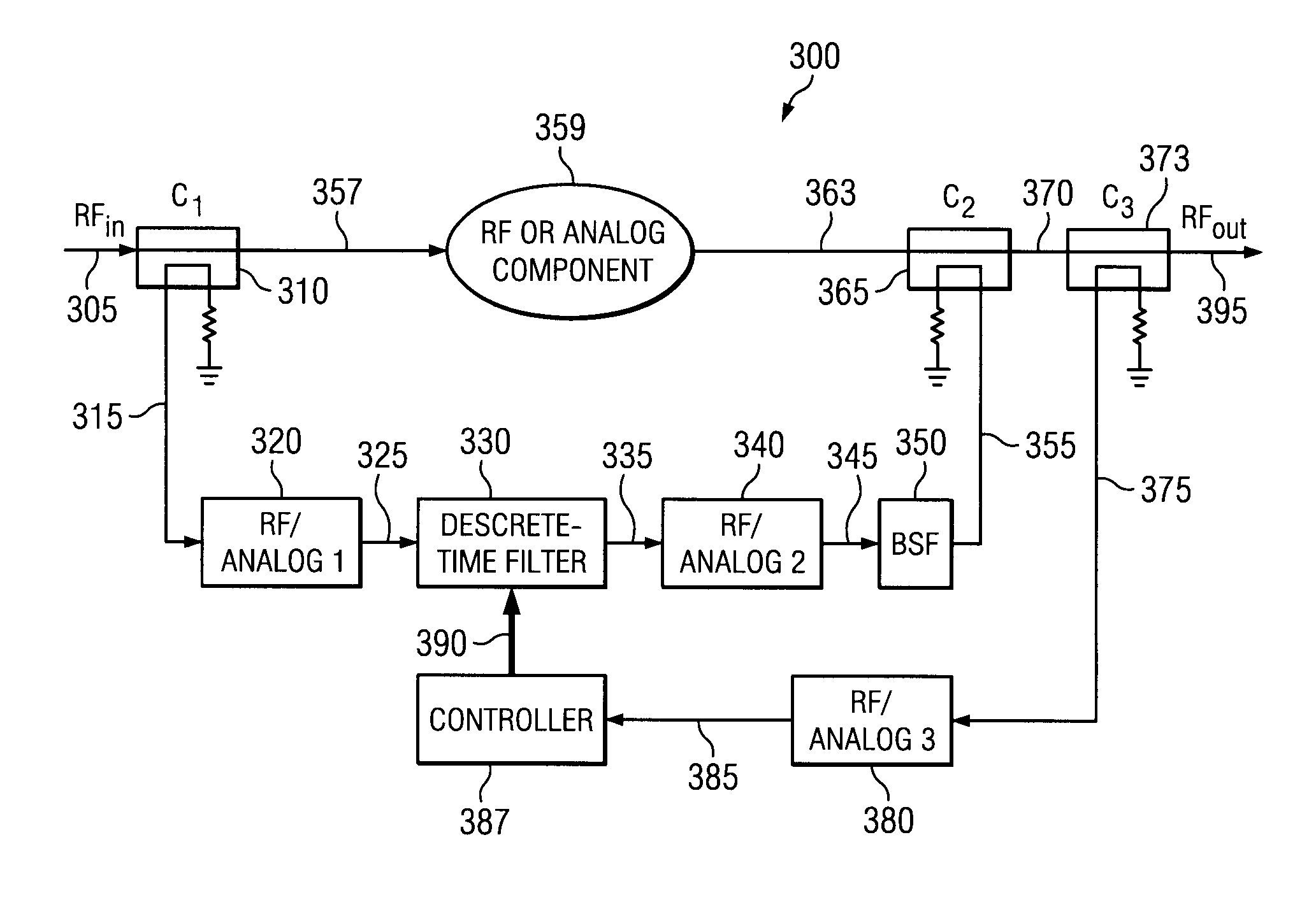

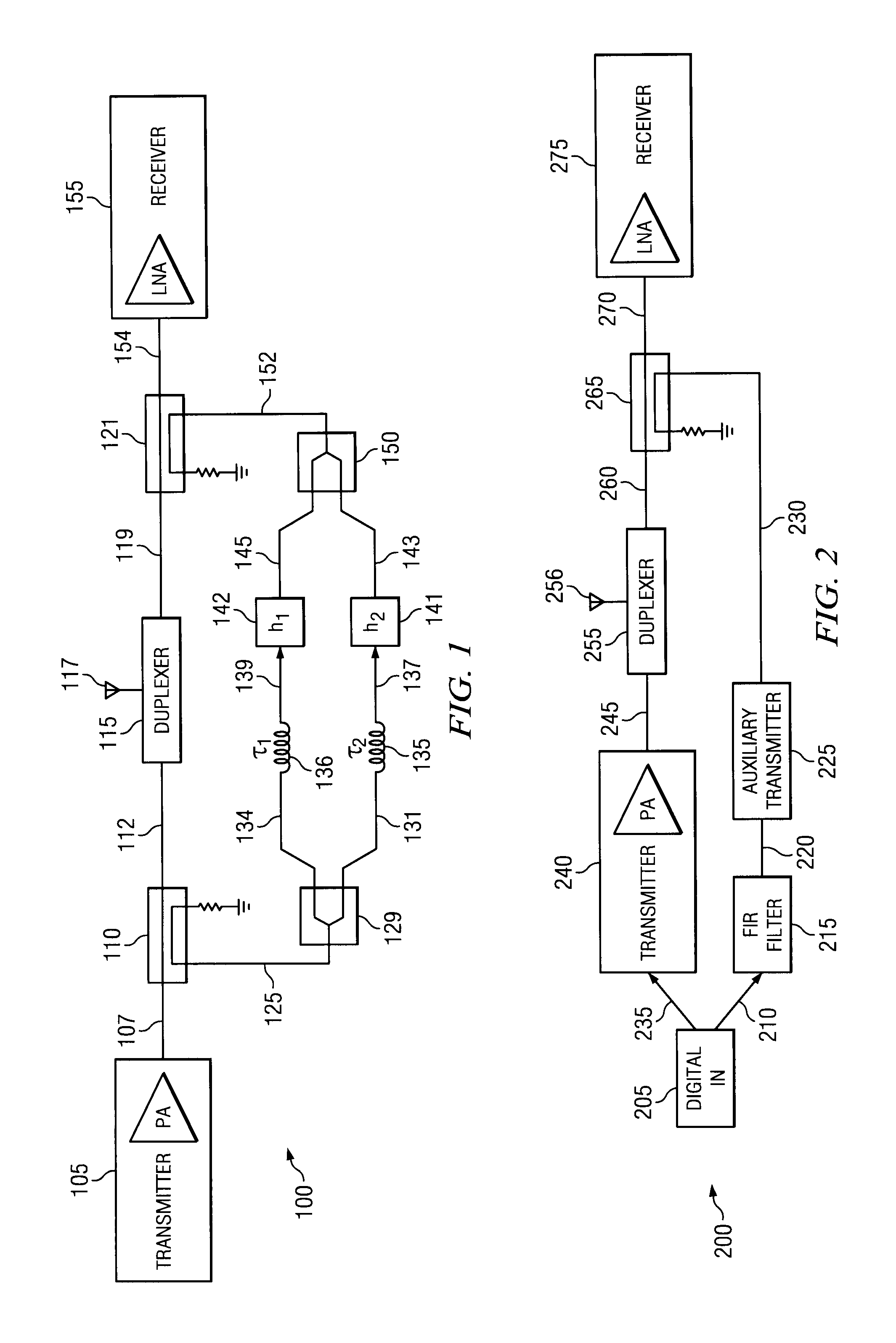

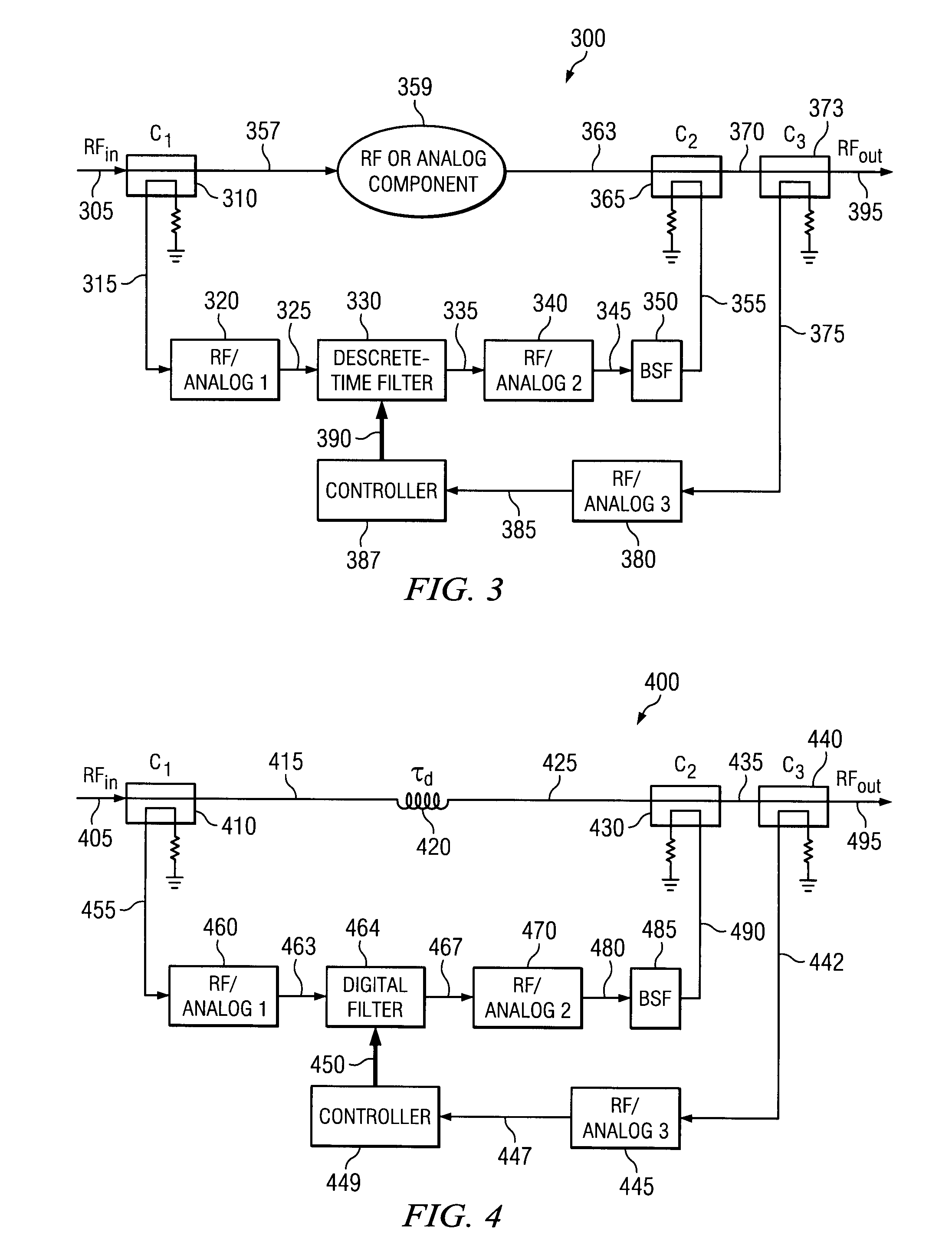

Frequency agile filter using a digital filter and bandstop filtering

InactiveUS8385871B2Large dynamic rangeHigh transmission powerTransmission control/equlisationDigital technique networkBandpass filteringFrequency changer

The present invention is a hybrid RF-digital signal processor-based filter for multiband radio architectures systems capable of spectrum re-farming and software defined radios. It performs low-loss frequency agile multiple notch filtering at RF where a large dynamic range exists at a filter input between signals in a stopband and passband. It is a frequency dependent signal attenuation apparatus having two paths connected together by directional couplers. The first path comprising a component such as a delay component or duplexer. The second path comprising a bandstop filter connected to a down converter, a digital filter, and an up converter. At the output of a power amplifier, the invention can be used to attenuate spurs, or noise within bands with strict emission constraints. At the input of a low noise amplifier, the invention can be used to attenuate blockers and transmitter noise outside of the receiver passband.

Owner:RPX CLEARINGHOUSE

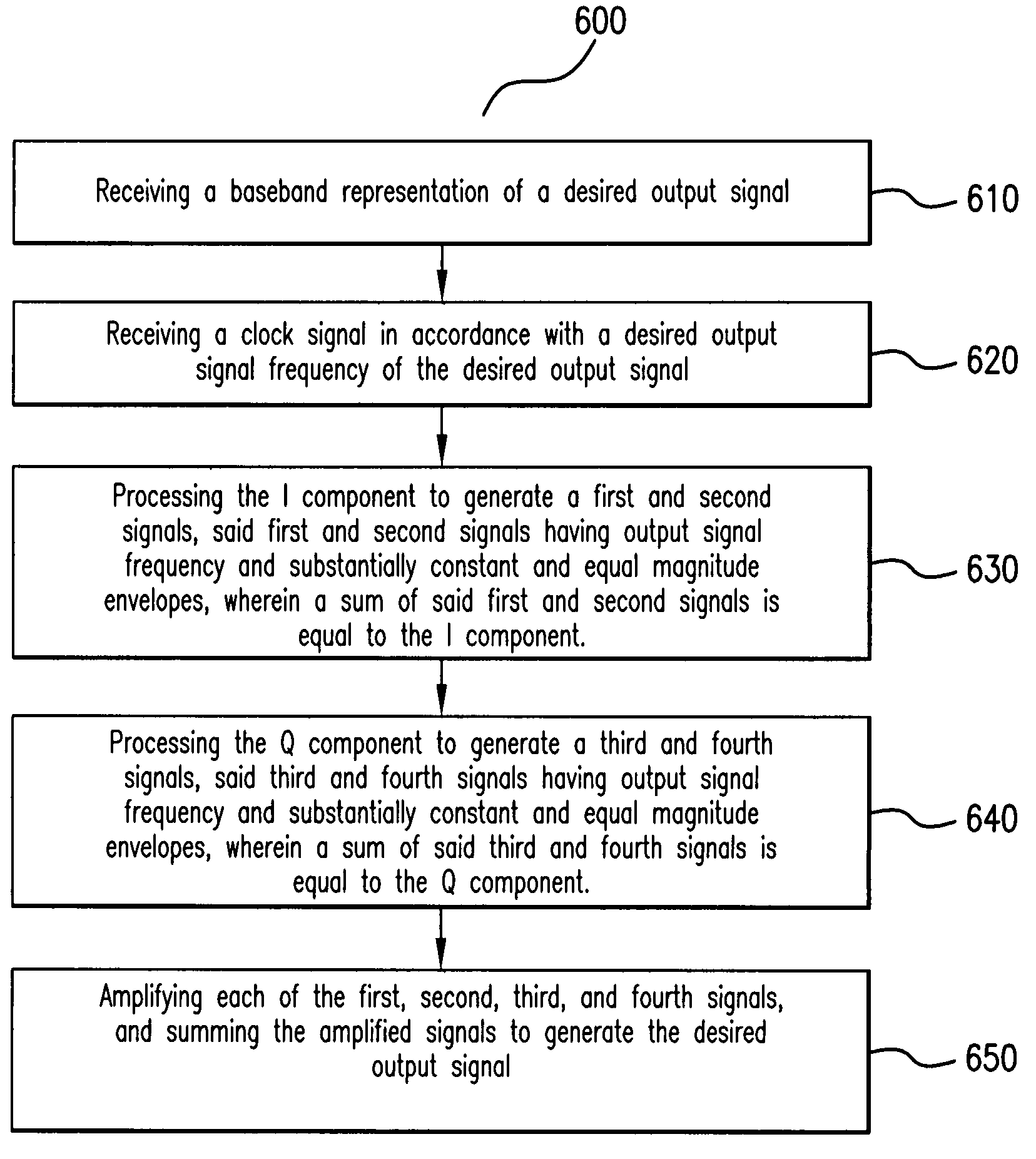

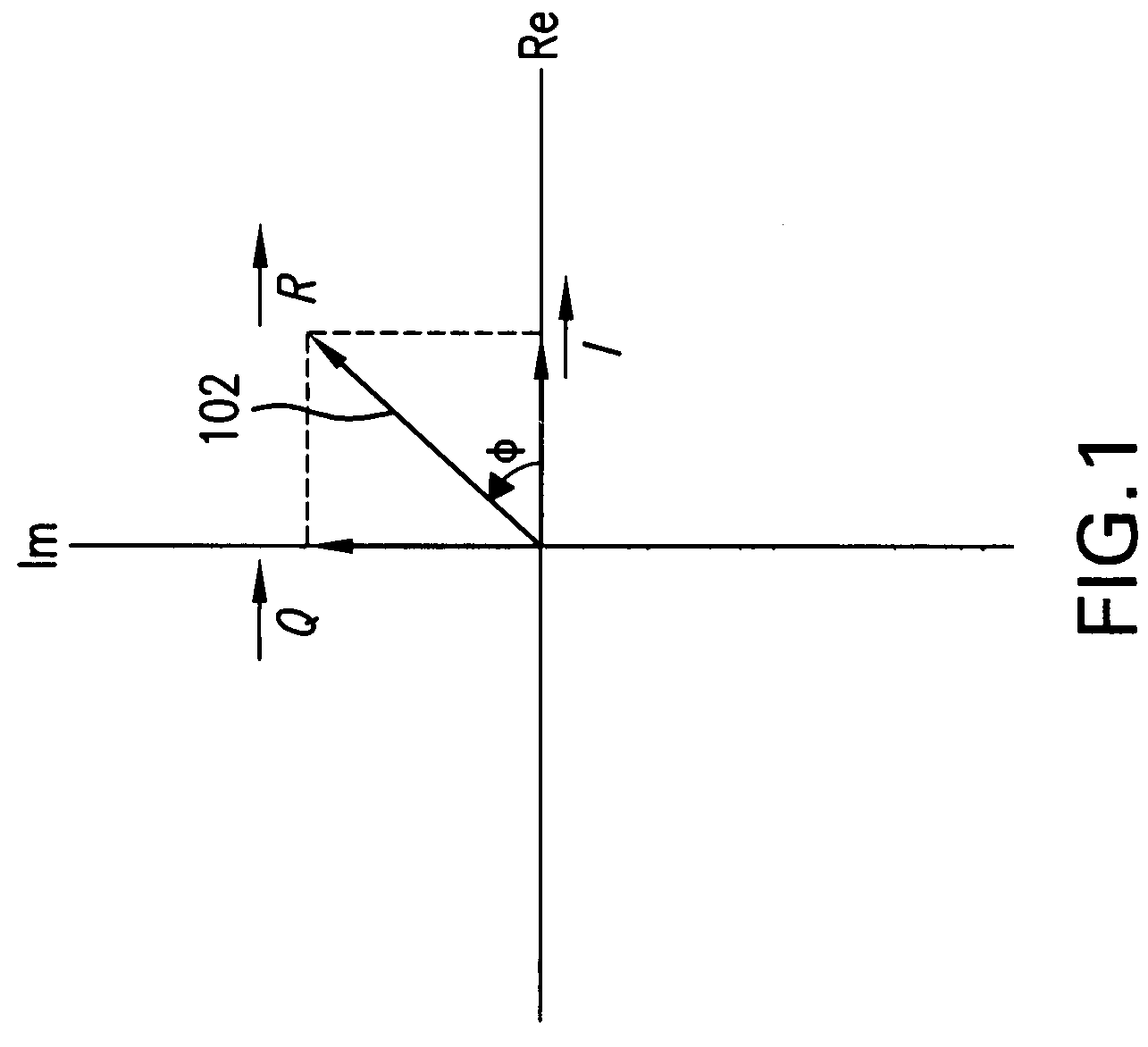

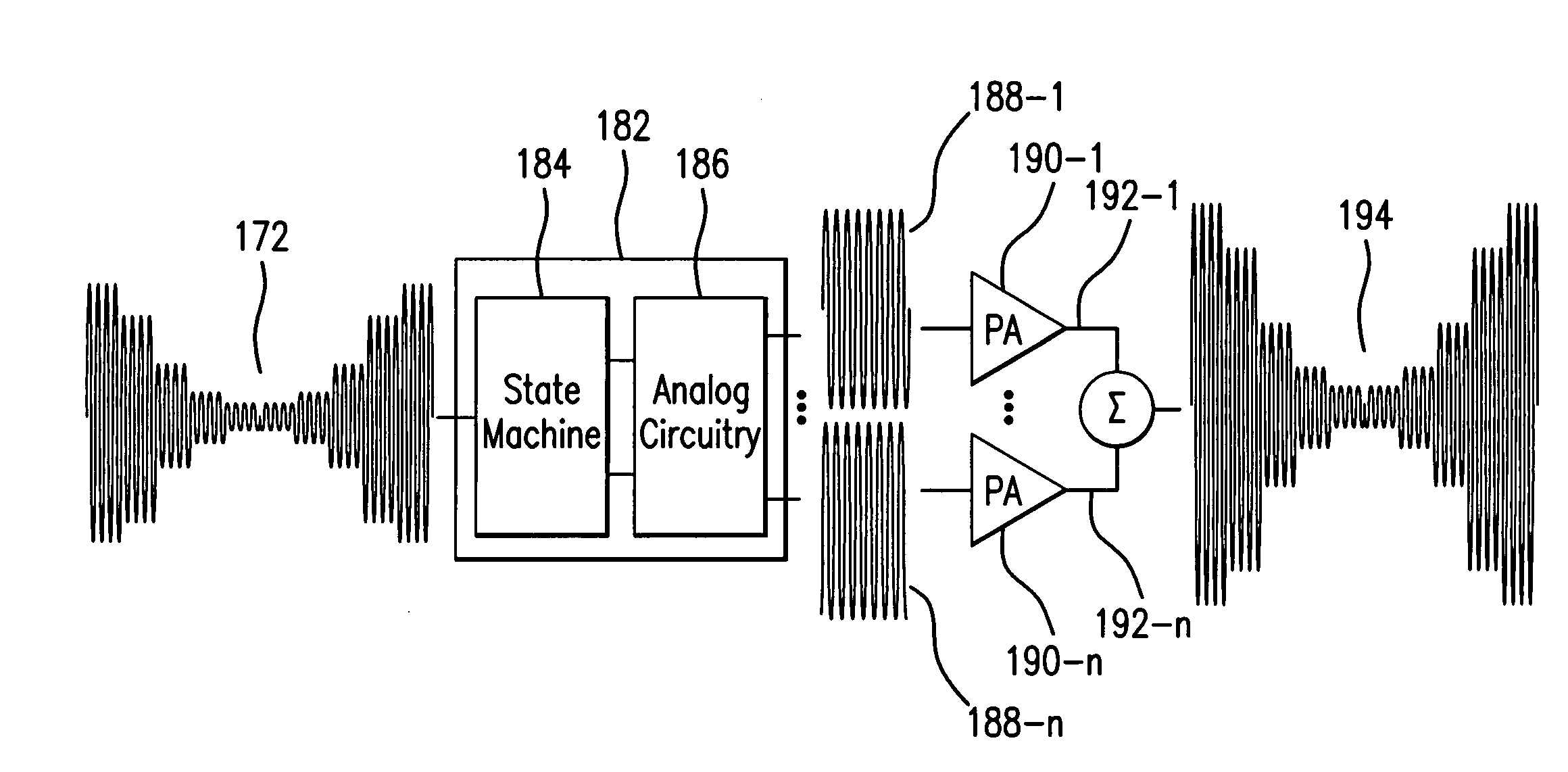

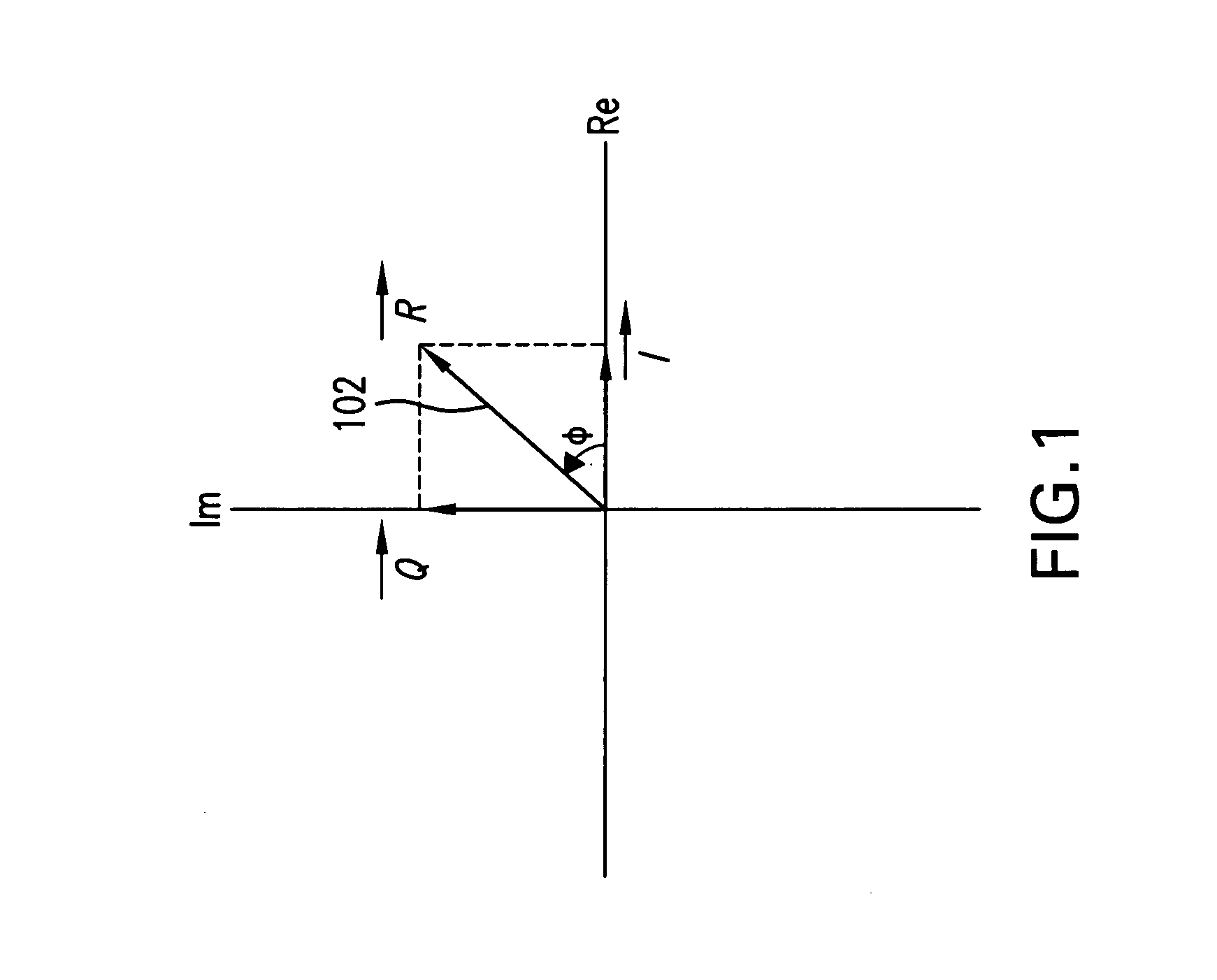

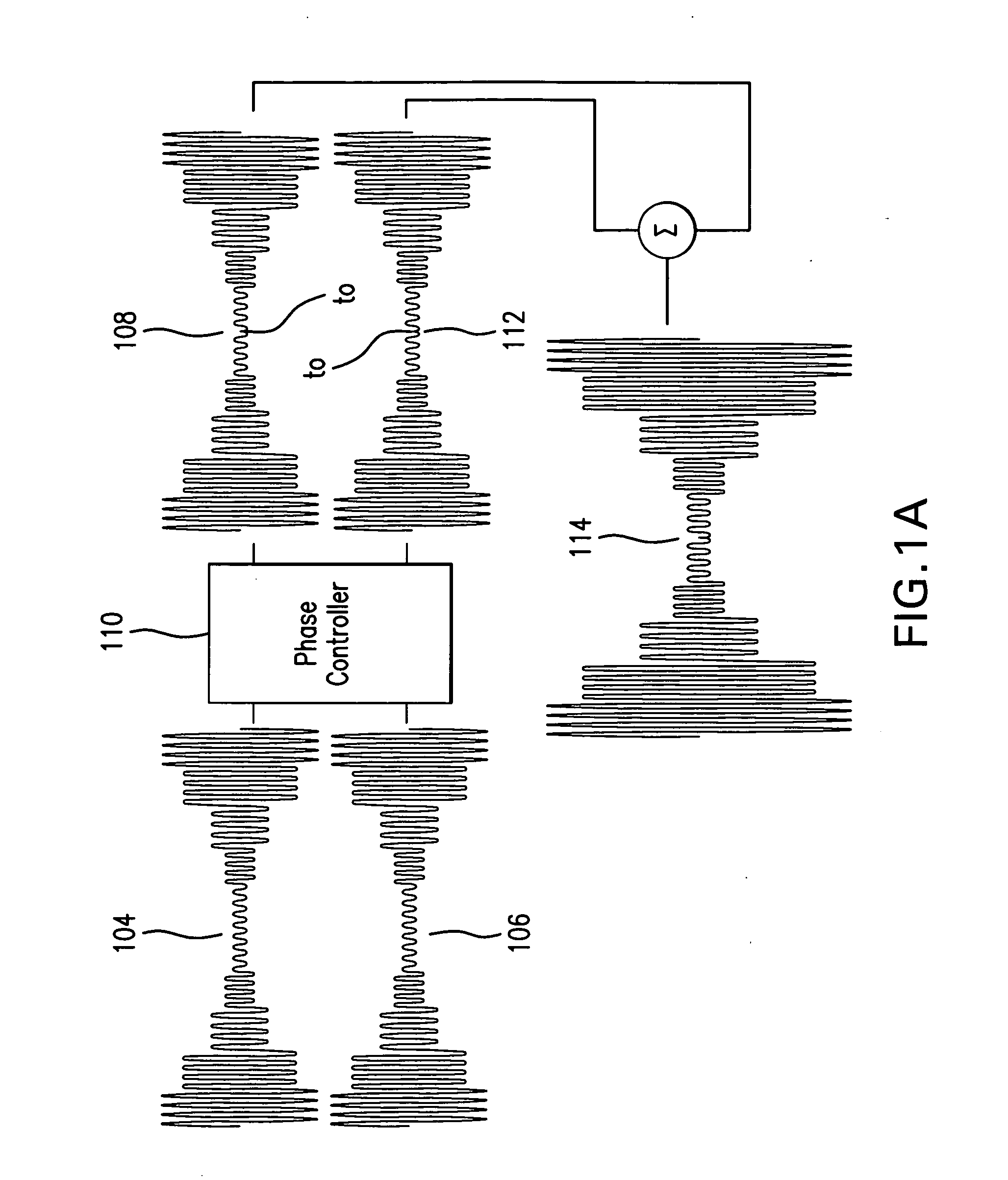

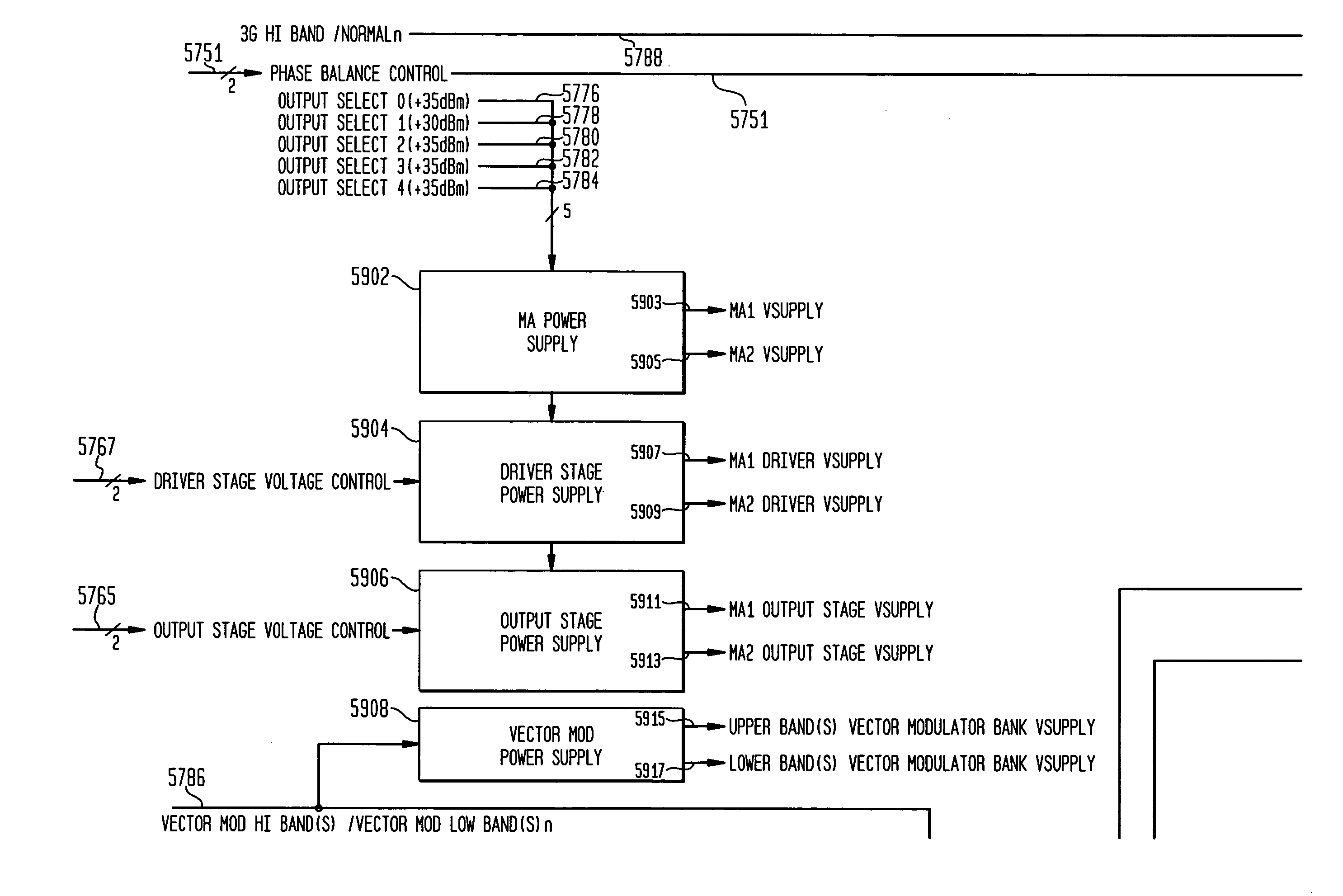

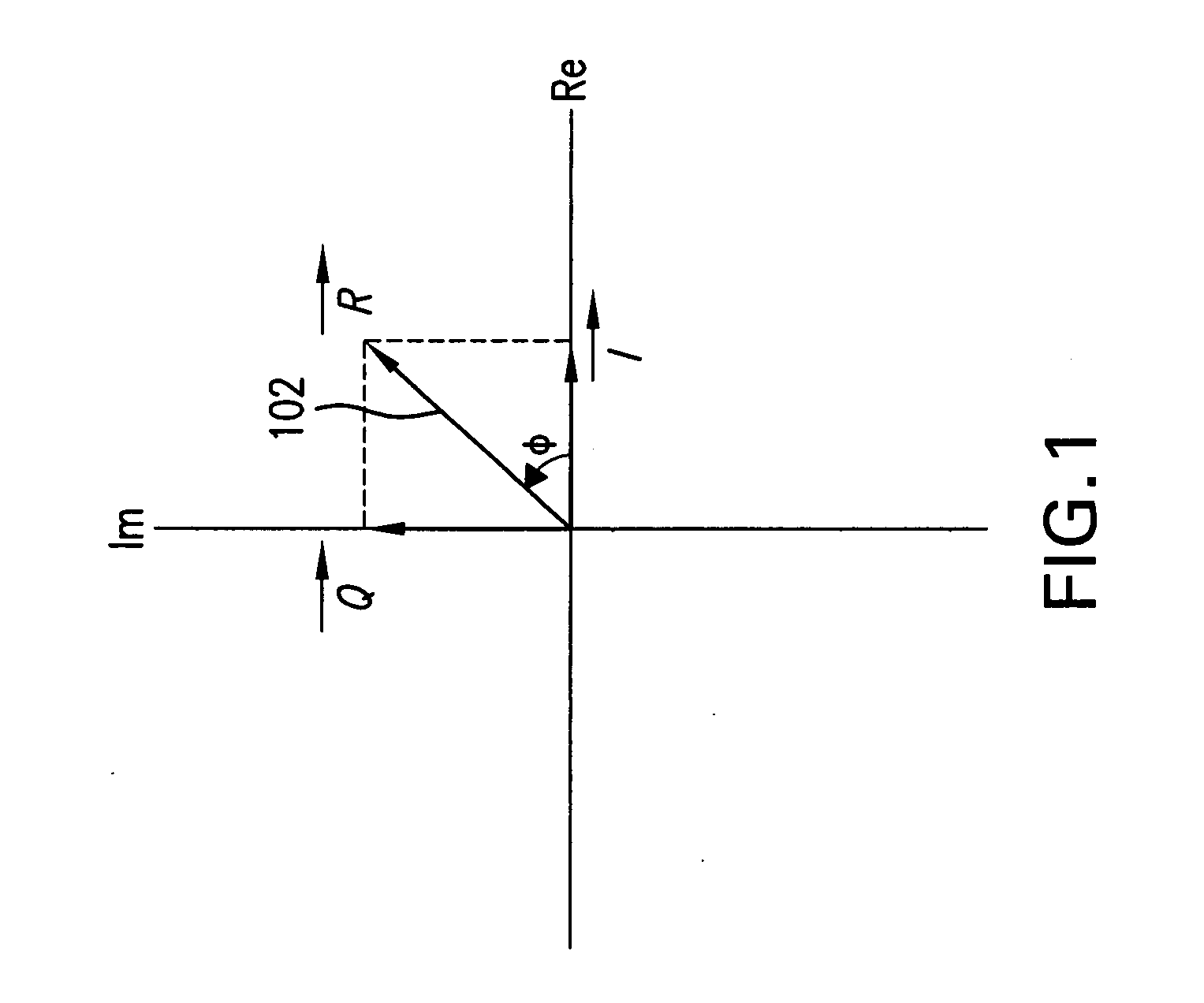

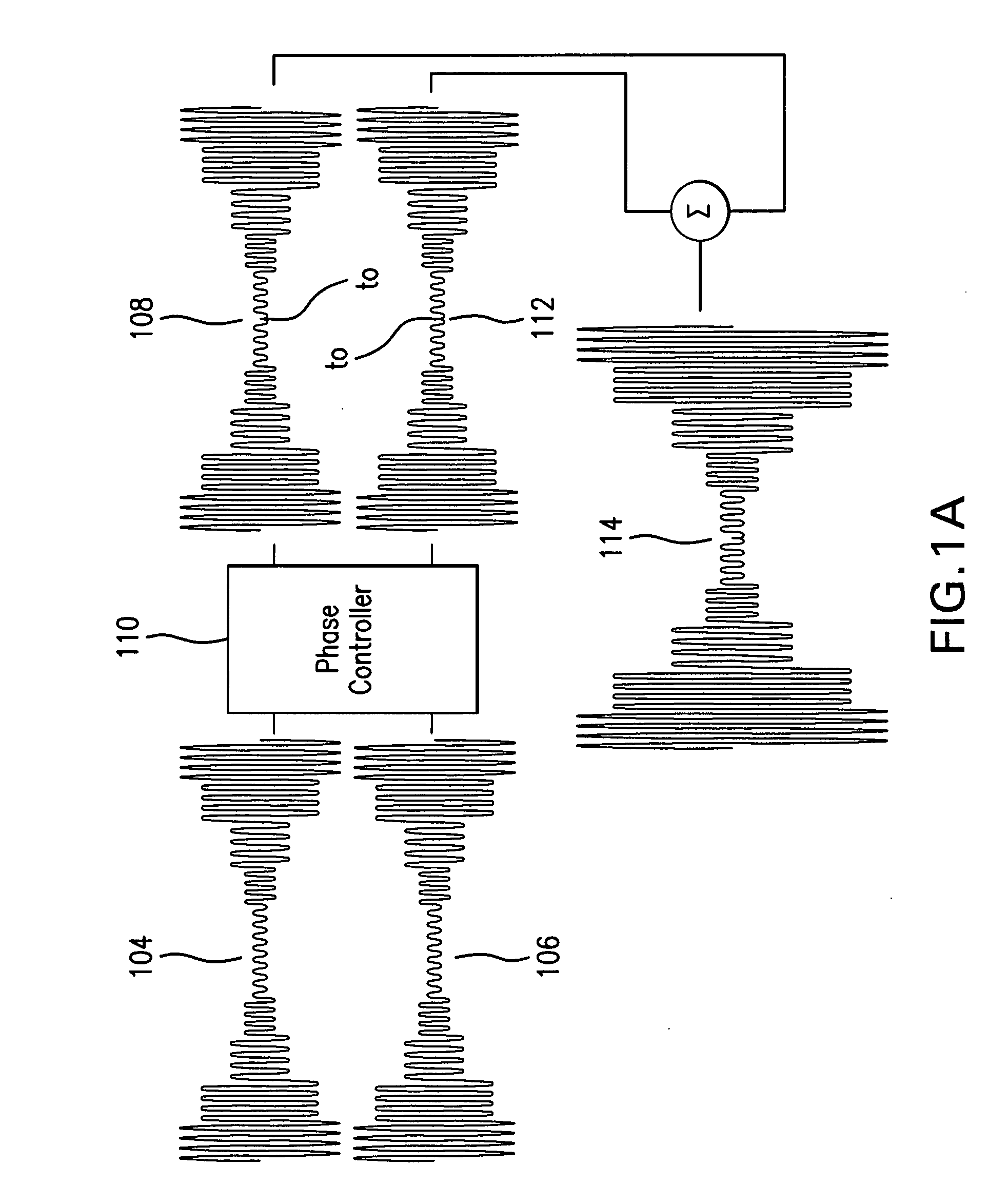

Systems and methods of RF power transmission, modulation, and amplification, including architectural embodiments of same

InactiveUS7885682B2Multiple-port networksResonant long antennasElectric power transmissionUp conversion

Methods and systems for vector combining power amplification are disclosed herein. In one embodiment, a plurality of signals are individually amplified, then summed to form a desired time-varying complex envelope signal. Phase and / or frequency characteristics of one or more of the signals are controlled to provide the desired phase, frequency, and / or amplitude characteristics of the desired time-varying complex envelope signal. In another embodiment, a time-varying complex envelope signal is decomposed into a plurality of constant envelope constituent signals. The constituent signals are amplified equally or substantially equally, and then summed to construct an amplified version of the original time-varying envelope signal. Embodiments also perform frequency up-conversion.

Owner:PARKER VISION INC

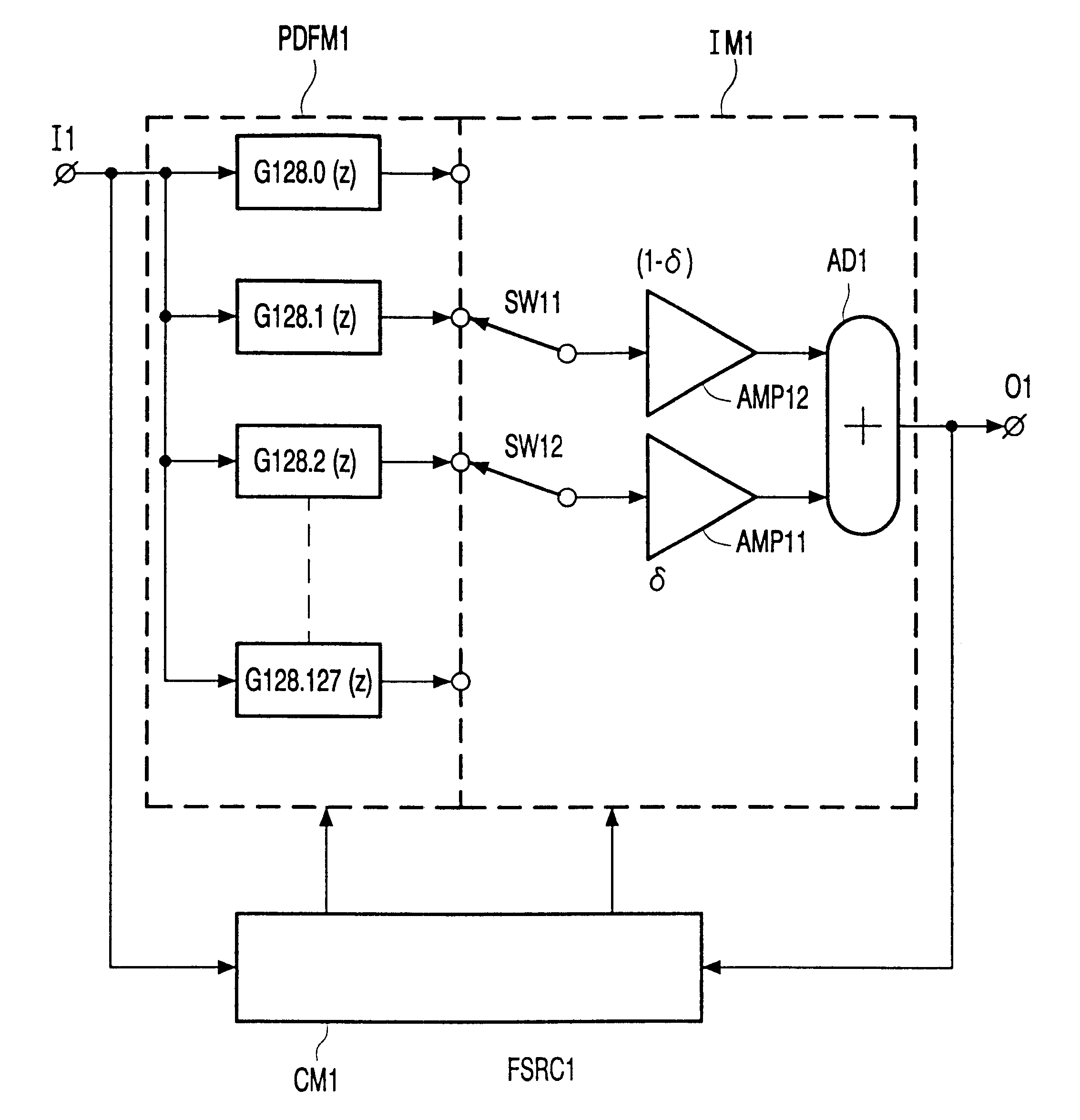

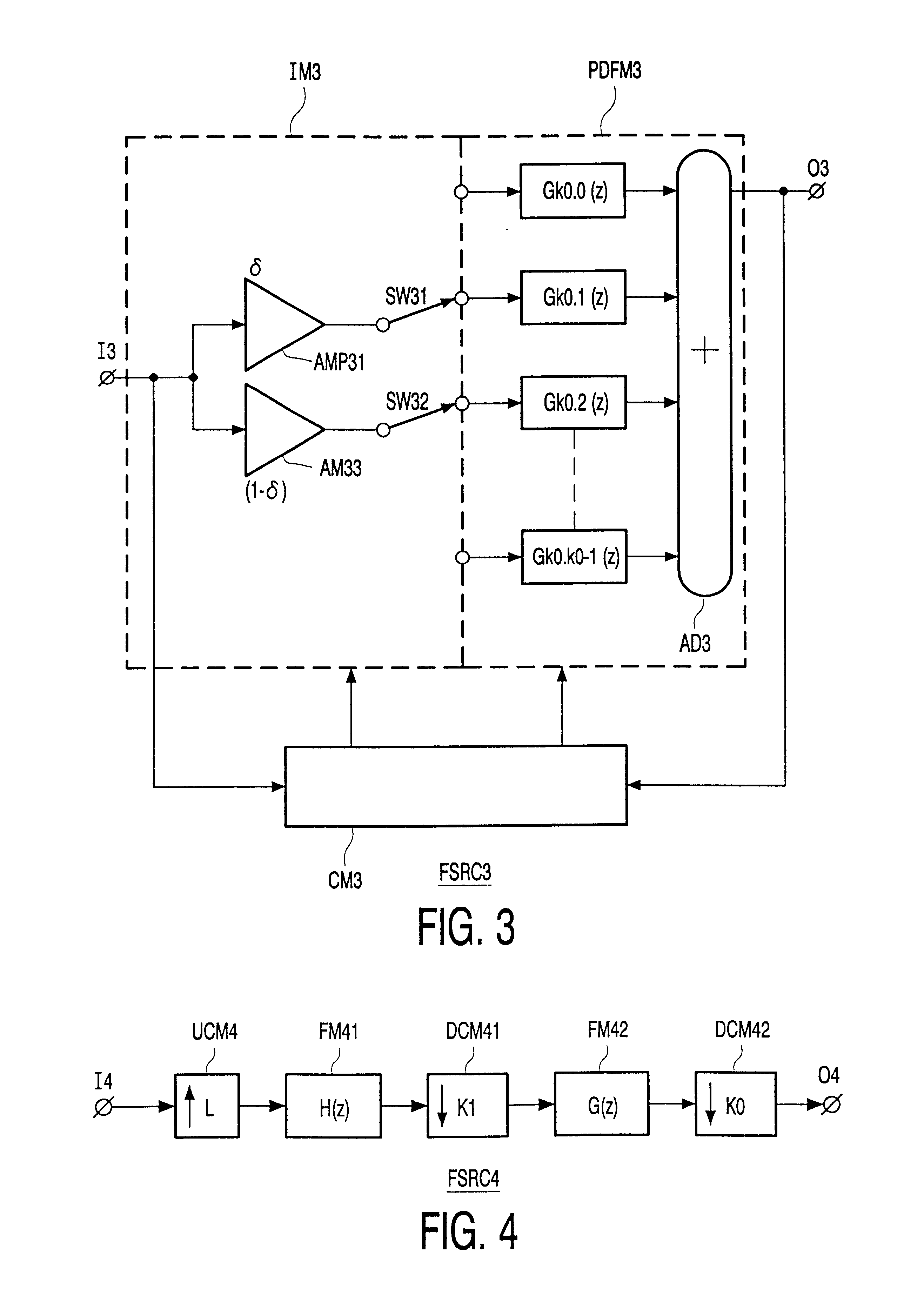

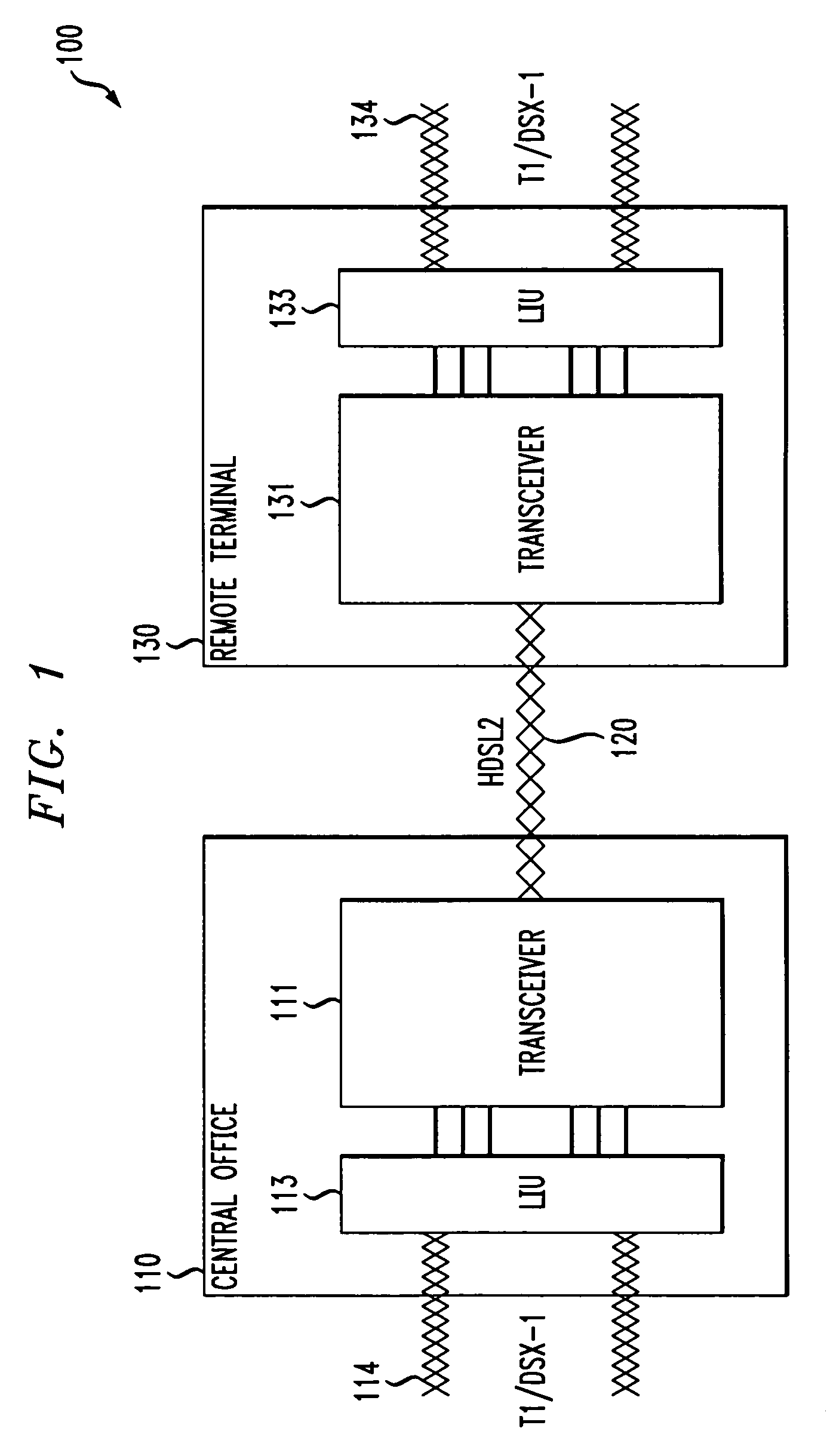

Sample rate converter

InactiveUS6411225B1Efficient flexible sample rate converterEasy to operateDigital technique networkDelta modulationSignal transitionPhysics

Sample rate converters are known, and are used to convert a signal with a first sample rate (sampling frequency) into a signal with a second sample rate (sampling frequency). To obtain a flexible sample rate converter with sampling frequencies that are not known beforehand, until now only sample rate converters with very high intermediate sampling frequencies are known. The invention provides a flexible sample rate converter, which is able to handle unknown input and output sampling frequencies. This is achieved by using polyphase decomposition filter means in combination with interpolation means.

Owner:NXP BV

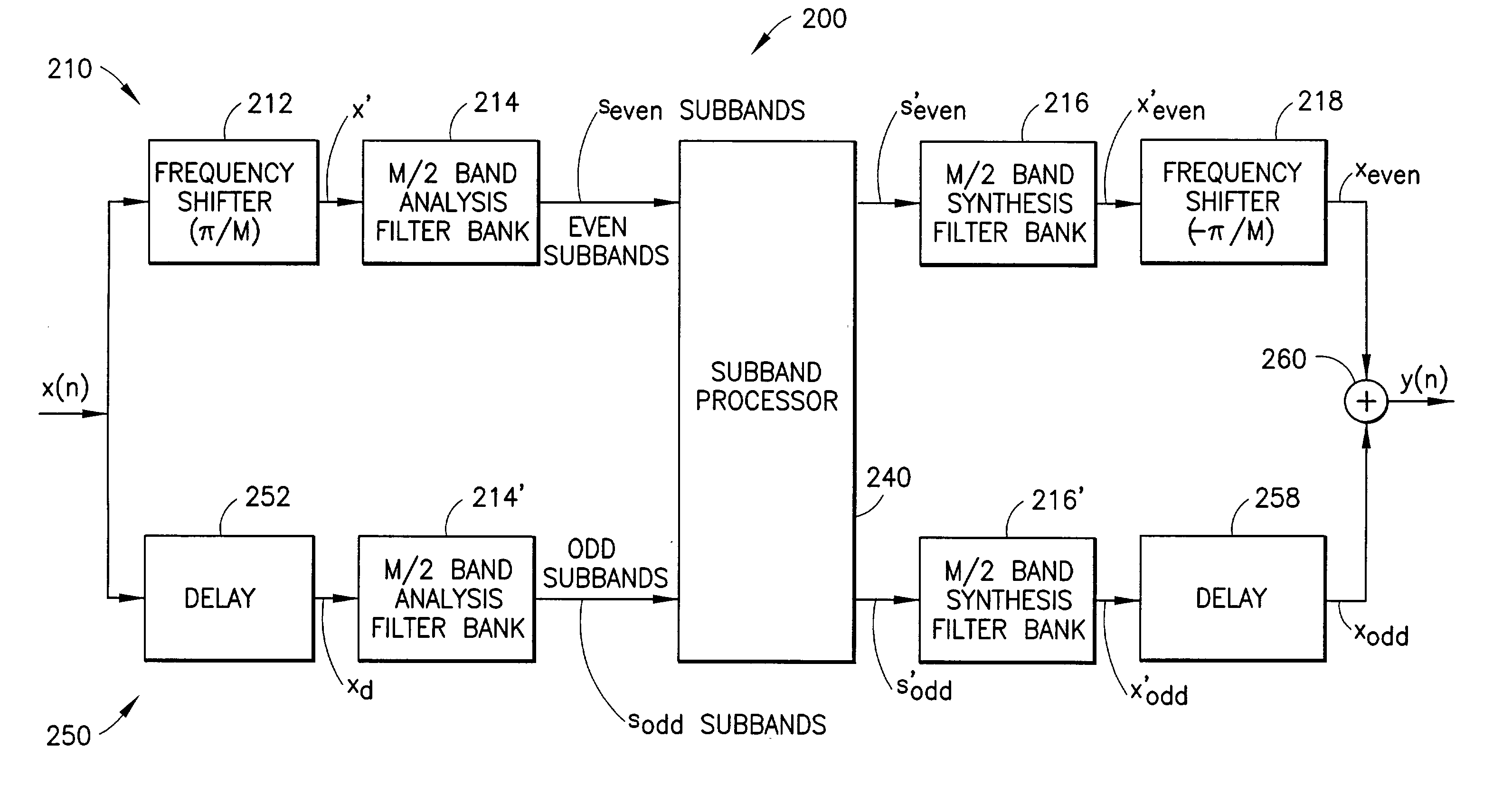

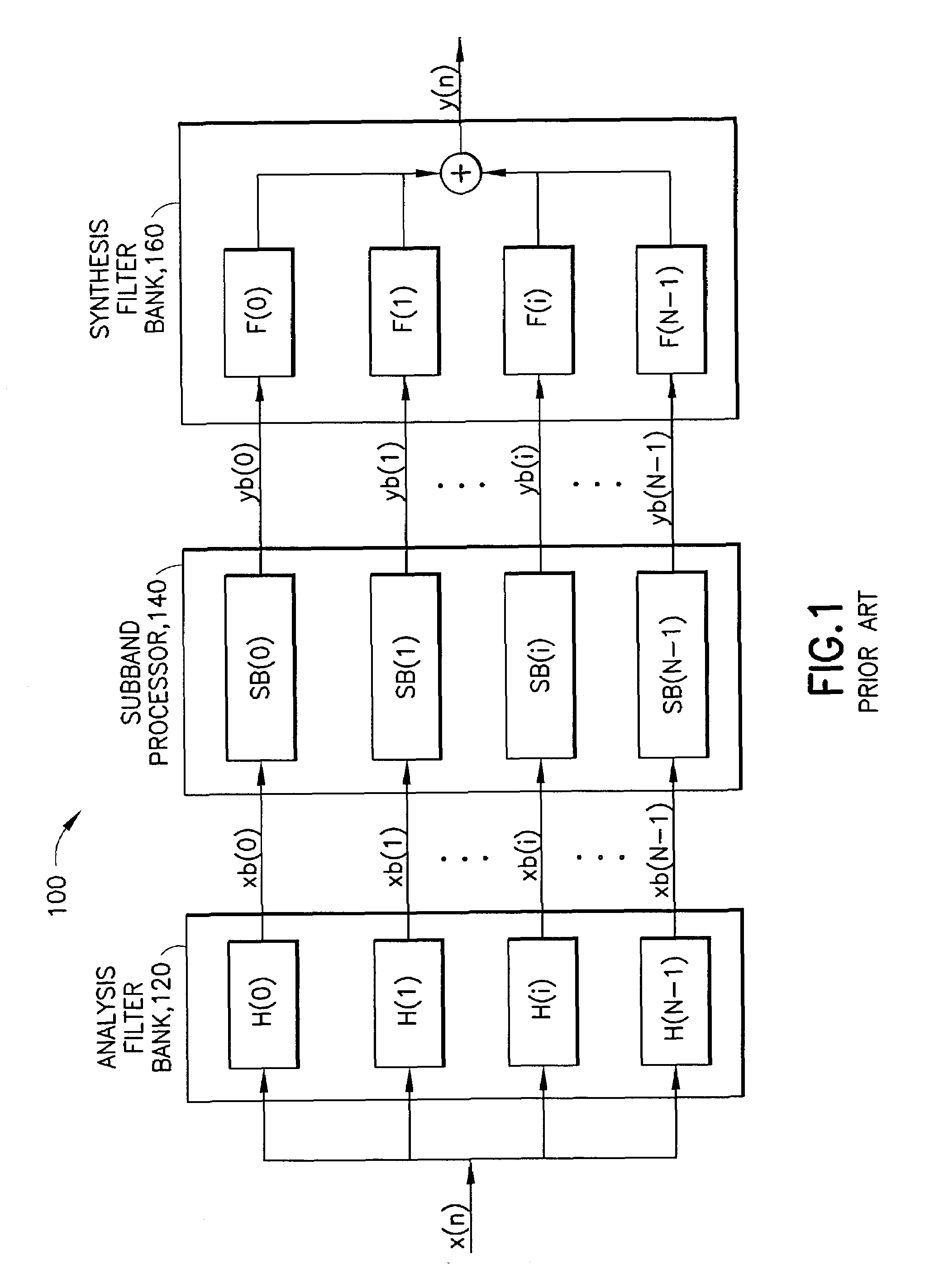

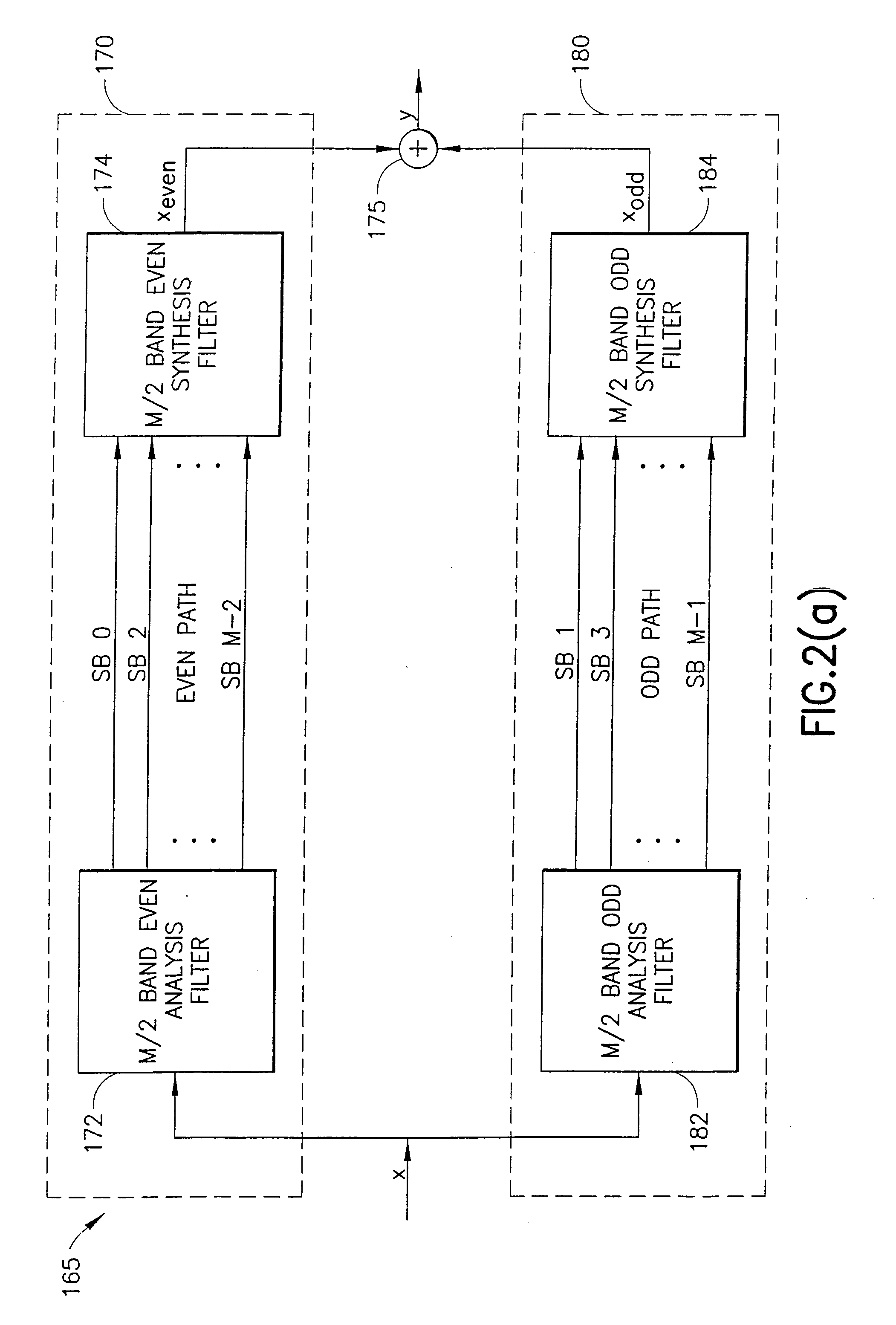

Oversampled filter bank for subband processing

InactiveUS6947509B1Aliasing between subbands is substantially reducedLower prototype filter orderDigital technique networkTransmissionEngineeringFrequency shift

An oversampled filter bank structure that can be implemented using popular and efficient fast filter banks to allow subband processing of an input signal with substantially reduced aliasing between subbands. Even subbands (SB0, SB2, SB4, . . . ) of an input signal (x(n)) are frequency-shifted (212, 1012, 1012′, 1012″) prior to analysis filtering (214, 214′, 214″) at a 2× oversampled filter bank, subband processing (240, 240′, 240″), and synthesis filtering (216, 216′, 216″). A subsequent frequency-shift (218, 218′) returns the even subbands to their original band positions. The odd subbands (SB1, SB3, SB5, . . . ) are delayed (252) to compensate for the processing time of the frequency shifting. Separate analysis (214, 214′) and synthesis (216, 216′) filter banks may be provided for the even and odd subbands, or common complex analysis (284) and synthesis (286) filter banks may be used. In another embodiment, the subbands are processed in four subband paths (Paths 0, 1, 2, 3), and 4× oversampling is used. A filter bank structure (1400) for 2-D data is also provided.

Owner:VERANCE

Systems and methods of RF tower transmission, modulation, and amplification, including embodiments for compensating for waveform distortion

InactiveUS20070249300A1Increase costLow costMultiple-port networksAmplifier modifications to reduce non-linear distortionTowerUp conversion

Methods and systems for vector combining power amplification are disclosed herein. In one embodiment, a plurality of signals are individually amplified, then summed to form a desired time-varying complex envelope signal. Phase and / or frequency characteristics of one or more of the signals are controlled to provide the desired phase, frequency, and / or amplitude characteristics of the desired time-varying complex envelope signal. In another embodiment, a time-varying complex envelope signal is decomposed into a plurality of constant envelope constituent signals. The constituent signals are amplified equally or substantially equally, and then summed to construct an amplified version of the original time-varying envelope signal. Embodiments also perform frequency up-conversion.

Owner:PARKER VISION INC

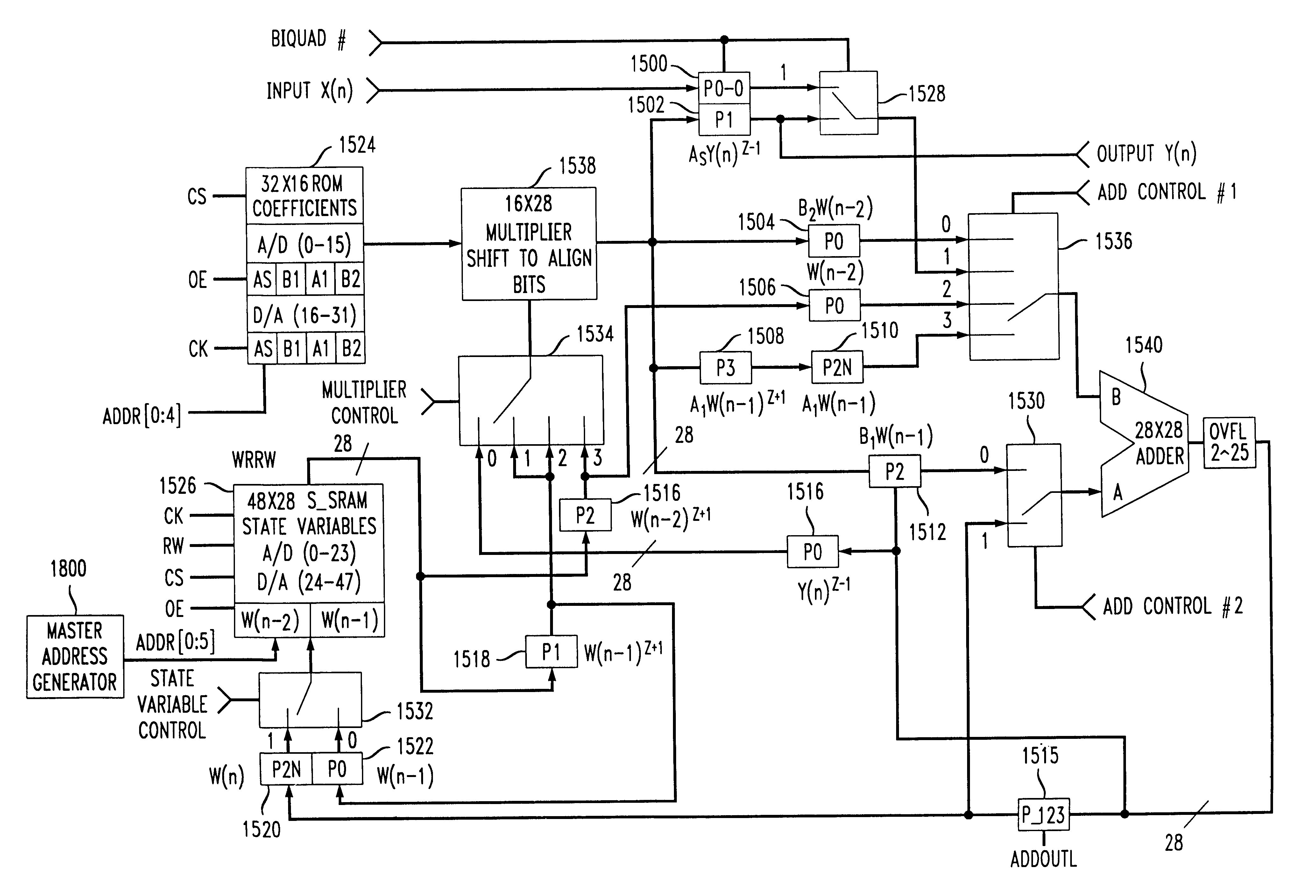

System for digital filtering in a fixed number of clock cycles

InactiveUS6175849B1Digital technique networkComplex mathematical operationsIir filteringState variable

An integrated circuit, e.g. an AC '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a DC buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A RAM is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional modules of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional modules.

Owner:WSOU INVESTMENTS LLC +1

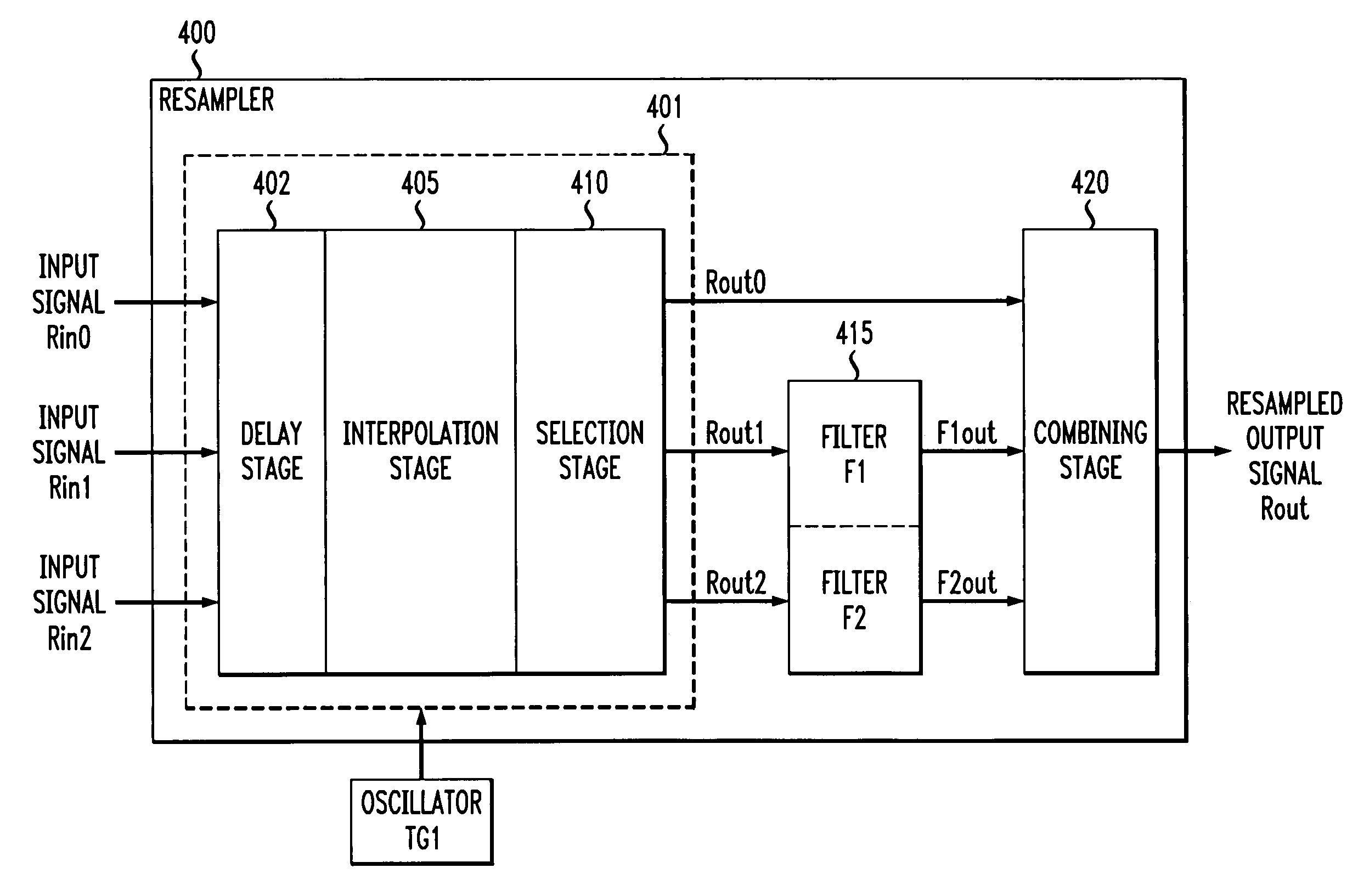

Interpolator, a resampler employing the interpolator and method of interpolating a signal associated therewith

InactiveUS6970511B1Adding significant additional complexityQuality improvementPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningSignal correlationComputer science

An interpolator, method of interpolating a one-bit signal and resampler employing the interpolator and method. The interpolator employs a cascaded architecture to interpolate a one-bit input signal received at an input thereof. In one embodiment, the interpolator includes a multiple order interpolation filter that generates a sample range from at least three input samples associated with the one-bit input signal. The interpolator further includes a linear interpolation filter, associated with the multiple order interpolation filter, that develops a plurality of samples within the sample range.

Owner:LUCENT TECH INC +1

Systems and methods of RF power transmission, modulation, and amplification, including embodiments for compensating for waveform distortion

ActiveUS20070248186A1Multiple-port networksAmplifier modifications to reduce non-linear distortionEngineeringFrequency characteristic

Methods and systems for vector combining power amplification are disclosed herein. In one embodiment, a plurality of signals are individually amplified, then summed to form a desired time-varying complex envelope signal. Phase and / or frequency characteristics of one or more of the signals are controlled to provide the desired phase, frequency, and / or amplitude characteristics of the desired time-varying complex envelope signal. In another embodiment, a time-varying complex envelope signal is decomposed into a plurality of constant envelope constituent signals. The constituent signals are amplified equally or substantially equally, and then summed to construct an amplified version of the original time-varying envelope signal. Embodiments also perform frequency up-conversion.

Owner:PARKER VISION INC

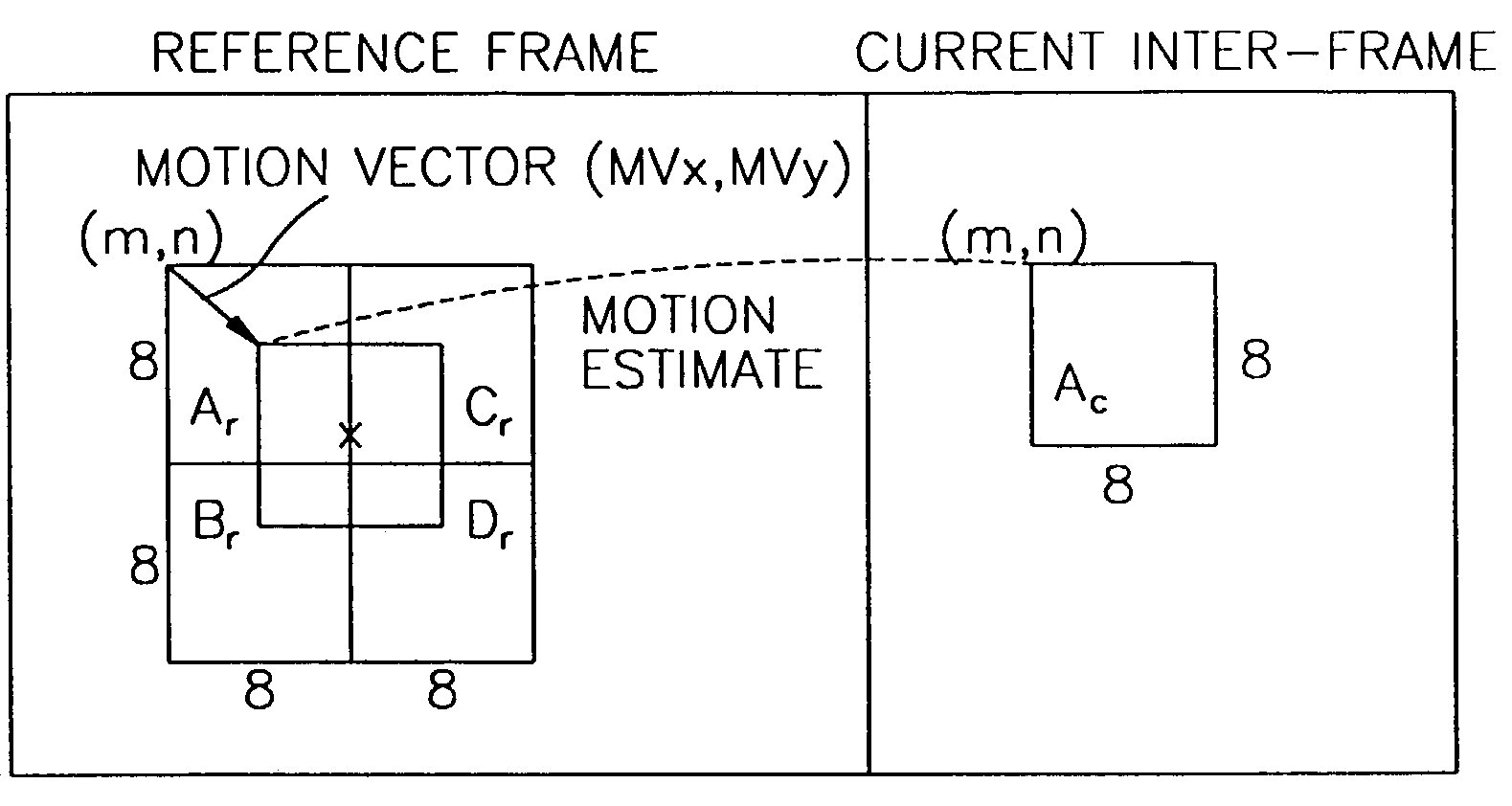

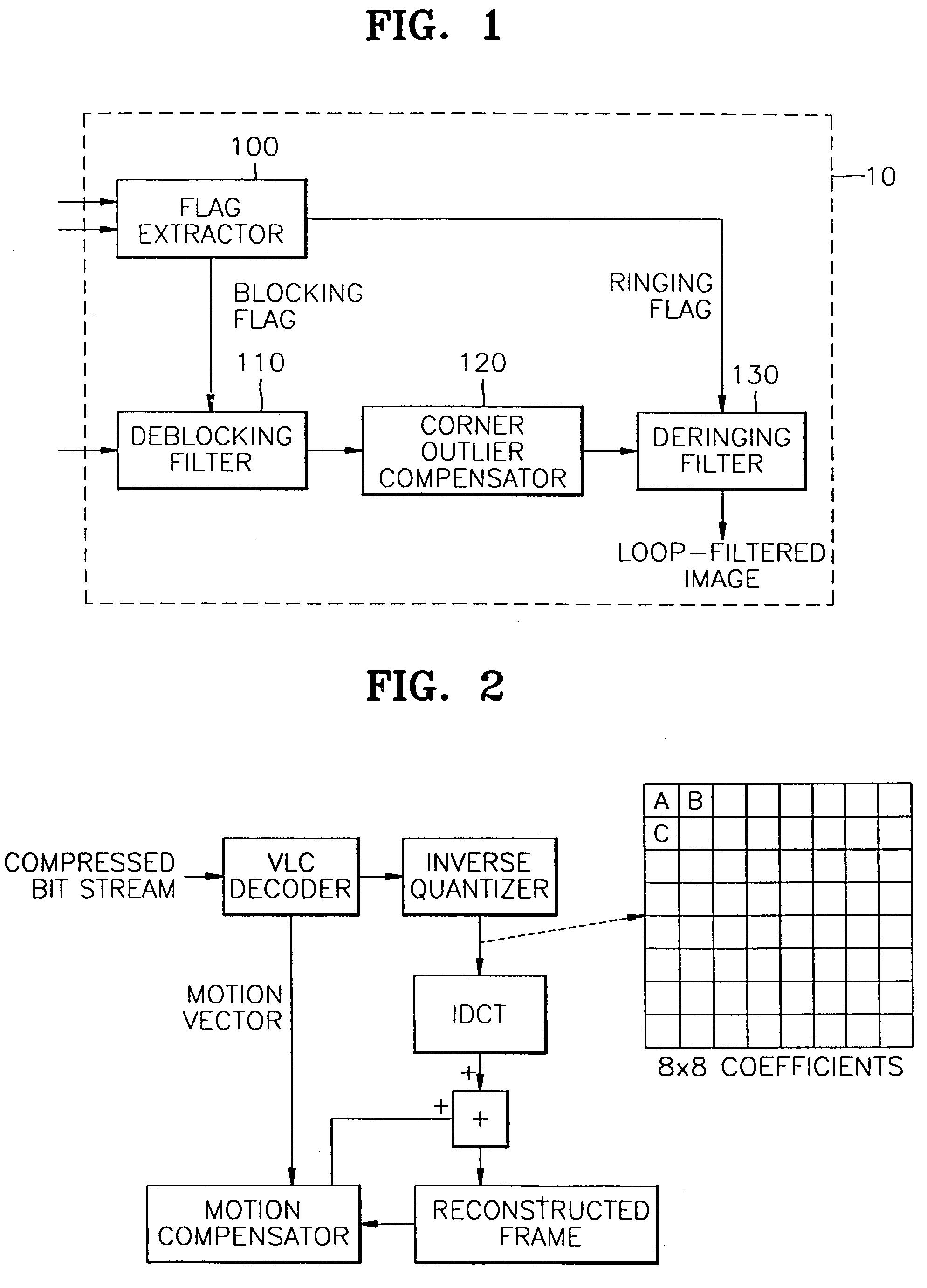

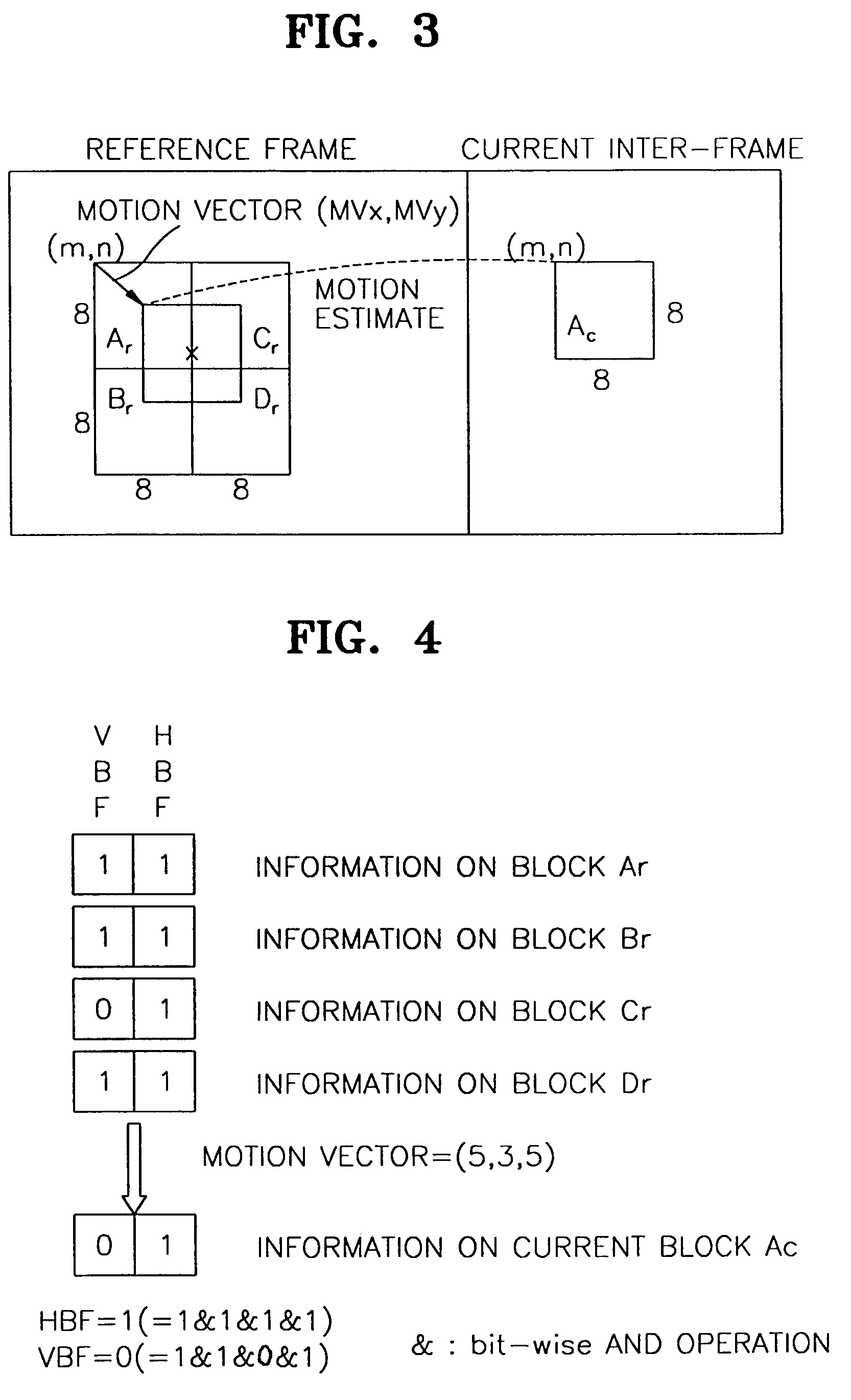

Loop-filtering method for image data and apparatus therefor

InactiveUS7251276B2Reducing quantization effectReduce impactTelevision system detailsImage enhancementLoop filterAdaptive filter

A loop-filtering method for reducing quantization effect generated when an image data is encoded and decoded, and an apparatus therefor. The loop-filtering method includes the steps of extracting a flag indicating whether the image data requires loop-filtering using the distribution of inverse quantized coefficients (IQCs) of an inverse quantized image data and a motion vector indicating the difference between the previous frame and the current frame. The image data corresponding to the flag is then filtered by a predetermined method if the extracted flag indicates a need for the loop-filtering. Using the flags and an adaptive filter reduces the quantization effect and is useful to reduce the amount of computation required for the filtering. Also, the filtering can be performed through parallel processing without multiplication and division, so that the complexity of hardware can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Systems and methods to determine elastic properties of materials

InactiveUS7107159B2Elastic propertyInherent ambiguityVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesTime domainHarmonic

The present invention provides systems and methods to used a measured driving-point response of a nonlinear material to determined one or more elastic properties of the material. The present invention takes advantage of the full information represented by the transient component, the steady-state component, the anharmonic components, and the nonlinear response components of a measured driving-point response of a real nonlinear material, without limitation in the use of large-amplitude forces. The elastic properties are determined by forming and solving a time-domain system of linear equations representing a differential equation model of the driving-point motions of the material. Based on a single, short duration, large-amplitude driving point measurement, both linear and nonlinear properties can be determined; both large-amplitude and near-zero amplitude properties can be determined; and elastic-wave speed and elastic moduli and their variation with depth can be determined.

Owner:GERMAN PETER THOMAS

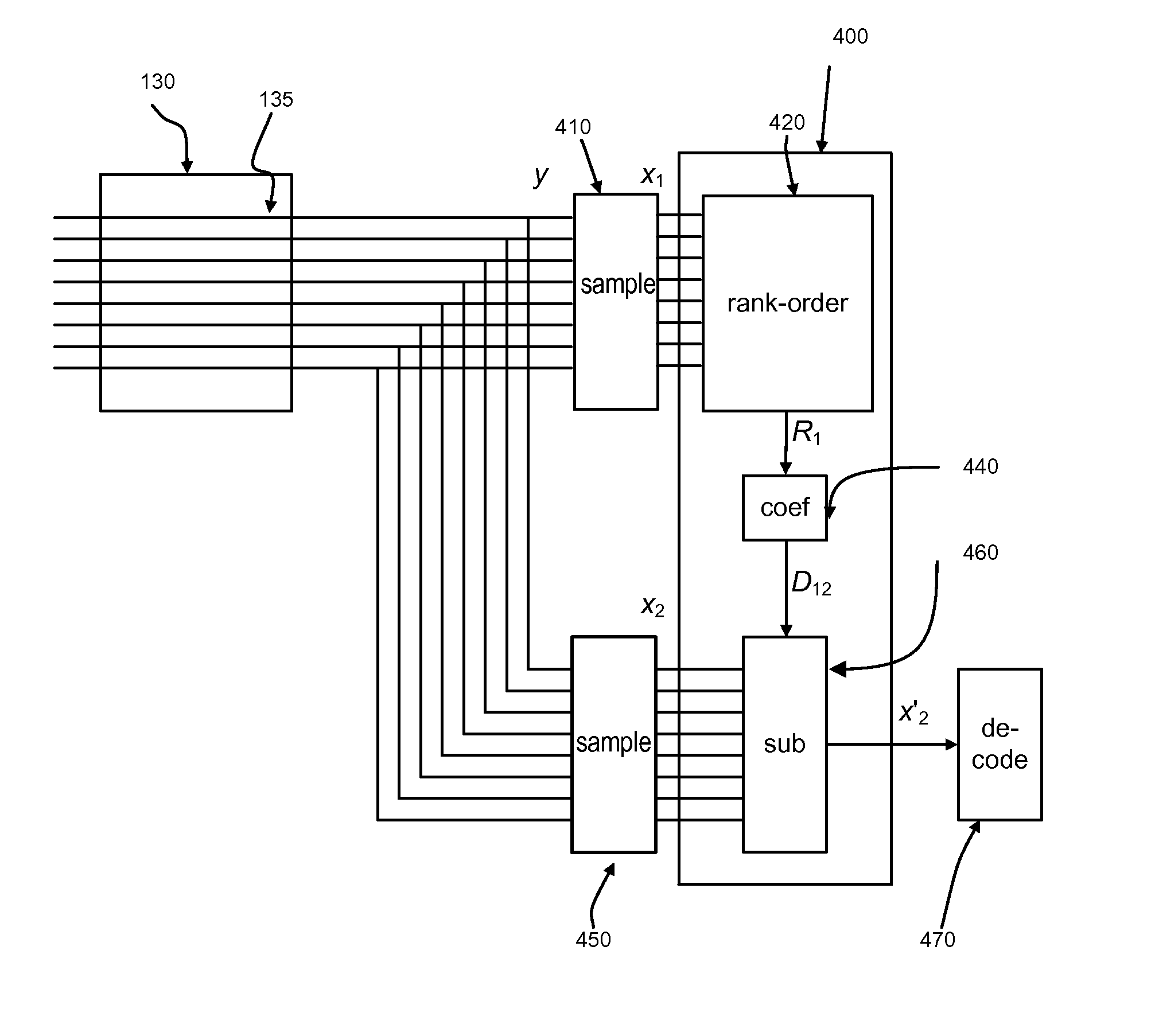

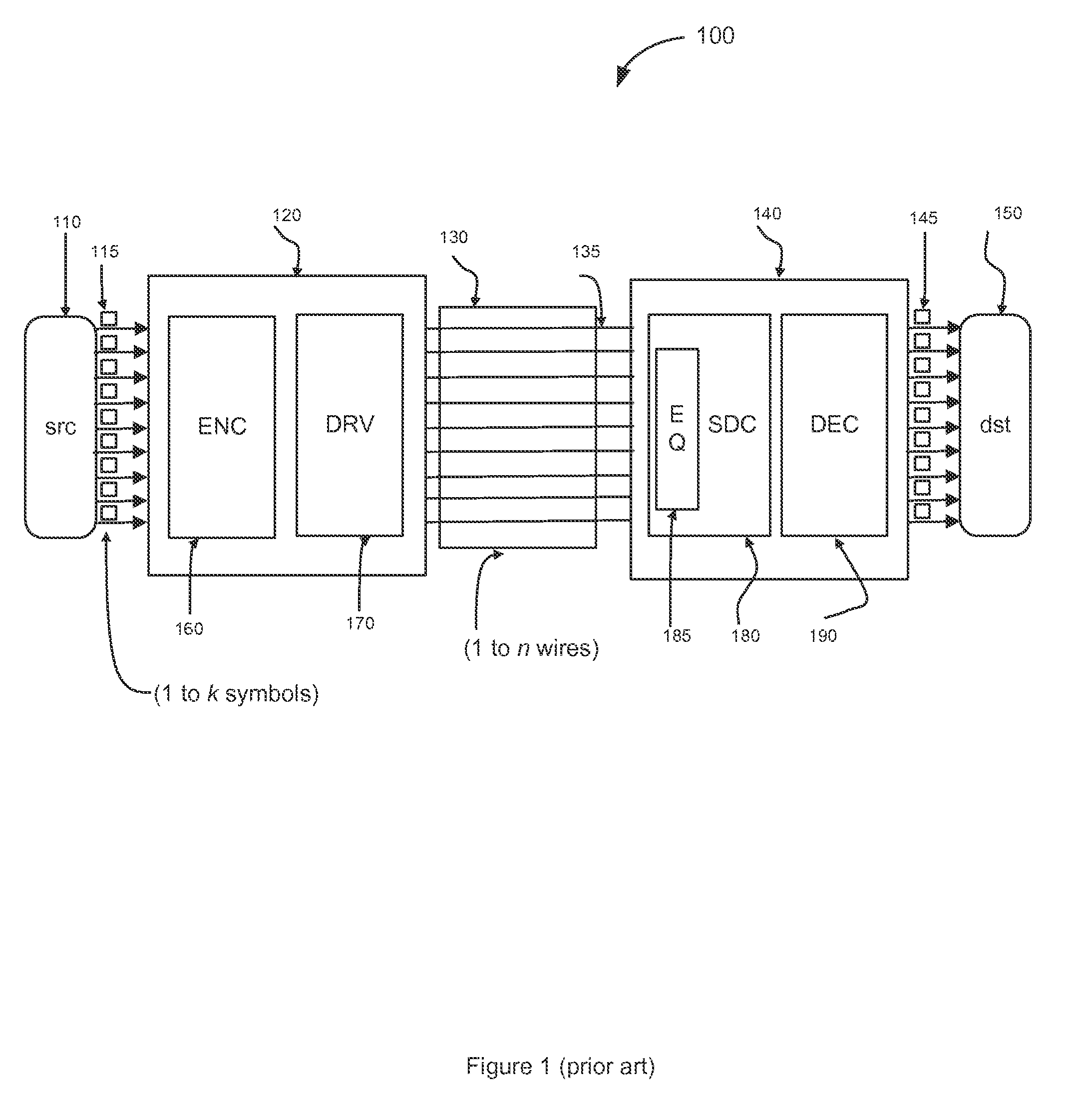

Rank-order equalization

For digital data transmitted using a vector signaling encoding, a rank-order equalizer cancels various channel noise such as inter-symbol interference. Further, rank-order units may be cascaded to achieve improved equalization over successive sample vector signals in a rank-order equalizer. Multiple rank-order equalizers further operate in parallel in a feed forward mode or in series in a feedback mode to provide a continuous vector signaling stream equalization.

Owner:KANDOU LABS

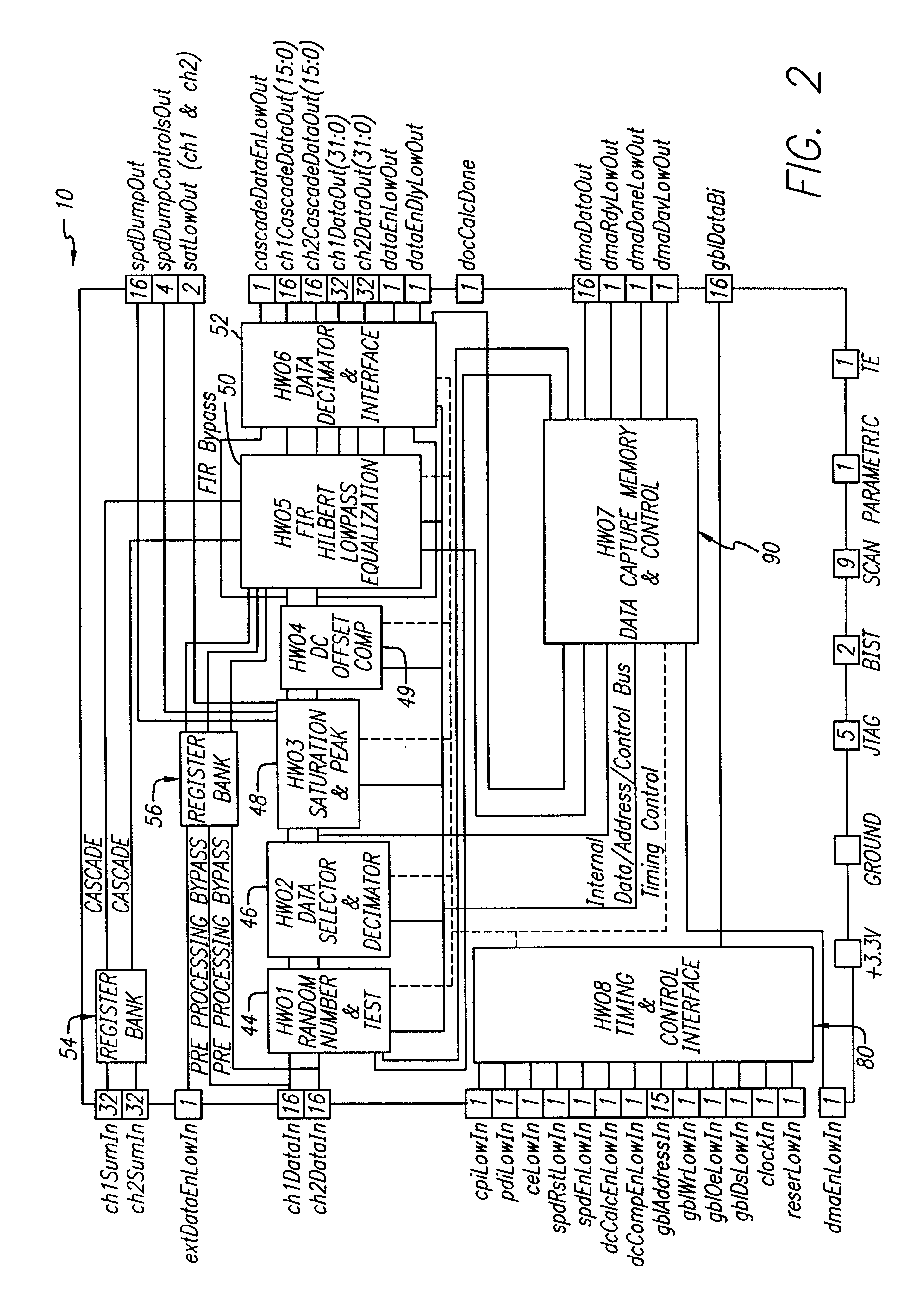

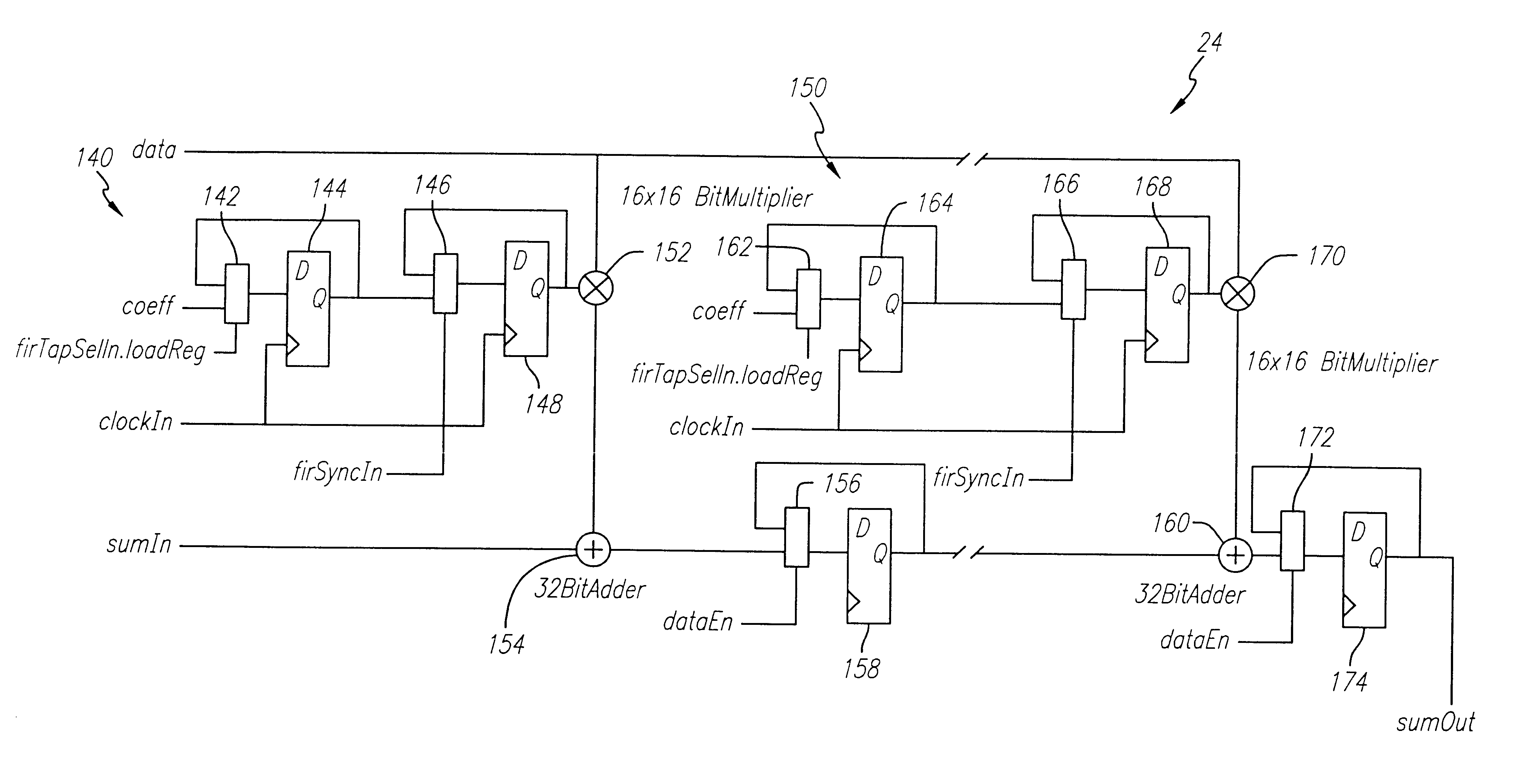

General purpose filter

InactiveUS6407694B1Television system detailsWave based measurement systemsGeneral purposeDigital signal processing

A versatile signal processor. The inventive signal processor includes a plurality of filters which are selectively interconnected to provide a variety of digital signal processing functions. In the illustrative embodiment, each filter is adapted to multiply input data by a coefficient. Further, each filter includes adders for accumulating the products. The coefficients are provided by an external processor which configures the general purpose filter to a particular function, such as a general purpose filter, a Hilbert filter, a finite impulse response filter, an equalizer, a beamforming network, a convolver, a correlator, or an application specific integrated circuit by way of example. When interconnected in accordance with the teachings provided herein, these circuits may be used to provide a digital receiver.

Owner:RAYTHEON CO

Recursive digital filter with reset

InactiveUS6167415ADigital technique networkComplex mathematical operationsIir filteringState variable

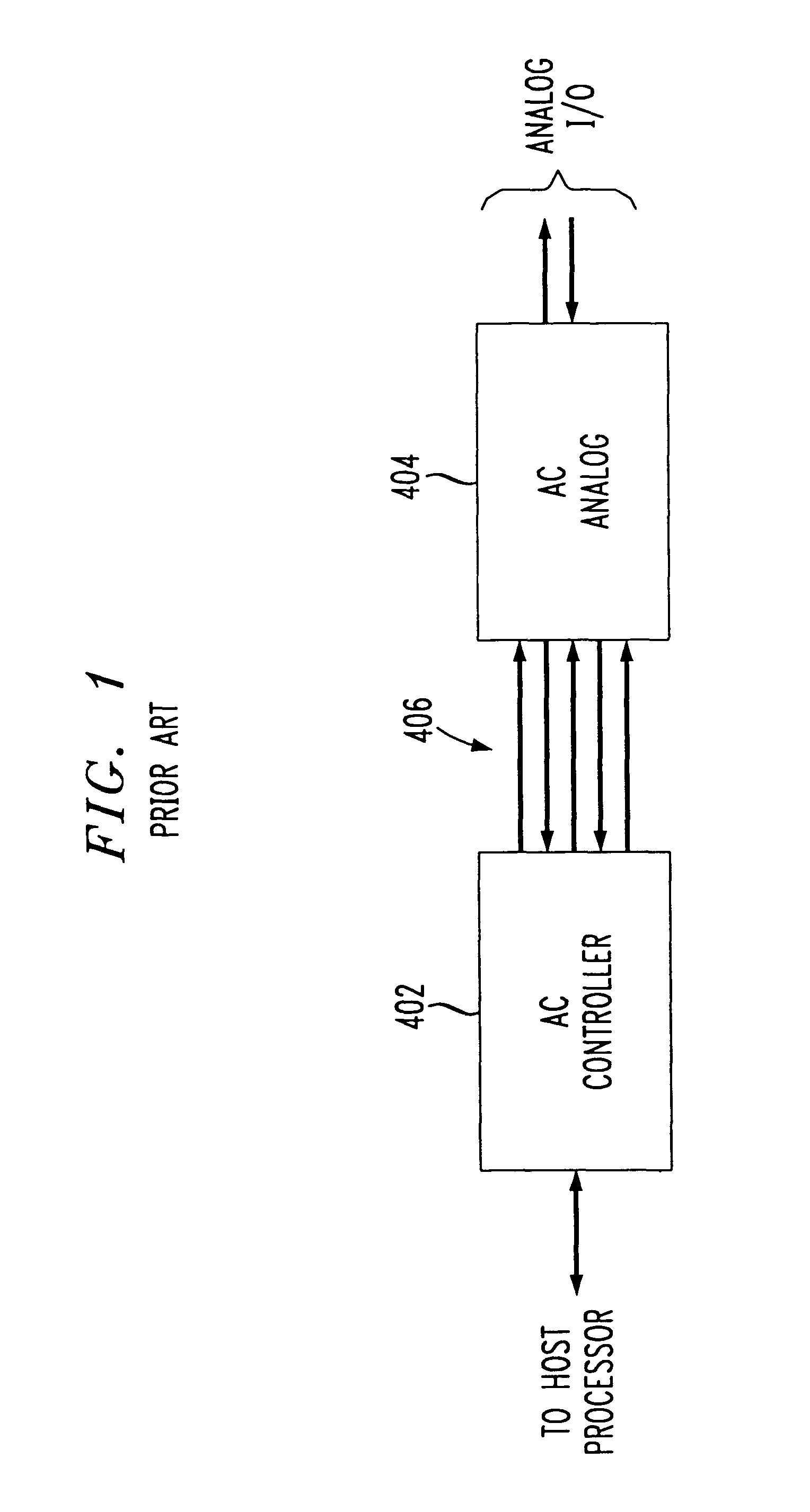

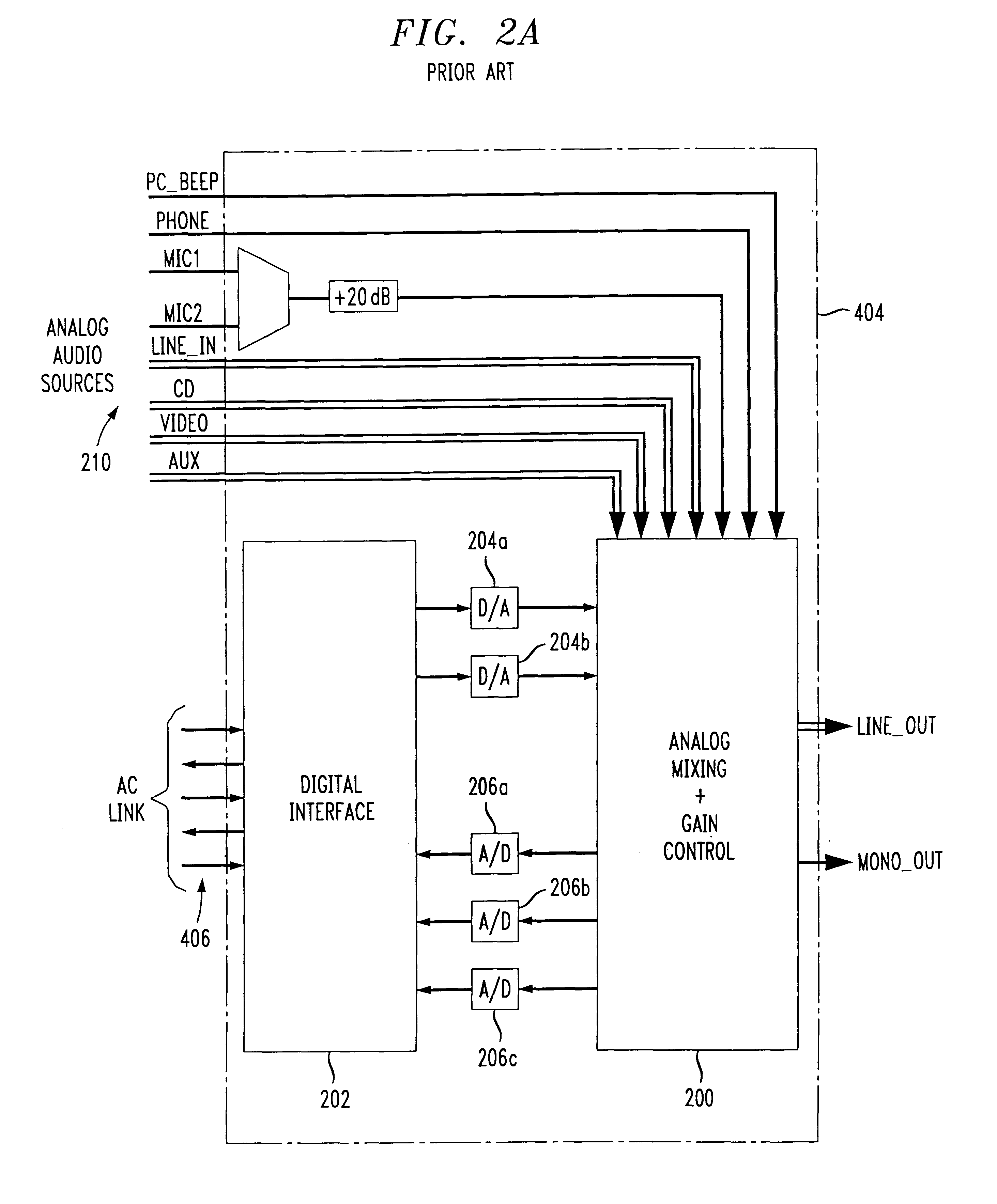

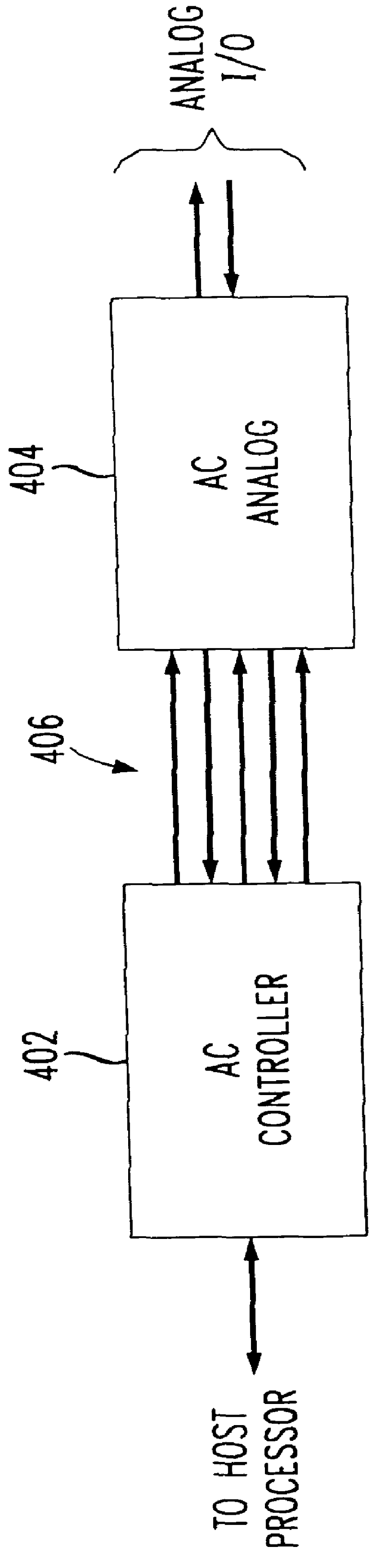

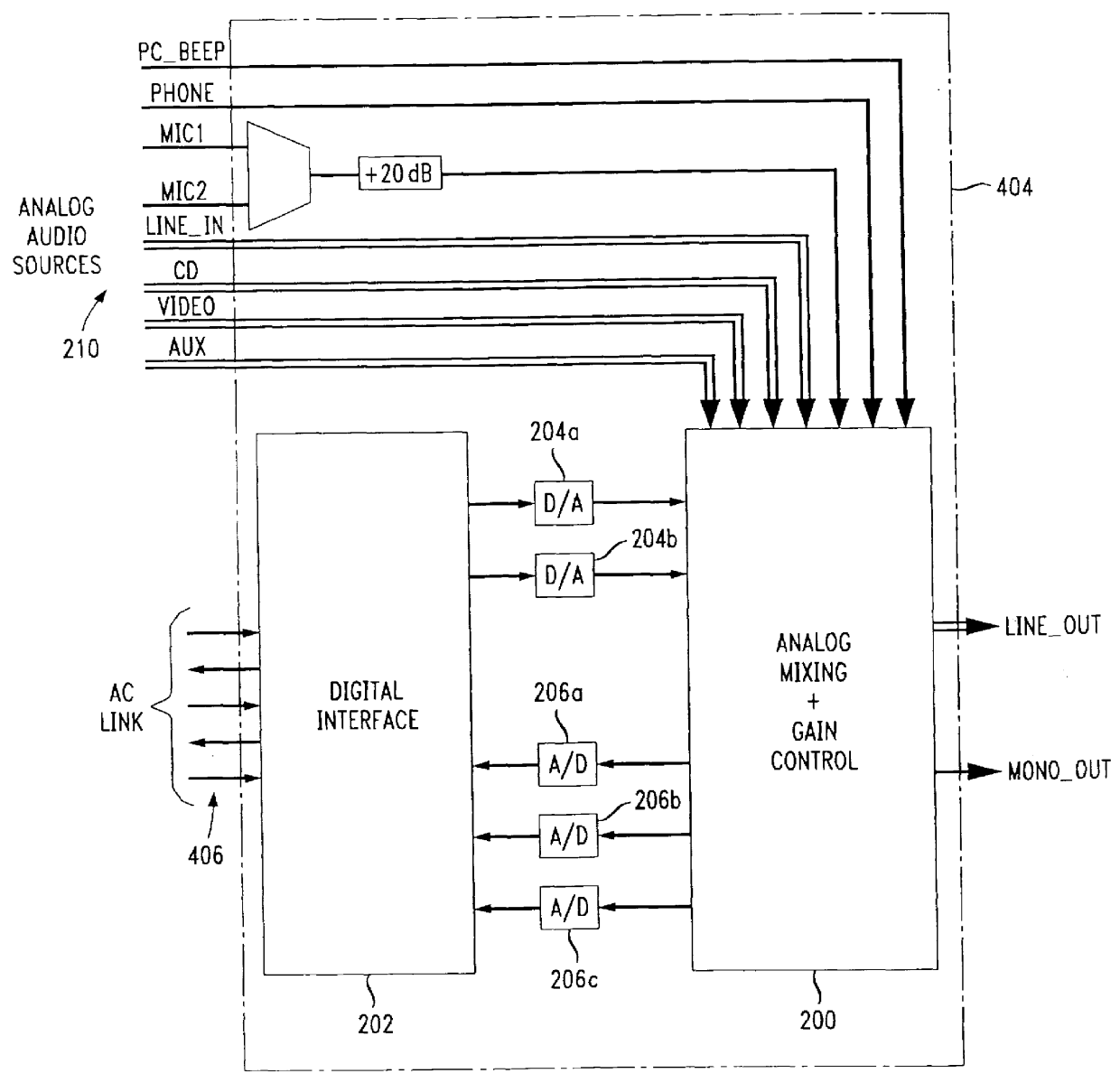

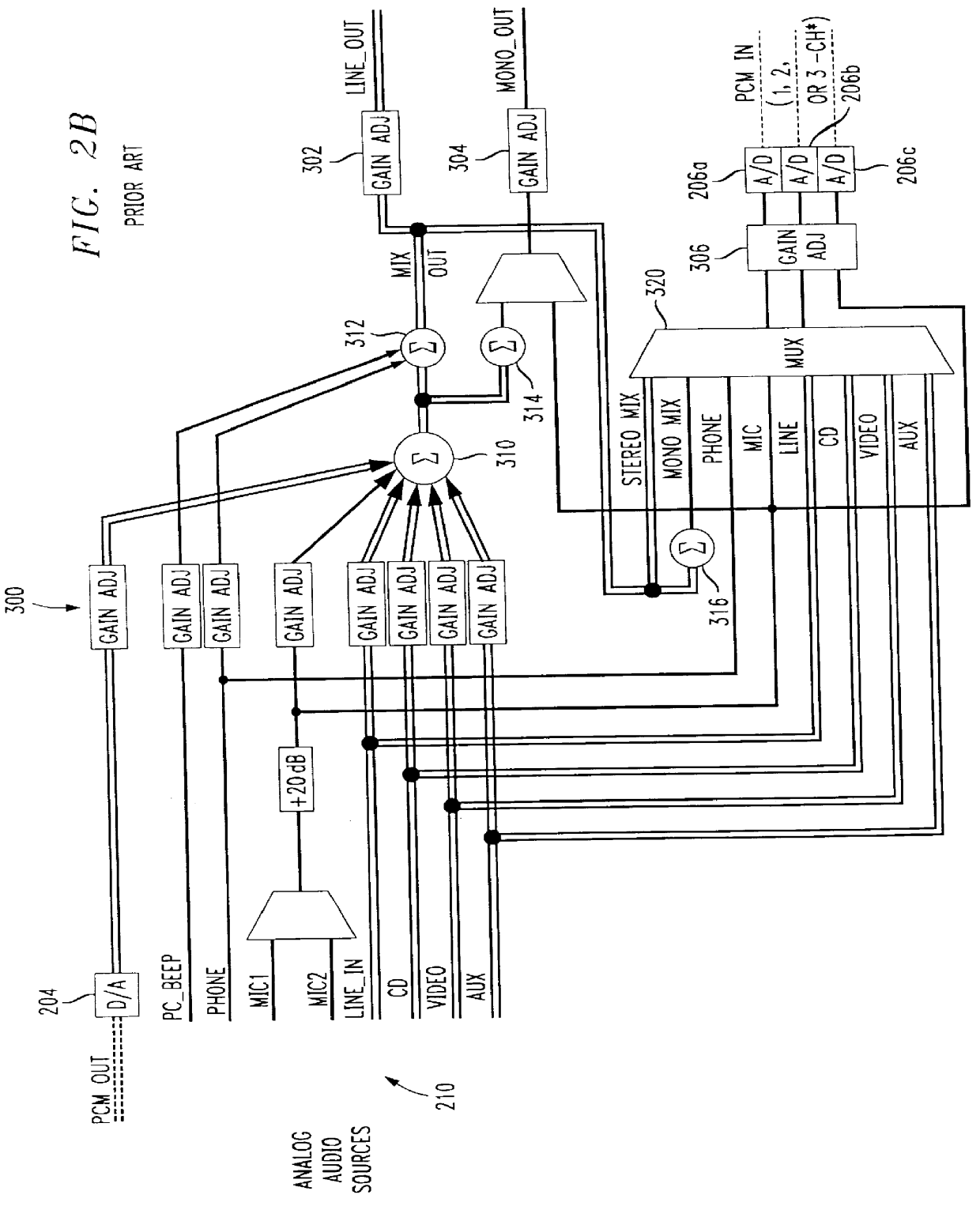

An integrated circuit, e.g. an Audio Codec (AC) '97 conforming audio codec, includes a digital filter and gain module including multiple channels of gain control and multiple channels of digital filtering. A gain control module includes an overflow check of data samples requiring differing lengths of clamping. Each channel of the digital filter includes a finite impulse response (FIR) filter, and an infinite impulse response (IIR) filter. The digital filtering is implemented largely in hardware independent of the number of channels required and / or independent of the required order of the filtering. Thus, filter channels can be added or additional filtering implemented merely by increasing the clock speed without changing the digital filter design. The FIR filter is capable of being reset each frame to prevent a direct current (DC) buildup at internal nodes. The IIR filter performs a plurality of 2nd order biquadratic equations in an overall average of as few as four clock cycles per 2nd order biquad. A random access memory (RAM) is used to store the state variables for the 2nd order biquadratic equations. The state variable RAM is reset by controlling the clear input of latches at an input and / or the output of the state variable RAM, and the state variable RAM is addressed by a delta counter which is independent of the particular number of filter channels or filter orders implemented. Test patterns may be inserted between functional blocks of an integrated circuit such as the disclosed audio codec by appropriate control of the preset and clear inputs to output latches of the functional blocks.

Owner:LUCENT TECH INC +1

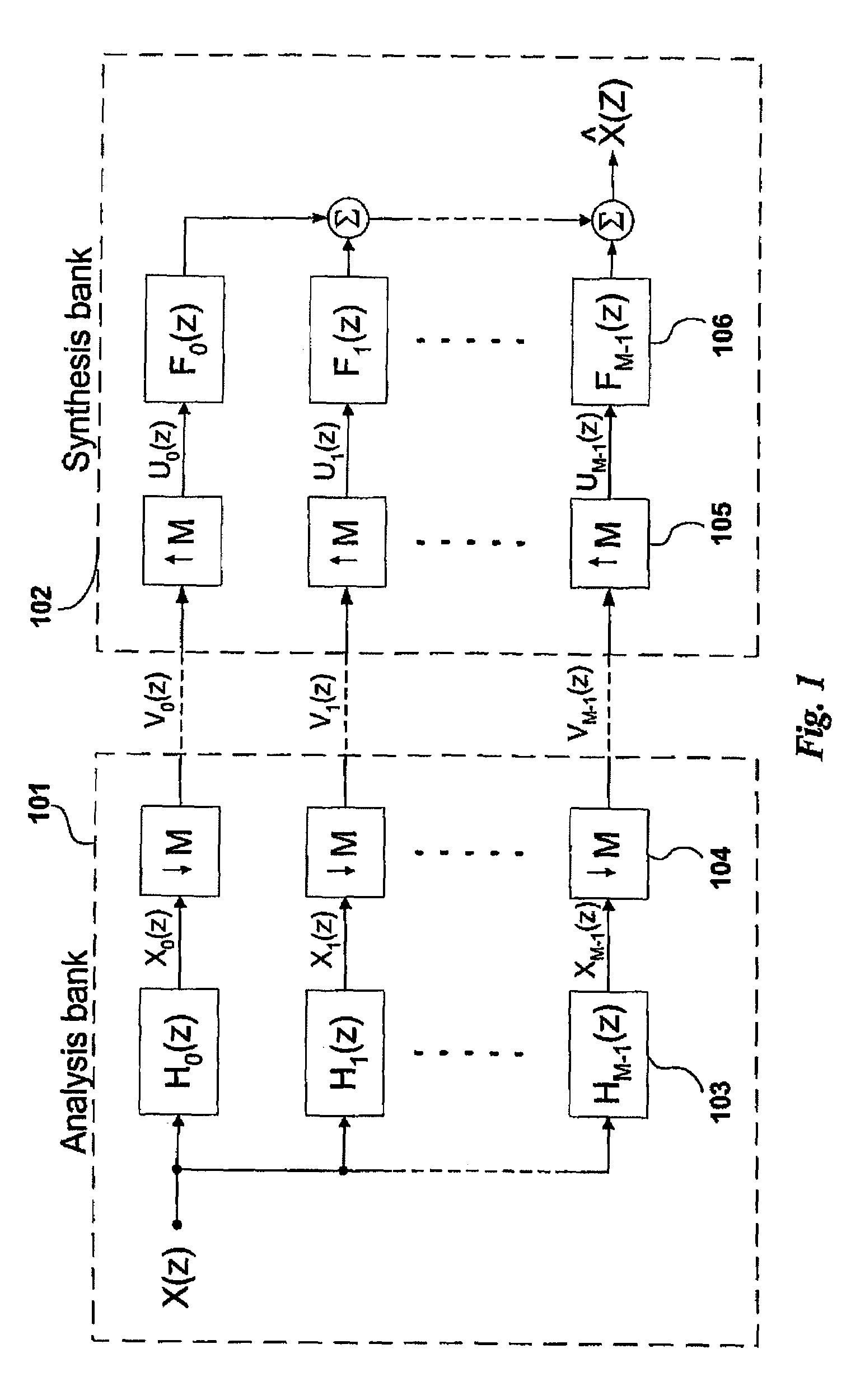

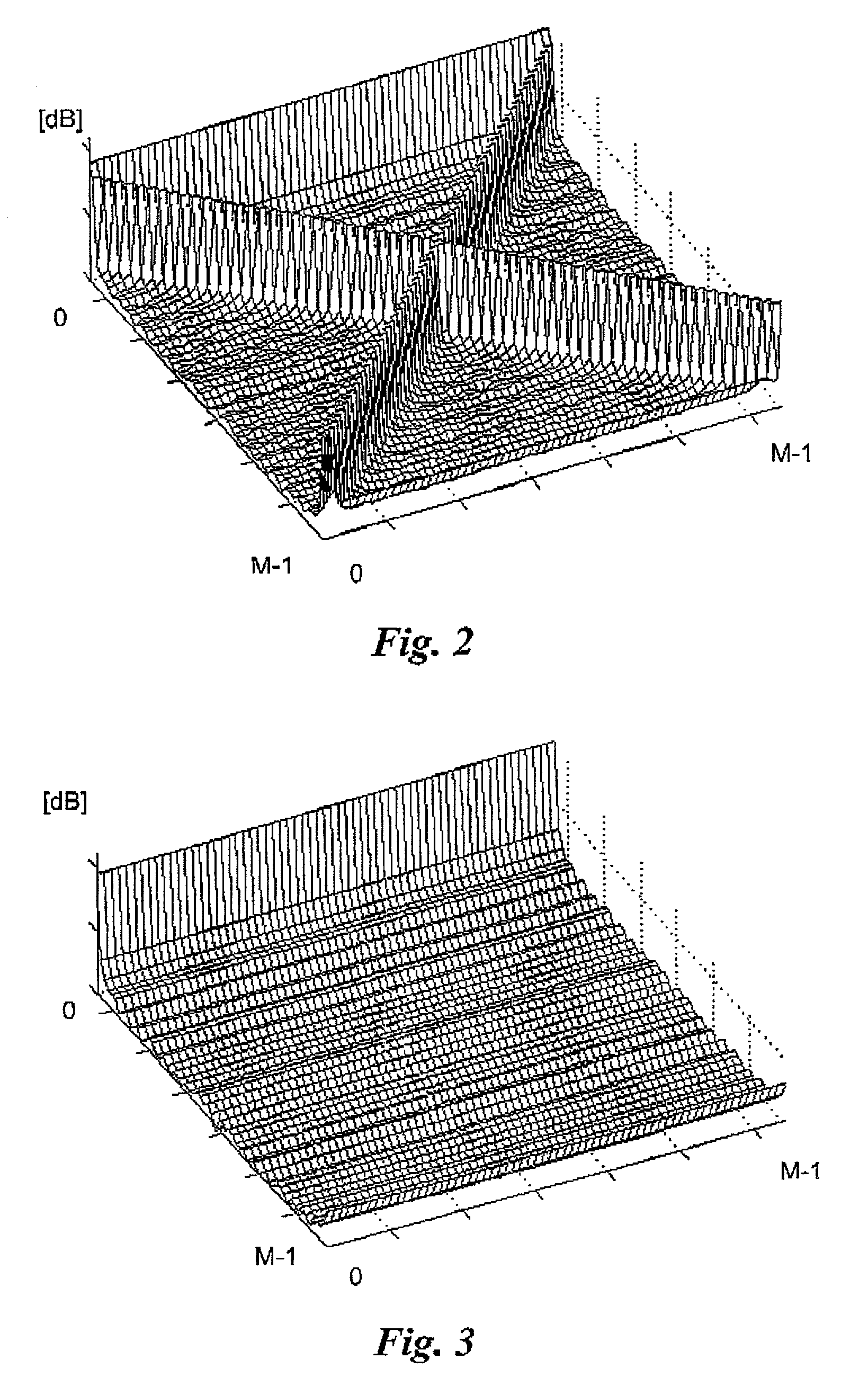

Aliasing reduction using complex-exponential modulated filterbanks

ActiveUS7242710B2Signal can be impairedMitigation of impairmentMultiple-port networksAdaptive networkFrequency spectrumComputer science

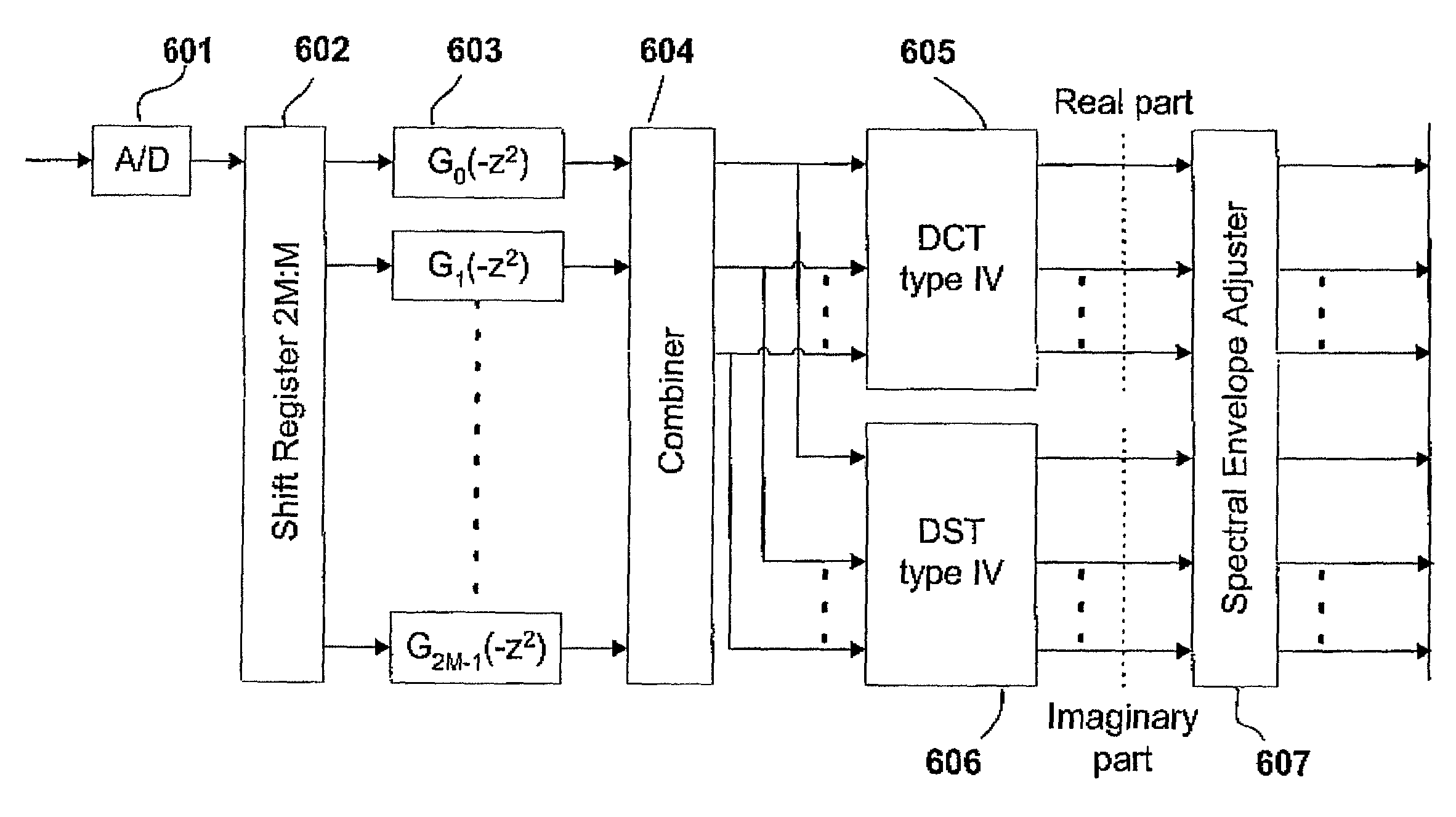

The present invention proposes a new method and apparatus for the improvement of digital filterbanks, by a complex extension of cosine modulated digital filterbanks. The invention employs complex-exponential modulation of a low-pass prototype filter and a new method for optimizing the characteristics of this filter. The invention substantially reduces artifacts due to aliasing emerging from independent modifications of subband signals, for example when using a filterbank as an spectral equalizer. The invention is preferably implemented in software, running on a standard PC or a digital signal processor (DSP), but can also be hardcoded on a custom chip. The invention offers essential improvements for various types of digital equalizers, adaptive filters, multiband companders and spectral envelope adjusting filterbanks used in high frequency reconstruction (HFR) systems.

Owner:DOLBY INT AB