Patents

Literature

57444results about "Complex mathematical operations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Optimization of microgrid energy use and distribution

ActiveUS20100179704A1Optimize energy distributionOptimize energy useBatteries circuit arrangementsLevel controlPersonalizationMicrogrid

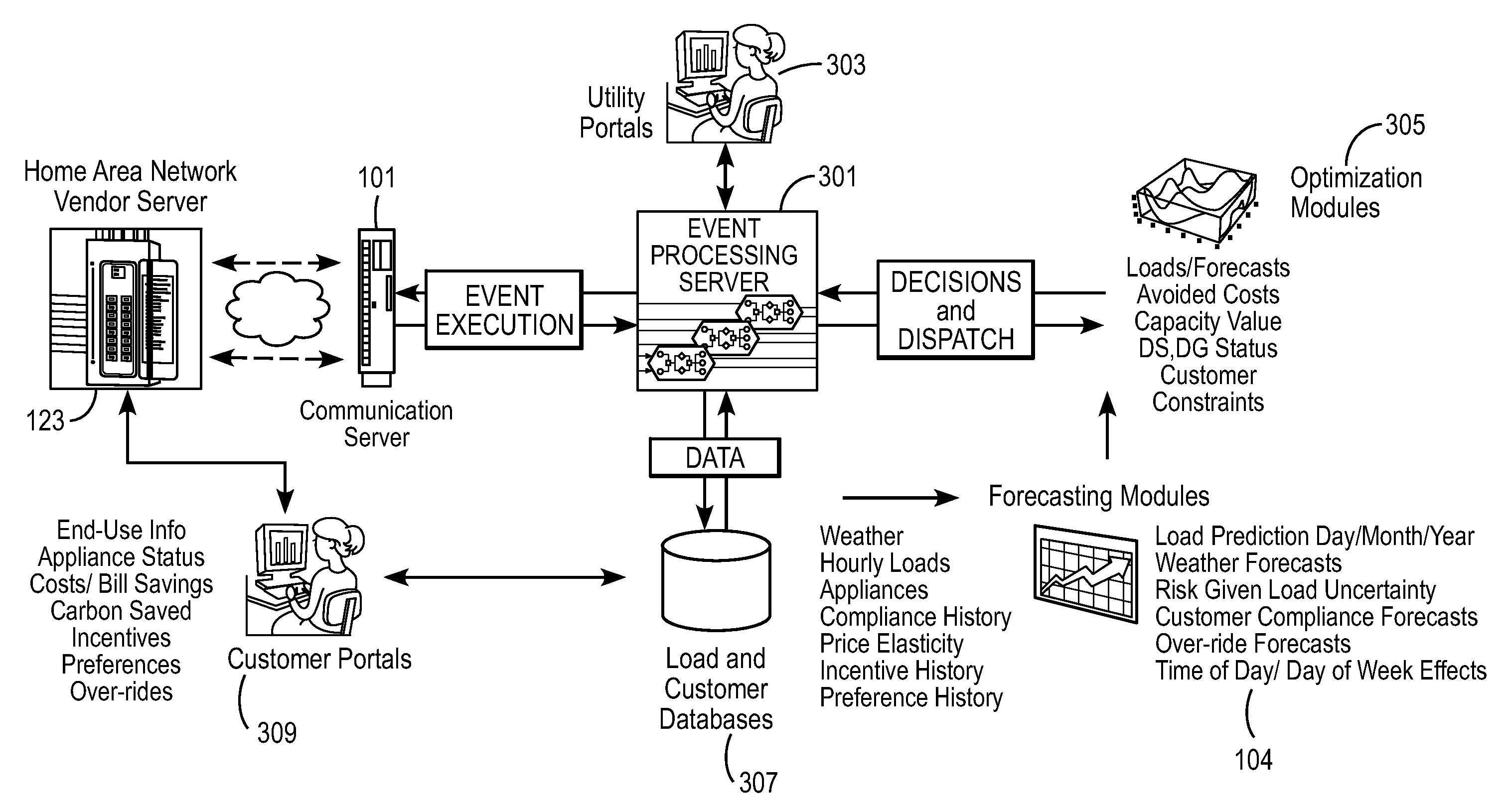

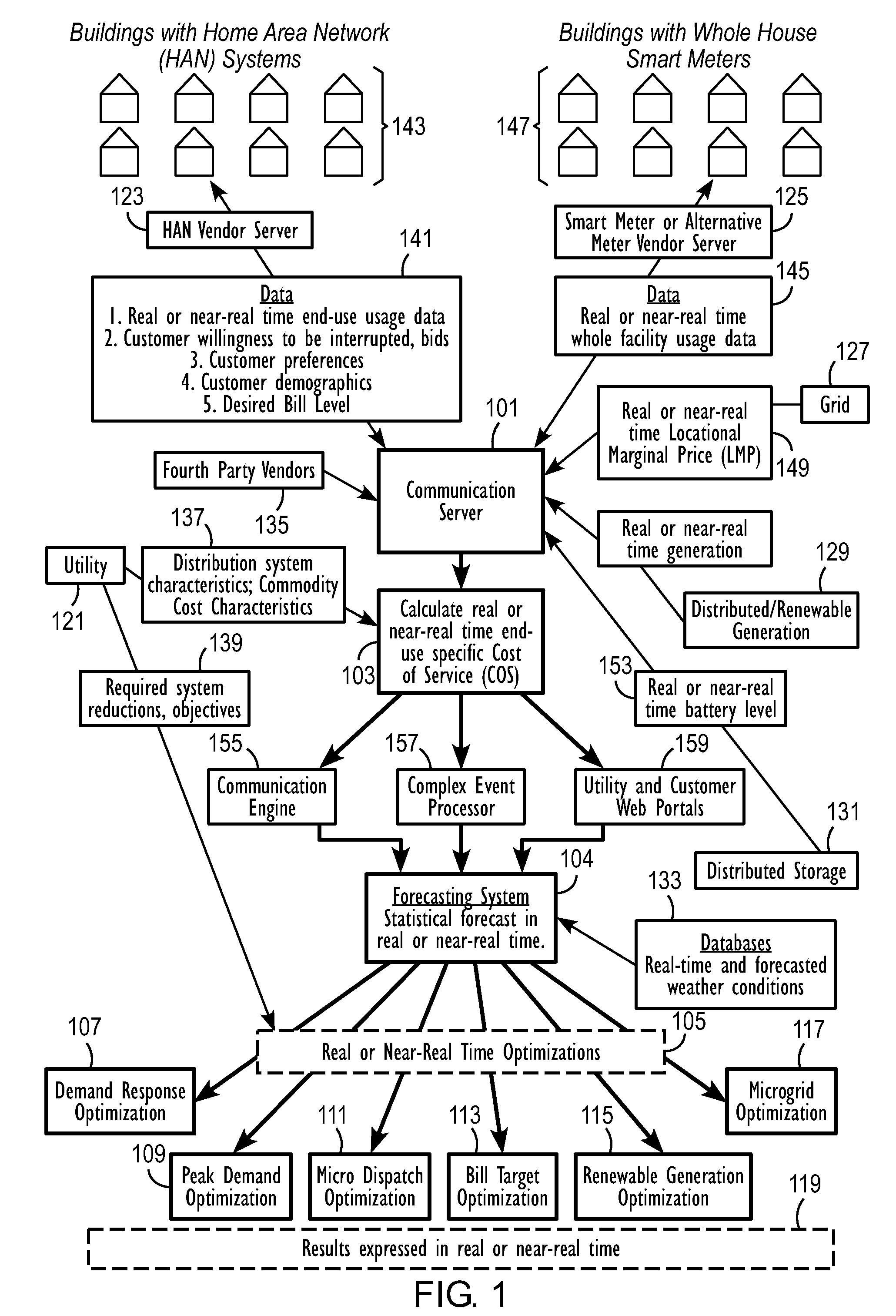

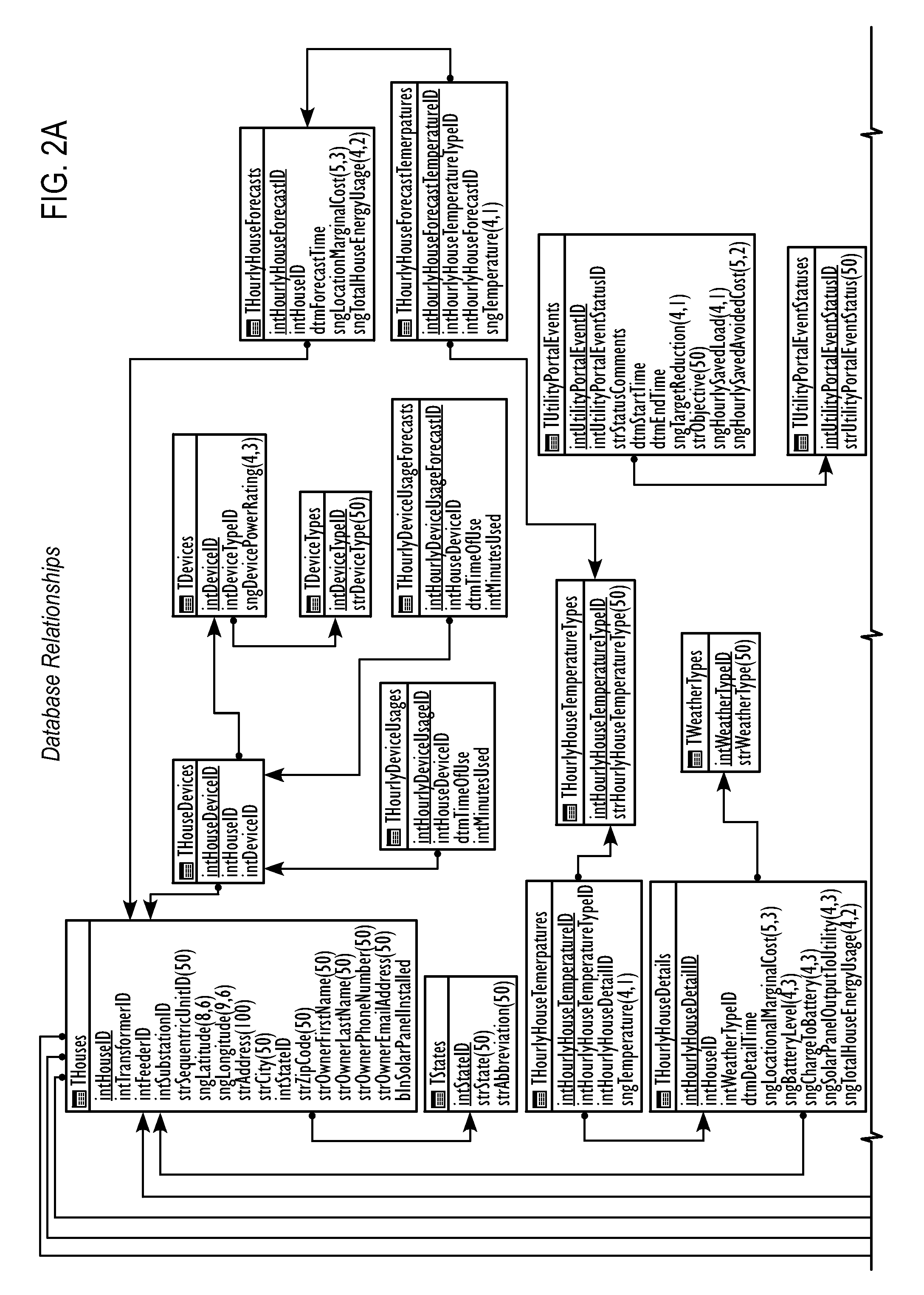

An energy distribution may include a server and one or more databases. The system may communicate with an energy provider to receive energy provider data, at least one information collector to receive information collector data such as individualized energy usage data, customer preferences, and customer or location characteristics, and the one or more databases for receiving data for optimization. The system may calculate a cost of service or avoided cost using at least one of the individualized energy usage data and a system generation cost at a nearest bus. The system may also forecast individualized demand by end-use, individualized demand by location, energy prices, or energy costs. The system may optimize energy distribution, energy use, cost of service, or avoided cost using the forecasted individualized demand by end-use, the forecasted individualized demand by location, the forecasted energy prices, and the forecasted energy costs.

Owner:INTEGRAL ANALYTICS

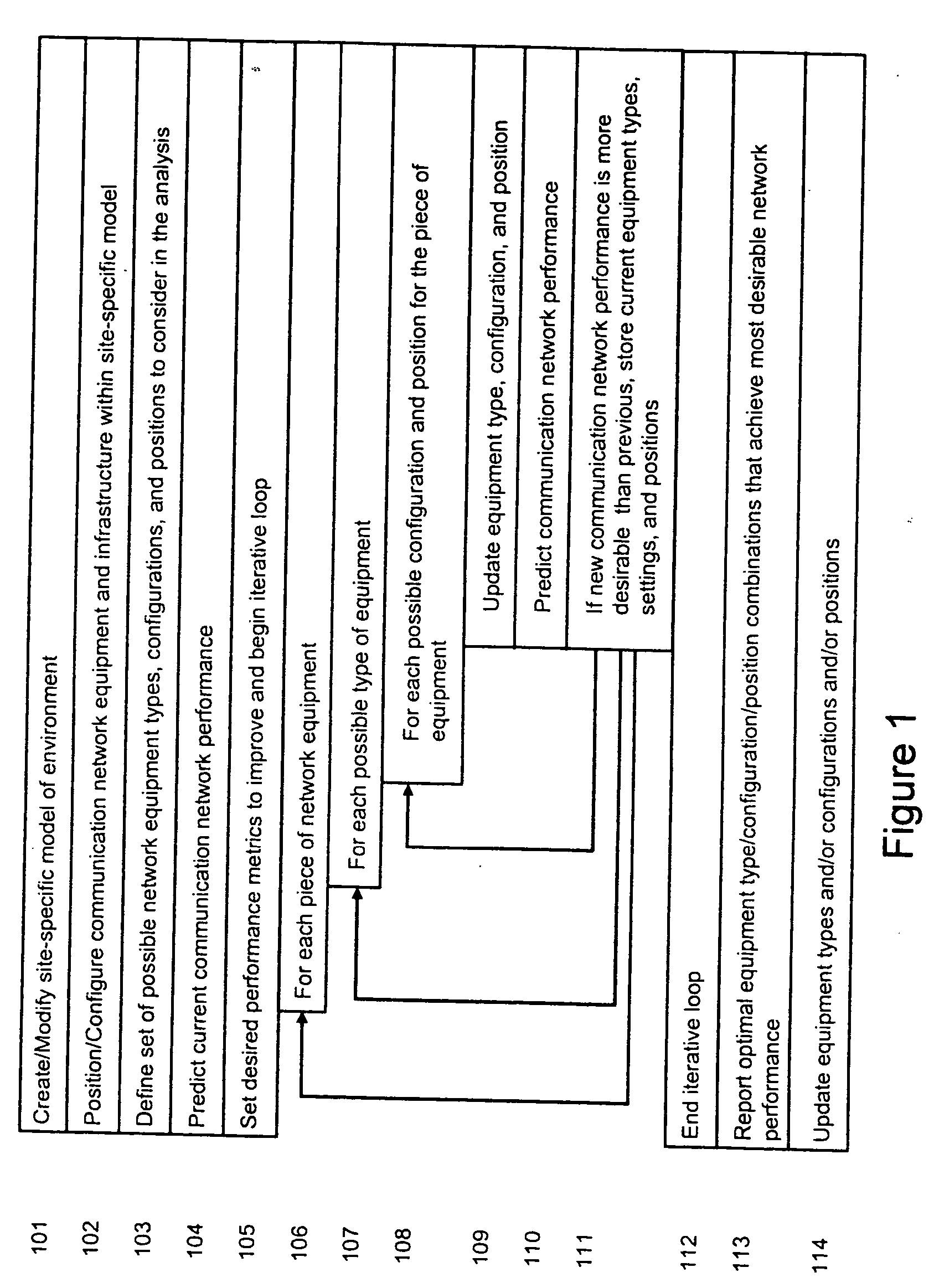

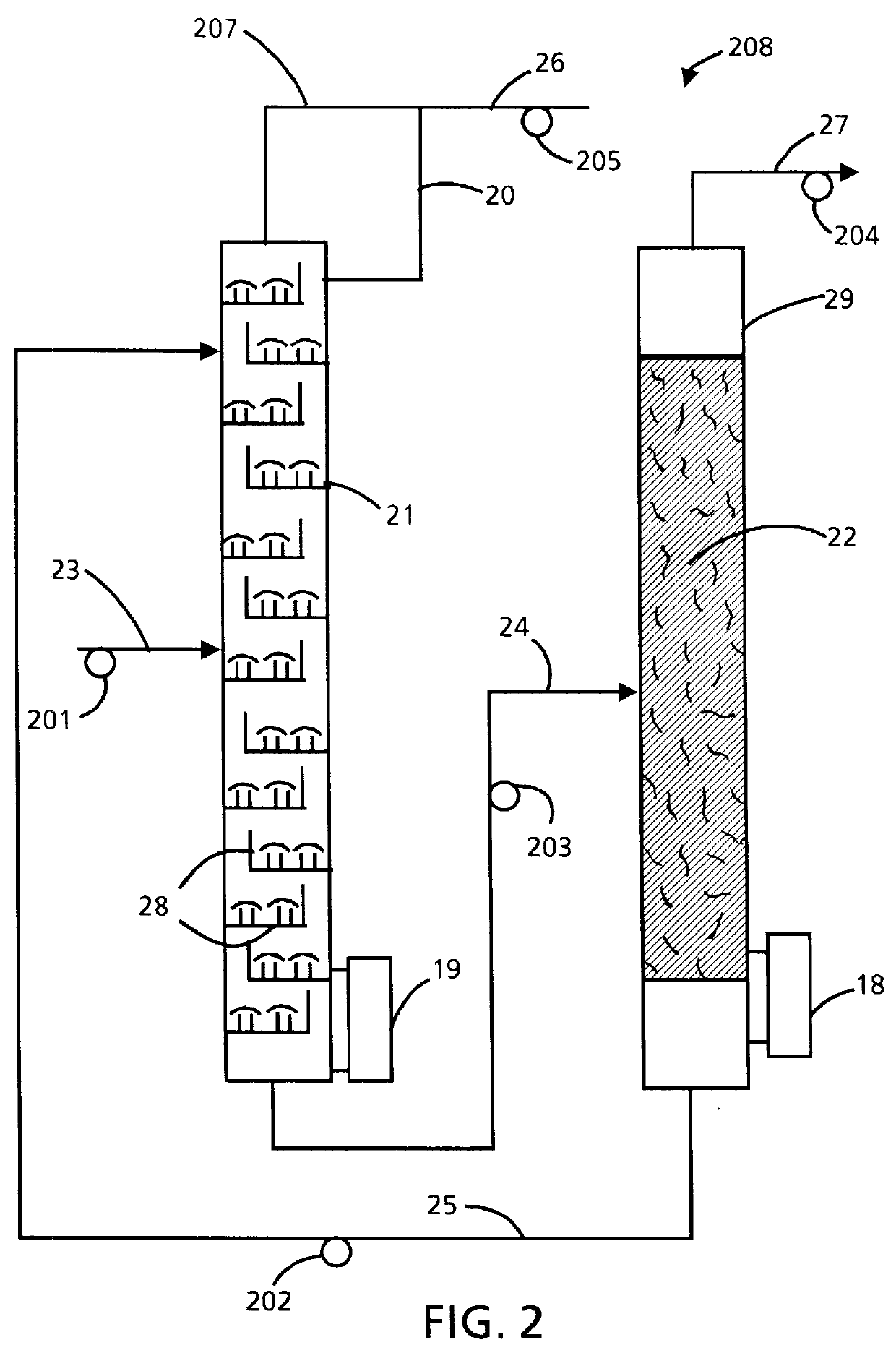

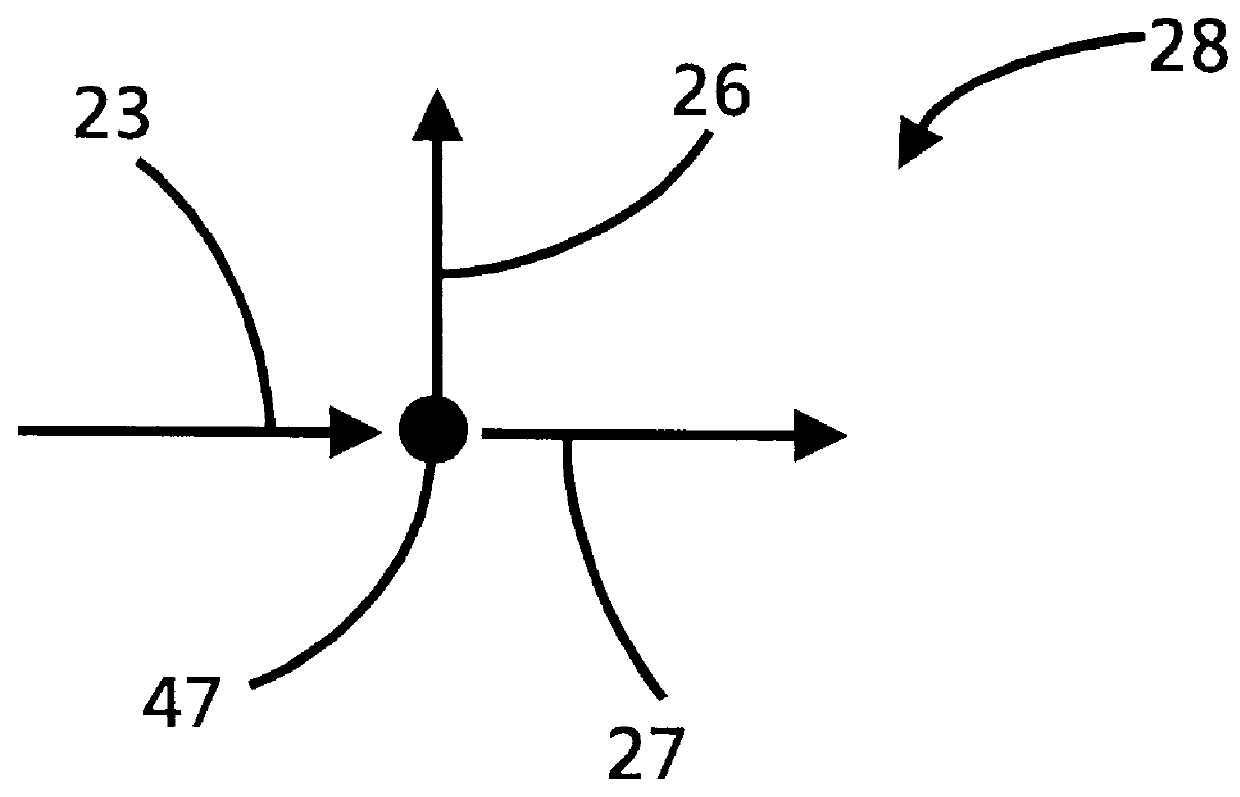

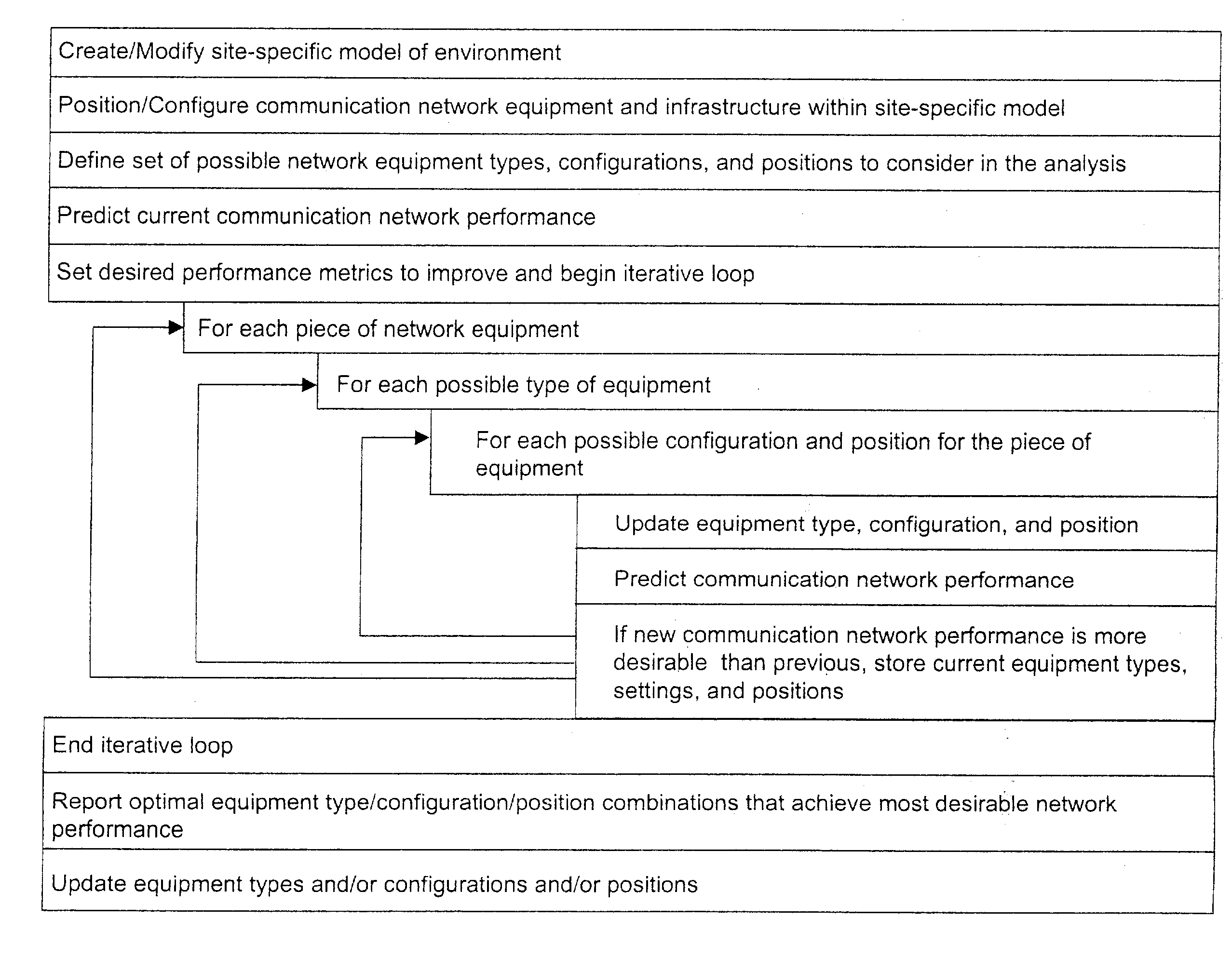

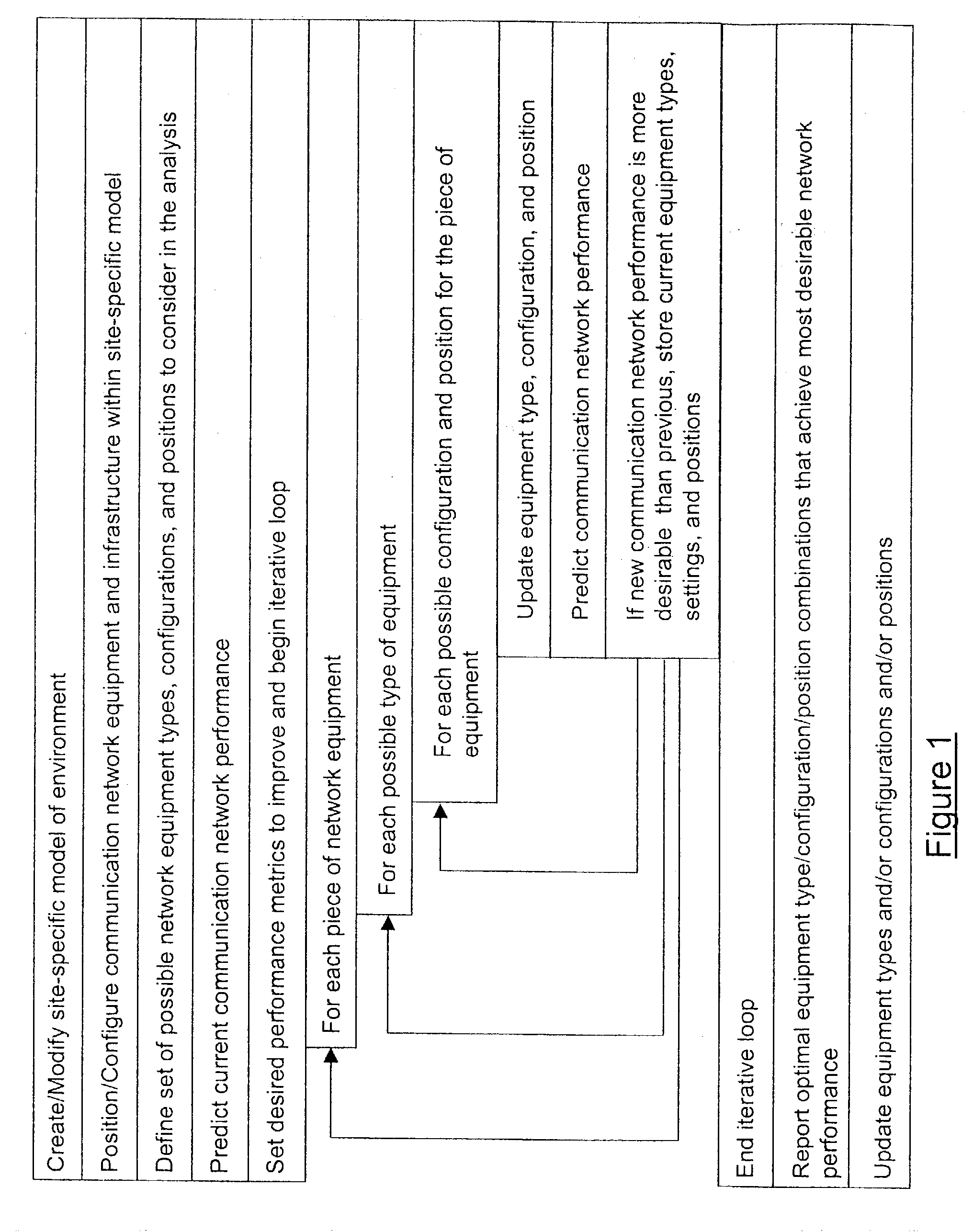

System and method for automated placement or configuration of equipment for obtaining desired network performance objectives and for security, RF tags, and bandwidth provisioning

ActiveUS20040236547A1Significant valueEasy to explainGeometric CADData taking preventionHard disc driveThe Internet

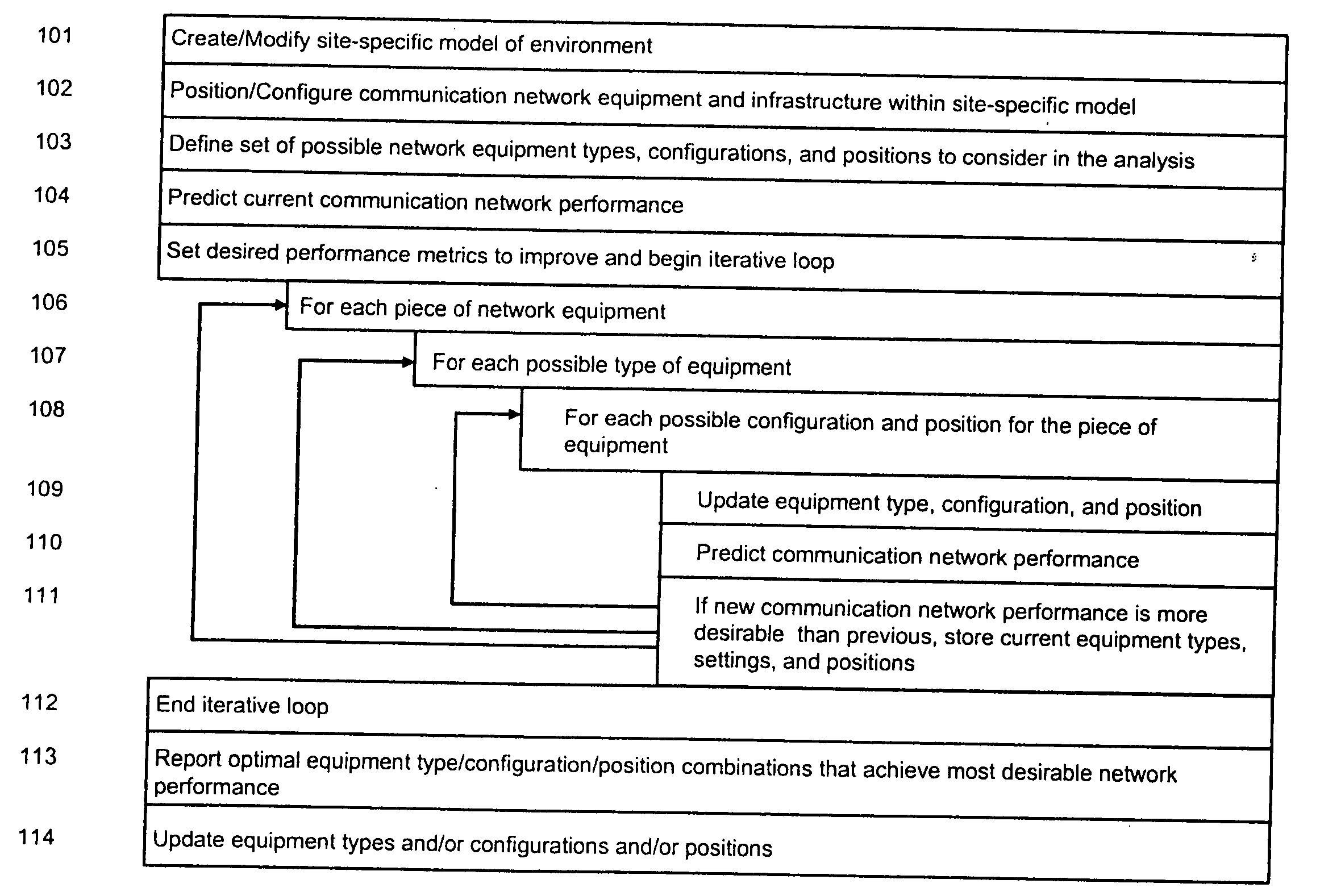

A method is presented for determining optimal or preferred configuration settings for wireless or wired network equipment in order to obtain a desirable level of network performance. A site-specific network model is used with adaptive processing to perform efficient design and on-going management of network performance. The invention iteratively determines overall network performance and cost, and further iterates equipment settings, locations and orientations. Real time control is between a site-specific Computer Aided Design (CAD) software application and the physical components of the network allows the invention to display, store, and iteratively adapt any network to constantly varying traffic and interference conditions. Alarms provide rapid adaptation of network parameters, and alerts and preprogrammed network shutdown actions may be taken autonomously. A wireless post-it note device and network allows massive data such as book contents or hard drive memory to be accessed within a room by a wide bandwidth reader device, and this can further be interconnected to the internet or Ethernet backbone in order to provide worldwide access and remote retrieval to wireless post-it devices.

Owner:EXTREME NETWORKS INC

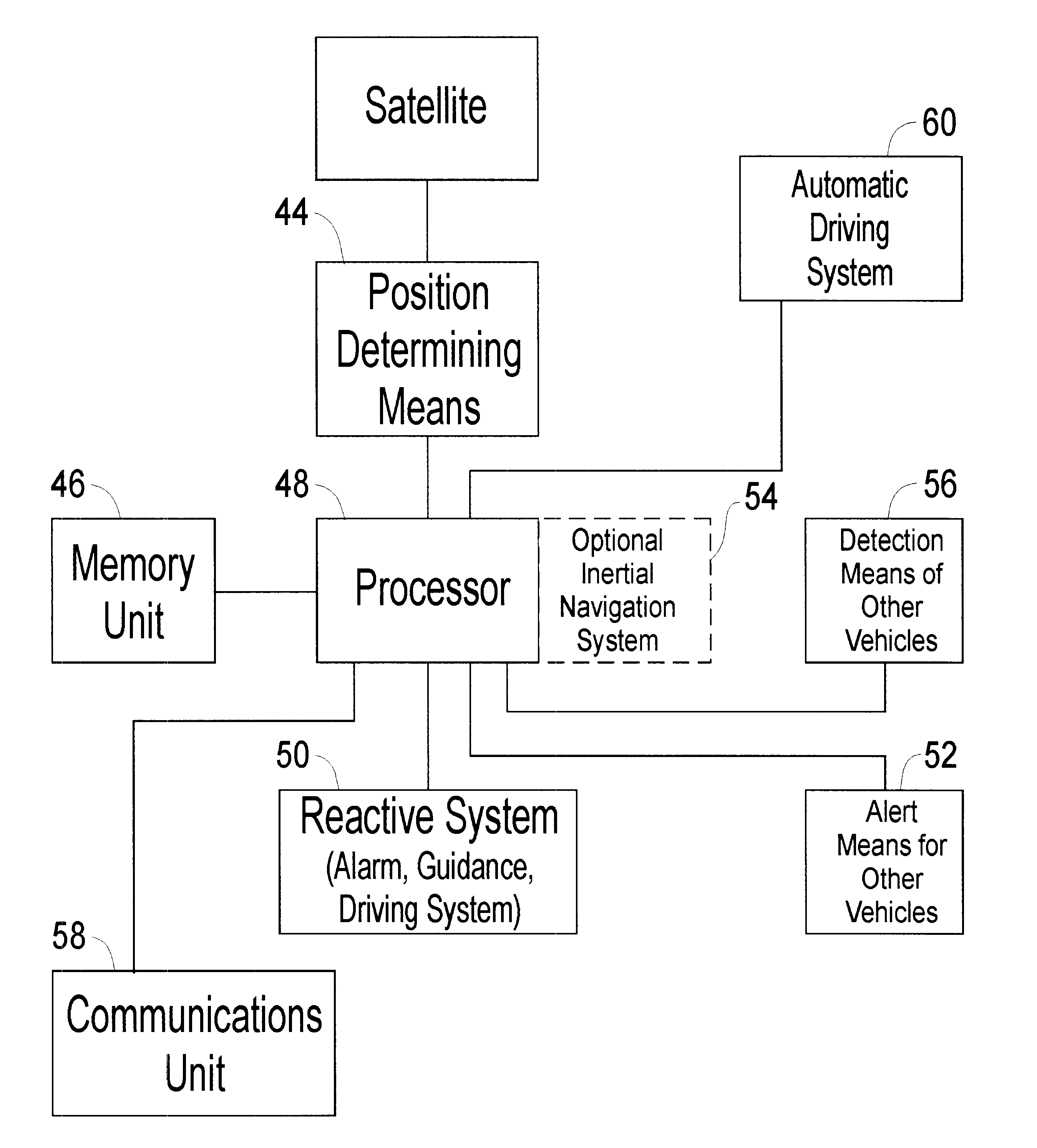

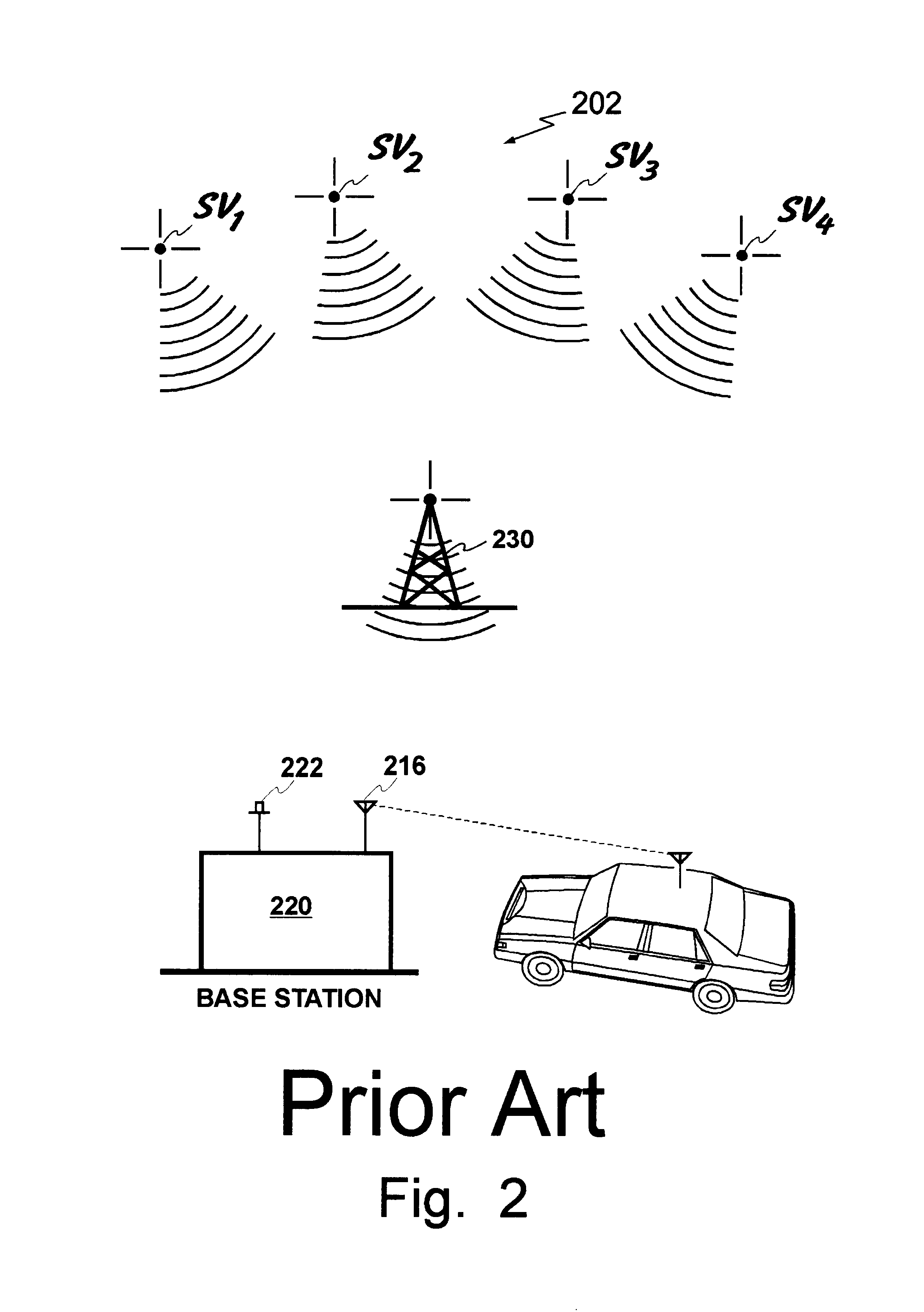

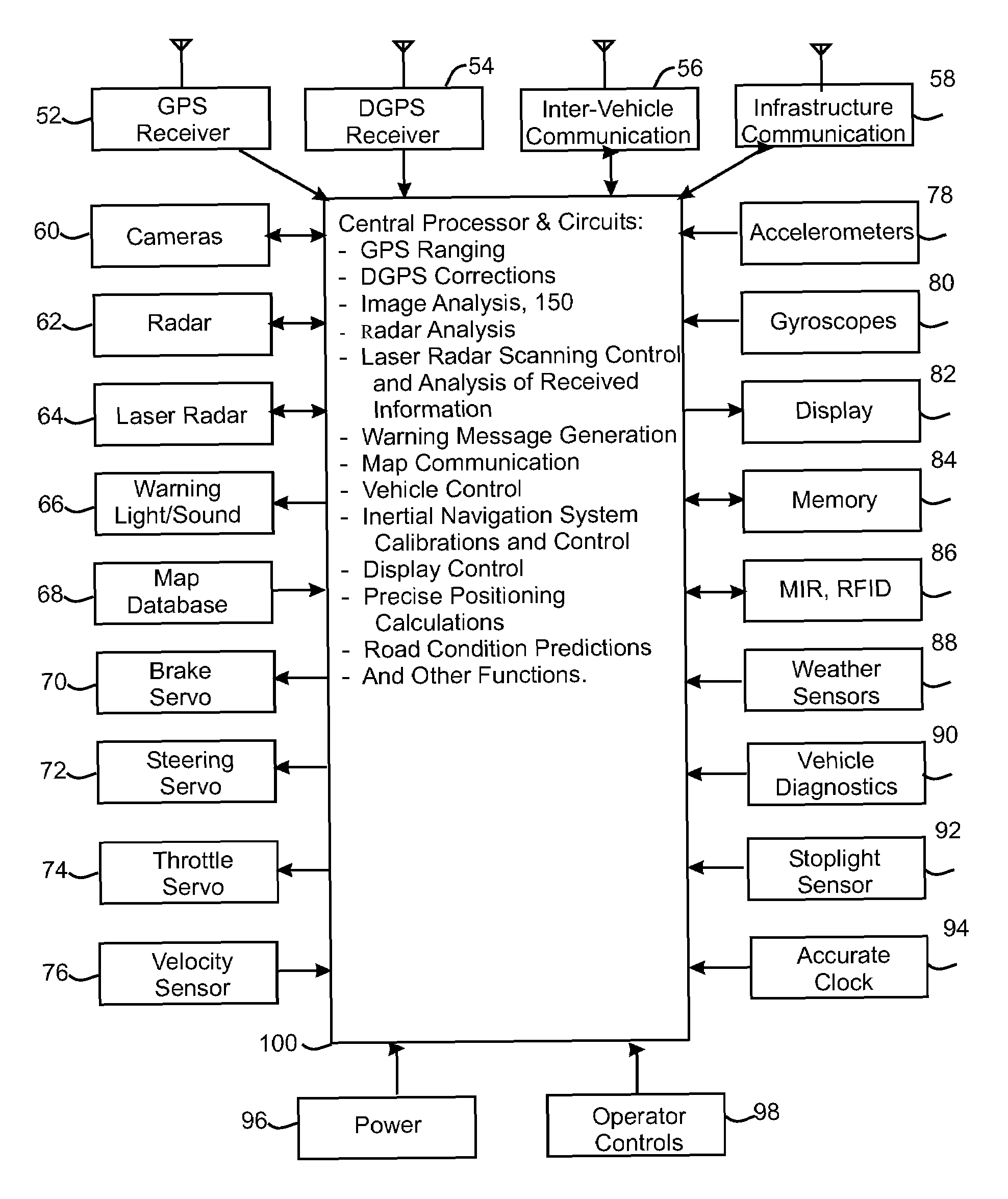

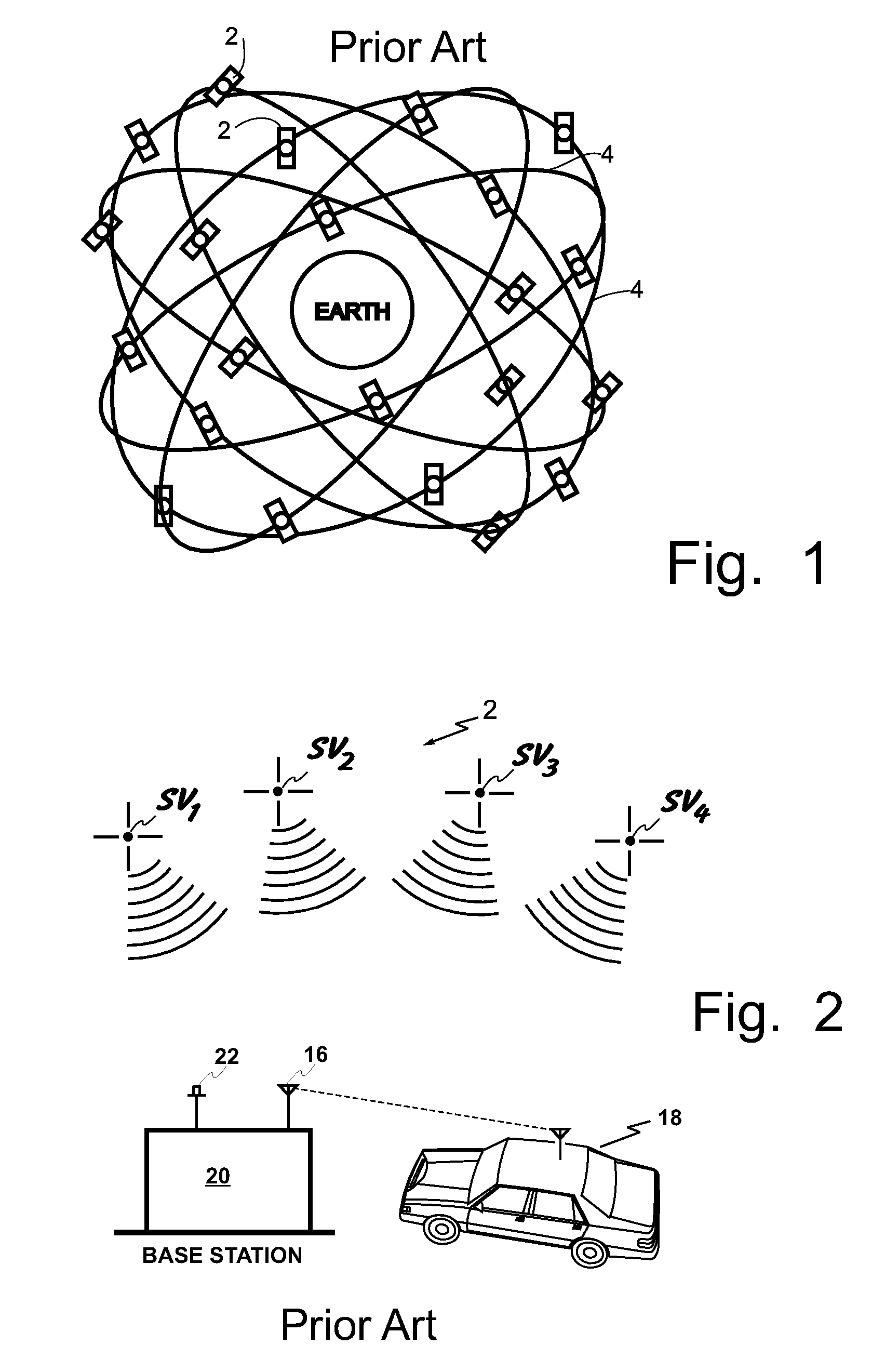

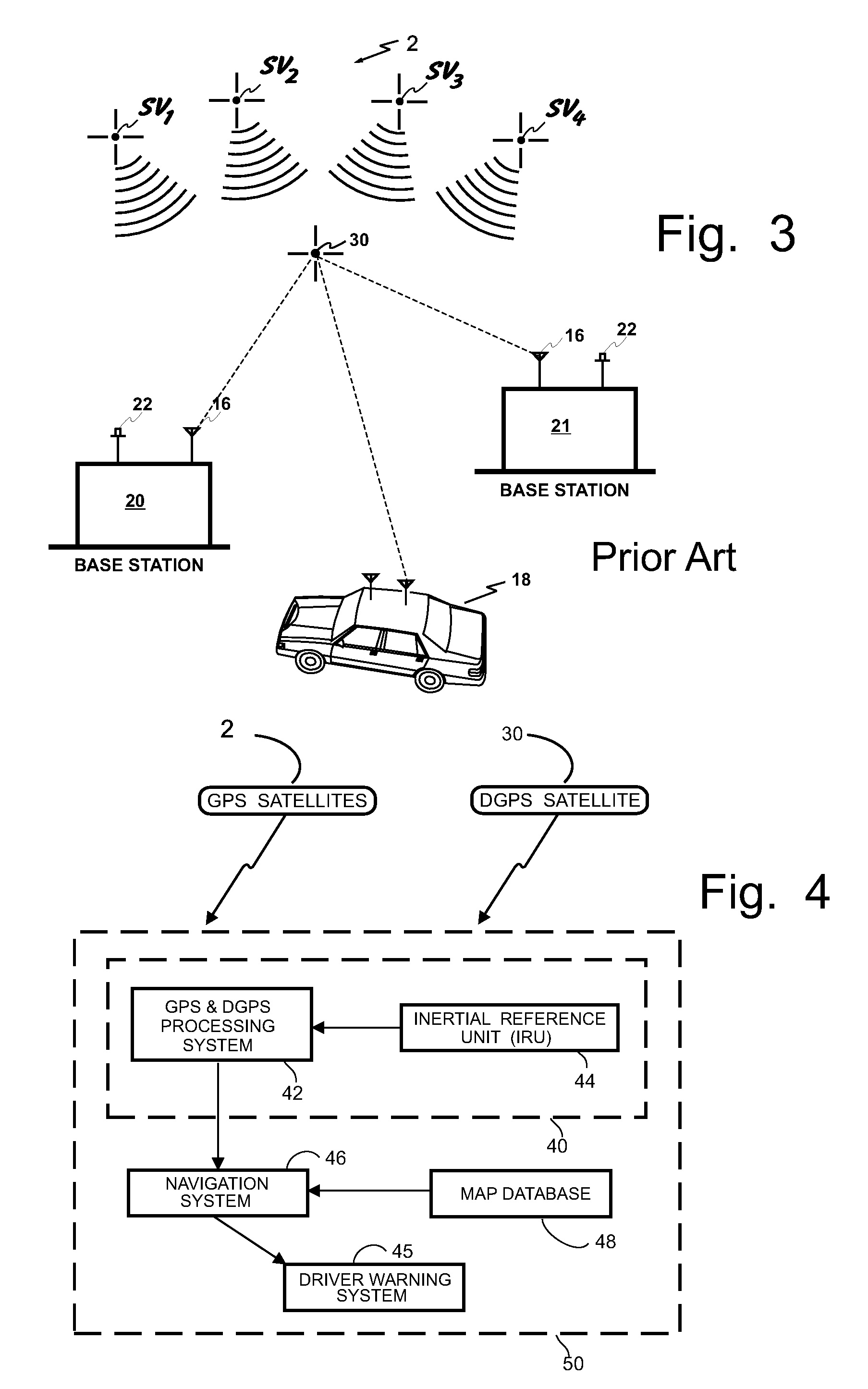

Accident avoidance system

InactiveUS6370475B1Increase typeAvoid accidentsAnti-collision systemsPosition fixationAccident avoidancePositioning system

System and method for preventing vehicle accidents in which the absolute position of the vehicle is determined, e.g., using a satellite-based positioning system such as GPS, and the location of the vehicle relative to the edges of the roadway is then determined based on the absolute position of the vehicle and stored data relating to edges of roadways on which the vehicle may travel. A system or component within the vehicle is initiated, e.g., an alarm or warning system, or the operation of a system or component is affected, e.g., an automatic guidance system, if the location of the vehicle approaches close to an edge of the roadway or intersects with an edge of the roadway.

Owner:AMERICAN VEHICULAR SCI

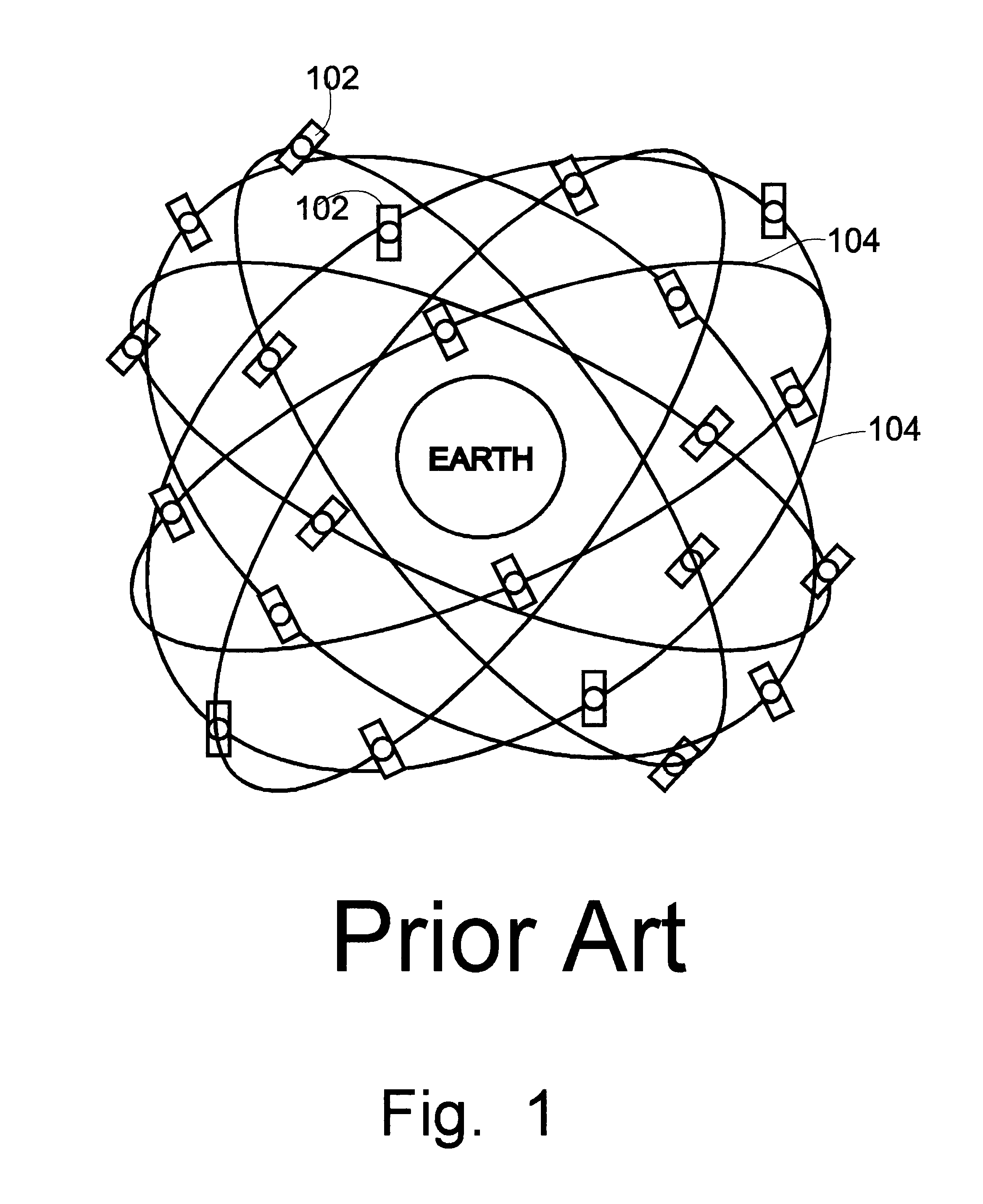

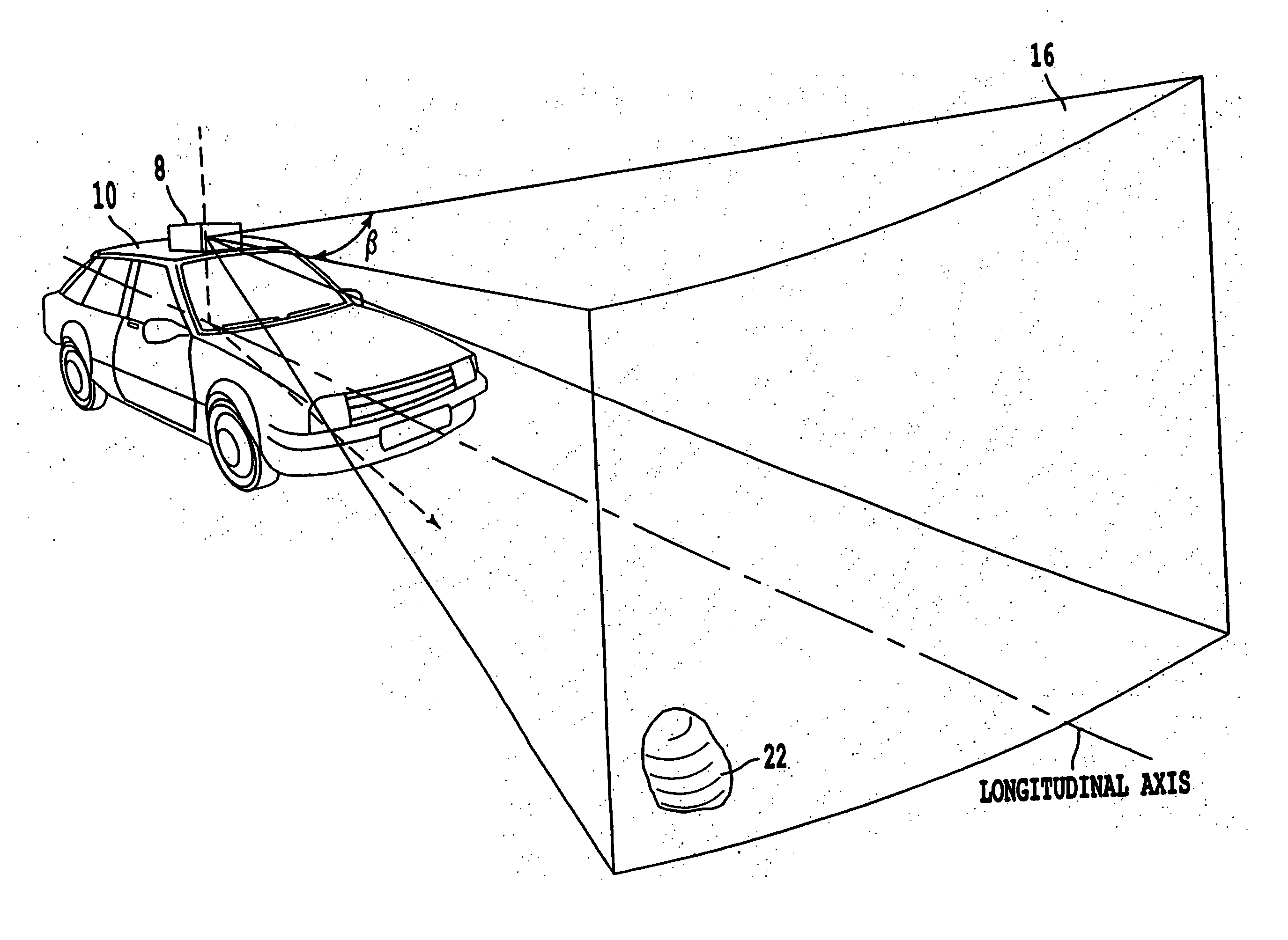

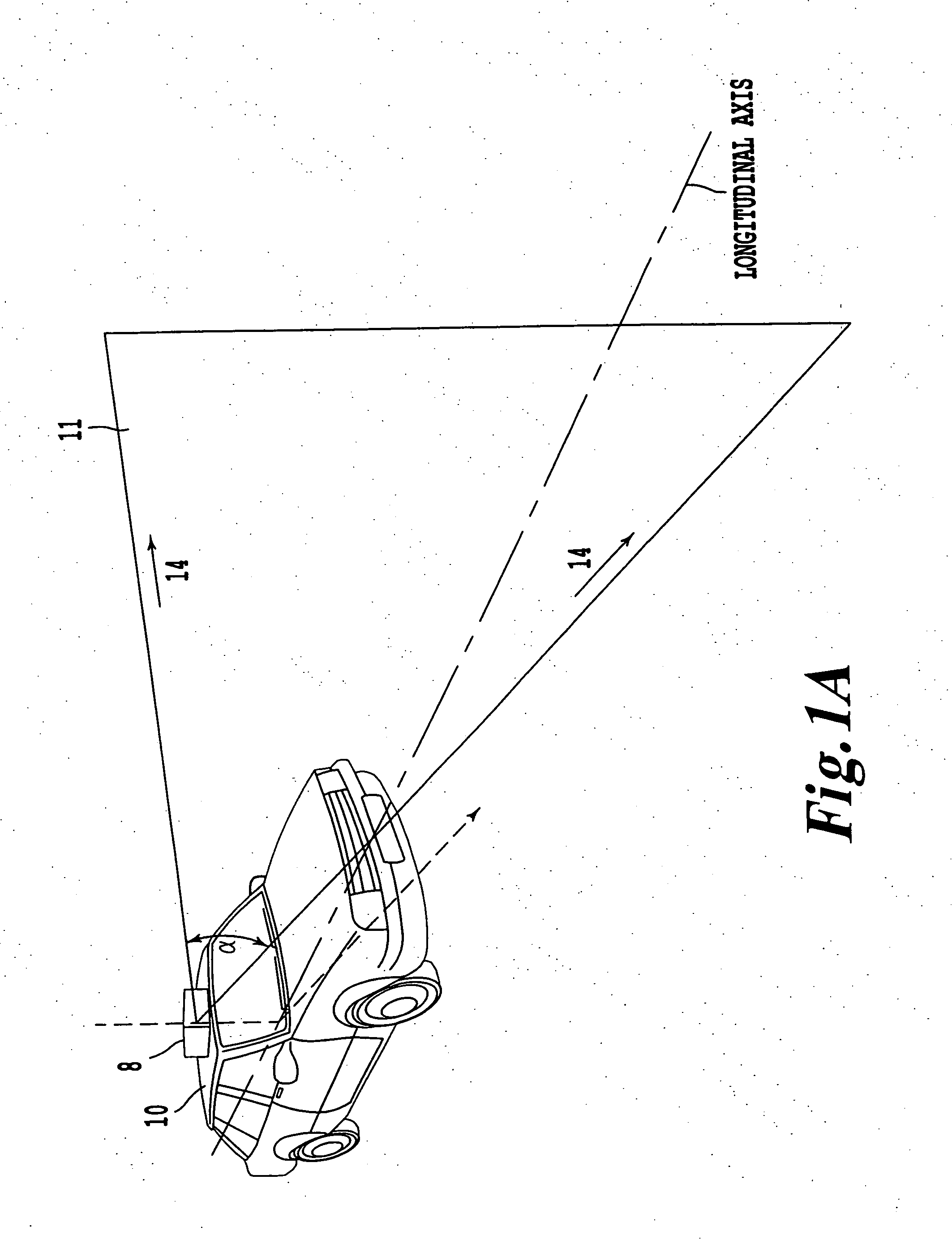

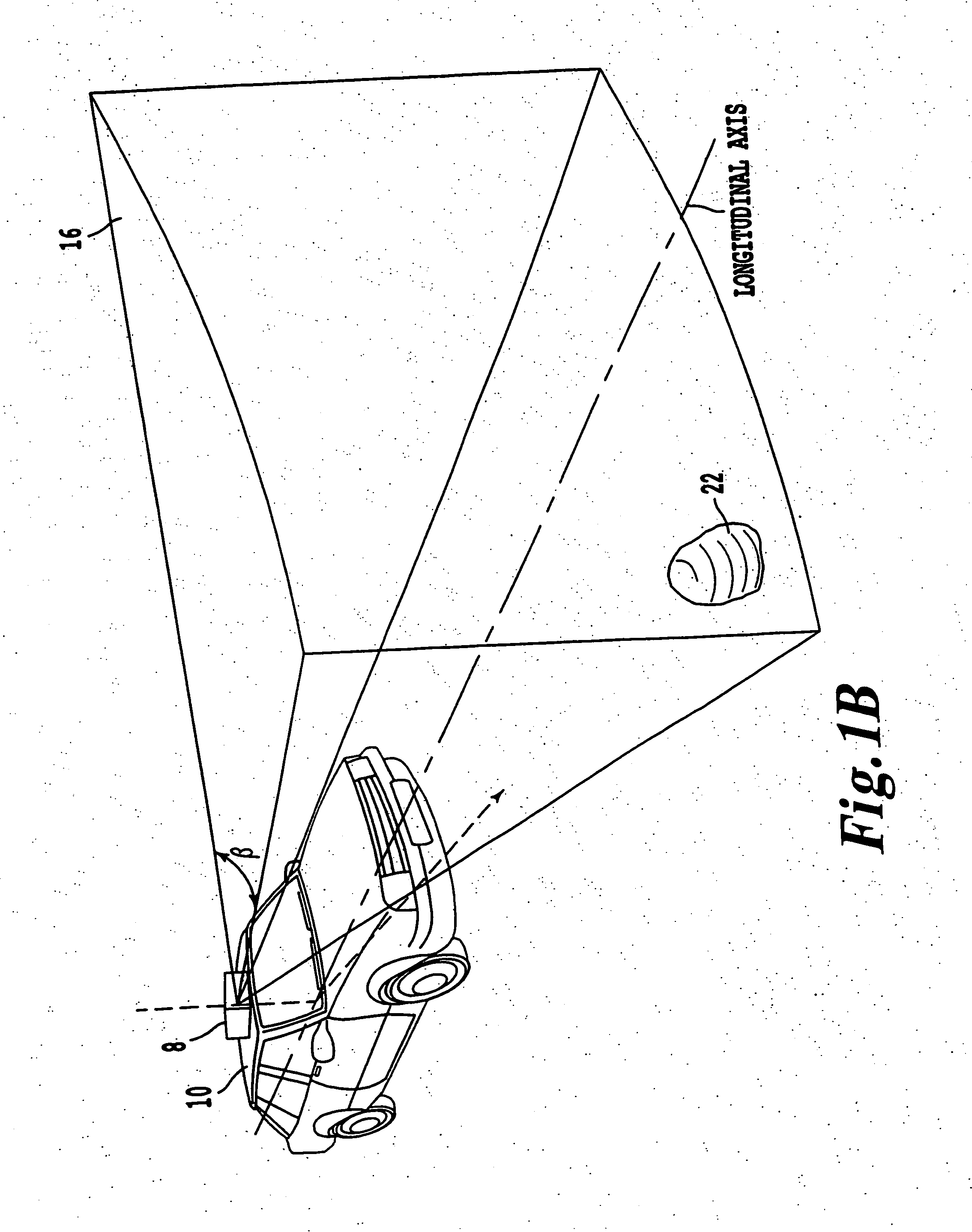

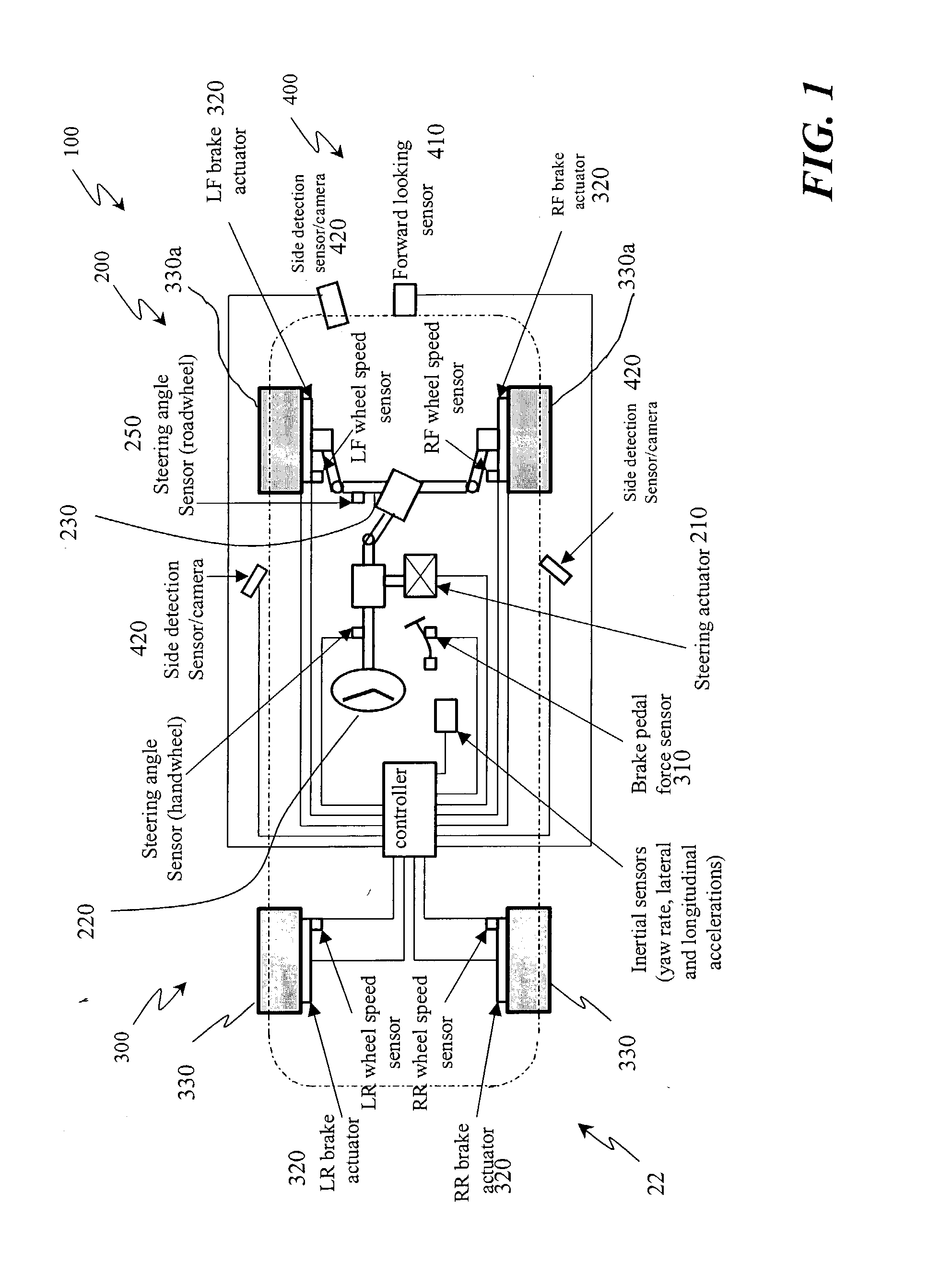

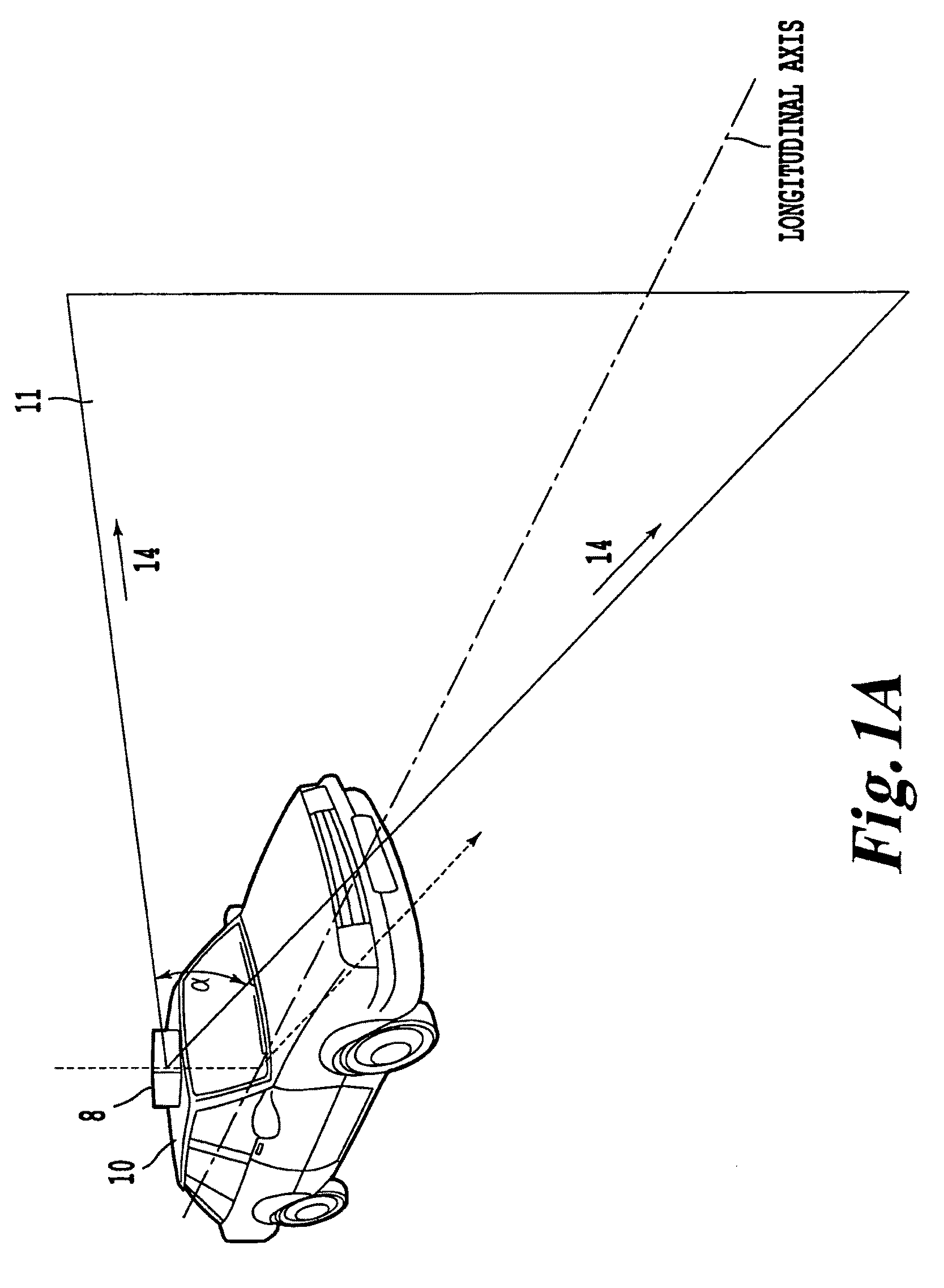

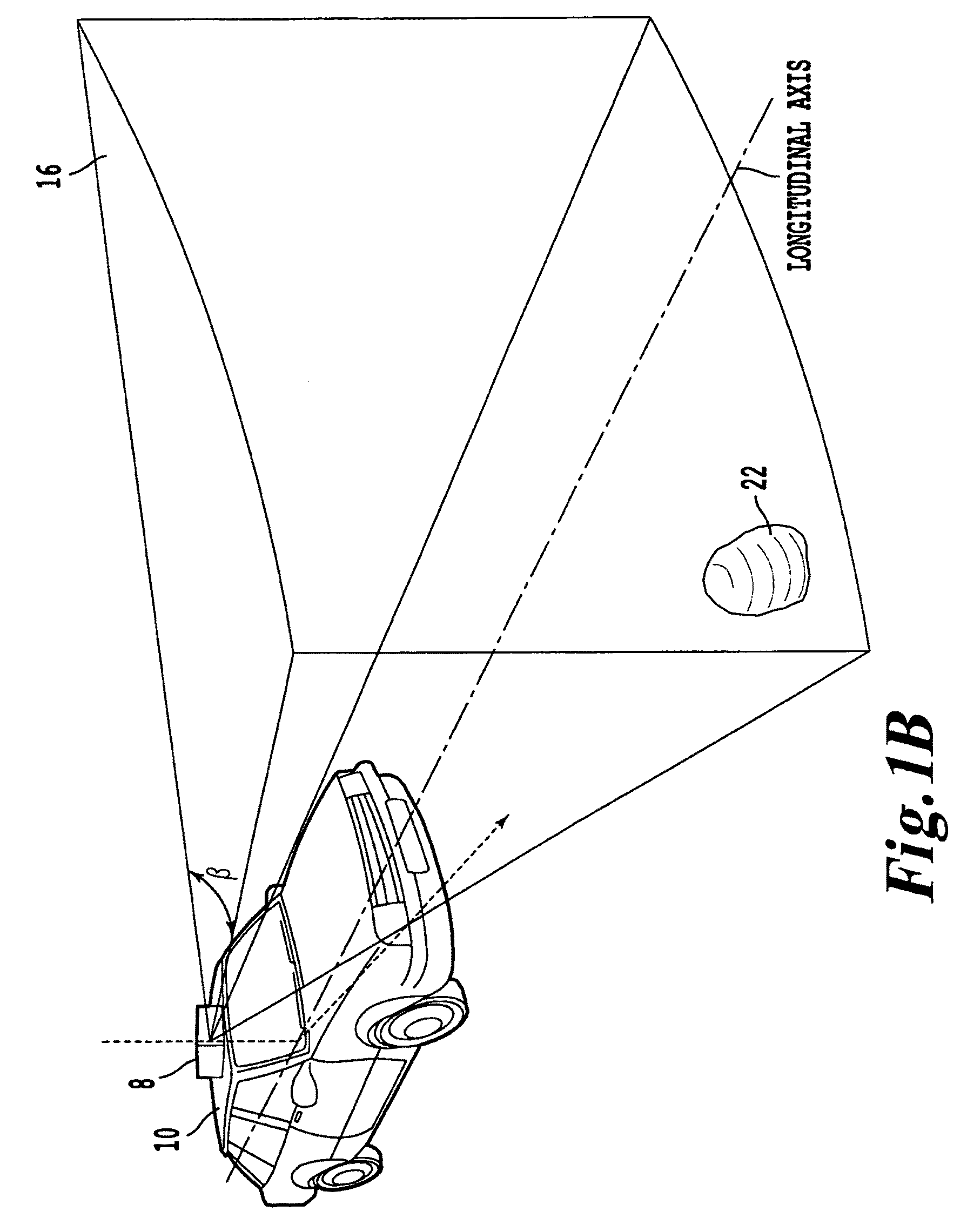

Navigation and control system for autonomous vehicles

ActiveUS20070219720A1Navigation instrumentsExternal condition input parametersControl systemLight beam

A navigation and control system including a sensor configured to locate objects in a predetermined field of view from a vehicle. The sensor has an emitter configured to repeatedly scan a beam into a two-dimensional sector of a plane defined with respect to a first predetermined axis of the vehicle, and a detector configured to detect a reflection of the emitted beam from one of the objects. The sensor includes a panning mechanism configured to pan the plane in which the beam is scanned about a second predetermined axis to produce a three dimensional field of view. The navigation and control system includes a processor configured to determine the existence and location of the objects in the three dimensional field of view based on a position of the vehicle and a time between an emittance of the beam and a reception of the reflection of the emitted beam from one of the objects.

Owner:SAMSUNG ELECTRONICS CO LTD

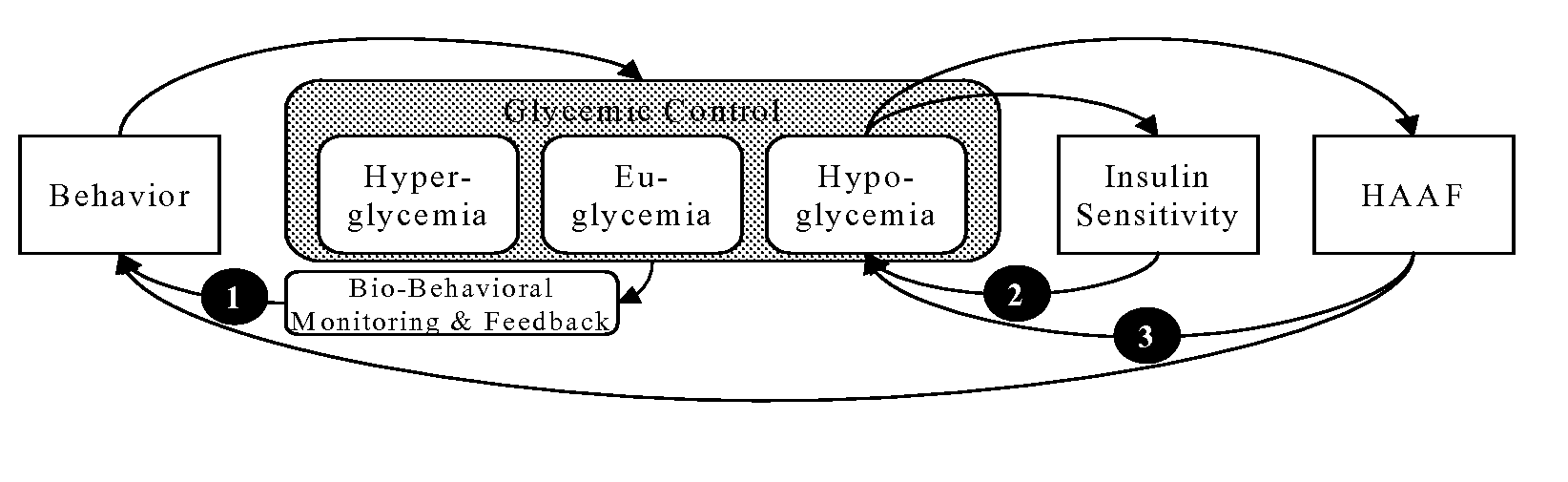

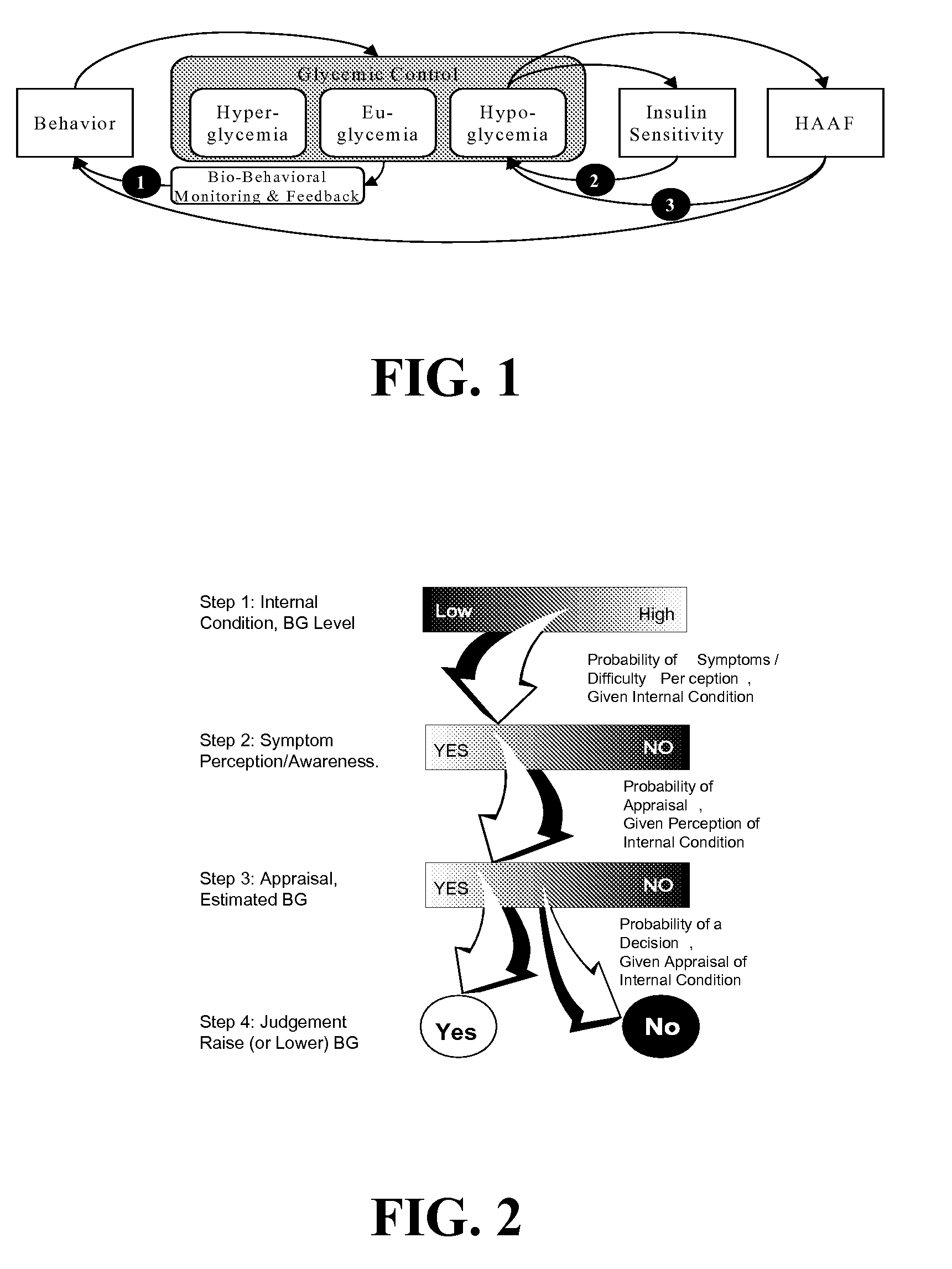

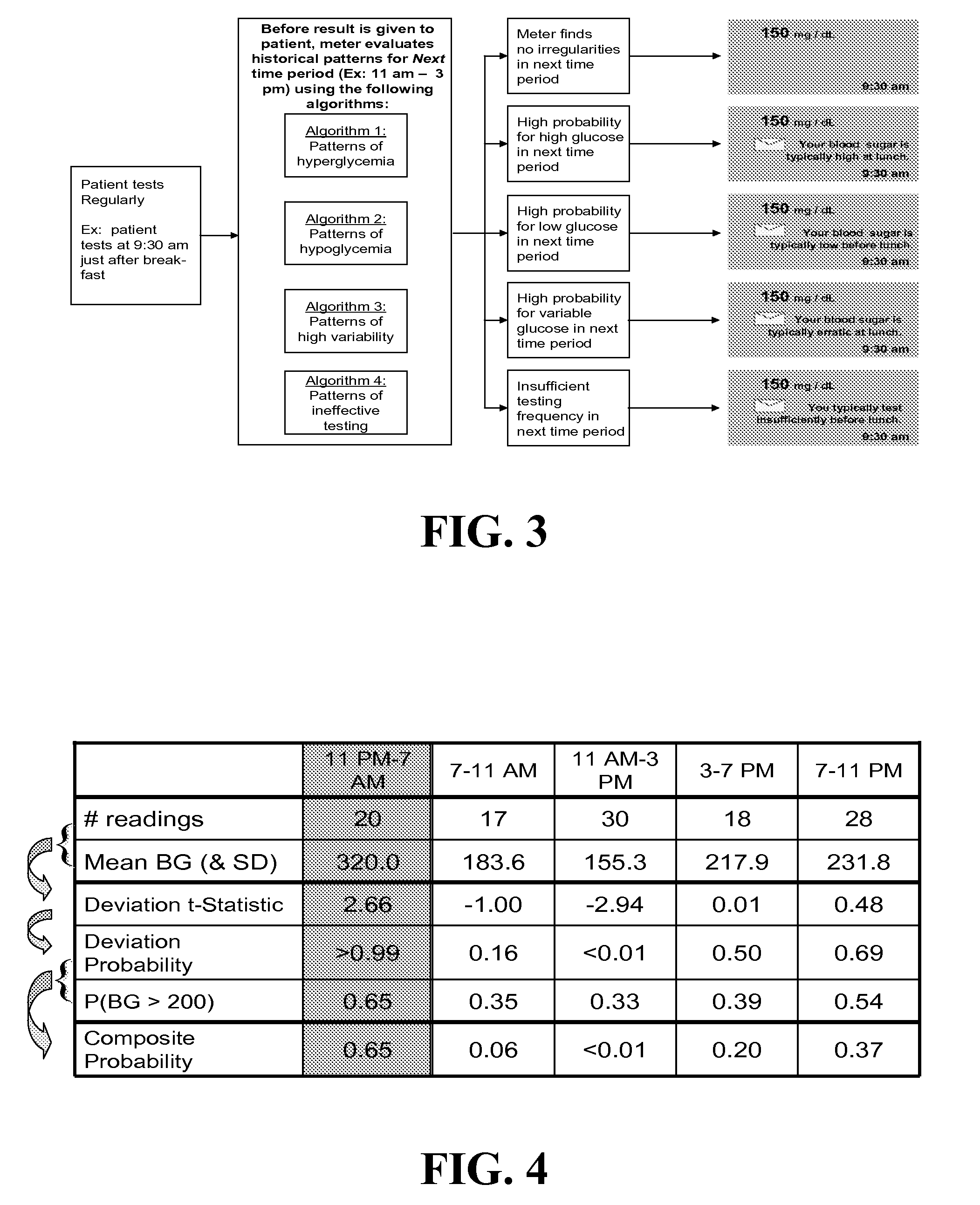

Systems, Methods and Computer Program Codes for Recognition of Patterns of Hyperglycemia and Hypoglycemia, Increased Glucose Variability, and Ineffective Self-Monitoring in Diabetes

InactiveUS20080154513A1Evaluate effectivenessEnhance existing SMBG devicesDrug and medicationsDigital computer detailsAcute hyperglycaemiaOptimal control

A method, system, and computer program product related to the maintenance of optimal control of diabetes, and is directed to predicting patterns of hypoglycemia, hyperglycemia, increased glucose variability, and insufficient or excessive testing for the upcoming period of time, based on blood glucose readings collected by a self-monitoring blood glucose device. The method, system, and computer program product pertain directly to the enhancement of existing home blood glucose monitoring devices, by introducing an intelligent data interpretation component capable of predicting and alerting the user to periods of increased risk for hyperglycemia, hypoglycemia, increased glucose variability, and ineffective testing, and to the enhancement of emerging self-monitoring blood glucose devices by the same features. With these predictions the diabetic can take steps to prevent the adverse consequences associated with hyperglycemia, hypoglycemia, and increased glucose variability.

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND +1

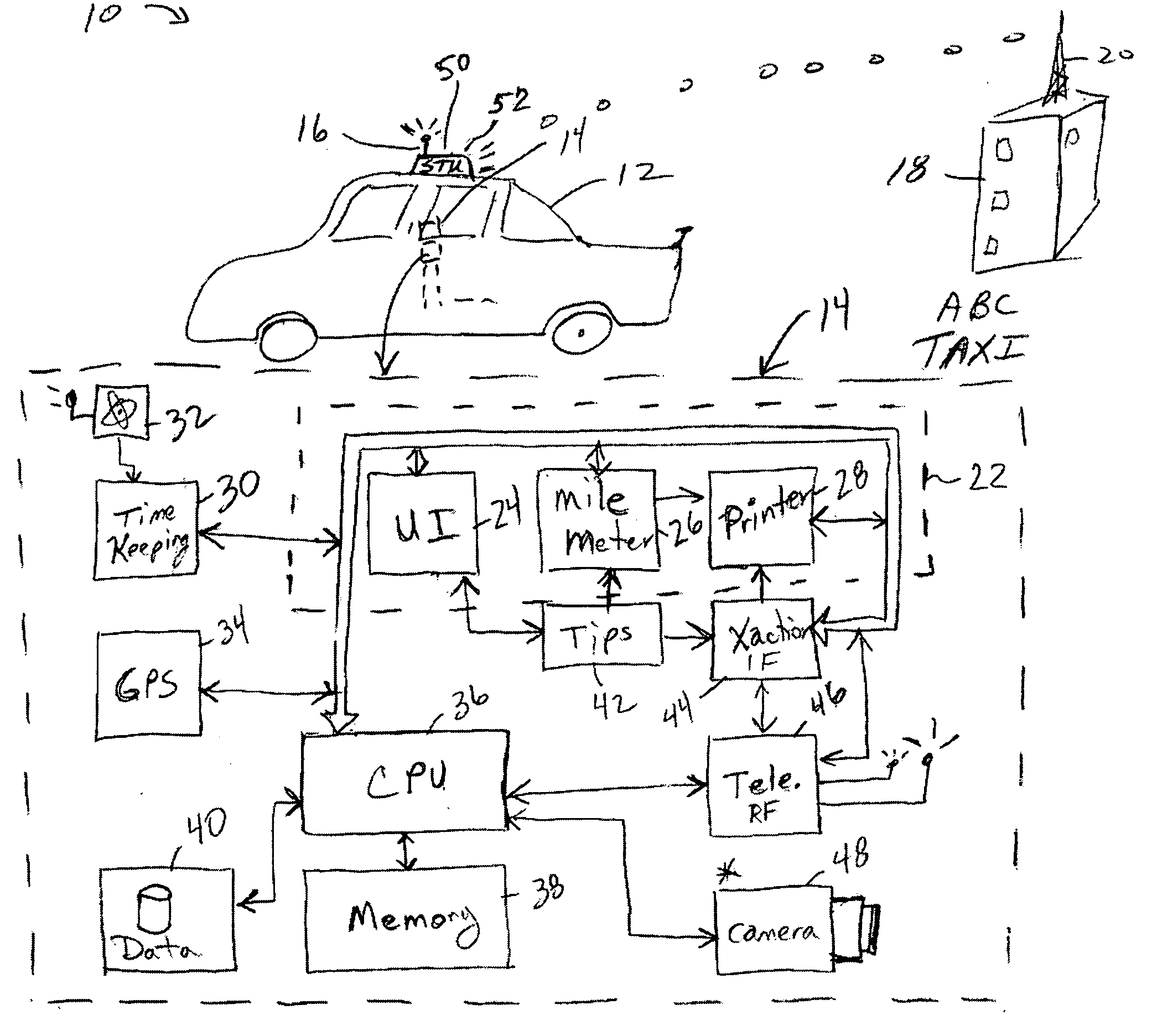

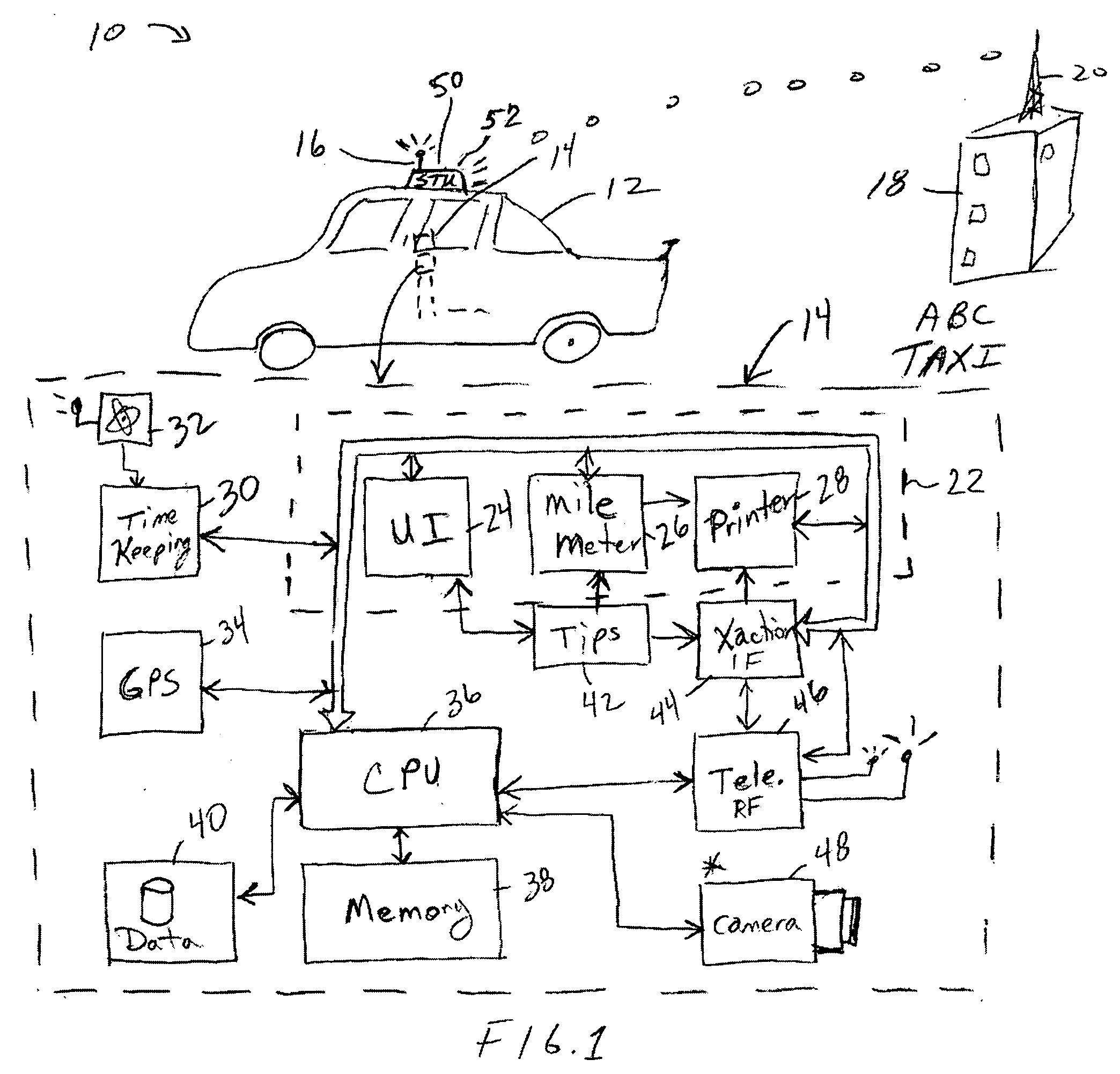

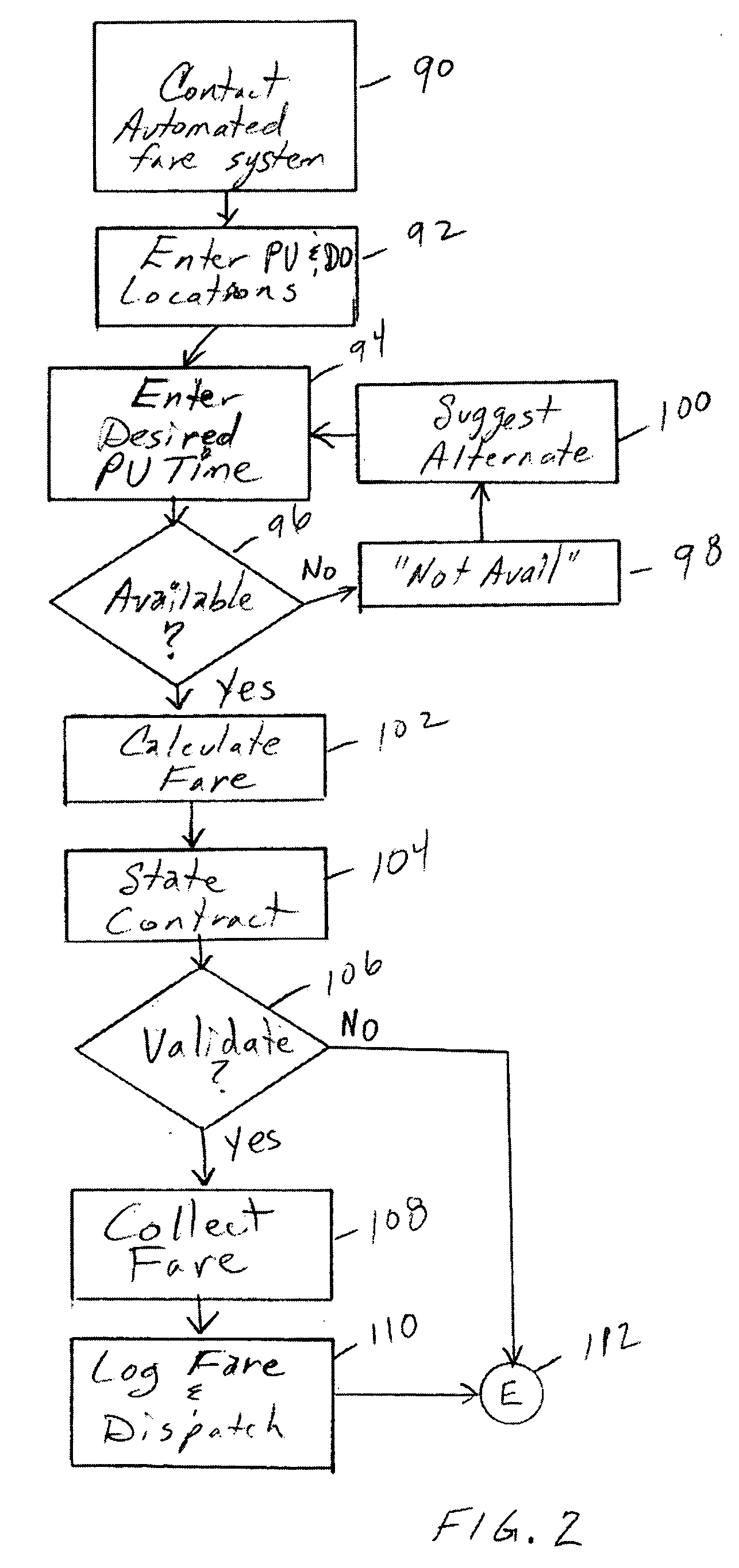

Conveyance scheduling and logistics system

InactiveUS20040260470A1Easy to modifyAvoid narrow scopeRoad vehicles traffic controlResourcesLogistics managementEngineering

An apparatus and method of reserving conveyance, such as taxis and limousines, in which the pickup locations, times, and contract are established and logged electronically. The system is configured to increase the assurance that the conveyance will arrive properly on time and on location, and that the patron will also keep their end of the agreement. The system preferably configured for disincentives for either party to not follow in accord with the contract.

Owner:RAST RODGER H

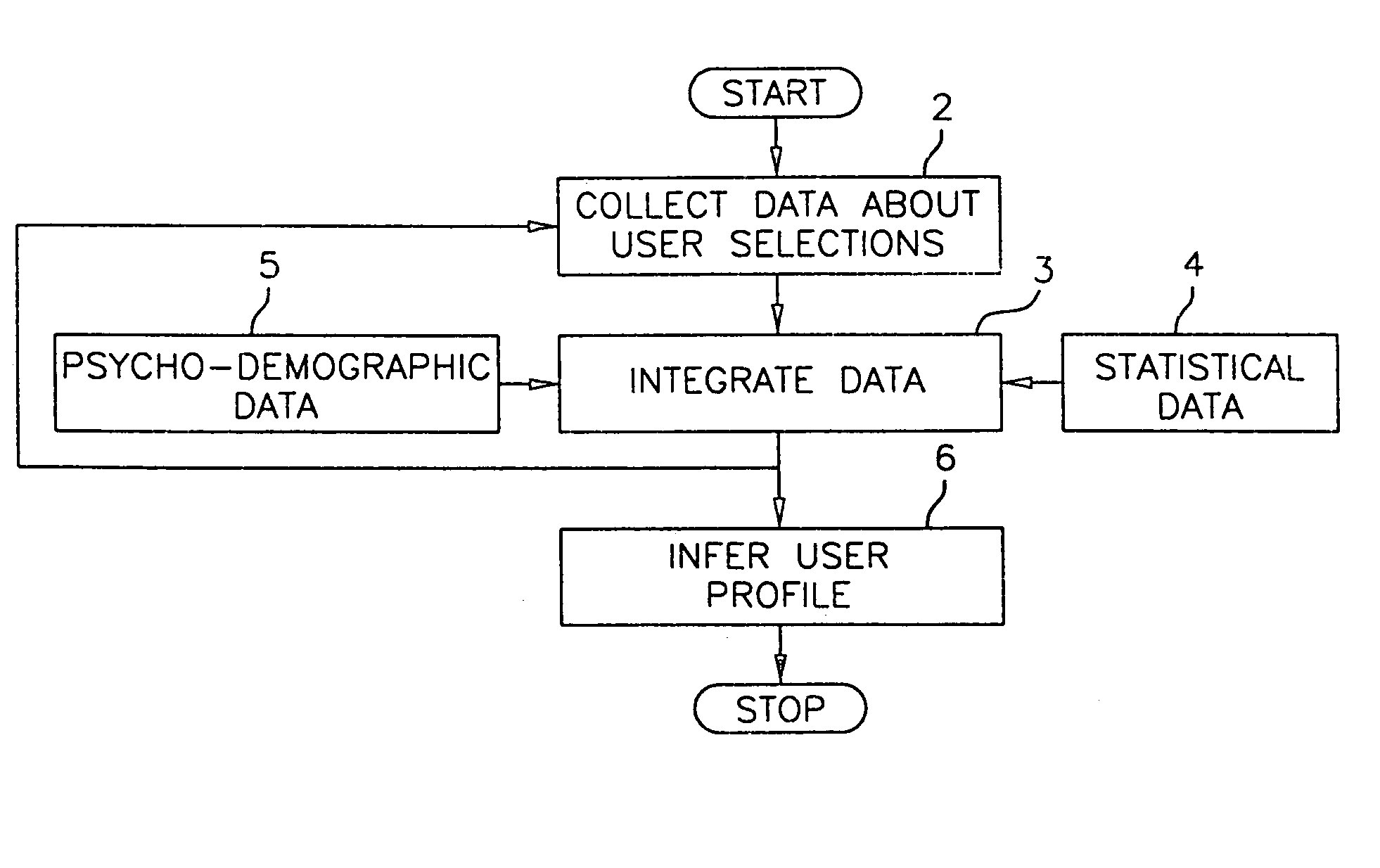

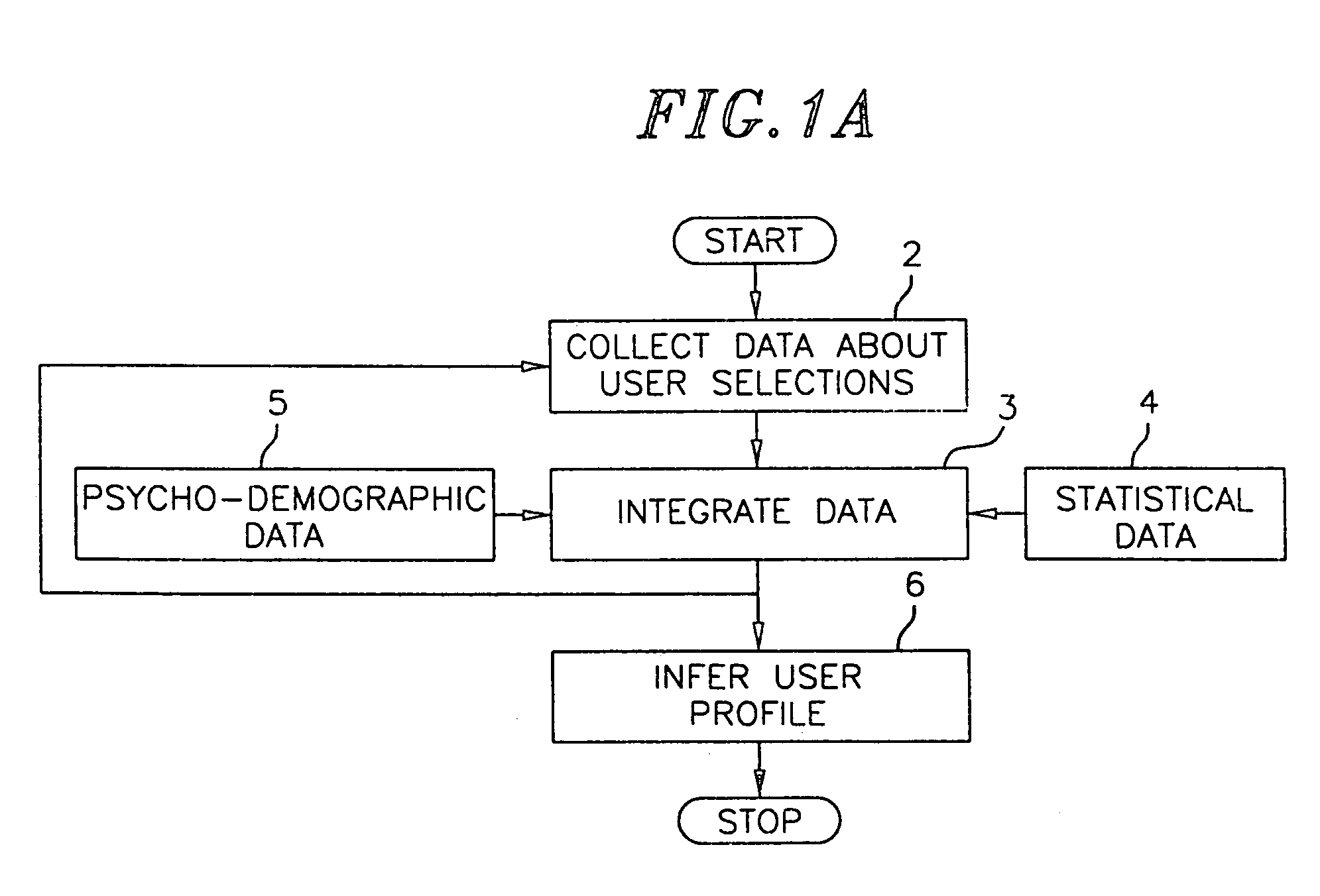

Smart agent based on habit, statistical inference and psycho-demographic profiling

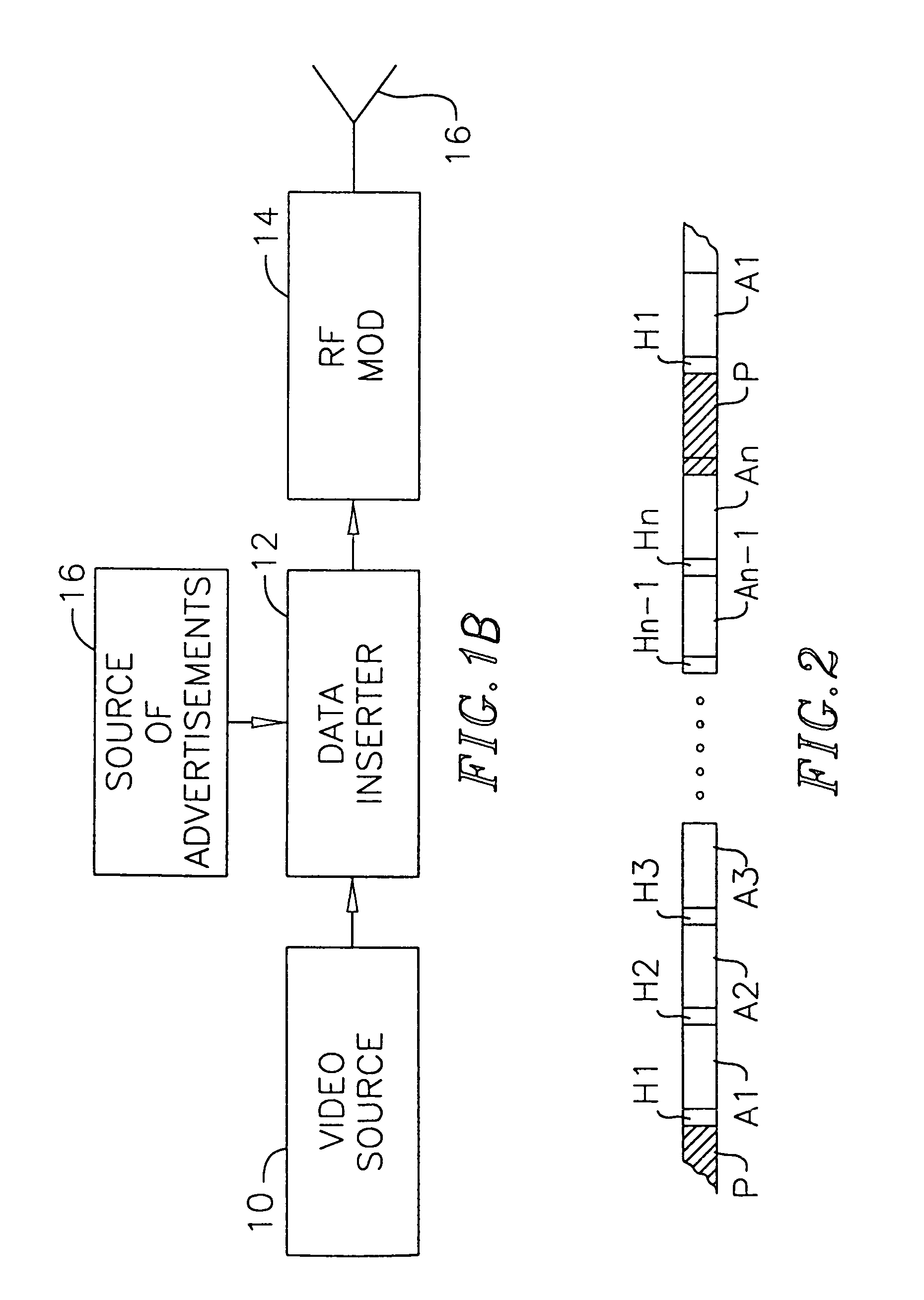

InactiveUS7003792B1Incur costIncur effortTelevision system detailsData processing applicationsHabitData mining

A smart agent (SA) is provided which resides locally in a local client device and by iterative means integrates the habit, statistics and psycho-demographic information of a user to infer the user's preferences. The SA may also utilize the preferences to filter information delivered to the local device. The invention further discloses a means of collecting, combining, integrating and inferring information from the user to arrive at a psycho-demographic profile of the user, and a means of utilizing such psycho-demographic profile to select or filter information delivered to the user, thereby achieving targeting. The invention also discloses a means of classifying and identifying the information delivered so that it can be matched, filtered or selected.

Owner:ROVI GUIDES INC

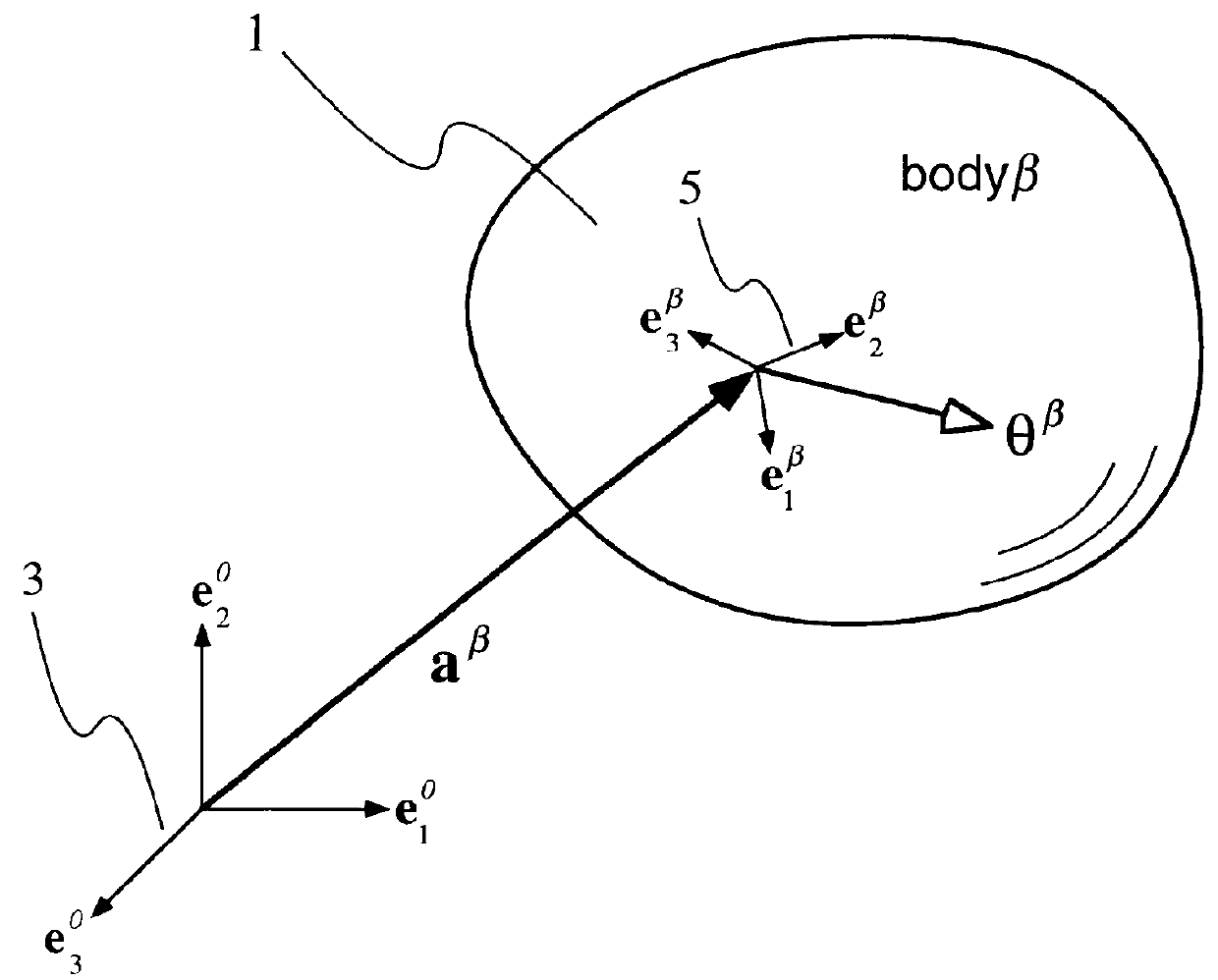

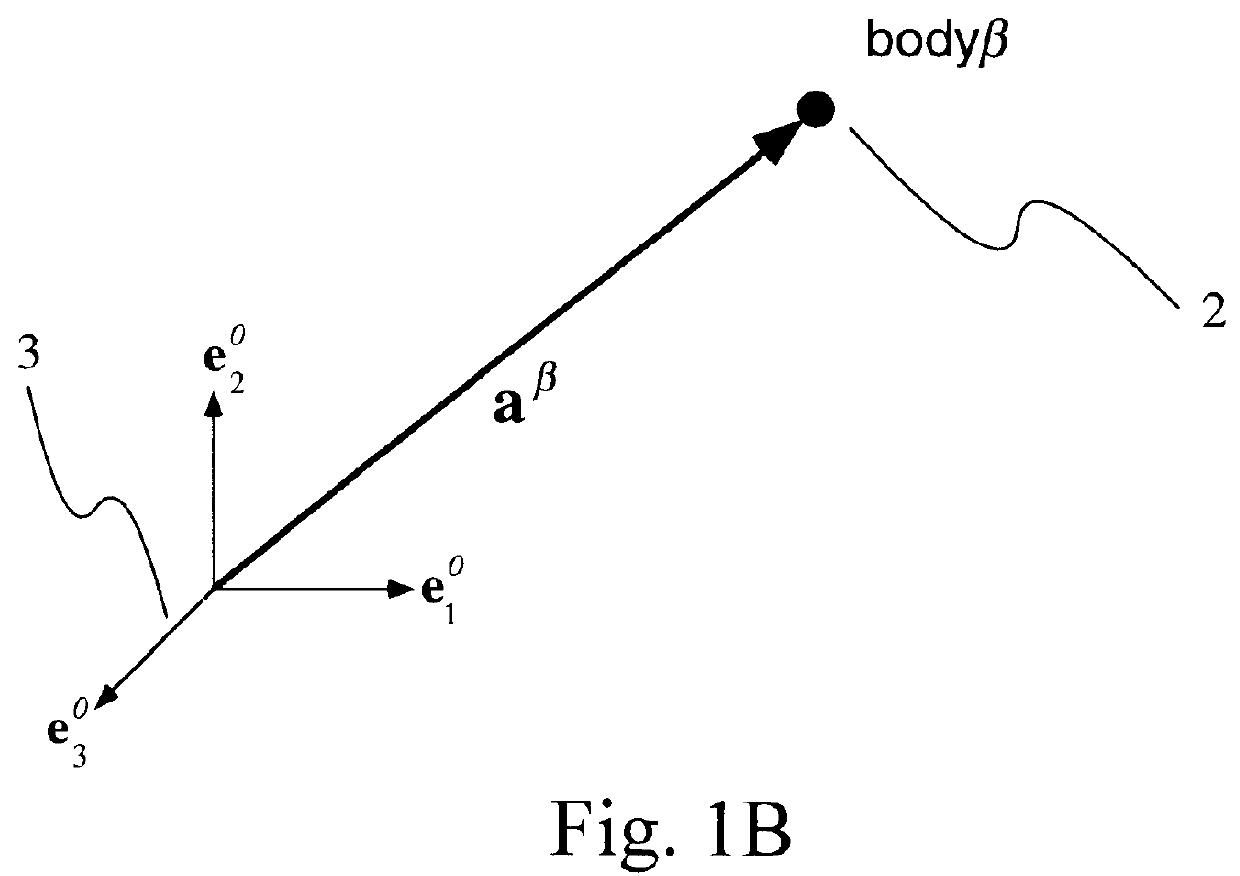

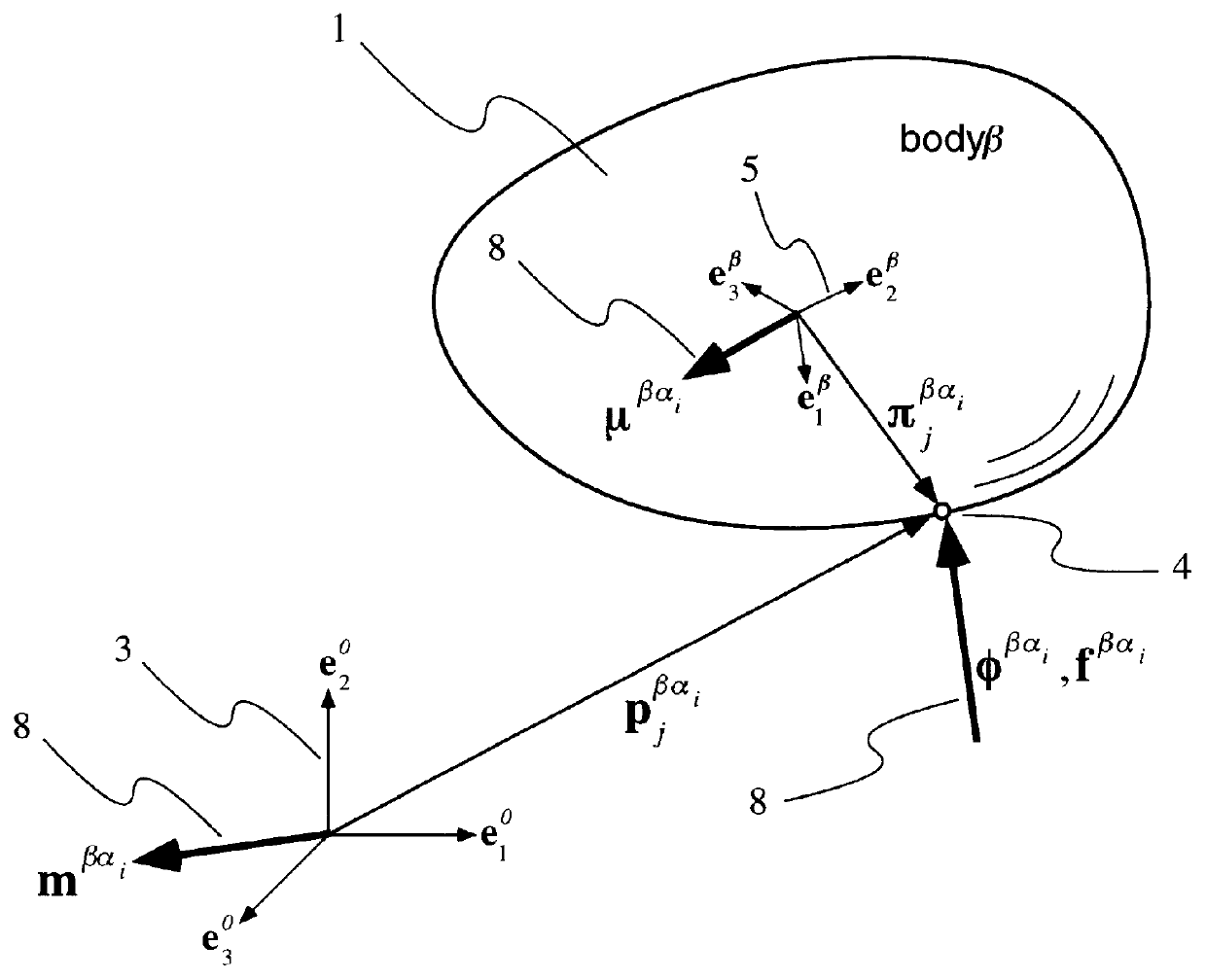

Three dimensional multibody modeling of anatomical joints

InactiveUS6161080AEasy to modifyPerson identificationAnalogue computers for chemical processesData selectionDimensional modeling

The present invention relates to a method of generating a three dimensional representation of one or more anatomical joints, wherein the representation comprises two or more movable bodies and one or more links, comprising the steps of inputting anatomically representative data of two or more movable bodies of the selected joint or joints; selecting one or more link types responsive to the representative data of the bodies; selecting link characteristics responsive to each selected link type; generating an equilibrium condition responsive to interaction between the bodies and the links; and displaying a three dimensional representation of the selected joint or joints responsive to the data generated from the equilibrium condition of the anatomical joint or joints. The present invention further relates to a system for generating a three dimensional representation of one or more anatomical joints, and a method of planning surgery of one or more anatomical joints.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

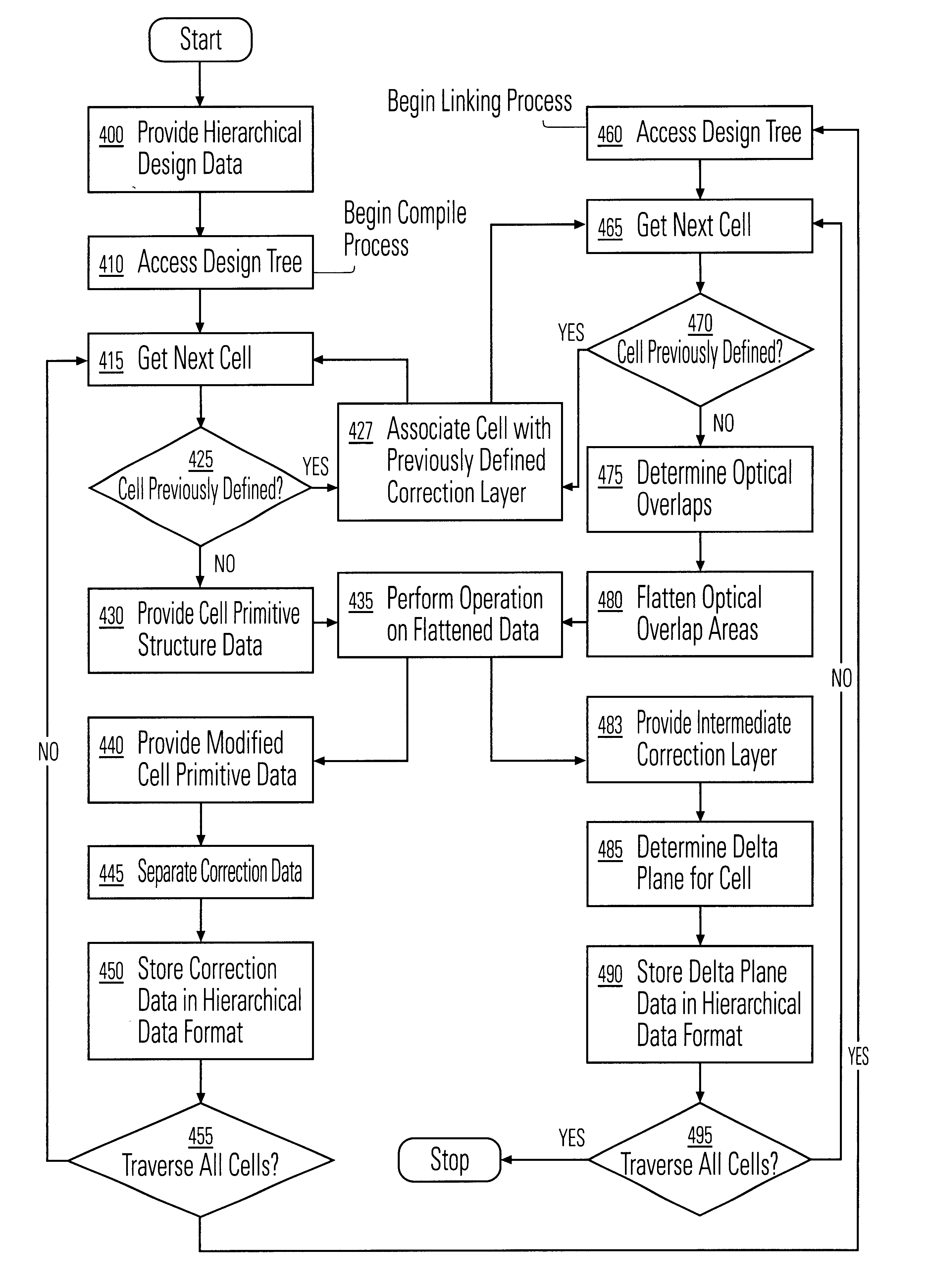

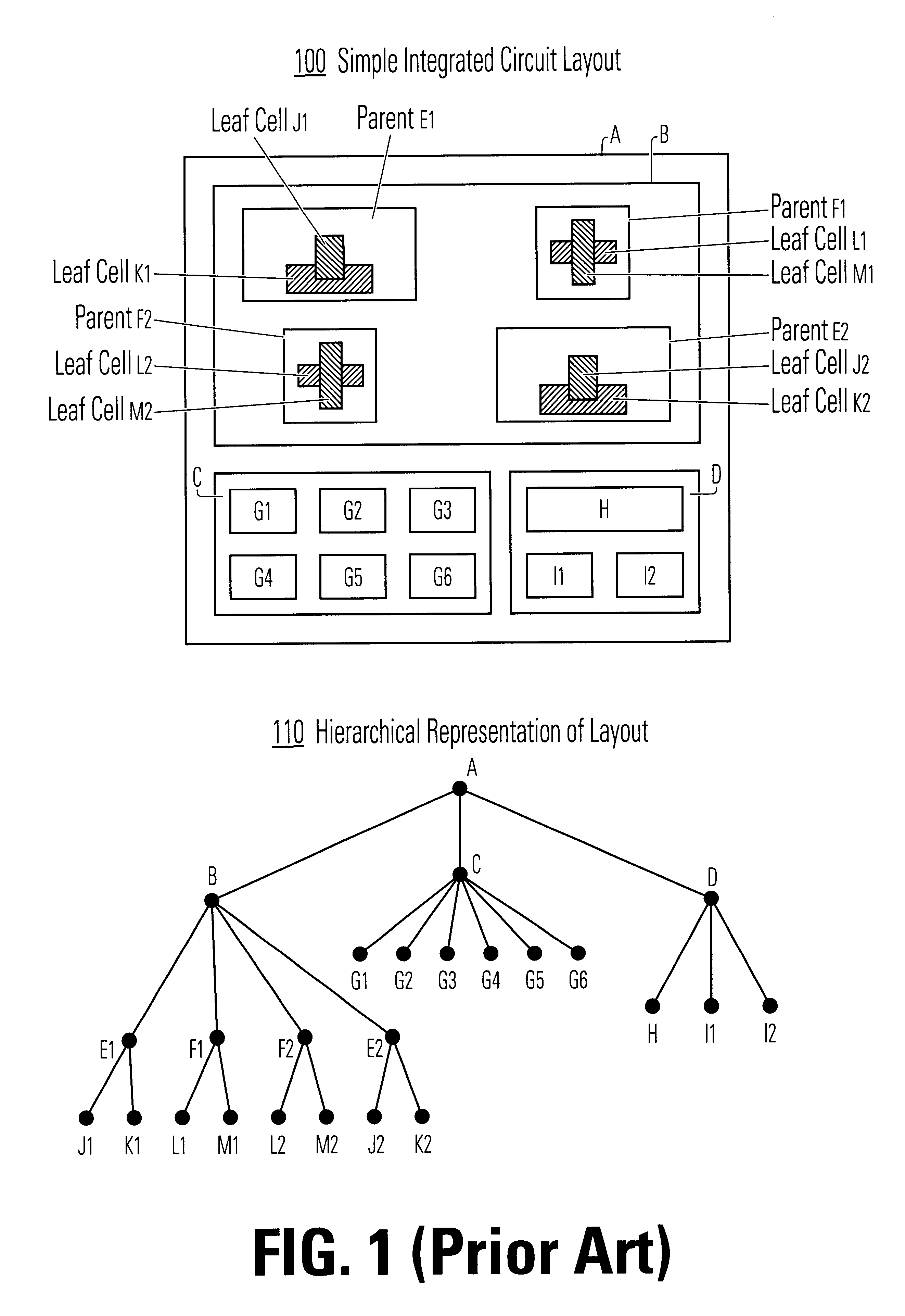

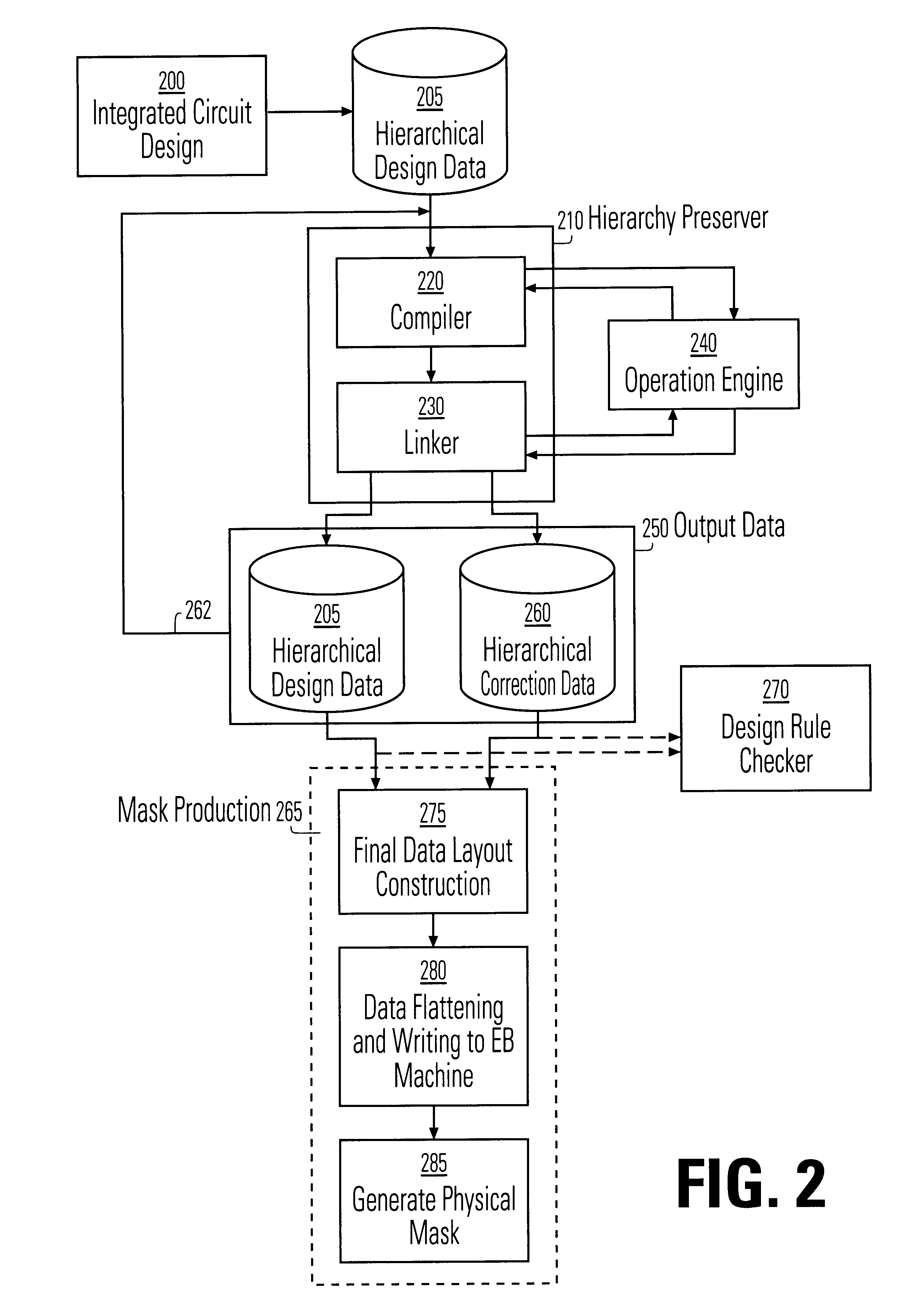

Data hierarchy layout correction and verification method and apparatus

InactiveUS6370679B1Computation using non-denominational number representationOriginals for photomechanical treatmentComputer architectureValidation methods

A method and apparatus for the correction of integrated circuit layouts for optical proximity effects which maintains the original true hierarchy of the original layout is provided. Also provided is a method and apparatus for the design rule checking of layouts which have been corrected for optical proximity effects. The OPC correction method comprises providing a hierarchically described integrated circuit layout as a first input, and a particular set of OPC correction criteria as a second input. The integrated circuit layout is then analyzed to identify features of the layout which meet the provided OPC correction criteria. After the areas on the mask which need correction have been identified, optical proximity correction data is generated in response to the particular set of correction criteria. Finally, a first program data is generated which stores the generated optical proximity correction data in a hierarchical structure that corresponds to the hierarchical structure of the integrated circuit layout. As the output correction data is maintained in true hierarchical format, layouts which are OPC corrected according to this method are able to be processed through conventional design rule checkers with no altering of the data.

Owner:SYNOPSYS INC

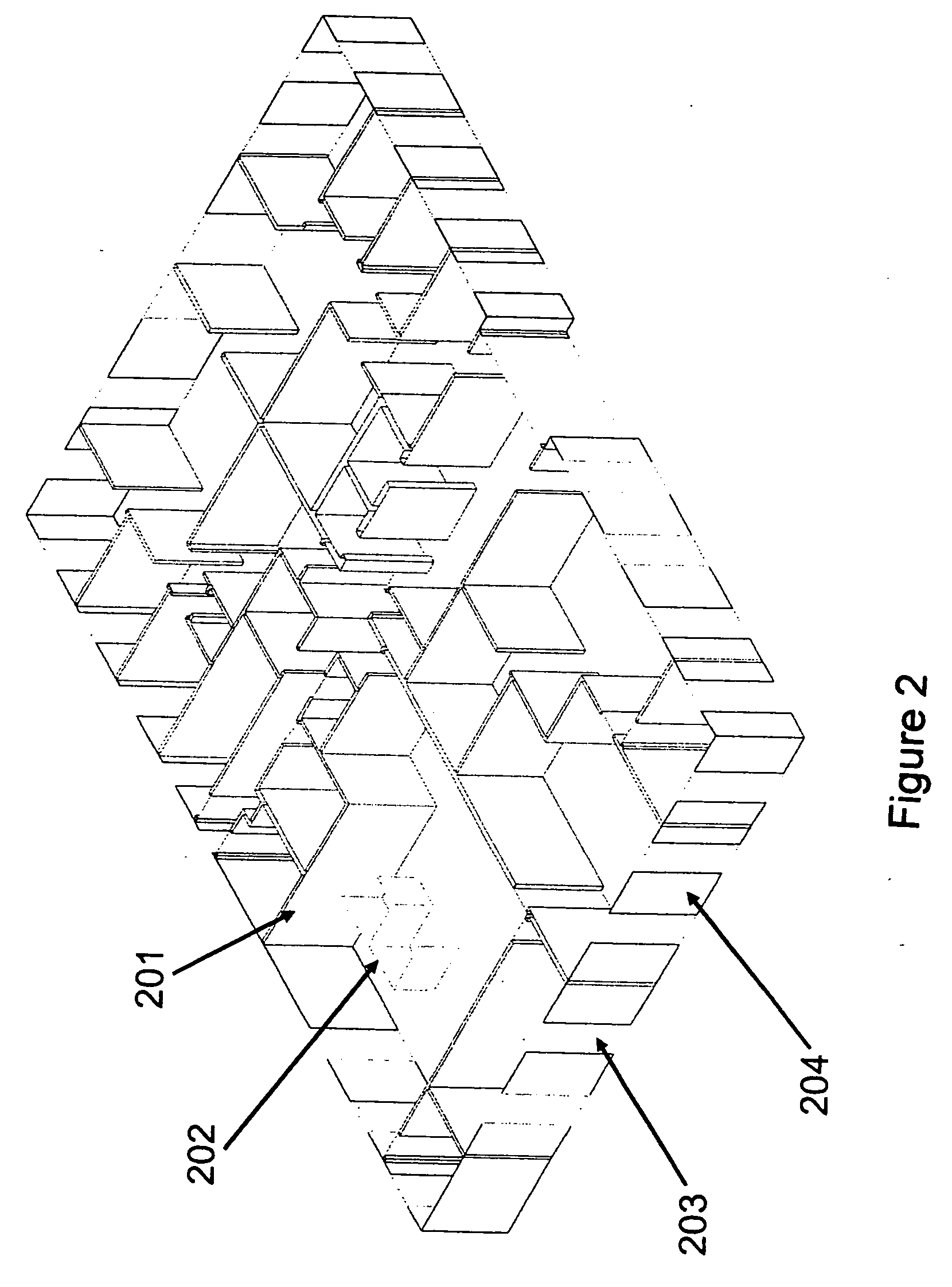

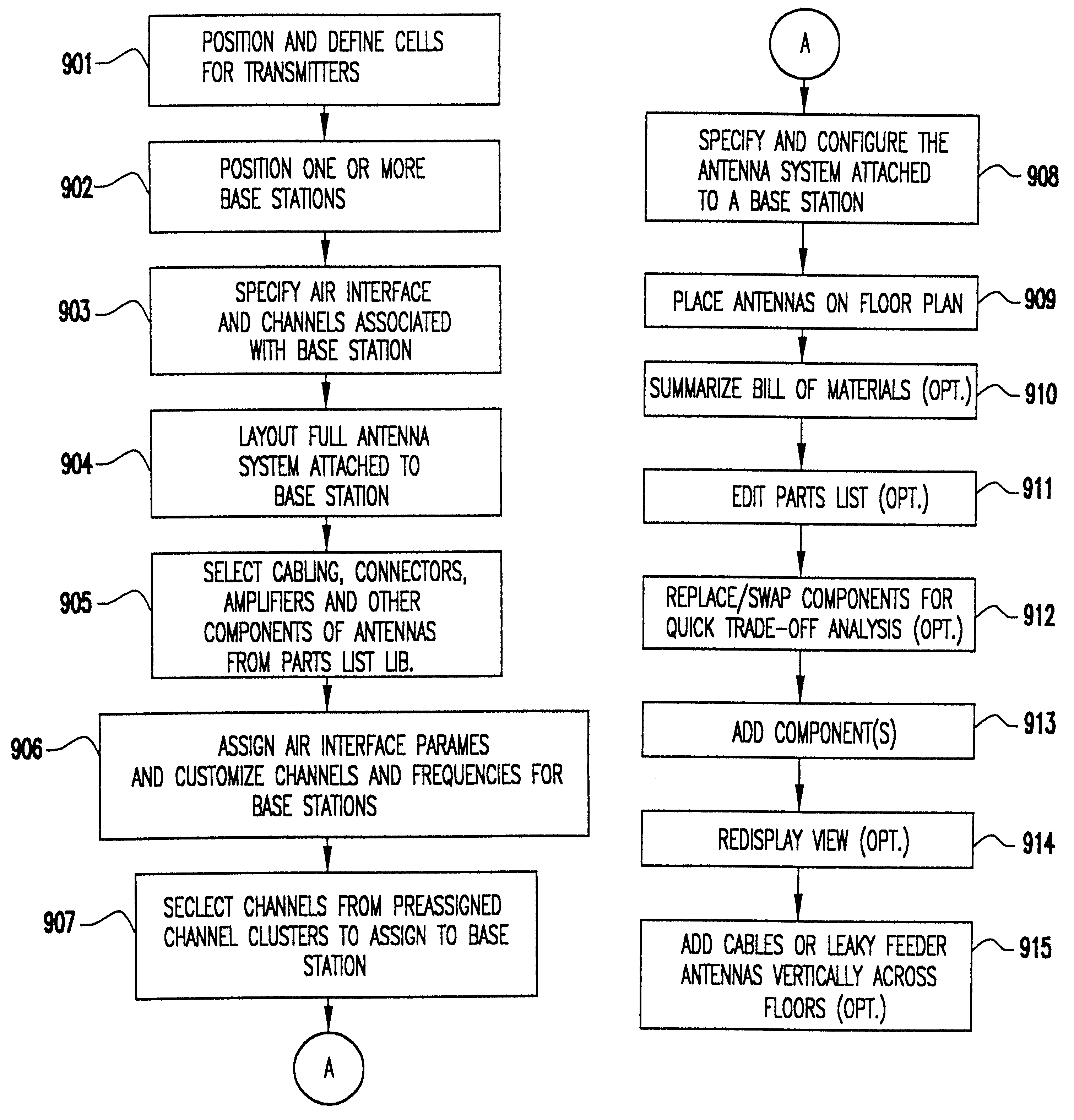

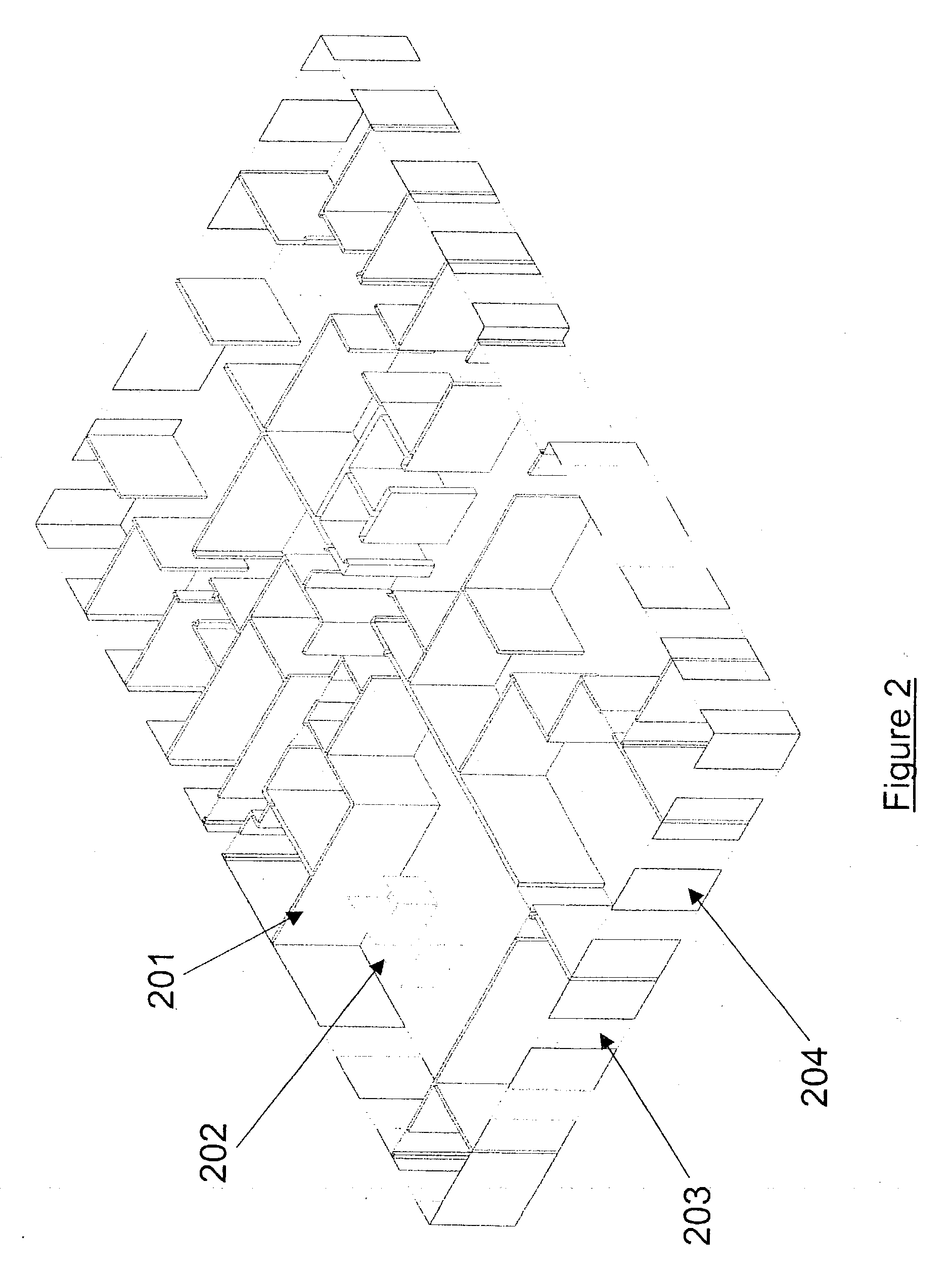

Method and system for automated optimization of antenna positioning in 3-D

InactiveUS6317599B1Quick fixSignificant valueMachines/enginesComputation using non-denominational number representationEngineeringRadio frequency

A method for engineering management and planning for the design of a wireless communications network in three-dimensions (3-D) combines computerized organization, database fusion, and radio frequency (RF) site-specific planning models. The method enables a designer to keep track of wireless system performance throughout the process of pre-bid design, installation and maintenance of a wireless system. Using a database of information that defines the desired environment, predictions of antenna coverage, system coverage and interference, and other wireless system performance criteria, such as frame error rate and network throughput, can be made. Watch points are created to ensure, in real time, that any modifications to the design of the wireless system do not degrade the performance of the system with respect to the watch point locations.

Owner:EXTREME NETWORKS INC

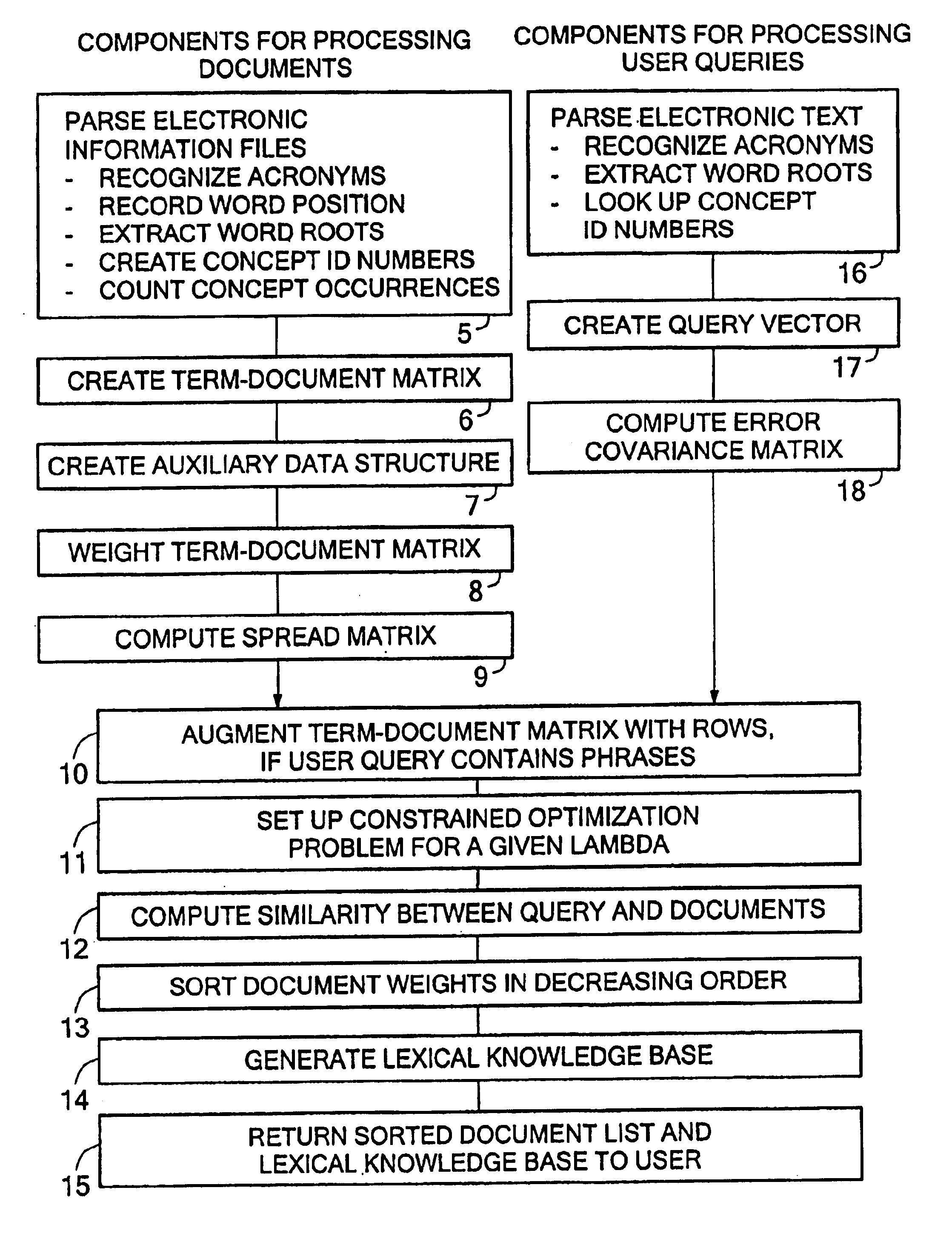

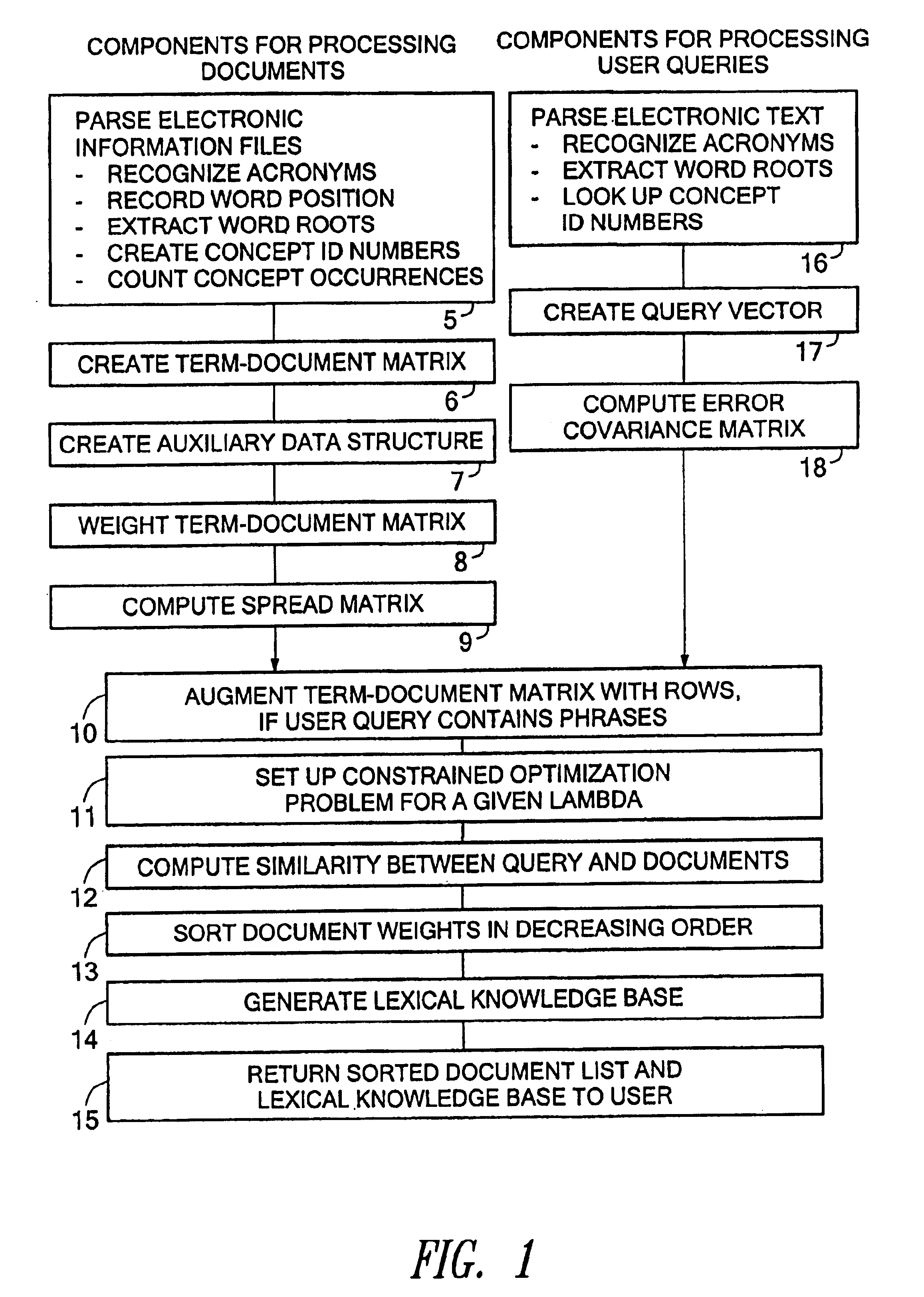

Internet navigation using soft hyperlinks

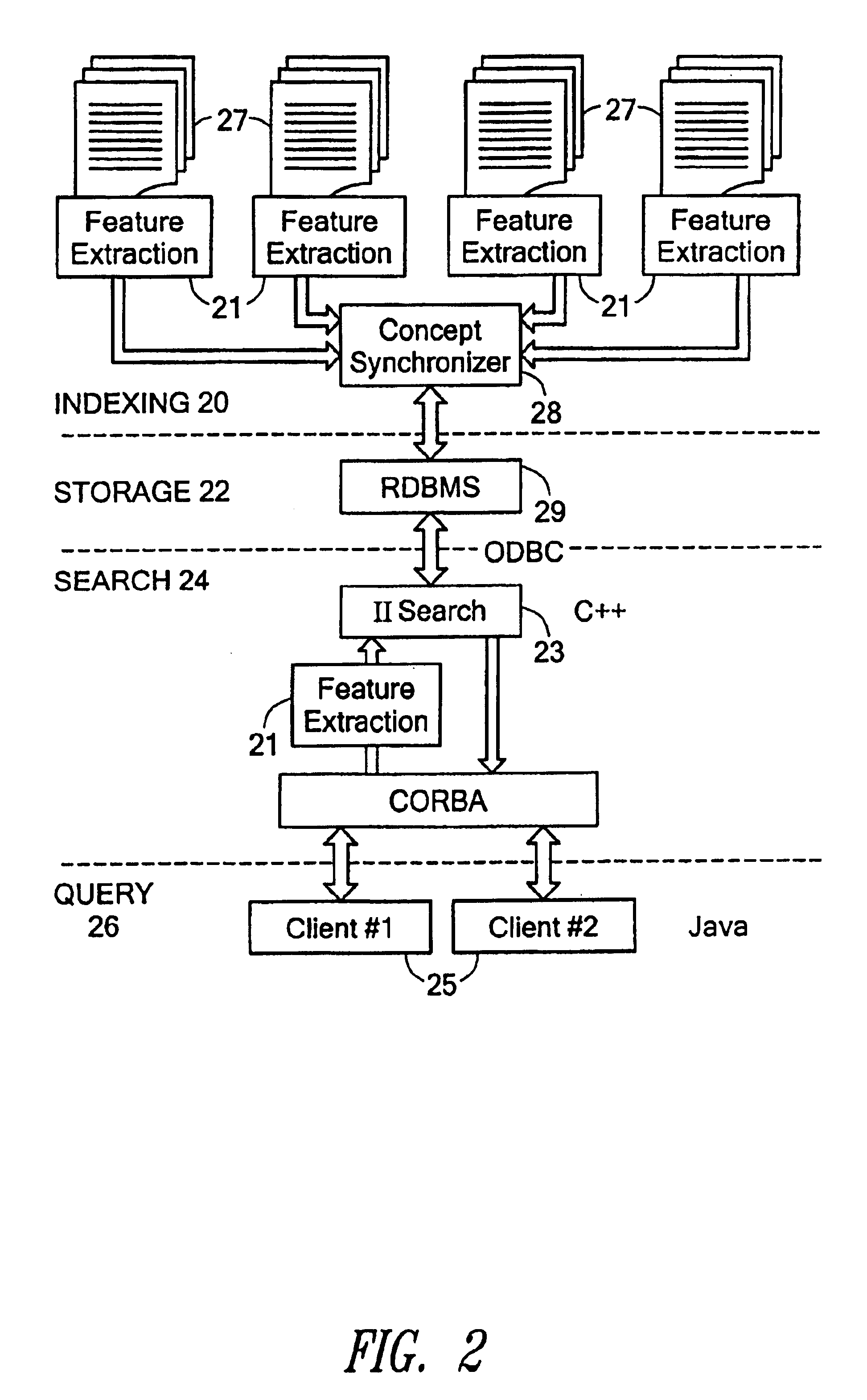

InactiveUS6862710B1High degree of correlationHigh degreeData processing applicationsWeb data indexingNavigation systemDocument preparation

A system for internet navigation using soft hyperlinks is disclosed, in connection with an illustrative information retrieval system with which it may be used. The navigation tool provides freedom to move through a collection of electronic documents independent of any hyperlink which has been inserted within an HTML page. A user can click on any term in a document page, not only those that are hyperlinked. For example, when a user clicks on an initial word within the document, the disclosed system employs a search engine in the background to retrieve a list of related terms. In an illustrative embodiment, a compass-like display appears with pointers indicating the first four terms returned by the search engine. These returned terms have the highest degree of correlation with the initial search term in a lexical knowledge base that the search engine constructs automatically. The disclosed system allows the user to move from the current document to one of a number of document lists which cover different associations between the initial word clicked on by the user and other terms extracted from within the retrieved list of related terms. The disclosed system may further allow the user to move to a document that is considered most related to the initial word clicked on by the user, or to a list of documents that are relevant to a phrase or paragraph selection indicated by the user within the current page.

Owner:FIVER LLC

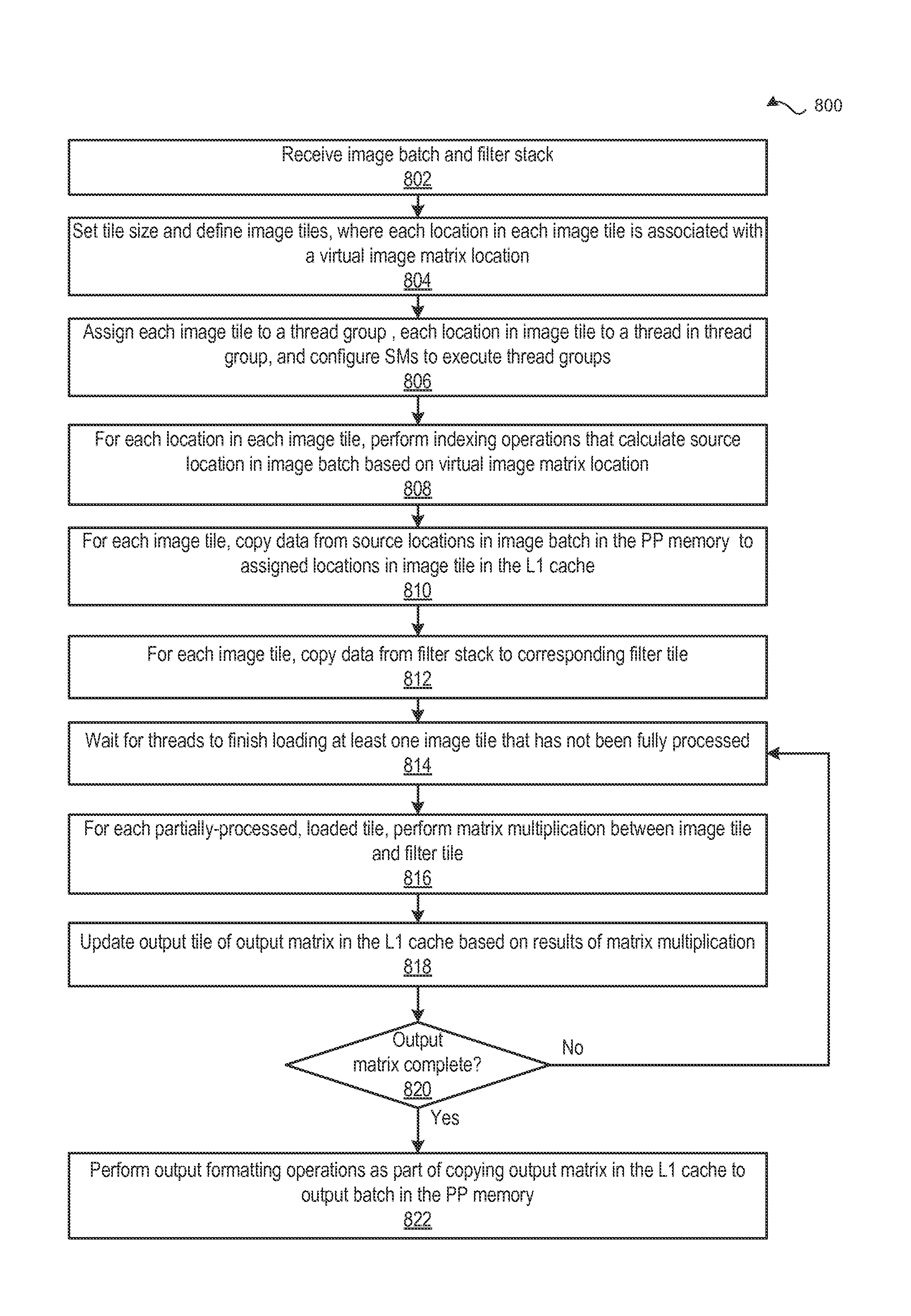

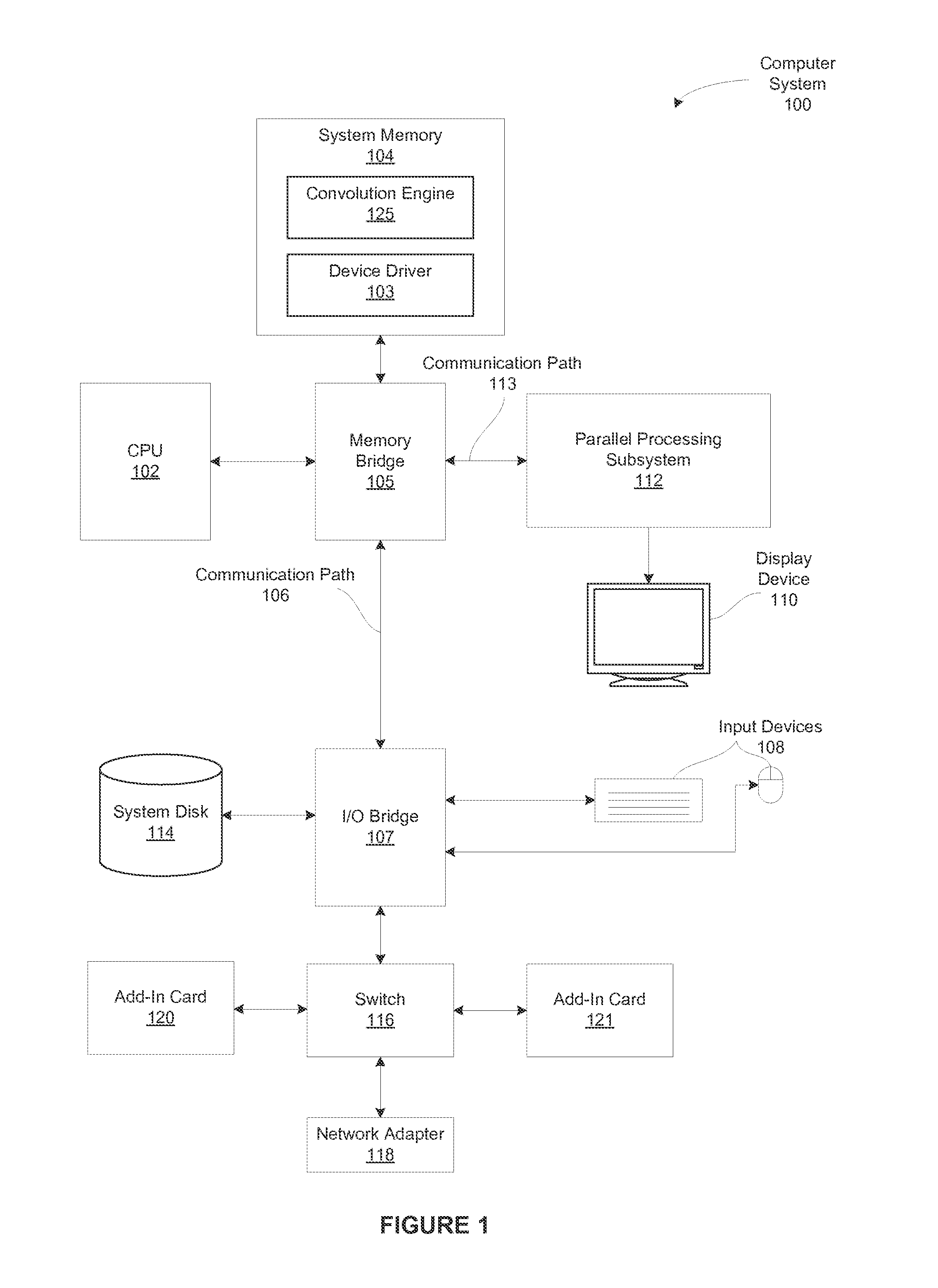

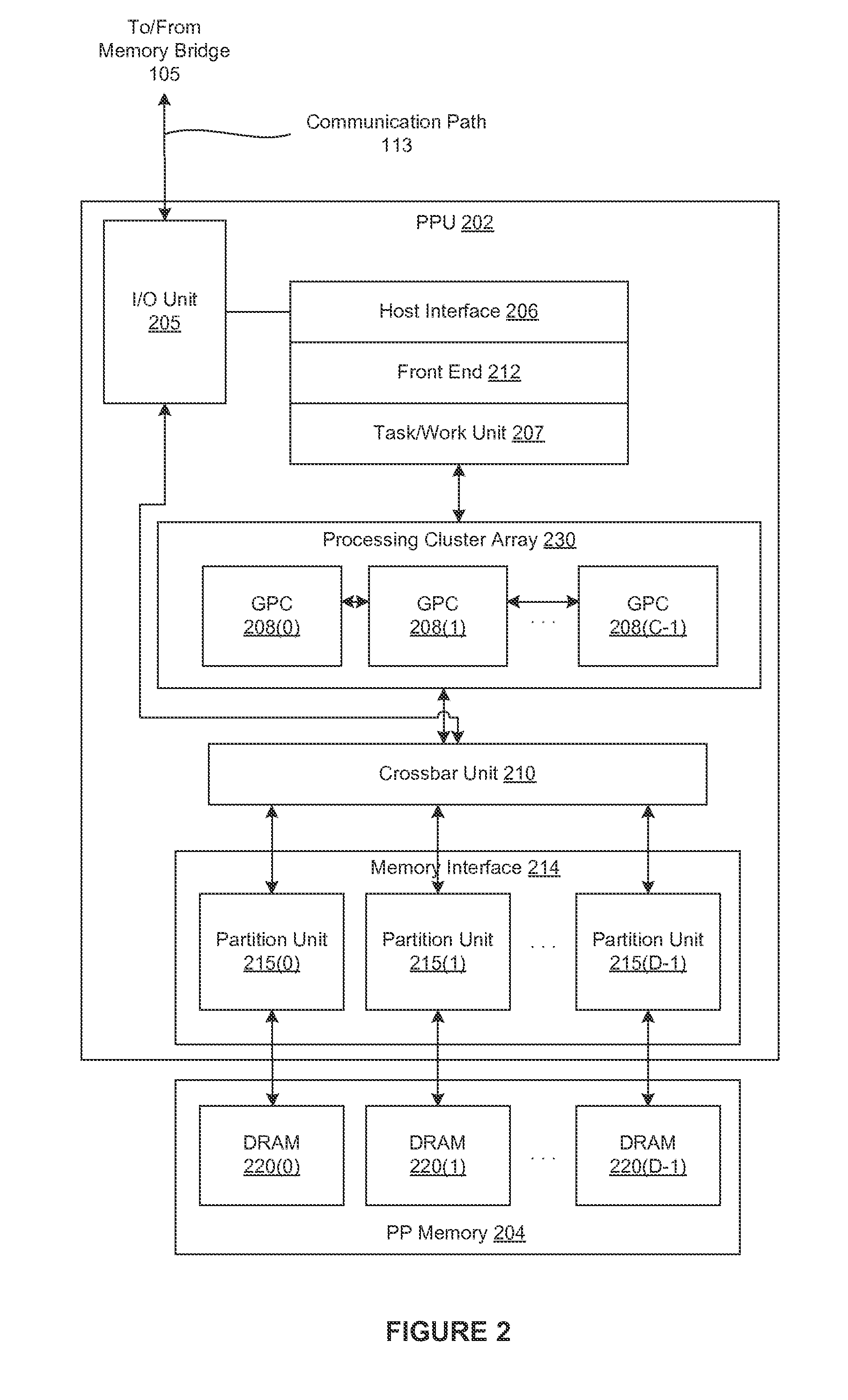

Performing multi-convolution operations in a parallel processing system

ActiveUS20160062947A1Easy to operateOptimizing on-chip memory usageBiological modelsComplex mathematical operationsLine tubingParallel processing

In one embodiment of the present invention a convolution engine configures a parallel processing pipeline to perform multi-convolution operations. More specifically, the convolution engine configures the parallel processing pipeline to independently generate and process individual image tiles. In operation, for each image tile, the pipeline calculates source locations included in an input image batch. Notably, the source locations reflect the contribution of the image tile to an output tile of an output matrix—the result of the multi-convolution operation. Subsequently, the pipeline copies data from the source locations to the image tile. Similarly, the pipeline copies data from a filter stack to a filter tile. The pipeline then performs matrix multiplication operations between the image tile and the filter tile to generate data included in the corresponding output tile. To optimize both on-chip memory usage and execution time, the pipeline creates each image tile in on-chip memory as-needed.

Owner:NVIDIA CORP

Simulation gridding method and apparatus including a structured areal gridder adapted for use by a reservoir simulator

InactiveUS6106561AHigh simulationSimulation results are accurateElectric/magnetic detection for well-loggingComputation using non-denominational number representationHorizonTriangulation

A Flogrid Simulation Gridding Program includes a Flogrid structured gridder. The structured gridder includes a structured areal gridder and a block gridder. The structured areal gridder will build an areal grid on an uppermost horizon of an earth formation by performing the following steps: (1) building a boundary enclosing one or more fault intersection lines on the horizon, and building a triangulation that absorbs the boundary and the faults; (2) building a vector field on the triangulation; (3) building a web of control lines and additional lines inside the boundary which have a direction that corresponds to the direction of the vector field on the triangulation, thereby producing an areal grid; and (4) post-processing the areal grid so that the control lines and additional lines are equi-spaced or smoothly distributed. The block gridder of the structured gridder will drop coordinate lines down from the nodes of the areal grid to complete the construction of a three dimensional structured grid. A reservoir simulator will receive the structured grid and generate a set of simulation results which are displayed on a 3D Viewer for observation by a workstation operator.

Owner:SCHLUMBERGER TECH CORP

System for real-time economic optimizing of manufacturing process control

InactiveUS6038540AEasy to operateEasy to deployMarket predictionsComplex mathematical operationsProcess measurementSelf adaptive

The present invention provides an adaptive process control and profit depiction system which is responsive to both process measurement input signals, economic inputs, and physical environment inputs. The process control system features an interactive optimization modeling system for determining manipulated process variables (also known as setpoints). These manipulated process variables are used to position mechanisms which control attributes of a manufacturing system, such as a valve controlling the temperature of a coolant or a valve controlling the flow rate in a steam line.

Owner:DOW GLOBAL TECH LLC

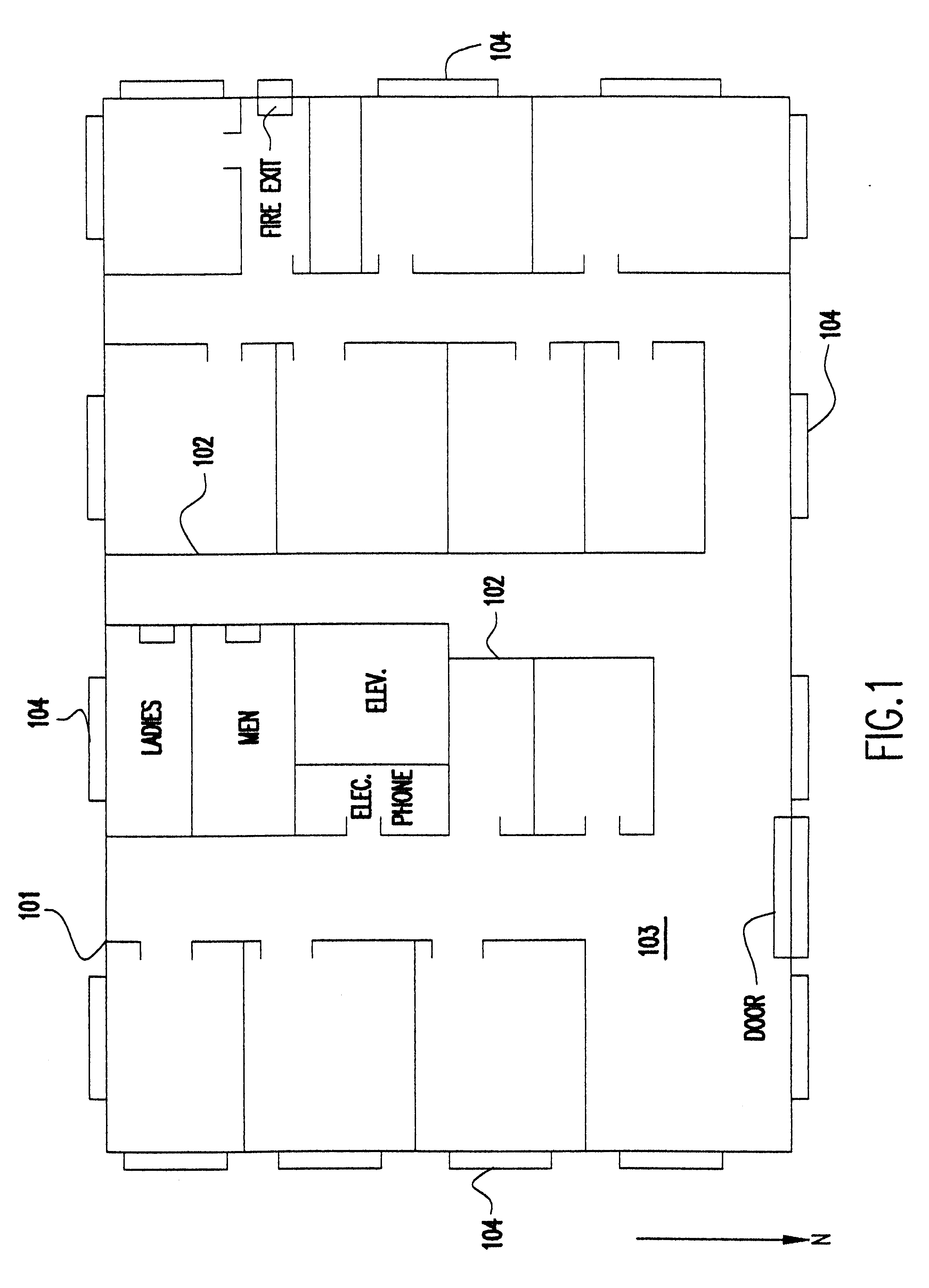

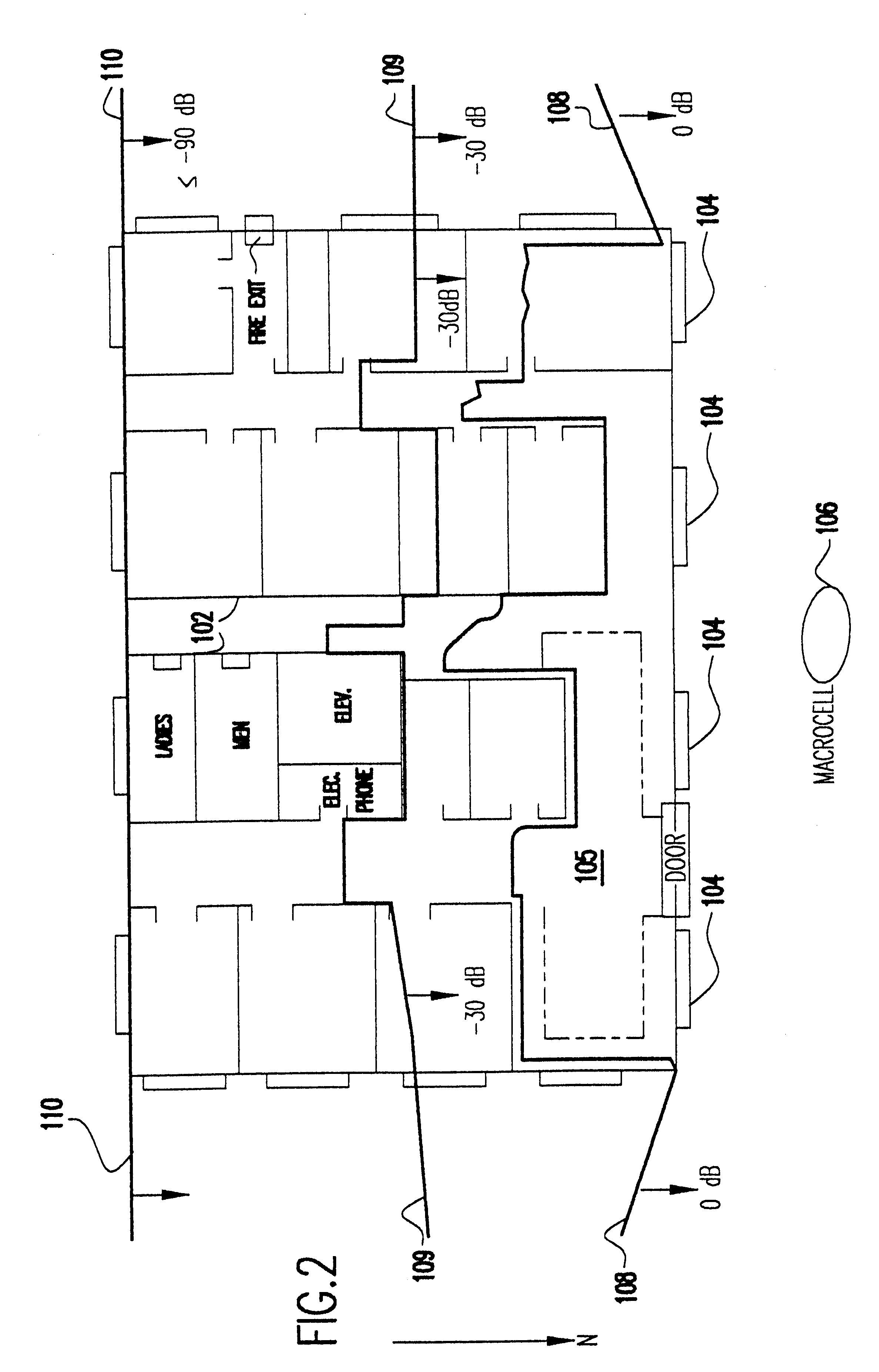

System and method for automated placement or configuration of equipment for obtaining desired network performance objectives

ActiveUS20040143428A1Significant valueEasy to explainGeometric CADProgram controlHard disc driveThe Internet

A method is presented for determining optimal or preferred configuration settings for wireless or wired network equipment in order to obtain a desirable level of network performance. A site-specific network model is used with adaptive processing to perform efficient design and on-going management of network performance. The invention iteratively determines overall network performance and cost, and further iterates equipment settings, locations and orientations. Real time control is between a site-specific Computer Aided Design (CAD) software application and the physical components of the network allows the invention to display, store, and iteratively adapt any network to constantly varying traffic and interference conditions. Alarms provide rapid adaptation of network parameters, and alerts and preprogrammed network shutdown actions may be taken autonomously. A wireless post-it note device and network allows massive data such as book contents or hard drive memory to be accessed within a room by a wide bandwidth reader device, and this can further be interconnected to the internet or Ethernet backbone in order to provide worldwide access and remote retrieval to wireless post-it devices.

Owner:EXTREME NETWORKS INC

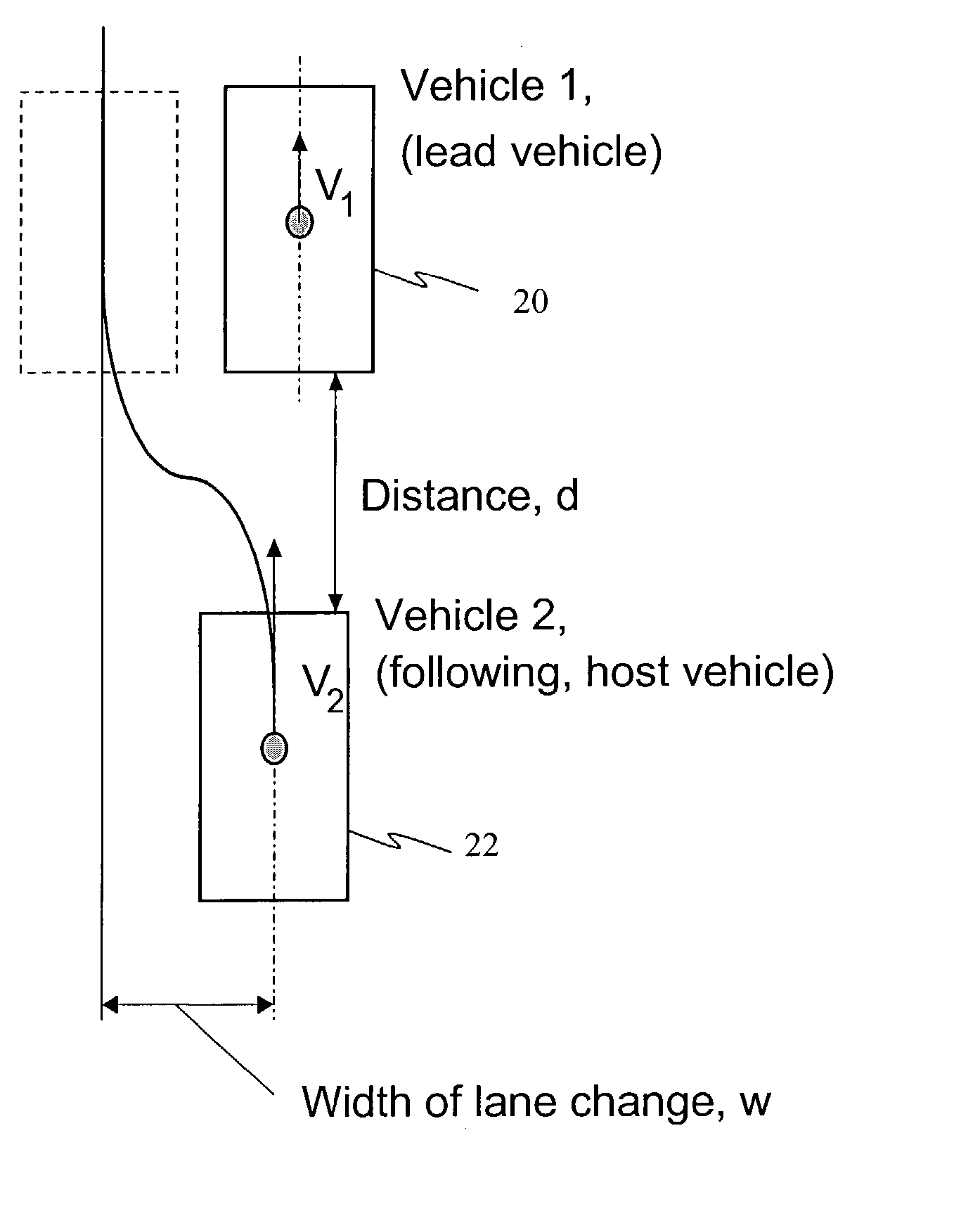

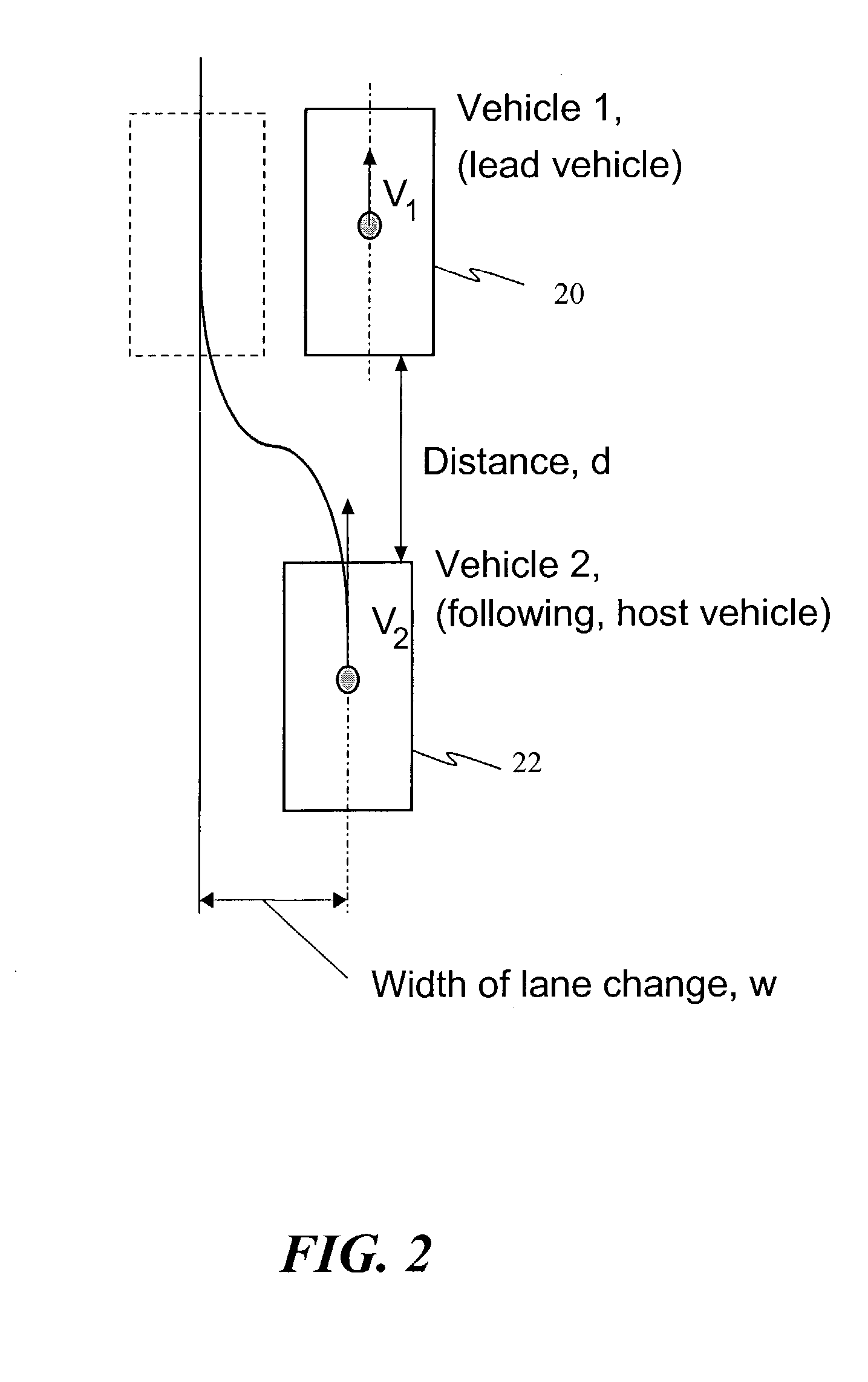

Collision avoidance with active steering and braking

A method for collision avoidance using automated braking and steering comprising: determining an actual distance to an obstacle in a path of a vehicle; determining a relative velocity between the obstacle and the vehicle; determining a first distance sufficient to avoid collision by braking only; determining a second distance sufficient to avoid collision by combined braking and steering around the obstacle. The method also includes: applying braking if at least one of, the first distance exceeds the actual distance and the first distance is within a selected threshold of the actual distance. If the actual distance exceeds the second distance and a lane change is permitted, steering control to affect a lane change is applied.

Owner:BWI +1

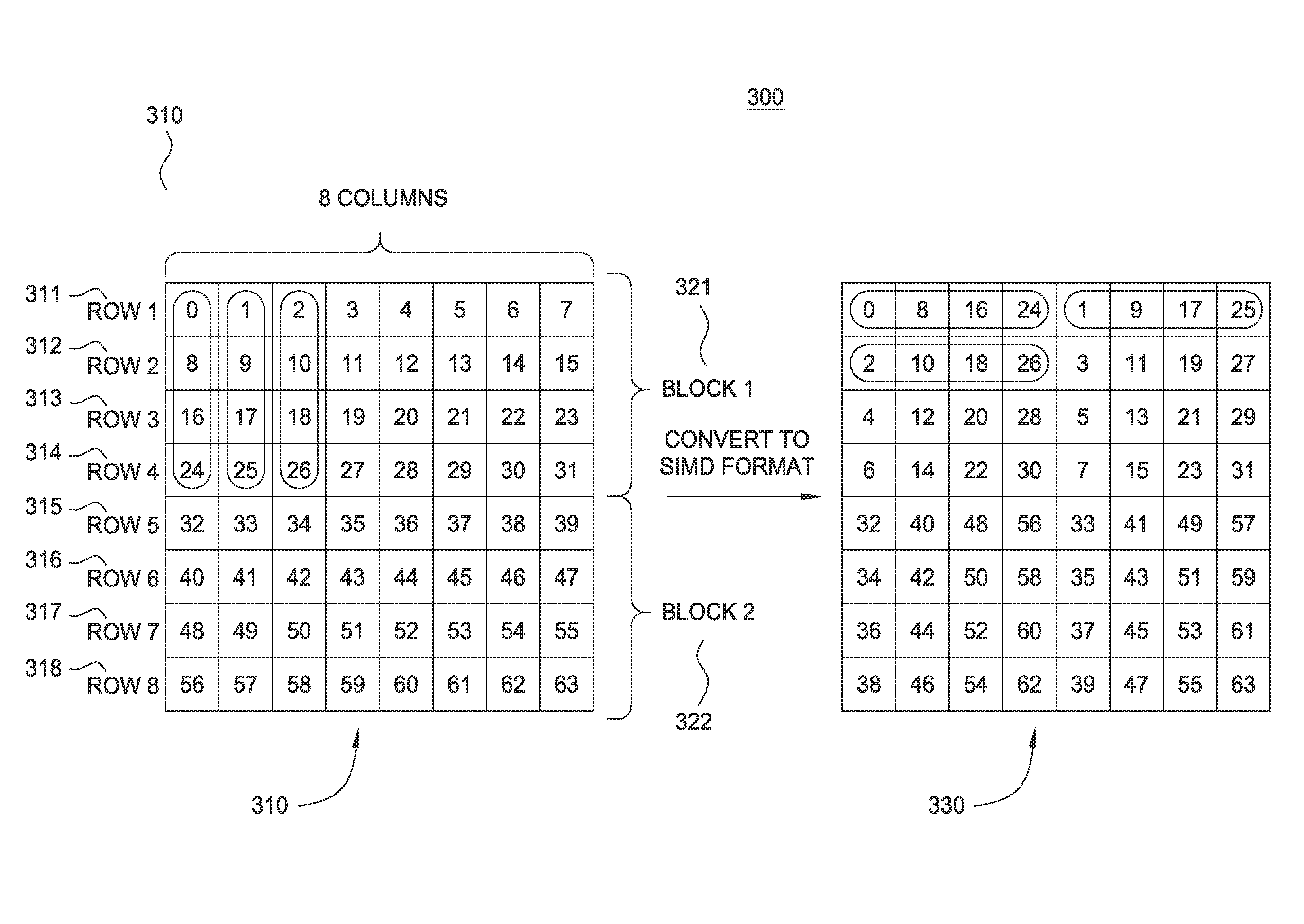

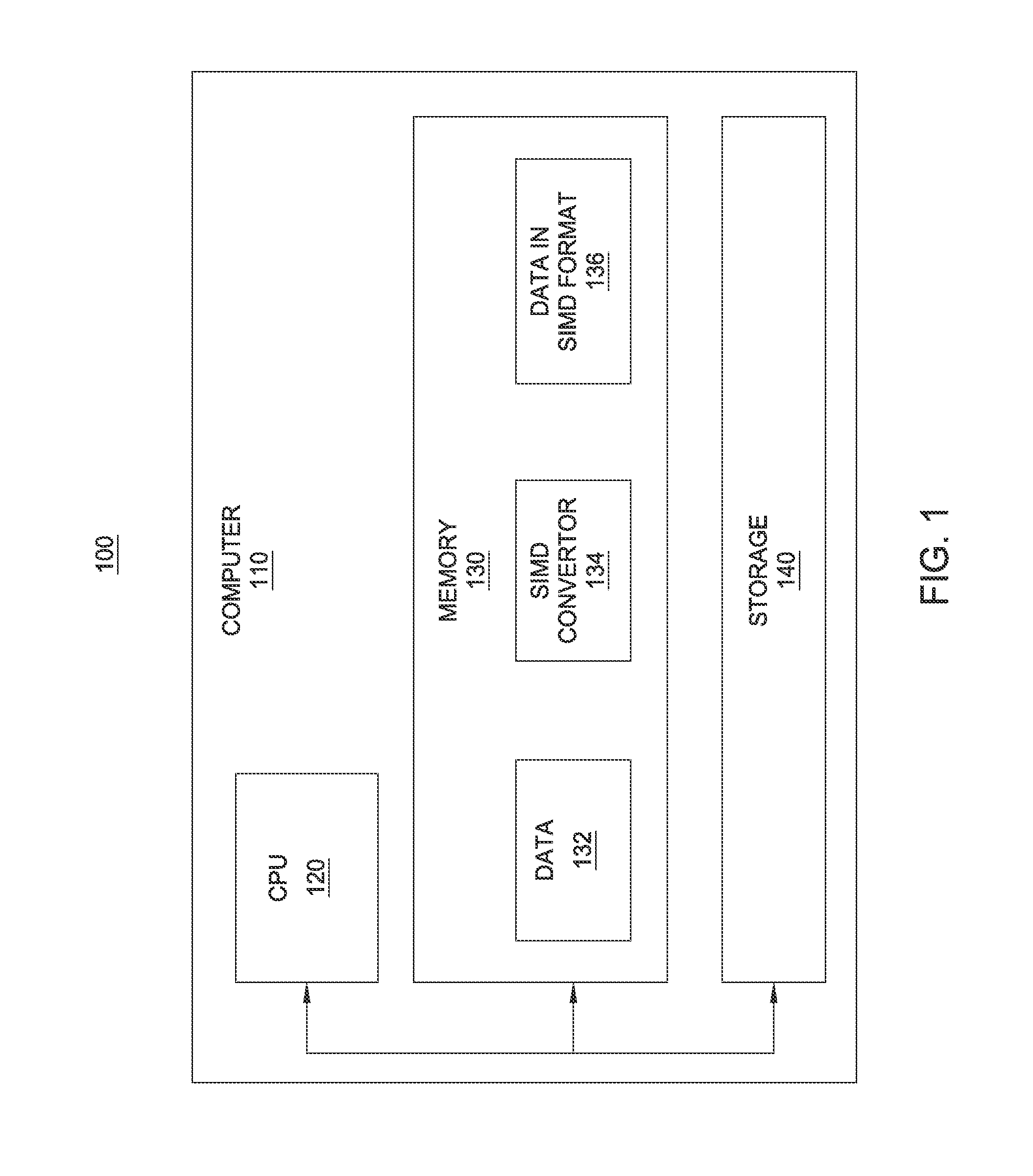

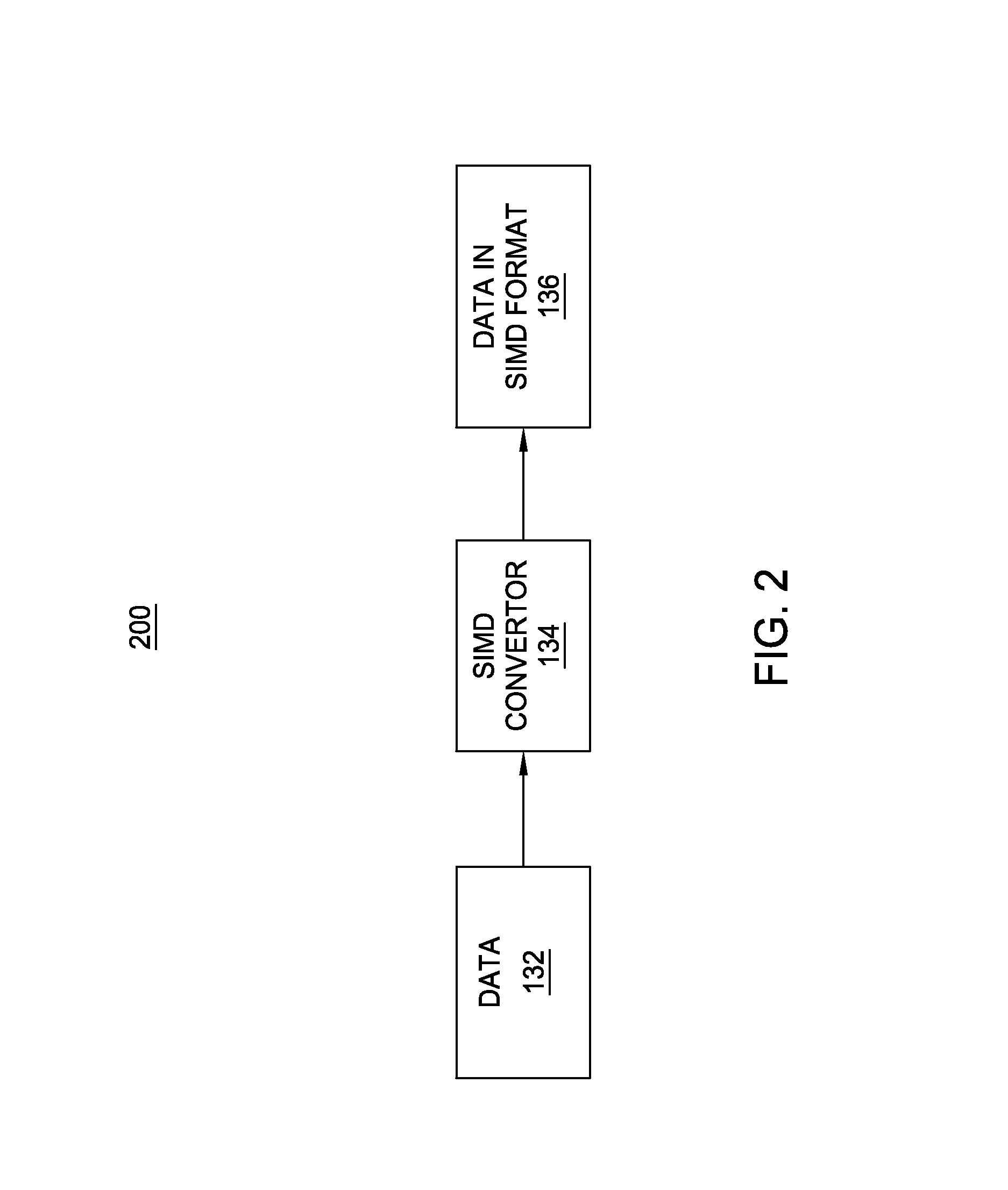

Processing array data on SIMD multi-core processor architectures

InactiveUS8484276B2Program control using stored programsGeneral purpose stored program computerFast Fourier transformFourier transform on finite groups

Owner:INT BUSINESS MASCH CORP

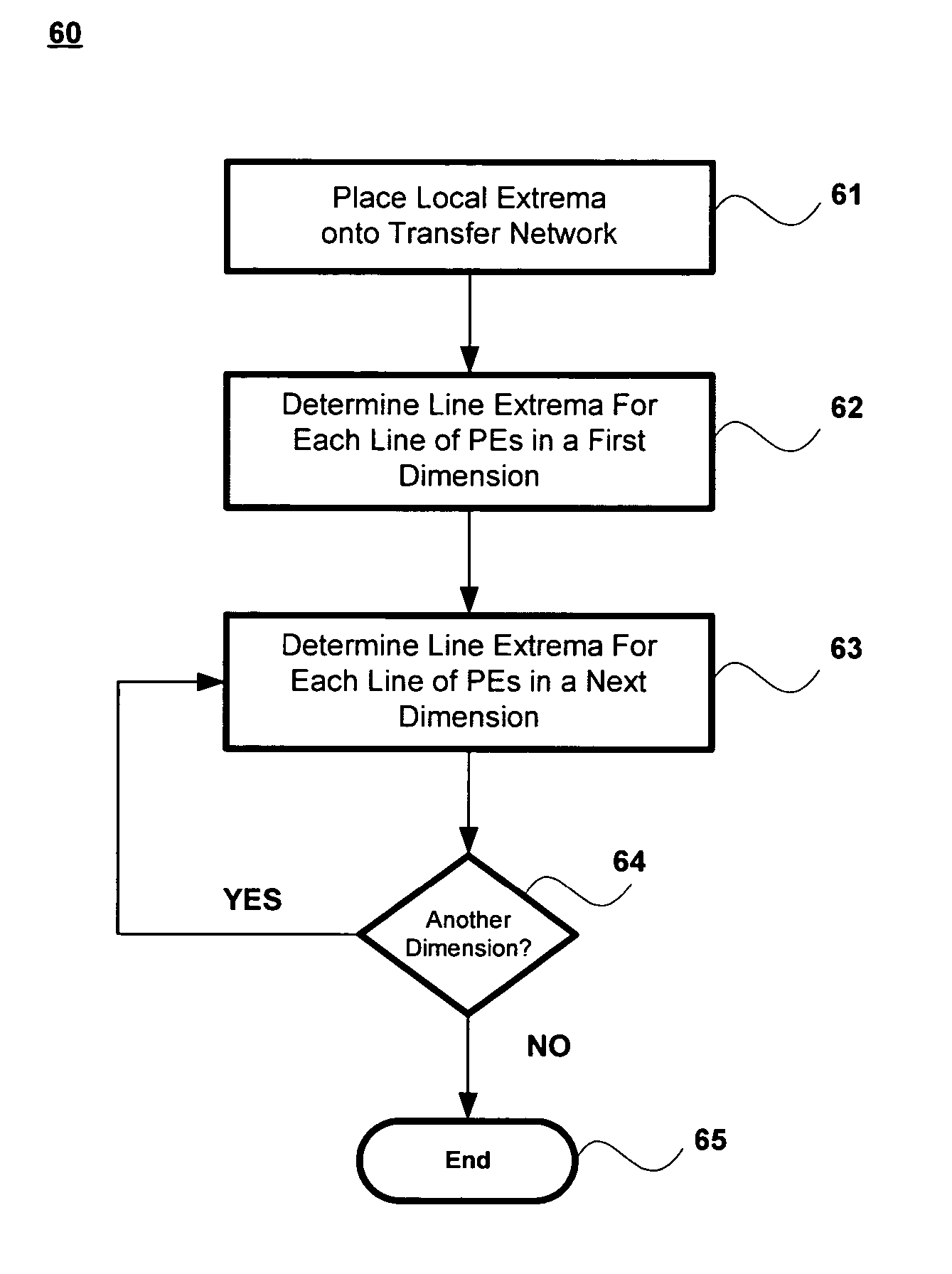

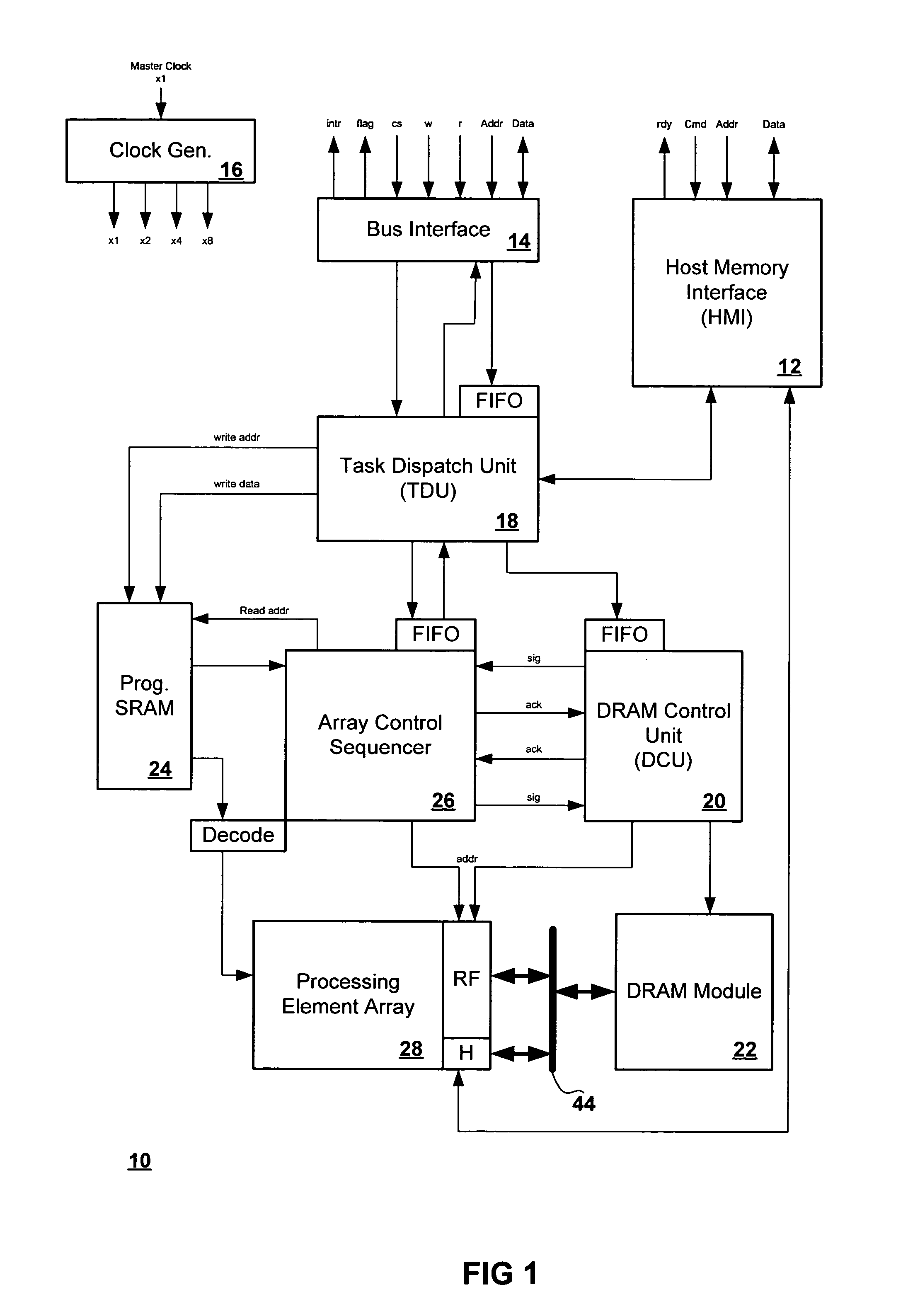

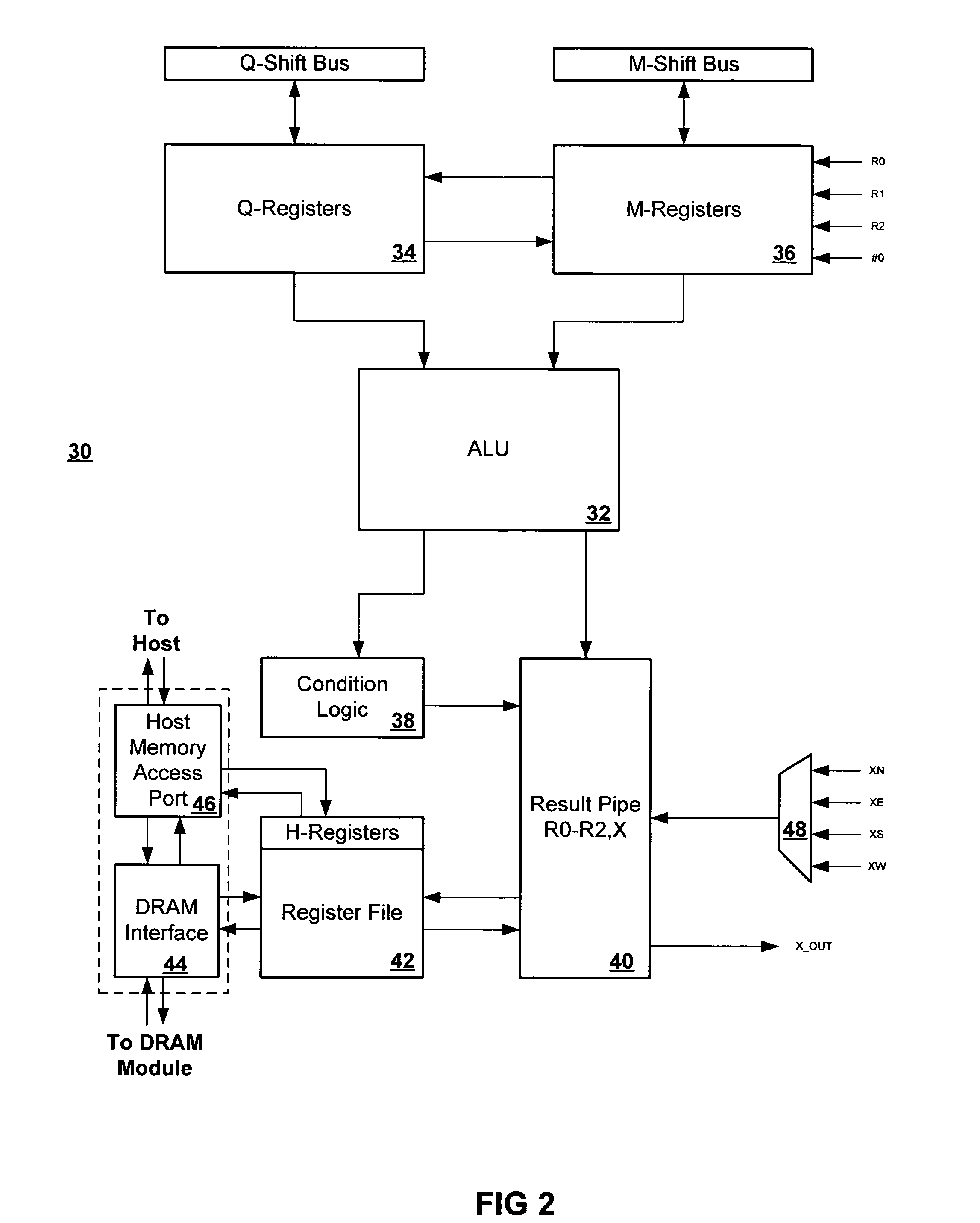

Method for finding global extrema of a set of shorts distributed across an array of parallel processing elements

ActiveUS7574466B2Single instruction multiple data multiprocessorsDigital data processing detailsProcessing elementParallel processing

A method for finding an extrema for an n-dimensional array having a plurality of processing elements, the method includes determining within each processing element a first dimensional extrema for a first dimension, wherein the first dimensional extrema is related to the local extrema of the processing elements in the first dimension and wherein the first dimensional extrema has a most significant byte and a least significant byte, determining within each processing element a next dimensional extrema for a next dimension of the n-dimensional array, wherein the next dimensional extrema is related to the first dimensional extrema and wherein the next dimensional extrema has a most significant byte and a least significant byte; and repeating the determining within each processing element a next dimensional extrema for each of the n-dimensions, wherein each of the next dimensional extrema is related to a dimensional extrema from a previously selected dimension.

Owner:MICRON TECH INC

Accident avoidance systems and methods

InactiveUS7295925B2Avoid accidentsAvoid and minimize effectVehicle seatsAnalogue computers for vehiclesCommunications systemEngineering

Method and system for preventing accidents between first and second vehicles includes a positioning system arranged in each vehicle for determining the absolute position thereof, a memory unit arranged in the first vehicle for storing data about travel lanes, a communication system for transmitting the position of the second vehicle to the first vehicle, a receiver system arranged in the first vehicle for receiving position information from the second vehicle, a processor coupled to the positioning system, the receiver system and the memory unit in the first vehicle for predicting a collision between the vehicles based on the position of the vehicles and travel lane data, and a reactive component arranged in the first vehicle and coupled to the processor. The reactive component is arranged to initiate an action or change its operation when a collision is predicted by the processor, e.g., sound or indicate an alarm.

Owner:AMERICAN VEHICULAR SCI

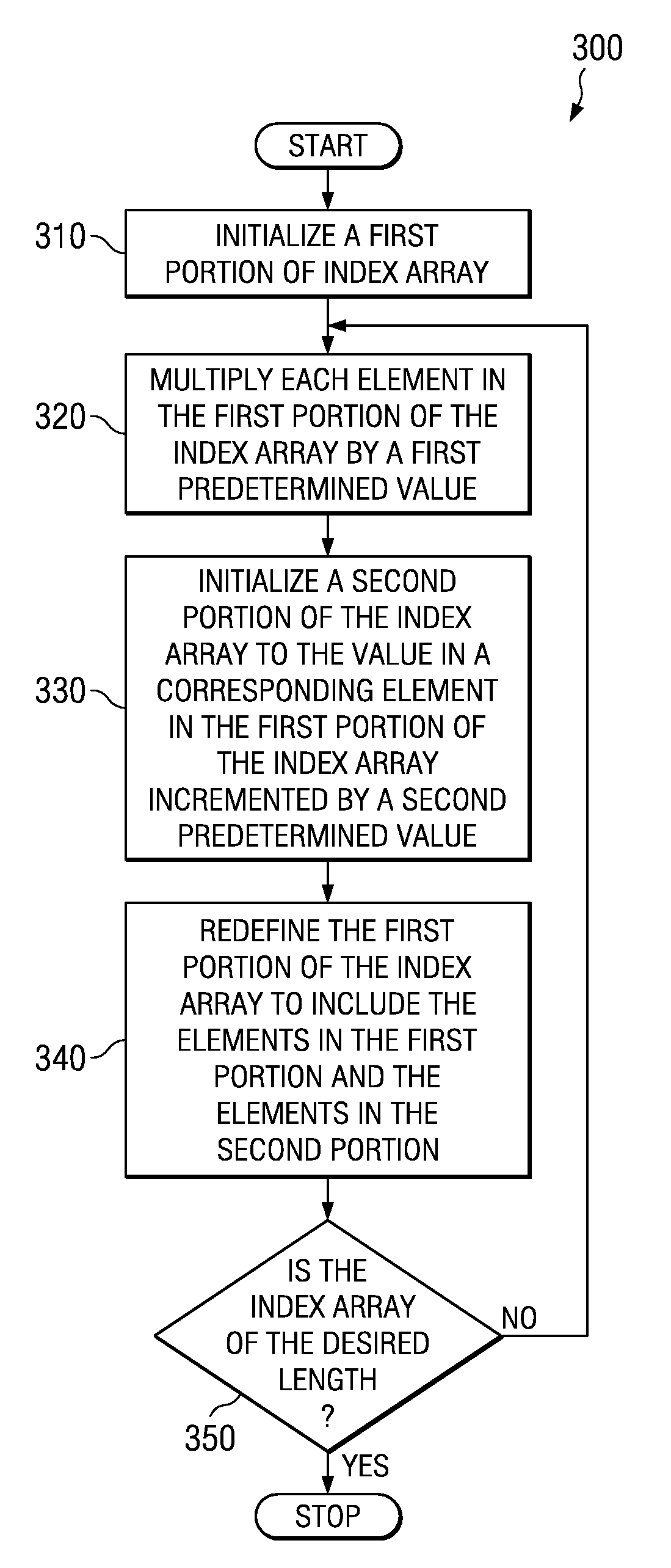

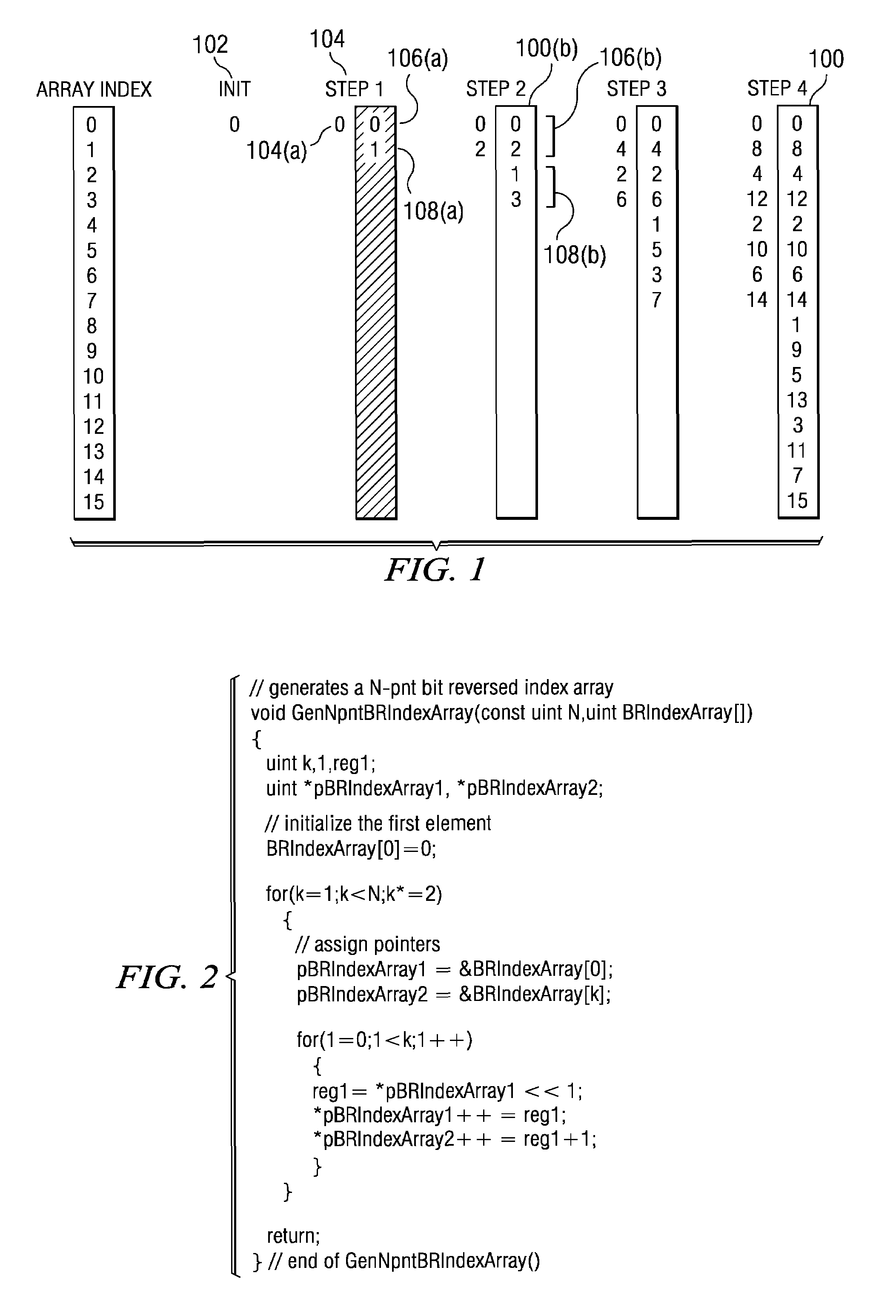

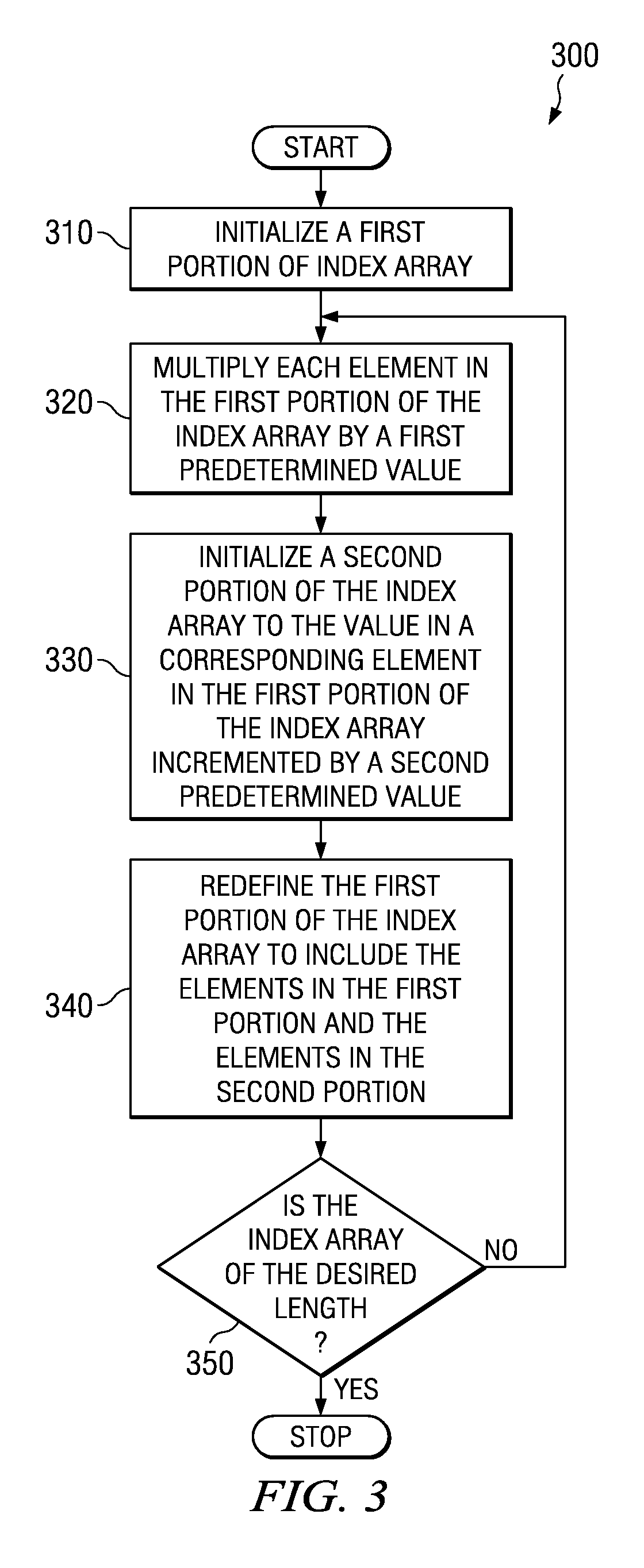

Method of generating a cycle-efficient bit-reverse index array for a wireless communication system

ActiveUS7406494B2Efficient hardwareGenerate efficientlyDigital computer detailsHandling data according to predetermined rulesCommunications systemReverse index

An efficient method of generating a bit-reverse index array in real time without performing any bit manipulation for a wireless communication system.

Owner:TEXAS INSTR INC

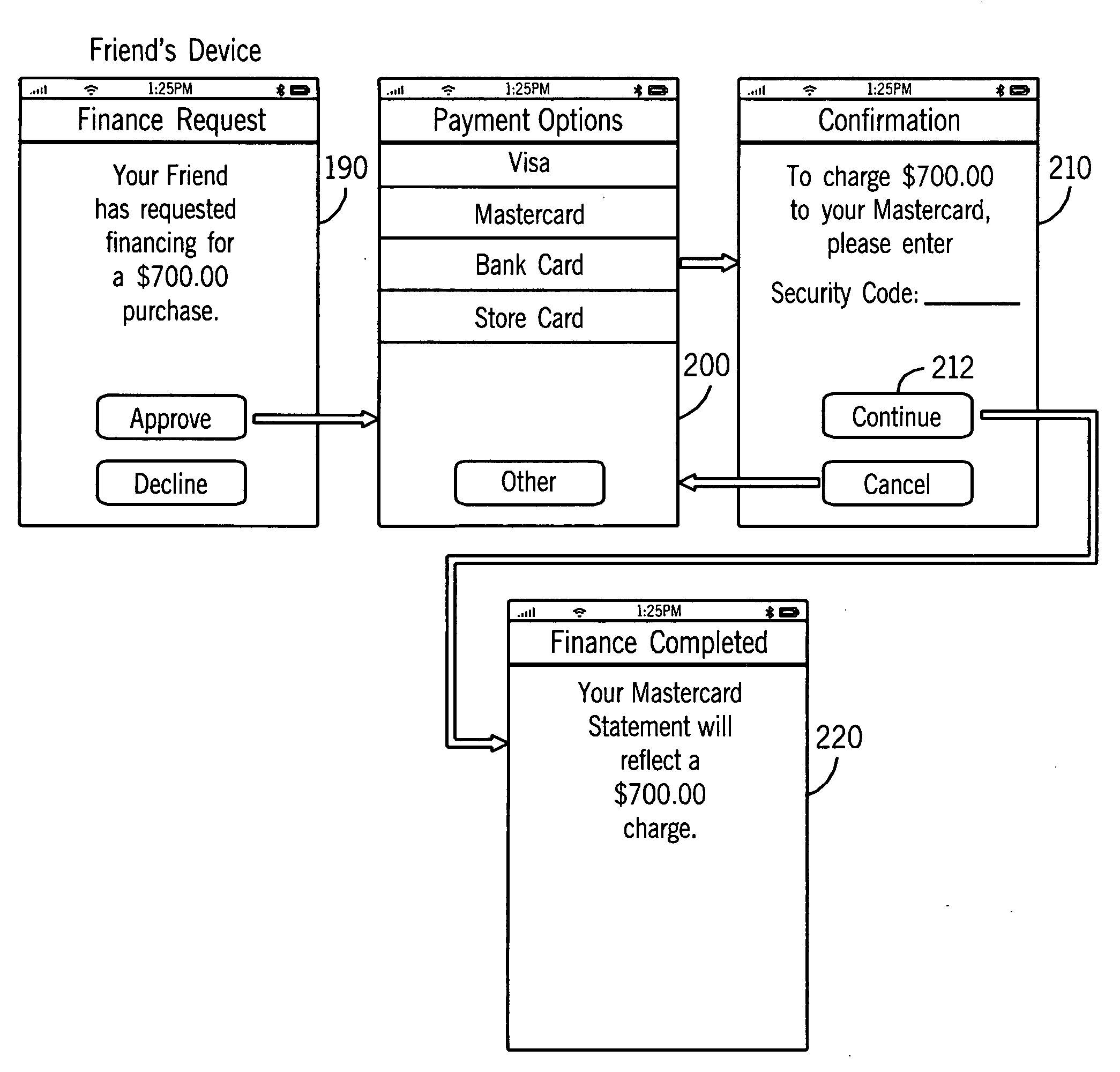

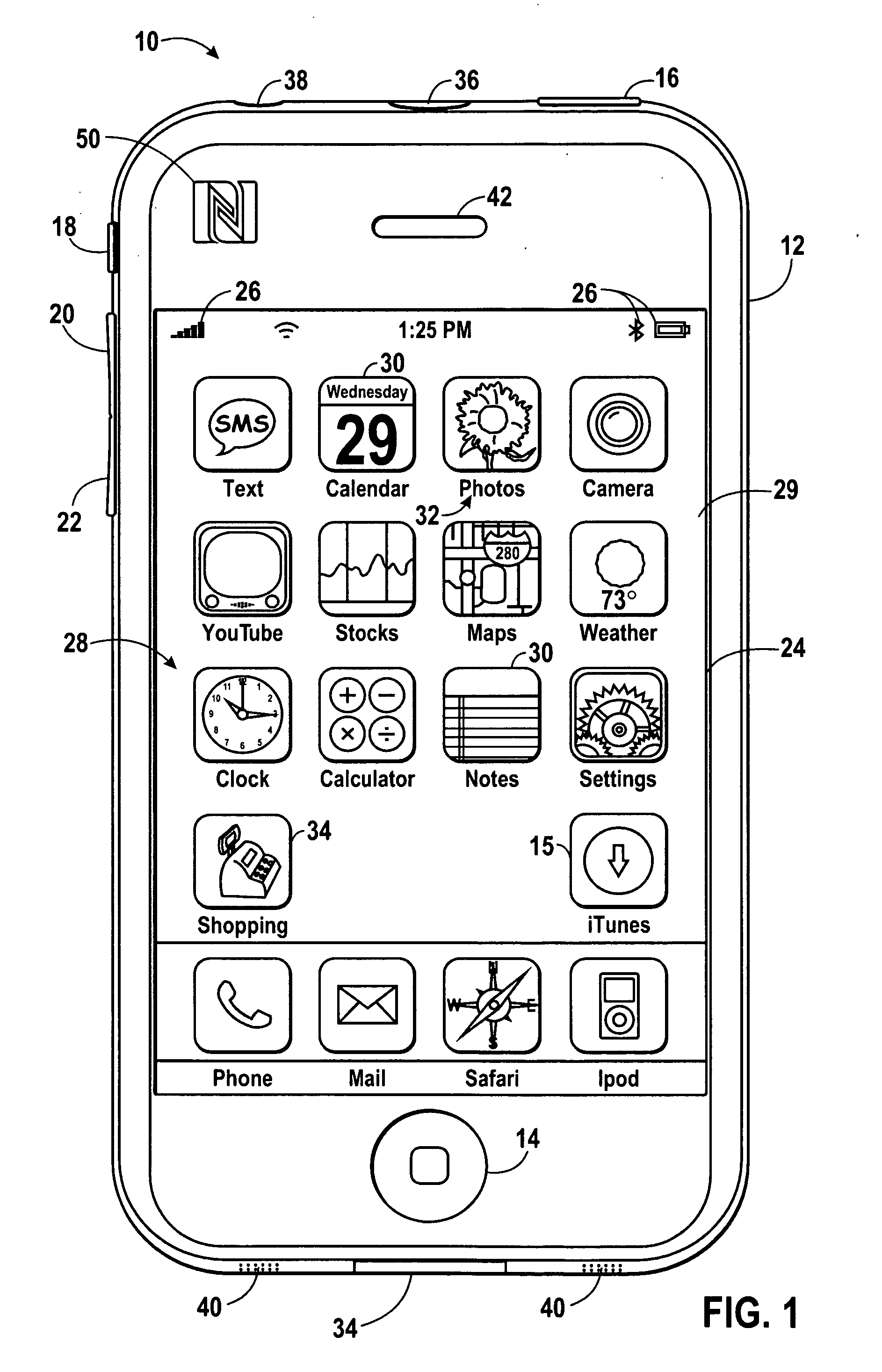

Smart menu options

InactiveUS20100082445A1Maximize the benefitsHand manipulated computer devicesFinanceContext basedHuman–computer interaction

Systems and methods are provided that allow for a portable electronic device to provide smart menus to a user based on a context of a transaction. Specifically, the method of using a portable electronic device may include opening a near field communication (NFC) channel with a point-of-purchase device and providing a smart menu based on a determined context. The portable electronic device may be configured to determine the context based at least in part upon acquiring sales transaction information for the point-of-purchase device. Additionally, the portable electronic device may be configured to determine the context based at least in part upon acquiring vendor identification information.

Owner:APPLE INC

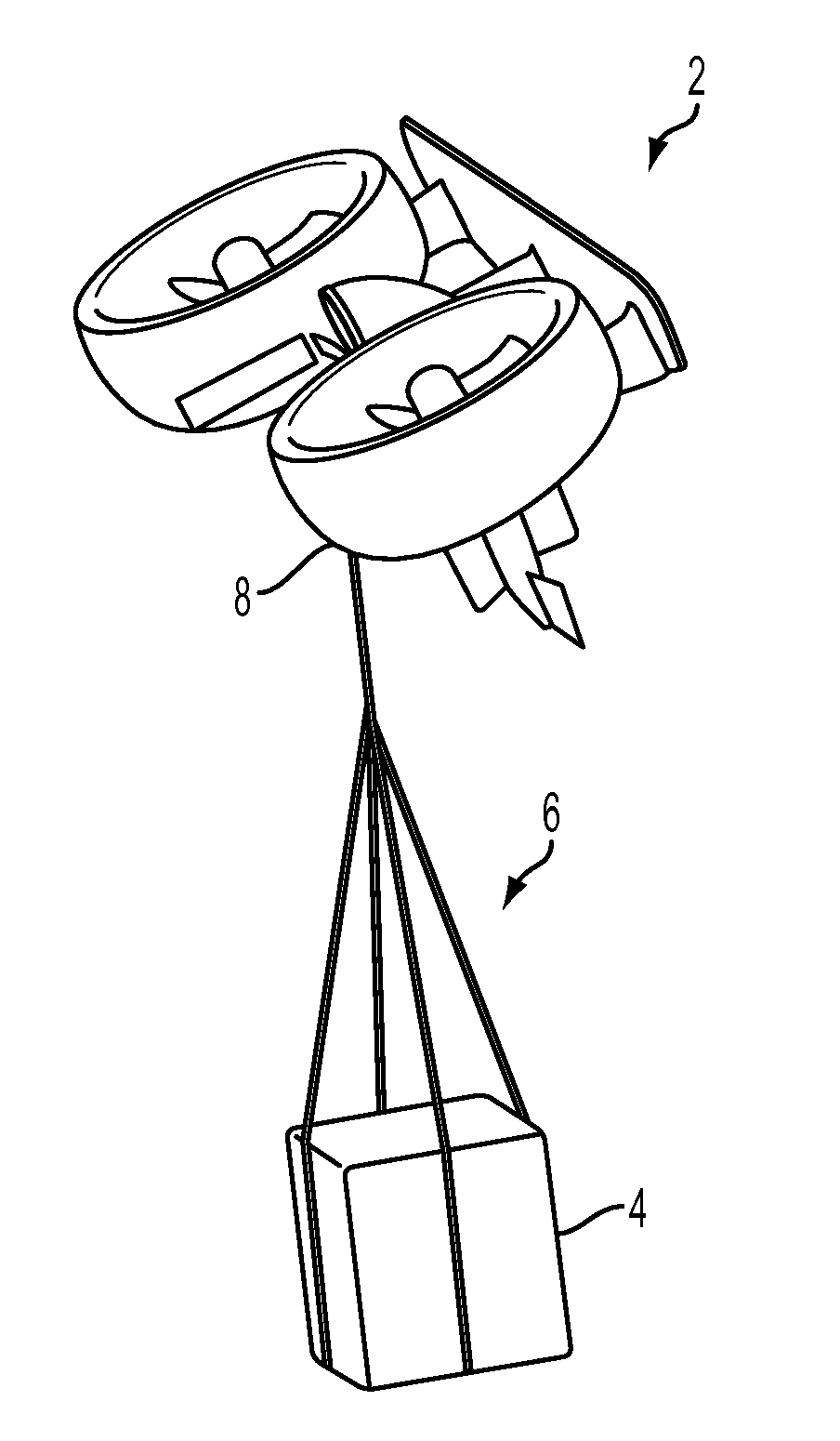

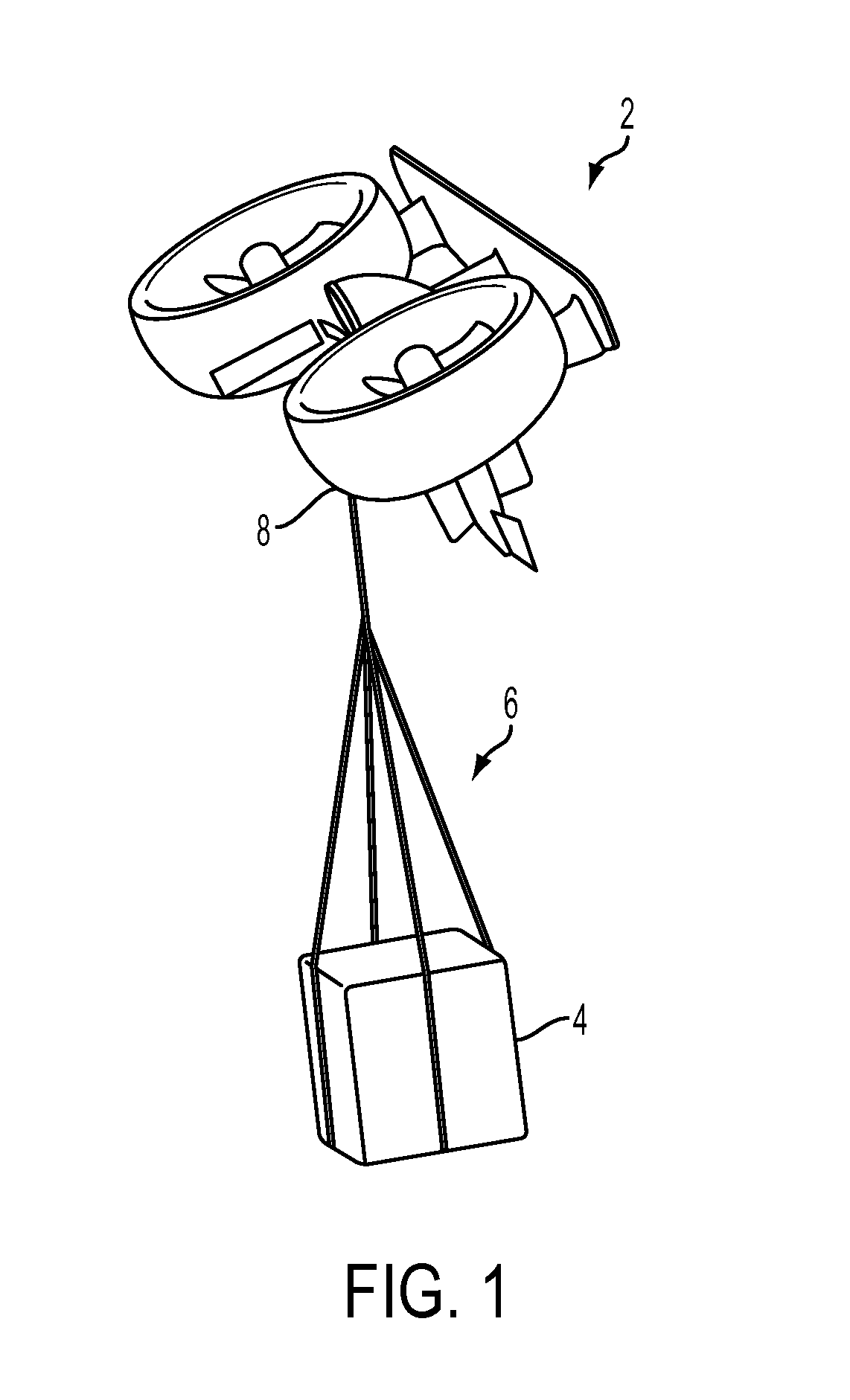

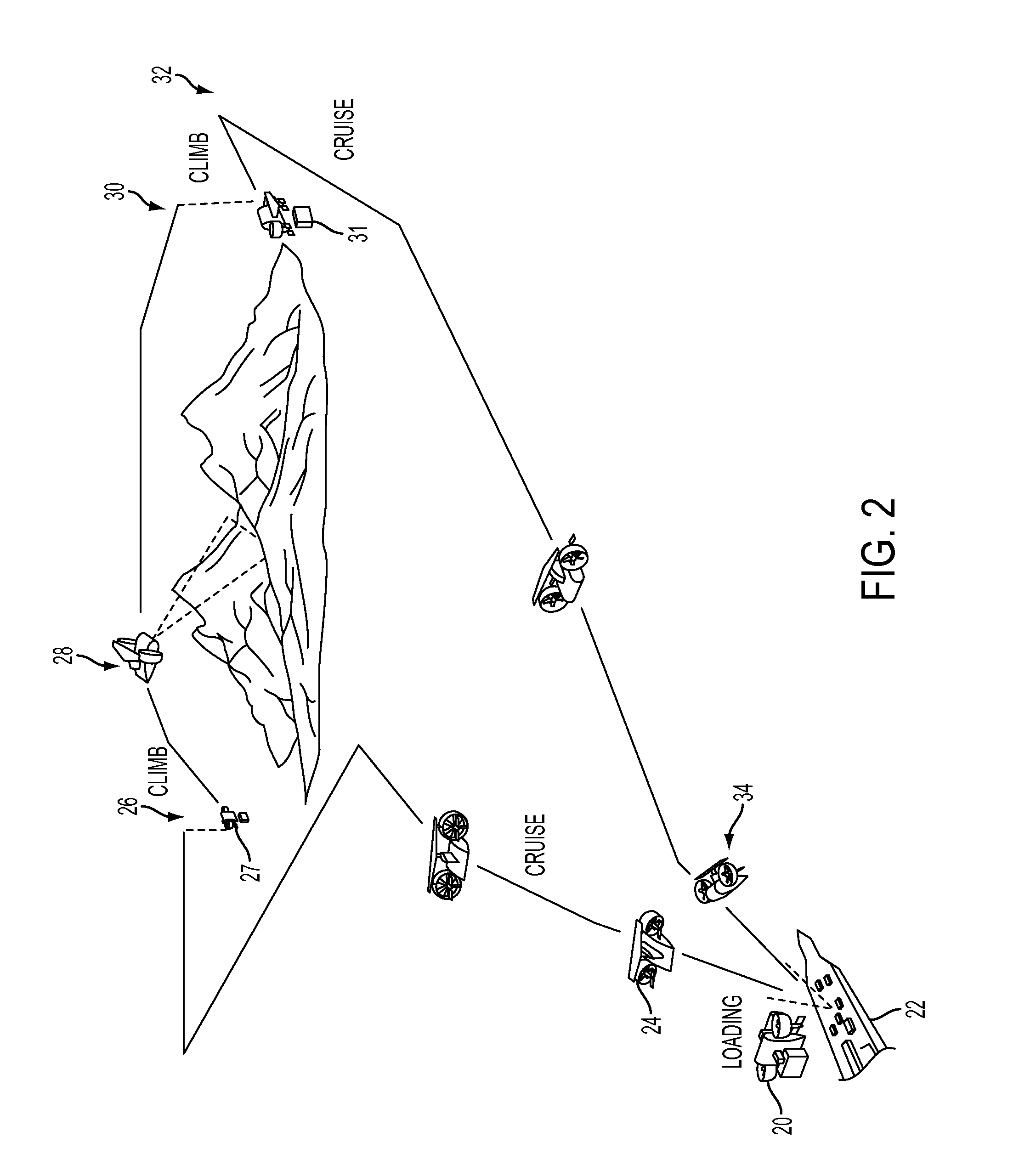

Autonomous Payload Parsing Management System and Structure for an Unmanned Aerial Vehicle

InactiveUS20110084162A1Improve versatilityIncrease in sizeStatic/dynamic balance measurementRemote controlled aircraftManagement systemControl logic

An unmanned aerial vehicle (UAV) for making partial deliveries of cargo provisions includes a UAV having one or more ducted fans and a structural interconnect connecting the one or more fans to a cargo pod. The cargo pod has an outer aerodynamic shell and one or more internal drive systems for modifying a relative position of one or more cargo provisions contained within the cargo pod. Control logic is configured to, after delivery of a partial portion of the cargo provisions contained within the cargo pod, vary a position of at least a portion of the remaining cargo provisions to maintain a substantially same center of gravity of the UAV relative to a center of gravity prior to delivery of the partial portion. Other center of gravity compensation mechanisms may also be controlled by the control logic to aid in maintaining the center of gravity of the UAV.

Owner:HONEYWELL INT INC

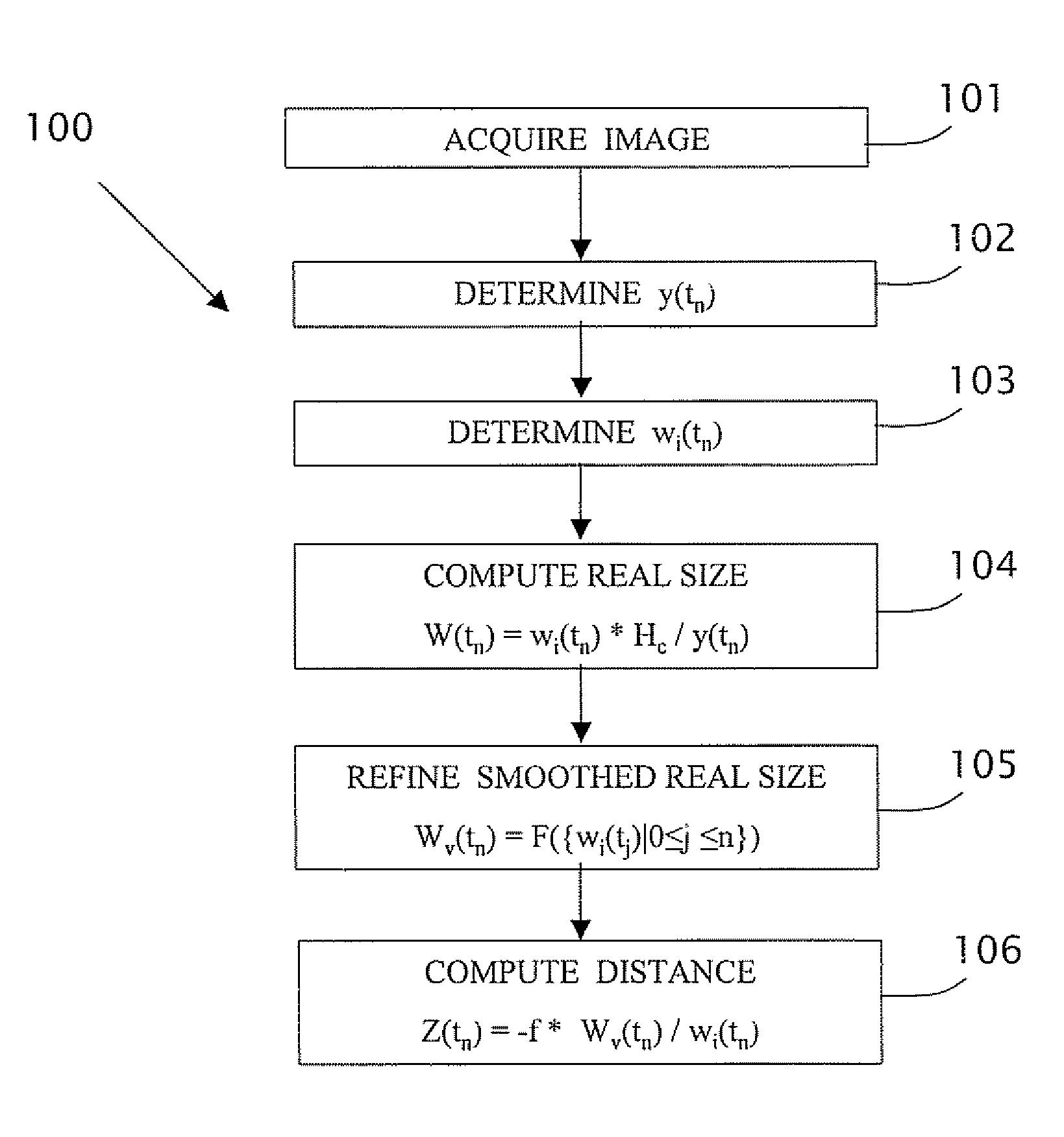

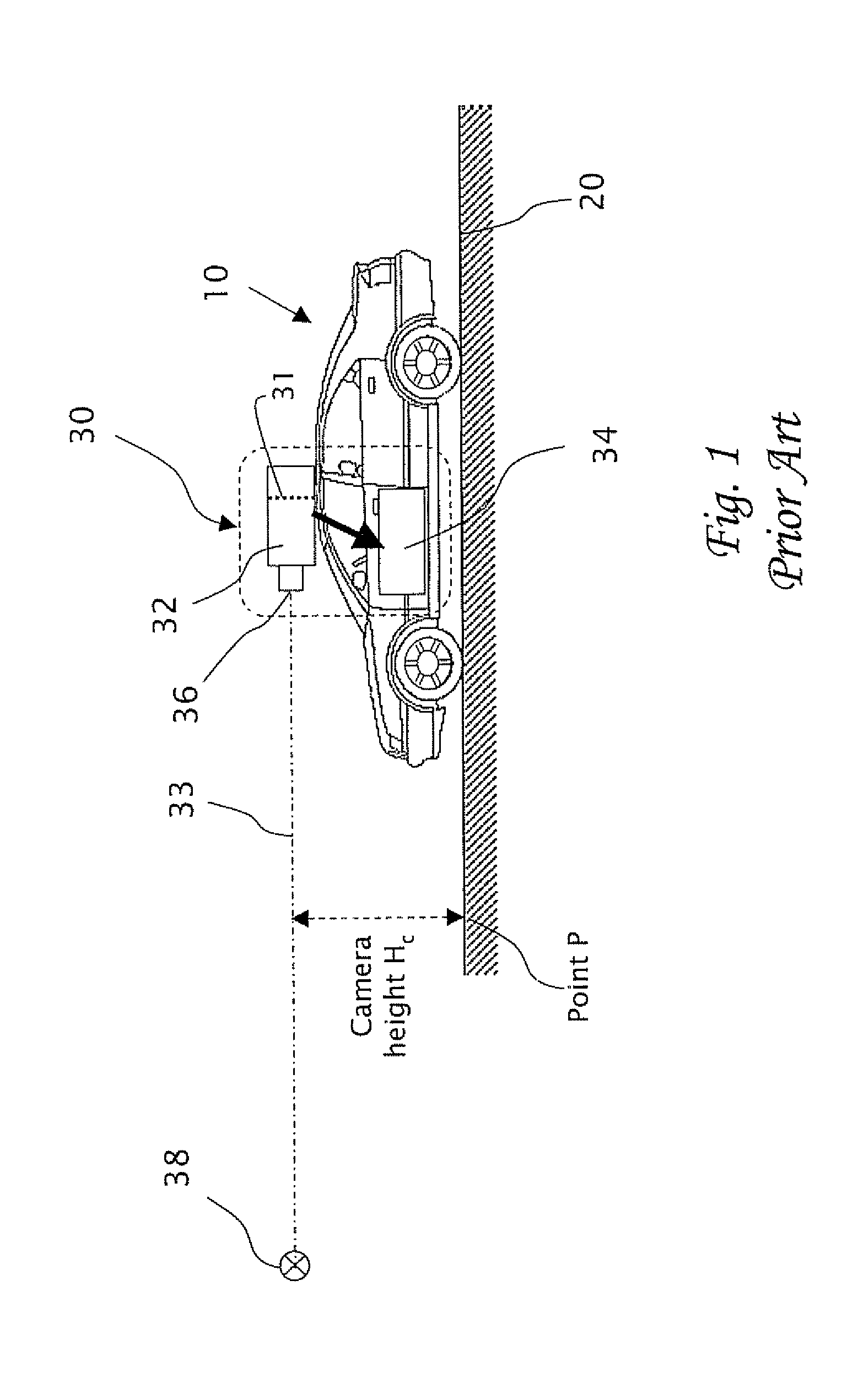

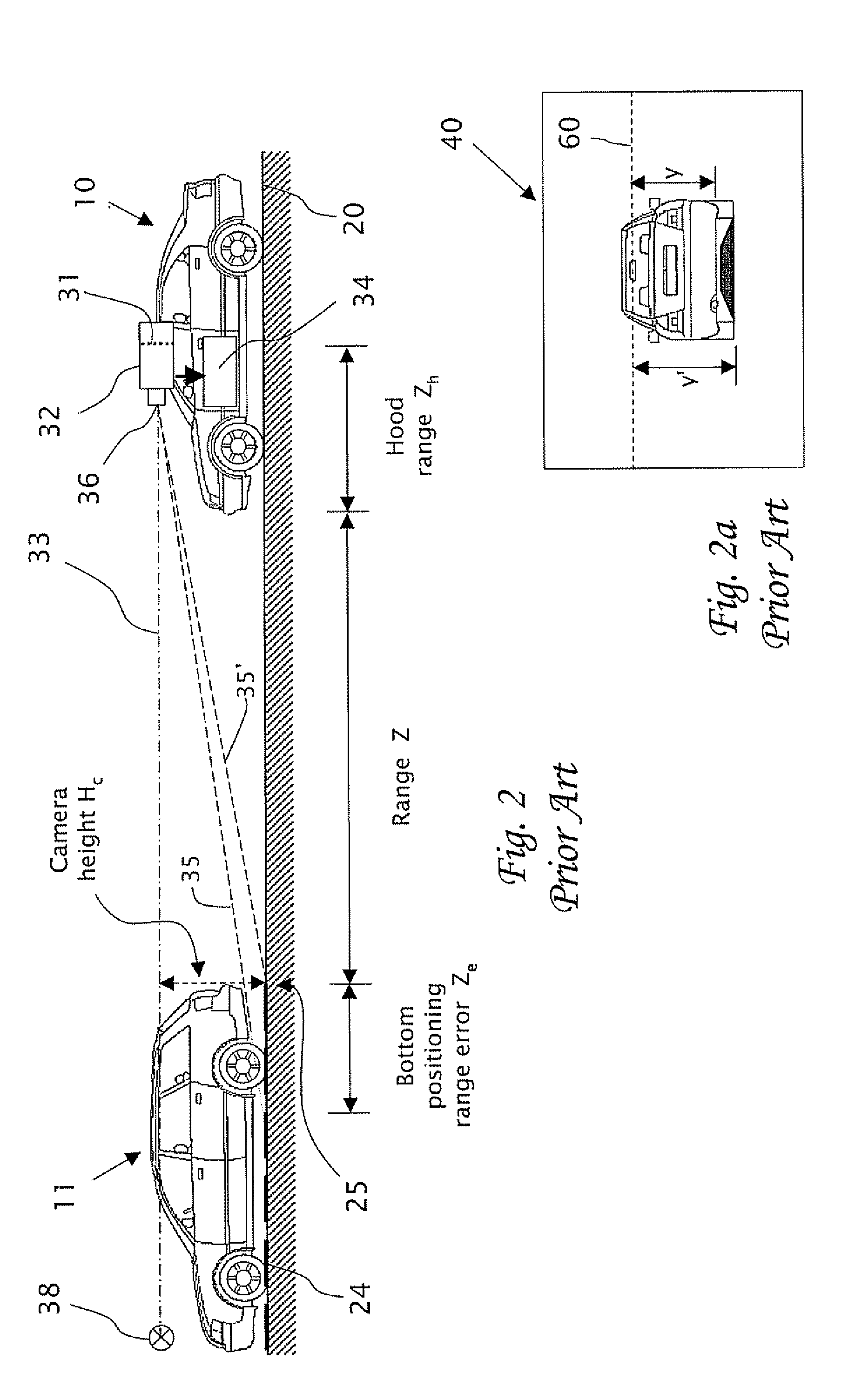

Estimating distance to an object using a sequence of images recorded by a monocular camera

In a computerized system including a camera mounted in a moving vehicle. The camera acquires consecutively in real time image frames including images of an object within the field of view of the camera. Range to the object from the moving vehicle is determined in real time. A dimension, e.g. a width, is measured in the respective images of two or more image frames, thereby producing measurements of the dimension. The measurements are processed to produce a smoothed measurement of the dimension. The dimension is measured subsequently in one or more subsequent frames. The range from the vehicle to the object is calculated in real time based on the smoothed measurement and the subsequent measurements. The processing preferably includes calculating recursively the smoothed dimension using a Kalman filter.

Owner:MOBILEYE VISION TECH LTD

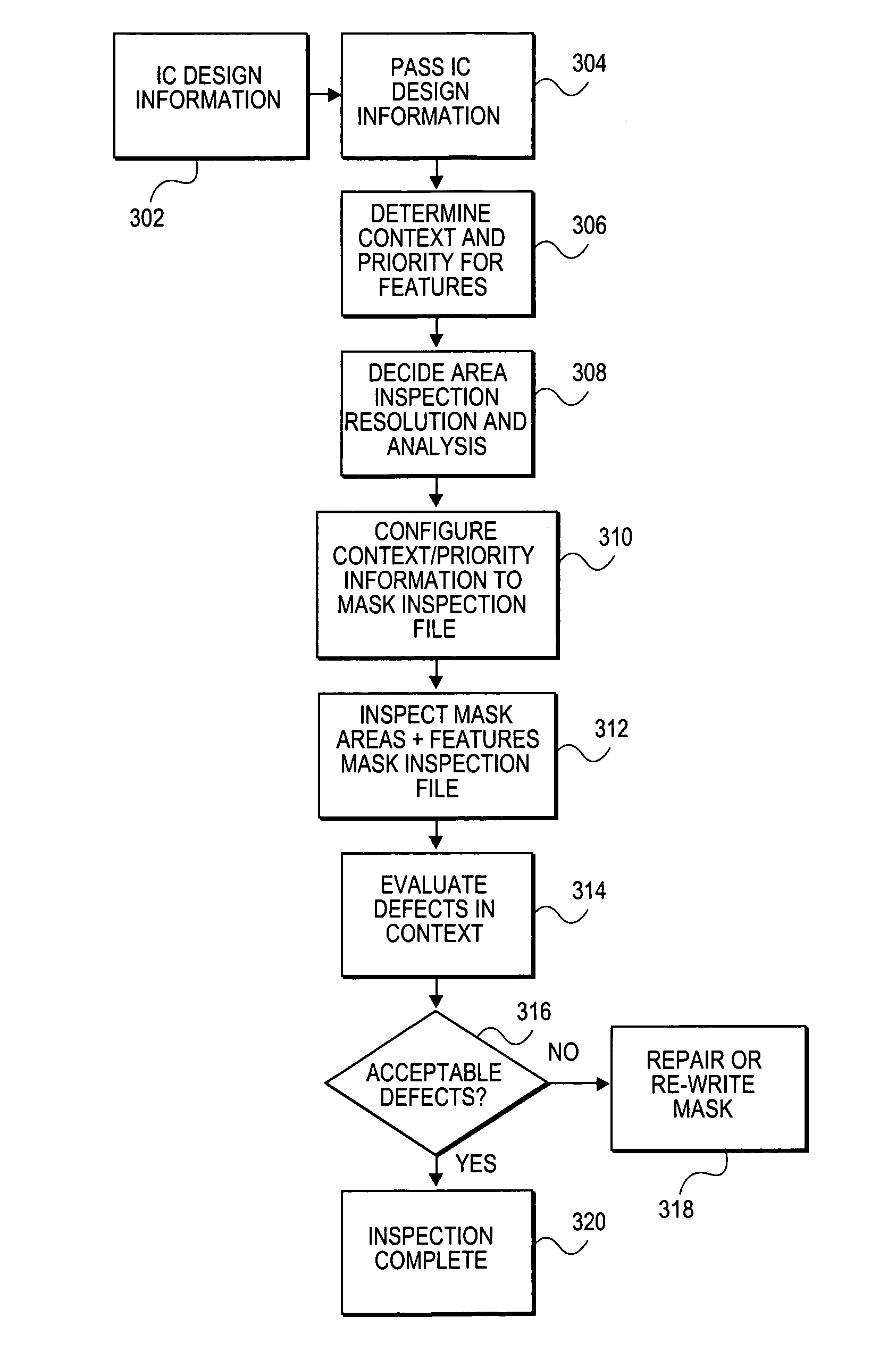

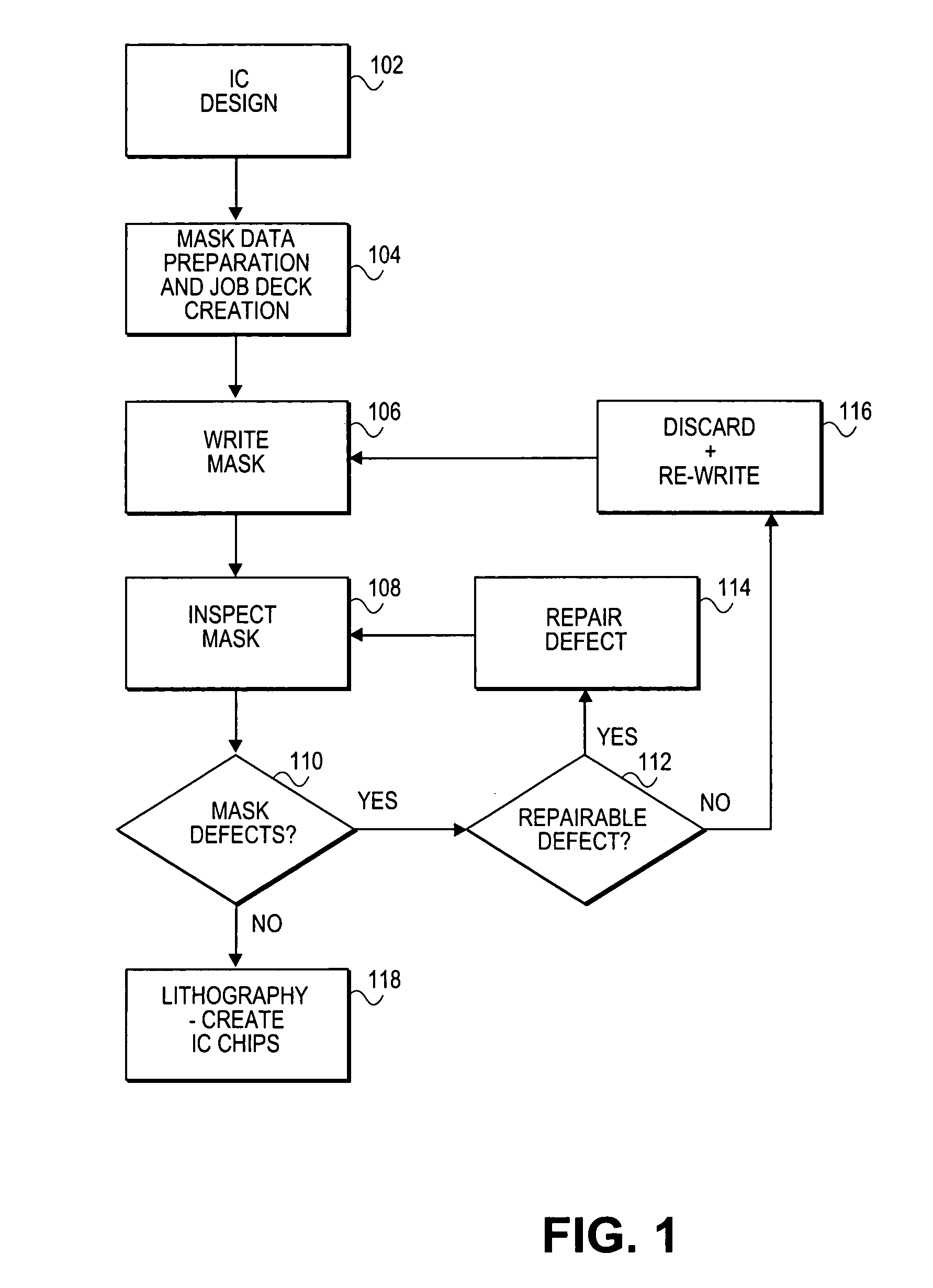

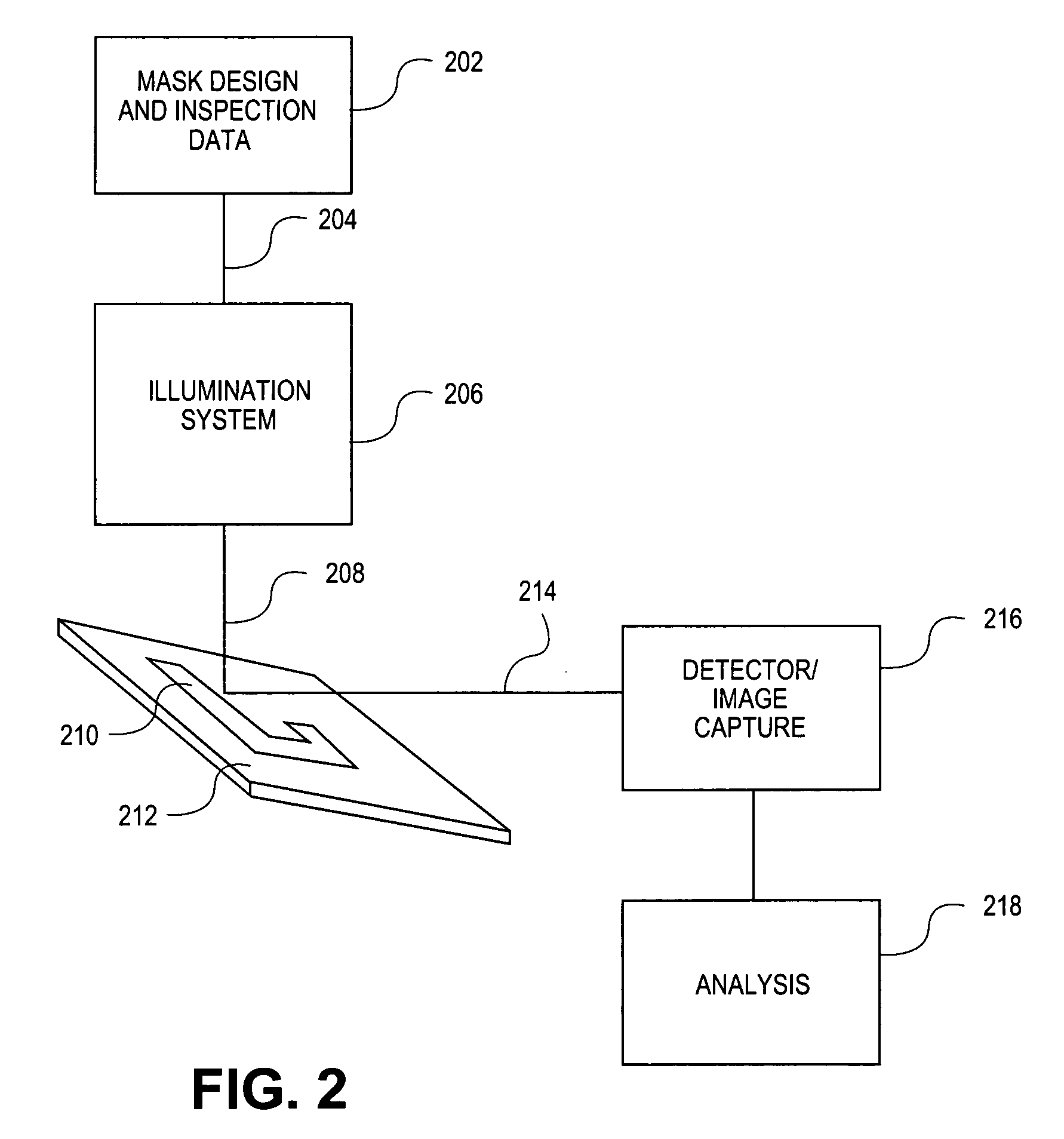

Method and system for context-specific mask inspection

InactiveUS7231628B2Electrical testingCharacter and pattern recognitionMask inspectionContext specific

A method for inspecting lithography masks includes generating integrated circuit design data and using context information from the integrated circuit design data to inspect a mask.

Owner:CADENCE DESIGN SYST INC

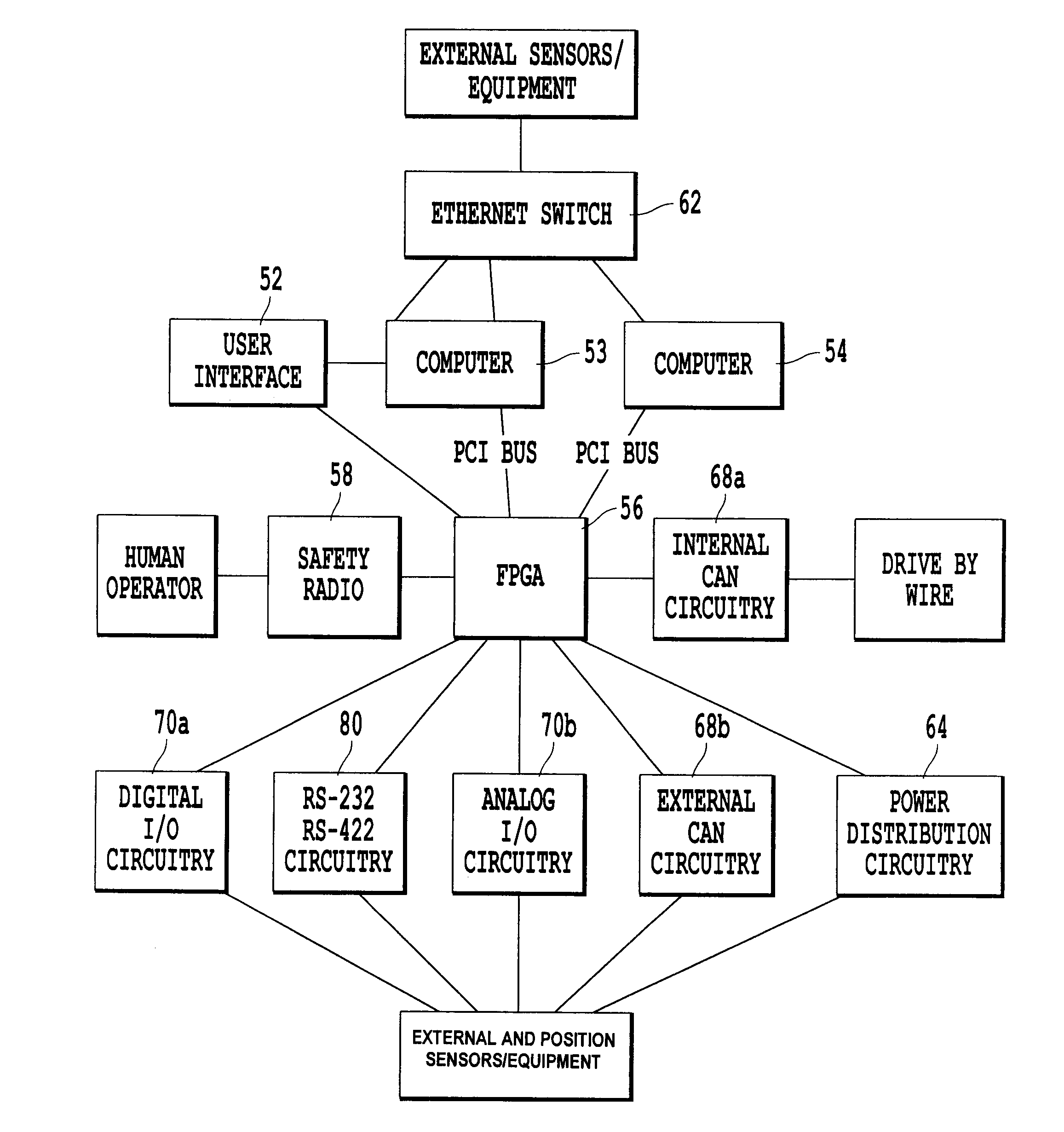

Control and systems for autonomously driven vehicles

ActiveUS8126642B2Reduce complexityImprove reliabilityInstruments for road network navigationAnti-collision systemsControl signalControl system

A navigation and control system including one or more position sensors configured to generate position signals indicative of the location and heading of a vehicle. The system includes one or more operation control mechanisms having inputs and producing outputs which control an operation of the vehicle and includes a self-contained autonomous controller disposed remote from the operation control mechanisms. The autonomous controller includes a processor configured to receive the position signals from the position sensors and to generate operation control signals defining an updated travel path for the vehicle, and a programmable interface providing communication among the position sensors, the operation control mechanisms, and the processor. The programmable interface is configured to normalize inputs to the processor from the position sensors and to generate compatible operation control signals applied as the inputs to the operation control mechanisms, whereby the self-contained autonomous controller is configurable for operation with a variety of different sensors and different operation control mechanisms.

Owner:SAMSUNG ELECTRONICS CO LTD

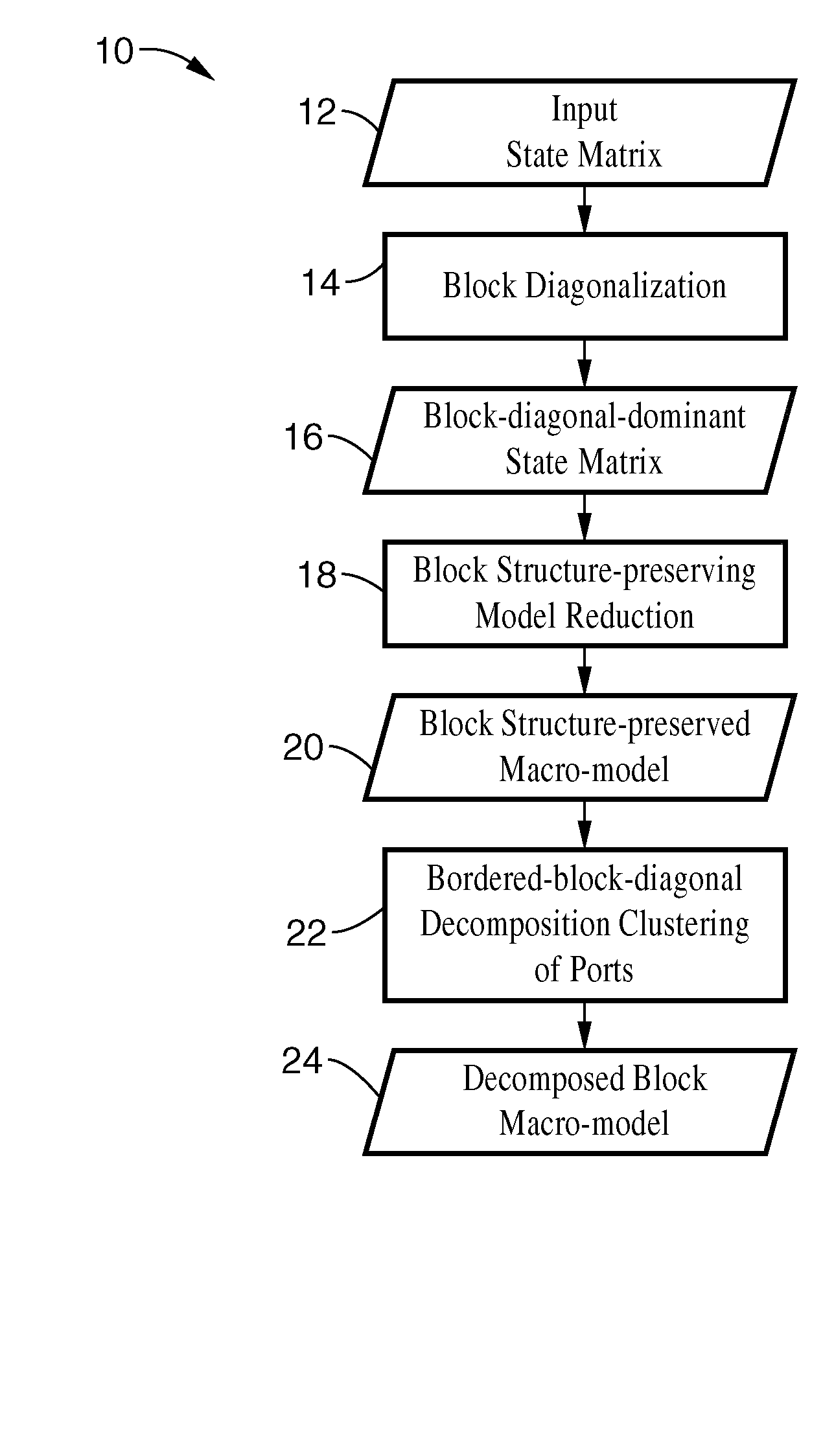

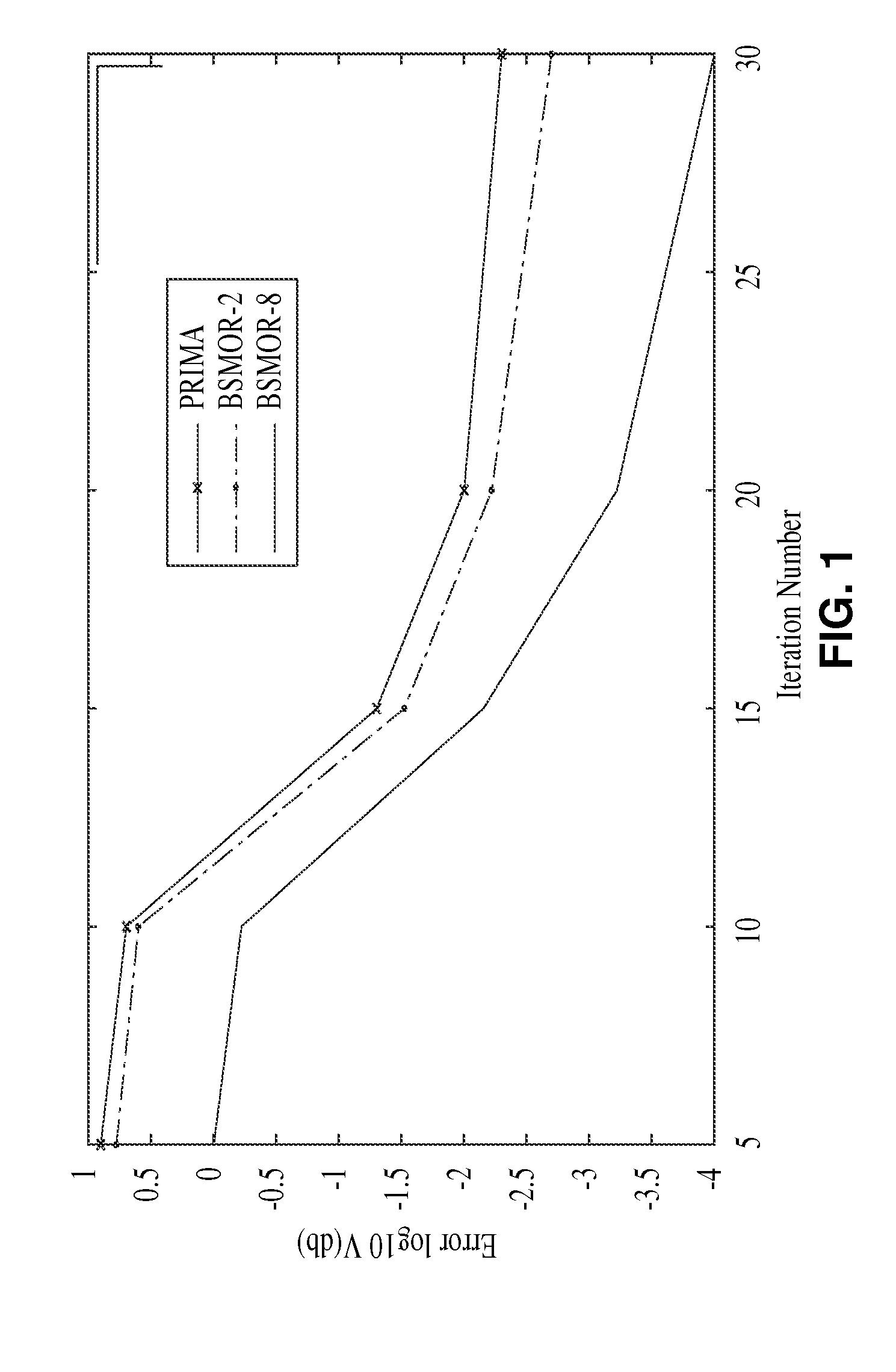

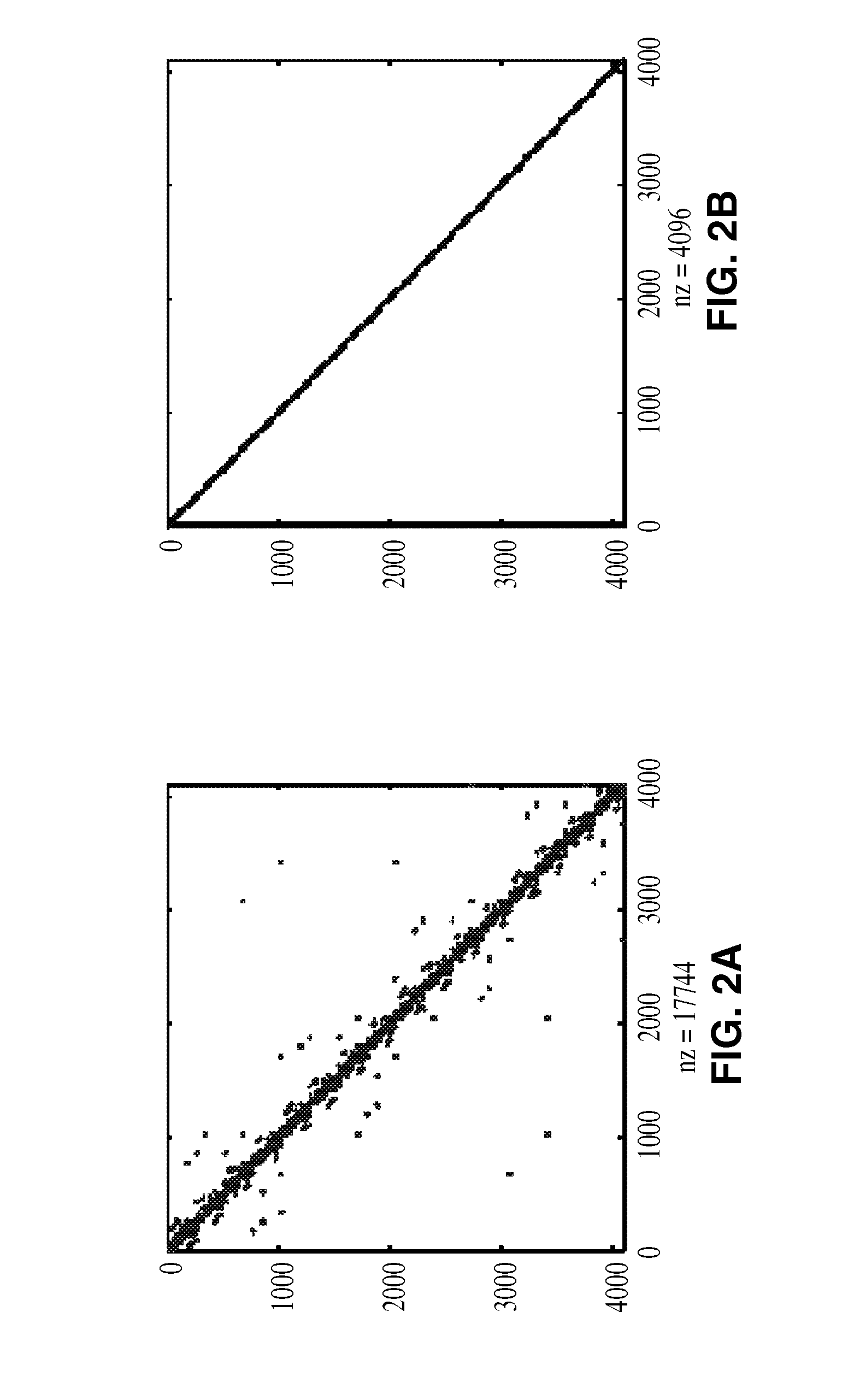

Structured and parameterized model order reduction

InactiveUS20080072182A1Reduce redundancyNon-uniformity is constantDetecting faulty computer hardwareComputation using non-denominational number representationStructured modelOrder reduction

Model-order reduction techniques are described for RLC circuits modeling the VLSI layouts. A structured model order reduction is developed to preserve the block-level sparsity, hierarchy and latency. In addition, a structured and parameterized model order reduction is developed to generate macromodels for design optimizations of VLSI layouts. The applications are thermal via allocation under the dynamic thermal integrity and via stapling to simultaneously optimize thermal and power integrity.

Owner:RGT UNIV OF CALIFORNIA

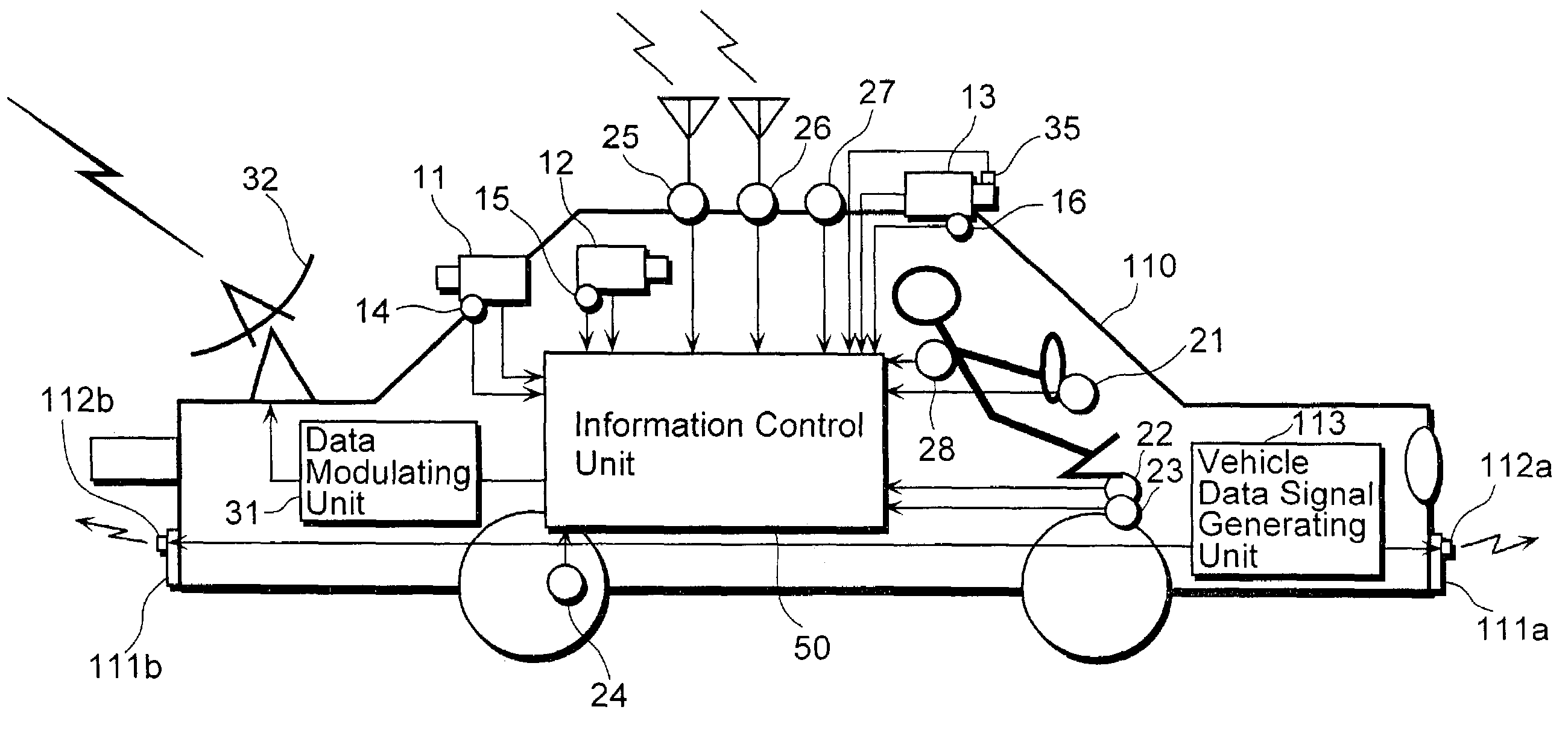

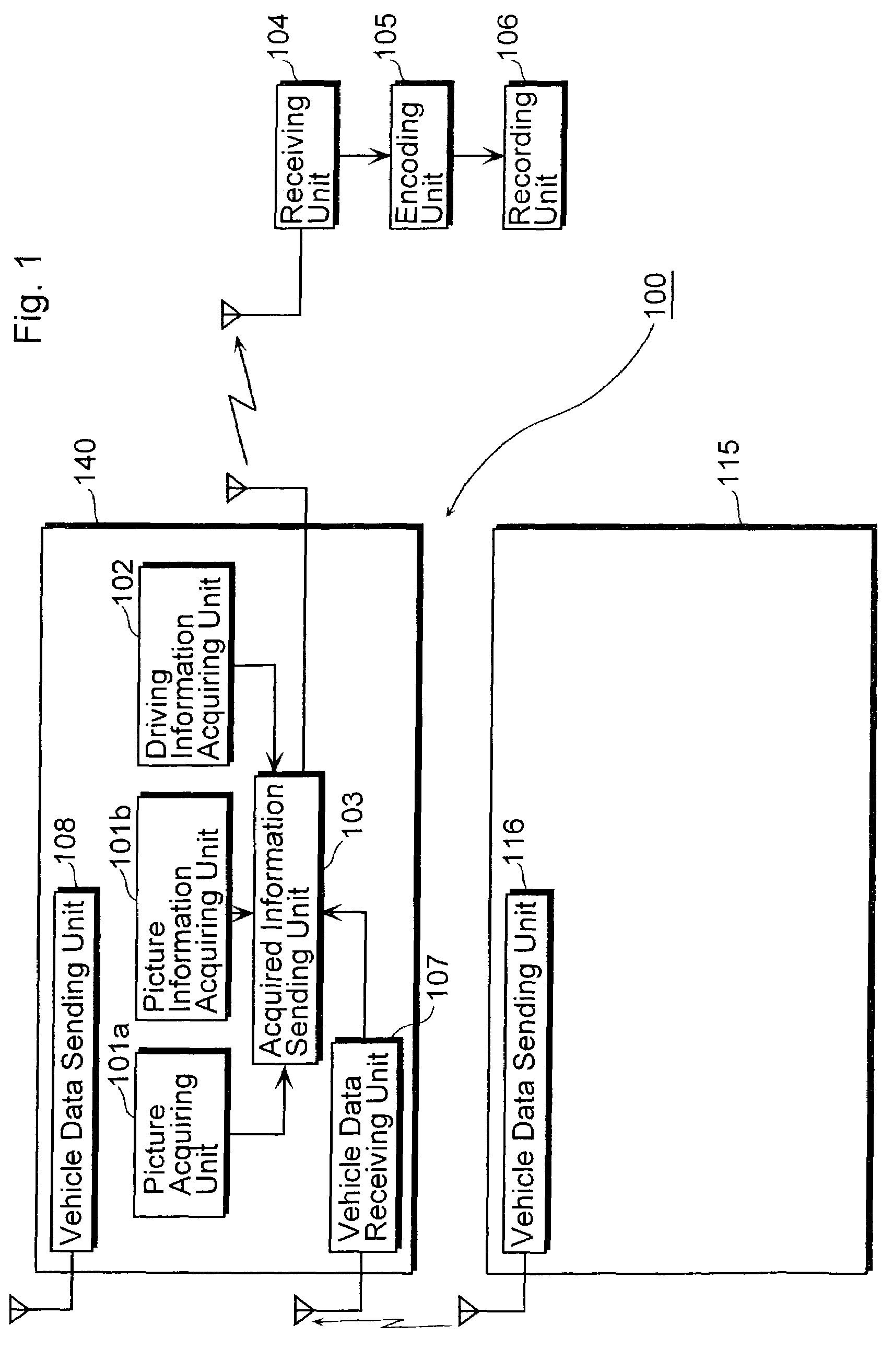

Vehicle information recording system

InactiveUS7254482B2Easy searchAnalogue computers for vehiclesInstruments for road network navigationReal-time computingRecording system

A vehicle information recording system 100 includes a picture acquiring unit 101a placed in a vehicle that takes a picture of surroundings and generates picture data showing the picture, a vehicle data receiving unit 107 placed in the vehicle that receives other vehicle data concerning another vehicle shown in the picture acquired by the picture acquiring unit 101a, an acquired information sending unit 103 placed in the vehicle that sends data including the picture data and the other vehicle data outside of the vehicle, a receiving unit 104 placed outside of the vehicle that receives the data sent by the acquired information sending unit 103, an encoding unit 105 placed outside of the vehicle that encodes the other vehicle data among the data received by the receiving unit 104 and adds the encoded data to the picture data as related data, and a recording unit 106 placed outside of the vehicle that records the picture data to which the other vehicle data is added by the encoding unit 105.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

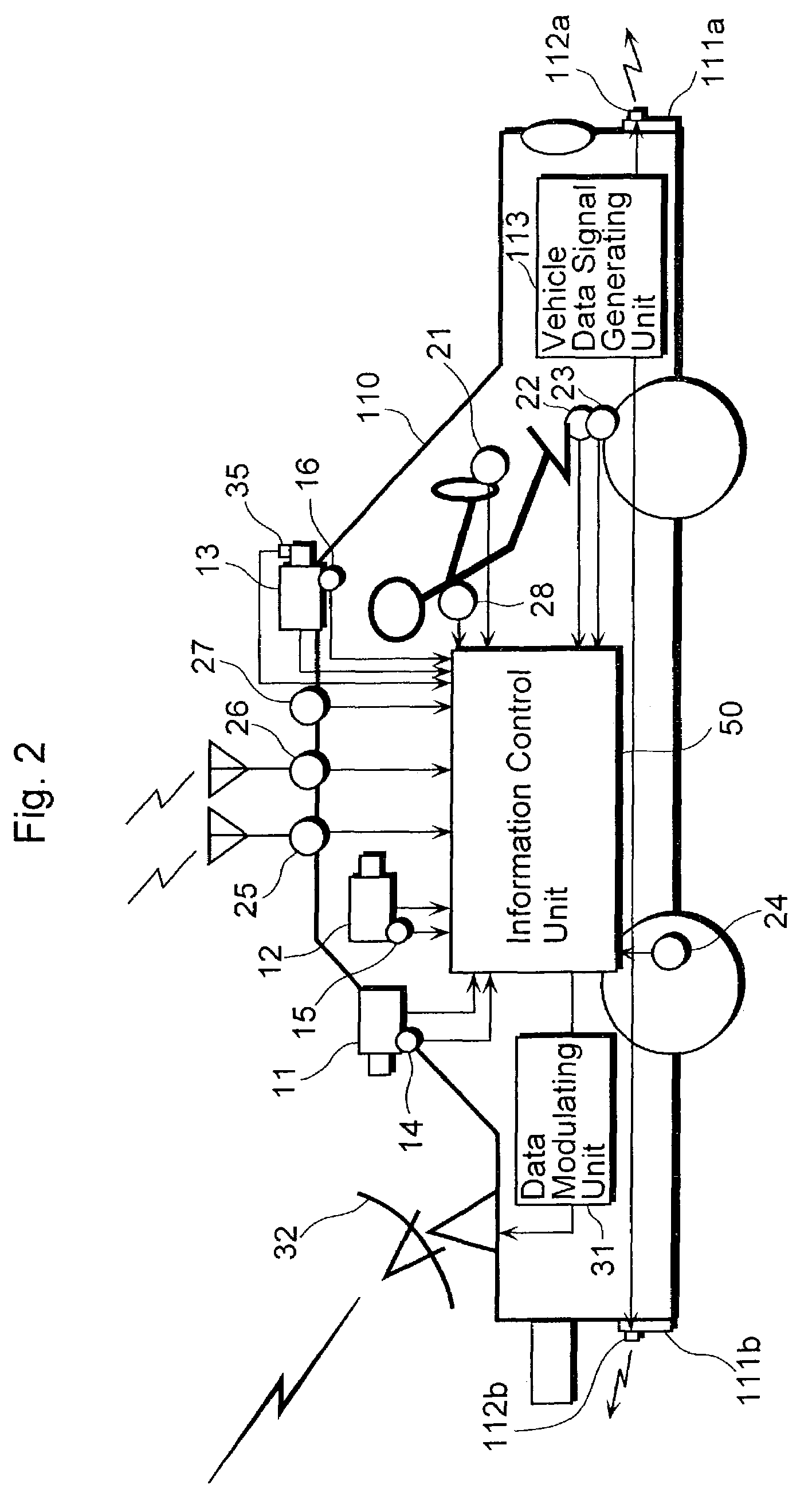

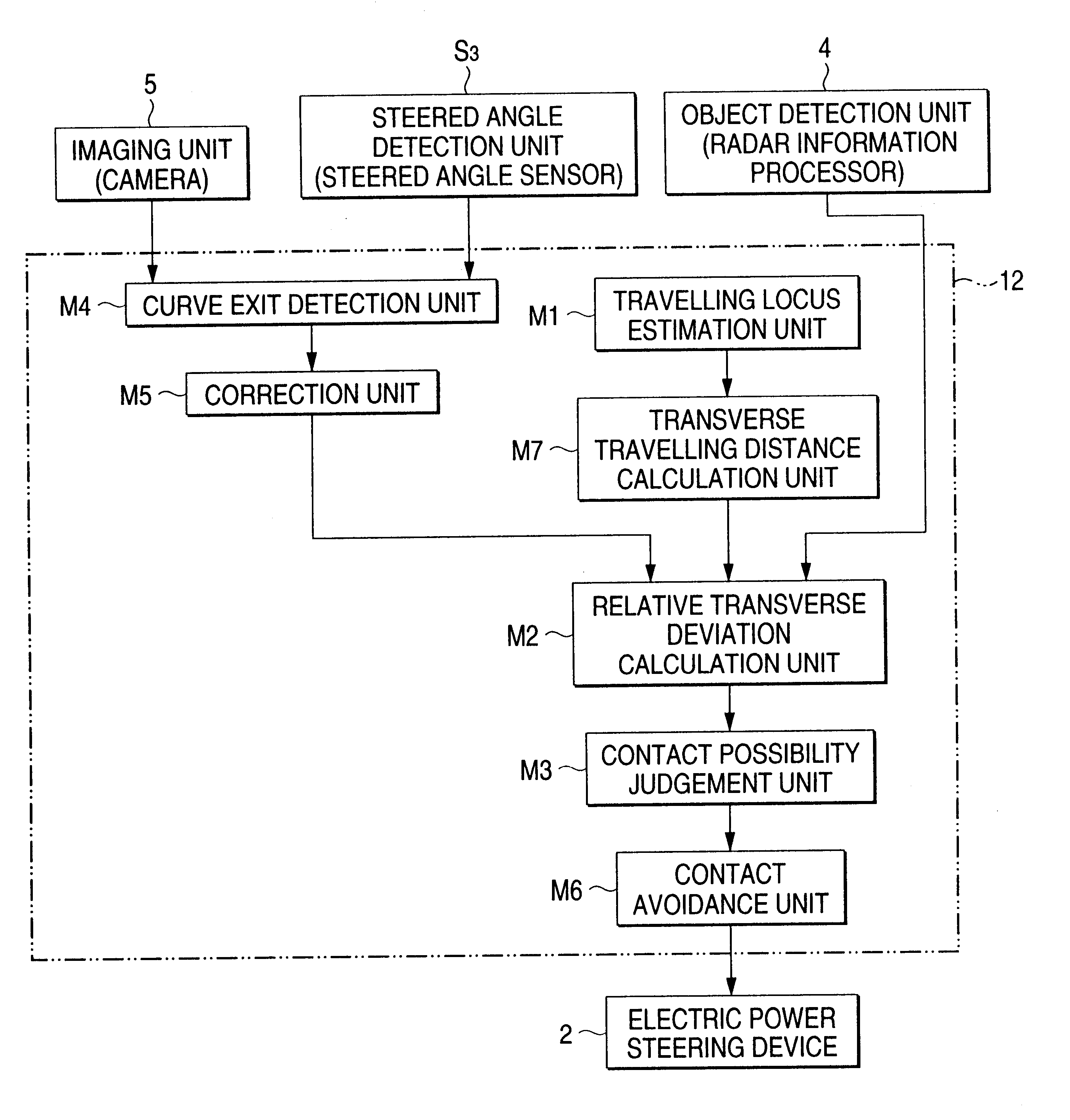

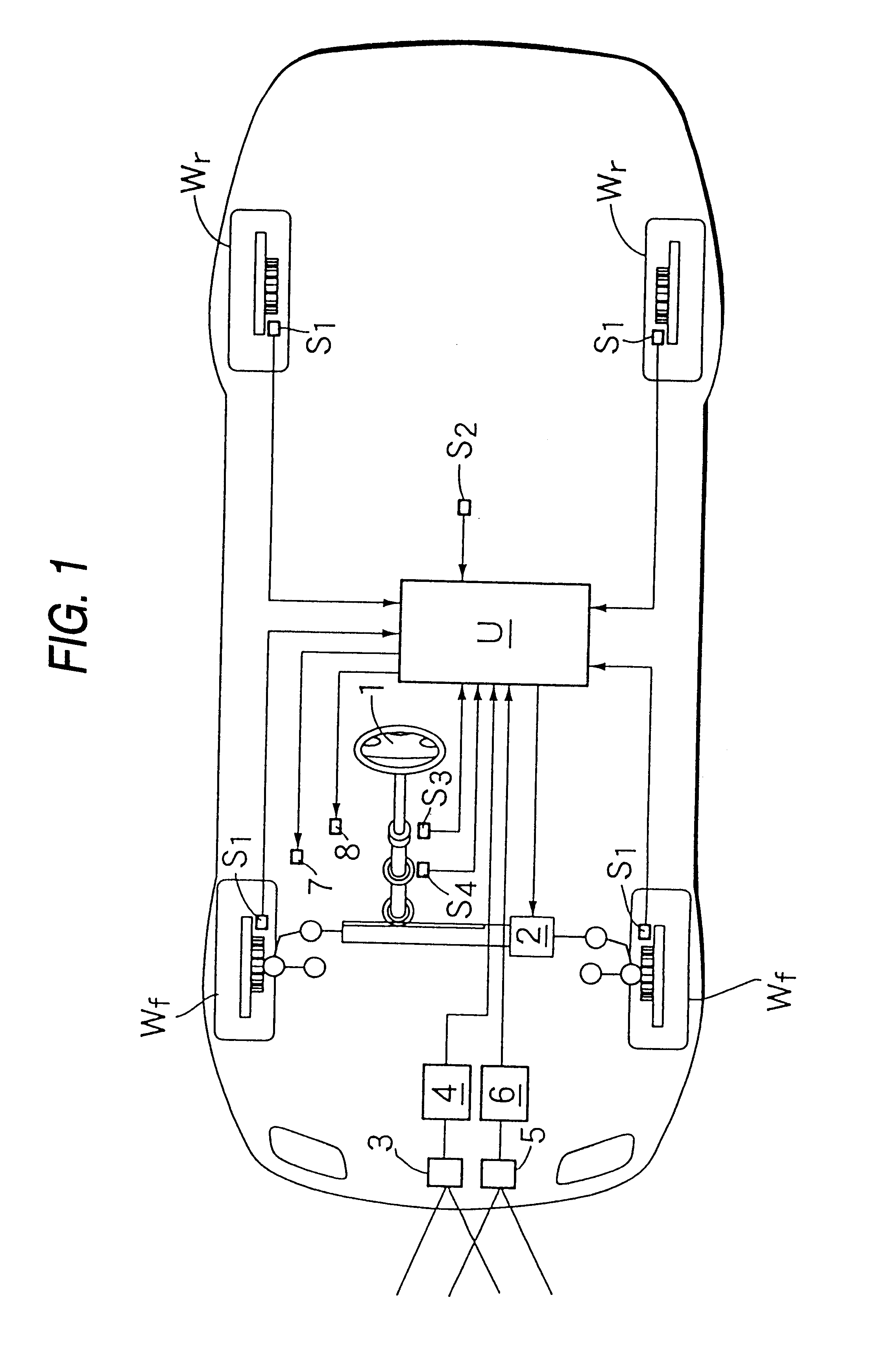

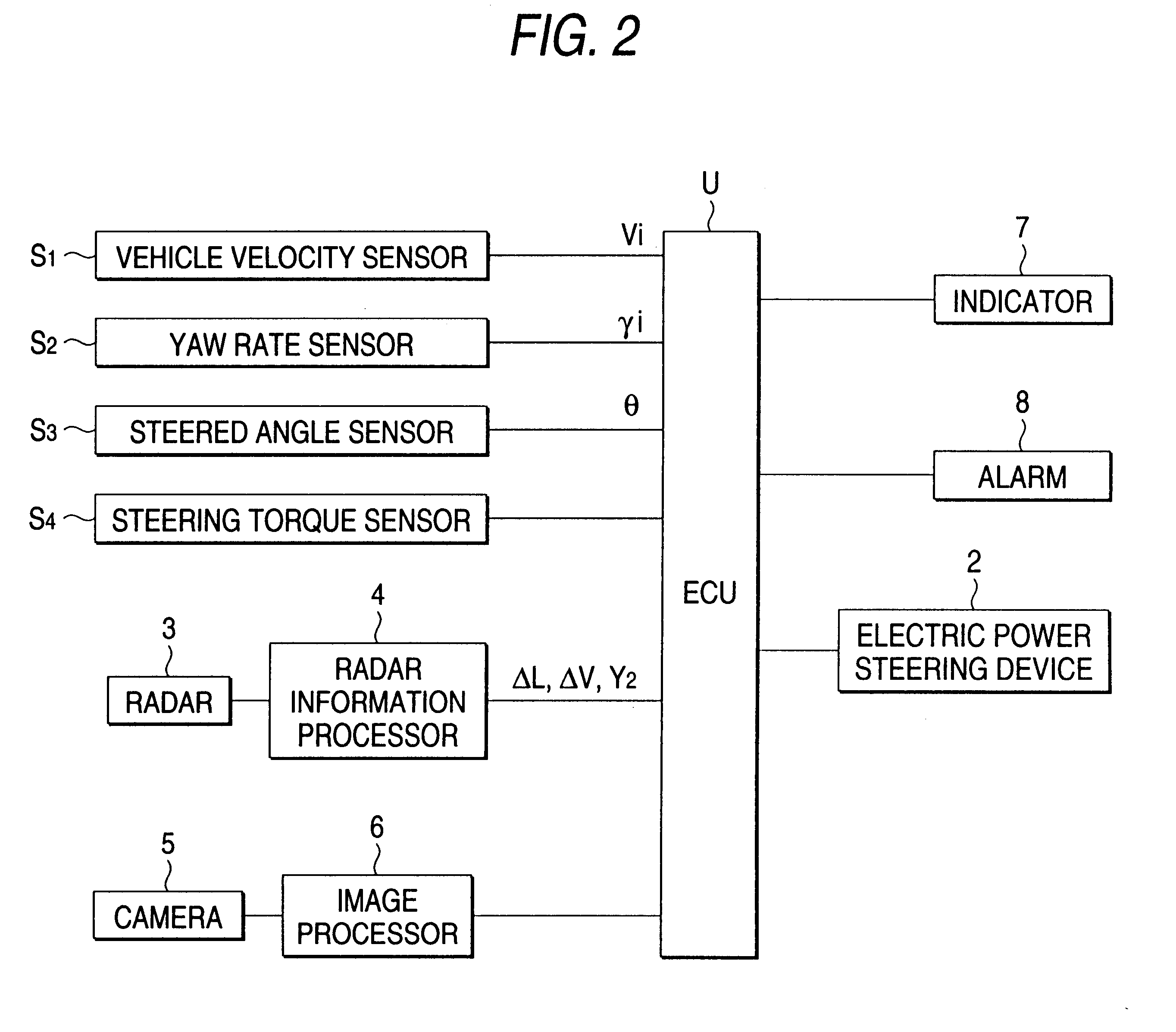

Safety running system for vehicle

InactiveUS6269308B1Digital data processing detailsPedestrian/occupant safety arrangementAutomatic steeringBody axis

In a safety running system, a transverse travelling distance resulting when a subject vehicle travels to a current position of an oncoming vehicle is calculated based on the vehicle velocity and yaw rate of the subject vehicle, a relative transverse distance of the oncoming vehicle relative to a vehicle body axis of the subject vehicle is calculated based on a relative distance, relative velocity and relative angle between the subject vehicle and the oncoming vehicle detected by a radar information processor. When a relative transverse deviation obtained by subtracting the transverse travelling distance from the relative transverse distance resides within a range and that state continues to exist over a predetermined time period, it is judged that there is a collision possibility of the subject vehicle with the oncoming vehicle, and automatic steering is performed so as to avoid a collision.

Owner:HONDA MOTOR CO LTD

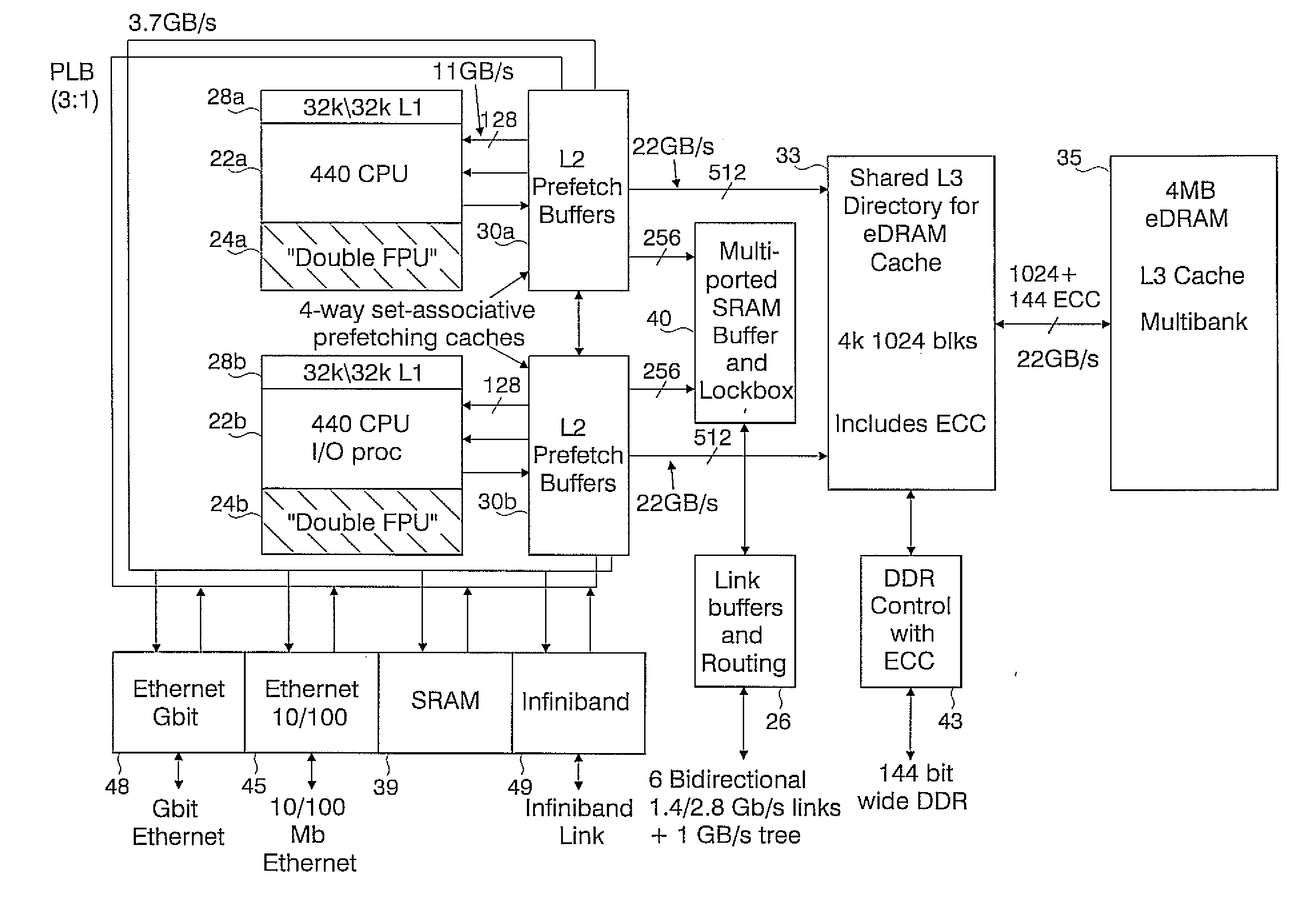

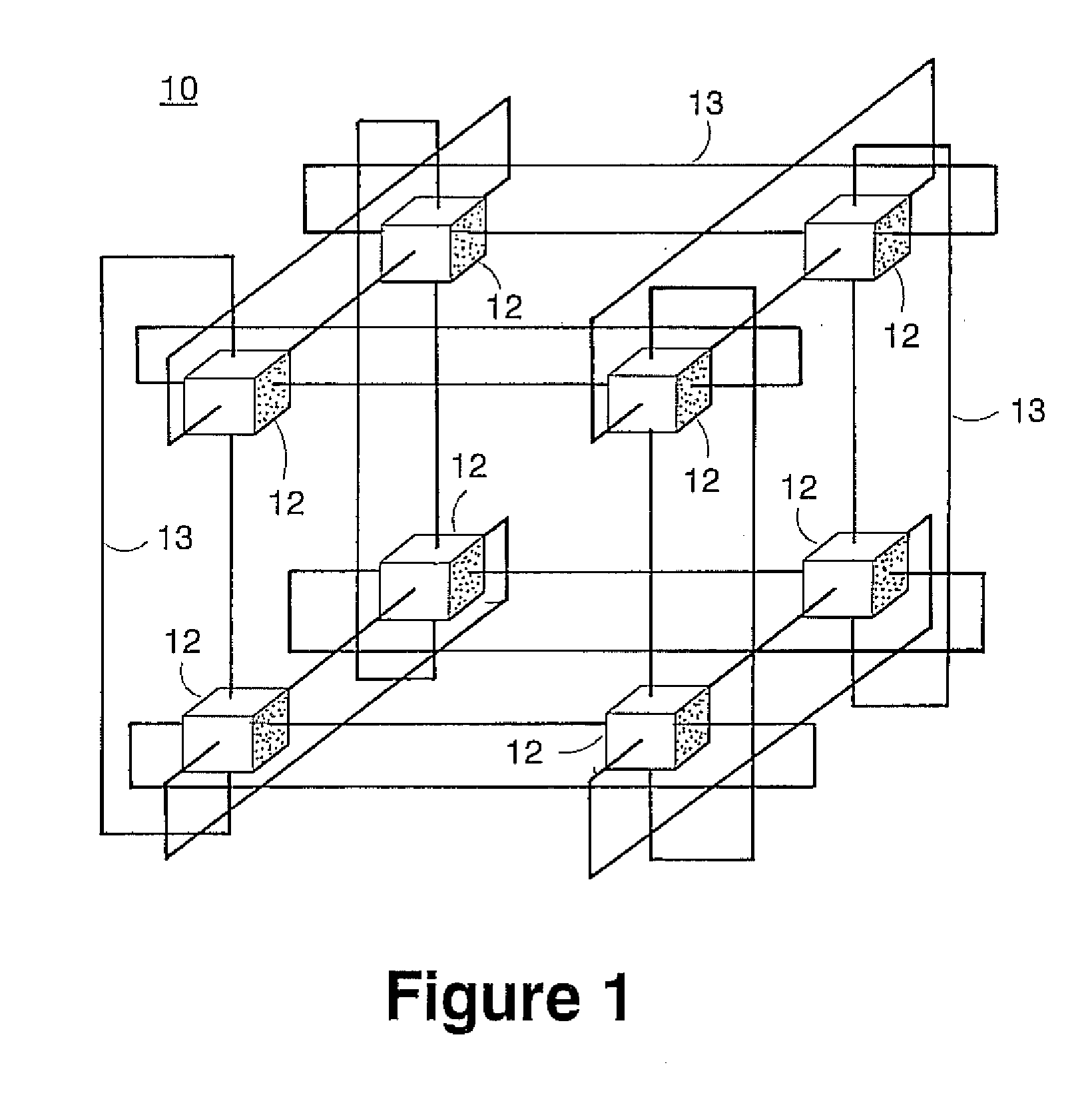

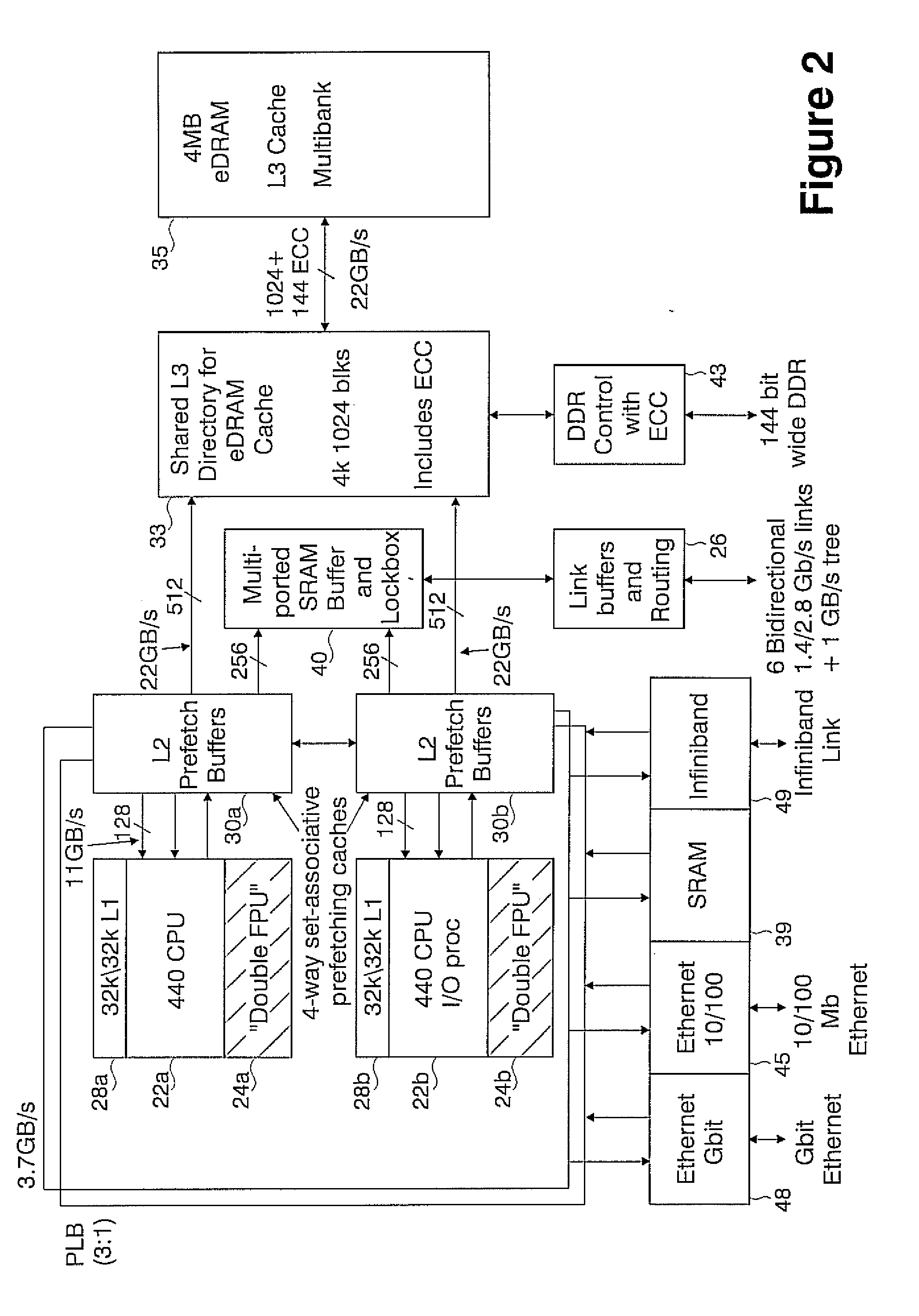

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

Method for the evolutionary design of biochemical reaction networks

The present invention relates to methods for achieving an optimal function of a biochemical reaction network. The methods can be performed in silico using a reconstruction of a biochemical reaction network of a cell and iterative optimization procedures. The methods can further include laboratory culturing steps to confirm and possibly expand the determinations made using the in silico methods, and to produce a cultured cell, or population of cells, with optimal functions. The current invention includes computer systems and computer products including computer-readable program code for performing the in silico steps of the invention.

Owner:RGT UNIV OF CALIFORNIA

Popular searches

Load forecast in ac network Analogue computers for electric apparatus Analogue computers for control systems Buying/selling/leasing transactions Material dimension control Mechanical power/torque control Power network operation systems integration Energy storage Power supply for data processing Ac network load balancing