Patents

Literature

1094 results about "Optical proximity correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

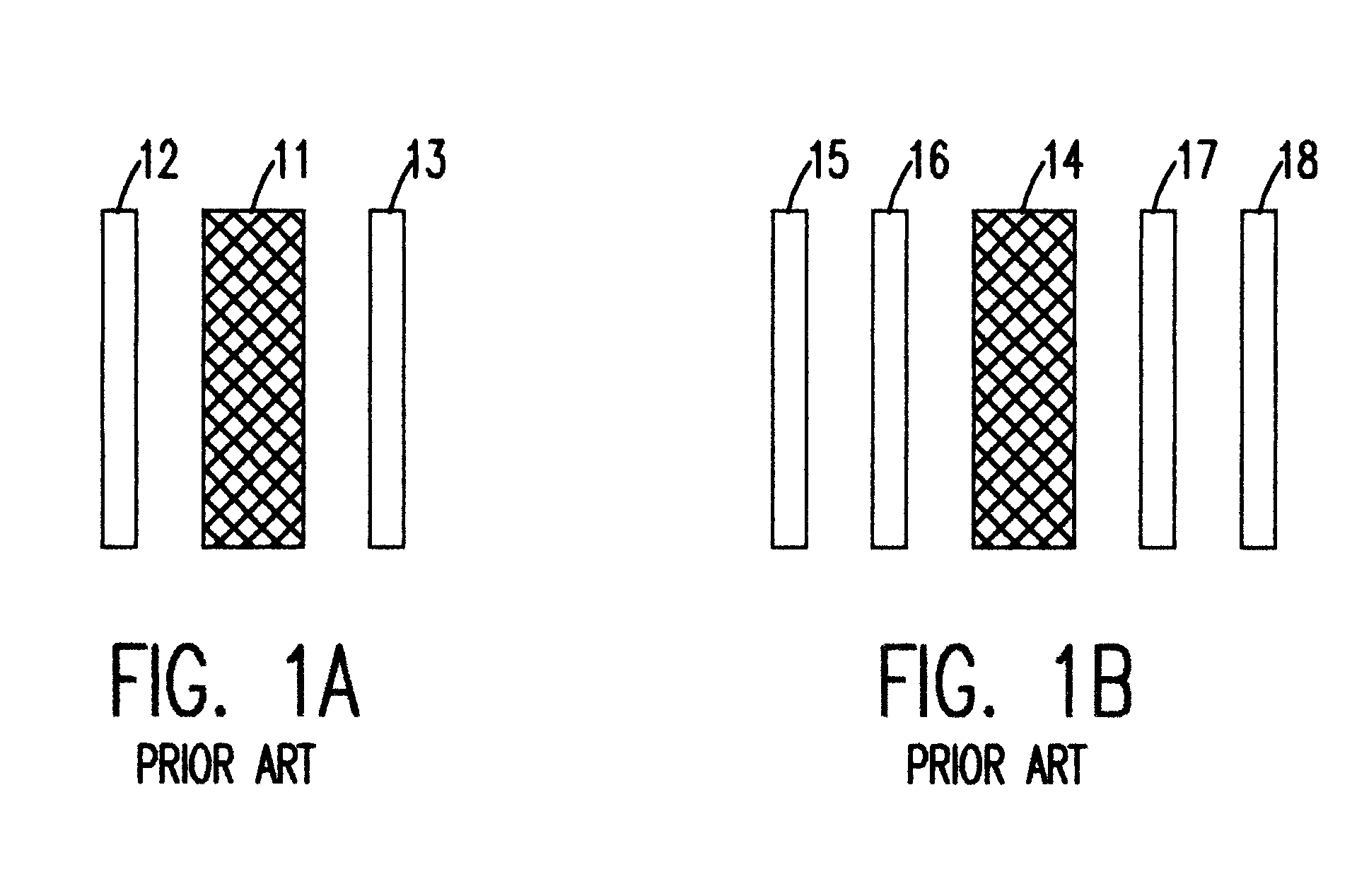

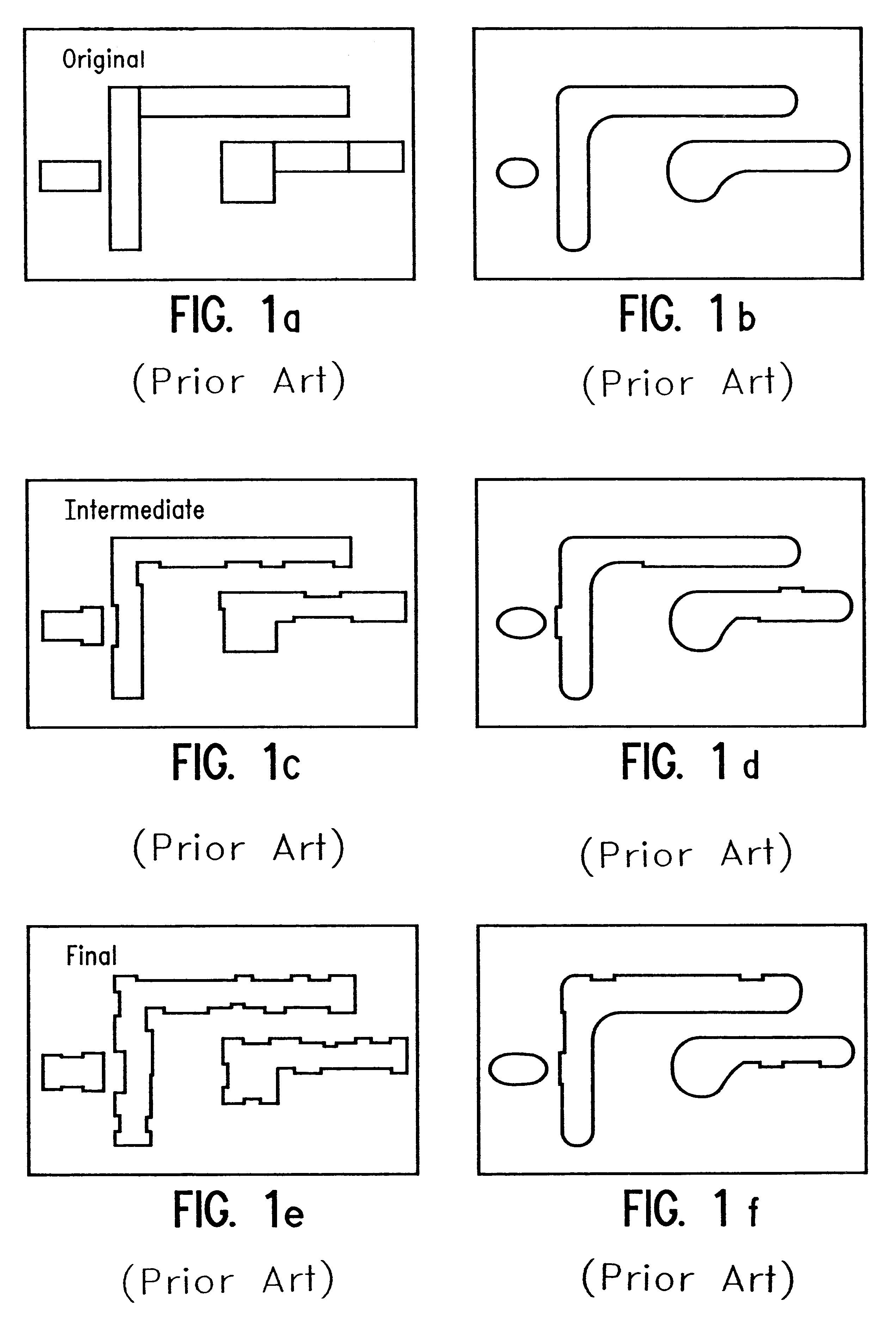

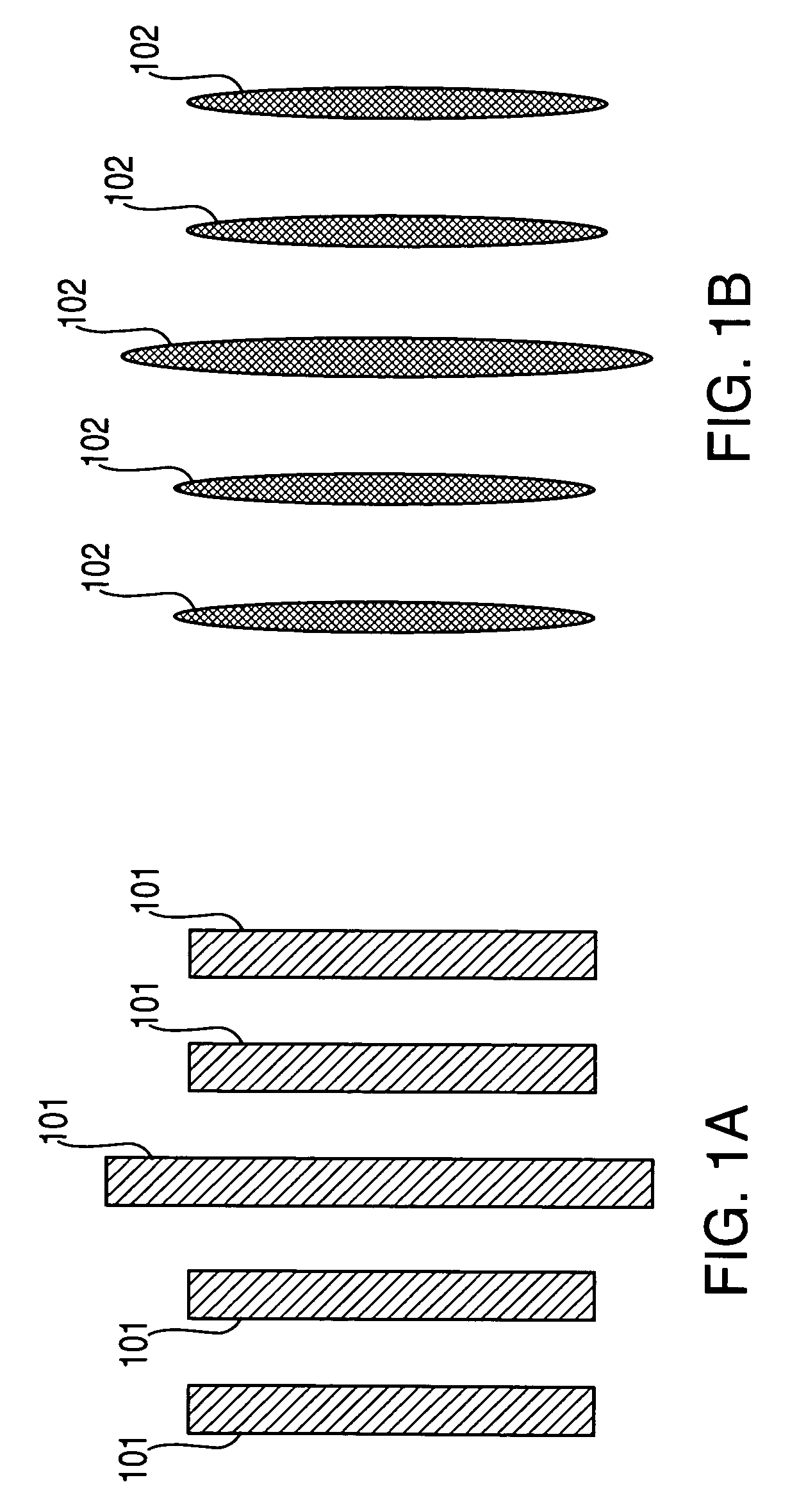

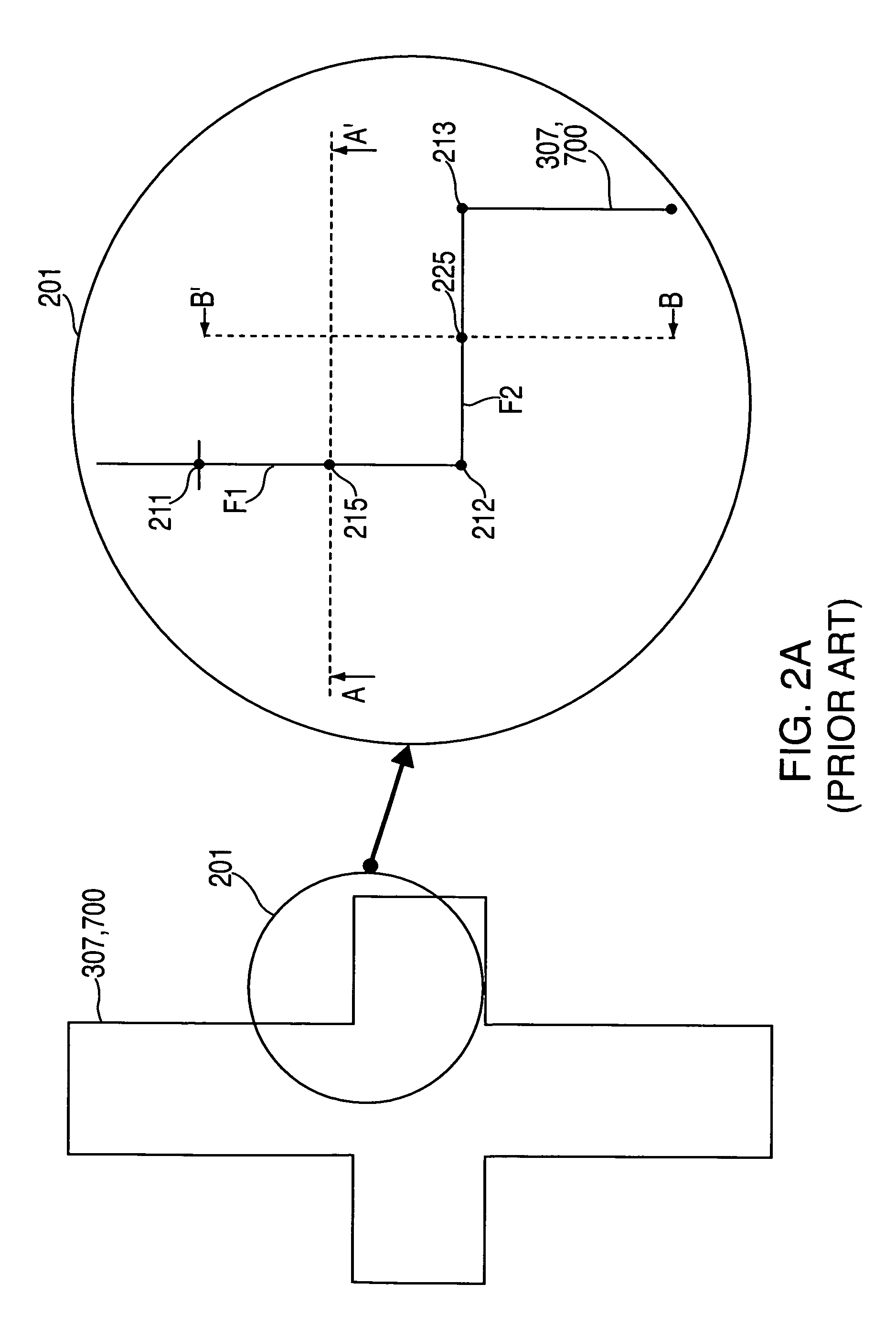

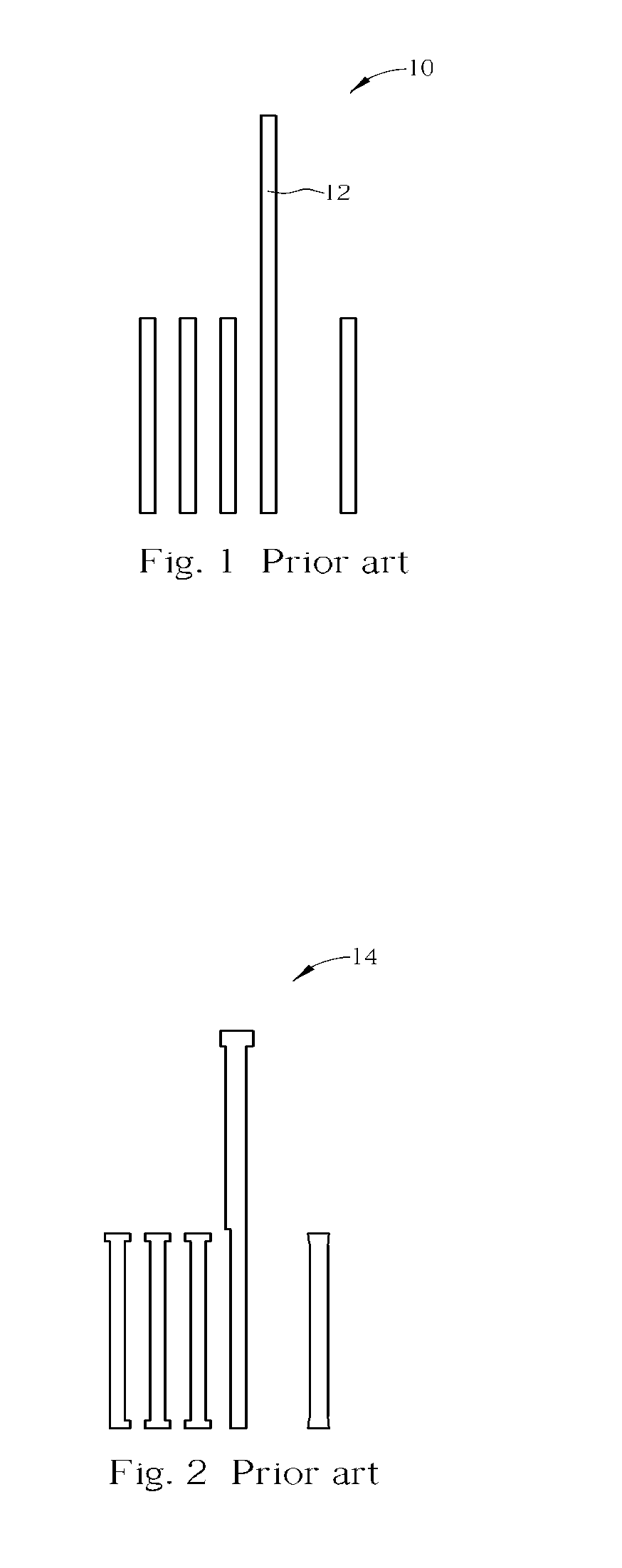

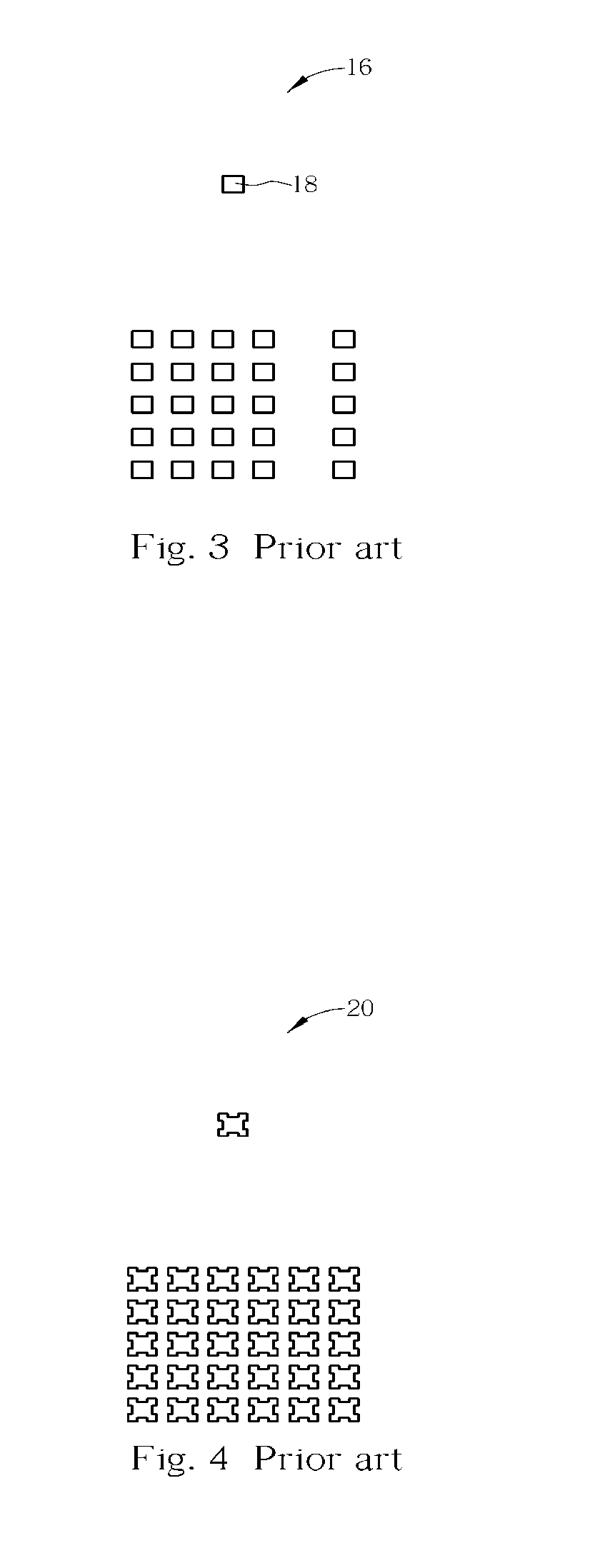

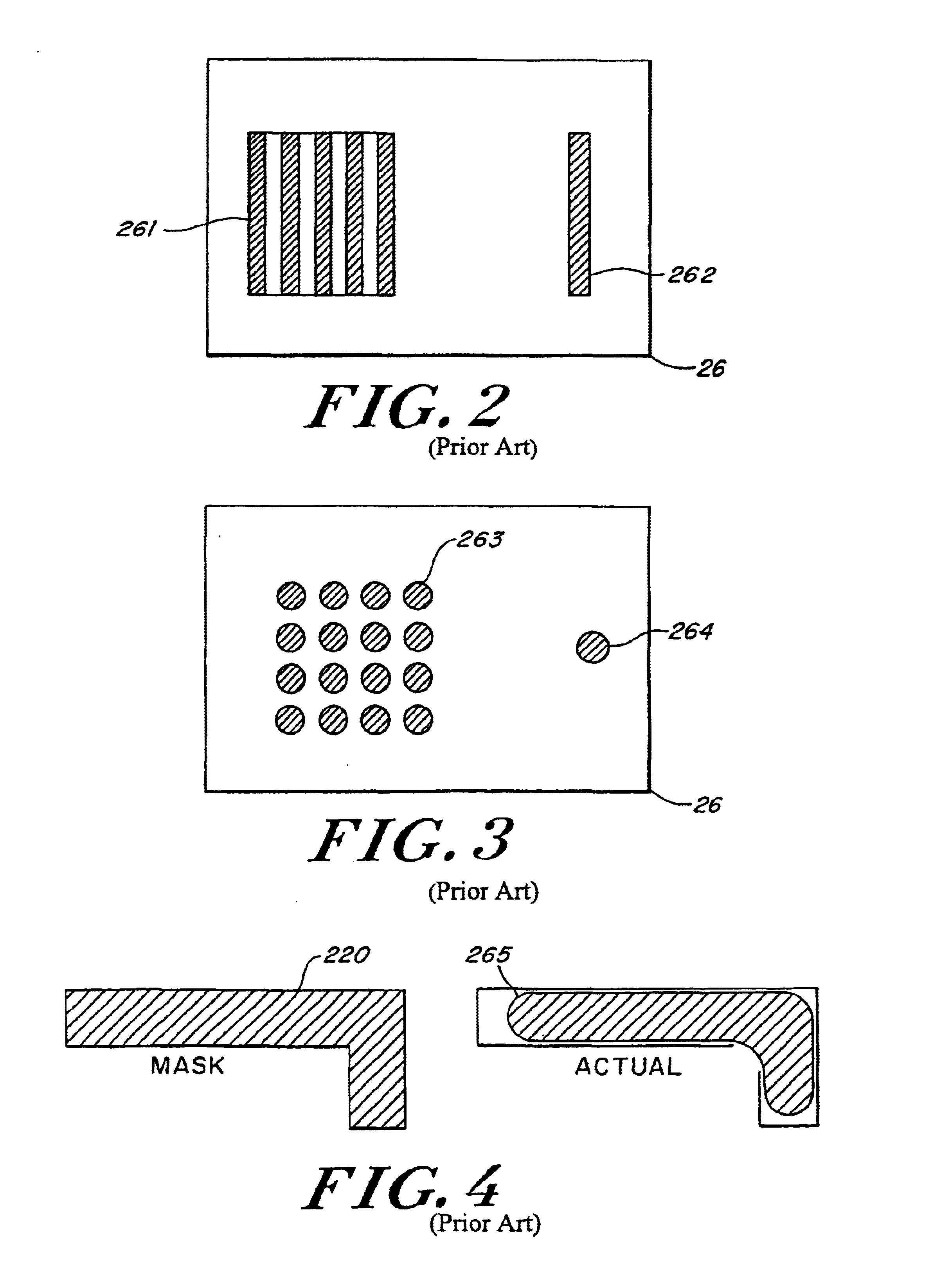

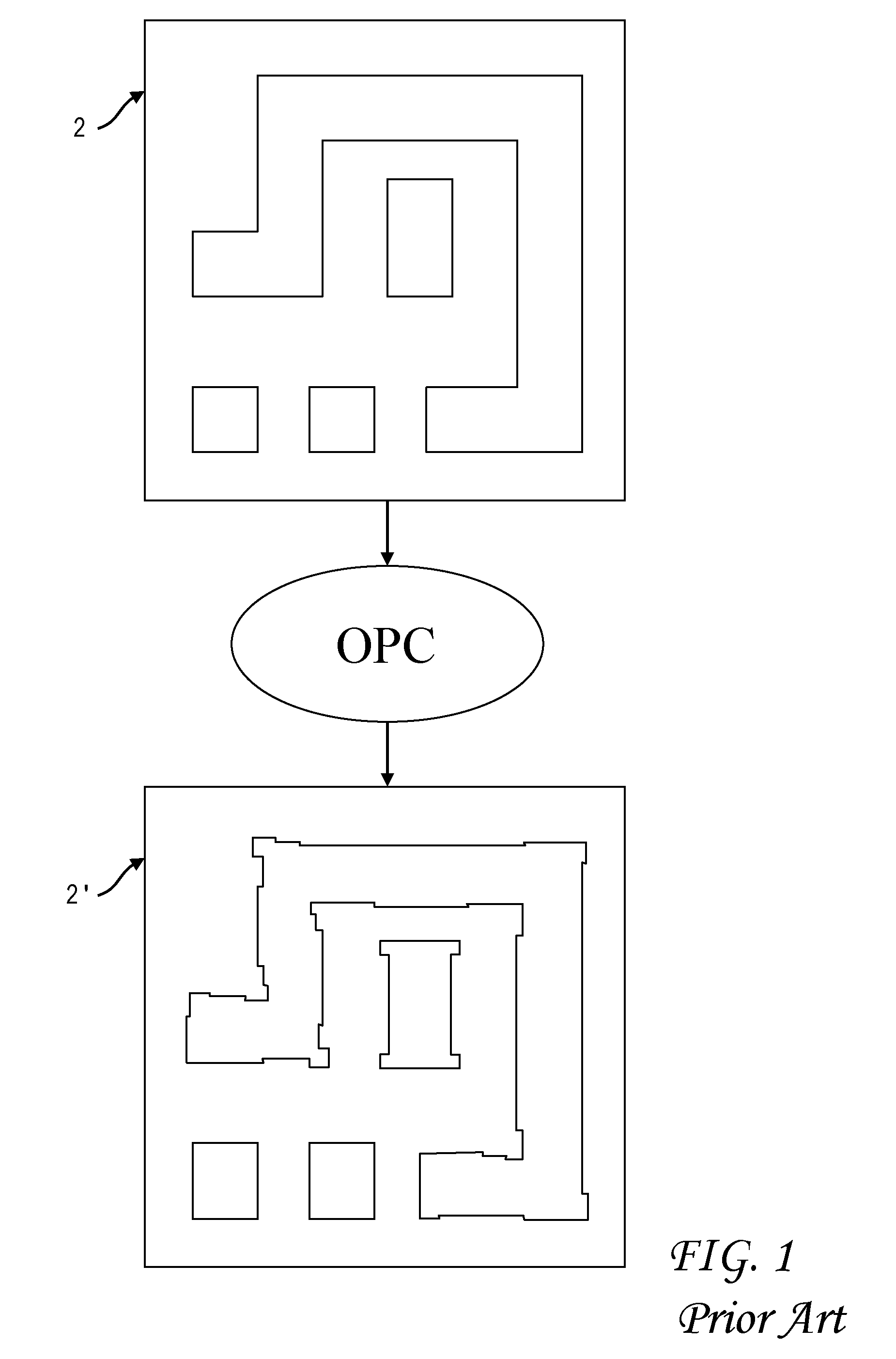

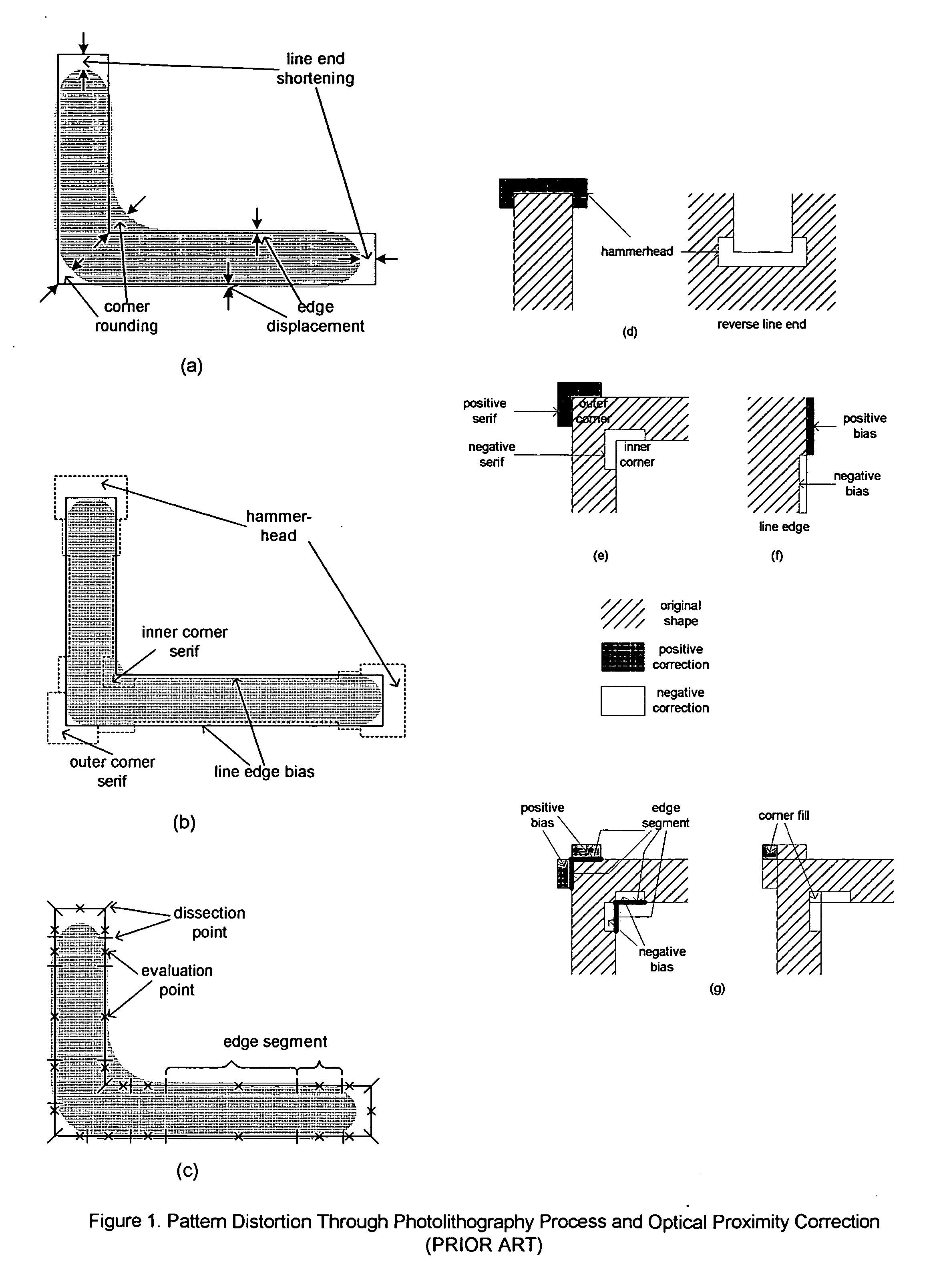

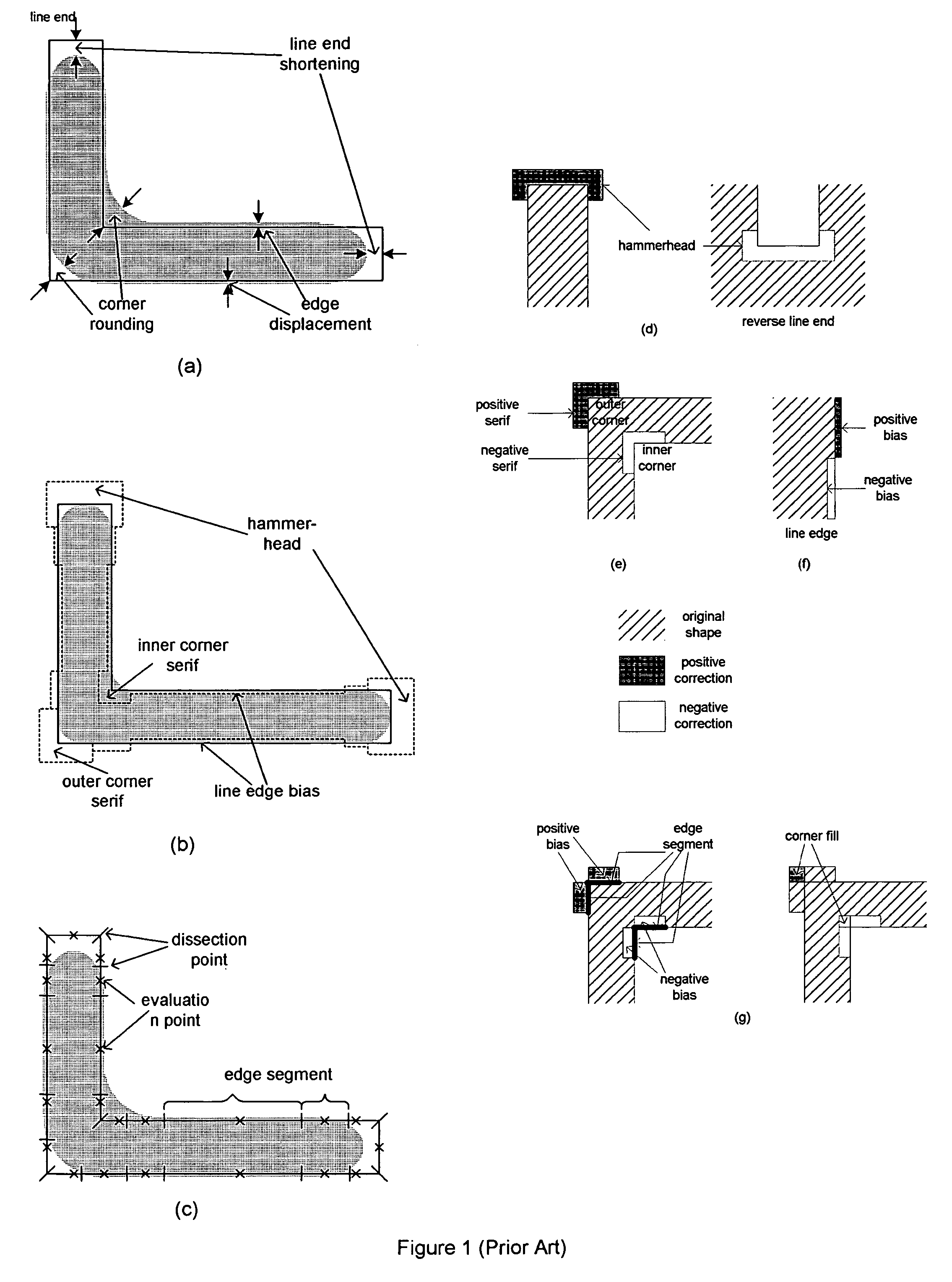

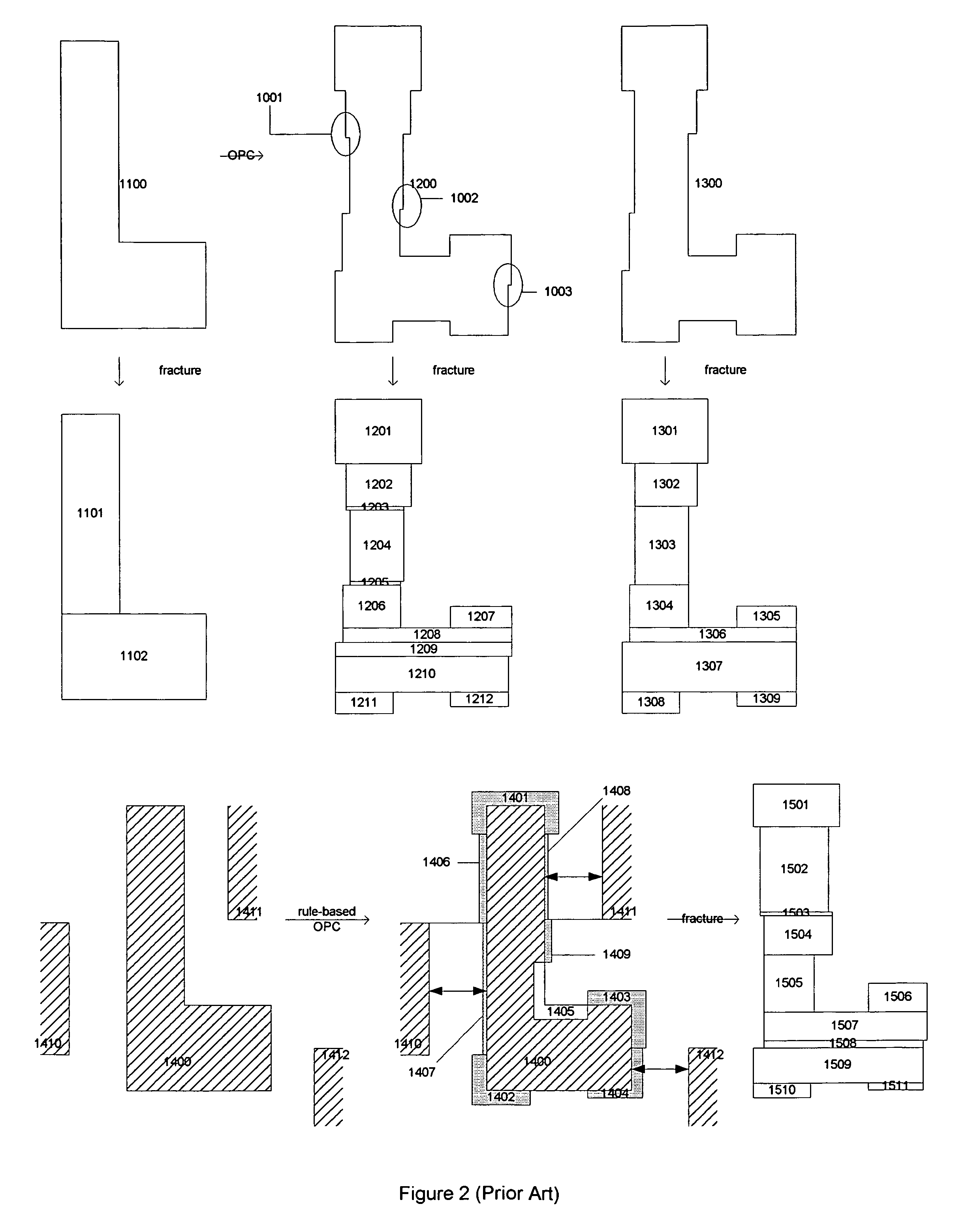

Optical proximity correction (OPC) is a photolithography enhancement technique commonly used to compensate for image errors due to diffraction or process effects. The need for OPC is seen mainly in the making of semiconductor devices and is due to the limitations of light to maintain the edge placement integrity of the original design, after processing, into the etched image on the silicon wafer. These projected images appear with irregularities such as line widths that are narrower or wider than designed, these are amenable to compensation by changing the pattern on the photomask used for imaging. Other distortions such as rounded corners are driven by the resolution of the optical imaging tool and are harder to compensate for. Such distortions, if not corrected for, may significantly alter the electrical properties of what was being fabricated. Optical proximity correction corrects these errors by moving edges or adding extra polygons to the pattern written on the photomask. This may be driven by pre-computed look-up tables based on width and spacing between features (known as rule based OPC) or by using compact models to dynamically simulate the final pattern and thereby drive the movement of edges, typically broken into sections, to find the best solution, (this is known as model based OPC). The objective is to reproduce on the semiconductor wafer, as well as possible, the original layout drawn by the designer.

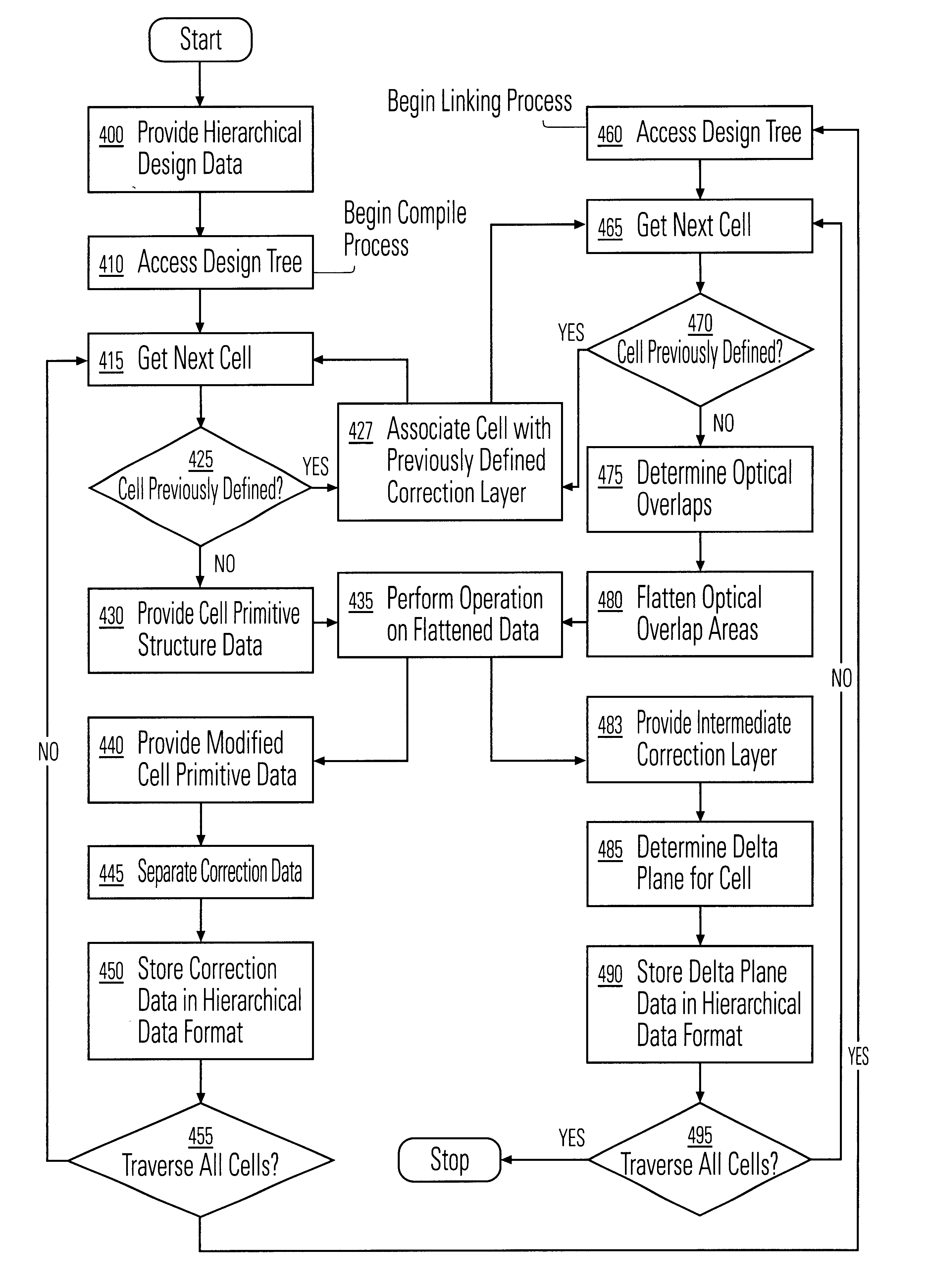

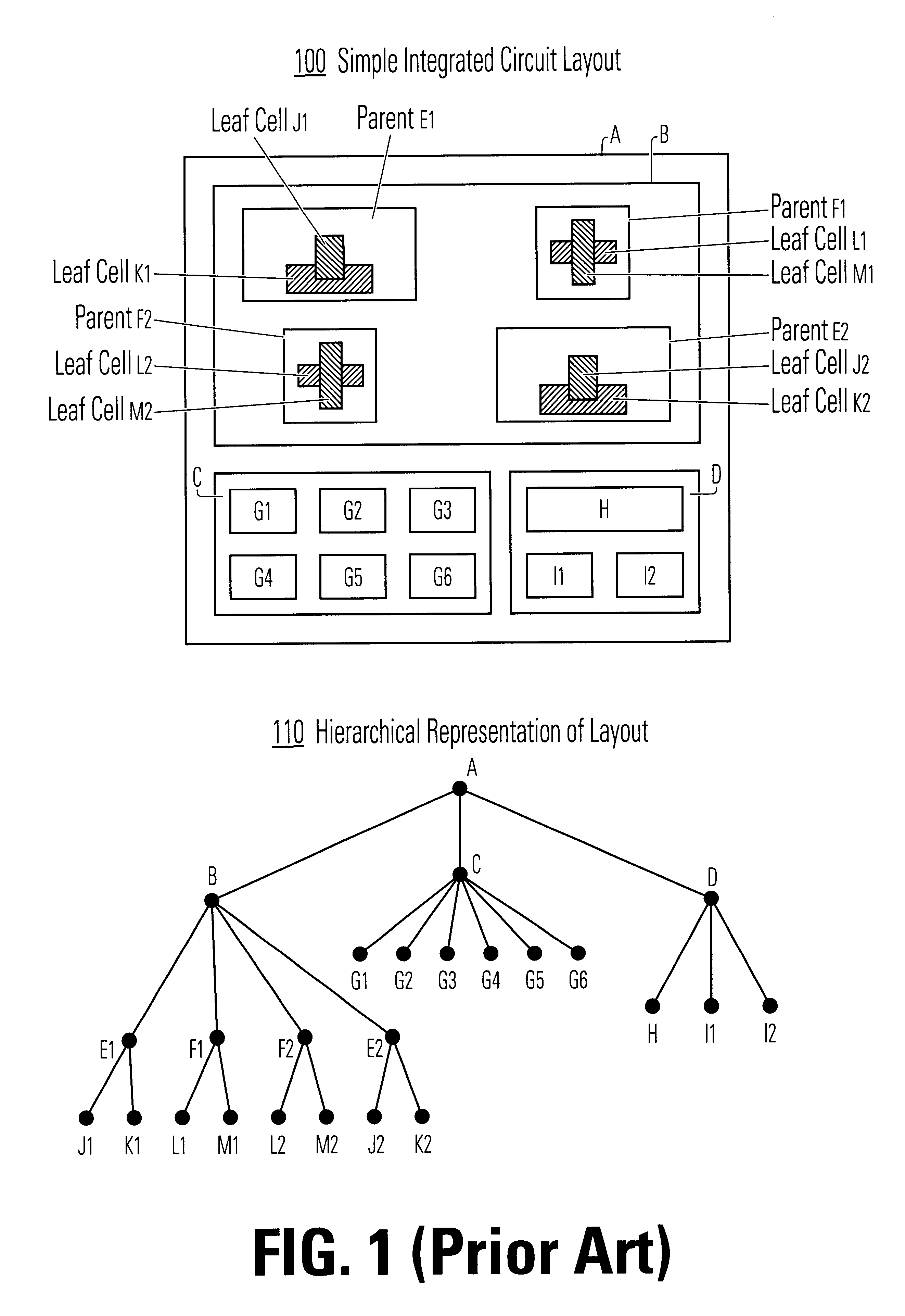

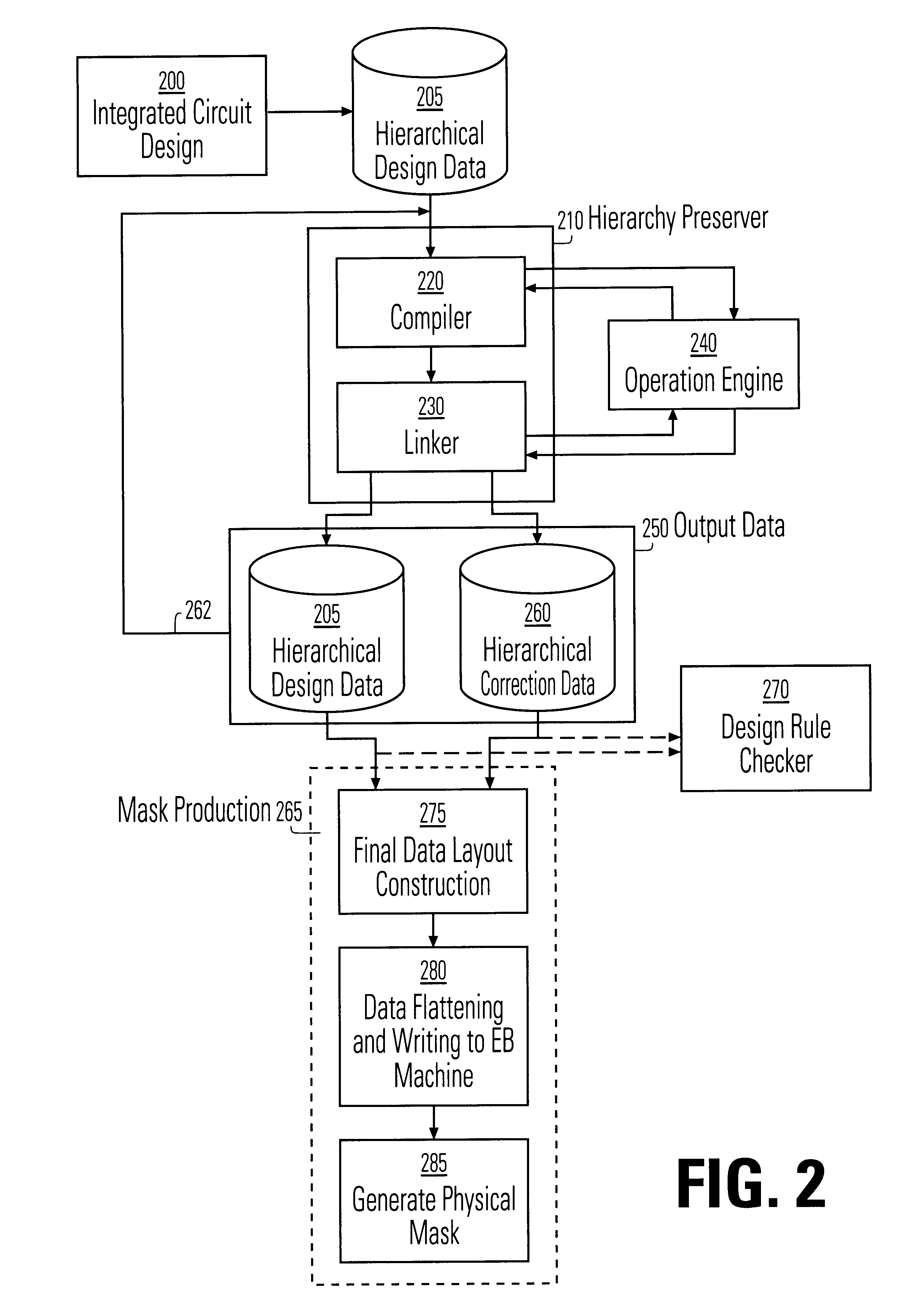

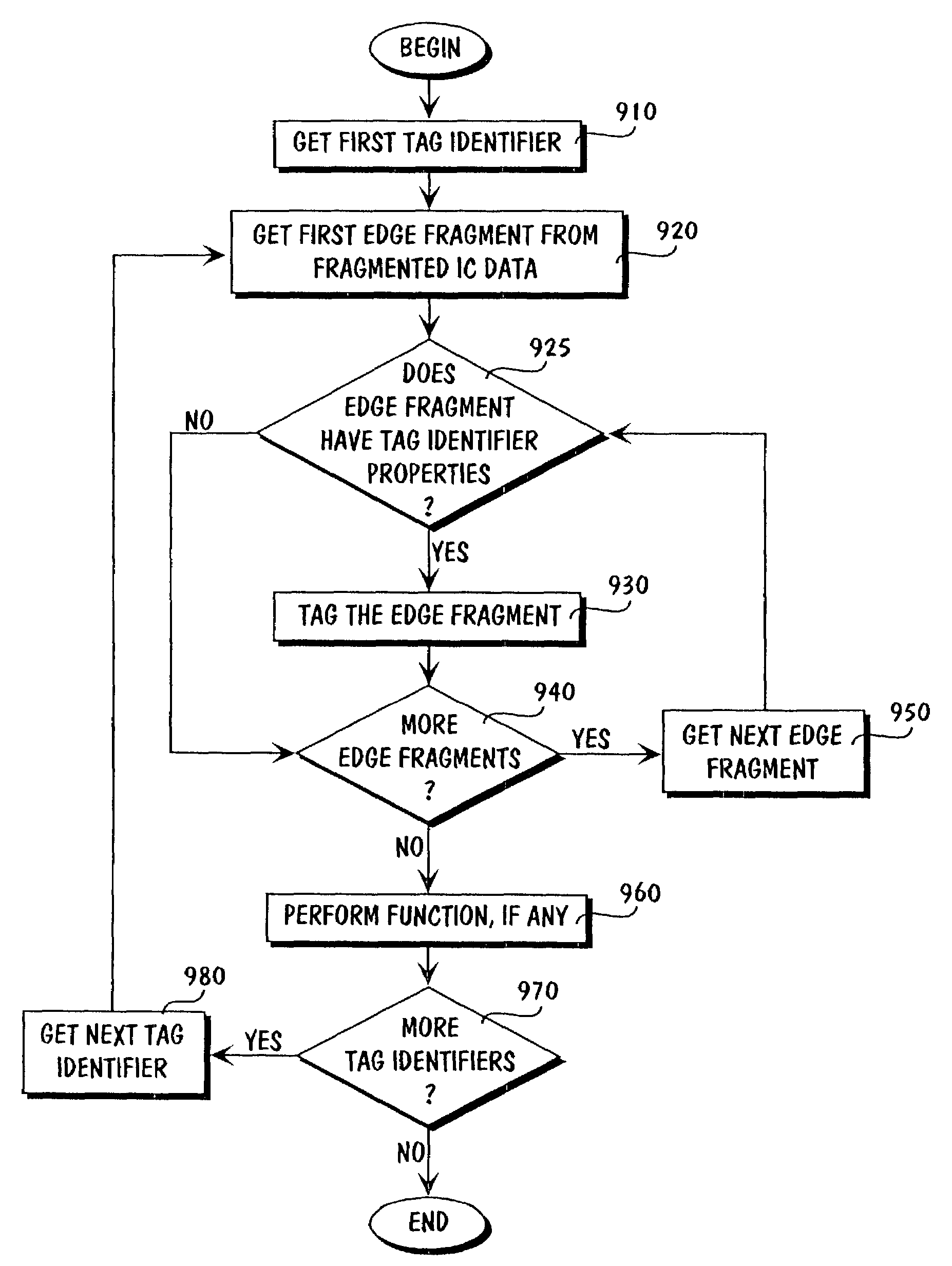

Data hierarchy layout correction and verification method and apparatus

InactiveUS6370679B1Computation using non-denominational number representationOriginals for photomechanical treatmentComputer architectureValidation methods

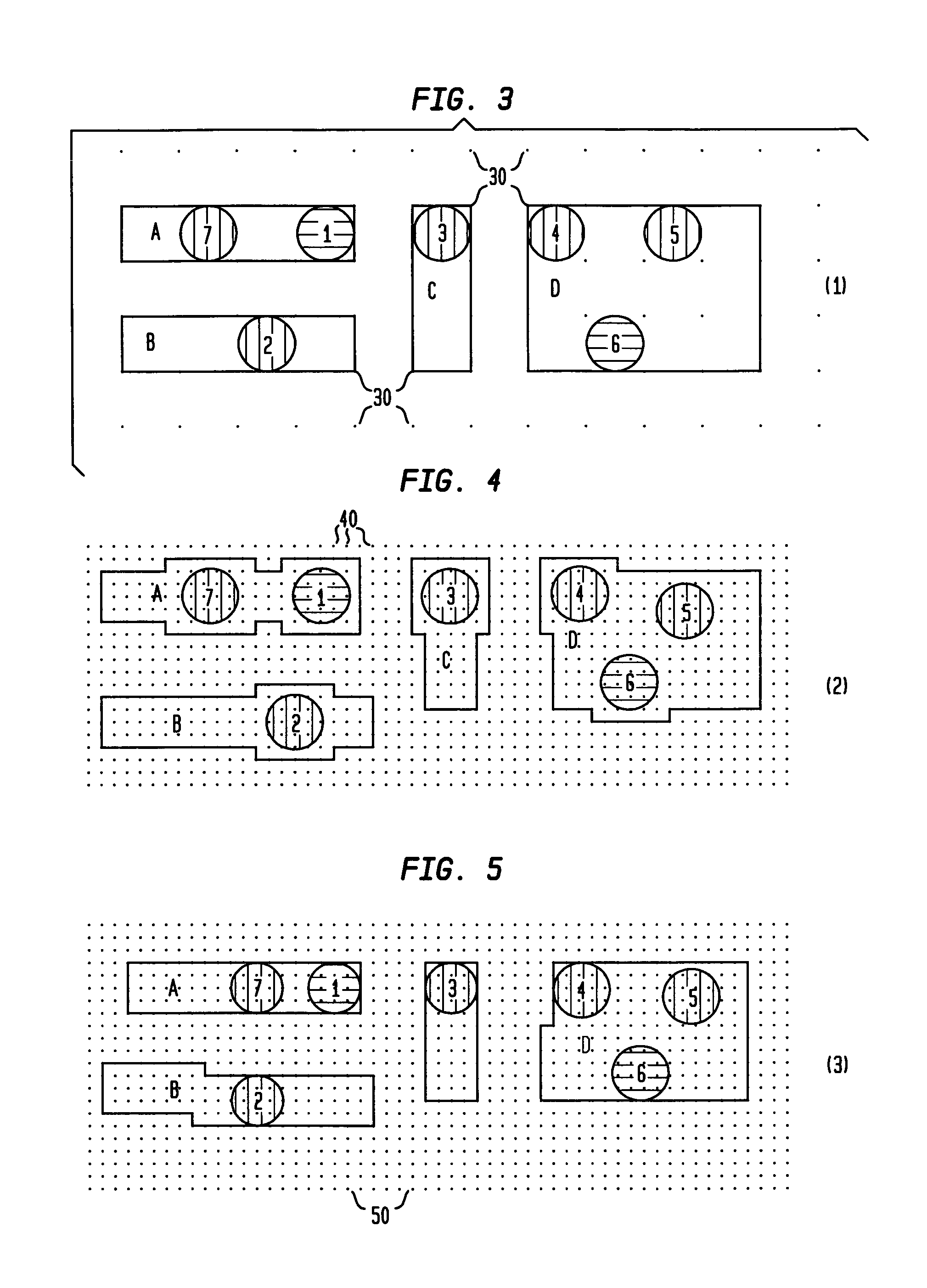

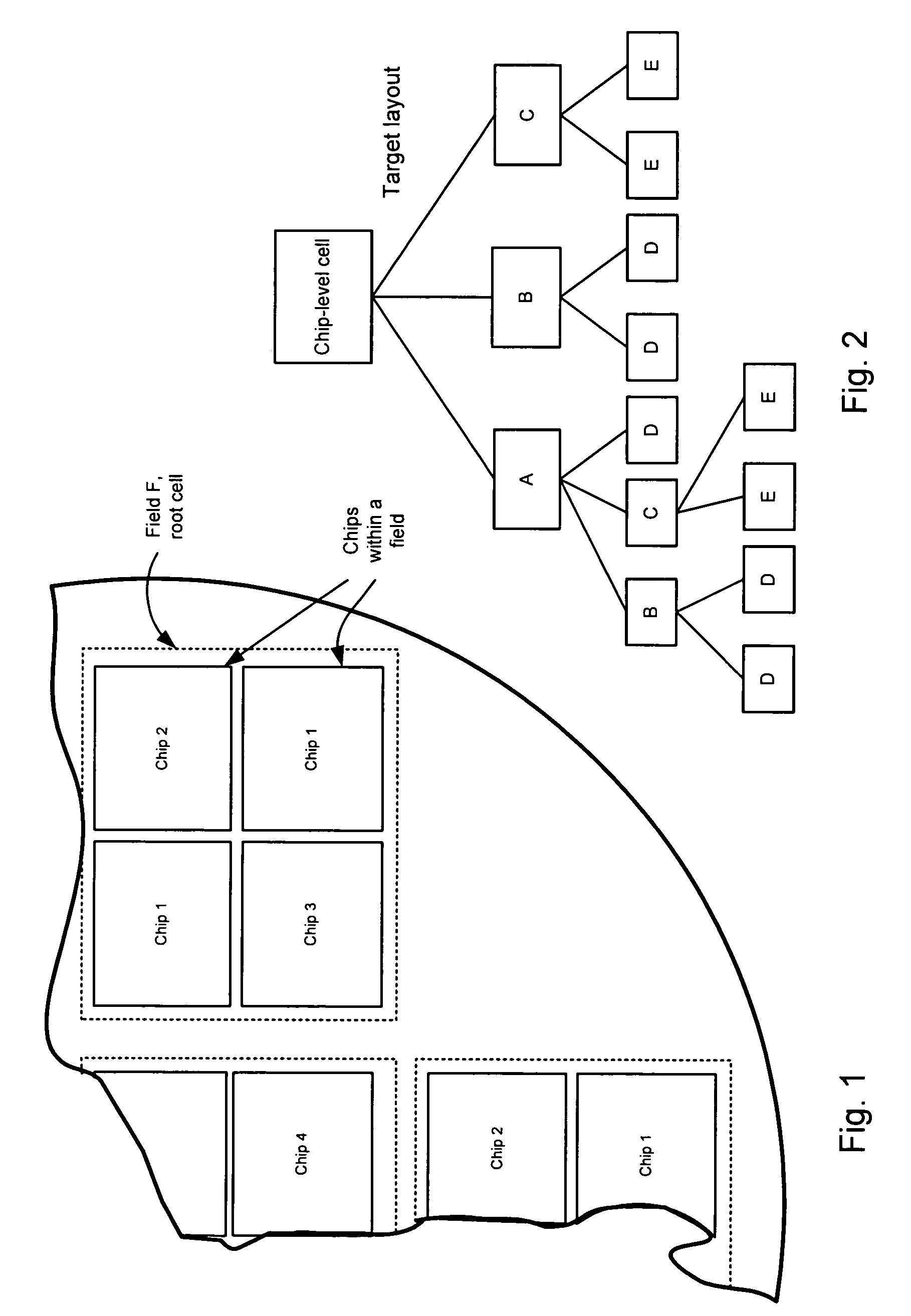

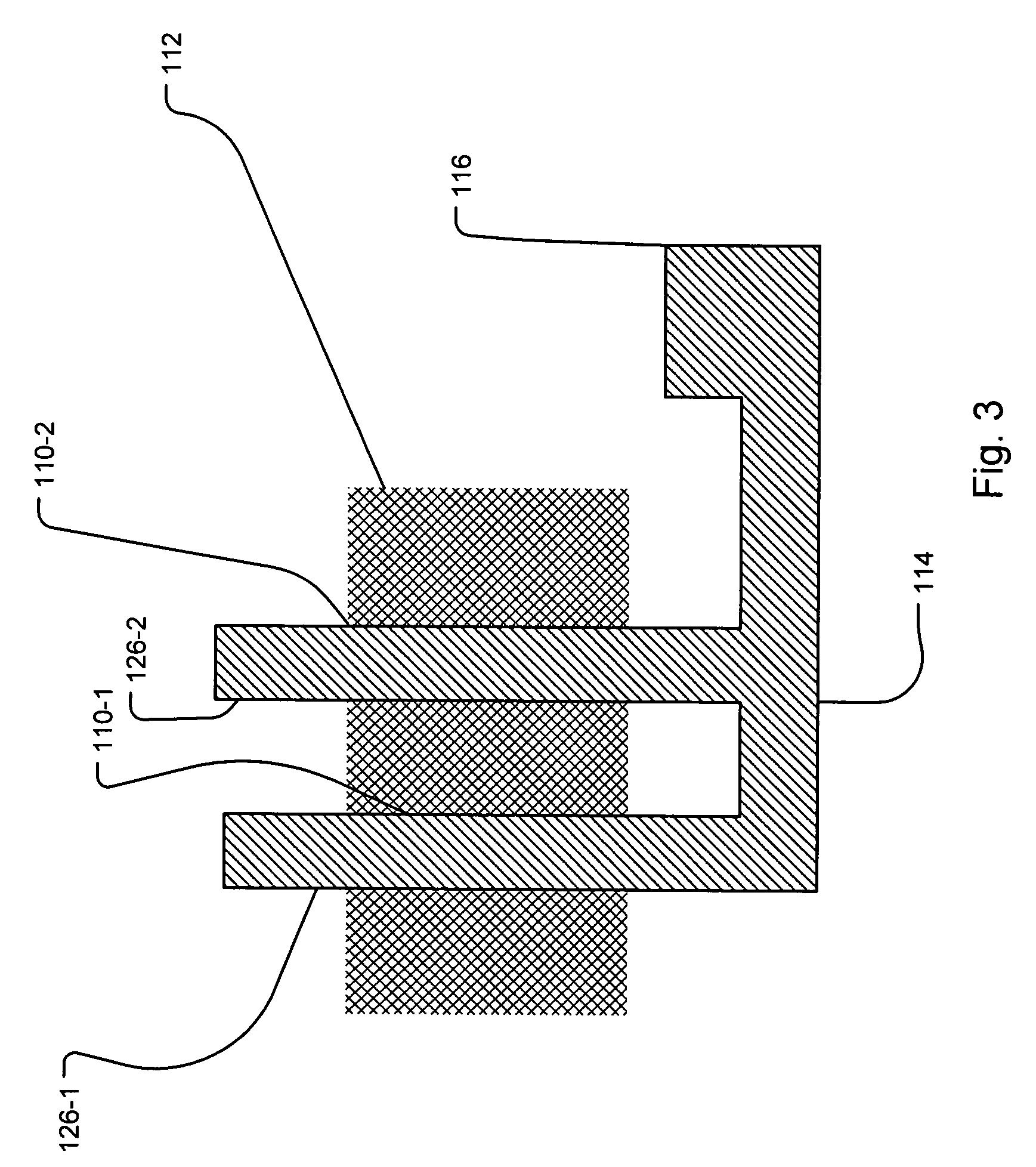

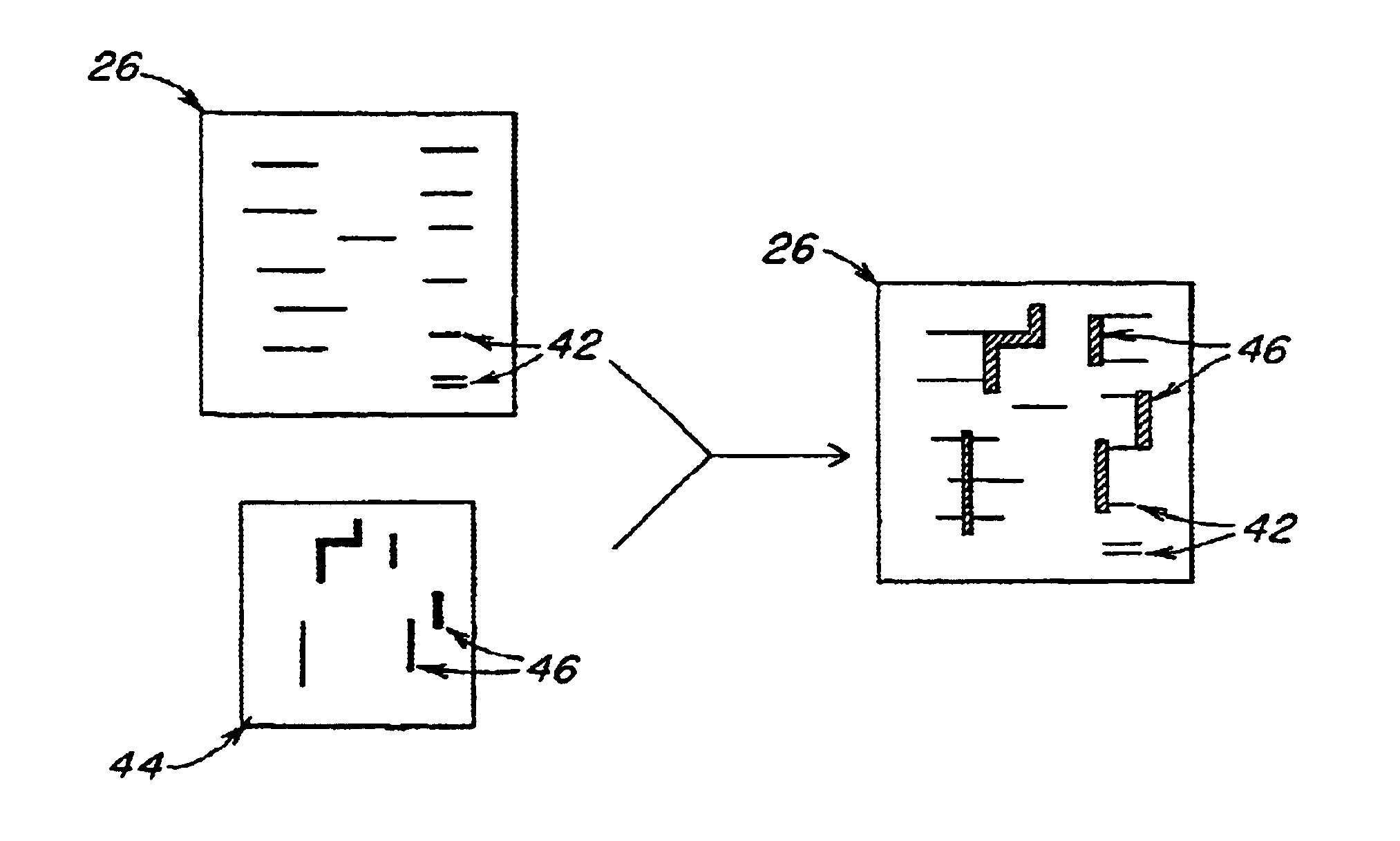

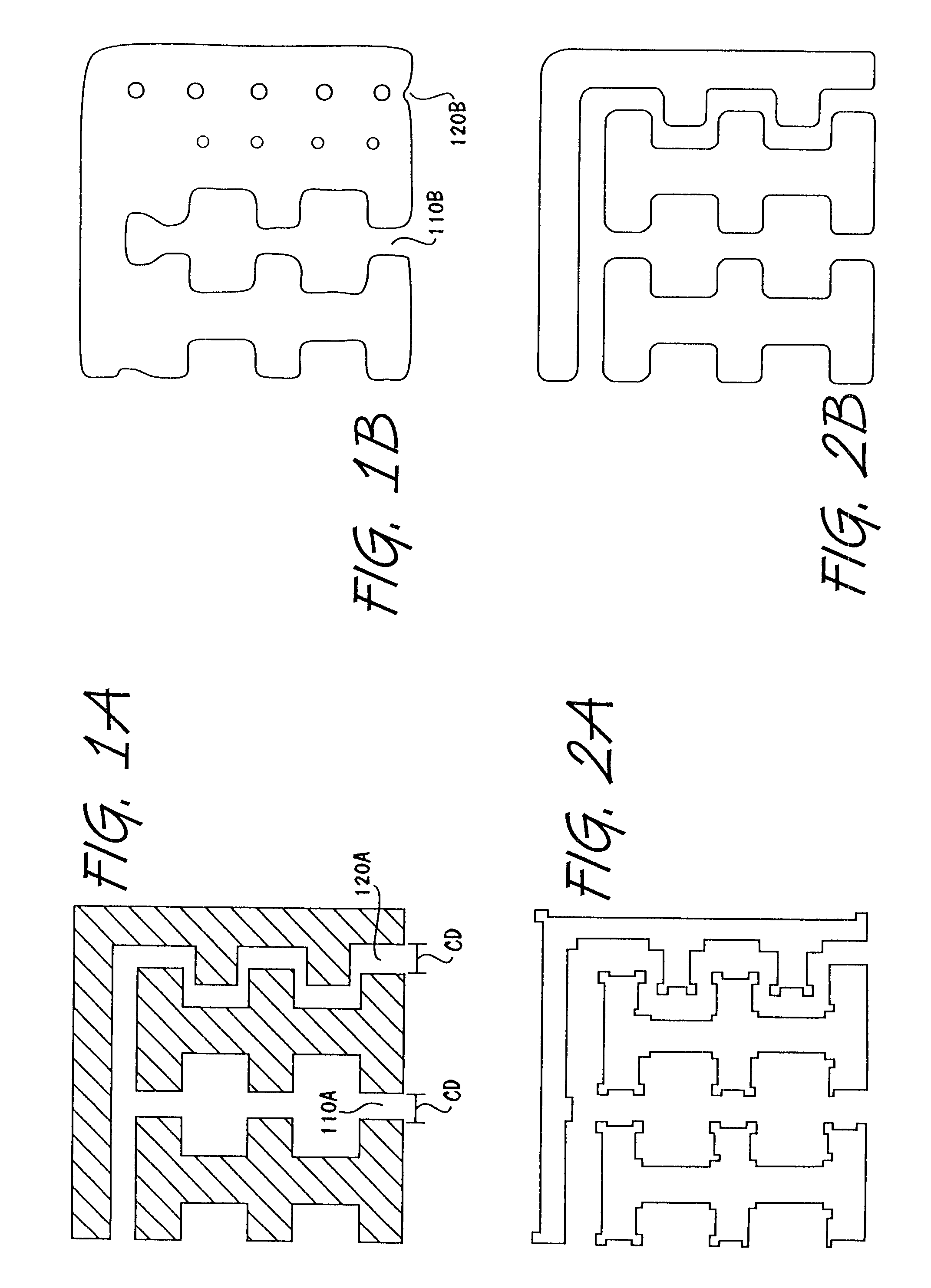

A method and apparatus for the correction of integrated circuit layouts for optical proximity effects which maintains the original true hierarchy of the original layout is provided. Also provided is a method and apparatus for the design rule checking of layouts which have been corrected for optical proximity effects. The OPC correction method comprises providing a hierarchically described integrated circuit layout as a first input, and a particular set of OPC correction criteria as a second input. The integrated circuit layout is then analyzed to identify features of the layout which meet the provided OPC correction criteria. After the areas on the mask which need correction have been identified, optical proximity correction data is generated in response to the particular set of correction criteria. Finally, a first program data is generated which stores the generated optical proximity correction data in a hierarchical structure that corresponds to the hierarchical structure of the integrated circuit layout. As the output correction data is maintained in true hierarchical format, layouts which are OPC corrected according to this method are able to be processed through conventional design rule checkers with no altering of the data.

Owner:SYNOPSYS INC

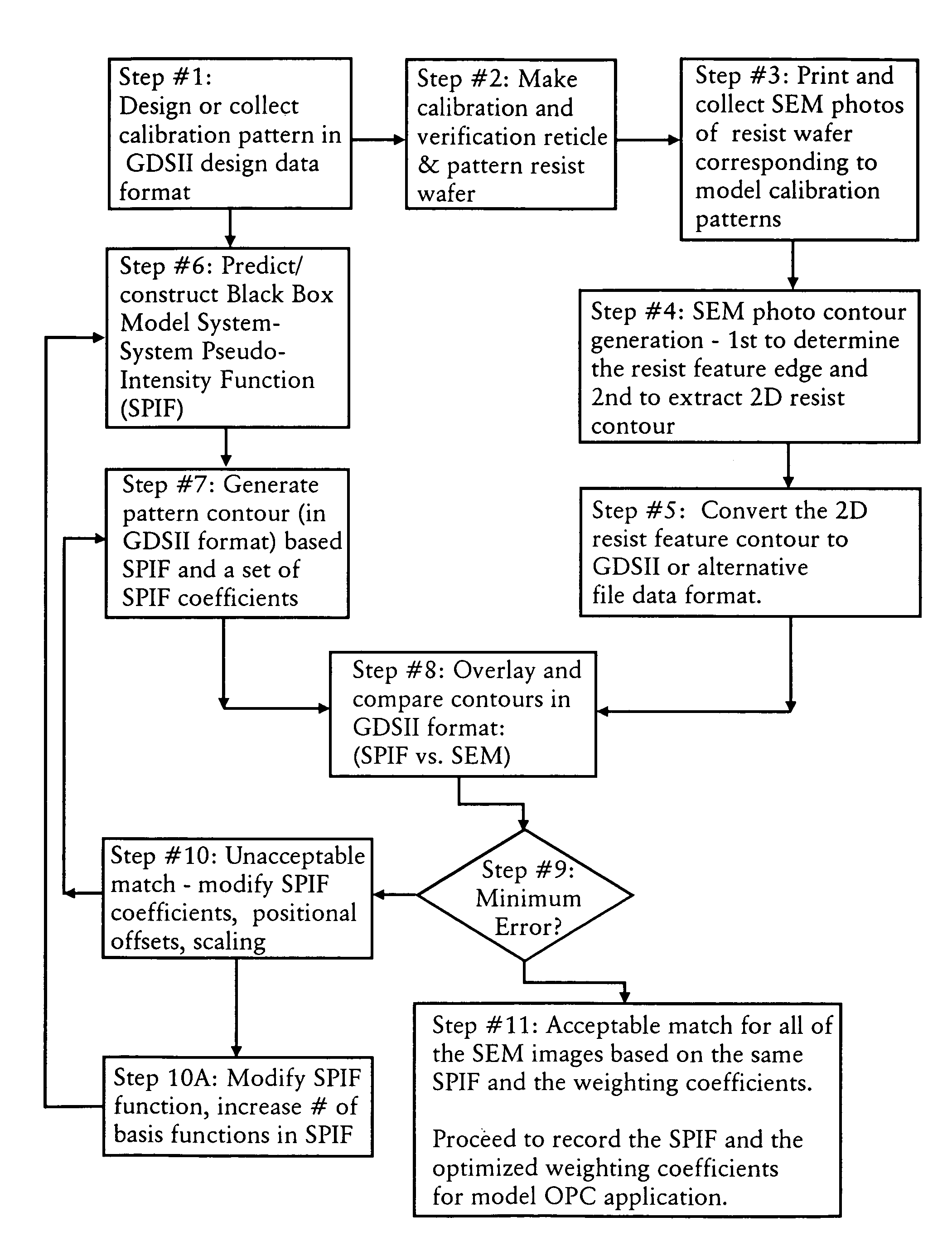

Method of two dimensional feature model calibration and optimization

InactiveUS7175940B2Minimize proximity effectAccurate performanceSemiconductor/solid-state device manufacturingCharacter and pattern recognitionPattern recognitionData format

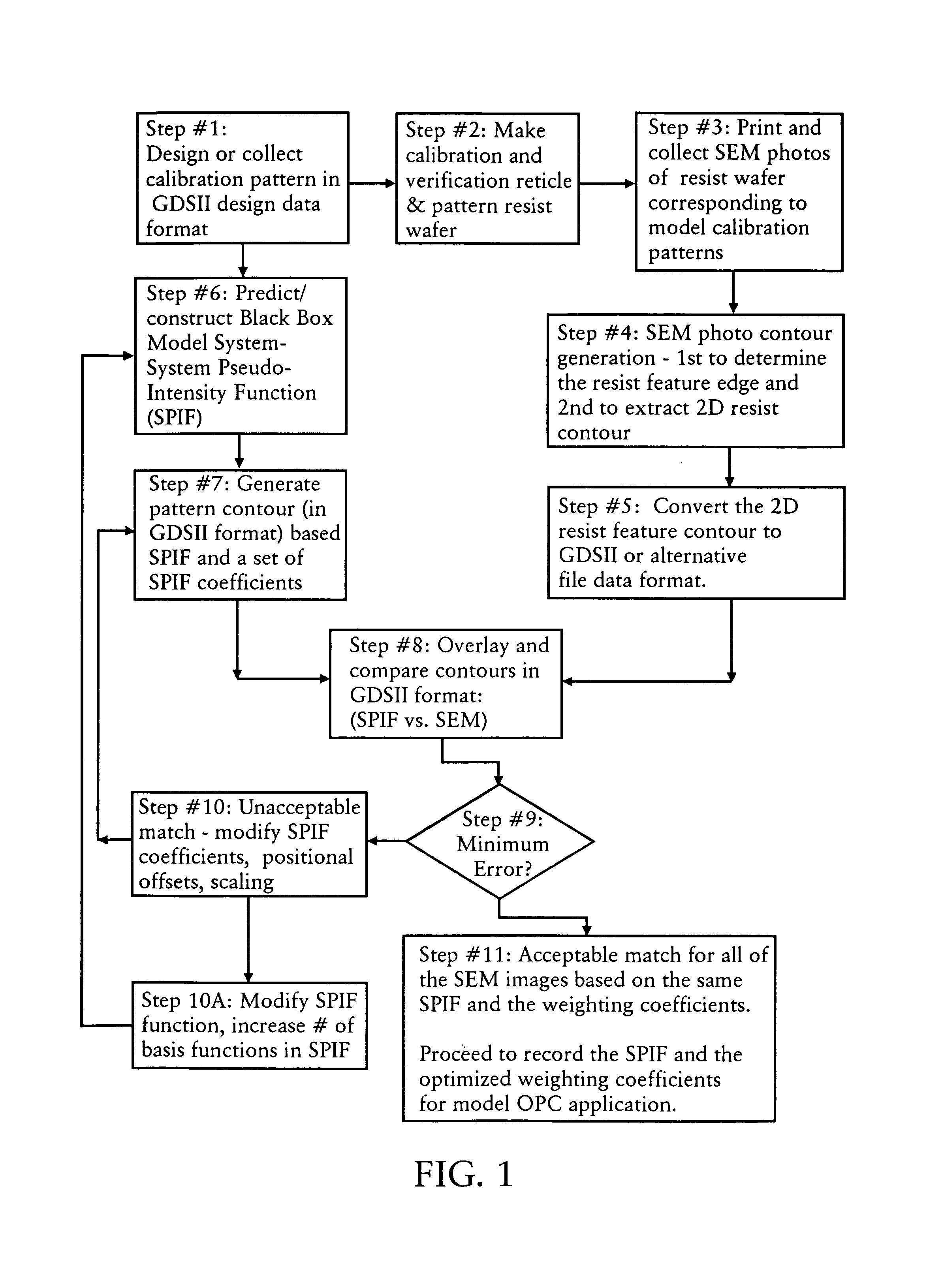

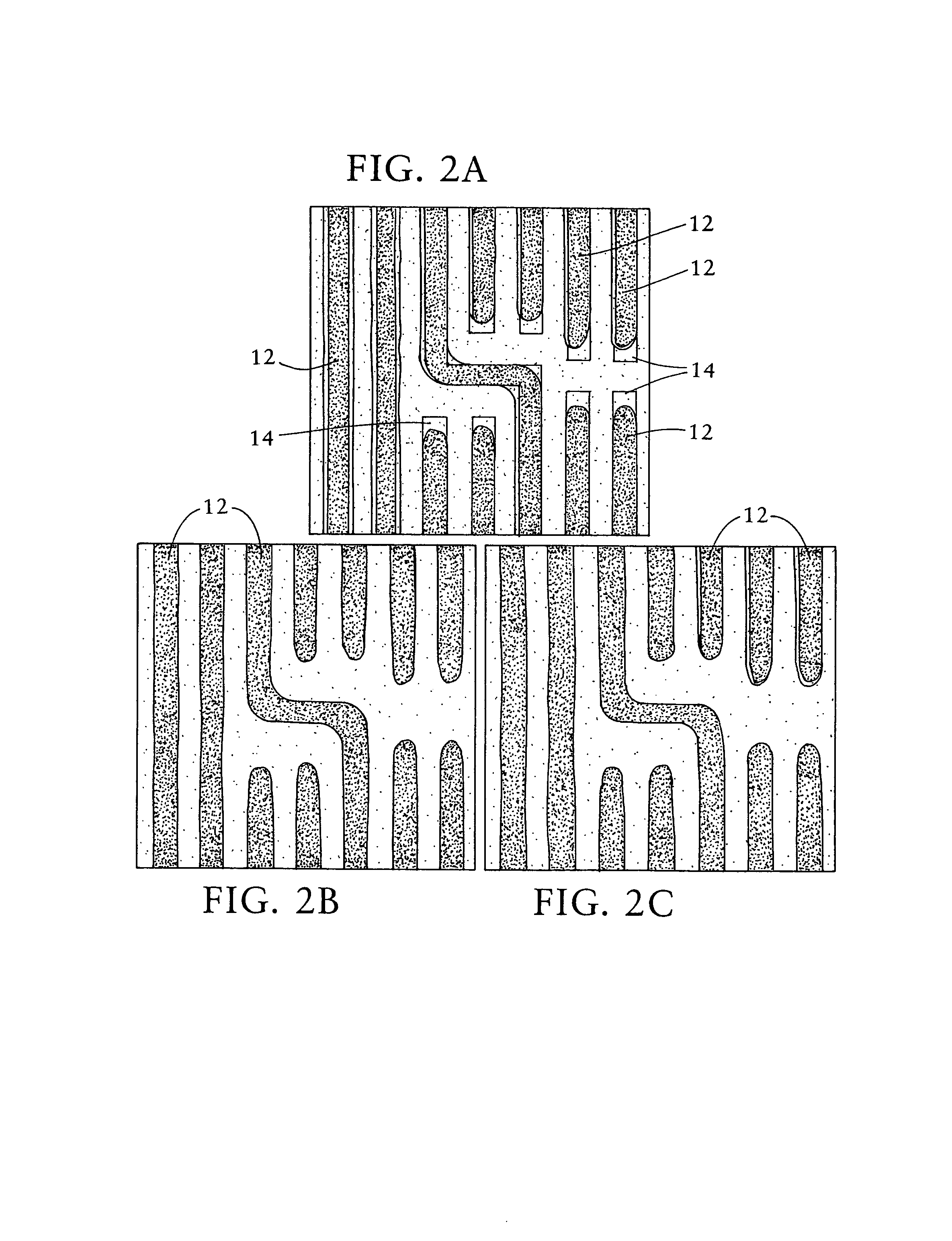

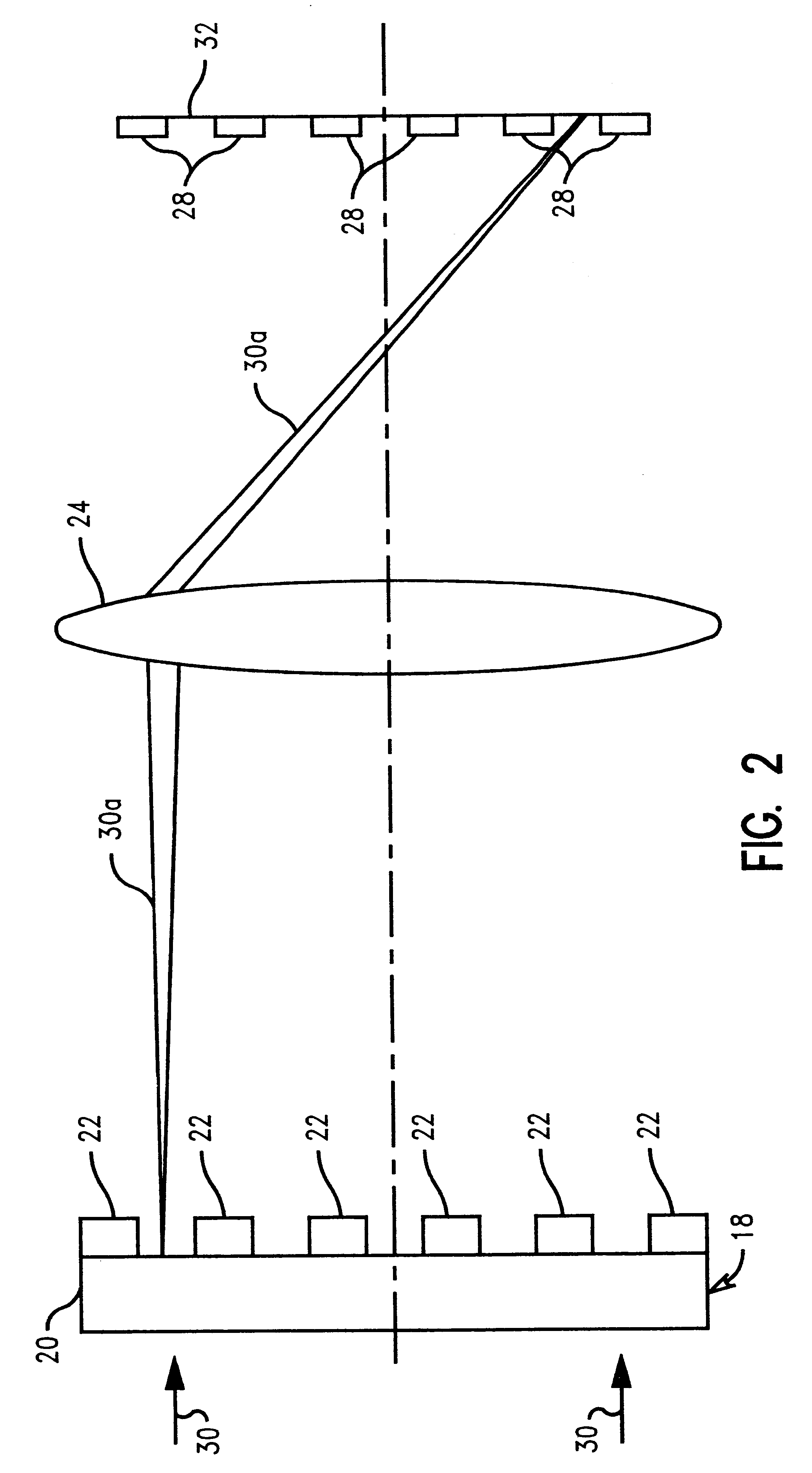

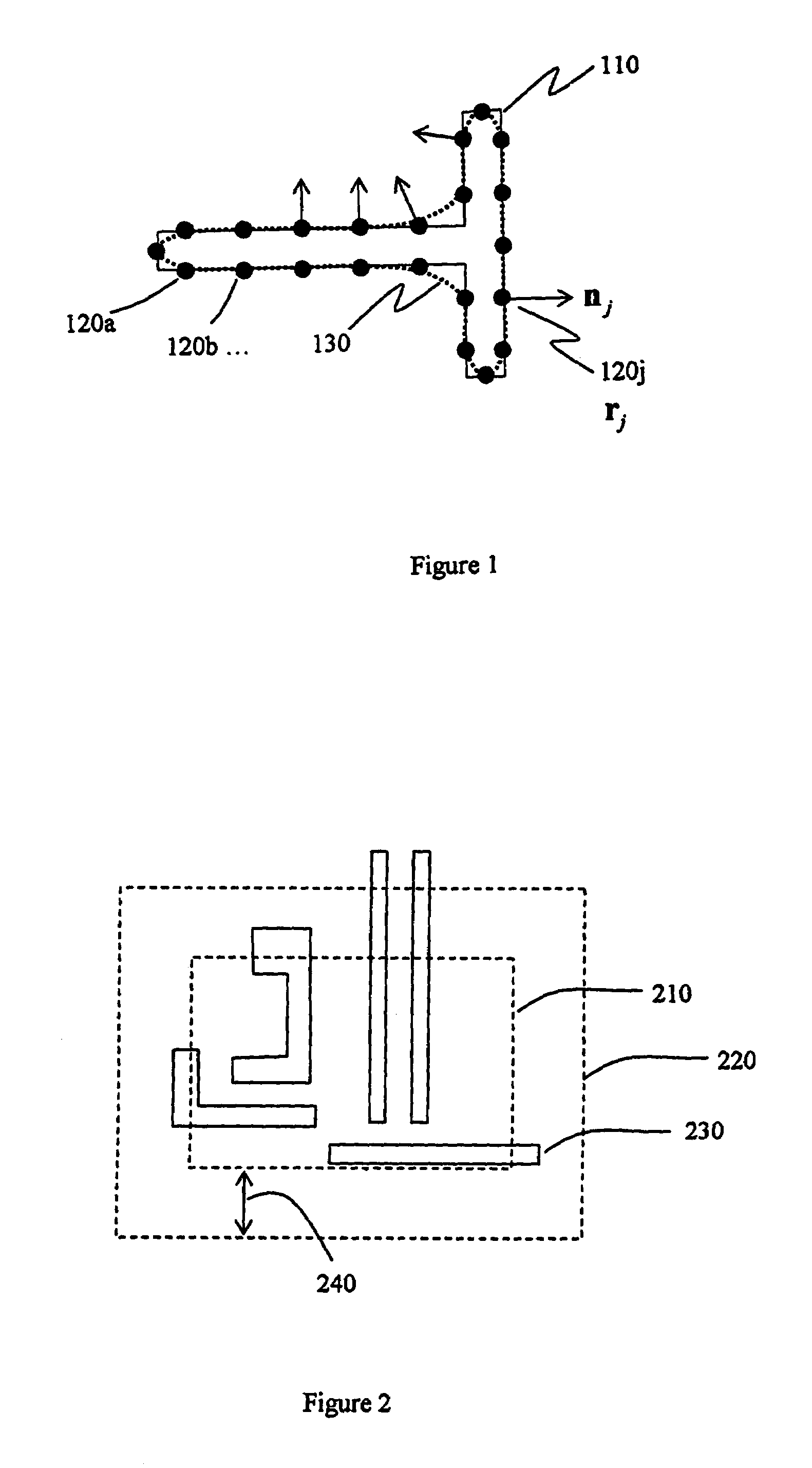

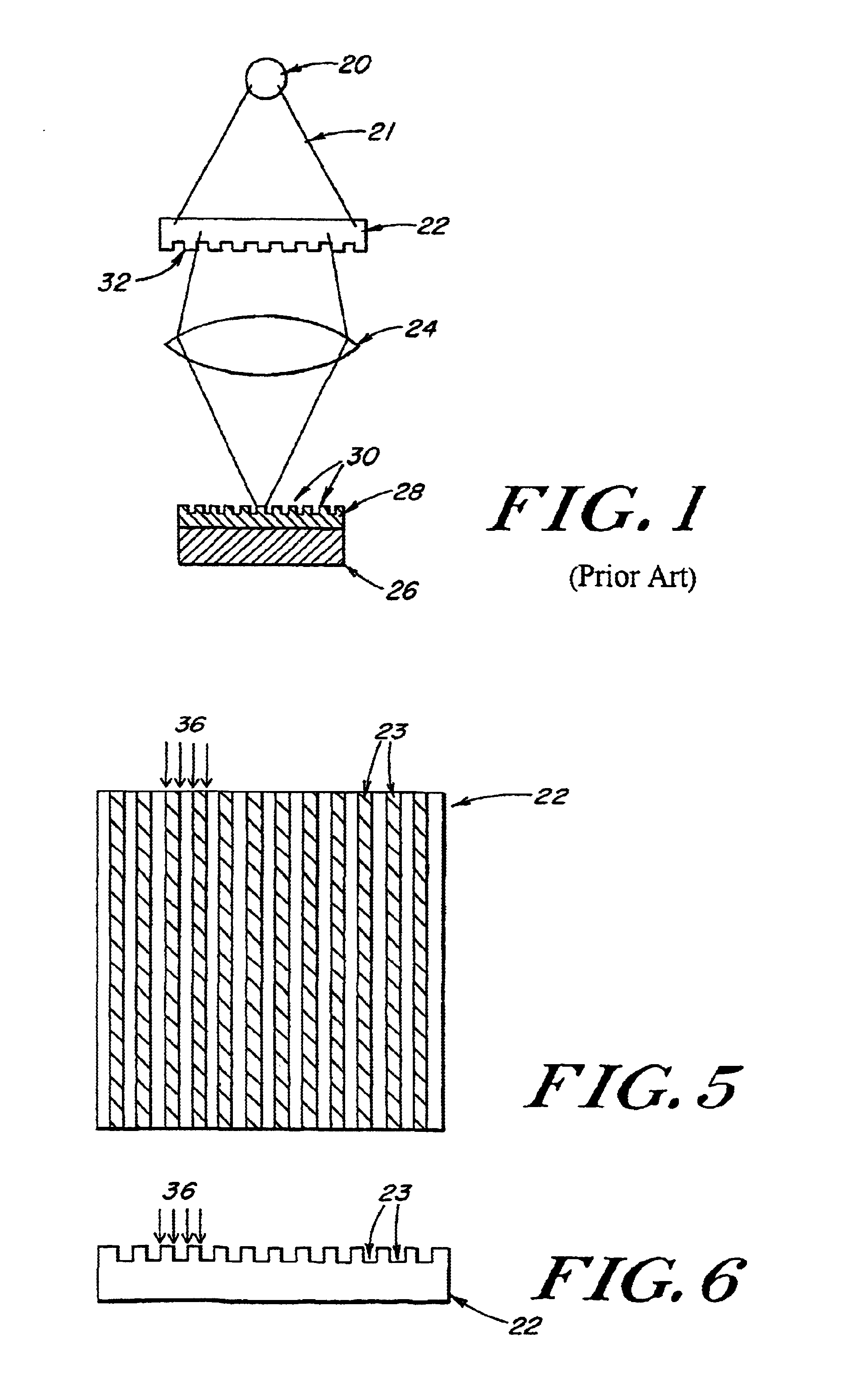

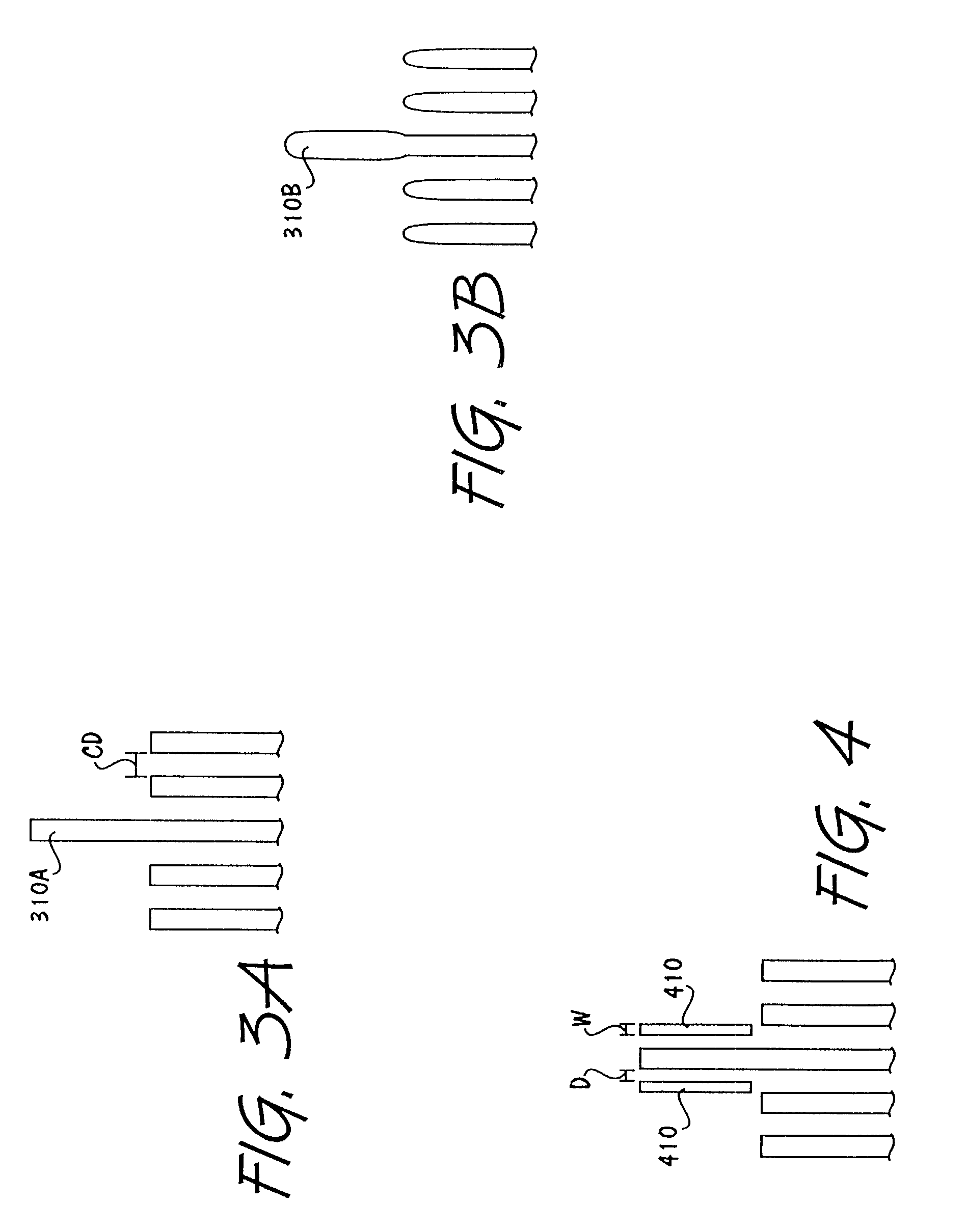

A method for generating a photolithography mask for optically transferring a pattern formed in the mask onto a substrate utilizing an imaging system. The method includes the steps of: (a) defining a set of calibration patterns, which are represented in a data format; (b) printing the calibration patterns on a substrate utilizing the given imaging system; (c) determining a first set of contour patterns corresponding to the calibration patterns imaged on the substrate; (d) generating a system pseudo-intensity function, which approximates the imaging performance of the imaging system; (e) determining a second set of contour patterns by utilizing the system pseudo-intensity function to define how the calibration patterns will be imaged in the substrate; (f) comparing the first set of contour patterns and the second set of contour patterns to determine the difference therebetween; (g) adjusting the system pseudo-intensity function until the difference between the first set of contour patterns and the second set of contour patterns is below a predefined criteria; and (h) utilizing the adjusted system pseudo-intensity function to modify the mask so as to provide for optical proximity correction.

Owner:ASML NETHERLANDS BV

Method to determine optical proximity correction and assist feature rules which account for variations in mask dimensions

InactiveUS6553559B2Photomechanical apparatusOriginals for photomechanical treatmentComputational physicsProcess window

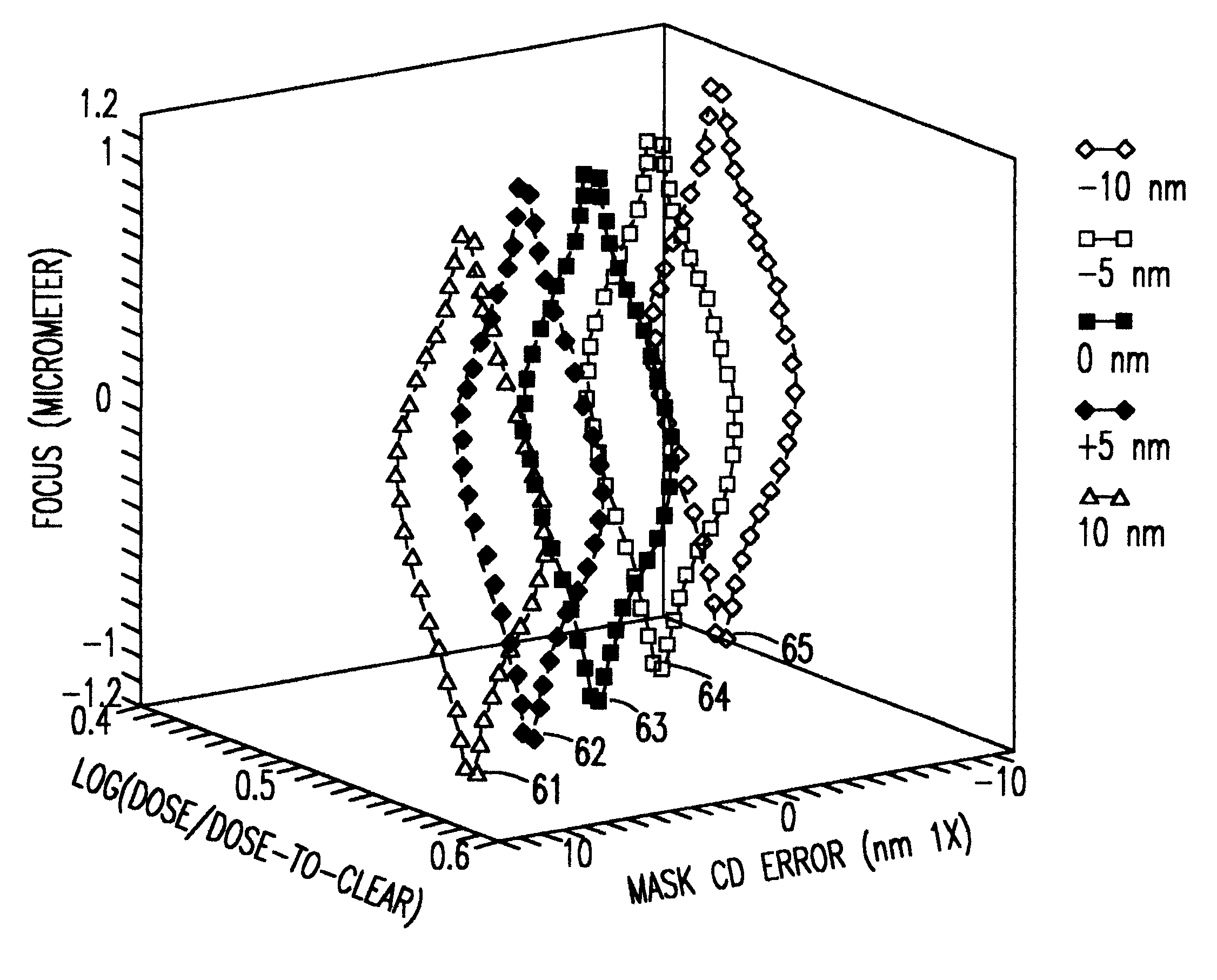

Optical proximity correction (OPC) and assist feature rules are generated using a process window (PW) analysis. A reference pitch is chosen and the mask bias is found that optimizes the process window. This can be done using standard process window analysis or through a weighted process window (WPW) analysis which accounts for focus and dose distributions that are expected in a real process. The WPW analysis gives not only the optimum mask bias, but also the center focus and dose conditions for the optimum process centering. A series of other pitches and mask biases are then analyzed by finding the common process window with the reference pitch. For the standard PW analysis, a common process window is found. For the WPW analysis, the WPW is computed at the center focus and dose conditions found for the reference pitch. If mask or lens errors are to be accounted for, then multiple structures can be included in the analysis. Once the common process windows for the mask features of interest have been computed, functional fits to the data can be found. Once the functional forms have been found for each of the OPC parameters, the rules table can be determined by solving for the spacings of interest in the design.

Owner:GLOBALFOUNDRIES U S INC

Process window based optical proximity correction of lithographic images

InactiveUS6578190B2Maximize rangeCharacter and pattern recognitionPhotomechanical exposure apparatusProcess windowPlanographic printing

Owner:GLOBALFOUNDRIES U S INC

Method for improving optical proximity correction

ActiveUS7350183B2Improve variationDefect minimizationPhotomechanical apparatusOriginals for photomechanical treatmentLine widthComputer science

Owner:GLOBALFOUNDRIES U S INC

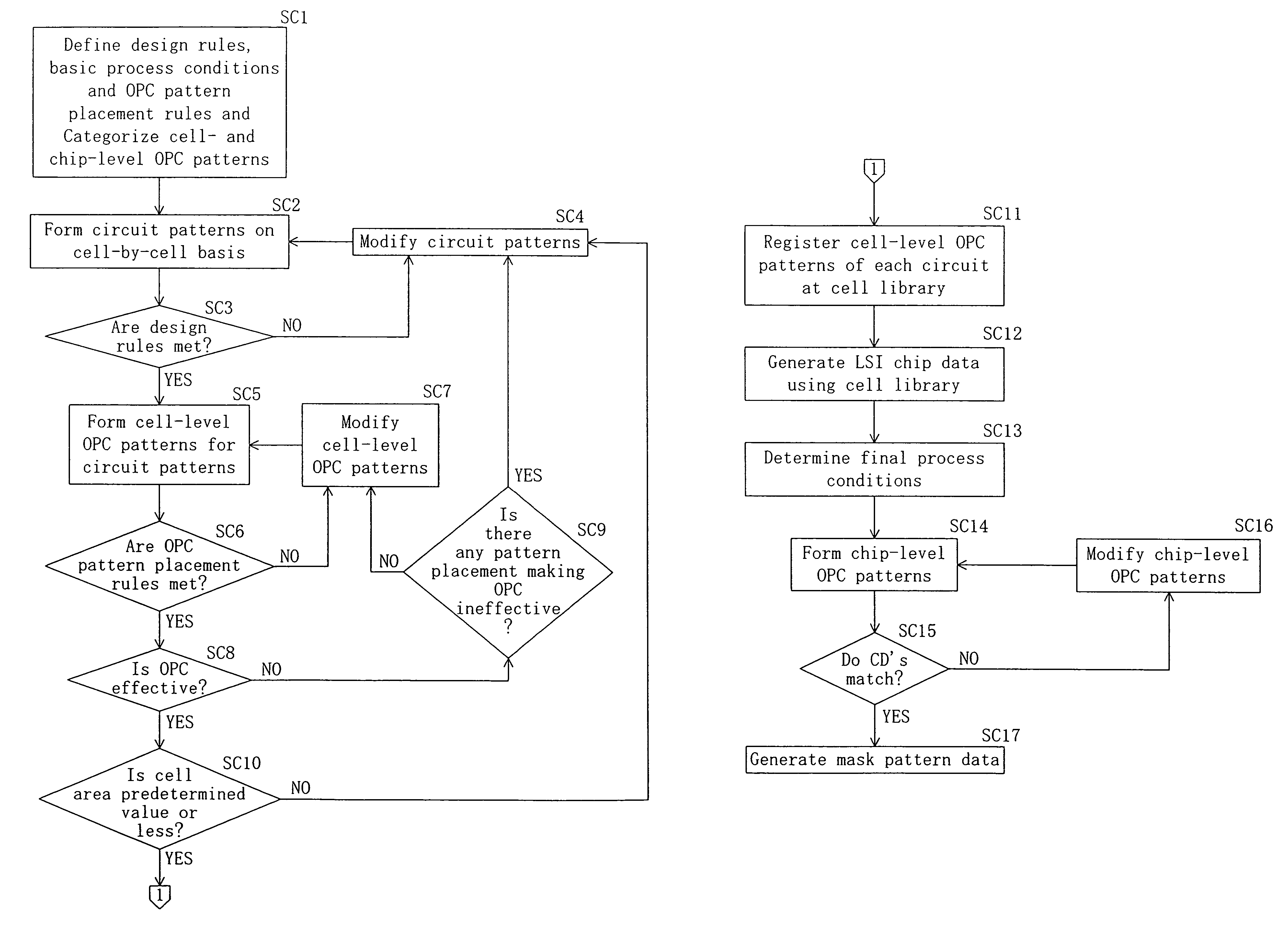

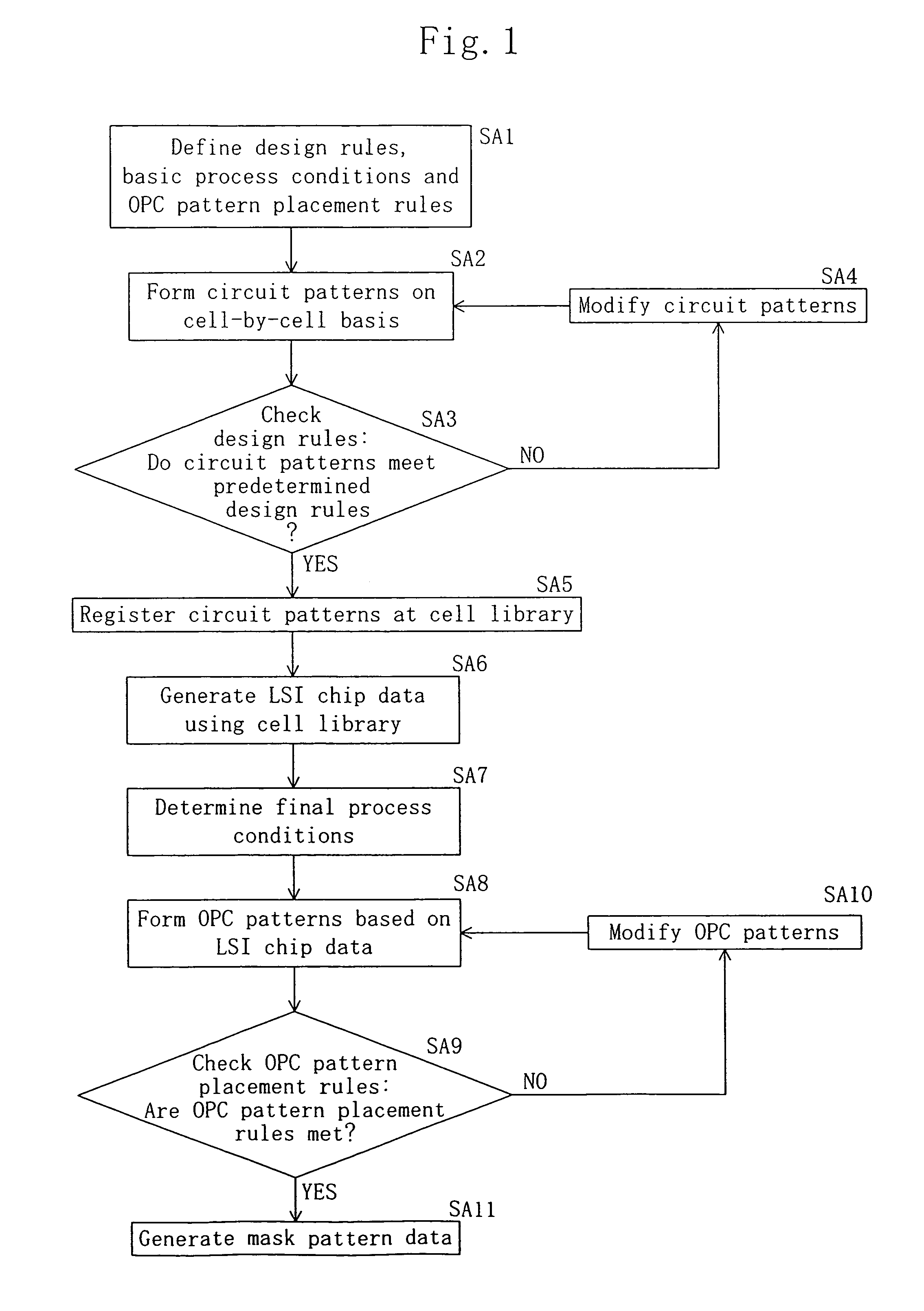

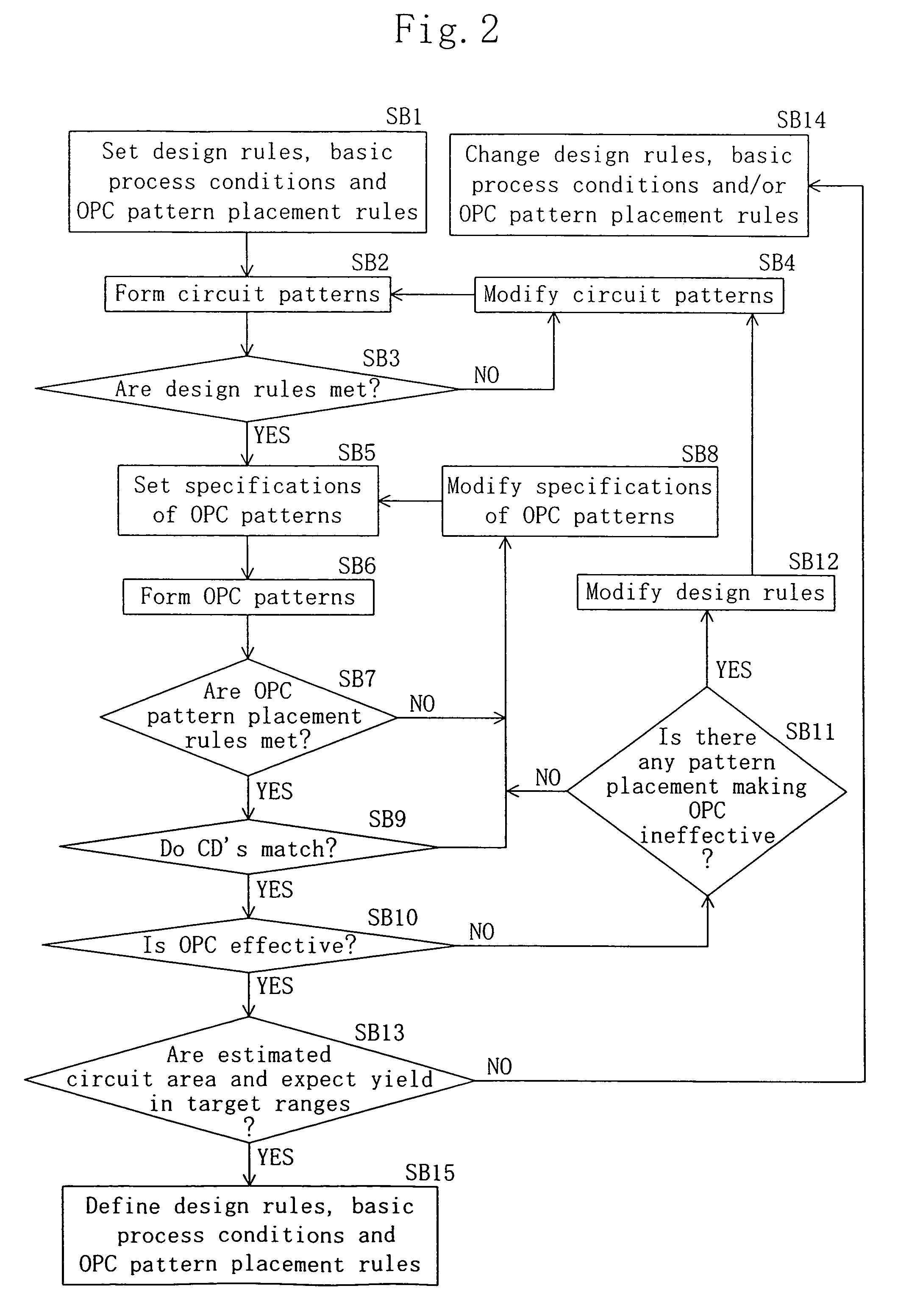

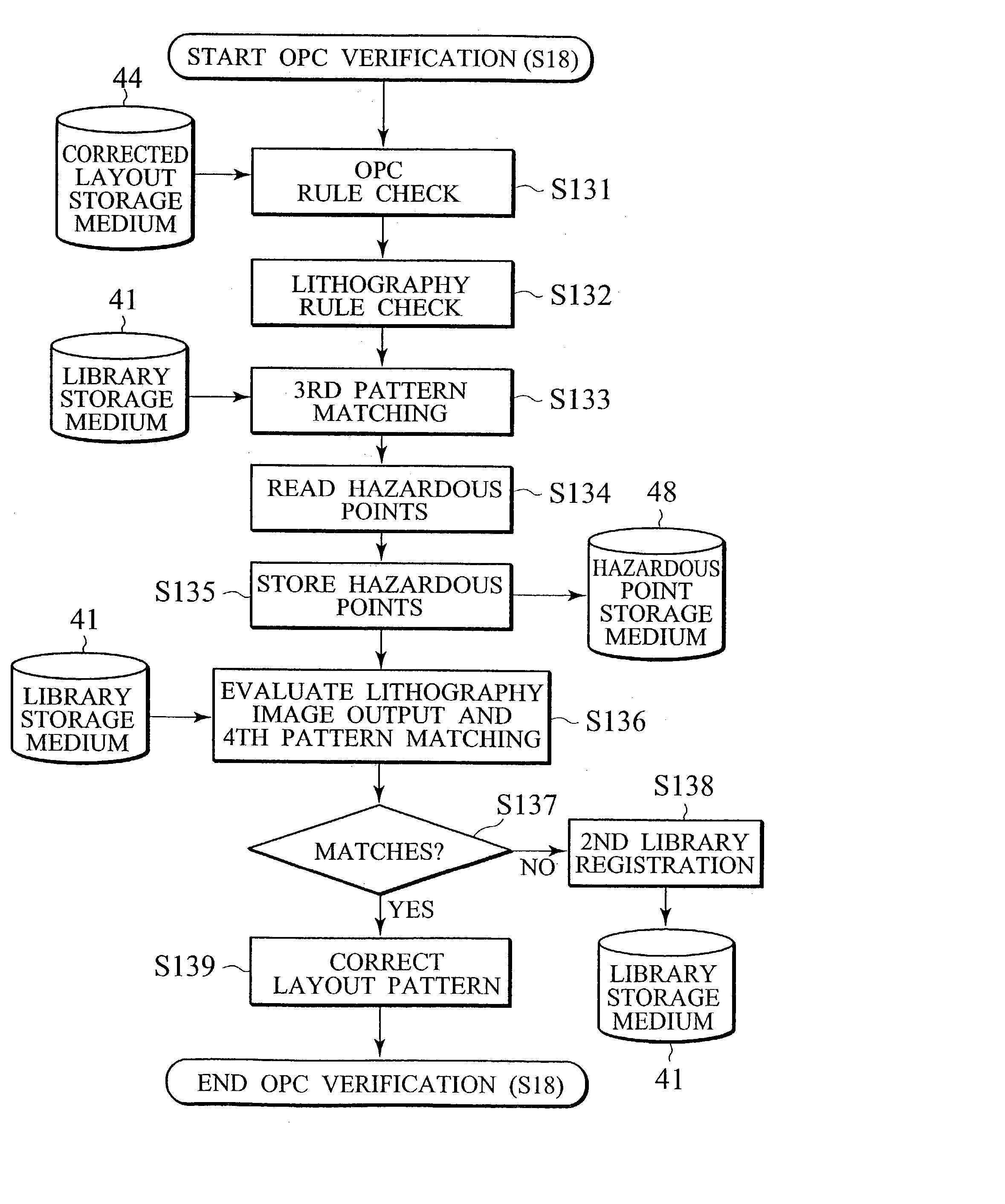

Method for planning layout for LSI pattern, method for forming LSI pattern and method for generating mask data for LSI

InactiveUS7103870B2Efficient executionEasy to manageCAD circuit designOriginals for photomechanical treatmentEngineeringOptical proximity correction

Owner:PANASONIC CORP

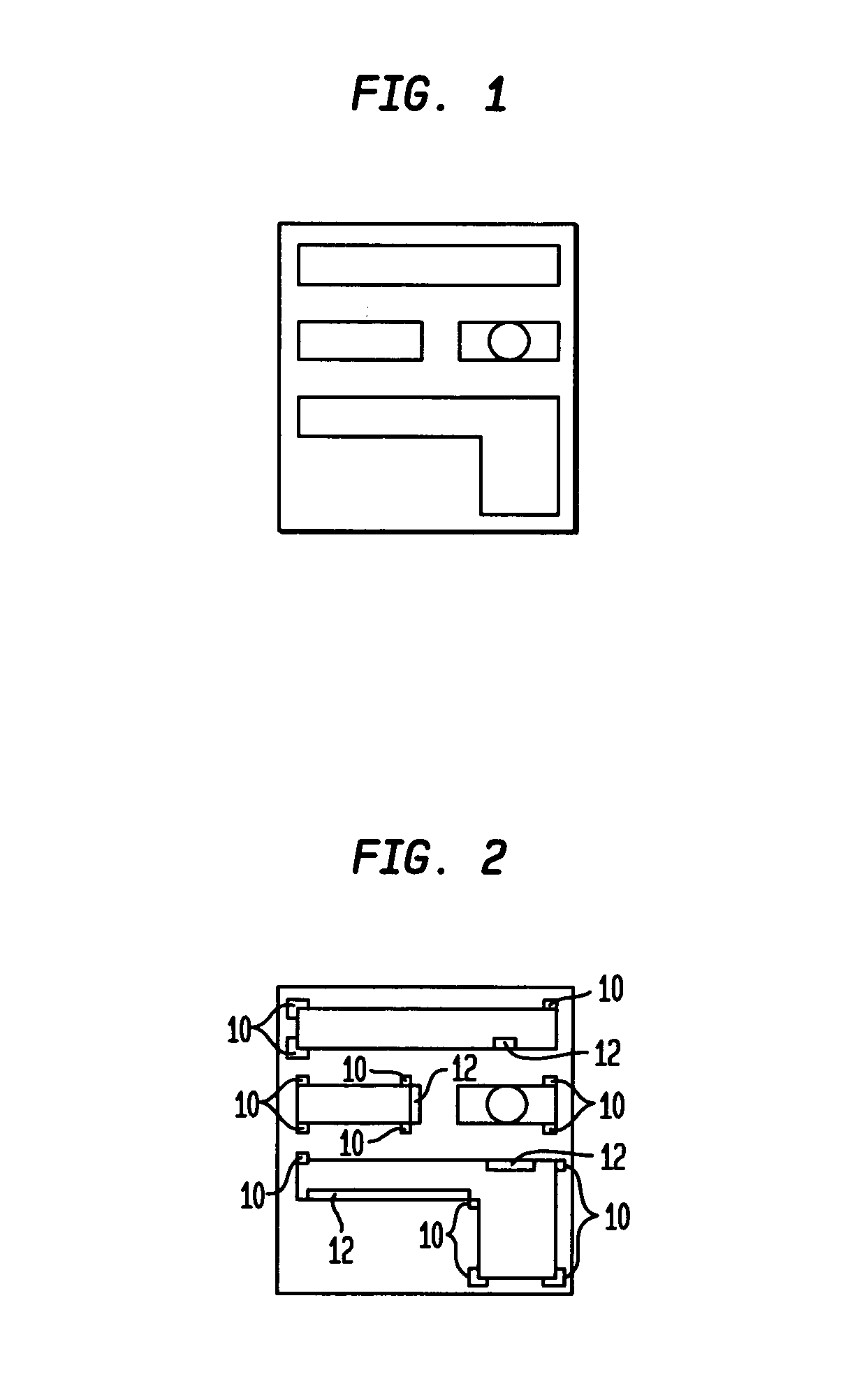

Circuit layout methodology using a shape processing application

InactiveUS7188322B2Low costSmall sizeCAD circuit designSpecial data processing applicationsManufacturing technologySoftware engineering

Owner:INT BUSINESS MASCH CORP

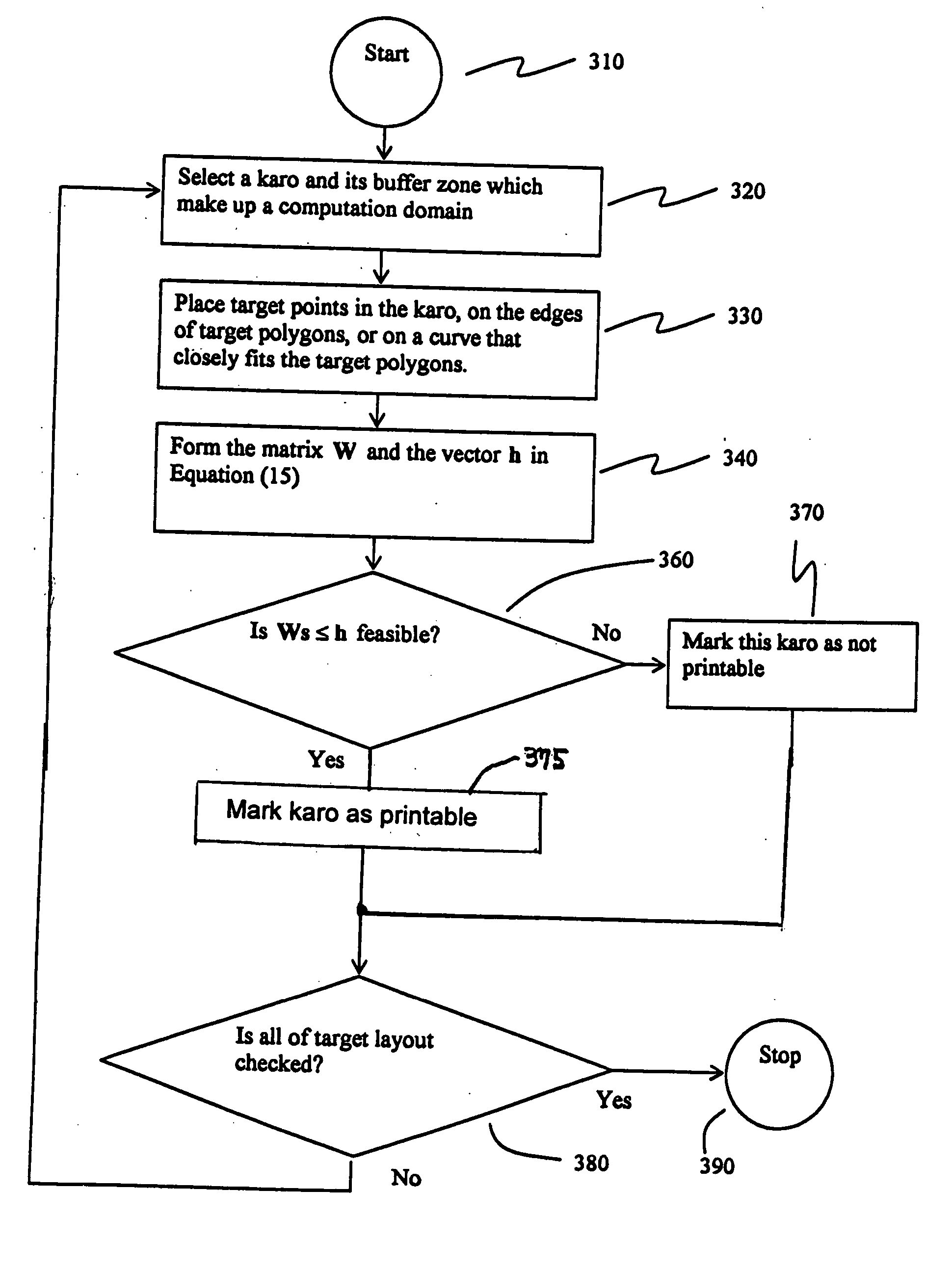

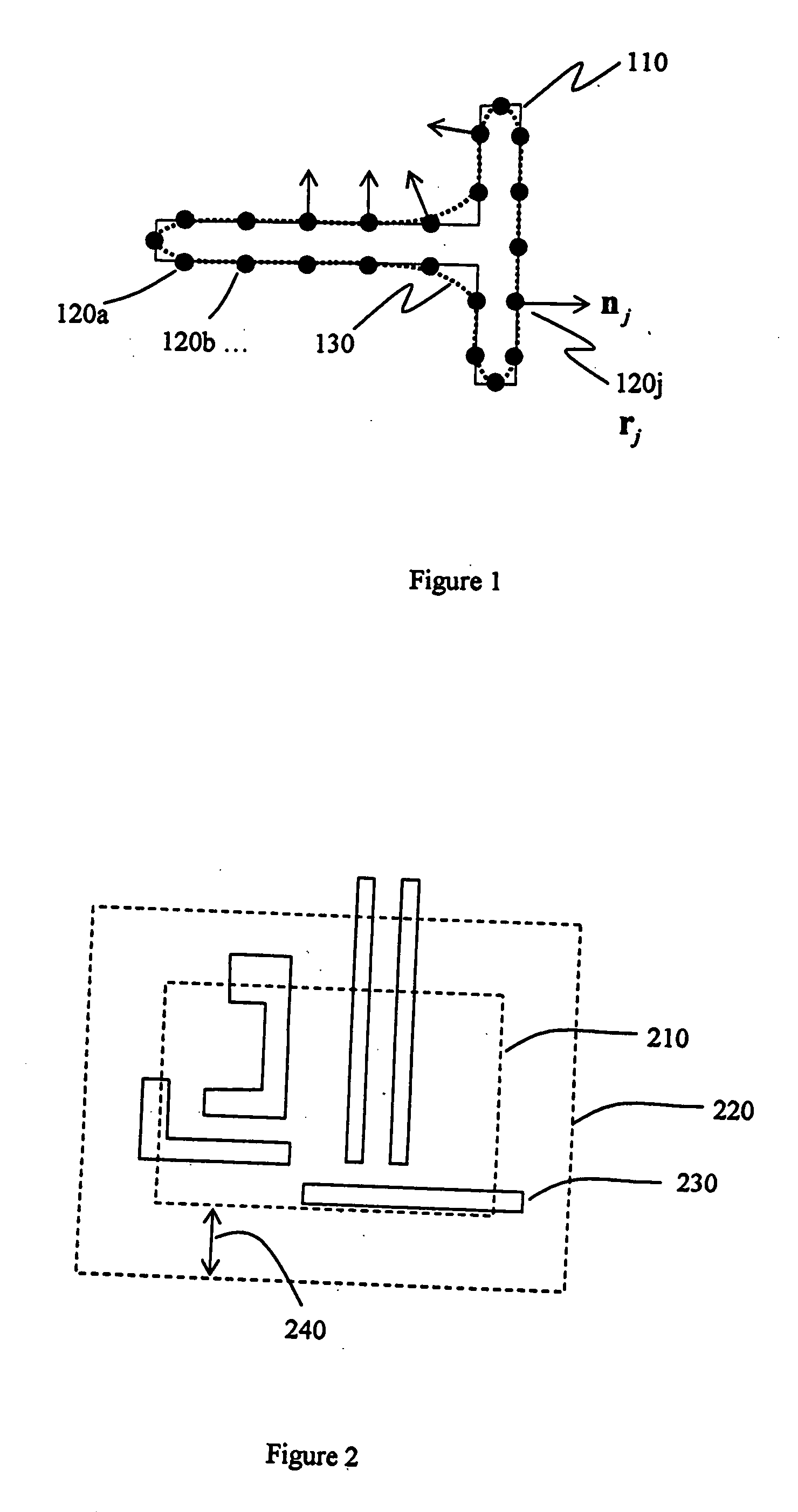

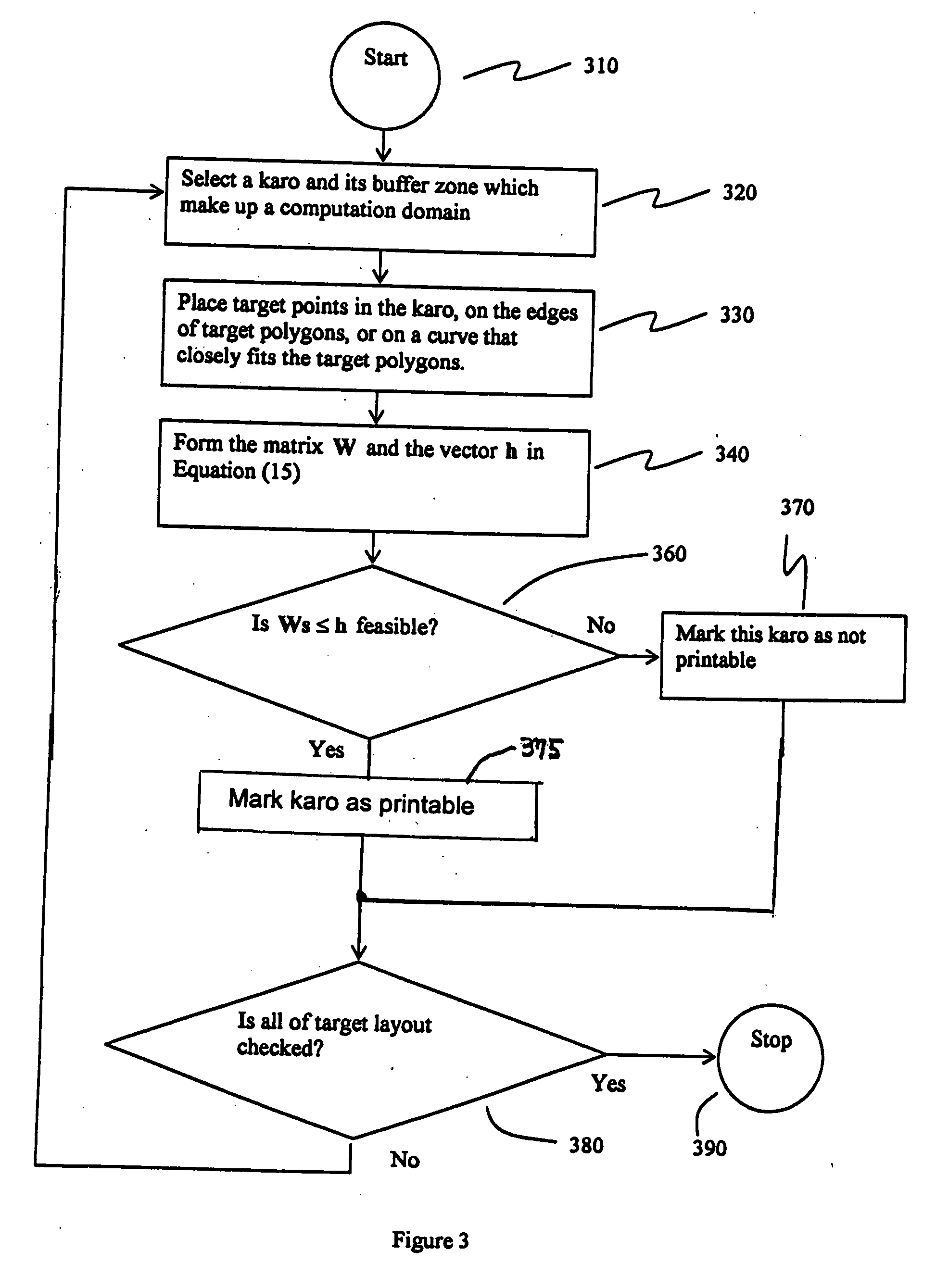

Method for checking printability of a lithography target

InactiveUS7568174B2Detecting faulty computer hardwarePhotomechanical apparatusOptical radiationLithographic artist

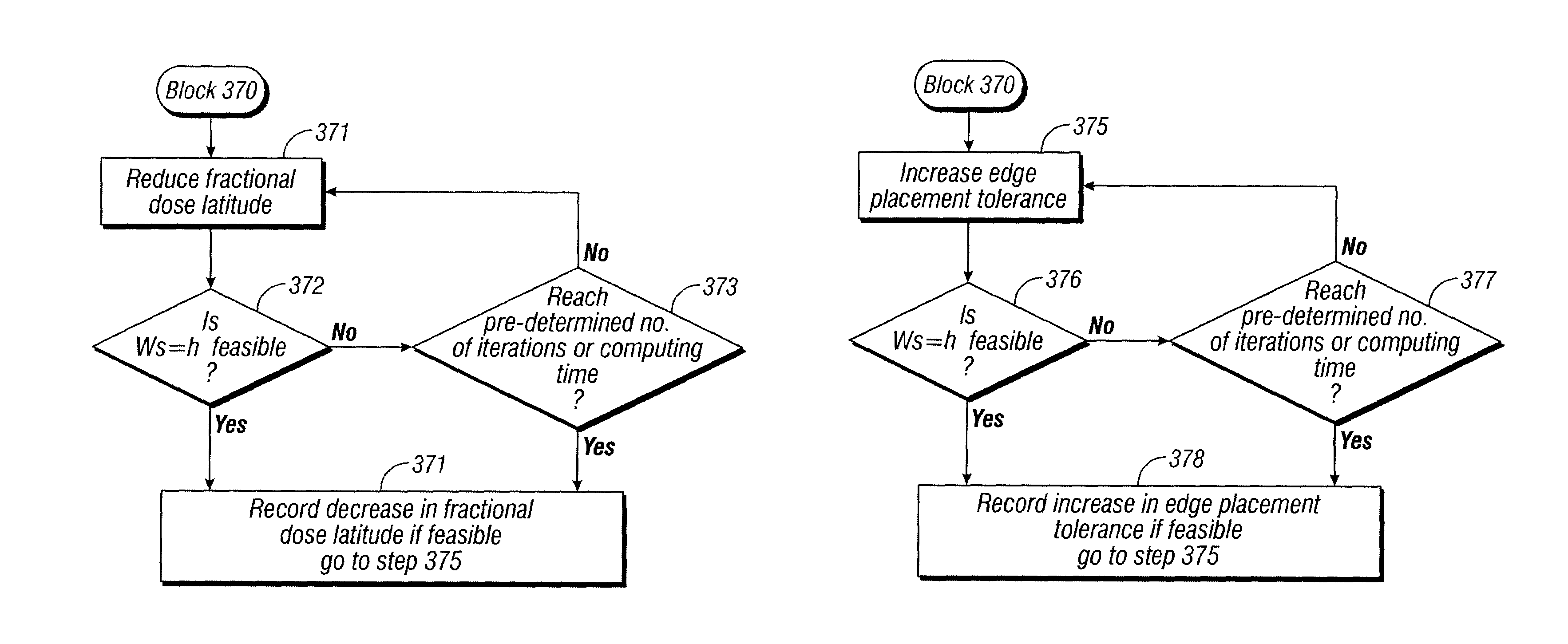

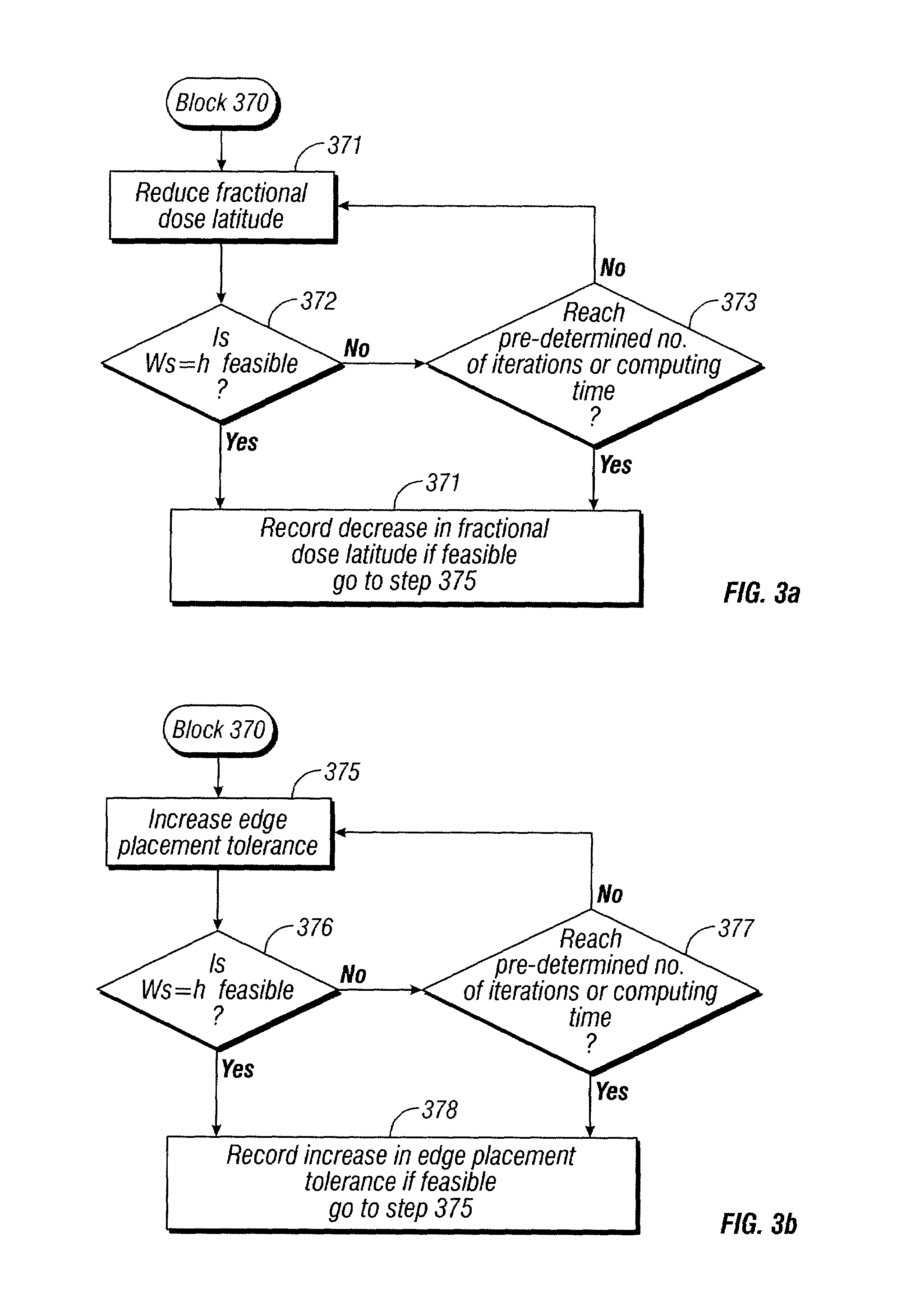

A technique for determining, without having to perform optical proximity correction, when the result of optical proximity correction will fail to meet the design requirements for printability. A disclosed embodiment has application to a process for producing a photomask for use in the printing of a pattern on a wafer by exposure with optical radiation to optically image the photomask on the wafer. A method is set forth for checking the printability of a target layout proposed for defining the photomask, including the following steps: deriving a system of inequalities that expresses a set of design requirements with respect to the target layout; and checking the printability of the target layout by determining whether the system of inequalities is feasible.

Owner:CADENCE DESIGN SYST INC

Method for checking printability of a lithography target

InactiveUS20070094634A1Detecting faulty computer hardwarePhotomechanical apparatusOptical radiationLithographic artist

A technique for determining, without having to perform optical proximity correction, when the result of optical proximity correction will fail to meet the design requirements for printability. A disclosed embodiment has application to a process for producing a photomask for use in the printing of a pattern on a wafer by exposure with optical radiation to optically image the photomask on the wafer. A method is set forth for checking the printability of a target layout proposed for defining the photomask, including the following steps: deriving a system of inequalities that expresses a set of design requirements with respect to the target layout; and checking the printability of the target layout by determining whether the system of inequalities is feasible.

Owner:CADENCE DESIGN SYST INC

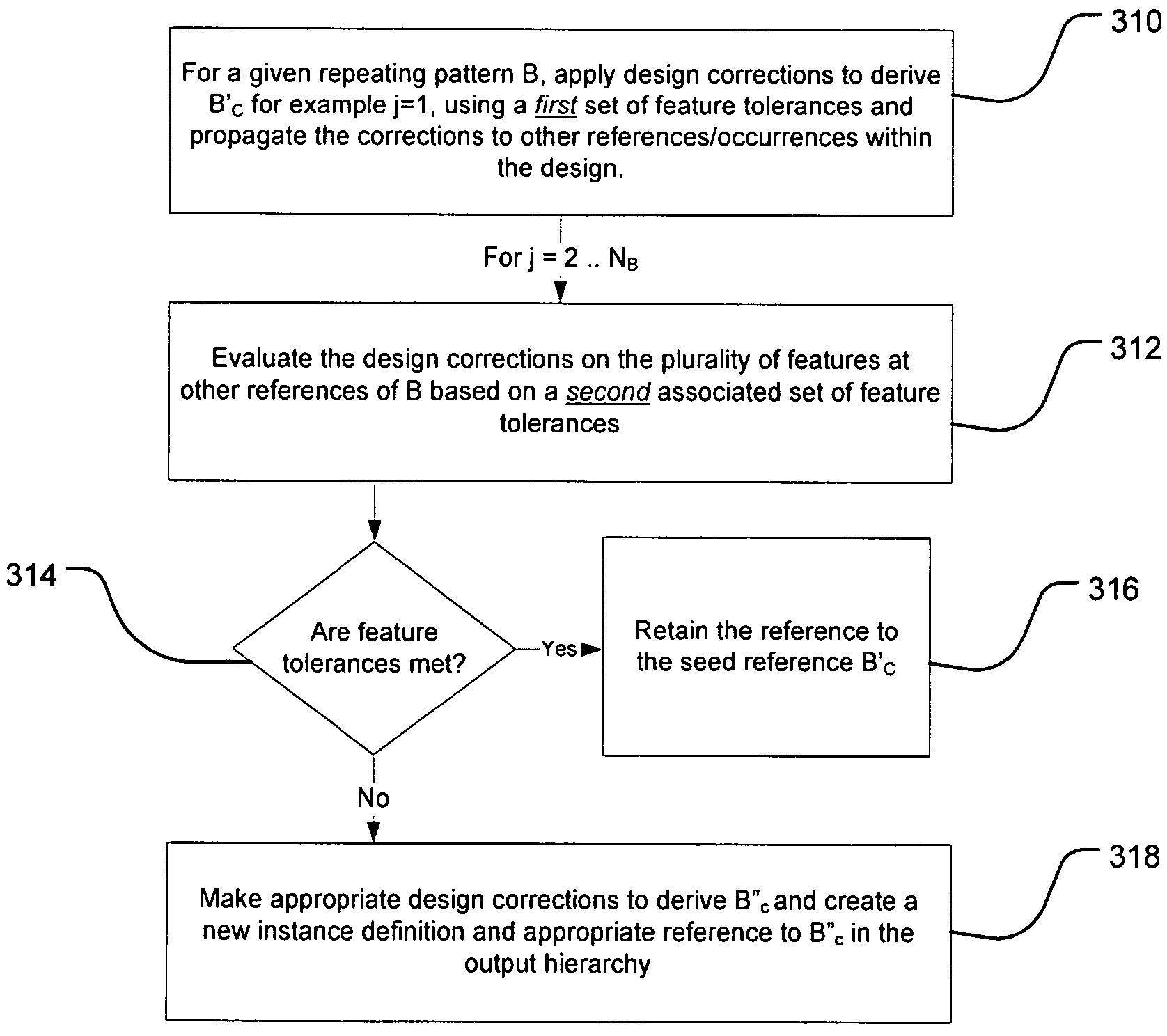

Method and system for managing design corrections for optical and process effects based on feature tolerances

ActiveUS7337421B2CAD circuit designSpecial data processing applicationsApplying knowledgeLithographic artist

Owner:CADENCE DESIGN SYST INC

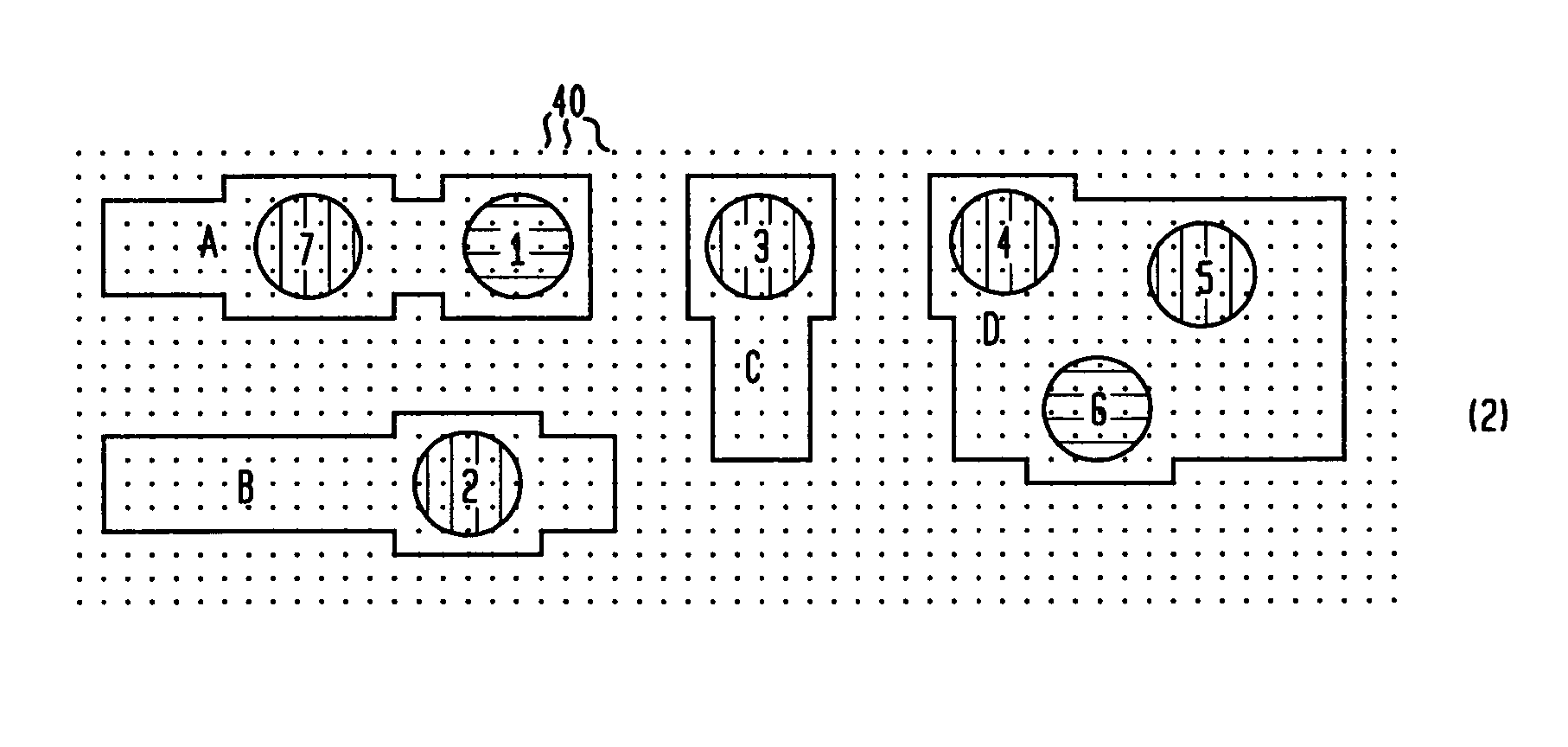

Method, apparatus and system for designing an integrated circuit including generating at least one auxiliary pattern for cell-based optical proximity correction

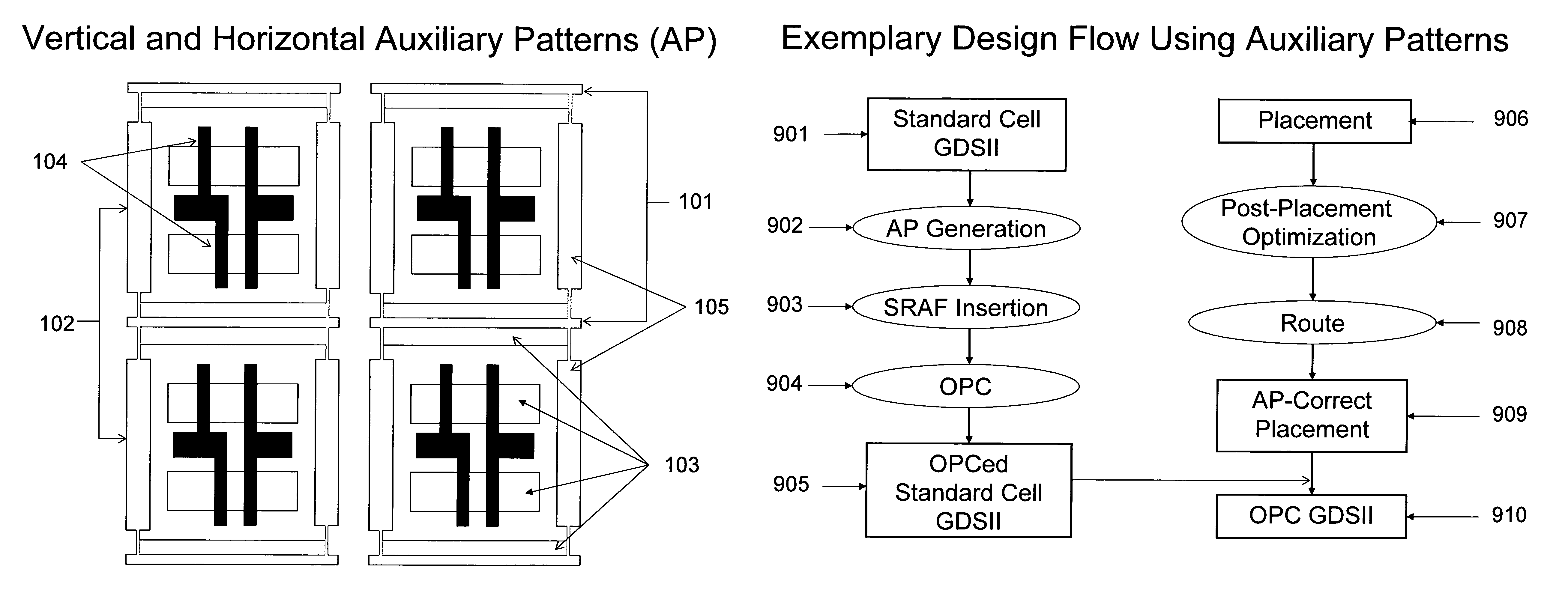

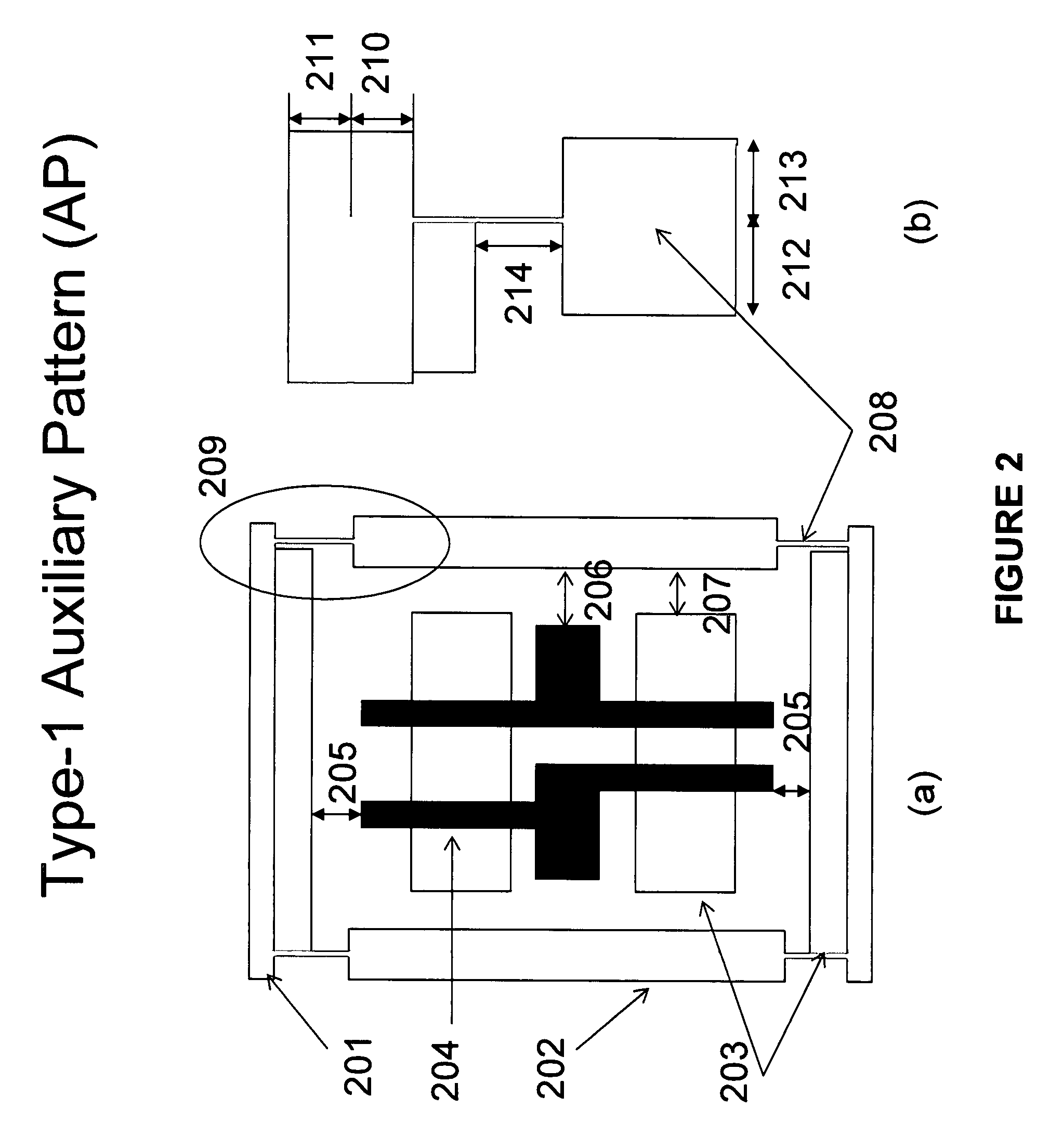

InactiveUS7873929B2Reduce running timeSemiconductor/solid-state device detailsSolid-state devicesCell basedObject function

Method and apparatus for designing an integrated circuit. A new layout is generated for at least one standard cell that incorporates an auxiliary pattern on a gate layer to facilitate cell-based optical proximity correction. An original placement solution is modified for a plurality of standard cells to permit incorporation of cells containing auxiliary patterns while improving an objective function of a resulting placement solution for the plurality of standard cells.

Owner:RGT UNIV OF CALIFORNIA

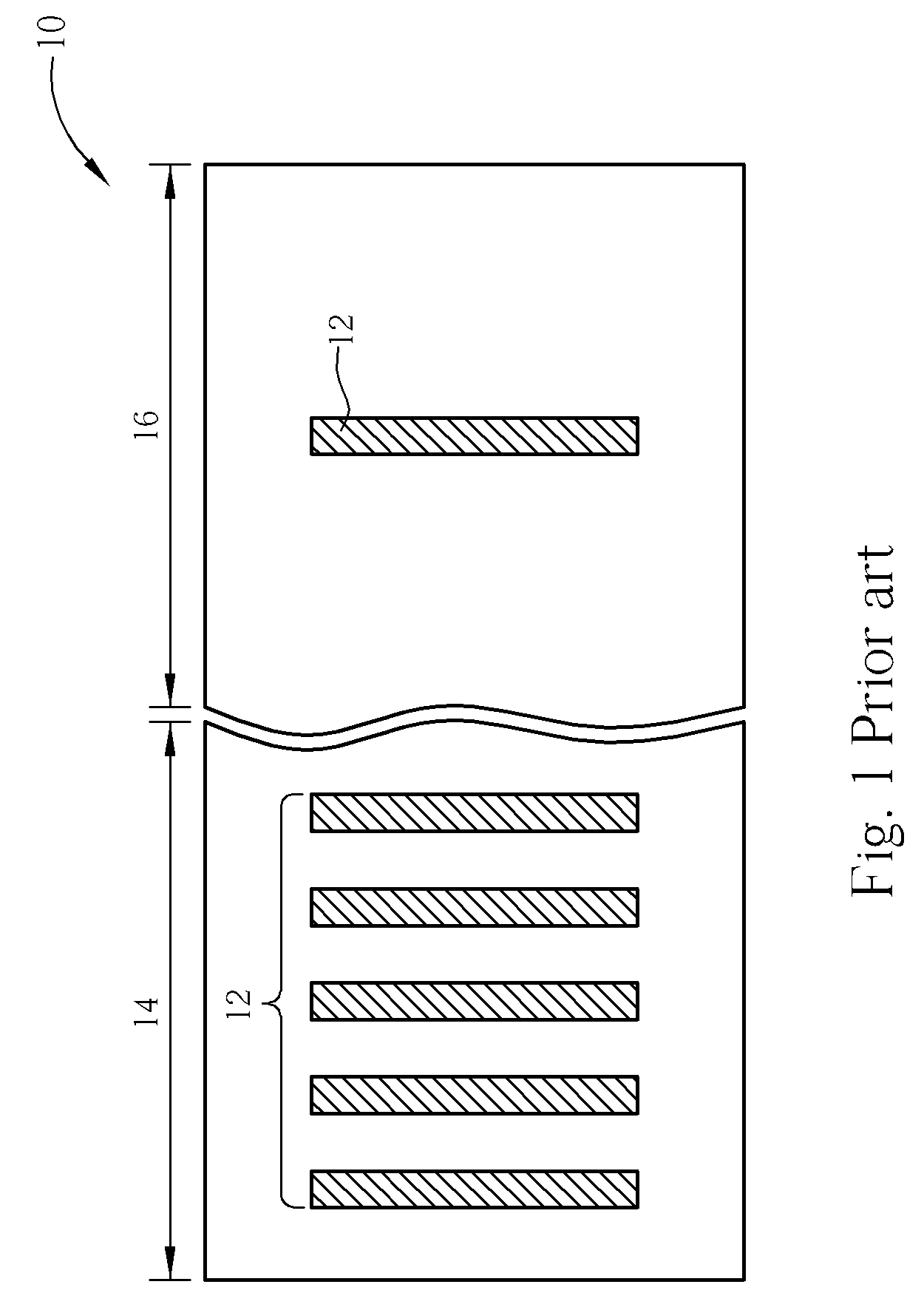

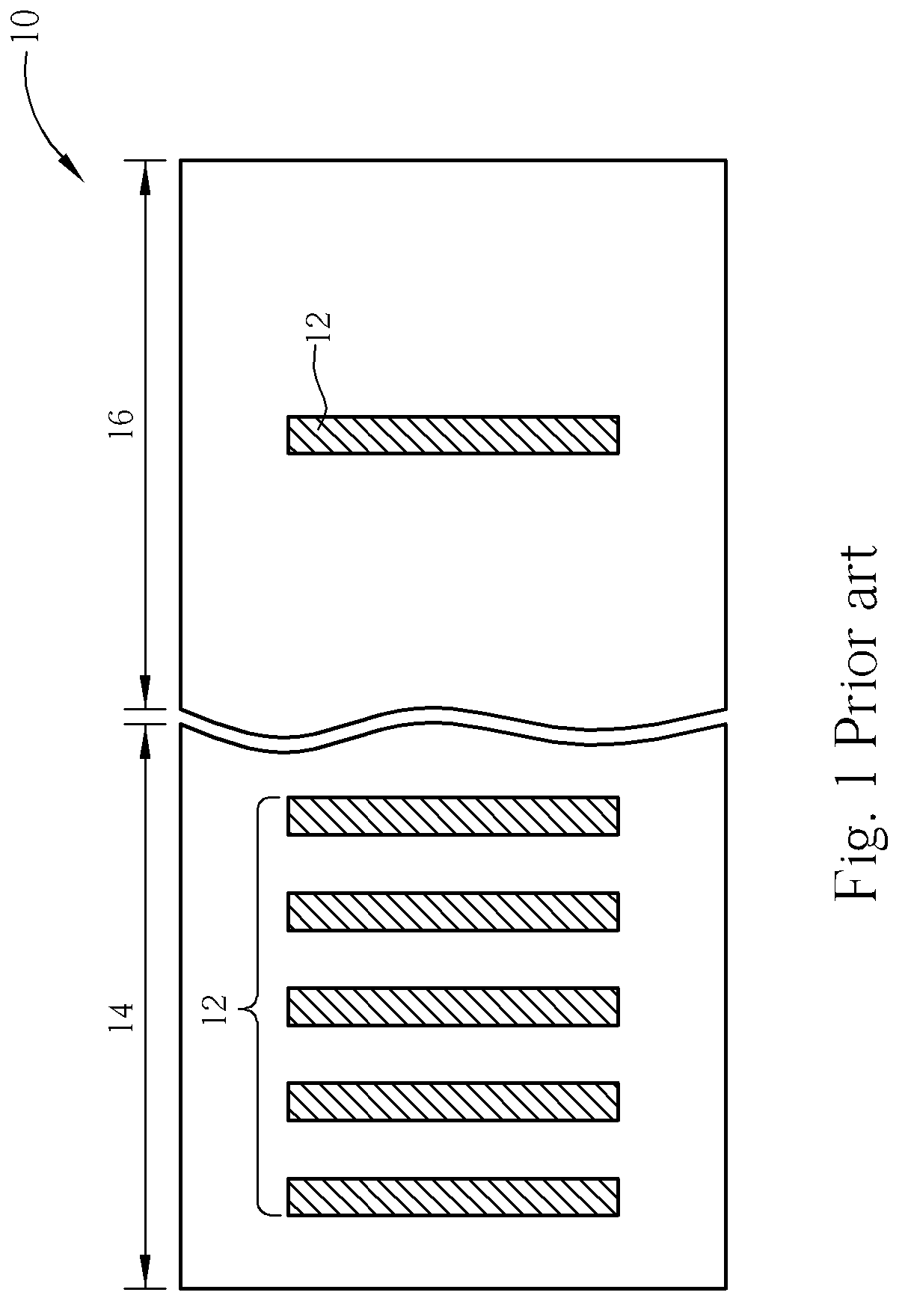

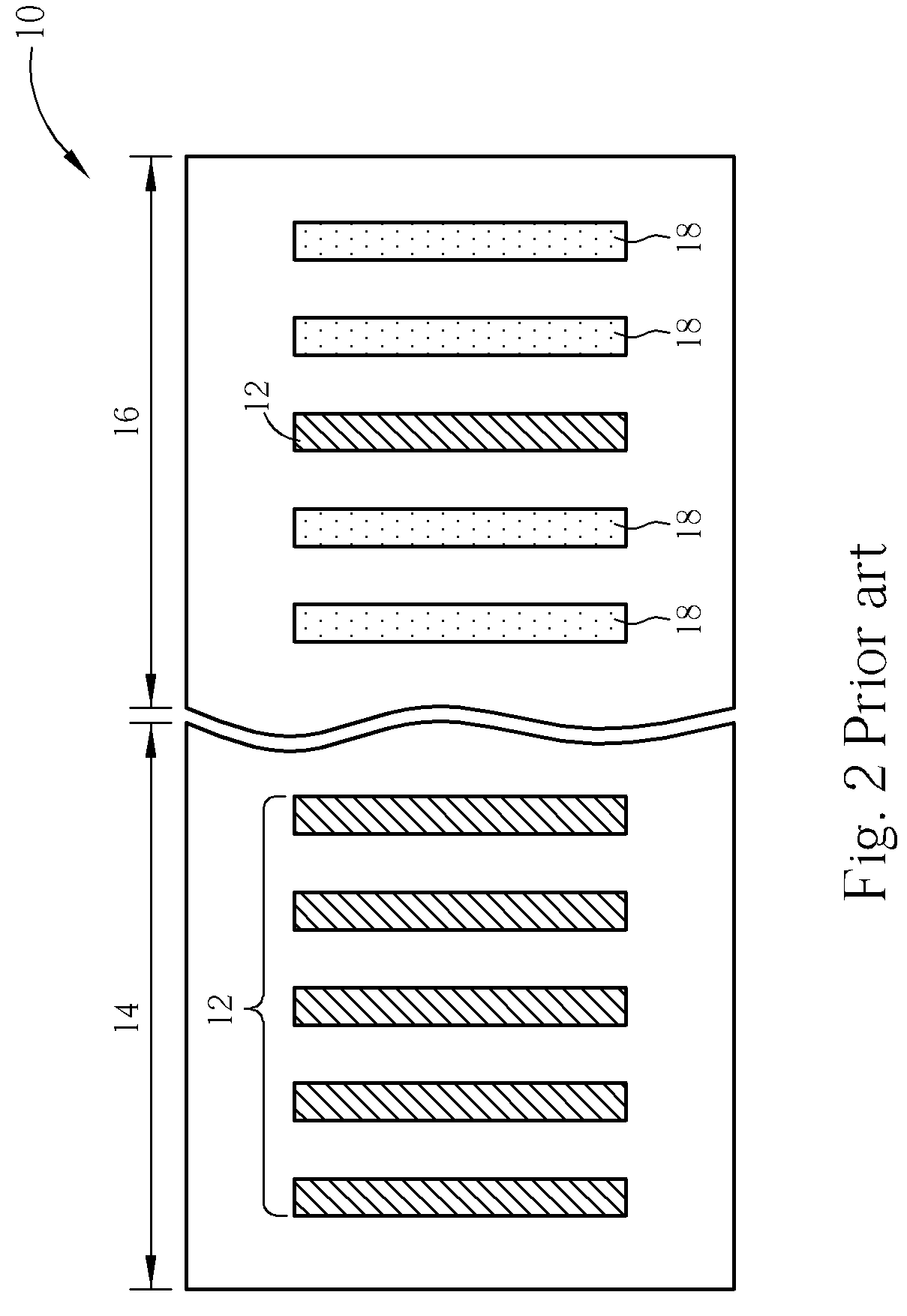

Optical proximity correction method

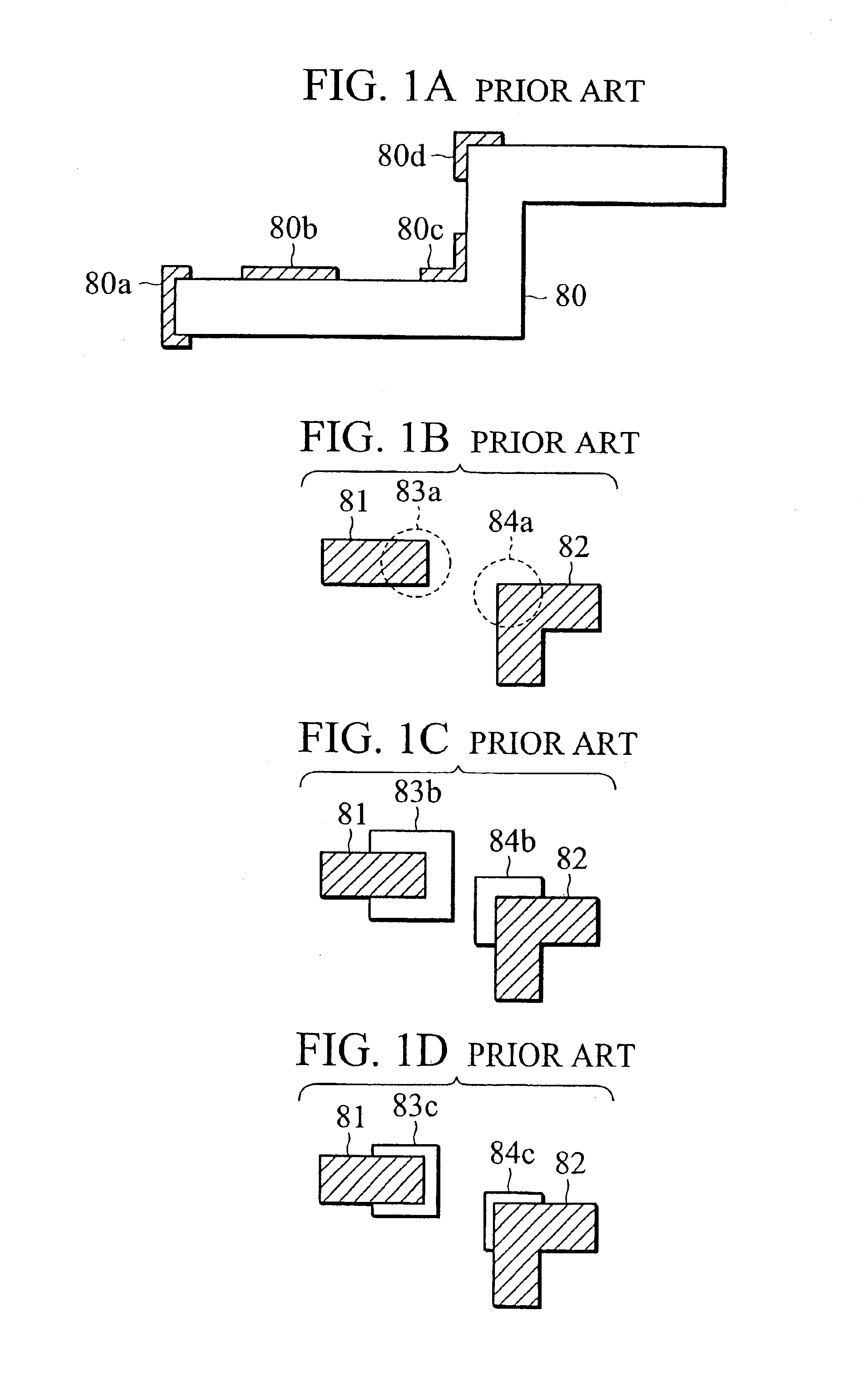

InactiveUS20050009344A1Reduce the differenceEasy to operateSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentGraphicsPhase difference

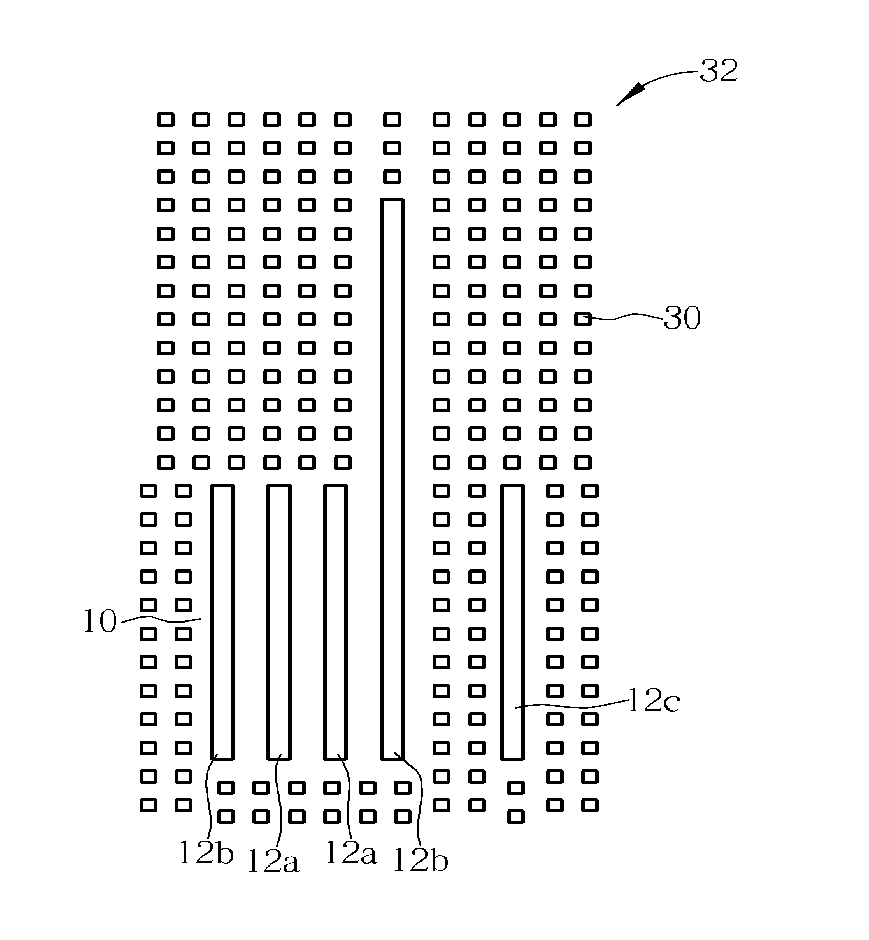

An integrated circuit layout includes dense figures and at least one isolated figure. A plurality of dummy patterns are formed to surround the isolated figure, so as to reduce the difference in pattern density of the integrated circuit layout. A transmitted light of the dummy patterns provides a phase difference of 0 or 180 degrees relative to a transmitted light of the integrated circuit layout. The integrated circuit layout and the plurality of dummy patterns are formed on a photo-mask.

Owner:UNITED MICROELECTRONICS CORP

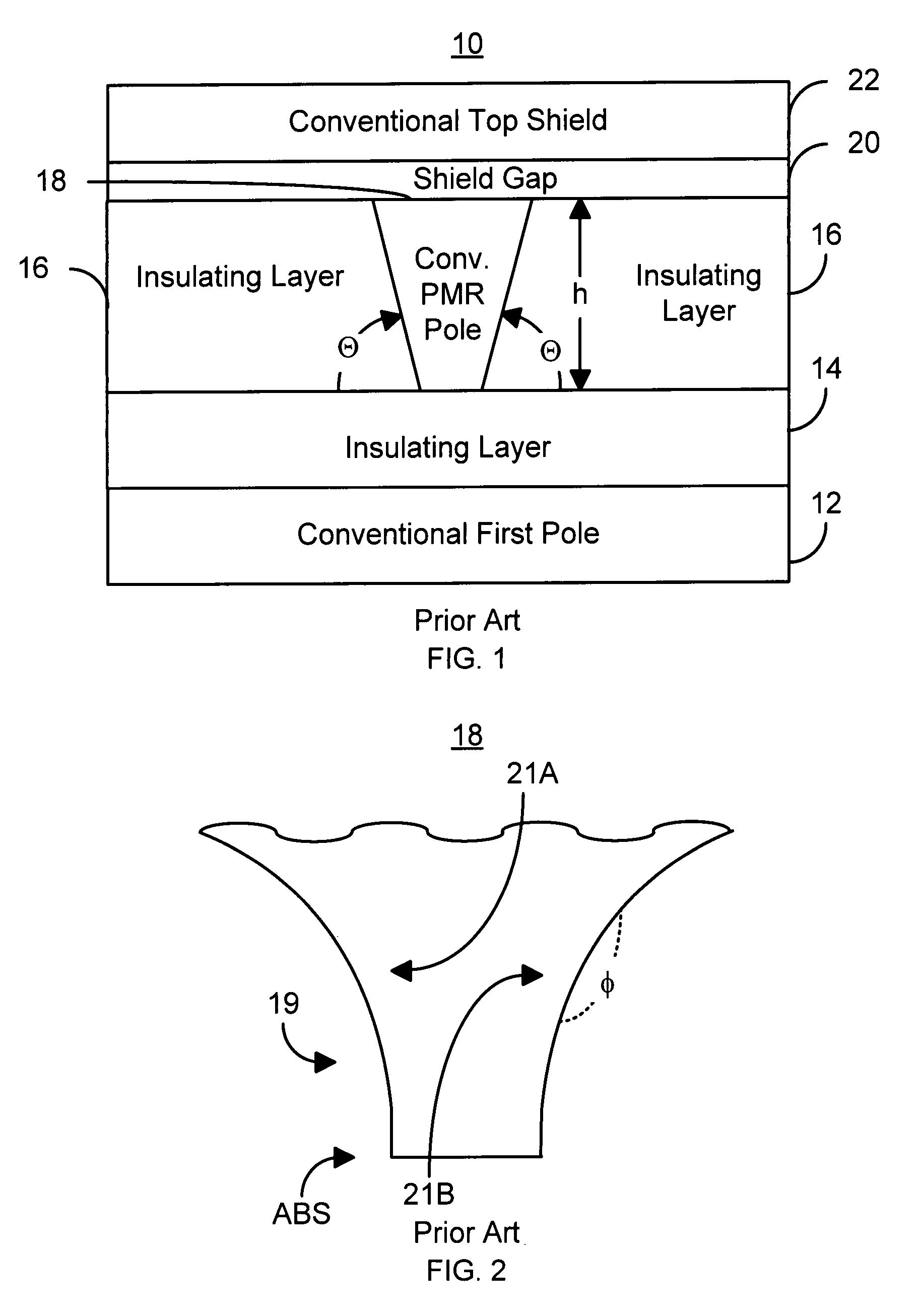

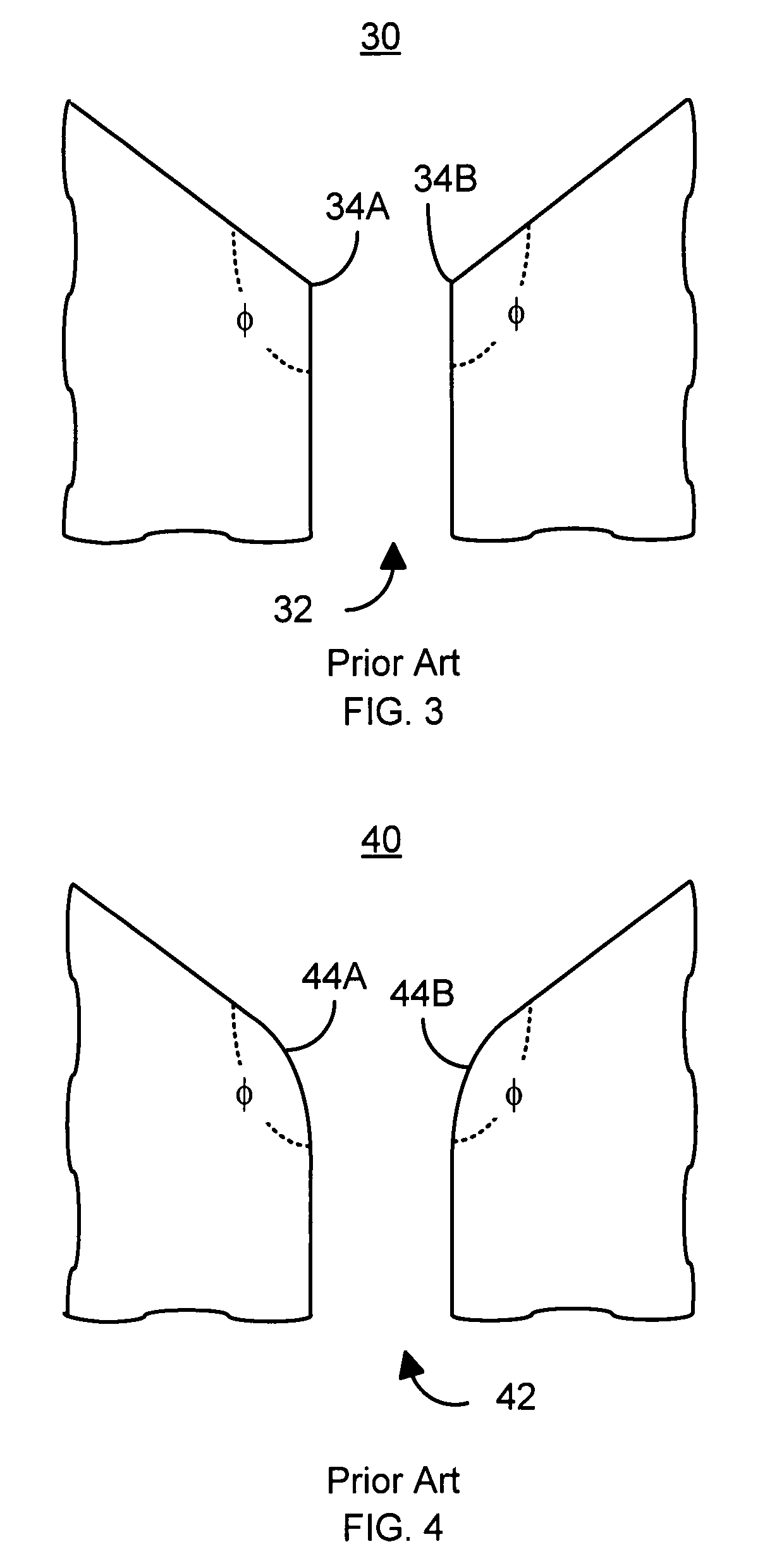

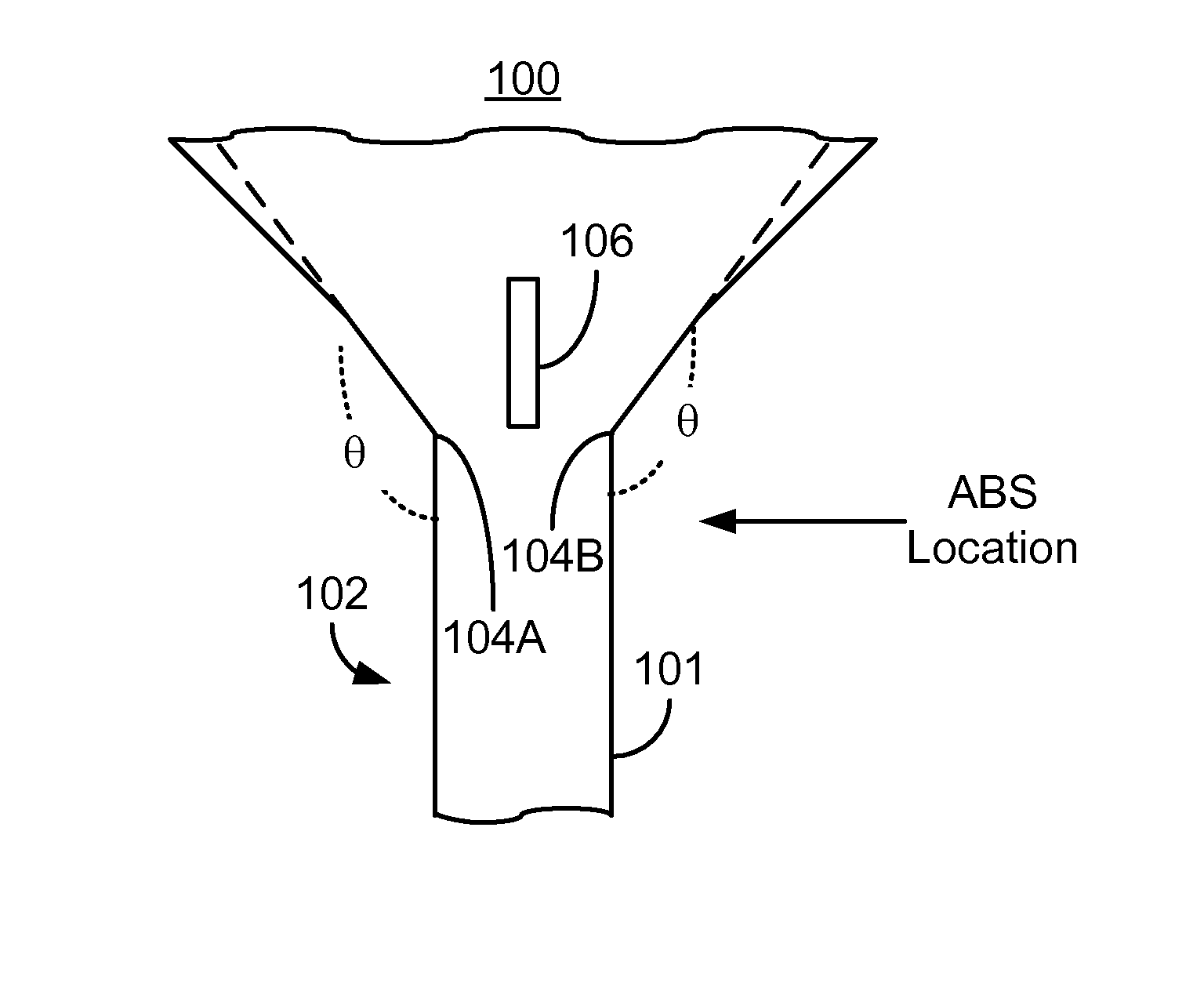

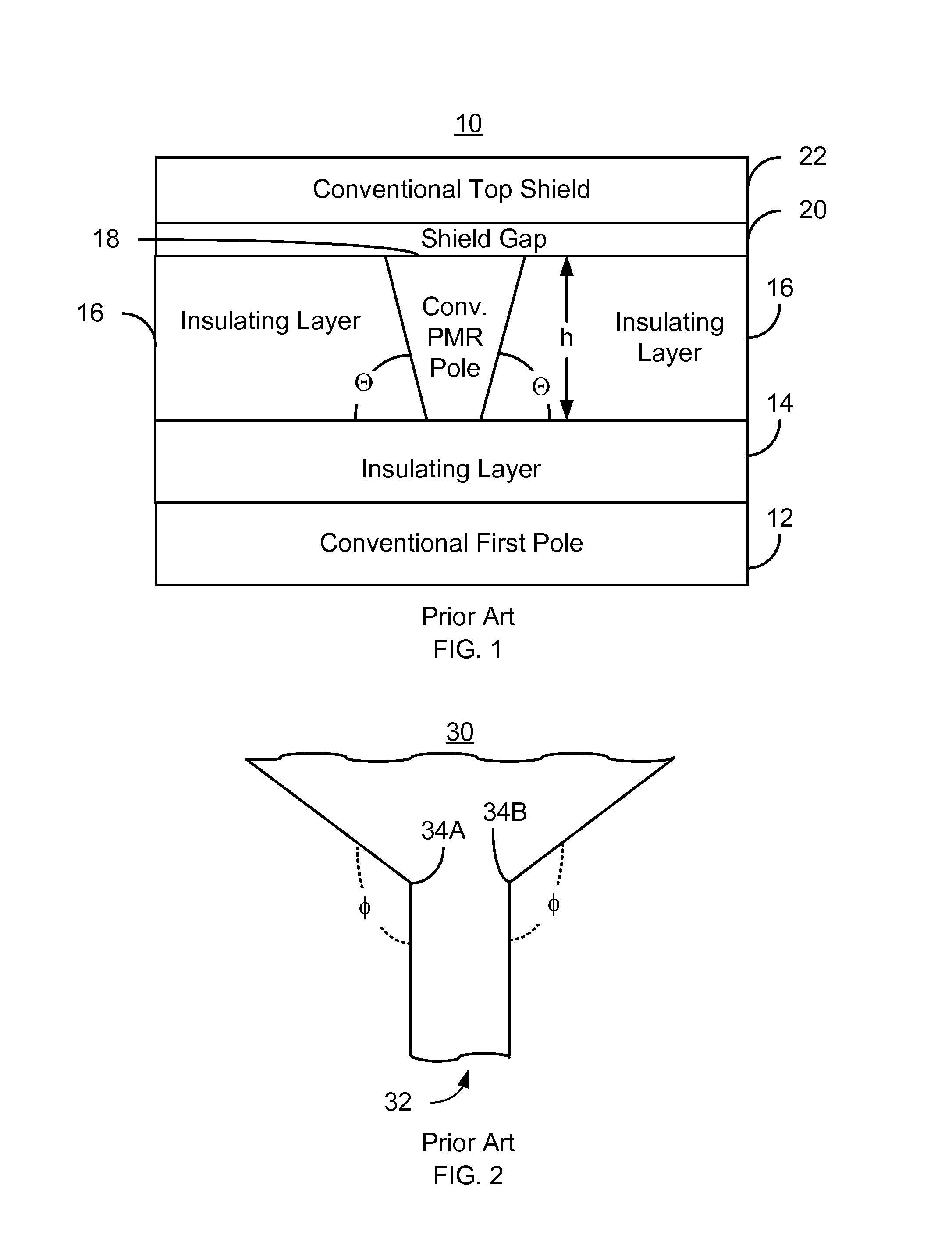

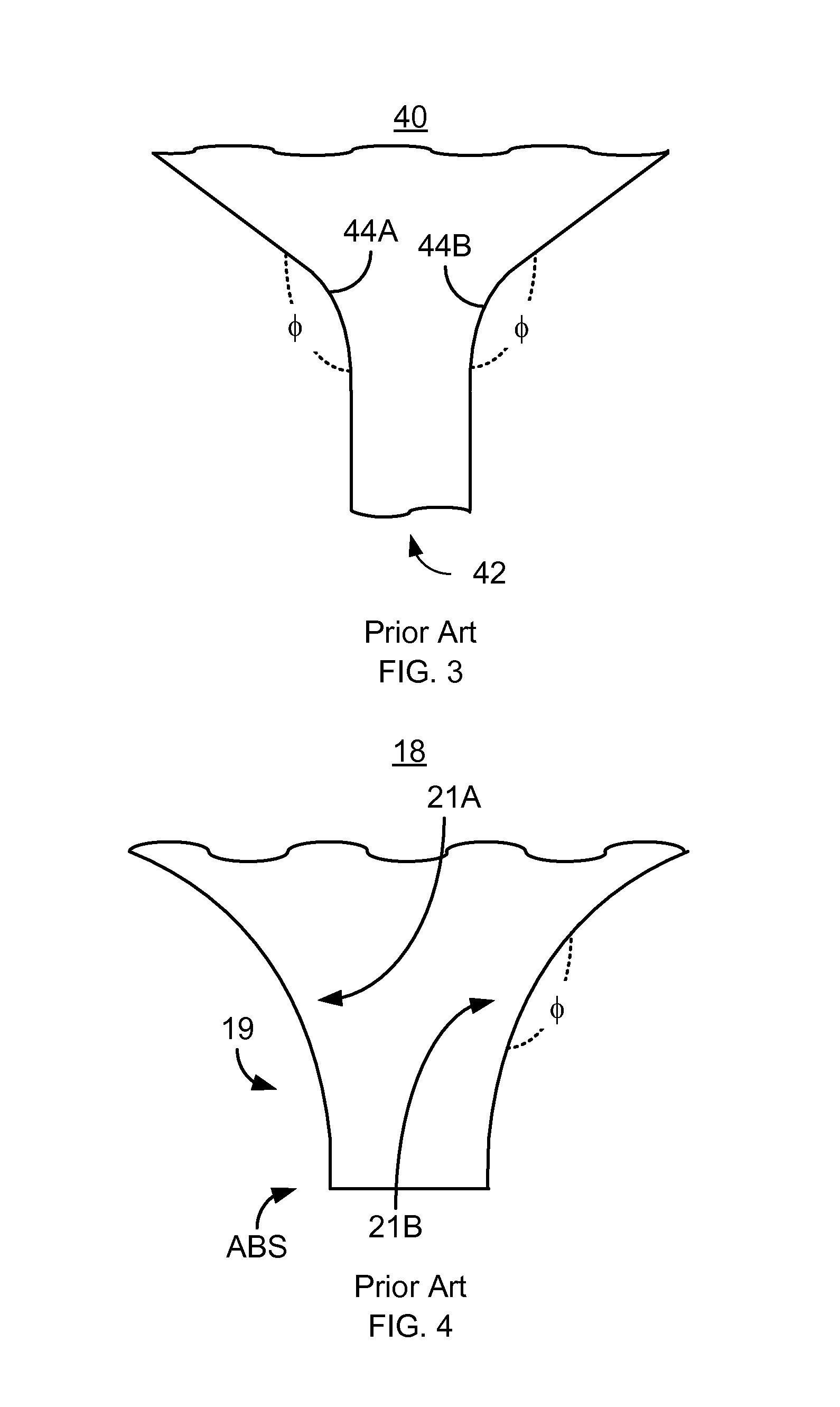

Method and system for providing optical proximity correction for structures such as a PMR nose

InactiveUS7736823B1Reduce proximity effectPhotomechanical apparatusRecord information storageTransducerOptical proximity correction

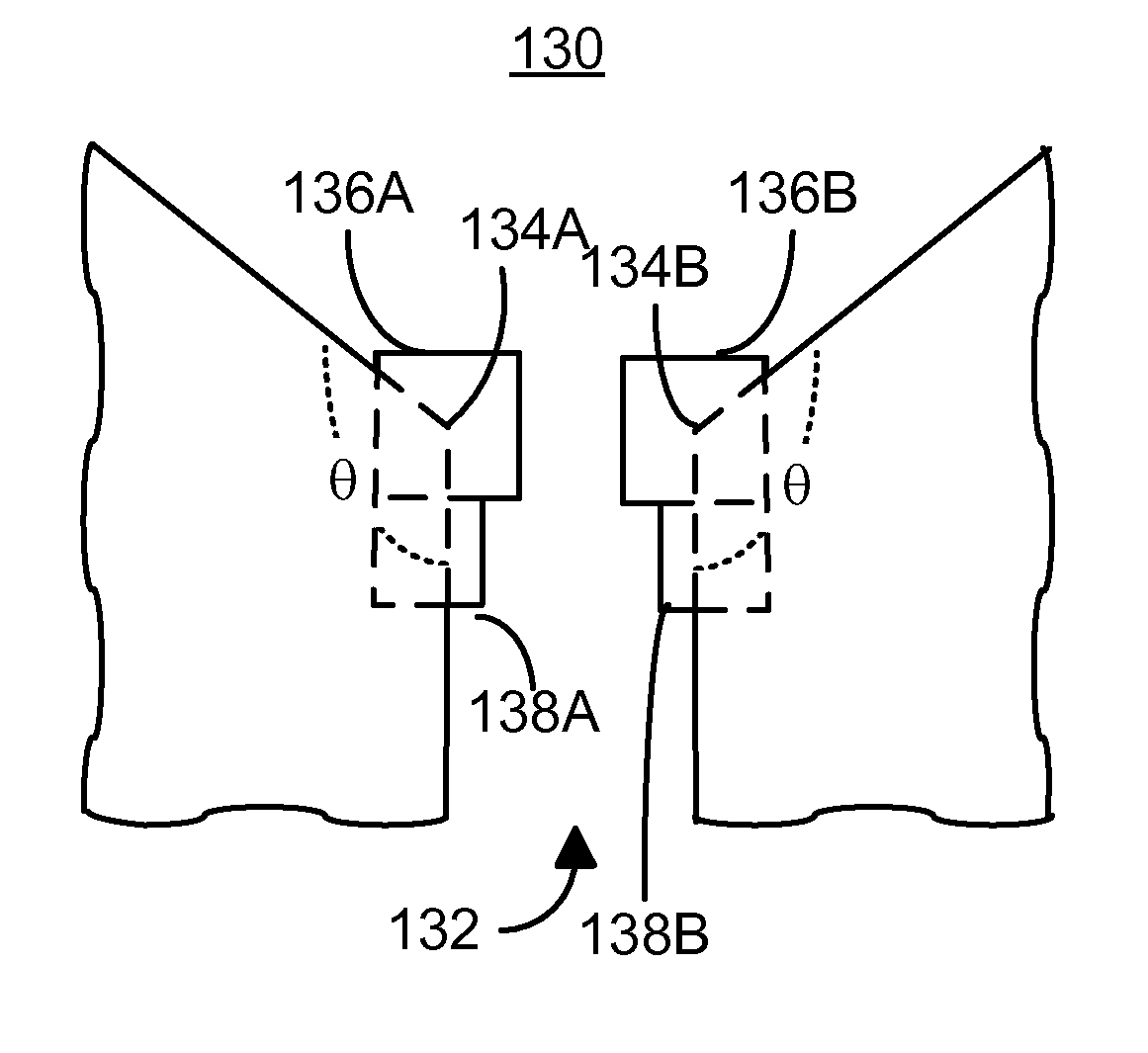

A mask for transferring a pattern for portion of a magnetic recording transducer is disclosed. The masks includes one corner corresponding to an angle of more than ninety degrees and less than one hundred eighty degrees. The mask also includes at least one rectangular serif residing at the corner.

Owner:WESTERN DIGITAL TECH INC +1

Method and system for providing optical proximity correction for structures such as a PMR nose

An optical mask for providing a pattern for portion of an electronic device, such as a magnetic recording transducer, is disclosed. The optical mask includes a device feature and at least one detached correction feature. The device feature includes a corner corresponding to a device corner of the pattern. The device corner has an angle of greater than zero degrees and less than one hundred eighty degrees. The at least one detached correction feature resides in proximity to but is physically separated from the corner. Each of the at least one detached correction feature is sub-resolution.

Owner:WESTERN DIGITAL TECH INC

Method of design and fabrication of integrated circuits using regular arrays and gratings

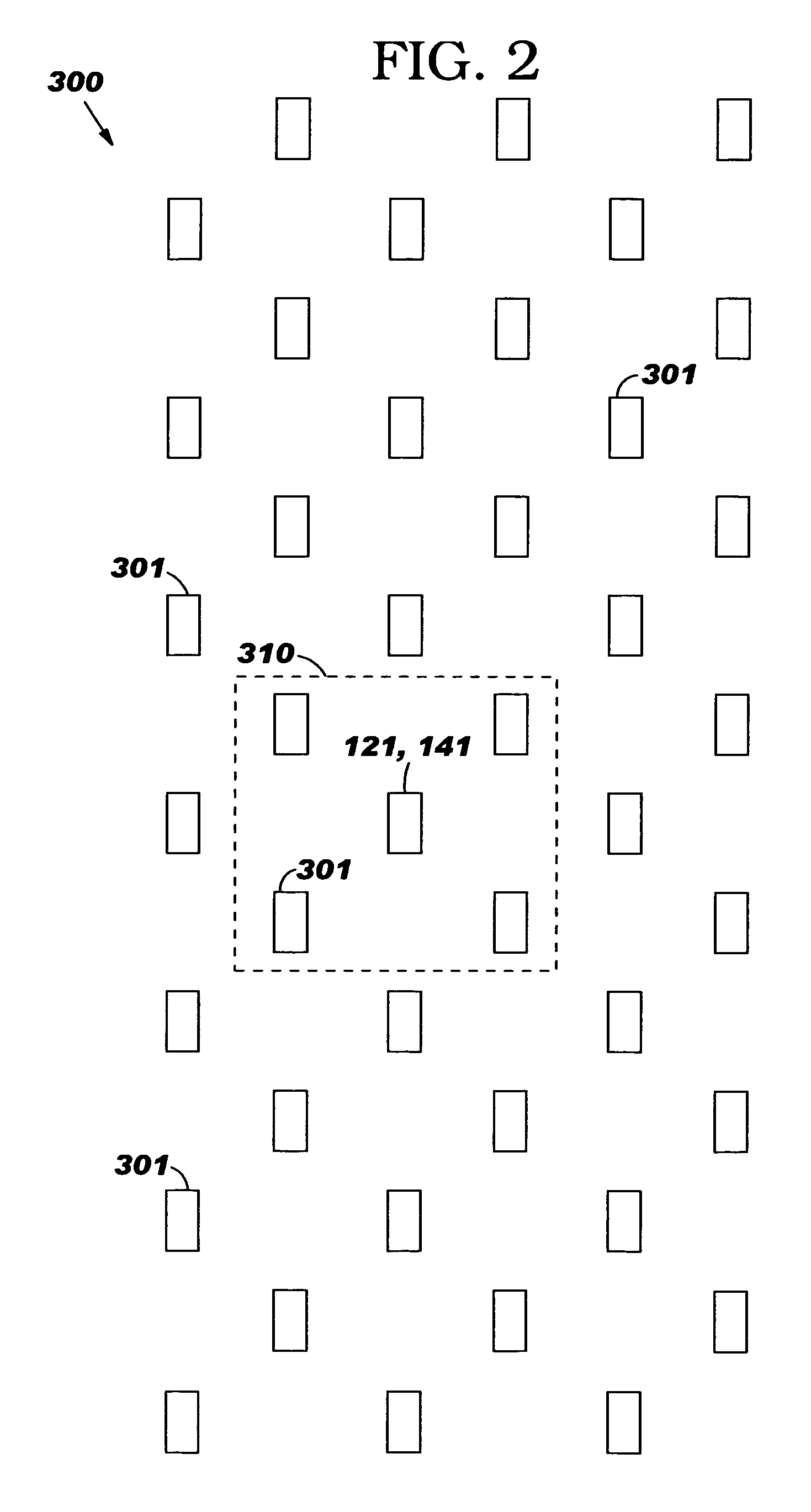

InactiveUS6818389B2Photo-taking processesSemiconductor/solid-state device manufacturingGratingRounding

A circuit fabrication and lithography process utilizes a mask including dense repetitive structures of features that result in a wide array of fine densely populated features on the exposed substrate film. Following this, a trimming procedure is performed to remove any unwanted fine patterned features providing multiple trimmed patterns on the substrate. An optional final step adds additional features as well as the interconnect features thus forming a circuit pattern. In this manner, all fine features may be generated using the exact same density of intensity patterns, and therefore, maximum consistency between features is established without the need for optical proximity correction. The secondary exposures are substantially independent from the initial dense-feature exposure in that the exposure of one set of features and the subsequent exposure of another set of features result in separate independent resist or masking layer reactions, thus minimizing corner rounding, line end shortening and other related spatial frequency effects and unwanted exposure memory effects.

Owner:MASSACHUSETTS INST OF TECH

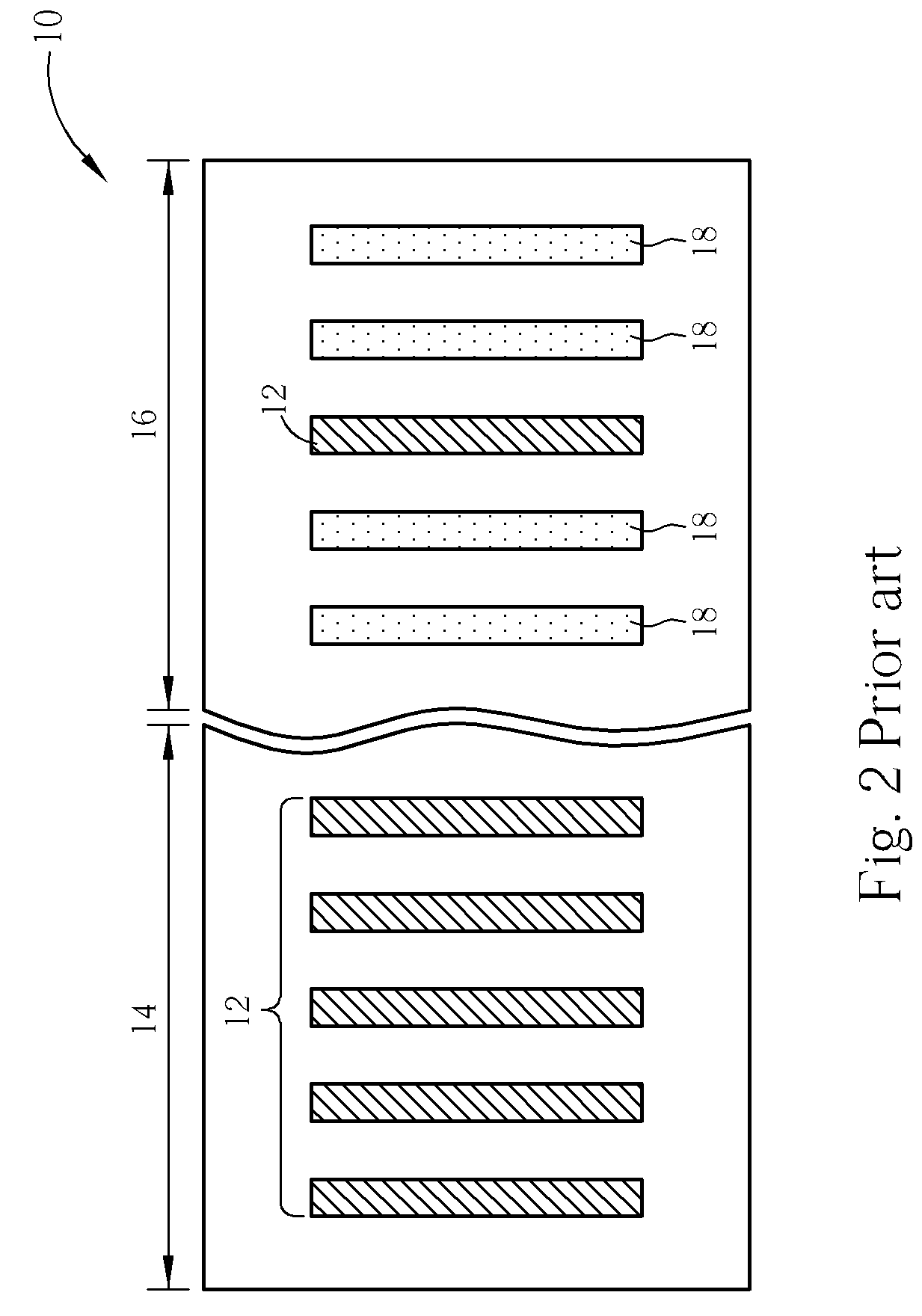

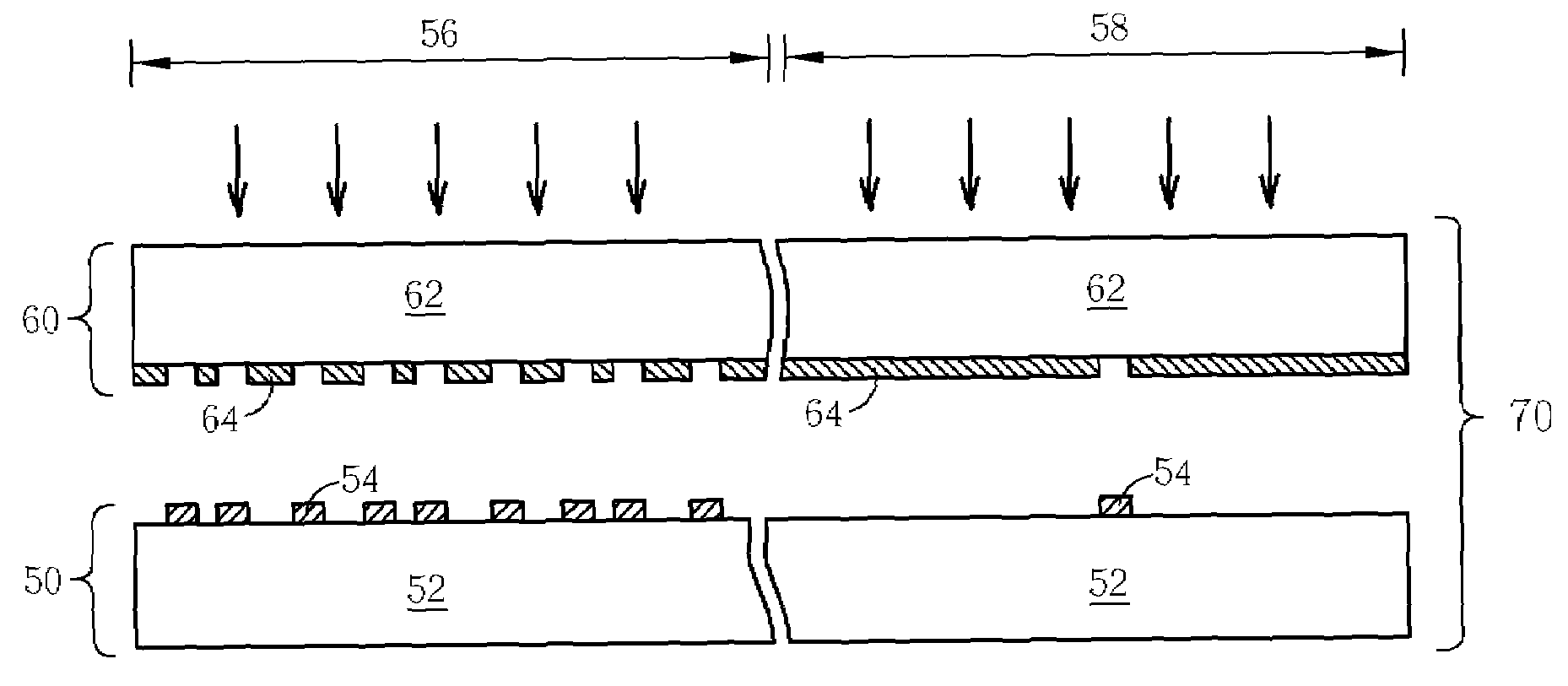

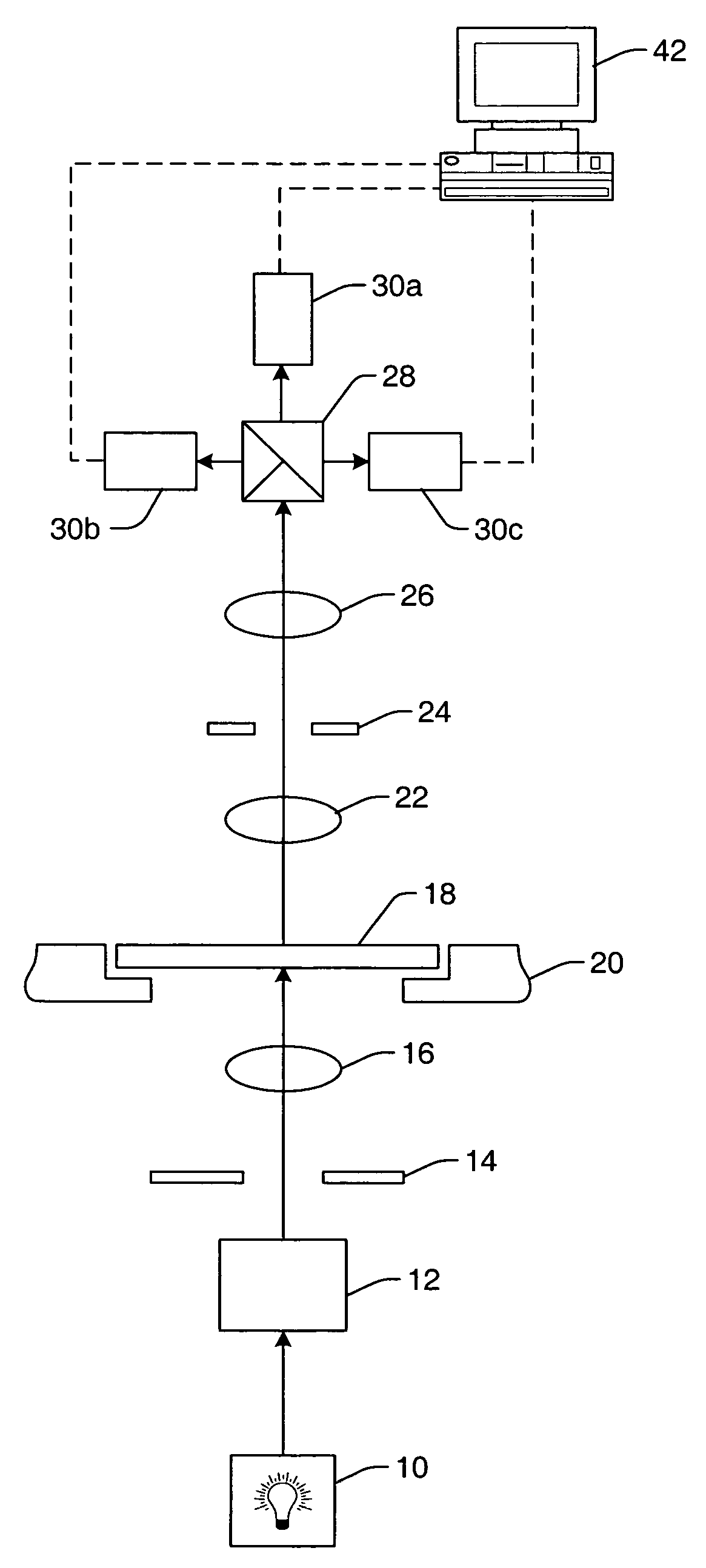

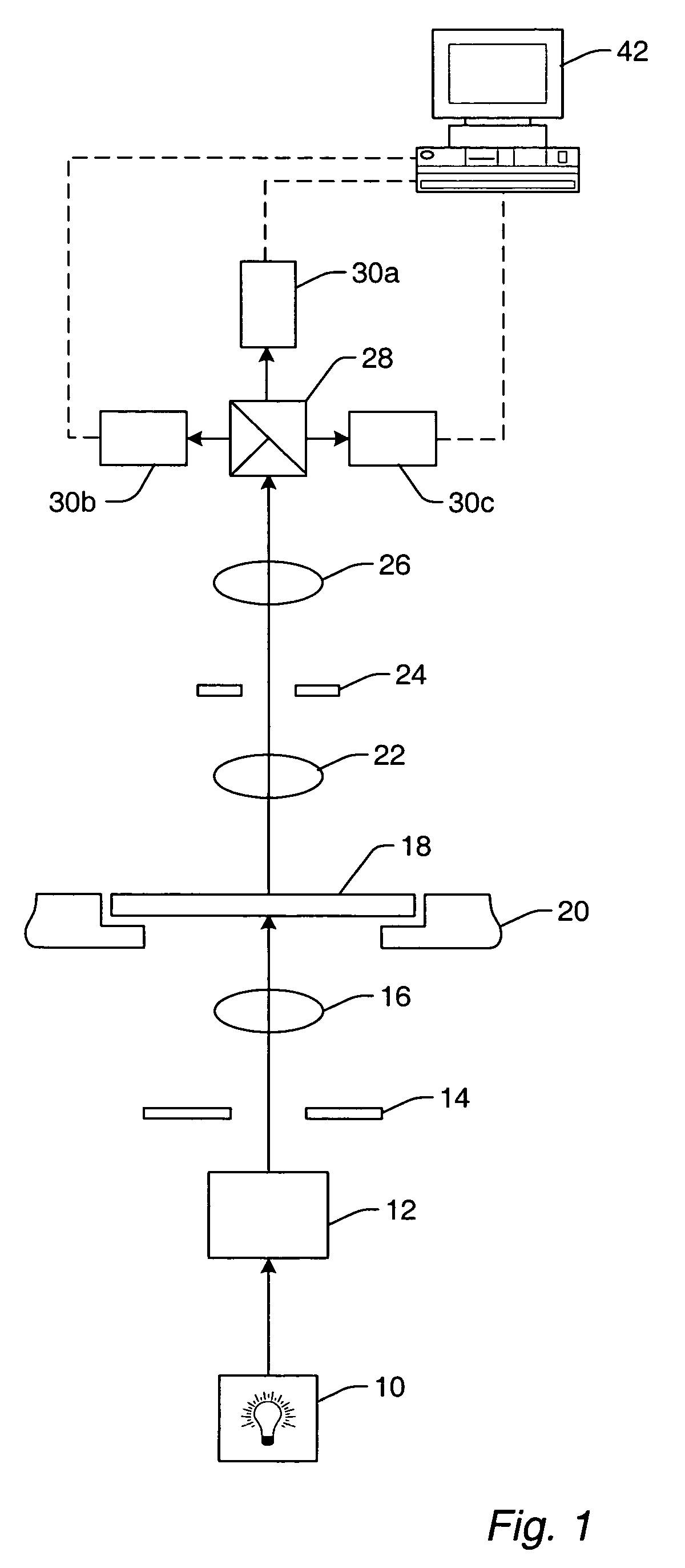

Reticle and optical proximity correction method

ActiveUS20070105023A1Low costIncrease flexibilityOriginals for photomechanical treatmentSpecial data processing applicationsOptical transmittanceReticle

An OPC method includes providing a primary mask having a primary pattern, forming an assist mask having a correction pattern substantially complementary to the primary pattern, and forming a reticle by overlapping the primary mask and the assist mask. The light transmittance of the correction pattern is adjustable so as to equalize the light intensity distribution of the primary mask.

Owner:MARLIN SEMICON LTD

Reticle and optical proximity correction method

ActiveUS7527900B2Increase flexibilityLow costOriginals for photomechanical treatmentSpecial data processing applicationsOptical transmittanceReticle

An OPC method includes providing a primary mask having a primary pattern, forming an assist mask having a correction pattern substantially complementary to the primary pattern, and forming a reticle by overlapping the primary mask and the assist mask. The light transmittance of the correction pattern is adjustable so as to equalize the light intensity distribution of the primary mask.

Owner:MARLIN SEMICON LTD

Methods and systems for inspecting reticles using aerial imaging and die-to-database detection

ActiveUS7123356B1Material analysis by optical meansCharacter and pattern recognitionReference imageAerial imaging

Methods and systems for inspecting a reticle are provided. In an embodiment, a method may include forming an aerial image of the reticle using a set of exposure conditions. The reticle may include optical proximity correction (OPC) features. The method may also include detecting defects on the reticle by comparing the aerial image to a reference image stored in a database. The reference image may be substantially optically equivalent to an image of the reticle that would be printed on a specimen by an exposure system under the set of exposure conditions. The reference image may not include images of the OPC features. Therefore, a substantial portion of the defects include defects that would be printed onto the specimen by the exposure system using the reticle under the set of exposure conditions. The method may also include indicating the defects that are detected in critical regions of the reticle.

Owner:KLA TENCOR CORP

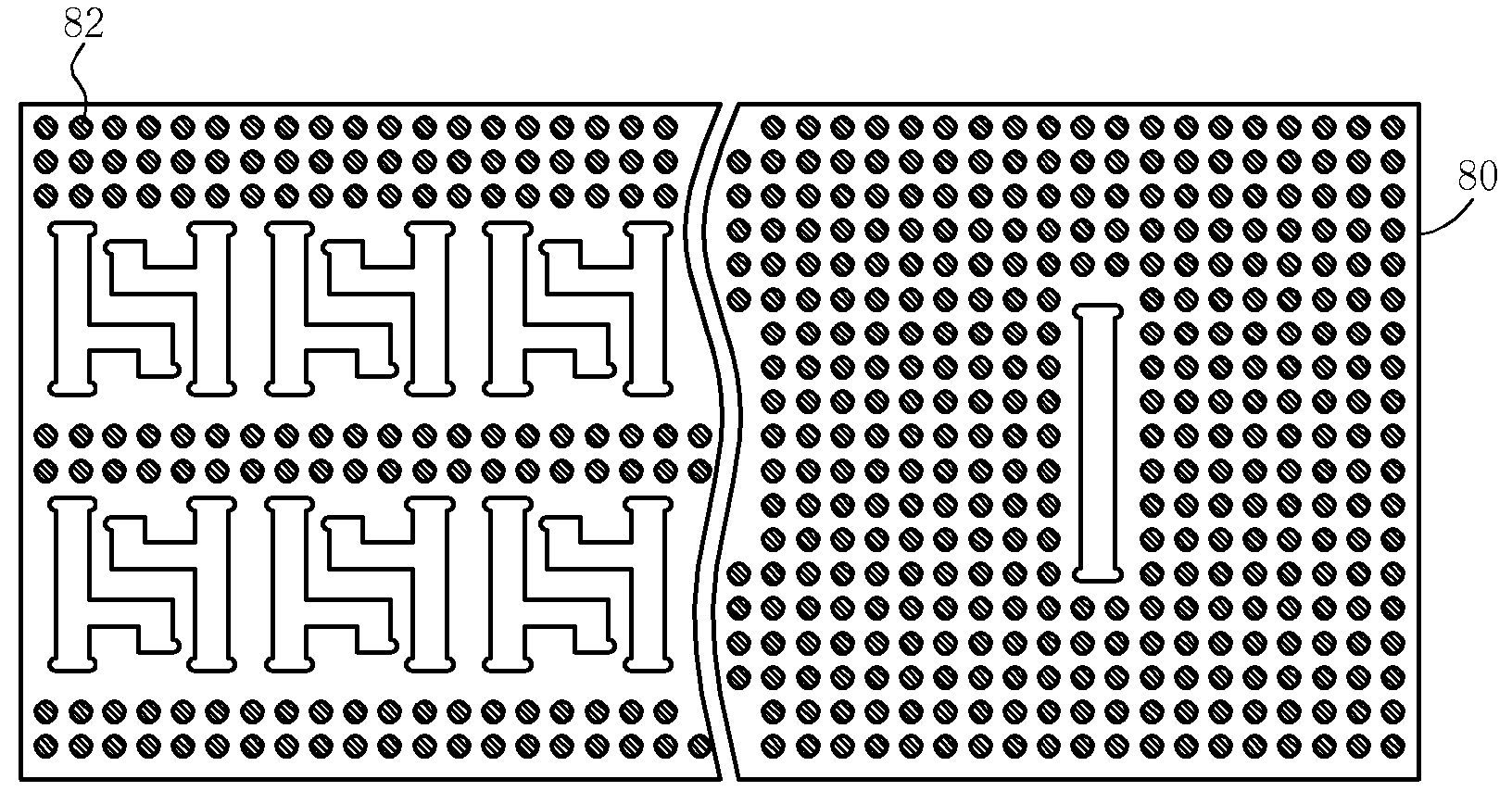

Circuit layout methodology

InactiveUS20060195809A1Simplifies design/layout ruleReduce data volumeCAD circuit designSpecial data processing applicationsManufacturing technologyData preparation

A circuit layout methology is provided for eliminating the extra processing time and file-space requirements associated with the optical proximity correction (OPC) of a VLSI design. The methodology starts with the design rules for a given manufacturing technology and establishes a new set of layer-specific grid values. A layout obeying these new grid requirements leads to a significant reduction in data preparation time, cost, and file size. A layout-migration tool can be used to modify an existing layout in order to enforce the new grid requirements.

Owner:IBM CORP

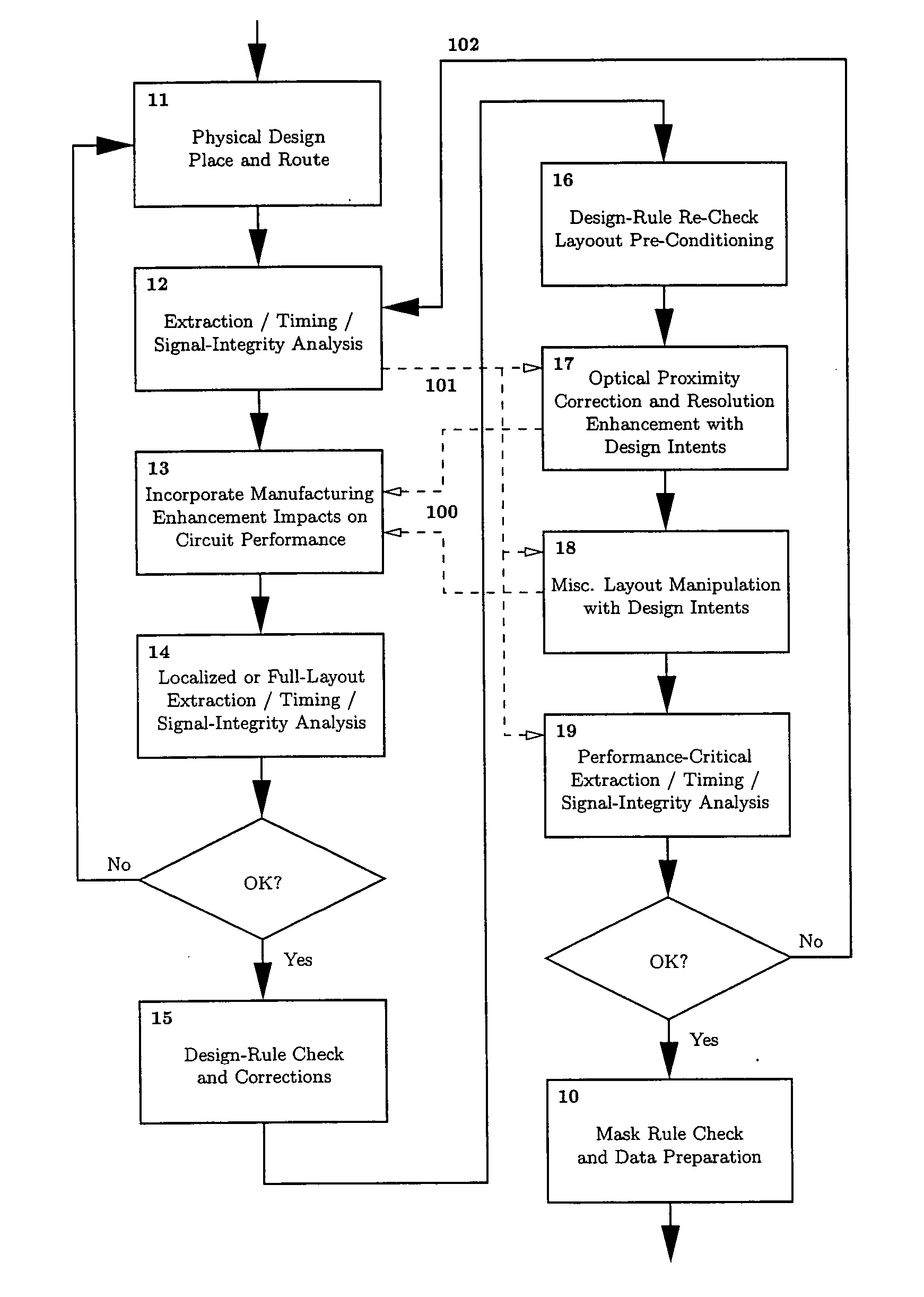

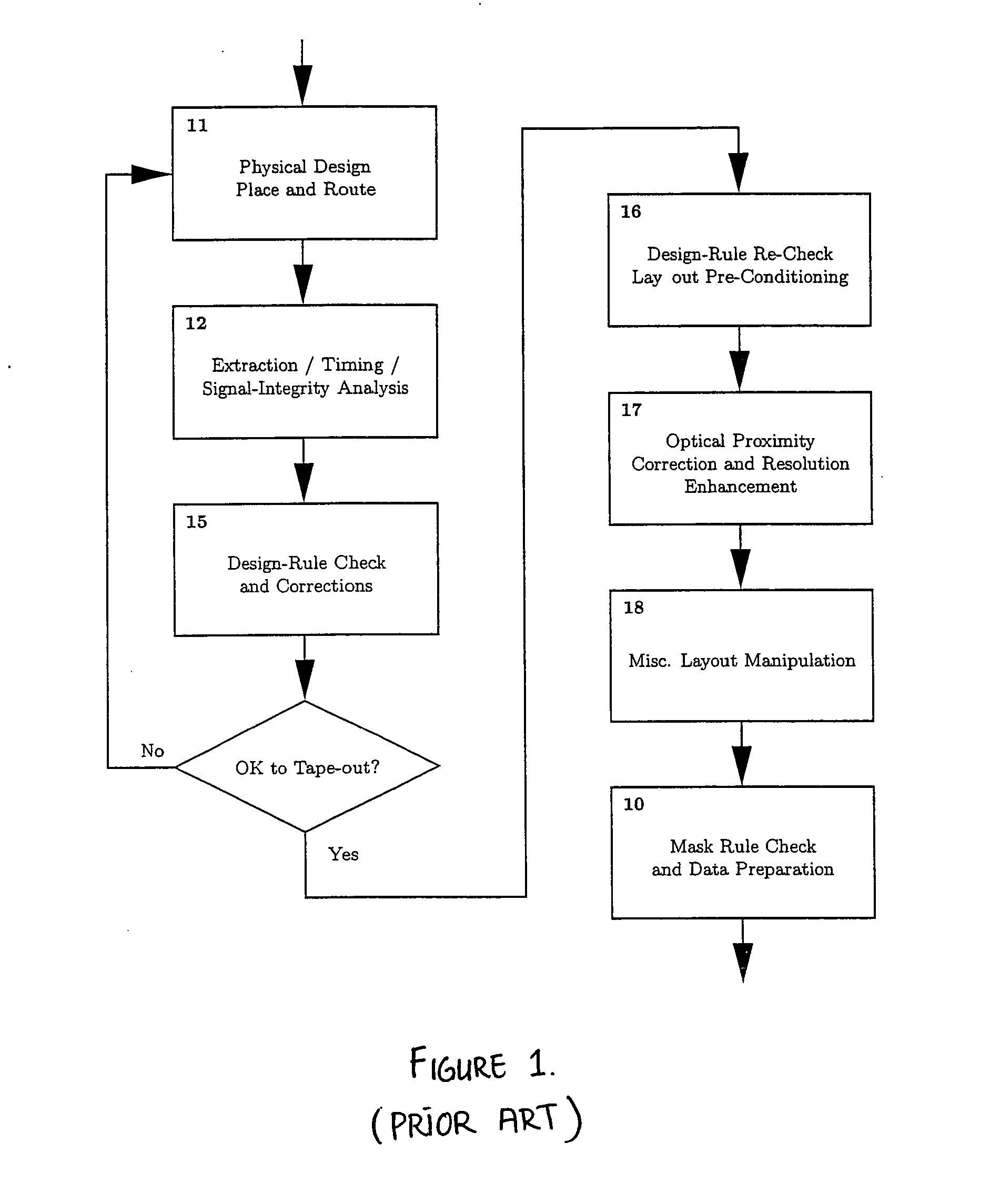

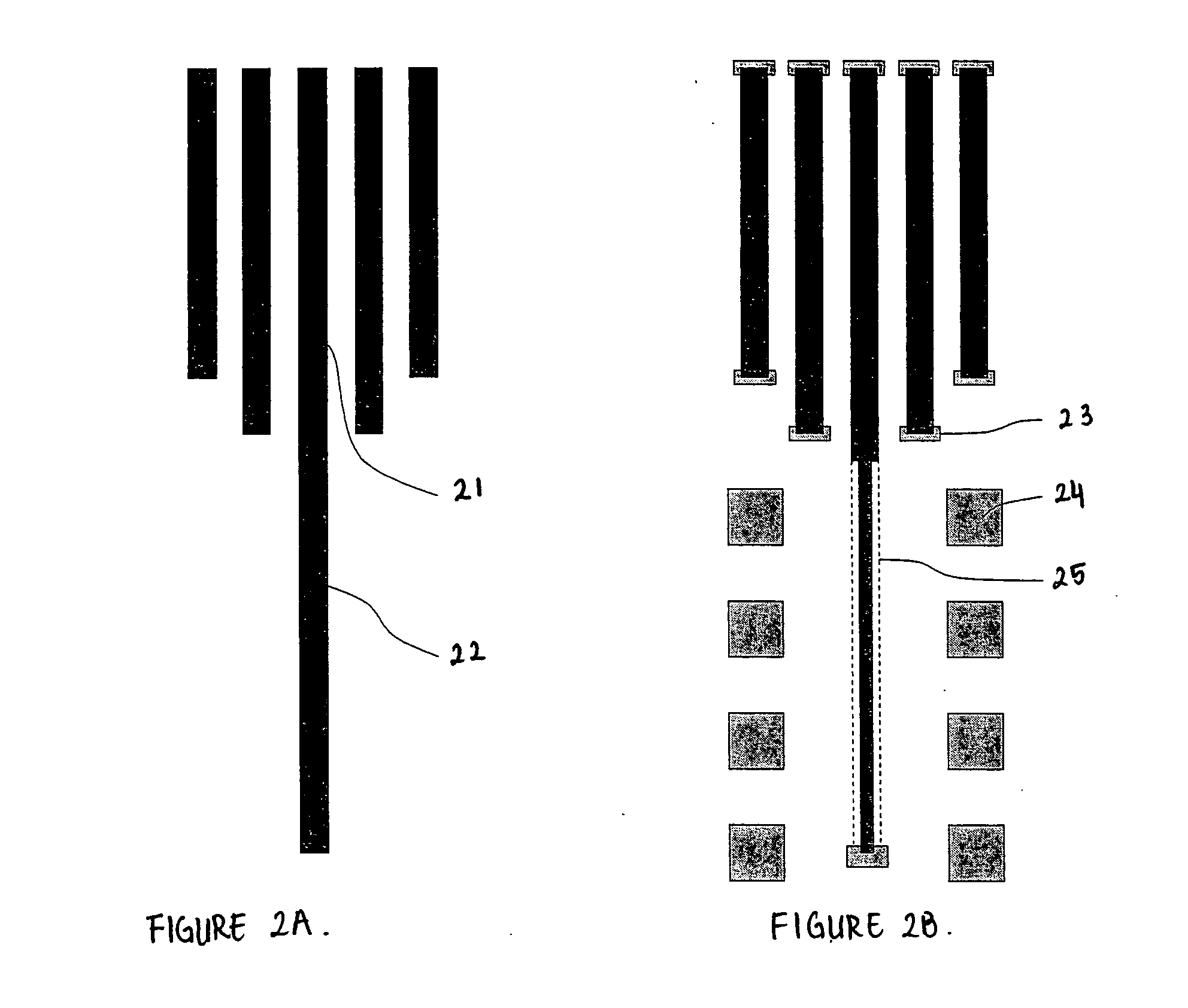

Method and platform for integrated physical verifications and manufacturing enhancements

InactiveUS20050044514A1High storageHigh memoryDigital computer detailsComputer aided designPhysical verificationEngineering

An automated design for manufacturability platform which provides integrated physical verification and manufacturing enhancement operations. The platform uses an efficient data structure capable of handling and manipulating both layout circuit and geometry characteristics, which permits a wide range of operations such as timing analysis, design-rule checking and optical proximity corrections on a single platform. This feature eliminates the need to translate layout representations between various tools without the requirement of using a common database. Moreover, the platform's common user interface enables encapsulated information exchange between the design and the manufacturing teams, permiting early consideration of manufacturing distortion or enhancement impact on circuit performance.

Owner:RPX CORP

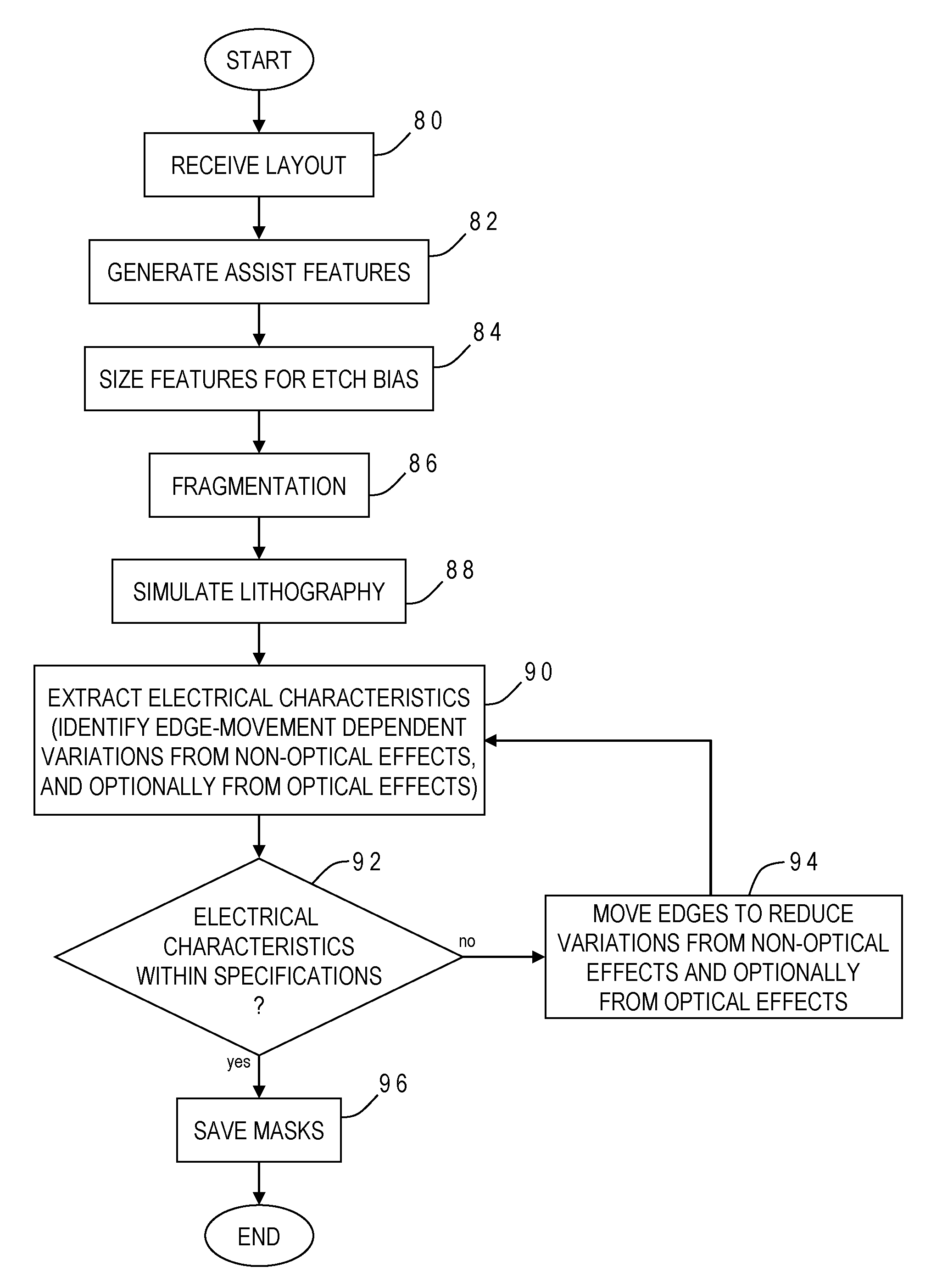

Electrically-driven optical proximity correction to compensate for non-optical effects

ActiveUS8103983B2Improve performancePhotomechanical apparatusOriginals for photomechanical treatmentCapacitanceEngineering

A contour of a mask design for an integrated circuit is modified to compensate for systematic variations arising from non-optical effects such as stress, well proximity, rapid thermal anneal, or spacer thickness. Electrical characteristics of a simulated integrated circuit chip fabricated using the mask design are extracted and compared to design specifications, and one or more edges of the contour are adjusted to reduce the systematic variation until the electrical characteristic is within specification. The particular electrical characteristic preferably depends on which layer is to be fabricated from the mask: on-current for a polysilicon; resistance for contact; resistance and capacitance for metal; current for active; and resistance for vias. For systematic threshold voltage variation, the contour is adjusted to match a gate length which corresponds to an on-current value according to pre-calculated curves for contour current and gate length at a nominal threshold voltage of the chip.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

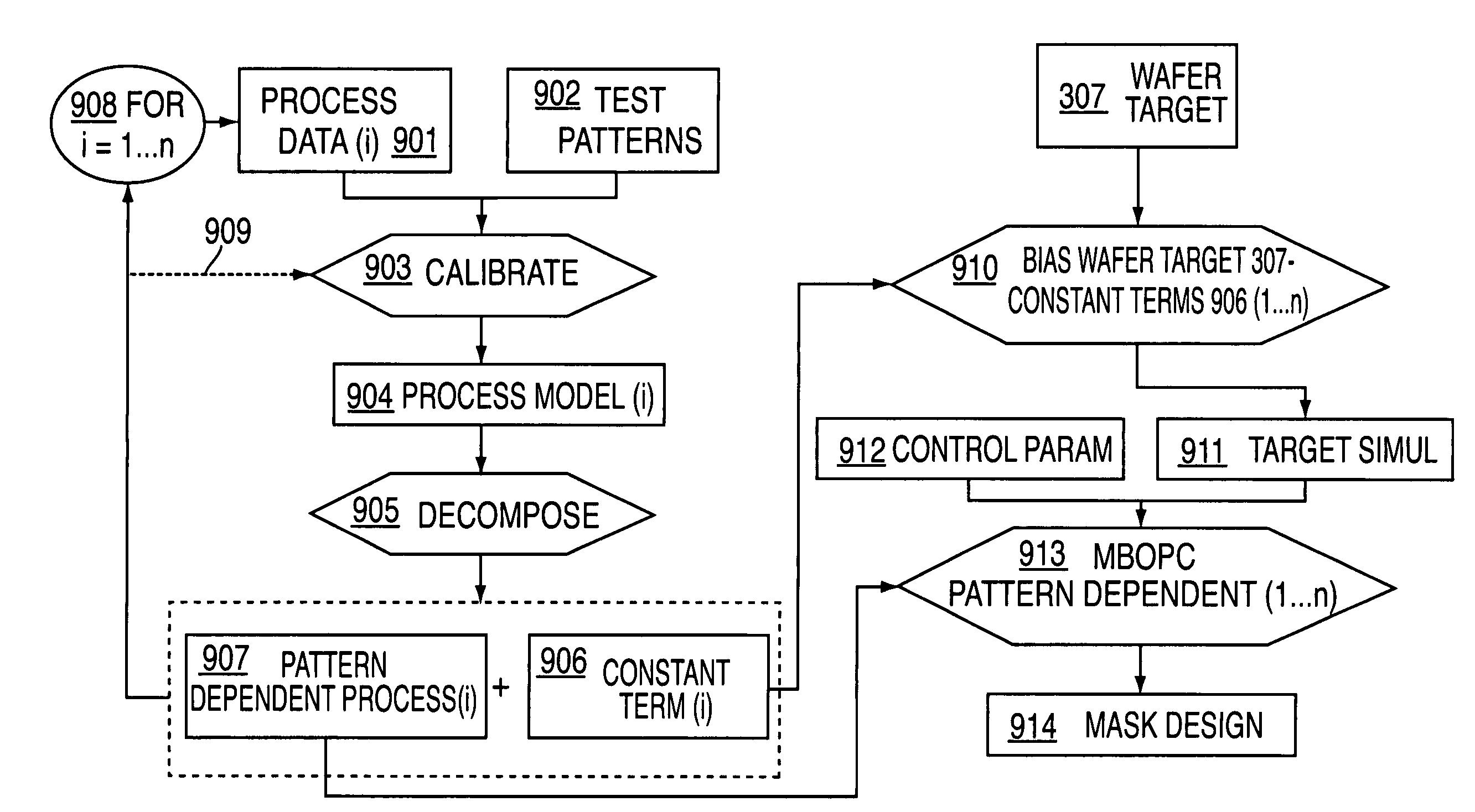

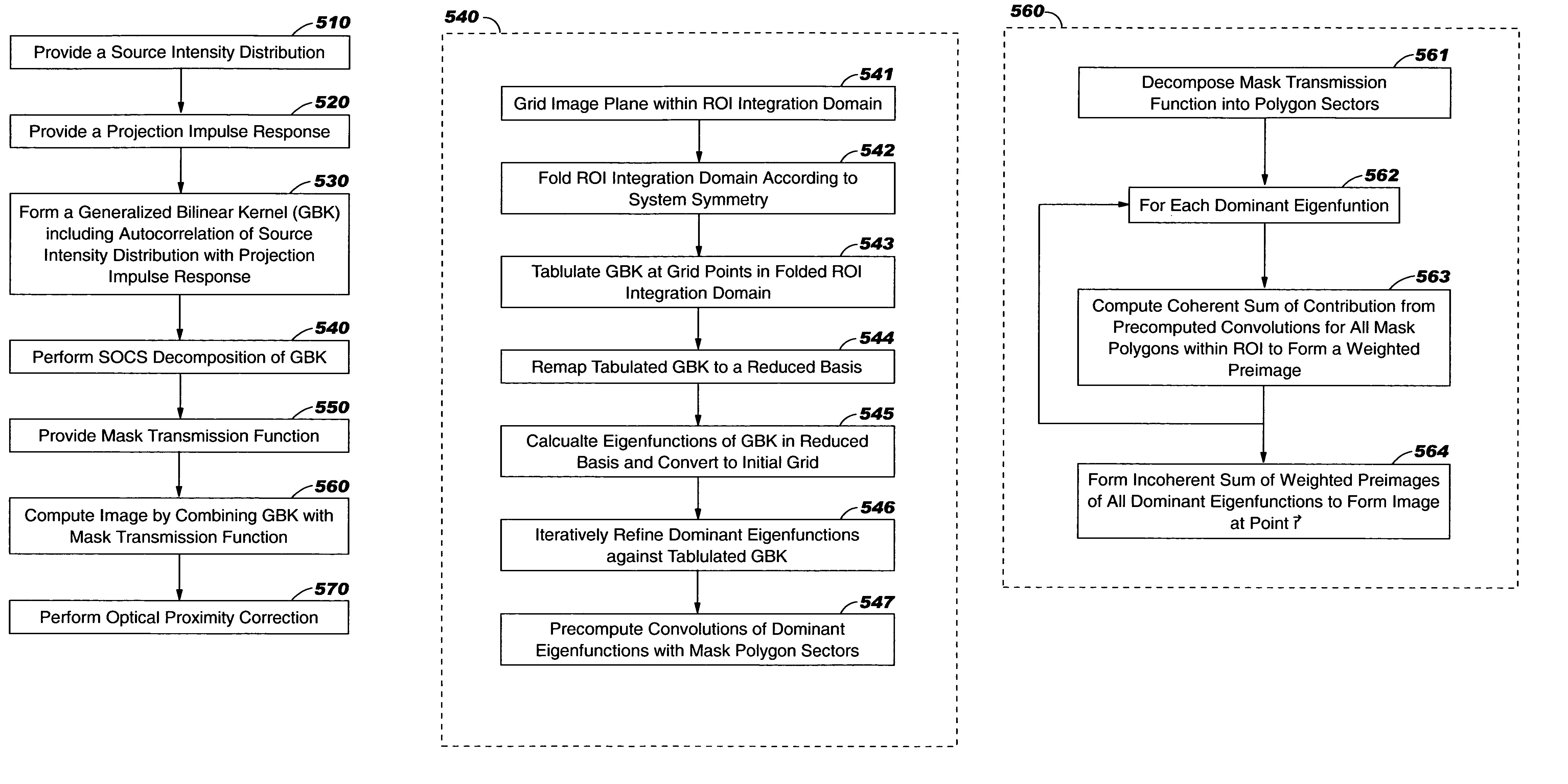

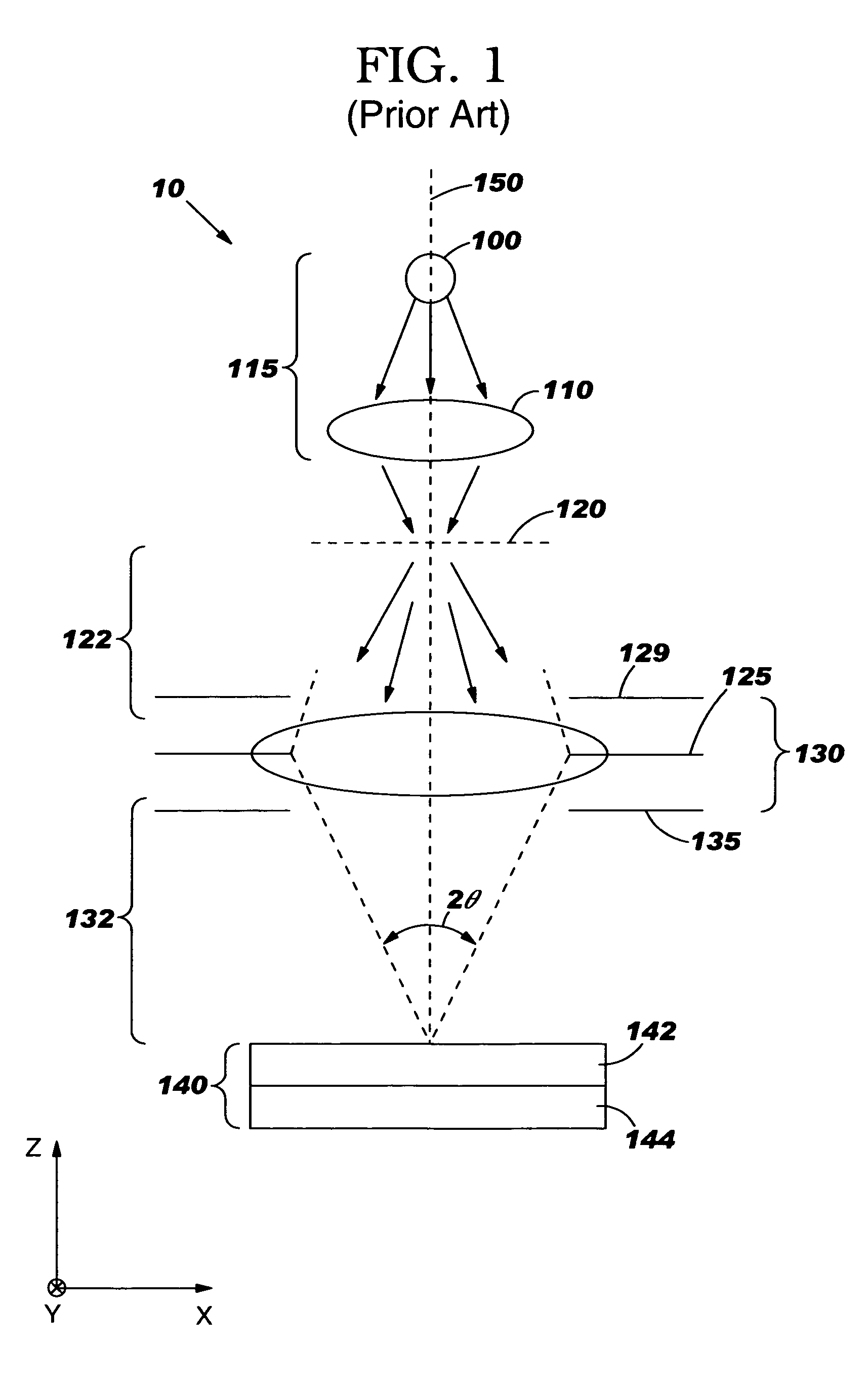

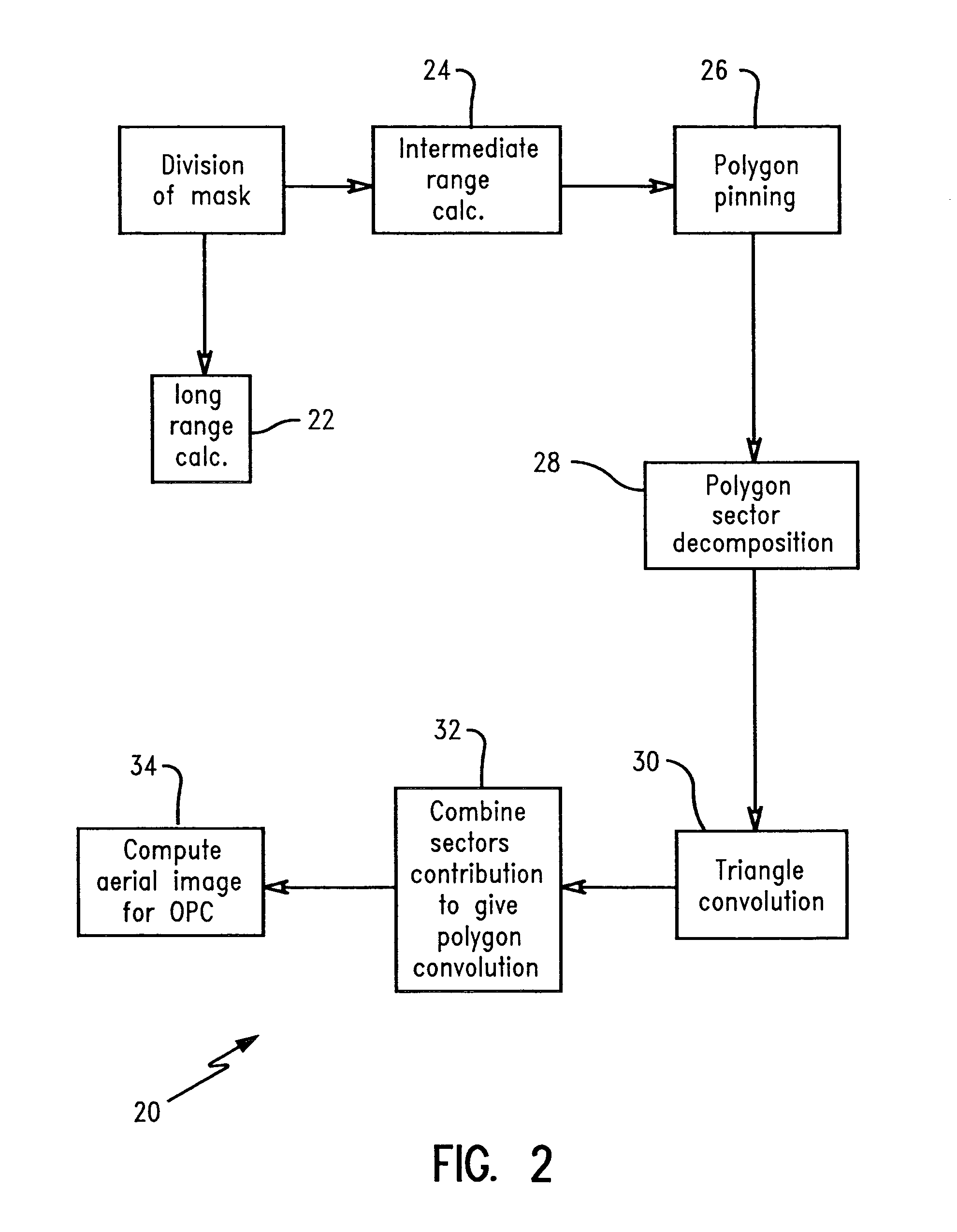

Fast model-based optical proximity correction

InactiveUS7079223B2Method is fastPhotomechanical exposure apparatusMicrolithography exposure apparatusResistDecomposition

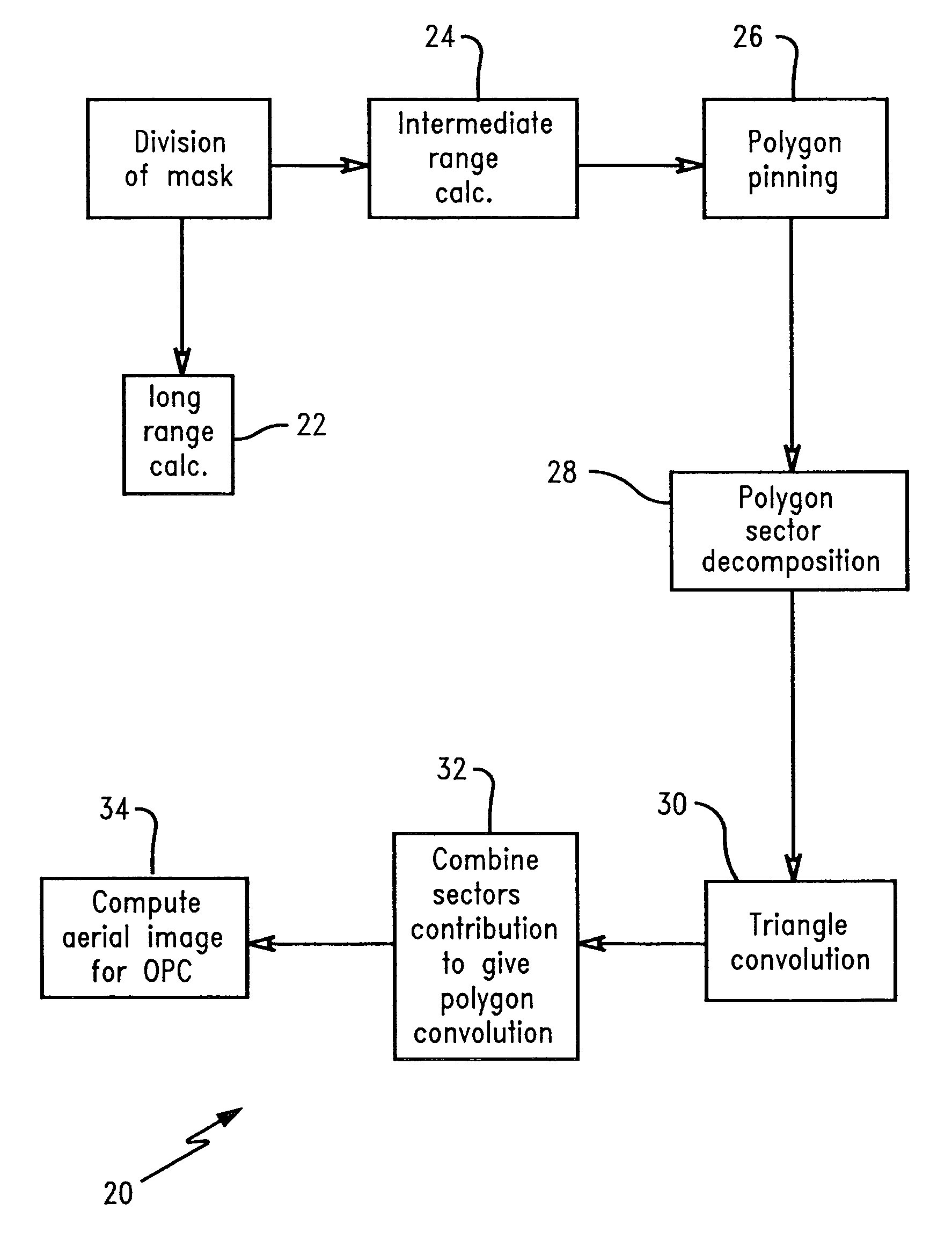

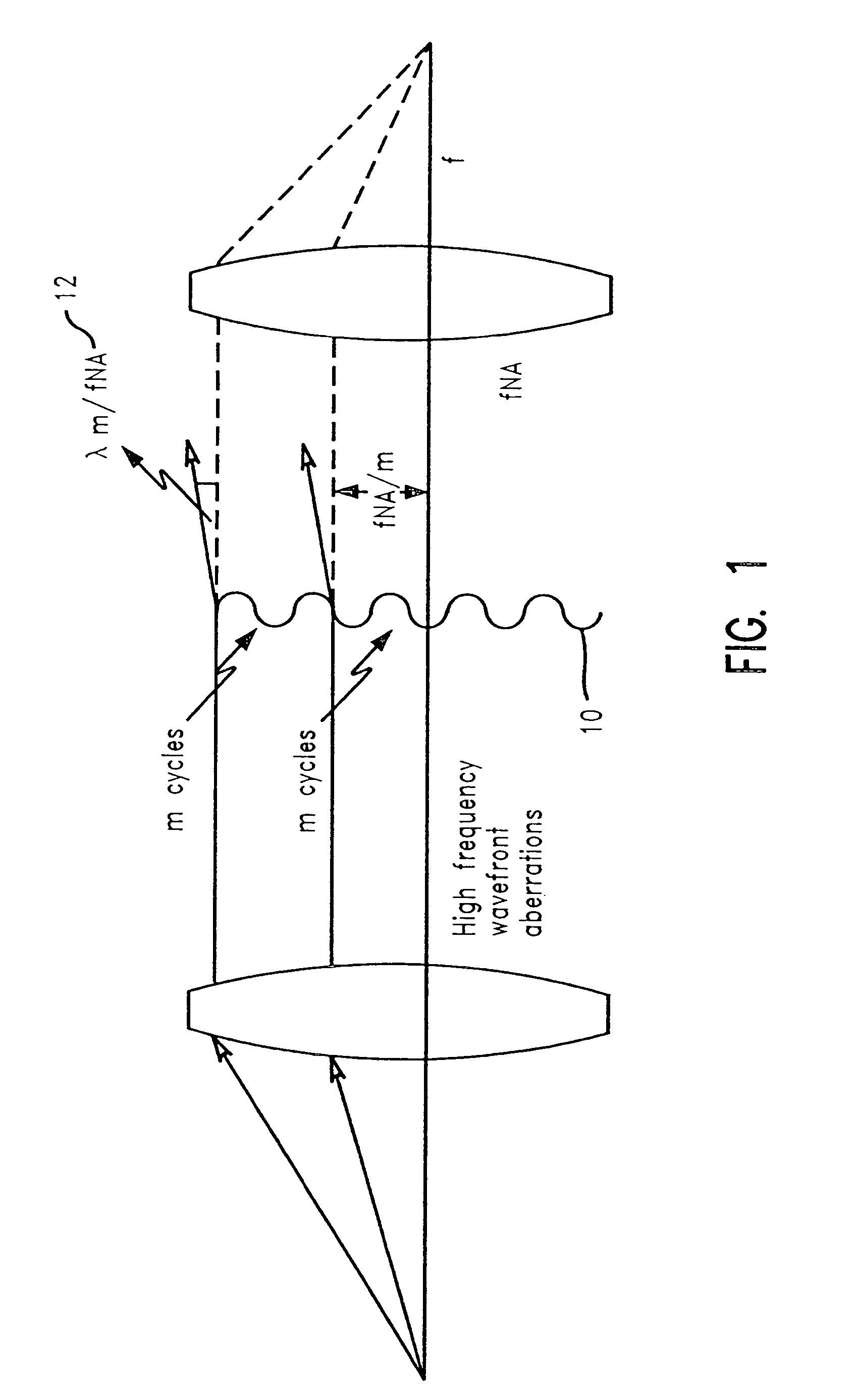

A method and system is provided for computing lithographic images that may take into account non-scalar effects such as lens birefringence, resist stack effects, tailored source polarizations, and blur effects of the mask and the resist. A generalized bilinear kernel is formed, which is independent of the mask transmission function, and which may then be treated using a decomposition to allow rapid computation of an image that includes such non-scalar effects. Weighted pre-images may be formed from a coherent sum of pre-computed convolutions of the dominant eigenfunctions of the generalized bilinear kernel with the appropriate mask polygon sectors. The image at a point may be formed from the incoherent sum of the weighted pre-images over all of the dominant eigenfunctions of the generalized bilinear kernel. The resulting image can then be used to perform model-based optical proximity correction (MBOPC).

Owner:GLOBALFOUNDRIES INC

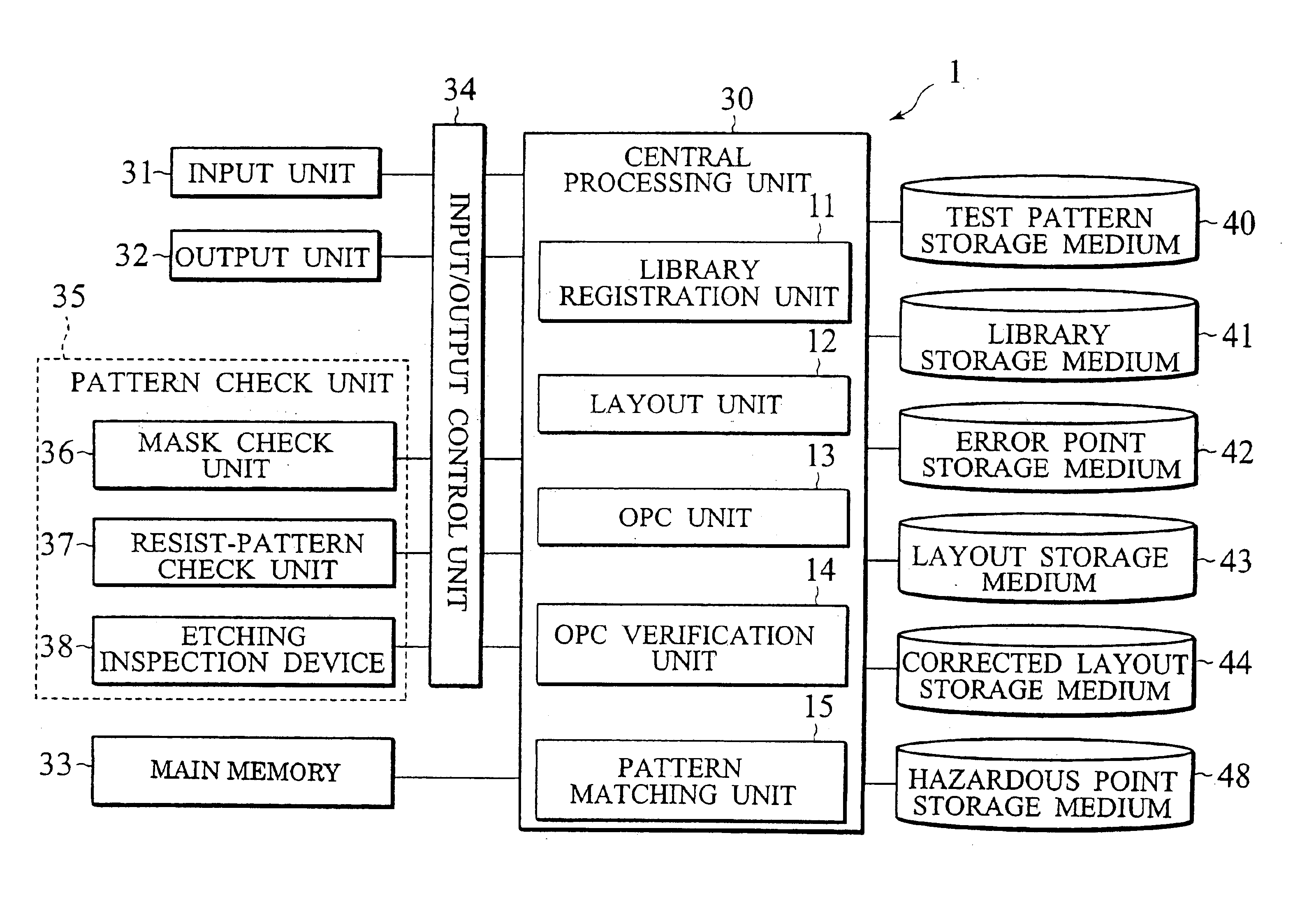

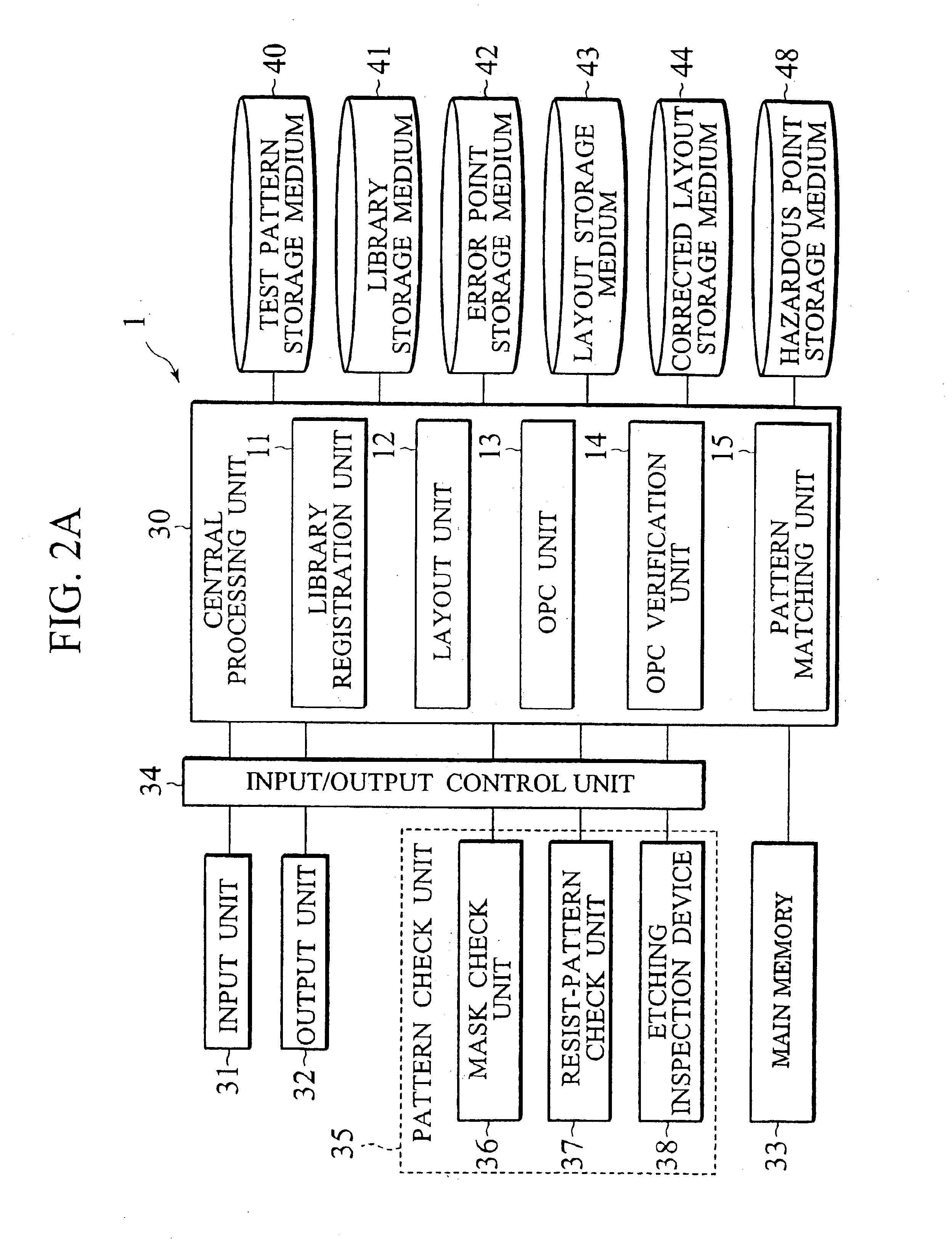

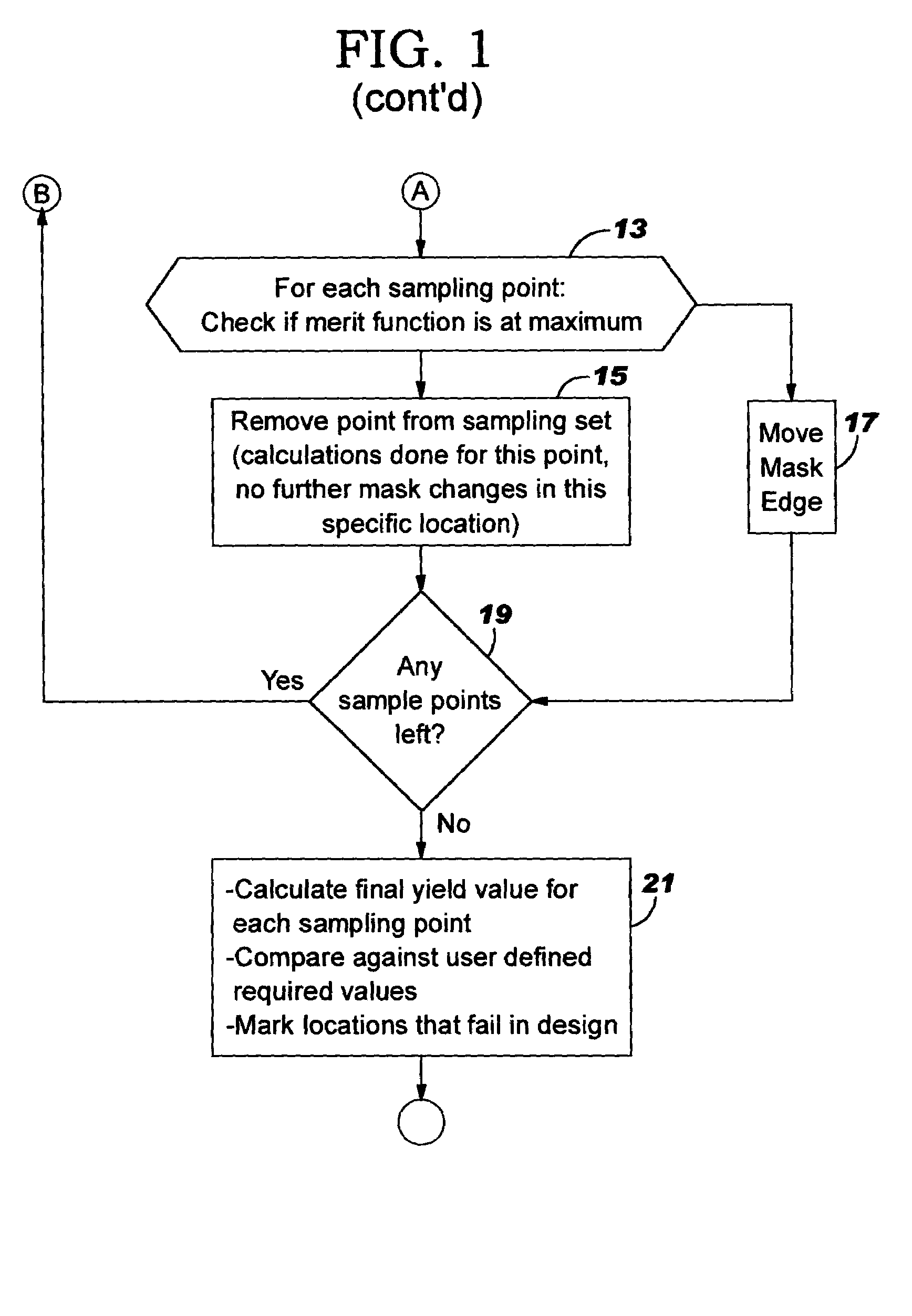

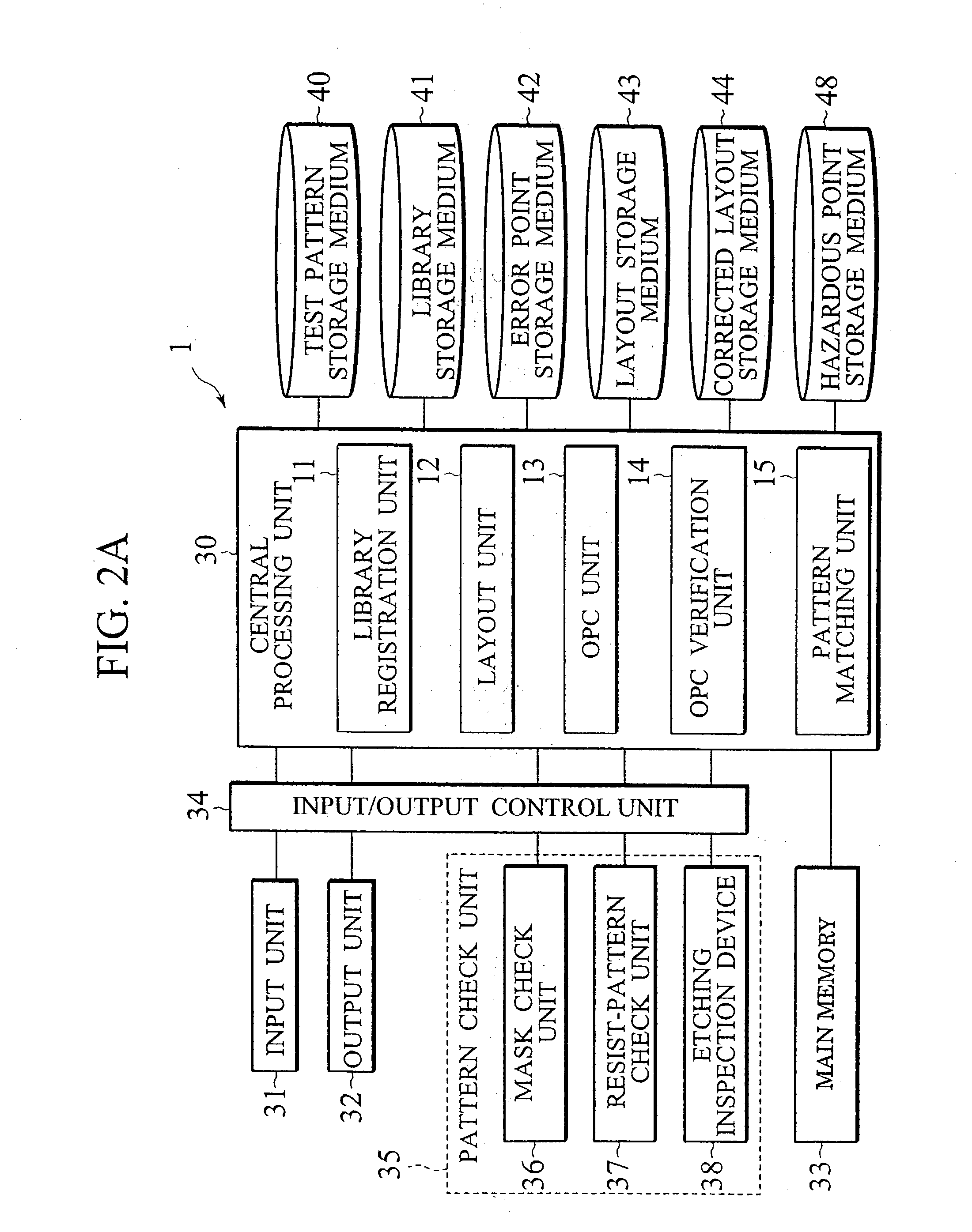

Method and system for optical proximity correction

InactiveUS6952818B2Photomechanical apparatusSemiconductor/solid-state device manufacturingPattern recognitionOptical proximity correction

Owner:KK TOSHIBA

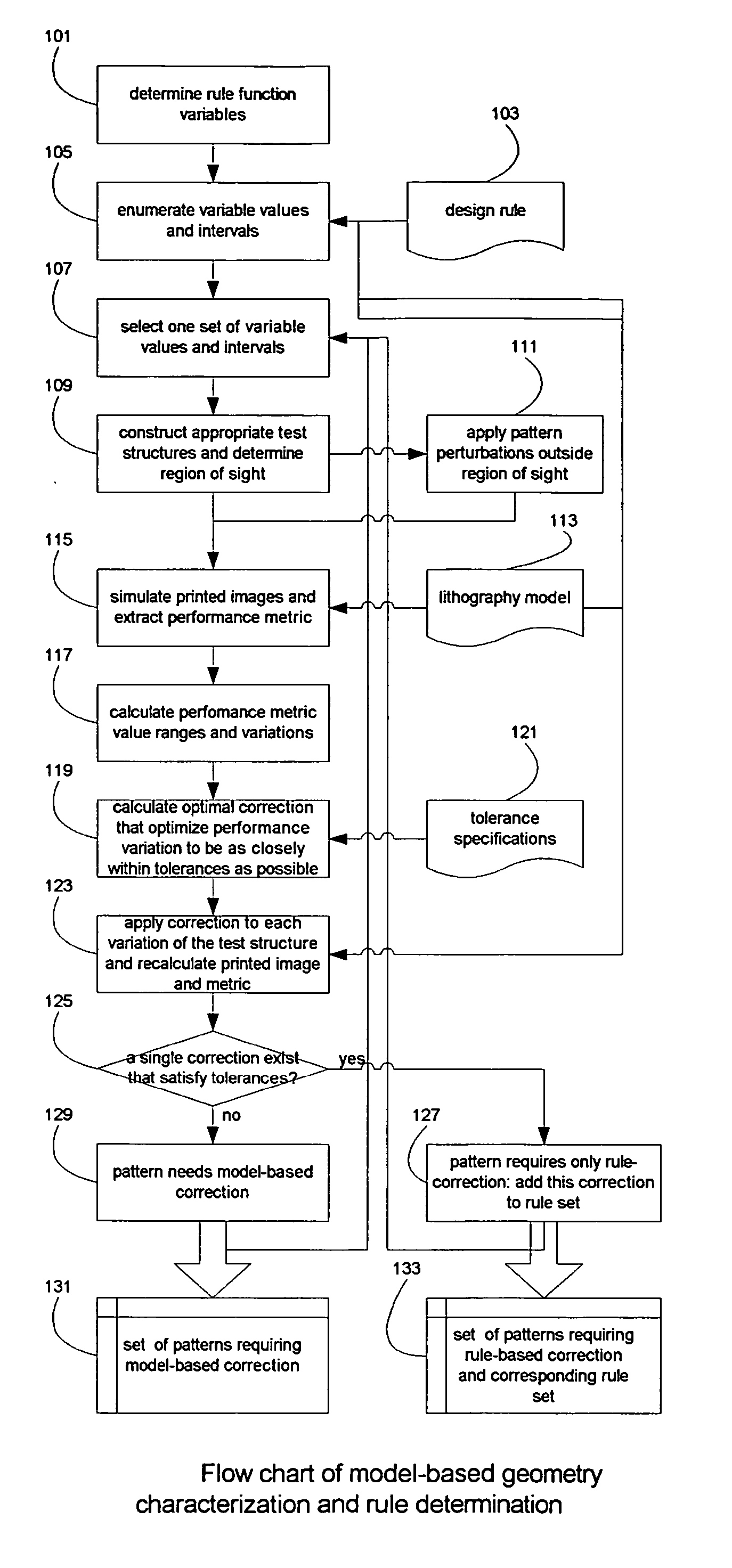

Model-based pattern characterization to generate rules for rule-model-based hybrid optical proximity correction

ActiveUS20060085772A1Photomechanical apparatusOriginals for photomechanical treatmentHybrid systemLithographic artist

A system and method are provided for analyzing layout patterns via simulation using a lithography model to characterize the patterns and generate rules to be used in rule-based optical proximity correction (OPC). The system and method analyze a series of layout patterns conforming to a set of design rules by simulation using a lithography model to obtain a partition of the pattern spaces into one portion that requires only rule-based OPC and another portion that requires model-based OPC. A corresponding hybrid OPC system and method are also introduced that utilize the generated rules to correct an integrated circuit (IC) design layout which reduces the OPC output complexity and improves turnaround time.

Owner:APPLIED MATERIALS INC

Mixed-mode optical proximity correction

InactiveUS7024655B2Photomechanical exposure apparatusMicrolithography exposure apparatusTreatment designEngineering

A mask is prepared by processing design data with various combinations of rule-based and model-based optical proximity correction. In one embodiment, the design data is first processed with a set of optical proximity correction rules to produce a rule-corrected design. The rule-corrected design is examined to identify a set of features to process with model-based optical proximity correction. Then, the set of features are processed with the model-based optical proximity correction.

Owner:COBB NICOLAS B

Extending the range of lithographic simulation integrals

ActiveUS7010776B2Semiconductor/solid-state device manufacturingCharacter and pattern recognitionLithographic artistAnalytical expressions

Owner:GLOBALFOUNDRIES U S INC

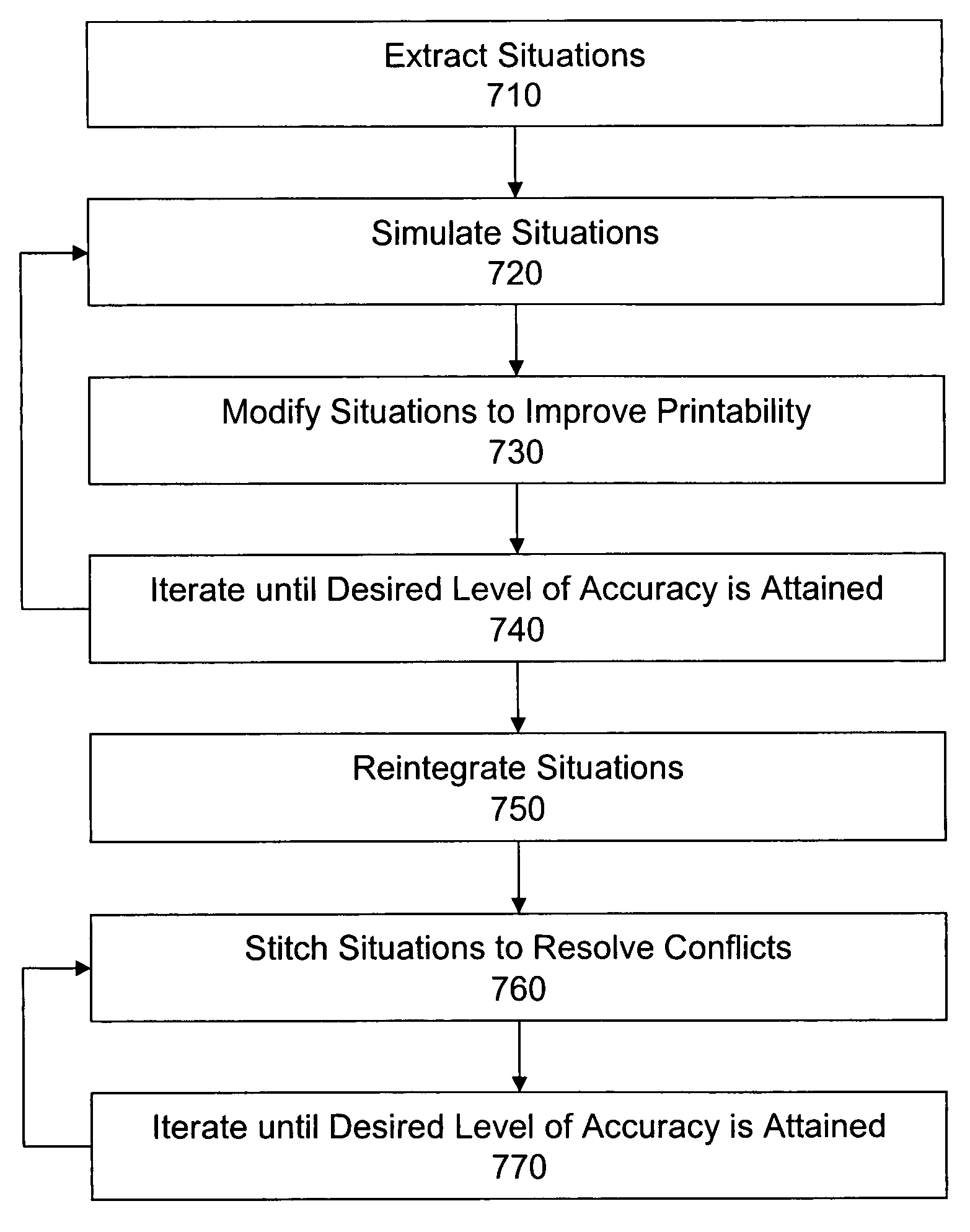

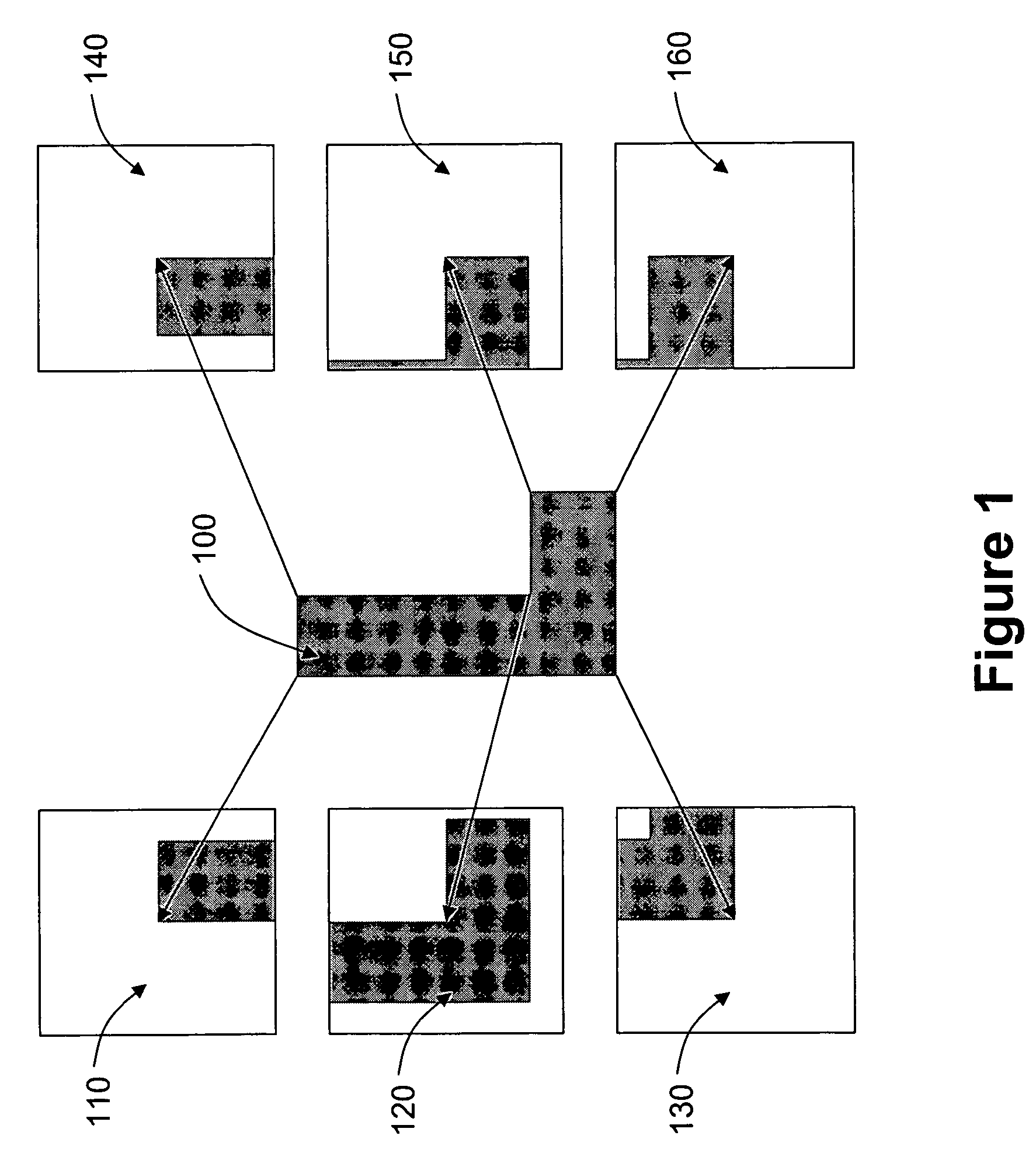

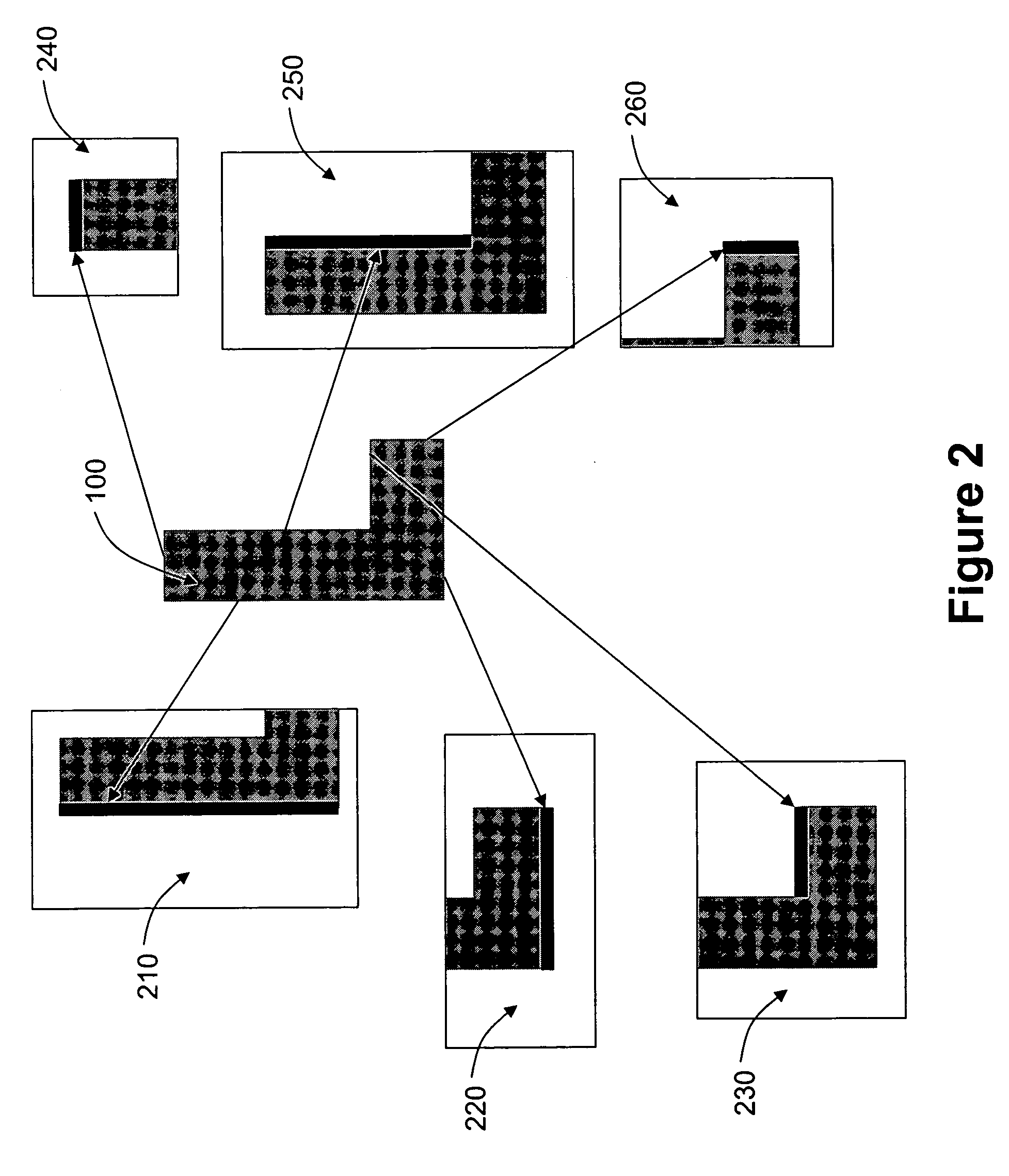

System and method for analysis and transformation of layouts using situations

ActiveUS7418693B1Efficient executionCAD circuit designTotal factory controlDensity analysisIntegrated circuit layout

Systems, methodologies and technologies for the analysis and transformation of integrated circuit layouts using situations are disclosed. A method for transforming an integrated circuit (IC) layout includes recognizing shapes within the IC layout, identifying features for each of the shapes and extracting situations for the respective features. Extracted situations can be used to improve optical proximity correction (OPC) of the IC layout. This improved OPC includes extracting the situations, simulating the situations to determine a set of the situations identified for modification based on failing to satisfy a desired OPC tolerance level, modifying the set of situations to improve satisfaction of the desired OPC tolerance level, and reintegrating the modified set of situations into the IC layout. Extracted situations can also be used to improve aerial image simulation of the IC layout. This improved aerial image simulation includes extracting the situations, simulating a subset of the situations to determine aerial images of the subset, and tiling the subset of situations to form a larger aerial image. Extracted situations can further be used to improve density analysis of the IC layout. This improved density analysis includes extracting the situations for a window of the IC layout, removing overlap from the window based on the extracted situations, calculating a density for each of the situations, and calculating a density for the window based on the density for each of the situations.

Owner:CADENCE DESIGN SYST INC

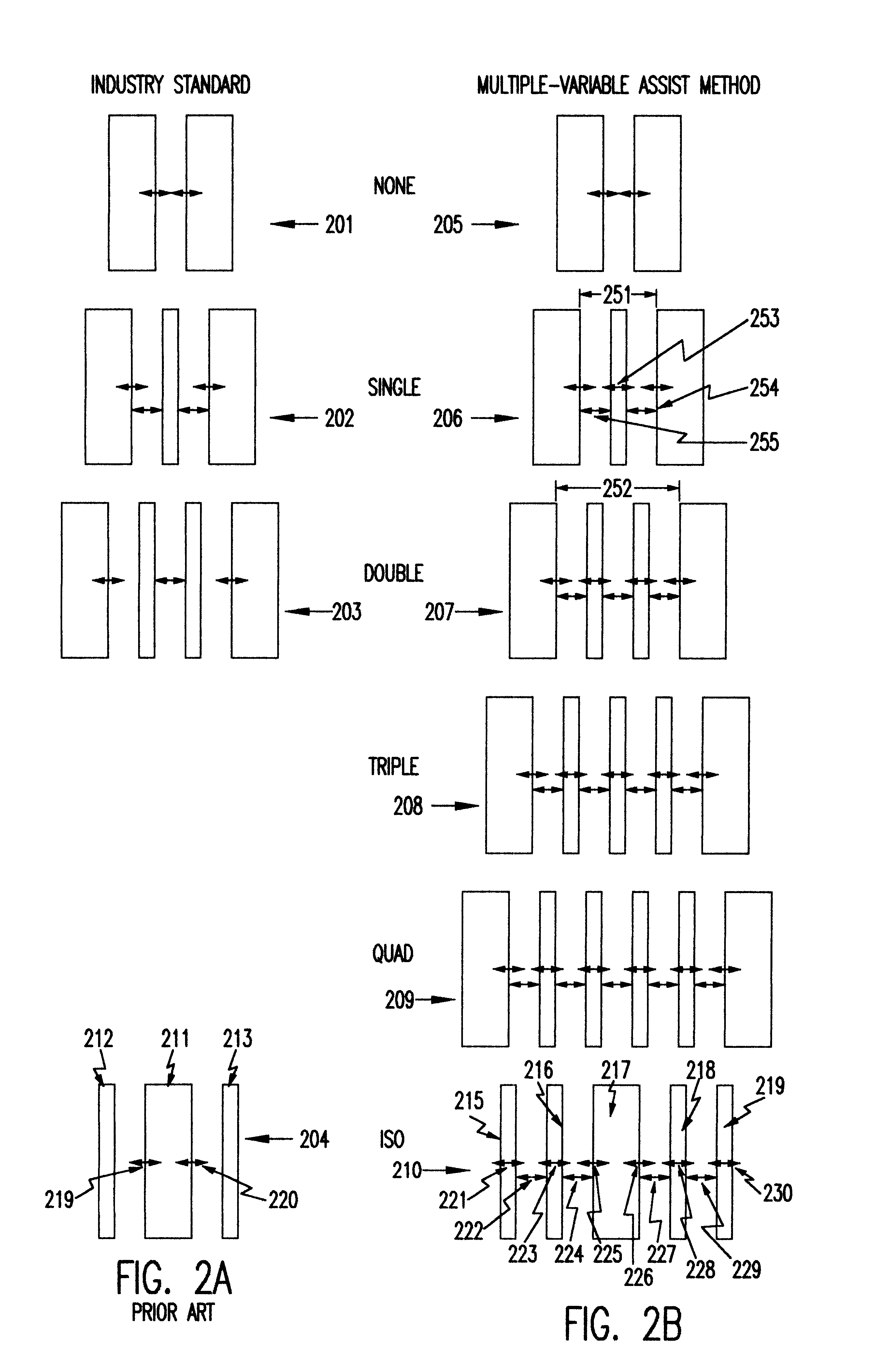

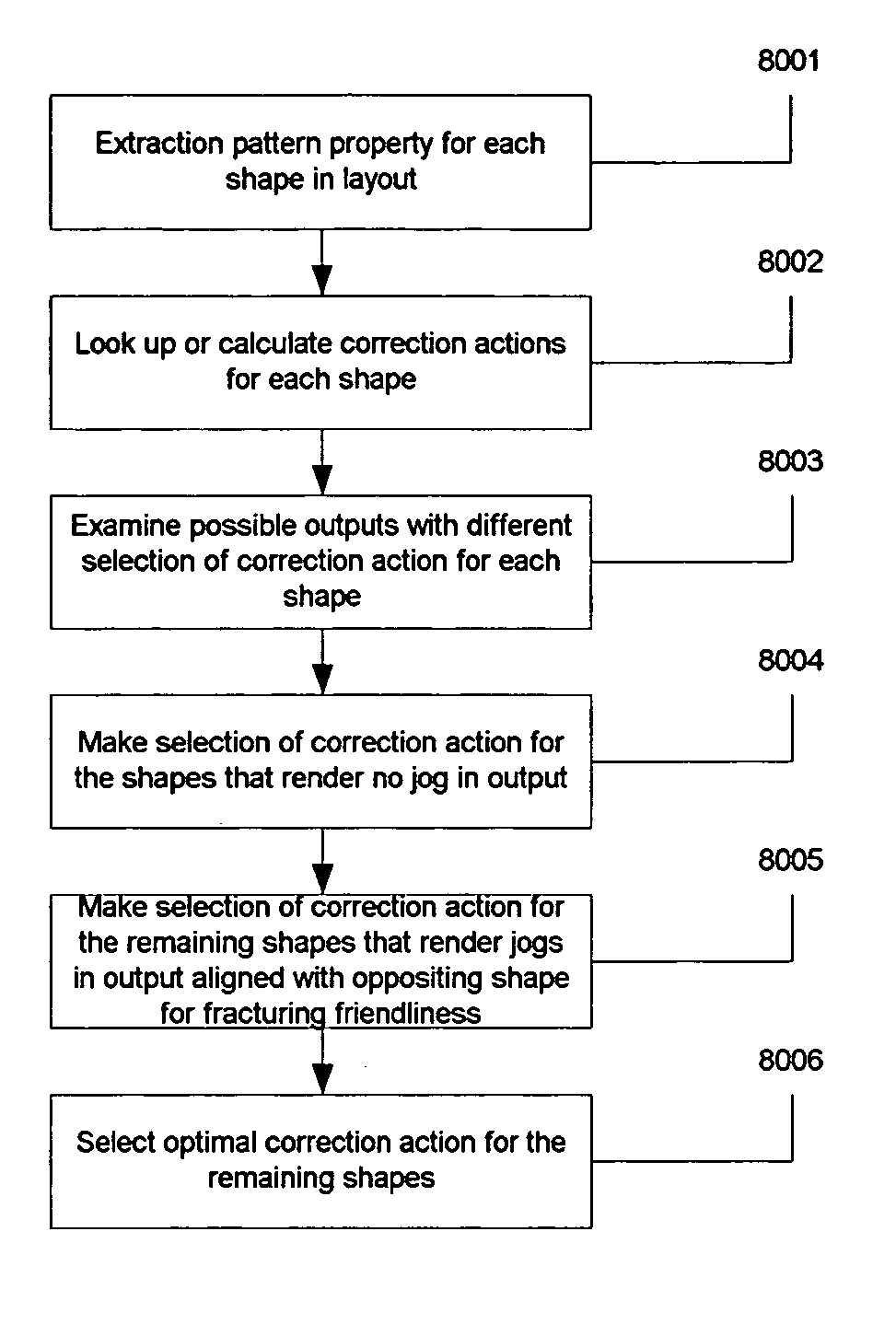

Creating and applying variable bias rules in rule-based optical proximity correction for reduced complexity

ActiveUS20060085773A1Minimizes OPC complexityAcceptable resultPhotomechanical apparatusOriginals for photomechanical treatmentAlgorithmDegrees of freedom

An optical proximity correction (OPC) based integrated circuit design system and method introduce a variable rule in which rules are specified in terms of multiple correction actions that yield acceptable results. This category of rules provides more degrees of freedom in actual application so that the rule-based OPC tool can intelligently select the proper valid rule that minimizes the OPC complexity or meets other objectives.

Owner:APPLIED MATERIALS INC

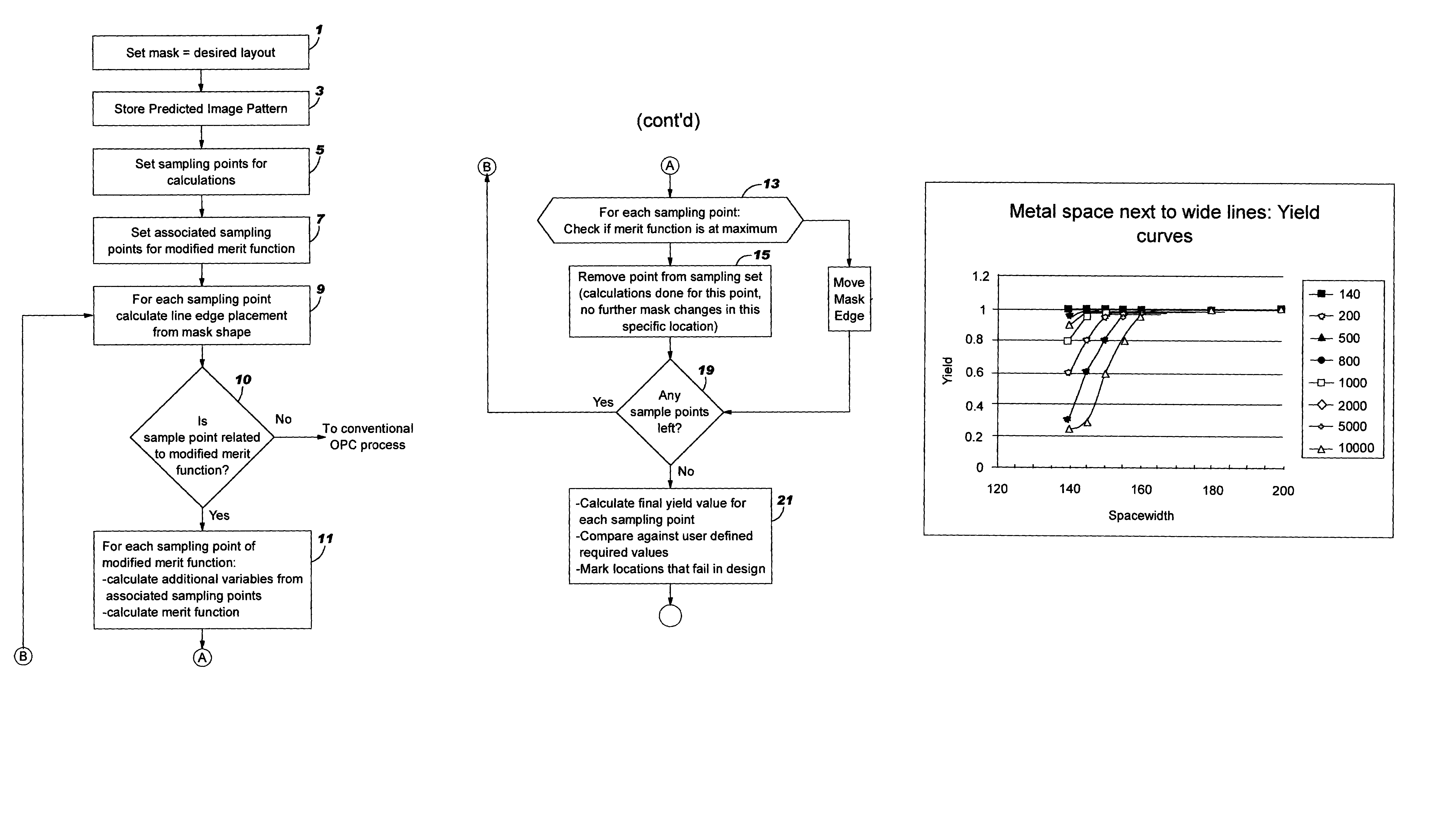

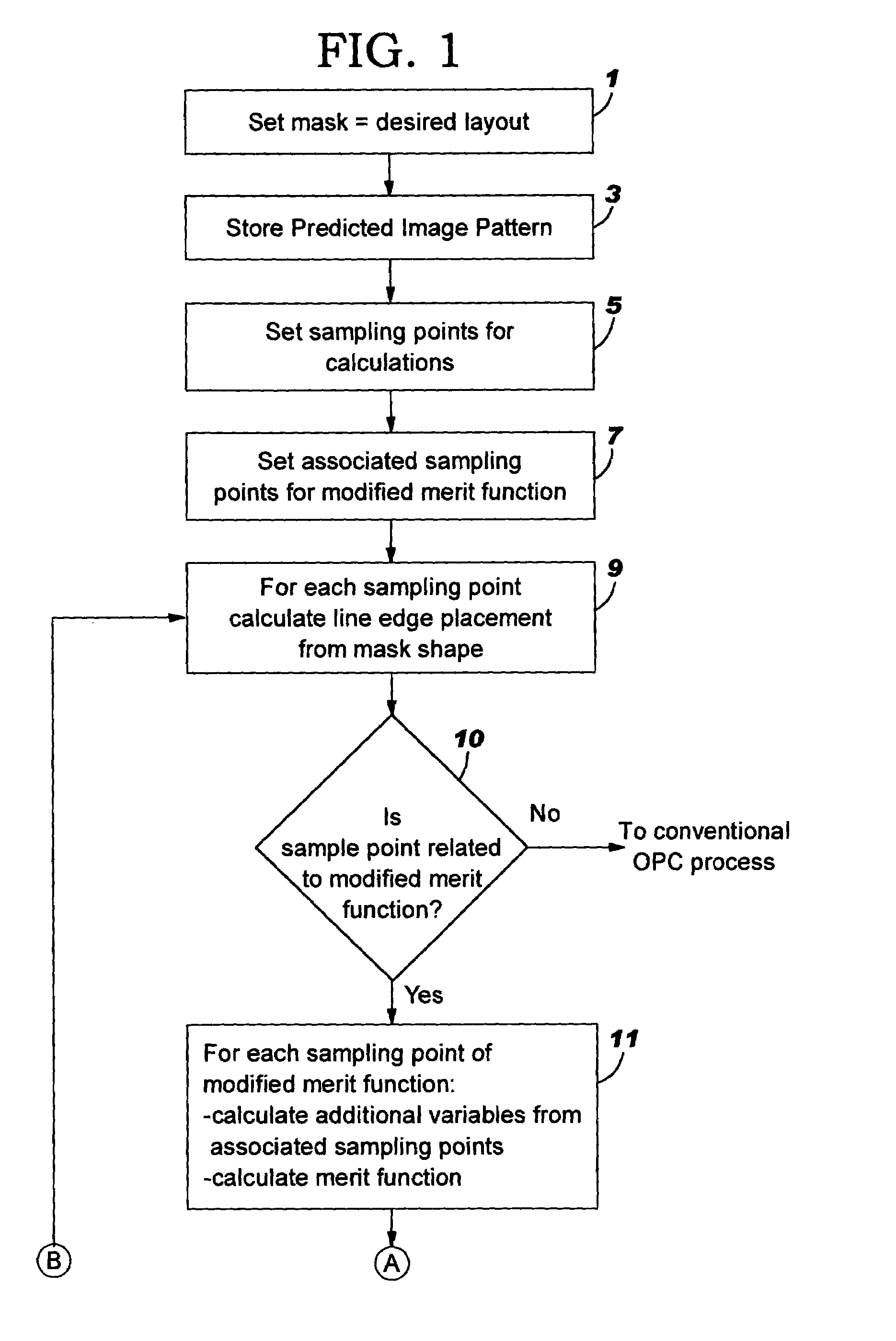

Method for interlayer and yield based optical proximity correction

InactiveUS6961920B2Improve lithographic processIncrease proximityPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringMerit function

An optical proximity correction method is provided using a modified merit function based upon yield. Known failure mechanisms related to layout geometries are used to derive yield functions based upon distance values between layout features, such as, edge features. In comparing the edge points on the predicted layout pattern with the corresponding point on the design layout pattern, a yield test is first undertaken before movement of the points on the predicted layout pattern to a position of higher yield. Where yield is acceptable, no further movement is made. Where incremental movement of points results in coming within acceptable proximity before acceptable yield is reached, the point is flagged for further consideration.

Owner:GLOBALFOUNDRIES INC