Patents

Literature

89 results about "Physical verification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

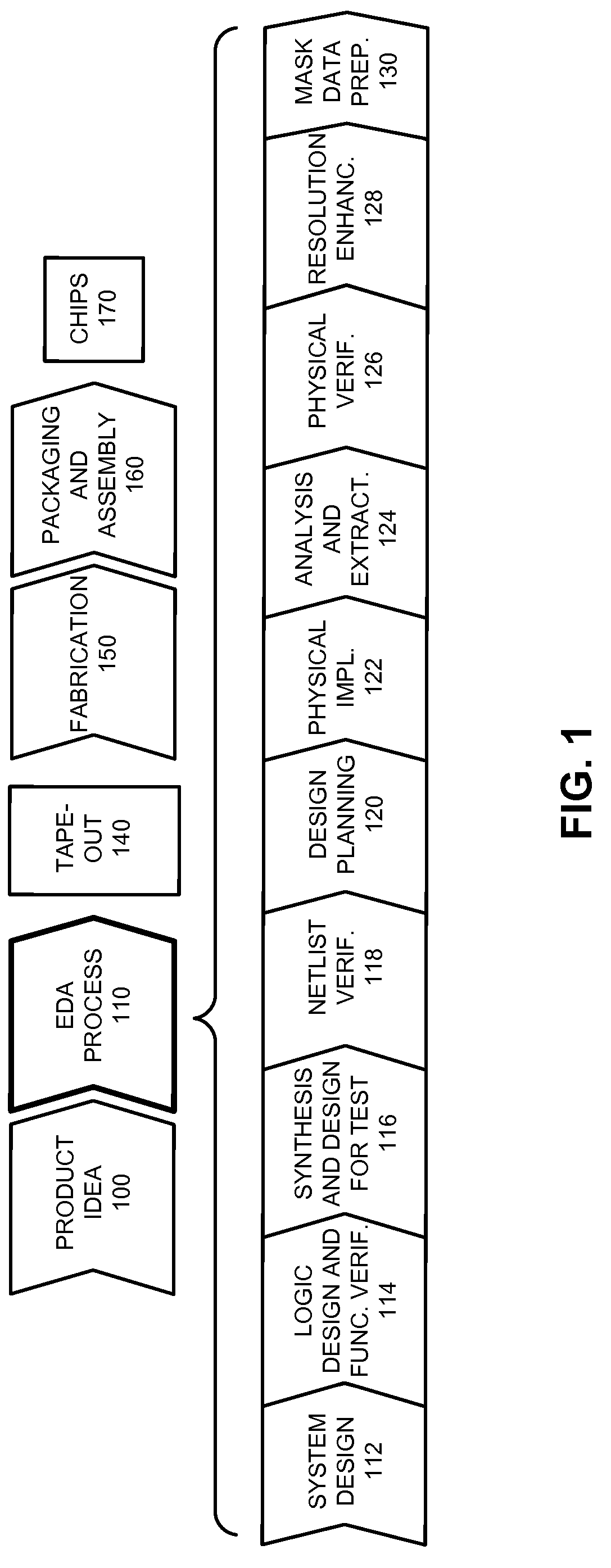

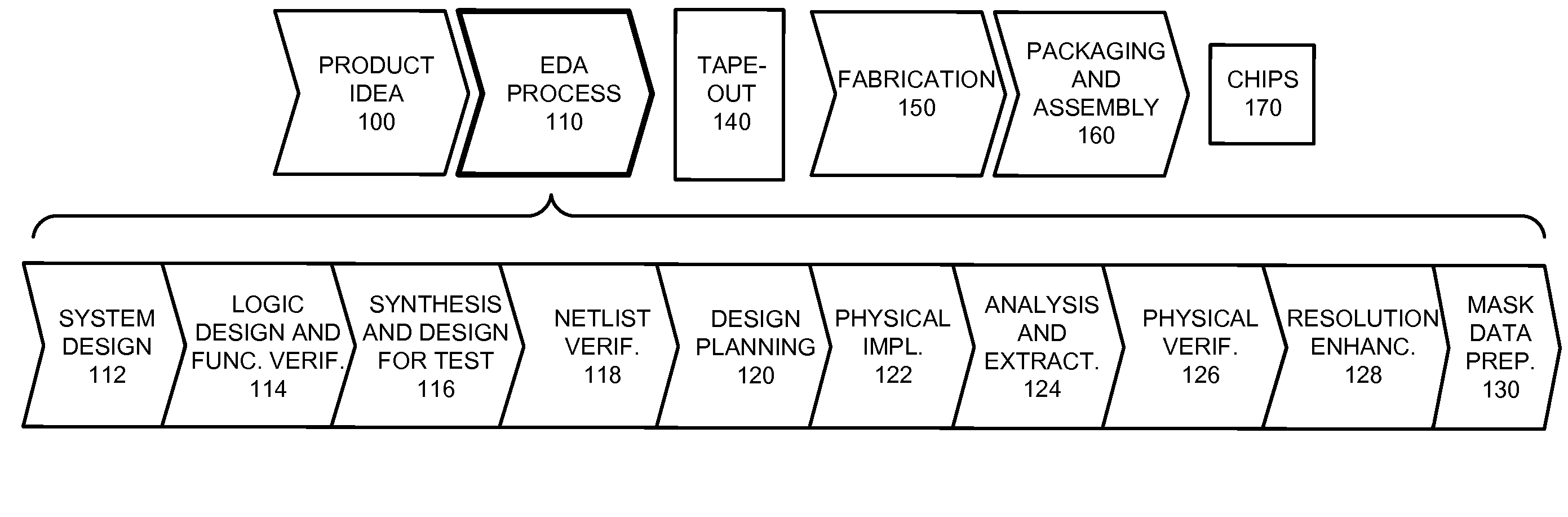

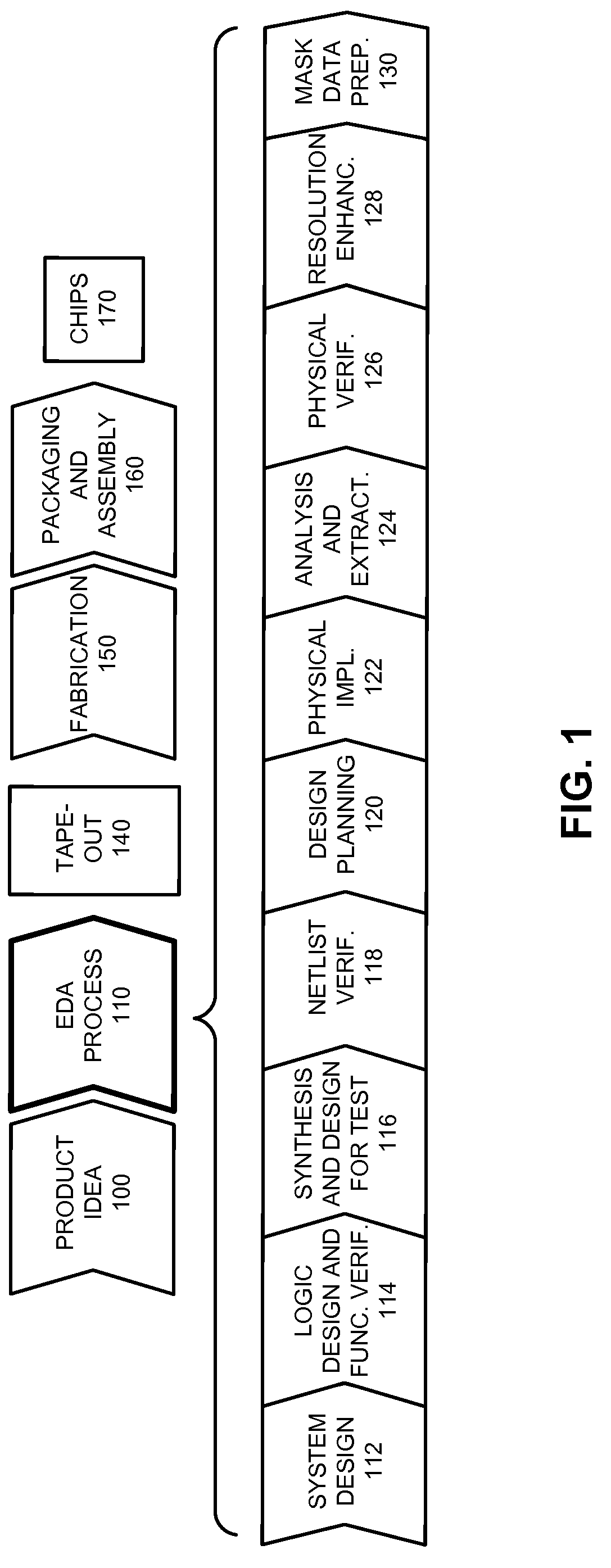

Physical verification is a process whereby an integrated circuit layout (IC layout) design is verified via EDA software tools to ensure correct electrical and logical functionality and manufacturability. Verification involves design rule check (DRC), layout versus schematic (LVS), XOR (exclusive OR), antenna checks and electrical rule check (ERC).

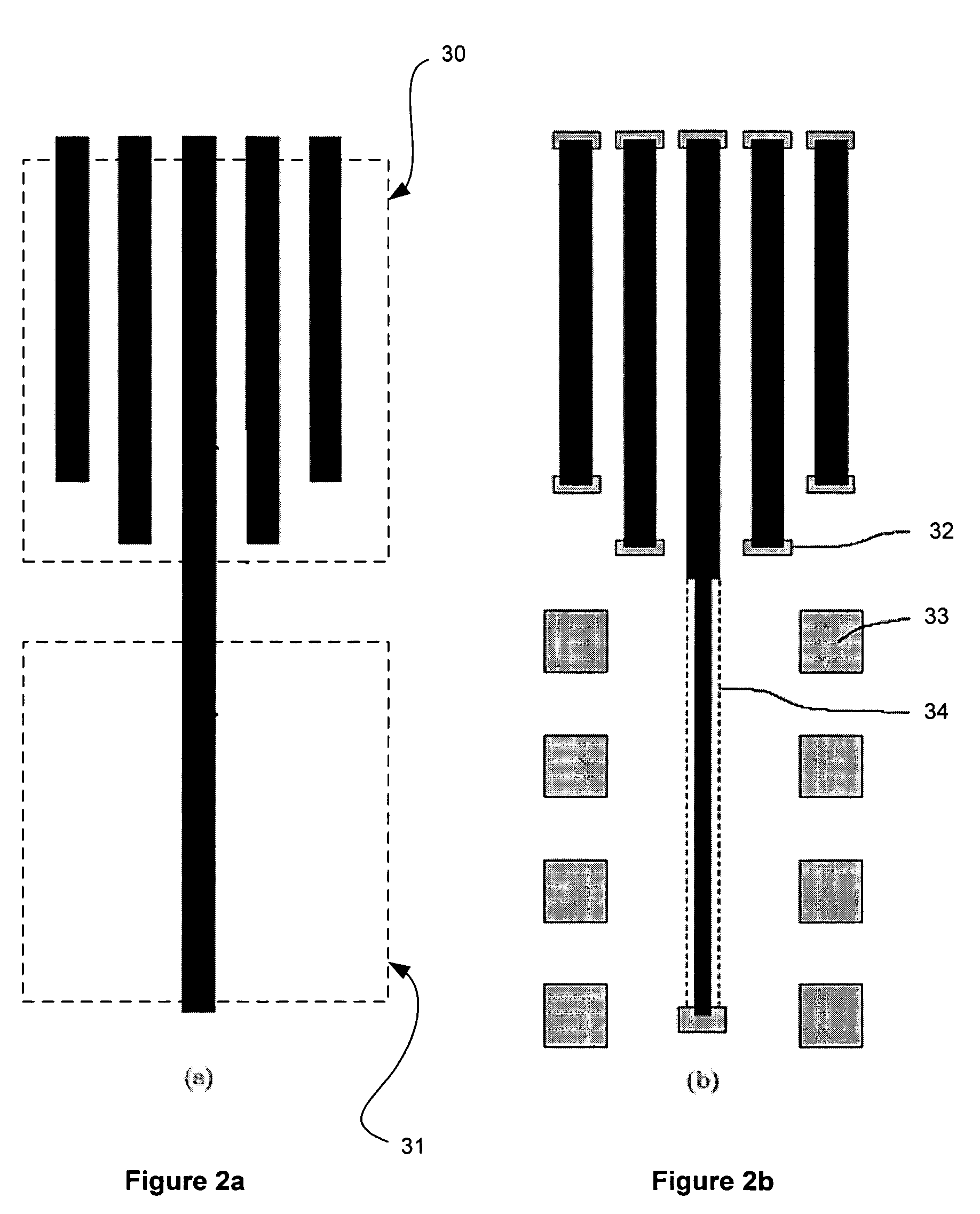

Method and apparatus for selective, incremental, reconfigurable and reusable semiconductor manufacturing resolution-enhancements

InactiveUS20050229130A1Improve manufacturabilityHigh yieldCAD circuit designSpecial data processing applicationsImage resolutionPhysical verification

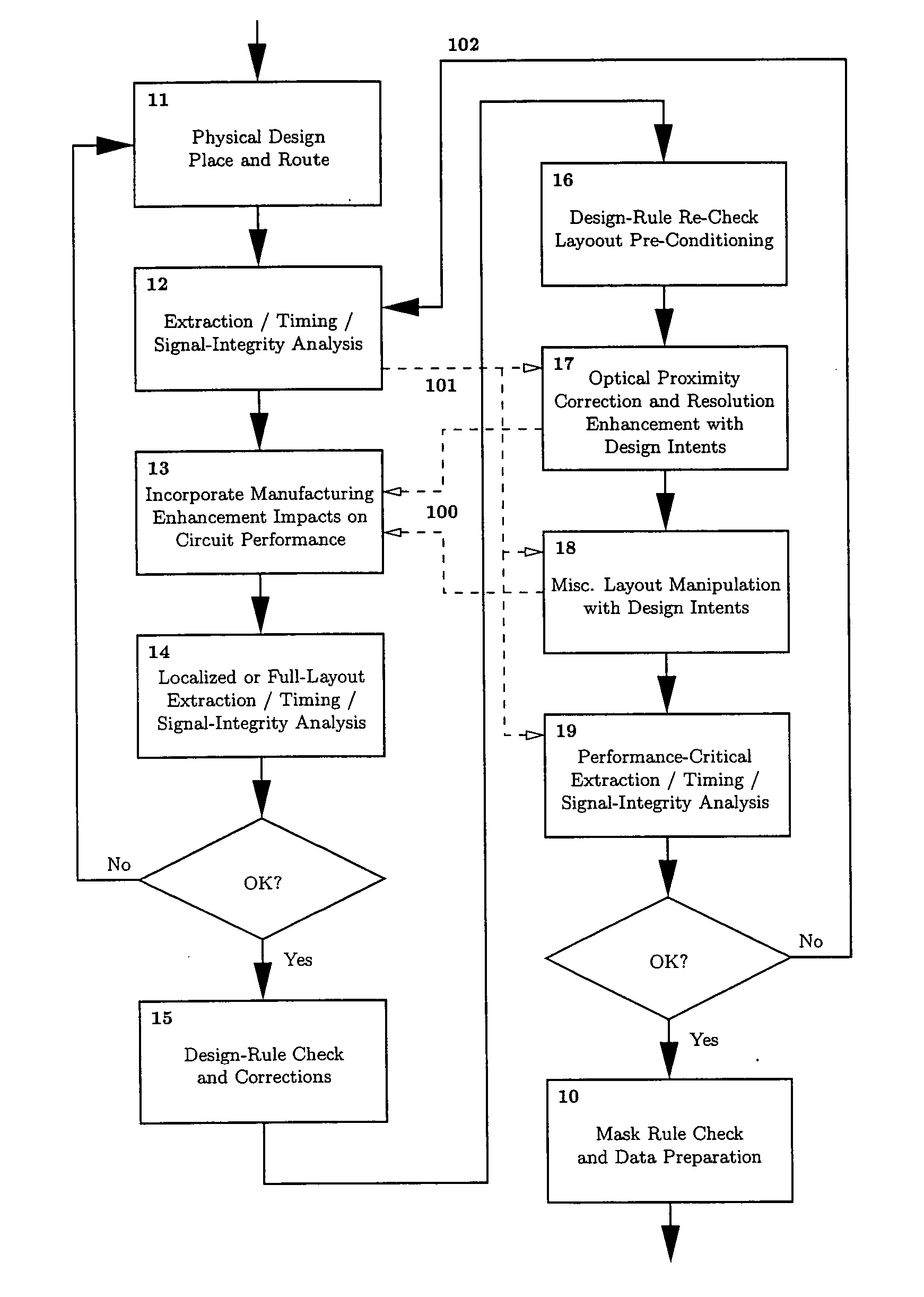

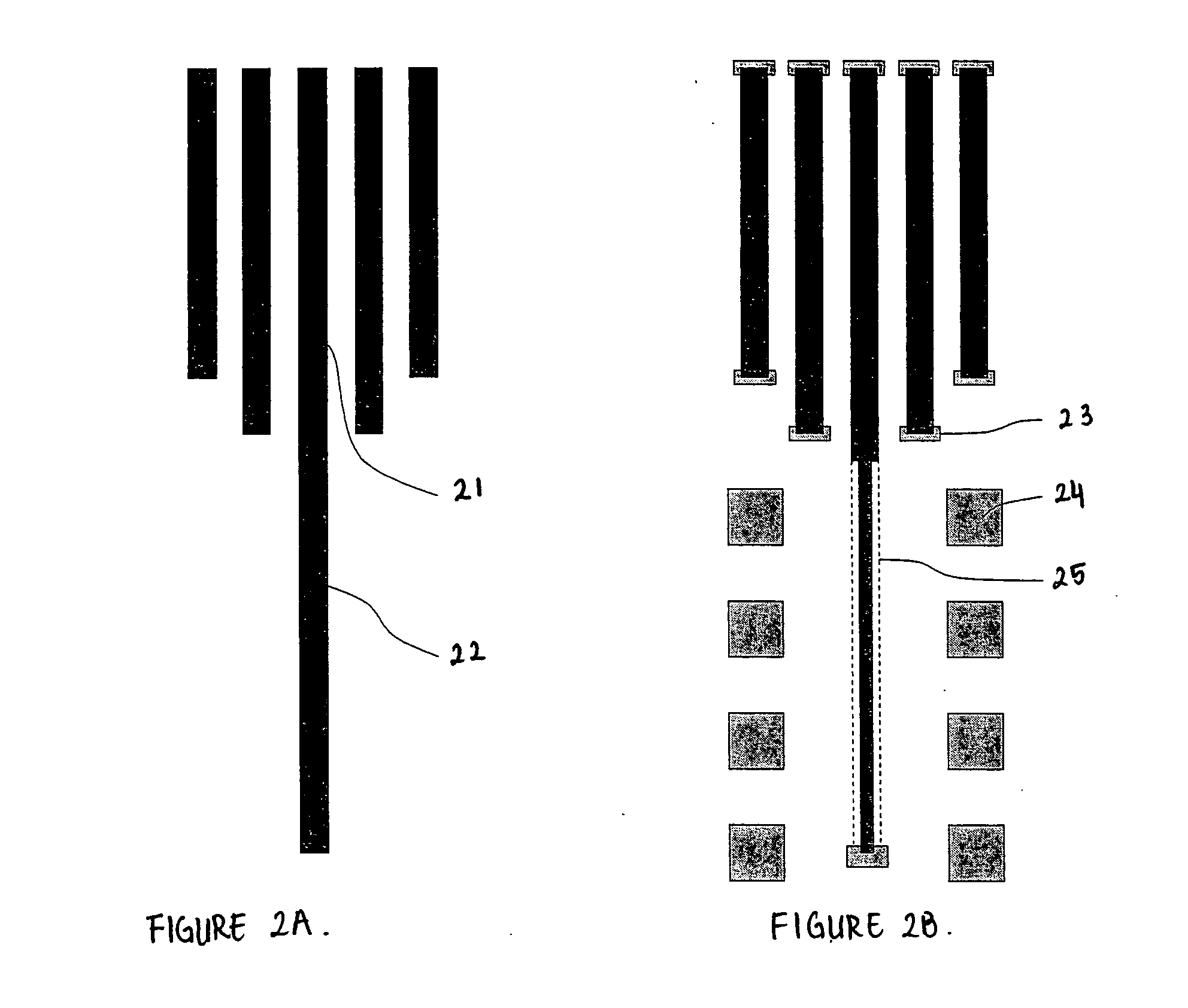

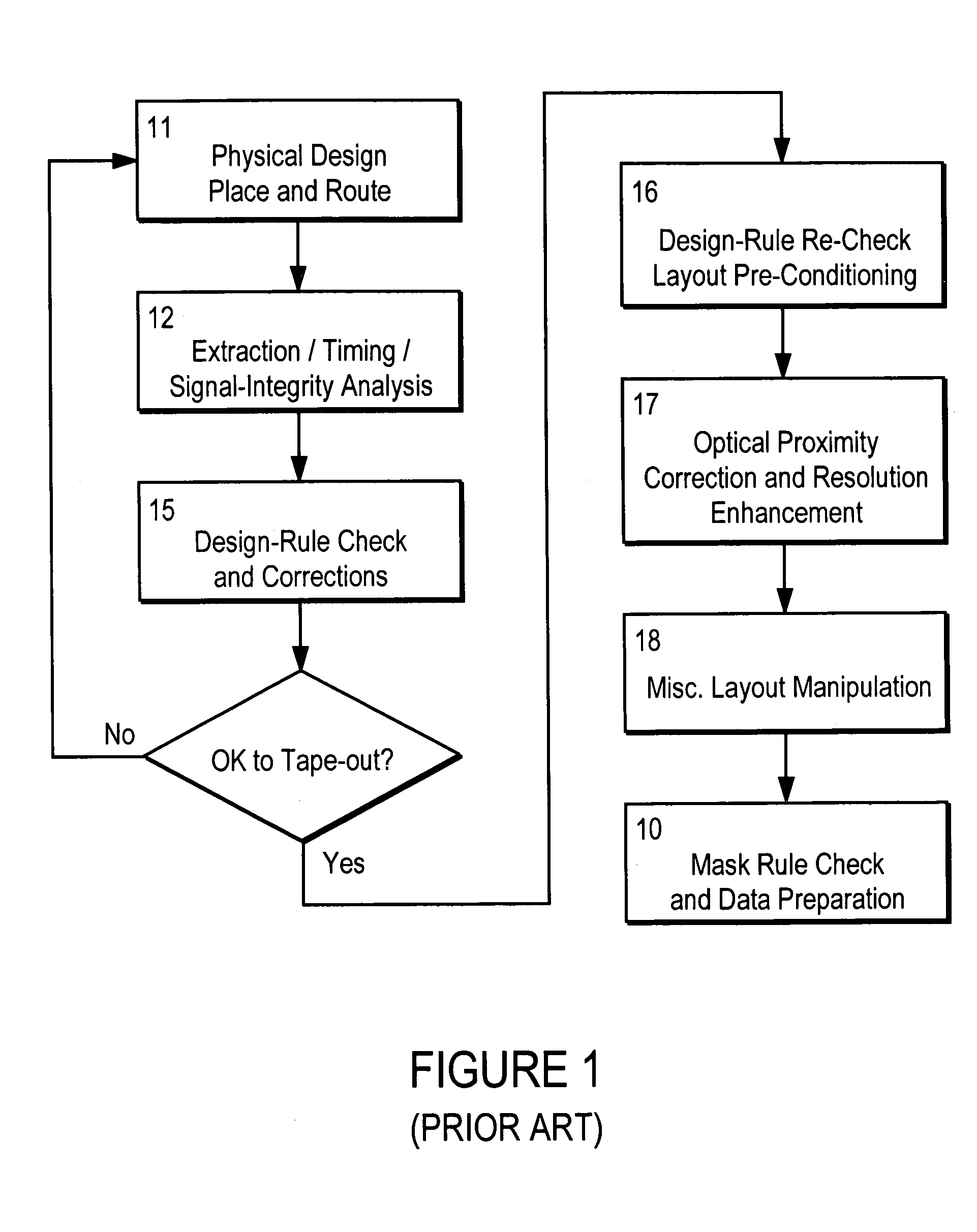

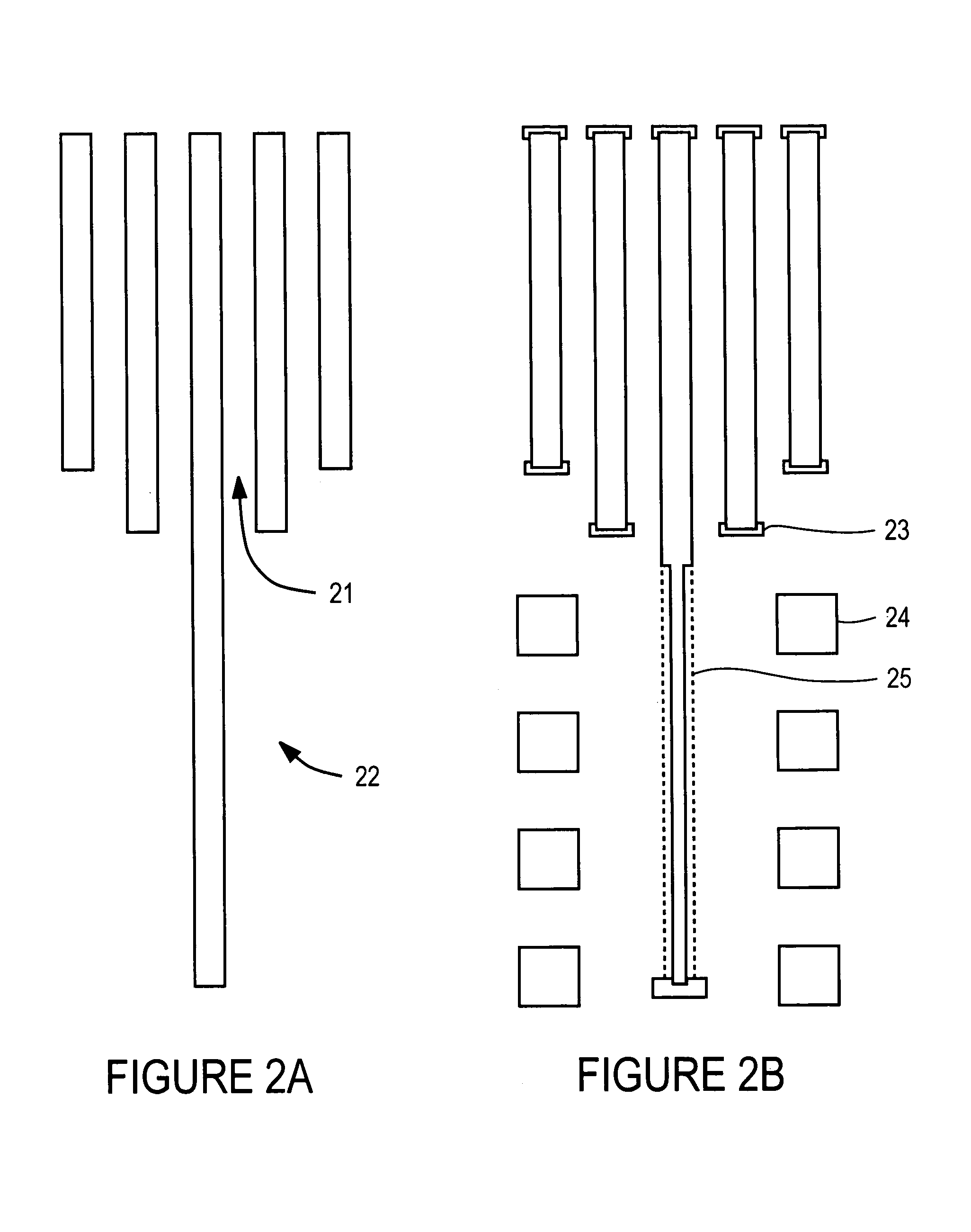

An automated design for manufacturability platform for integrated physical verification and manufacturing enhancement operations. Given original layouts and one or more associated resolution-enhanced layouts, intermediate resolution-enhancement state layouts are reconstructed, and selective localized resolution-enhancement reconfigurations, modifications, and / or perturbations are introduced on any existing enhancements in order to improve manufacturability and yield.

Owner:RPX CORP

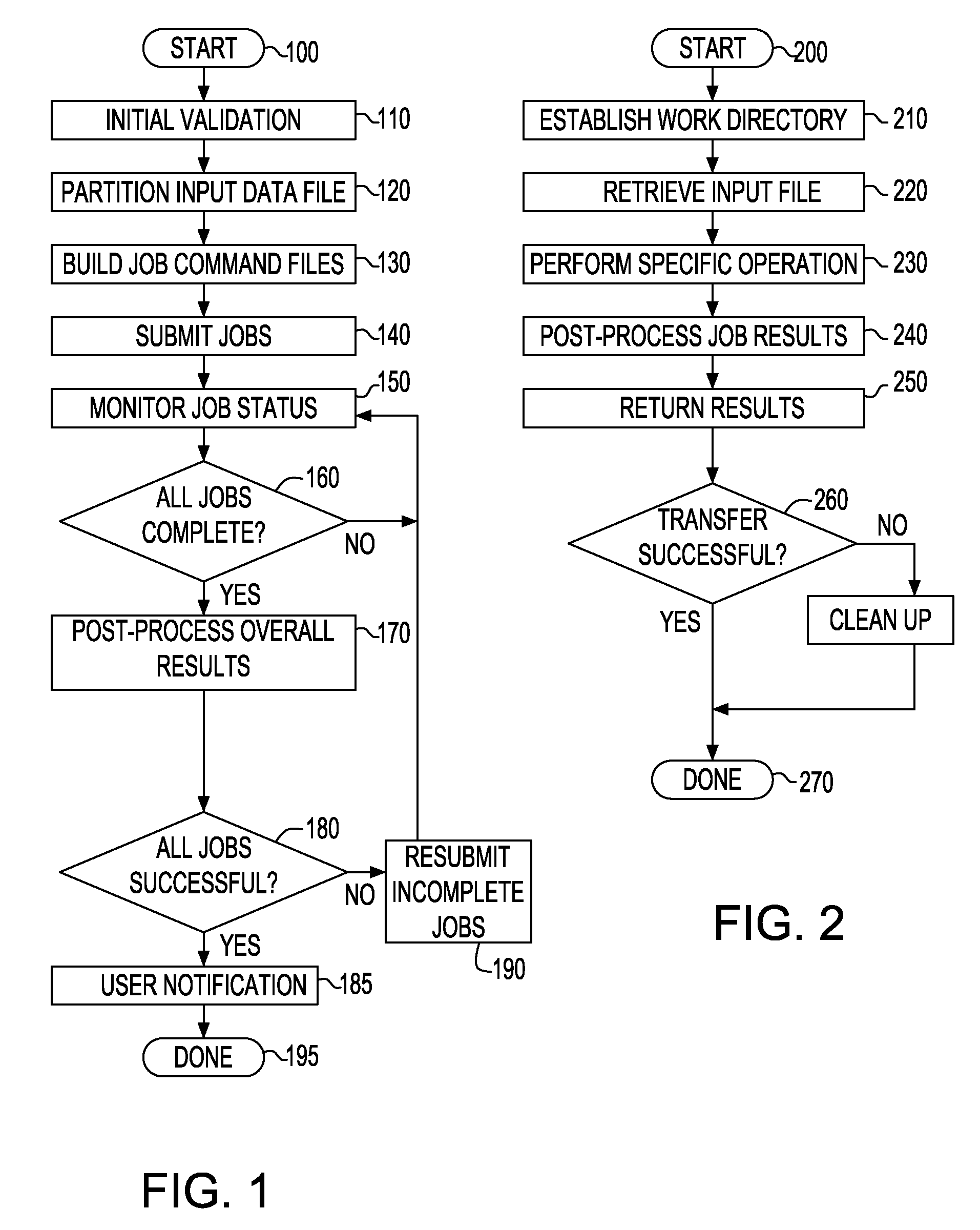

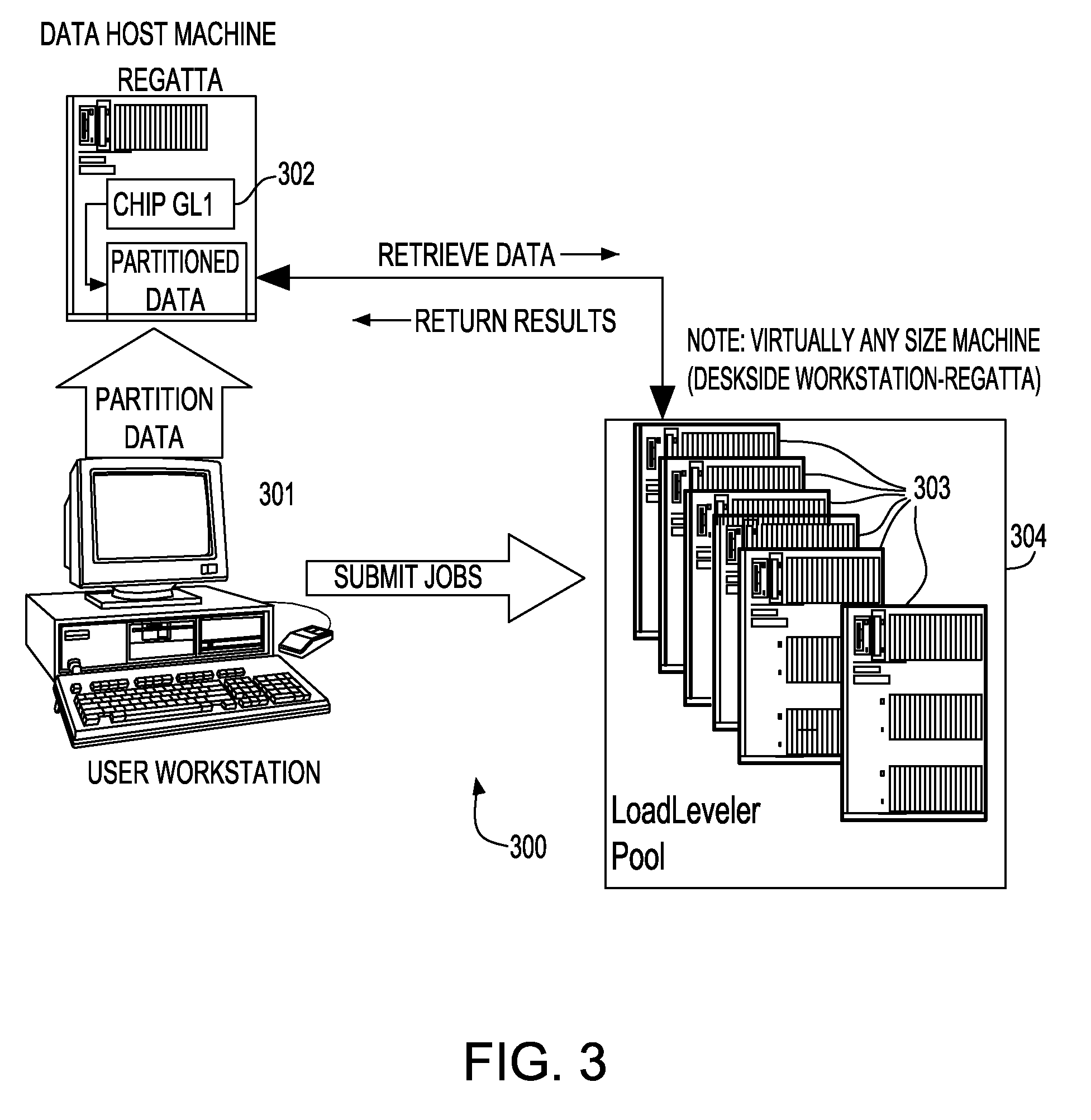

Method and apparatus for parallel data preparation and processing of integrated circuit graphical design data

InactiveUS7434185B2Improve scalabilityIncrease loadDetecting faulty computer hardwareOriginals for photomechanical treatmentGraphicsComputer architecture

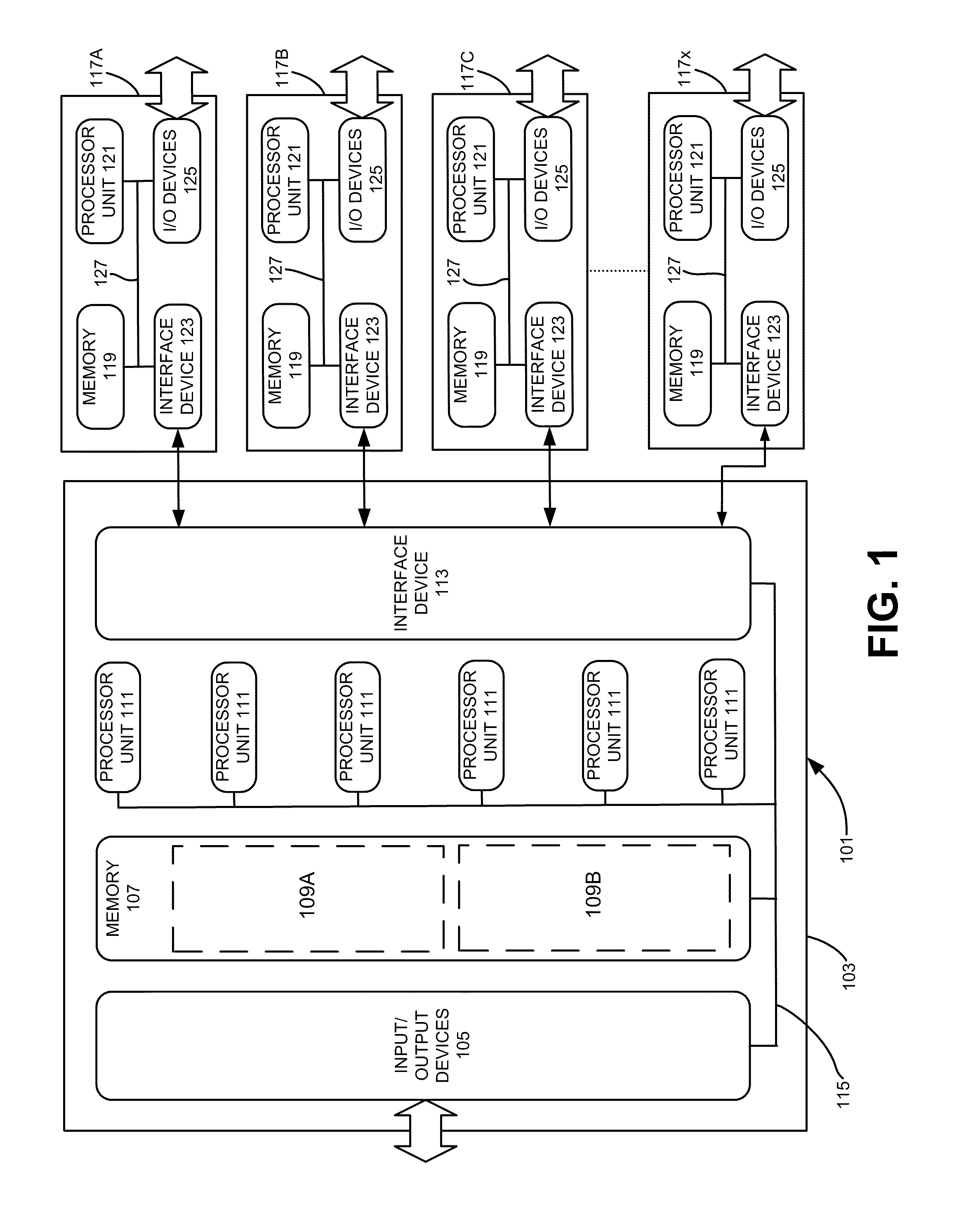

A method for implementing an ORC process to facilitate physical verification of an integrated circuit (IC) graphical design. The method includes partitioning the IC graphical design data into files by a host machine such that the files correspond to regions of interest or partitions with defined margins, dispersing the partitioned data files to available cpus within the network, processing of each job by the cpu receiving the file, wherein artifacts arising from bisection of partitioning margins during the partitioning, including cut-induced false errors, are detected and removed, and the shape-altering effects of such artifact errors are minimized and transmitting the results of processing at each cpu to the host machine for aggregate processing.

Owner:GLOBALFOUNDRIES INC

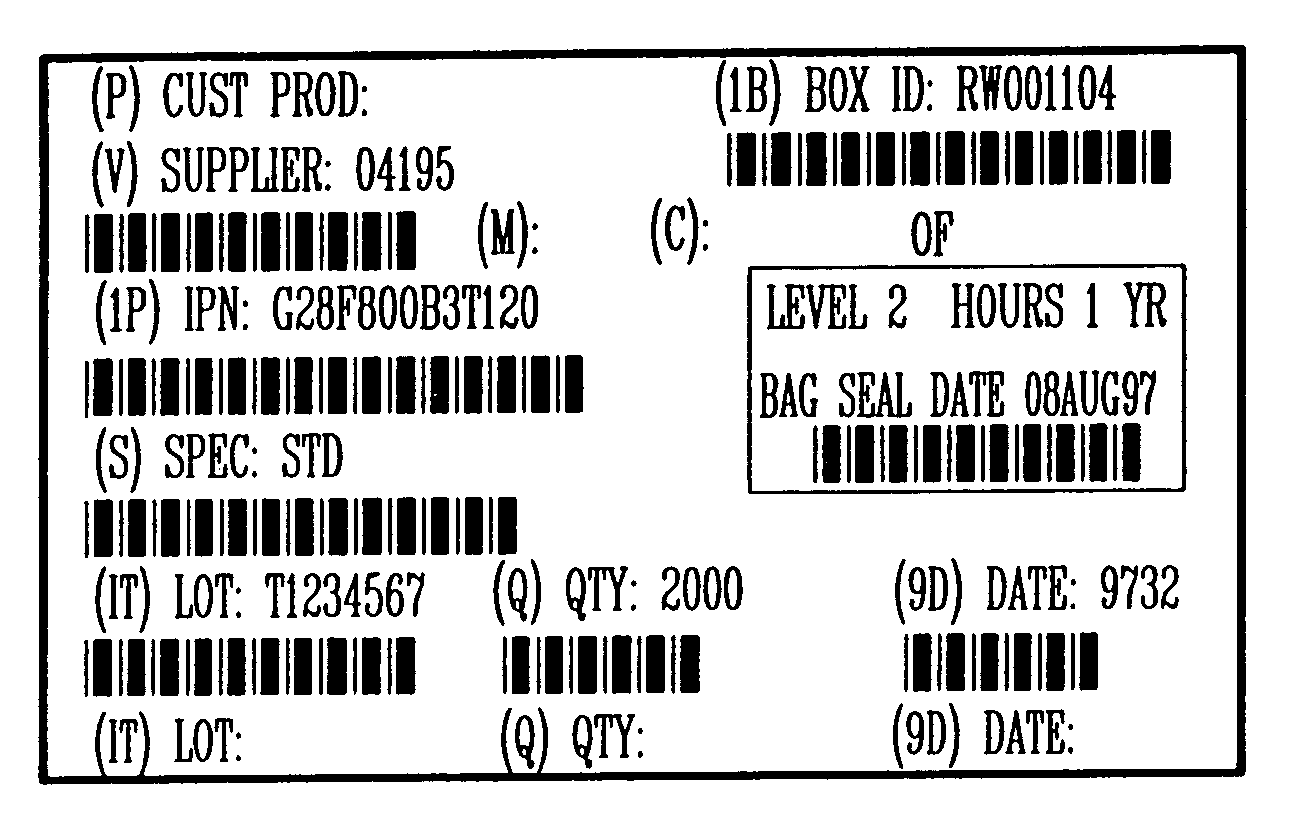

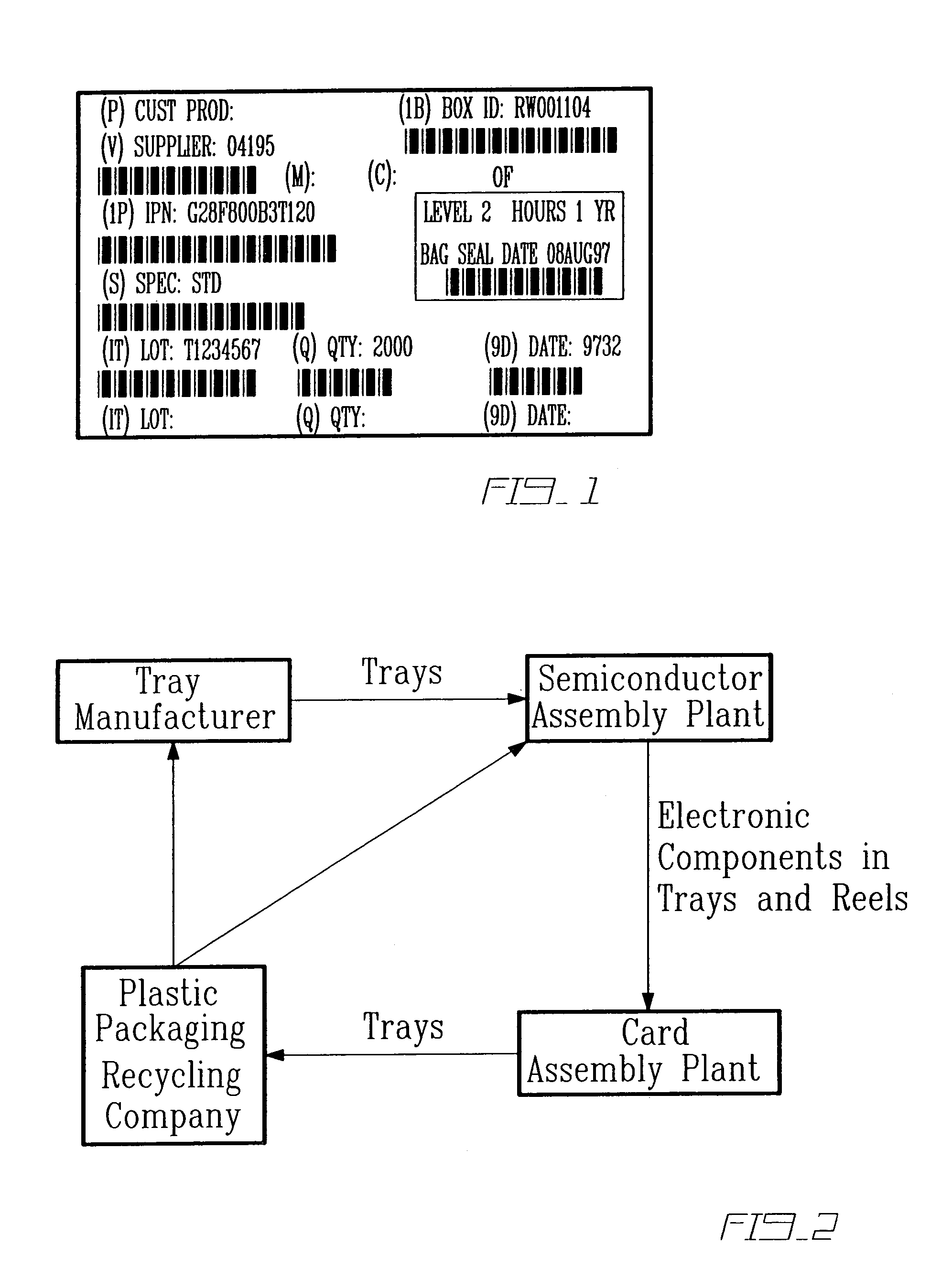

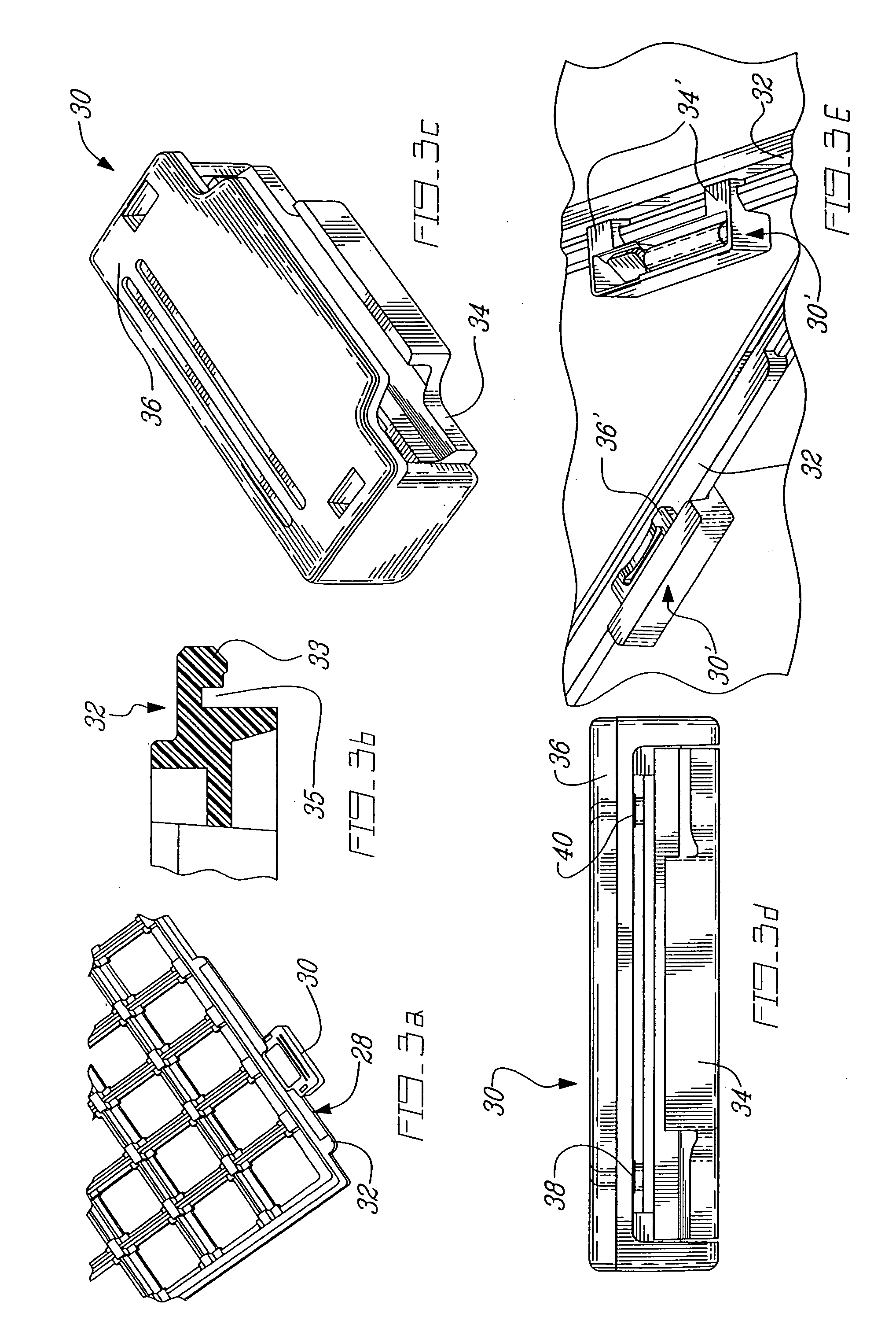

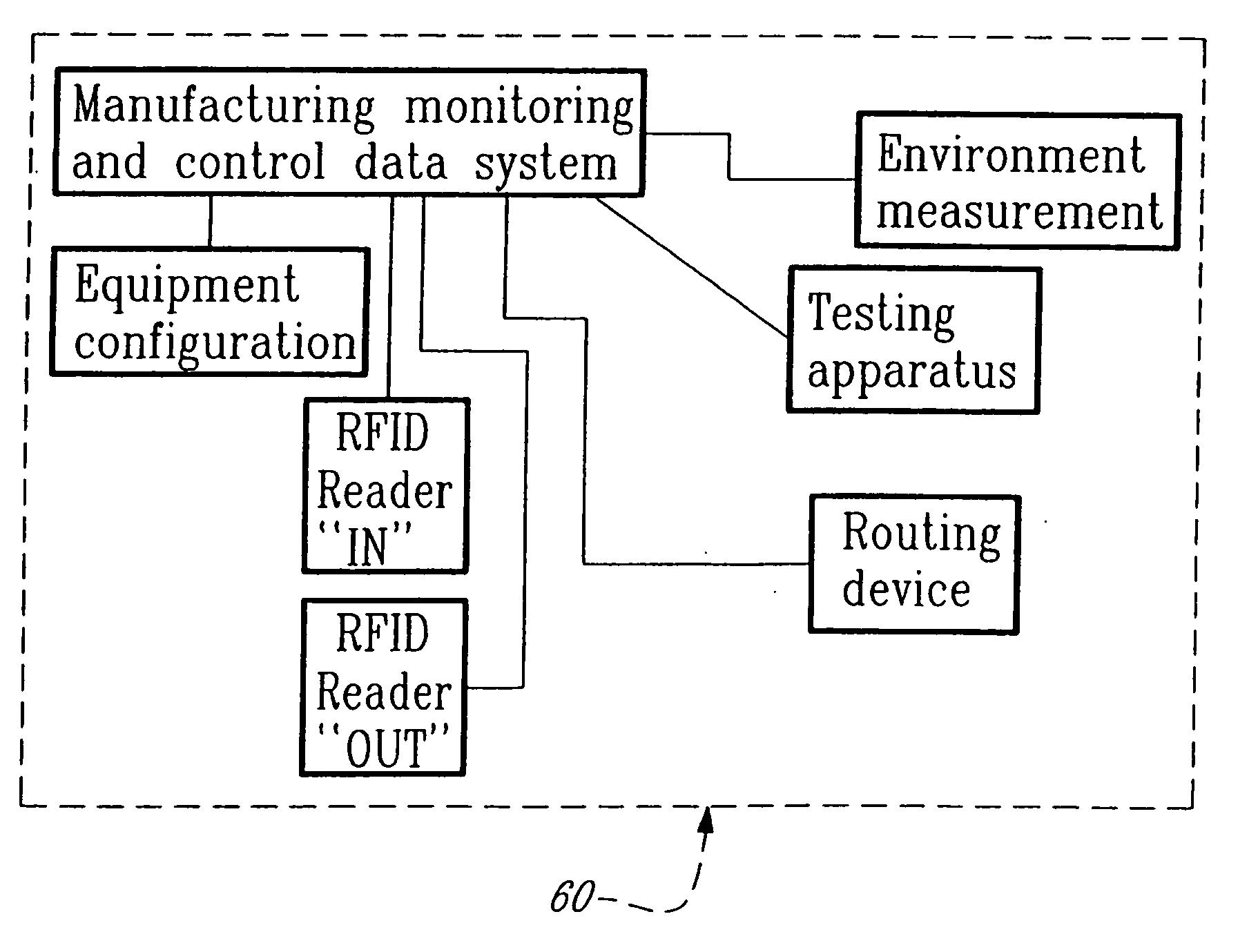

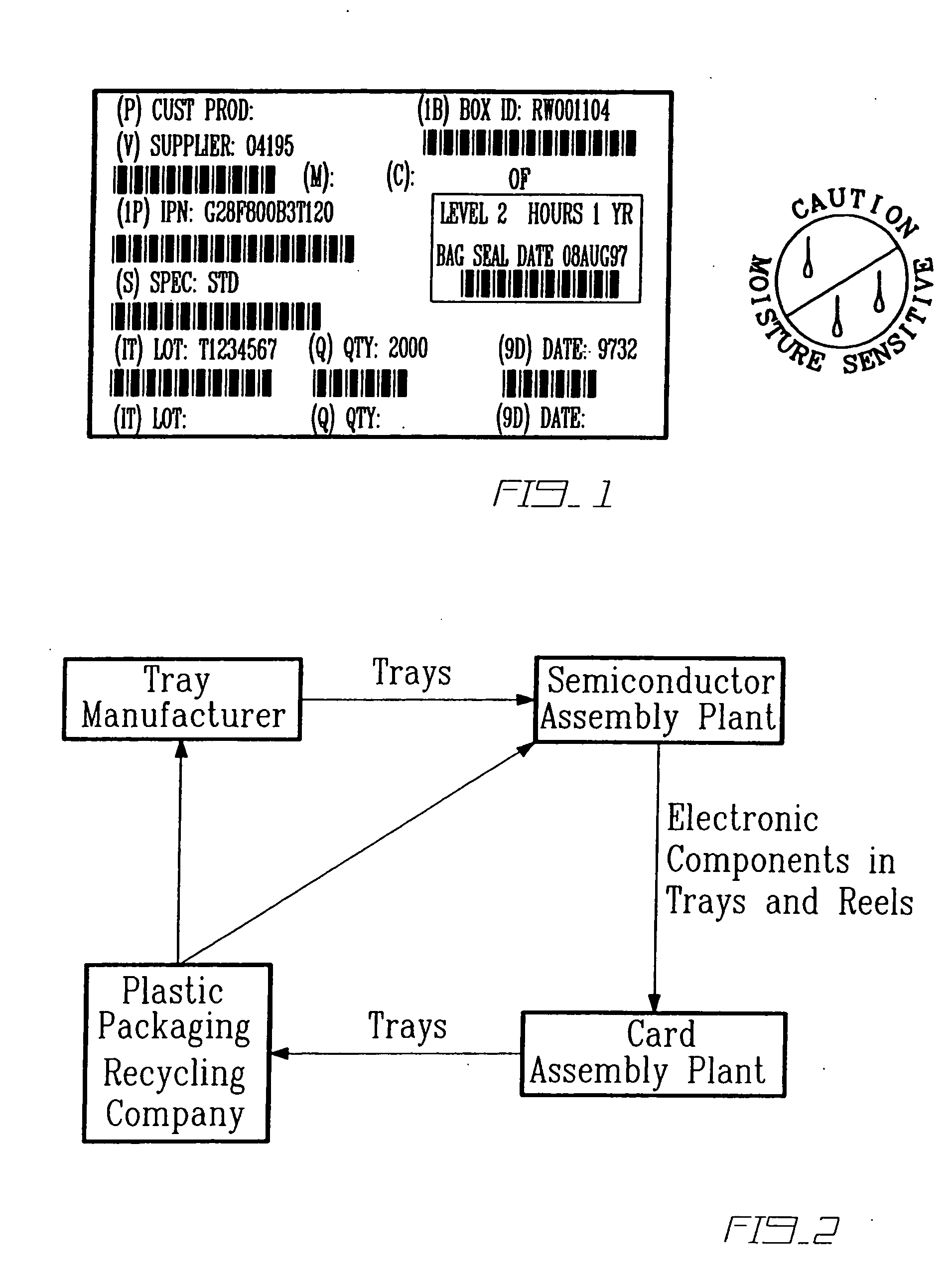

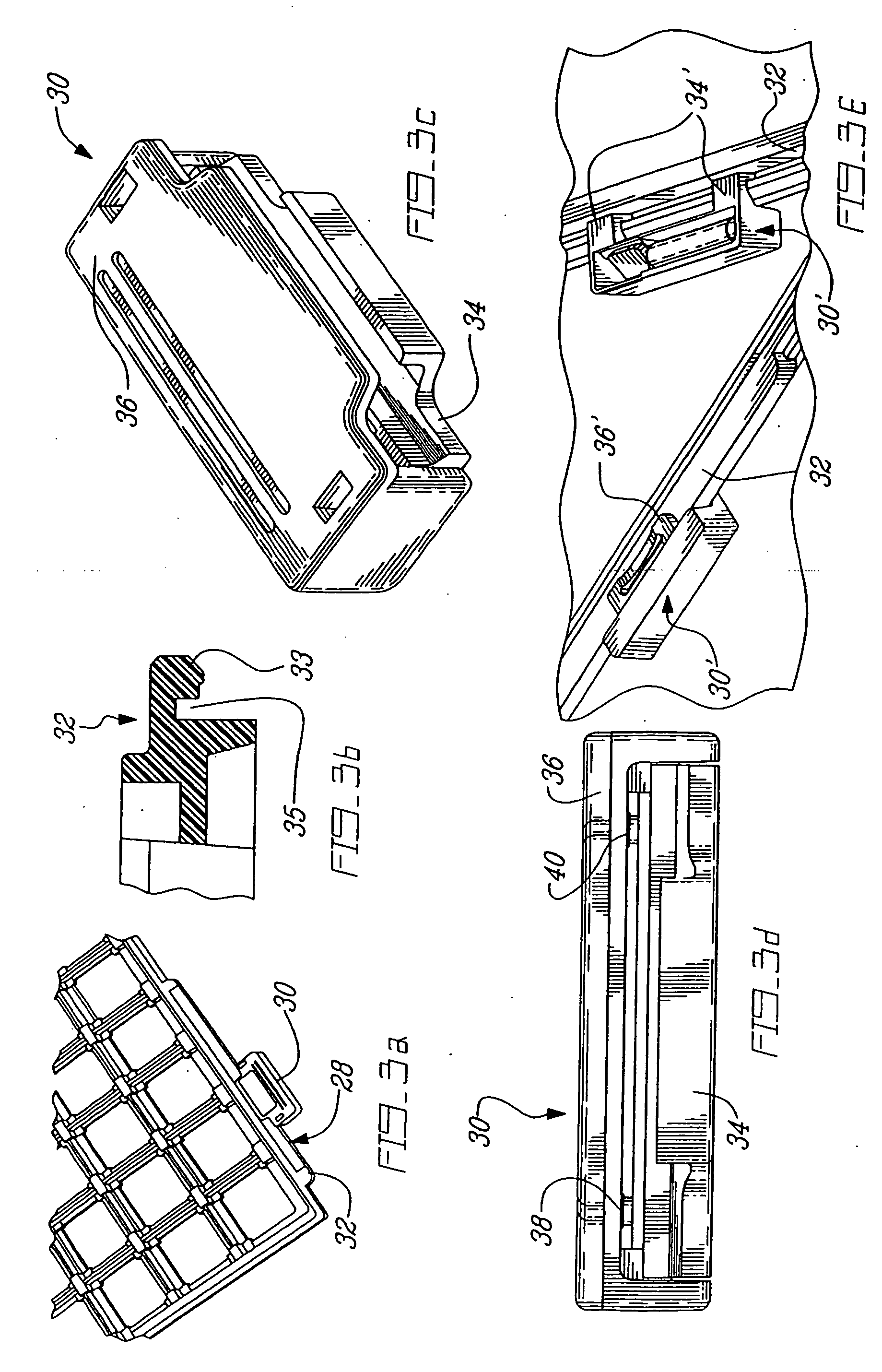

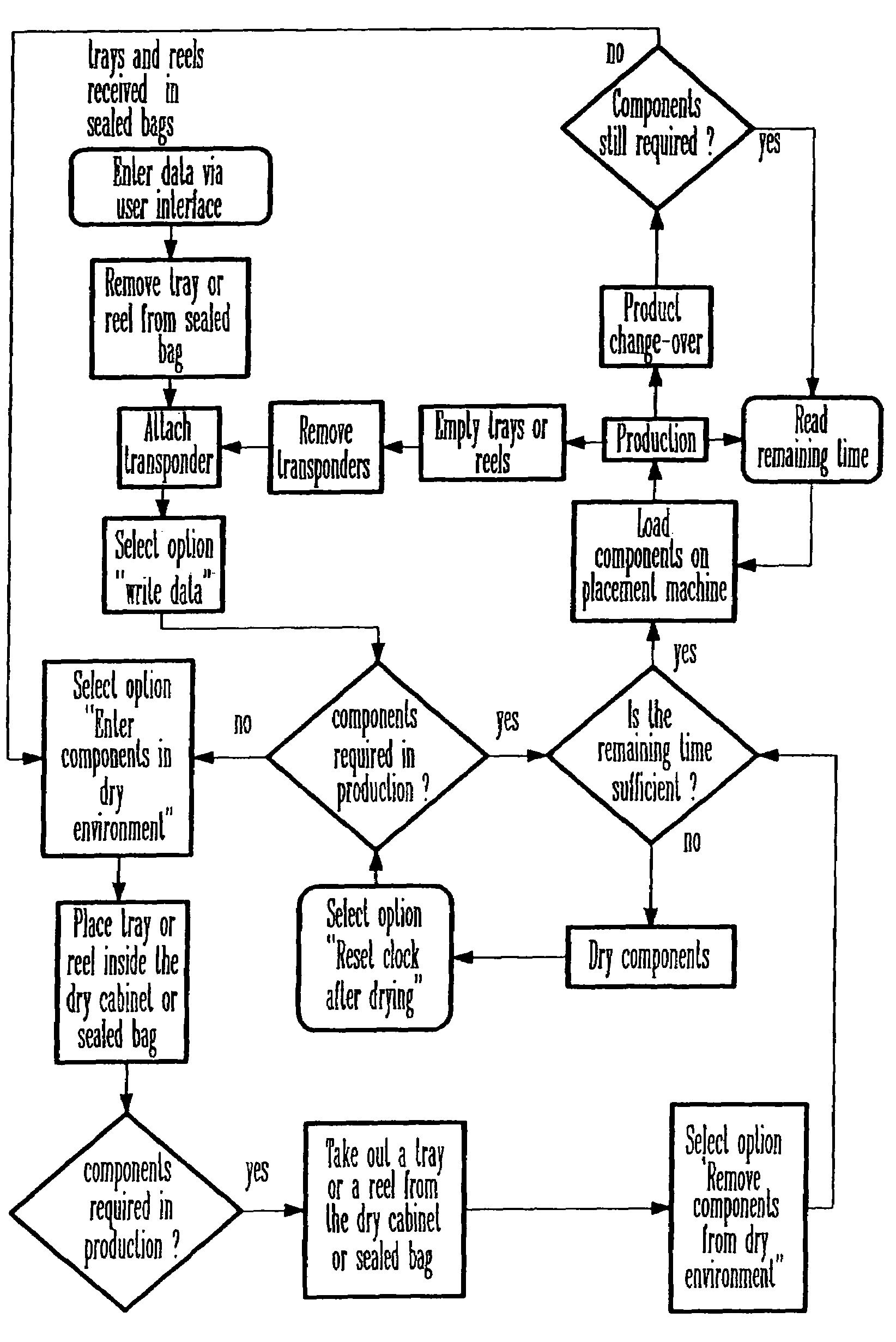

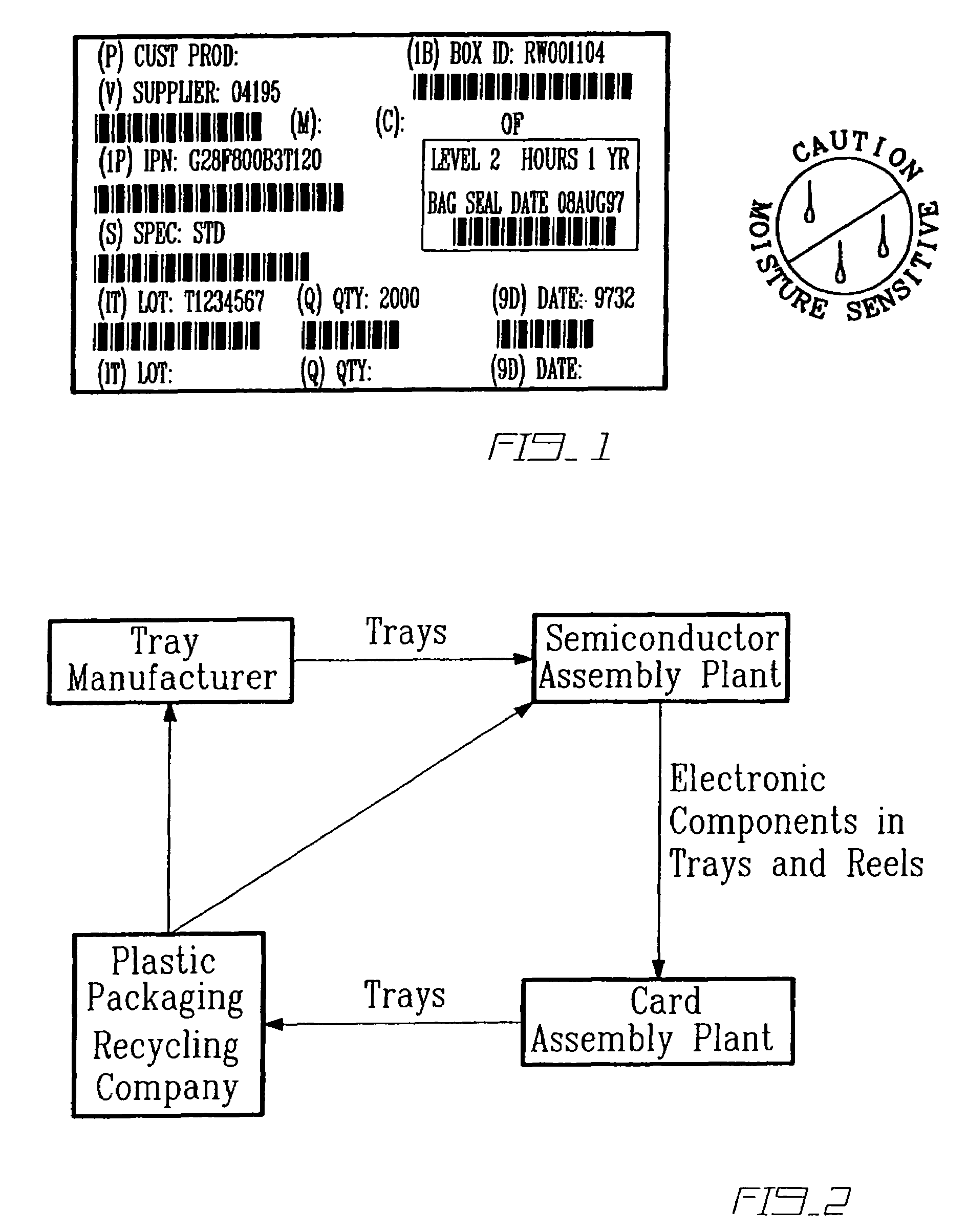

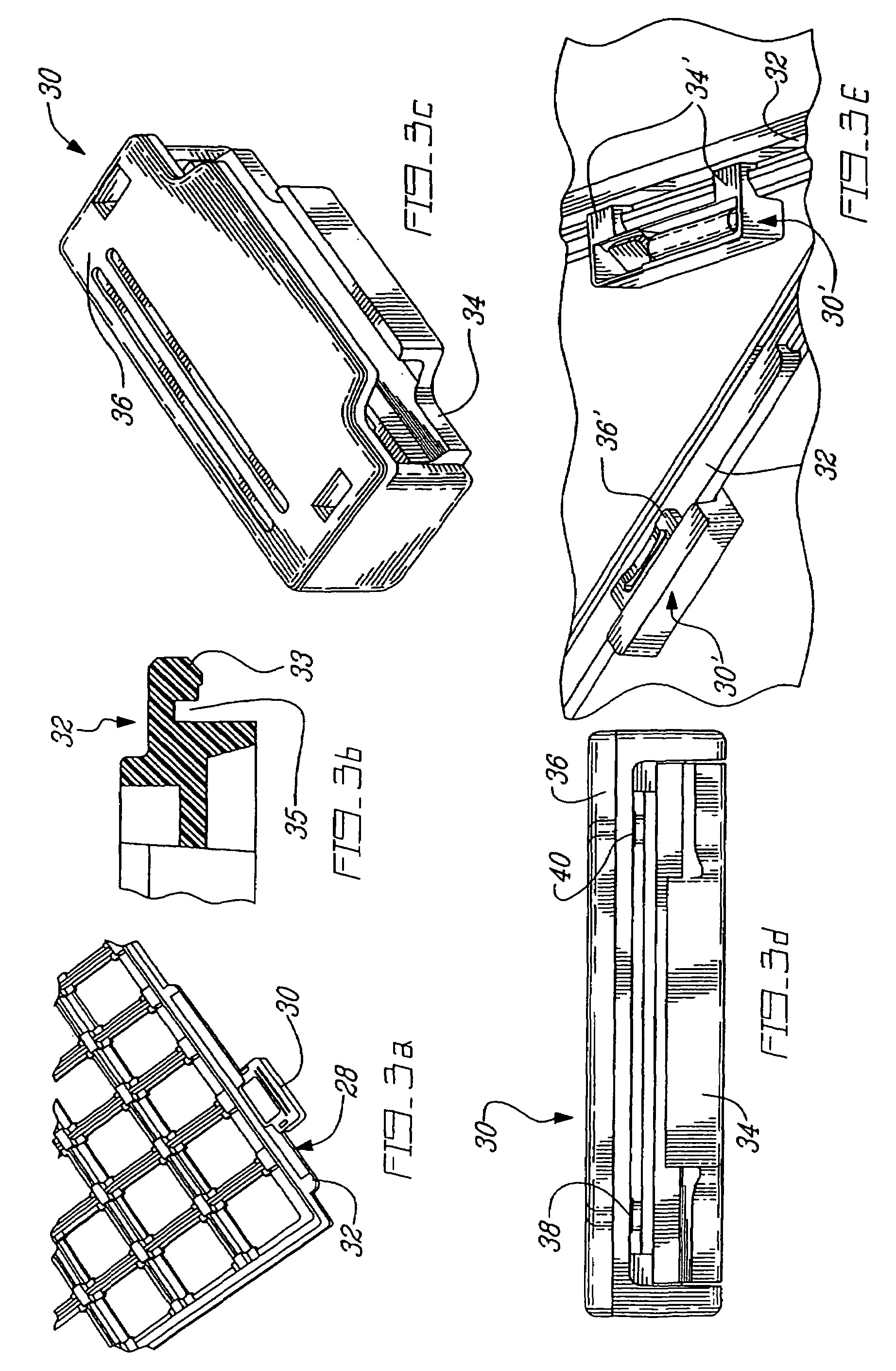

Automated manufacturing control system

InactiveUS7069100B2Reduce human interactionDigital data processing detailsTotal factory controlHuman interactionMachine

An automated manufacturing control system is proposed to greatly reduce the human interaction relative to the data transfer, physical verification and process control associated with the movement of components, tooling and operators in a manufacturing system. This is achieved by the use of data carriers which are attached to the object(s) to be traced. These data carriers (12) can store all the relevant identification, material and production data to required by the various elements, e.g. stations, of the manufacturing system. Various readers, integrated with controllers and application software, are located at strategic points of the production area, including production machines and storage areas, to enable automatic data transfer and physical verification that the right material is at the right place at the right time, using the right tooling.

Owner:COGISCAN

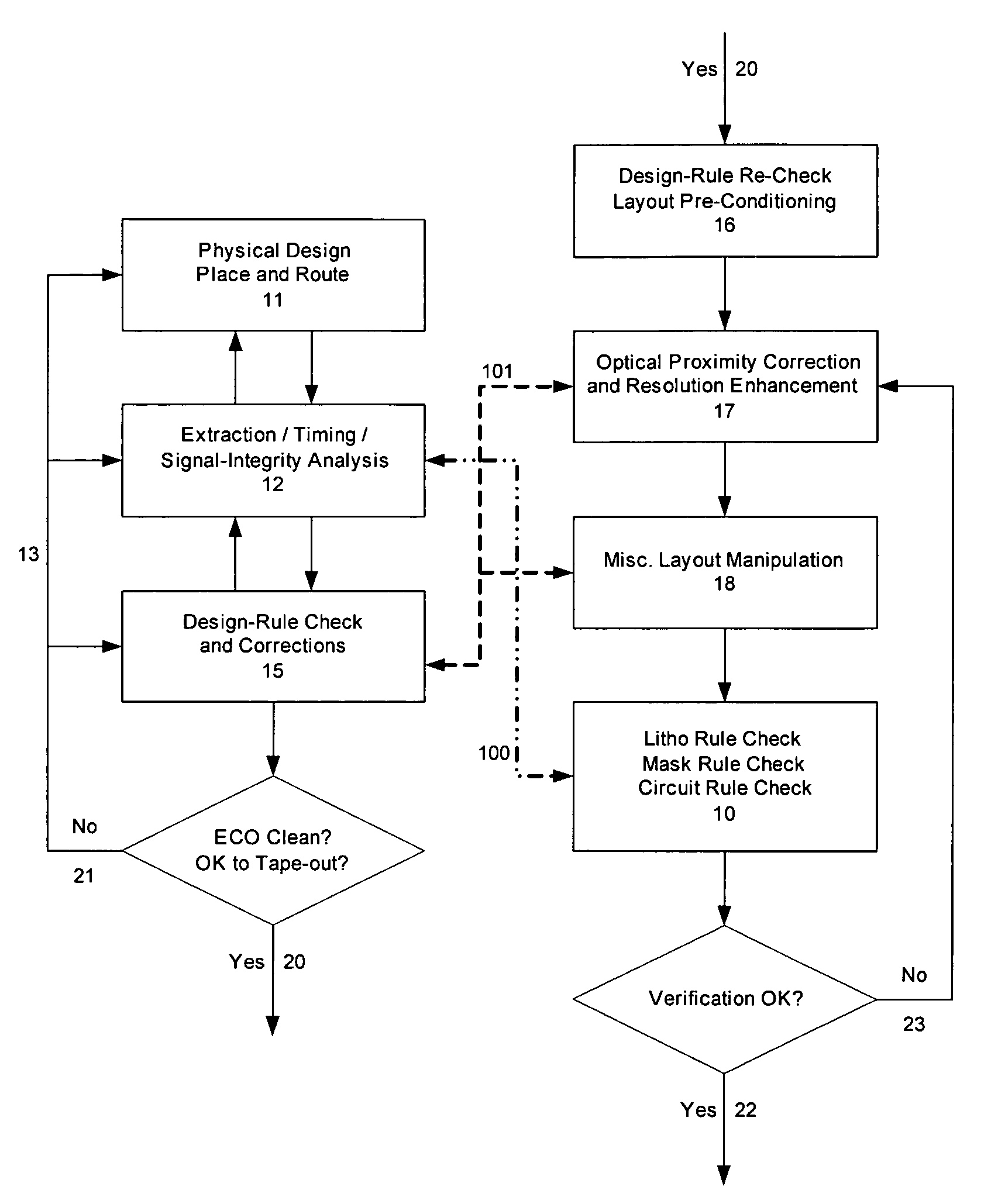

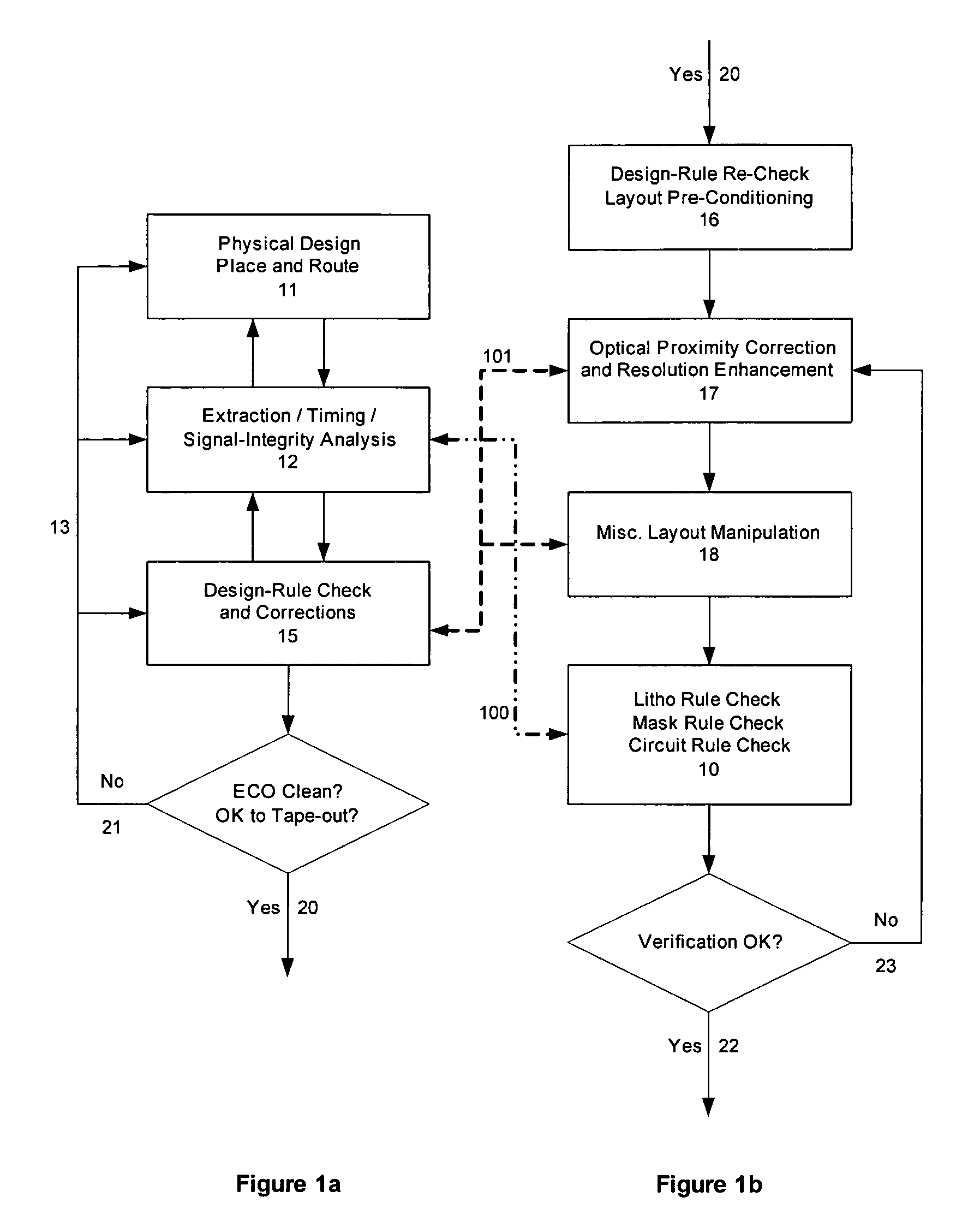

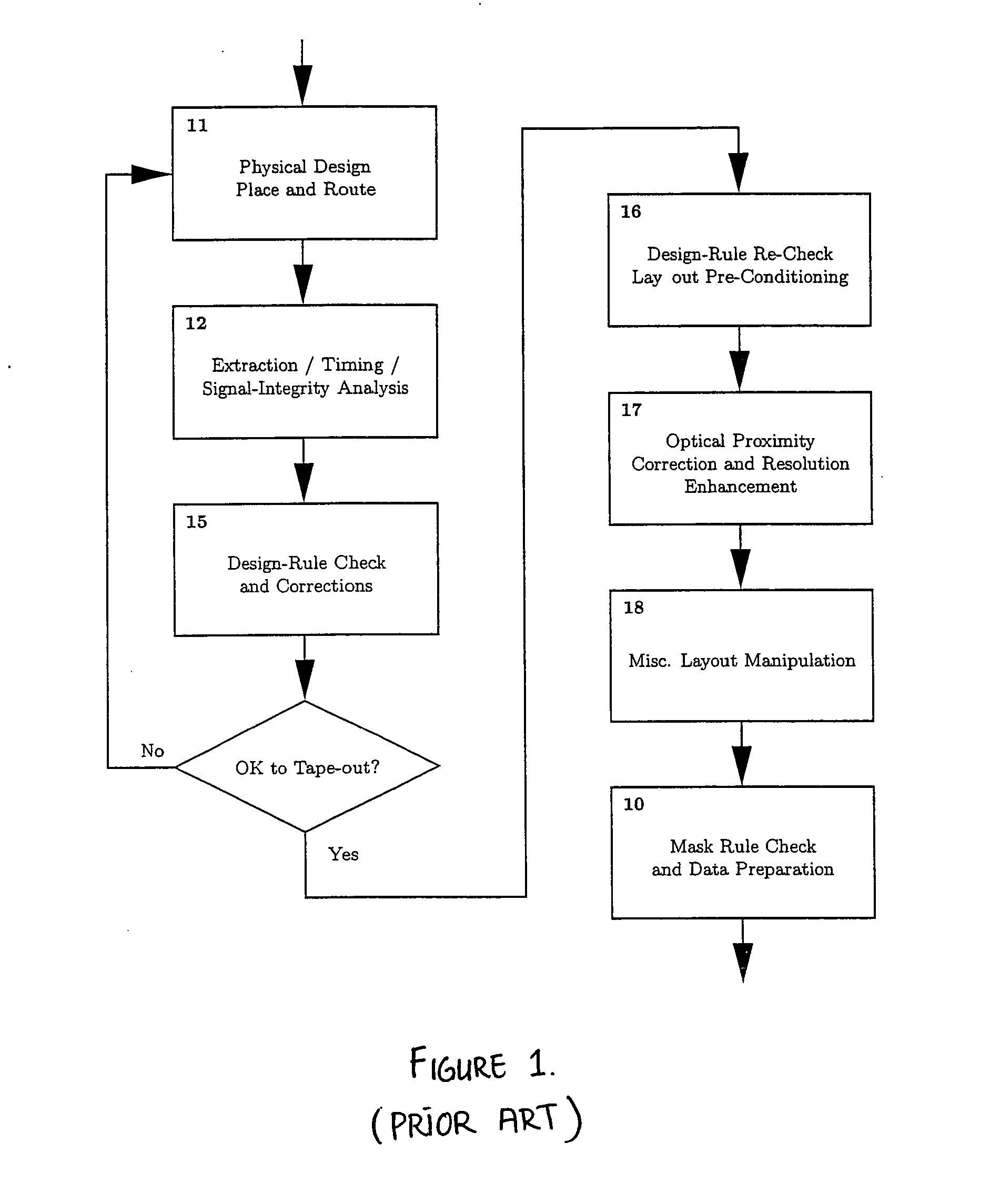

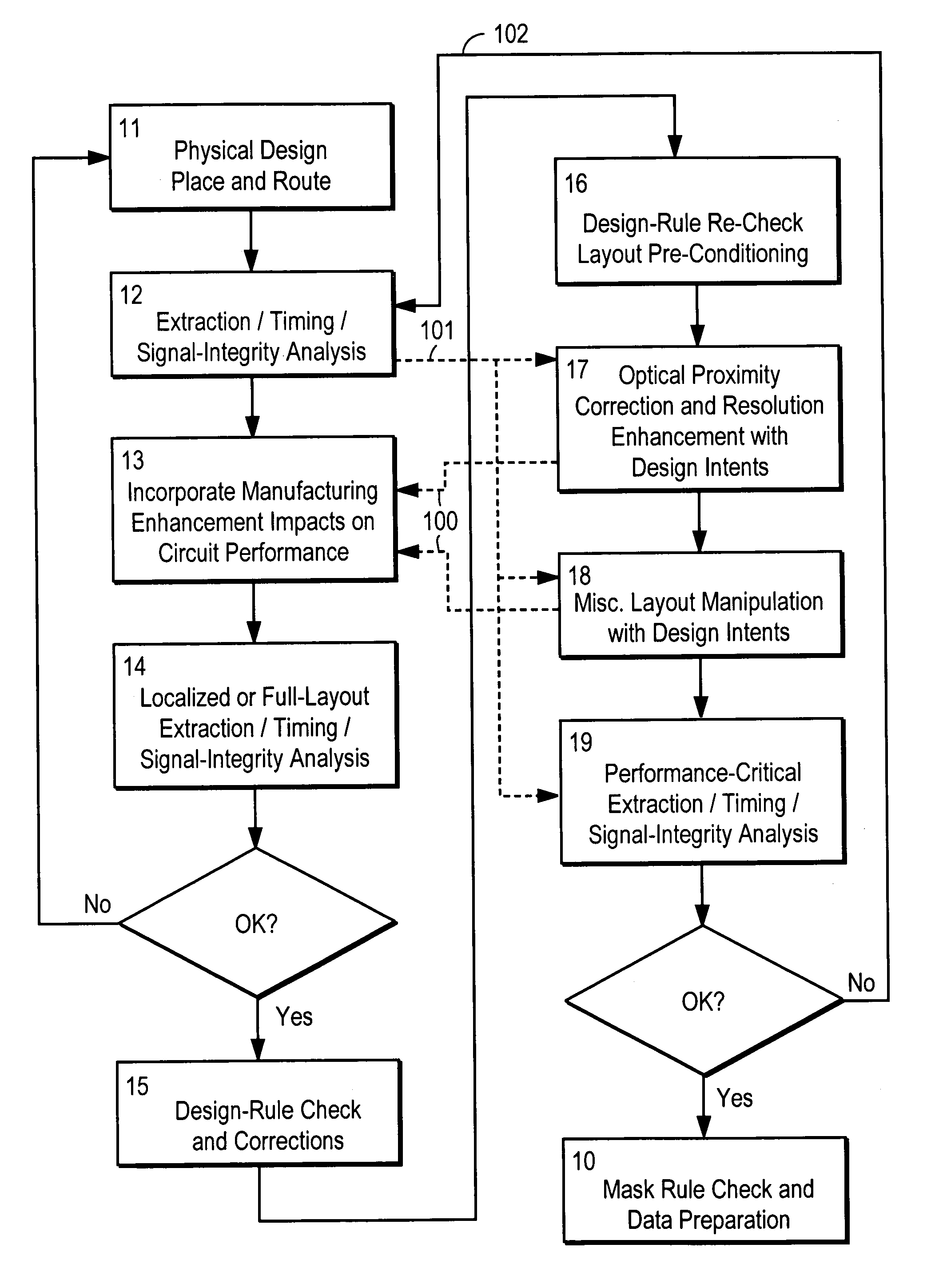

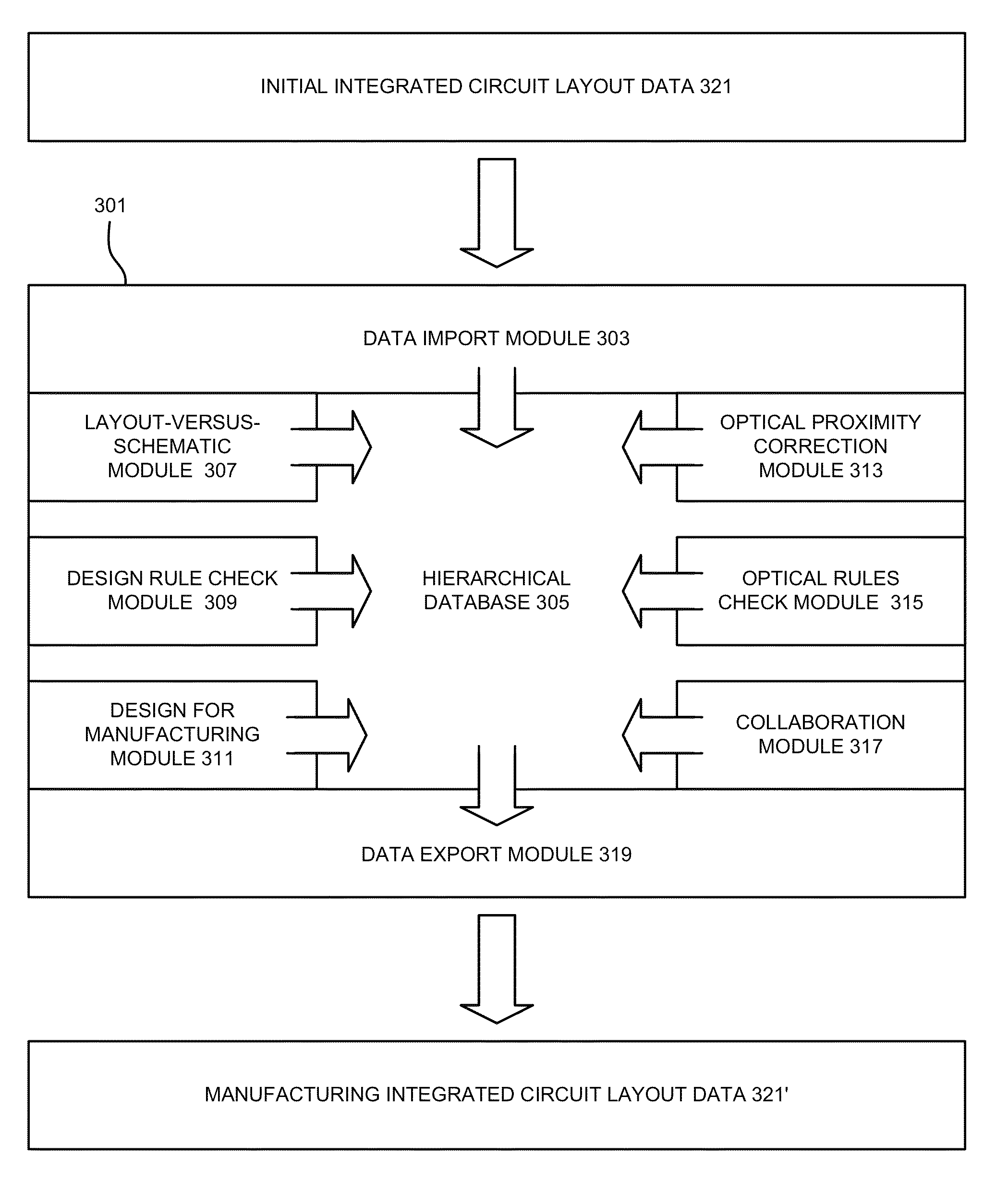

Method and platform for integrated physical verifications and manufacturing enhancements

InactiveUS20050044514A1High storageHigh memoryDigital computer detailsComputer aided designPhysical verificationEngineering

An automated design for manufacturability platform which provides integrated physical verification and manufacturing enhancement operations. The platform uses an efficient data structure capable of handling and manipulating both layout circuit and geometry characteristics, which permits a wide range of operations such as timing analysis, design-rule checking and optical proximity corrections on a single platform. This feature eliminates the need to translate layout representations between various tools without the requirement of using a common database. Moreover, the platform's common user interface enables encapsulated information exchange between the design and the manufacturing teams, permiting early consideration of manufacturing distortion or enhancement impact on circuit performance.

Owner:RPX CORP

Automated manufacturing control system

InactiveUS20060200261A1Reduce human interactionTotal factory controlSpecial data processing applicationsHuman interactionManufacturing technology

Owner:COGISCAN

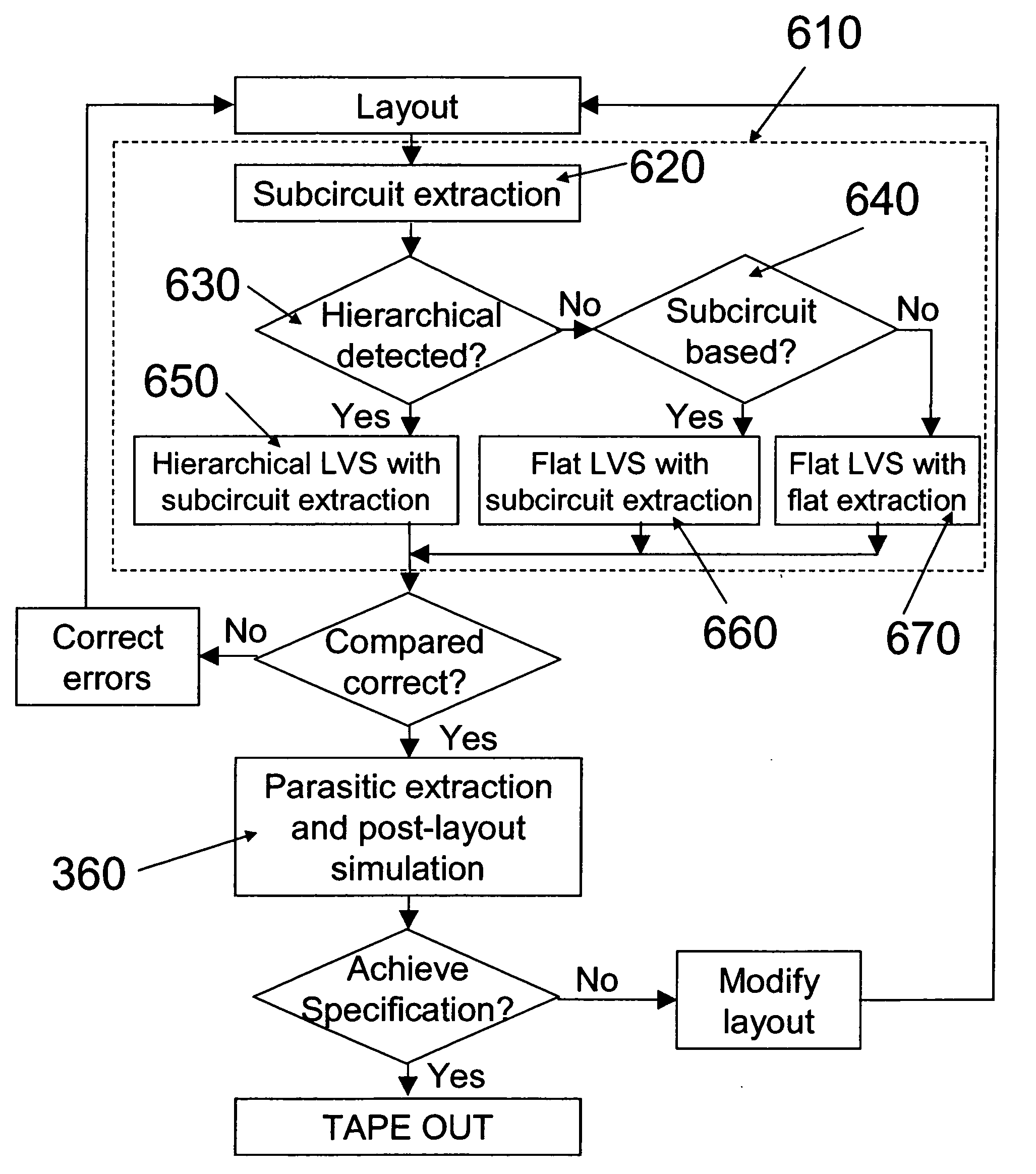

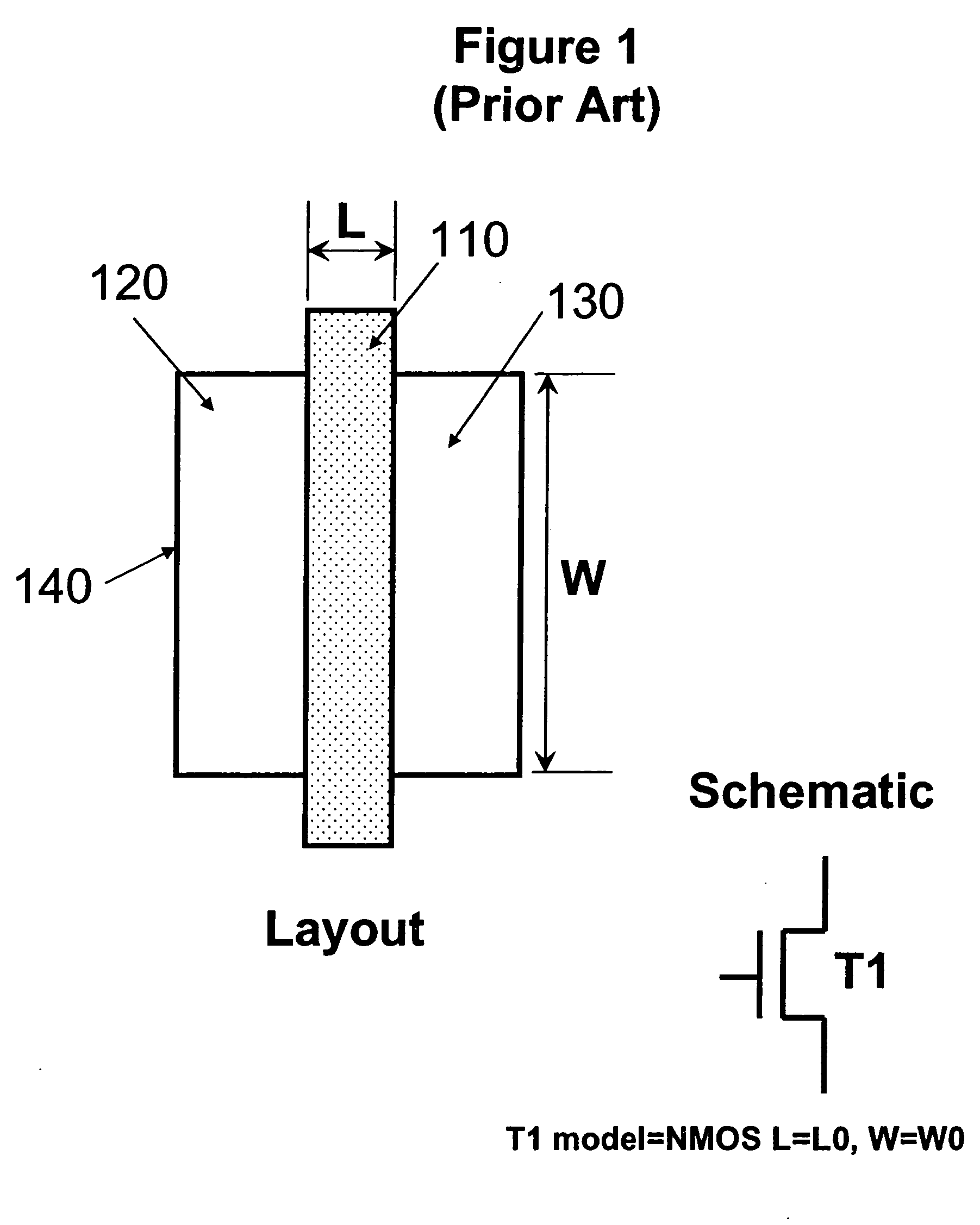

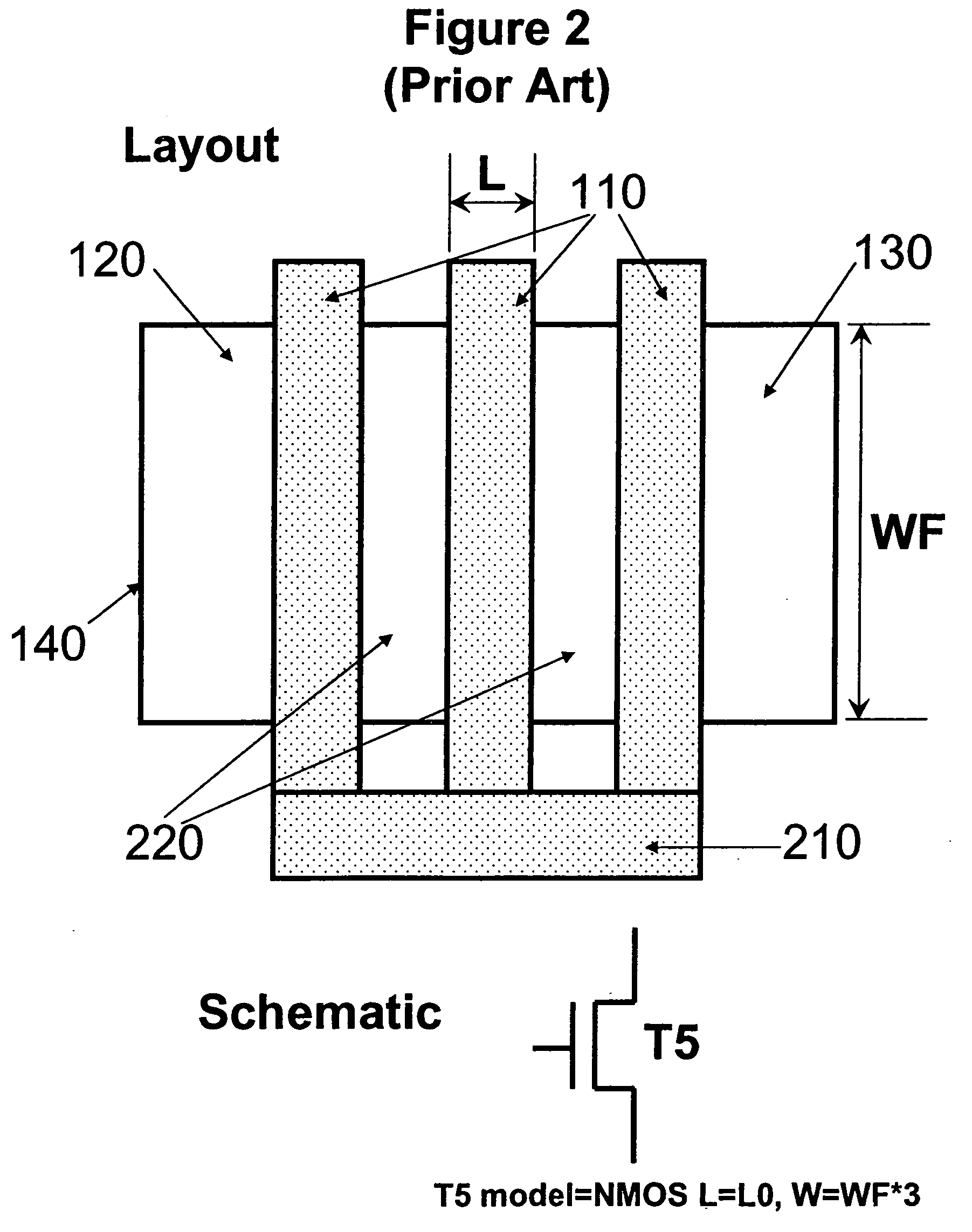

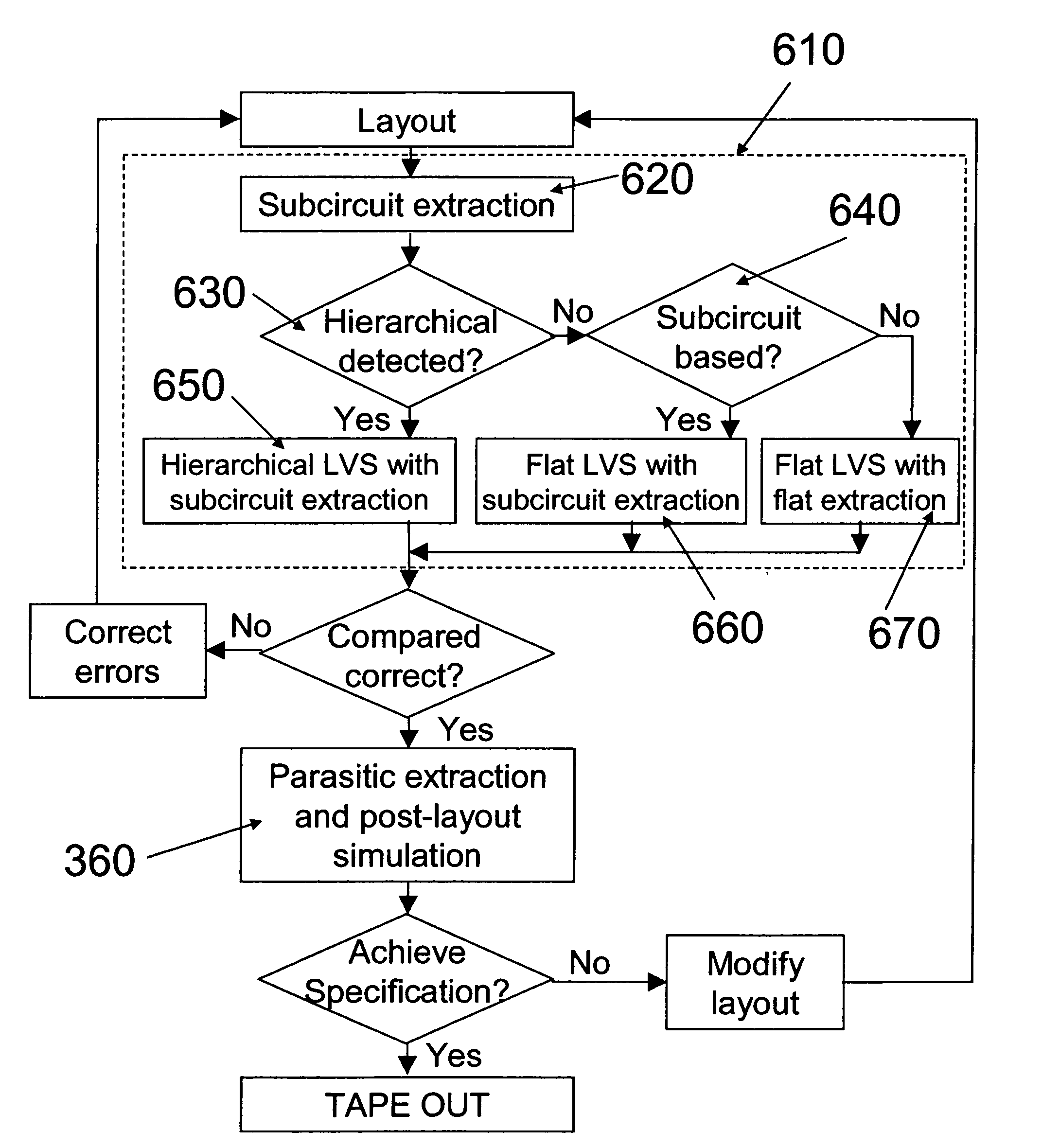

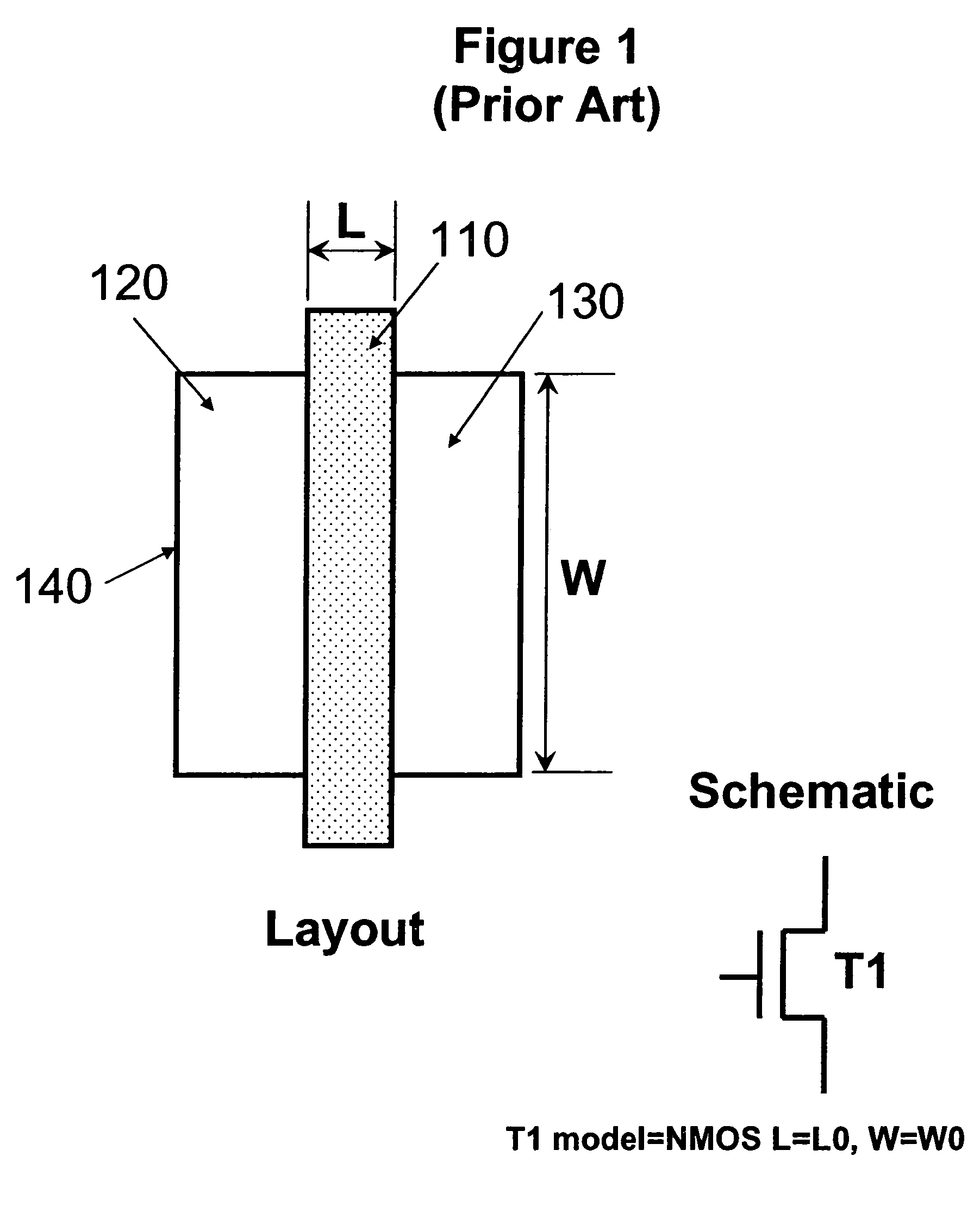

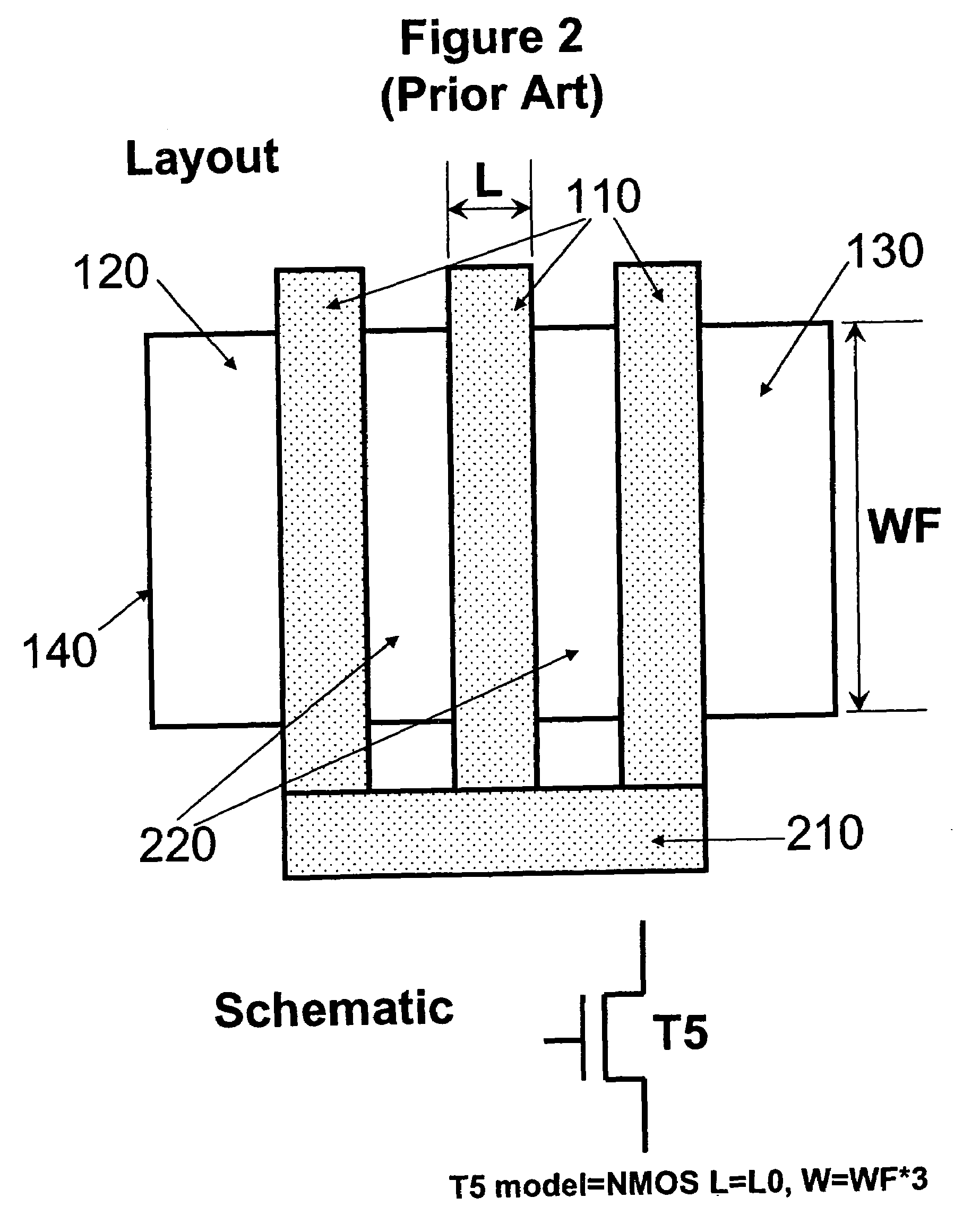

Method of checking the layout versus the schematic of multi-fingered MOS transistor layouts using a sub-circuit based extraction

InactiveUS20050216873A1Improve trustEasy to identifyCAD circuit designSoftware simulation/interpretation/emulationDevice PropertiesComputer architecture

A sub-circuit based extraction method which extracts a multi-finger MOS transistor directly as a sub-circuit is described. By adding three marking layers, the method provides the layout extracted netlist with a complete list of device geometric parameters corresponding to the device properties as presented in the sub-circuit model based schematic netlist. By performing a layout-versus-schematic comparison based on all geometric parameters extracted, the layout checking is performed in a complete and accurate way where each device parameter is checked against the corresponding design schematic. This complete and accurate geometric parameter comparison enhances the confidence level of the layout physical verification.

Owner:IBM CORP

Automated manufacturing control system

InactiveUS7286888B2Reduce human interactionTotal factory controlSpecial data processing applicationsHuman interactionManufacturing technology

Owner:COGISCAN

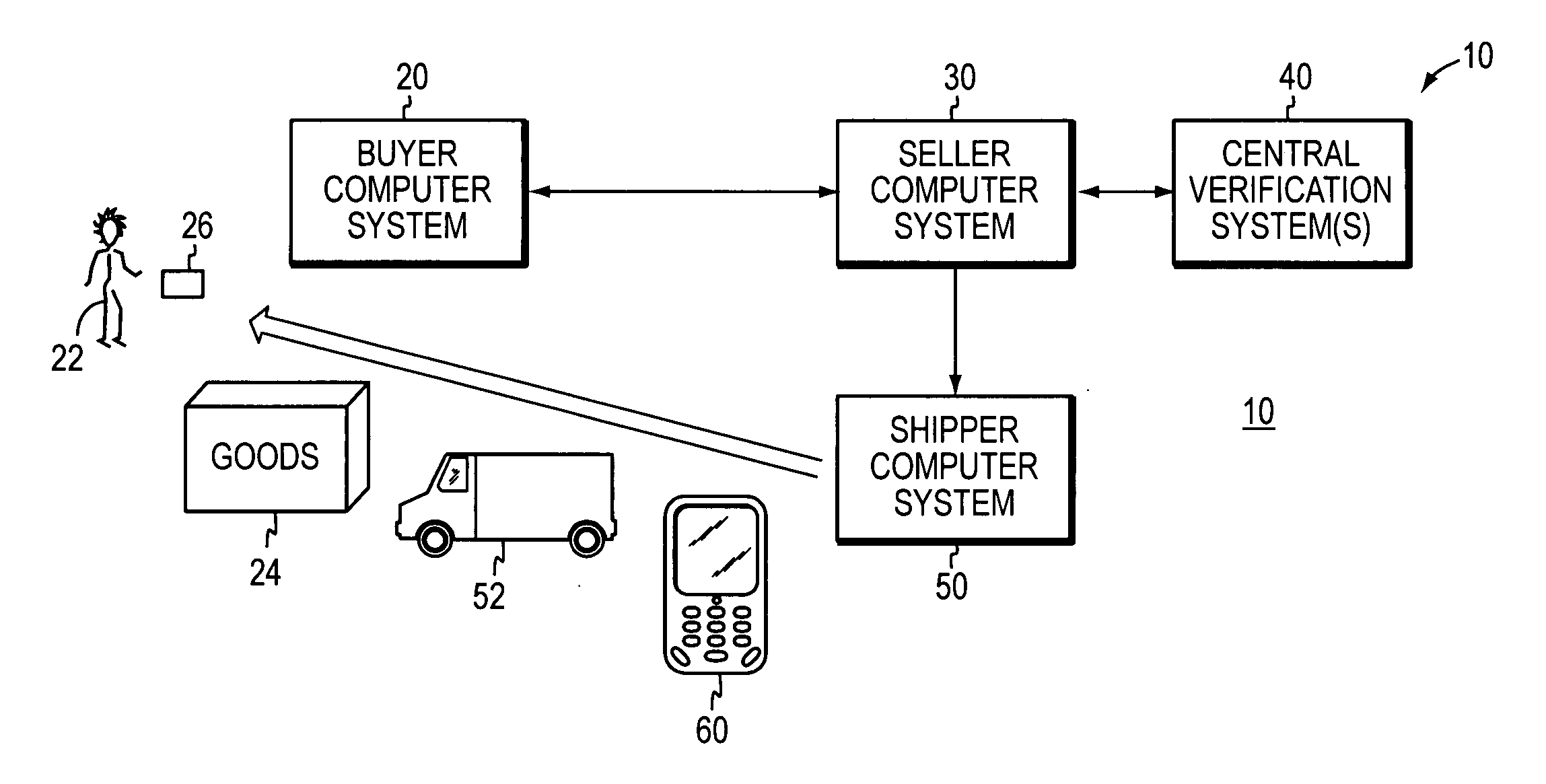

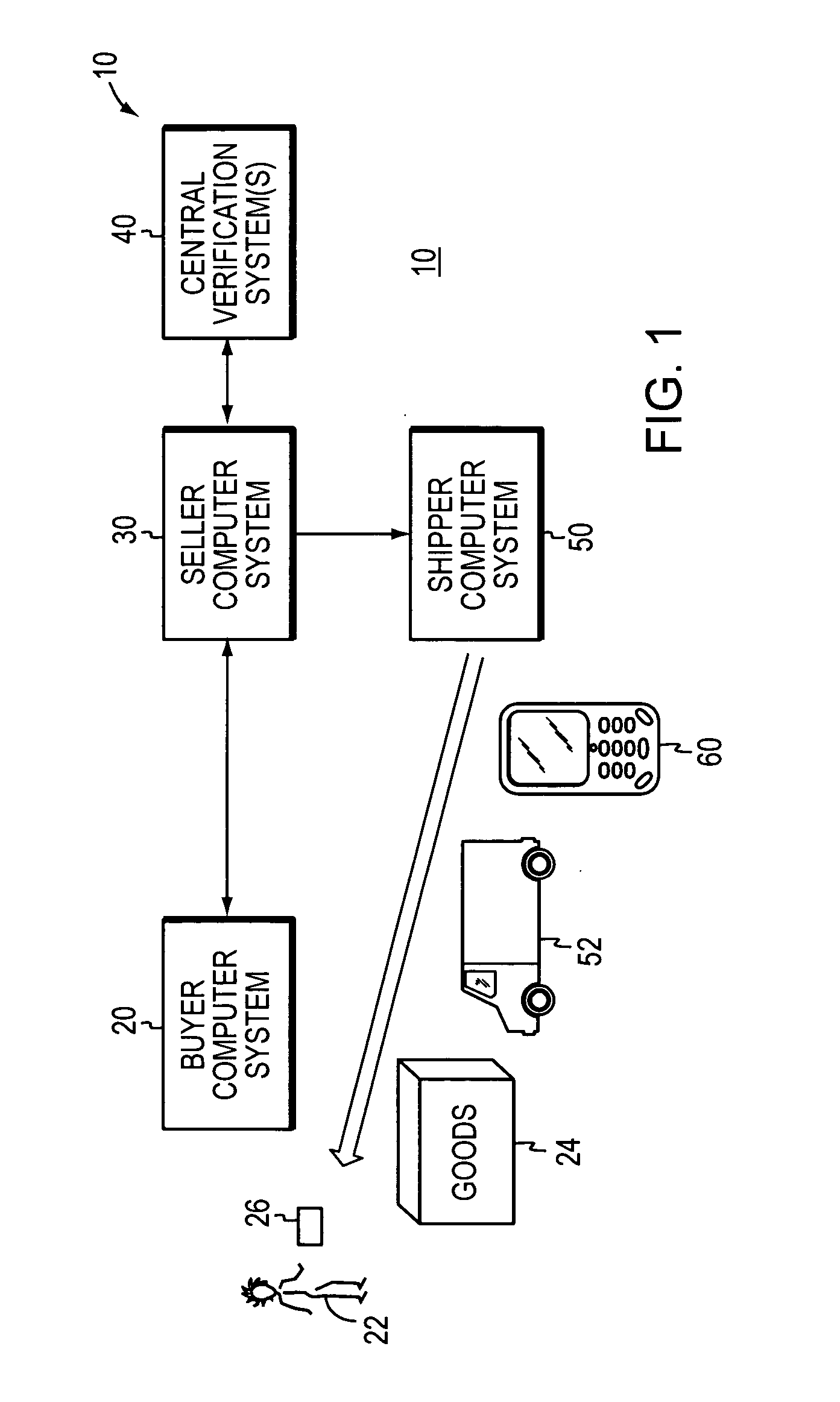

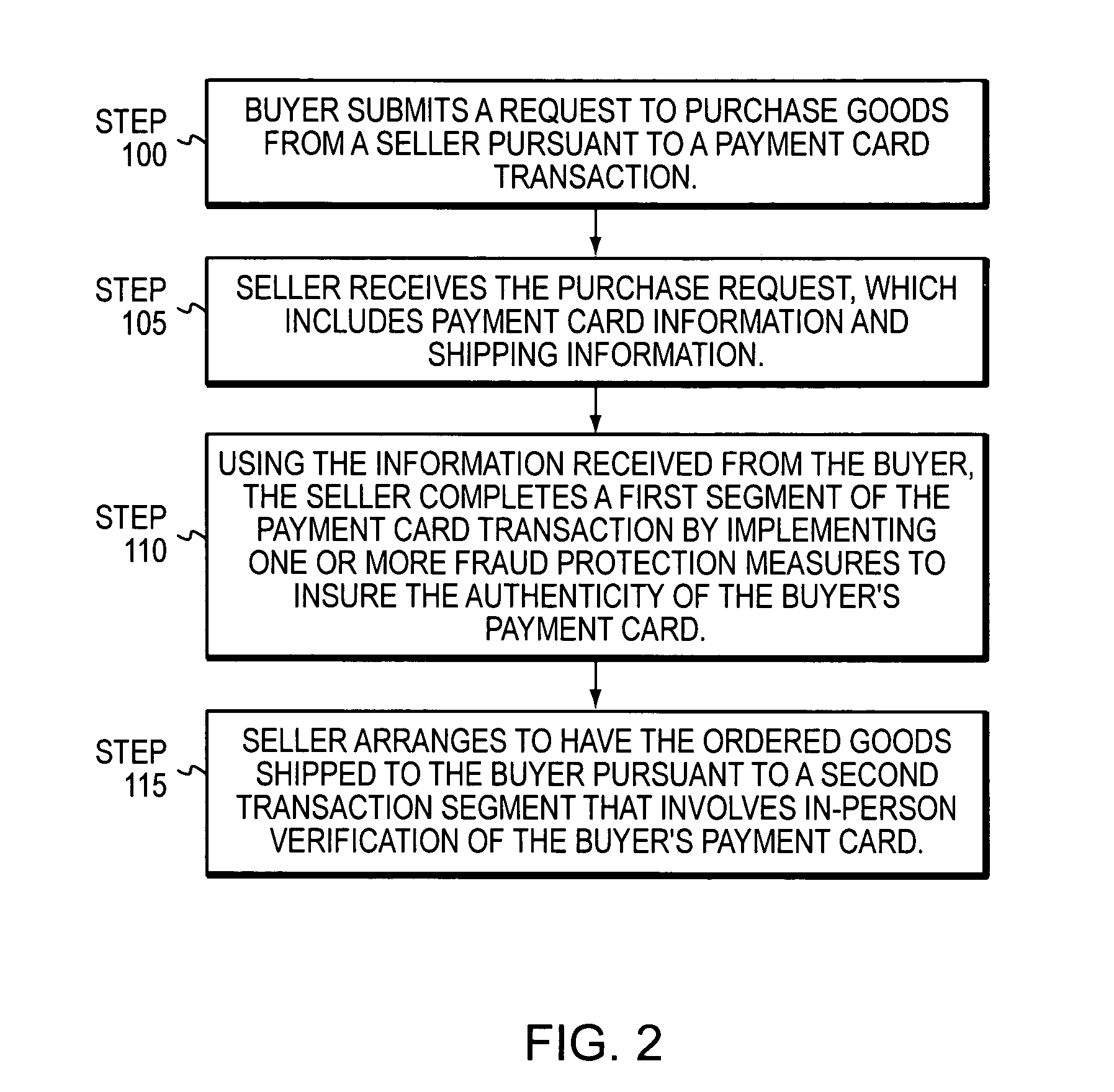

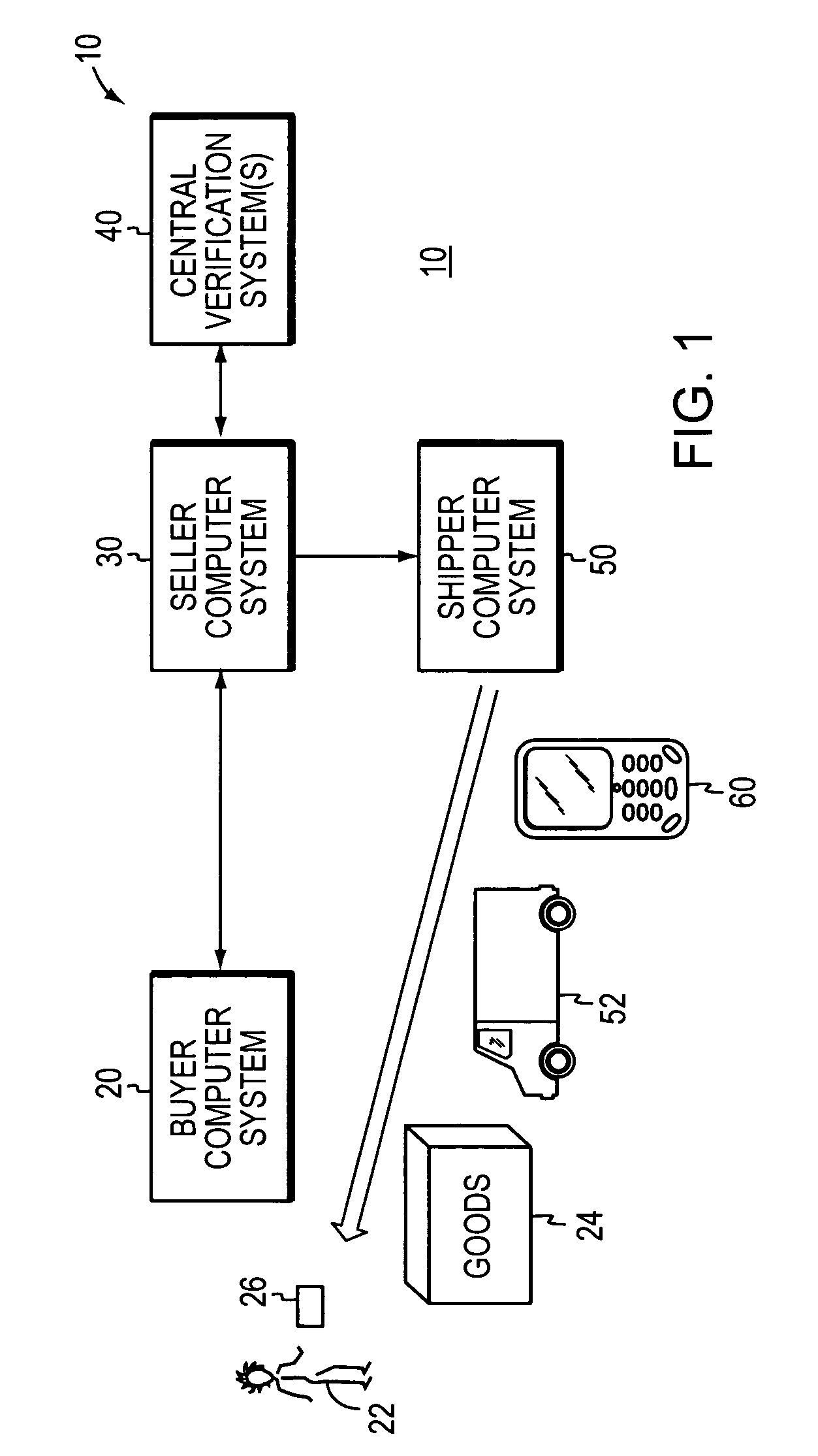

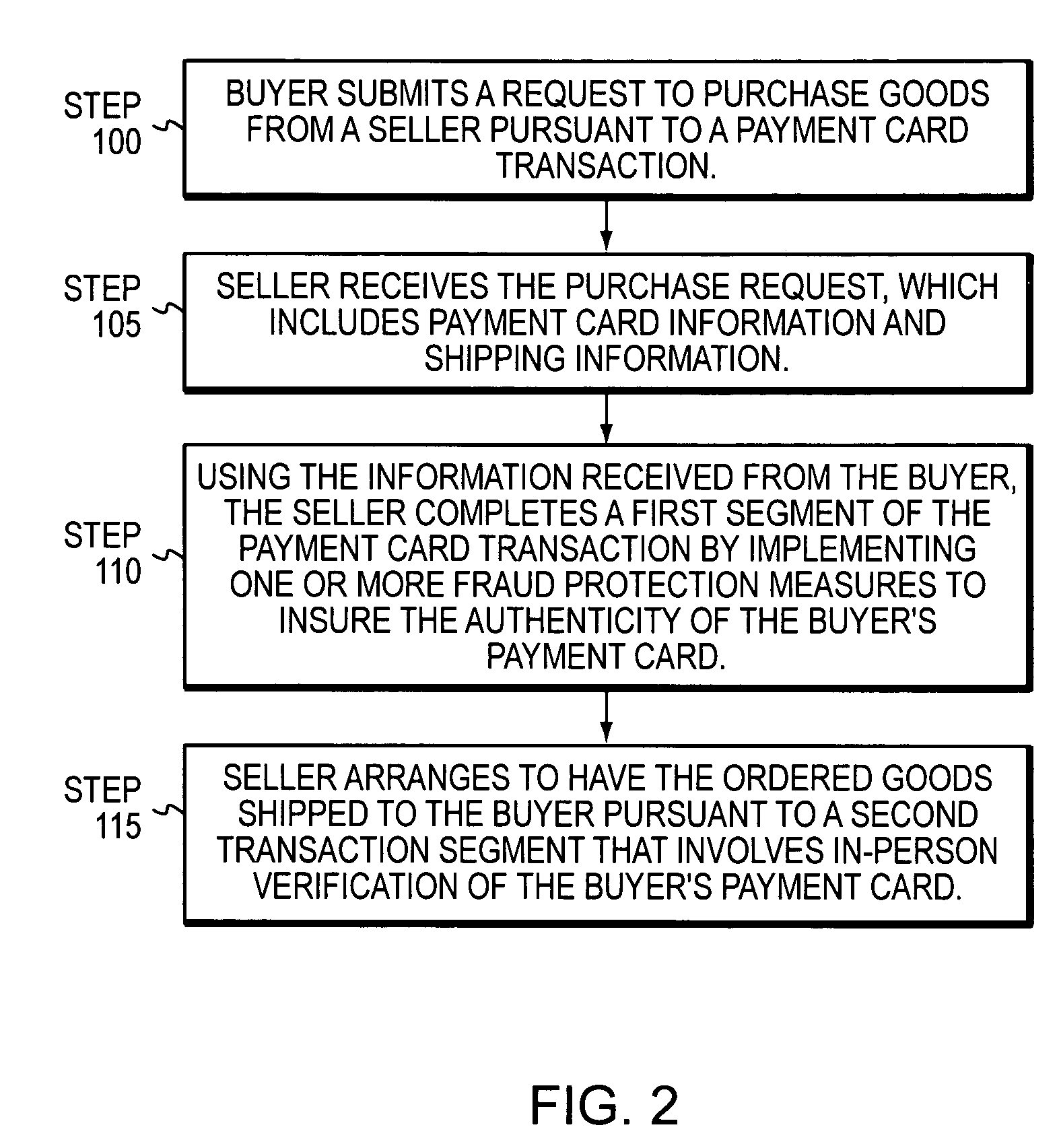

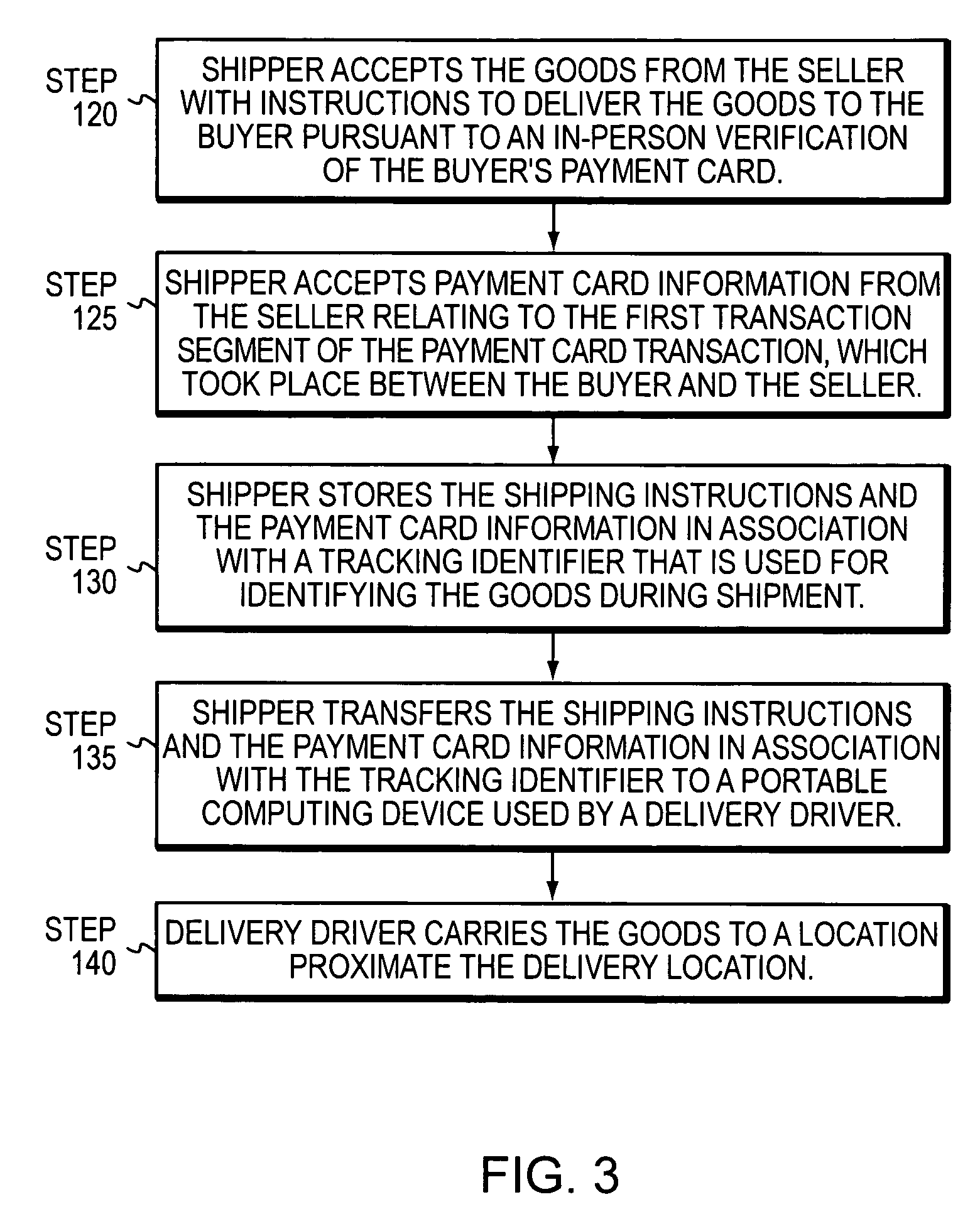

Delivery systems and methods involving verification of a payment card from a handheld device

The present invention relates generally to systems and methods that facilitate the prevention of fraud occurring in connection with credit cards, debit cards, smart cards and other payment cards that are used in transactions involving goods sold by a seller, delivered by a shipper, and purchased by a buyer. Specifically, the present invention provides systems and methods that allow for physical verification of a payment card (e.g., credit card) upon delivery of goods that are purchased in the context of a remote transaction between a buyer and a seller, including, for example, goods that are ordered via phone, mail order, fax or the Internet.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

Method and platform for integrated physical verifications and manufacturing enhancements

InactiveUS7100134B2Optimize circuit designDigital computer detailsComputer aided designPhysical verificationEngineering

An automated design for manufacturability platform which provides integrated physical verification and manufacturing enhancement operations. The platform uses an efficient data structure capable of handling and manipulating both layout circuit and geometry characteristics, which permits a wide range of operations such as timing analysis, design-rule checking and optical proximity corrections on a single platform. This feature eliminates the need to translate layout representations between various tools without the requirement of using a common database. Moreover, the platform's common user interface enables encapsulated information exchange between the design and the manufacturing teams, permiting early consideration of manufacturing distortion or enhancement impact on circuit performance.

Owner:RPX CORP

Method of checking the layout versus the schematic of multi-fingered MOS transistor layouts using a sub-circuit based extraction

InactiveUS7139990B2Improve trustEasy to identifyCAD circuit designSoftware simulation/interpretation/emulationComputer architectureDevice Properties

A sub-circuit based extraction method which extracts a multi-finger MOS transistor directly as a sub-circuit is described. By adding three marking layers, the method provides the layout extracted netlist with a complete list of device geometric parameters corresponding to the device properties as presented in the sub-circuit model based schematic netlist. By performing a layout-versus-schematic comparison based on all geometric parameters extracted, the layout checking is performed in a complete and accurate way where each device parameter is checked against the corresponding design schematic. This complete and accurate geometric parameter comparison enhances the confidence level of the layout physical verification.

Owner:IBM CORP

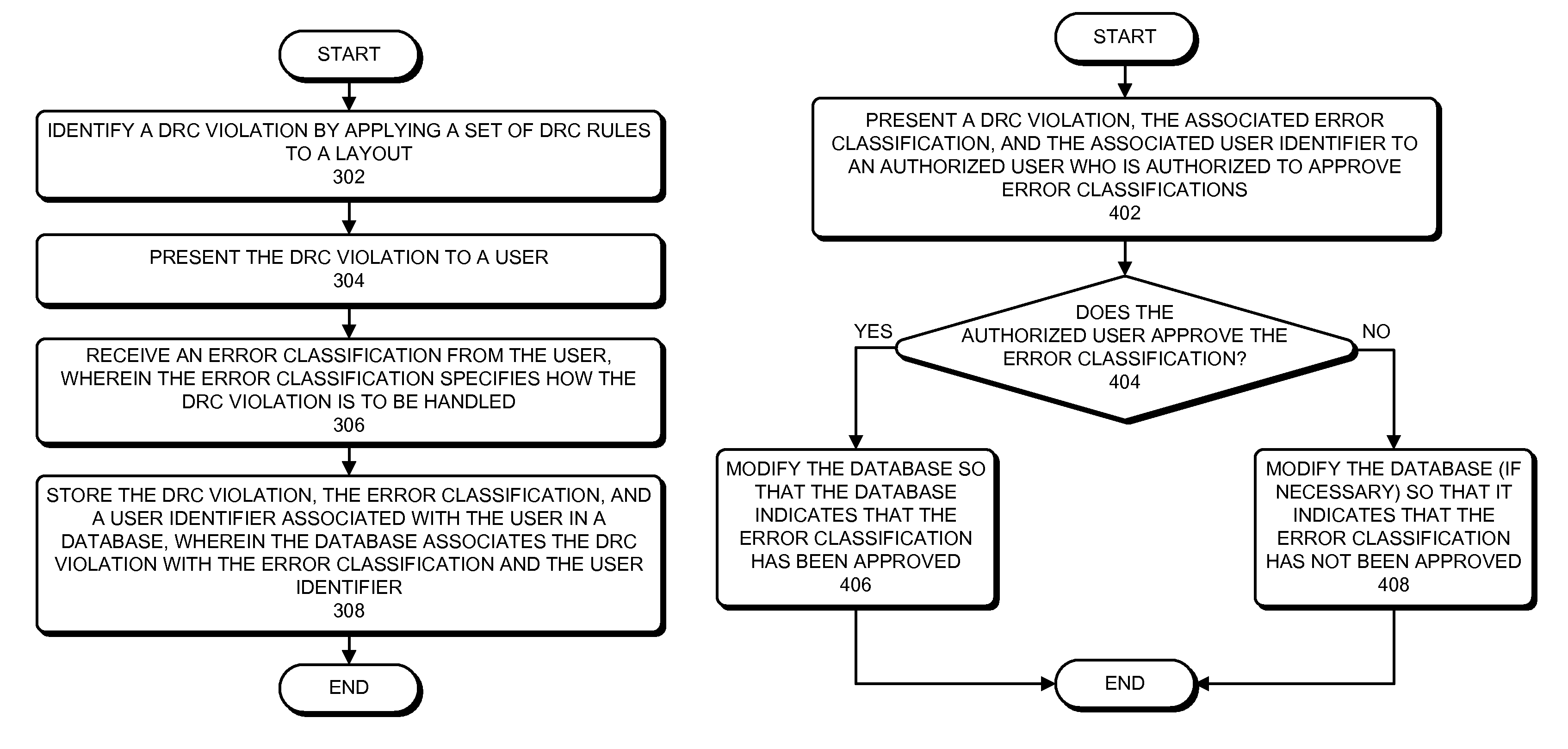

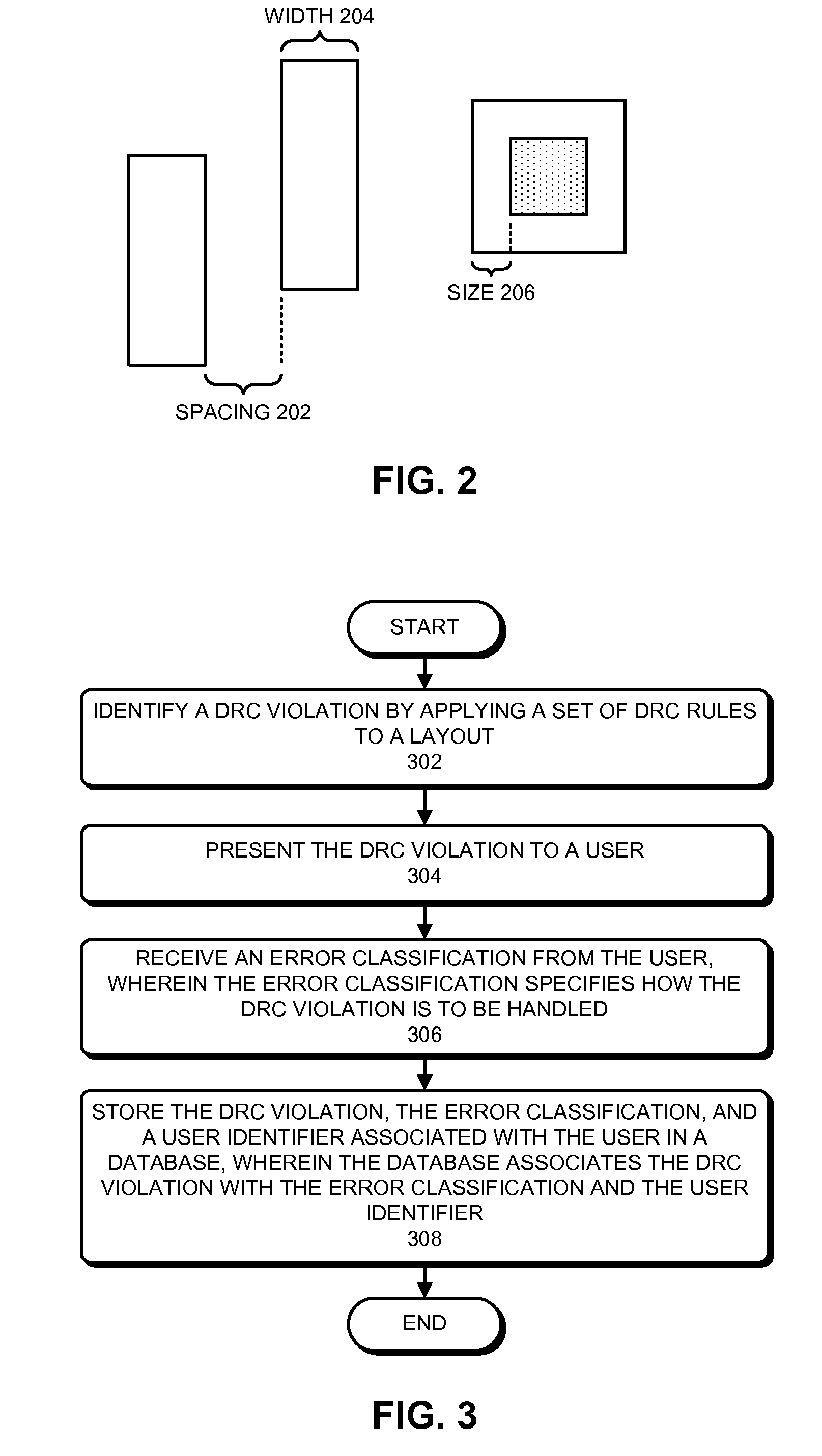

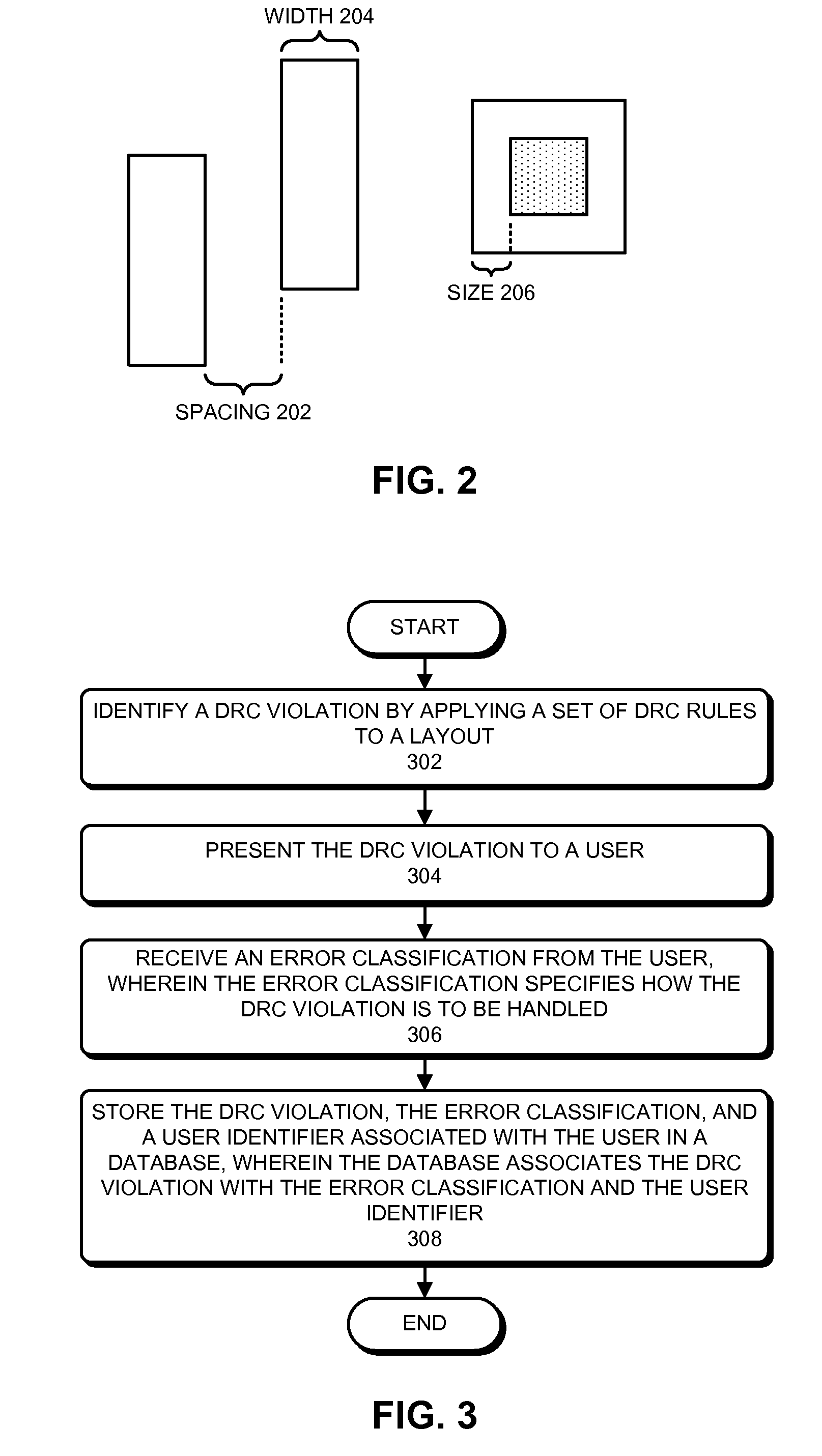

Method and apparatus for managing violations and error classifications during physical verification

ActiveUS8091055B2Increase probabilitySpeeding up applicationDigital data processing detailsComputer programmed simultaneously with data introductionPhysical verificationUser identifier

Owner:SYNOPSYS INC

Method and apparatus for managing violations and error classifications during physical verification

ActiveUS20100192113A1Increase probabilitySpeeding up applicationDigital data processing detailsComputer programmed simultaneously with data introductionPhysical verificationUser identifier

Some embodiments provide a system for managing violations during physical verification. The system may identify a design-rule-check (DRC) violation by applying a set of DRC rules to a layout. The system can then receive an error classification from the user which specifies how the DRC violation is to be handled. Next, the system can store the DRC violation, the user-selected error classification, and a user identifier associated with the user in a database. If the user is not authorized to approve the error classification, the database can indicate that the error classification has not been approved. Later, a user who is authorized to approve the error classification can approve the error classification. The system can determine if a cell is known, and if so, the system can use the violations and error classifications stored in the database to speed up the verification process.

Owner:SYNOPSYS INC

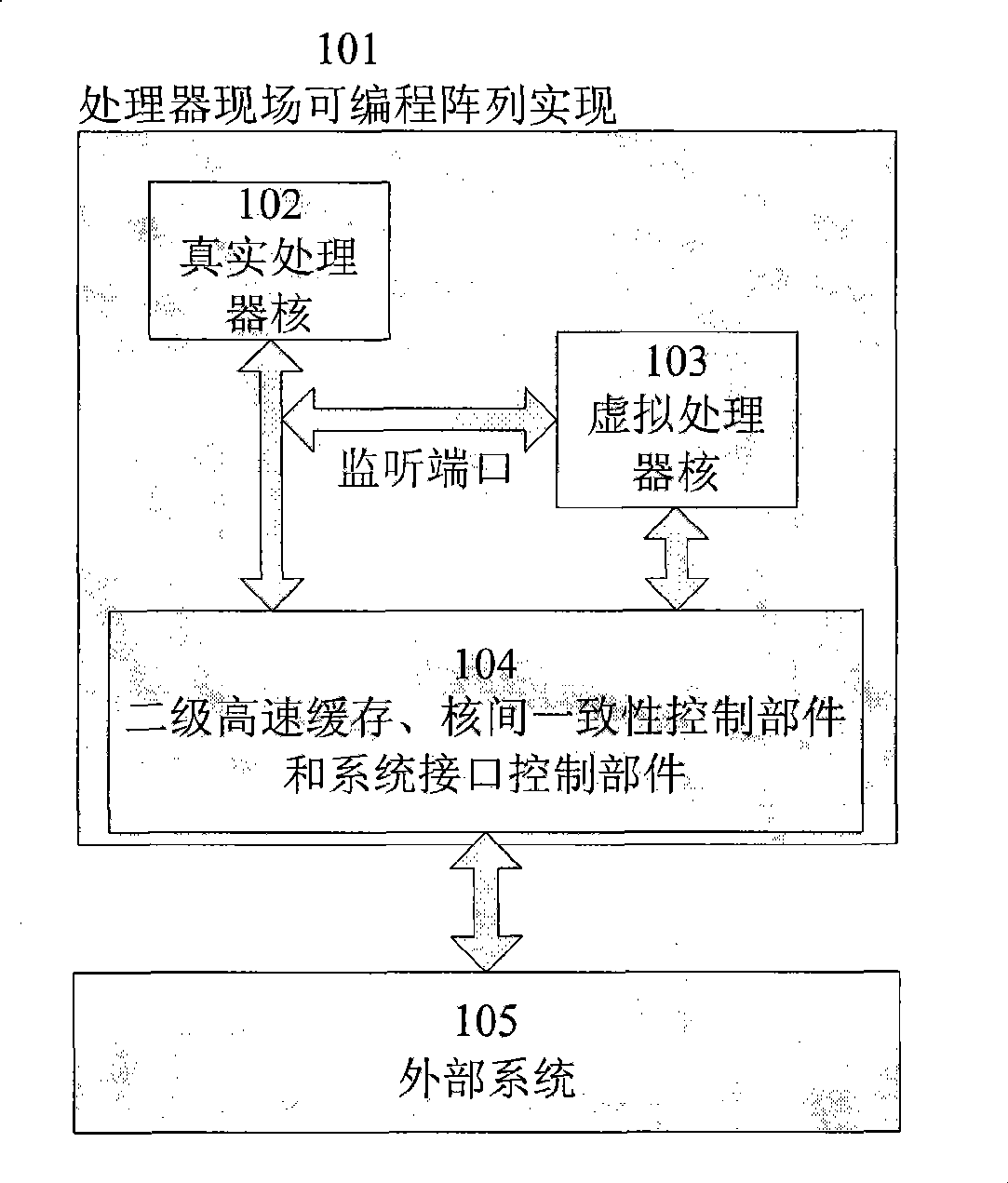

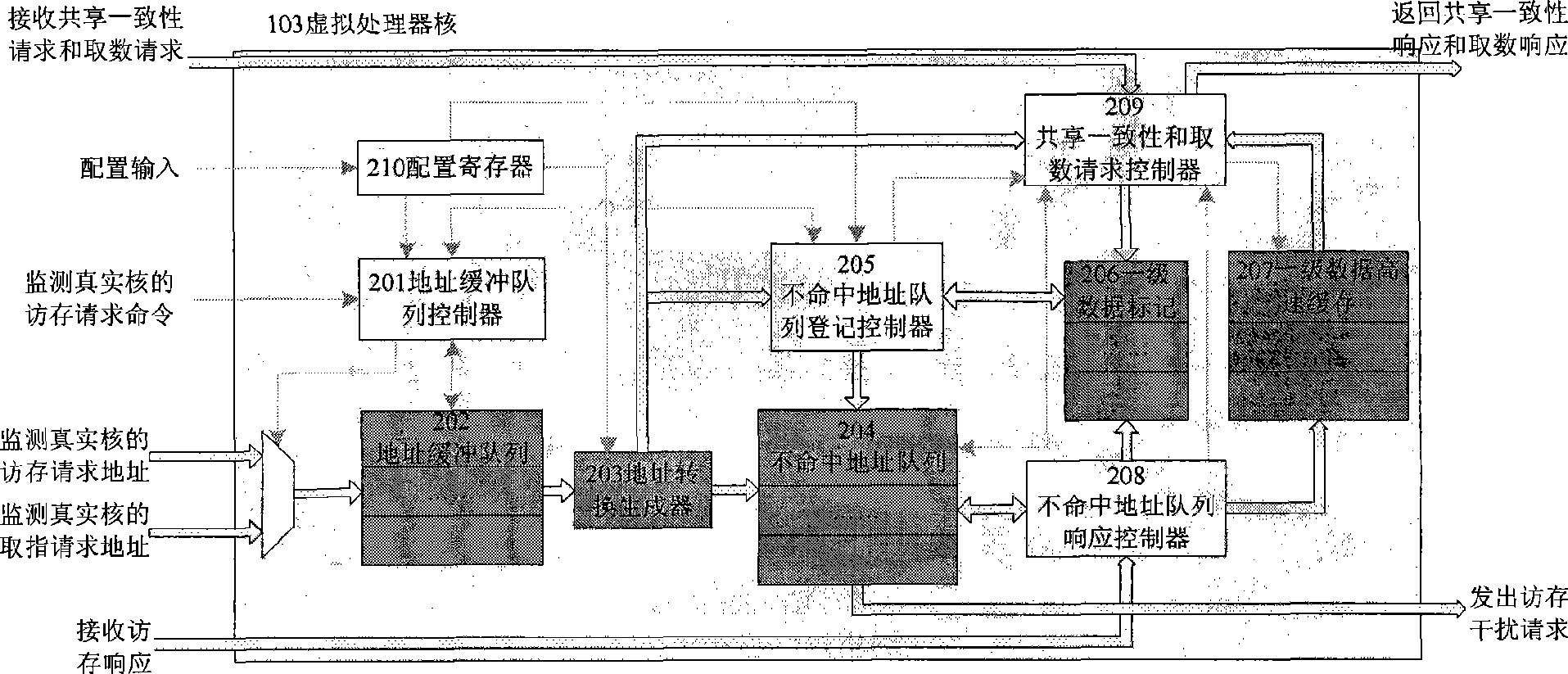

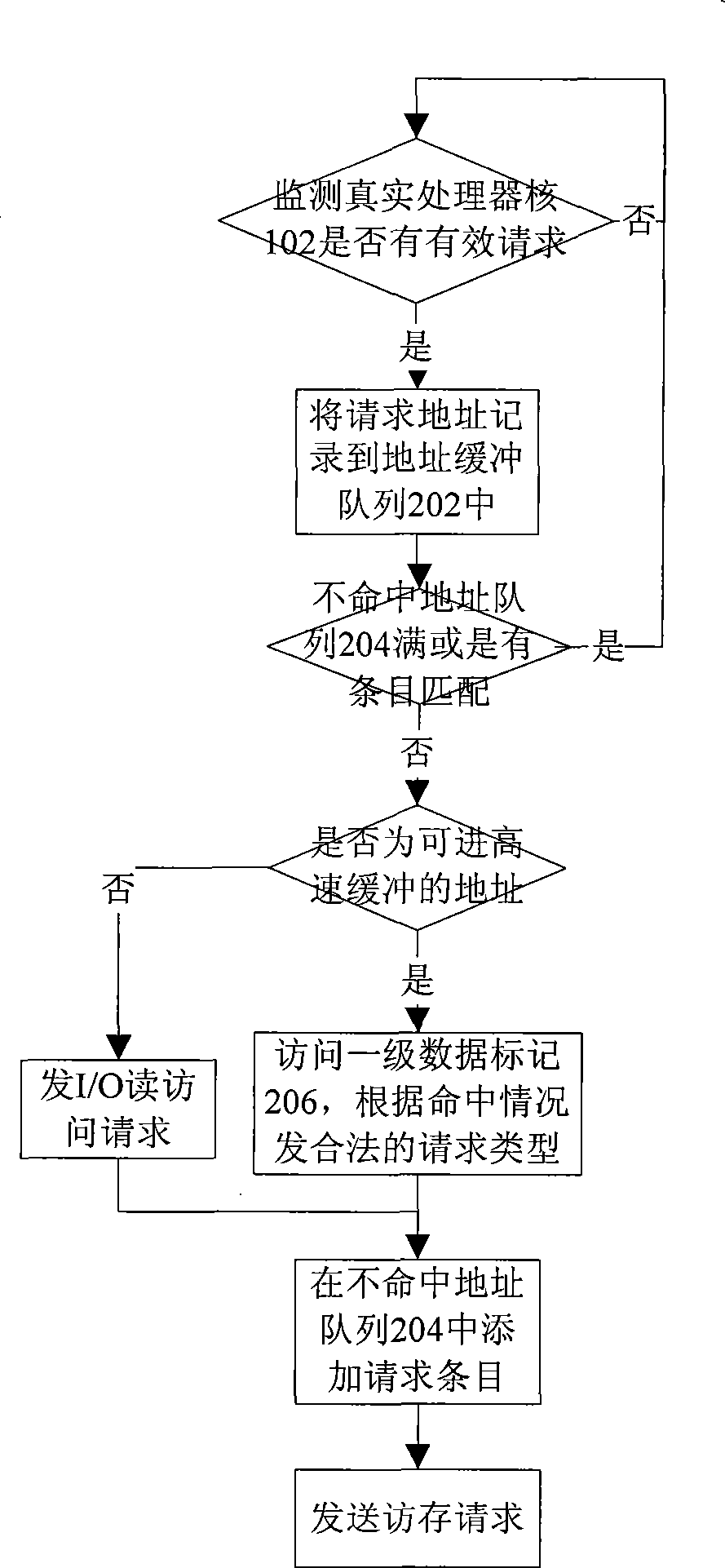

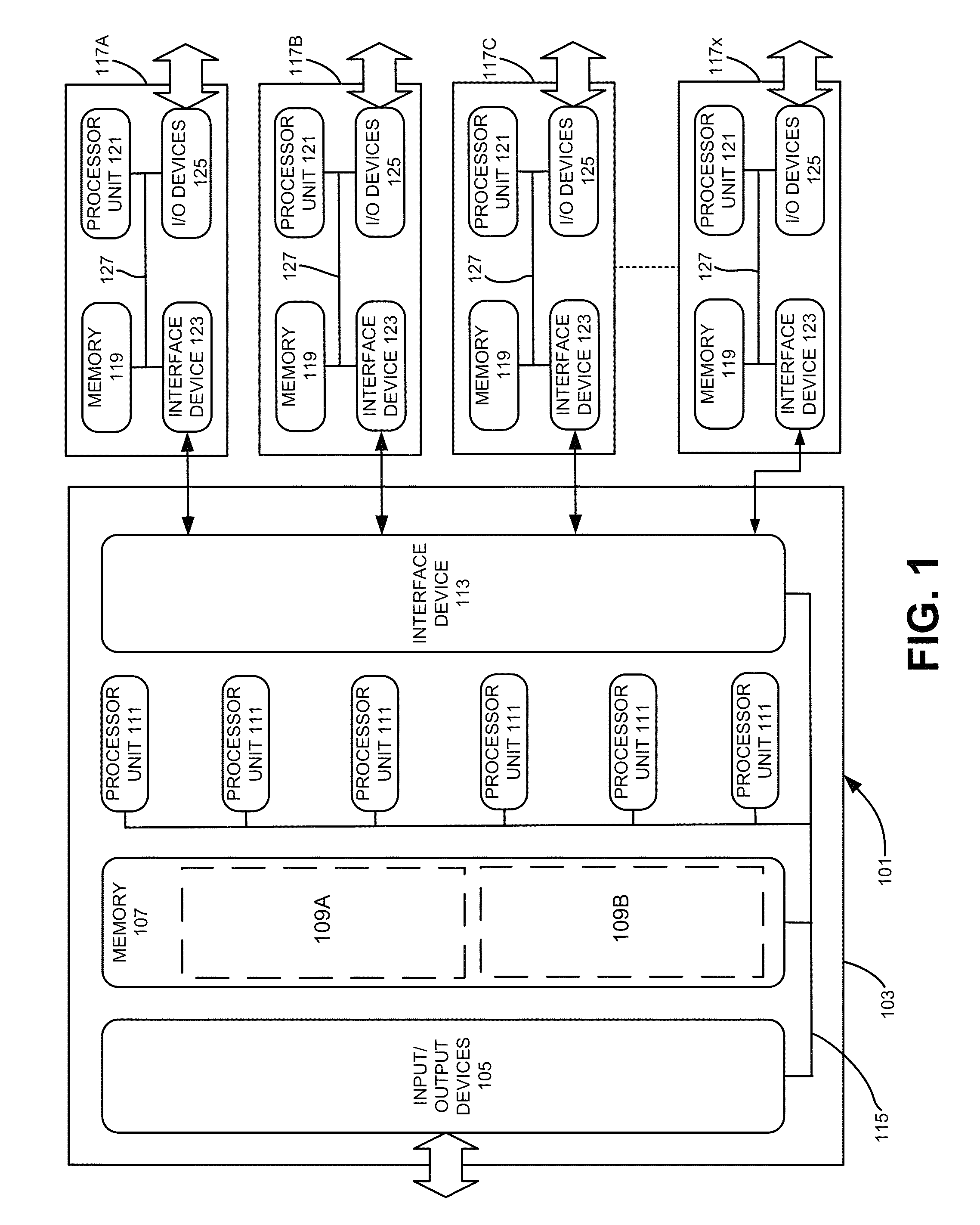

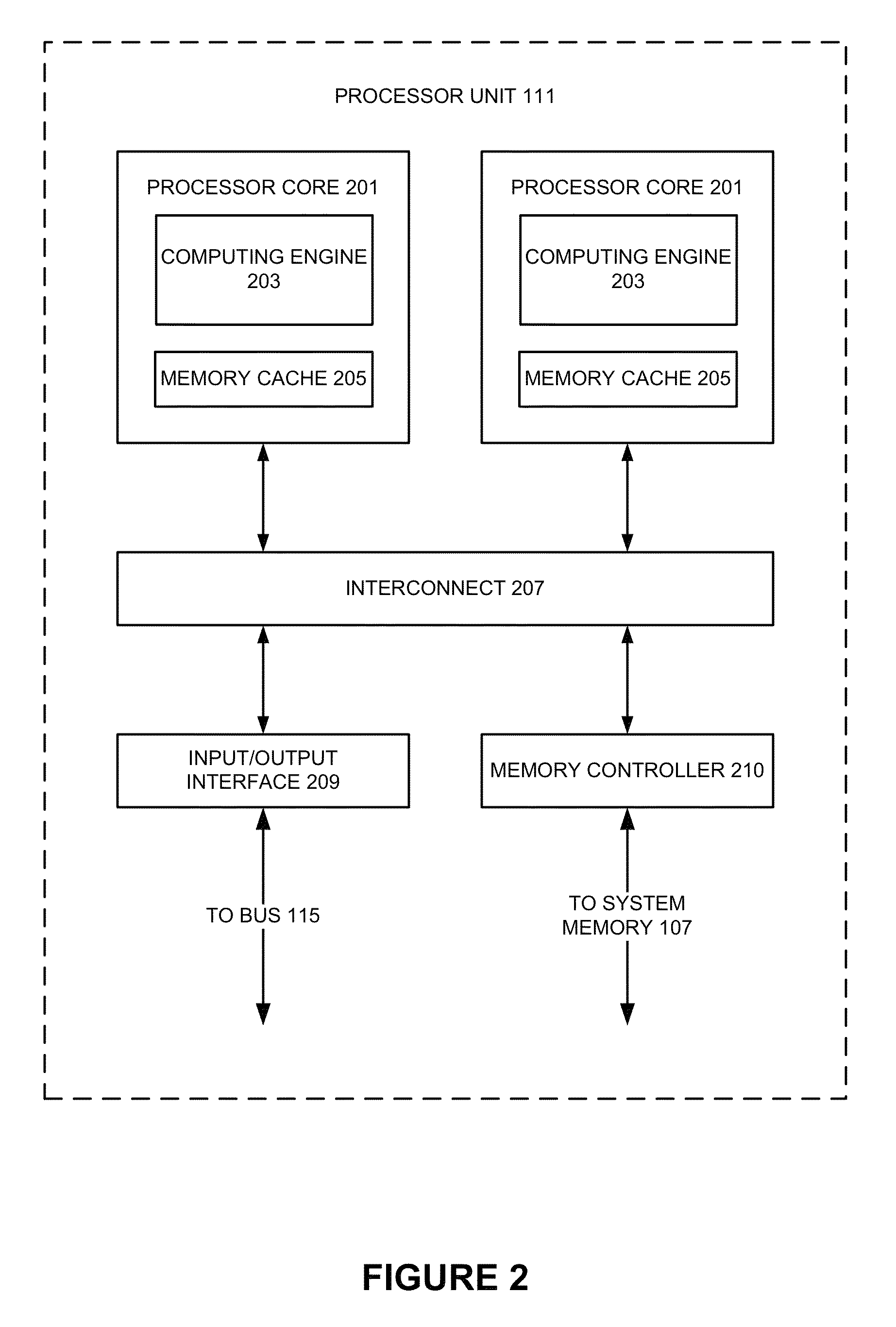

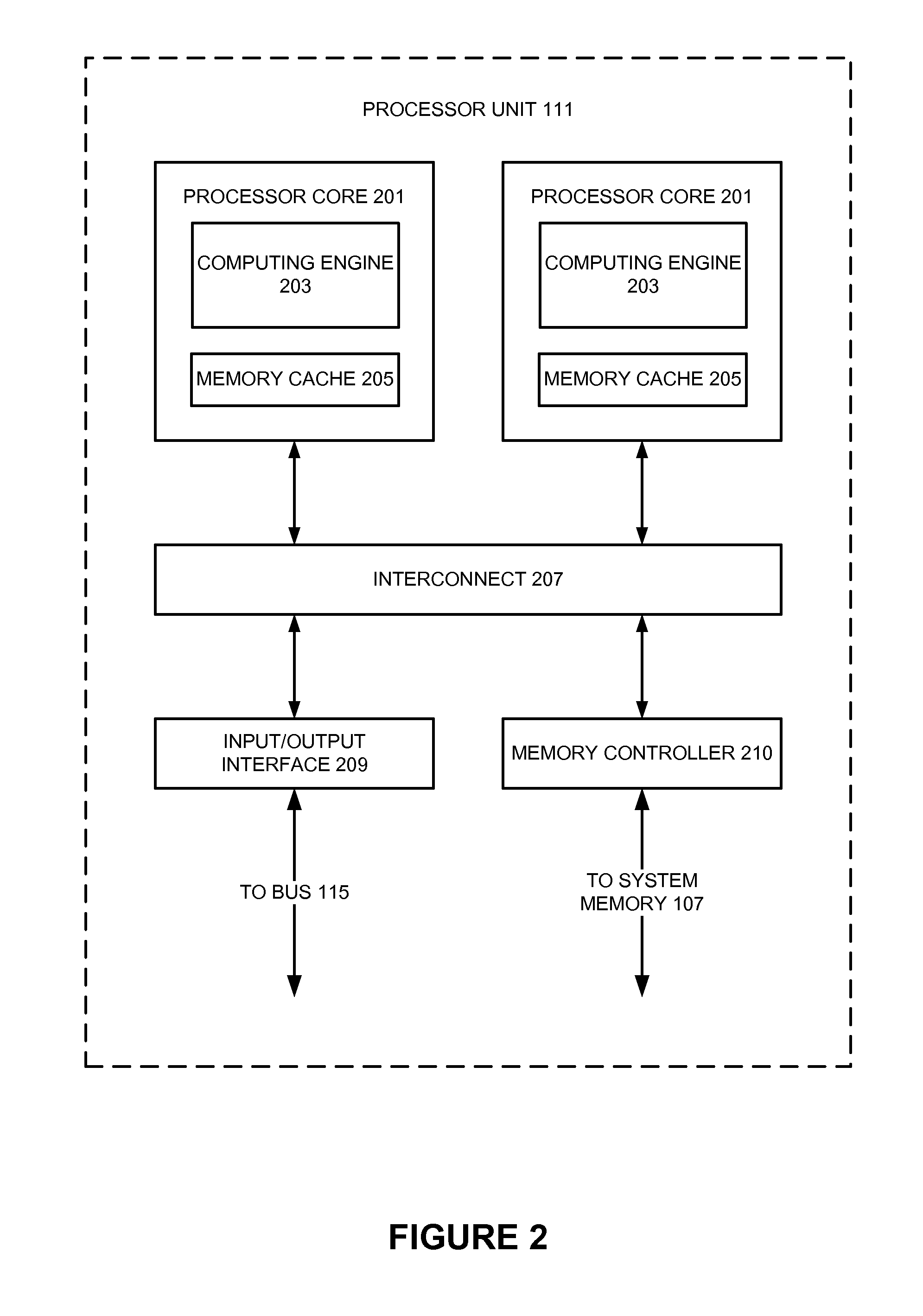

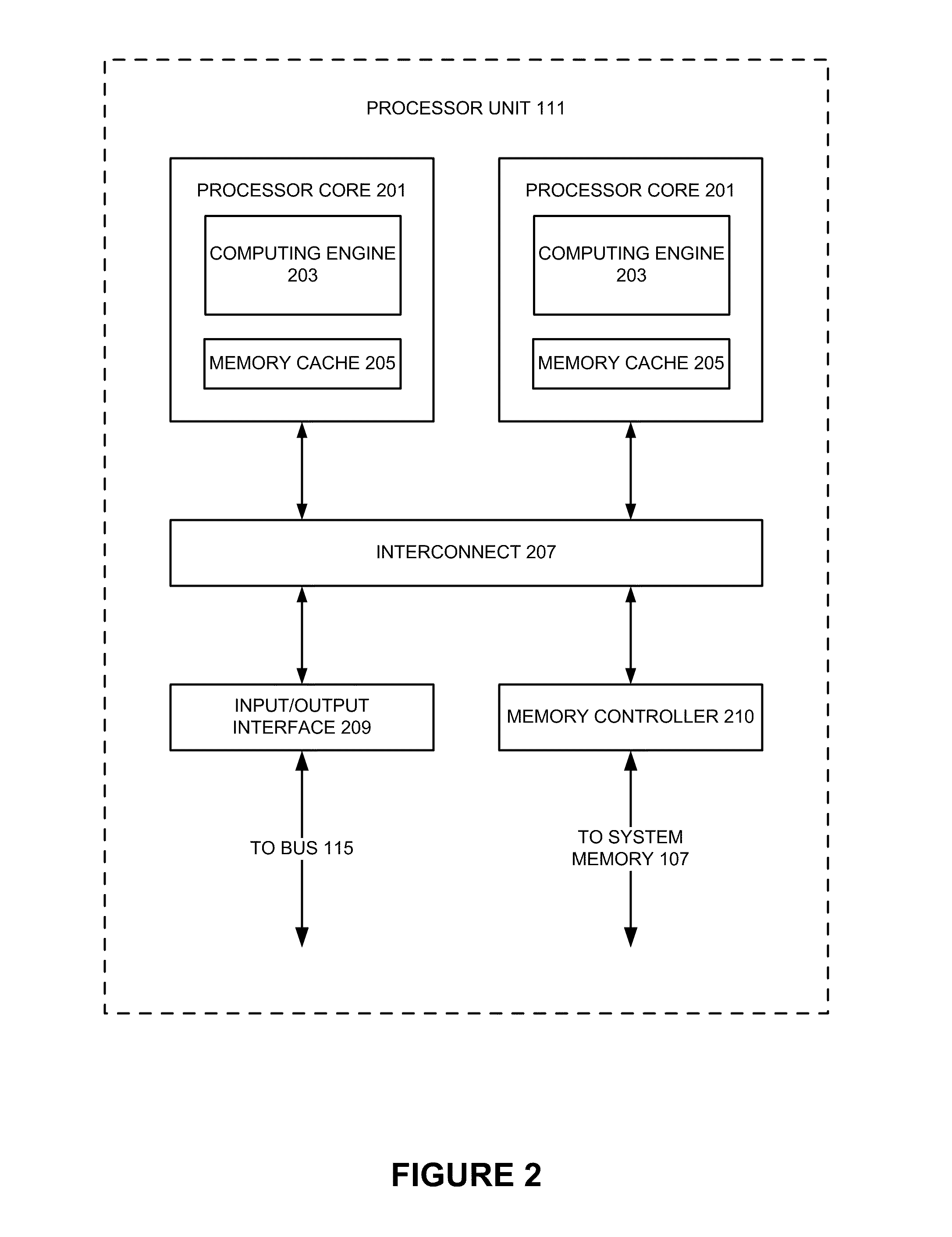

Consistency physical verification device of multicore processor Cache

ActiveCN101446987AReduce the cost of FPGA physical verificationImprove verification efficiencySpecial data processing applicationsValidation methodsPhysical verification

The invention discloses a consistency physical verification device of a multicore processor Cache, to provide a consistency physical verification device with low cost and high efficiency for the multicore processor Cache. Based on a field programmable gate-array (FPGA) verification platform of a single core processor, the device is embedded with a virtual processor core (103) to verify the consistency of the multicore processor Cache. The virtual processor core (103) can imitate the multicore processor to automatically generate shared memory access request and automatically store the correctness of results. The device can verify the correctness of the consistency of the multicore processor Cache on the FPGA verification platform of a single core processor, which reduces FPGA physical verification cost of the multicore processor and improves the consistency verification efficiency of the multicore processor Cache; synchronously, using such verification method in a simulation verification can reduce the complexity of the simulation verification and increase the speed of the simulation verification.

Owner:上海高性能集成电路设计中心

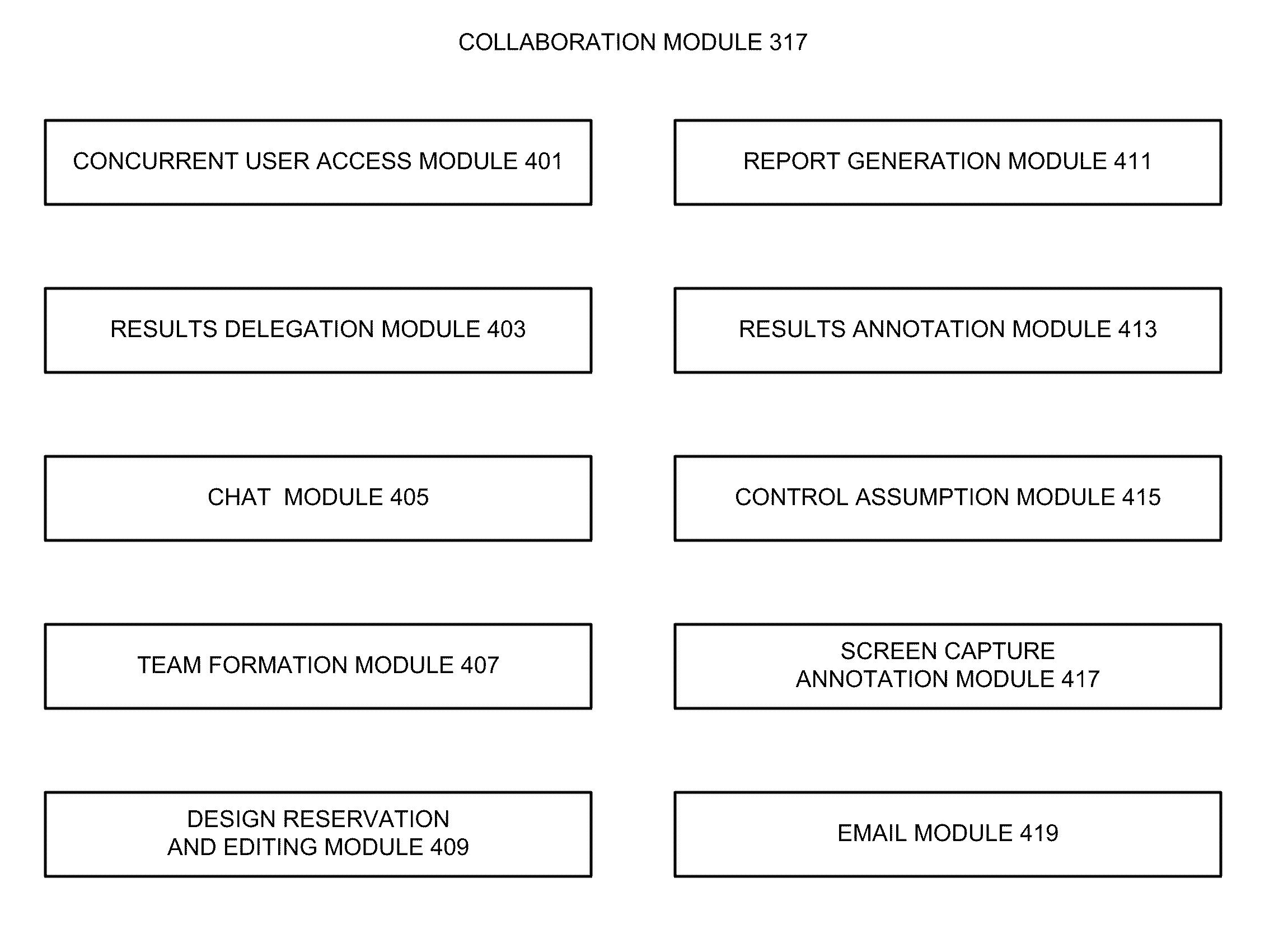

Collaborative environment for physical verification of microdevice designs

A collaborative environment for performing physical verification processes on integrated circuit designs. Multiple physical verification results may be stored in a “unified” results database / directory (e.g., unified at least from a user's perspective), where results from various verification processes, such as Design-Rule-Check (DRC) processes, Layout-Versus-Schematic comparison (LVS) processes, Design-For-Manufacturing (DFM) processes Optical Proximity Correction (OPC) processes, and Optical Rule Check (ORC) processes are accessible from the same style of user interface, which may be a graphical user interface. The basic abilities for design team-based interactions can be equally available to each process involved in the physical verification of an integrated circuit design.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

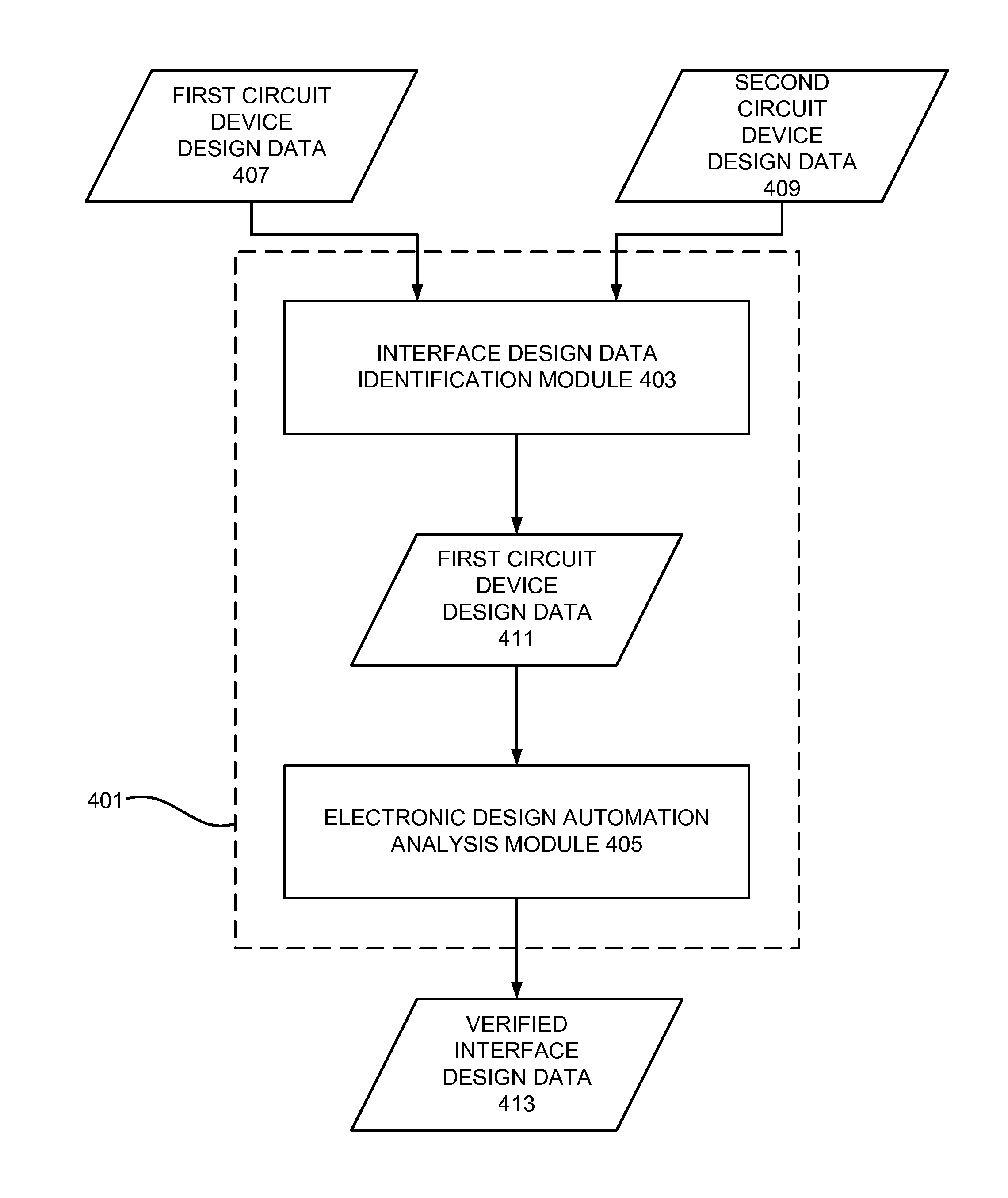

Stacked Integracted Circuit Verification

InactiveUS20110185323A1Precise routingComputer aided designSpecial data processing applicationsInterface designPhysical verification

Techniques for performing physical verification processes for stacked integrated circuit devices. An interface between a first two-dimensional integrated circuit device and a second two-dimensional integrated circuit device is identified. The design data for the identified layers in the first and second two-dimensional integrated circuit devices are then combined and physically verified as a single set of interface design data. The design data for the first two-dimensional integrated circuit device and the second two-dimensional integrated circuit device are then separately physically verified. Once the interface design data, the first two-dimensional integrated circuit device design data and the second two-dimensional integrated circuit device design data have been physically verified, the verified design can be recombined to form verified design data corresponding to a stacked integrated circuit device.

Owner:HOGAN WILLIAM MATTHEW +2

Failure point positioning method for semiconductor power device failure analysis

InactiveCN102854429AConvenient to judge timeViolent reactionElectrical testingElectrical resistance and conductanceLight beam

The invention provides a failure point positioning method for semiconductor power device failure analysis. The failure point positioning method comprises the following steps of: performing chemical corrosion on a metal aluminum layer covering the surface of a power device by utilizing a chemical corrosion stripping technology, completely removing the aluminum layer, and completely keeping a barrier layer below the metal aluminum layer; positioning the front side of the power device by utilizing a micro light microscope and a light beam induced resistance variation technology, simulating electric conditions under the failure conditions, electrifying by using a point needle method, simulating the electric conditions, and finding possible failure points; and performing physical verification of electronic package assembly failure analysis by utilizing the positioning result of an electronic package assembly failure analysis tool on the previous steps, and finding the final physical failure point. The failure point positioning method has the advantages that the metal aluminum layer is effectively stripped, and the integrity of the barrier layer is kept; and moreover, the positioning speed and efficiency of the semiconductor power device failure point are greatly improved, and an extremely high precision is kept.

Owner:SHANGHAI FALAB TEST

Delivery systems and methods involving verification of a payment card from a handheld device

The present invention relates generally to systems and methods that facilitate the prevention of fraud occurring in connection with credit cards, debit cards, smart cards and other payment cards that are used in transactions involving goods sold by a seller, delivered by a shipper, and purchased by a buyer. Specifically, the present invention provides systems and methods that allow for physical verification of a payment card (e.g., credit card) upon delivery of goods that are purchased in the context of a remote transaction between a buyer and a seller, including, for example, goods that are ordered via phone, mail order, fax or the Internet.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

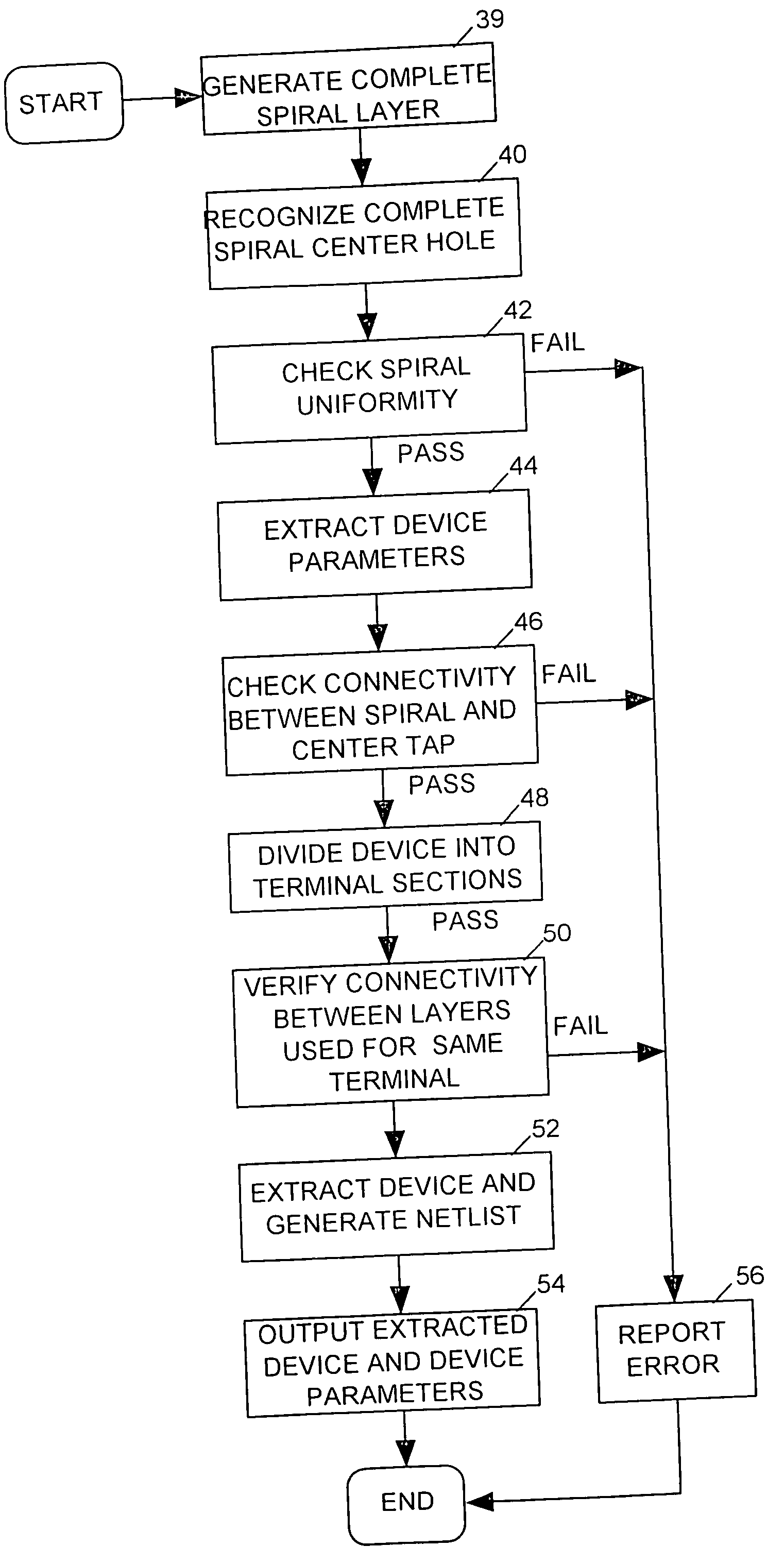

IC layout physical verification method

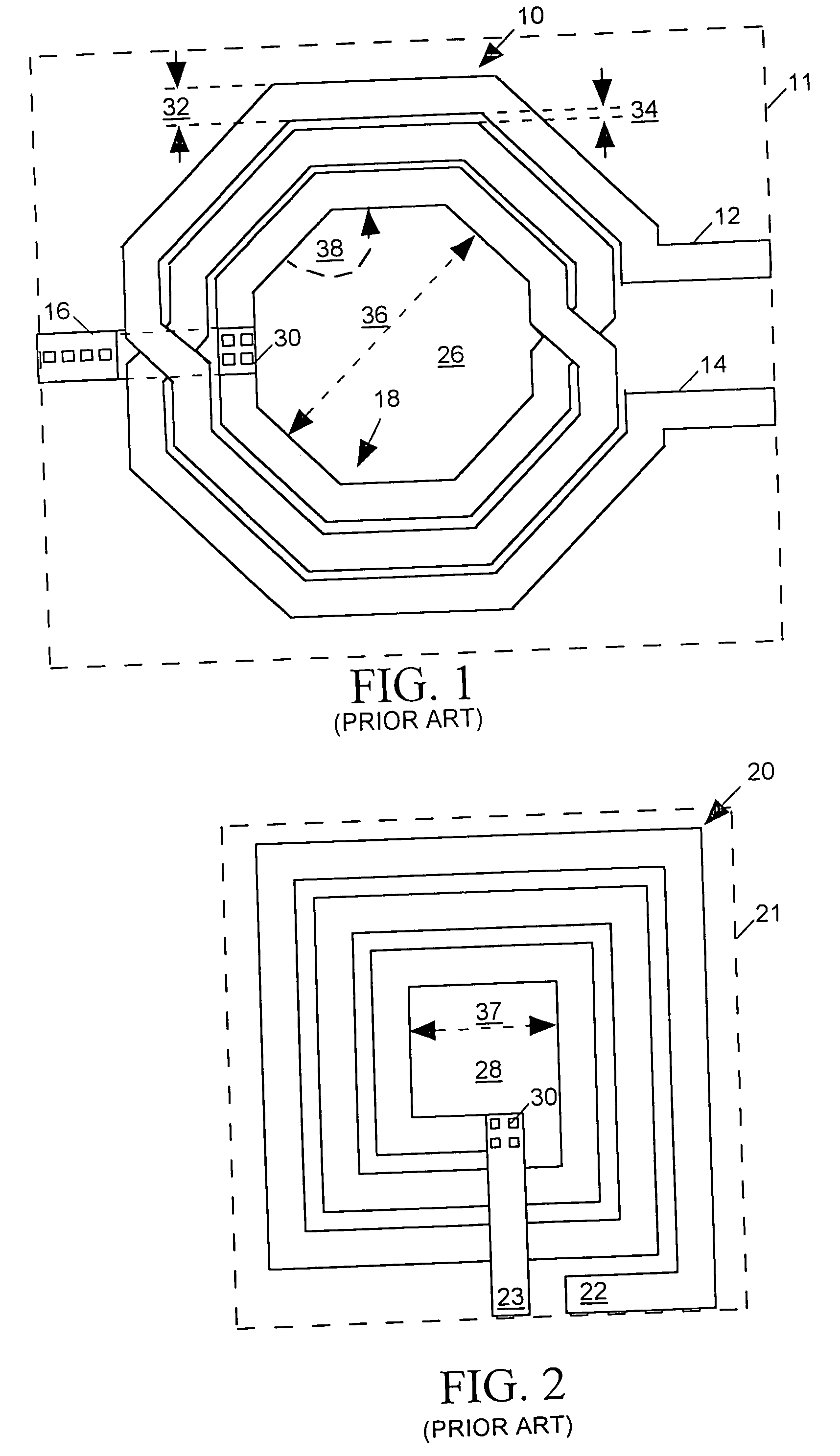

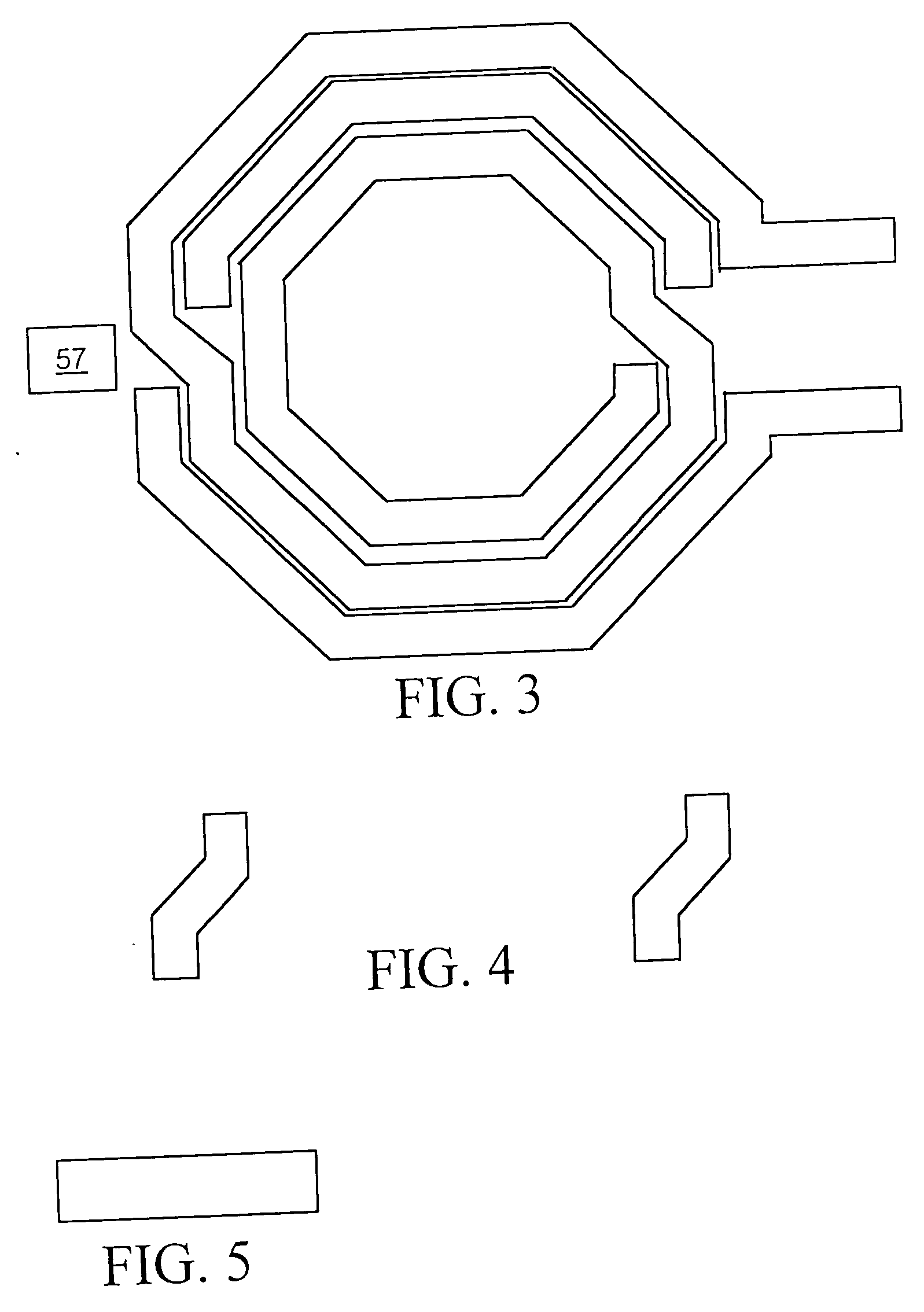

InactiveUS20050229126A1Analogue computers for electric apparatusComputation using non-denominational number representationHelical linePhysical verification

Responding to a single command, a layout versus schematic (LVS) tool processes layout data describing positions of conductors on layers of an IC to produce data representing a shape recognition layer depicting boundary shapes of spirals of drawn inductors. The boundary shape of a spiral is the shape of the spiral as viewed from above with all of the layers of conductive material forming the spiral superimposed. The LVS tool then processes the shape recognition layer data to identify the type and position of each drawn inductor, to determine whether each inductor's spiral turns are of uniform width and spacing, to detect connectivity violations, and to determine parameters relating to the shape of the spiral from which its inductance can be computed.

Owner:CADENCE DESIGN SYST INC

Collaborative Environment For Physical Verification Of Microdevice Designs

ActiveUS20110016444A1For easy referencePromote collaborationDetecting faulty computer hardwareOffice automationComputer architectureLayout Versus Schematic

A collaborative environment for performing physical verification processes on integrated circuit designs. Multiple physical verification results may be stored in a “unified” results database / directory (e.g., unified at least from a user's perspective), where results from various verification processes, such as Design-Rule-Check (DRC) processes, Layout-Versus-Schematic comparison (LVS) processes, Design-For-Manufacturing (DFM) processes Optical Proximity Correction (OPC) processes, and Optical Rule Check (ORC) processes are accessible from the same style of user interface, which may be a graphical user interface. The basic abilities for design team-based interactions can be equally available to each process involved in the physical verification of an integrated circuit design.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

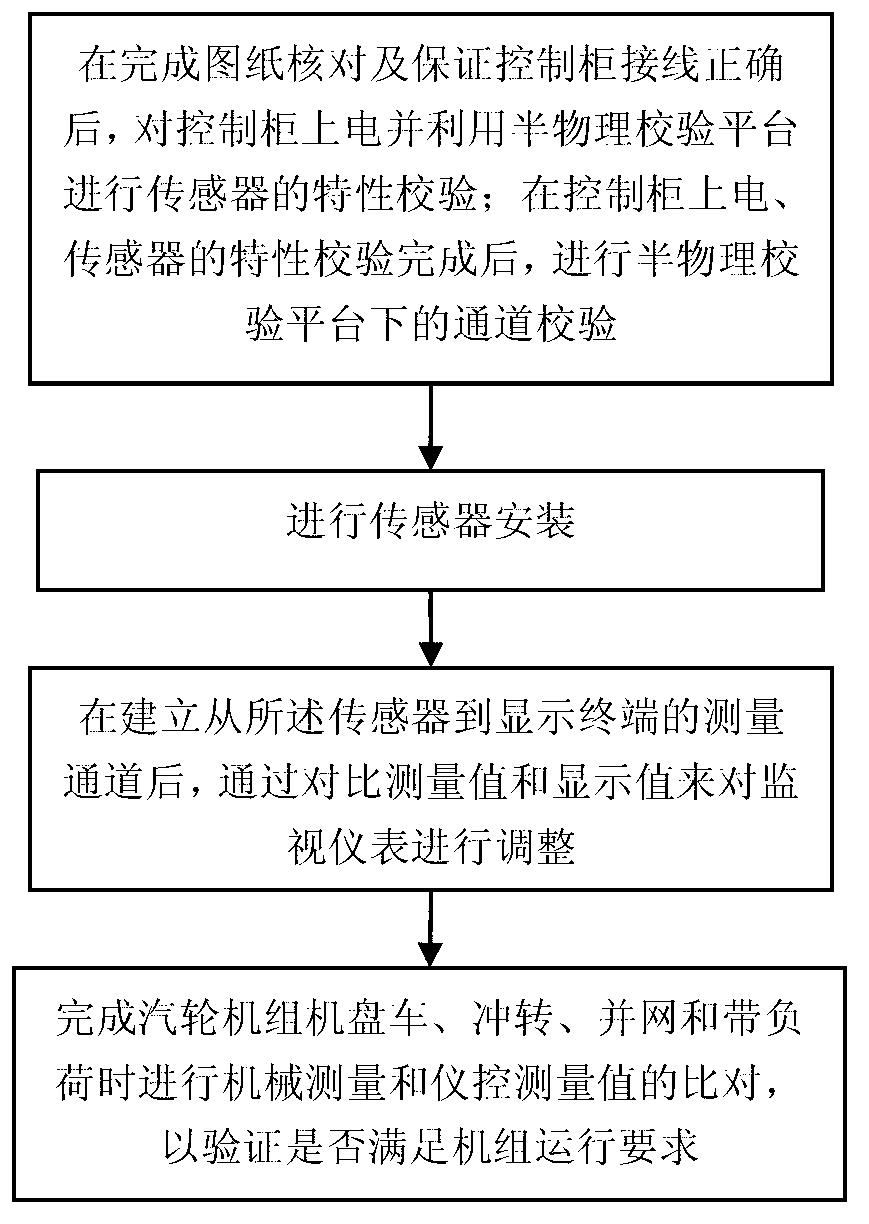

Debugging method of nuclear power plant half-speed turbine monitoring system

ActiveCN102997957ASolve the problem that static feature checking cannot be performedAvoid downtimeInstrumentsElectricityPhysical verification

The invention discloses a debugging method of a nuclear power plant half-speed turbine monitoring system. The debugging method includes the following steps that S1, after a drawing is checked, and correct wiring of a control cabinet is guaranteed, the control cabinet is powered up, and verification of sensor characteristics is conducted by using a semi-physical verification platform; and after the control cabinet is powered up and the verification of the sensor characteristics is finished, verification of a channel below the semi-physical verification platform is conducted; S2, a sensor is installed; S3, after a measuring channel from the sensor to a display terminal is built, a monitoring instrument is adjusted by comparing a measuring value and a display value; and S4, jiggering, impulse starting and grid combining of a turbine unit are finished, and comparison of mechanical measurement and instrument control measuring value is conducted during on-load so as to verify whether unit operation requirements are met. The debugging method can solve the problem that static characteristic inspection can not be conducted before installing of the sensor, and cost is saved.

Owner:中广核工程有限公司 +1

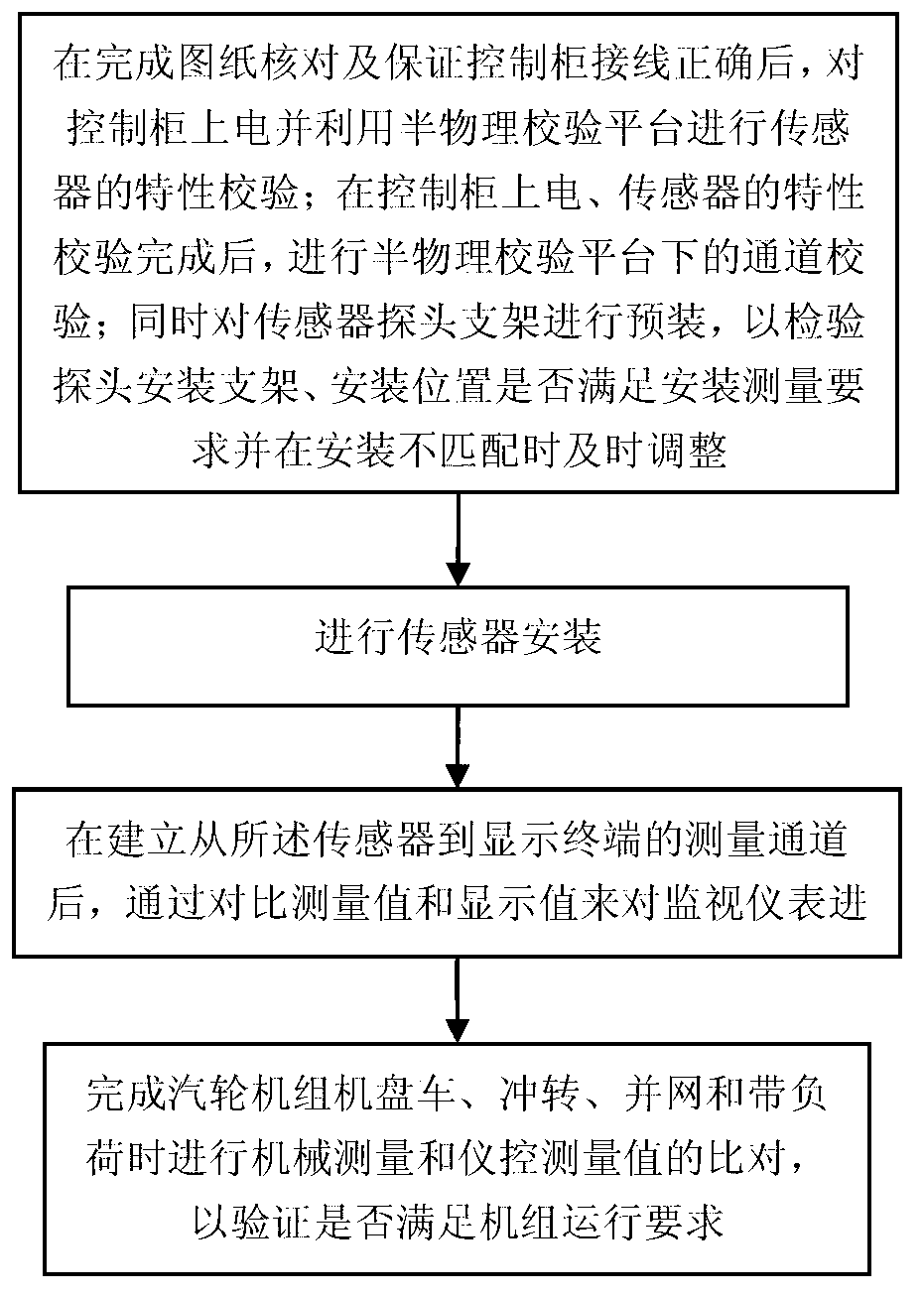

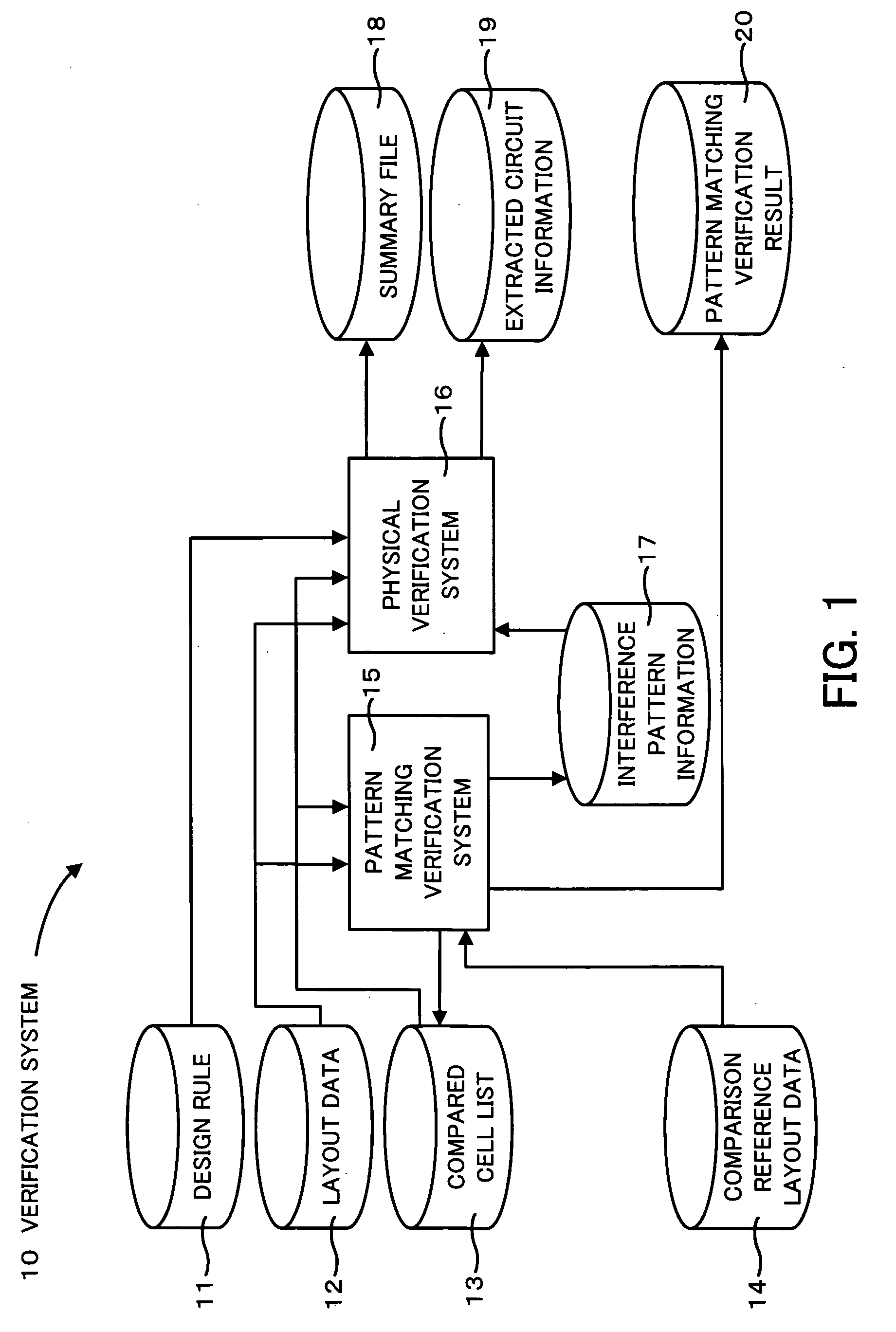

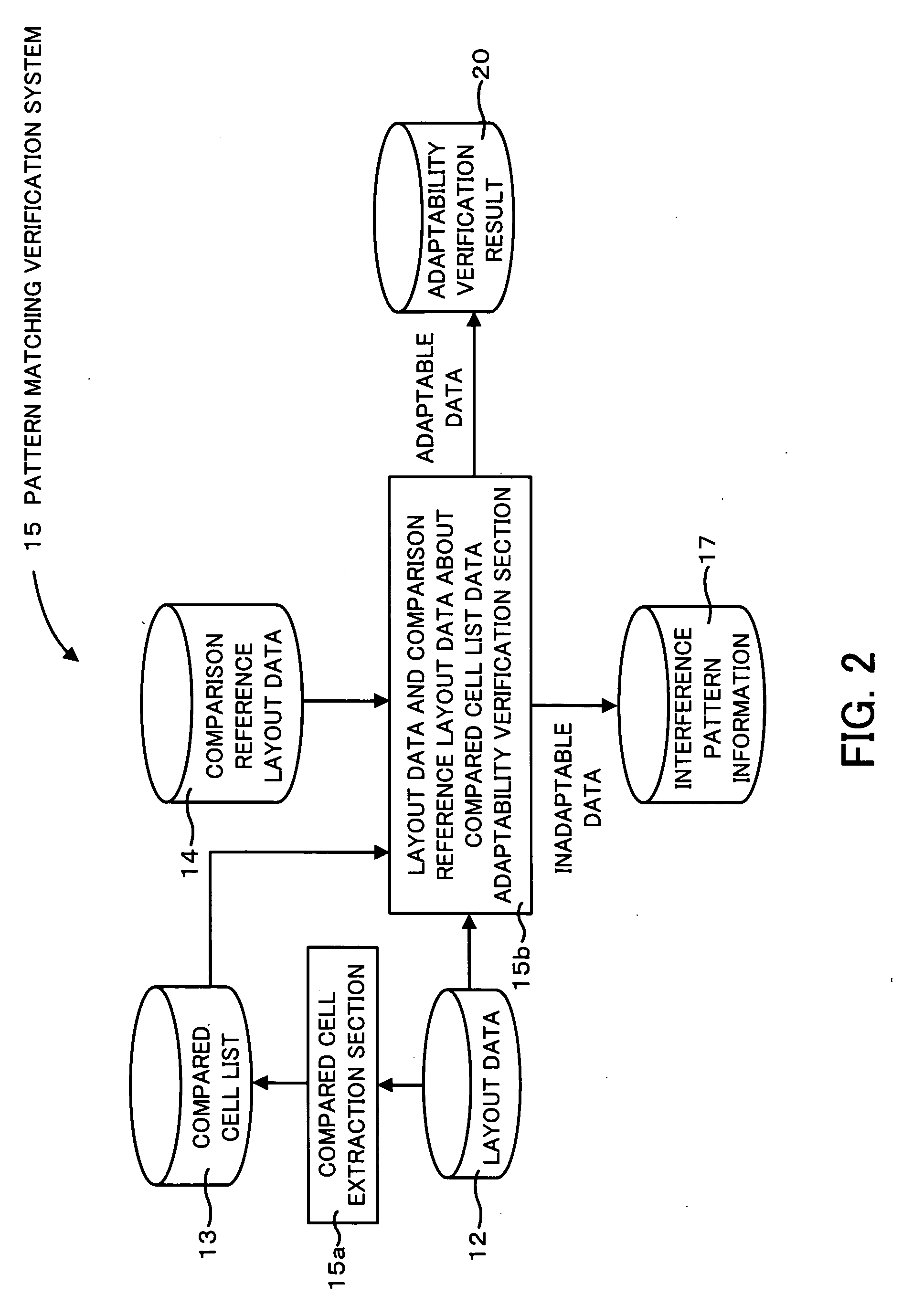

Semiconductor device verification system and semiconductor device fabrication method

InactiveUS20080010623A1Highly integratedComputer aided designSoftware simulation/interpretation/emulationComputer architecturePattern matching

A semiconductor device verification system capable of verifying operation with great accuracy. A pattern matching verification system outputs interference pattern information. A physical verification system compiles the interference pattern information and a design rule and extracts a design rule applied to the interference pattern information. The physical verification system then refers to the design rule to verify a compared cell list and the interference pattern information. As a result, the physical verification system can perform physical verification of layout data without skipping data regarding the compared cell list.

Owner:SOCIONEXT INC

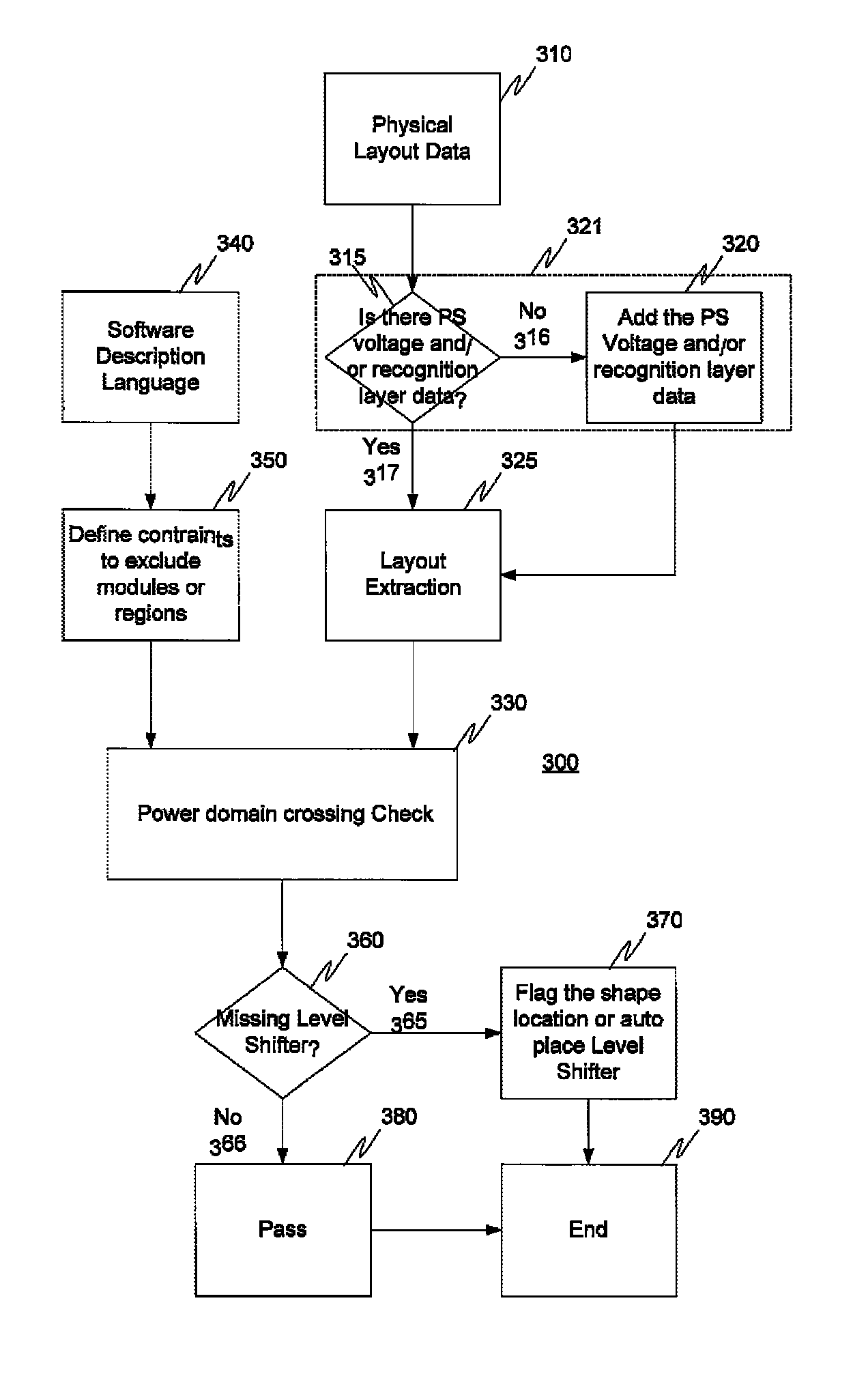

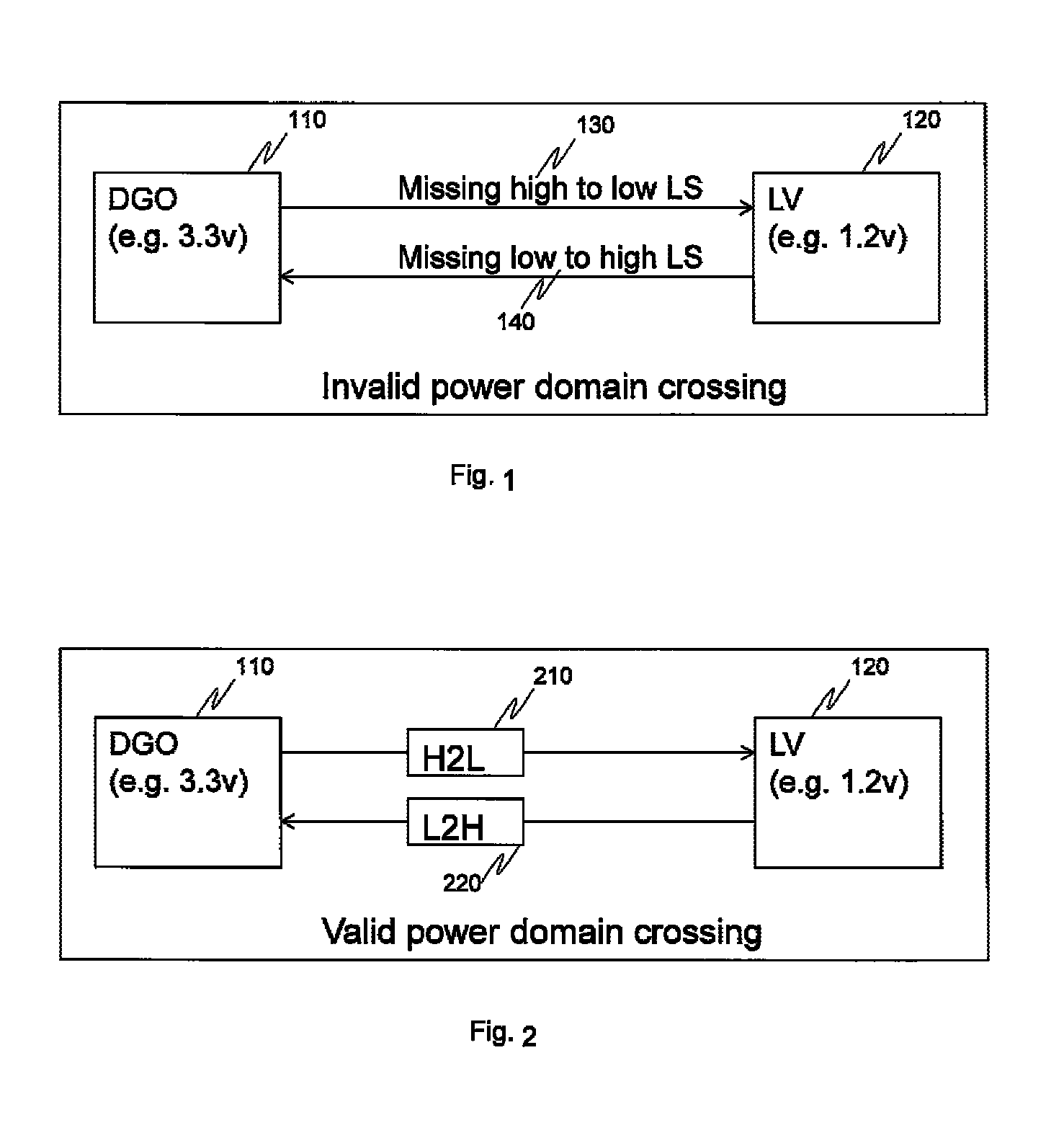

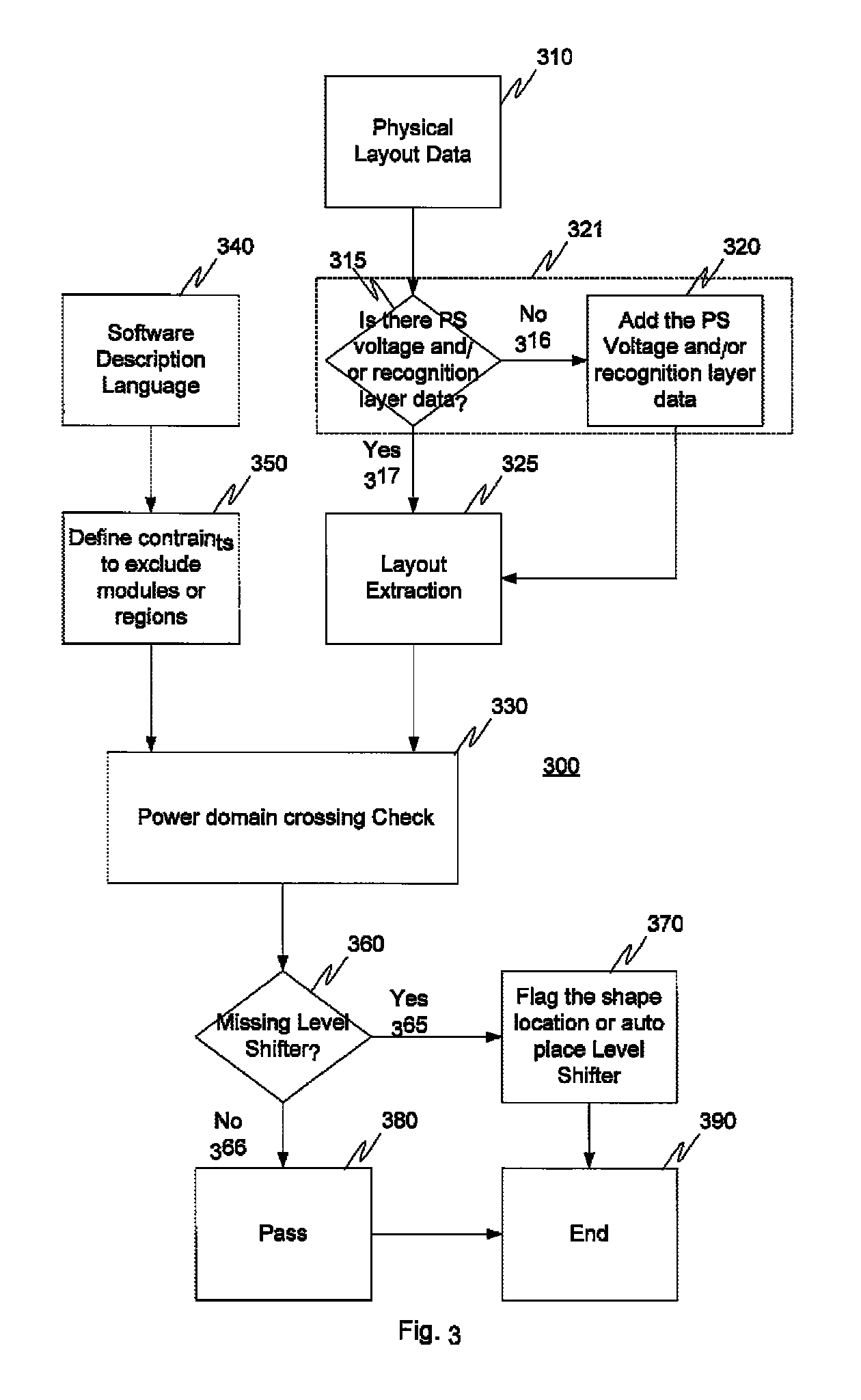

Multi-voltage domain circuit design verification method

ActiveUS8601426B1Computer aided designSoftware simulation/interpretation/emulationSystems analysisPhysical verification

A level shifter physical verification system identifies missing level shifters in a multi-voltage domain integrated circuit design. The system analyzes a physical layout design data file for design to identify domains and signals that cross domains, and connected nets of devices within the IC design having one or more missing level shifters.

Owner:NXP USA INC

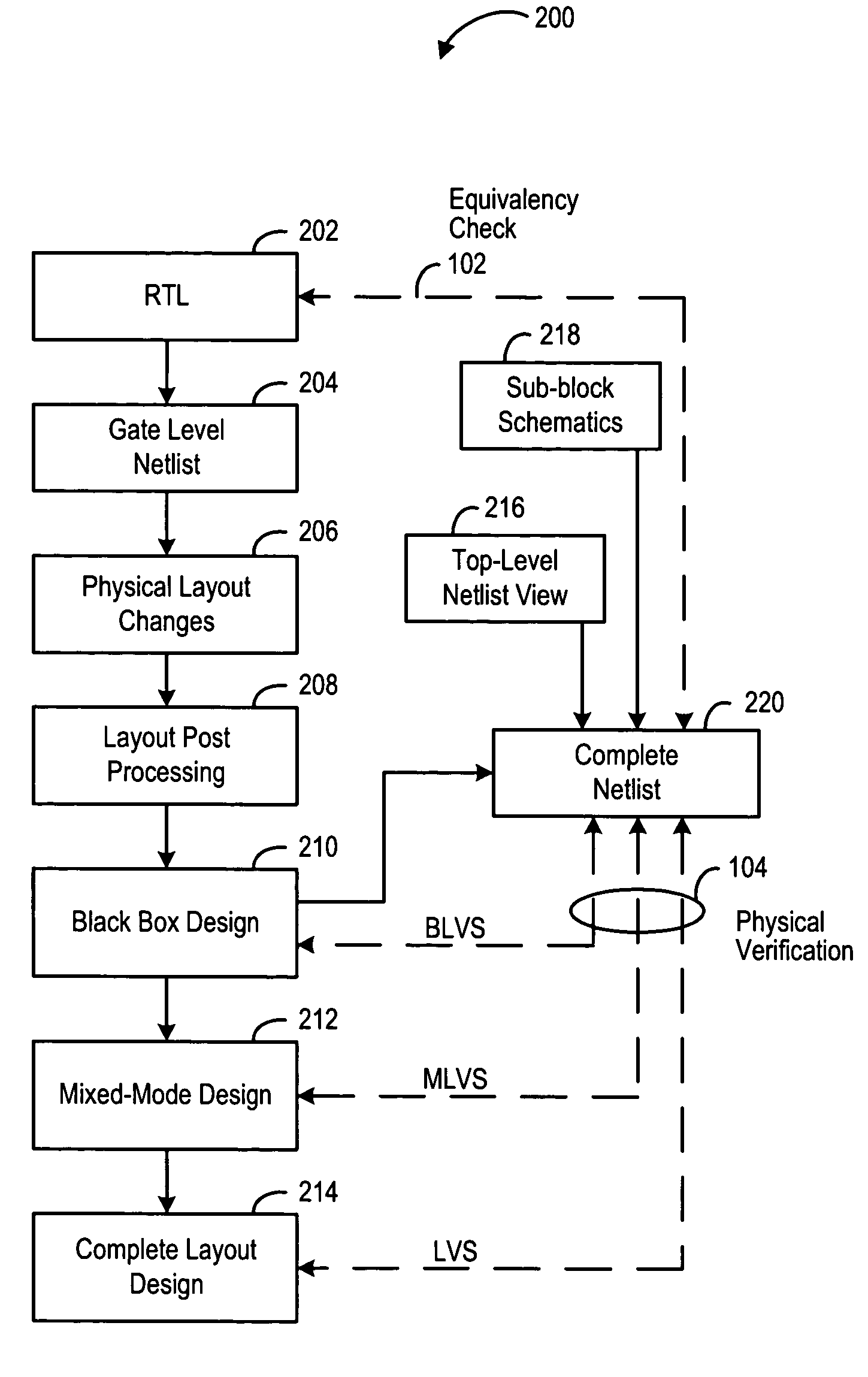

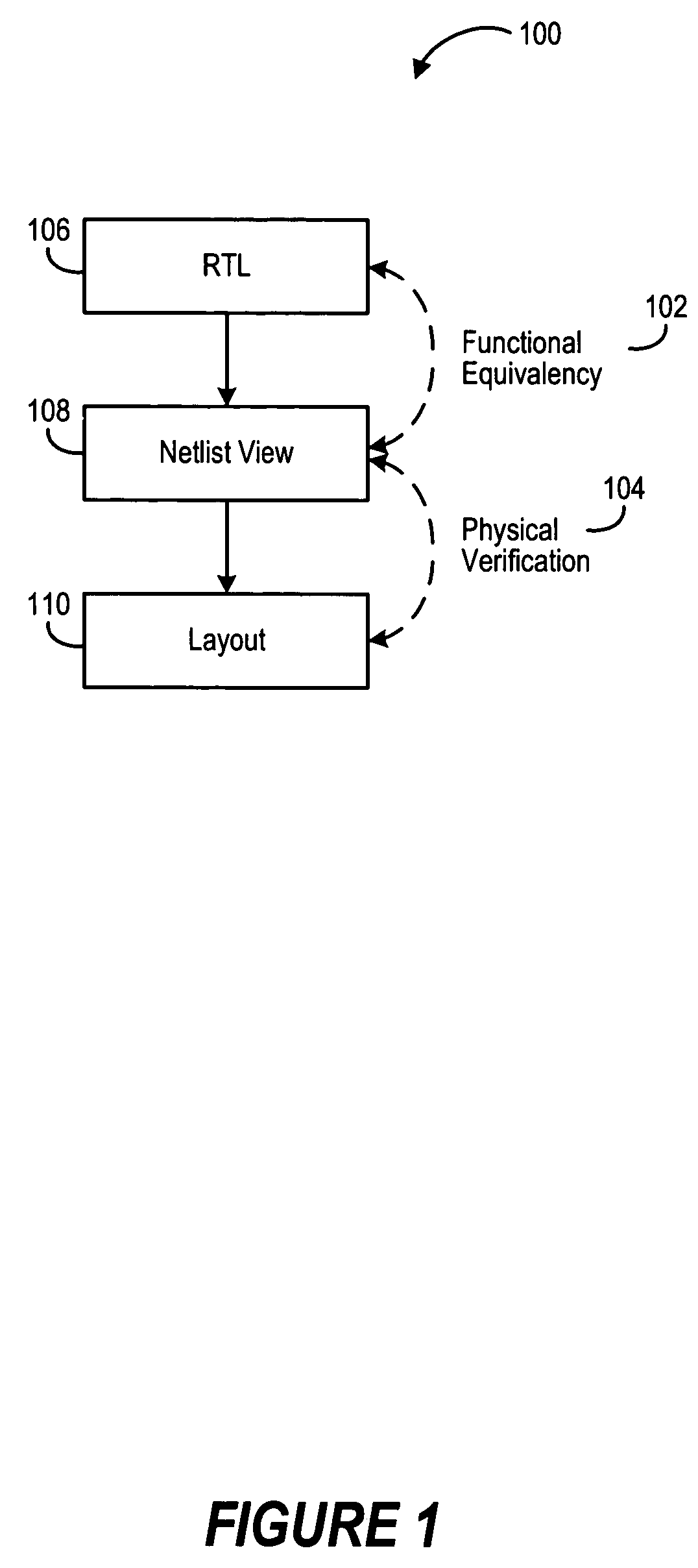

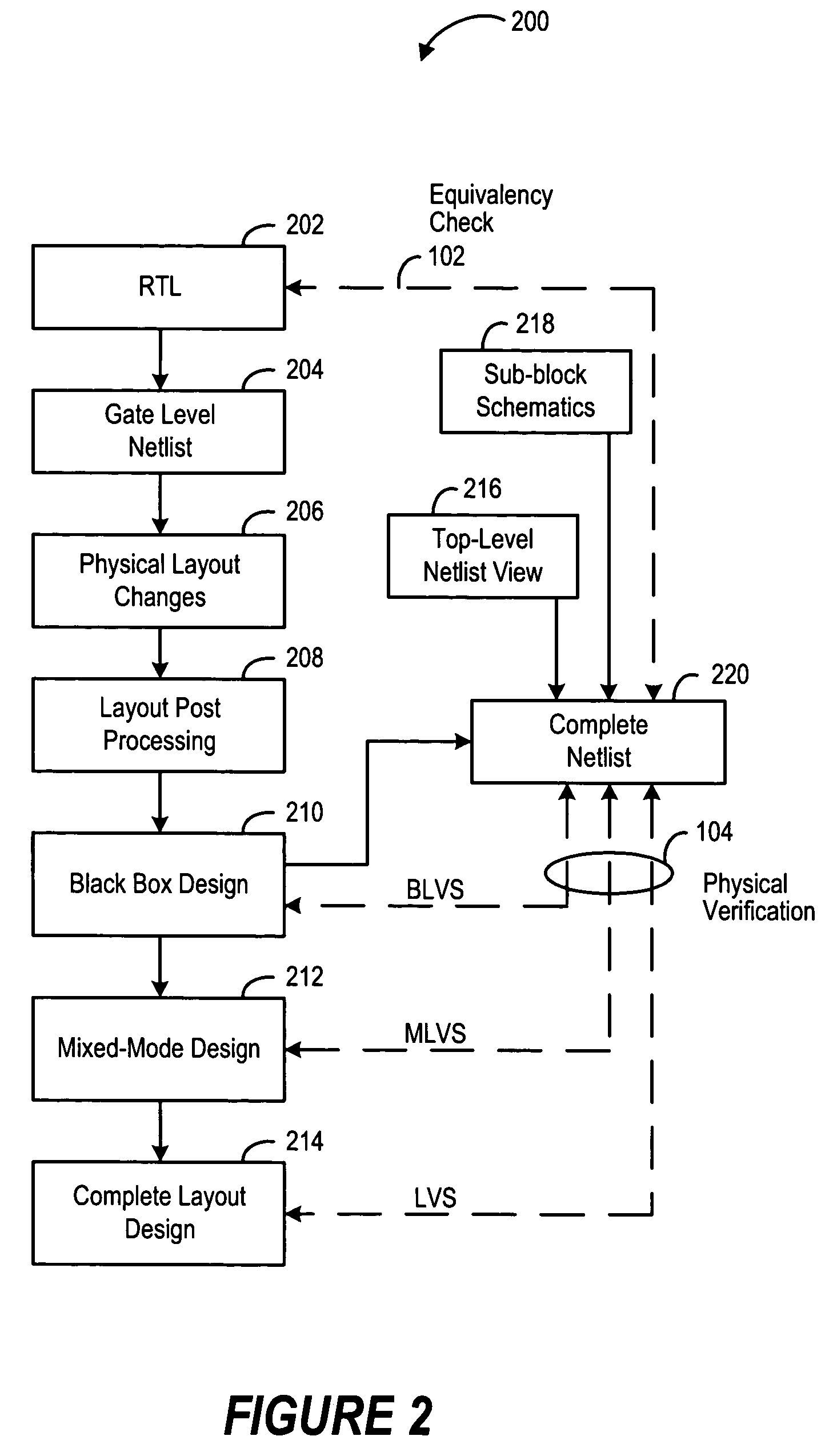

Fullchip functional equivalency and physical verification

ActiveUS7404161B2Efficient modificationStay connectedCAD circuit designSoftware simulation/interpretation/emulationPhysical verificationComputer science

A method for maintaining equivalency between the reference Register Transfer Logic (RTL) and the physical layout design of an integrated circuit by way of maintaining a reference netlist derived from symbolic connectivity.

Owner:ORACLE INT CORP

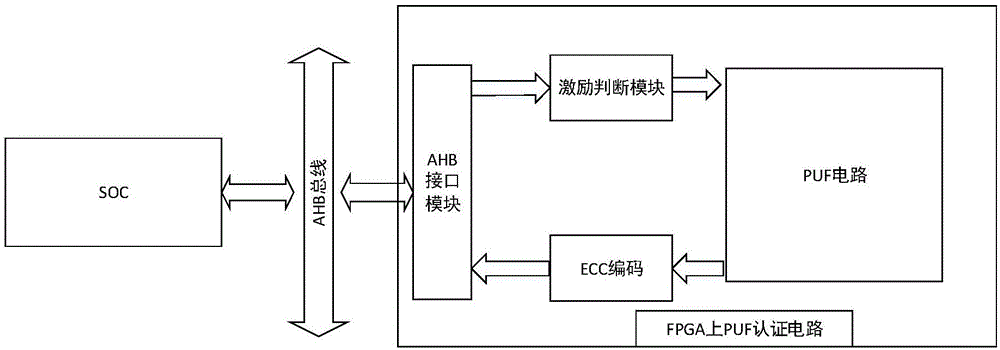

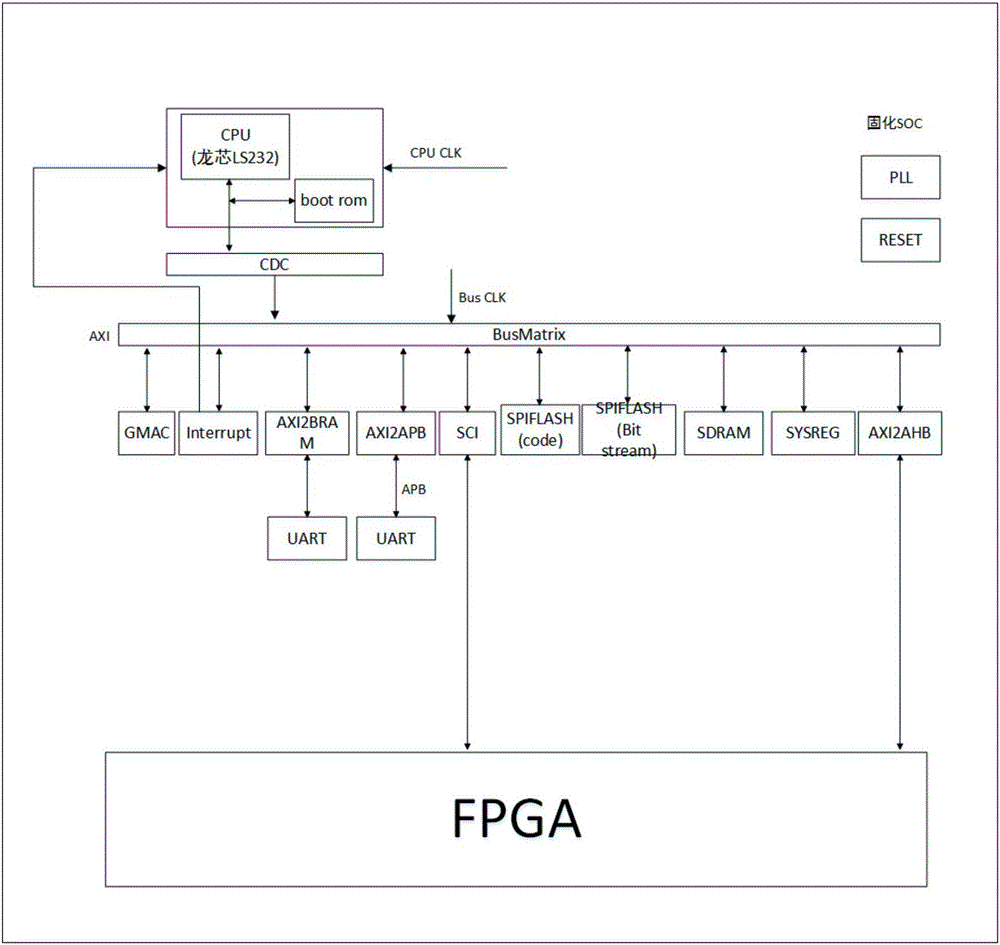

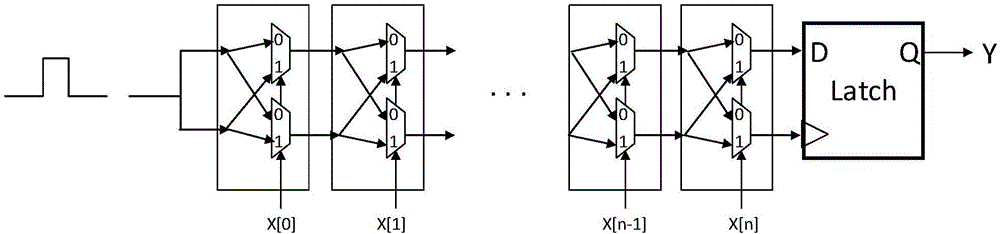

Dynamic configurable secret key authentication system based on system-on-a-programmable-chip (SoPC)

InactiveCN106817223AImprove securityImplement changesUser identity/authority verificationComputer hardwarePhysical verification

The purpose of the present invention is to provide a dynamic configurable key authentication system based on SoPC for the deficiencies of the prior art. This invention is mainly used in the security field, especially the system key authentication in the electronic information field. The main feature is that, using the completely self-developed SoPC chip and the development board based on the chip design, an innovative key authentication system is proposed, the key cannot be physically cloned, and the PUF circuit part combines the two current mainstream methods , and the PUF code can be changed by using the dynamic configuration of the CPU to the FPGA, giving full play to the cooperation between the CPU and the FPGA, and all the incentives can only be used once, making the key authentication extremely safe and reliable. This method has been approved by the development board. Physical verification proves that it is completely feasible and has great reference significance for the current certification system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

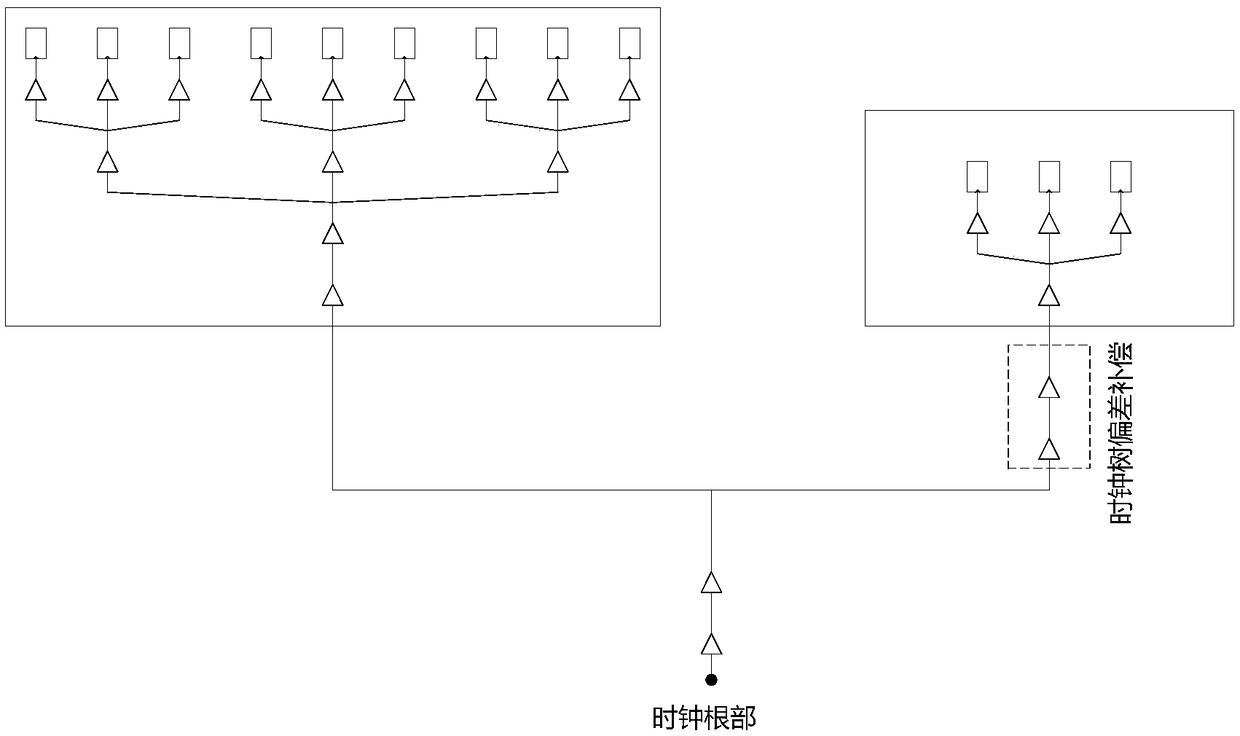

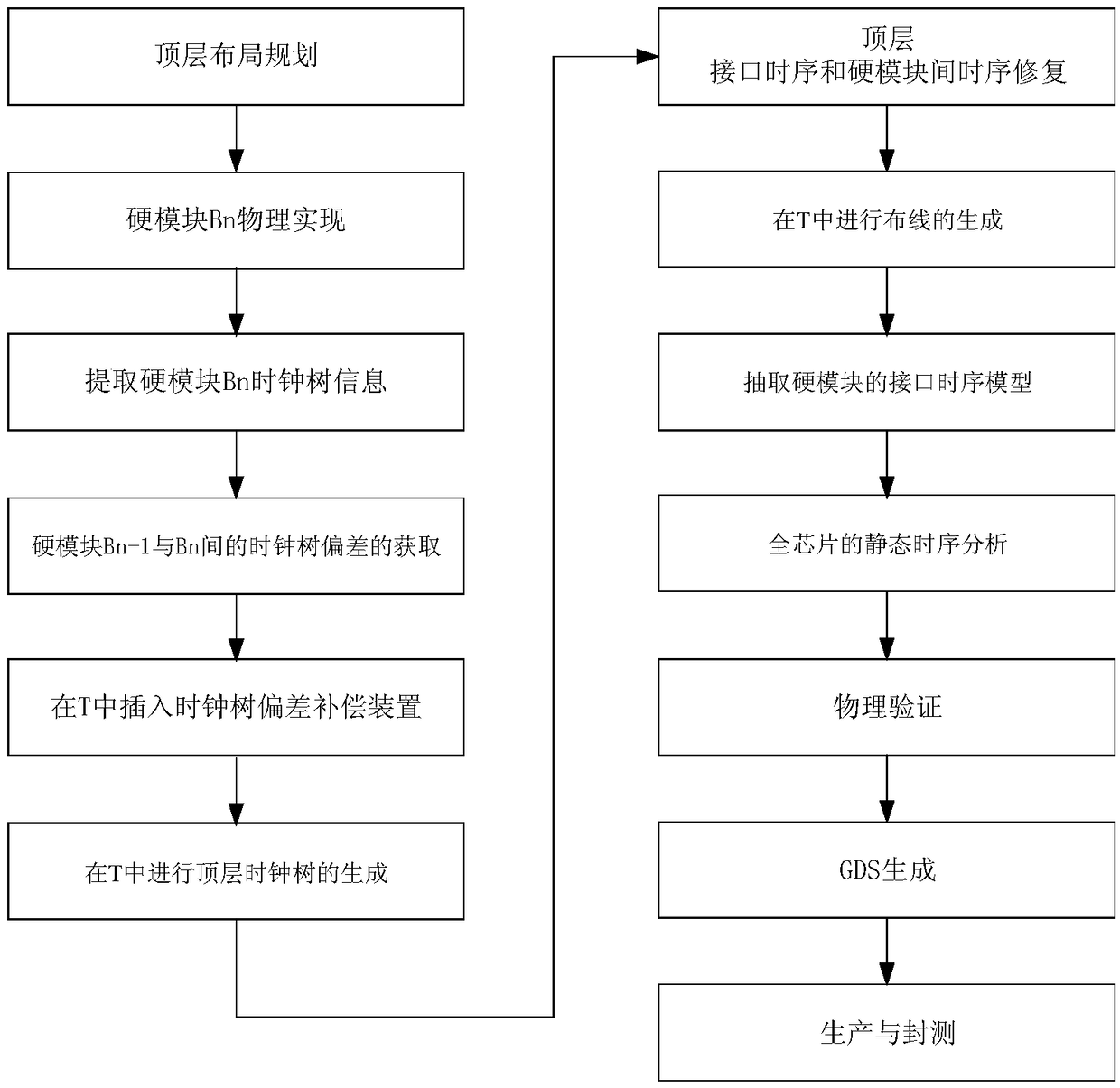

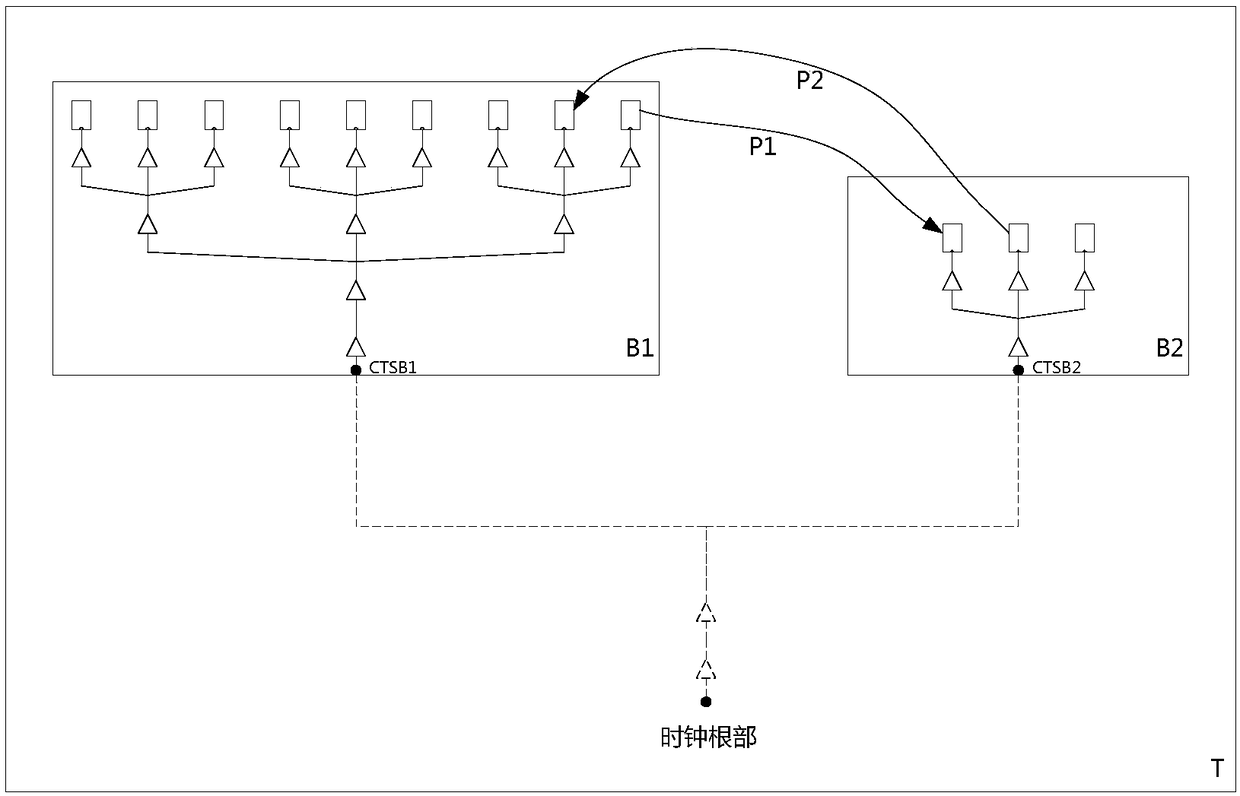

Clock-tree layout flow method and clock-tree deviation compensation device in integrate circuit

ActiveCN109376467AReduce hierarchyReduce difficultySpecial data processing applicationsStatic timing analysisPhysical verification

Owner:WUHAN INSTITUTE OF TECHNOLOGY

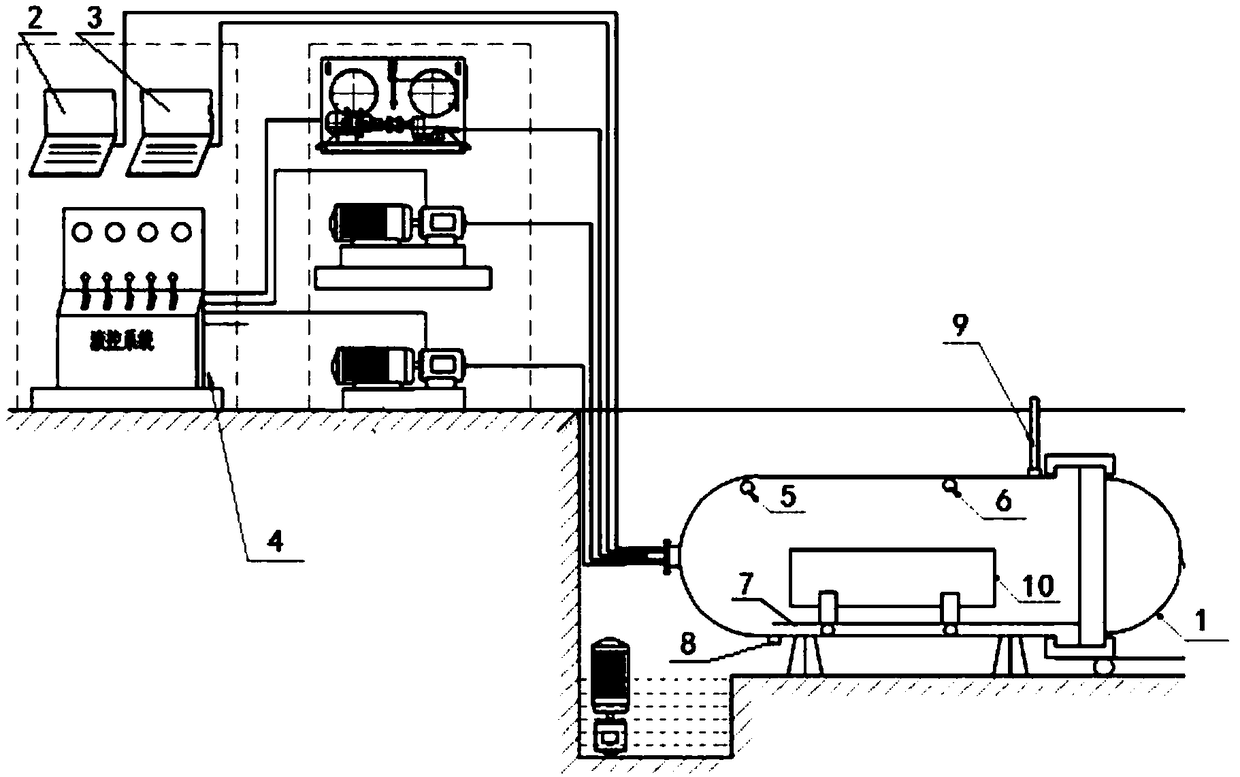

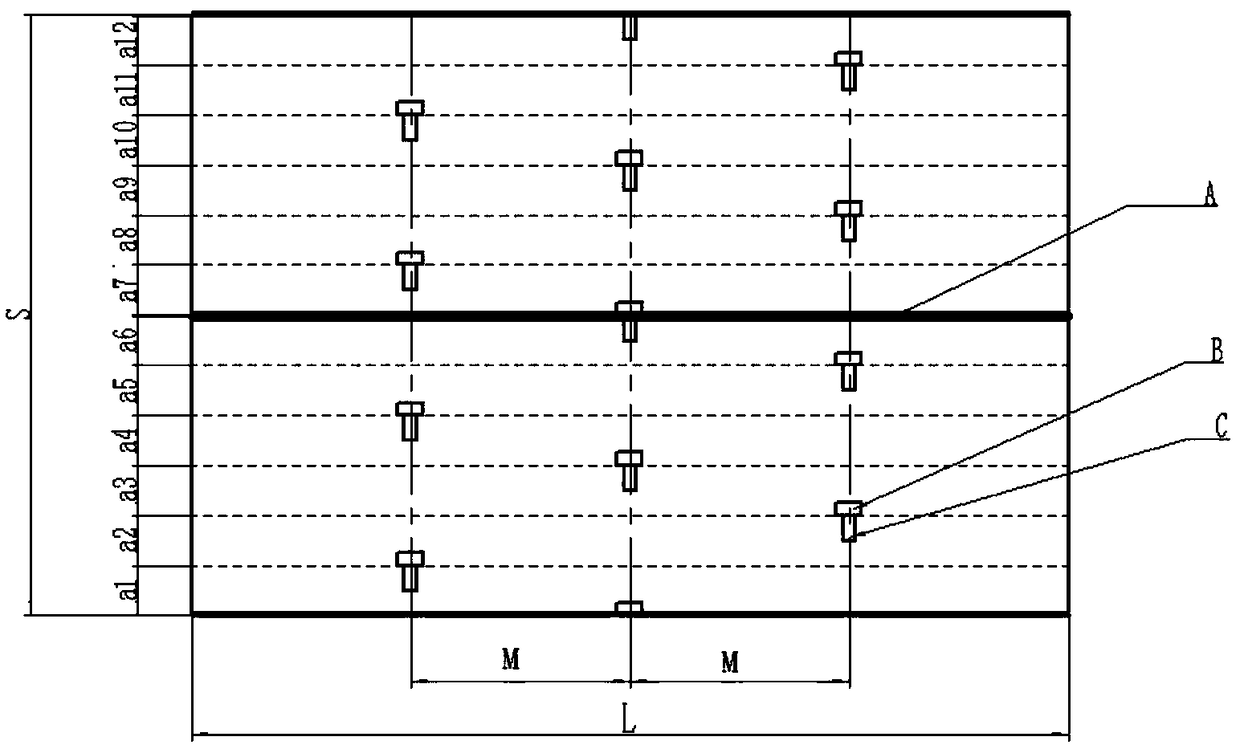

Test method for external pressure resistance of steel pipe for submarine pipeline

InactiveCN109163855AEffective evaluation of external pressure resistanceOptimized Design SpecificationsDetection of fluid at leakage pointMaterial strength using tensile/compressive forcesPhysical verificationTest analysis

The invention discloses a test method for the external pressure resistance of a steel pipe for a submarine pipeline. The test method mainly includes selection of test equipment, design of a steel pipespecimen, test of the sealing performance of the steel pipe specimen, test of the external pressure resistance of the steel pipe specimen and evaluation of the external pressure resistance of the steel pipe specimen. The test method is mainly applicable to the test of the external pressure resistance of the steel pipe for the submarine pipeline under the external pressure load of surrounding environmental water, especially for the test of the external pressure resistance of a high-strength thick-walled steel pipe for a deep-sea pipeline within the water depth of 3500 meters or less. Through adoption of the method, physical verification and test analysis of the external pressure resistance of the steel pipe for the deep-sea pipeline can be realized; comprehensive performance evaluation ofindexes such as mechanical properties and appearance geometric dimensions of the steel pipe for the submarine pipeline can be realized; and the test result play an important guidance role in the design and control of indexes such as materials, wall thicknesses, mechanical properties and appearance dimensions of steel pipes for submarine pipeline projects.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

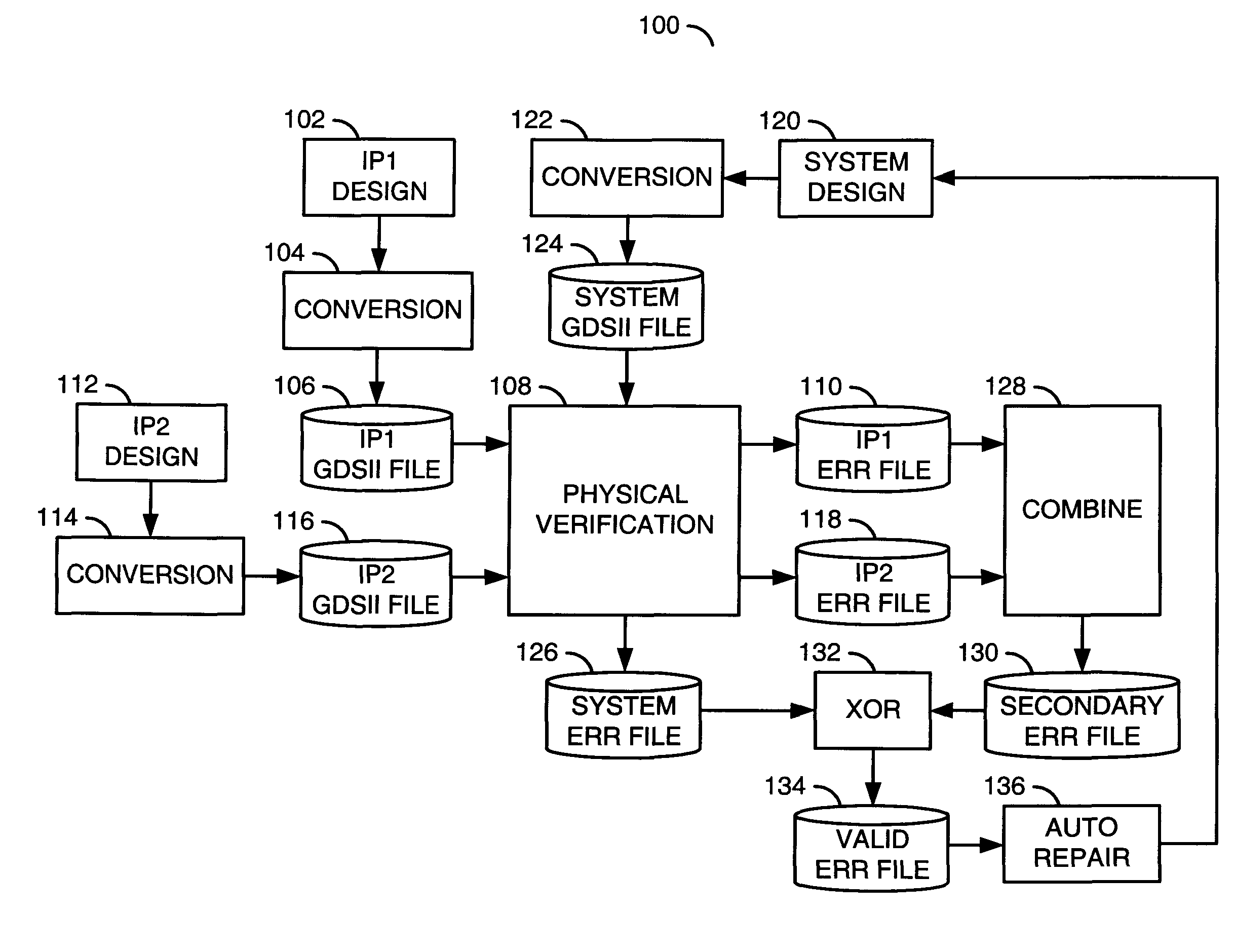

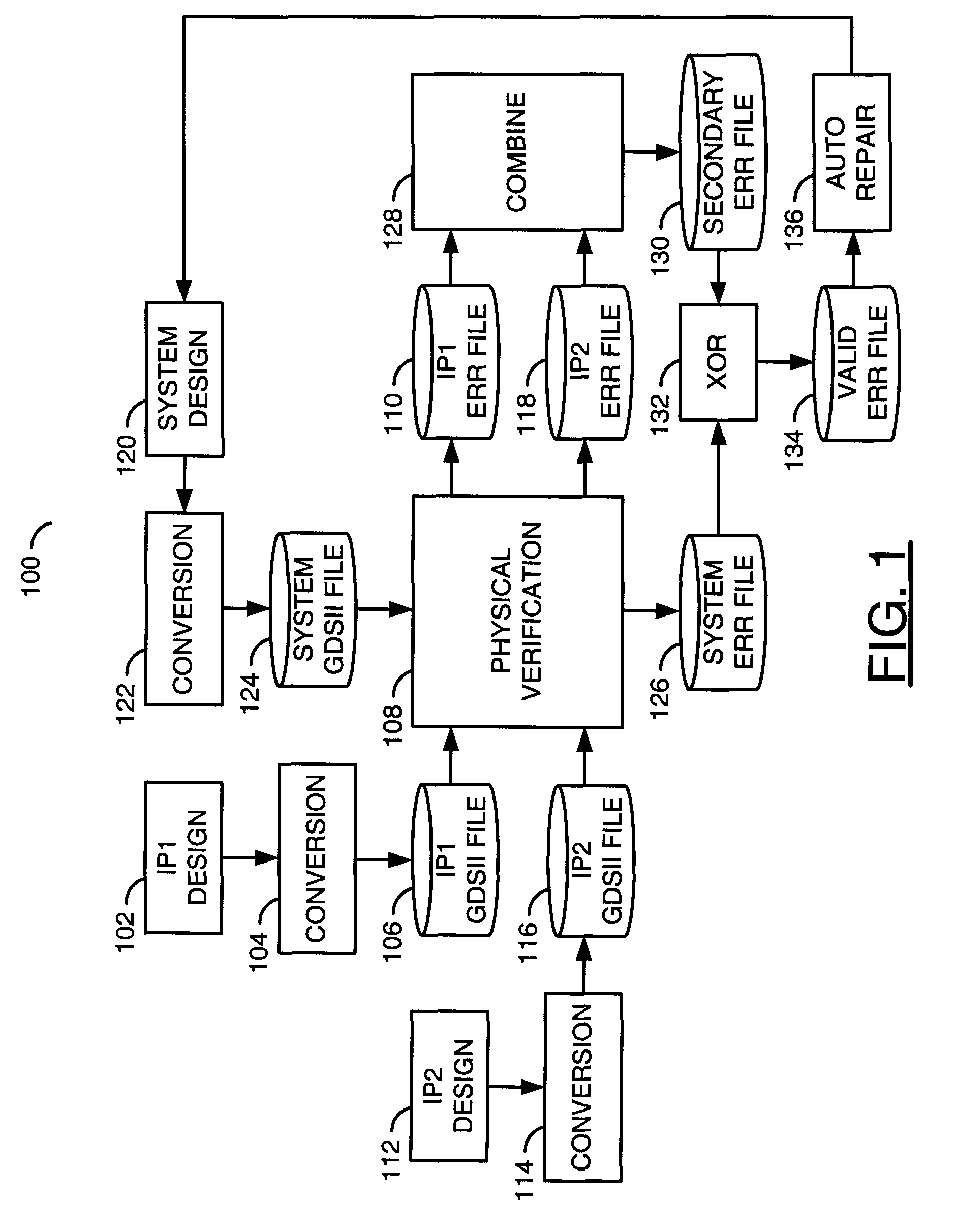

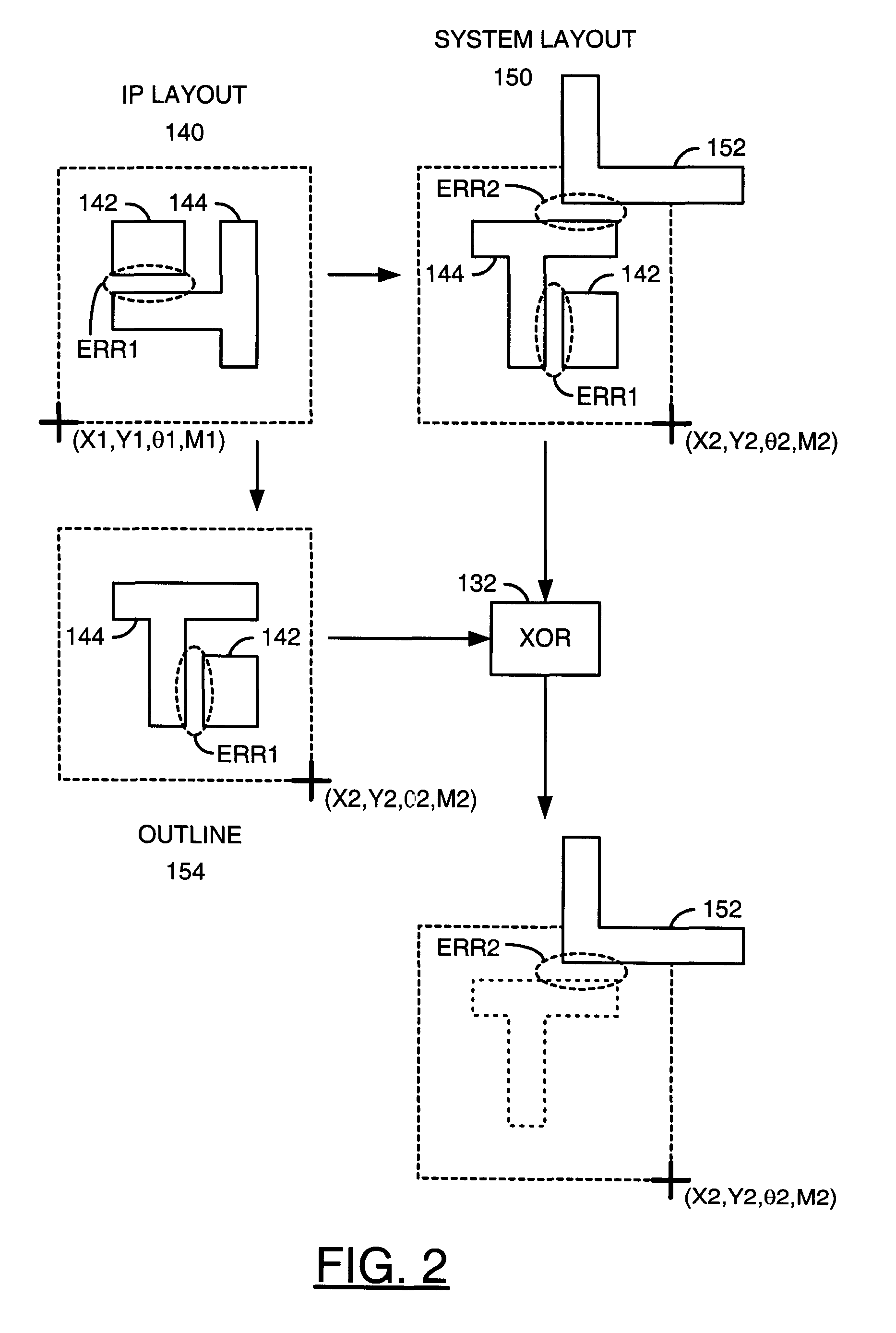

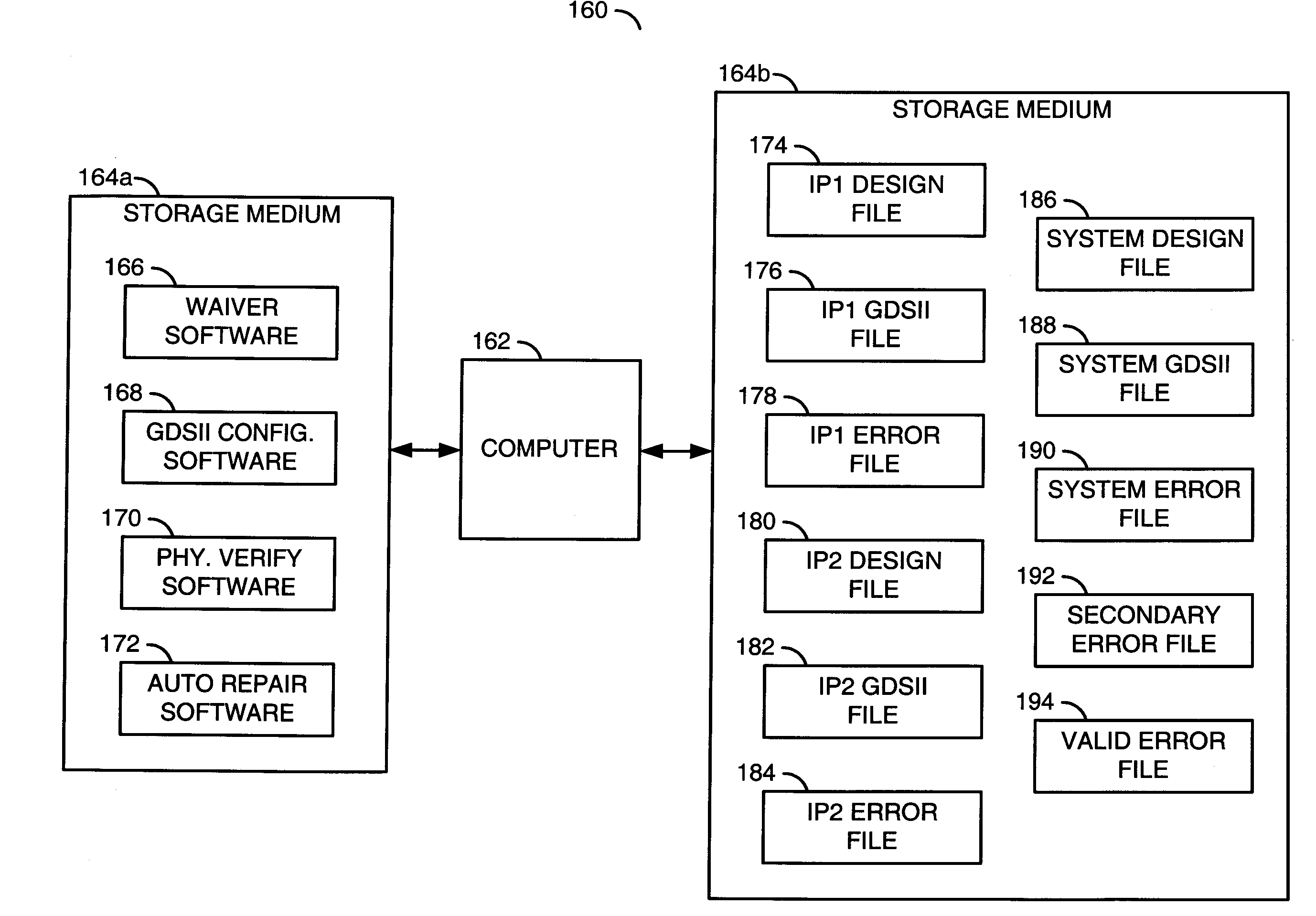

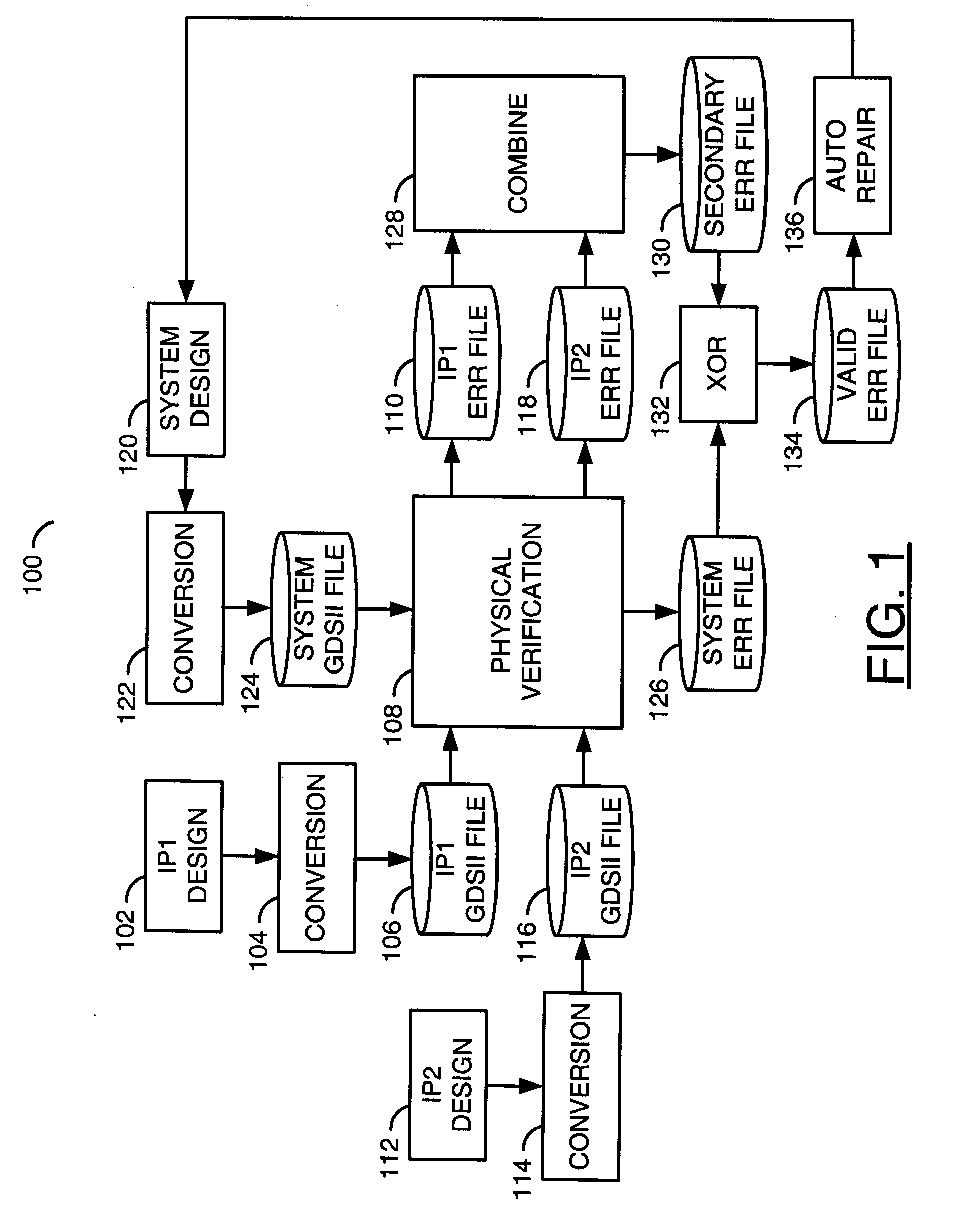

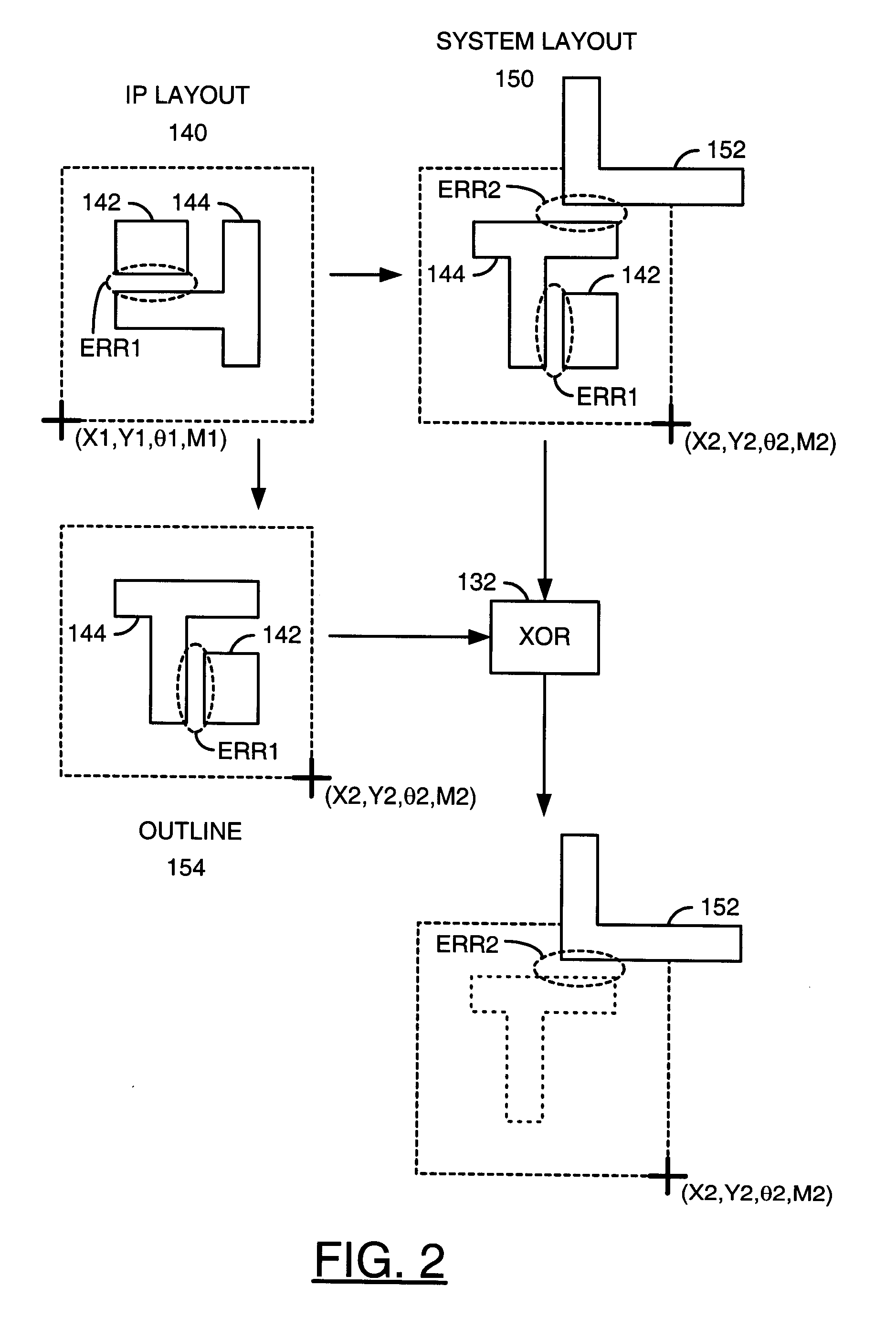

Waiver mechanism for physical verification of system designs

InactiveUS8046726B2Reduce in quantityDetecting faulty computer hardwareComputer aided designComputer hardwareSystems design

A method of waiving verification failures is disclosed. The method generally includes the steps of (A) generating a plurality of circuit error files by performing a plurality of physical verifications on a plurality of circuit designs, the circuit error files containing a plurality of circuit errors of the circuit designs, (B) generating a system error file by performing an additional physical verification on a system design, the system error file containing a plurality of system errors of the system design, the system design incorporating the circuit designs and (C) generating a valid error file by removing the circuit errors from the system error file, the valid error file containing a plurality of valid errors comprising a subset of the system errors.

Owner:BELL SEMICON LLC

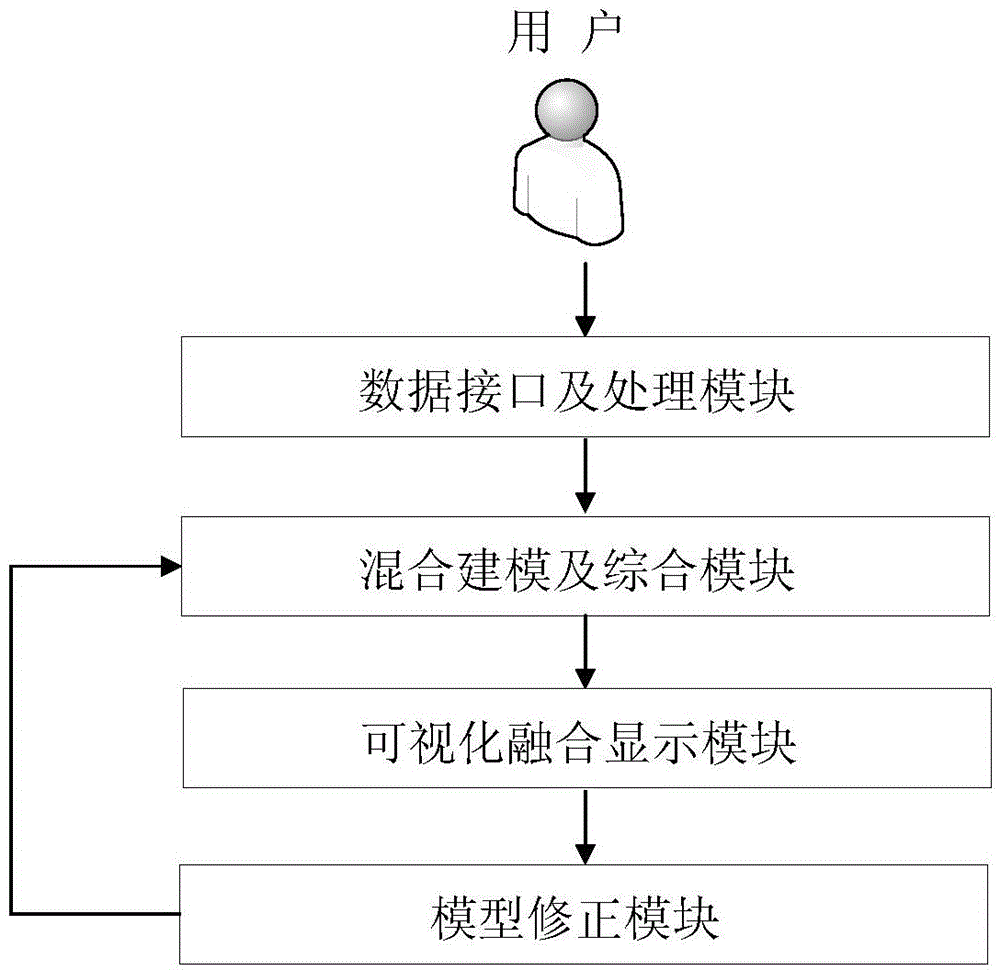

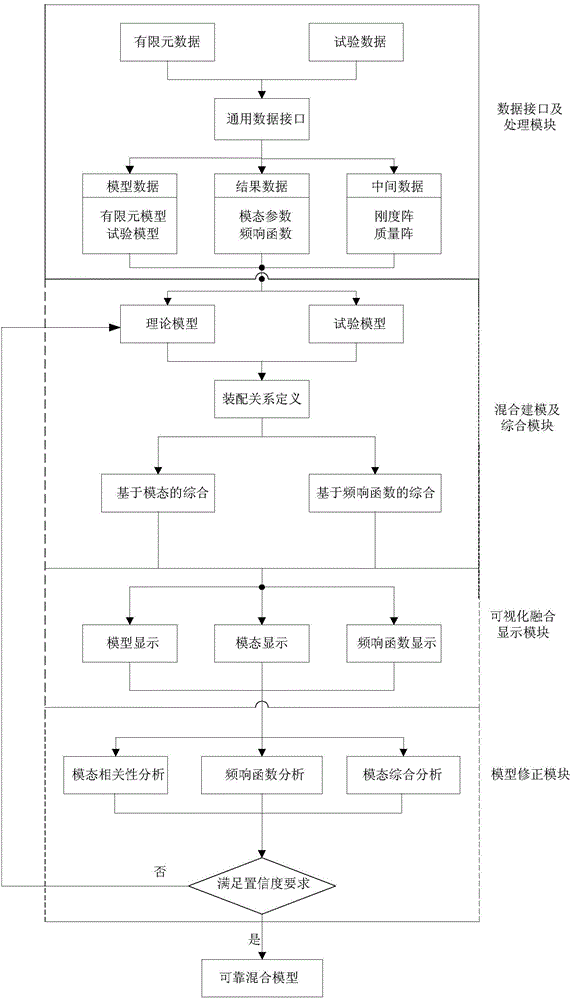

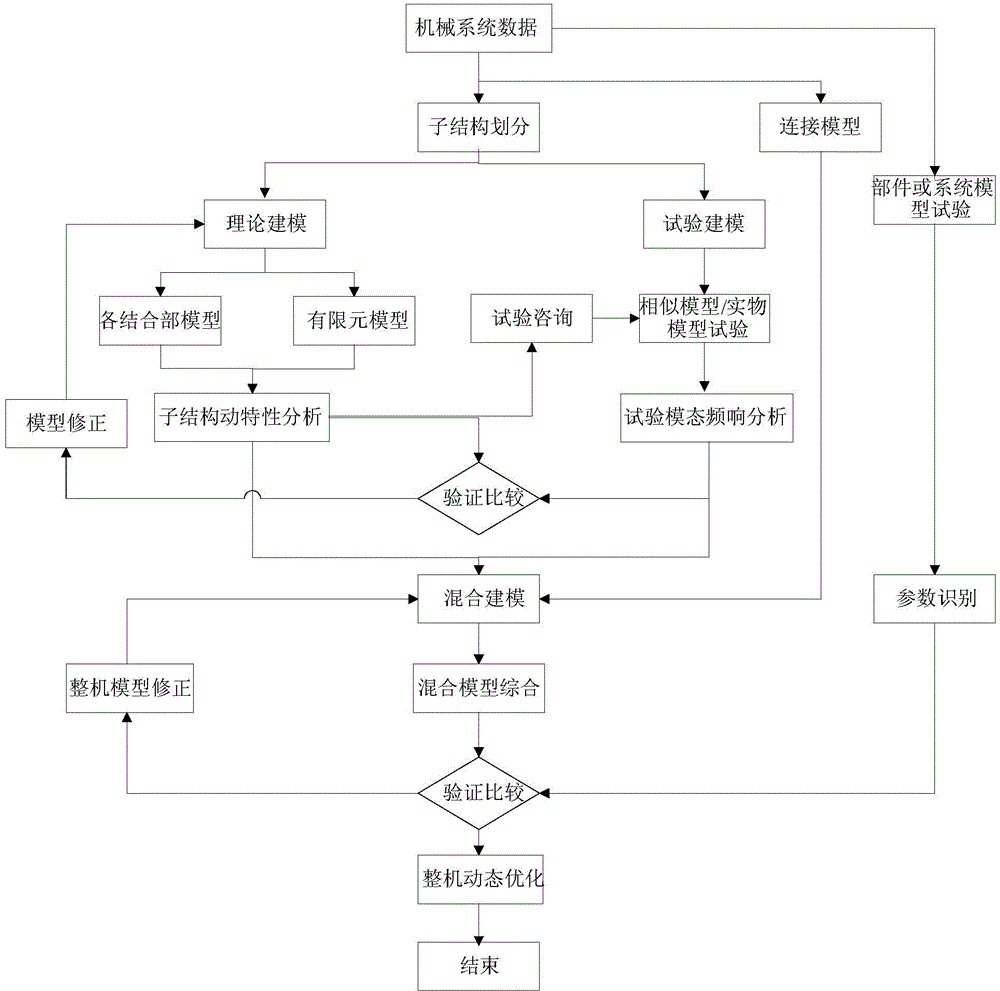

Virtools based multivariate data fusion virtual test display system

ActiveCN104318005AEasy to testRealize the "integration of virtual and realSpecial data processing applicationsElement modelPhysical field

The invention relates to a Virtools based multivariate data fusion virtual test display system, which comprises a data interface and processing module, a hybrid modeling and integrated module, a visual fusion display module, and a model correction module. A finite element method calculation (virtual test) and physical test methods carry out the calculation or test verification on all sub-structures, and a finite element model (virtual test model) is corrected according to physical test result data; meanwhile, a test trend indicated by the virtual test is utilized to guide the physical test to perfect the physical verification test scheme; finally, the overlapping display of comprehensive test environment of a complicated system is carried out according to a hybrid model established by a virtual test model and physical test data, and an LOD management technology is adopted in an overlapping display model, so that the overlapping display efficiency of physical field data in Virtools is improved.

Owner:CHINA ACAD OF LAUNCH VEHICLE TECH

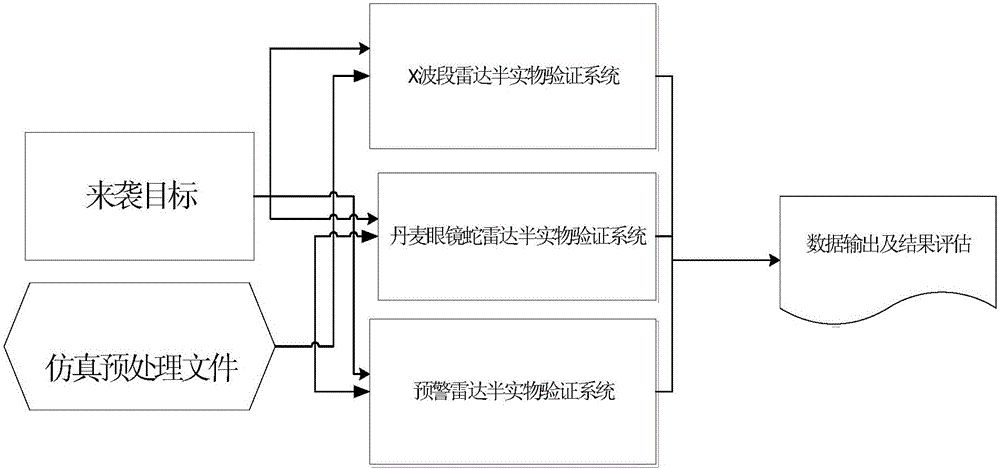

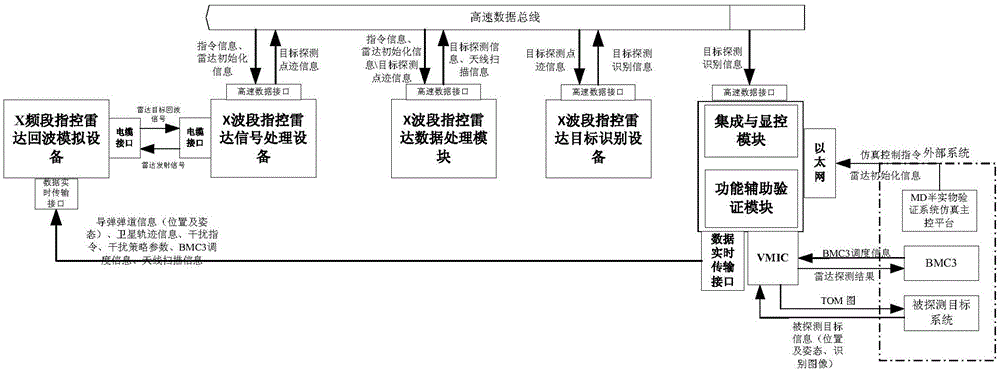

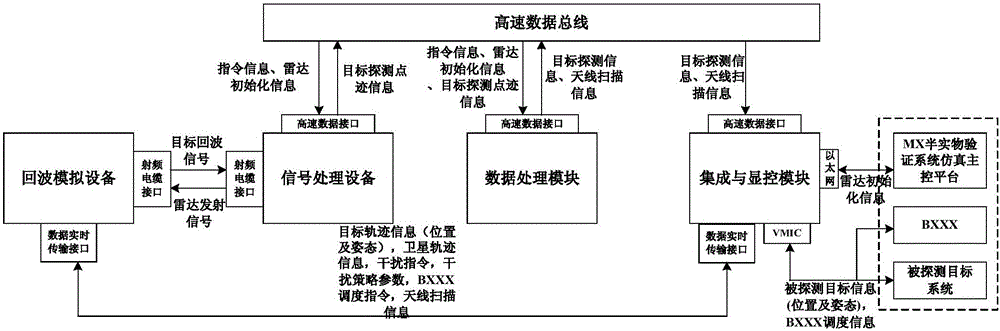

Time-division multiplexing technology-based networked ground-based radar semi-physical system

ActiveCN106546978AComplete simulationImprove realismRadio wave reradiation/reflectionGround based radarCommand and control

The present invention relates to a time-division multiplexing technology-based networked ground-based radar semi-physical system. The system includes an X-band command and control radar semi-physical verification system, a Cobra Dane radar semi-physical verification system and an early warning radar semi-physical verification system; the three verification systems work jointly so as to simulate required battlefield environments more completely, and therefore, fidelity is high, implementation possibility is higher; and a time-division technology, semi-physical model and functional auxiliary verification module-combined method is adopted, and therefore, the costs of actually-created semi-physical equipment are decreased, a test method is simplified, and test difficulty is reduced.

Owner:CHINA ACAD OF LAUNCH VEHICLE TECH

Waiver mechanism for physical verification of system designs

InactiveUS20100070936A1Reduce in quantityDetecting faulty computer hardwareComputer aided designComputer hardwareSystems design

A method of waiving verification failures is disclosed. The method generally includes the steps of (A) generating a plurality of circuit error files by performing a plurality of physical verifications on a plurality of circuit designs, the circuit error files containing a plurality of circuit errors of the circuit designs, (B) generating a system error file by performing an additional physical verification on a system design, the system error file containing a plurality of system errors of the system design, the system design incorporating the circuit designs, (C) generating a valid error file by removing the circuit errors from the system error file, the valid error file containing a plurality of valid errors comprising a subset of the system errors and (D) storing the valid error file in a recording medium.

Owner:BELL SEMICON LLC