Clock-tree layout flow method and clock-tree deviation compensation device in integrate circuit

A technology of integrated circuits and compensation devices, which is applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of small effective time window, large clock tree delay, and cost, so as to accelerate the timing convergence cycle and shorten the time to market Time, Difficulty Reduction Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

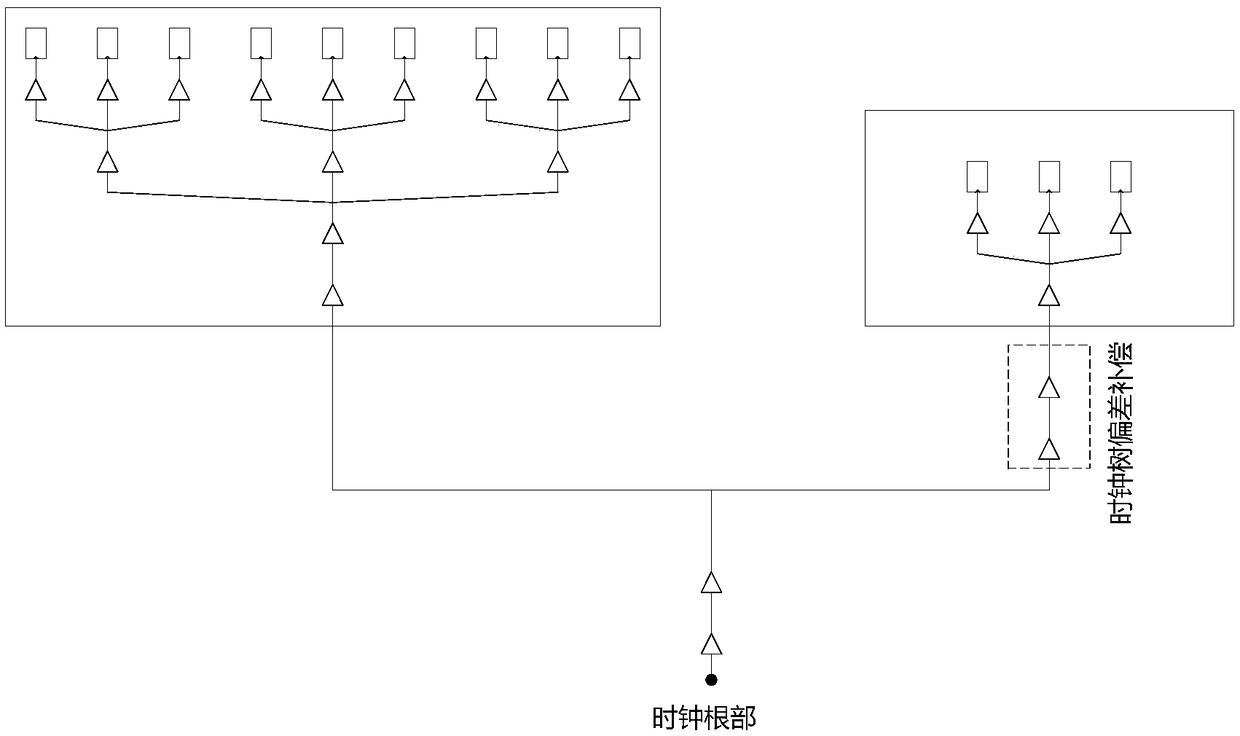

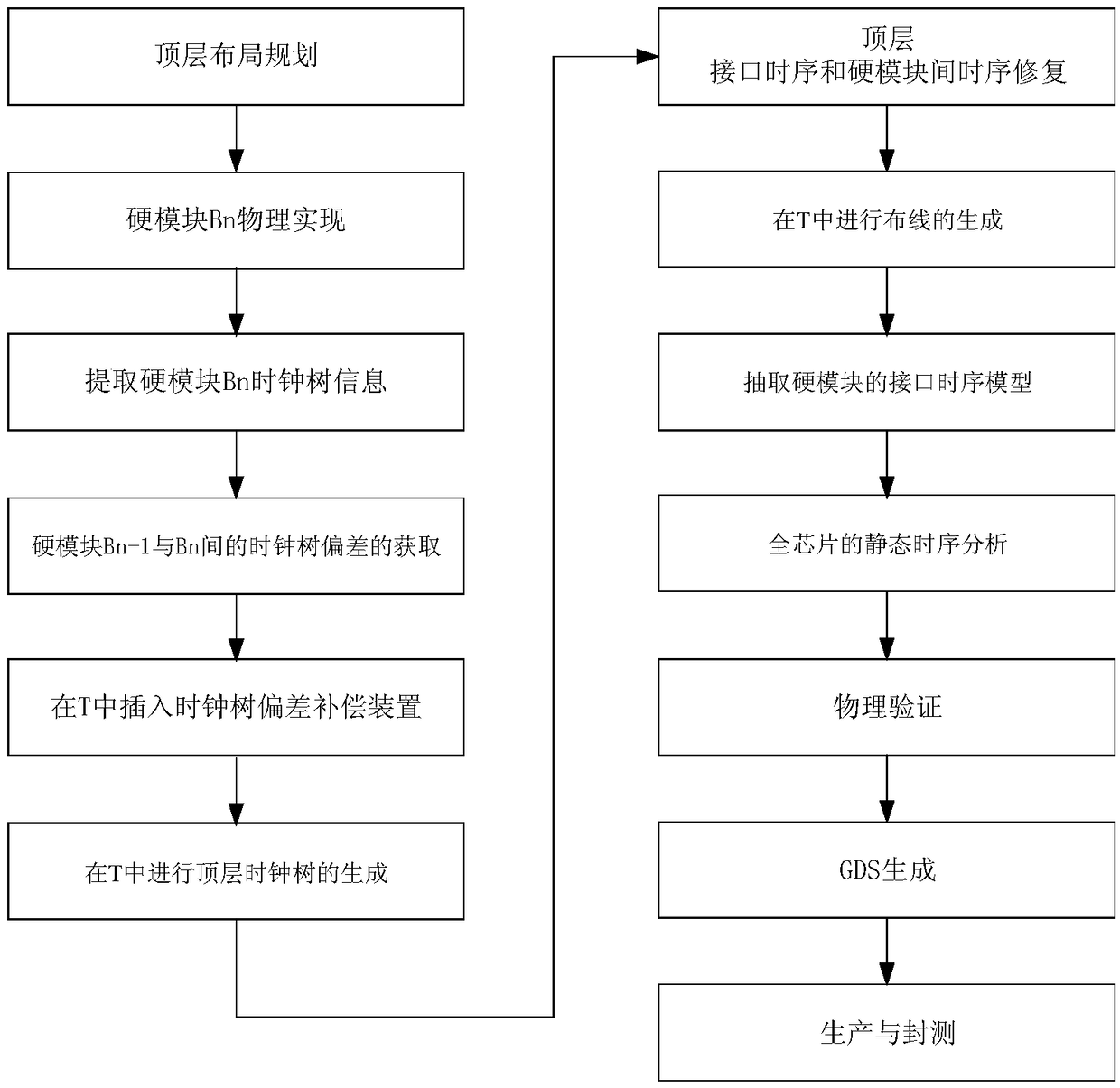

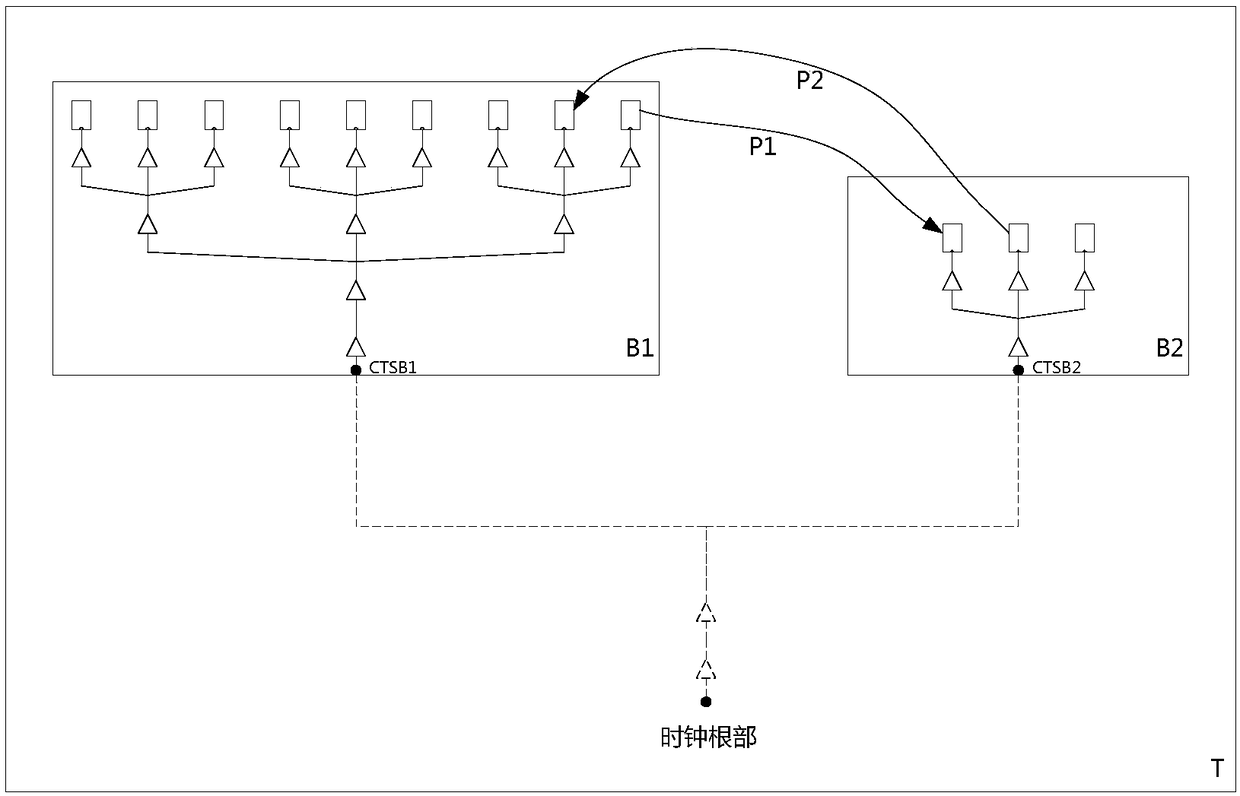

[0049] The method for laying out a clock tree in an integrated circuit according to an embodiment of the present invention is as follows: figure 2 shown, including the following steps:

[0050] Step 1: Top level layout. First, divide and place the hard modules on the top layer. After many iterations and experiments, there will be no wiring congestion and timing violations in the subsequent layout and wiring process. Within a certain range, such as ensuring that the static pressure drop is less than 3%-5%, and the dynamic pressure drop is less than 10%-15%. Each hard module is denoted a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More