Patents

Literature

133 results about "Timing closure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

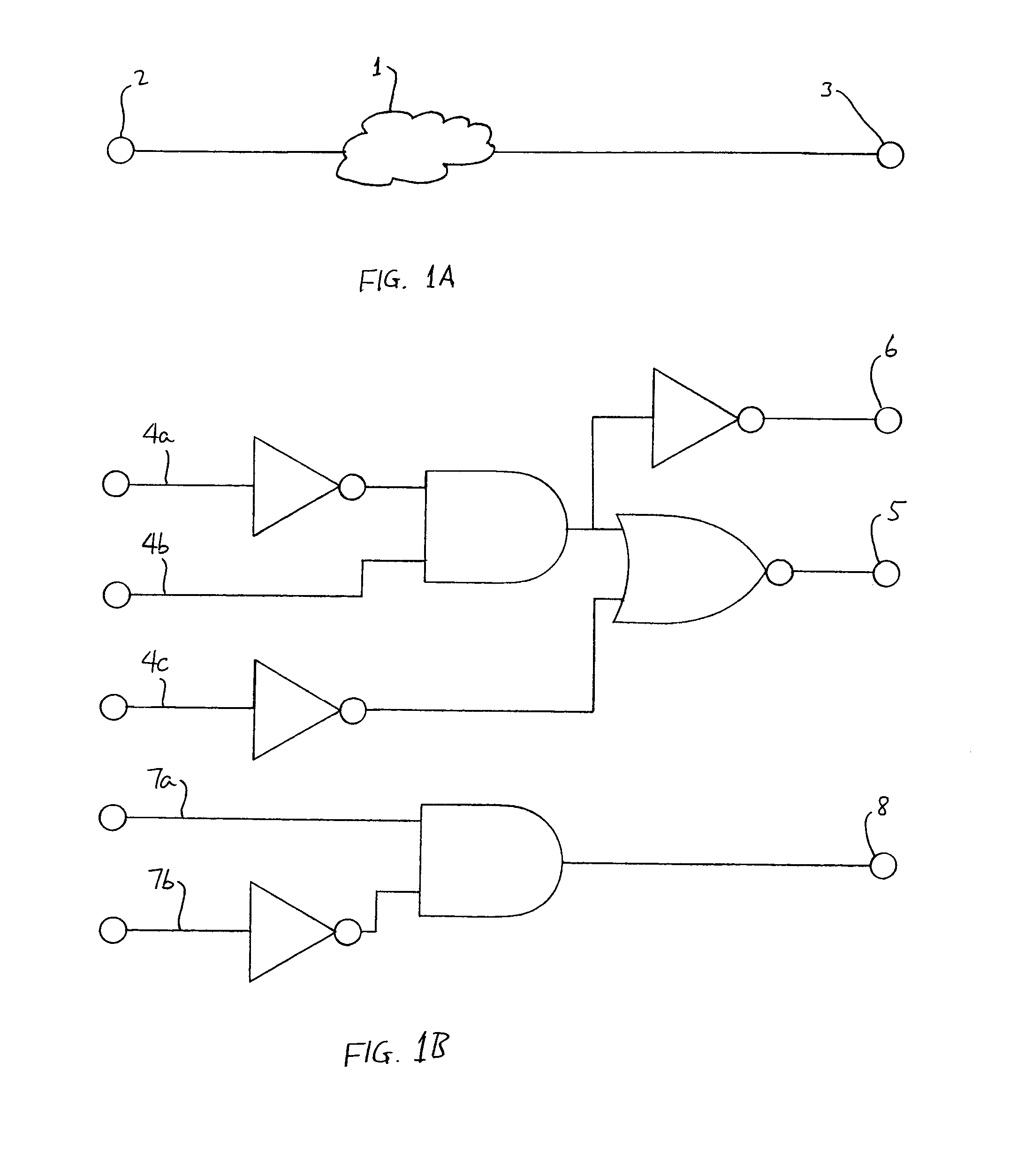

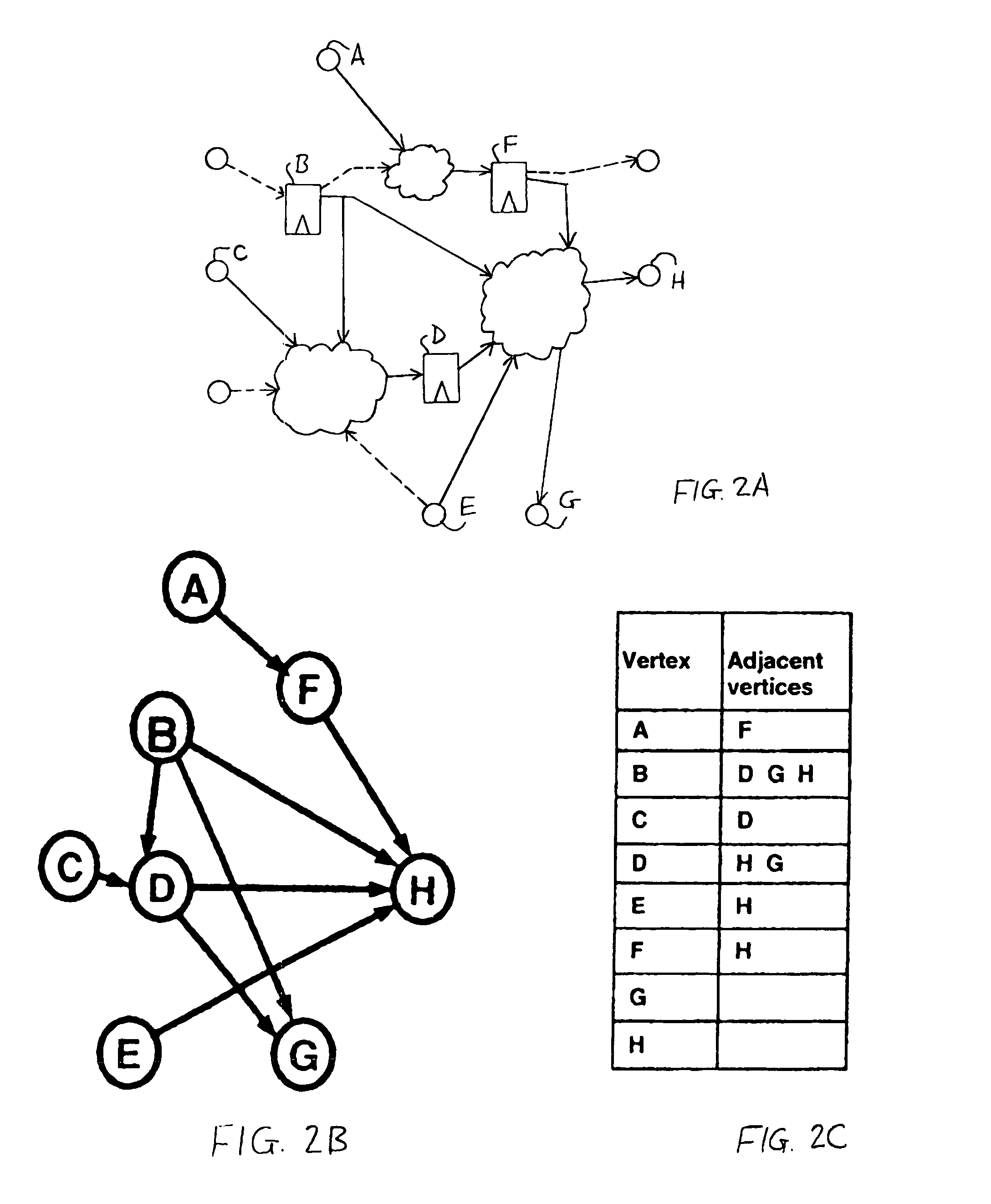

Timing closure is the process by which a logic design consisting of primitive elements such as combinatorial logic gates (and, or, not, nand, nor, etc.) and sequential logic gates (flip flops, latches, memories) is modified to meet its timing requirements. Unlike in a computer program where there is no explicit delay to perform a calculation, logic circuits have intrinsic and well defined delays to propagate inputs to outputs. In simple cases, the user can compute the path delay between elements manually. If the design is more than a dozen or so elements this is impractical. For example, the time delay along a path from the output of a D-Flip Flop, through combinatorial logic gates, then into the next D-Flip Flop input must satisfy (be less than) the time period between synchronizing clock pulses to the two flip flops. When the delay through the elements is greater than the clock cycle time, the elements are said to be on the critical path. The circuit will not function when the path delay exceeds the clock cycle delay so modifying the circuit to remove the timing failure (and eliminate the critical path) is an important part of the logic design engineer's task.

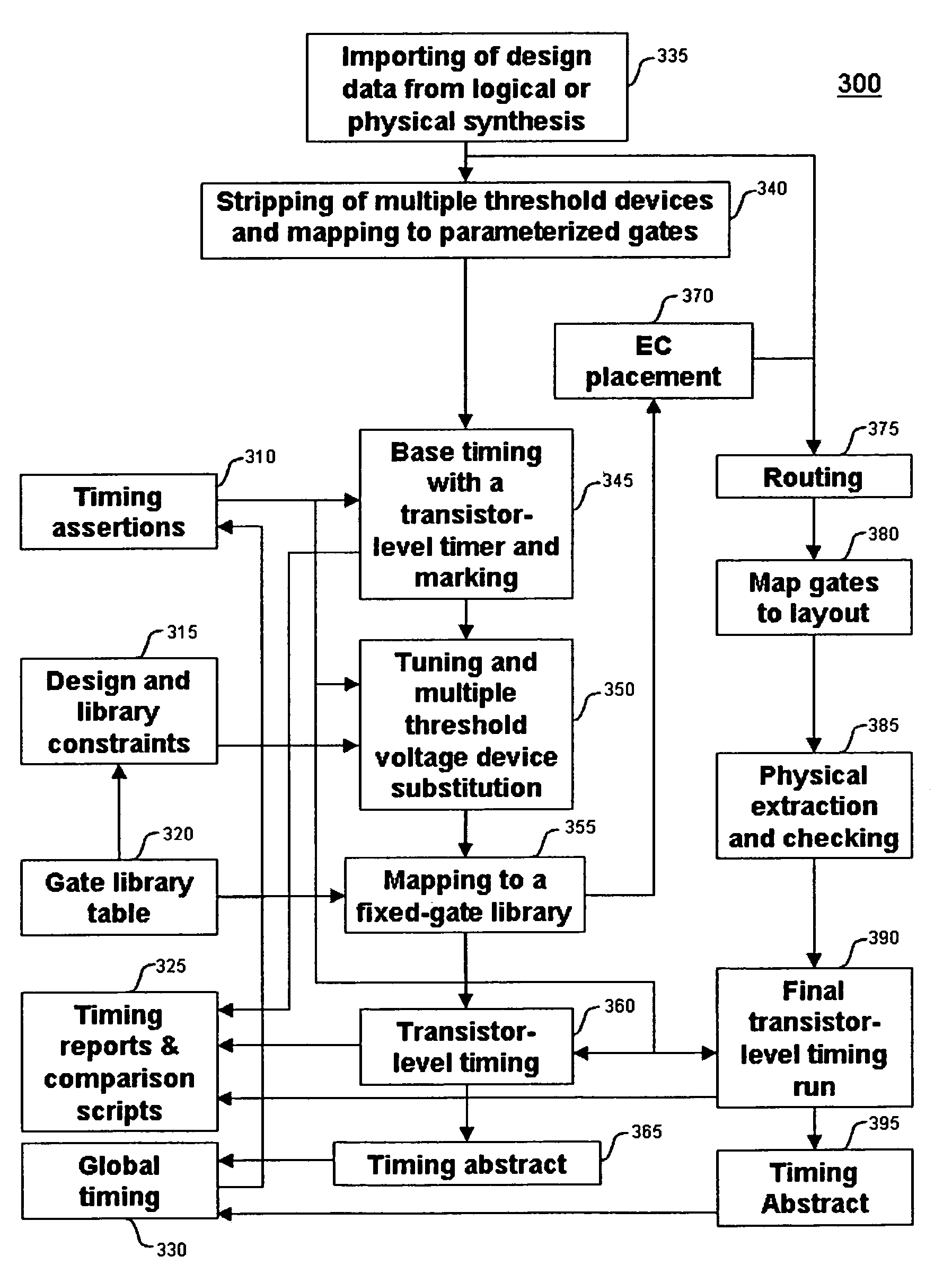

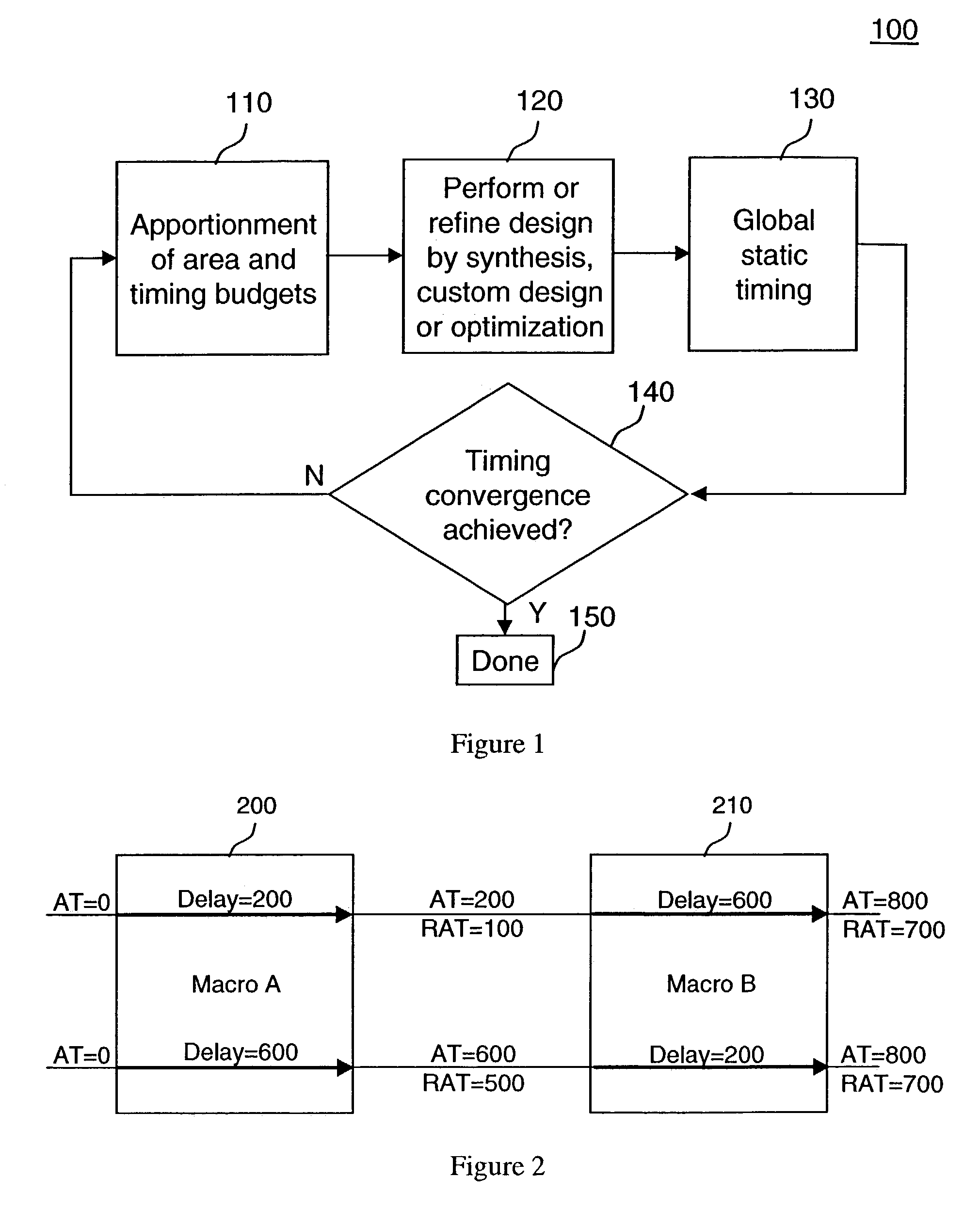

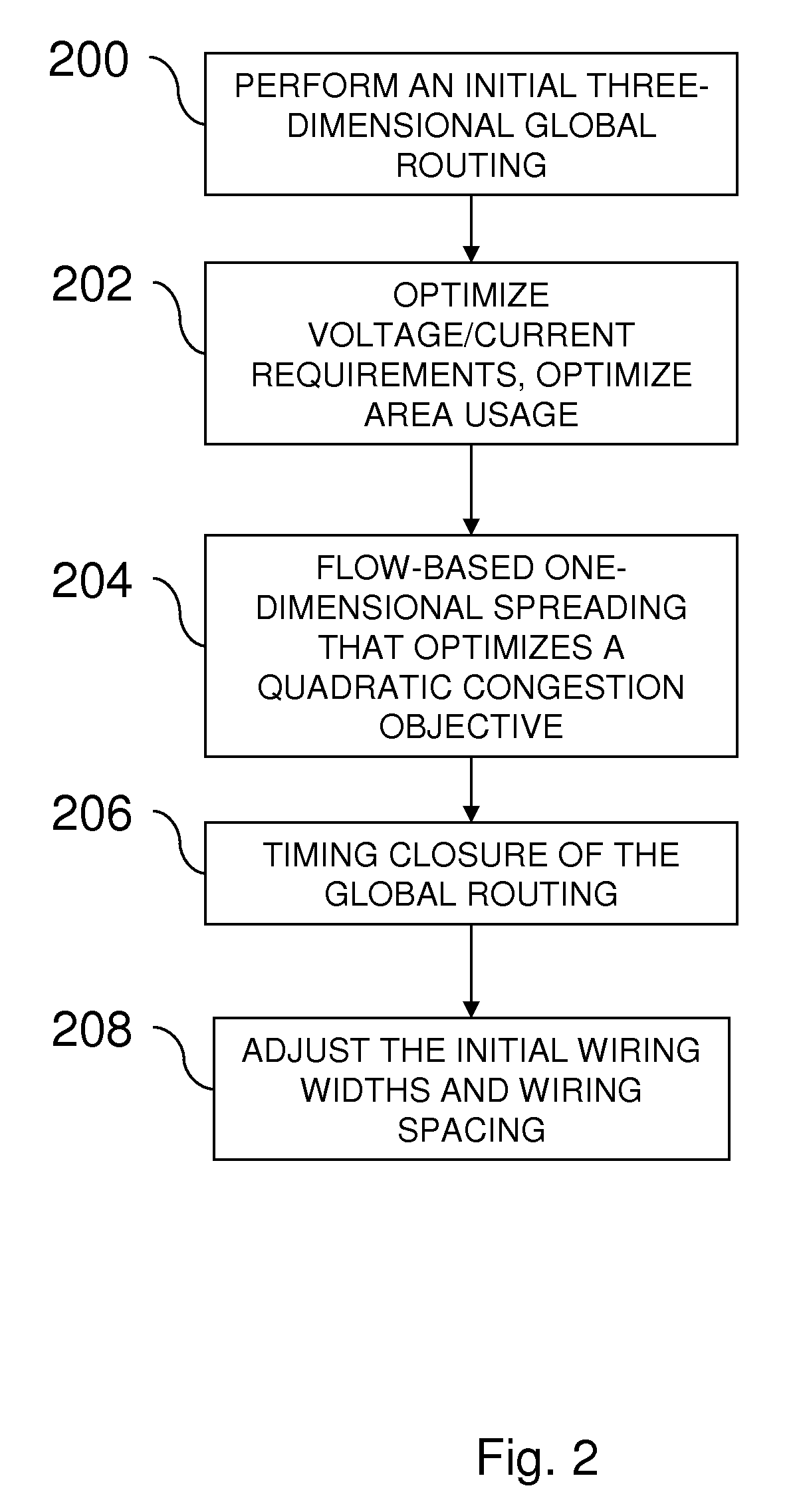

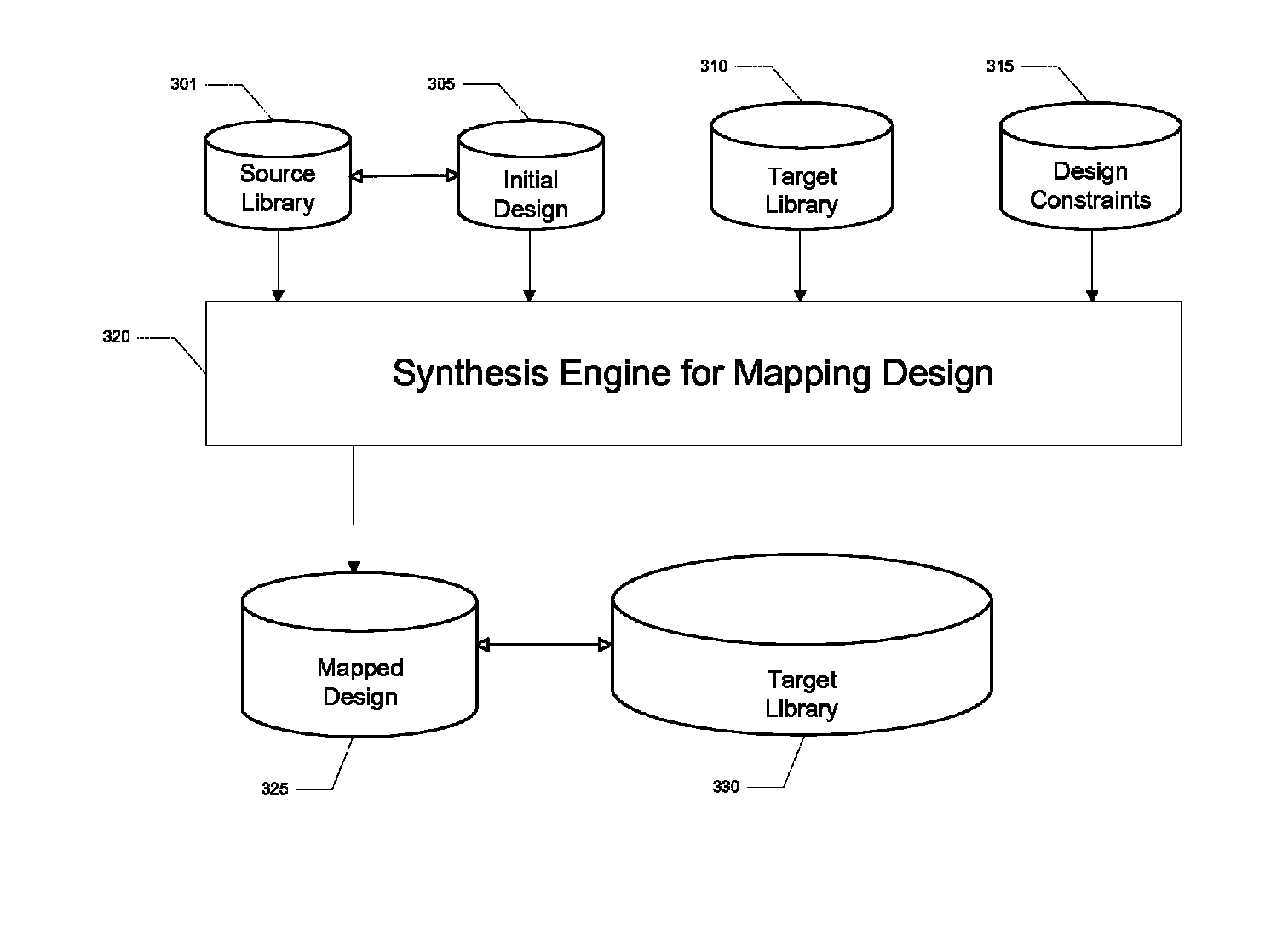

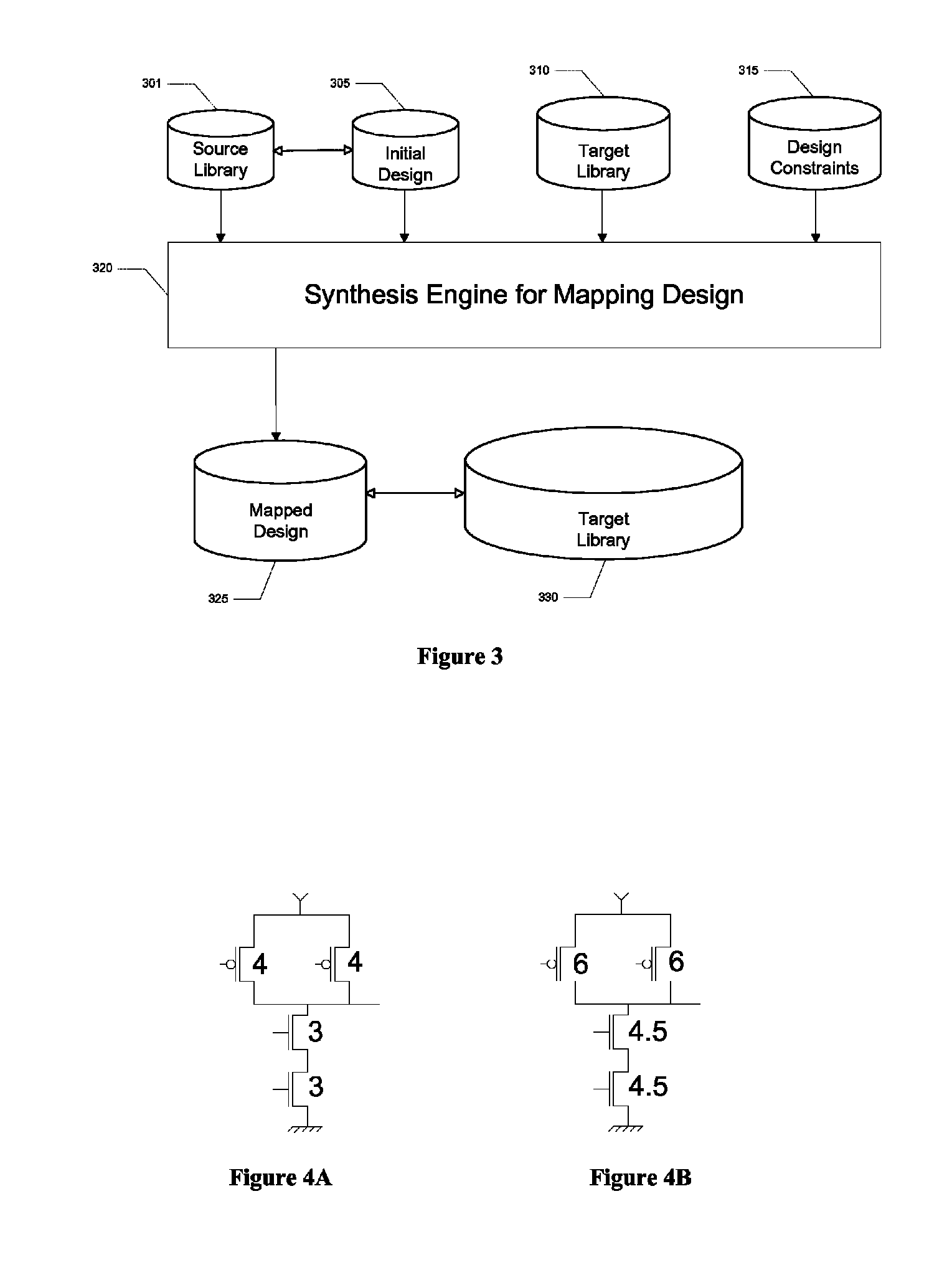

Method for tuning a digital design for synthesized random logic circuit macros in a continuous design space with optional insertion of multiple threshold voltage devices

InactiveUS7093208B2Efficient and effective methodologyError minimizationDigital storageComputer aided designContinuous designCritical section

A Digital Design Method which may be automated is for obtaining timing closure in the design of large, complex, high-performance digital integrated circuits. The methodincludes the use of a tuner on random logic macros that adjusts transistor sizes in a continuous domain. To accommodate this tuning, logic gates are mapped to parameterized cells for the tuning and then back to fixed gates after the tuning. Tuning is constrained in such a way as to minimize “binning errors” when the design is mapped back to fixed cells. Further, the critical sections of the circuit are marked in order to make the optimization more effective and to fit within the problem-size constraints of the tuner. A specially formulated objective function is employed during the tuning to promote faster global timing convergence, despite possibly incorrect initial timing budgets. The specially formulated objective function targets all paths that are failing timing, with appropriate weighting, rather than just targeting the most critical path. Finally, the addition of multiple threshold voltage gates allows for increased performance while limiting leakage power.

Owner:GLOBALFOUNDRIES INC

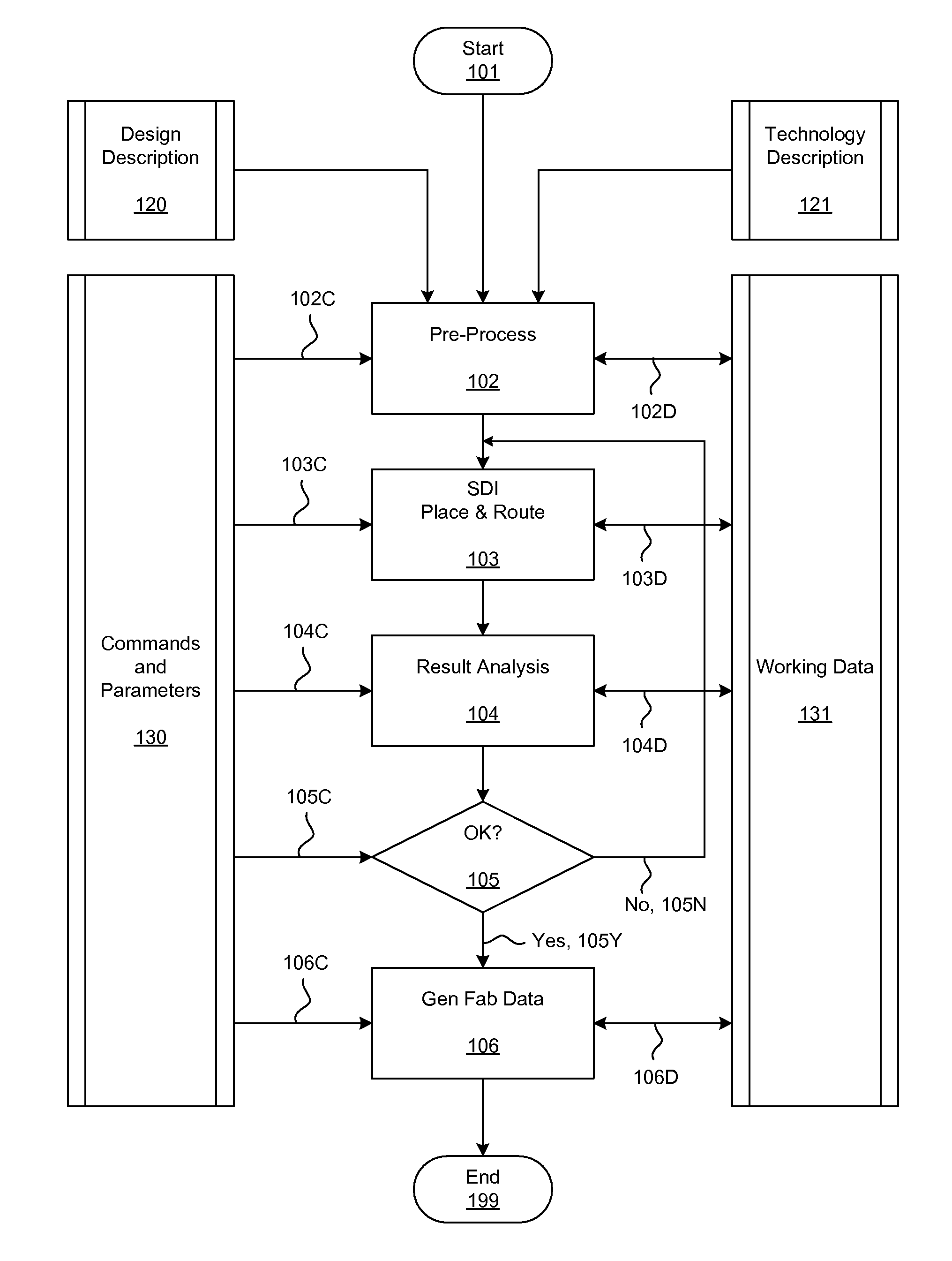

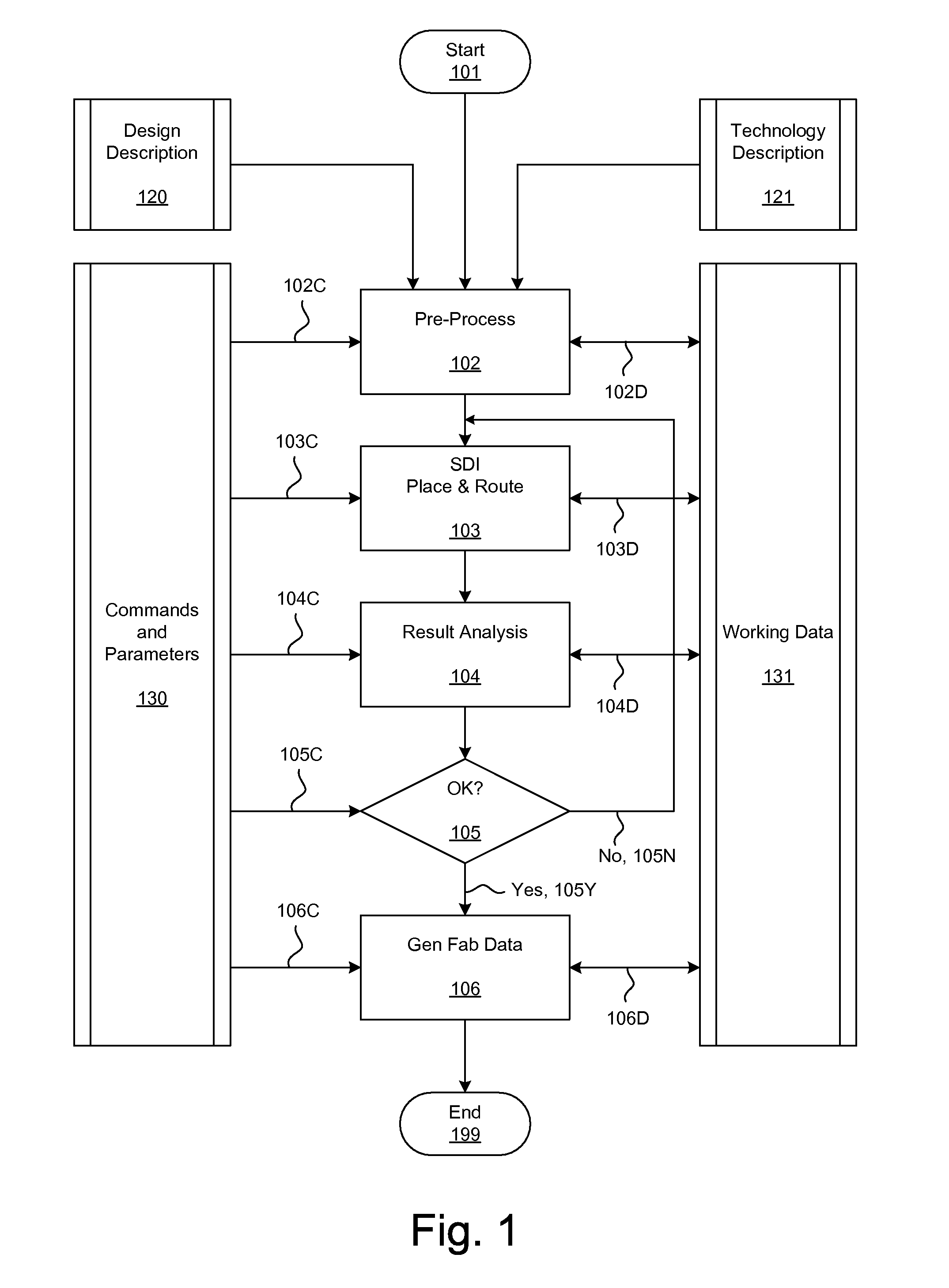

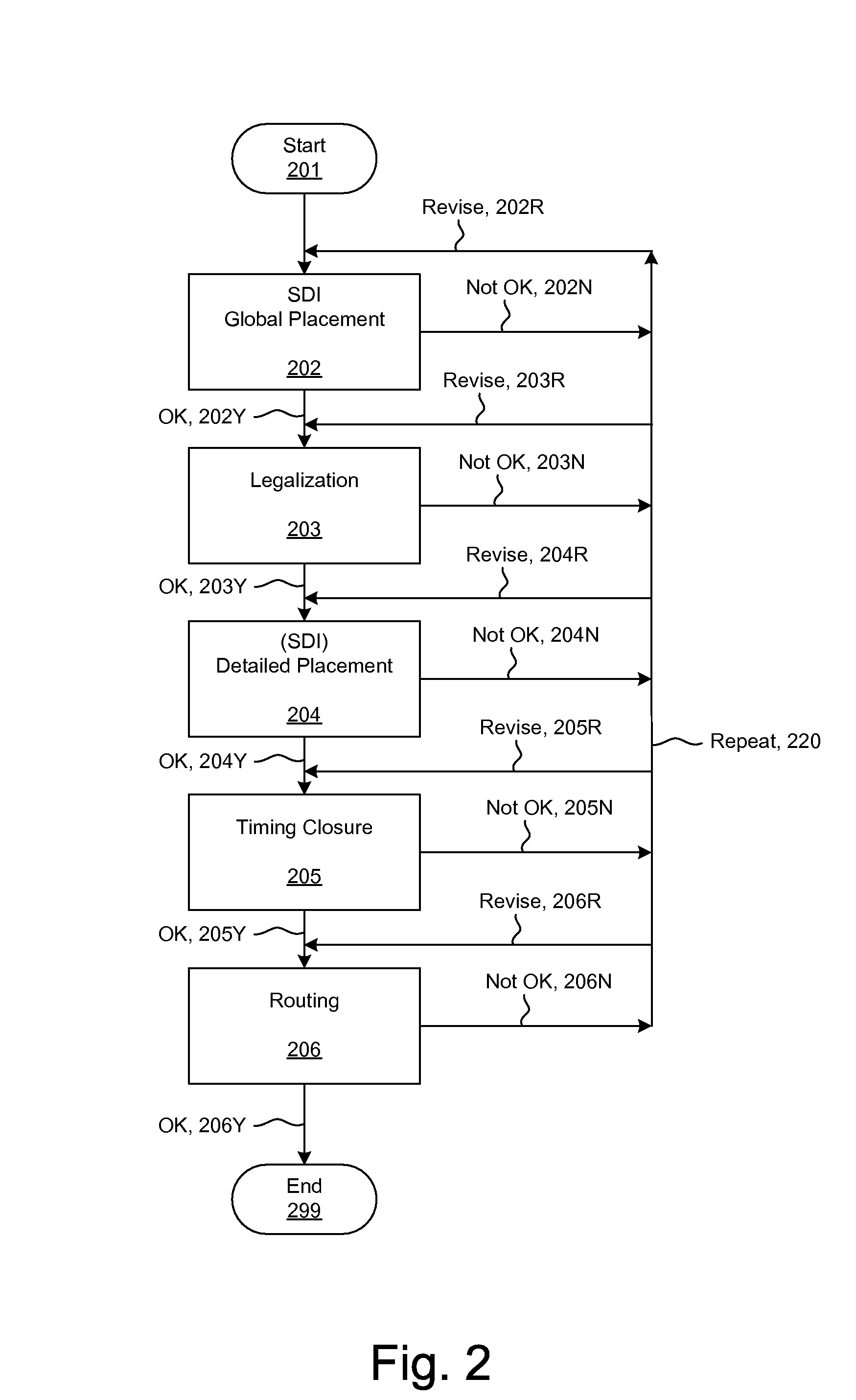

Methods and systems for placement and routing

ActiveUS20090254874A1Influence optimizeImprove performanceCAD circuit designSoftware simulation/interpretation/emulationElectrical resistance and conductanceCapacitance

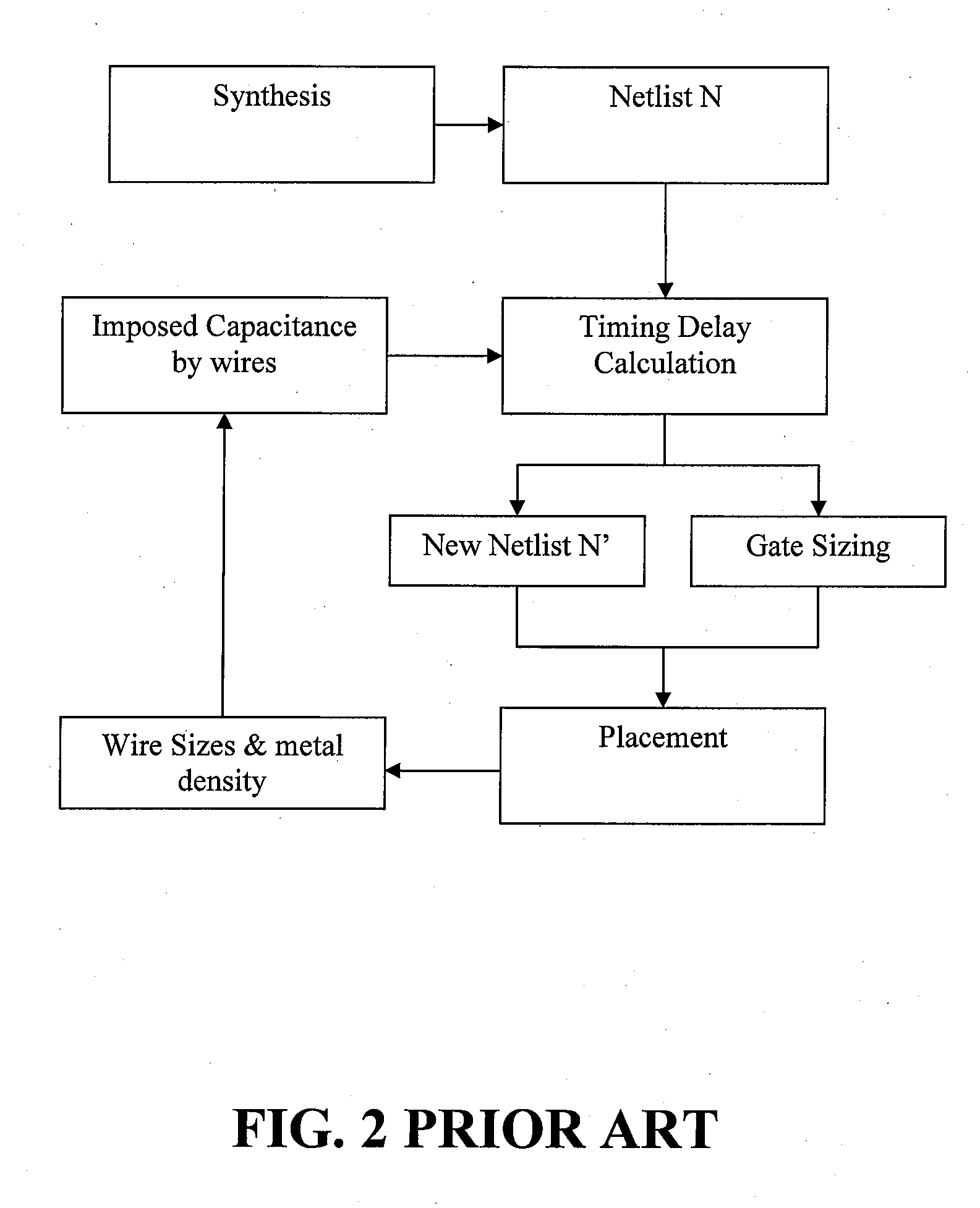

Techniques for placement of integrated circuit elements include global placement, detailed placement, timing closure, and routing. The integrated circuit is described by a netlist specifying interconnections of morphable devices. The detailed placement uses, for example, Simultaneous Dynamical Integration, wherein the morphable-devices correspond to nodes influenced by forces, including timing forces. The timing forces are derived, for example, from a timing graph; path delay; slack; and drive resistance of the elements. The timing closure uses timing-driven buffering and timing-driven resizing to reduce maximum delay and / or transition time, and / or to fix hold time. Nets having high capacitance and / or fanout, and timing critical nets are preferentially processed. Timing-driven buffering applies buffering solutions to segments of route trees, combines solutions of adjoining segments, and prunes sets of solutions. Timing-driven resizing morphably replaces selected elements with upsized versions thereof.

Owner:CALLAHAN CELLULAR L L C

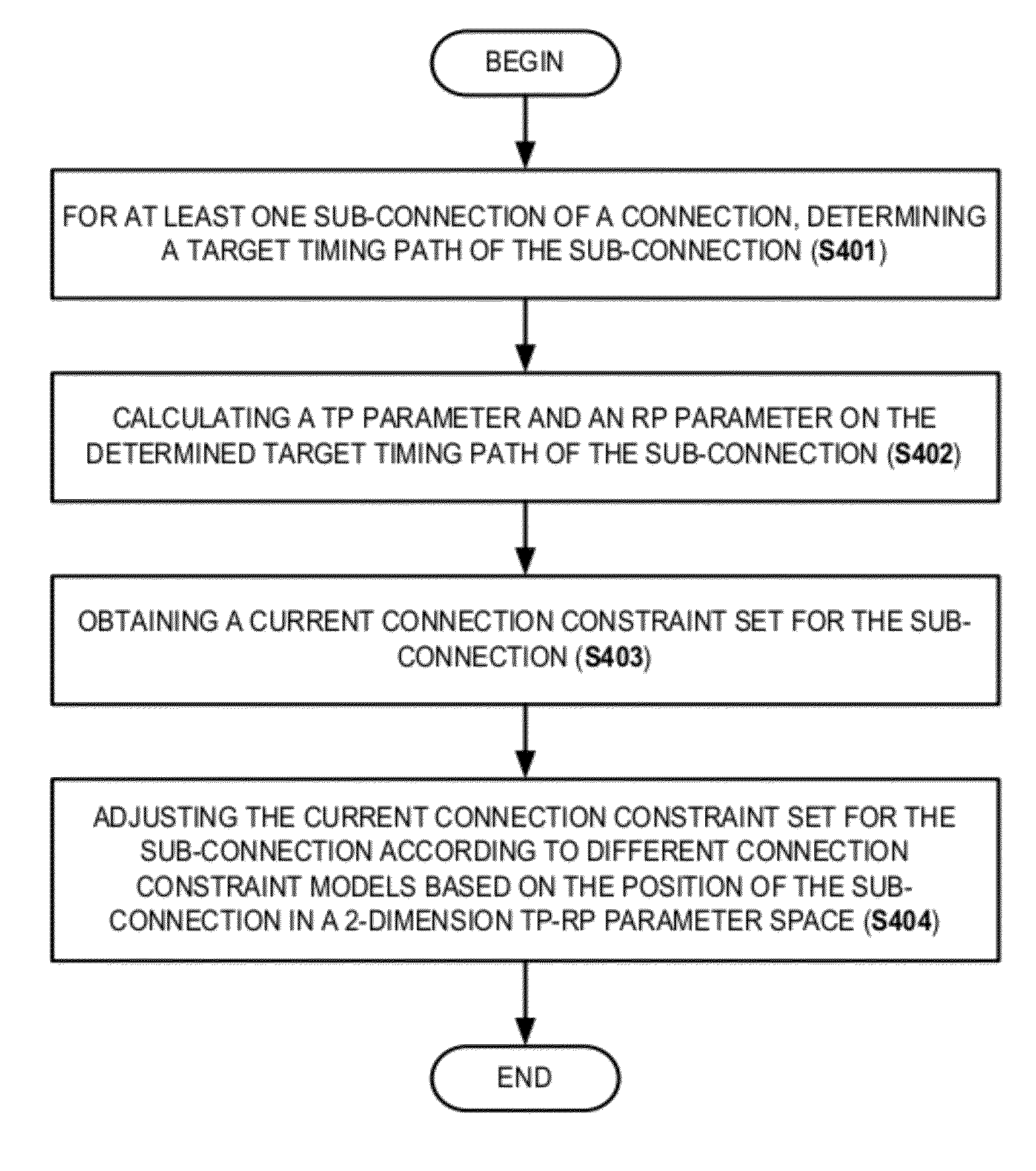

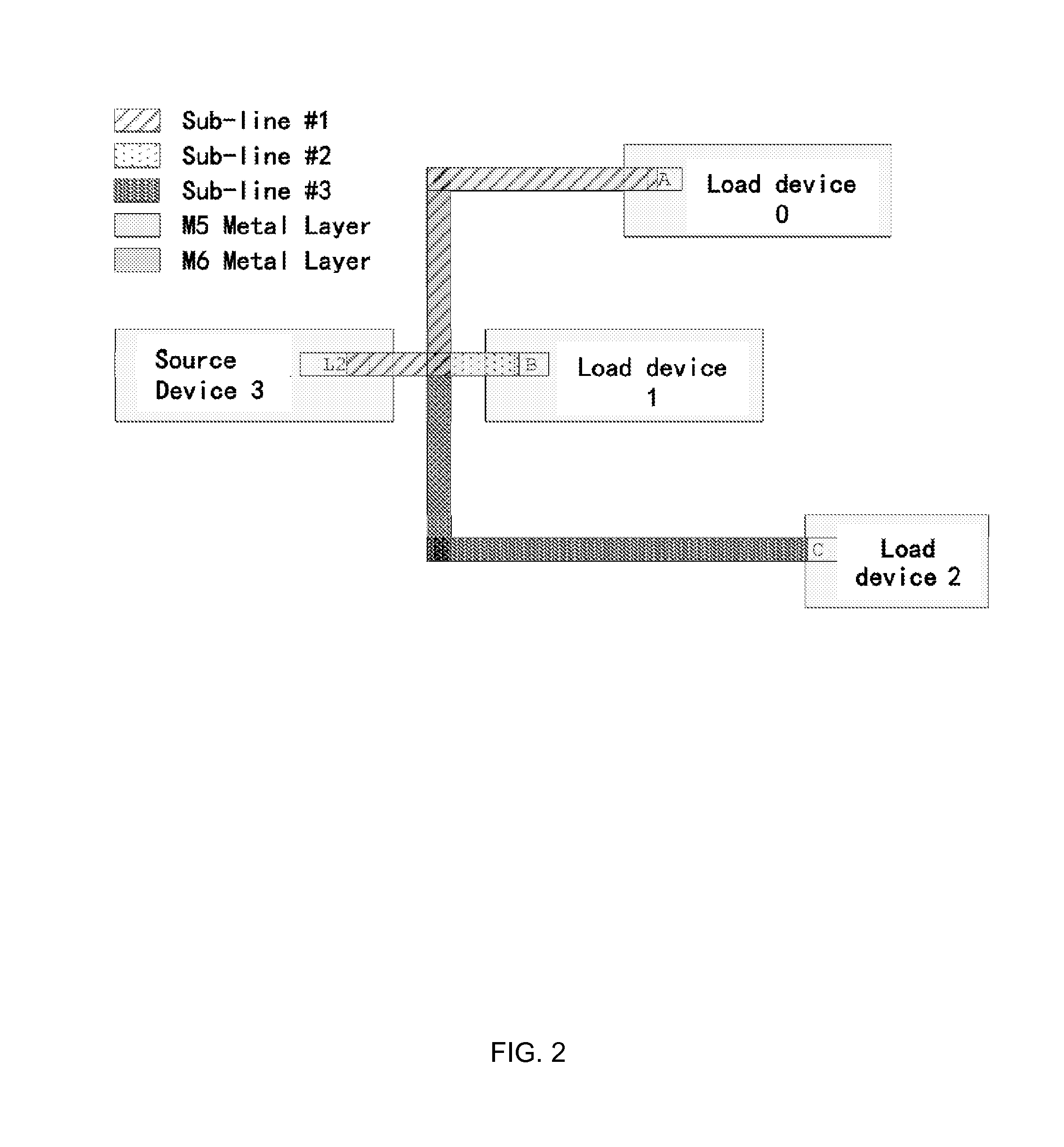

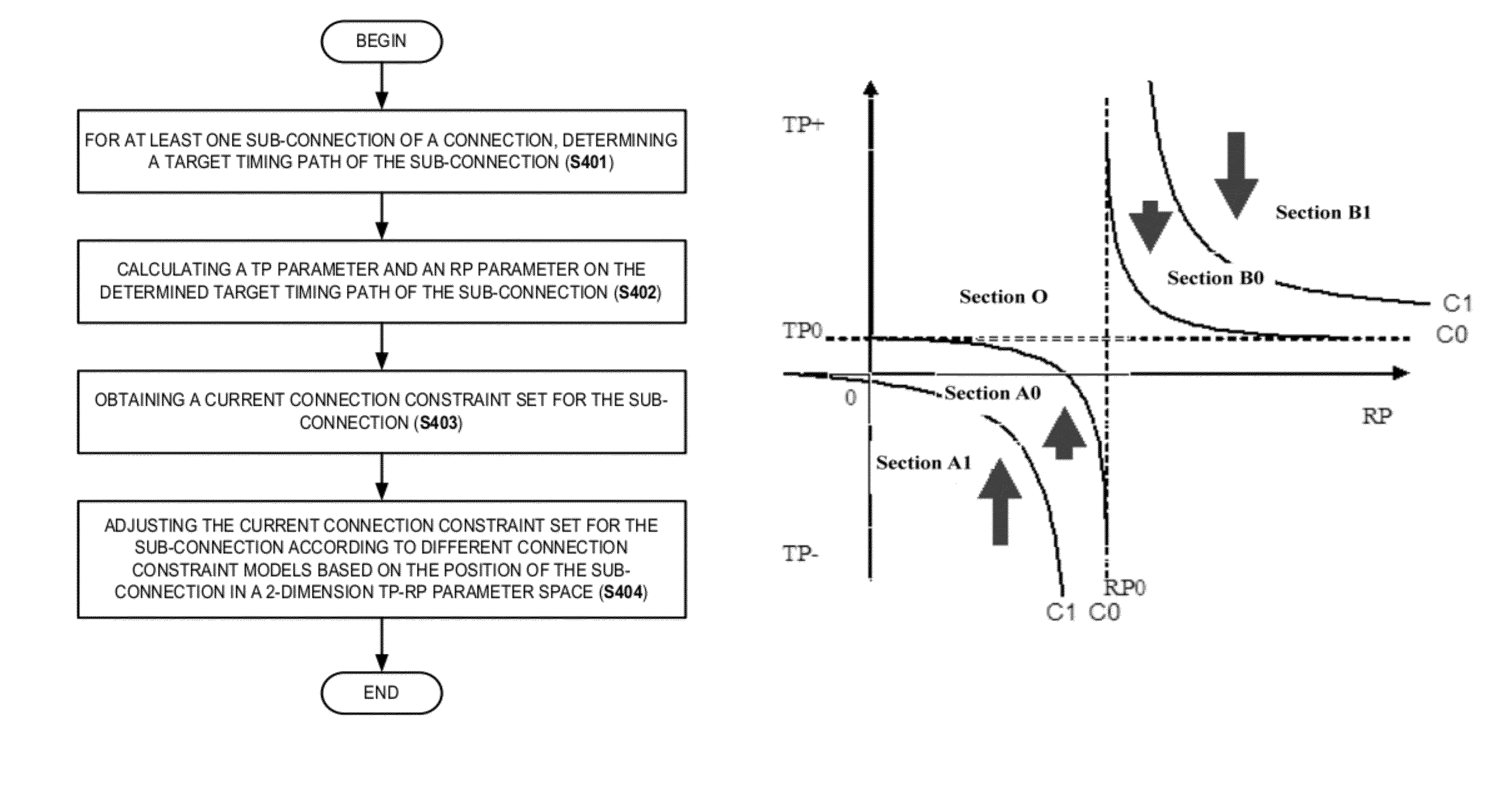

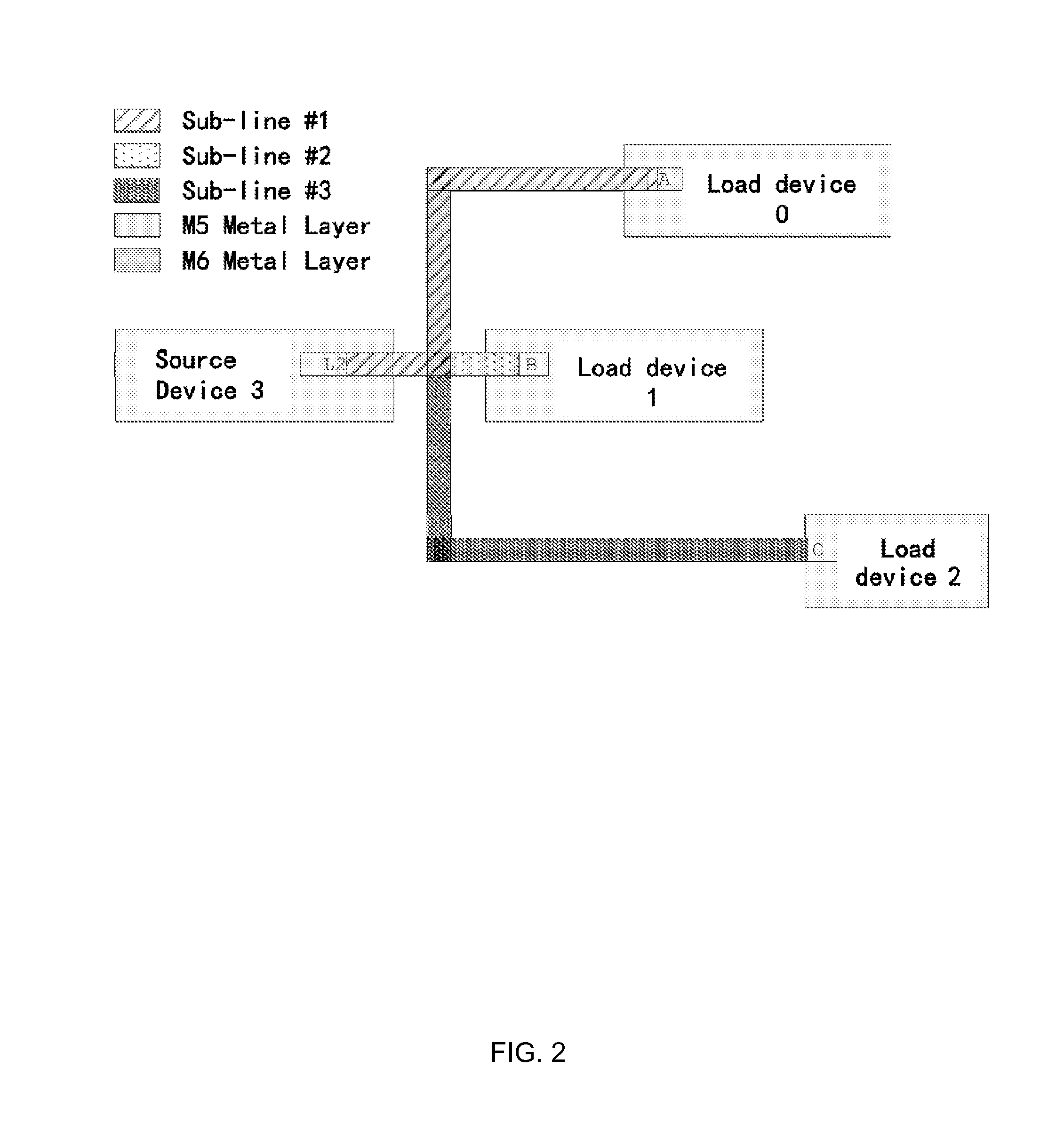

Constraint optimization of sub-net level routing in asic design

ActiveUS20120110541A1Difficult to balanceComputer aided designSoftware simulation/interpretation/emulationPathPingAlgorithm

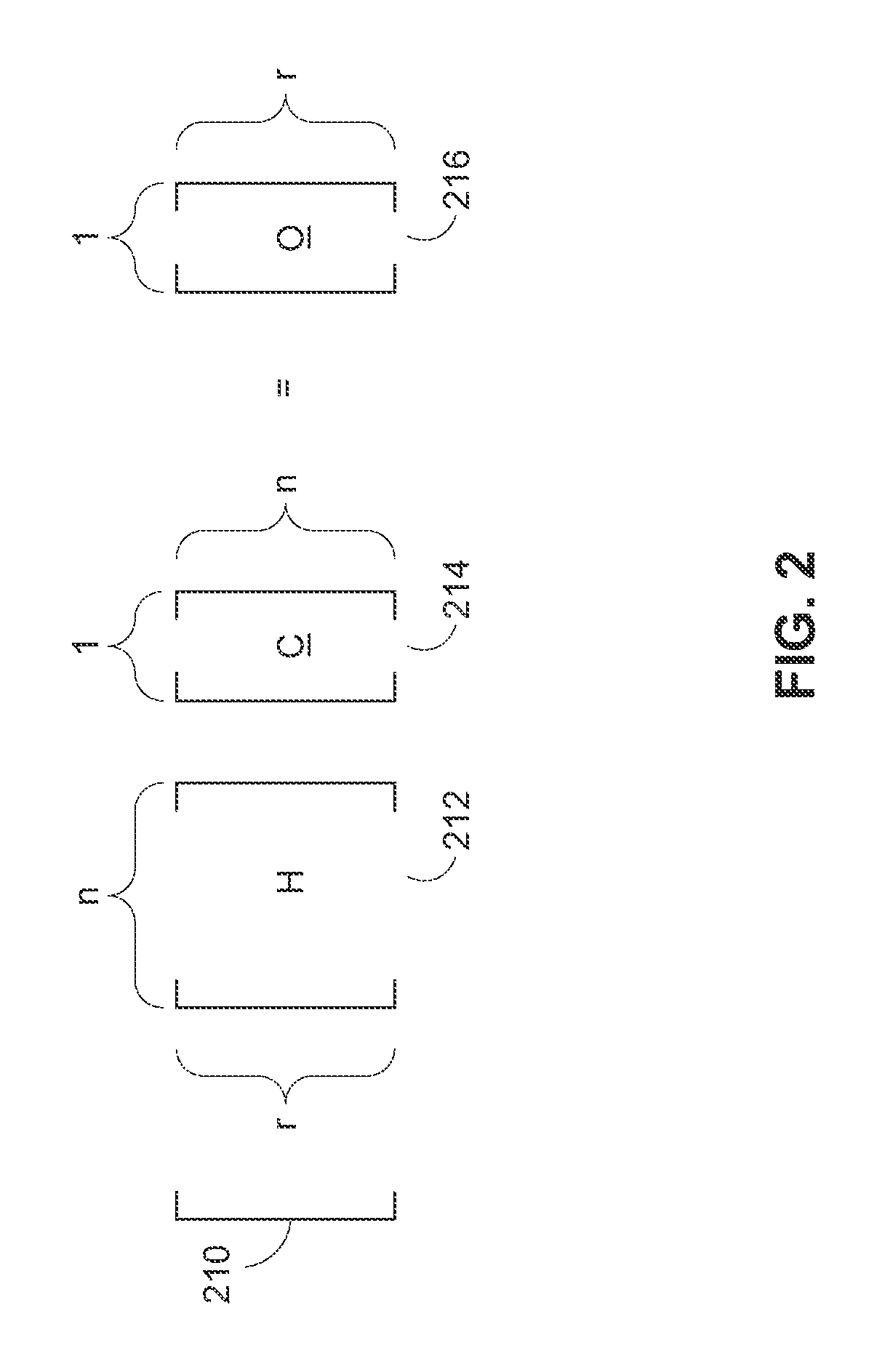

Functionality can be implemented for optimizing connection constraints in an integrated circuit design. A target timing path associated with a first of a plurality of sub-connections of the integrated circuit is determined. A timing probability value and a route probability value associated with the first of the plurality of sub-connections is determined based, at least in part, on the target timing path associated with the first of the plurality of sub-connections. The timing probability value indicates a probability that timing closure is satisfied on the target timing path. The route probability value indicates a probability that a physical routing track on the target timing path associated with the first of the plurality of sub-connections resolves congestion. A current connection constraint associated with the first of the plurality of sub-connections is modified in accordance with a connection constraint model to which the first of the plurality of sub-connections corresponds.

Owner:GLOBALFOUNDRIES US INC

Constraint optimization of sub-net level routing in asic design

ActiveUS8543964B2Computer aided designSoftware simulation/interpretation/emulationTiming closureCircuit design

Functionality can be implemented for optimizing connection constraints in an integrated circuit design. A target timing path associated with a first of a plurality of sub-connections of the integrated circuit is determined. A timing probability value and a route probability value associated with the first of the plurality of sub-connections is determined based, at least in part, on the target timing path associated with the first of the plurality of sub-connections. The timing probability value indicates a probability that timing closure is satisfied on the target timing path. The route probability value indicates a probability that a physical routing track on the target timing path associated with the first of the plurality of sub-connections resolves congestion. A current connection constraint associated with the first of the plurality of sub-connections is modified in accordance with a connection constraint model to which the first of the plurality of sub-connections corresponds.

Owner:GLOBALFOUNDRIES US INC

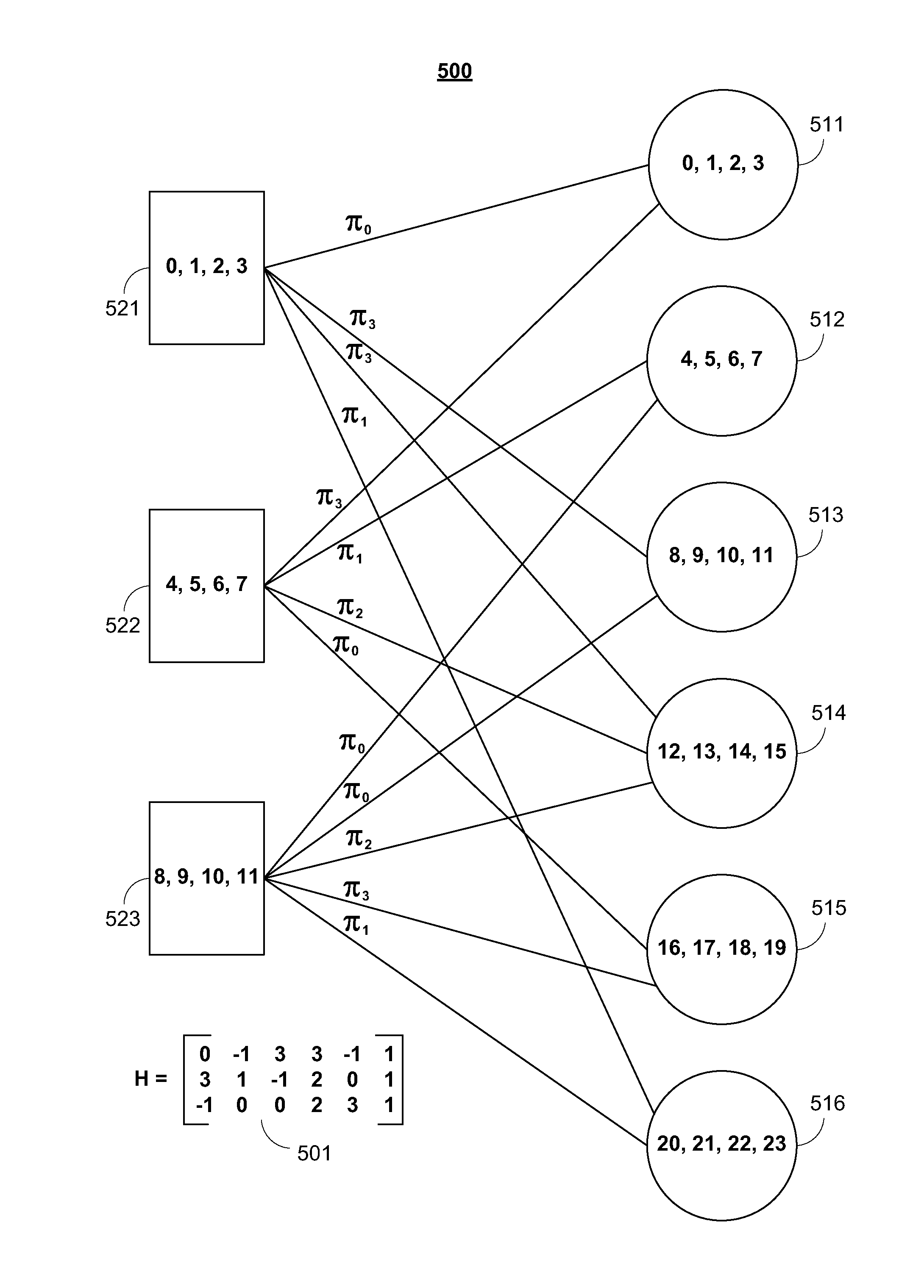

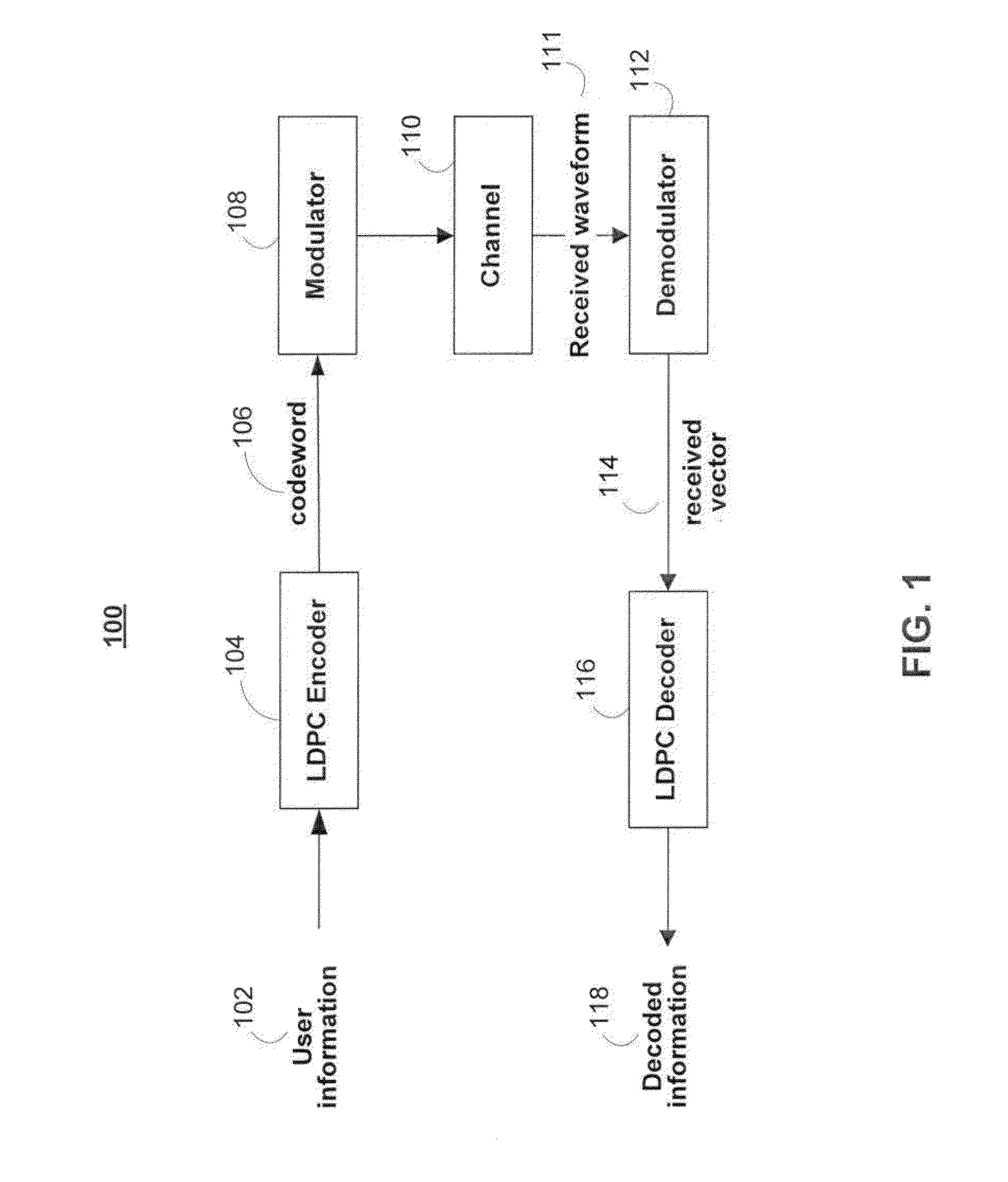

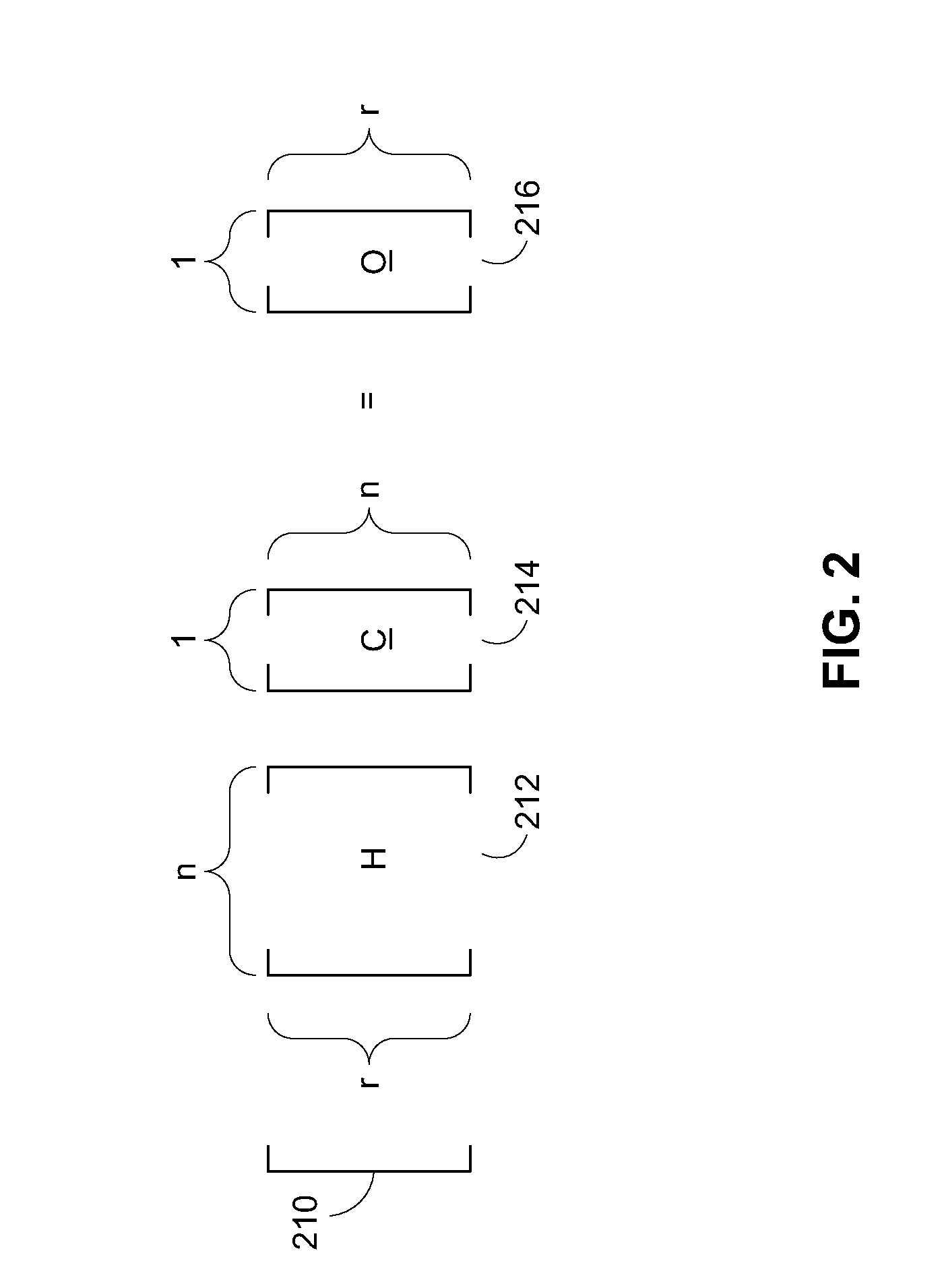

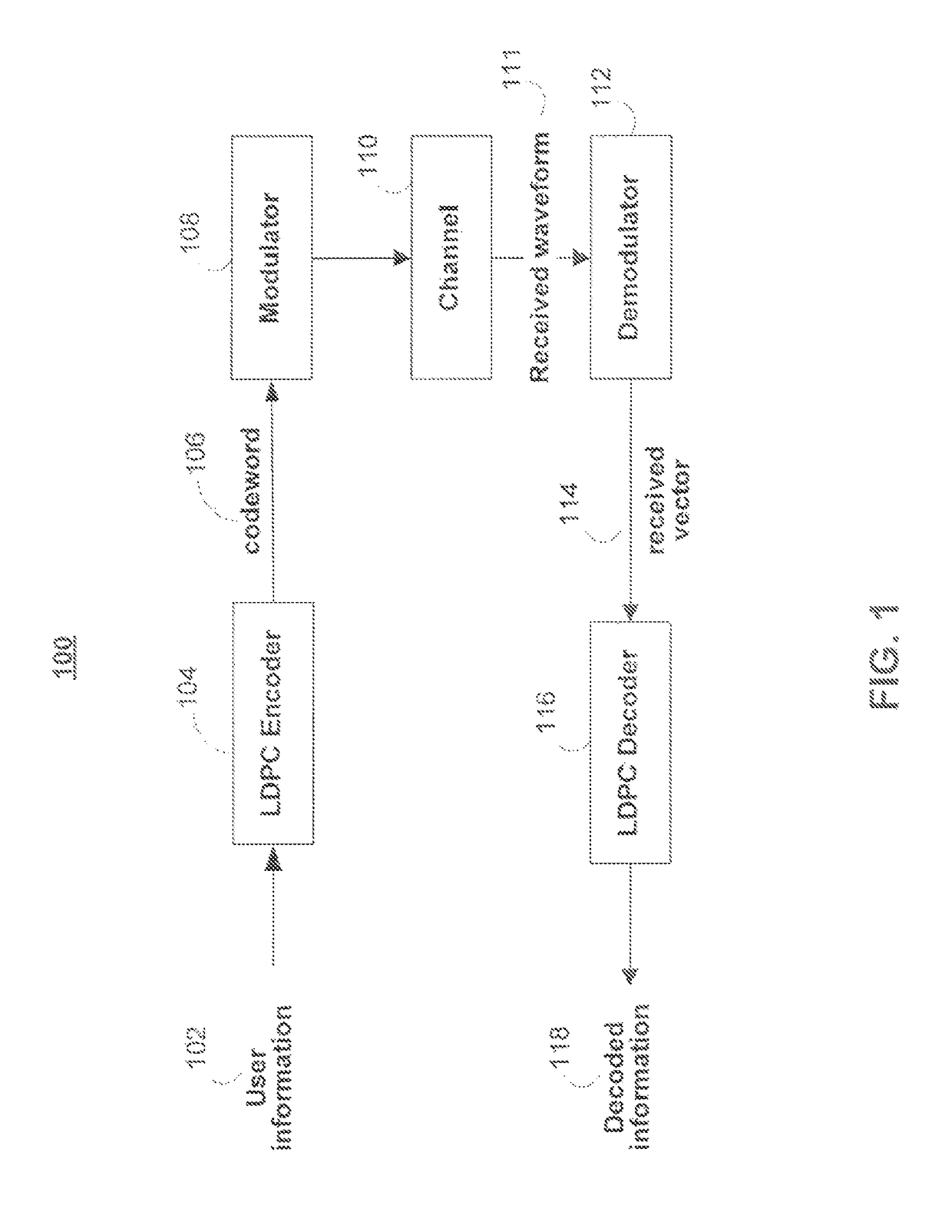

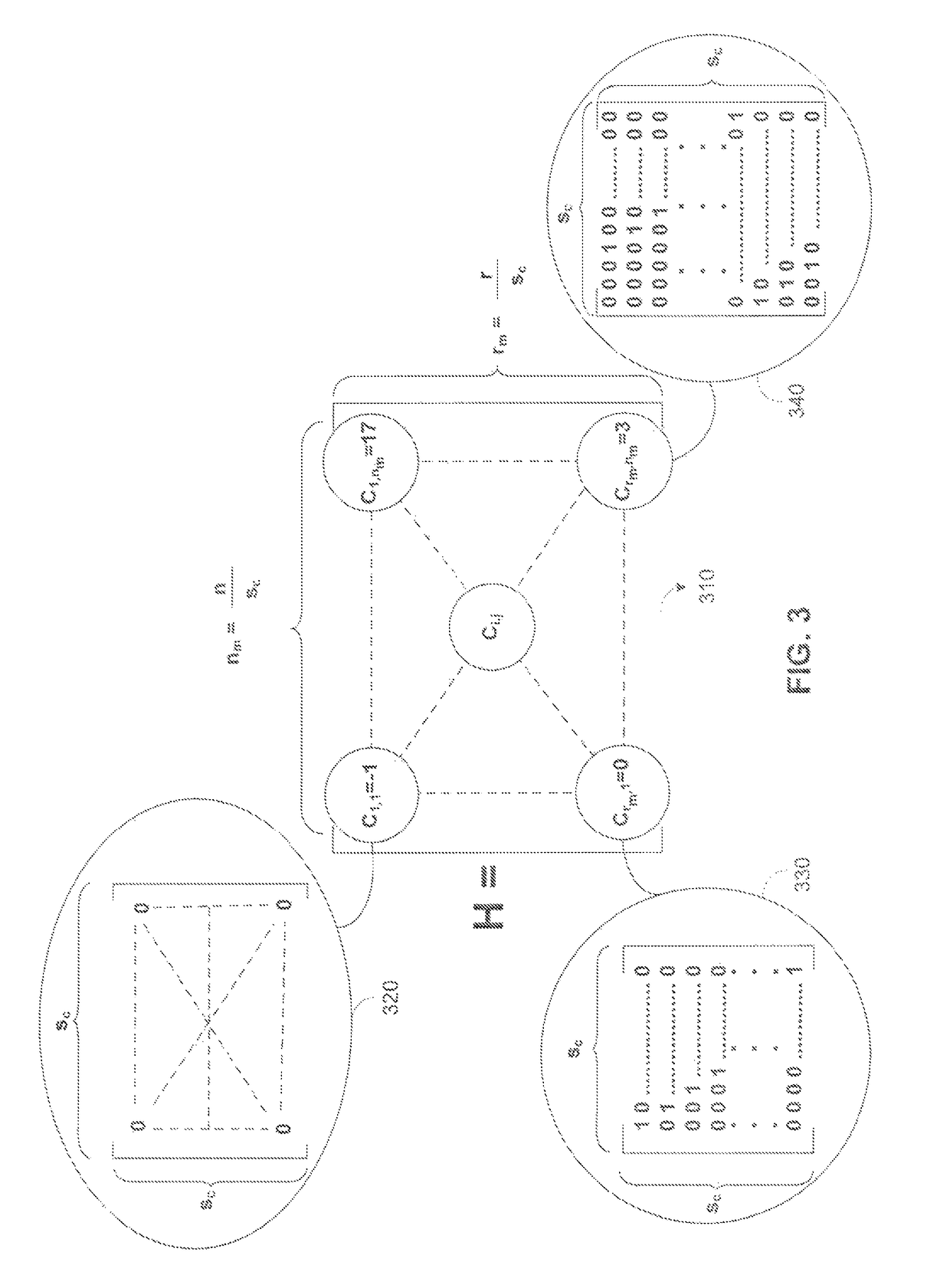

Layered quasi-cyclic LDPC decoder with reduced-complexity circular shifter

ActiveUS8291283B1Improve computing efficiencyDecreased routing congestionError detection/correctionCode conversionRound complexityParallel computing

This disclosure relates generally to data decoding, and more particularly to iterative decoders for data encoded with a low-density parity check (LDPC) encoder. LDPC decoders are disclosed that use reduced-complexity circular shifters that may be used to decode predefined or designed QC-LDPC codes. In addition, methods to design codes which may have particular LDPC code performance capabilities and which may operate with such decoders using reduced-complexity circular shifters are provided. The generation of quasi-cyclic low density parity check codes and the use of circular shifters by LDPC decoders, may be done in such a way as to provide increased computational efficiency, decreased routing congestion, easier timing closure, and improved application performance.

Owner:MARVELL ASIA PTE LTD

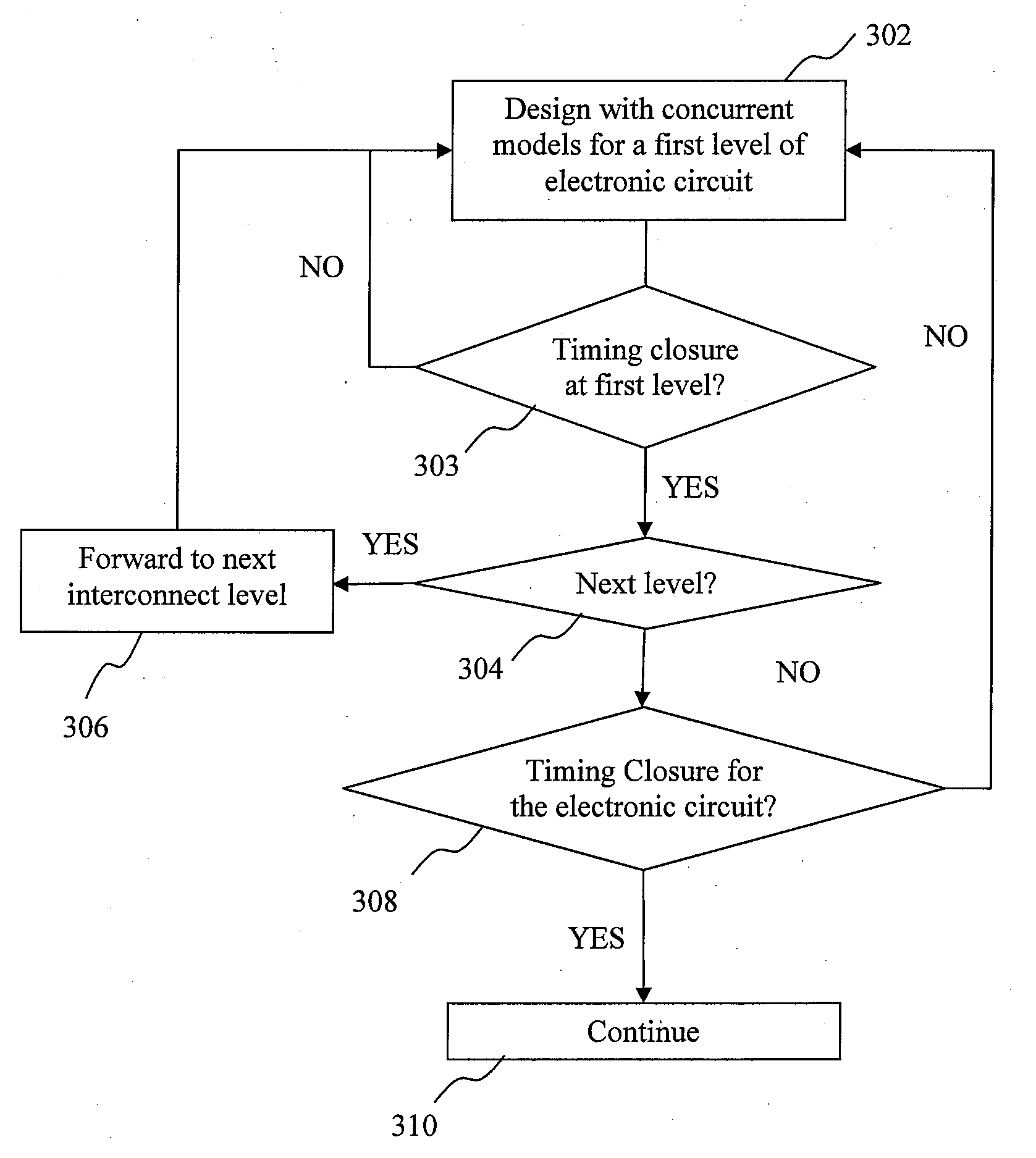

Method, system, and computer program product for timing closure in electronic designs

ActiveUS20080163148A1Effective and accurate methodologyAccurate predictionDesign optimisation/simulationCAD circuit designMetrologyComputer architecture

Disclosed is an improved method, system, and computer program product for timing closure with concurrent models for fabrication, metrology, lithography, and / or imaging processing analyses for electronic designs. Some embodiments of the present invention disclose a method for timing closure with concurrent process model analysis in which a design tool with such concurrent models generates a design for the one or more interconnect levels. The method or system then analyzes the effects of the concurrent models to predict feature dimension variations based upon the concurrent models. The method or system then modifies the design files to reflect the variations and determines one or more parameters based upon the concurrent models. One embodiment then determines the impact of concurrent models upon the electrical and timing performance.

Owner:CADENCE DESIGN SYST INC

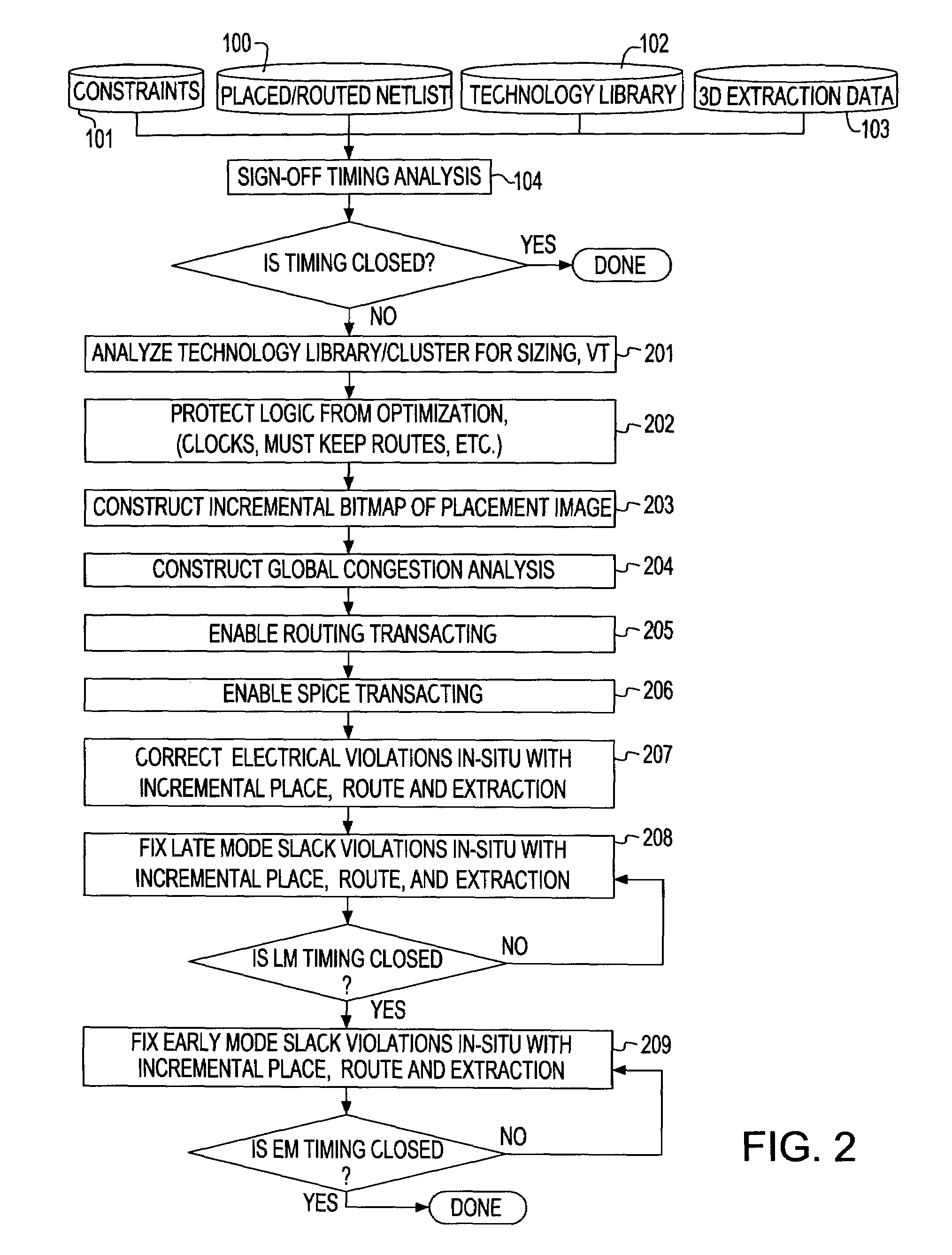

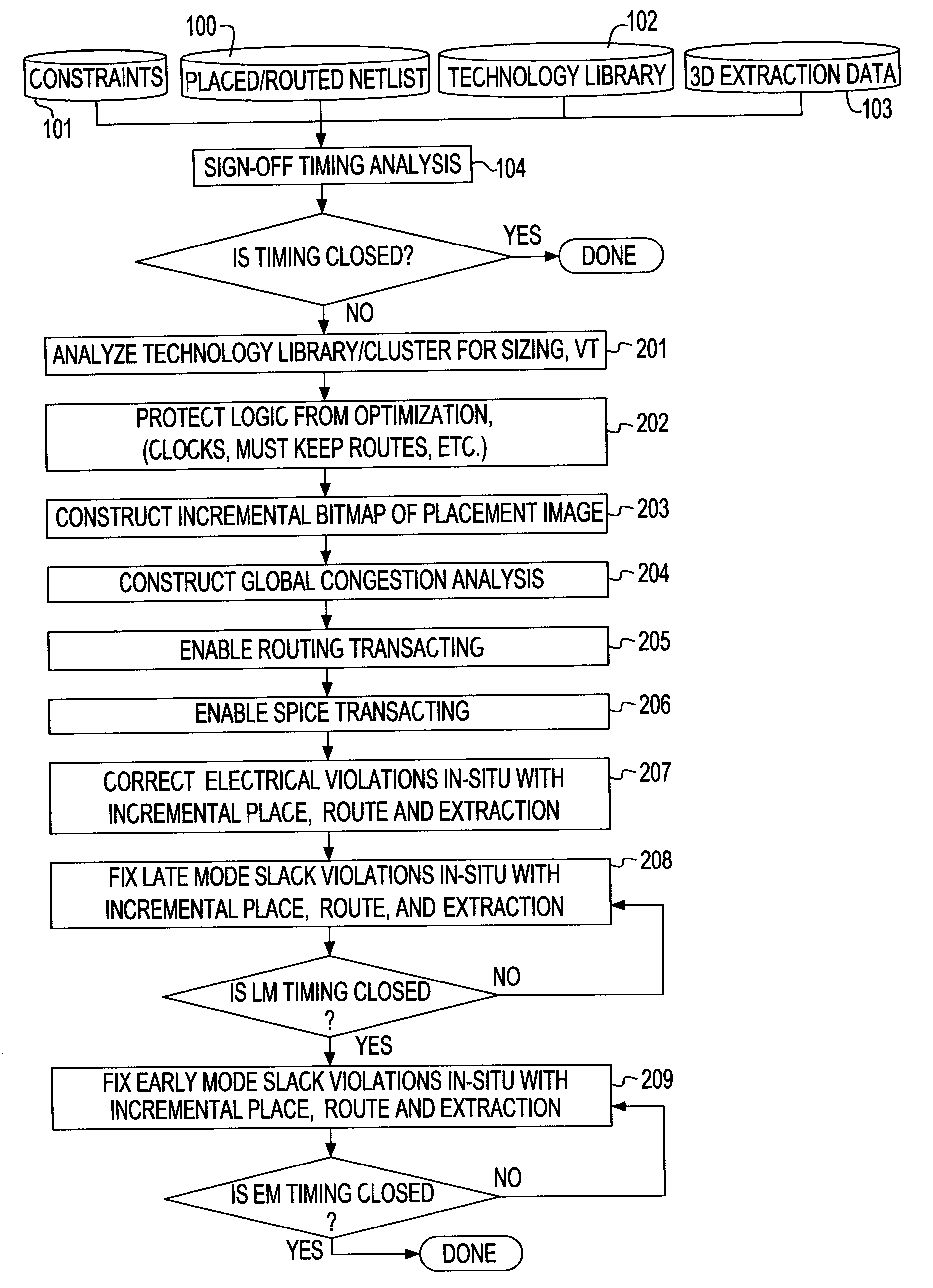

System and method for sign-off timing closure of a VLSI chip

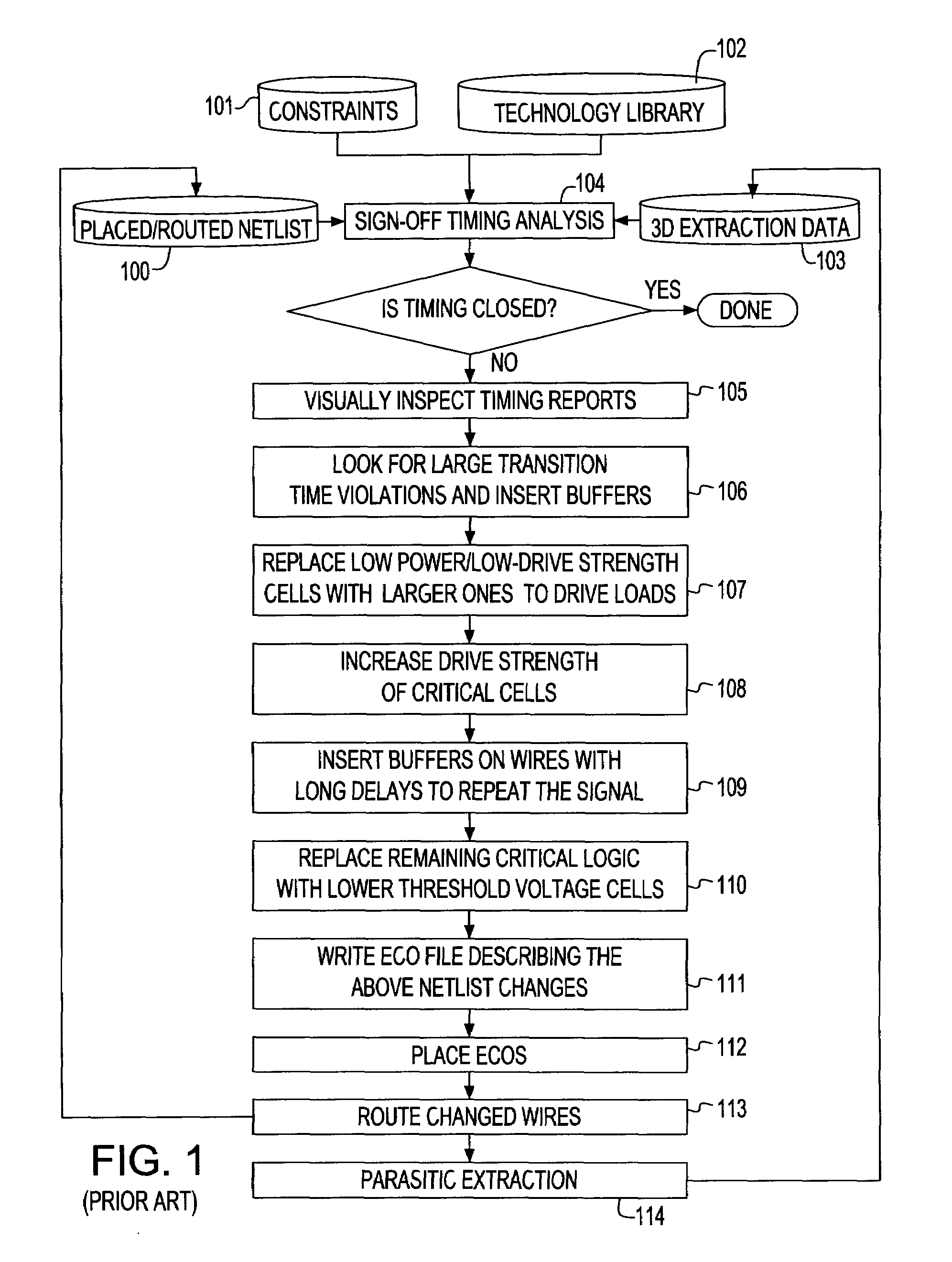

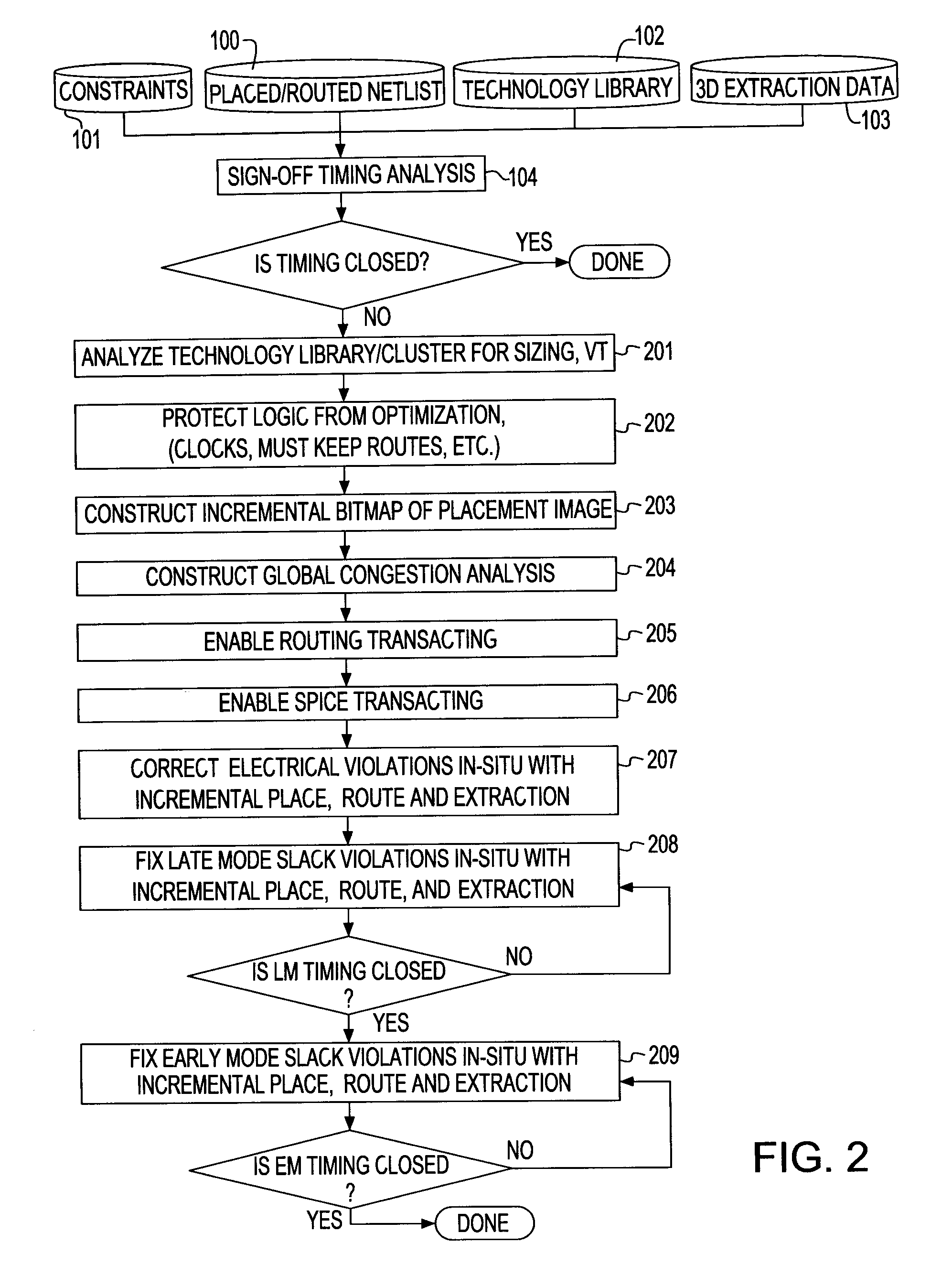

InactiveUS7581201B2Efficiently improve the timing and electrical violationsMinimal placement and routing disruptionCAD circuit designSoftware simulation/interpretation/emulationCapacitancePathPing

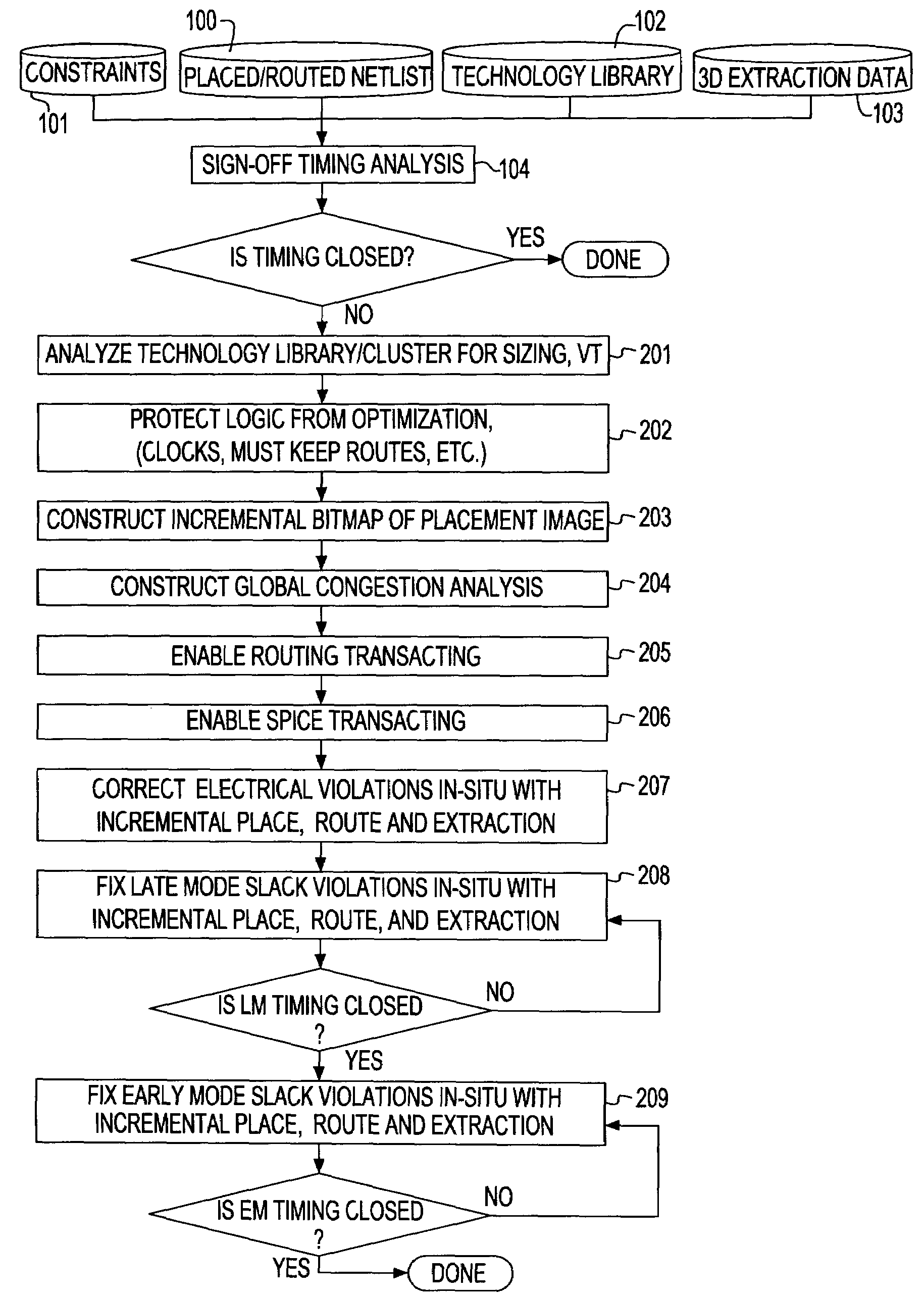

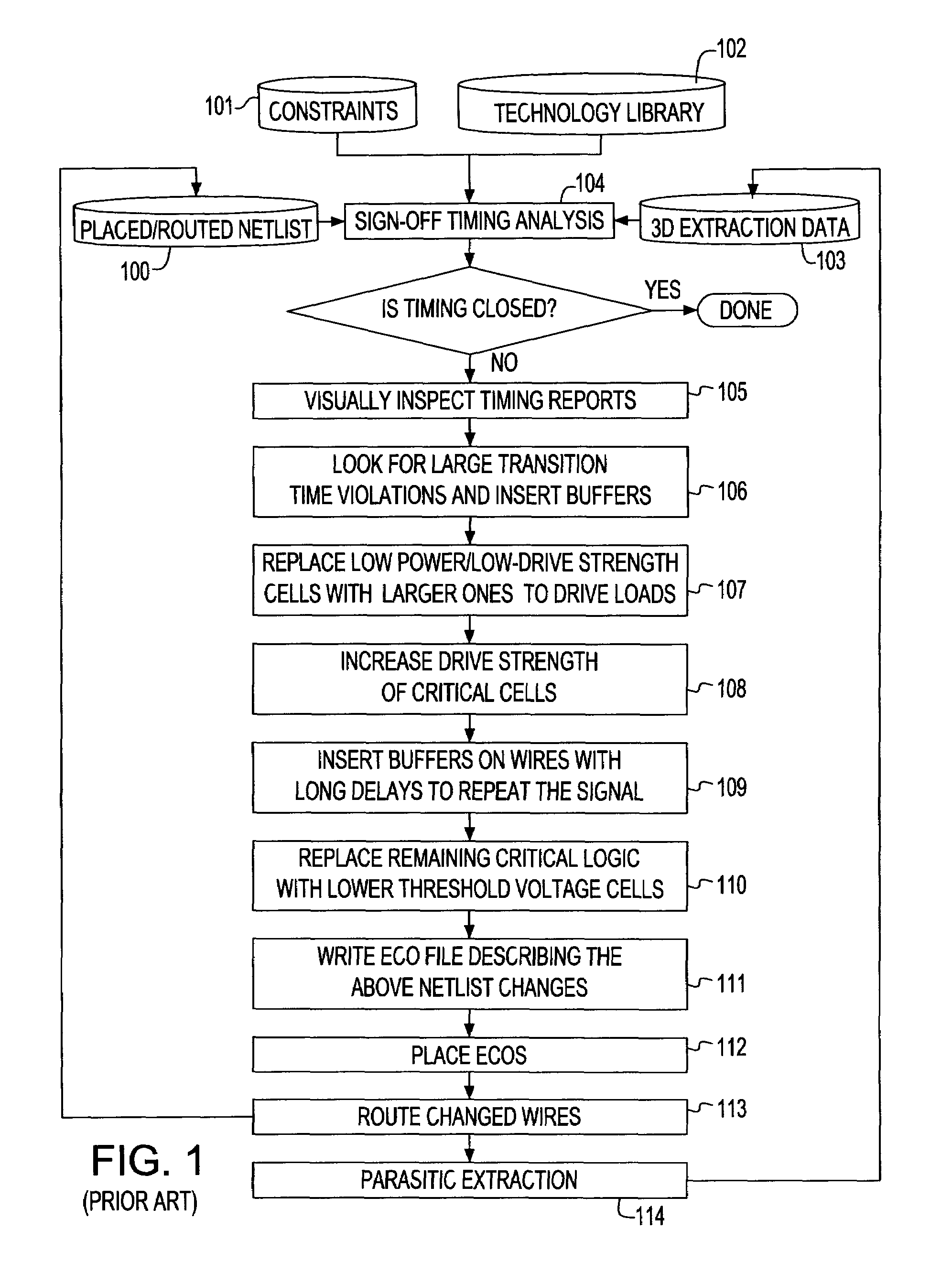

A method for performing timing optimization of a detail routed netlist, incorporating statistical variability information, common path pessimism reduction, and capacitative coupling information, in a tightly coupled, incremental manner with minimal perturbations to the placement, routing, and asserted parasitic information. The method corrects violations in a placed and routed design of a VLSI circuit chip, where the design is represented by a netlist describing logical and physical characteristics of the design and by a corresponding timing graph, the method including the steps of: identifying violations in the design; iteratively eliminating the violations by incrementally transforming the logical and the physical characteristics of the design, incorporating in the design only legal placements and routes; and applying incremental timing to evaluate the transformations, and updating the existing timing graphs to reflect changes consisting of the legal placements and routes.

Owner:INT BUSINESS MASCH CORP

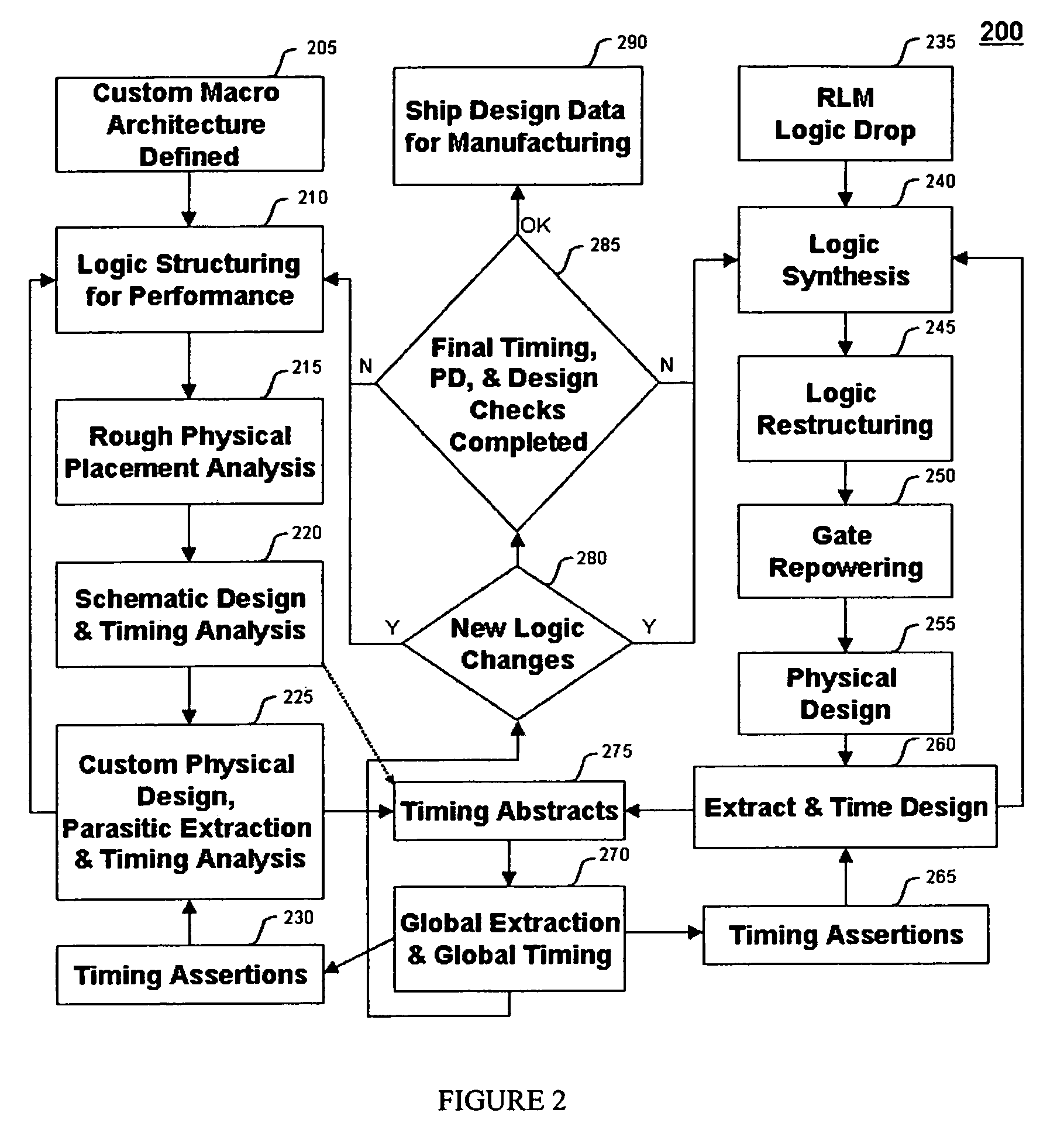

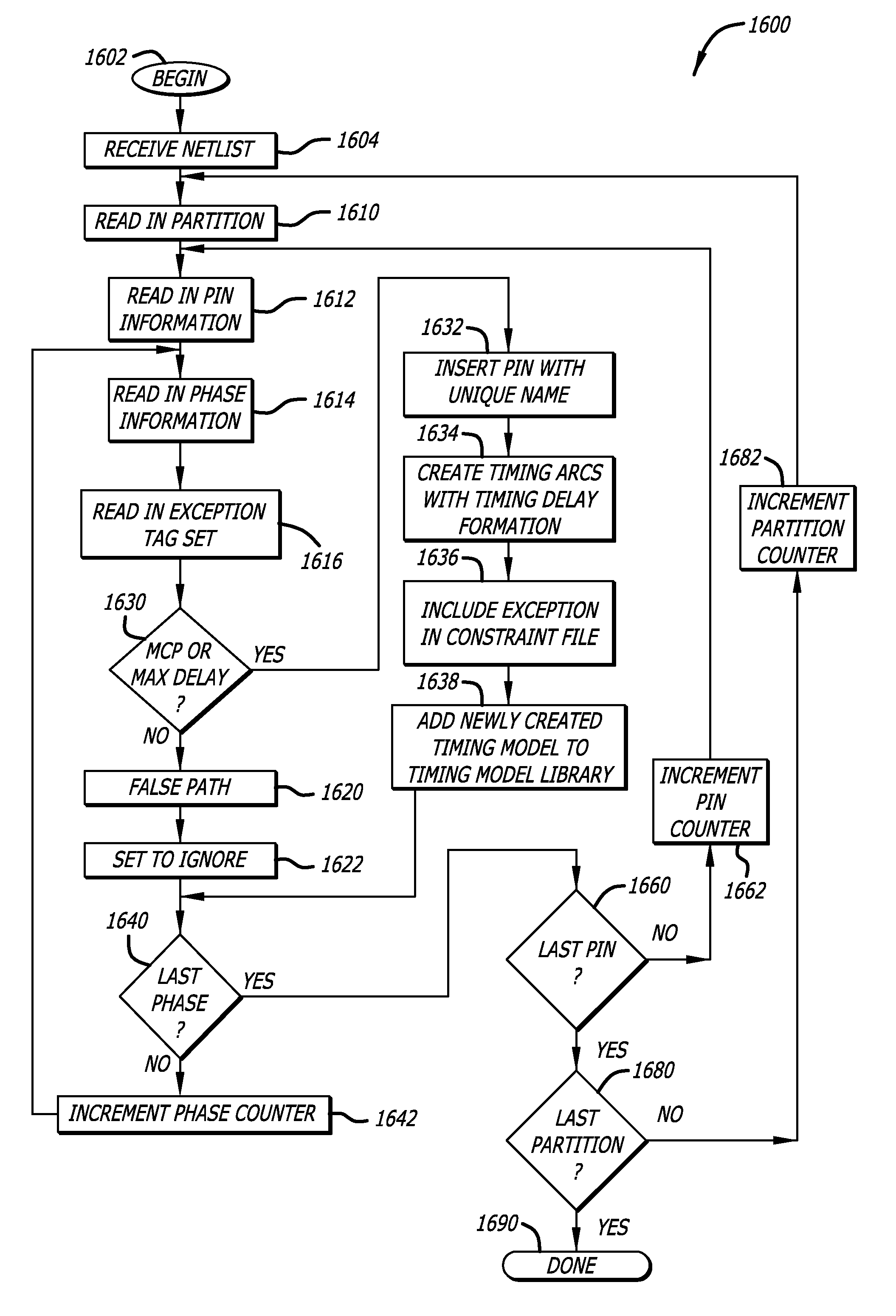

Multi-phase models for timing closure of integrated circuit designs

ActiveUS8640066B1Accurate modelingDetecting faulty computer hardwareComputer aided designFalse pathHierarchical design

In one embodiment, a method of designing an integrated circuit is disclosed, including receiving a first partition block for a top level of a hierarchical design of an integrated circuit; analyzing each pin of the first partition block for an attribute associated with the pin indicating a timing exception; and if a timing exception other than false path is indicated then generating an internal timing pin in a first timing graph model of the first partition block for each timing exception, and adding a timing arc and a dummy arc coupled to the internal timing pin in the first timing graph model of the first partition block. The internal timing pin adds a timing exception constraint for each timing exception. Timing of the top level may then be analyzed with the first timing graph model to determine if timing constraints, including the added timing exception constraints, are met.

Owner:CADENCE DESIGN SYST INC

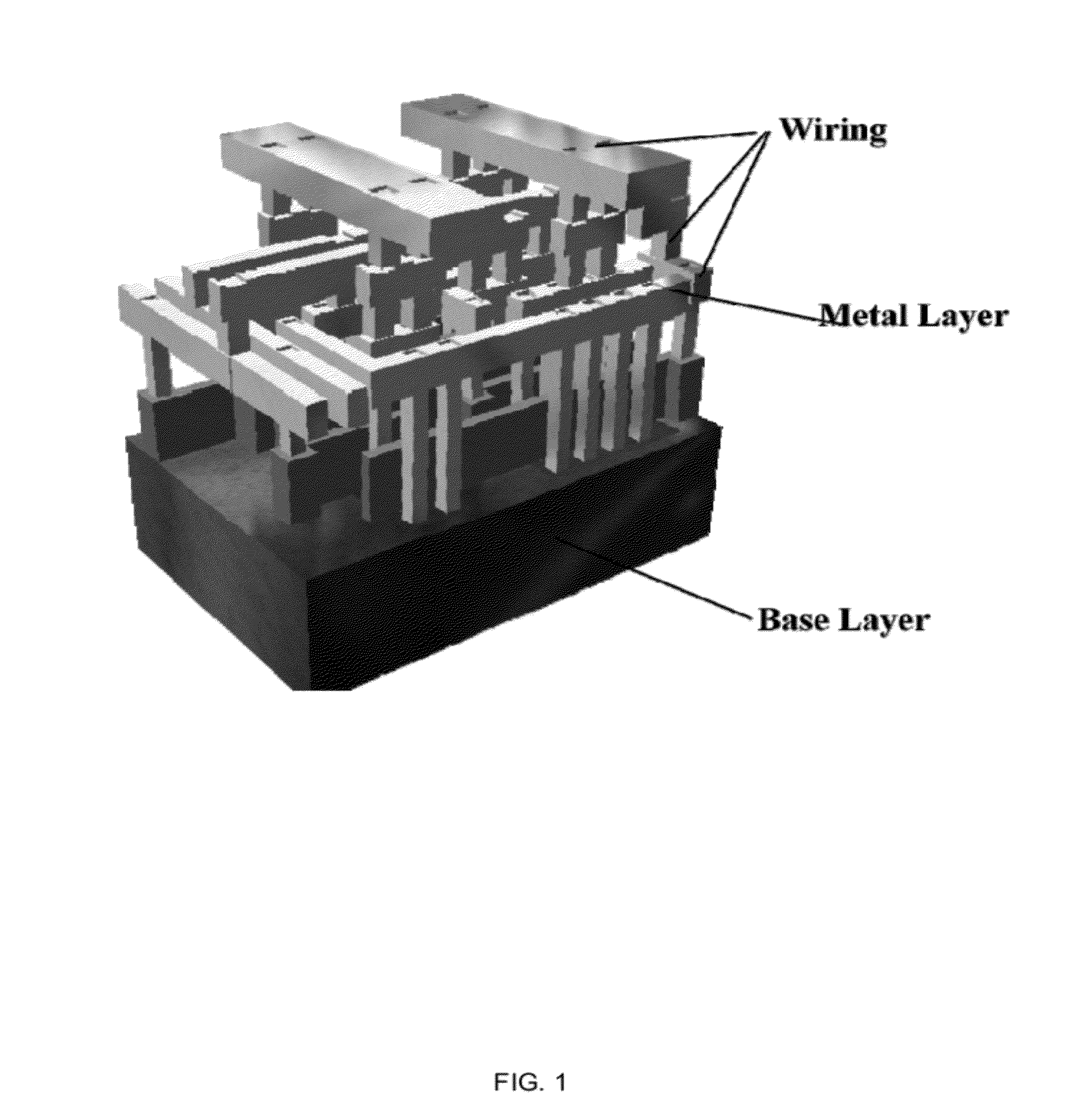

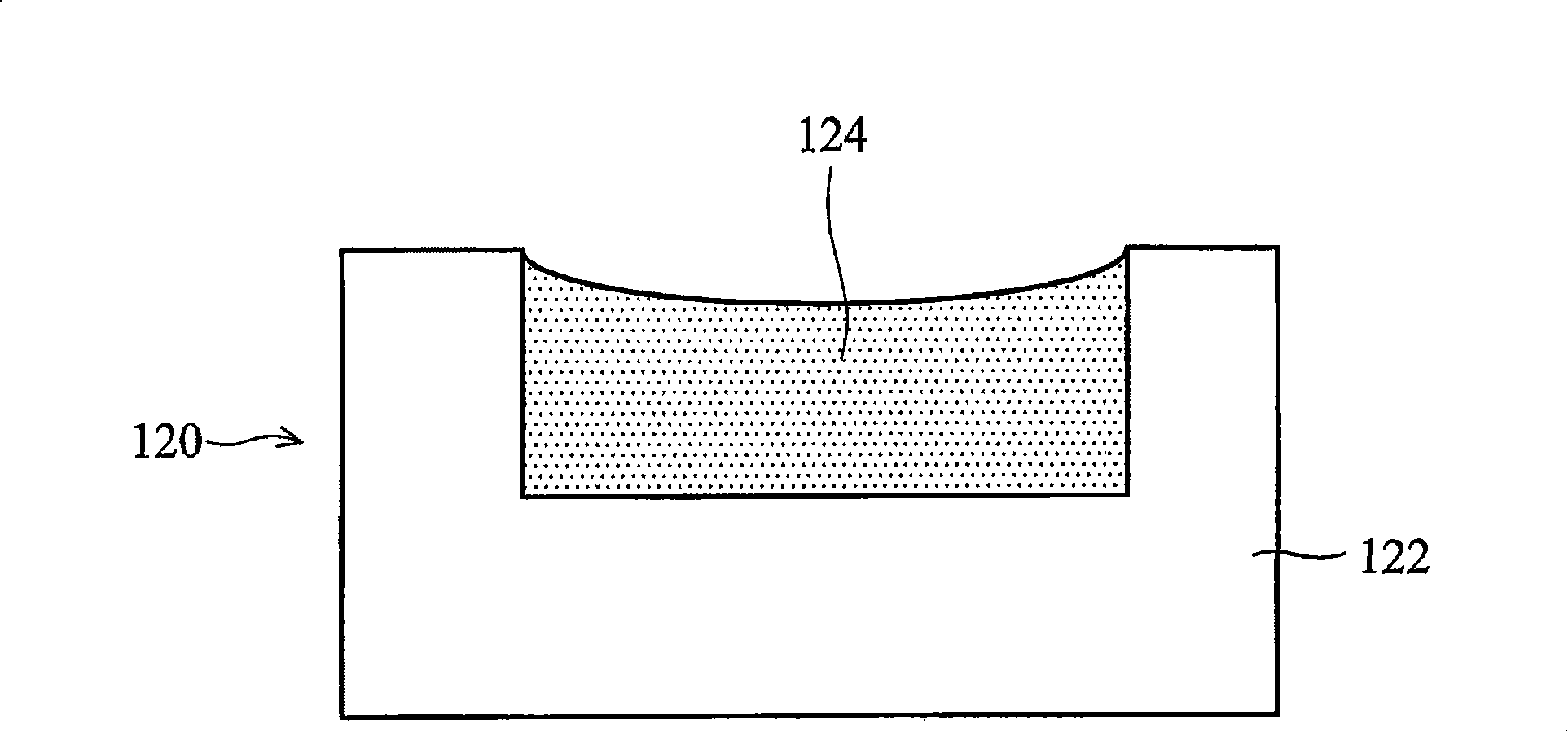

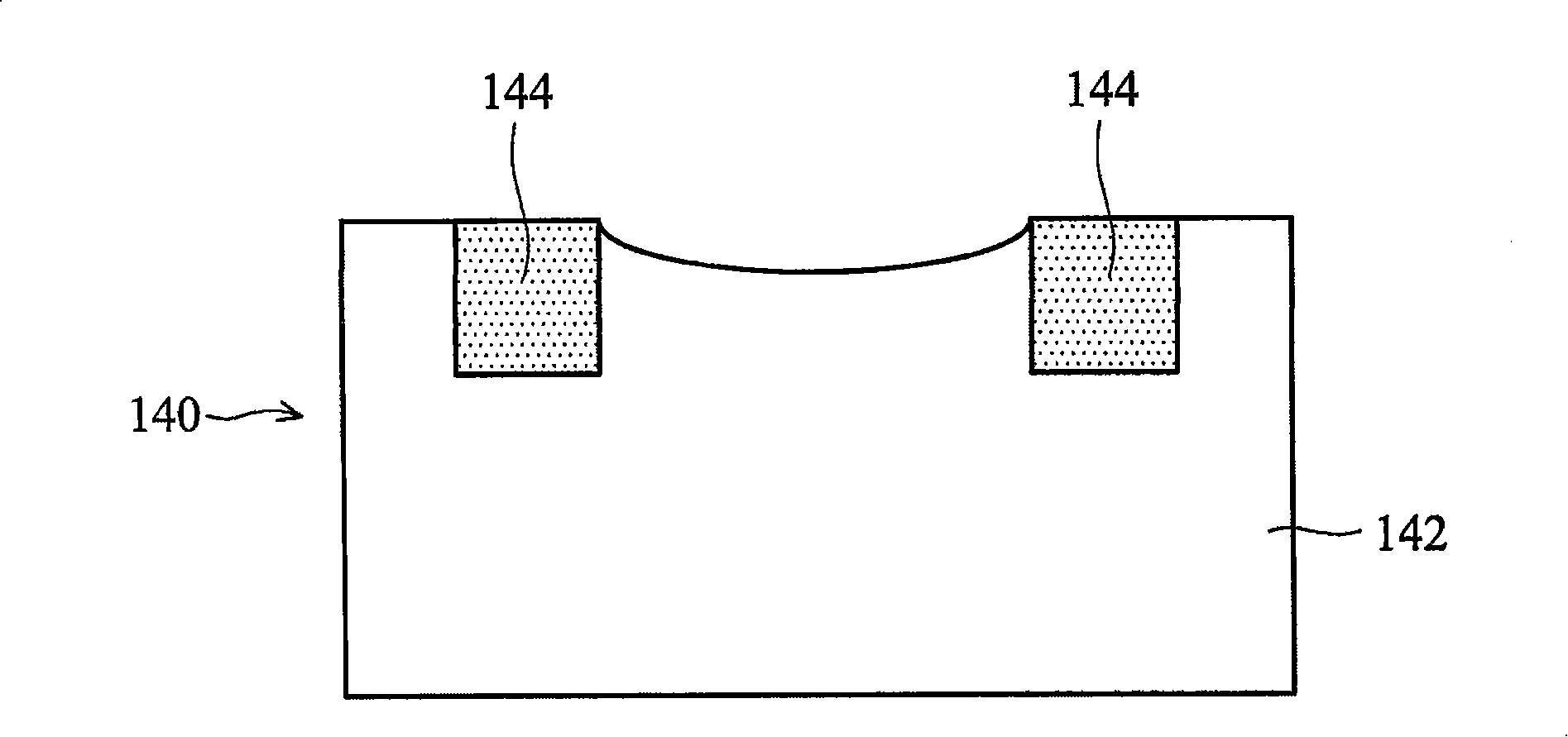

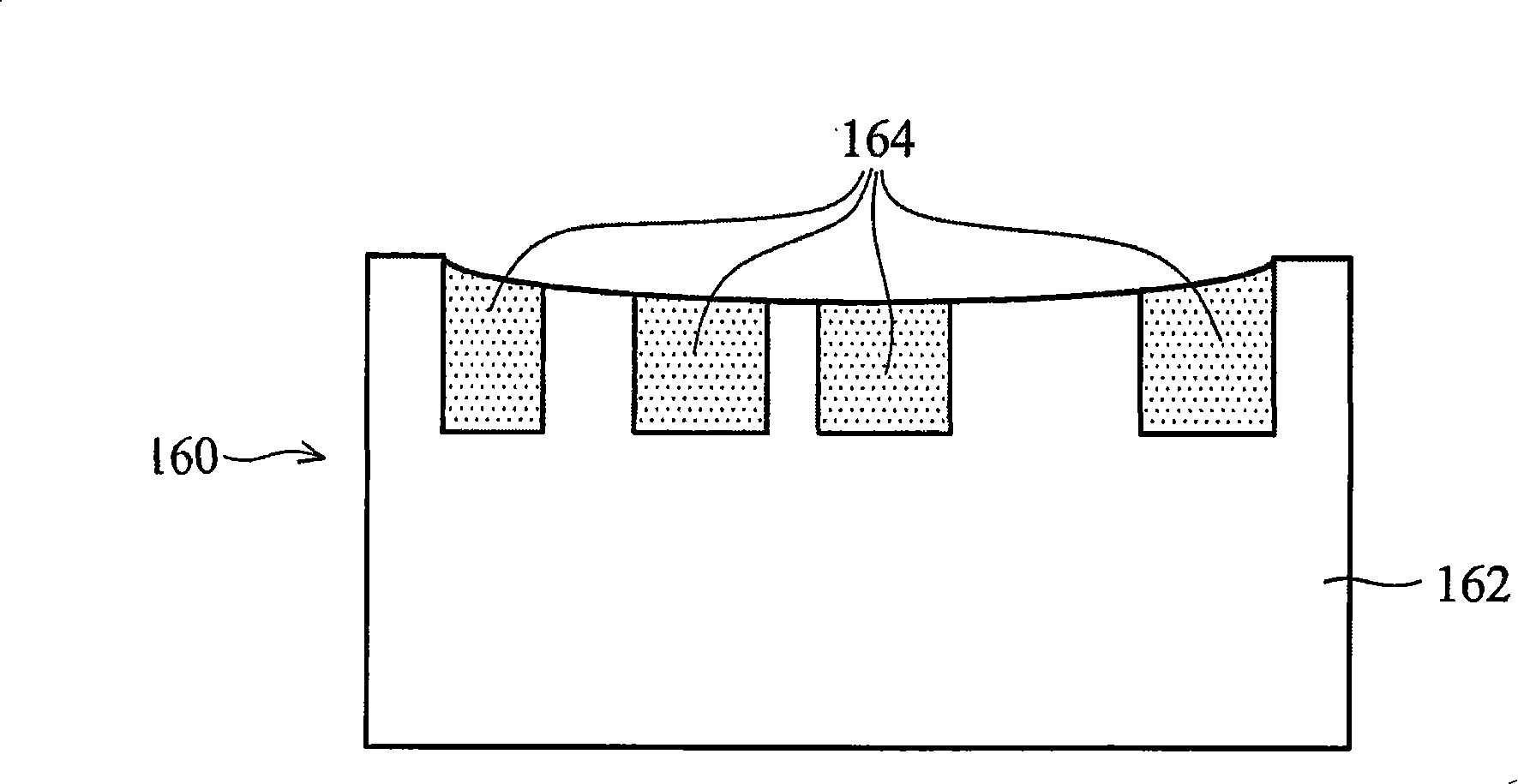

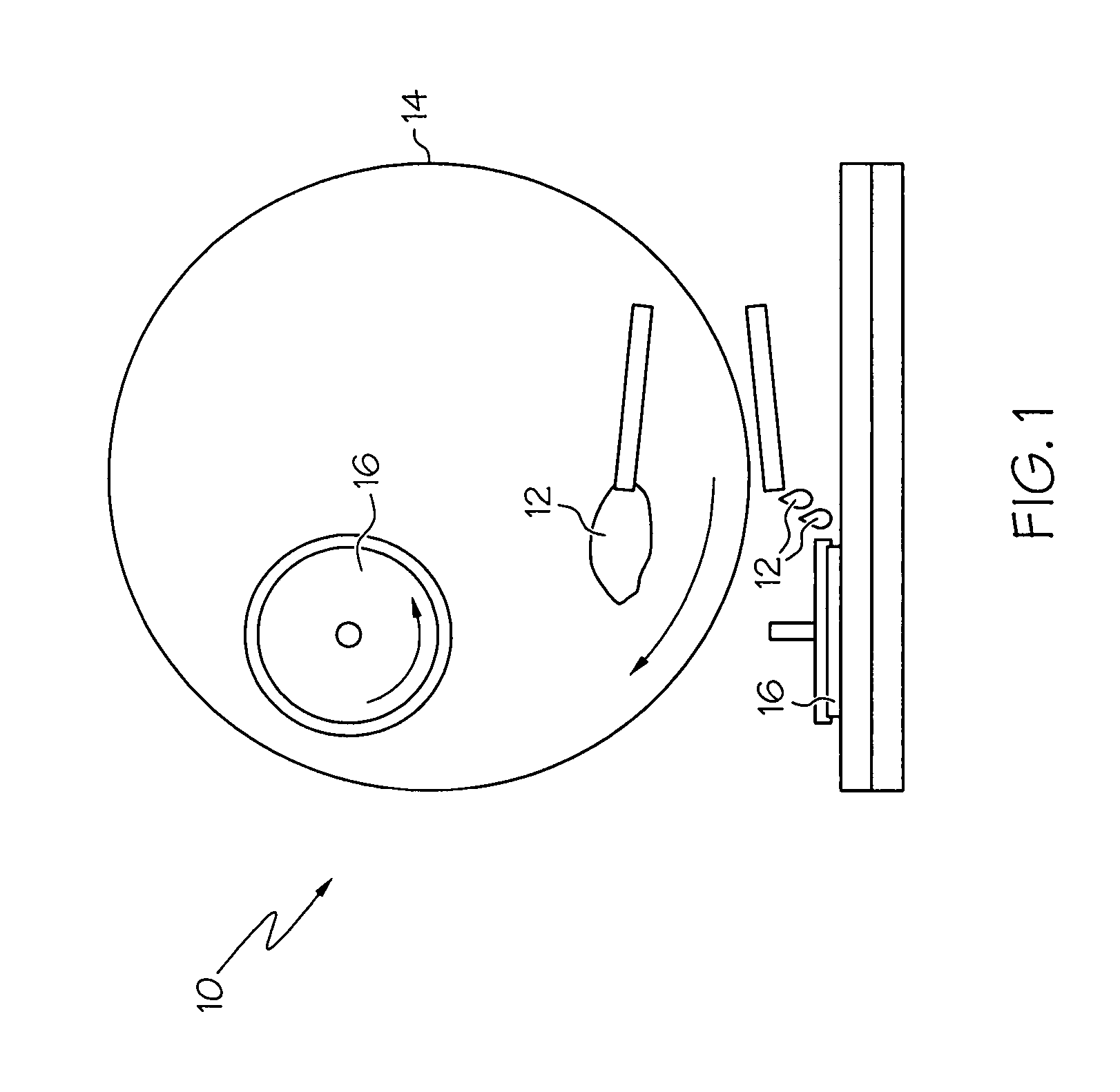

Method of filling redundancy for semiconductor manufacturing process and semiconductor device

ActiveCN101231667AReduce in quantityReduce consumptionSemiconductor/solid-state device detailsSolid-state devicesGraphicsCPU time

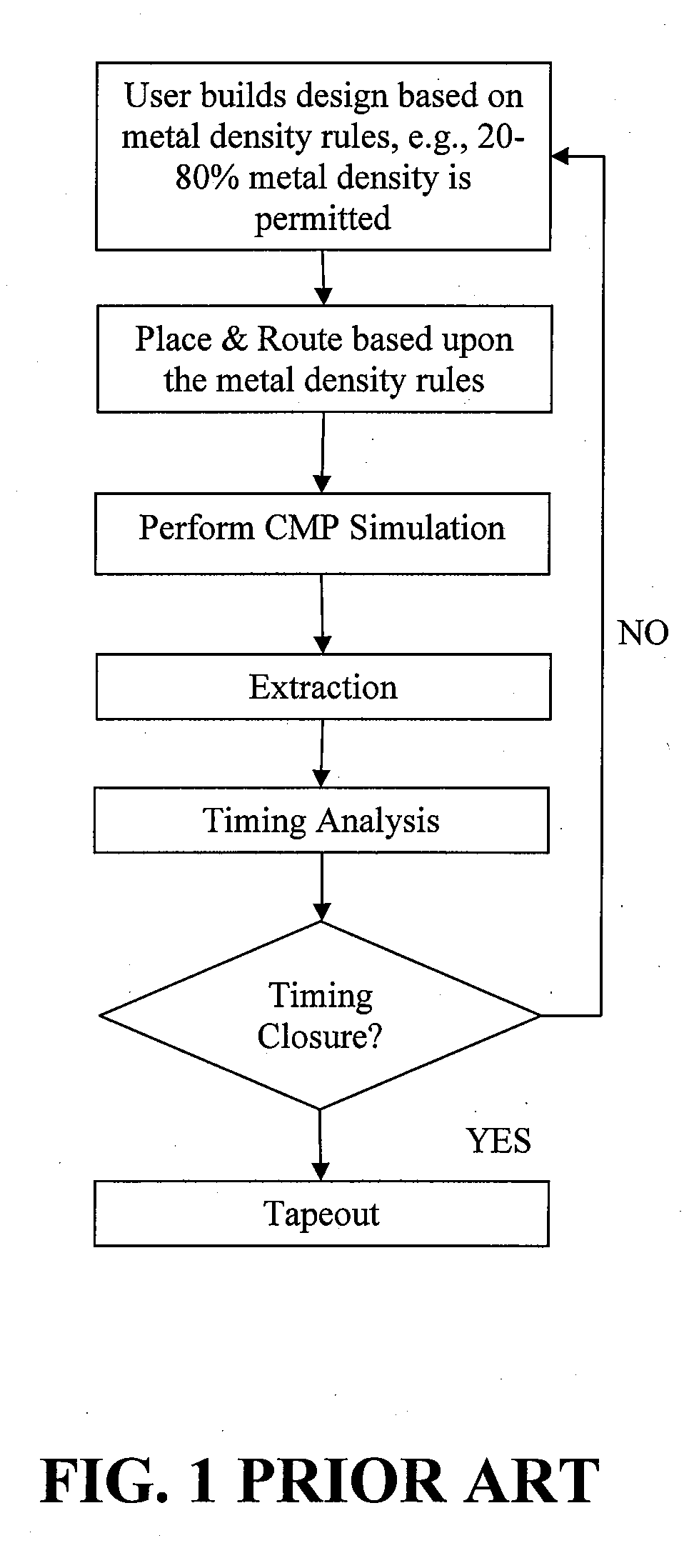

A dummy filling method for a semiconductor manufacturing process provides a circuit pattern and generates a density report of the circuit pattern to identify a feasible area for dummy insertion. The method also includes using the density report to simulate a planarization manufacturing process and identifying hot spots on the circuit pattern, filling virtual redundant patterns in the feasible area, and then adjusting the density report. The method simulates the planarization process using the adjusted density report until the hot spot is removed. The invention can reduce the amount of redundant metal in circuit design and save photomask time, CPU time, and signal storage memory. This will help design timing closure (time closure) faster and easier.

Owner:TAIWAN SEMICON MFG CO LTD

System and method for sign-off timing closure of a VLSI chip

InactiveUS20080209376A1Reduce variability effectAvoid a lot of timeCAD circuit designSoftware simulation/interpretation/emulationCapacitanceCoupling

A method for performing timing optimization of a detail routed netlist, incorporating statistical variability information, common path pessimism reduction, and capacitative coupling information, in a tightly coupled, incremental manner with minimal perturbations to the placement, routing, and asserted parasitic information. The method corrects violations in a placed and routed design of a VLSI circuit chip, where the design is represented by a netlist describing logical and physical characteristics of the design and by a corresponding timing graph, the method including the steps of: identifying violations in the design; iteratively eliminating the violations by incrementally transforming the logical and the physical characteristics of the design, incorporating in the design only legal placements and routes; and applying incremental timing to evaluate the transformations, and updating the existing timing graphs to reflect changes consisting of the legal placements and routes.

Owner:IBM CORP

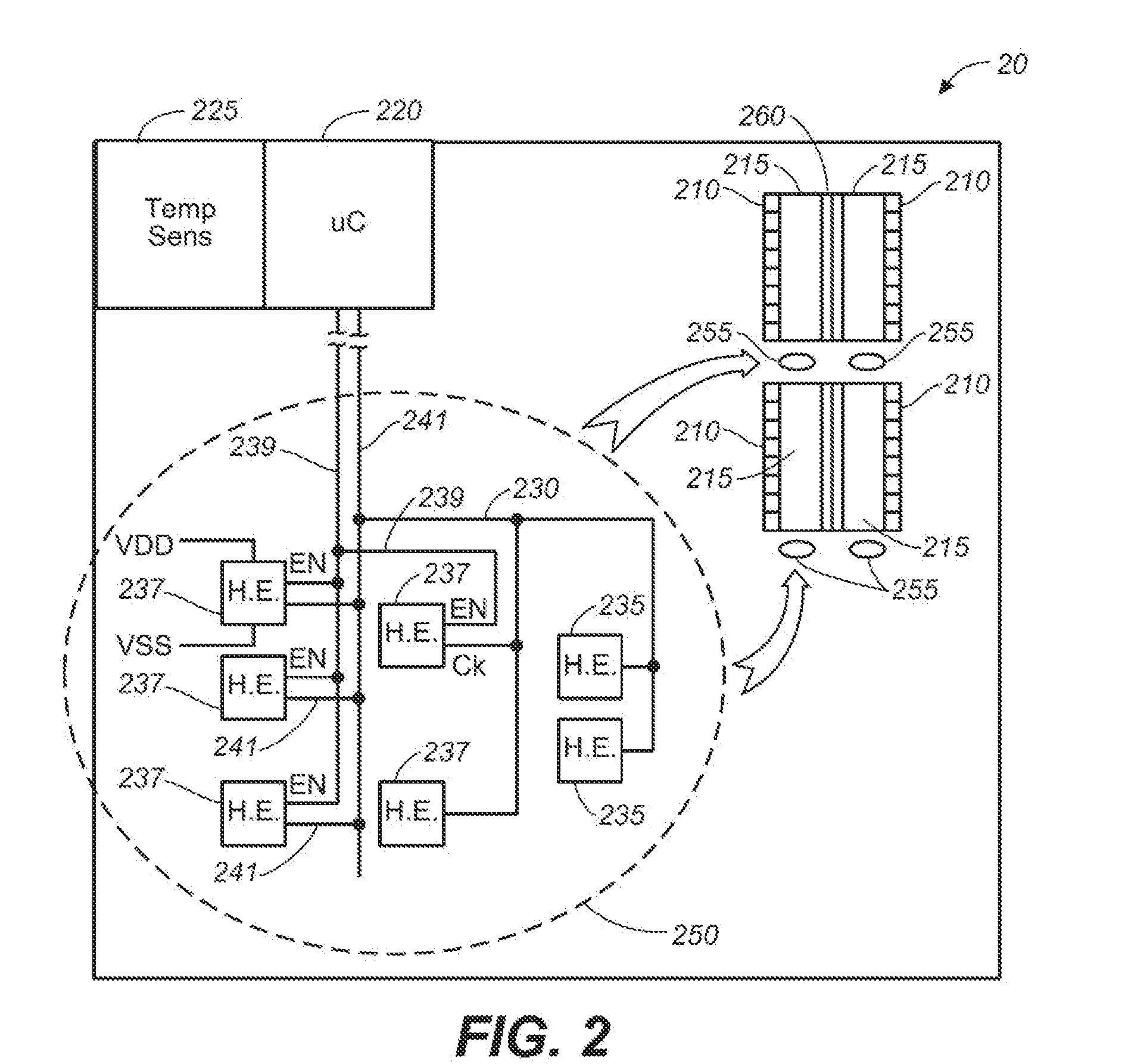

Temperature Controlled Structured ASIC Manufactured on a 28 NM CMOS Process Lithographic Node

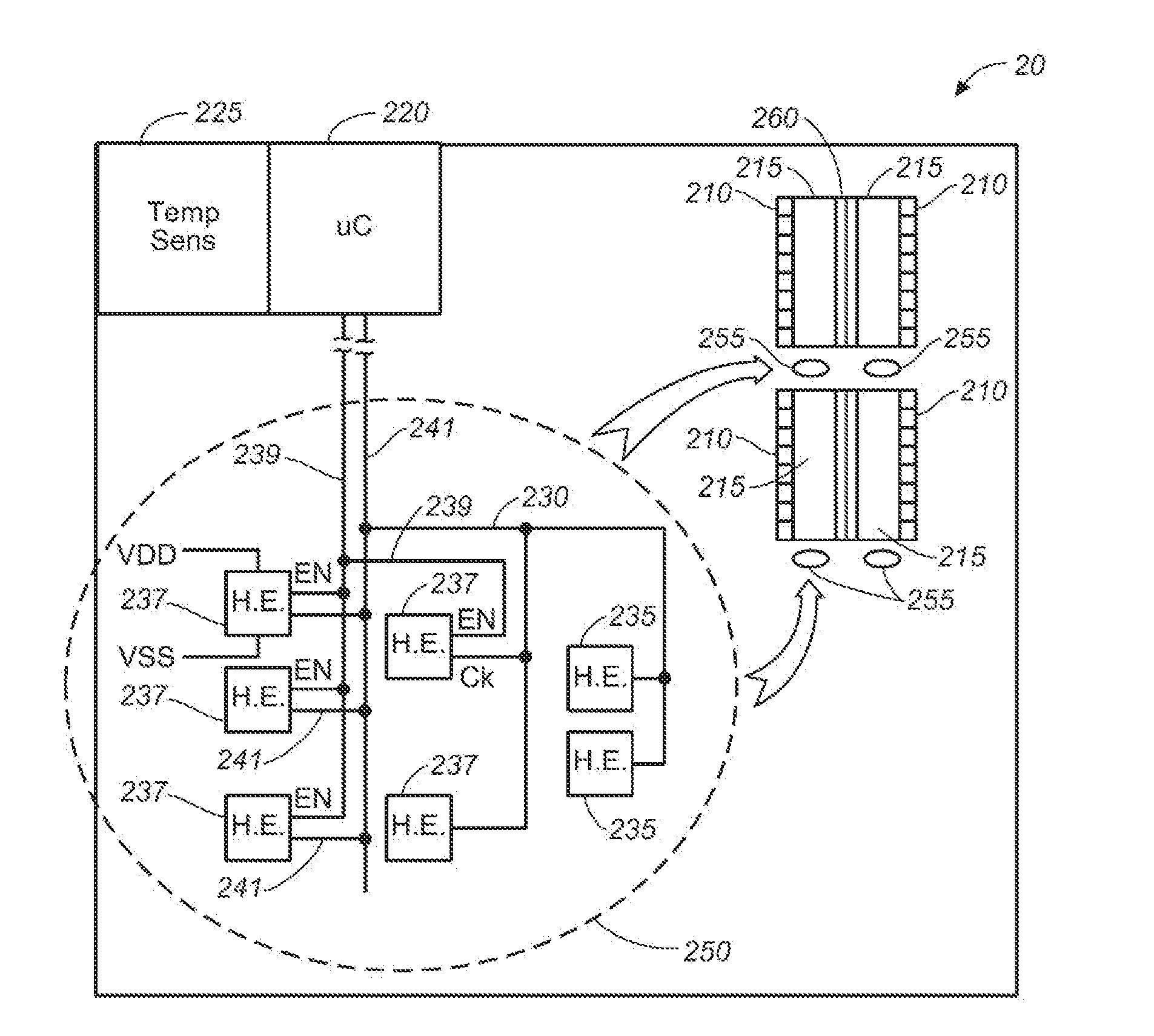

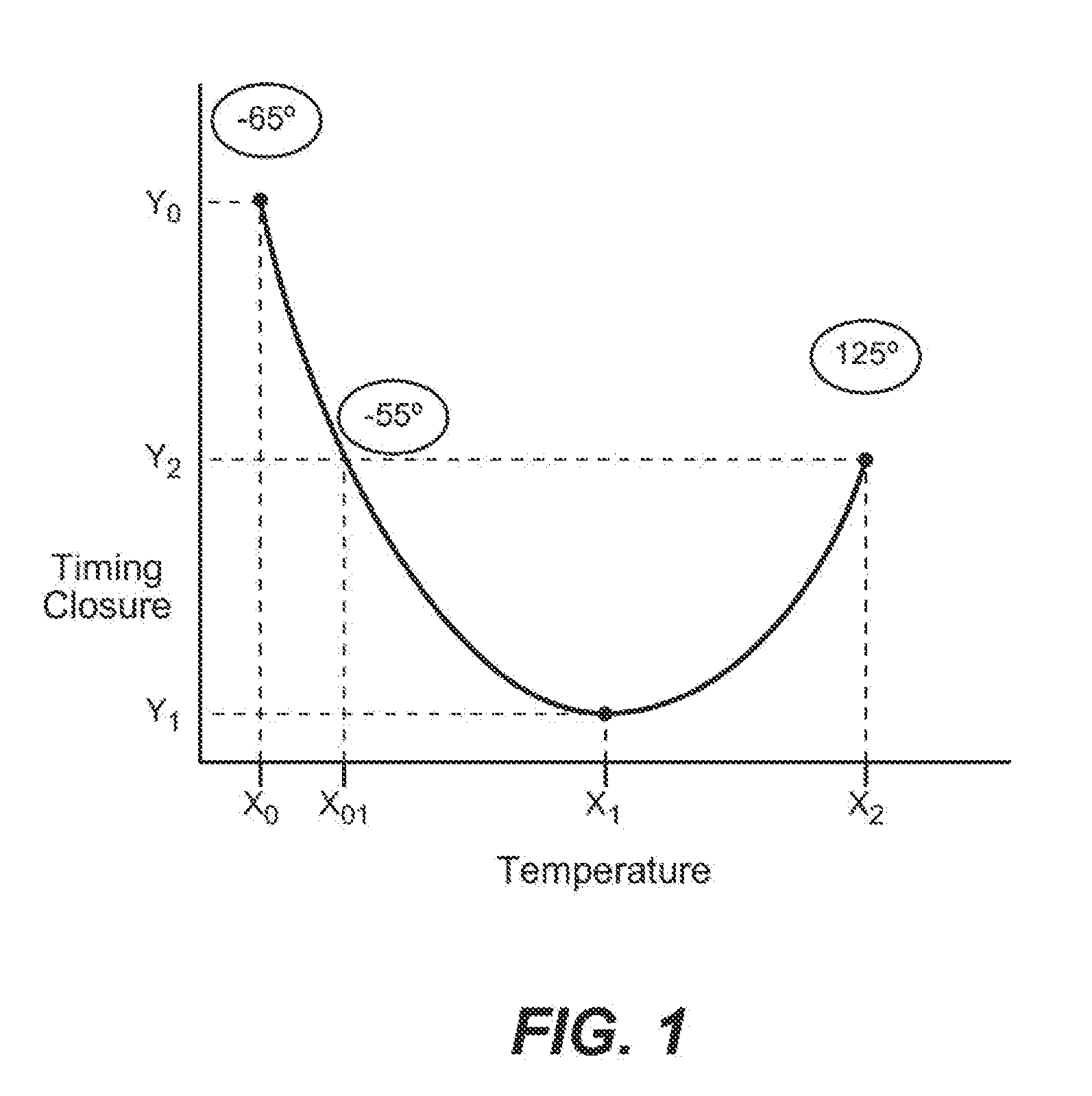

InactiveUS20140105246A1Temperatue controlDigital data processing detailsTemperature controlEngineering

A temperature control for a Structured ASIC chip, manufactured using a CMOS process is shown. A circuit employing temperature feedback using a microprocessor and active heating elements, that in a preferred embodiment uses decoupling cell capacitors, is employed to actively heat a die when the temperature of the die drops below a predetermined minimum temperature, in order to achieve timing closure in the chip.

Owner:INTEL CORP

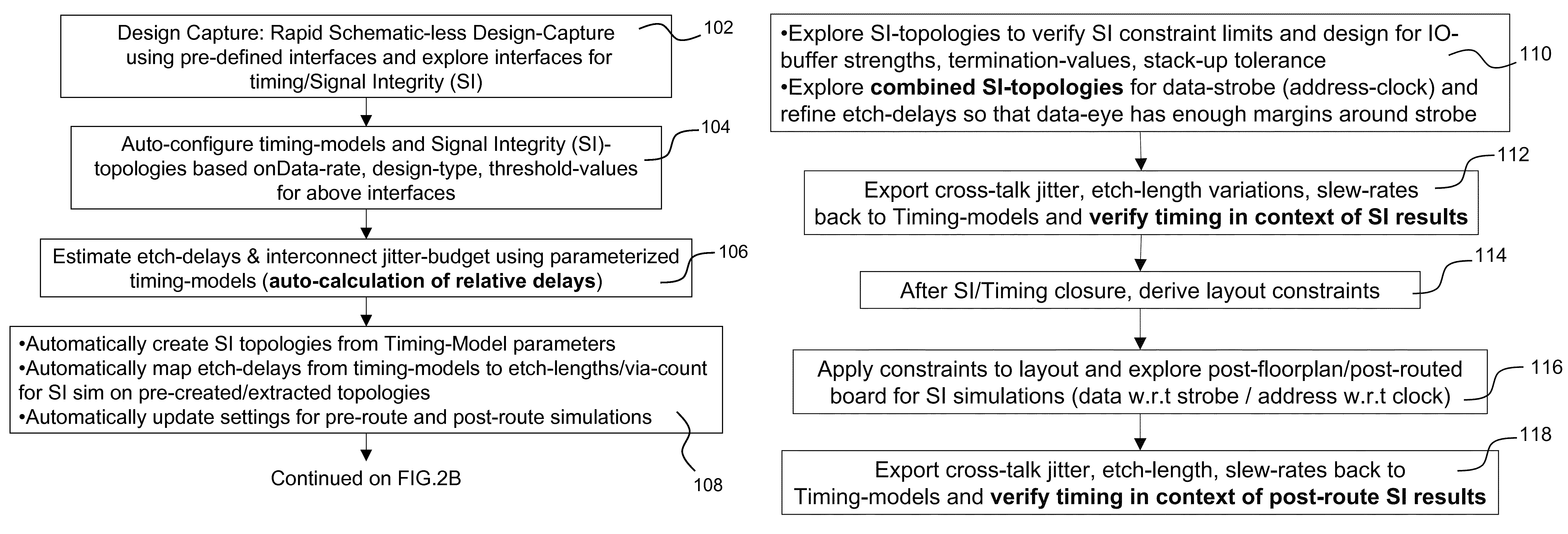

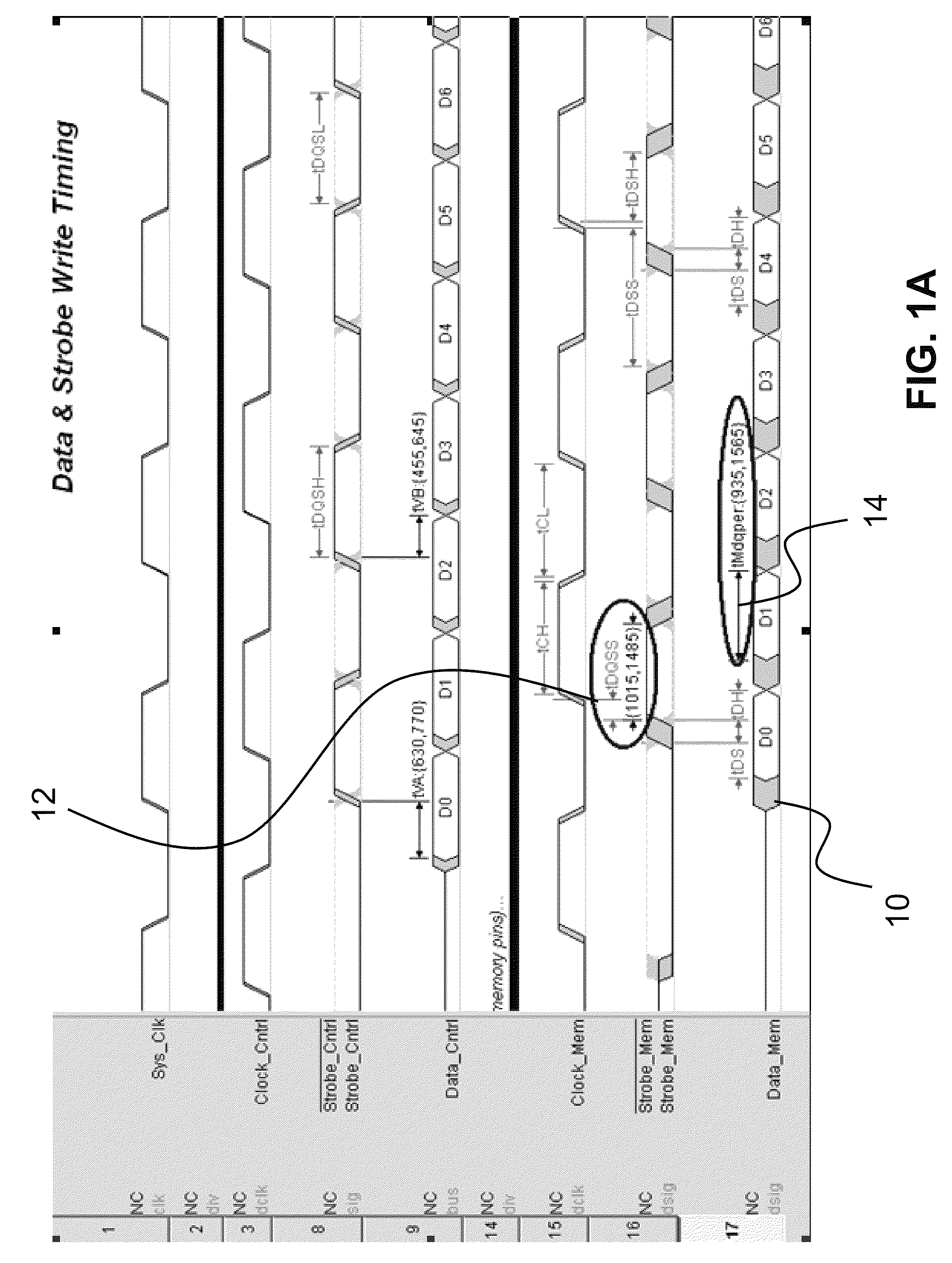

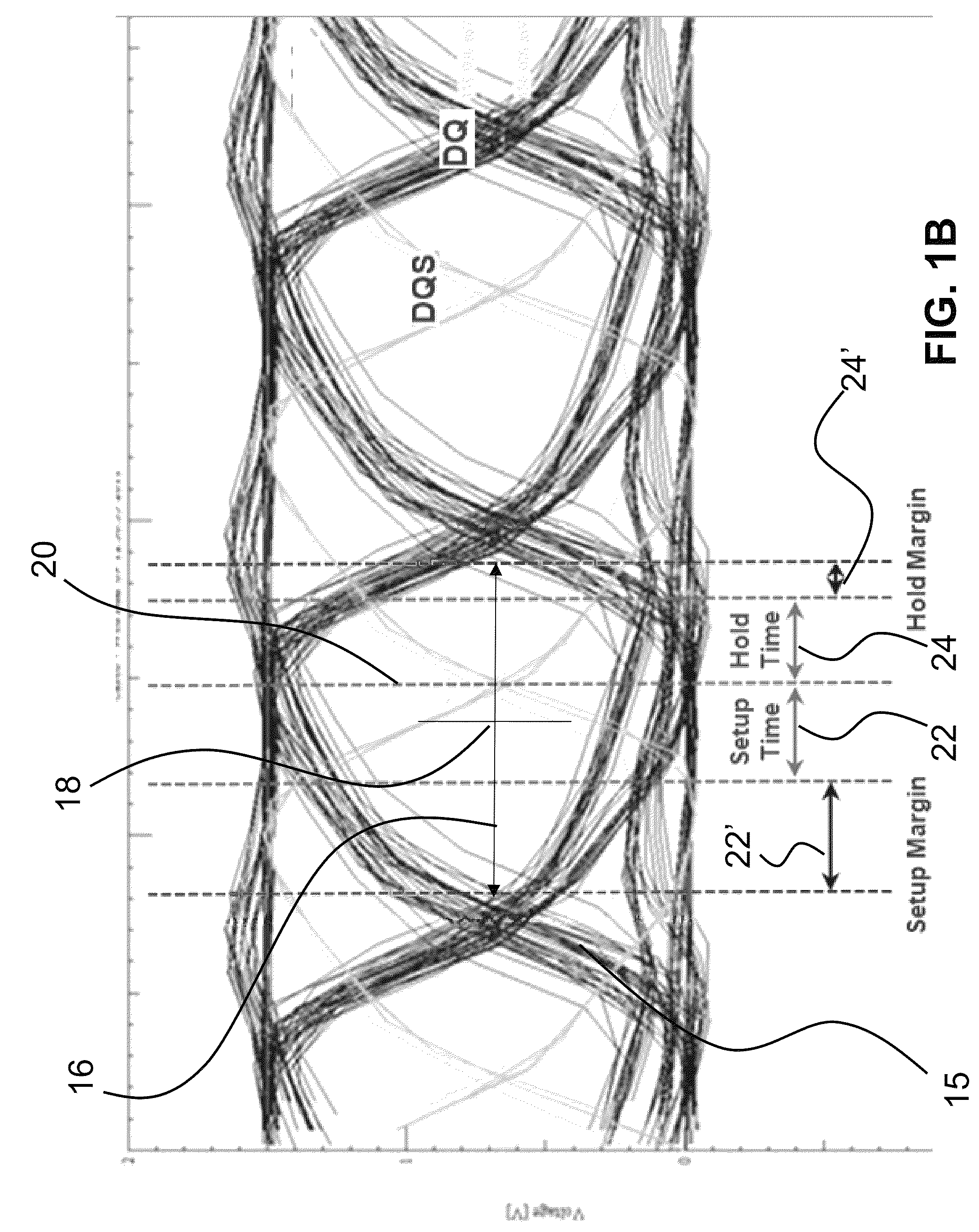

System and method for parametric intercoupling of static and dynamic analyses for synergistic integration in electronic design automation

InactiveUS8566767B1Shorten the timeImprove design flexibilityAnalogue computers for electric apparatusDetecting faulty computer hardwareElectronic systemsAnalysis tools

A system and method are provided for actuating static and dynamic analysis tools in parametrically intercoupled manner for synergistic optimization of an electronic system design. The system and method execute a timing designer process for selectively actuating the static analysis tool to conduct timing analysis based on at least one predetermined timing model and generate a plurality of estimated values for certain signal parameters to be in compliance with predetermined timing constraints. A signal exploration process is executed to receive the estimated values from the timing designer process and configure the resources of the dynamic analysis tool responsive thereto. The signal exploration process actuates the dynamic analysis tool to conduct electrical integrity analysis based on transient simulation and generate a plurality of simulated values for signal parameters. The simulated values are back annotated to the timing designer process for timing closure.

Owner:CADENCE DESIGN SYST INC

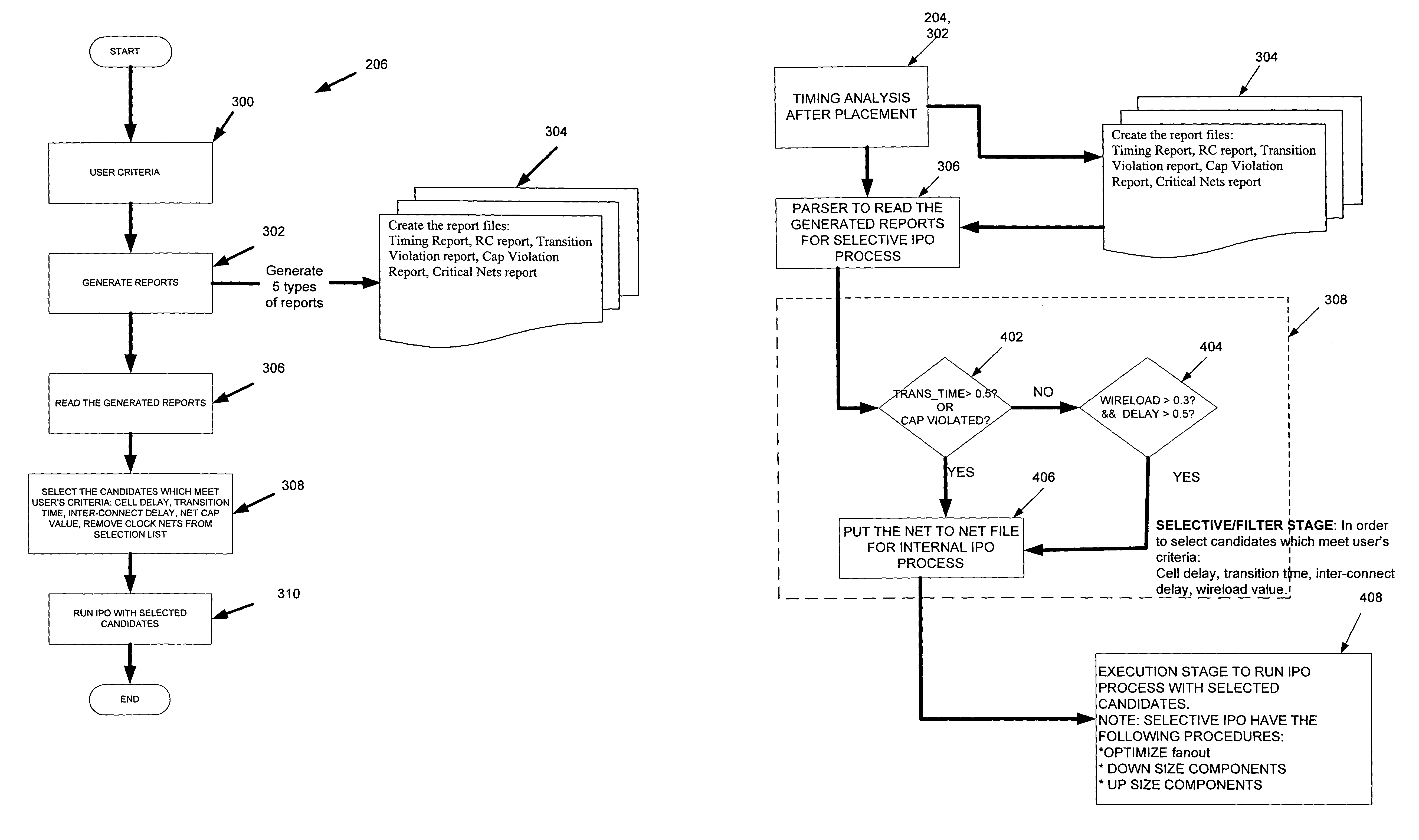

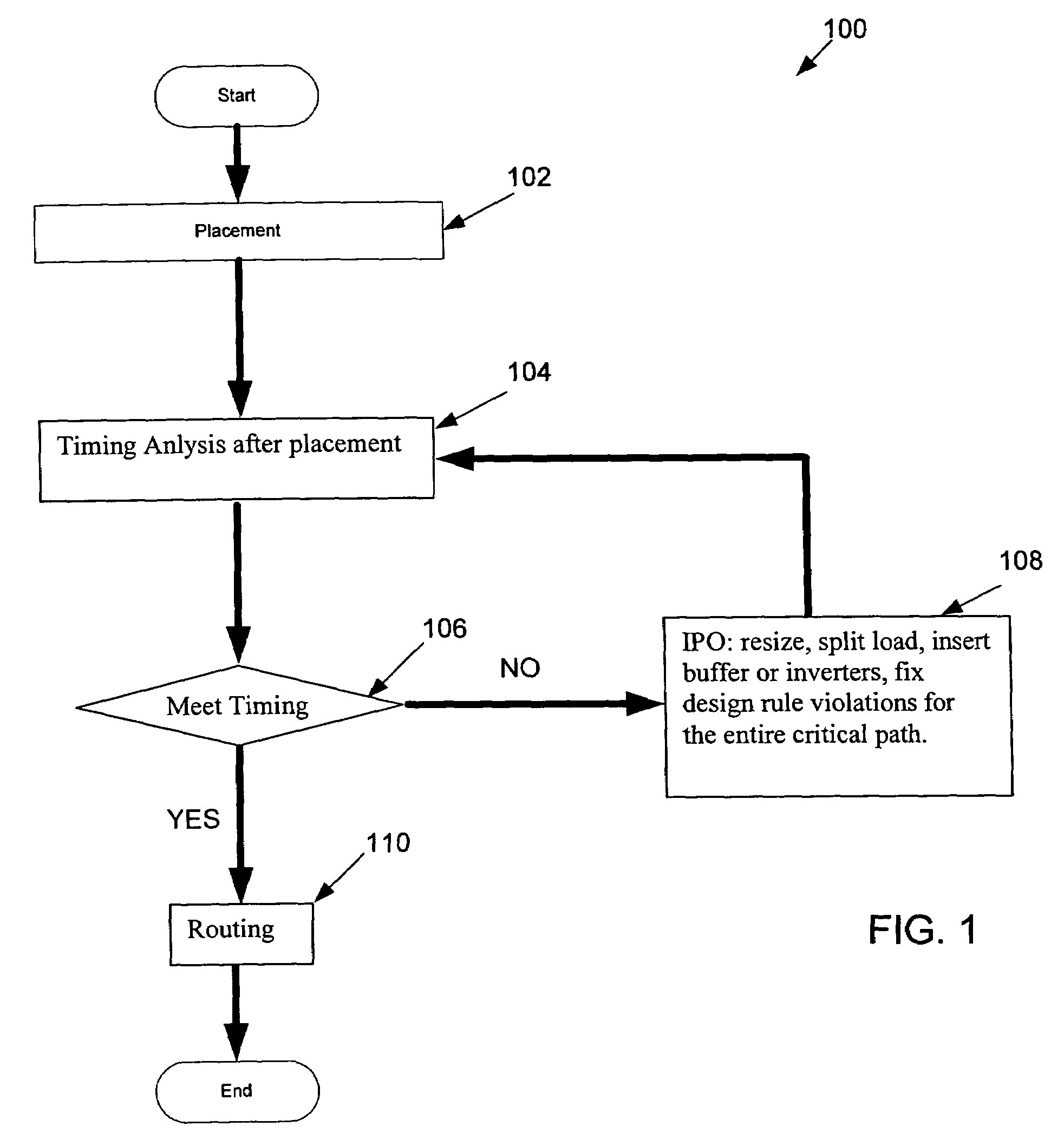

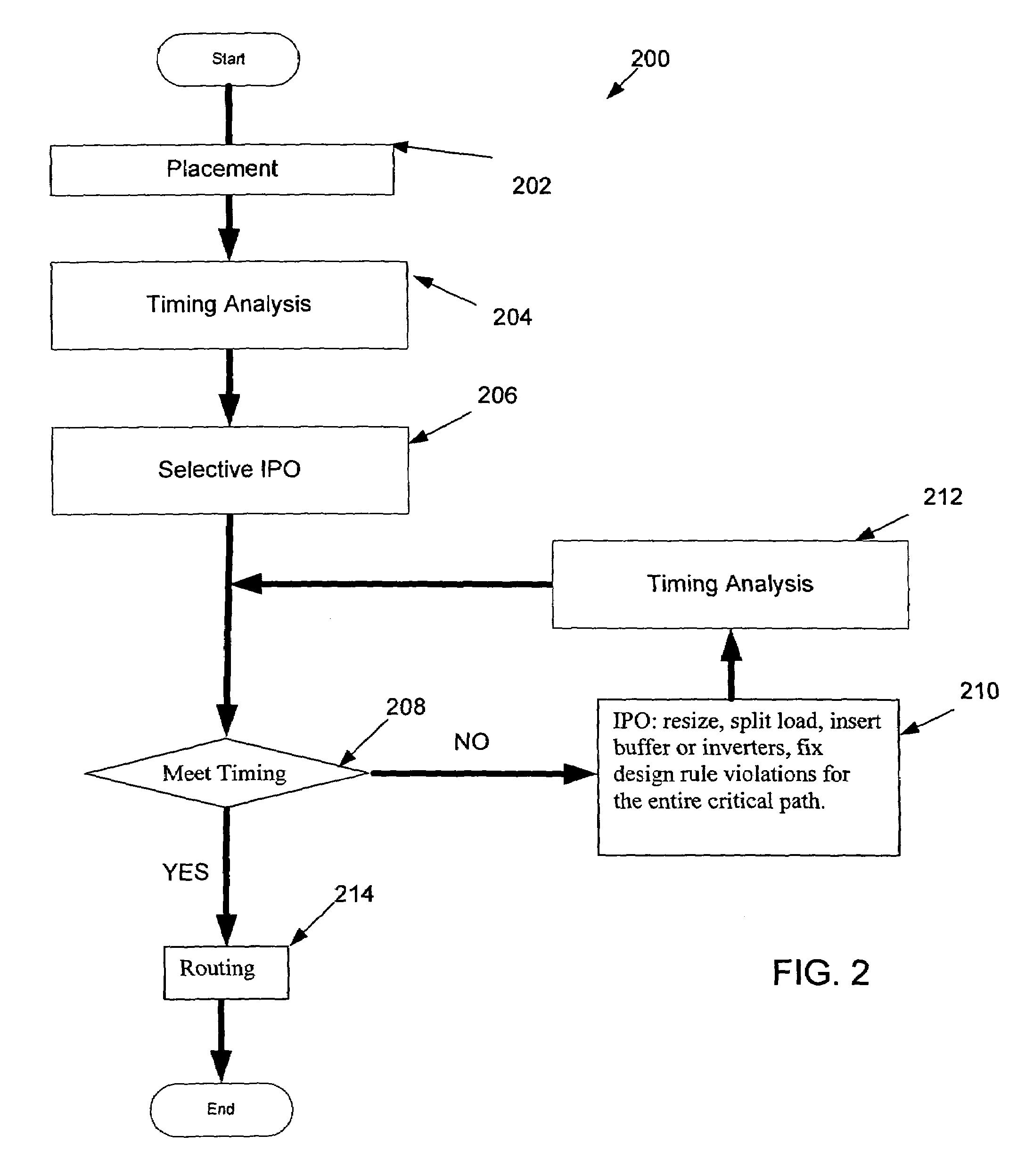

Method for faster timing closure and better quality of results in IC physical design

ActiveUS7149992B2Quality improvementFaster run timeCAD circuit designSoftware simulation/interpretation/emulationWorst negative slackUser input

A selective IPO procedure based on the concept of a “timing violation potential” prioritizes the components and nets in a critical path. User input criteria is used to select the components or nets (or both) which have the larger “timing violation potential;” only those components and nets are then operated on. After a selective IPO step, the total number of critical paths is reduced, as well as the worst negative slacks (WNS) of the critical path compared to the traditional IPO method.

Owner:VIA TECH INC

Layered quasi-cyclic LDPC decoder with reduced-complexity circular shifter

ActiveUS8473806B1Improve computing efficiencyReduce congestionError detection/correctionCode conversionRound complexityParallel computing

This disclosure relates generally to data decoding, and more particularly to iterative decoders for data encoded with a low-density parity check (LDPC) encoder. LDPC decoders are disclosed that use reduced-complexity circular shifters that may be used to decode predefined or designed QC-LDPC codes. In addition, methods to design codes which may have particular LDPC code performance capabilities and which may operate with such decoders using reduced-complexity circular shifters are provided. The generation of quasi-cyclic low density parity check codes and the use of circular shifters by LDPC decoders, may be done in such a way as to provide increased computational efficiency, decreased routing congestion, easier timing closure, and improved application performance.

Owner:MARVELL ASIA PTE LTD

Design stage mitigation of interconnect variability

Owner:GLOBALFOUNDRIES U S INC

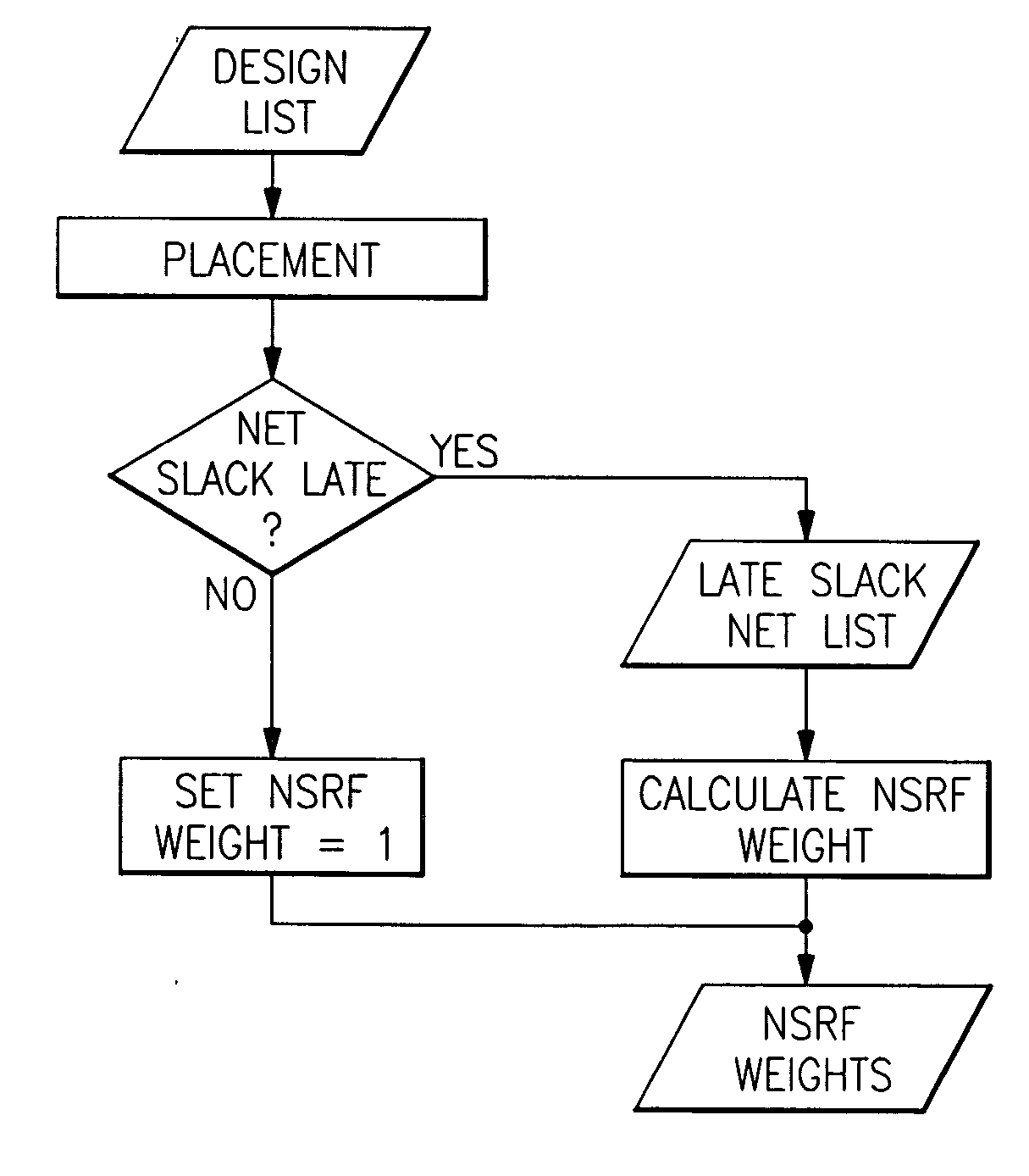

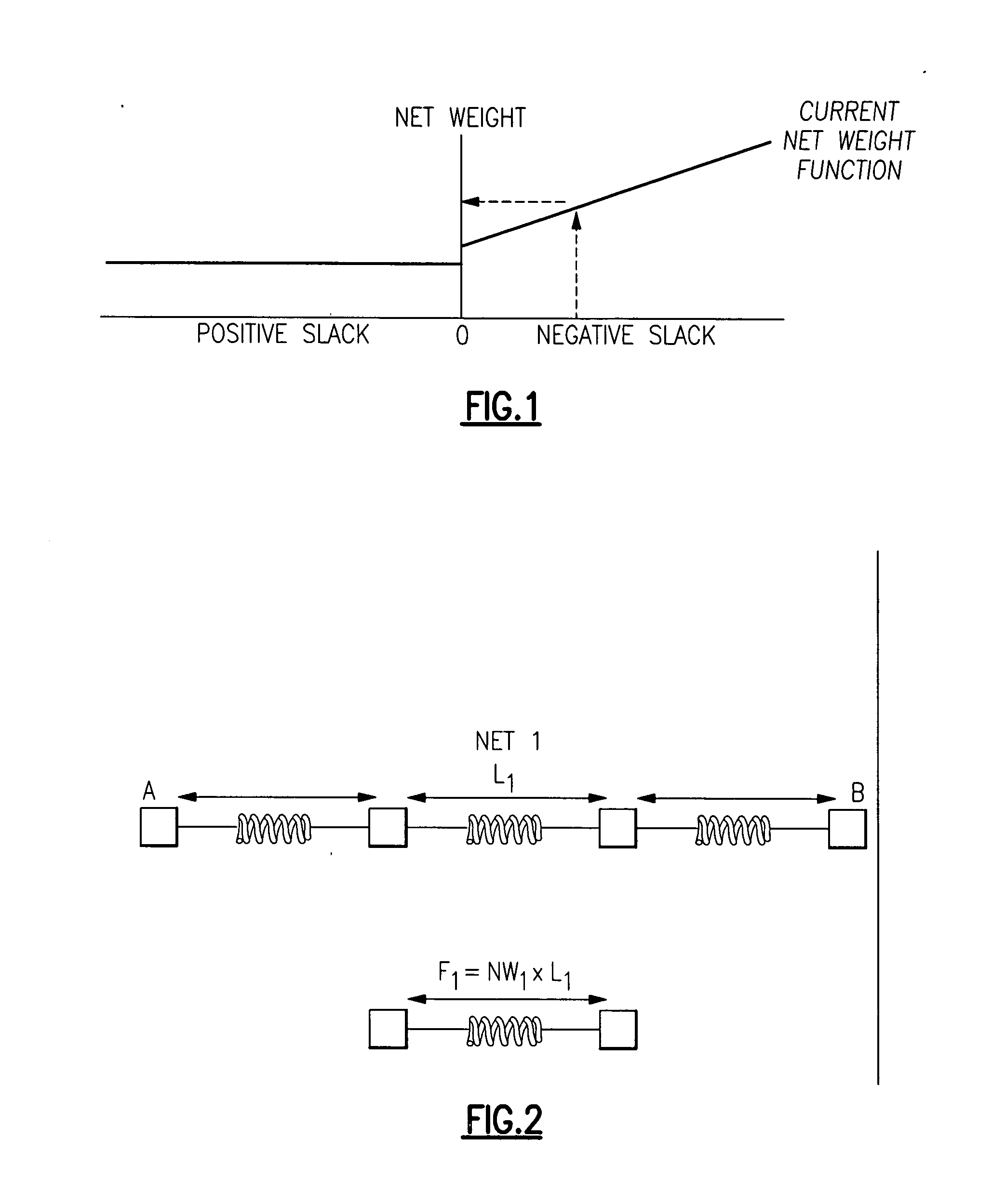

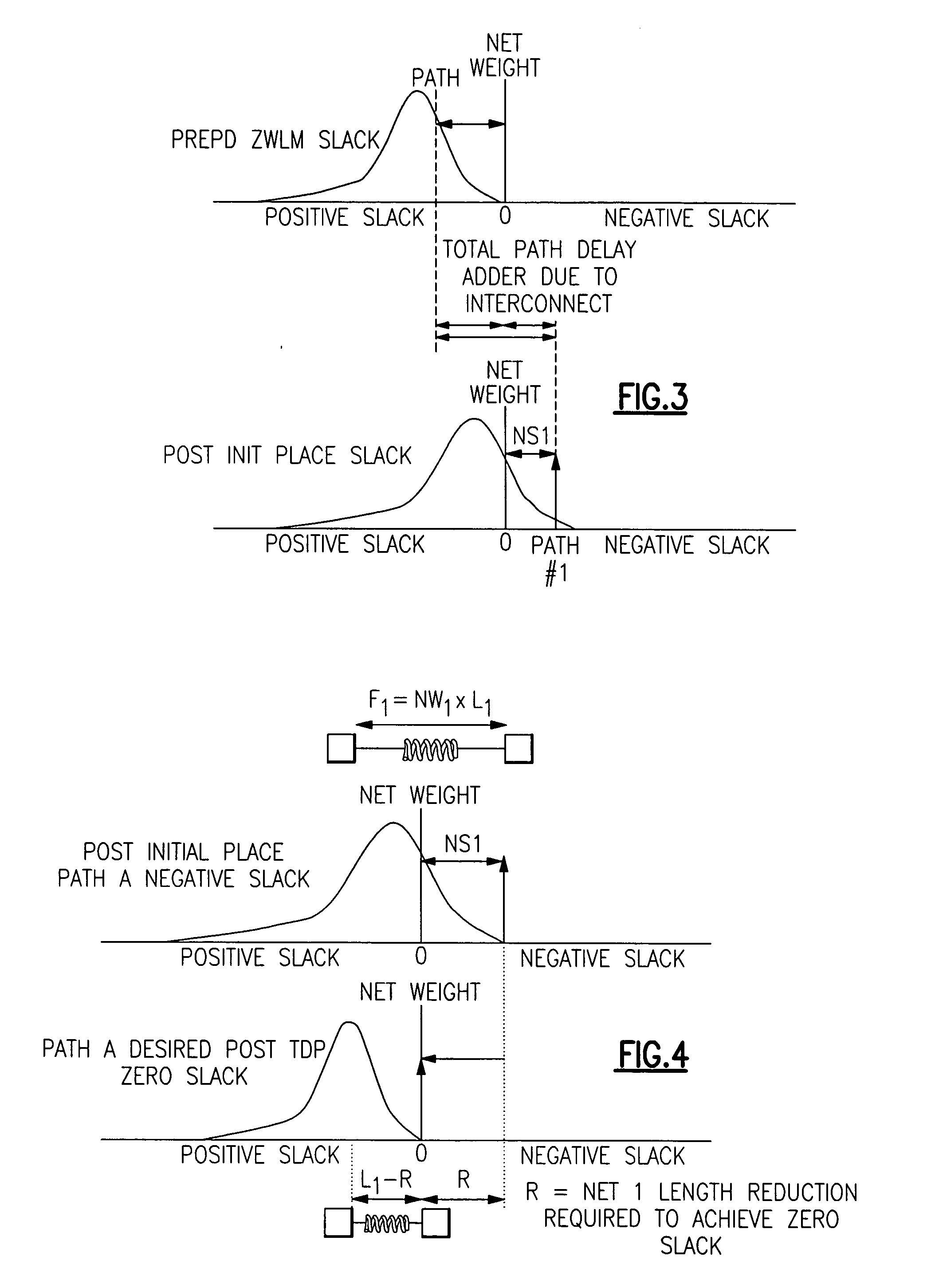

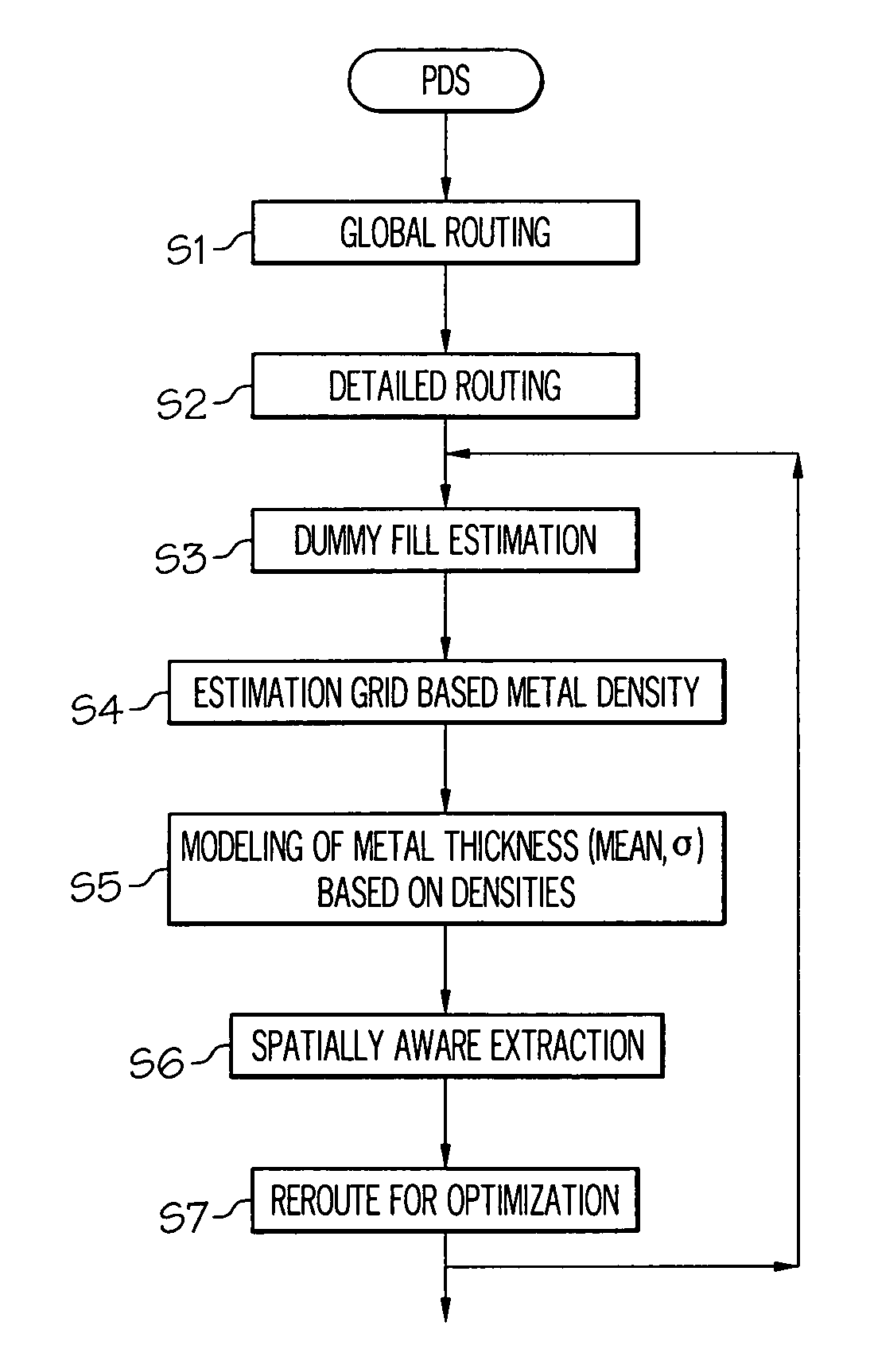

Negative slack recoverability factor - a net weight to enhance timing closure behavior

InactiveUS20060015836A1Enhance timing closure behaviorOvercomes shortcomingComputer aided designSoftware simulation/interpretation/emulationLoad modelTiming closure

More “timing closure efficient” Timing Driven Placements by implementing our new net weight for negative slack paths to enhance timing closure behavior is provided by a NSRF (Negative Slack Recover Factor). This new weight would not be based on the absolute amount of negative slack in a path, but rather it would be based on the proportion or percentage of the path's total net delay adder that must be recovered in order to achieve timing closure (zero slack). After an initial or previous placement has been created, then a list of paths with timing violations with a Negative Slack Recover Factor (NSRF) is created for each net in each of the timing paths on the list of paths, and then calculating a NSRF net weight factor for use in subsequent placements and also assigning nets in the list of paths with no timing violations a NSRF default value of one.. The NSRF value is calculated as equaling (ZWLM slack value +negative slack value) / ZWLM slack value=(1+(negative slack value / ZWLM slack value)), where ZWLM is a Zero Wire Load Model (ZWLM) value of timing wherein all wire parasitics are removed from consideration in the timing.

Owner:GLOBALFOUNDRIES INC

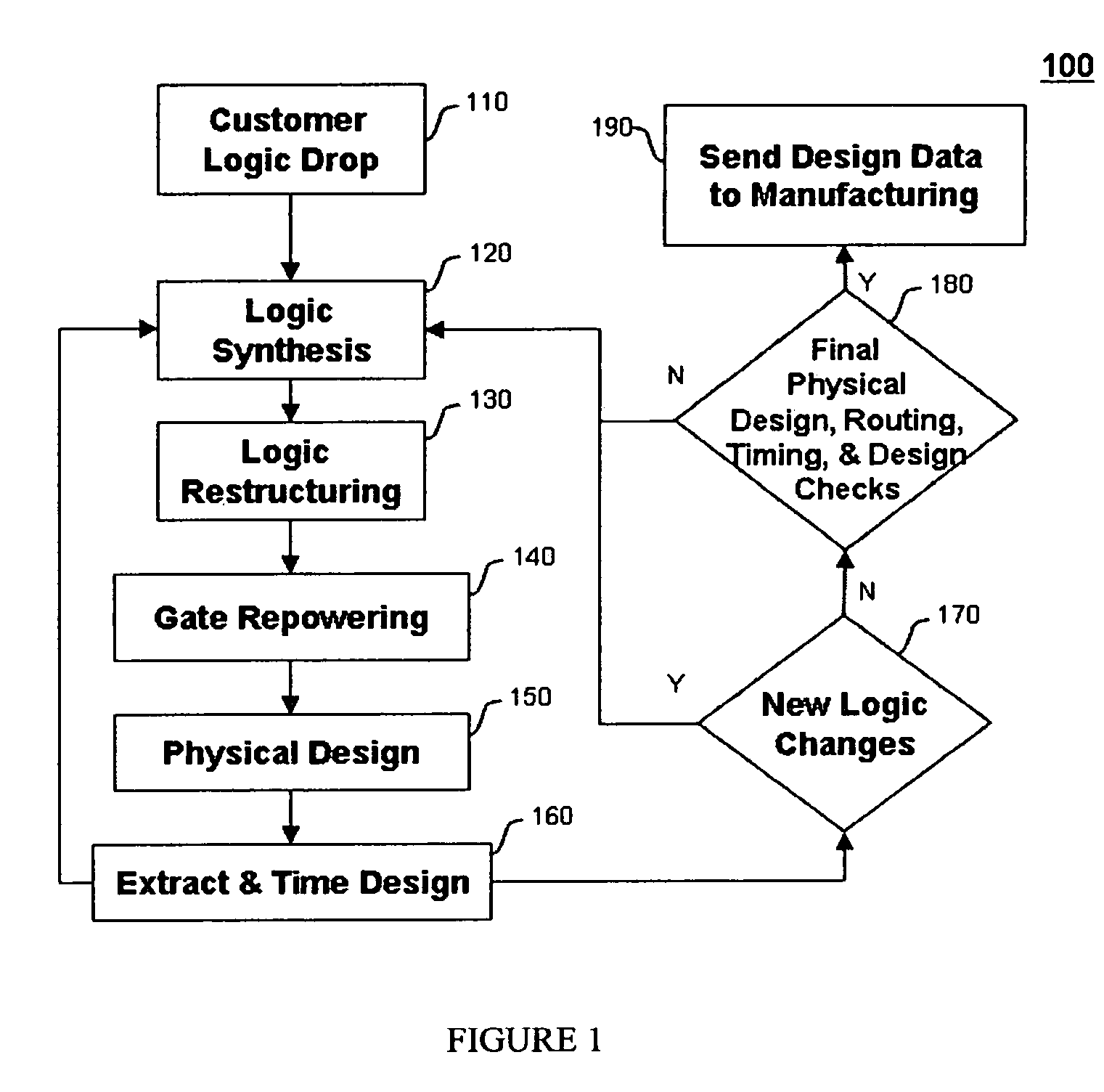

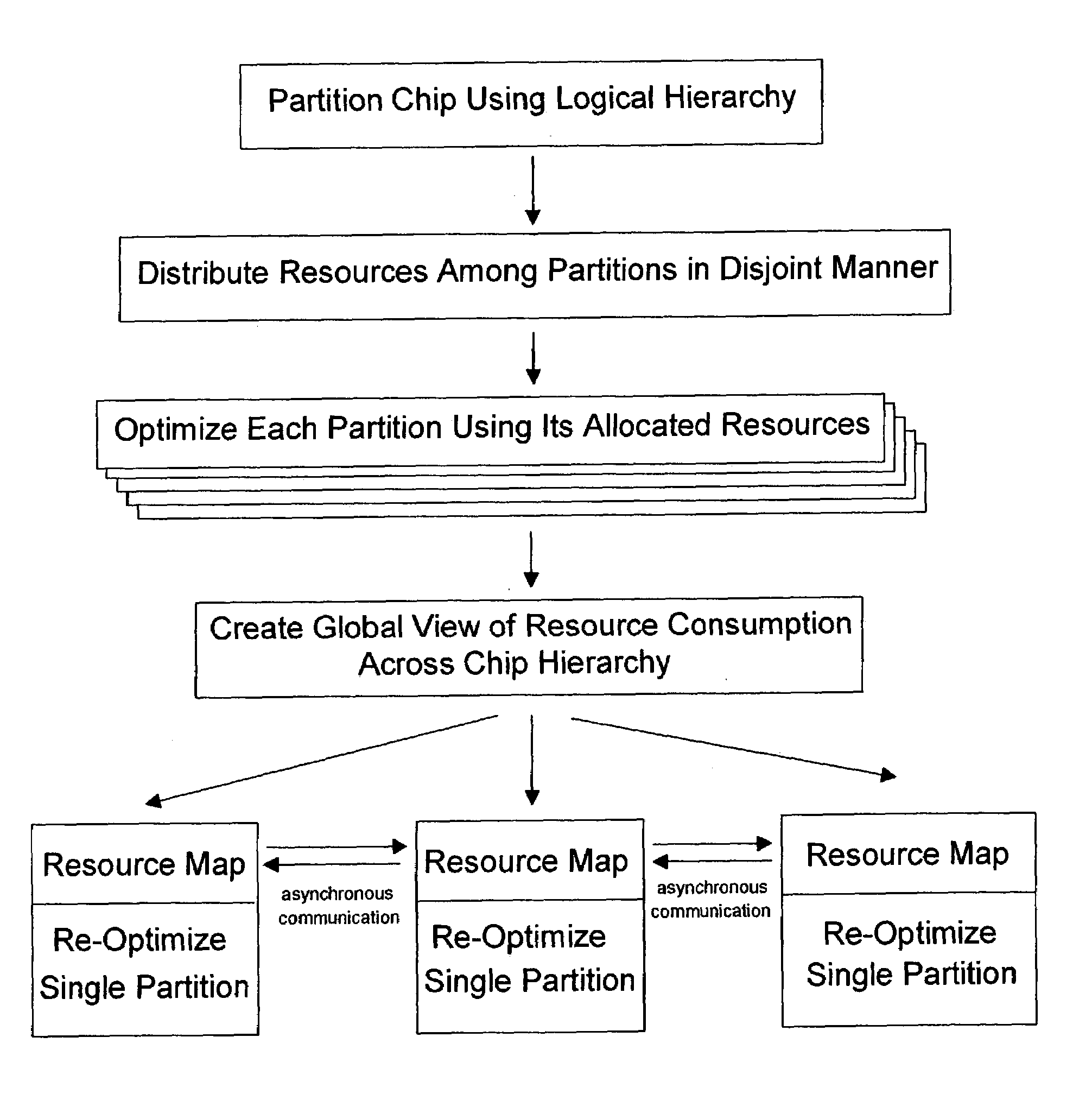

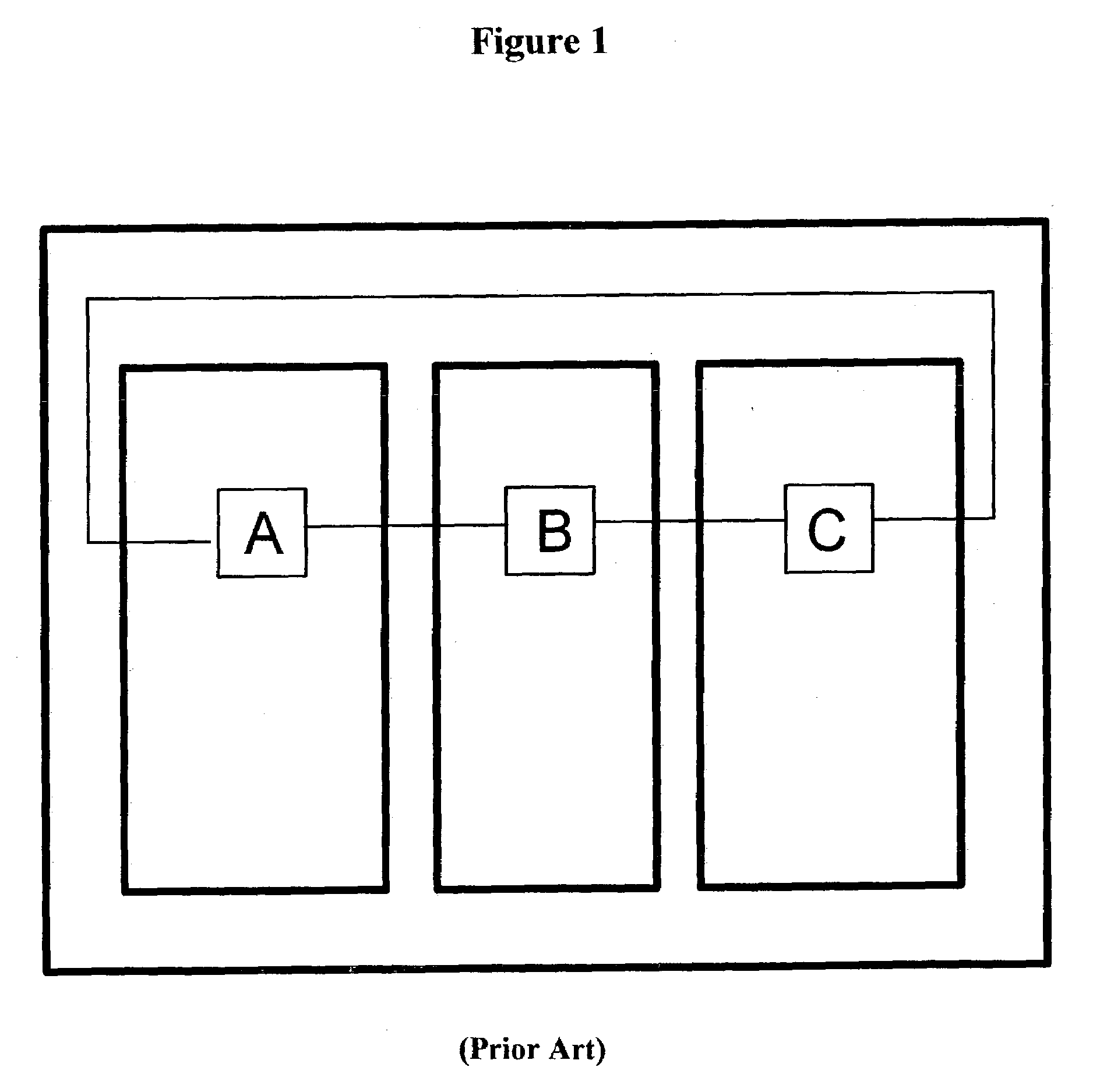

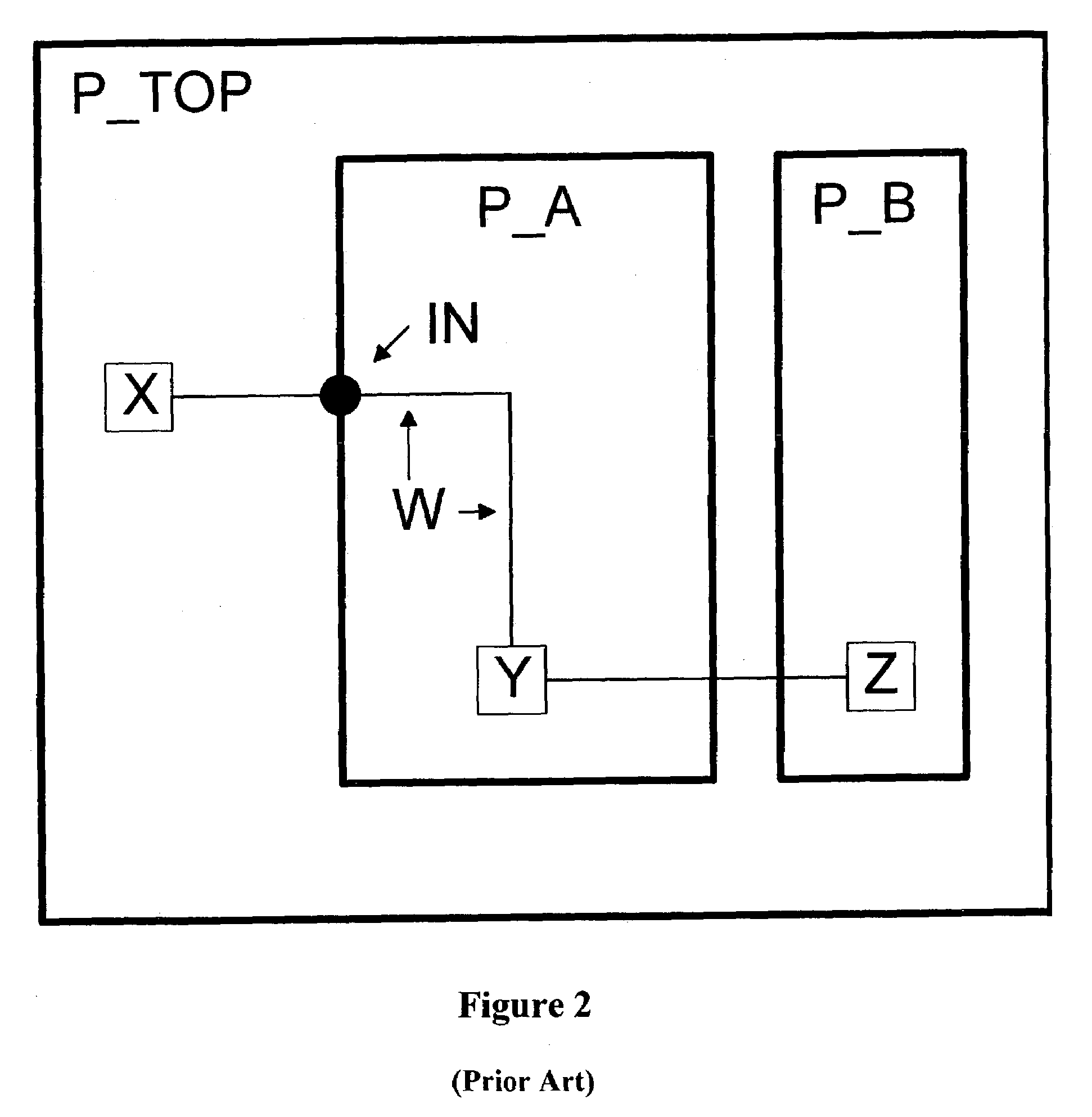

Method for performing timing closure on VLSI chips in a distributed environment

InactiveUS7178120B2Quality improvementComputer aided designSoftware simulation/interpretation/emulationSingle processPresent method

A method for performing timing closure on VLSI chips in a distributed environment is described. Abstracting the physical and timing resources of a chip and providing an asynchronous method of updating that abstraction allows multiple partitions of a chip to be optimized concurrently. A global view of physical and timing resources is supplied to local optimizations which are applied concurrently to achieve timing closure. Portions of the hierarchy are optimized in separate processes. Partitioning of the chip is performed along hierarchical lines, with each process owning a single partition in the hierarchy. The processes may be executed by a single computer, or spread across multiple computers in a local network. While optimizations performed by a single process are only applied to its given portion of the hierarchy, decisions are made in the context of the entire hierarchy. These optimizations include placement, synthesis, and routing. The present method can also be expanded to include other resources, such as routing resource, power supply current, power / thermal budget, substrate noise budget, and the like, all of which being able to be similarly abstracted and shared.

Owner:IBM CORP

Timing closure methodology

InactiveUS20050120319A1Easy maintenanceAvoidance of costly timing analysisSemiconductor/solid-state device manufacturingDesign optimisation/simulationIntegrated circuit layoutTiming closure

An automated method for designing an integrated circuit layout using a computer based upon an electronic circuit description and based upon cells which are selected from a cell library, each of the cells having an associated area, comprising the steps of: (a) placing each of the cells in the integrated circuit layout so that the cells can be coupled together by wires to form a circuit path having an associated predetermined delay constraint wherein the cells are coupled together based upon the electronic circuit description input to the computer; (b) connecting the cells together with the wires to form the circuit path; and (c) adjusting an area of at least one of the cells to satisfy the associated predetermined delay constraint of the circuit path.

Owner:IBM CORP +1

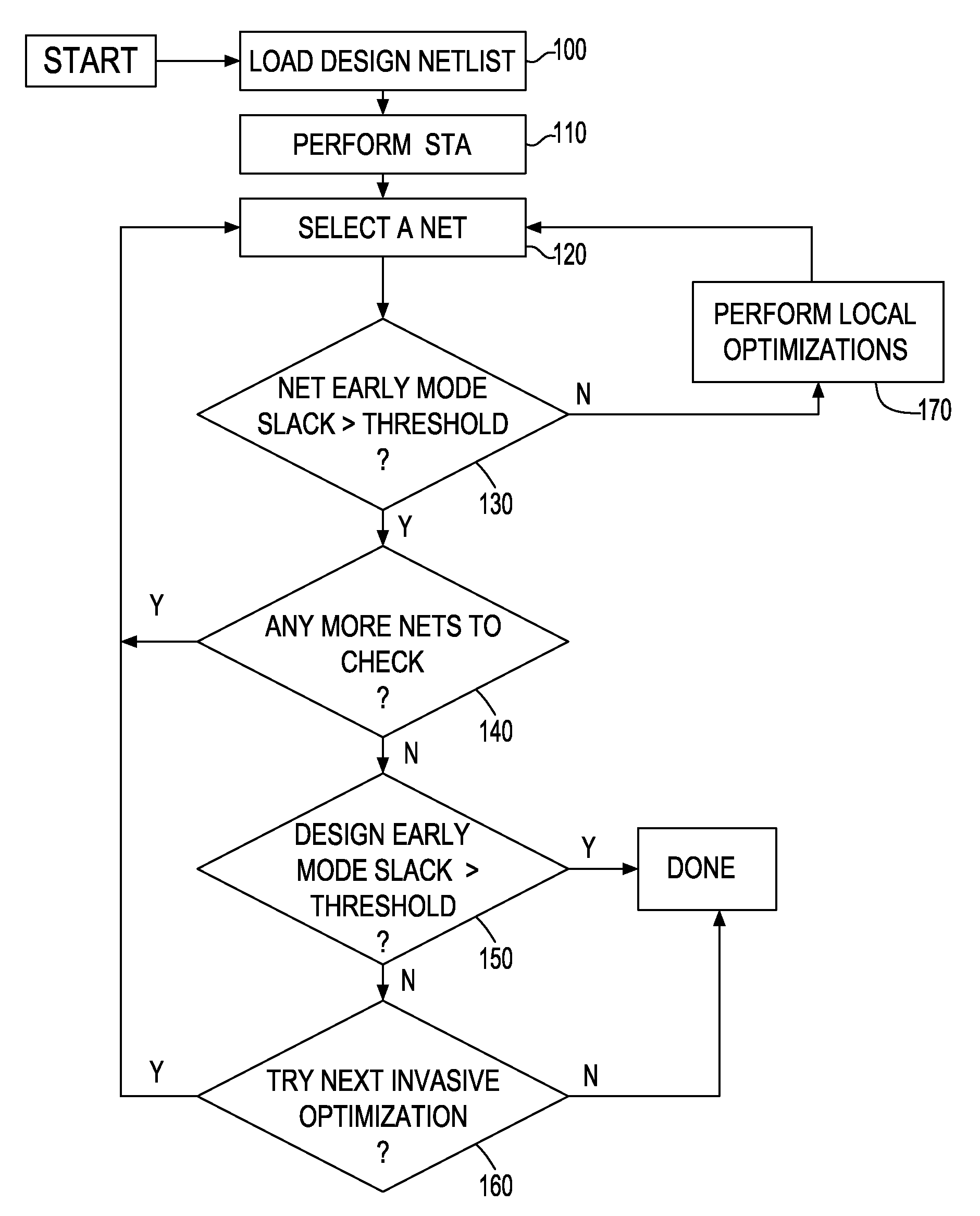

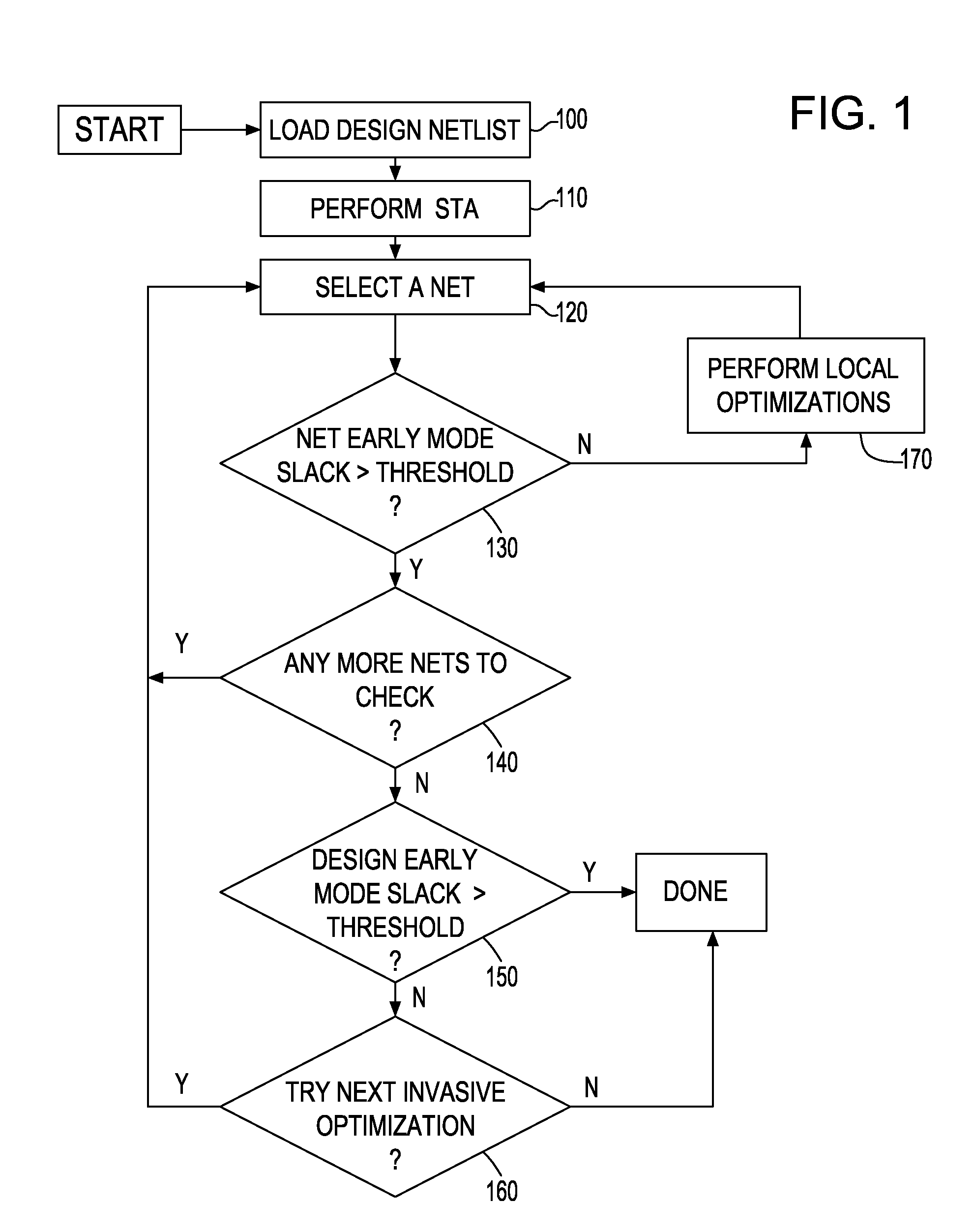

Method of minimizing early-mode violations causing minimum impact to a chip design

InactiveUS7996812B2Minimize disruptionAccurate timingComputer aided designSoftware simulation/interpretation/emulationFast pathEngineering

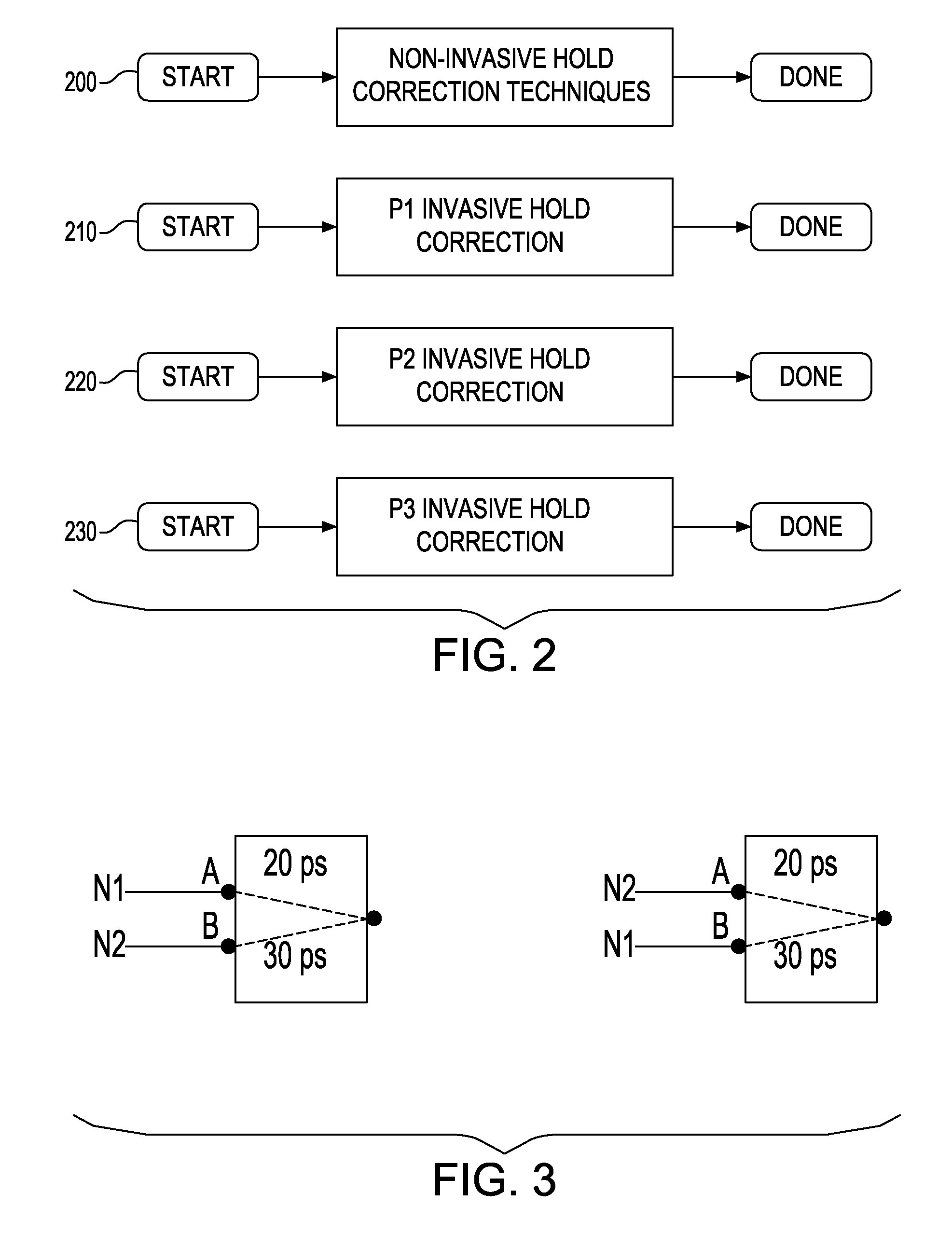

A system and a method for correcting early-mode timing violations that operate across the process space of a circuit design. Optimizations are performed to replace padding that increase path delays on fast paths. At the stage in the design process where early-mode violations are addressed, placement, late-mode timing closure, routing, and detailed electrical and timing analysis are assumed to have been completed. The optimizations are designed to be effective in delaying fast paths while minimizing the impact on already-completed work on the chip, in contrast to relying only on adding pads that can have a negative impact on all of these quantities. The optimizations are classified according to their invasiveness and are followed by their deployment. The deployment is designed to minimize using delay pads, reduce design disruptions, and minimize effects on other aspects of the design.

Owner:MENTOR GRAPHICS CORP

Method for variability constraints in design of integrated circuits especially digital circuits which includes timing closure upon placement and routing of digital circuit or network

InactiveUS20080105904A1Reduced characteristicsSuppress mutationSolid-state devicesSemiconductor/solid-state device manufacturingTiming closureSignal delay

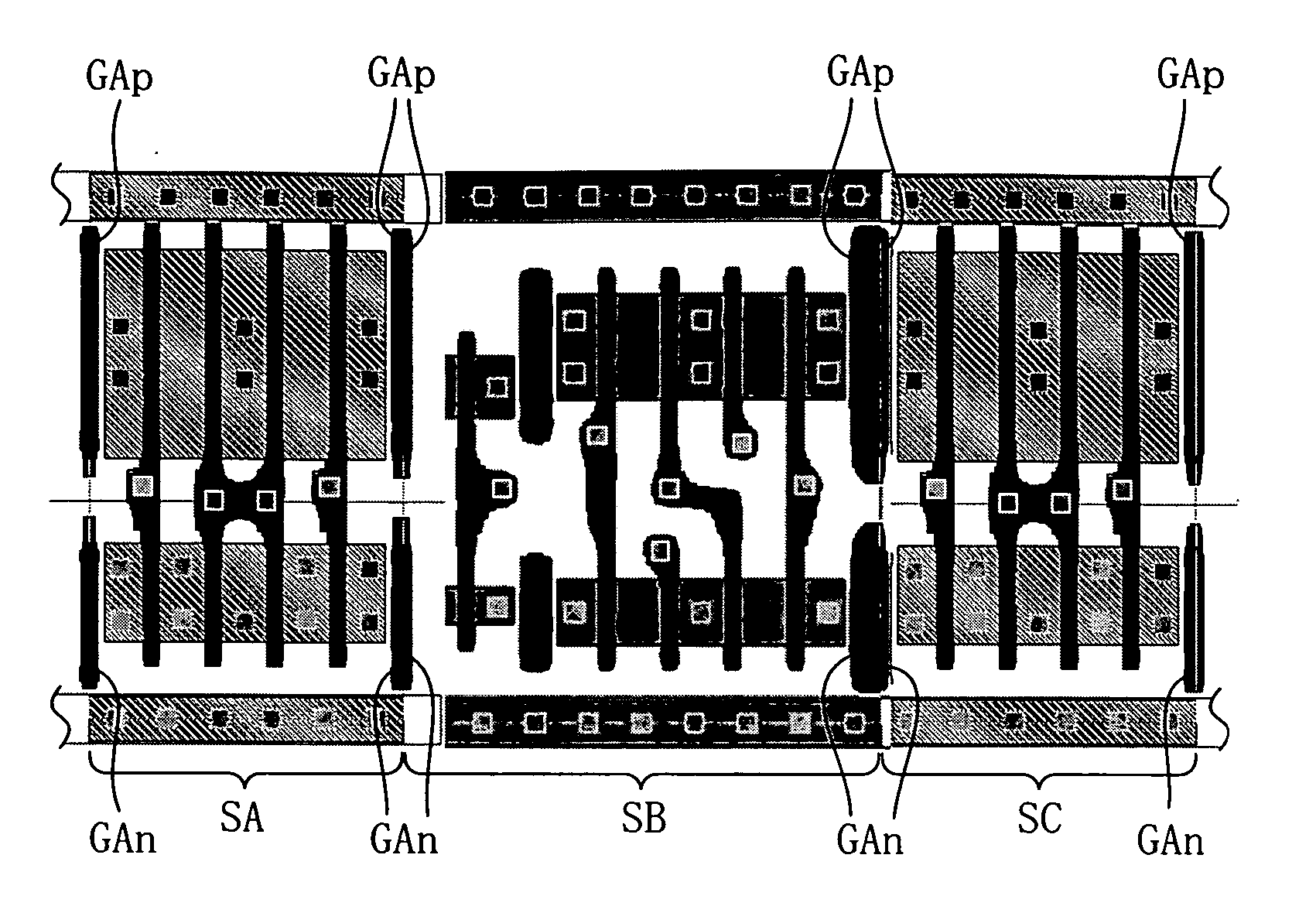

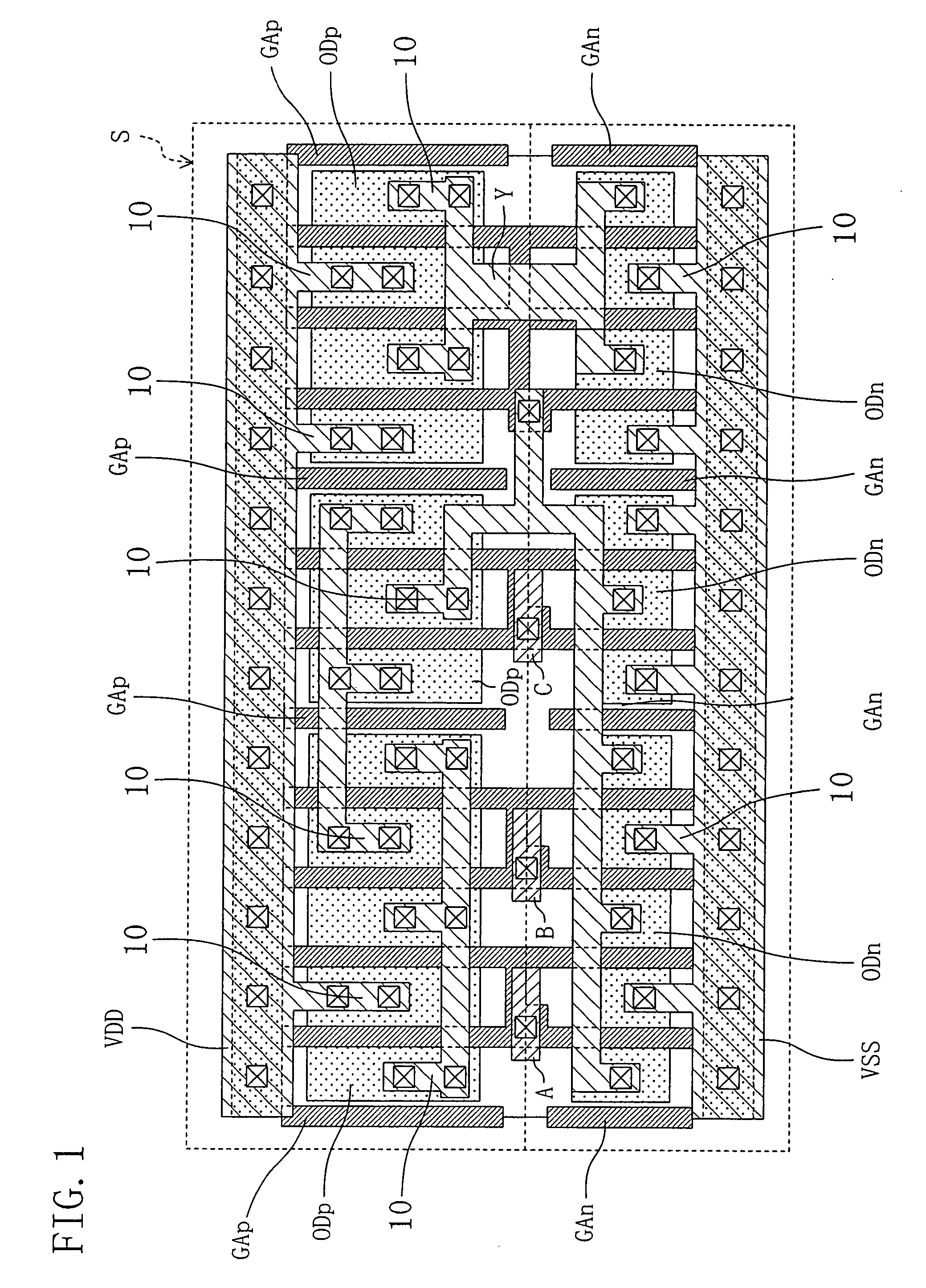

In a standard cell, dummy transistors have p-type and n-type dummy gate electrodes. The dummy transistors are in an OFF state all the time. The gate length of each of the dummy gate electrodes is extended over an end portion of a diffusion region toward the inside of the standard cell. Thus, the total surface area and the total perimeter of respective gate electrodes of all transistors provided in the standard cell are increased. As a result, for example, even though shapes of gate electrodes of transistors vary between the standard cell and each of other standard cells, transistor characteristics are substantially equal among the standard cells. Therefore, variations in delays of signals generated between the standard cells can be suppressed.

Owner:PANASONIC CORP

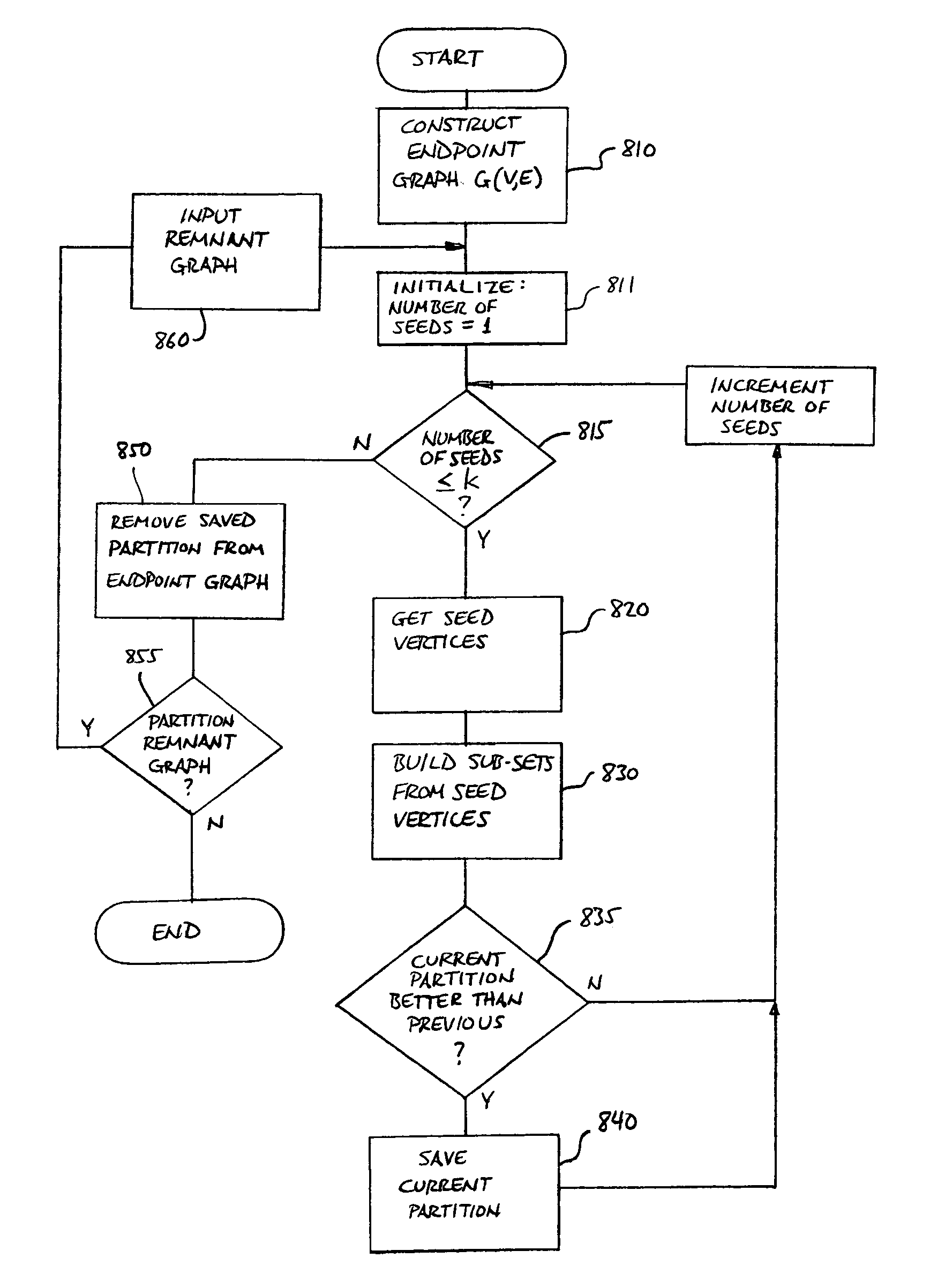

Method to identify geometrically non-overlapping optimization partitions for parallel timing closure

ActiveUS7047506B2Convenient timeEliminate needComputer aided designSoftware simulation/interpretation/emulationTime criticalAlgorithm

Owner:TWITTER INC

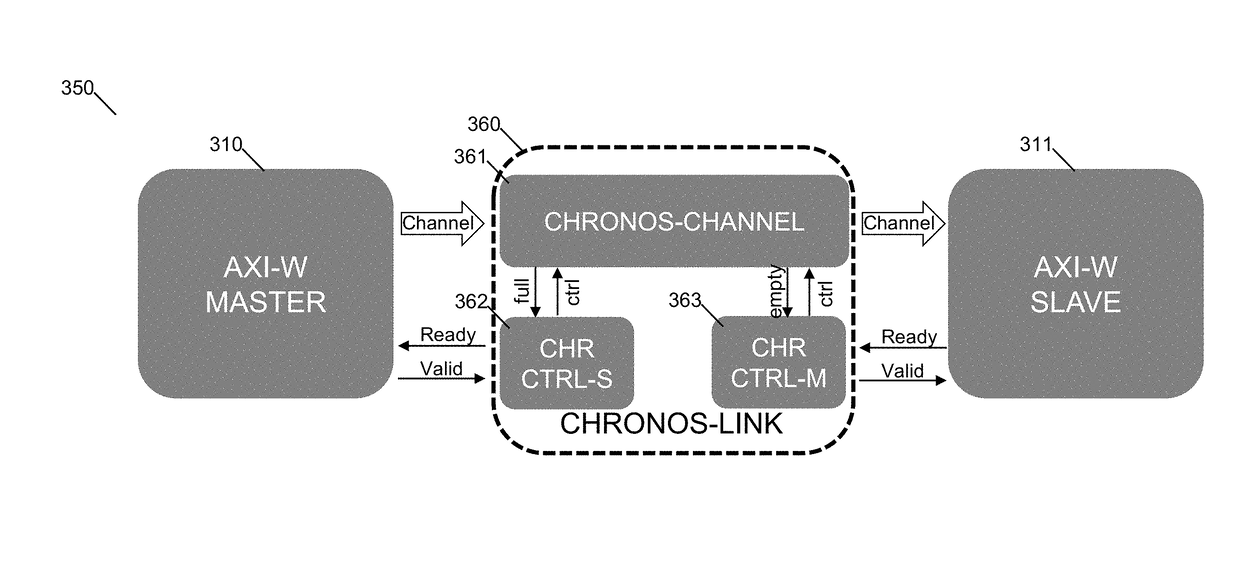

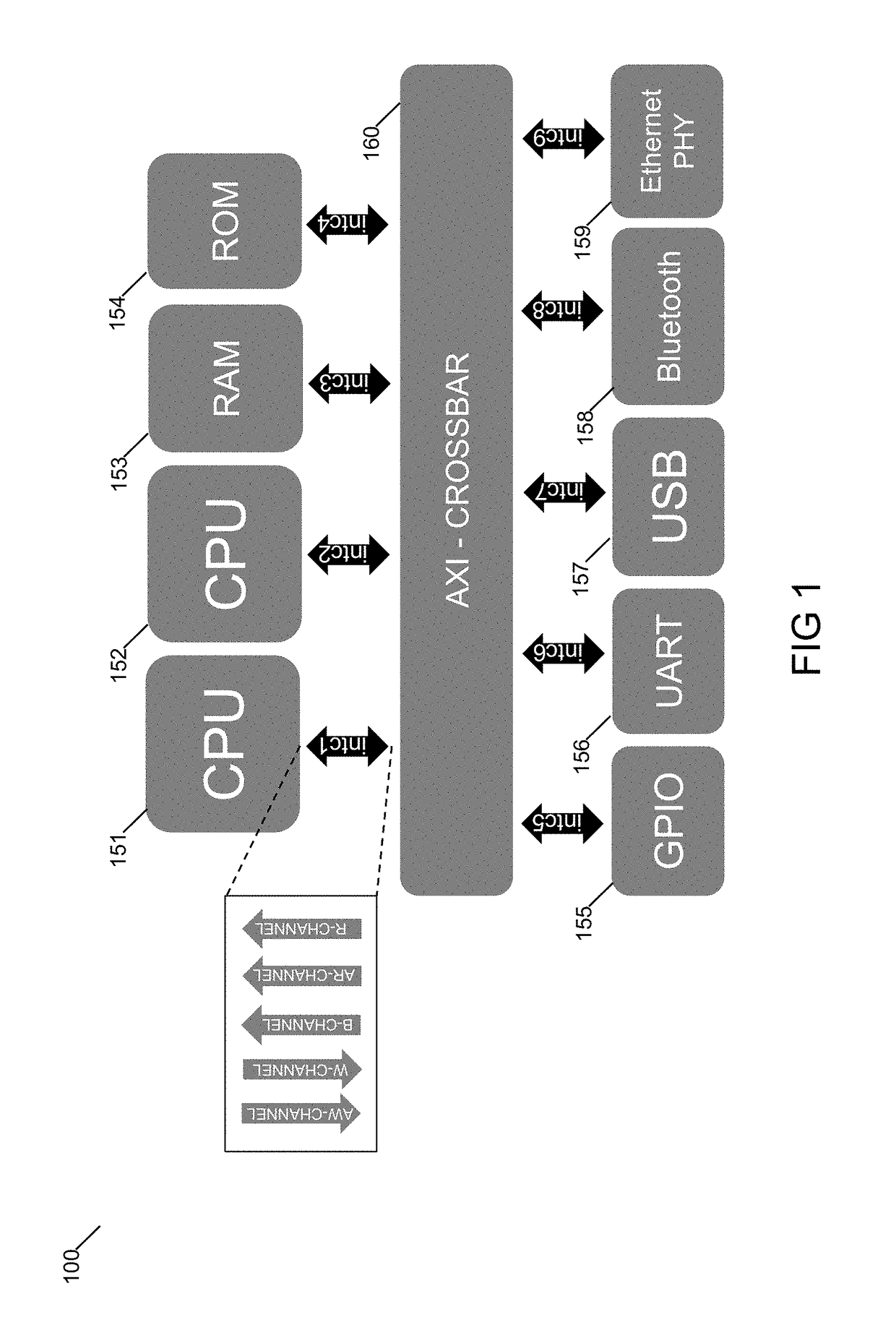

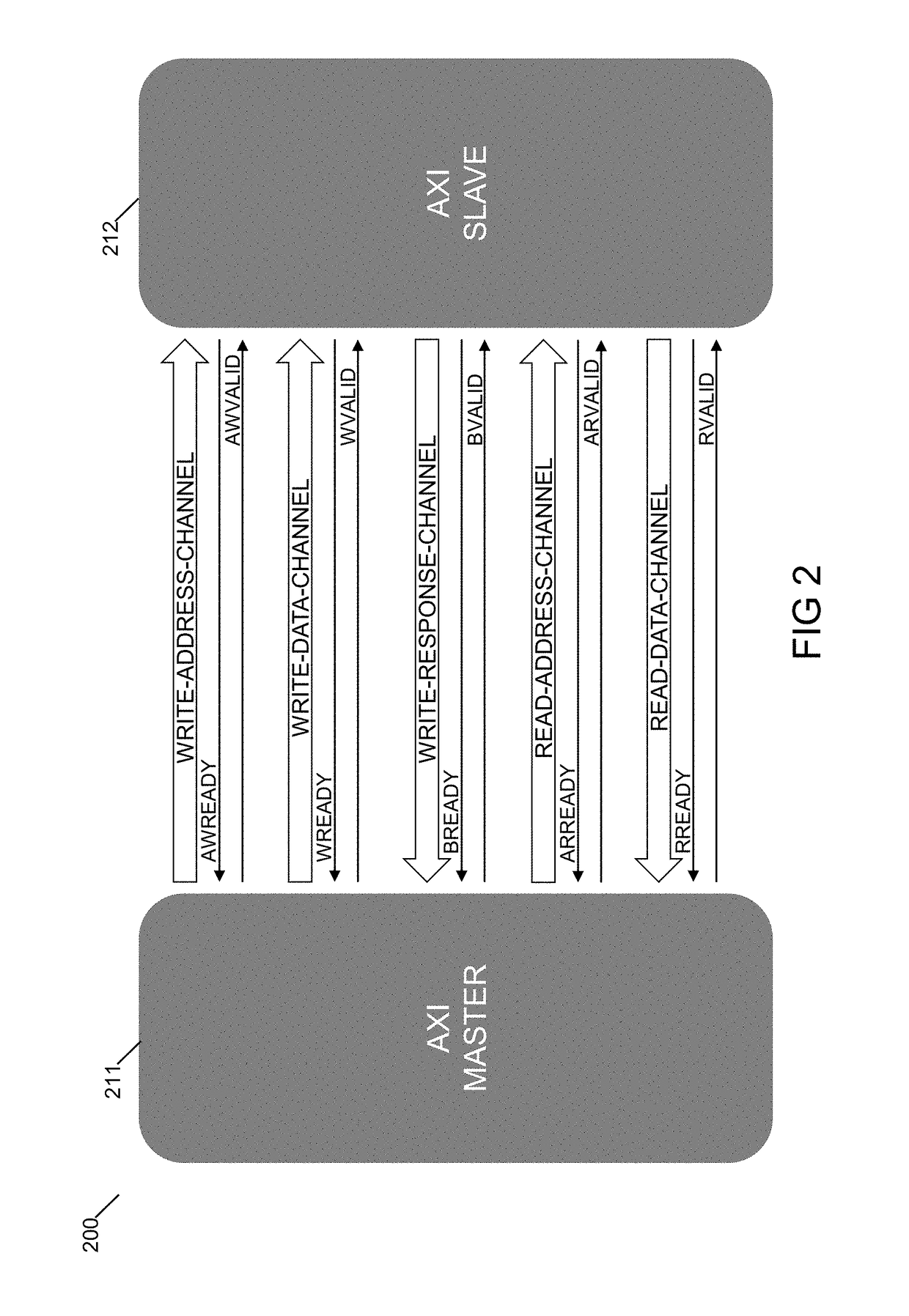

Application specific integrated circuit link

ActiveUS9977853B2Reduce overheadEfficient data transferCAD circuit designSpecial data processing applicationsIntellectual propertyClock tree synthesis

Systems and methods for application specific integrated circuit design using Chronos links are disclosed. A Chronos Link is an ASIC on-chip and off-chip interconnect communication protocol that allows interfaces to transmit and receive information. The protocol may utilize messages or signals to indicate the availability and / or readiness of information to be exchanged between a producer and a consumer allowing the communication to be placed on hold and to be resumed seamlessly. A method includes inserting gaskets and channel repeaters connected to interfaces of multiple intellectual property (IP) blocks in order to replace traditional links with Chronos Links; performing simplified floorplanning; performing simplified placement; performing simplified clock tree synthesis (CTS) and routing; and performing simplified timing closure.

Owner:CHRONOS TECH LLC

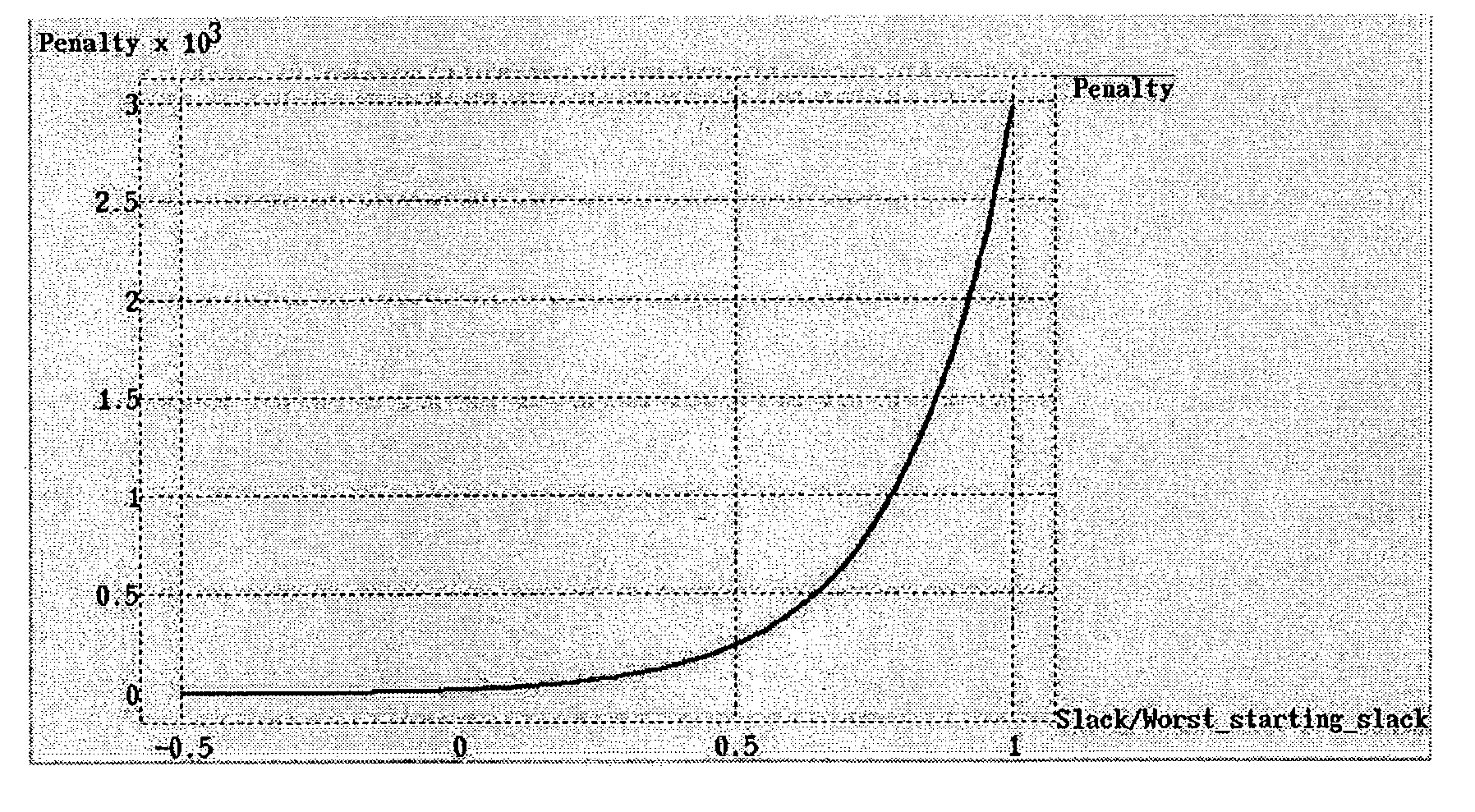

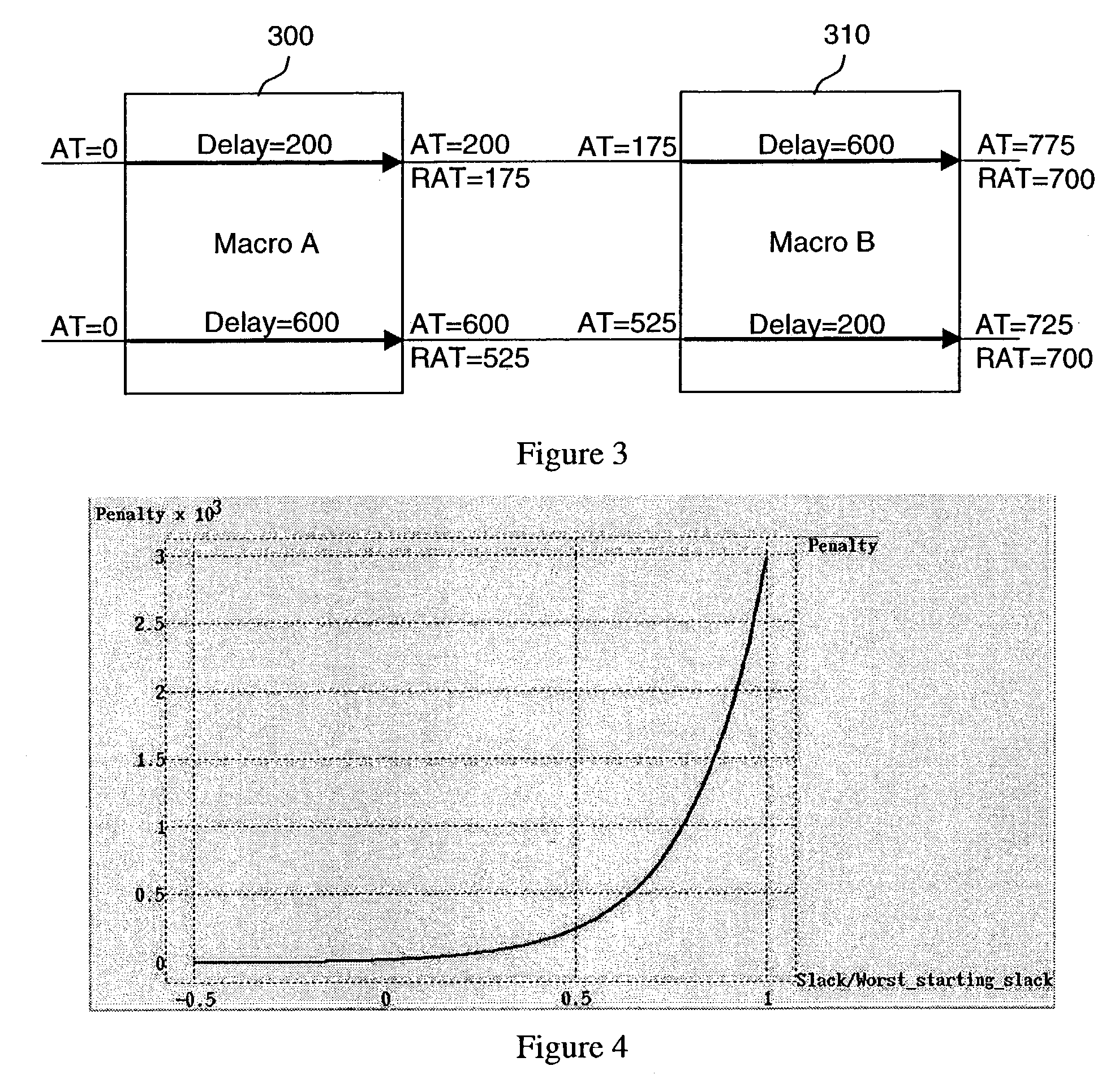

Method of achieving timing closure in digital integrated circuits by optimizing individual macros

InactiveUS7003747B2Computer aided designSoftware simulation/interpretation/emulationEngineeringTiming closure

Disclosed is a method for enhanced efficiency and effectiveness in achieving timing closure of large, complex, high-performance digital integrated circuits. Circuit macros are re-optimized and re-tuned in the timing closure loop by means of a reformulated objective function that allows the optimizer to improve the slack of all signals rather than just the most critical one(s). The incentive to improve the timing of a sub-critical signal is a diminishing function of the criticality of the signal. Thus all signals are improved during the optimization, with the highest incentive to improve on the most critical signals, leading to faster and more effective overall timing closure.

Owner:GLOBALFOUNDRIES INC

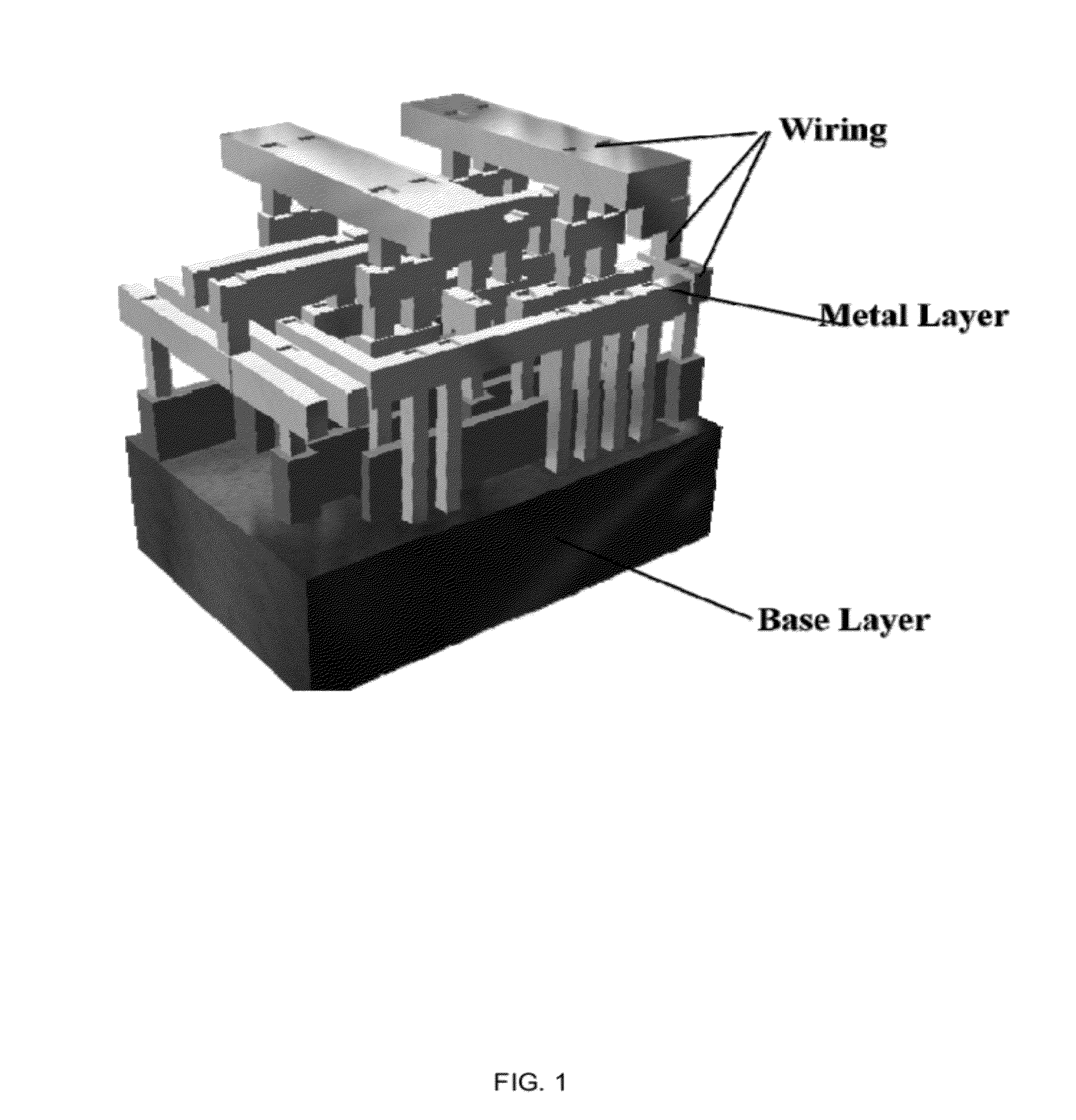

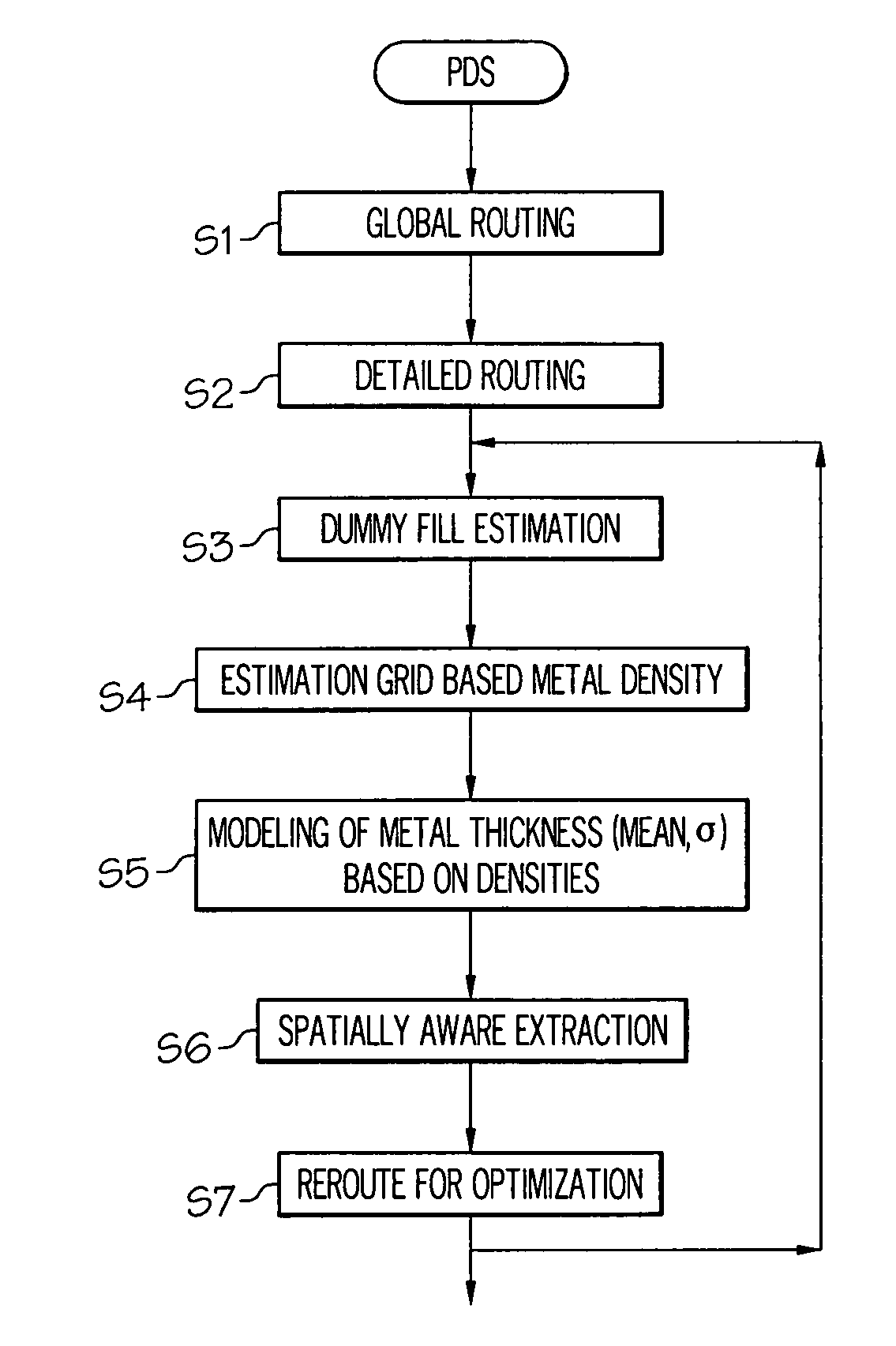

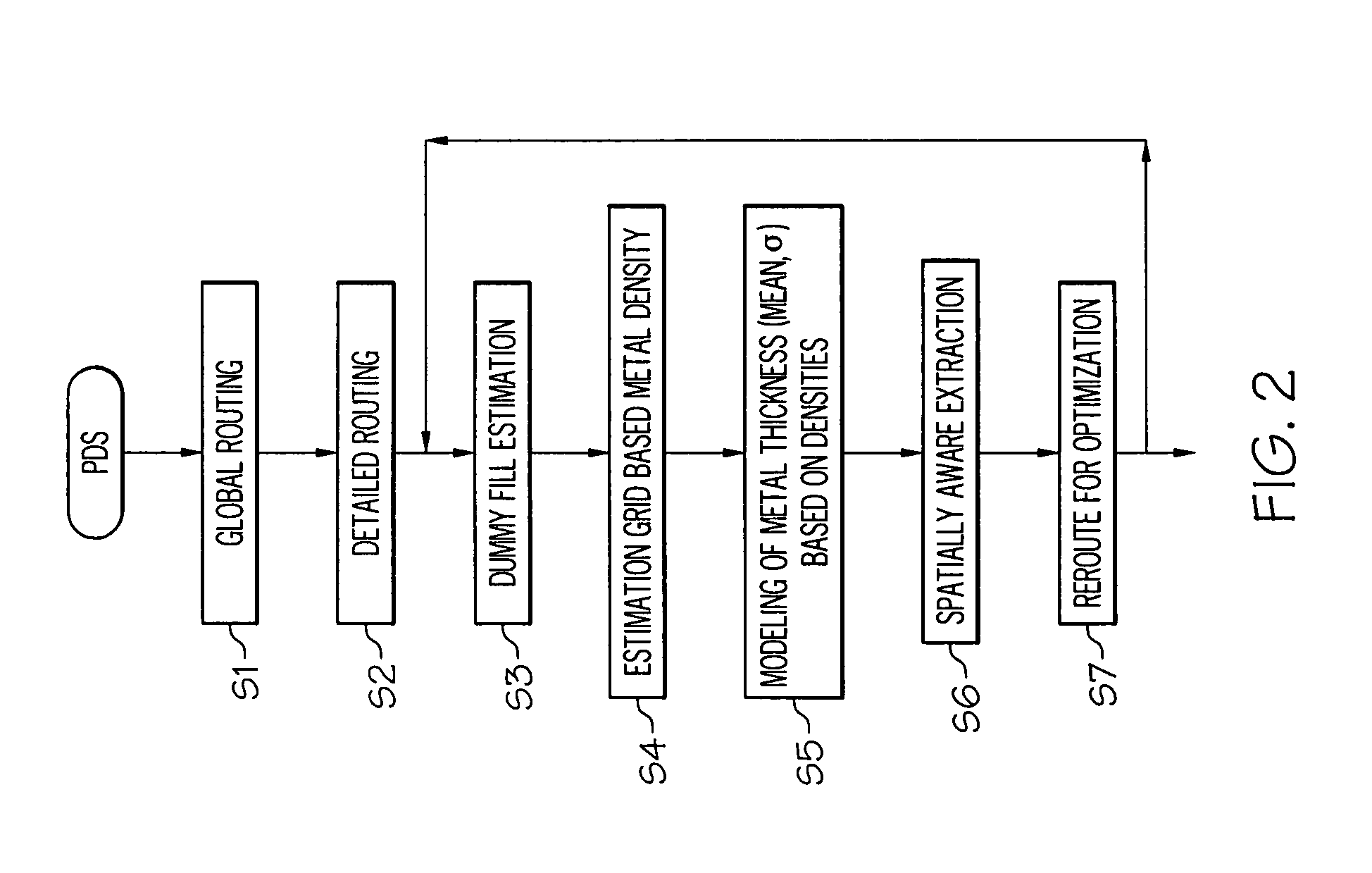

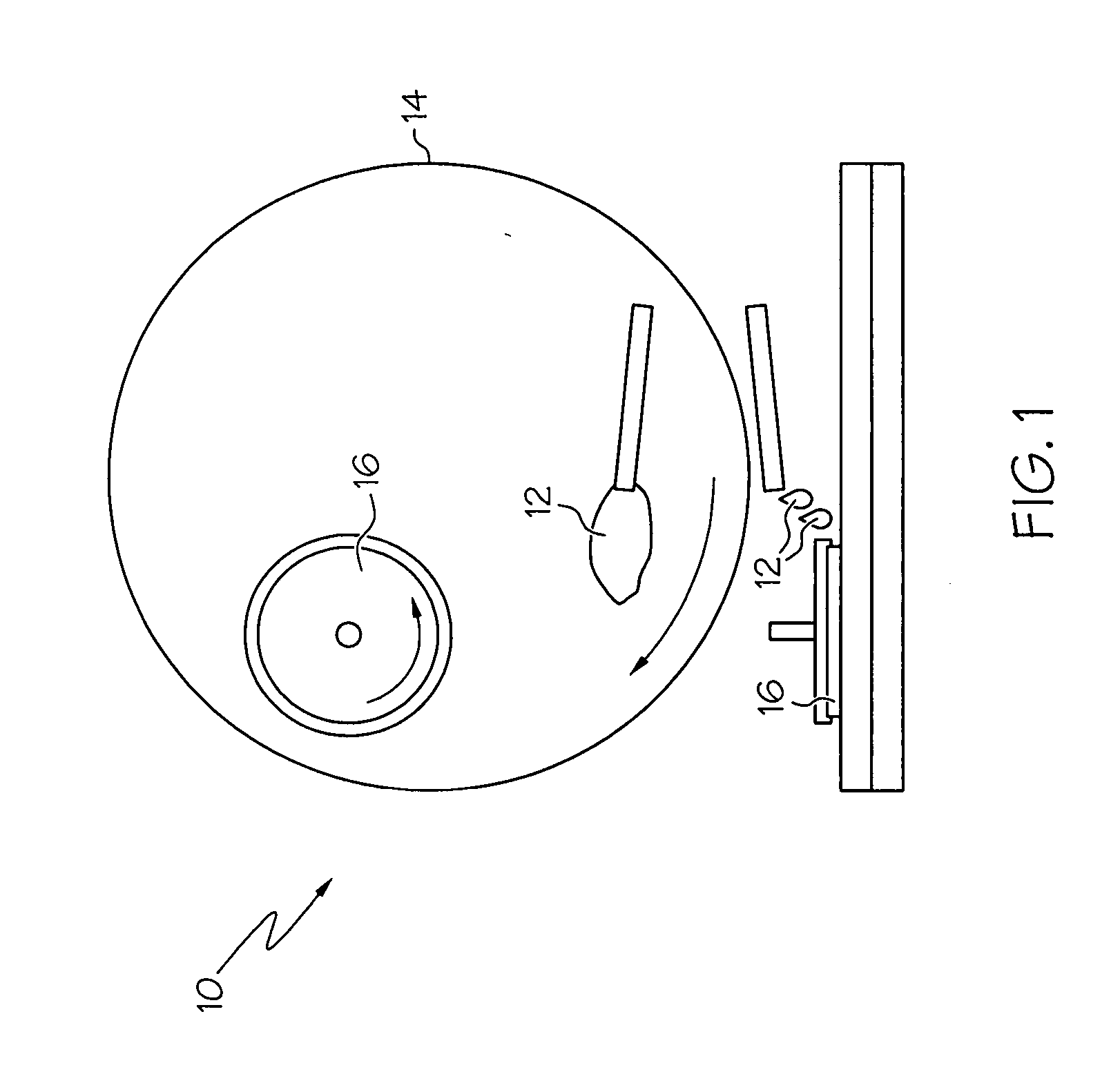

Design stage mitigation of interconnect variability

ActiveUS20070214446A1Reduce the impactReduce impactCAD circuit designTotal factory controlGrid basedEngineering

The present invention provides a method, system and program product for mitigating effects of interconnect variability during a design stage of a chip. Under the technique of the present invention, a global and detailed routing of interconnects of the chip are determined. Thereafter, a dummy fill estimation and a grid based metal density estimation are performed. Then, based on a CMP model, a variable map of metal thicknesses is obtained. Based on the variable map, wiring nets of the chip that are sensitive to metal variability (e.g., that fail to meet timing closure due to metal thickness loss / gain in the CMP process) are identified. These wiring nets are then re-routed for optimization of the chip.

Owner:GLOBALFOUNDRIES US INC

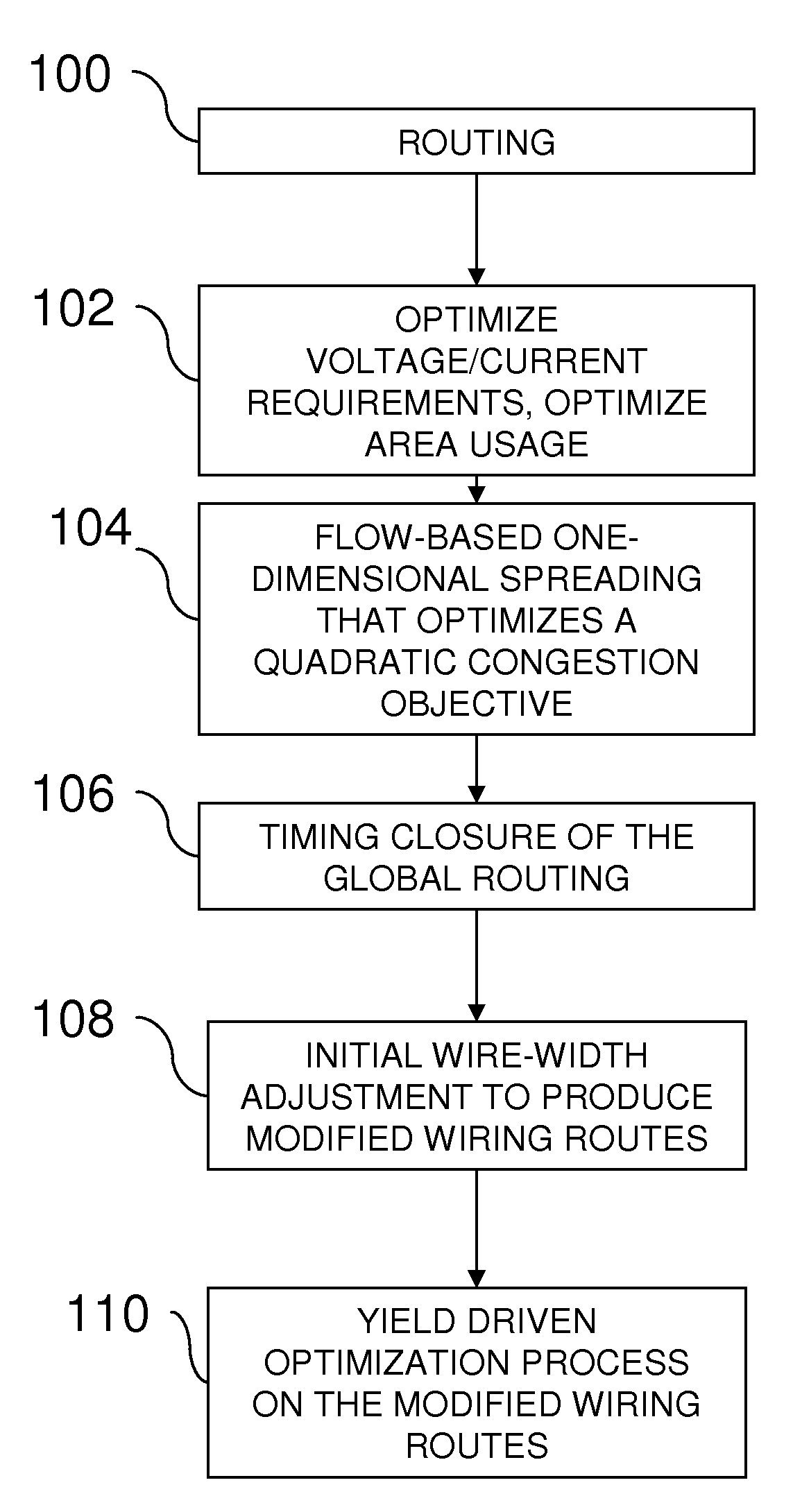

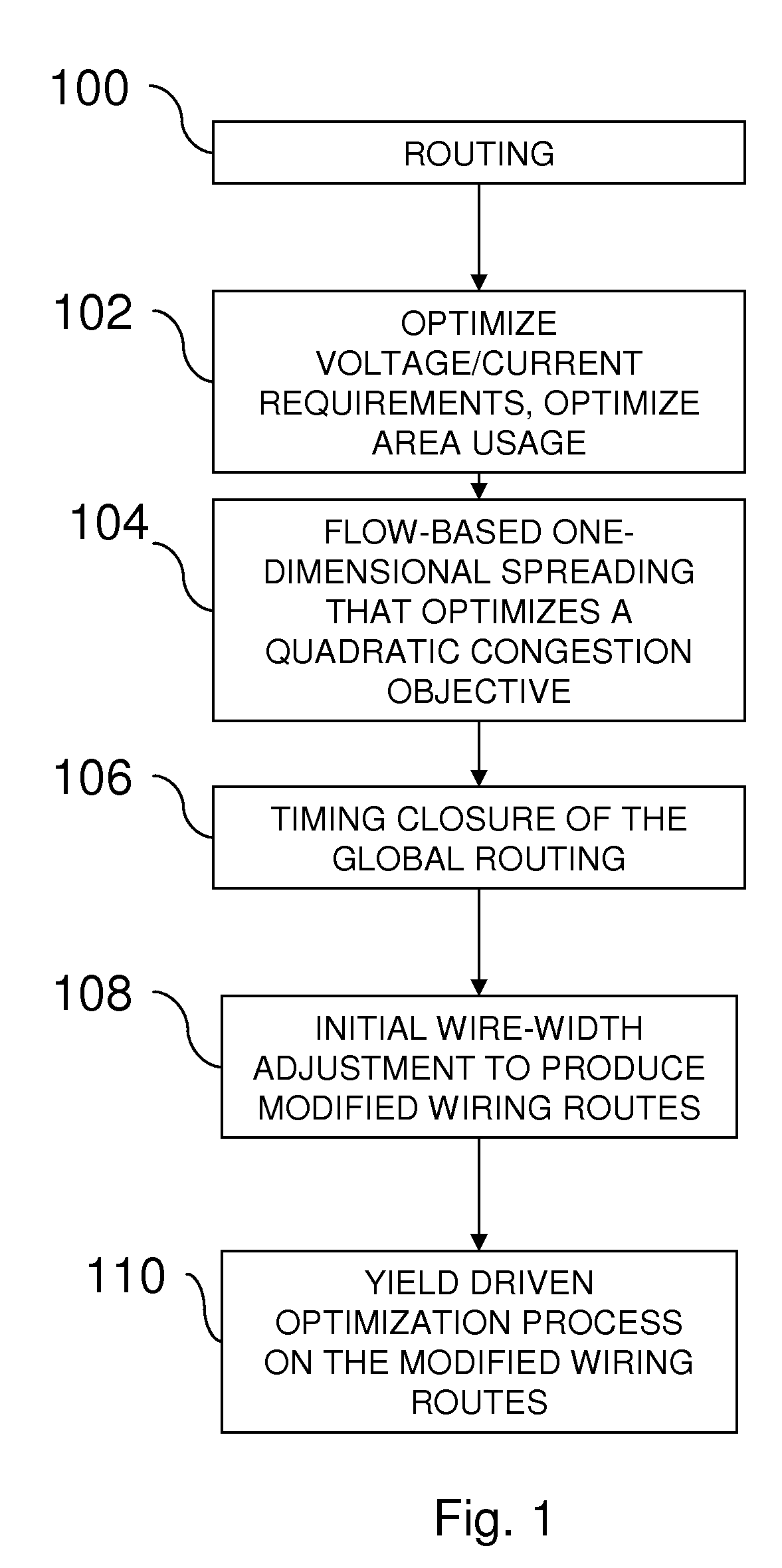

Method for IC wiring yield optimization, including wire widening during and after routing

InactiveUS20100023913A1Good yieldReduce areaComputer aided designSoftware simulation/interpretation/emulationTiming closureIc routing

Owner:GLOBALFOUNDRIES INC

Library sizing

ActiveUS8015517B1Effective timeConfiguration CADCAD circuit designComputer architectureTiming closure

A cell library is automatically designed. An emphasis of a design methodology is on automatic determination of the desired or needed cell sizes and variants. This method exploits different variants on drive strengths, P / N ratios, topology variants, internal buffering, and so forth. The method allows generating libraries that are more suitable for efficient timing closure.

Owner:SILVACO INC

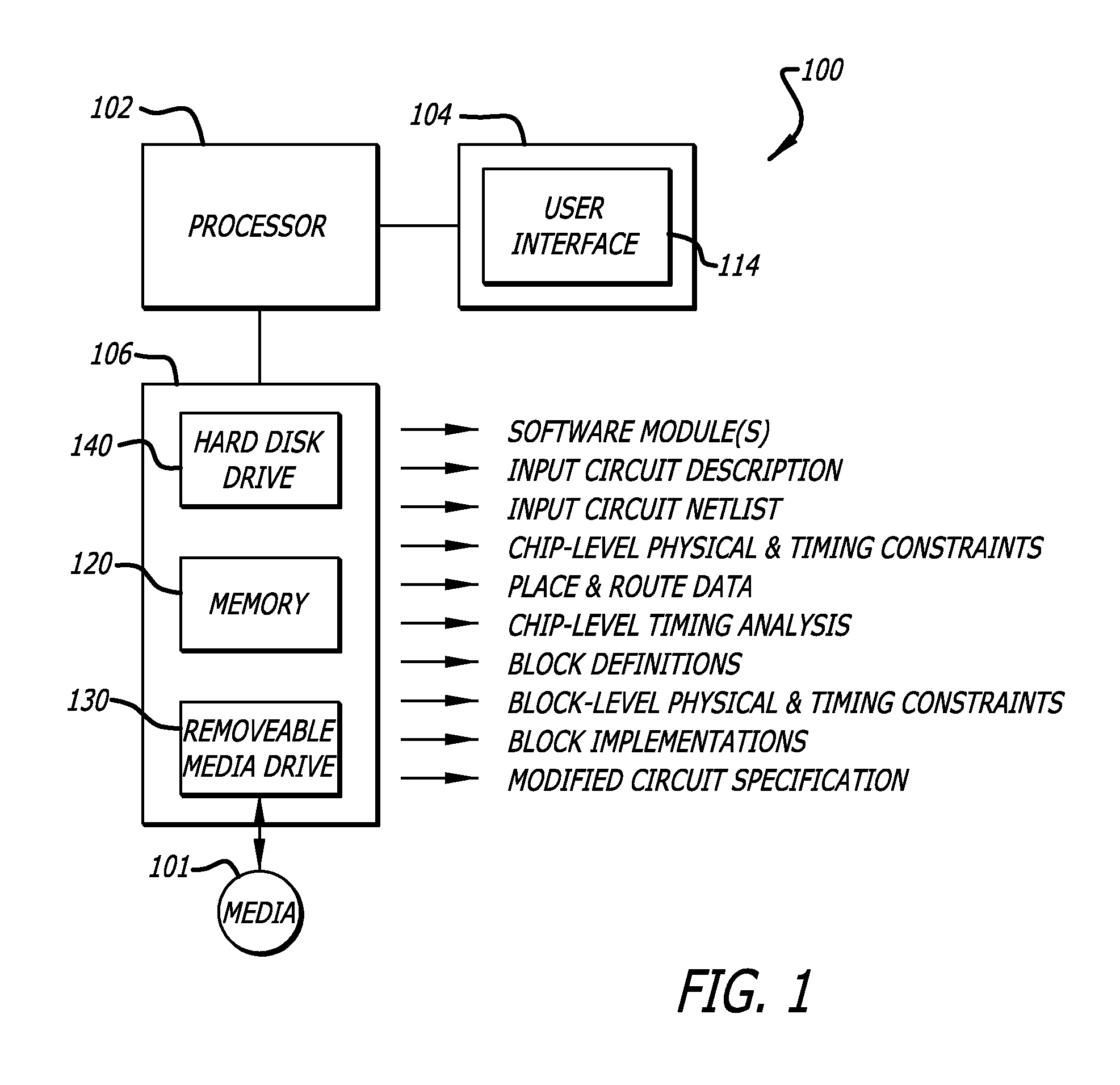

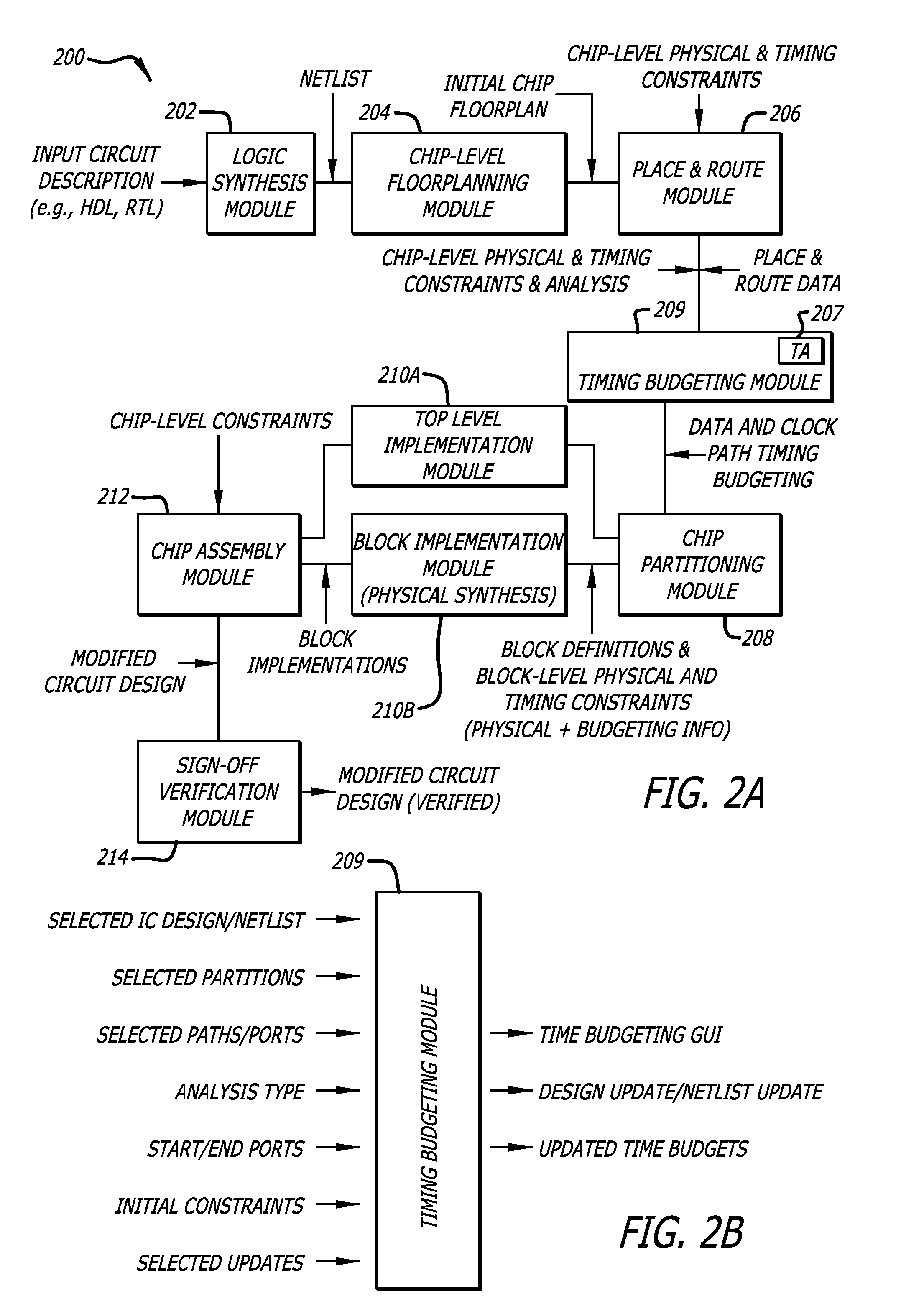

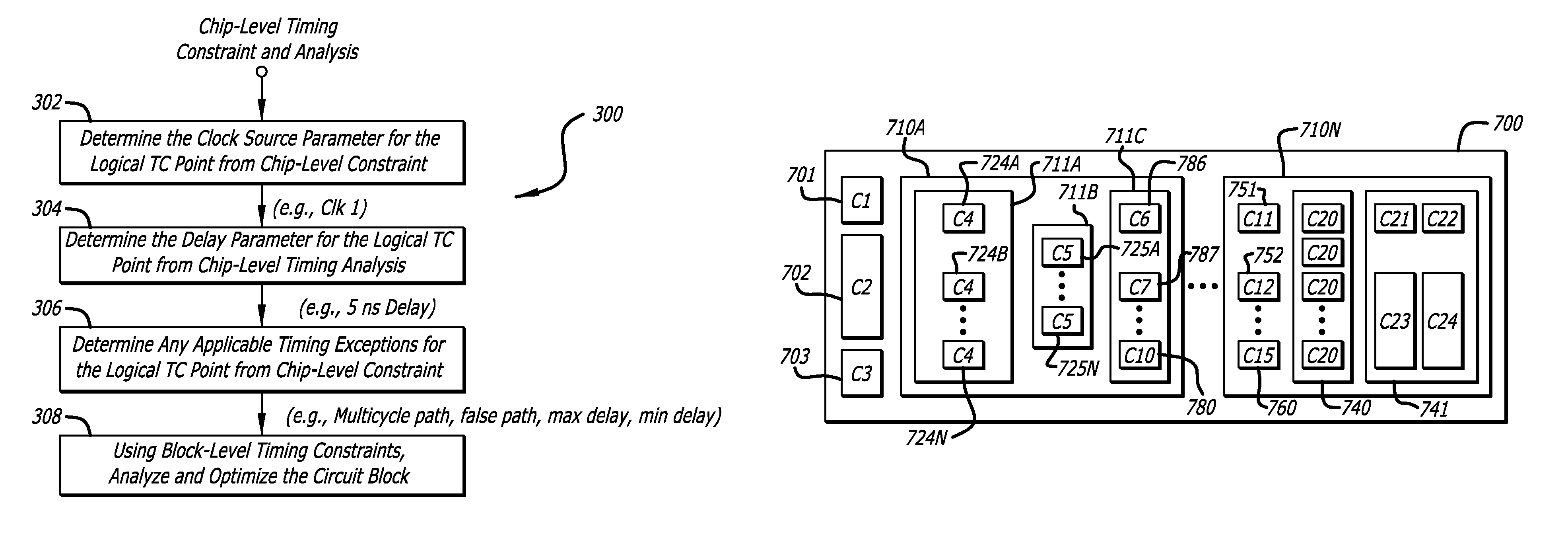

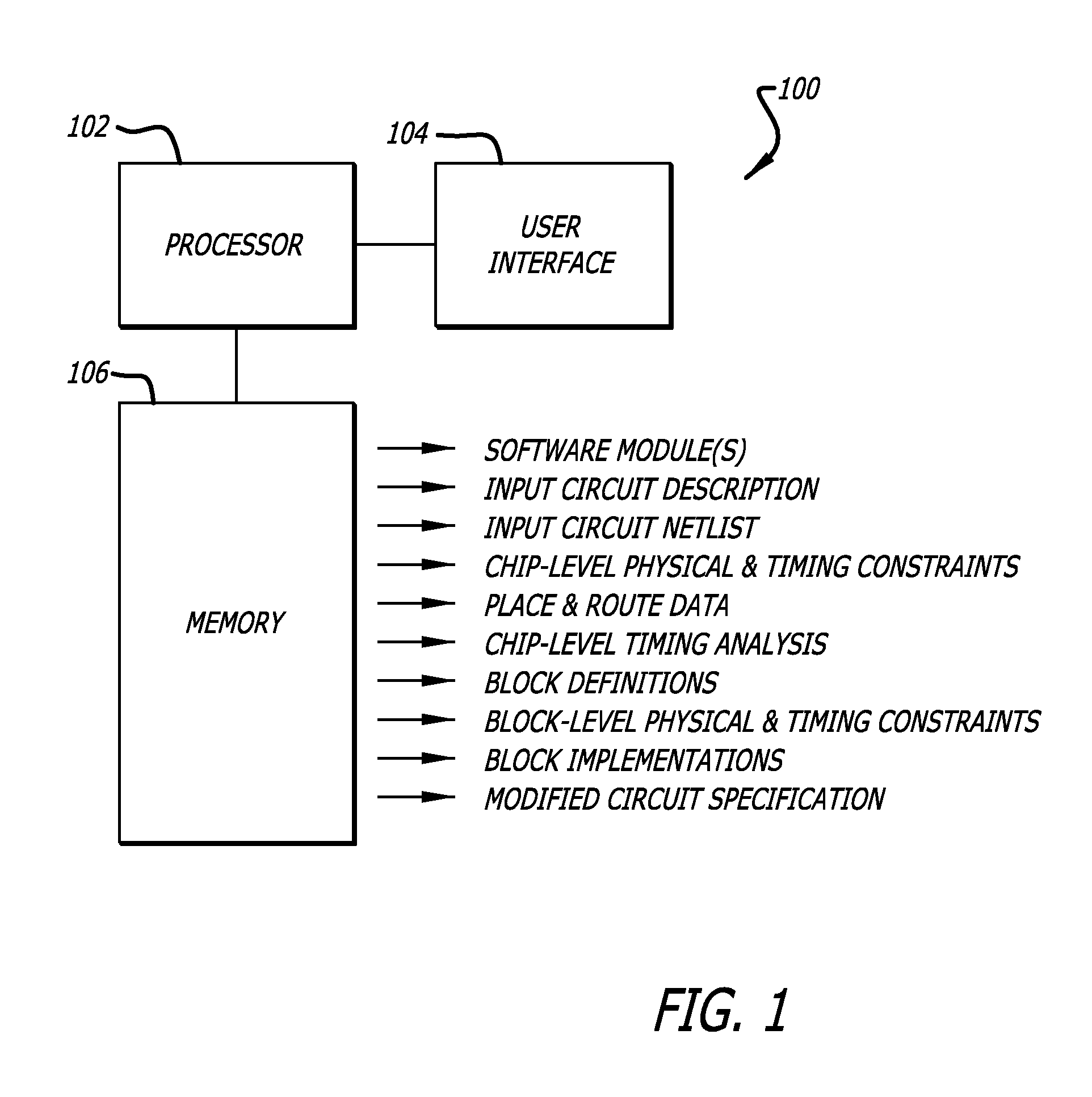

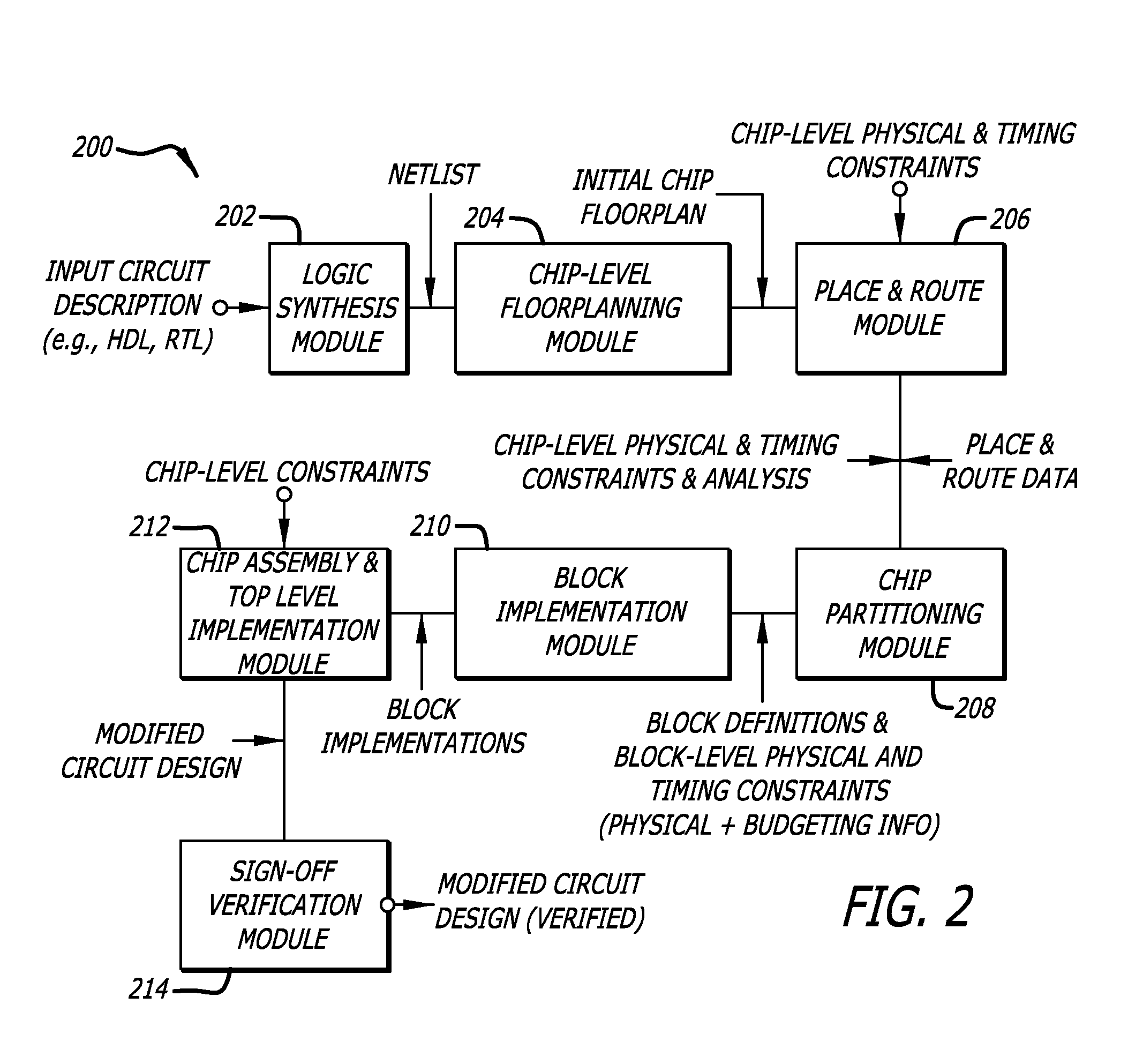

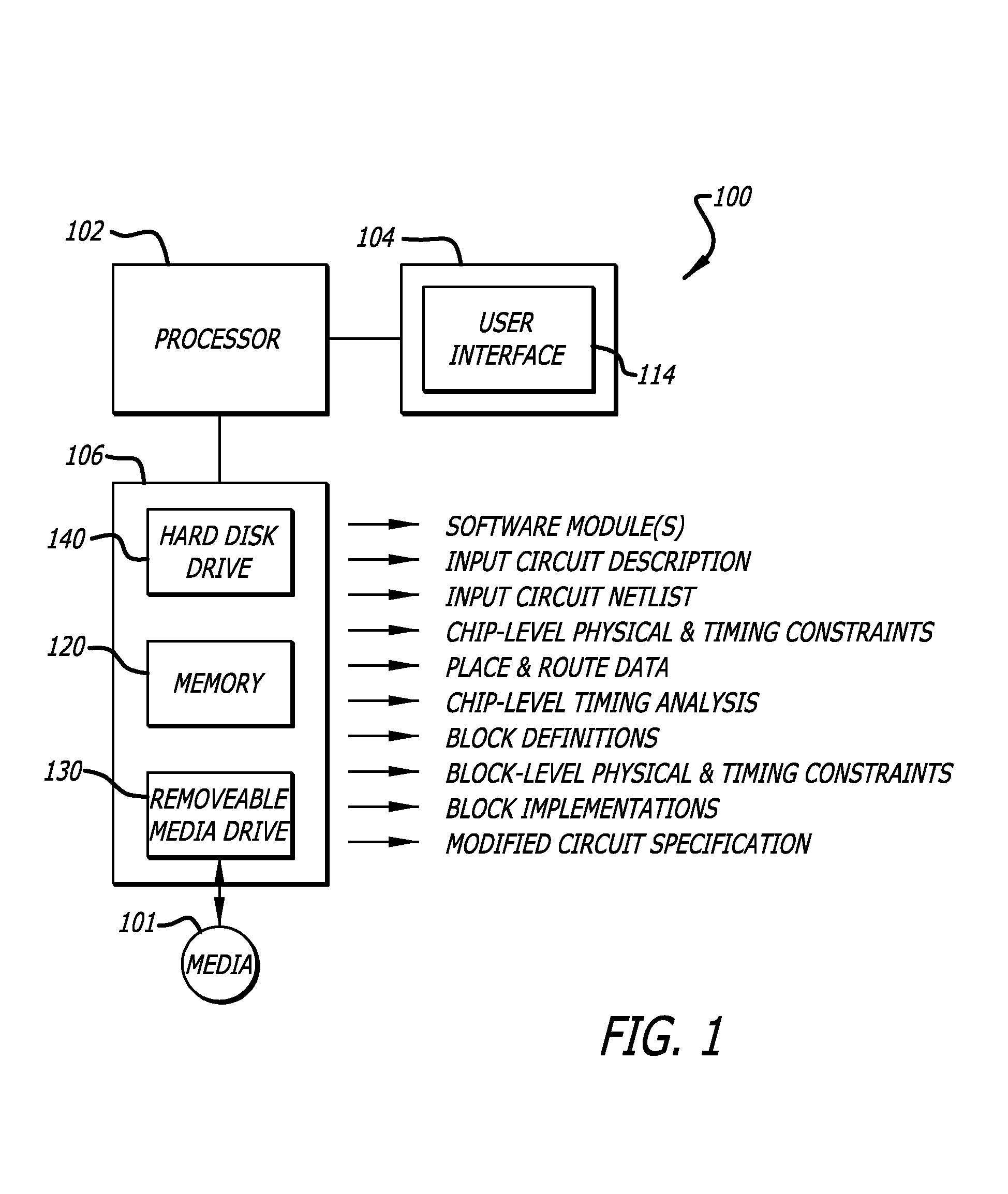

System and method of generating hierarchical block-level timing constraints from chip-level timing constraints

ActiveUS7926011B1Computer programmed simultaneously with data introductionComputer aided designPropagation delayDatapath

A system and method of designing an integrated circuit capable of deriving timing constraints for individual block-level circuits of an integrated circuit that are derived from the chip-level timing constraints and analysis. The block-level timing constraints are in the form of one or more logical timing constraint points at the input and output ports of block-level circuits. Each logical timing constraint points specifies a clock source used to clock data through the port, a delay parameter specifying data propagation delay backward from an input port and forward from an output port, and any timing exception associated with the data path. Using the logical timing constraint point, the circuit design system performs independent timing analysis and optimization of each block-level circuit. The system then reassembles the block-level circuits into a modified chip-level circuit for which timing closure can be achieved.

Owner:CADENCE DESIGN SYST INC

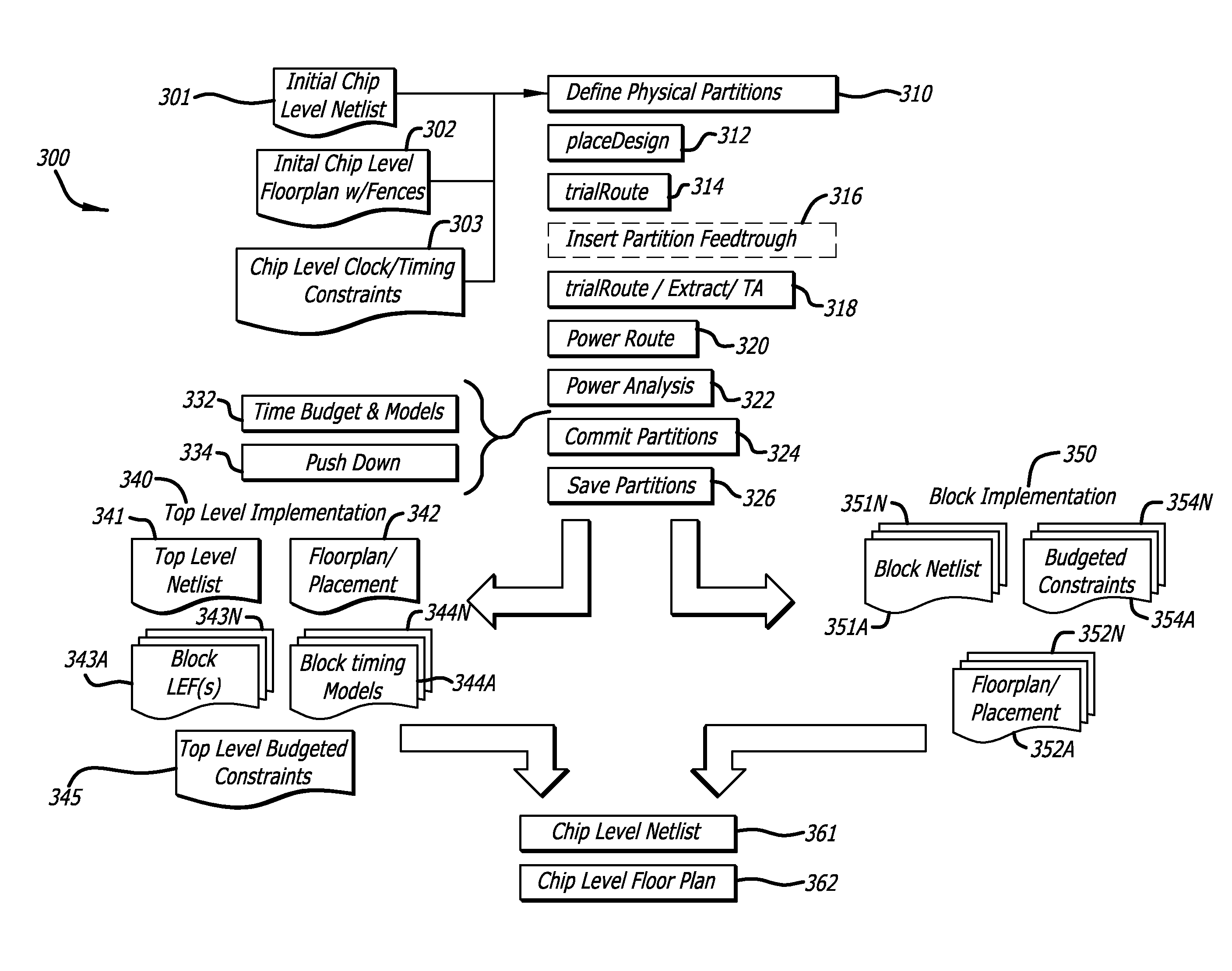

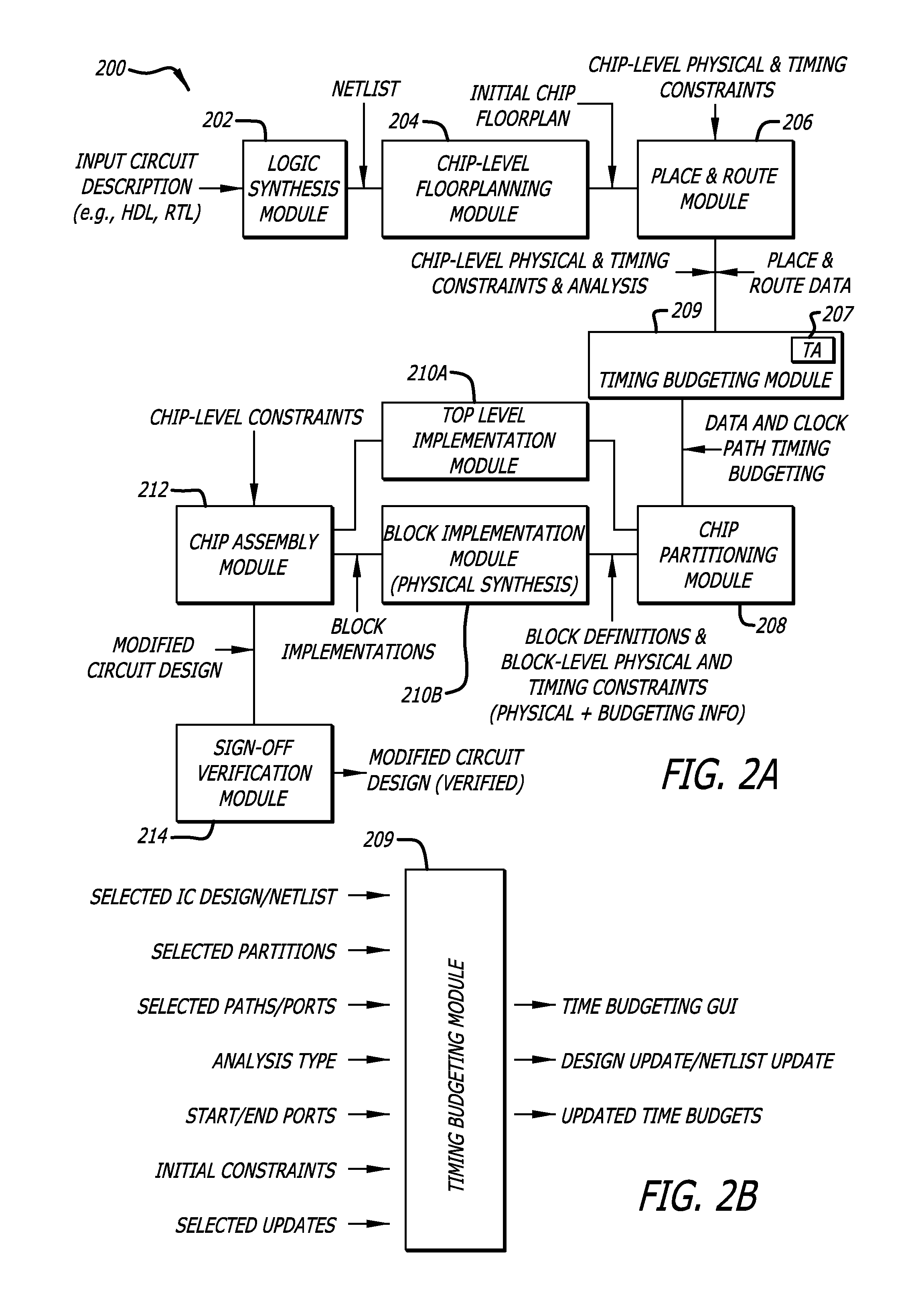

Systems for single pass parallel hierarchical timing closure of integrated circuit designs

ActiveUS8539402B1Computer programmed simultaneously with data introductionCAD circuit designDatapathTiming closure

In one embodiment of the invention, a method includes partitioning an integrated circuit design into a hierarchy of a top level and a plurality of partitions, wherein the top level includes a top level netlist and each partition includes a partition netlist; receiving data path timing budgets and clock path timing budgets for each of the plurality of partitions of the integrated circuit design; and generating a timing budget model of each partition in response to the respective data path timing budgets and clock path timing budgets, wherein each timing budget model includes an intra-partition clock timing constraint for each respective partition for independent implementation of the top level.

Owner:CADENCE DESIGN SYST INC

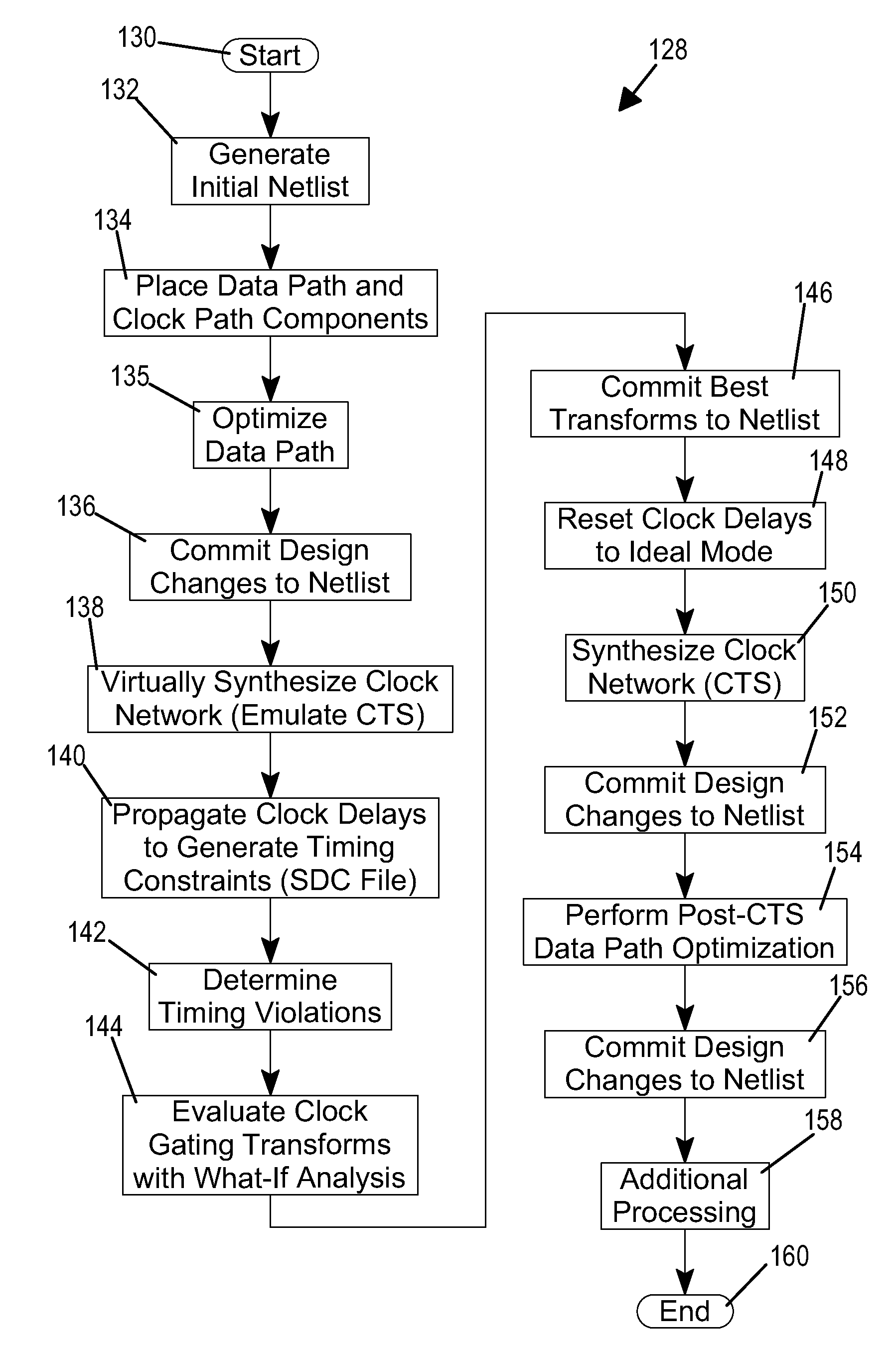

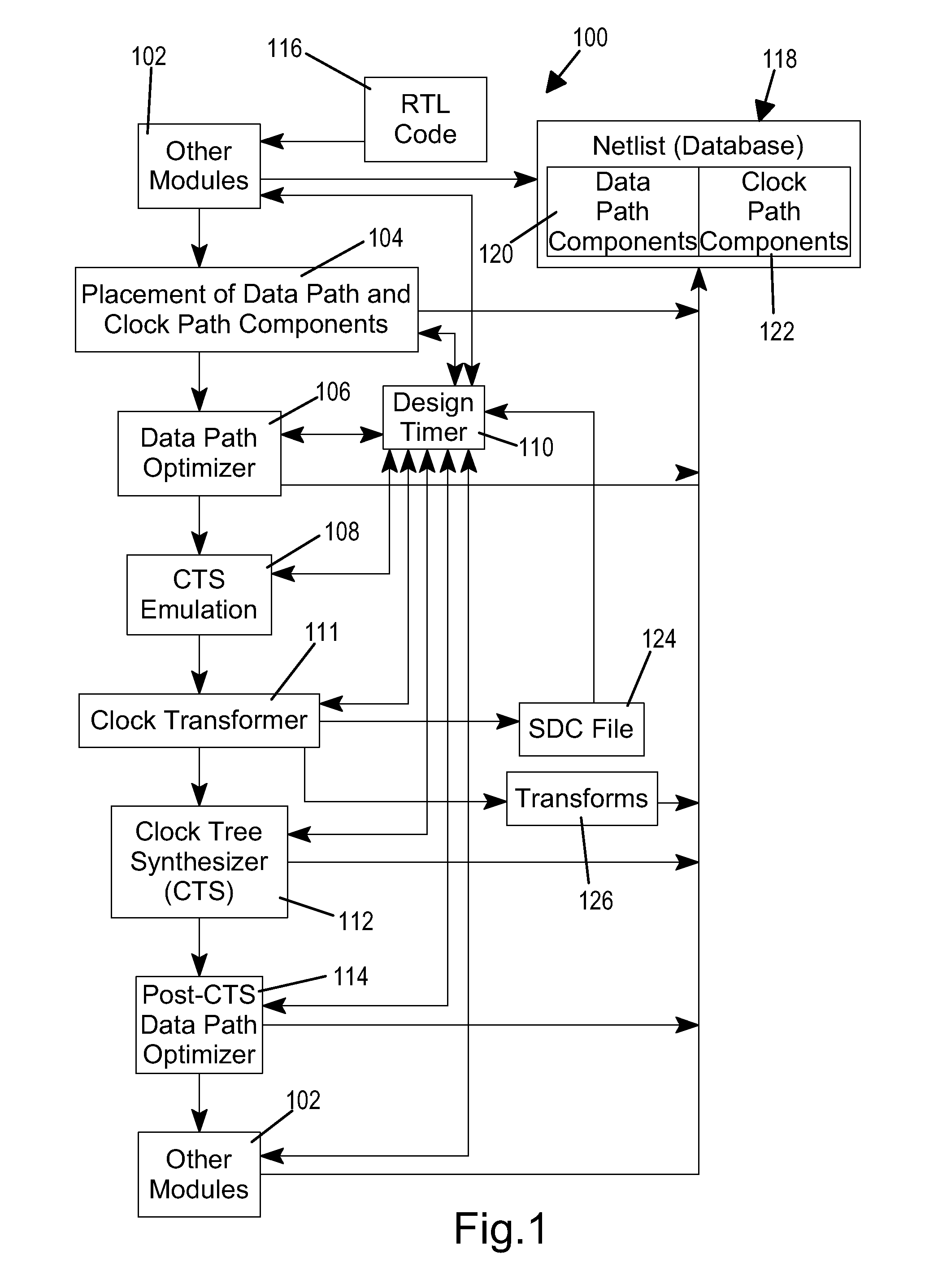

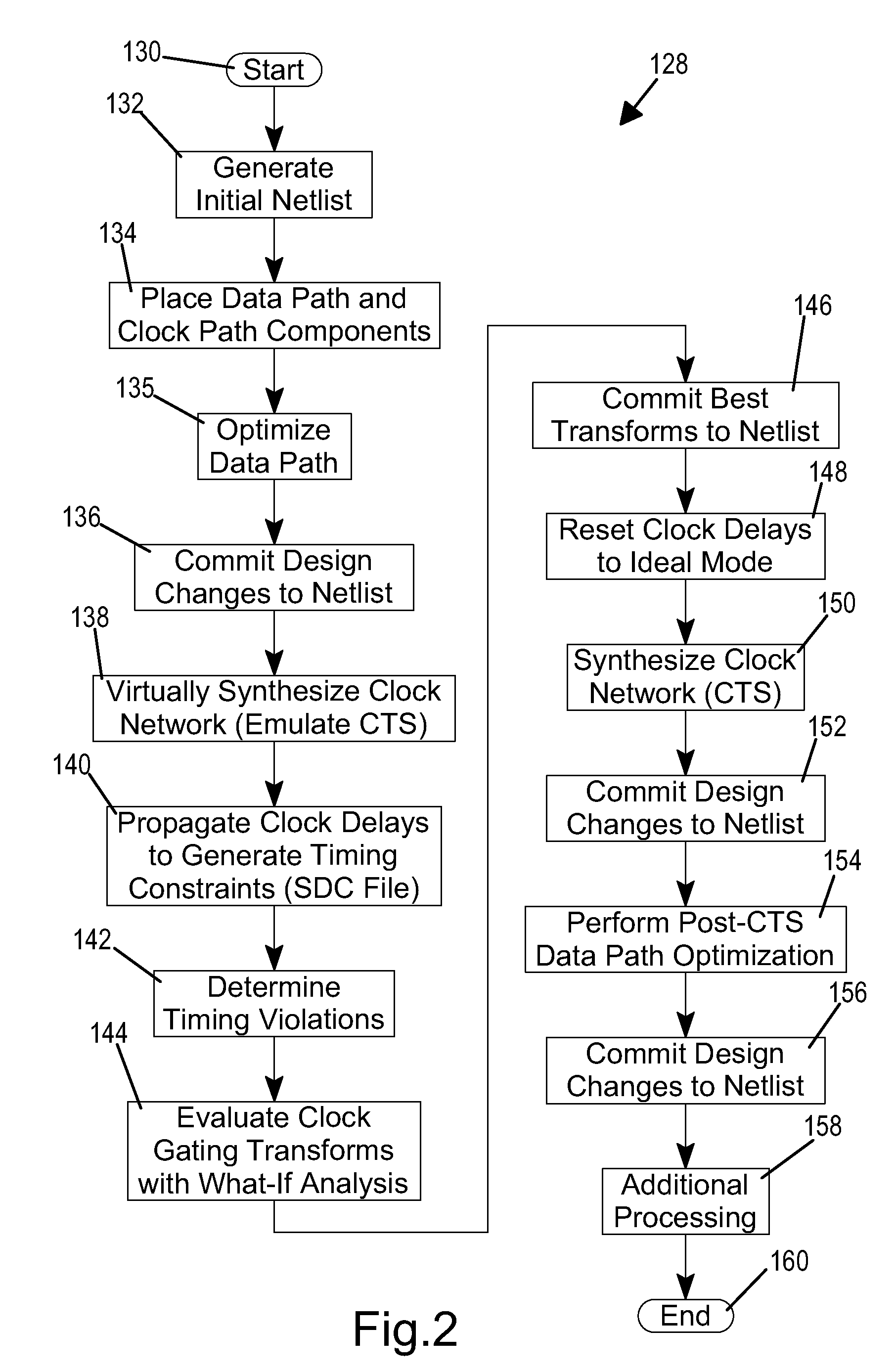

Achieving Clock Timing Closure in Designing an Integrated Circuit

ActiveUS20100070941A1Simple designCAD circuit designSoftware simulation/interpretation/emulationClock networkDatapath

Achieving clock timing closure in designing an integrated circuit involves virtually synthesizing a clock network for the integrated circuit design to generate virtual clock buffering in the clock network before a point in the design flow at which the clock network is actually synthesized and committed to a netlist. Timing violations are determined for clock gates generated by the virtual clock buffering. Clock gating transforms are evaluated for the clock gates having the timing violations, based on recalculated clock and data path delays, to incrementally virtually synthesize the clock network. The clock gating transforms that result in the best timing gains are committed to the netlist. The clock network is then actually synthesized for the integrated circuit design, and design changes, due to the actual clock network synthesis, are committed to the netlist.

Owner:CADENCE DESIGN SYST INC

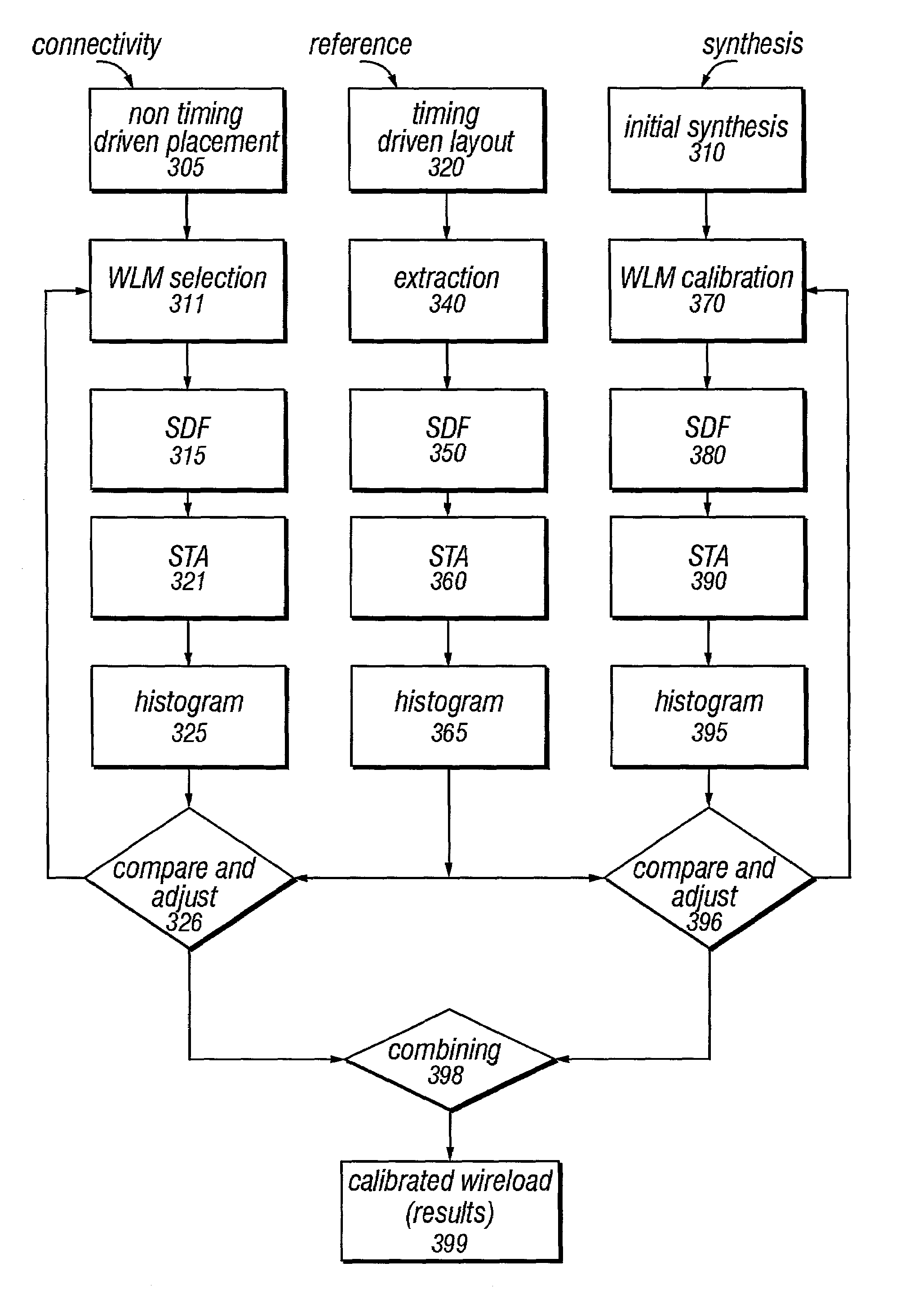

Calibrating a wire load model for an integrated circuit

InactiveUS7149991B2Computer aided designSoftware simulation/interpretation/emulationElectronic systemsLoad model

A method is taught for determining a calibrated wire load model. The calibrated wire load model can be used to reach timing closure for an integrated circuit. The method includes; determining a reference timing description; determining a wire load model based on synthesis; determining a wire load model based connectivity; comparing the wire load model based on connectivity to the reference timing description. The method teaches adjusting the wire load model based on connectivity to determine a wire load model which faciliates timing closure. The method also teaches comparing the wire load model (based on synthesis) with the reference timing description. The disclosure contemplates a computer program product based upon the method taught. The disclosure further contemplates an integrated circuit designed based on the method taught. In another embodiment a computer system or another electronic system includes an integrated circuit designed by the method taught.

Owner:RENESAS ELECTRONICS AMERICA