Patents

Literature

107 results about "Virtual clock" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Virtual clock definition For paths going through a primary input port, the tool needs to know the frequency of the clock driving the signal in order to create a proper timing path. Similarly for output ports, the tool needs to know the frequency of the flop capturing the signal. This is why we define a virtual clock.

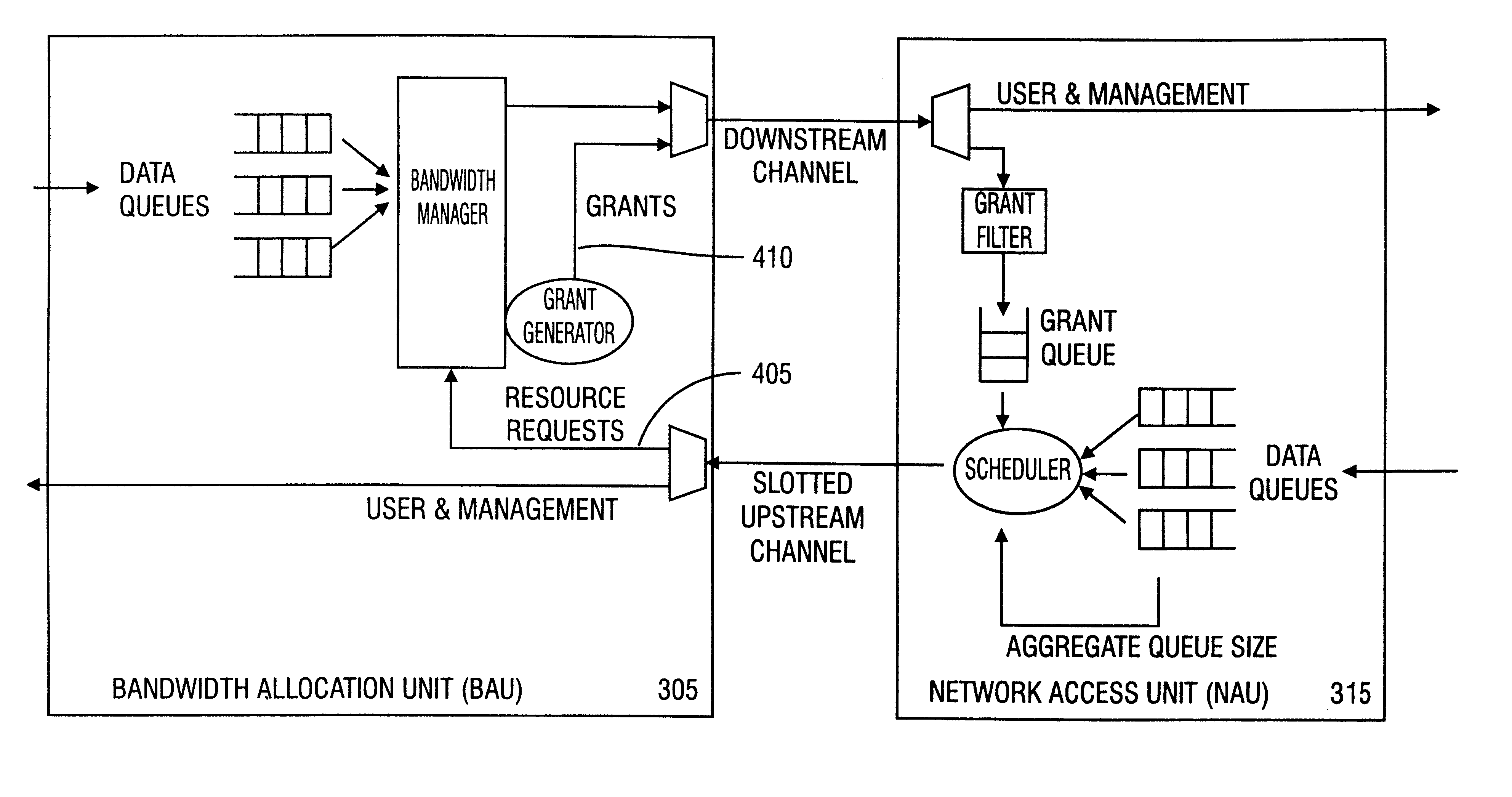

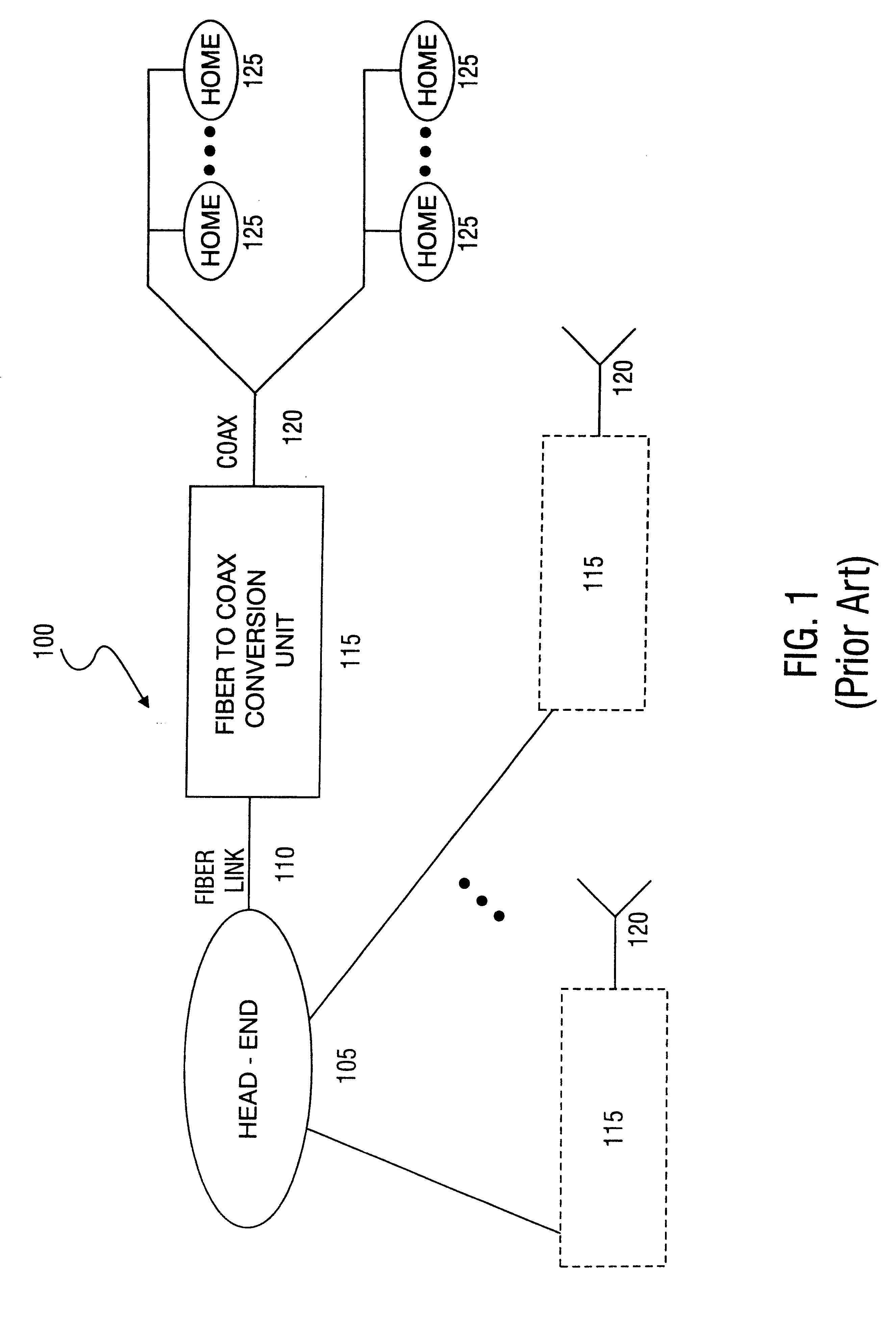

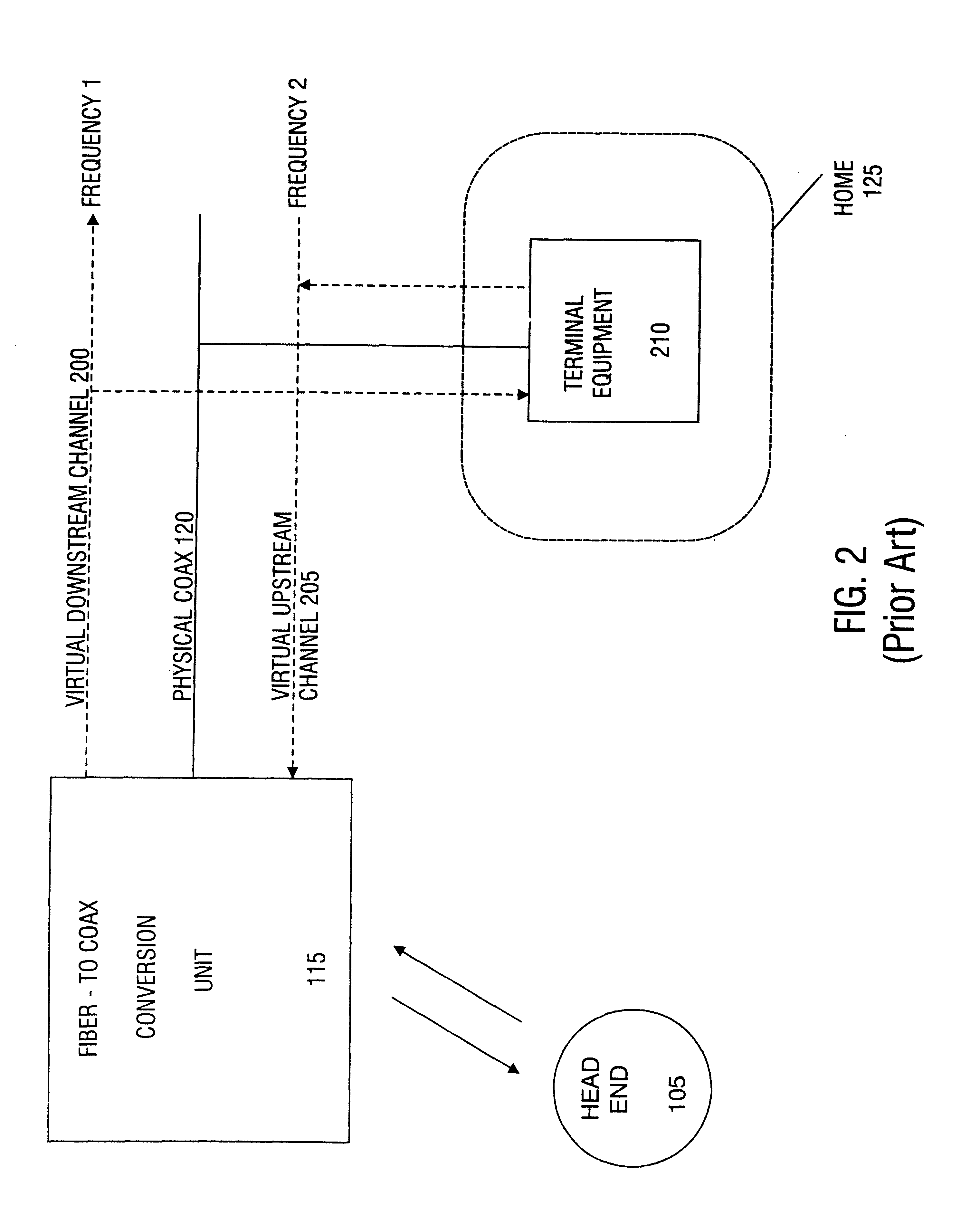

Method for providing integrated packet services over a shared-media network

InactiveUS6563829B1Good serviceError preventionTransmission systemsQos quality of serviceExchange network

A method in accordance with the invention allocates bandwidth, fairly and dynamically, in a shared-media packet switched network to accommodate both elastic and inelastic applications. The method, executed by or in a head-end controller, allocates bandwidth transmission slots, converting requests for bandwidth into virtual scheduling times for granting access to the shared media. The method can use a weighted fair queuing algorithm or a virtual clock algorithm to generate a sequence of upstream slot / transmission assignment grants. The method supports multiple quality of service (QoS) classes via mechanisms which give highest priority to the service class with the most stringent QoS requirements.

Owner:AMERICAN CAPITAL FINANCIAL SERVICES

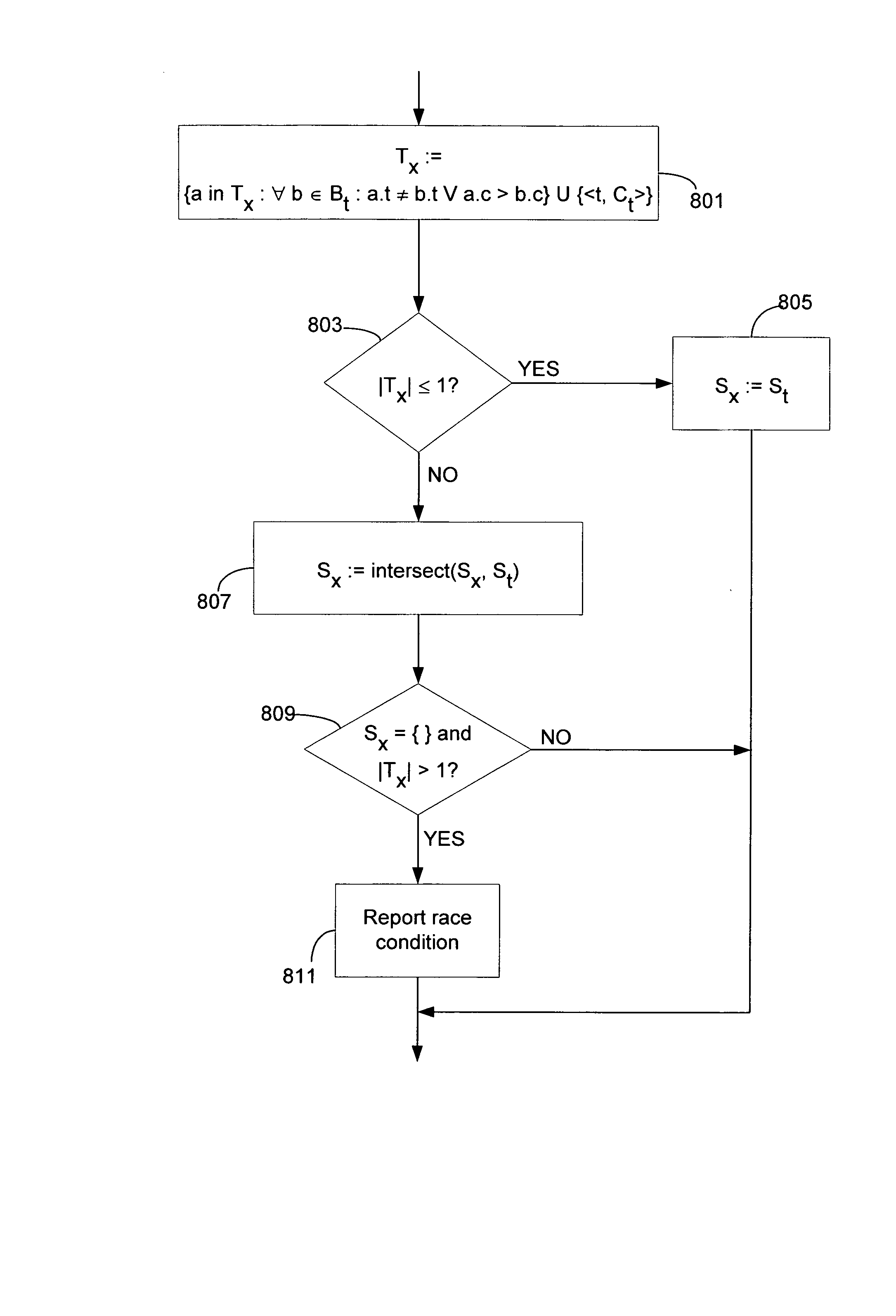

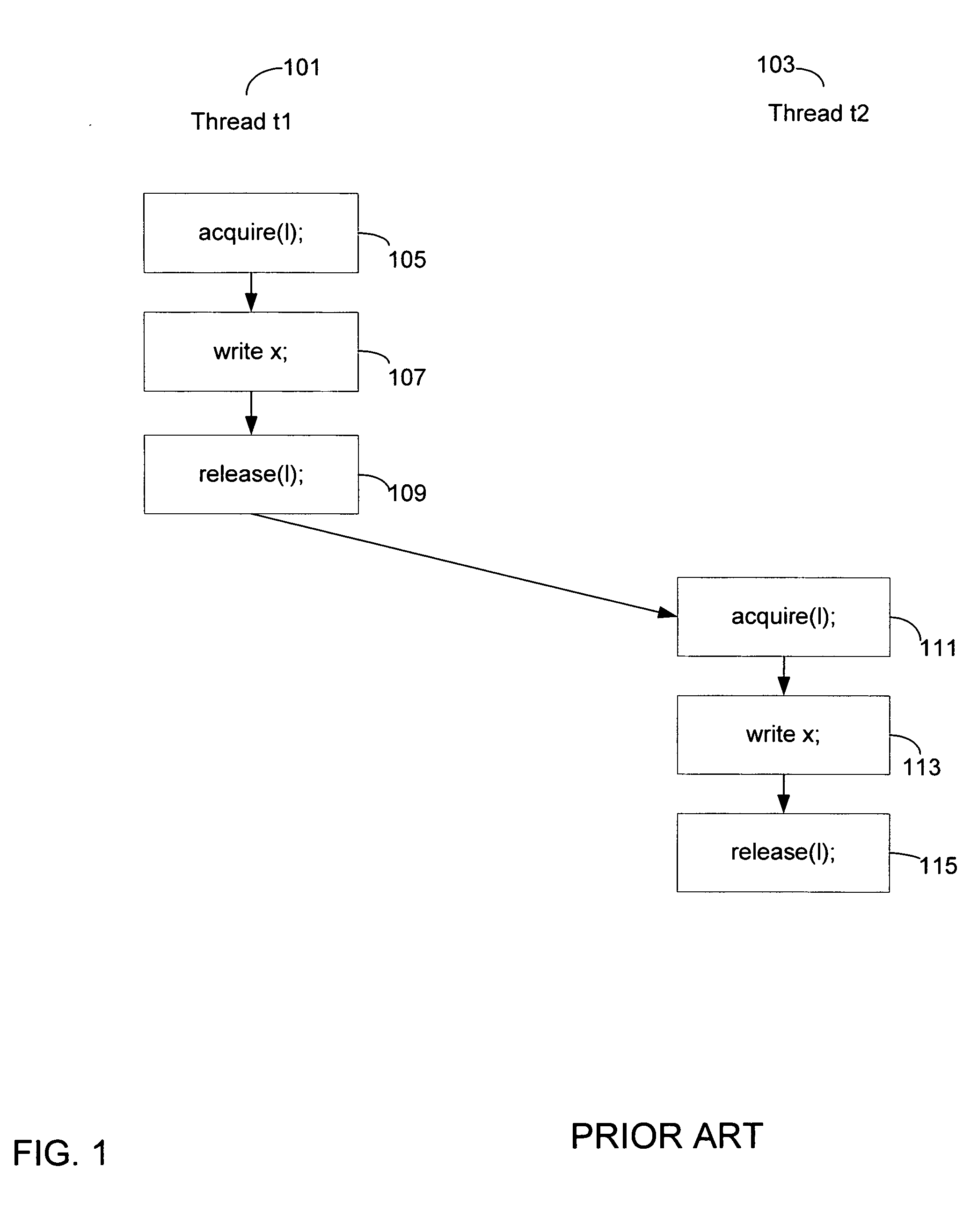

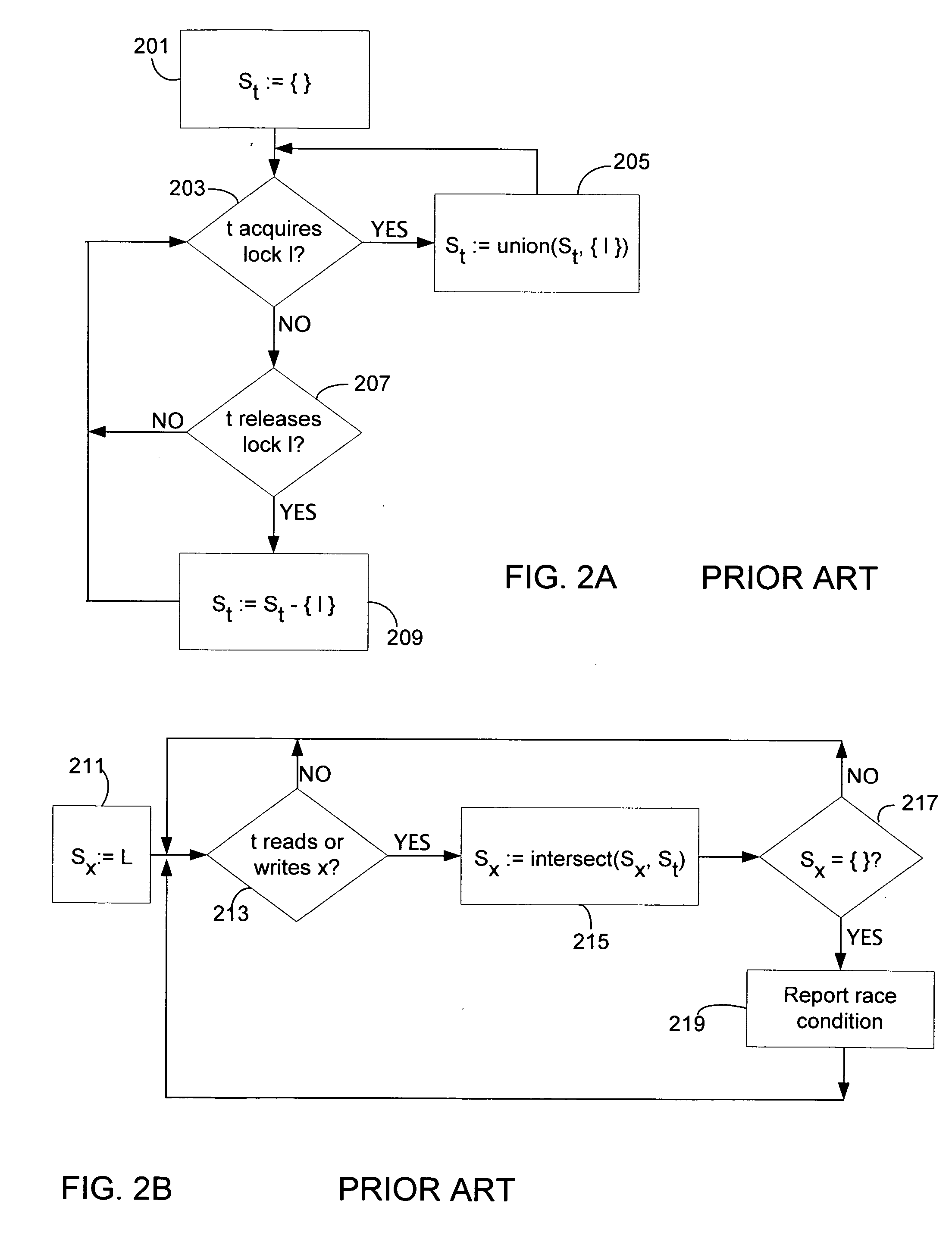

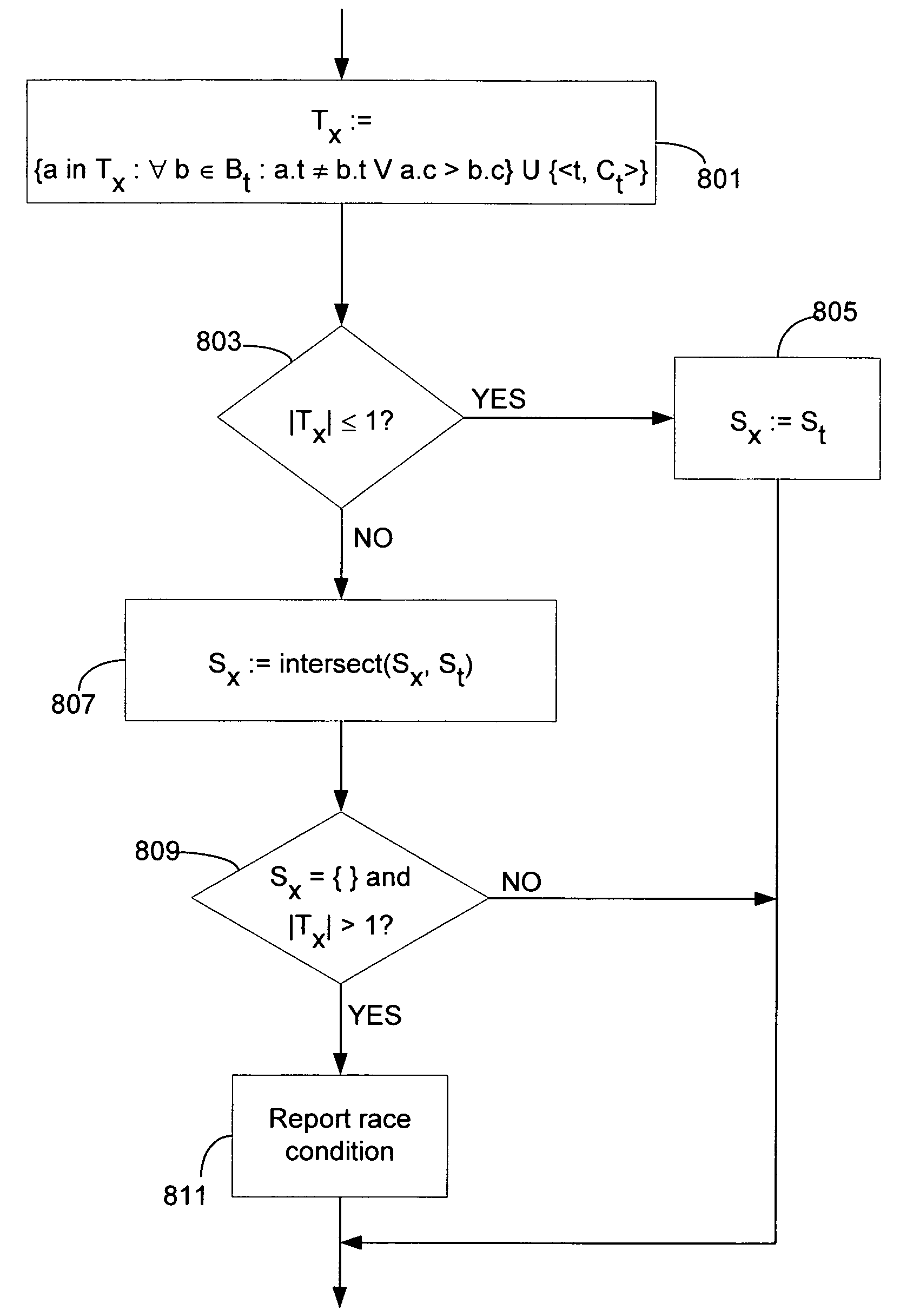

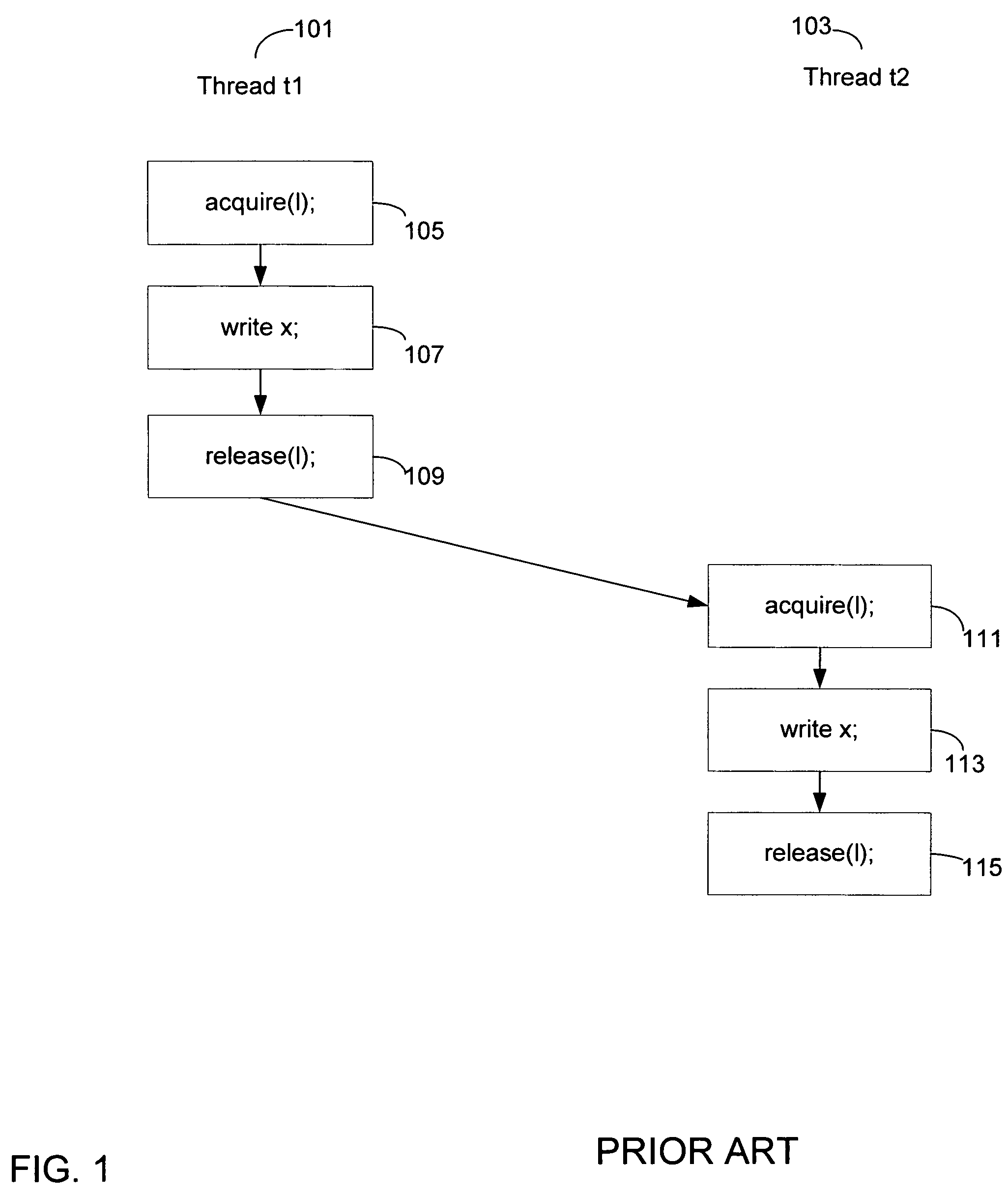

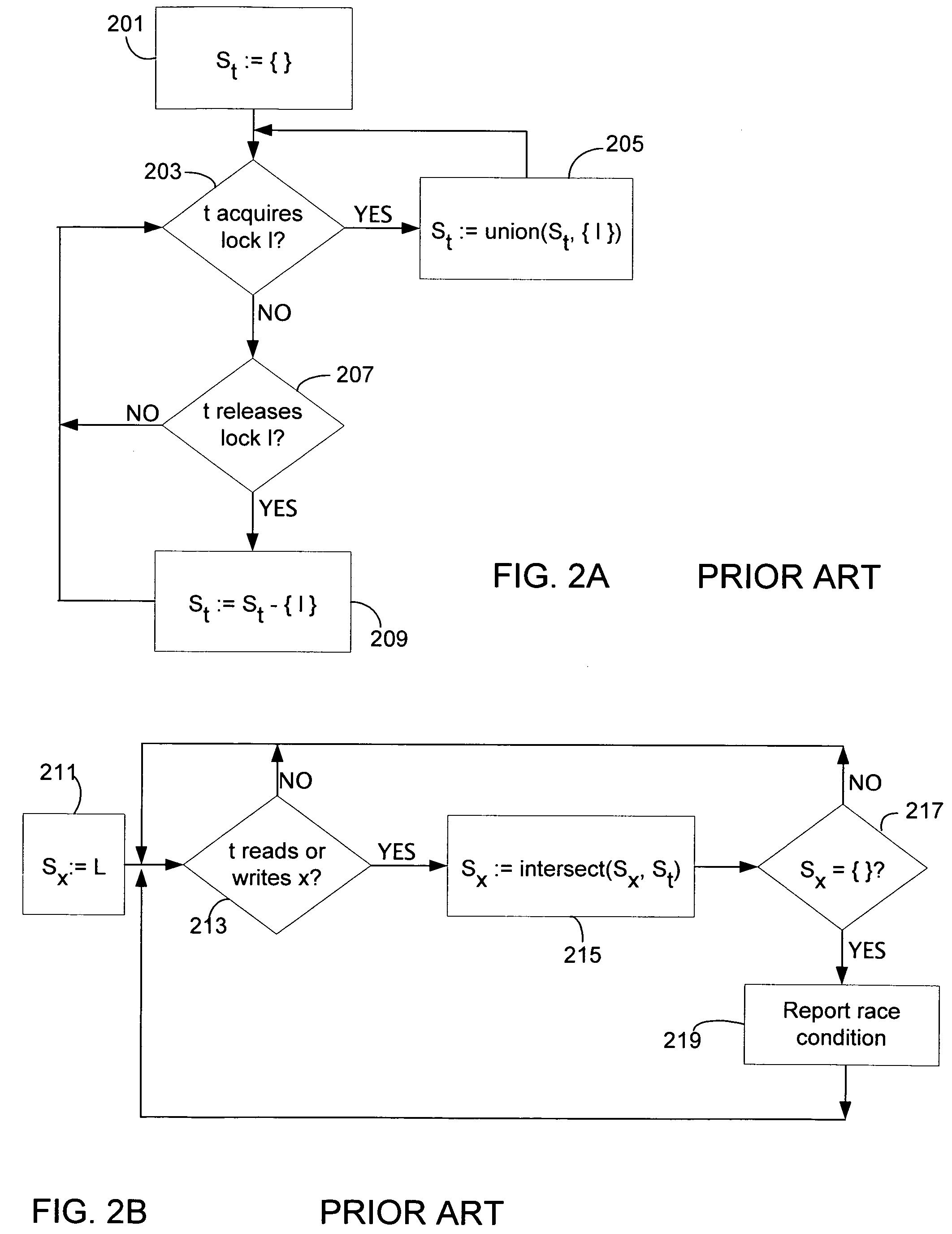

Method and system for detecting potential races in multithreaded programs

A dynamic race detection system and method overcomes drawbacks of previous lockset approaches, which may produce many false positives, particularly in the context of thread fork / join and asynchronous calls. For each shared memory location, a set of locks that are protecting the location and a set of concurrent thread segments that are accessing the location are maintained. To maintain these sets, each thread maintains a set of locks it is currently holding and a set of thread segments ordered before its current thread segment. Each thread also maintains a virtual clock that is incremented when it forks a second thread. A thread segment is a pair comprising a thread identifier and a virtual clock value. A data race is reported when the lockset for a particular shared memory location is empty and the cardinality of the set of concurrent threads for that memory location is greater than one.

Owner:MICROSOFT TECH LICENSING LLC

Method and system for detecting potential races in multithreaded programs

A dynamic race detection system and method overcomes drawbacks of previous lockset approaches, which may produce many false positives, particularly in the context of thread fork / join and asynchronous calls. For each shared memory location, a set of locks that are protecting the location and a set of concurrent thread segments that are accessing the location are maintained. To maintain these sets, each thread maintains a set of locks it is currently holding and a set of thread segments ordered before its current thread segment. Each thread also maintains a virtual clock that is incremented when it forks a second thread. A thread segment is a pair comprising a thread identifier and a virtual clock value. A data race is reported when the lockset for a particular shared memory location is empty and the cardinality of the set of concurrent threads for that memory location is greater than one.

Owner:MICROSOFT TECH LICENSING LLC

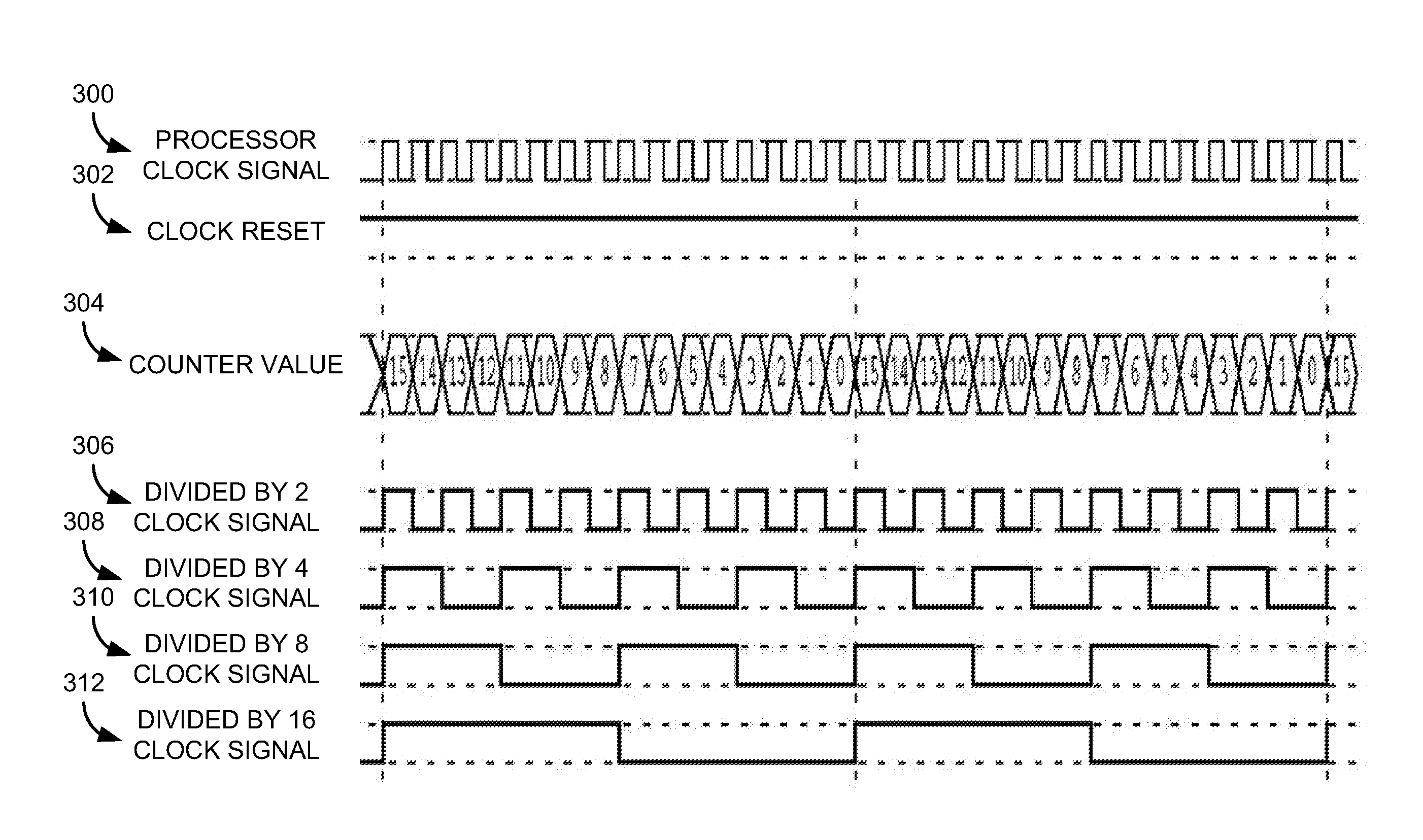

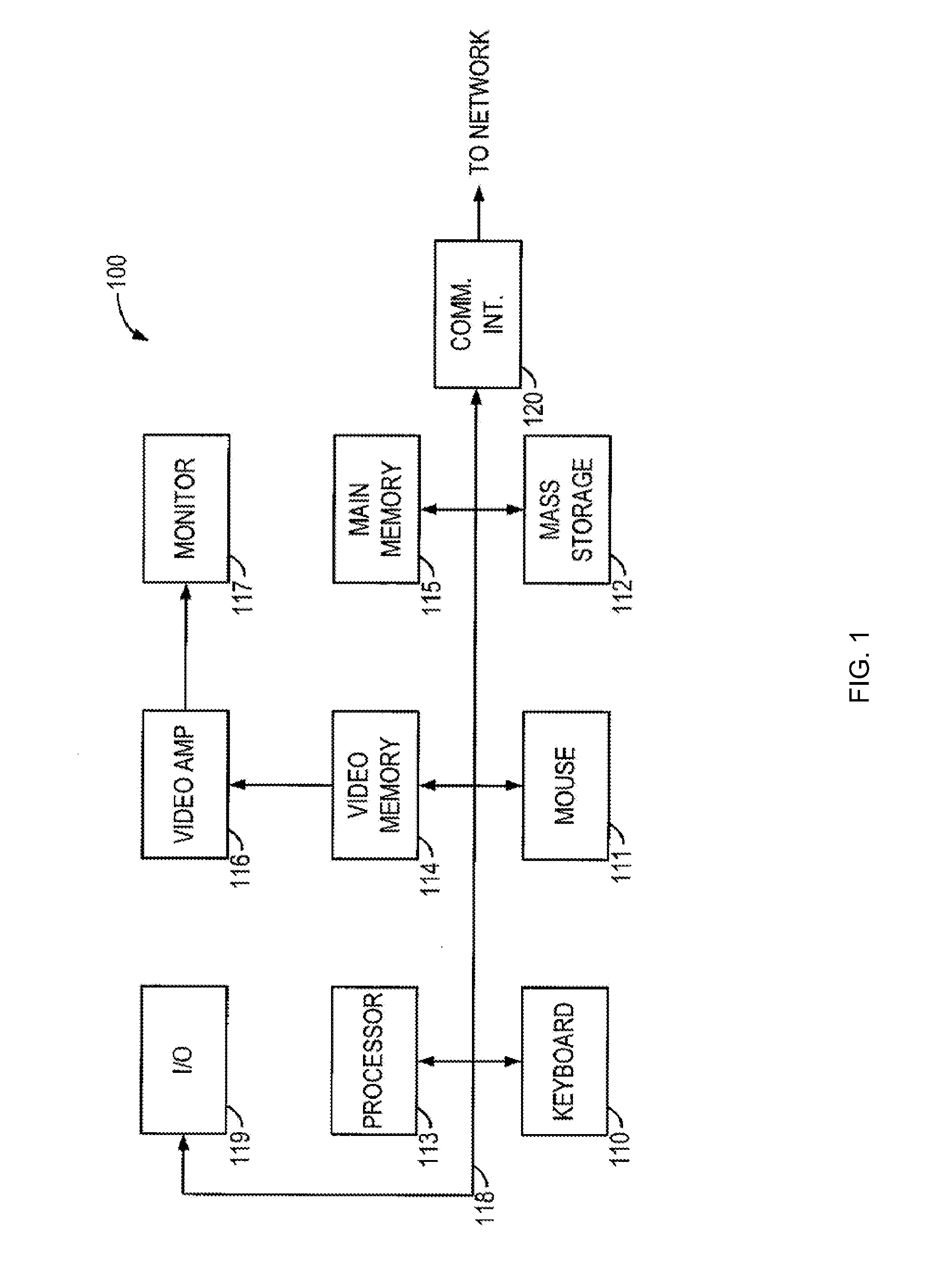

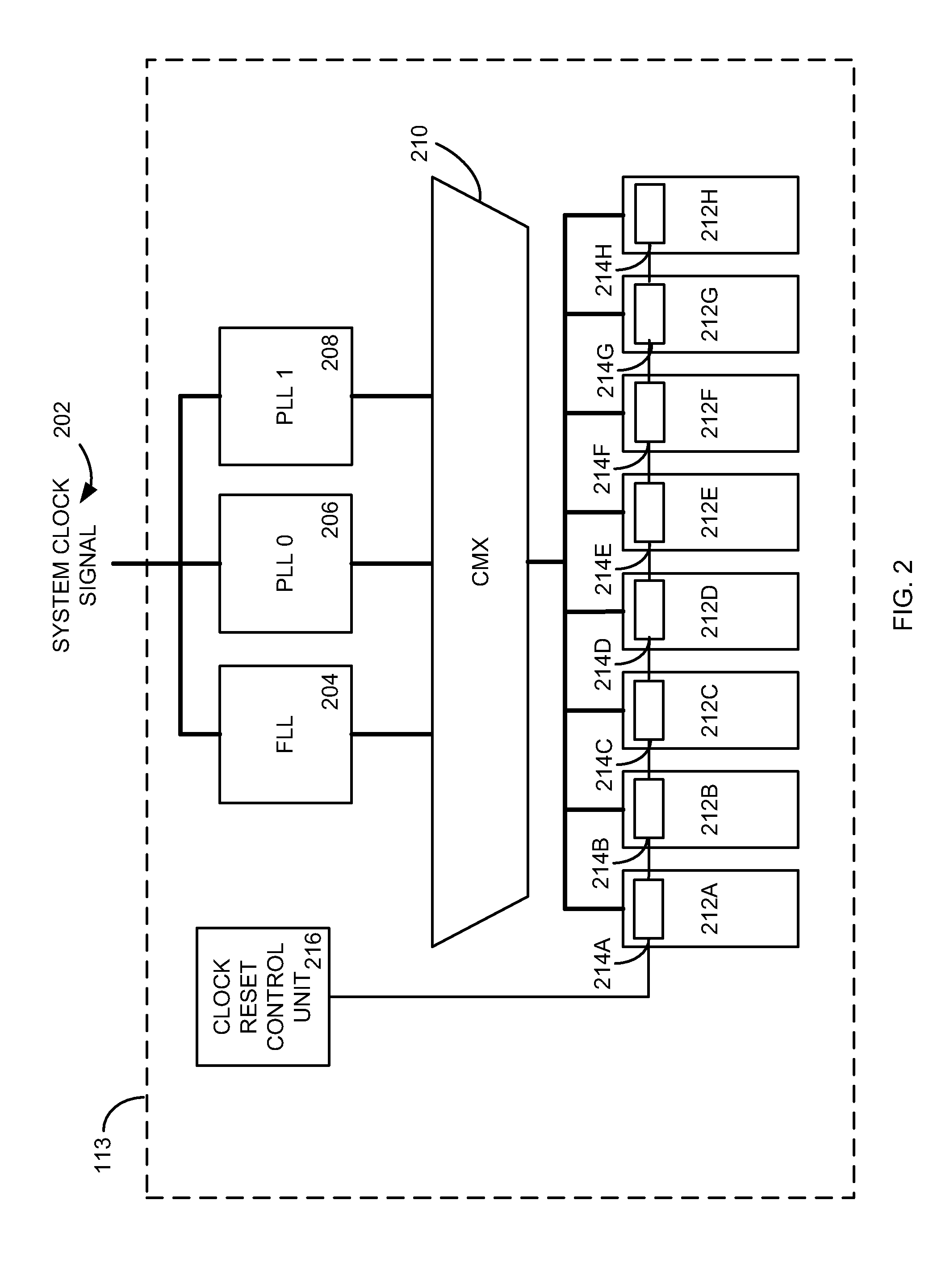

Method and apparatus for distributed generation of multiple configurable ratioed clock domains within a high speed domain

ActiveUS20140082396A1Generating/distributing signalsTransmission path multiple useClock rateComputer science

Implementations of the present disclosure involve an apparatus and / or method for providing one or more clock signals within a processing device. In particular, one or more counter devices may be integrated into a microprocessor design that operates on a system clock signal to provide ratioed synchronous clock signals for use by the microprocessor. Additionally, one or more synchronization pulse signals are also generated from the one or more counter devices to facilitate communication between domains of the microprocessor that may operate on separate clock frequencies. Such synchronization pulse signals may also provide for a virtual clock signal within a clock domain to create a low frequency logic cluster within a high frequency domain of the microprocessor. A synchronous, low frequency reset signal is also disclosed to synchronize the counting devices to the system clock without the need for an additional high frequency signal path in the microprocessor design.

Owner:ORACLE INT CORP

Method and apparatus for predicting clock skew for incomplete integrated circuit design

ActiveUS7107200B1Analogue computers for electric apparatusComputer aided designEngineeringLarge distance

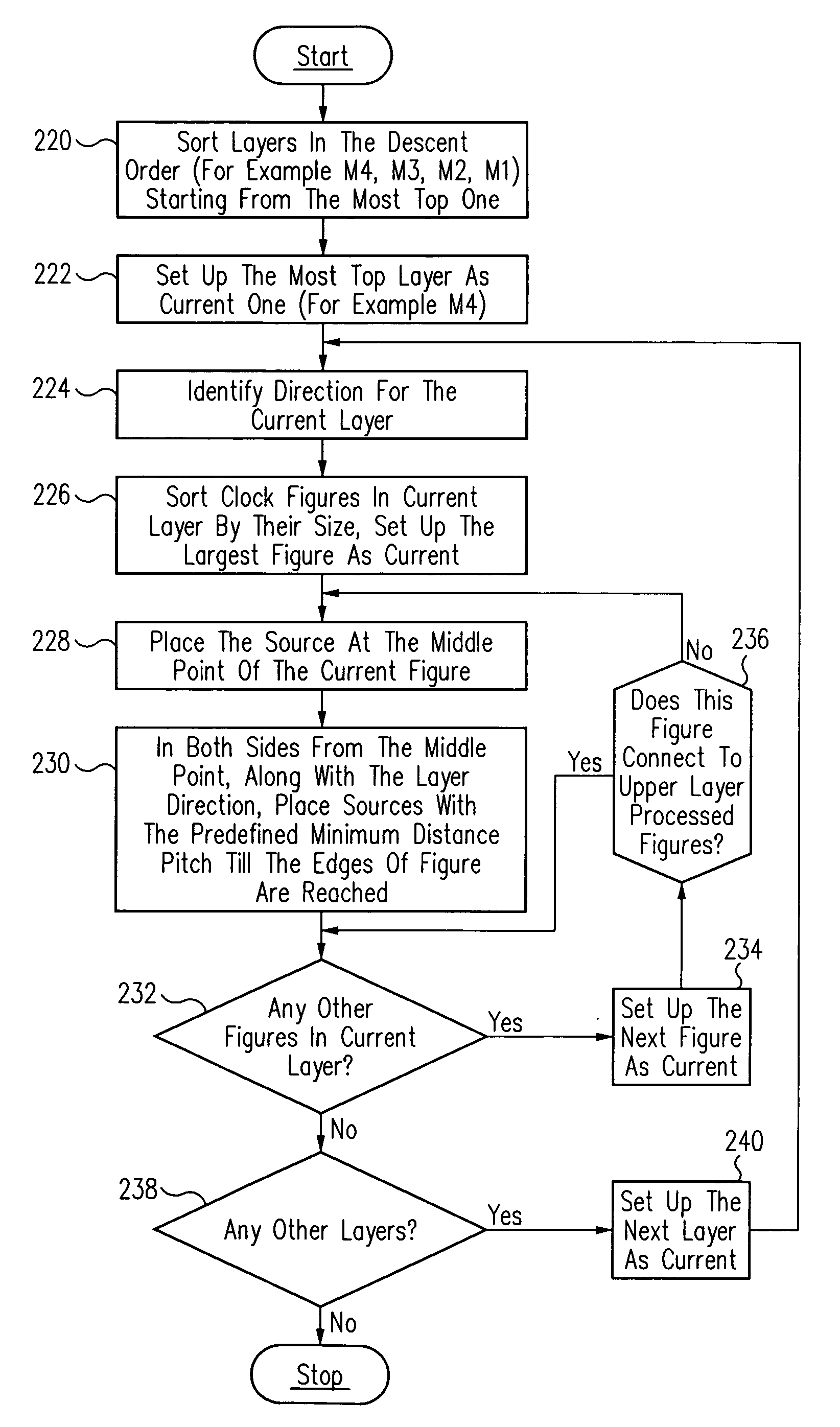

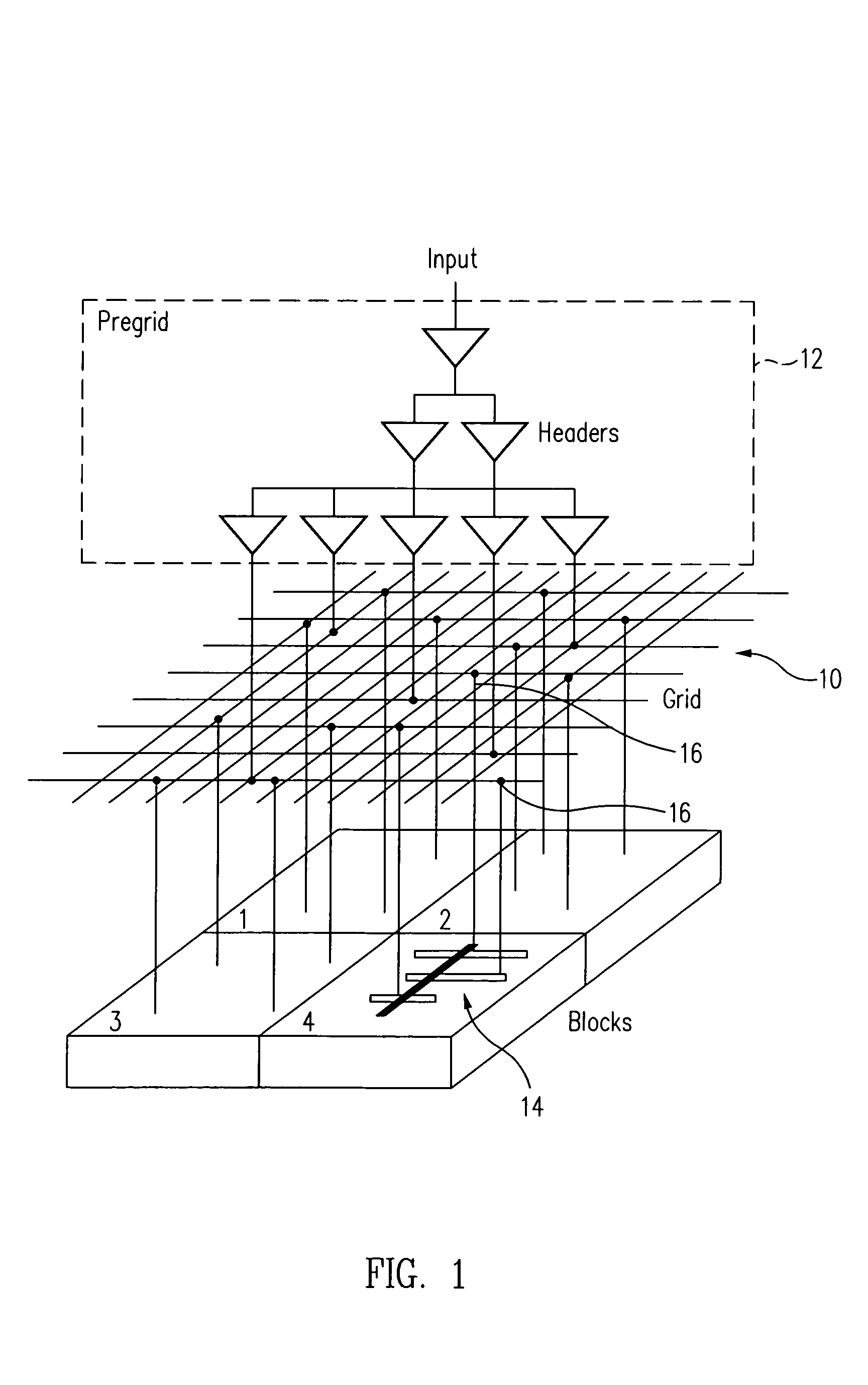

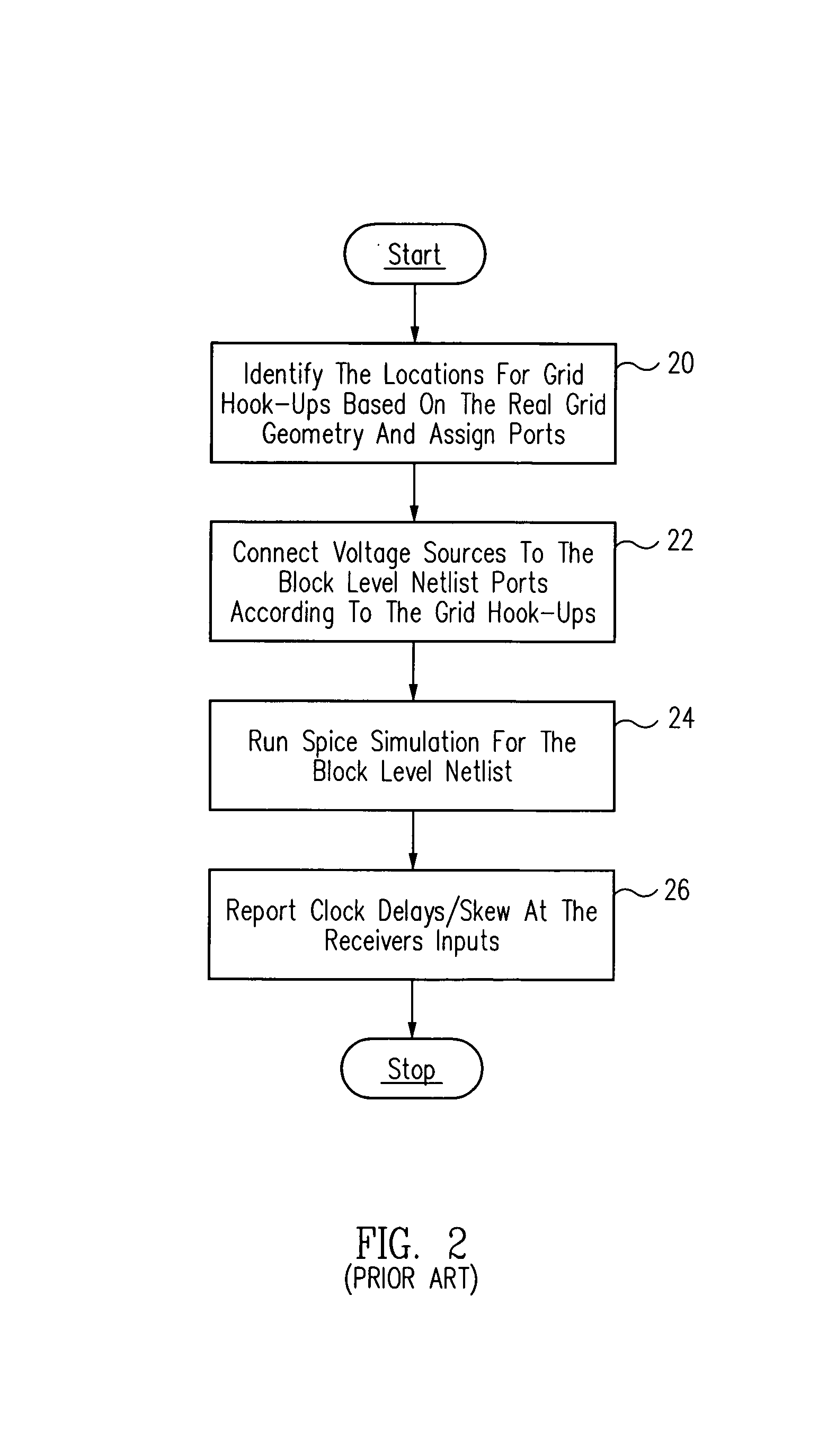

Prediction of a clock skew for an incomplete integrated circuit design, includes (a) selecting a first metal layer having at least one clock design figure, (b) placing, for a minimum clock skew prediction, clock source locations on the clock design figure in accordance with a first predetermined minimum distance between adjacent clock source locations, (c) placing, for a maximum clock skew prediction, a clock source location on a largest clock design figure in the first layer, such that the clock source location has a largest distance from a via to a lower layer, and (d) placing, for an intermediate clock skew prediction, clock source locations on intersections between the clock design figure and a virtual clock grid created for the first metal layer, the virtual clock grid having a predetermined offset from a design boundary and a predetermined pitch between grid lines.

Owner:ORACLE INT CORP

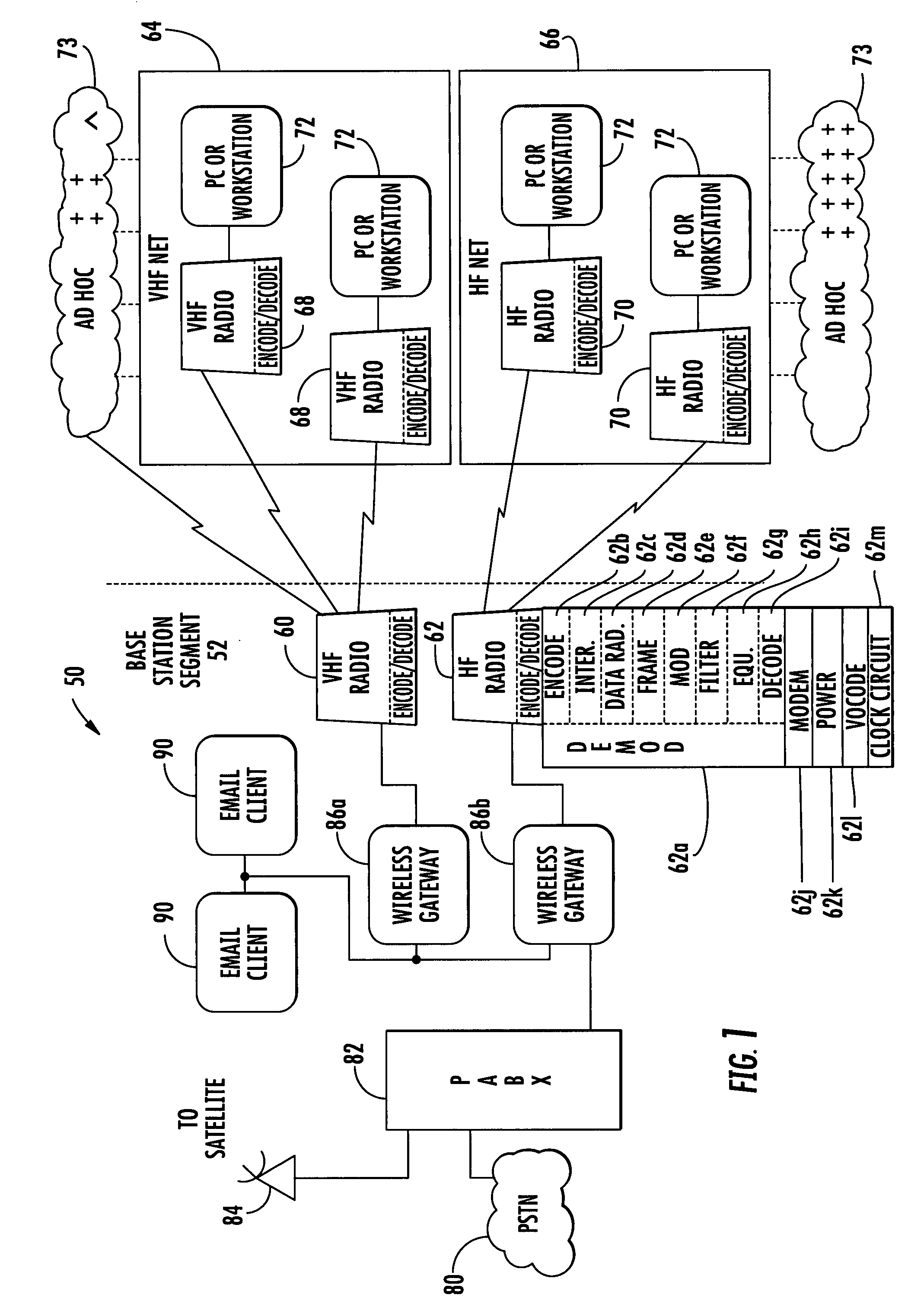

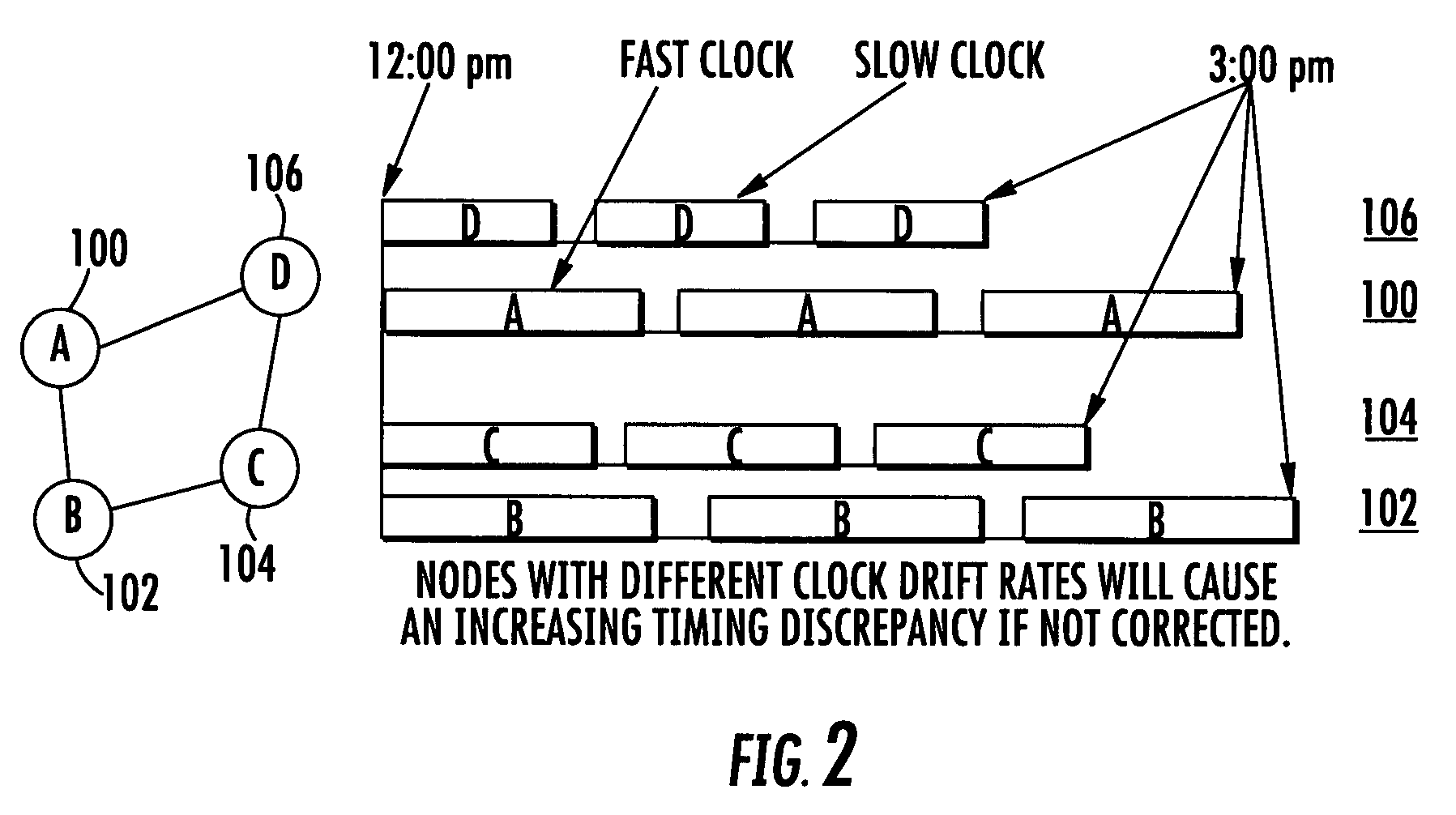

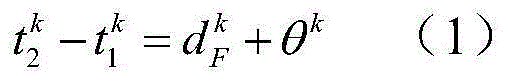

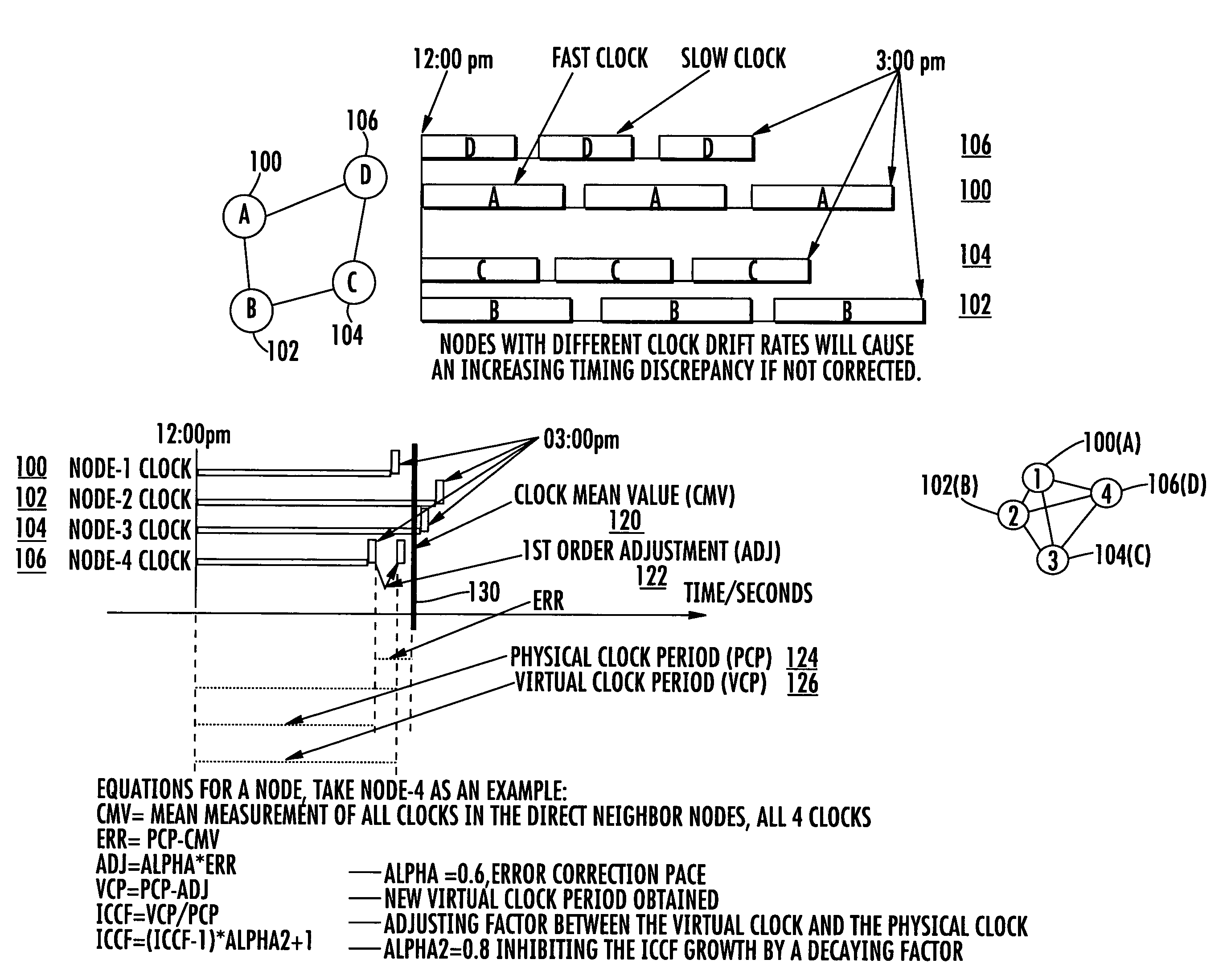

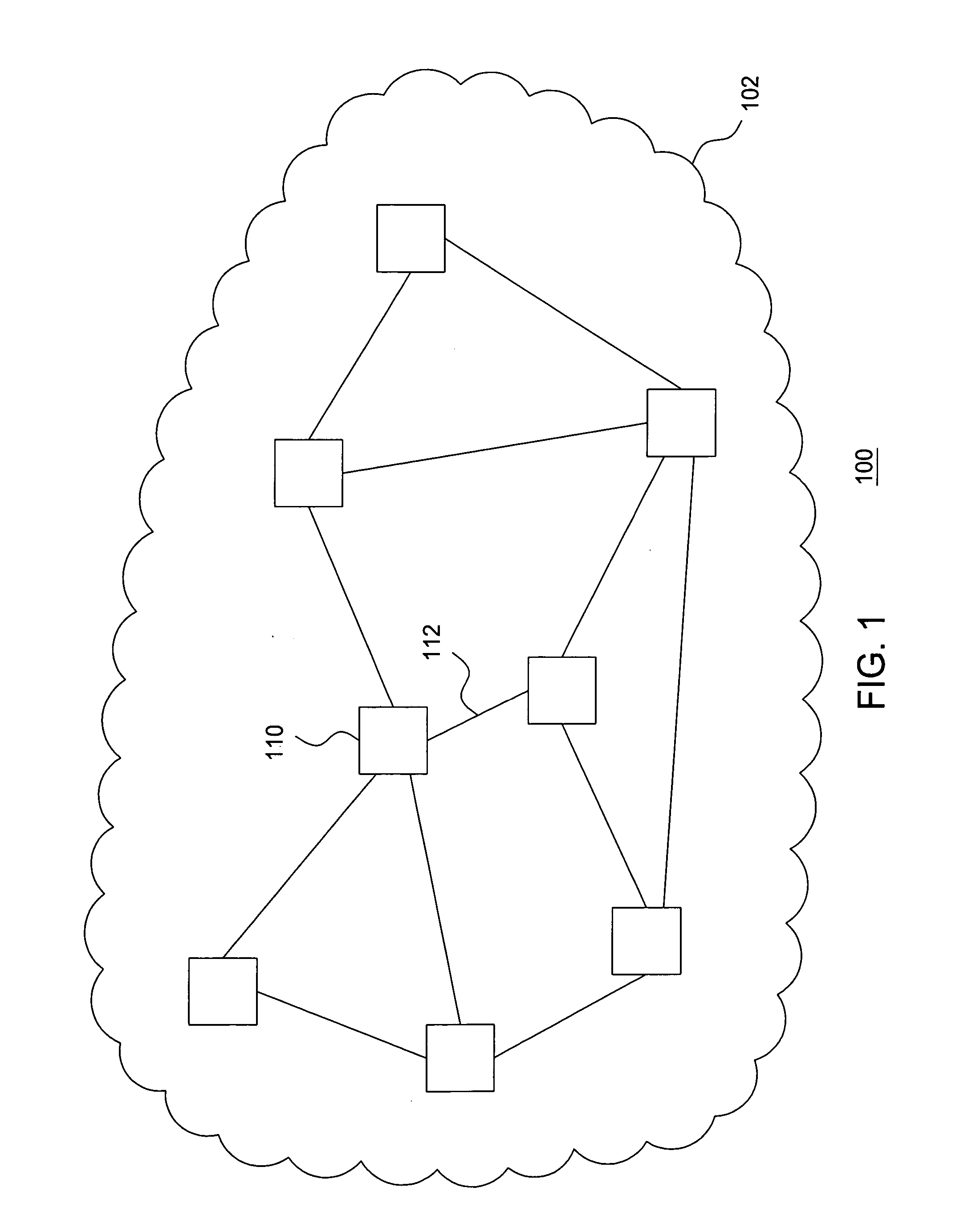

TDMA mobile ad-hoc network (MANET) with second order timing and tracking

InactiveUS20080240050A1Error preventionFrequency-division multiplex detailsTelecommunications linkCommunication link

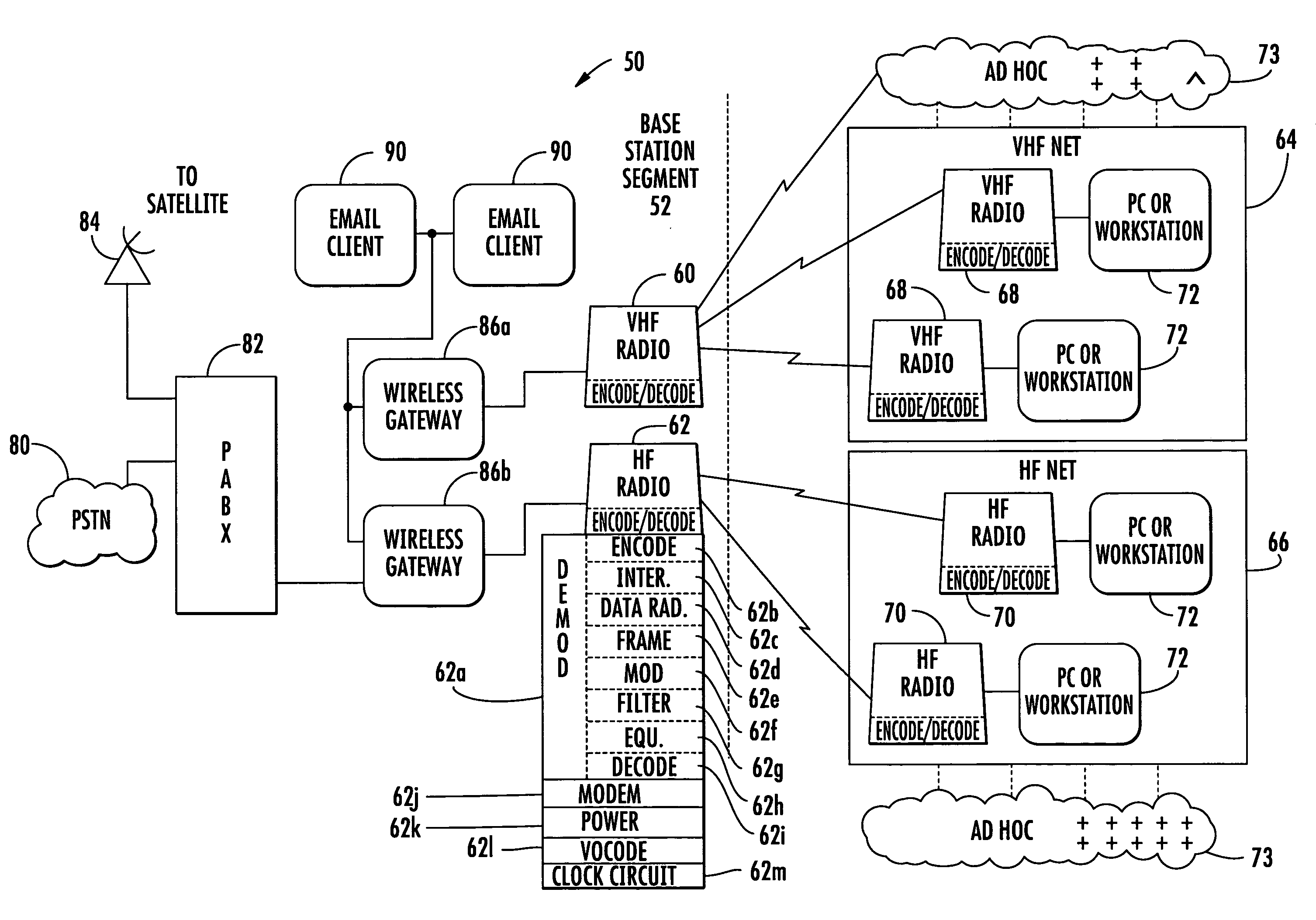

A communication system includes a plurality of mobile nodes forming a mobile ad-hoc network (MANET) and having a network clock time. A plurality of wireless communications links connects the mobile nodes together. Each mobile node includes a communications device and controller for transmitting and routing data packets wirelessly to other mobile nodes via the wireless communications link using a Time Division Multiple Access (TDMA) data transmission. Each mobile node includes a clock circuit having a digital clock time. A clock circuit is operative for processing a second order internal clock compensation factor as a learned and accumulated value for establishing a virtual clock time to correct any clock timing errors of the physical clock time from the network clock time.

Owner:STINGRAY IP SOLUTIONS LLC

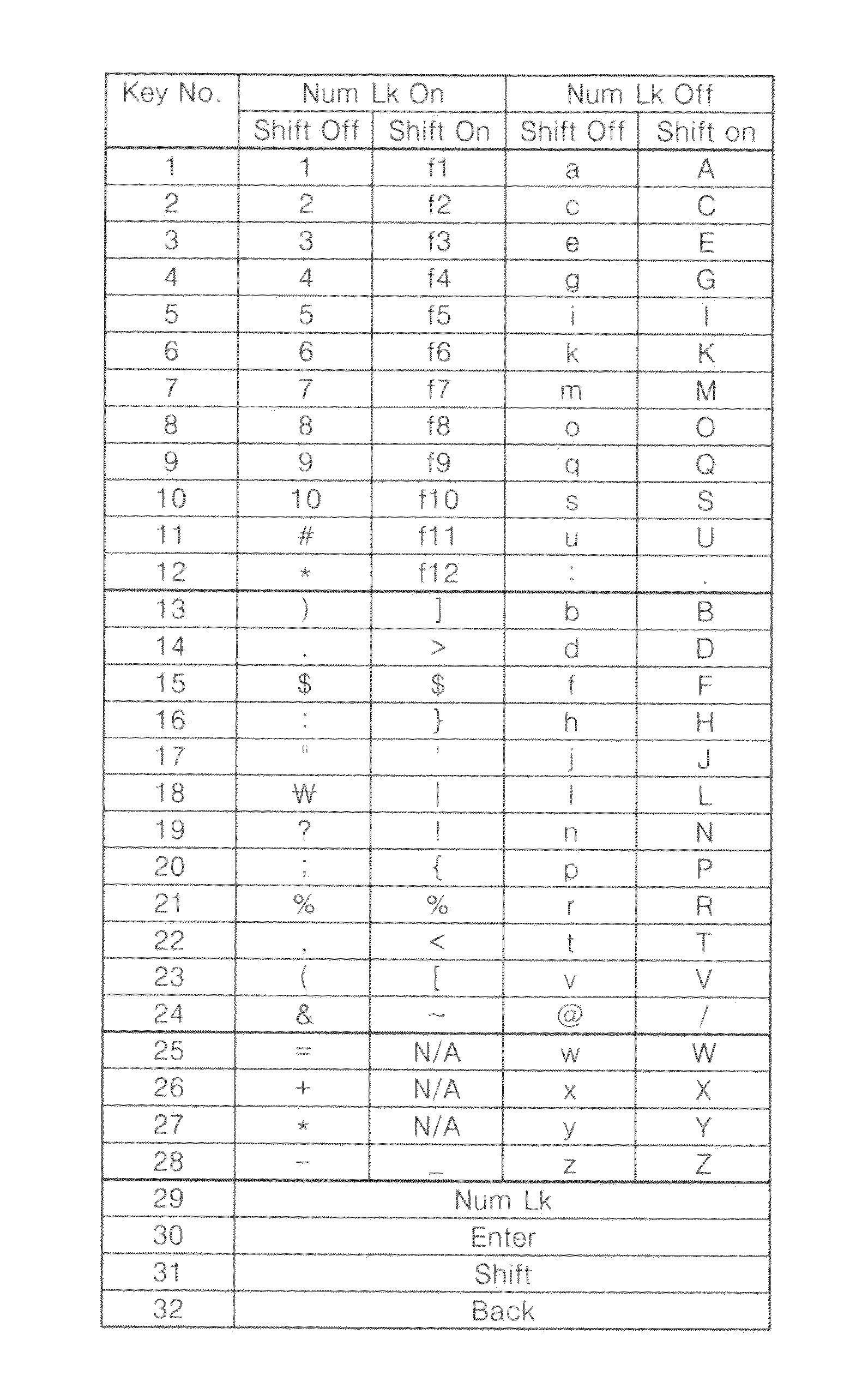

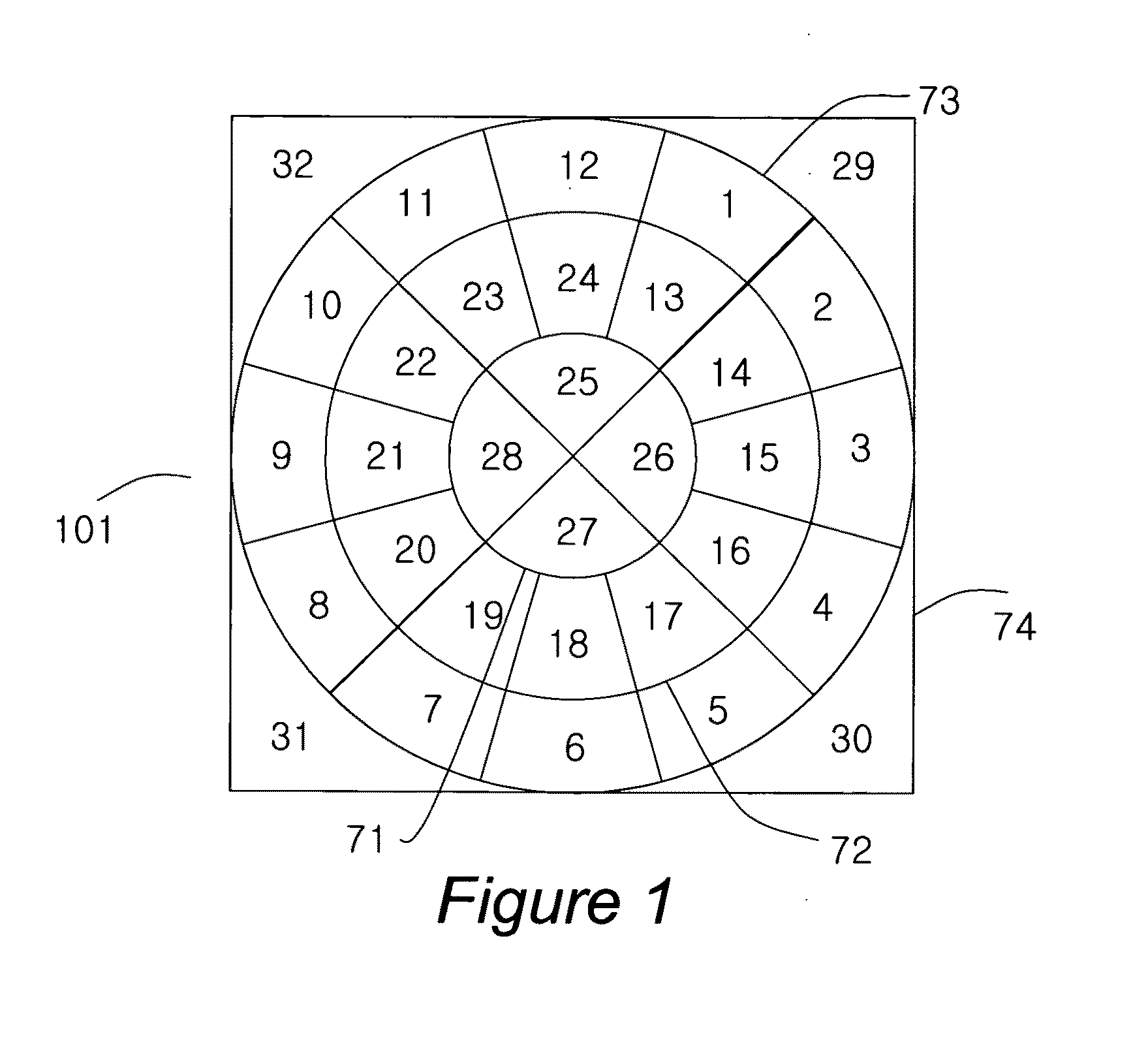

Clock face keyboard

ActiveUS20100266323A1Easy to learnEasy to useDetails for portable computersOther printing apparatusRadial positionComputer science

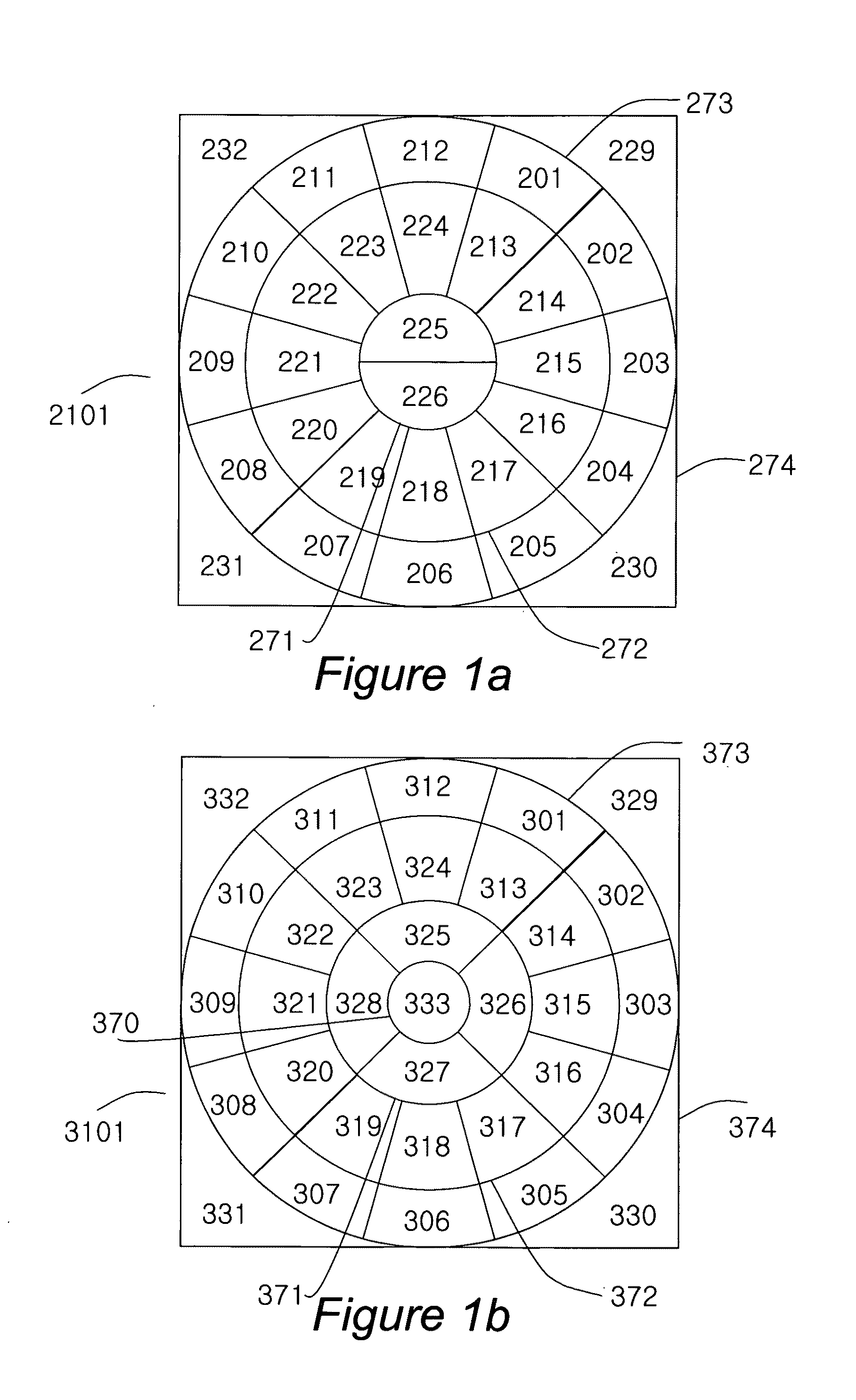

An alphanumeric keyboard that is easy to learn, easy to use, and mountable on a handset for one-hand operation, comprises a virtual clock face having the center for the rotation of virtual hands, first set of twelve hourly radial positions, from one o'clock to twelve o'clock, surrounding the center, second set of twelve hourly radial positions, from one o'clock to twelve o'clock, surrounding the center and nearer to the center than the first set of twelve hourly radial positions, twenty four key areas, each key area being uniquely associated with one hourly radial position of the first and second sets, wherein each key area is substantially of 30 degree annular sector shape and contiguous to the adjacent key areas associated with the adjacent hourly radial positions, wherein all twenty four key areas are substantially of equal area, at least thirteen alphabetic keys placed at predetermined hourly radial positions of the first and second sets, and wherein each key has an indicia surface that is within the associated key area for being pressed by a finger. The associated radial direction or time may be marked on the key surface for visual or tactile differentiation.

Owner:MIN BYUNG KON

Method for testing lip synchronization for multimedia audio/video stream

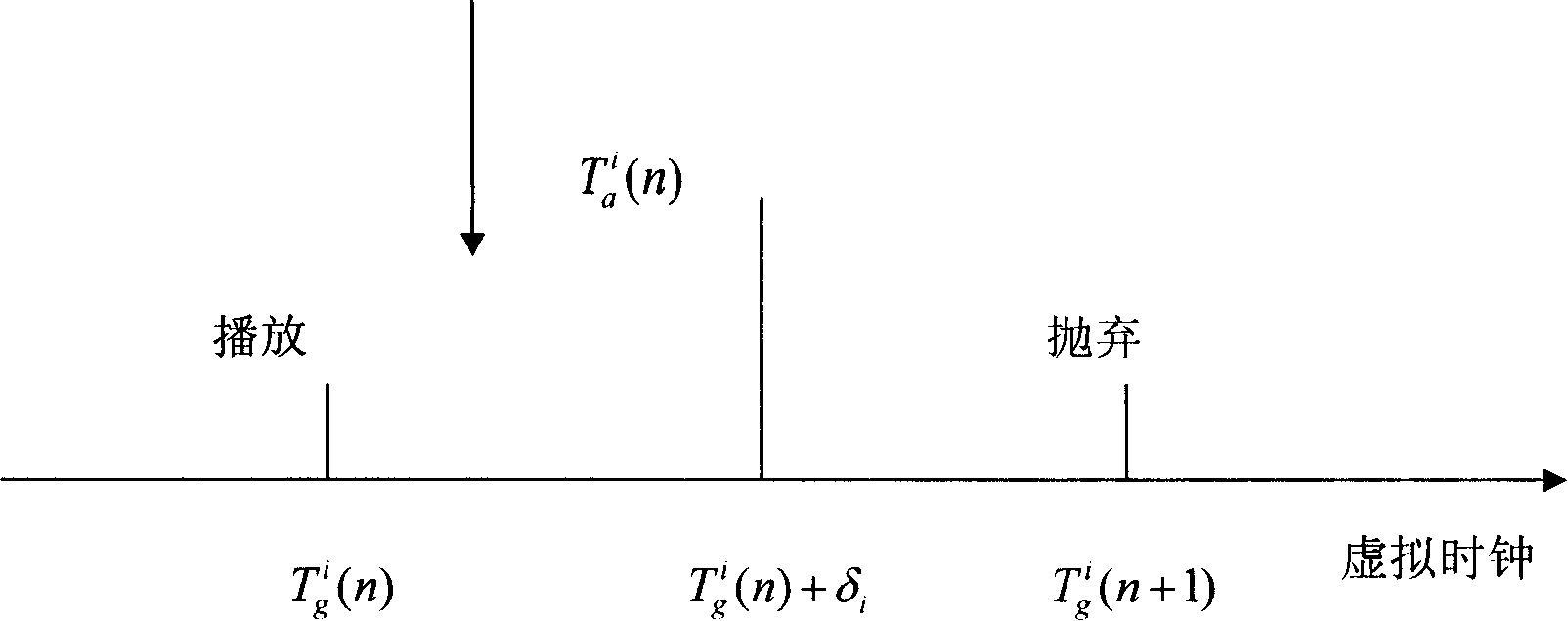

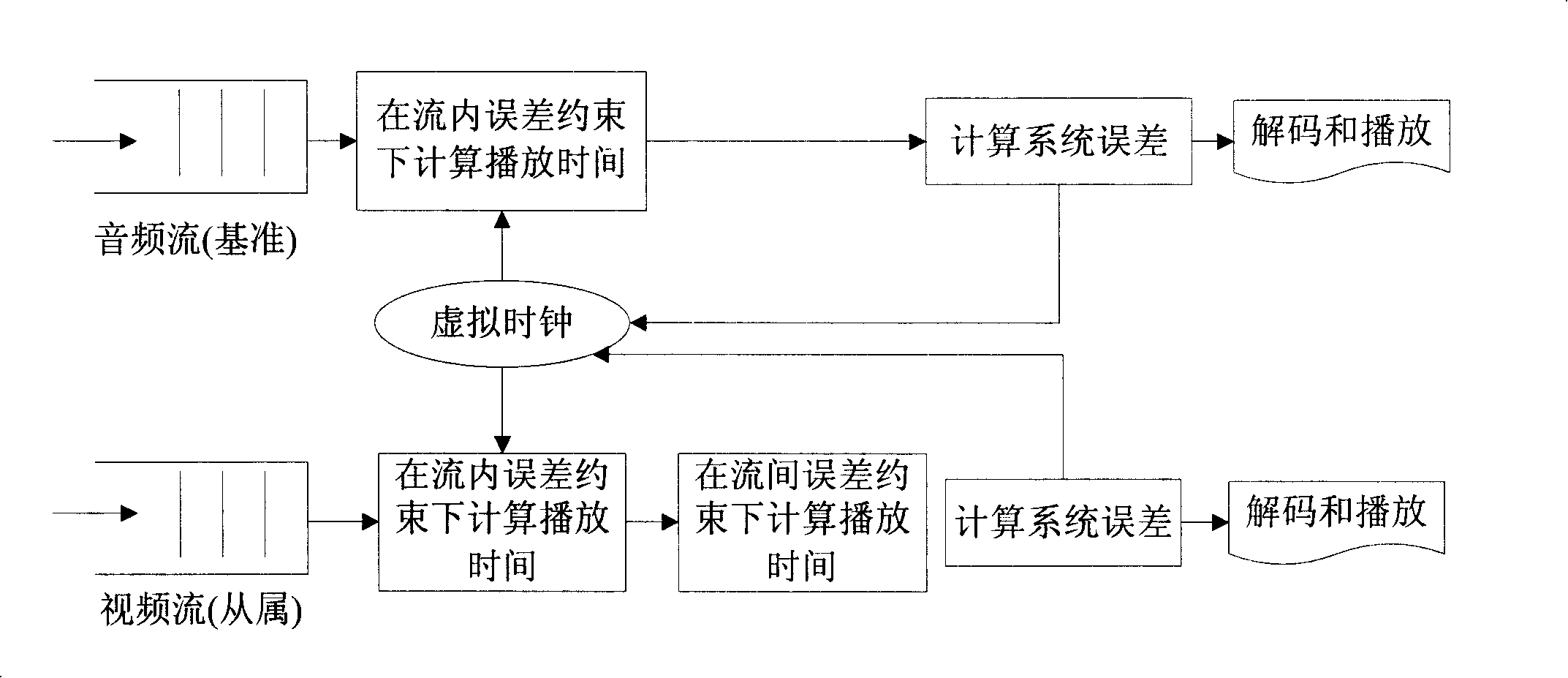

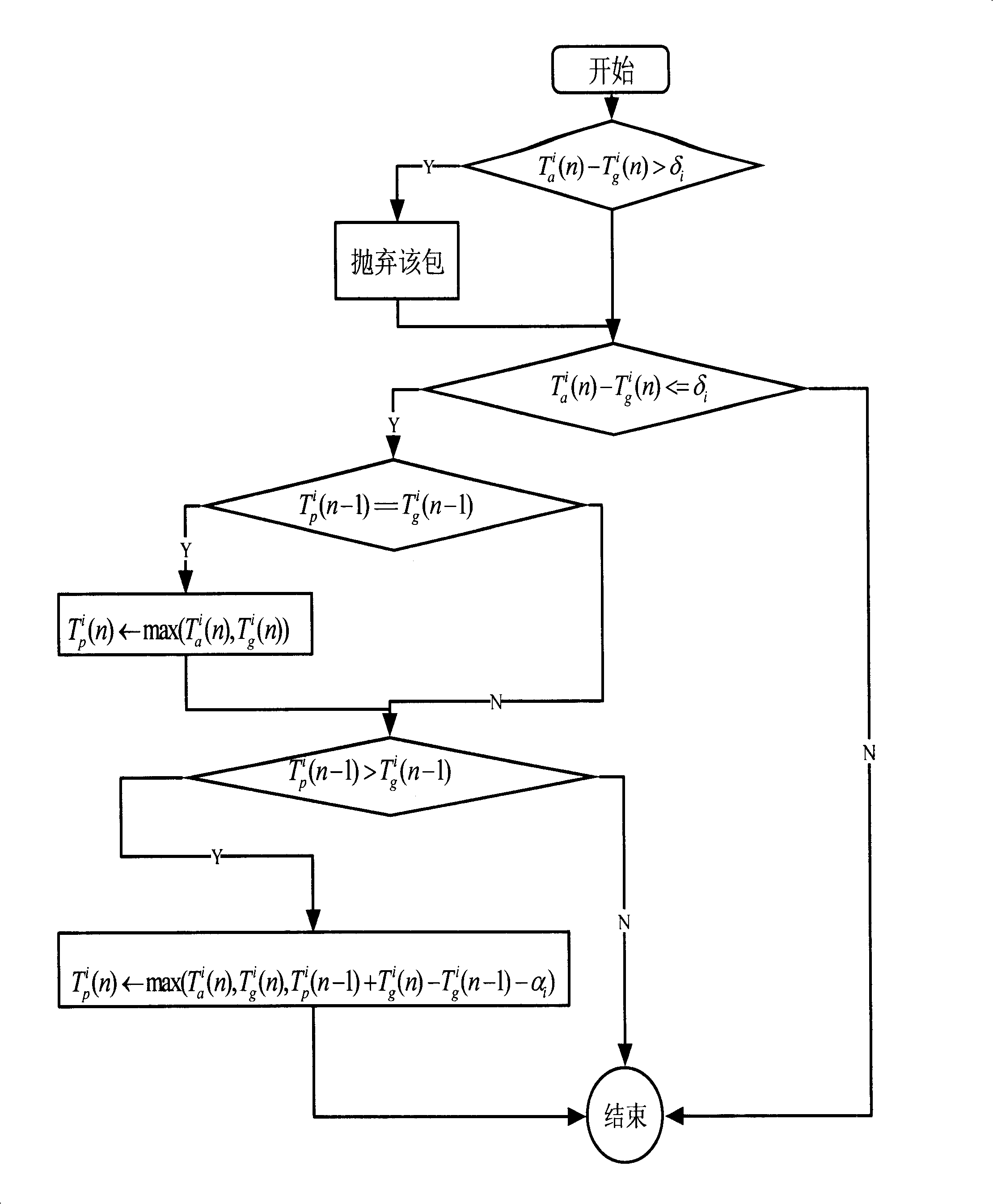

ActiveCN101212690AImprove app lip sync performanceTelevision systemsData synchronizationReal-time clock

The invention discloses a regulating method of lip synchronization of multimedia video and audio stream, which relates to the regulating method of lip synchronization. In order to solve the problem that the existing method can not well realize the lip synchronization of the multimedia stream, the regulating method is invented. The regulating method builds a virtual clock model on the basis of a real-time clock of a decoding end of the multimedia video and audio stream; according to the calculation results of adaptive delay algorithm and synchronized control algorithm, the virtual clock is adjusted and the lip synchronization of multimedia video and audio stream is available, thus greatly improving lip synchronization performance applied to multimedia and internet.

Owner:ZTE CORP

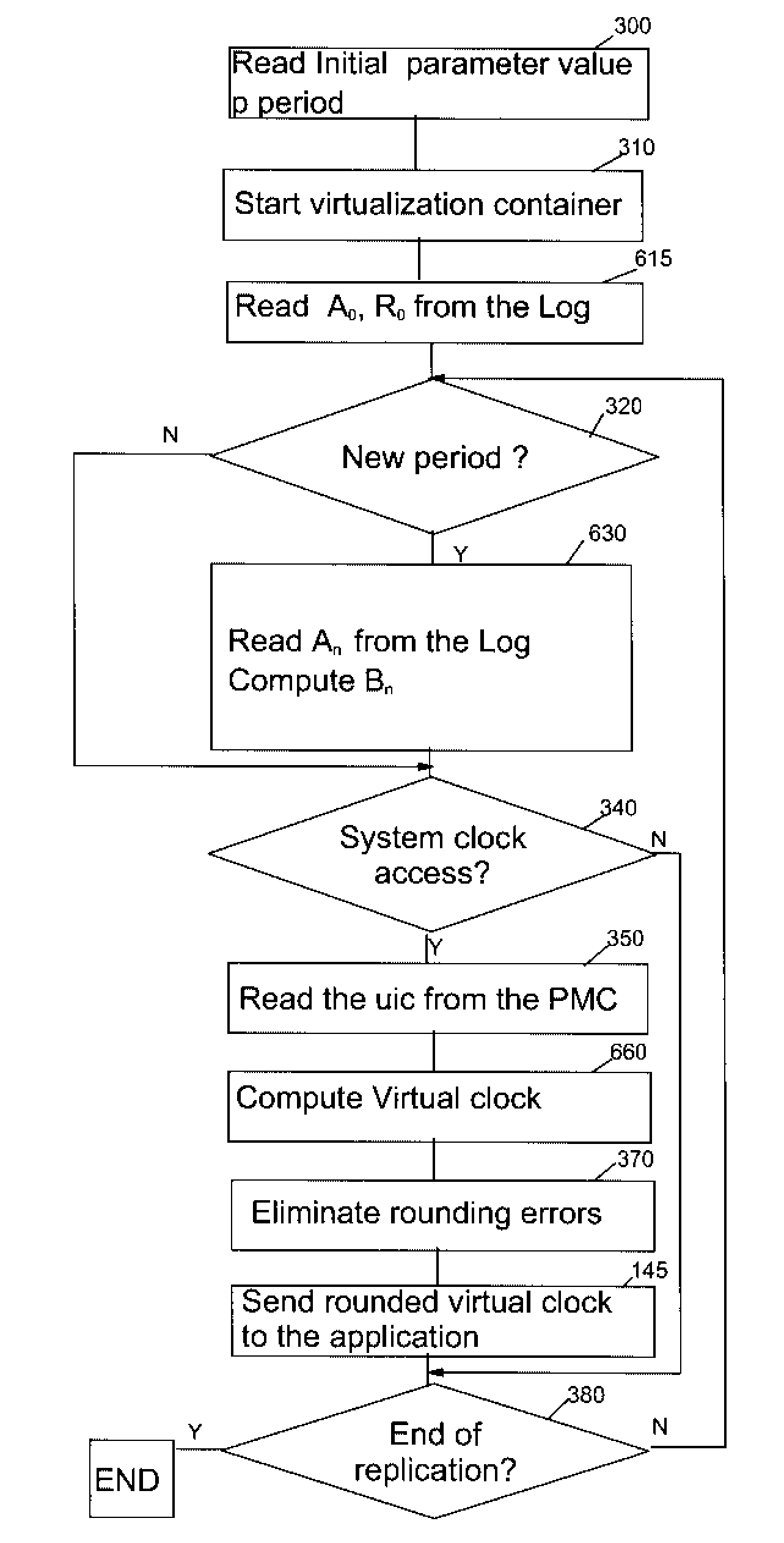

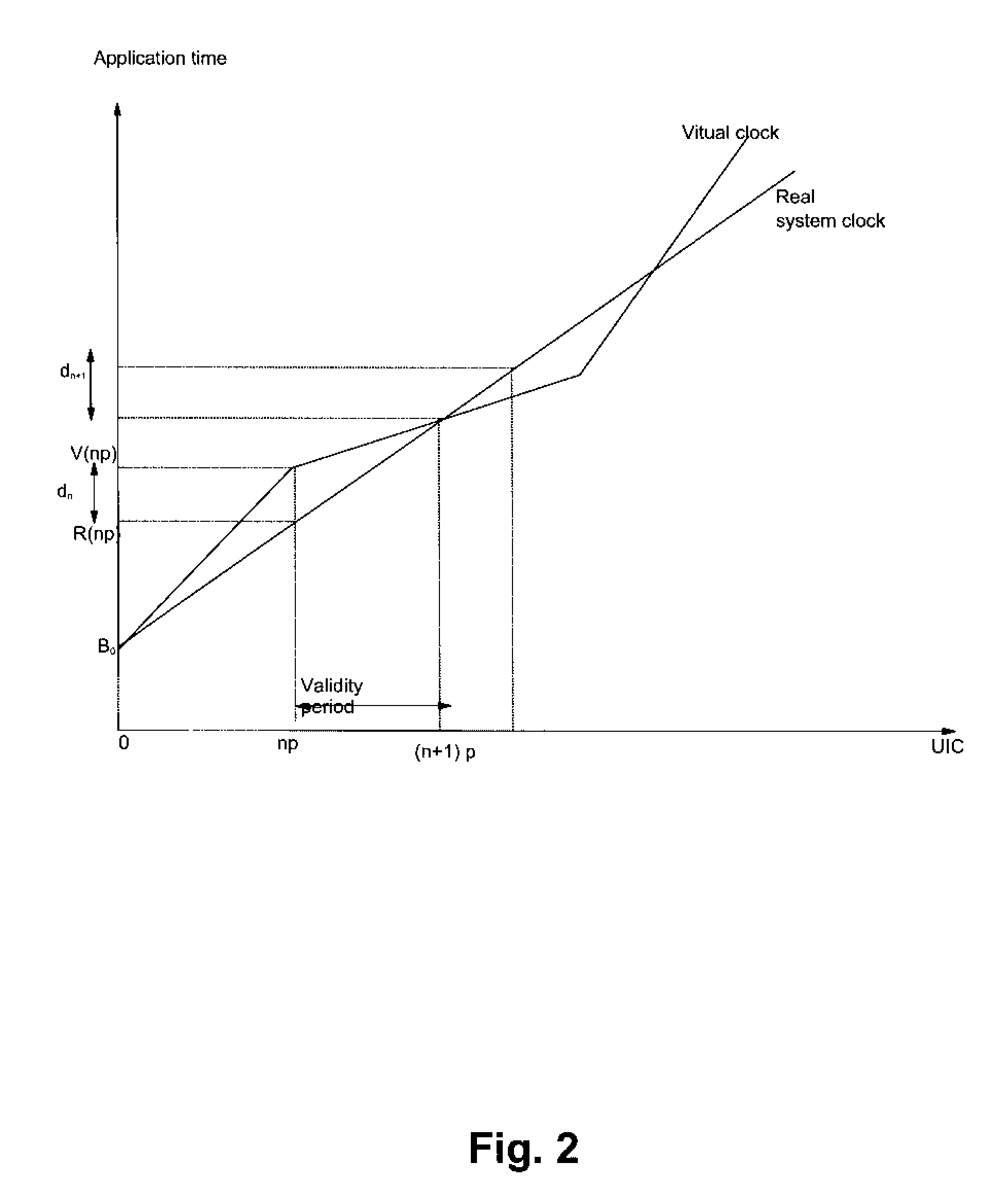

Method and system for providing a deterministic virtual clock

InactiveUS20080155299A1Efficient and reliableAllow useError detection/correctionGenerating/distributing signalsVirtualizationComputer hardware

A method and system for providing a virtual clock on a computer by multiplying the number of instructions executed by the average instruction execution time. It is however not reliable to use this generic computation for virtualization of application in a fault tolerant system because the virtual clock computed like this quickly deviates from the system clock. A virtual clock computation is provided which includes periodic readjustment of the virtual to the system clock. Also, the errors coming from rounding of the number of executing instruction are suppressed.Taking the assumption that the user instruction counters are maintained synchronized in the operational and the replication computers, replacing the system clock access by a virtual clock when virtualizing applications thus turning the system clock acquisition into a deterministic event. Replicating the system clock access can be thus done by reexecuting the application code in the replication machine avoiding transfer of information at each system clock access of the virtualized application programs.

Owner:IBM CORP

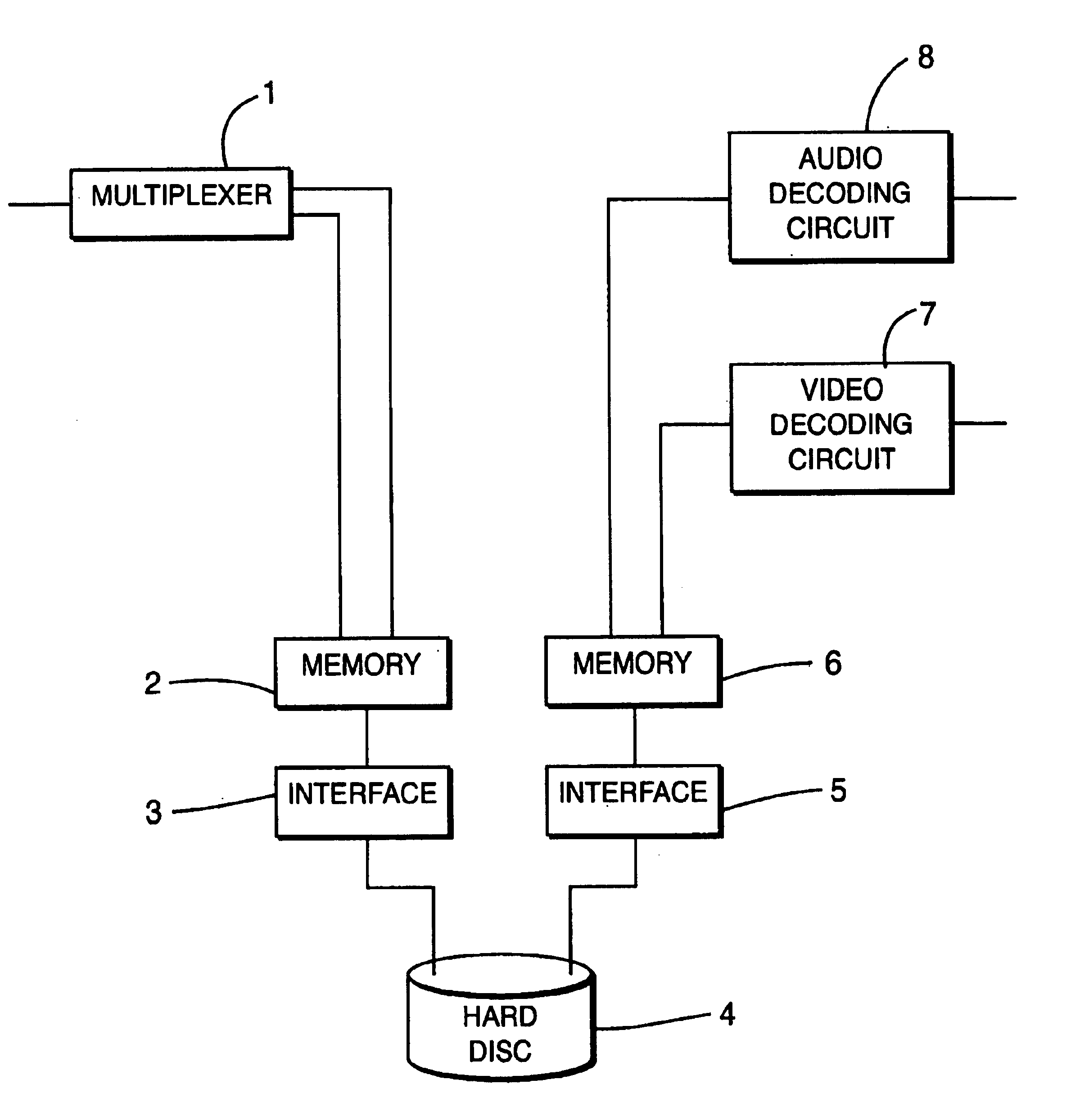

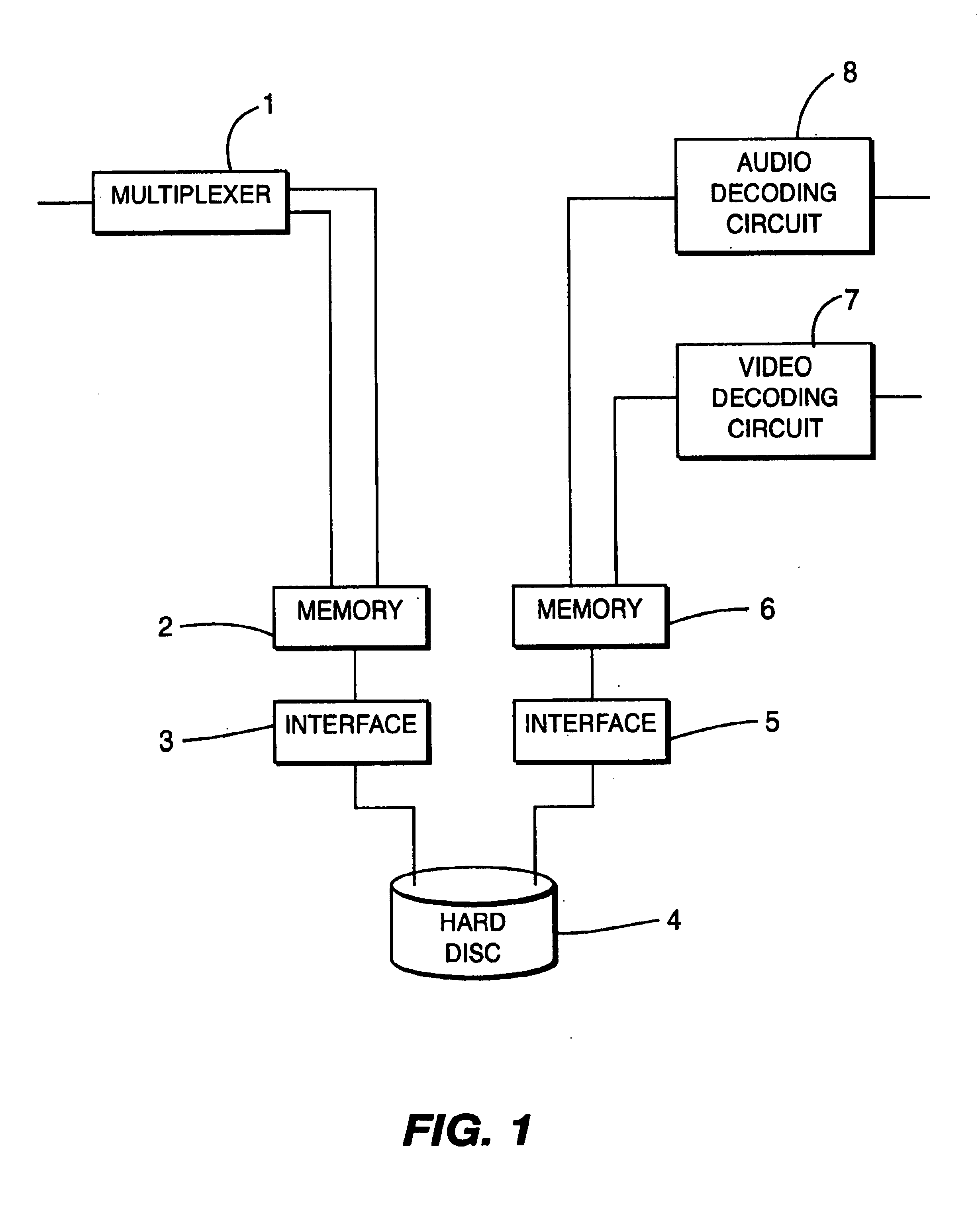

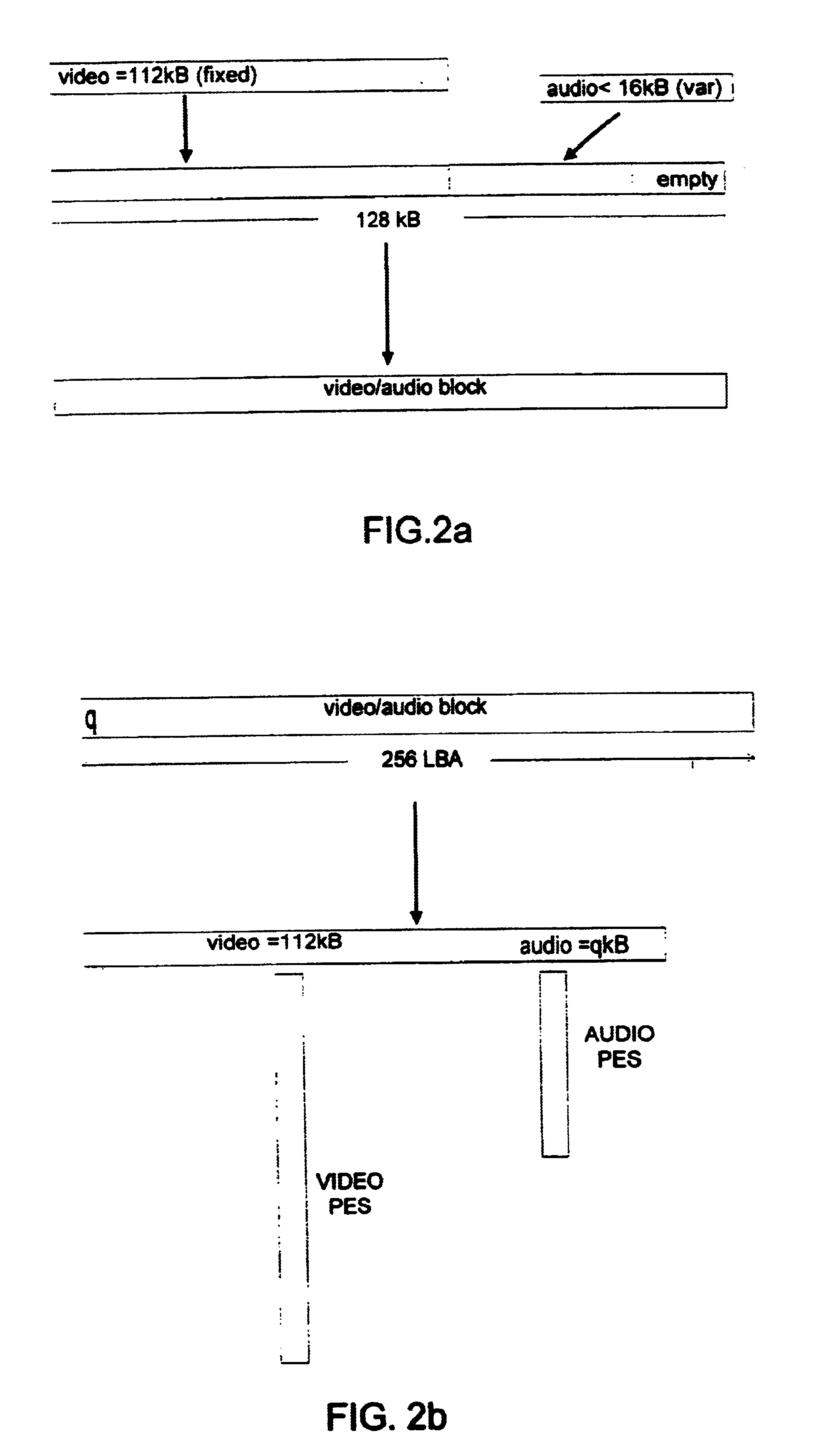

Process and device for synchronizing an MPEG decoder

InactiveUS6948185B1Easy to implementAvoid failureTelevision system detailsPulse modulation television signal transmissionComputer networkTelevision receivers

A process for synchronizing an MPEG decoder, characterized by the process of calculating an actual instant of presentation Tpres of the video of an image, this instant relating to a local clock LSTC, further calculating an offset STOC between Tpres, being the calculated instant of presentation and the PTS label corresponding to the instant of presentation desired by the coder for the video of this image, so as to define a virtual clock VSTC=STCO+LSTC, the presentation of the video corresponding to this image being made at the PTS dates relating to the virtual clock VSTC, wherein this process relates to satellite decoders, MPEG decoders, as well, as digital TV receivers, utilizing a hard disk for recording coded data.

Owner:MAGNOLIA LICENSING LLC

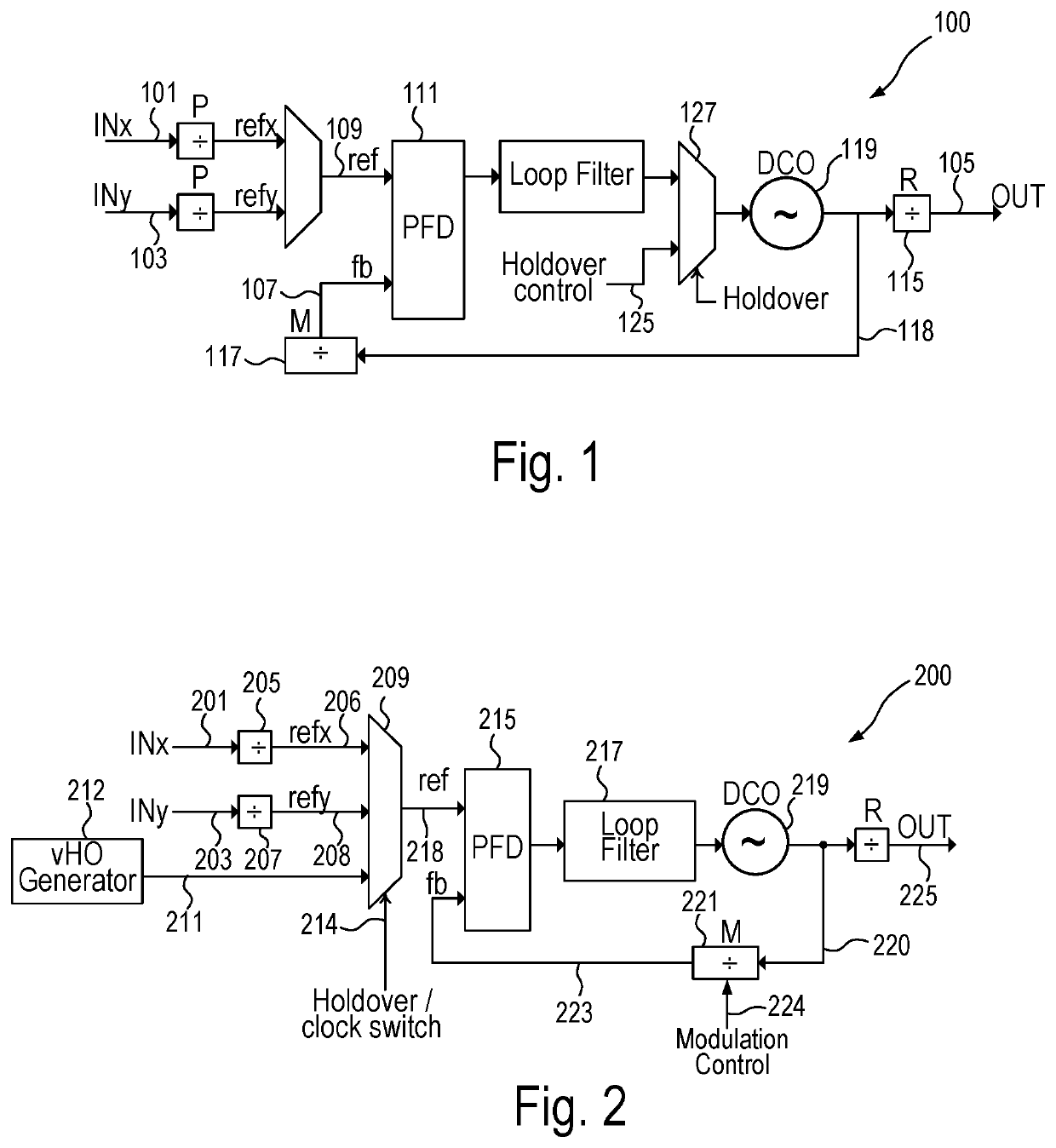

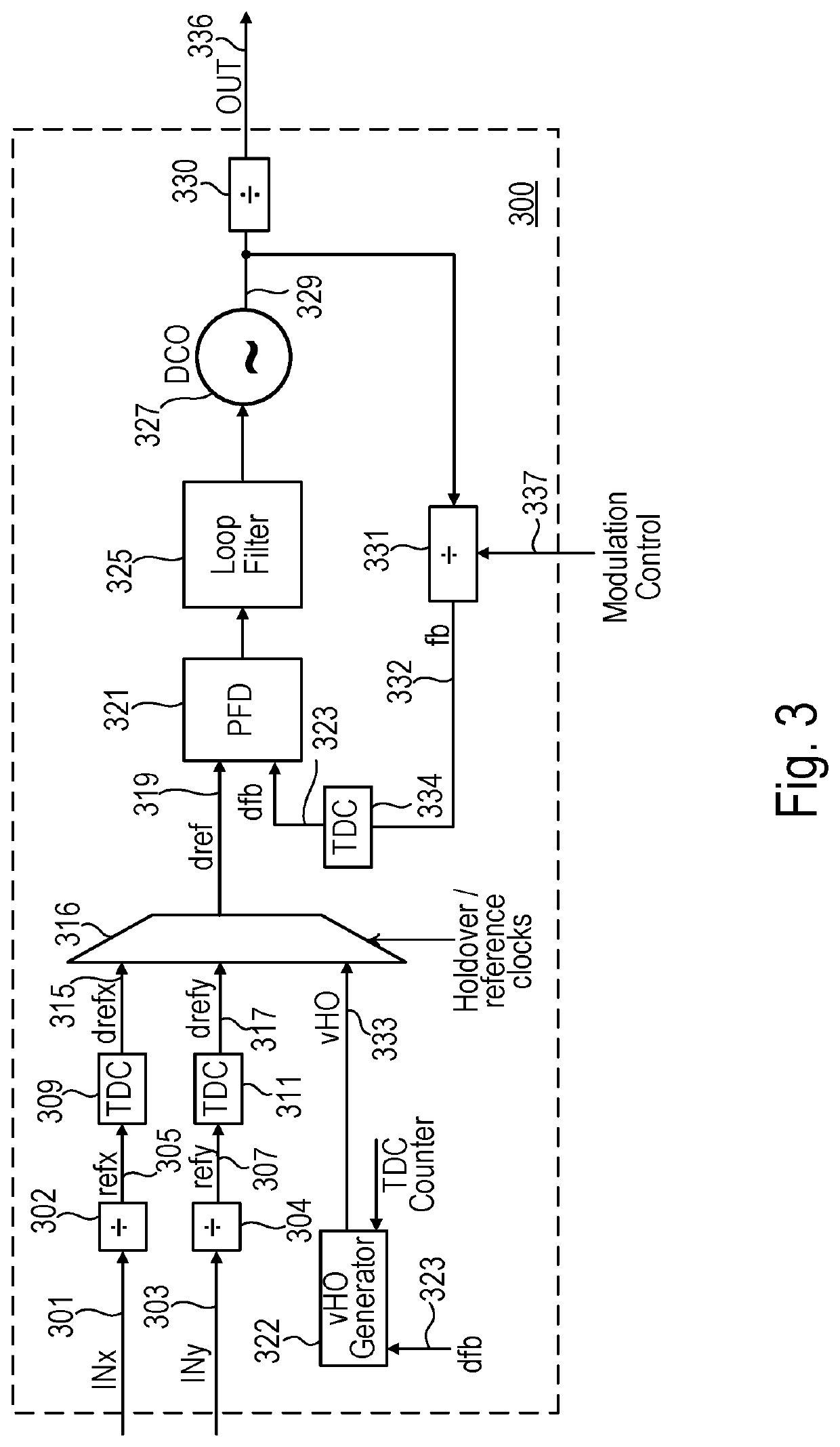

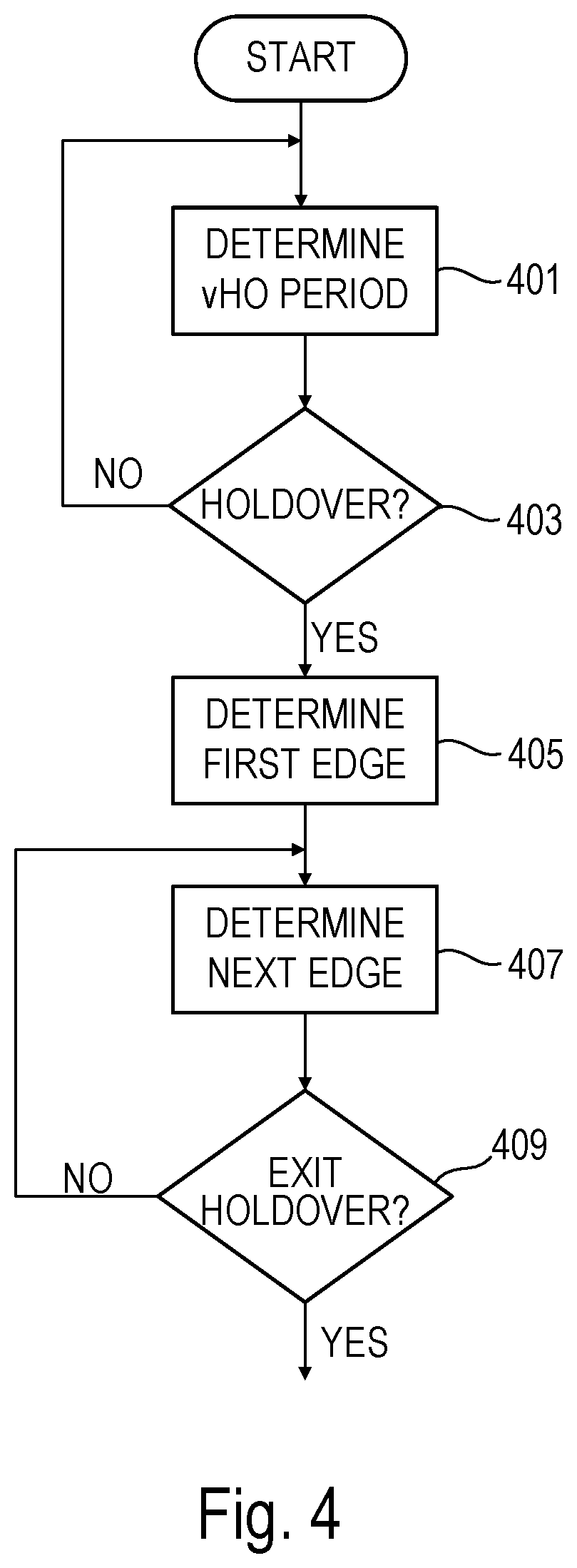

Use of a virtual clock in a PLL to maintain a closed loop system

A PLL uses a virtual clock signal during holdover and / or startup to maintain a closed loop for the PLL and allow for phase / frequency adjustment of the PLL output through the feedback divider during holdover / startup when reference clock(s) supplied to the PLL are unavailable. The virtual clock signal is a series of digital values separated by a time period, where the digital values indicate transitions of the virtual clock signal and the time period corresponds to a period of the virtual clock signal. A selector circuit selects as a digital reference clock signal the virtual clock signal in a holdover or startup mode and another reference clock signal in normal operation.

Owner:SKYWORKS SOLUTIONS INC

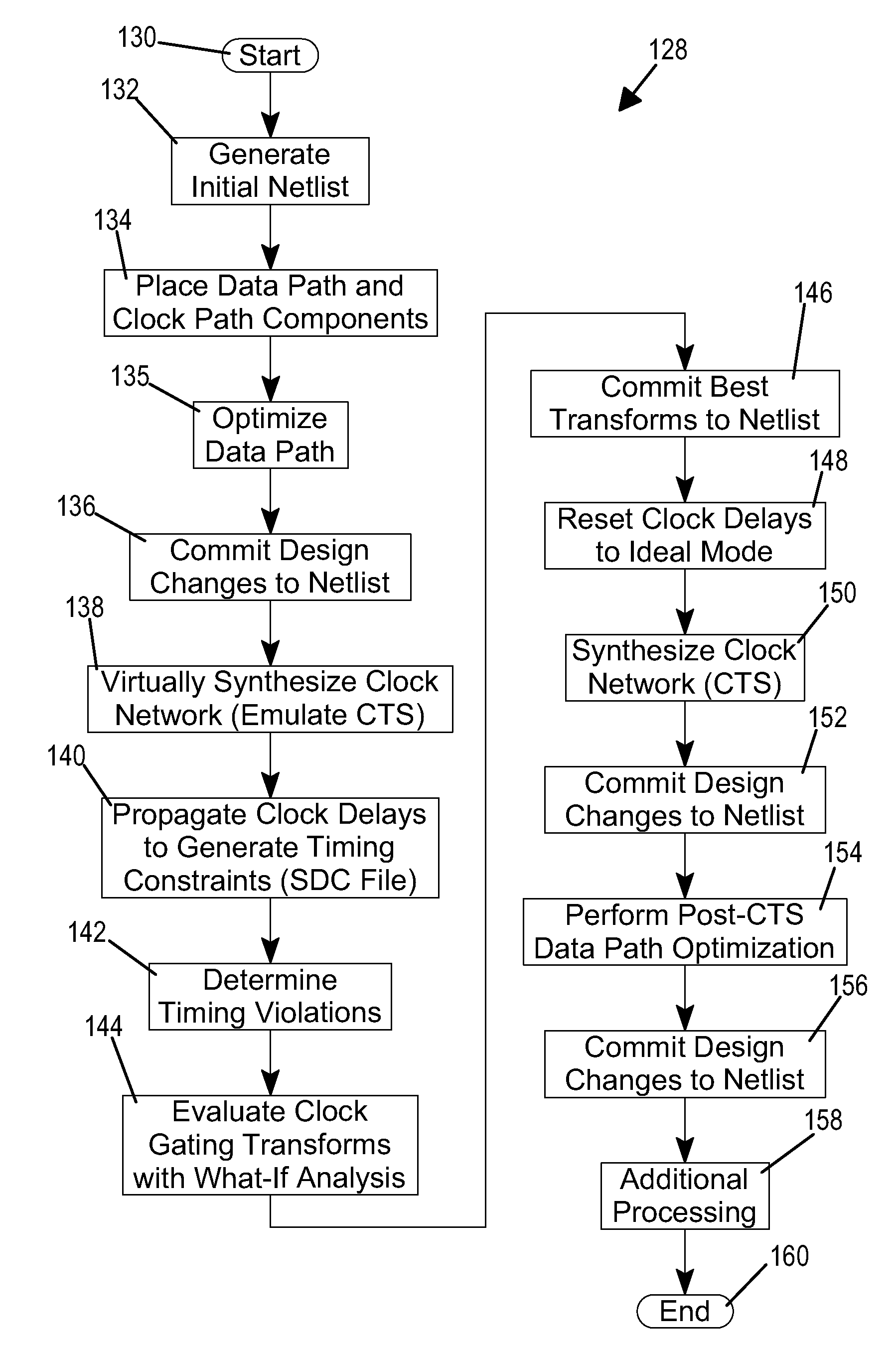

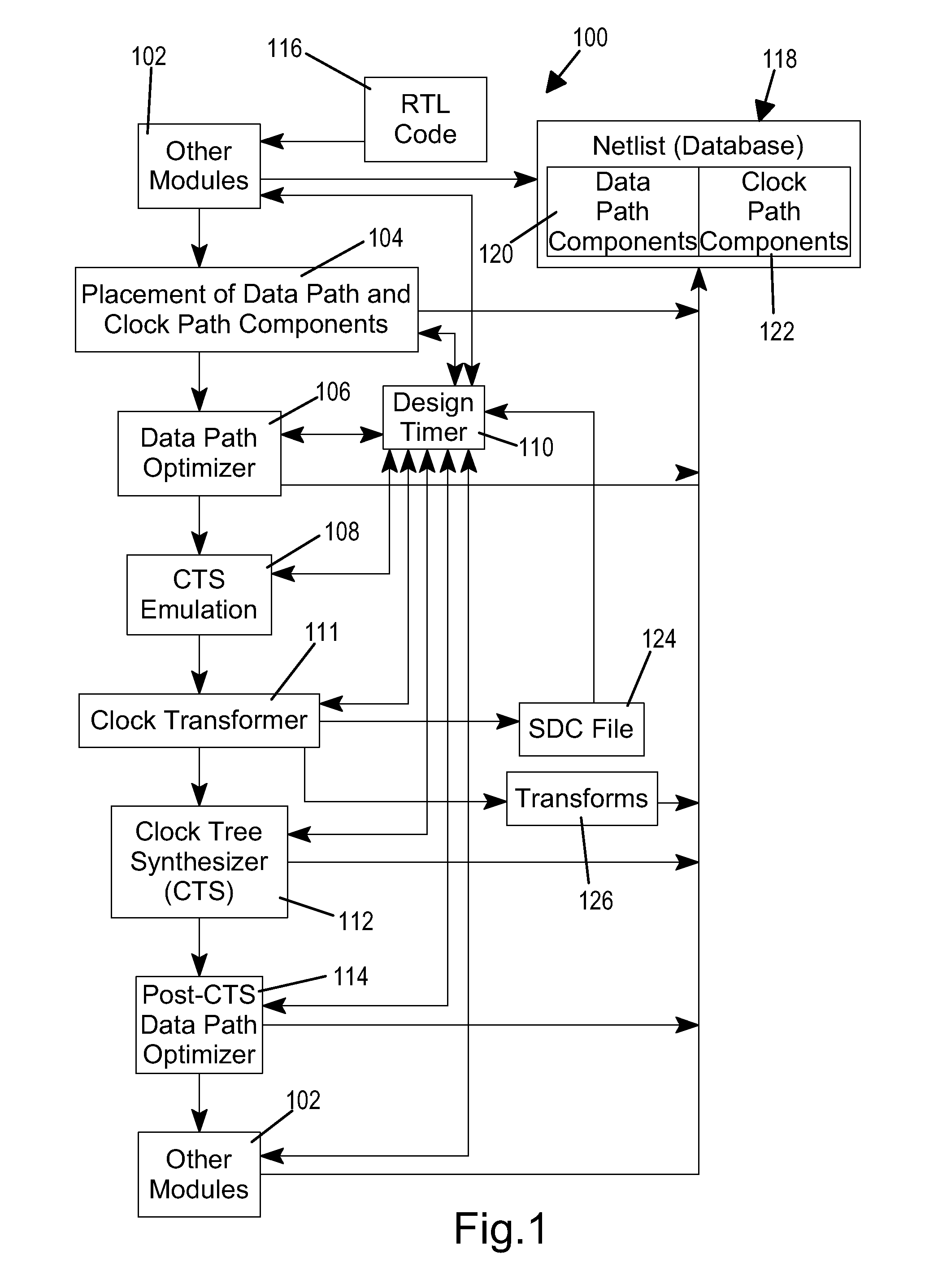

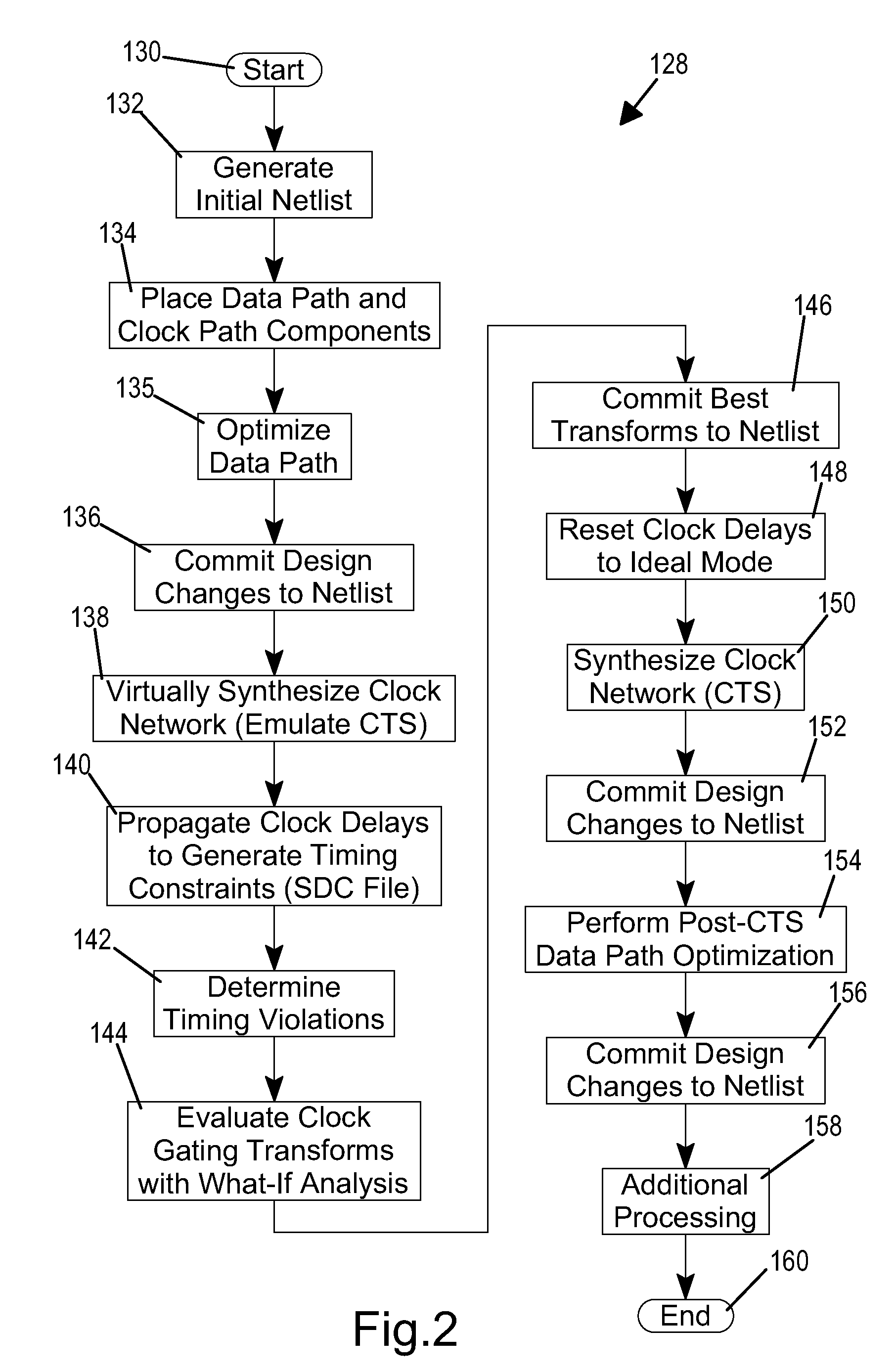

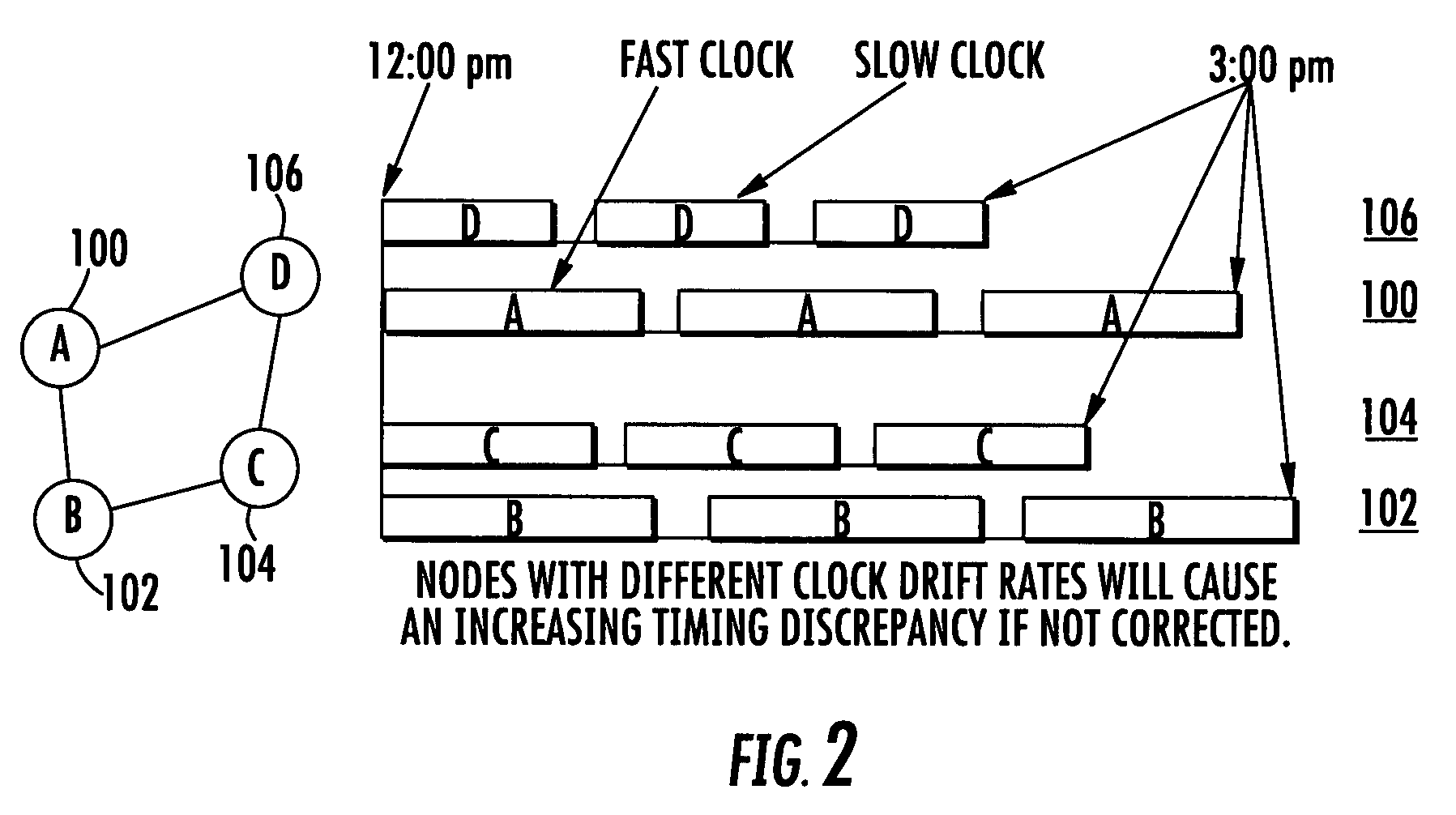

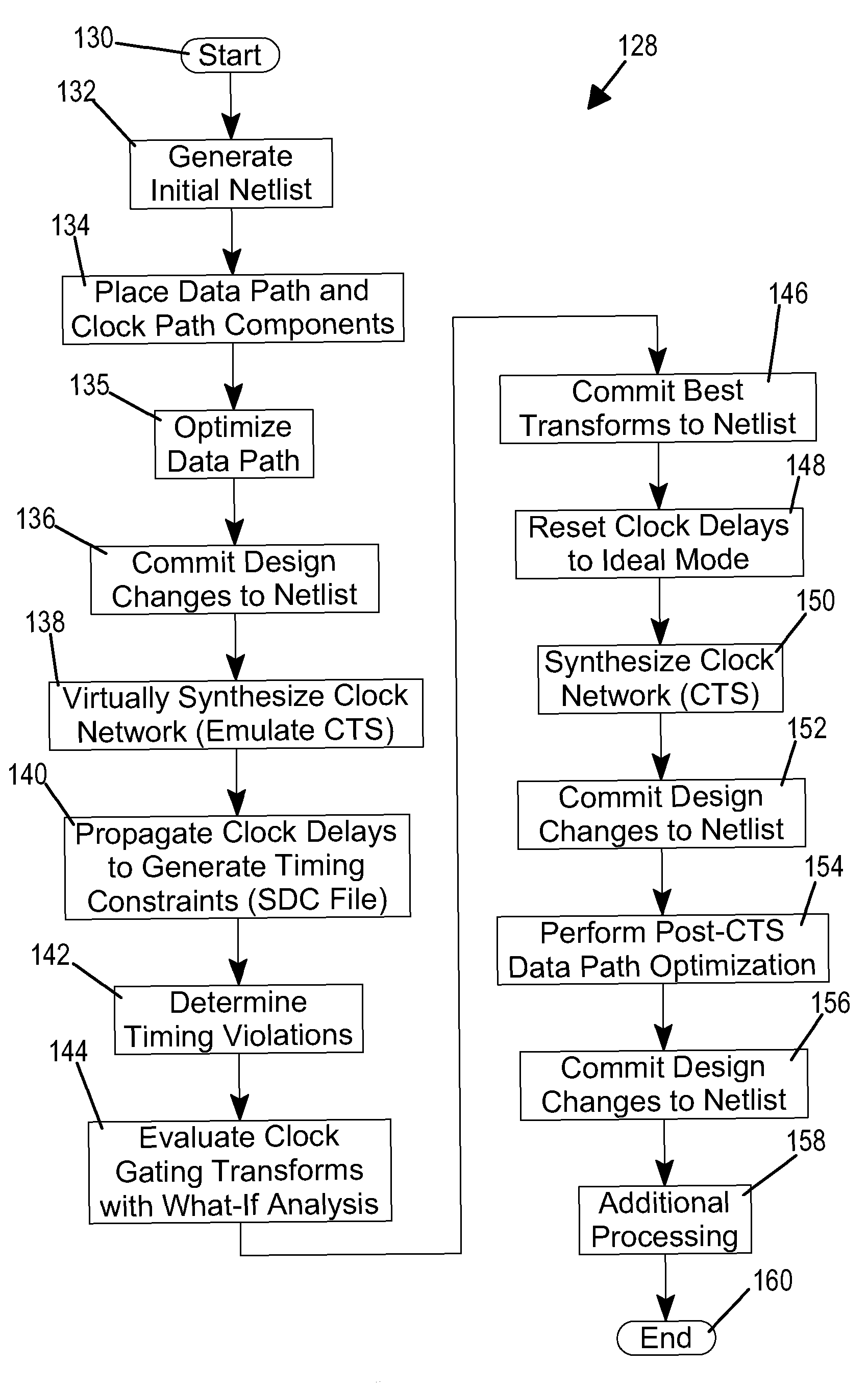

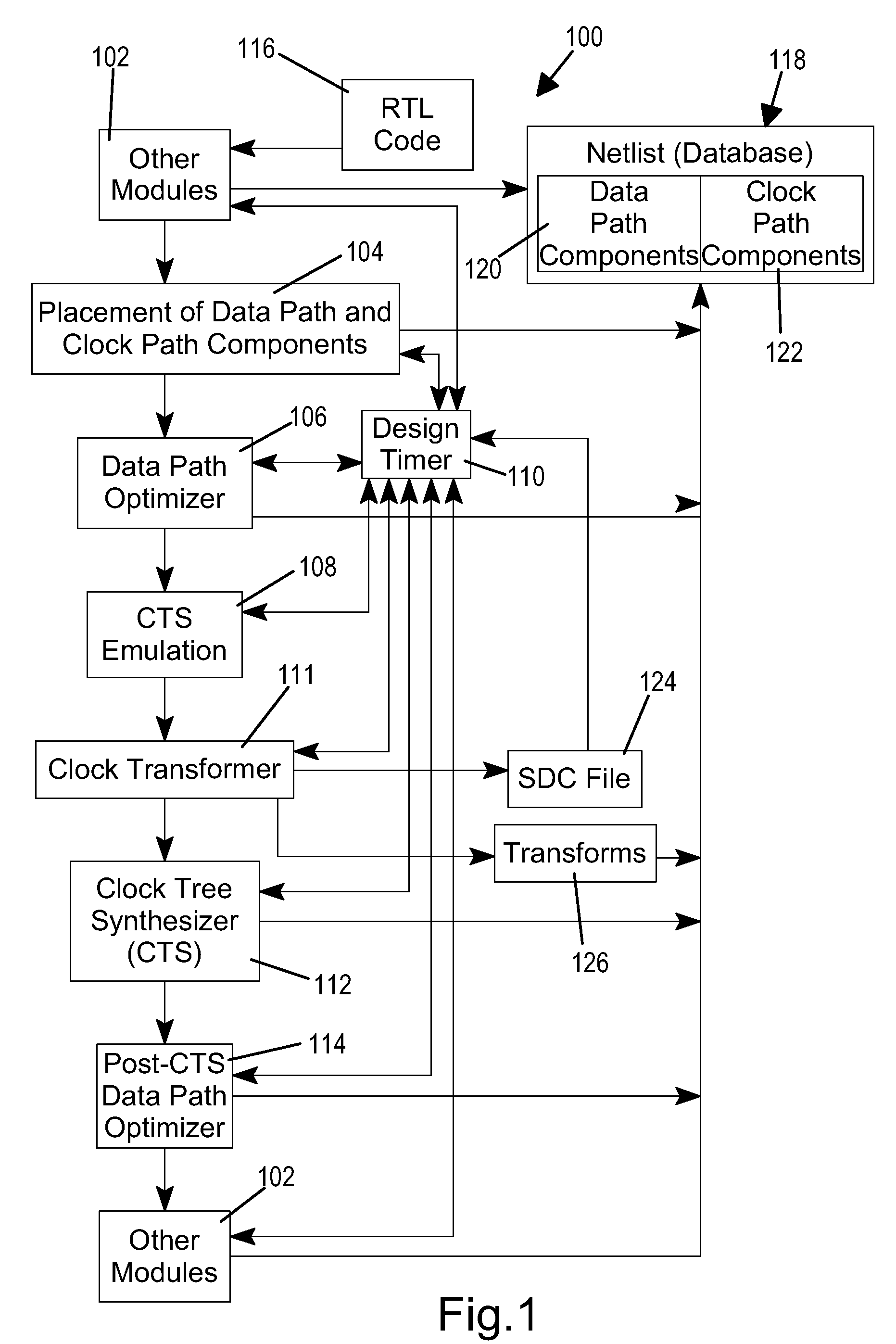

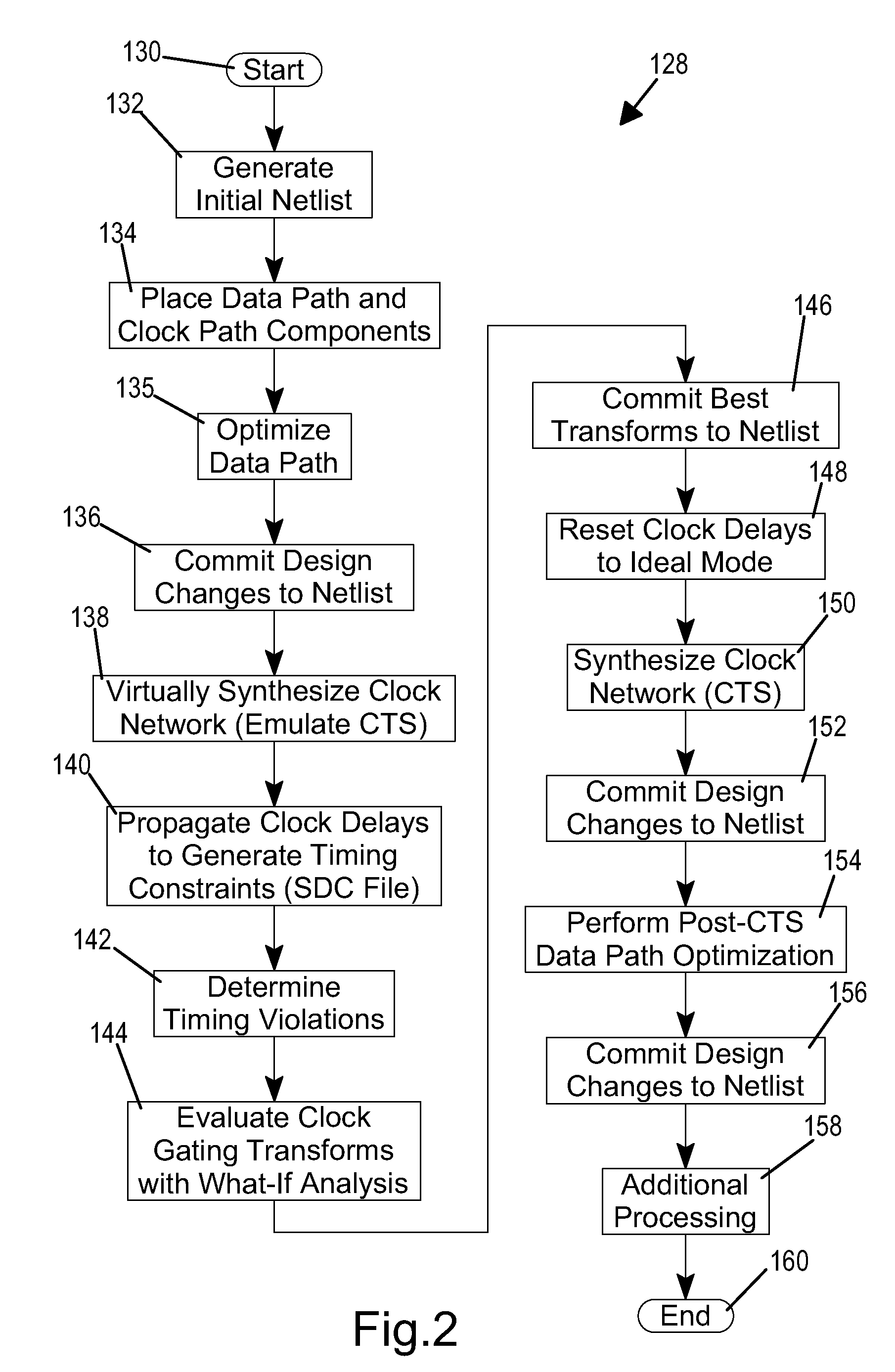

Achieving Clock Timing Closure in Designing an Integrated Circuit

ActiveUS20100070941A1Simple designCAD circuit designSoftware simulation/interpretation/emulationClock networkDatapath

Achieving clock timing closure in designing an integrated circuit involves virtually synthesizing a clock network for the integrated circuit design to generate virtual clock buffering in the clock network before a point in the design flow at which the clock network is actually synthesized and committed to a netlist. Timing violations are determined for clock gates generated by the virtual clock buffering. Clock gating transforms are evaluated for the clock gates having the timing violations, based on recalculated clock and data path delays, to incrementally virtually synthesize the clock network. The clock gating transforms that result in the best timing gains are committed to the netlist. The clock network is then actually synthesized for the integrated circuit design, and design changes, due to the actual clock network synthesis, are committed to the netlist.

Owner:CADENCE DESIGN SYST INC

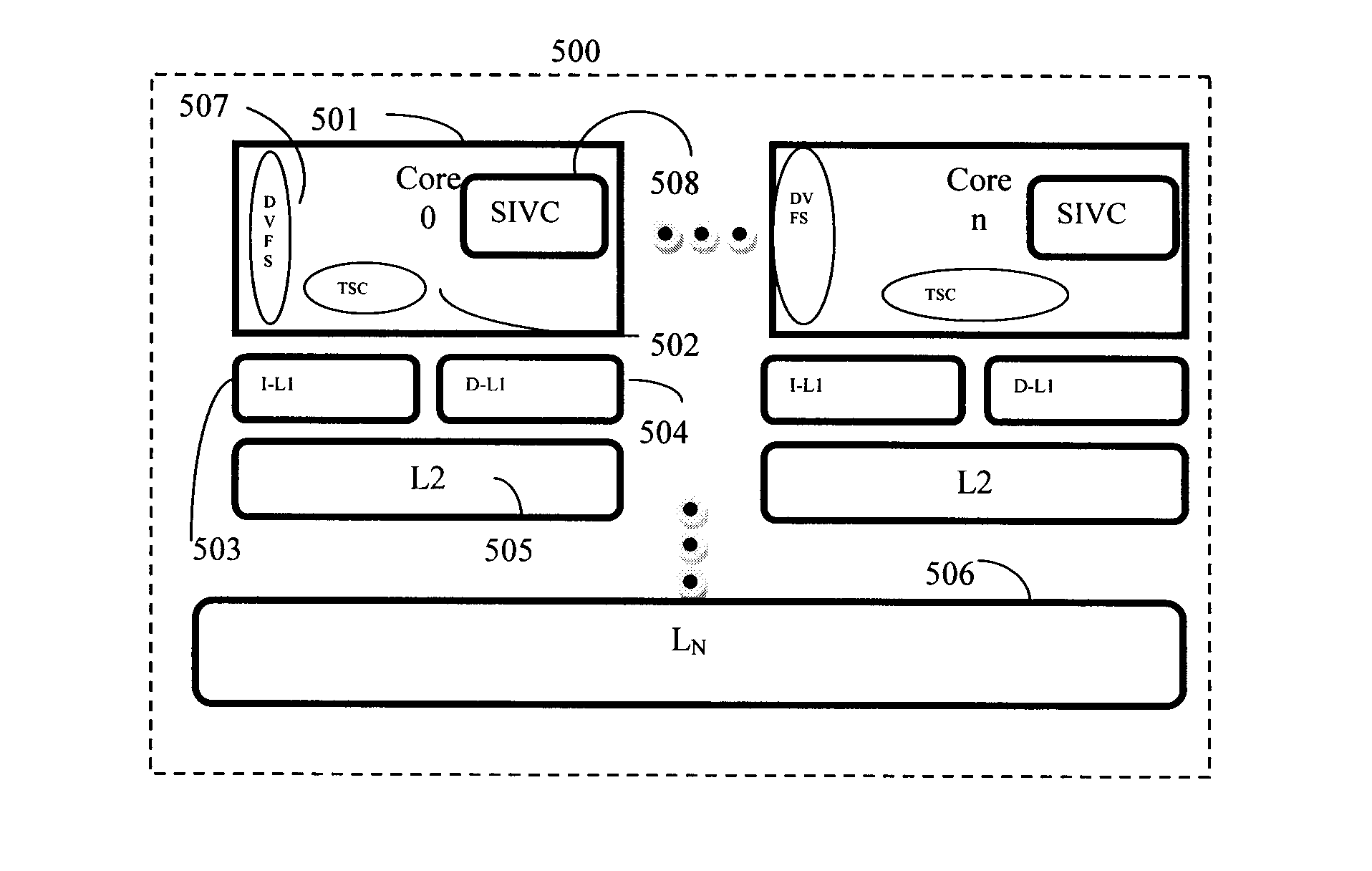

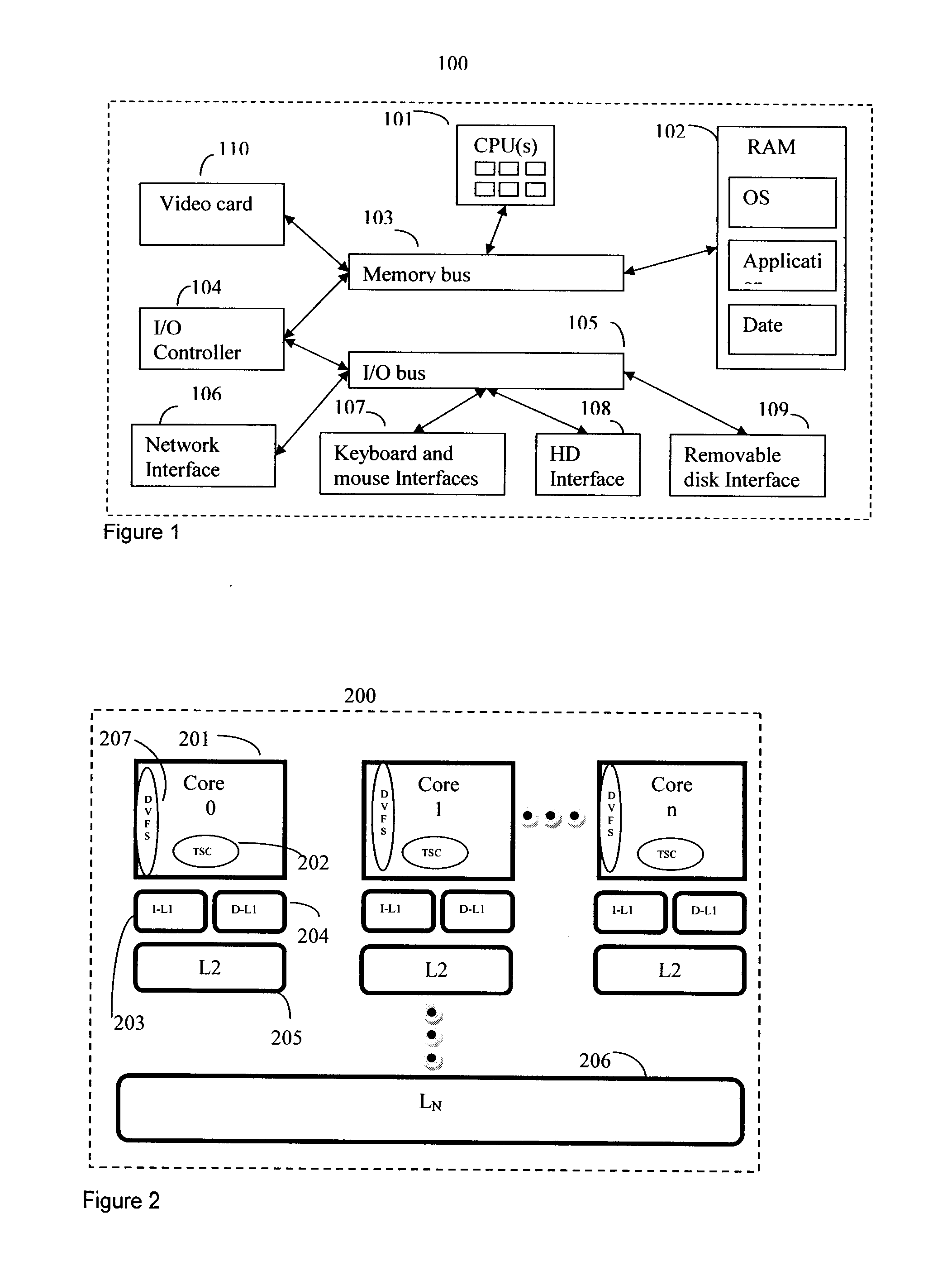

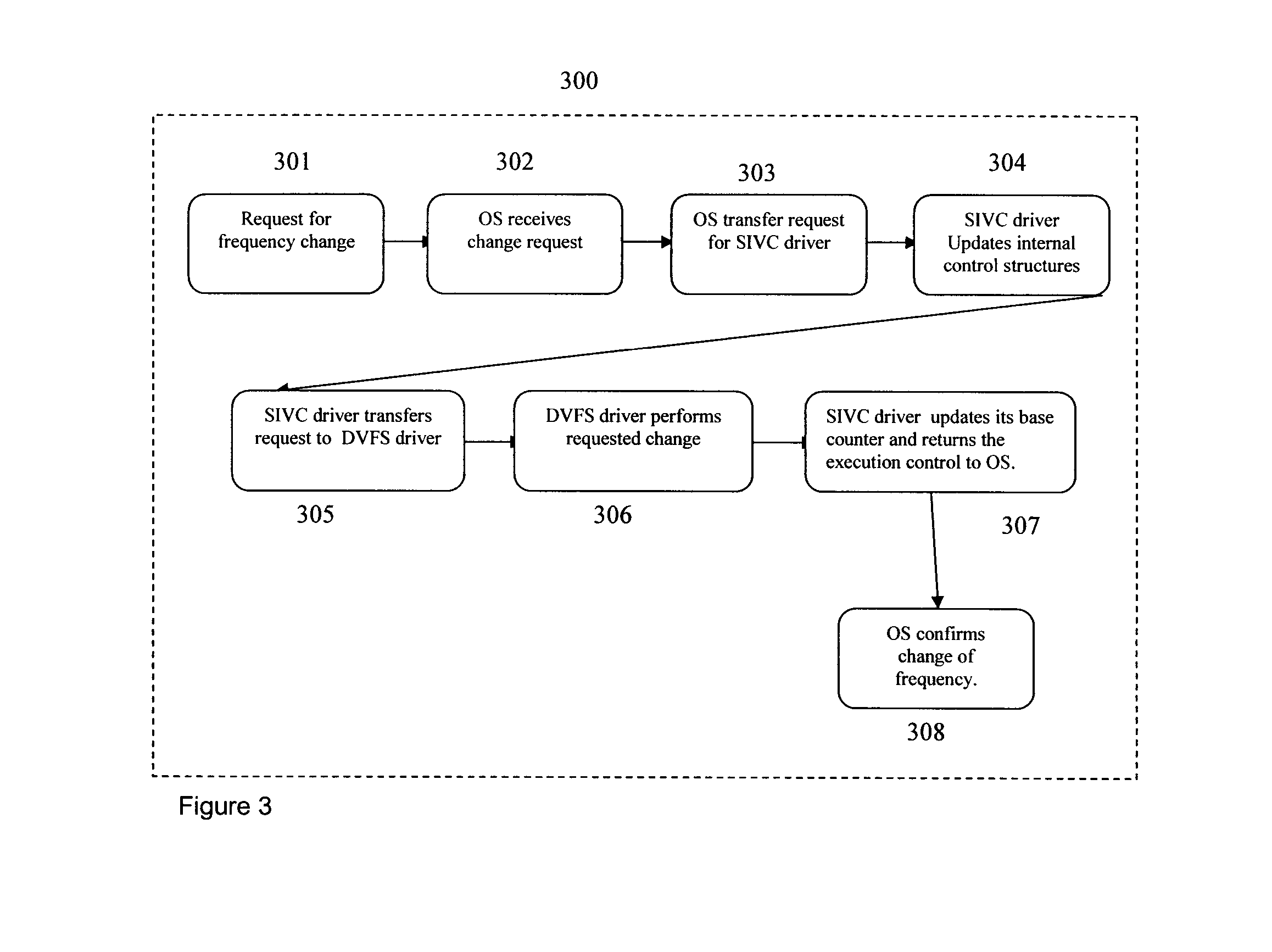

Strictly increasing virtual clock for high-precision timing of programs in multiprocessing systems

The present invention relates to a method of building virtual clocks that guarantee strictly increasing and high precision timekeeping of programs executed on multiprocessor systems. Specifically, a multiprocessor system is defined as a computing system composed of multiple processing units, where a processing unit is formed of multiple processor cores which operate asynchronously with each other. In addition each processor core has a time counter and operates with one of multiple operating frequencies and can change the operating frequency dynamically. The method builds a high-precision Strictly Increasing Virtual Clock (SIVC) on top of a computer system's time counter which is used as the reference time counter to which a control layer is implemented for capturing the system events that can advance or delay the elapsed time count of system clocks. In this way, SIVC can provide to the computer system a time counter which produces strictly increasing and high-precision values. A program will access SIVC information by using either an operating system call or a hardware instruction. A computer program will create a SIVC on top of a selected computer system's time counter and by isolating it from differences in time count caused by internal changes of the computer system such as internal replacements of a time counter by the system. The present invention guarantees that the SIVC values are strictly increasing and highly precise.

Owner:DE AMORIM CLAUDIO LUIS +2

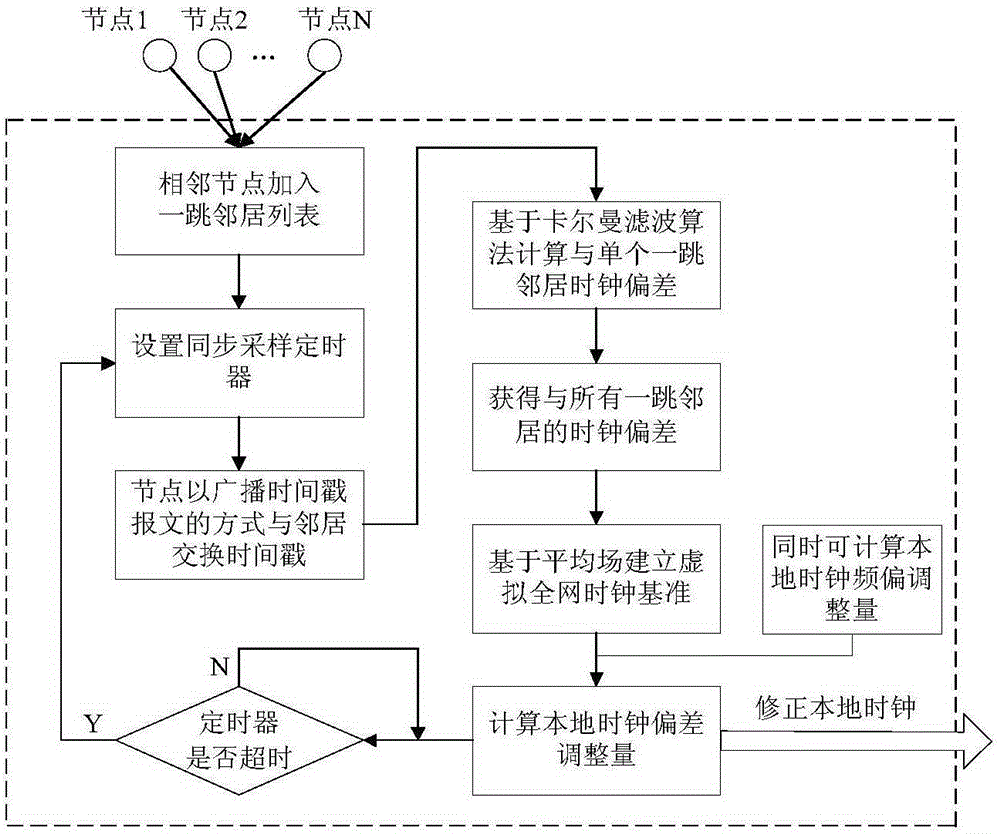

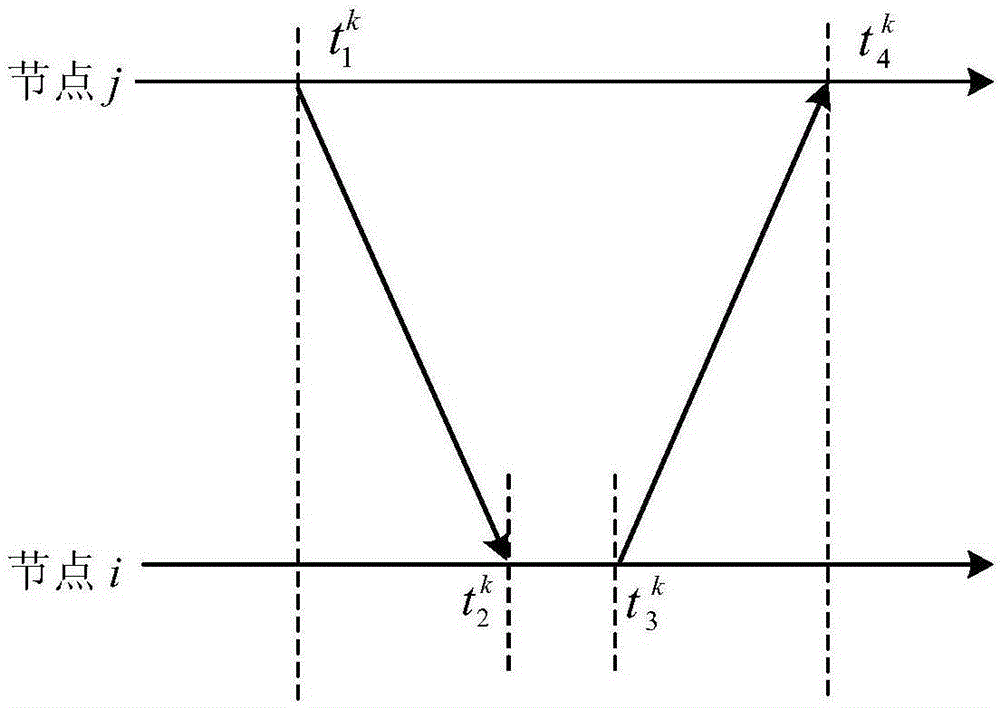

Distributed multi-hop wireless network clock synchronization method based on mean field

ActiveCN105188126ASolve the technical problem that the clock reference is difficult to determineSolve difficult technical problemsSynchronisation arrangementNetwork topologiesIsing modelEnergy minimization

The invention discloses a distributed multi-hop wireless network clock synchronization method based on a mean field, and aims to solve the technical problem that a clock reference is difficult to determine in an existing distributed clock synchronization method. According to the technical scheme, the method comprises the following steps: realizing bidirectional time stamp exchange in a broadcast way firstly; making a clock difference overall effect between nodes be equivalent to a mean field; establishing a clock synchronization model of a network based on a spatial Markov random field; introducing a neighbor system and a clique potential according to the equivalence between the Markov random field and a Gibbs random field to obtain a clock synchronization energy function based on a mean field Ising model; and giving a clock synchronization algorithm adopting energy minimization optimization, namely, a whole-network clock distributed synchronization algorithm based on a mean field model. Through adoption of a whole-network clock synchronization method based on the mean field model, a whole-network virtual clock reference is determined through a mean action between the nodes, so that the technical problem that the clock reference is difficult to determine in the distributed clock synchronization method in the prior art is solved.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

TDMA mobile ad-hoc network (MANET) with second order timing and tracking

InactiveUS7974402B2Multiplex system selection arrangementsSynchronisation arrangementTelecommunications linkCommunication link

Owner:STINGRAY IP SOLUTIONS LLC

Achieving clock timing closure in designing an integrated circuit

ActiveUS8095900B2Simple designCAD circuit designSoftware simulation/interpretation/emulationClock networkDatapath

Achieving clock timing closure in designing an integrated circuit involves virtually synthesizing a clock network for the integrated circuit design to generate virtual clock buffering in the clock network before a point in the design flow at which the clock network is actually synthesized and committed to a netlist. Timing violations are determined for clock gates generated by the virtual clock buffering. Clock gating transforms are evaluated for the clock gates having the timing violations, based on recalculated clock and data path delays, to incrementally virtually synthesize the clock network. The clock gating transforms that result in the best timing gains are committed to the netlist. The clock network is then actually synthesized for the integrated circuit design, and design changes, due to the actual clock network synthesis, are committed to the netlist.

Owner:CADENCE DESIGN SYST INC

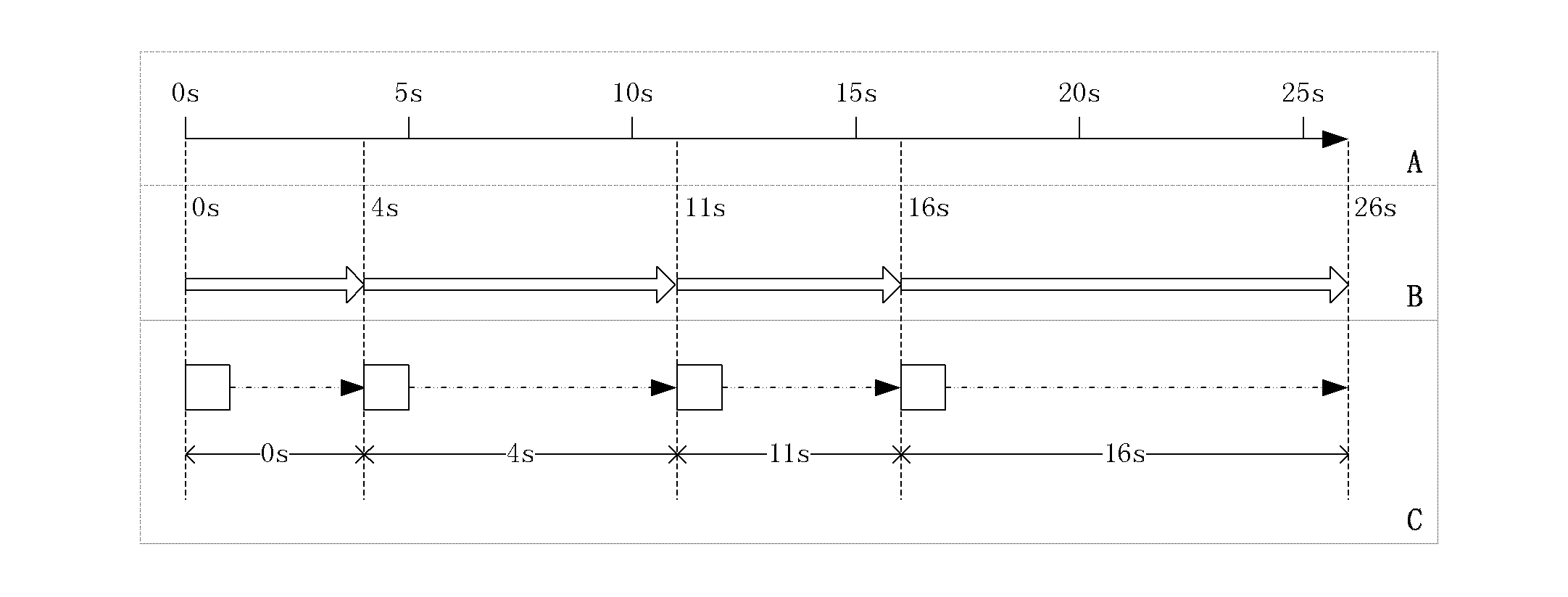

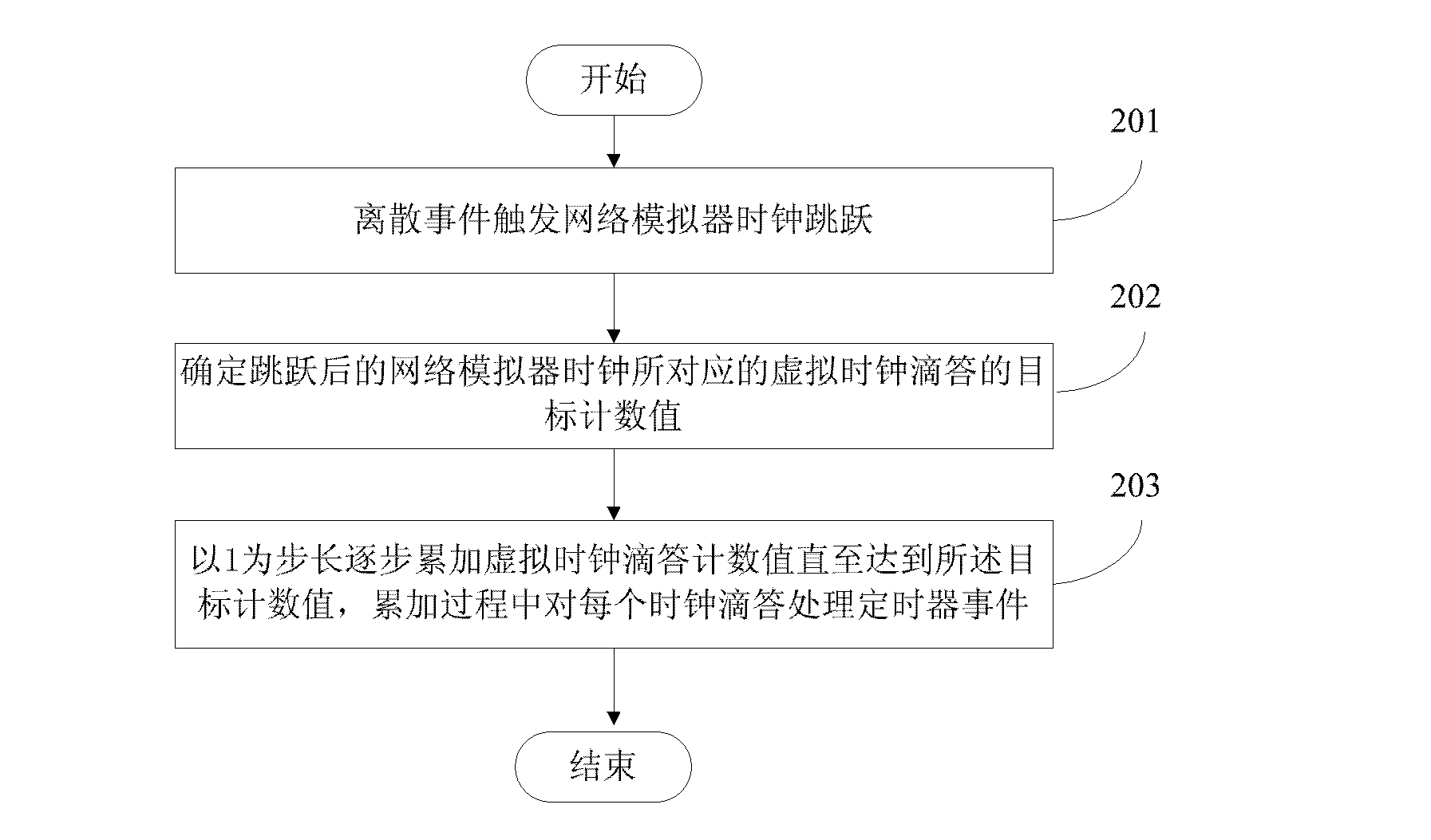

Clock synchronization method for network simulation environment of discrete event

ActiveCN102662428AAvoid distortionProgram synchronisationGenerating/distributing signalsTimerDistortion

The invention provides a clock synchronization method for network simulation environment of discrete event. The method comprises the steps of: 1) determining a virtual clock tick count value corresponding to occurrence time of a discrete event when the discrete event occurs, and sending the tick count value as a target count value to a kernel-state program; controlling operation of all timers of real software accessing to a network simulation environment of discrete event by using the virtual clock tick count value; 2) summating the virtual clock tick count value gradually by using 1 as step length to reach the target count value by the kernel-state program; for a real software accessing to a network simulation environment of discrete event, determining whether the timer of the real software overtimes or not each time when the virtual clock tick count value is added by 1. The method of the invention assists in avoiding distortion caused by time inconsistence between simulation environment and real environment. In the invention, the real software can be applied in network simulation environment of discrete event directly without modification.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

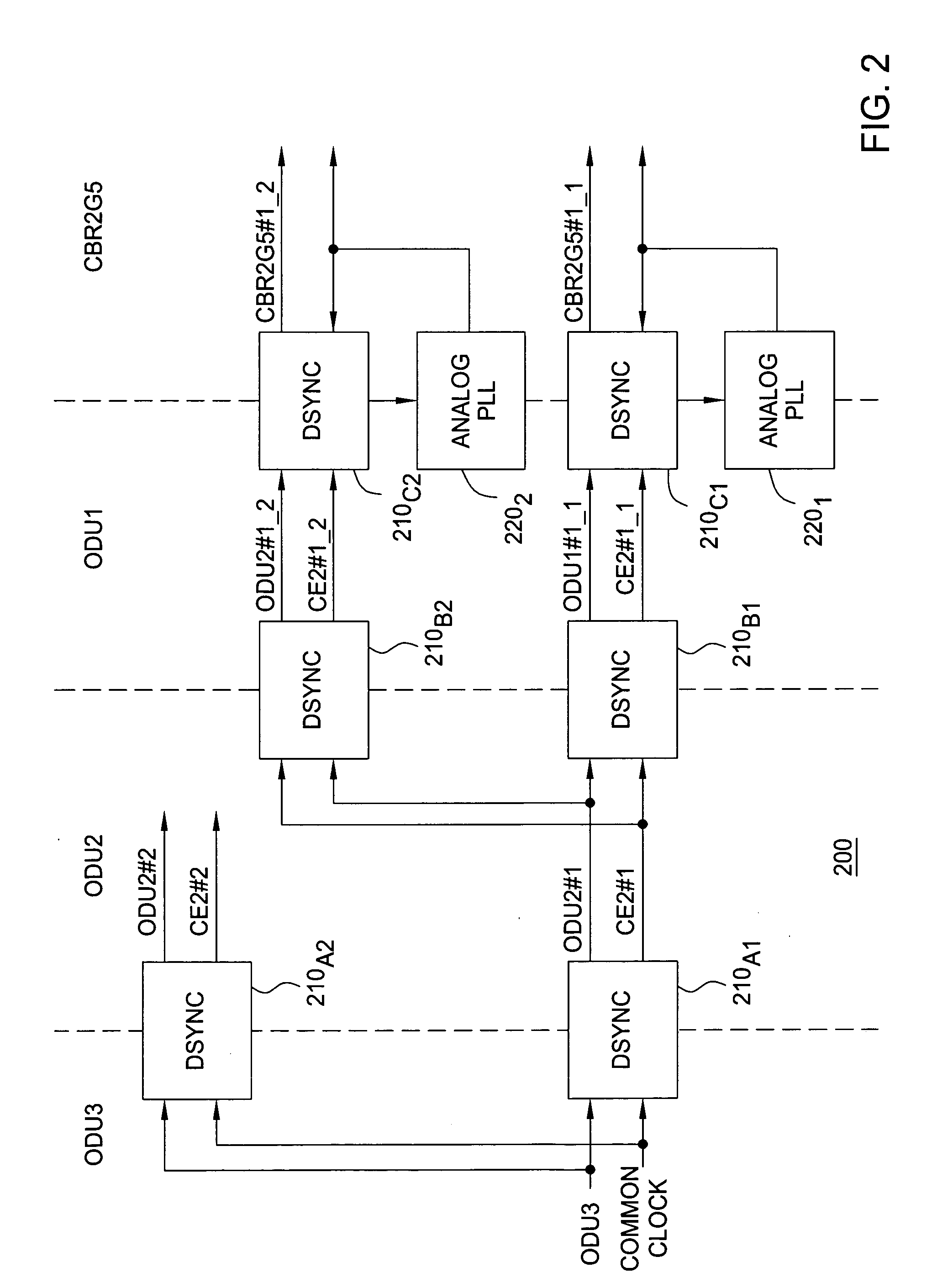

Method and apparatus for generating virtual clock signals

The invention includes a method and apparatus for generating virtual clock signals for differing hierarchies in a communication system conveying data frames of differing hierarchies. Specifically, a method according to one embodiment of the invention includes receiving data frames of a first hierarchy, receiving at least one input clock signal, and generating a virtual clock signal using the at least one input clock signal and a clock enable signal. The clock enable signal is generated using at least one of a data rate ratio and a clock rate ratio. The virtual clock signal is adapted for converting at least a portion of the data frames of the first hierarchy to data frames of a second hierarchy. The frequency of the virtual clock signal is determined by applying the clock enable signal to a common clock signal.

Owner:WSOU INVESTMENTS LLC

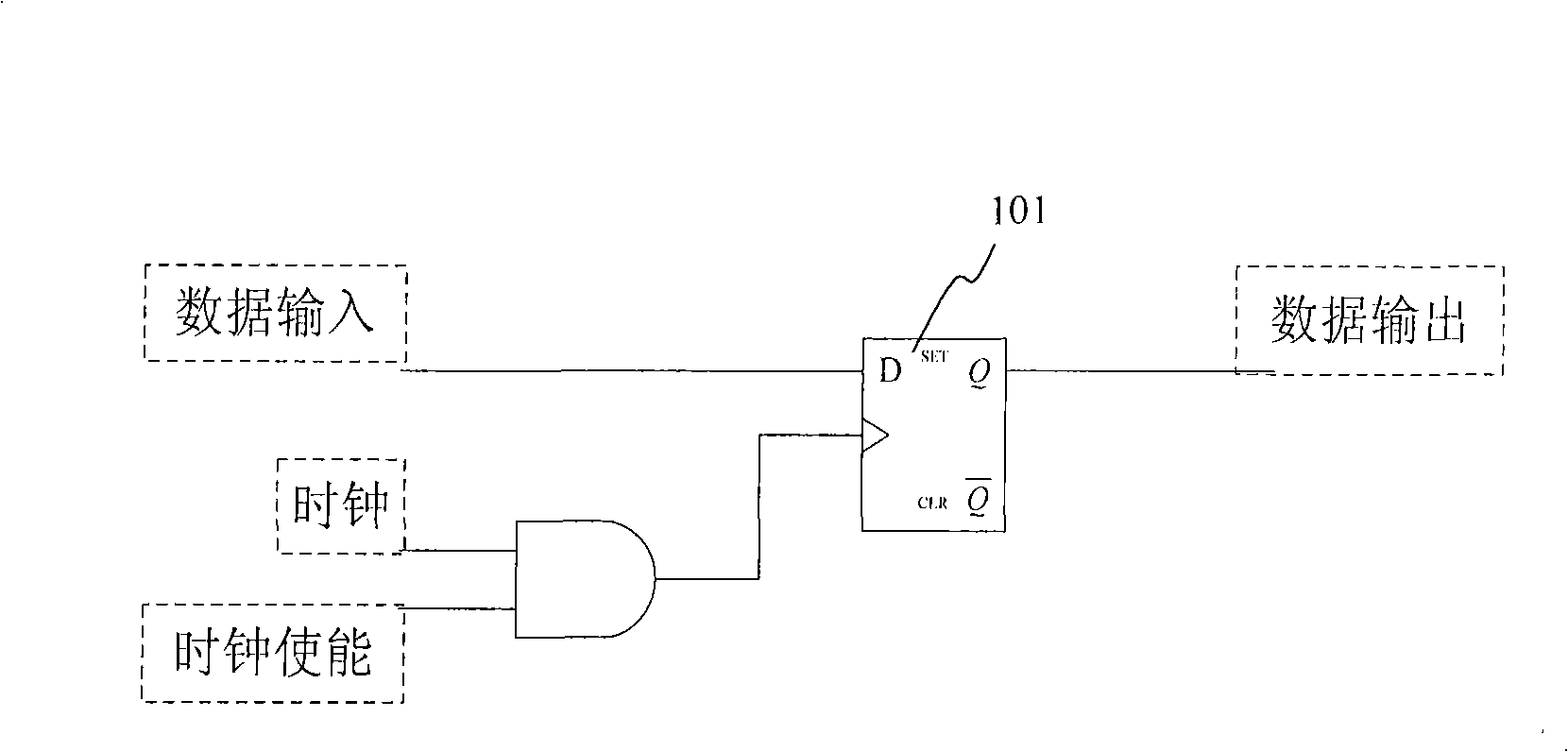

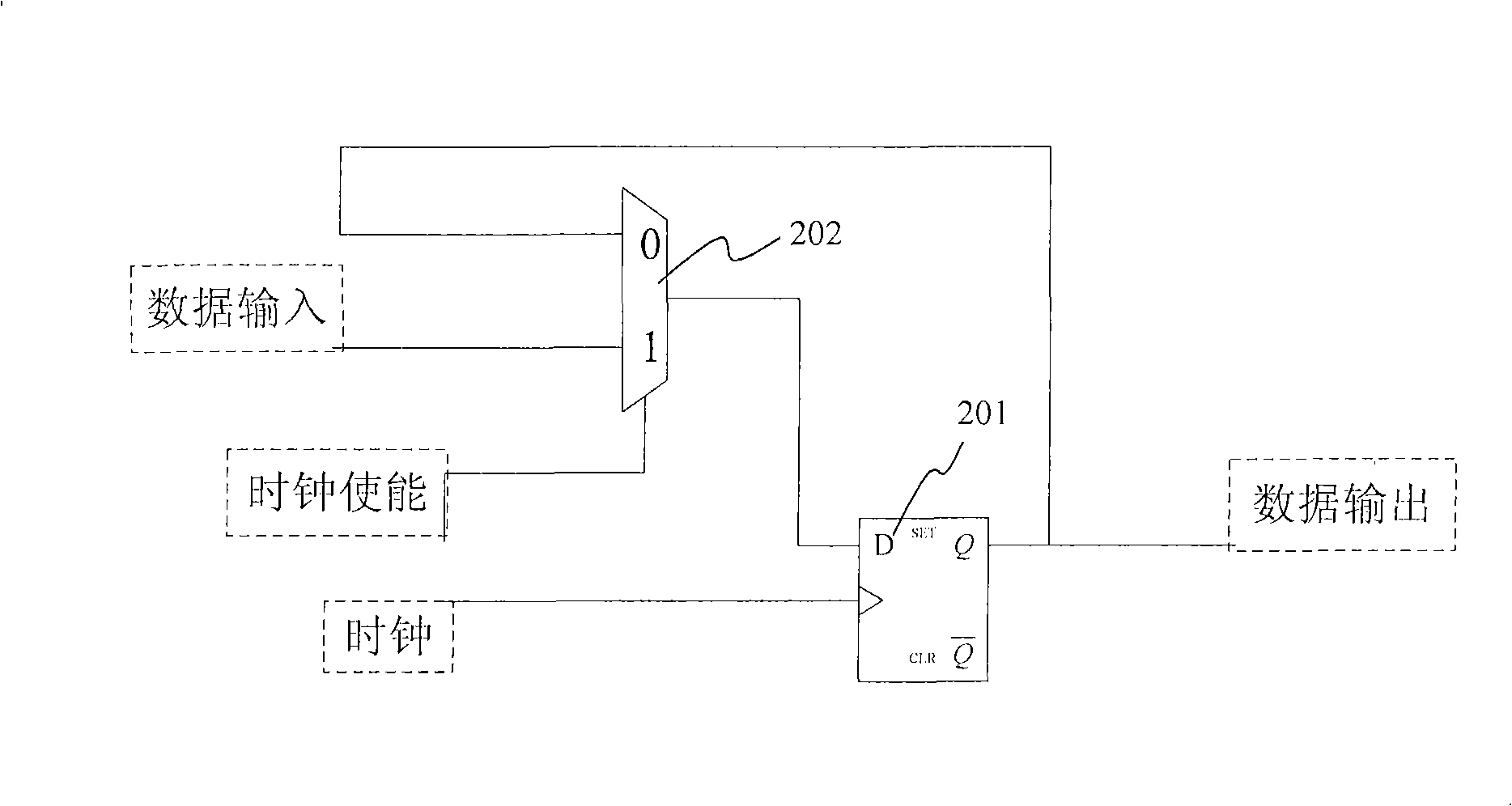

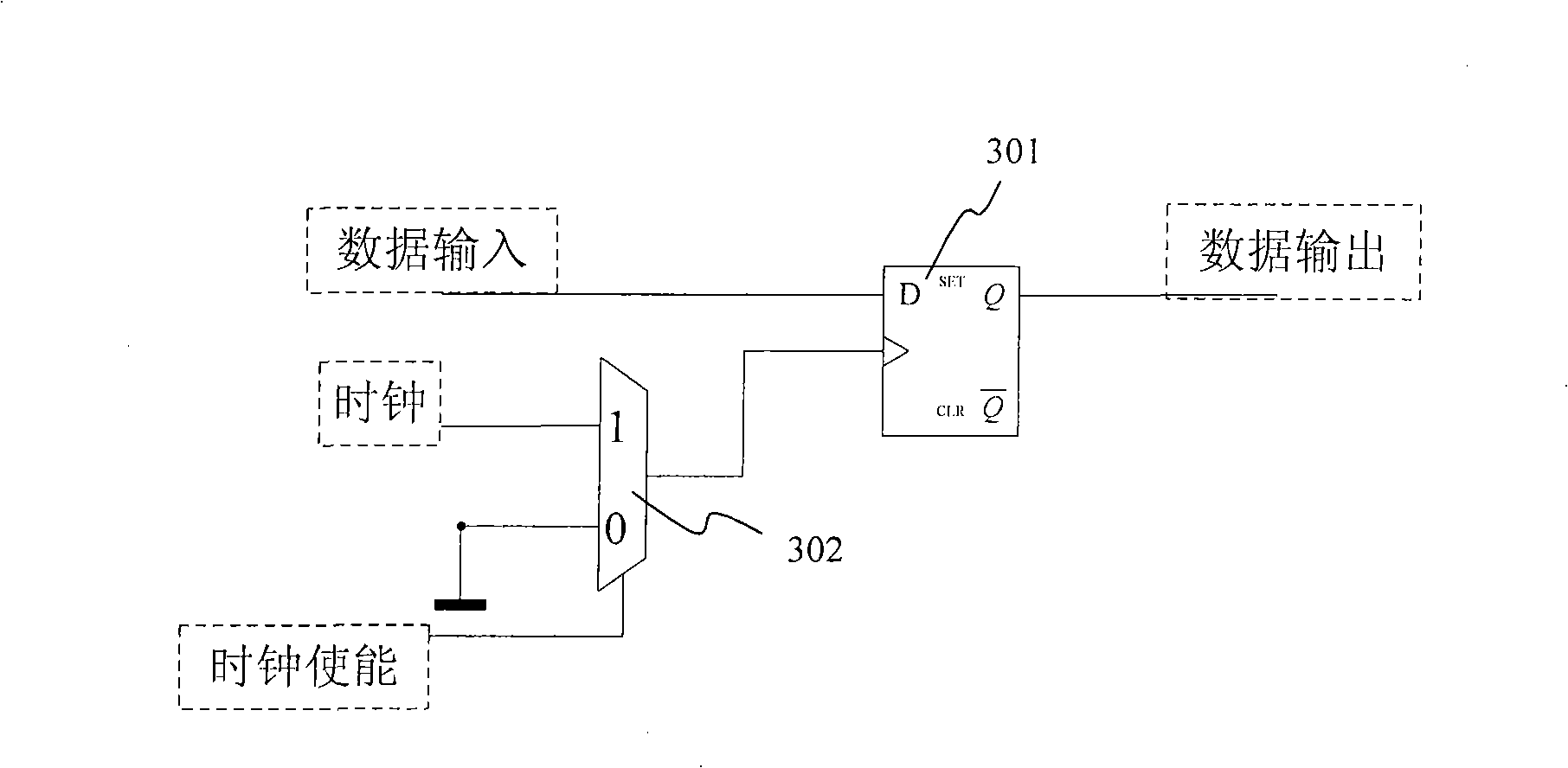

Gating clock for on-site programmable gate array and implementing method thereof

InactiveCN101303711AMeeting Clock Tree RequirementsMeet the needs of design verificationSpecial data processing applicationsGate arrayClock tree

The invention provides a gated clock in a field programmable gate array and a realizing method thereof; the gated clock includes a plurality of triggers, and a global clock cache multi-route selector the output end of which is connected with the clock input ends of the triggers; the global clock cache multi-route selector is used for leading the input of the clock input ends of the triggers to be a clock signal when a clock enabling signal is effective and leading the input of the clock input ends of the triggers to be zero when the clock enabling signal is ineffective. In the invention, a plurality of triggers are connected with the same BUFGMUX, thereby reducing the consumption of a plurality of areas. The gating mode is consistent with a real ASIC; the clock enabling signal is synchronous with the phase relation of the clock; when the enabling signal is ineffective, the actual clock inputted into the trigger is zero; therefore, more accurate evolution can be carried out on the power consumption; the demands of a clock tree in FPGA can be met; the invention is simple and practical.

Owner:VIMICRO CORP

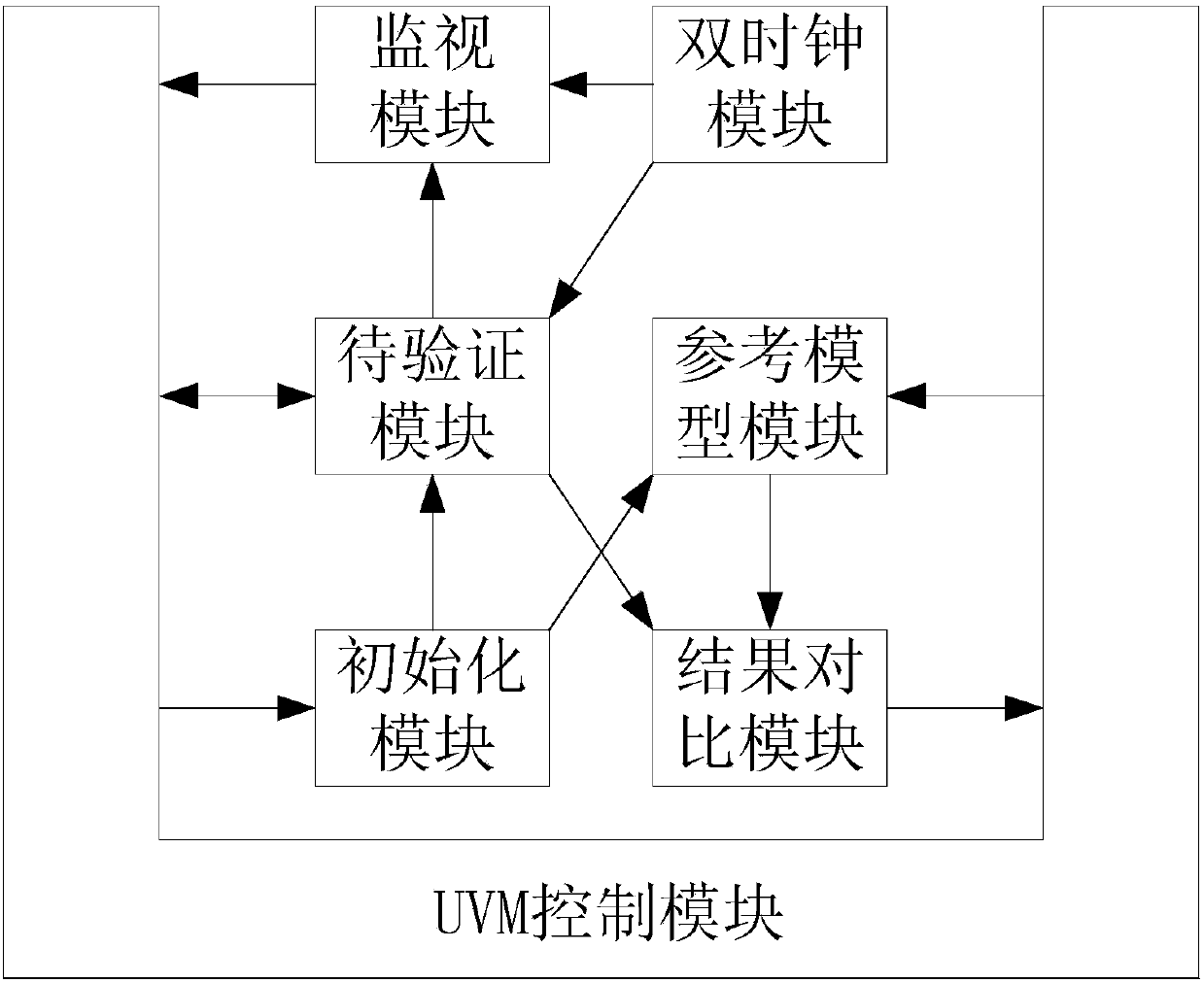

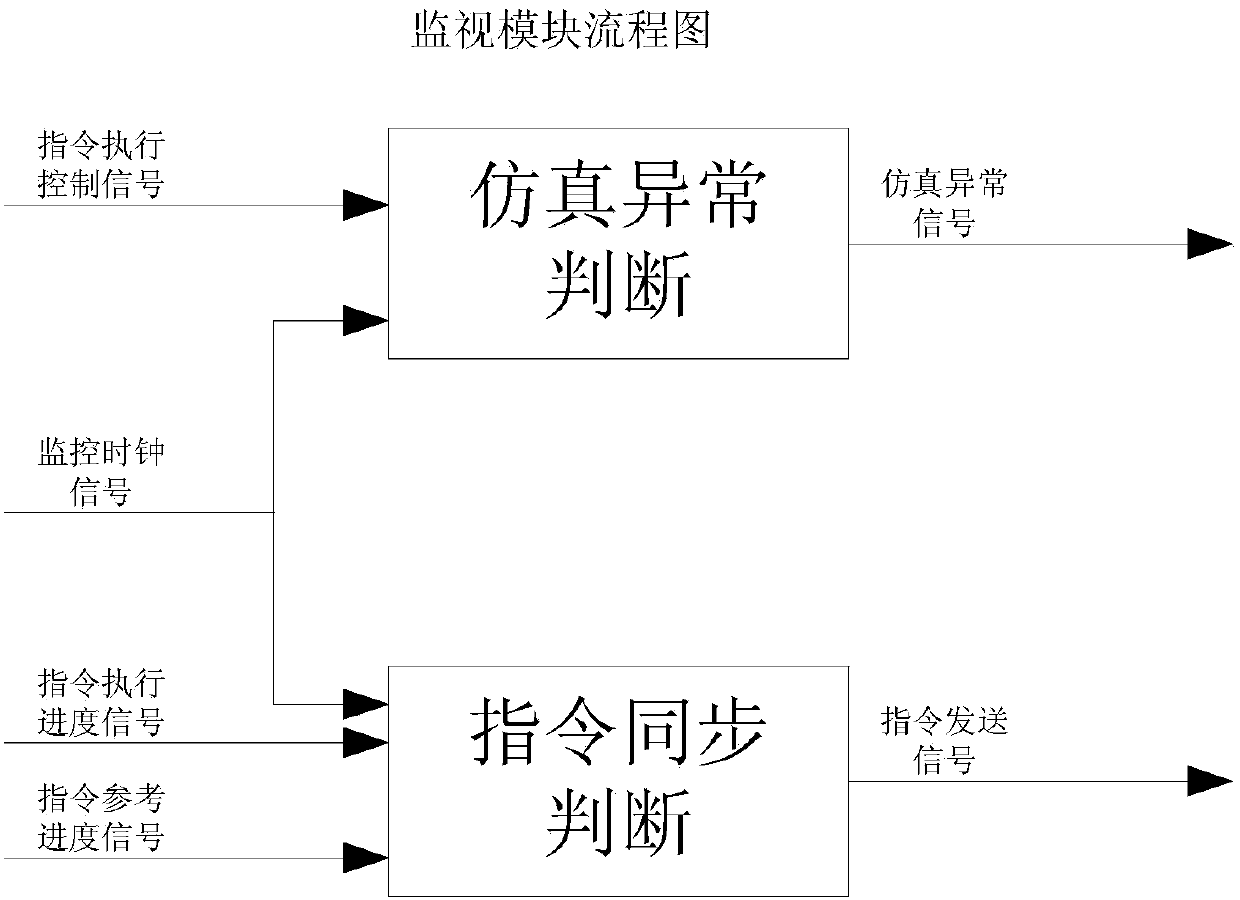

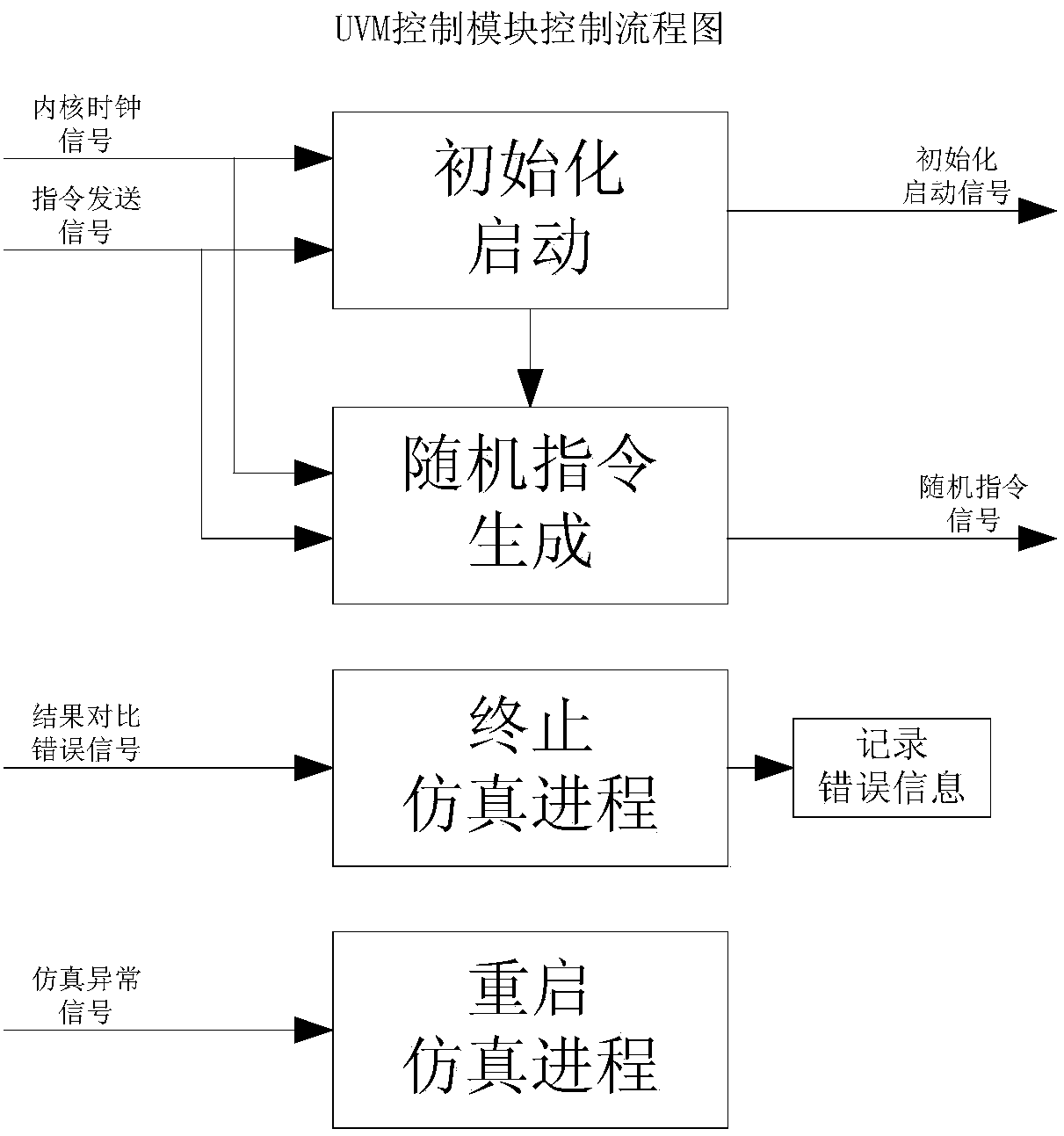

SoC verification platform with high efficiency and high coverage rate for virtual clock synchronization

ActiveCN108038283AFlexible configurationResolve synchronizationSpecial data processing applicationsReference modelComputer module

The invention relates to an SoC verification platform with high efficiency and high coverage rate for virtual clock synchronization. The SoC verification platform comprises a dual clock module used for generating two clock signals required by a system, a module to be verified used for executing random instructions and feeding back an execution result, a reference model module used for providing acomparison result of the module to be verified for the system, an initialization module used for providing programs required for initialization, a monitoring module used for monitoring the operating state of the module to be verified, a result comparison module used for checking the execution result of the module to be verified and a control module used for controlling the operation flow of the entire system. An SoC random instruction synchronization test platform can provide a solution for the problem that the instructions in the module to be verified in the SoC verification platform are difficult to synchronize with the instructions in a reference model, so that a lot of verification time is saved, the work difficulty is reduced, and the coverage rate of verification is increased.

Owner:BEIJING MXTRONICS CORP +1

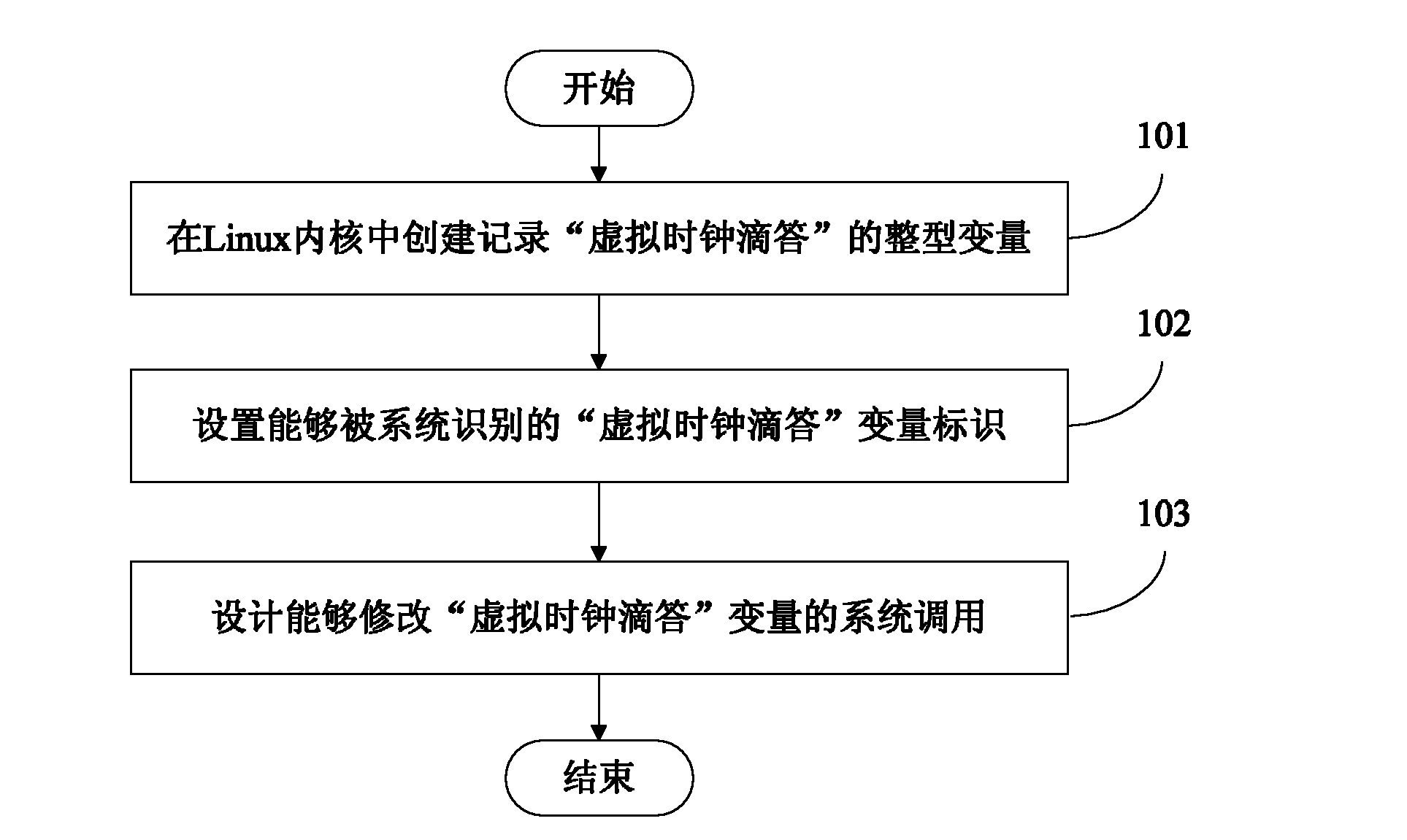

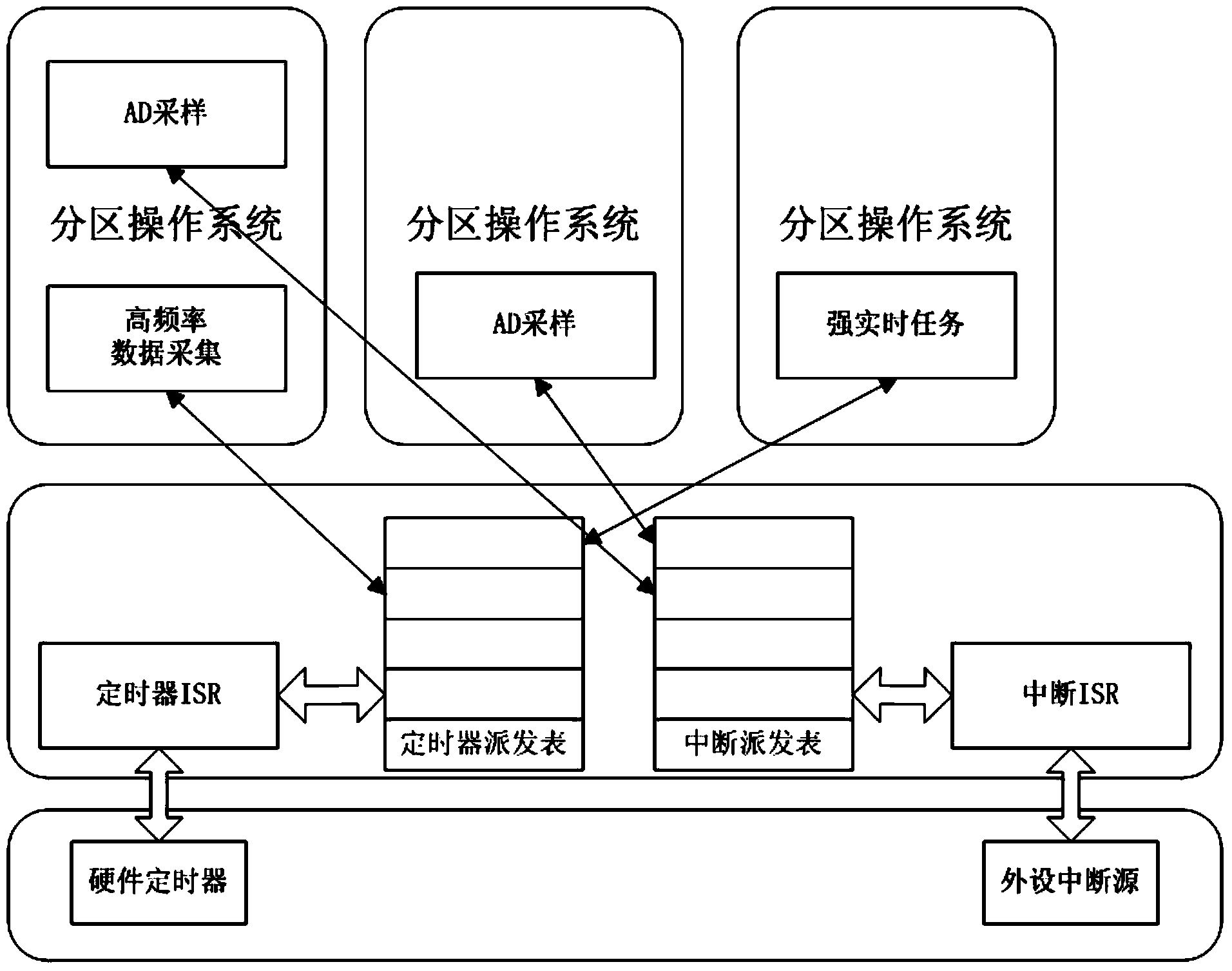

Method for realizing hard real time virtual timer response of embedded virtual machine

ActiveCN103853598ALower latencyAchieve sharingSoftware simulation/interpretation/emulationVirtual timeTimer

Owner:北京神舟航天软件技术股份有限公司

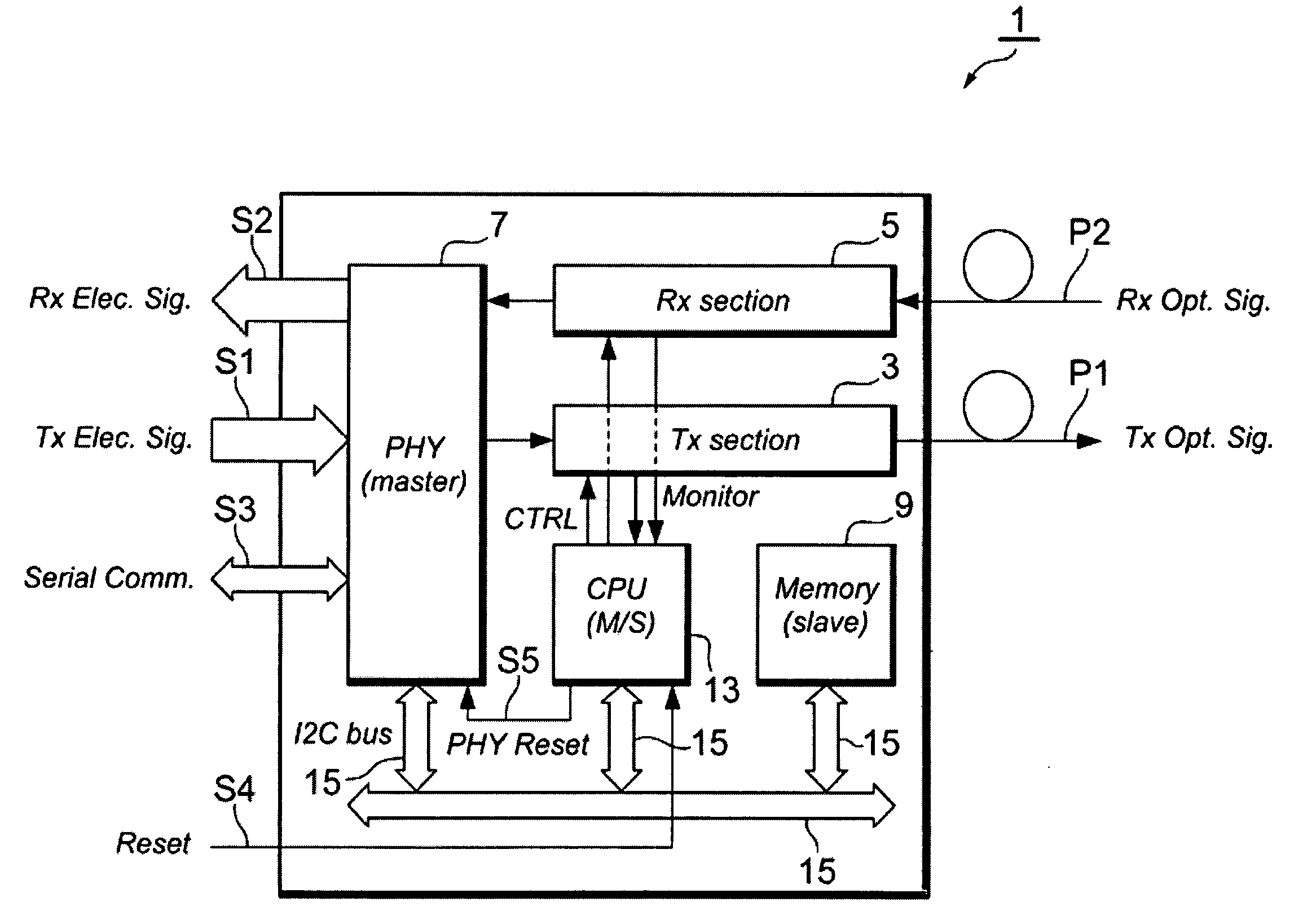

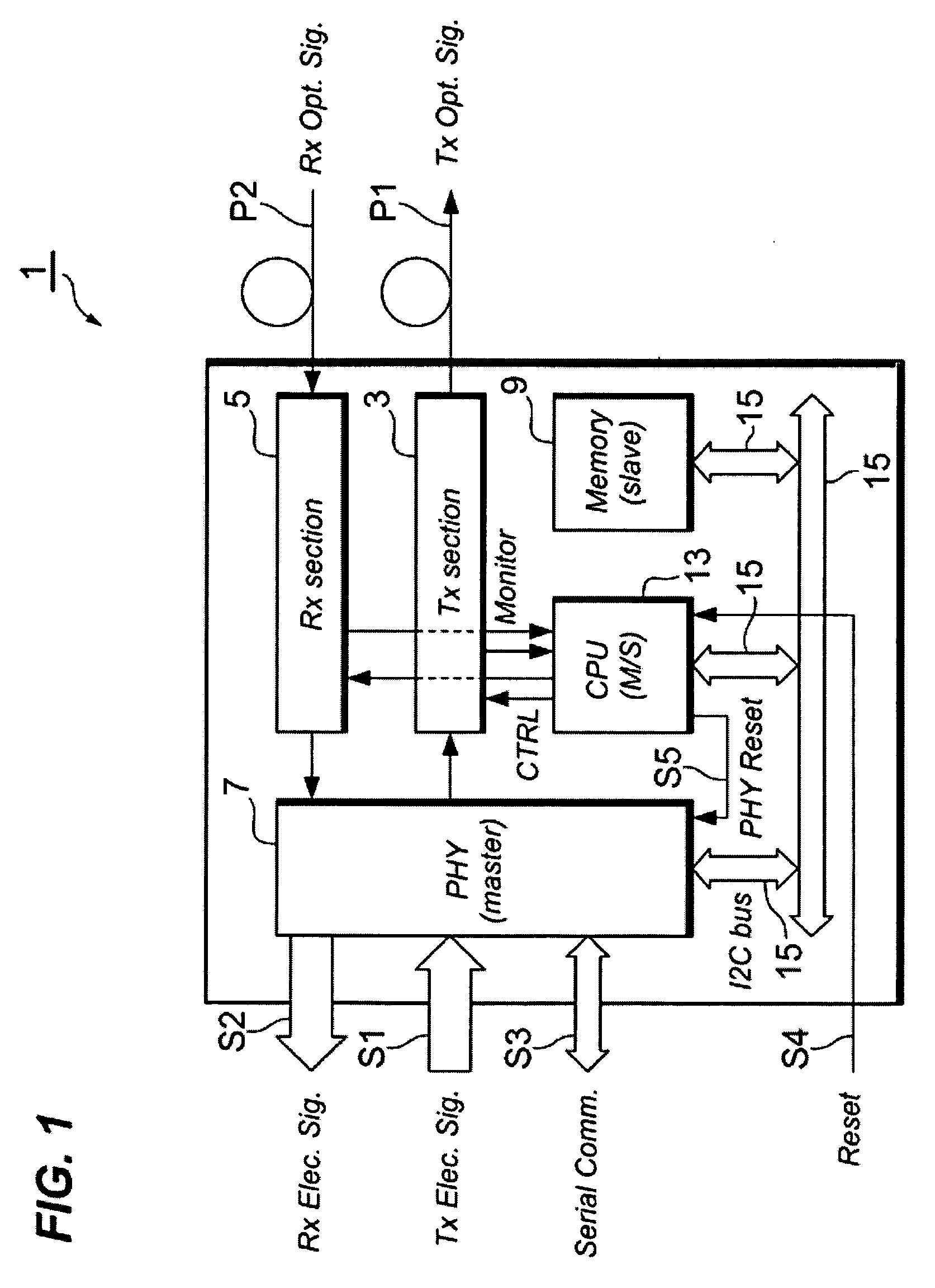

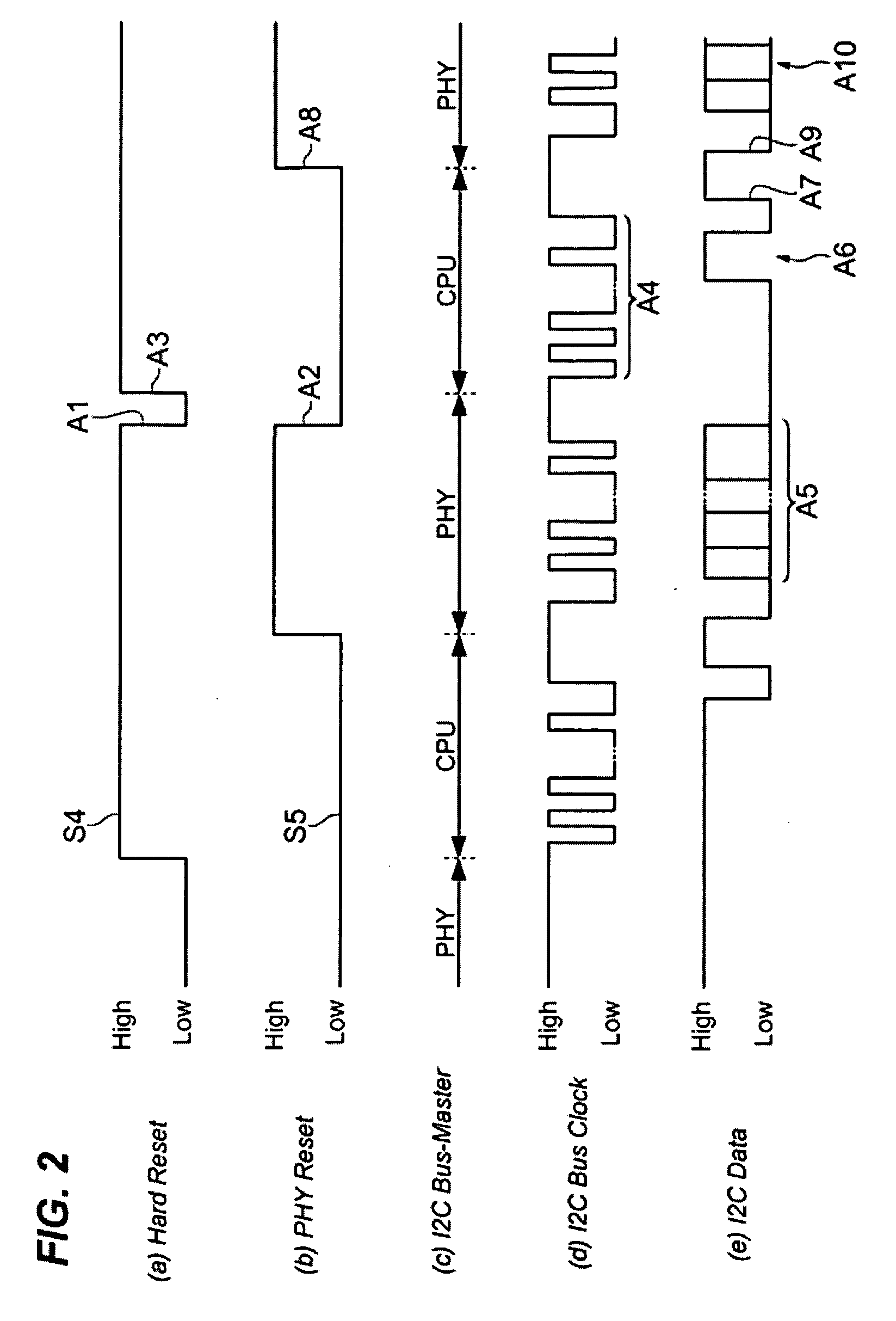

Optical data link stably operable for duplicated reset

InactiveUS20080131139A1Bus-type electromagnetic networksTransmission monitoring/testing/fault-measurement systemsPhysical layerEmbedded system

The preset invention provides an optical data link that prevents the internal I2C bus system from being hung up. The data link provides a CPU able to receive a reset signal and an IC (PHY) to control the physical layer to communicate with the outside of the data link, and they are coupled via the internal I2C bus system. When the data link receives a reset signal, the PHY behaves as the slave device, while, the controller behaves as the master device to output dummy clocks on the clock line of the I2C bus so as to sweep left data on the data line of the I2C bus.

Owner:SUMITOMO ELECTRIC IND LTD

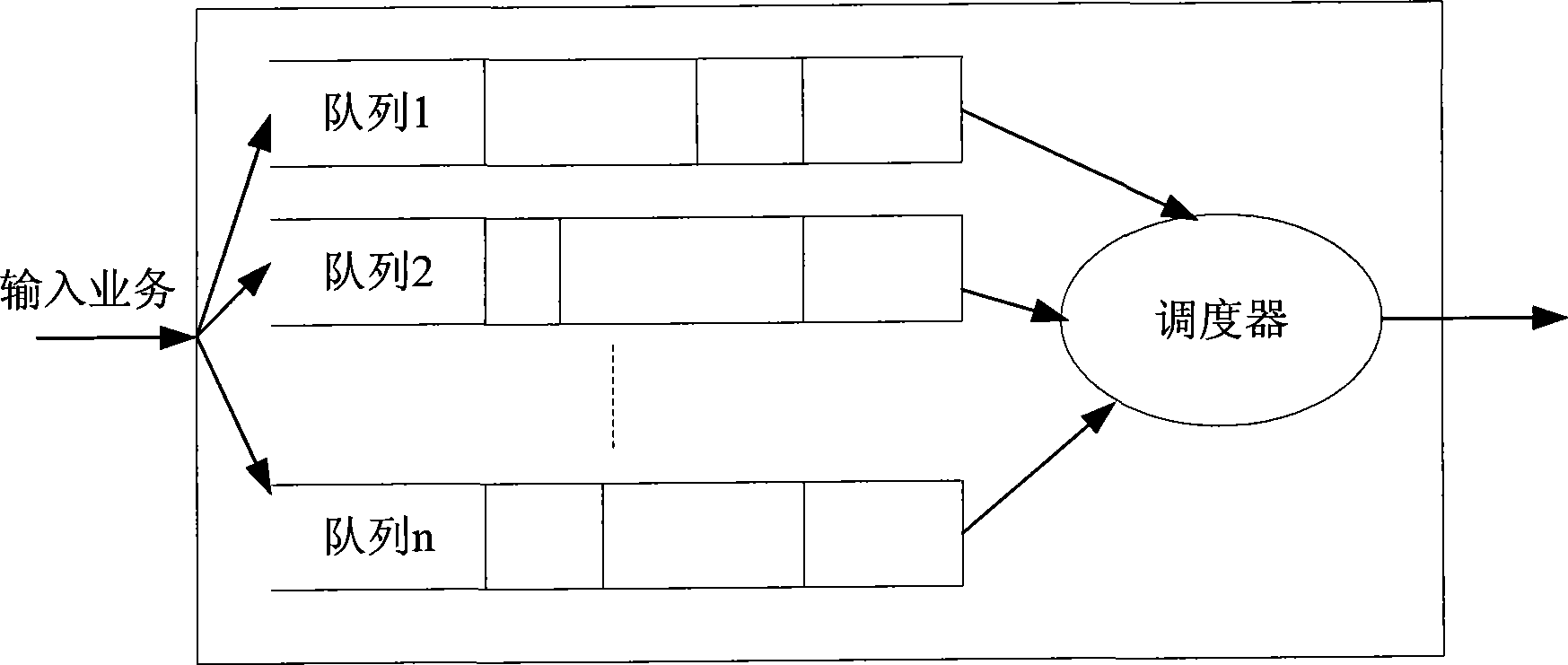

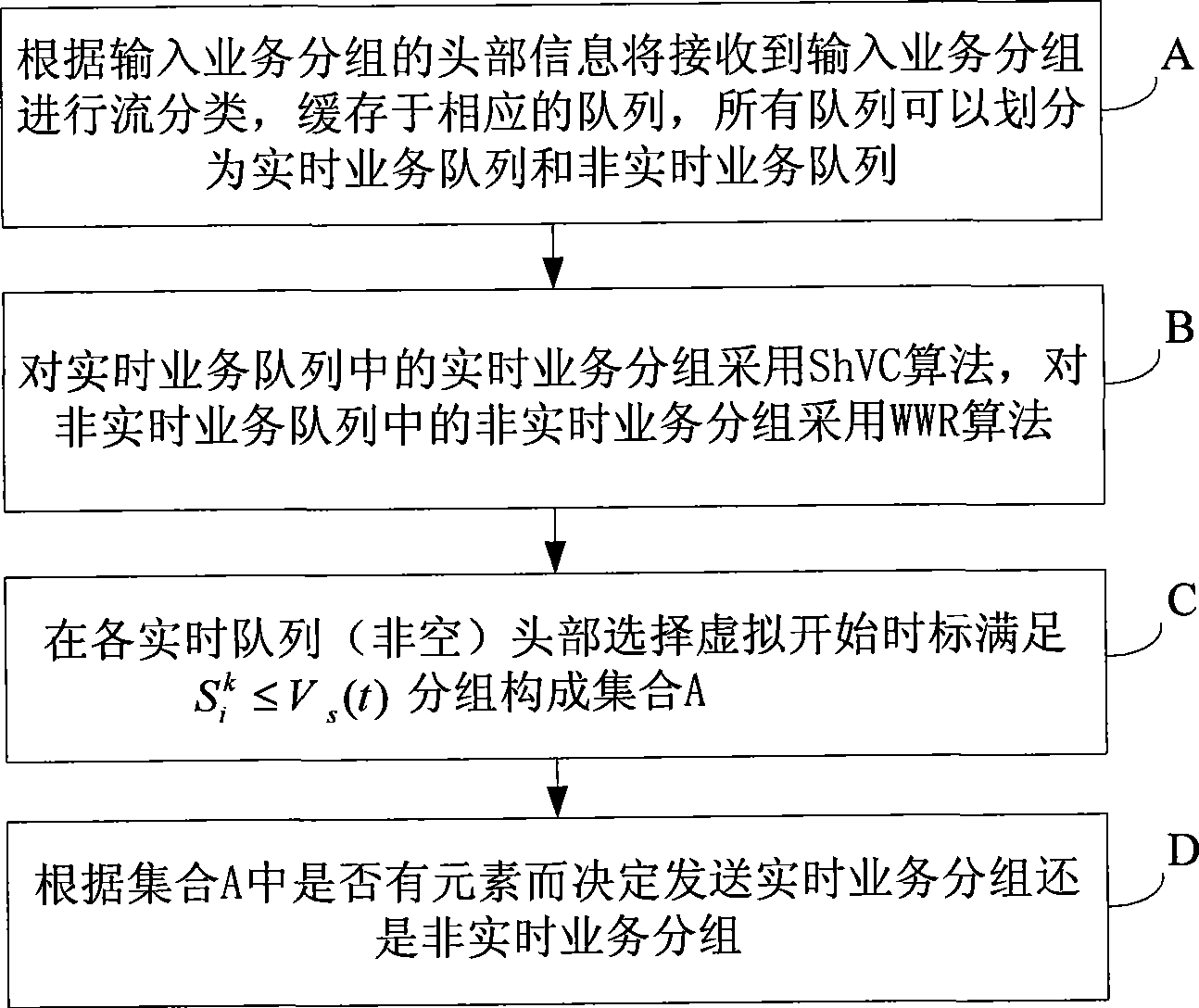

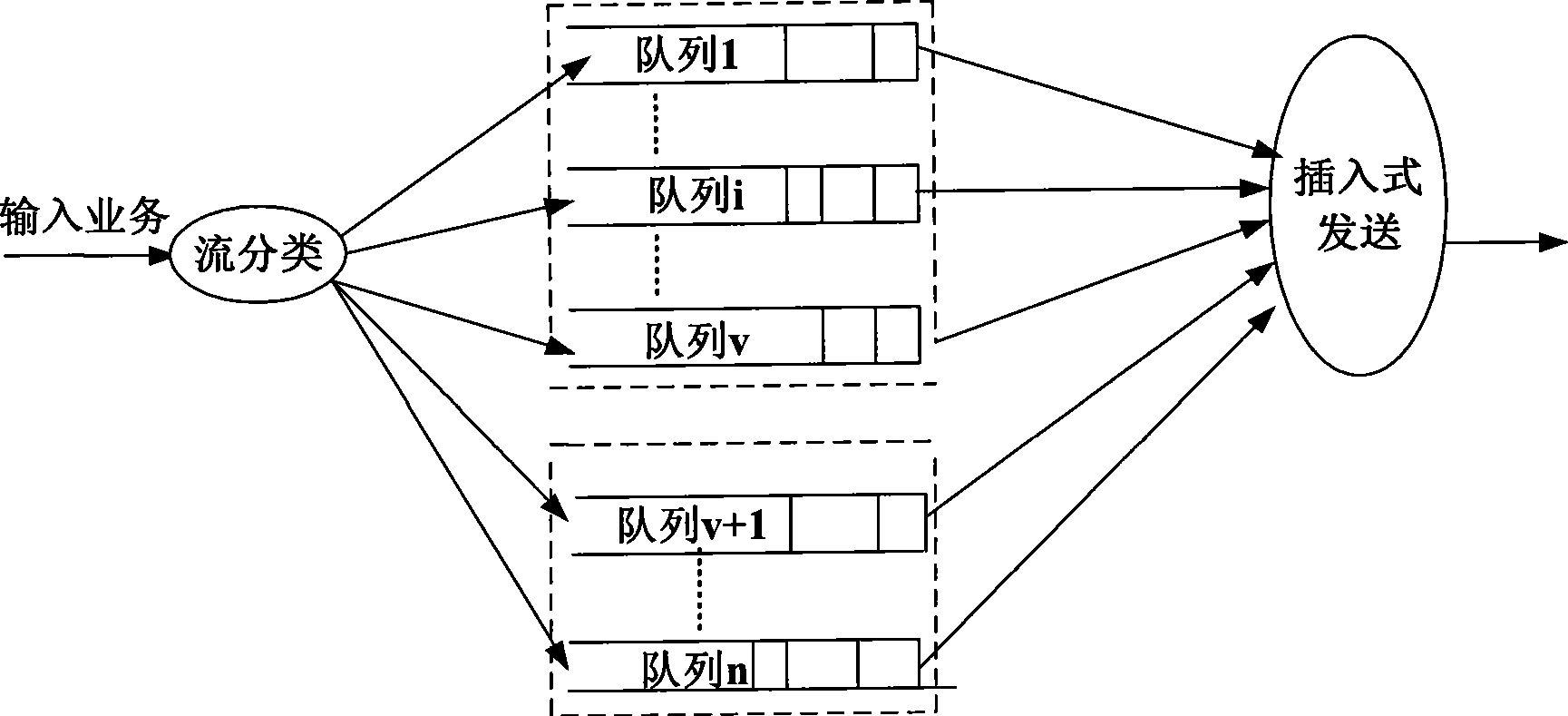

Method and apparatus for scheduling packet

InactiveCN101465794AUniform outputTimely outputData switching networksNon real timeReal time services

The embodiment of the invention discloses a packet scheduling algorithm and a device thereof, belonging to communication field. The packet scheduling algorithm includes the following steps: partitioning the service packets into real-time service packets and non-real-time service packets according to headers of the service packets; judging whether legal real-time service packets exist in the real-time service packets according to shaping virtual clock algorithm, if yes, sending out the legal real-time service packets, and if no, sending out the non-real-time service packets; if new legal real-time service packets appear during the process of sending out the non-real-time service packets, suspending the sending of the non-real-time service packets and sending out the new legal real-time service packets. The device comprises a sort module, a judge module, a real-time service sending module, a non-real-time sending module and a notification module. The packet scheduling algorithm and the device can ensure that the sending of the real-time service packets is free from the influence of the non-real-time service packets and can avoid the occasion that the non-real-time service packets wait for too long. Therefore, the packet scheduling algorithm and the device have strong practicability, reliability and effectiveness.

Owner:HUAWEI TECH CO LTD

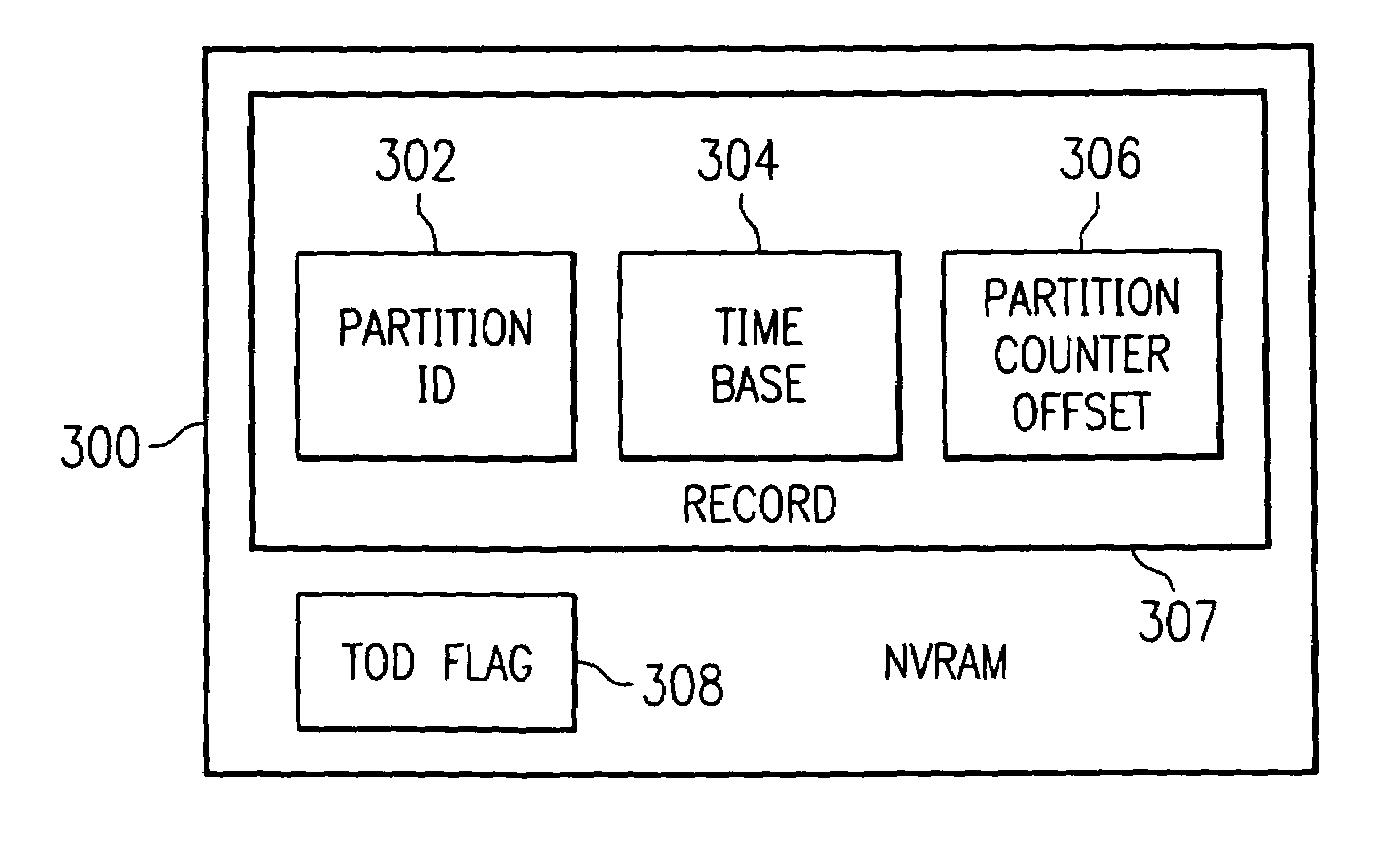

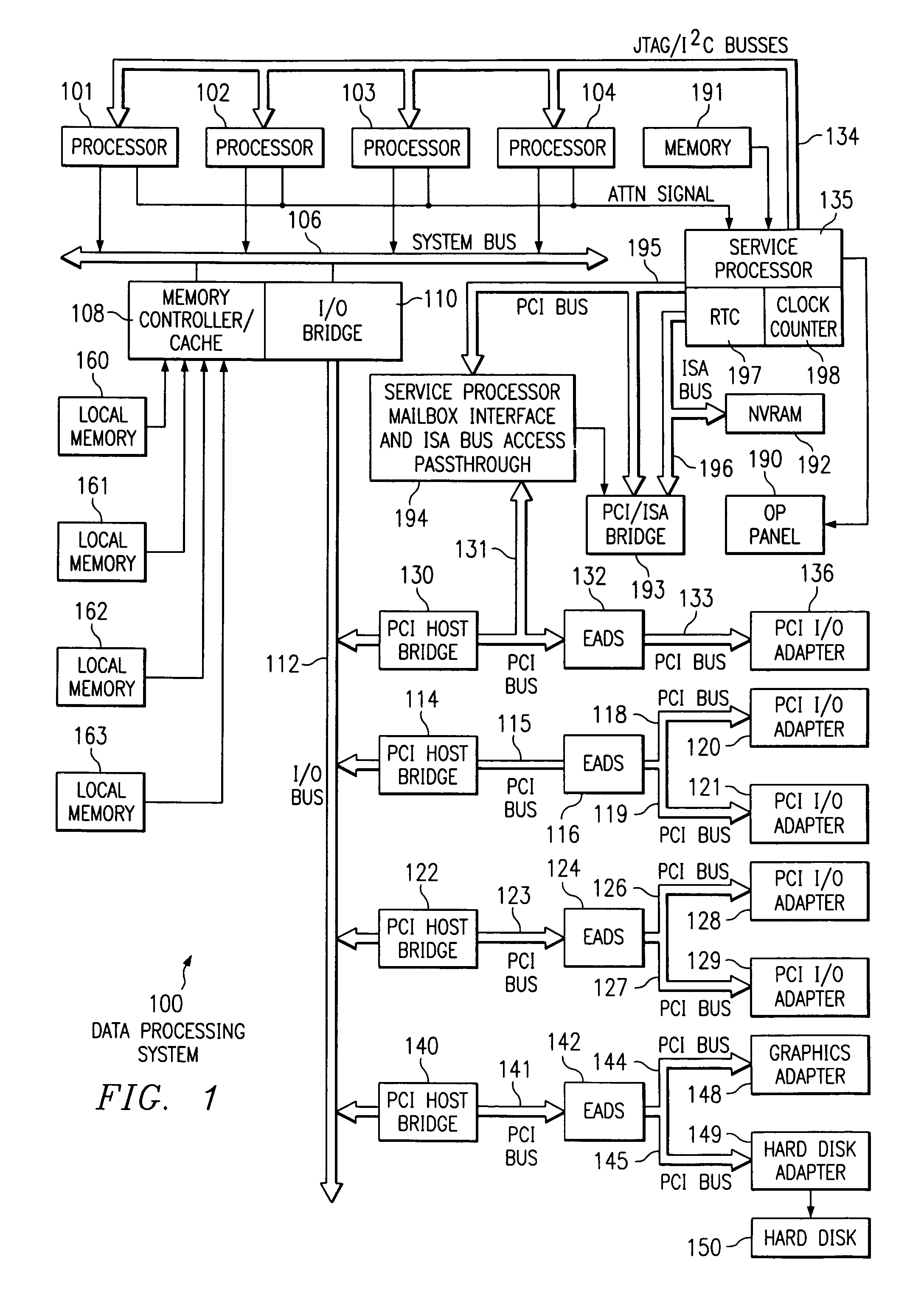

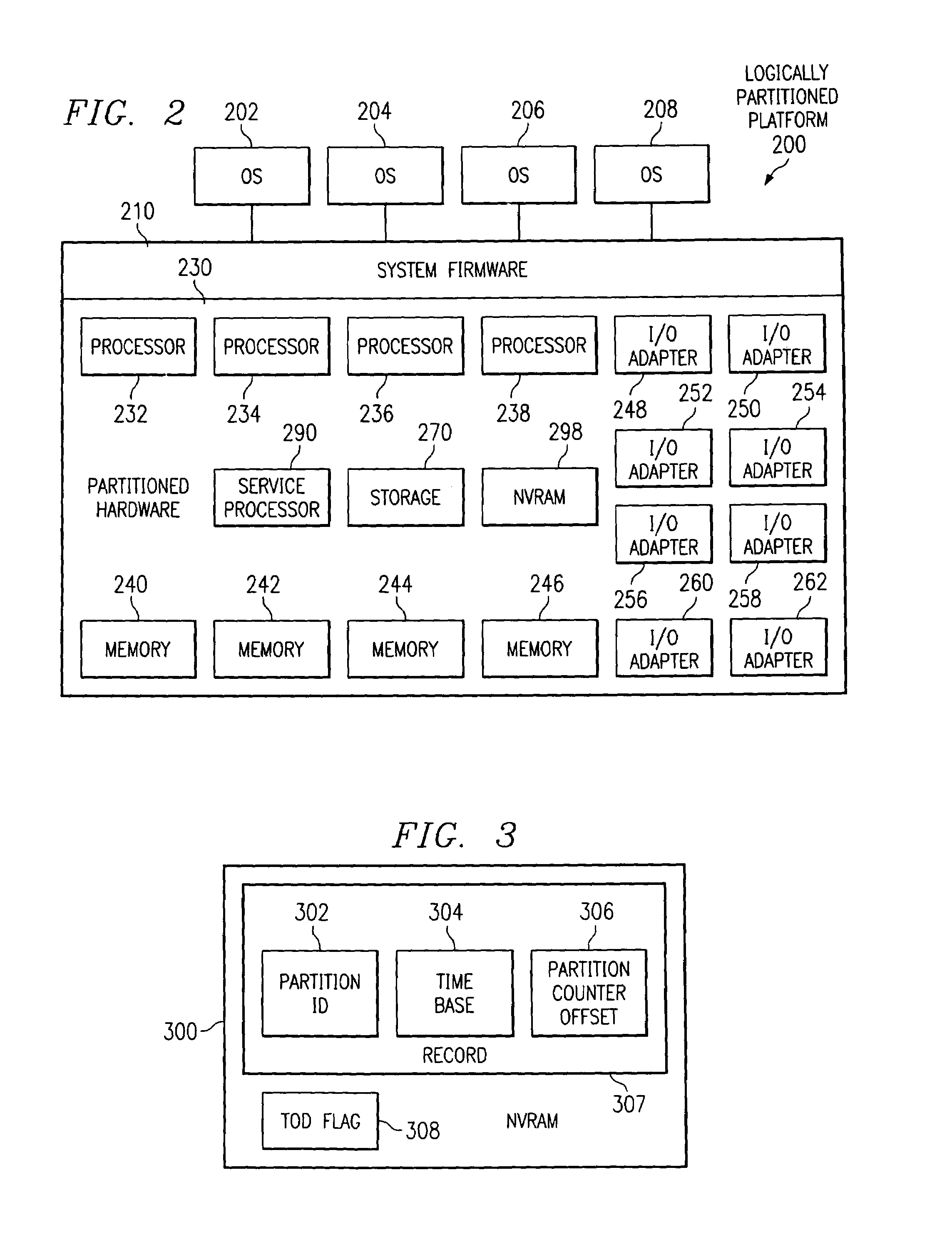

Method and apparatus for generating a virtual clock in a data processing system

InactiveUS6968473B2Multiple digital computer combinationsGenerating/distributing signalsData processing systemTime of day

A method, apparatus, and computer instructions for managing a set of virtual clocks in a data processing system with multiple partitions. A “set-time-of-day” command is used in connection with each virtual clock to define a basis for its local date / time state via the following elements: (1) a partition peculiar time base reference value, and (2) a partition peculiar time offset reference value which corresponds to the state of an elapsed time counter at the point in time when the time base reference value is established. The partition time base reference and offset reference values are stored in memory. When executing a “get-time-of-day” command, these are retrieved along with the current state of the elapsed time counter facility to compute the current date / time state of the virtual clock for the partition.

Owner:IBM CORP

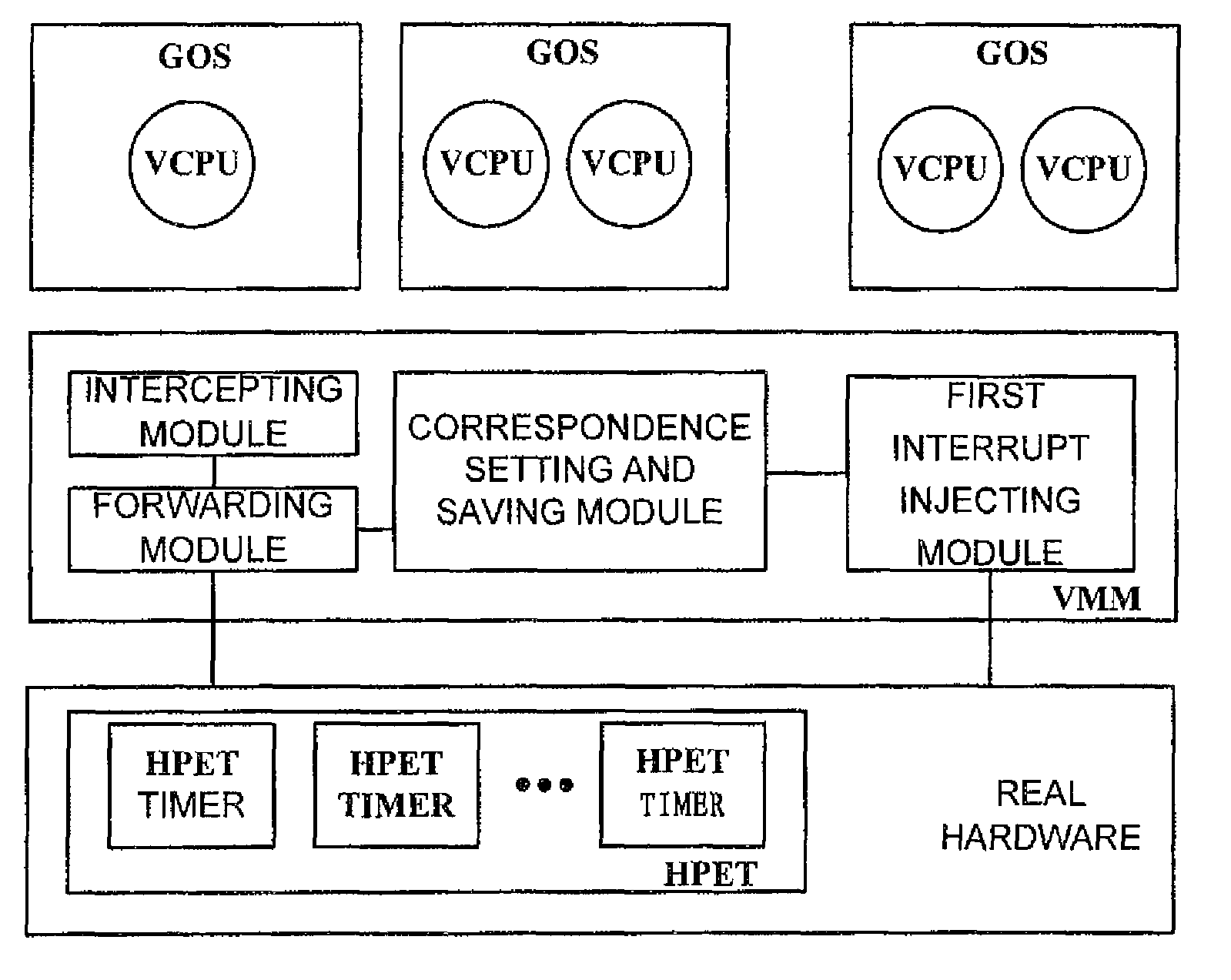

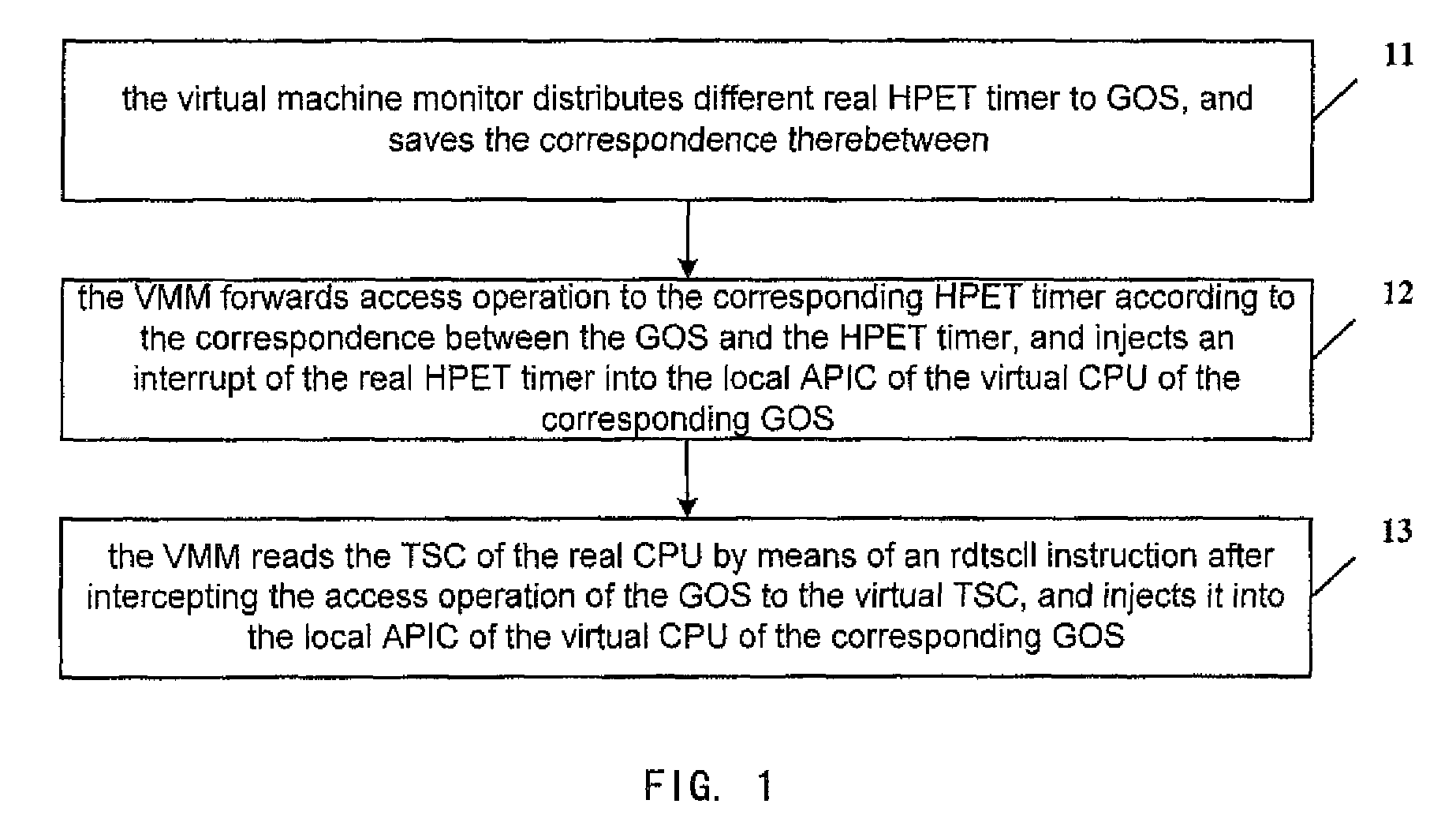

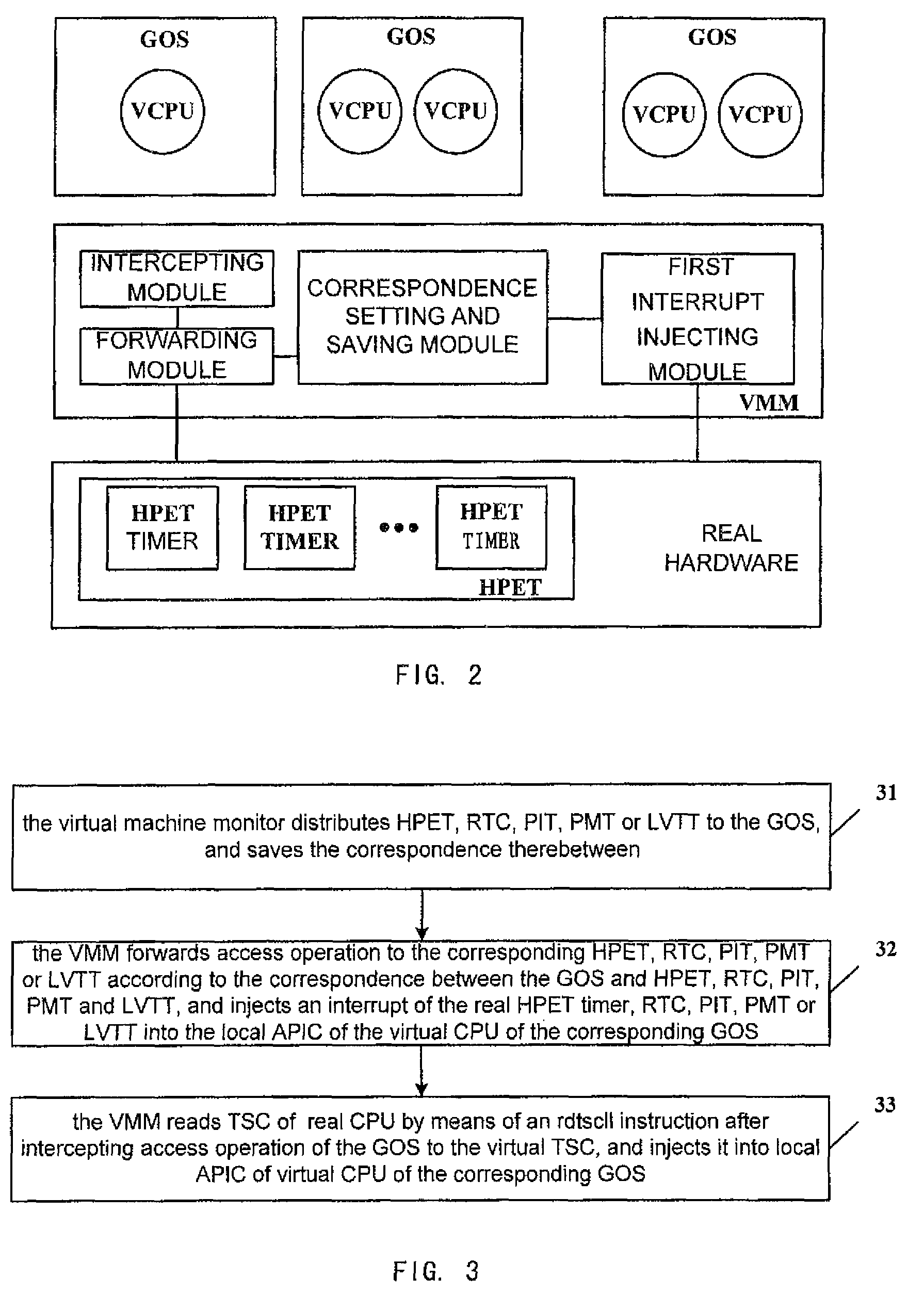

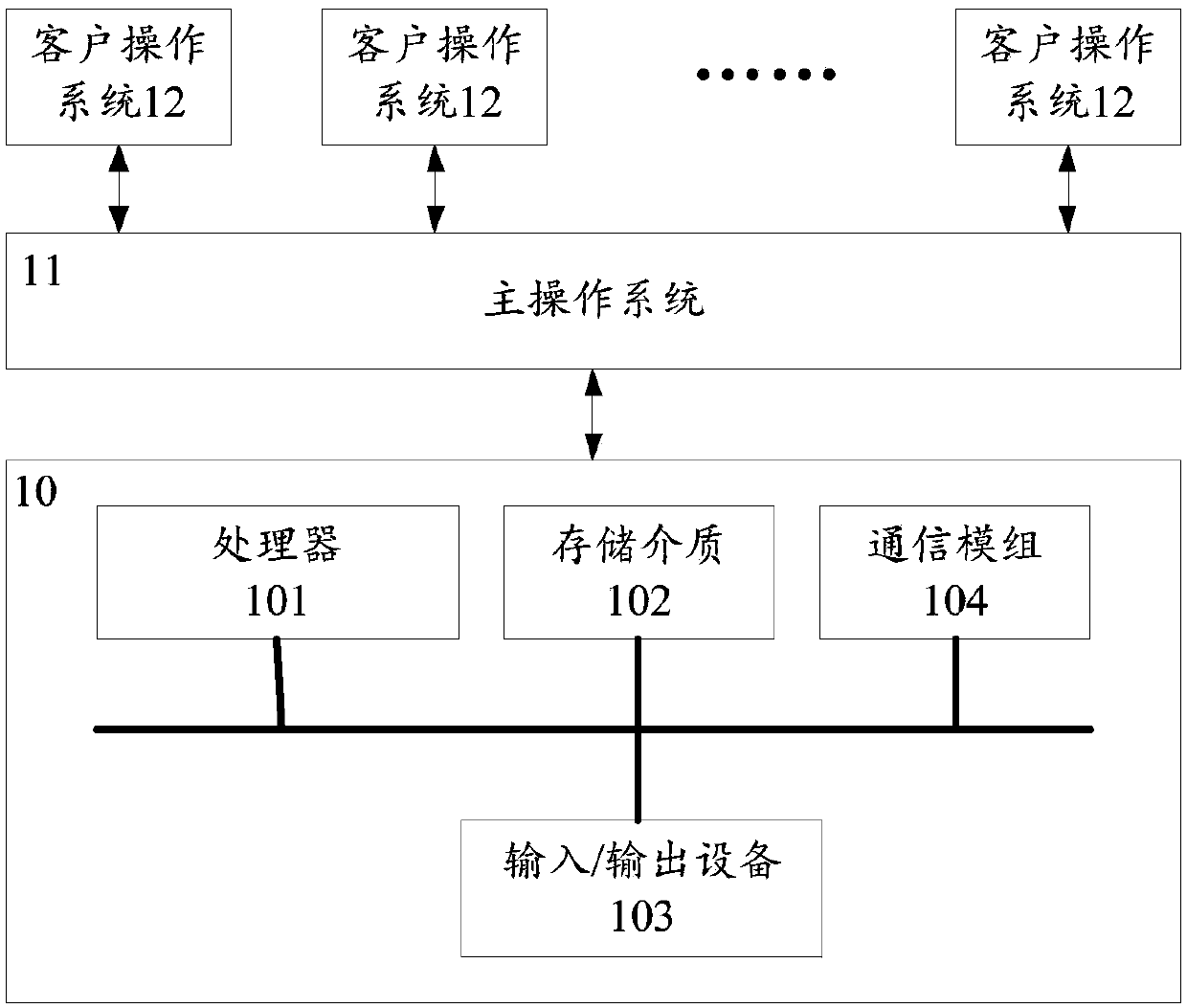

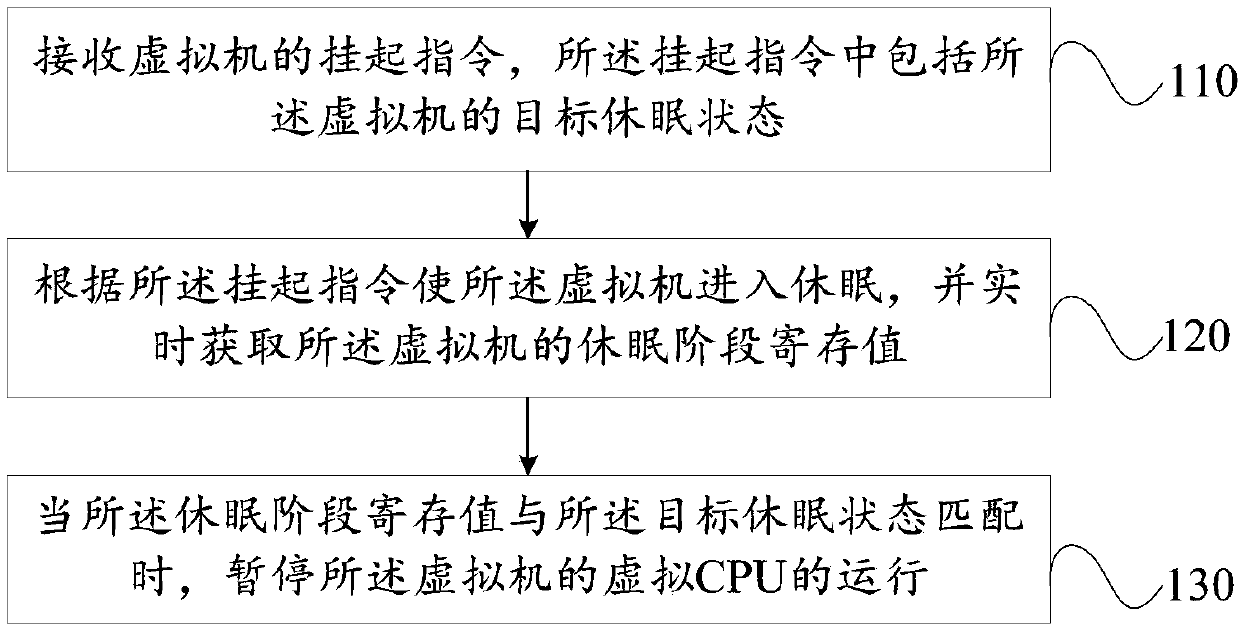

Virtual machine monitor, virtual machine system and clock distribution method thereof

ActiveUS8086890B2Accurate serviceProgram controlGenerating/distributing signalsVirtual file systemReal-time clock

A virtual machine monitor, a virtual machine system and a clock distribution method thereof. The clock distribution method includes: distributing real clock resource to a Guest Operation System (GOS), and saving correspondence between said GOS and said real clock resource; intercepting an access operation of said GOS to a virtual clock resource; sending said access operation to the corresponding real clock resource according to said correspondence, and then performing a write operation, or injecting an interrupt of said real clock resource into a local Advanced Programmable Interrupt Controllers (APIC) of a virtual CPU of the corresponding GOS of said GOSs.

Owner:LENOVO (BEIJING) LTD

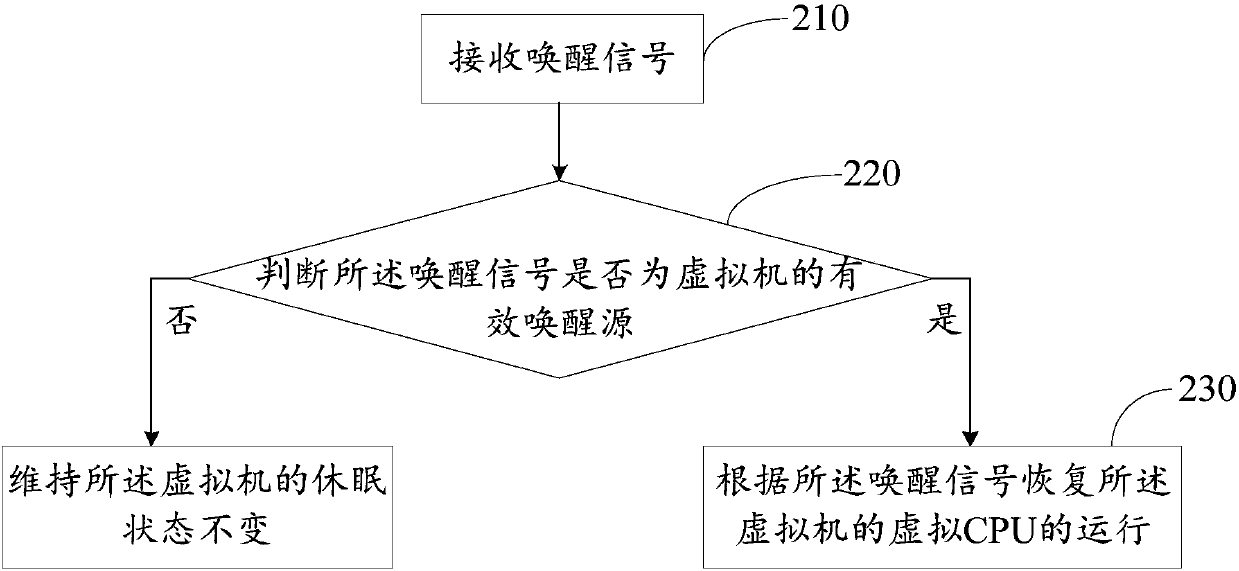

Method and device for managing state of virtual machine and intelligent terminal

PendingCN107810488APending implementationAchieving a full hangResource allocationEnergy efficient computingSleep stateState management

The embodiments of the present invention provide a method and a device for managing state of a virtual machine and an intelligent terminal, wherein, the method includes: receiving a suspend instruction of a virtual machine, the suspend instruction includes a target machine-sleep state of the virtual machine; and the virtual machine is put into dormancy according to the suspend instruction, and thevirtual machine is acquired in real time. The sleep stage register value of the machine; when the sleep stage register value matches the target sleep state, the operation of the virtual CPU of the virtual machine is suspended. Through the above technical solution, the embodiment of the present invention can achieve complete suspension of the virtual machine, avoid false wakeup of an interrupt signal generated by the virtual machine by the virtual clock, and improve the energy-saving effect of the system.

Owner:CLOUDMINDS (SHENZHEN) ROBOTICS SYST CO LTD

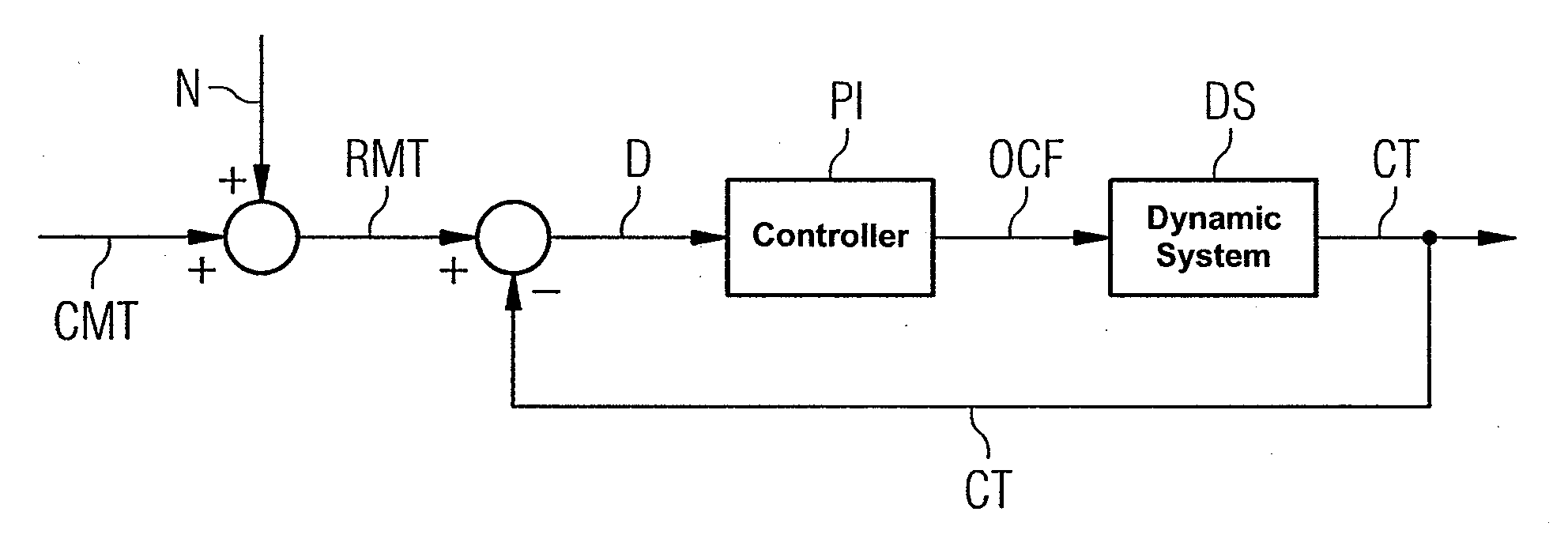

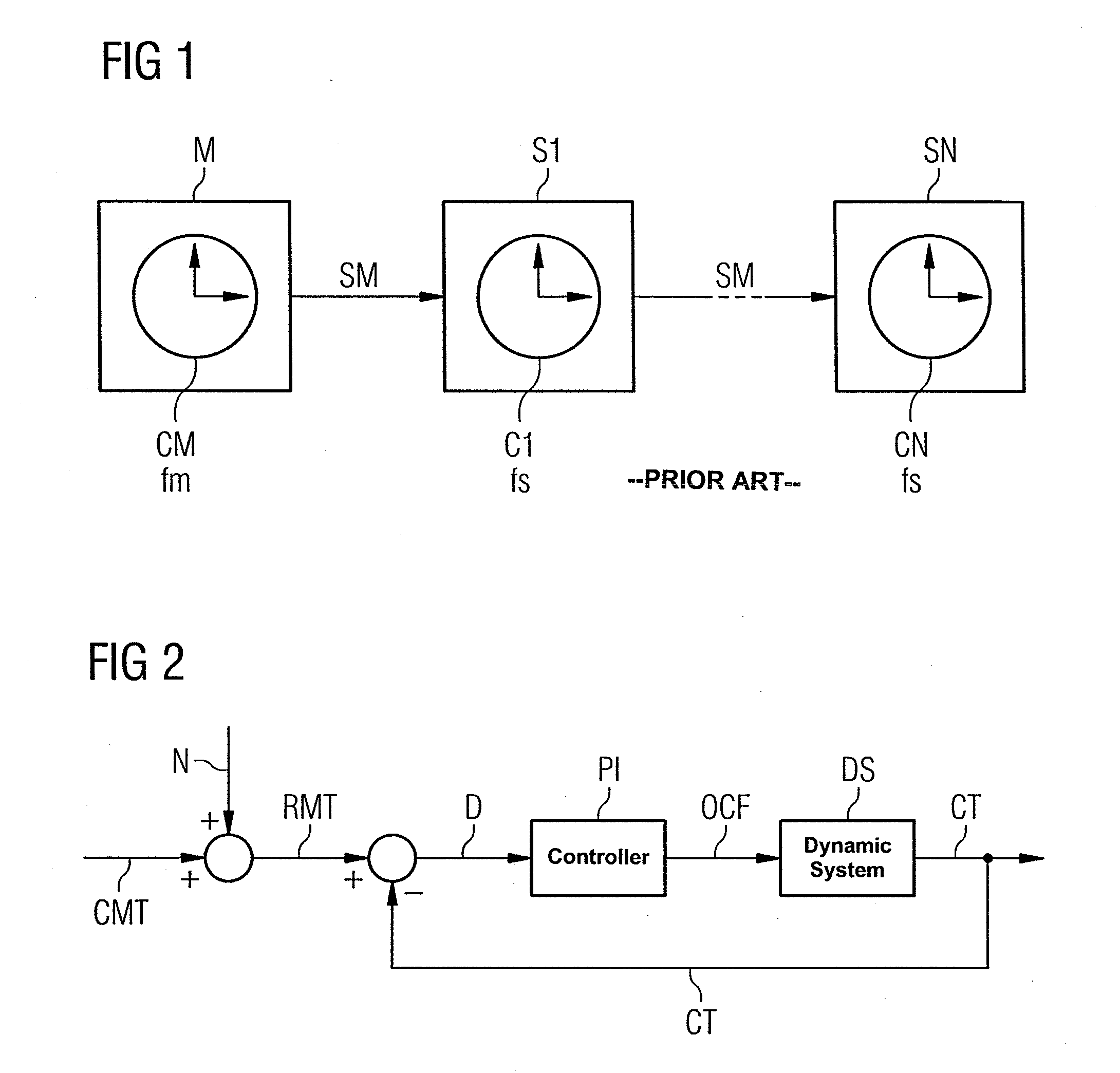

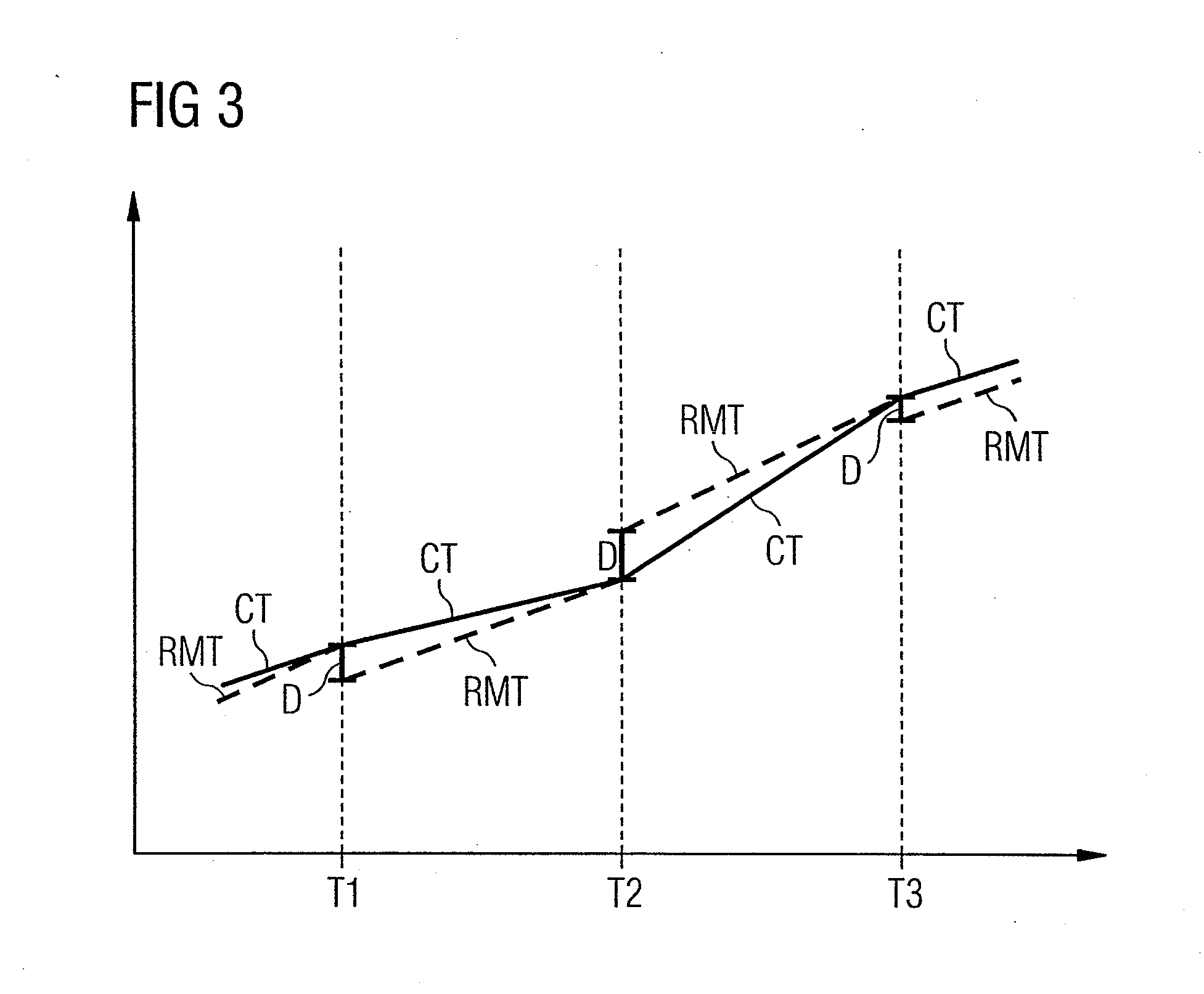

Device and Method for Time Synchronization in a Communication Network

ActiveUS20110064177A1Improve referenceGood estimateTime-division multiplexSynchronising arrangementTime criticalPROFINET

A device and method for time synchronization in a communication network, wherein a virtual clock is produced by a controller in each network node based on the PROFINET-Standard and / or the Precision Transparent Clock Protocol. In contrast to known methods for estimating the time, the time of the virtual clock does not undergo sudden changes. The virtual clock includes a controlled, continuous path. As a result, the virtual clock is particularly suitable for time-critical applications. Here, the estimation of the time of a reference clock is improved by 18-35%. Accordingly, a markedly greater number of network nodes may be synchronized with a predetermined level of accuracy for the time synchronization.

Owner:SIEMENS AG

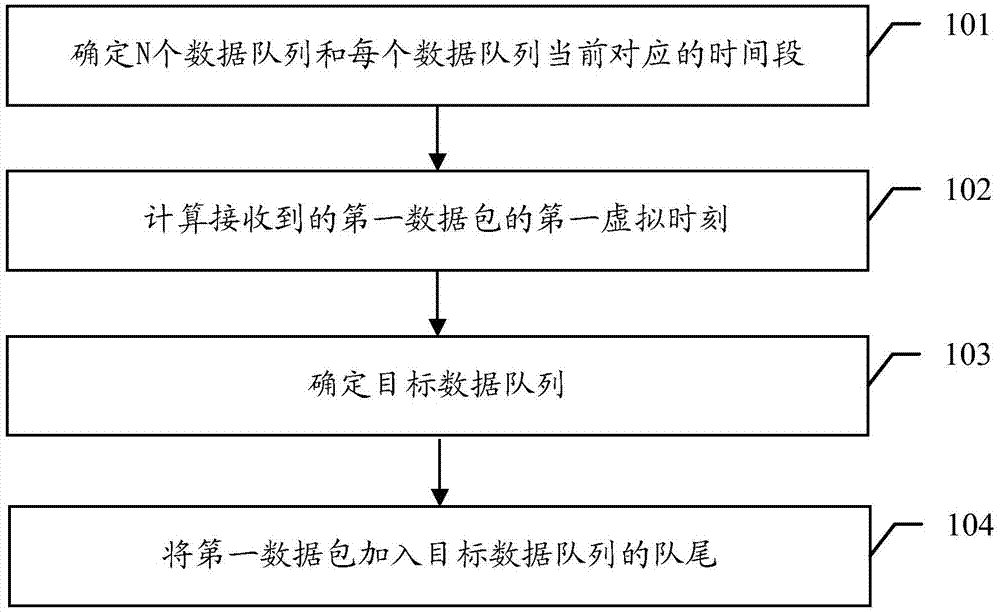

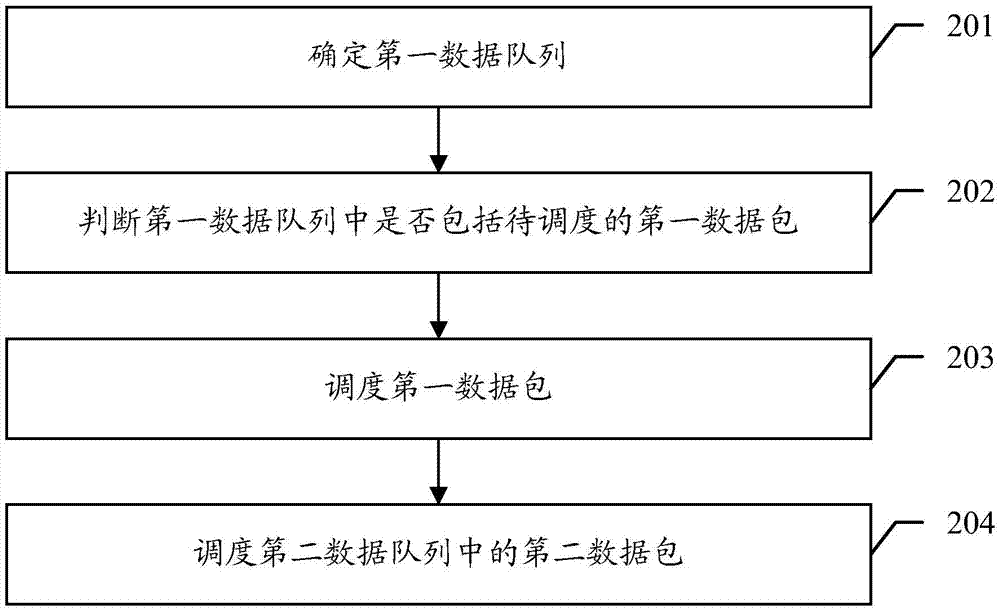

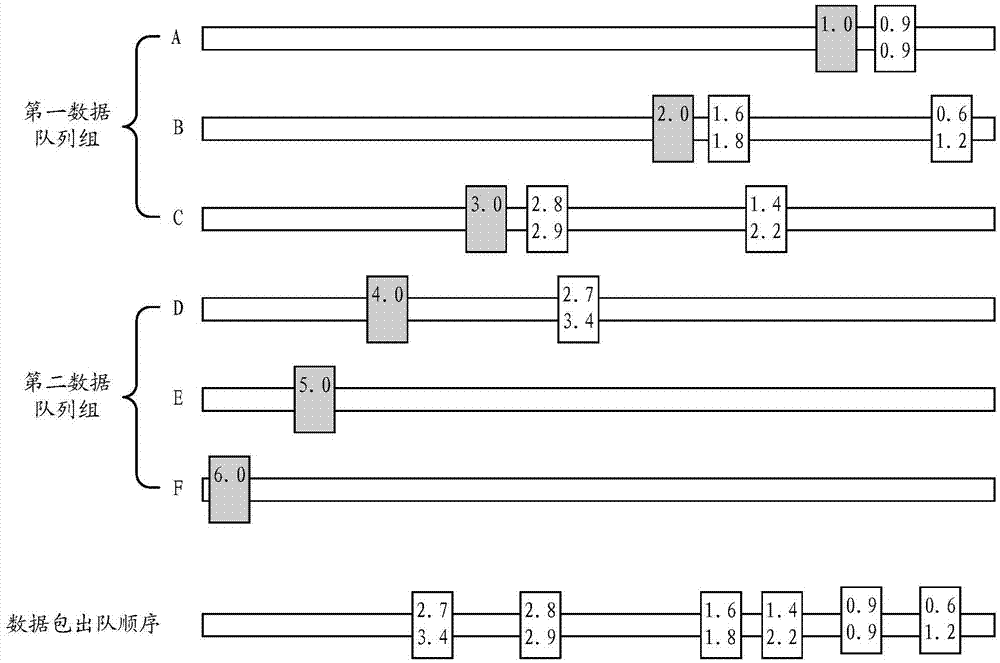

Data stream shaping method and device, and data scheduling method and device

The embodiment of the invention discloses a data stream shaping method. The method is used for reducing queue jumping operation of data packets and realizing data stream shaping in a network. A data stream shaping device calculates first virtual time of receiving a first data packet according to a virtual clock method, and selects a target data queue for the first data packet from N data queues according to the first virtual time and a time period corresponding to each data queue in the N data queues, wherein the N is an integer greater than or equal to 2. After determining the target data queue, the data stream shaping device adds the first data packet to the tail of t he target data queue. The embodiment of the invention also provides a related data scheduling method and device and a computing device.

Owner:XFUSION DIGITAL TECH CO LTD

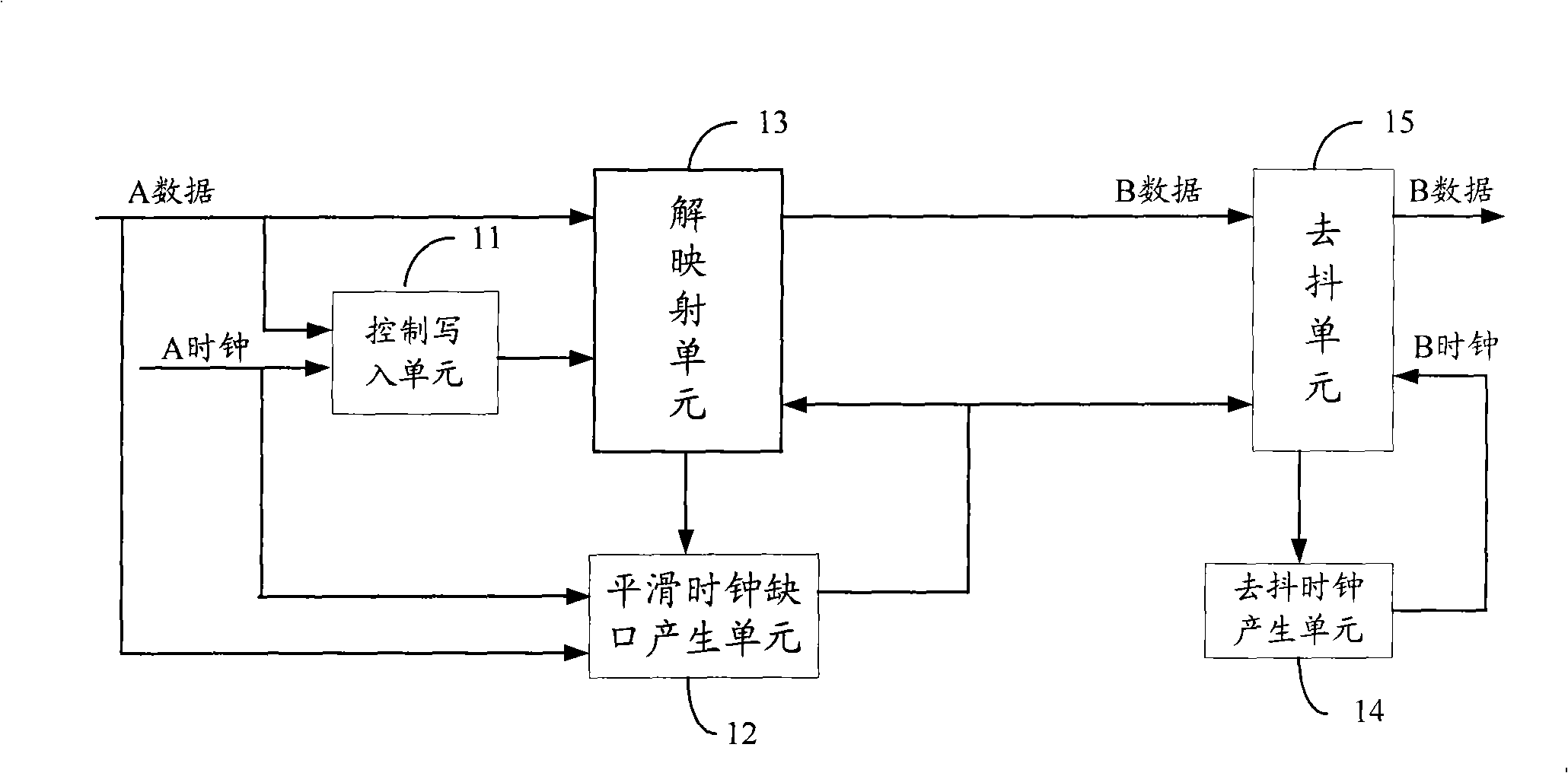

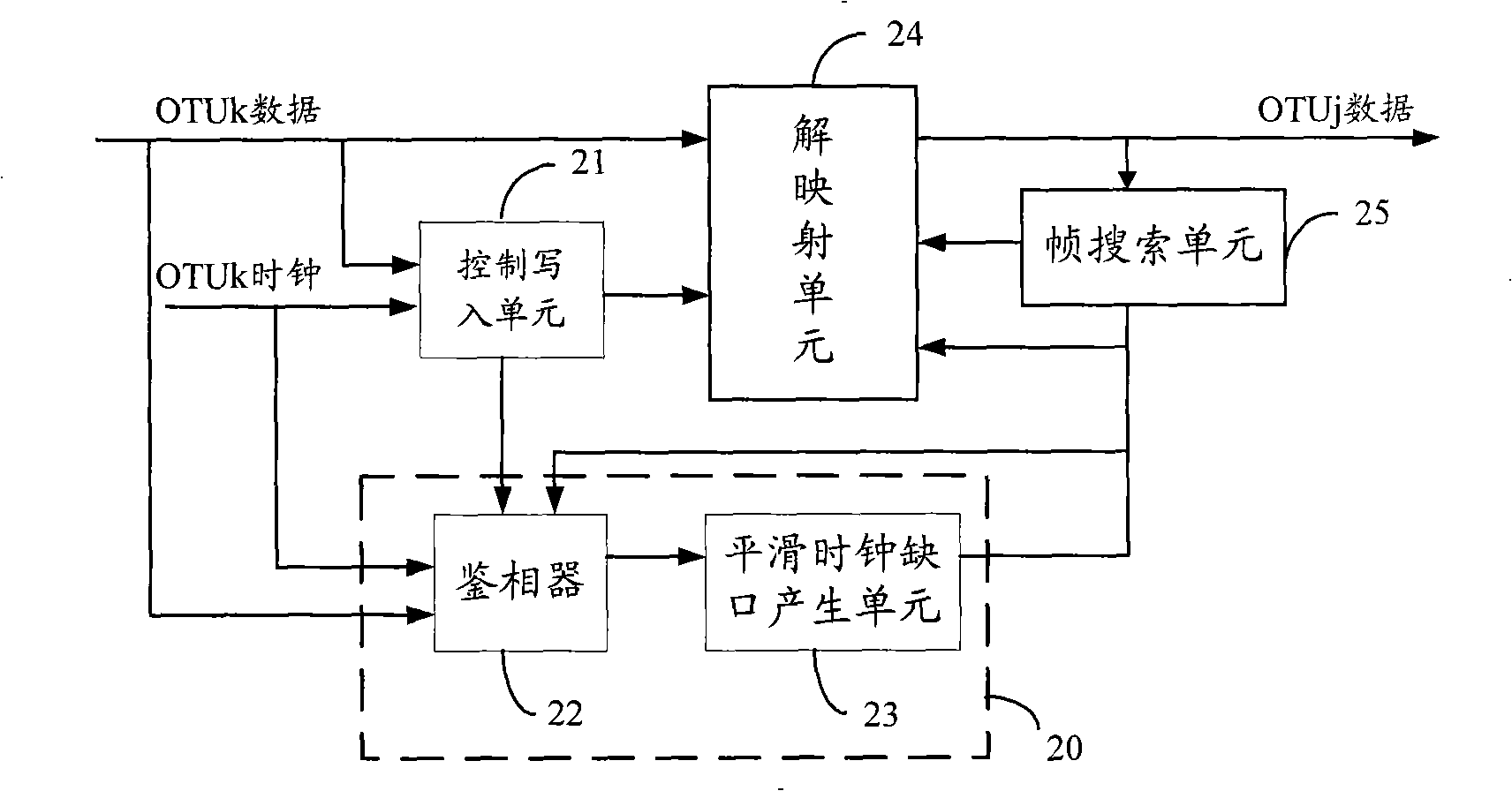

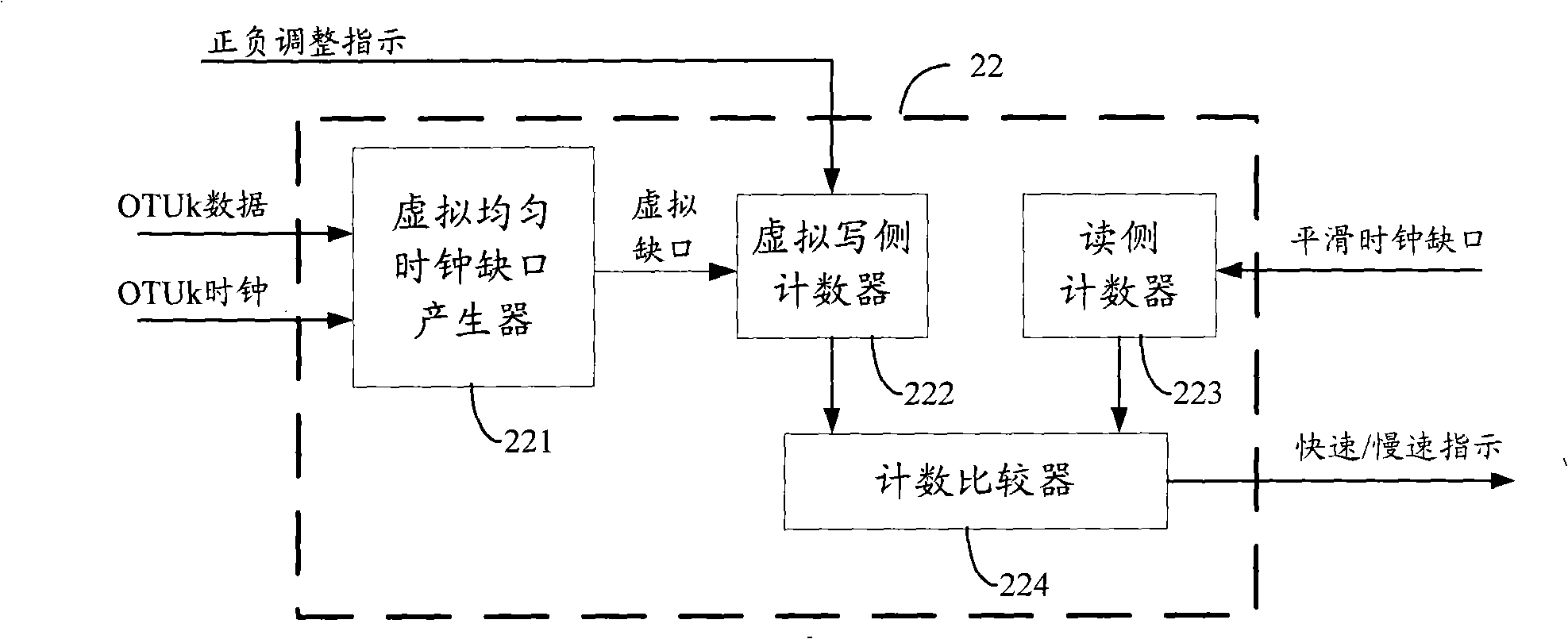

Method and apparatus for removing jitter in demapping, method and apparatus for obtaining clock, phase discriminator

InactiveCN101277162AImprove performanceGet jitterTime-division multiplexDiscriminatorComputer hardware

The invention provides a dithering-removal method and device in de-mapping, a clock obtain method and device, and a phase detector. The dithering-removing method in de-mapping includes: data required de-mapping is processed de-mapping and is cached according with data writer clock; data writer virtual clock and data reader precast clock is obtained according with data required de-mapping and corresponding clock; data writer virtual clock and data reader precast clock are compared, data reader clock is generated according with the comparison result; data after being de-mapping is read according with the data reader clock. The technical solution provided by the invention can obtain dithering condition generated in de-mapping course effectively, filter dithering generated in data de-mapping course effectively by adjusting clock in time, and obtain data output with high performance.

Owner:HUAWEI TECH CO LTD

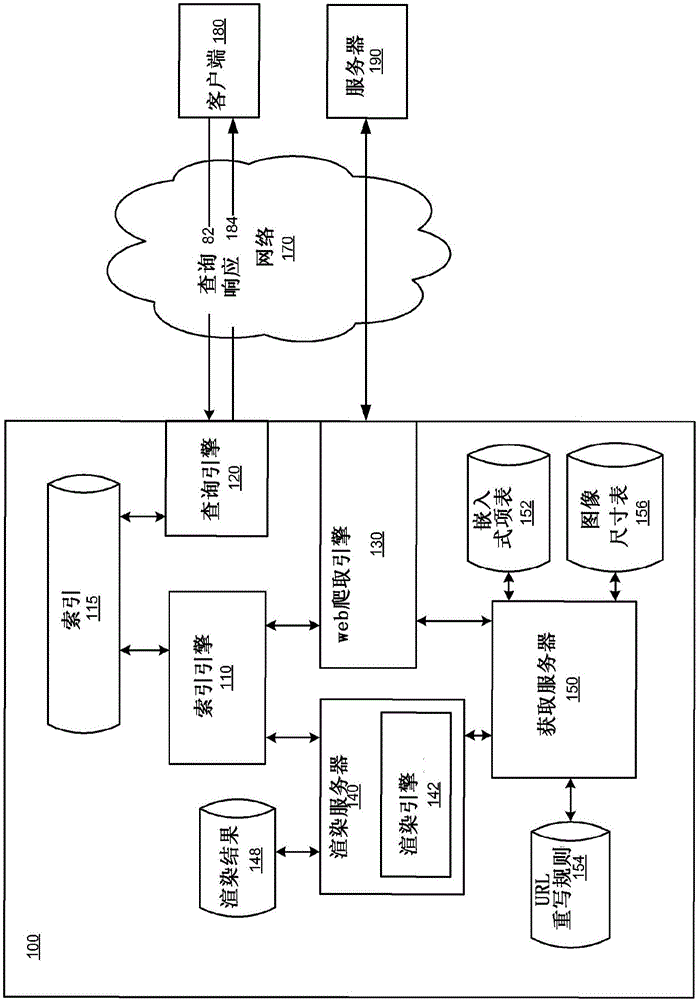

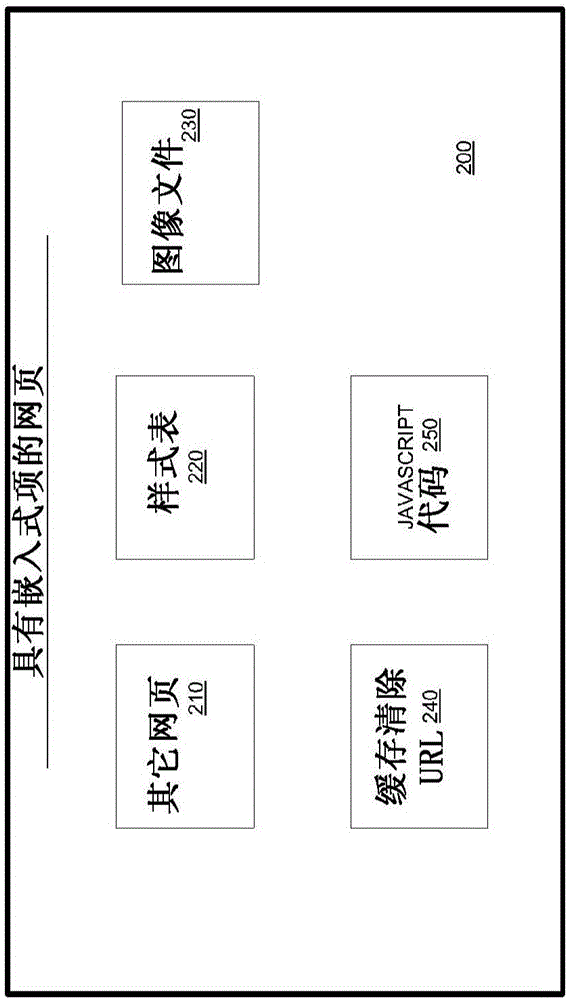

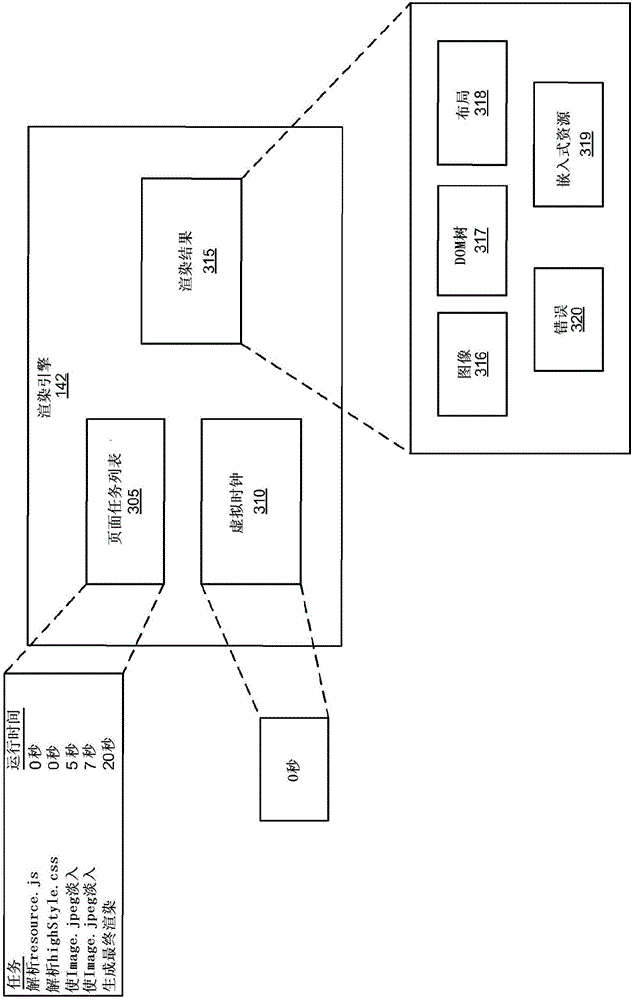

Batch-optimized render and fetch architecture

ActiveCN106462582AAvoid common mistakesAvoid timeout errorsText processingSpecial data processing applicationsRewrite ruleWeb page

Implementations include a batch-optimized render and fetch architecture. An example method performed by the architecture includes receiving a request from a batch process to render a web page and initializing a virtual clock and a task list for rendering the web page. The virtual clock stands still when a request for an embedded item is outstanding and when a task is ready to run. The method may also include generating a rendering result for the web page when the virtual clock matches a run time for a stop task in the task list, and providing the rendering result to the batch process. Another example method includes receiving a request from a batch process to render a web page, identifying an embedded item in the web page, and determining, based on a rewrite rule, that the embedded item has content that is duplicative of content for a previously fetched embedded item.

Owner:GOOGLE LLC