Patents

Literature

436 results about "Digital clock" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A digital clock is a type of clock that displays the time digitally (i.e. in numerals or other symbols), as opposed to an analog clock, where the time is indicated by the positions of rotating hands.

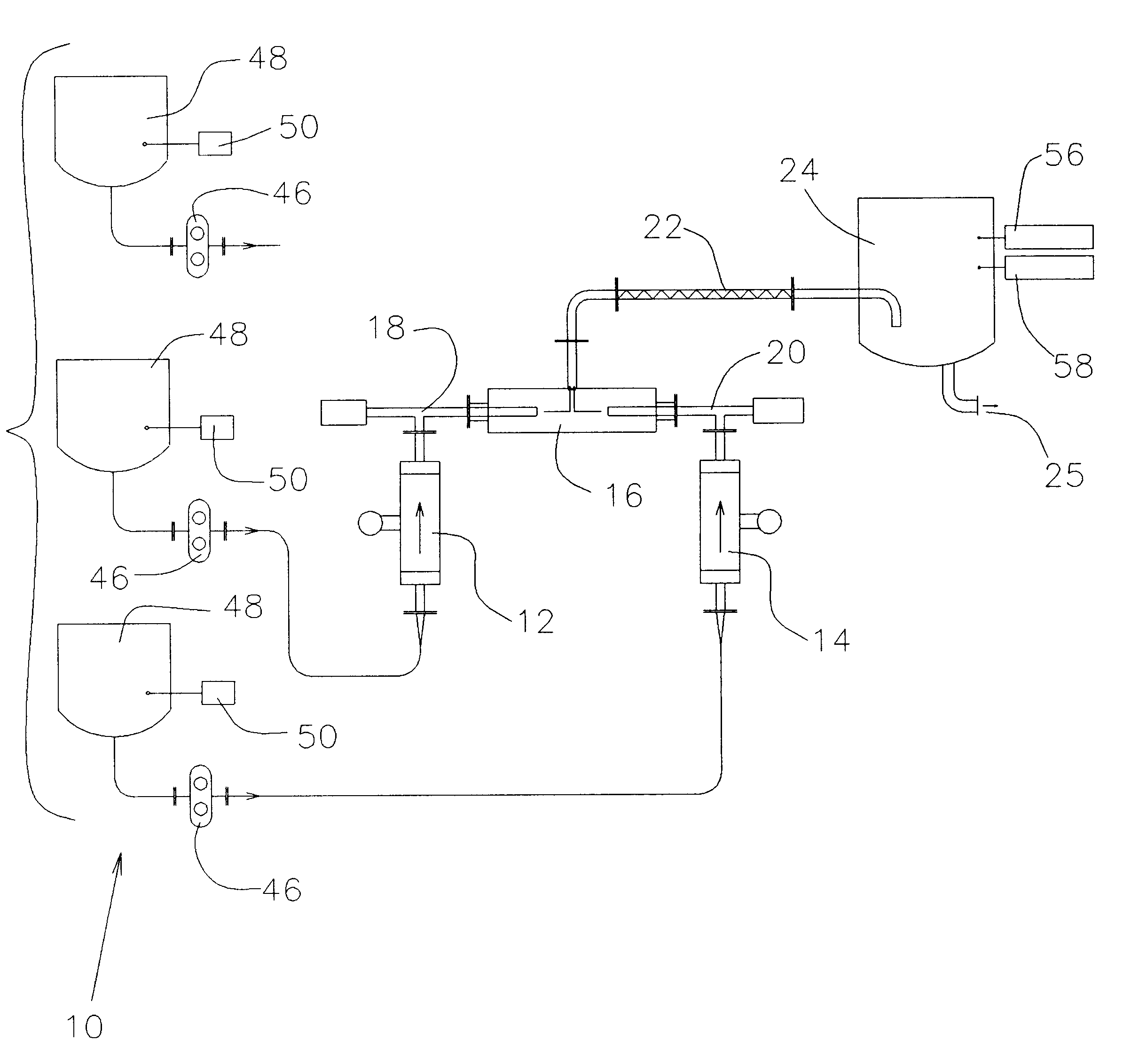

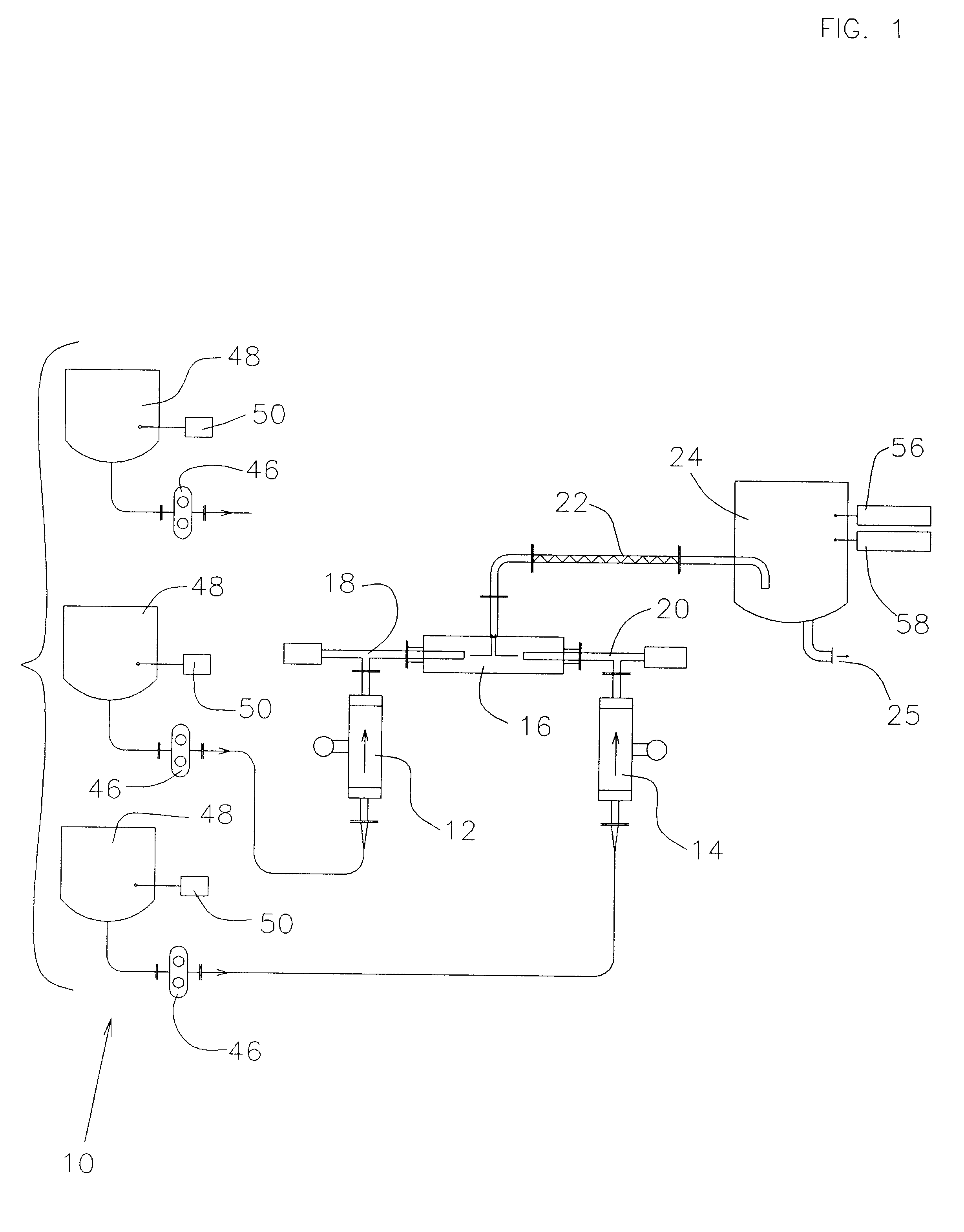

Continuous liquid stream digital blending system

InactiveUS6186193B1More disadvantageSimplifies software and set-up computationLiquid fillingControlling ratio of multiple fluid flowsHybrid systemDigital clock

The present invention consists of a method and apparatus providing for the continuous stream blending, preferably on a mass ratio basis, of two or more liquids. Each individual liquid stream is synchronously dosed in precise mass ratio to a common mixing point. The flow of each stream is on-off or digital. Repeated mass ratio doses of defined and matching flow interval, referred to as synchronous digital flow, interspersed with a defined interval of no flow, constitutes digital flow at a net rate sufficient to meet or exceed some required take-away of the blended liquids. In one preferred embodiment, each dose stream flow is produced and measured by a four element apparatus preferably consisting of a servo motor and controller, a precision positive displacement pump, a Coriolis mass meter and a precision flow stream shut-off device. The servo motor and controller establish and control a periodic and intermittent flow rate necessary to displace a defined mass dose in a precisely defined flow interval. The flow interval is measured against a precision millisecond digital clock. The Coriolis mass meter is used only to totalize mass flow to define the desired mass dose during the defined digital flow interval. The flow stream shut-off device ensures precise delivery of the mass dose to the common mixing point. The flow rate of a stream is automatically adjusted by the control electronics until the required mass dose is delivered in the defined flow interval.

Owner:ODEN MACHINERY

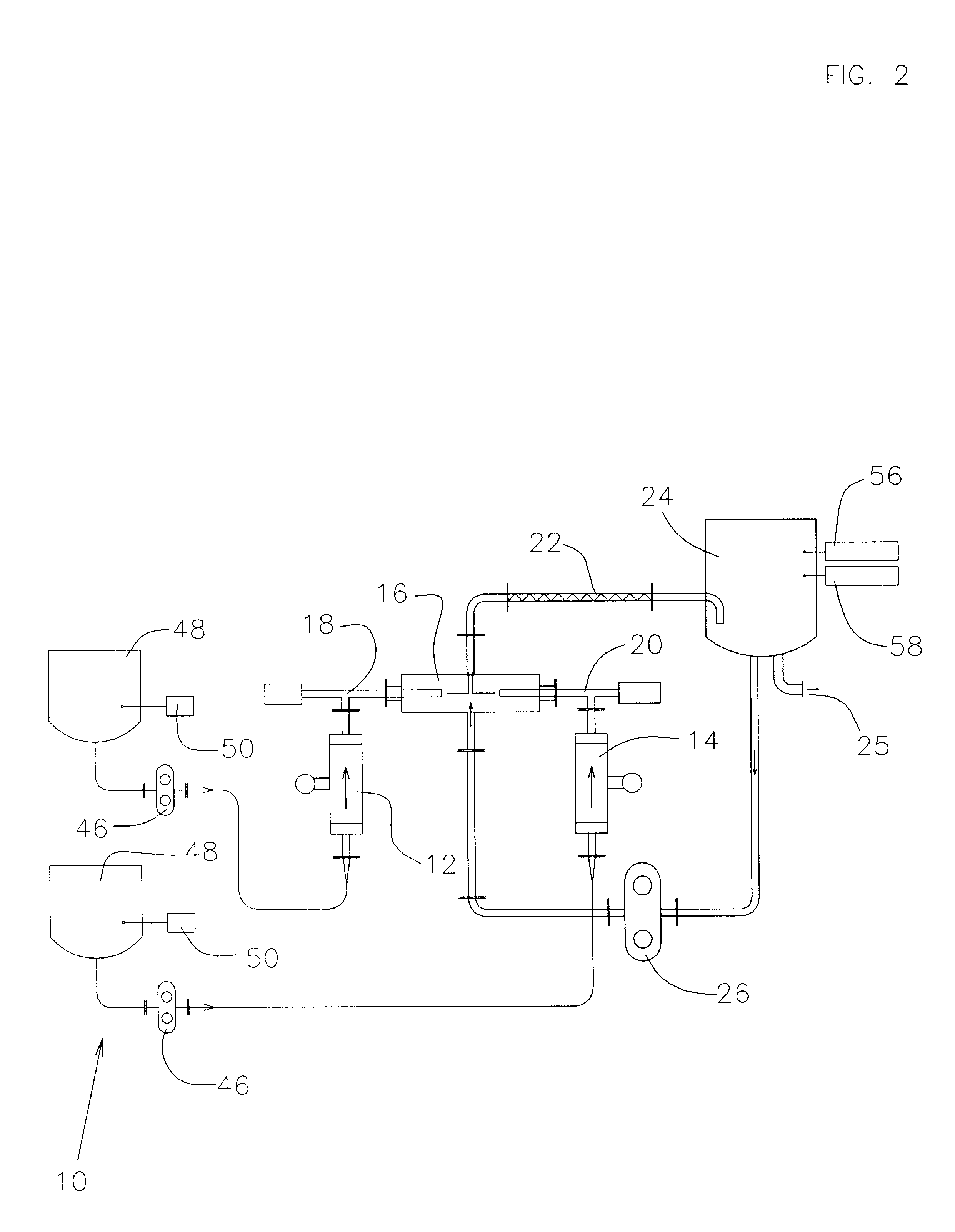

Direct radio frequency generation using power digital-to-analog conversion

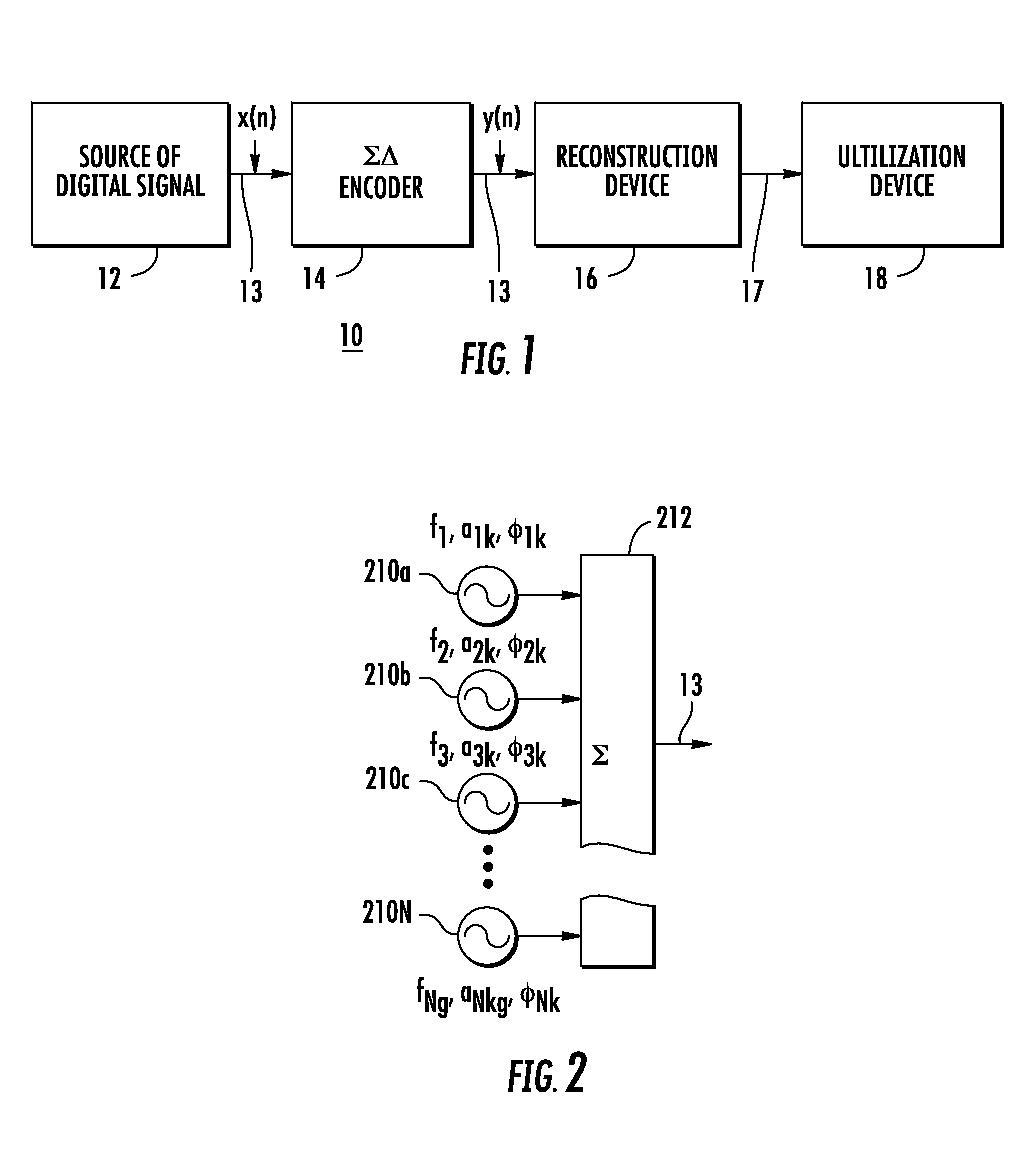

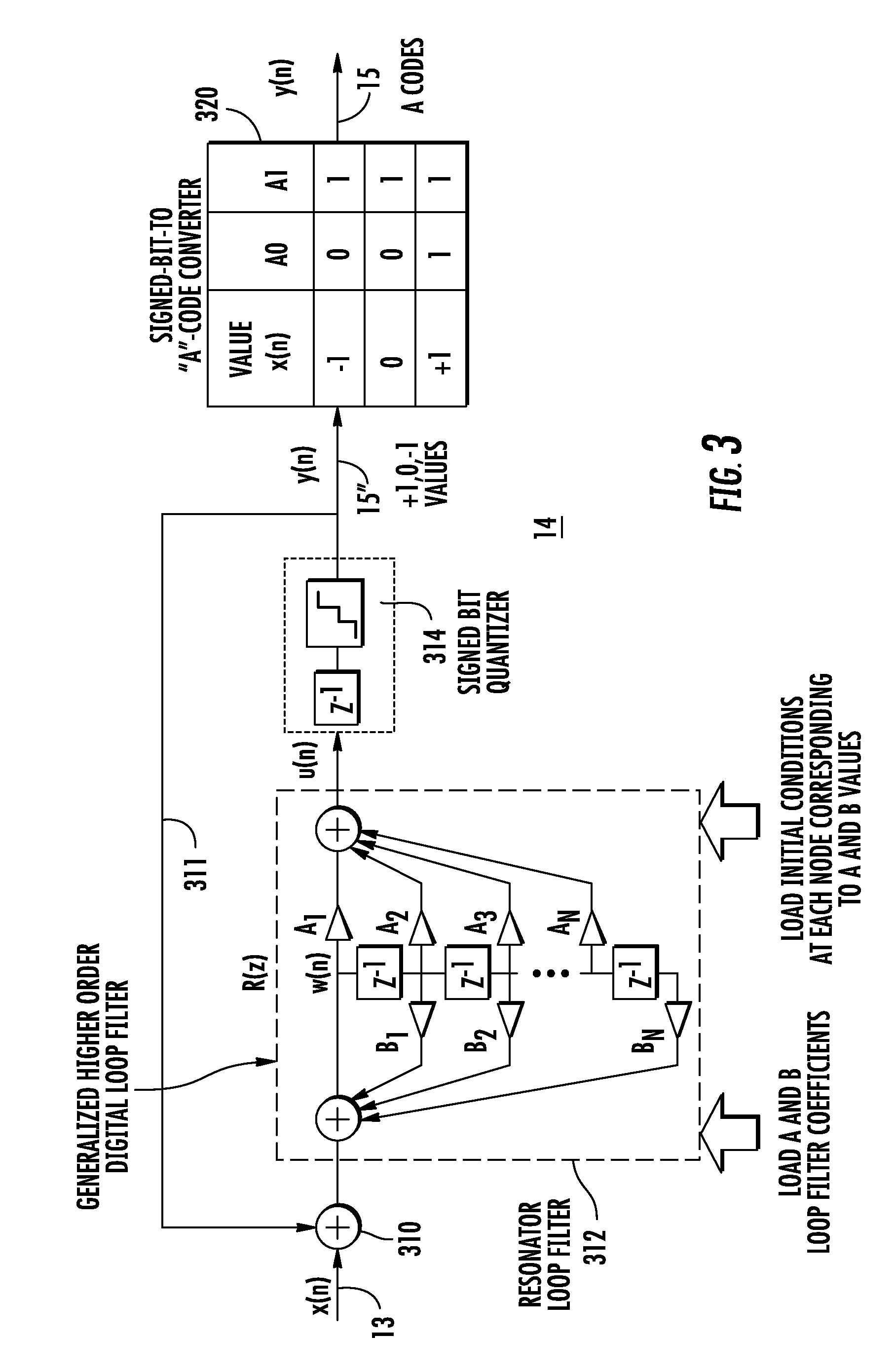

An RF signal source receives wideband digital signals representing the instantaneous amplitude of the desired RF, and ΣΔ converts to ternary ΣΔ signals. The ternary ΣΔ signals are delayed in a transversal filter and the delayed signals are converted to currents for application to a traveling-wave summer for producing the desired RF. The traveling-wave summer may be a transmission line. The currents may be weighted with a filter response in order to limit the bandwidth of the RF signals. The RF may be coupled out through an antialiasing filter. The digital clocks may be delayed to correspond with the delays of the combiner, to impart directionality to the summed signals.

Owner:LOCKHEED MARTIN CORP

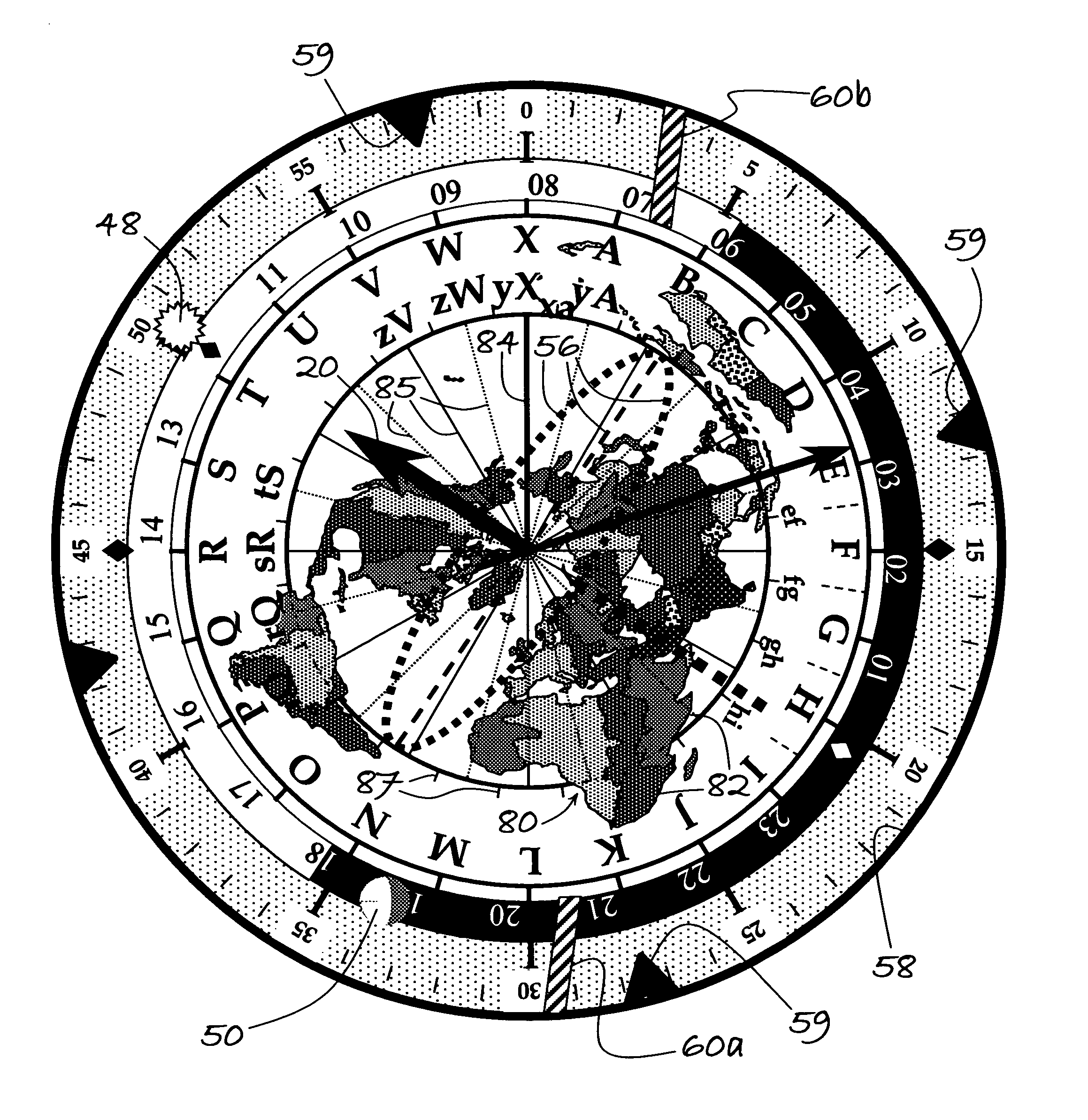

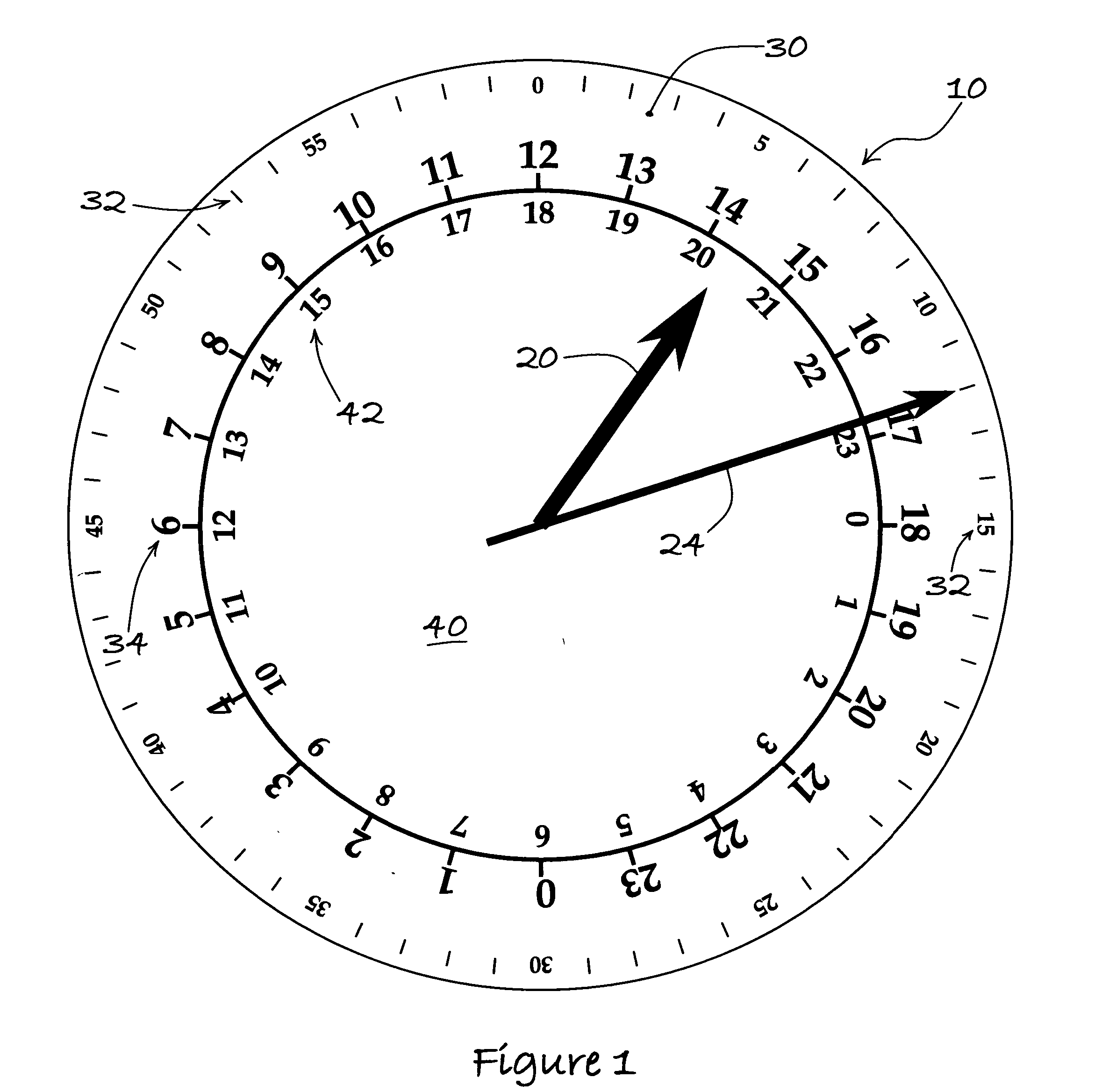

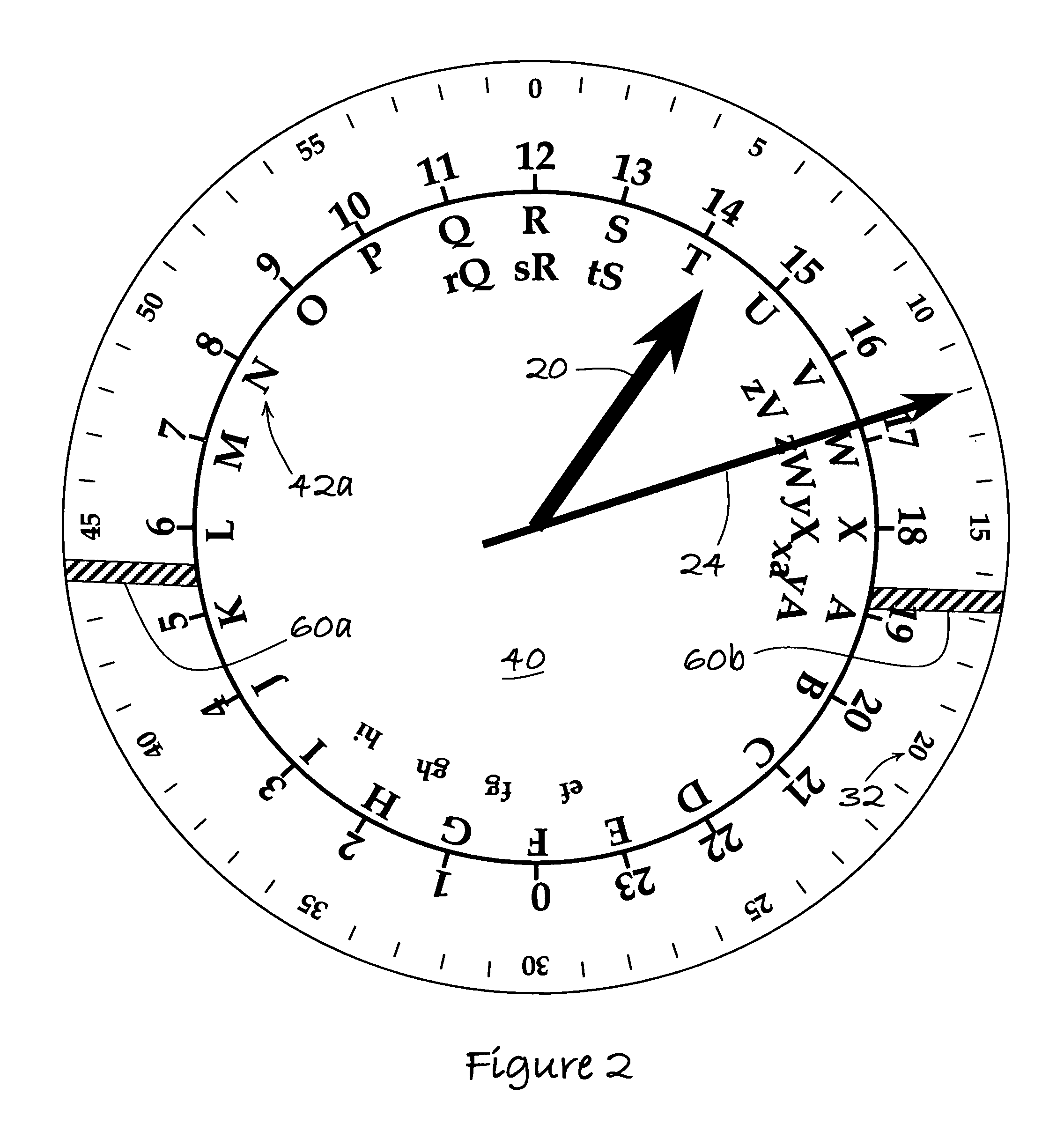

System and method for a clock using a time standard where global time works cooperatively with all local time zones

InactiveUS20050105397A1Clear and easy conversionVisual indicationRadio transmissionTime of useSolstice

A global time reckoning system simultaneously indicates local time and global time. The global time reckoning system can be practiced with standard clock timer drivers, including electromechanical and digital clock motors, in combination with a novel global time system clock face to allow a user to reckon time locally or anywhere on the globe without time zone conversion calculations. The global time system clock face has multiple time scales, at least one of which is driven by the clock drive in cooperation with an hour indicator (e.g., an hour hand). The global time system clock face simultaneously displays global time (relative to any location on the globe) and local time. Additionally, the global time reckoning system, with the appropriate clock timer driver is adaptable to indicate a number of other global time related information, including sunrise / sunset, days of the week, lunar phase and solstices / equinoxes.

Owner:TUASON CHRISTOPHER

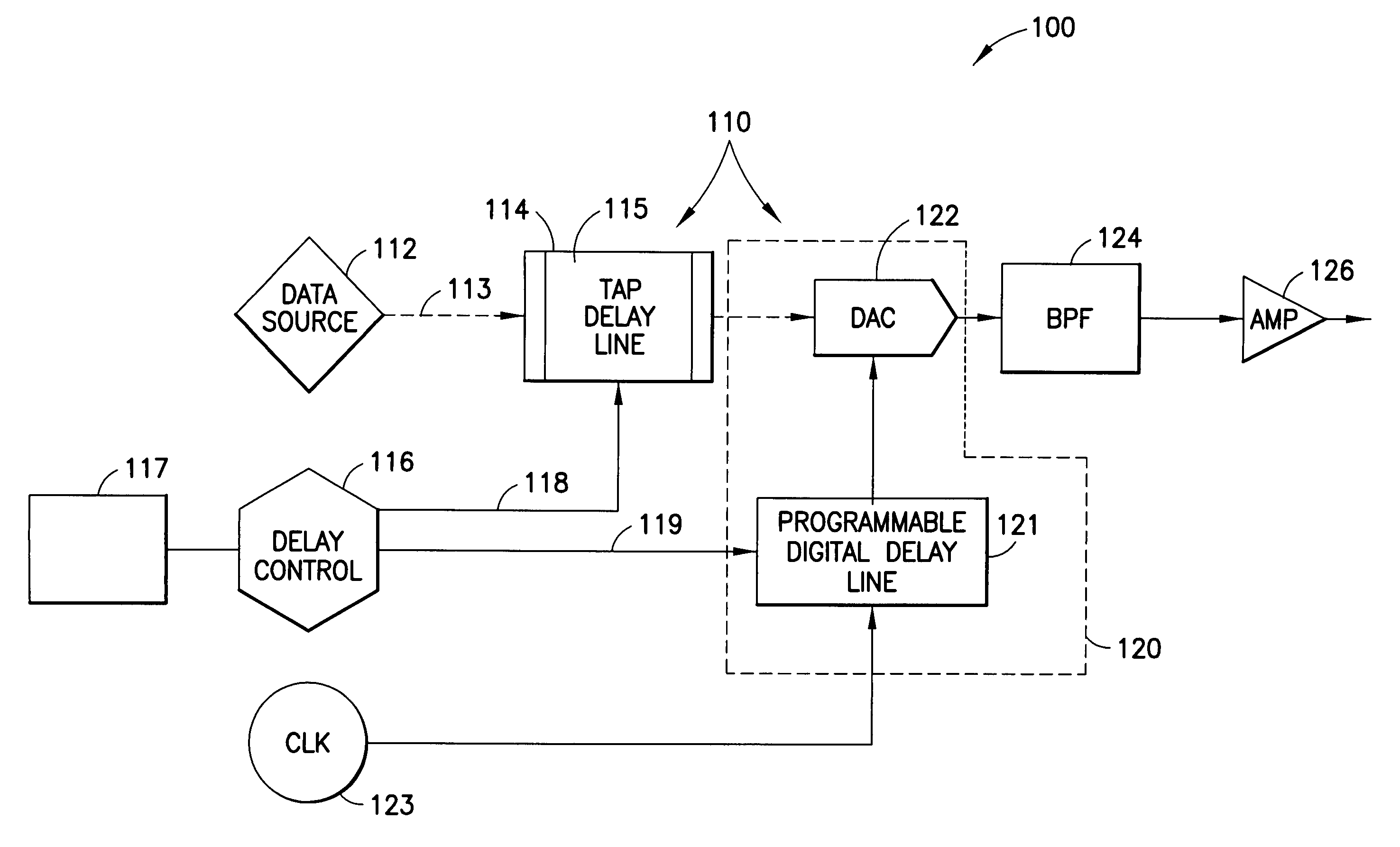

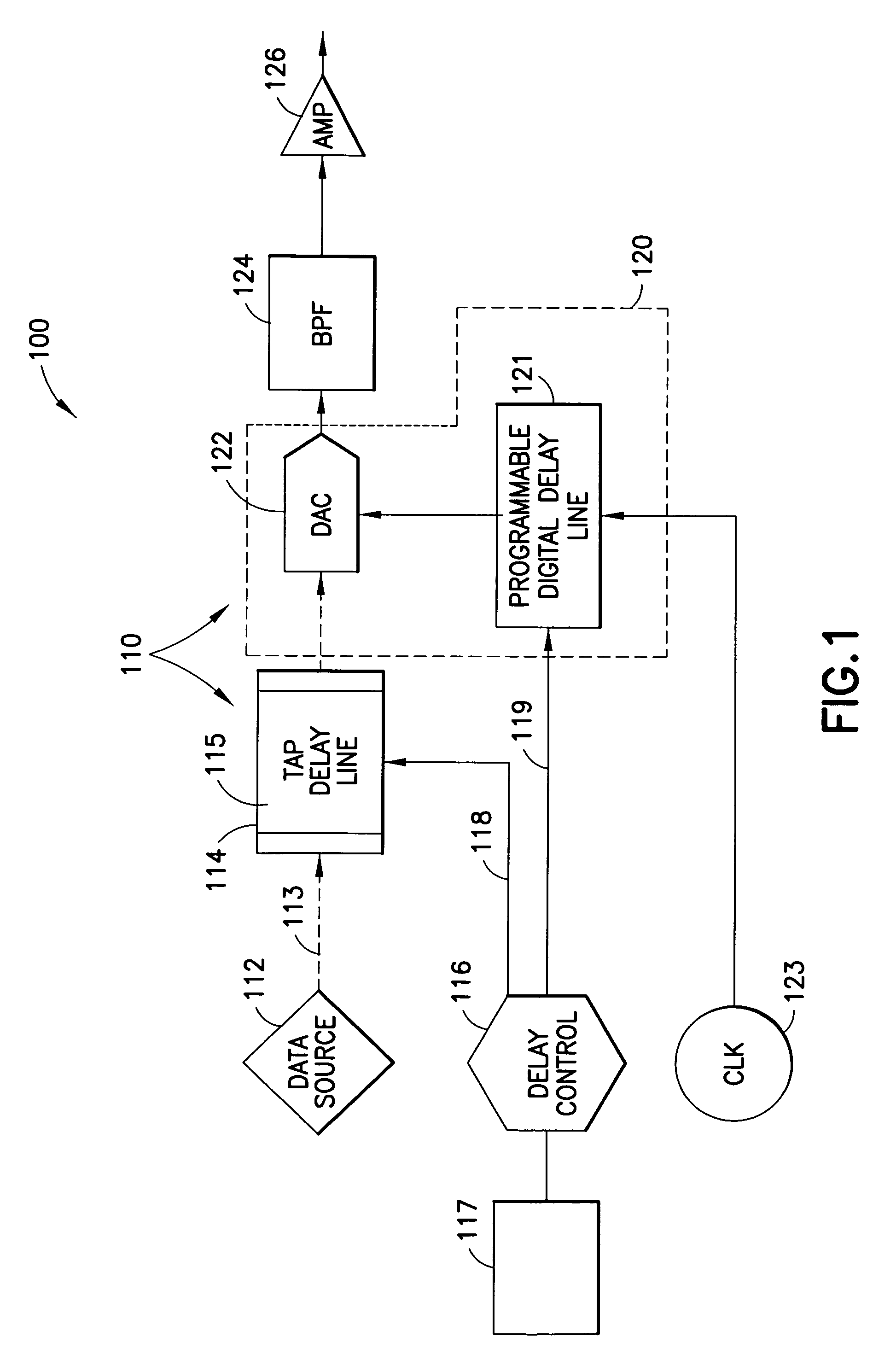

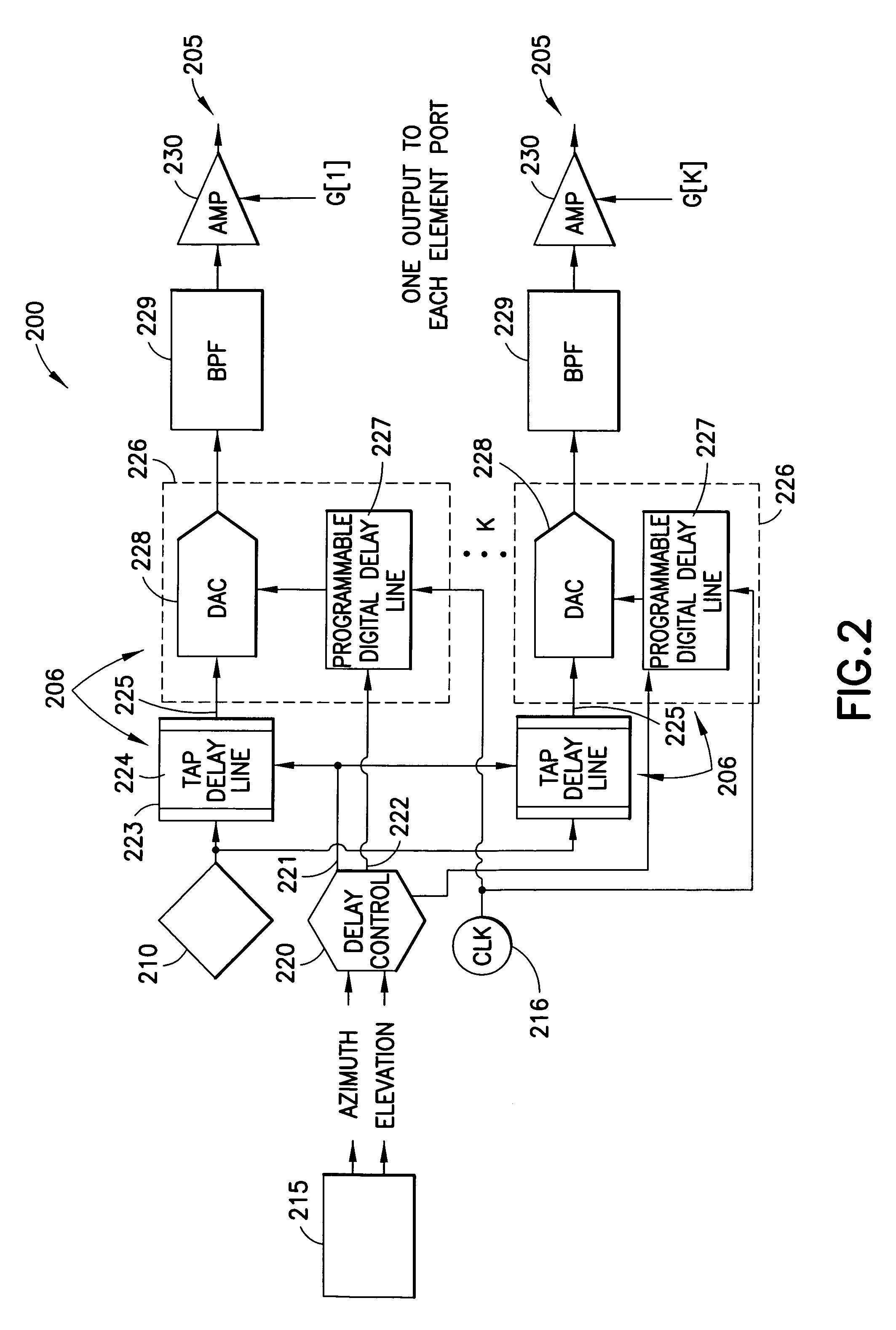

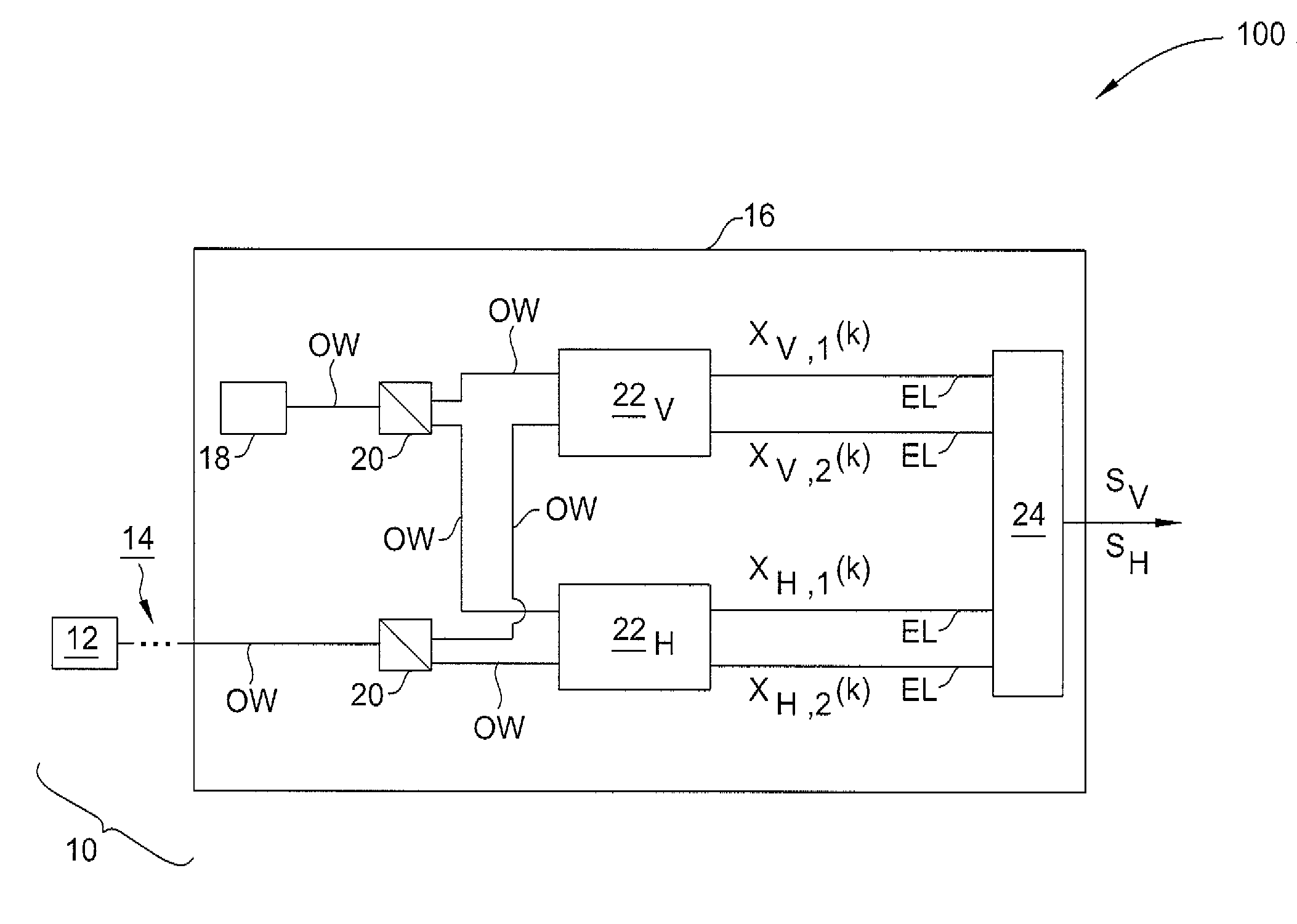

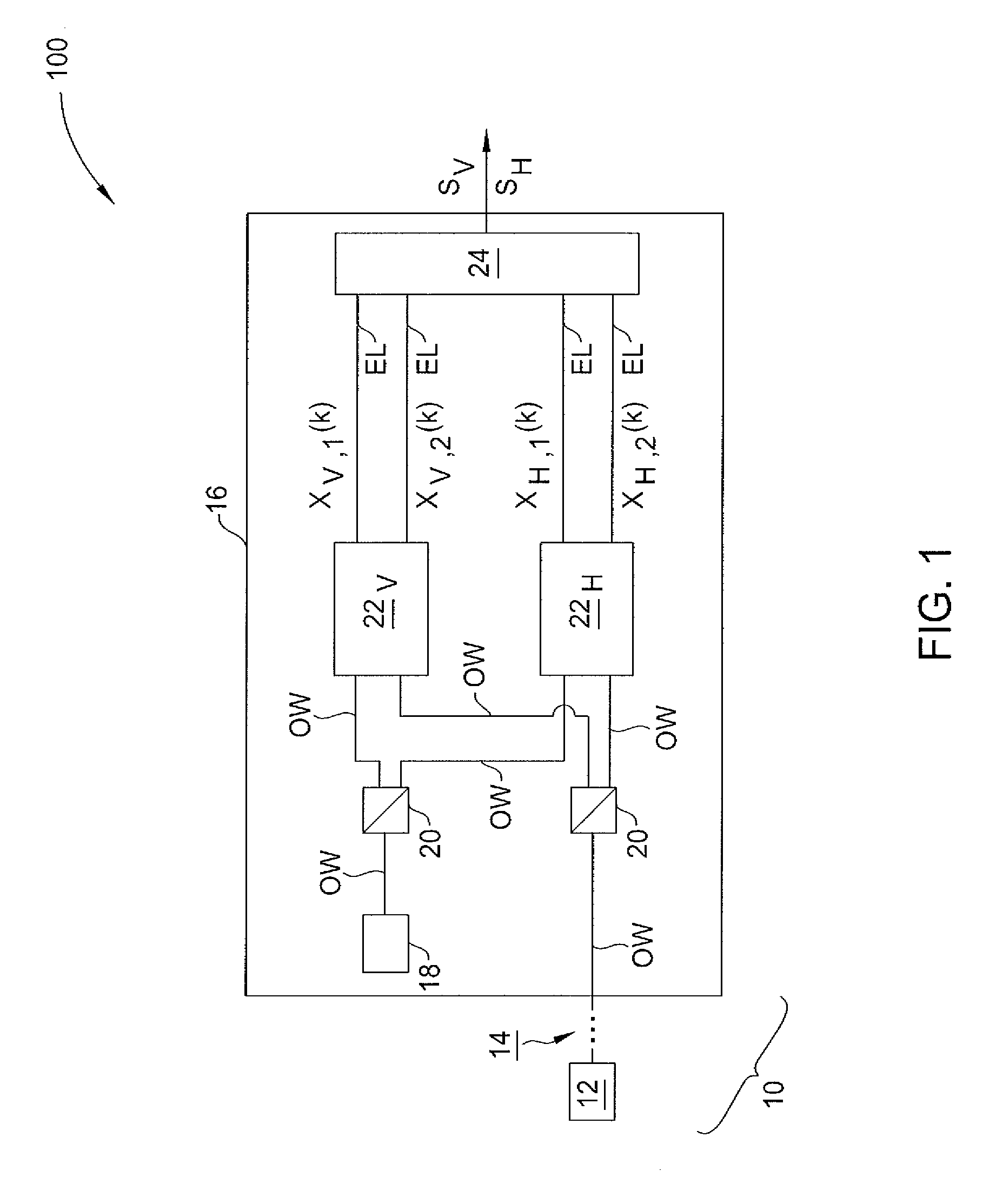

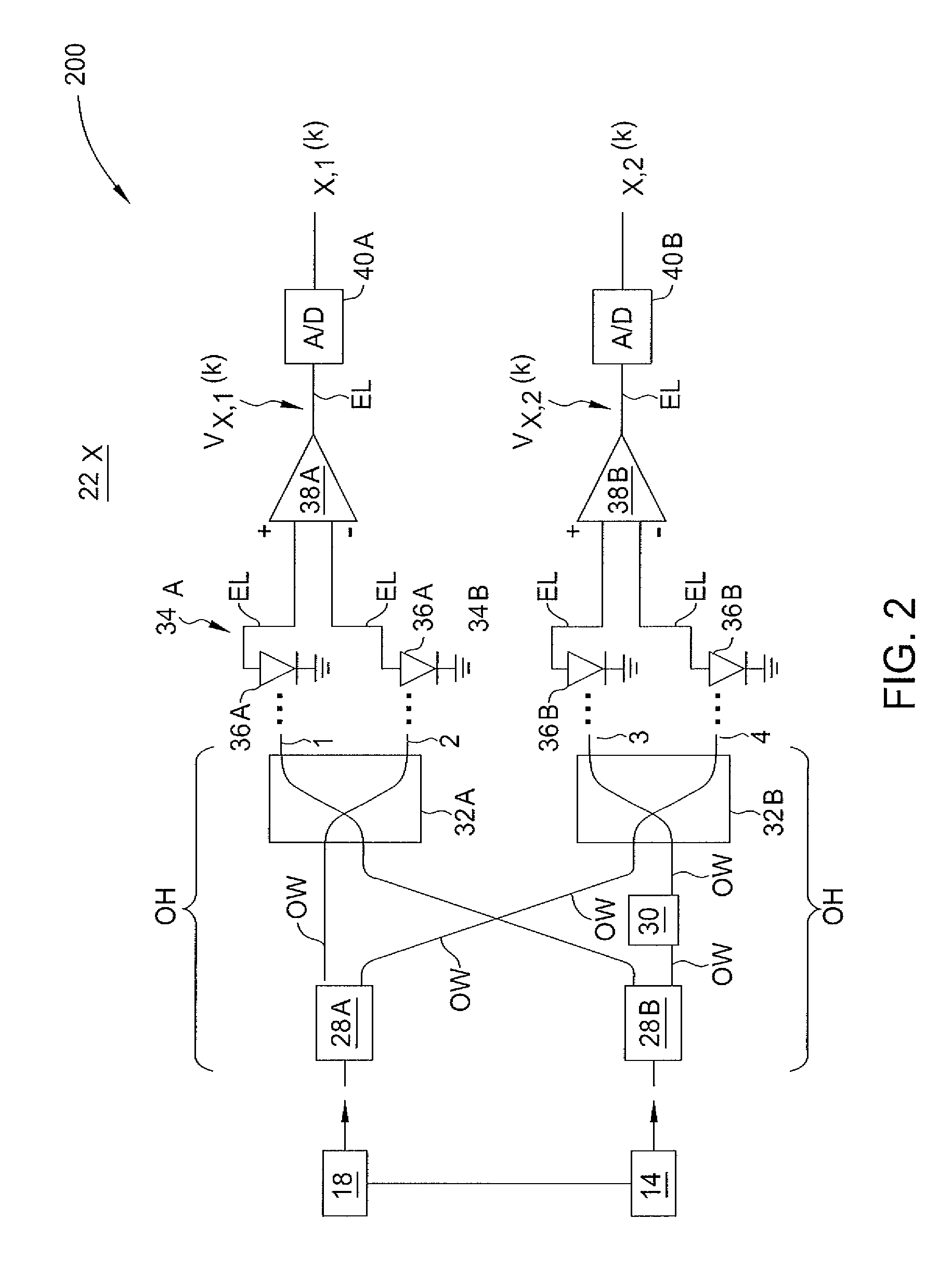

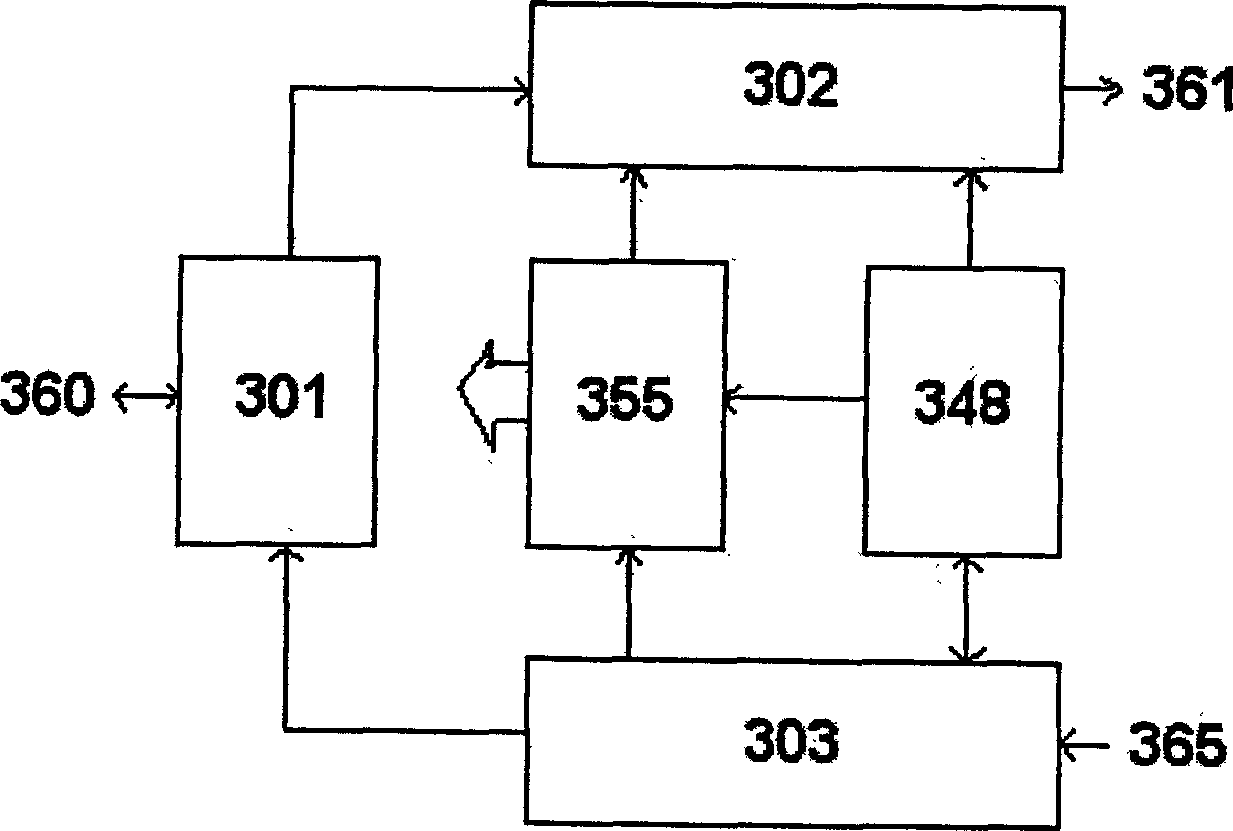

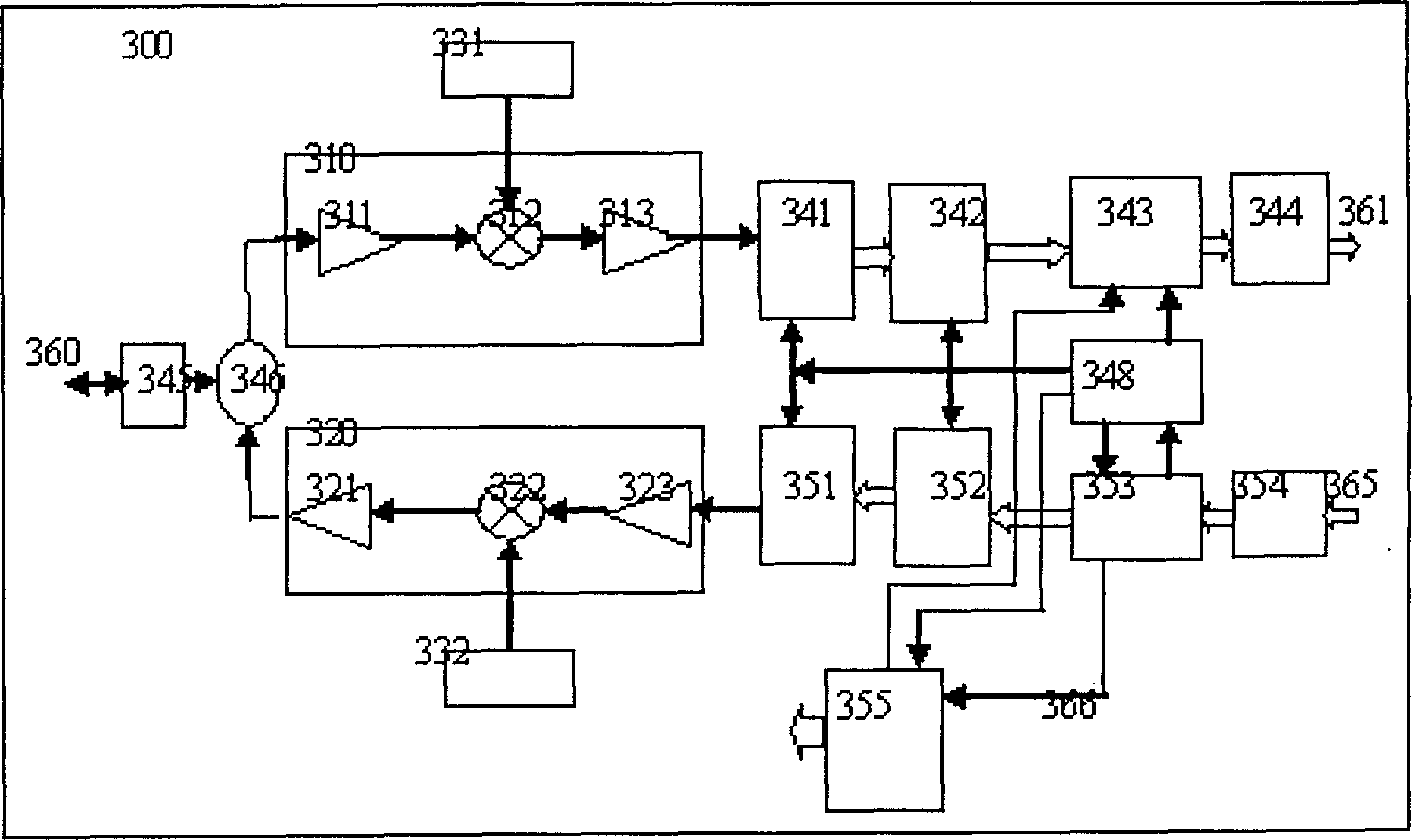

Methods and apparatus for implementing a wideband digital beamforming network

The present invention concerns methods and apparatus for implementing a true-time-delay wideband digital beamformer. In true-time-delay wideband digital beamformers of the present invention, improved control over beam properties formed by the combination of the beamformer and a multi-element antenna coupled to the beamformer is achieved through finer control of delays imparted to data signals. In beamformers of the present invention, data is delayed using a coarse control that provides a delay in whole increments of a clock cycle of a digital clock reference and a fine control that provides a delay corresponding to a fraction of a whole clock cycle of the digital clock reference. In the true time delay method of the present invention, transmission and reception across a wide frequency band is accommodated. In the true time delay method of the present invention, multiple simultaneous beams are formed independently, beam-to-beam, across a wide frequency band.

Owner:RAYTHEON CO

High-precision time interval measurement method based on phase modulation

InactiveCN102540865AMany technical meansEasy to implementElectric unknown time interval measurementObservational errorMeasurement device

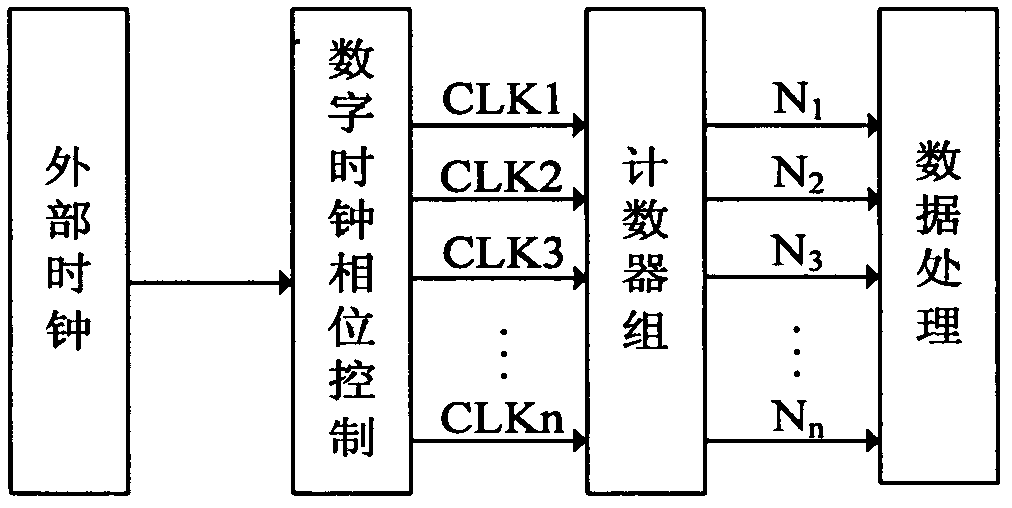

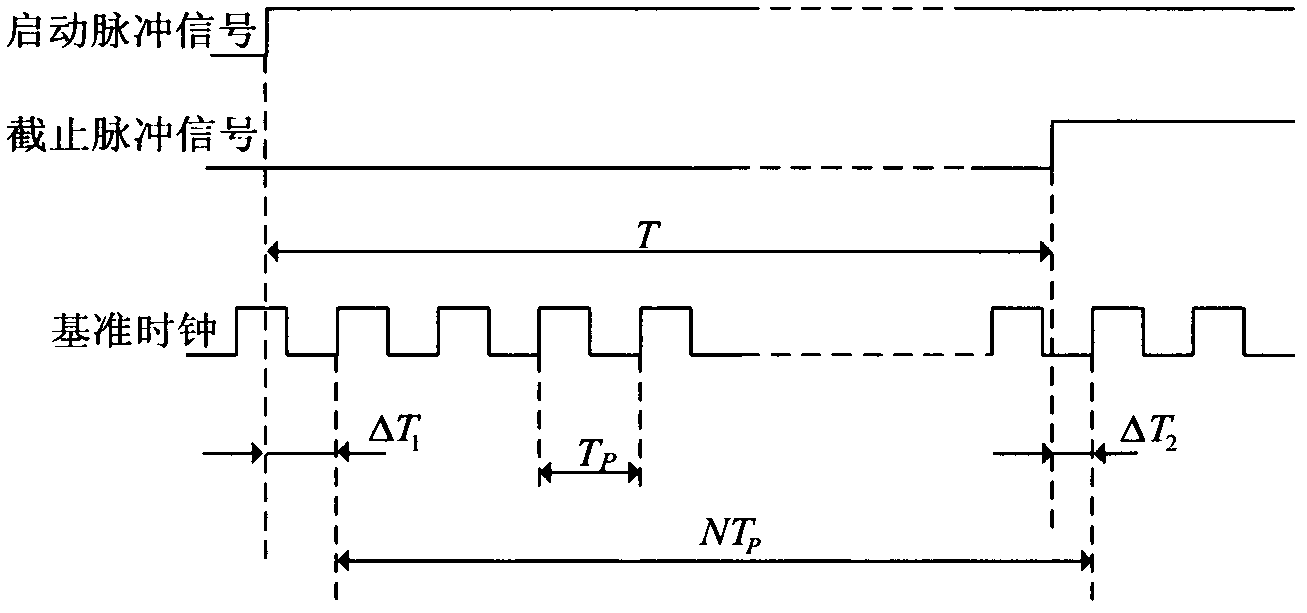

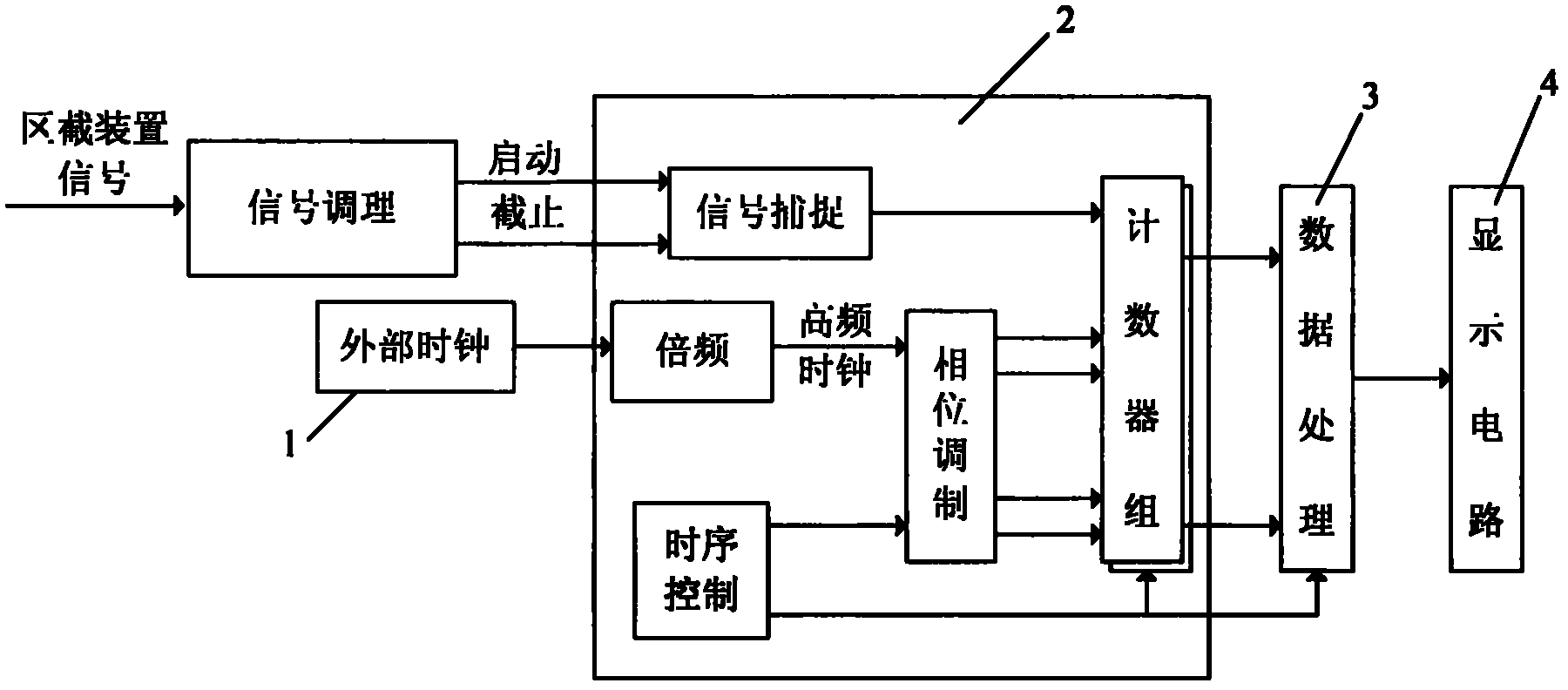

The invention discloses a high-precision time interval measurement method based on phase modulation. Under the control of digital clock phase-shift, a path of high-frequency and low-jitter clock is transformed to N paths of clock signals having same frequency and fixed phase difference, and is taken as a counter reference clock; a counter is driven to count respectively in N paths of clock periods; two paths of clock signals, which have the smallest error, are extracted by utilizing the clock phase information; through the combination with the clock period and the counted values, the measurement valve of the time interval is worked out. Compared with the method using a single clock for counting, the high-precision time interval measurement method effectively reduces the measurement principle error, and can improve the measurement resolution ratio to 1 / n of the reference clock. A measurement device is connected with a signal conditioning module, an FPGA module, a singlechip module and a display circuit module sequentially according to the signal processing order, and realizes high measurement precision, high measurement resolution ratio, high measurement speed, real time display, and stable and reliable work under a certain crystal oscillation frequency; and the integration in the FPGA is easy, and the expansion is flexible. The high-precision time interval measurement method can be used for measuring the speed in a high-speed motion.

Owner:XIAN MODERN CHEM RES INST

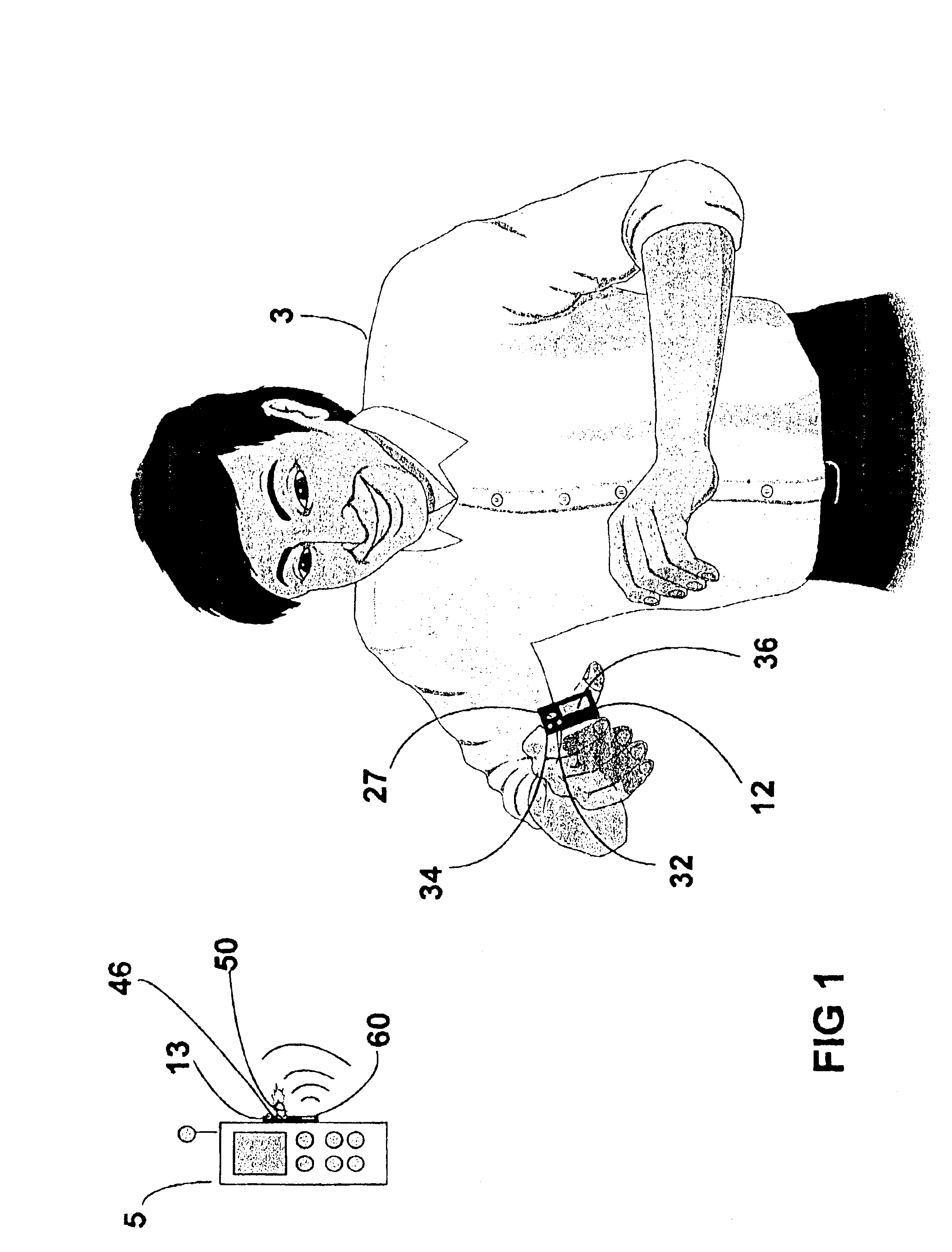

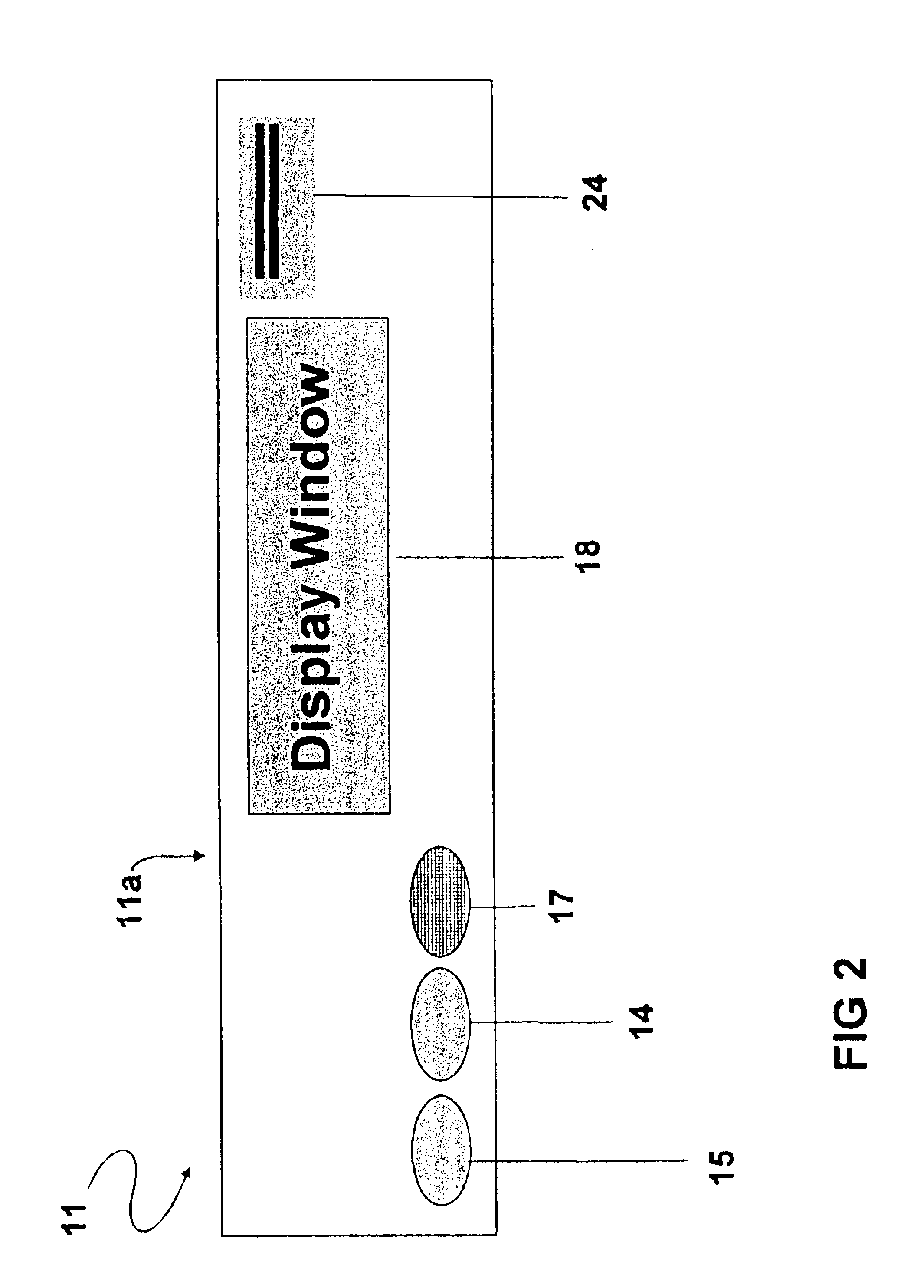

Devices for locating/keeping track of objects, animals or persons

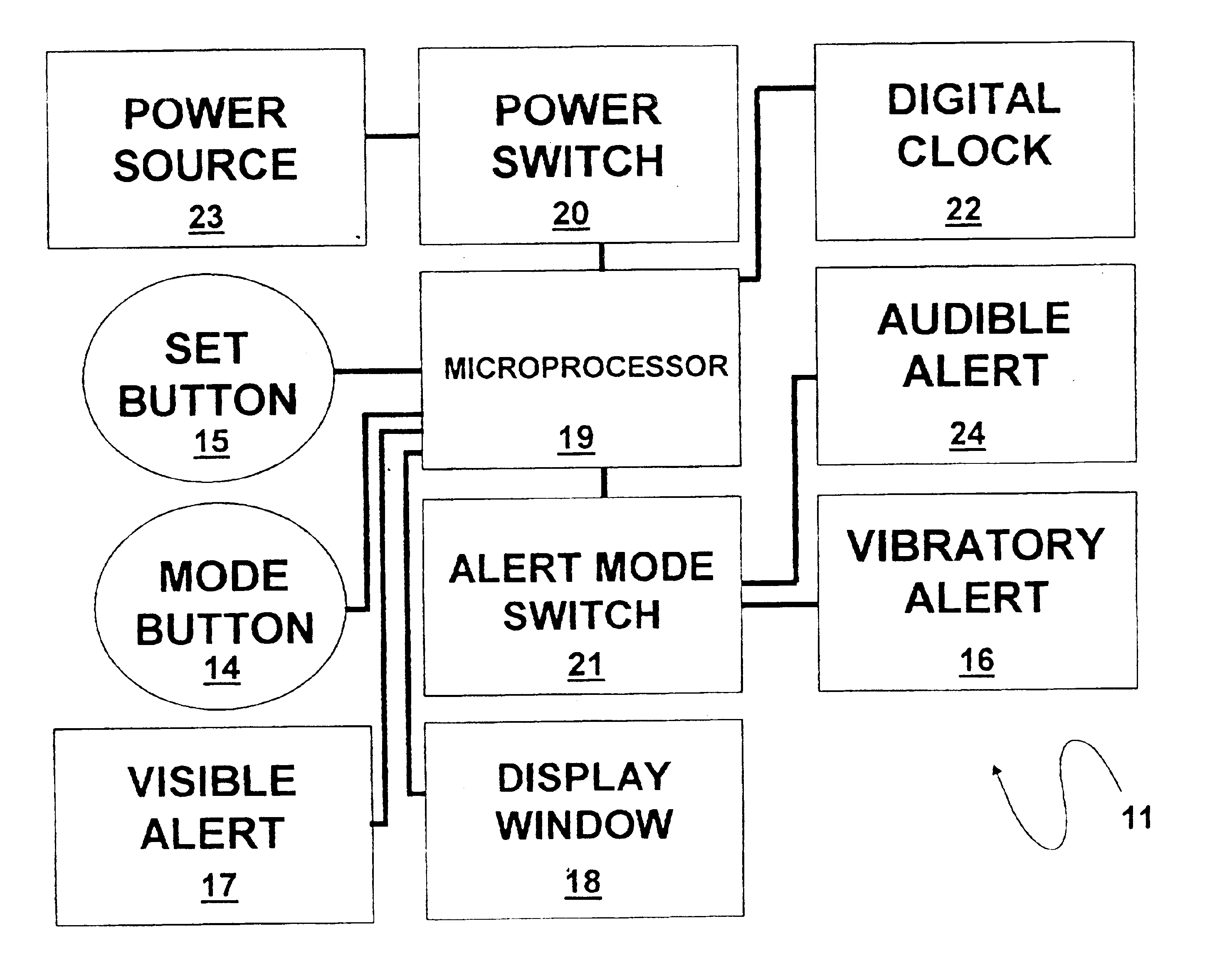

Devices for enabling a user to locate an object, animal or person or reminding the user of the location of an object, animal or person. In a non-transmitter / receiver embodiment, the device includes at least one alert mechanism which is connected to a digital clock or other timer and microprocessor which times transmission of alert signals emitted from the alert mechanism or mechanisms. The operational components of the device may be contained in a housing which is attached to the object, animal or person to be located. In a remote transmitter / receiver embodiment, the device includes a transmitter which transmits activation signals at preset times to activate an alert feature of a paired remote receiver which is provided on the object, animal or person to be located or tracked. The transmitter may include an on-command button for manual transmission of the activation signals to the receiver. The receiver may have a visible alert mode in combination with a selected audible or vibratory alert mode. In an on-board transmitter / receiver embodiment, the device includes a transmitter which is housed together with a receiver in a single unit. In that case, the transmitter of one unit can transmit preset timed activation signals to the receiver of a different unit which is placed on the object, animal or person. Alternatively, the transmitter of one unit can transmit preset timed activation signals to the receiver of the same unit placed on the object, animal or person.

Owner:CALHOUN RICKY R +1

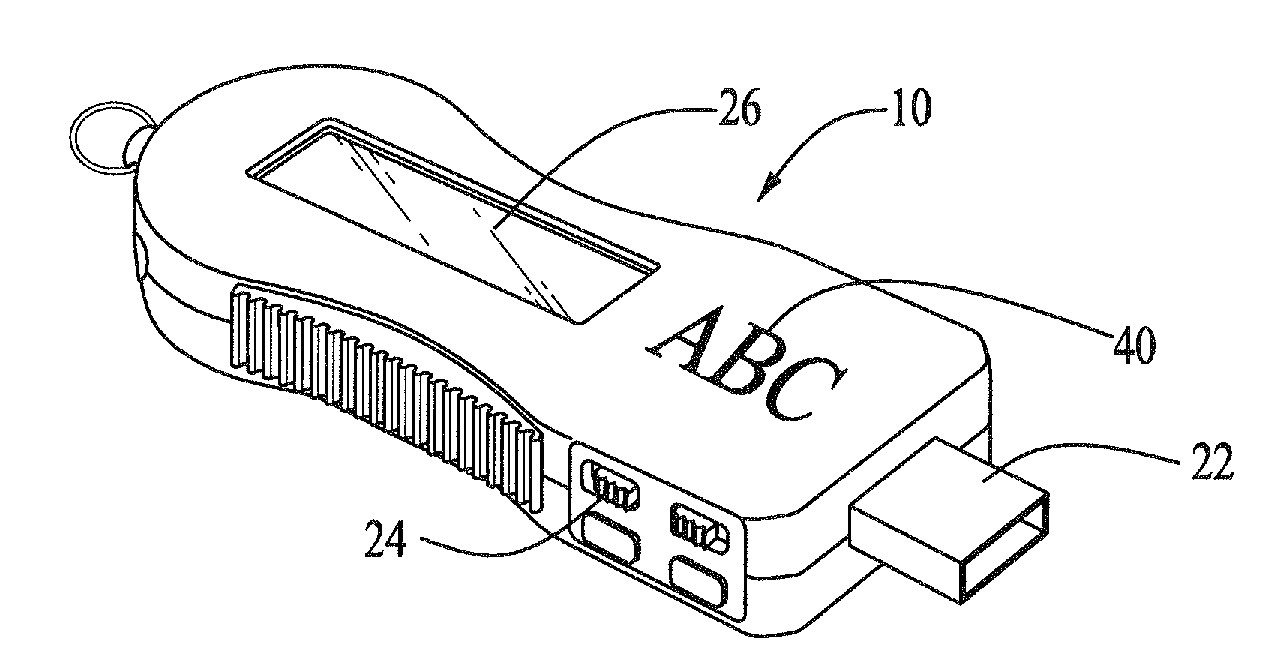

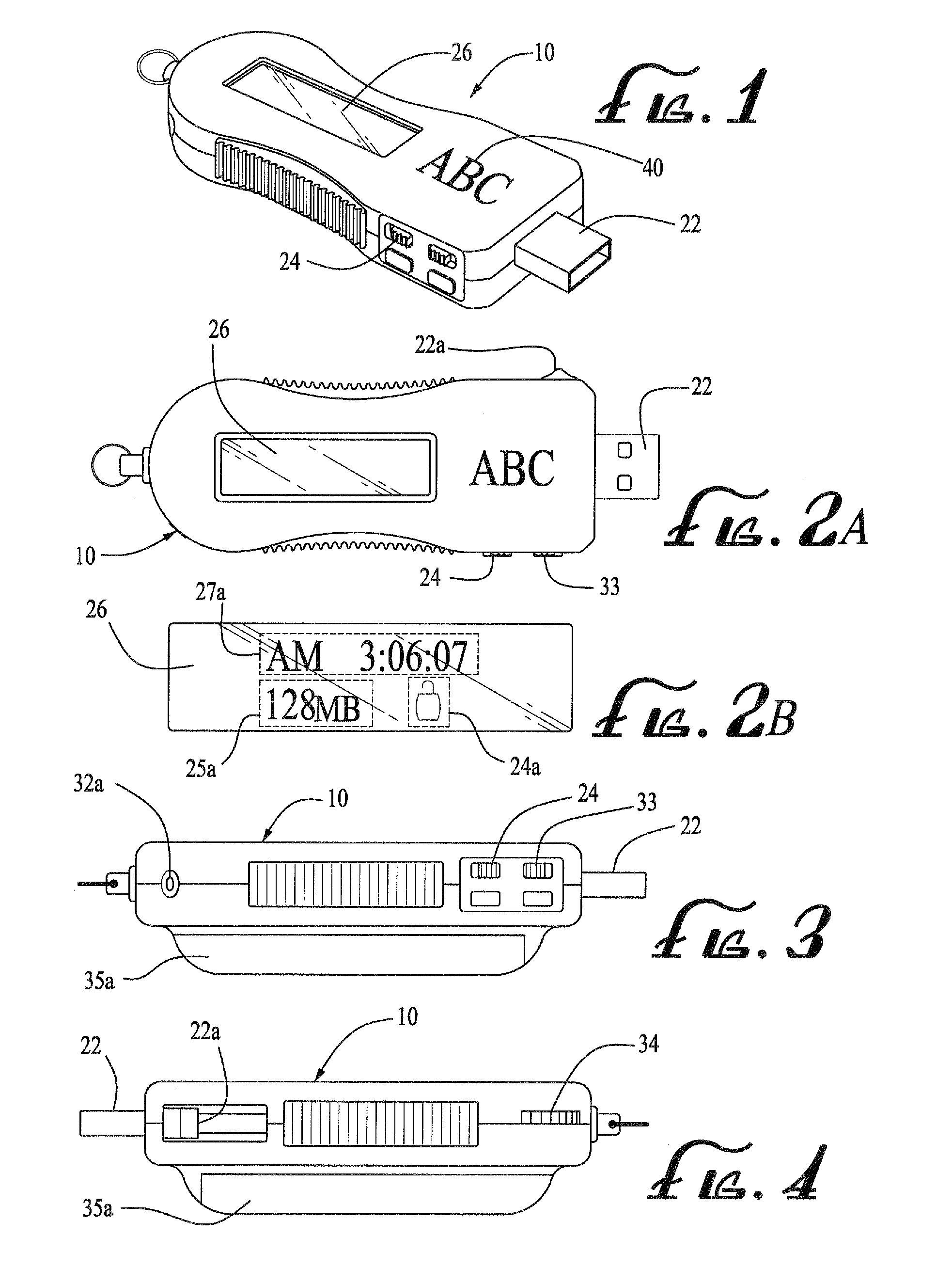

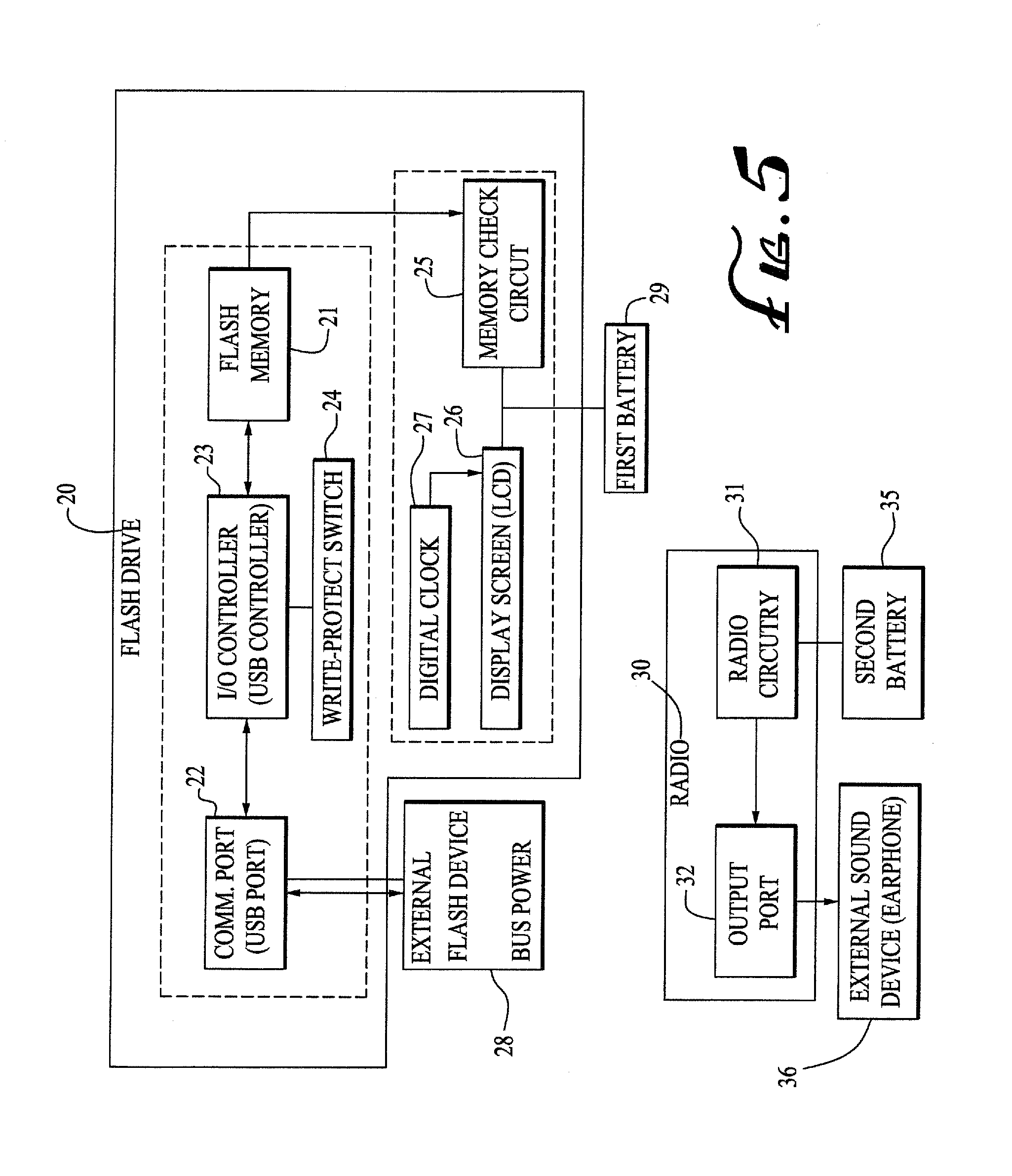

Flash drive-radio combination

InactiveUS20080133832A1Low production costSmall sizeRecord carriers used with machinesMemory systemsElectricityDigital clock

A flash drive incorporating a FM scanner radio, of which the circuitry is electrically isolated from each other and separately powered to reduce production cost and size. The flash drive-radio combination comprises a radio and a flash drive encased in a housing. The radio is configured only to search, receive, and convert to audio signals, radio signals that lies within only the broadcast FM bands, and the flash drive comprises a flash memory, a bidirectional communication port, a controller, and preferably, a display unit for displaying used and available memory in the flash memory. A write protect switch, a channel scan button, a digital clock may be further included in the present invention.

Owner:SUN COAST MERCHANDISE

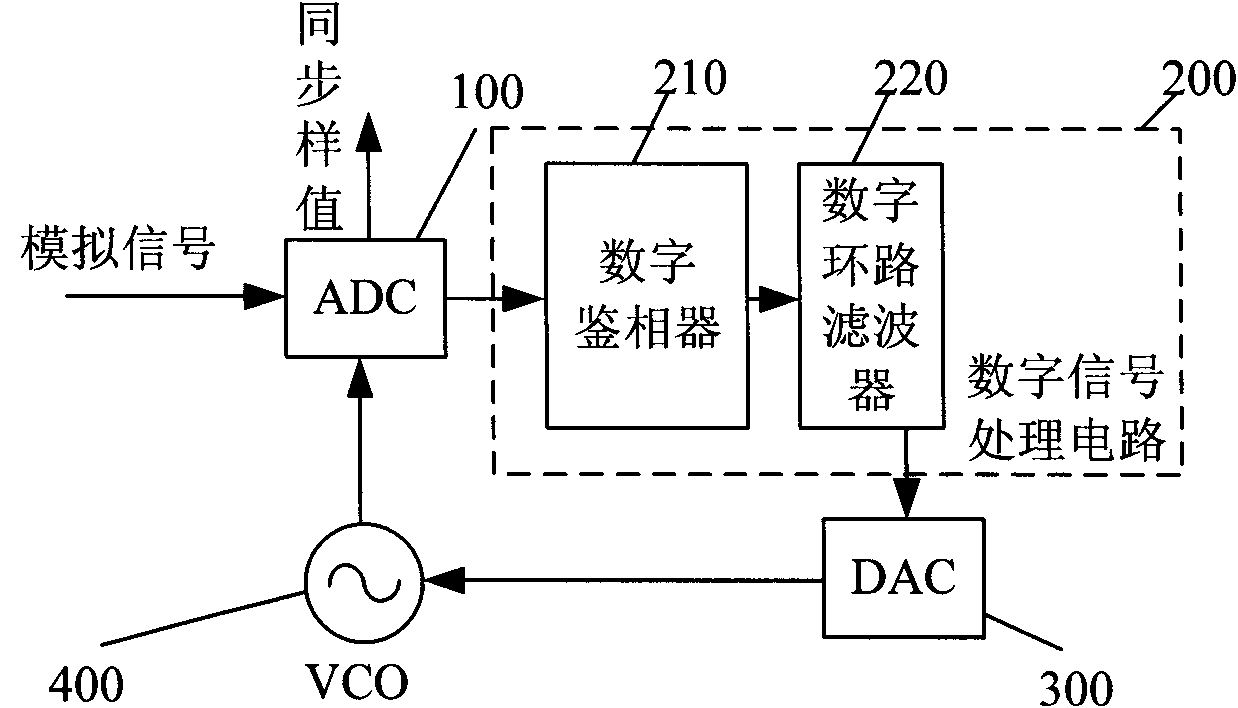

Clock recovery device and method

InactiveCN101820340AModulated-carrier systemsSynchronisation error detectionDigital signal processingEngineering

The invention discloses a clock recovery device and a clock recovery method. The clock recovery device comprises an analog-to-digital converter, a digital signal processing circuit, a digital-to-analog converter and a voltage-controlled oscillator which are connected in turn, wherein the voltage-controlled oscillator is connected with the analog-to-digital converter; the analog-to-digital converter is used for converting received analog signals into digital signals, and sending the digital signals to the digital signal processing circuit; the digital signal processing circuit is used for carrying out phase demodulation and filtering processing on the received digital signals so as to obtain digital clock error signals, and sending the digital clock error signals to the digital-to-analog converter; the digital-to-analog converter is used for converting the received digital clock error signals into control voltage signals, and sending the control voltage signals to the voltage-controlled oscillator; and the voltage-controlled oscillator is used for generating a synchronous clock according to the received control voltage signals, and outputting the synchronous clock to the analog-to-digital converter. The invention can provide a reference clock for chips in a digital circuit.

Owner:ZTE CORP +1

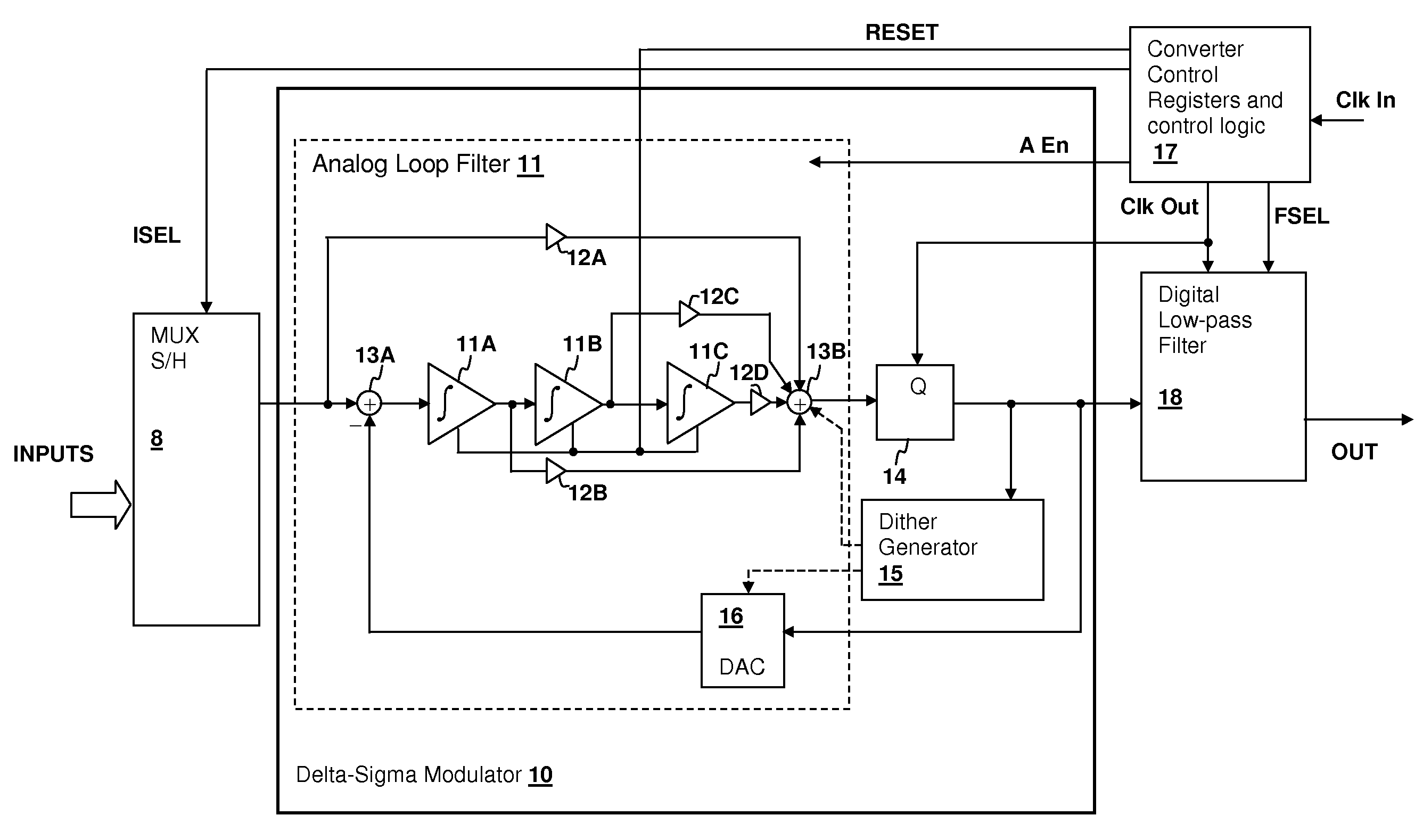

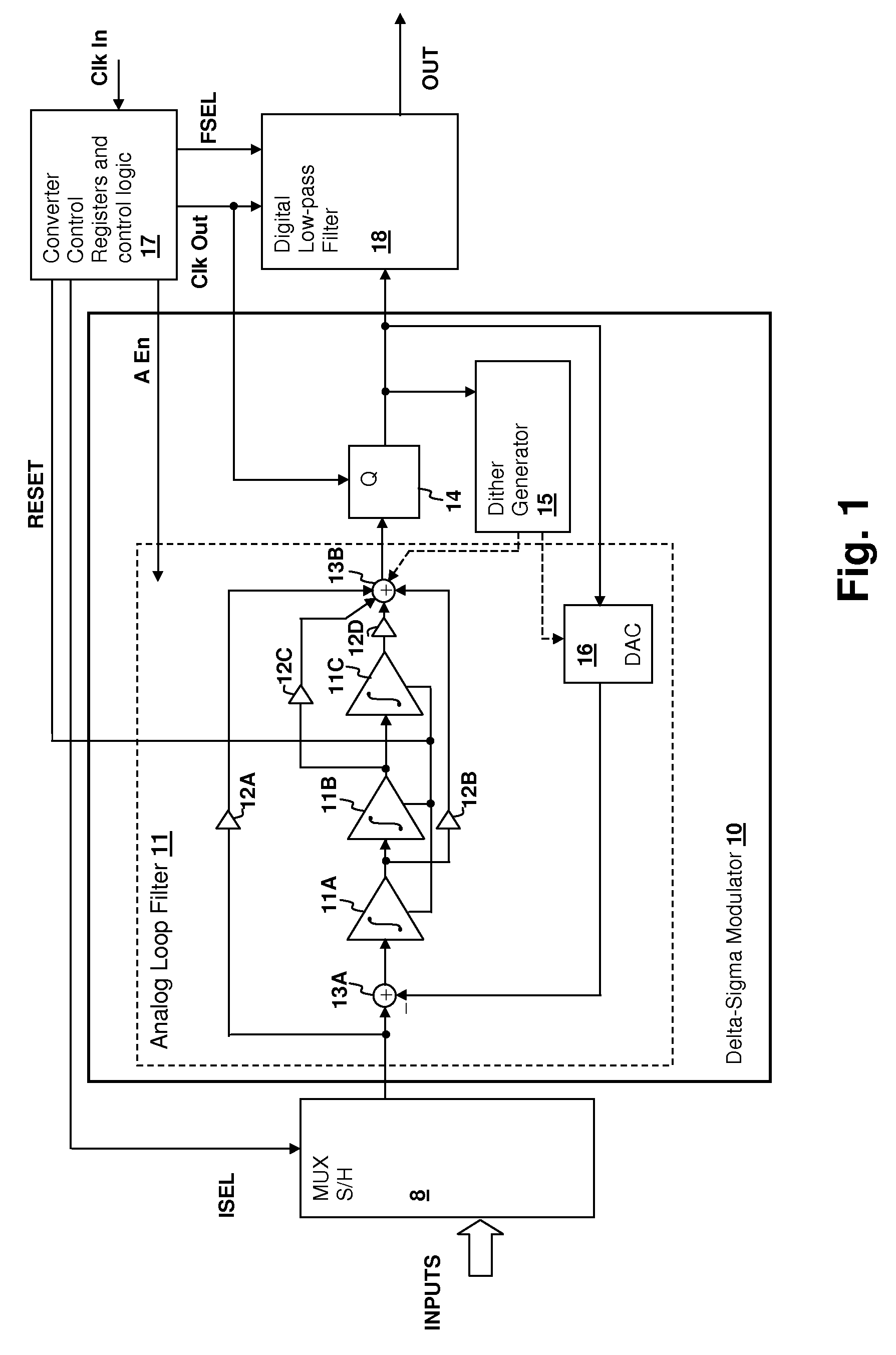

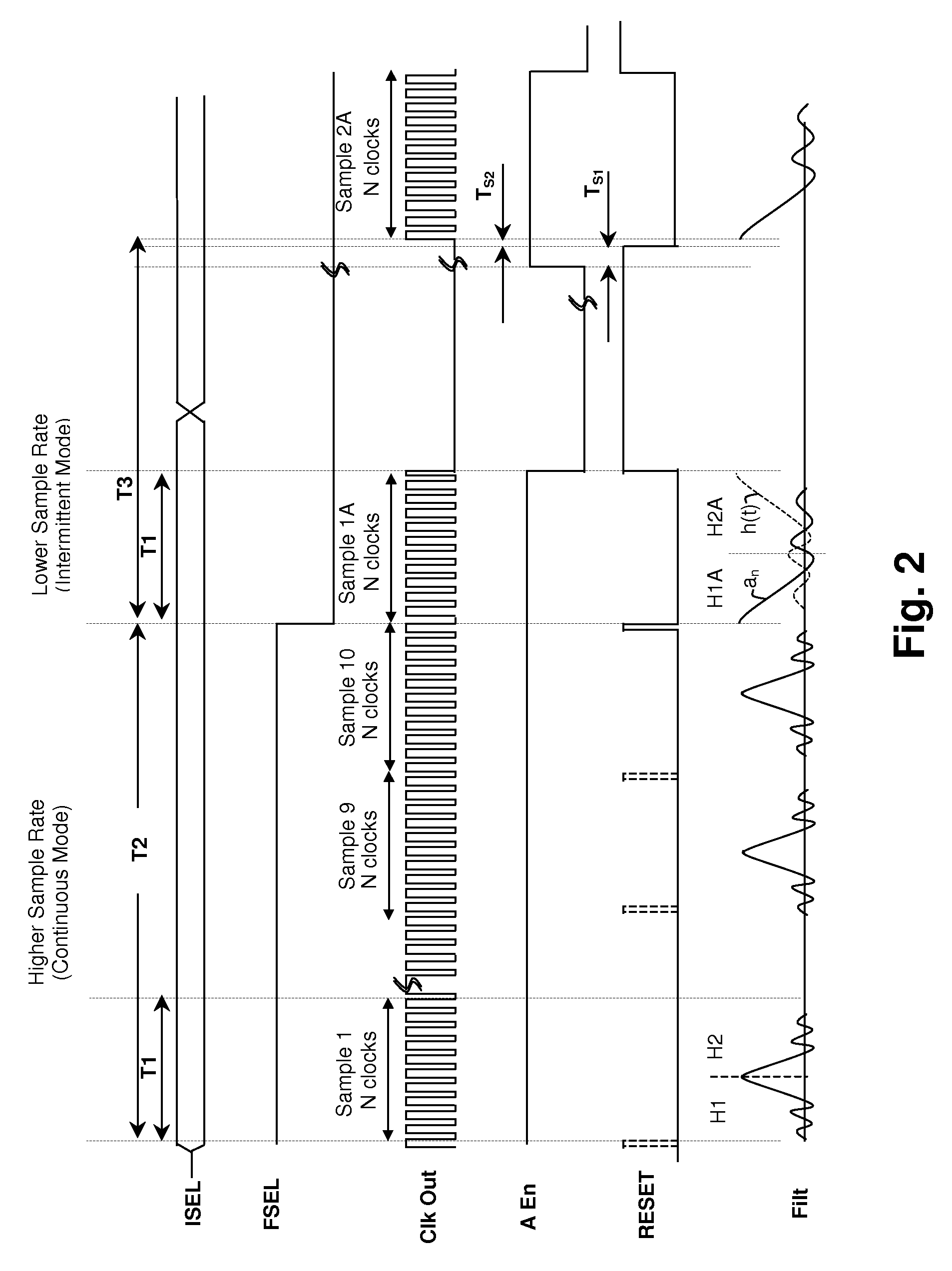

Delta-sigma analog-to-digital converter (ADC) having an intermittent power-down state between conversion cycles

ActiveUS7365667B1Electric signal transmission systemsAnalogue conversionLoop filterDigital down converter

A delta-sigma analog to digital converter (ADC) having an intermittent power down state between conversion cycles provides for power consumption savings when the converter is in a lower sample rate operating mode. Clocks provided to the digital portions of the converter are disabled, except for a periodic interval in which a conversion is performed at the higher selectable sample rate of the converter. The analog portions of the converter can also be disabled, but are re-enabled for a predetermined time period and reset before the digital clocks are enabled, so that the loop filter and feedback value supplied from the quantizer to the loop filter are stable prior to each conversion.

Owner:CIRRUS LOGIC INC

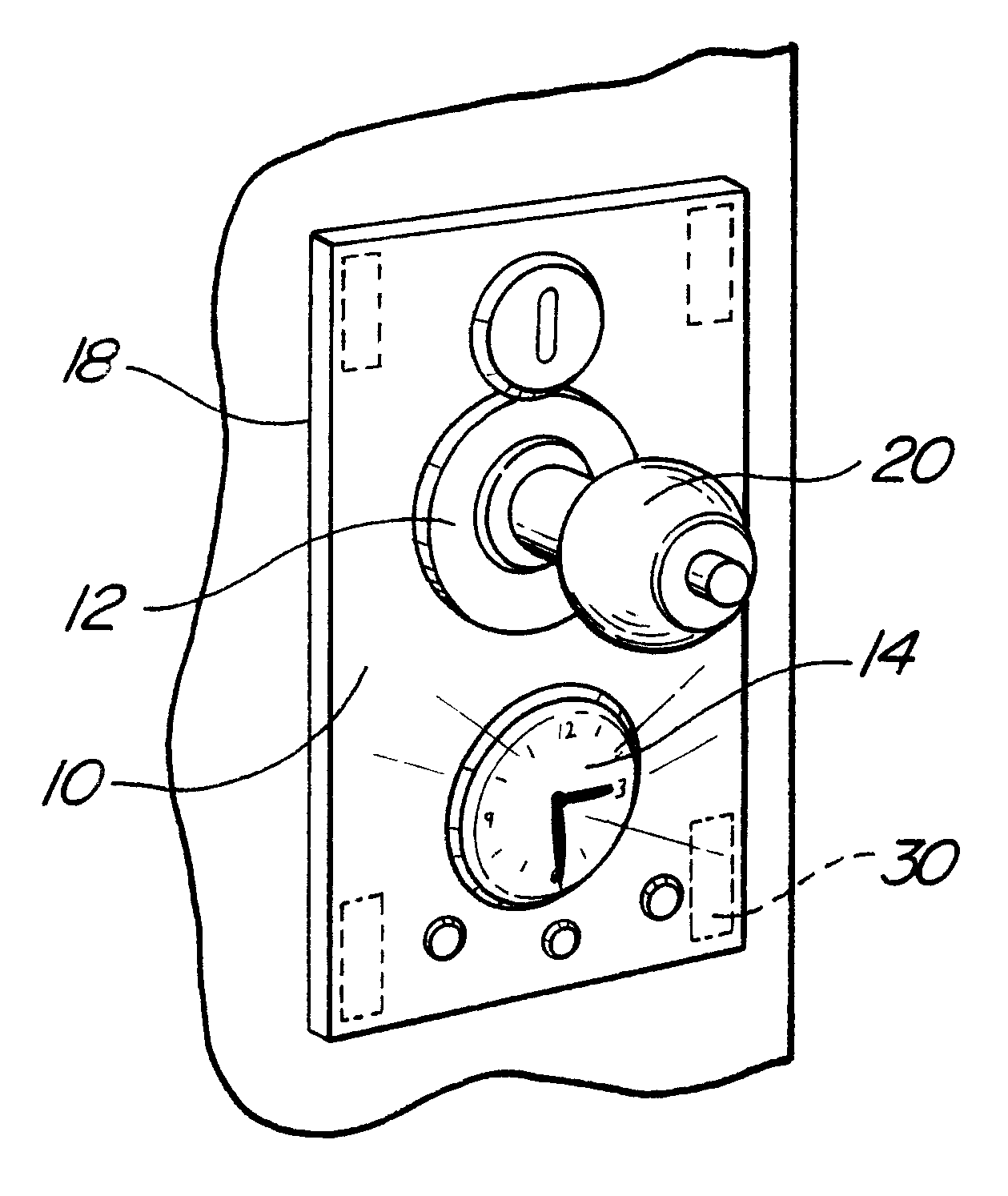

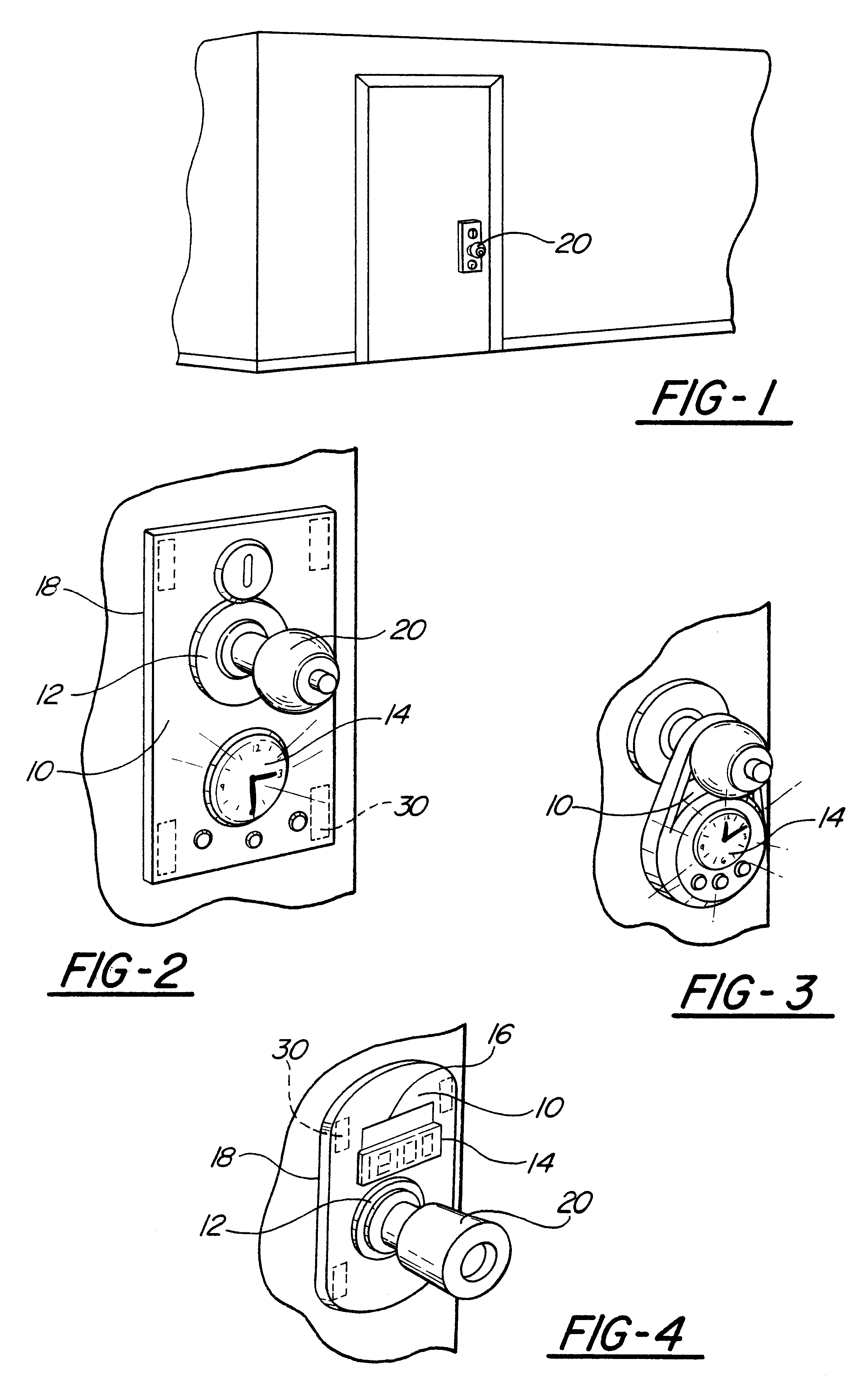

Illuminated article for a door having a handle

An article is described for providing illumination for a door handle in reduced lighting conditions. The article includes a mounting device and a method for illuminating the door handle. The method for illuminating may comprise a timekeeping device such as a light emitting display digital clock.

Owner:HOLLOWAY KATIE

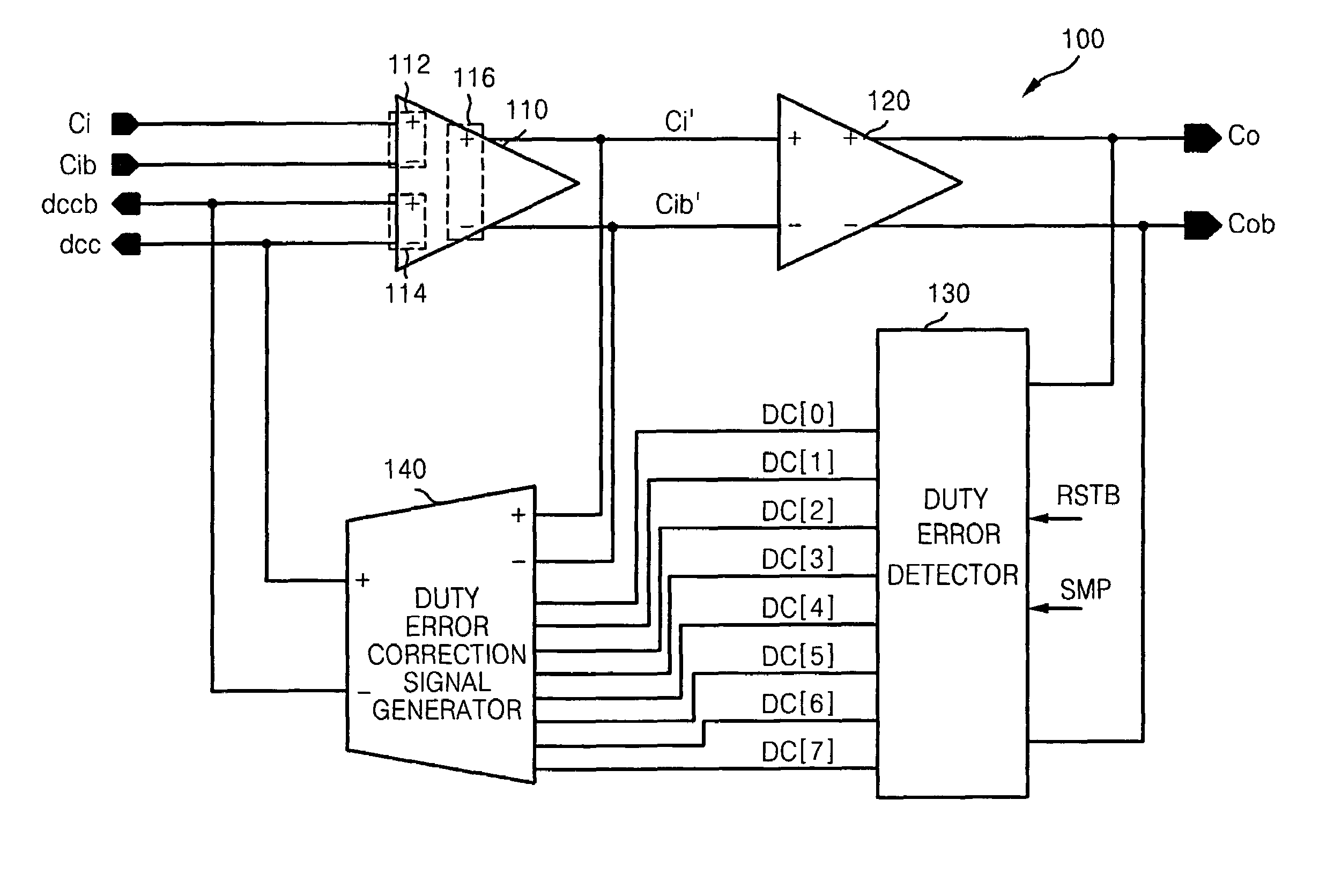

Duty cycle correction circuit and duty cycle correction method

ActiveUS7501870B2Improve accuracyReduced settling timeDigital storageElectric pulse generatorDigital clockEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

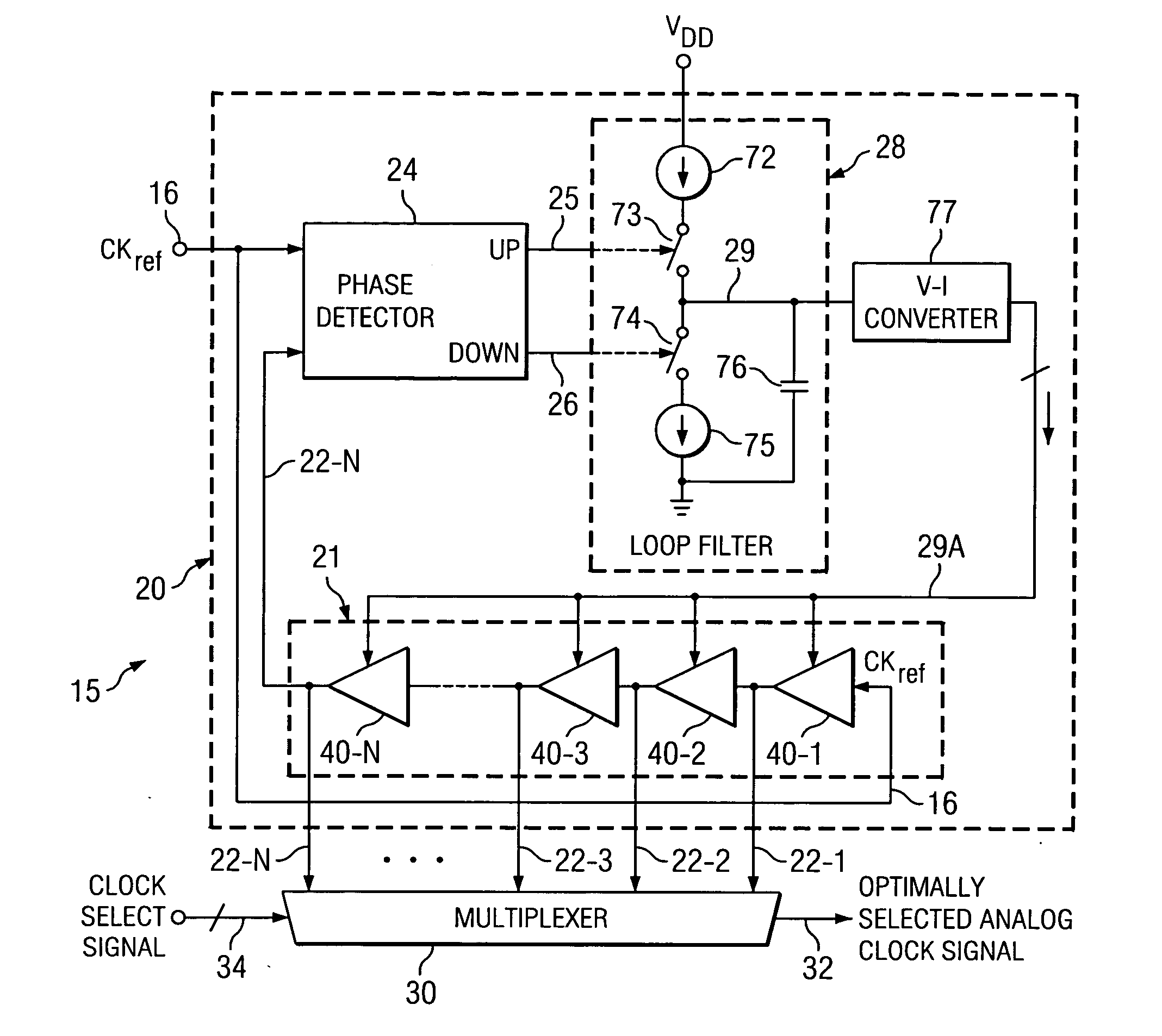

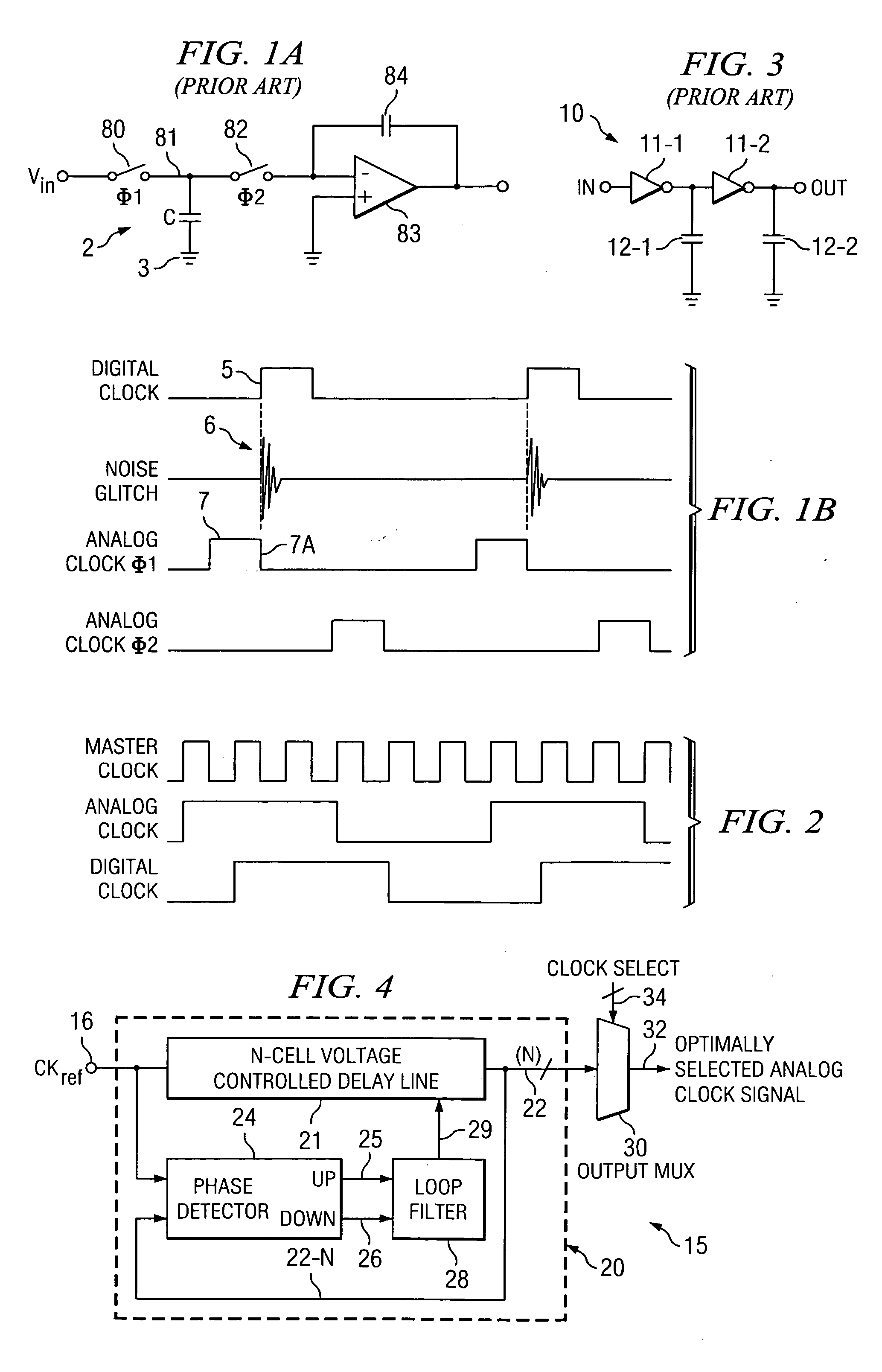

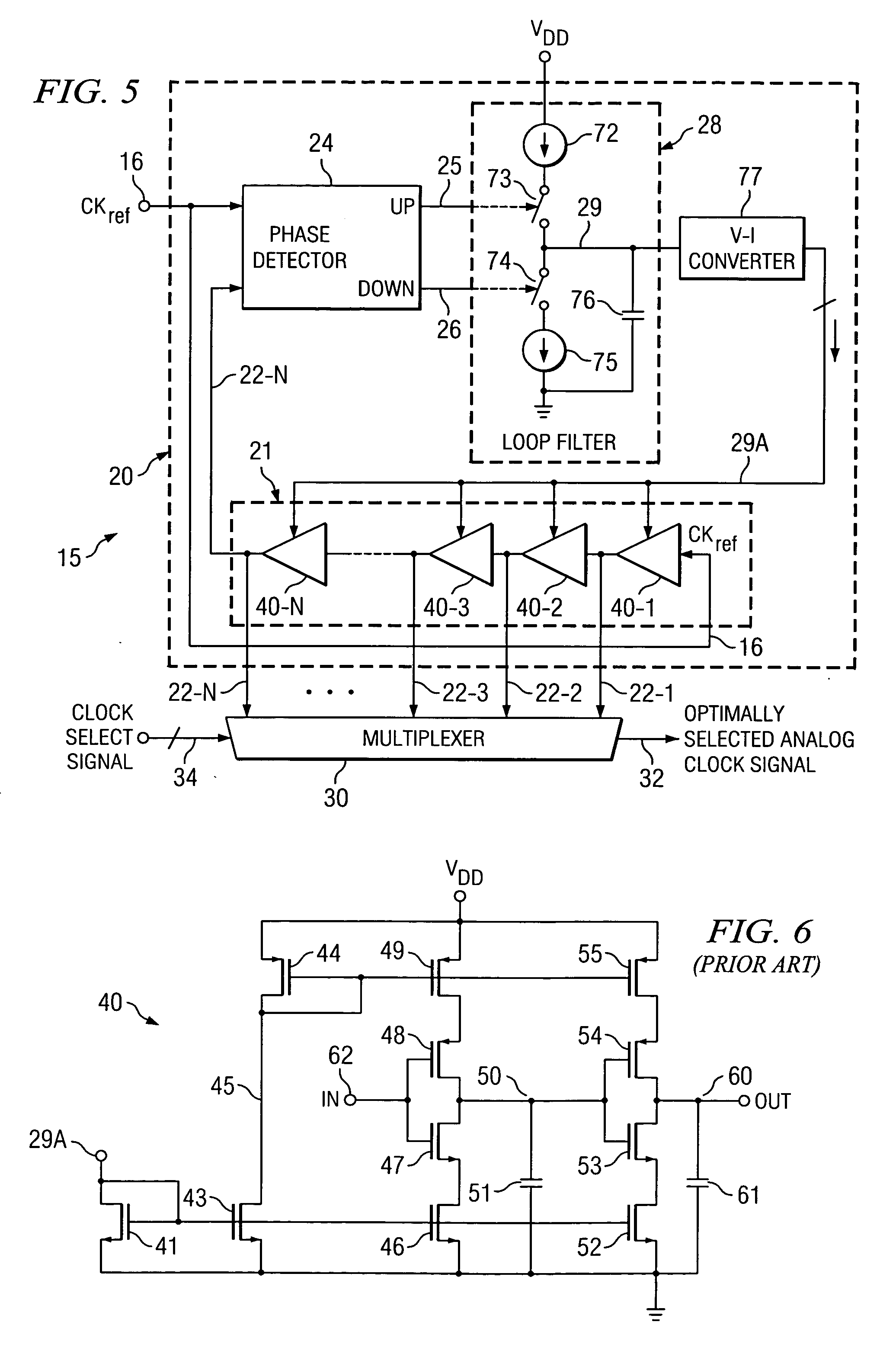

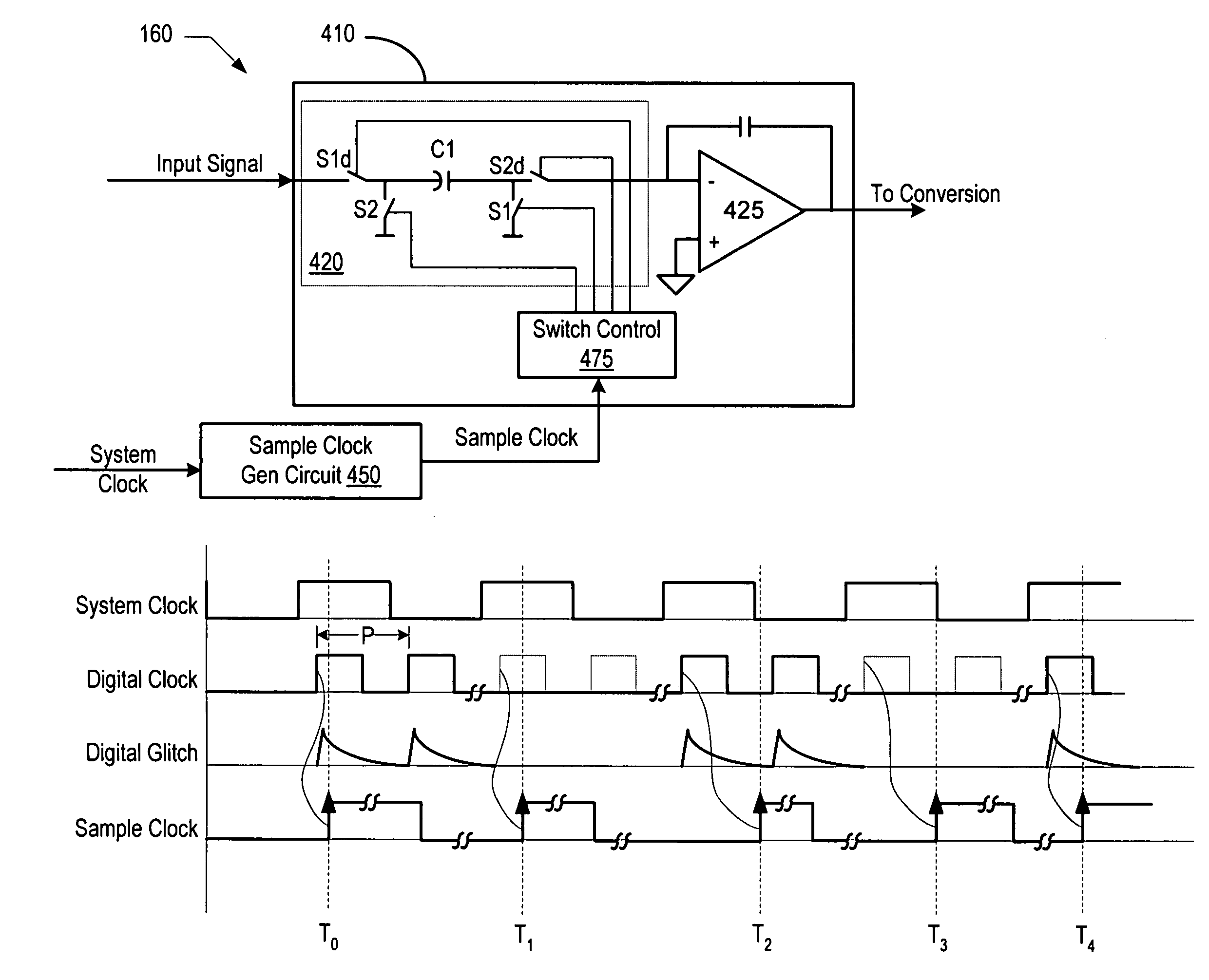

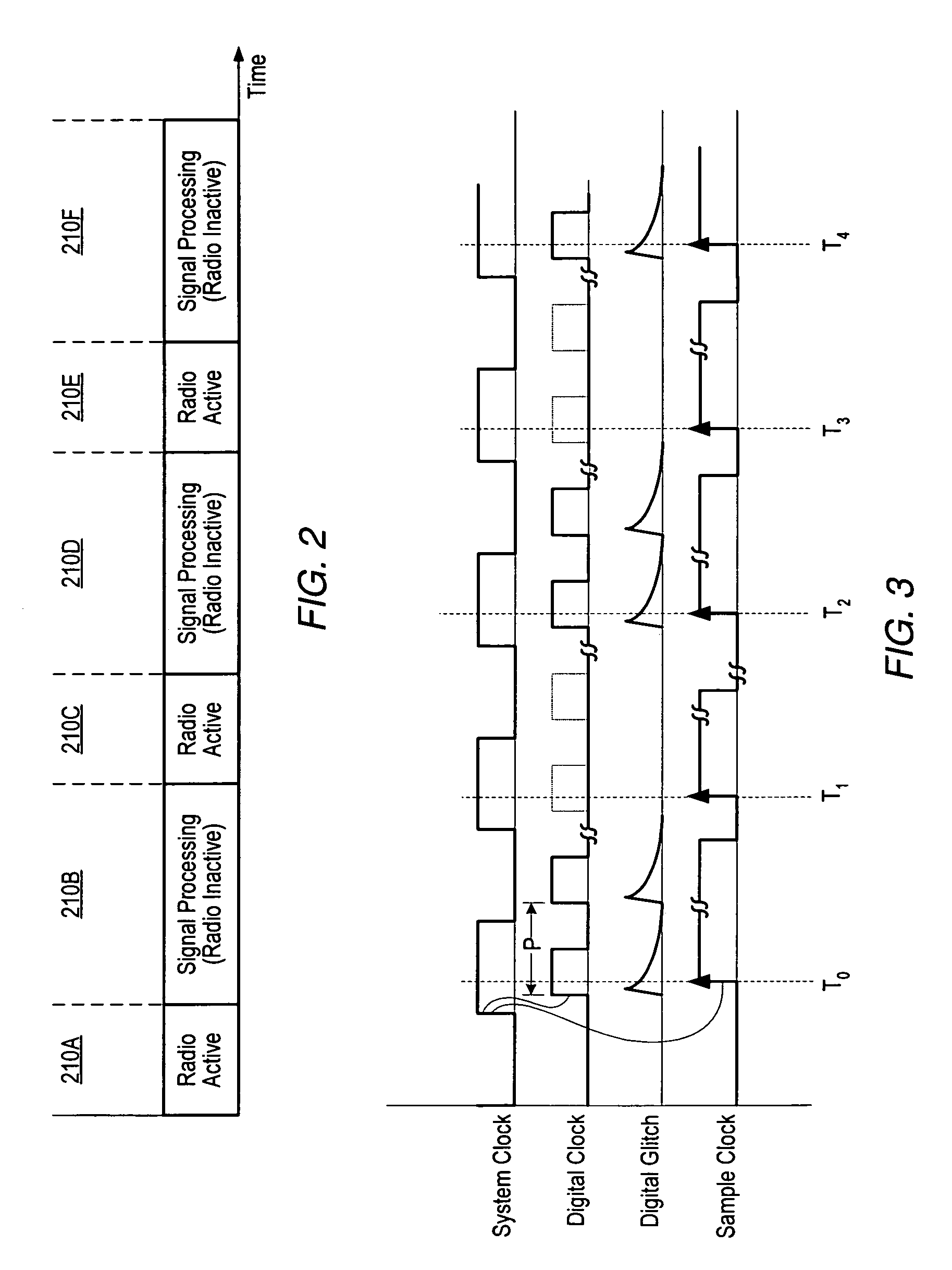

Delay locked loop circuitry and method for optimizing delay timing in mixed signal systems

InactiveUS20060038596A1Minimizing degradationAvoid problemsAnalogue/digital conversionPulse automatic controlMultiplexerDigital clock

A mixed signal system includes a digital circuit (17) clocked by a digital clock signal, an analog circuit (18) clocked by an analog clock signal, and clock generation circuitry (15) including a delay locked loop (20) including a N-cell delay line (21) having an input for receiving a reference clock signal and a plurality of delay outputs (22), and a multiplexer (30) having a plurality of inputs coupled to the plurality of delay outputs (22), respectively. A selection signal (34) causes the multiplexer (30) to couple a selected one of the delay outputs (22) to an output (32) of the multiplexer (30) so as to cause the analog clock signal and the digital clock signal to be sufficiently skewed from each other to minimize an inaccuracy in the analog circuit (18) caused by a noise glitch associated with the digital clock signal.

Owner:TEXAS INSTR INC

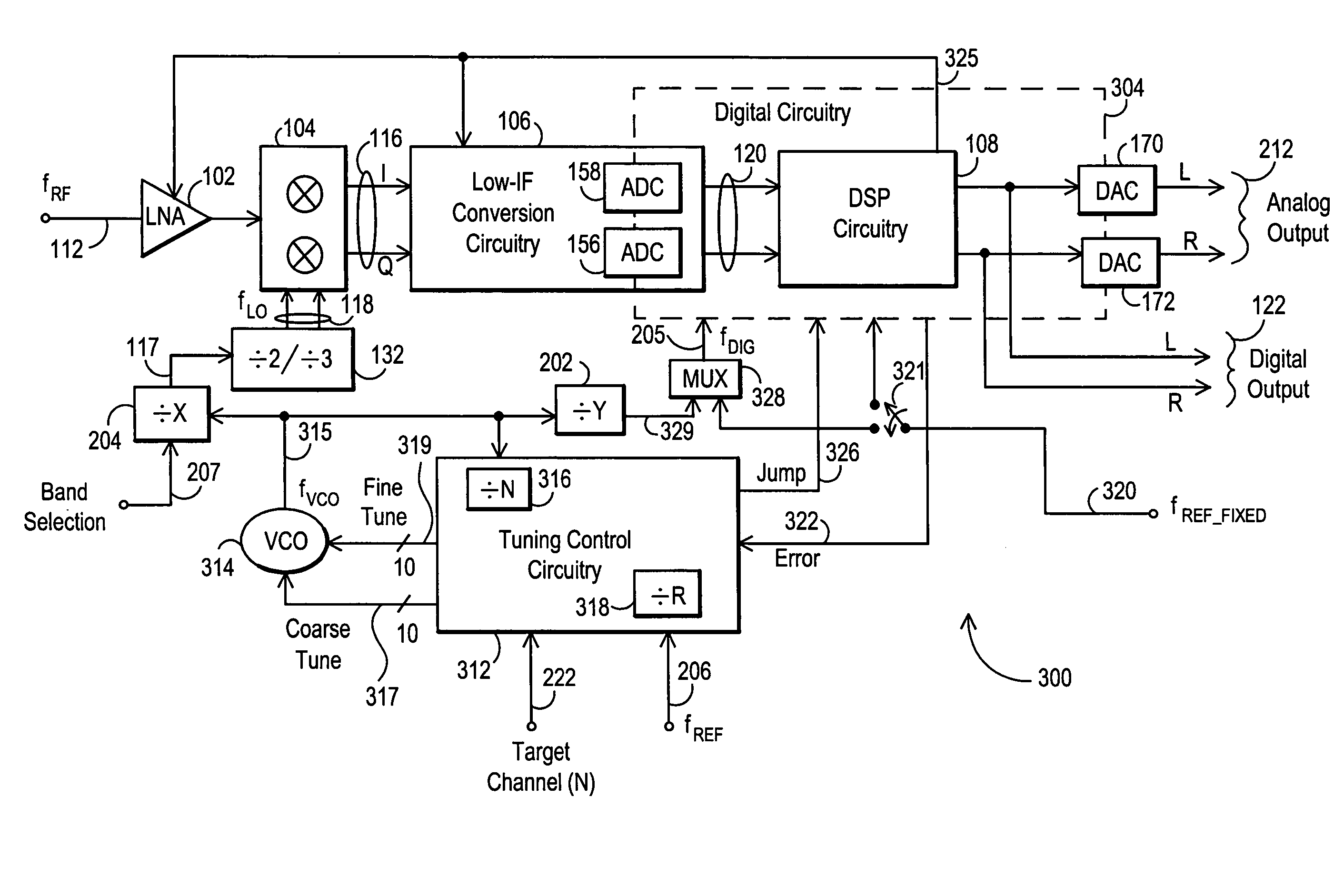

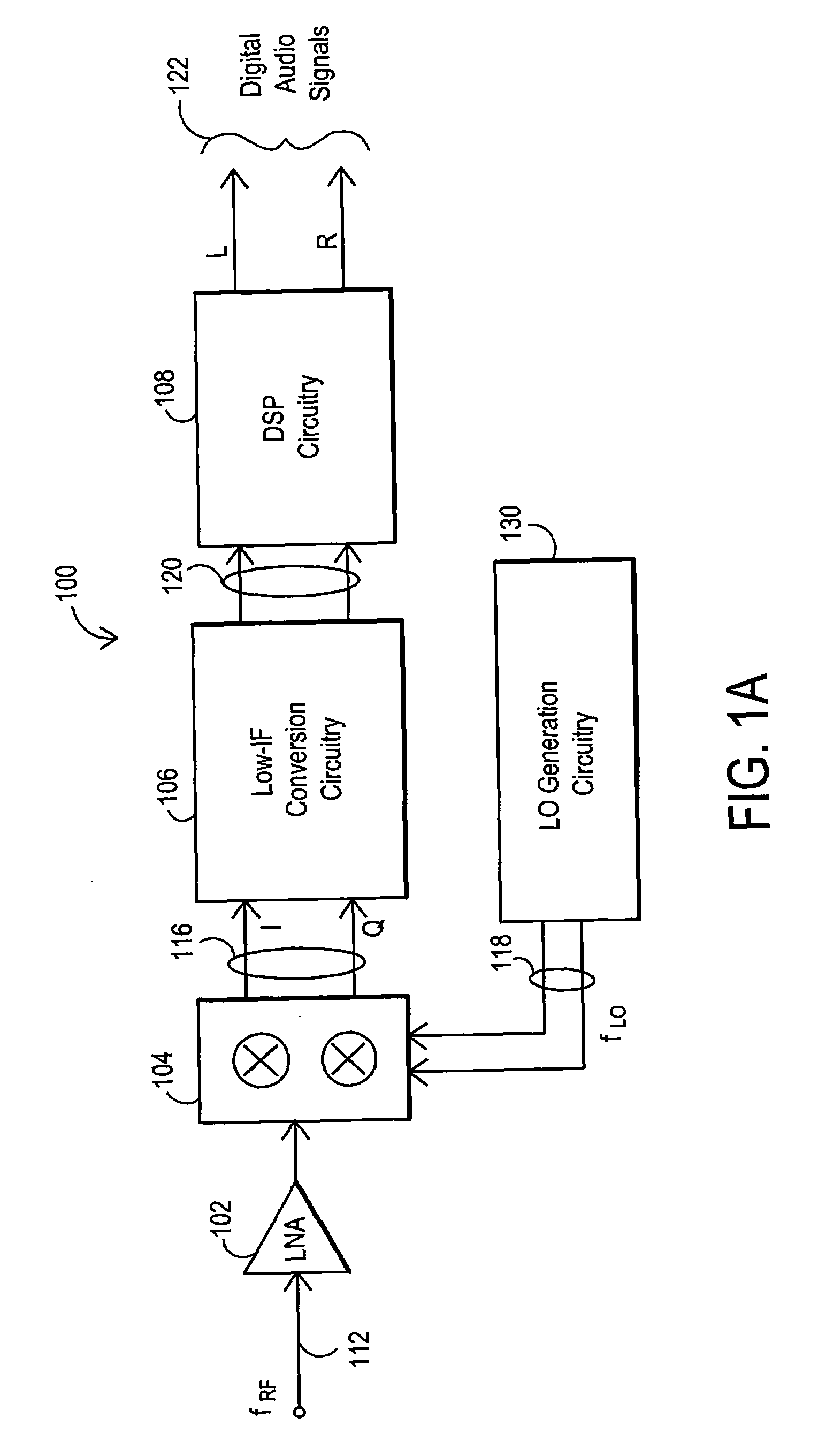

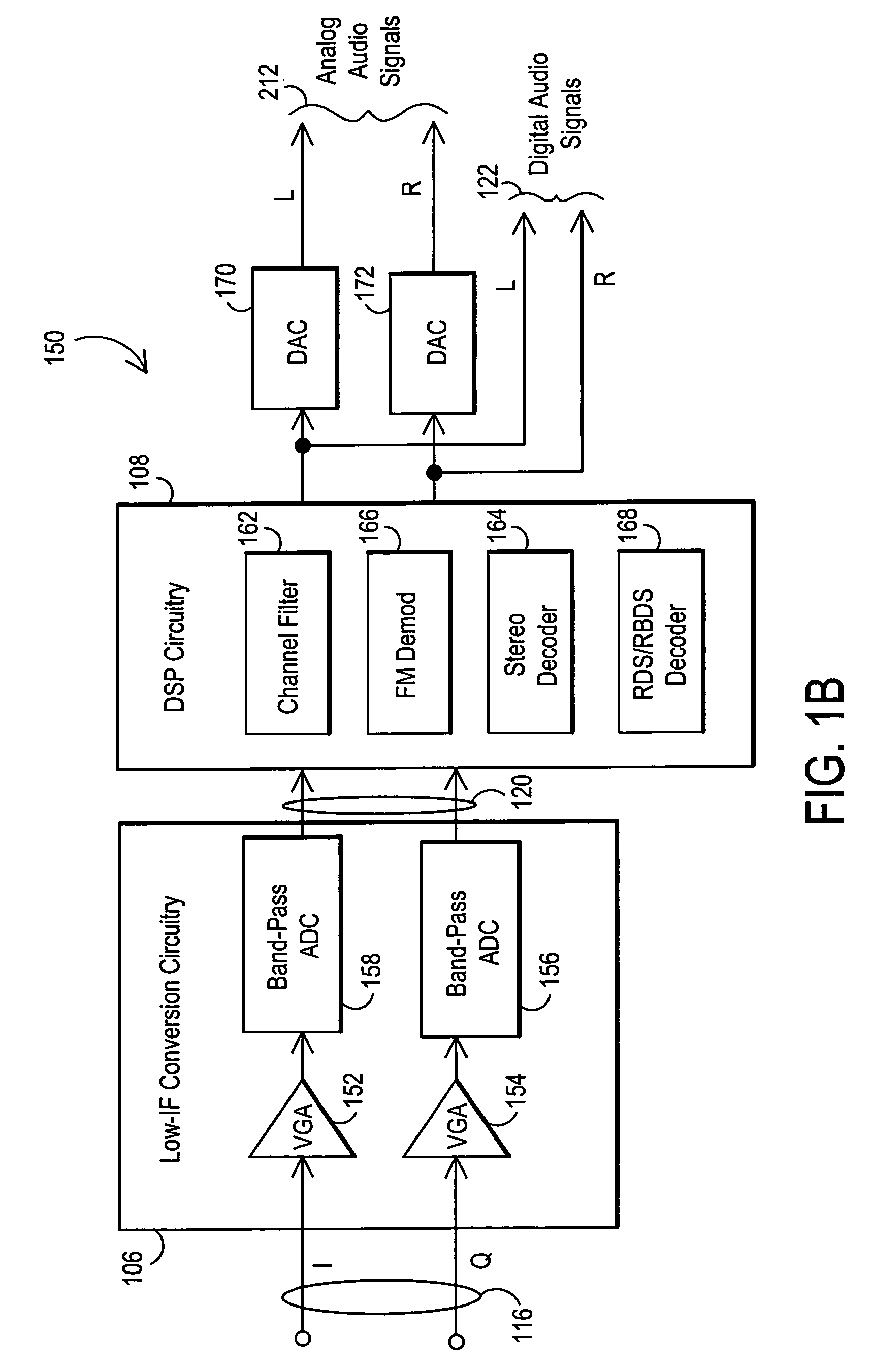

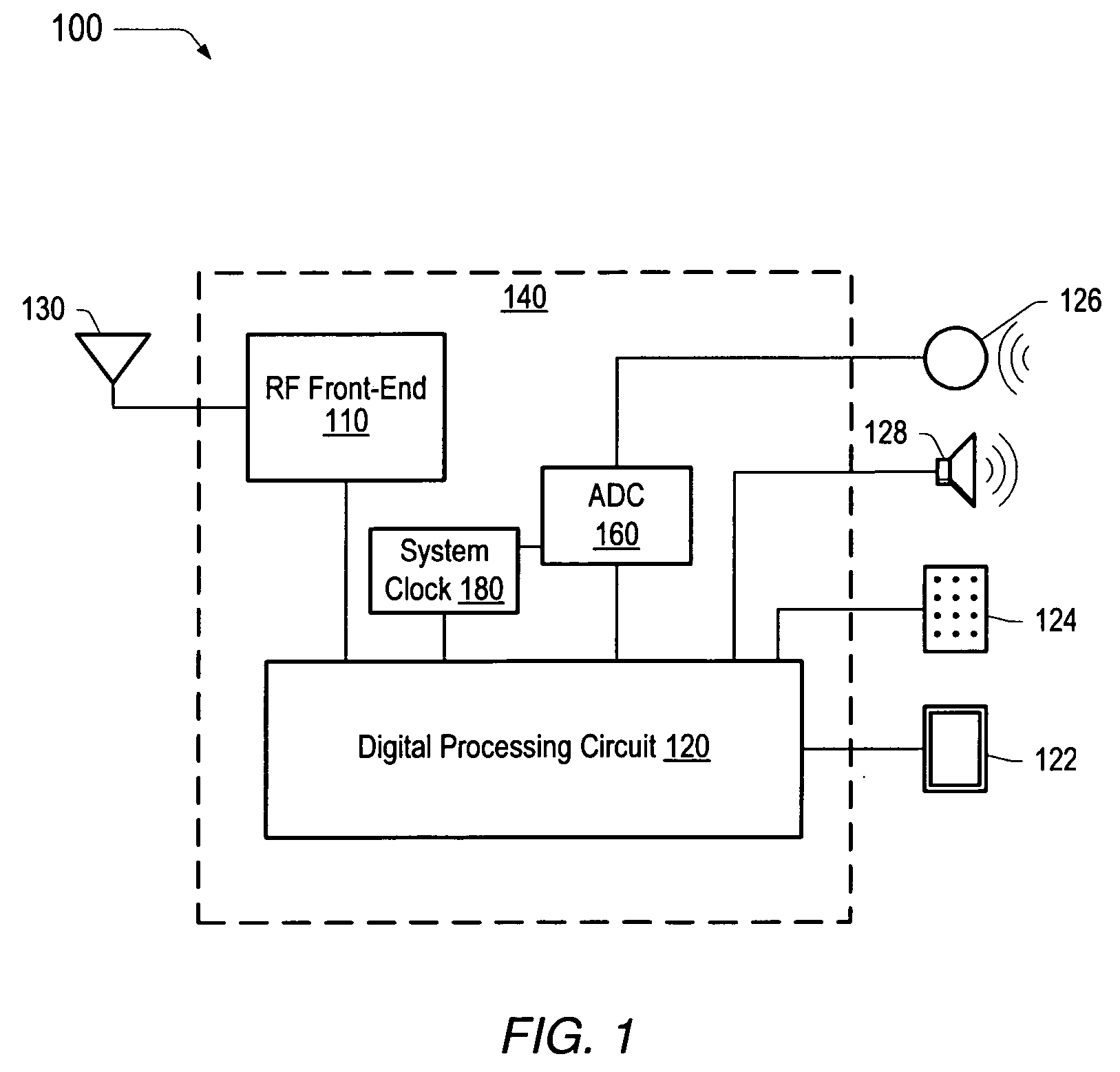

Ratiometric clock systems for integrated receivers and associated methods

A ratiometric clock system for an integrated receiver and associated method are disclosed that provide an advantageous solution for combining digital signal processing (DSP) circuitry on the same integrated circuit as mixer and local oscillator (LO) generation circuitry. The generation circuitry generates an oscillation signal that is passed through a first divider to generate mixing signals for the mixer and that is passed through a second divider to generate a digital clock signal that is utilized by the DSP circuitry. This digital clock signal can be utilized by integrated analog-to-digital conversion circuitry, as well.

Owner:SILICON LAB INC

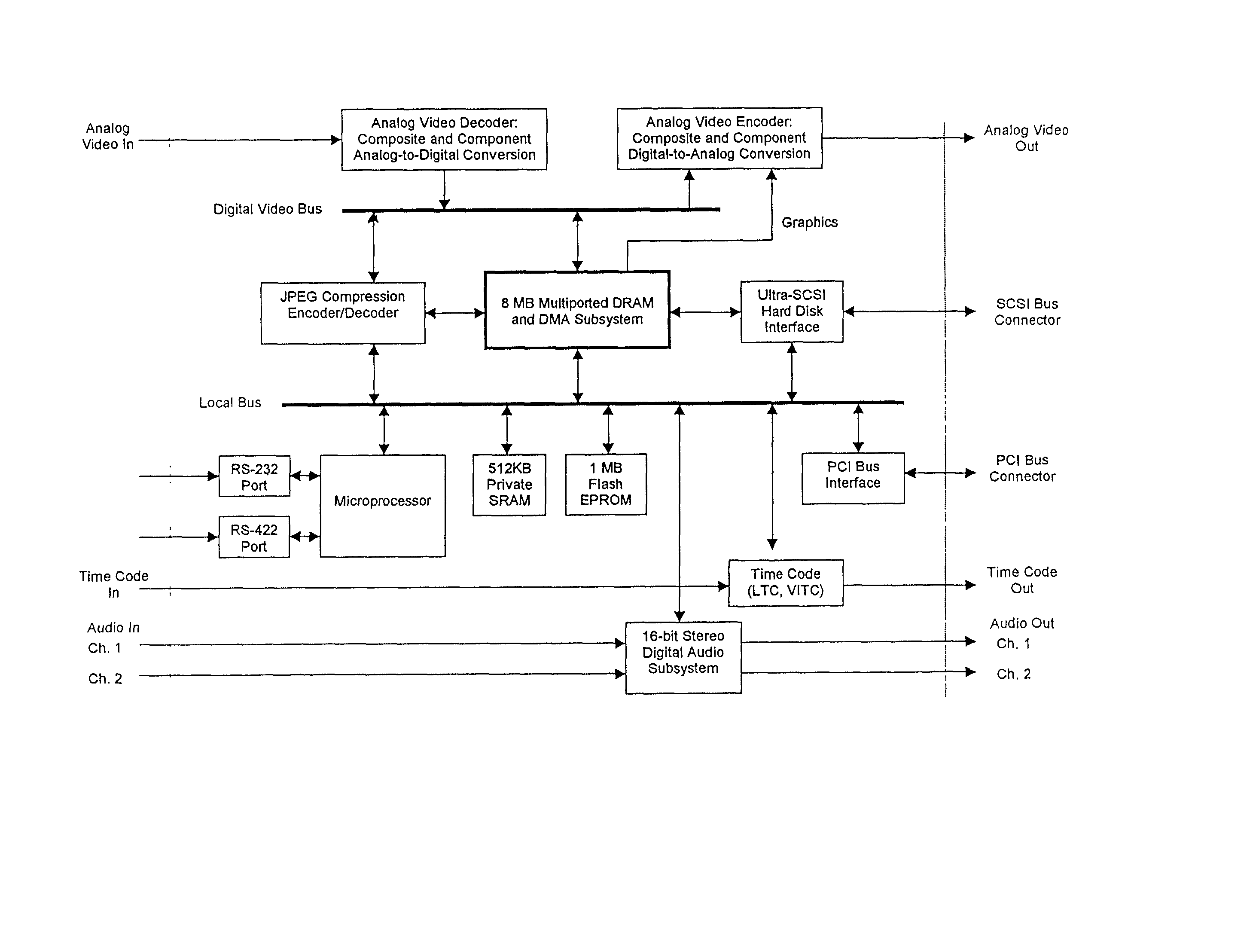

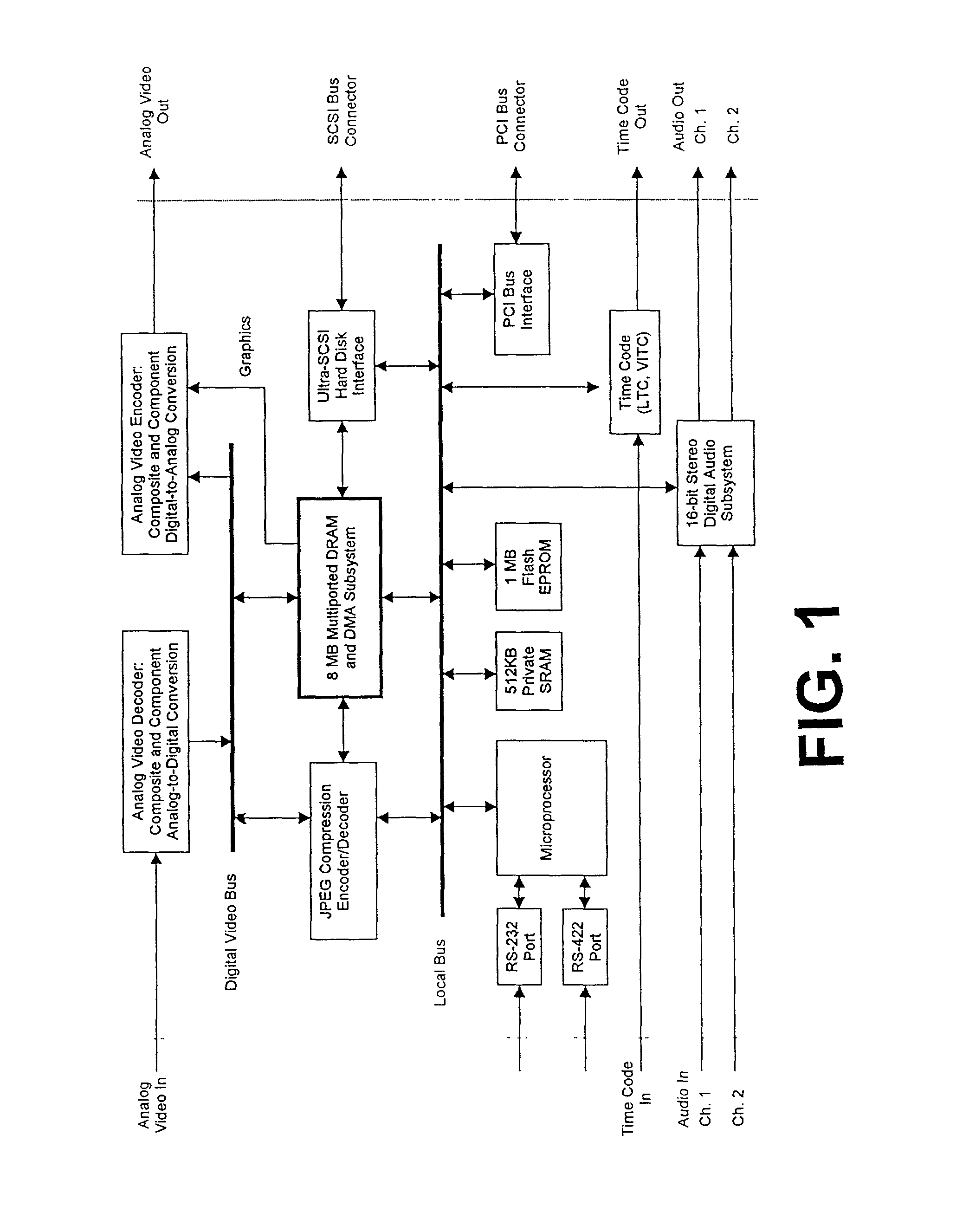

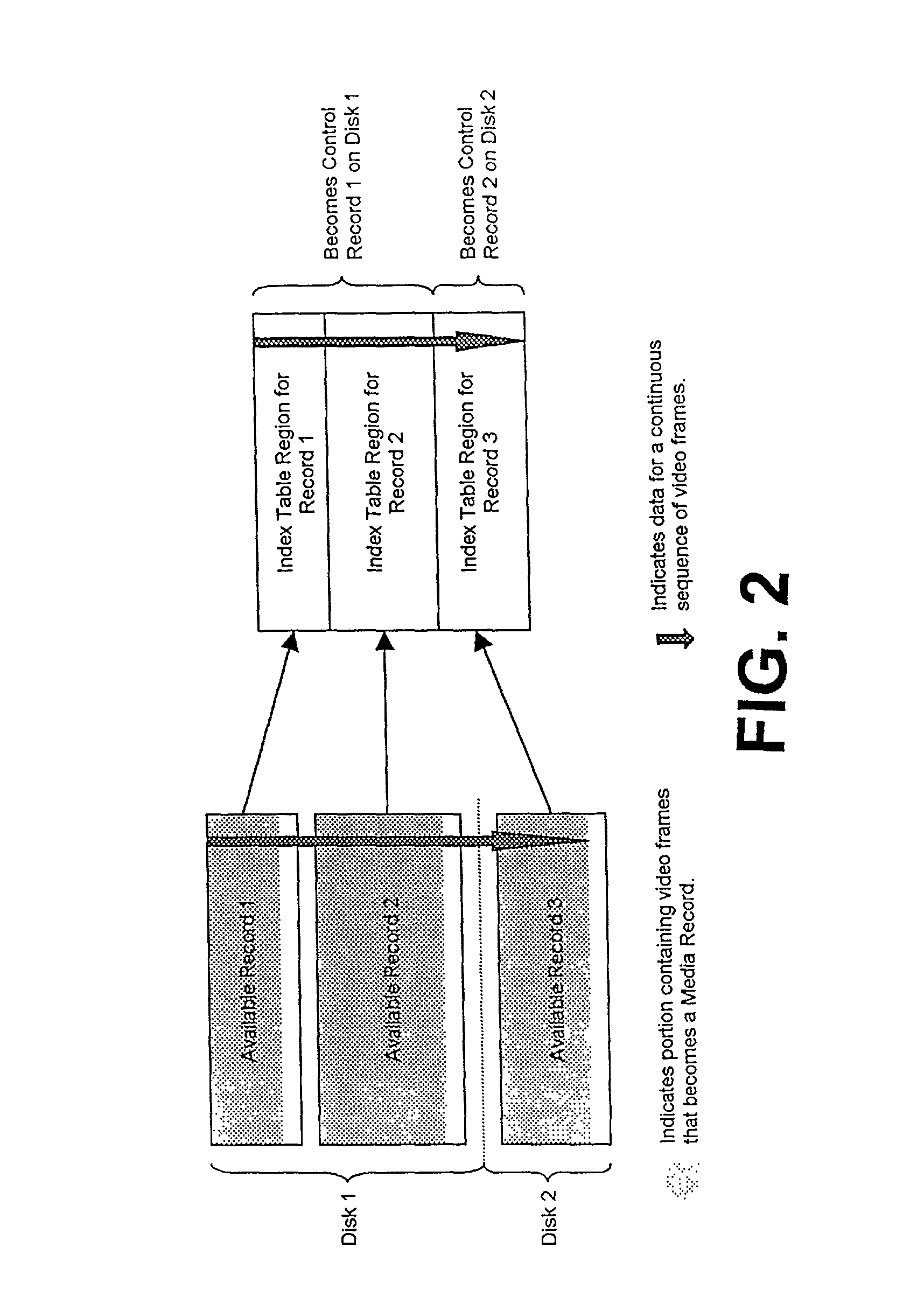

Digital video recorder

InactiveUS20020131765A1Data transfer speed is fastTelevision system detailsColor television detailsHard disc driveBus interface

A unique high performance digital video recorder having a number of novel features. The recorder's electronics are all on a unitary printed circuit board. The recorder also requires at least one hard disk drive and audio and video input analog signals (from a source such as video camera or broadcast media) as well as a suitable monitor for receiving output audio and video analog signals. A external time code generator (i.e., VITC digital clock) is also required for synchronization. Also required are various manual control devices (i.e., panel controls) for mode selection. The electronics of the preferred embodiment comprise A-to-D and D-to-A converters, a hard disk interface, a JPEG compression encoder / decoder, a multi-port DRAM and DMA subsystem, a microprocessor with RS-232 and RS-422 access ports, various working memory devices and bus interfaces and a 16-bit stereo digital audio subsystem. Novel features of the preferred embodiment include use of an index table for disk addresses of recorded frames, a multi-port memory controller in the form of a field programmable gate array (FPGA), loop recording using dual channels, and dynamic JPEG compression compensation.

Owner:FFV SYST

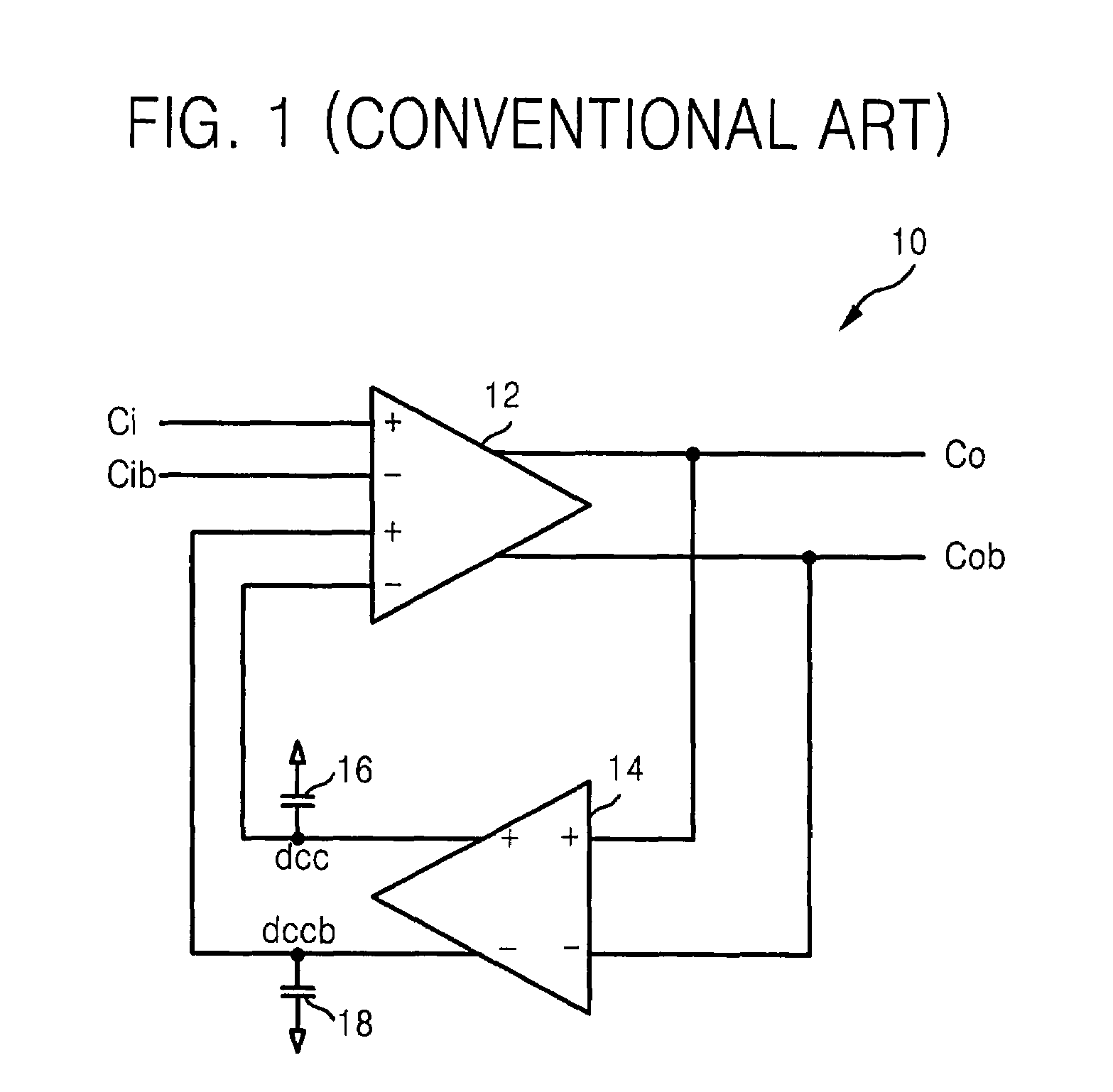

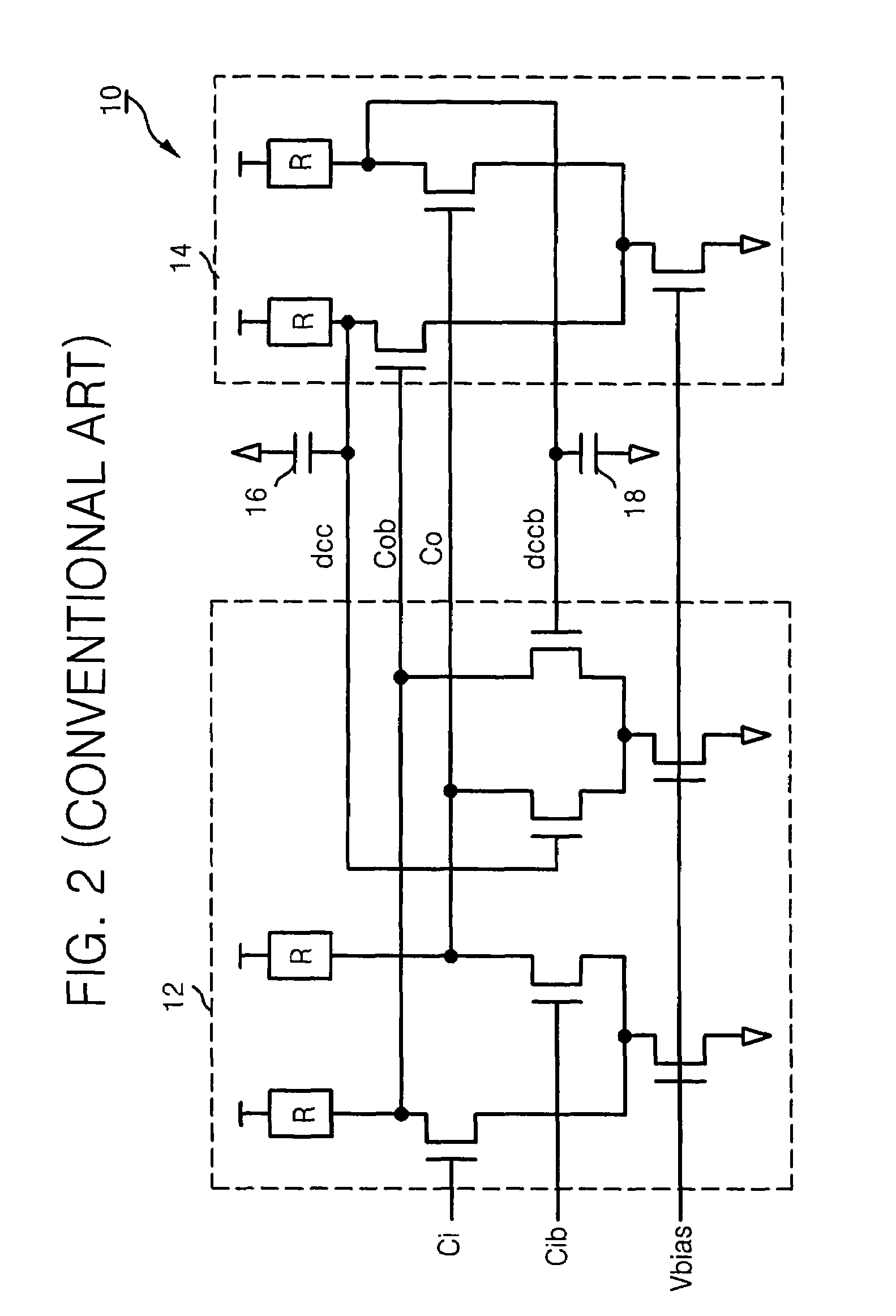

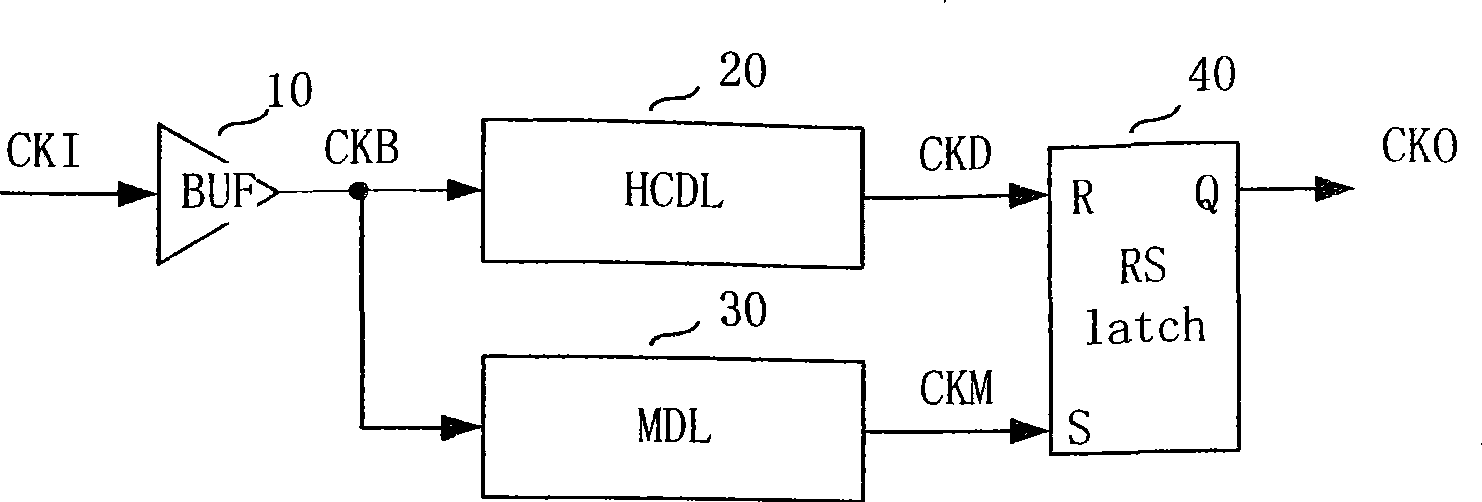

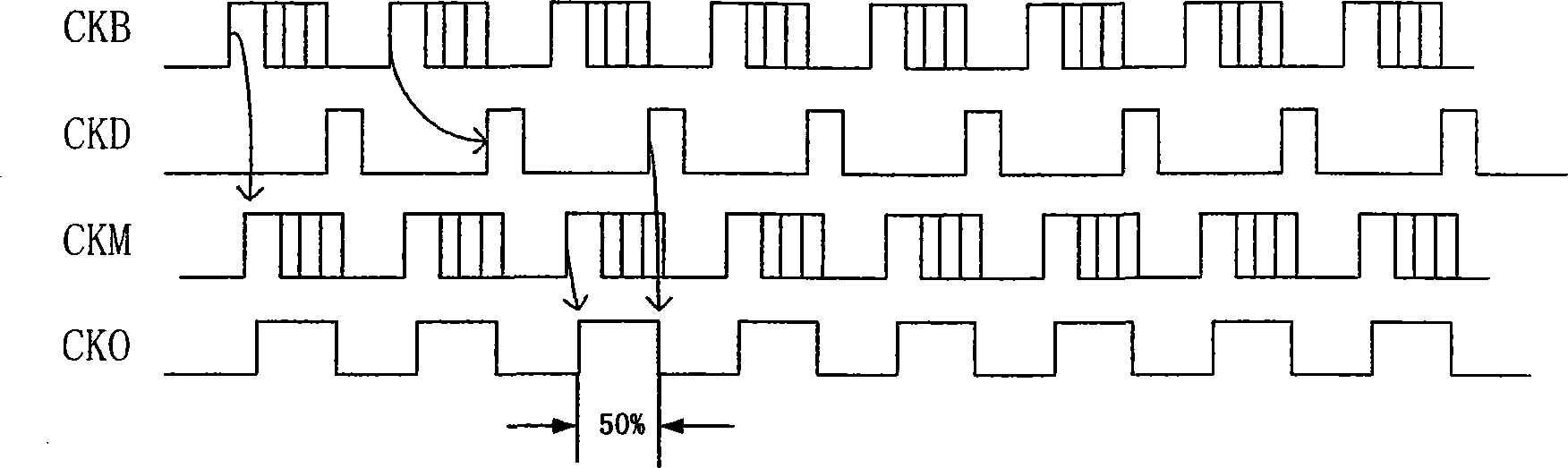

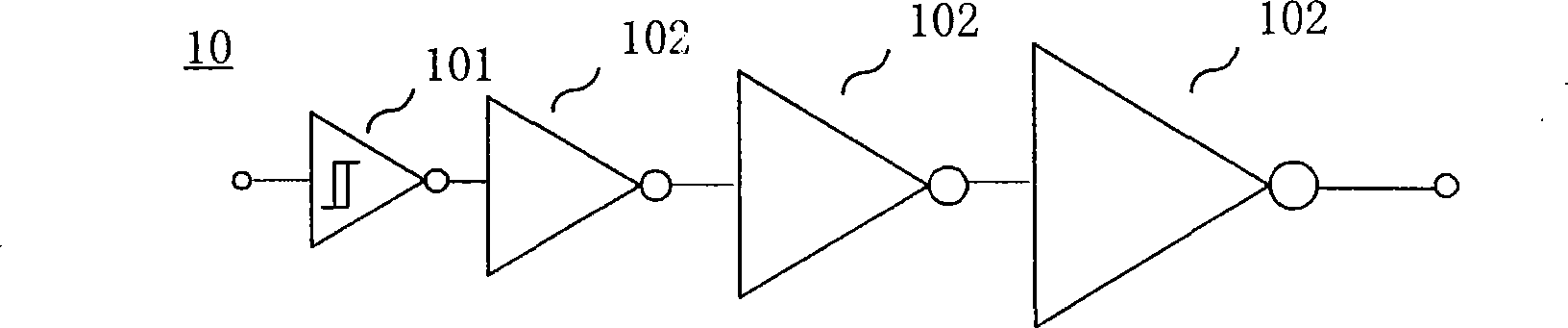

Digital clock duty ratio calibrating circuit

InactiveCN101478300AQuick buildNo cumulative effectContinuous to patterned pulse manipulationDigital signal processingCommunications system

The invention relates to a digital clock dutyfactor calibration circuit, which is mainly used for calculating the dutyfactor of a system clock in a high-speed data communication system and a DSP system (such as a high-speed data storage device, a pipelining processor, etc.). In the circuit, an input terminal of an input buffer (10) is connected with an original input clock signal (CKI) to be calculated; the output terminal signal of the input buffer (10) that is an input clock signal after being buffered (CKB), the output terminal signal of a half cycle delay line HCDL (20) that is a half cycle delay clock signal (CKD) and the output terminal signal of a matching delay-line (30) that is a matching delay clock signal (CKM) are respectively connected with a reset input terminal R and a set input terminal S of an RS trigger (40); the signal at an output terminal Q of the RS trigger (40) is a calibration clock signal (CKO) with dutyfactor of 50 percent after being calculated; and the input buffer (10) plays the role of ensuring the fan-out ability of the clock signal on a subsequent circuit.

Owner:SOUTHEAST UNIV

Clock masking scheme in a mixed-signal system

Owner:SIGEAR EURO

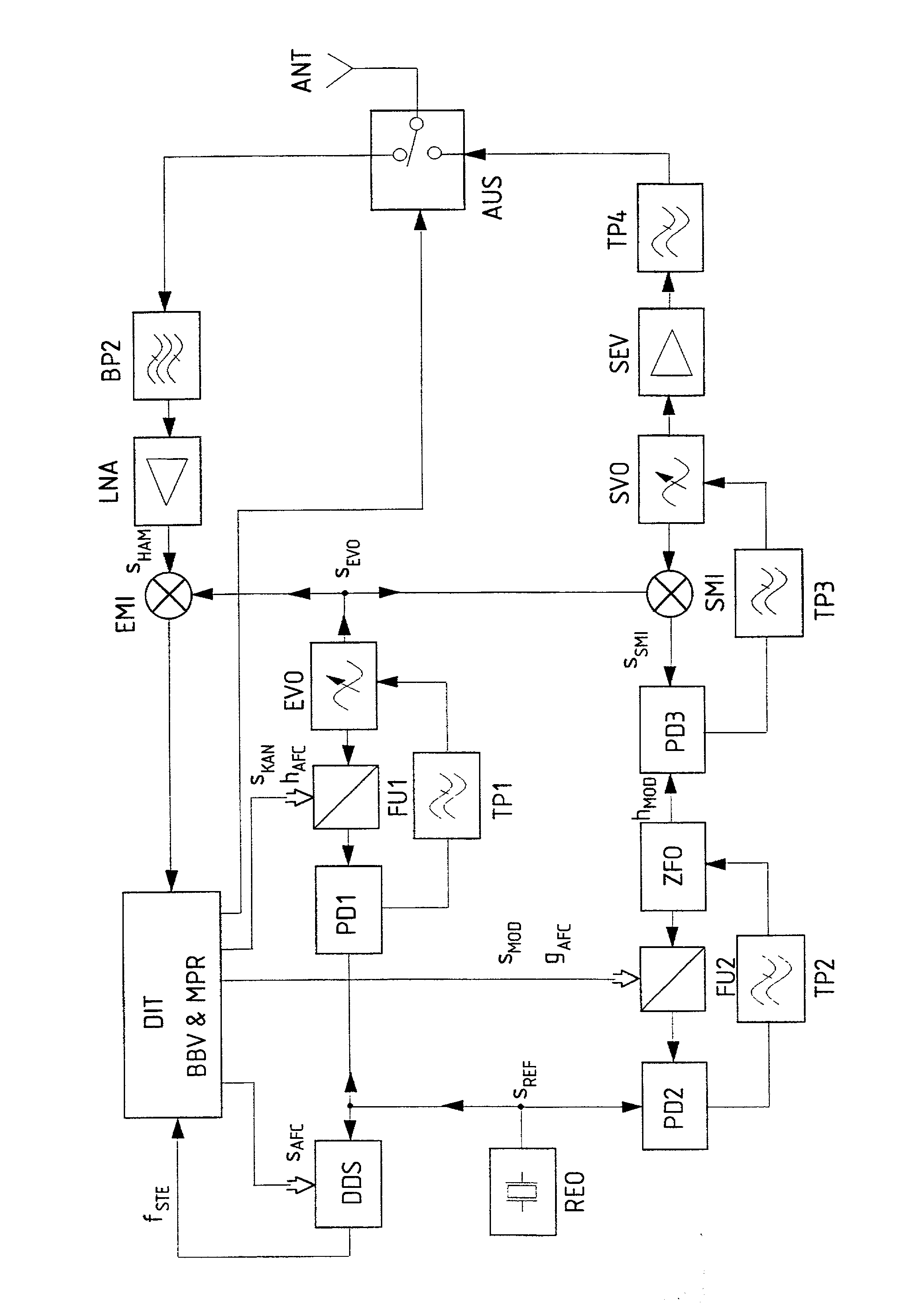

Transmitter-receiver

InactiveUS7076215B1Avoid harmonicsReduced shieldingPulse automatic controlElectrial characteristics varying frequency controlDigital tuningDiscriminator

A transceiver having an RF receiver, in particular VHF receiver, with digital signal processing in a digital part. The transceiver having an input part, at least one mixer and an intermediate frequency / baseband processing device, having a local channel oscillator, to which a first phase locked loop with a phase discriminator and an adjustable first frequency converter are assigned, and having a reference oscillator for the phase locked loop and the control clock of the digital signal processing device, in which, in order to acquire the control clock, a digital clock synthesizer is provided to which an output signal of the reference oscillator is supplied, and a control signal is supplied by the digital part in the form of a digital tuning word, the frequency of the reference oscillator being selected such that its order of magnitude is at least equal to the bandwidth of one or more of the reception bands used, and none of its harmonics occur in a reception channel.

Owner:CINTERION WIRELESS MODULES

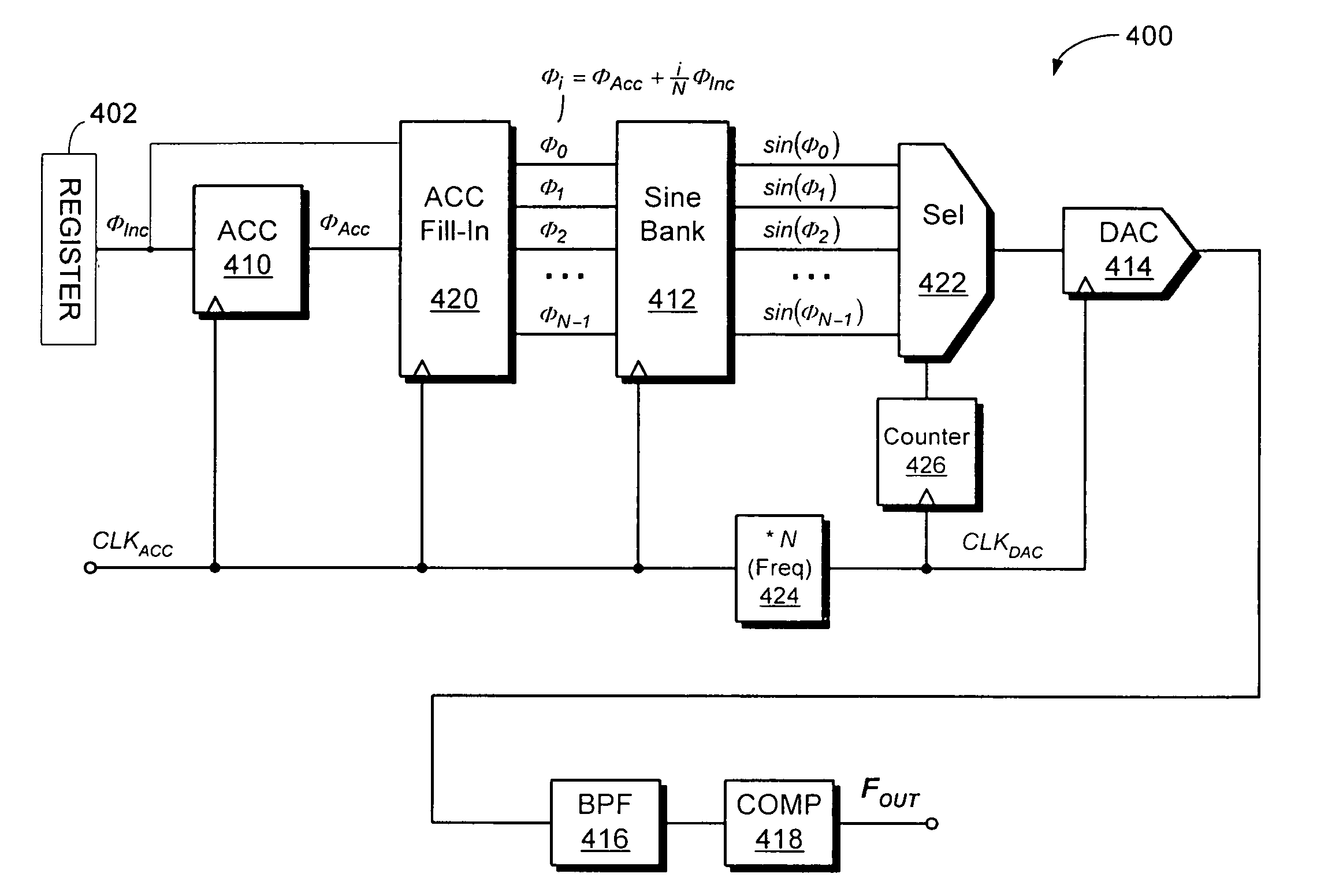

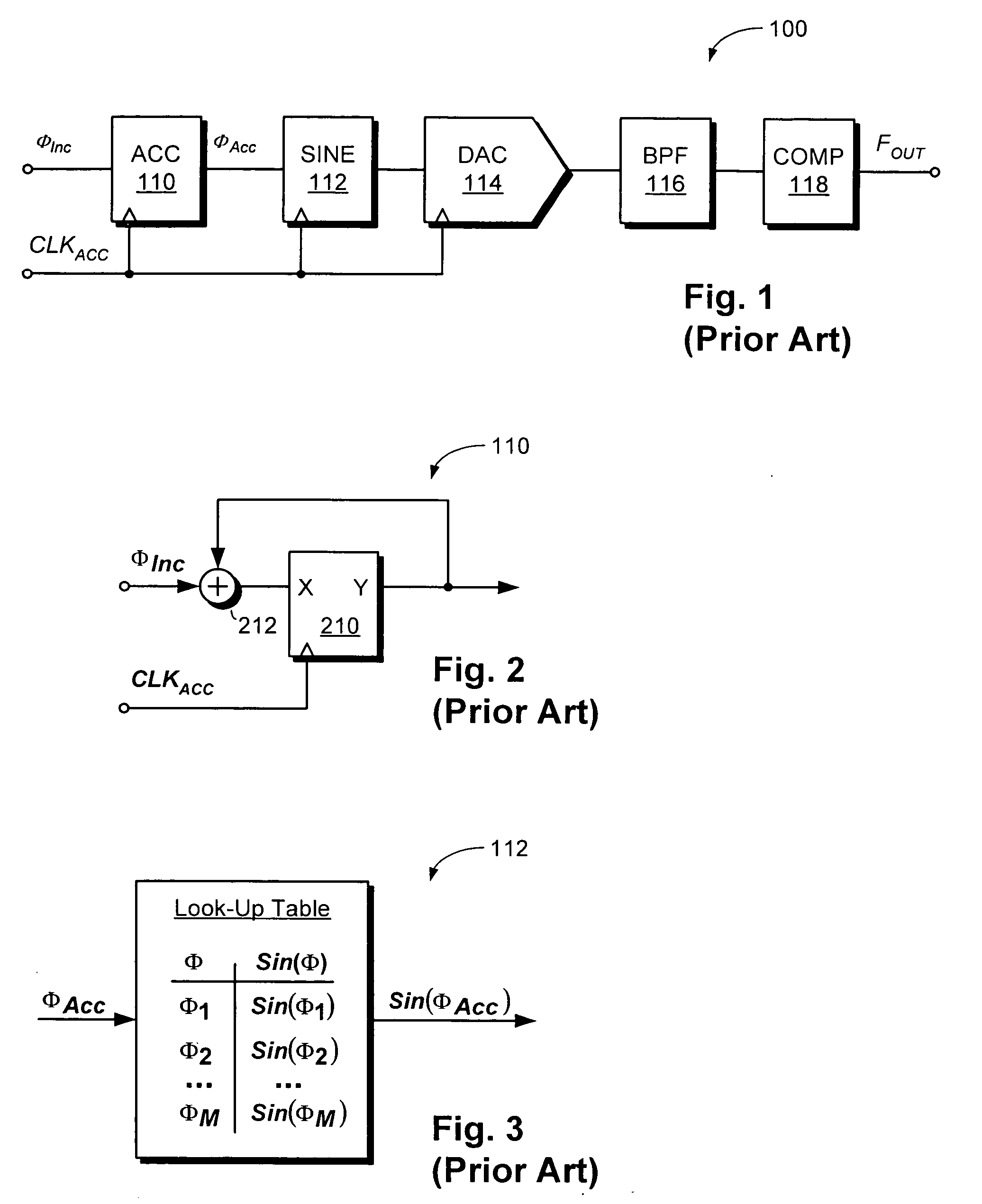

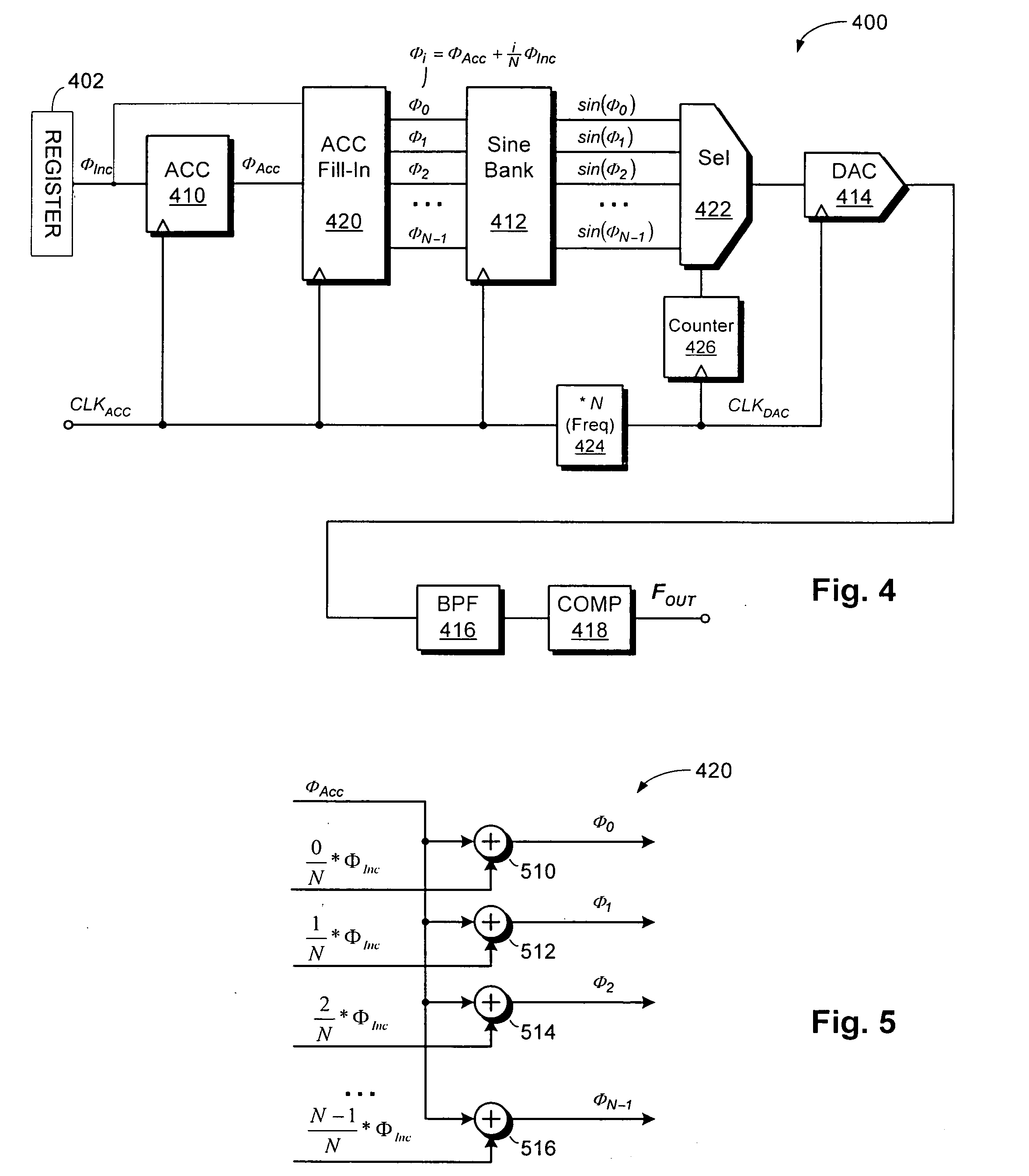

High resolution synthesizer with improved signal purity

ActiveUS20050135524A1Increase sampling rateElectrical testingGenerating/distributing signalsCMOSData stream

An automatic test system using a DDS signal generator to create a signal with high spectral purity or a low jitter digital clock. The low jitter clock has variable frequency and is programmed to control other test functions, such as the generation of arbitrary waveforms. The DDS uses a high resolution, high sampling rate DAC to generate a sine wave that is converted to a digital clock. The architecture of the DDS signal generator allows low cost CMOS circuitry to be used to generate the data stream that feeds the high sample rate DAC.

Owner:TERADYNE

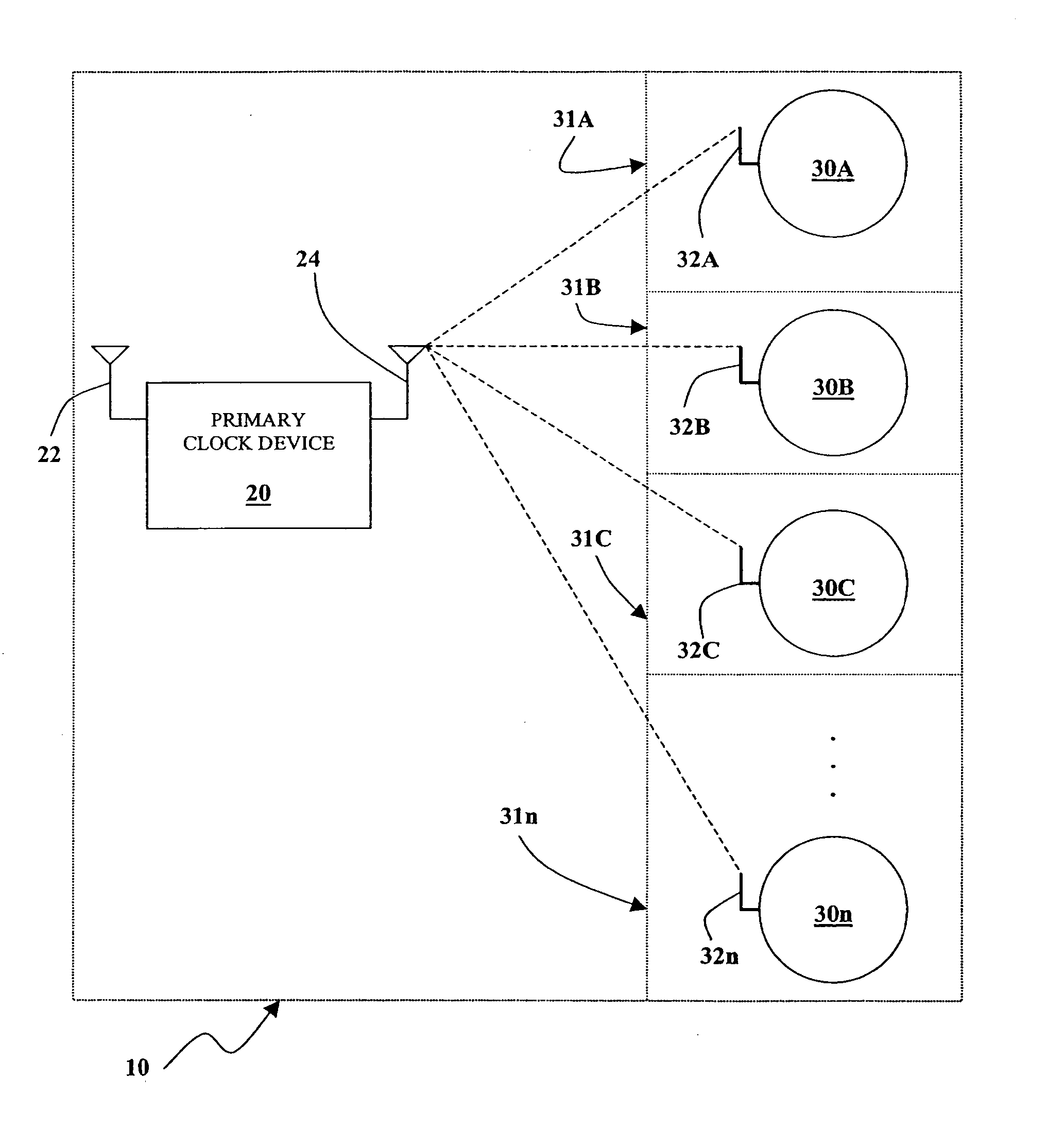

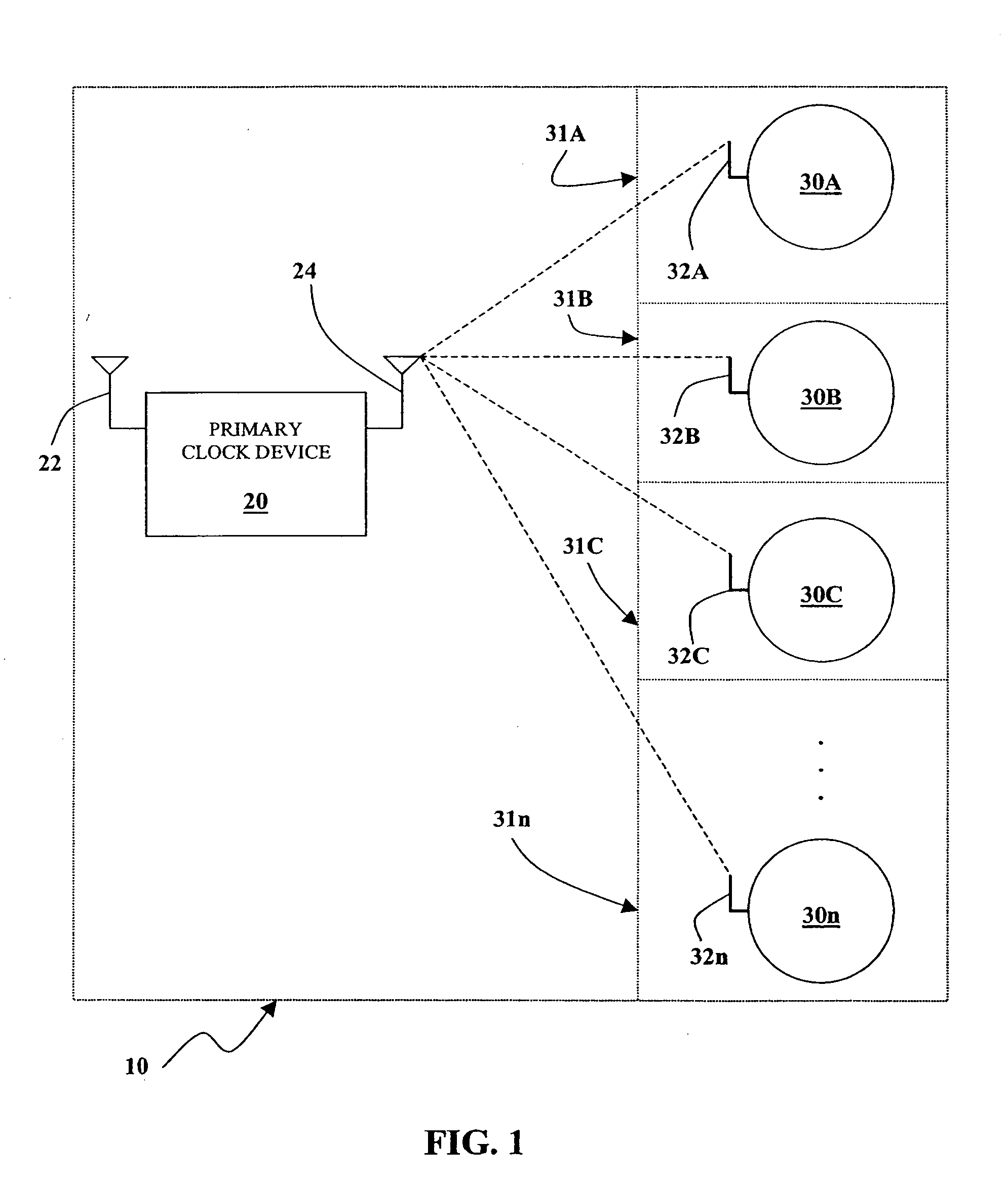

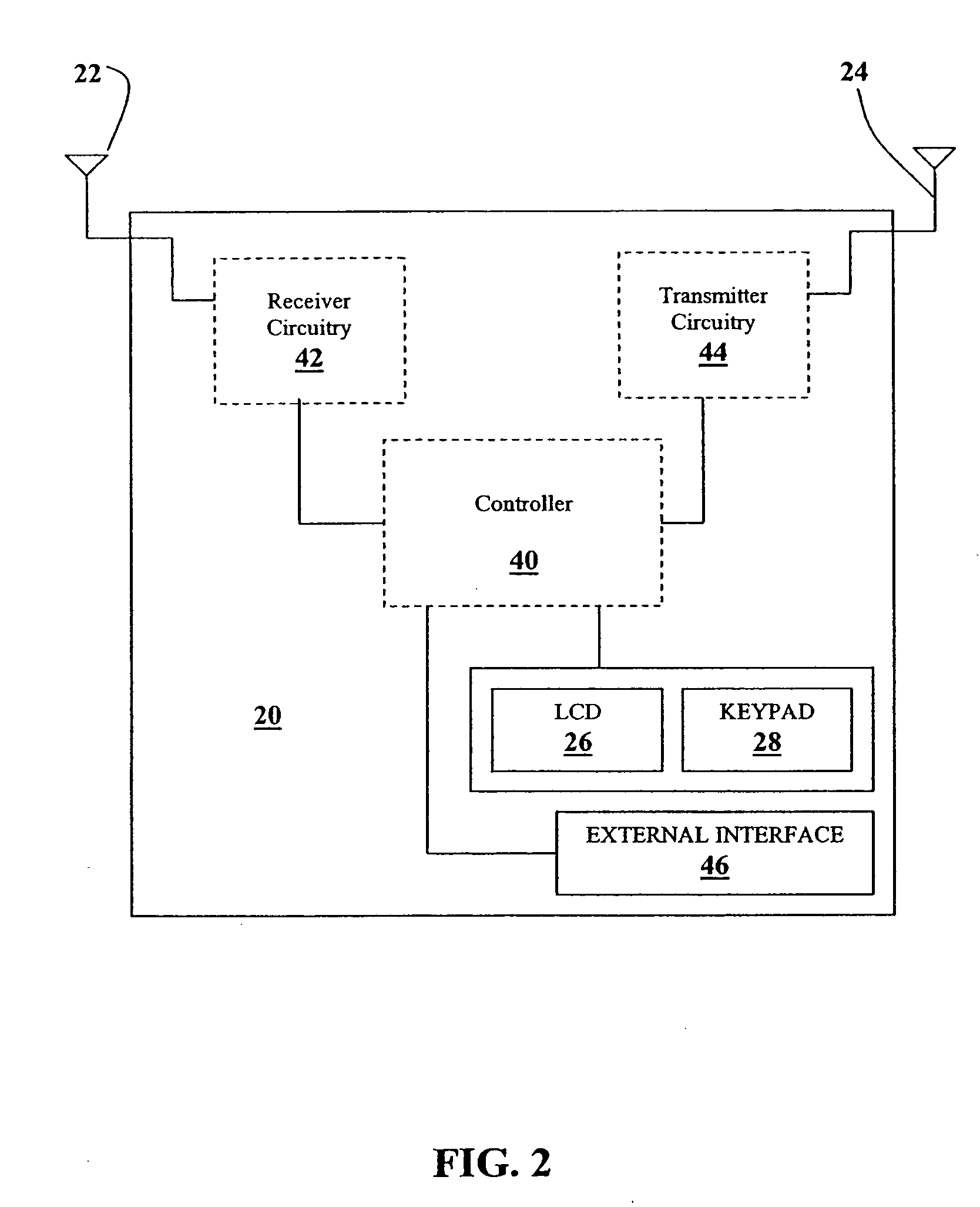

Wireless clock system

InactiveUS20050259722A1Eliminate requirementsInexpensive and easy to installSinusoidal oscillation interference reductionSynchronising arrangementDigital clockTime signal

A wireless clock system is disclosed. The system includes a primary clock device and at least one secondary clock device, where the secondary clock device is an analog clock, a digital clock, or a signal device. The primary clock device is adapted to wirelessly receive a reference time signal and wirelessly broadcast a master time signal based upon the reference signal to the secondary clock device. The secondary clock device wirelessly receives the signal and updates its displayed time accordingly. The secondary clock device can include a controller adapted to translate the wirelessly received signal into an alternate format recognized by a secondary clock device movement to synchronize the secondary clock device movement to the nearest second. The secondary clock device can further include an adapter module for compatibility with a wired clock system

Owner:AMERICAN TIME & SIGNAL

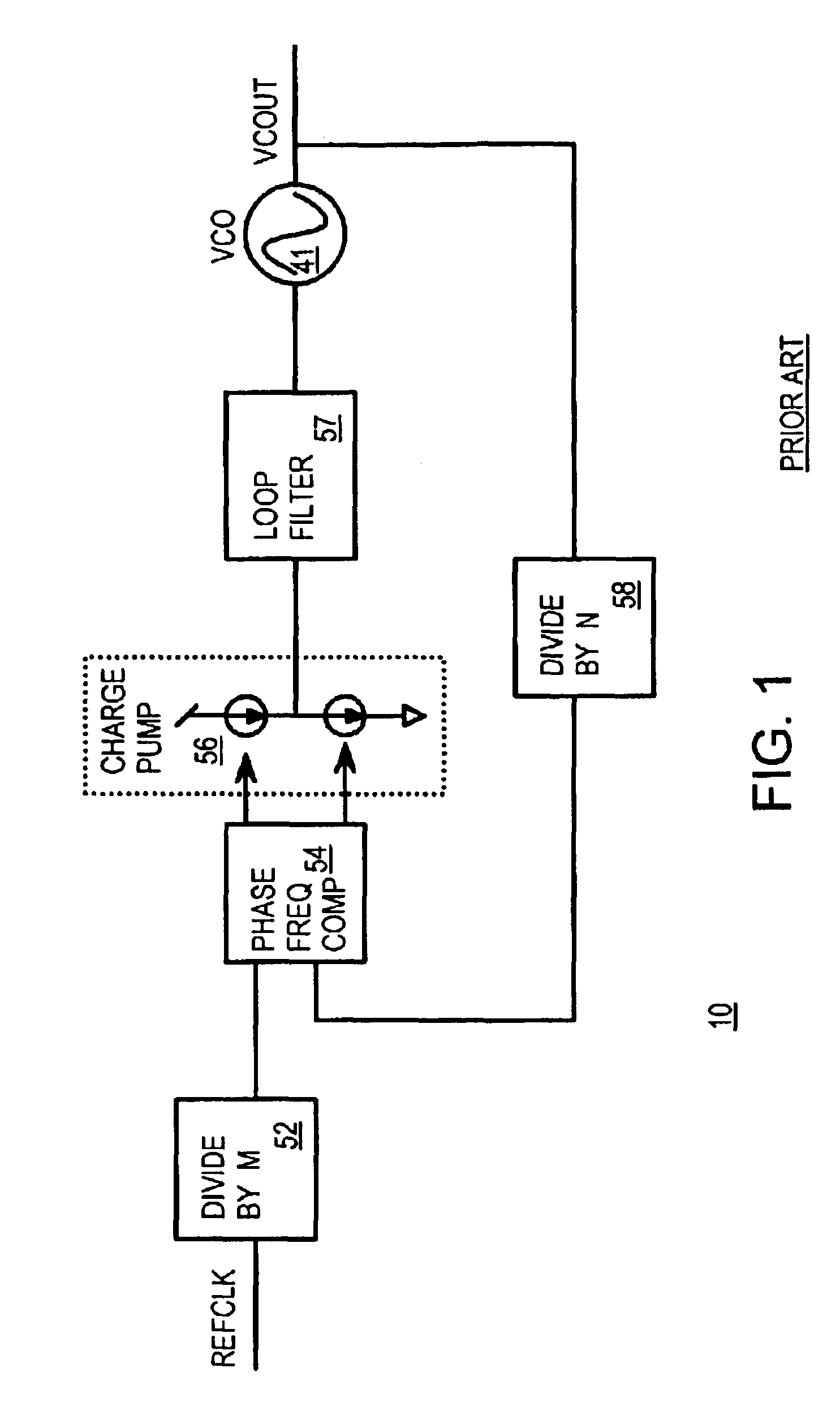

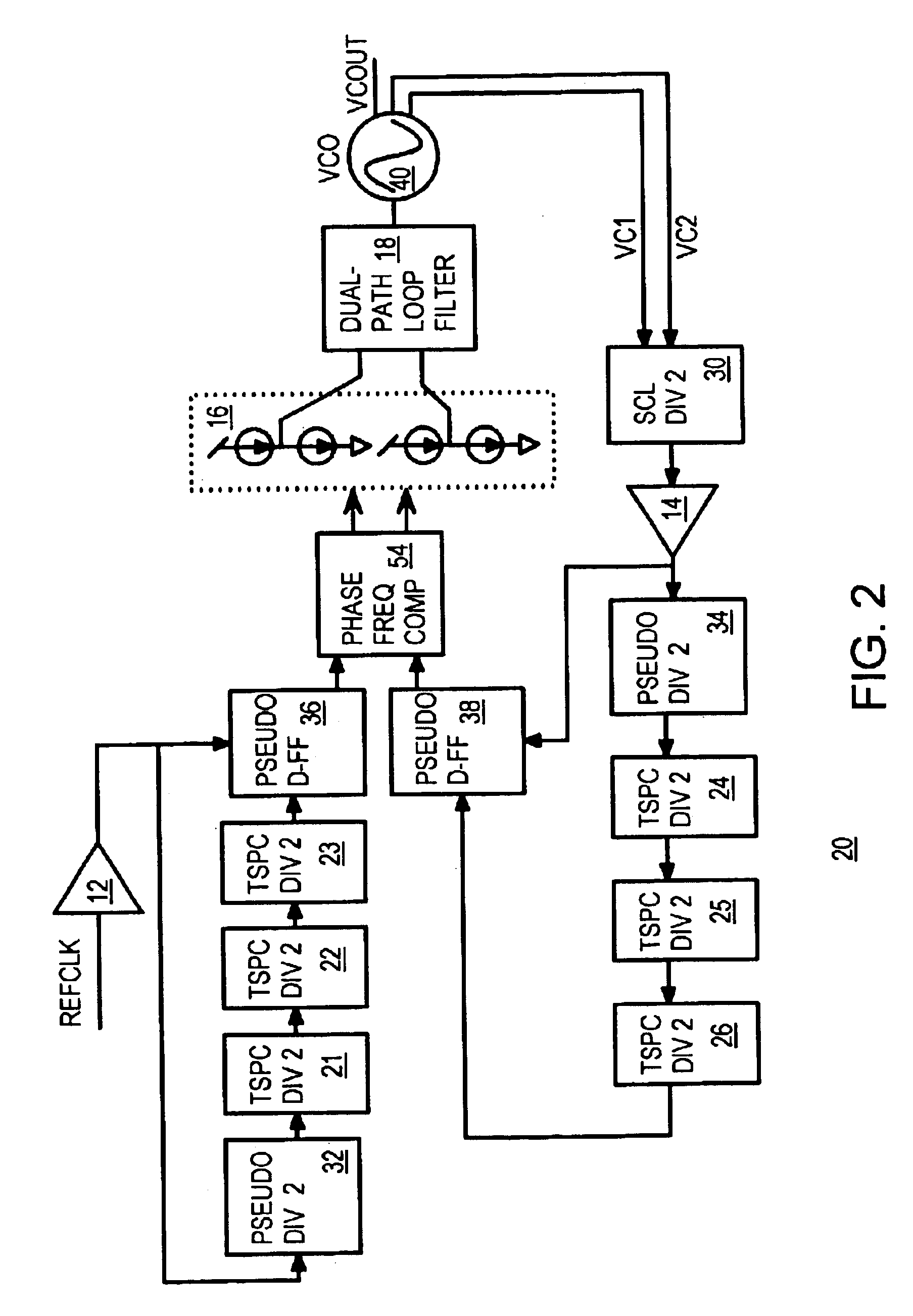

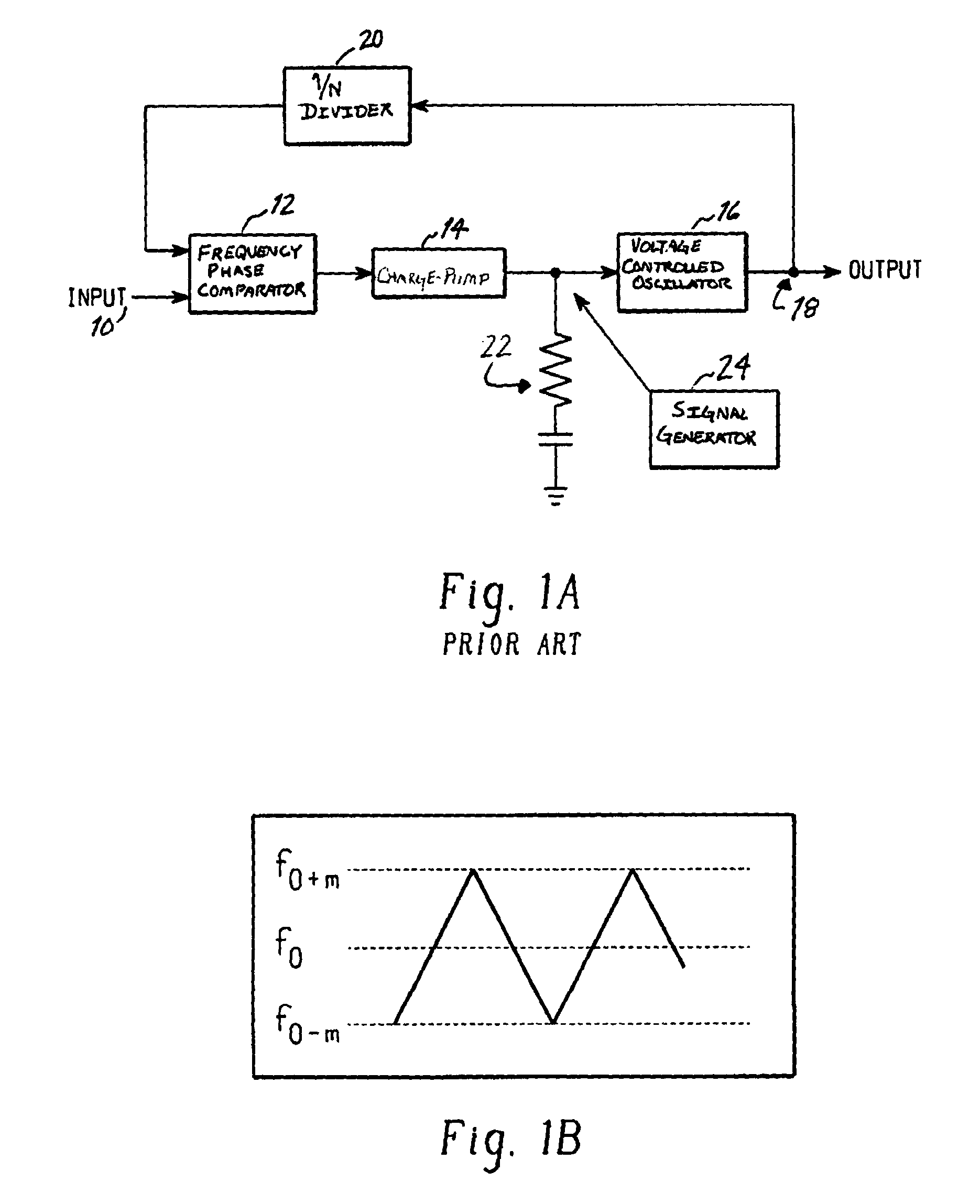

Double-data rate phase-locked-loop with phase aligners to reduce clock skew

InactiveUS6859109B1Pulse automatic controlPulse generation by logic circuitsDouble data rateDigital clock

A phase-locked loop (PLL) has an analog divider in the feedback path that receives either the in-phase or quadrature-phase pair of outputs from a voltage-controlled oscillator (VCO) while the other pair, 90-degree out-of-phase, of outputs from the VCO is used for the PLL output. Phases between the PLL's input and output are inherently aligned. The analog output of the analog divider is converted to a digital clock signal and applied to a cascade of digital dividers to generate a reduced feedback clock. The reduced feedback clock is applied to the D input and the digital clock signal is applied to the clock input of a pseudo D-flip-flop that drives the feedback input of a phase-frequency detector that drives the charge pump to the VCO input. Another cascade of digital dividers and pseudo D-flip-flop re-align the reference clock input to the phase-frequency detector. Analog and digital re-alignment circuits reduce internal skew.

Owner:DIODES INC

Digital clock and data recovery scheme

ActiveUS8095019B2Amplitude-modulated carrier systemsAmplitude demodulationDigital clockComputer science

A method and apparatus providing clock and data recovery within an optical receiver using three CMA FIR filters with different group delays where filter coefficients are adapted to provide for a filter exhibiting a group delay of one sample period from which symbols for further processing are provided.

Owner:RPX CORP

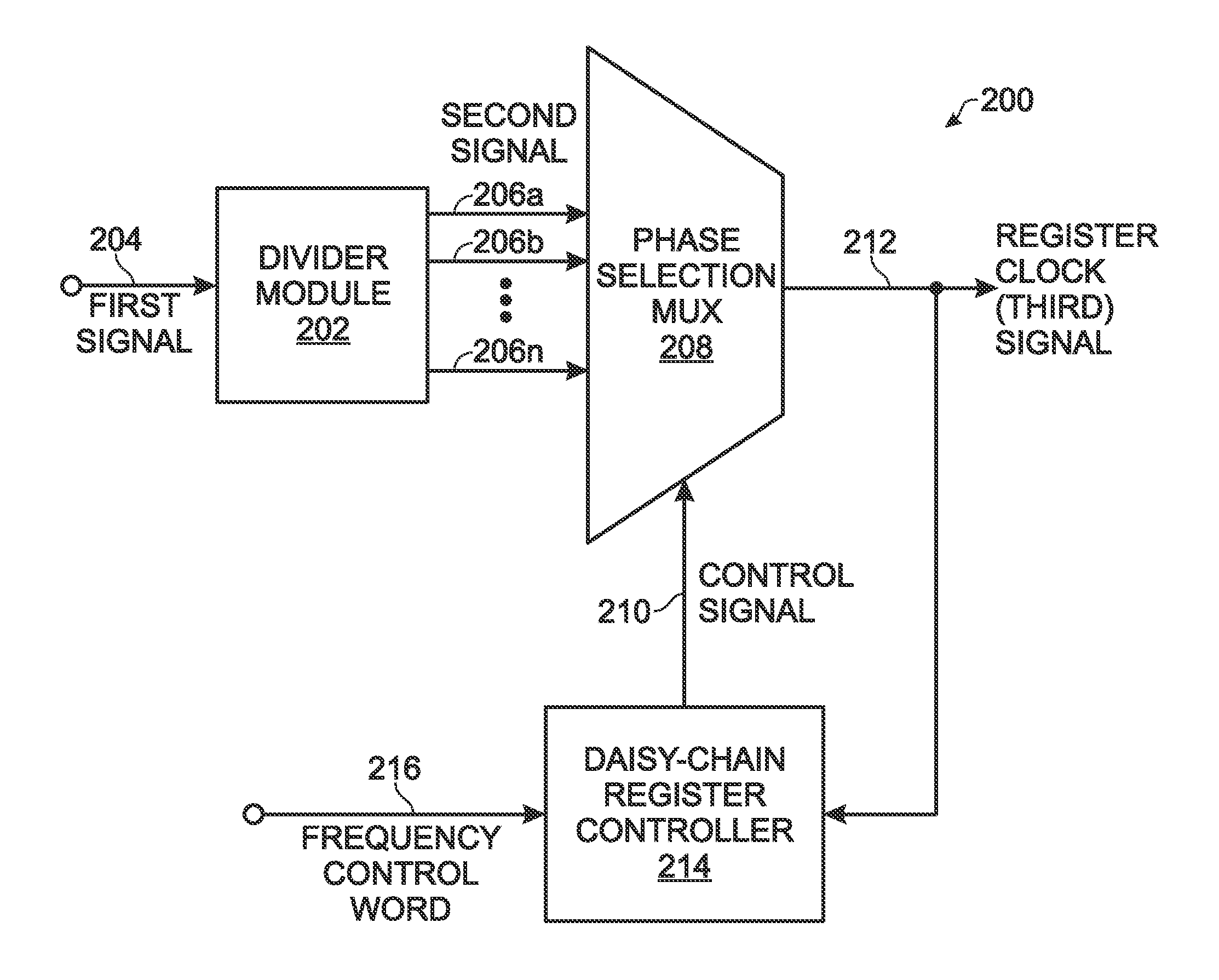

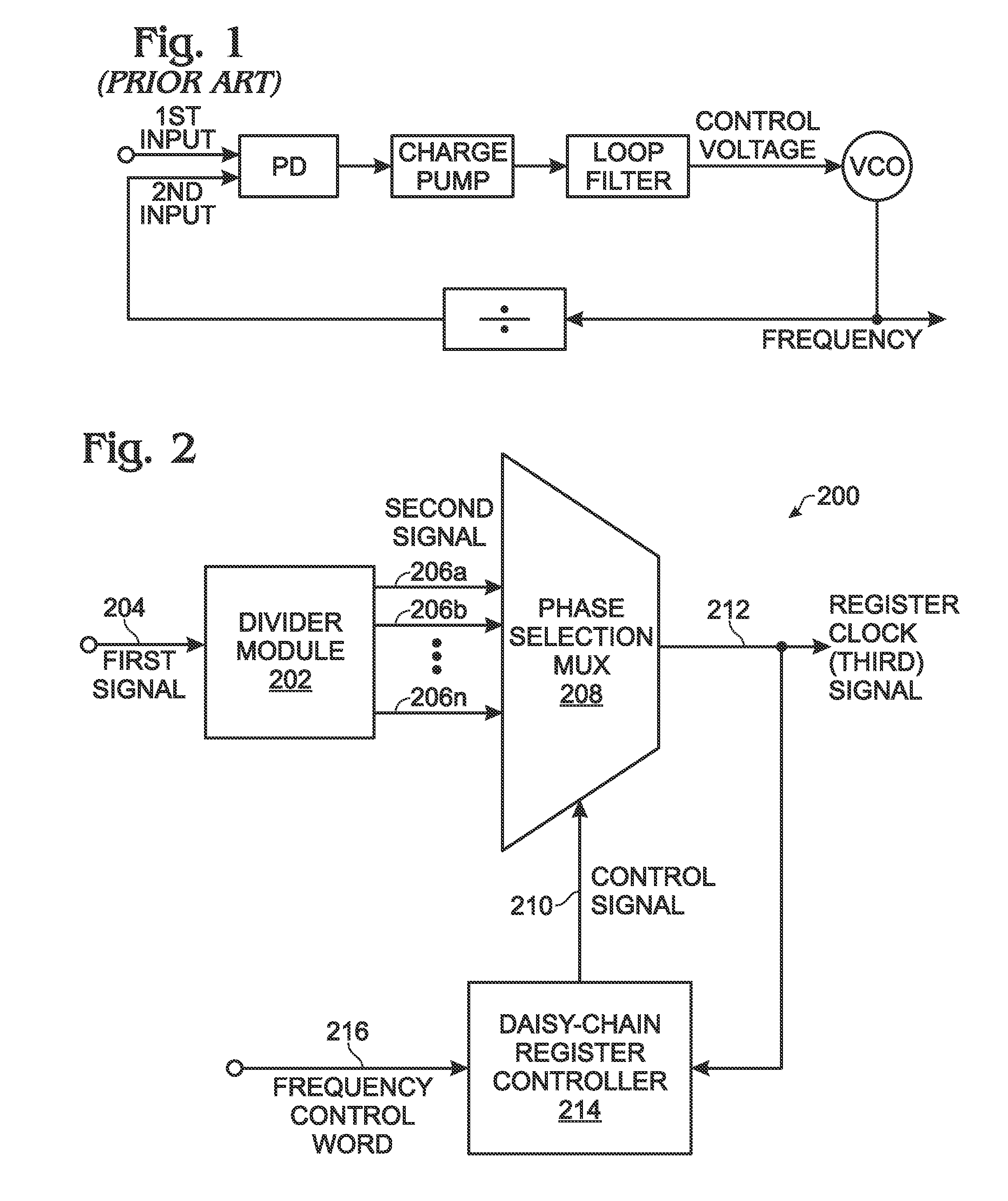

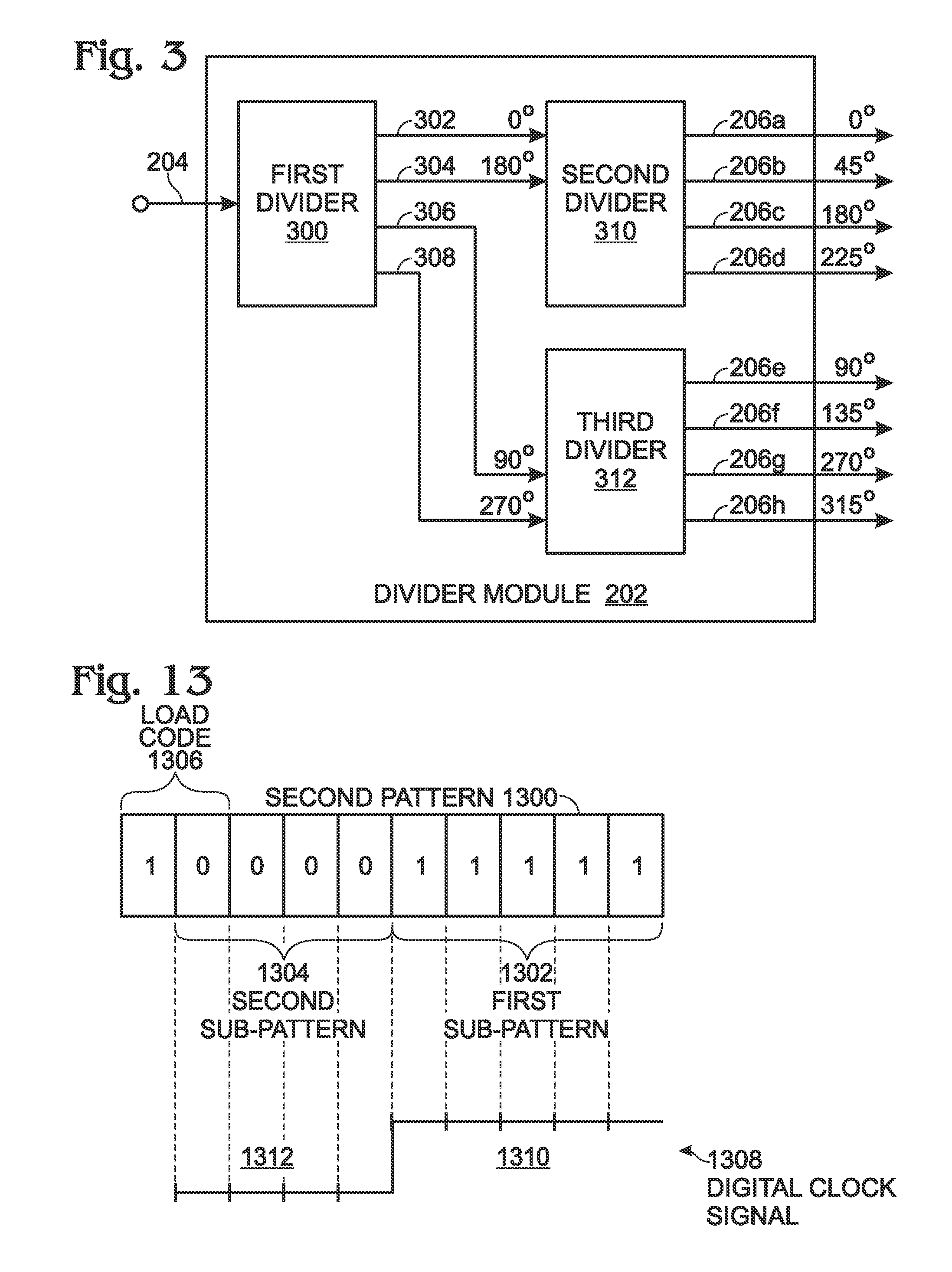

Digitally Clock with Selectable Frequency and Duty Cycle

ActiveUS20090201066A1Reduce the amount of powerHigh input signalPulse automatic controlCounting chain pulse countersDigital clockProcessor register

A system and method are provided for controlling the duty cycle and frequency of a digitally generated clock. The method accepts a first clock signal having a fixed first frequency. A frequency control word with a first pattern is loaded into a first plurality of serially-connected registers. A duty cycle control word with a second pattern is loaded into a second plurality of serially-connected registers. A register clock signal is generated in response to the first clock and the first pattern. Then, a digital clock signal is generated having a frequency and duty cycle responsive to the register clock signal and the second pattern.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

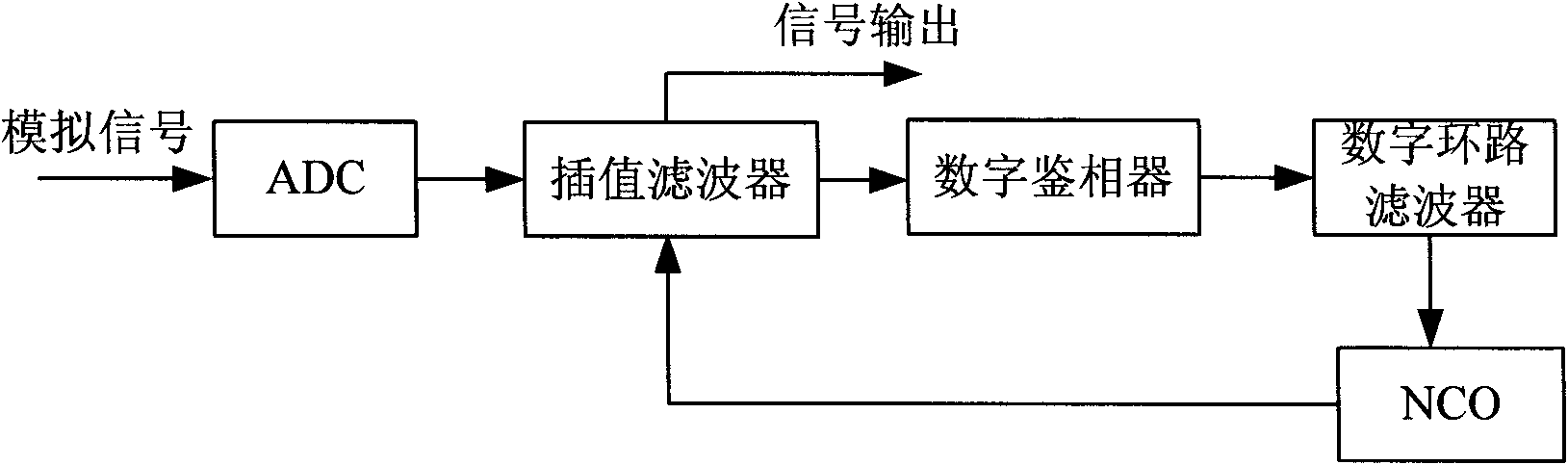

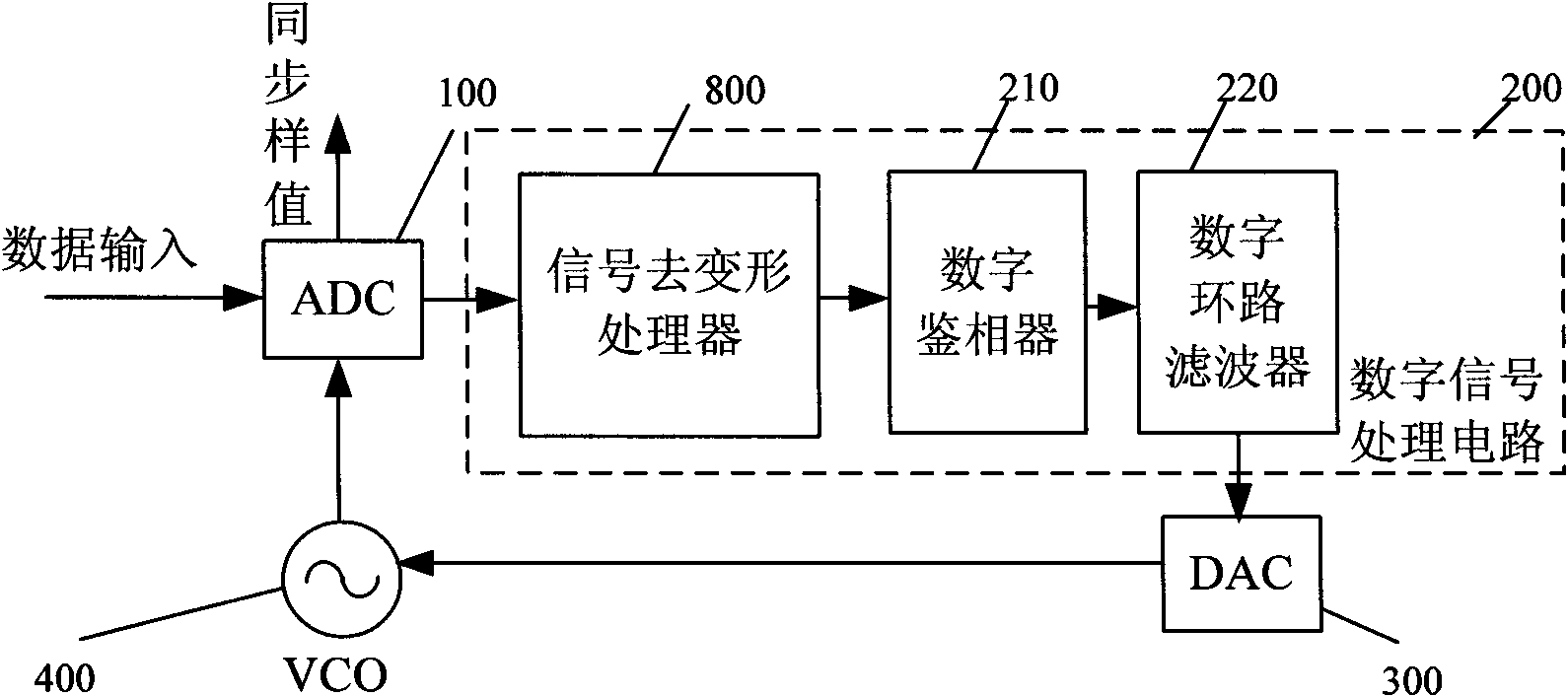

Signal processing system and method

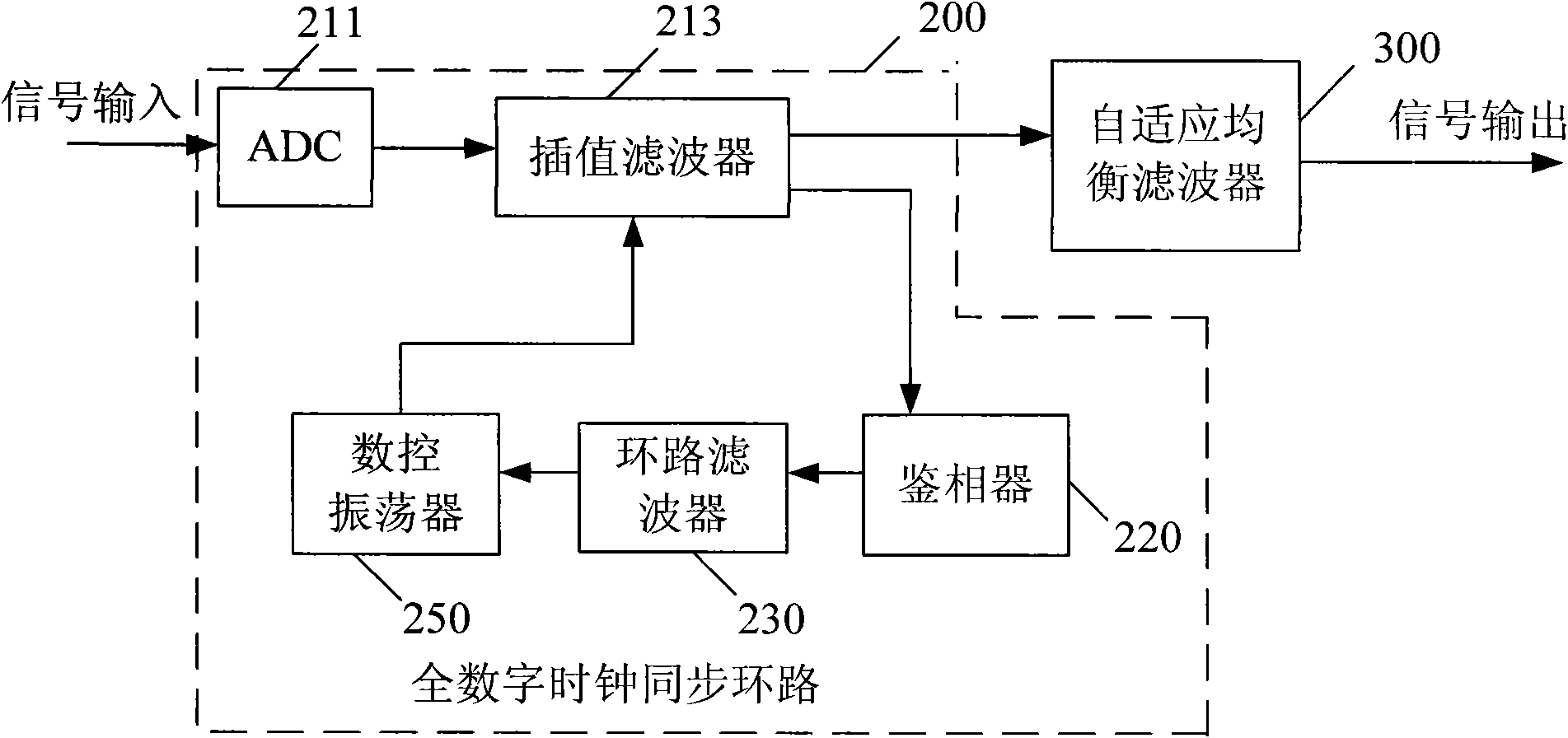

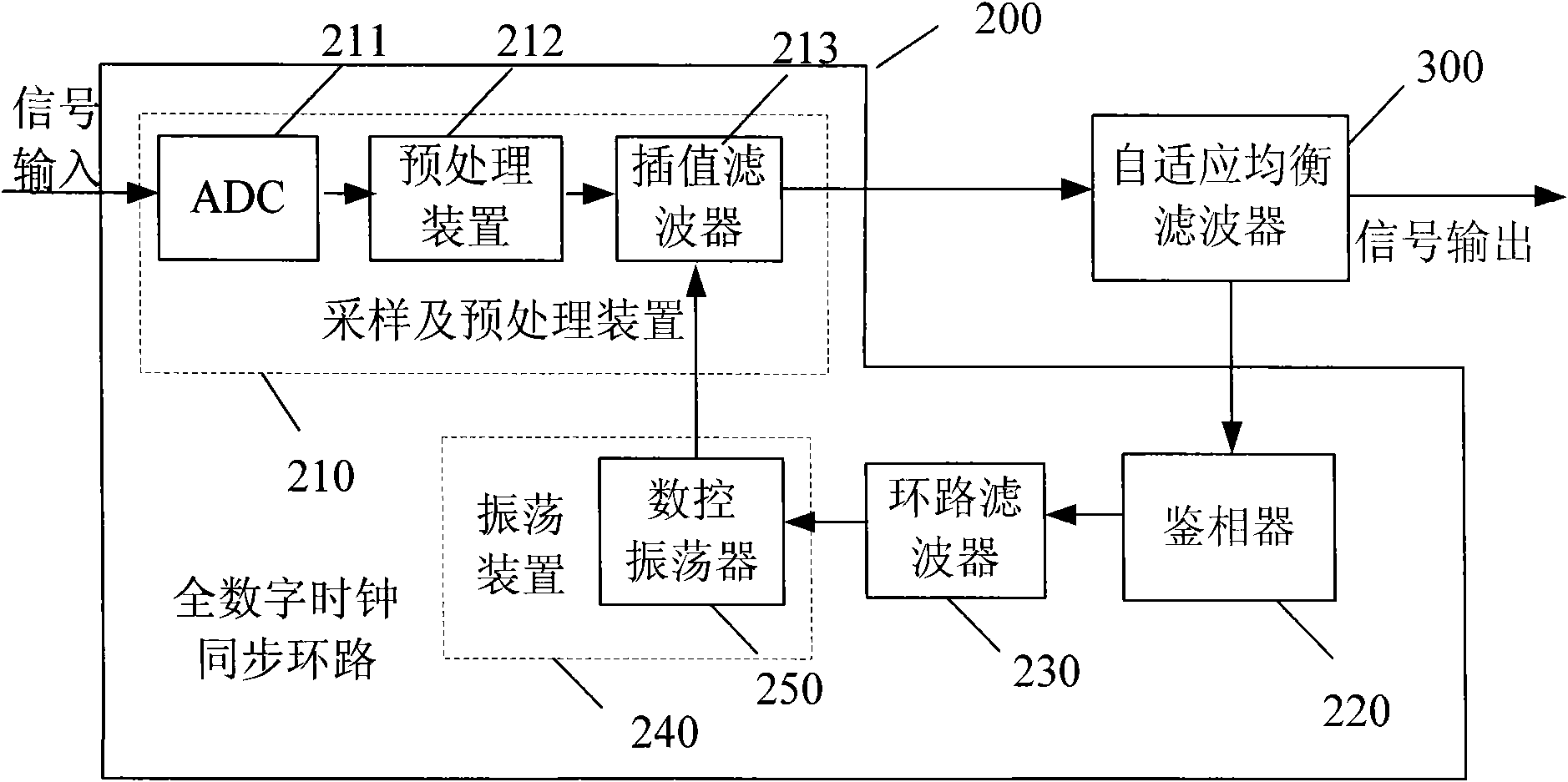

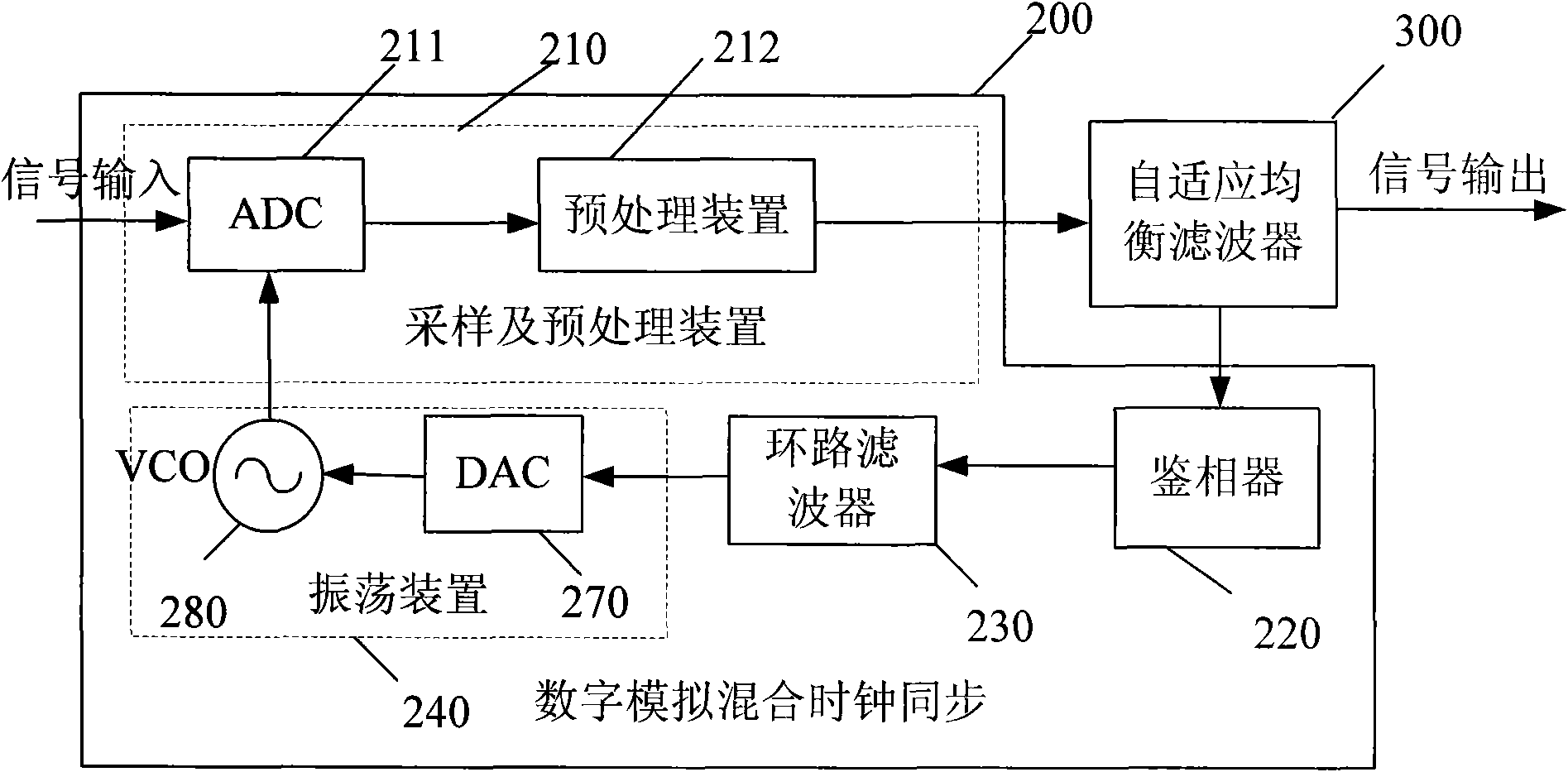

InactiveCN101841327AEliminate crosstalkEasy to handlePulse automatic controlEqualizationTransmission system

The invention discloses a signal processing system and a signal processing method. A sampling and preprocessing device samples and preprocesses input signals according to oscillation signals output by an oscillation device, and sends obtained sampling values to an adaptive equalization filter to perform equalization; the signals after the equalization are divided into two paths, wherein one path is a signal output, while the other path is sent to a phase demodulator; the phase demodulator detects the phase error of each sampling value to obtain a phase error signal which is sent to a loop filter to filter noises and high-frequency components of the phase error signal so as to obtain a digital clock error signal; the digital clock error signal is sent to the oscillation device which generates the oscillation signals according to the digital clock error signal; and the oscillation signals are sent to the sampling and preprocessing device. In the system and the method, the adaptive equalization filter is embedded in a clock synchronization loop to perform the equalization during clock synchronization, so the influence, caused by signal distortion, on phase demodulation is weakened, the clock synchronization and equalization are performed effectively, the signal crosstalk of a communication transmission system is eliminated, and the signal processing capacity of a receiving end is improved.

Owner:ZTE CORP +1

Method and system for sampling a signal

InactiveUS7209061B2Electric signal transmission systemsAnalogue conversionDigital clockComputer science

A system includes a digital circuit that may be clocked by a digital clock signal having an associated clock period. The system also includes a sample clock generation circuit coupled to a sampling circuit. The sample clock generation circuit may be configured to receive an input clock having a fixed phase relationship with respect to the digital clock signal. The sample clock generation circuit may also generate a sample clock having a first sampling edge corresponding to a first relative offset within the clock period and a subsequent sampling edge corresponding to a different relative offset within the clock period. The sampling circuit may be configured to sample a designated signal upon a first sampling instance corresponding to the first sampling edge and to sample the designated signal upon a subsequent sampling instance corresponding to the subsequent sampling edge.

Owner:SILICON LAB INC

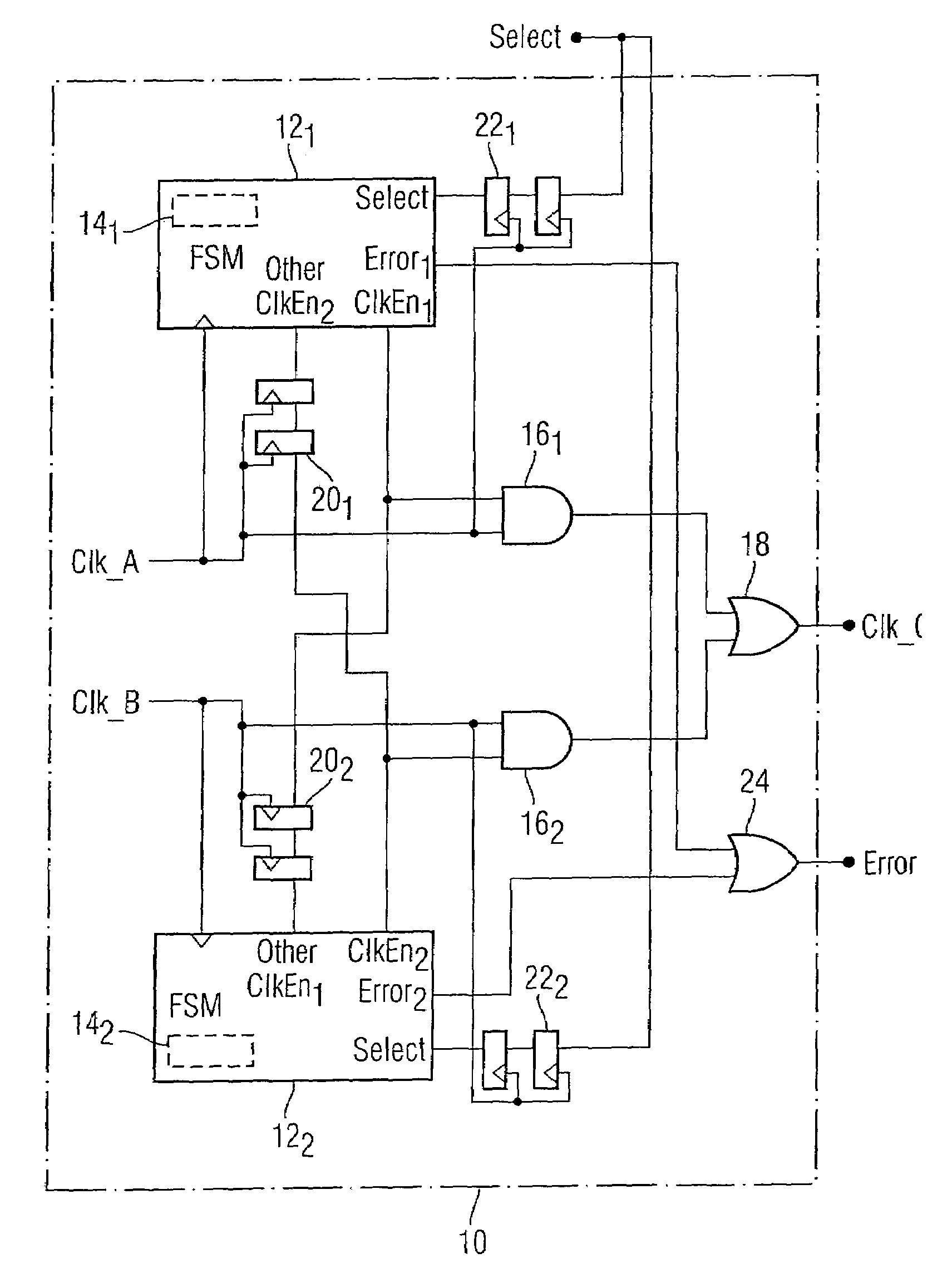

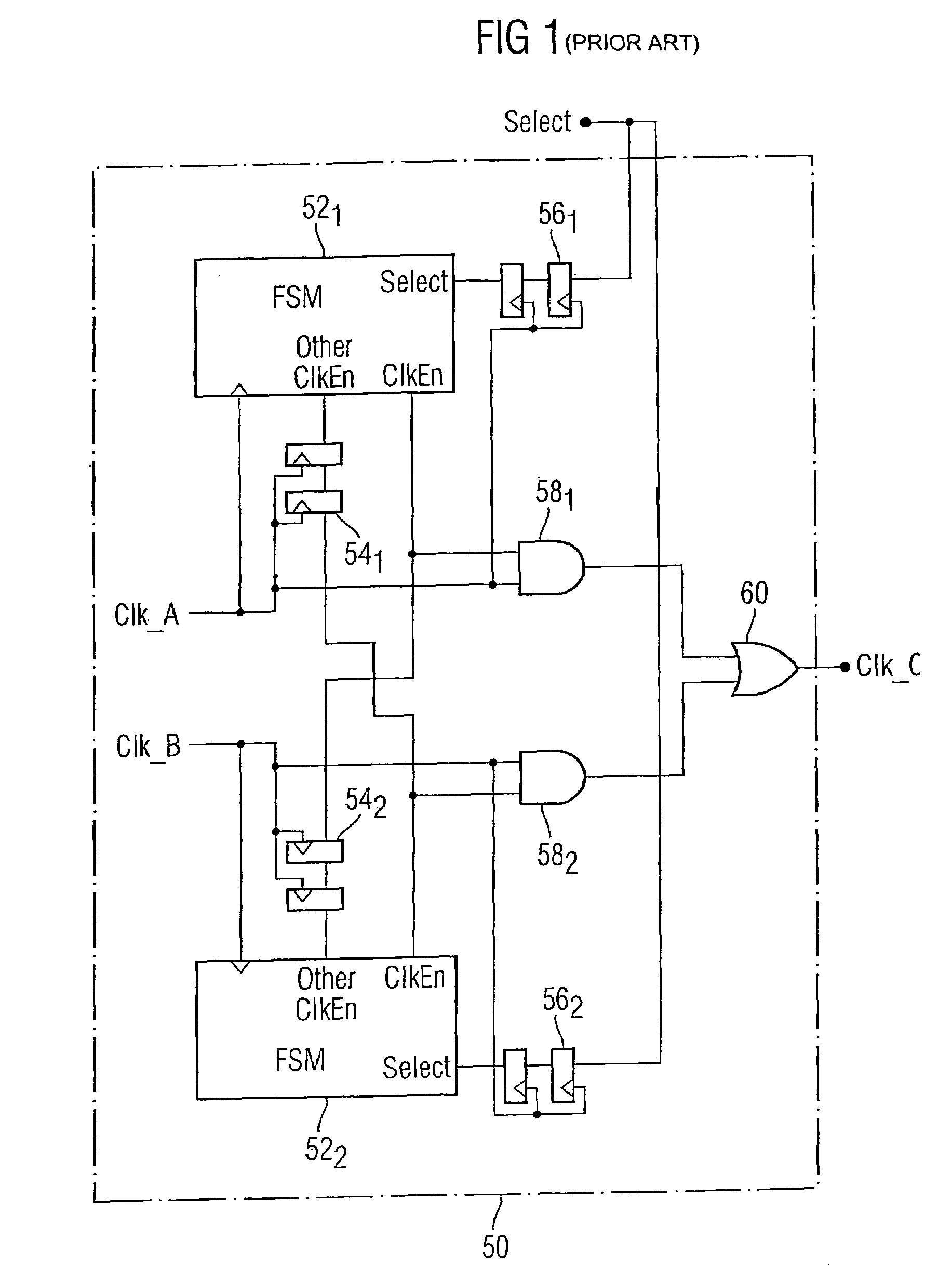

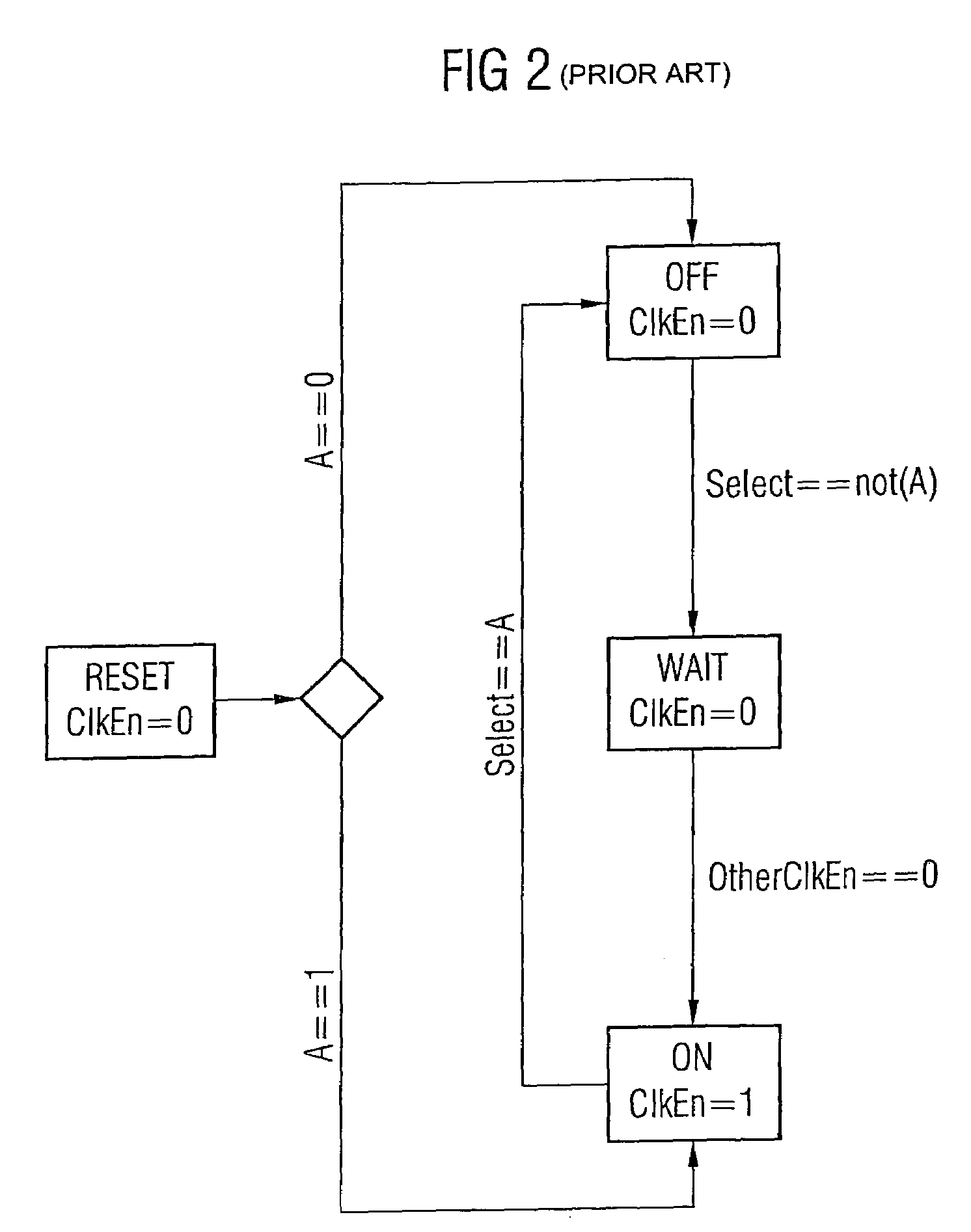

Digital clock switching means

A digital clock switching circuit and method is disclosed and is operable to deadlock-free switch a digital clock source for an integrated circuit. The circuit includes a first finite state machine associated with a first clock source and a second finite state machine associated with a second clock source. The finite state machines are connected to each other and monitor the current state of the other finite state machine. Each finite state machine receives an input select signal to control which clock source should be active and passed to a clock output. Each finite state machine includes a counter, wherein the counter associated with the active clock source is initialized to a first predetermined value when the input select signal indicates a switching off of the active clock source. The finite state machine associated with the active clock source enters a CHECK state and varies a count at each clock cycle. If the other finite state machine verifies a presence of its clock source before the counter reaches a second predetermined value the switch of the active clock source is effected.

Owner:INFINEON TECH AG

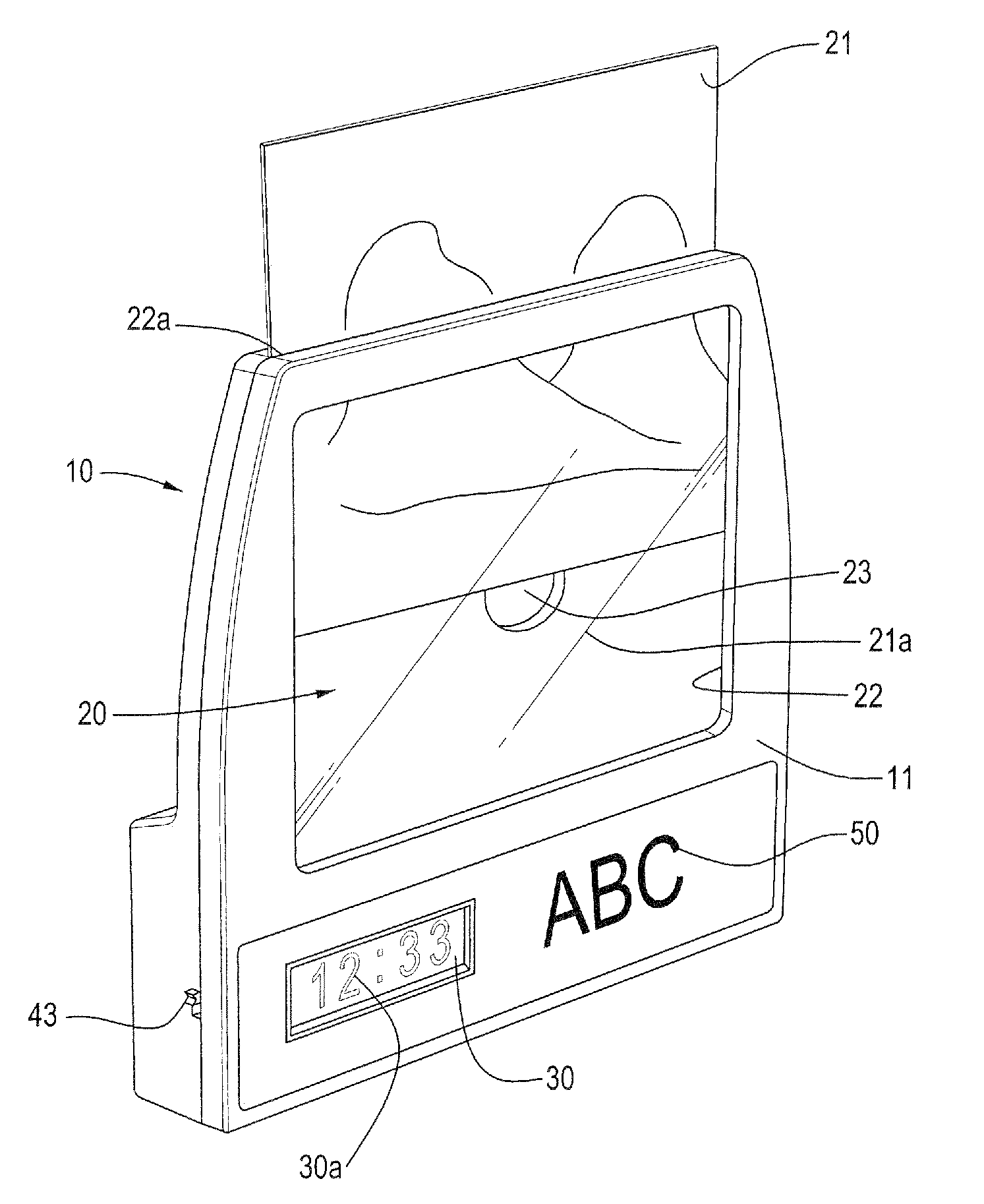

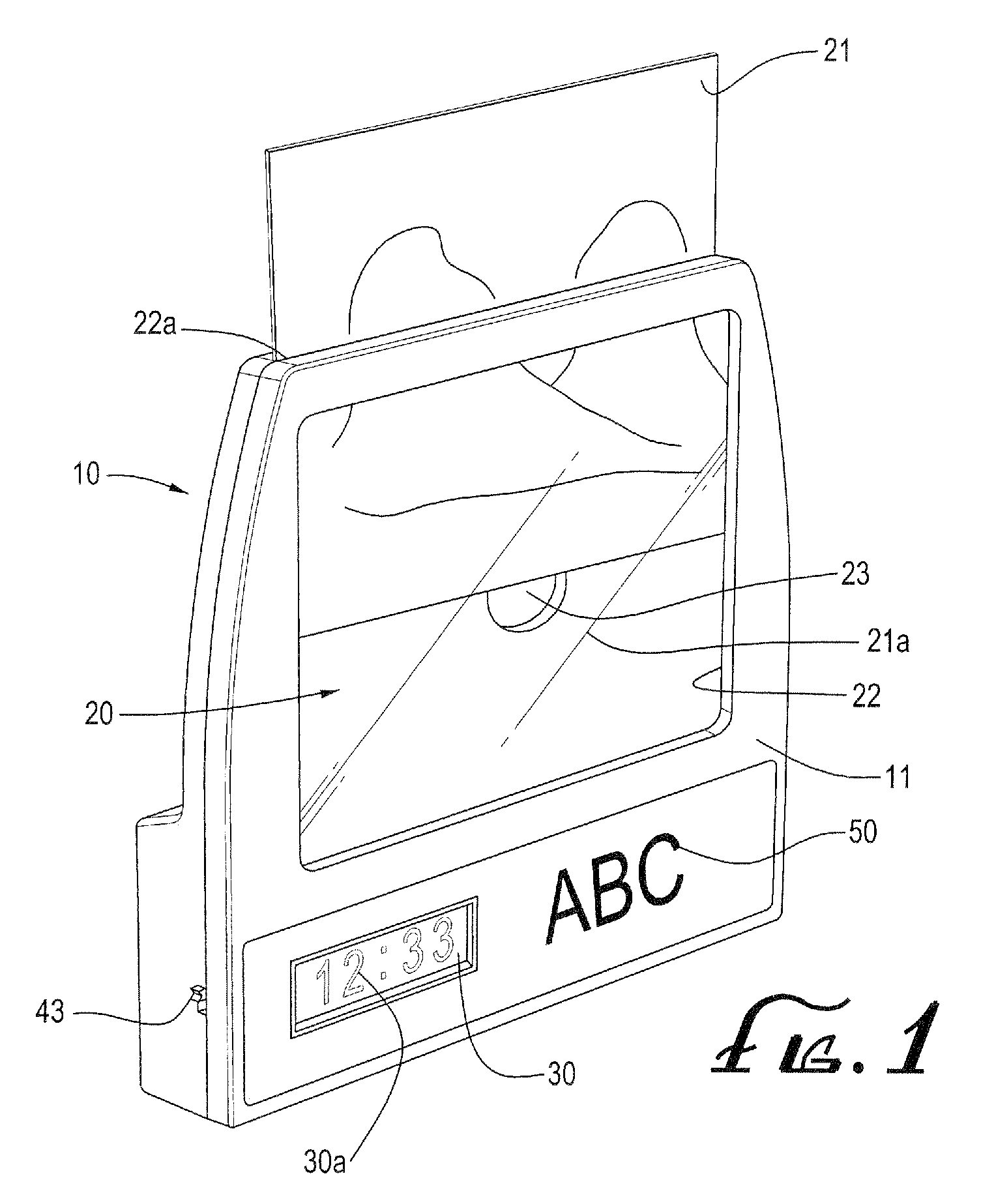

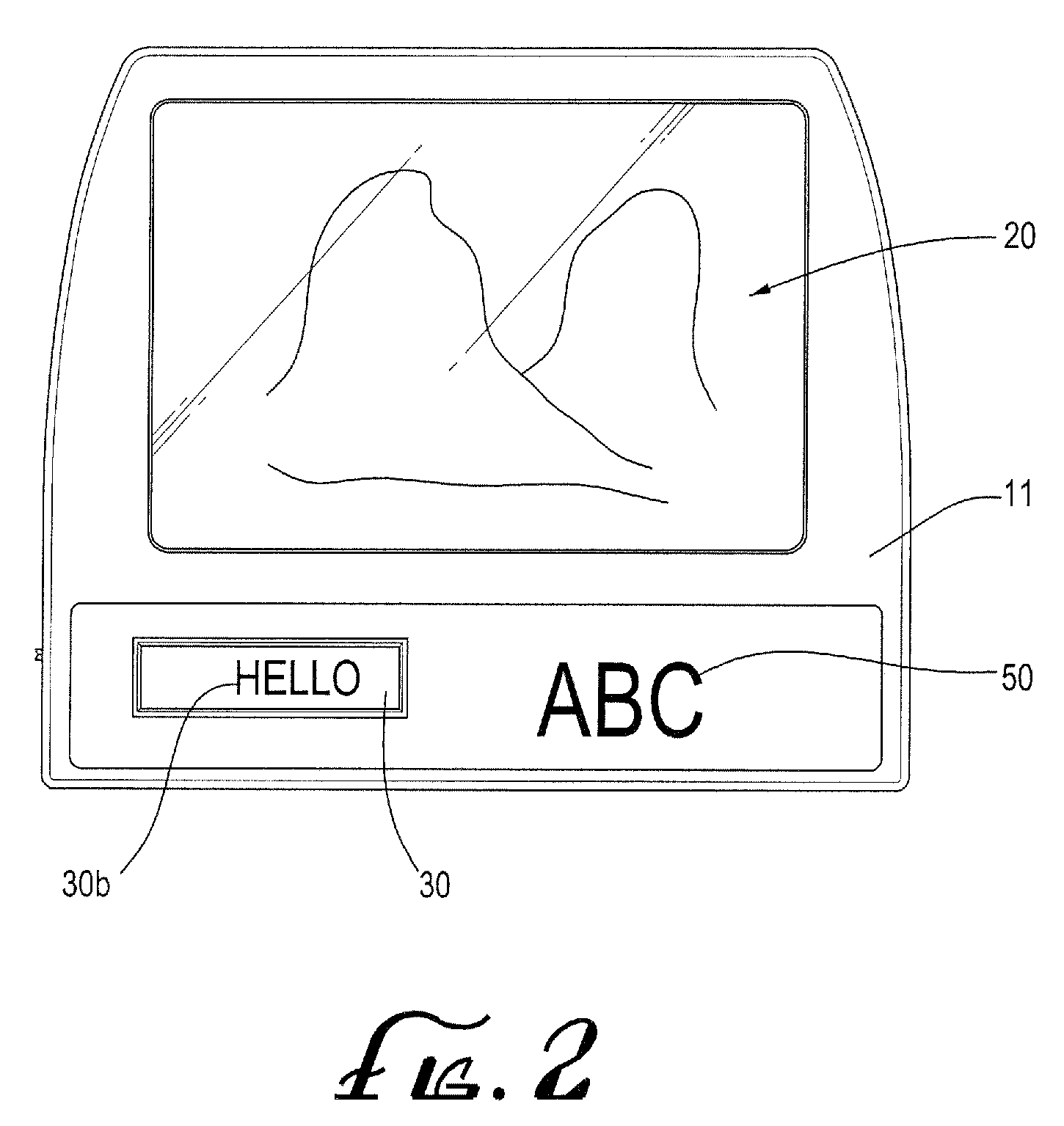

Multi-function picture frame

InactiveUS20080129646A1More attentionEffective attentionMechanical clocksPicture framesGraphicsDigital clock

A multi-function desktop photo frame configured to interchangeably display graphic images in either a conventional paper format or digital format, and incorporating some of widely used office functions. In the preferred embodiment, the photo frame includes an AM / FM radio and an LCD screen on which an alphanumeric message, inputted by a user via a message input unit, scrolls for effectively reminding the user of important messages. Further, the photo frame may include other common office electronics such as a digital clock and / or a thermometer.

Owner:SUN COAST MERCHANDISE

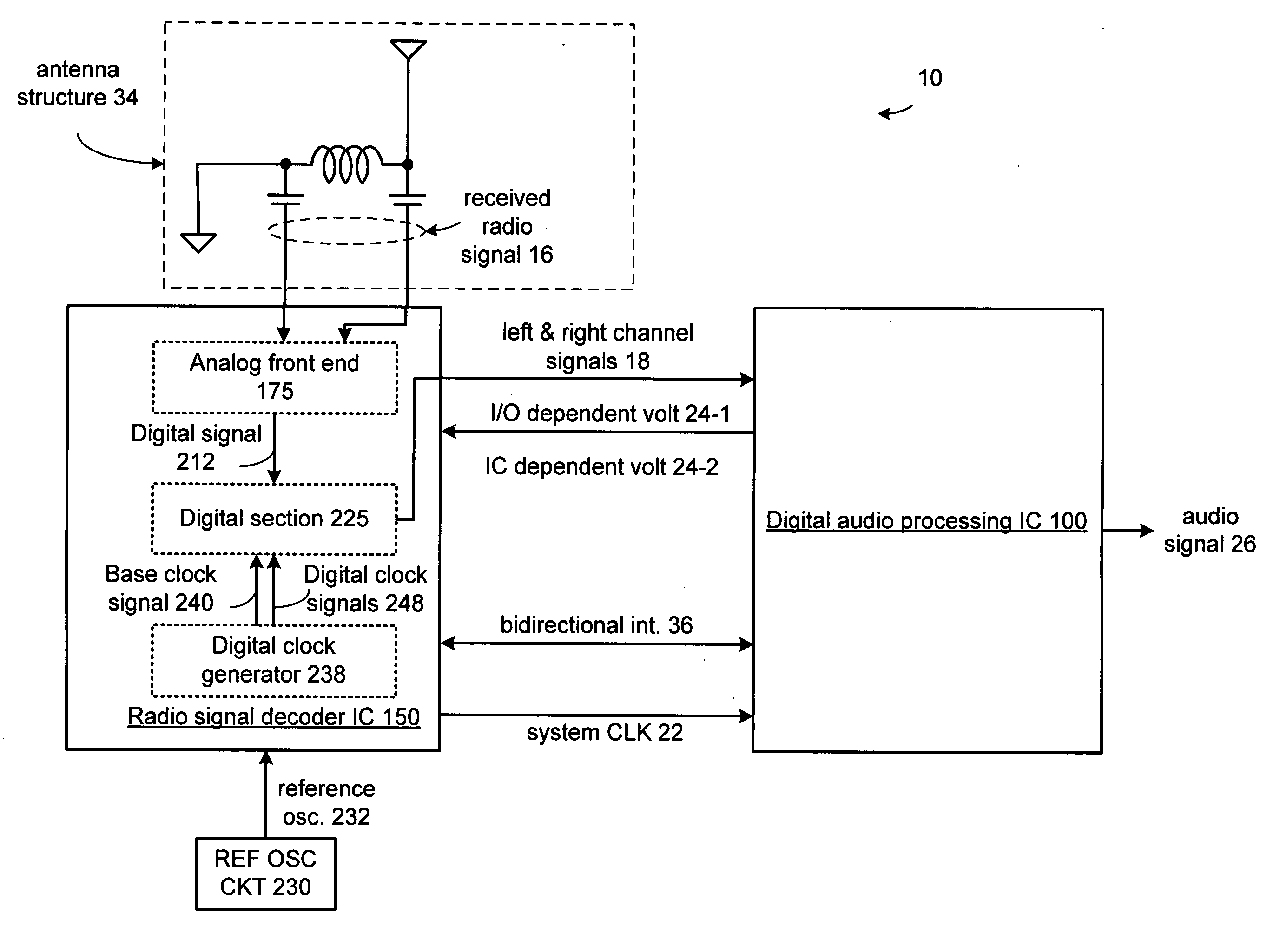

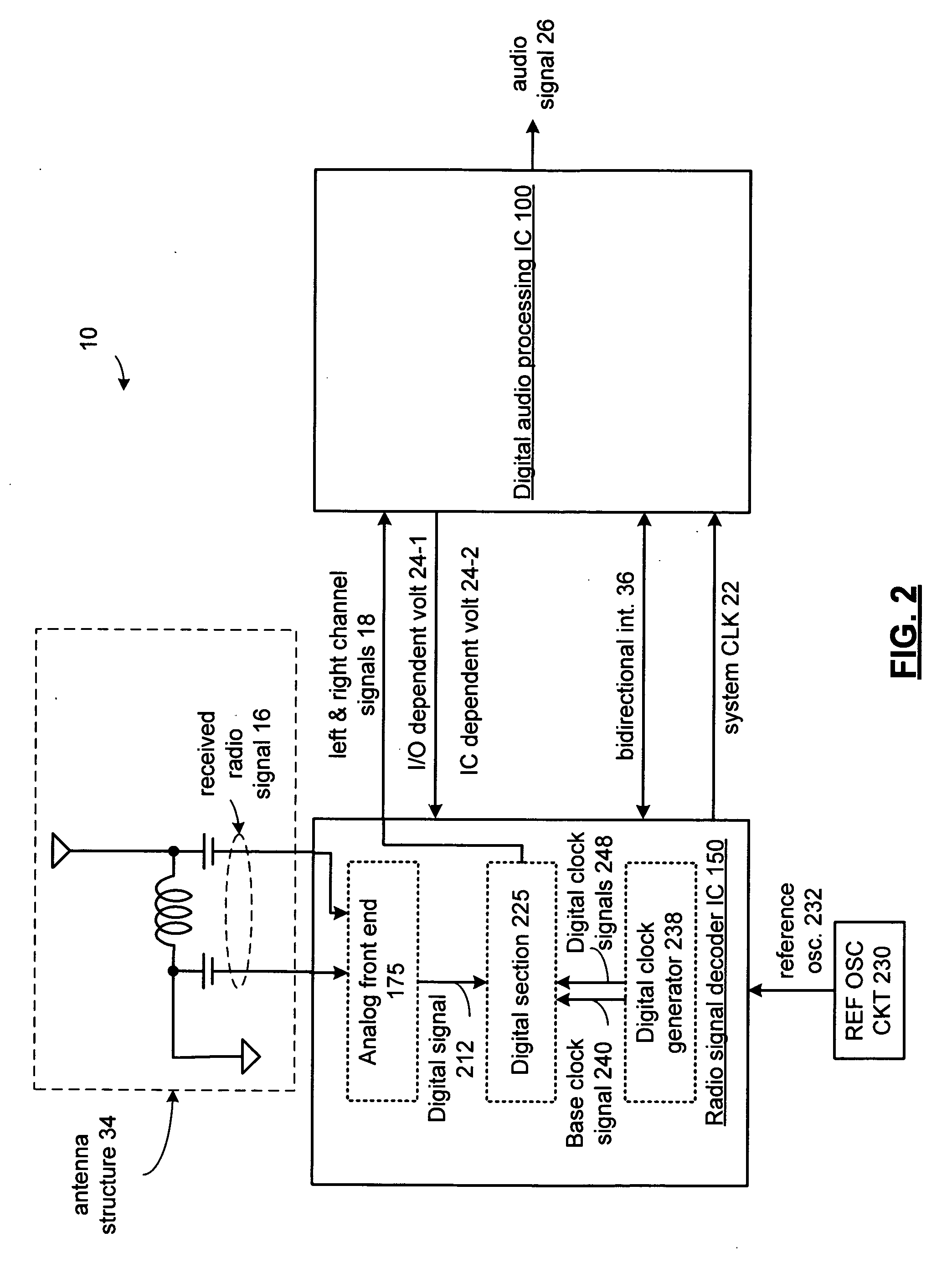

Digital clock controller, radio receiver, and methods for use therewith

InactiveUS20070165747A1Reduce noiseAnalogue/digital conversionElectric signal transmission systemsRadio receiverDigital clock

A digital clock generator includes a base clock generator for generating a base clock signal at a variable base clock frequency in response to a control signal. A digital clock controller generates a digital clock signal having a substantially constant number of digital clock cycles over a predetermined period.

Owner:NORTH STAR INNOVATIONS

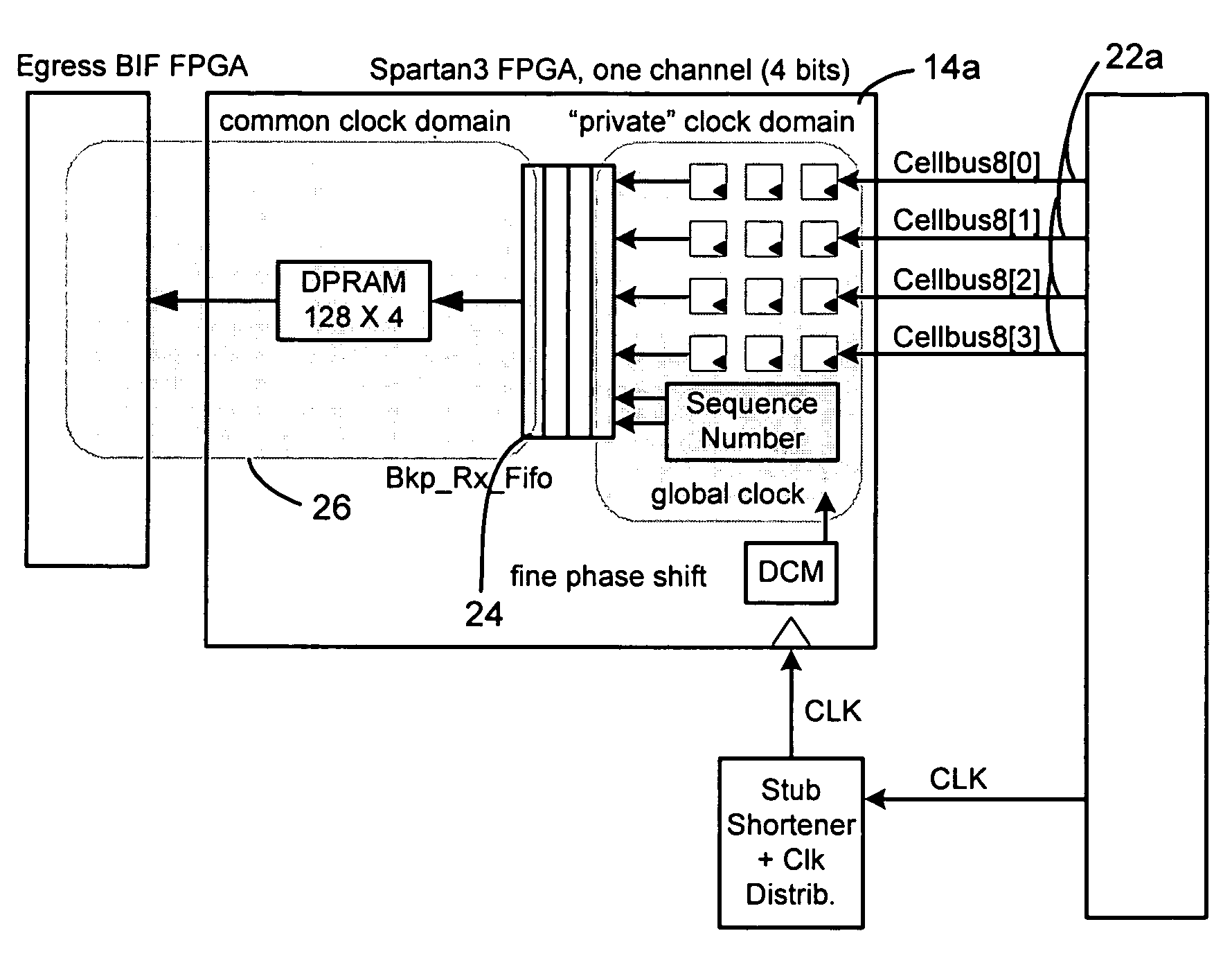

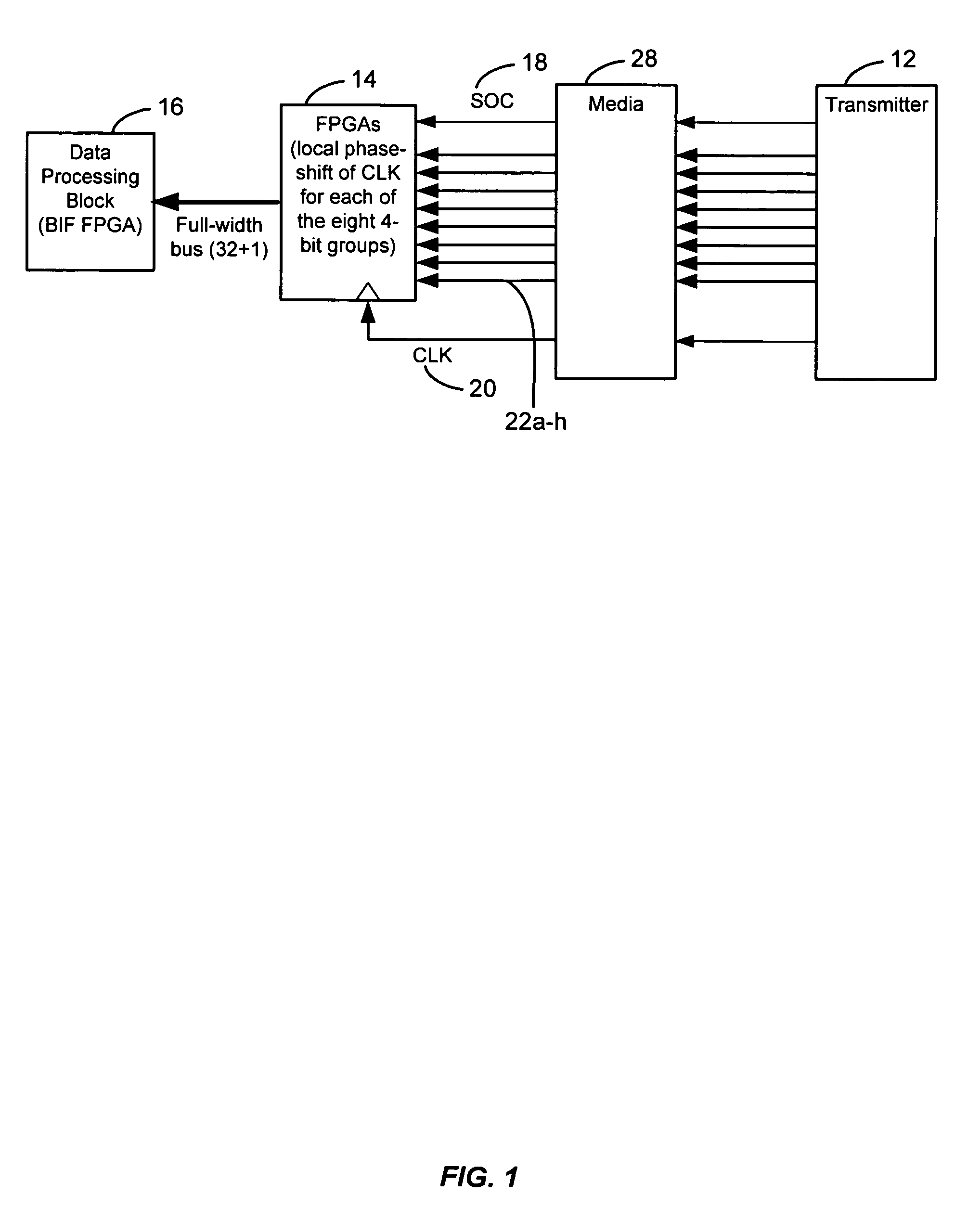

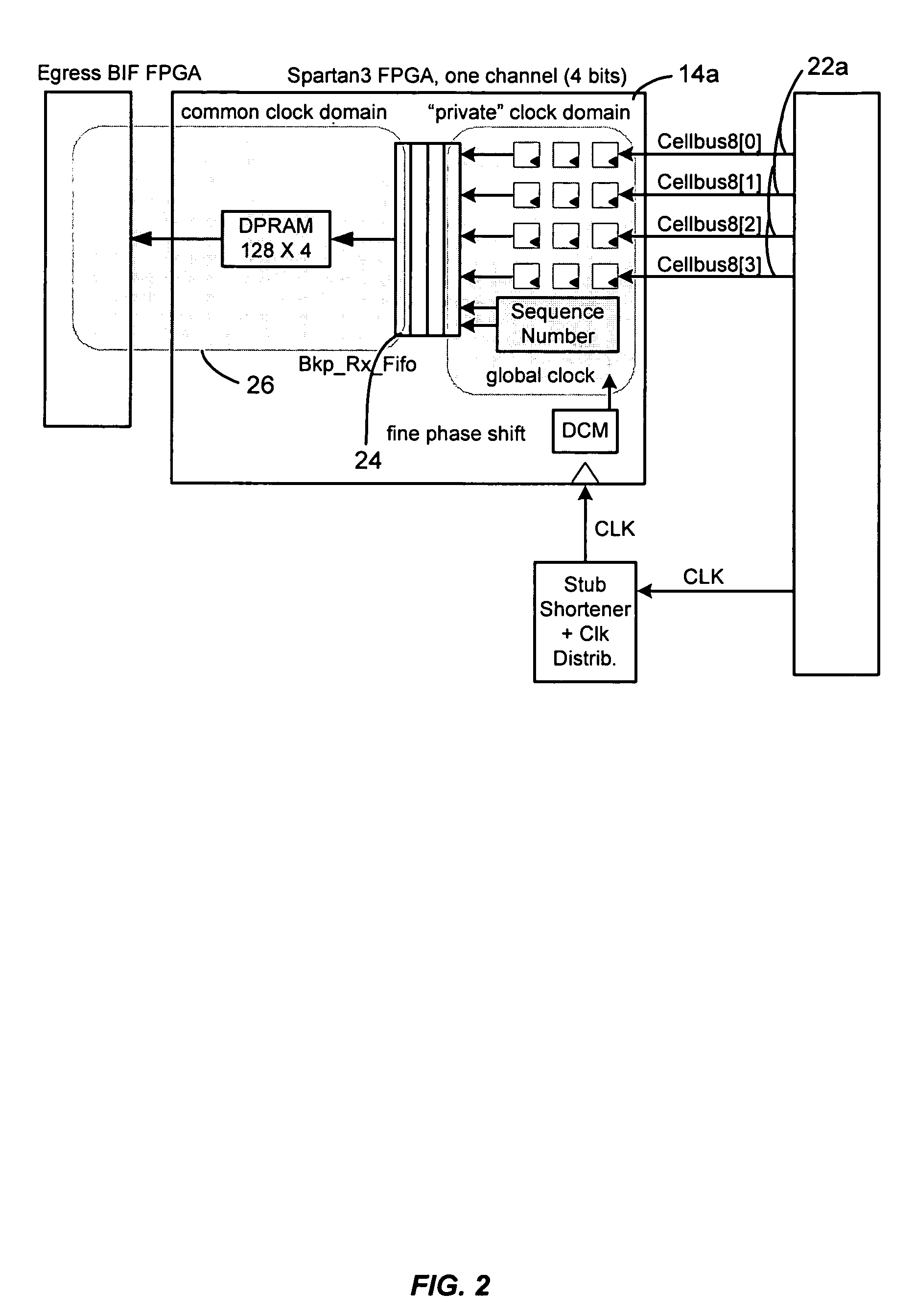

Method and system for recovering and aligning synchronous data of multiple phase-misaligned groups of bits into a single synchronous wide bus

A system for recovering and aligning synchronous data transmissions is disclosed. The system includes a transmitter configured to transmit a source clock signal and a number of data groups over a number of channels with different latencies / propagation delays. The data groups are transmitted during the same clock cycle pursuant to the source clock signal. Each data group is transmitted over a corresponding media channel. The system also includes a receiver configured to receive the source clock signal and the data groups over the corresponding channels and to re-align or recover the wide word that comes in on the channels that are skewed. The receiver further includes: for each channel, (a) a local clock configured to generate a local clock signal based on the source clock signal, the local clock signal being phase-shifted from the source clock signal by a predetermined amount of phase shift, (b) a logic device configured to clock in the data group received over the channel using the local clock signal, (c) a sequence number generator configured to generate a sequence number associated with the data group, (d) a FIFO configured to store and output the clocked-in data group and the associated sequence number, (e) a memory device configured to store the clocked-in data group from the FIFO using the associated sequence number as a memory address, the memory device further configured to output a predetermined portion of its contents after a predetermined capacity threshold is reached. The transmitter is further configured to transmit a start-of-cell signal to the receiver. The sequence number generators are synchronized upon receiving an alignment cell, which is identified by a start-of-cell signal having a specific value for a predetermined cycle period. In one implementation, the receiver is implemented using a number of field programmable gate arrays and the local clocks are implemented using digital clock managers associated with the field programmable gate arrays.

Owner:RIBBON COMM OPERATING CO INC

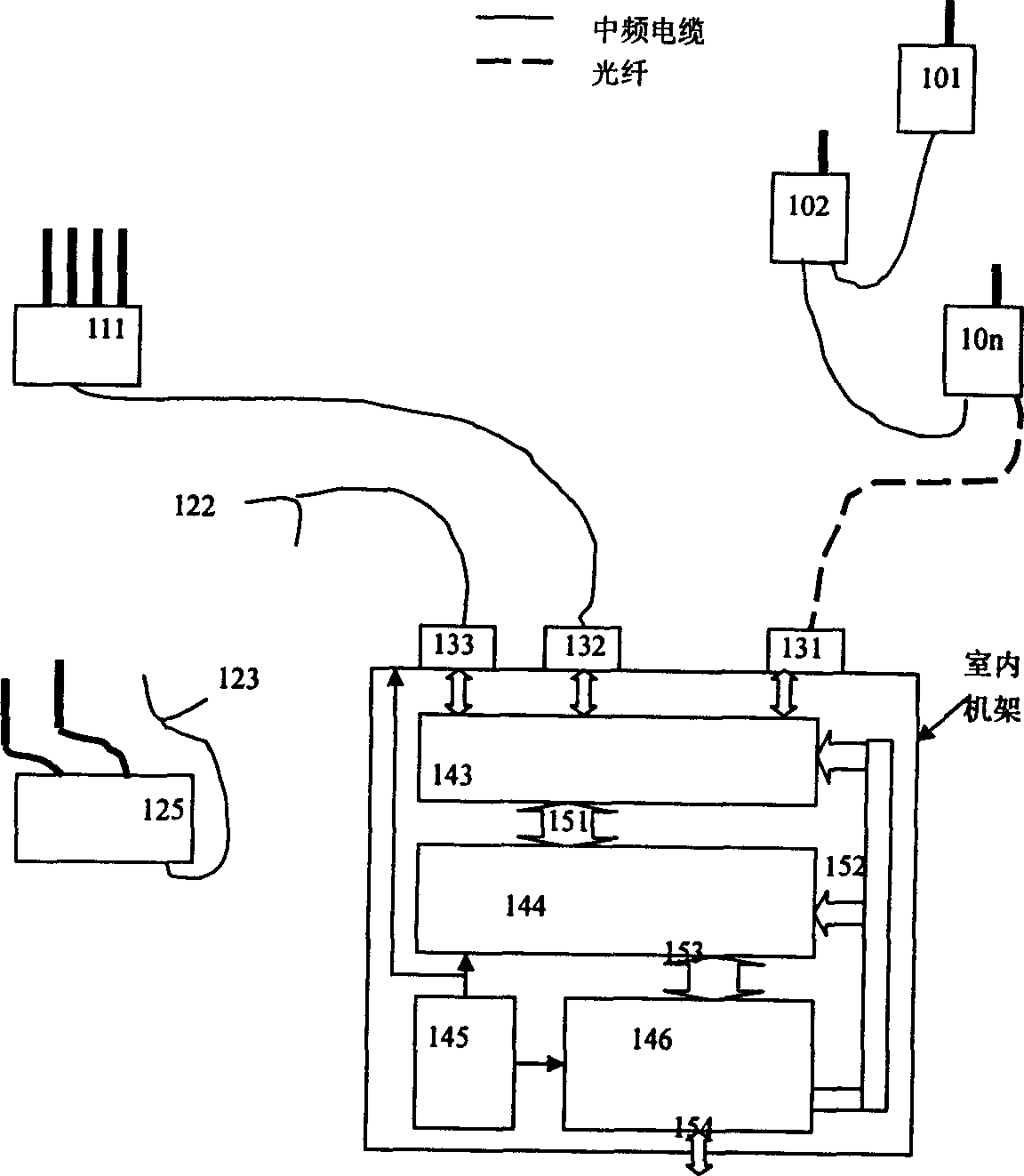

TD-SCDMA system base station radio-frequency digital long-drawn optical fiber transmitting method and apparatus

ActiveCN1812292ATroubleshoot connection transfer issuesReduce complexityRadio-over-fibreDigital signal processingFiber

This invention is fiber-optical transmission method for drawing far away the TD-SCDMA system base station radio-frequency digit. The radio-frequency signal receiver-transmitter in wireless base station and base band digital signal processing part in wireless base station are separated and drawn far away to antenna neighborhood. After digitizing the intermediate-frequency port of radio-frequency signal receiver-transmitter, the received and transmitted digital data stream signal, controlling or detecting digital signal and referenced clock signal are respectively modulated to corresponding light wavelength. After making the optical signals corresponded to each radio-frequency receiver-transmitter confluent, an optical fiber is used to up-transmitting and down-transmitting respectively. At the receiving end, the confluent signal is split in terms of wavelength. The split signals are demodulated to corresponding digital signals respectively. This invention also provides the radio-frequency signal receiver-transmitter and indoor base station interface card matching this transmission method.

Owner:成都芯通软件有限公司

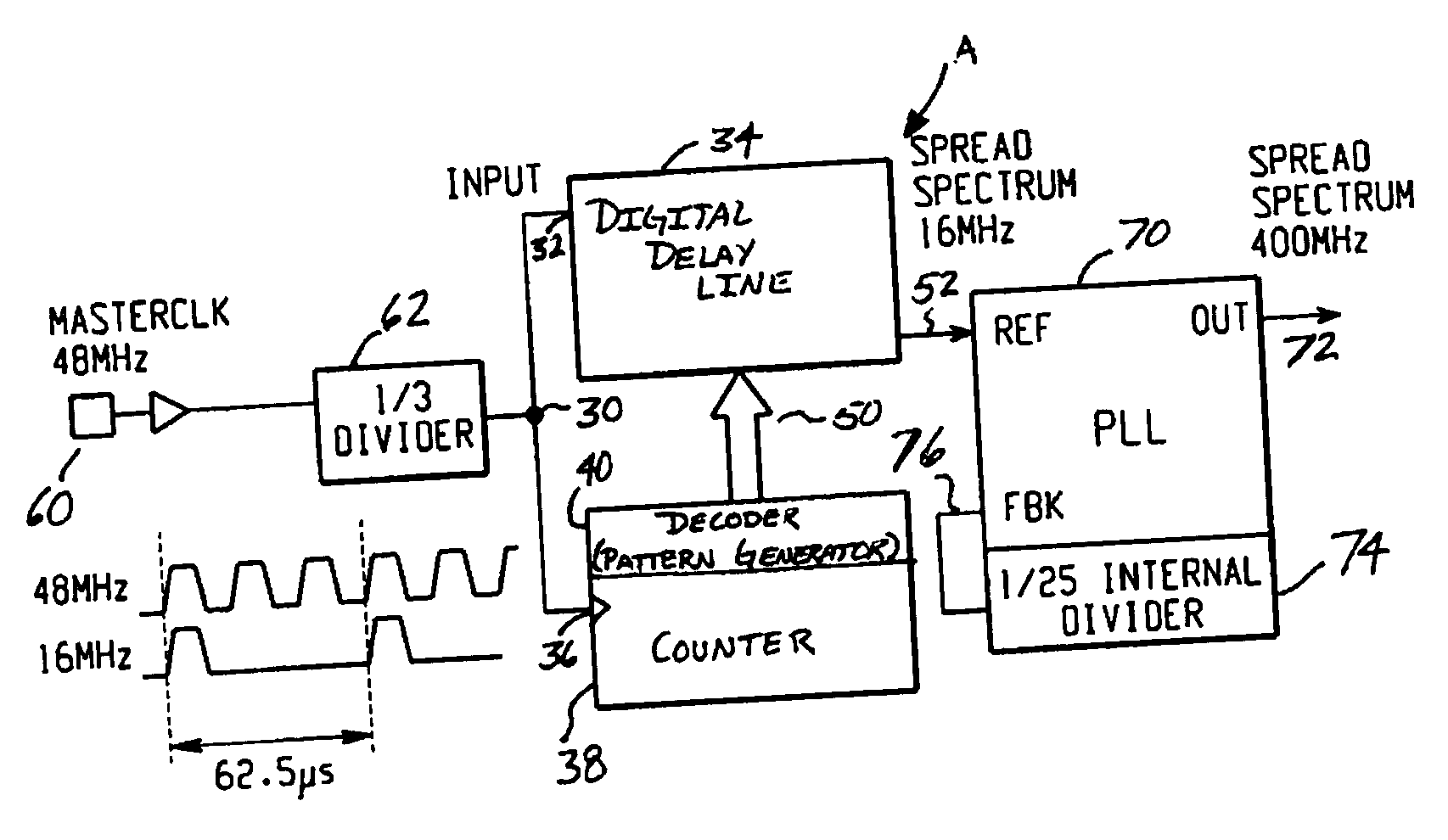

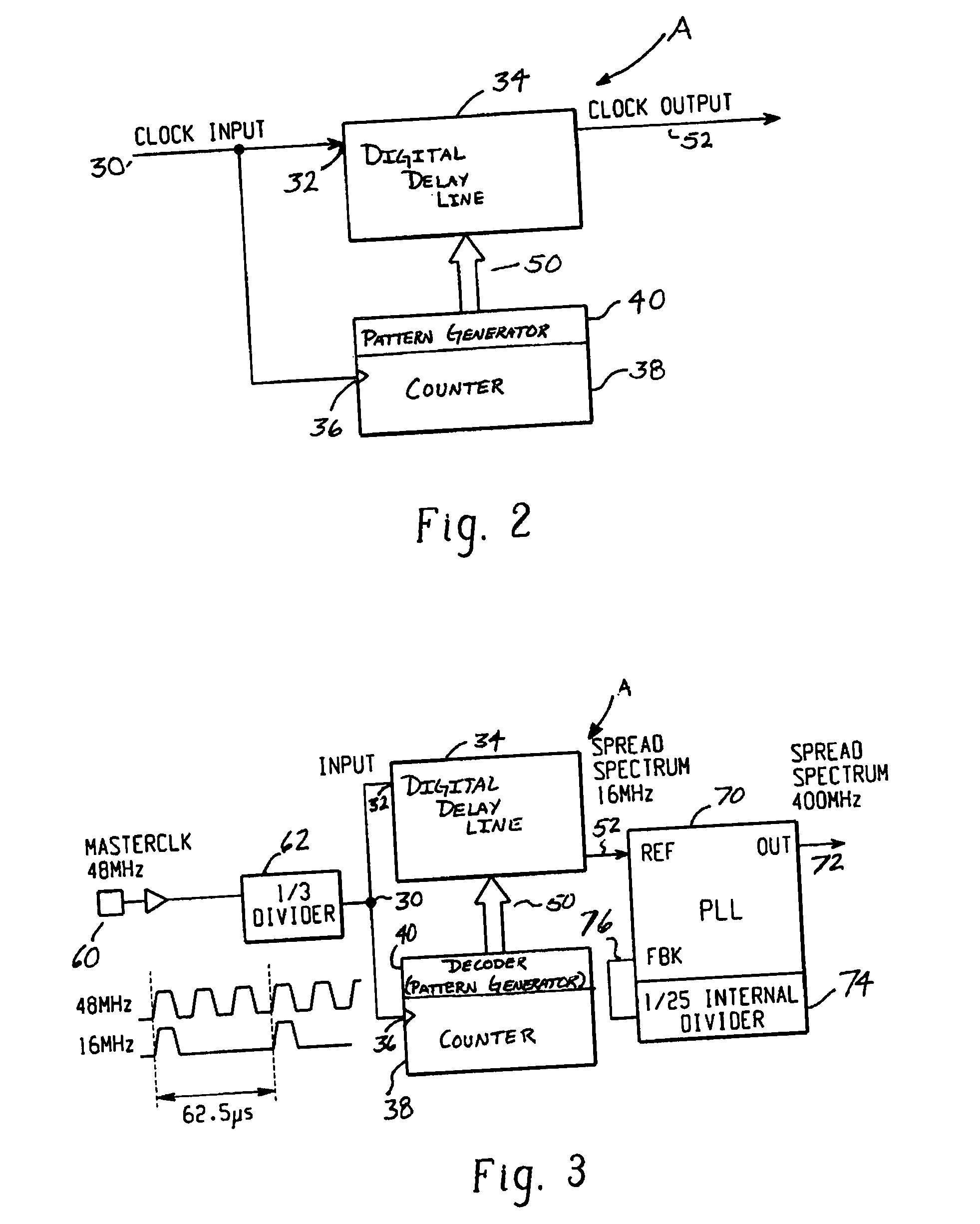

Spread spectrum clock generator

InactiveUS20050069019A1Angle modulation detailsDigital data processing detailsDigital dataDigital clock

A clock signal generator varies a frequency of a digital clock over a selected range of frequencies. The generator employs a divider for lowering a frequency of a clock signal. A counter increments synchronously with the signal, and causes a selected sequence of outputs to be generated by a pattern generator. The pattern generator output forms an input to a digitally controllable delay line which receives the lower frequency clock signal. The pattern generator causes the digital delay line to vary a frequency of the lowered frequency clock signal between selected boundaries. The varying frequency clock signal is then raised up again such that a final clock has a varying frequency, and will exhibit less EMI spiking during switching of an associated, synchronous digital data device. The solid state nature of the generator allows for simple fabrication, inexpensive manufacture and ready integration into digital circuitry, such as multifunction integrated circuits.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS