Patents

Literature

5353 results about "Field-programmable gate array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence the term "field-programmable". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an Application-Specific Integrated Circuit (ASIC). Circuit diagrams were previously used to specify the configuration, but this is increasingly rare due to the advent of electronic design automation tools.

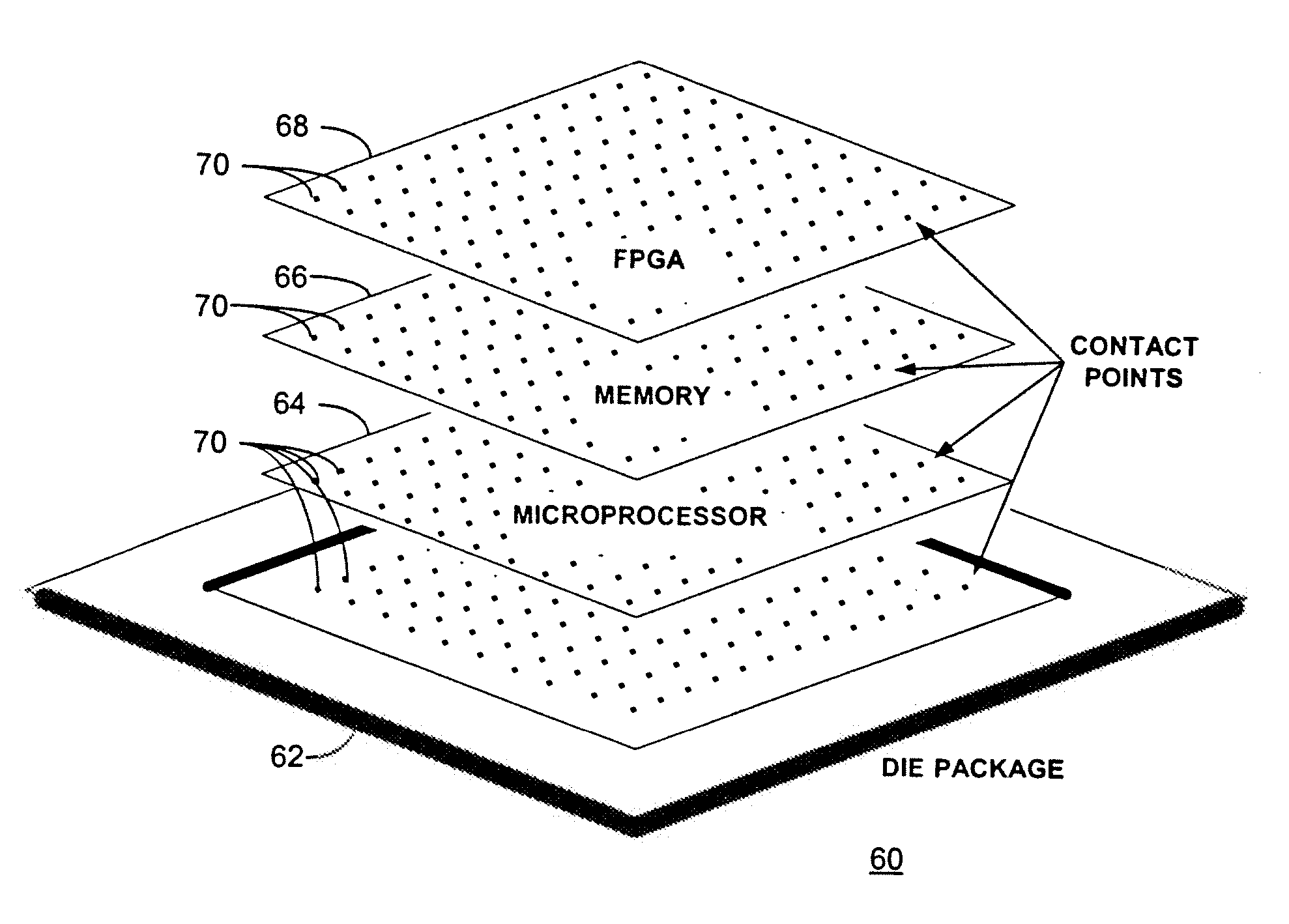

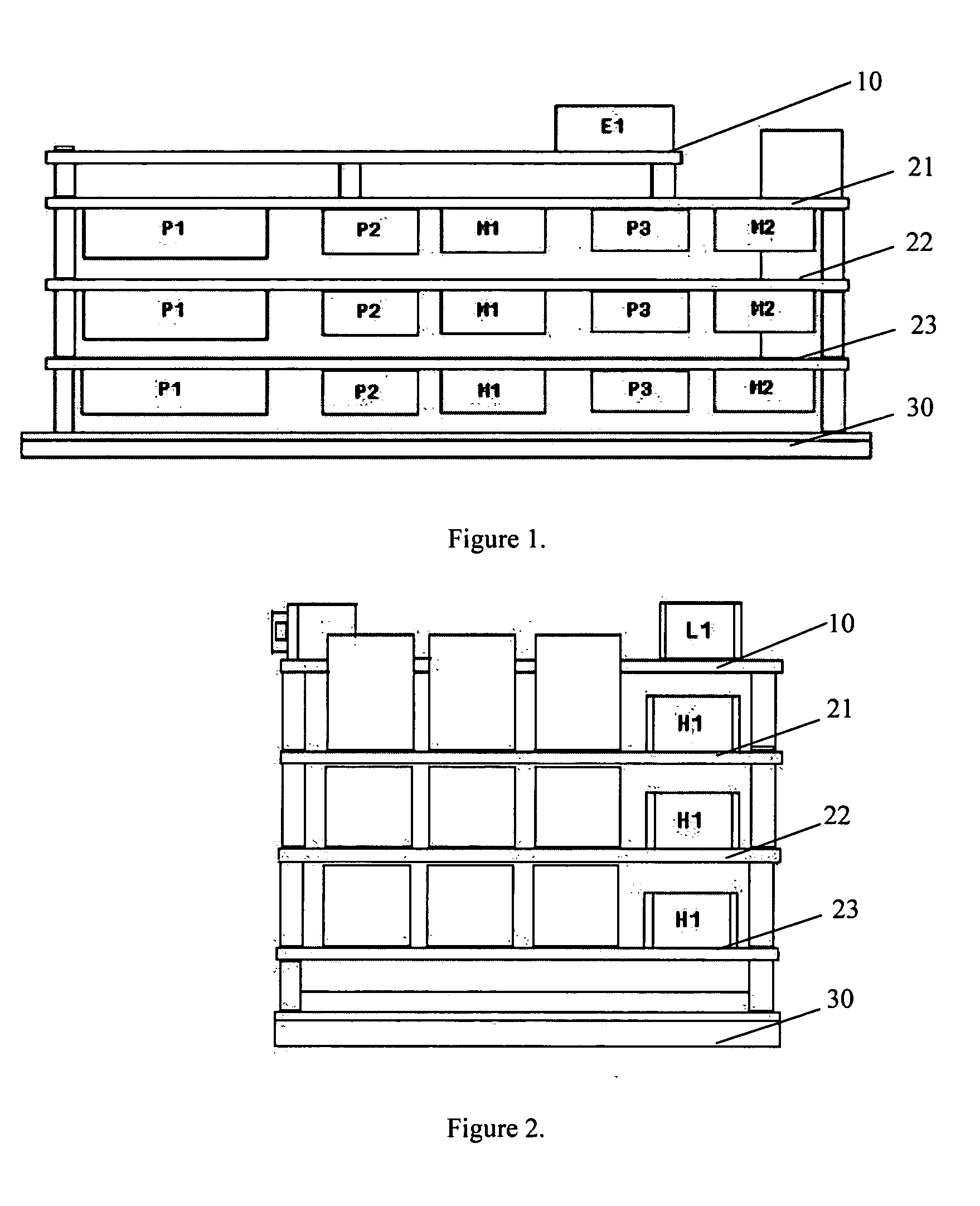

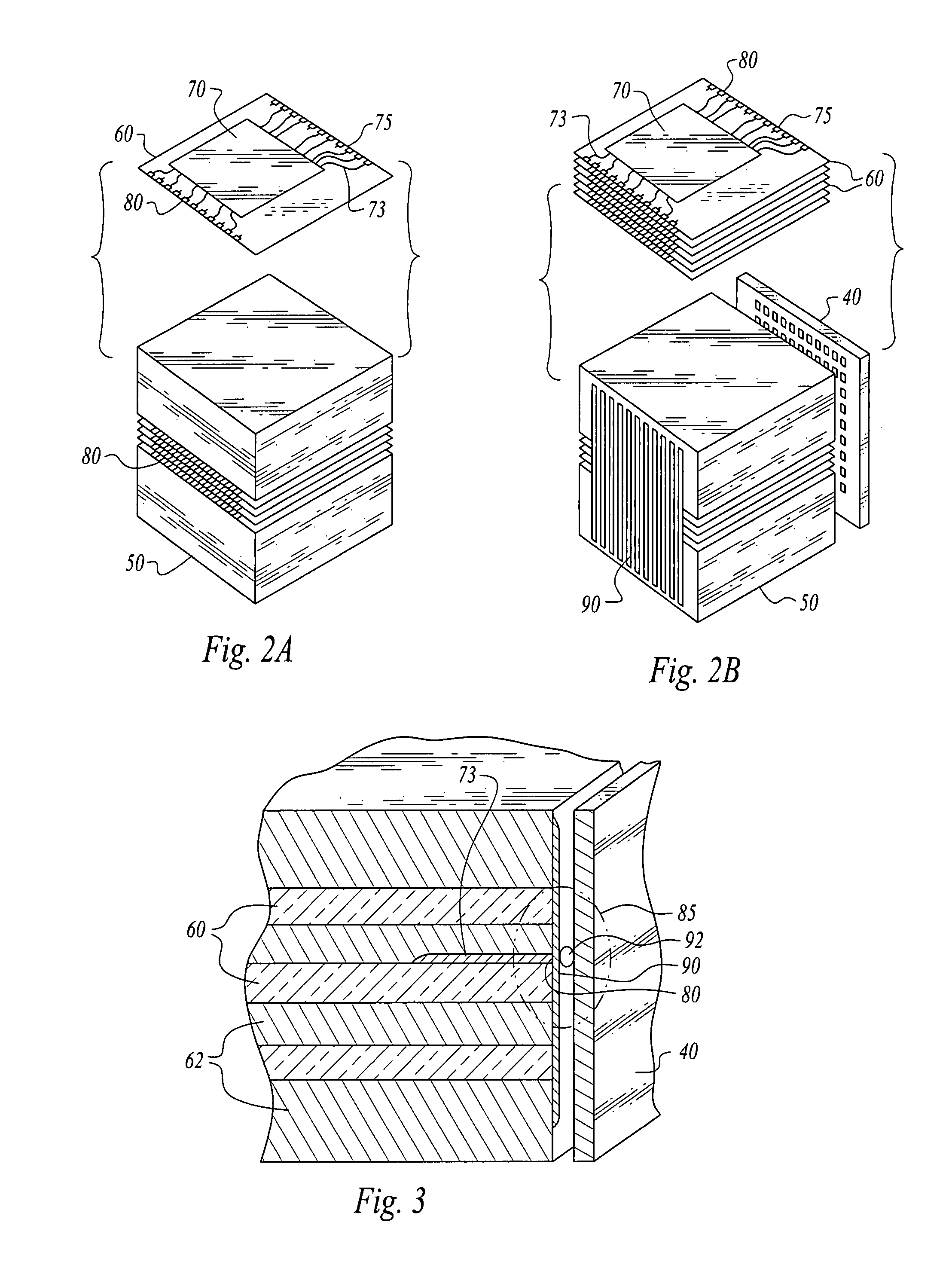

Reconfigurable processor module comprising hybrid stacked integrated circuit die elements

InactiveUS20060195729A1Energy efficient ICTError detection/correctionEngineeringField-programmable gate array

A reconfigurable processor module comprising hybrid stacked integrated circuit (“IC”) die elements. In a particular embodiment disclosed herein, a processor module with reconfigurable capability may be constructed by stacking one or more thinned microprocessor, memory and / or field programmable gate array (“FPGA”) die elements and interconnecting the same utilizing contacts that traverse the thickness of the die. The processor module disclosed allows for a significant acceleration in the sharing of data between the microprocessor and the FPGA element while advantageously increasing final assembly yield and concomitantly reducing final assembly cost.

Owner:ARBOR GLOBAL STRATEGIES LLC

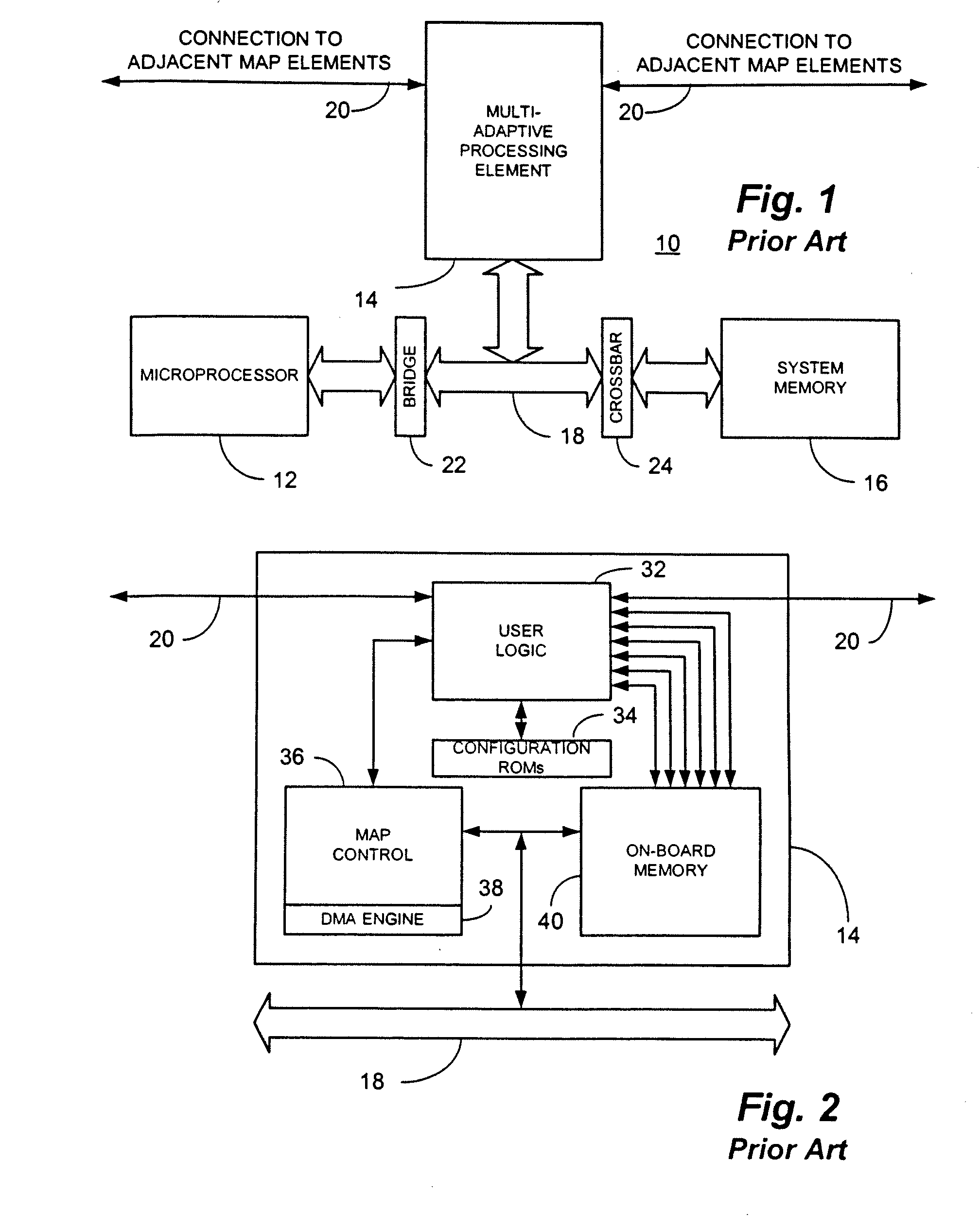

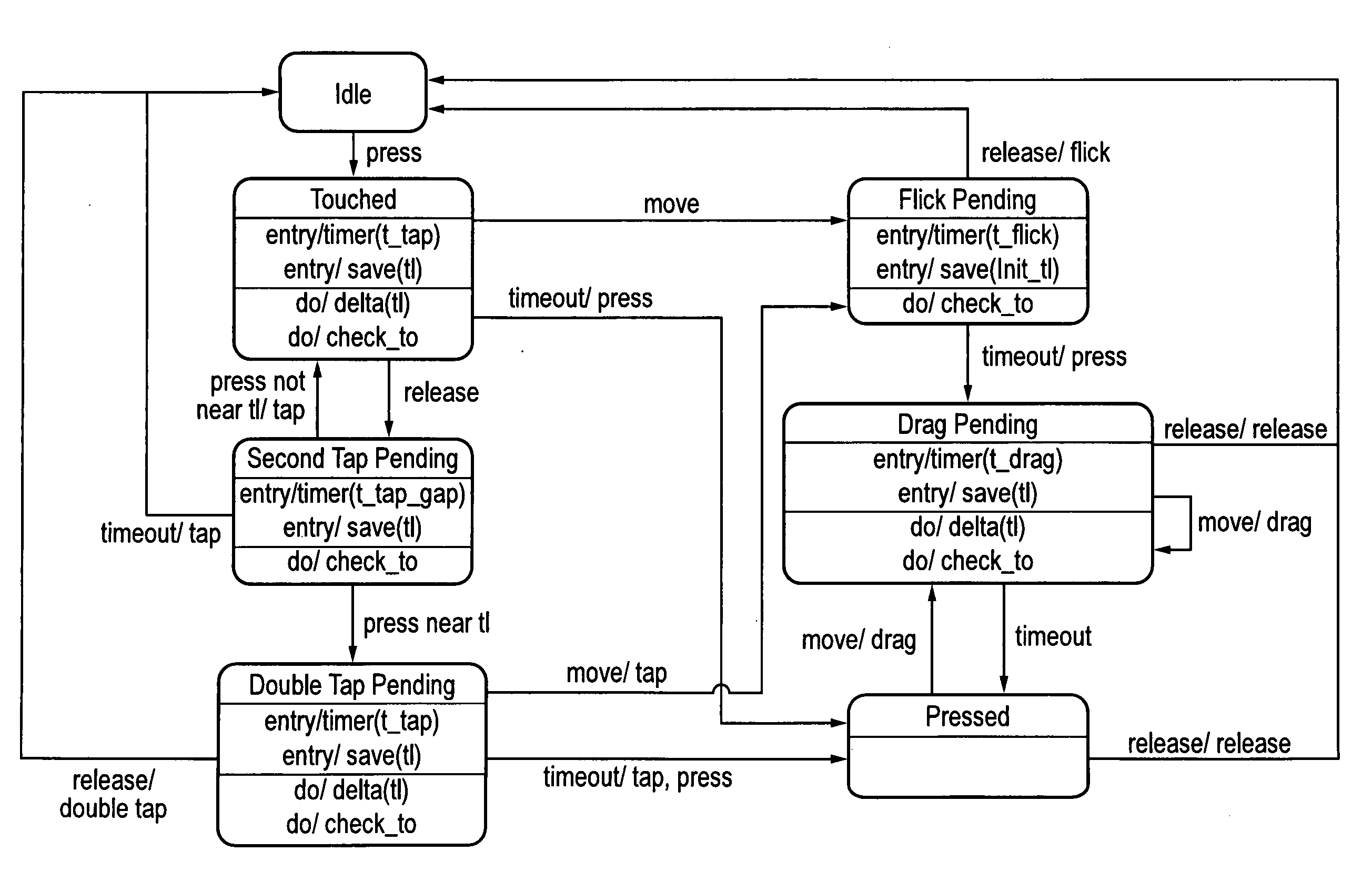

Gesture Recognition

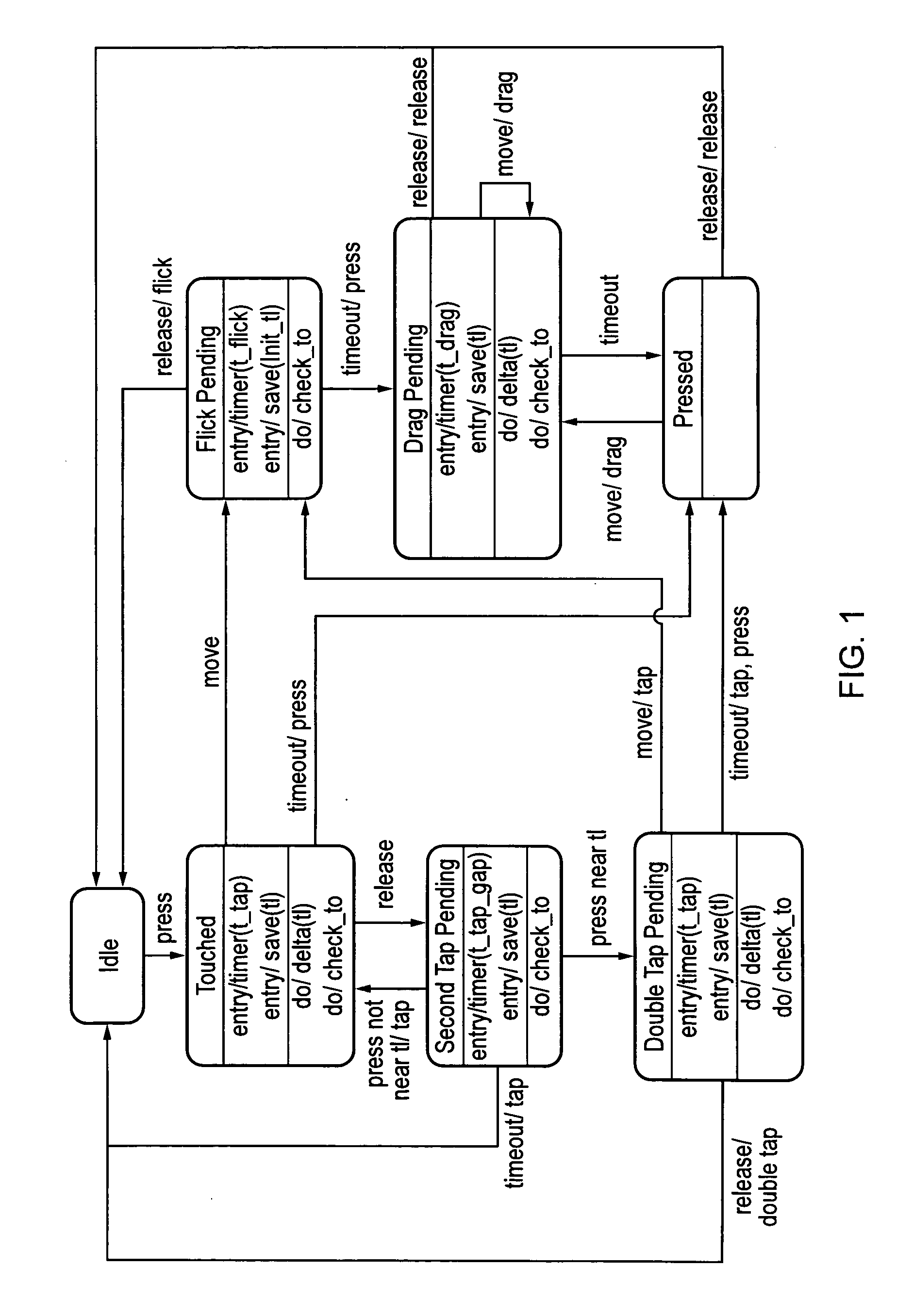

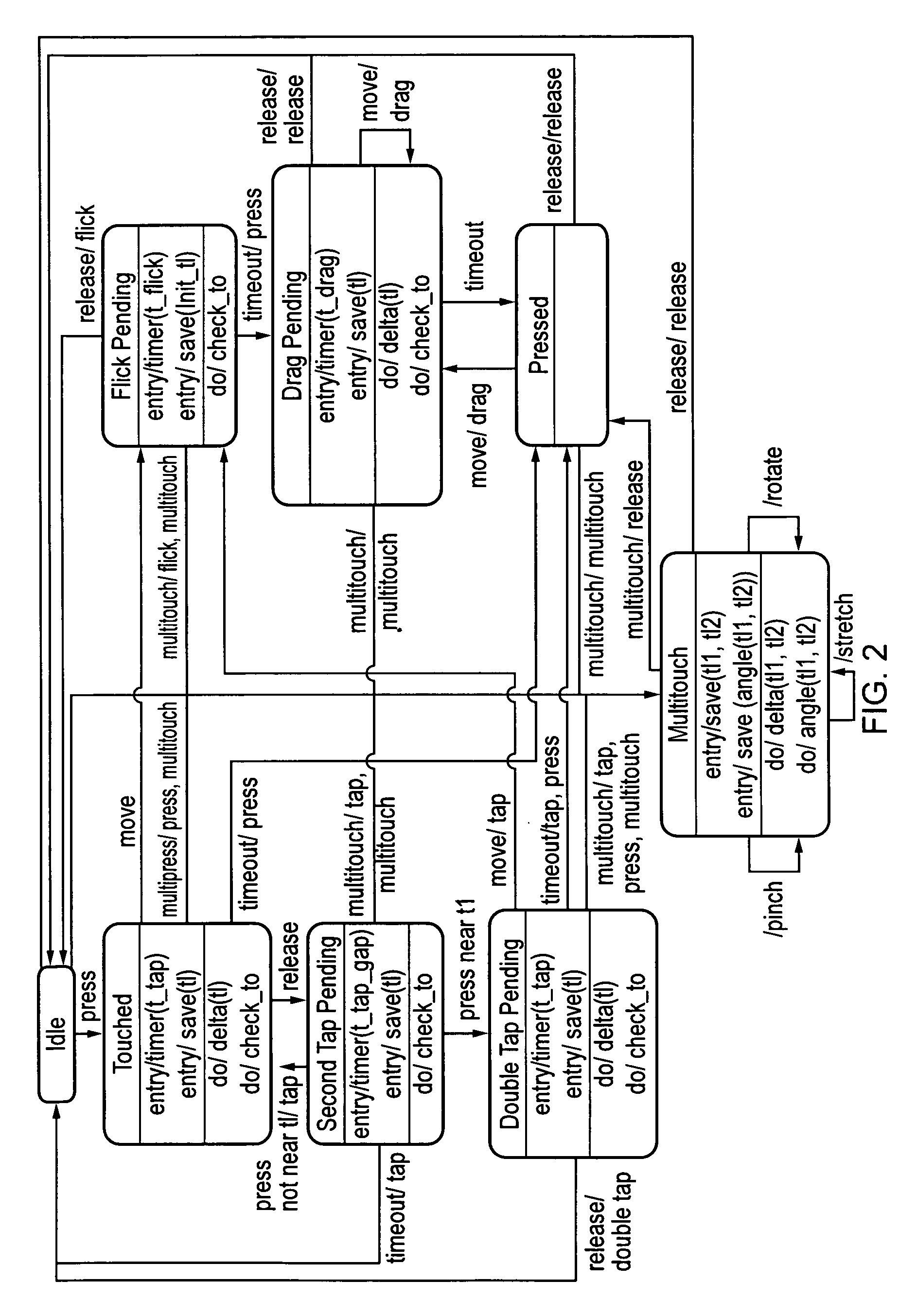

ActiveUS20090273571A1Transmission systemsCharacter and pattern recognitionMicrocontrollerProgrammable logic device

A state machine gesture recognition algorithm for interpreting streams of coordinates received from a touch sensor. The gesture recognition code can be written in a high level language such as C and then compiled and embedded in a microcontroller chip, or CPU chip as desired. The gesture recognition code can be loaded into the same chip that interprets the touch signals from the touch sensor and generates the time series data, e.g. a microcontroller, or other programmable logic device such as a field programmable gate array.

Owner:SOLAS OLED LTD

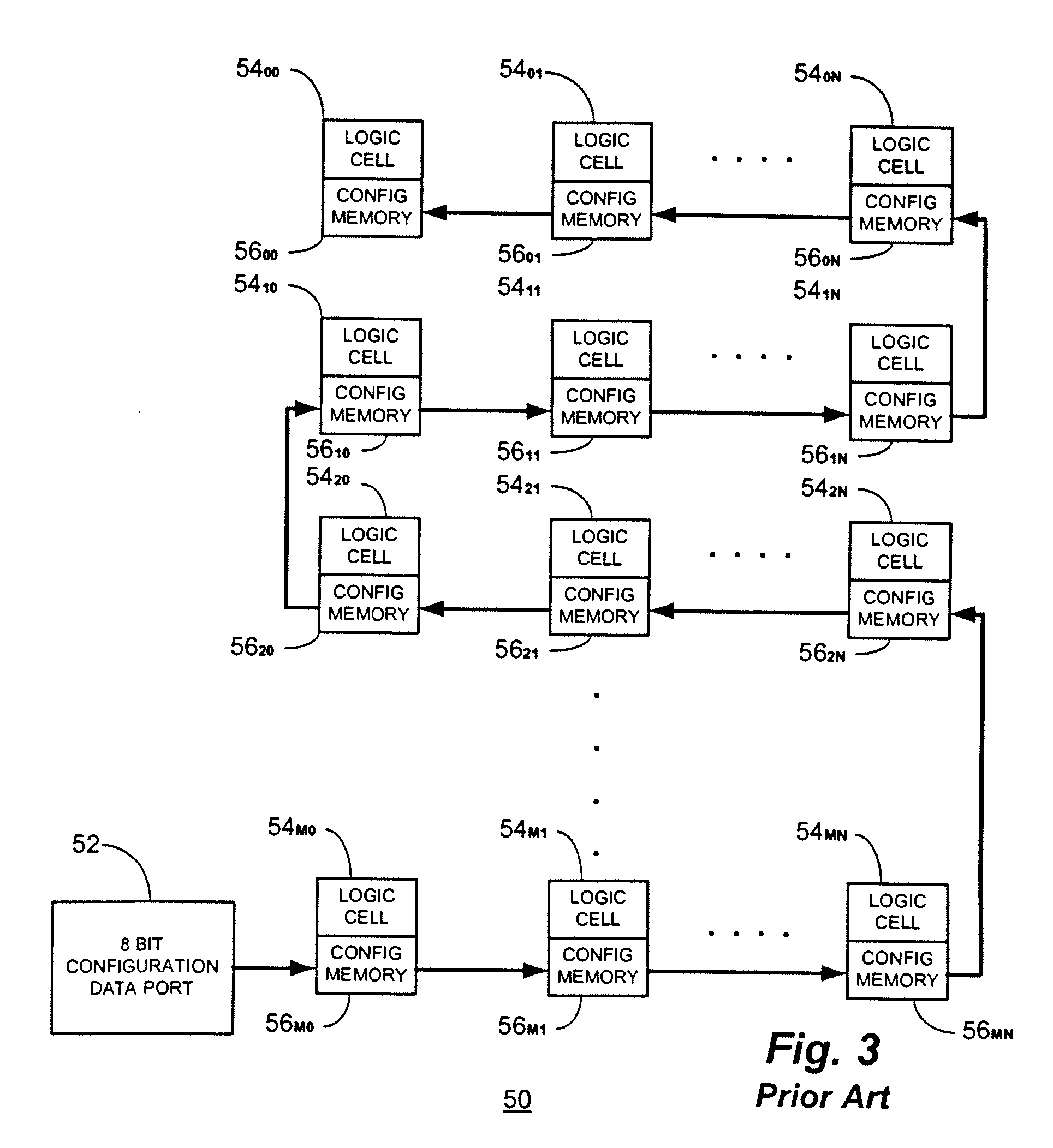

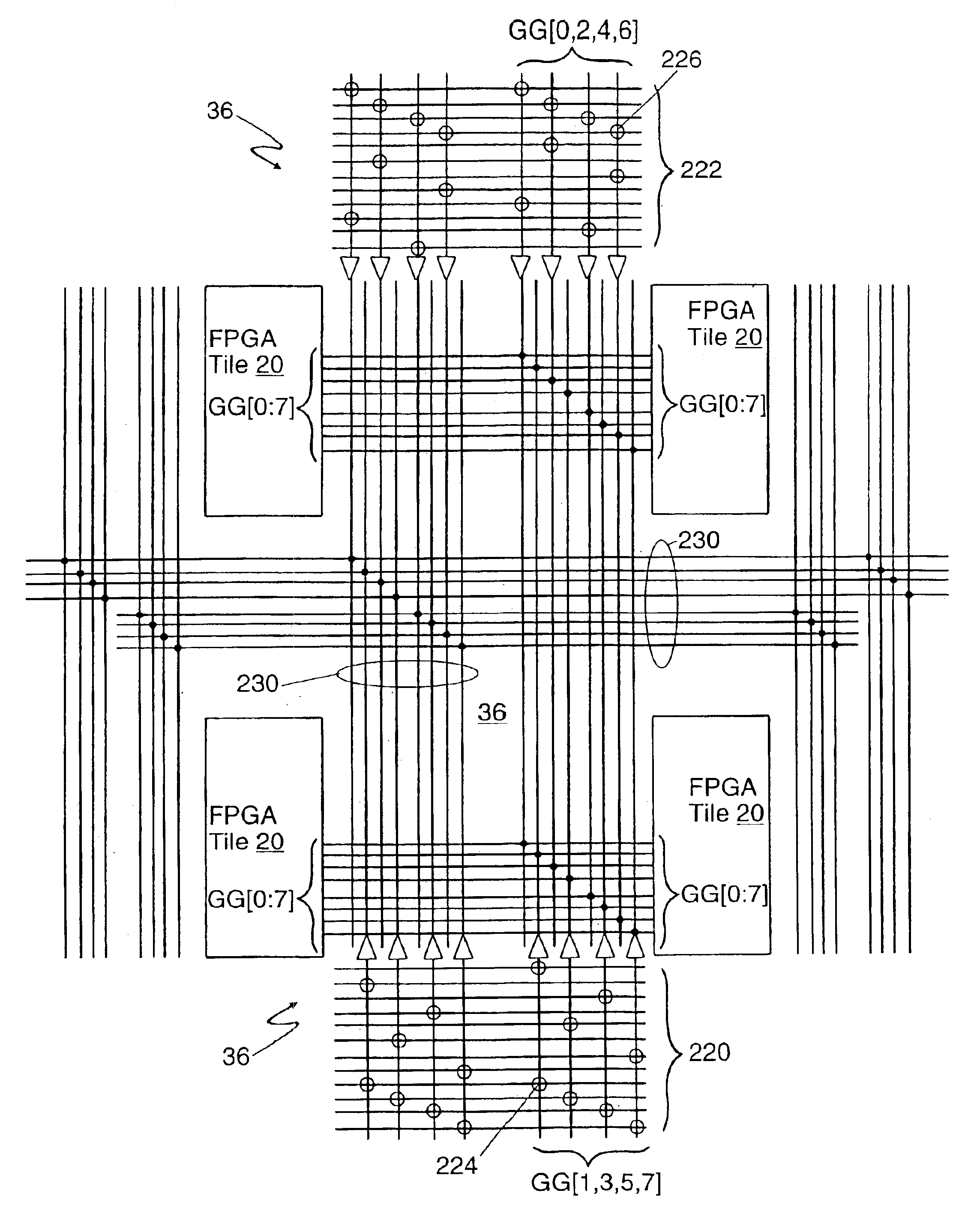

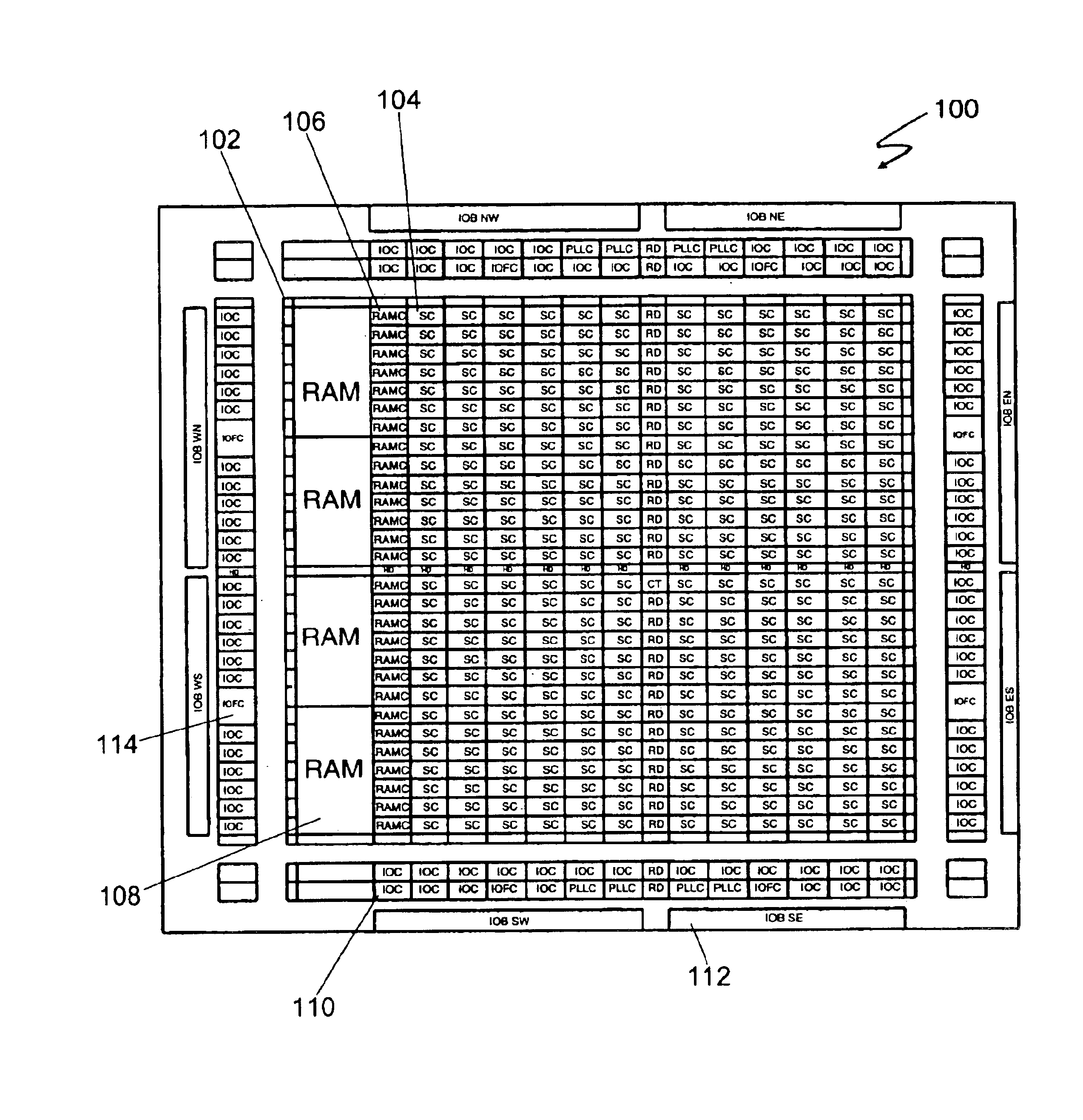

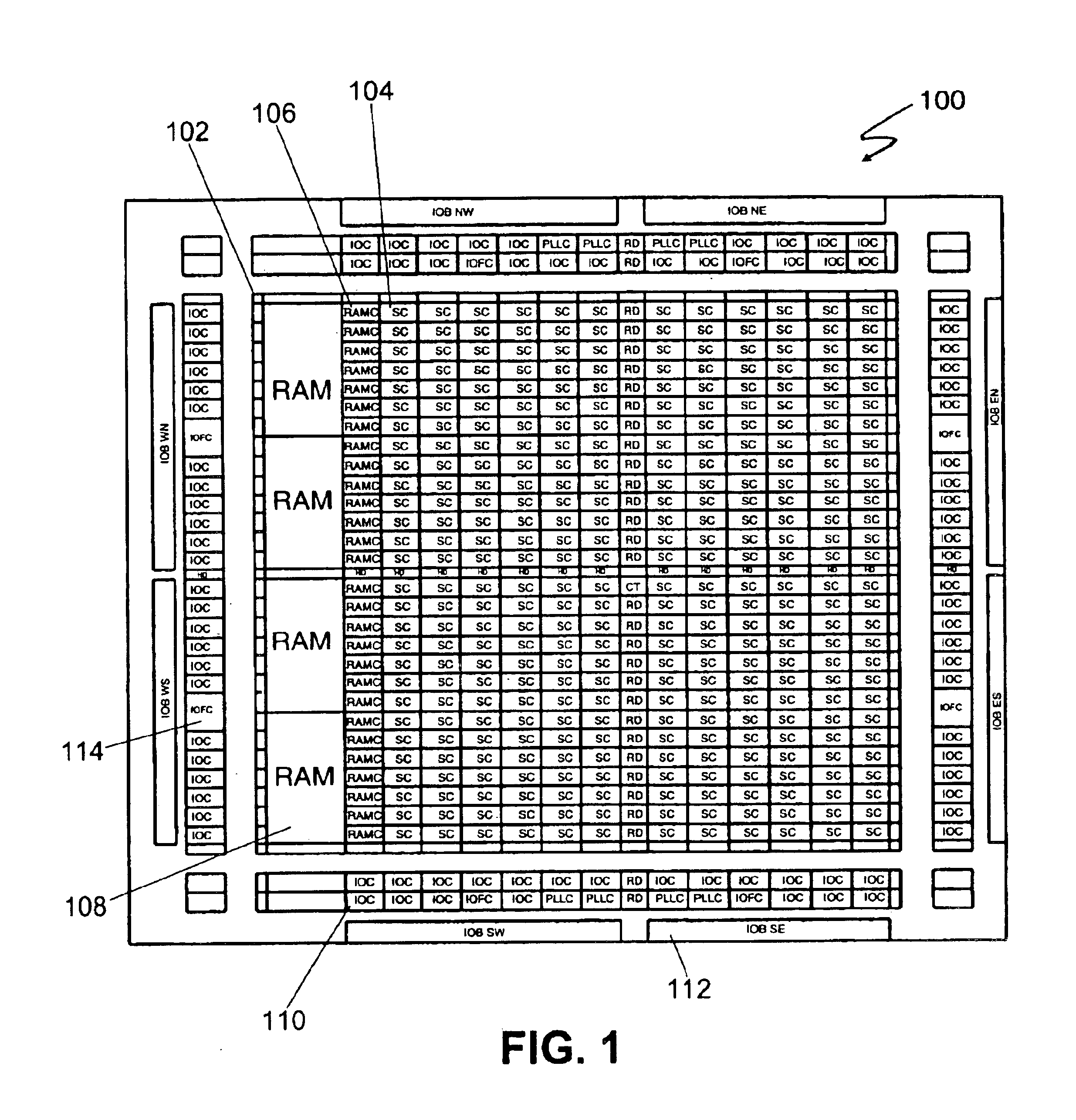

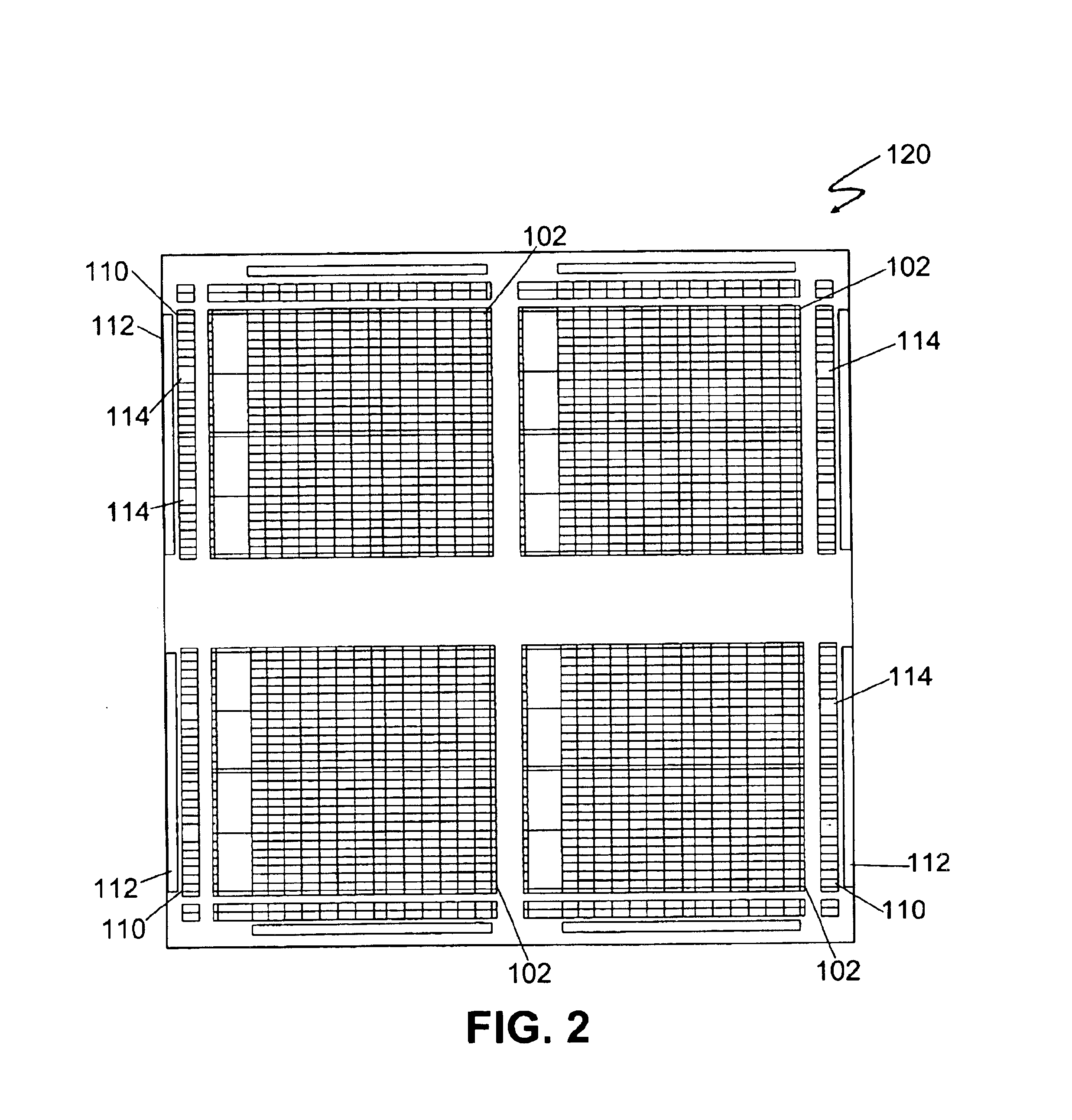

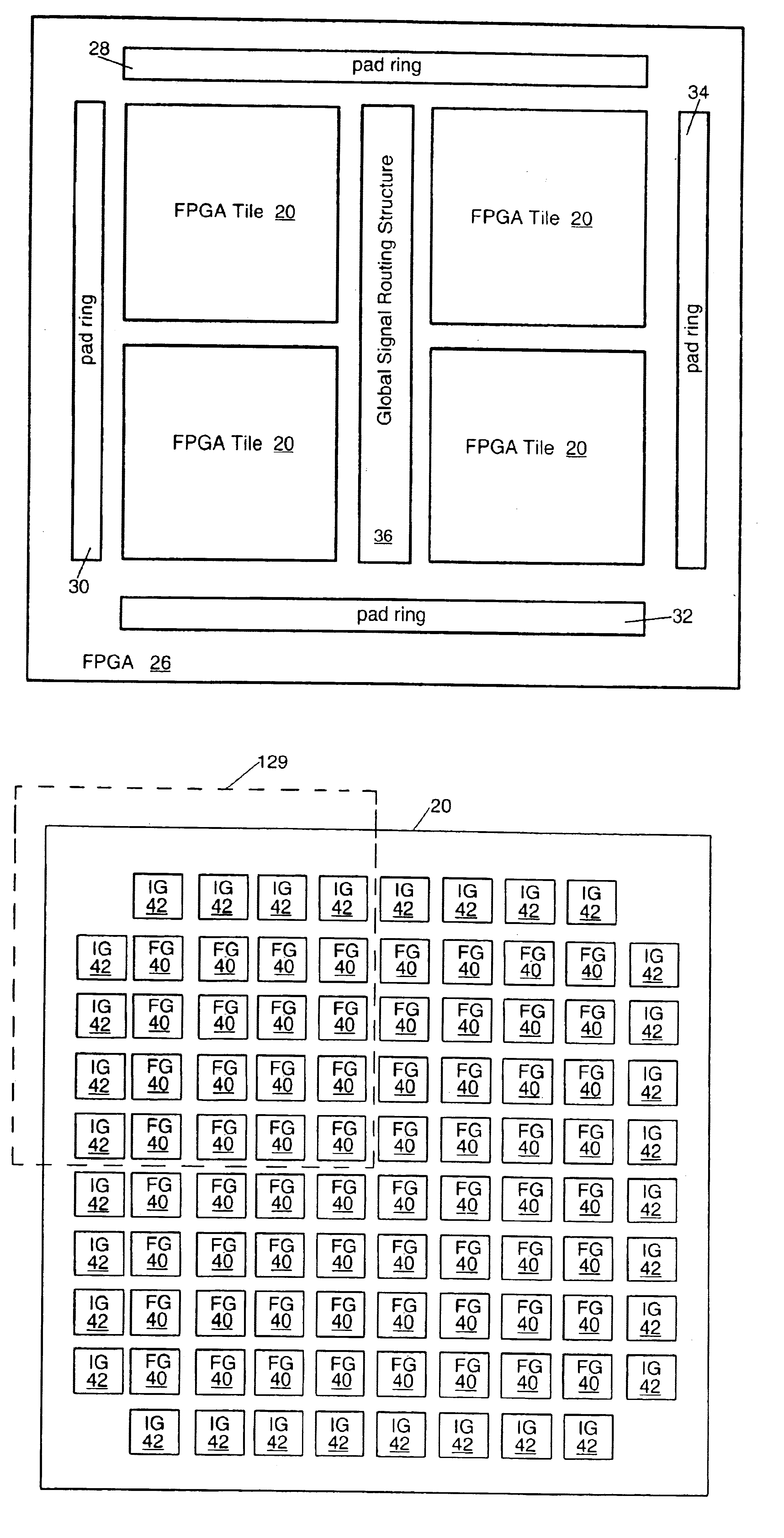

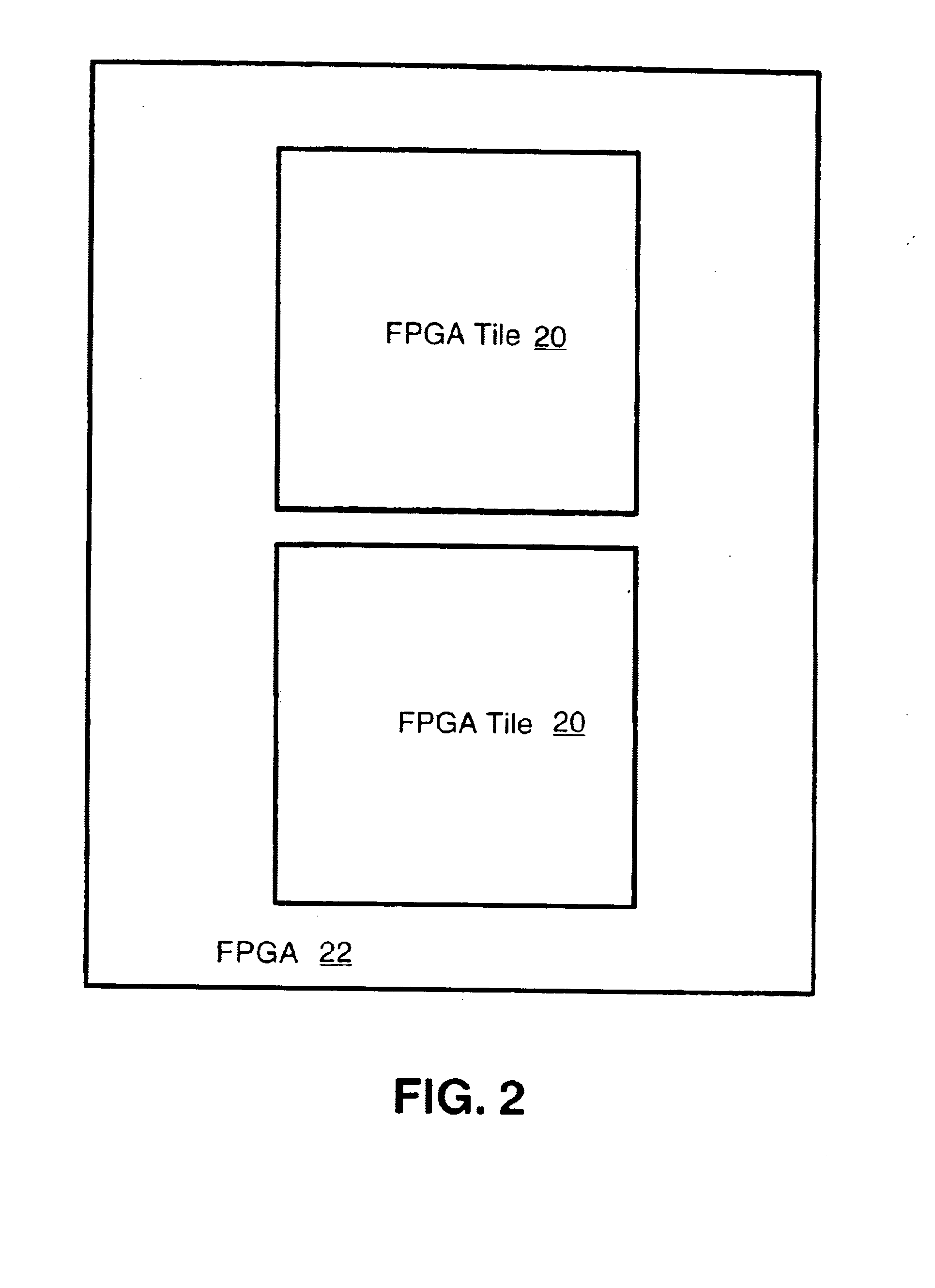

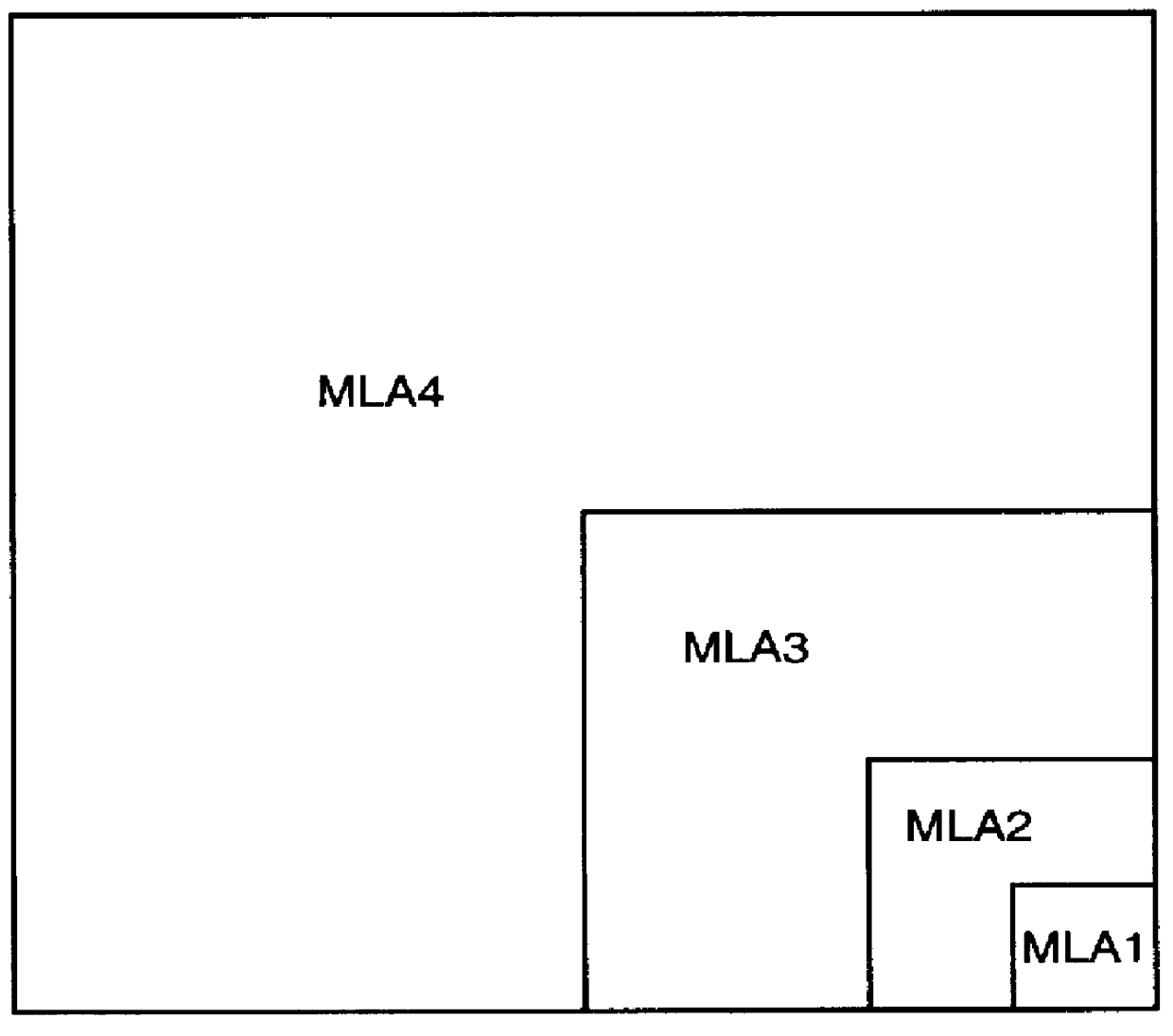

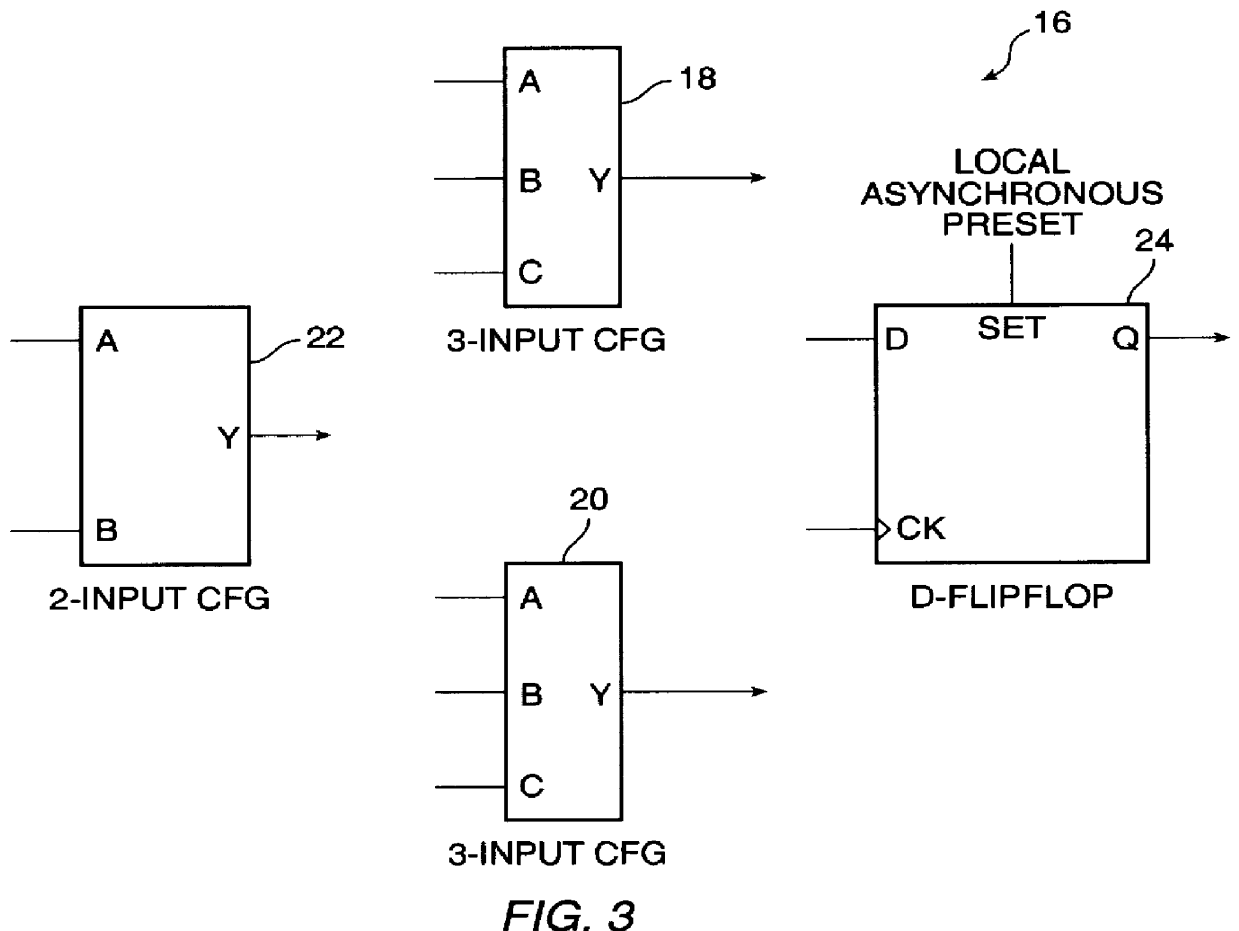

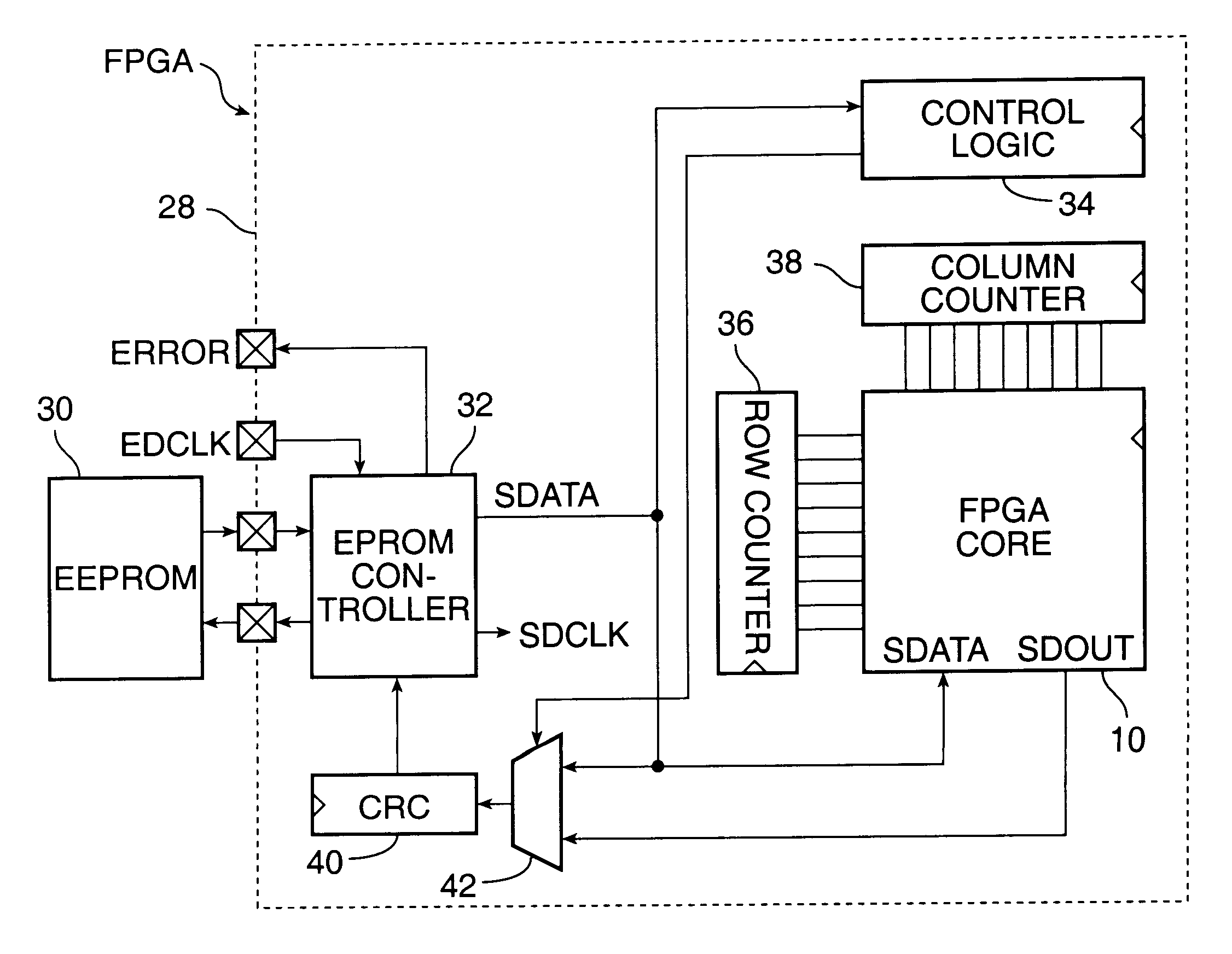

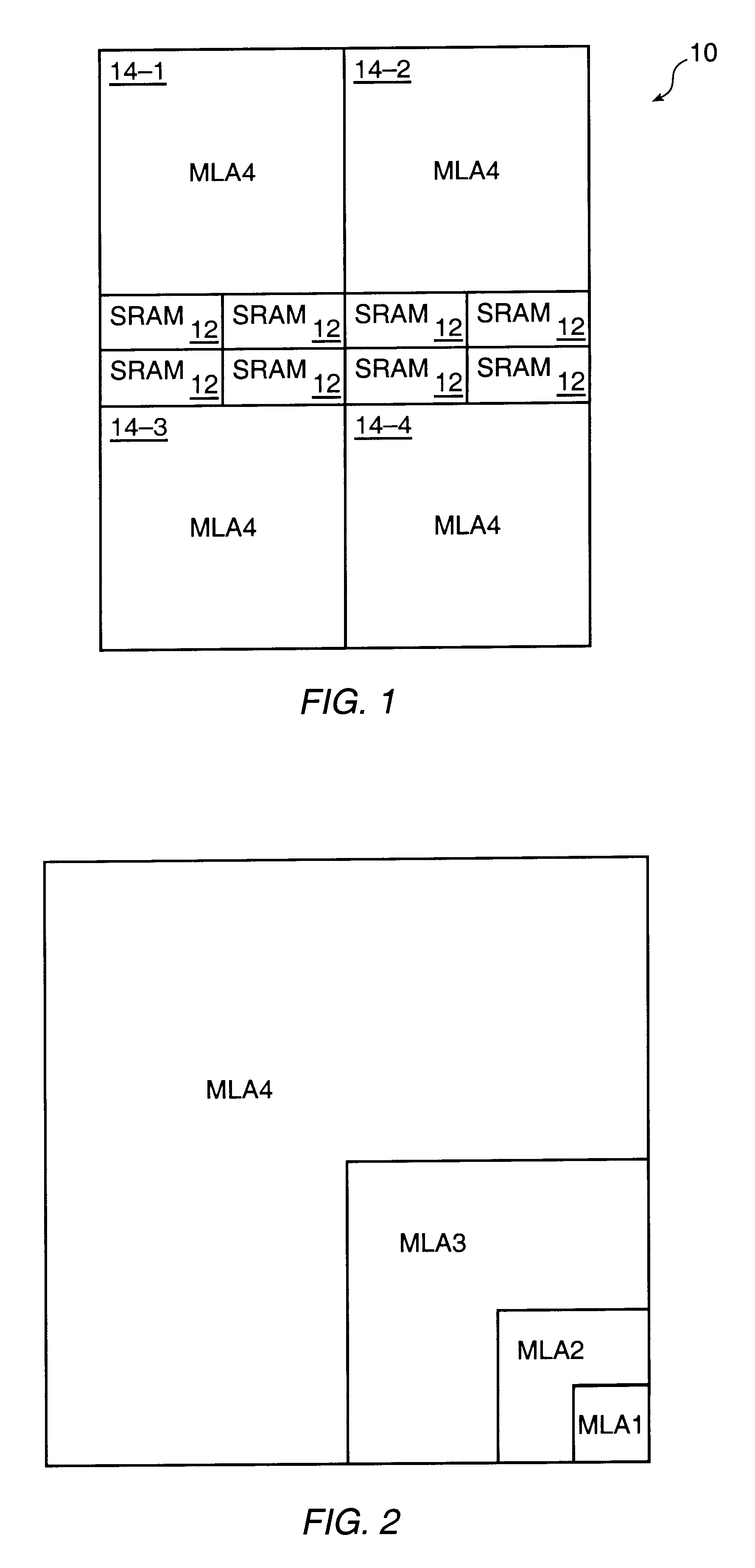

Tileable field-programmable gate array architecture

InactiveUS6888375B2Solid-state devicesCAD circuit designElectrical conductorField-programmable gate array

An apparatus includes a field-programmable gate array (FPGA). The FPGA includes a first FPGA tile, and the first FPGA tile includes a plurality of functional groups (FGs), a third set of routing conductors, in addition to a first set of routing conductors and a second set of routing conductors and a plurality of interface groups (IGs). The plurality of FGs are arranged in rows and columns with each of the FGs being configured to receive tertiary input signals as well as regular input signals, perform a logic operation, and generate regular output signals. The third set of routing conductors is coupled to the first set of output ports of the FGs and configured to receive signals, route signals within the first FPGA tile, and provide input signals to the third set of input ports of the FGs. The plurality of IGs surround the plurality of FGs such that one IG is positioned at each end of each row and column. Each of the IGs is coupled to the third set of routing conductors and configured to transfer signals from the third set of routing conductors to outside of the first FPGA tile.

Owner:MICROSEMI SOC

Tileable field-programmable gate array architecture

InactiveUS7015719B1Solid-state devicesLogic circuits using elementary logic circuit componentsElectrical conductorEngineering

An apparatus includes an FPGA, which includes a first FPGA tile including a plurality of FGs, a first, second, and third set of routing conductors, and a plurality of IGs. The FGs are arranged in rows and columns with each FG being configured to receive tertiary and regular input signals, perform a logic operation, and generate regular output signals. The third set of routing conductors is coupled to the first set of output ports of the FGs and configured to receive signals, route signals within the FPGA tile, and provide input signals to the third set of input ports of the FGs. The IGs surround the FGs such that one IG is positioned at each end of each row and column. Each IG is coupled to the third set of routing conductors and configured to transfer signals from the third set of routing conductors to outside the first FPGA tile.

Owner:MICROSEMI SOC

Synchronous first-in/first-out block memory for a field programmable gate array

The present invention comprises a field programmable gate array that has a plurality of dedicated first-in / first-out memory logic components. The field programmable gate array includes a plurality of synchronous random access memory blocks that are coupled to a plurality of dedicated first-in / first-out memory logic components and a plurality of random access memory clusters that are programmably coupled to the plurality of dedicated first-in / first-out memory logic components and to the plurality of synchronous random access memory blocks.

Owner:MICROSEMI SOC

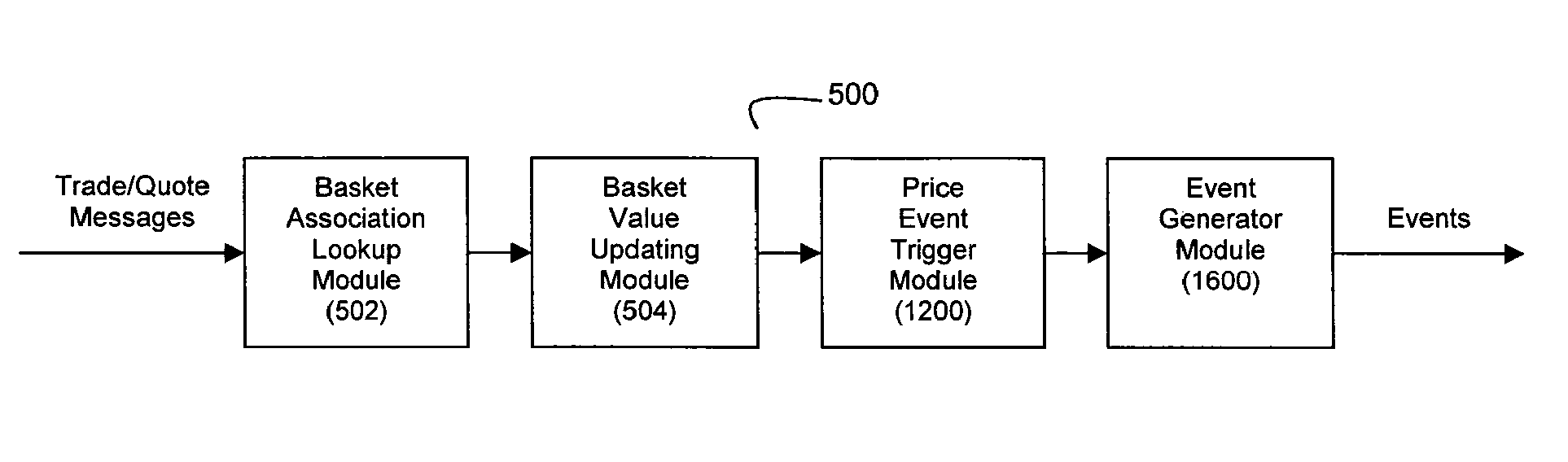

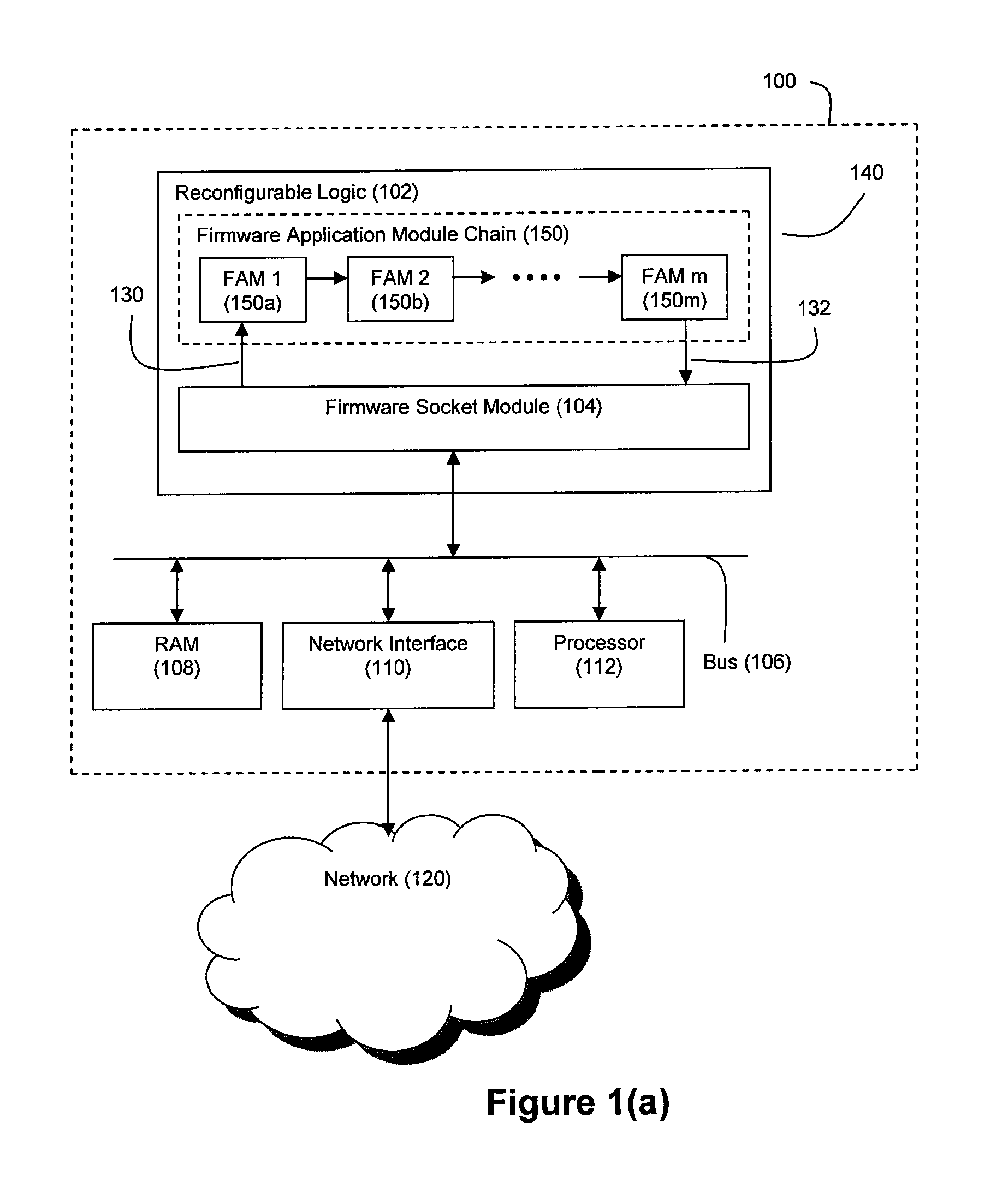

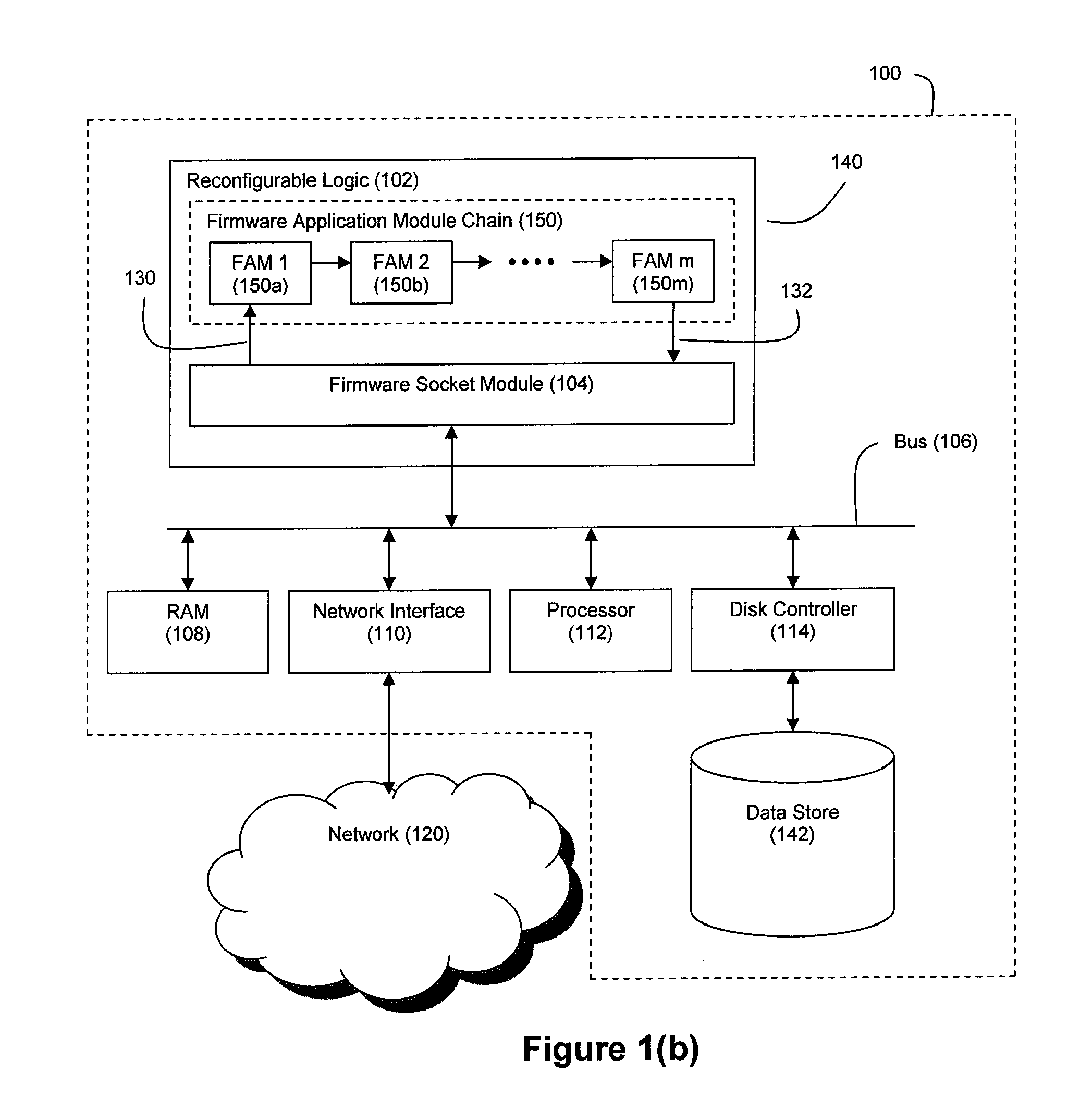

Method and System for Low Latency Basket Calculation

A basket calculation engine is deployed to receive a stream of data and accelerate the computation of basket values based on that data. In a preferred embodiment, the basket calculation engine is used to process financial market data to compute the net asset values (NAVs) of financial instrument baskets. The basket calculation engine can be deployed on a coprocessor and can also be realized via a pipeline, the pipeline preferably comprising a basket association lookup module and a basket value updating module. The coprocessor is preferably a reconfigurable logic device such as a field programmable gate array (FPGA).

Owner:EXEGY INC

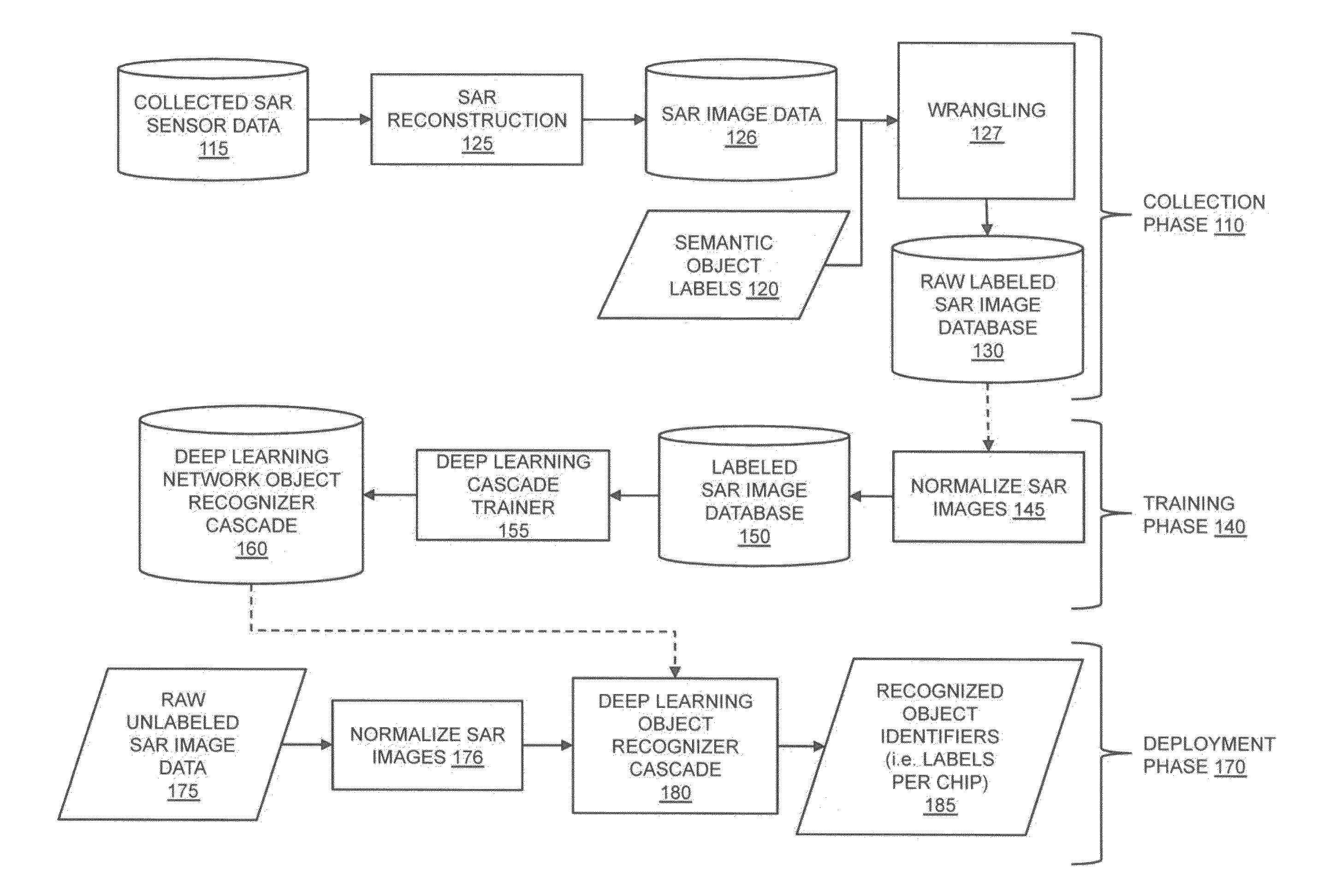

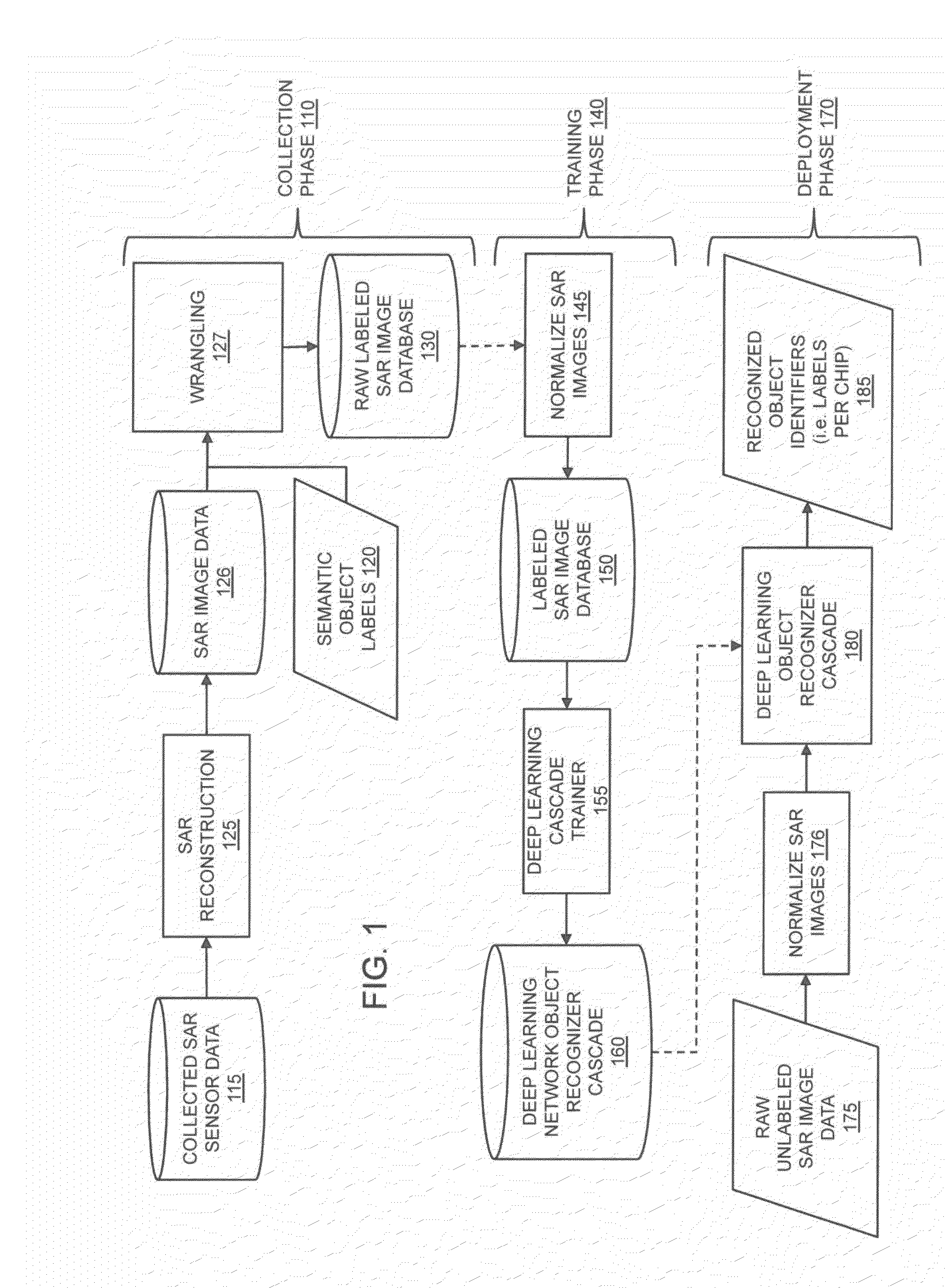

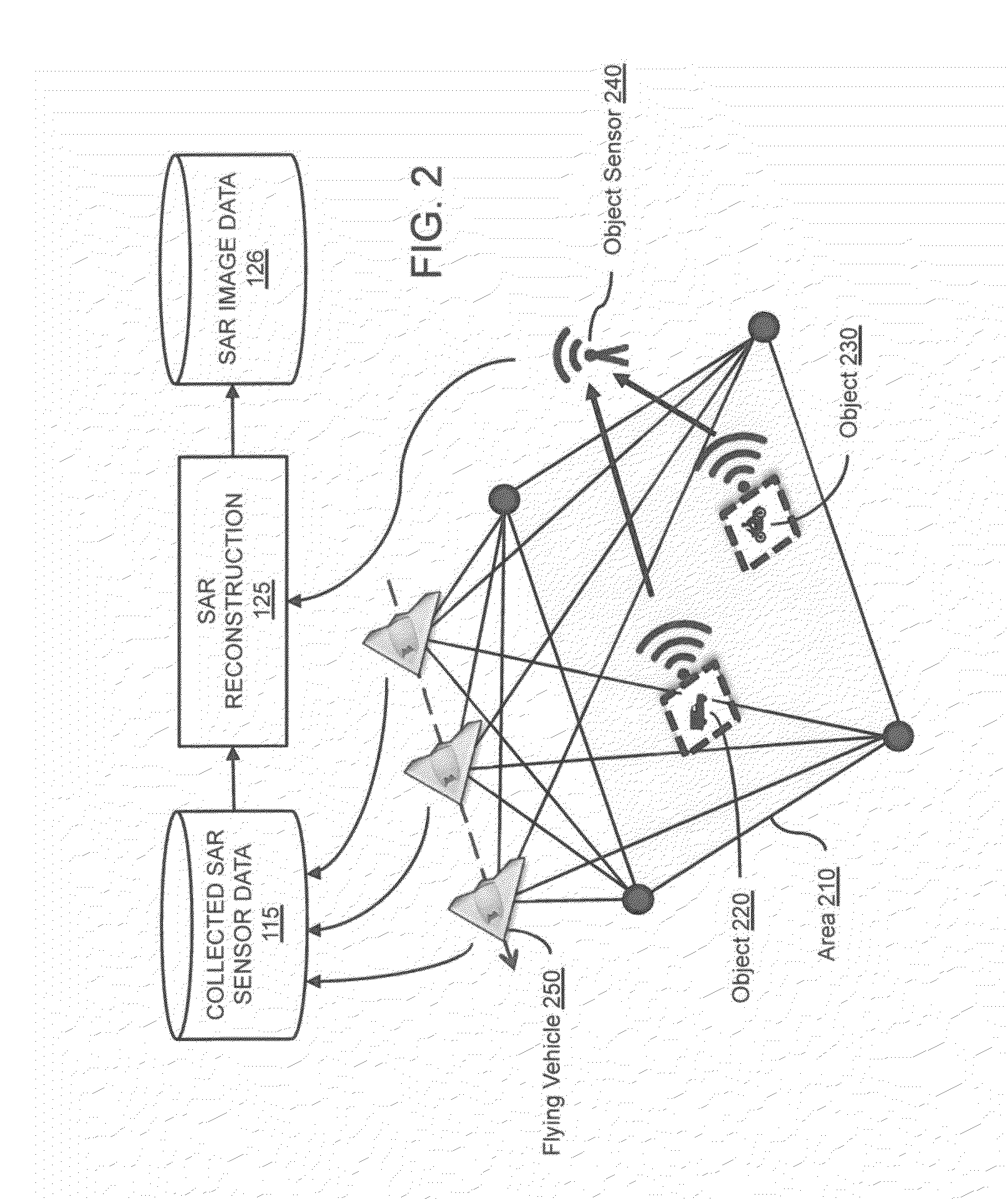

Systems and methods for recognizing objects in radar imagery

ActiveUS20160019458A1Low in size and weight and power requirementImprove historical speed and accuracy performance limitationDigital computer detailsDigital dataPattern recognitionGraphics

The present invention is directed to systems and methods for detecting objects in a radar image stream. Embodiments of the invention can receive a data stream from radar sensors and use a deep neural network to convert the received data stream into a set of semantic labels, where each semantic label corresponds to an object in the radar data stream that the deep neural network has identified. Processing units running the deep neural network may be collocated onboard an airborne vehicle along with the radar sensor(s). The processing units can be configured with powerful, high-speed graphics processing units or field-programmable gate arrays that are low in size, weight, and power requirements. Embodiments of the invention are also directed to providing innovative advances to object recognition training systems that utilize a detector and an object recognition cascade to analyze radar image streams in real time. The object recognition cascade can comprise at least one recognizer that receives a non-background stream of image patches from a detector and automatically assigns one or more semantic labels to each non-background image patch. In some embodiments, a separate recognizer for the background analysis of patches may also be incorporated. There may be multiple detectors and multiple recognizers, depending on the design of the cascade. Embodiments of the invention also include novel methods to tailor deep neural network algorithms to successfully process radar imagery, utilizing techniques such as normalization, sampling, data augmentation, foveation, cascade architectures, and label harmonization.

Owner:GENERAL DYNAMICS MISSION SYST INC

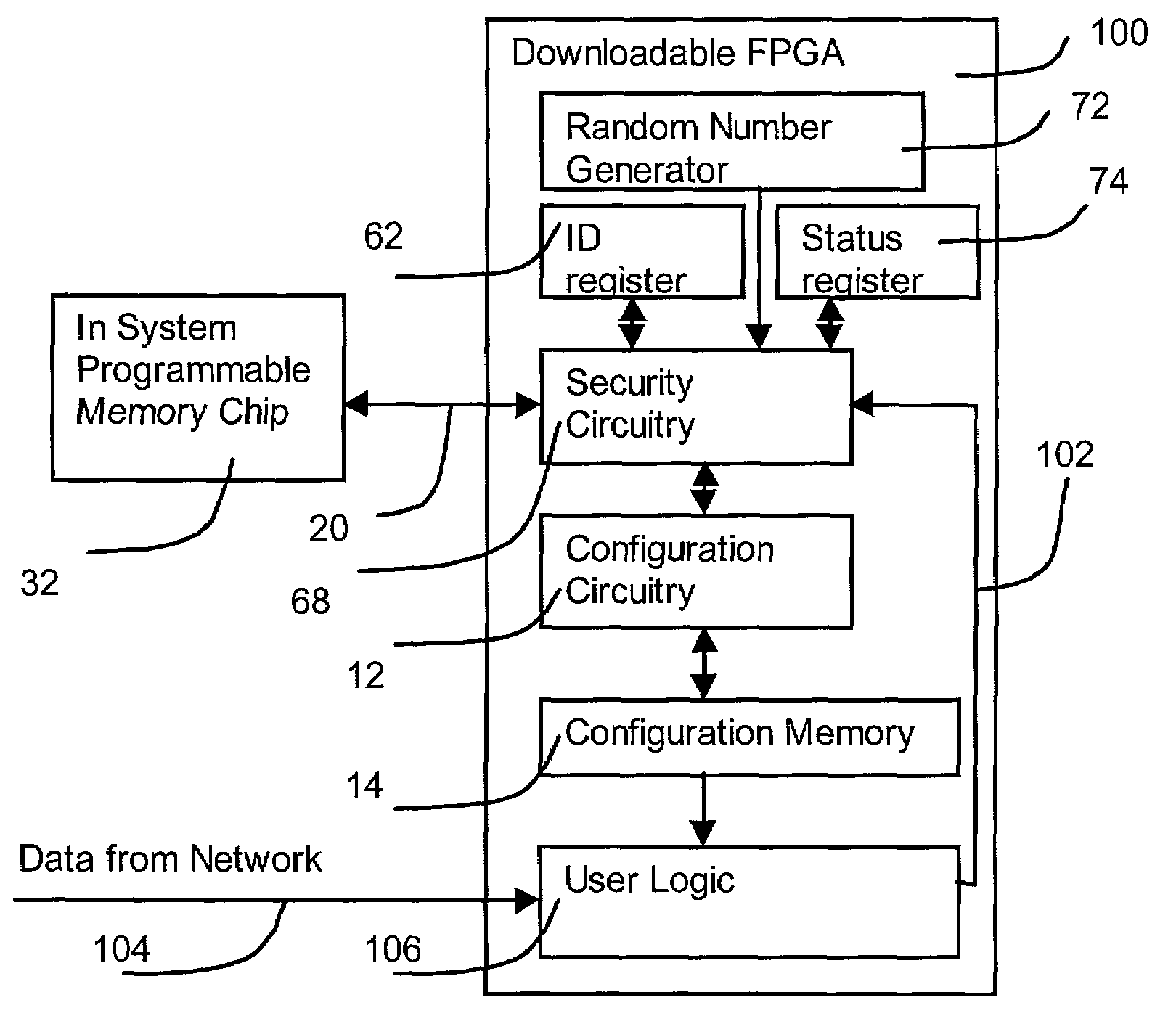

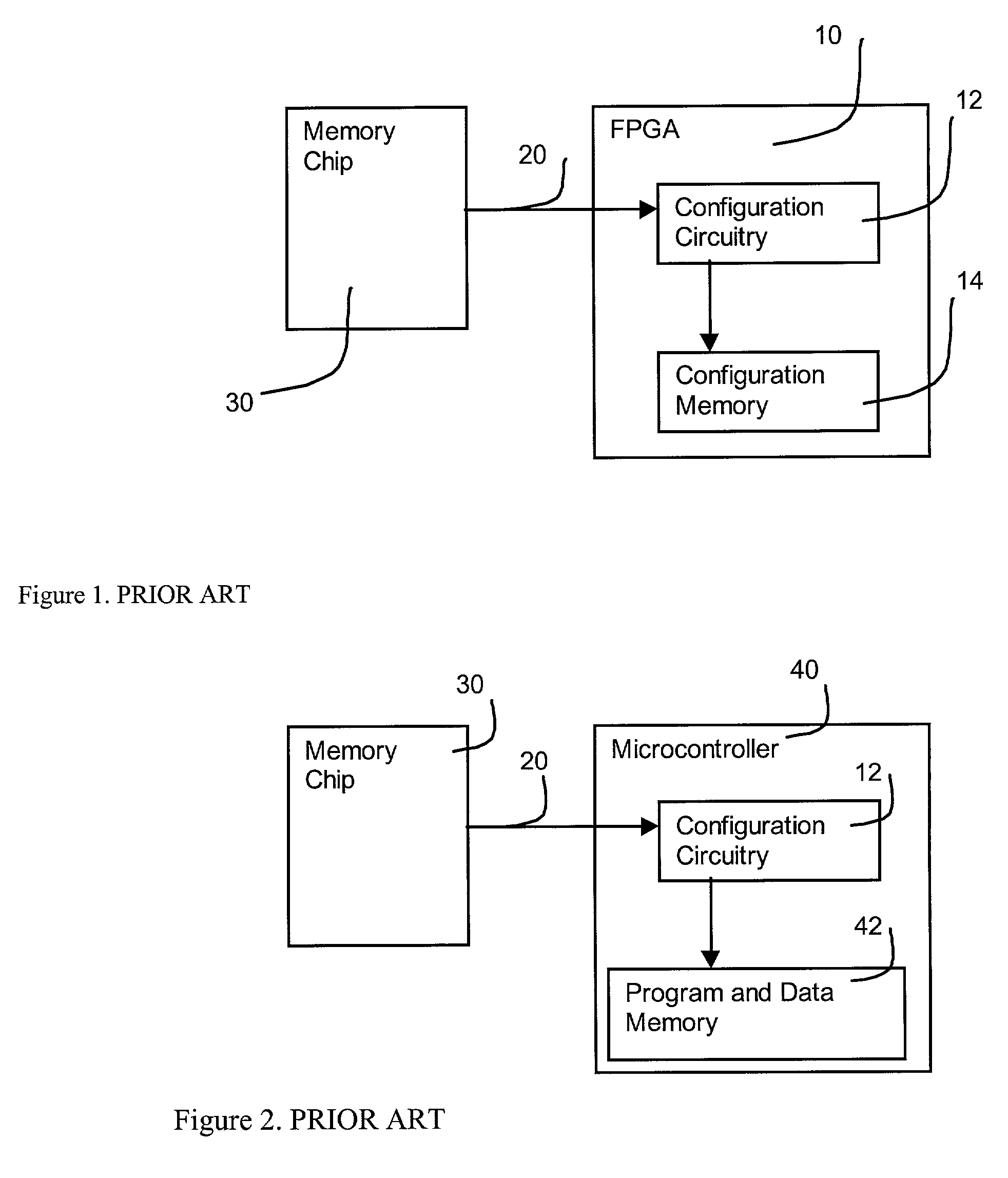

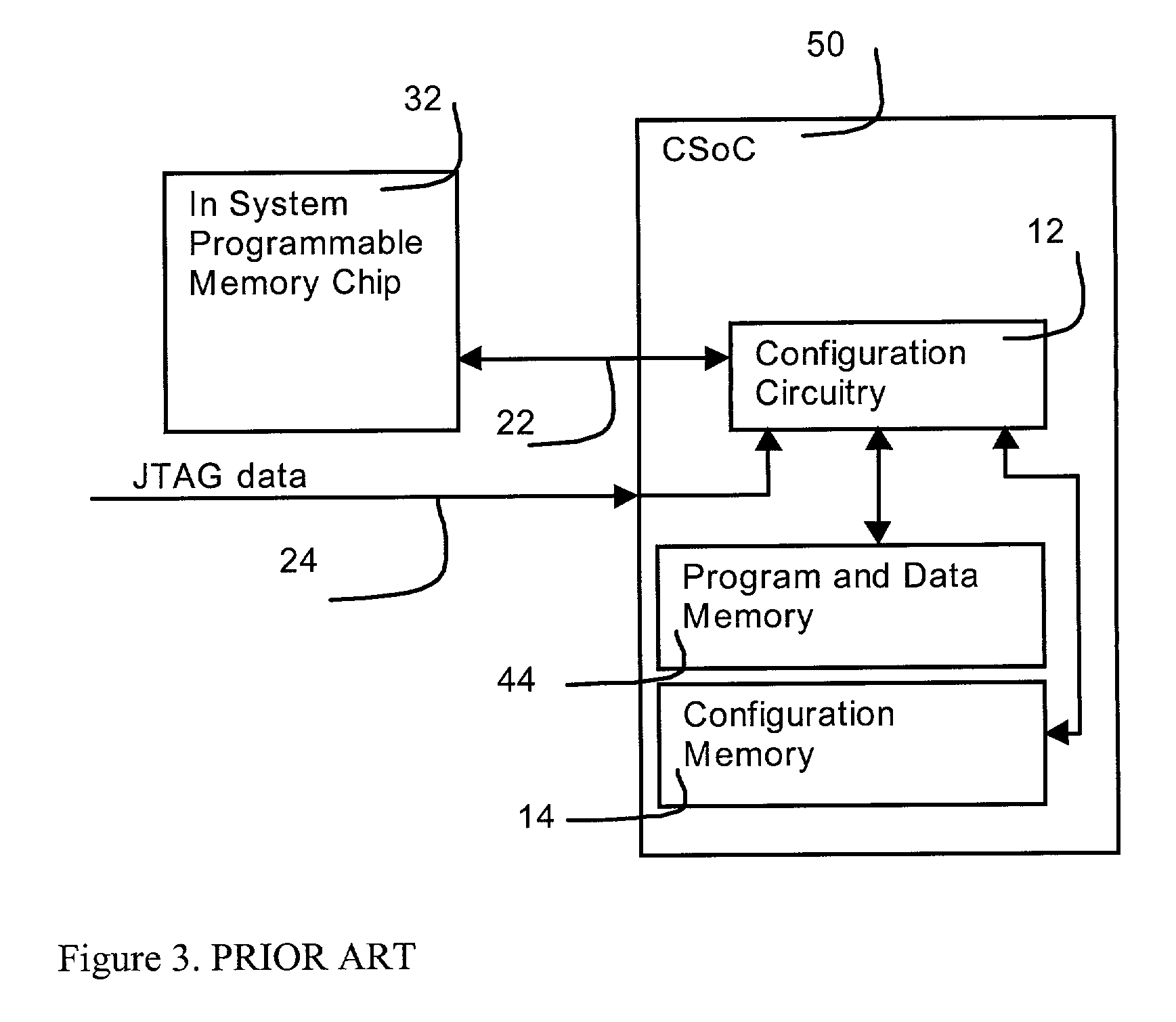

Method and apparatus for secure configuration of a field programmable gate array

InactiveUS7203842B2Digital data processing detailsUnauthorized memory use protectionField-programmable gate arrayNon-volatile memory

A field programmable gate array (70) has security configuration features to prevent monitoring of the configuration data for the field programmable gate array. The configuration data is encrypted by a security circuit (64) of the field programmable gate array using a security key (62). This encrypted configuration data is stored in an external nonvolatile memory (32). To configure the field programmable gate array, the encrypted configuration data is decrypted by the security circuit (64) of the field programmable gate array using the security key stored in the field programmable gate array.

Owner:ALGOTRONIX

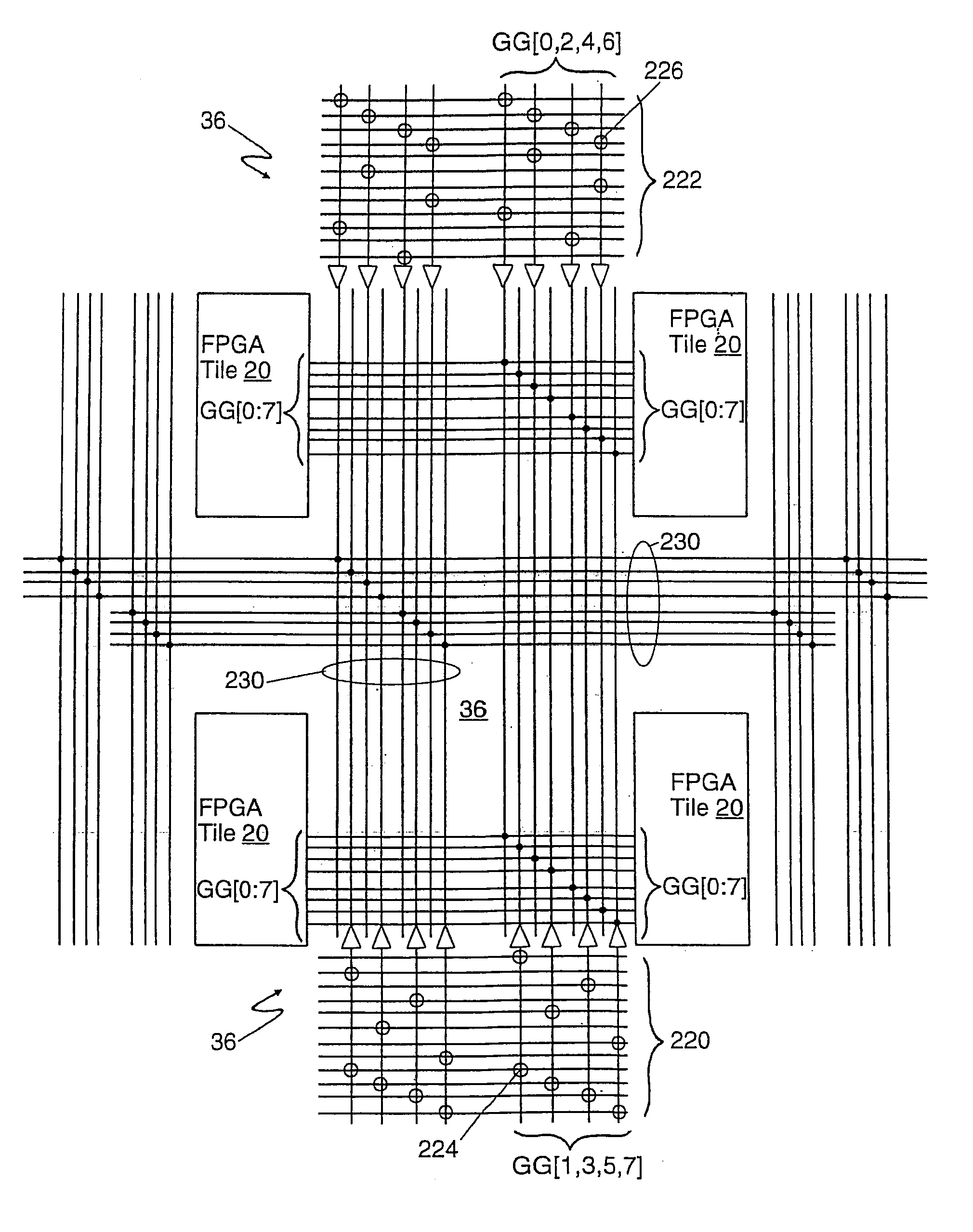

Routing structures for a tileable field-programmable gate array architecture

A field-programmable gate array (FPGA), comprising: a first FPGA tile, the first FPGA tile comprising a plurality of functional groups (FGs), a regular routing structure, and a plurality of interface groups (IGs). The plurality of FGs are arranged in rows and columns with each of the FGs being configured to receive regular input signals, perform a logic operation, and generate regular output signals. The regular routing structure is coupled to the FGs and configured to receive the regular output signals, route signals within the first FPGA tile, and provide the regular input signals to the FGs. The plurality of IGs surround the plurality of FGs such that one IG is positioned at each end of each row and column. Each of the IGs is coupled to the regular routing structure and configured to transfer signals from the regular routing structure to outside of the first FPGA tile. The first FPGA tile also comprising a secondary routing structure independent of the regular routing structure, coupled to each of the IGs, configured to transfer signals from said first FPGA tile to at least one other FPGA tile. The disclosed apparatus also provides for a routing structure between IGs and RAM blocks. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understand that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:MICROSEMI SOC

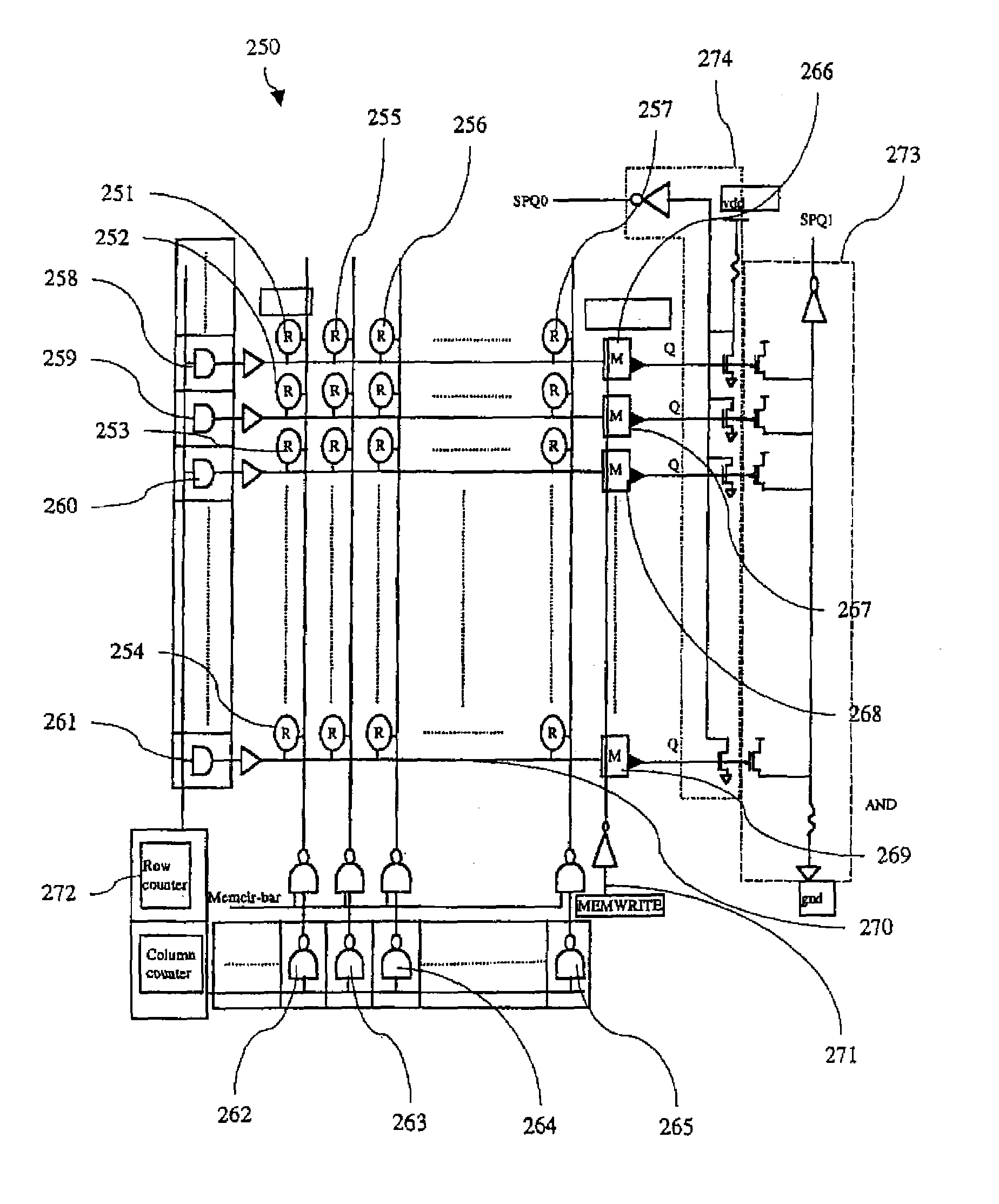

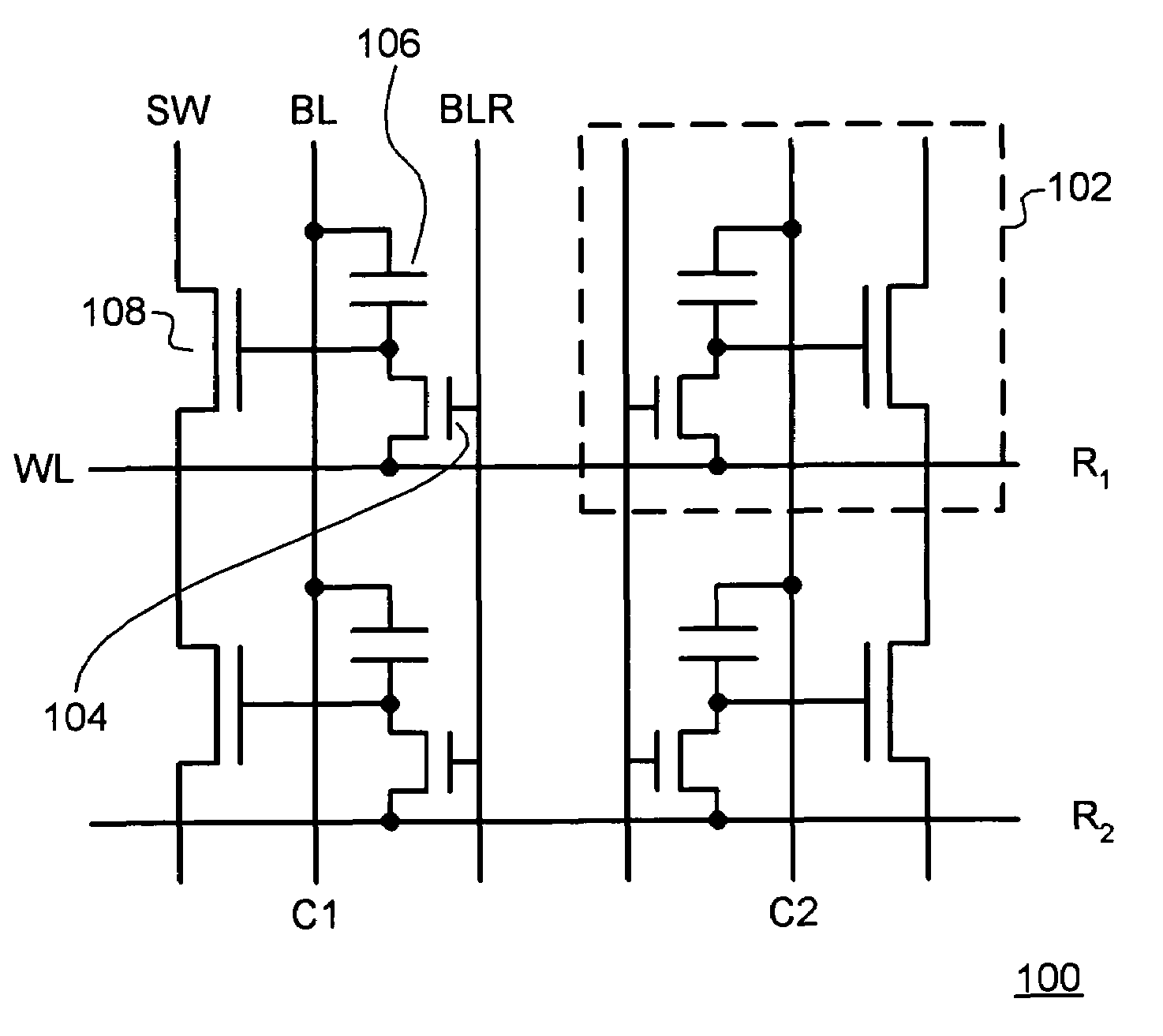

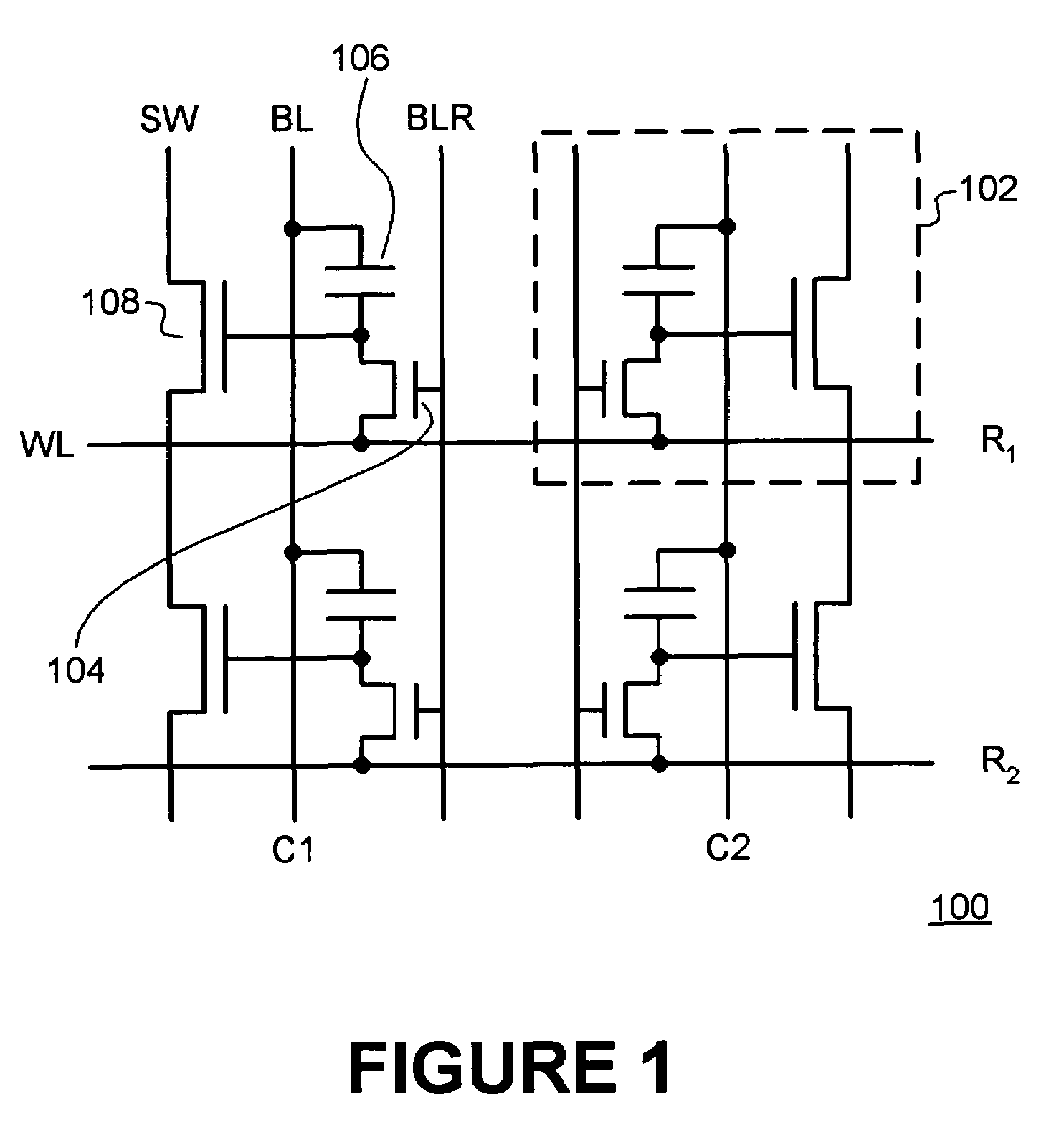

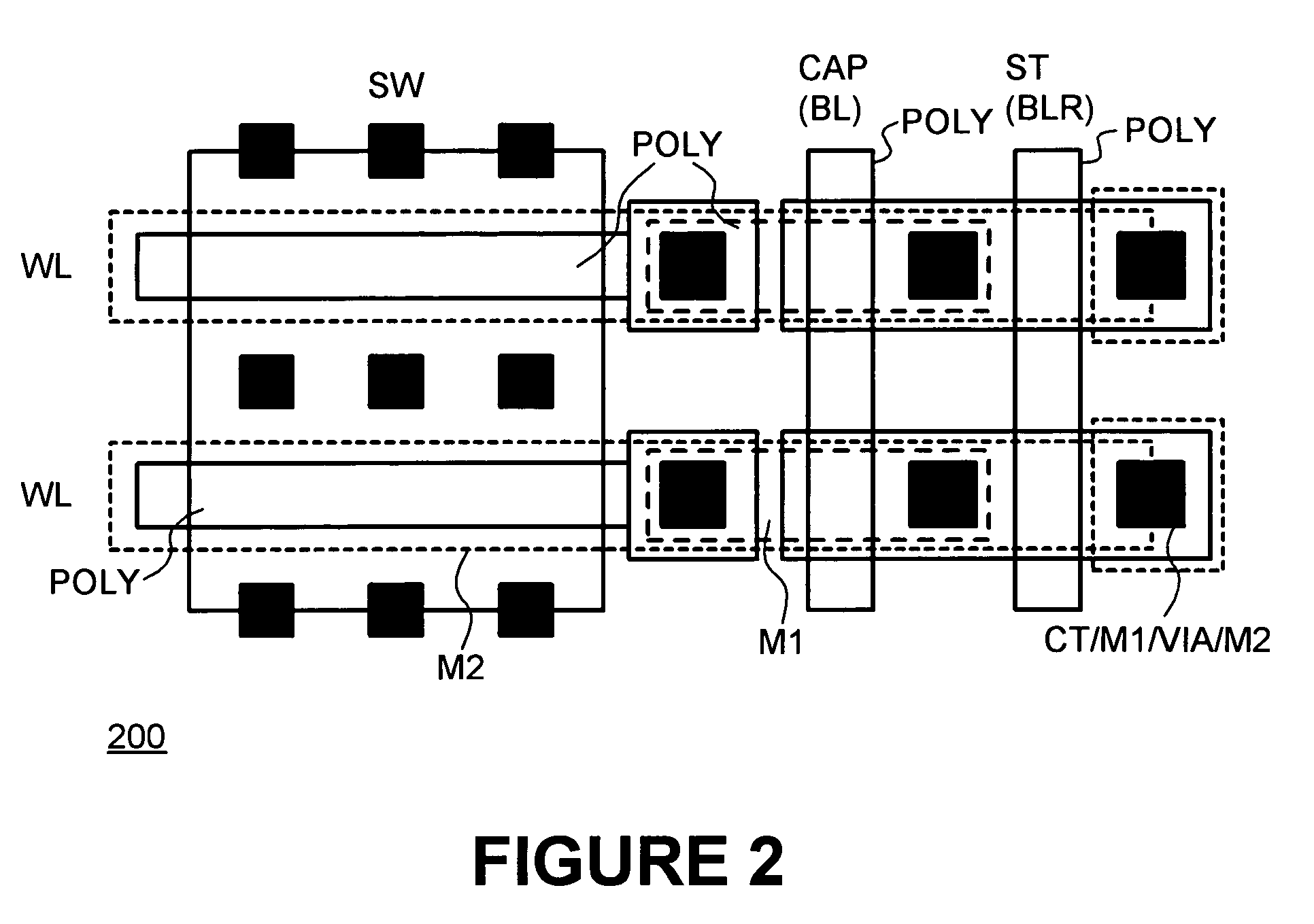

Method and apparatus of memory clearing with monitoring RAM memory cells in a field programmable gated array

A field-programmable gate array (FPGA) having an array of RAM memory cells comprising at least one row of RAM memory cells, each RAM cell of the at least one row of RAM memory cells coupled to a row driver line; a row decoder coupled to a first end of the row driver line of each at least one row of RAM memory cells. A monitoring memory cell is coupled to a row driver line. Each monitoring memory cell is also coupled to a memory writing line. An FPGA also has RAM memory cells that act as the programming mechanism. The FPGA further has erase circuitry for clearing the RAM memory cells for reprogramming of the FPGA. The FPGA is erased by providing at least one monitoring memory cell coupled to the erase circuitry. A memory clear phase is initiated on at least one monitoring memory cell. The monitoring memory cell then indicts the cell has been cleared.

Owner:ACTEL CORP

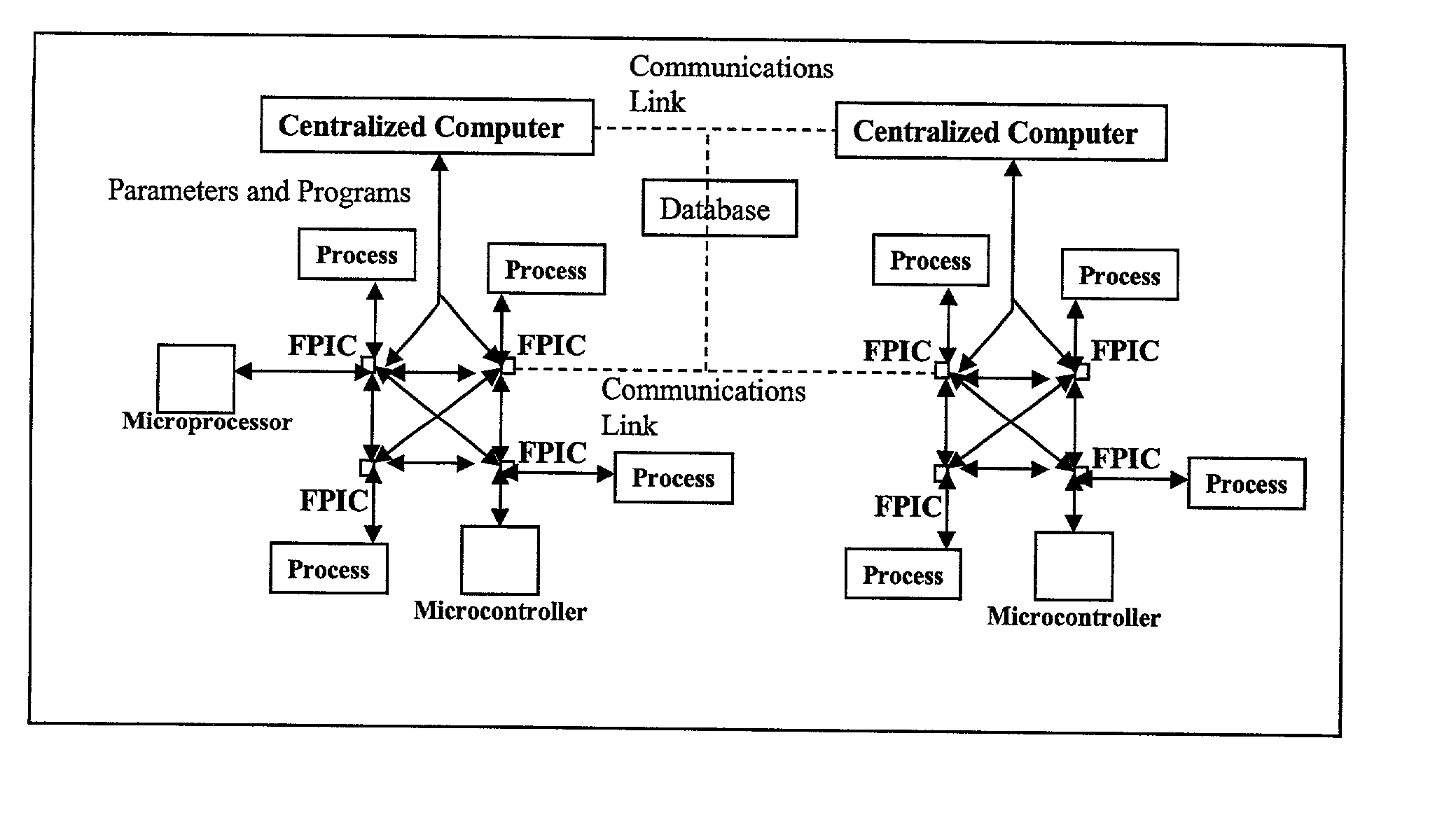

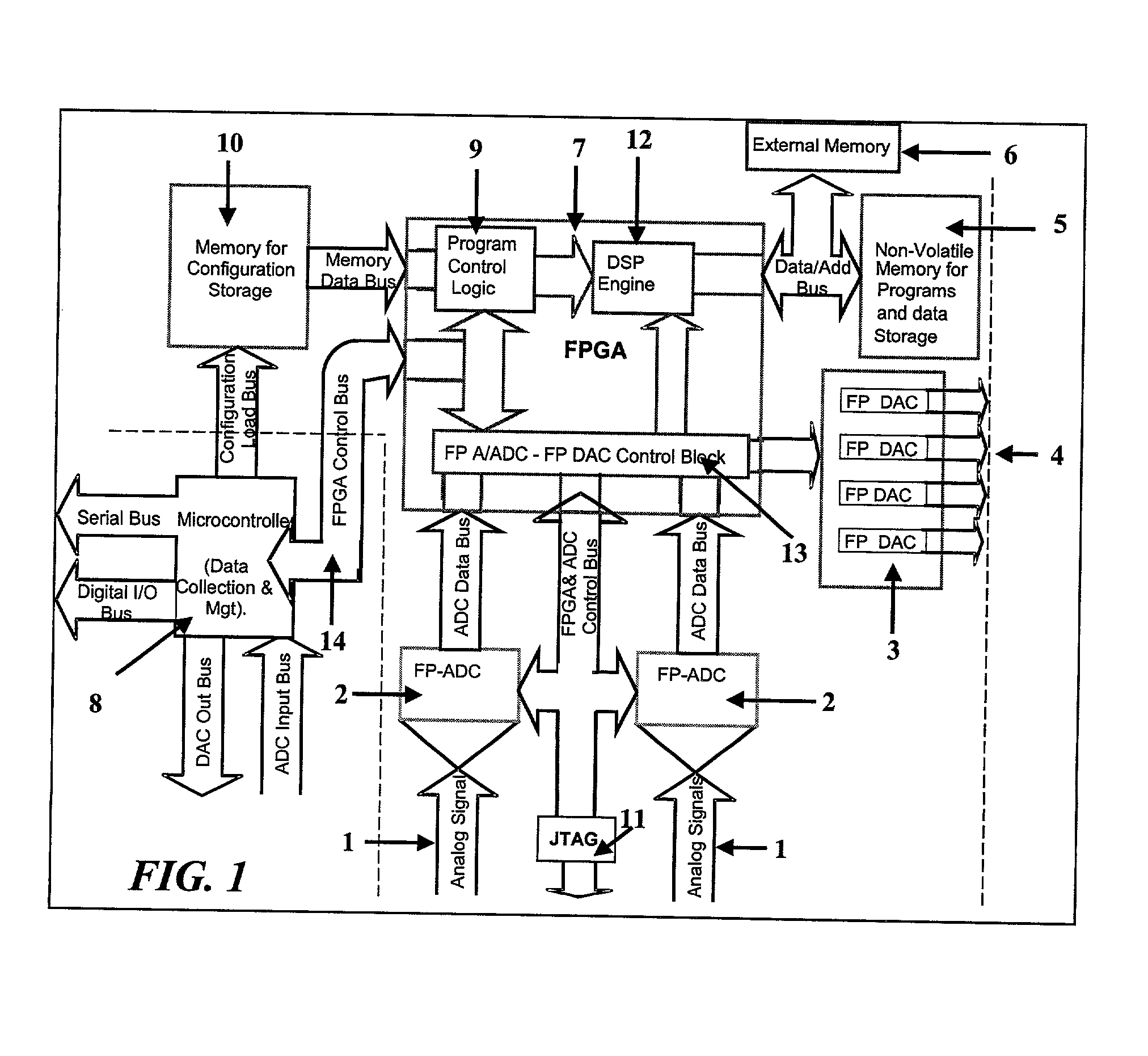

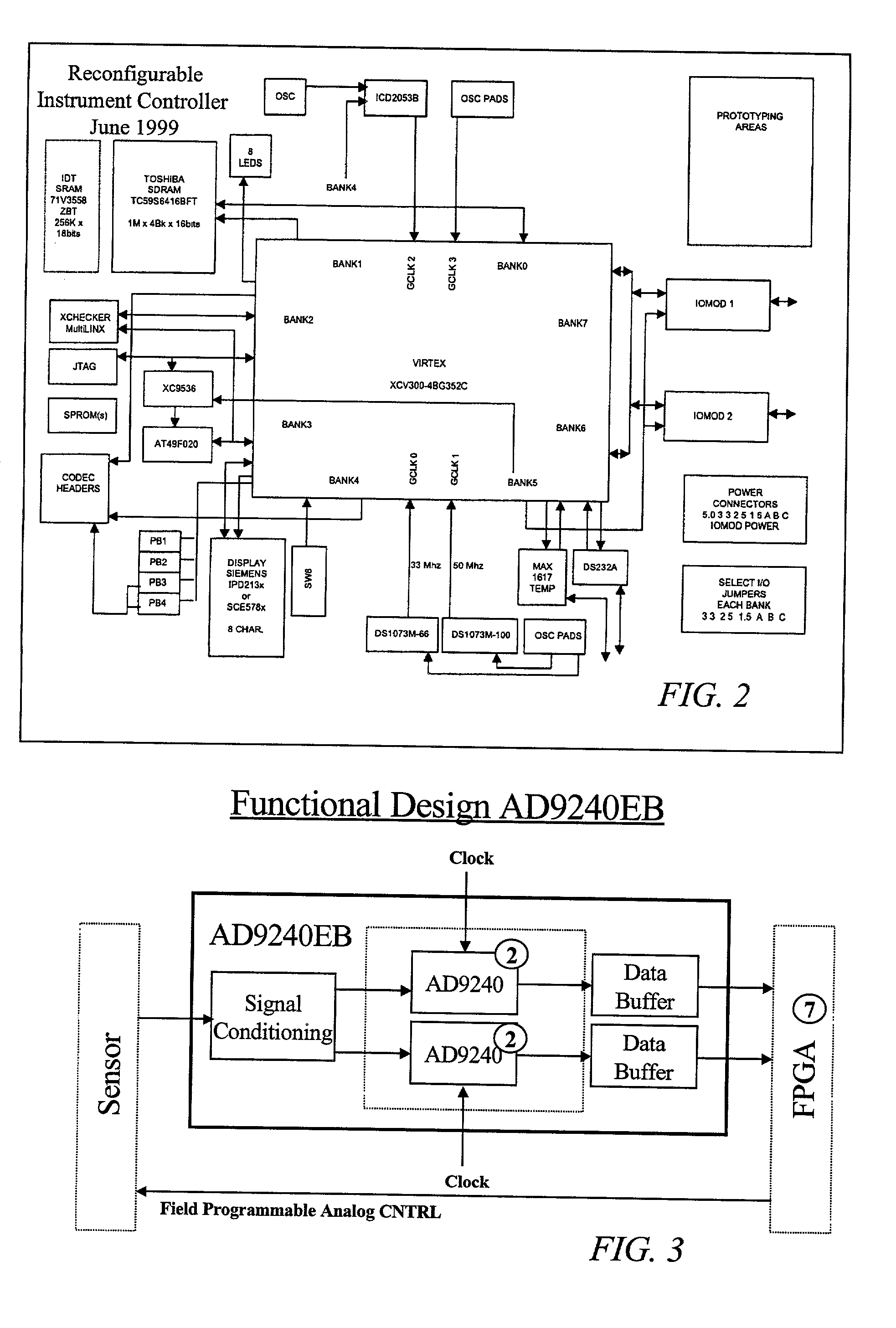

High performance hybrid micro-computer

The Field Programmable Instrument Controller (FPIC) is a stand-alone low to high performance, clocked or unclocked multi-processor that operates as a microcontroller with versatile interface and operating options. The FPIC can also be used as a concurrent processor for a microcontroller or other processor. A tightly coupled Multiple Chip Module design incorporates non-volatile memories, a large field programmable gate array (FPGA), field programmable high precision analog to digital converters, field programmable digital to analog signal generators, and multiple ports of external mass data storage and control processors. The FPIC has an inherently open architecture with in-situ reprogrammability and state preservation capability for discontinuous operations. It is designed to operate in multiple roles, including but not limited to, a high speed parallel digital signal processing; co-processor for precision control feedback during analog or hybrid computing; high speed monitoring for condition based maintenance; and distributed real time process control. The FPIC is characterized by low power with small size and weight.

Owner:BLEMEL KENNETH G

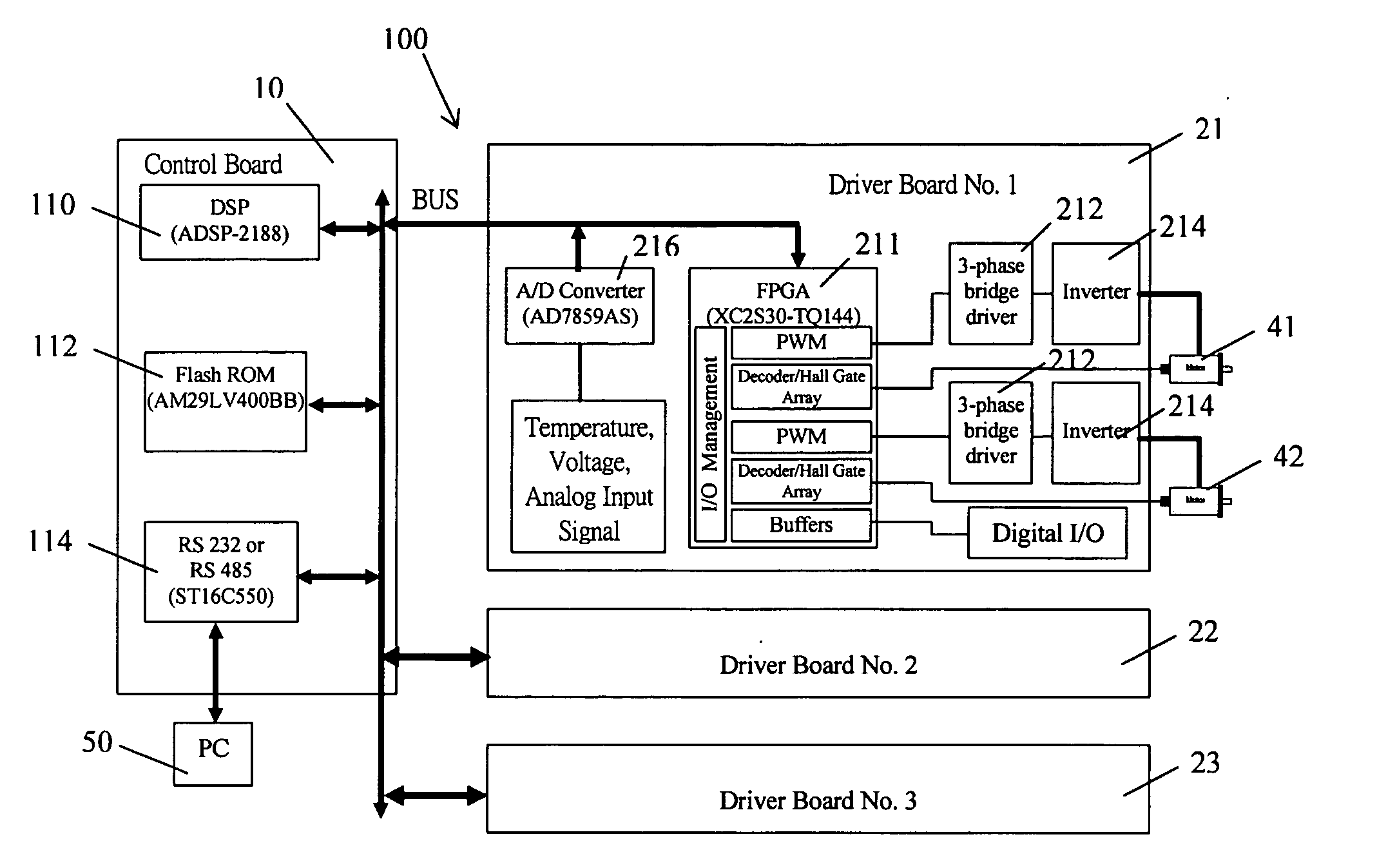

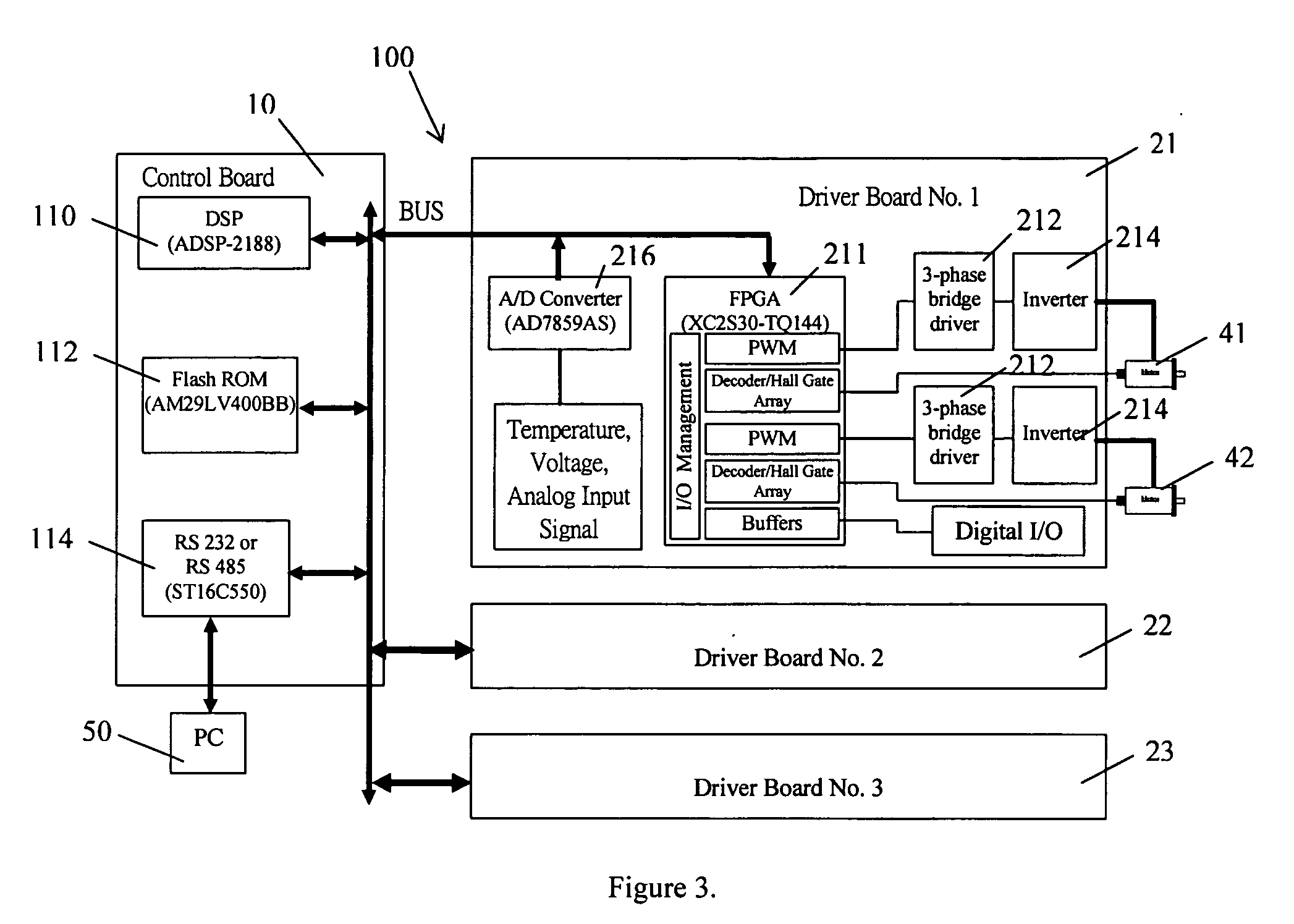

Modular multi-axis motion control and driving system and method thereof

InactiveUS20060100723A1Improve performanceReduced dimensionSynchronous motors startersAC motor controlMOSFETNetwork service

A modular multi-axis motion control and driving system is developed by using advanced Digital Signal Processor (DSP) and Field Programmable Gate Array (FPGA) technologies. A modular multi-axis motion control and driving system comprises: a control board comprising a DSP and Flash ROM connected to each other, for performing position control and current control of said system; a plurality of driver boards, connected to the control board through a bus, each of which comprise a FPGA device and a plurality of MOSFET power amplifier, for driving a plurality of servo motors; a computer, connected to said control board, for providing graphic user interface, through which motor setting, current and position loop tuning and diagnostic can be performed; Wherein, a control program, system parameters and FPGA configuration file are stored in said Flash ROM, when the system power is on, the DSP automatically executes an loader firmware to transfer the control program from said Flash ROM to the memory of DSP for execution, then the DSP reads the FPGA configuration file from the Flash ROM and configure the FPGA in the driver board, after that, the control program runs into a circulation loop to do system diagnose, network service and check command queue, while the current and position controls are implemented in an interrupt service.

Owner:DYNACITY TECH HK

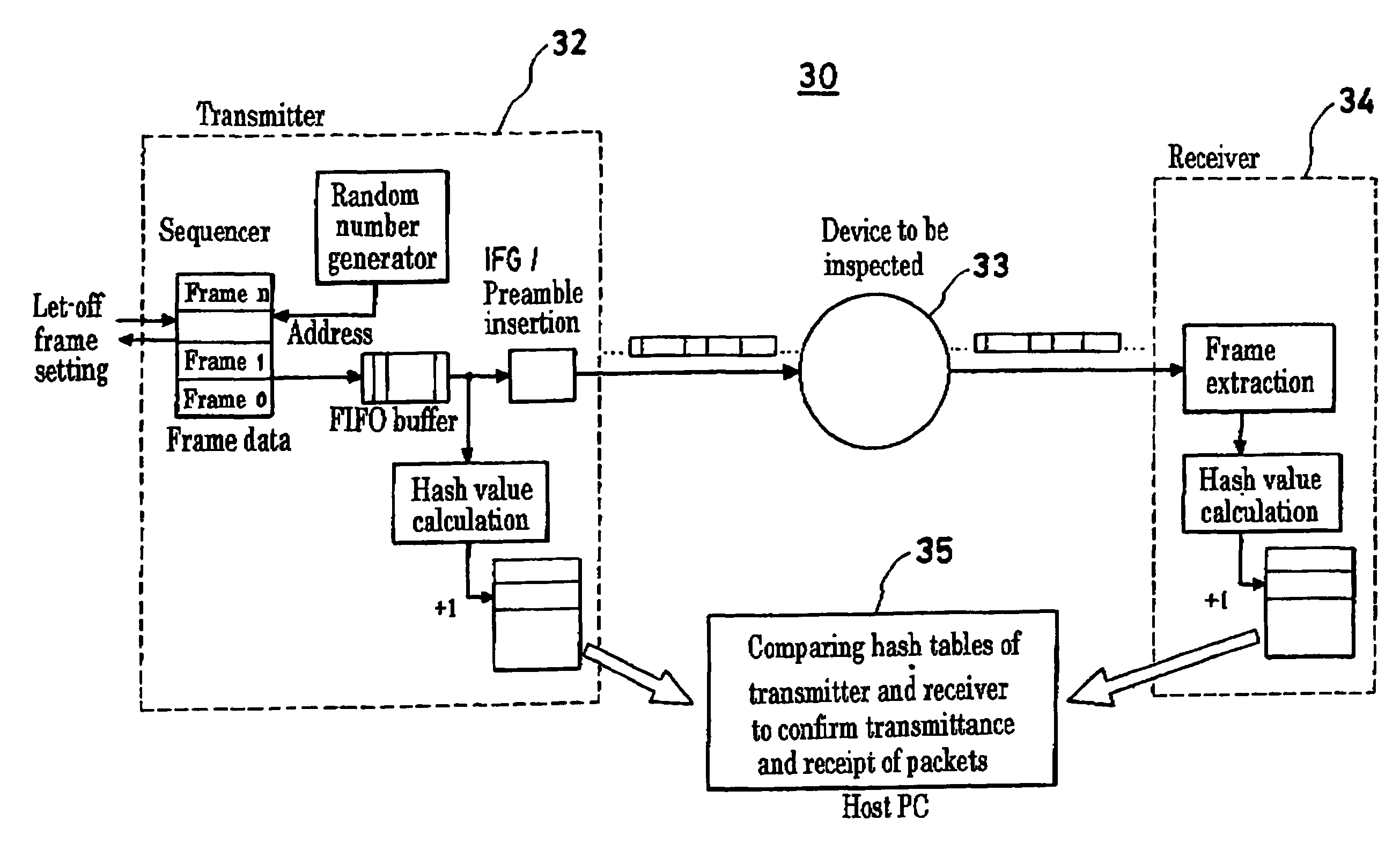

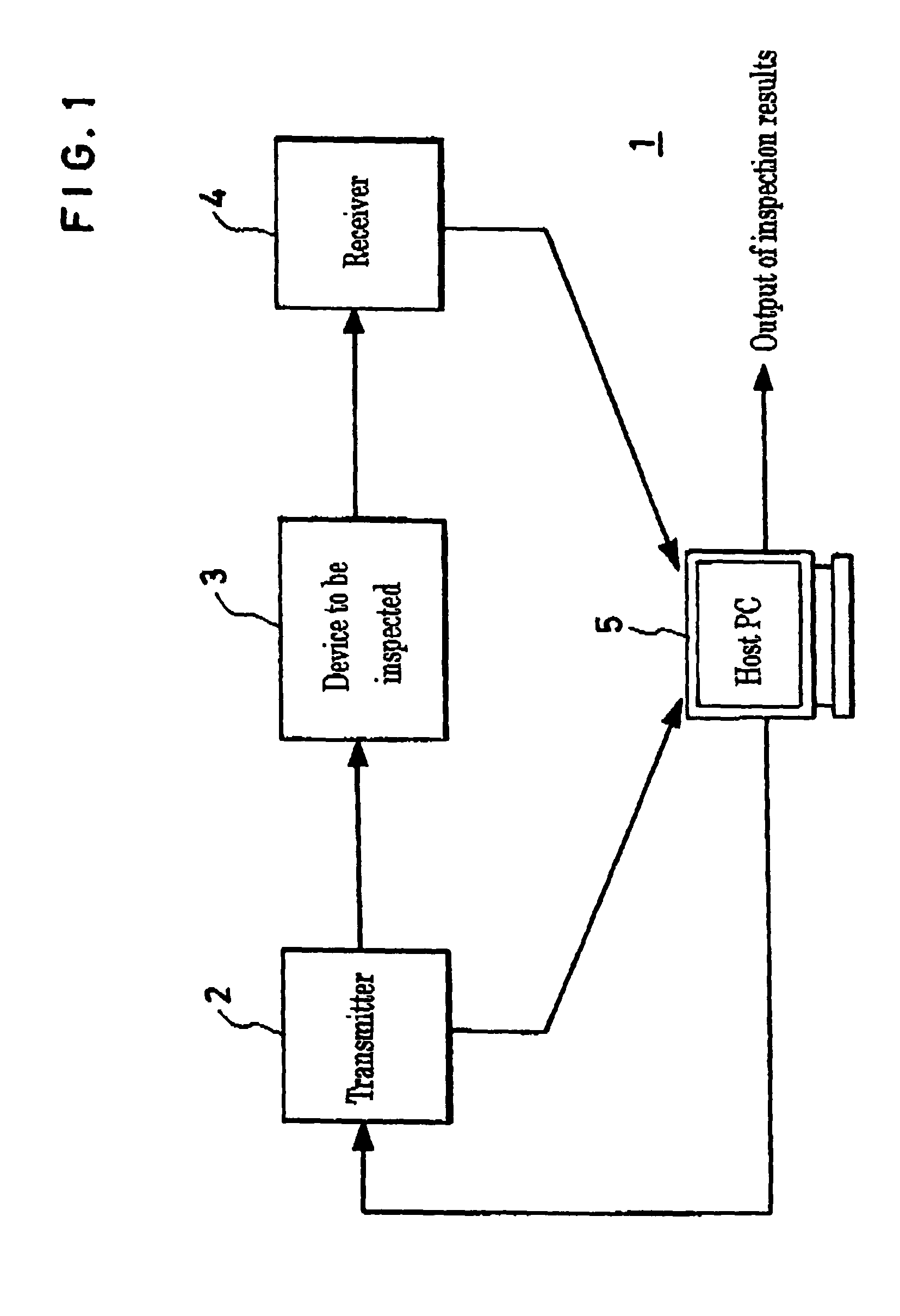

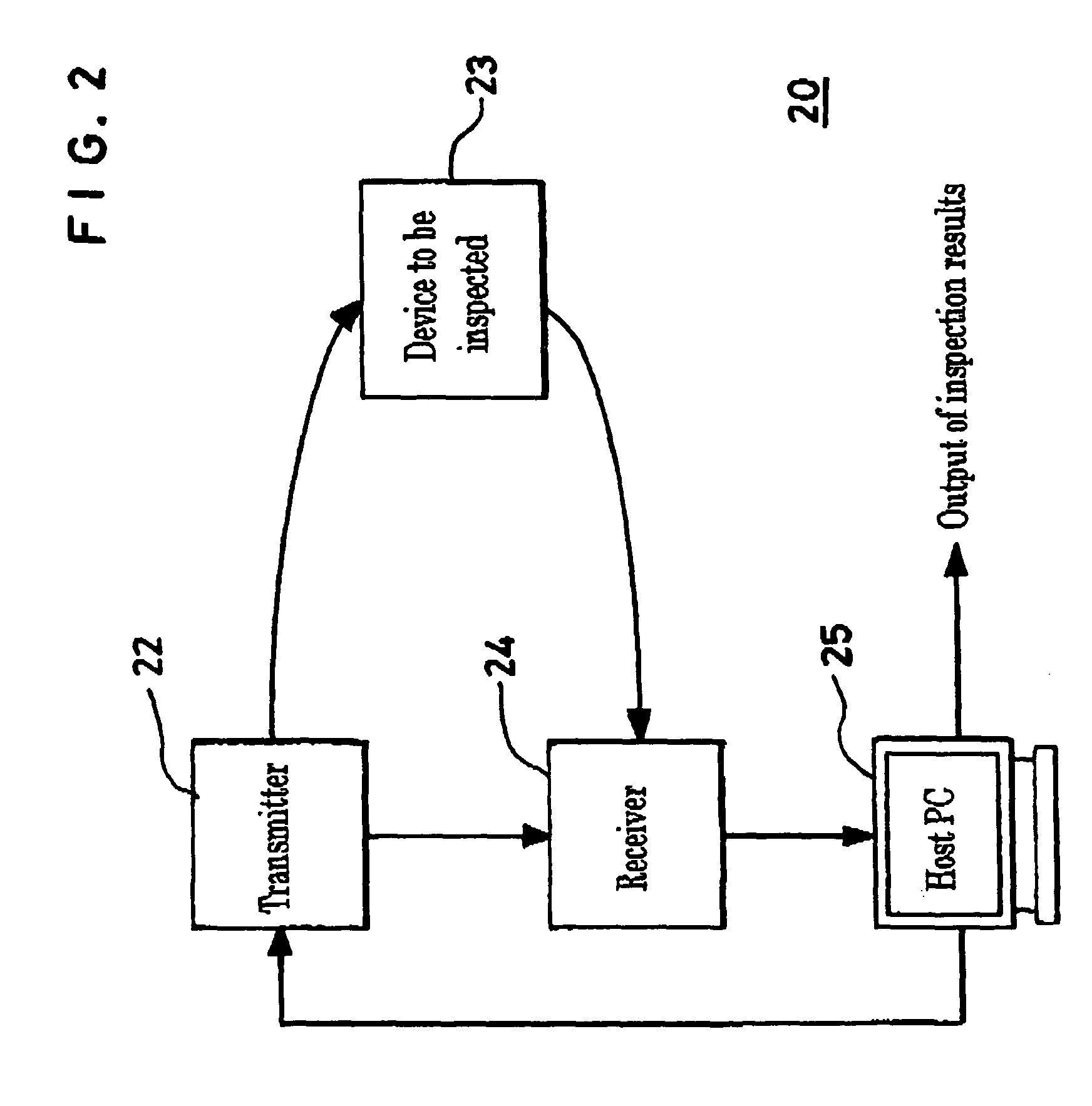

FPGA-based network device testing equipment for high load testing

InactiveUS7953014B2High load in testIncrease speedError preventionFrequency-division multiplex detailsPhysical layerPattern generation

Network device testing equipment capable of testing network devices using small size packets and for a transferring ability and a filtering ability at a media speed is described. A configuration is adopted in which a Field Programmable Gate Array (FPGA) included in a transmitter or receiver on one or both of transmitting and receiving sides is connected directly to a physical layer chip of a network and computers on both the transmitting and receiving sides are connected thereto. Each of the FPGAs of the transmitter and receiver has a circuit which has an integrated function of transmitting a packet pattern generation function and a packet-receiving function, thereby enabling a test and an inspection in real time. When inspecting the filtering function, a hash table storing therein a hash value and a list of occurrence frequencies for hash values is utilized. In order to avoid the hash values of different packets from having a same value, the hash function is configured so as to avoid that the same hash value is given to different packets or, when packet values have a common hash value, the packet is re-shaped into a packet having a different hash value.

Owner:NAT INST OF ADVANCED IND SCI & TECH +2

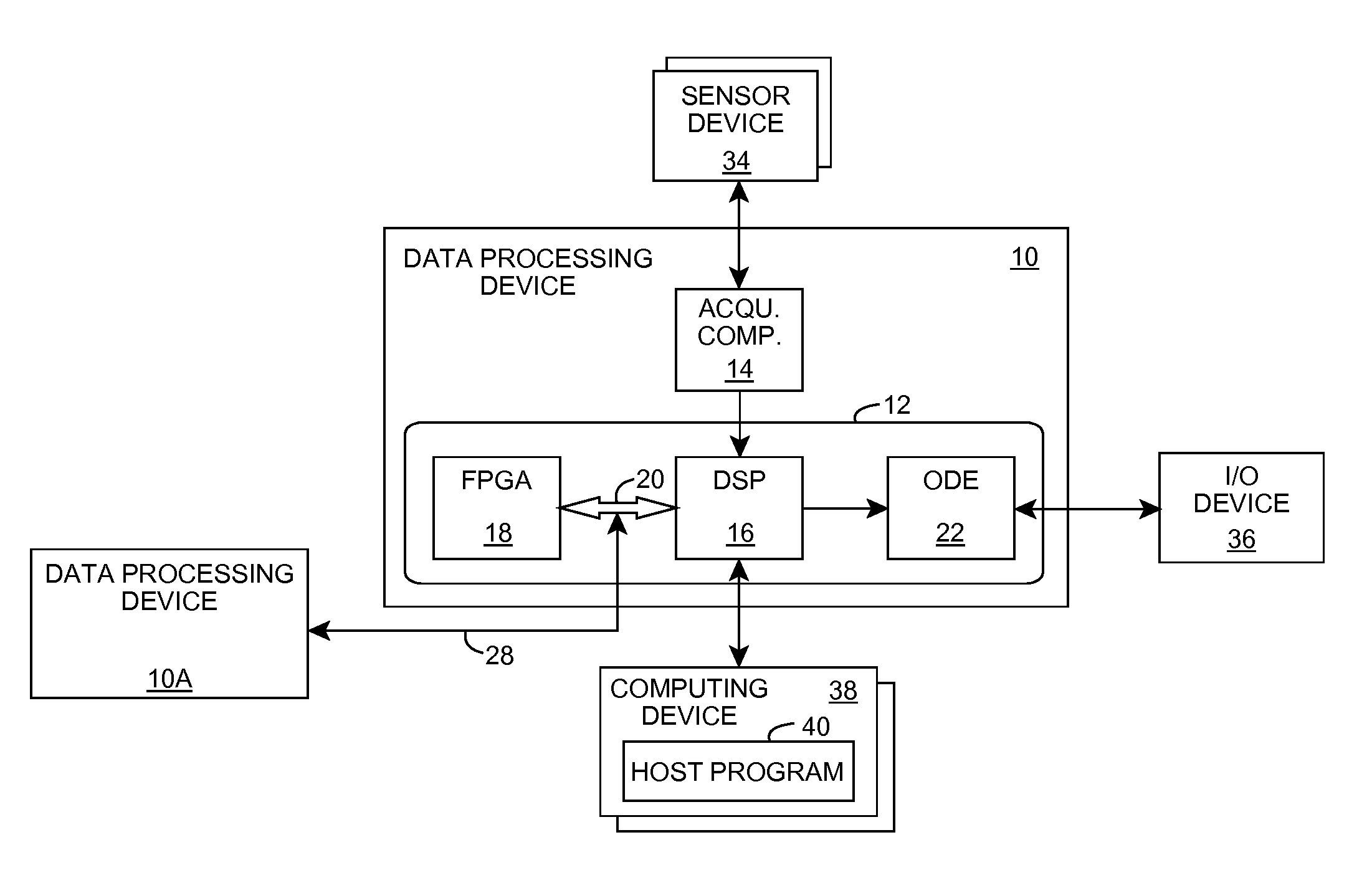

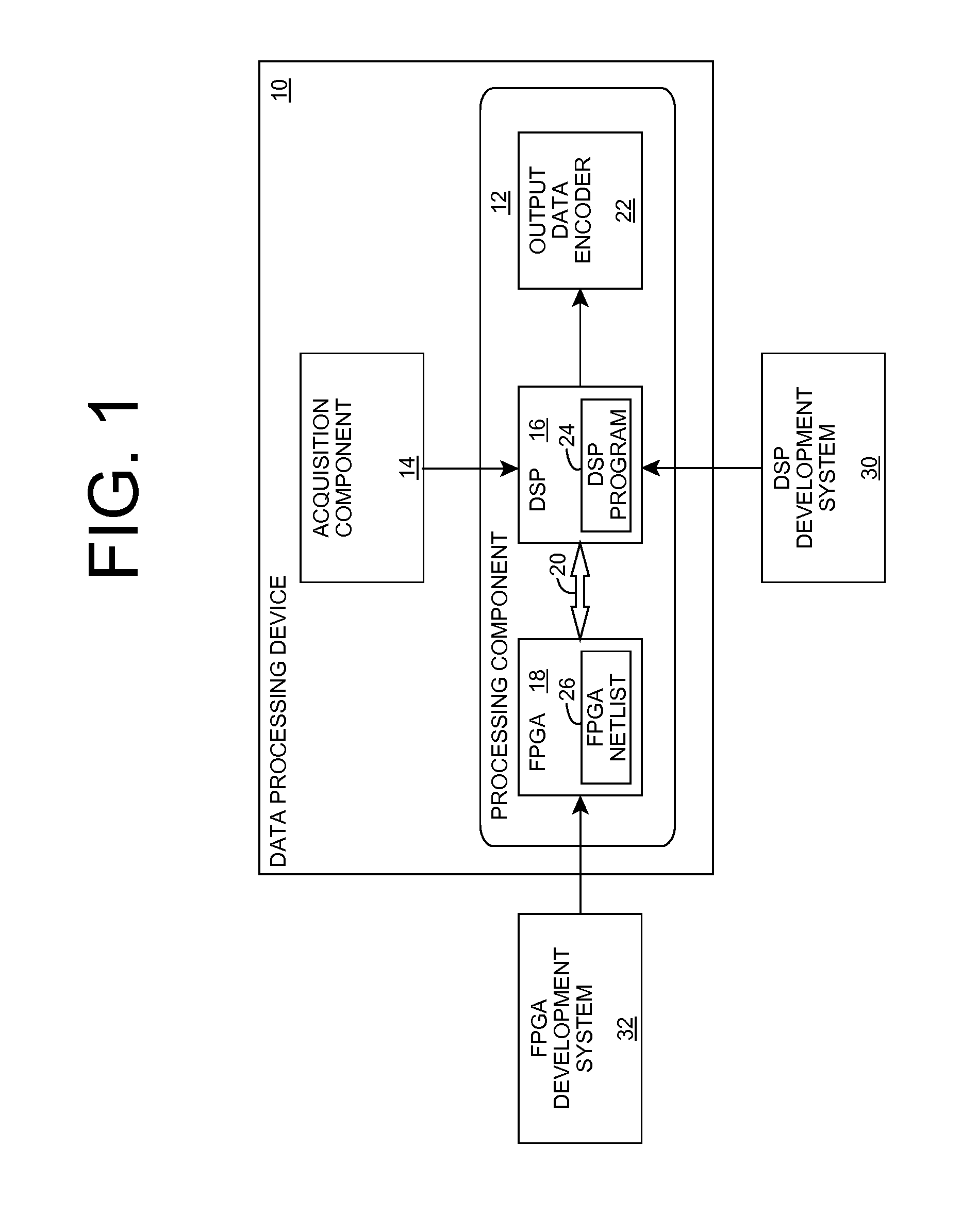

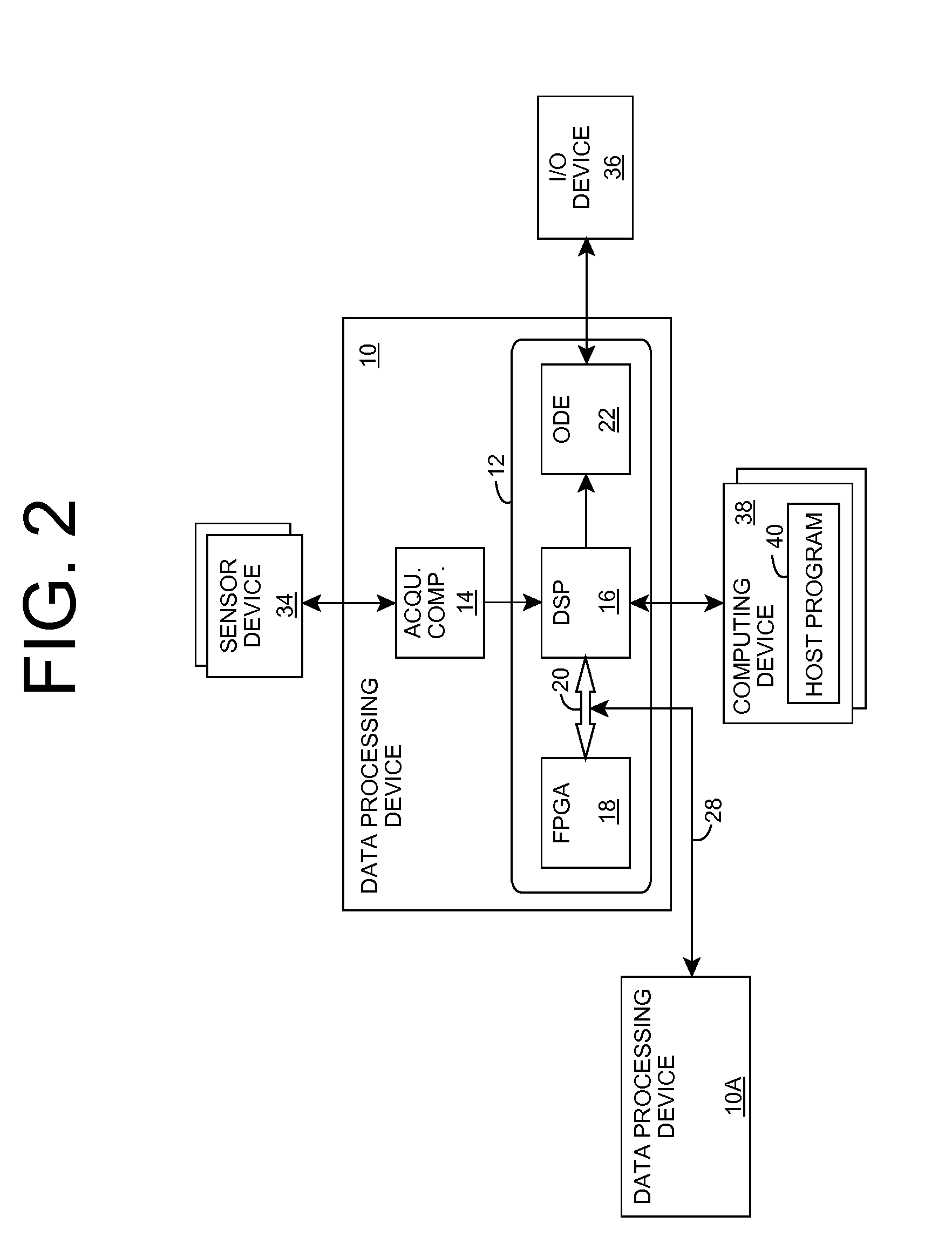

Sensor data processing using DSP and FPGA

InactiveUS20080177507A1Reduce the amount requiredReduce total powerAmplifier modifications to reduce noise influenceDigital computer detailsExternal memory interfaceField-programmable gate array

A system for managing sensor data, such as video data, includes a processing component for generating processed data based on the sensor data. The processing component can include a digital signal processor (DSP), the DSP including a computer usable medium for storing the processed data, a field programmable gate array (FPGA), and an external memory interface for transferring data between the DSP and the FPGA.

Owner:INT ELECTRONICS MACHINES

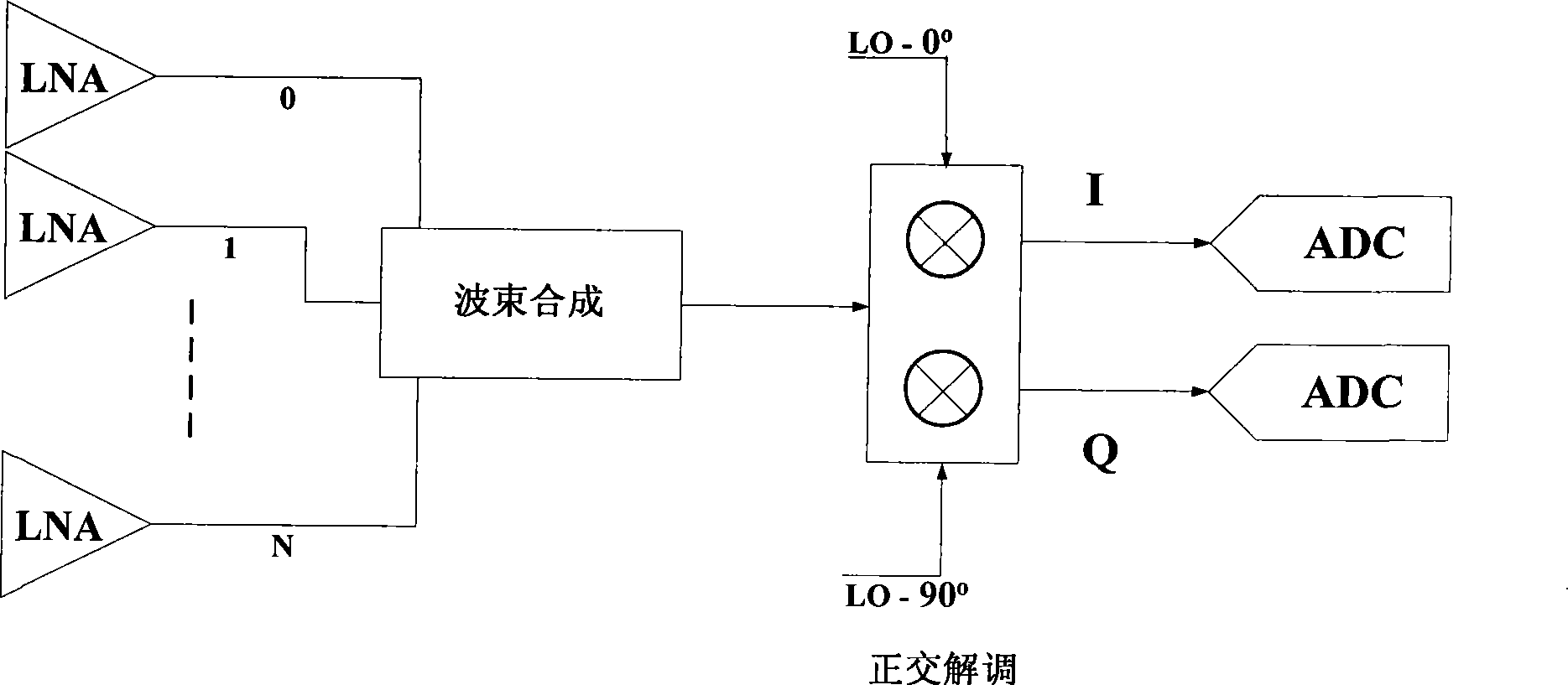

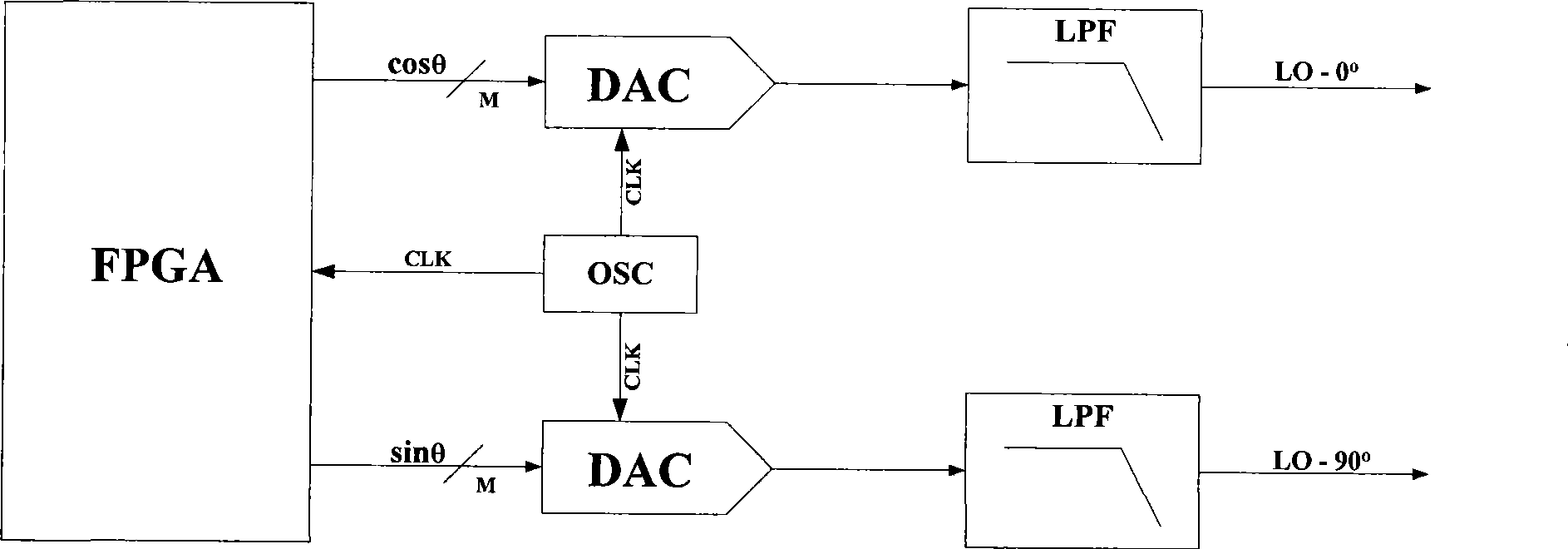

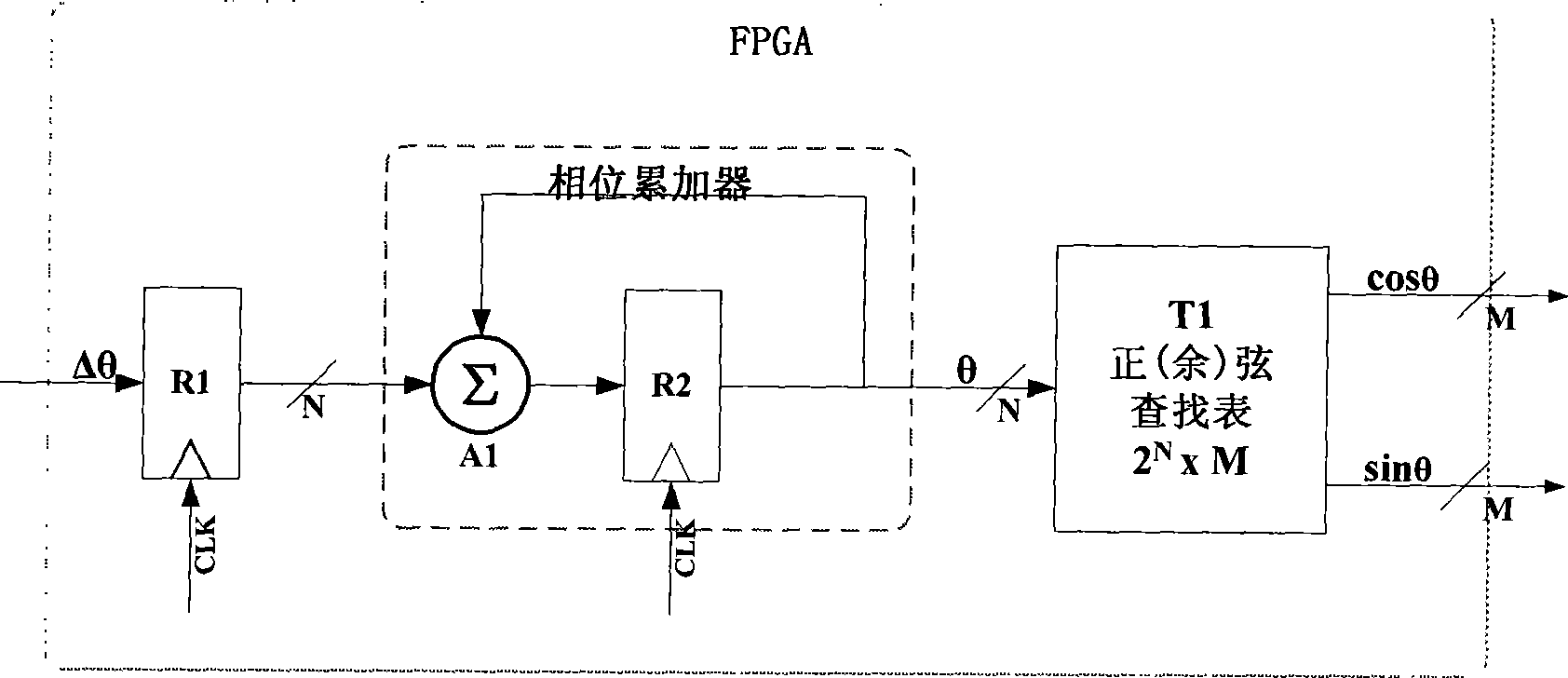

Device for producing orthogonal local oscillation signal in continuous Doppler ultrasound imaging system

InactiveCN101474081AReduce Design ComplexityReduce manufacturing costBlood flow measurement devicesDoppler Ultrasound ImagingSonification

The invention discloses a continuous Doppler US imaging system orthogonal intrinsic signal generation device, which comprise a field programmable gate array (FPGA), a crystal oscillator, a first digital-analog converter and a second digital-analog converter. The output end of the field programmable gate array (FPGA) is connected with the input ends of the first digital-analog converter and the second digital-analog converter; the crystal oscillator is respectively connected with the field programmable gate array (FPGA), the first digital-analog converter and the second digital-analog converter; the crystal oscillator is used for supplying synchronizing clock signals to the field programmable gate array (FPGA), the first digital-analog converter and the second digital-analog converter; the field programmable gate array (FPGA) is used for outputting the sine value corresponding to the phase value to the first digital-analog converter according to the input phase value and outputting the cosine value corresponding to the phase value to the second digital-analog converter; the first digital-analog converter is used for converting the sine value into the corresponding analog signals; the second digital-analog converter is used for converting the cosine value into the corresponding analog signals.

Owner:SHENZHEN LANDWIND IND

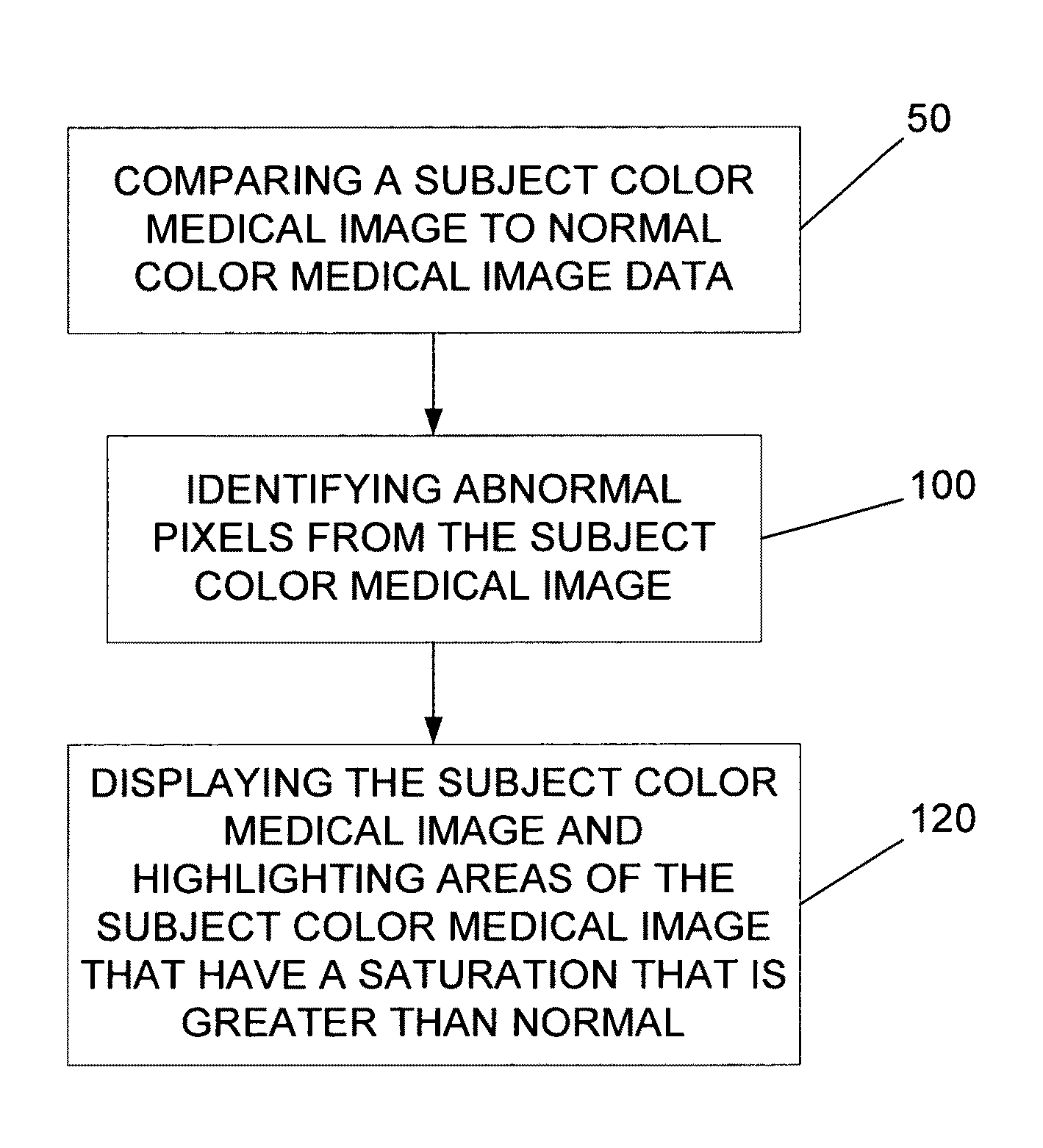

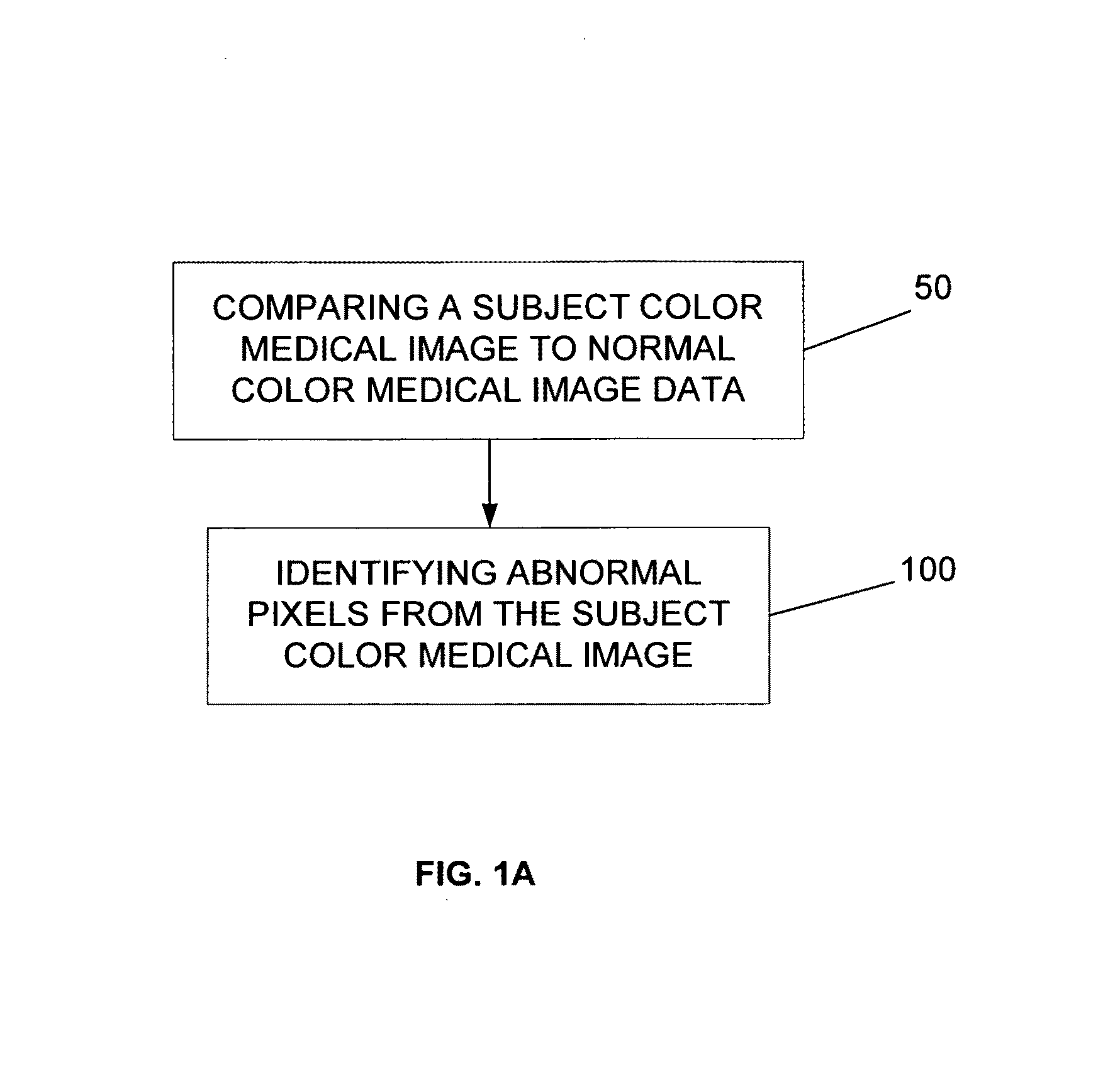

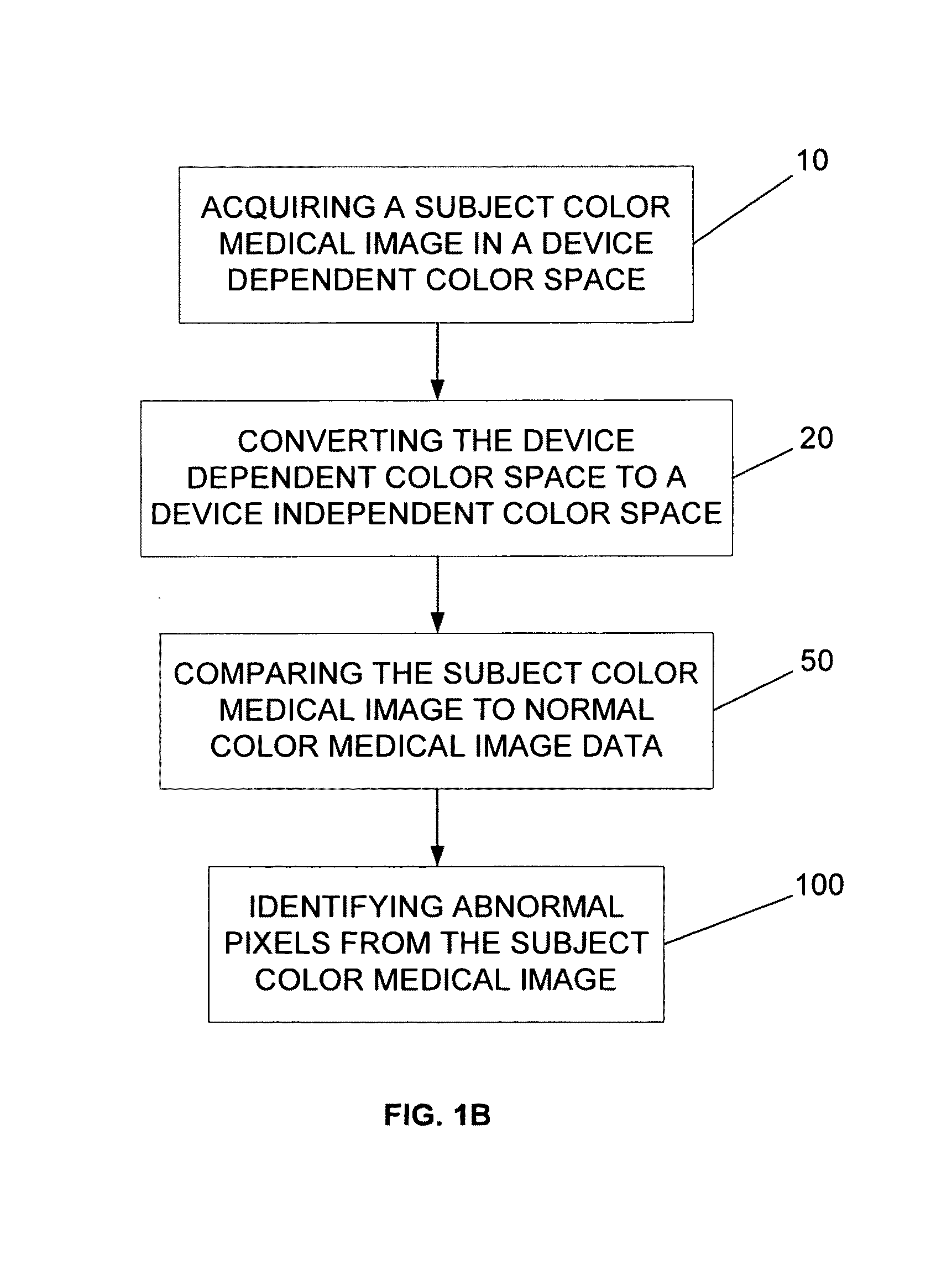

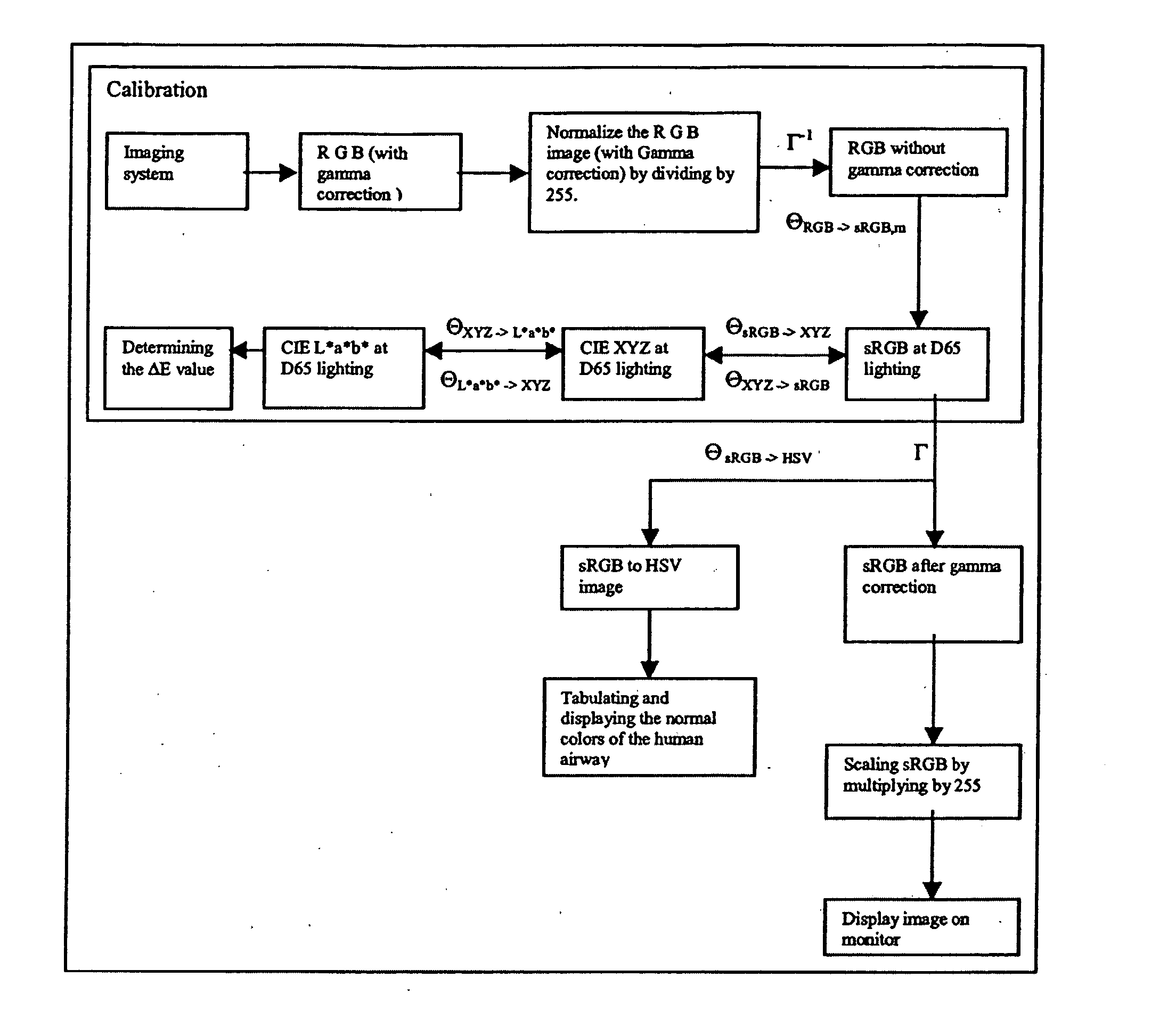

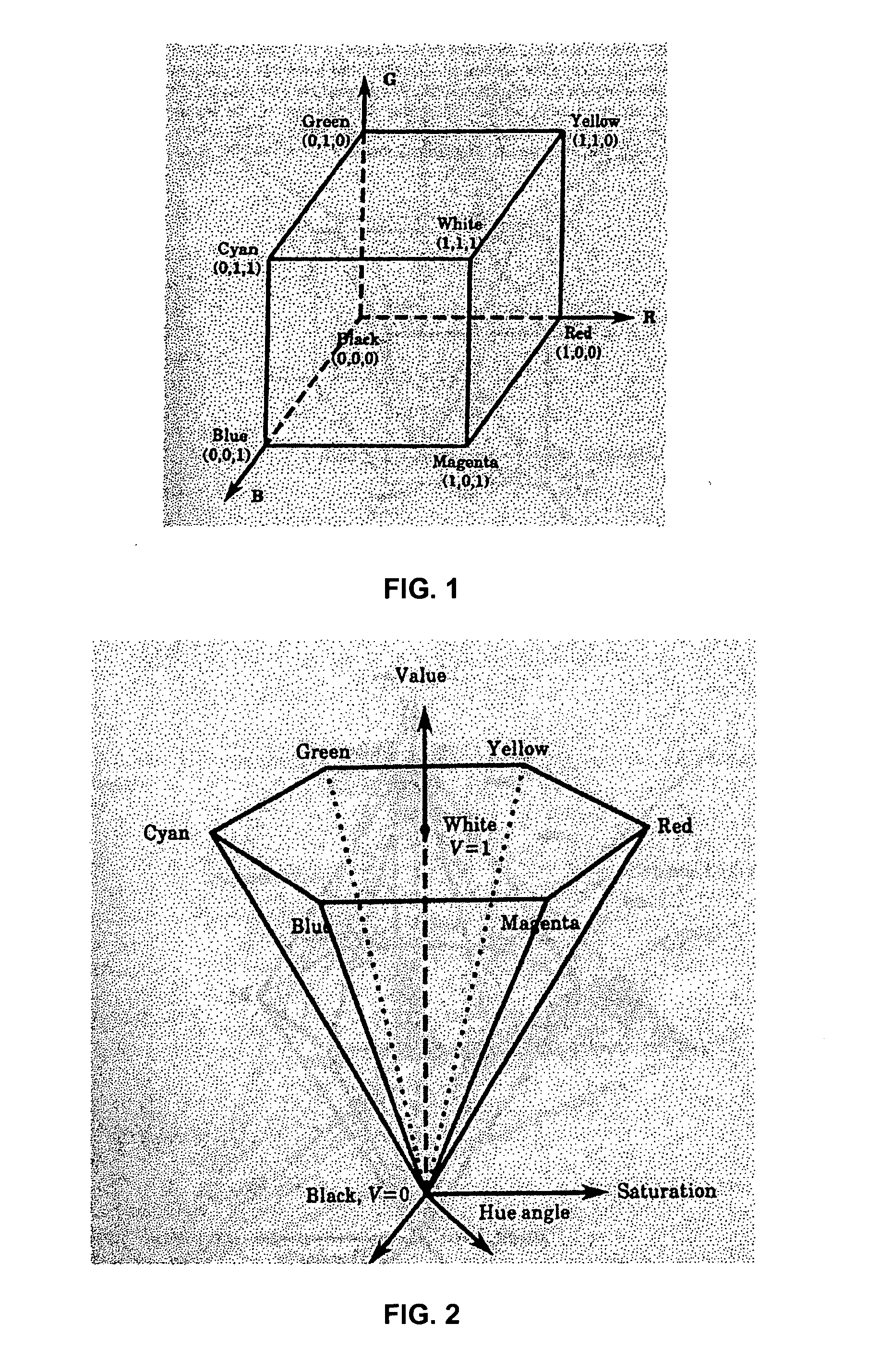

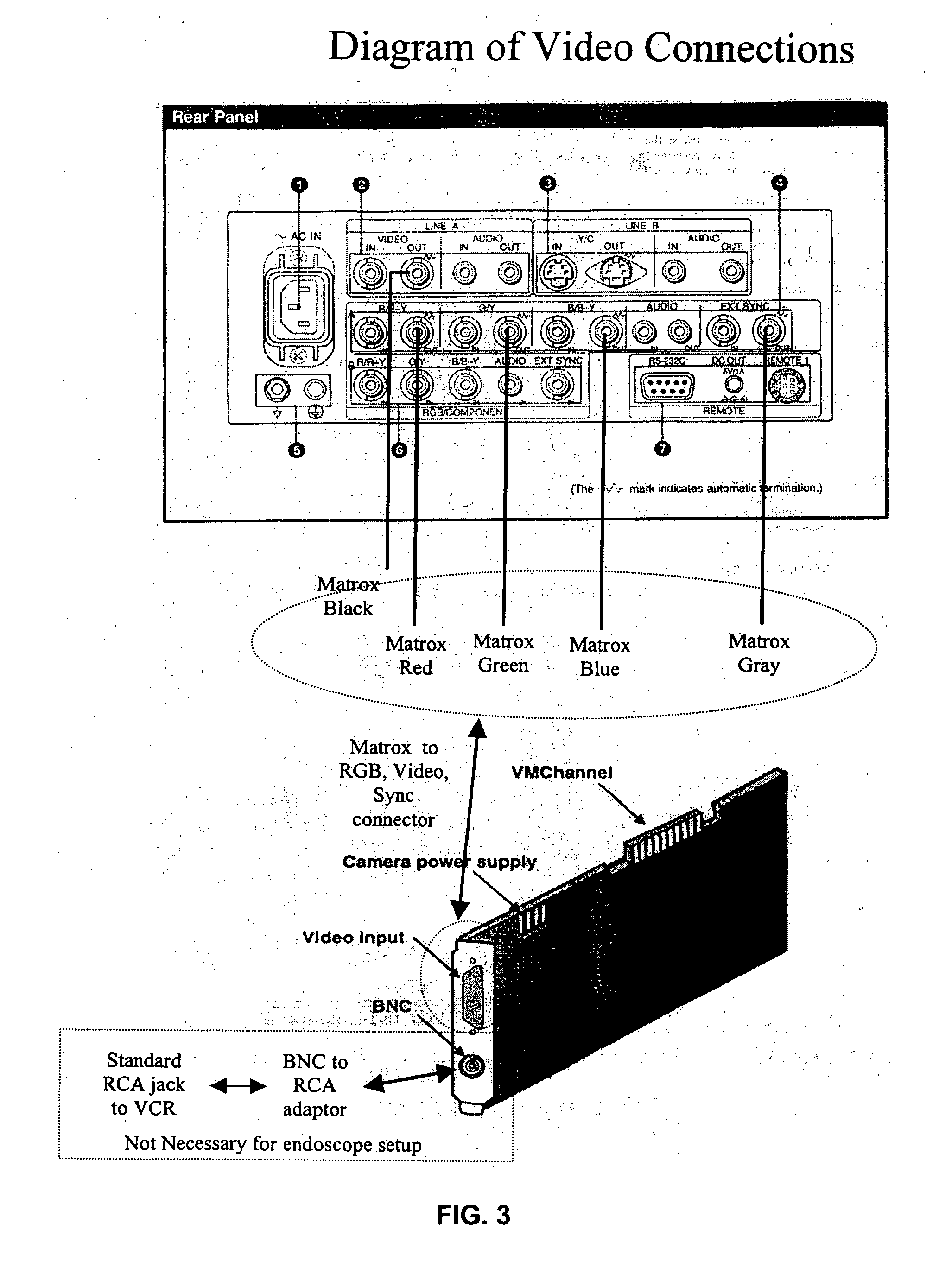

Methods and devices useful for analyzing color medical images

InactiveUS7613335B2Image enhancementImage analysisPattern recognitionApplication-specific integrated circuit

In one embodiment, a method that includes comparing a subject color medical image to normal color medical image data; and identifying abnormal pixels from the subject color medical image. Another embodiment includes a computer readable medium comprising machine readable instructions for implementing one or more steps of that method. Another embodiment includes a device that has a field programmable gate array configured to perform one or more of the steps of that method. Another embodiment includes a device that has an application specific integrated circuit configured to perform one or more of the steps of that method.

Owner:UNIV OF IOWA RES FOUND

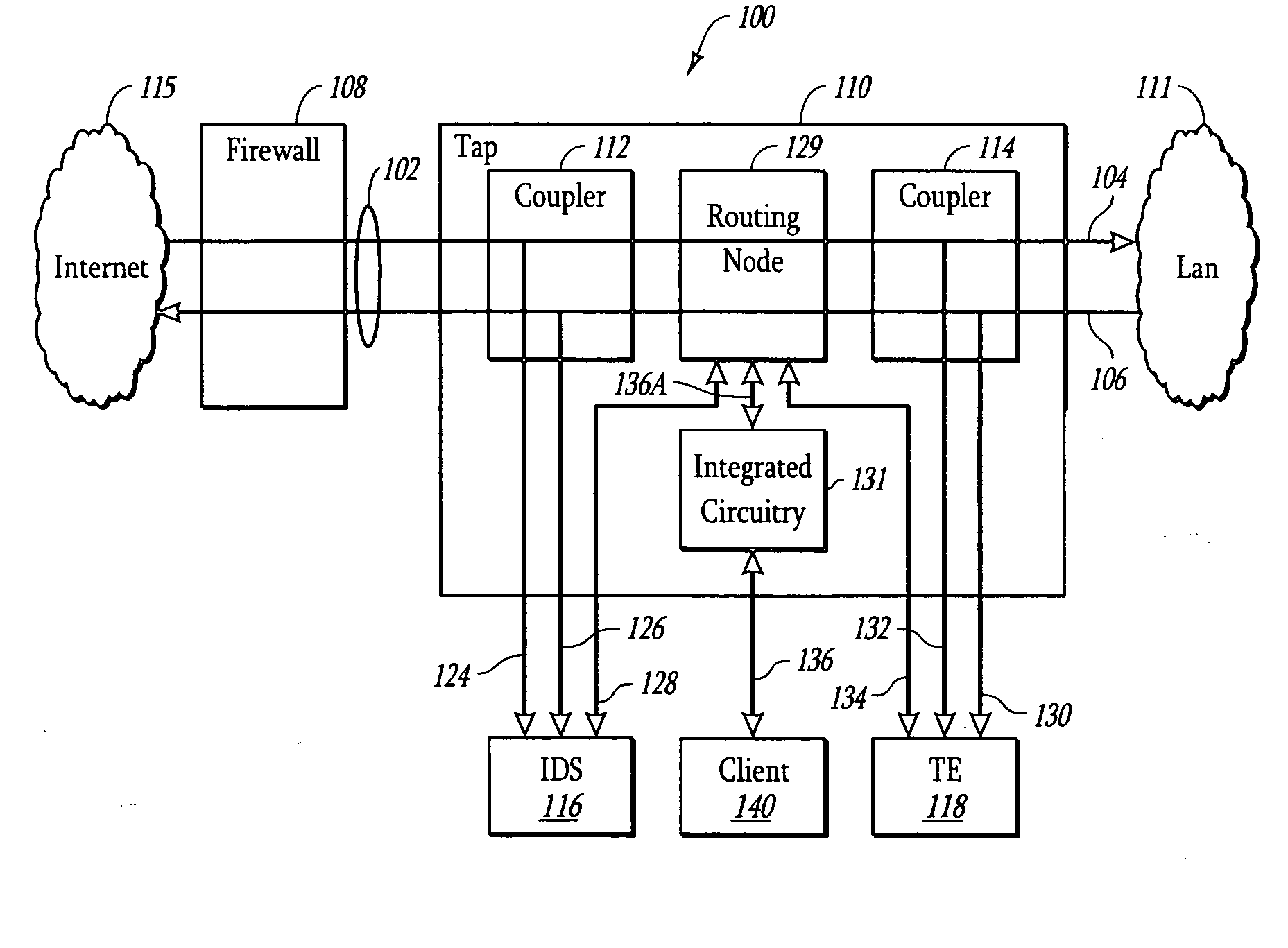

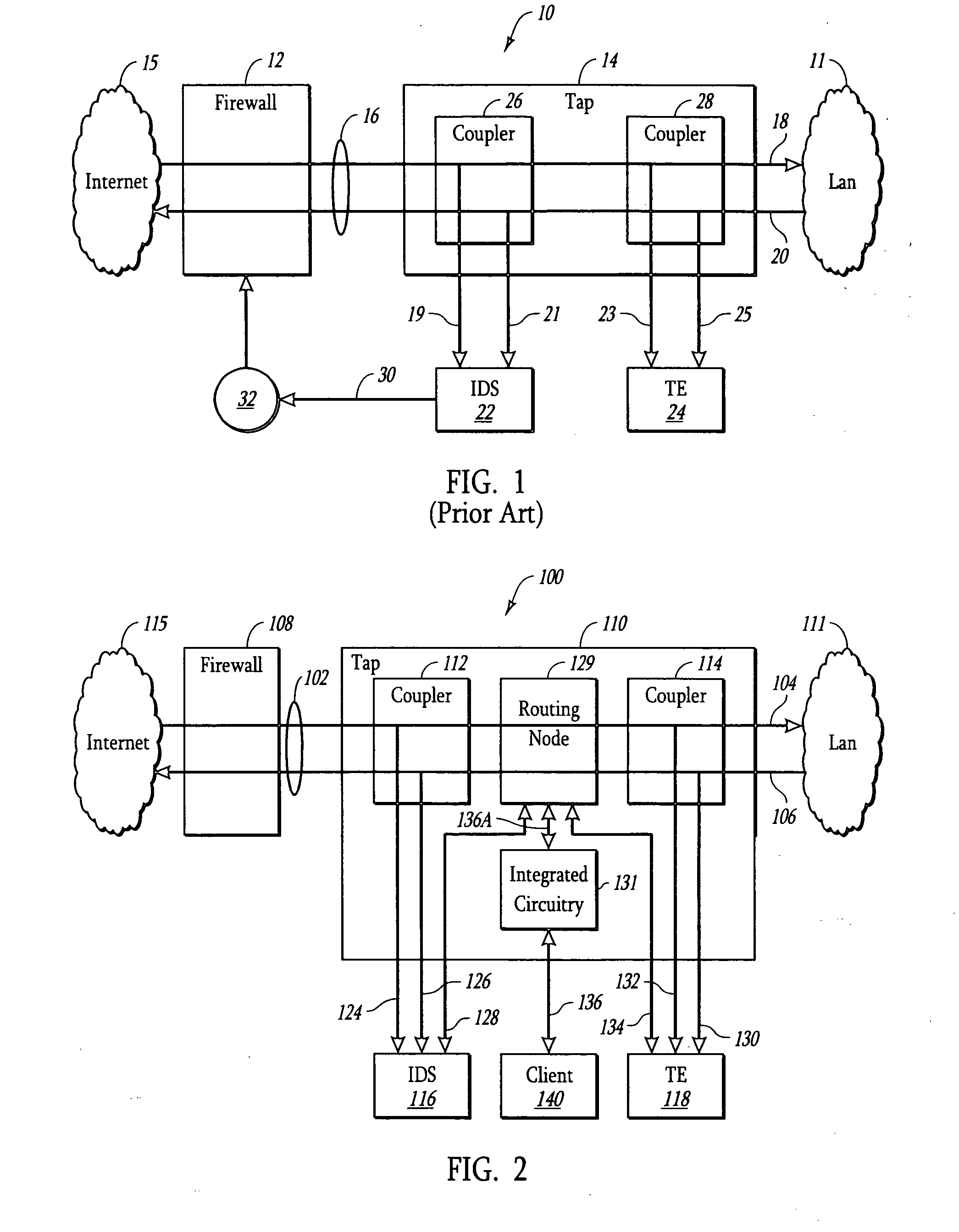

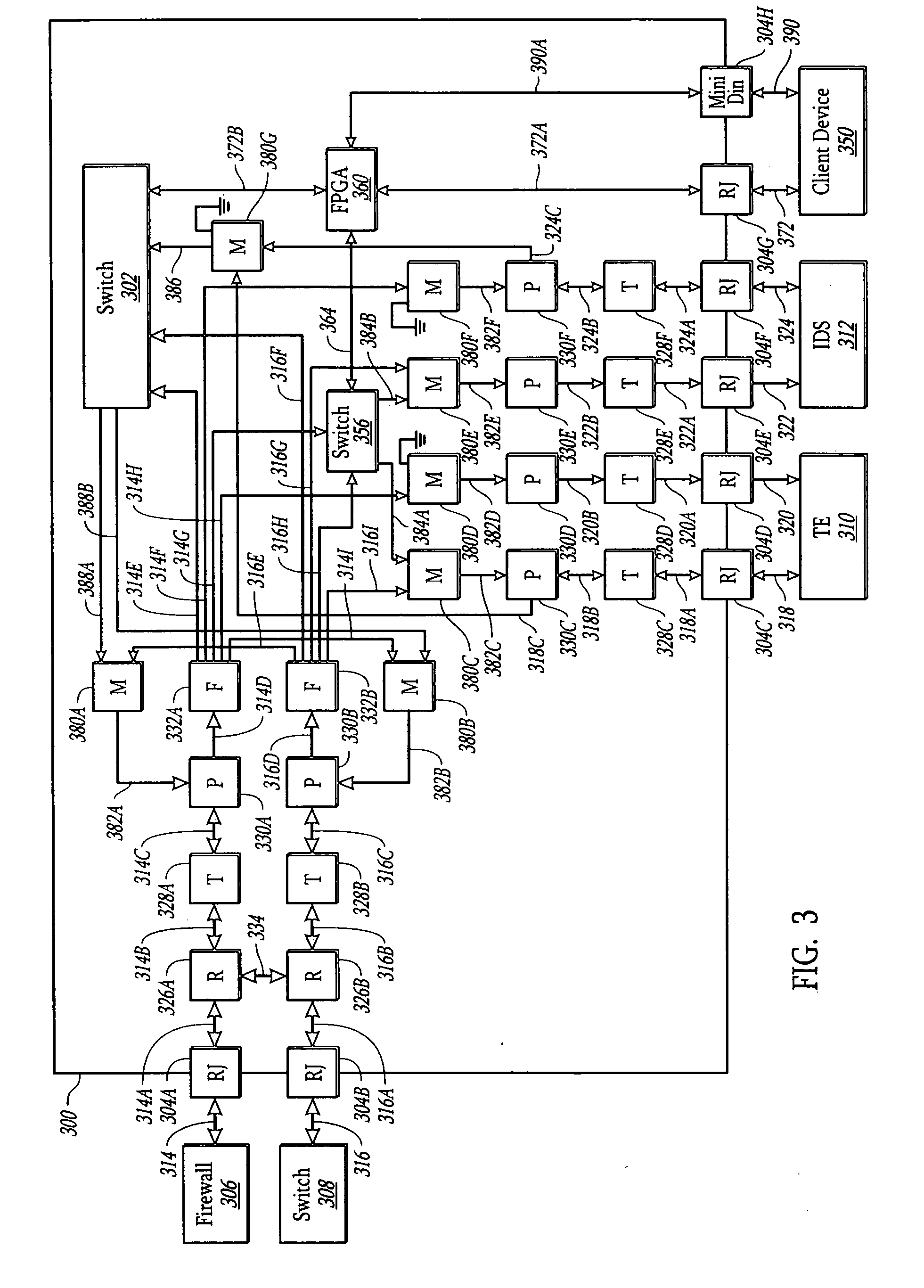

Network tap for use with multiple attached devices

InactiveUS20050129033A1Function increaseEliminate needMultiplex system selection arrangementsData switching by path configurationNetwork tapData transmission

Owner:FINISAR

Methods and devices useful for analyzing color medical images

InactiveUS20050036668A1Image enhancementImage analysisPattern recognitionApplication-specific integrated circuit

In one embodiment, a method that includes comparing a subject color medical image to normal color medical image data; and identifying abnormal pixels from the subject color medical image. Another embodiment includes a computer readable medium comprising machine readable instructions for implementing one or more steps of that method. Another embodiment includes a device that has a field programmable gate array configured to perform one or more of the steps of that method. Another embodiment includes a device that has an application specific integrated circuit configured to perform one or more of the steps of that method.

Owner:UNIV OF IOWA RES FOUND

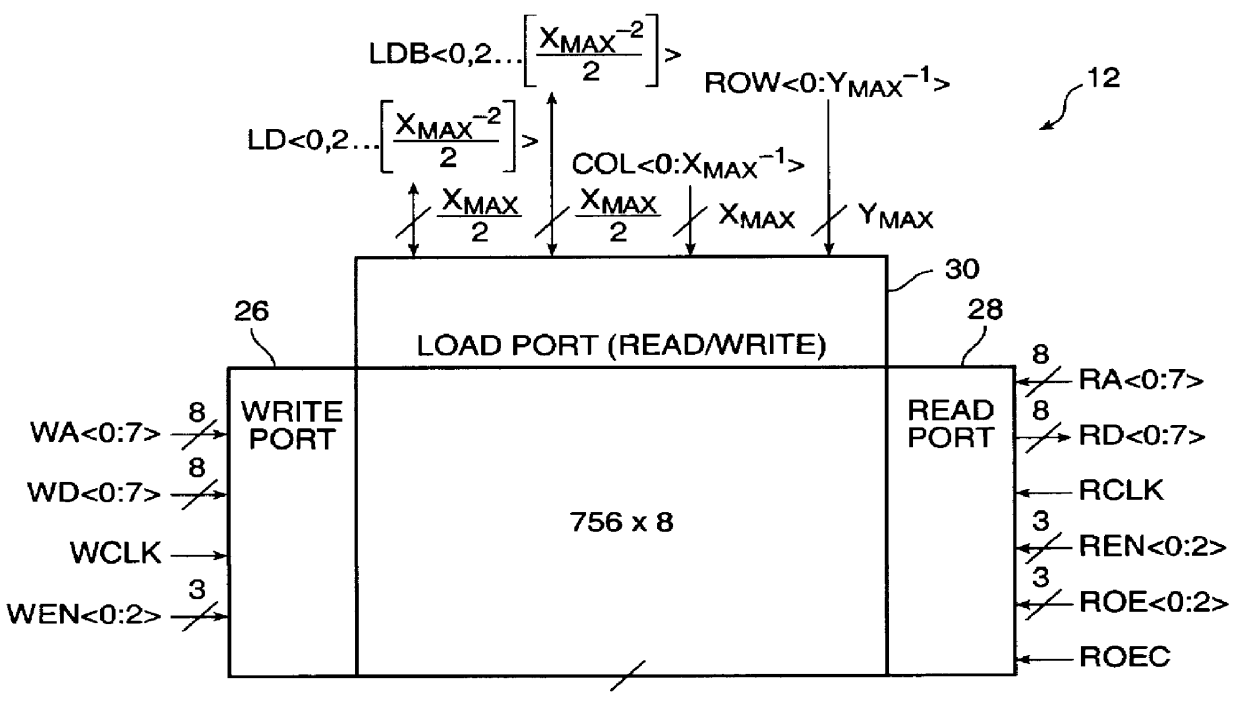

Embedded static random access memory for field programmable gate array

InactiveUS6049487AHigh impedance stateSolve conflictsDetecting faulty hardware by configuration testRead-only memoriesStatic random-access memoryRandom access memory

A dual ported (simultaneous read / write) SRAM block with an additional load port that interacts with the circuitry employed in the loading and testing of the configuration data of the FPGA core is disclosed. Each SRAM block contains circuits in both the read port and the write port that permit the SRAM blocks to be connected into deeper and wider configurations by without any additional logic as required by the prior art. An address collision detector is provided such that when both read and write ports in the SRAM block access the same address simultaneously a choice between the data being read can be made between the data presently in the SRAM block or the new data being written to the SRAM block.

Owner:MICROSEMI SOC

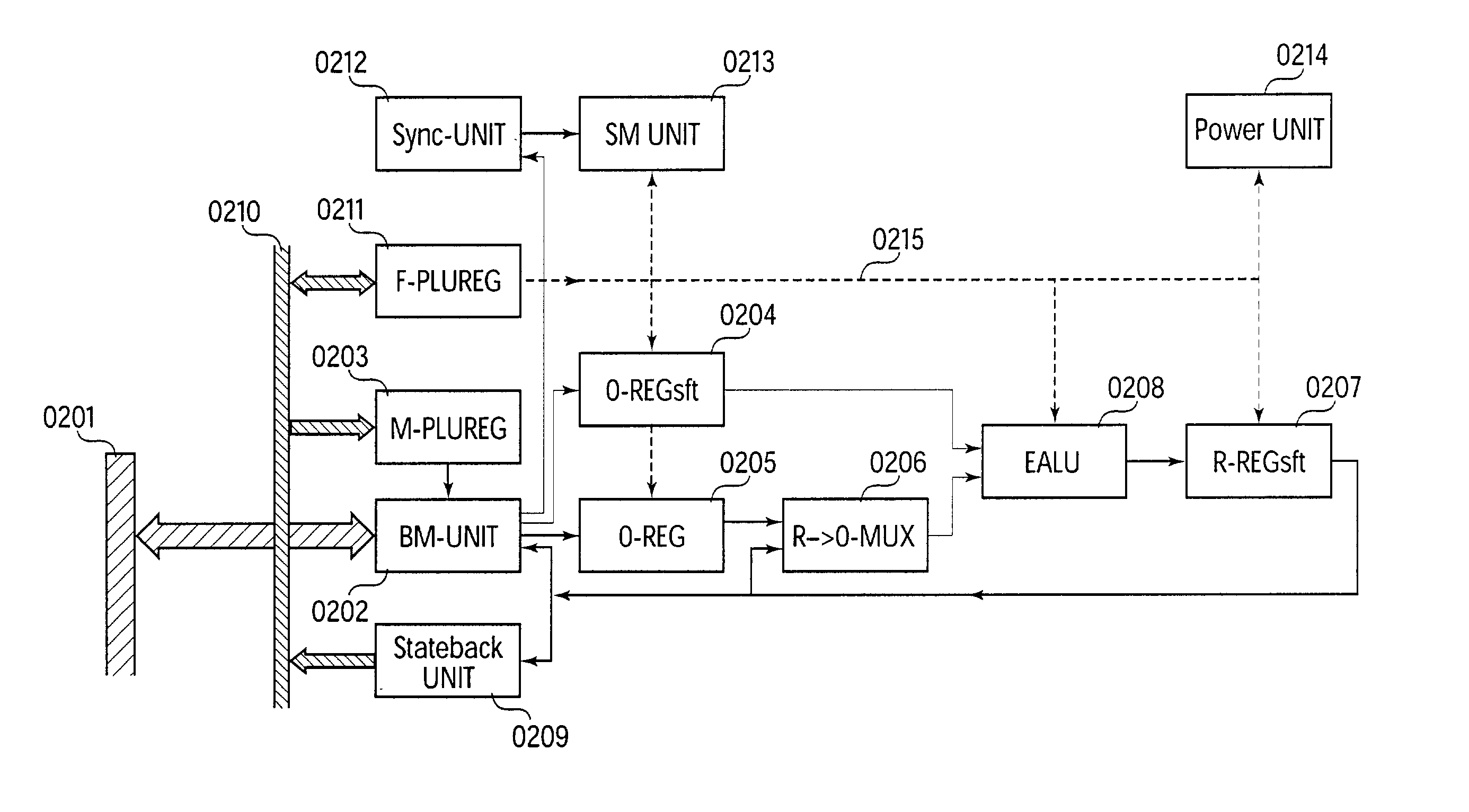

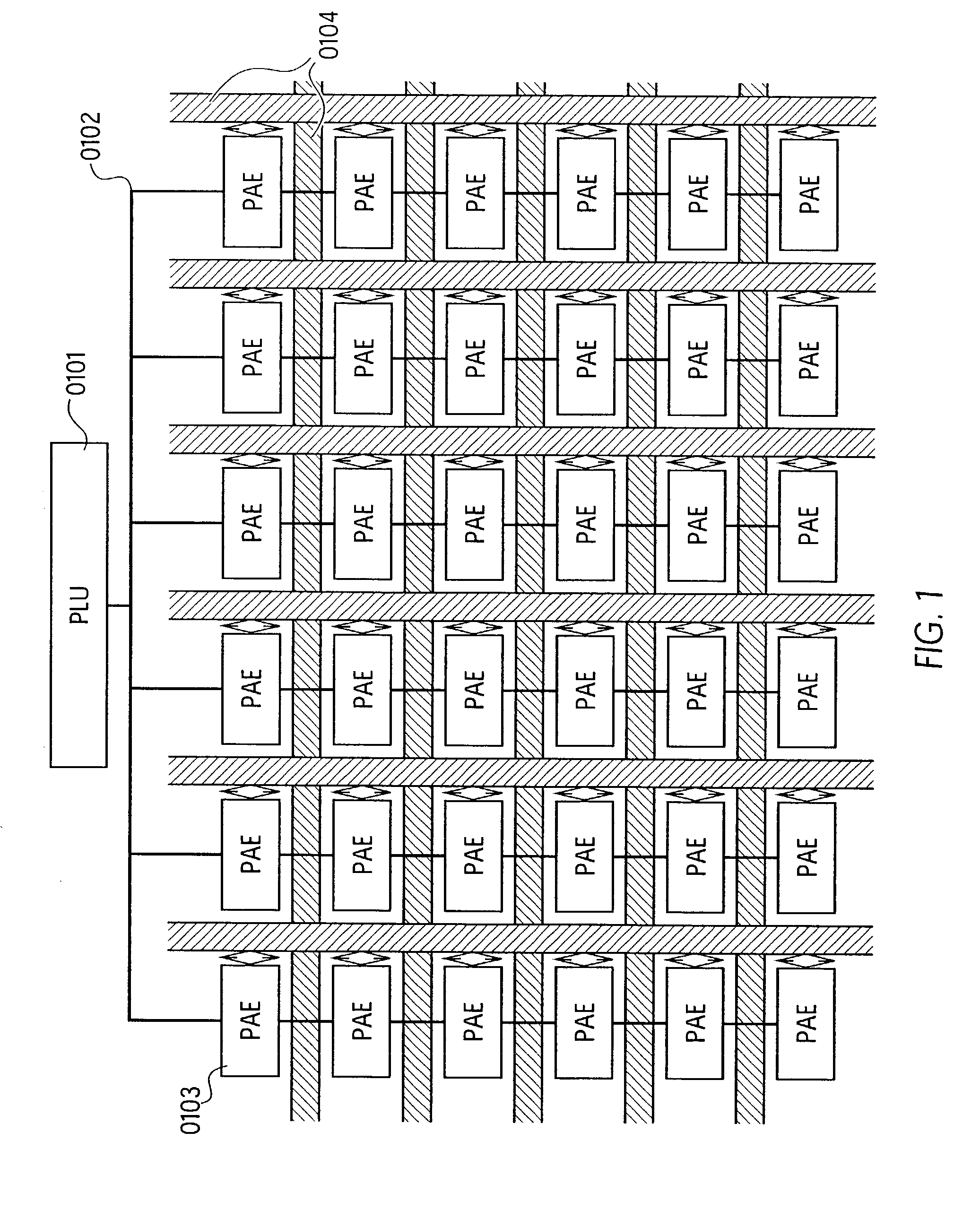

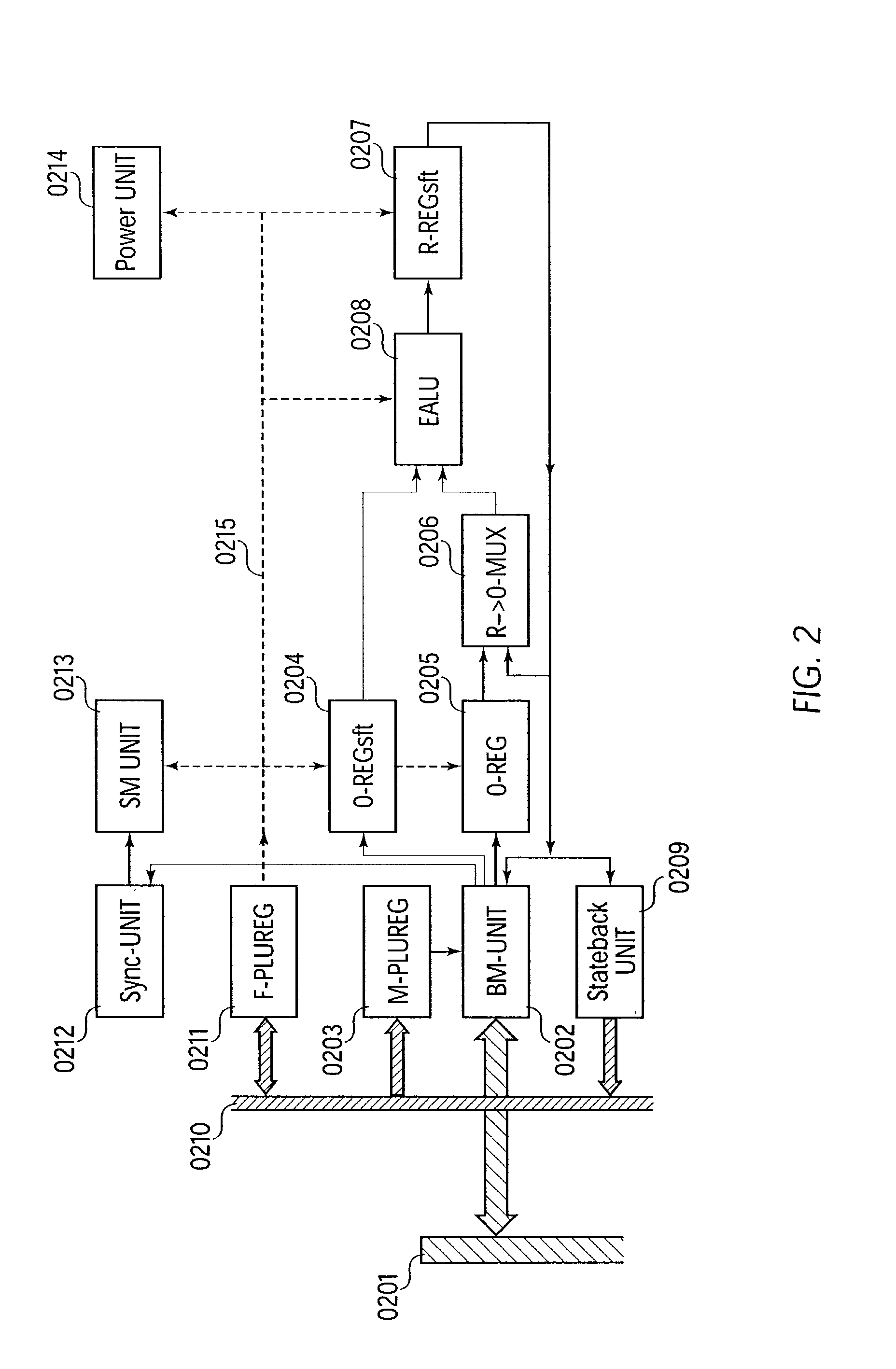

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

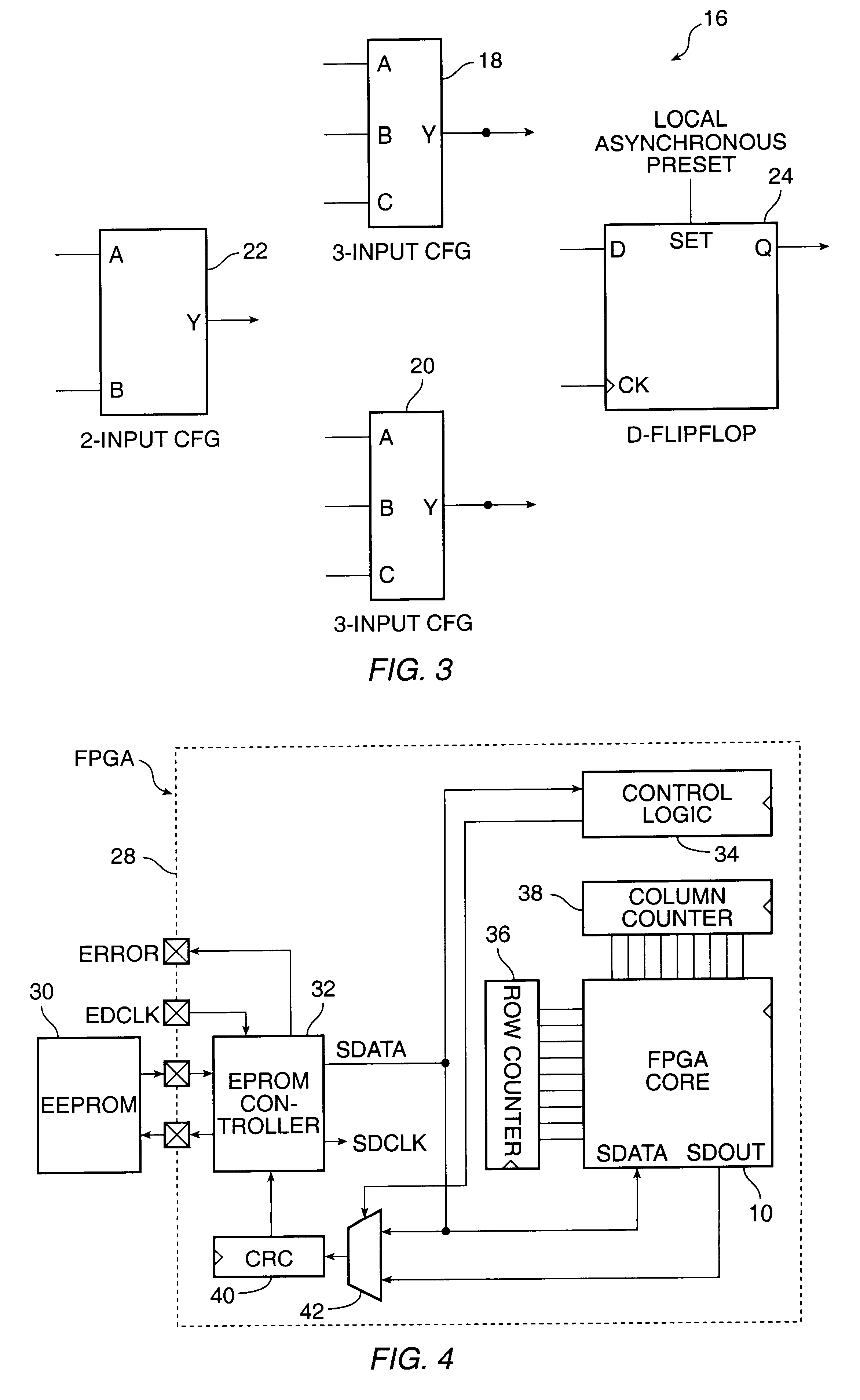

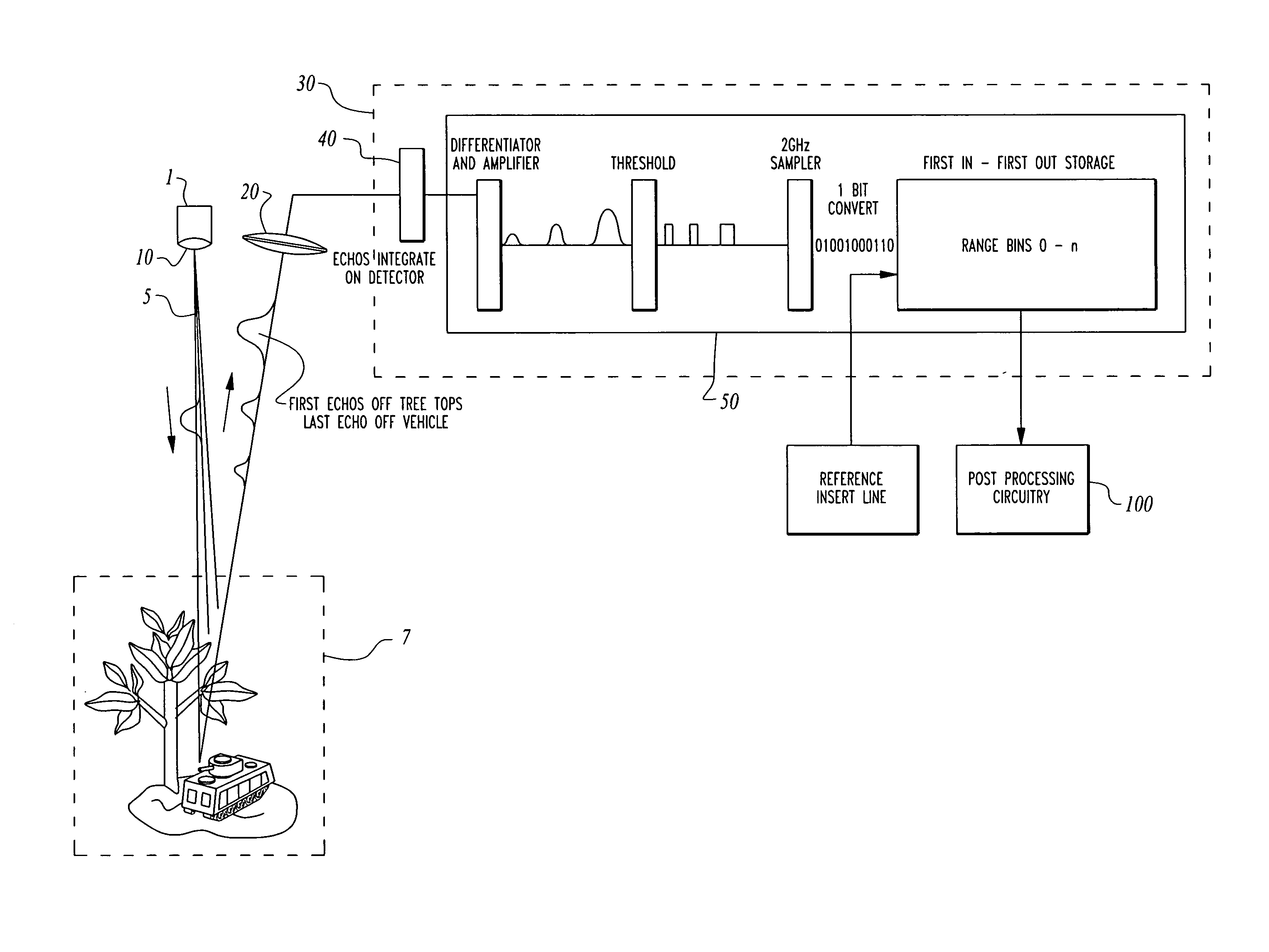

Methods for errors checking the configuration SRAM and user assignable SRAM data in a field programmable gate array

A method for detecting an error in data stored in configuration SRAM and user assignable SRAM in a FPGA comprises the steps of providing a serial data stream into the FPGA from an external source, loading data from the serial data stream into the configuration SRAM in response to address signals generated by row column counters, loading data from the serial data stream into the user assignable SRAM in response to address signals generated by row and column counters, loading a seed and signature from the serial data stream into a cyclic redundancy checking circuit, cycling data out of the configuration SRAM and the user assignable SRAM by the row and column counters; performing error checking on the data that has been cycled out of the configuration SRAM and out of the user assignable SRAM by the cyclic redundancy checking circuit, and generating an error signal when an error is detected by the error checking circuit.

Owner:MICROSEMI SOC

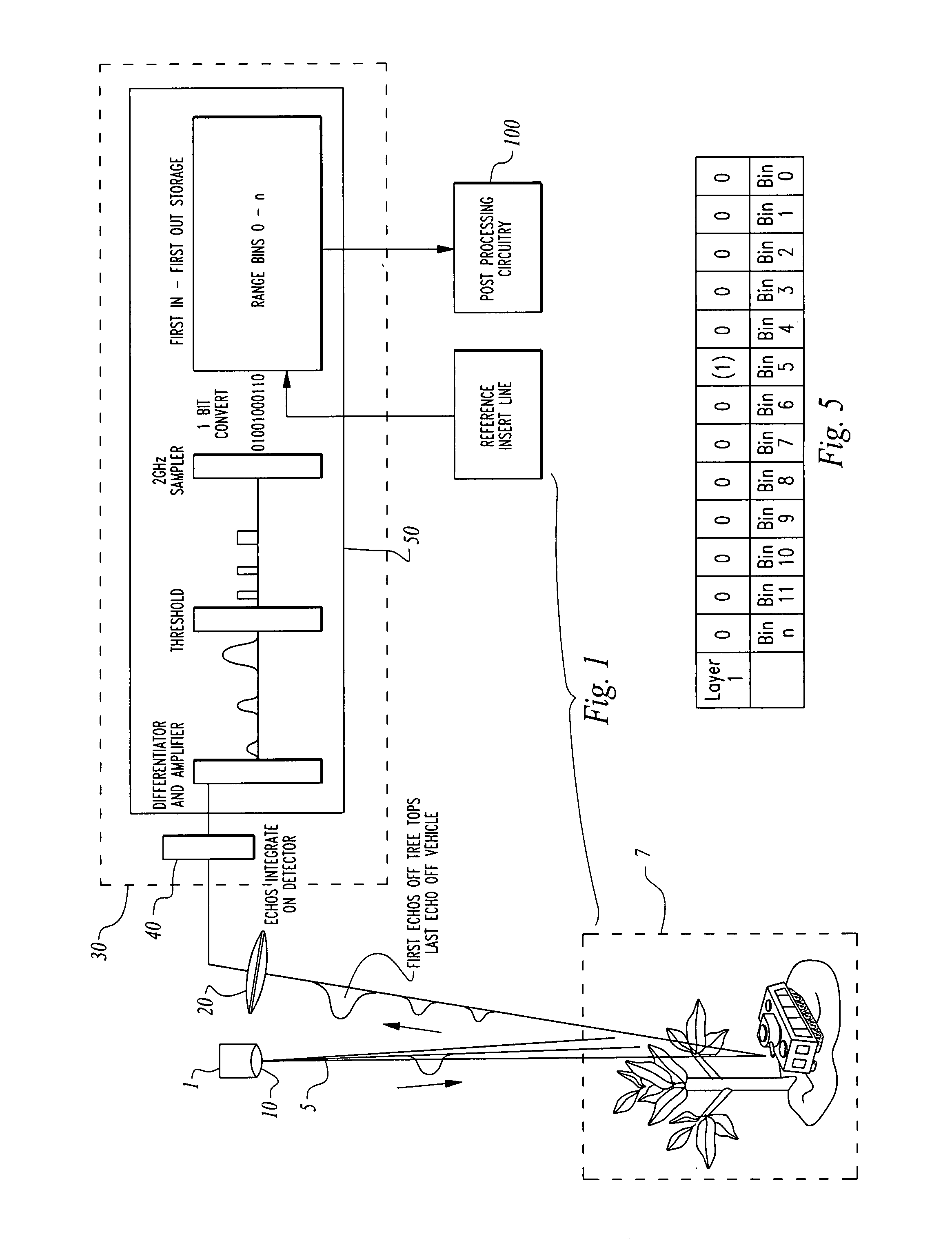

Three-dimensional ladar module with alignment reference insert circuitry

ActiveUS7436494B1Minimize layer-to-layerMinimize channel-to-channel “ jitter ”Optical rangefindersElectromagnetic wave reradiationShift registerSignal processing circuits

A 3-D LADAR imaging system incorporating stacked microelectronic layers is provided. A light source such as a laser is imaged upon a target through beam shaping optics. Photons reflected from the target are collected and imaged upon a detector array though collection optics. The detector array signals are fed into a multilayer processing module wherein each layer includes detector signal processing circuitry. The detector array signals are amplified, compared to a user-defined threshold, digitized and fed into a high speed FIFO shift register range bin. Dependant on the value of the digit contained in the bins in the register, and the digit's bin location, the time of a photon reflection from a target surface can be determined. A T0 trigger signal defines the reflection time represented at each bin location by resetting appropriate circuitry to begin processing.A reference insert circuit inserts data into the FIFO registers at a preselected location to provide a reference point at which all FIFO shift register data may be aligned to accommodate for timing differences between layers and channels. The bin data representing the photon reflections from the various target surfaces are read out of the FIFO and processed using appropriate circuitry such as a field programmable gate array to create a synchronized 3-D point cloud for creating a 3-D target image.

Owner:NYTELL SOFTWARE LLC

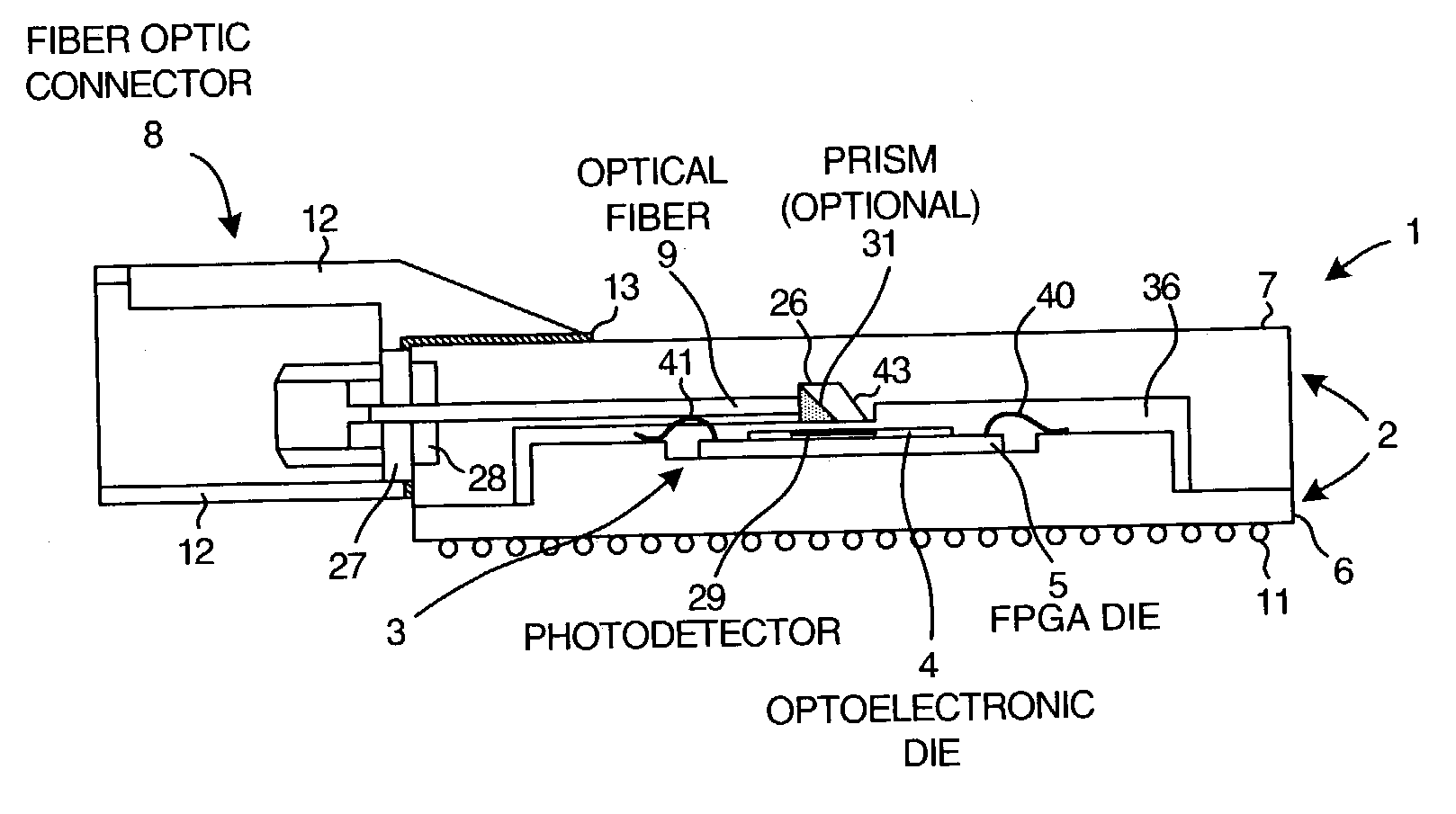

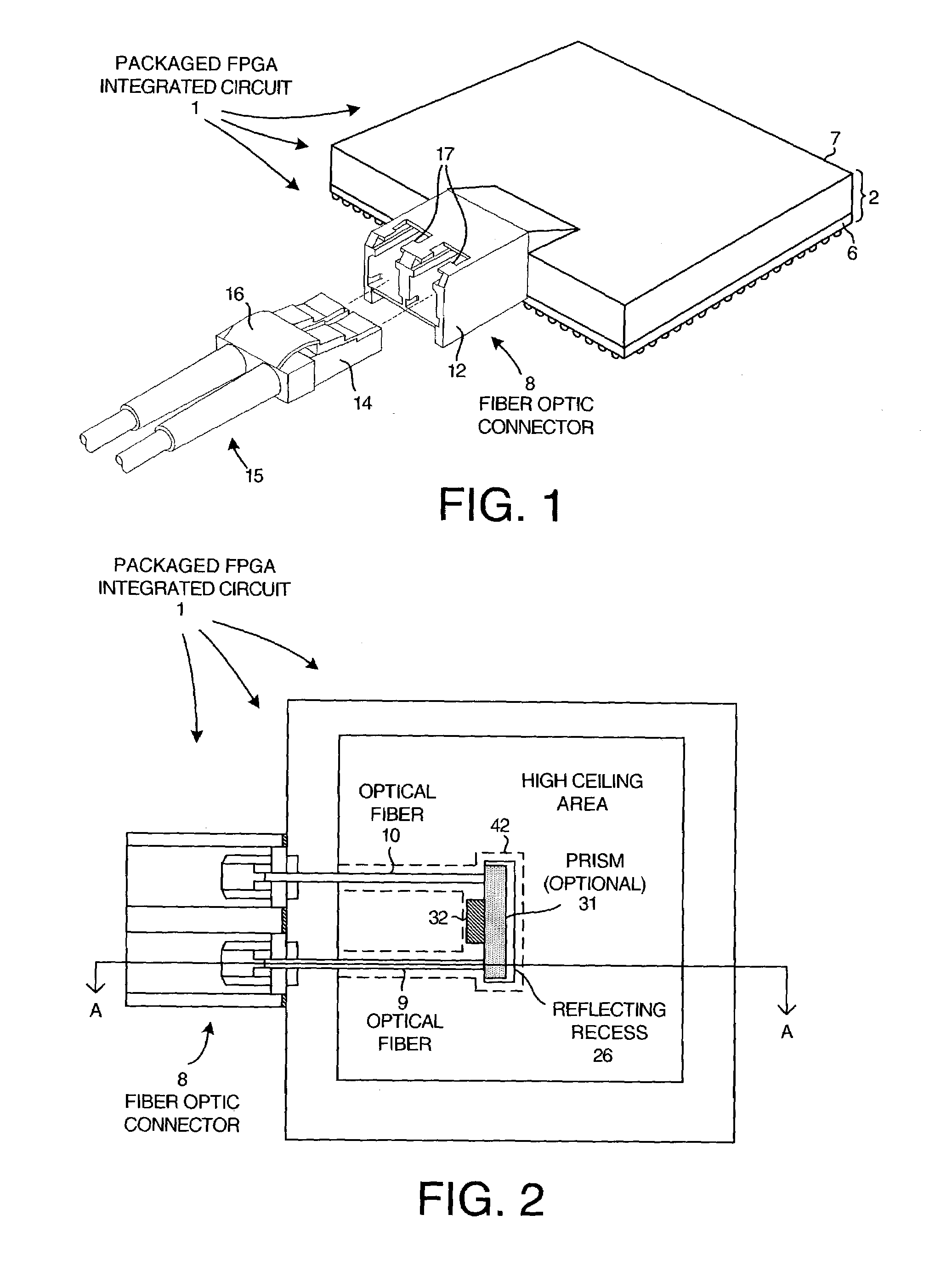

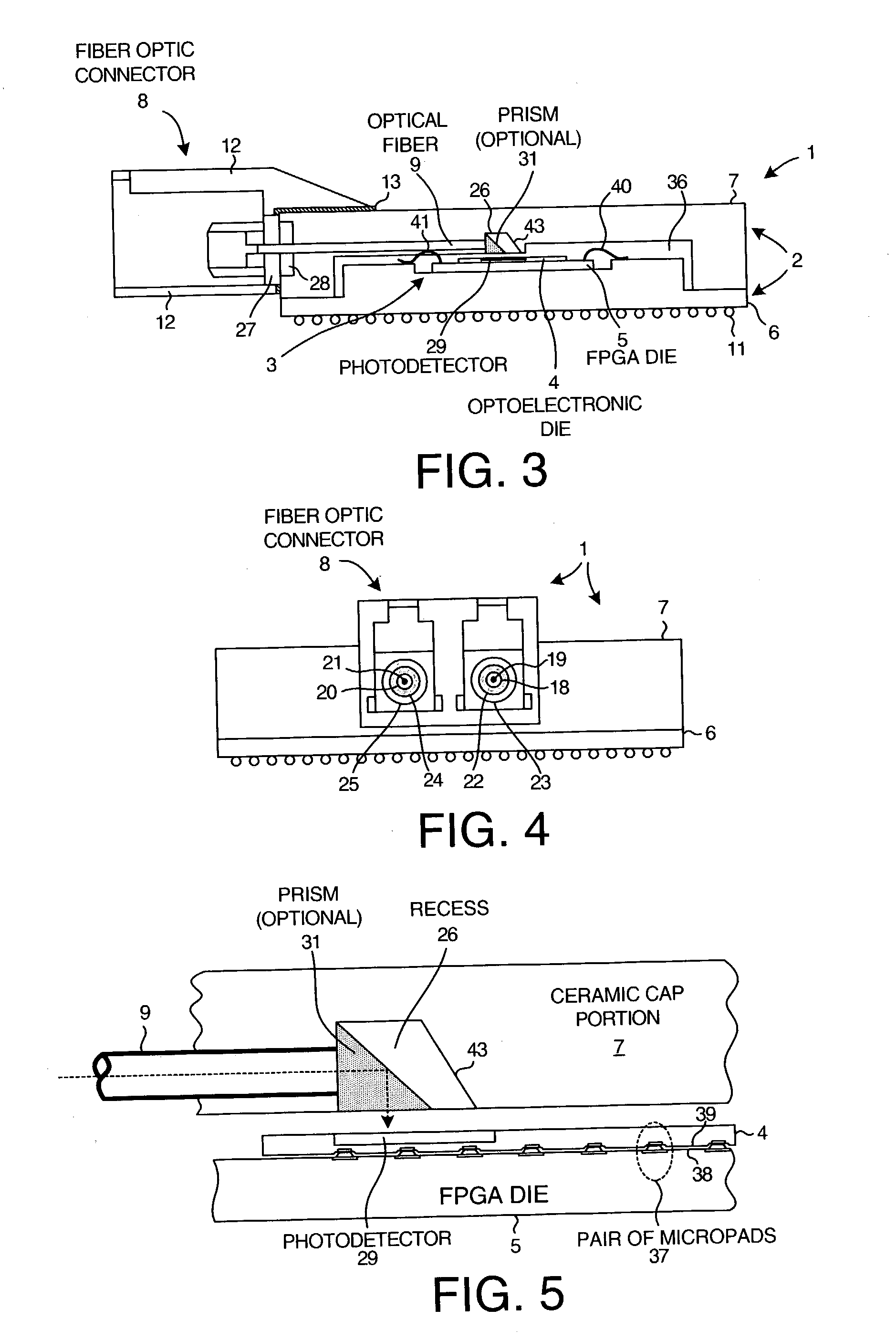

Fiber optic field programmable gate array integrated circuit packaging

ActiveUS6945712B1Thin profileReduce power consumptionSolid-state devicesCoupling light guidesFiberPhotodetector

An FPGA is readily connectable to a high-speed fiber optic link by snap fitting an external fiber optic cable into an accommodating duplex fiber optic connector of a low-profile packaged FPGA integrated circuit. The low-profile packaged FPGA integrated circuit includes a die-bonded assembly disposed within a co-fired multilayer ceramic integrated circuit package. The die-bonded assembly includes the optoelectronic die, the bottom surface of which is die-bonded and electrically interconnected by micropads to the upper surface of the core of an FPGA integrated circuit die. A first optical fiber communicates light from the connector, through the package, and to a photodetector on the optoelectronic die. A second optical fiber communicates light from a laser diode on the optoelectronic die, through the package, and to the connector. In some embodiments, a micromirror device is disposed within the package to redirect light between the optoelectronic die and the optical fibers.

Owner:XILINX INC

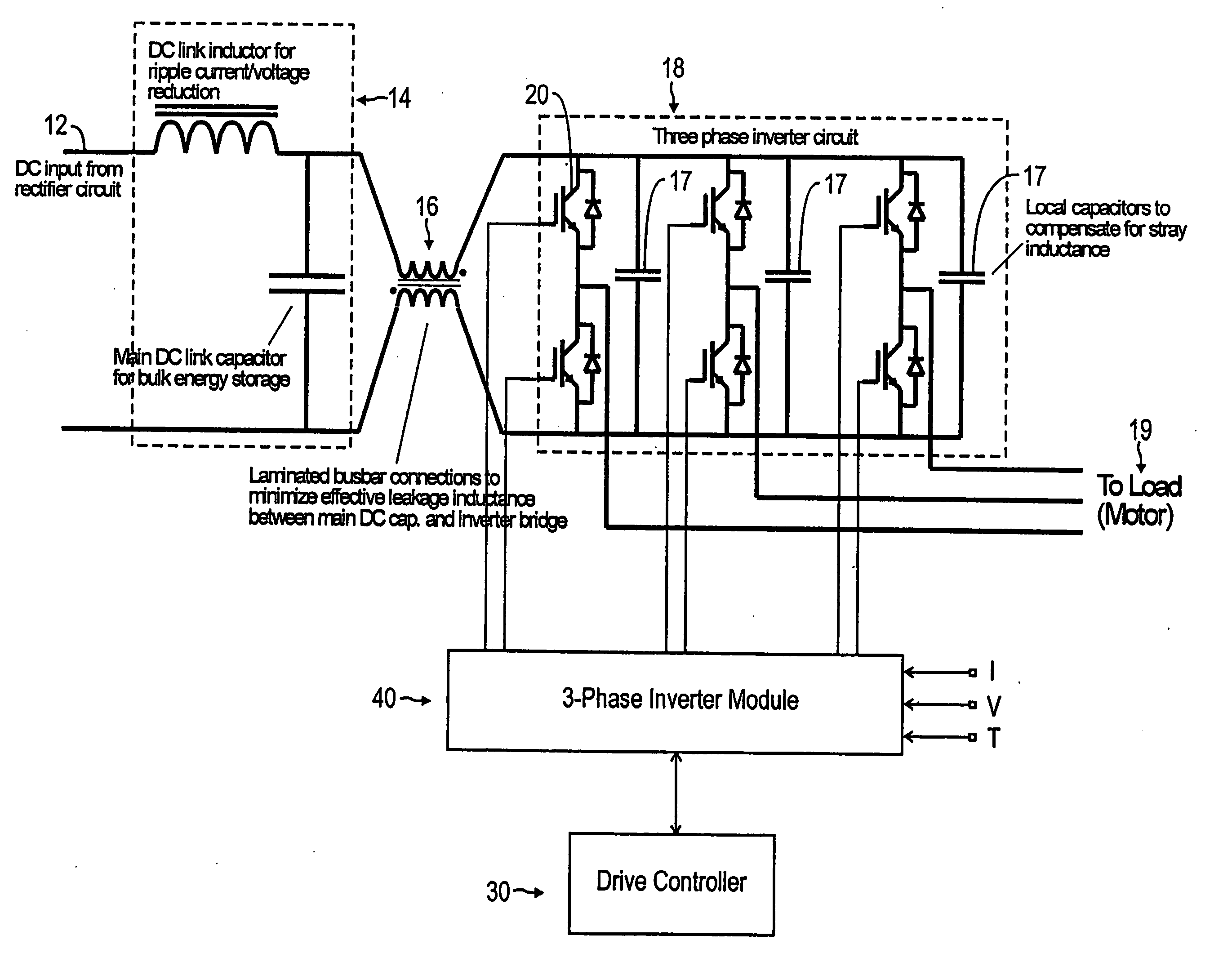

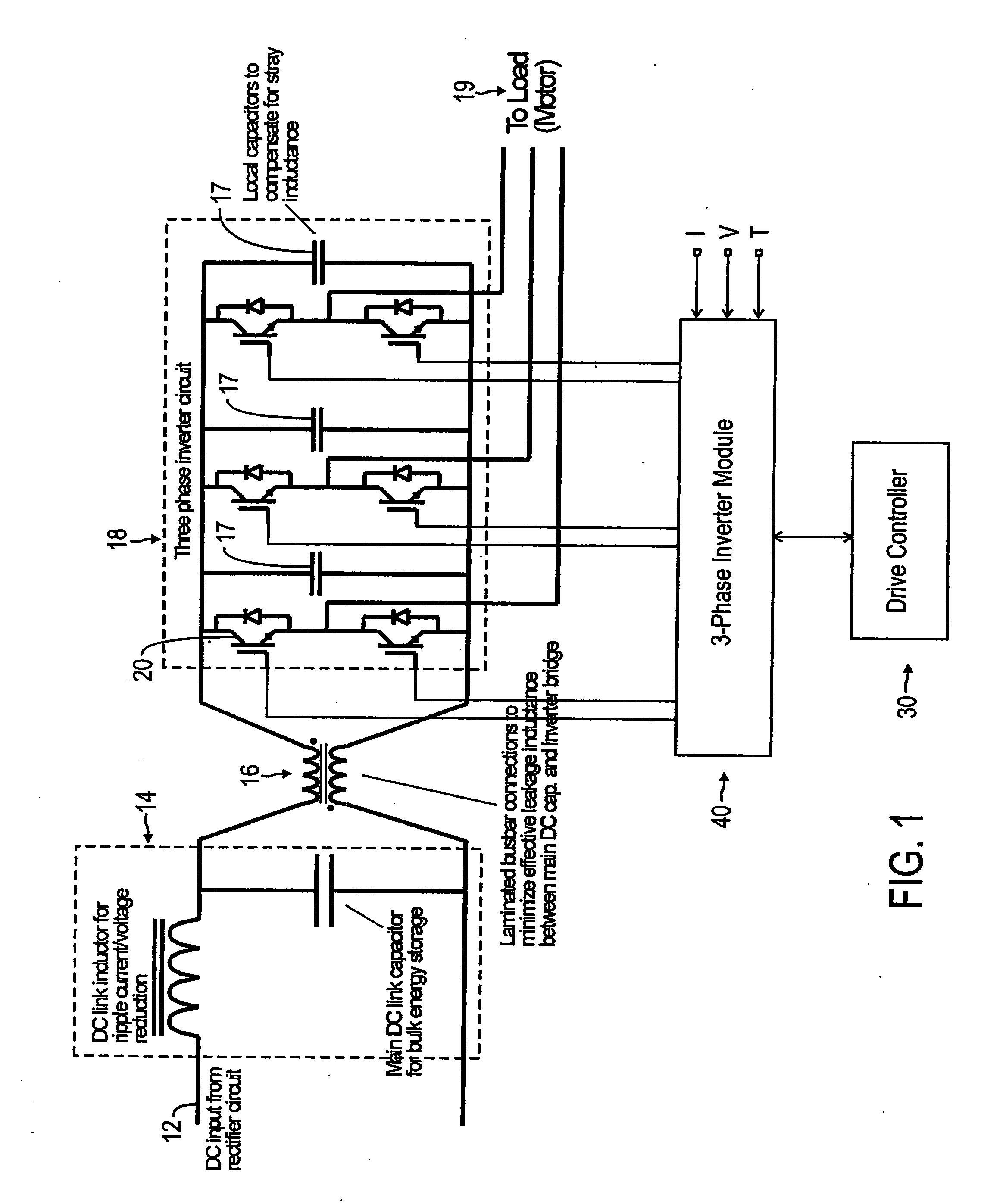

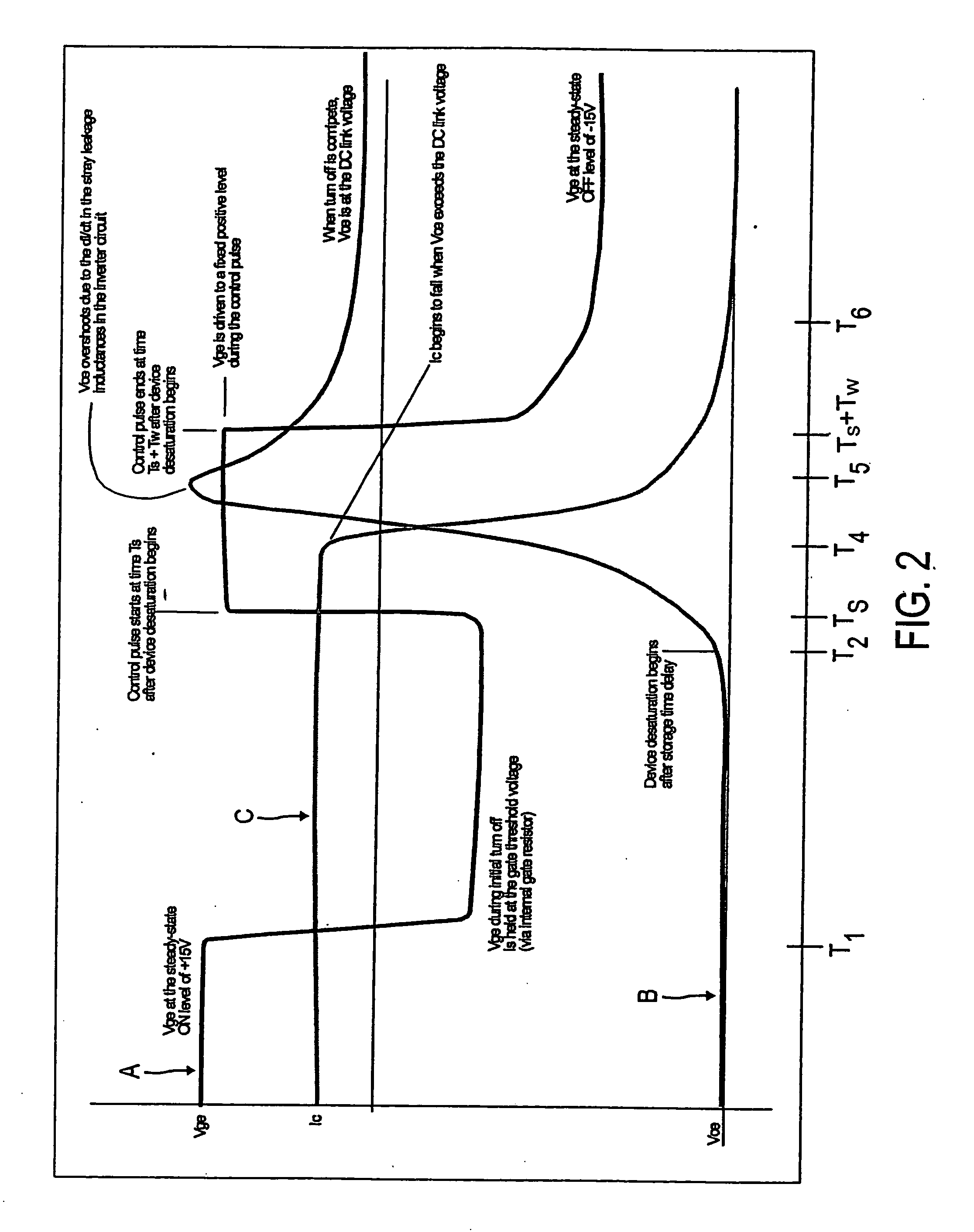

Adaptive gate drive for switching devices of inverter

An adaptive gate drive for an inverter includes control circuitry having a Field Programmable Gate Array (FPGA) and includes power circuitry having a plurality of FETs for operating a switching device, such as a Trench Gate Insulated Gate Bipolar Transistor (IGBT device). The control circuitry provides switching signals for operating the switching device. In addition, the control circuitry receives signals of output current of the IGBT device, temperature of the IGBT device, and DC link voltage. The FPGA has a plurality of operating points stored therein. Each operating point has corresponding parameters for a control signal that is used to control the turn-on or turn-off behavior of the IGBT device. During operation, the control circuitry compares the measured current, voltage and temperature operating points stored in the FPGA and sends the corresponding parameters to the gate drive circuit. The gate drive modifies the signal on the gate of the IGBT accordingly and thereby optimizes the turn-on and / or turn-off behavior of the device based on actual operating conditions.

Owner:LETOURNEAU TECH DRILLING SYST

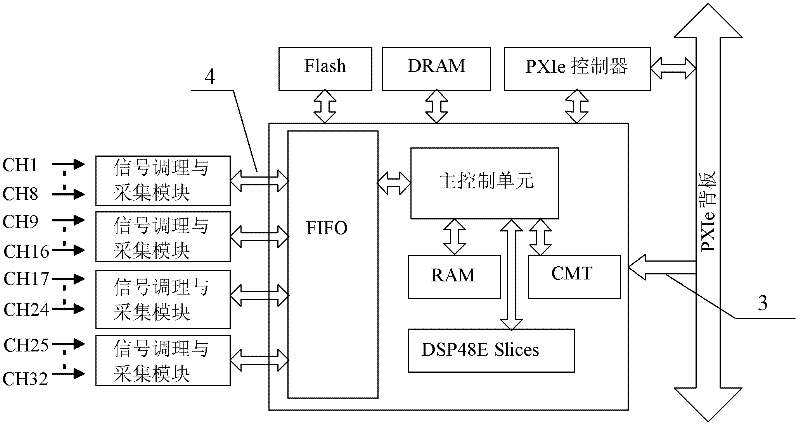

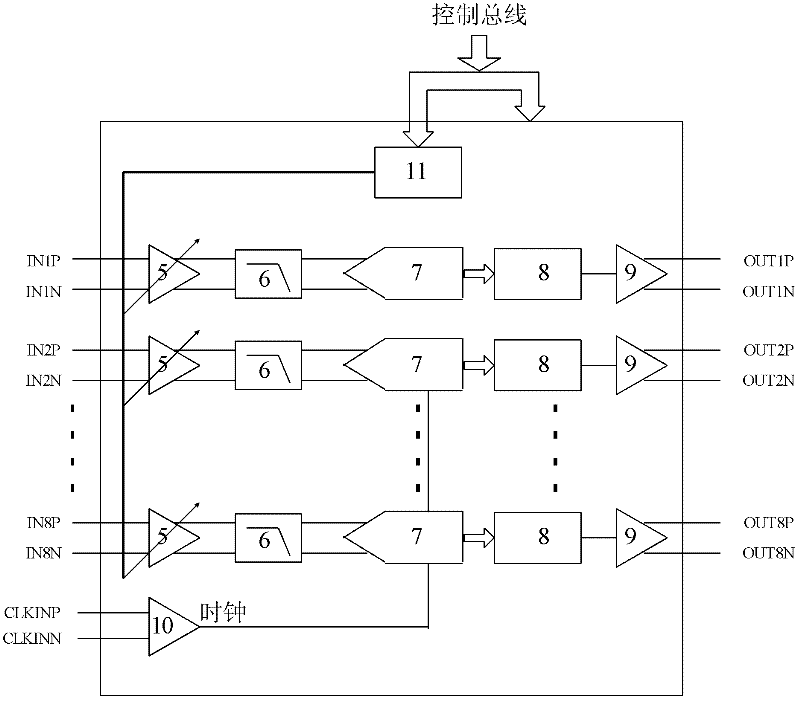

Extensible multichannel parallel real-time data acquisition device and method

ActiveCN102521182AEasy to scale massivelyGood parallel data processing capabilityElectric digital data processingComputer moduleData transmission

The invention discloses an extensible multichannel parallel real-time data acquisition device and method. The device comprises a PXIe (PCI (Peripheral Component Interconnect) Extensions for Instrumentation Express) backboard, a CPU (Central Processing Unit) board card and a plurality of FPGA (Field-Programmable Gate Array) acquisition cards; the PXIe backboard comprises a CPU motherboard slot, a clock board slot, a plurality of FPGA board card slots and a PCIe (Peripheral Component Interface Express) / PCI switching bridge; the data transmission between the CPU board card and the FPGA acquisition cards is achieved by PCIe switches, and the P2P (Peer-to-Peer) data transmission is carried out among the FPGA acquisition cards; a clock module provides a system differential clock, differential synchronization signals and differential star-shaped triggers through a clock bus and is downwardly compatible with a PXI clock; and the FPGA board card slots realize the compatibility between a PXI and a Compact PCIe board card through a PCI bus and the PCIe / PCI switching bridge. The invention further provides the method based on the device. The device and the method have the advantages of high sampling rate, fast data transmission and easiness for the large-scale extension of a plurality of board cards.

Owner:SOUTH CHINA NORMAL UNIVERSITY

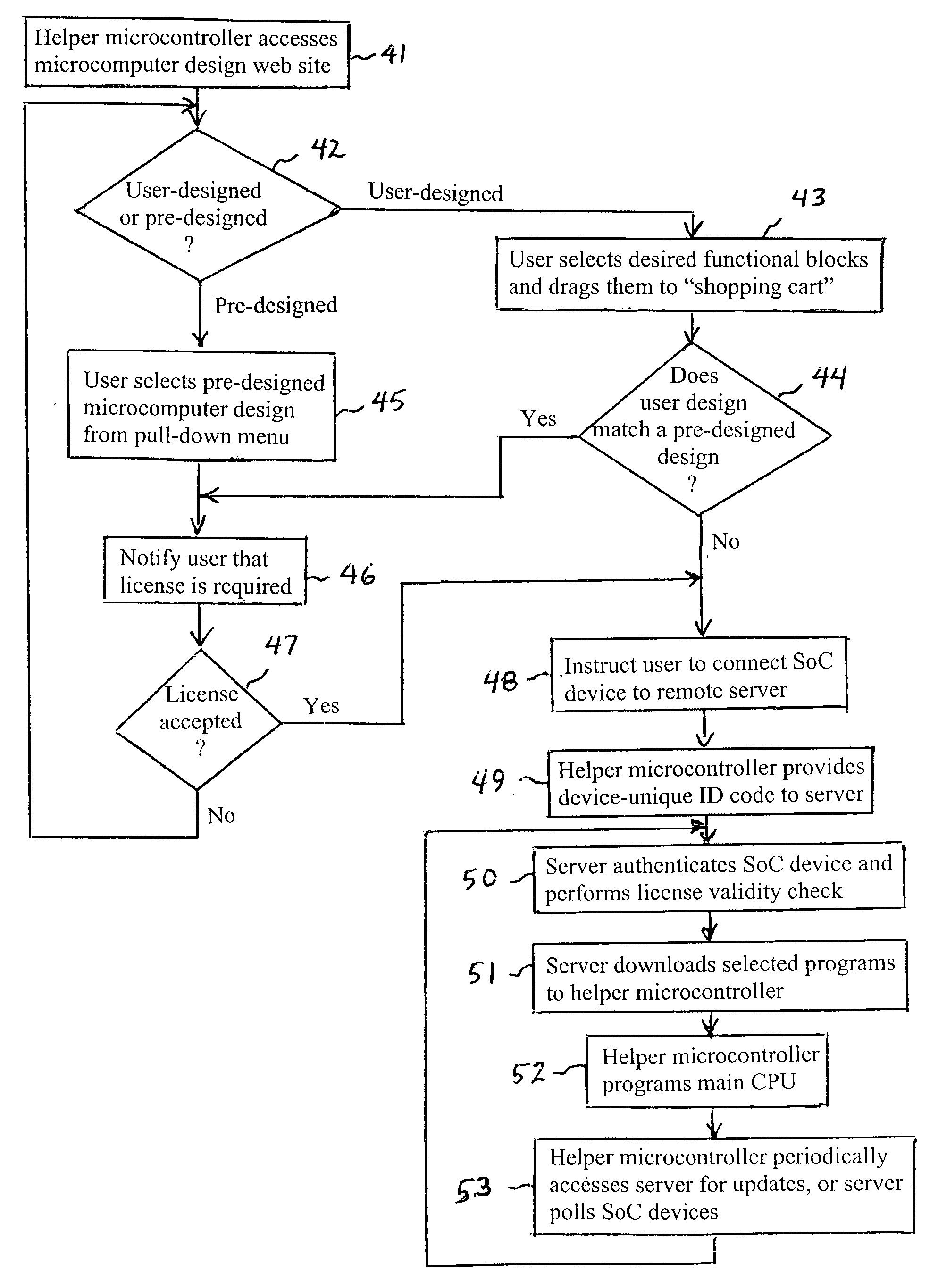

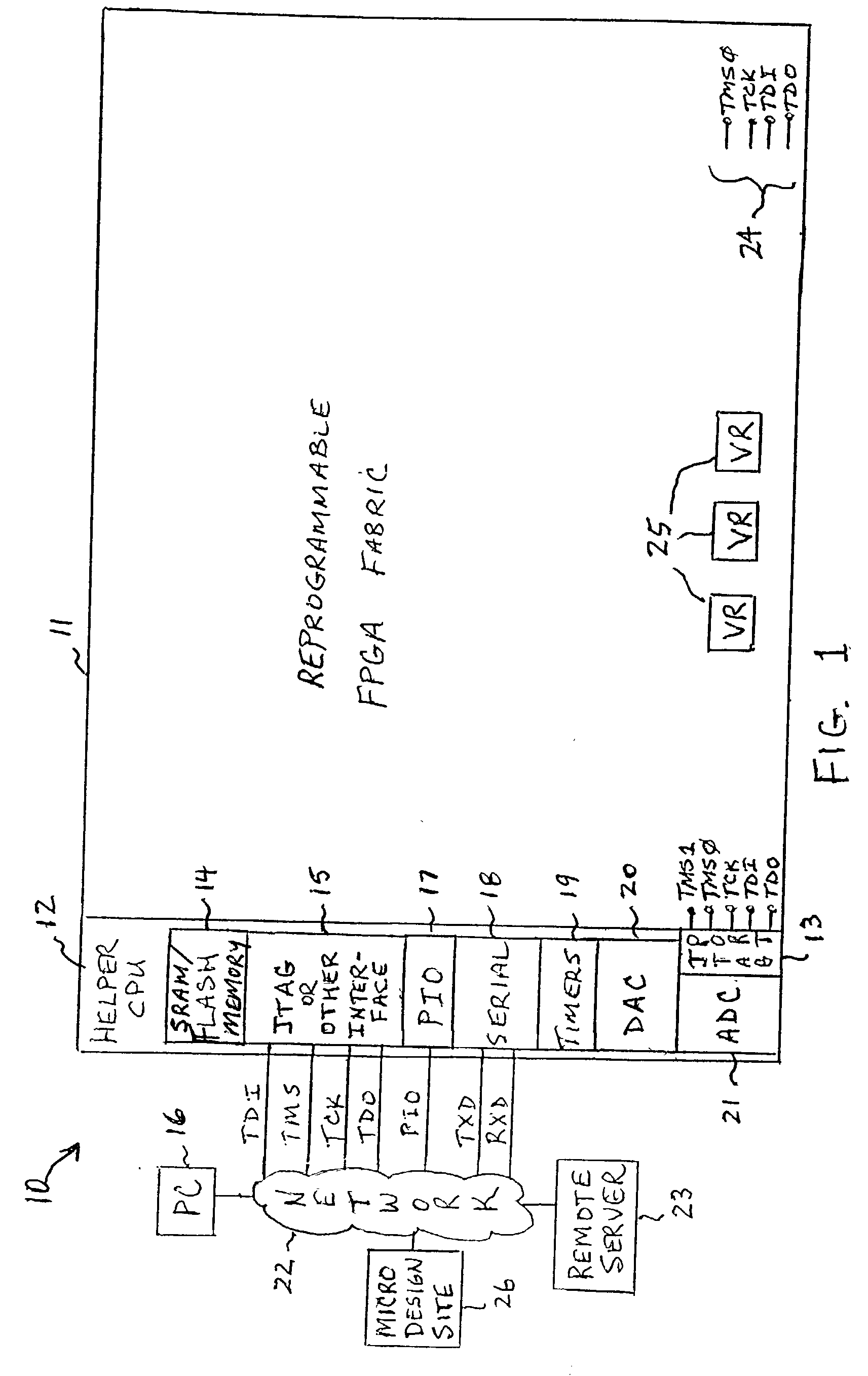

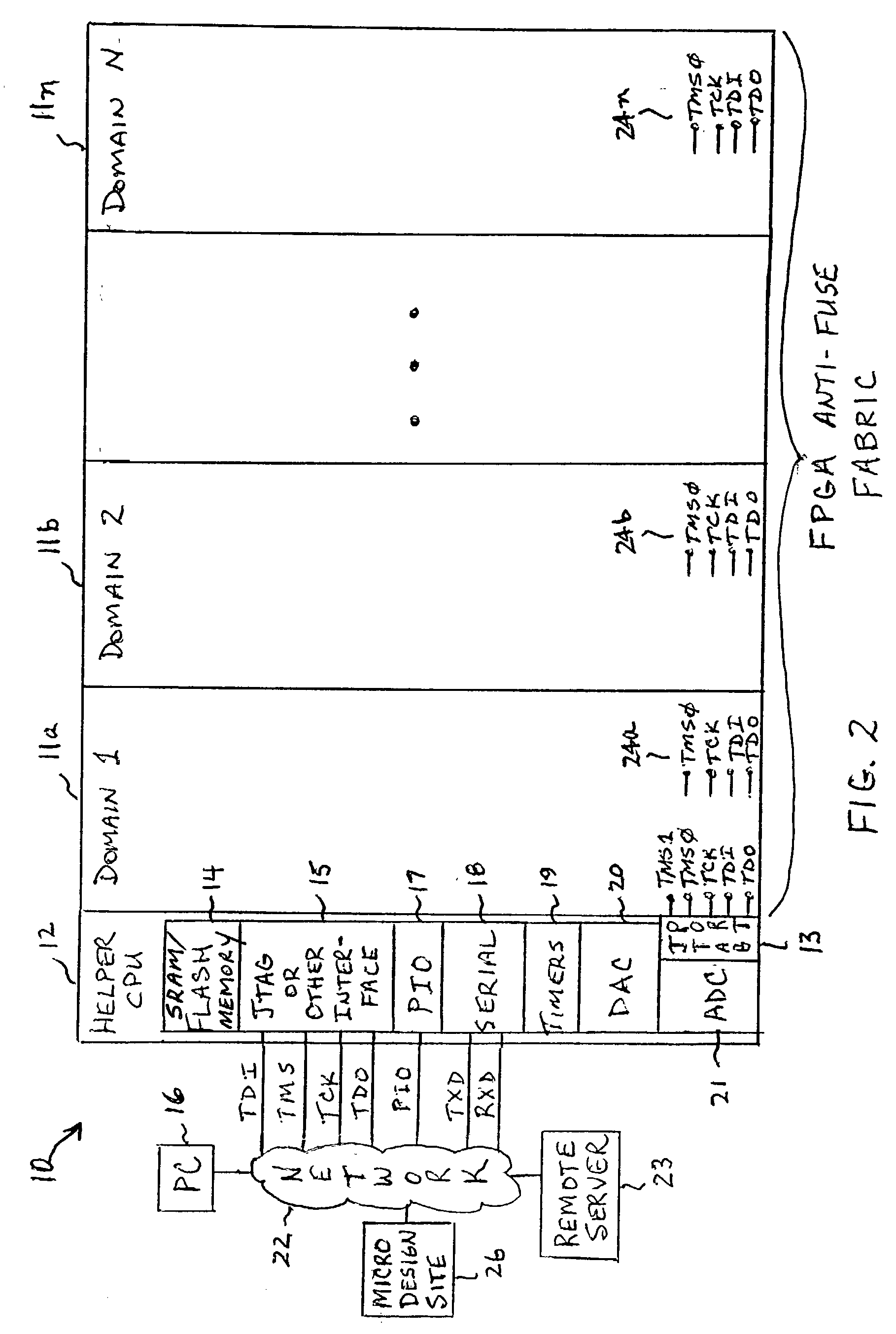

Self-programmable microcomputer and method of remotely programming same

InactiveUS20030217306A1Error preventionDetecting faulty hardware by remote testMicrocontrollerMicrocomputer

A user-configurable and / or self-configurable System on a Chip (SoC) device and corresponding remote programming method enabling the SoC to be reprogrammed multiple times from a remote chip file server. Once programmed with the desired SoC design, the device can be debugged remotely in real-time by one or more users. The device includes a helper microcontroller / programmer, and a Field Programmable Gate Array (FPGA) fabric which is divided into a plurality of programmable logic and clock driver domains that may be independently programmed by way of the helper microcontroller. Once programmed, the helper microcontroller can serve as a real-time monitor / data exchange sub-controller and / or may be used by the end application.

Owner:HARTHCOCK JERRY D +1

Combination field programmable gate array allowing dynamic reprogrammability and non-votatile programmability based upon transistor gate oxide breakdown

Owner:LATTICE SEMICON CORP +1

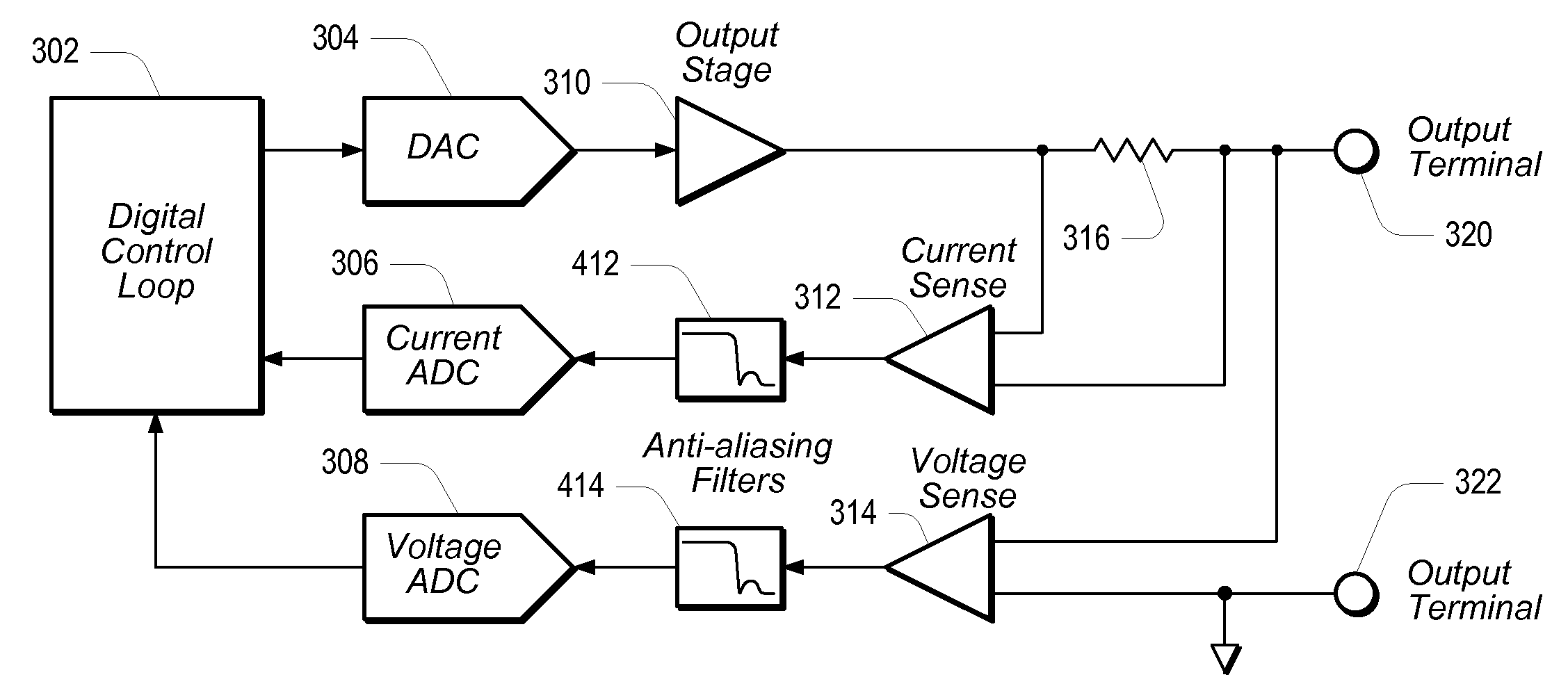

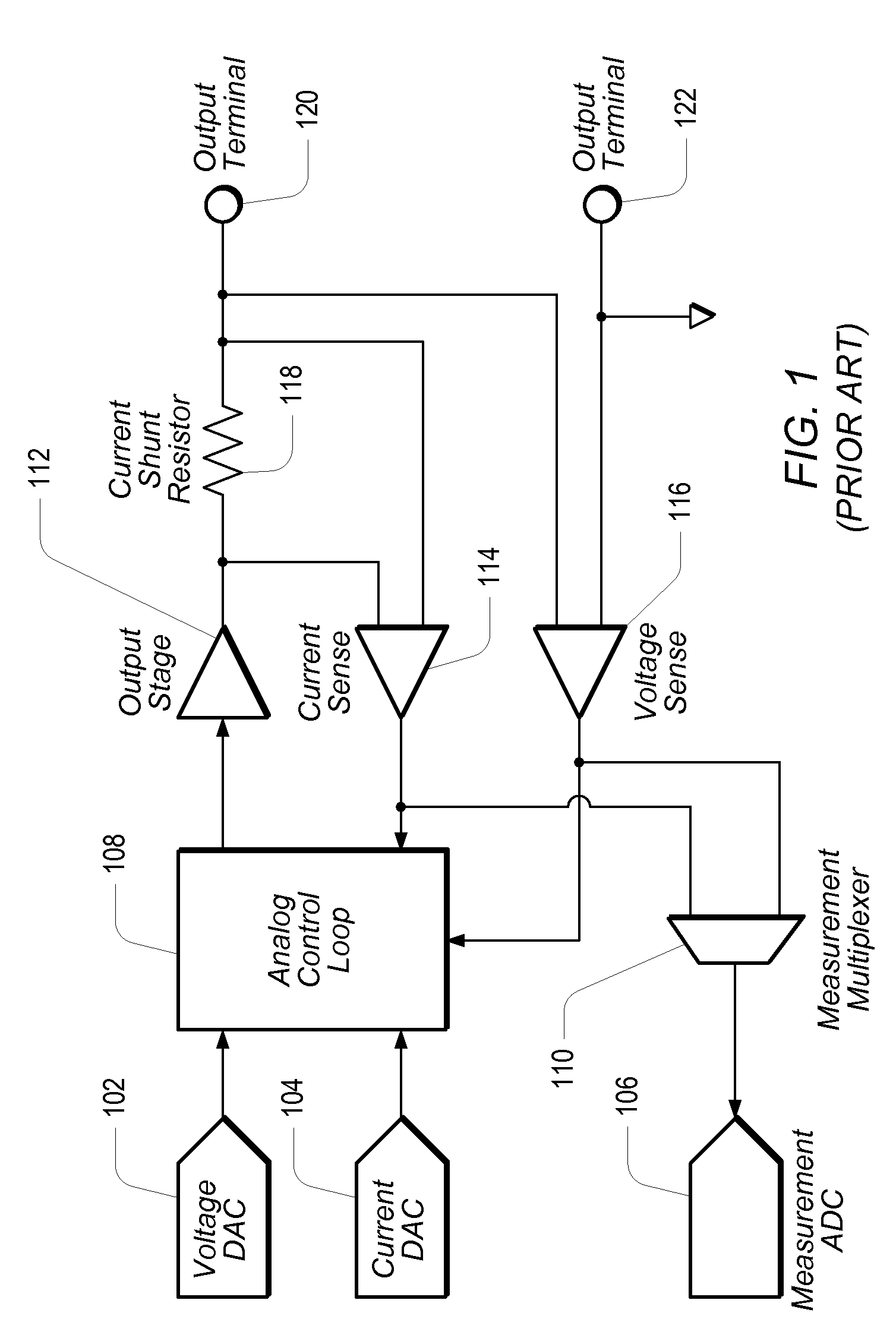

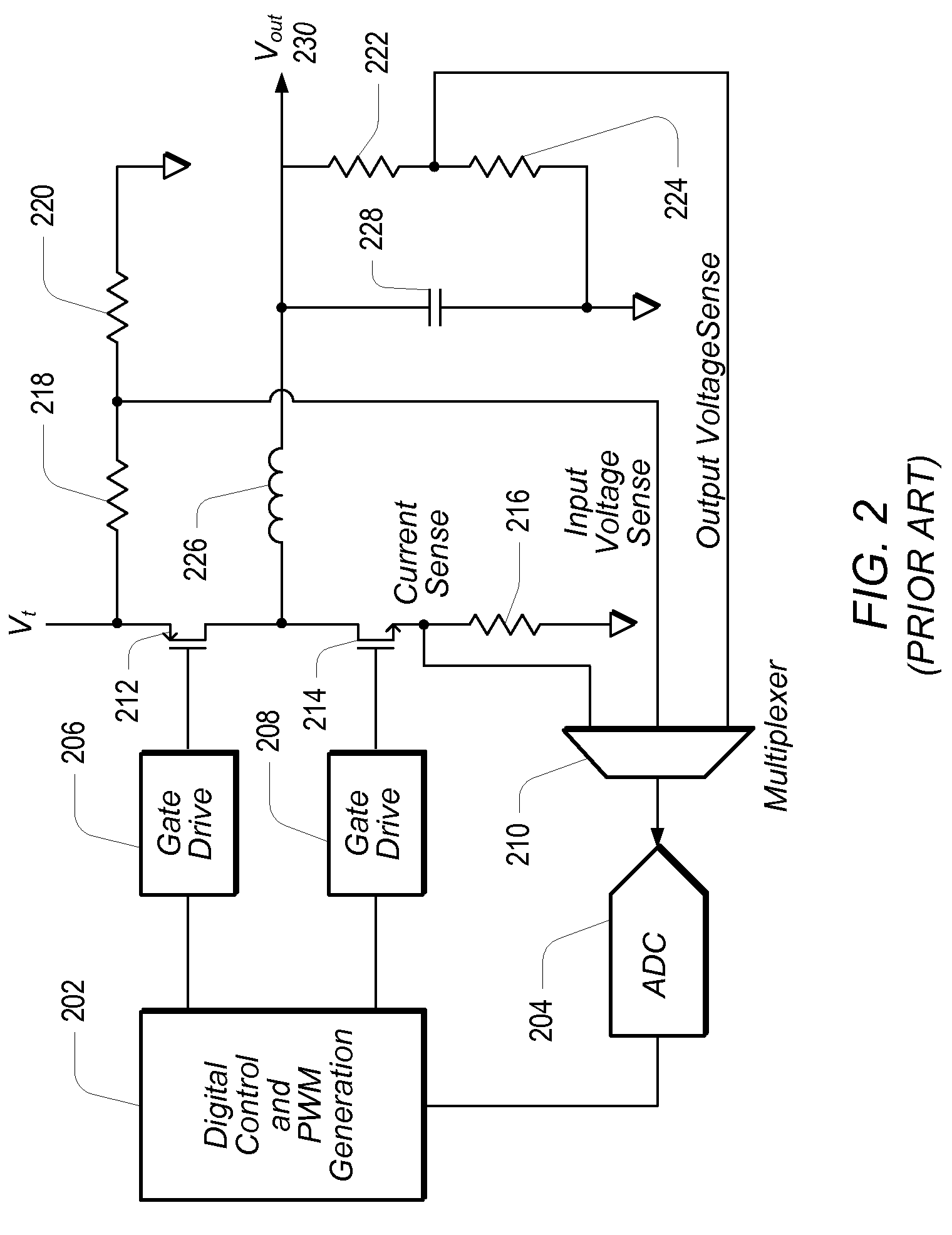

Source-Measure Unit Based on Digital Control Loop

ActiveUS20090121908A1Increase flexibilityConvenient and accurateElectric signal transmission systemsElectric devicesDigital signal processingMeasuring output

A source-measure unit (SMU) may be implemented with a control loop configured in the digital domain. The output voltage and output current may be measured with dedicated ADCs (analog-to-digital converters). The readings obtained by the ADCs may be compared to a setpoint, which may be set in an FPGA (field programmable gate array) or DSP (digital signal processing) chip. The FPGA or DSP chip may then be used to produce an output to drive a DAC (digital-to-analog converter) until the output voltage and / or output current reach the respective desired levels. The readback values may be obtained by averaging the voltage and / or current readings provided by the ADCs. The averaging may be weighted to improve noise rejection. The digital control loop provides added flexibility to the SMU and a decrease in the accuracy requirements on the DAC, while also for solving potential range-switching issues that may arise within the SMU.

Owner:NATIONAL INSTRUMENTS

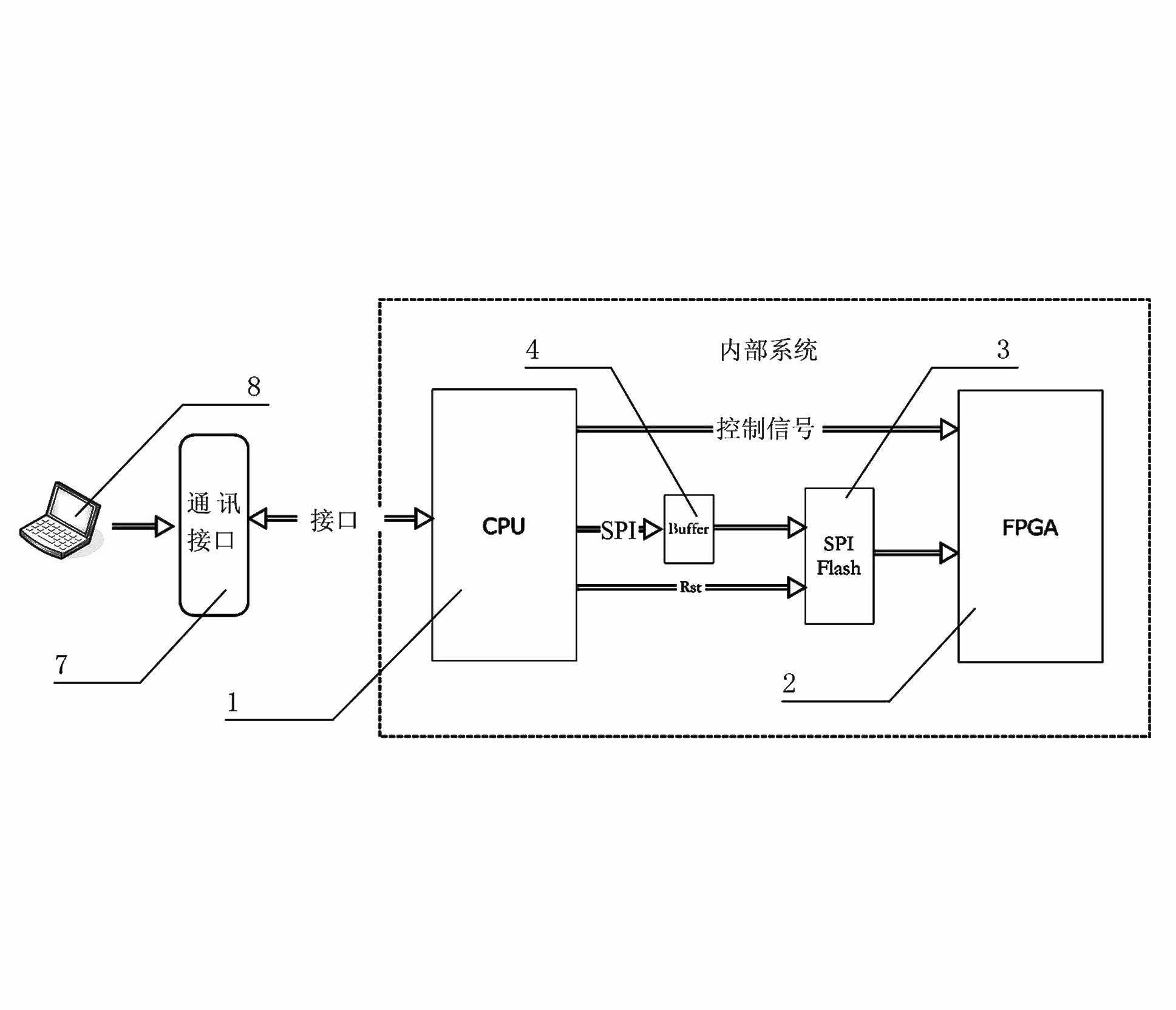

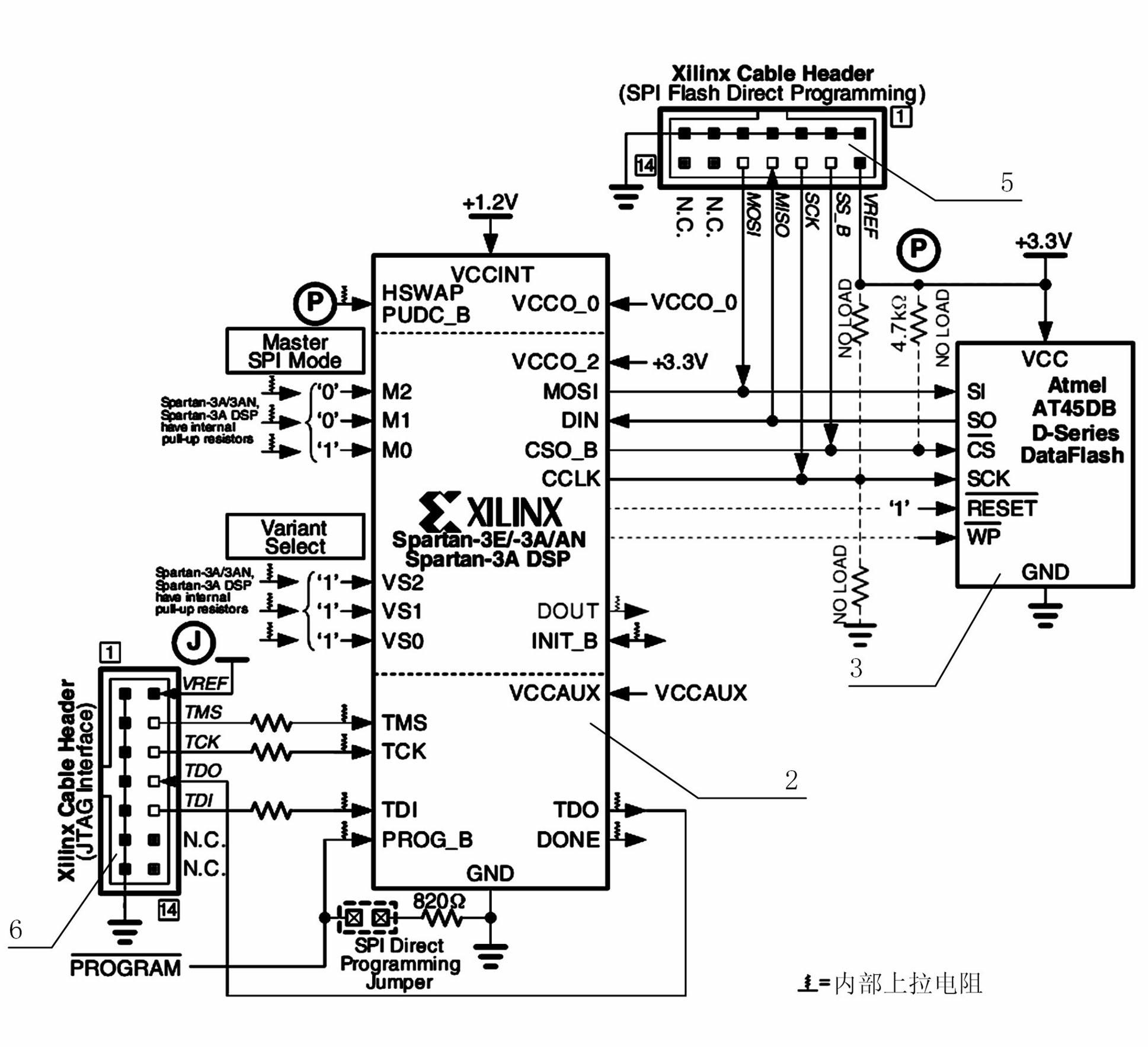

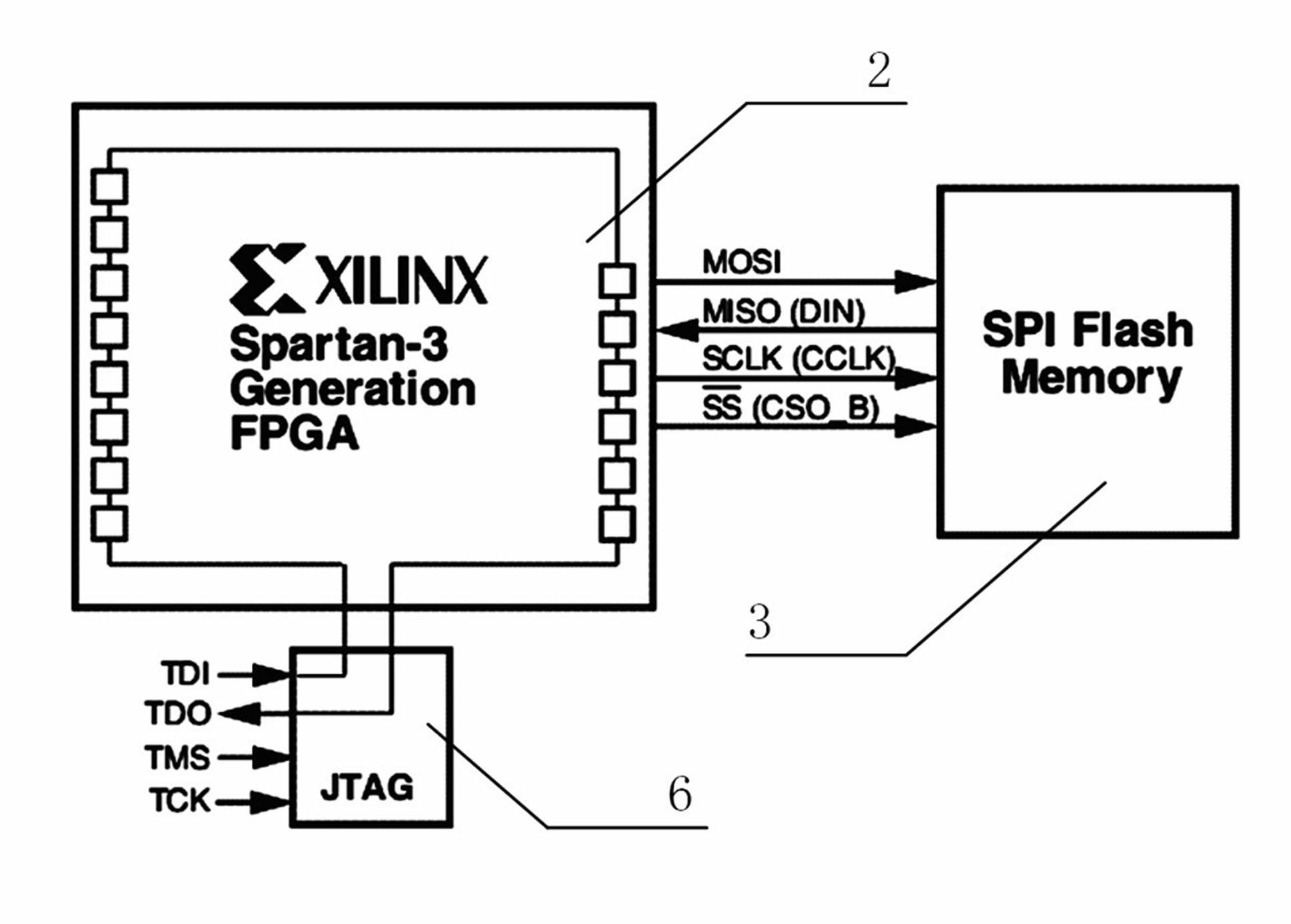

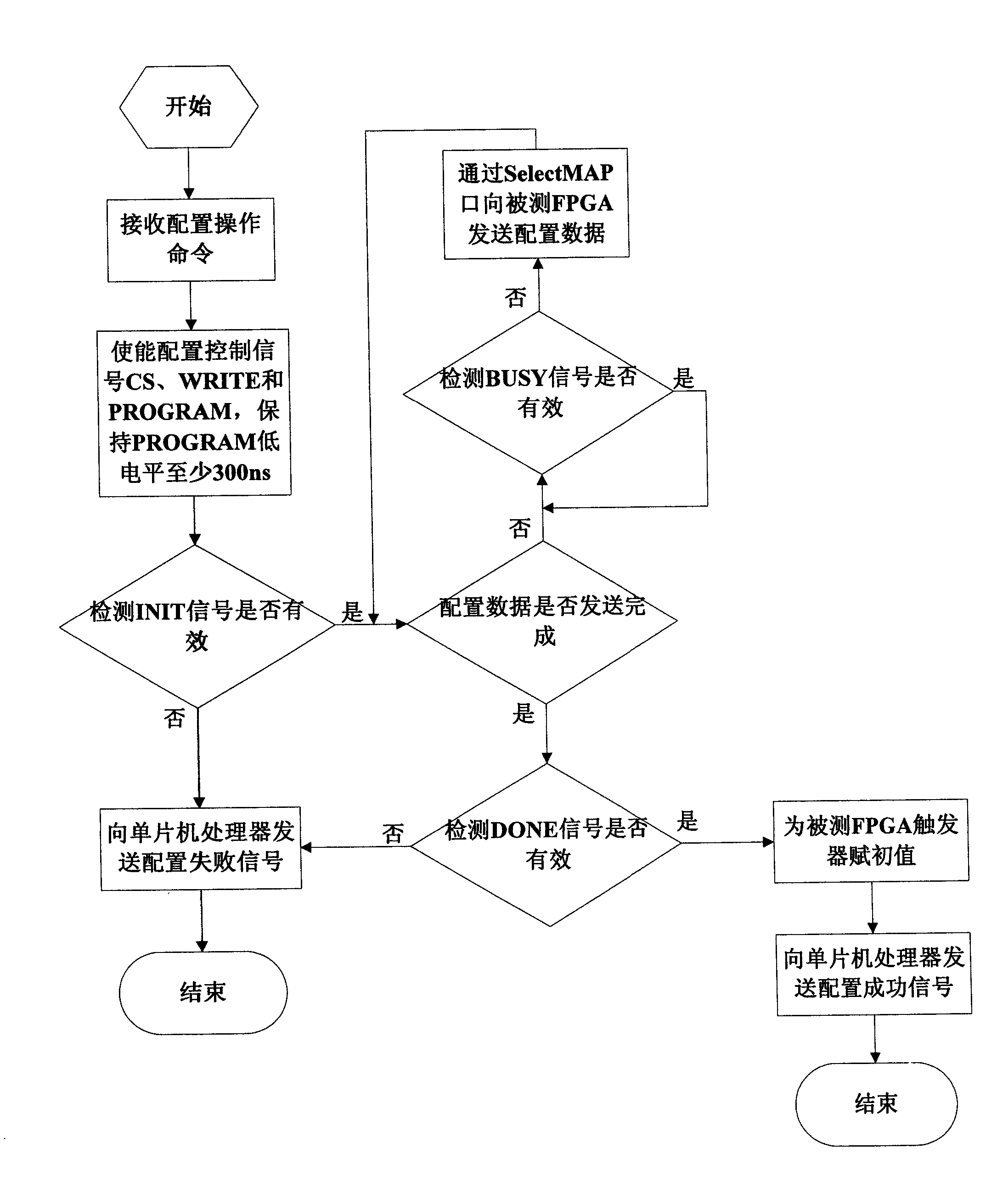

System for updating FPGA (Field Programmable Gate Array) configuration program from a long distance based on control of processor and method therefor

ActiveCN102609286AAvoid disassemblyReal-time online updateProgram loading/initiatingCommunication interfaceField-programmable gate array

The invention discloses a system for updating an FPGA (Field Programmable Gate Array) configuration program from a long distance based on the control of a processor and a method for updating the FPGA configuration program from a long distance based on the control of the processor. The system comprises a processor module, an FPGA module, an SPI (Serial Peripheral Interface) memory module and a buffer module, wherein the processor module is connected with the SPI memory module and is connected with a communication interface, the SPI memory module is connected with the FPGA module, and the processor module is connected with the SPI memory module by the buffer module. When the configuration program of an FPGA requires to be updated, an upper computer or a terminal downloads the FPGA configuration program into the SPI memory module through the communication interface and the processor module, and the FPGA module can automatically load the configuration program memorized in the SPI memory module in a MasterSPI mode. According to the system and the method, the FPGA configuration program is updated from a long distance, the function of updating the configuration program on line under the non-outage situation is realized, and therefore, the system and the method are particularly suitable for on-site application.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

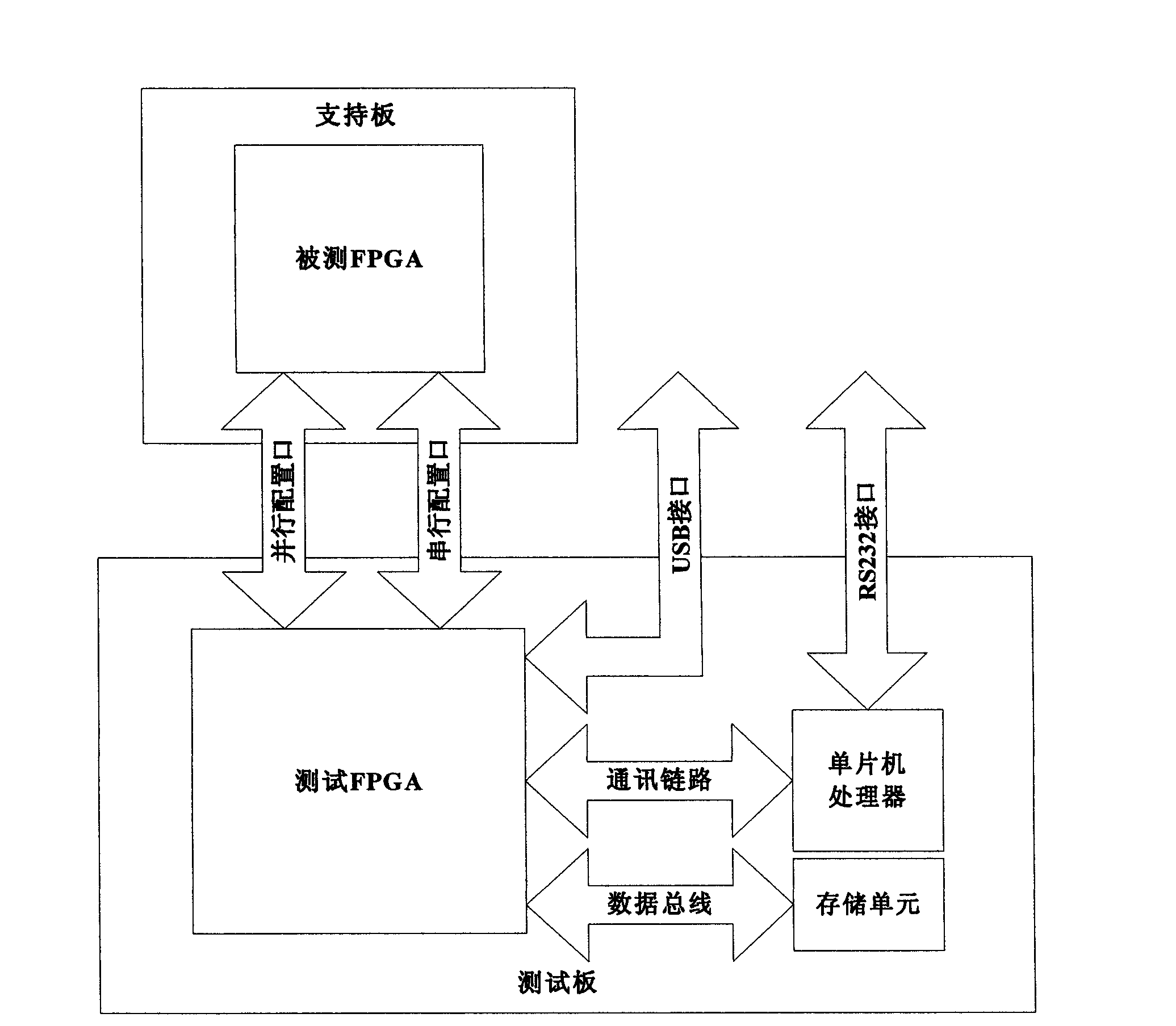

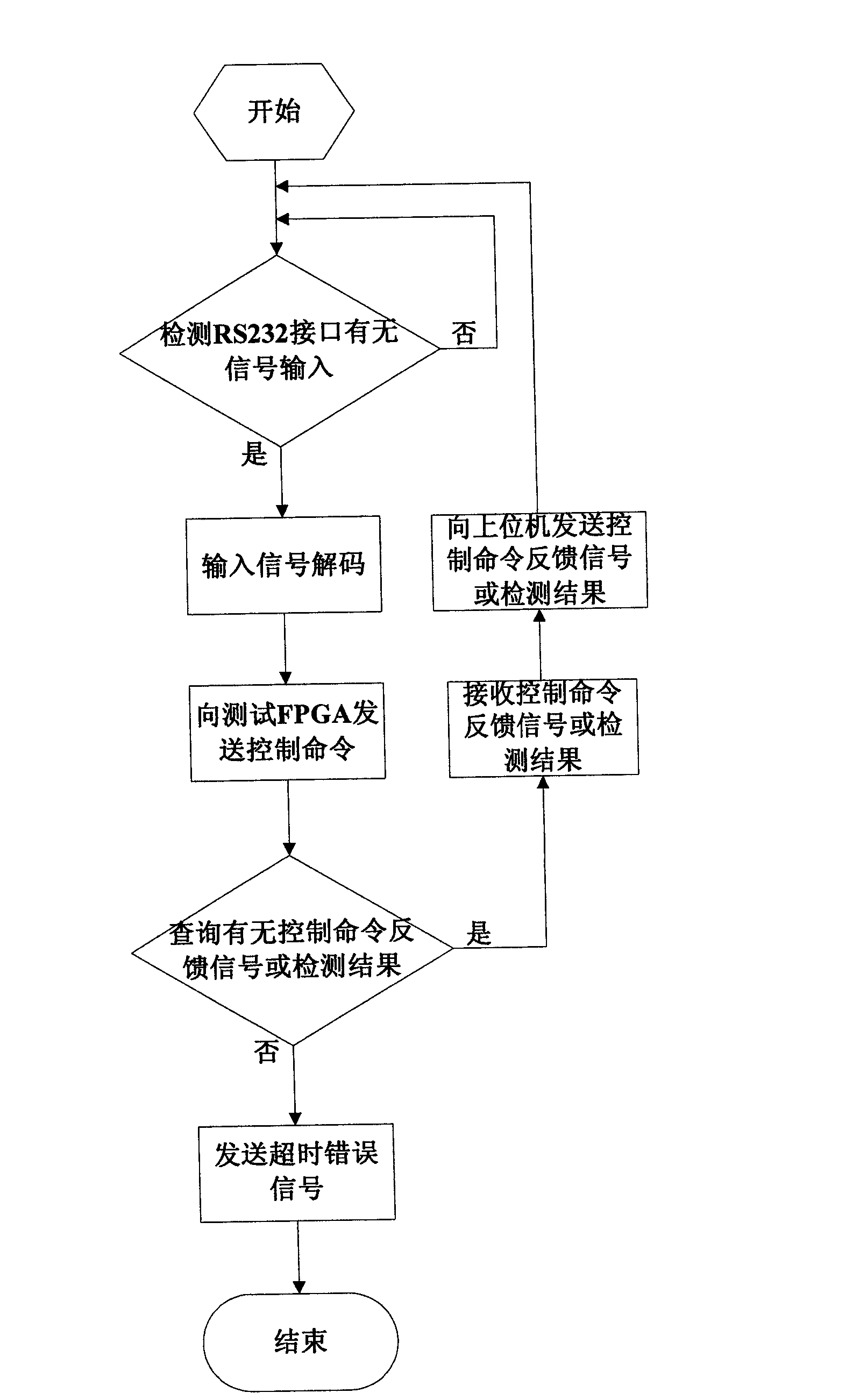

Test system and method for single event effect of SRAM (System Random Access Memory) type FPGA (Field Programmable Gate Array)

ActiveCN102332307AEasy to operateImplement rollover detectionStatic storagePilot systemRandom access memory

The invention provides a test system and method for a single event effect of an SRAM (System Random Access Memory) type FPGA (Field Programmable Gate Array). The test system comprises a single chip microcomputer processor, an RS232 interface circuit, a USB (Universal Serial Bus) interface circuit, a test FPGA and a storage unit. The test system and method can be used for fault injection tests of a configuration memory and a BRAM (Battery Random Access Memory) of the SRAM type FPGA, and single event function interrupting detection, single event locking detection and single event turning detection including single event turning detection for a configuration storage region, the BRAM and a trigger of the SRAM type FPGA are realized. The invention has the advantages of simplicity in operation, entirety in detection, high accuracy, good real-time property and strong universality.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY