Patents

Literature

1555results about How to "Reduce Design Complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Channel equalization system and method

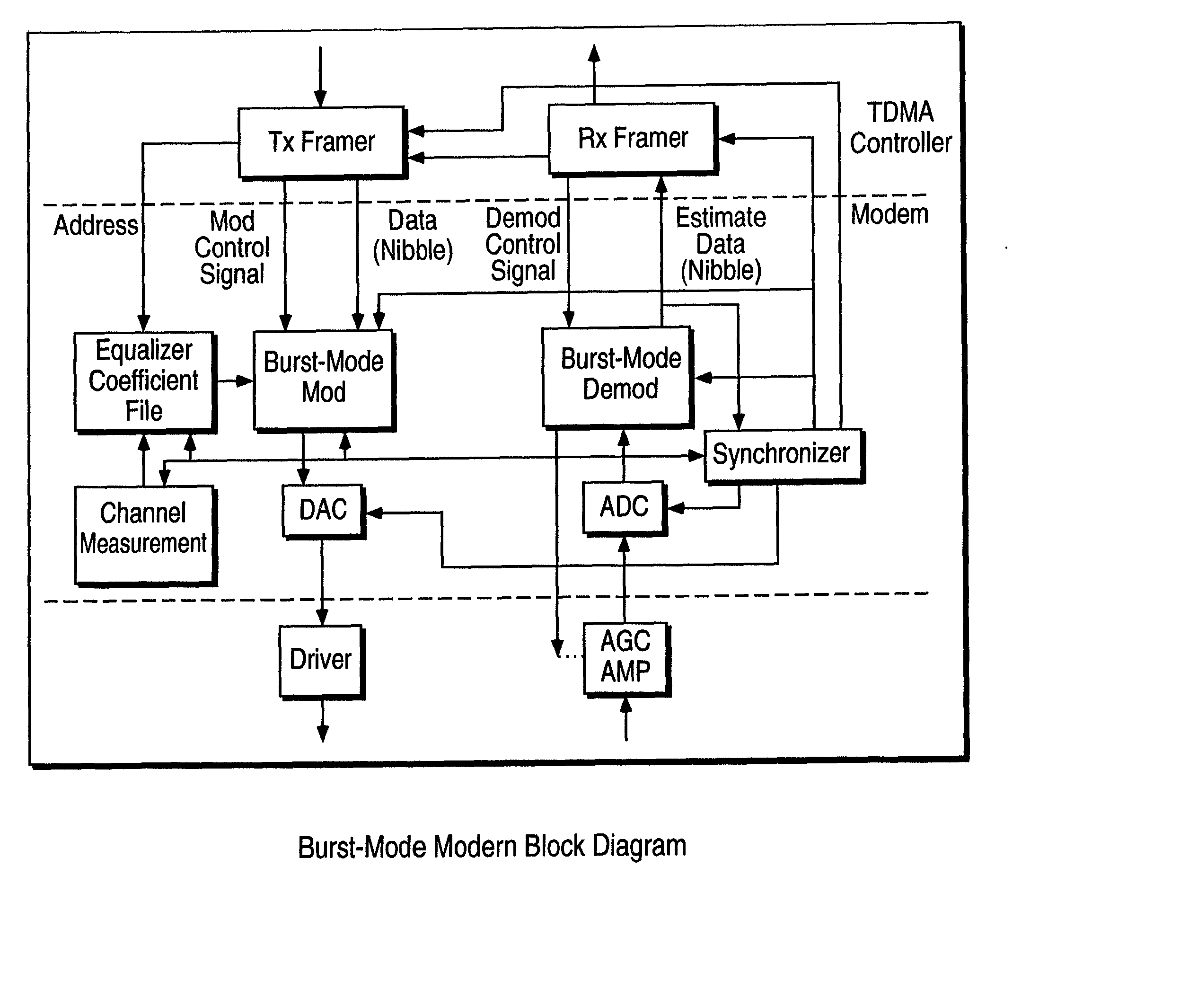

InactiveUS20030016770A1Increase high performance and data rate capacityLow costMultiple-port networksChannel dividing arrangementsData transmissionTTEthernet

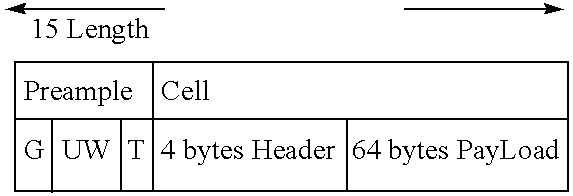

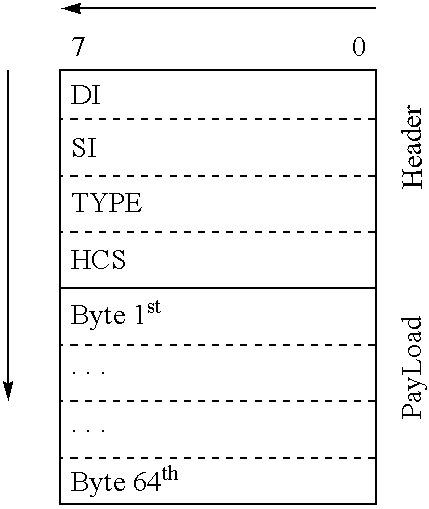

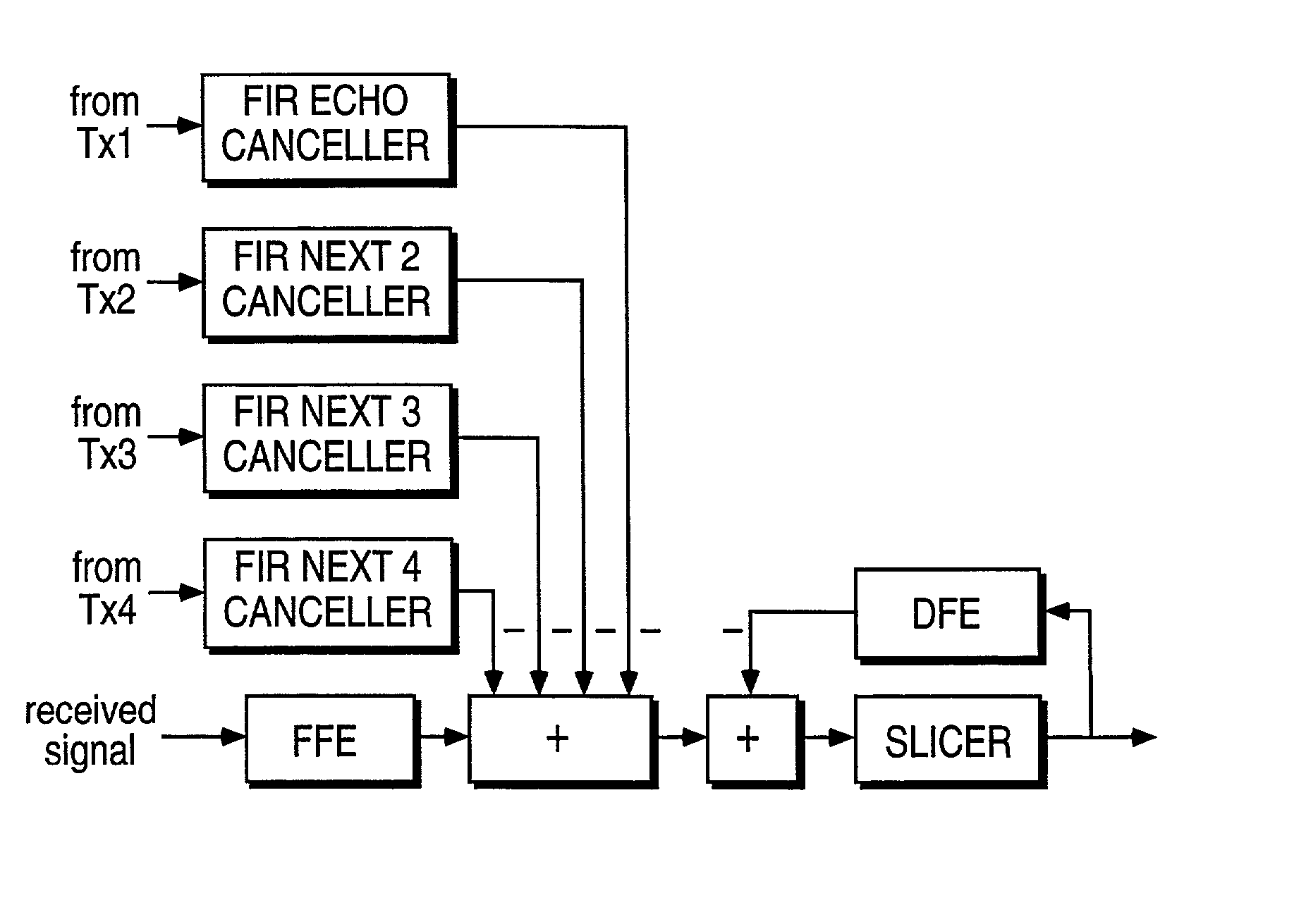

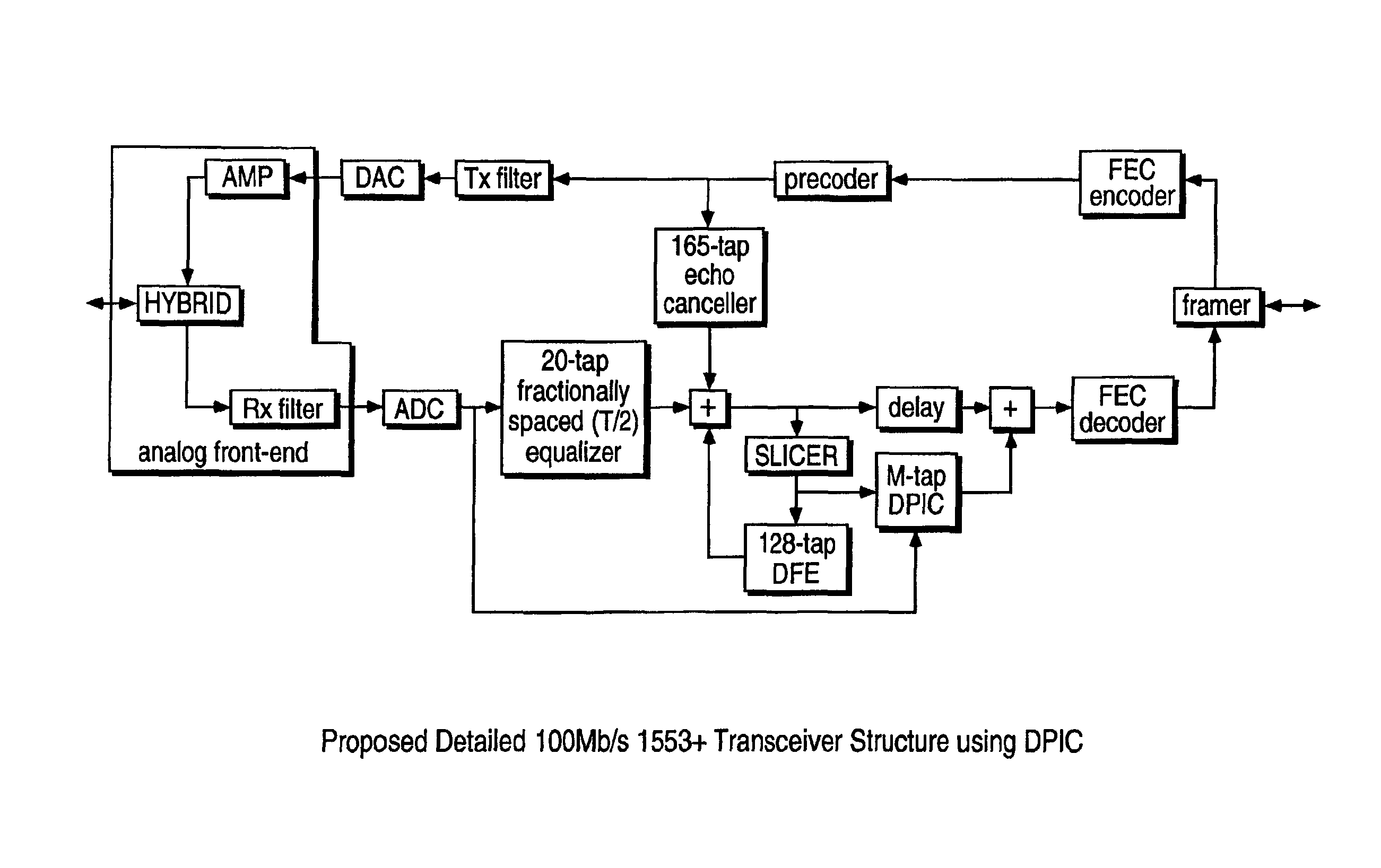

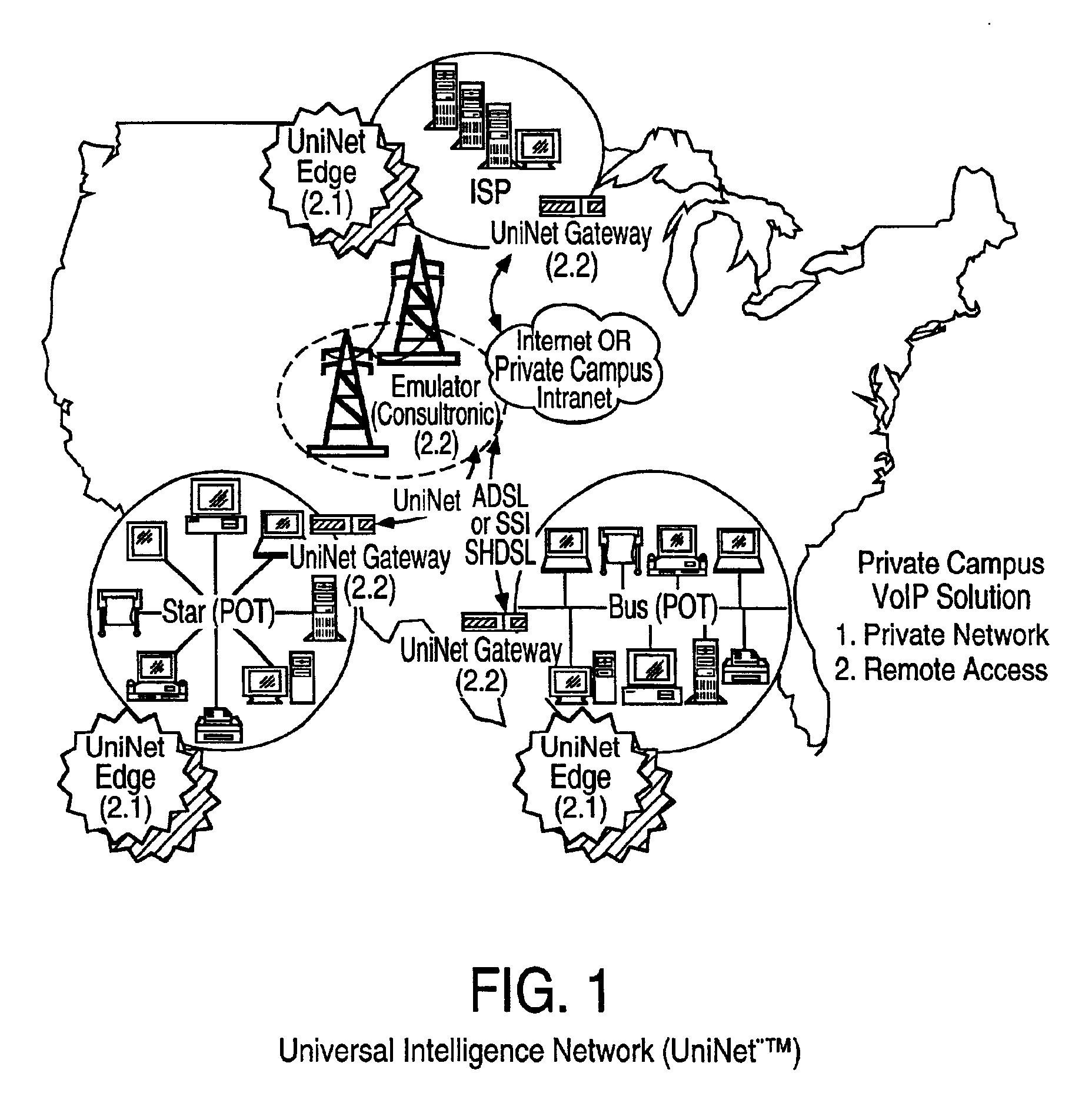

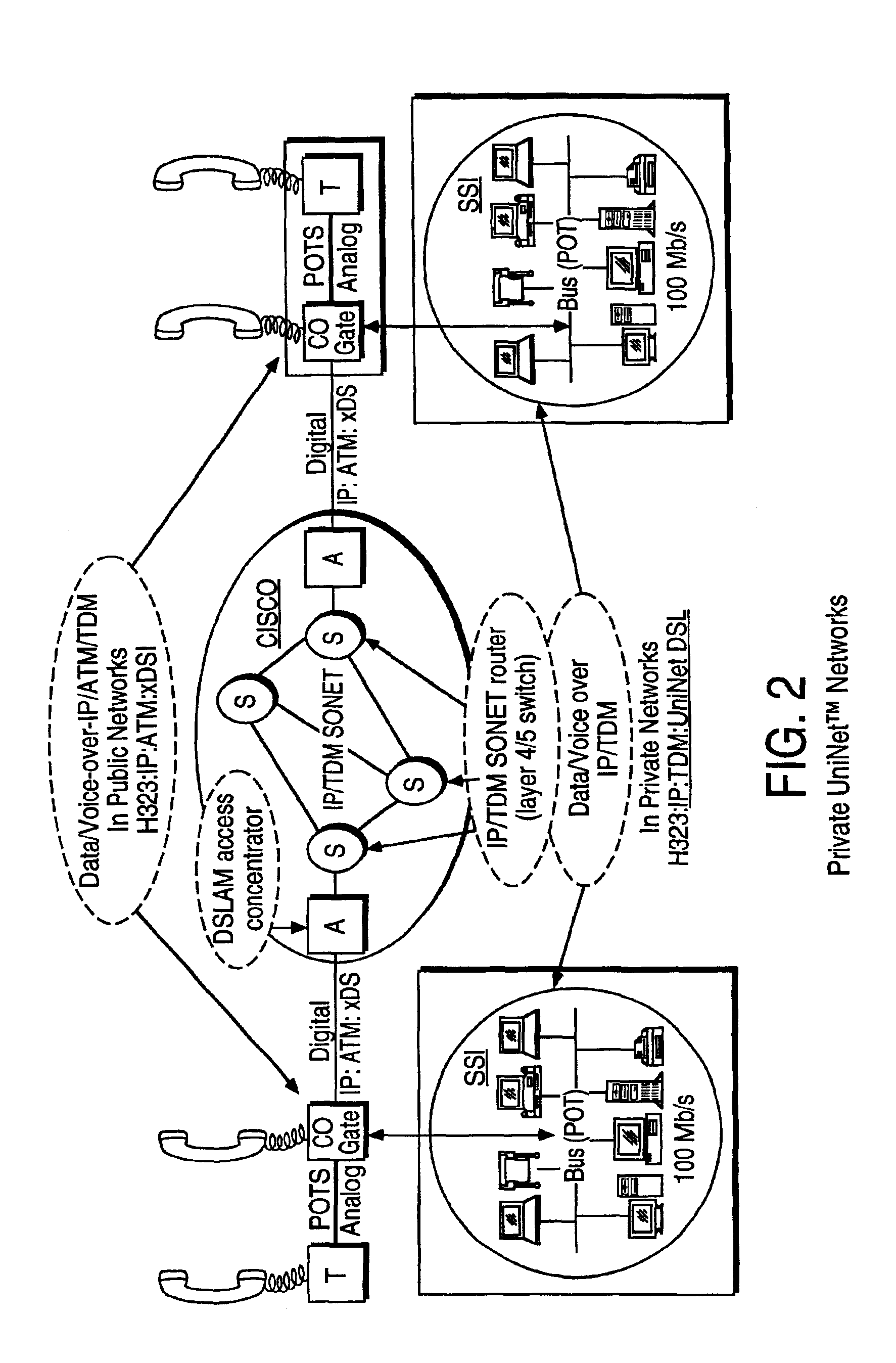

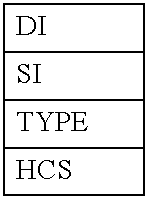

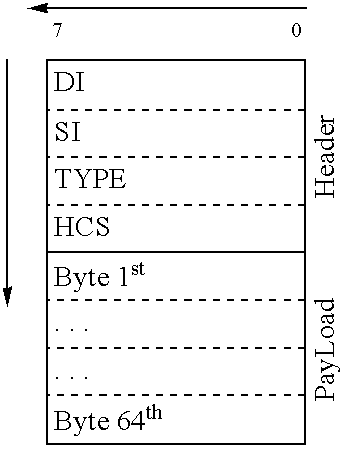

A system and method for delivering increases speed, security, and intelligence to wireline and wireless systems. The present invention includes a new generation Fast Circuit Switch (packet / circuit) Communication processors and platform which enables a new Internet Exchange Networking Processor Architecture at the edge and core of every communication system, for next generation Web Operating System or Environment (WOE) to operate on with emphasis of a non-local processor or networking processor with remote web computing capabilities. A Unified Network Communication & Processor System or UniNet is a New generation network architecture of packet / circuit communication processors or Internet networking processor, that increases speeds over any communication channels and topologies, synchronizing, enabling, improving, controlling and securing all of the data transmission of web applications over existing wireline and wireless infrastructure while providing seamless integration to the legacy telecom & data corn backbone. The present invention is capable of operating on any topology with distributed intelligence and data switching / routing, which is located at the edge. This method not only alleviates the ever increasing data processing bottleneck which is currently done by the data communication and telecom switch and routers, but it also enables new and next generation Internet Processor architecture. The UniNet is also a flexible solution for the novel concept that the capability of a network interface should depend on the level of service assigned to a service access point, not the capacity of the total network, such as transaction services with a short burst of messages with short access delay. The present invention increases channel capacity by using a parallel or multi-channel structure in such wireless and wireline at the edge or the core of. This new architecture of the present invention uses parallel bitstreams in a flexible way and distributed switching / routing technique, is not only to avoid the potential bottlenet of centralized switches, but also to increase speed with intelligence that is seamlessly integrating into the Fiber Optic Backbone such as WDM and SONET of the MAN / WAN network with a Real-time guarantees, different types of traffic (such as Stringent synchronous, isochronous, and asynchronous data messages) with different demands, and privacy & security of multi access and integrated services environment.

Owner:B C LEOW

Channel equalization system and method

InactiveUS6904110B2Increase high performance and data rate capacityLow costMultiple-port networksChannel dividing arrangementsFiberEngineering

A system and method for delivering increases speed, security, and intelligence to wireline and wireless systems. The present invention increases channel capacity by using a parallel or multi-channel structure in such wireless and wireline at the edge or the core of. This new architecture of the present invention uses parallel bitstreams in a flexible way and distributed switching / routing technique, is not only to avoid the potential bottlenet of centralized switches, but also to increase speed with intelligence that is seamlessly integrating into the Fiber Optic Backbone such as WDM and SONET of the MAN / WAN network with a Real-time guarantees, different types of traffic (such as Stringent synchronous, isochronous, and asynchronous data messages) with different demands, and privacy & security of multi access and integrated services environment.

Owner:B C LEOW

Channel adaptive equalization precoding system and method

InactiveUS20030086515A1Increase high performance and data rate capacityLow costChannel dividing arrangementsError detection/prevention using signal quality detectorPrecodingOperational system

A system and method for delivering increased speed, security, and intelligence to wireline and wireless systems. The present invention includes a new generation Fast Circuit Switch (packet / circuit) Communication processors and platform which enables a new Internet Exchange Networking Processor Architecture at the edge and core of every communication system, for next generation Web Operating System or Environment (WOE) to operate on with emphasis of a non-local processor or networking processor with remote web computing capabilities.

Owner:TRANS FRANCOIS +1

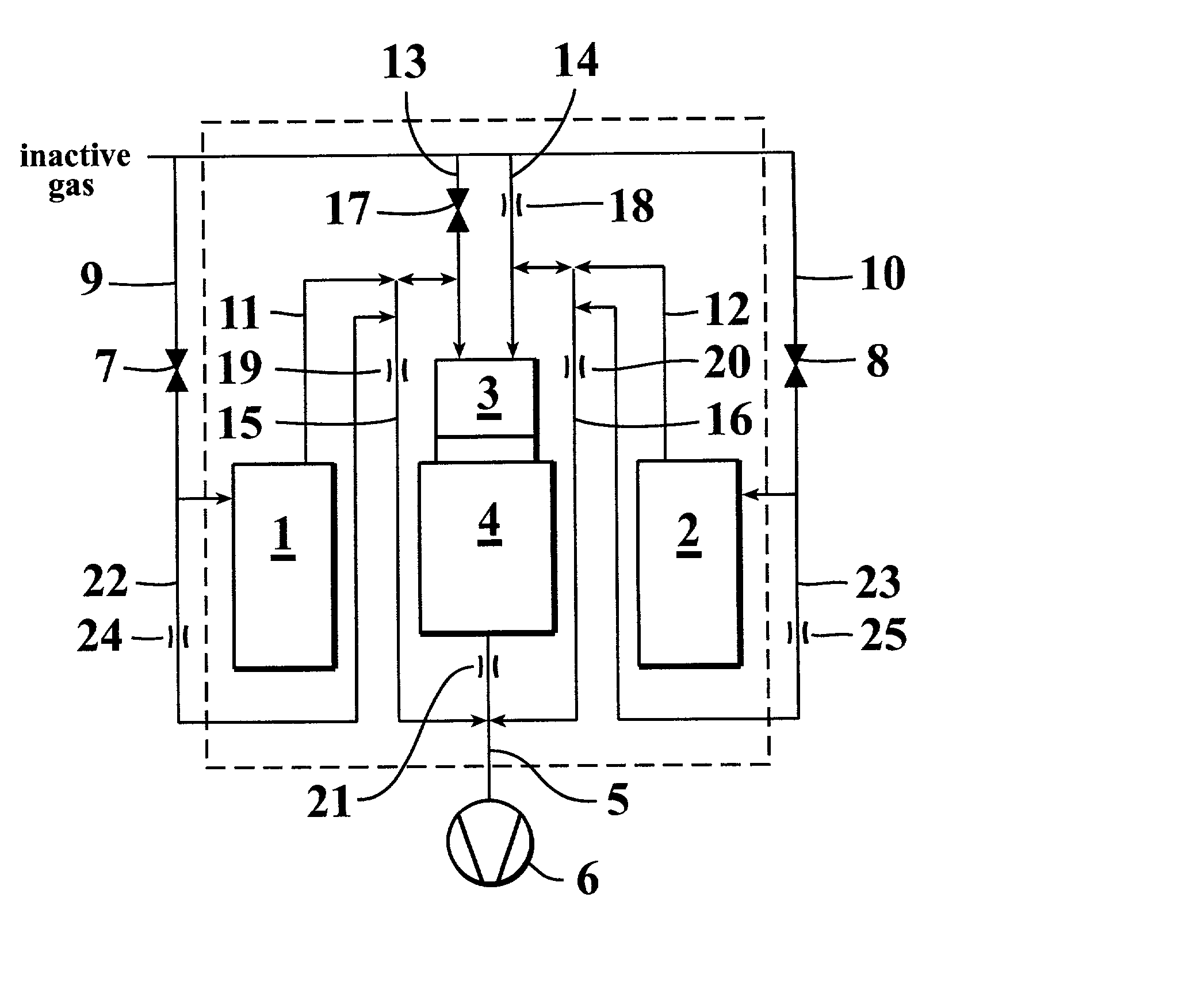

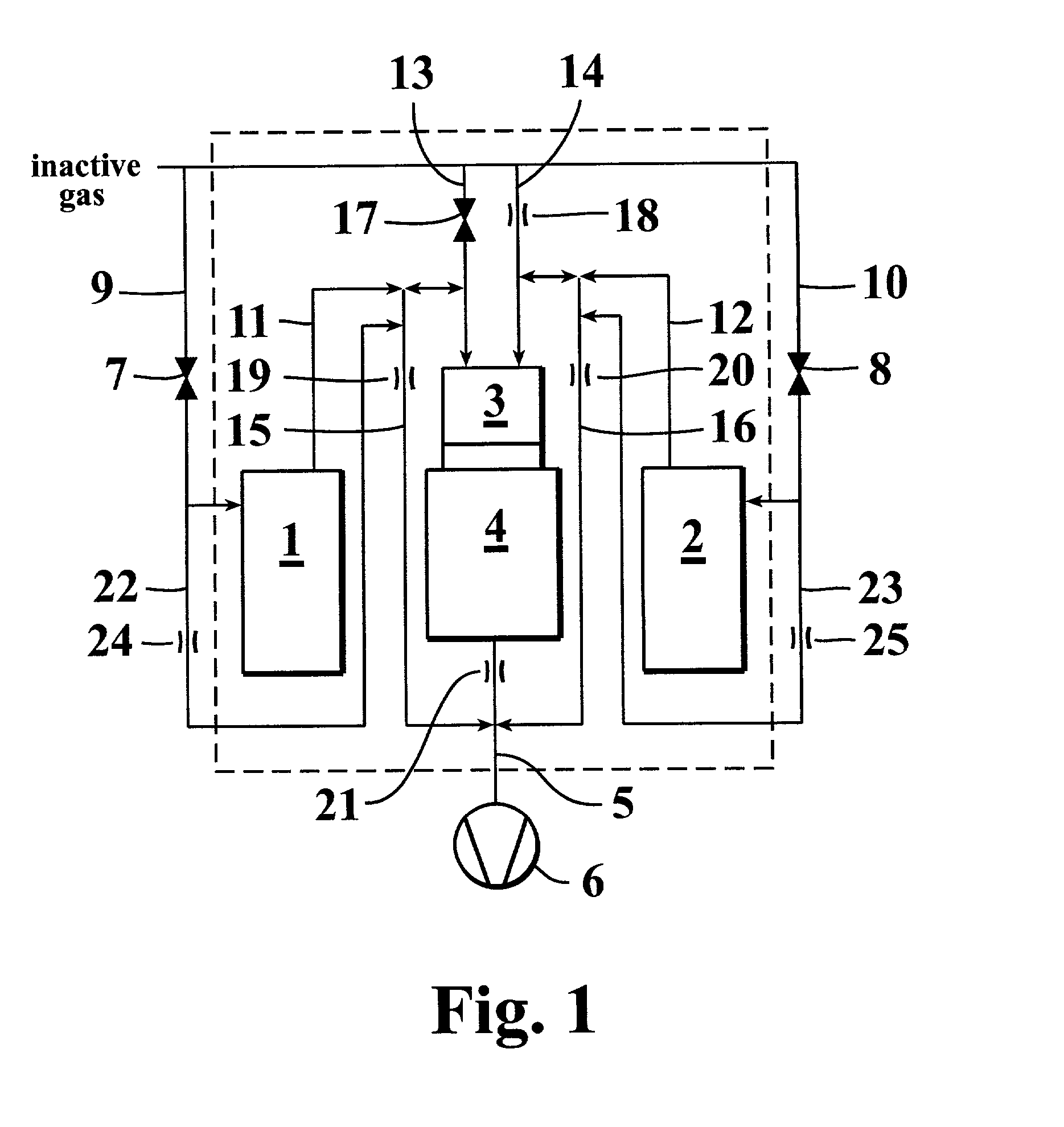

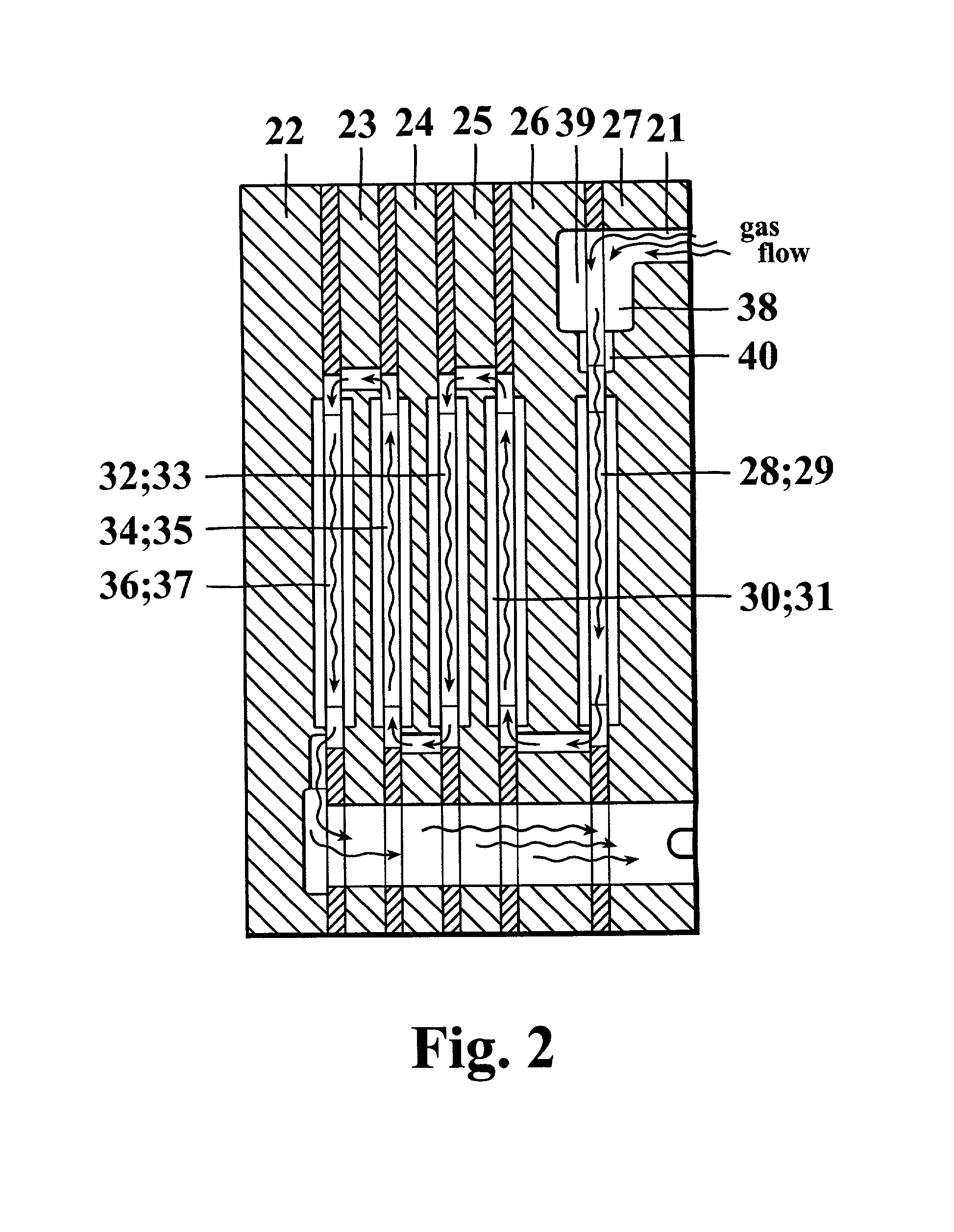

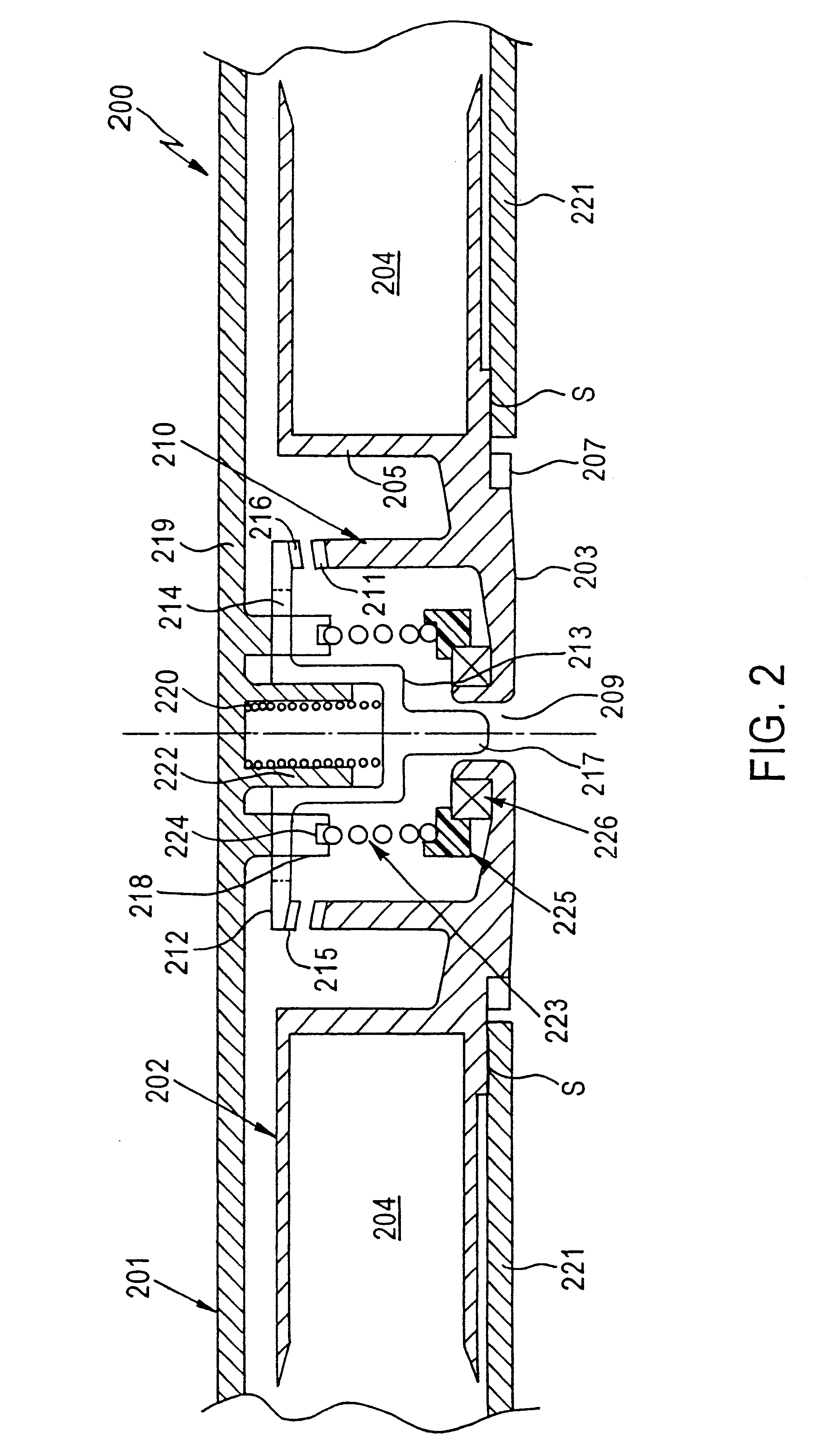

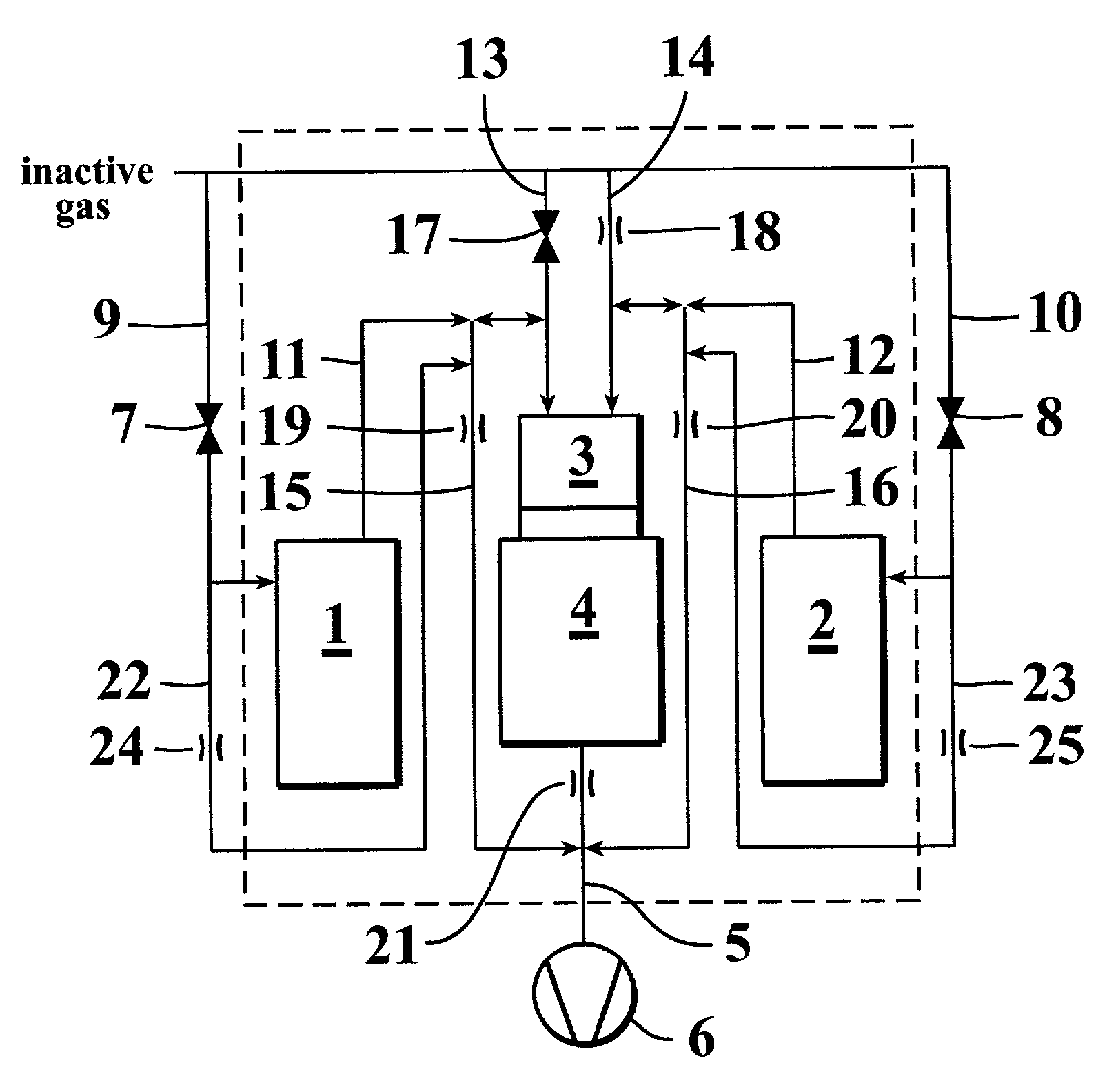

Method and apparatus of growing a thin film onto a substrate

InactiveUS20020108570A1Good film uniformitySimple and efficientPolycrystalline material growthSemiconductor/solid-state device manufacturingInlet channelGas phase

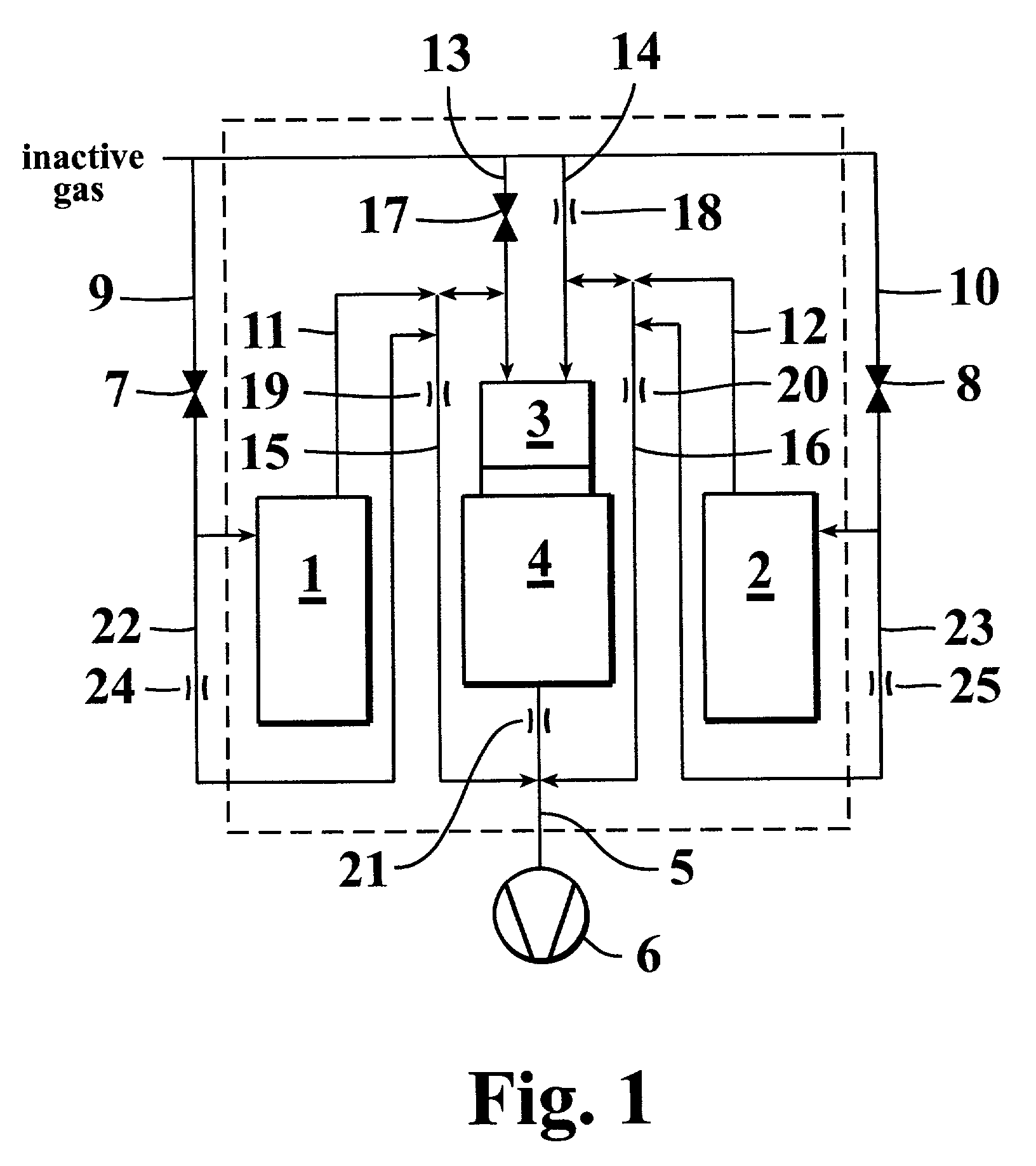

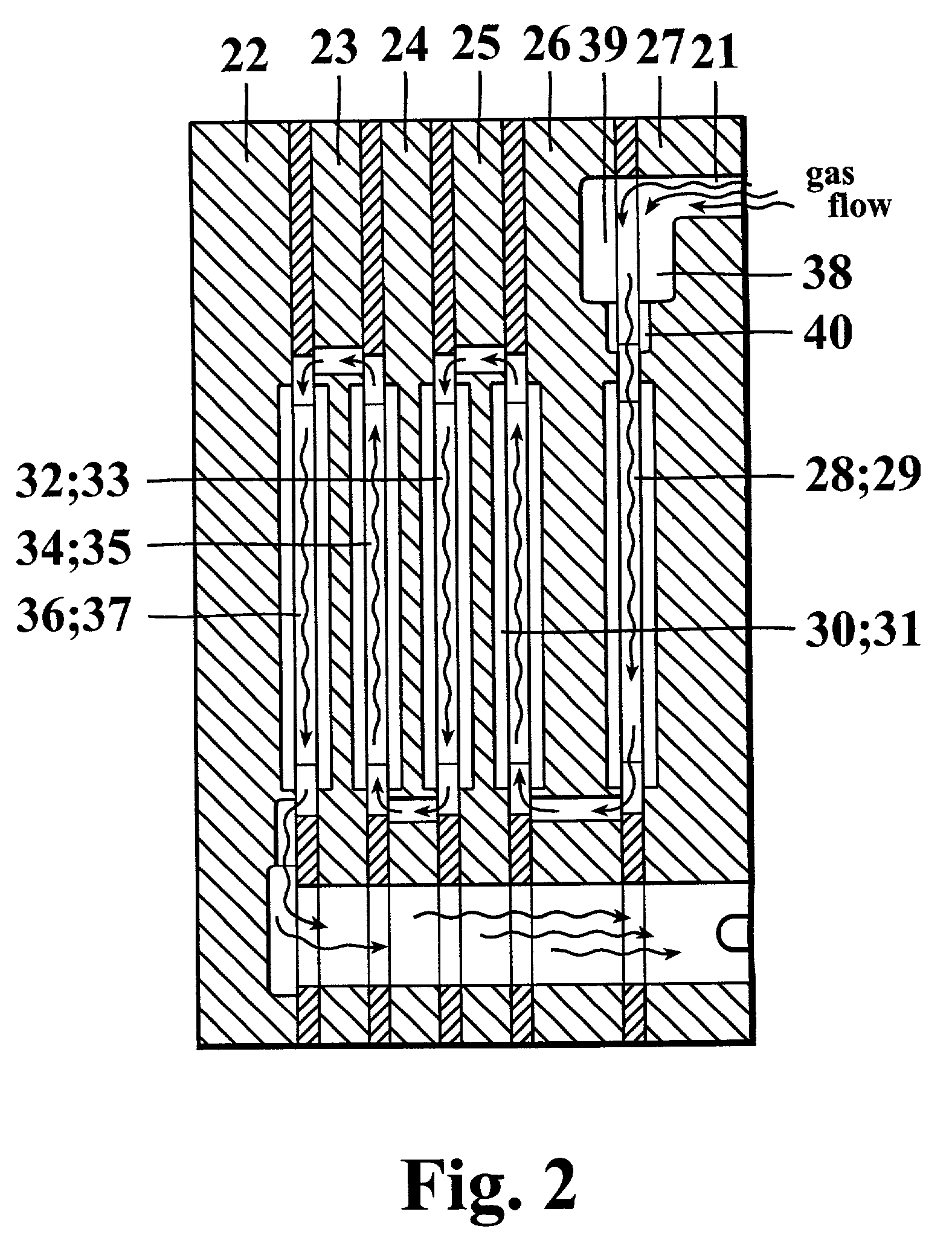

A method and an apparatus for growing a thin film onto a substrate by the ALD process. The apparatus comprises a reaction chamber into which the substrate can be disposed; a plurality of inlet channels communicating with said reaction chamber, said inlet channels being suited for feeding the reactants employed in a thin-film growth process in the form of vapor-phase pulses into said reaction chamber; at least one outlet channel communicating with said reaction chamber, said outlet channel being suited for the outflow of reaction products and excess amounts of reactants from said reaction space; and a pre-reaction chamber arranged immediately upstream of the reaction chamber, said pre-reaction chamber forming a first reaction zone, in which the reactants of successive vapor-phase pulses can be reacted with each other in the vapor phase to form a solid product, whereas said reaction chamber forming a second reaction zone can be operated under conditions conducive to ALD growth of a thin film.

Owner:ASM INTERNATIONAL

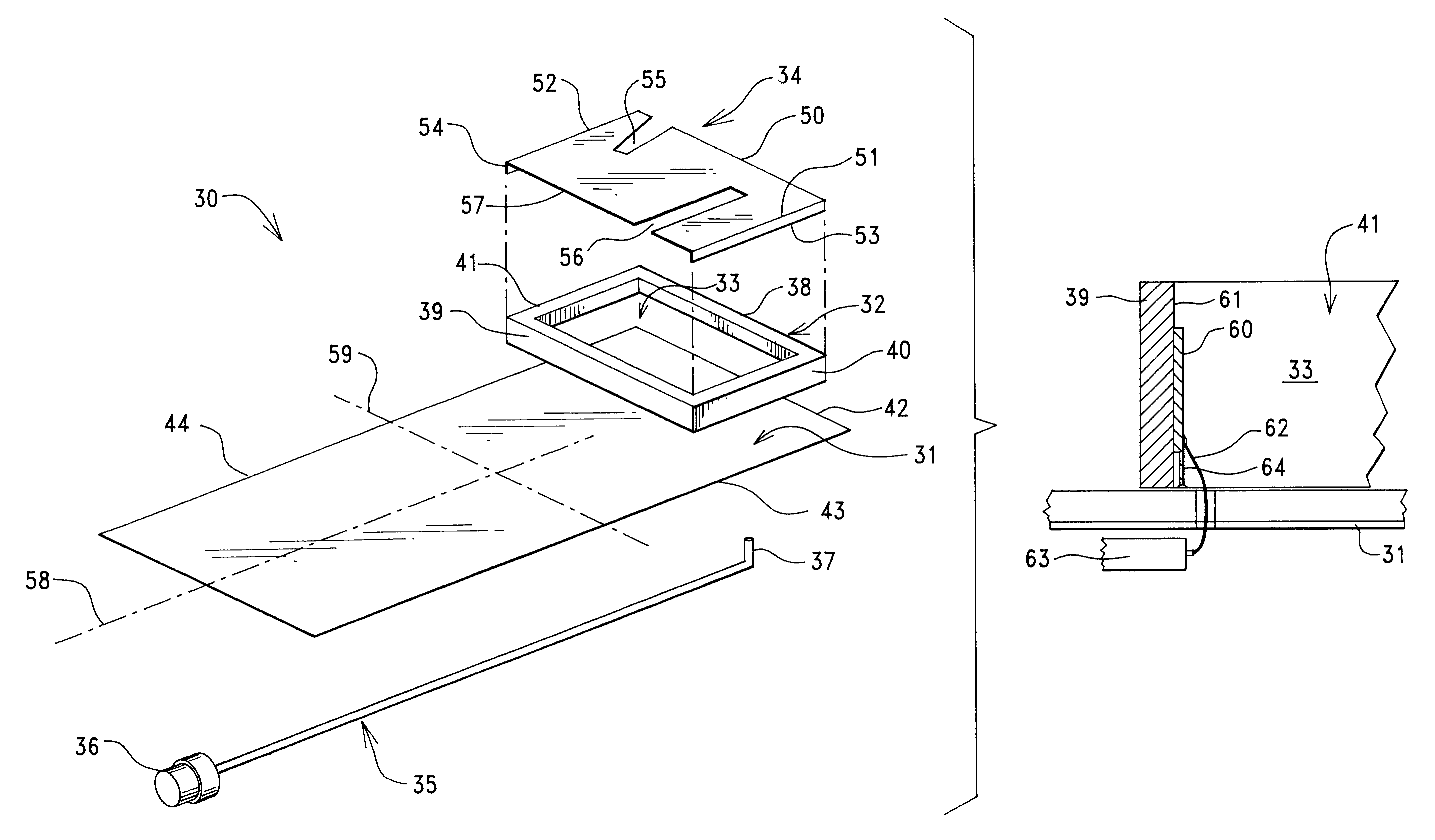

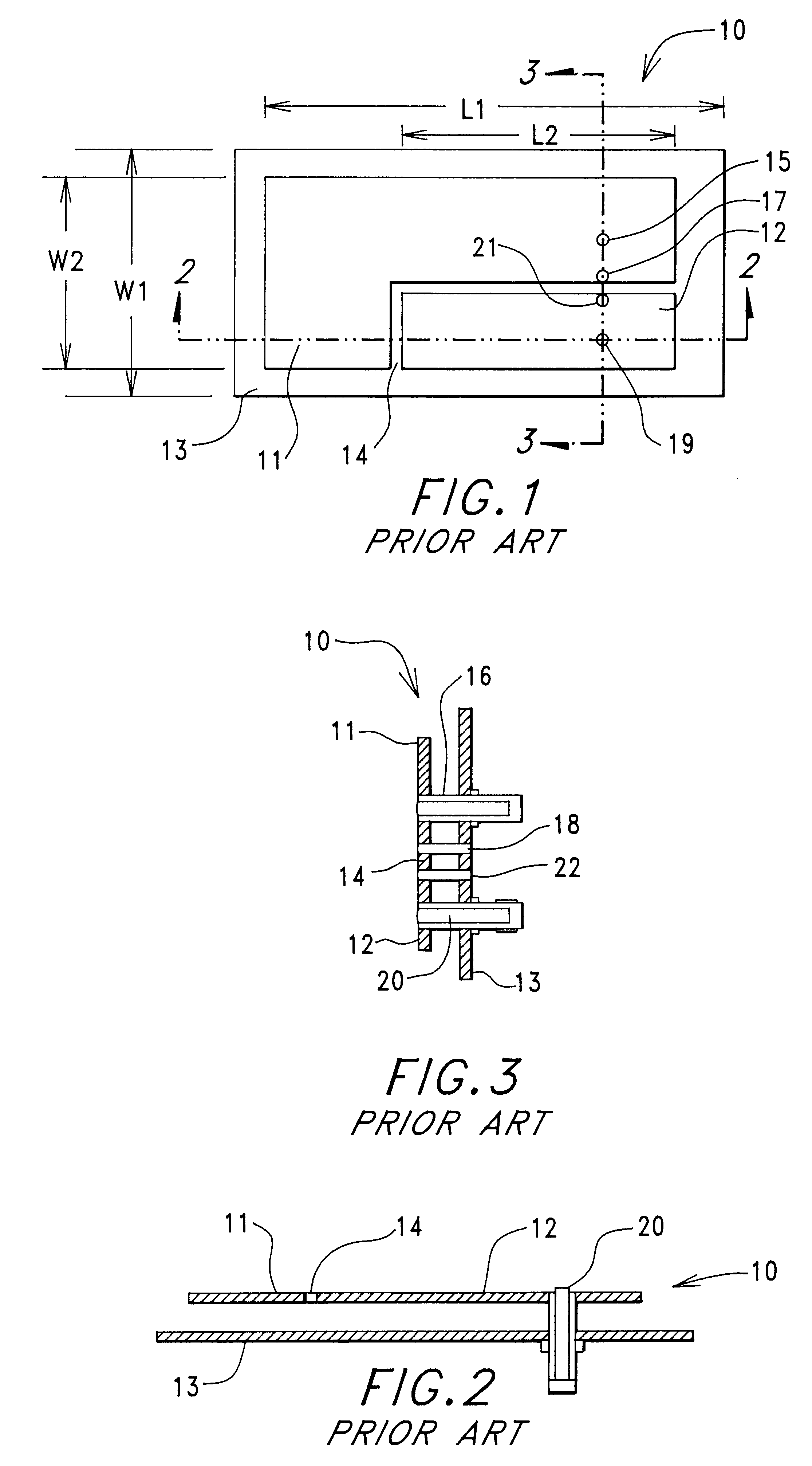

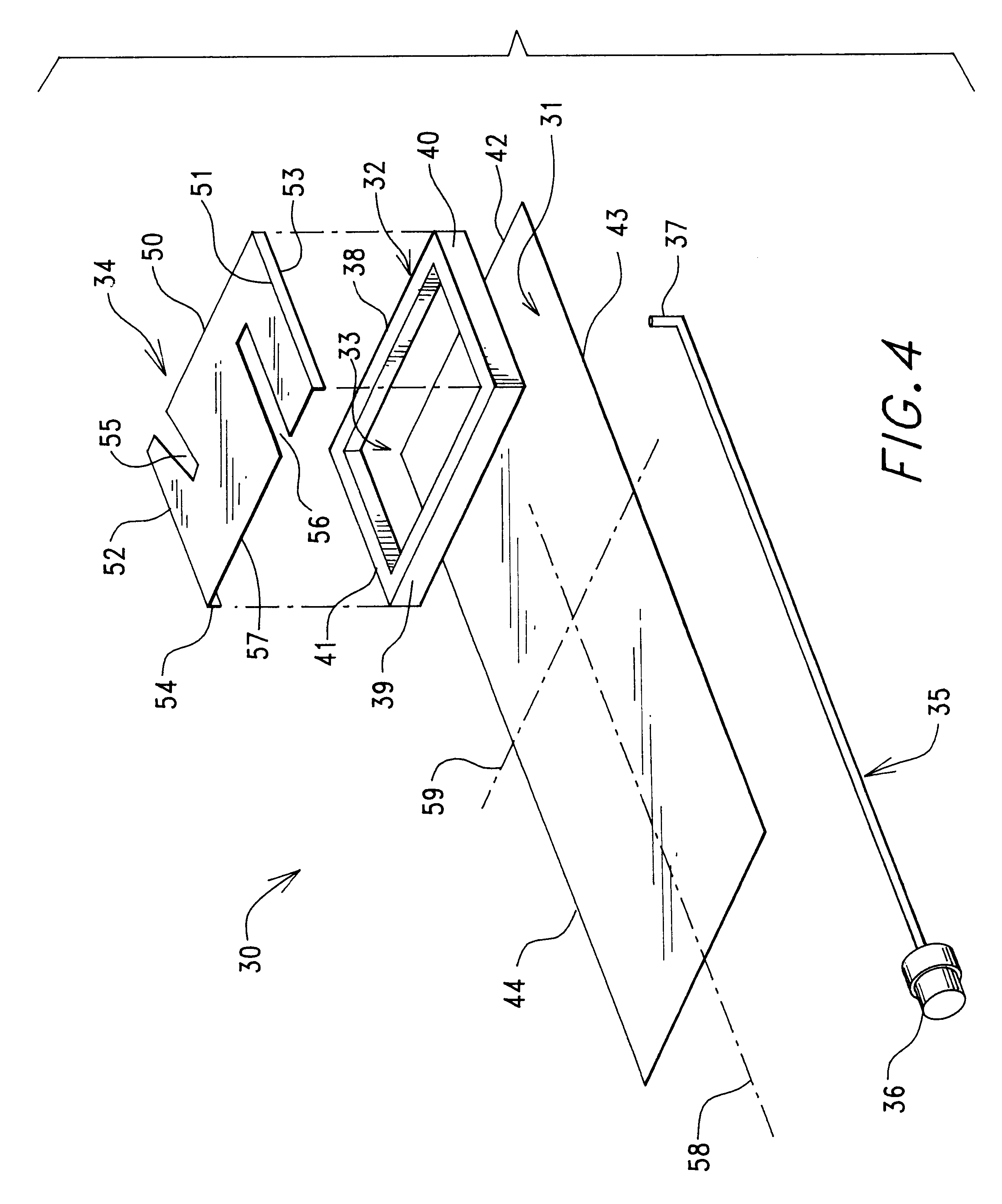

Dual feel multi-band planar antenna

InactiveUS6670923B1Reduce Design ComplexityCompromise performanceSimultaneous aerial operationsAntenna supports/mountingsMulti bandPlanar inverted f antenna

A three-band, two-antenna, assembly includes a planar inverted-F antenna (PIFA) having a radiating / receiving element that is spaced from and extends generally parallel to a ground plane element. The planar radiating / receiving element of an inverted-F antenna (IFA) is located in an open space that exists between the radiating / receiving element of the PIFA and the ground plane element. The radiating / receiving element of the IFA extends either perpendicular to, or parallel to, the radiating / receiving element of the PIFA. The radiating / receiving element of the PIFA includes one or more open slot configurations that operate to provide dual resonant frequencies for the IPFA (AMPS / PCS or GSM / DCS). The radiating / receiving element of the IFA operates in a non-cellular frequency band (ISM or GPS).

Owner:LAIRD CONNECTIVITY LLC

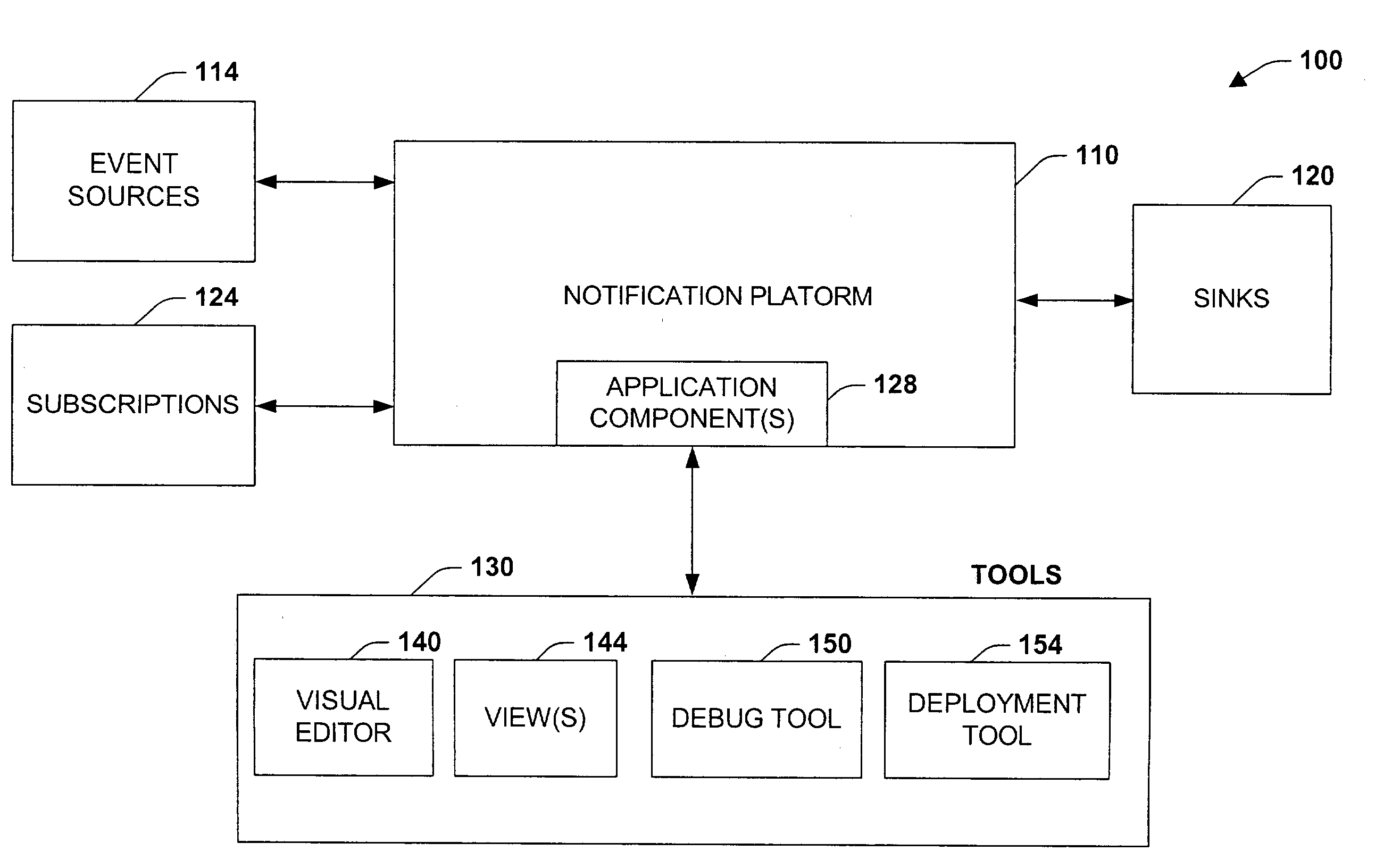

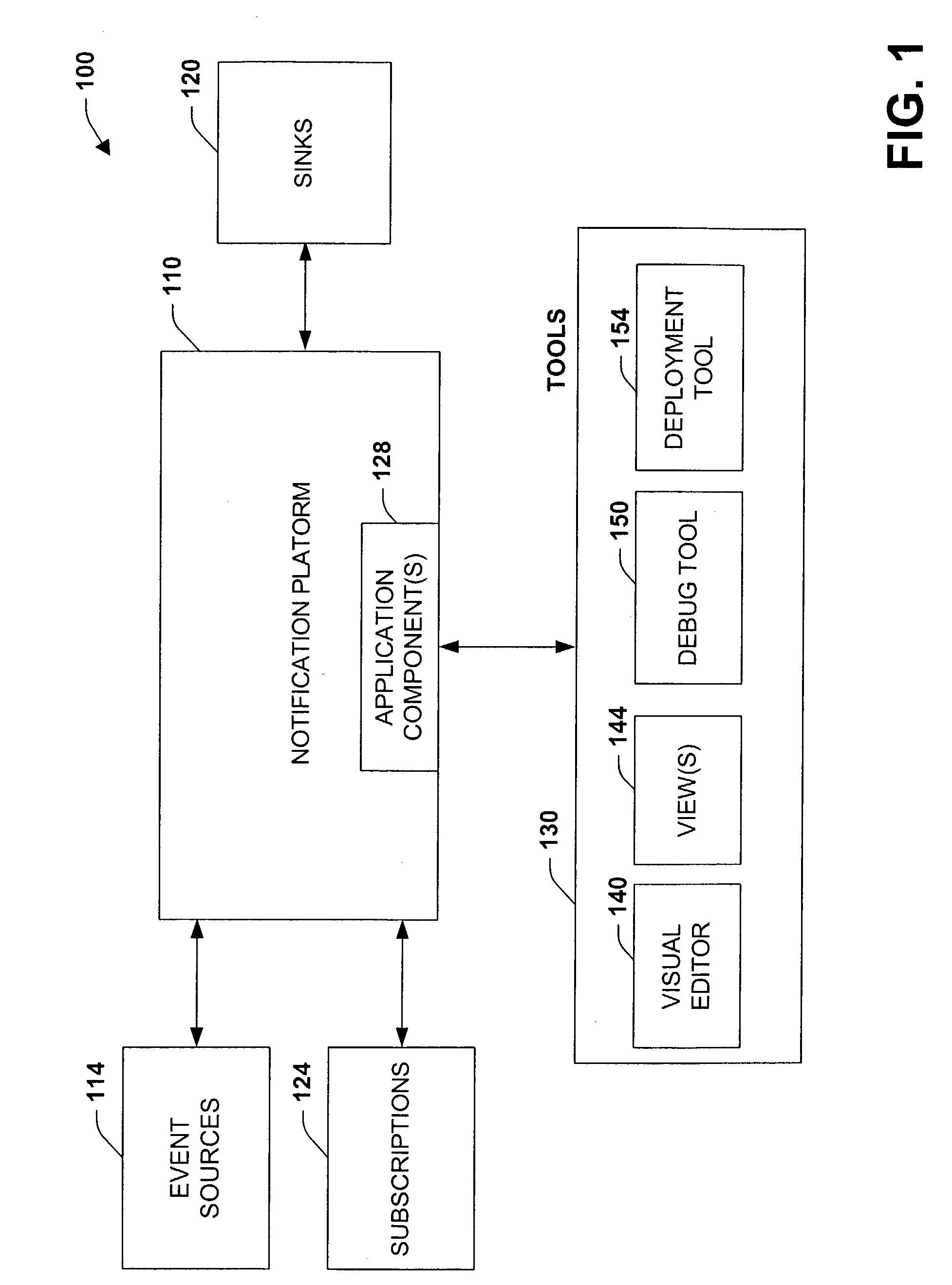

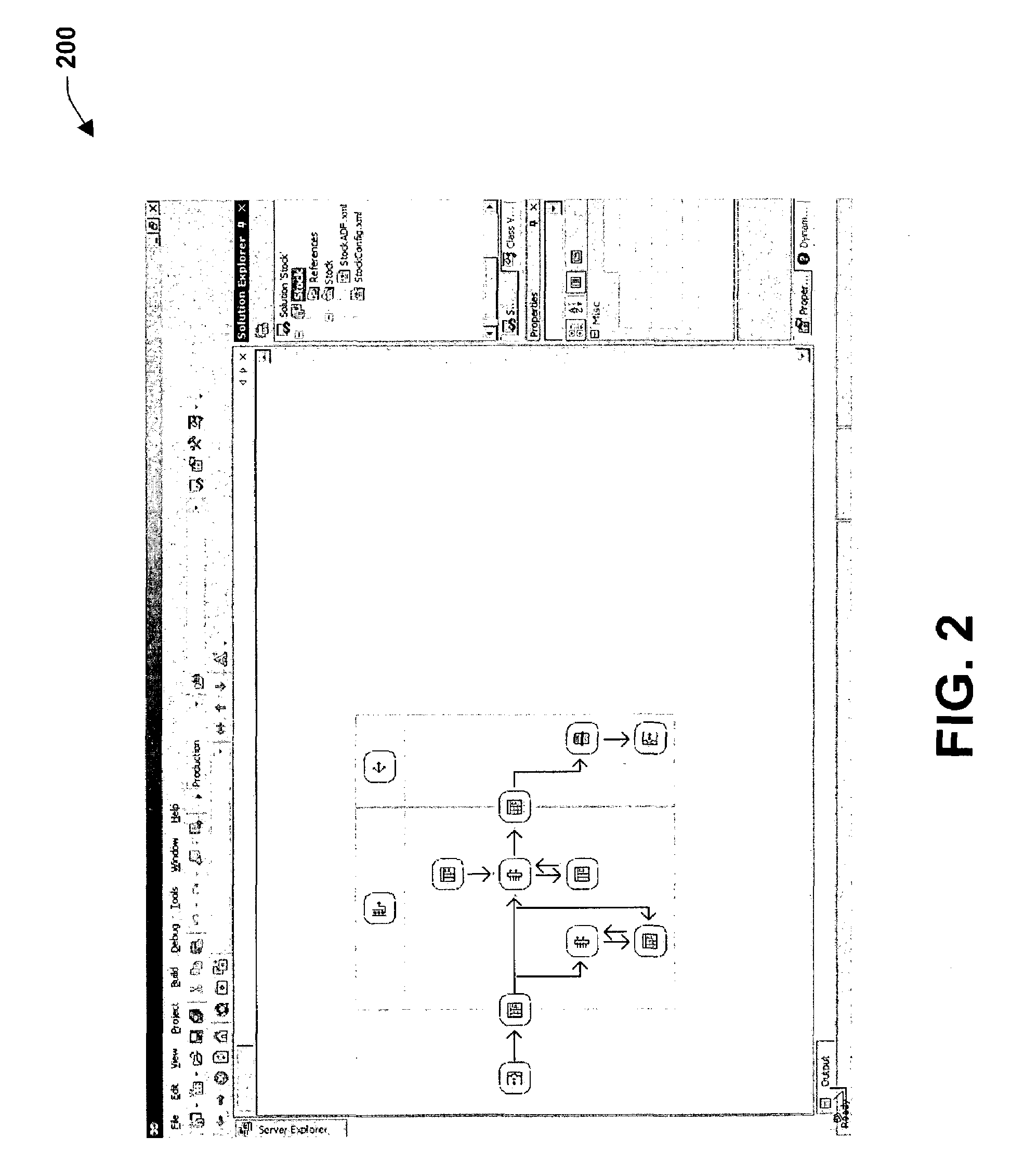

User interface system and methods for providing notification(s)

InactiveUS7360202B1Facilitates efficient design and debug and management and deploymentImprove development experienceData processing applicationsDigital data processing detailsSoftware engineeringApplication software

The present invention relates to a system and methodology to facilitate development, debug, and deployment of a notification platform application. This includes providing various editor and display tools that interact with diverse components of the application in the context of a dynamic framework and development environment adapted to the nuances of the components. Visual displays and interfaces are provided that depict the various components of an application along with the relationships between the components. Developers are then directed though the components of the application in a visual manner, wherein various editors can be invoked to design a portion of the application relating to the selected component. Other aspects include providing a debug environment for troubleshooting a notification application along with deployment options to install and execute the application.

Owner:MICROSOFT TECH LICENSING LLC

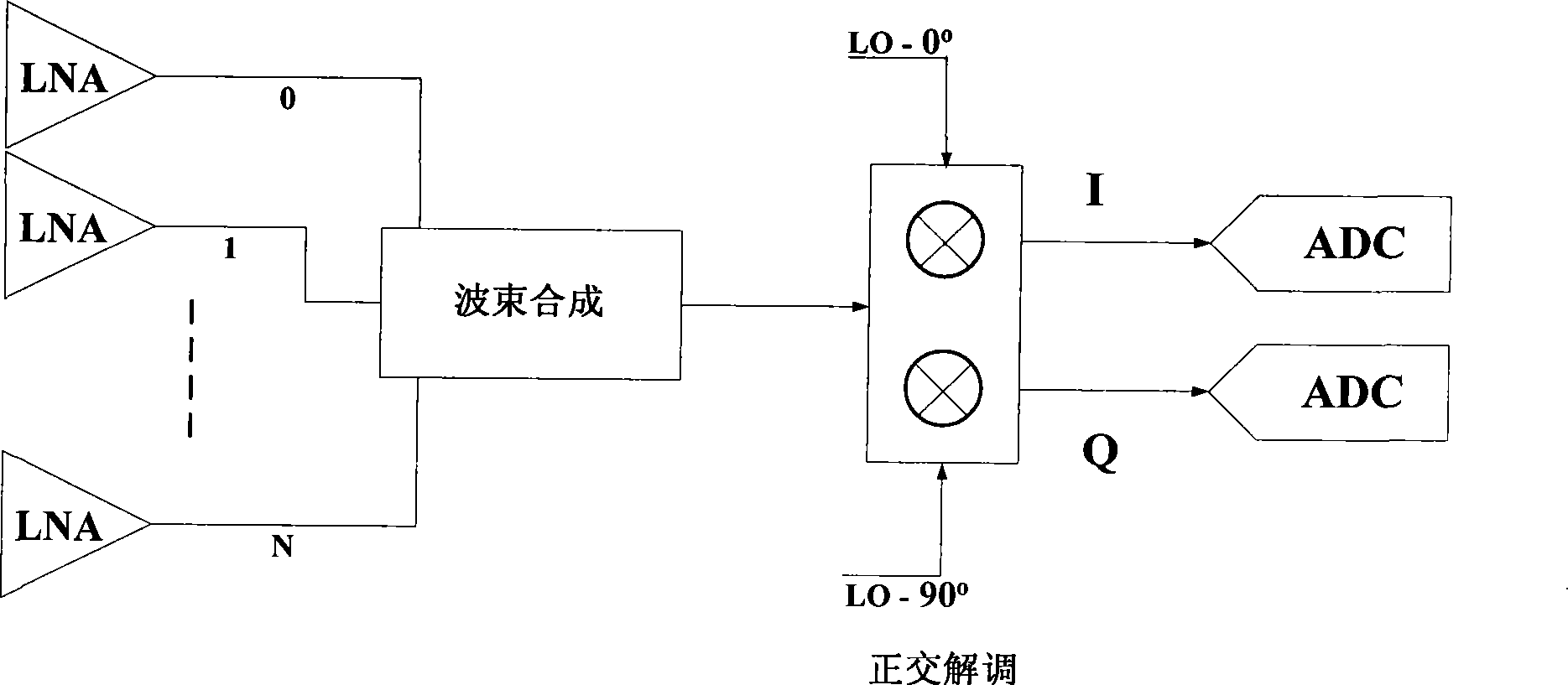

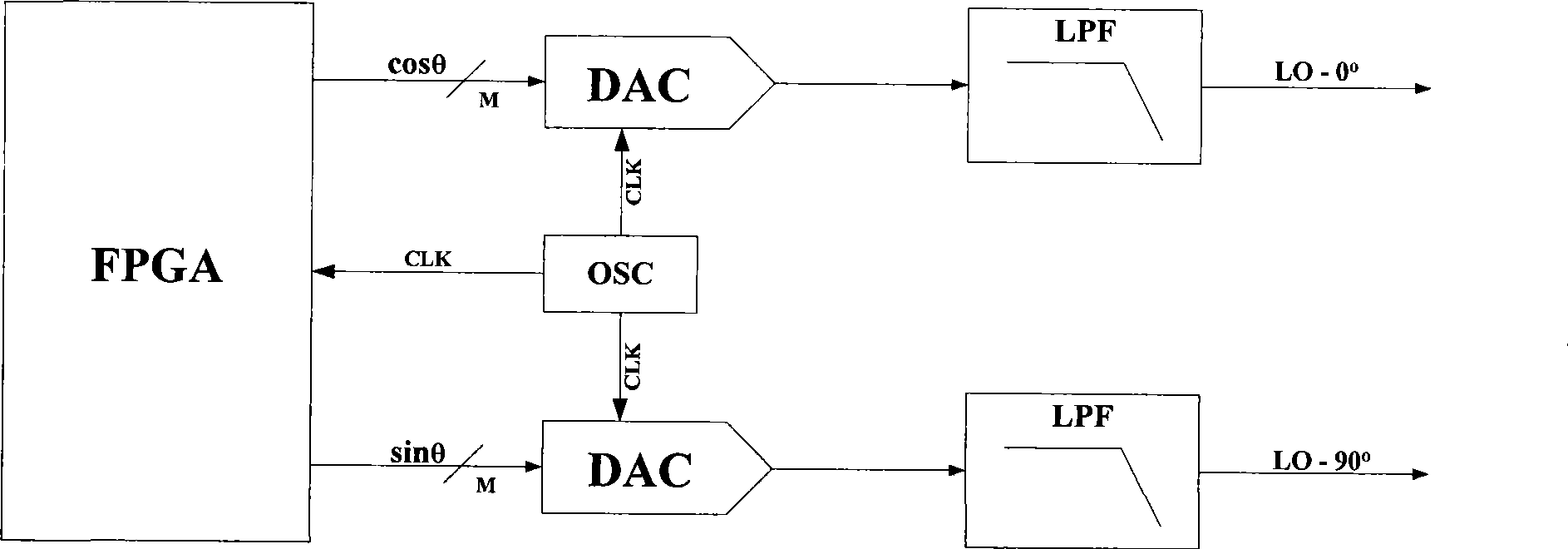

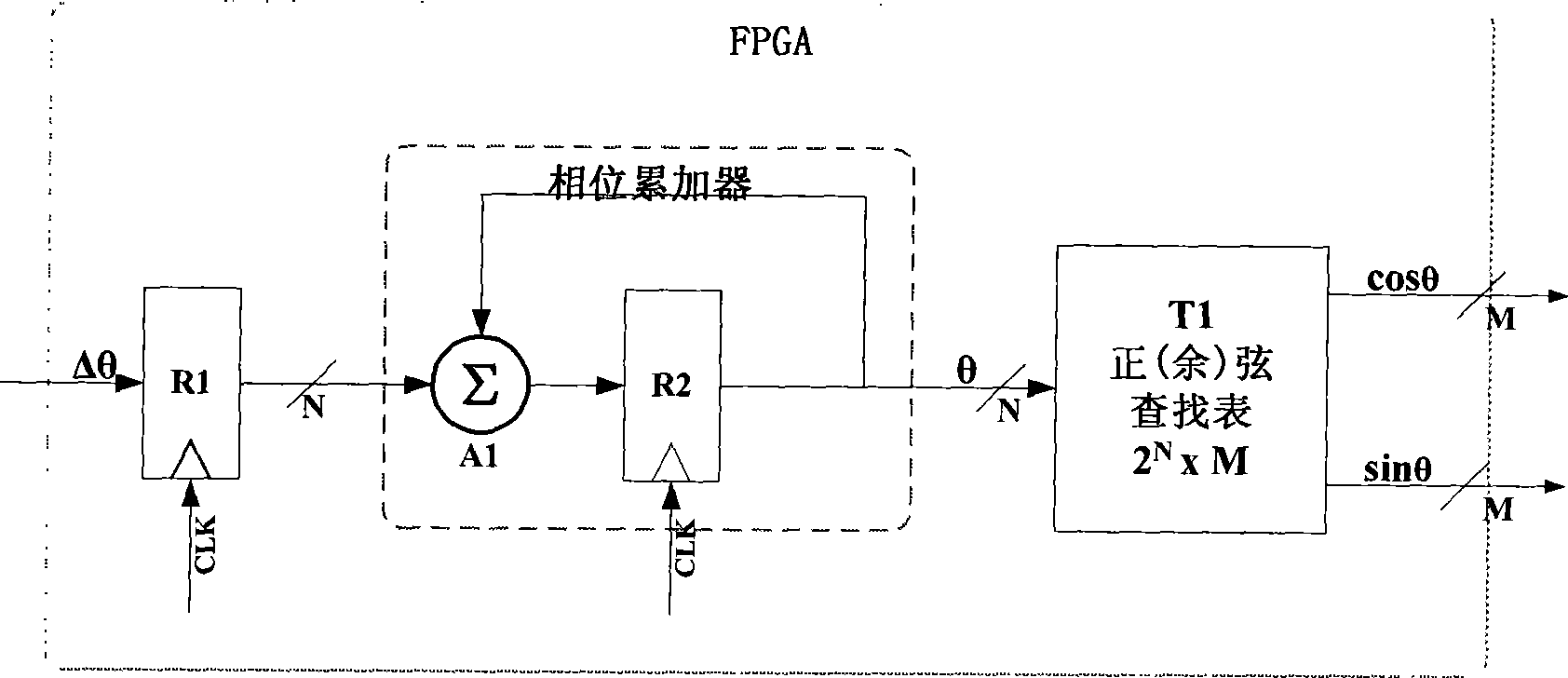

Device for producing orthogonal local oscillation signal in continuous Doppler ultrasound imaging system

InactiveCN101474081AReduce Design ComplexityReduce manufacturing costBlood flow measurement devicesDoppler Ultrasound ImagingSonification

The invention discloses a continuous Doppler US imaging system orthogonal intrinsic signal generation device, which comprise a field programmable gate array (FPGA), a crystal oscillator, a first digital-analog converter and a second digital-analog converter. The output end of the field programmable gate array (FPGA) is connected with the input ends of the first digital-analog converter and the second digital-analog converter; the crystal oscillator is respectively connected with the field programmable gate array (FPGA), the first digital-analog converter and the second digital-analog converter; the crystal oscillator is used for supplying synchronizing clock signals to the field programmable gate array (FPGA), the first digital-analog converter and the second digital-analog converter; the field programmable gate array (FPGA) is used for outputting the sine value corresponding to the phase value to the first digital-analog converter according to the input phase value and outputting the cosine value corresponding to the phase value to the second digital-analog converter; the first digital-analog converter is used for converting the sine value into the corresponding analog signals; the second digital-analog converter is used for converting the cosine value into the corresponding analog signals.

Owner:SHENZHEN LANDWIND IND

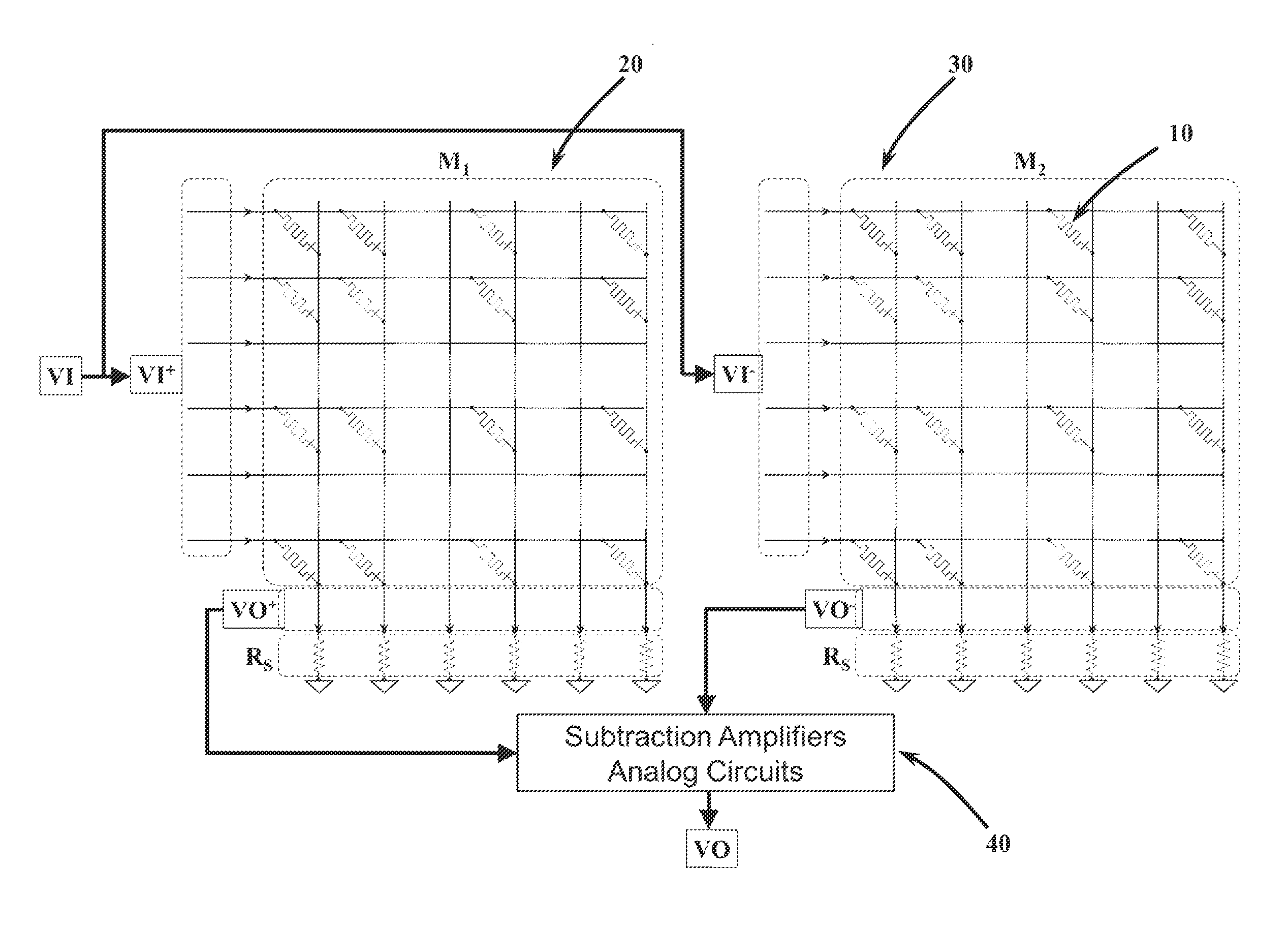

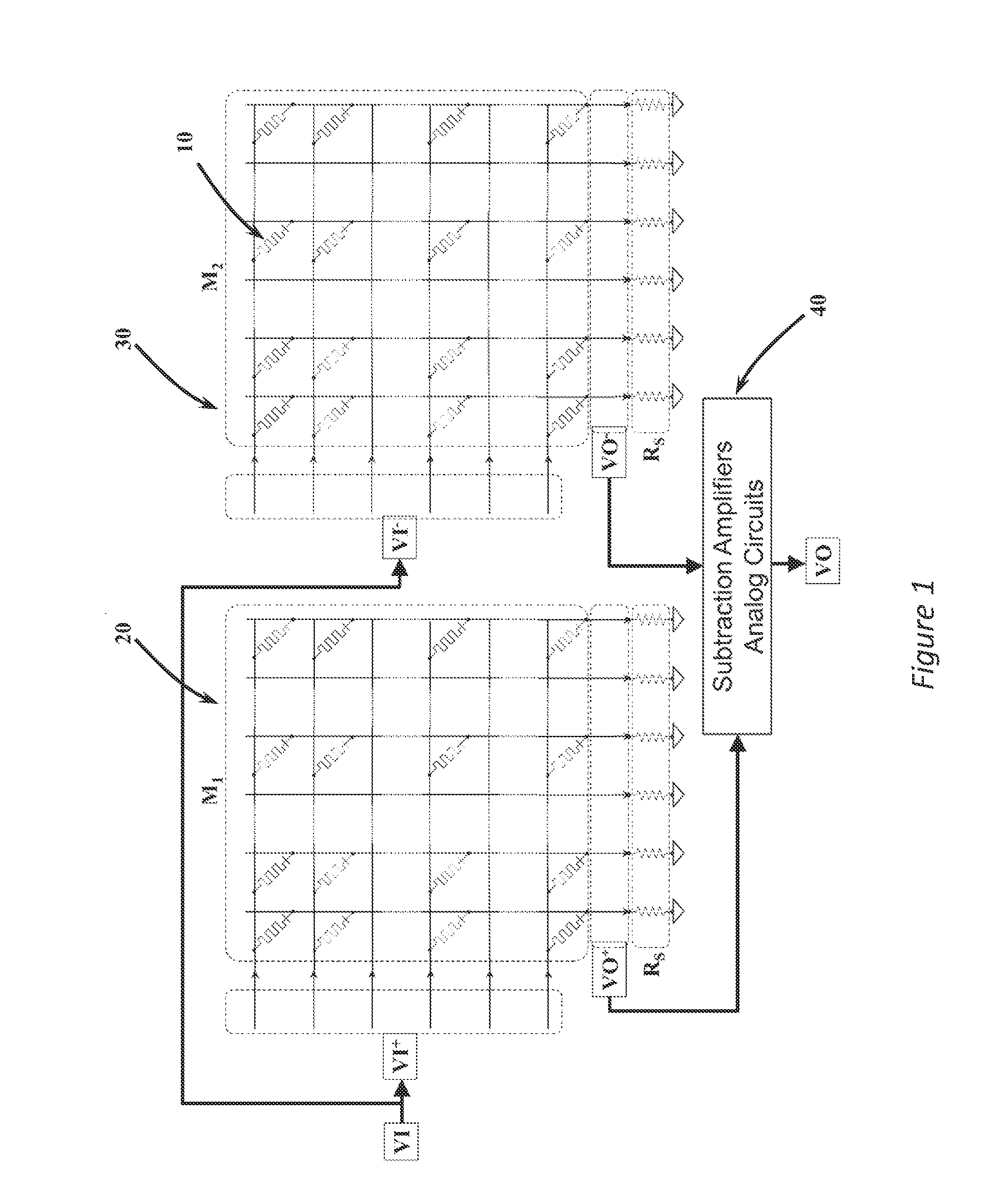

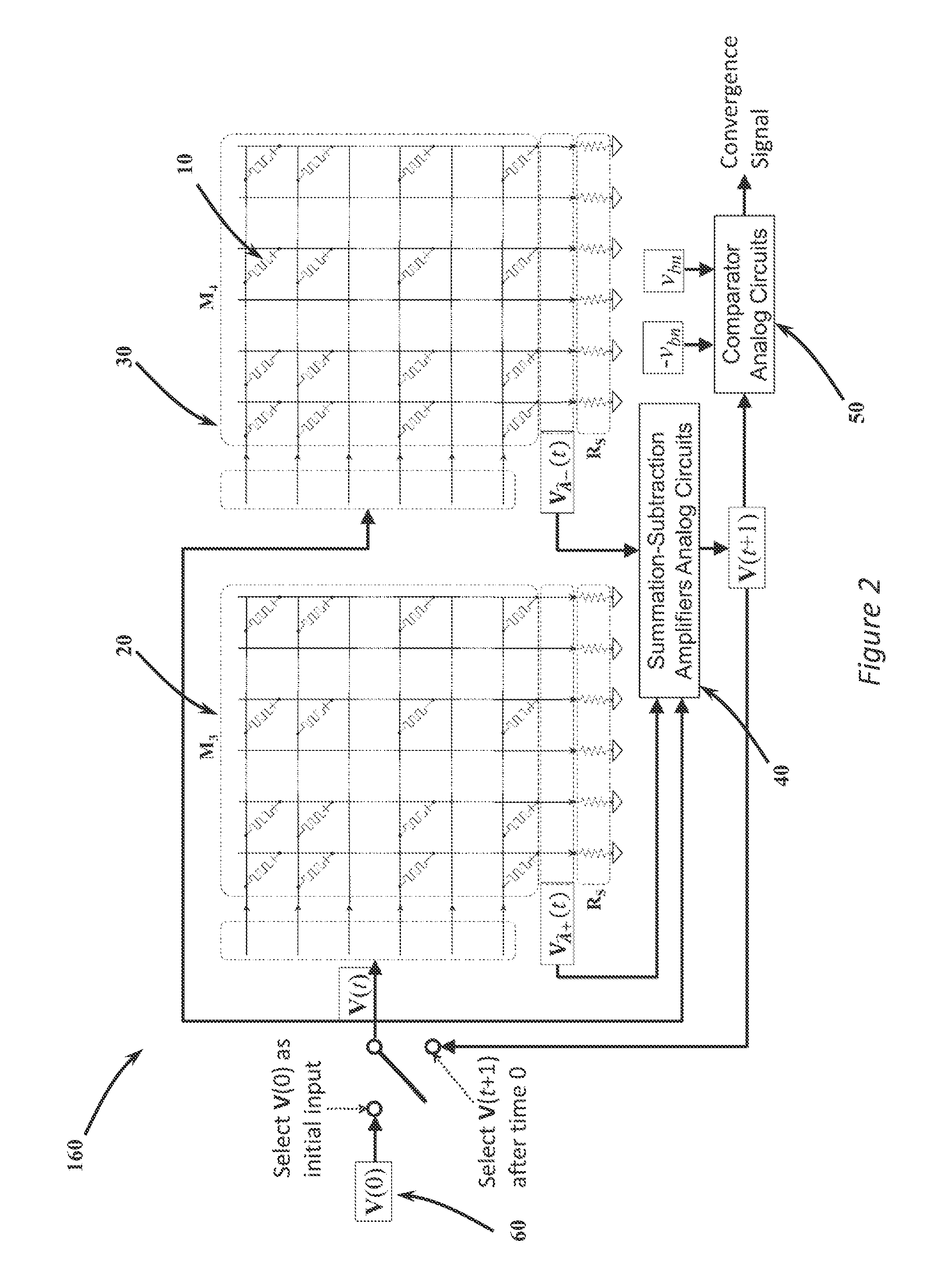

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems

ActiveUS20150170025A1Reduce Design ComplexityConvenient and accurateDigital computer detailsDigital storageObservational errorElectrical resistance and conductance

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems. Invention provides iterative training of memristor crossbar arrays for neural networks by applying voltages corresponding to selected training patterns. Error is detected and measured as a function of the actual response to the training patterns versus the expected response to the training pattern.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

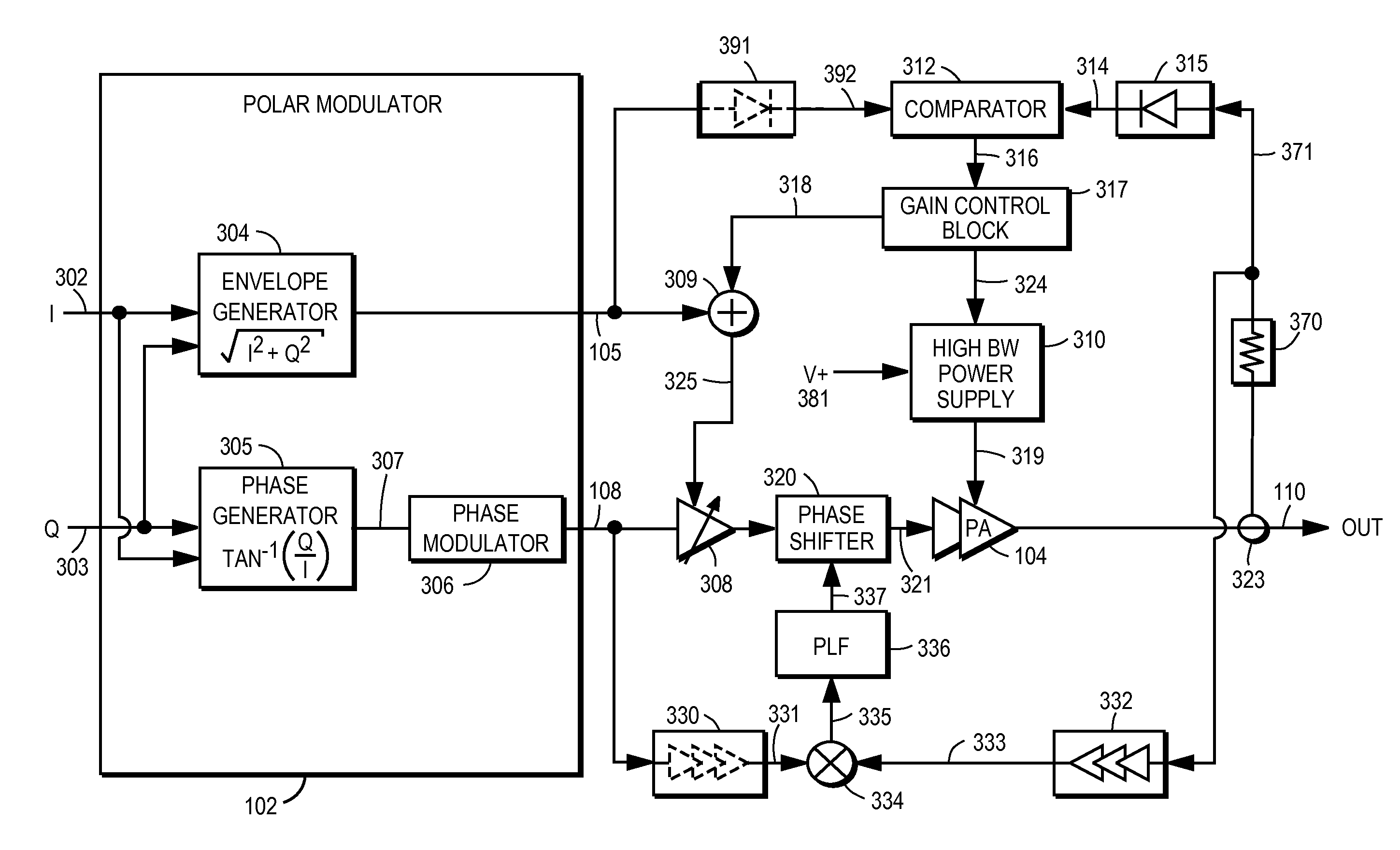

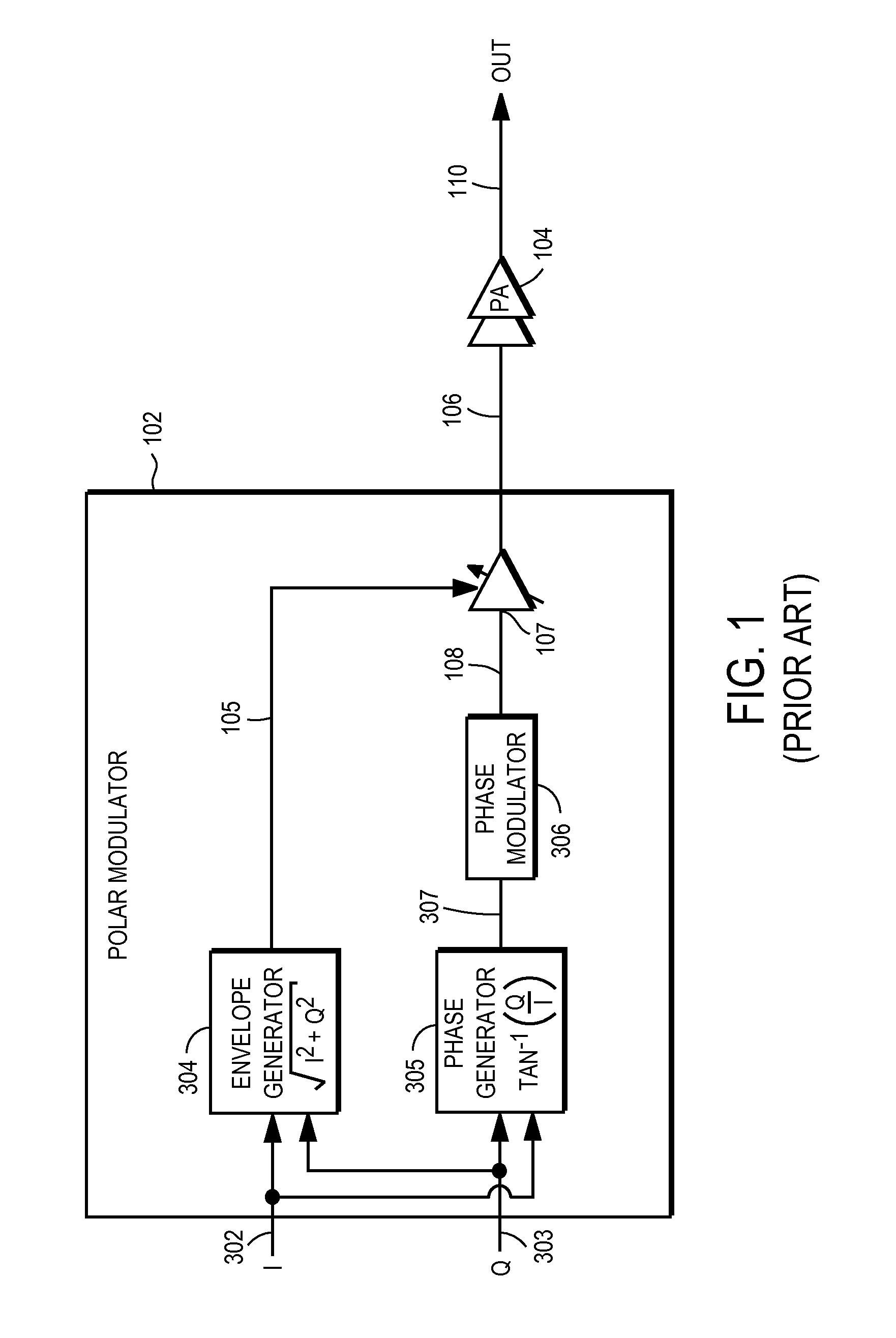

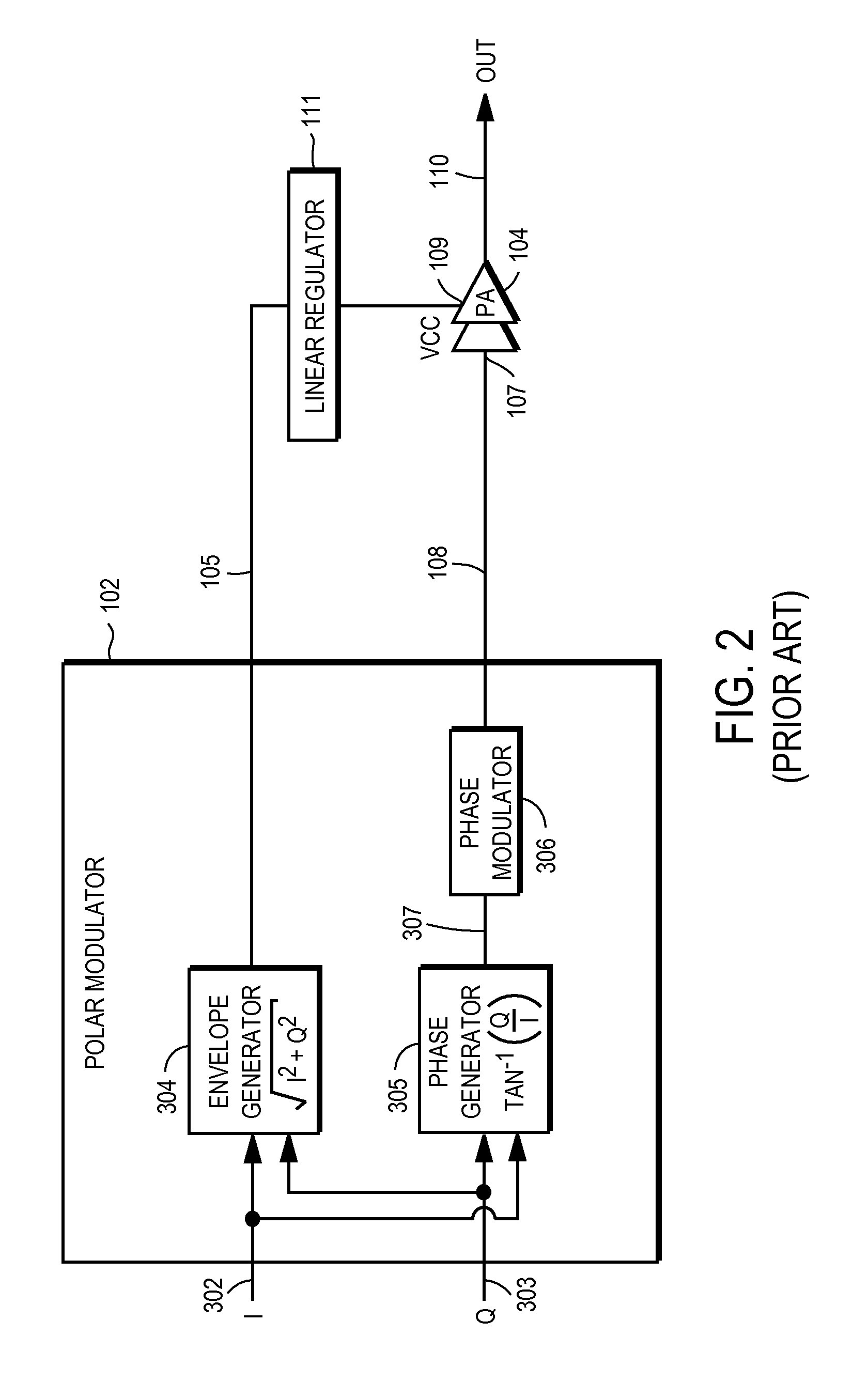

Power Amplifier Controller With Polar Transmitter

ActiveUS20100311365A1Reduce phase distortionMinimize the differenceAmplifier modifications to reduce non-linear distortionResonant long antennasAudio power amplifierEngineering

A power amplifier controller controls a power amplifier and is coupled to a polar modulator. The polar modulator generates an amplitude component and a phase-modulated component of the desired RF modulated signal, and outputs to the power amplifier controller. The power amplifier controller regenerates a combined phase and amplitude modulated RF signal to generate an input signal to a power amplifier by adjusting the gain of a VGA based on the amplitude component of the desired RF modulated signal. Concurrently, the power amplifier controller both controls an adjusted supply voltage to the PA and adjusts the gain of the VGA based upon an amplitude correction signal or amplitude error signal.

Owner:QUANTANCE

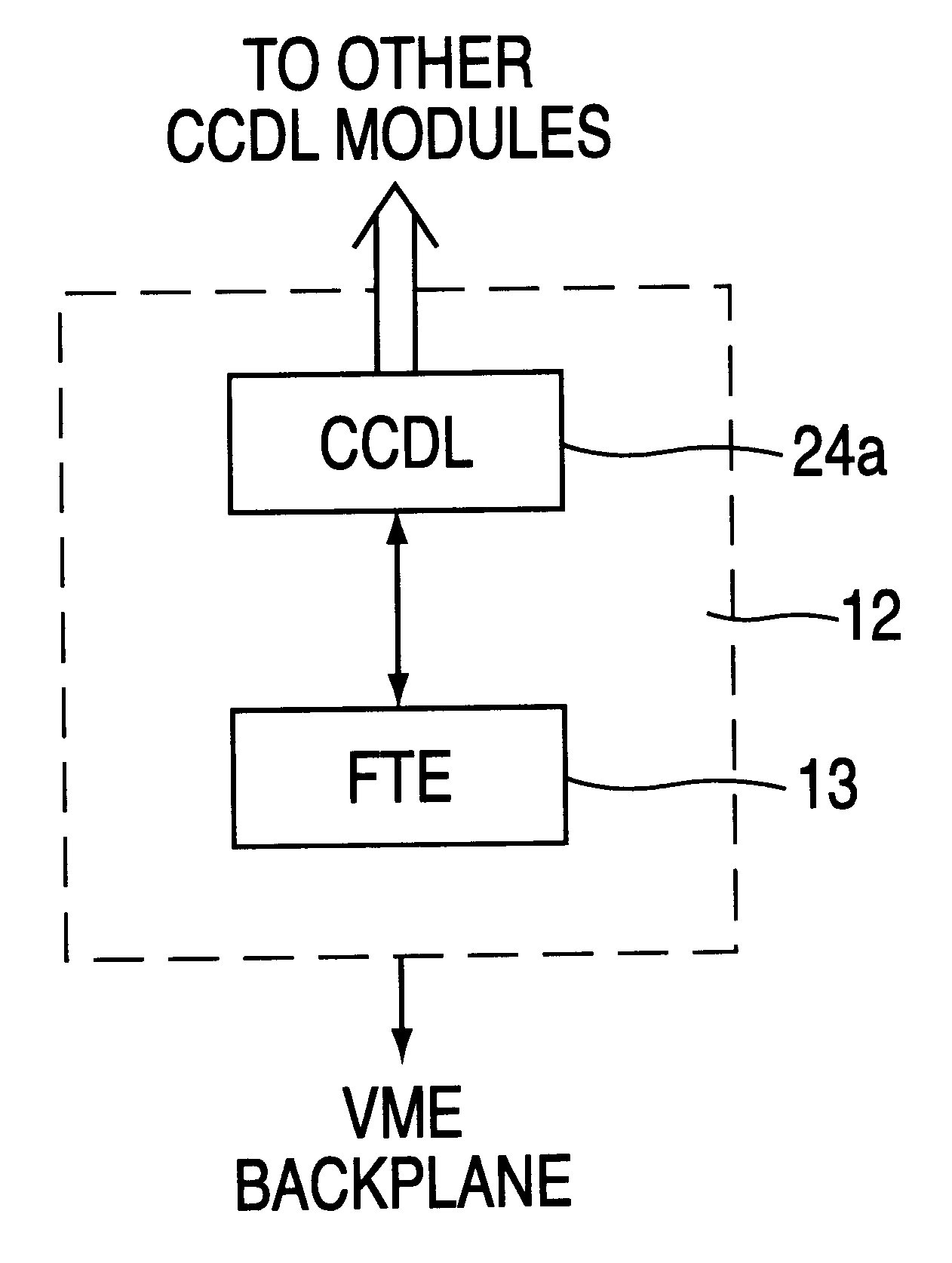

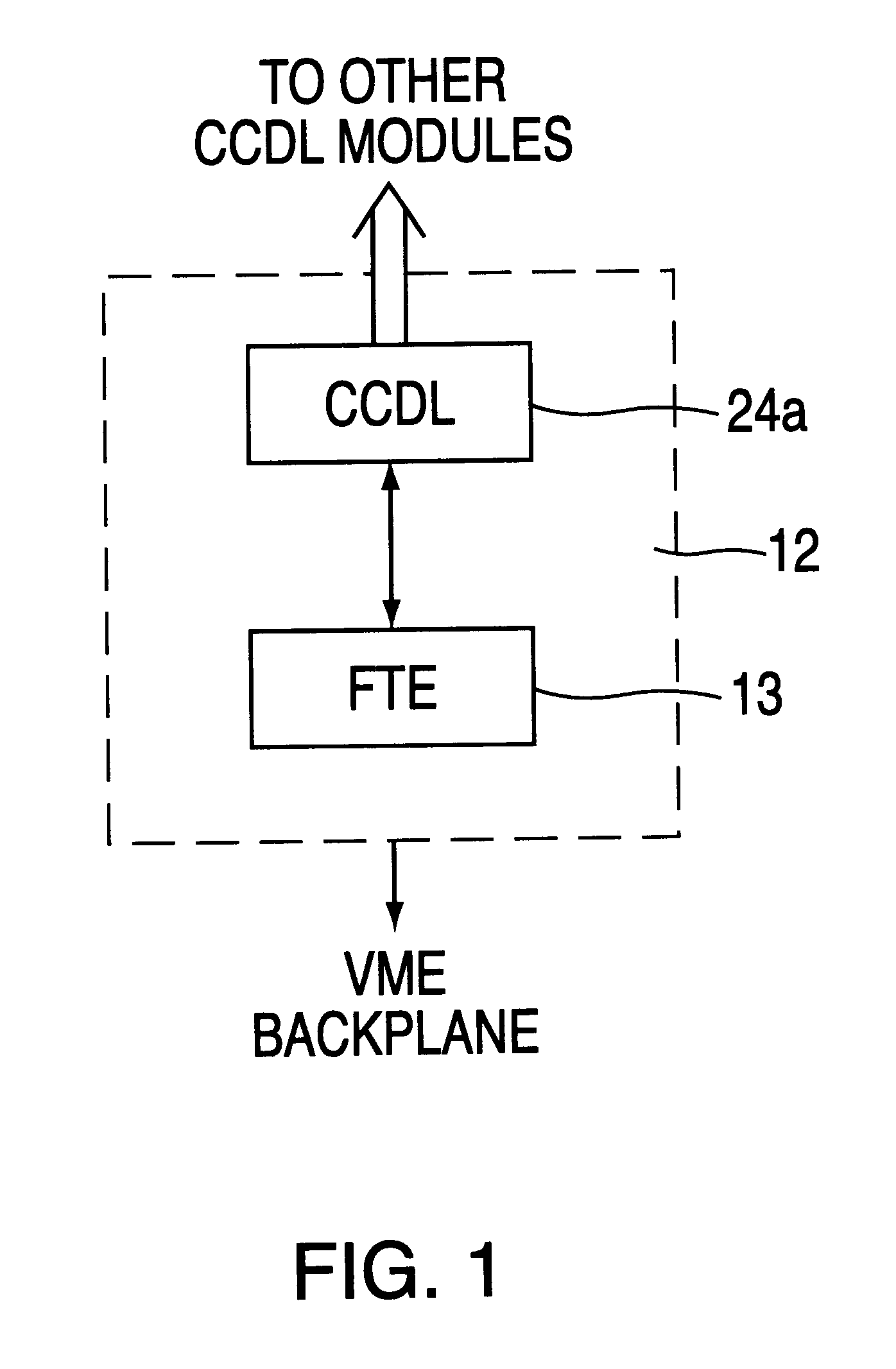

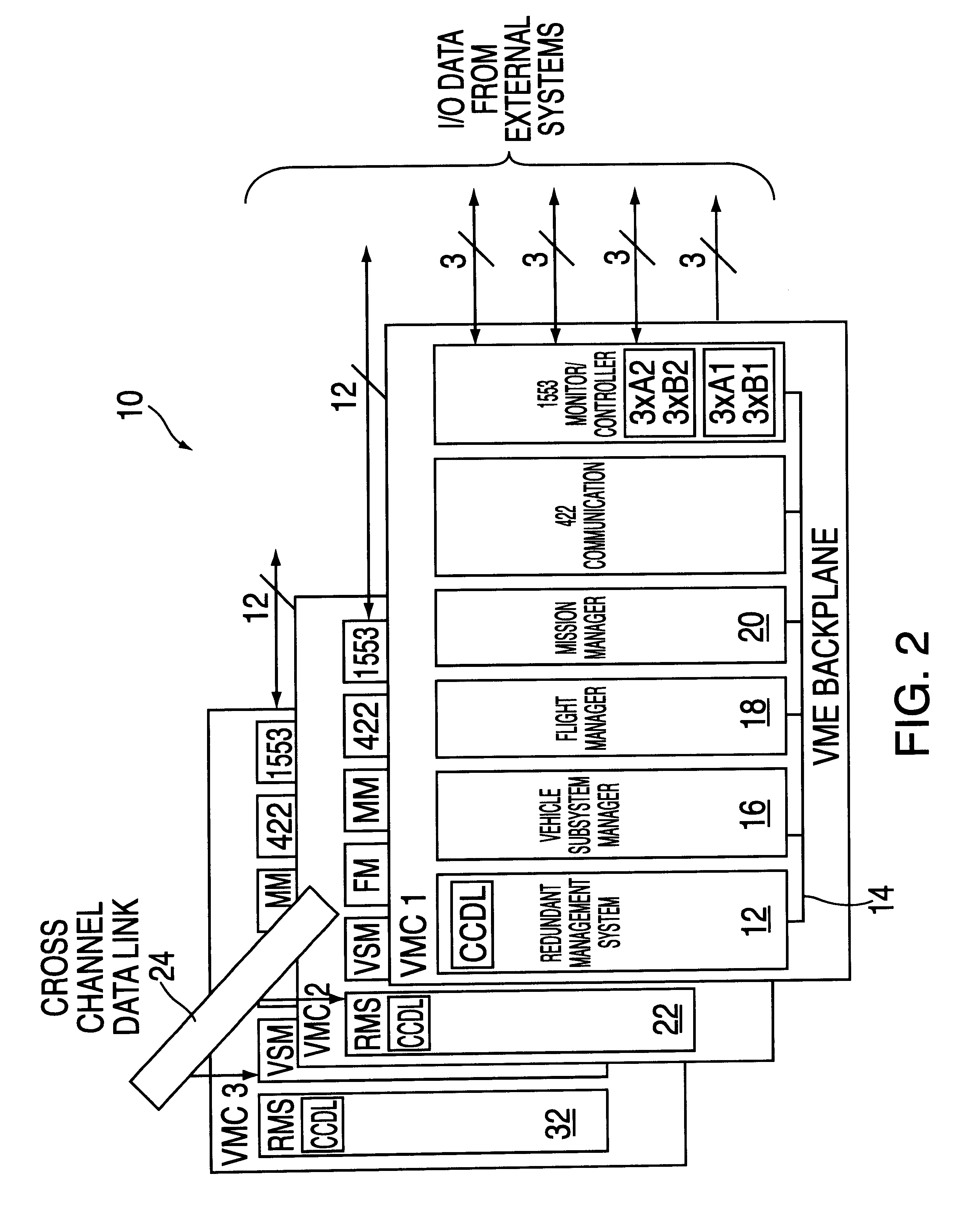

Method and apparatus for managing redundant computer-based systems for fault tolerant computing

InactiveUS6178522B1Reduce Design ComplexityReliability increasing modificationsProgram synchronisationEffective solutionSystem integrity

A stand alone Redundancy Management System (RMS) provides a cost-effective solution for managing redundant computer-based systems in order to achieve ultra-high system reliability, safety, fault tolerance, and mission success rate. The RMS includes a Cross Channel Data Link (CCDL) module and a Fault Tolerant Executive (FE) module. The CCDL module provides data communication for all channels, while the FTE module performs system functions such as synchronization, data voting, fault and error detection, isolation and recovery. System fault tolerance is achieved by detecting and masking erroneous data through data voting, and system integrity is ensured by a dynamically reconfigurable architecture that is capable of excluding faulty nodes from the system and re-admitting healthy nodes back into the system.

Owner:ALLIEDSIGNAL INC

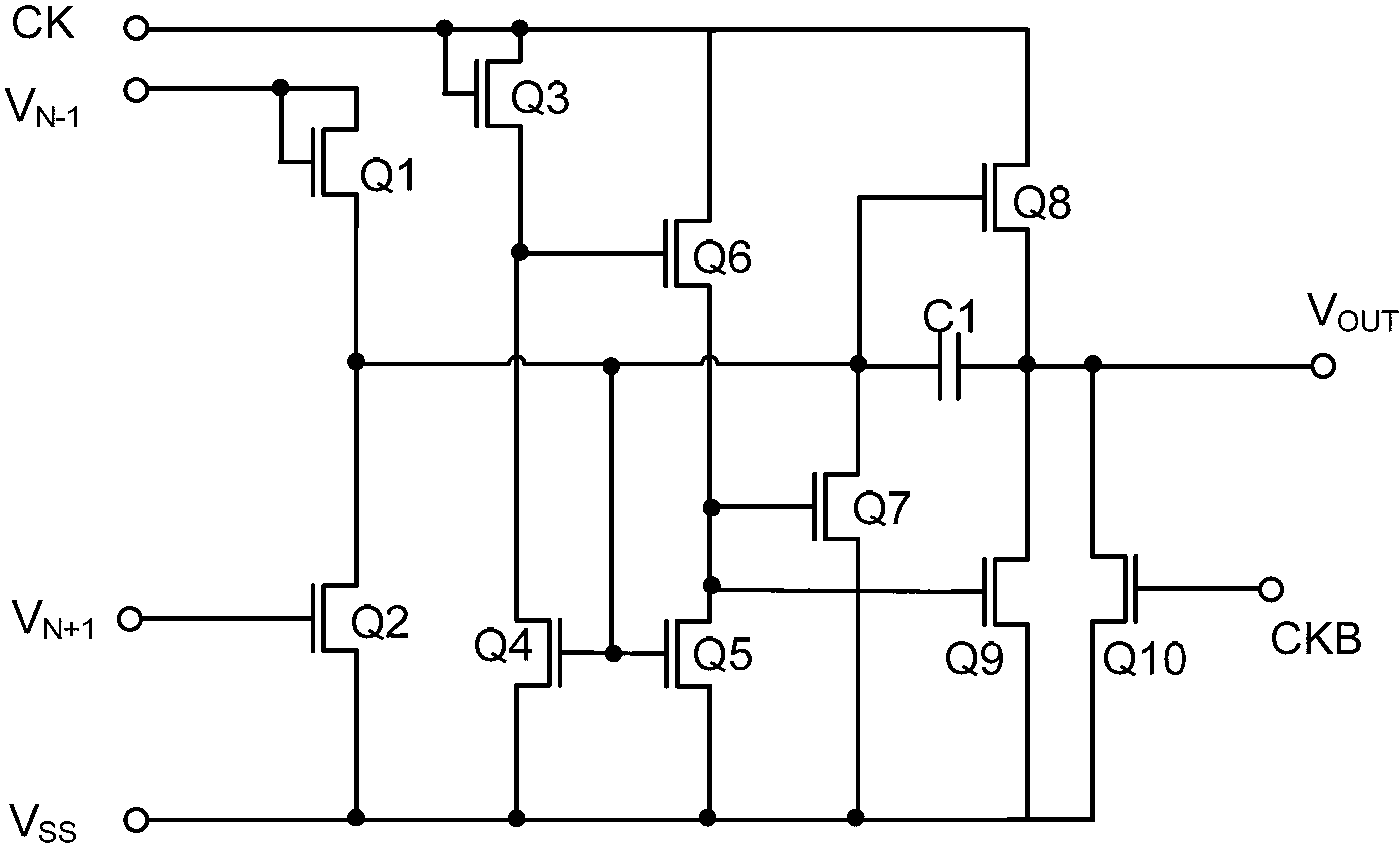

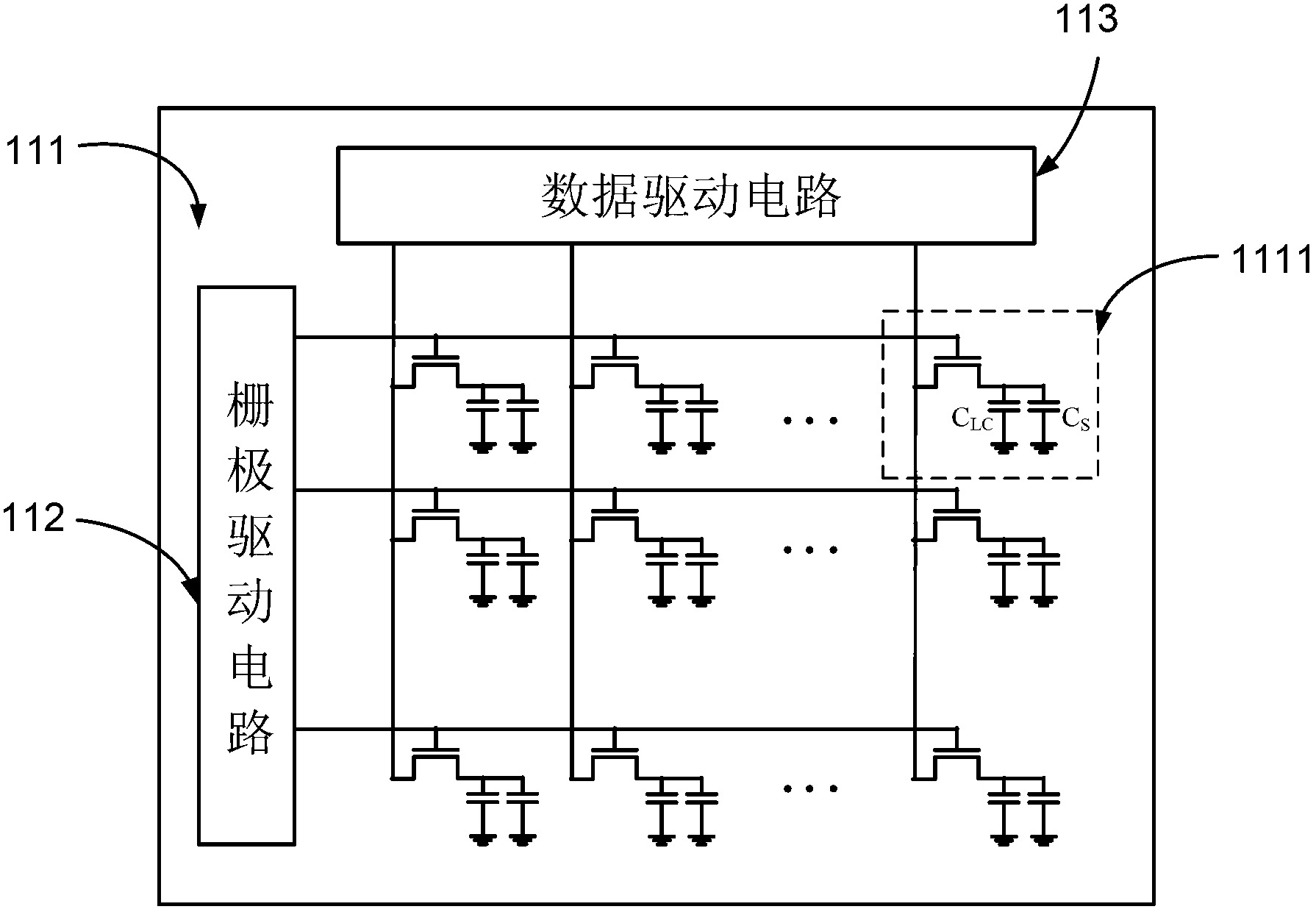

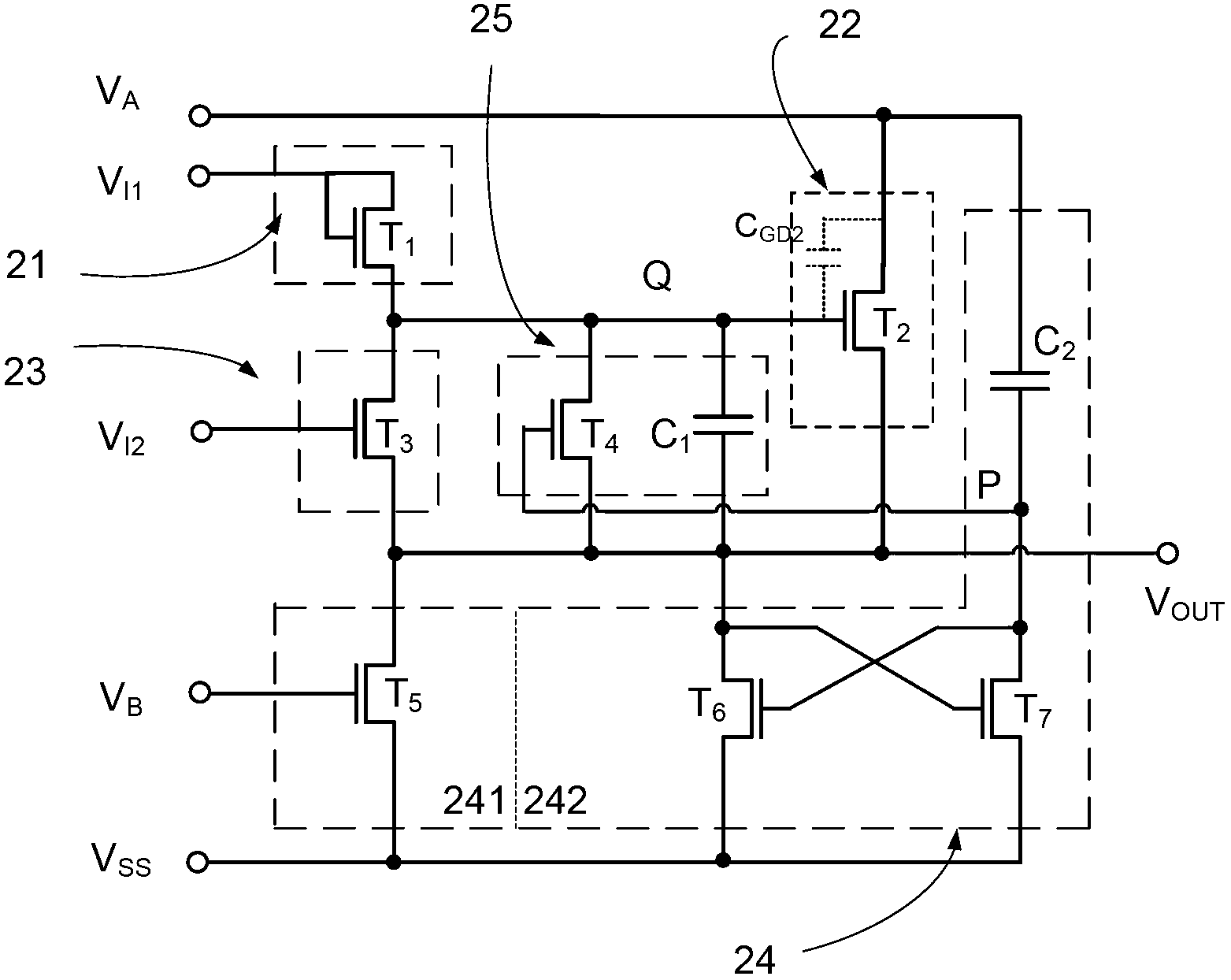

Shift register cell, gate driving circuit, data driving circuit and display

ActiveCN103077689AShorten the timeShorten rise timeStatic indicating devicesDigital storageShift registerElectricity

The invention discloses a shift register cell, a gate driving circuit, a data driving circuit and a display, wherein the shift register cell comprises a first signal input end, a second signal input end, a first clock signal input end, a pull-down control signal input end, a signal output end (VOUT), an input module (21), a driving module (22), a driving control end pull-down delay module (23), a clock feed through inhibition module (25) and a low-level retention module (24). According to the invention, the signal output end can quickly discharge by a charging transistor in the driving module by prolonging discharging time for a driving control end in the shift register cell; and the electricity leakage of the transistor in the clock feed through inhibition module is inhibited, so that work speed and integration degree of the circuit are improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

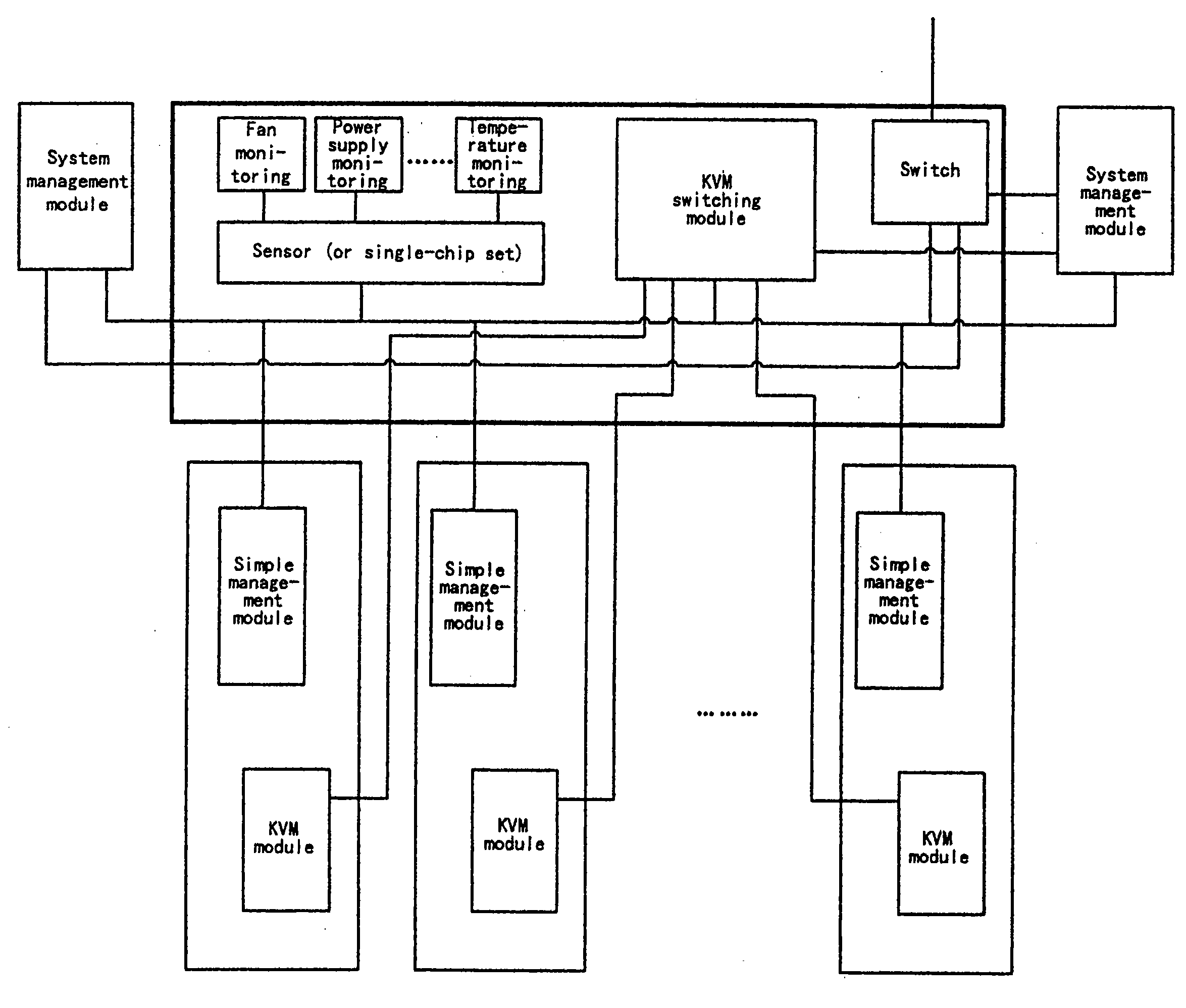

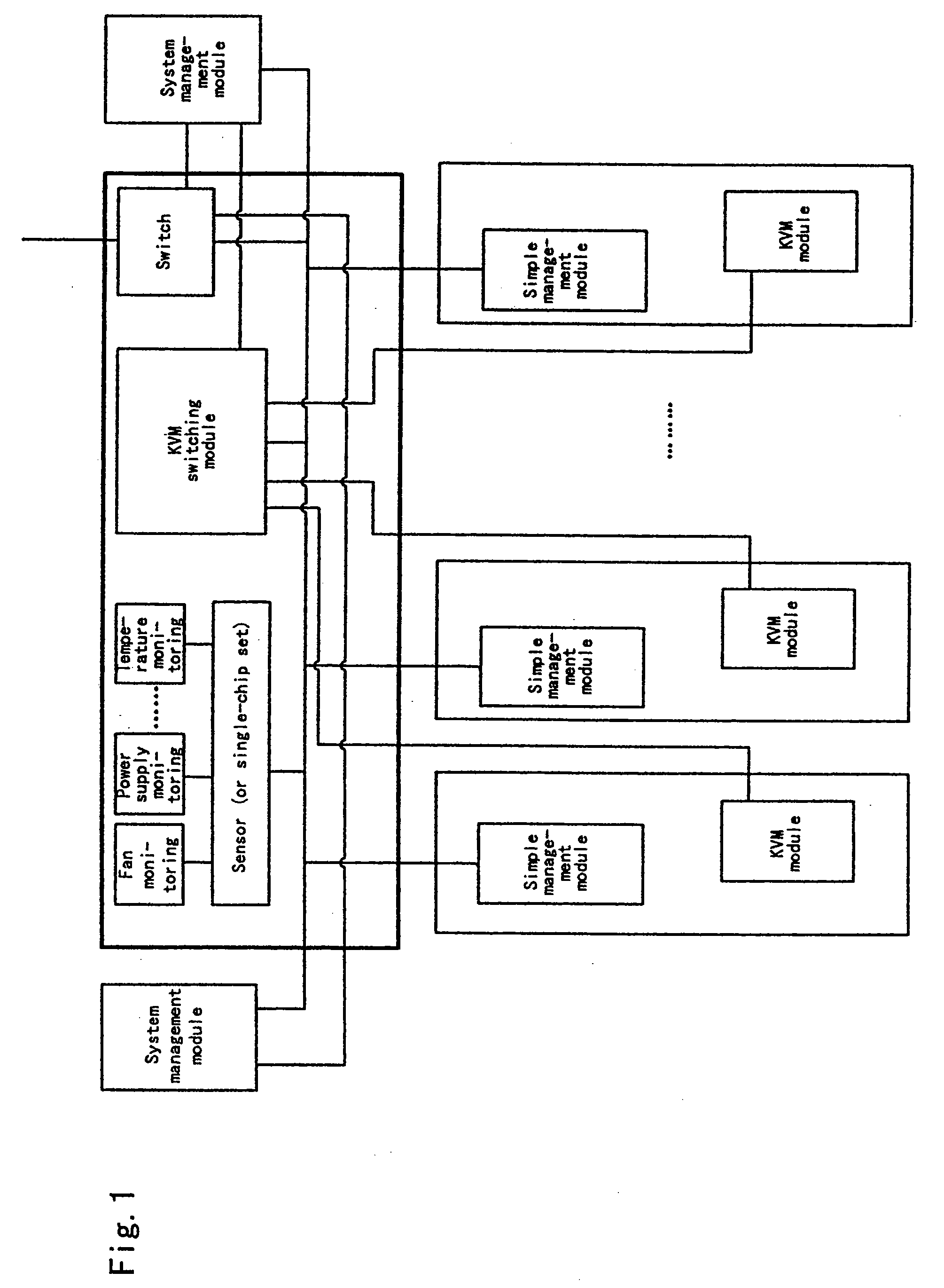

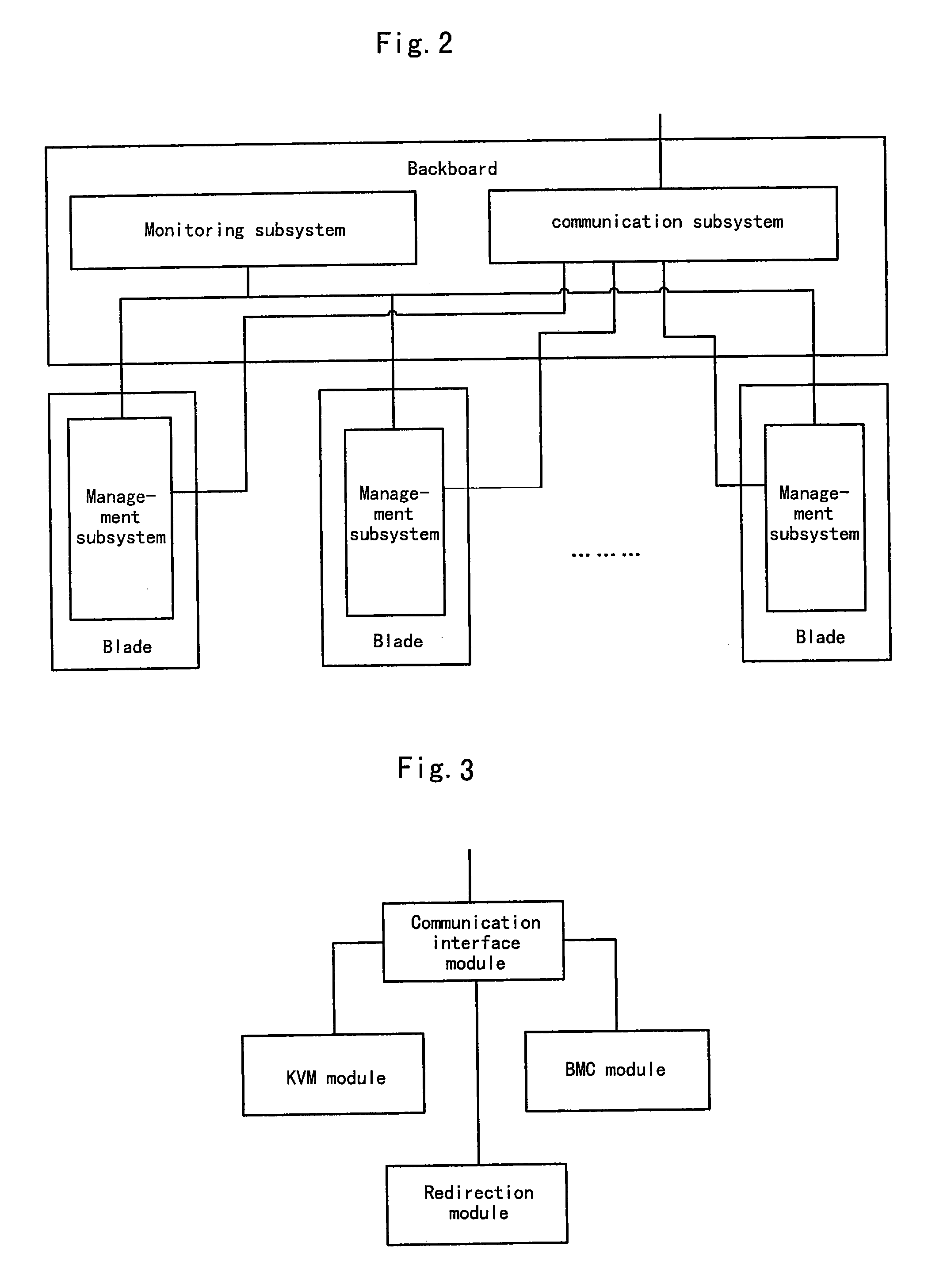

Blade server management system

ActiveUS20080162691A1Improve stability and reliabilitySimplify System DesignDigital computer detailsHardware monitoringEmbedded systemBlade server

The present invention discloses a blade server management system comprising a plurality of management subsystems provided on each blade in a blade server and connected to each other via a local area network, each of which implements remote control and self-management for the corresponding blade, and said management subsystems including at least one master management subsystem for monitoring the operation parameters of the blade server through a monitoring subsystem; a communication subsystem provided on a backboard for connecting a external network and said local area network made up of said management subsystems; and a monitoring subsystem provided on the backboard and connected to said management subsystems for monitoring the operation parameters of the blade server based on a command from the master management subsystem. The blade server management system of the present invention has high system reliability and stability as well as a simple routing design while reducing the complexity of system design.

Owner:LENOVO SOFTWARE +1

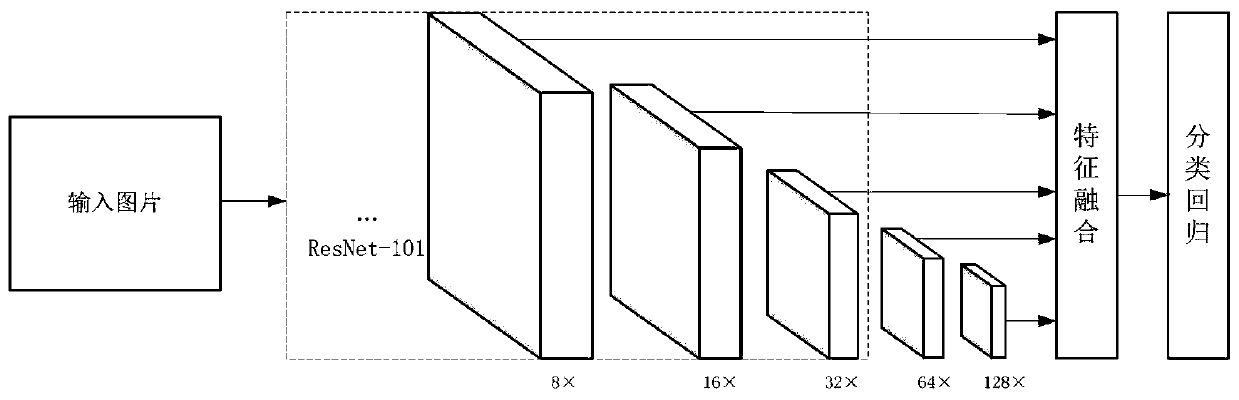

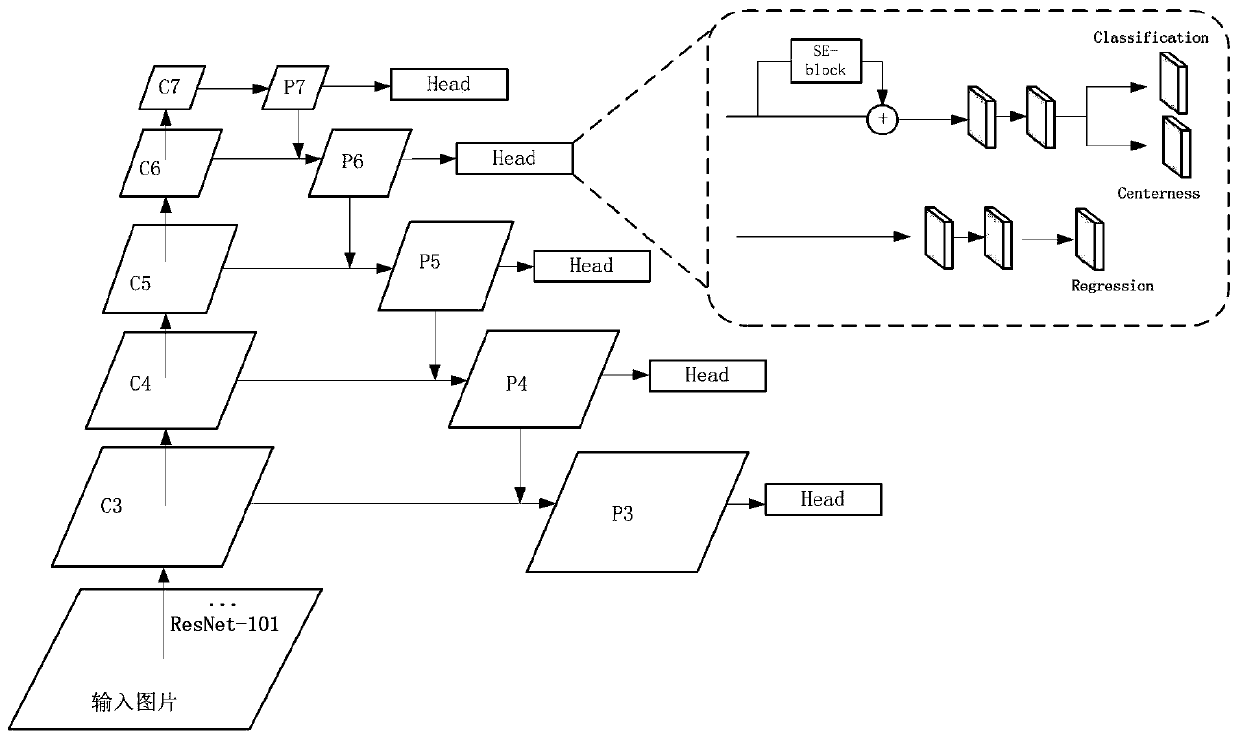

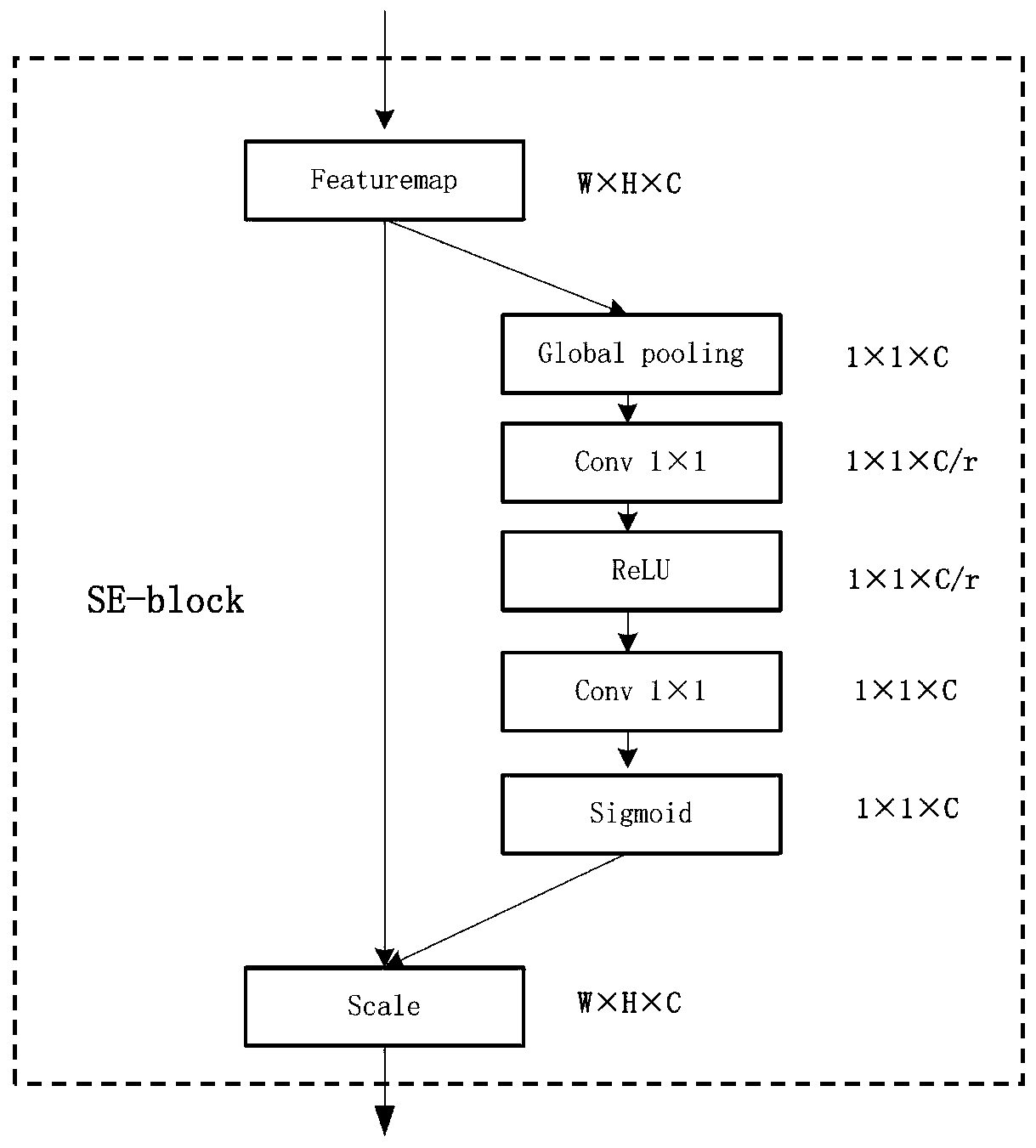

Target detection method based on SSD improvement

ActiveCN111126472AEasy to detectRich feature map informationCharacter and pattern recognitionNeural architecturesAlgorithmEngineering

The invention provides a target detection method based on SSD improvement, and the method selects ResNet-101 to replace VGG-16 as a basic network of a whole model, and provides richer feature map information. A feature fusion strategy is adopted, so that the detection effect of multi-scale prediction of a network prediction layer on a small target is improved to a certain extent; an SE-block module is added to a classification branch and used for capturing global environment information of the feature map and outputting the feature map with channel weight, so that classification is more accurate; and a Centerness parallel to the classification prediction layer is added to suppress a low-quality bounding box so as to improve the detection precision. According to the method, anchor-frame-free detection is adopted, all hyper-parameters related to the anchor frame are avoided, the hyper-parameter amount is greatly reduced through the adopted prediction bounding box strategy, the network design complexity is reduced, and the training stage becomes very simple. According to the method, a loss function adopts a focalloss function, so that the model detection precision is improved while the detection speed is kept.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

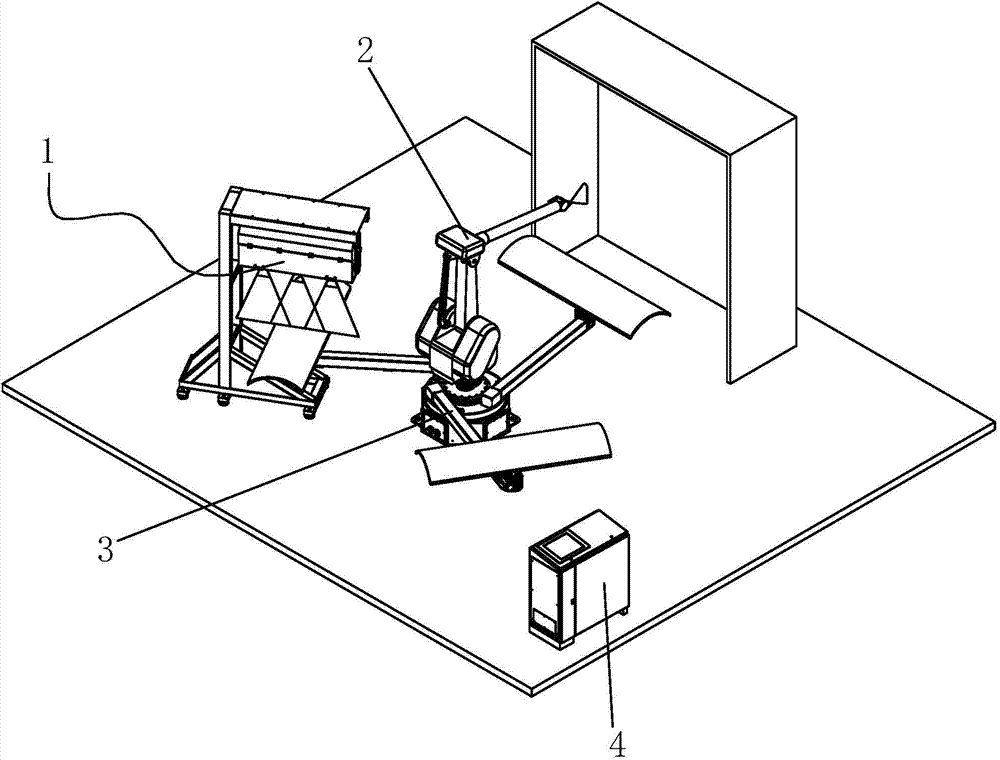

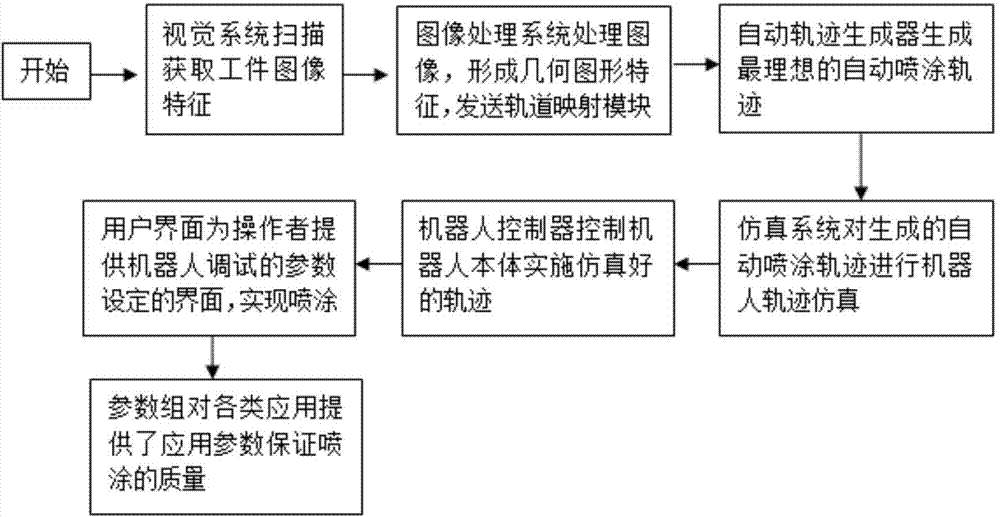

Control method of robot automatic spraying system

The invention discloses a control method for a robot automatic spraying system. The control method of the robot automatic spraying system comprises the following steps of (1) acquiring feature data of a workpiece to be sprayed; (2) processing acquired data by using an image processing system; (3) automatically generating a track; (4) simulating; (5) controlling a user interface; (6) determining a spraying parameter; and (7) performing spraying. The control method of the robot automatic spraying system has the advantages of high automation degree, high machining precision, wide application range and the like. Different workpiece spraying tracks can be generated automatically, the operation difficulty of a user is reduced, the traditional manual programming on single different-model workpieces to be sprayed is replaced, consumed time on spraying is shortened, and the production efficiency is improved.

Owner:希美埃(芜湖)机器人技术有限公司

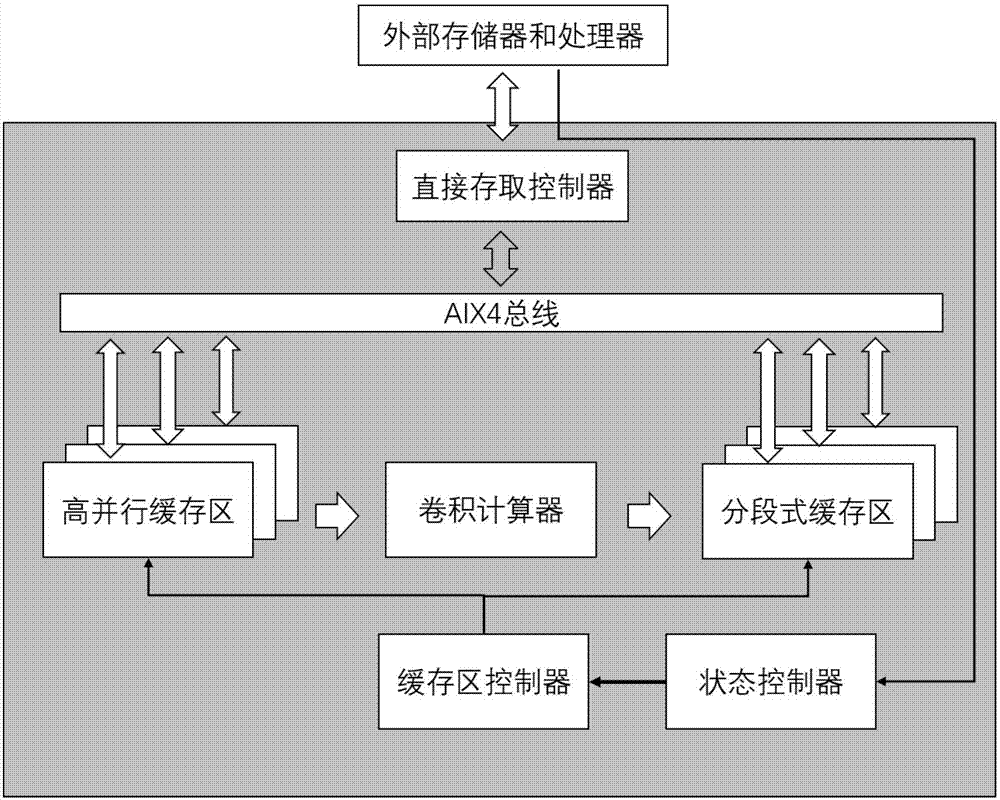

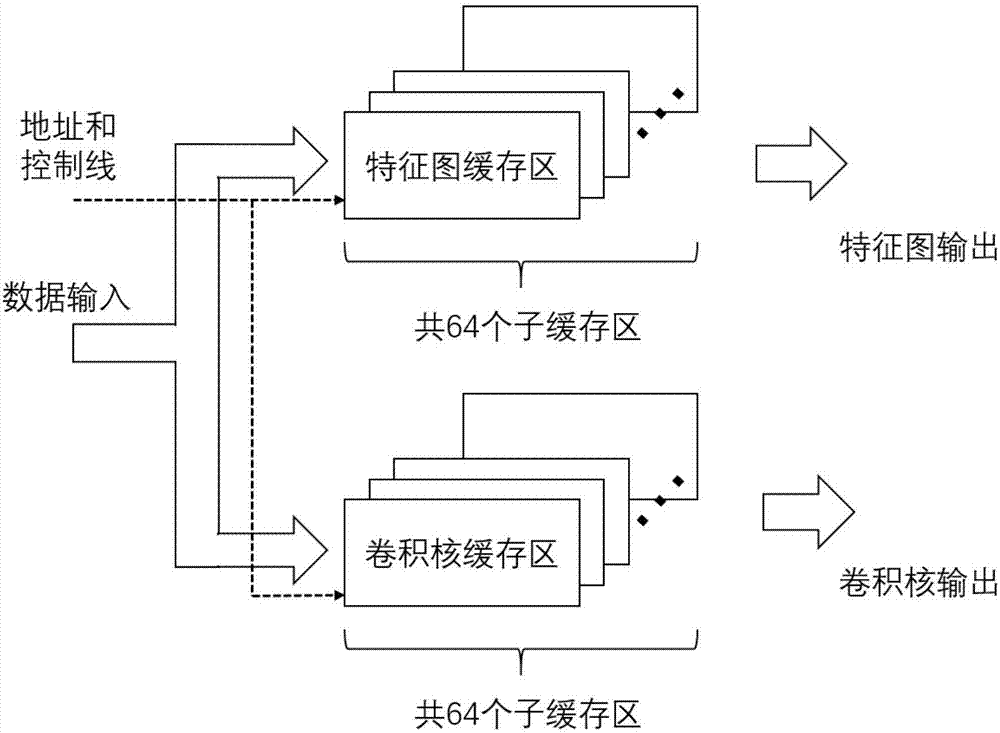

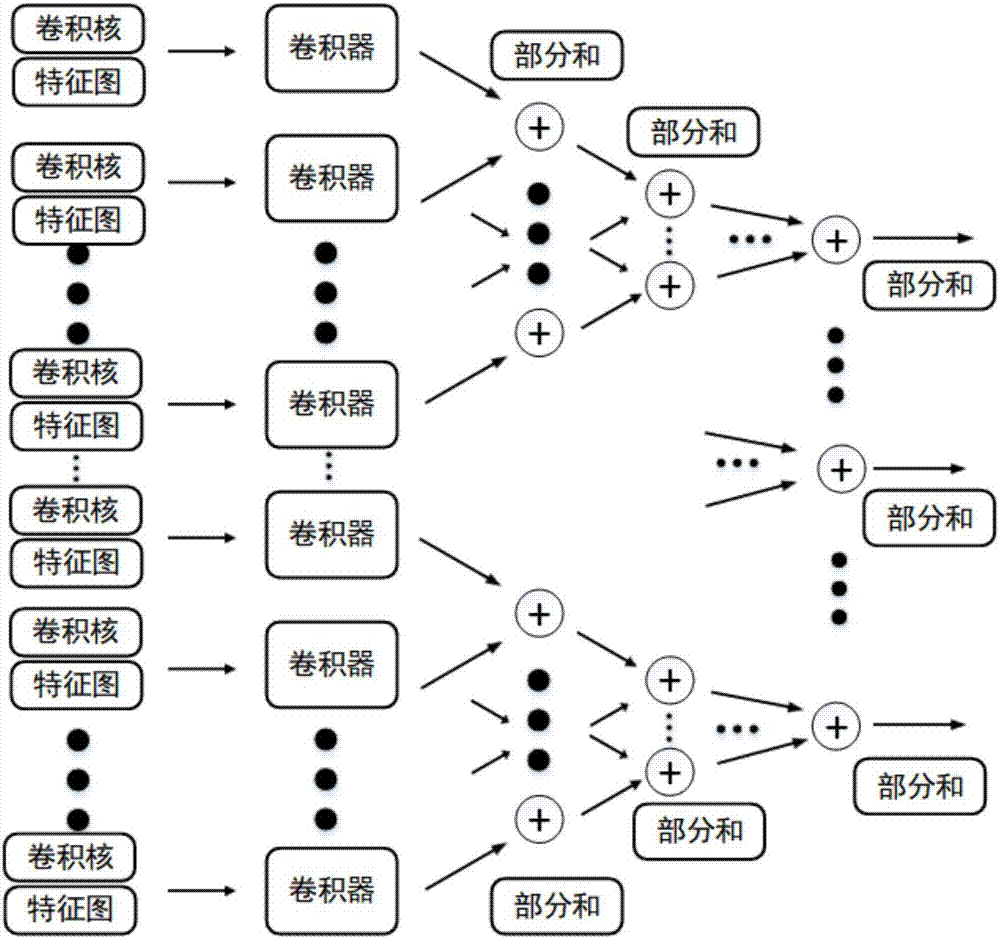

FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure

InactiveCN107392309AImprove versatilityIncrease computing speedPhysical realisationData conversionFace detectionHardware structure

The invention discloses an FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure which comprises a universal AXI4 high-speed bus interface, a universal GPIO (general purpose input / output) interface, a universal convolver, a universal read-write control unit, a universal state controller and a universal convolution result buffer. Universal memory hardware is provided, and high-parallel read-write operations are supported; the universal convolver can be used for accurate configuration of fixed point numbers, configuration of convolution operation levels and high-parallel convolution operation in coordination with high-parallel read-write operations after data storage; the universal read-write control unit includes ram, rom and Fifo read-write control logics and address generating logics; the universal state controller makes corresponding unit operating reactions aiming at a convolution layer and read-write and calculation processes to control an integral calculation process; the universal convolution result buffer is used for high-speed parallel caching and sending of a processing result to a bus according to a convolution result sectional accumulation method. By verification in application to Yolo algorithm based human face detection and CNN (convolutional neural network) based human face recognition, high operating speed and high data precision are embodied.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS +1

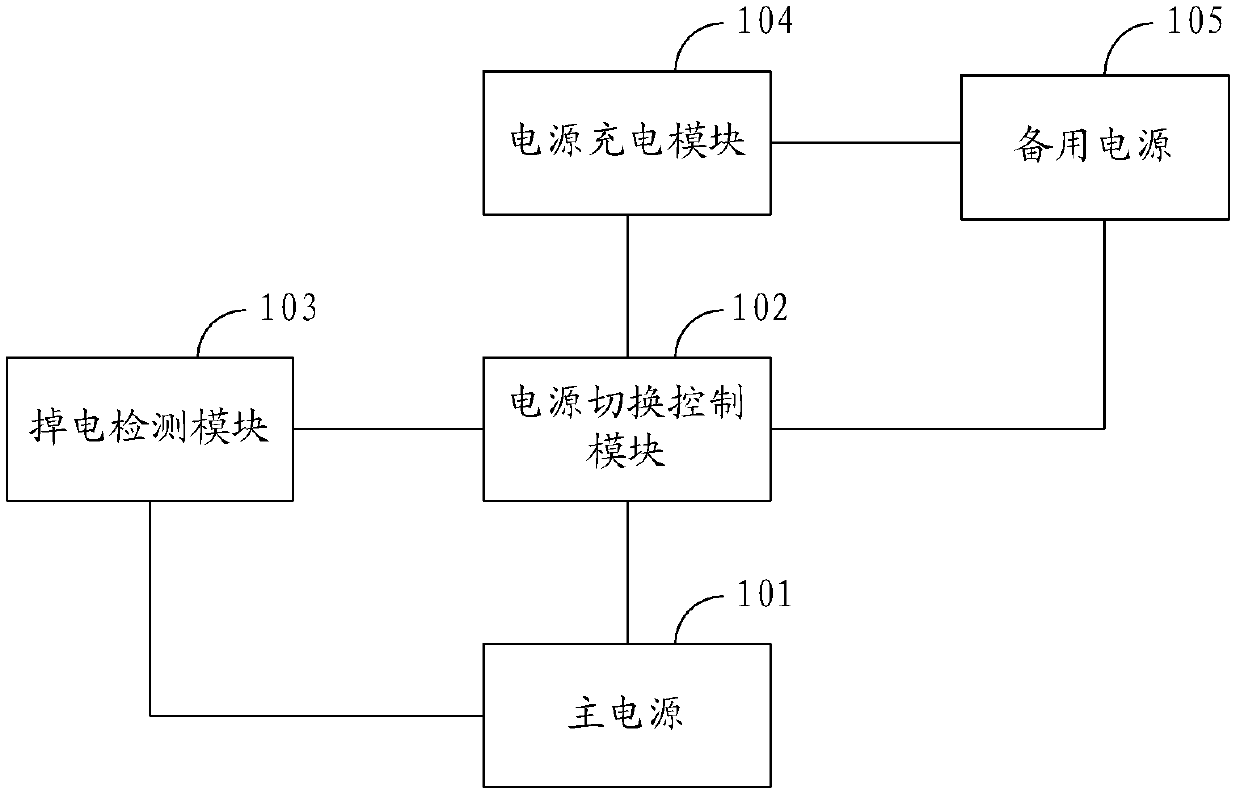

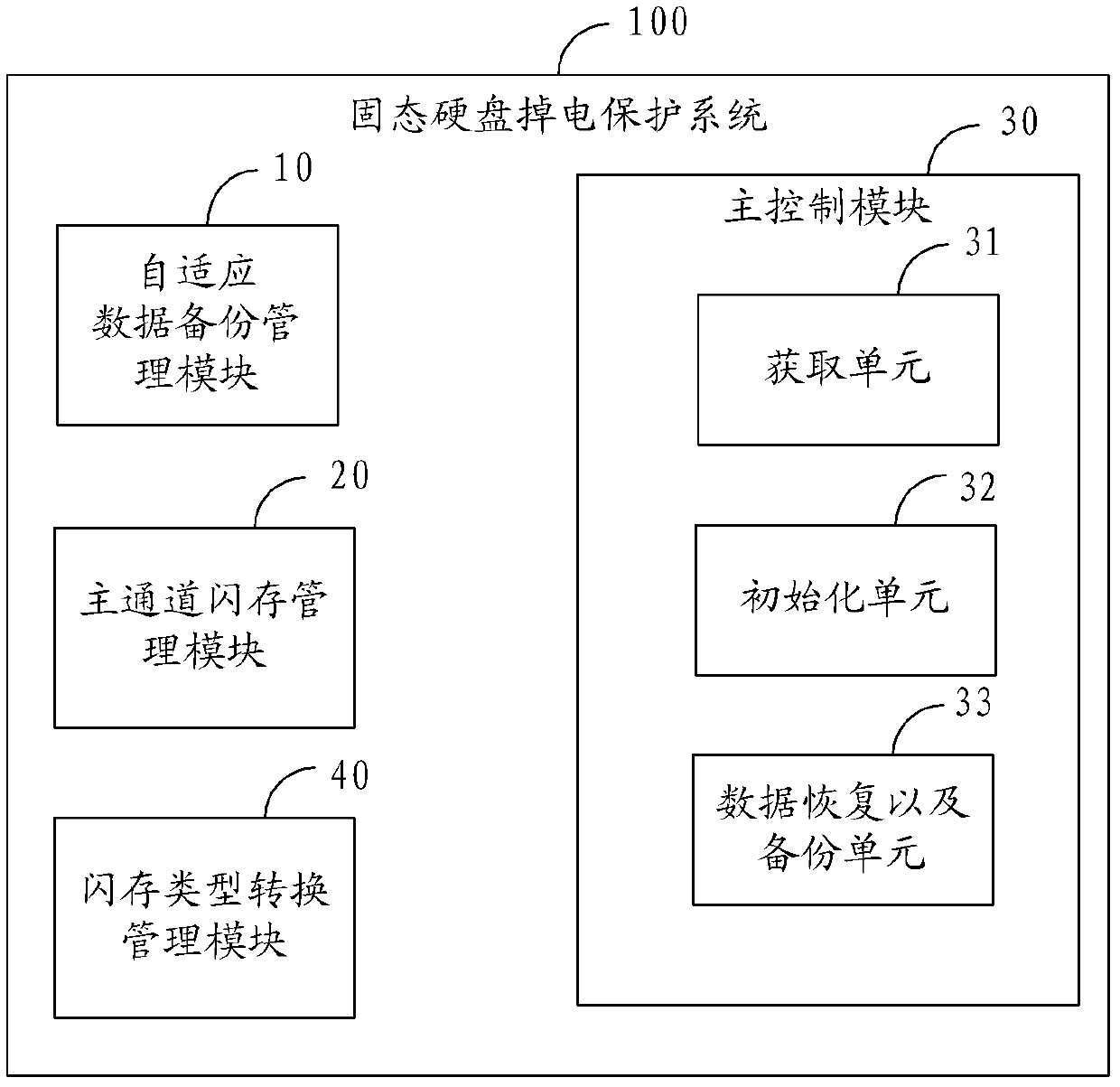

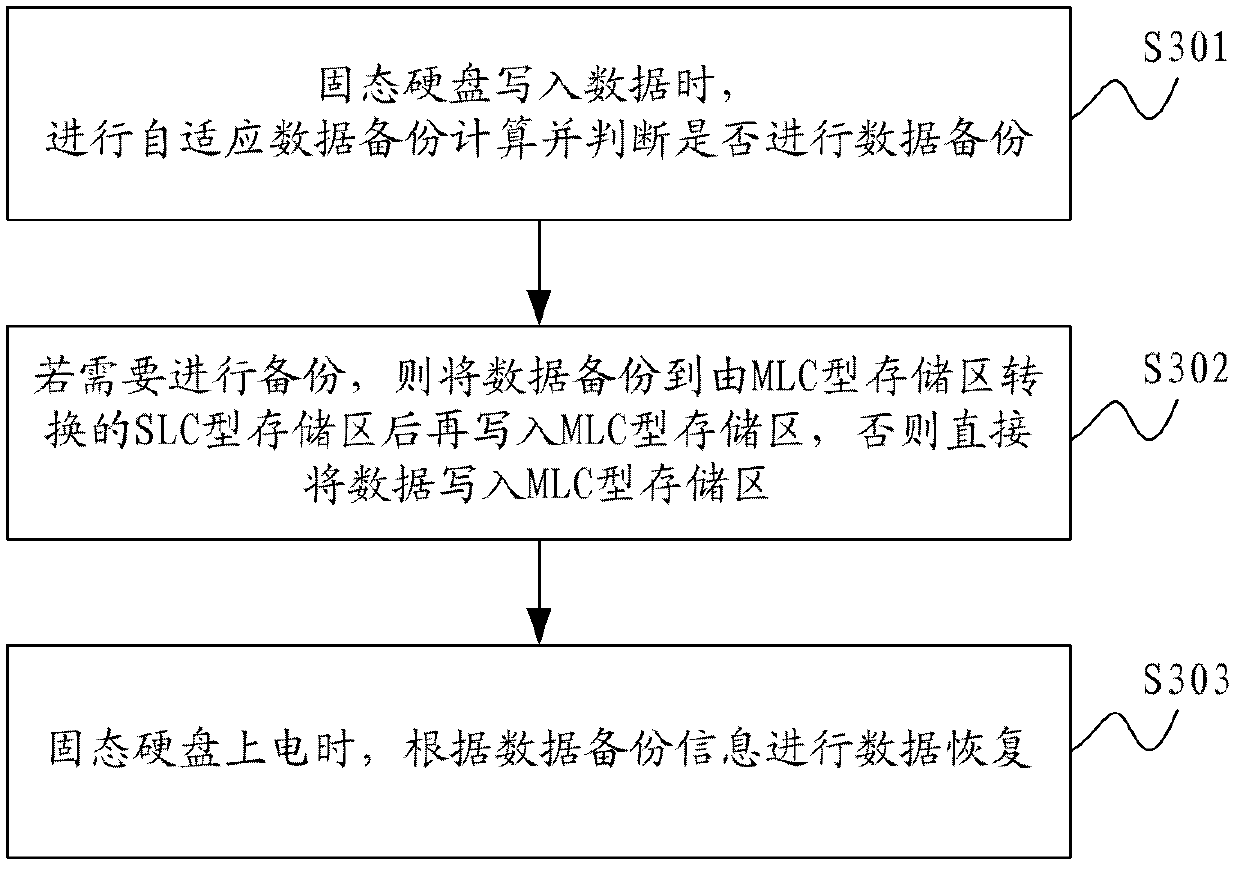

Solid state disc and power failure protection method and system thereof

InactiveCN102591748AAvoid destructionSolve the damageRedundant operation error correctionElectricitySingle level

The invention is applied to the fields of solid state discs and information storage and provides a solid state disc and a power failure protection method and a system thereof. The method comprises the steps of performing self-adaption data backup computation and judging whether to proceed data backup when data is written into the solid state disc; if backup is required, backuping the data to a single level cell (SLC) type storage area converted from a multi level cell (MLC) type storage area, then writing the data into the MLC type storage area, otherwise directly writing the data into the MLC type storage area; and when the solid state disc is powered on, the data is recovered according to data backup information. Therefore, the solid state disc and the power failure protection method and the system of the solid state disc can solve the problem of data damage of coupling pages in Nand Flash caused by abnormal power failure by means of a self-adaption backup technology on the basis that hardware design cost and complexity are not increased.

Owner:RAMAXEL TECH SHENZHEN

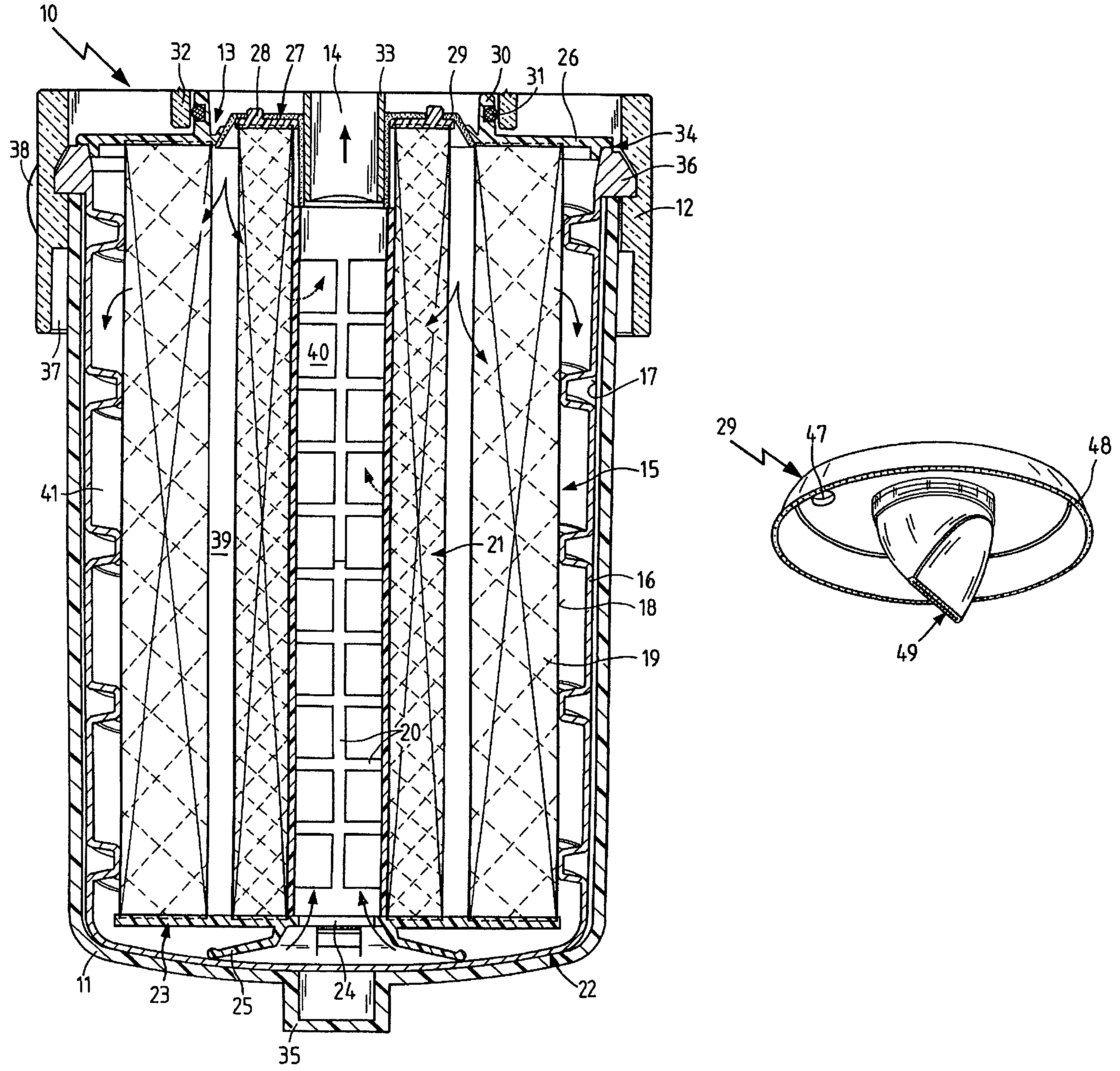

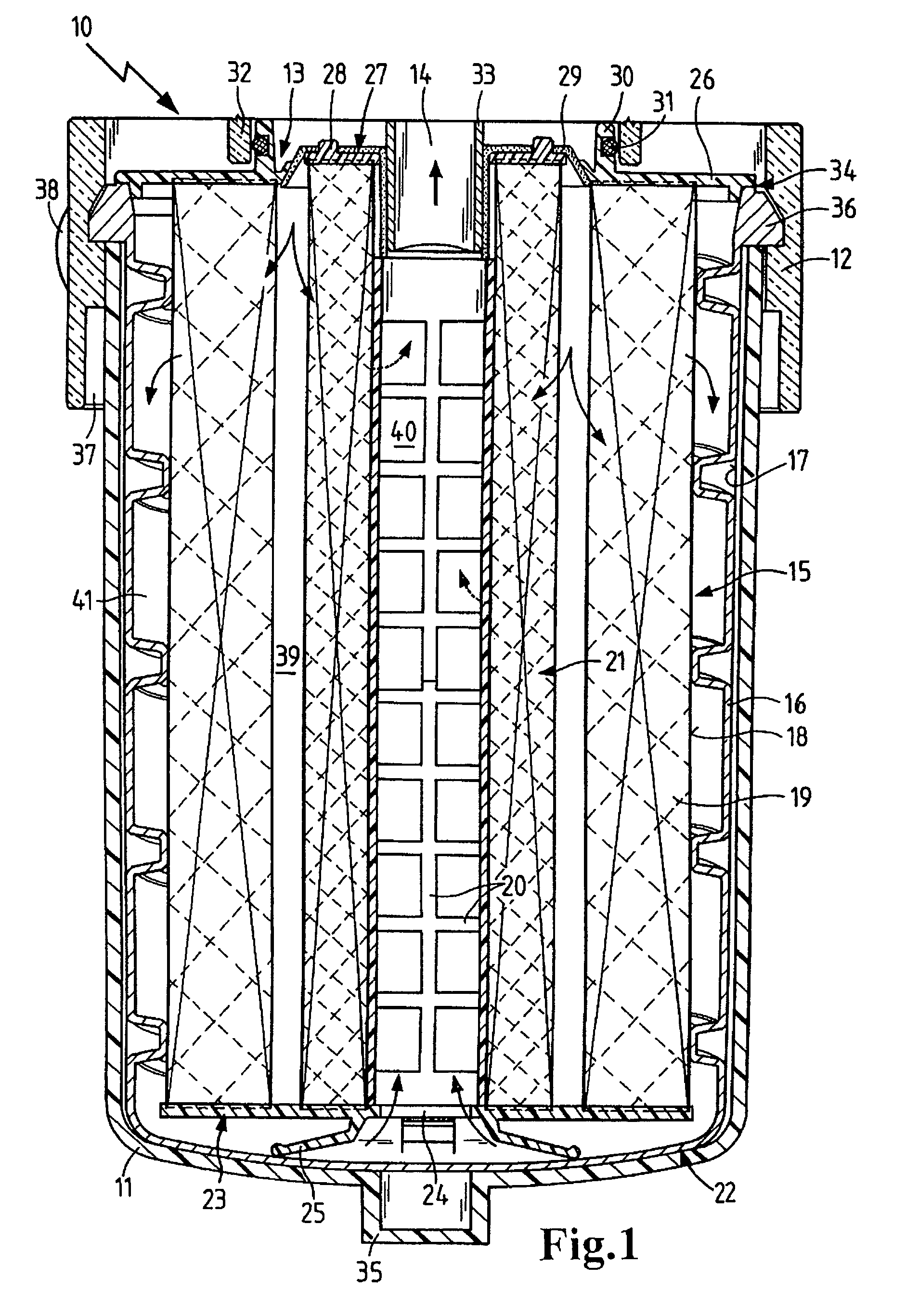

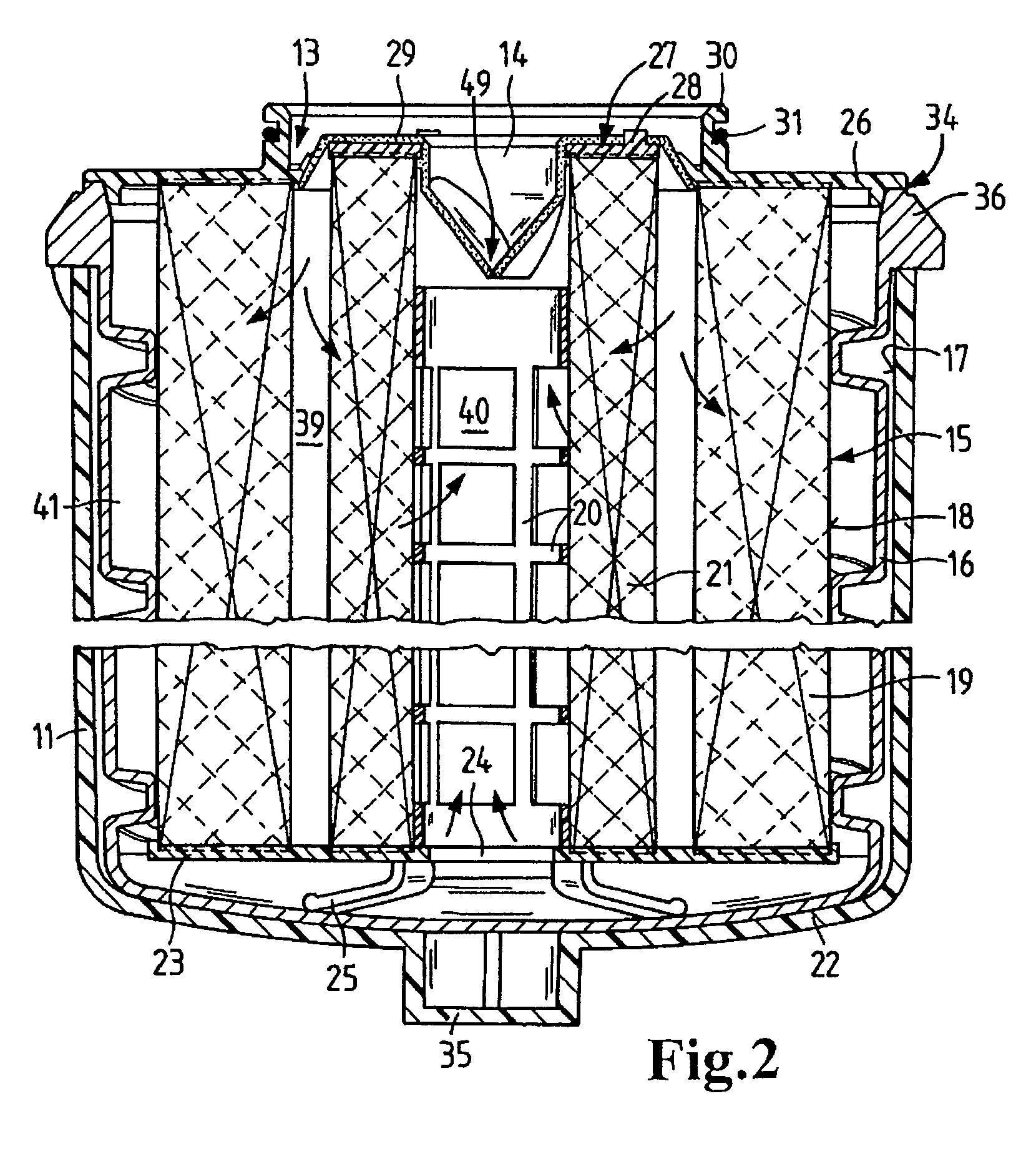

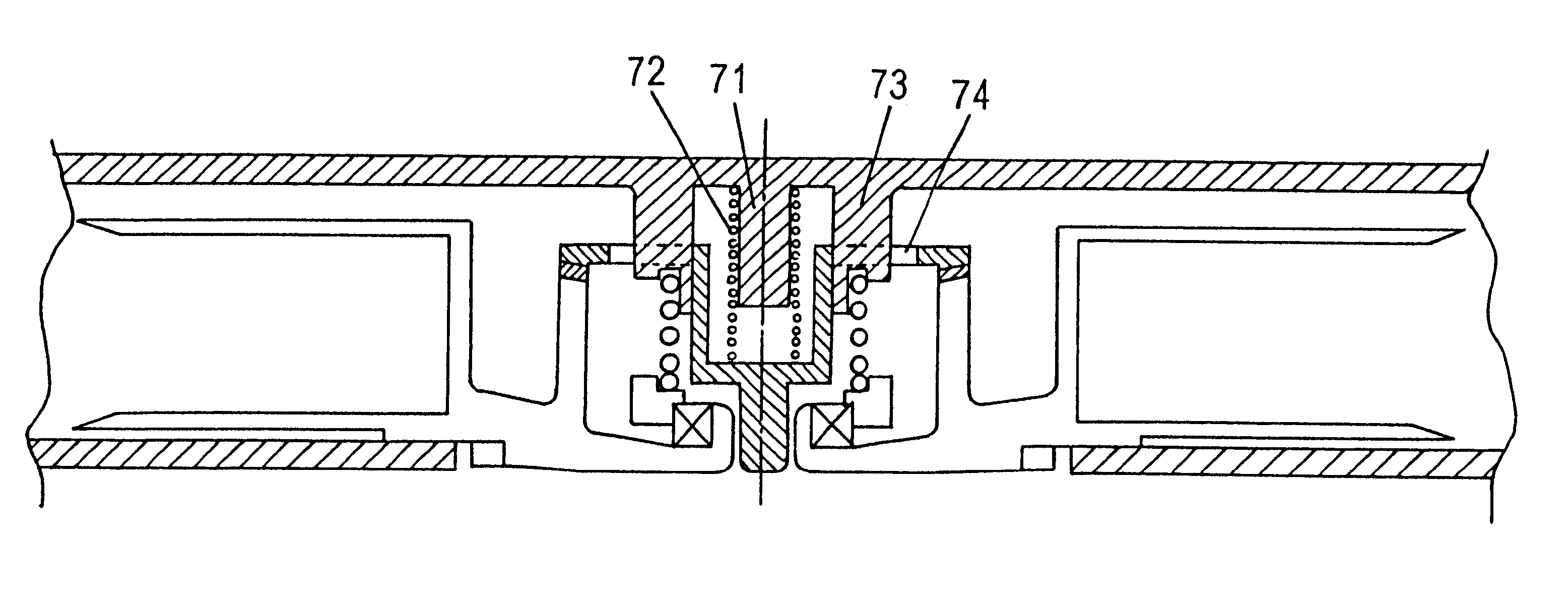

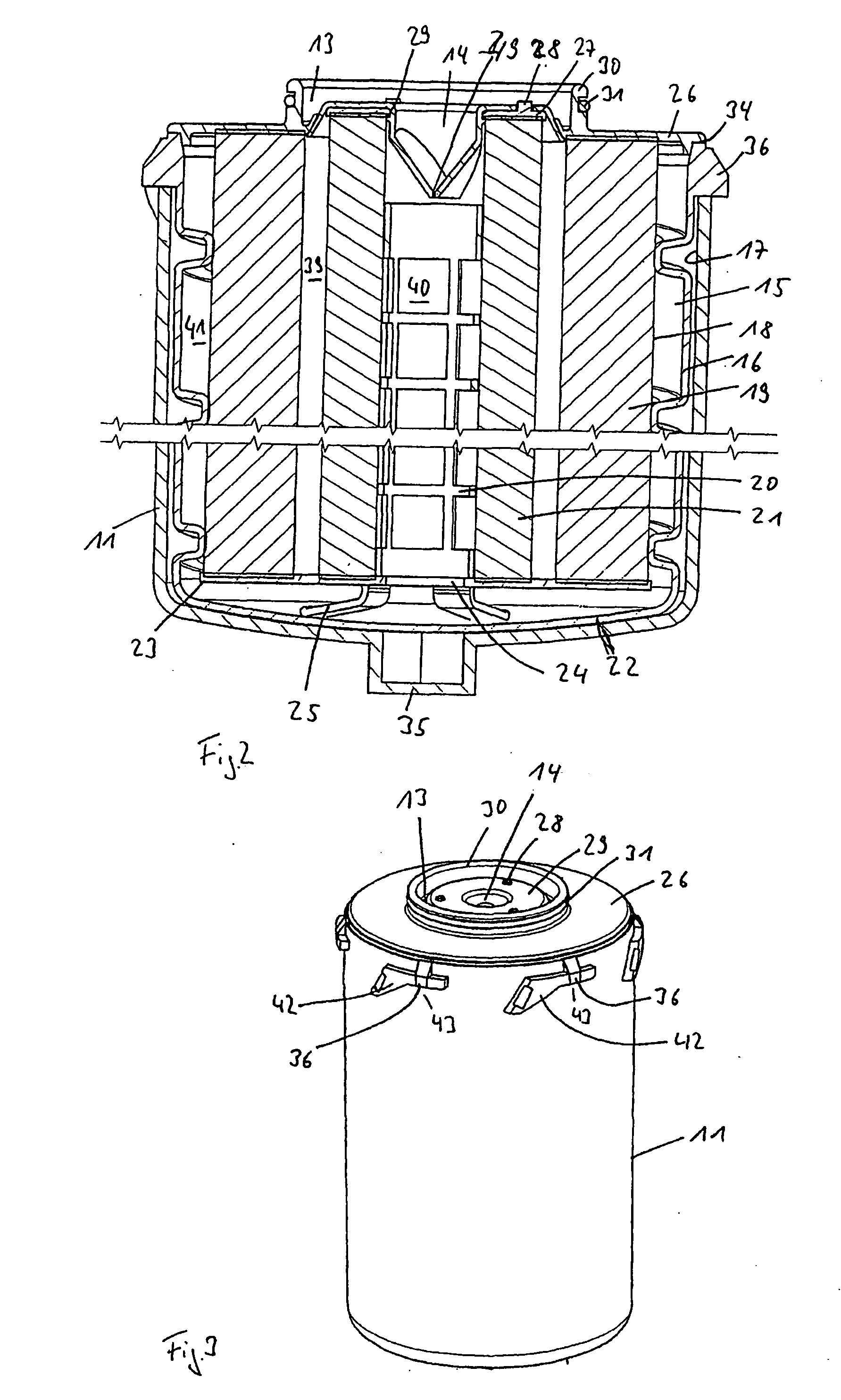

Liquid filter

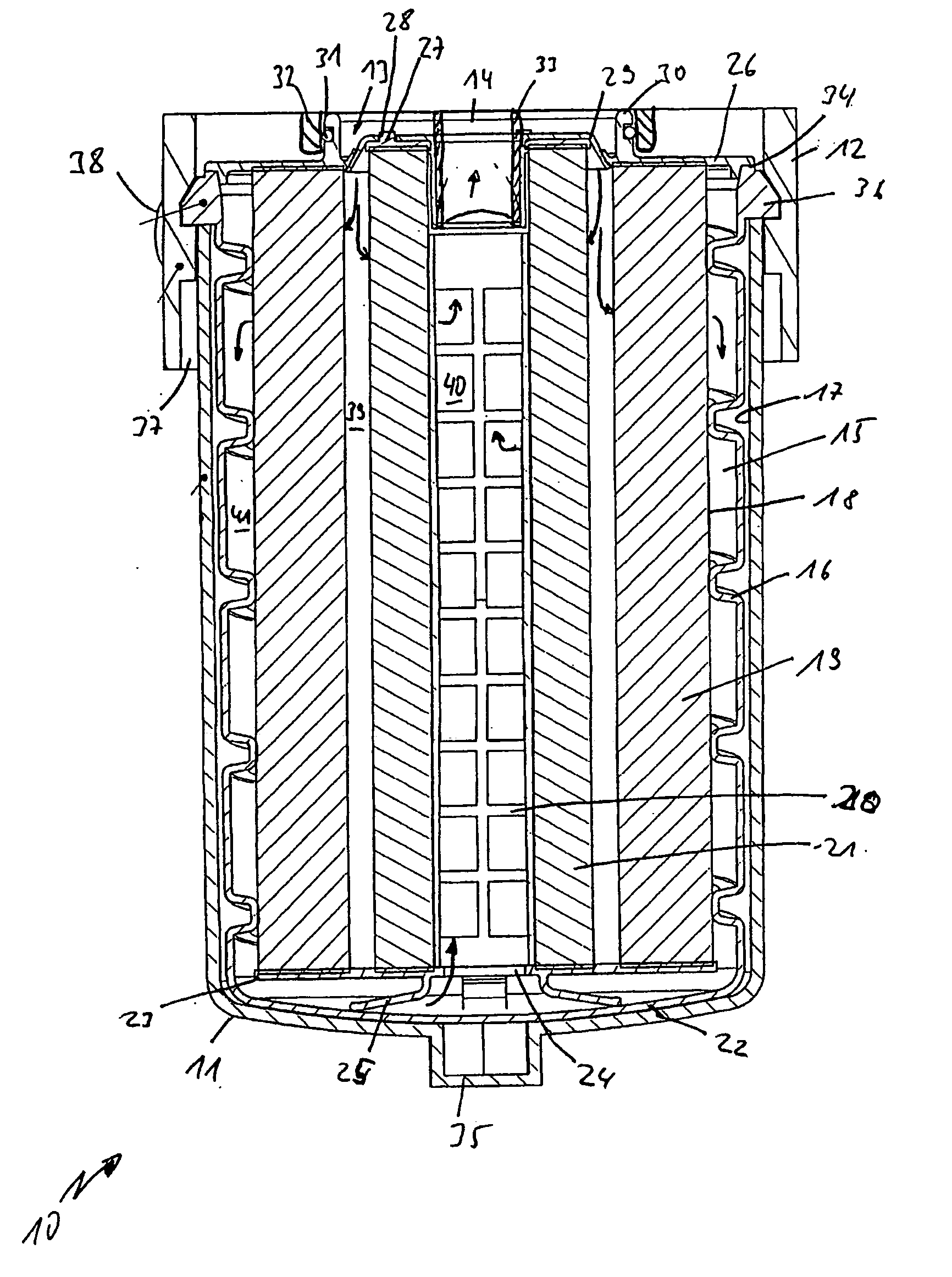

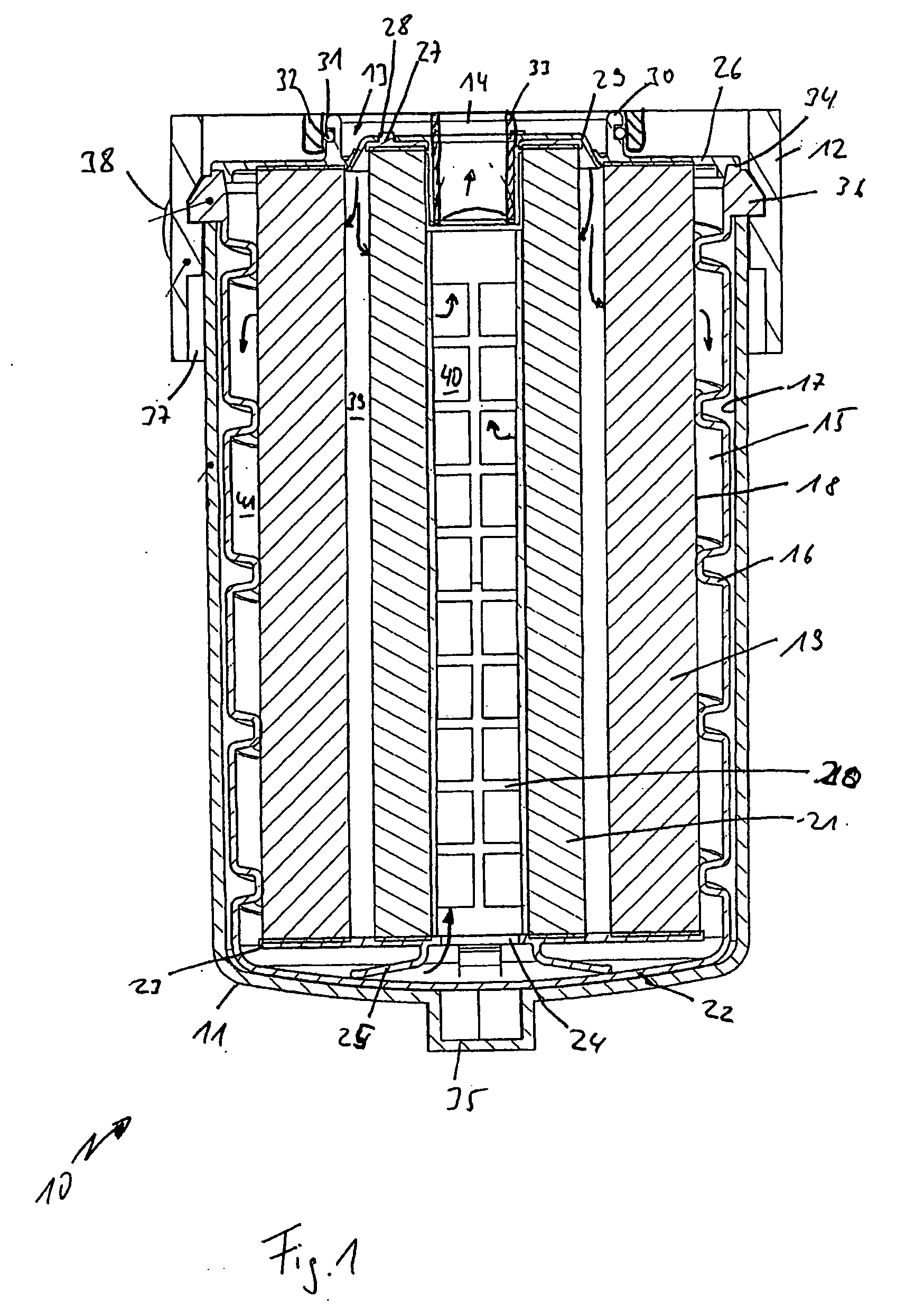

InactiveUS7744758B2Reduce Design ComplexitySimple structureSemi-permeable membranesSedimentation separationEngineeringInternal combustion engine

Owner:MANN HUMMEL GMBH

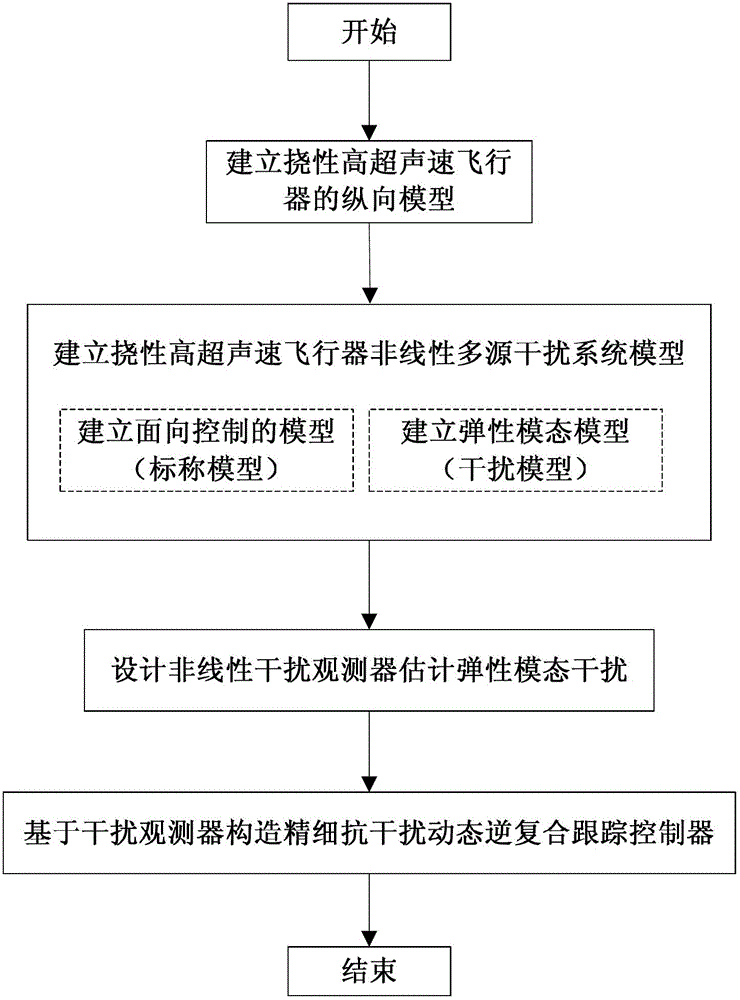

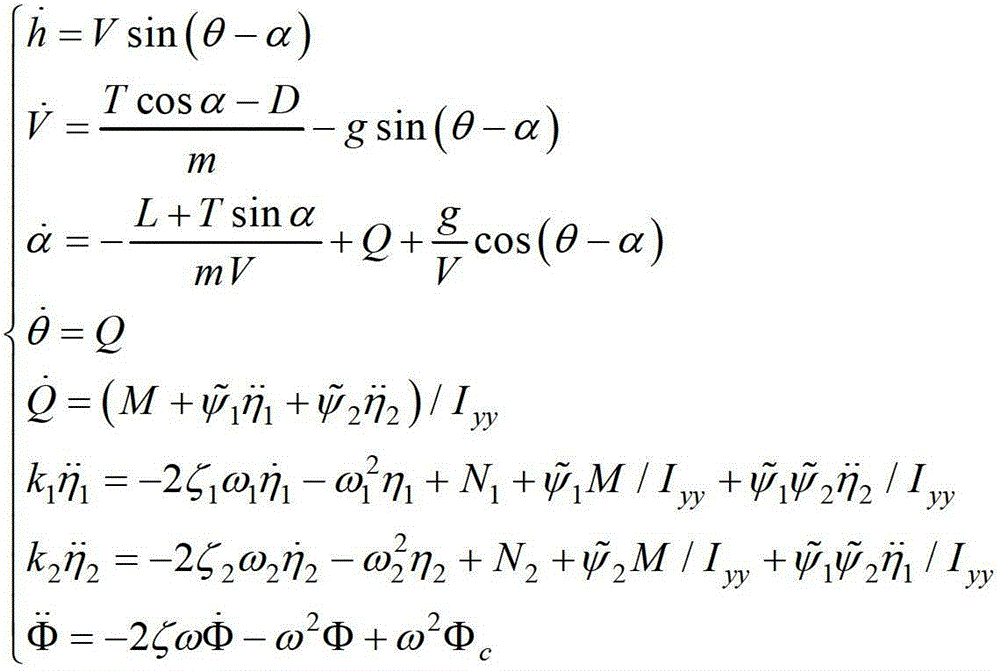

Fine anti-interference tracking controller of flexible hypersonic vehicle

ActiveCN102749851ALittle impact on performanceSuppress interferenceAdaptive controlObservational errorControl oriented

The invention relates to a fine anti-interference tracking controller of a flexible hypersonic vehicle. A method for constructing the fine anti-interference tracking controller comprises the following steps of: (1) building a longitudinal model of the flexible hypersonic vehicle; (2) building a multisource interference system model of the flexible hypersonic vehicle based on the longitudinal model in the step (1): firstly, building a control-oriented nominal model; then regarding an elastic mode as interference and building an elastic mode interference model; and finally, building a multisource interference system model by combining the above two models and considering measurement errors, parameter uncertainty, external interference, etc.; (3) designing a nonlinear disturbance observer to estimate the elastic mode interference based on the multisource interference system model in the step (2); and (4) constructing the fine anti-interference dynamic reverse composite tracking controller based on the nonlinear disturbance observer in the step (3). The fine anti-interference tracking controller has the advantages of high anti-interference performance, rapid tracking speed, high control accuracy, etc., and applies to high accuracy tracking control of the height and the speed of the flexible hypersonic vehicle.

Owner:BEIHANG UNIV

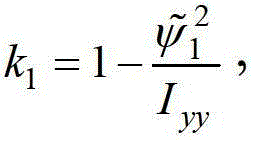

Reel lock and coupling engagement mechanisms for a cartridge

InactiveUS6318657B1Improve reliabilityShorten the timePicture changing apparatusRecord information storageCouplingMagnetic tape

A tape cartridge is provided with reliable reel lock and motor / reel coupling mechanisms whose functions are both accomplished during a single motion of the cartridge relative to the drive motor. The motor / reel coupling includes a circular set of gear teeth on the bottom of the tape reel which meshes with a complementary set of gear teeth on a motor coupling rotated by the motor when the cartridge is loaded into the tape drive and the cartridge and motor are moved towards each other. An engagement force to maintain the coupling is provided by an engagement spring in the cartridge which biases the reel towards the motor. Reel locking is accomplished by providing a second circular set of gear teeth on a top side of the tape reel which meshes with a complementary set of gear teeth provided on a slidably mounted locking bracket inside the tape cartridge. A lock spring normally biases the locking bracket towards the top of the tape reel, thus locking the reel when the cartridge is not engaged with the motor. When the cartridge and the drive motor are moved towards each other, the motor coupling engages the bottom of the tape reel, and a projection on the motor coupling extends into the tape cartridge to slide the locking bracket out of engagement with the teeth on the top of the tape reel, thereby unlocking the reel. Thus, reel unlocking and motor / reel coupling are accomplished with a single motion by reliable mechanisms.

Owner:QUANTUM CORP

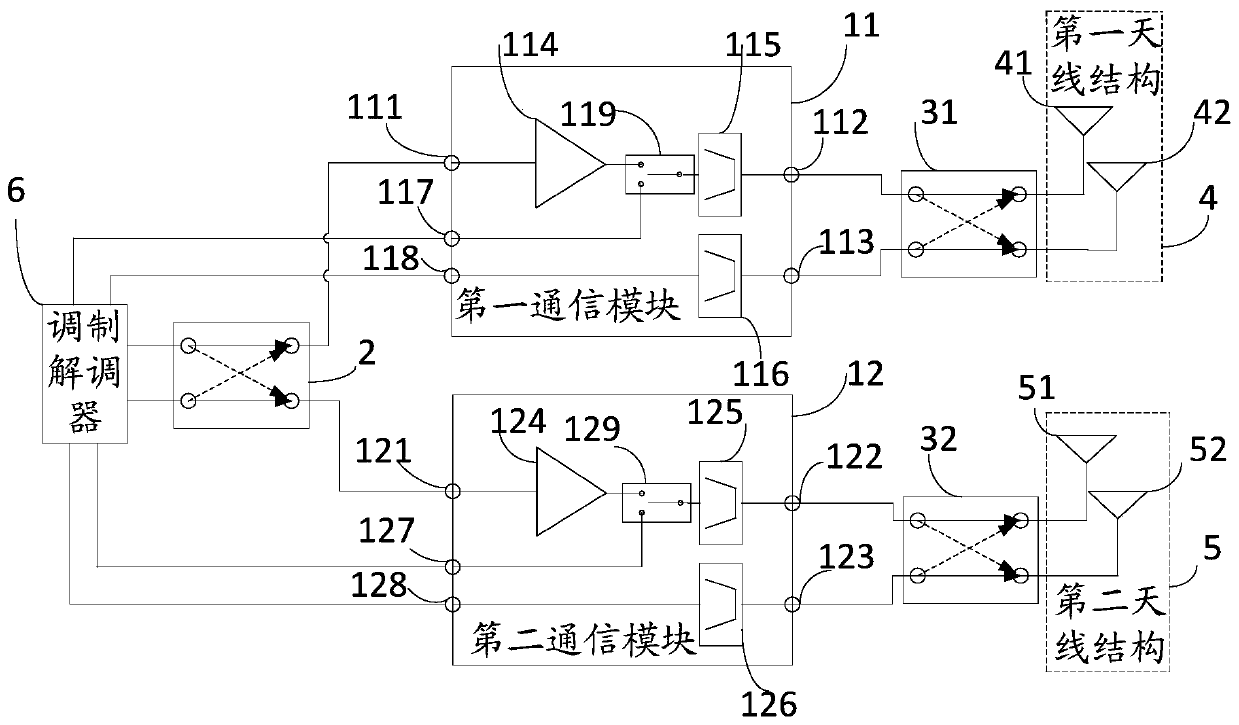

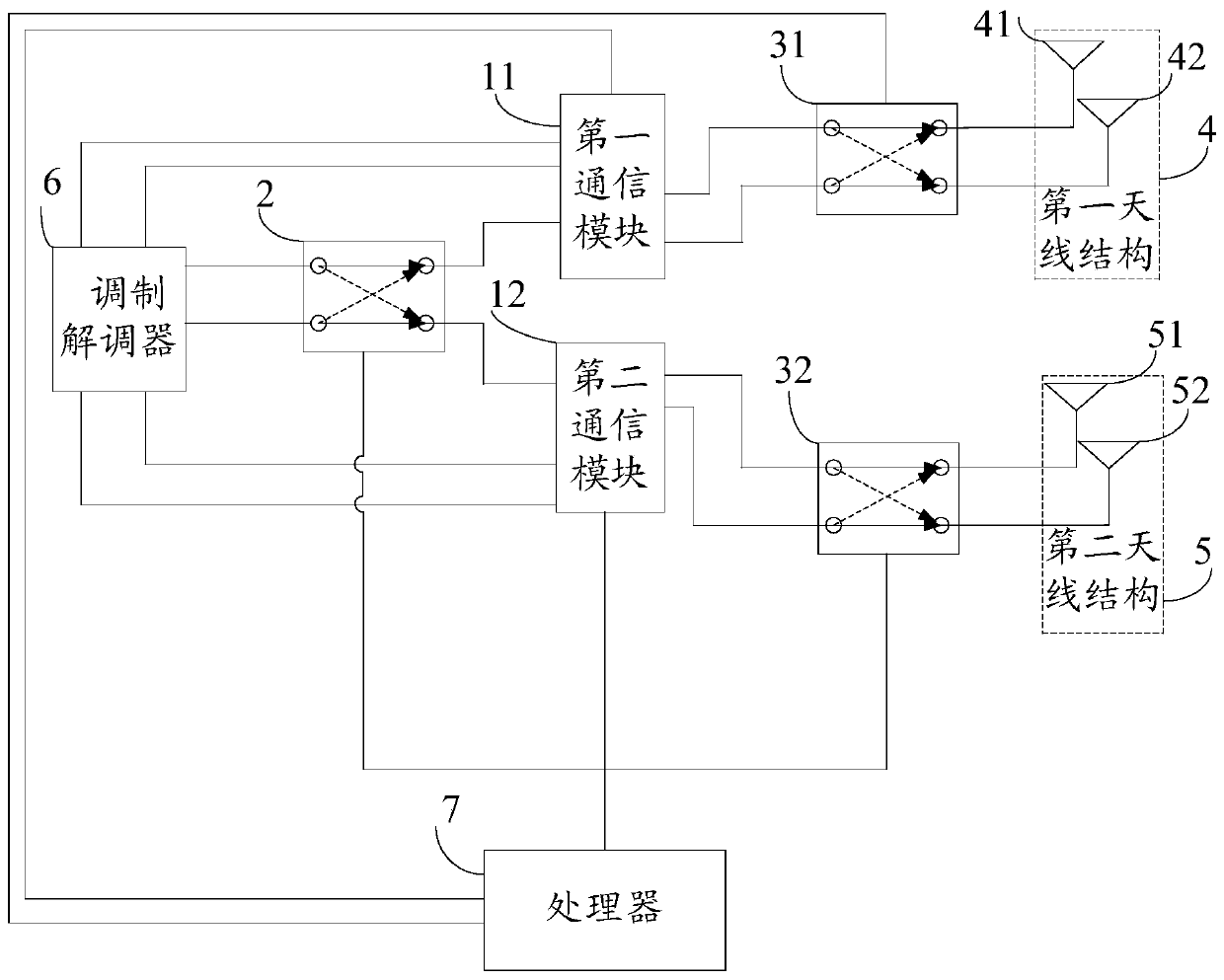

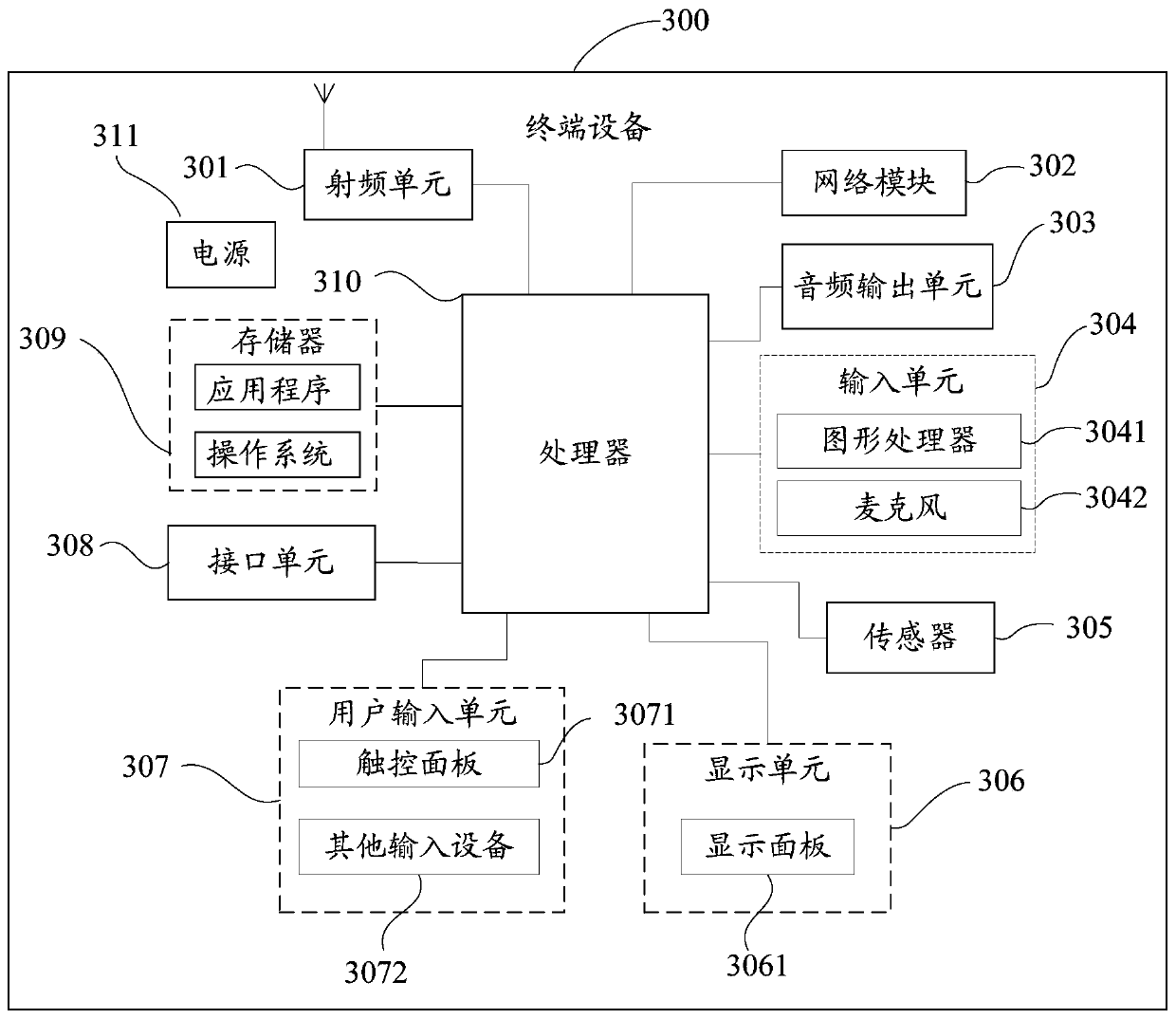

Signal transceiving device and terminal equipment

ActiveCN109802699ASmall insertion lossImprove performanceSpatial transmit diversityRadio transmissionTerminal equipmentEngineering

The invention provides a signal receiving and transmitting device and terminal equipment. The signal receiving and transmitting device comprises a first communication module and a second communicationmodule, a first switch is respectively connected with the first end of the first communication module and the first end of the second communication module; a second switch is connected with the second end of the first communication module; a first antenna structure is connected with the second switch; a third switch is connected with the second end of the second communication module; a second antenna structure is connected with the third switch; Wherein the first communication module corresponds to a first transmitting link and two receiving links, and the second communication module corresponds to a second transmitting link and two receiving links; At least one of the first transmitting link and the second transmitting link is conducted during signal transmitting, and two receiving linkscorresponding to the first communication module and the second communication module are conducted during signal receiving. According to the invention, the insertion loss of a receiving link can be reduced, the performance of a transmitting link is improved, the routing length is reduced, and the compatibility of 1T4R and 2T4R modes is realized.

Owner:VIVO MOBILE COMM CO LTD

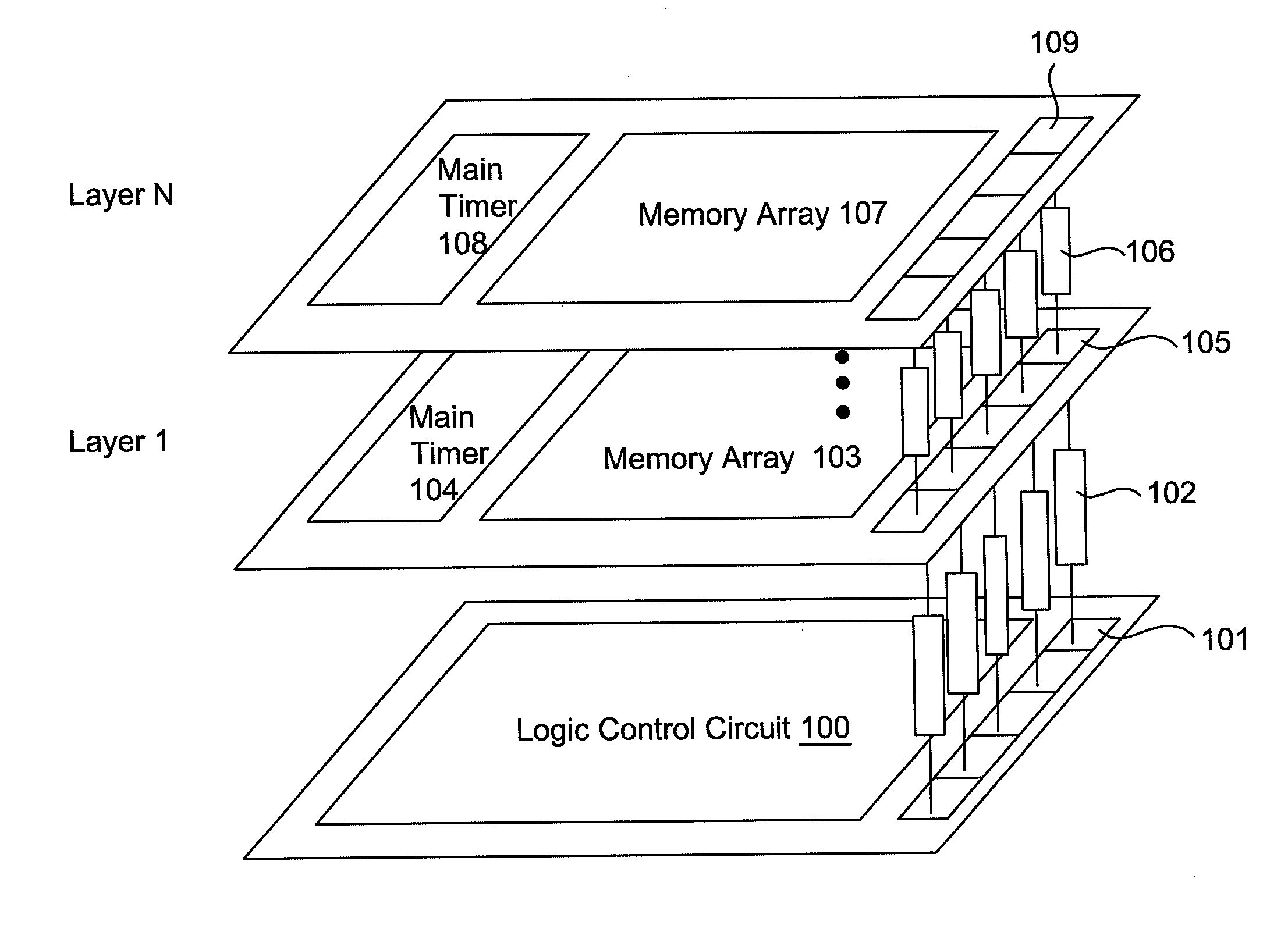

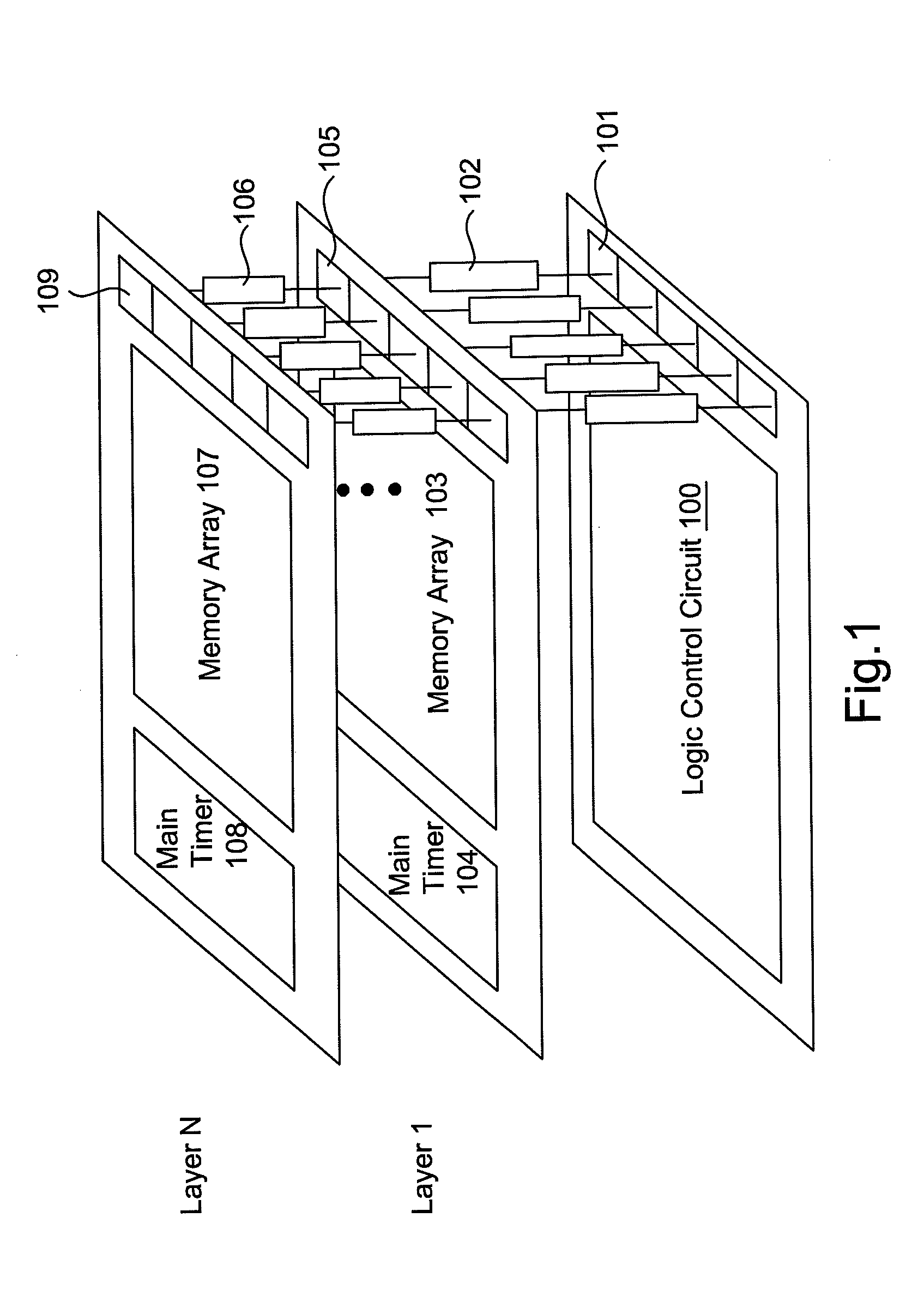

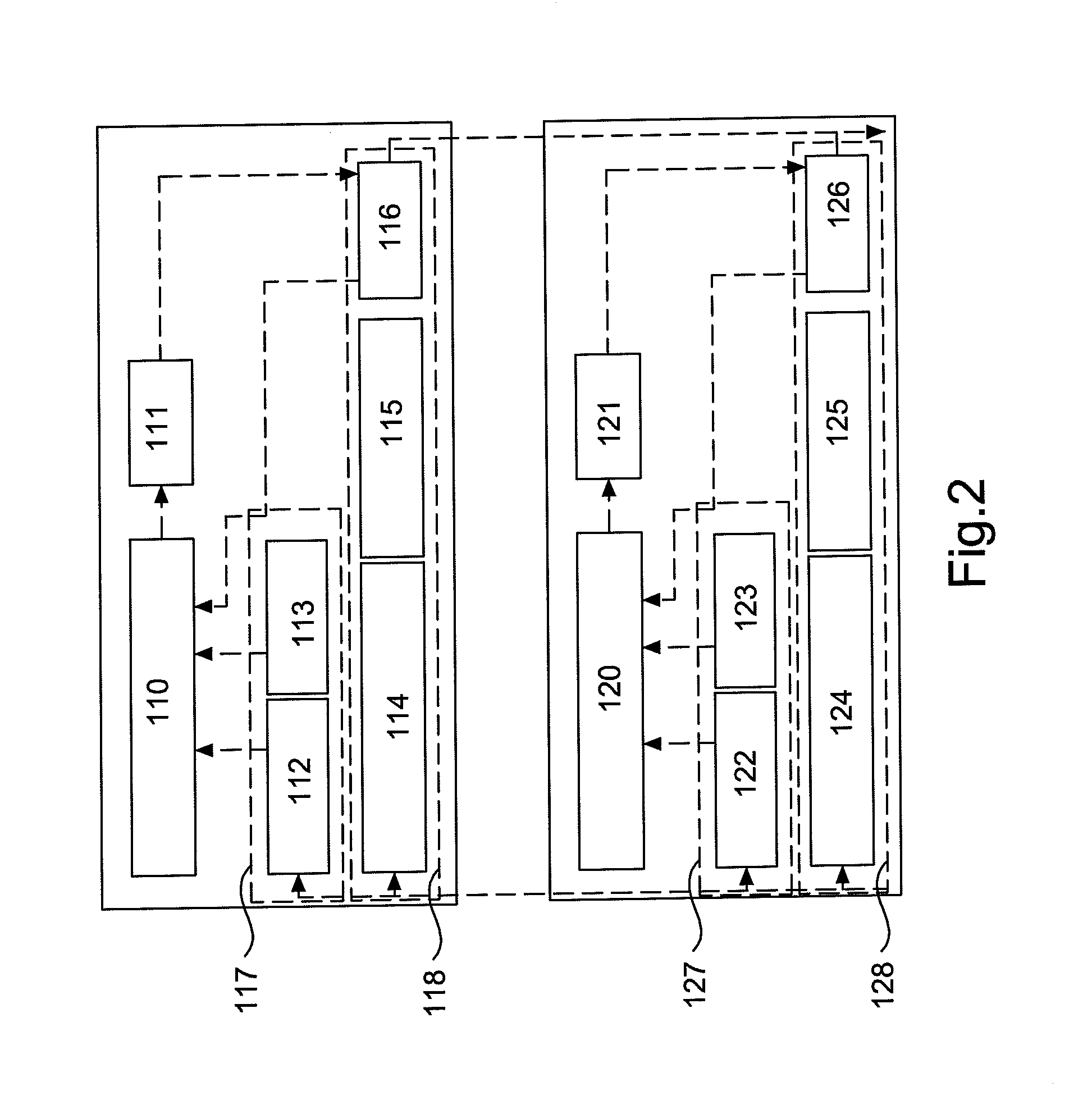

Control scheme for 3D memory IC

The present invention discloses a control scheme for 3D memory IC that includes a master chip and at least one slave chip. The master chip includes a main memory core, a first local timer, an I / O buffer, a first pad and a second pad. The at least one slave chip is stacked with the master chip. Each of the slave chip includes a slave memory core, a second local timer and a third pad. A first TSV is coupled to the first pad and the third pad. A logic control circuit layer includes a logic control circuit and a fourth pad, and the logic control circuit is coupled to the fourth pad. A second TSV is coupled to the second pad and the fourth pad.

Owner:NATIONAL TSING HUA UNIVERSITY

Method and apparatus of growing a thin film onto a substrate

InactiveUS7105054B2Reduce concentrationGood film uniformityPolycrystalline material growthSemiconductor/solid-state device manufacturingInlet channelGas phase

A method and an apparatus for growing a thin film onto a substrate by the ALD process. The apparatus comprises a reaction chamber into which the substrate can be disposed; a plurality of inlet channels communicating with said reaction chamber, said inlet channels being suited for feeding the reactants employed in a thin-film growth process in the form of vapor-phase pulses into said reaction chamber; at least one outlet channel communicating with said reaction chamber, said outlet channel being suited for the outflow of reaction products and excess amounts of reactants from said reaction space; and a pre-reaction chamber arranged immediately upstream of the reaction chamber, said pre-reaction chamber forming a first reaction zone, in which the reactants of successive vapor-phase pulses can be reacted with each other in the vapor phase to form a solid product, whereas said reaction chamber forming a second reaction zone can be operated under conditions conducive to ALD growth of a thin film.

Owner:ASM INTERNATIONAL

Liquid filter

InactiveUS20060191836A1Compact designSave spaceSemi-permeable membranesSedimentation separationEngineeringInternal combustion engine

A liquid filter, especially oil filter for an internal combustion engine, having a cup-shaped housing with a liquid inlet and a liquid outlet, a filter element arranged with a seal between the inlet and outlet, and a one-piece barrier membrane arranged in the area of the opening of the cup-shaped housing such that the liquid inlet and / or the liquid outlet can be closed by the barrier membrane.

Owner:MANN HUMMEL GMBH

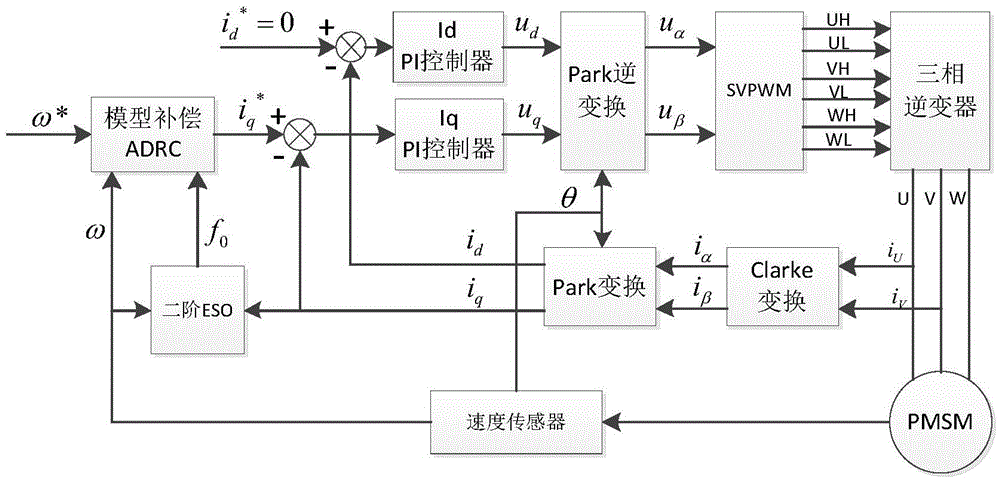

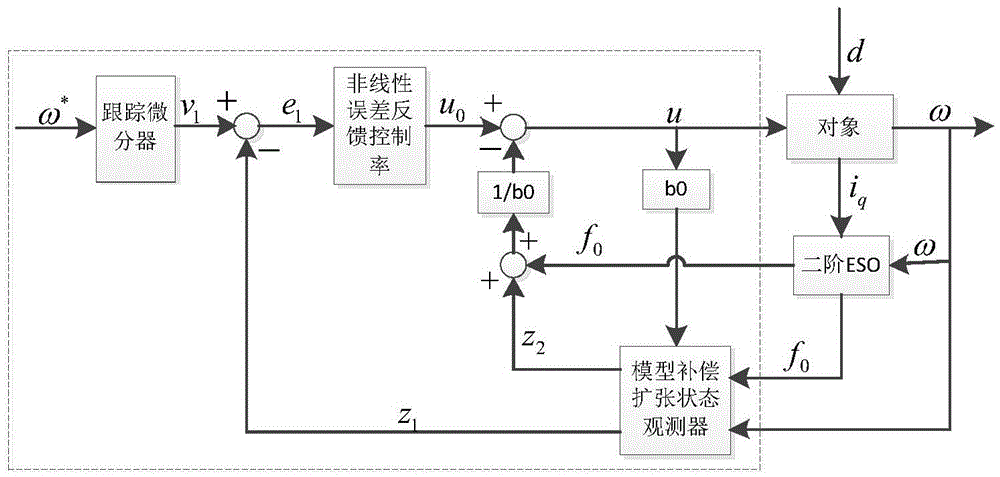

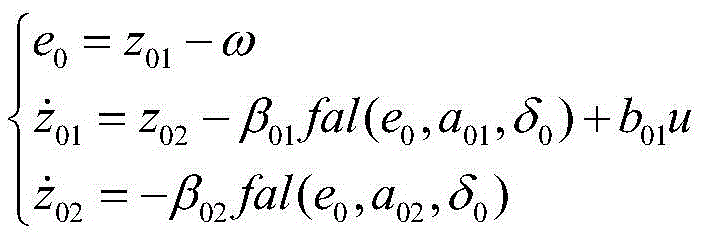

PMSM servo system control method based on improved model compensation ADRC

ActiveCN105680750AReduce the burden of estimationImprove estimation performanceElectronic commutation motor controlVector control systemsActive disturbance rejection controlEngineering

The invention discloses a PMSM servo system control method based on an improved model compensation ADRC, aims at the problems that the system disturbance amplitude estimated by an extended state observer is high and changes sharply, estimation precision is difficult to guarantee and obtaining of better control performance of an active disturbance rejection controller is limited, and provides an improved model compensation active disturbance rejection control method. Firstly a second-order extended state observer (ESO) is adopted to observe a total disturbance compensation model of the system, and then the disturbance compensation model is utilized to be compensated to a speed loop active disturbance rejection controller in the design of the speed loop ADRC. According to the method, observation capacity of the ESO for system disturbance can be fully utilized so that the ESO in the ADRC is enabled not to estimate total disturbance quantity, estimation burden of the ESO in the active disturbance rejection controller can be reduced, estimation capacity of the system for total disturbance can be enhanced, compensation capacity of the system for various types of disturbance can be effectively enhanced and robustness and anti-disturbance capability of the system can be enhanced.

Owner:WUXI XINJIE ELECTRICAL

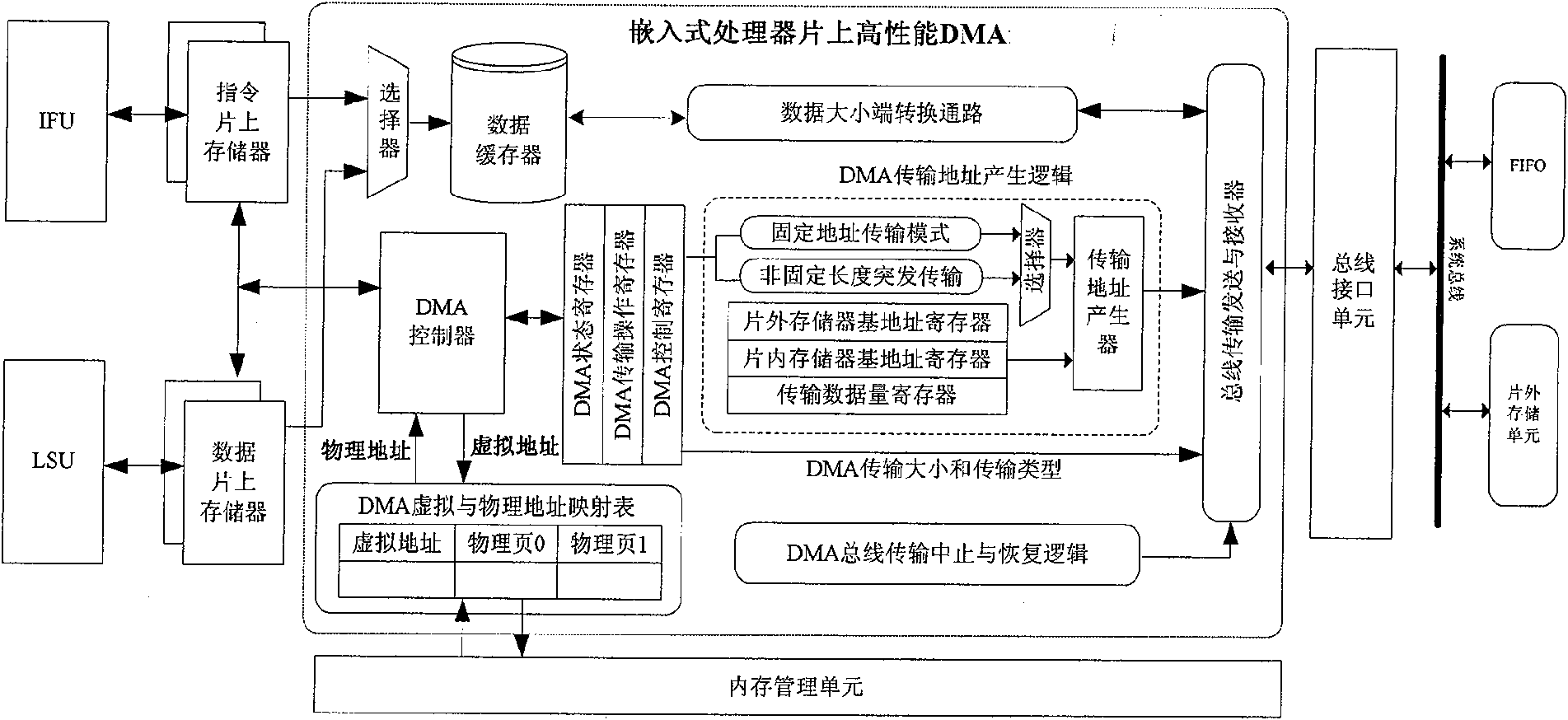

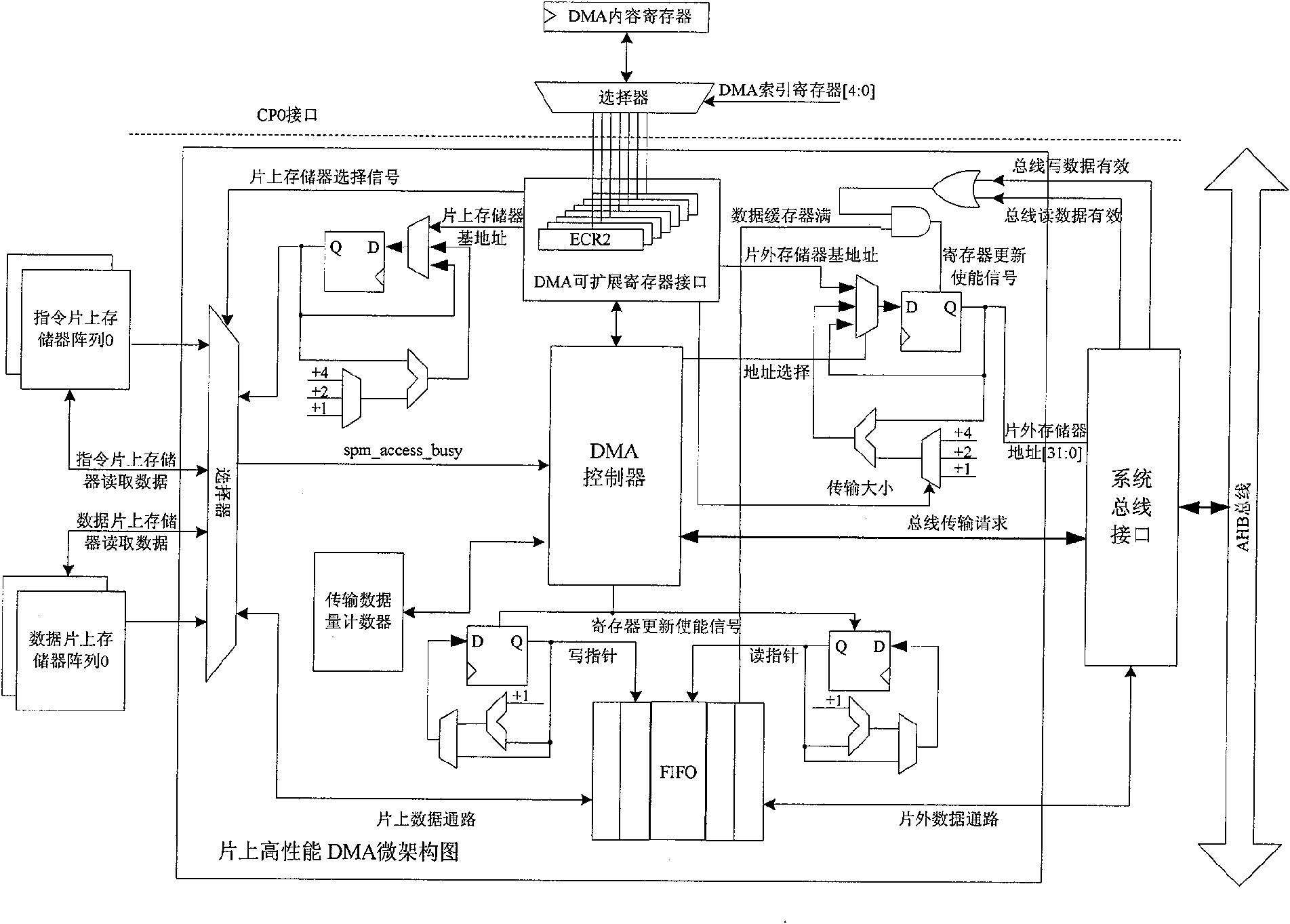

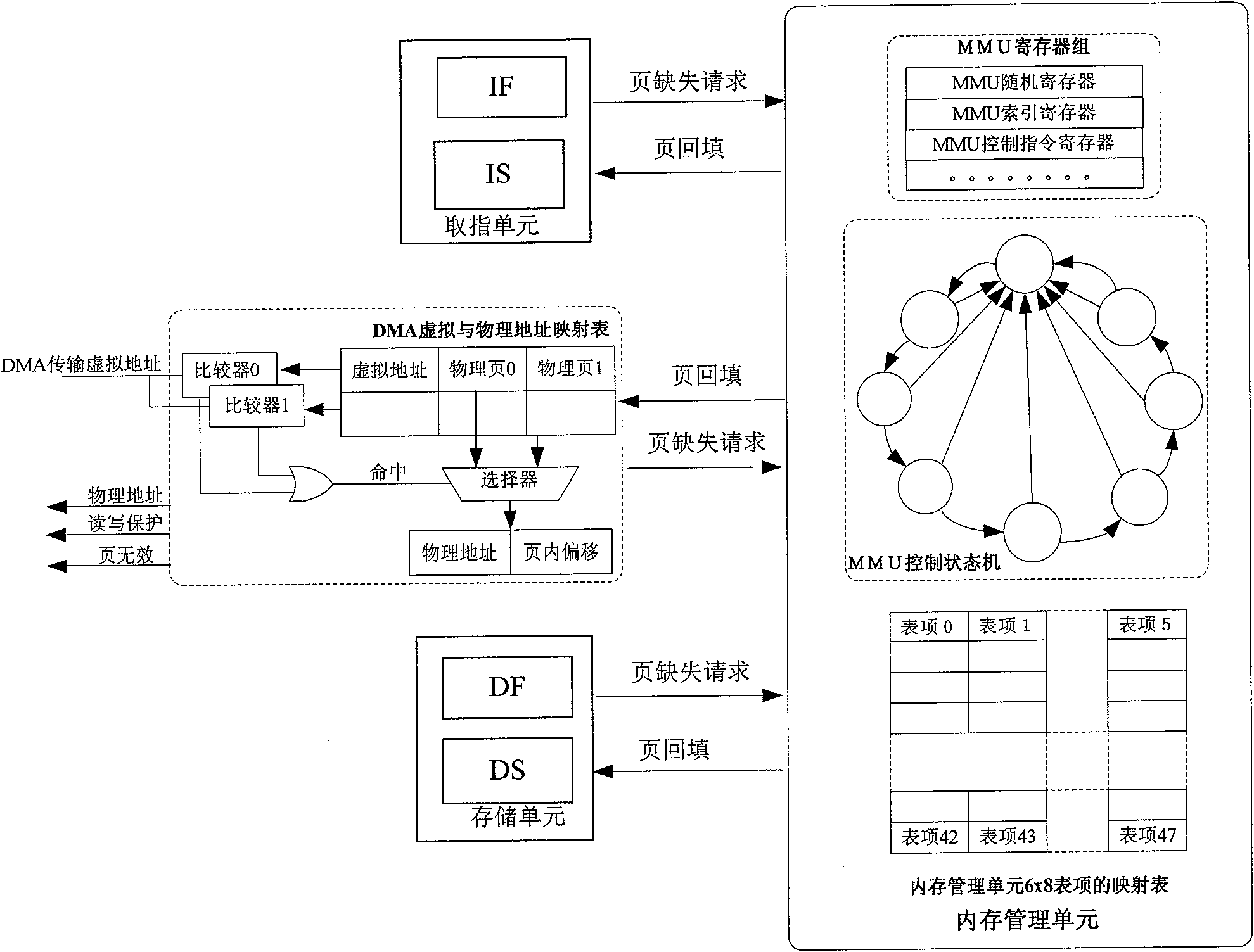

High performance DMA on embedded type processor chip

ActiveCN101556565AImprove performanceIncrease independenceElectric digital data processingPage address registerIp address

The invention relates to a high performance DMA on an embedded type processor chip. The high performance DMA comprises a data buffer used for caching the data read from an on-chip memory, the data sent to a bus interface unit, the data received from the bus interface unit, and the data written into the on-chip memory; a data big-endian and little-endian convertor; a DMA controller used for initializing a state register, a control register, an initial address register and a data size register; a DMA transmission address generating logic module used for automatically calculating the transmission address of the next data on an on-chip external memory and generating chip selection and read and write signals of the on-chip memory according to the on-chip address, and simultaneously updating a data size counter till the counter changes to zero; and a bus transmission transmitter and receiver. The high performance DMA has the advantages that the development difficulty is low, the cost of the hardware is low, the transplantation is convenient, the expansibility is flexible, the data transmission speed is high, and the performance of the processor is greatly enhanced.

Owner:C SKY MICROSYST CO LTD

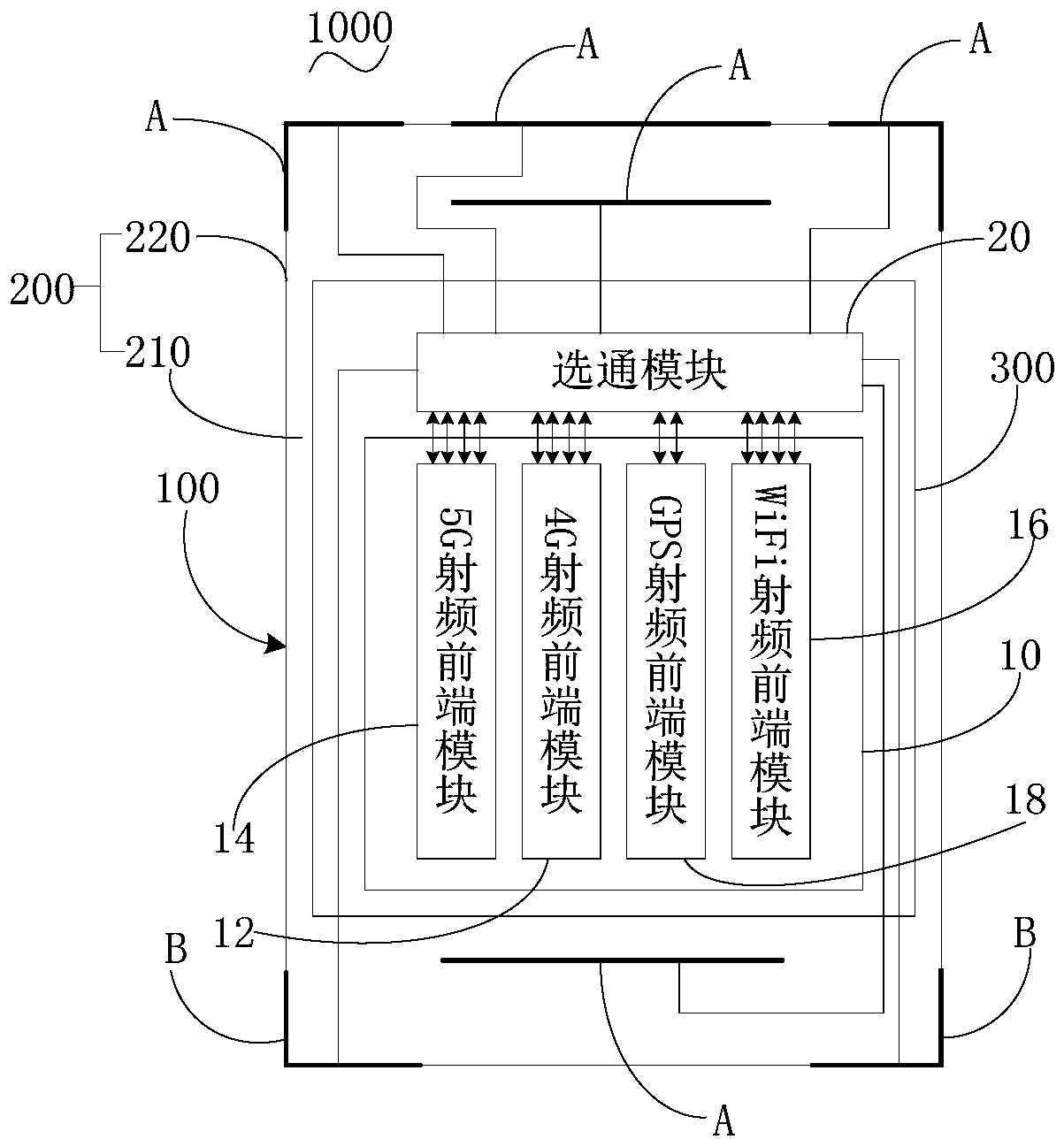

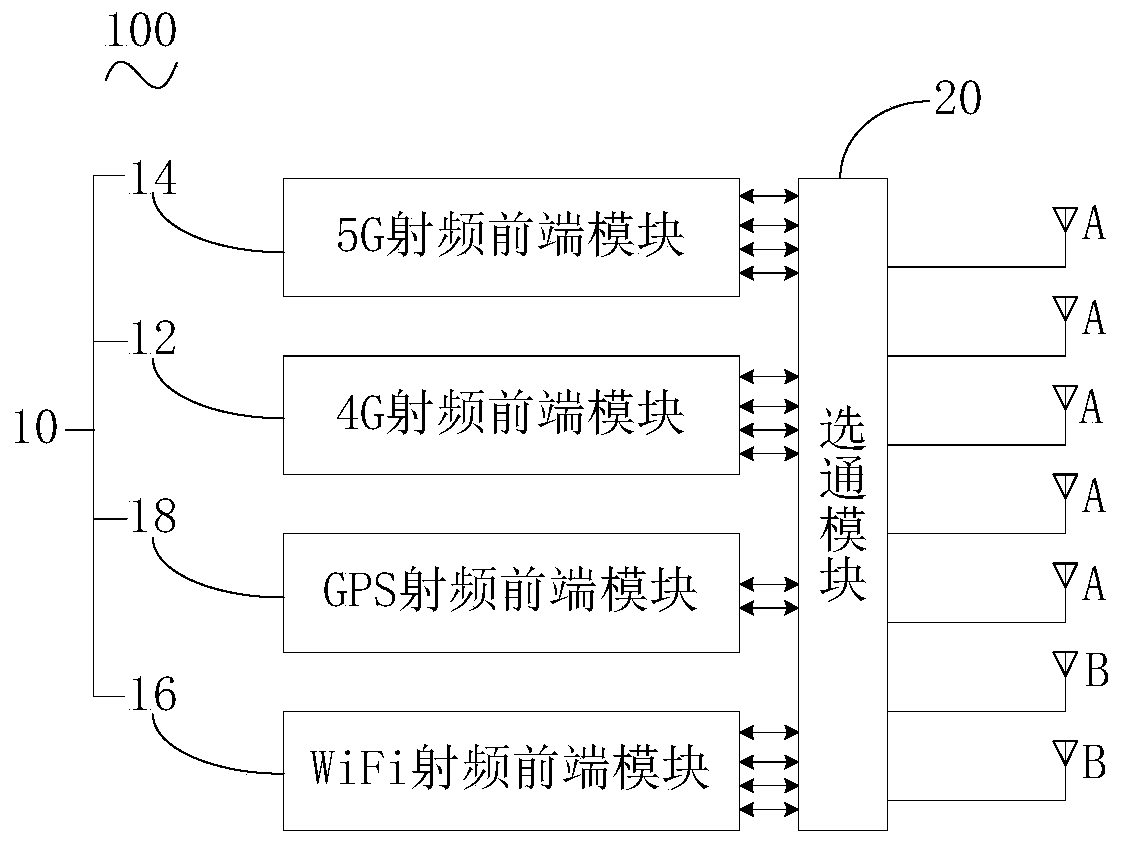

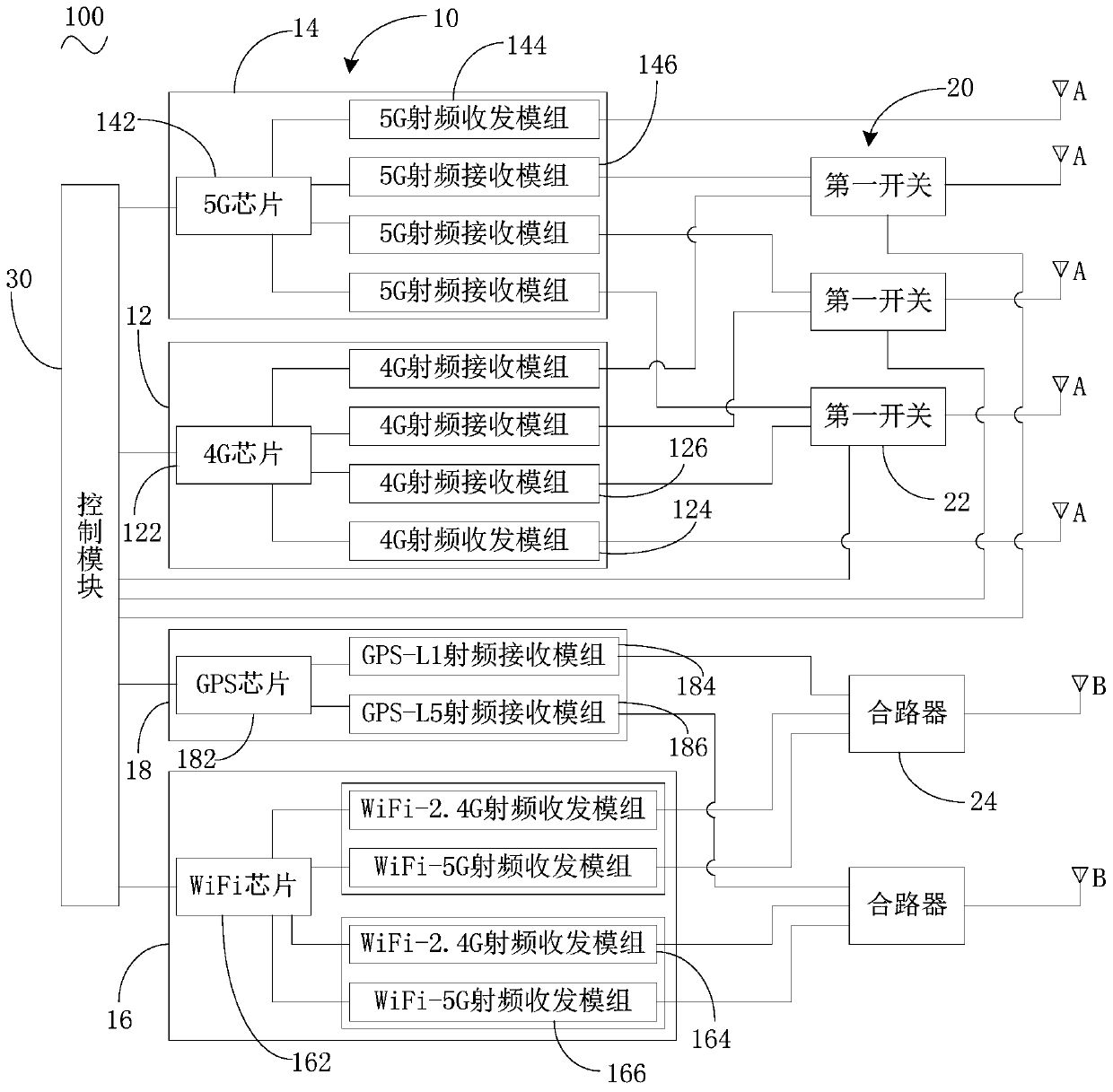

Antenna multiplexing radio frequency device and terminal

ActiveCN109831223AReduced Quantity RequirementsLow costRadio transmissionMultiplexingComputer terminal

The invention discloses an antenna multiplexing radio frequency device and a terminal. The antenna multiplexing radio frequency device comprises a plurality of radio frequency antennas, a plurality ofwireless antennas, a radio frequency circuit and a gating module. The radio frequency circuit comprises a 4G radio frequency front end module, a 5G radio frequency front end module, a WiFi radio frequency front end module and a GPS radio frequency front end module. And part of the radio frequency antennas are connected with the 4G radio frequency front-end module and the 5G radio frequency front-end module through the gating module. All wireless antennas are connected with the WiFi radio frequency front-end module and the GPS radio frequency front-end module through the gating module. The embodiment of the invention discloses an antenna multiplexing radio frequency device. The 5G radio frequency front-end module and the 4G radio frequency front-end module can multiplex part of radio frequency antennas, and the WiFi radio frequency front-end module and the GPS radio frequency front-end module can multiplex all wireless antennas, so that the requirement of a multimode communication terminal on the number of antennas is reduced, and meanwhile, the cost and the design complexity of the terminal are reduced.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

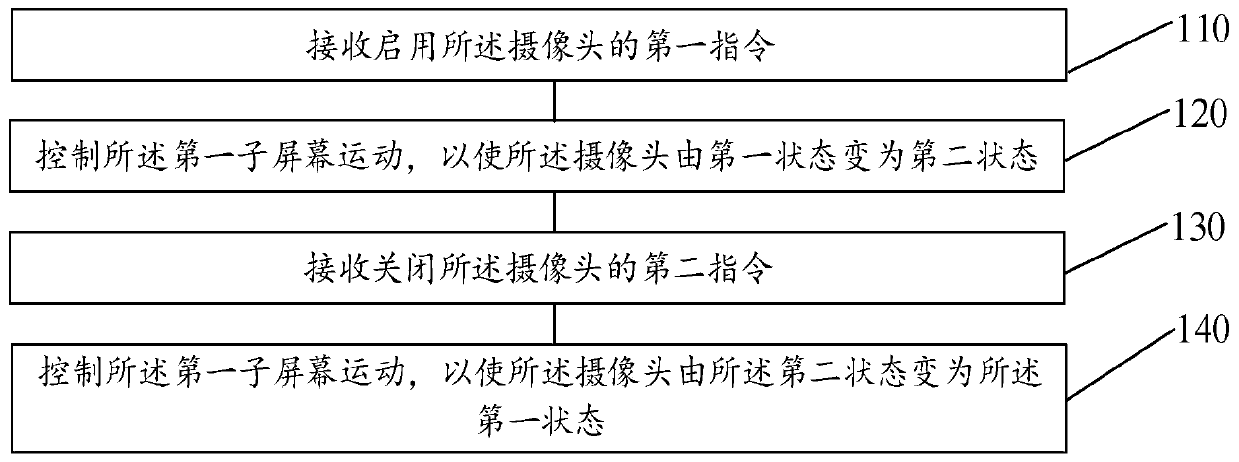

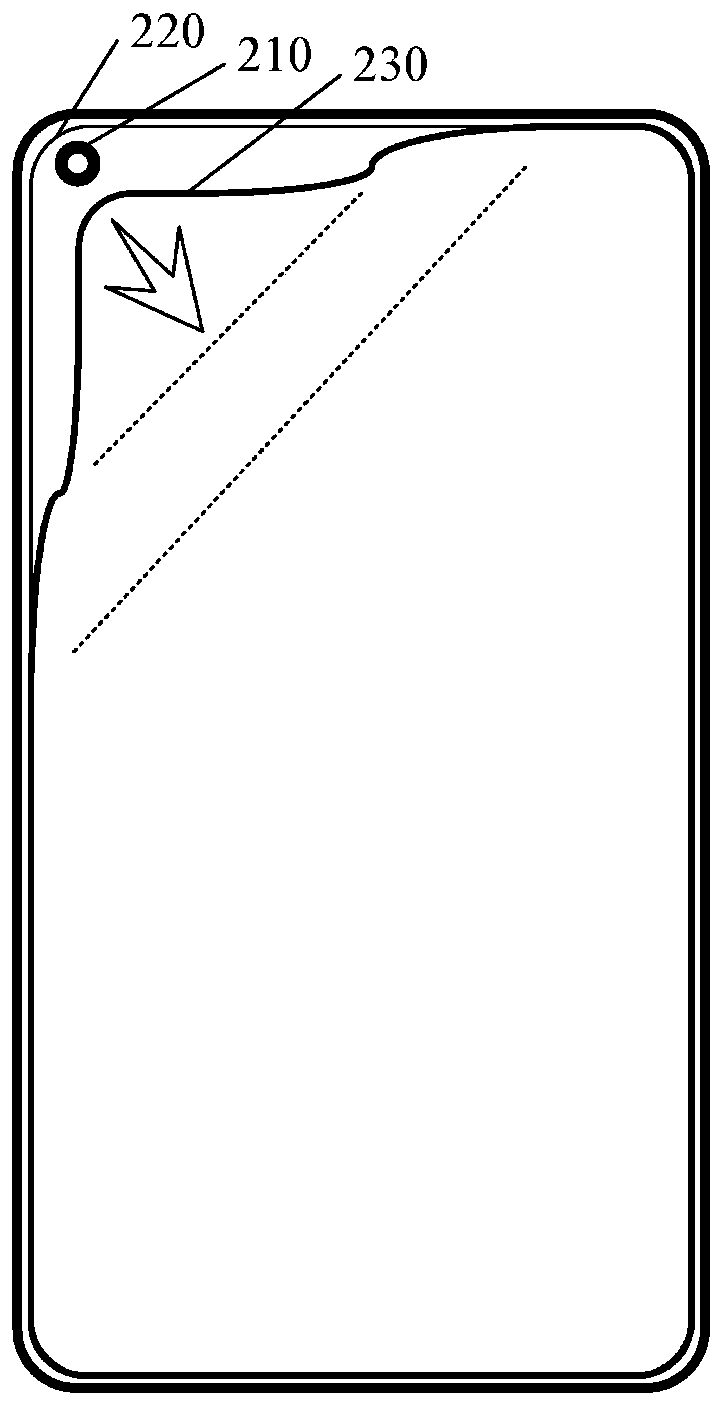

Screen control method, terminal and storage medium

ActiveCN109756594AIncrease the screen ratioIncrease the display areaDetails for portable computersTelephone set constructionsComputer hardwareComputer graphics (images)

Owner:VIVO MOBILE COMM CO LTD

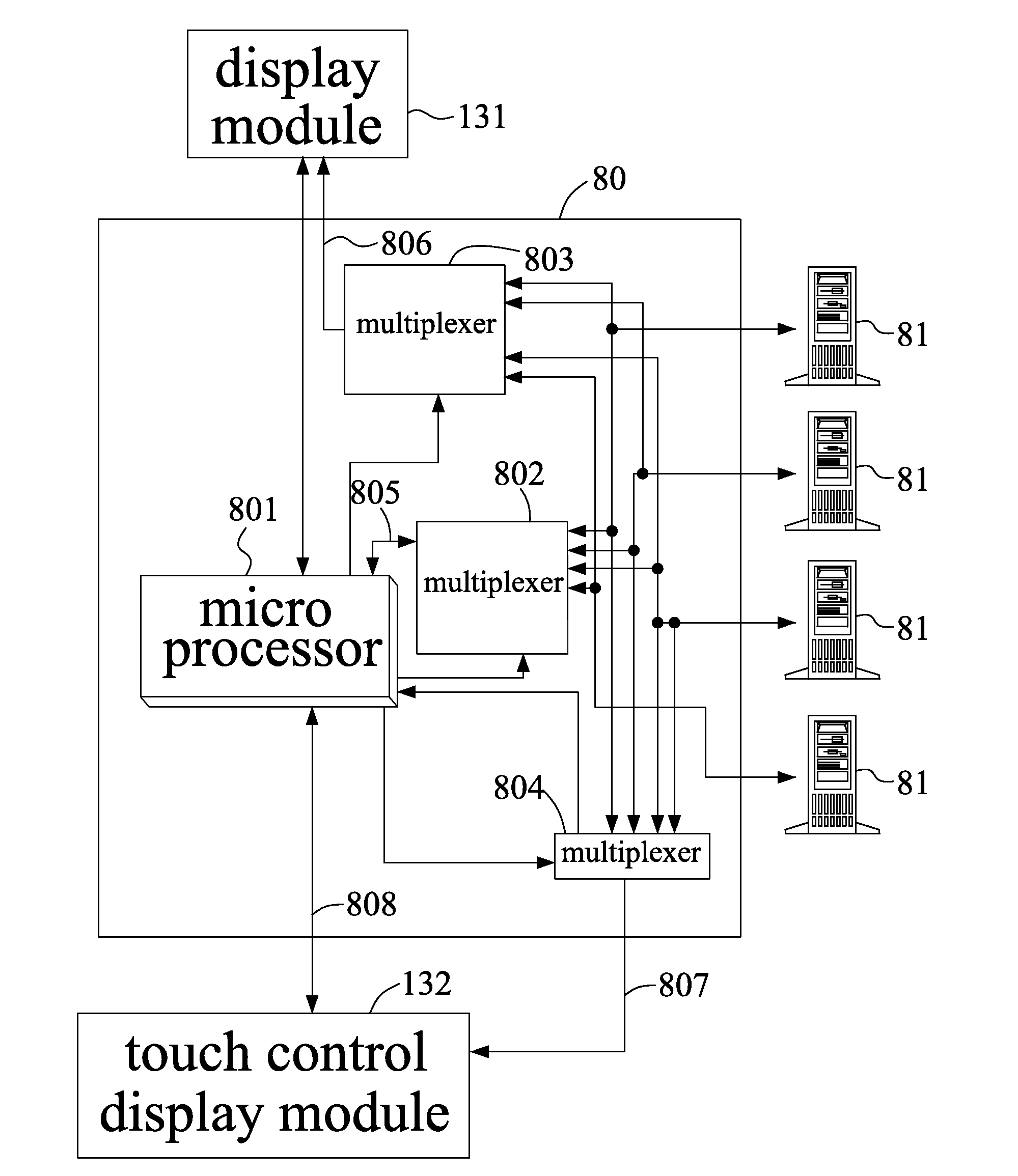

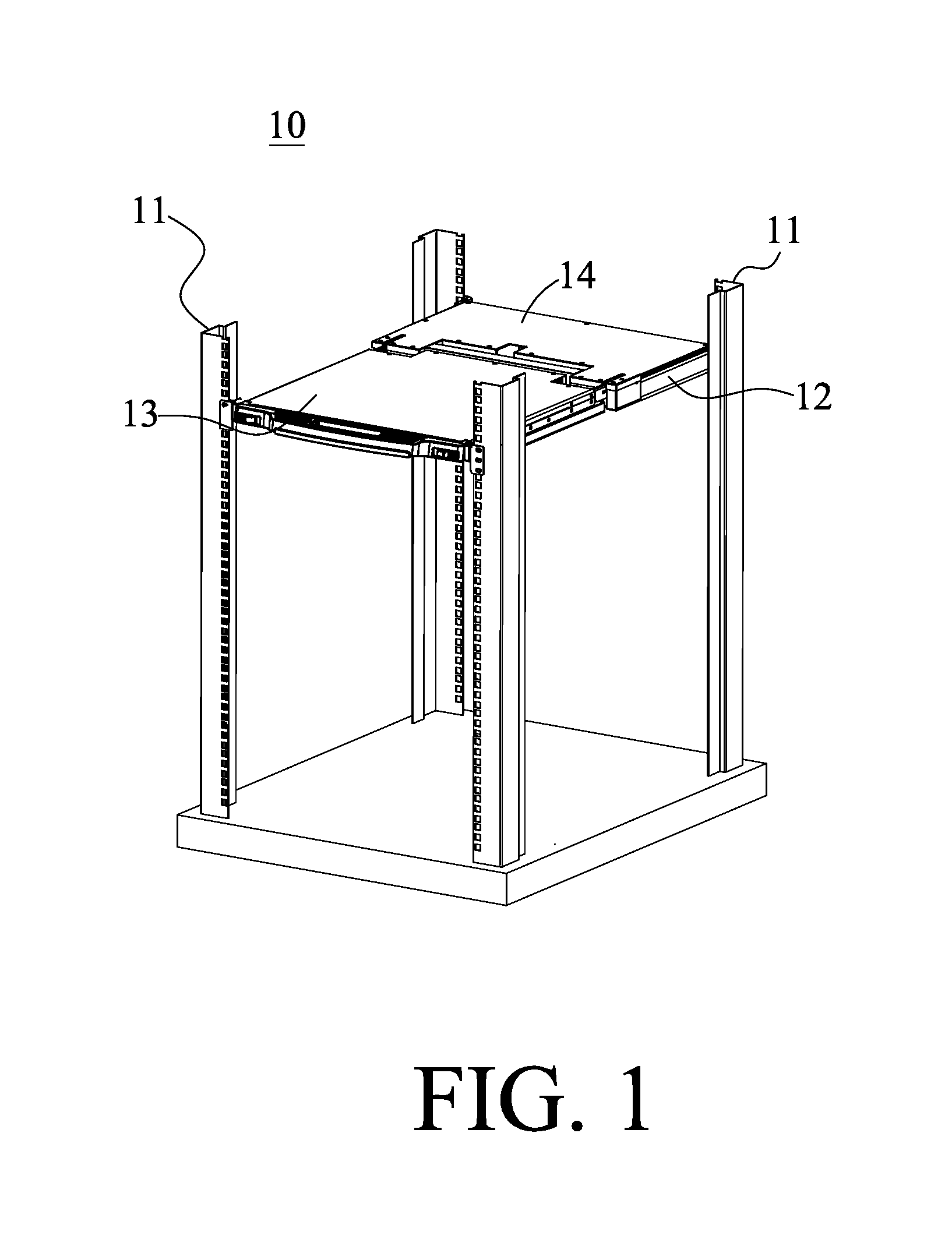

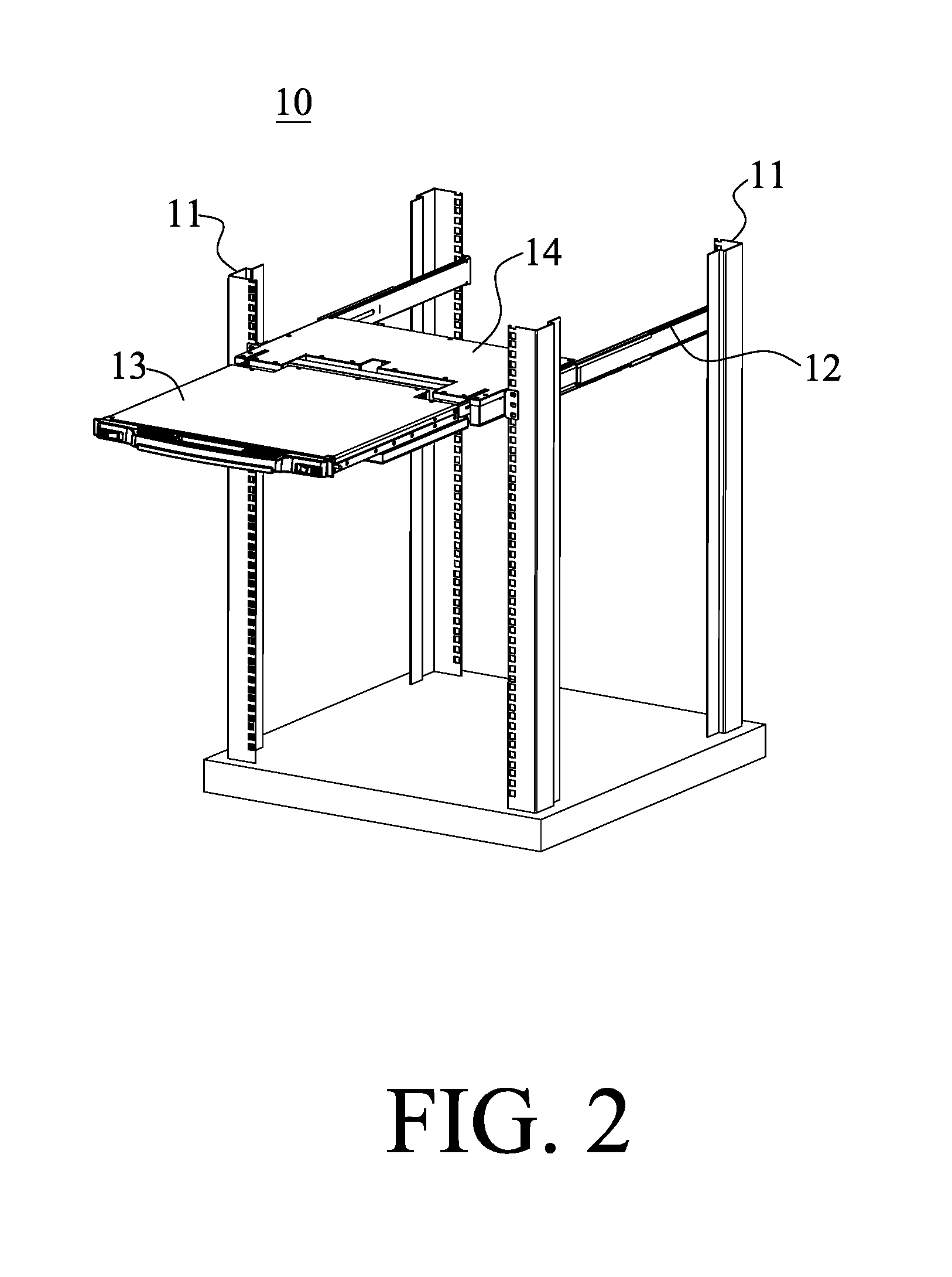

Equipment with dual screens for controlling multi-computers and the operating method thereof

ActiveUS20110225537A1Improve management efficiencyGreat viewing areaServersDigital data processing detailsLiquid-crystal displayComputer science

An equipment for controlling a plurality of computers and the operating method thereof are provided. The equipment electrically connects to a Liquid Crystal Display (LCD) module and a touch LCD module and a plurality of computer respectively, where the LCD module receives and displays an image of one of the plurality of computers, the touch LCD module displays an imaging inputting interface and at least one of the images corresponding to the plurality of computers, and the imaging inputting interface receives a command to control the specific computer.

Owner:ATEN INT CO

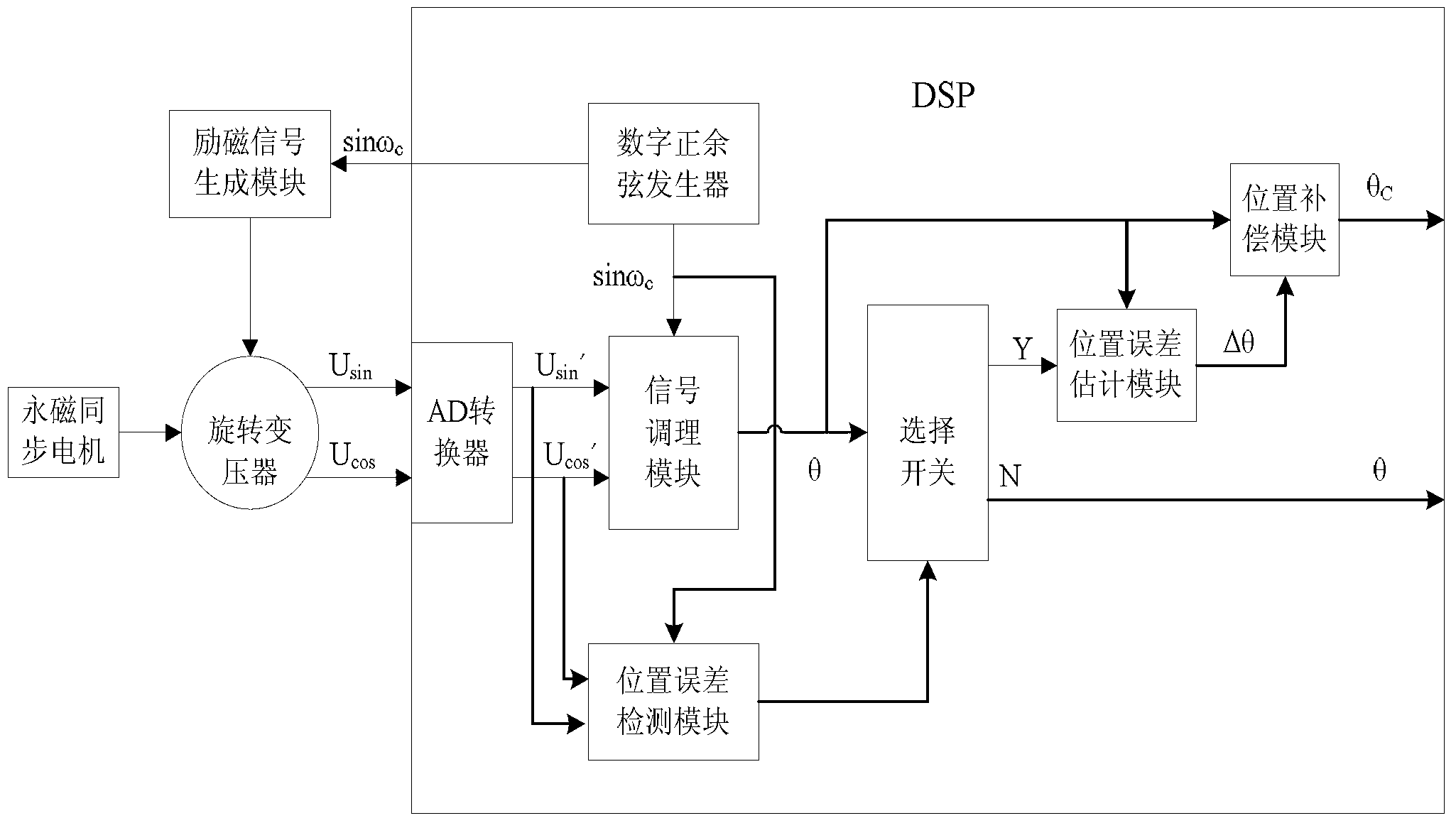

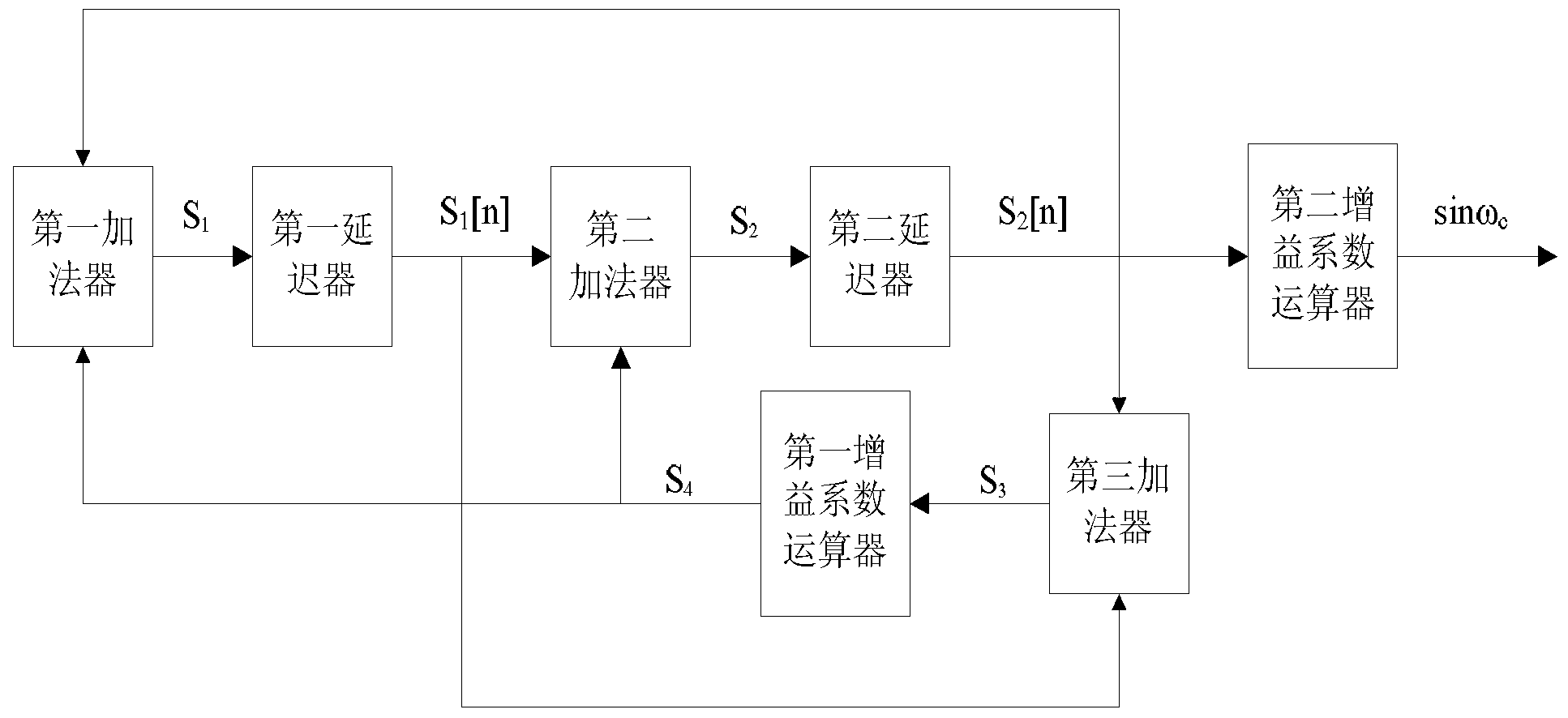

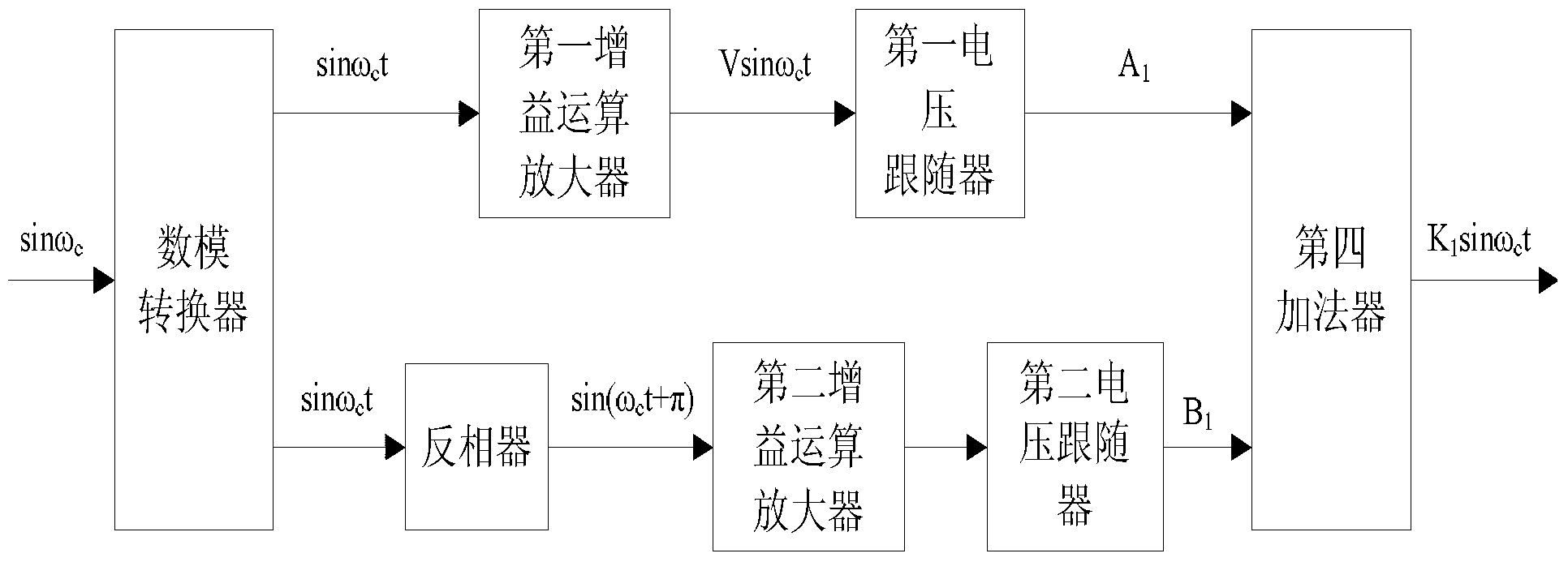

Rotating transformer digital converter capable of on-line failure detection and fault-tolerant control

ActiveCN103256946AHigh precisionEasy to detectConverting sensor output electrically/magneticallyKaiman filterEngineering

The invention discloses a rotating transformer digital converter capable of on-line failure detection and fault-tolerant control. According to the method, an electric automobile PMSM is used for controlling matched utilization of a microprocessor DSP and the rotating transformer so as to achieve a PMSM rotor position of a drive system of the PMSM. Failures of the rotor position of the drive system of the PMSM can be detected real-timely. Meanwhile, a kalman filter is adopted for identifying errors of the rotor position, and realizing self-adaptive fault-tolerant control, and therefore precision of acquiring the rotor position is improved.

Owner:HEFEI UNIV OF TECH

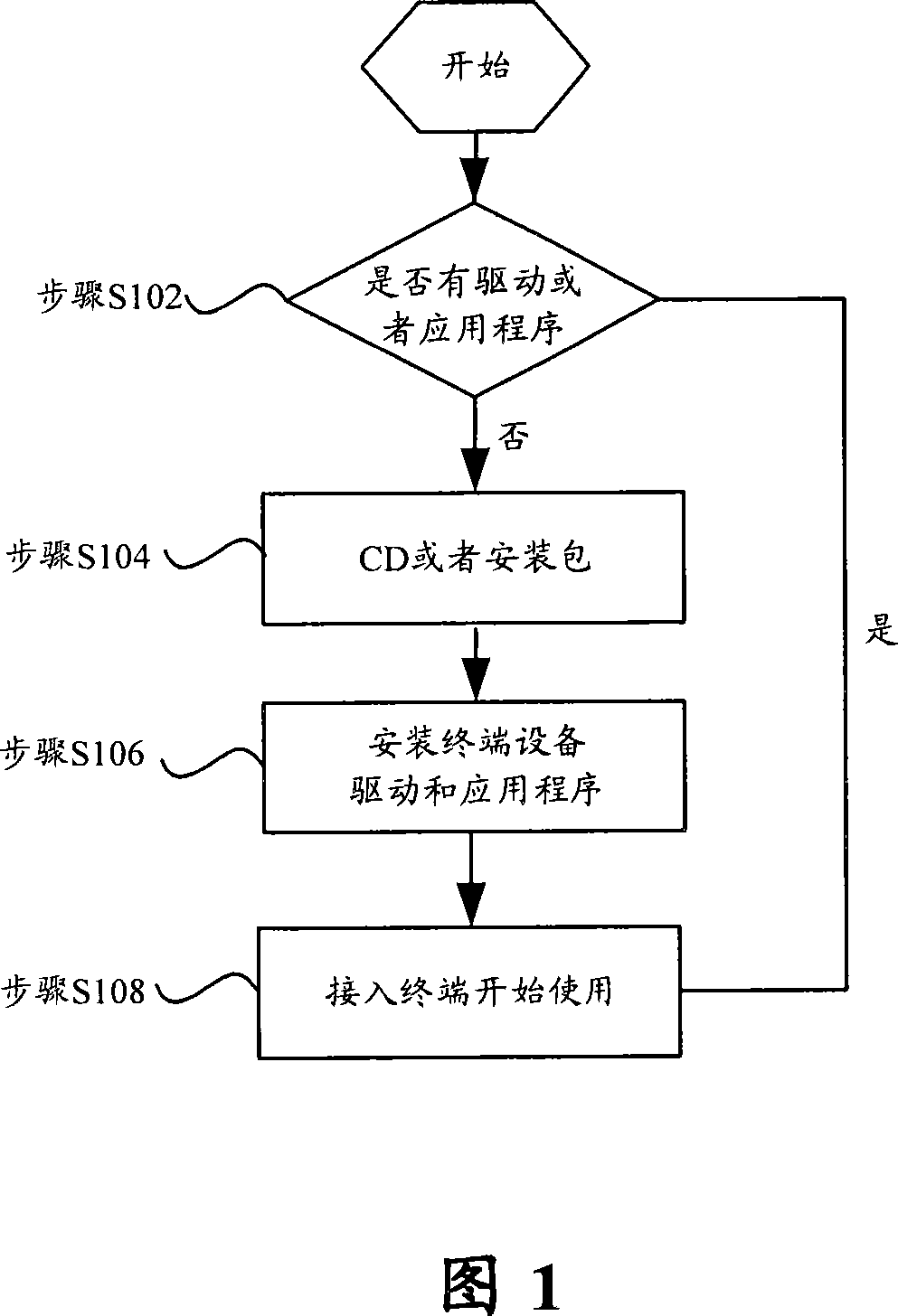

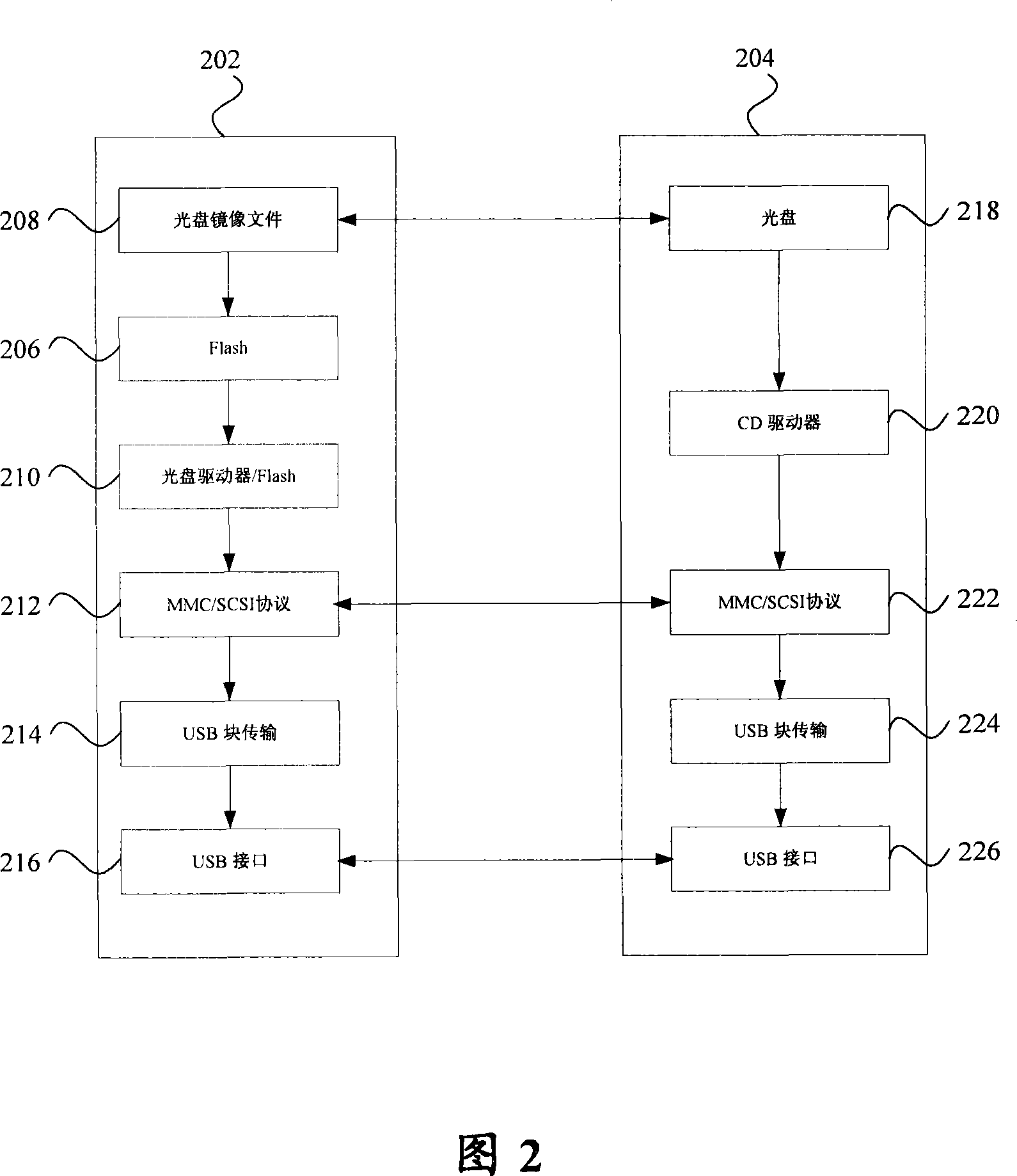

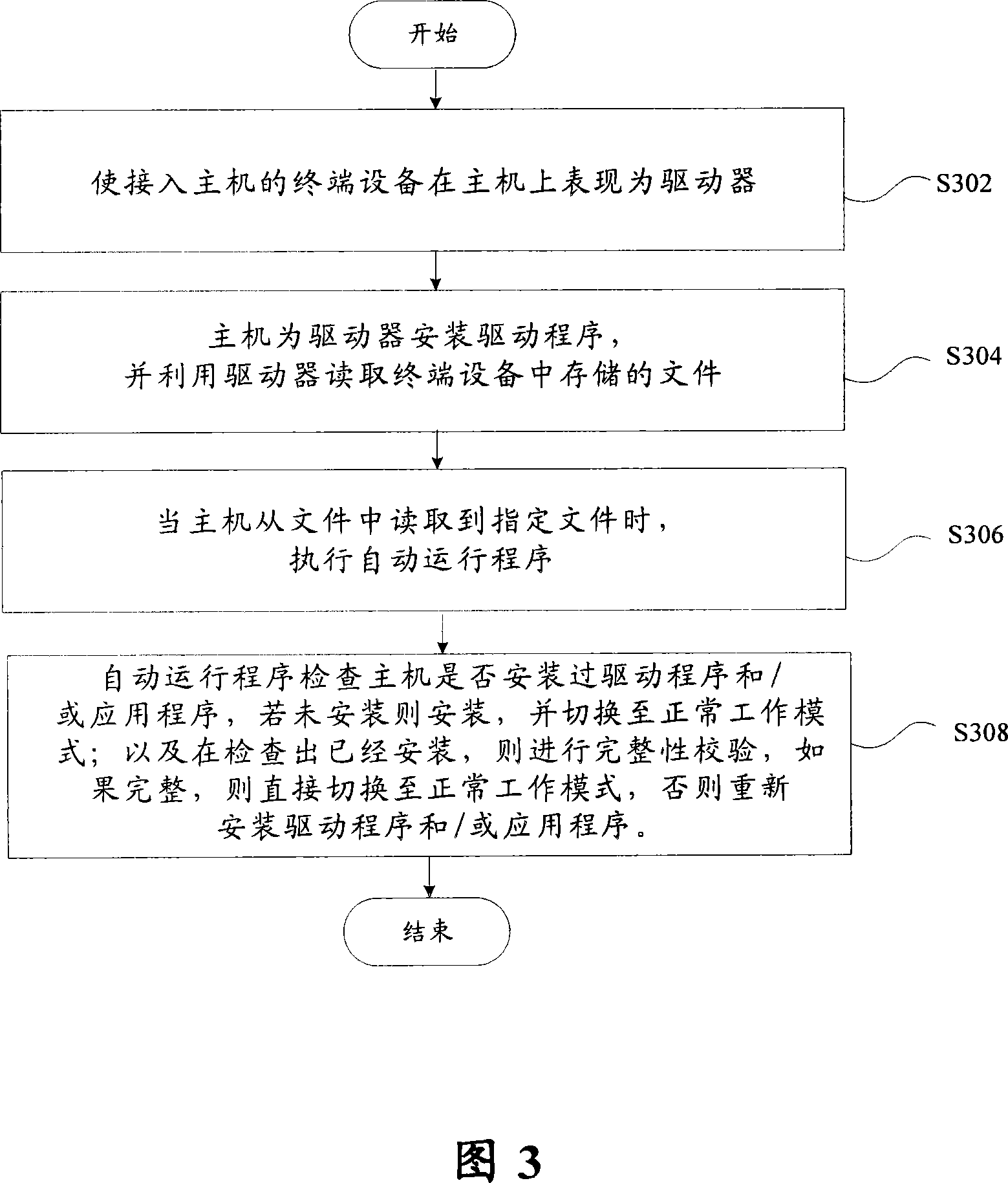

Terminal unit self-installing and self-starting system and method thereof

InactiveCN101110039AReduce Design ComplexityLow costProgram loading/initiatingWork patternApplication software

The utility model discloses a self-installing and self-starting system of the terminal equipment and the method thereof. The method comprises the procedures as below: the terminal equipment connected with the mainframe is used as the driver; the mainframe can install the driver program into the driver and read the documents stored in the terminal equipment; when the specific document is found, the program can be automatically run and the check on whether the driver program and / or the application program has been installed can be made; if the driver program and / or the application program has not been installed, the system can install the programs thereof and switch into the normal working pattern; otherwise, the check on the program completeness can be made. If the program is completely installed, the system can directly switch into the normal working pattern, otherwise, the driver program and / or the application program can be reinstalled. The utility model can automatically install the driver program and the application program for the terminal equipment pursuant to the conditions of the mainframe and automatically start up the terminal equipment.

Owner:ZTE CORP