Patents

Literature

523 results about "Multi-level cell" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

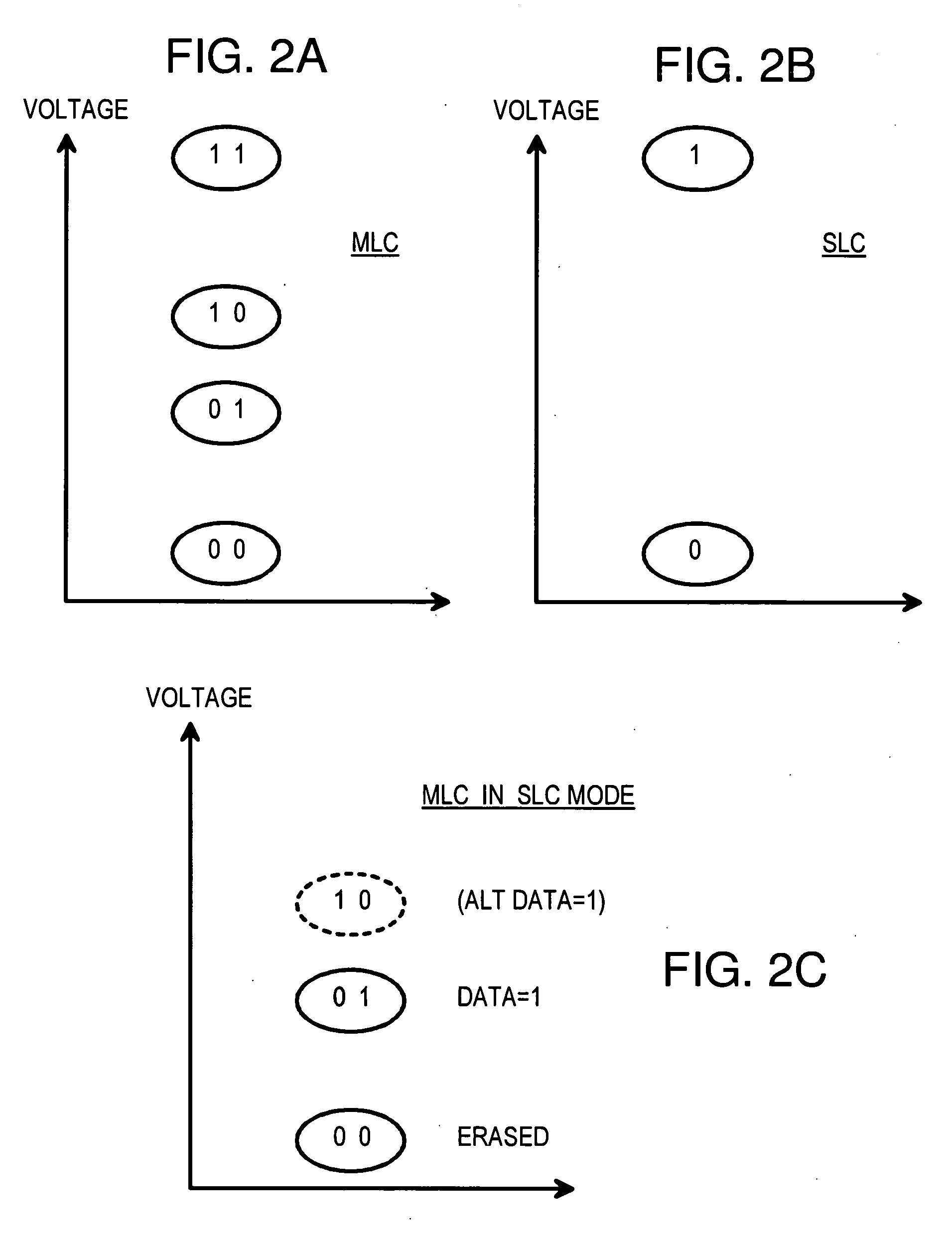

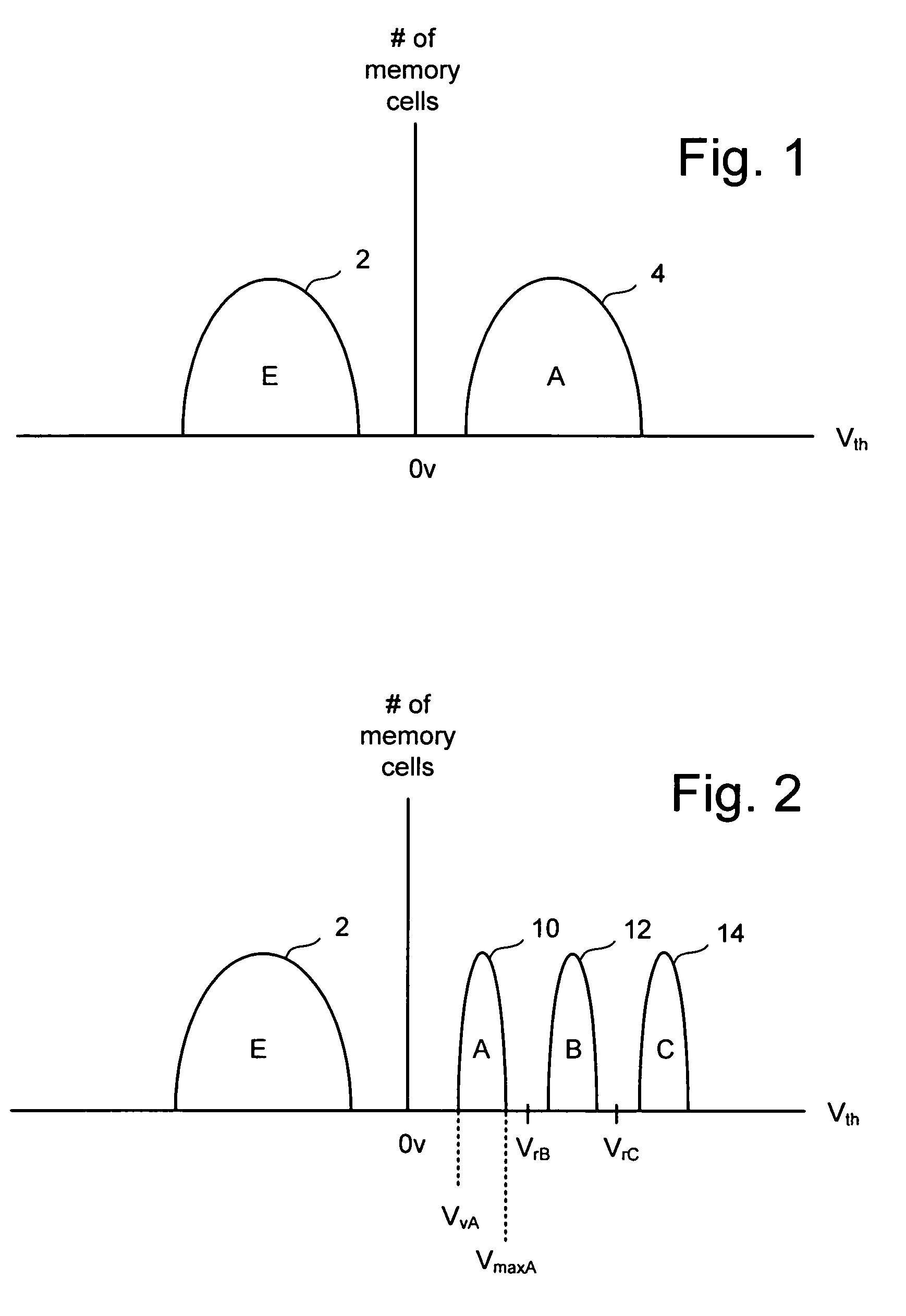

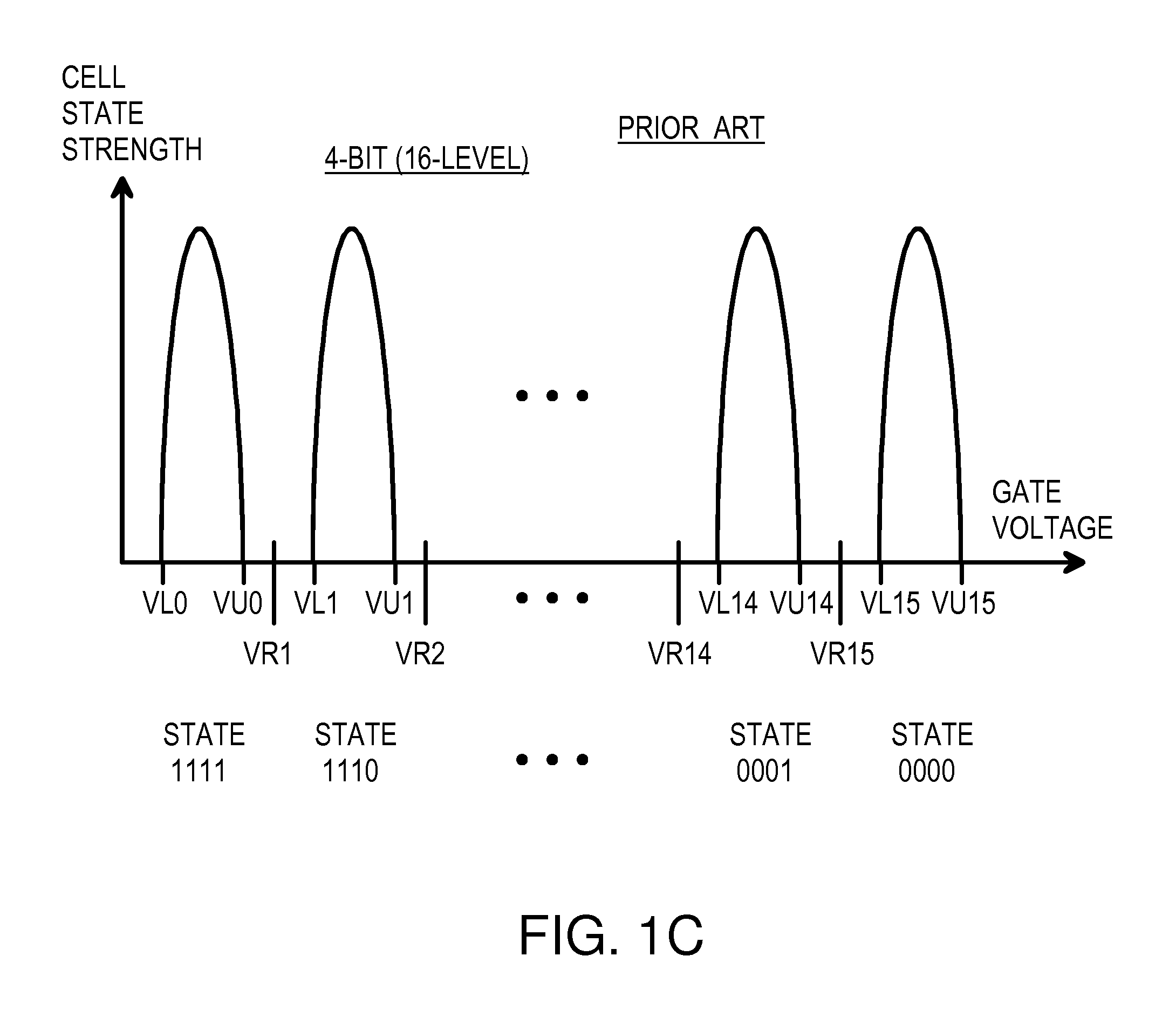

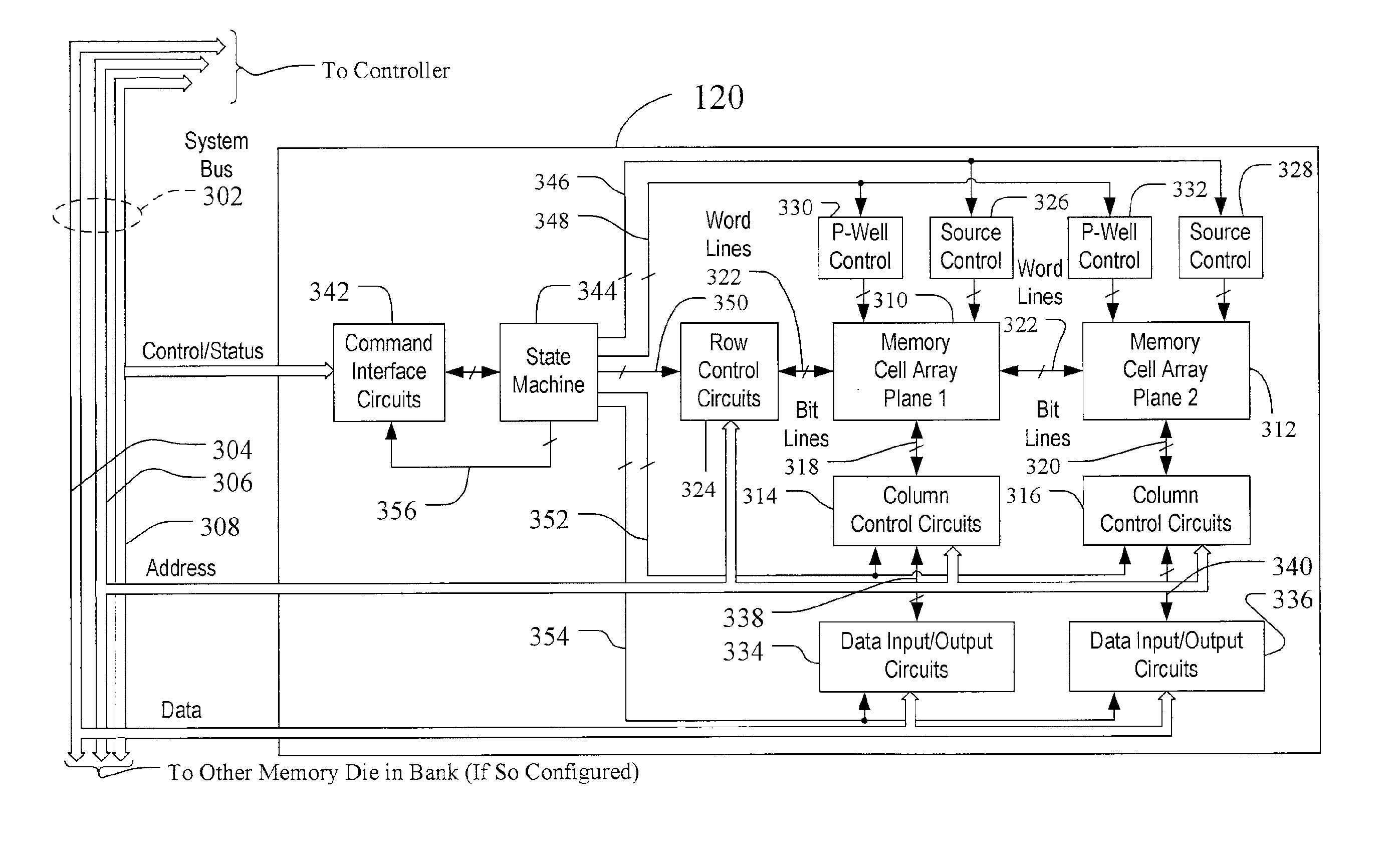

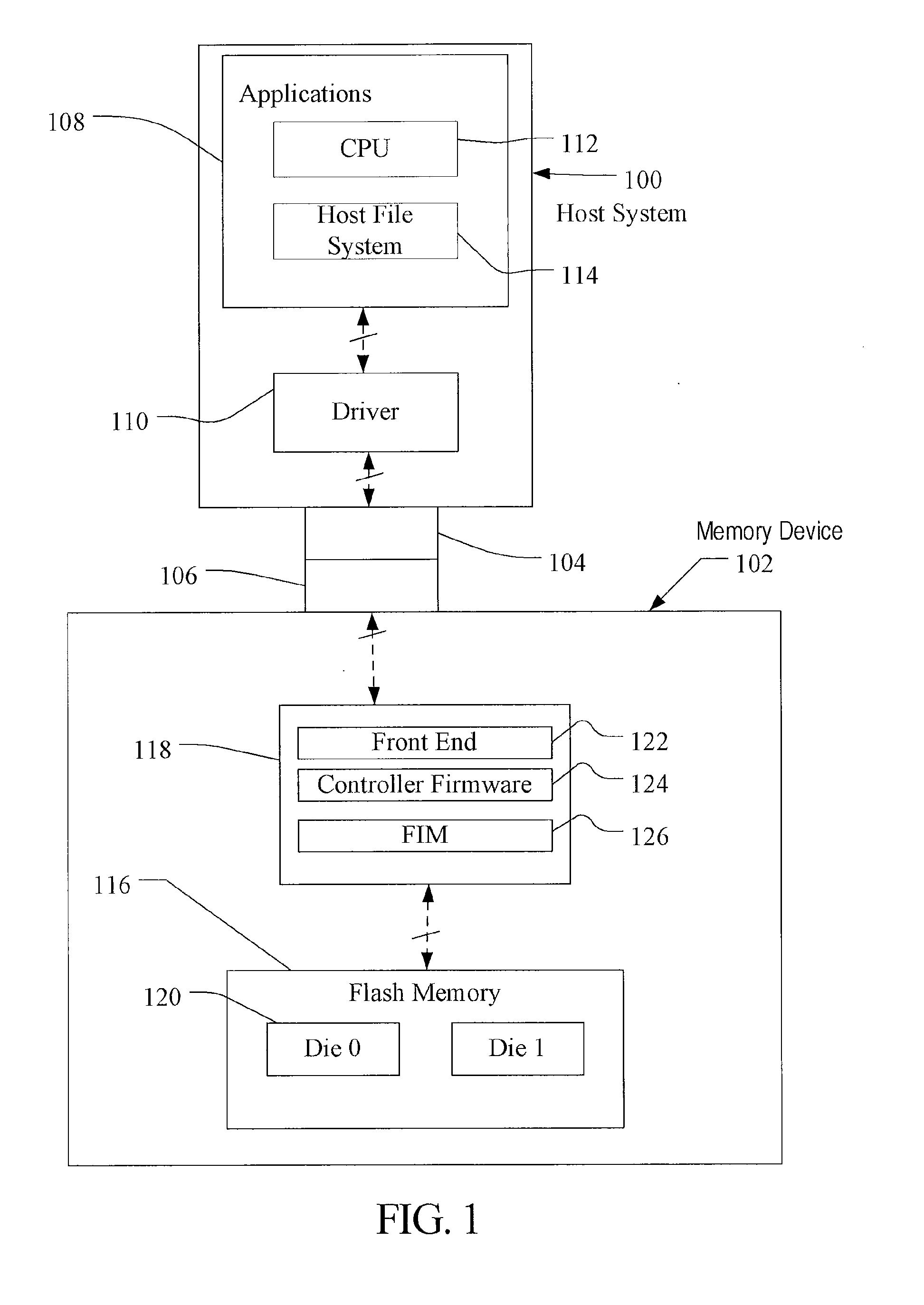

In electronics, a multi-level cell (MLC) is a memory cell/element capable of storing more than a single bit of information, compared to a single-level cell (SLC) which can store only one bit per memory cell/element. A memory cell typically consists of a single MOSFET (metal-oxide-semiconductor field-effect transistor), thus multi-level cells reduce the number of MOSFETs required to store the same amount of data as single-level cells.

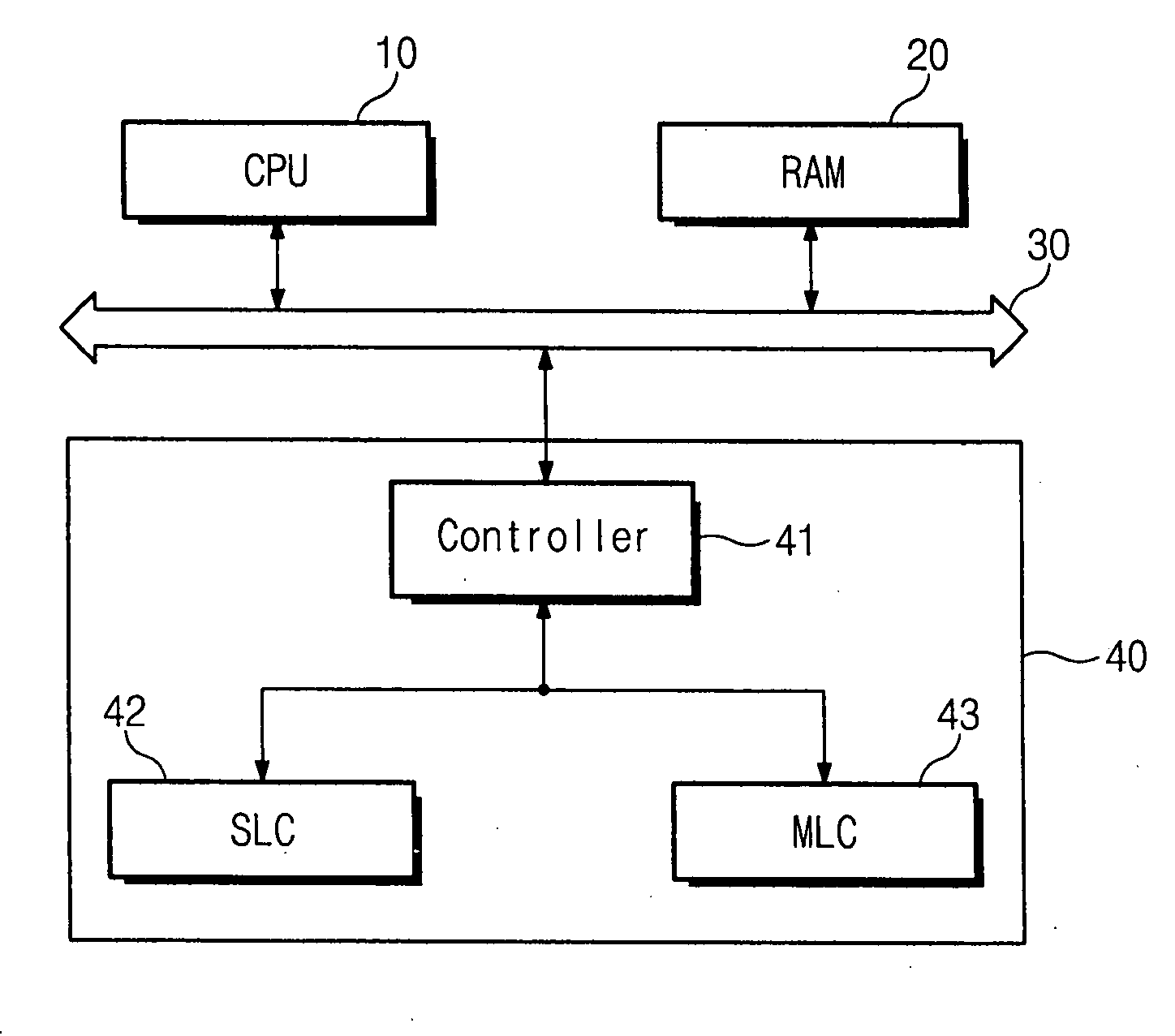

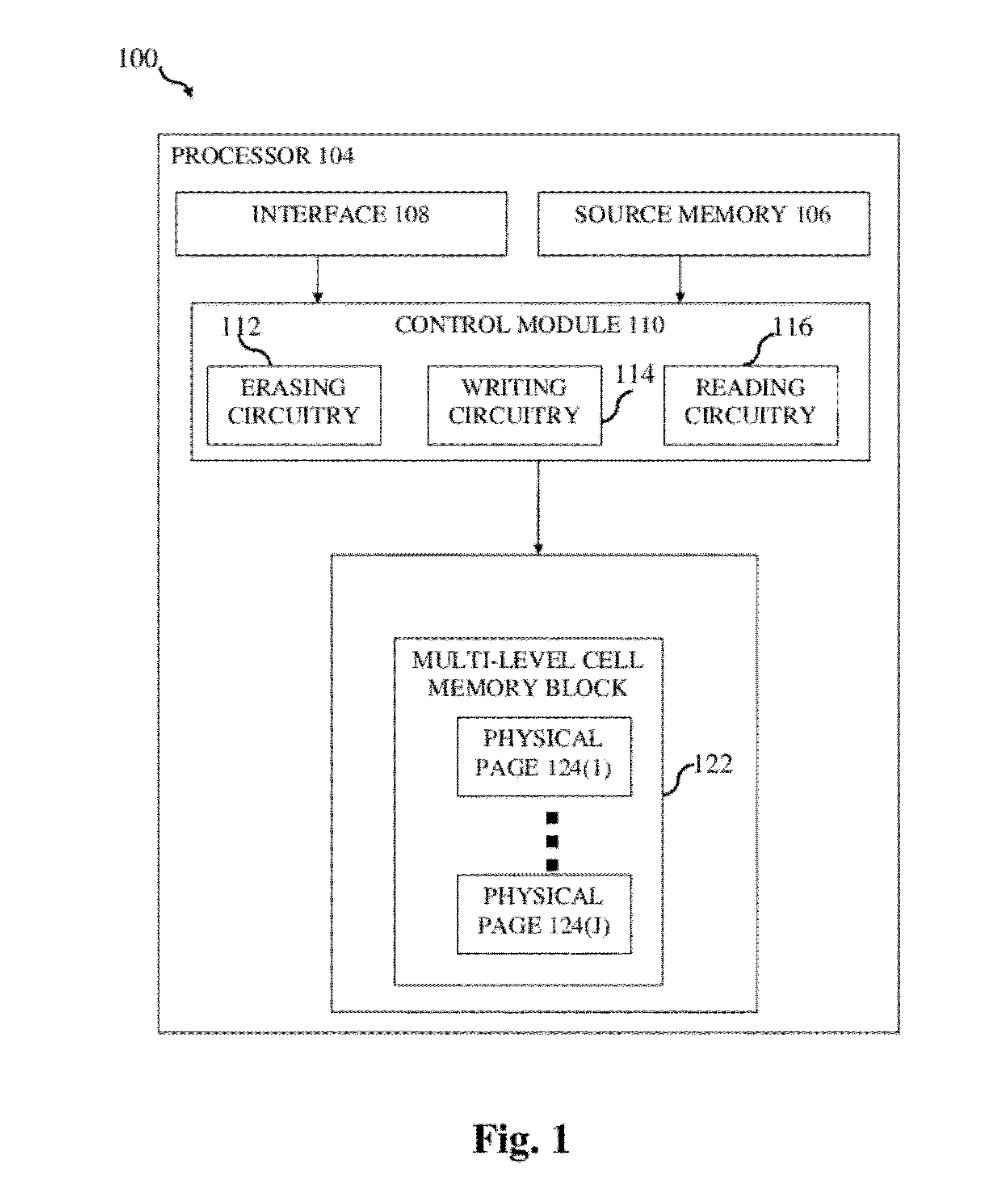

Flash memory device with multi-level cells and method of writing data therein

ActiveUS20080104309A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMulti-level cellAddress mapping

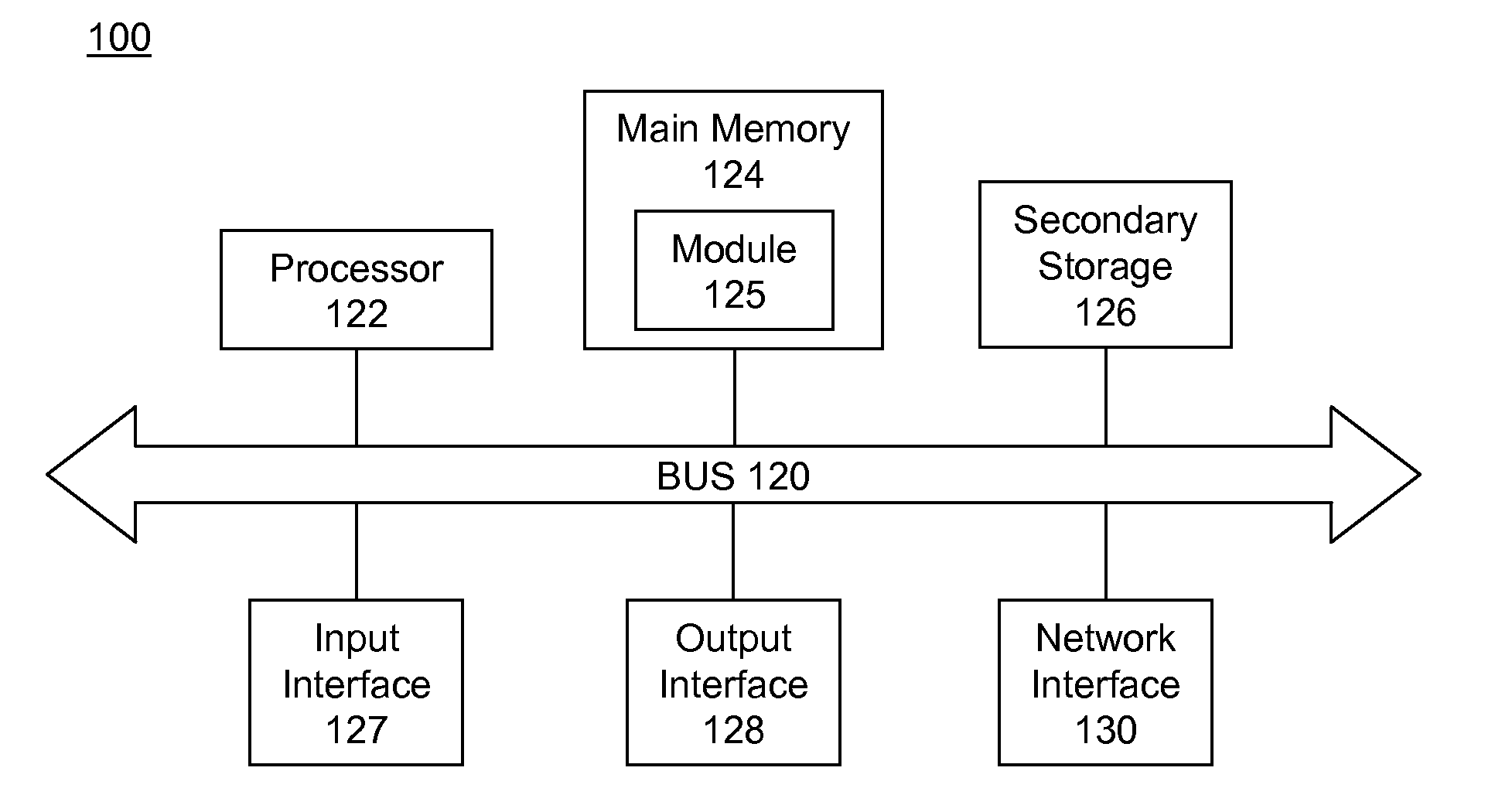

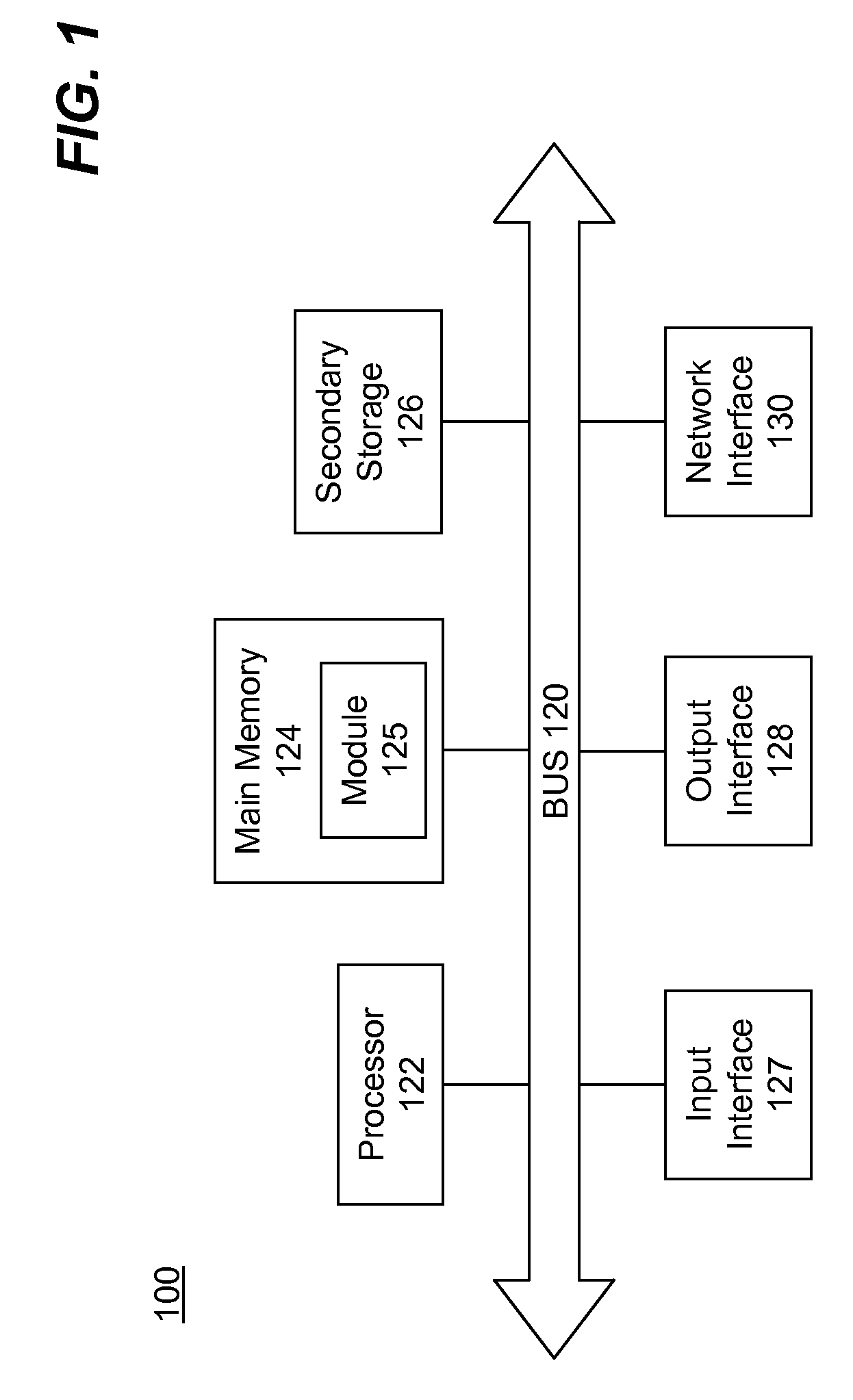

In one aspect, a method of writing data in a flash memory system is provided. The flash memory system forms an address mapping pattern according to a log block mapping scheme. The method includes determining a writing pattern of data to be written in a log block, and allocating one of SLC and MLC blocks to the log block in accordance with the writing pattern of the data.

Owner:SAMSUNG ELECTRONICS CO LTD

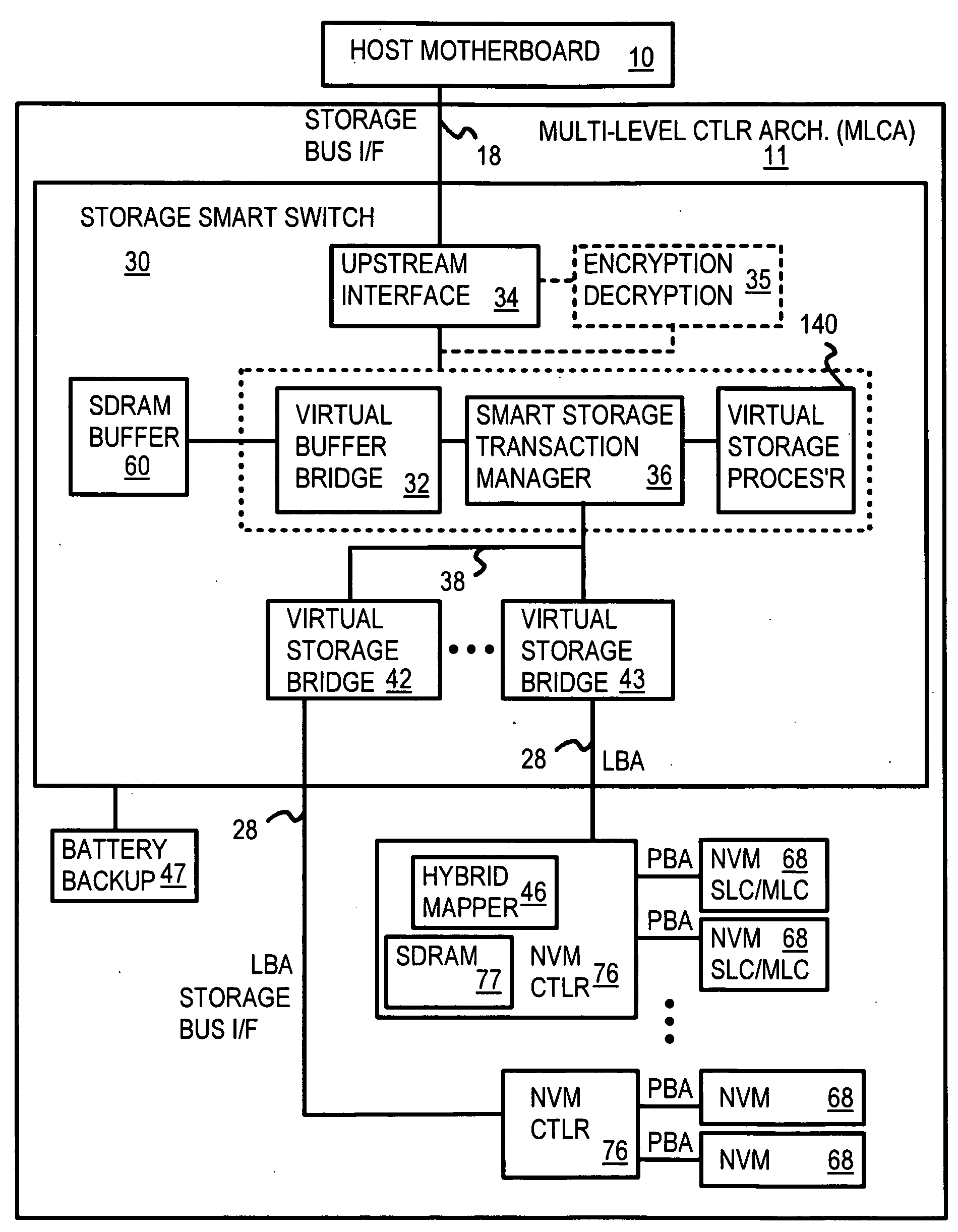

Hybrid 2-Level Mapping Tables for Hybrid Block- and Page-Mode Flash-Memory System

InactiveUS20090193184A1Memory architecture accessing/allocationMemory adressing/allocation/relocationVirtual fieldFrequency counter

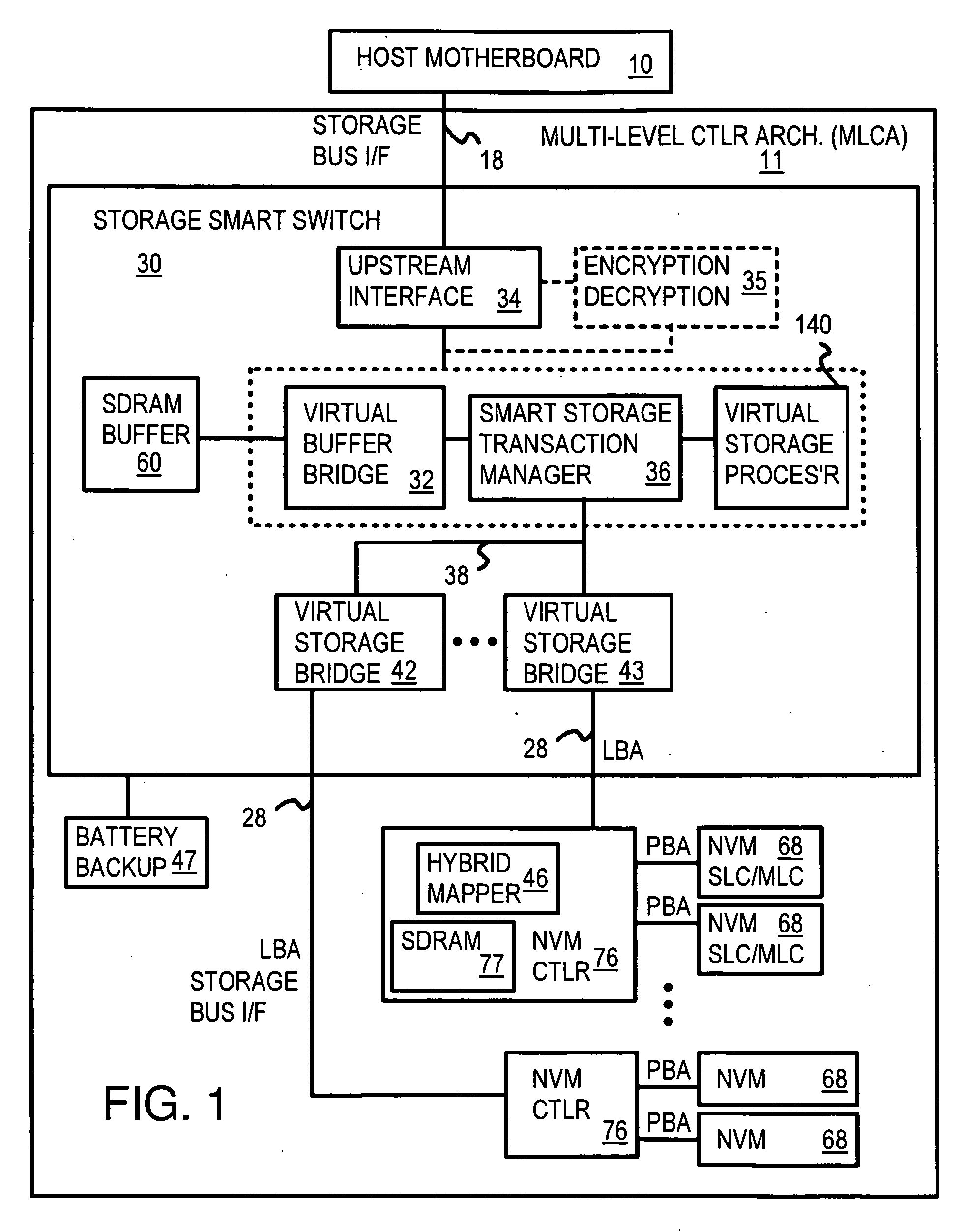

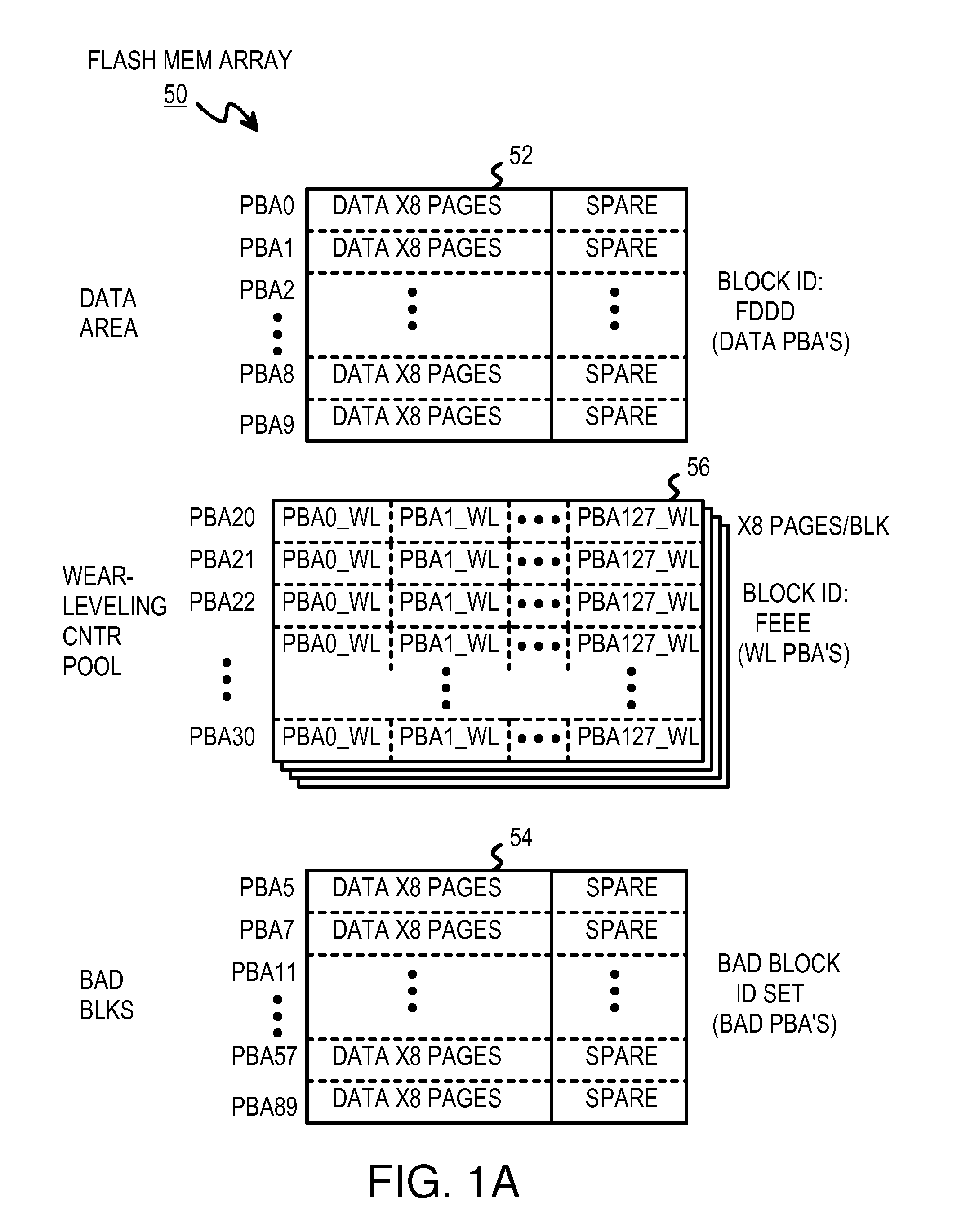

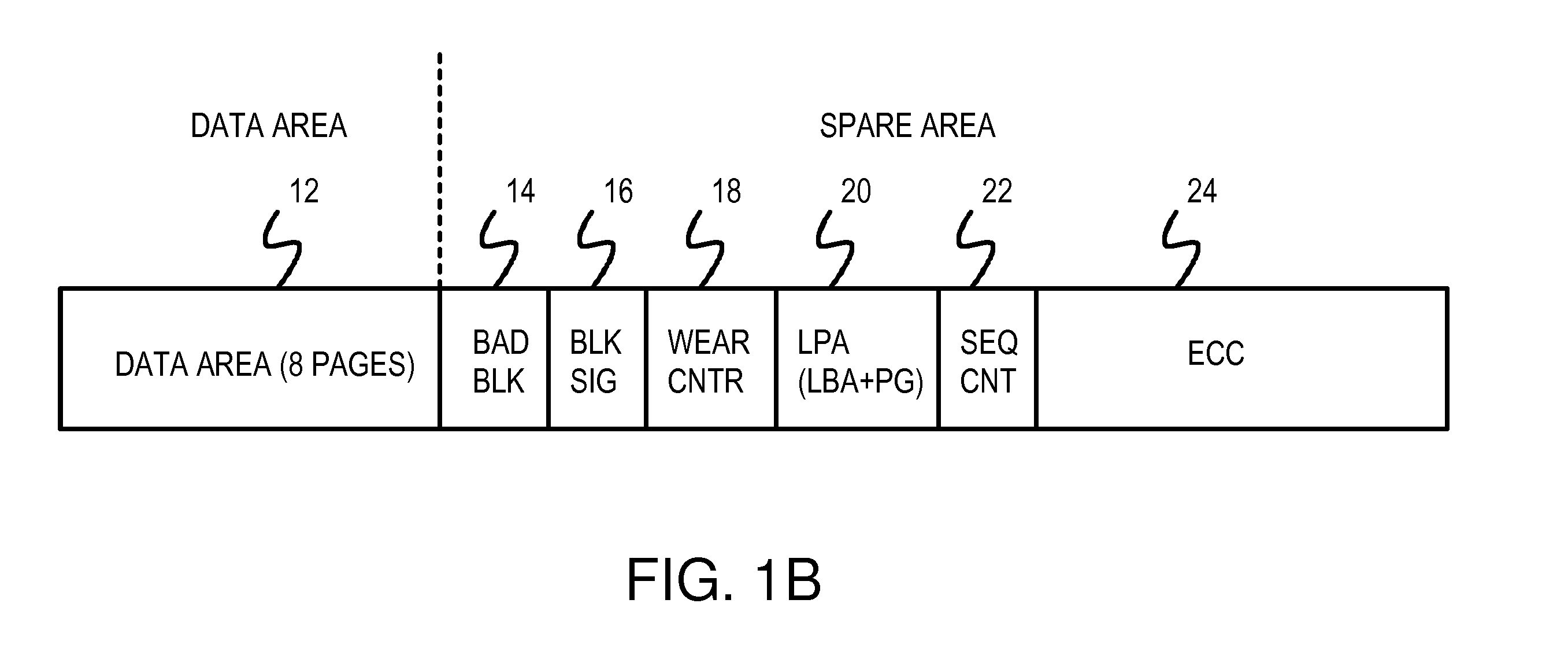

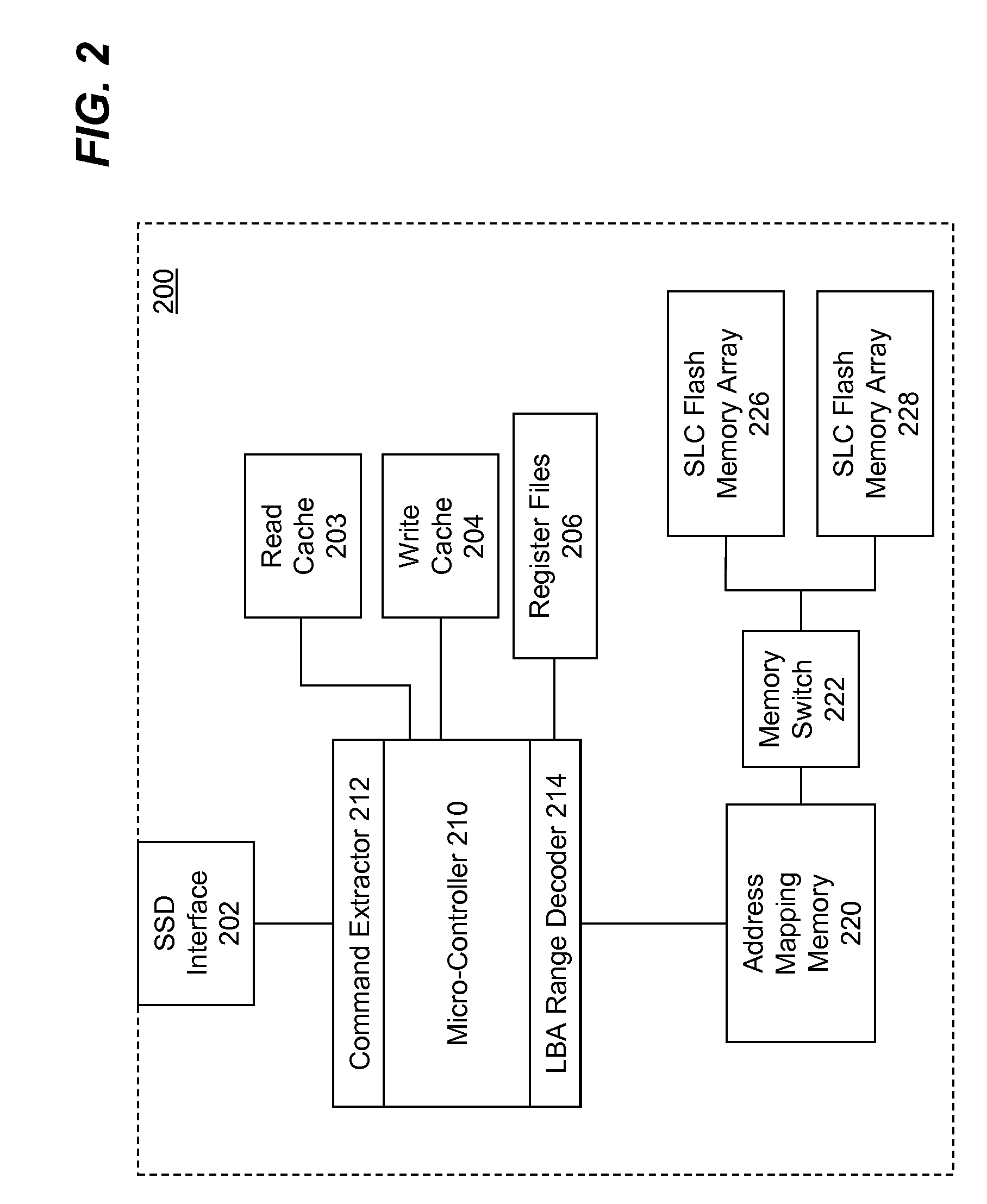

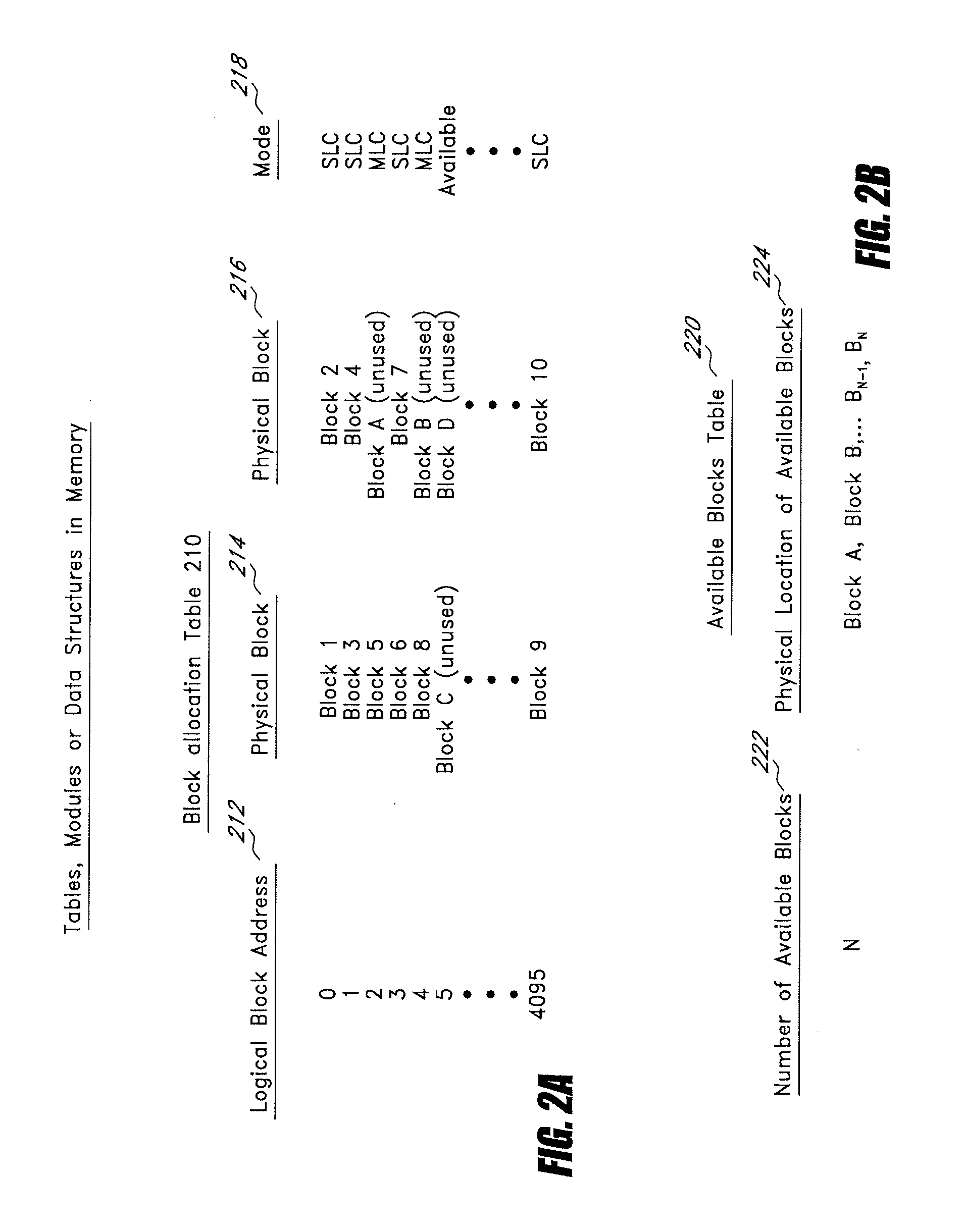

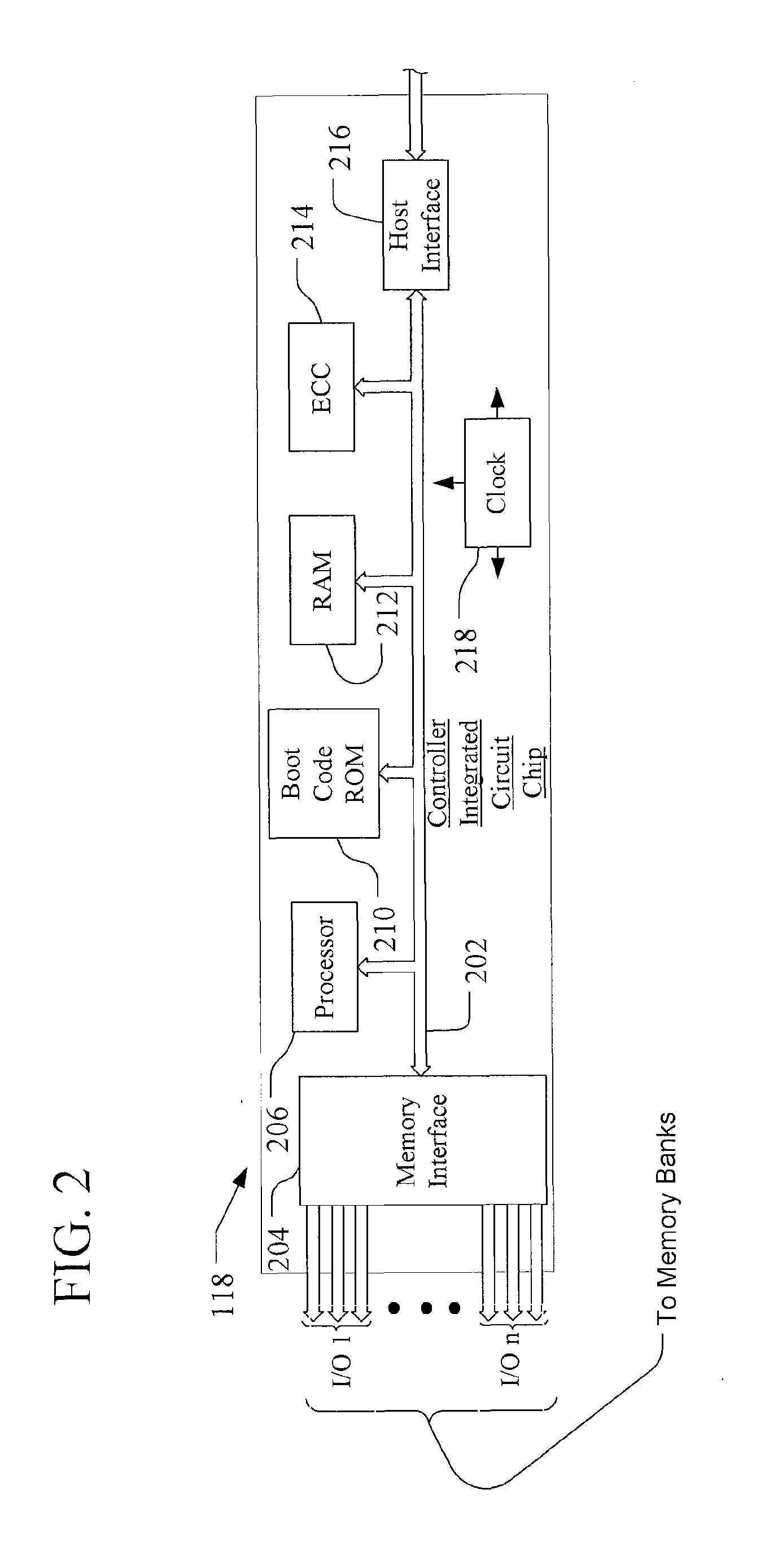

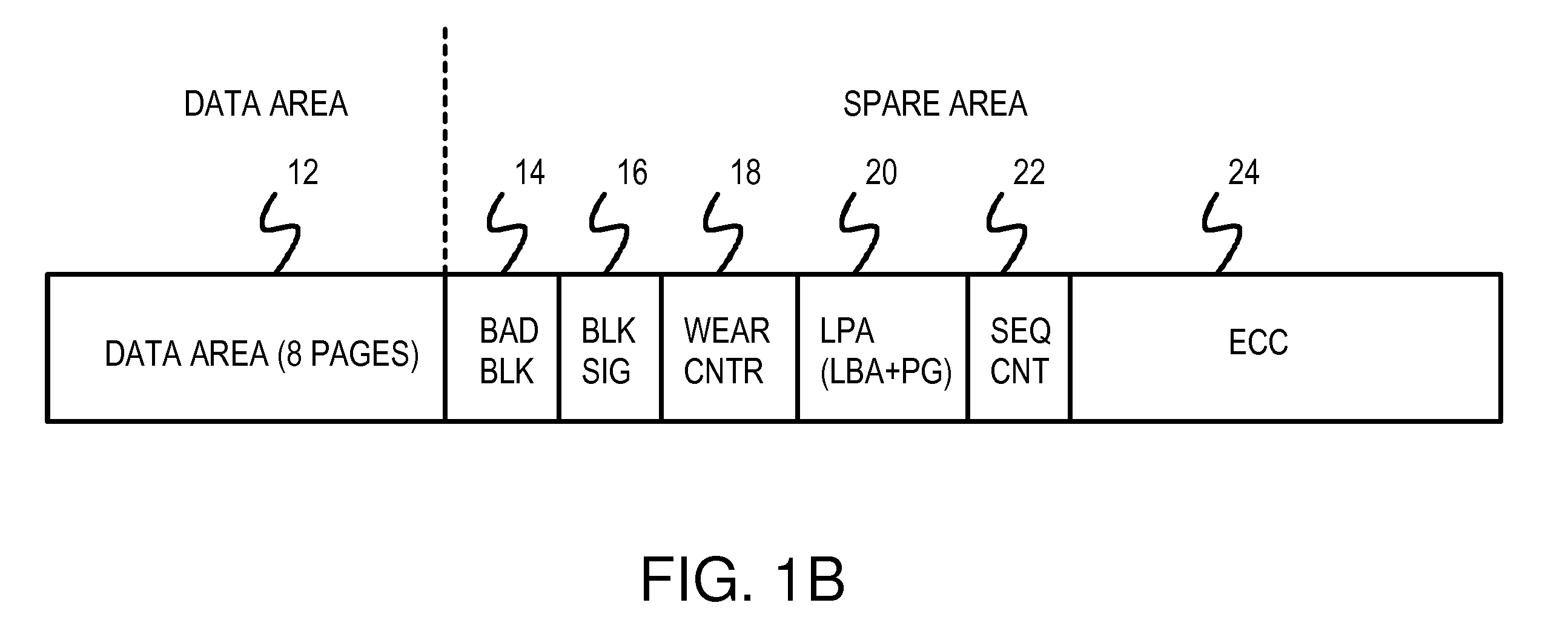

A hybrid solid-state disk (SSD) has multi-level-cell (MLC) or single-level-cell (SLC) flash memory, or both. SLC flash may be emulated by MLC that uses fewer cell states. A NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Most data is block-mapped and stored in MLC flash, but some critical or high-frequency data is page-mapped to reduce block-relocation copying. A hybrid mapping table has a first-level and a second level. Only the first level is used for block-mapped data, but both levels are used for page-mapped data. The first level contains a block-page bit that indicates if the data is block-mapped or page-mapped. A PBA field in the first-level table maps block-mapped data, while a virtual field points to the second-level table where the PBA and page number is stored for page-mapped data. Page-mapped data is identified by a frequency counter or sector count. SRAM space is reduced.

Owner:SUPER TALENT ELECTRONICS

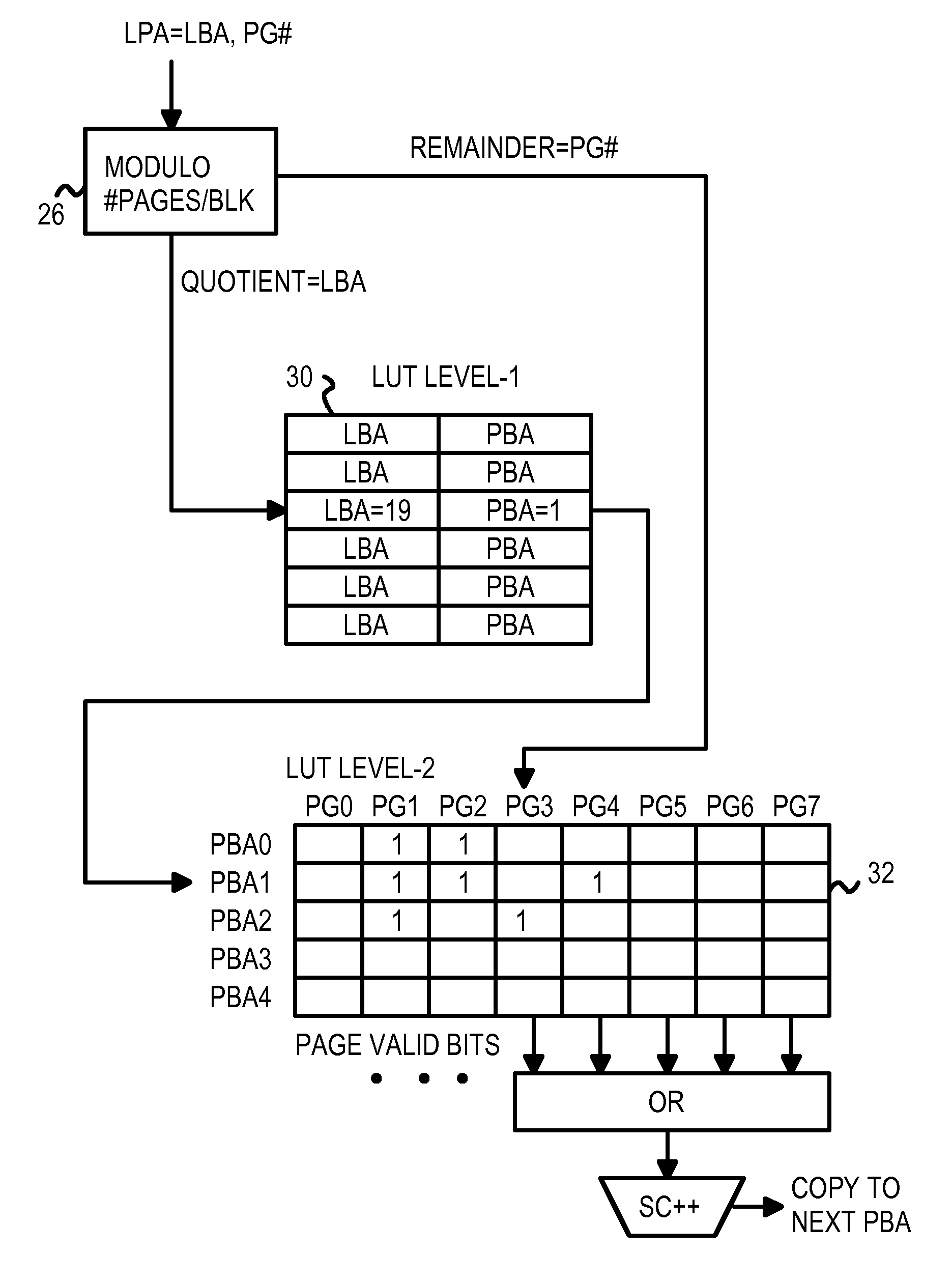

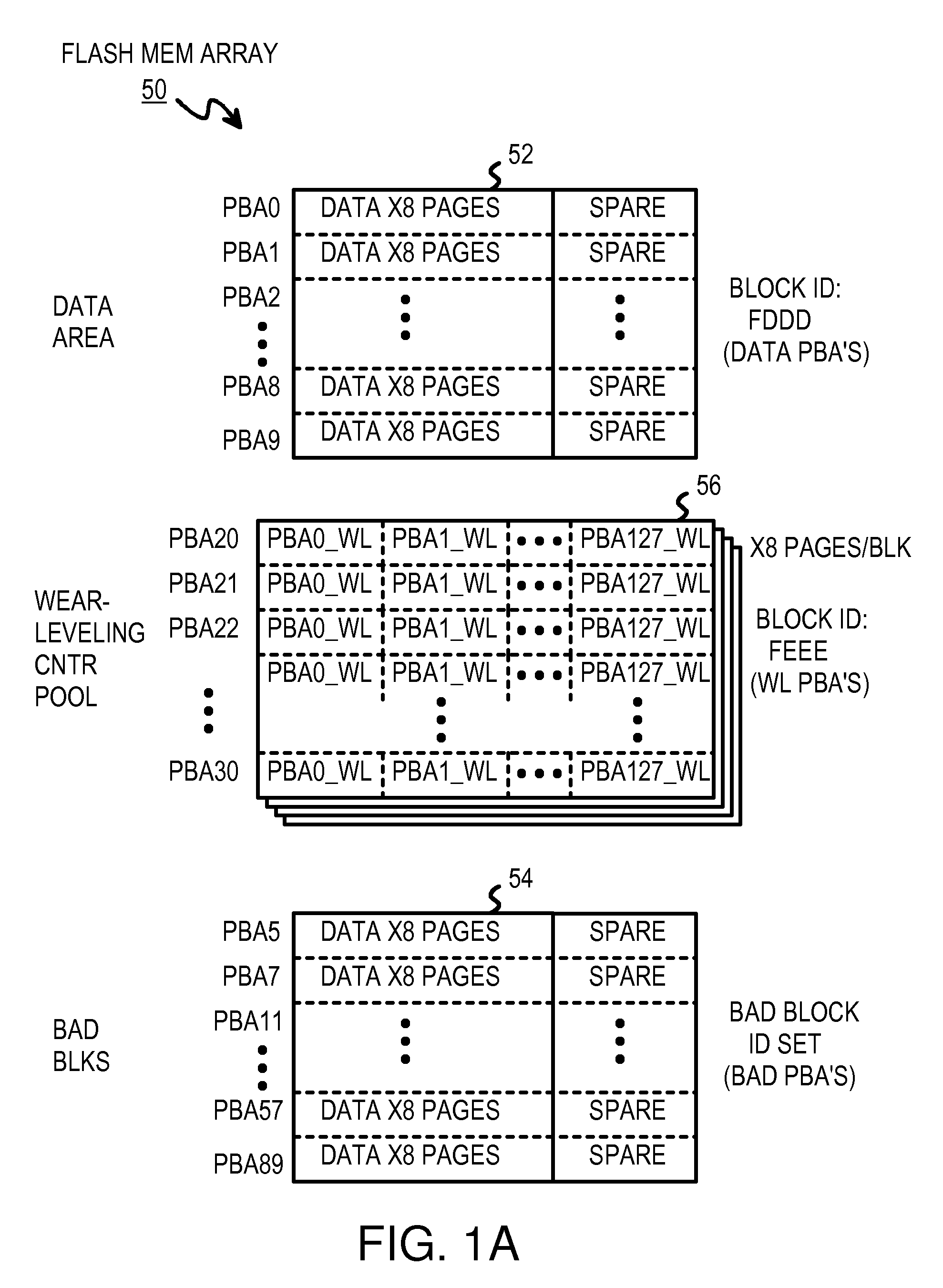

Two-Level RAM Lookup Table for Block and Page Allocation and Wear-Leveling in Limited-Write Flash-Memories

InactiveUS20070204128A1Memory architecture accessing/allocationRead-only memoriesRandom access memoryLogical block addressing

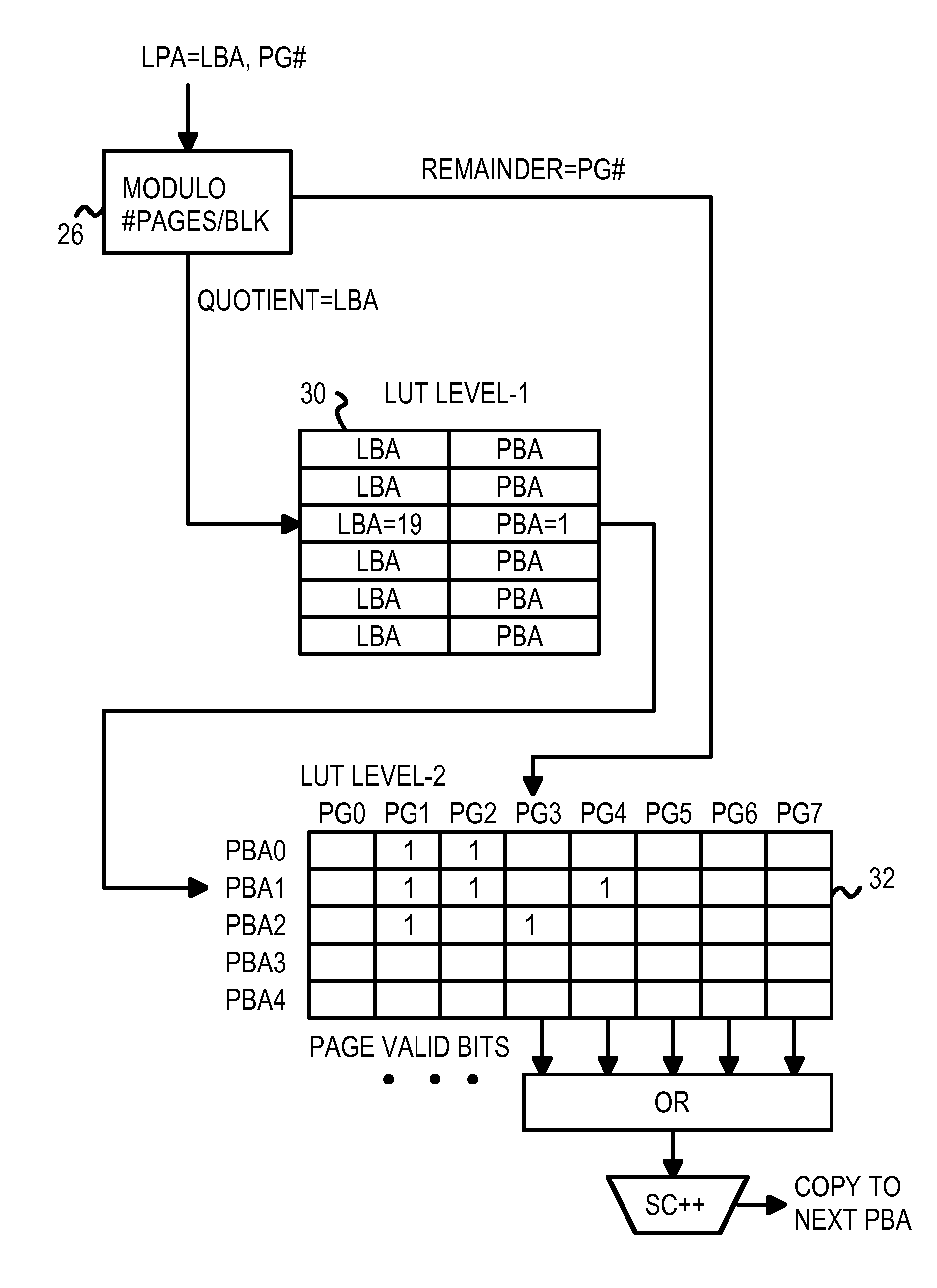

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

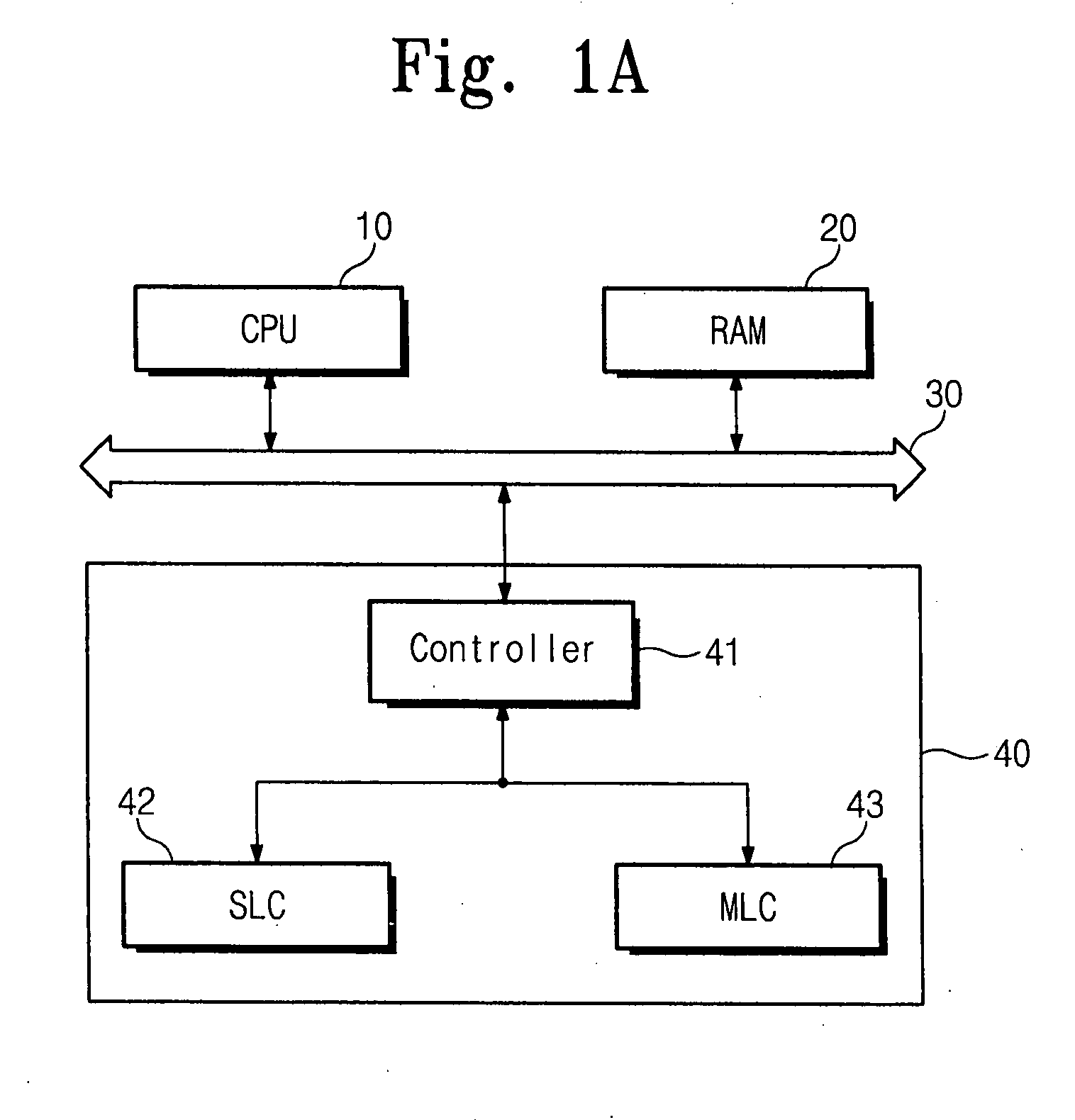

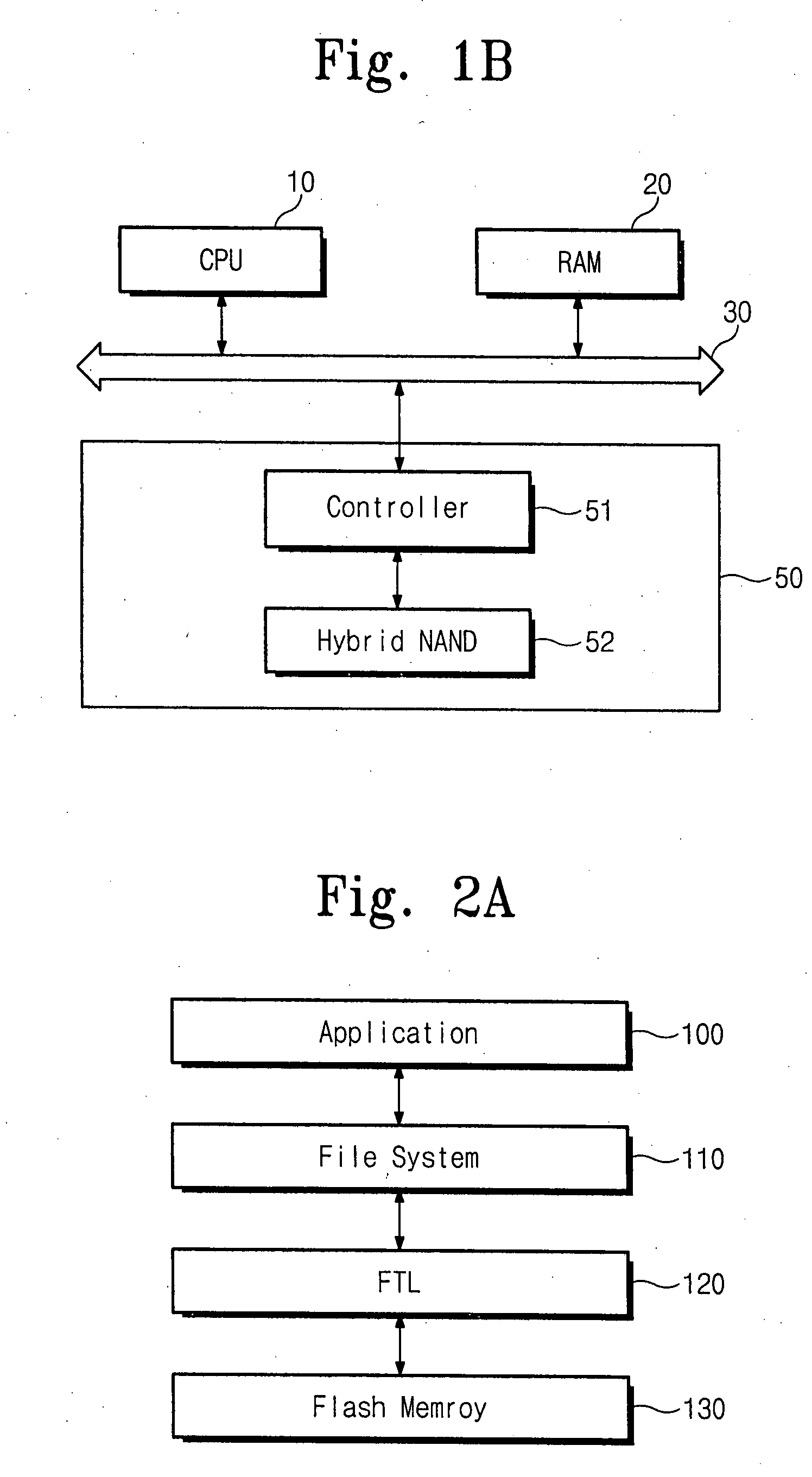

Hybrid SSD Using A Combination of SLC and MLC Flash Memory Arrays

InactiveUS20080215800A1Reduce manufacturing costAcceptable levelMemory architecture accessing/allocationInternal/peripheral component protectionData fileSingle level

Hybrid solid state drives (SSD) using a combination of single-level cell (SLC) and multi-level cell (MLC) flash memory arrays are described. According to one aspect of the present invention, a hybrid SSD is built using a combination SLC and MLC flash memory arrays. The SSD also includes a micro-controller to control and coordinate data transfer from a host computing device to either the SLC flash memory array of the MLC flash memory array. A memory selection indicator is determined by triaging data file based on one or more criteria, which include, but is not limited to, storing system files and user directories in the SLC flash memory array and storing user files in the MLC flash memory array; or storing more frequent access files in the SLC flash memory array, while less frequent accessed files in the MLC flash memory array.

Owner:SUPER TALENT TECH CORP

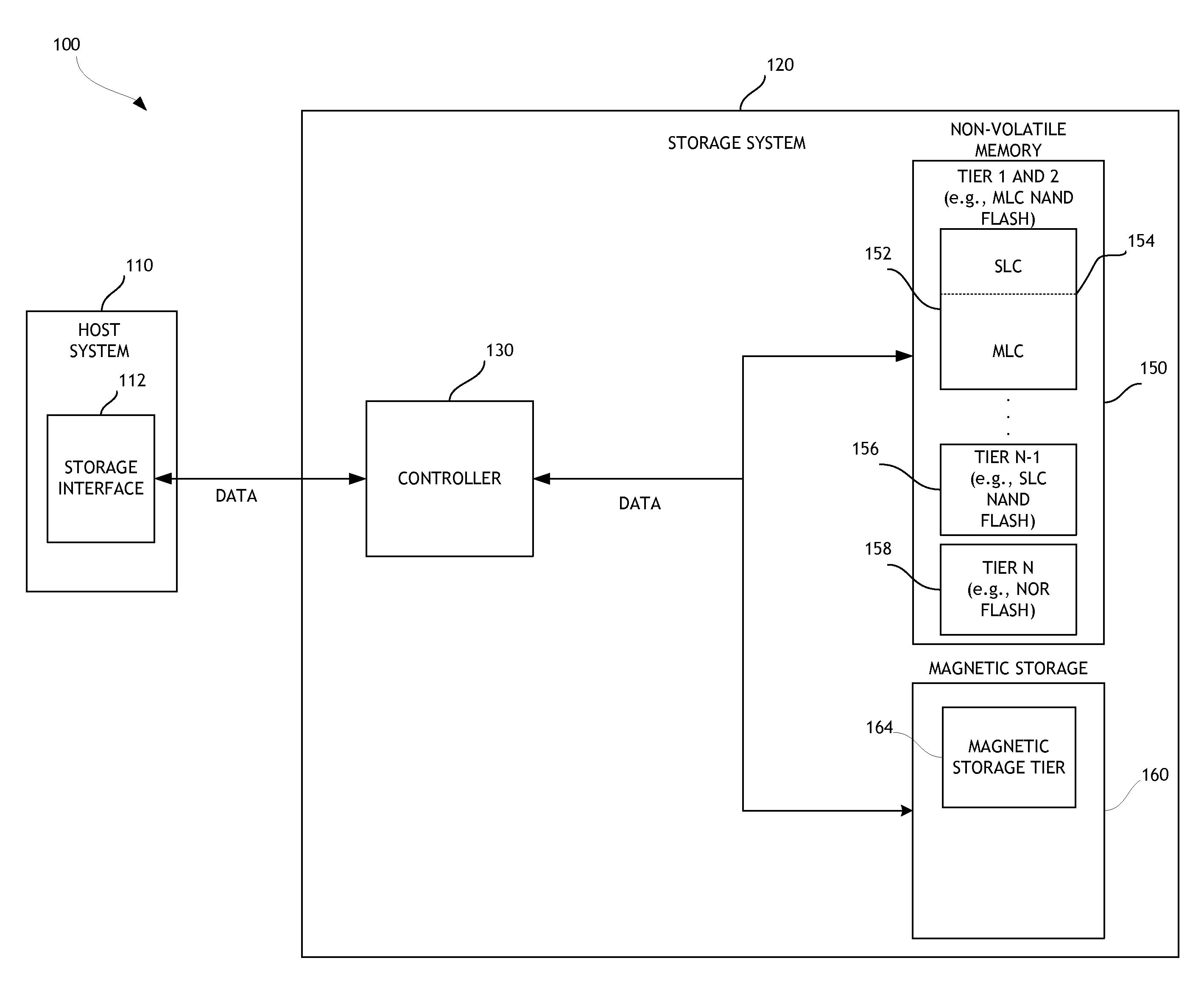

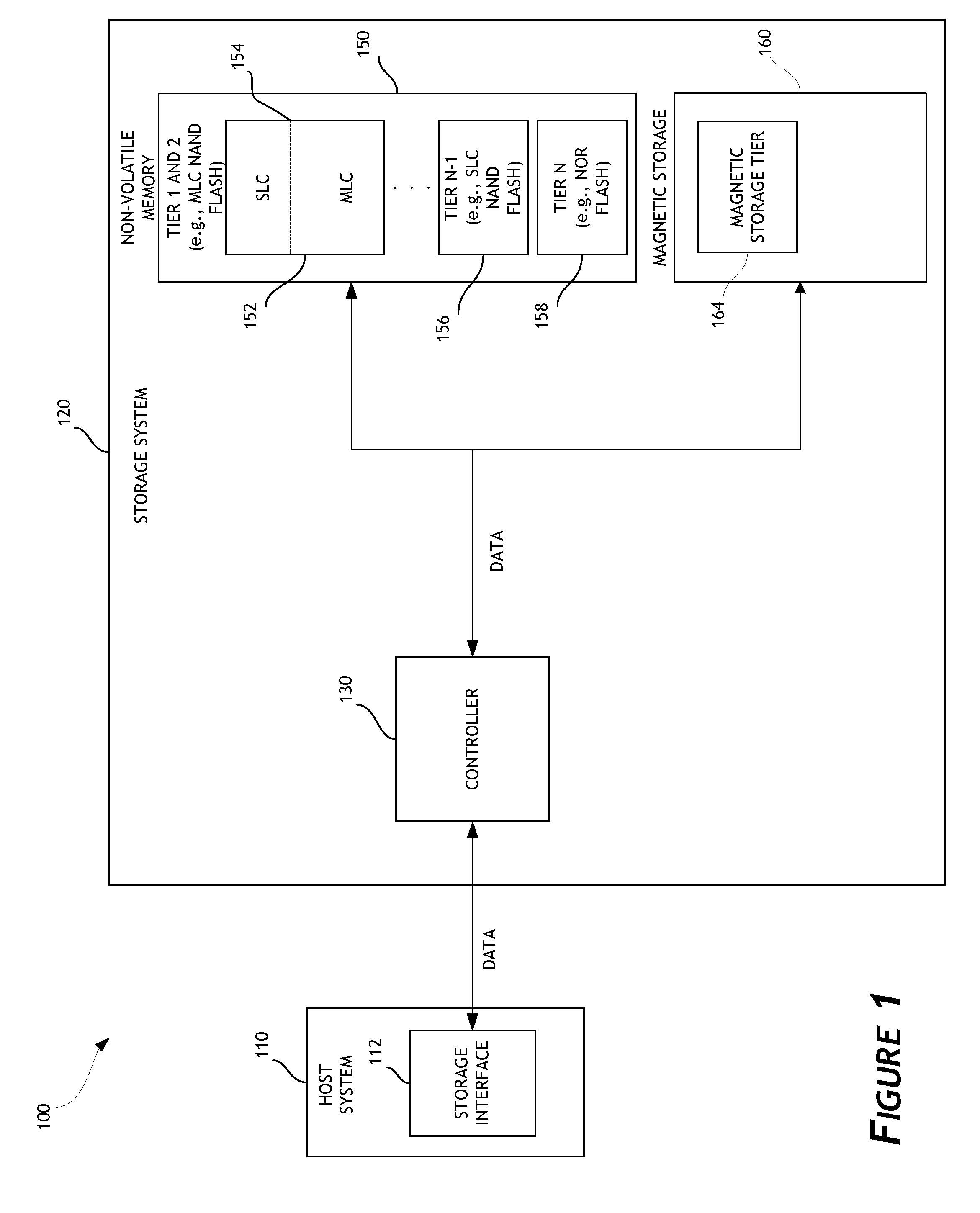

Disk drive data caching using a multi-tiered memory

ActiveUS20130132638A1Limit usable lifeReduce dataMemory architecture accessing/allocationEnergy efficient ICTSingle levelComputer science

A disk drive is disclosed that utilizes multi-tiered solid state memory for caching data received from a host. Data can be stored in a memory tier that can provide the required performance at a low cost. For example, multi-level cell (MLC) memory can be used to store data that is frequently read but infrequently written. As another example, single-level cell (SLC) memory can be used to store data that is frequently written. Improved performance, reduced costs, and improved power consumption can thereby be attained.

Owner:WESTERN DIGITAL TECH INC

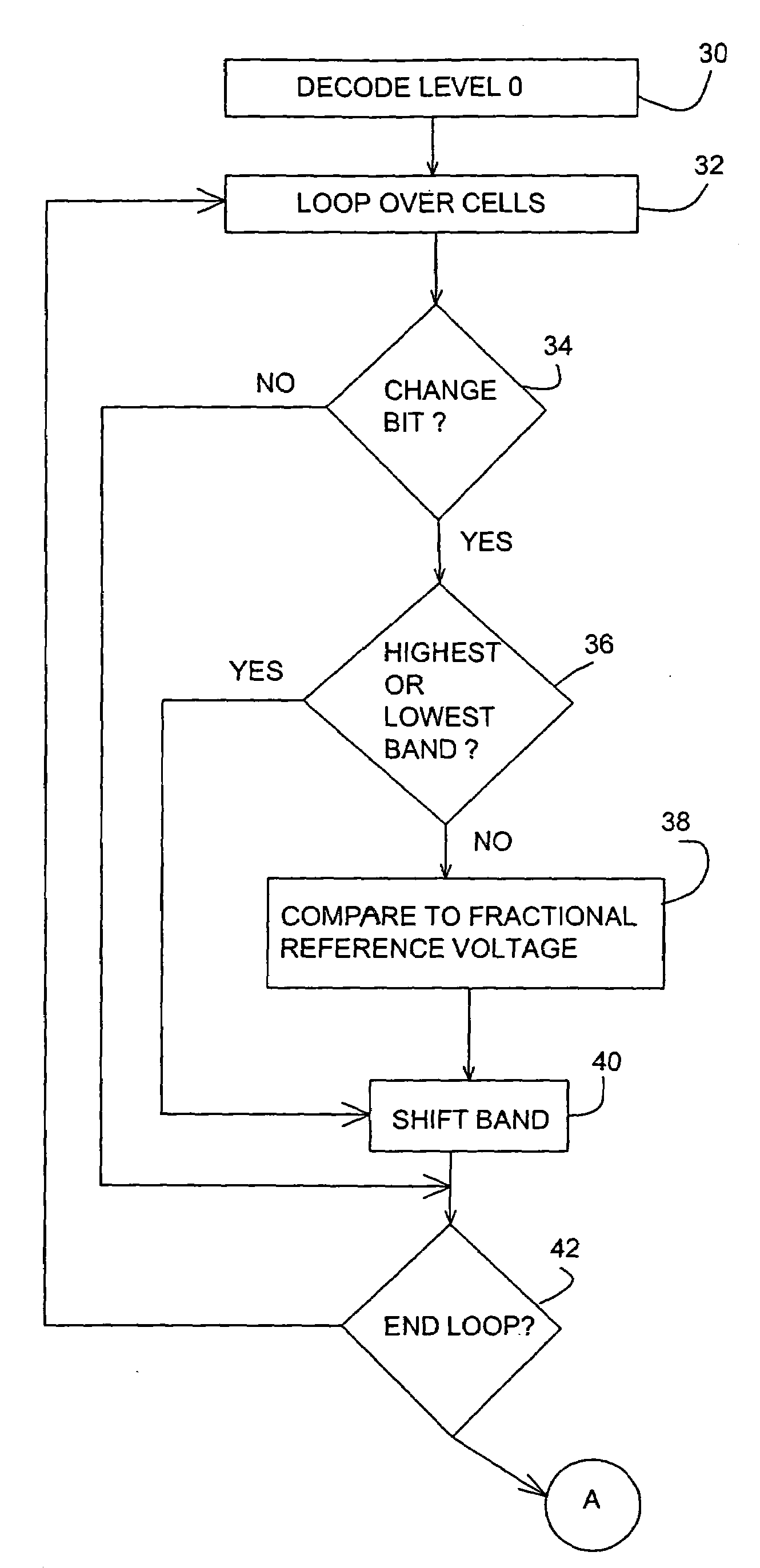

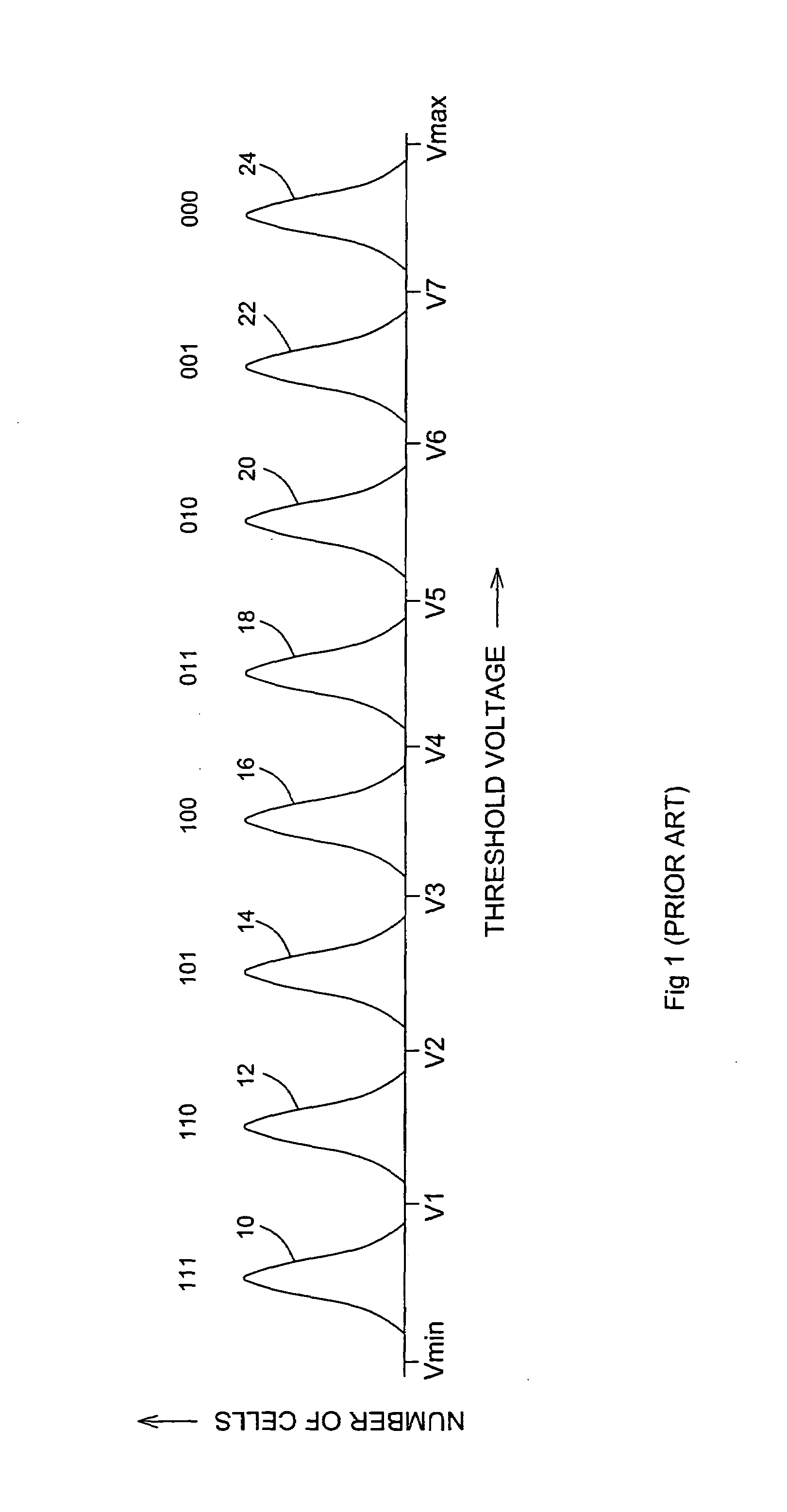

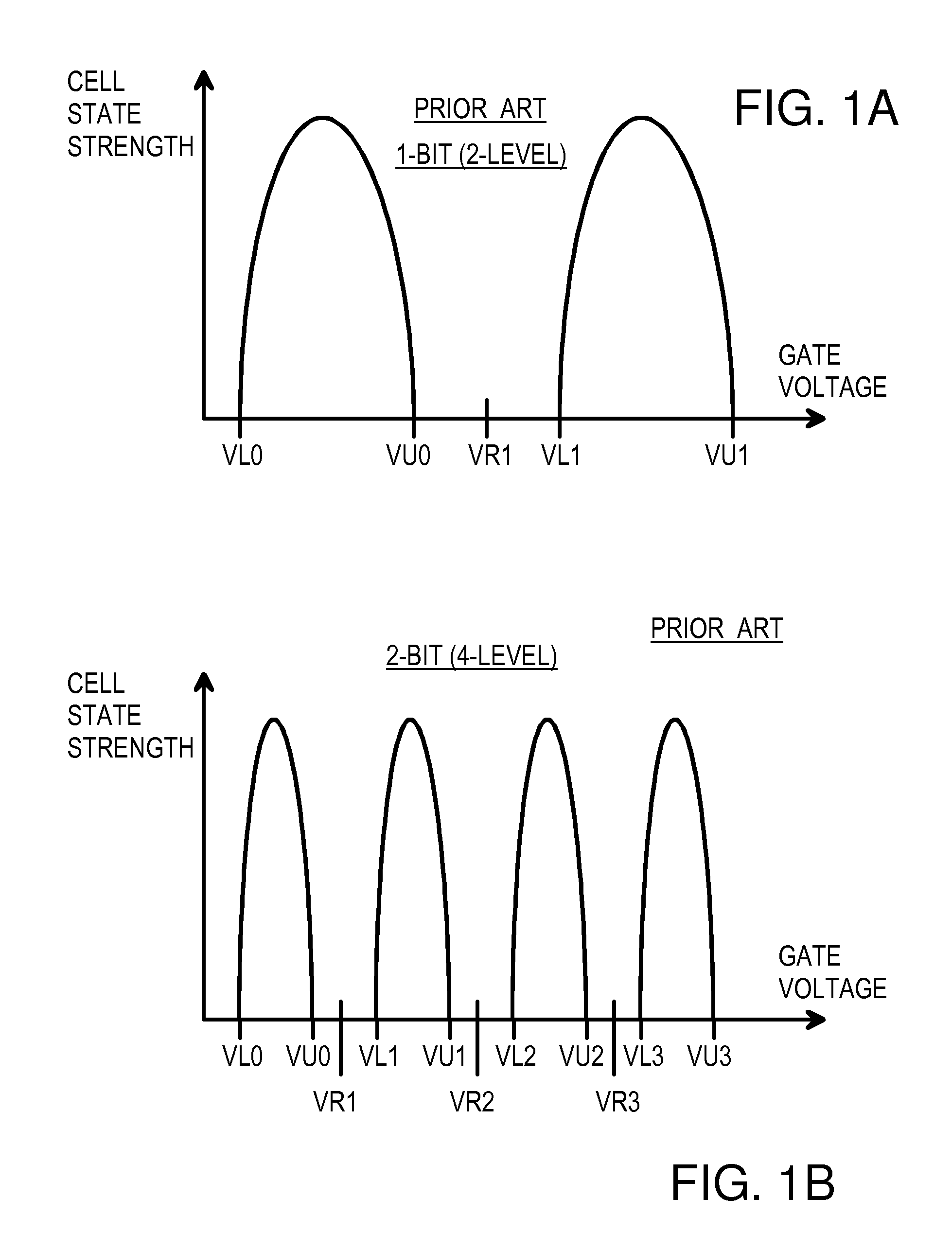

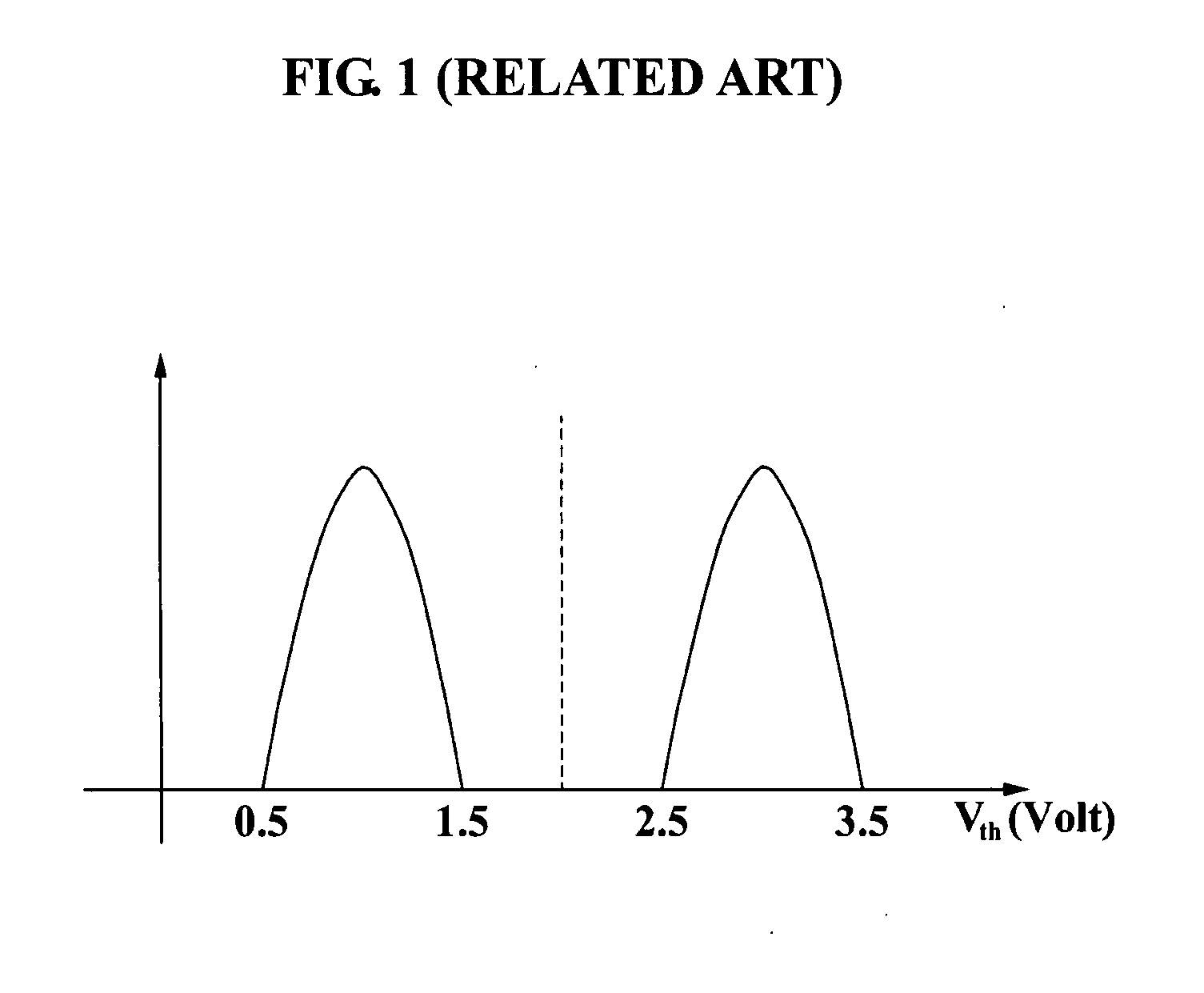

Methods of increasing the reliability of a flash memory

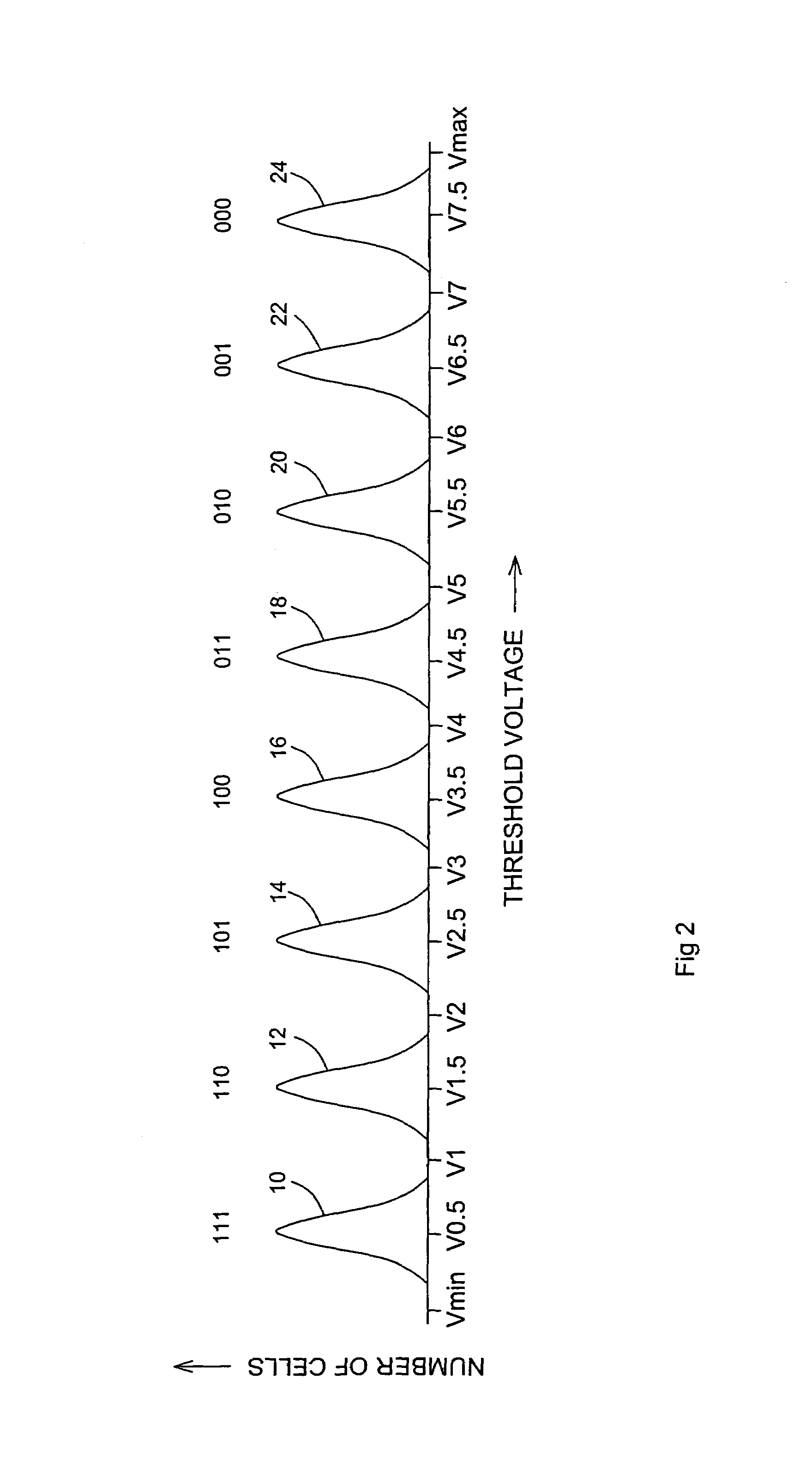

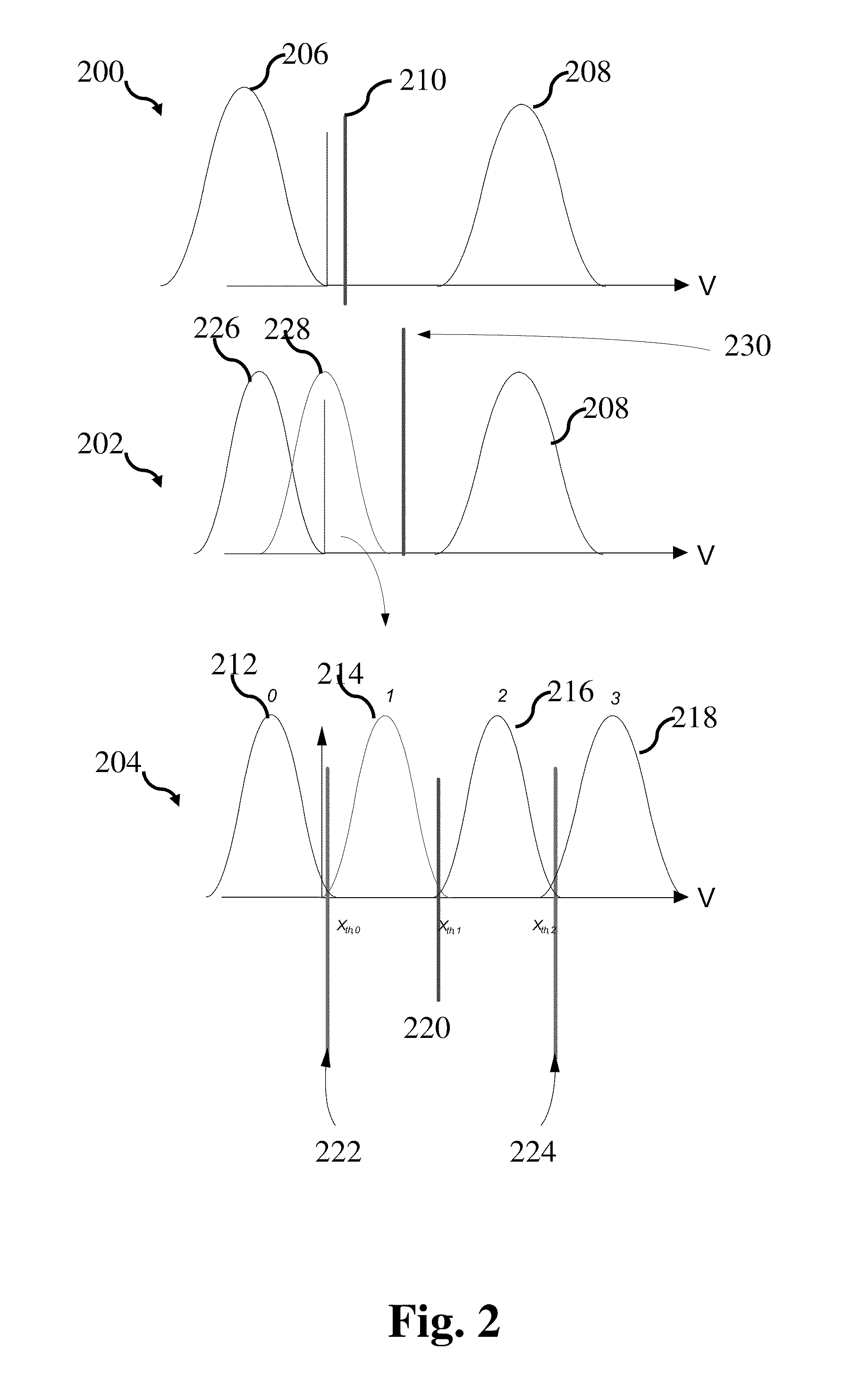

A multi-level flash memory cell is read by comparing the cell's threshold voltage to a plurality of integral reference voltages and to a fractional reference voltage. Multi-level cells of a flash memory are programmed collectively with data and redundancy bits at each significance level, preferably with different numbers of data and redundancy bits at each significance level. The cells are read collectively, from lowest to highest significance level, by correcting the bits at each significance level according to the redundancy bits and adjusting the bits of the higher significance levels accordingly. The adjustment following the correction of the least significant bits is in accordance with comparisons of a cell's threshold voltages to fractional reference voltages.

Owner:RAMOT AT TEL AVIV UNIV LTD

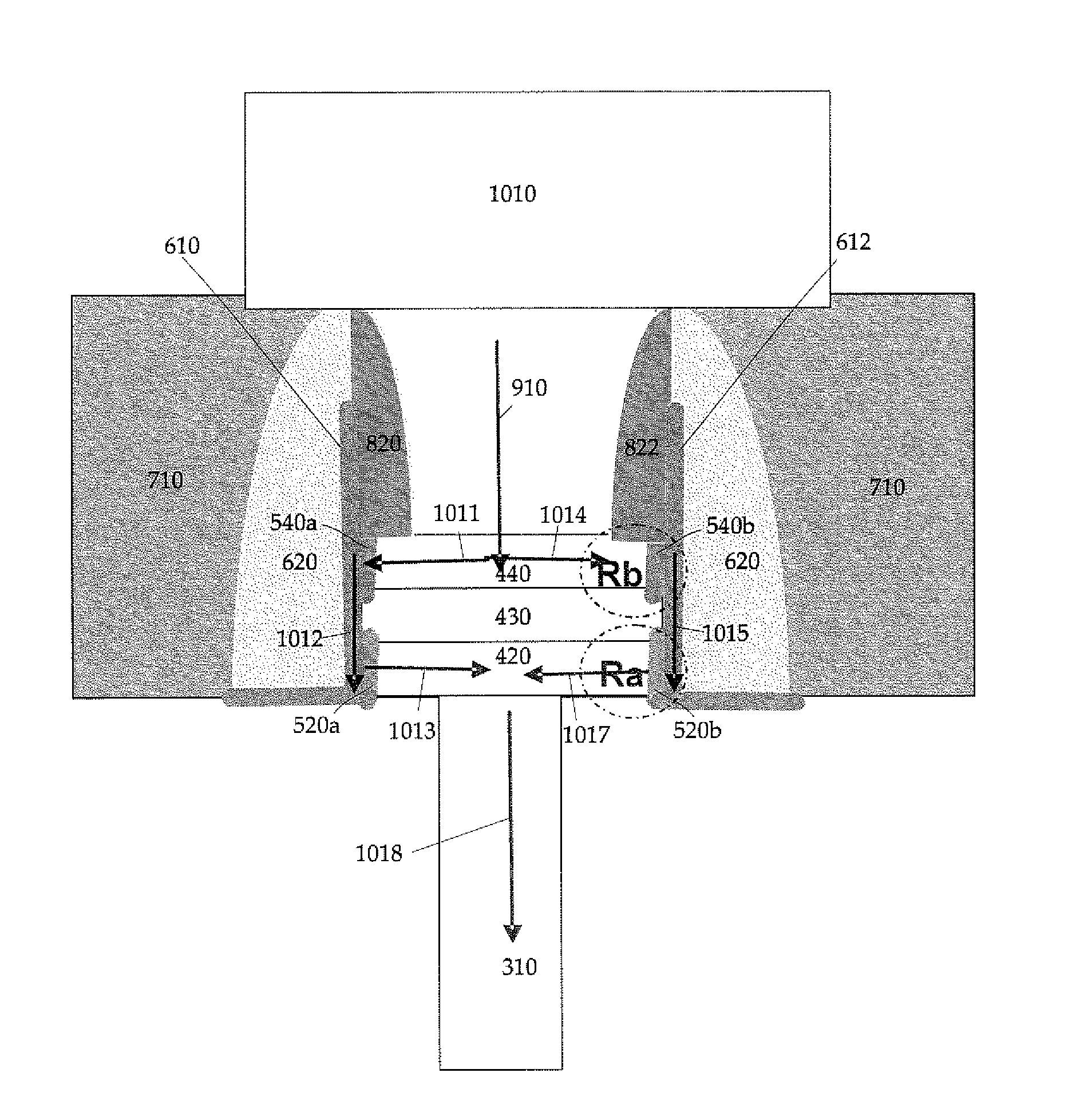

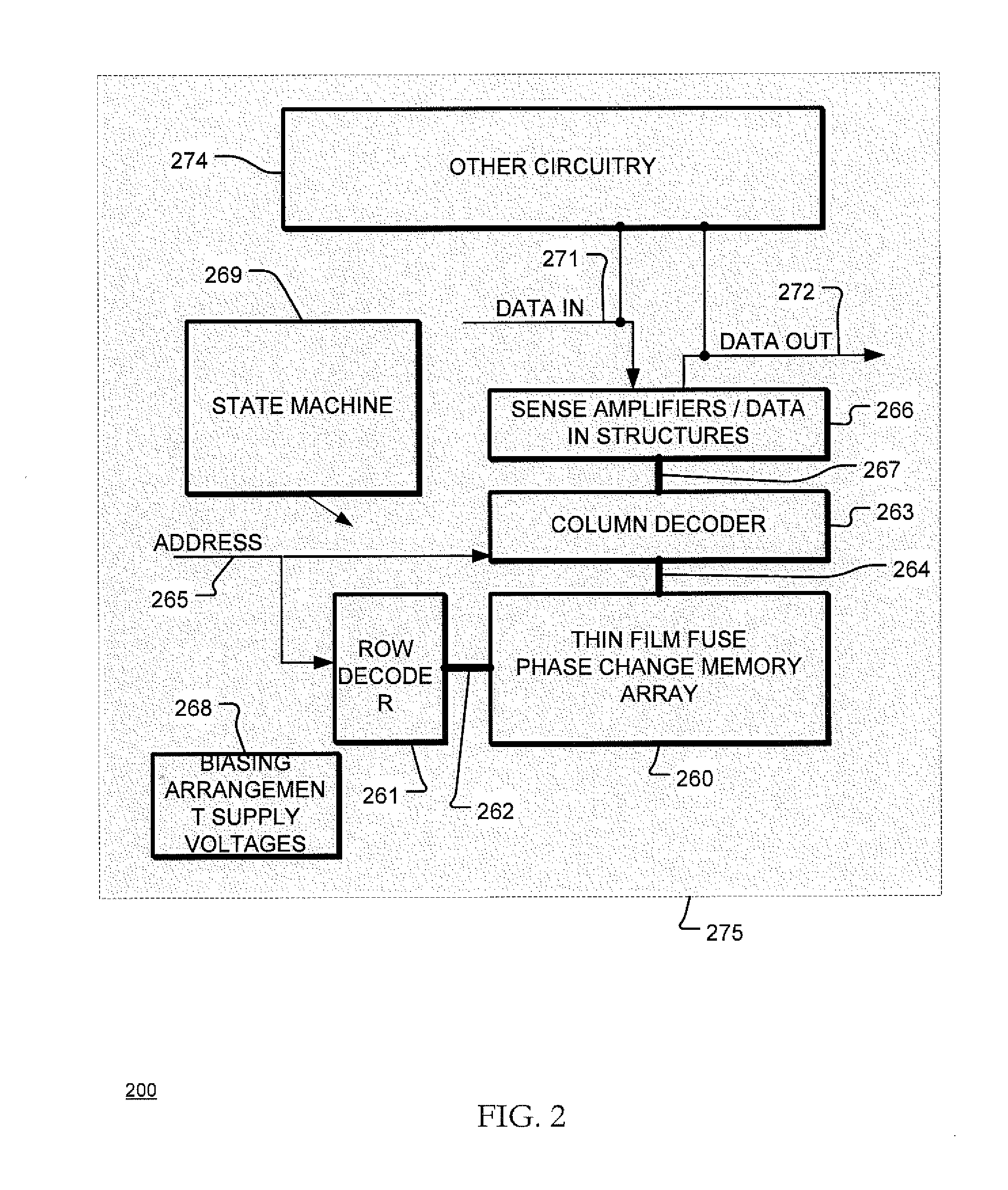

Multi-level cell resistance random access memory with metal oxides

ActiveUS7697316B2High densityElectrical apparatusElectric analogue storesRandom access memoryElectrical battery

A bistable resistance random access memory comprises a plurality of programmable resistance random access memory cells where each programmable resistance random access memory cell includes multiple memory members for performing multiple bits for each memory cell. The bistable RRAM includes a first resistance random access member connected to a second resistance random access member through interconnect metal liners and metal oxide strips. The first resistance random access member has a first resistance value Ra, which is determined from the thickness of the first resistance random access member based on the deposition of the first resistance random access member. The second resistance random access member has a second resistance value Rb, which is determined from the thickness of the second resistance random access member based on the deposition of the second resistance random access member.

Owner:MACRONIX INT CO LTD

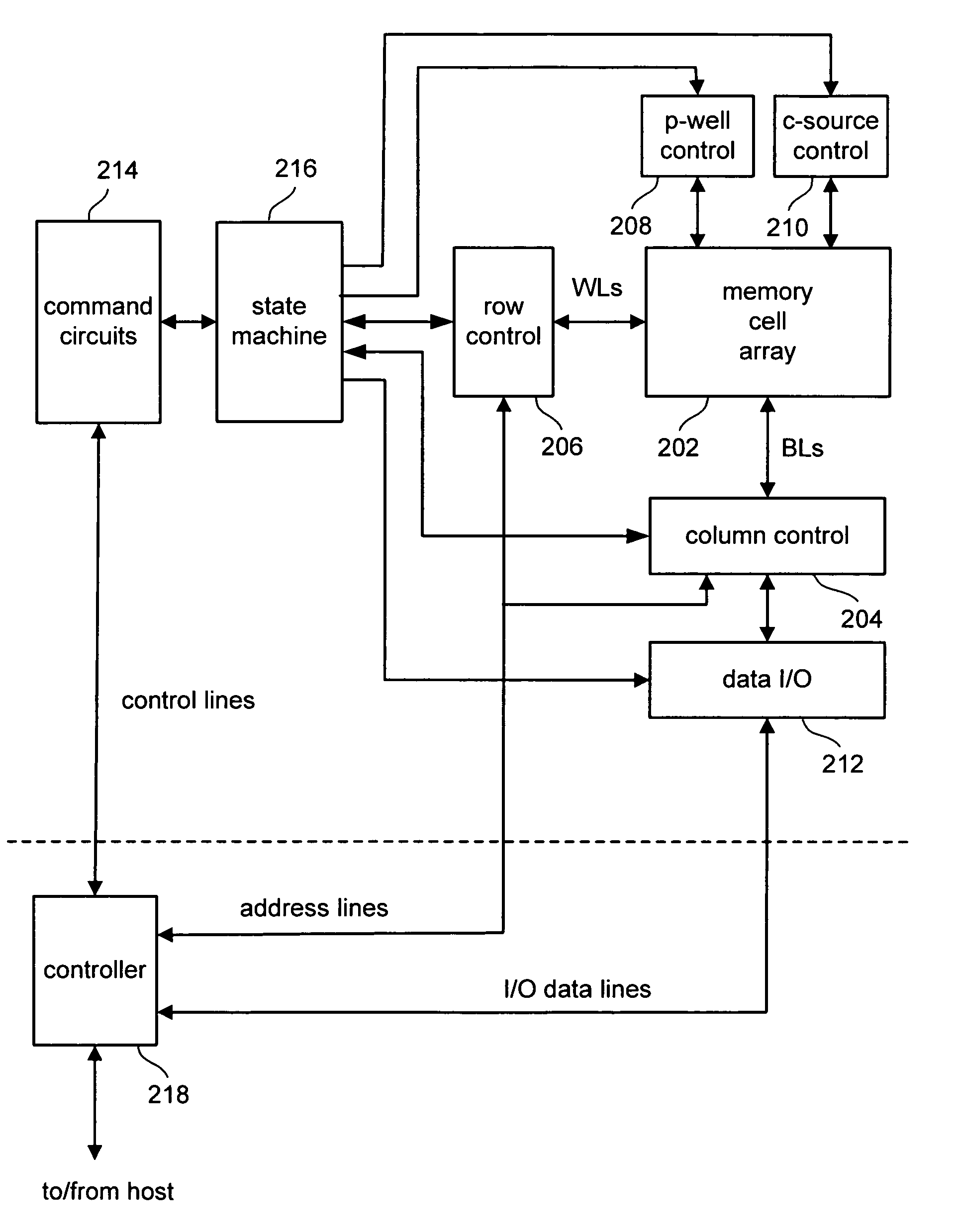

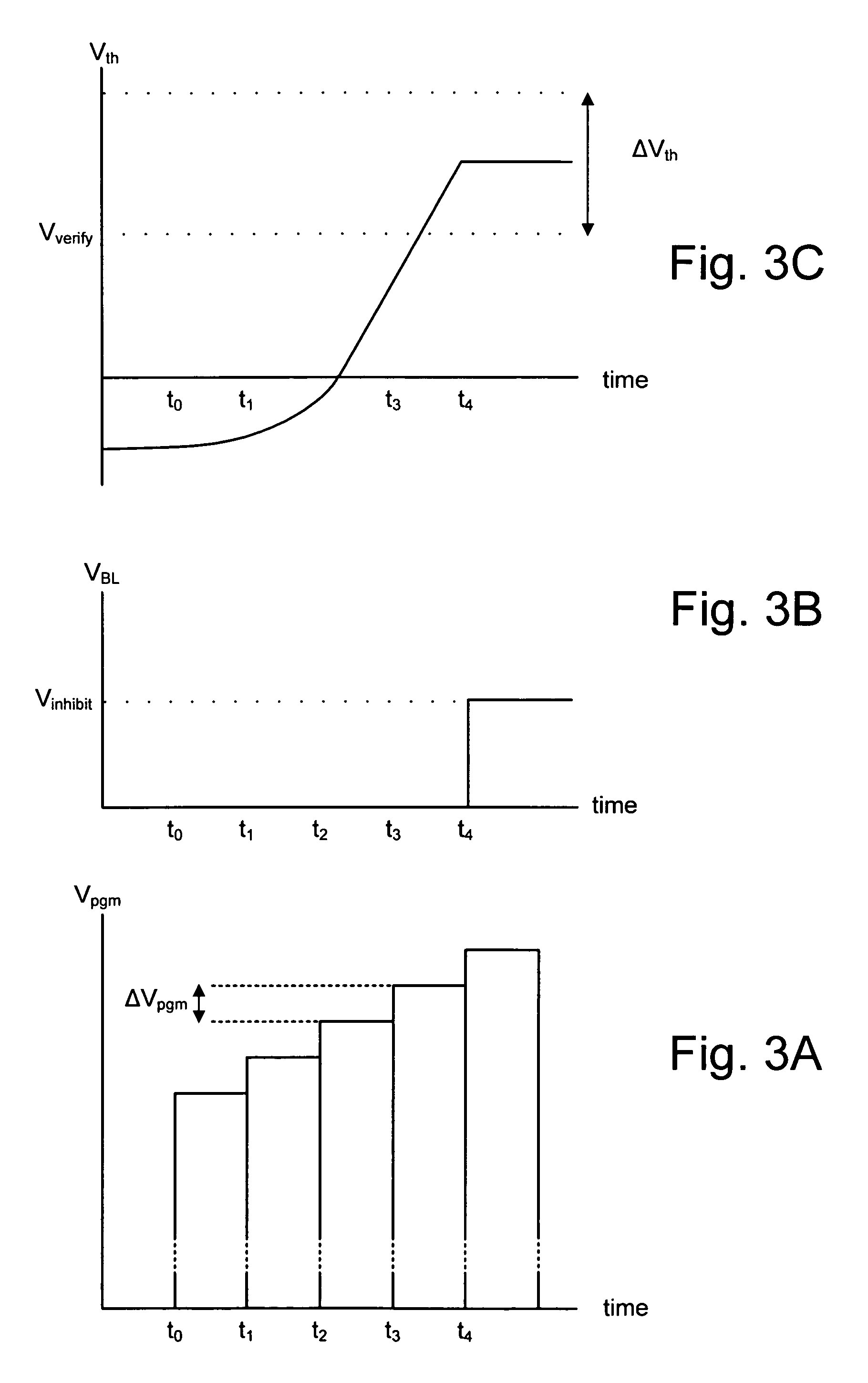

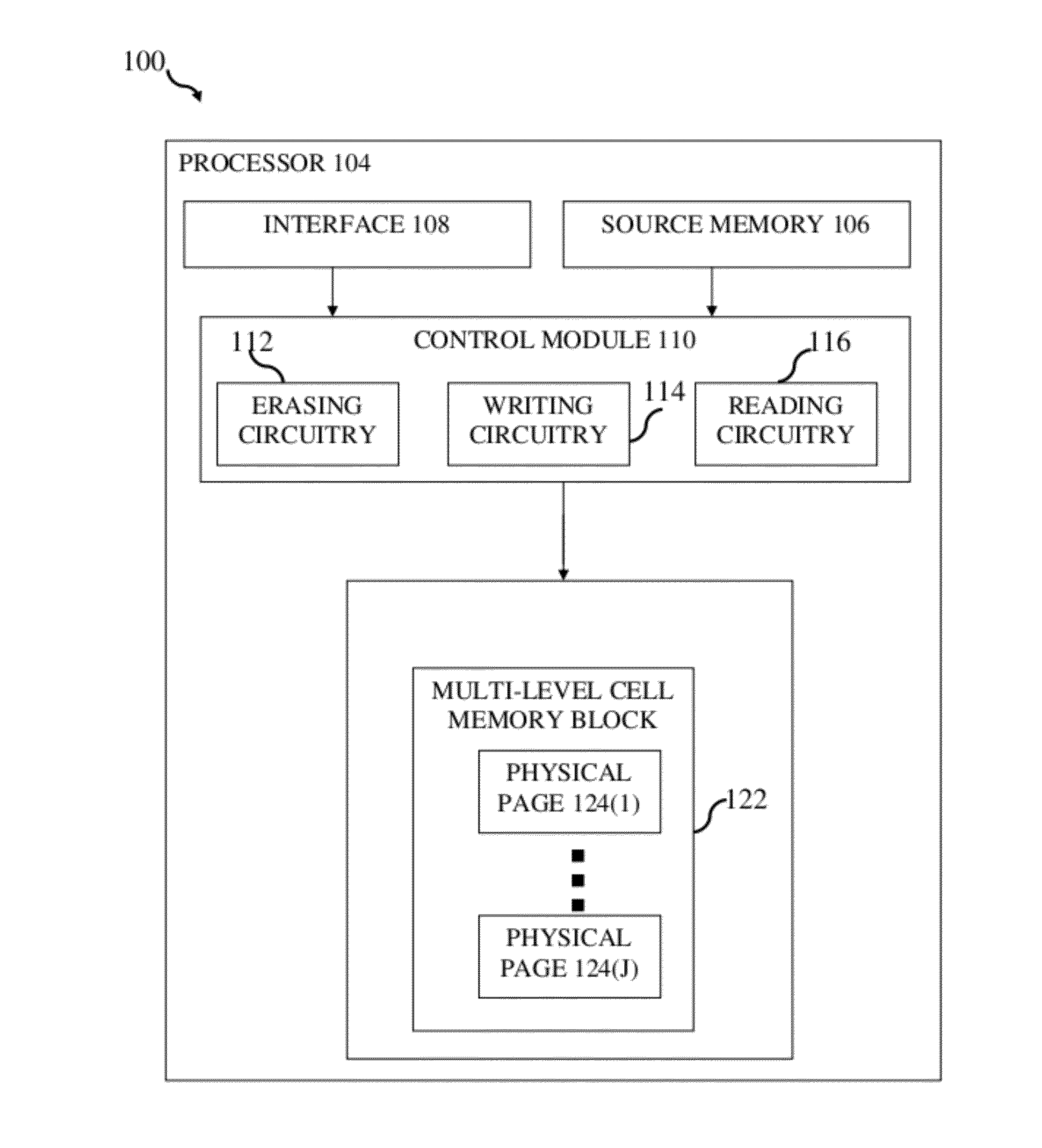

Faster programming of higher level states in multi-level cell flash memory

A program voltage signal implemented as a series of increasing program voltage pulses is applied to a set of non-volatile storage elements. Different increment values can be used when programming memory cells to different memory states. A smaller increment value can be used when programming memory cells to lower threshold voltage memory states and a larger increment value used when programming memory cells to higher threshold voltage memory states such as the highest memory state in an implementation. When non-volatile storage elements of a set are programmed to different memory states under simultaneous application of a single program voltage signal, programming can be monitored to determine when lower state programming is complete. The increment value can then be increased to complete programming to the highest memory state. Coarse / fine programming methodology can be incorporated for the highest memory state when the increment value is increased to maintain the threshold distribution within a reasonable range.

Owner:SANDISK TECH LLC

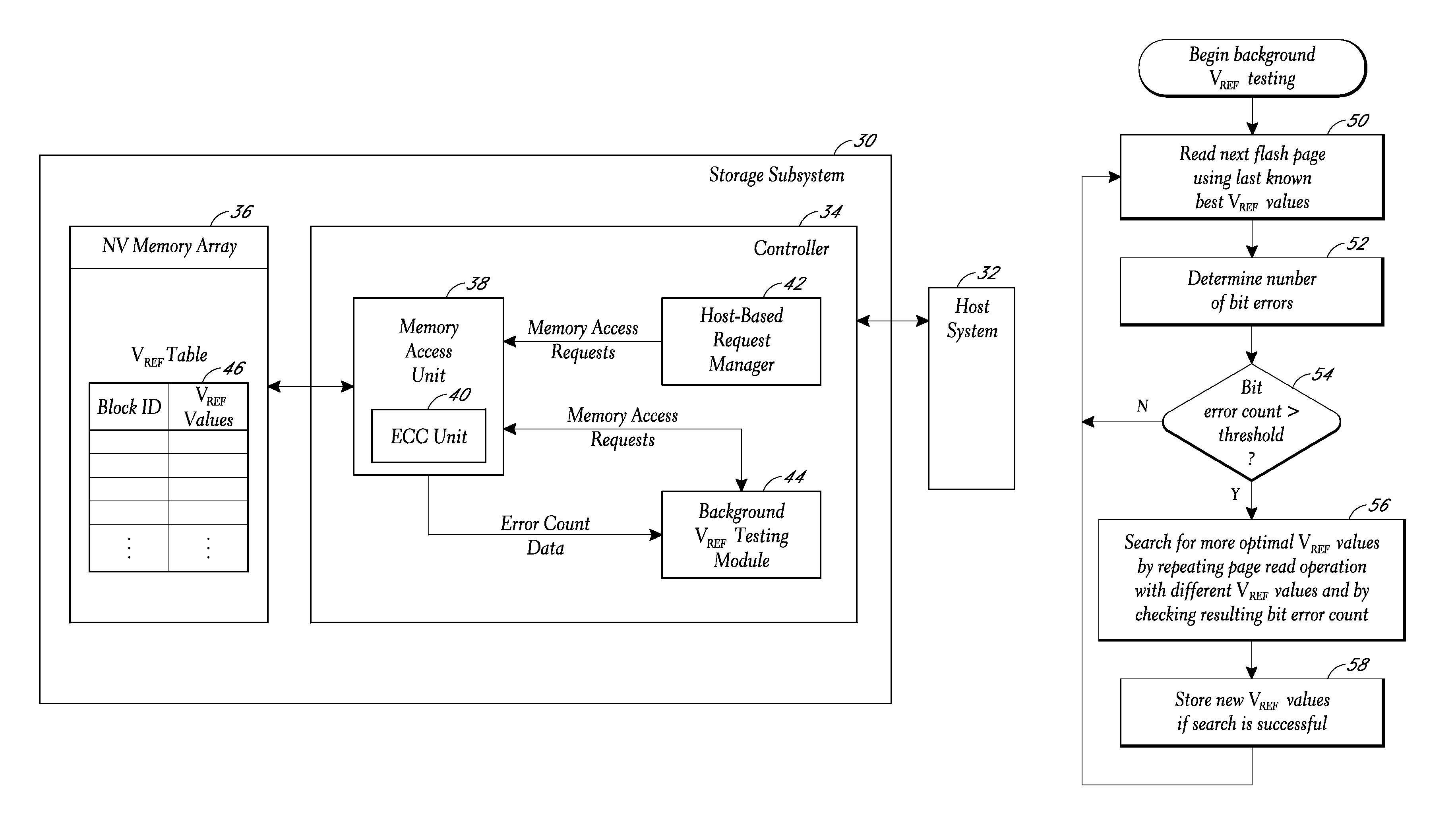

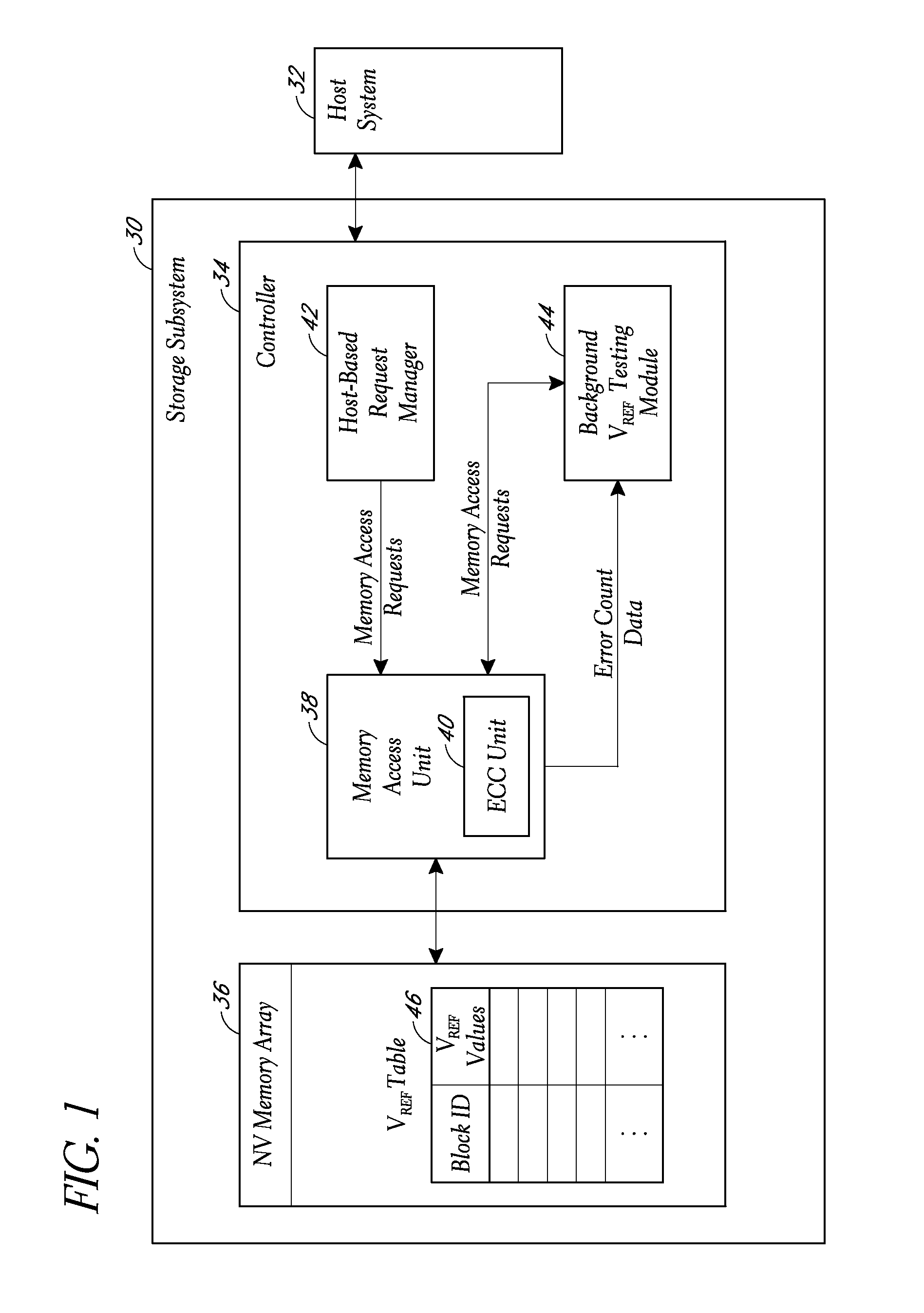

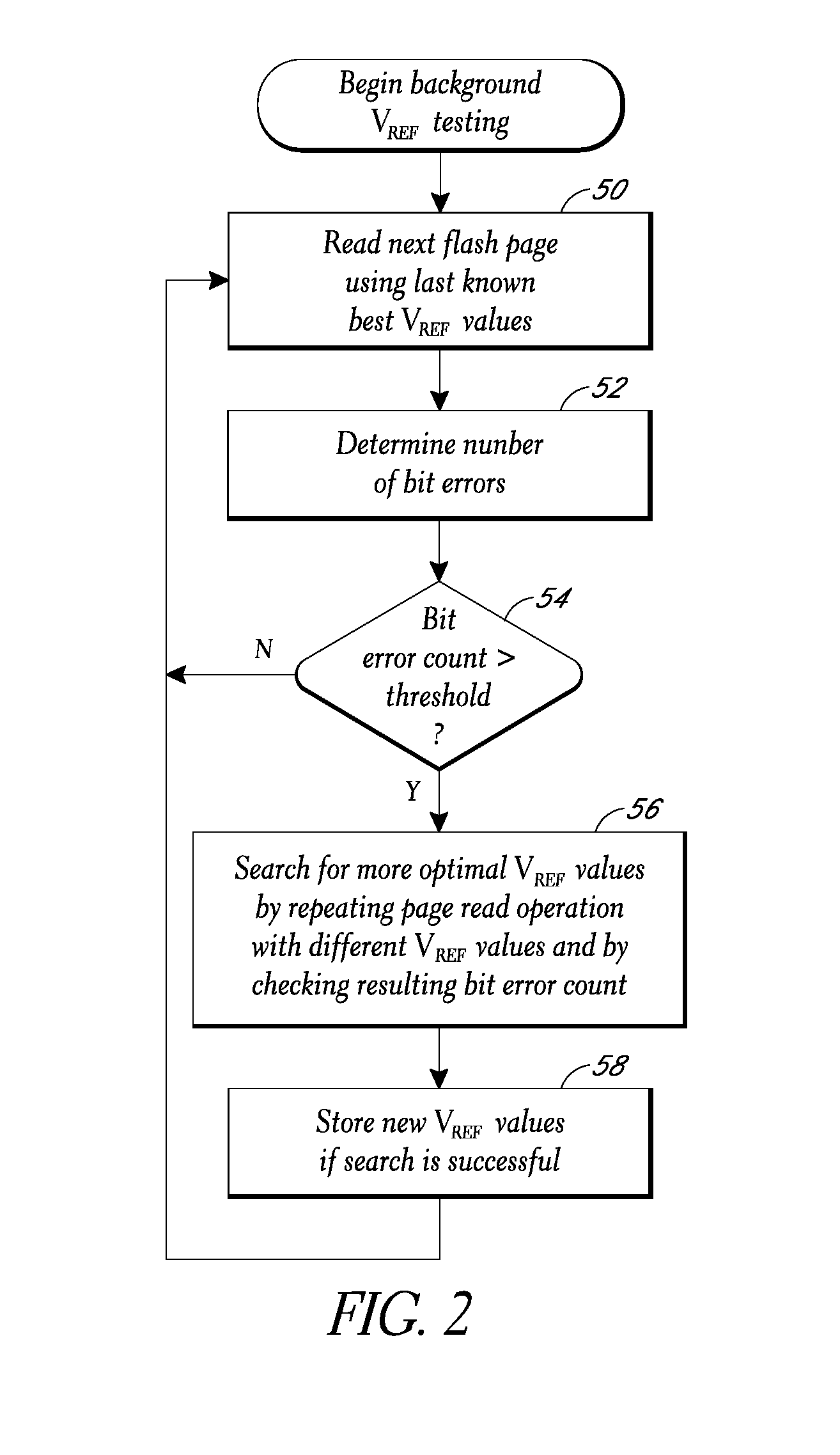

Background selection of voltage reference values for performing memory read operations

A storage subsystem implements a background process for selecting voltage reference values to use for reading data from a non-volatile memory array, such as an array of multi-level cell (MLC) flash memory. The process involves performing background read operations using specific sets of voltage reference values while monitoring the resulting bit error counts. The selected voltage reference values for specific pages or other blocks of the array are stored in a table. Read operations requested by a host system are executed using the corresponding voltage reference values specified by the table.

Owner:WESTERN DIGITAL TECH INC

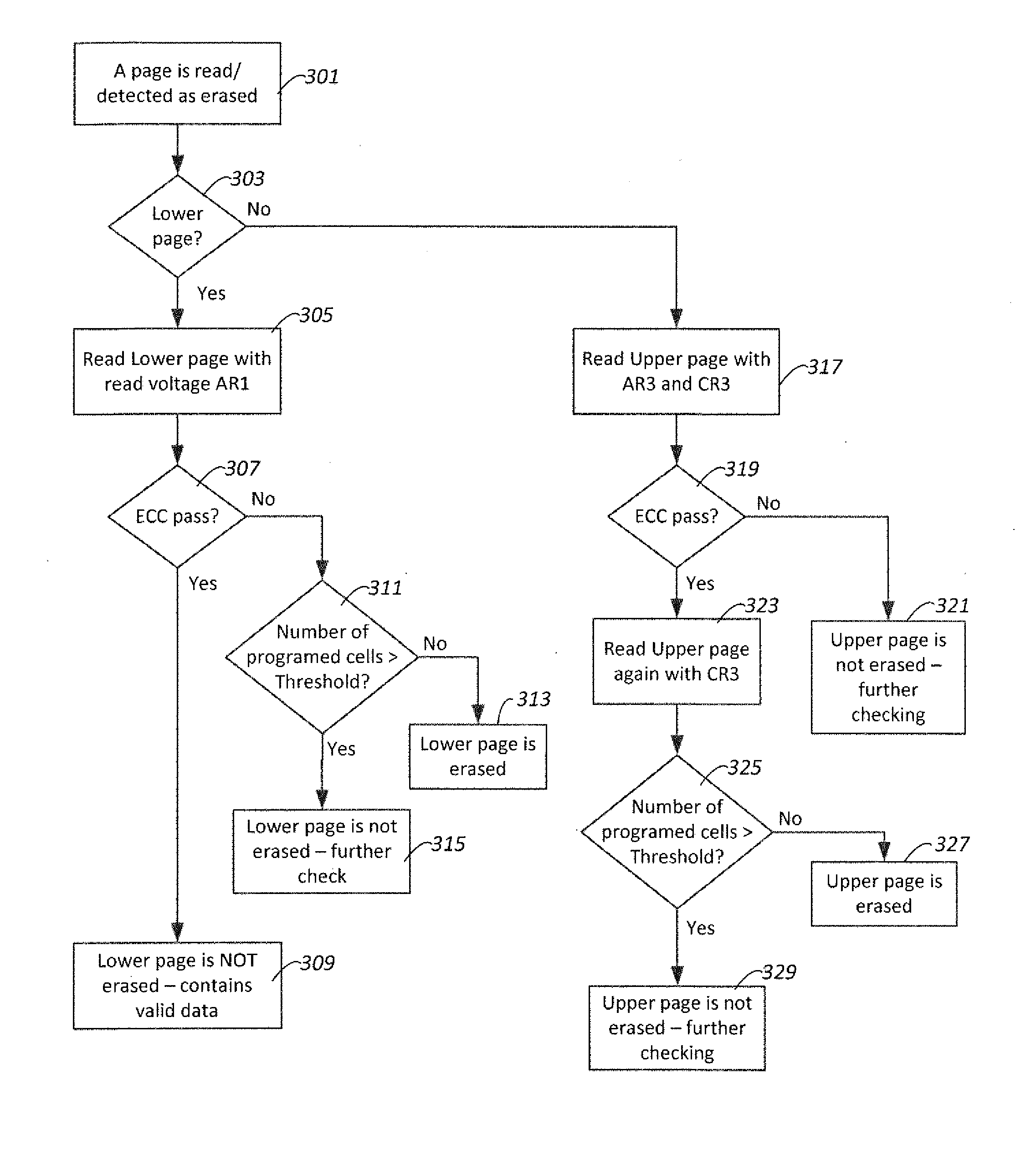

Erased Page Confirmation in Multilevel Memory

ActiveUS20140075252A1Error detection/correctionRead-only memoriesMultilevel memoryTwo-step verification

In a multi-level cell memory array, a flag that indicates that a logical page is unwritten is subject to a two-step verification. In a first verification step, the logical page is read, and ECC decoding is applied. If the first verification step indicates that the logical page is unwritten, then a second verification step counts the number of cells that are not in an unwritten condition.

Owner:SANDISK TECH LLC

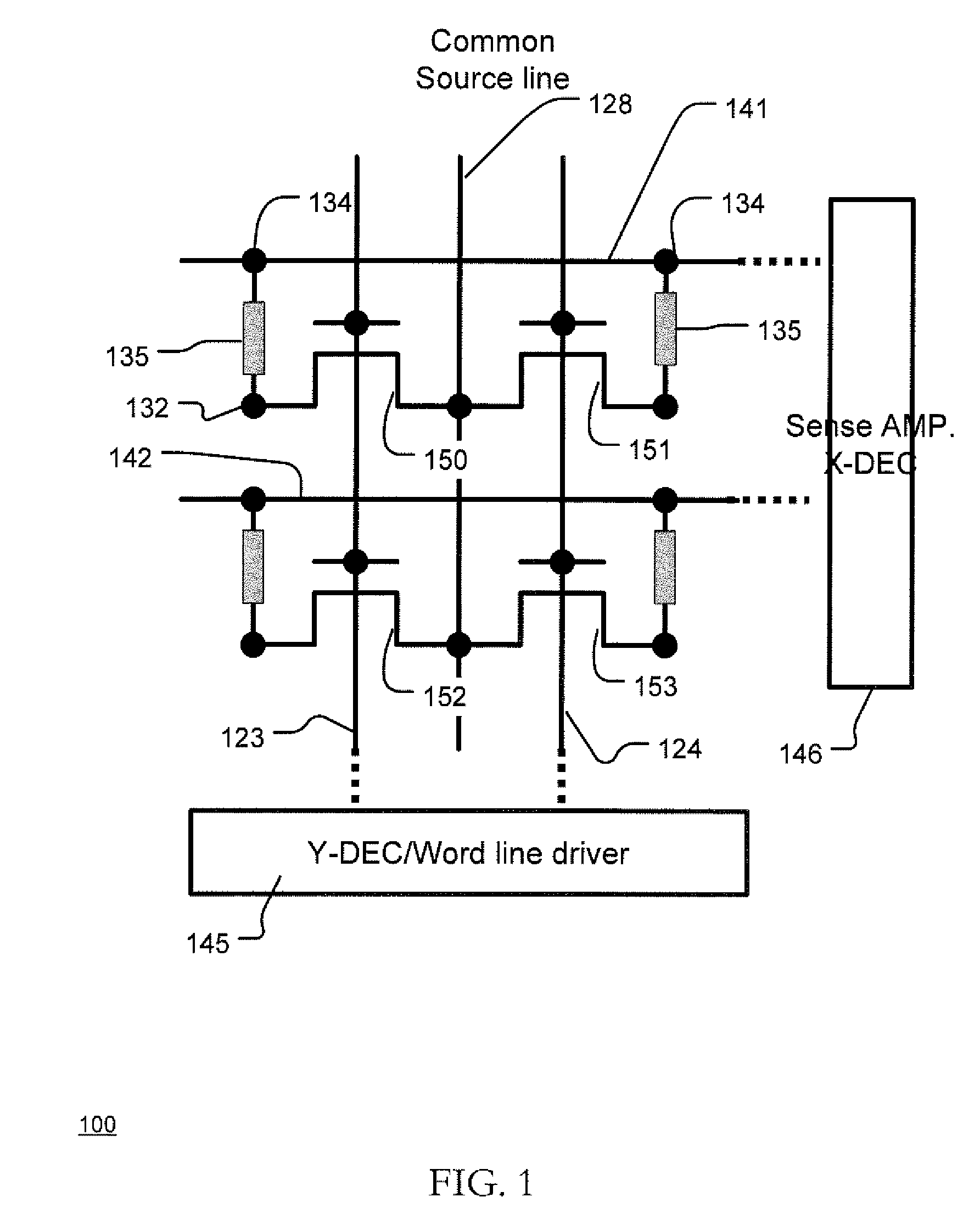

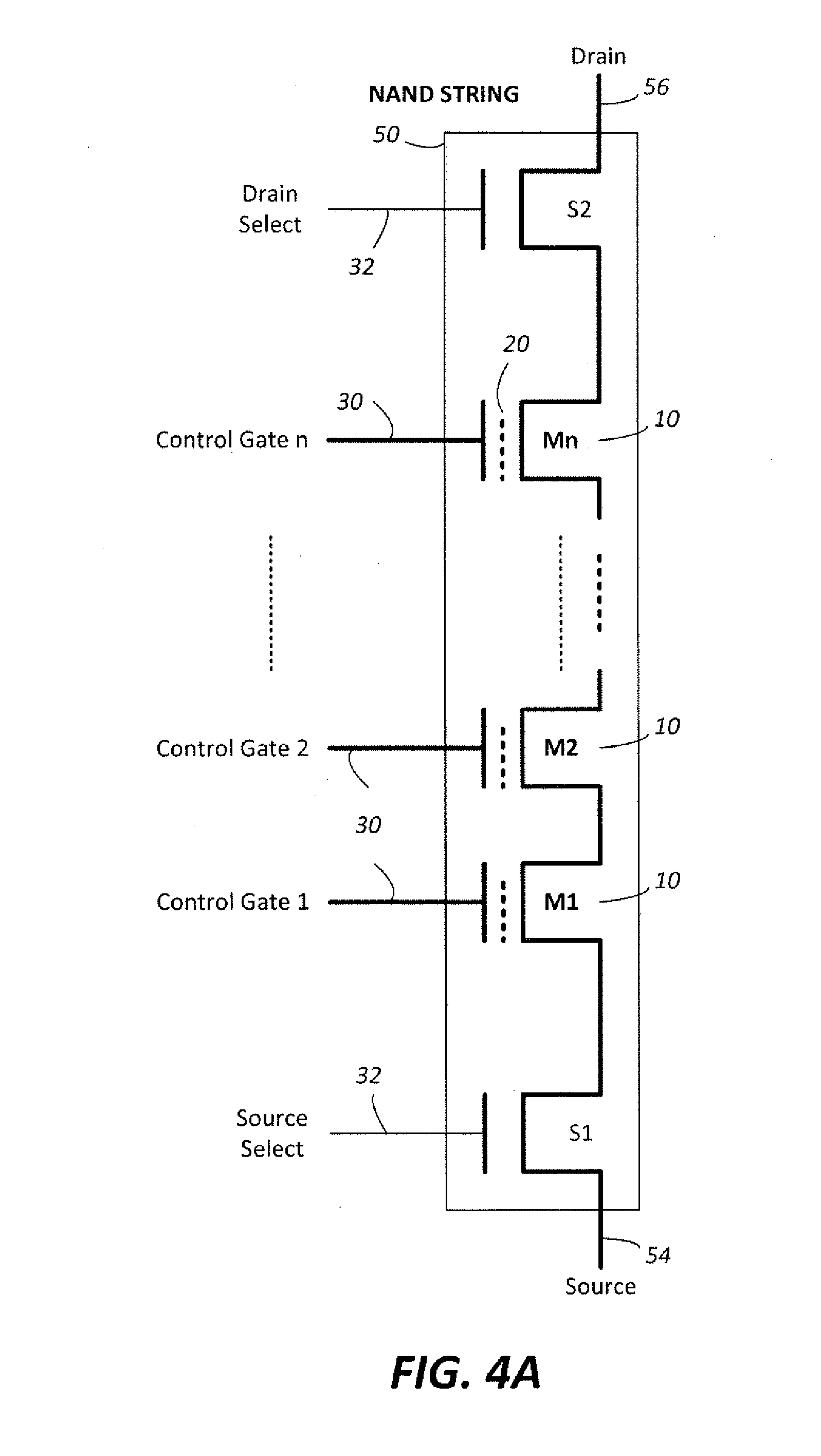

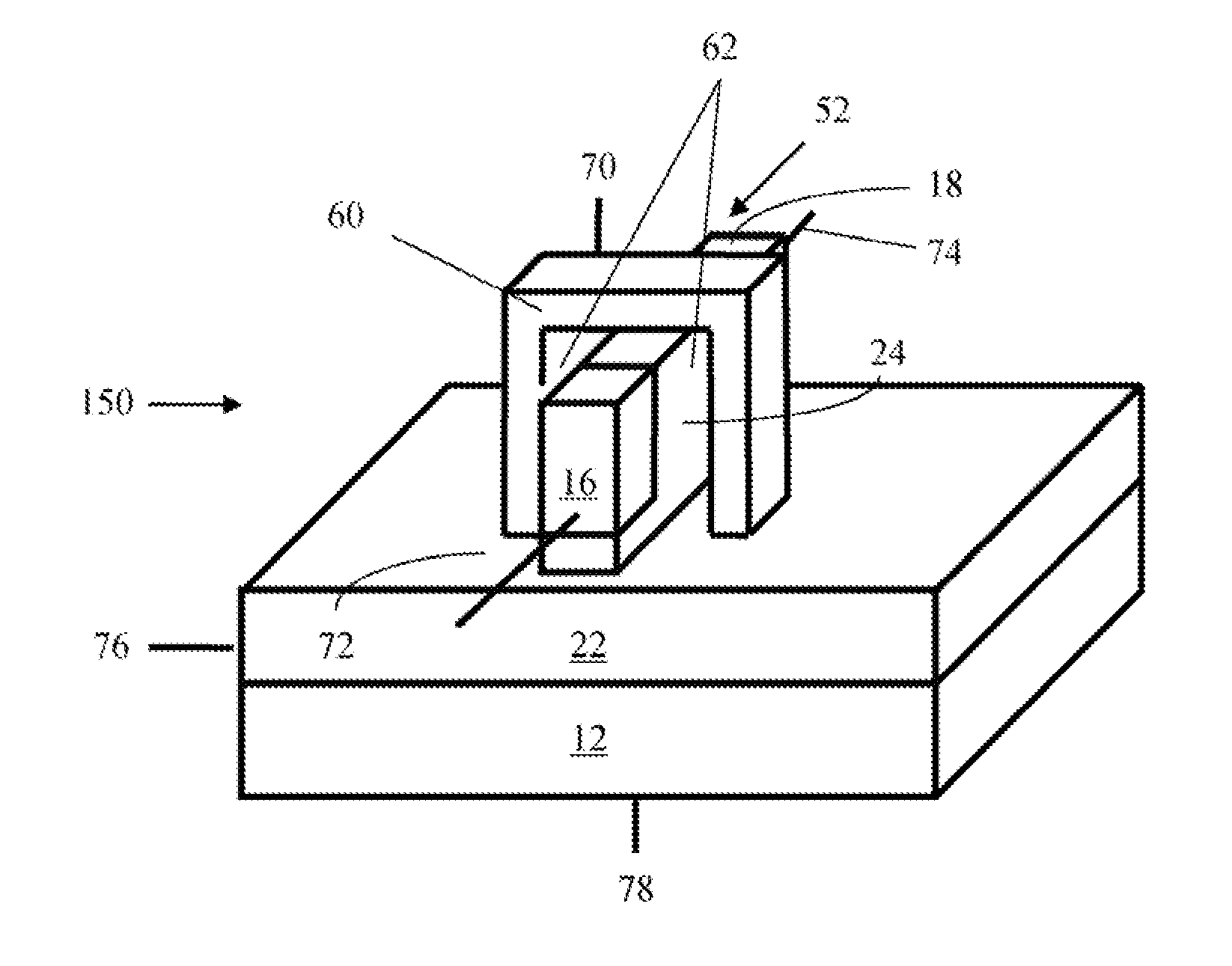

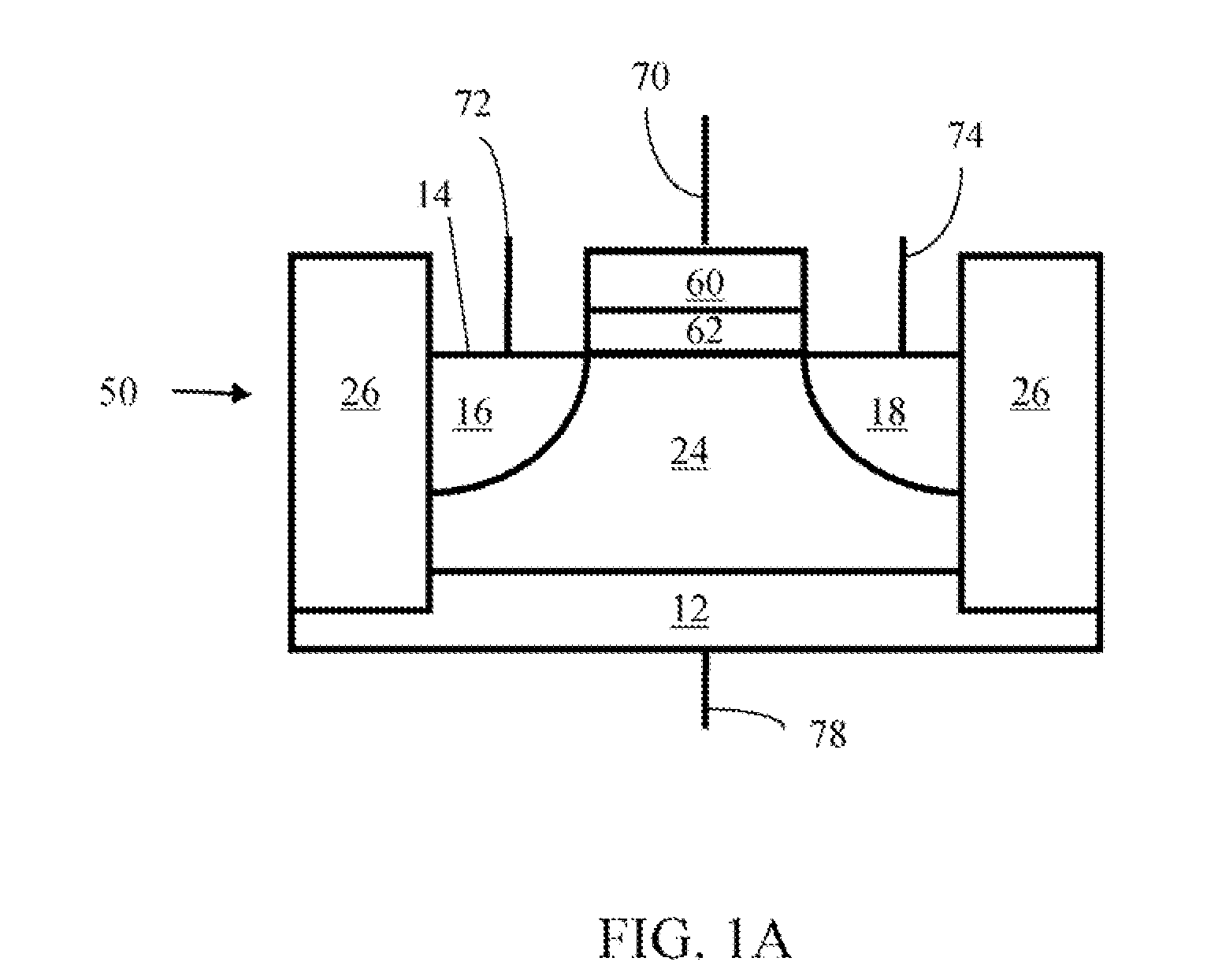

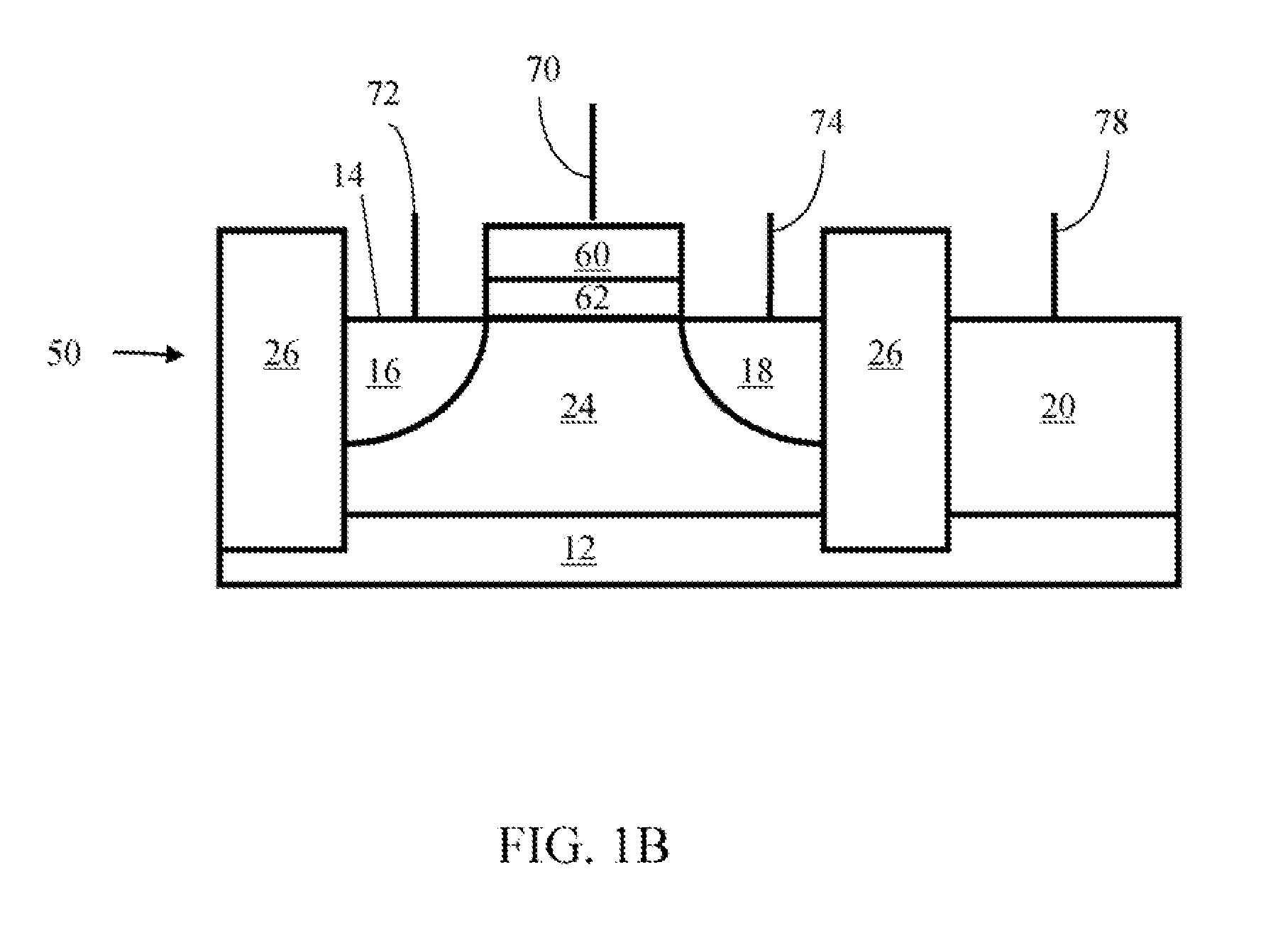

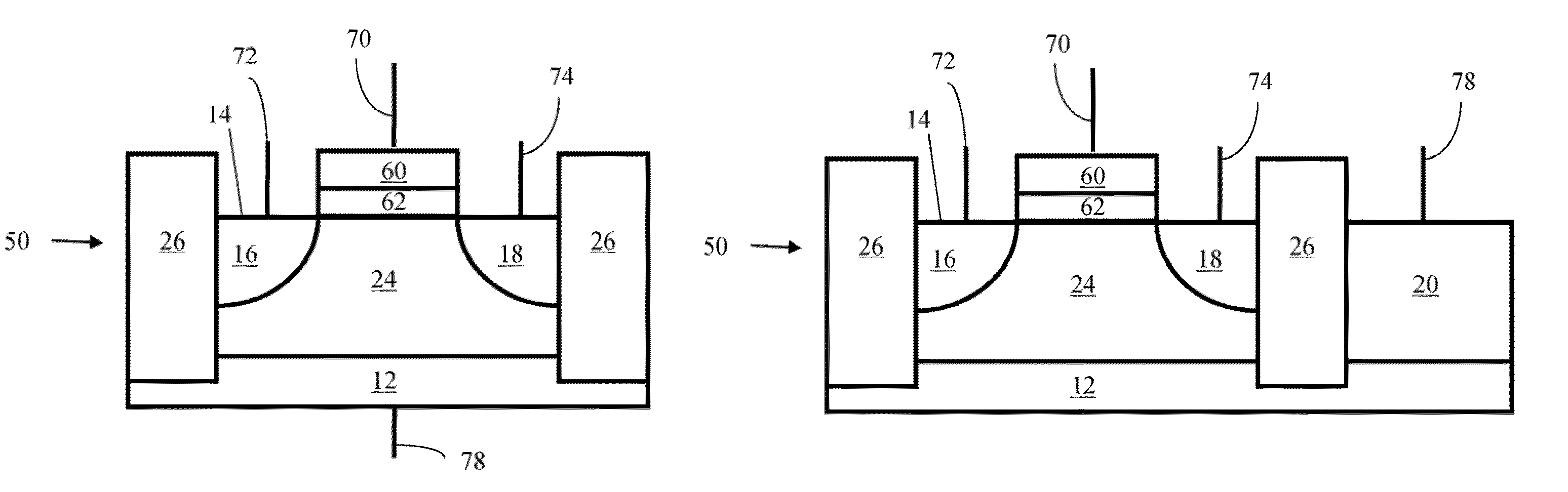

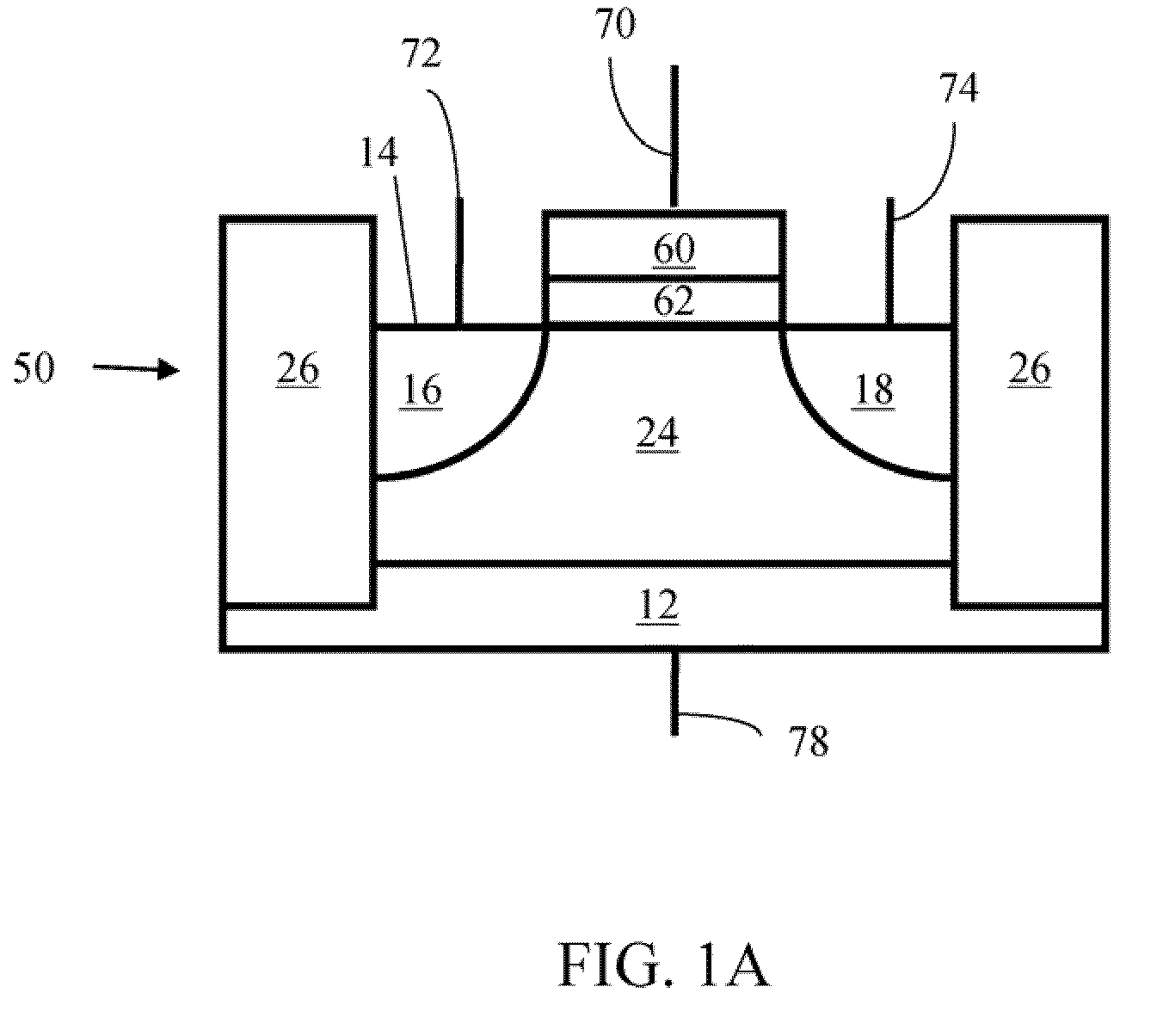

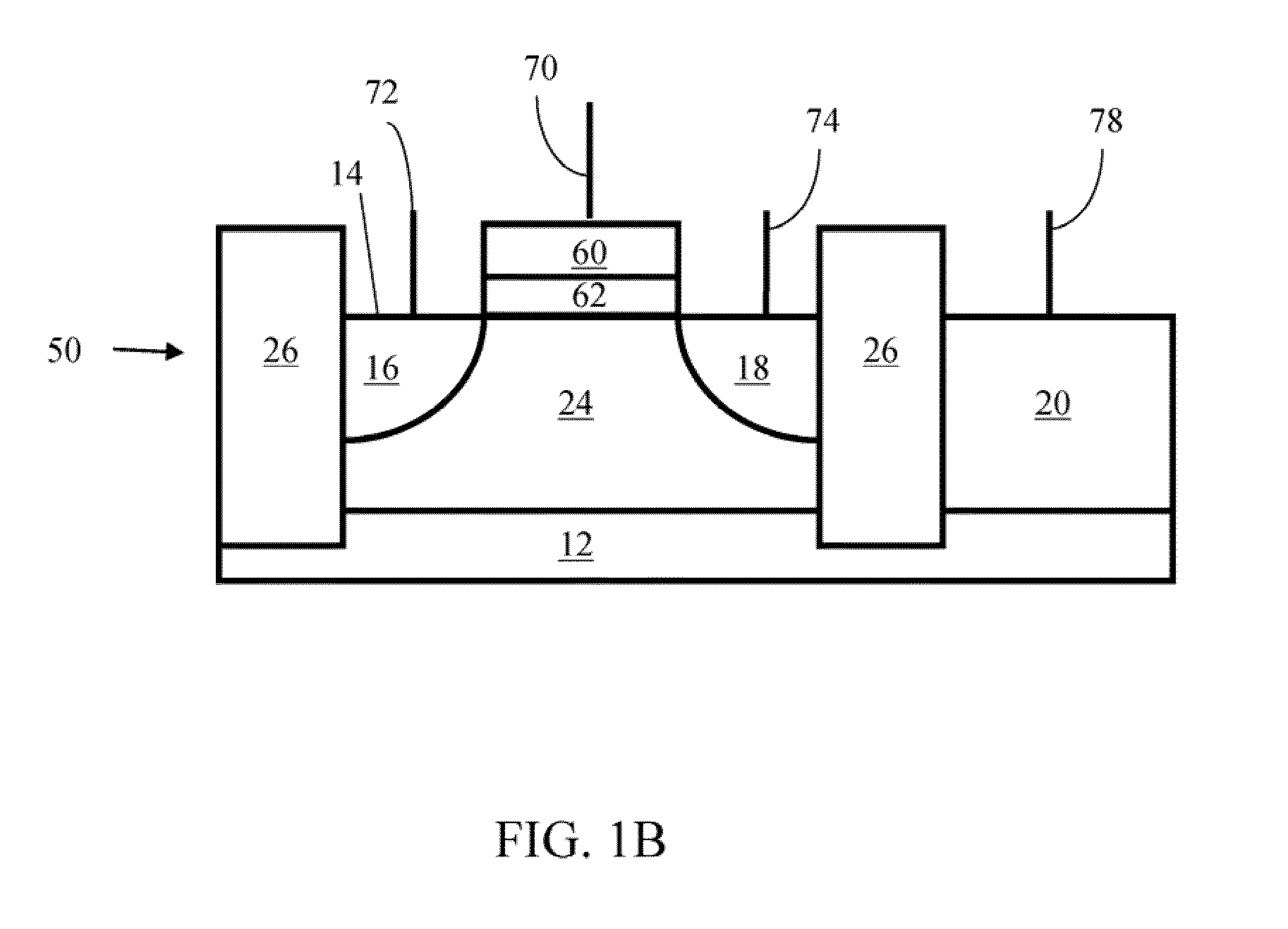

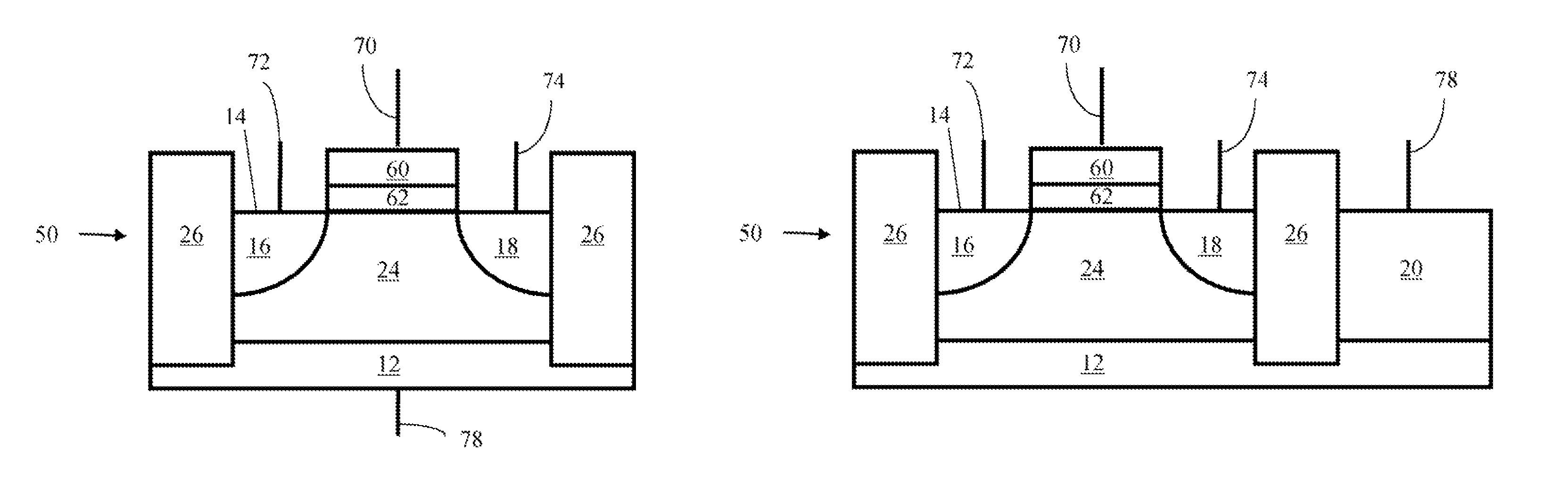

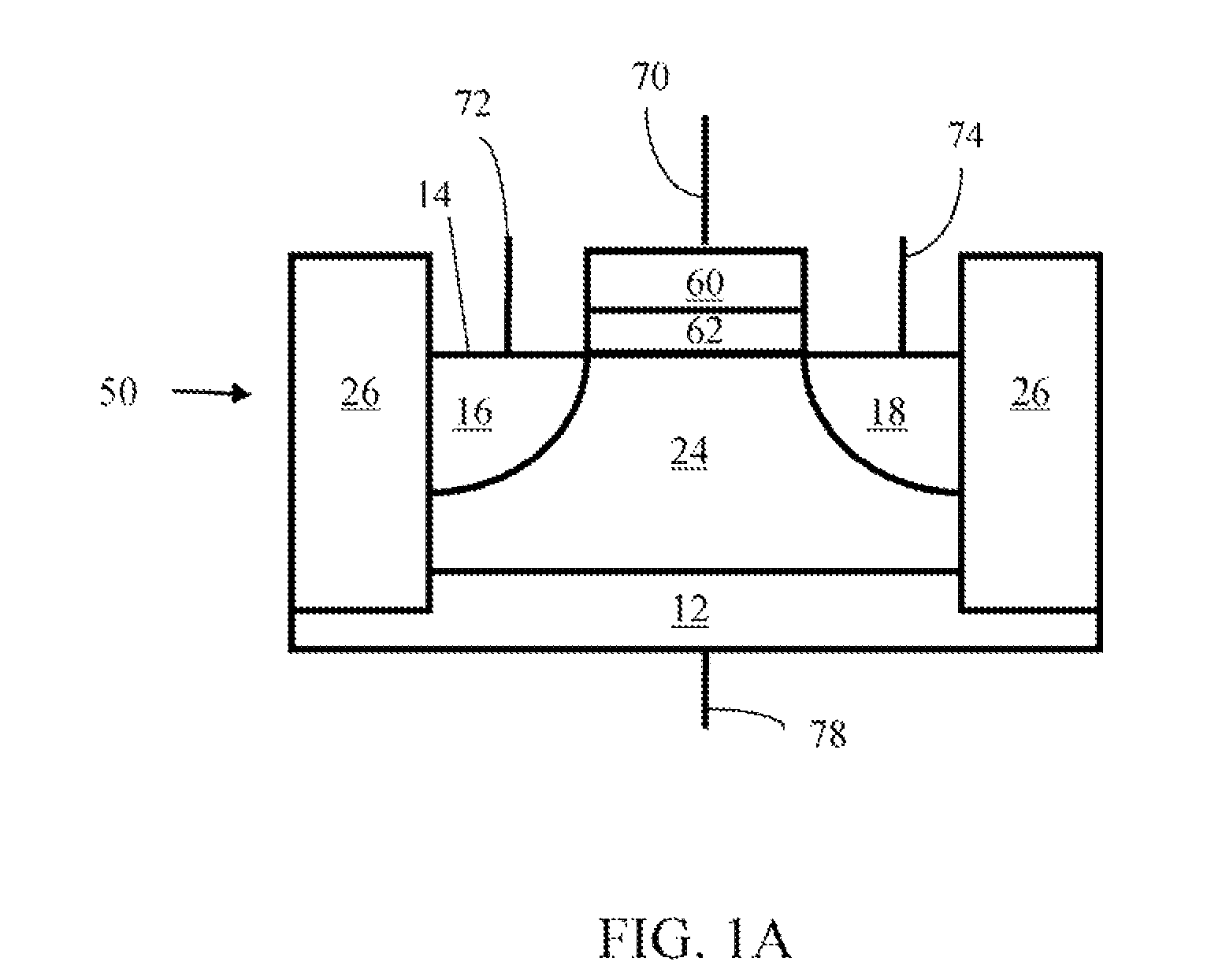

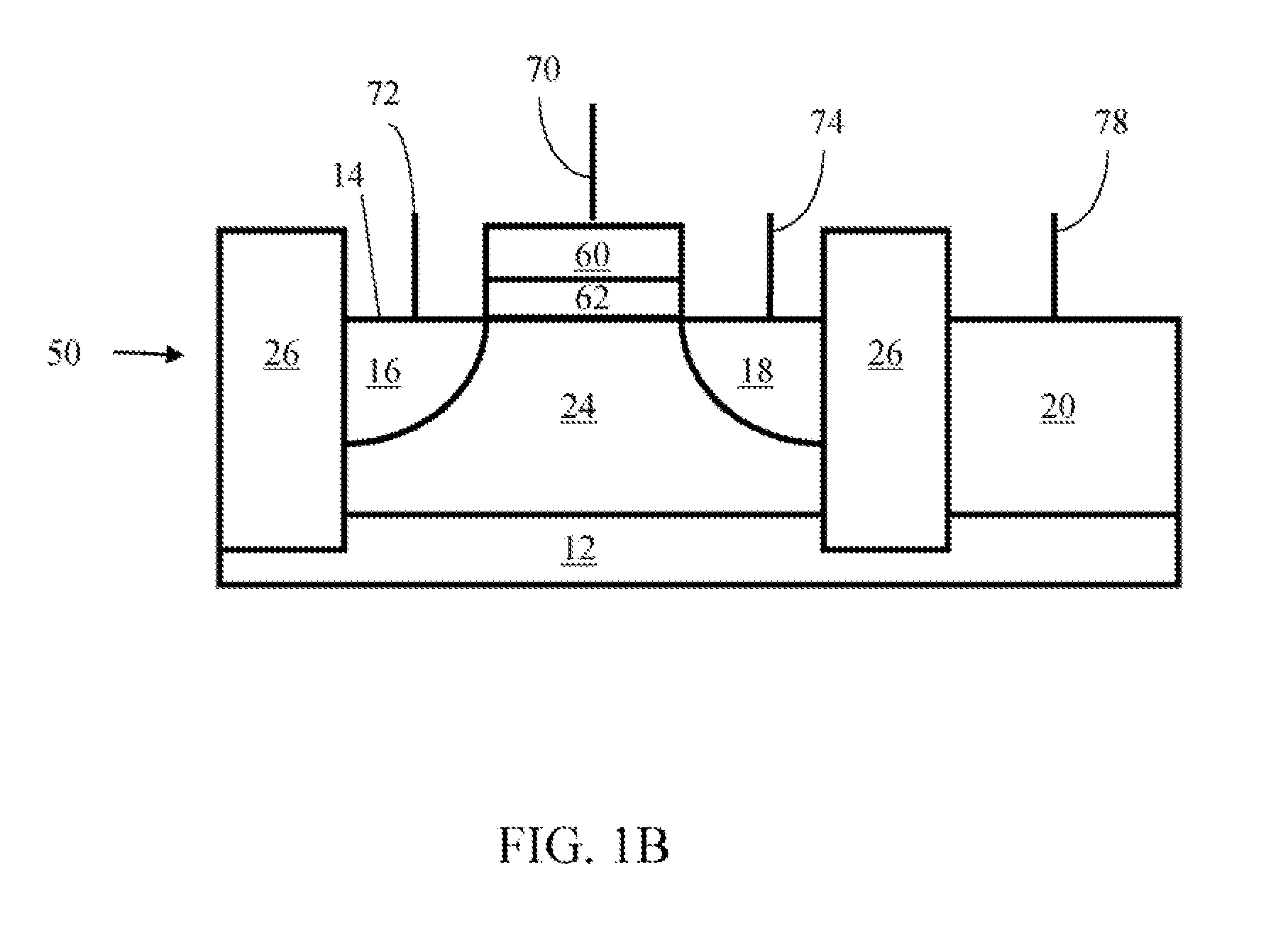

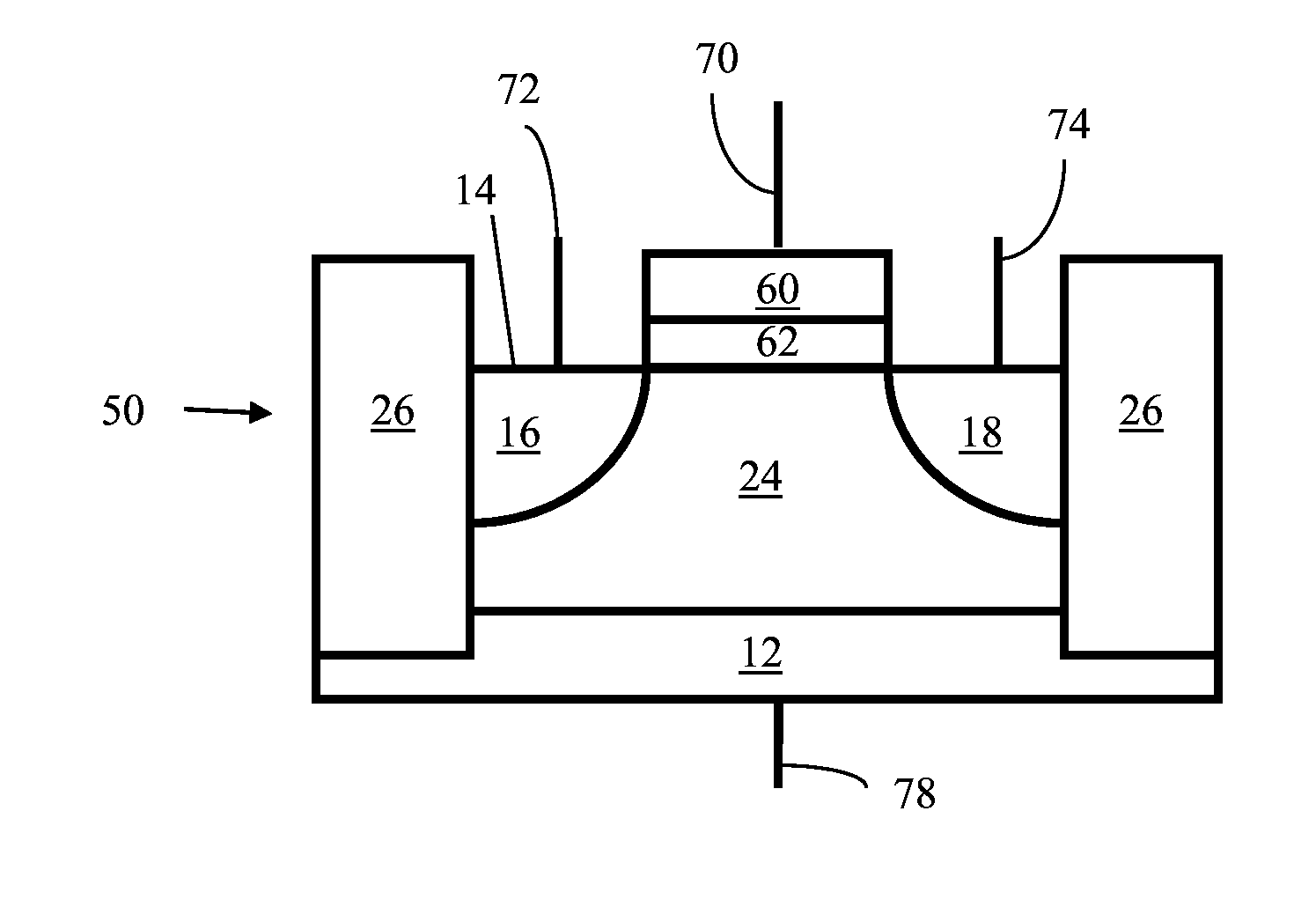

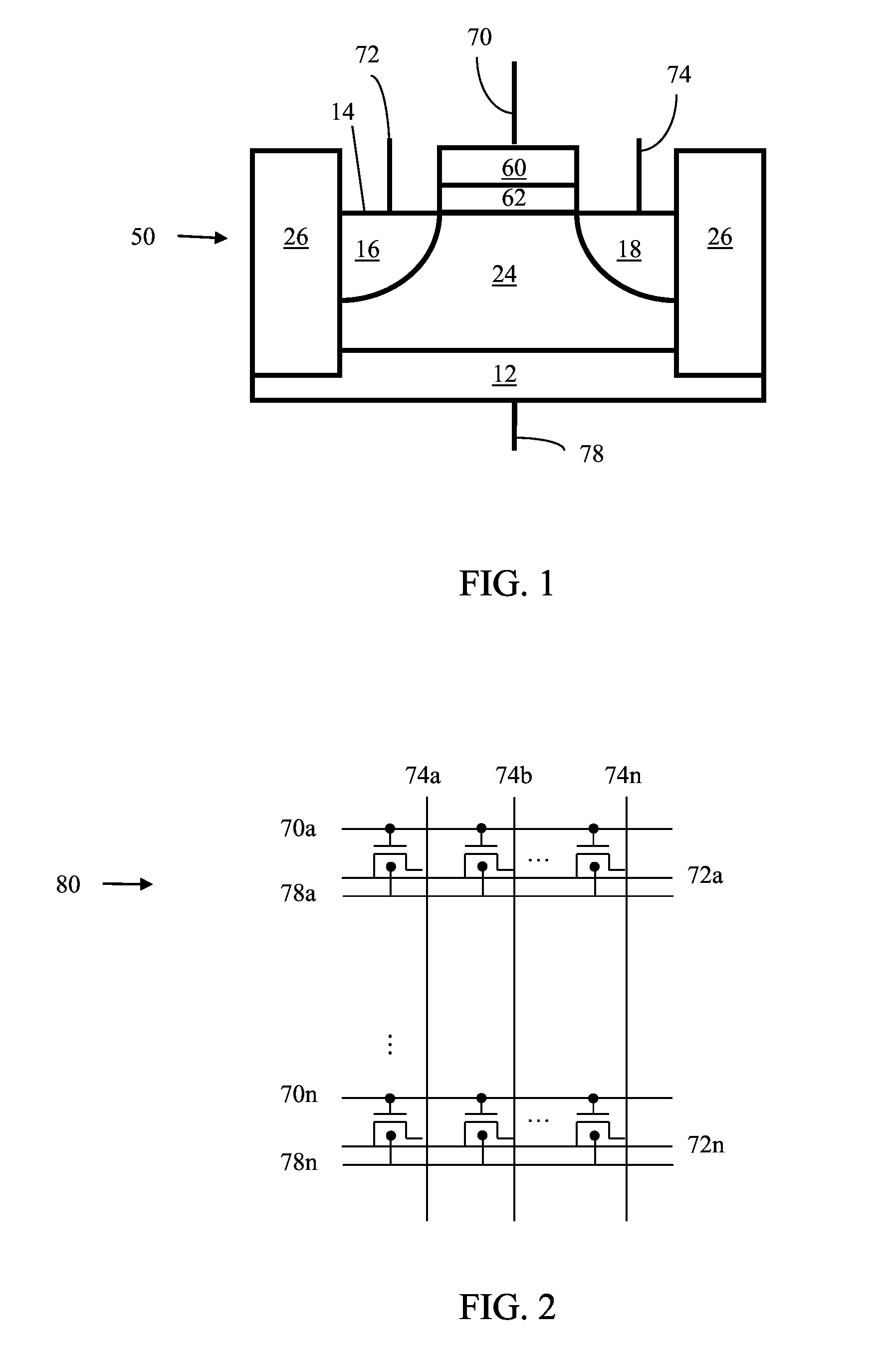

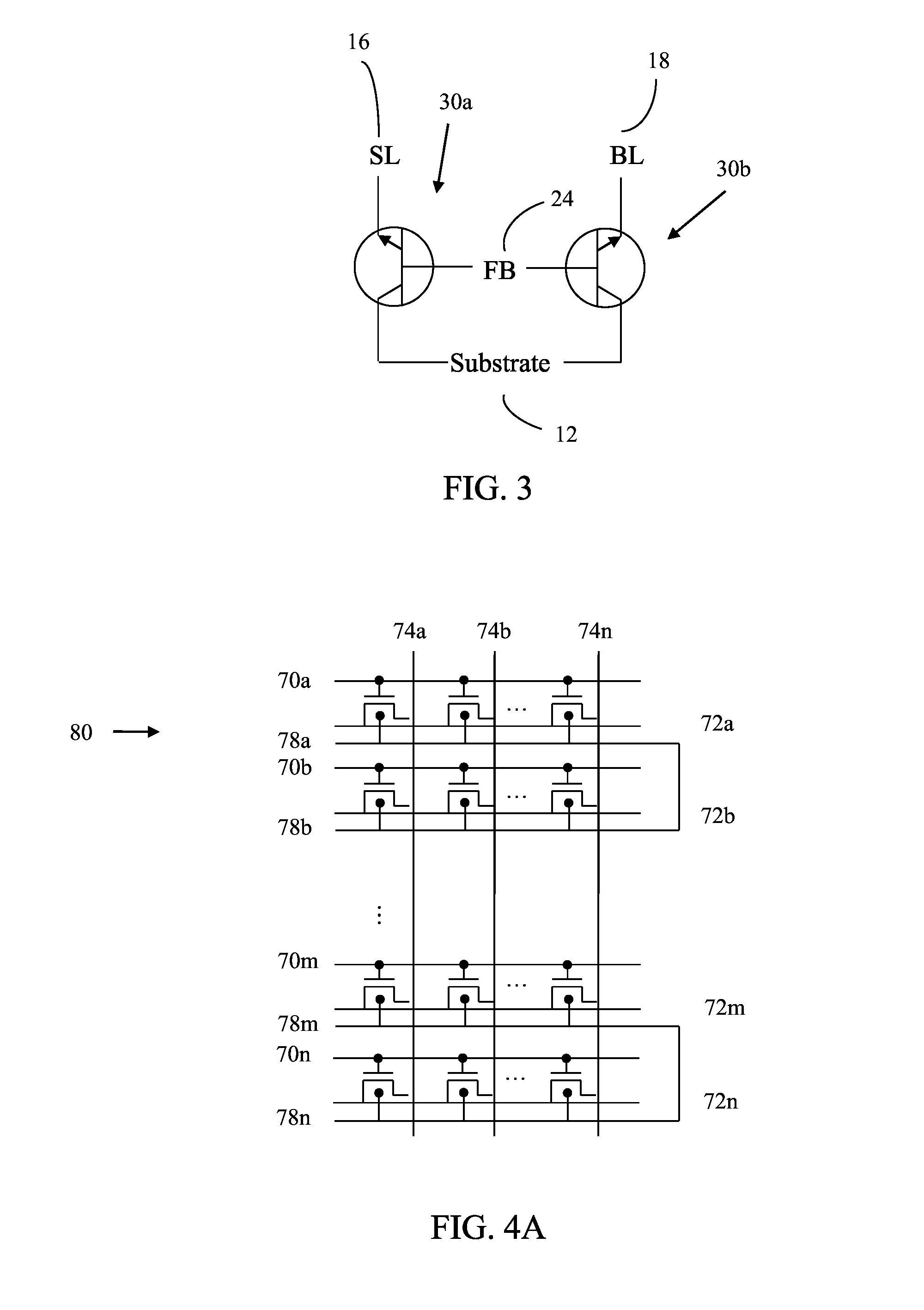

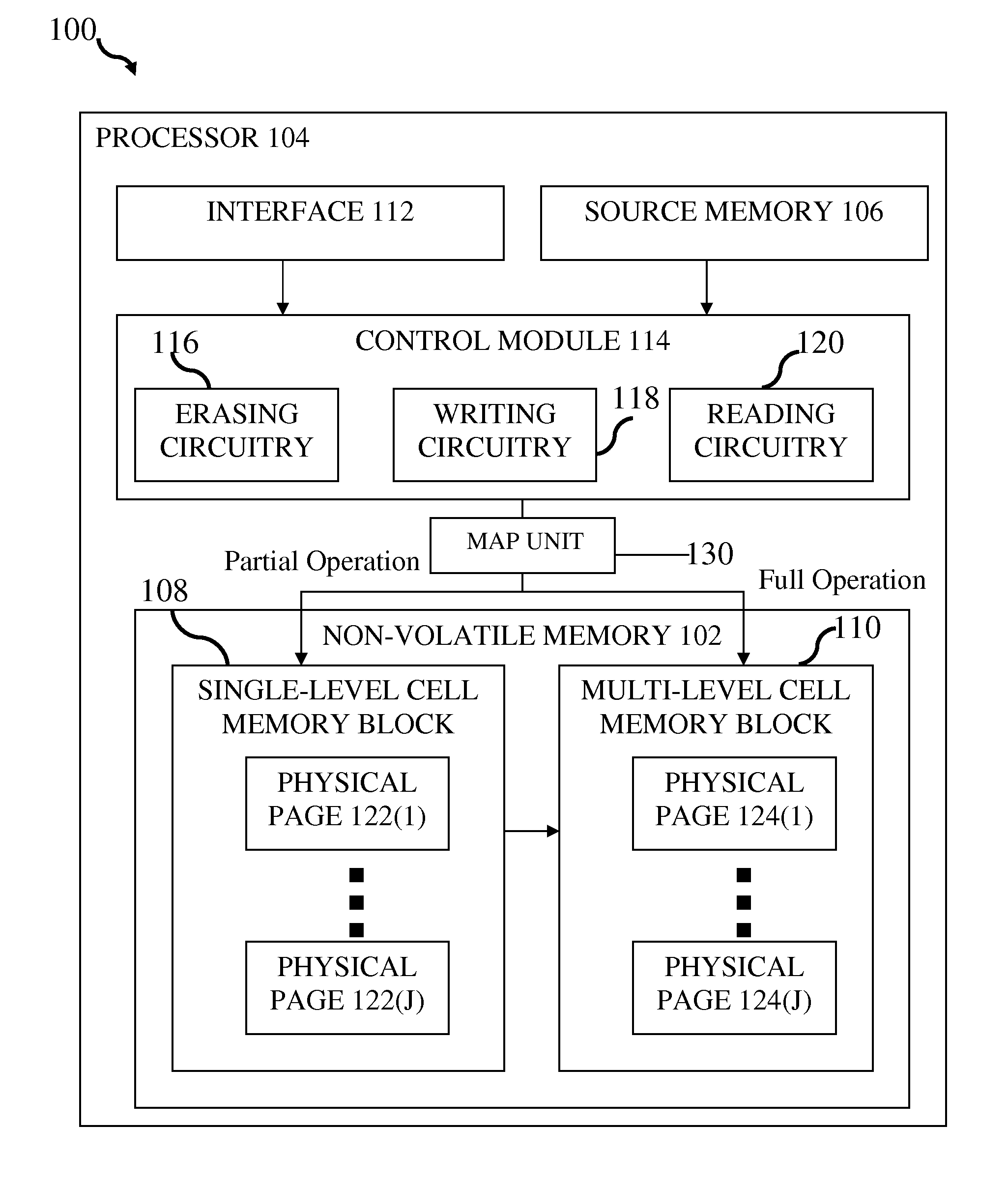

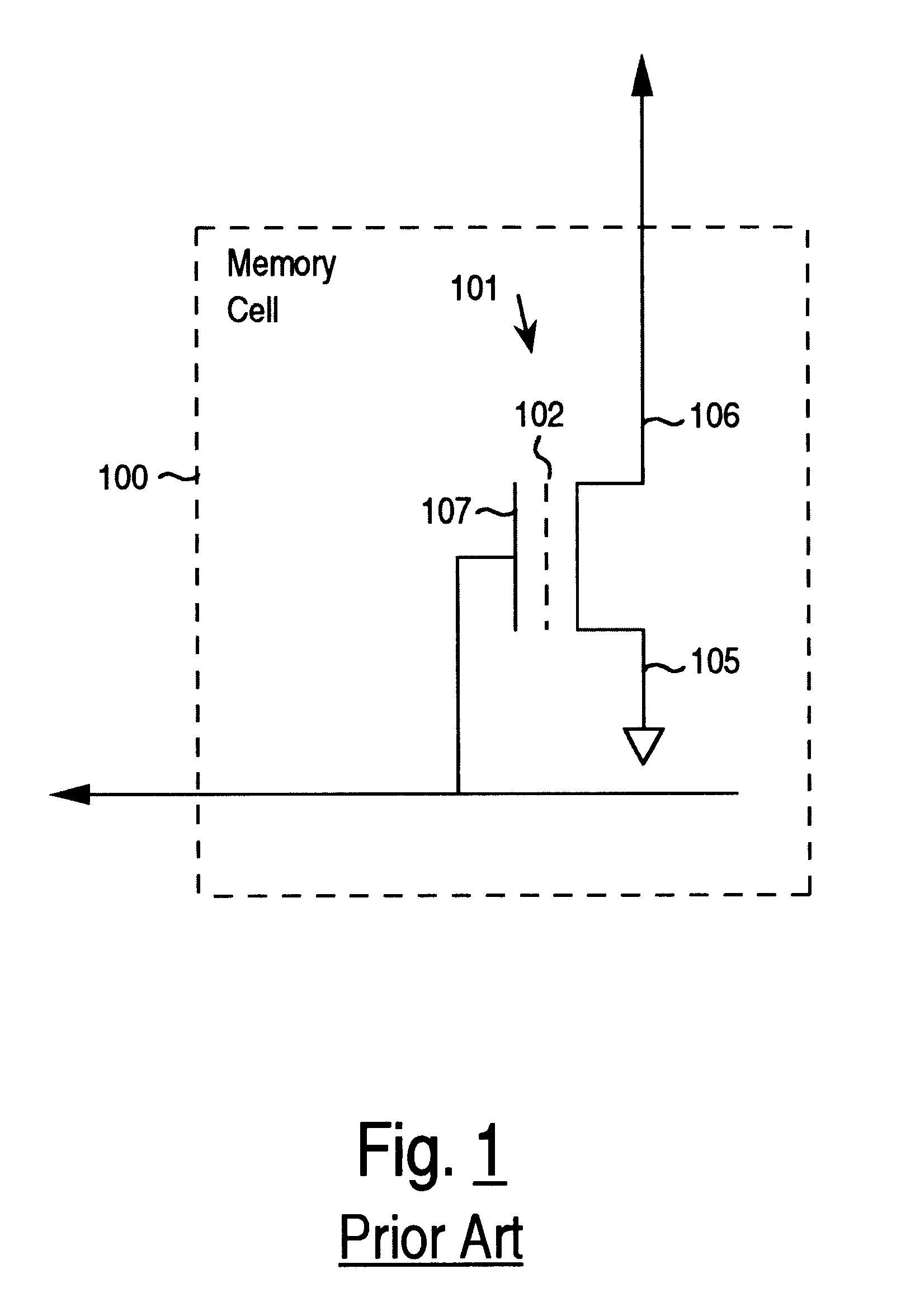

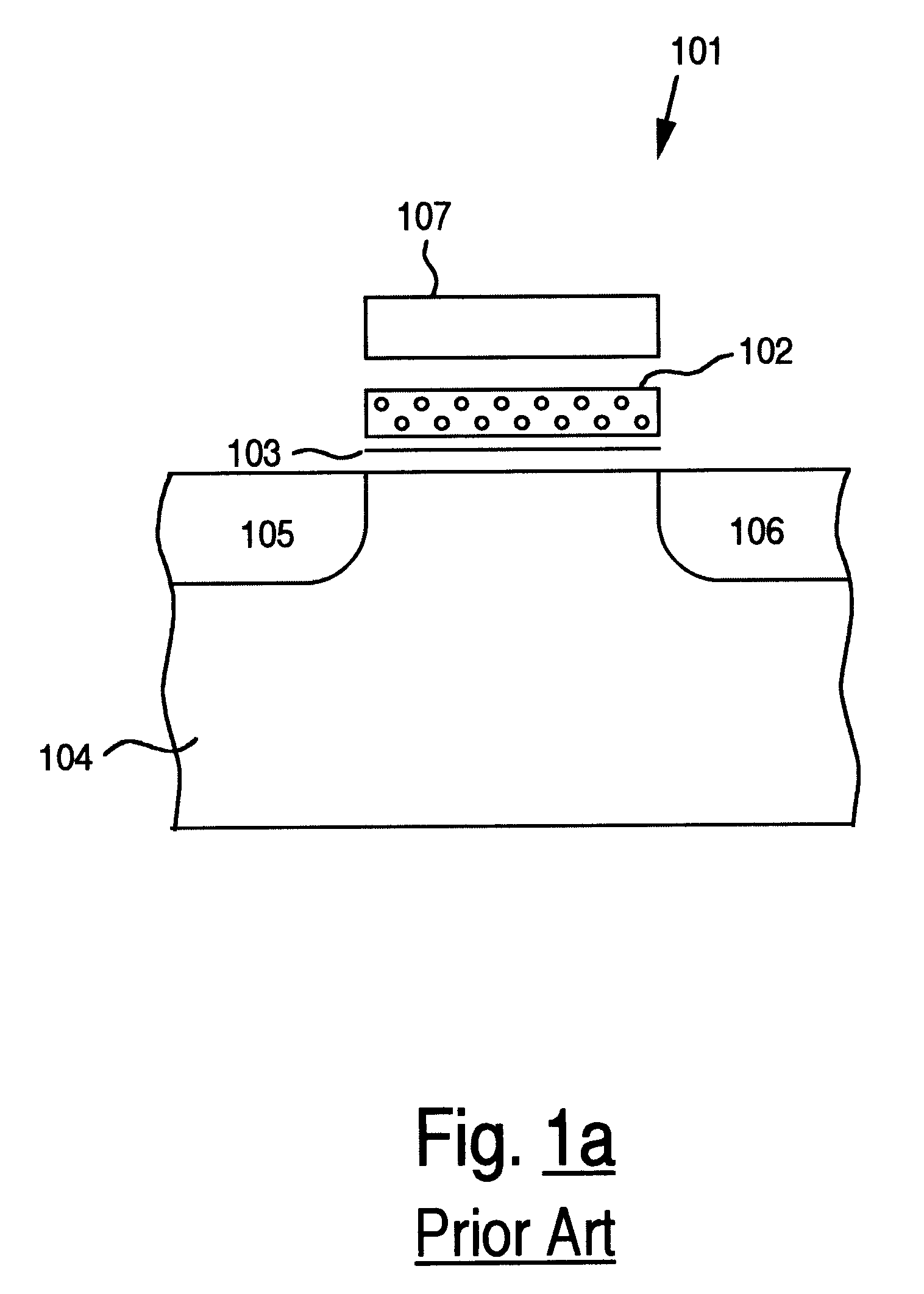

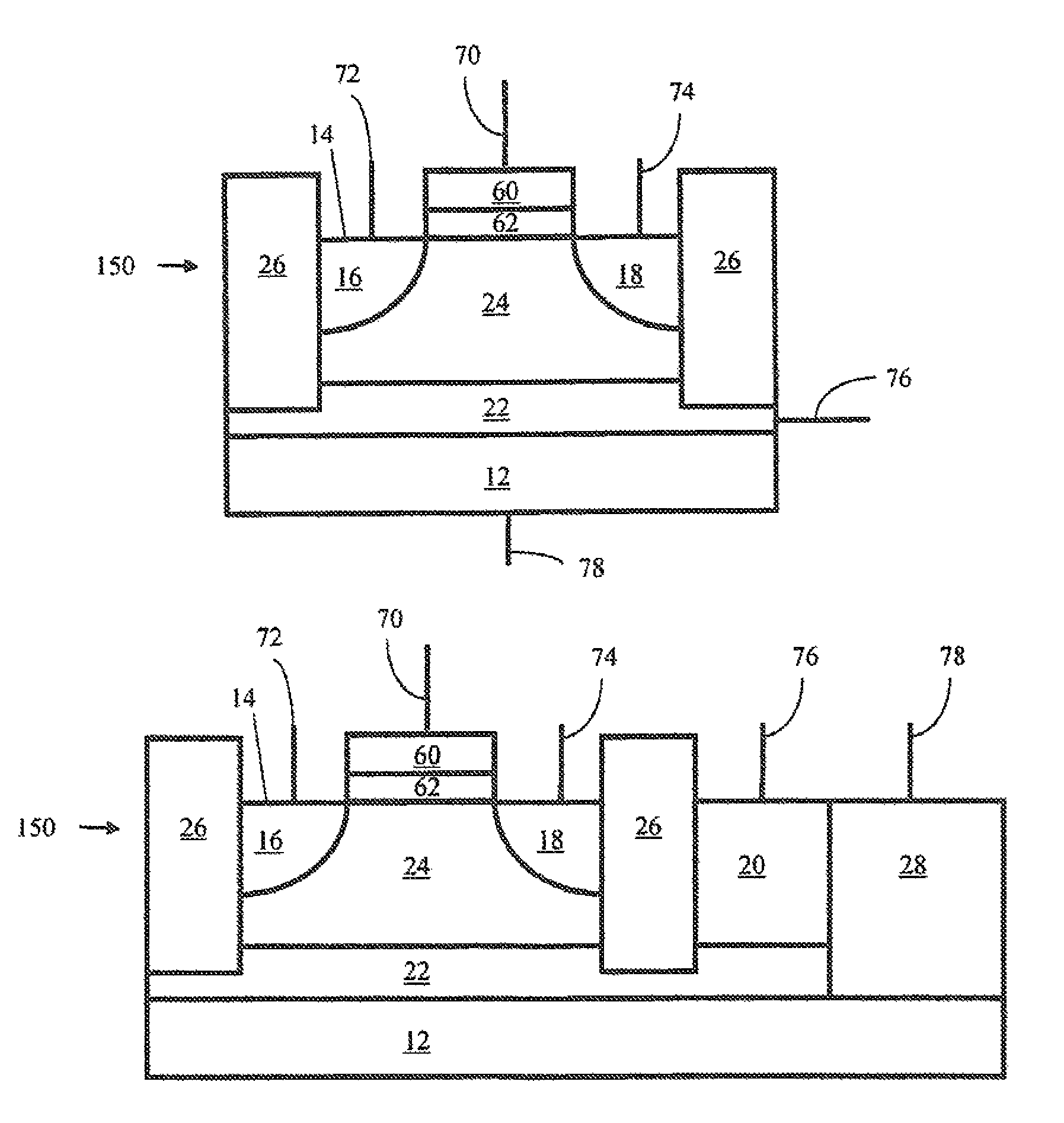

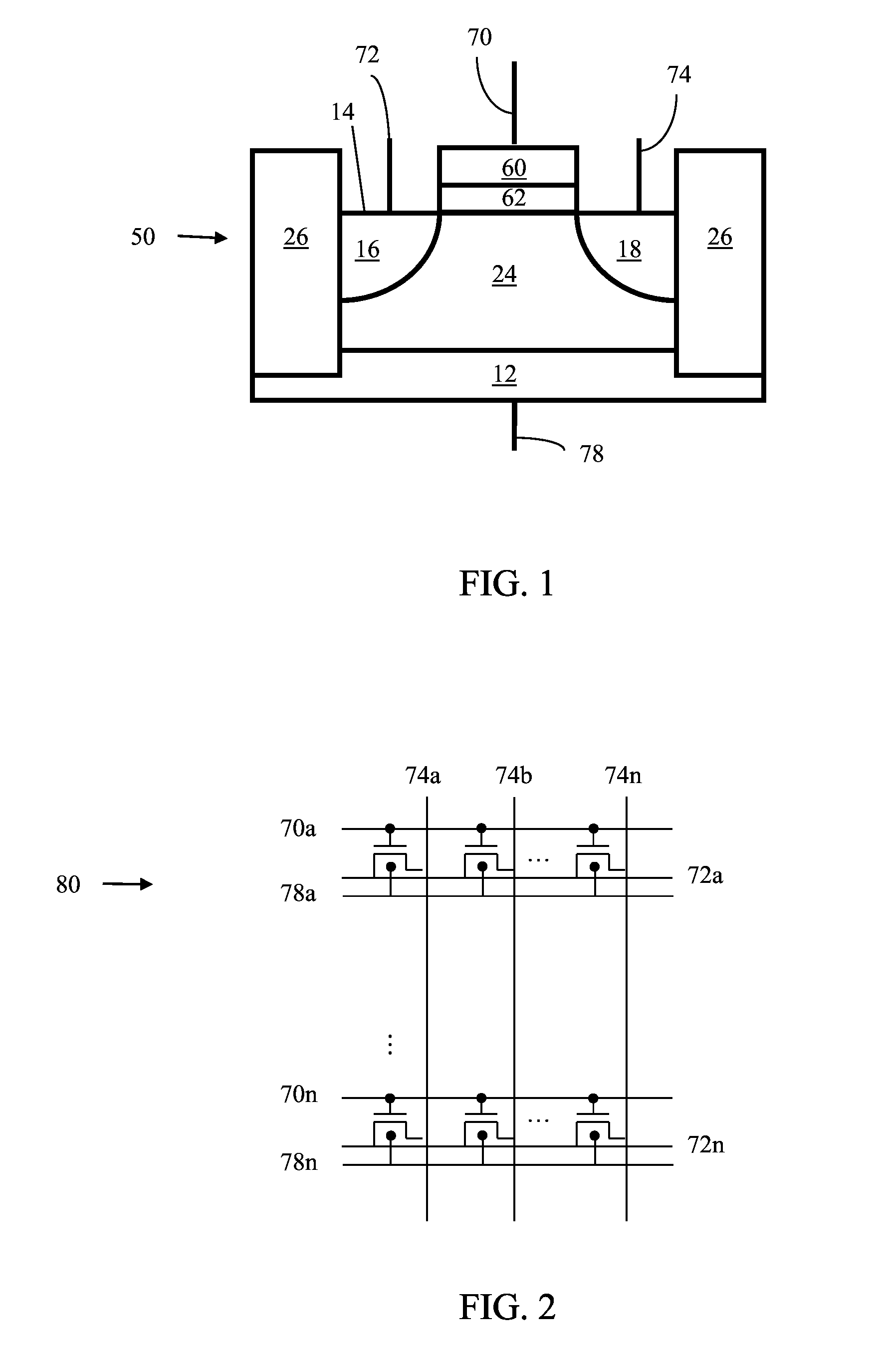

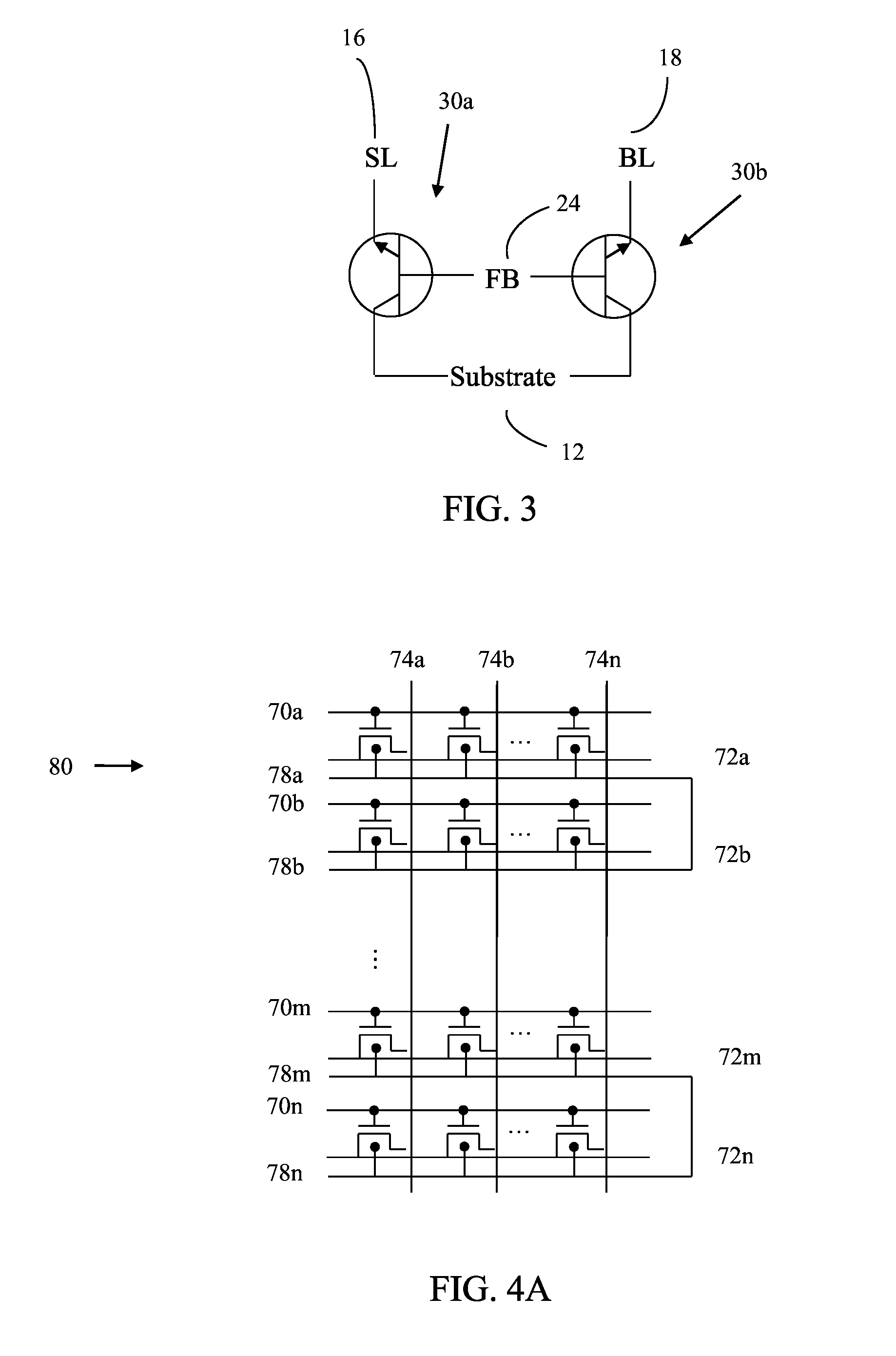

Semiconductor memory having electrically floating body transistor

ActiveUS20120012915A1Large memory windowLarger memory windowTransistorSolid-state devicesCharge injectionBack bias

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; a gate positioned between said first and second regions; and a back-bias region configured to inject charge into or extract charge out of said floating body region to maintain said state of the memory cell. Application of back bias to the back bias region offsets charge leakage out of the floating body and performs a holding operation on the cell. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device.

Owner:ZENO SEMICON

Semiconductor memory having electrically floating body transistor

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; a gate positioned between said first and second regions; and a back-bias region configured to inject charge into or extract charge out of said floating body region to maintain said state of the memory cell. Application of back bias to the back bias region offsets charge leakage out of the floating body and performs a holding operation on the cell. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device.

Owner:ZENO SEMICON

Semiconductor memory having electrically floating body transistor

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; a gate positioned between said first and second regions; and a back-bias region configured to inject charge into or extract charge out of said floating body region to maintain said state of the memory cell. Application of back bias to the back bias region offsets charge leakage out of the floating body and performs a holding operation on the cell. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device.

Owner:ZENO SEMICON

Semiconductor Memory Device Having Electrically Floating Body Transistor, Semiconductor Memory Device Having Both Volatile and Non-Volatile Functionality and Method of Operating

ActiveUS20130015517A1Larger memory windowReduce in quantityTransistorSolid-state devicesElectricityMulti-level cell

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; and a gate positioned between said first and second regions. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device. Methods of operating memory cells are also provided.

Owner:ZENO SEMICON

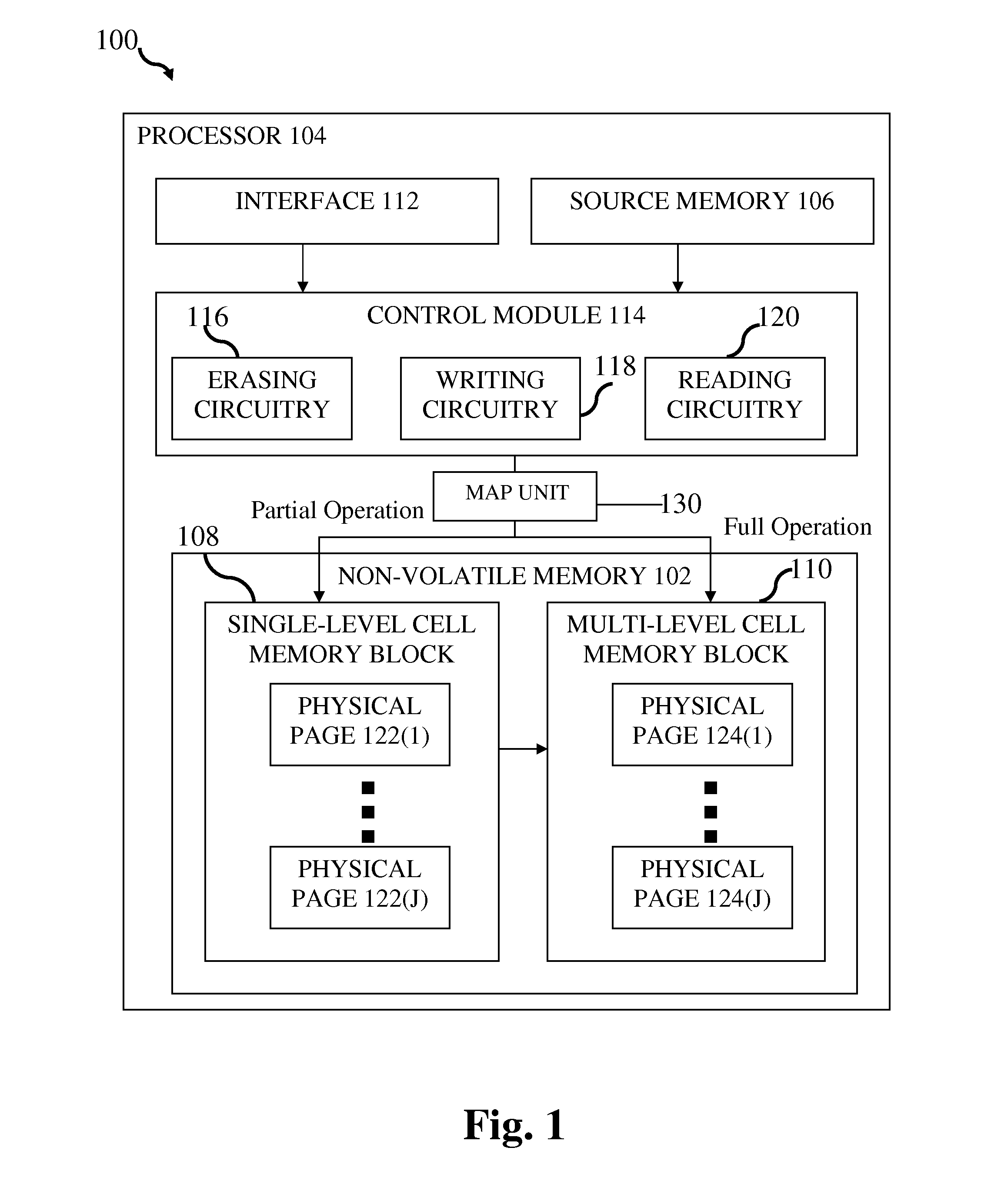

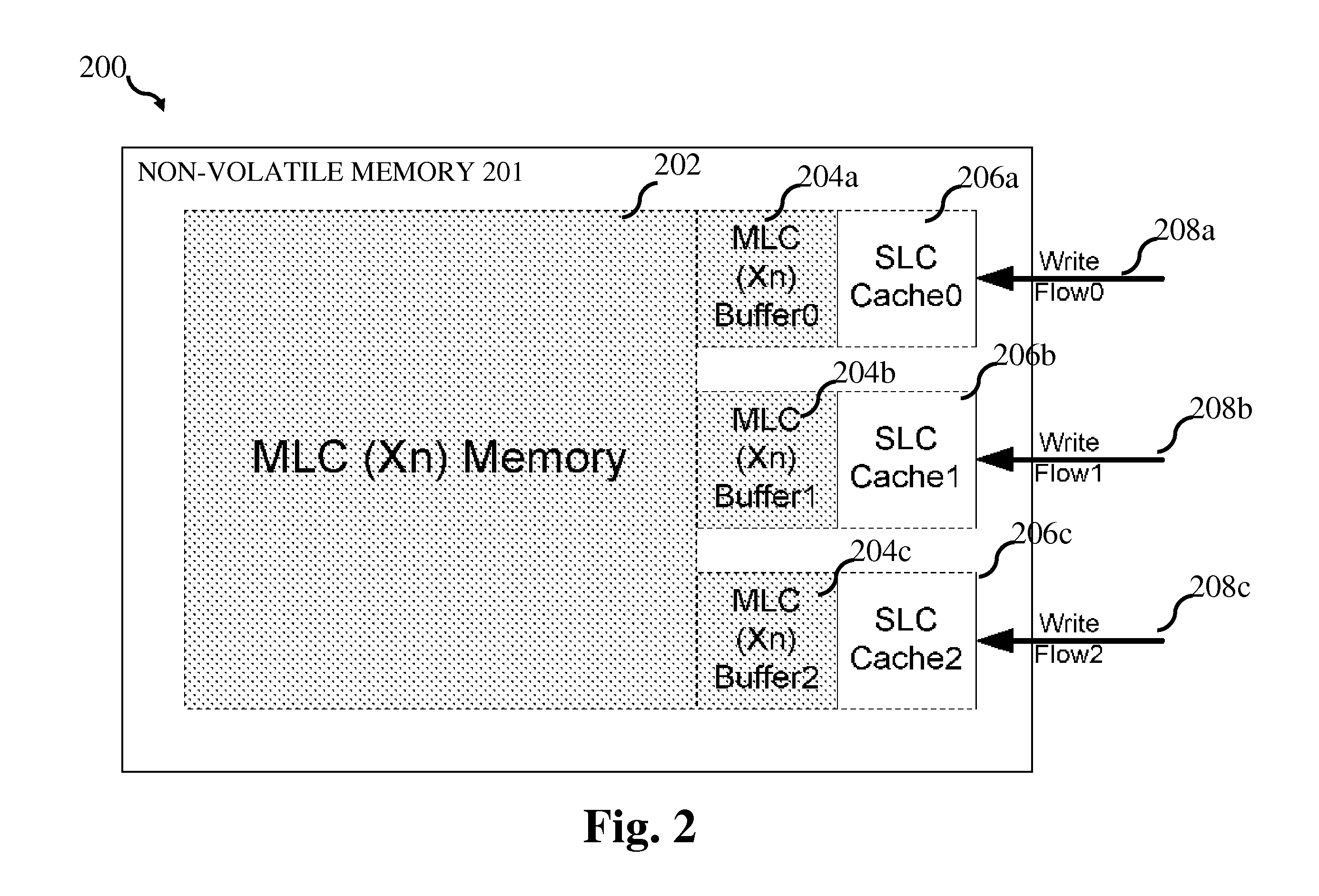

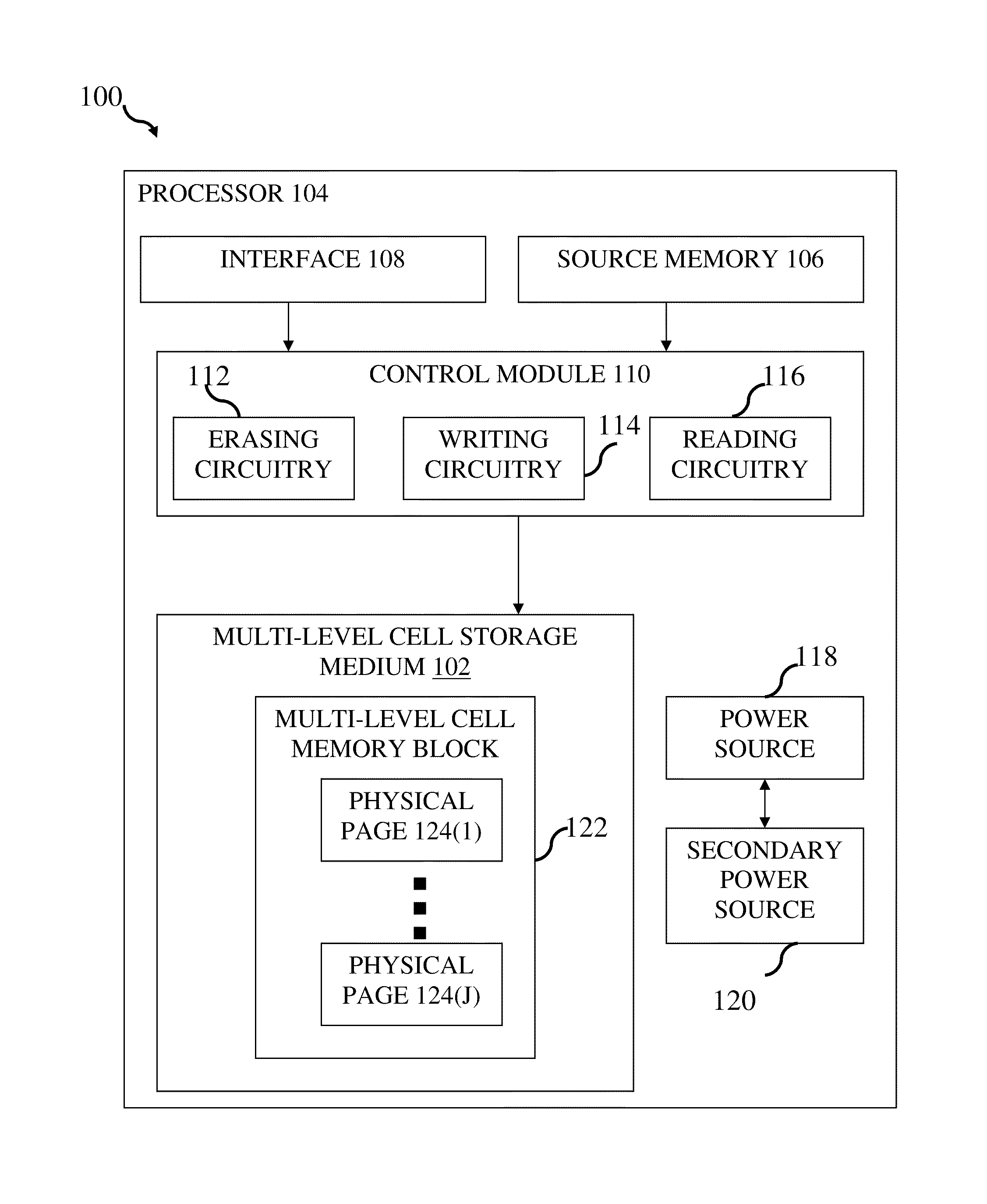

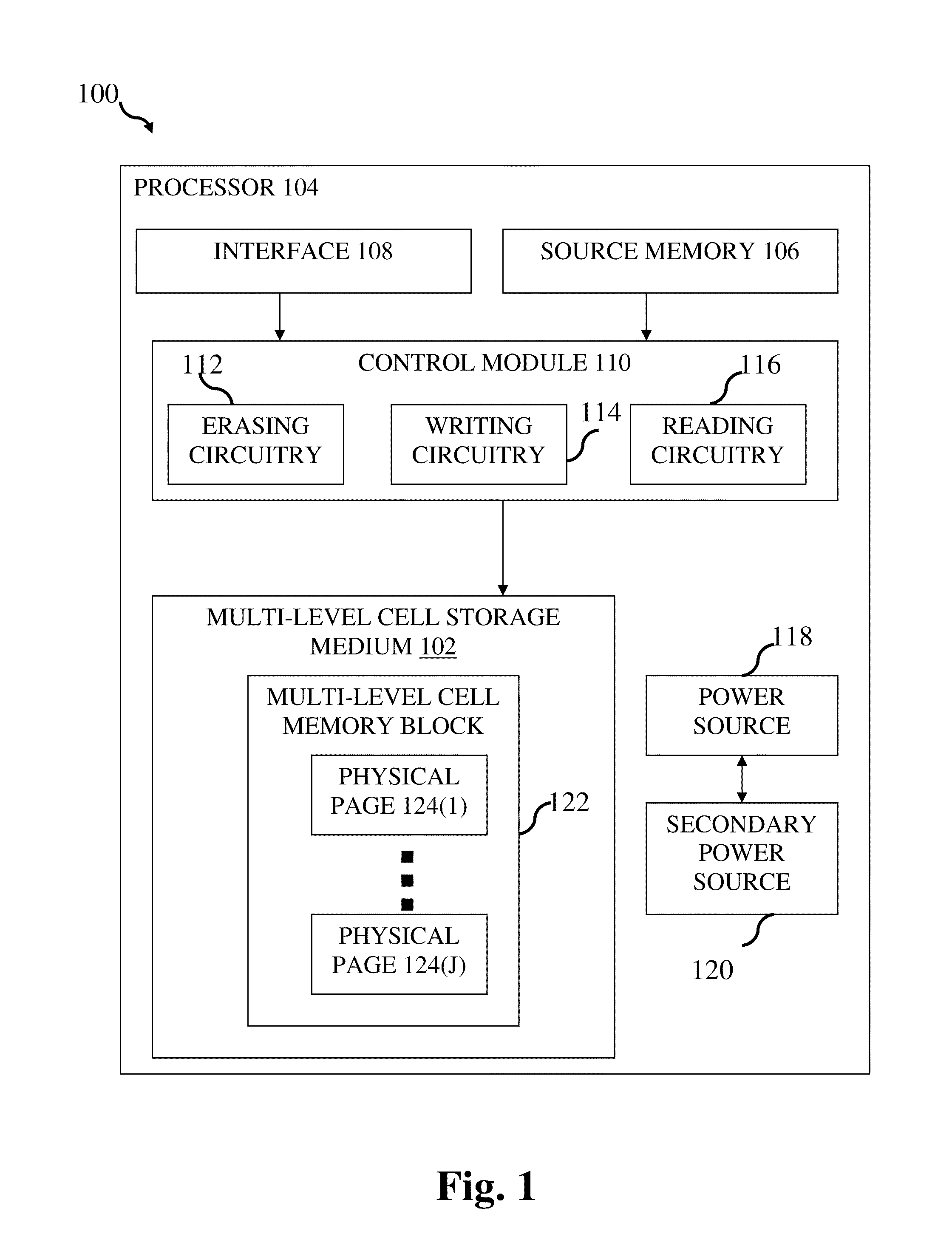

System and method for operating a non-volatile memory including a portion operating as a single-level cell memory and a portion operating as a multi-level cell memory

InactiveUS20110252187A1Reduce in quantityMemory architecture accessing/allocationMemory adressing/allocation/relocationData setSingle level

System and method for storing data in a non-volatile memory including a multi-level cell and single-level cell memory portions. To write a dataset to the non-volatile memory, if the size of the dataset is equal to the size of pages in the multi-level cell memory portion, the dataset may be written directly to the multi-level cell memory portion to fill an integer number of pages in a single write operation. However, if the size of the dataset is different than the size of the multi-level cell memory pages, at least a portion of the dataset may be temporarily written to the single-level cell memory portion until data is accumulated in a plurality of write operations having a size equal the size of the multi-level cell memory pages. The accumulated data may fill an integer number of the pages in the multi-level cell memory portion in a single write operation.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

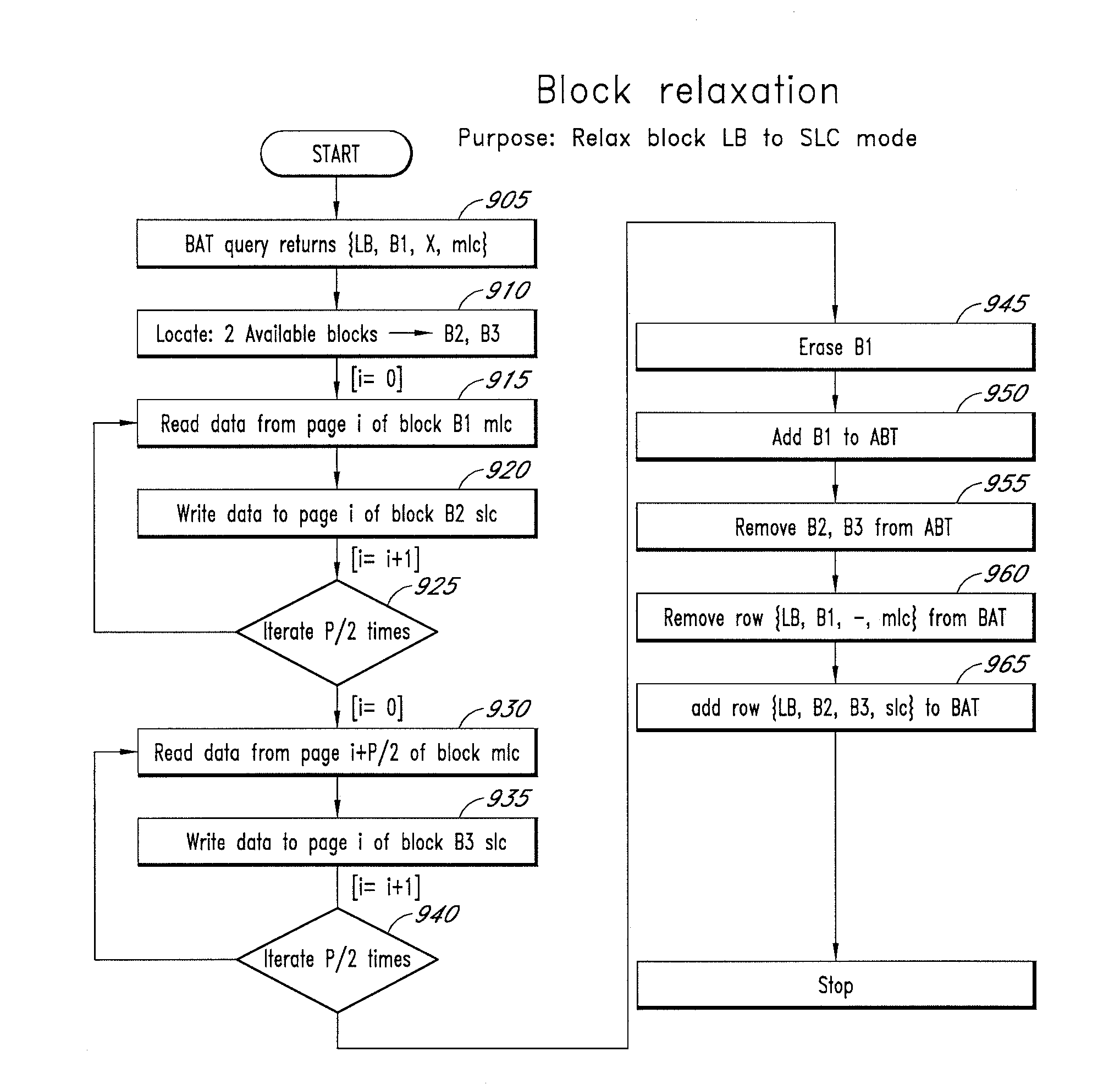

Dynamic slc/mlc blocks allocations for non-volatile memory

InactiveUS20100122016A1Memory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingSingle level

Apparatus and methods are disclosed, such as those that provide dynamic block allocations in NAND flash memory between single-level cells (SLC) and multi-level cells (MLC) based on characteristics. In one embodiment, a memory controller dynamically switches between programming and / or reprogramming blocks between SLC mode and MLC mode based on the amount of memory available for use. When memory usage is low, SLC mode is used. When memory usage is high, MLC mode is used. Dynamic block allocation allows a memory controller to obtain the performance and reliability benefits of SLC mode while retaining the space saving benefits of MLC mode.

Owner:ROUND ROCK RES LLC

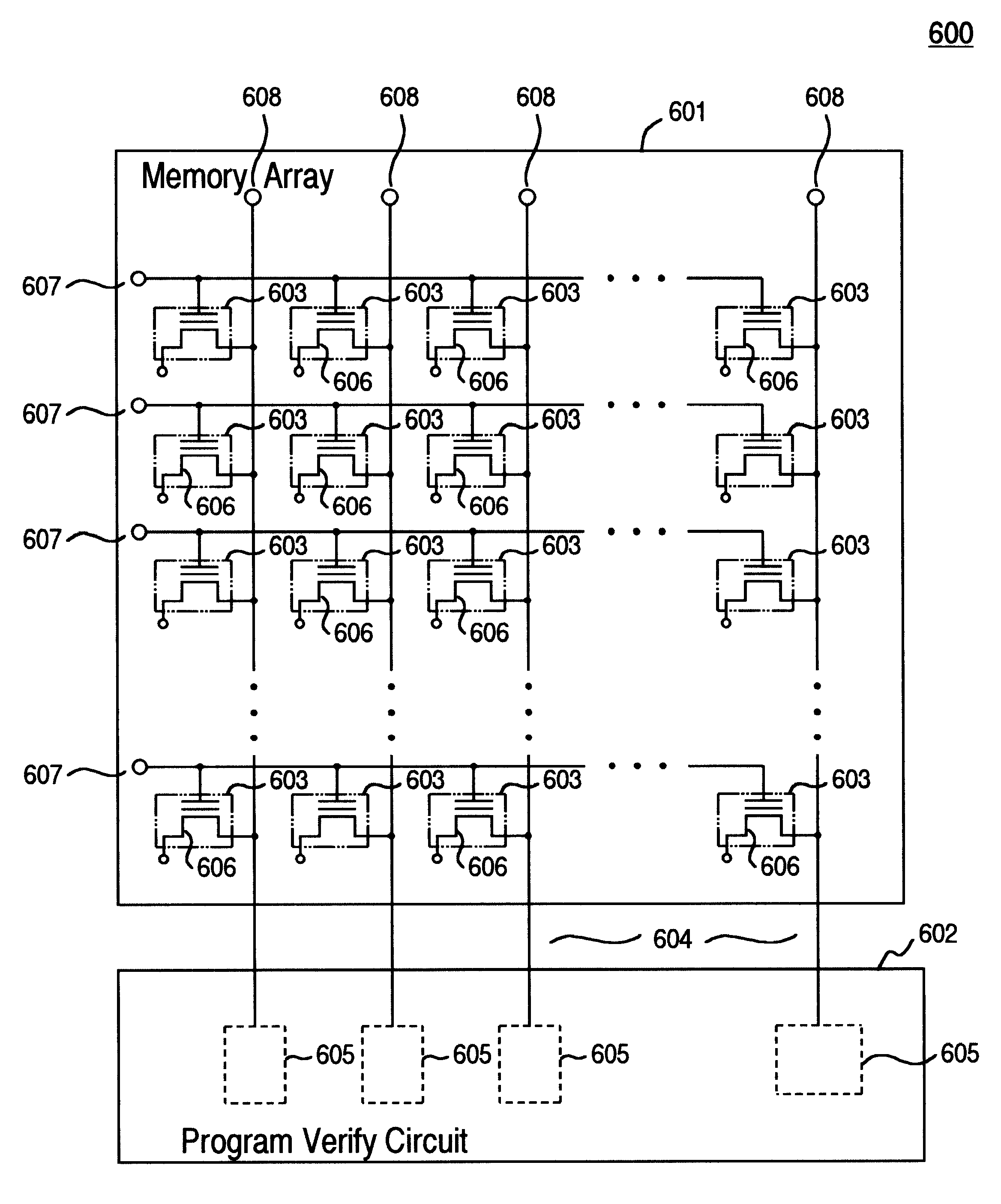

Staircase program verify for multi-level cell flash memory designs

InactiveUS6538923B1Improve performanceAvoid programmingRead-only memoriesDigital storageComputer architectureVoltage pulse

A system for concurrently verifying programming of logical data in a multi-level-cell (MLC) flash memory device having a plurality of memory cells each configured to store N bits of logical data where N>=2. The MLC flash memory device has a plurality of memory cells capable of being storing N-bits of data in one of 2N distinct data storage levels, each data storage level corresponding to a discrete N-bit combination of logical data. The data storage levels include a default level, called the erased level, and 2N-1 program levels, including a lowest program level, 2N-2 intermediate program levels and a highest program level. For each memory cell to be verified as programmed, an N-bit combination of data to be verified is loaded into a program-verify circuit and a stepped voltage pulse having 2N-1 steps is applied to each memory cell. The stepped voltage pulse includes an initial step, at least one intermediate step and a final step with the initial step substantially equal to a program-verify voltage for the highest program level of the MLC flash memory within a the highest program level, each successive intermediate step is substantially equal to a program-verify voltage corresponding to an intermediate program level and the final step of the voltage pulse is substantially equal to a program-verify voltage for the lowest program level. Concurrently with the application of the stepped voltage pulse to each memory cell, the data storage level is verified as substantially within a program level corresponding to the N-bit combination for the memory cell. Subsequent to verifying the data storage level for a memory cell, the verified memory cell is inhibited form further application of a program pulse.

Owner:MONTEREY RES LLC

System and method for data recovery in multi-level cell memories

ActiveUS20120005558A1Read-only memoriesError correction/detection using block codesParallel computingMulti-level cell

A system and method are provided for data recovery in a multi-level cell memory device. One or more bits may be programmed sequentially in one or more respective levels of multi-level cells in the memory device. An interruption of programming a subsequent bit in a subsequent second or greater level of the multi-level cells may be detected. Data may be recovered from the multi-level cells defining the one or more bits programmed preceding the programming interruption of the second or greater level.

Owner:AVAGO TECH INT SALES PTE LTD

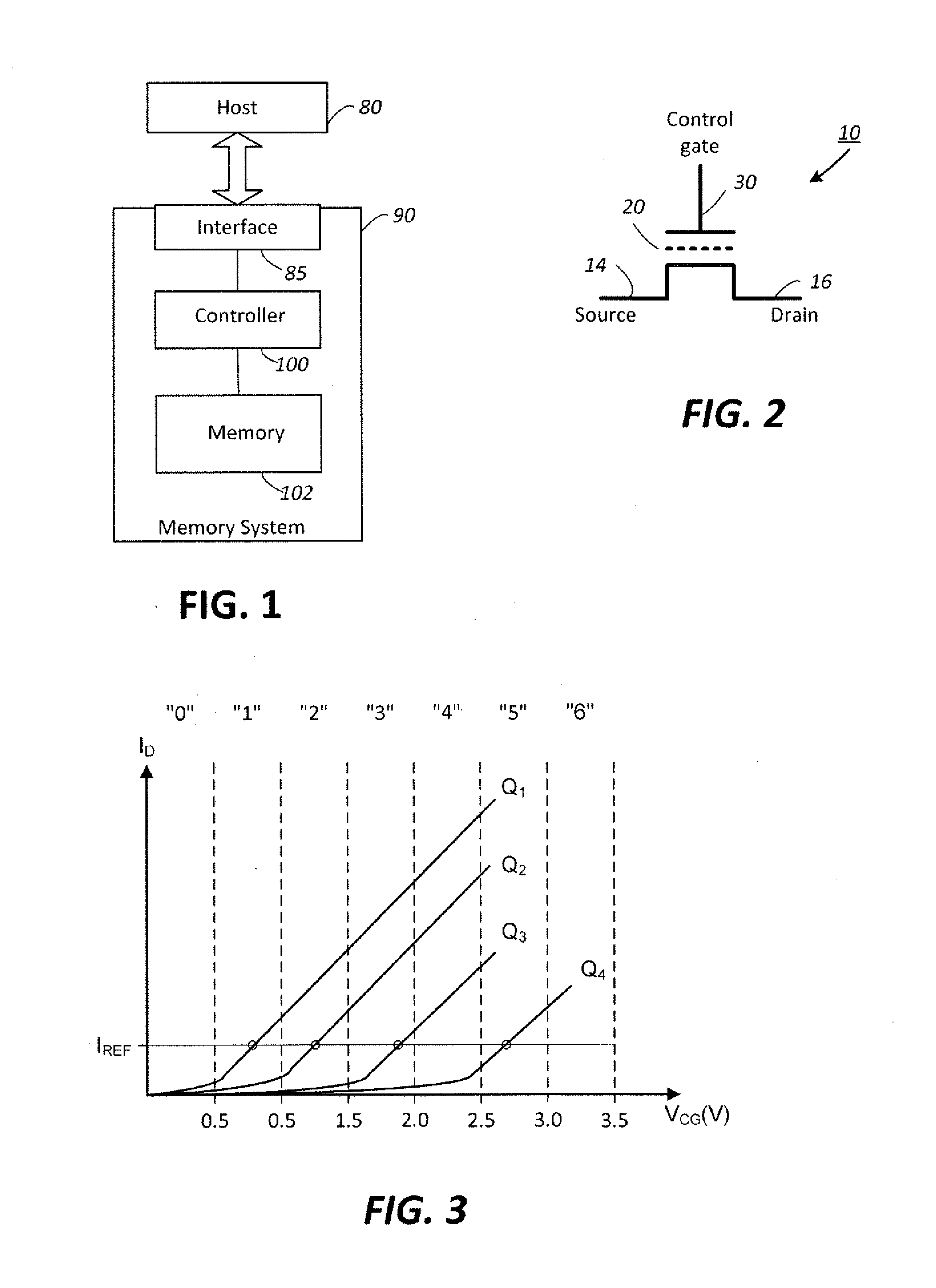

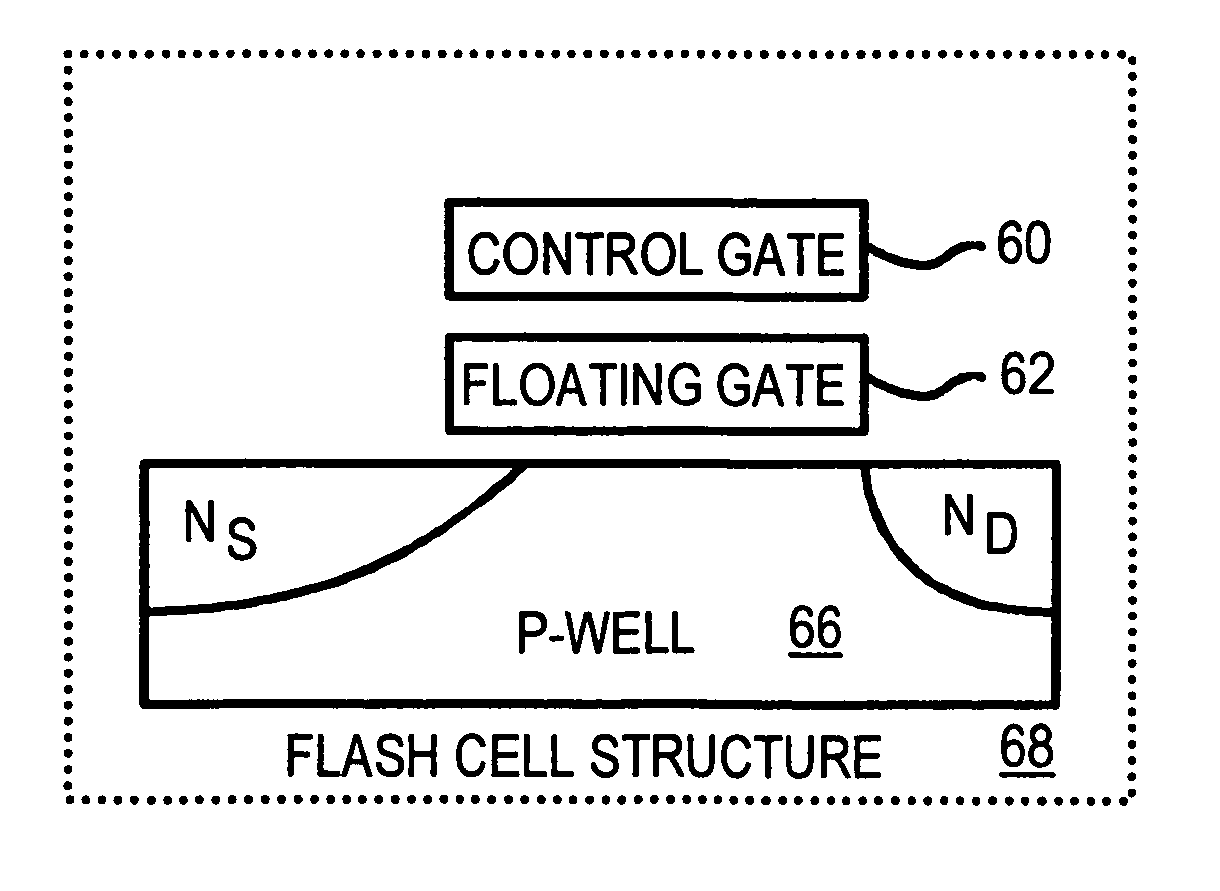

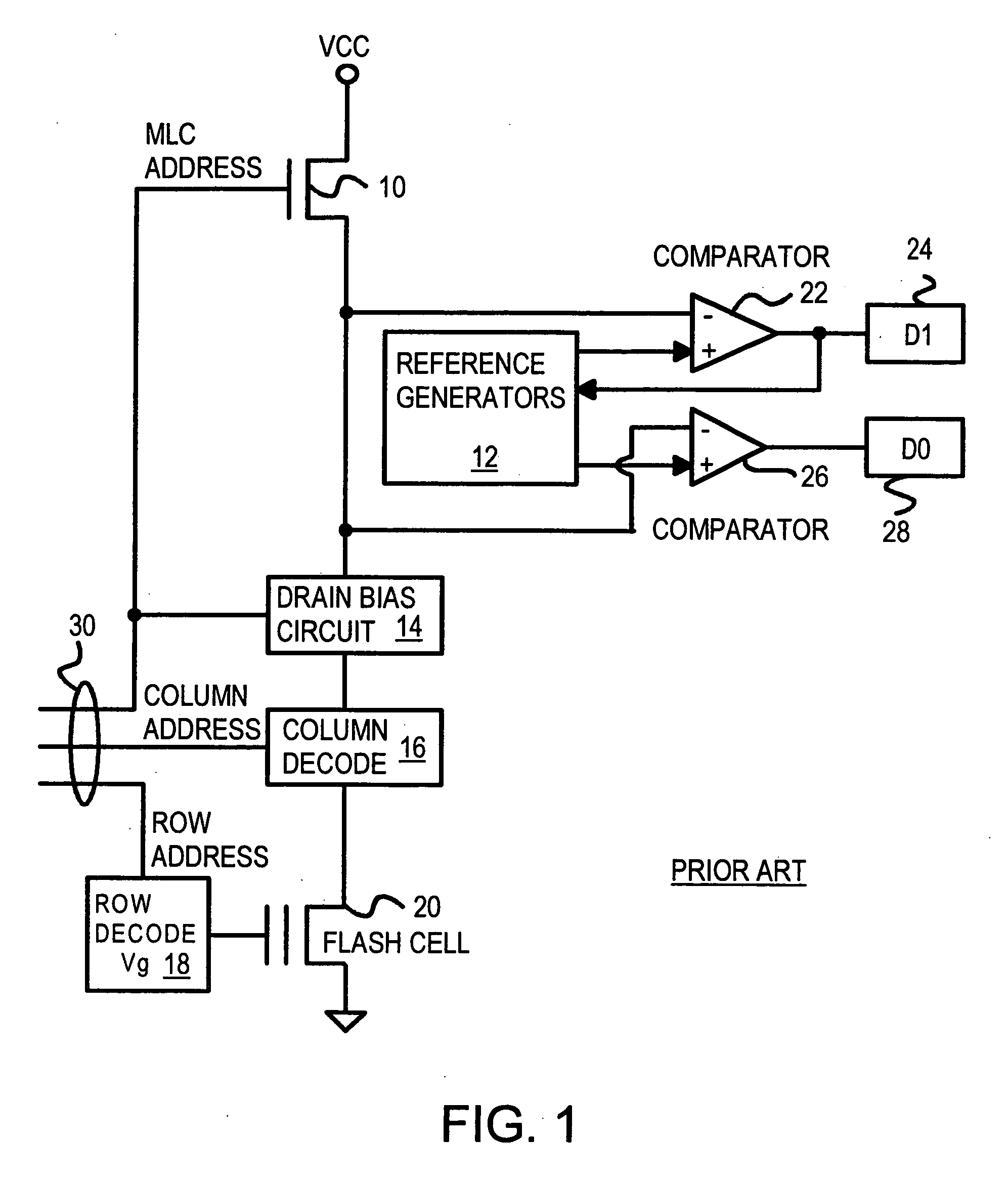

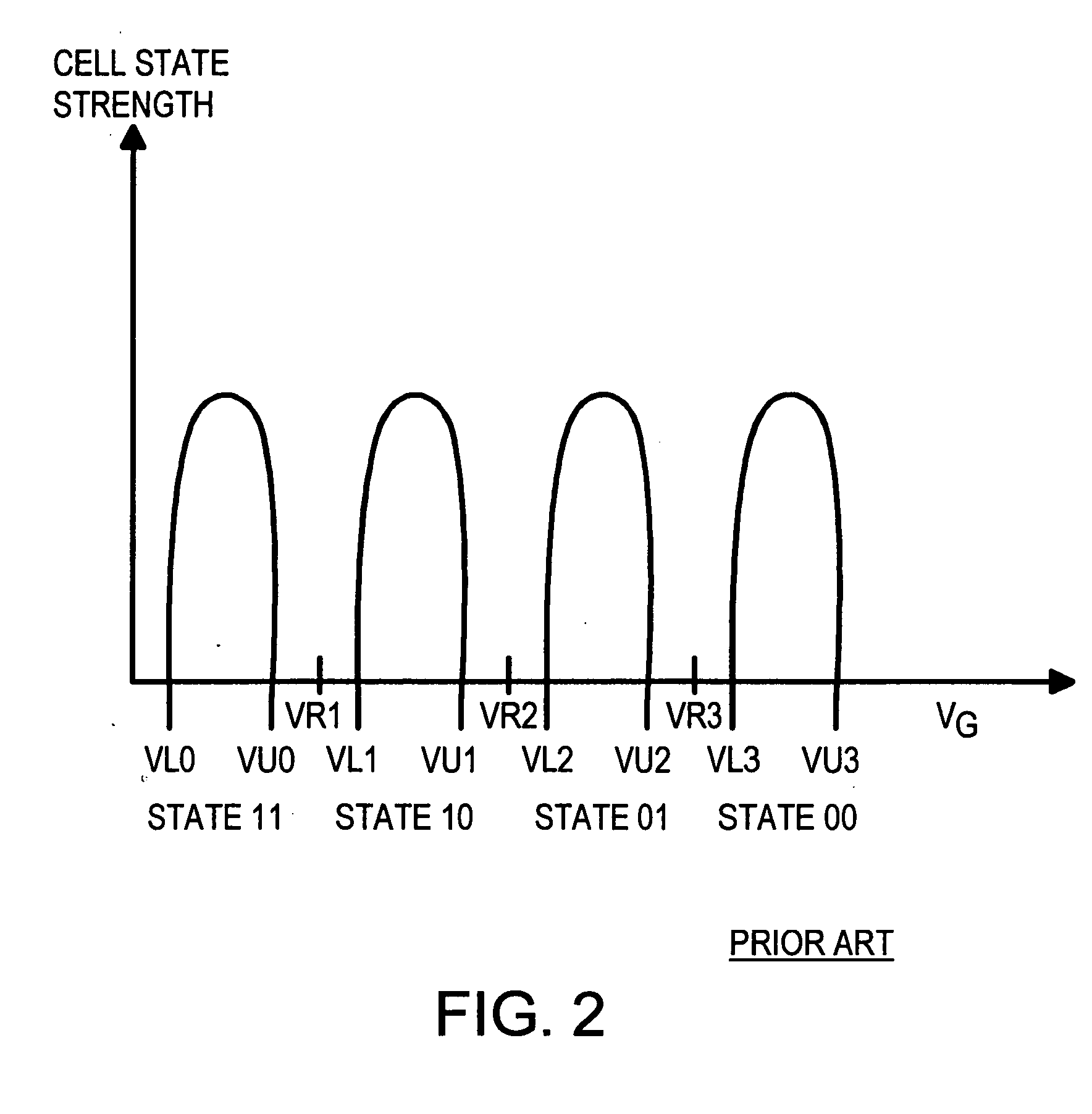

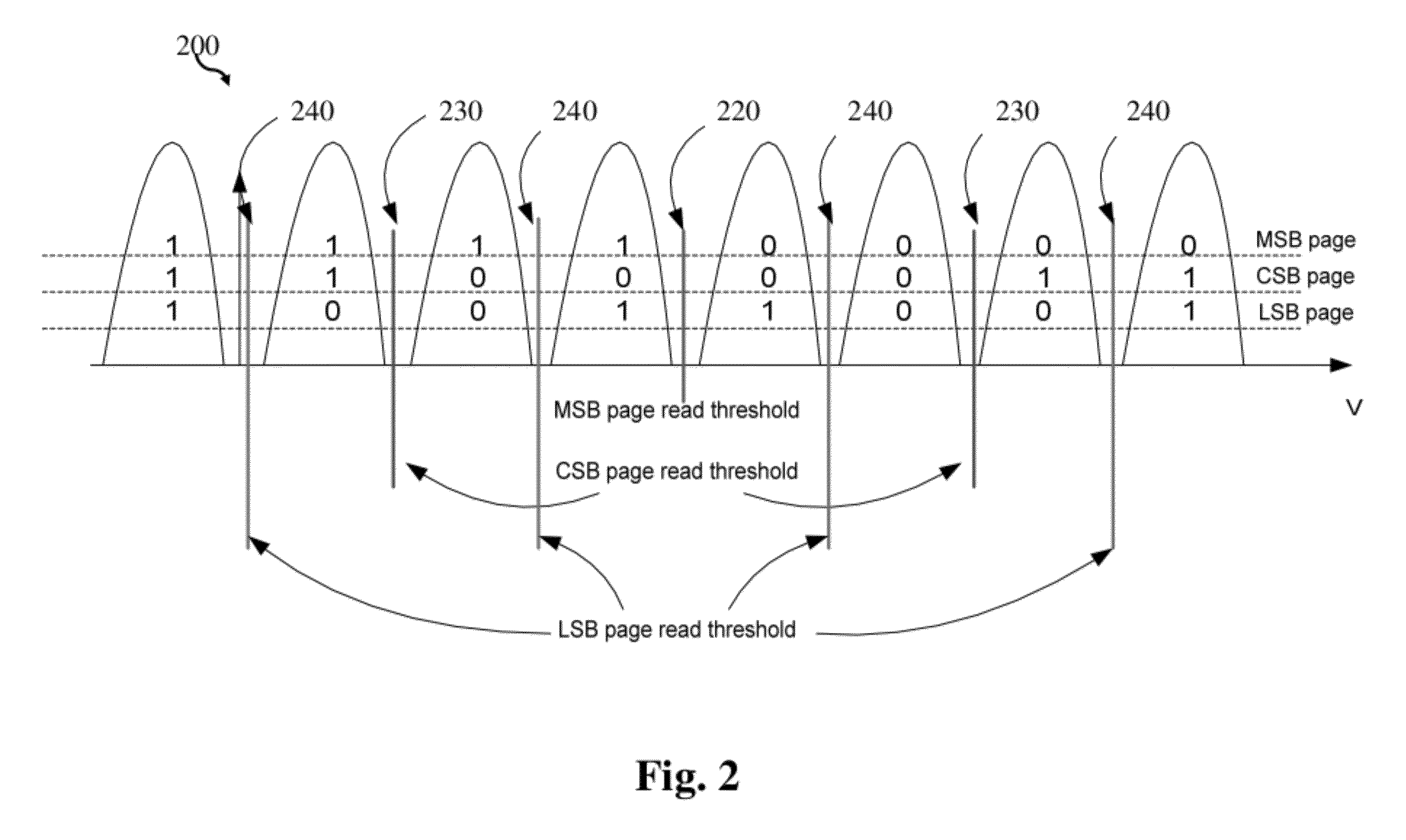

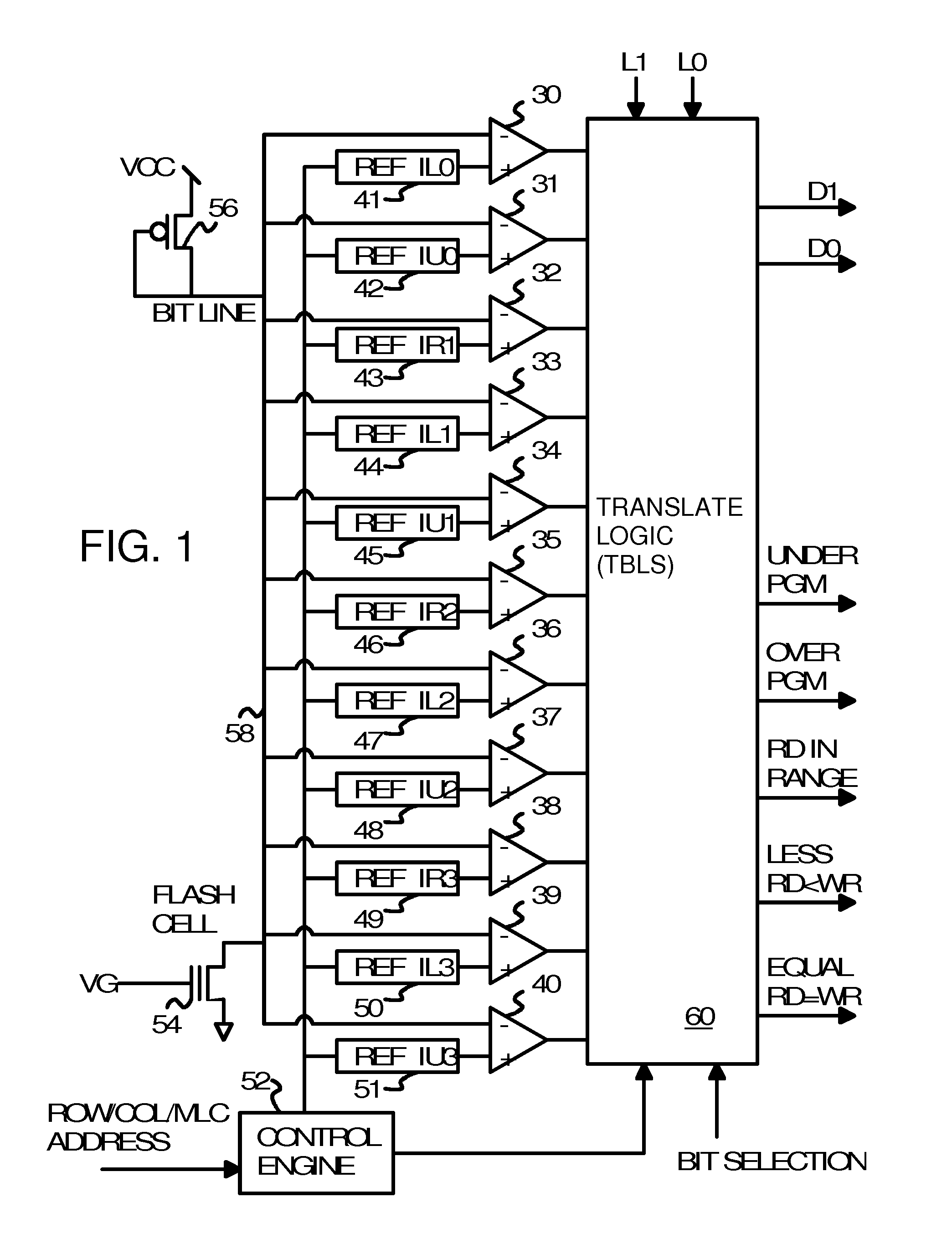

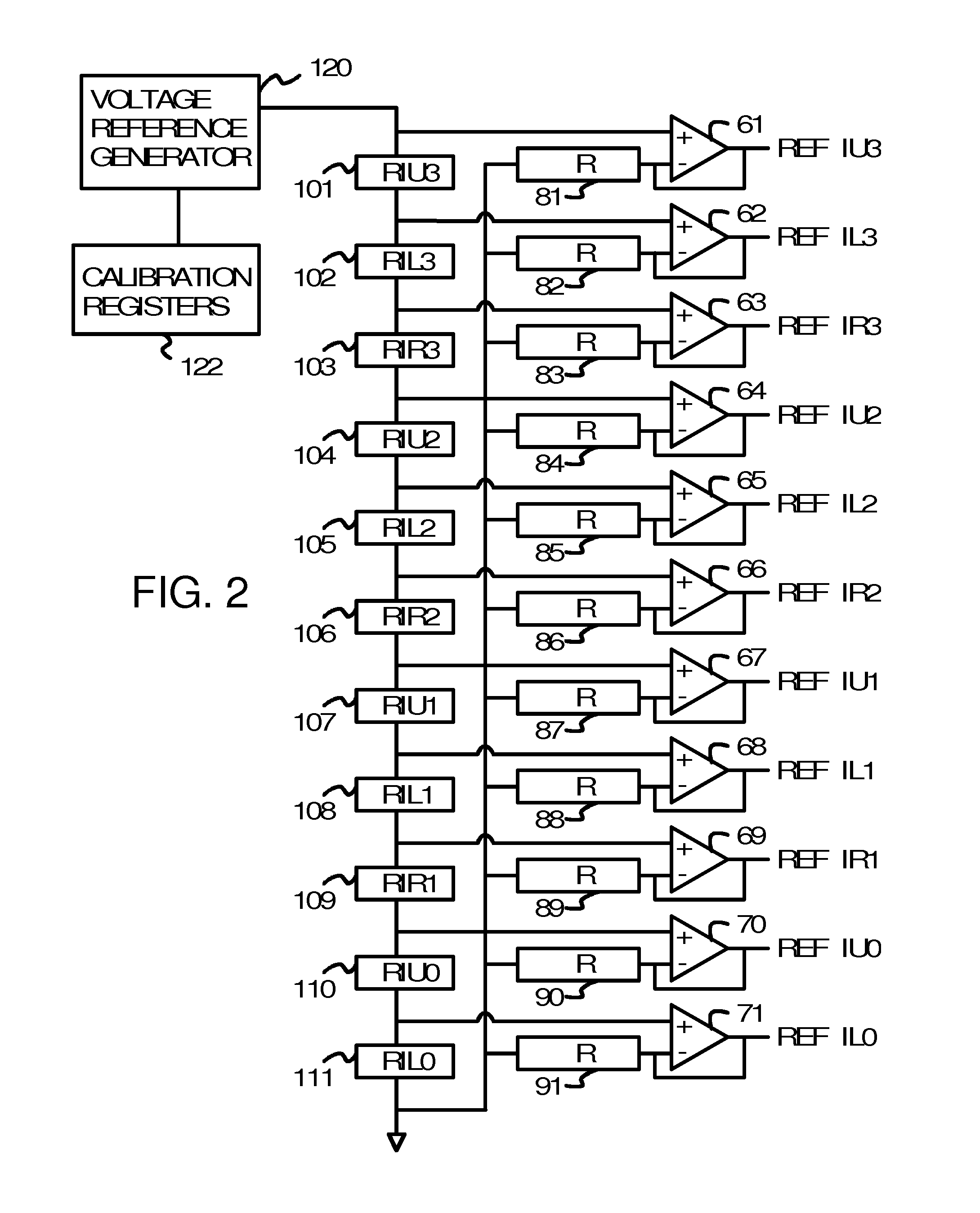

Flash memory device and architecture with multi level cells

A FLASH memory has an array of FLASH cells that each store N multiple bits of information as charge stored on a floating gate. Reference voltages or currents are generated for each boundary between the 2N states or levels and for an upper limit and a lower limit reference for each state. A selected bit line driven by a selected FLASH cell generates a sense node that is compared to a full range of 3*2N-1 comparators in parallel. The compare results are decoded to determine which state is read from the selected FLASH cell. An in-range signal is activated when the sense node is between the upper and lower limit references. The target programming count or programming pulses is adjusted during calibration to sense in the middle of the upper and lower limit references. Margin between references is adjusted by calibration codes that select currents for summing.

Owner:SUPER TALENT TECH CORP

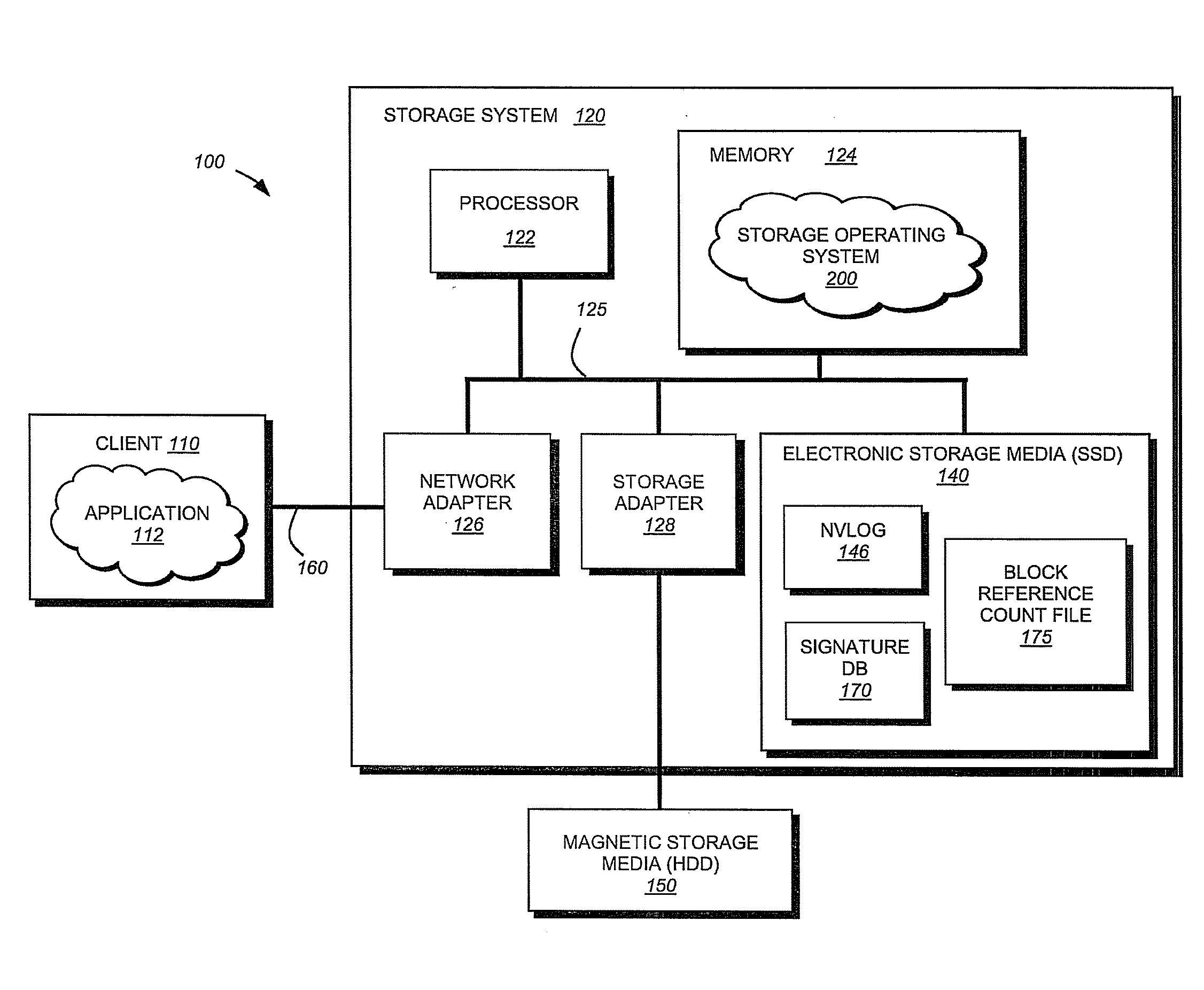

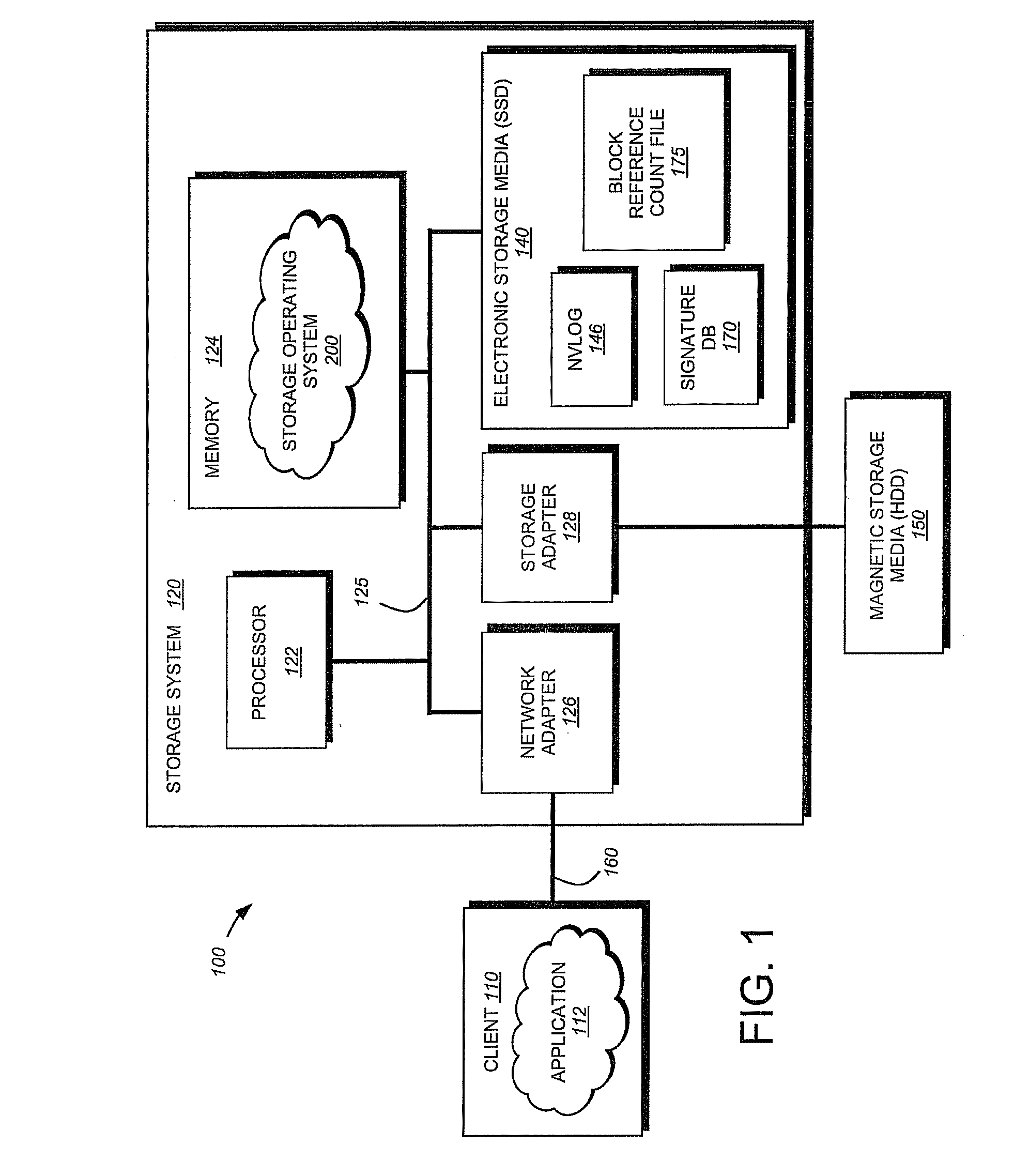

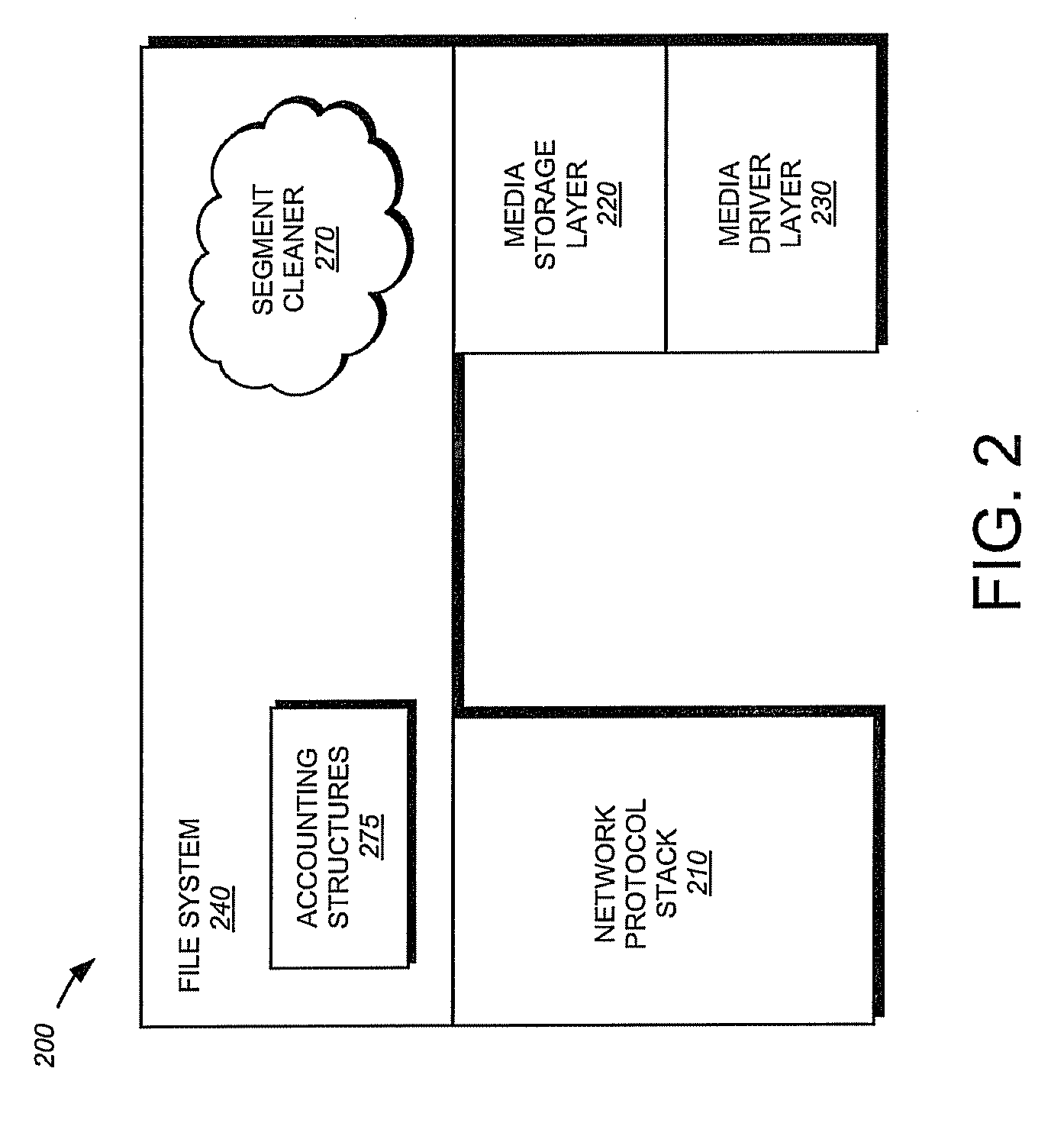

Flash-based data archive storage system

InactiveUS20100281207A1Large capacityMore capacityEnergy efficient ICTMemory loss protectionMass storageMagnetic tape

A flash-based data archive storage system having a large capacity storage array constructed from a plurality of dense flash devices is provided. The flash devices are illustratively multi-level cell (MLC) flash devices that are tightly packaged to provide a low-power, high-performance data archive system having substantially more capacity per cubic inch than more dense tape or disk drives. The flash-based data archive system may be adapted to employ conventional data de-duplication and compression methods to compactly store data. Furthermore, the flash-based archive system has a smaller footprint and consumes less power than the tape and / or disk archive system.

Owner:NETWORK APPLIANCE INC

System and method for accelerated sampling

A system and method for reading memory cells in a multi-level cell memory device. A set of thresholds may be received for reading a current page of the memory cells. The set of threshold may include hard decision thresholds for hard decoding, soft decision thresholds for soft decoding, erase thresholds for erase decoding and / or other combinations of thresholds. The set of thresholds may be divided into a plurality of groups of thresholds. The current page may be simultaneously read using multiple thresholds, where each of the multiple thresholds is divided into a different group of thresholds.

Owner:AVAGO TECH INT SALES PTE LTD

Cell-Downgrading and Reference-Voltage Adjustment for a Multi-Bit-Cell Flash Memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

SLC-MLC Wear Balancing

ActiveUS20130173844A1Memory architecture accessing/allocationRead-only memoriesSingle levelMulti-level cell

A method and system for SLC-MLC Wear Balancing in a flash memory device is disclosed. The flash memory device includes a single level cell (SLC) portion and a multi-level cell (MLC) portion. The age of the SLC portion and the MLC portion may differ, leading potentially to one portion wearing out before the other. In order to avoid this, a controller is configured to receive an age indicator from one or both of the SLC portion and the MLC portion, determine, based on the age indicator, whether to modify operation of the SLC portion and / or the MLC portion, and in response to determining to modifying operation, modify the operation of the at least one of the SLC portion or the MLC portion. The modification of the operation may thus balance wear between the SLC and MLC portions, thereby potentially extending the life of the flash memory device.

Owner:SANDISK TECH LLC

Swappable Sets of Partial-Mapping Tables in a Flash-Memory System With A Command Queue for Combining Flash Writes

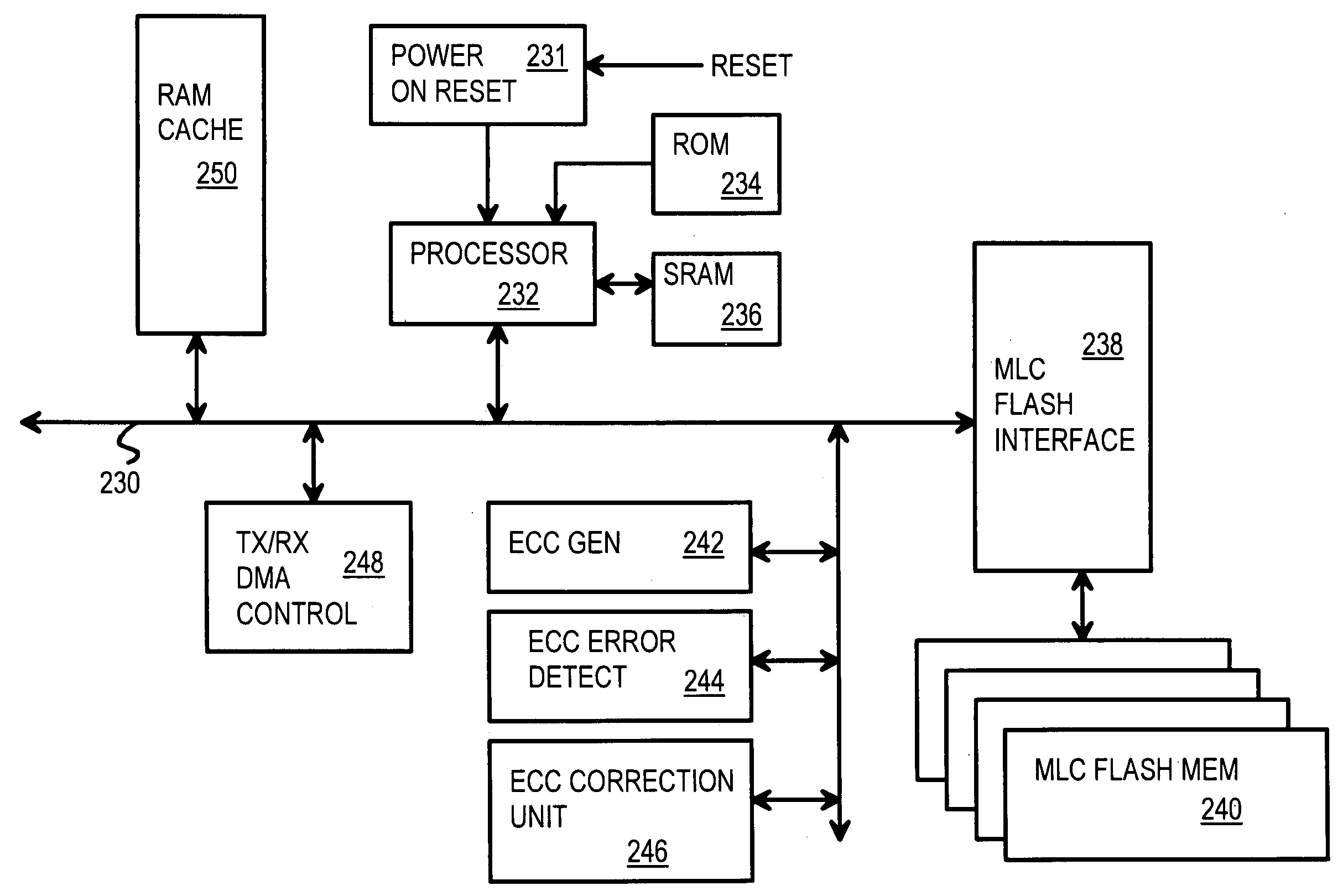

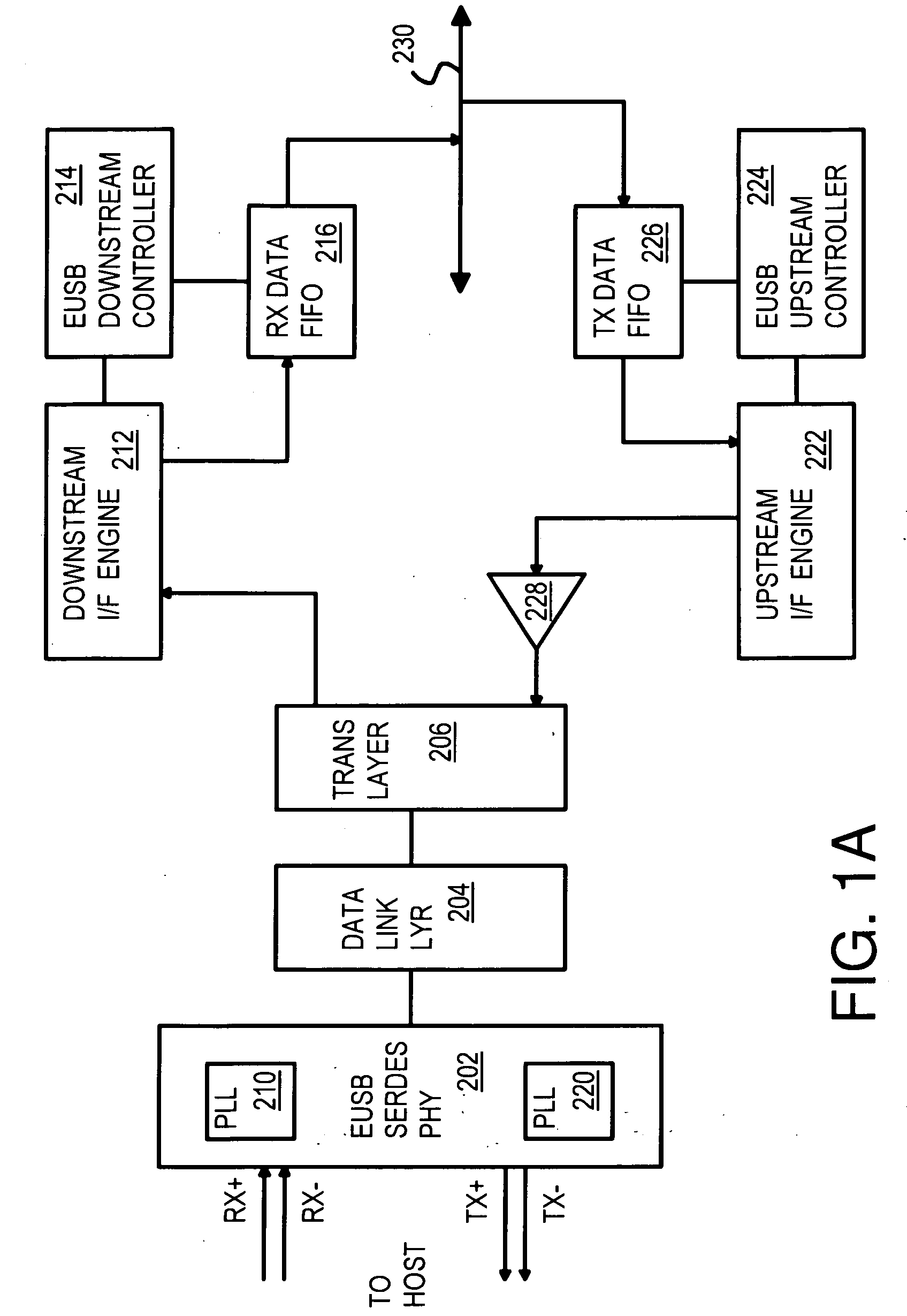

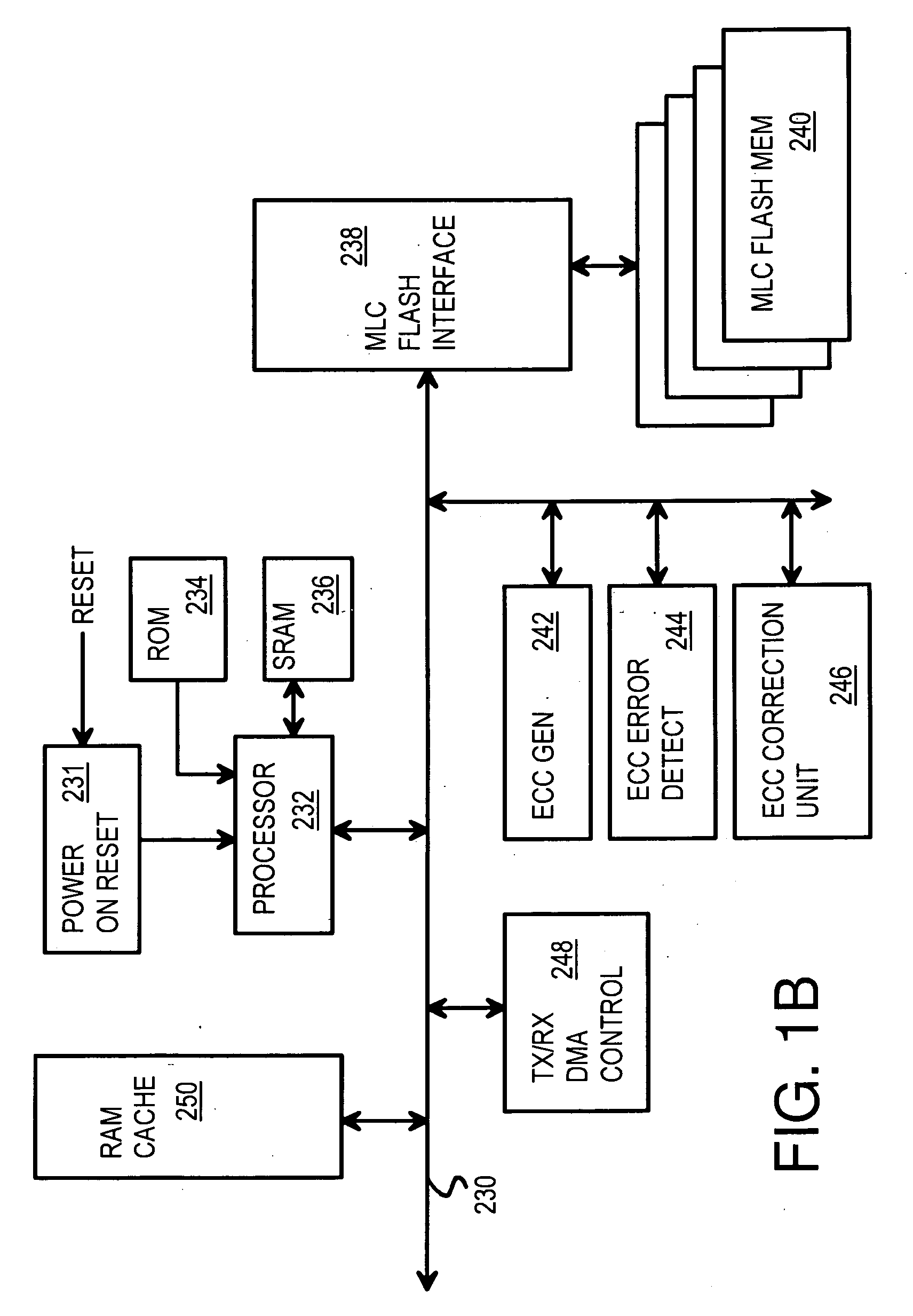

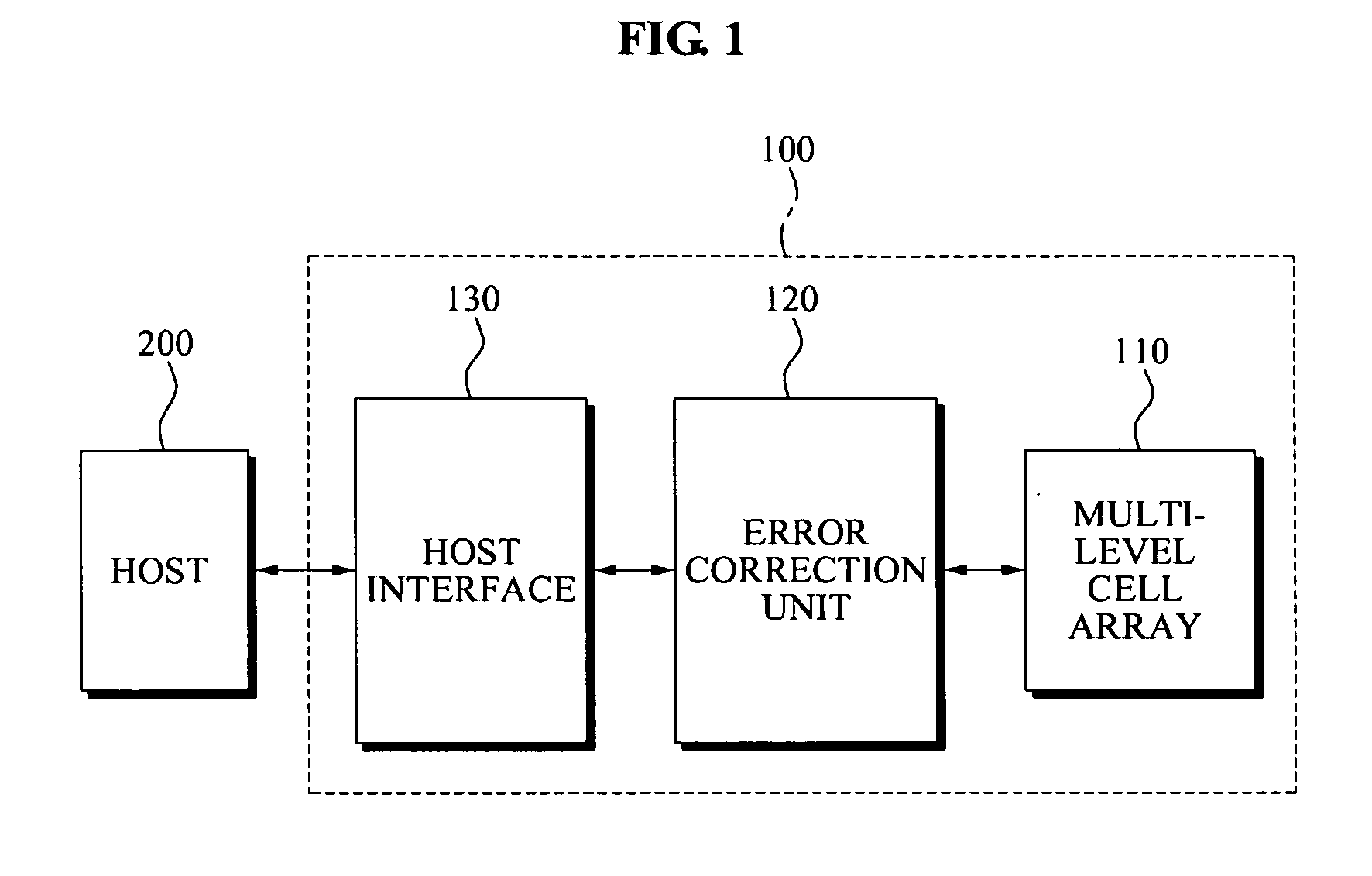

InactiveUS20090113121A1Memory architecture accessing/allocationDistillation regulation/controlFlash memory controllerMulti-level cell

A flash controller has a flash interface accessing physical blocks of multi-level-cell (MLC) flash memory. An Extended Universal-Serial-Bus (EUSB) interface loads host commands into a command queue where writes are re-ordered and combined to reduce flash writes. A partial logical-to-physical L2P mapping table in a RAM has entries for only 1 of N sets of L2P mapping tables. The other N−1 sets are stored in flash memory and fetched into the RAM when a L2P table miss occurs. The RAM required for mapping is greatly reduced. A data buffer stores one page of host write data. Sector writes are merged using the data buffer. The data buffer is flushed to flash when a different page is written, while the partial logical-to-physical mapping table is flushed to flash when a L2P table miss occurs, when the host address is to a different one of the N sets of L2P mapping tables.

Owner:SUPER TALENT TECH CORP

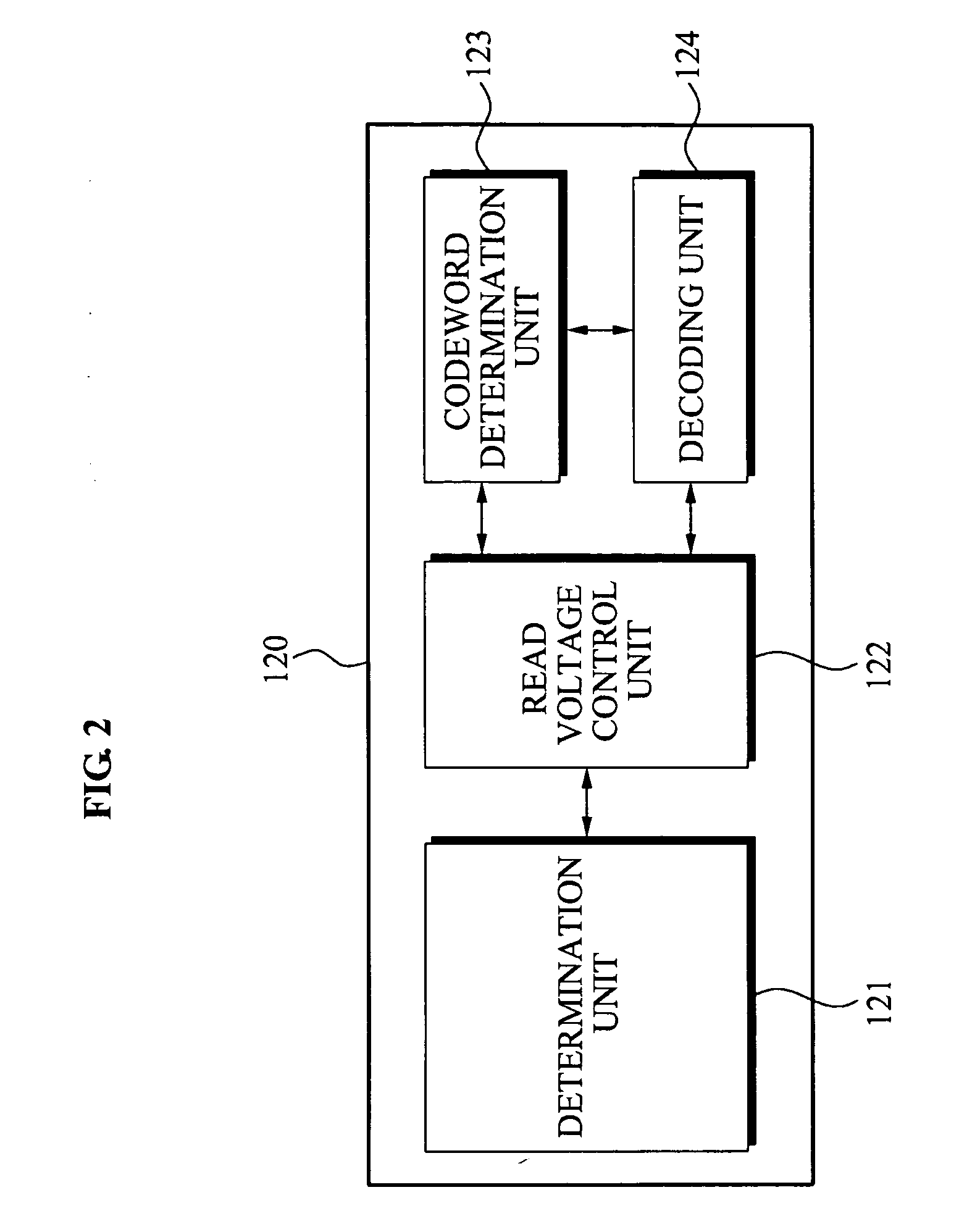

Error correction apparatus, method thereof and memory device comprising the apparatus

InactiveUS20090292972A1Effective correctionIncrease probabilityRead-only memoriesCode conversionComputer hardwareError correcting

An error correction apparatus, a method thereof, and a memory device including the apparatus are provided. The error correction apparatus may include: a determination unit configured to determine whether a number of errors in a read word being read and extracted from a multi-level cell (MLC) exists in an error correcting capability range; a read voltage control unit configured to either increase or decrease a read voltage applied to the MLC when the number of errors in the read word is outside the error correcting capability range; and a codeword determination unit configured to analyze a bit error based on the increase or decrease of the read voltage, and to select a codeword corresponding to the analyzed bit error based on a selected read error pattern. Through this, it may be possible to efficiently correct a read error that occurs when the data of the memory device is maintained for a long time.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device having electrically floating body transistor, semiconductor memory device having both volatile and non-volatile functionality and method or operating

ActiveUS9153309B2Larger memory windowReduce in quantityTransistorSolid-state devicesElectricityEngineering

A semiconductor memory cell includes a floating body region configured to be charged to a level indicative of a state of the memory cell; a first region in electrical contact with said floating body region; a second region in electrical contact with said floating body region and spaced apart from said first region; and a gate positioned between said first and second regions. The cell may be a multi-level cell. Arrays of memory cells are disclosed for making a memory device. Methods of operating memory cells are also provided.

Owner:ZENO SEMICON

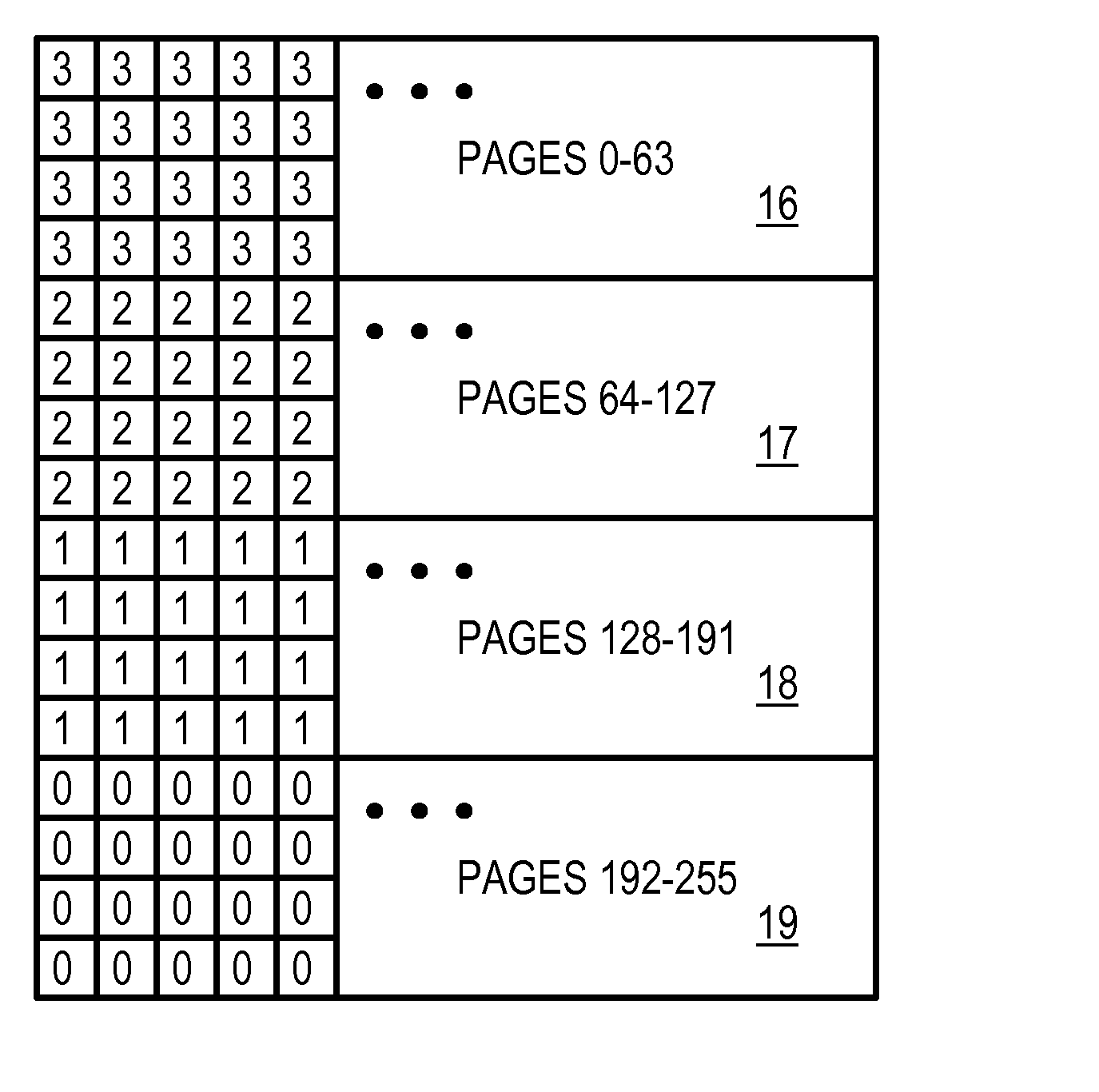

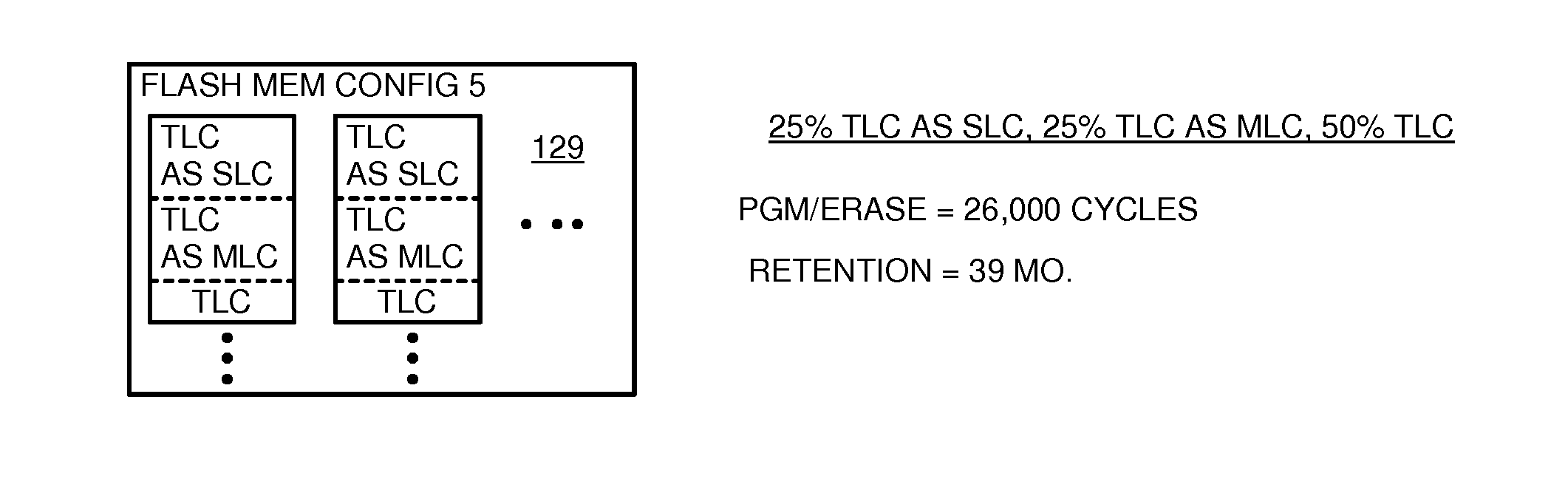

Endurance and retention flash controller with programmable binary-levels-per-cell bits identifying pages or blocks as having triple, multi, or single-level flash-memory cells

InactiveUS9123422B2Memory architecture accessing/allocationMemory adressing/allocation/relocationTruth valueRetention time

An retention flash controller reads assigned-level bits from a bad block / erase count table or from a page status table that indicate when flash memory cells operate as Triple-Level-Cell (TLC), Multi-Level-Cell (MLC), or Single-Level-Cell (SLC). Pages that fail as TLC or MLC are downgraded for use as SLC pages by changing the assigned-level bits. The level bits adjust truth tables used by translation logic that receives inputs from voltage comparators reading a bit line. The range of voltages for each logic level may be adjusted by the truth tables or by programmable registers. The programming voltage or programming pulses may be adjusted to increase endurance and the number of permitted program-erase cycles while reducing retention times before a refresh is needed of the flash cells. Mixed configurations of flash memory have MLC blocks and MLC as SLC blocks, or other combinations.

Owner:SUPER TALENT TECH CORP

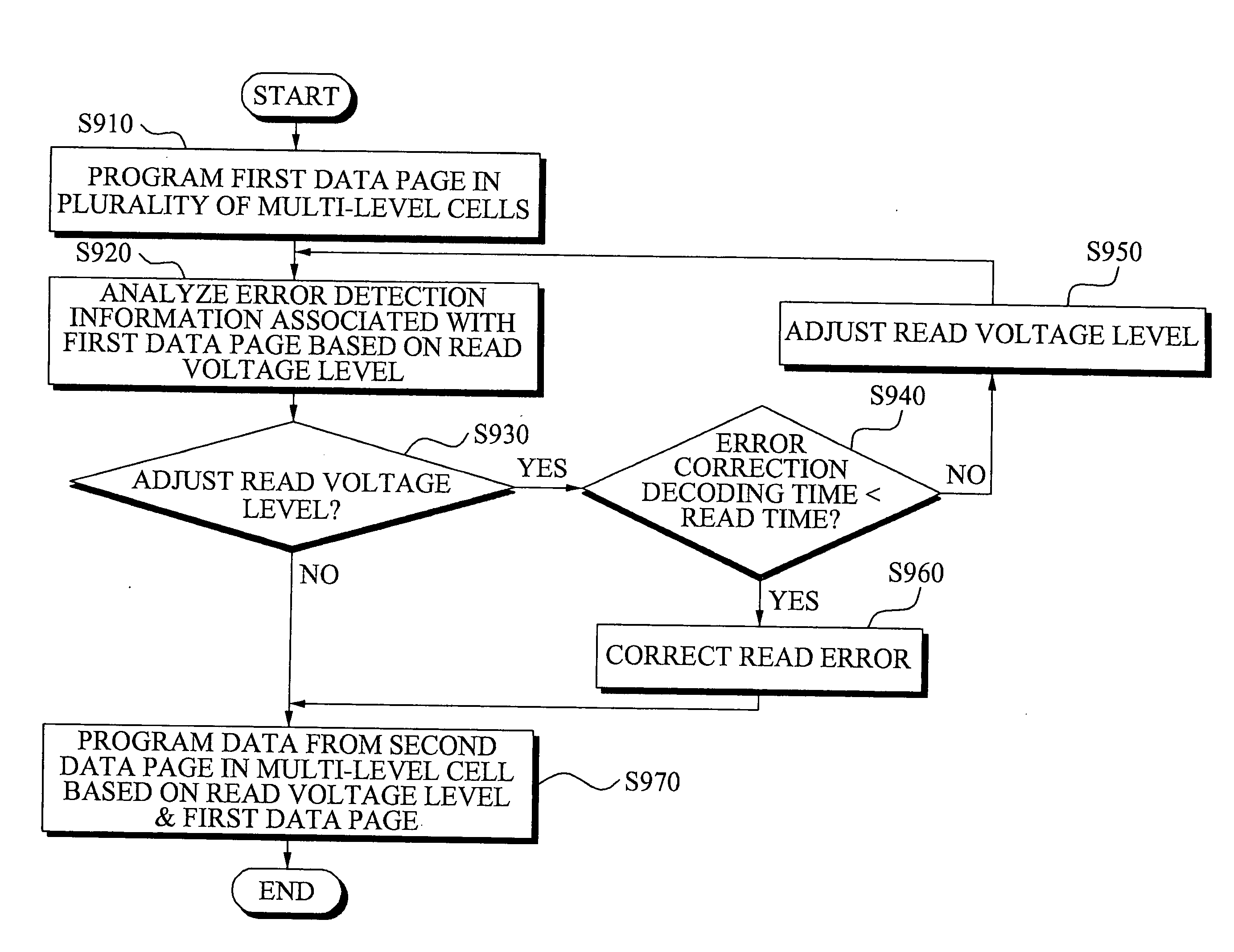

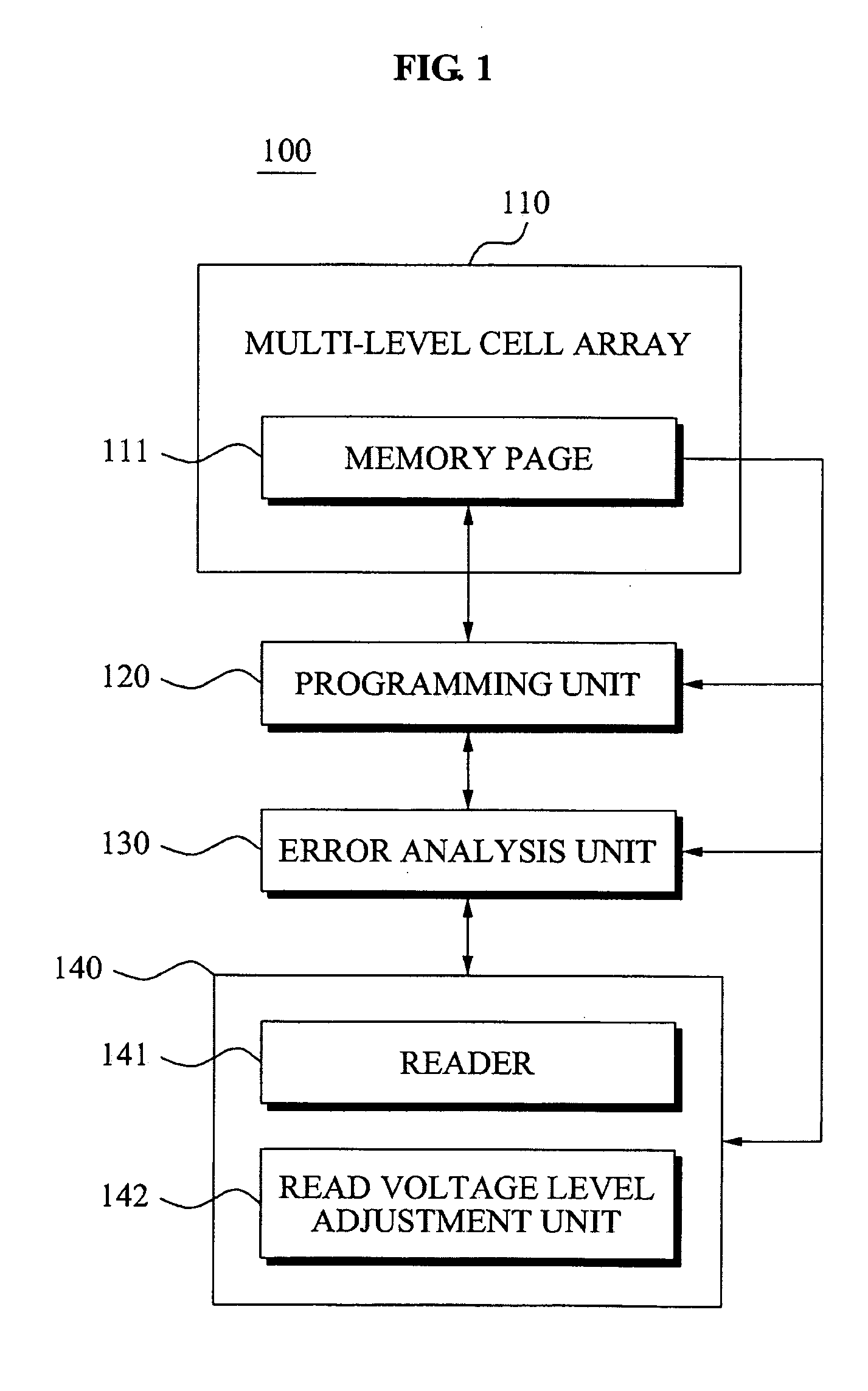

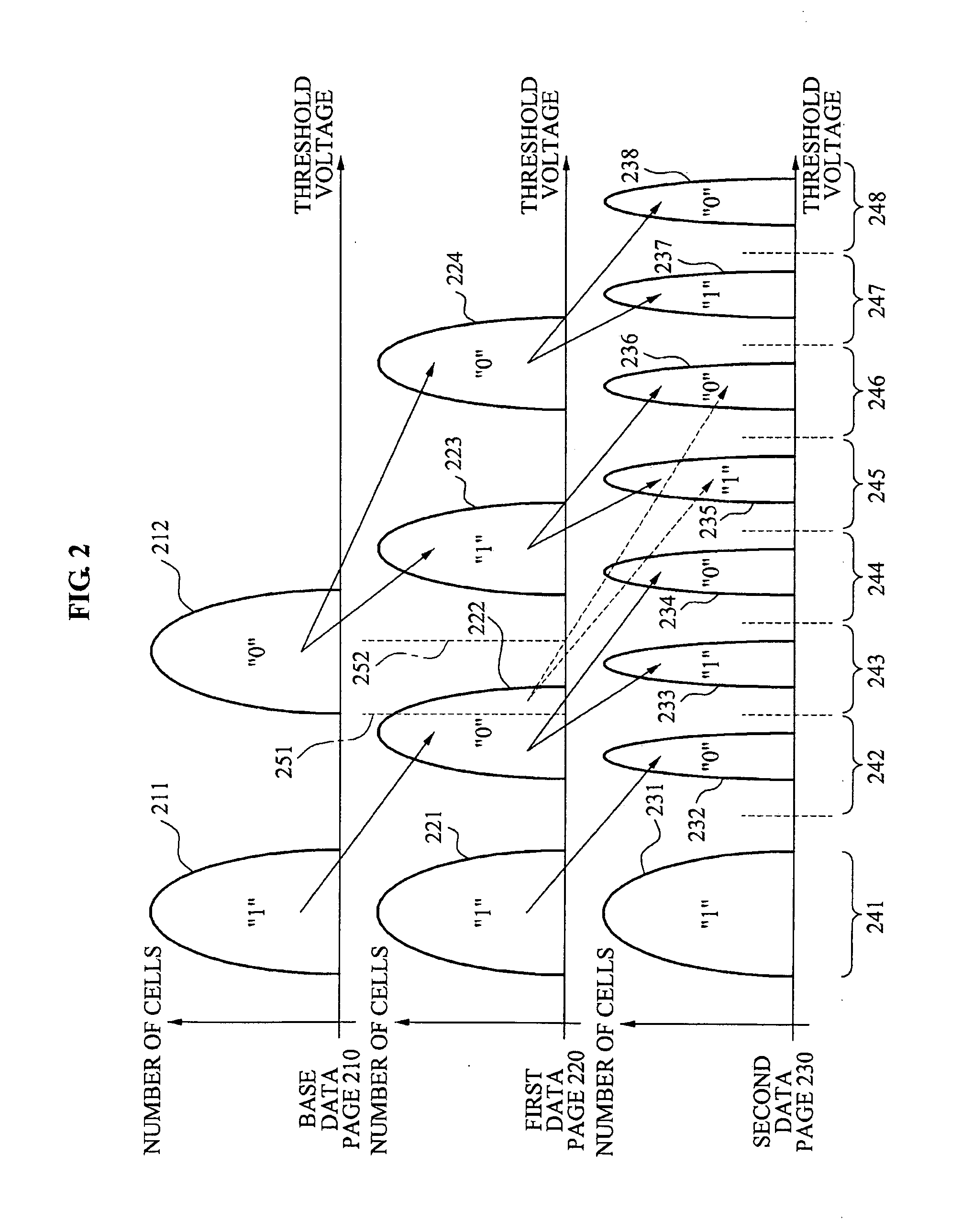

Memory device and memory programming method

ActiveUS20100002506A1Reduce errorsRead-only memoriesDigital storageMulti-level cellReal-time computing

Provided are memory devices and memory programming methods. A memory device may include: a multi-level cell array that includes a plurality of multi-level cells; a programming unit that programs a first data page in the plurality of multi-level cells and programs a second data page in a multi-level cell from among the plurality of multi-level cells in which the first data page is programmed; an error analysis unit that analyzes read error information corresponding to the first data page based on a read voltage level to determine whether to correct a read error based on the analyzed read error information; and a controller that adjusts the read voltage level of the first data page depending on the determination result. Through this, it is possible to reduce an error occurrence when reading and / or programming a data page.

Owner:SAMSUNG ELECTRONICS CO LTD

Two-level RAM lookup table for block and page allocation and wear-leveling in limited-write flash-memories

InactiveUS7660941B2Memory architecture accessing/allocationRead-only memoriesLogical block addressingRandom access memory

A restrictive multi-level-cell (MLC) flash memory prohibits regressive page-writes. When a regressive page-write is requested, an empty block having a low wear-level count is found, and data from the regressive page-write and data from pages stored in the old block are written to the empty block in page order. The old block is erased and recycled. A two-level look-up table is stored in volatile random-access memory (RAM). A logical page address from a host is divided by a modulo divider to generate a quotient and a remainder. The quotient is a logical block address that indexes a first-level look-up table to find a mapping entry with a physical block address that selects a row in a second-level look-up table. The remainder locates a column in the row in the second-level look-up table. If any page-valid bits above the column pointed to by the remainder are set, the write is regressive.

Owner:SUPER TALENT TECH CORP

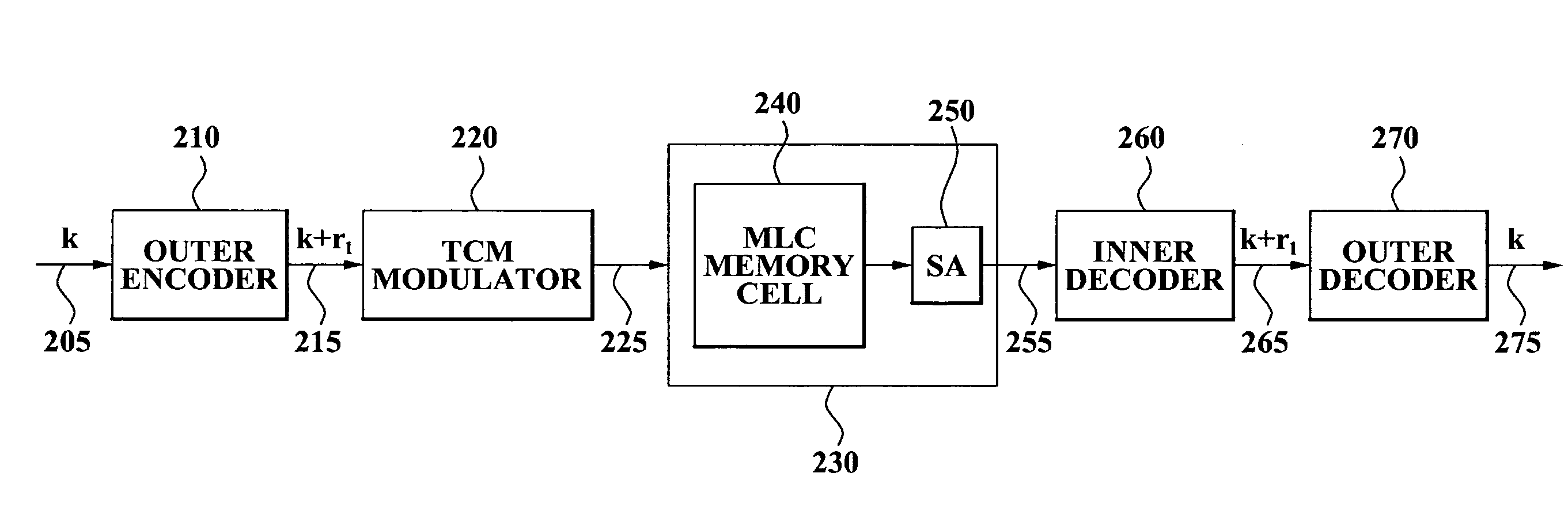

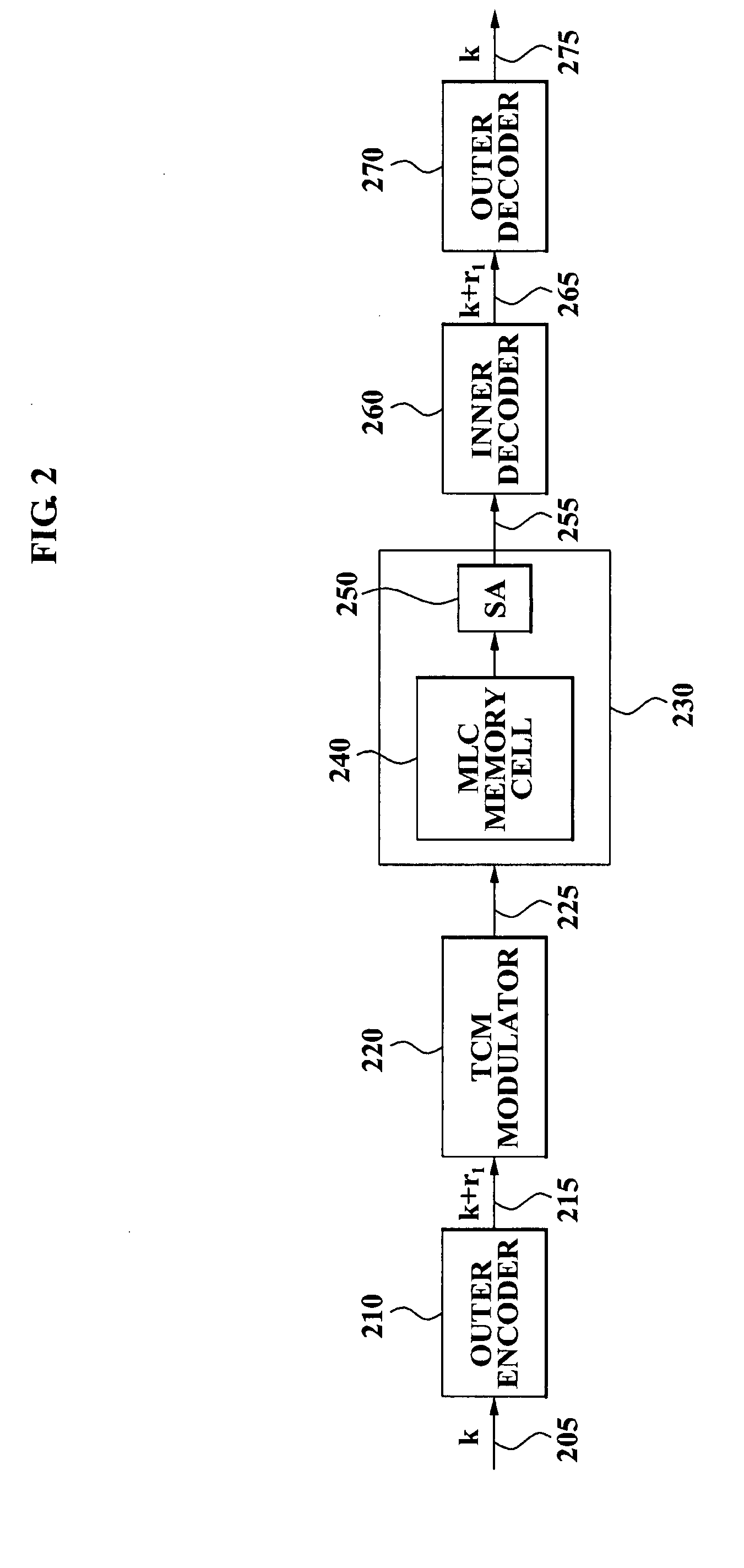

Multi-level cell memory devices using trellis coded modulation and methods of storing data in and reading data from the memory devices

ActiveUS20080137413A1Improve storage densityData representation error detection/correctionRead-only memoriesComputer architectureMulti-level cell

A multi-level cell (MLC) memory device may include: a MLC memory cell; an outer encoder that encodes data using a first encoding scheme to generate an outer encoded bit stream; and a TCM modulator that applies a program pulse to the MLC memory cell to write the data in the MLC memory cell. The program pulse may be generated by TCM modulating the outer encoded bit stream. A method of storing data in a MLC memory device, reading data from the MLC memory device, or storing data in and reading data from the MLC memory device may include: encoding data using a first encoding scheme to generate an outer encoded bit stream; and applying a program pulse to a MLC memory cell of the MLC memory device to write the data in the MLC memory cell. The program pulse may be generated by TCM modulating the outer encoded bit stream.

Owner:SAMSUNG ELECTRONICS CO LTD