Patents

Literature

3474 results about "Data bits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Data bits. The number of bits used to represent one character of data. When transmitting ASCII text via modem, either seven or eight bits may be used.

Programmable magnetic data storage card

ActiveUS7044394B2Reduce financial riskSimple and inexpensive and effectiveAcutation objectsApparatus for flat record carriersMicrocomputerComing out

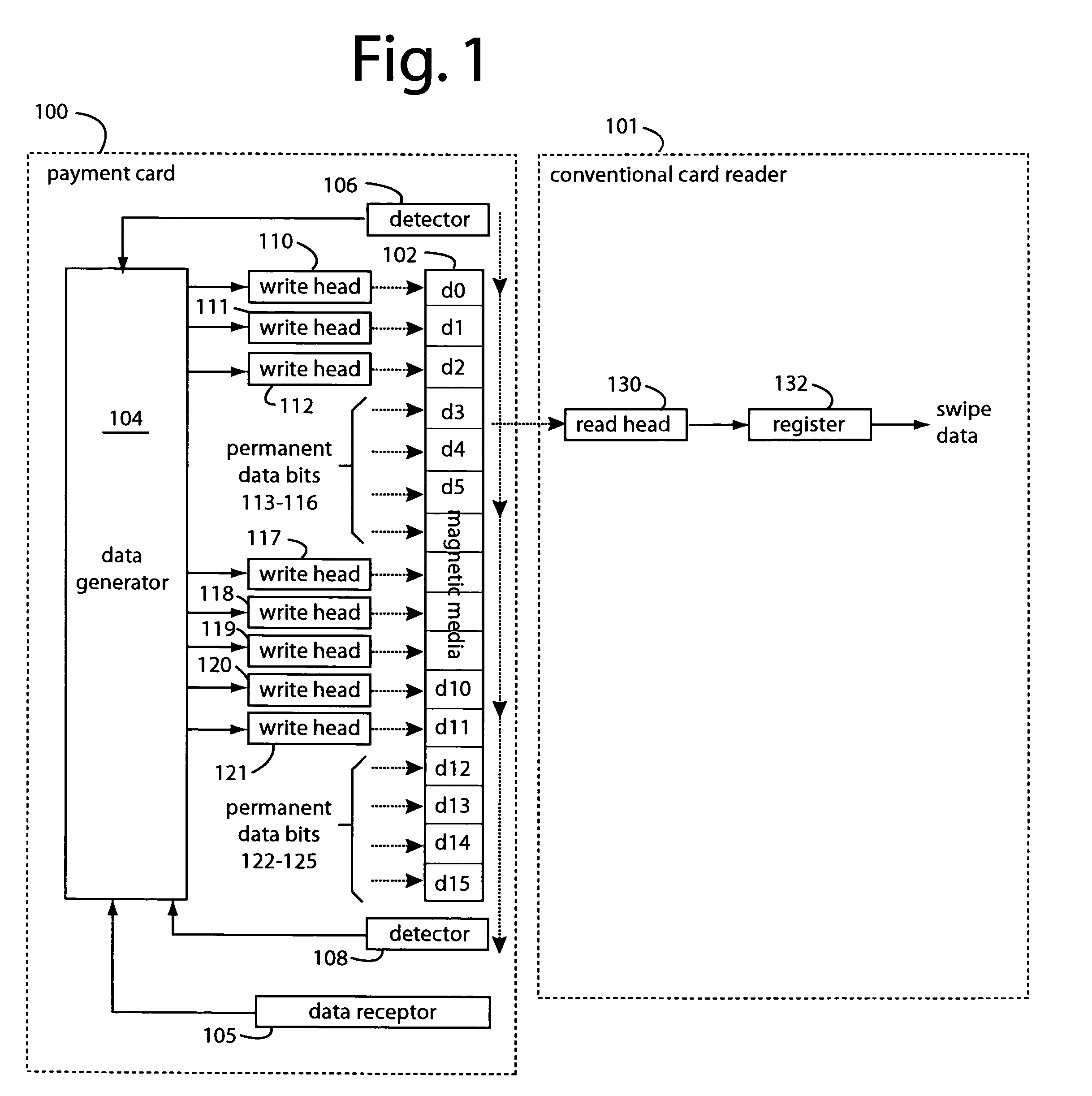

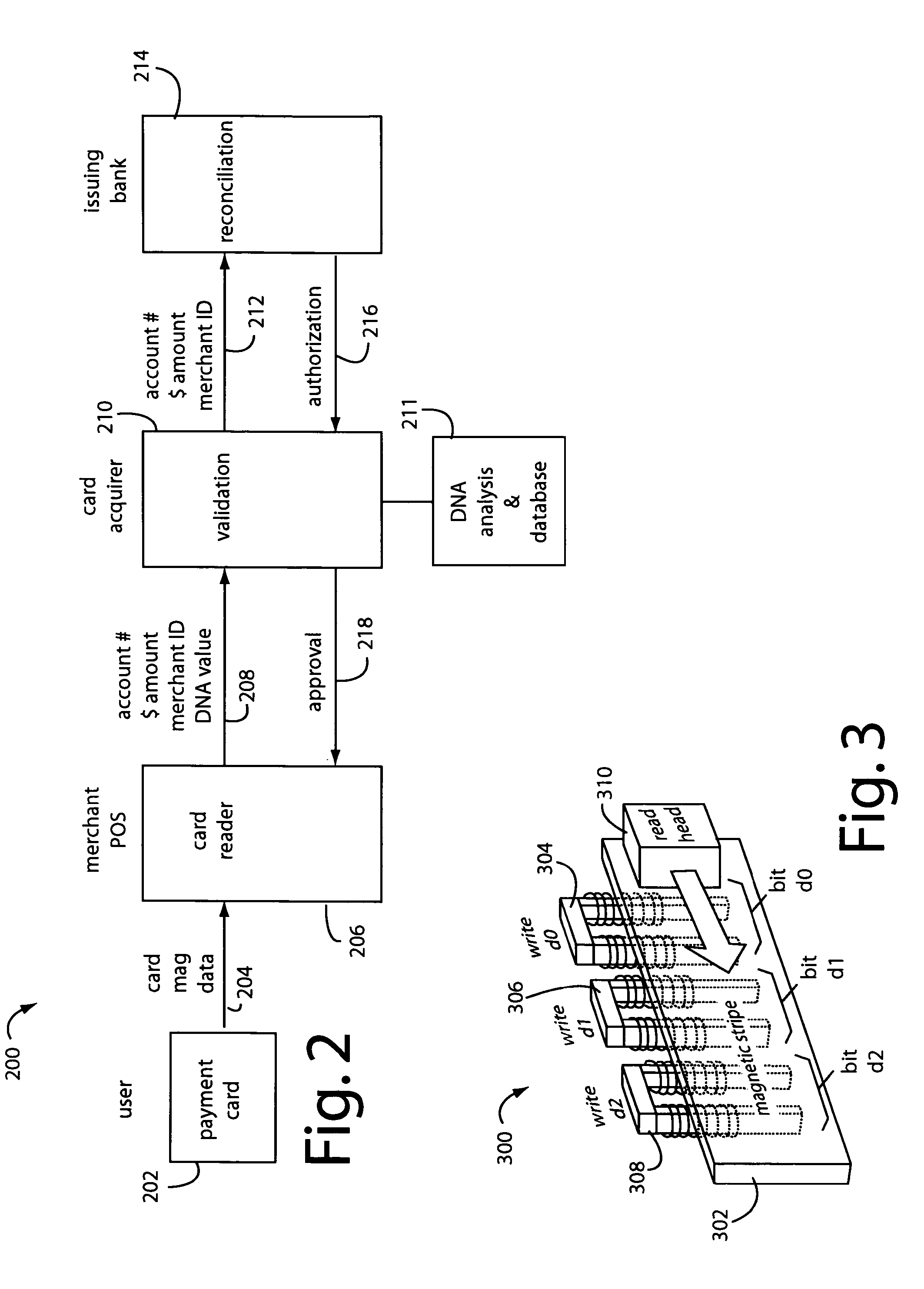

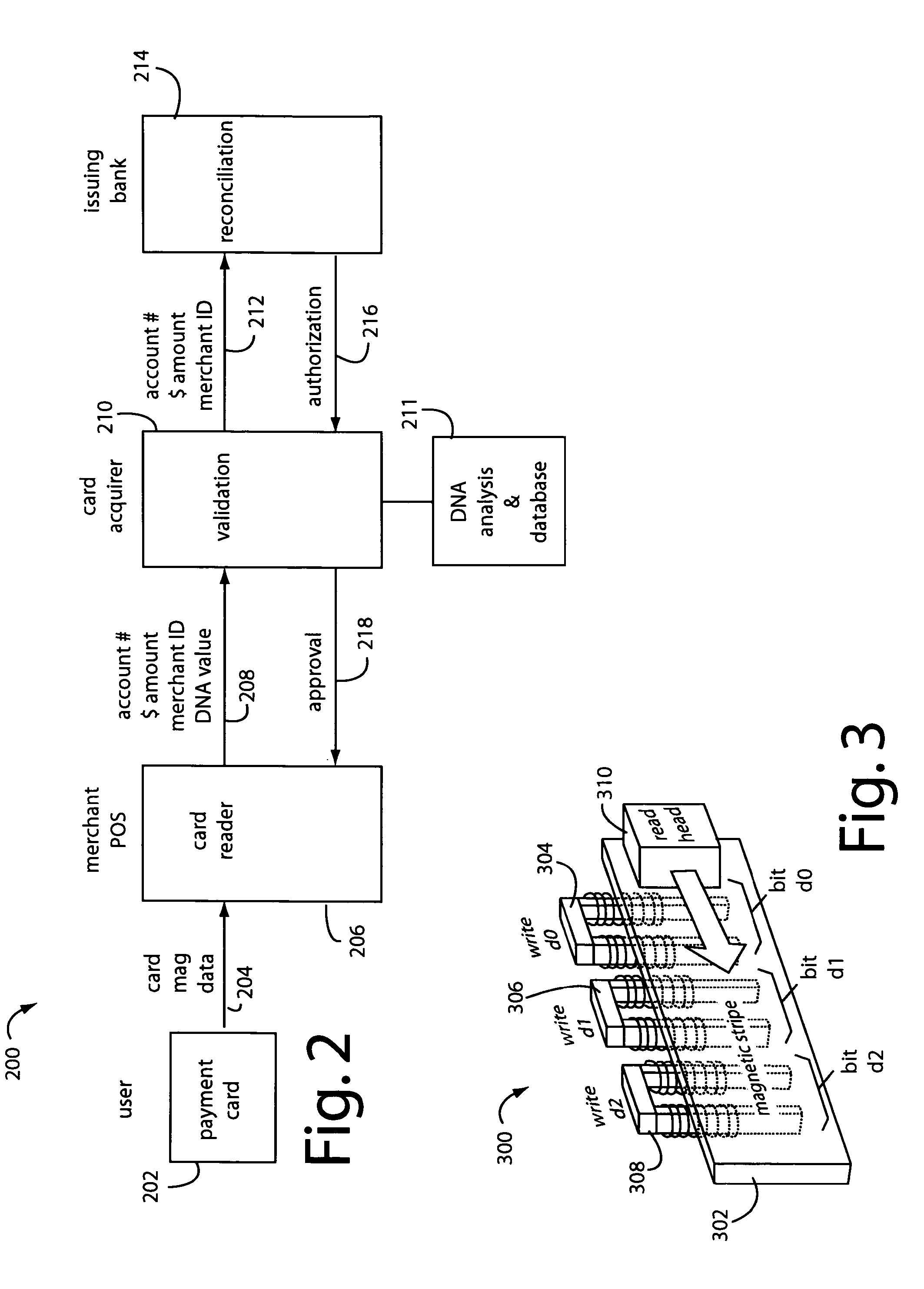

A payment card comprises a plastic card with a magnetic stripe for user account data. Internal to the plastic card, and behind the magnetic stripe, a number of fixed-position magnetic write heads allow the user account data to be automatically modified. For example, a data field that counts the number of times the card has been scanned is incremented. A payment processing center keeps track of this usage-counter data field, and will not authorize transaction requests that come out of sequence. For example, as can occur from a magnetic clone of a card that has been skimmed and tried later. A card-swipe detector embedded in the plastic card detects each use in a scanner, and it signals an internal microcomputer which changes data bits sent to the write heads. Once scanned, the payment card can also disable any reading of the user account data for a short fixed period of time.

Owner:FITBIT INC

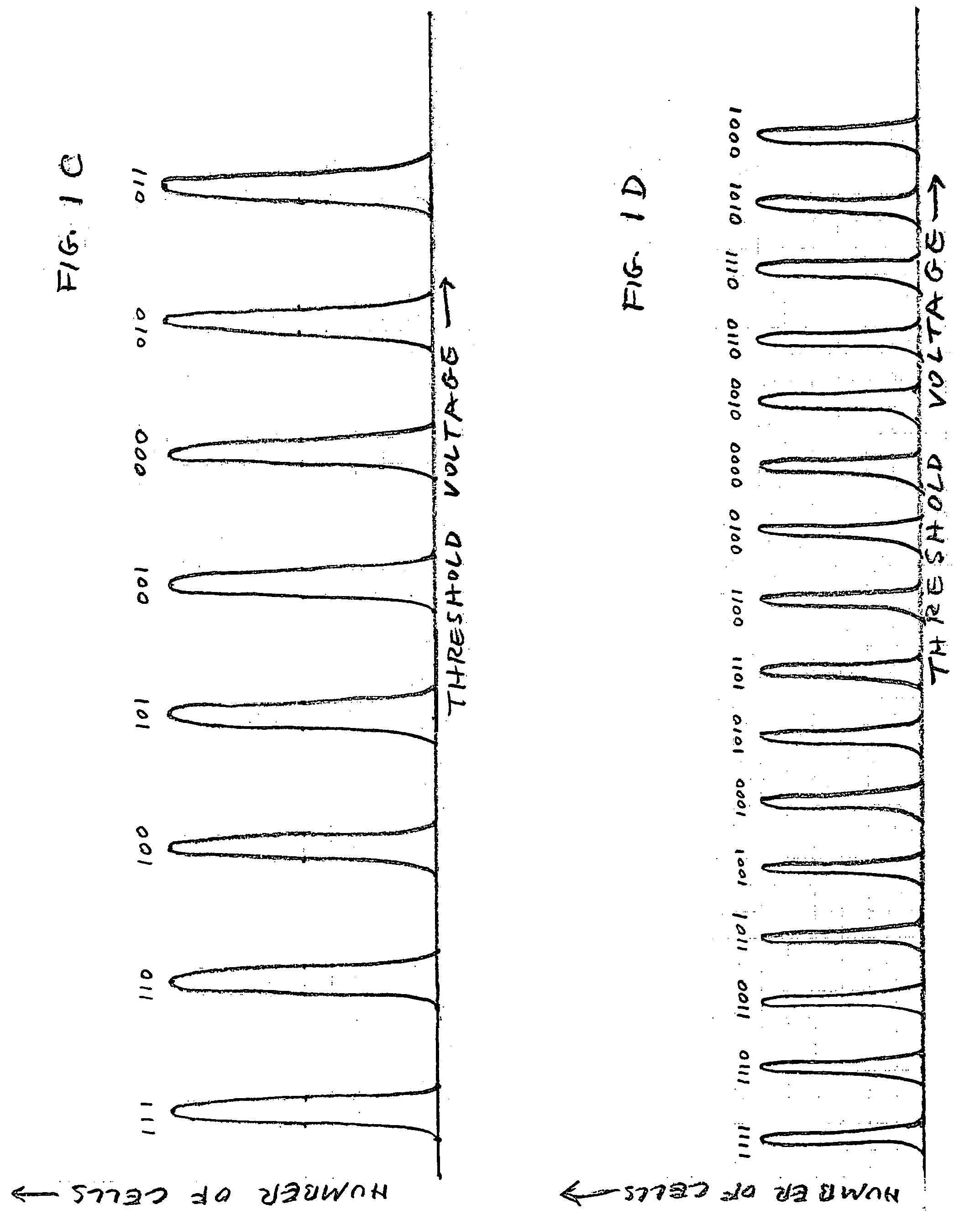

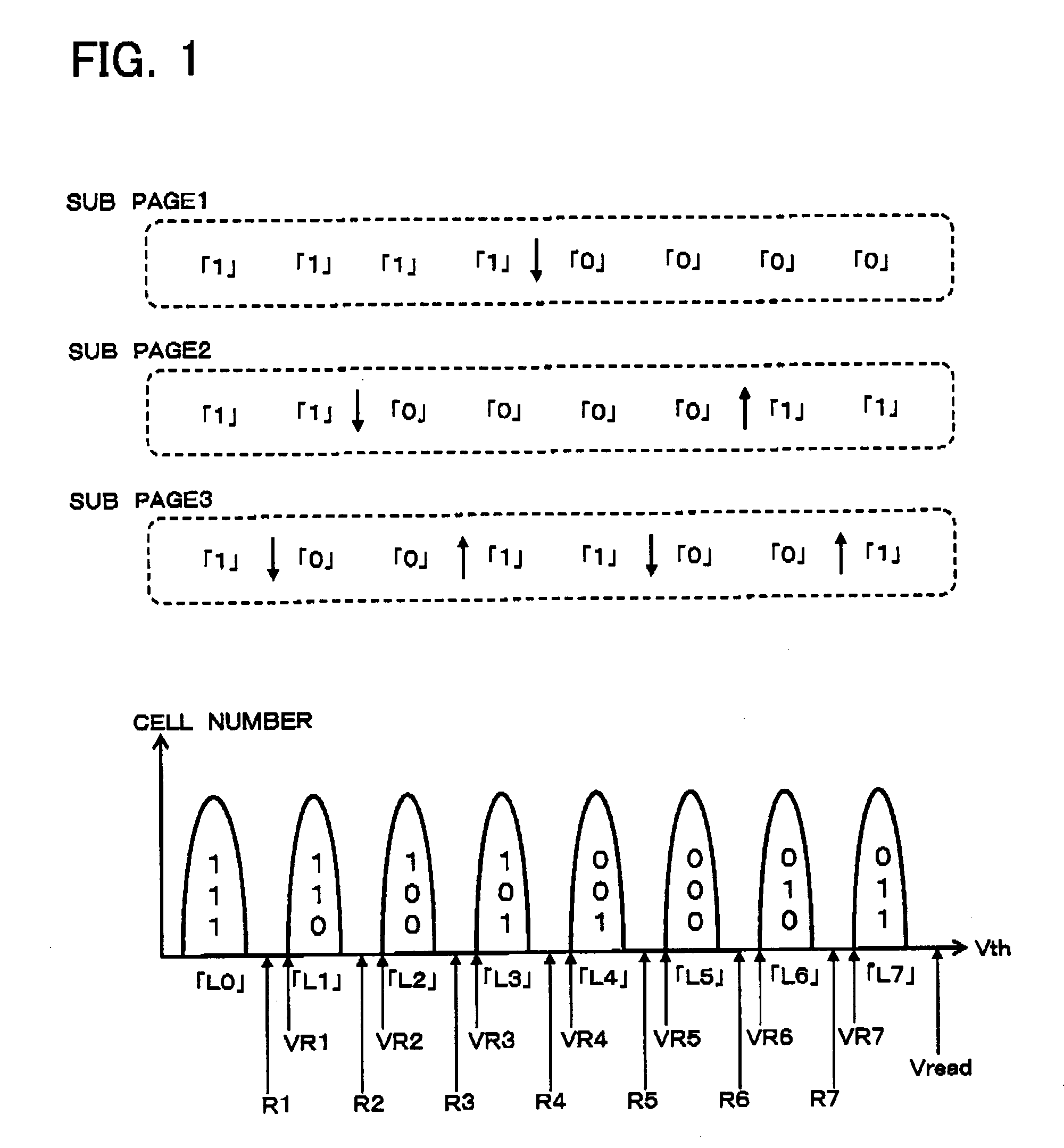

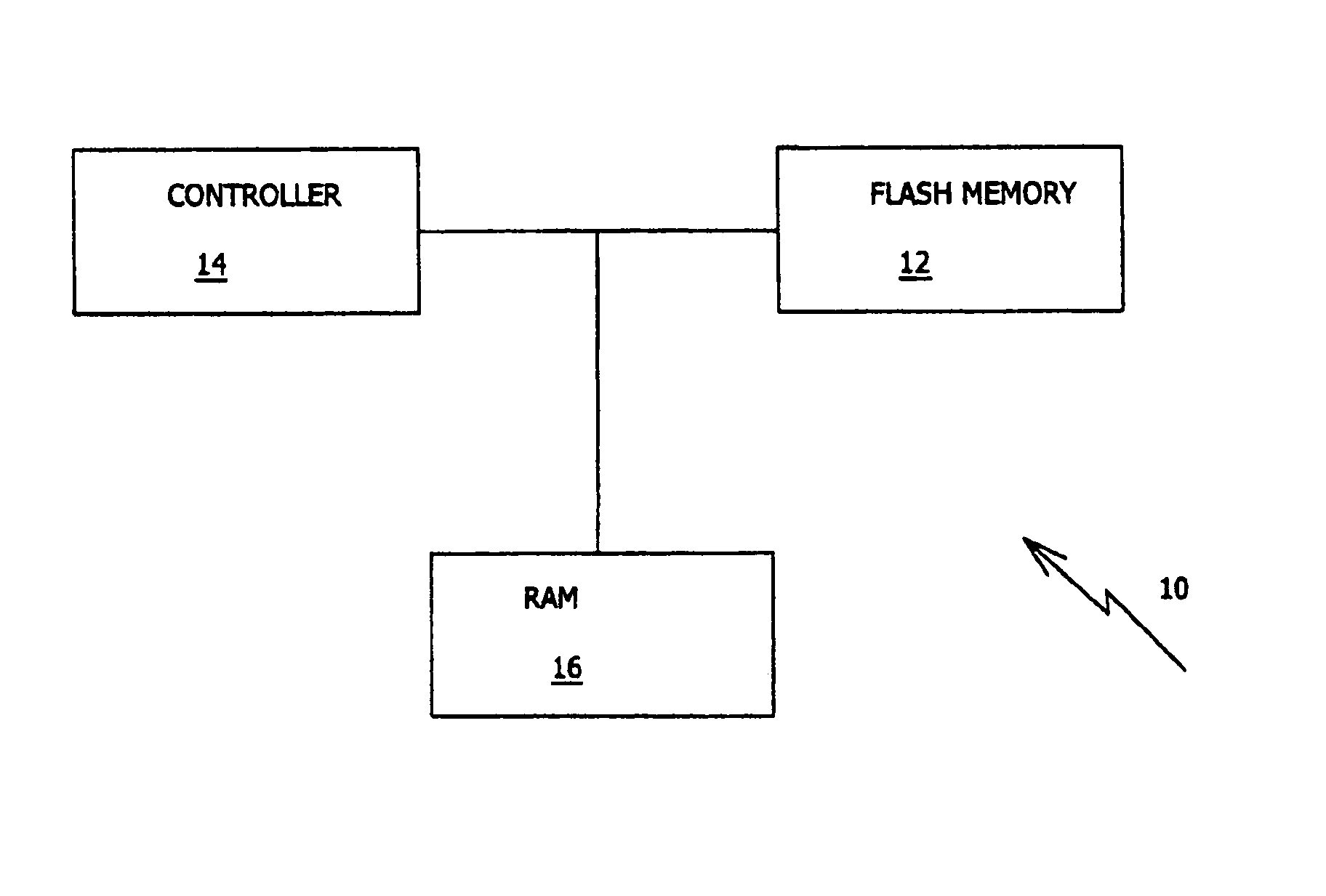

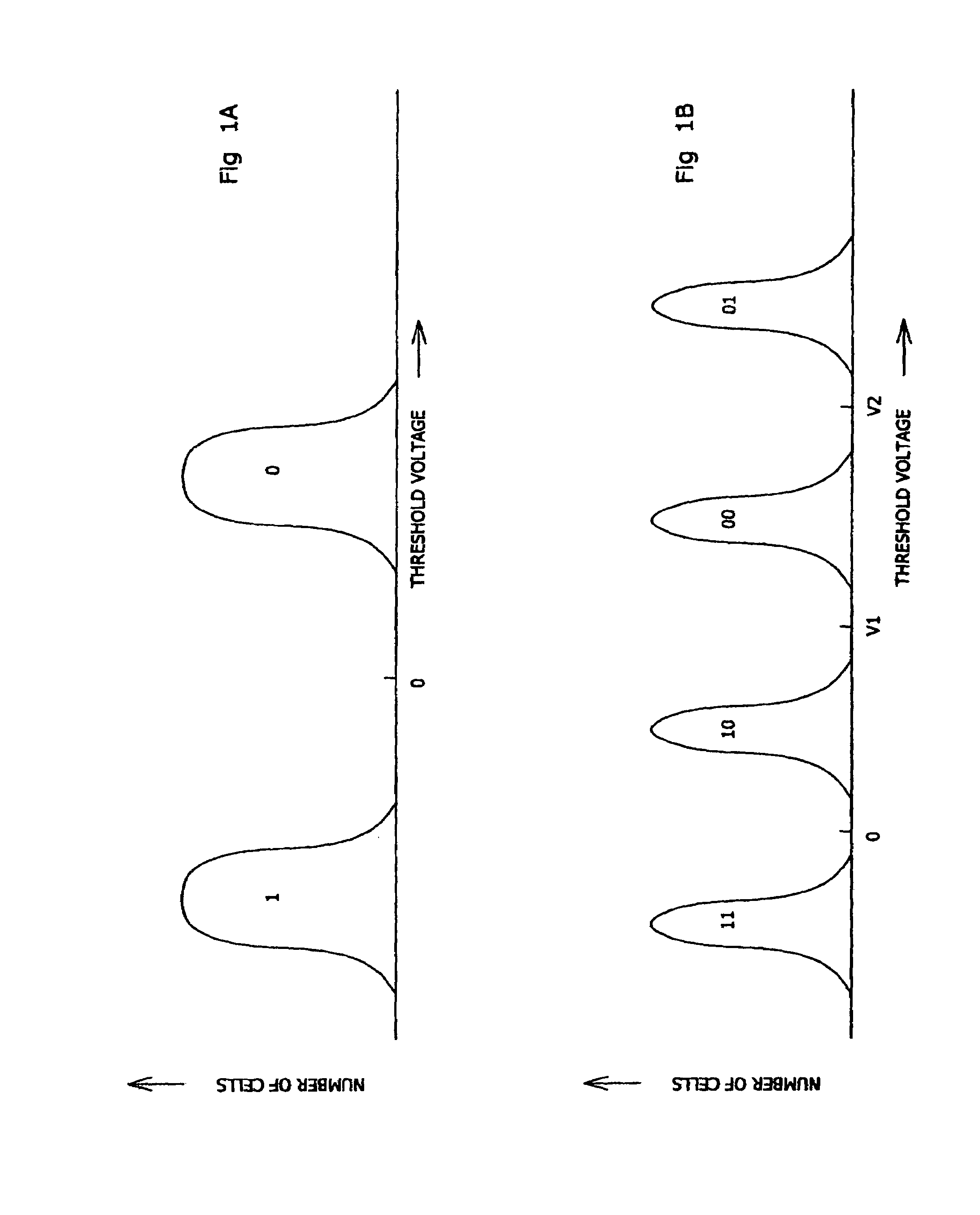

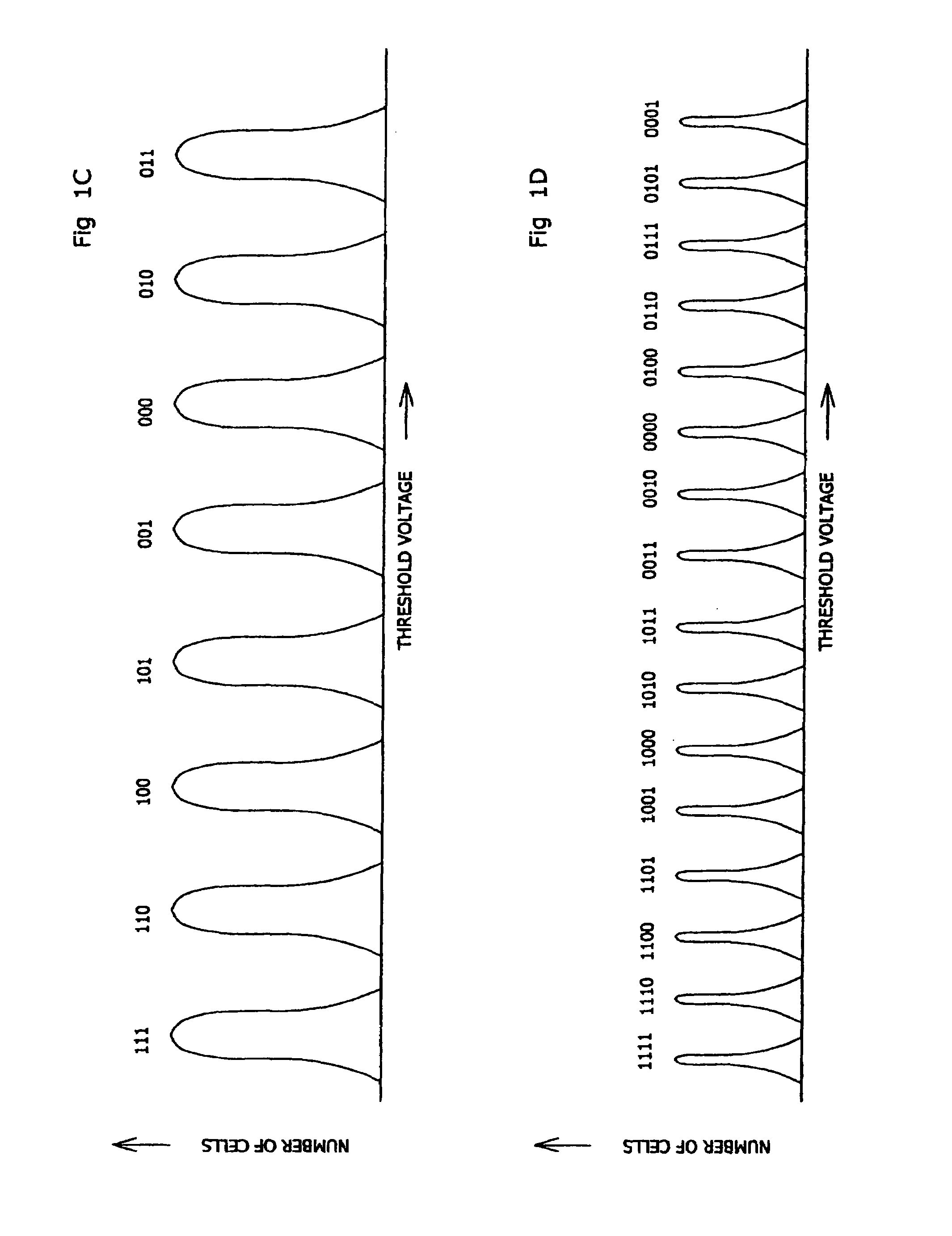

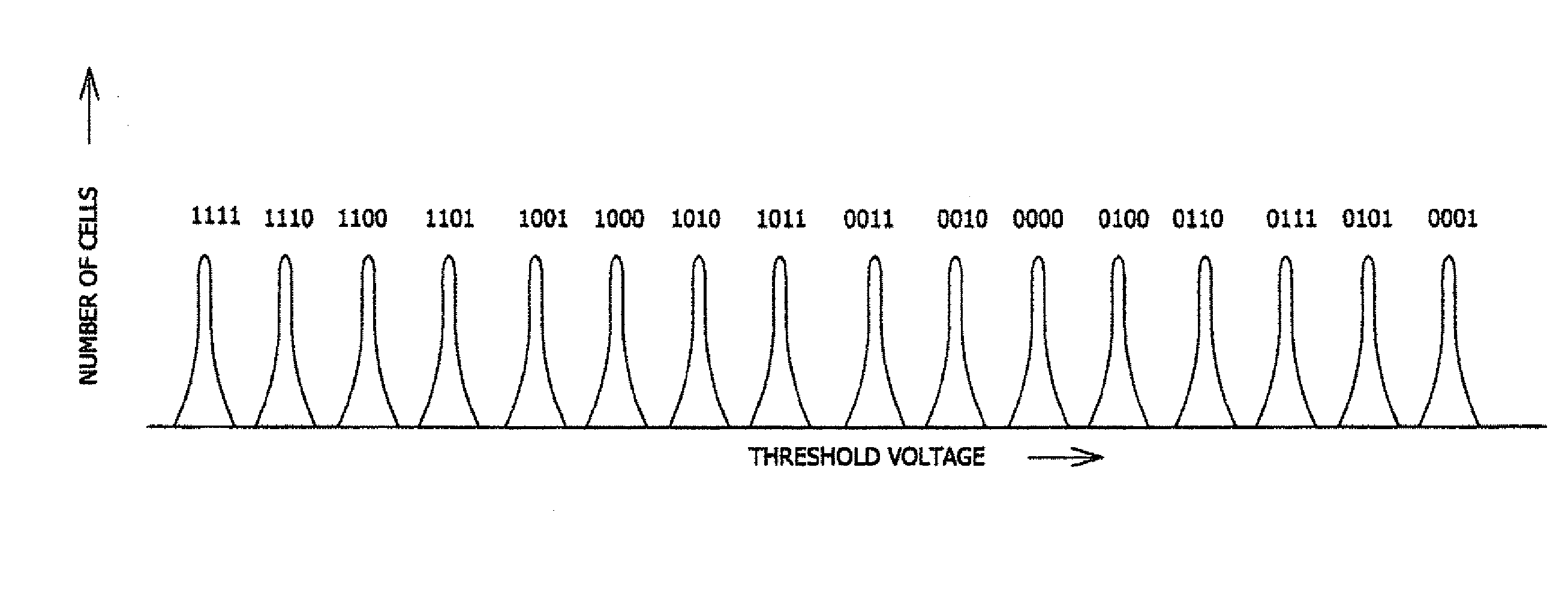

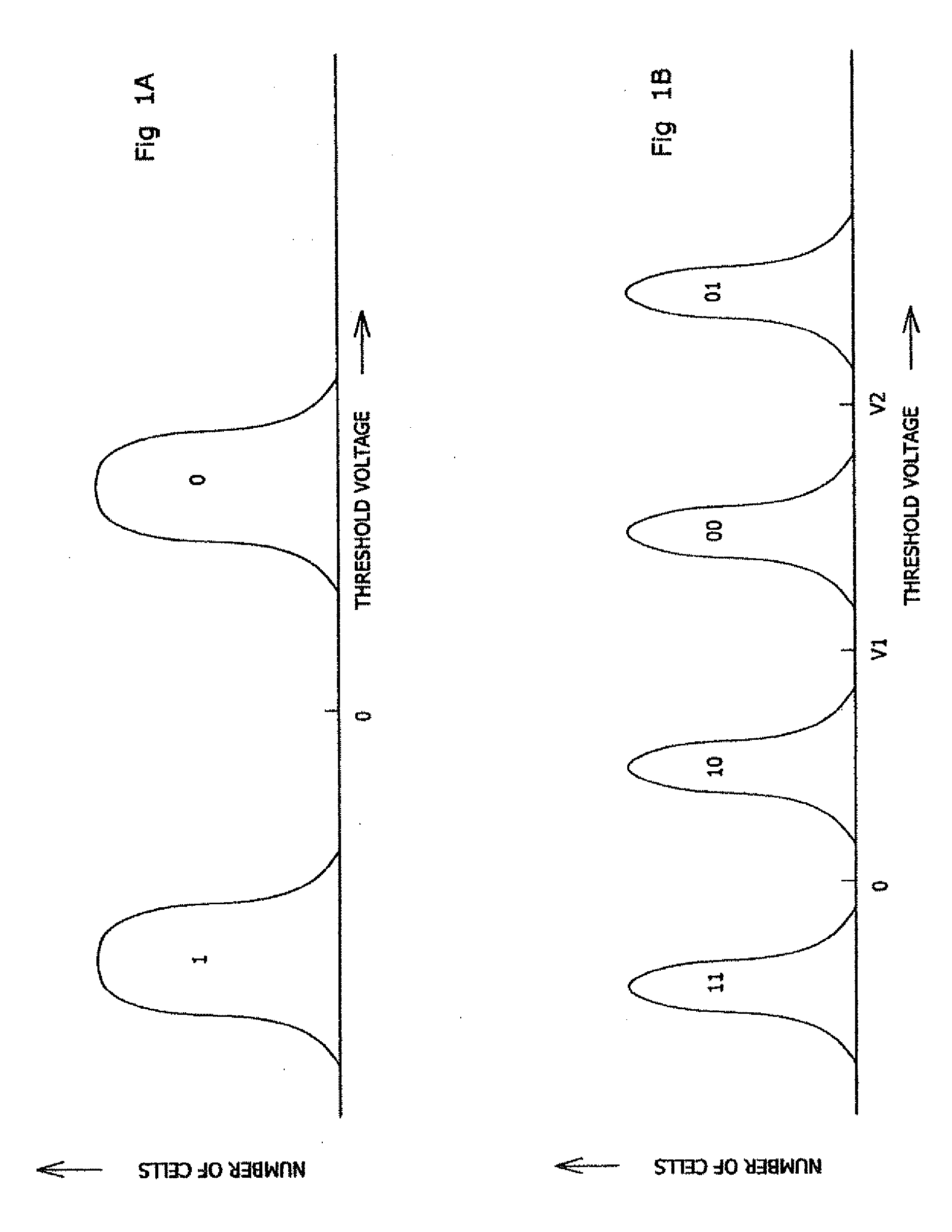

States encoding in multi-bit flash cells for optimizing error rate

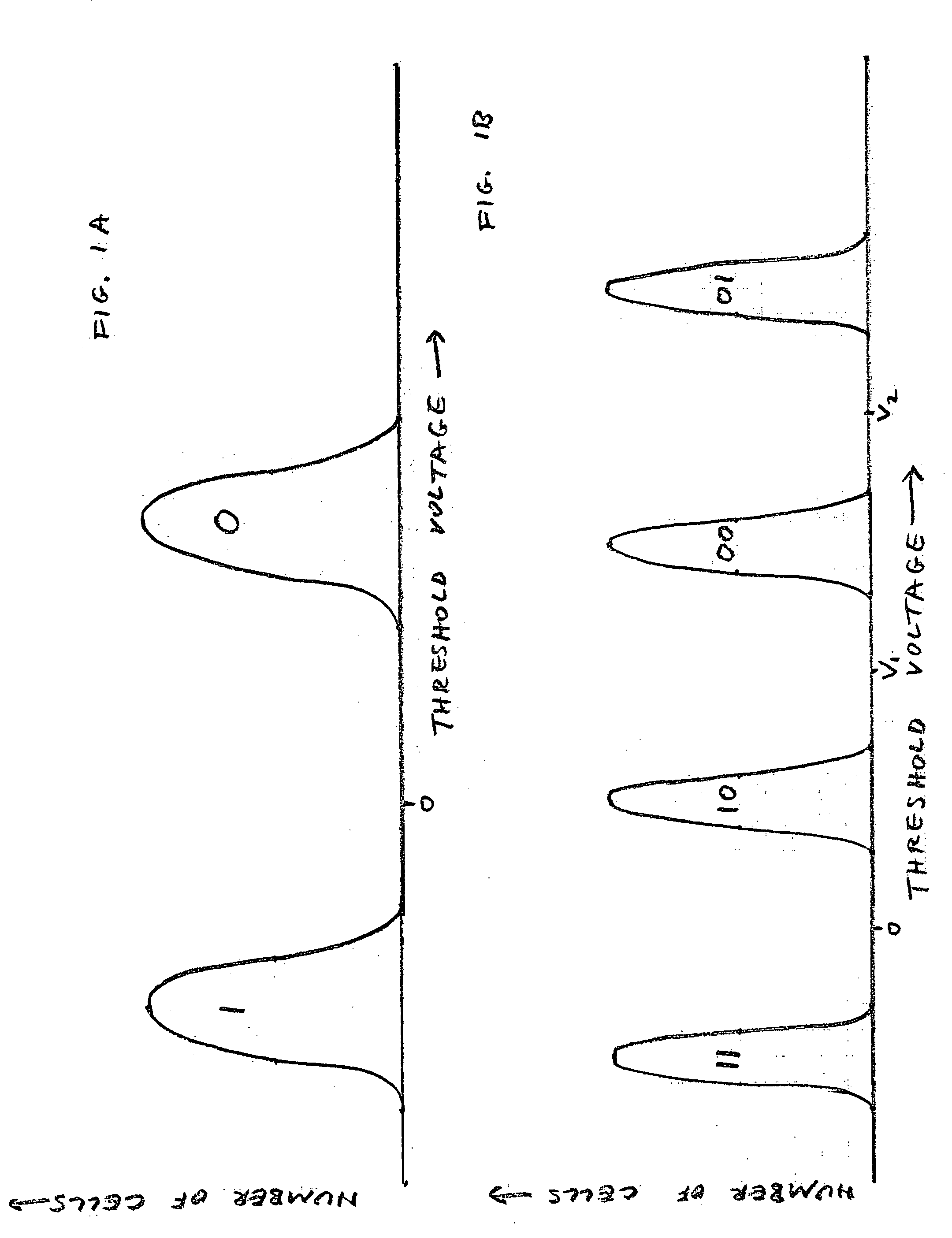

InactiveUS20050213393A1Equally distributedRead-only memoriesDigital storageTest error rateData error

Owner:SANDISK IL

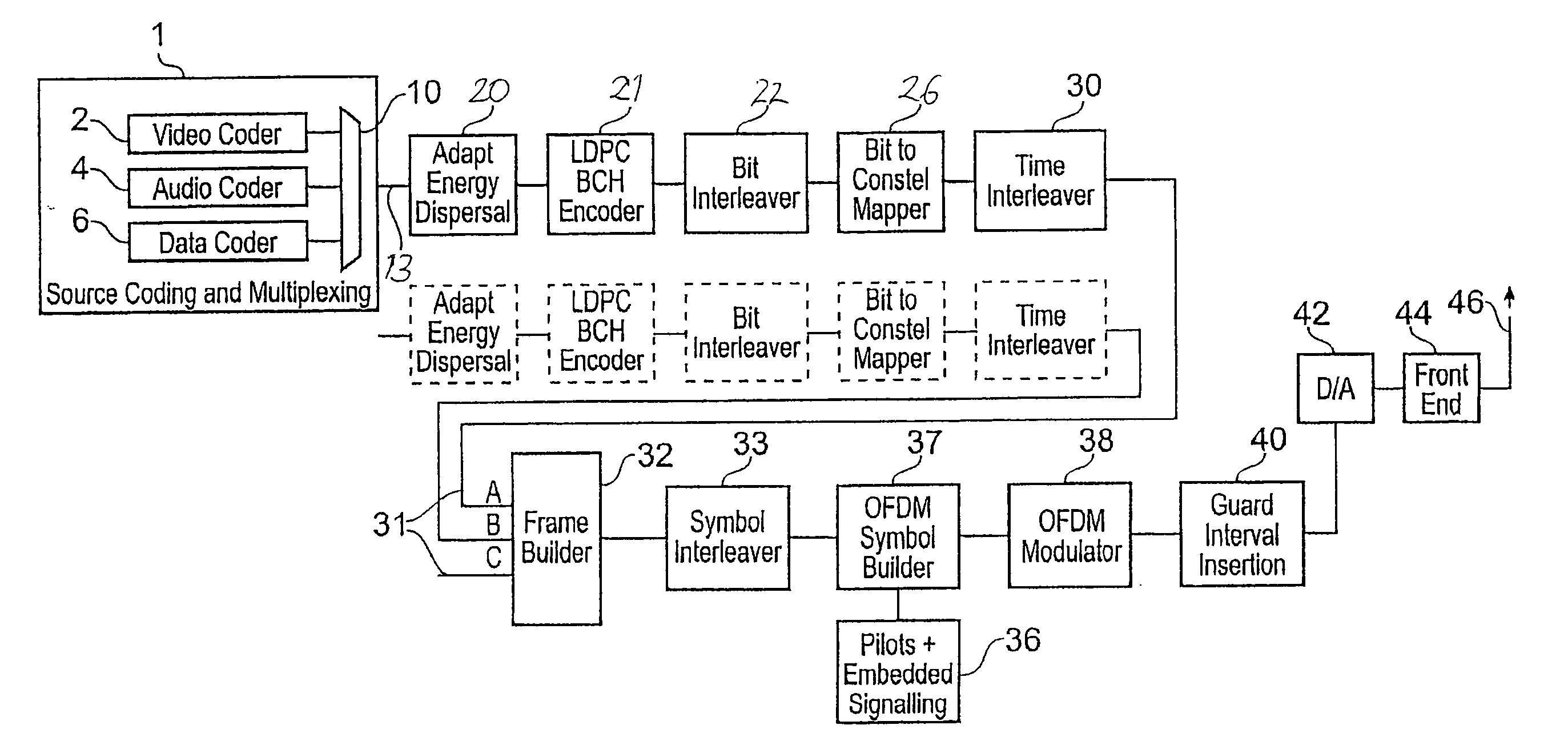

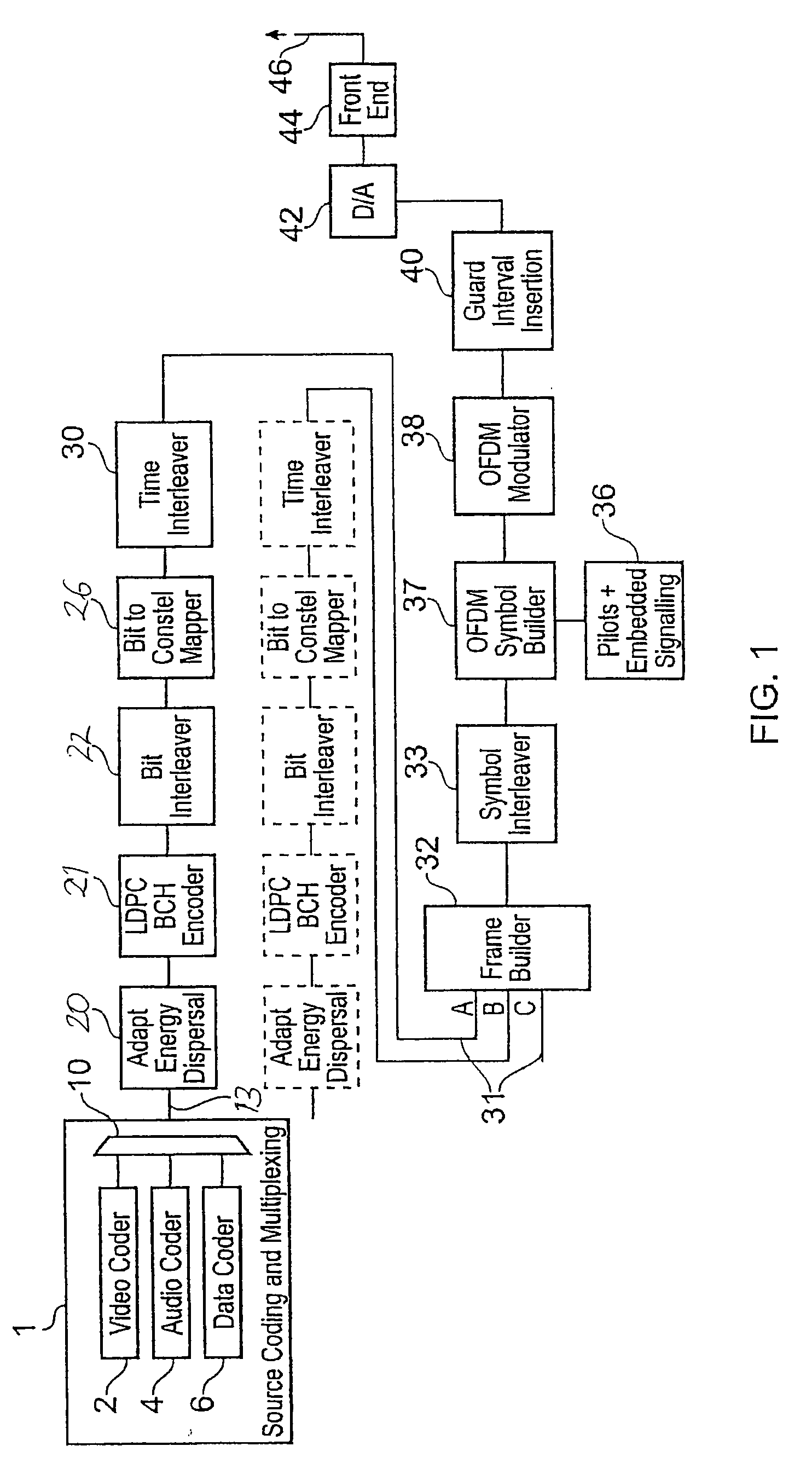

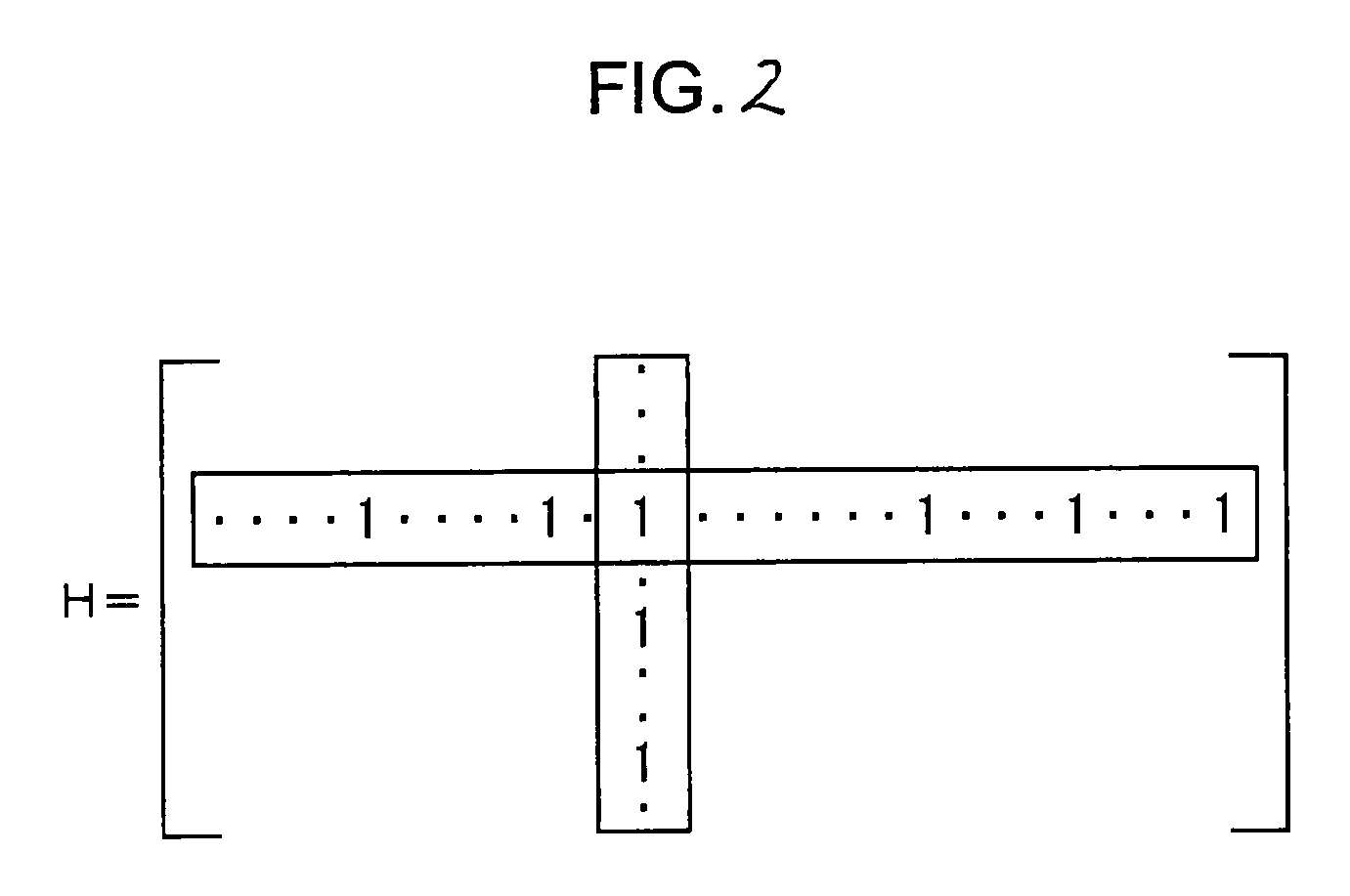

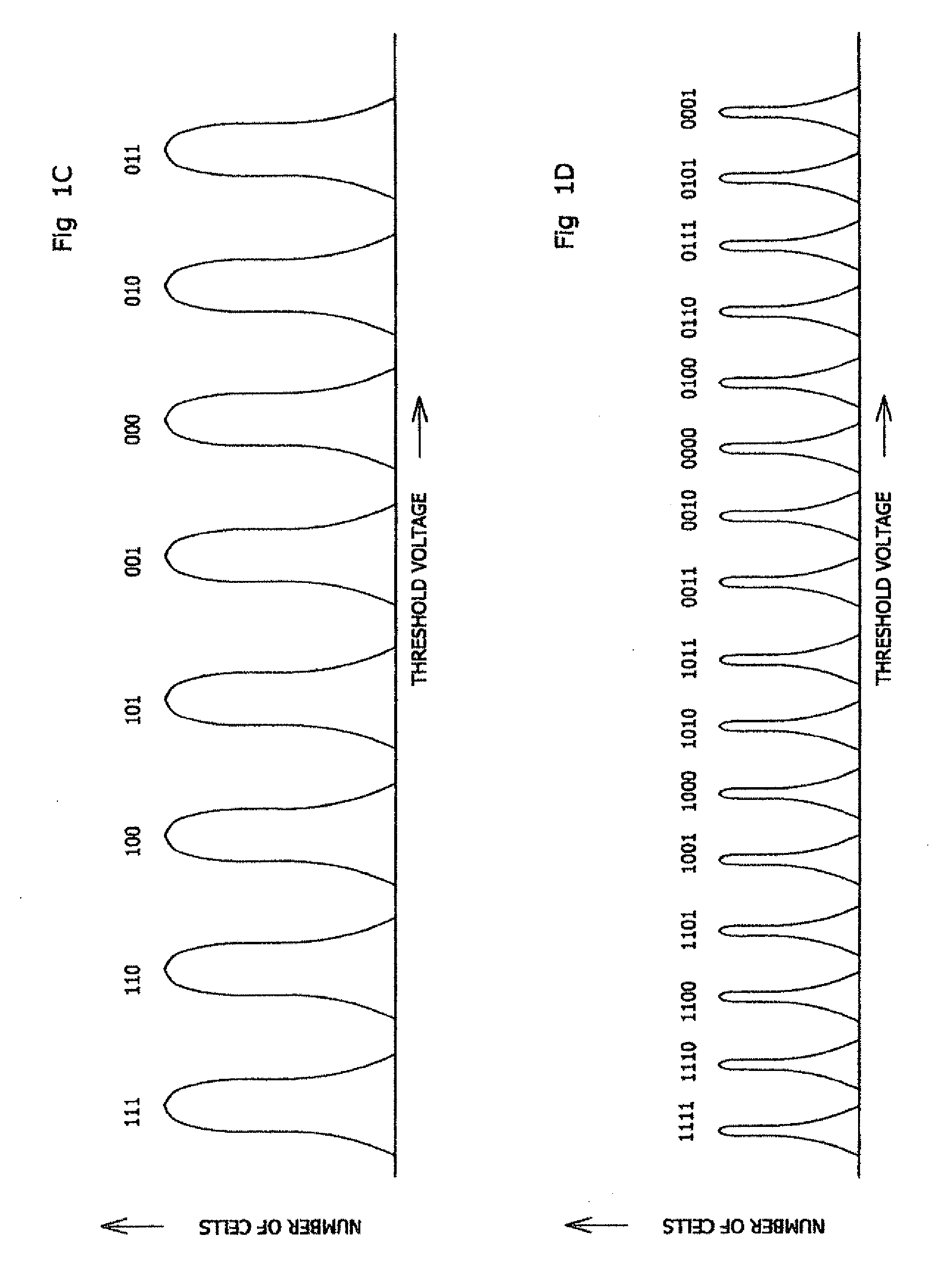

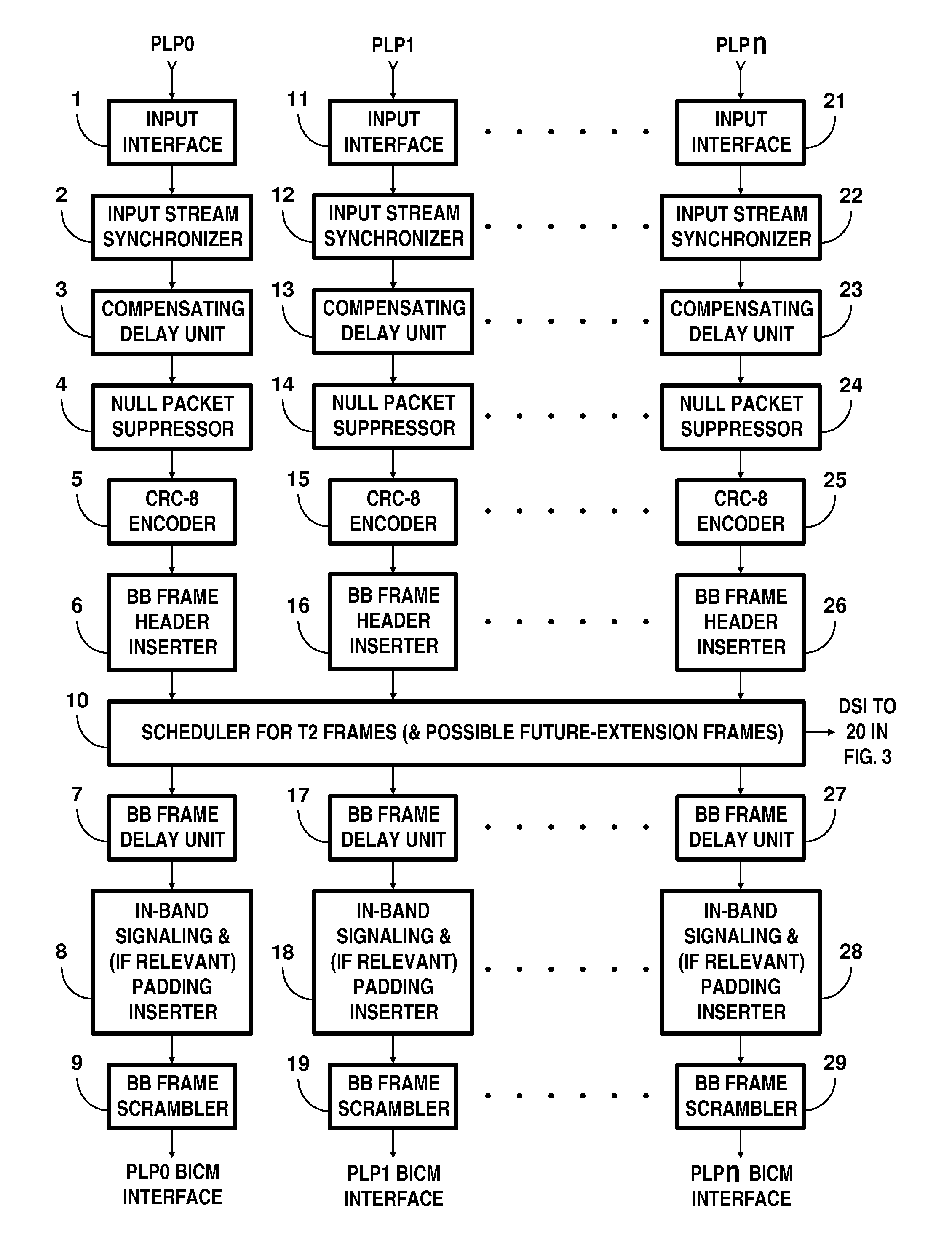

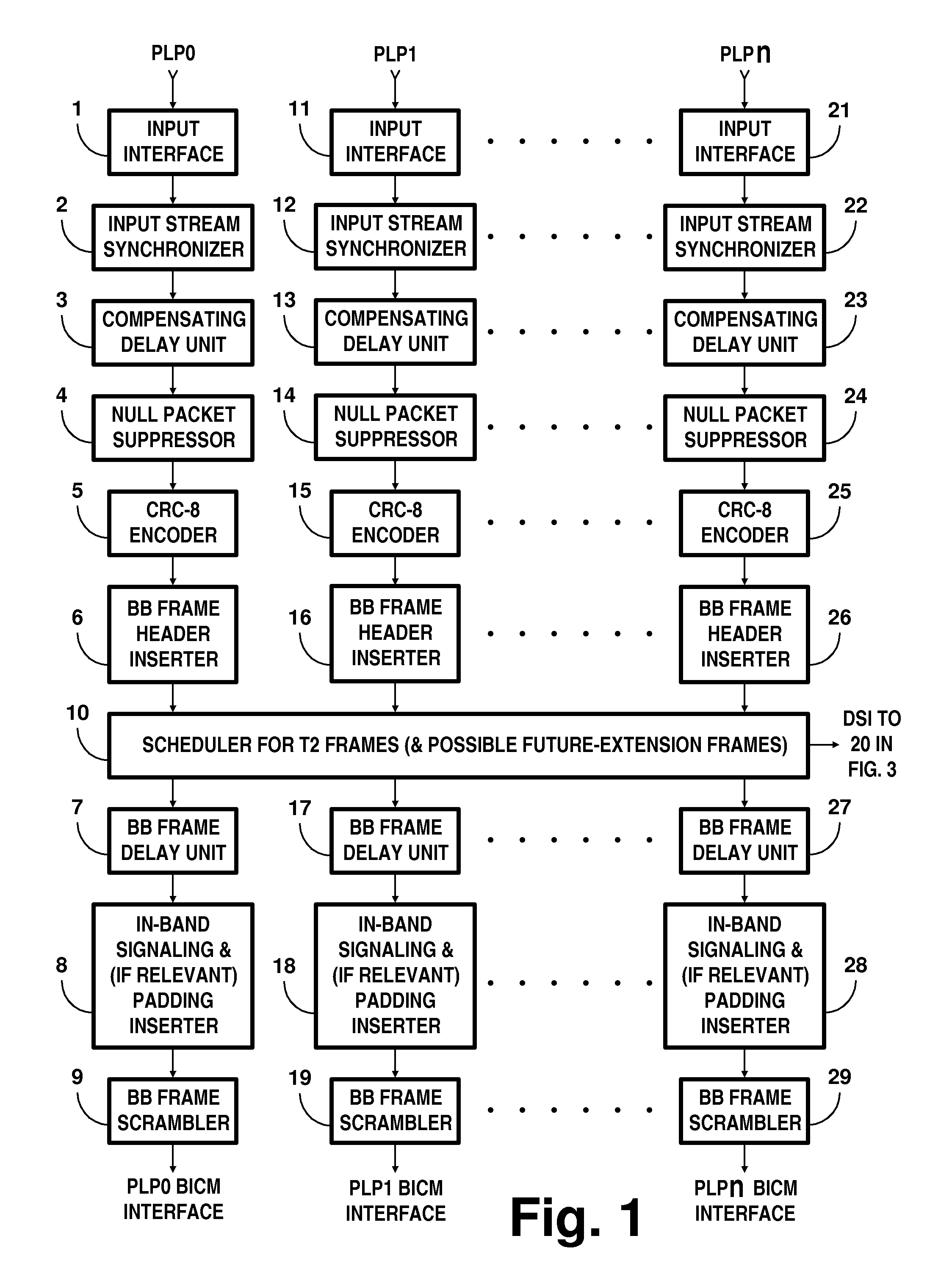

Data processing apparatus and method

ActiveUS20090125780A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError detection/correctionCarrier signalTheoretical computer science

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals. A symbol interleaver is arranged in operation to read-into a symbol interleaver memory the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals, and to read-out of the interleaver memory the data symbols for the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on the sub-carrier signals. The set of addresses are generated by an address generator which has been optimised to interleave the data symbols on to the sub-carrier signals of the OFDM carrier signals for a given operating mode of the OFDM system, such as a 32K operating mode for DVB-T2 or DVB-C2.

Owner:SATURN LICENSING LLC

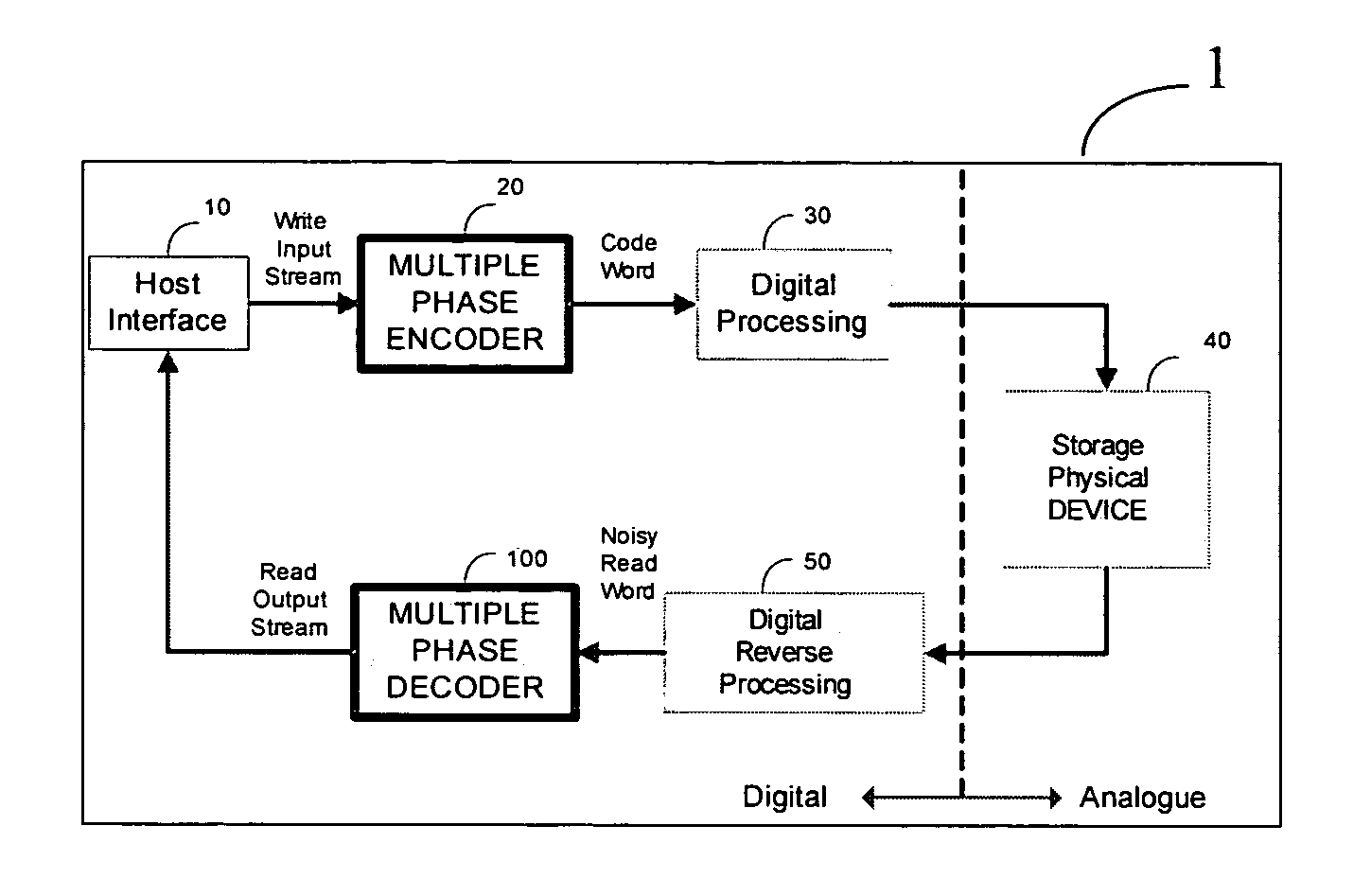

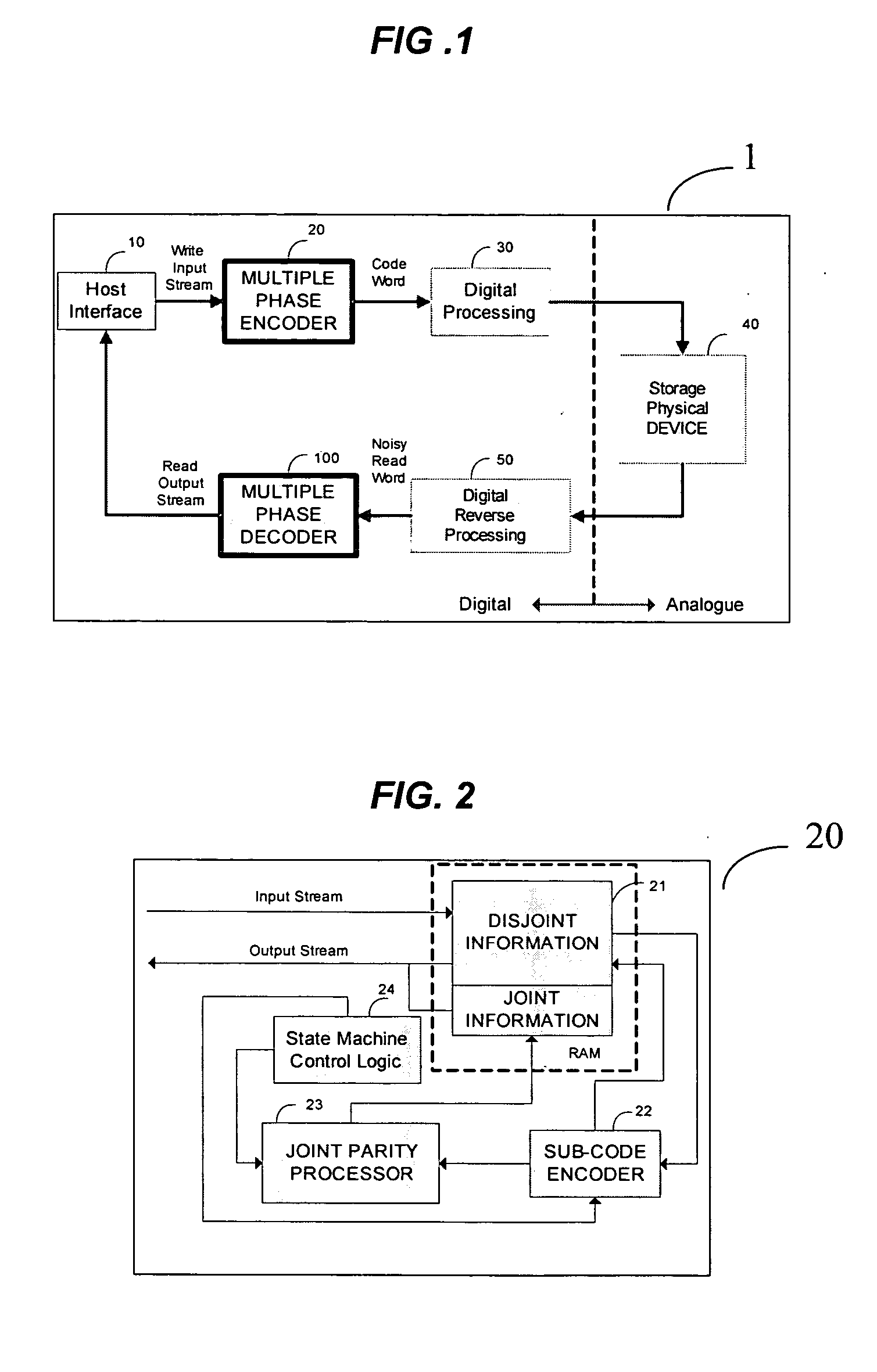

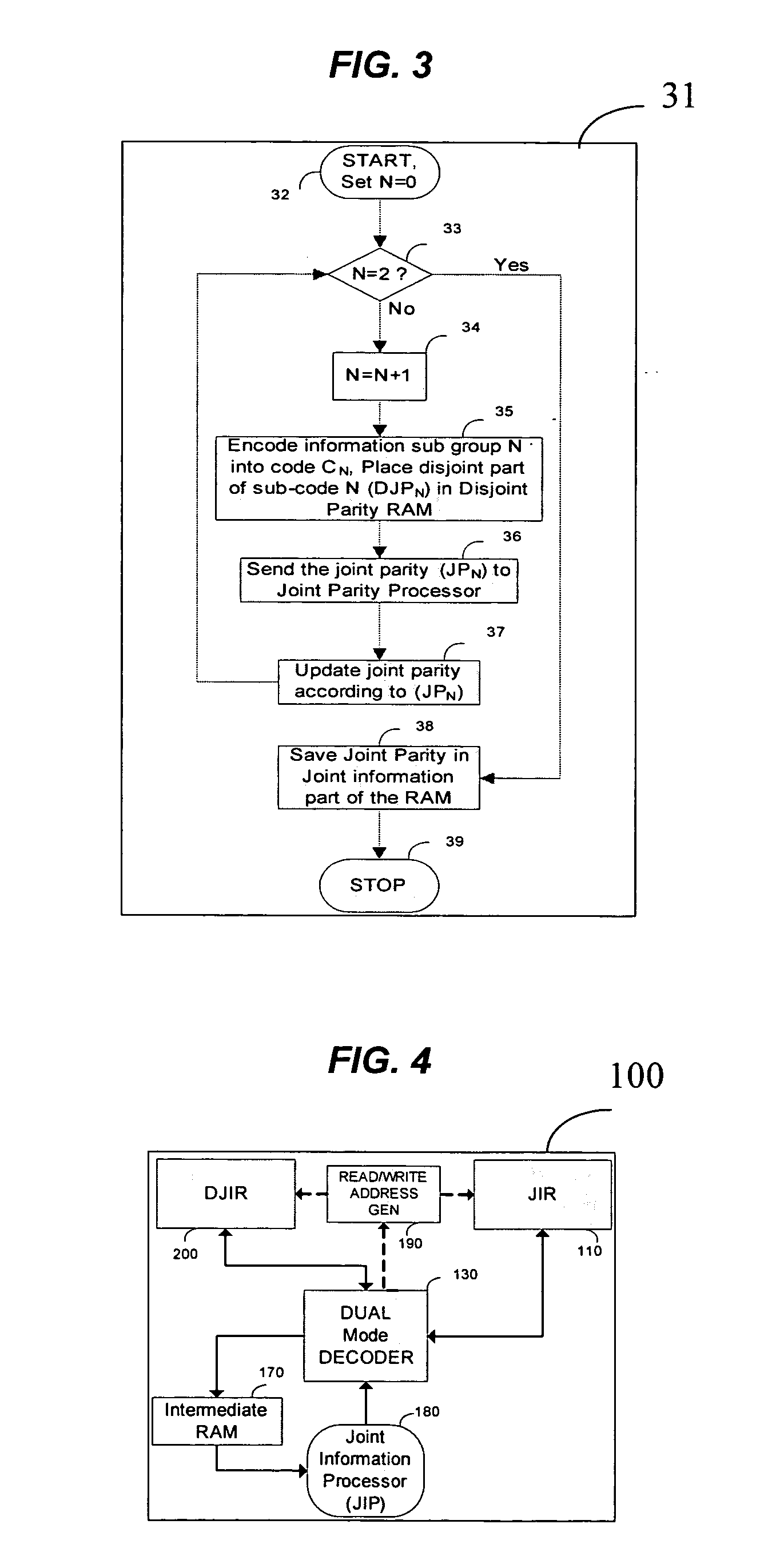

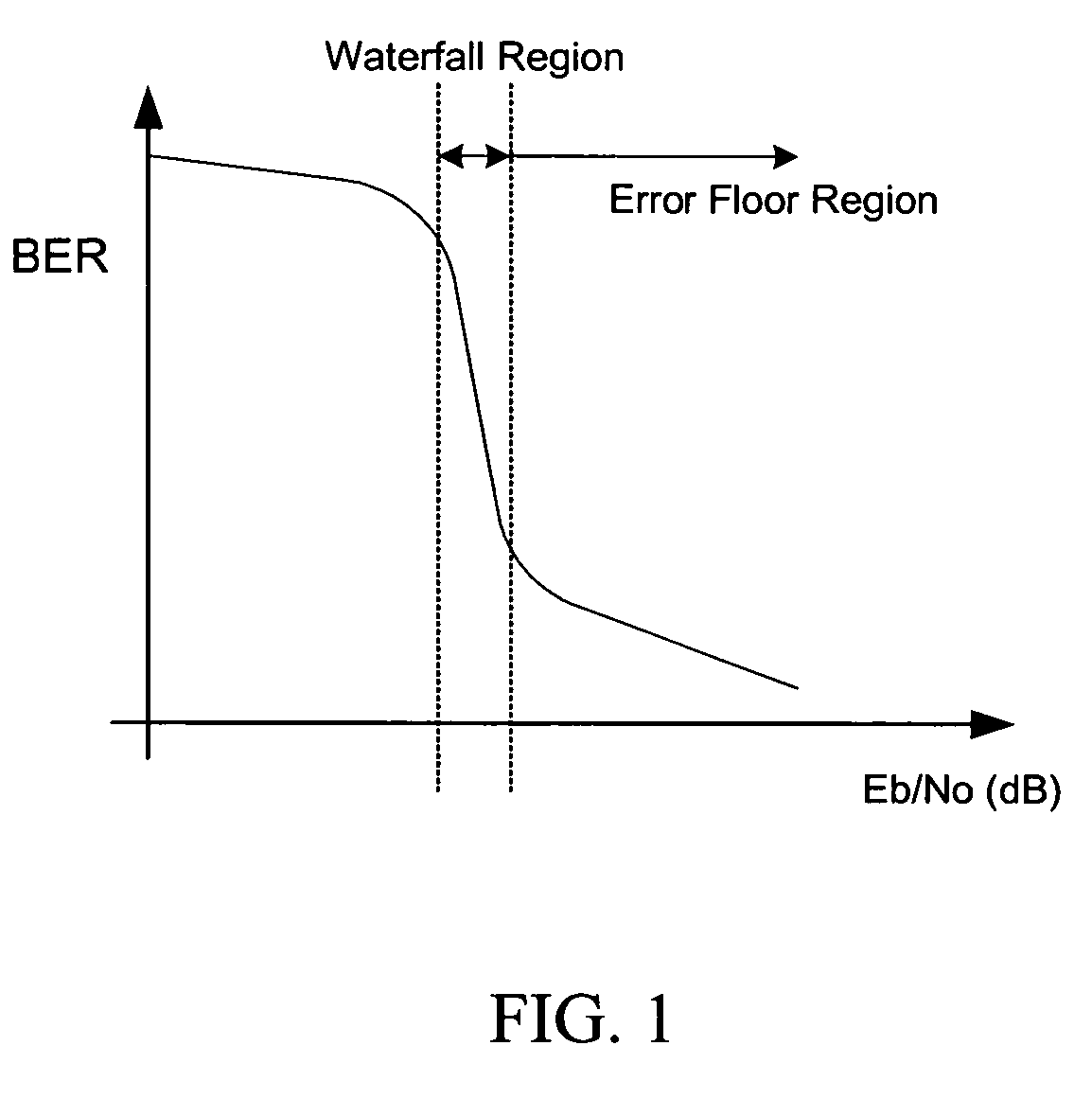

Method and device for multi phase error-correction

InactiveUS20070124652A1Error detection/correctionCode conversionTheoretical computer scienceMulti phase

Data bits to be encoded are split into a plurality of subgroups. Each subgroup is encoded separately to generate a corresponding codeword. Selected subsets are removed from the corresponding codewords, leaving behind shortened codewords, and are many-to-one transformed to condensed bits. The final codeword is a combination of the shortened codewords and the condensed bits. A representation of the final codeword is decoded by being partitioned to a selected subset and a plurality of remaining subsets. Each remaining subset is decoded separately. If one of the decodings fails, the remaining subset whose decoding failed is decoded at least in part according to the selected subset. If the encoding and decoding are systematic then the selected subsets are of parity bits.

Owner:RAMOT AT TEL AVIV UNIV LTD

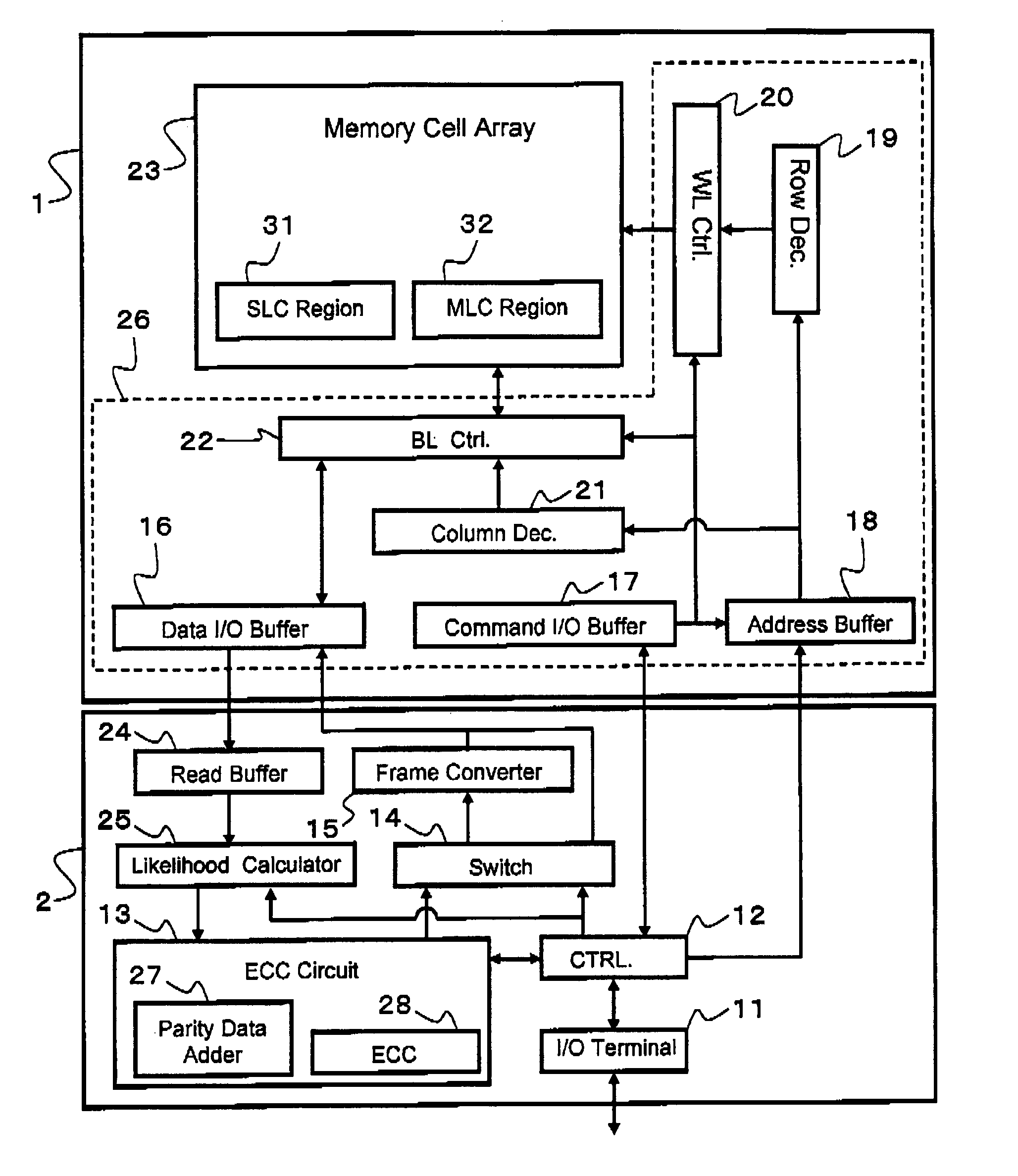

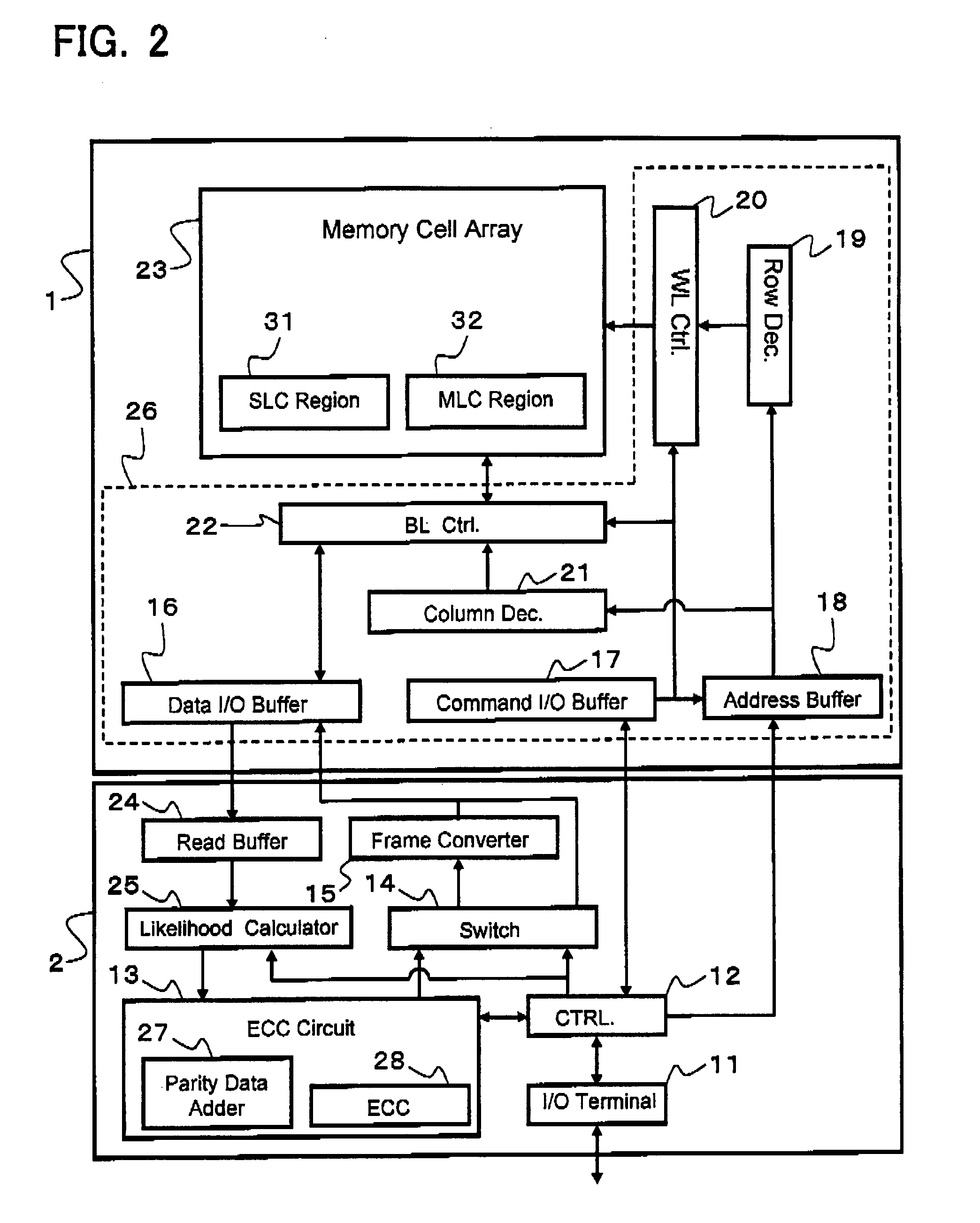

Non-volatile semiconductor memory device

ActiveUS20080301532A1Read-only memoriesError correction/detection using block codesThreshold voltageData bits

A non-volatile semiconductor memory device comprises a memory cell array including a plurality of memory cells arrayed capable of storing information of N bits (N≧2) in accordance with variations in threshold voltage. A parity data adder circuit adds parity data for error correction to every certain data bits to be stored in the memory cell array. A frame converter circuit uniformly divides frame data containing the data bits and the parity data into N pieces of subframe data. A programming circuit stores the subframe data divided into N pieces in respective N sub-pages formed corresponding to the information of N bits.

Owner:KIOXIA CORP

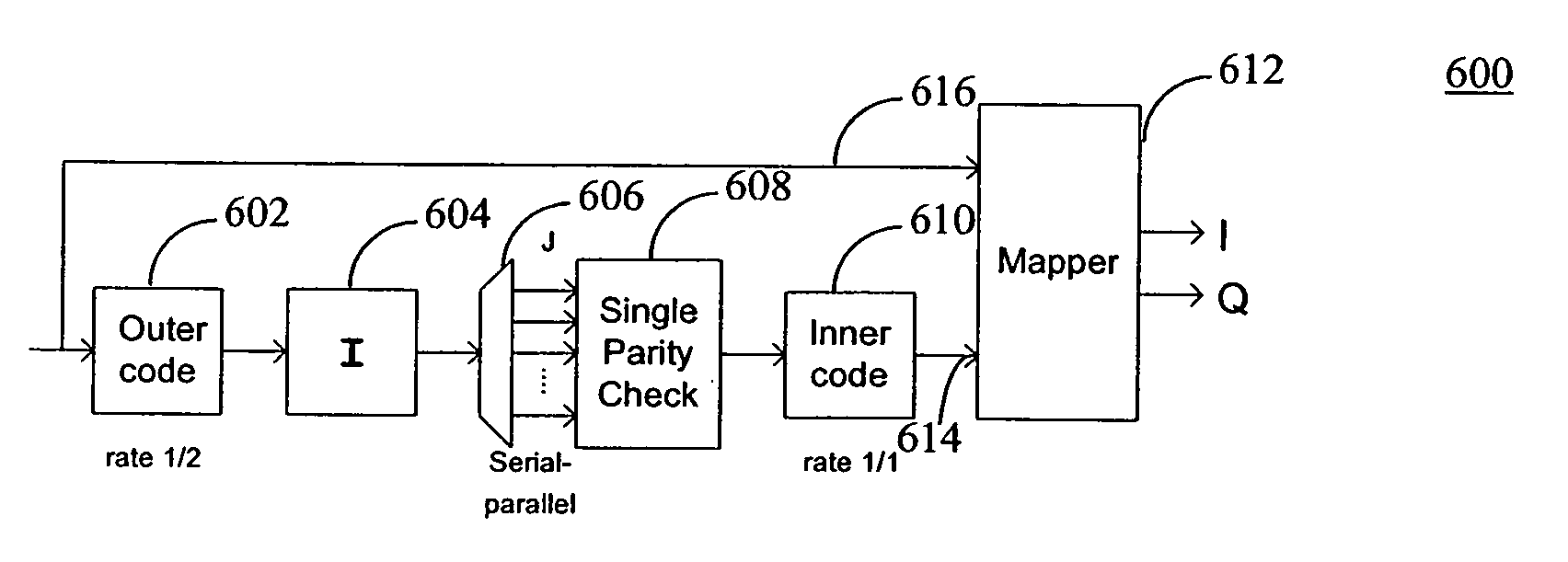

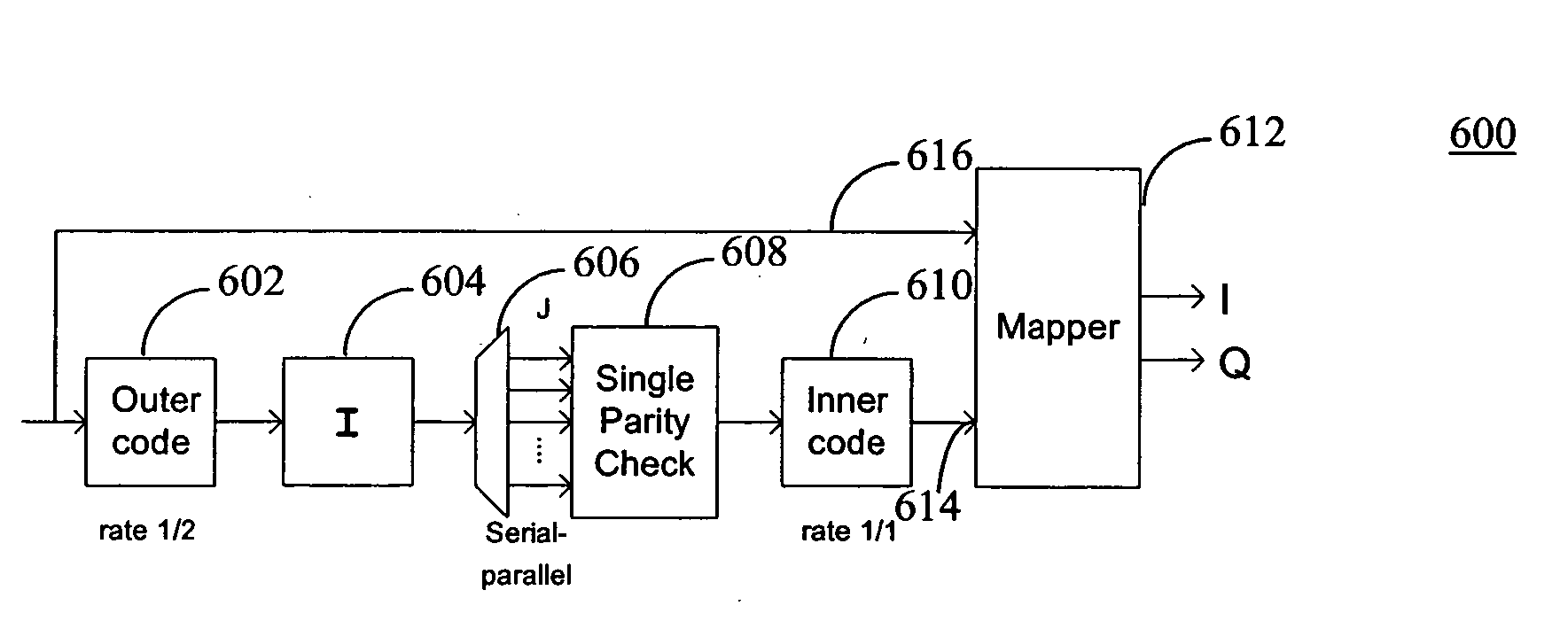

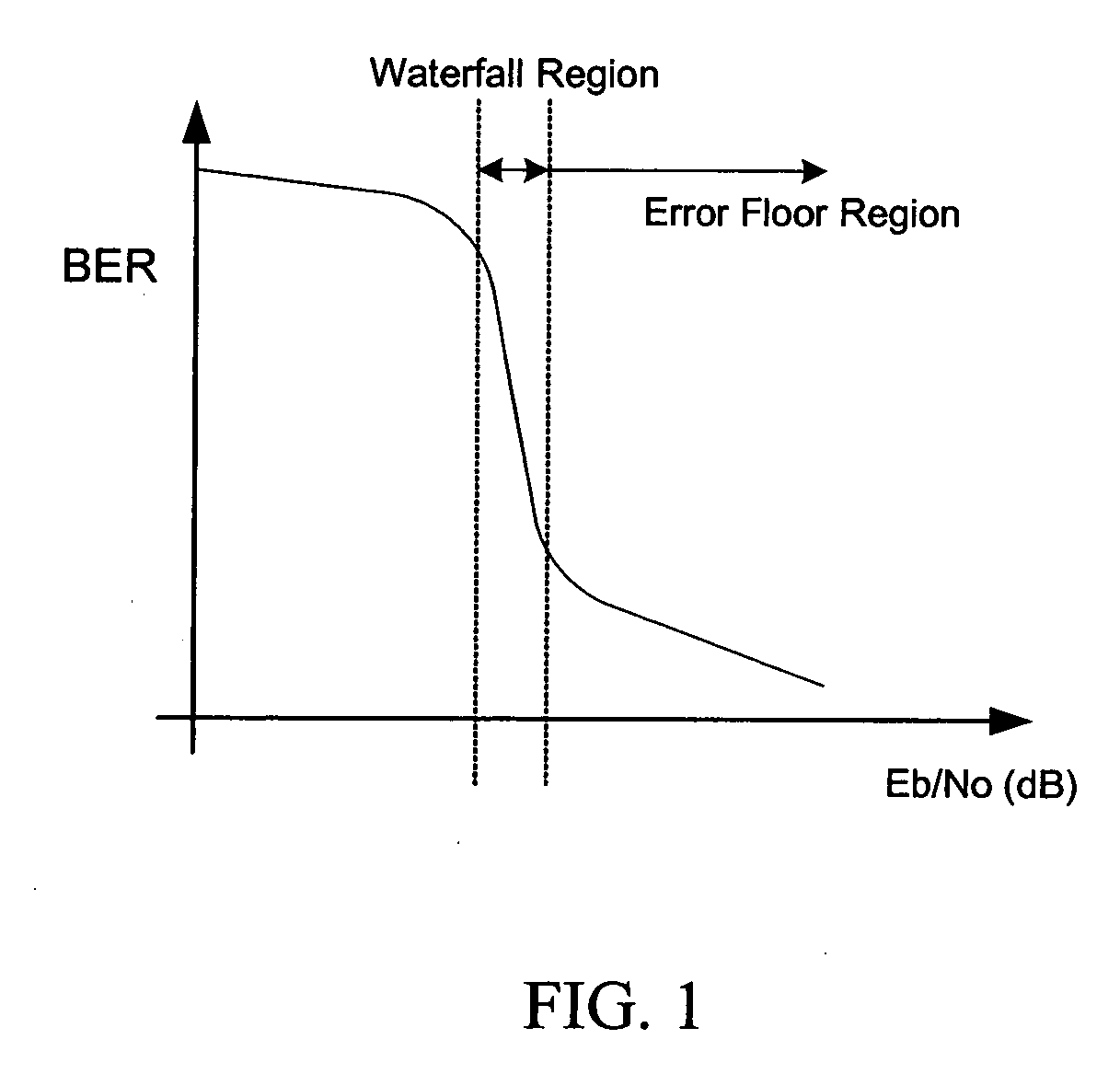

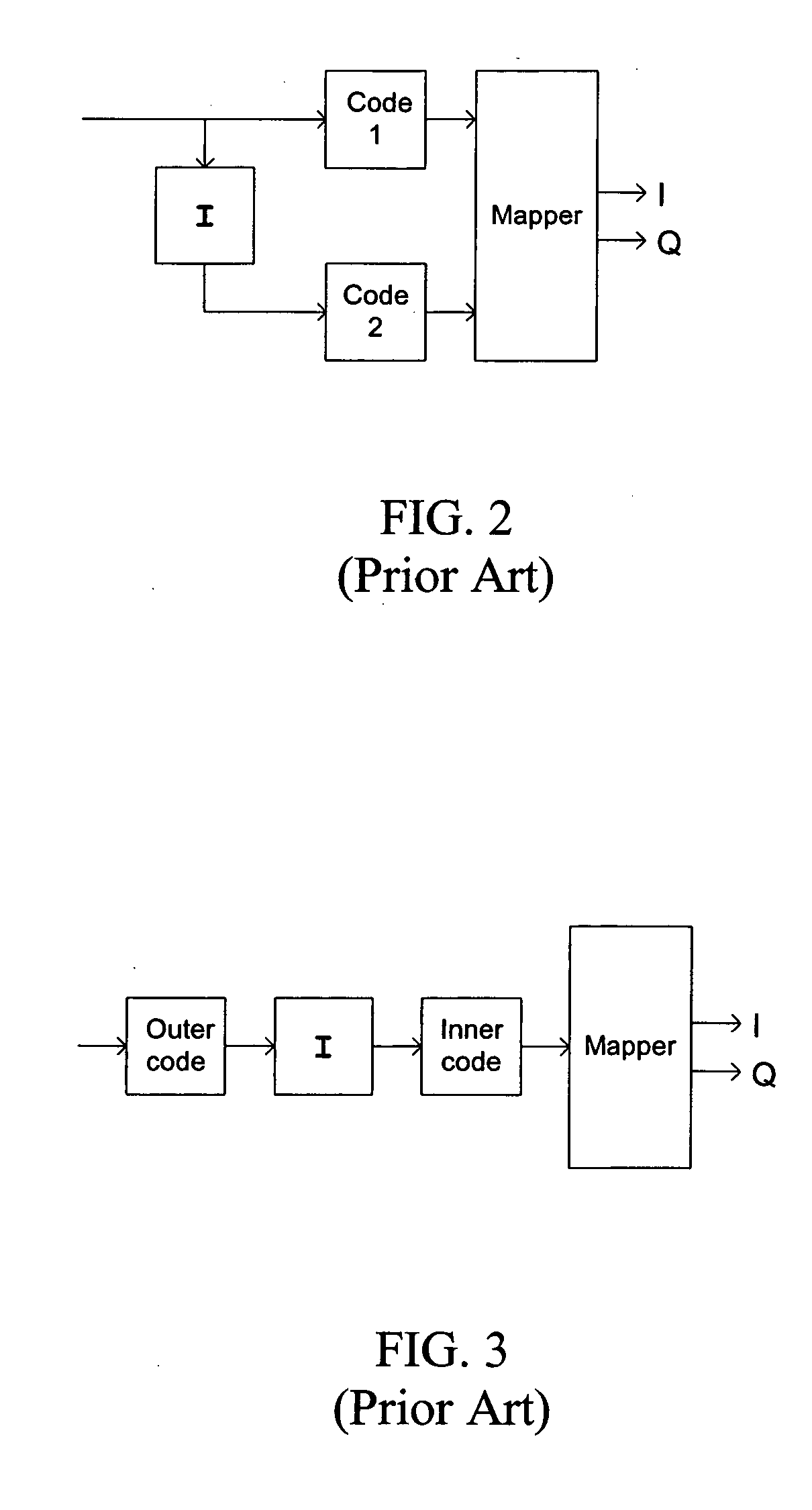

Method and apparatus for communications using improved turbo like codes

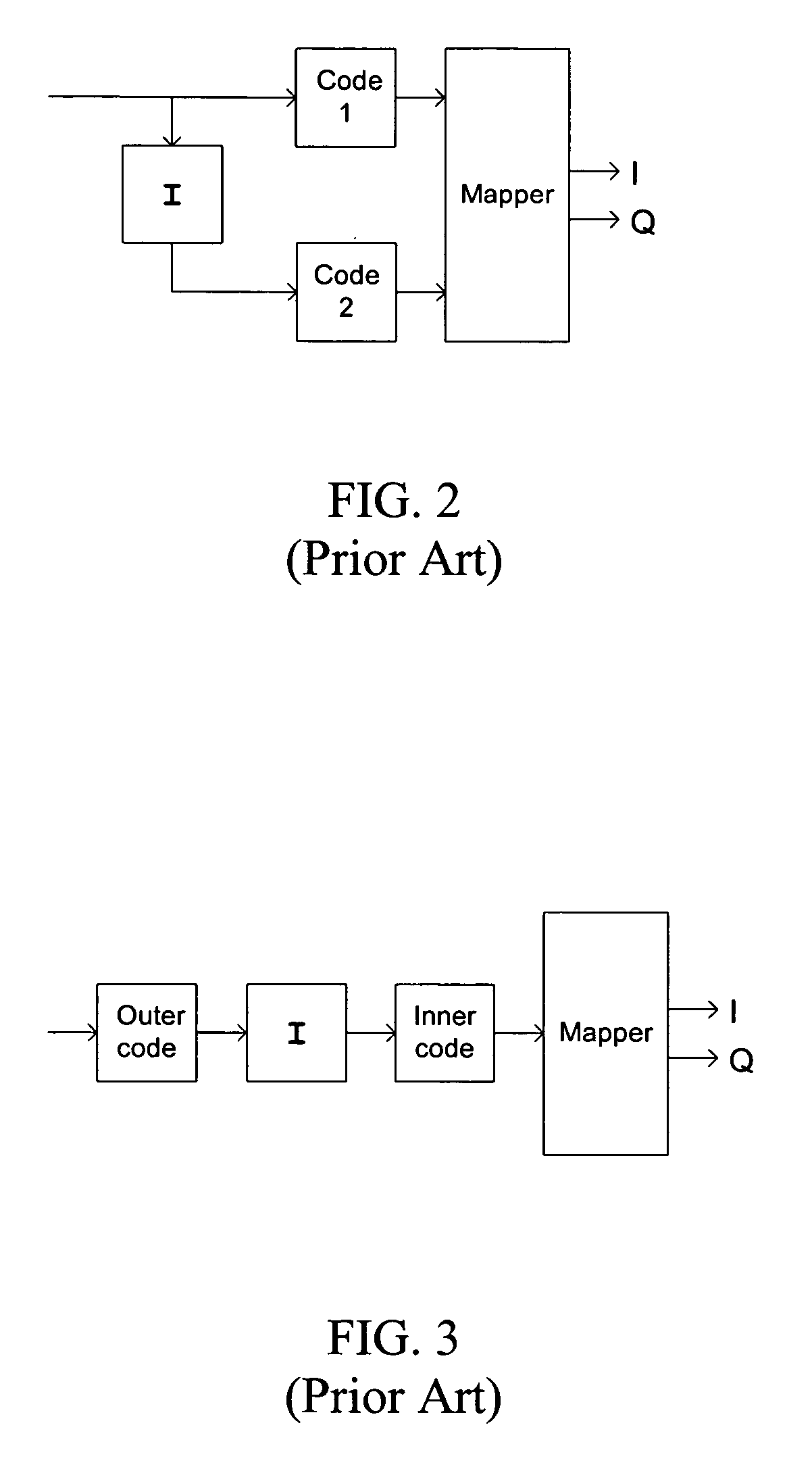

ActiveUS20060031737A1Data representation error detection/correctionCode conversionSingle parity checkConvolutional code

Methods, apparatuses, and systems are presented for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits, processing the outer encoded bits using an interleaver and a single parity check (SPC) module to produce intermediate bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, processing the inner encoded bits using a puncture module to produce punctured bits, and combining the data bits and the punctured bits to produce encoded outputs. Methods, apparatuses, and systems are also presented for performing data decoding based on soft channel metrics derived from a channel using various iterative techniques.

Owner:TRELLIS WARE TECH

Method of error correction in MBC flash memory

InactiveUS20070089034A1Reduce wasteHigh bit error rateStatic storageRedundant data error correctionData bitsFlash memory

A plurality of logical pages is stored in a MBC flash memory along with corresponding ECC bits, with at least one of the MBC cells storing bits from more than one logical page, and with at least one of the ECC bits applying to two or more of the logical pages. When the pages are read from the memory, the data bits as read are corrected using the ECC bits as read. Alternatively, a joint, systematic or non-systematic ECC codeword is computed for two or more of the logical pages and is stored instead of those logical pages. When the joint codeword is read, the logical bits are recovered from the codeword as read. The scope of the invention also includes corresponding memory devices, the controllers of such memory devices, and also computer-readable storage media bearing computer-readable code for implementing the methods.

Owner:RAMOT AT TEL AVIV UNIV LTD

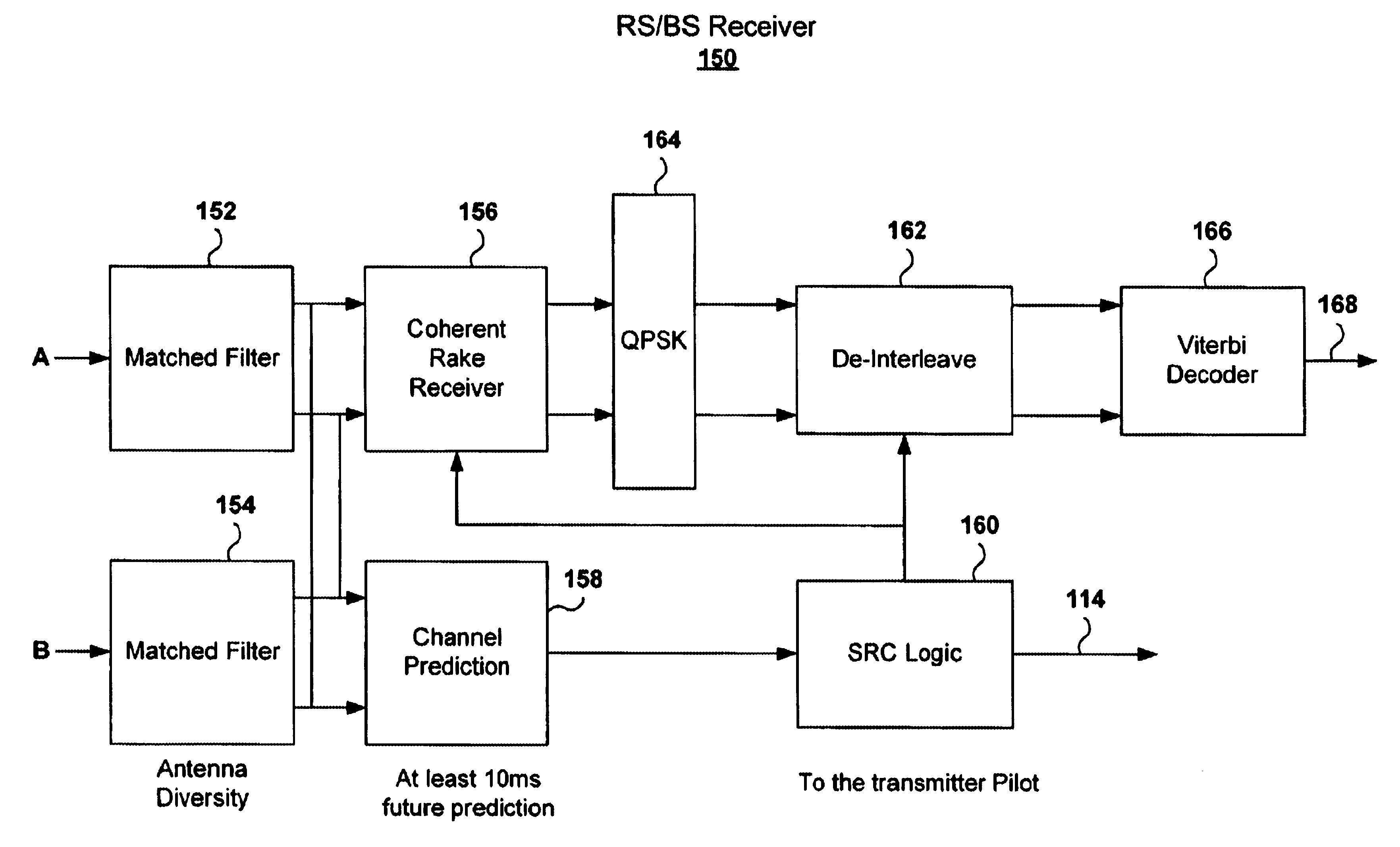

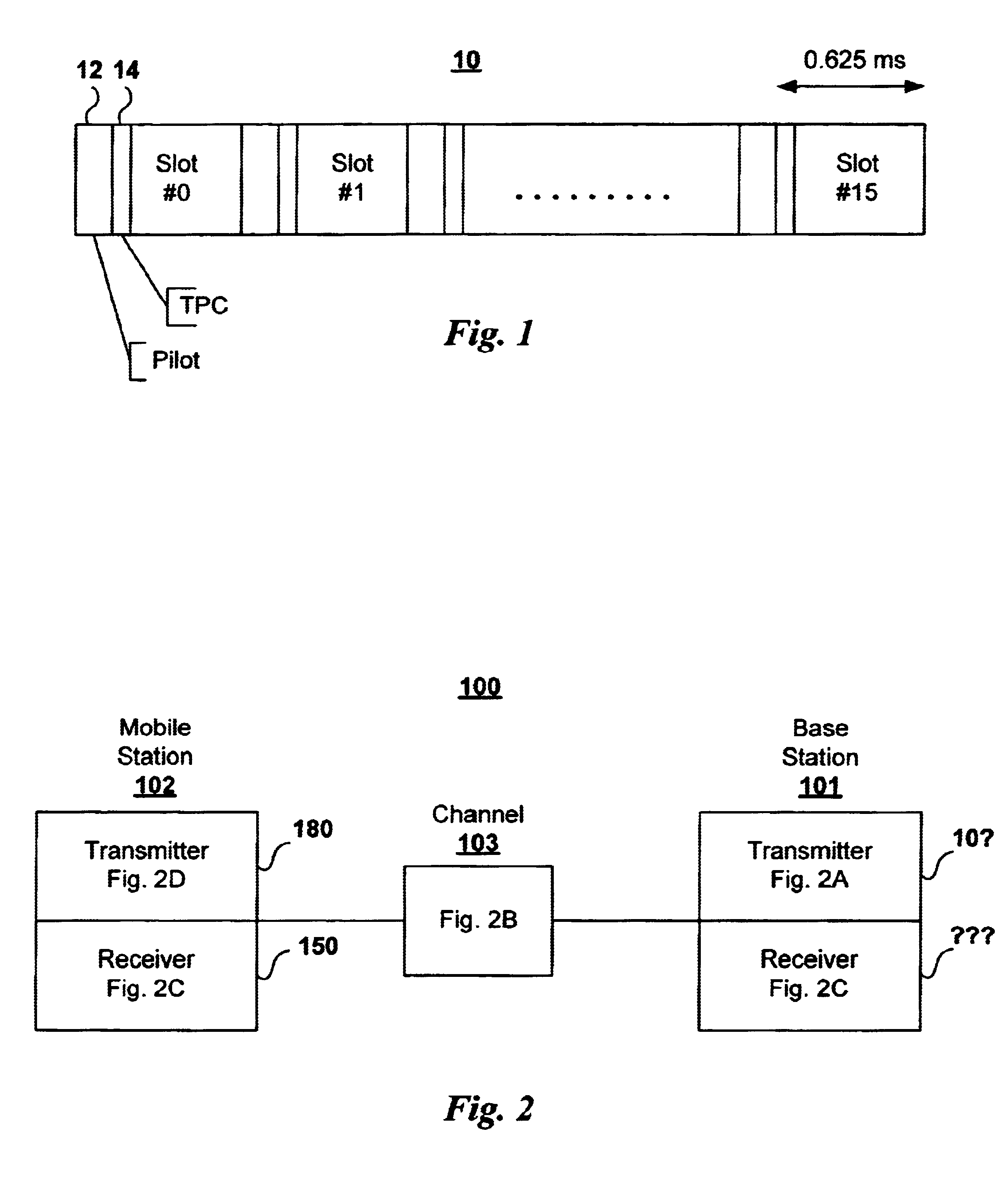

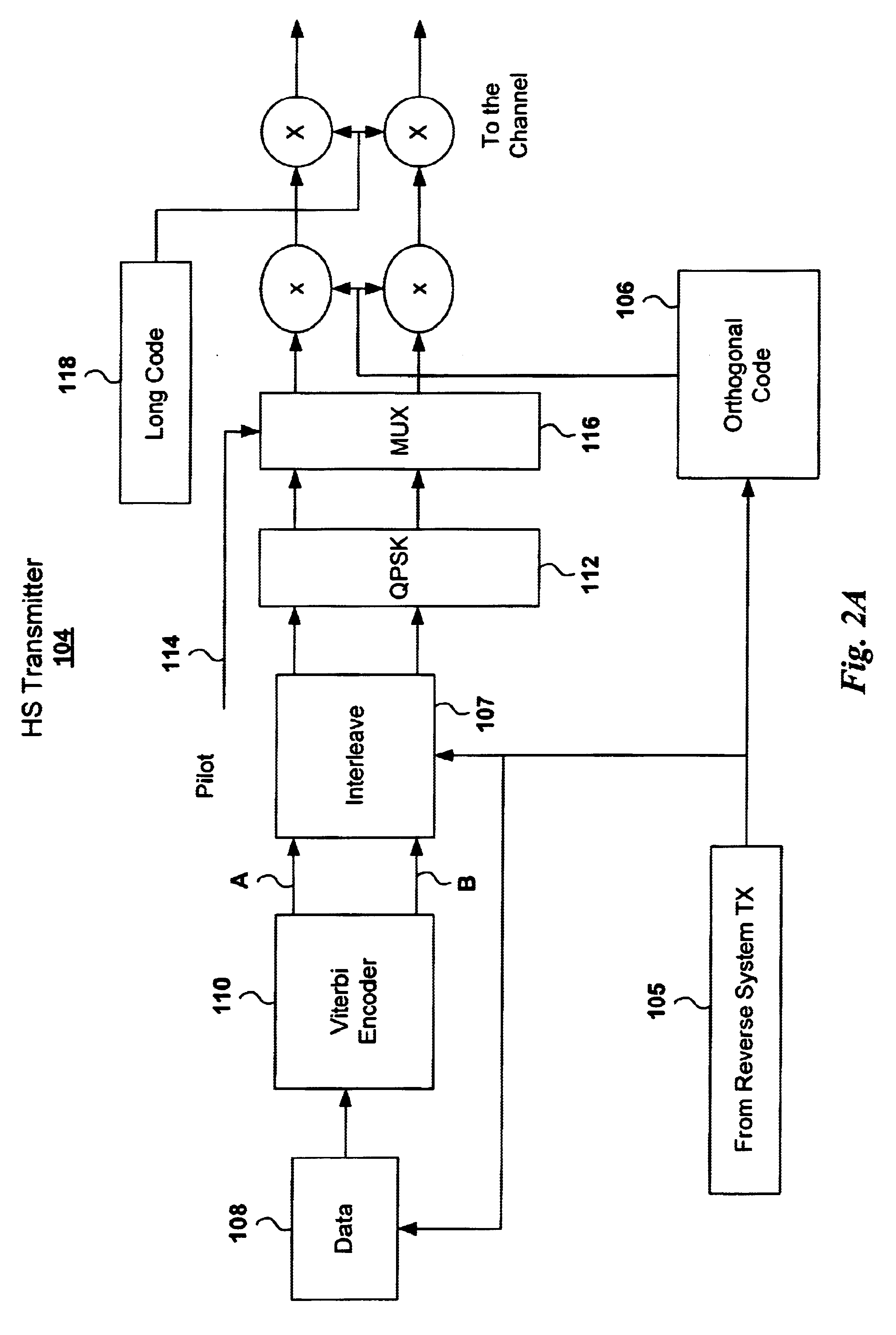

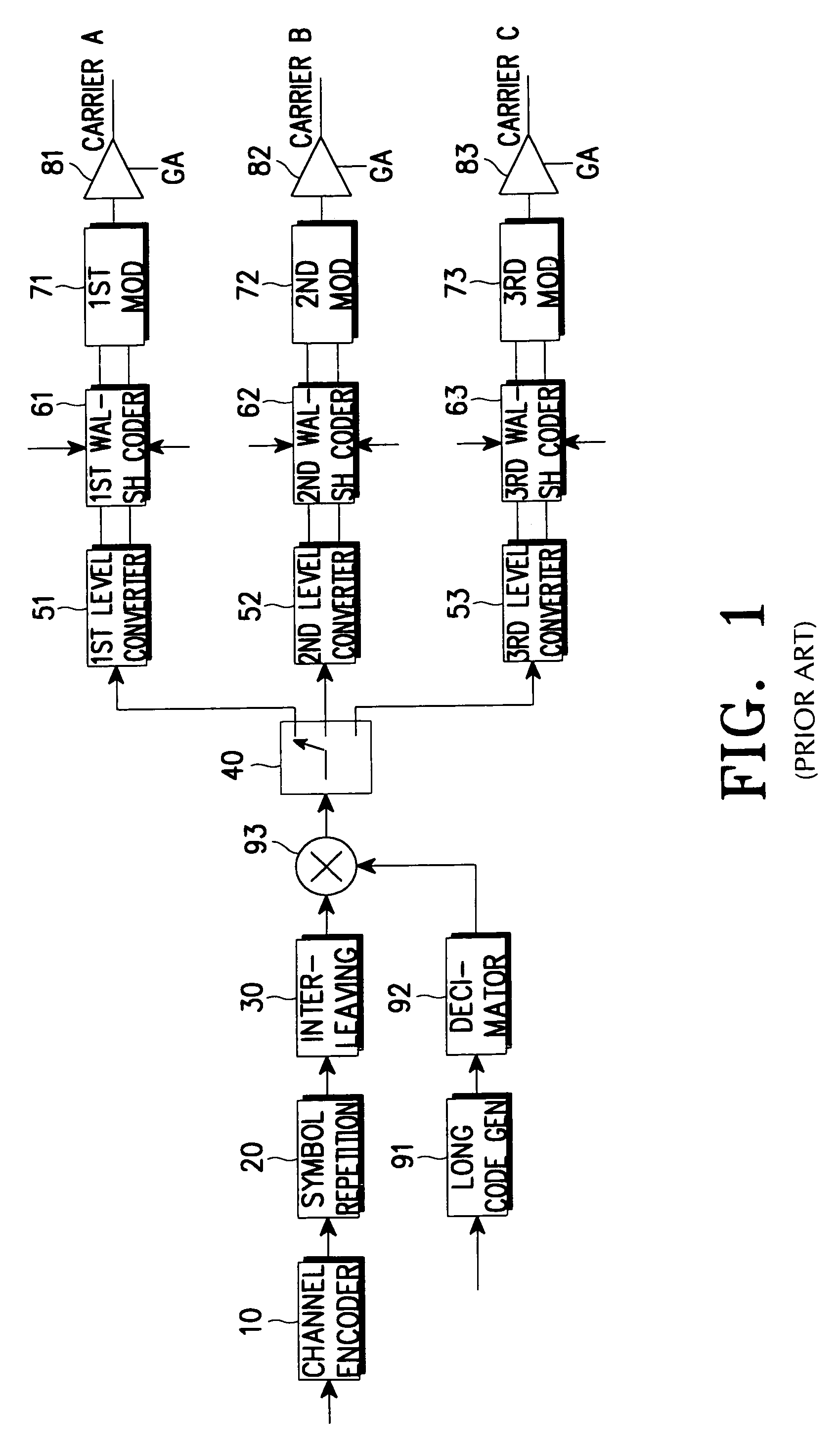

Adaptive power control based on a rake receiver configuration in wideband CDMA cellular systems (WCDMA) and methods of operation

InactiveUS6621808B1Maximizes controlMaximize throughputPower managementTransmission control/equalisingChannel powerOperational system

A WCDMA system includes a Base Station (BS) or forward transmitter and a pilot channel that transmits control signals between a Mobile Station (MS) and BS to reconfigure their transmitter / receiver according to the prediction of the channel power and channel power probability density function separated into three distinct equal probable regions. Data signals are encoded using a one-half Viterbi encoder and interleaved. The interleaved data bits are modulated using Quadrature Phase Shift Keying (QPSK) modulation. The QPSK data is multiplexed with the pilot channel and spread by an appropriate code in an OFDM transmitter modified by a long code. Output of the transmitter may be provided to two diverse antennas for reliable communications to the receiver. Data may be received at two diverse antennas. The outputs are provided to match filters coupled to a coherent rake receiver and a channel prediction system. The future attenuation of the channel coefficients and power are determined by the prediction system for several milliseconds. The power levels of each finger in the Rake receiver can be predicted and the strongest ones used in determining the optimum transmitter power or rate control for operating the system transmitters and receivers based on computing a long range power prediction of each finger of a rake receiver.

Owner:WISTRON CORP

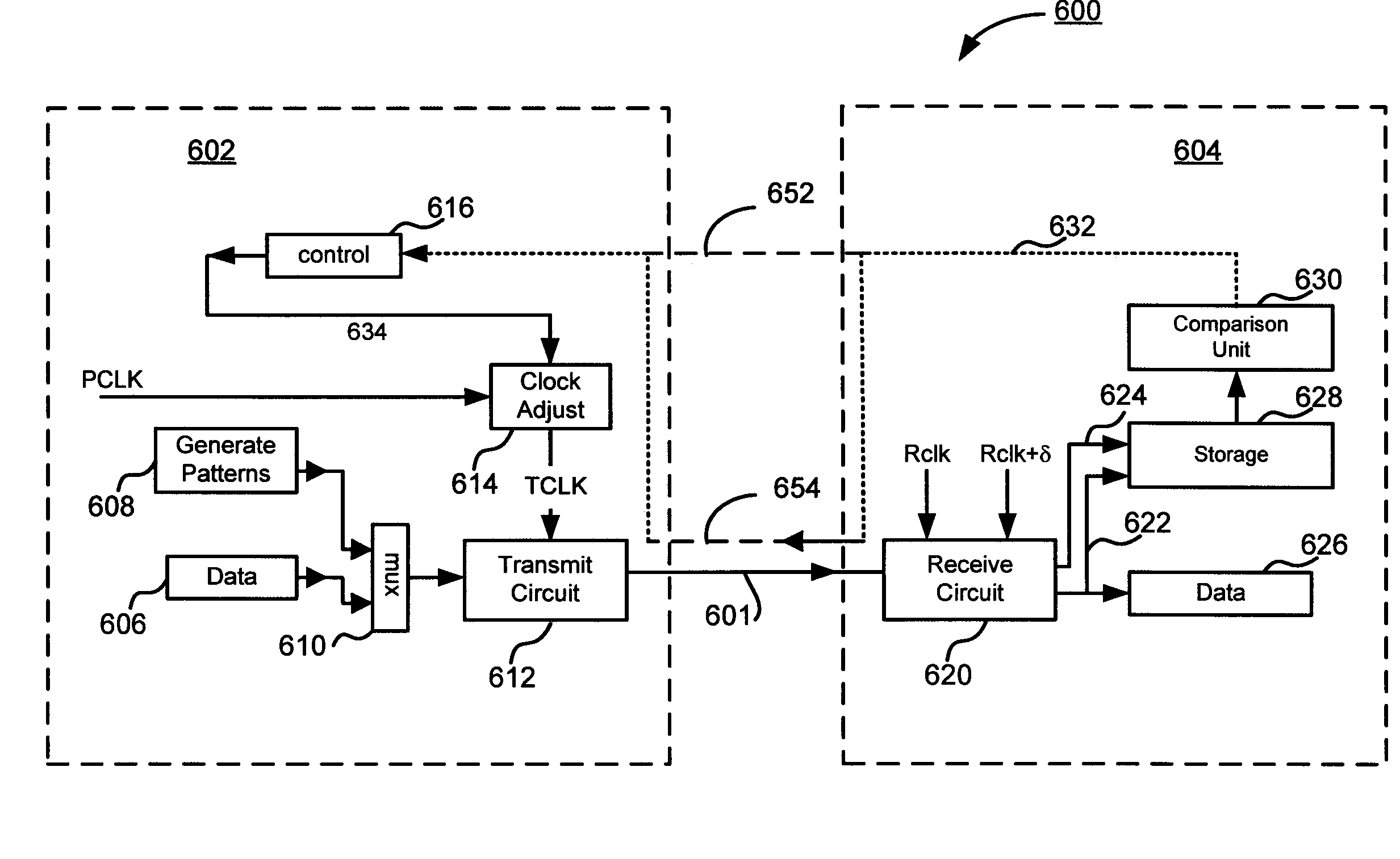

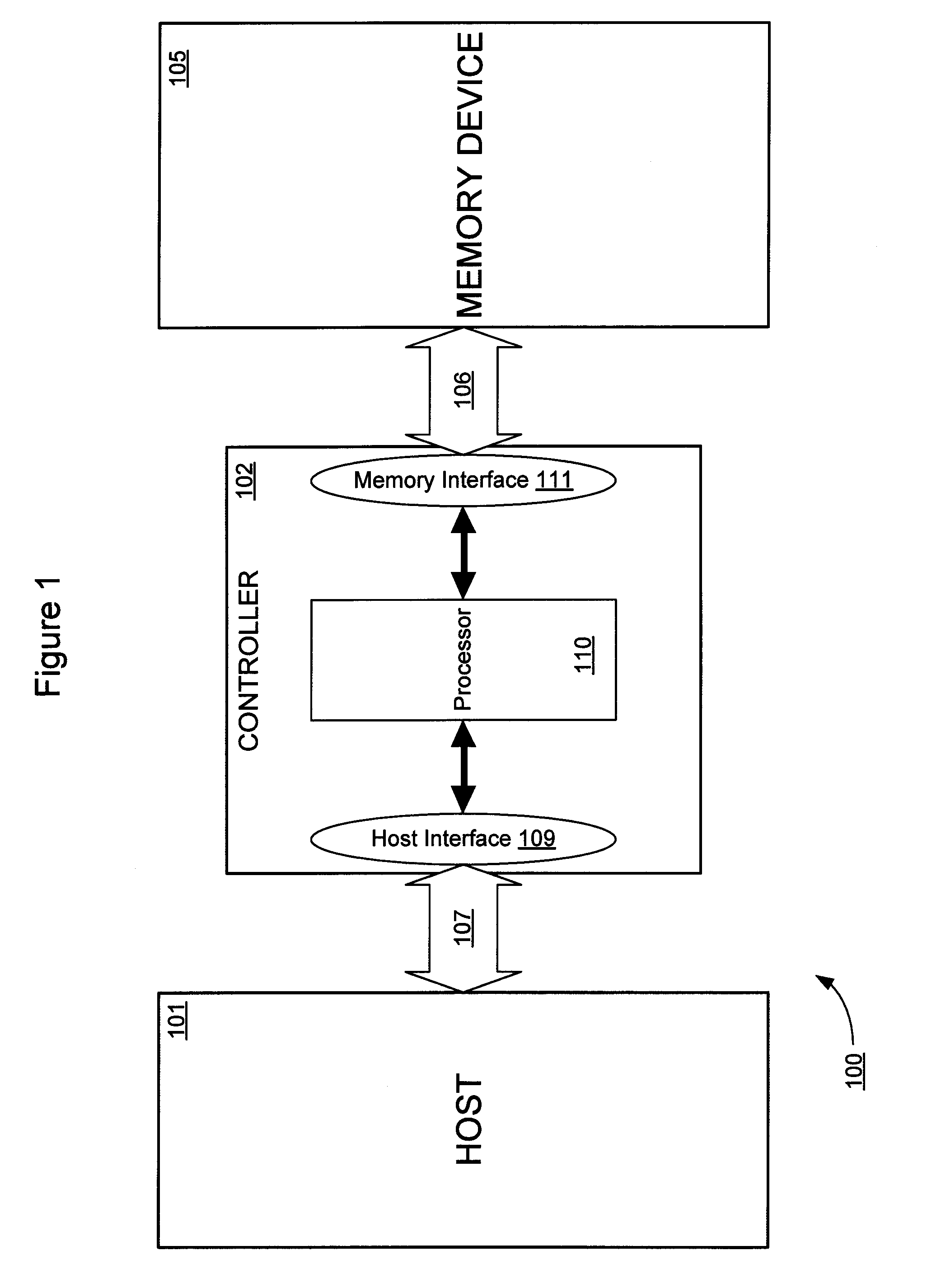

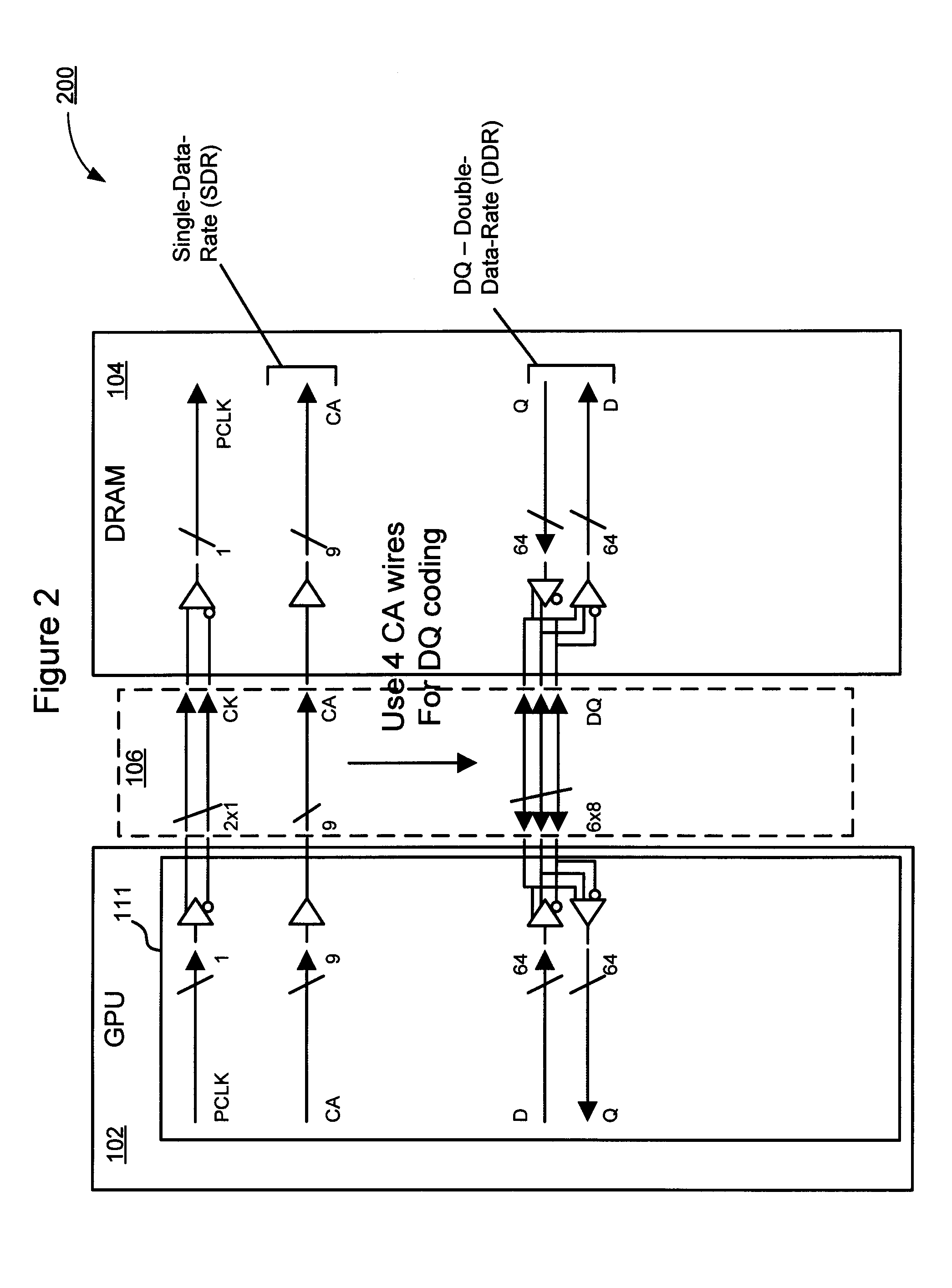

Techniques for improved timing control of memory devices

InactiveUS20100180143A1Digital storageGenerating/distributing signalsElectrical conductorTelecommunications link

Techniques for improved timing control of memory devices are disclosed. In one embodiment, the techniques may be realized as a memory controller to communicate with a memory device via a communications link. The memory controller may comprise a memory interface to exchange data with the memory device via a set of N conductors according to at least one clock, the data being encoded such that each M bits of data are represented by at least one symbol and each symbol is associated with a combination of signal levels on a group of n conductors, wherein M<N and n is equal to at least one and at most N. The memory may also comprise clock control logic to receive timing calibration information from the memory device and to output a signal to adjust a phase of the at least one clock based on the timing calibration information.

Owner:RAMBUS INC

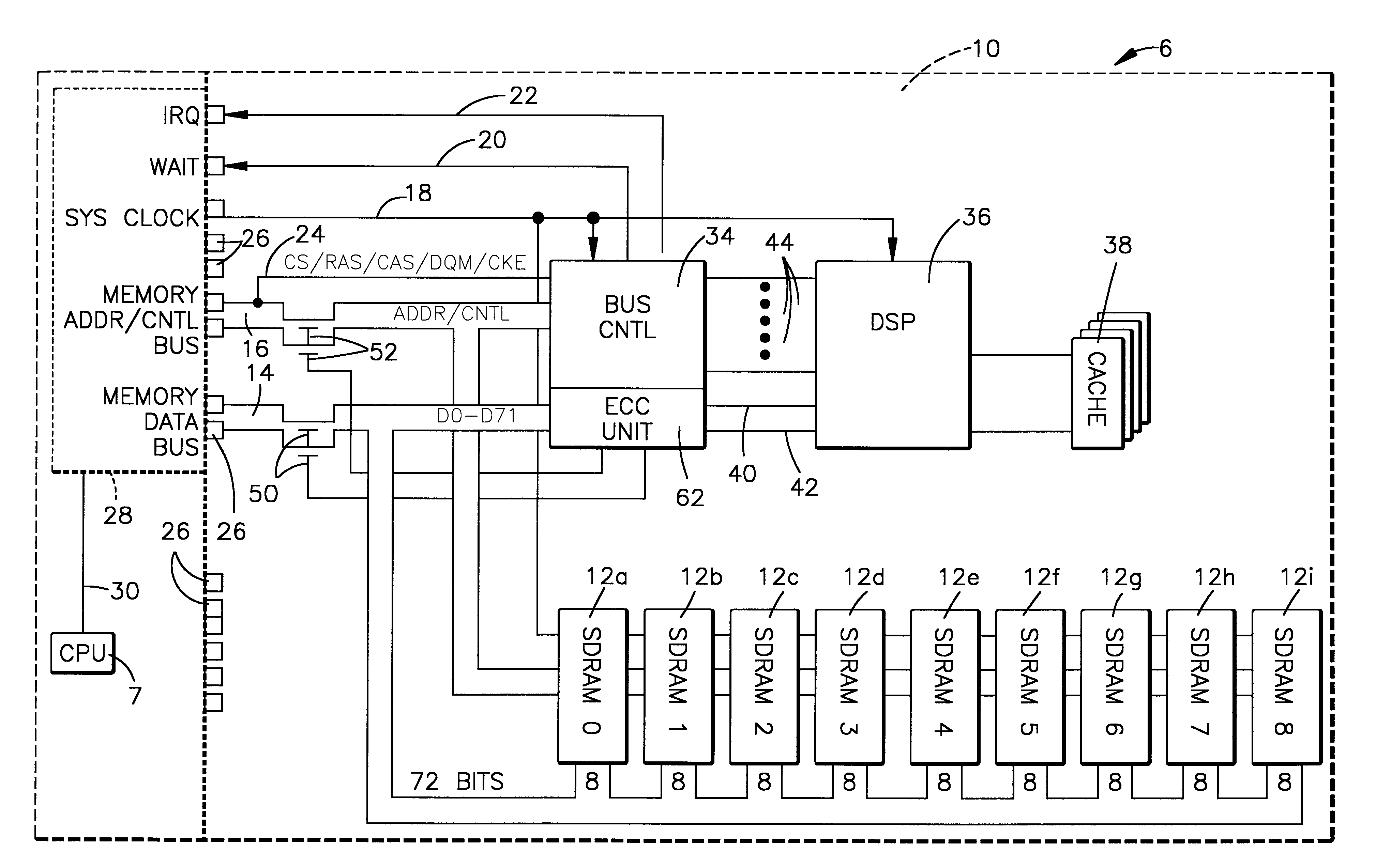

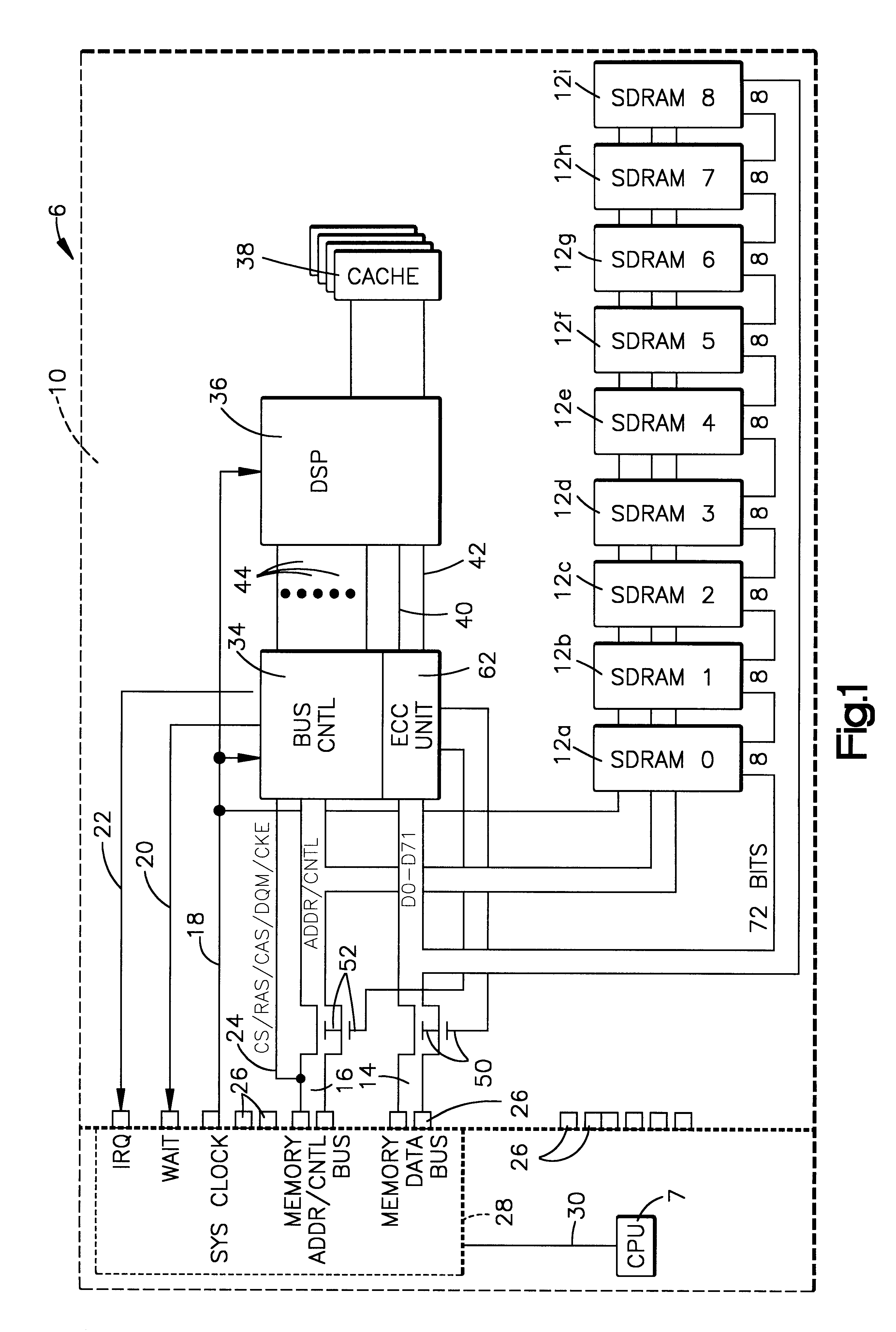

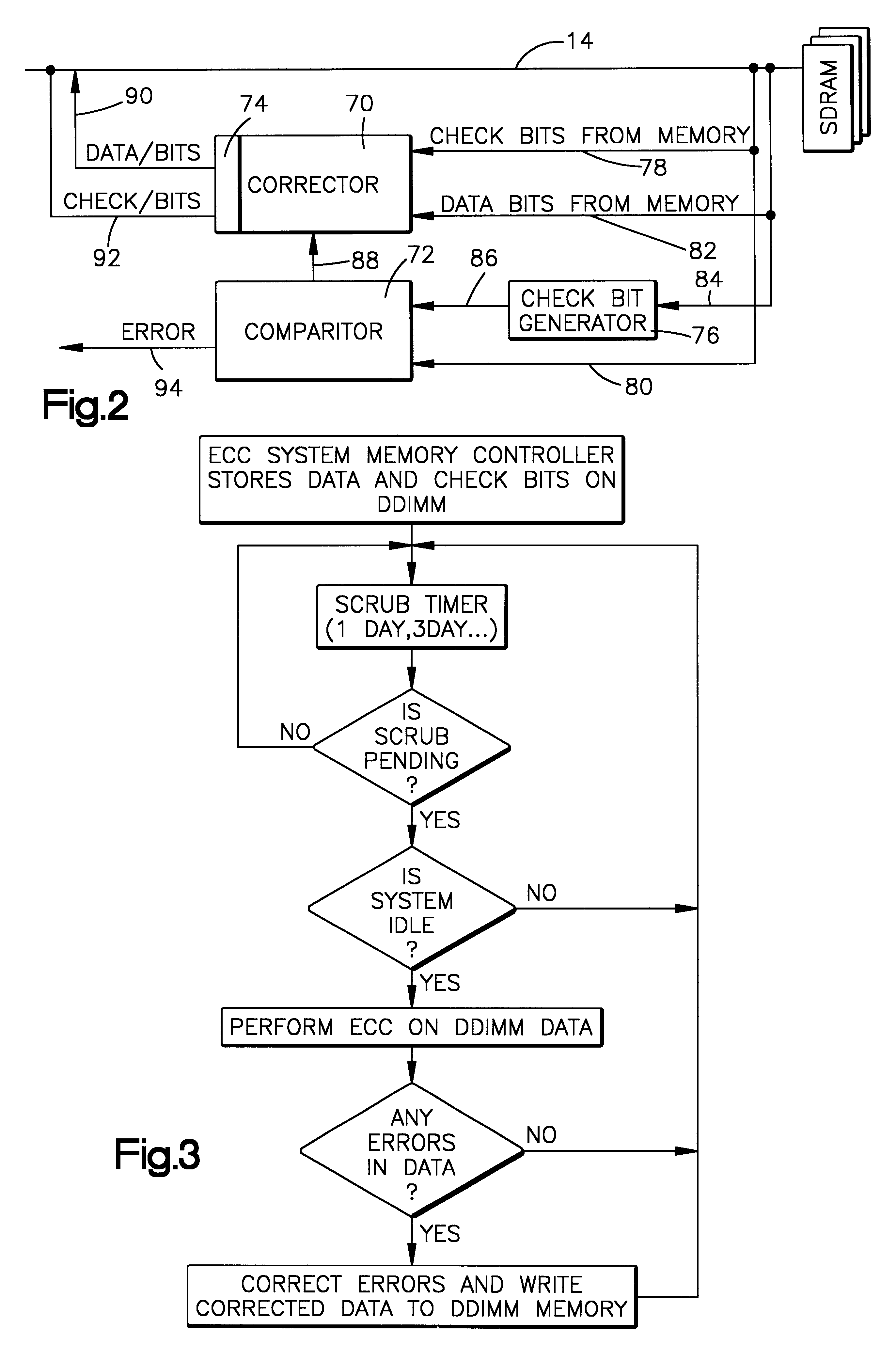

On-board scrubbing of soft errors memory module

A memory module for attachment to a computer system having a memory bus and a method of using the memory module for error correction by scrubbing soft errors on-board the module is provided. The module includes a printed circuit card with memory storage chips on the card to store data bits and associated ECC check bits. Tabs are provided on the circuit card to couple the card to the memory bus of the computer system. Logic circuitry selectively operatively connects and disconnects the memory chip and the memory bus. A signal processor is connected in circuit relationship with the memory chips. The logic circuitry selectively permits the signal processor to read the stored data bits and associated check bits from the memory chips, recalculate the check bits from the read stored data bits, compare the recalculated check bits with the stored check bits, correct all at least one bit errors in the store data bits and stored associated check bits and re-store the correct data bits and associated check bits in the memory chips. When the memory chips and the memory bus are disconnected, single bit soft errors occurring during storage of the data bits and check bits are corrected periodically before the data is read from the memory chips to the data bus on a read operation.

Owner:IBM CORP

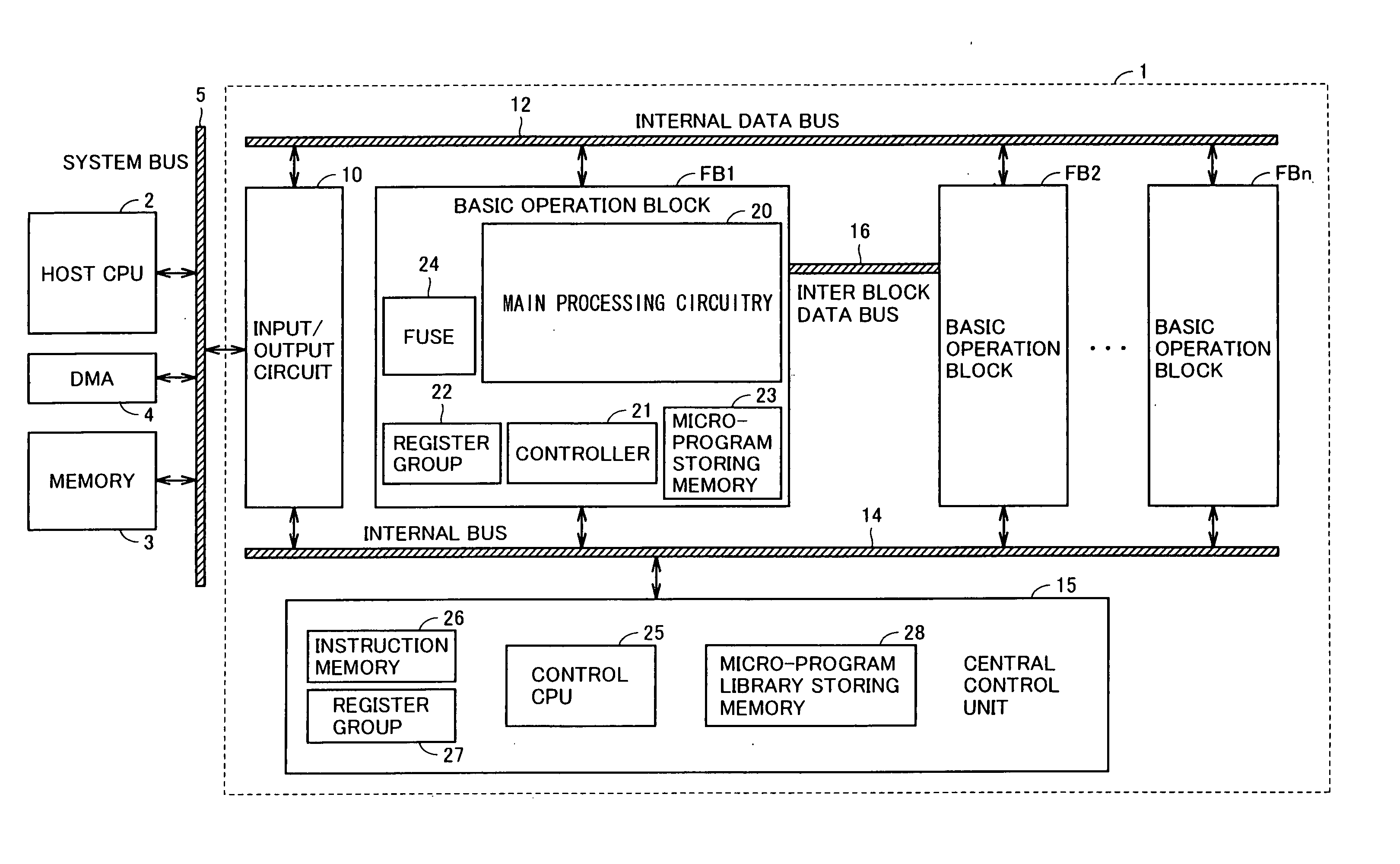

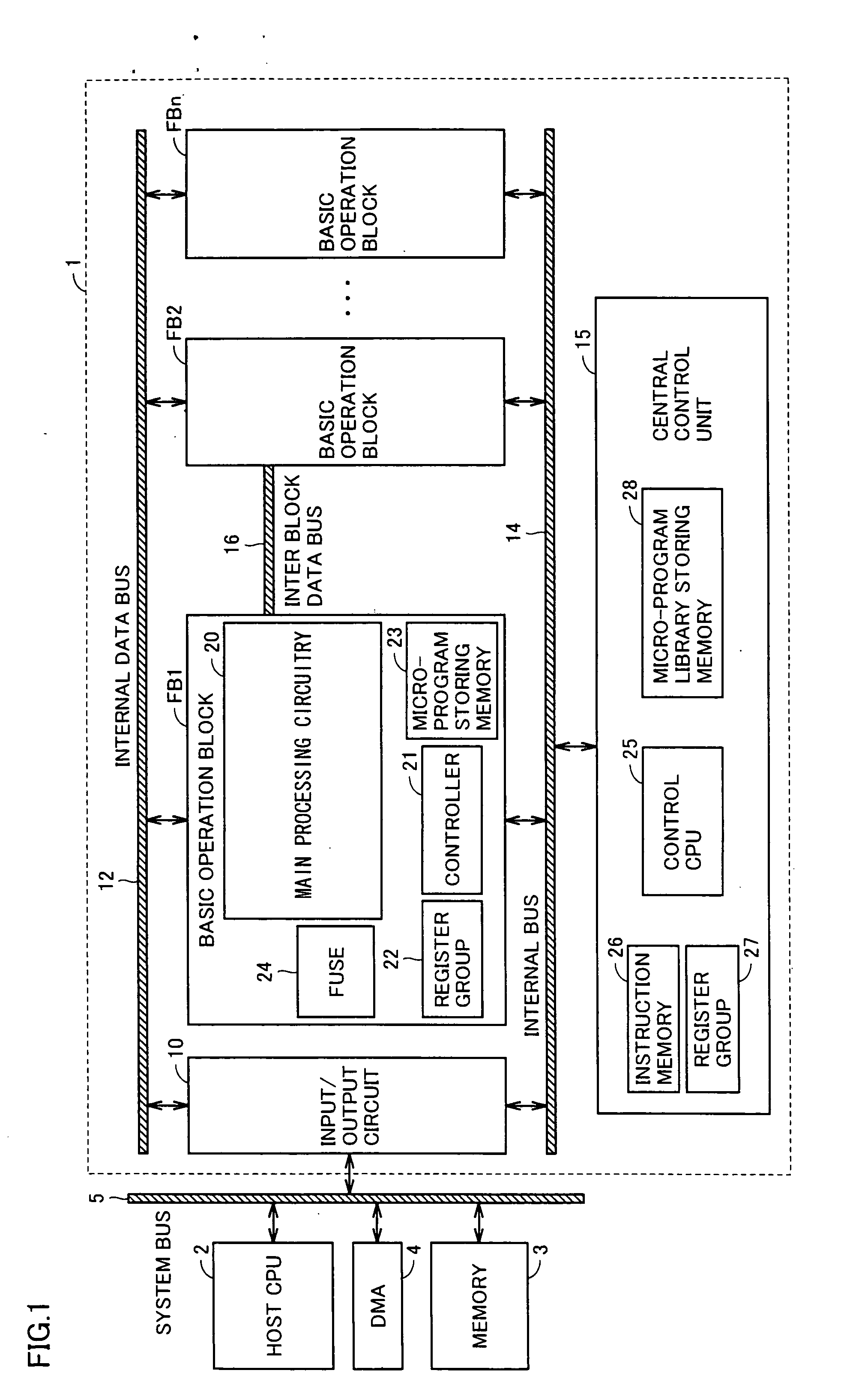

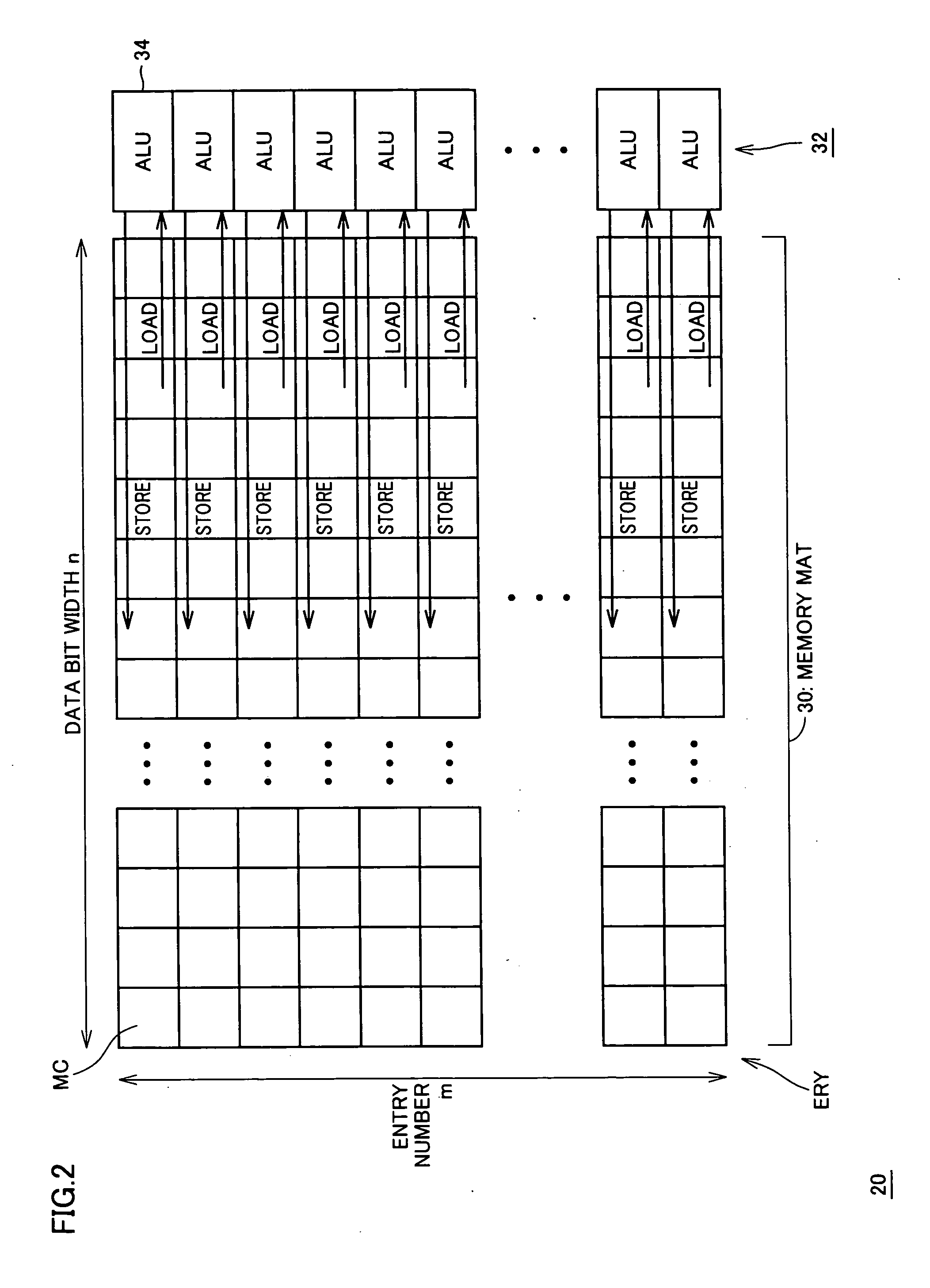

Semiconductor device and semiconductor signal processing apparatus

InactiveUS20050285862A1Operation control becomes easyEasy to processImage memory managementMultiple digital computer combinationsArithmetic logic unitDevice material

A memory cell mat is divided into a plurality of entries, and an arithmetic logic unit is arranged corresponding to each entry. Between the entries and the corresponding arithmetic logic units, arithmetic / logic operation is executed in bit-serial and entry-parallel manner. Where parallel operation is not very effective, data is transferred in entry-serial and bit-parallel manner to a group of processors provided at a lower portion of the memory mat. In this manner, a large amount of data can be processed at high speed regardless of the contents of operation or data bit width.

Owner:RENESAS ELECTRONICS CORP

Method and apparatus for communications using turbo like codes

The present invention relates to methods, apparatuses, and systems for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits processing the outer encoded bits using an interleaver and a logical unit to produce intermediate bits, wherein the logical unit receives a first number of input bits and produces a second number of corresponding output bits, the second number being less than the first number, and wherein the logical unit takes each of the first number of input bits into account in producing the second number of output bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, wherein the inner convolutional code is characterized by at least two states, and combining the data bits and the inner encoded bits to produce encoded outputs.

Owner:TRELLIS WARE TECH

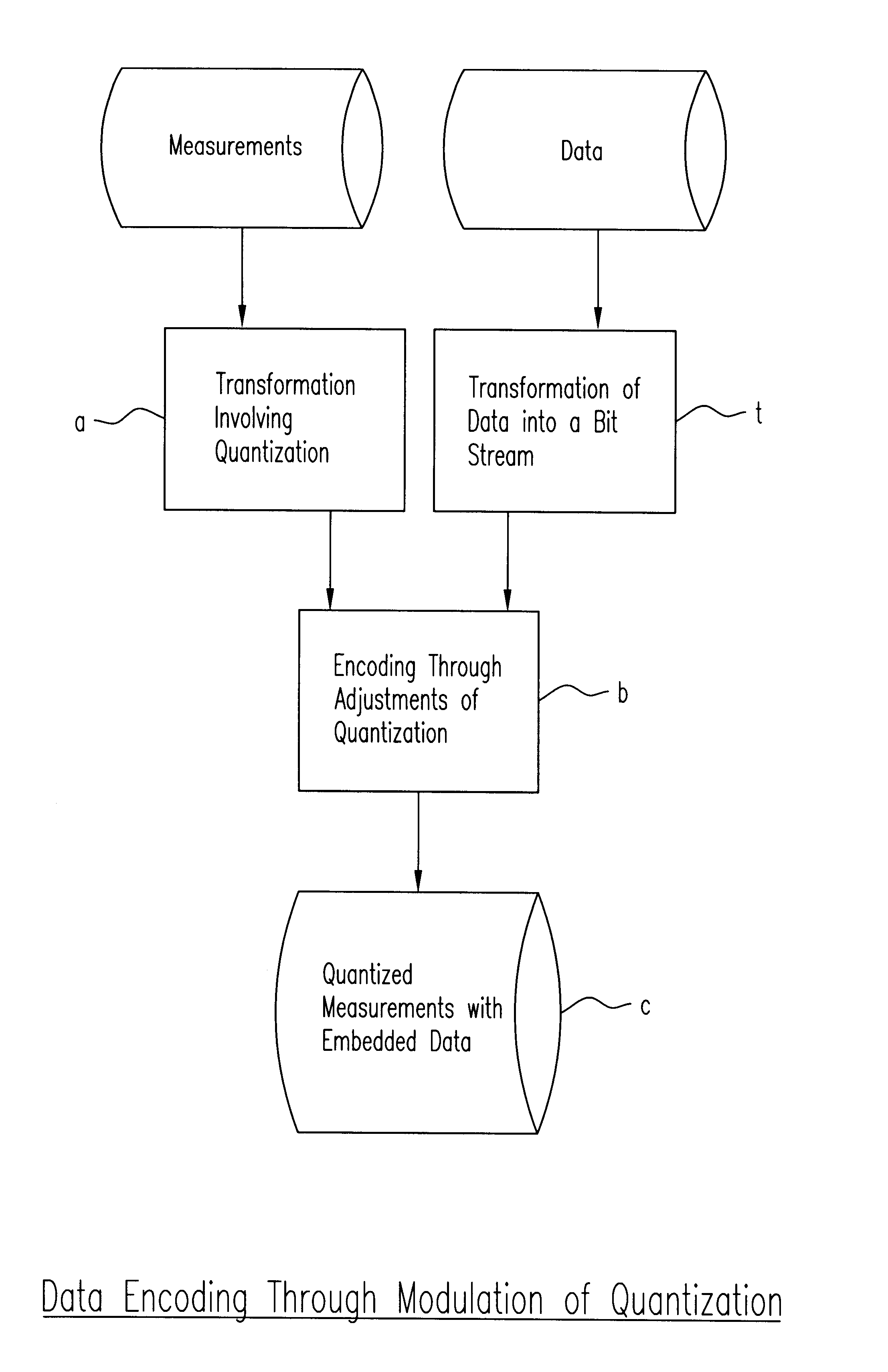

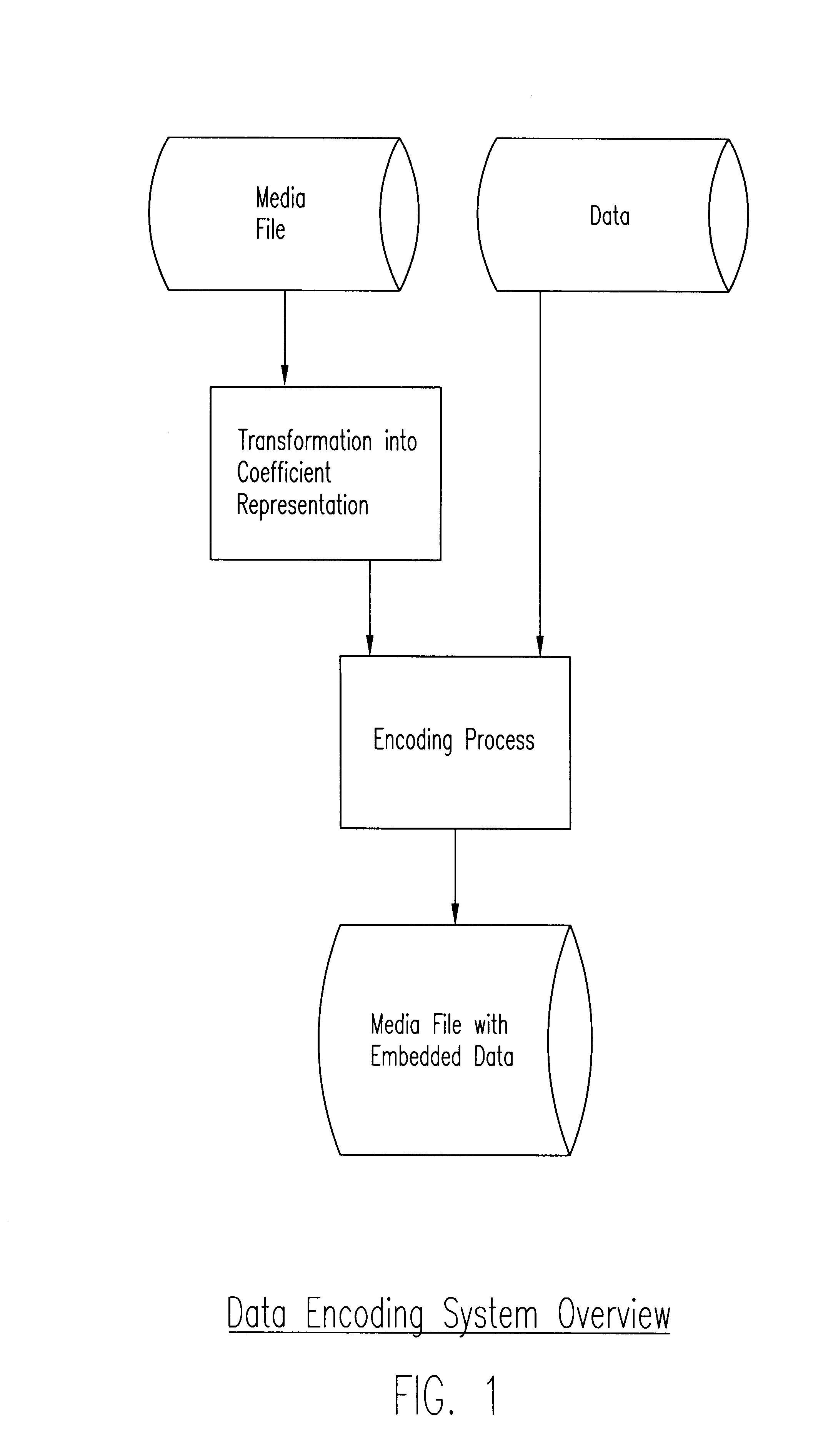

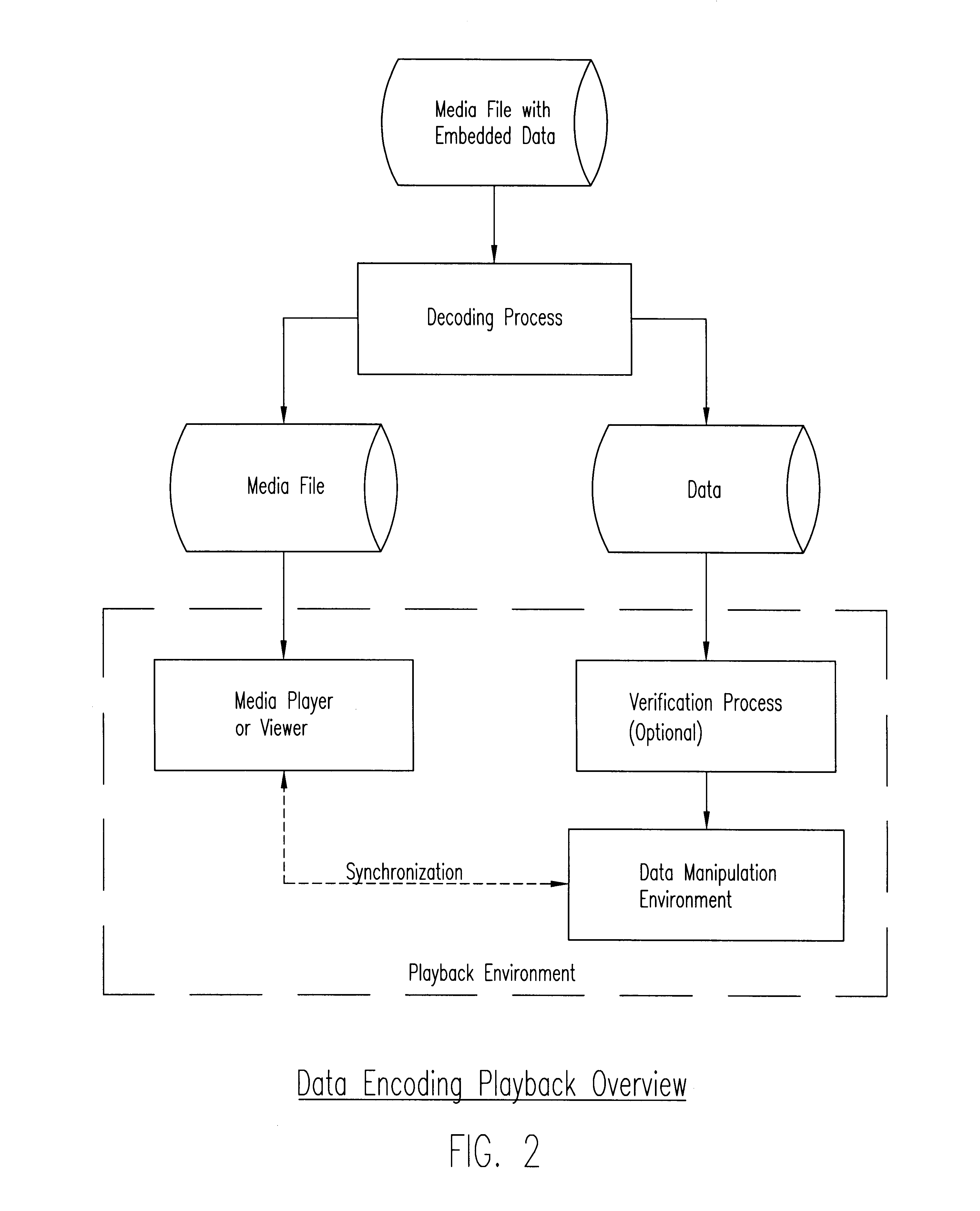

Method of and apparatus for high-bandwidth steganographic embedding of data in a series of digital signals or measurements such as taken from analog data streams or subsampled and/or transformed digital data

InactiveUS6768980B1Pulse modulation television signal transmissionSpeech analysisDigital dataData stream

A novel technique for high-bandwidth steganographic embedding of supplemental data in a series of digital signals or measurements, such as taken from analog data streams or subsampled and / or transformed digital data, wherein the series of measurements are derived through functional transformations and involving quantization and / or aliasing, with the supplemental data bits modulating or modifying the quantized and / or aliased components with only slight adjustments thereof to embed the supplemental data without substantially affecting the quality of the measurements; and all, preferably, through not exclusively, with the use of least-significant-bit parity encoding designed to choose the appropriate components to be so modulated or modified

Owner:TIME WARNER CABLE ENTERPRISES LLC

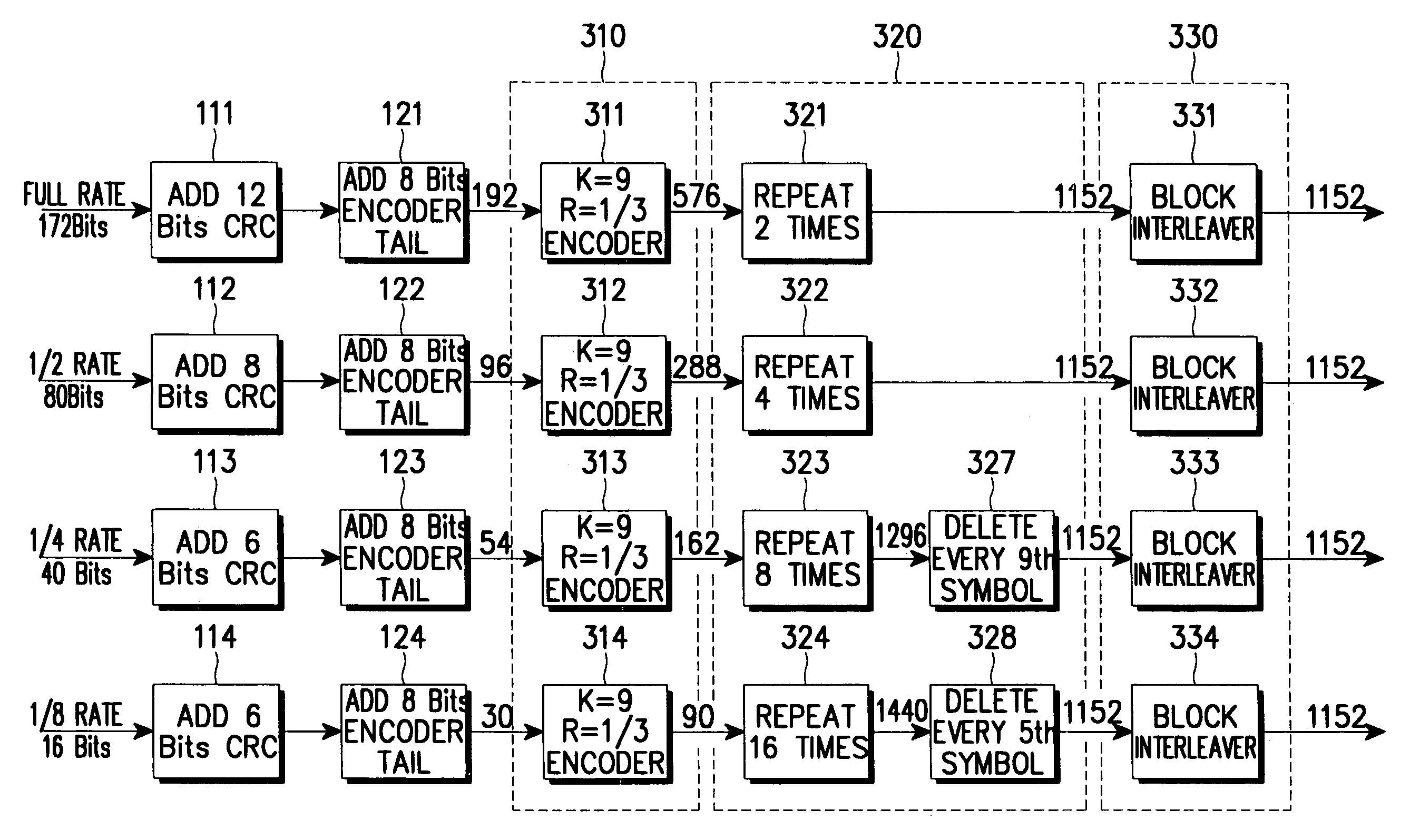

Forward link device of multicarrier communication system and method for realizing the same

InactiveUS6993062B1Improve transmission performanceImprove performanceMultiplex system selection arrangementsCriteria allocationCommunications systemCarrier signal

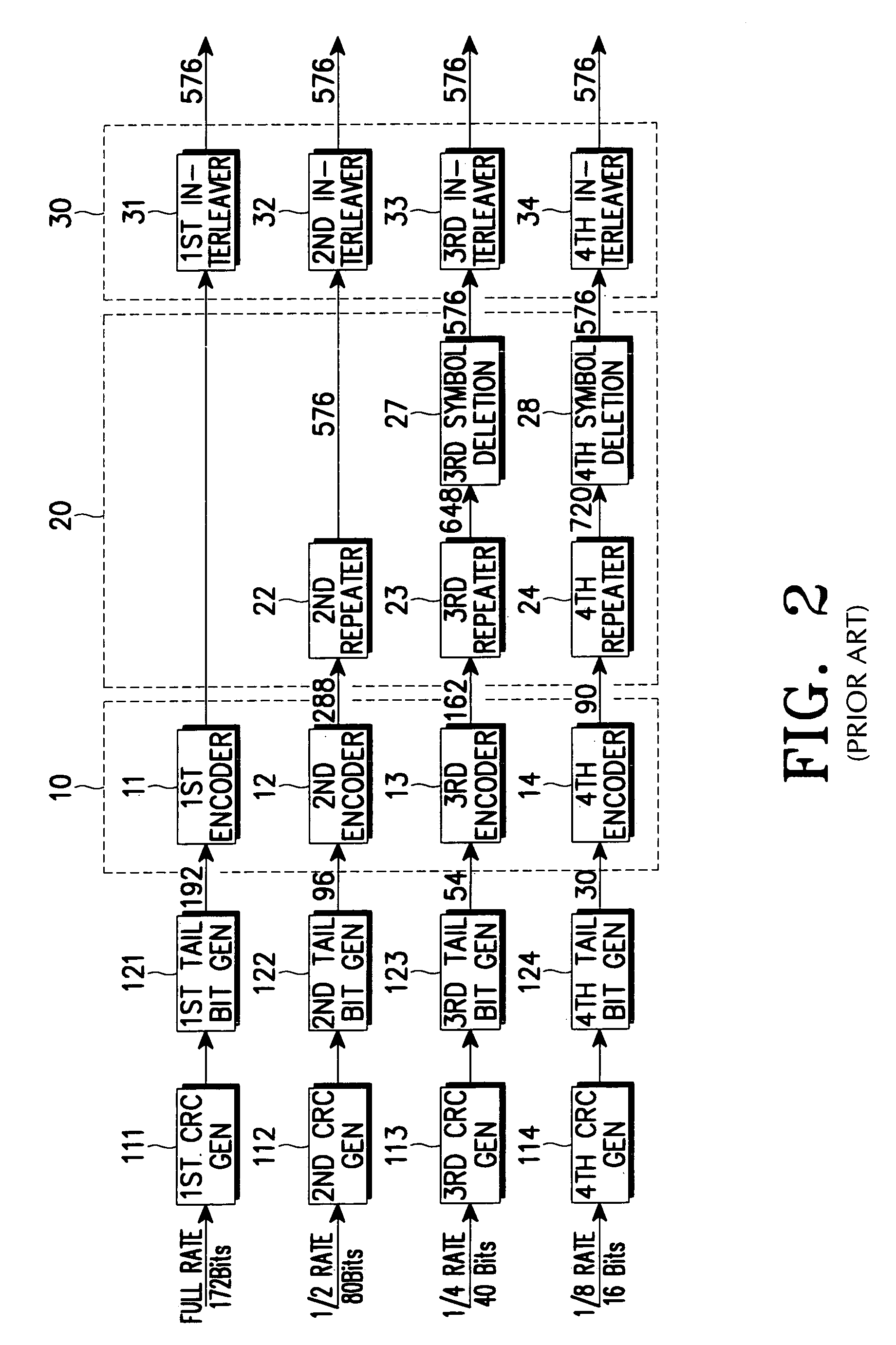

A forward link device of a multicarrier CDMA communication system with an overlay scheme in which a multicarrier system and an IS-95 system share same frequency bands. In the forward link device, four encoders encode input data of corresponding rates with a 1 / 3 coding rate, respectively. A first repeater repeats two times full rate symbols output from the first encoder, and second to fourth repeaters repeat symbols output from the second to fourth encoders, respectively, according to a predetermined number of times, to match the number of corresponding output symbols to the number of full rate symbols. First to fourth interleavers interleave the symbols output from the first to fourth repeaters, respectively, to uniformly distribute the symbols of the same data bit to the carriers.

Owner:SAMSUNG ELECTRONICS CO LTD

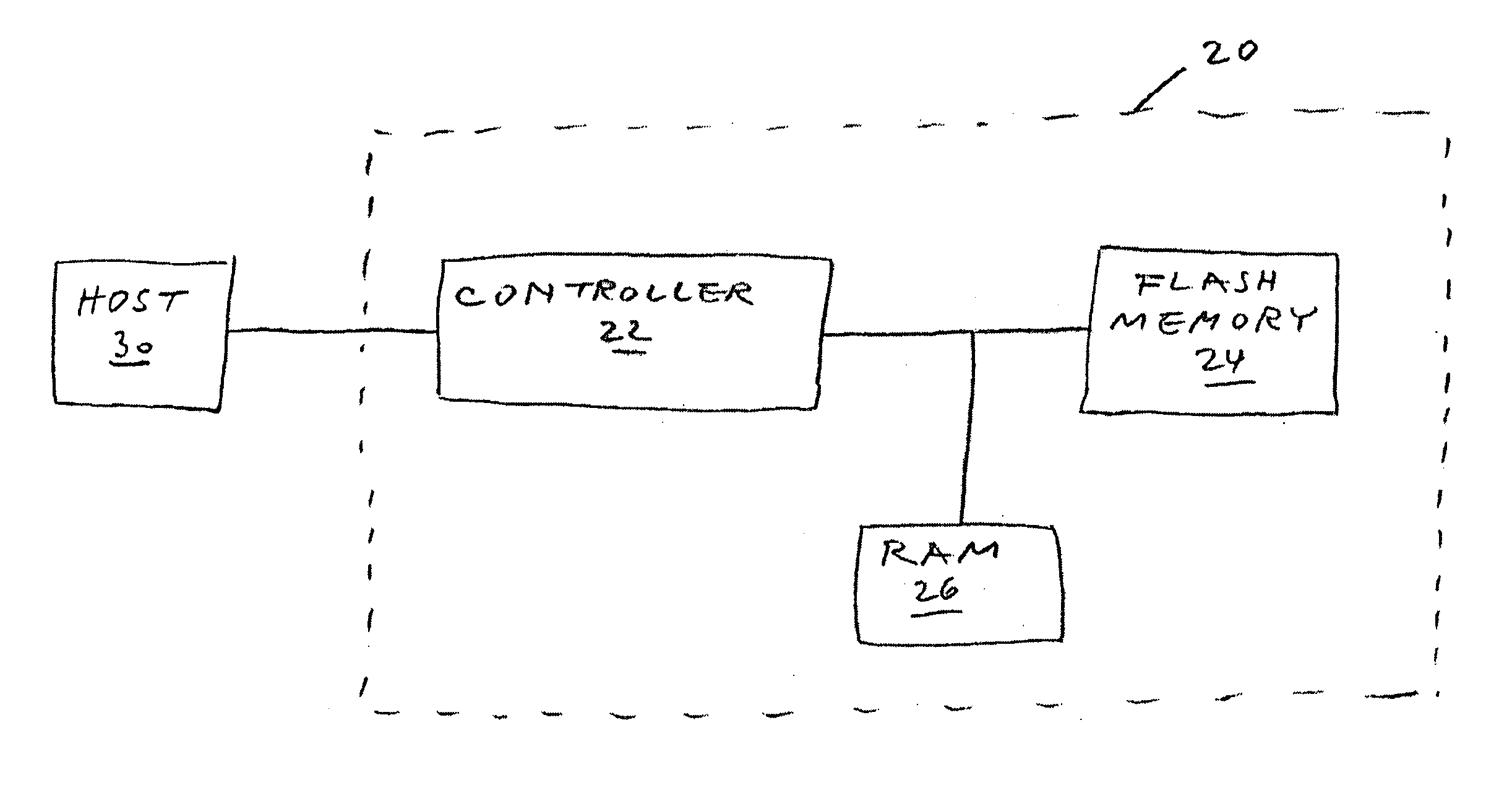

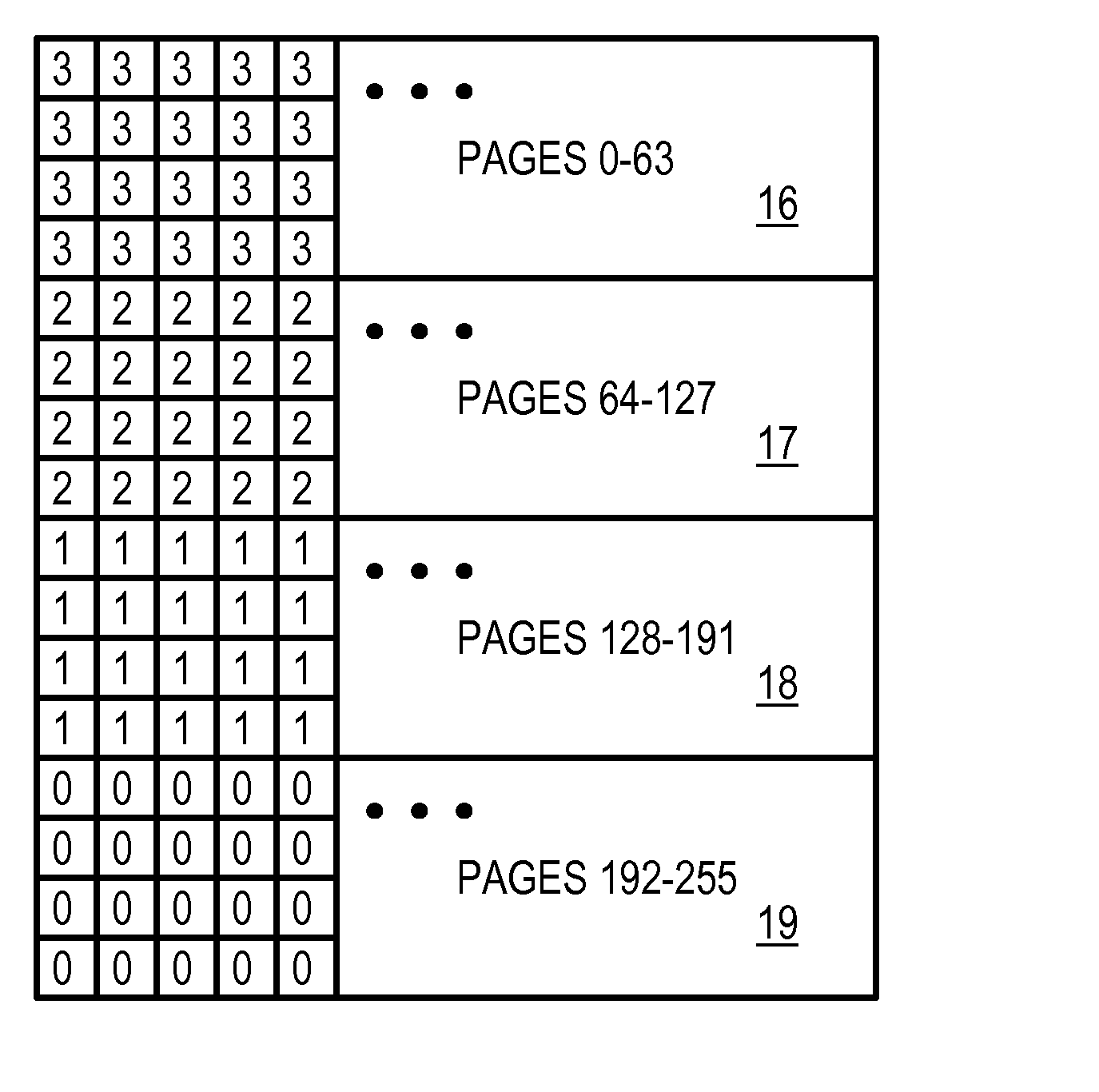

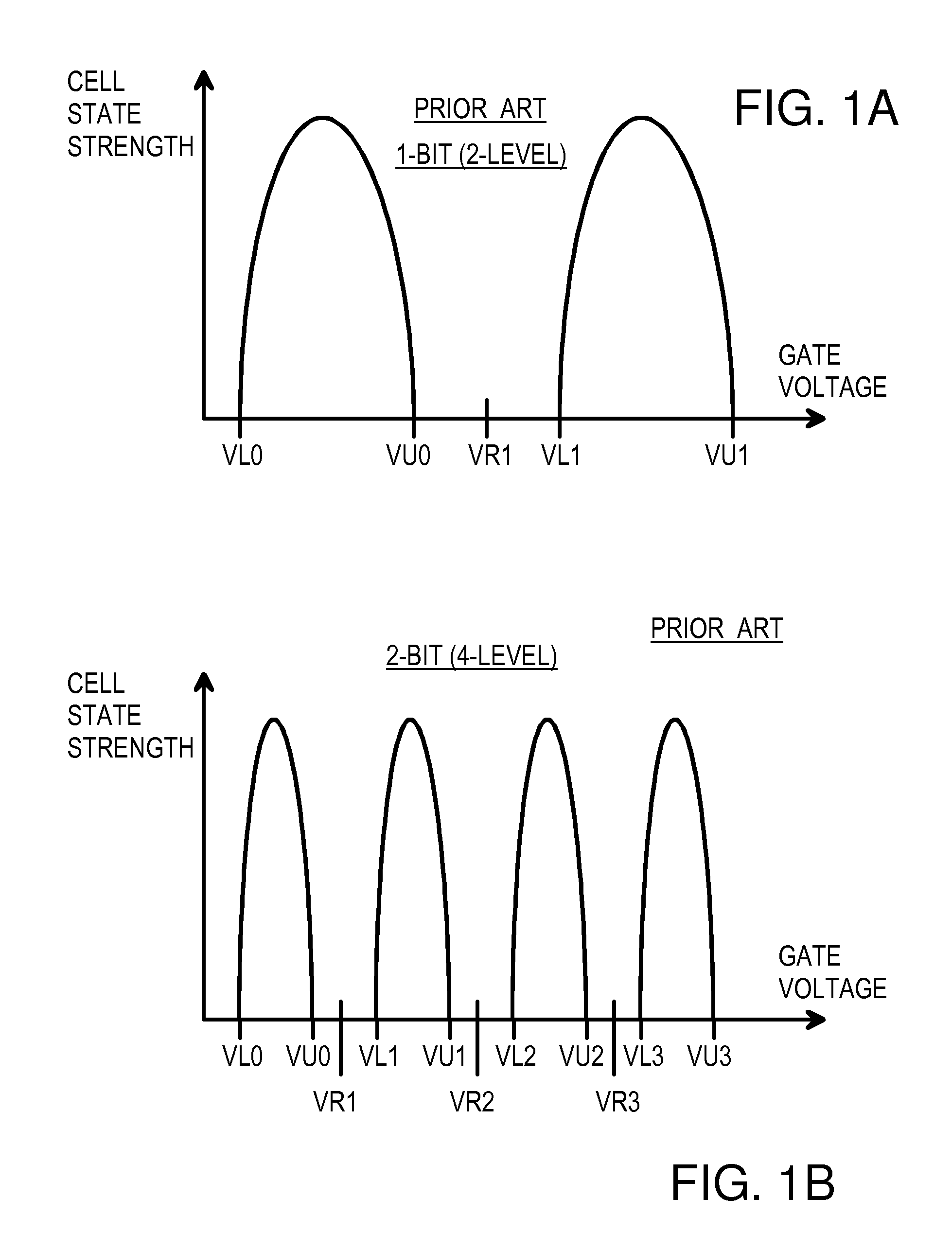

Cell-Downgrading and Reference-Voltage Adjustment for a Multi-Bit-Cell Flash Memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

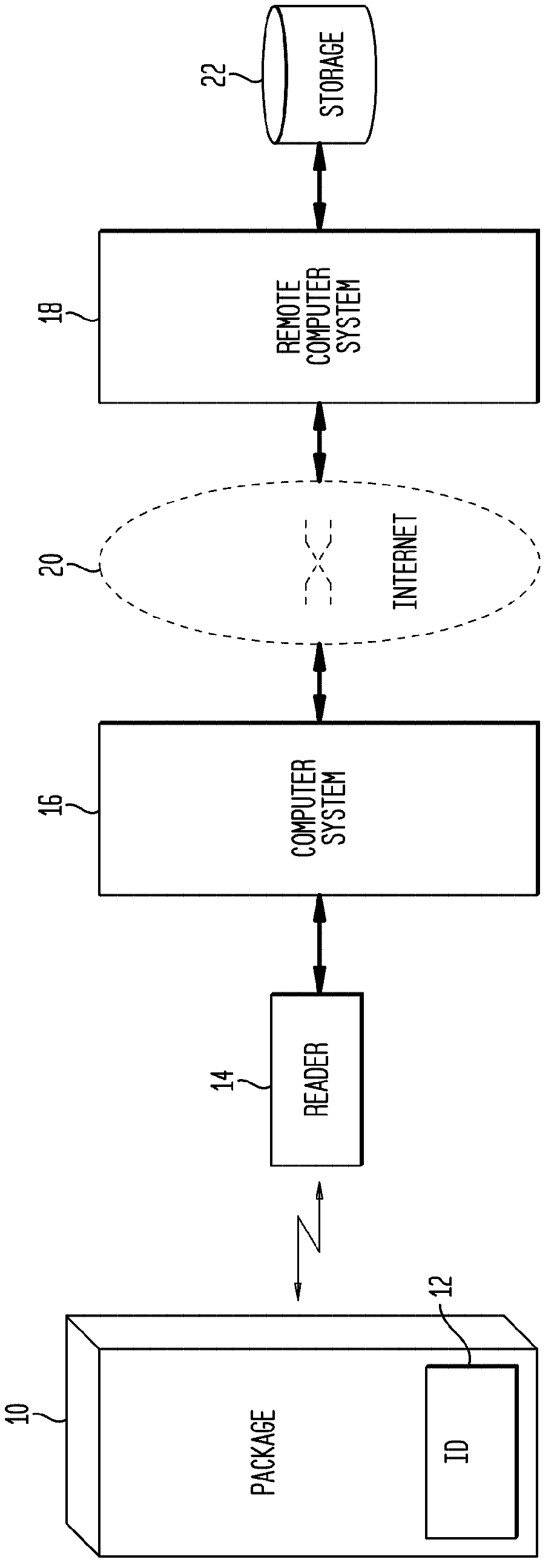

Controlled remote product internet access and distribution

InactiveUS20010054082A1Multiple digital computer combinationsSpecial data processing applicationsComputerized systemInternet access

<heading lvl="0">Abstract of Disclosure< / heading> A system for accessing a remote computer network. The system comprising (a) a package; (b) an identification tag coupled to the package that stores identifying data unique to the package; (c) an interrogator located external to the package; and (d) a computer system coupled to the interrogator for exchanging information with a remote site. The interrogator transmits a query to the identification tag and the identification tag responds by communicating the identifying data to the computer system, thereby accessing the remote computer network.

Owner:INT PAPER CO

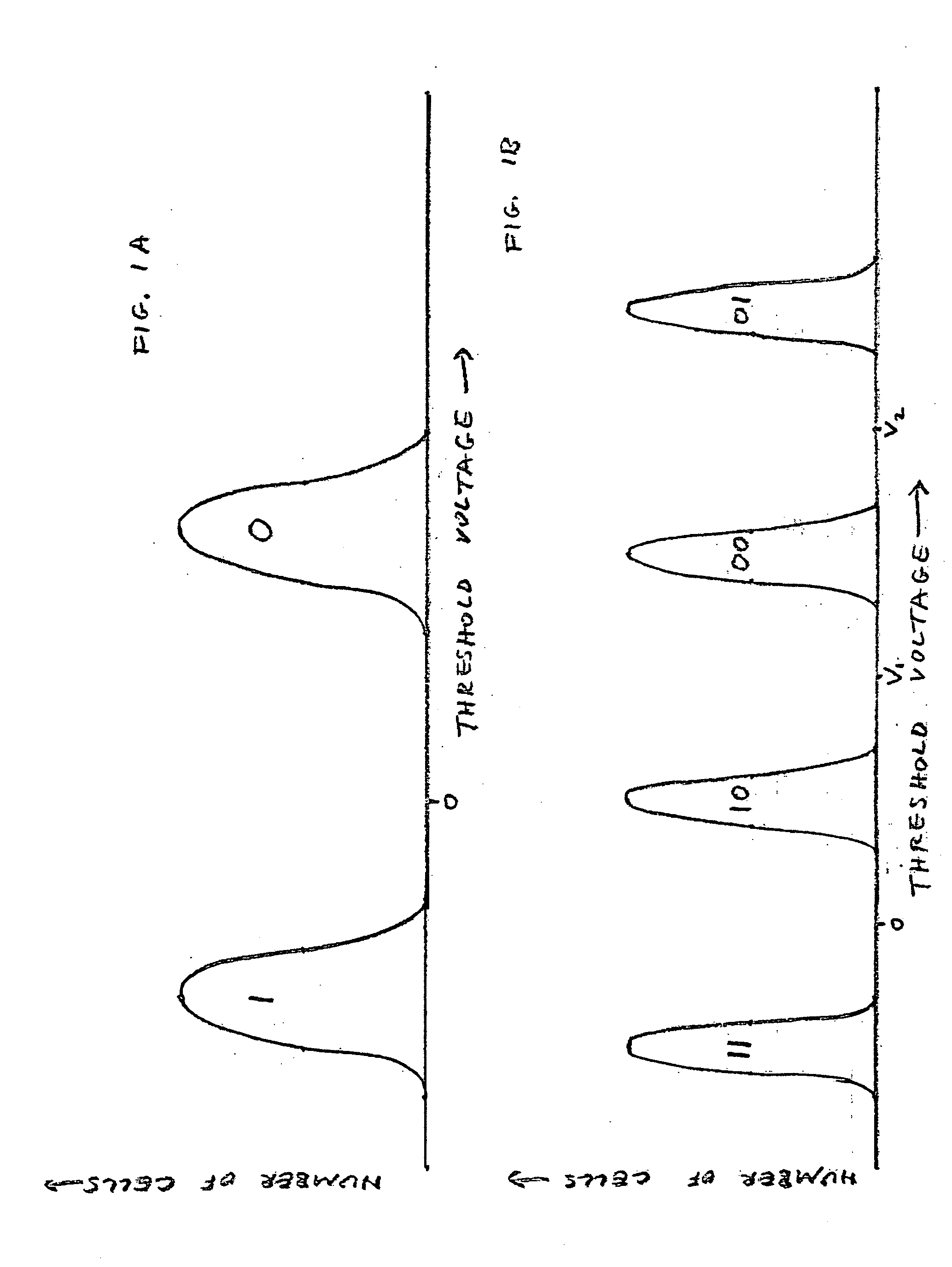

States encoding in multi-bit flash cells

ActiveUS7310347B2Read-only memoriesData switching by path configurationComputer scienceThreshold voltage

Owner:WESTERN DIGITAL ISRAEL LTD

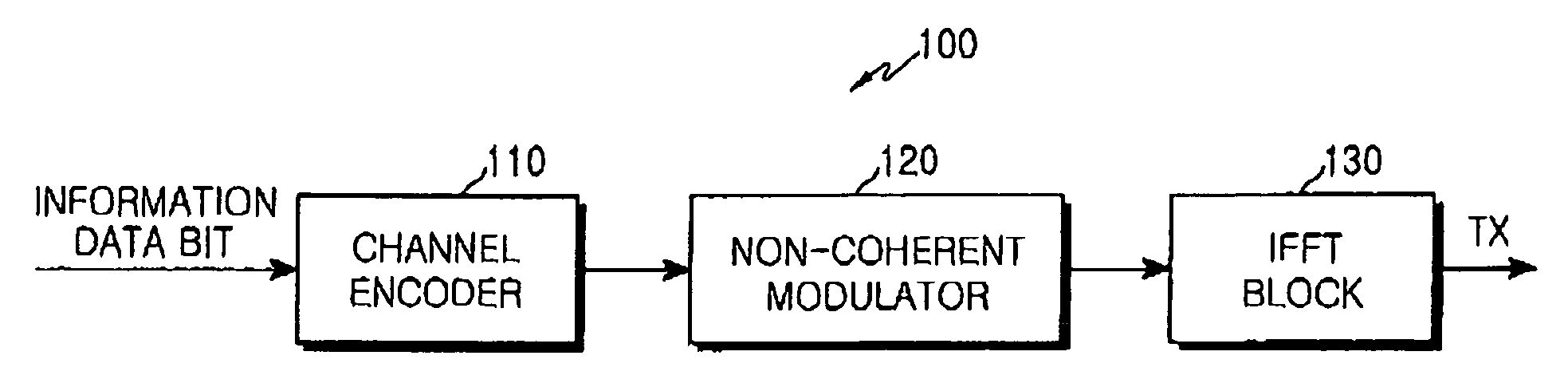

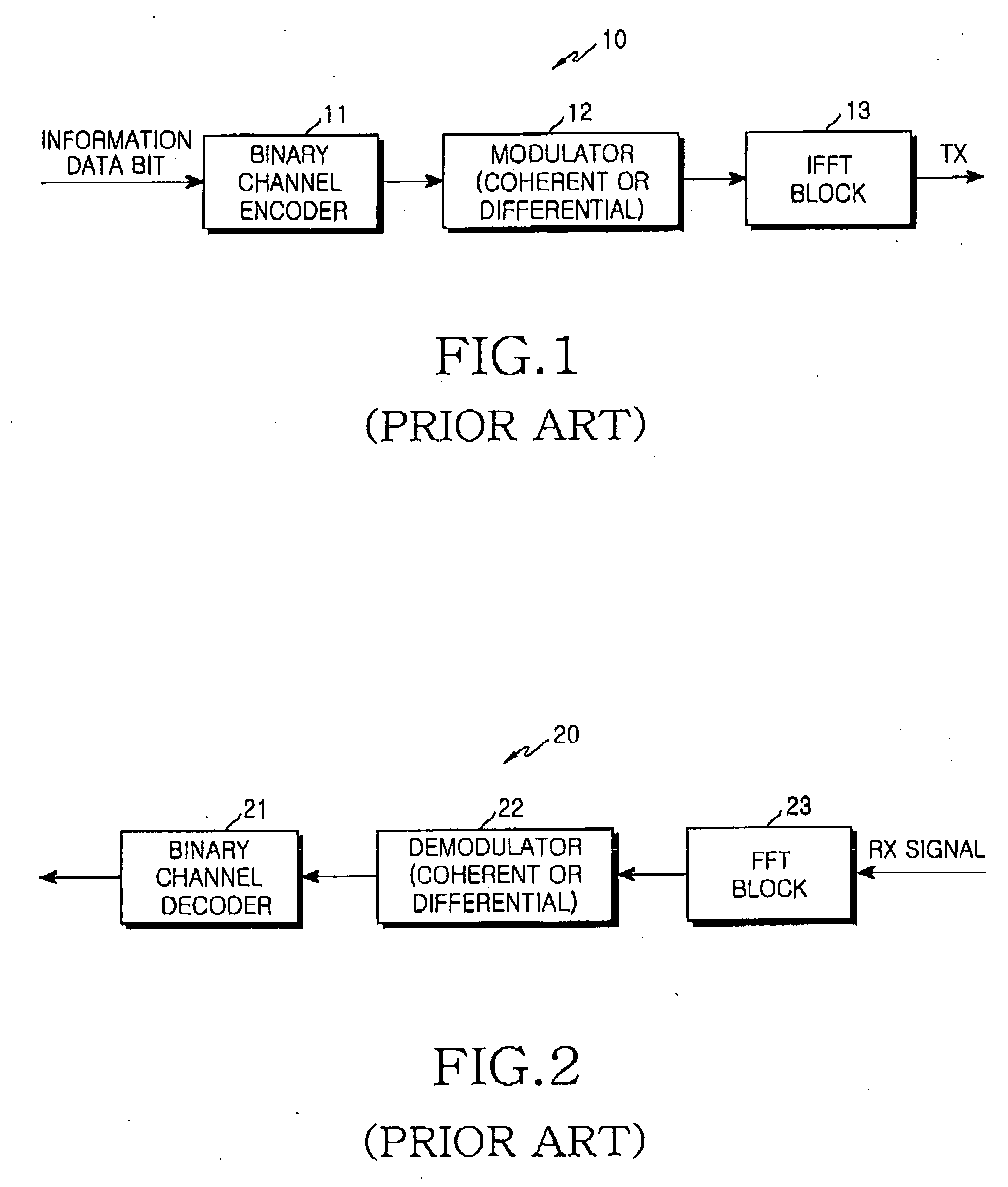

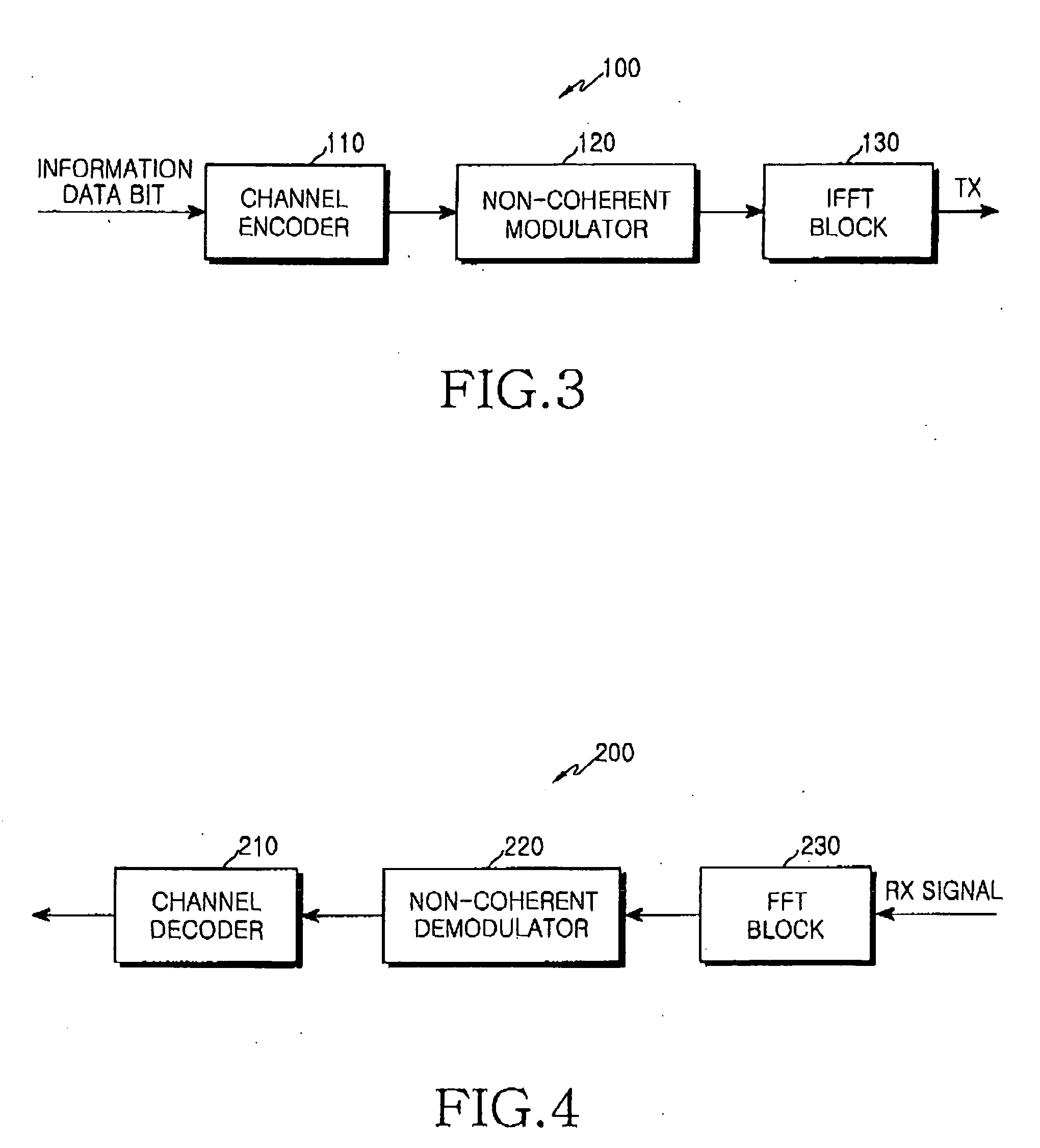

Method and apparatus for transmitting uplink acknowledgement information in an OFDMA communication system

ActiveUS20050286402A1Guaranteed normal transmissionImprove reliabilityError prevention/detection by using return channelTransmission path divisionFast Fourier transformCommunications system

A method and apparatus for transmitting uplink acknowledge information (ACK) in a communication system using an orthogonal frequency division multiple access (OFDMA) scheme. The method includes receiving a data bit for the uplink ACK; outputting codewords corresponding to the data bit; performing quadrature phase shift keying (QPSK) modulation on symbols for ACK vector indexes corresponding to the codewords for the received data bit; performing inverse fast Fourier transform (IFFT) on a transmission signal having subcarrier clusters to which the modulated transmission symbols are allocated; and transmitting the IFFT-processed transmission signal.

Owner:SAMSUNG ELECTRONICS CO LTD

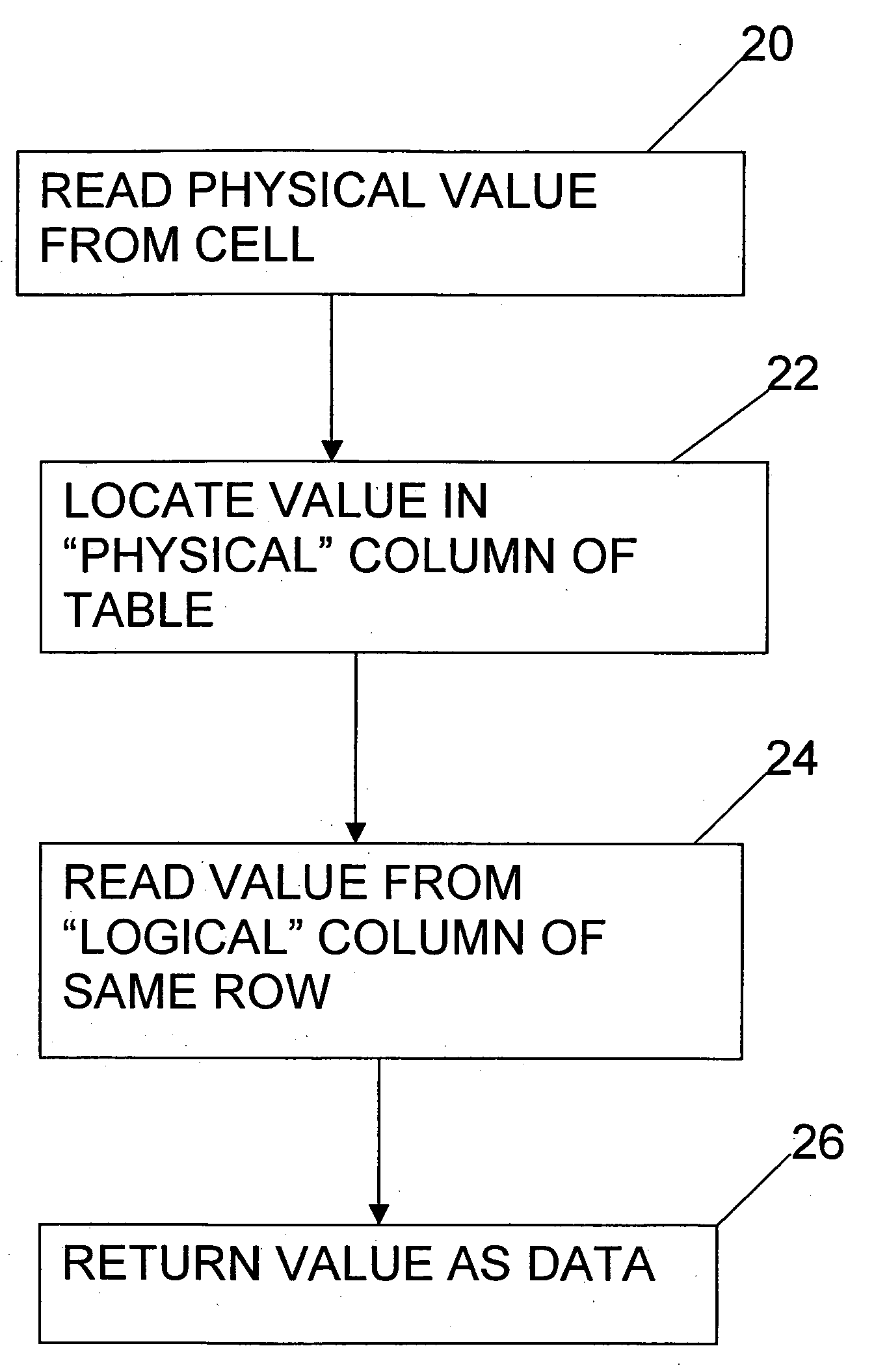

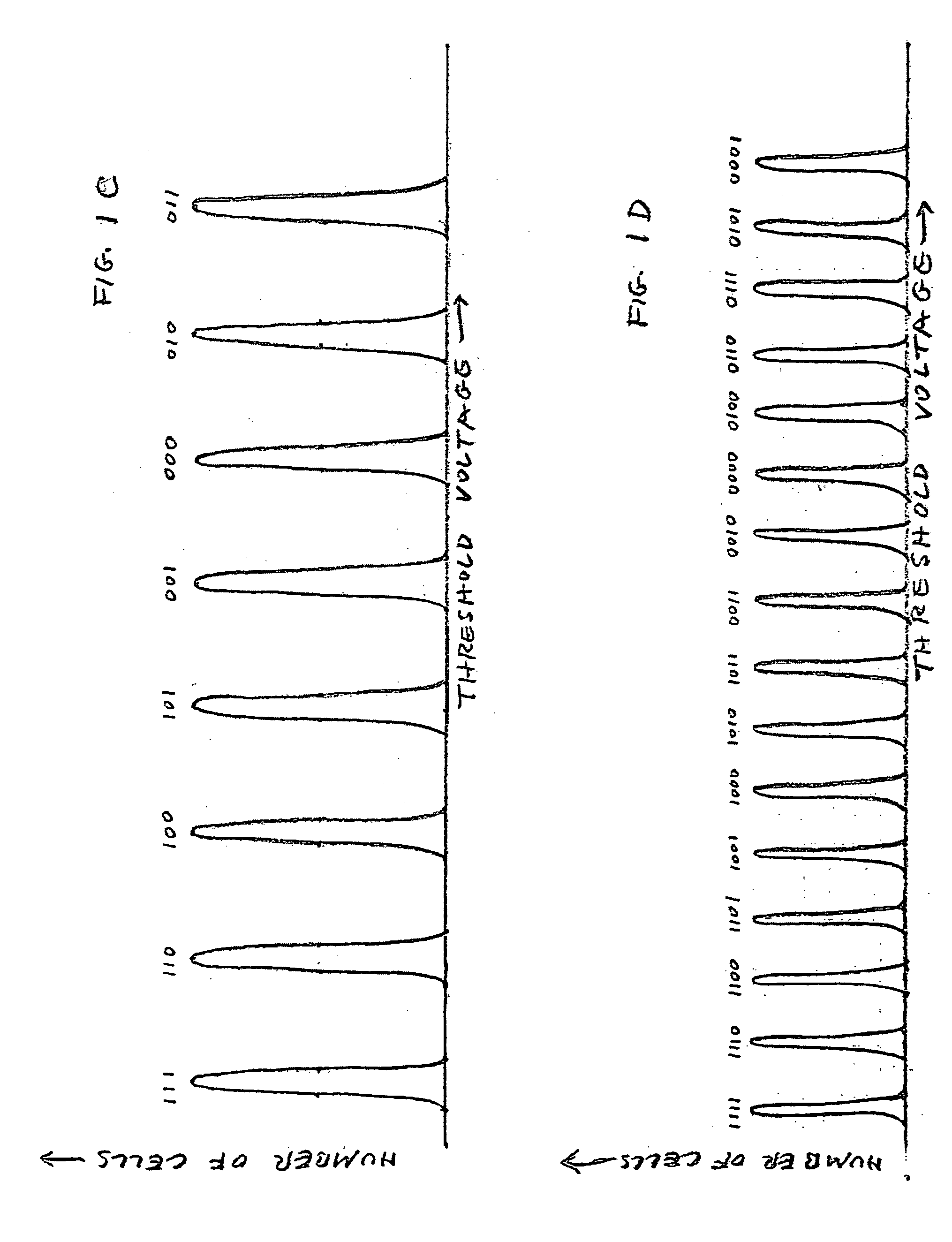

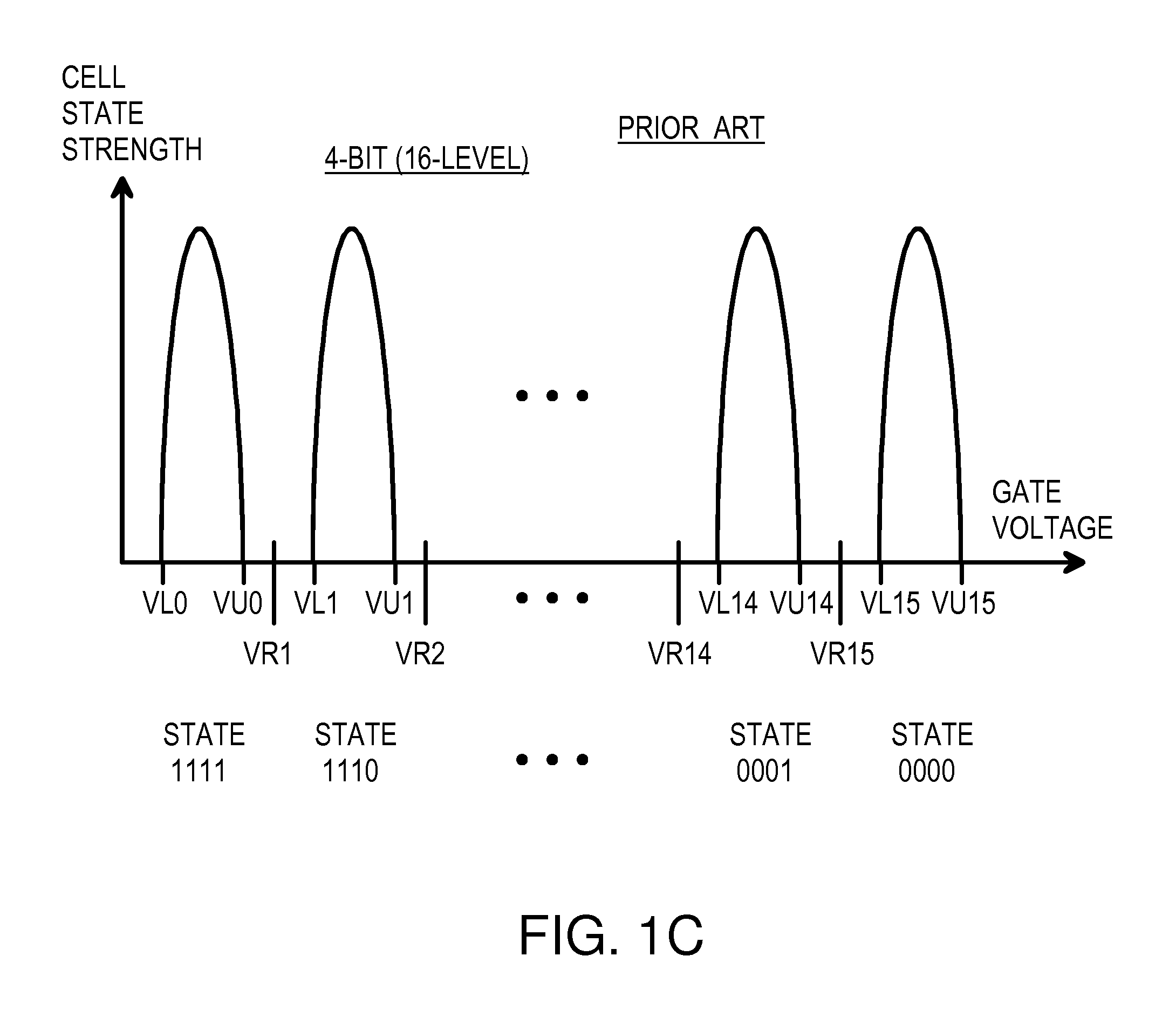

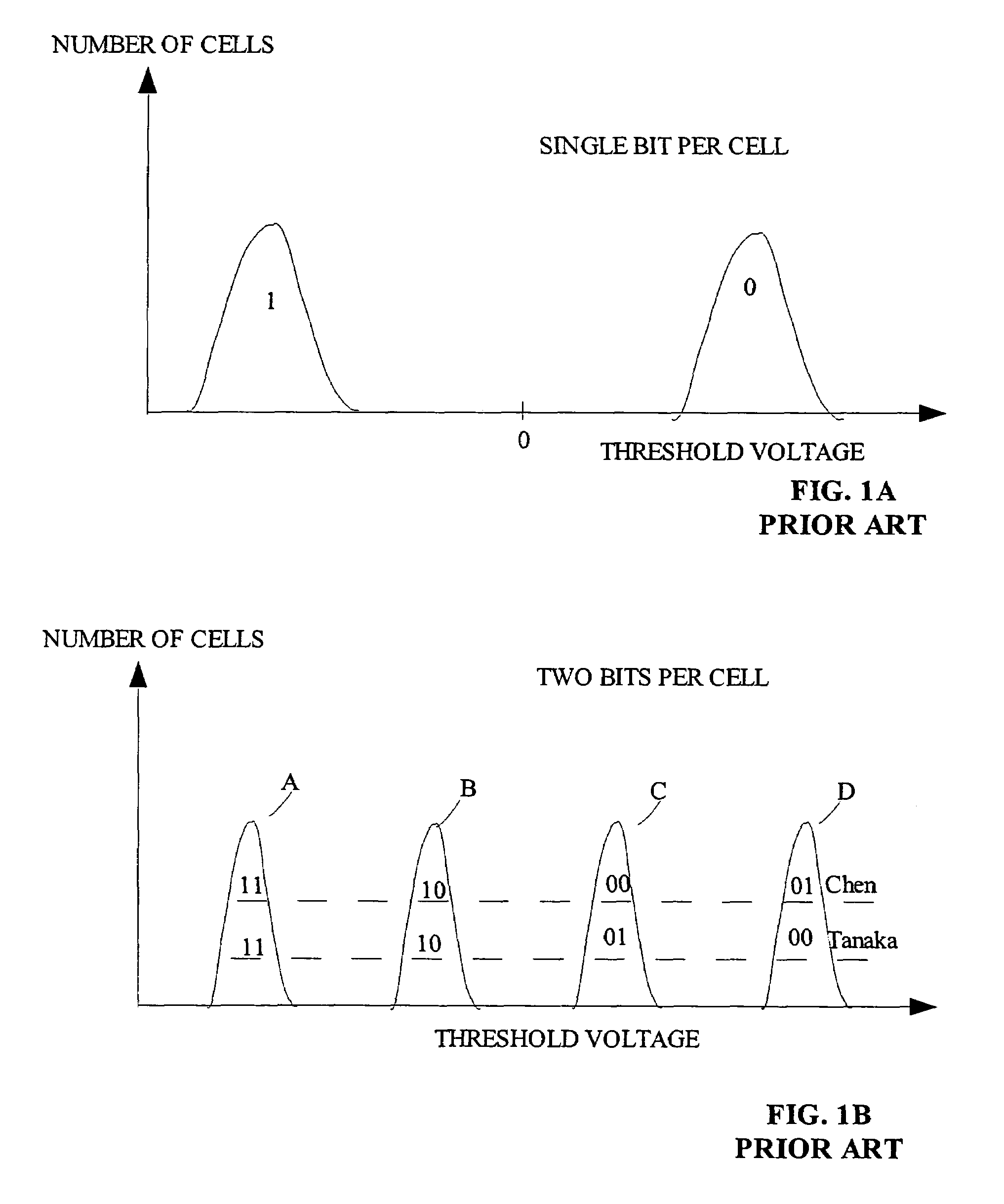

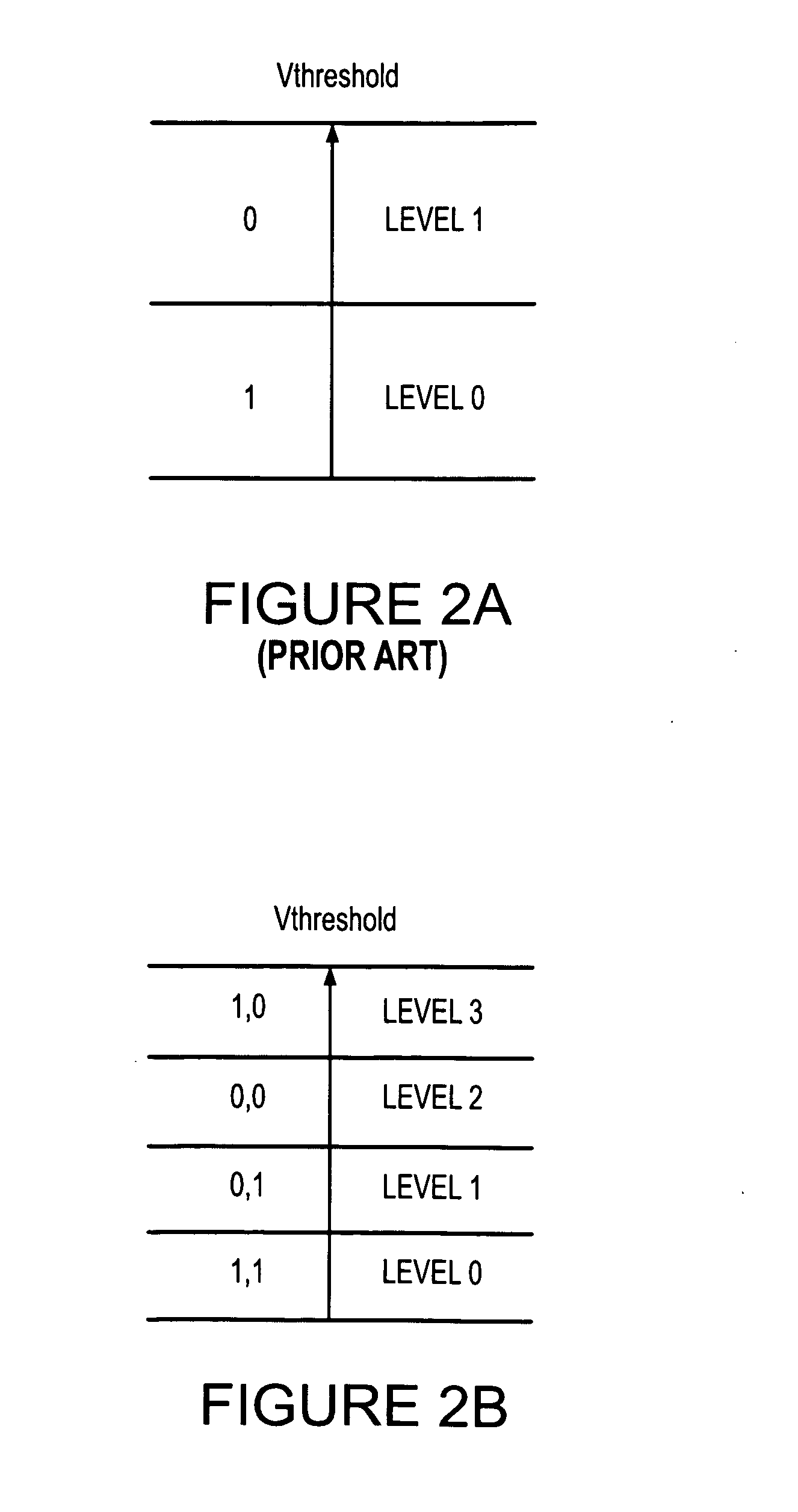

States encoding in multi-bit flash cells for optimizing error rate

ActiveUS20080104312A1Equally distributedMemory adressing/allocation/relocationRead-only memoriesData errorCell state

Memory cells are programmed and read, at least M=3 data bits per cell, according to a valid nonserial physical bit ordering with reference to a logical bit ordering. The logical bit ordering is chosen to give a more even distribution of error probabilities of the bits, relative to the probability distributions of the data error and the cell state transition error, than would be provided by the physical bit ordering alone. Preferably, both bit orderings have 2M−1 transitions. Preferably, the logical bit ordering is evenly distributed. The translation between the bit orderings is done by software or hardware.

Owner:WESTERN DIGITAL ISRAEL LTD

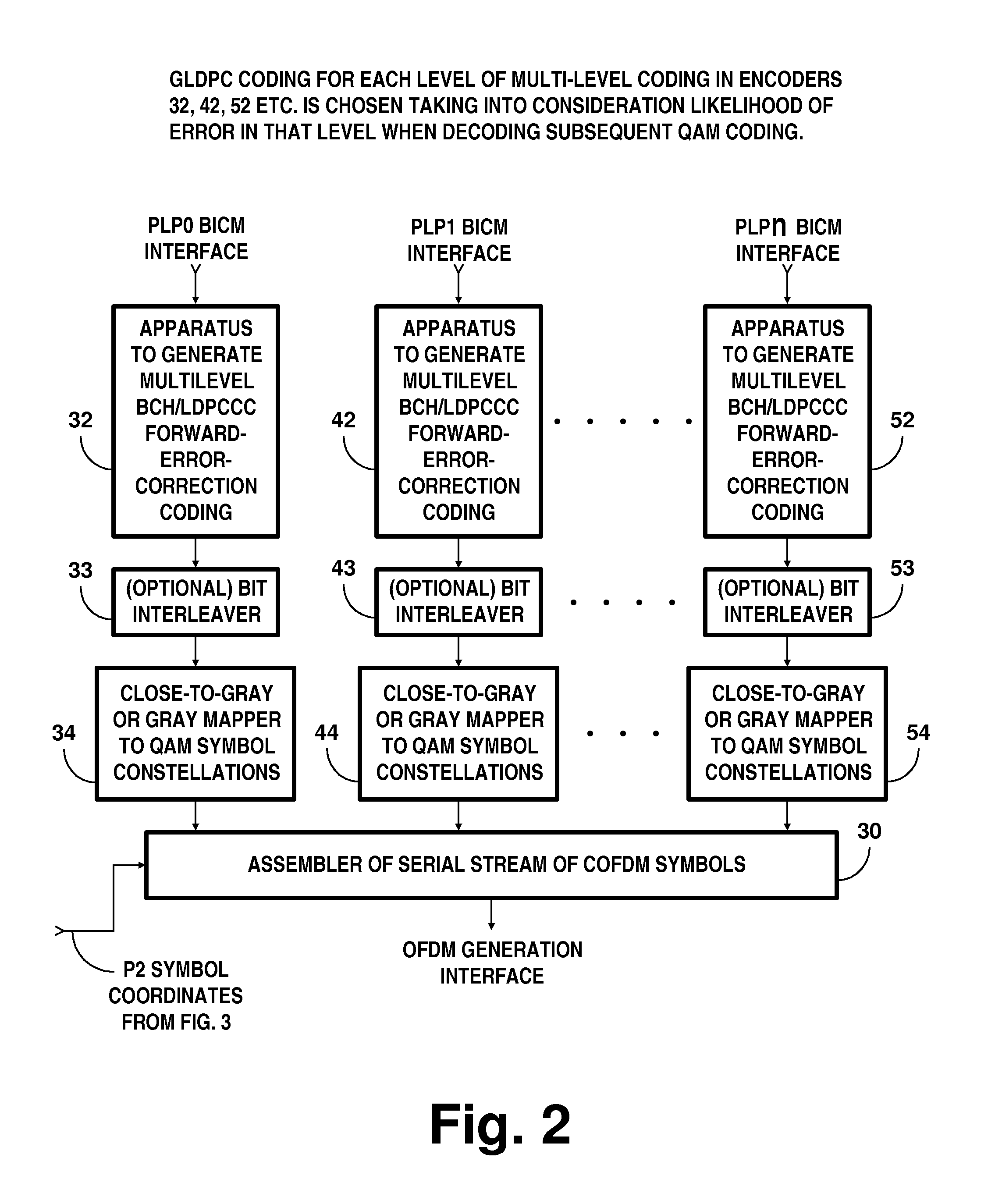

Digital television broadcasting system using coded orthogonal frequency-division modulation and multilevel LDPC convolutional coding

InactiveUS20150358648A1Facilitate parallel independent decodingError preventionError correction/detection using concatenated codesCarrier signalRadio frequency

In transmitter apparatus for a digital television (DTV) broadcasting system, internet-protocol (IP) packets of digital television information are subjected to multilevel concatenated Bose-Chaudhuri-Hocquenghem (BCH) coding and low-density parity-check convolutional coding (LDPCCC) before being bit-interleaved and mapped to quadrature-amplitude-modulation (QAM) constellations. The QAM constellations are used in coded orthogonal frequency-division modulation (COFDM) of plural carrier waves up-converted to a radio-frequency broadcast television channel. In receiver apparatus for the DTV broadcasting system the results of de-mapping QAM constellations recovered from demodulating the COFDM carrier waves are de-interleaved, and the constituent LDPCCC codewords are decoded to recover constituent BCH codewords of the multilevel BCH coding. The constituent BCH codewords are decoded to correct remnant bit errors in them. Then, IP packets of digital television information are reconstituted from the systematic data bits in those BCH codewords.

Owner:LIMBERG ALLEN LEROY

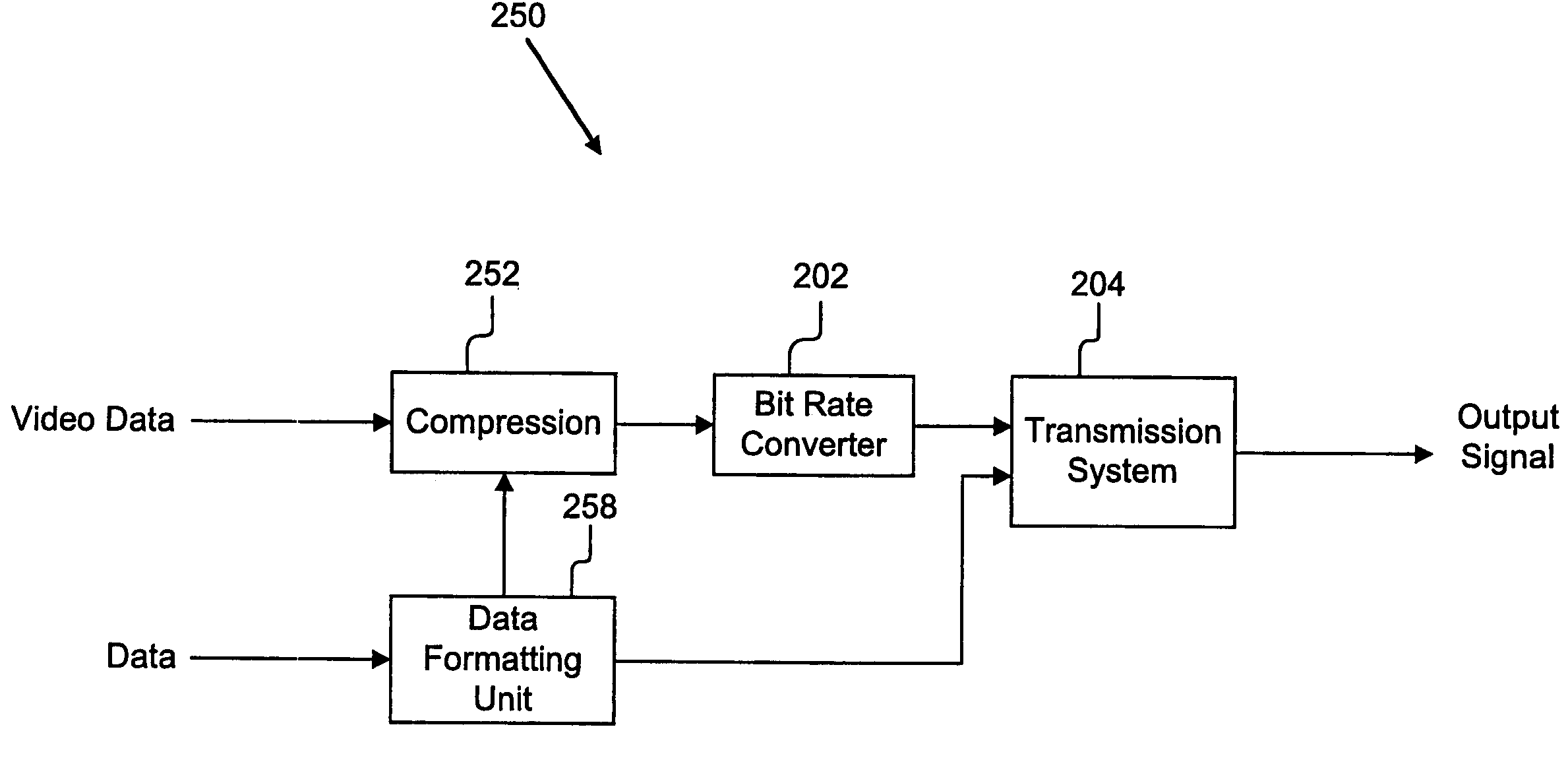

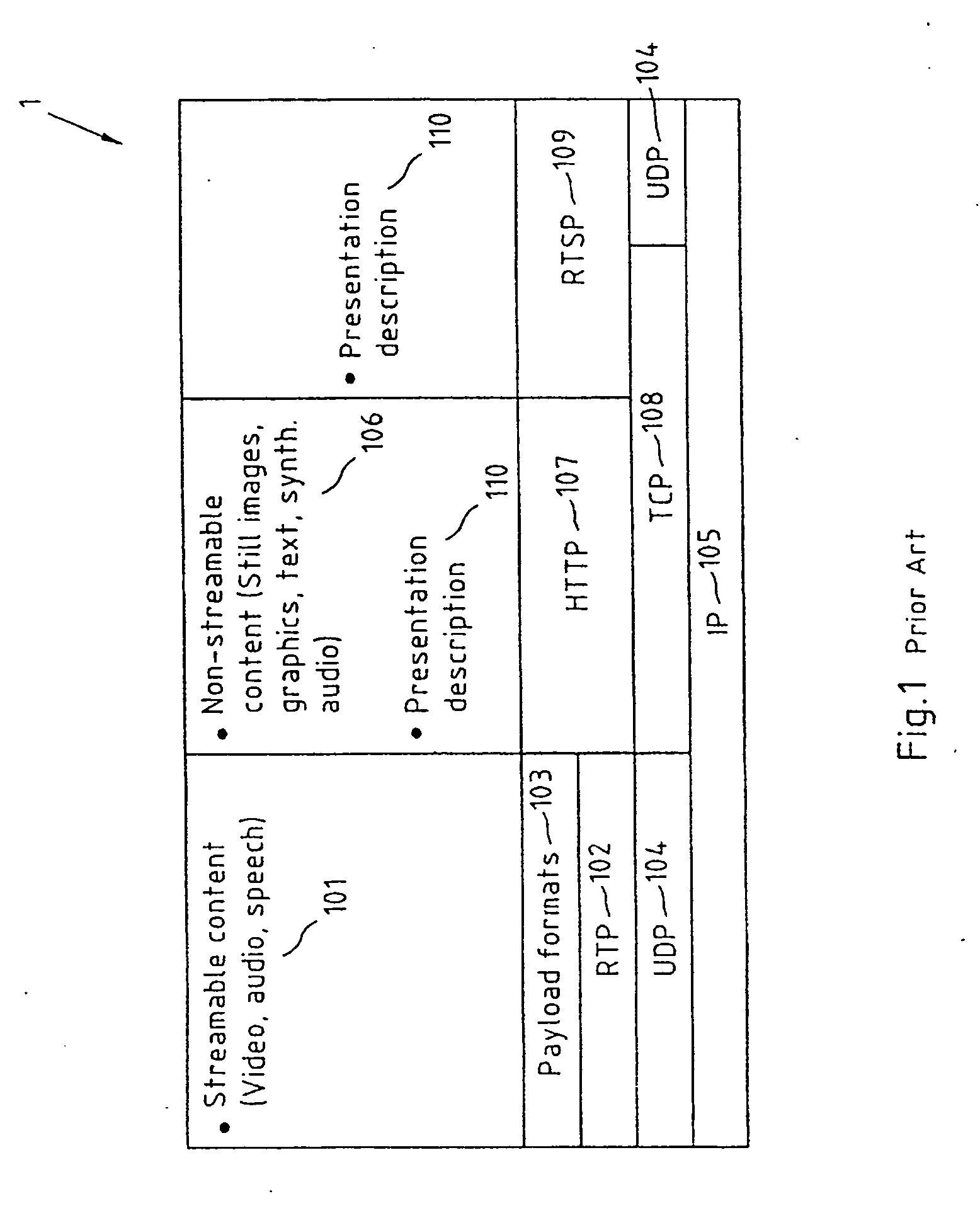

System and method for transporting a compressed video and data bit stream over a communication channel

InactiveUS7505480B1Eliminate needError preventionFrequency-division multiplex detailsAccess networkComputer science

Digitally compressed video / audio bit streams, when transmitted over digital communication channels such as digital subscriber loop (DSL) access networks, ATM networks, satellite, or wireless digital transmission facilities, can be corrupted due to lack of sufficient channel bandwidth. This invention describes schemes to ensure lossless transmission of bit streams containing pre-compressed video signals within the communication channels. The schemes herein comprises a rate conversion system that converts the bit rate of a pre-compressed video bit stream from one bit rate to another, and that is integrated with a digital communication channel, and a means to convey the maximum channel transmission rate to the rate conversion system to allow satisfactory transmission of the bit stream from the input of the rate converter through the transmission facility.

Owner:V BITS +1

Velocity enhancement for OFDM systems

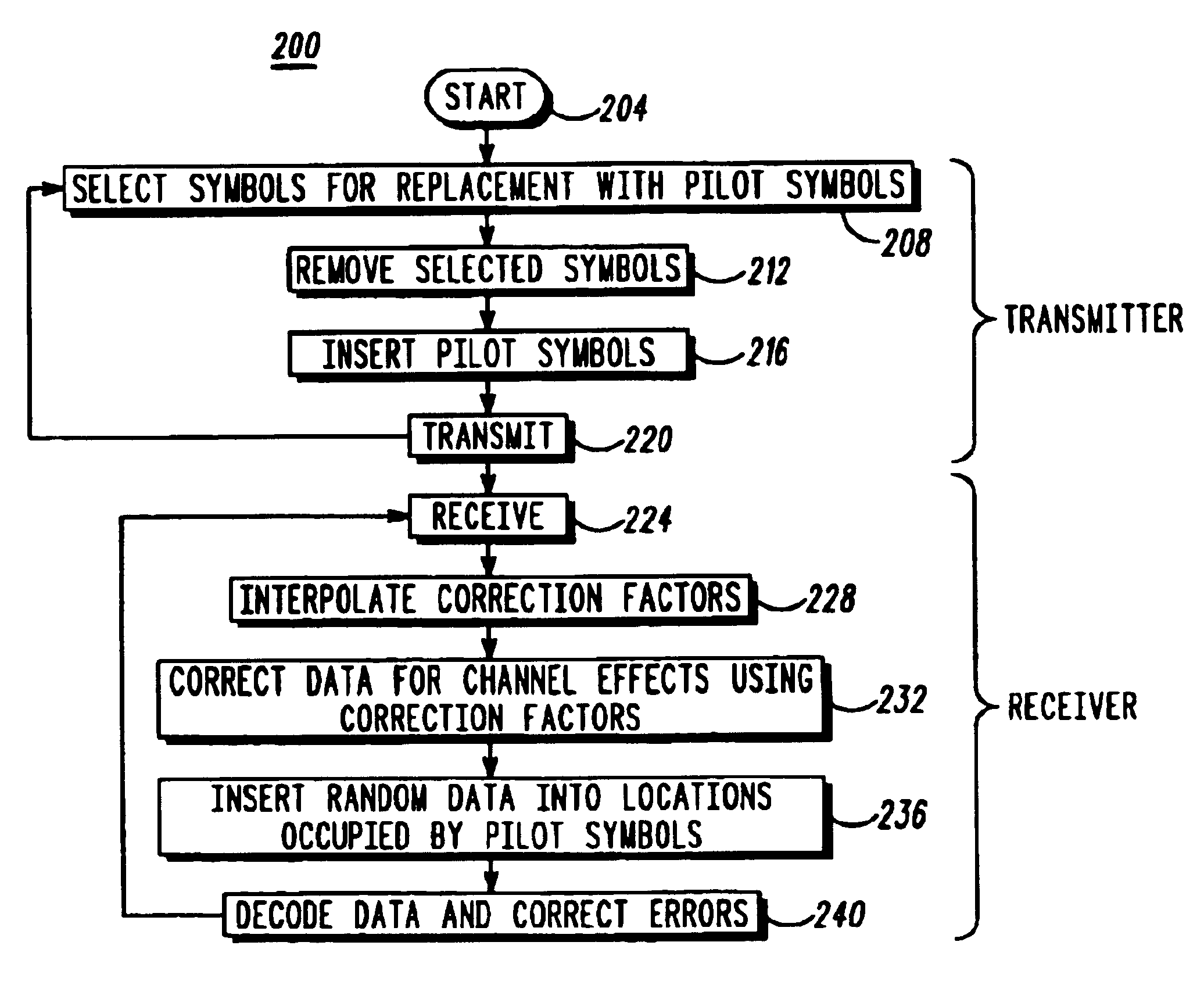

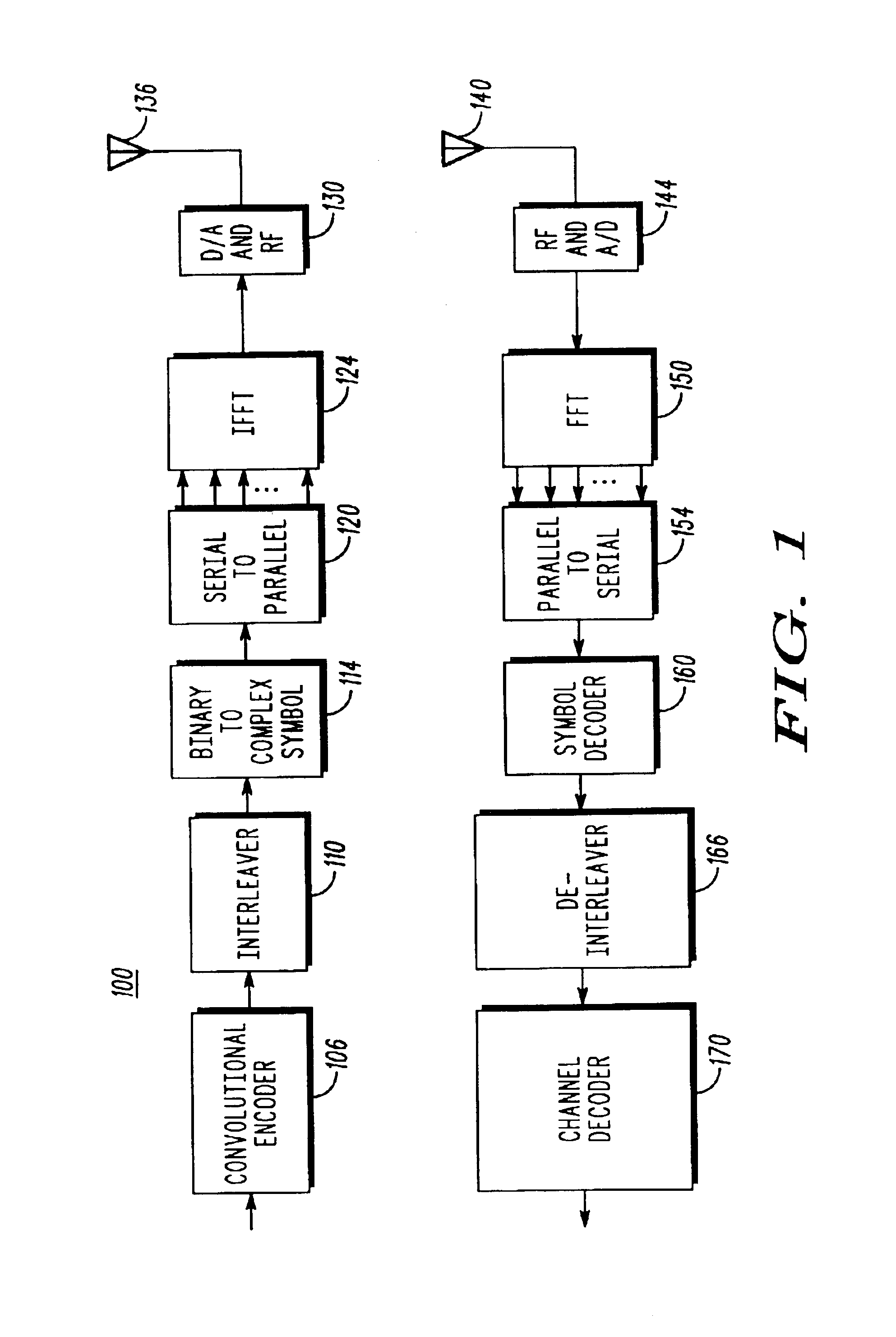

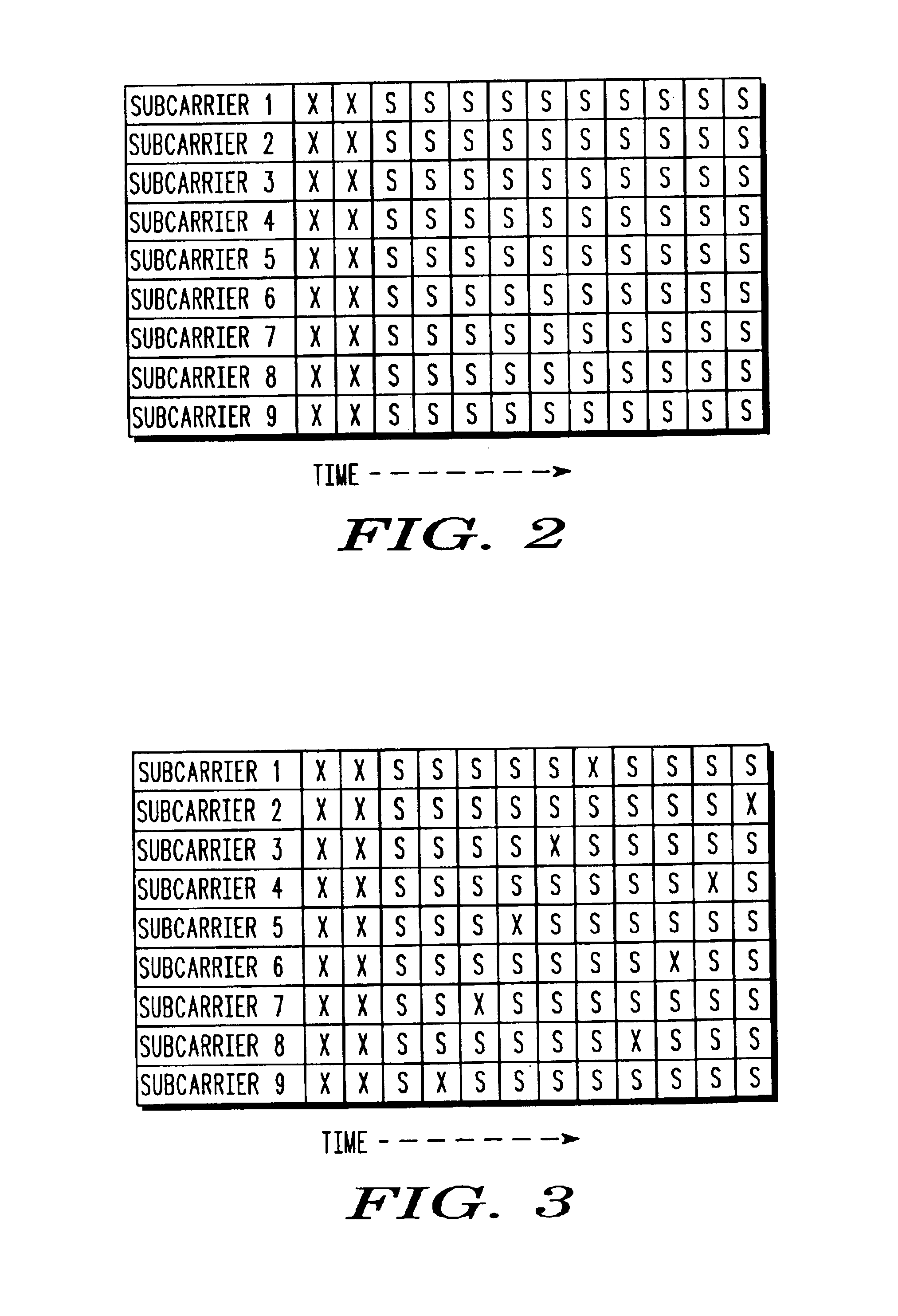

An orthogonal frequency division multiplexing (OFDM) transmitter method, consistent with certain embodiments of the present invention arranges OFDM data symbols representing data bits for transmission in a packet. A prescribed pattern of OFDM data symbols are removed (212) and replaced (216) with pilot symbols. The packet is then transmitted (220) to an OFDM receiver that receives the packet (224) and determines a channel correction factor from the pilot pattern. The receiver then estimates a plurality of channel correction factors, one for each of the plurality of OFDM symbols representing data (228) and uses these correction factors to correct the OFDM symbols representing data (232). Arbitrary data are then inserted in place of the pilot symbols (236). The OFDM symbols representing data along with the arbitrary data are then decoded using an error correction decoder that corrects the errors induced by substitution of the pilot symbols for data symbols (240).

Owner:GOOGLE TECH HLDG LLC

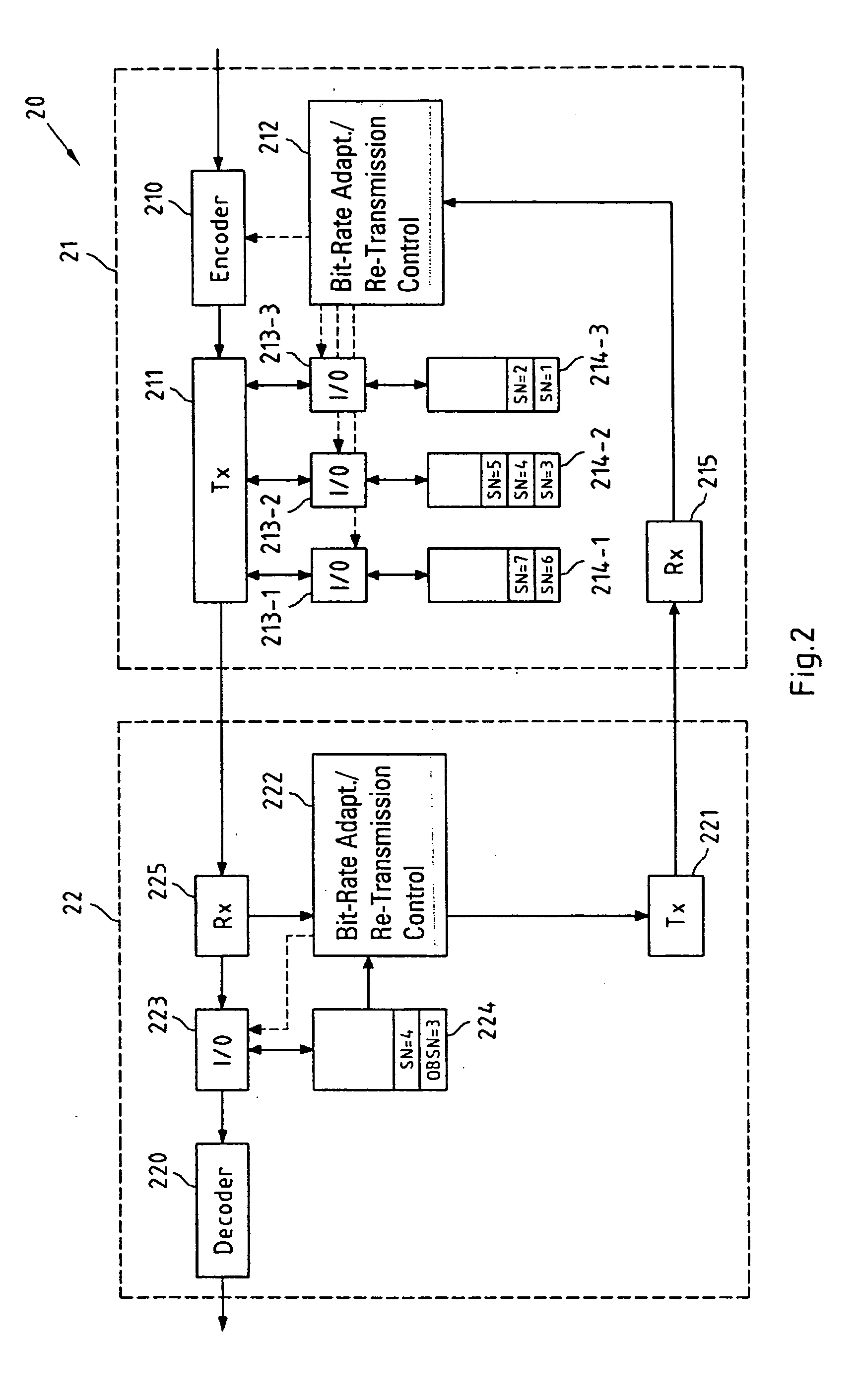

Cooperation between packetized data bit-rate adaptation and data packet re-transmission

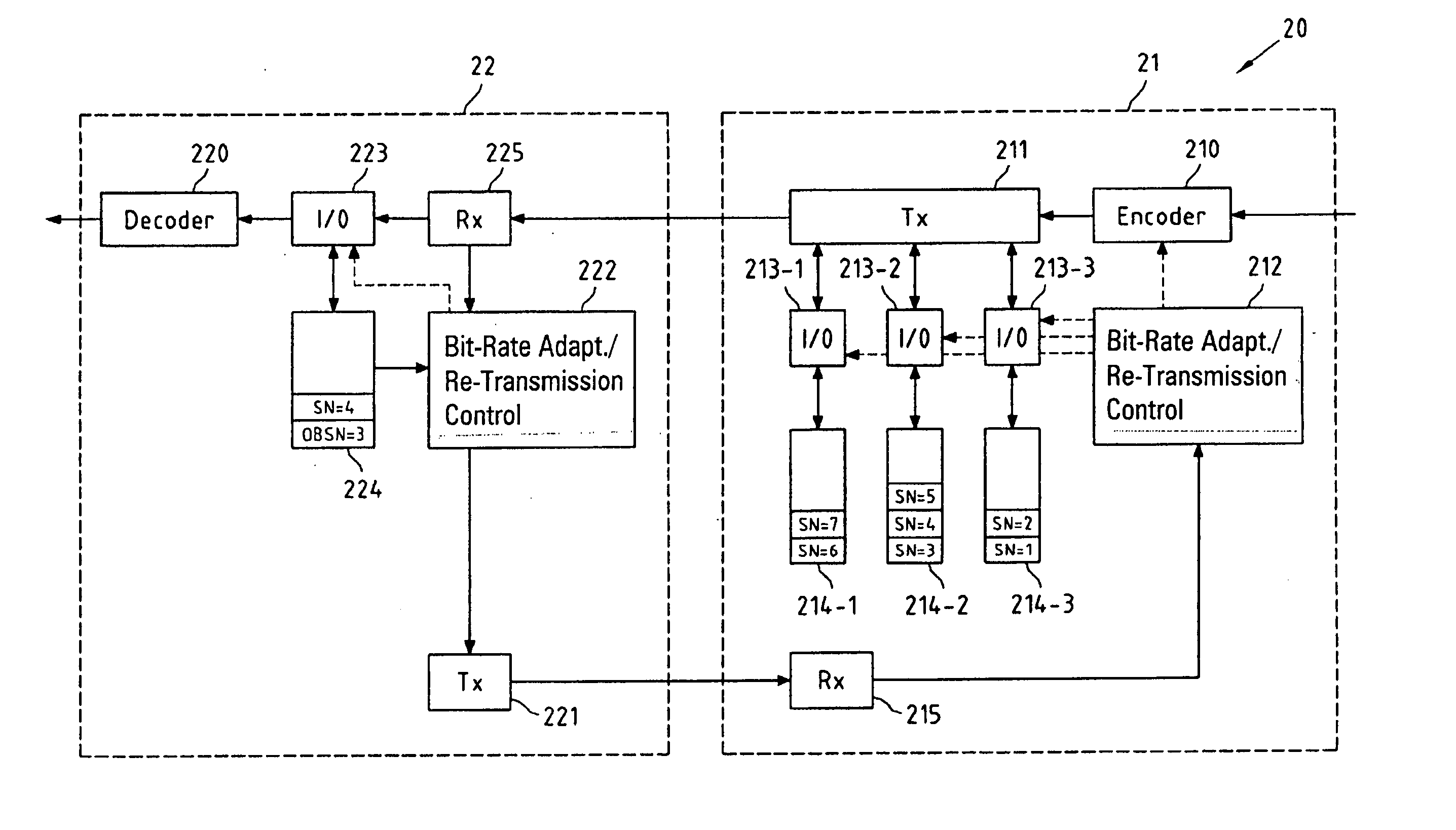

InactiveUS20050254508A1Cooperate wellAvoid delayError prevention/detection by using return channelTransmission systemsData packRate adaptation

A method for improving a cooperation between a packetized data bit-rate adaptation and a data packet re-transmission transmits data packets from a server to a client with a first bit-rate; stores transmitted data packets in a server buffer; stores transmitted data packets in a client buffer; signals impairment information related to an impairment of transmitted data packets during transmitting to the server, wherein the signaled impairment information is analyzed by the server to decide if a re-transmission of data packets stored in the server buffer is required; and signals client buffer information related to a state of the client buffer to the server, wherein the client buffer information is analyzed by the server to decide if a re-transmission of data packets is required.

Owner:NOKIA CORP

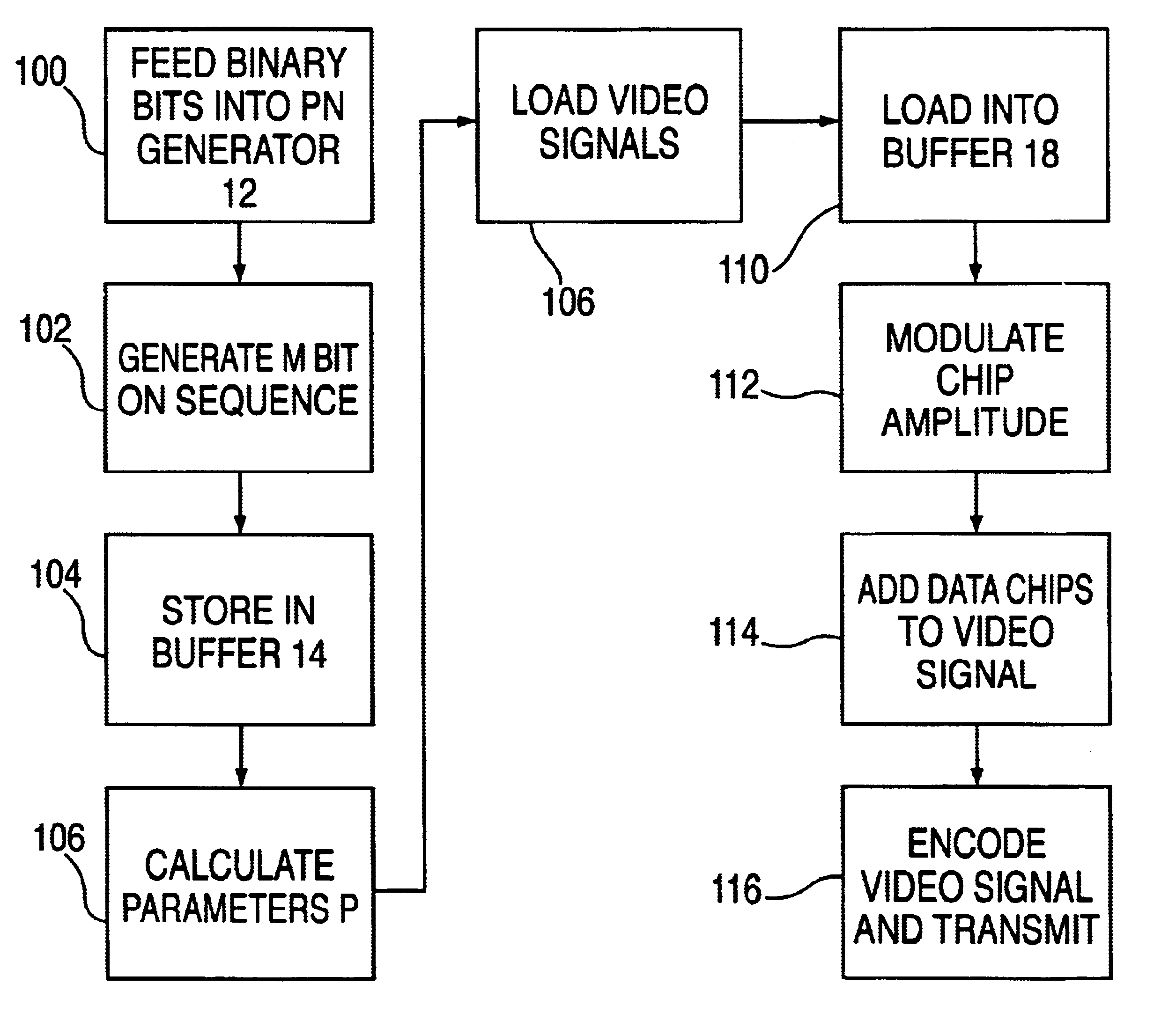

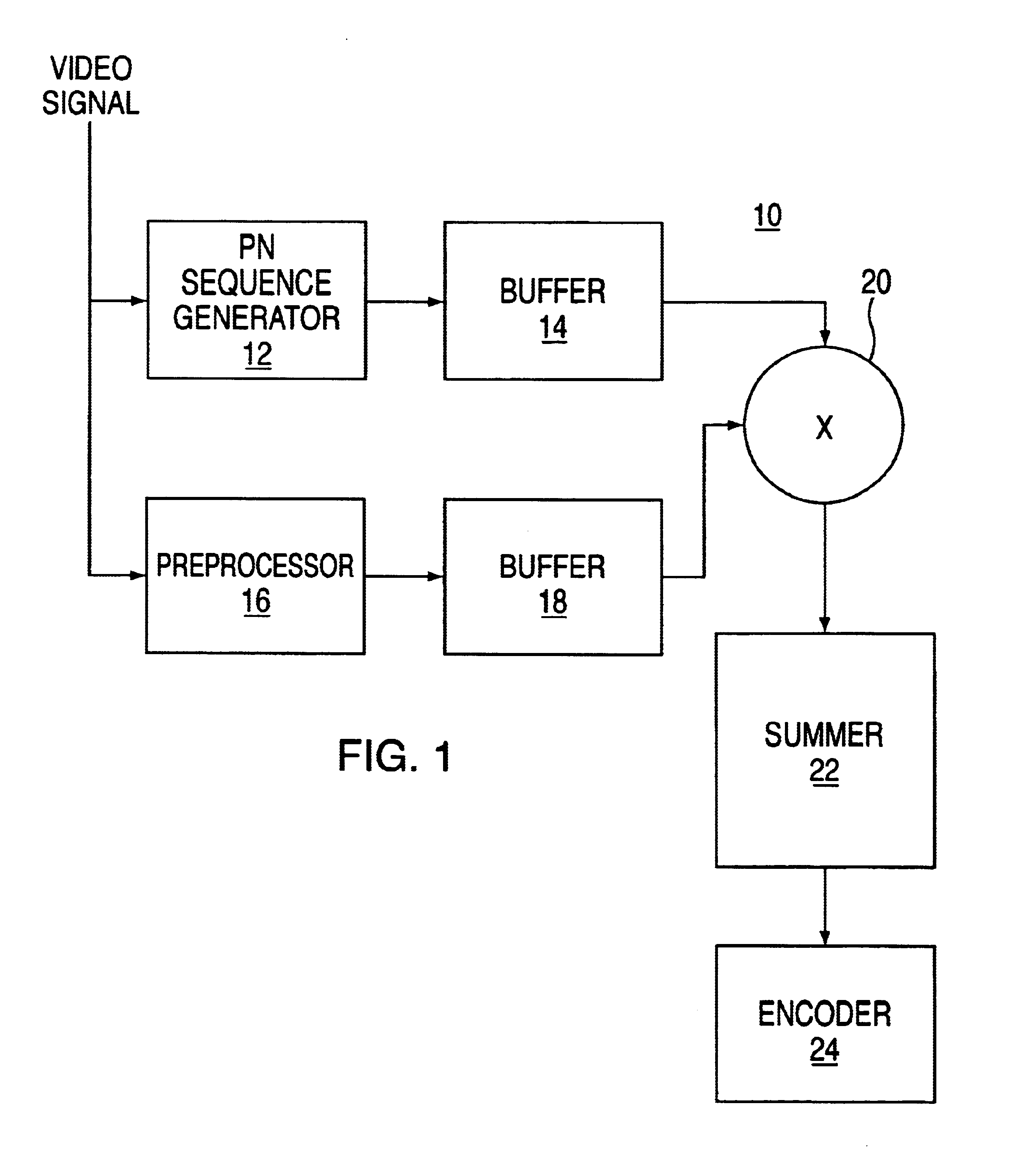

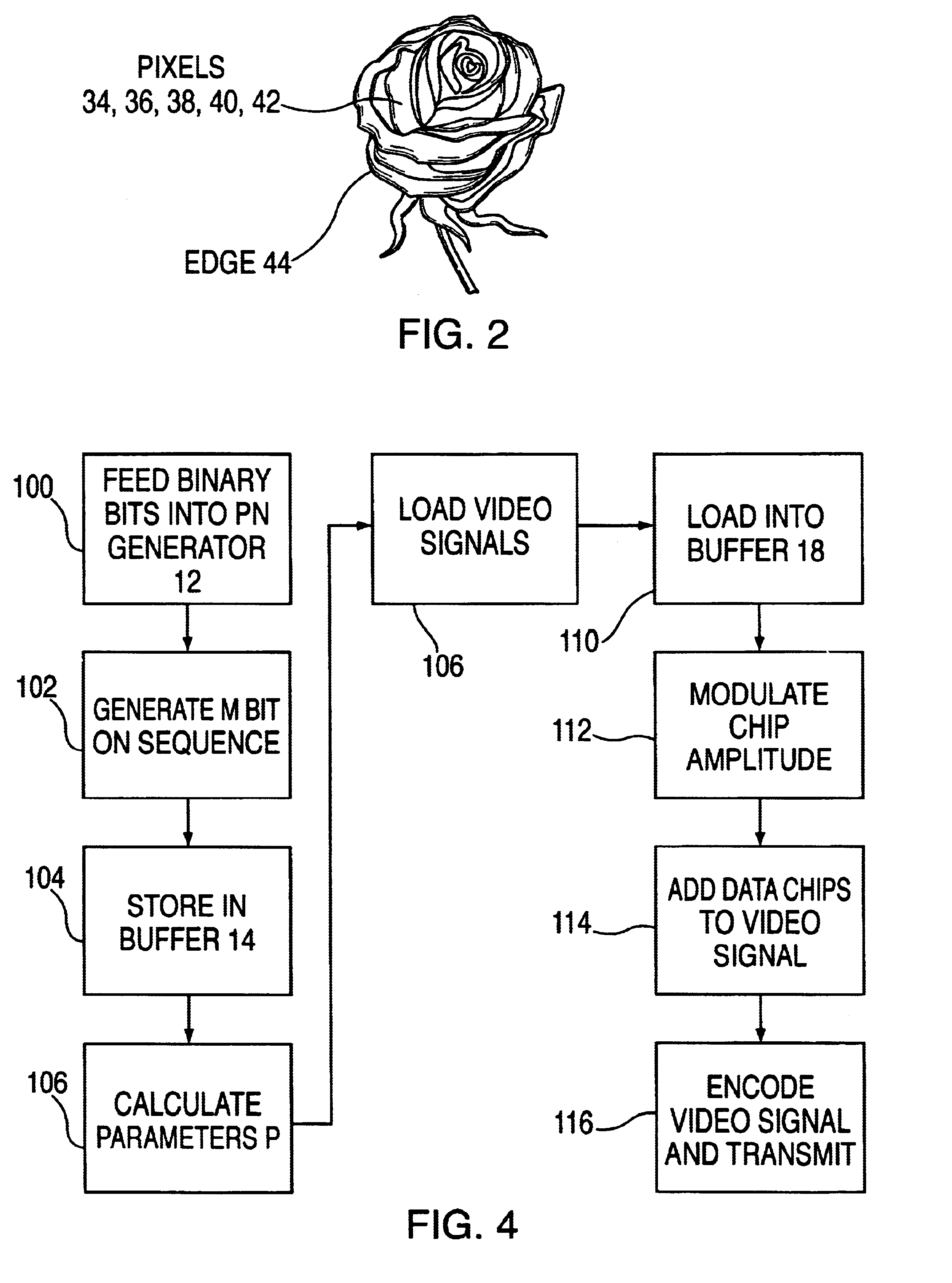

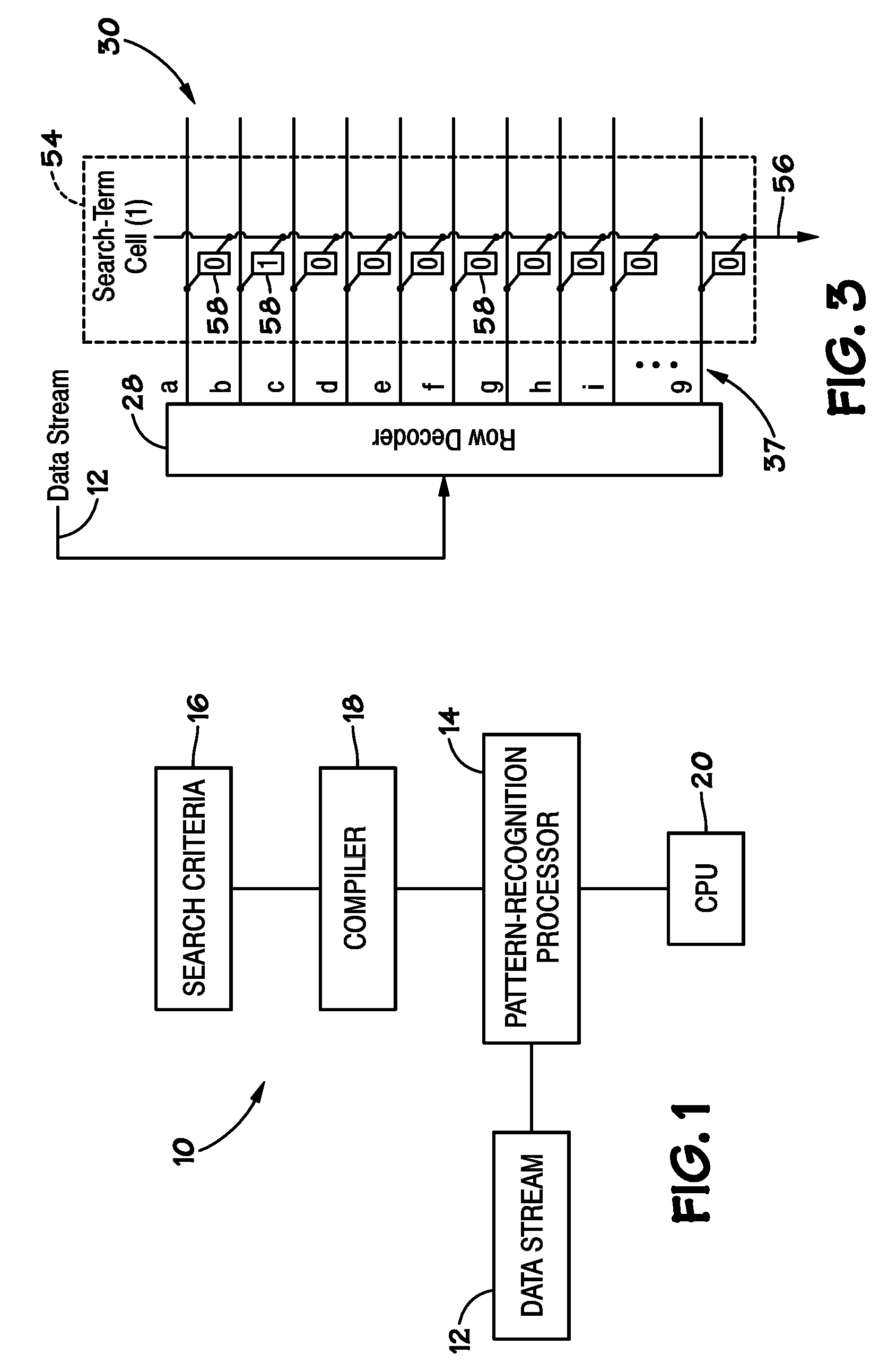

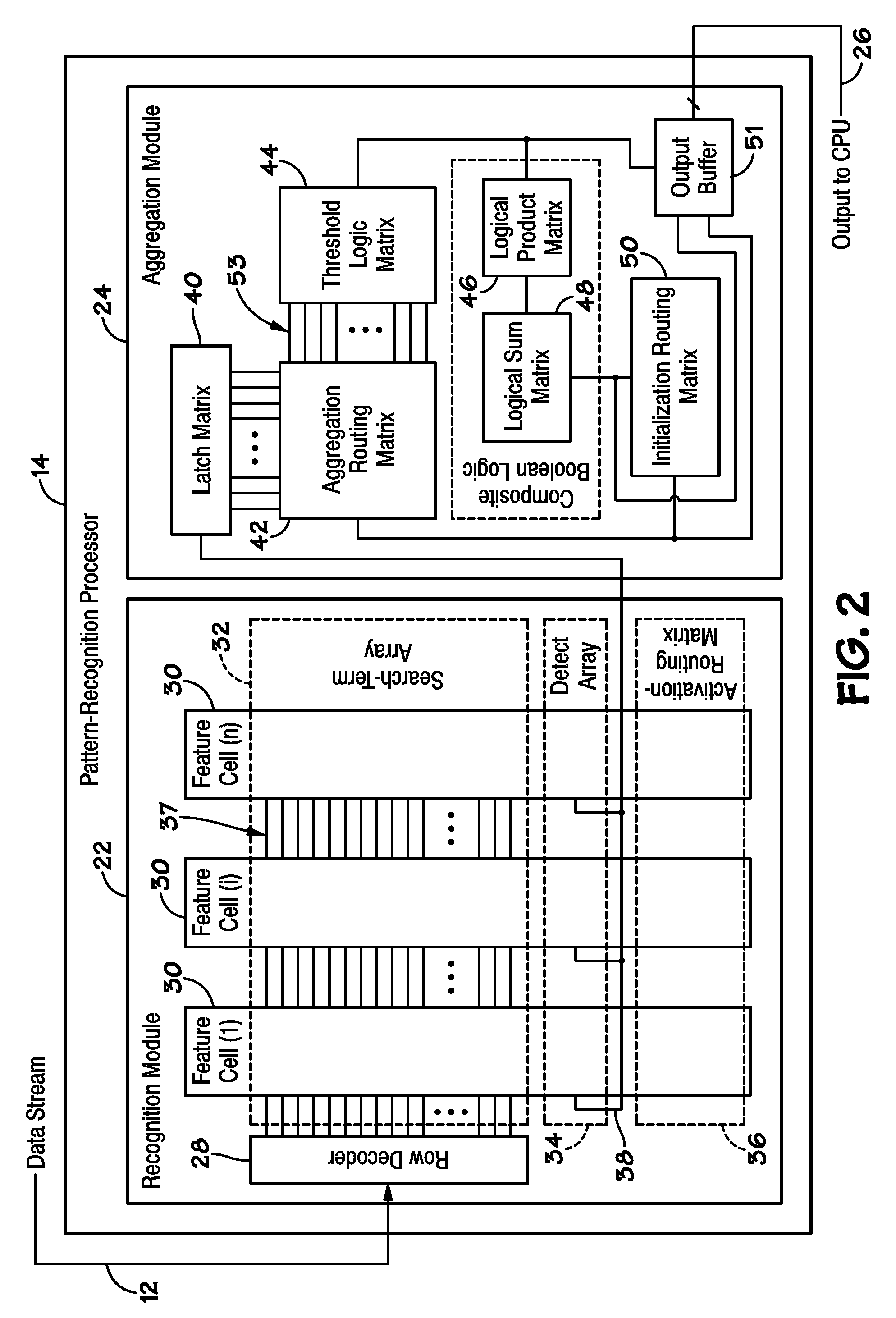

Method for transmitting data on a viewable portion of a video signal

InactiveUS6661905B1Improve reliabilityImprove efficiency and qualityCharacter and pattern recognitionSimultaneous/sequential multiple television signal transmissionComputer scienceLine scan

A method of encoding data in the visible portion of a transmitted video signal without degrading display of the received video signal, and for decoding the data in the received video signal. Each group of data bits to be transmitted, referred to a data symbol, is associated with one of a number of longer predetermined sequences of chips. Each chip sequence is divided into a multiplicity of lines of chips, and each line of chips together with its inverse are embedded, in pairwise fashion, in respective pairs of line scans of the video signal prior to its transmission. Received pairs of line scans are operated upon to detect the lines of chips they represent, and each of the number of chip sequences is correlated with the detected line of chips to derive a correlation magnitude. The chip sequence with the largest correlation magnitude is selected as the chip sequence whose data symbol was transmitted. The number of data lines exceeds the number of video lines required to define a video framer. In addition, each line has an amplitude which is modulated in accordance with a data carrying parameter determined by analyzing spatial and / or temporal characteristics of the video signal.

Owner:KOPLAR INTERACTIVE SYST INT

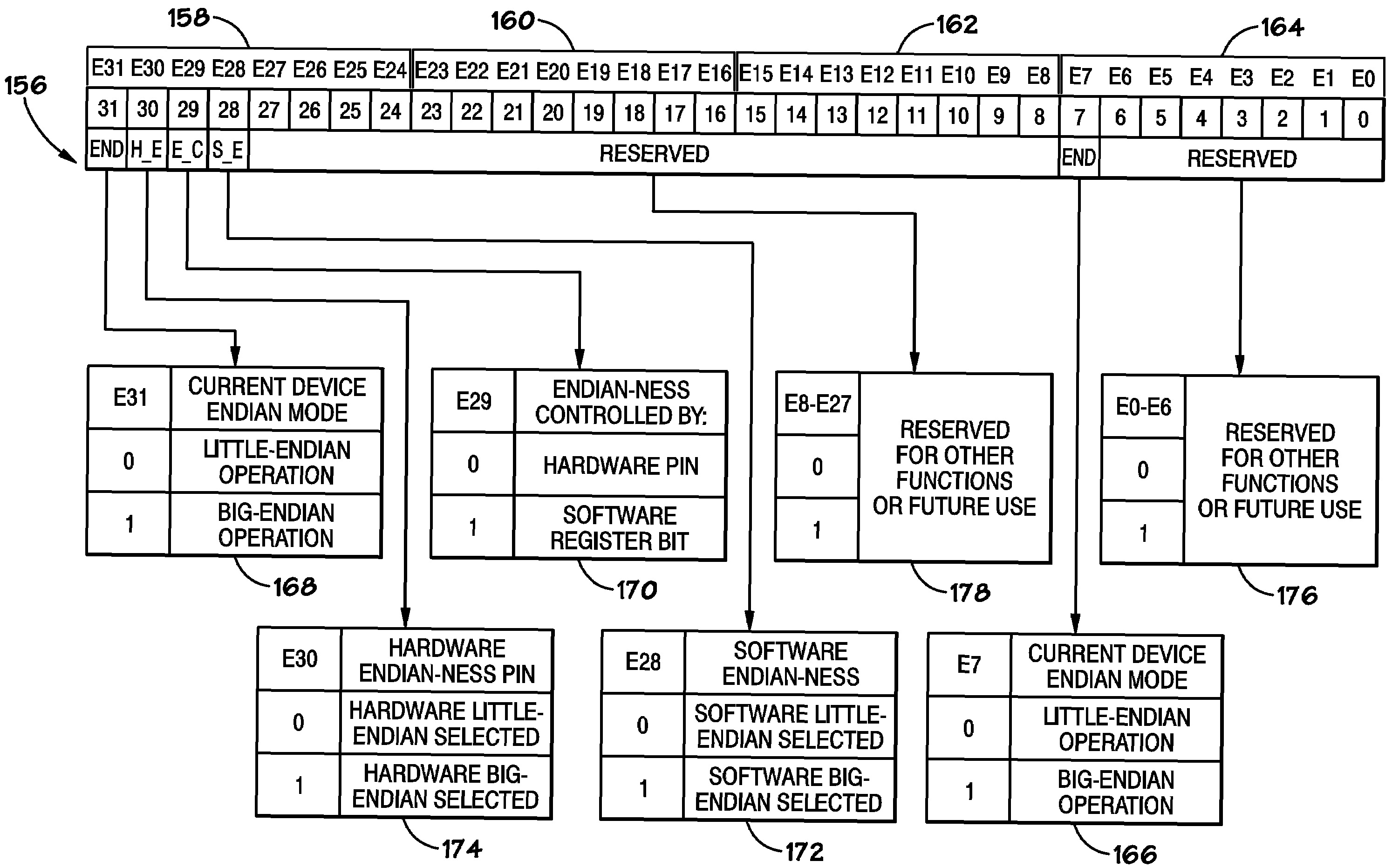

Systems and Methods for Managing Endian Mode of a Device

Systems, methods, and devices for managing endian-ness are disclosed. In one embodiment, a device is configured to selectively operate in one of a big-endian operating mode or a little-endian operating mode. The device may include a register in which the current endian mode of the device is indicated in at least two different bit positions within the register. The at least two different bit positions may be chosen such that a data bit in one of the bit positions would be read by a system if the device and system operate in the same endian mode, while a data bit in another of the chosen bit positions would be read by the system if the device and system are operating in different endian modes from one another. In some embodiments, the endian mode of the device may be controlled by a hardware input or a software input.

Owner:MICRON TECH INC

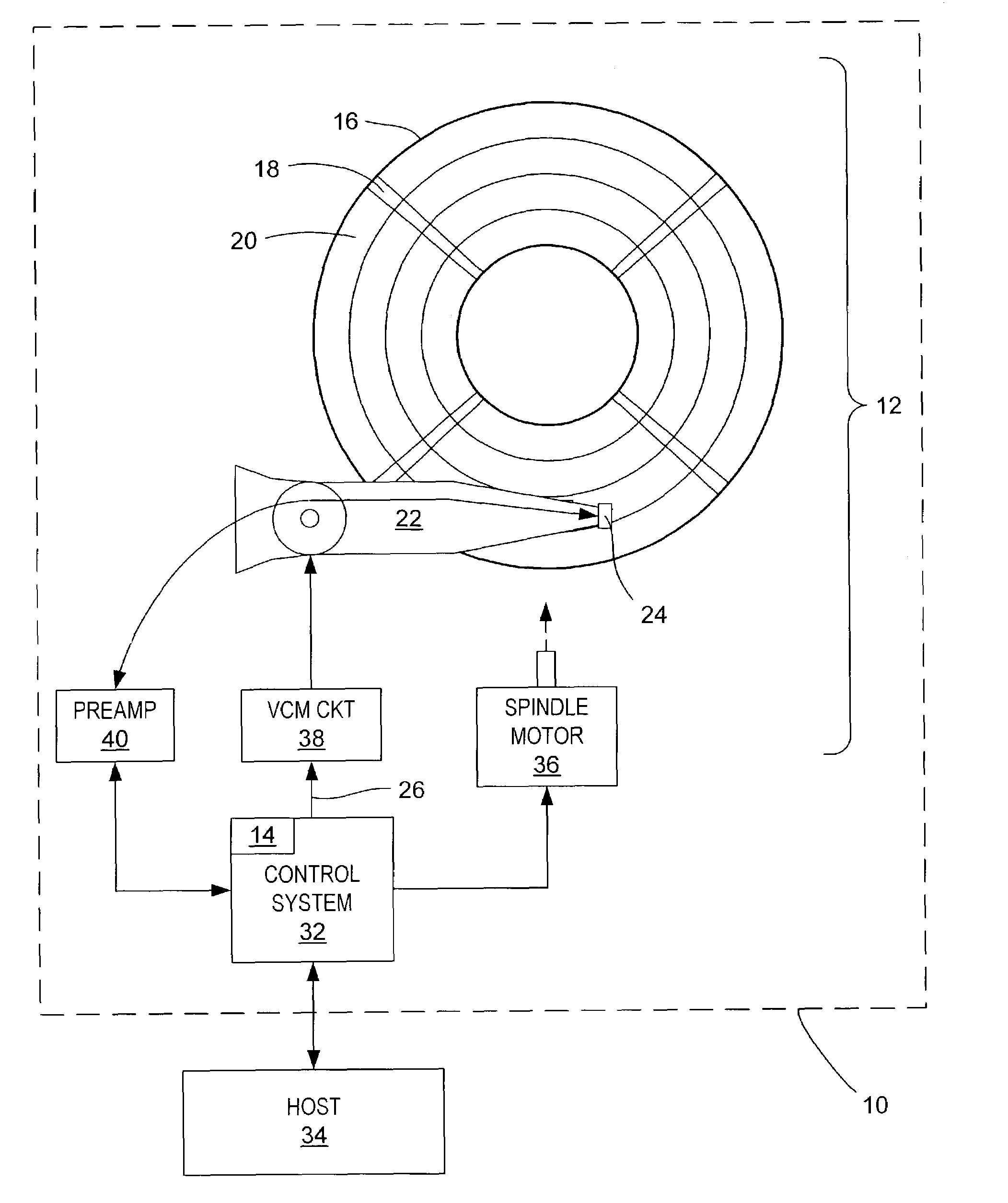

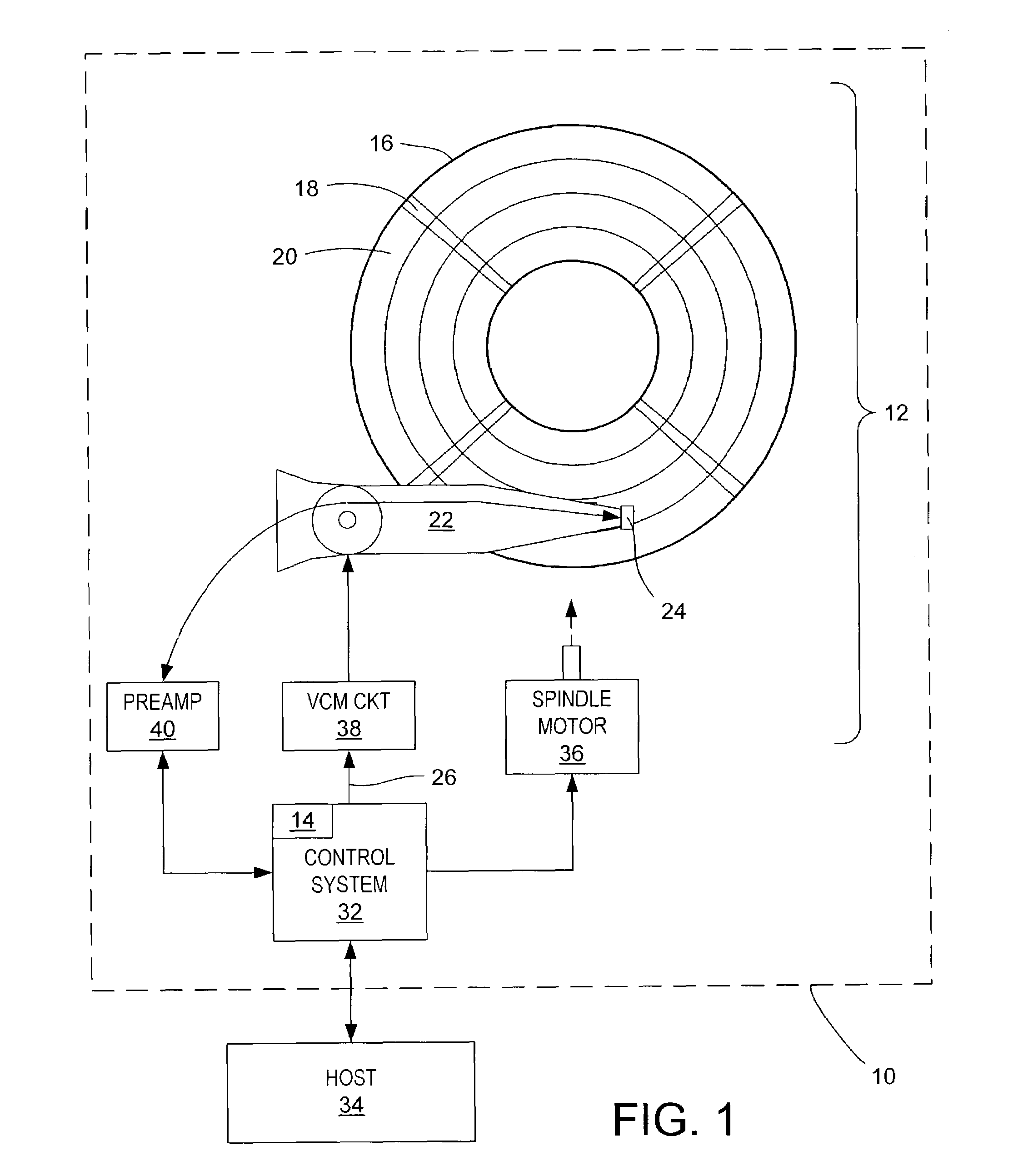

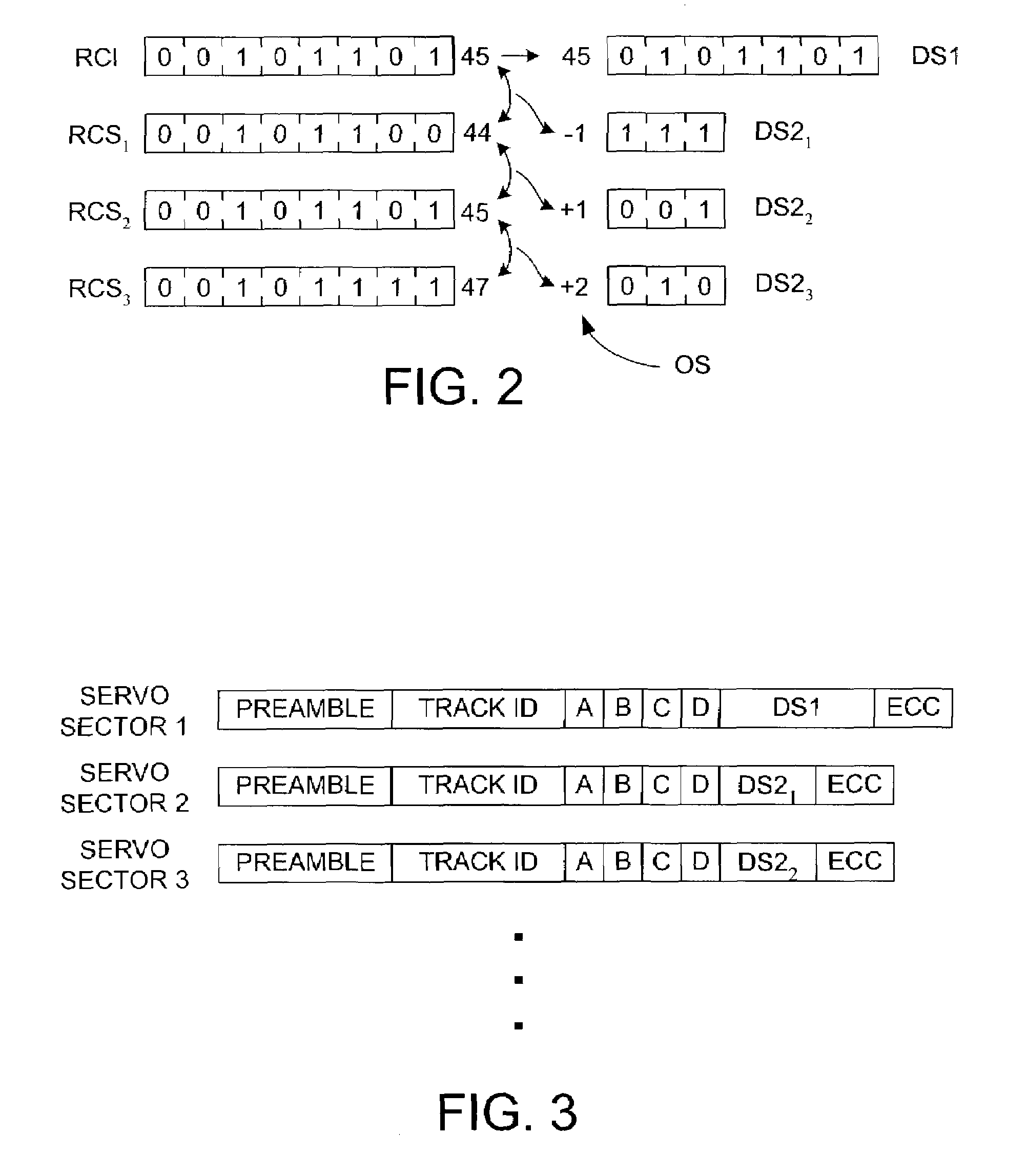

Disk drive having internal data structures for efficiently storing repeatable runout cancellation information

InactiveUS6972922B1Reduce the impactReduce impactRecord information storageAlignment for track following on disksData structureData bits

A disk drive includes a sampled servo controller for periodically adjusting a control effort signal during a track-following operation based on embedded distributed position information and repeatable runout (RRO) cancellation values for reducing effects of RRO in the distributed position information during track following. A magnetic disk in the disk drive stores RRO information relating to predetermined RRO cancellation values for a data storage track. The RRO information for the data storage track includes at least one first data structure having a first predetermined number of data bits for representing an initial RRO cancellation value, and includes at least one second data structure having a second predetermined number of data bits associated with a respective subsequent RRO cancellation value. The first predetermined number of data bits is greater than the second predetermined number of data bits.

Owner:WESTERN DIGITAL TECH INC

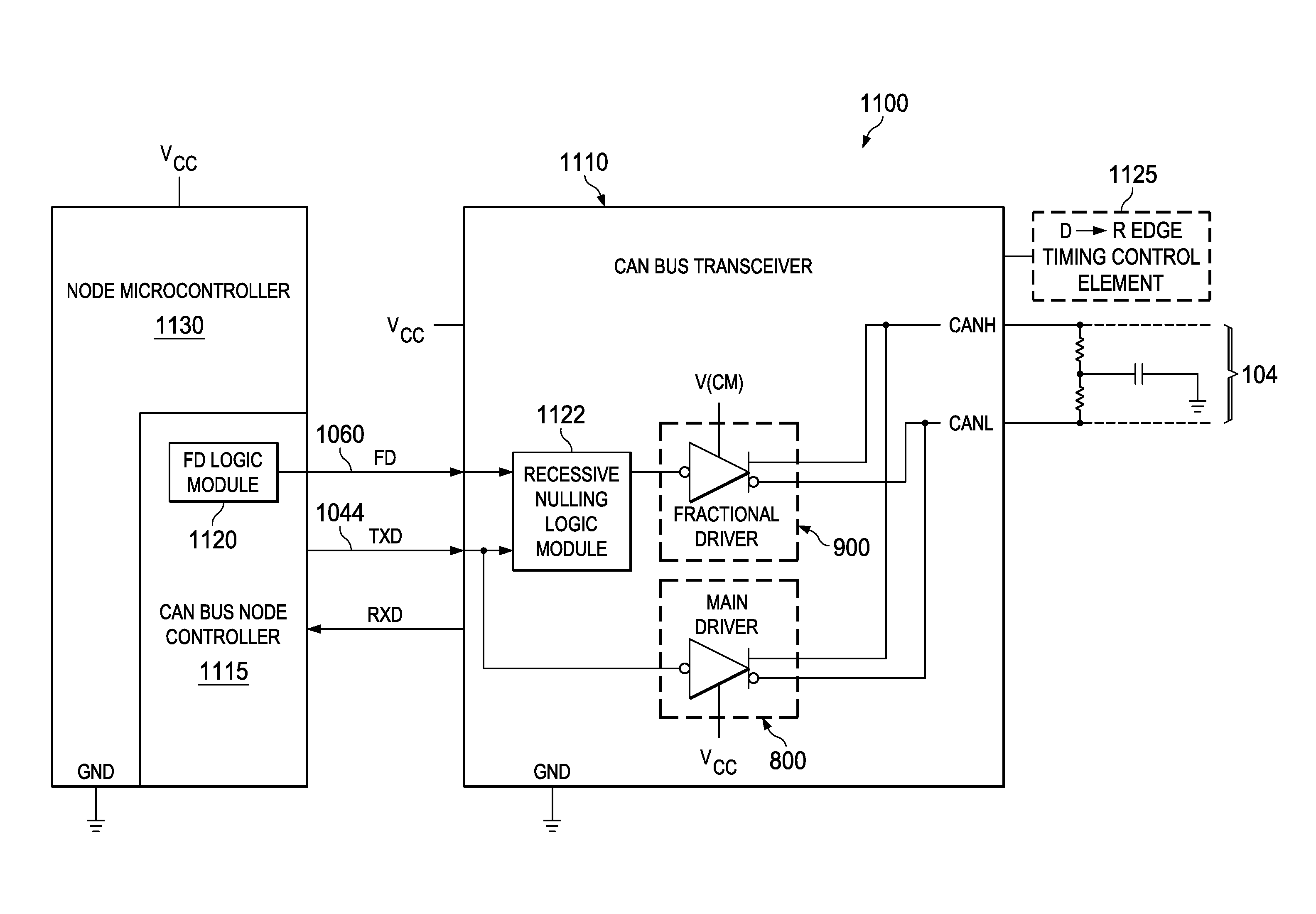

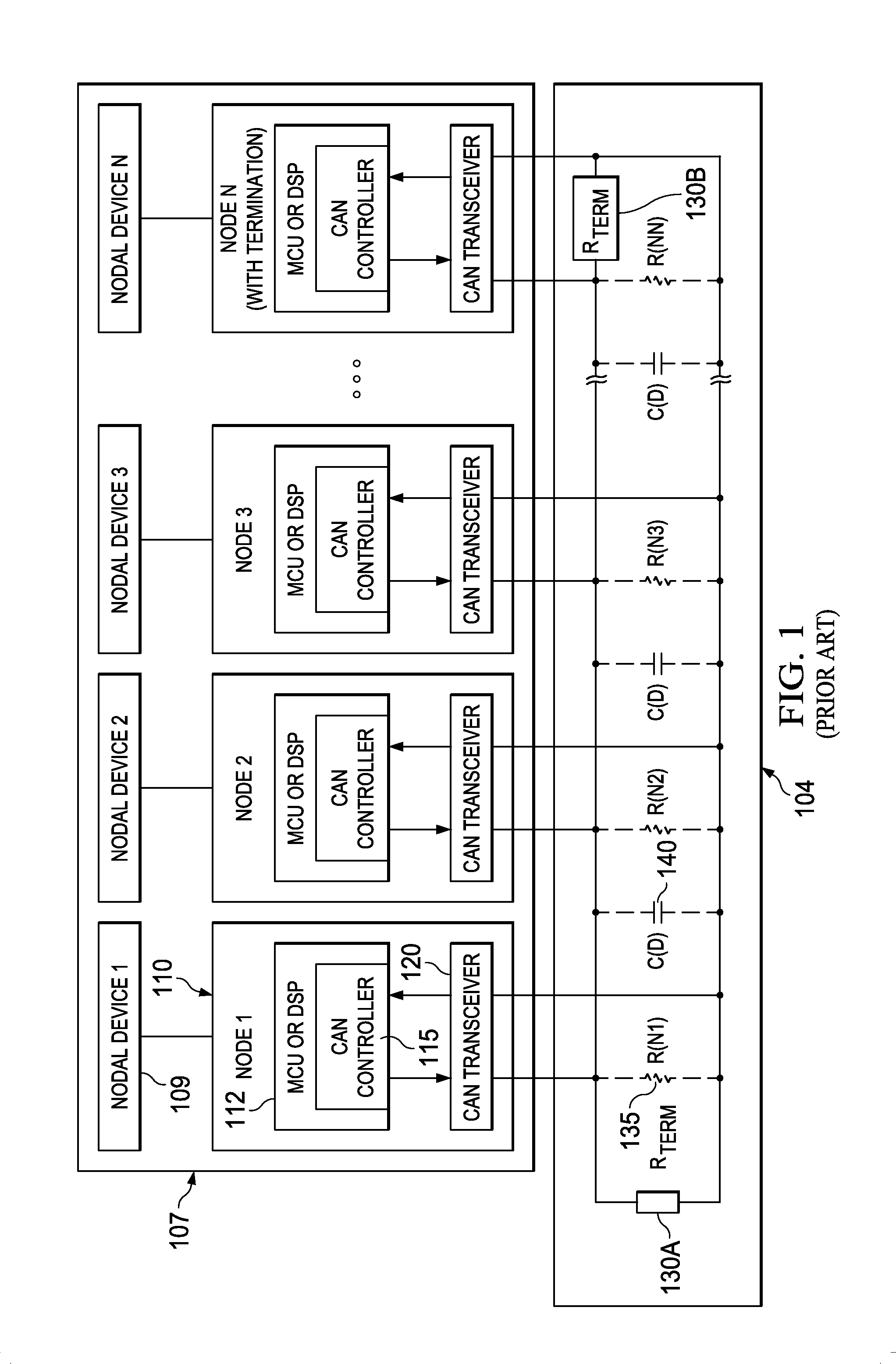

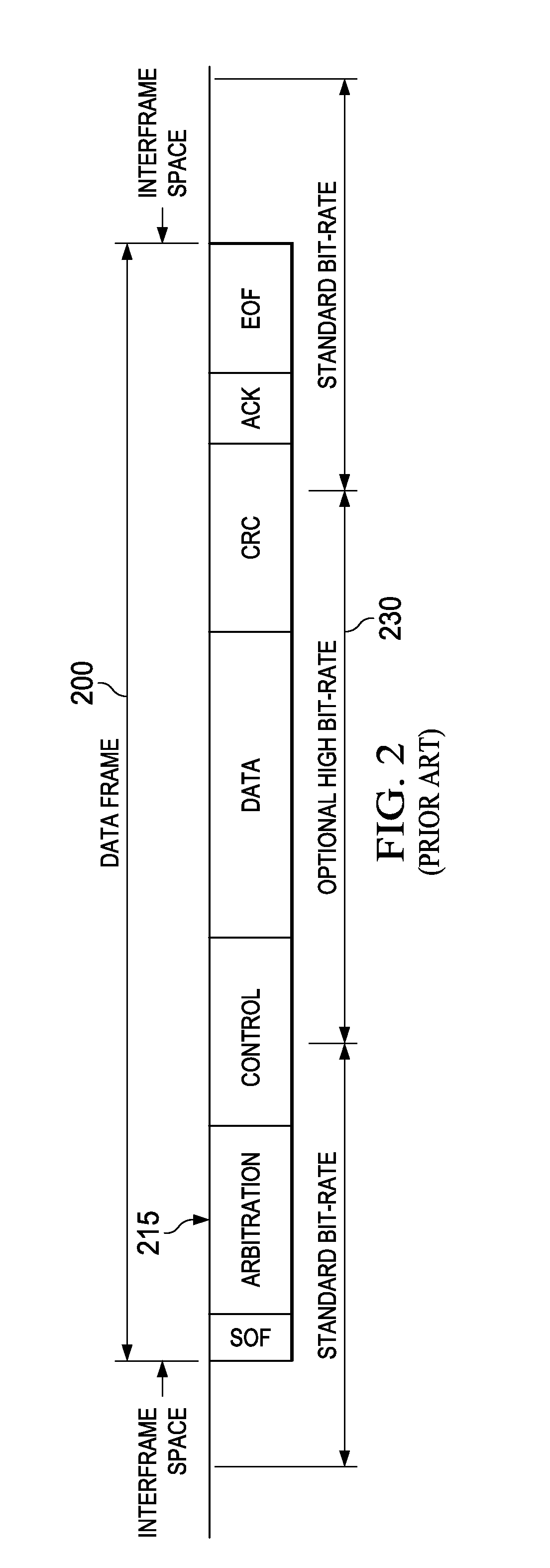

Can bus edge timing control apparatus, systems and methods

ActiveUS20140156893A1Easy dischargeSacrificing integrityData switching networksElectric digital data processingArea networkEngineering

Structures and methods herein insert one or more parallel “recessive nulling” driver impedances across a controller area network (CAN) bus starting at the time of a dominant-to-recessive data bit transition and extending for a selected recessive nulling time period. Doing so increases a rate of decay of a CAN bus dominant-to-recessive differential signal waveform, permits a shortened recessive bit time period, and allows for increased CAN bus bandwidth. Various modes of operation are applicable to various CAN bus node topologies. Recessive nulling may be applied to only the beginning portion of a recessive bit following a dominant bit (“LRN mode”) or to the entire recessive bit time (“HRN mode”). And, some embodiments may apply LRN operations to some recessive CAN frame bits and HRN operations to others.

Owner:TEXAS INSTR INC

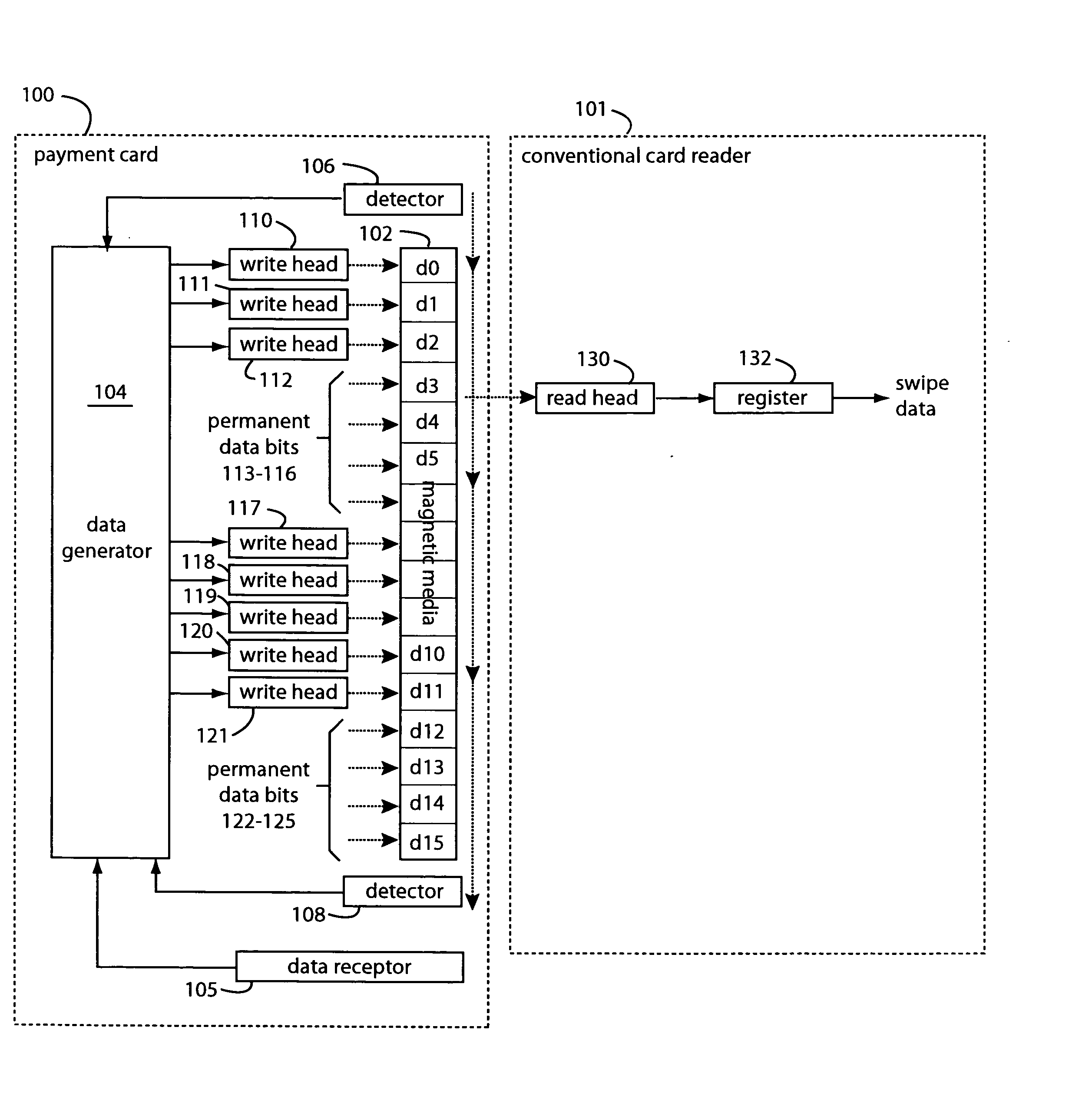

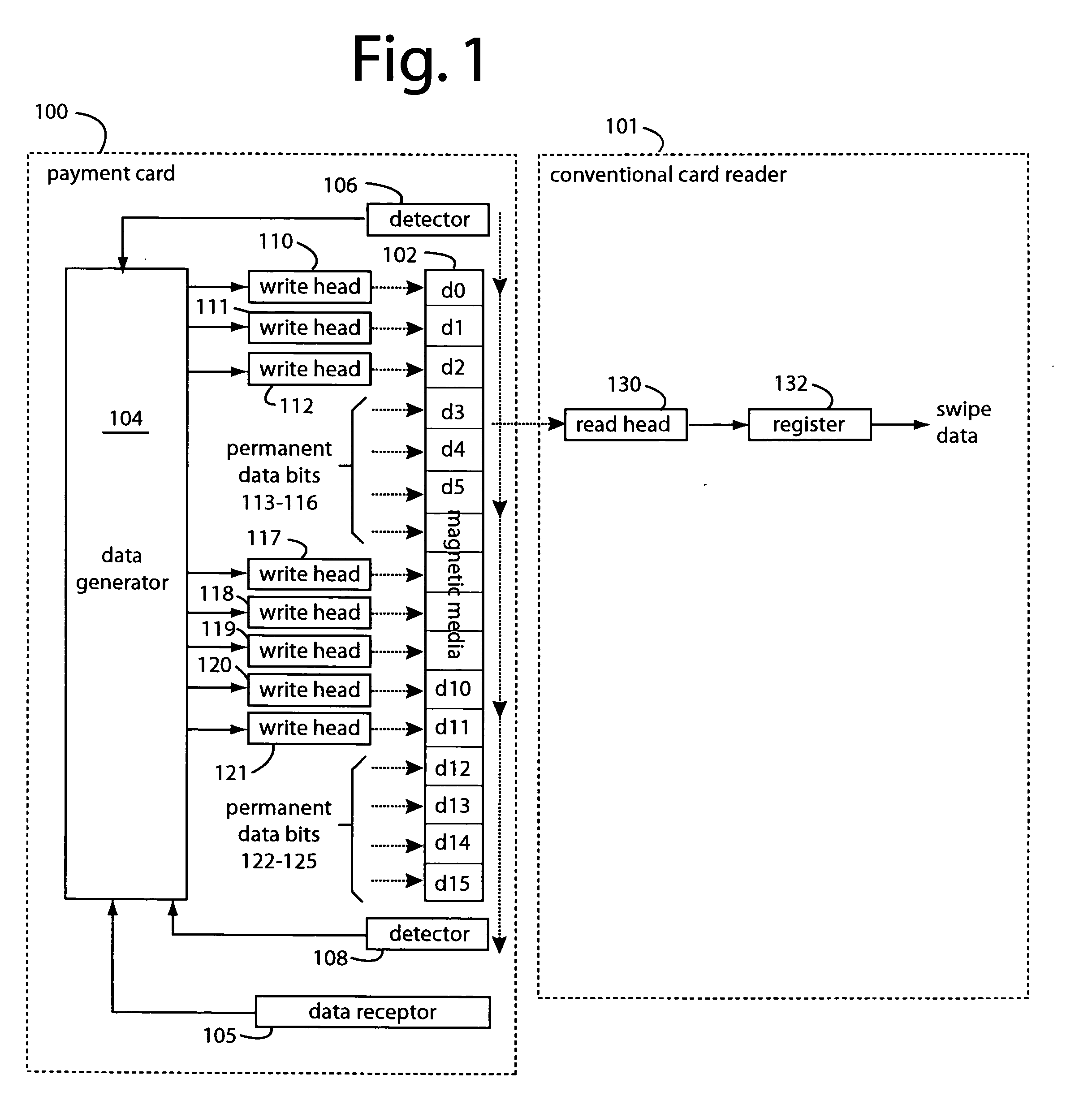

Programmable magnetic data storage card

ActiveUS20050133606A1Reduce riskSimple and inexpensive and effectiveAcutation objectsApparatus for flat record carriersComing outMicrocomputer

A payment card comprises a plastic card with a magnetic stripe for user account data. Internal to the plastic card, and behind the magnetic stripe, a number of fixed-position magnetic write heads allow the user account data to be automatically modified. For example, a data field that counts the number of times the card has been scanned is incremented. A payment processing center keeps track of this usage-counter data field, and will not authorize transaction requests that come out of sequence. For example, as can occur from a magnetic clone of a card that has been skimmed and tried later. A card-swipe detector embedded in the plastic card detects each use in a scanner, and it signals an internal microcomputer which changes data bits sent to the write heads. Once scanned, the payment card can also disable any reading of the user account data for a short fixed period of time.

Owner:FITBIT INC

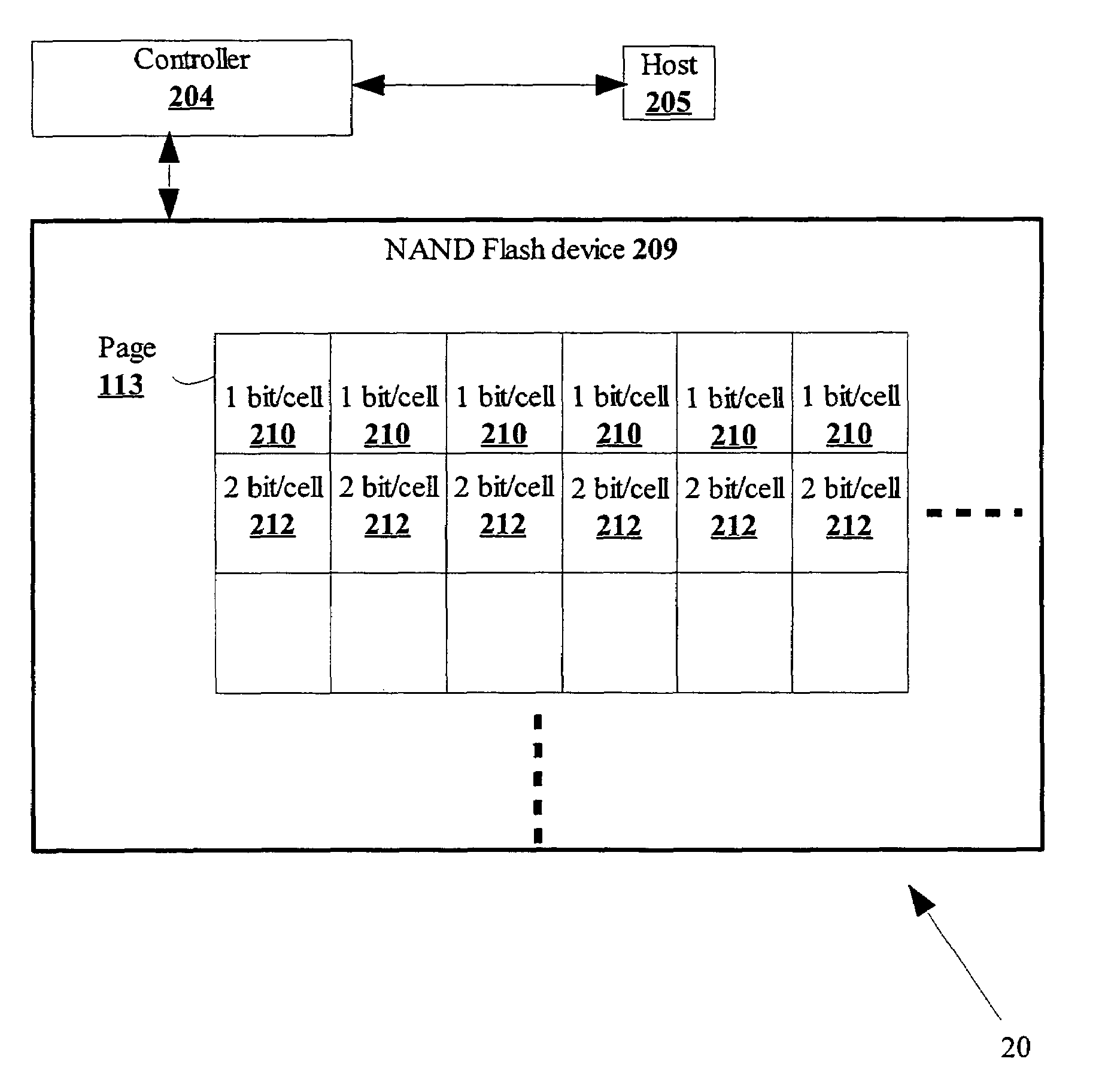

Method of managing a multi-bit cell flash memory with improved reliablility and performance

A method of storing data by providing a flash memory device including a plurality of memory cells; each of the memory cells is capable of storing data bits. First data bits are stored into memory cells used for storing M bits per cell, the memory cells are allocated to a page of the memory. Second data bits are stored into other memory cells, the other memory cells used for storing N bits per cell are allocated to the page and upon storing of the first data bits and upon storing the second data bits, the page uses at the same time at least one of the memory cells with M bits per cell and at least one of the other memory cells with N bits per cell with N less than M.

Owner:WESTERN DIGITAL ISRAEL LTD

Method and system for minimizing number of programming pulses used to program rows of non-volatile memory cells

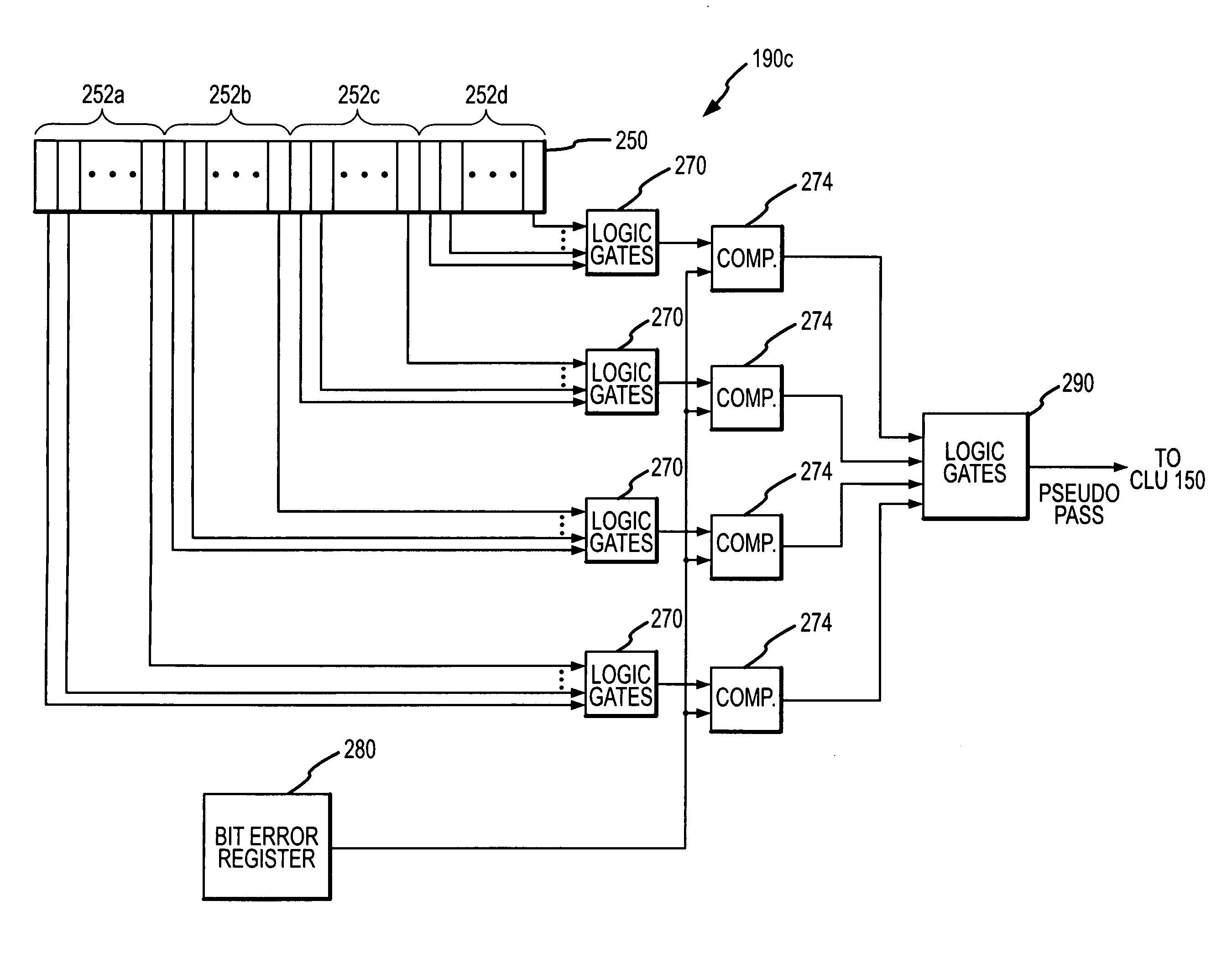

A flash memory device programs cells in each row in a manner that minimizes the number of programming pulses that must be applied to the cells during programming. The flash memory device includes a pseudo pass circuit that determines the number of data errors in each of a plurality of subsets of data that has been programmed in the row. The size of each subset corresponds to the number of read data bits coupled from the memory device, which are simultaneously applied to error checking and correcting circuitry. During iterative programming of a row of cells, the pseudo pass circuit indicates a pseudo pass condition to terminate further programming of the row if none of the subsets of data have a number of data errors that exceeds the number of data errors that can be corrected by the error checking and correcting circuitry.

Owner:MICRON TECH INC