Patents

Literature

776 results about "Error check" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

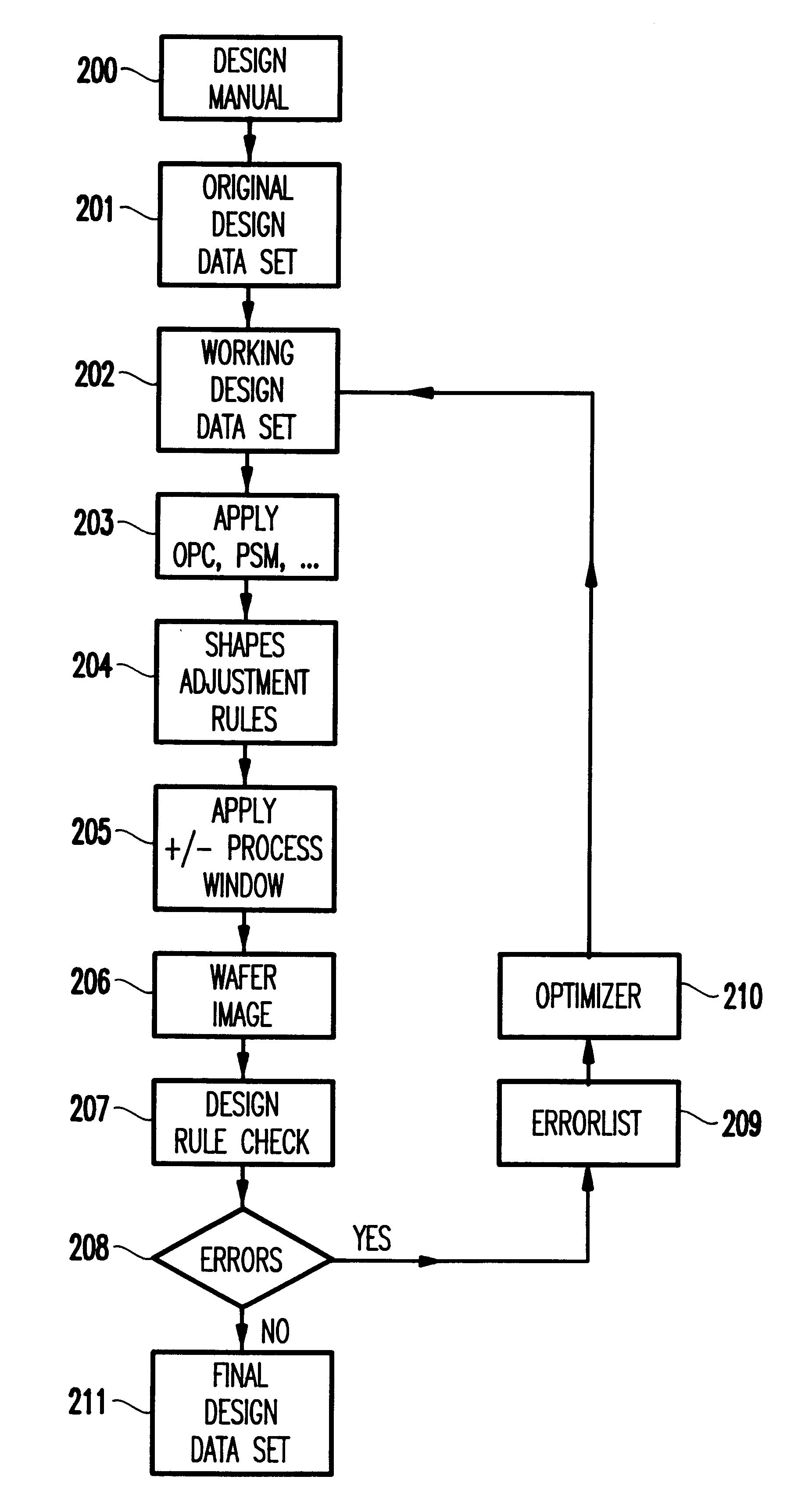

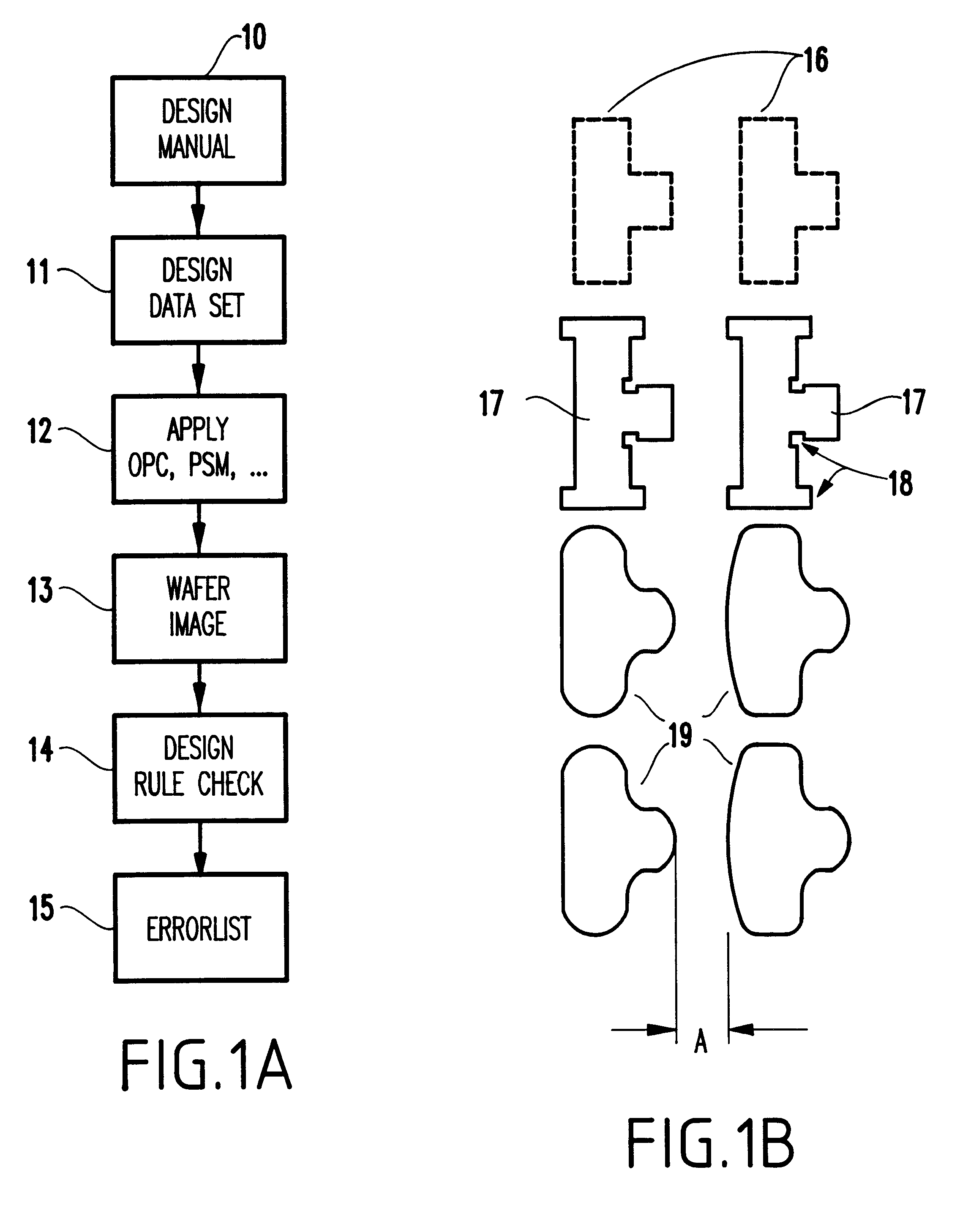

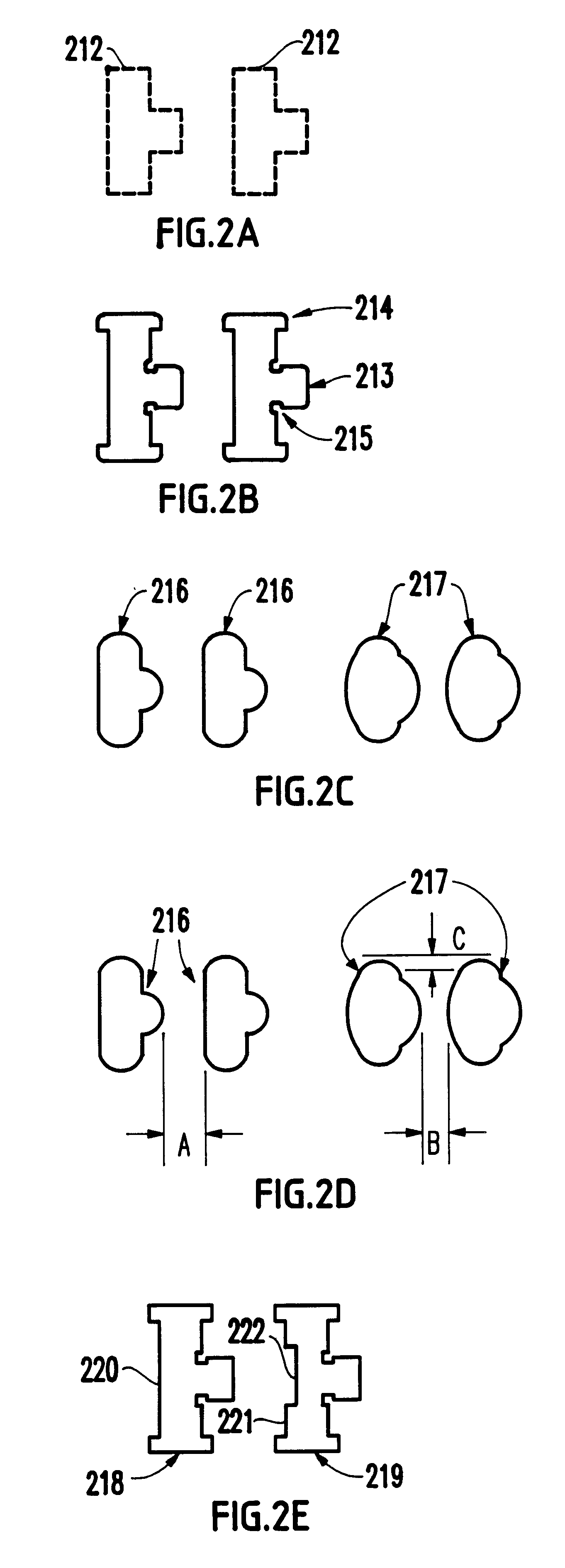

Auto correction of error checked simulated printed images

A method and computer system are provided for checking integrated circuit designs for design rule violations. The method may include generating a working design data set, creating a wafer image data set, comparing the wafer image data set to the design rules to produce an error list and automatically altering the working design data set when the comparing indicates a design rule violation. The method further automatically repeats the creating, the comparing and the automatically altering until no design rule violations occur or no solution to the errors exists.

Owner:IBM CORP

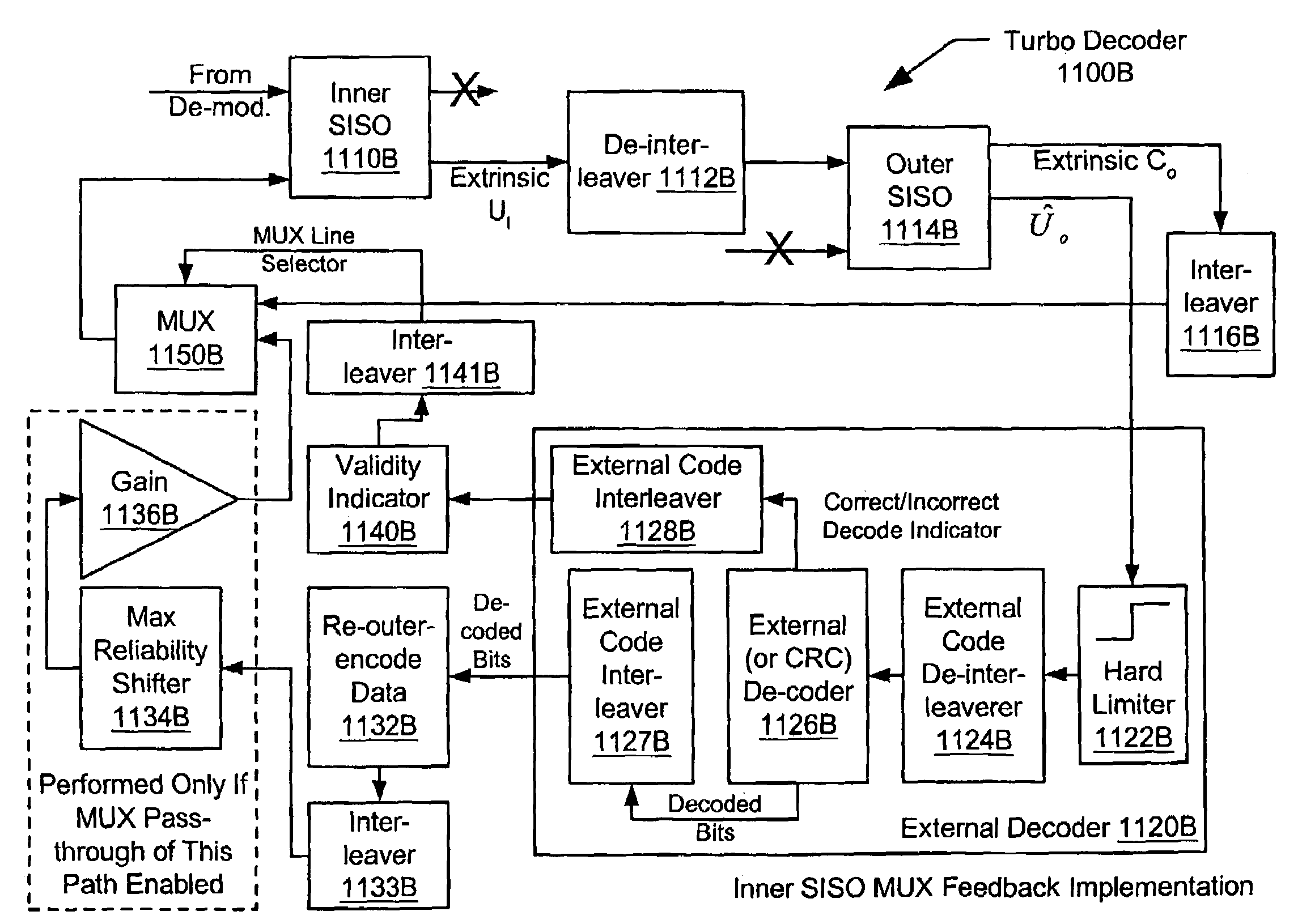

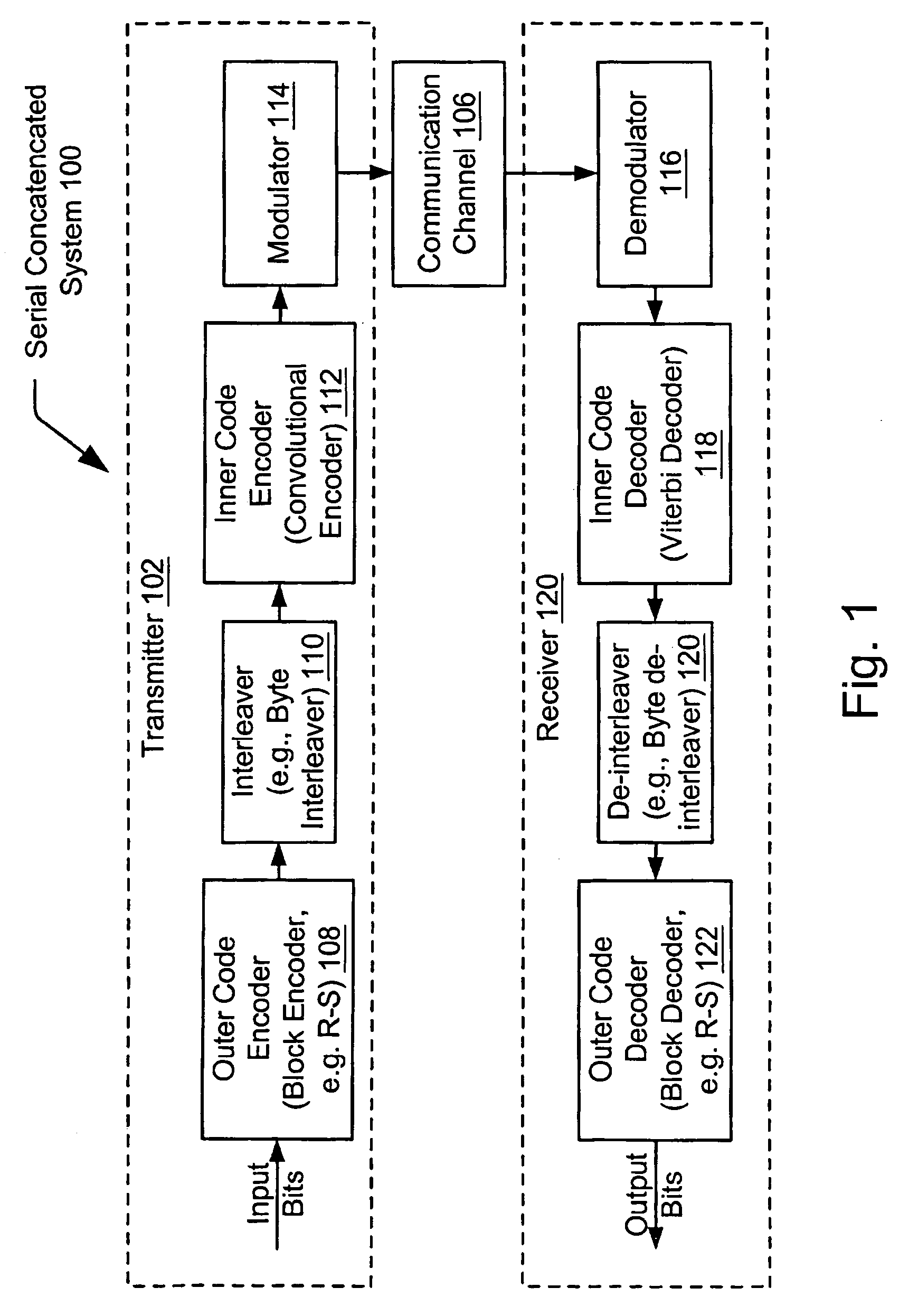

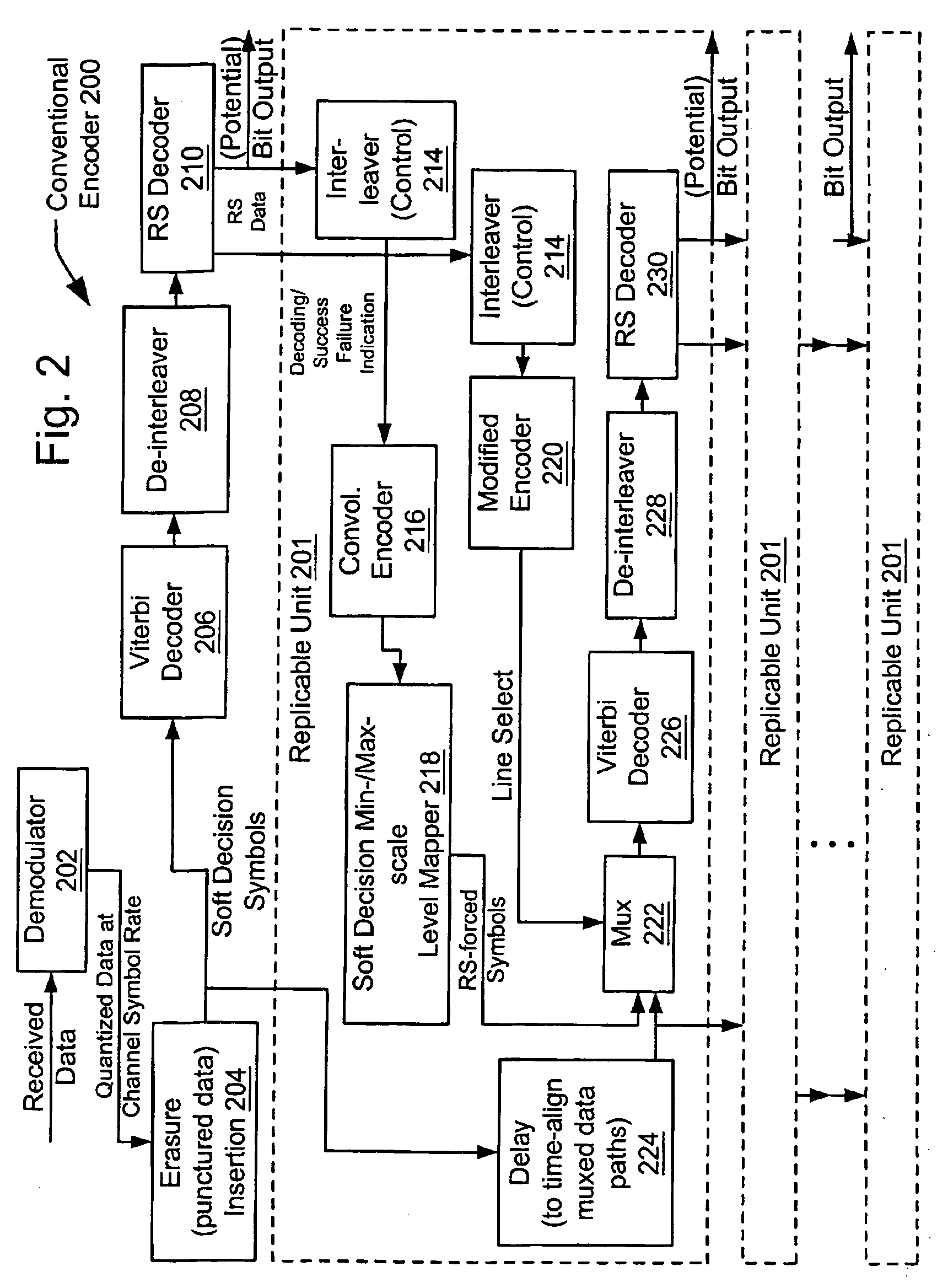

Iterative decoder employing multiple external code error checks to lower the error floor

InactiveUS7310768B2Code conversionError correction/detection by combining multiple code structuresError checkDegree of certainty

Owner:ENTROPIC COMM INC

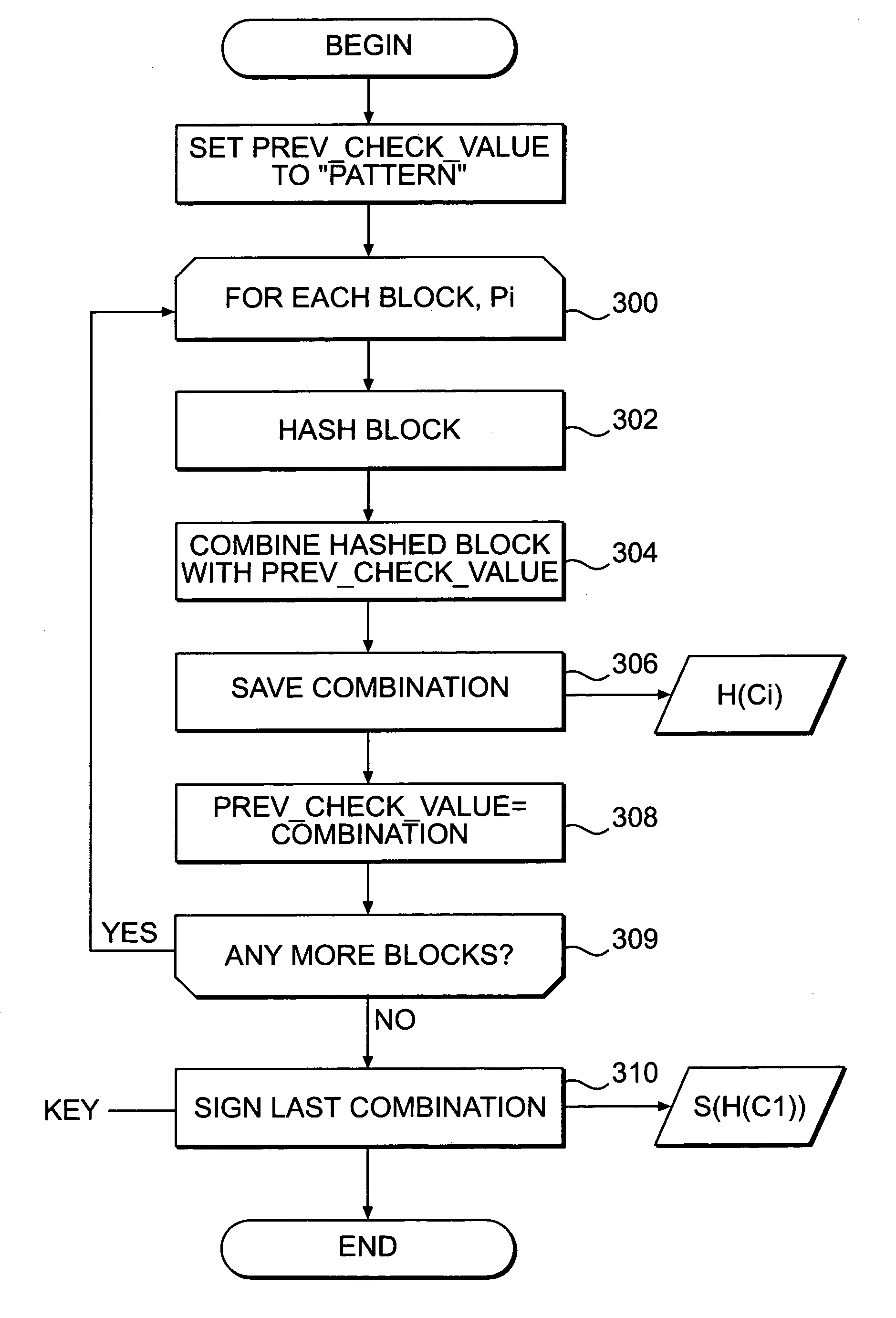

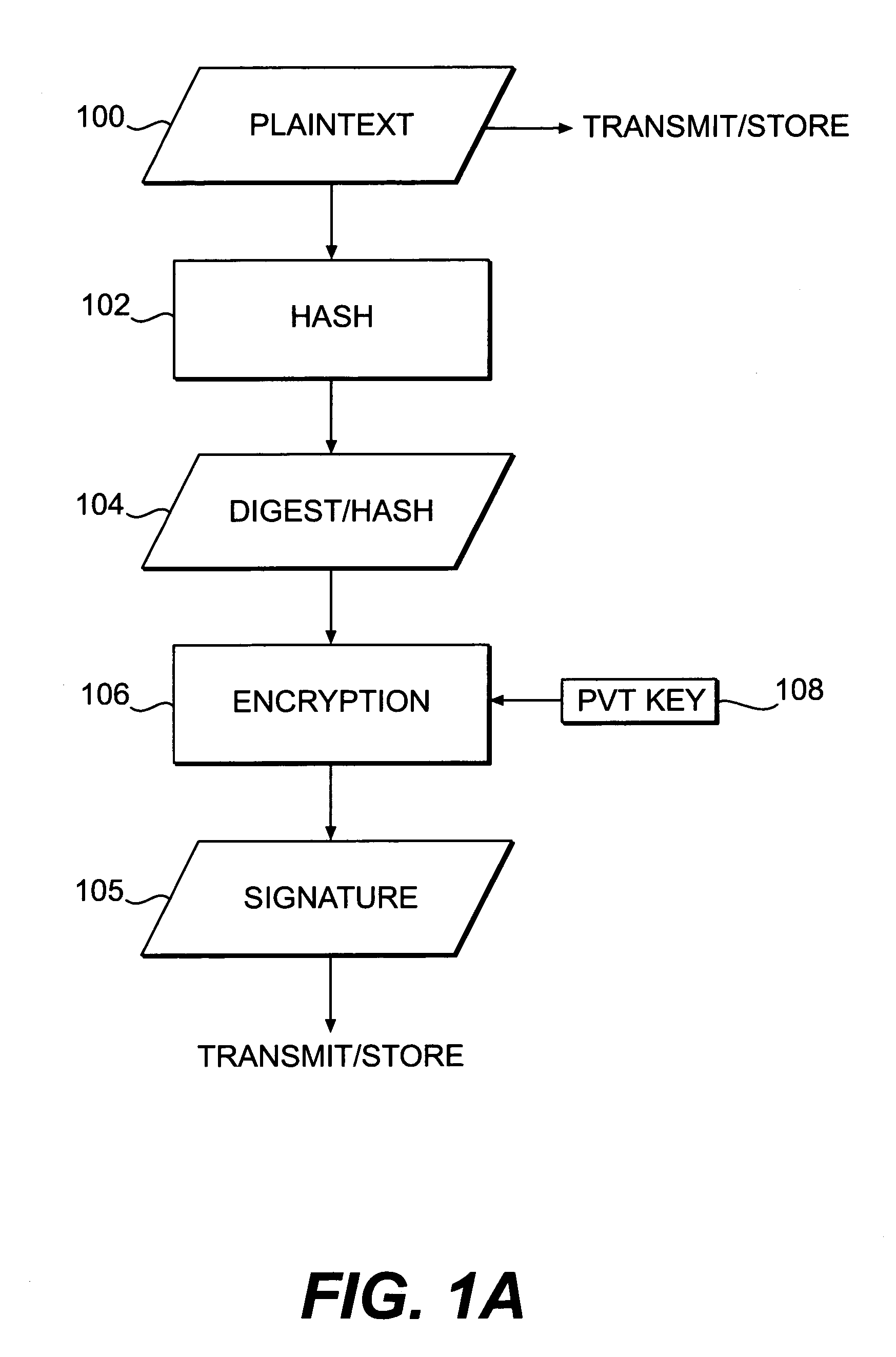

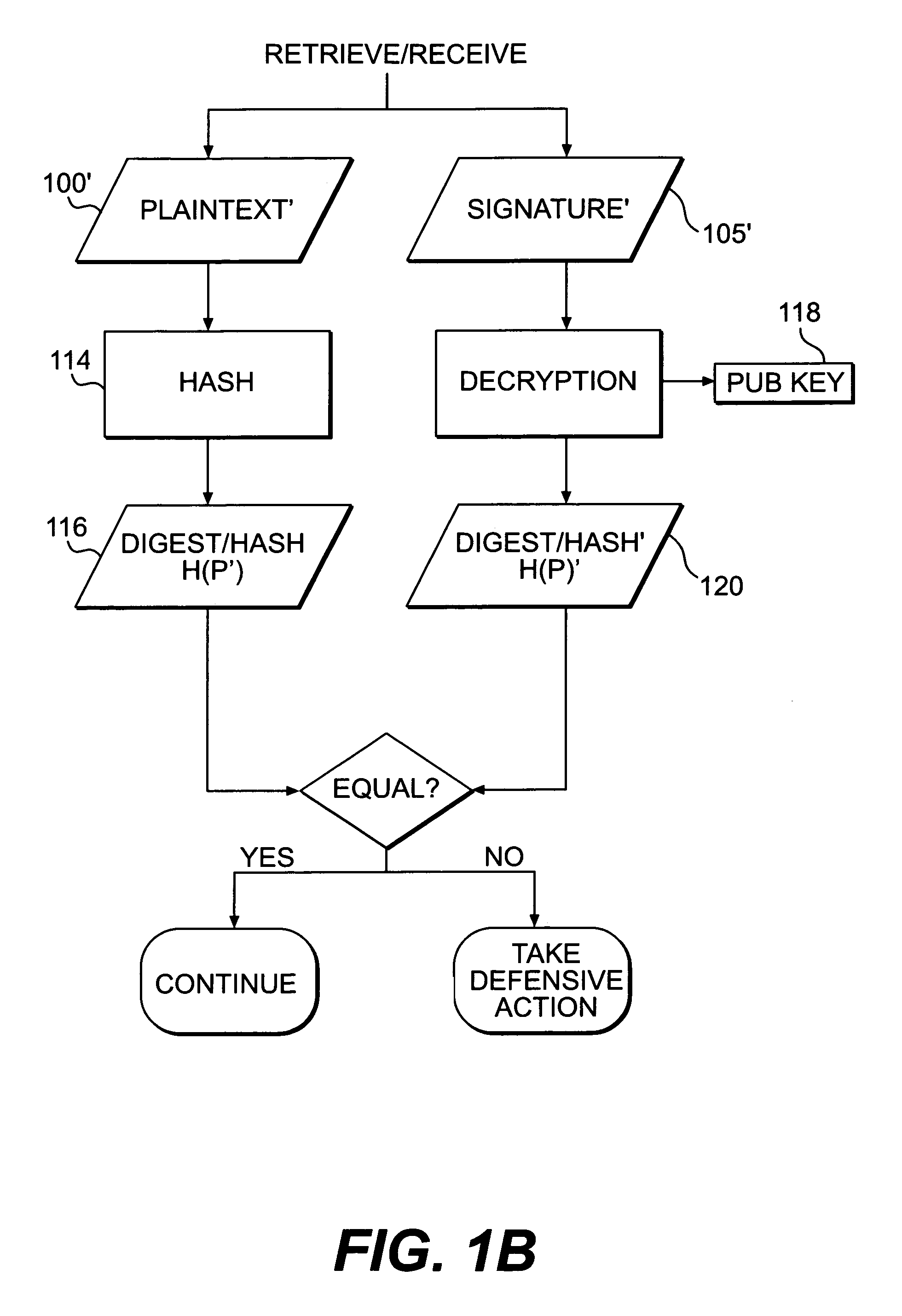

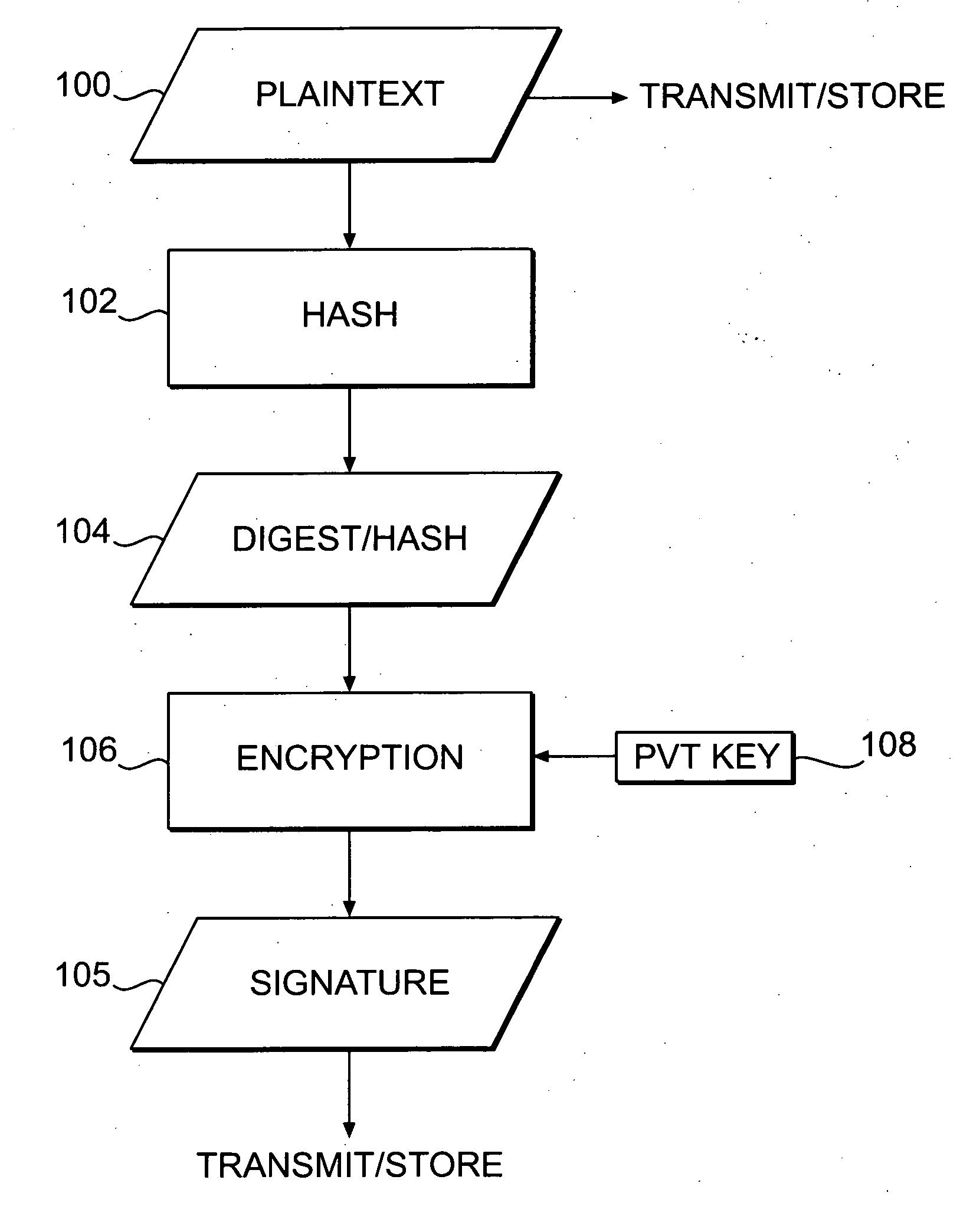

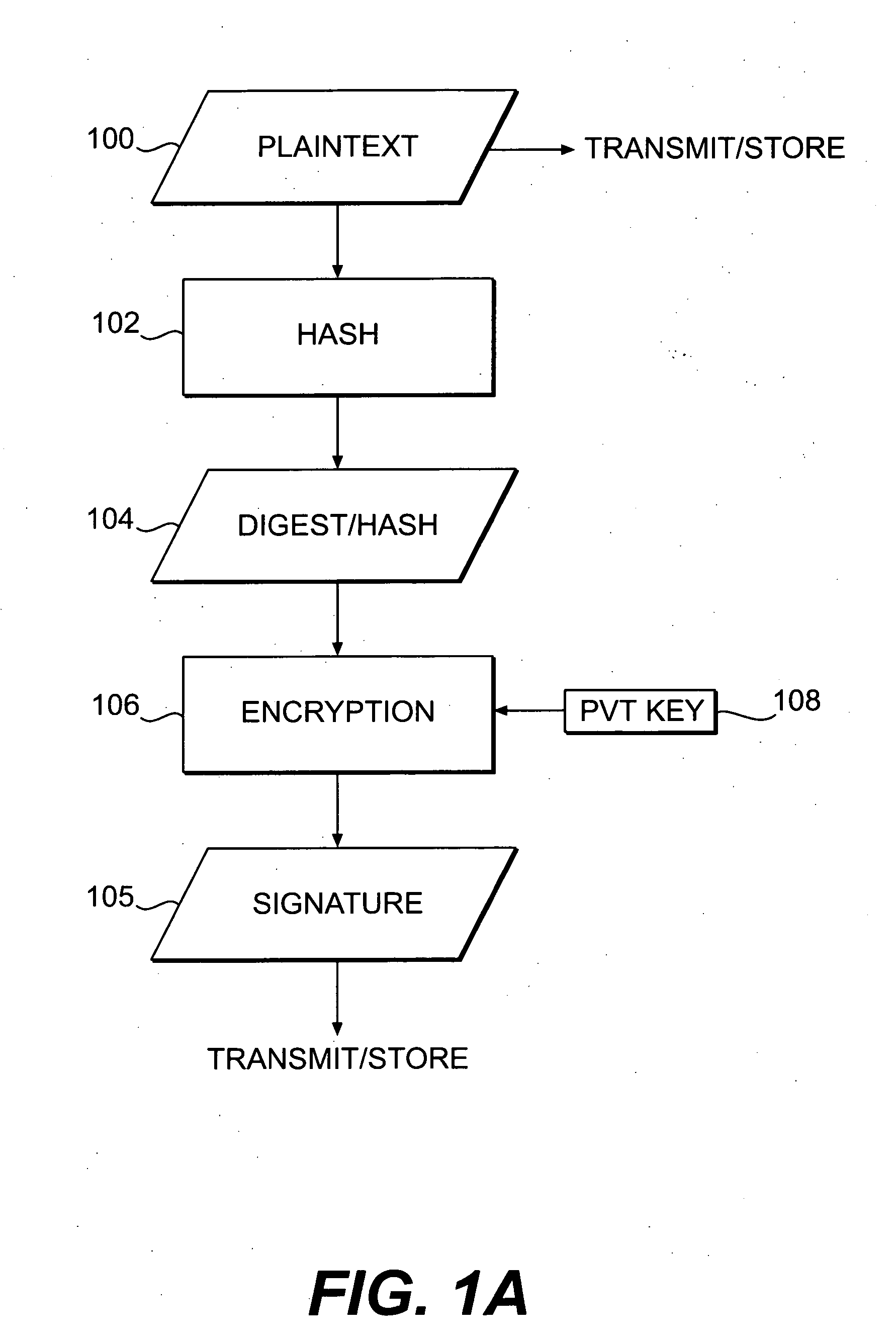

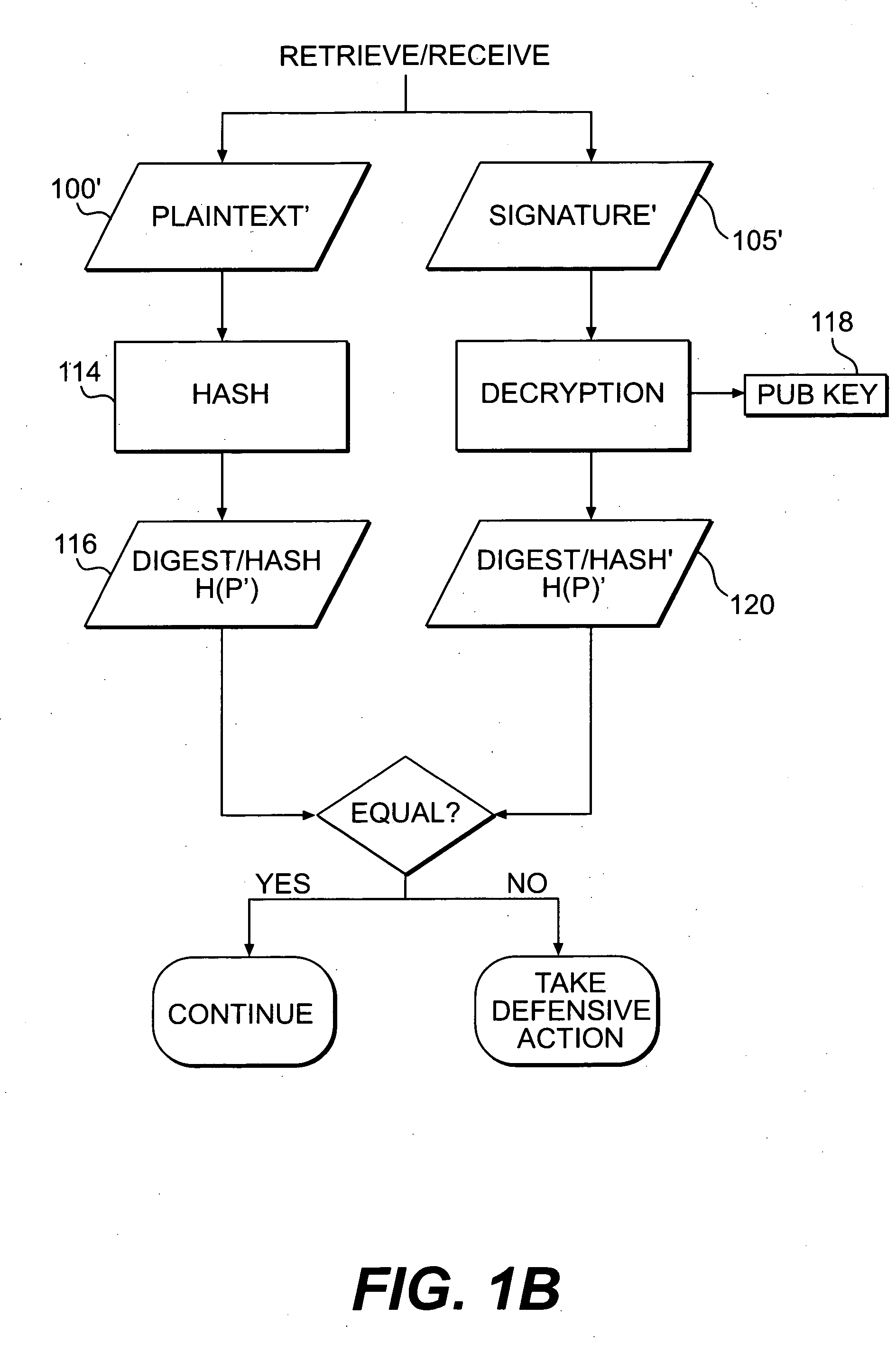

Systems and methods for authenticating and protecting the integrity of data streams and other data

InactiveUS6959384B1Authentication is convenientDetecting errorUser identity/authority verificationDigital data protectionError checkFault tolerance

Systems and methods are disclosed for enabling a recipient of a cryptographically-signed electronic communication to verify the authenticity of the communication on-the-fly using a signed chain of check values, the chain being constructed from the original content of the communication, and each check value in the chain being at least partially dependent on the signed root of the chain and a portion of the communication. Fault tolerance can be provided by including error-check values in the communication that enable a decoding device to maintain the chain's security in the face of communication errors. In one embodiment, systems and methods are provided for enabling secure quasi-random access to a content file by constructing a hierarchy of hash values from the file, the hierarchy deriving its security in a manner similar to that used by the above-described chain. The hierarchy culminates with a signed hash that can be used to verify the integrity of other hash values in the hierarchy, and these other hash values can, in turn, be used to efficiently verify the authenticity of arbitrary portions of the content file.

Owner:INTERTRUST TECH CORP

Systems and methods for authenticating and protecting the integrity of data streams and other data

InactiveUS20050235154A1Authentication is convenientDetecting errorUser identity/authority verificationDigital data protectionError checkFault tolerance

Systems and methods are disclosed for enabling a recipient of a cryptographically-signed electronic communication to verify the authenticity of the communication on-the-fly using a signed chain of check values, the chain being constructed from the original content of the communication, and each check value in the chain being at least partially dependent on the signed root of the chain and a portion of the communication. Fault tolerance can be provided by including error-check values in the communication that enable a decoding device to maintain the chain's security in the face of communication errors. In one embodiment, systems and methods are provided for enabling secure quasi-random access to a content file by constructing a hierarchy of hash values from the file, the hierarchy deriving its security in a manner similar to that used by the above-described chain. The hierarchy culminates with a signed hash that can be used to verify the integrity of other hash values in the hierarchy, and these other hash values can, in turn, be used to efficiently verify the authenticity of arbitrary portions of the content file.

Owner:INTERTRUST TECH CORP

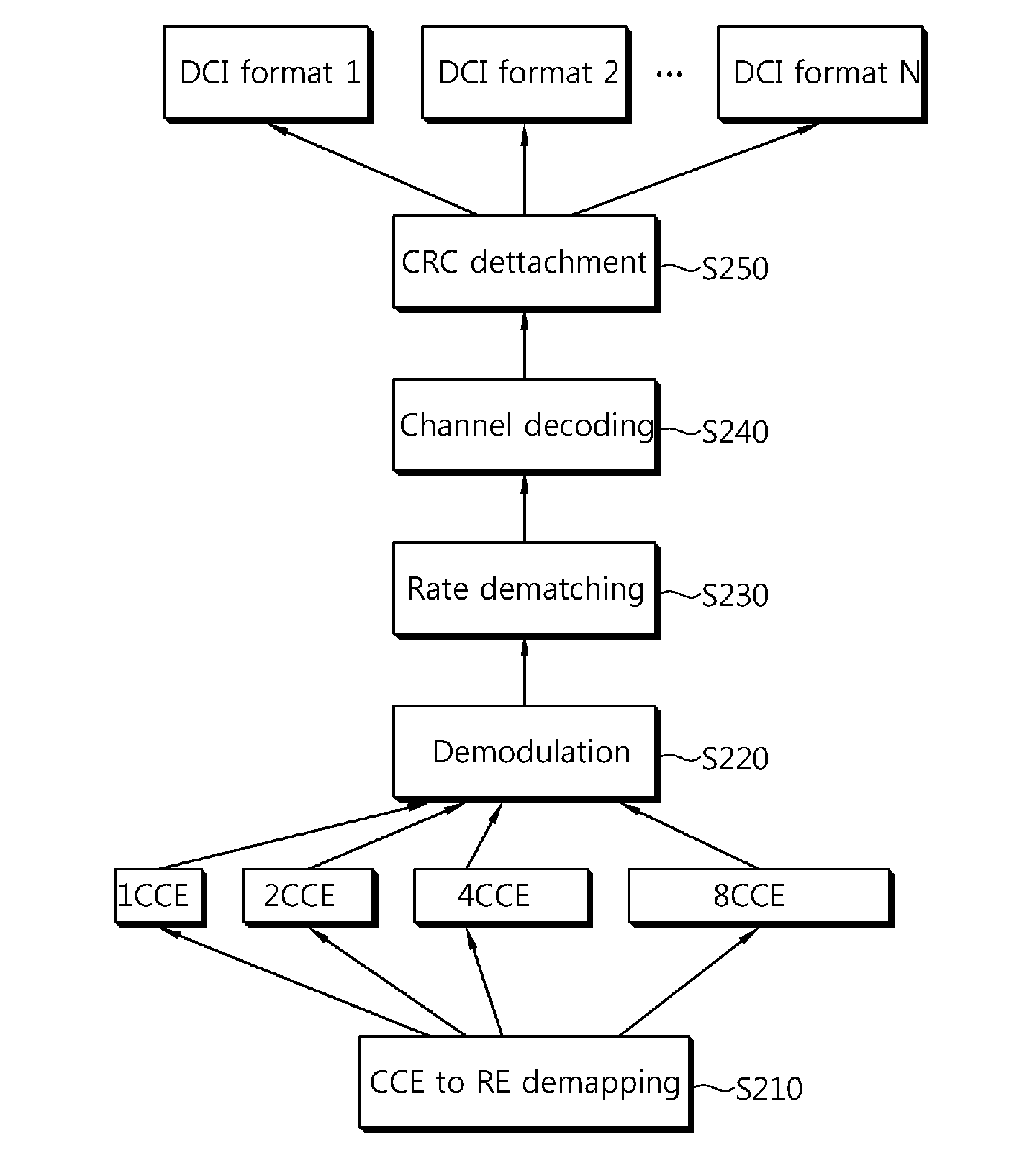

Method for detecting control information in wireless communication system

ActiveUS20110083066A1Improve accuracyAccurate detectionCode conversionSignal allocationError checkCommunications system

A method for detecting control information in a wireless communication system is provided. The method includes checking a cyclic redundancy check (CRC) error by monitoring control channels, determining whether a value of an error check field is equal to a specific value, and, if the value of the error check field is equal to the specific value, detecting the control information on the control channel.

Owner:LG ELECTRONICS INC

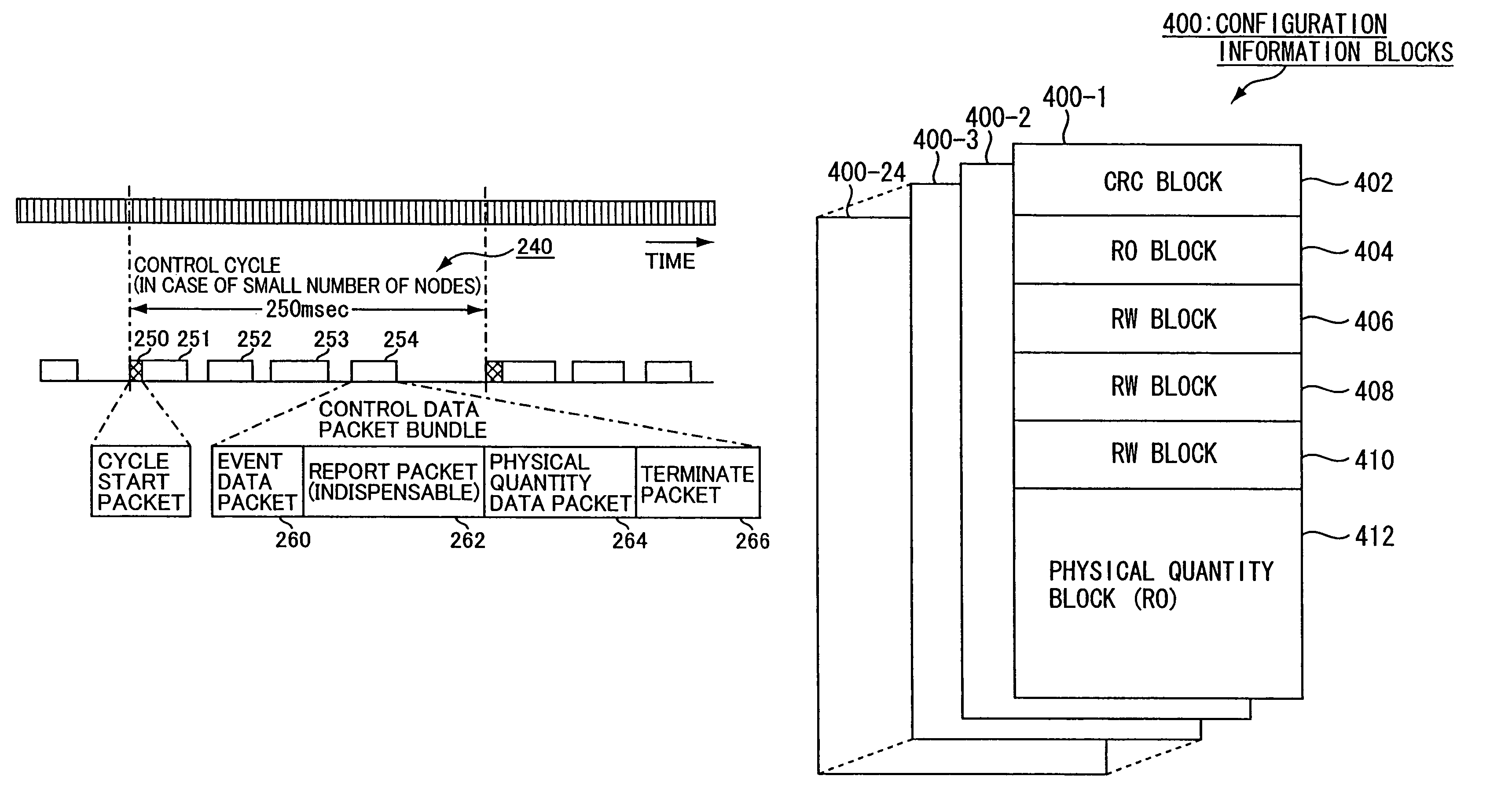

Signal transmission apparatus

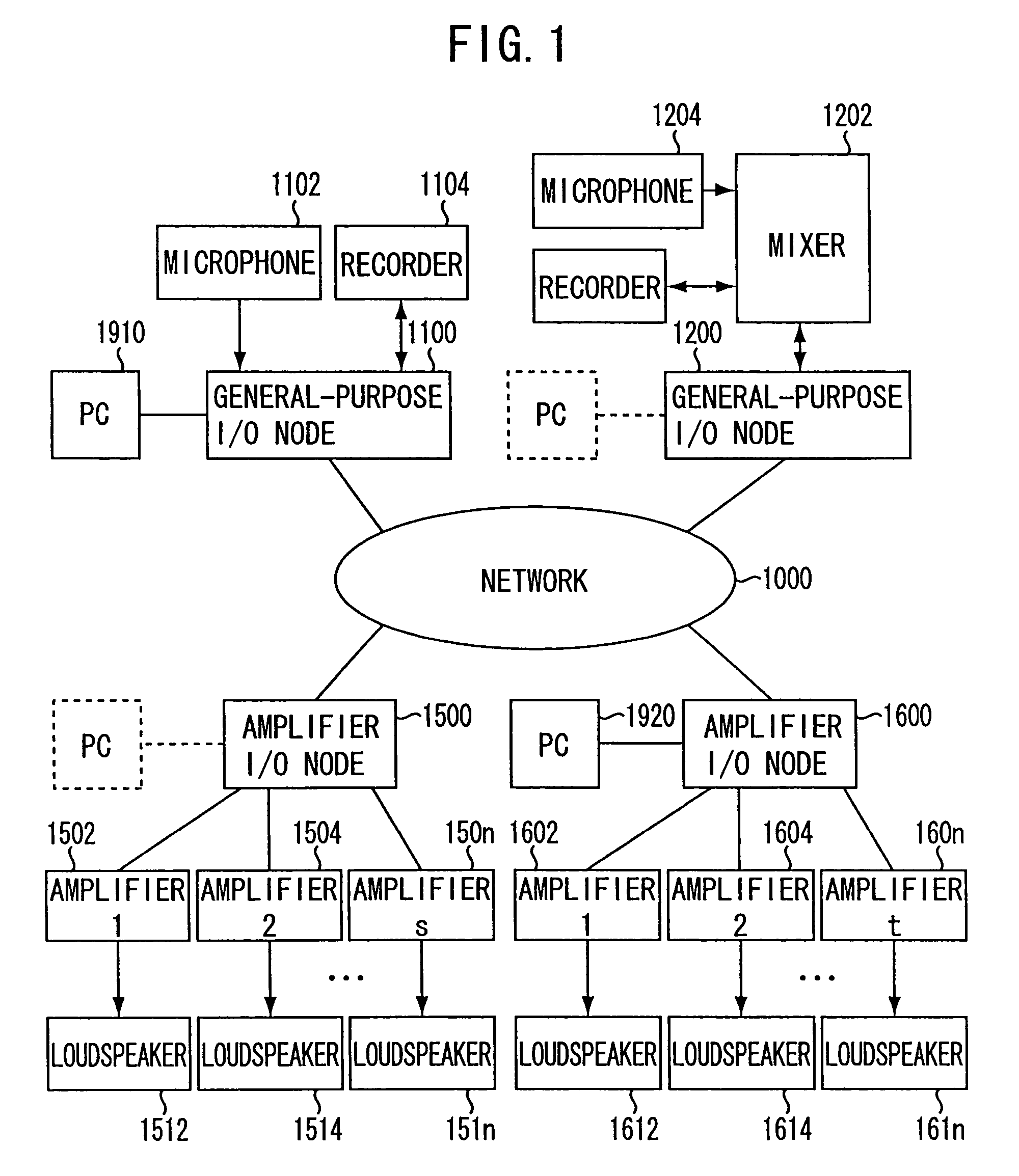

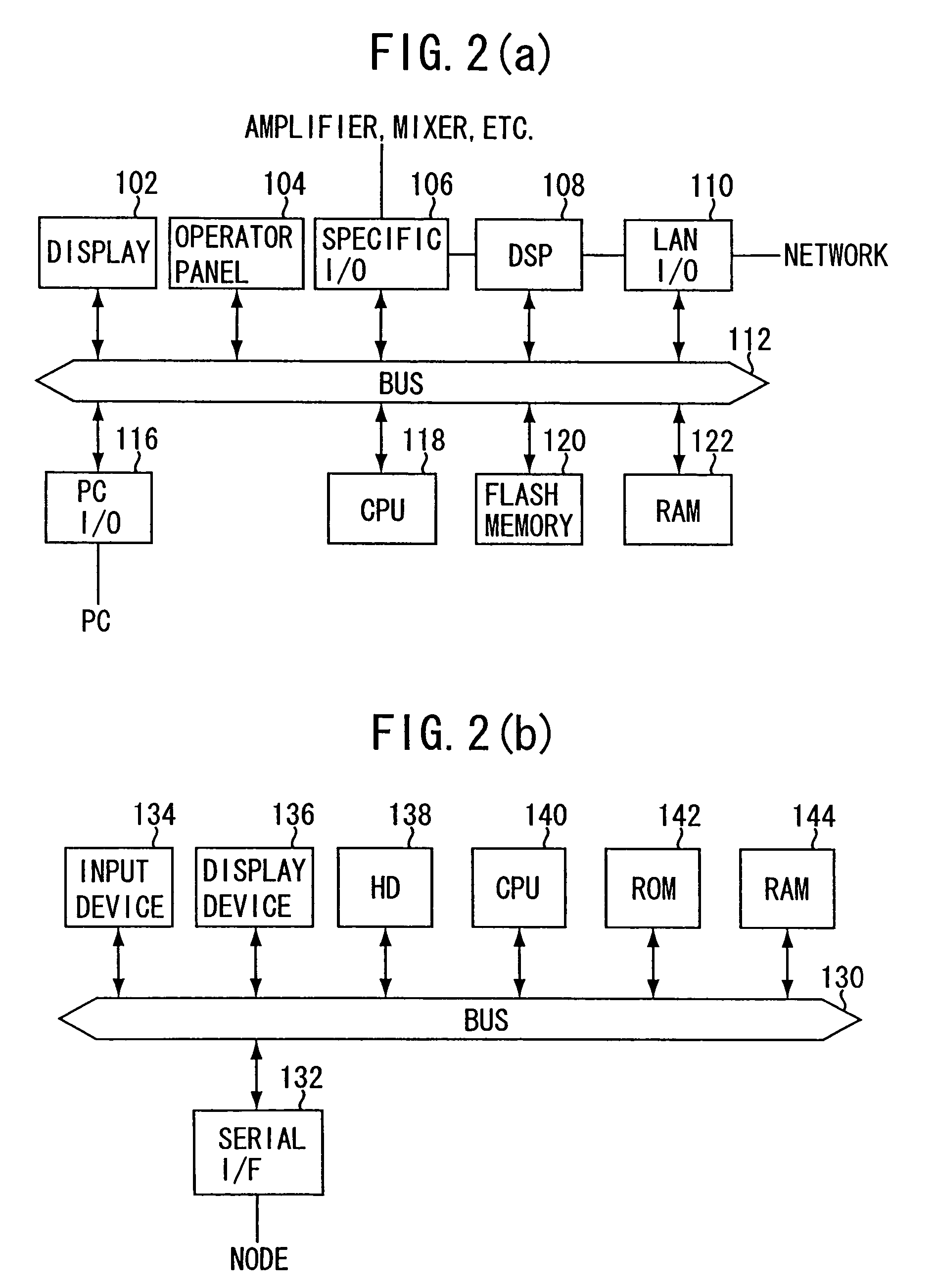

A signal transmission apparatus is connected to a network as one node among a plurality of nodes involved in the network which is provided with an audio signal transmission period for transmitting a plurality of channels of audio signals each transmission cycle and a control data transmission period for transmitting control data of the plurality of the nodes each control cycle by using an idle time period other than the audio signal transmission period. In the signal transmission apparatus, a storage section stores configuration information of the one node. A transmitting section transmits the control data including an error checking code of the configuration information. A receiving section receives request data from another node, the request data requesting the one node for transmission of an information block of the configuration information. A control section controls the transmitting section to transmit the information block in response to the request data.

Owner:YAMAHA CORP

Error detection/correction code which detects and corrects component failure and which provides single bit error correction subsequent to component failure

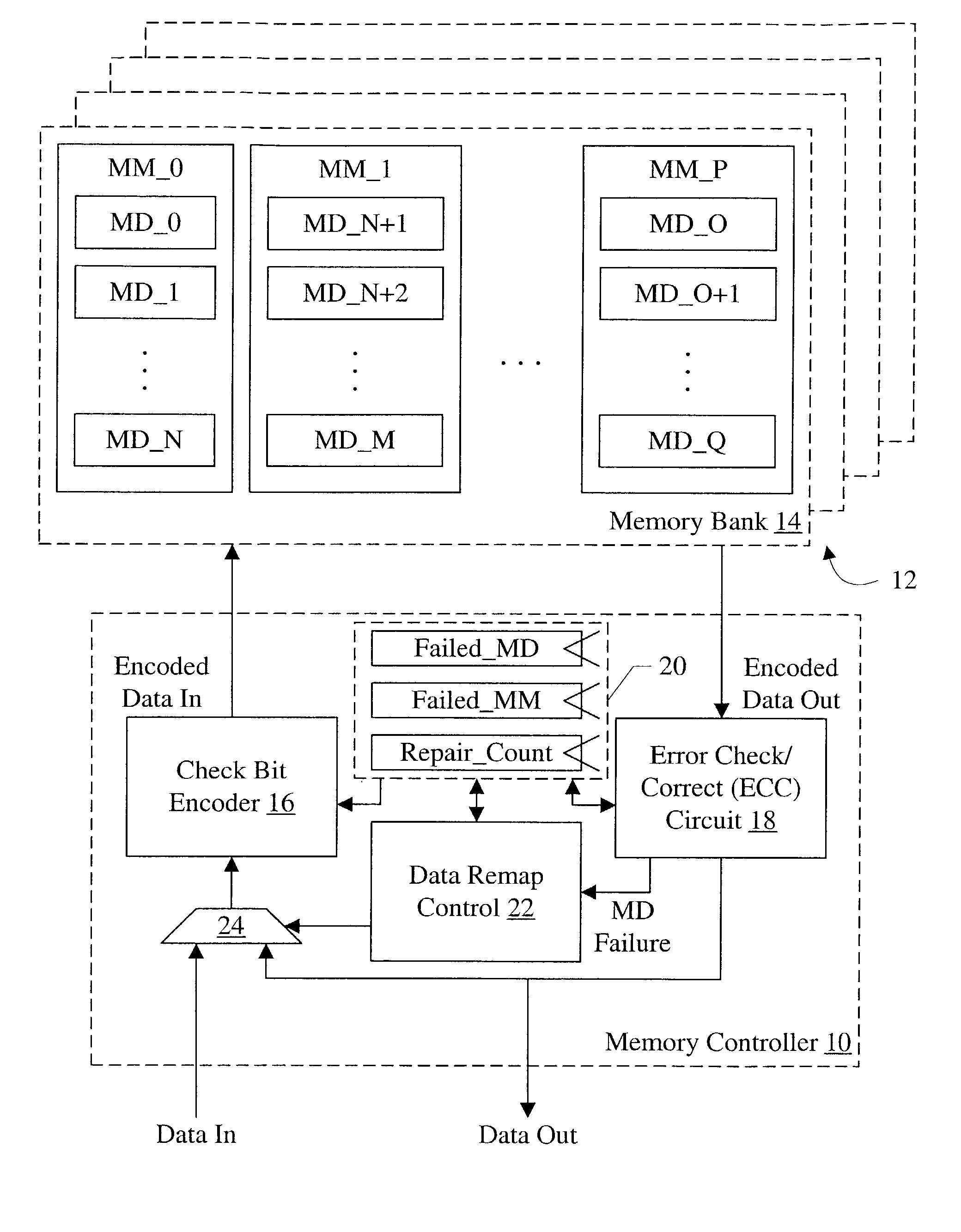

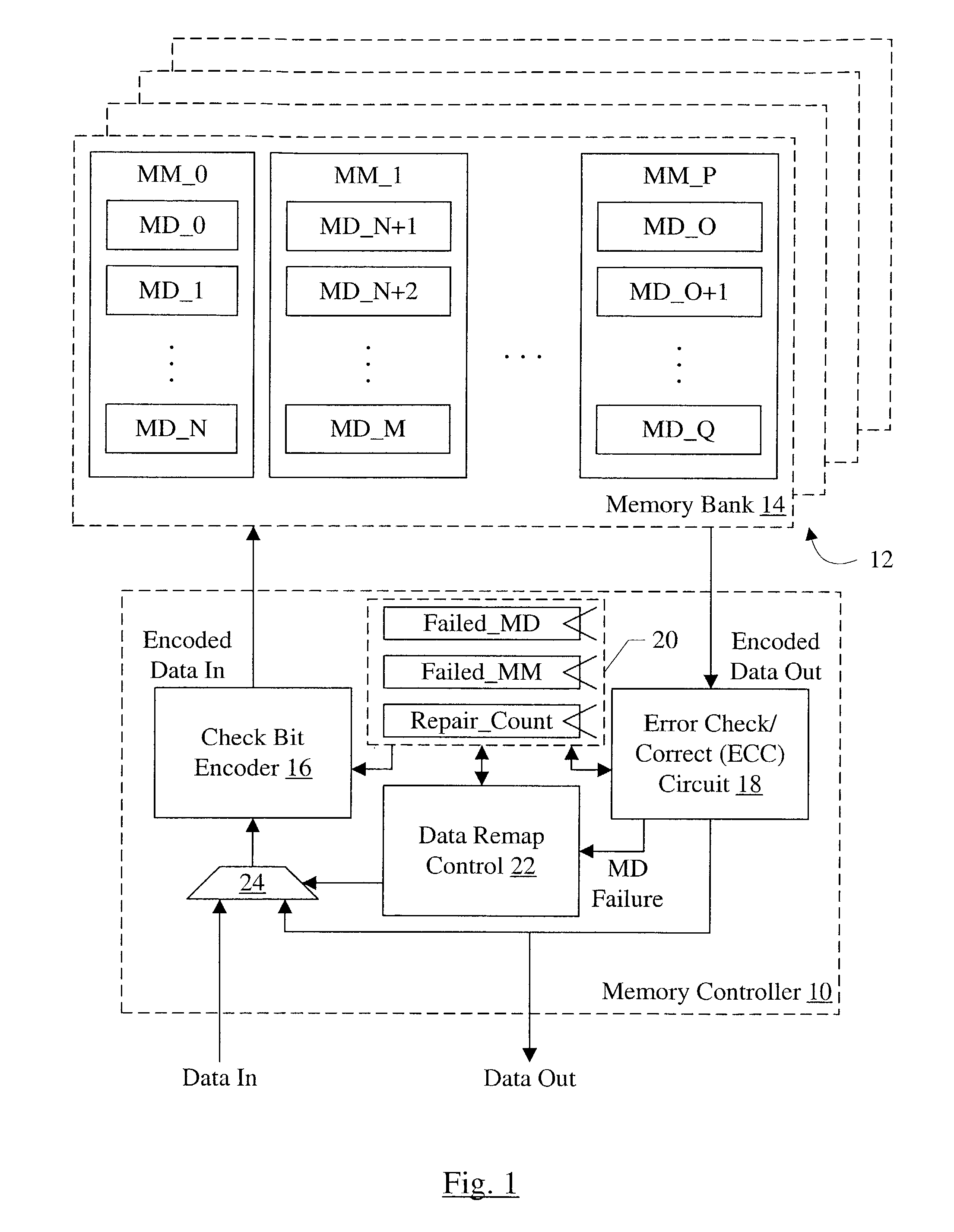

A memory controller comprises a check bit encoder circuit and a check / correct circuit. The check bit encoder circuit is coupled to receive a data block to be written to a memory comprising a plurality of memory devices, and is configured to encode the data block with a plurality of check bits to generate an encoded data block. The plurality of check bits are defined to provide at least: (i) detection and correction of a failure of one of the plurality of memory devices; and (ii) detection and correction of a single bit error in the encoded data block following detection of the failure of one of the plurality of memory devices. The check / correct circuit is coupled to receive the encoded data block from the memory and is configured to decode the encoded data block and perform at least the detection of (i) and (ii) on the encoded data block.

Owner:ORACLE INT CORP

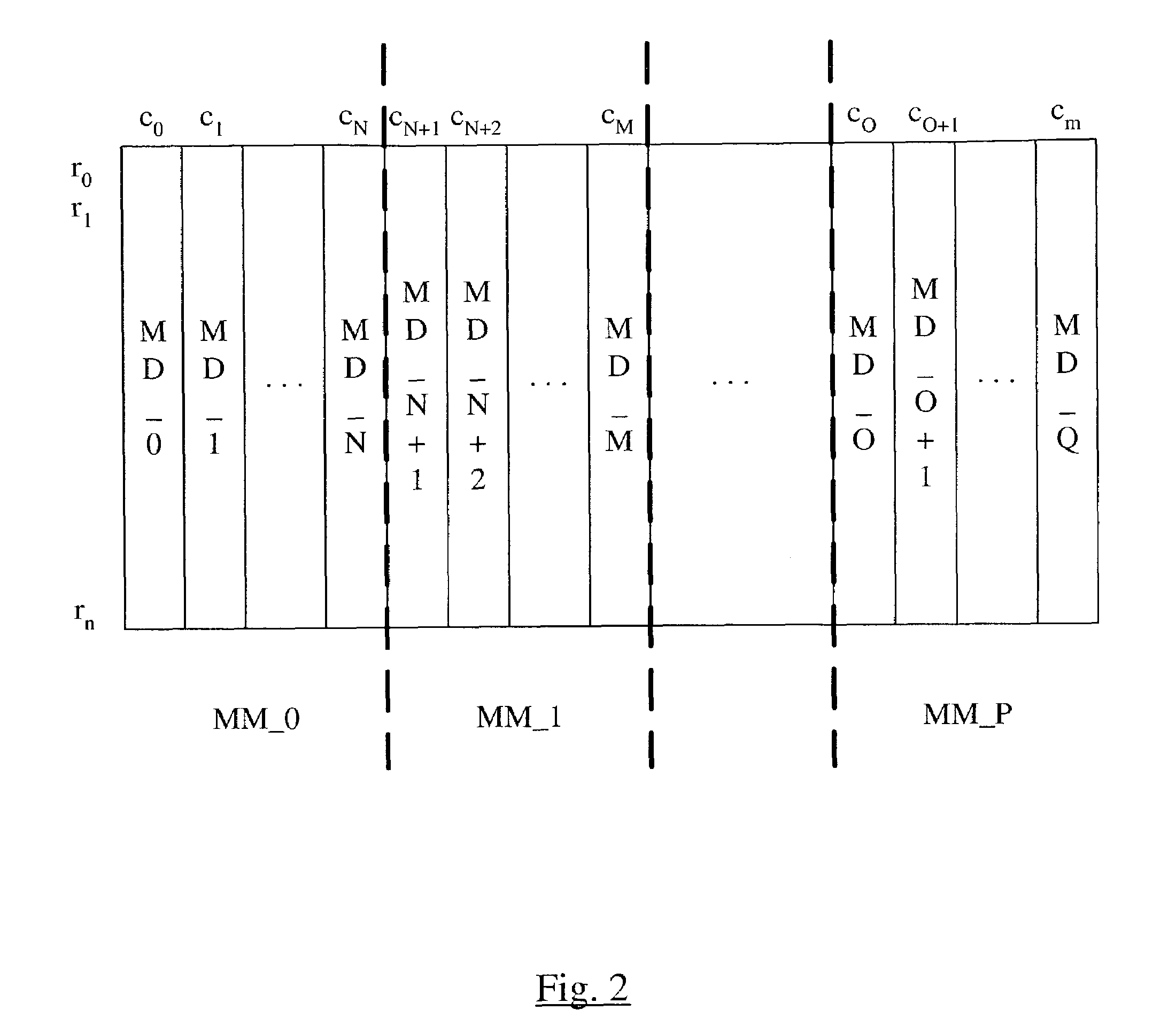

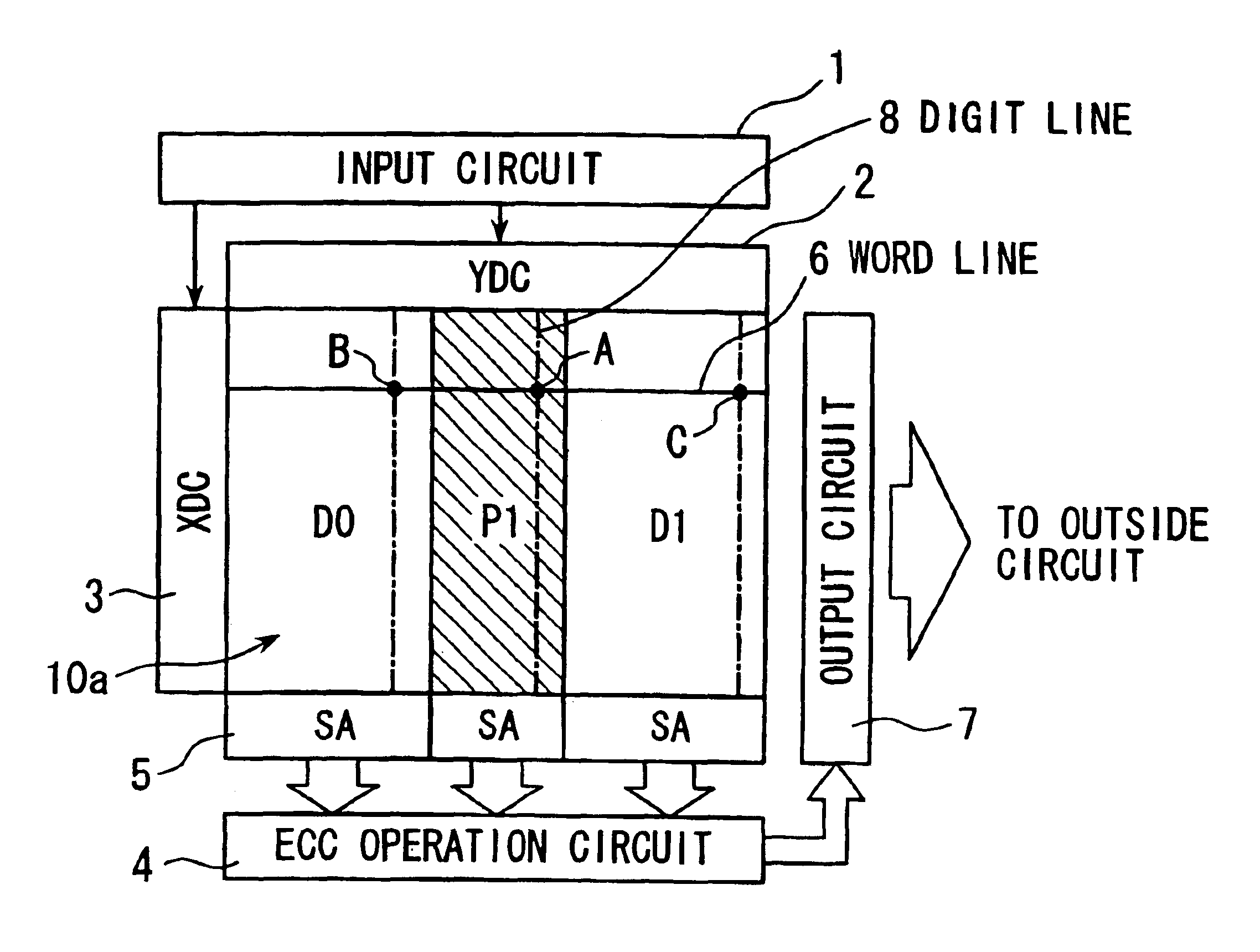

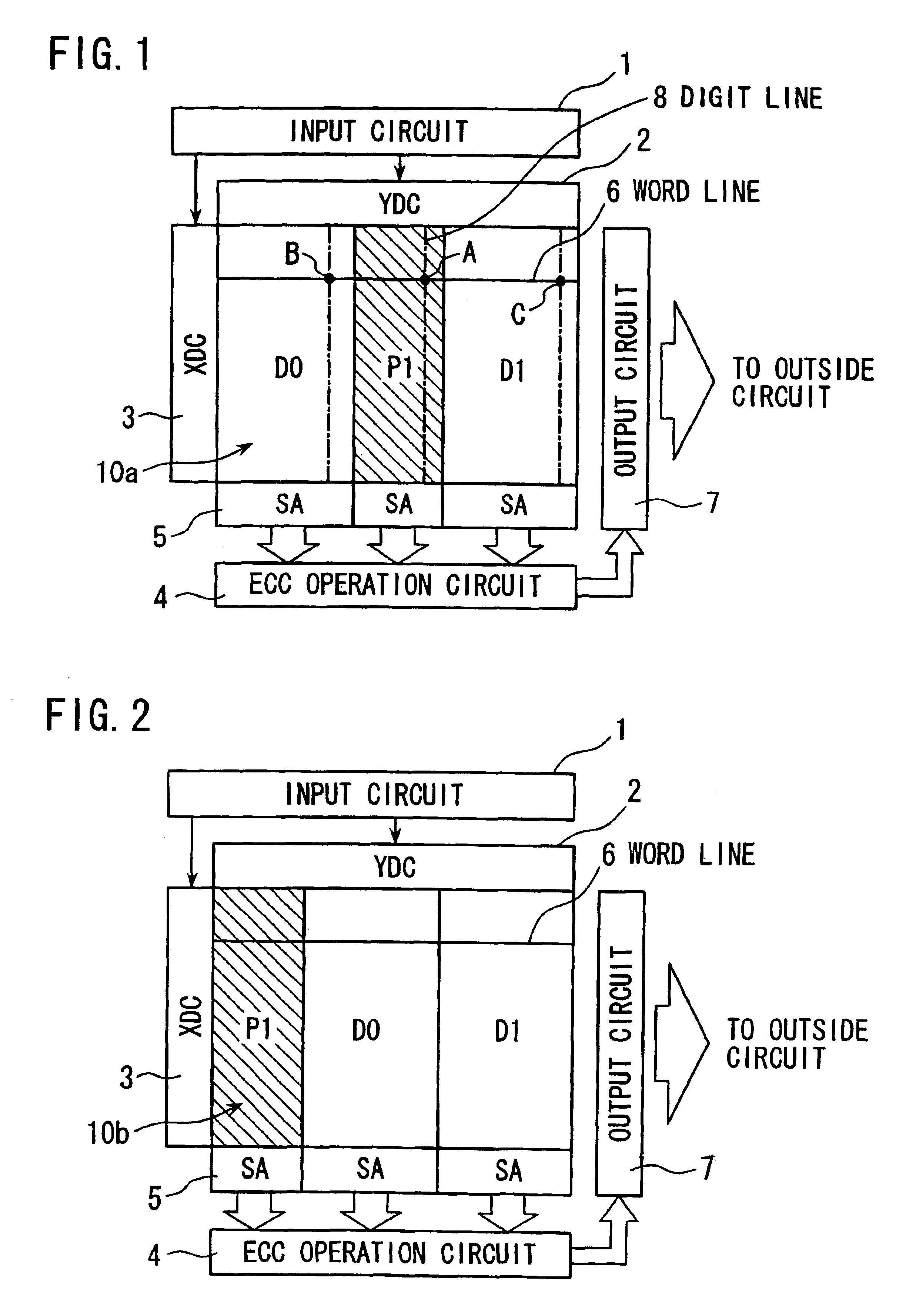

Semiconductor memory device having ECC type error recovery circuit

InactiveUS6851081B2Easy to measureEasy to readMemory loss protectionEmergency protective arrangements for automatic disconnectionType errorError check

A semiconductor memory device having an error check and correction (ECC) type error recovery circuit in which disposition of ECC cells is improved. The memory device comprises: a memory cell array including a plurality of normal cell array portions and an ECC cell array portion; an X decoder for selecting one of word lines in the memory cell array, the word lines extending from the X decoder to the memory cell array; an ECC operation circuit for performing error check and correction based on cell data read out from a selected word line, the cell data including data from normal cells and ECC cells of the selected word line. The ECC memory cell array portion is disposed at a location other than the far end of the word lines from the X decoder, that is, the ECC cell array portion is disposed at a location in which read out speed of data from ECC cell or cells does not become the worst speed in the memory device. Therefore, the worst data read out speed can be measured from outside.

Owner:RENESAS ELECTRONICS CORP

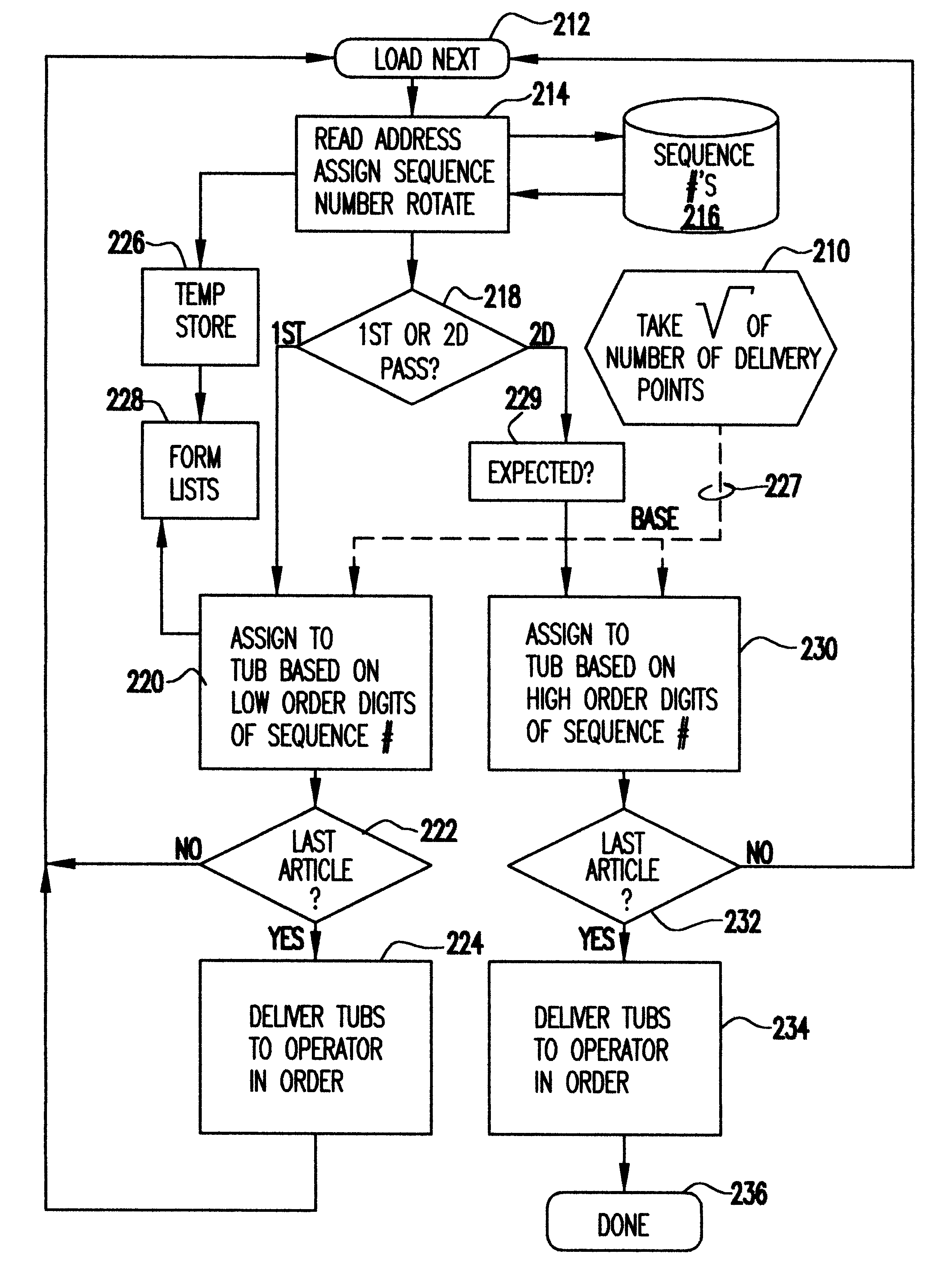

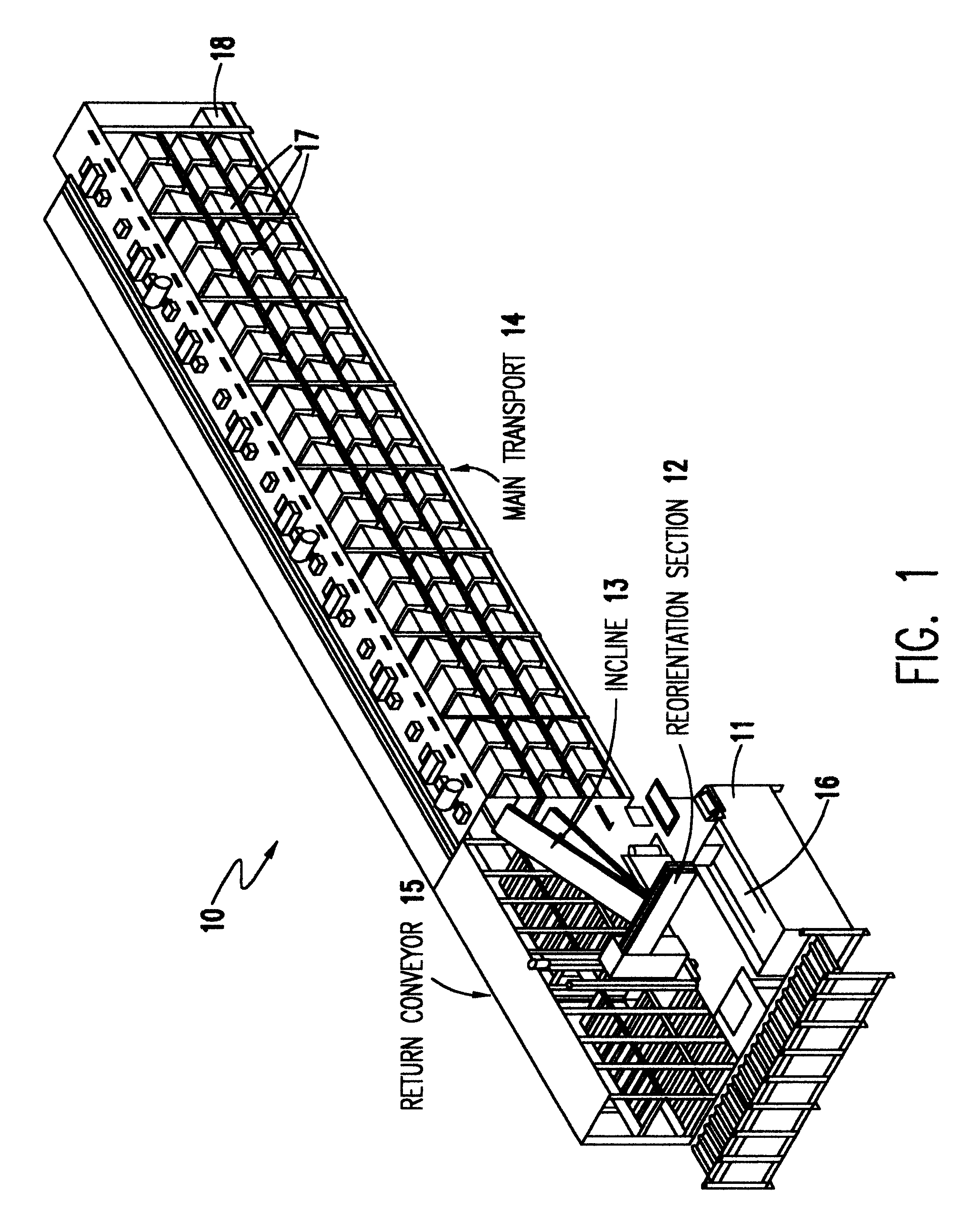

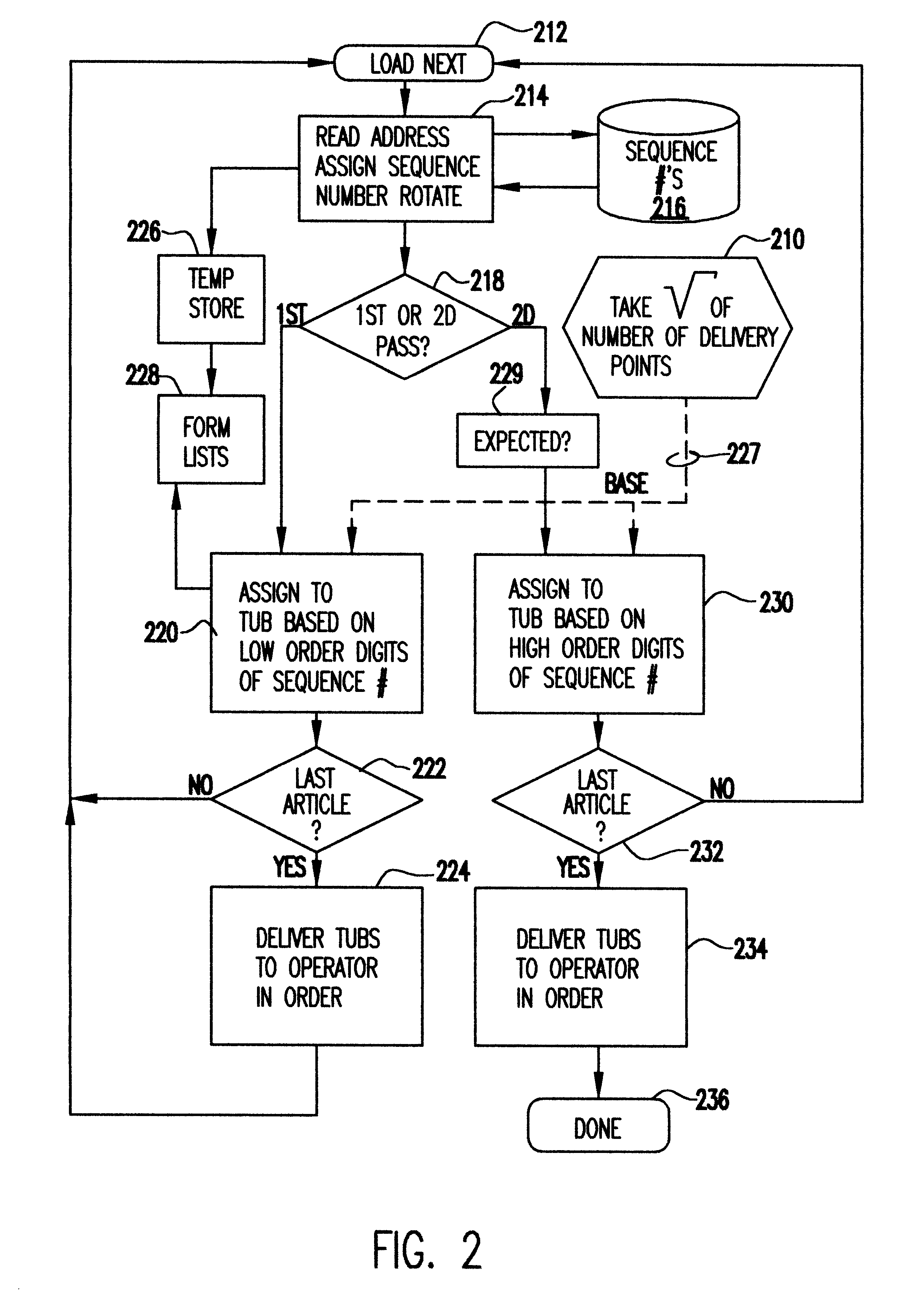

Object sortation for delivery sequencing

A sortation process provides high-speed sorting of randomly ordered articles into a desired order in a plurality of ordered bins or tubs such as standard USPS tubs in two passes, without additionally marking the articles in any way or requiring additional processes to do so. Optical character recognition or bar code reading performed on an image of the article provides a sequence number which is used to place the articles in respective bins or tubs during a first pass. The process then presents the content of the bins or tubs in order for a second pass during which they are placed in final desired order among a final ordered group of bins or tubs. During the first pass, sequence number information can be collected and used for error checking against the order of articles in each bin or tub during a second pass. The final output of the process provides the articles in standard (e.g. USPS) tubs face up and in delivery order.

Owner:LOCKHEED MARTIN CORP

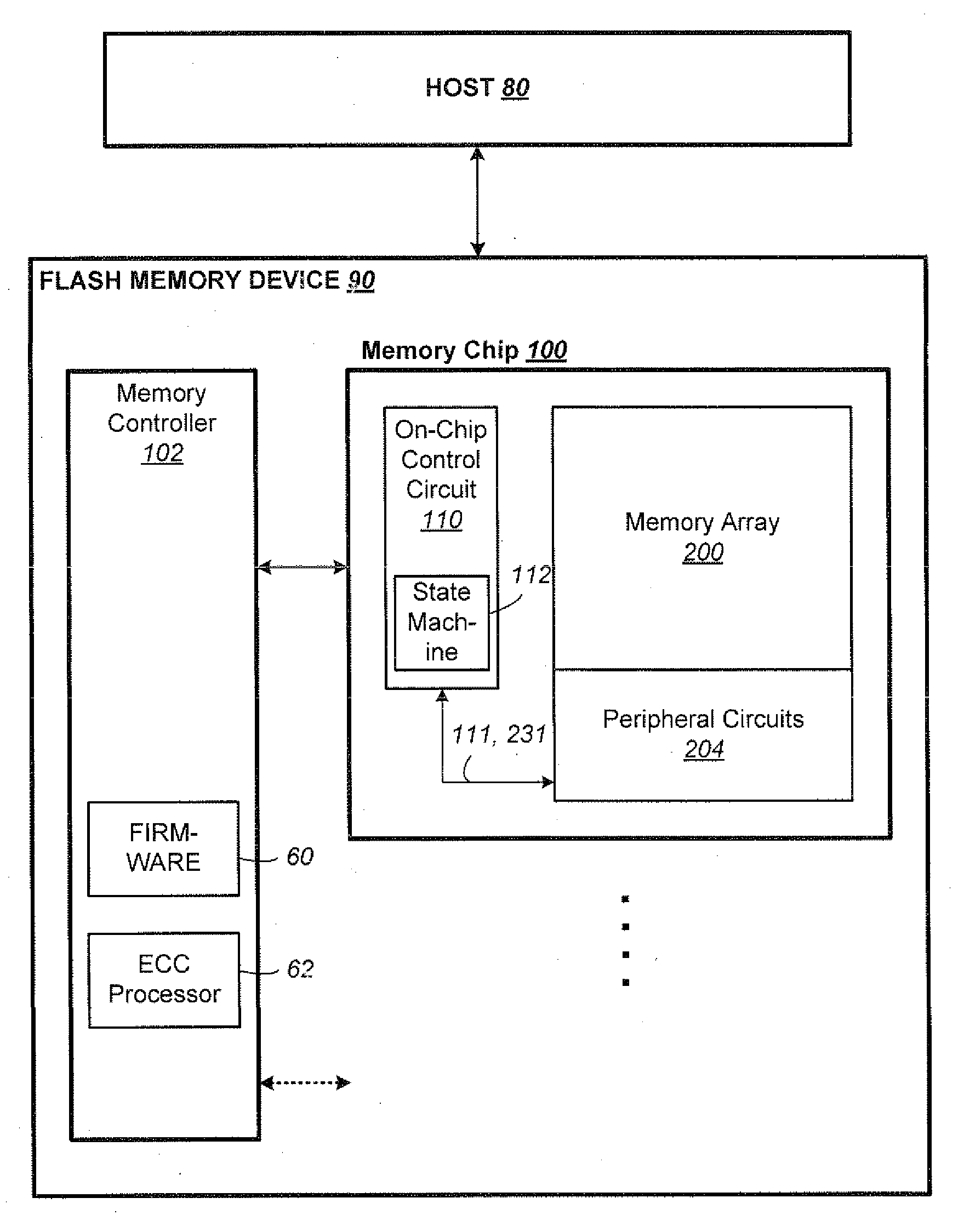

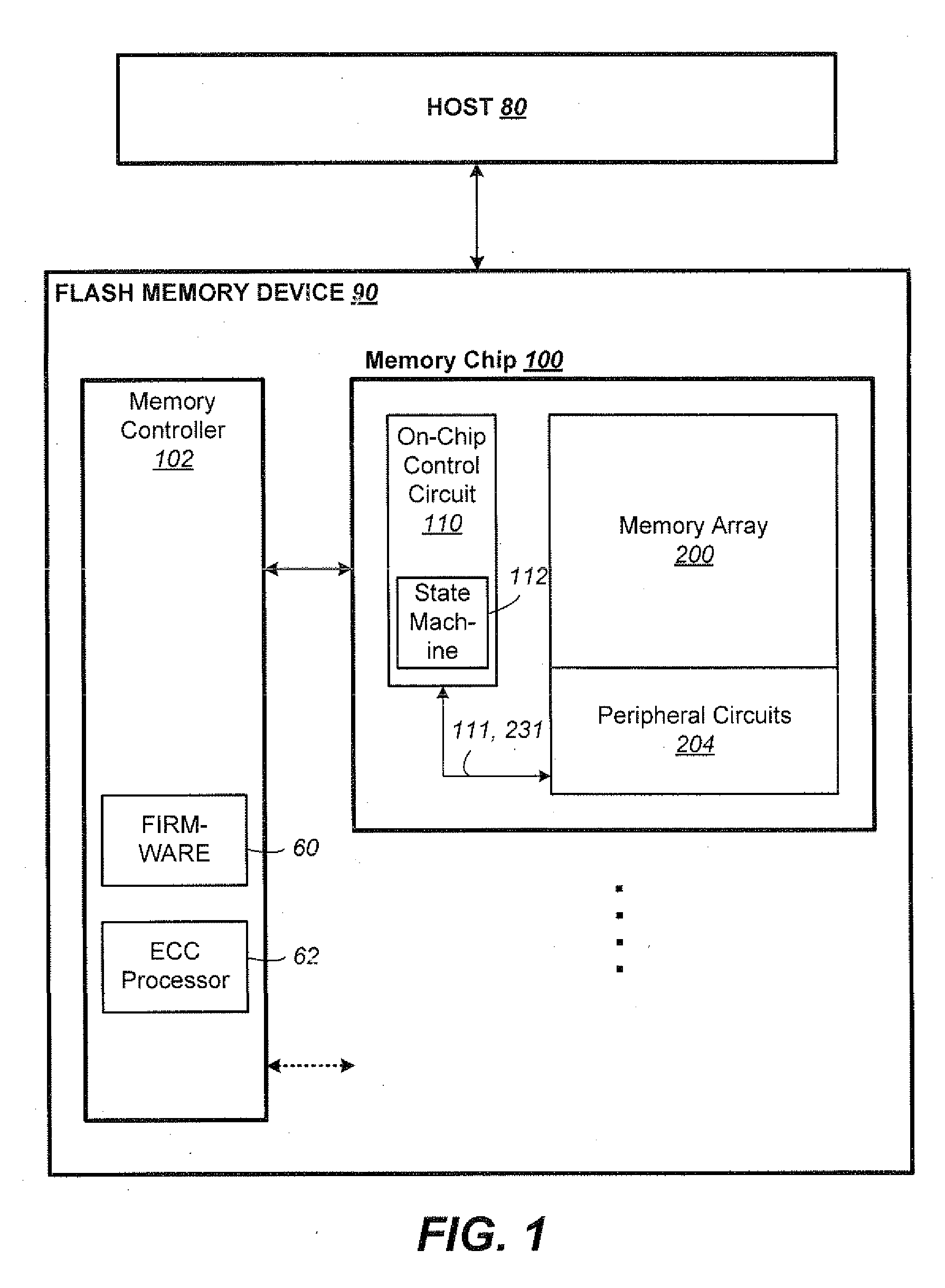

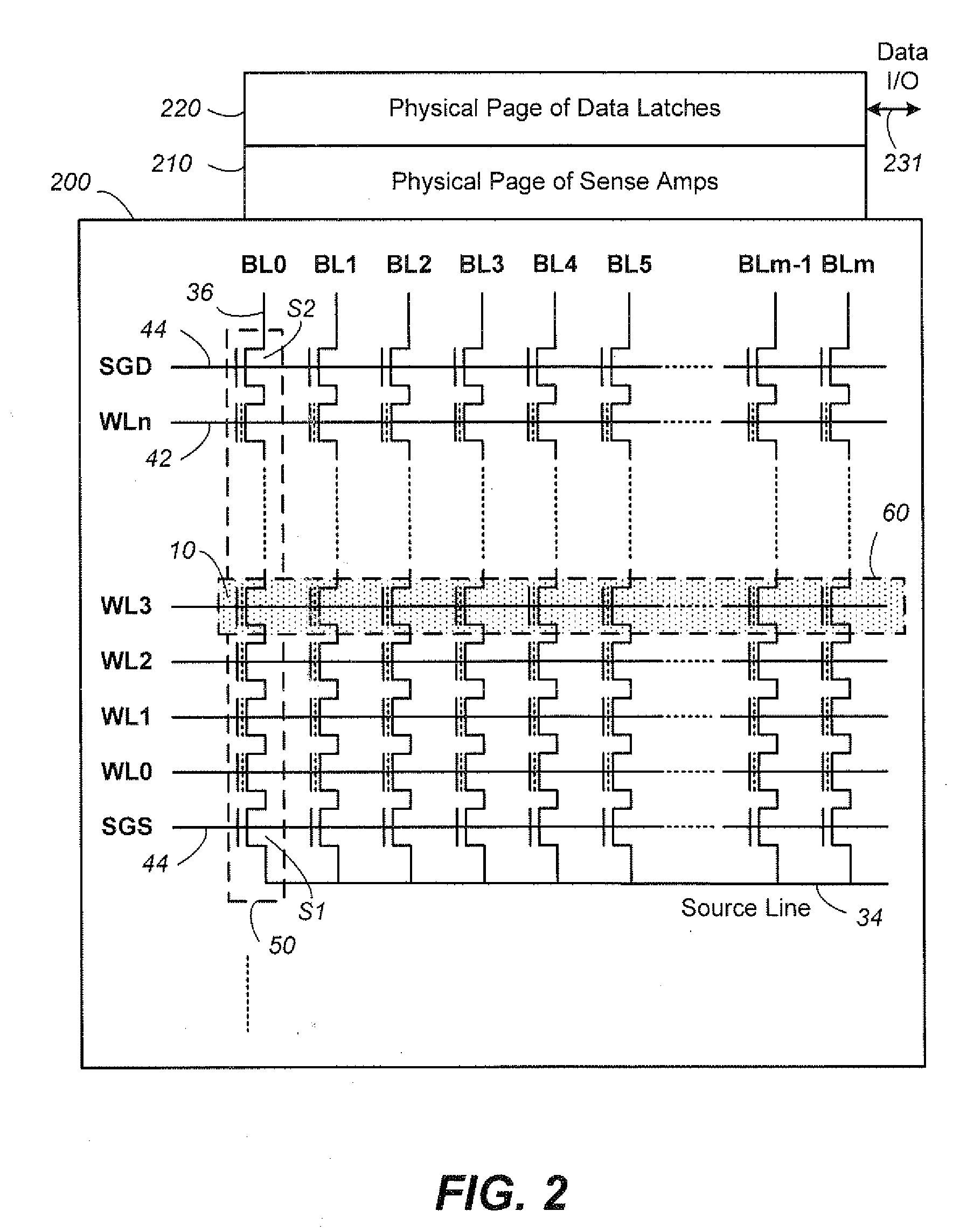

Method and system for minimizing number of programming pulses used to program rows of non-volatile memory cells

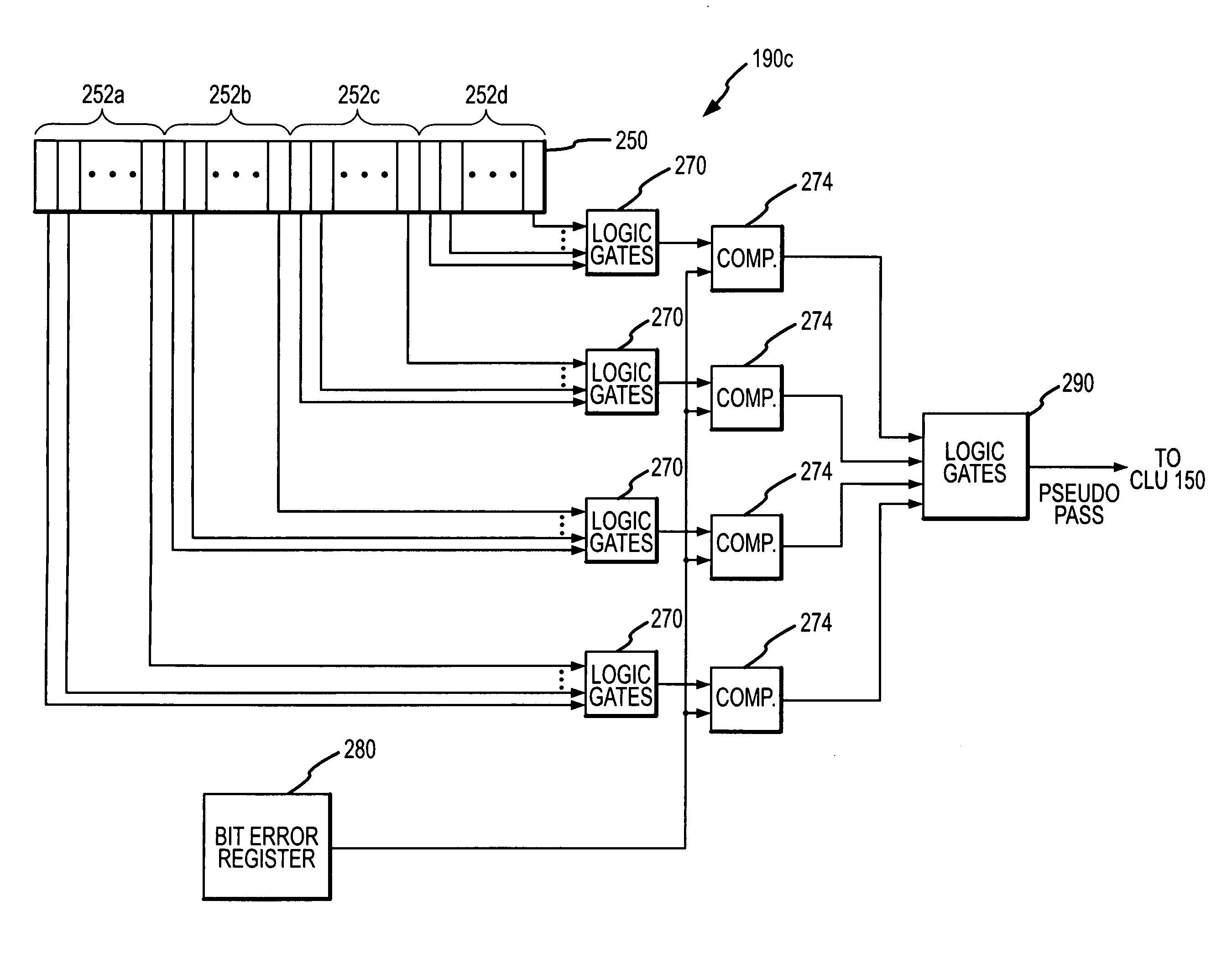

A flash memory device programs cells in each row in a manner that minimizes the number of programming pulses that must be applied to the cells during programming. The flash memory device includes a pseudo pass circuit that determines the number of data errors in each of a plurality of subsets of data that has been programmed in the row. The size of each subset corresponds to the number of read data bits coupled from the memory device, which are simultaneously applied to error checking and correcting circuitry. During iterative programming of a row of cells, the pseudo pass circuit indicates a pseudo pass condition to terminate further programming of the row if none of the subsets of data have a number of data errors that exceeds the number of data errors that can be corrected by the error checking and correcting circuitry.

Owner:MICRON TECH INC

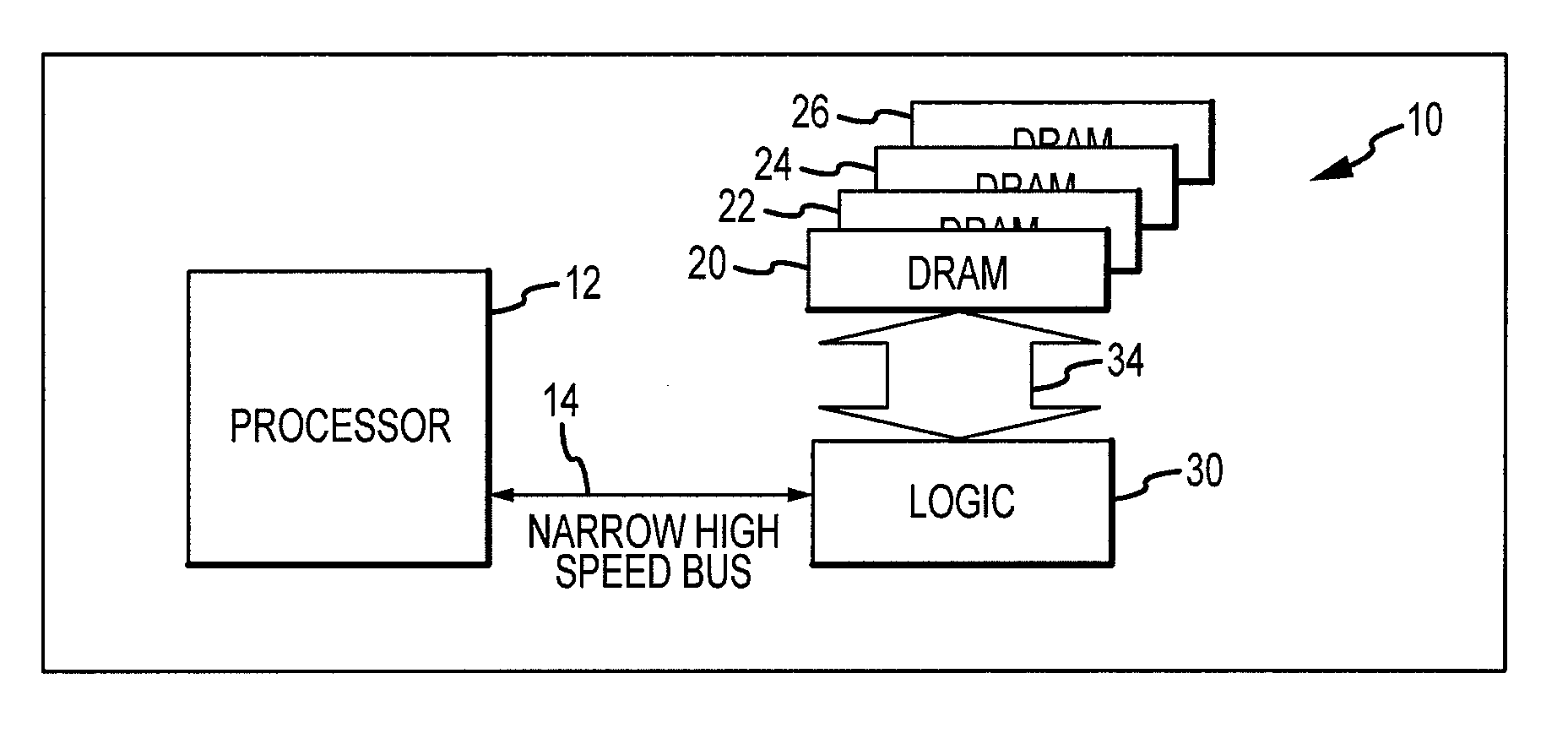

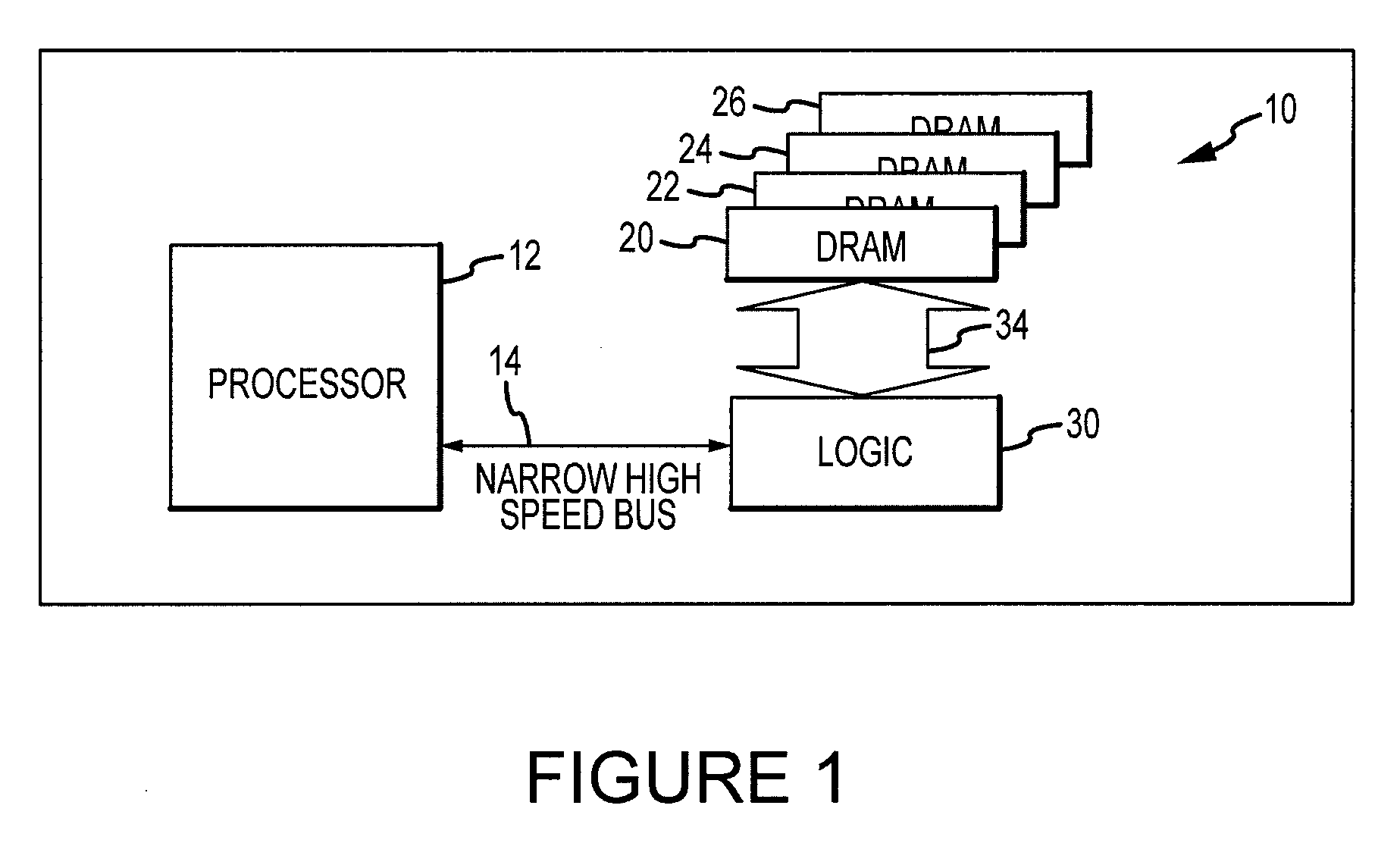

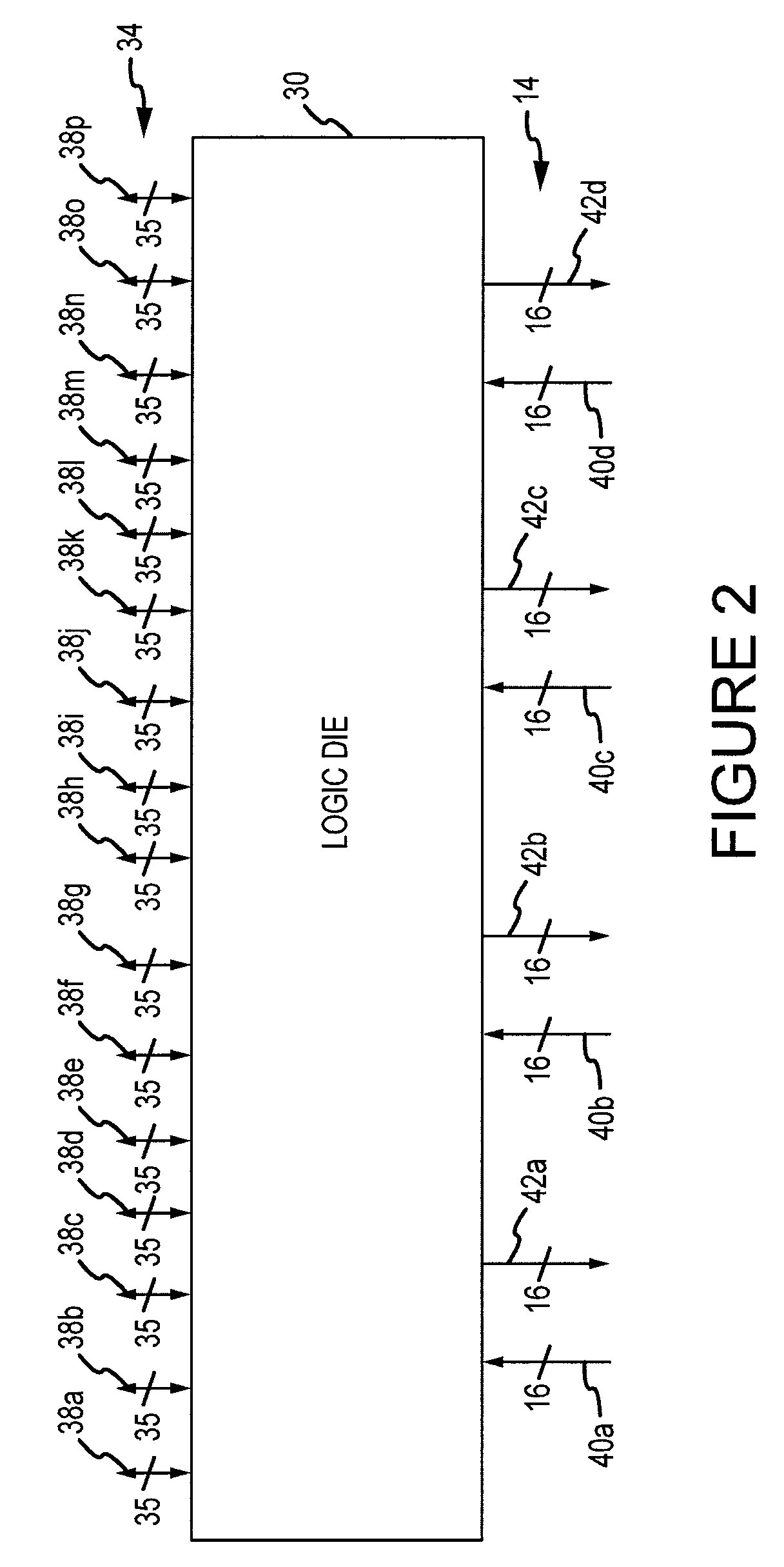

Memory system and method using a memory device die stacked with a logic die using data encoding, and system using the memory system

A memory system and method using at least one memory device die stacked with and coupled to a logic die by interconnects, such as through silicon vias. One such logic die includes an ECC system generating error checking and correcting (“ECC) bits corresponding to write data. The write data are transmitted to the memory device dice in a packet containing a serial burst of a plurality of parallel data bits. The ECC bits are transmitted to the memory device dice using through silicon vias that are different from the vias through which data are coupled. Such a logic die could also include a data bus inversion (“DBI”) system encoding the write data using a DBI algorithm and transmitting to the memory device dice DBI bits indicating whether the write data have been inverted. The DBI bits are transmitted using through silicon vias that are shared with the ECC bits when they are unused for transferring the ECC bits.

Owner:MICRON TECH INC

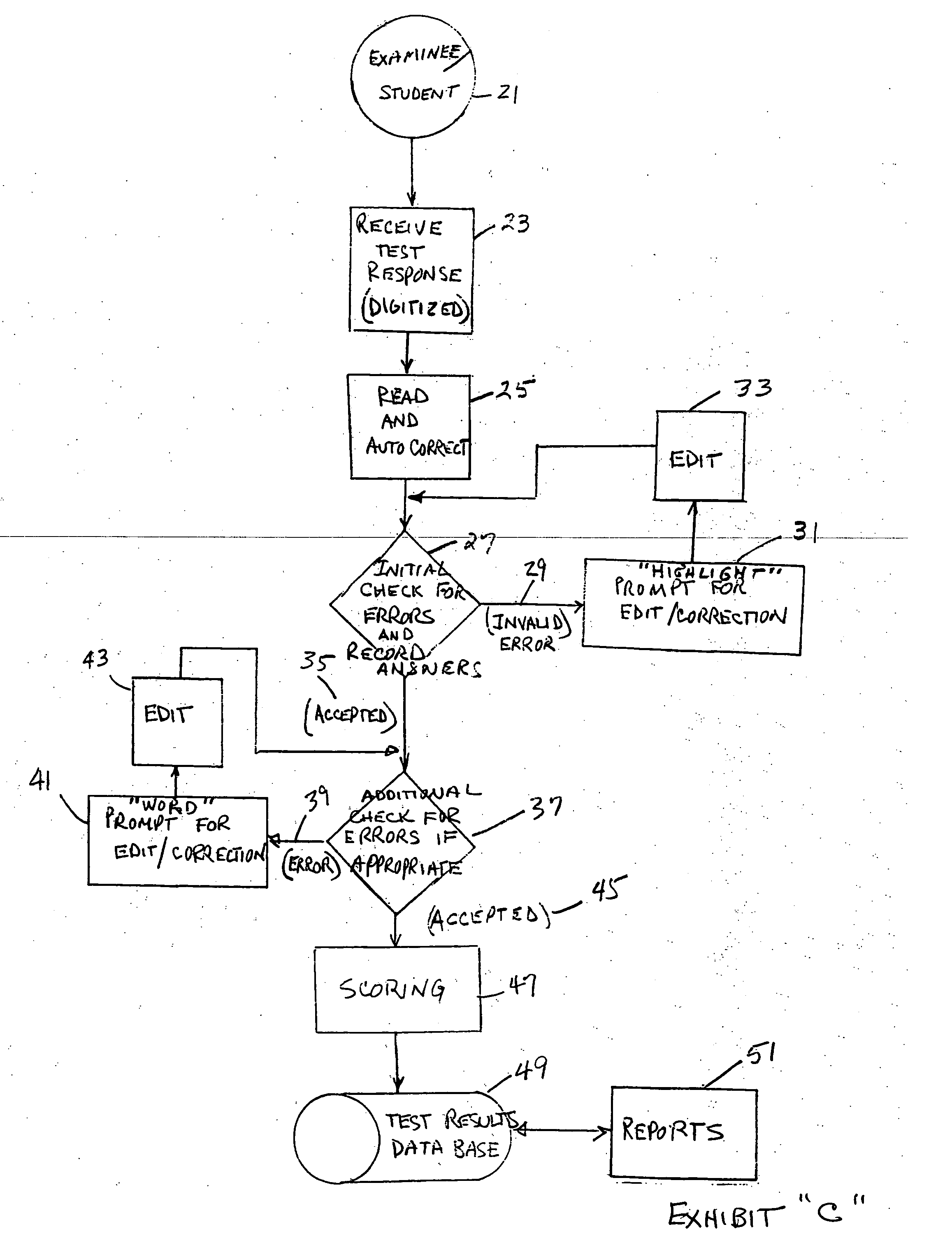

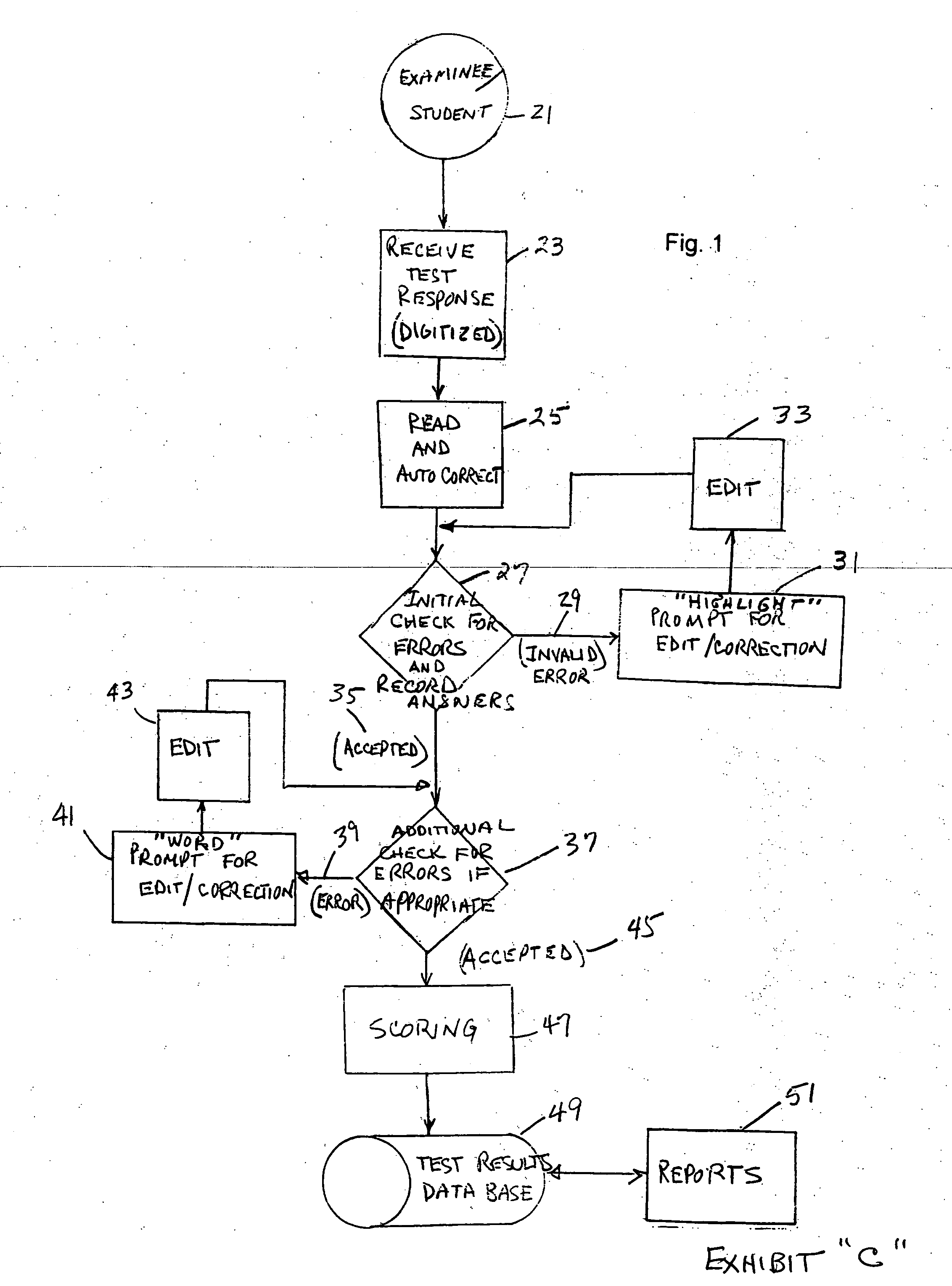

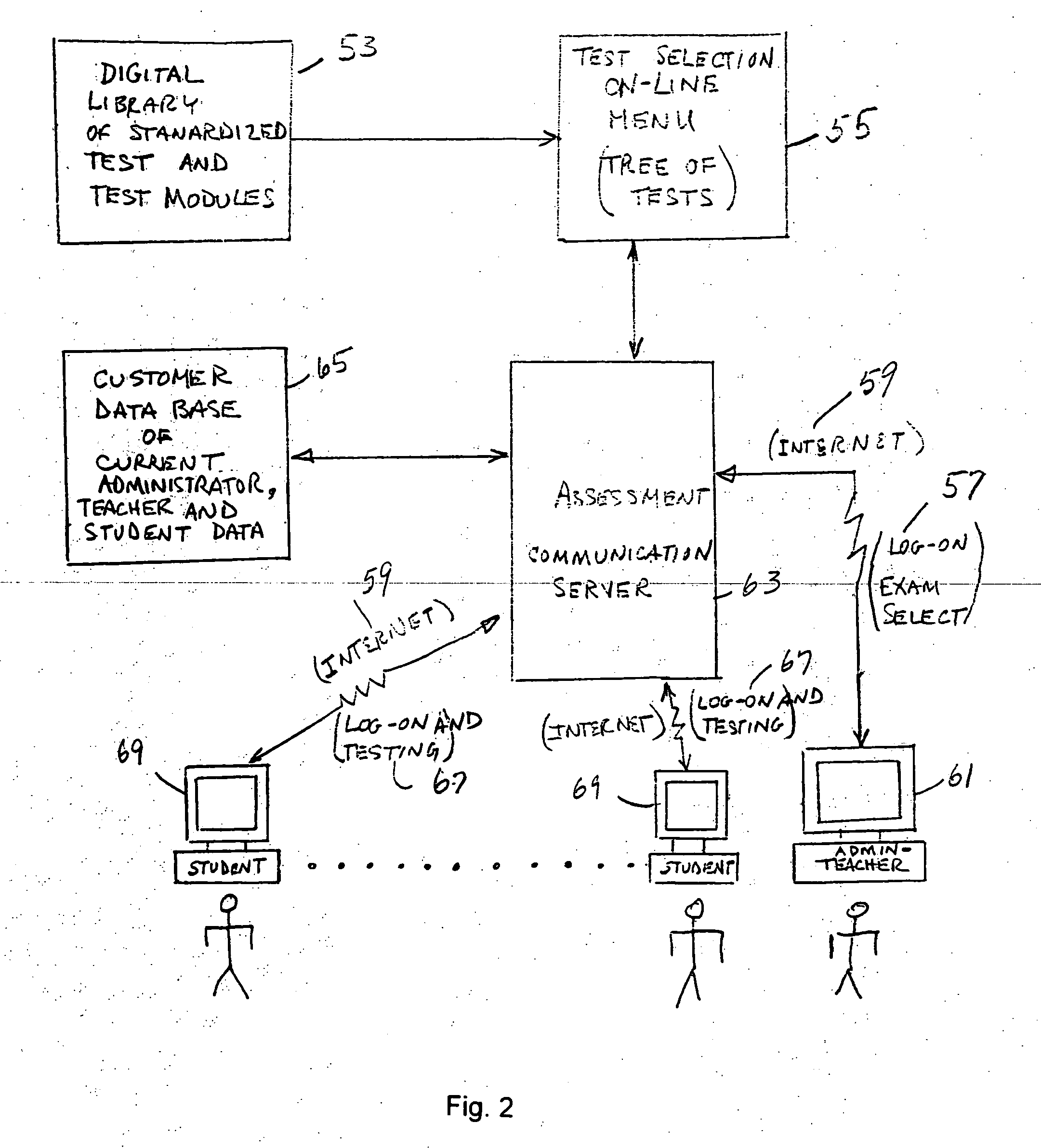

Unified web-based system for the delivery, scoring, and reporting of on-line and paper-based assessments

InactiveUS20060003306A1Reduce processing timePrecise positioningMechanical appliancesError checkThe Internet

A hardware and software implemented, standardize testing, scoring and reporting system has a network interface, being either LAN or the Internet. A test is selected from a library, assigned to a group of examinees, and a record is made of the assignment. The test is available on-line, or downloaded, or both. Downloaded tests are saved as PDF files and printed into booklets. Examinees record answers on bubble sheets, which are scanned at the customer site or shipped to a processing plant. Individual scanned answer sheets provided data for individual scanned records. Scanning software performs an initial auto-correct and then performs an initial check for errors in scanned records. Tests are batched for later inspection. Scanned records with errors are classified as invalid and the test papers are separated. Prompts are generated for a human test paper inspection and scanned record editing. Accepted batches of scanned records are sent to a scanned records server where a second scanned records error check is performed. Prompts are sent to the appropriate scanning station for further human editing of invalid scanned records. Once all records are valid they are scored and the test results stored in a database, which is accessed by a reporting subsystem associated with an on-line server.

Owner:VANTAGE TECH KNOWLEDGE ASSESSMENT

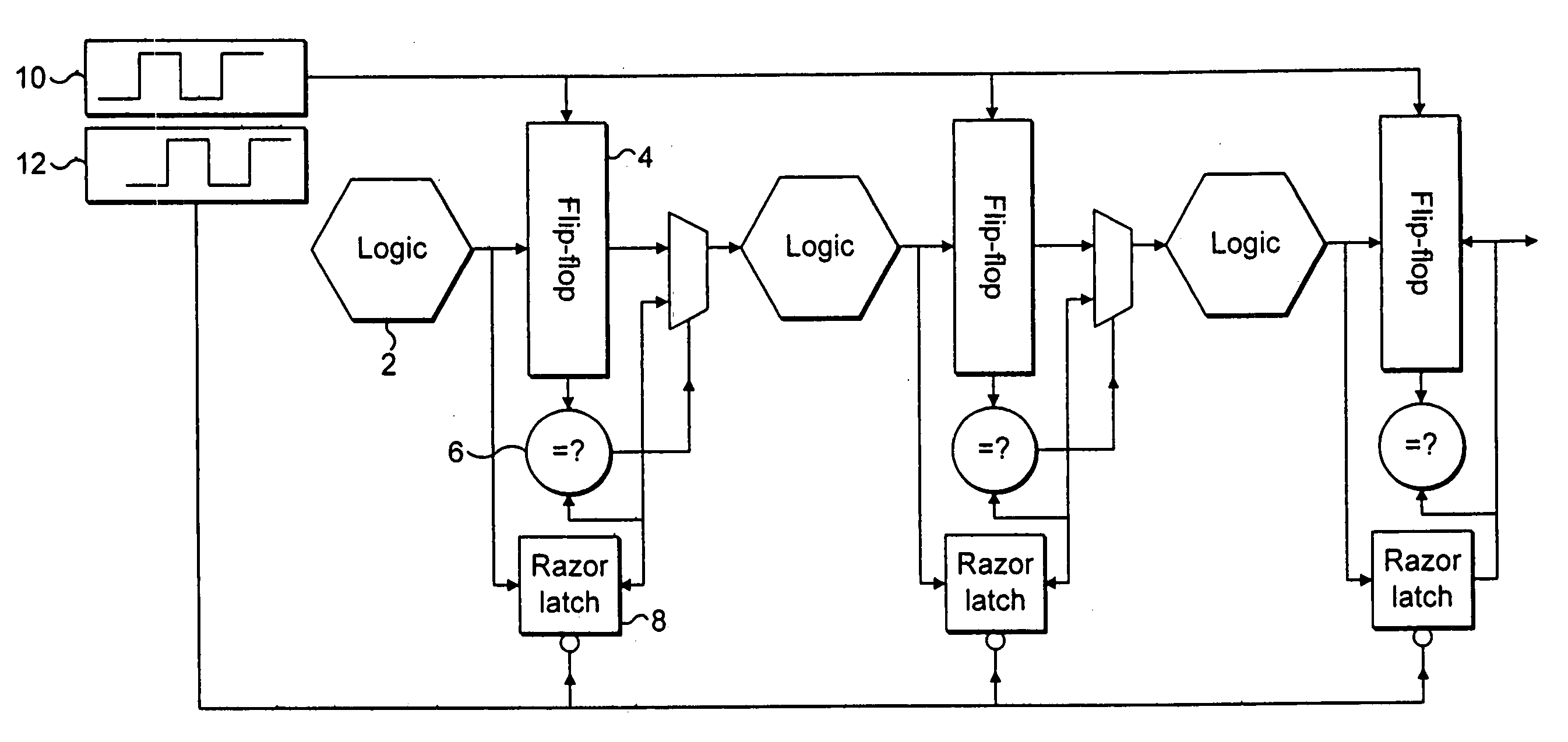

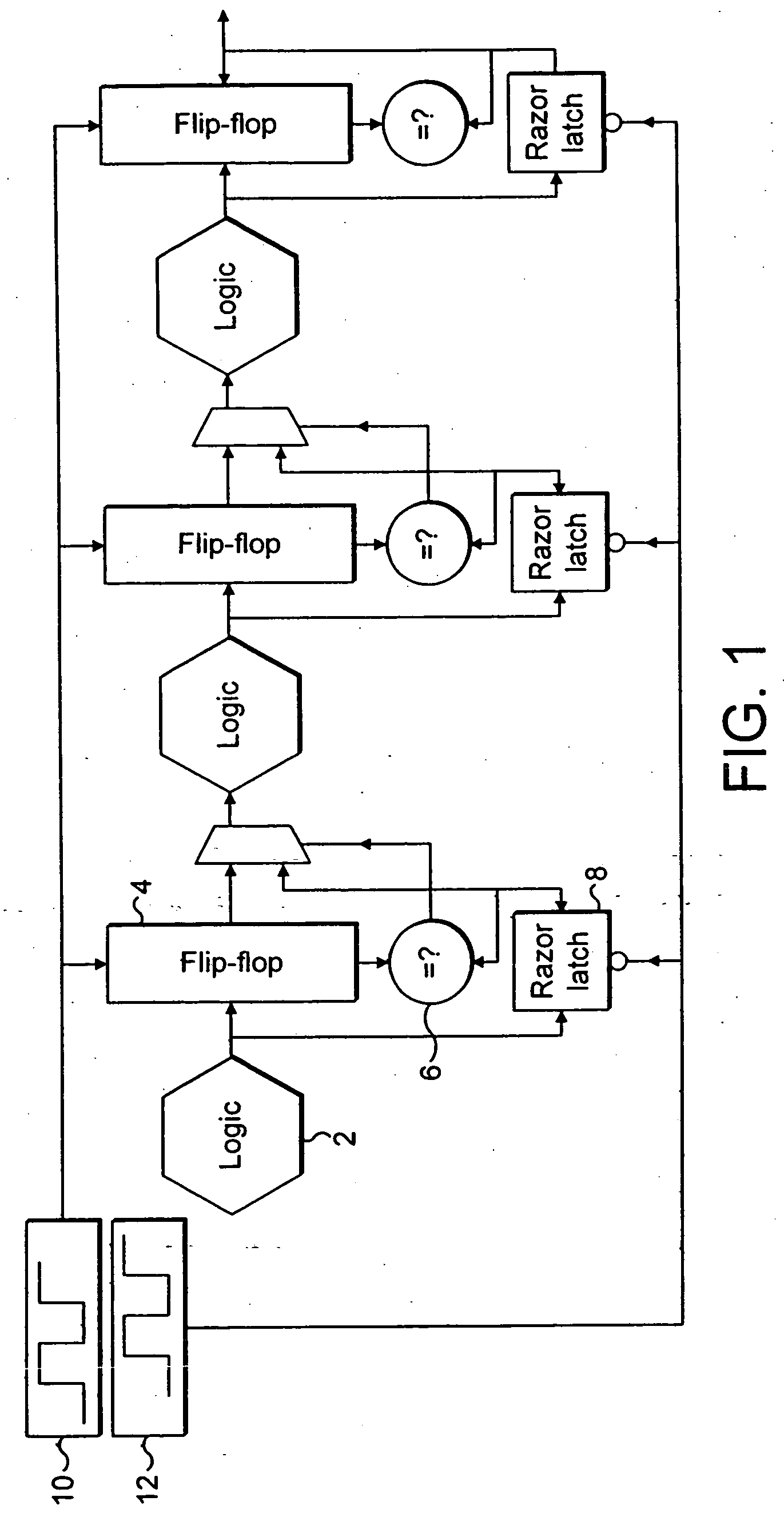

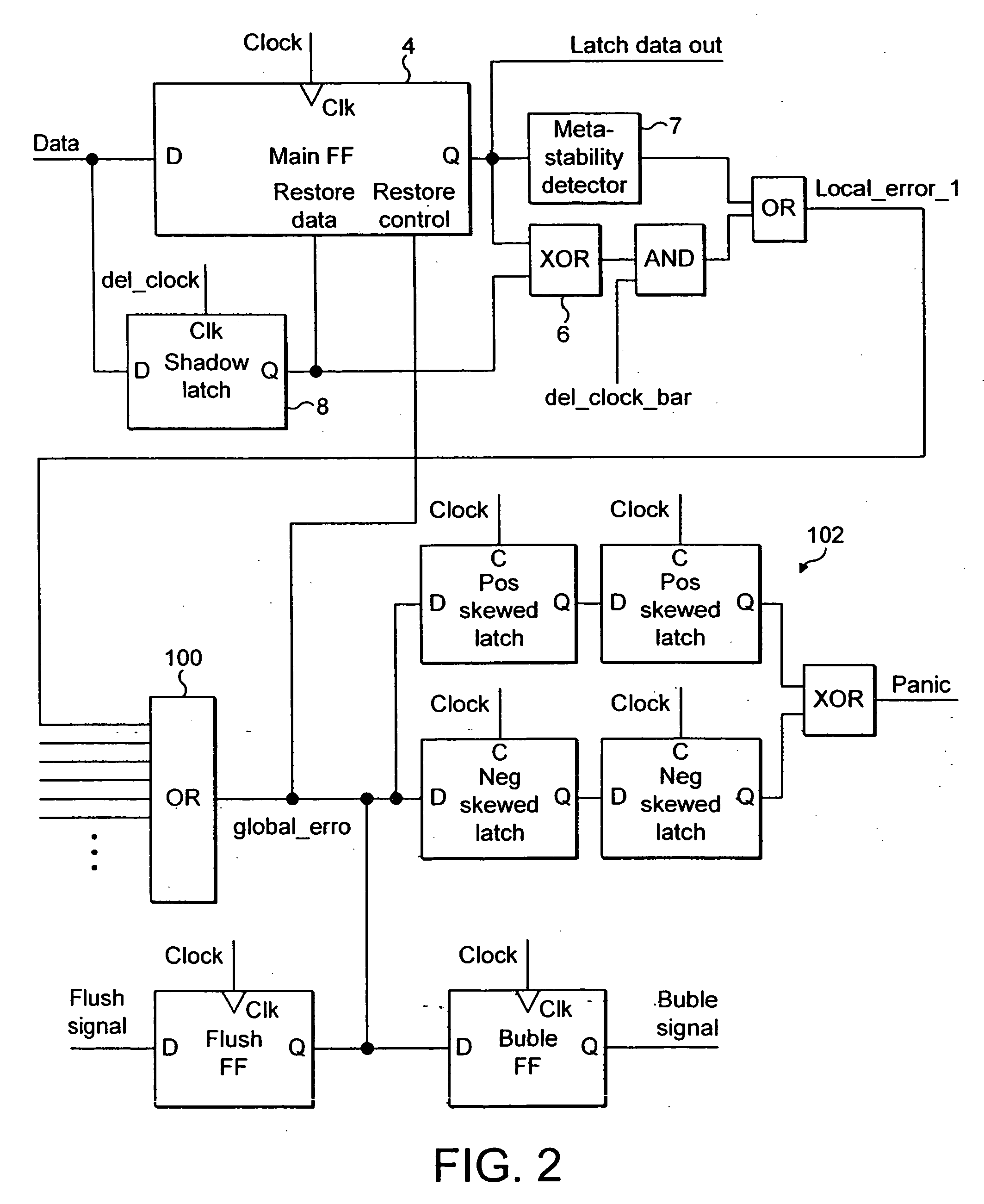

Error recovery within processing stages of an integrated circuit

ActiveUS20050246613A1Easy to modifyReduce the possibilityCode conversionFrequency/rate-modulated pulse demodulationError checkClock rate

An integrated circuit includes a plurality of processing stages each including processing logic 1014, a non-delayed signal-capture element 1016, a delayed signal-capture element 1018 and a comparator 1024. The non-delayed signal-capture element 1016 captures an output from the processing logic 1014 at a non-delayed capture time. At a later delayed capture time, the delayed signal-capture element 1018 also captures a value from the processing logic 1014. An error detection circuit 1026 and error correction circuit 1028 detect and correct random errors in the delayed value and supplies an error-checked delayed value to the comparator 1024. The comparator 1024 compares the error-checked delayed value and the non-delayed value and if they are not equal this indicates that the non-delayed value was captured too soon and should be replaced by the error-checked delayed value. The non-delayed value is passed to the subsequent processing stage immediately following its capture and accordingly error recovery mechanisms are used to suppress the erroneous processing which has occurred by the subsequent processing stages, such as gating the clock and allowing the correct signal values to propagate through the subsequent processing logic before restarting the clock. The operating parameters of the integrated circuit, such as the clock frequency, the operating voltage, the body biased voltage, temperature and the like are adjusted so as to maintain a finite non-zero error rate in a manner that increases overall performance.

Owner:ARM LTD +1

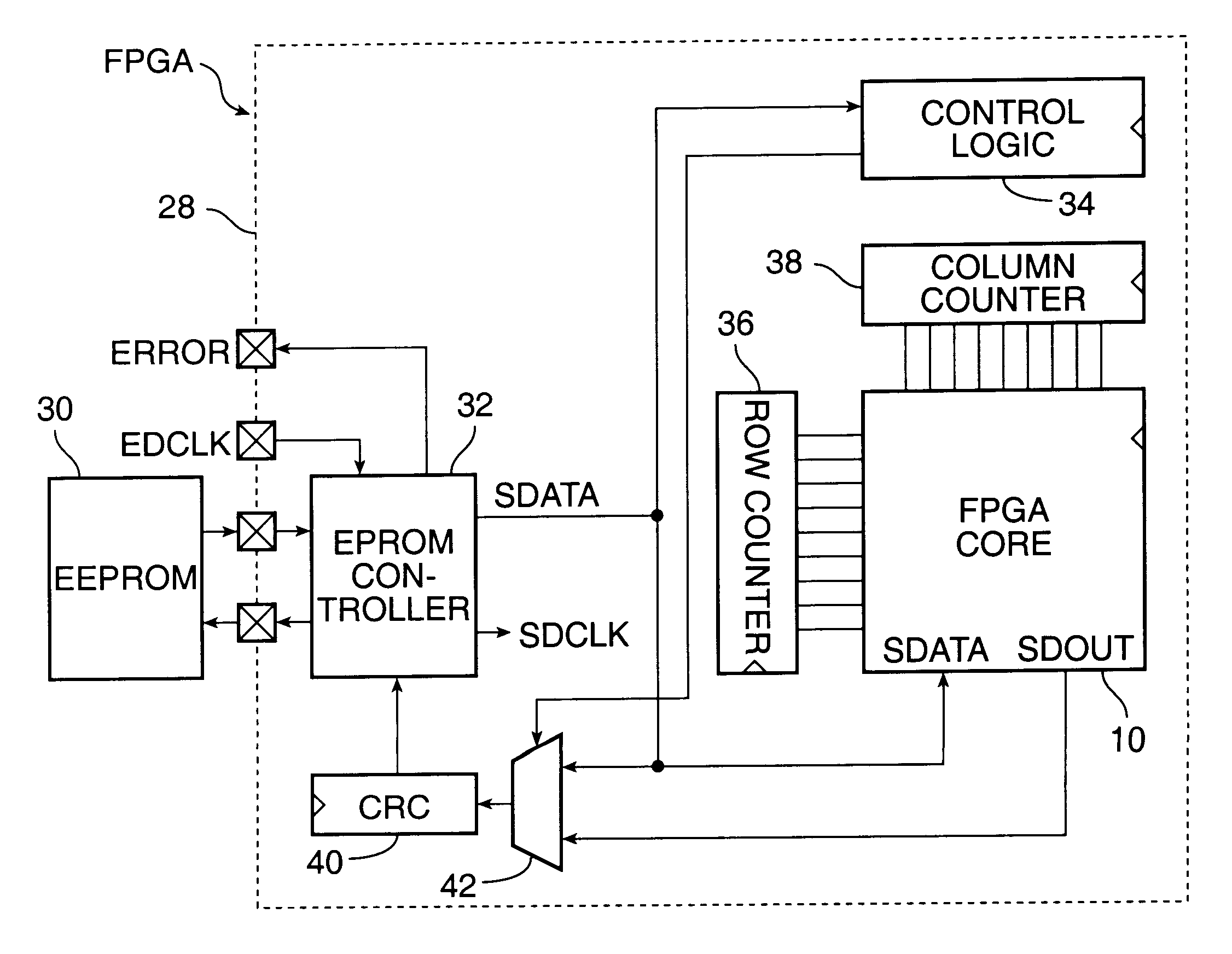

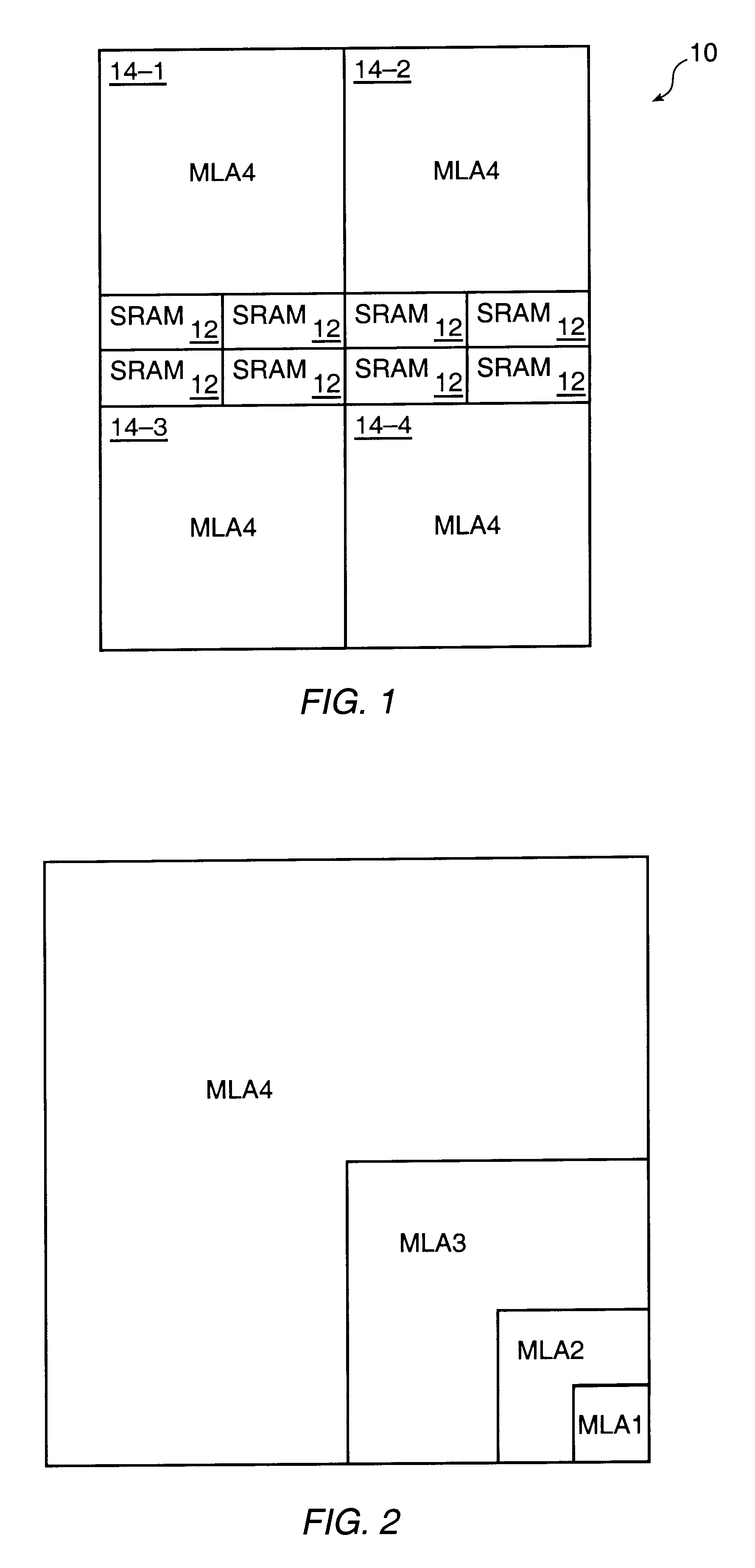

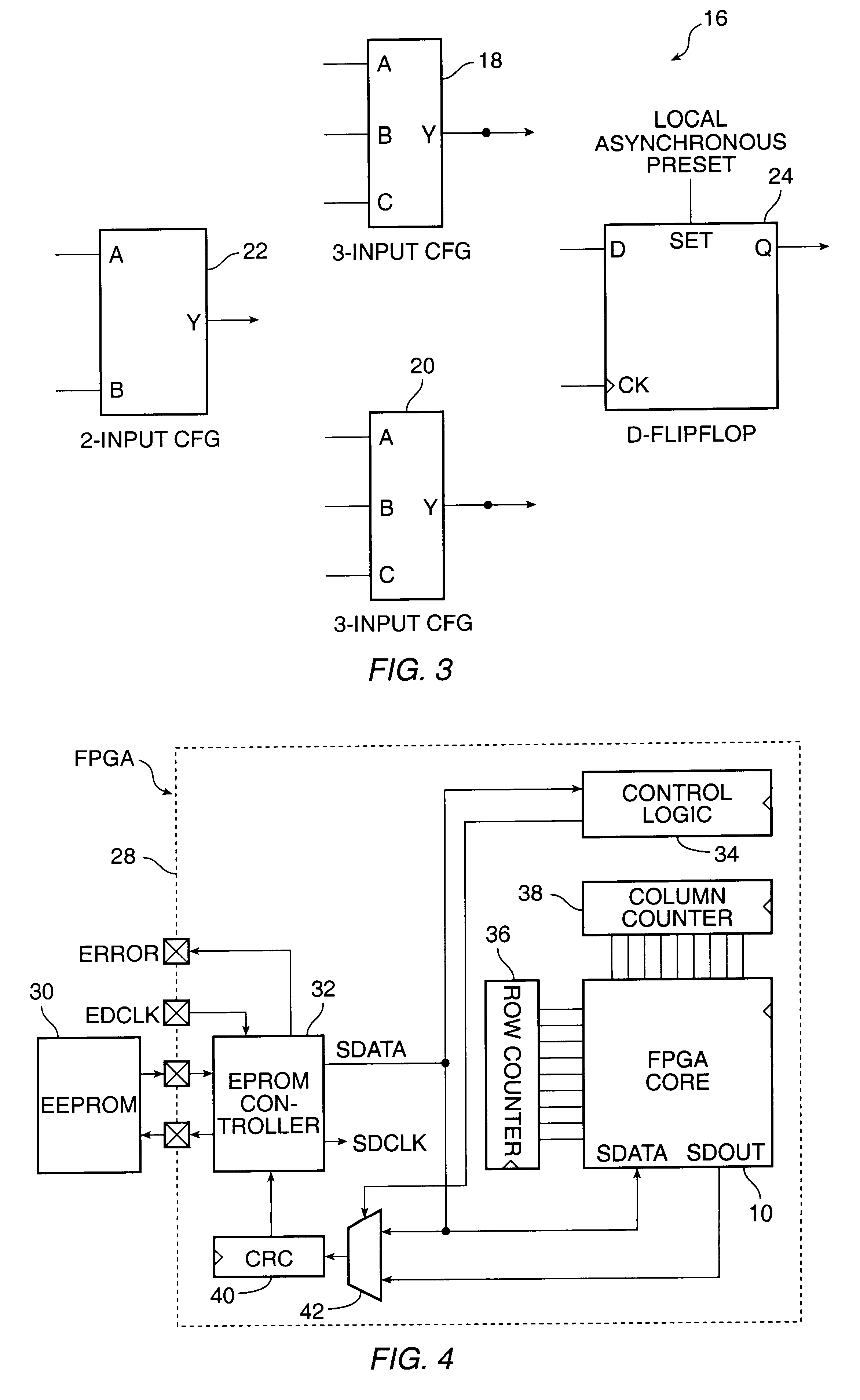

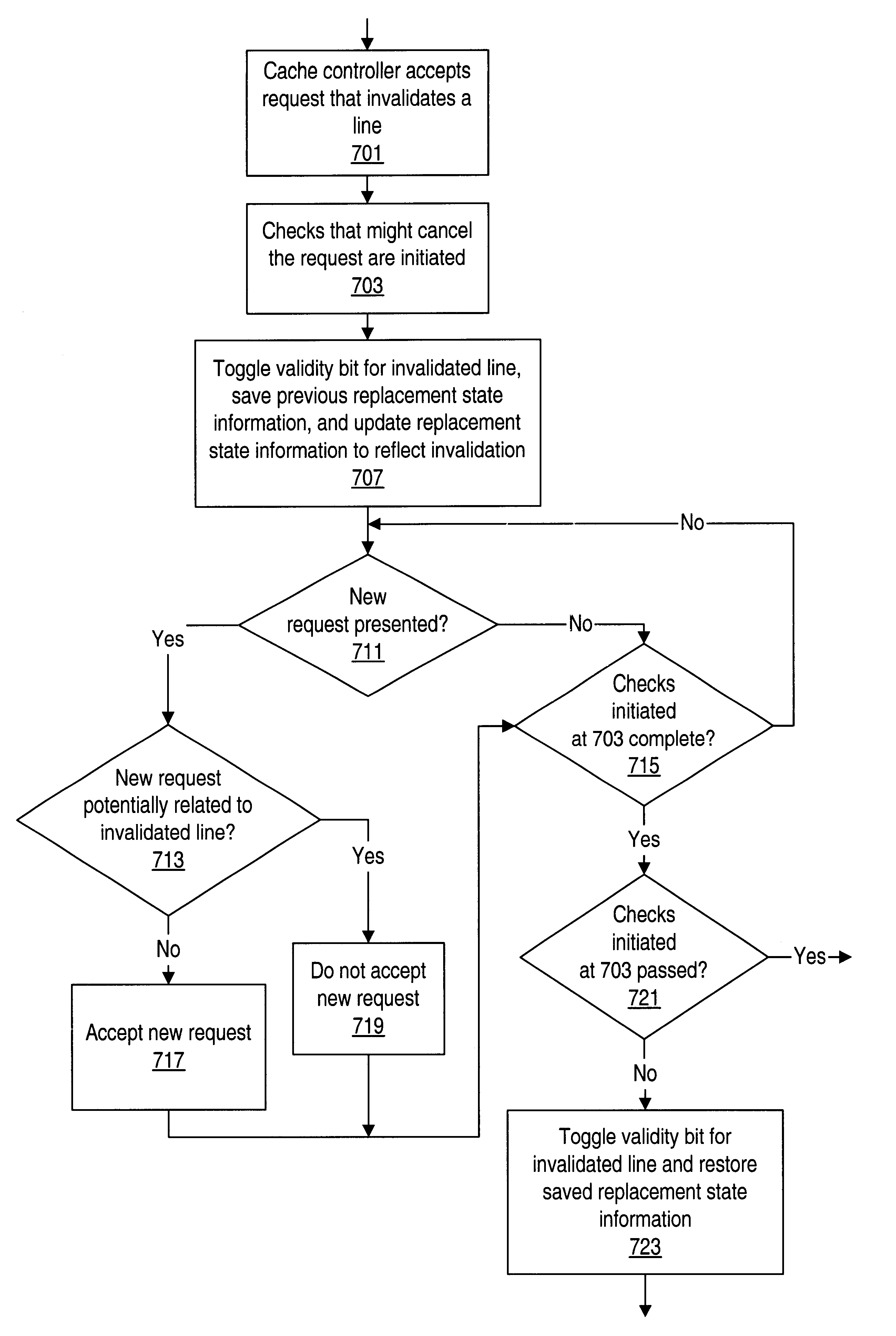

Methods for errors checking the configuration SRAM and user assignable SRAM data in a field programmable gate array

A method for detecting an error in data stored in configuration SRAM and user assignable SRAM in a FPGA comprises the steps of providing a serial data stream into the FPGA from an external source, loading data from the serial data stream into the configuration SRAM in response to address signals generated by row column counters, loading data from the serial data stream into the user assignable SRAM in response to address signals generated by row and column counters, loading a seed and signature from the serial data stream into a cyclic redundancy checking circuit, cycling data out of the configuration SRAM and the user assignable SRAM by the row and column counters; performing error checking on the data that has been cycled out of the configuration SRAM and out of the user assignable SRAM by the cyclic redundancy checking circuit, and generating an error signal when an error is detected by the error checking circuit.

Owner:MICROSEMI SOC

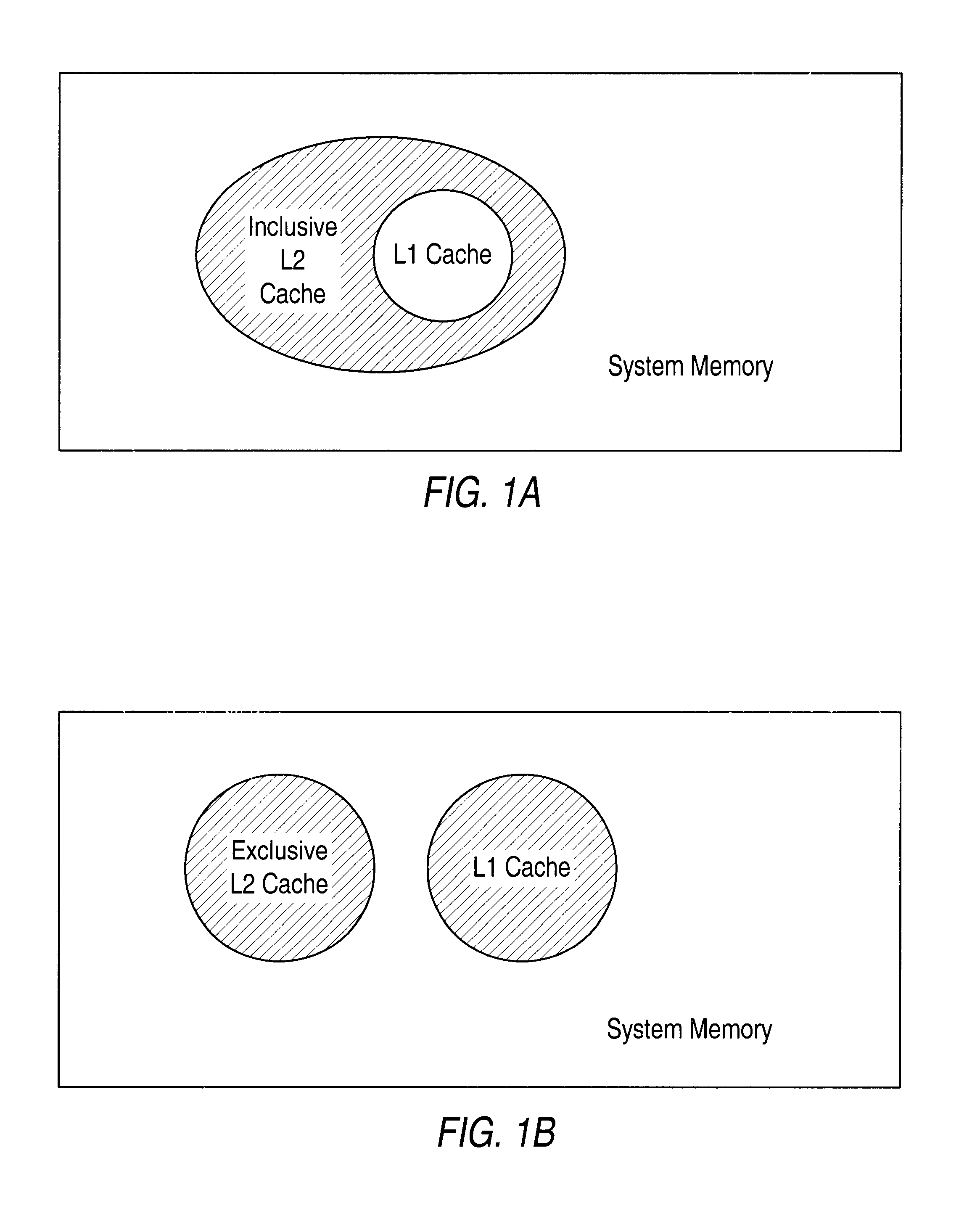

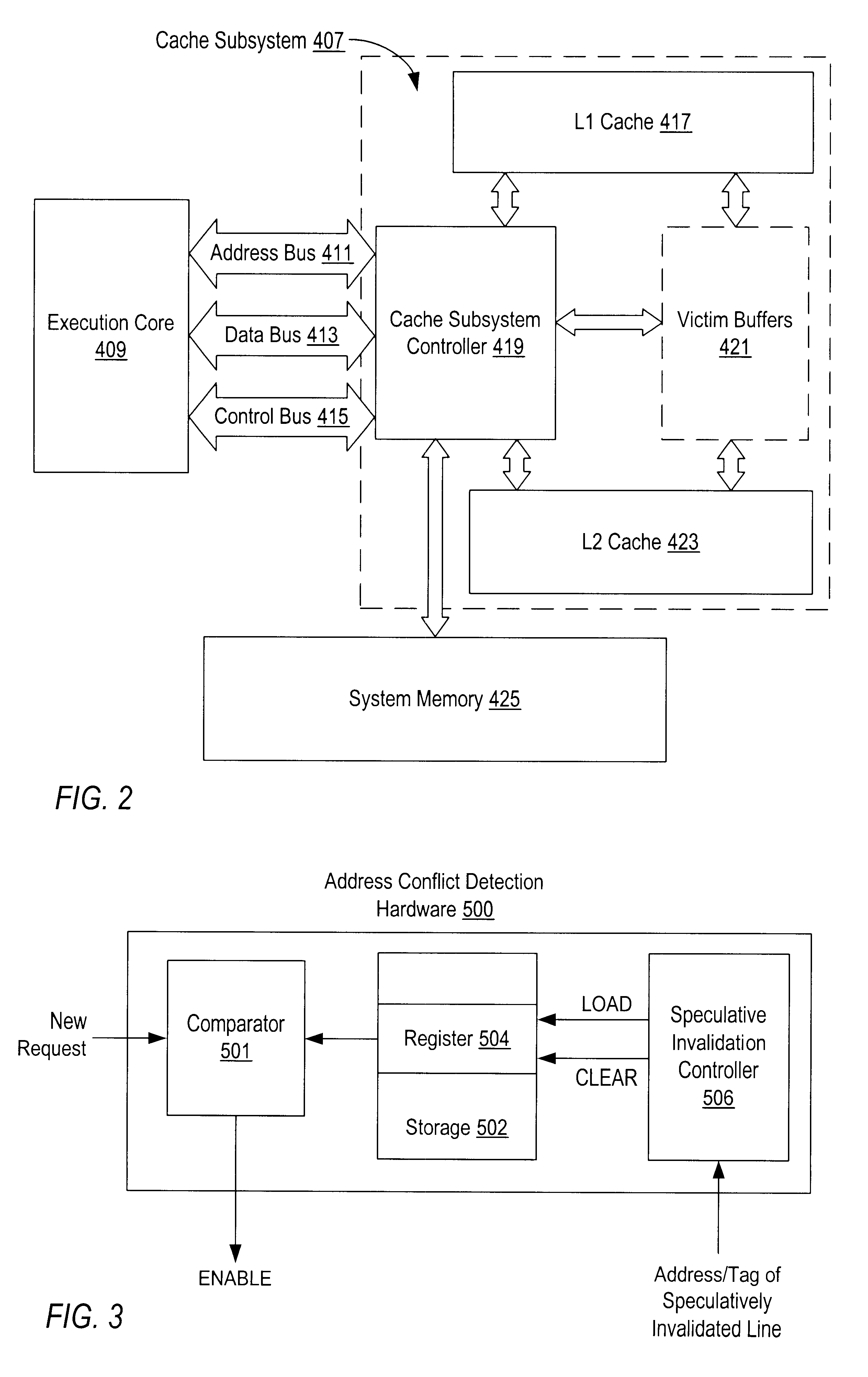

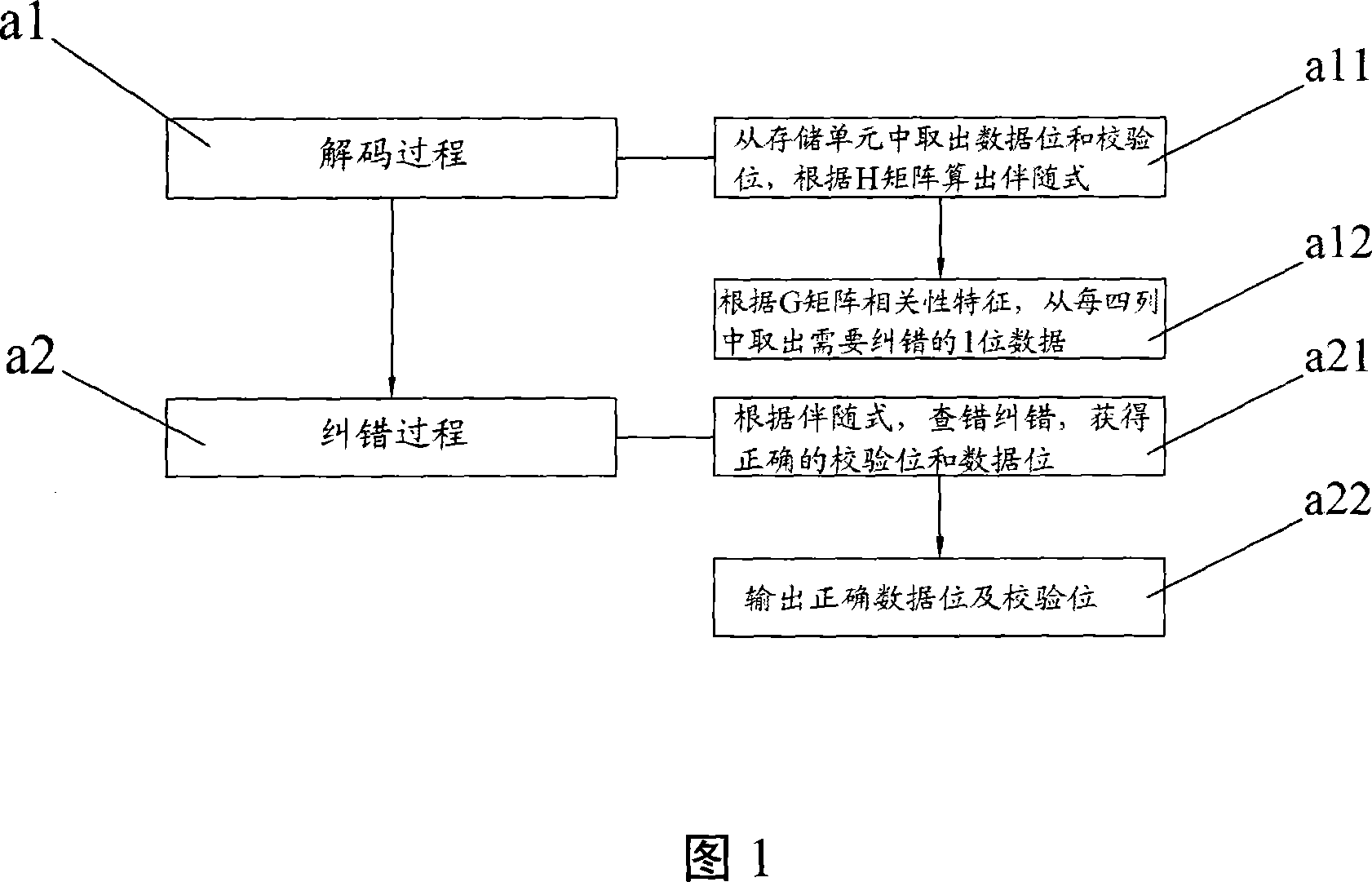

Method and system for speculatively invalidating lines in a cache

InactiveUS6725337B1Memory architecture accessing/allocationMemory adressing/allocation/relocationError checkParallel computing

A cache controller configured to speculatively invalidate a cache line may respond to an invalidating request or instruction immediately instead of waiting for error checking to complete. In case the error checking determines that the invalidation is erroneous and thus should not be performed, the cache controller protects the speculatively invalidated cache line from modification until error checking is complete. This way, if the invalidation is later found to be erroneous, the speculative invalidation can be reversed. If error checking completes without detecting any errors, the speculative invalidation becomes non-speculative.

Owner:GLOBALFOUNDRIES US INC

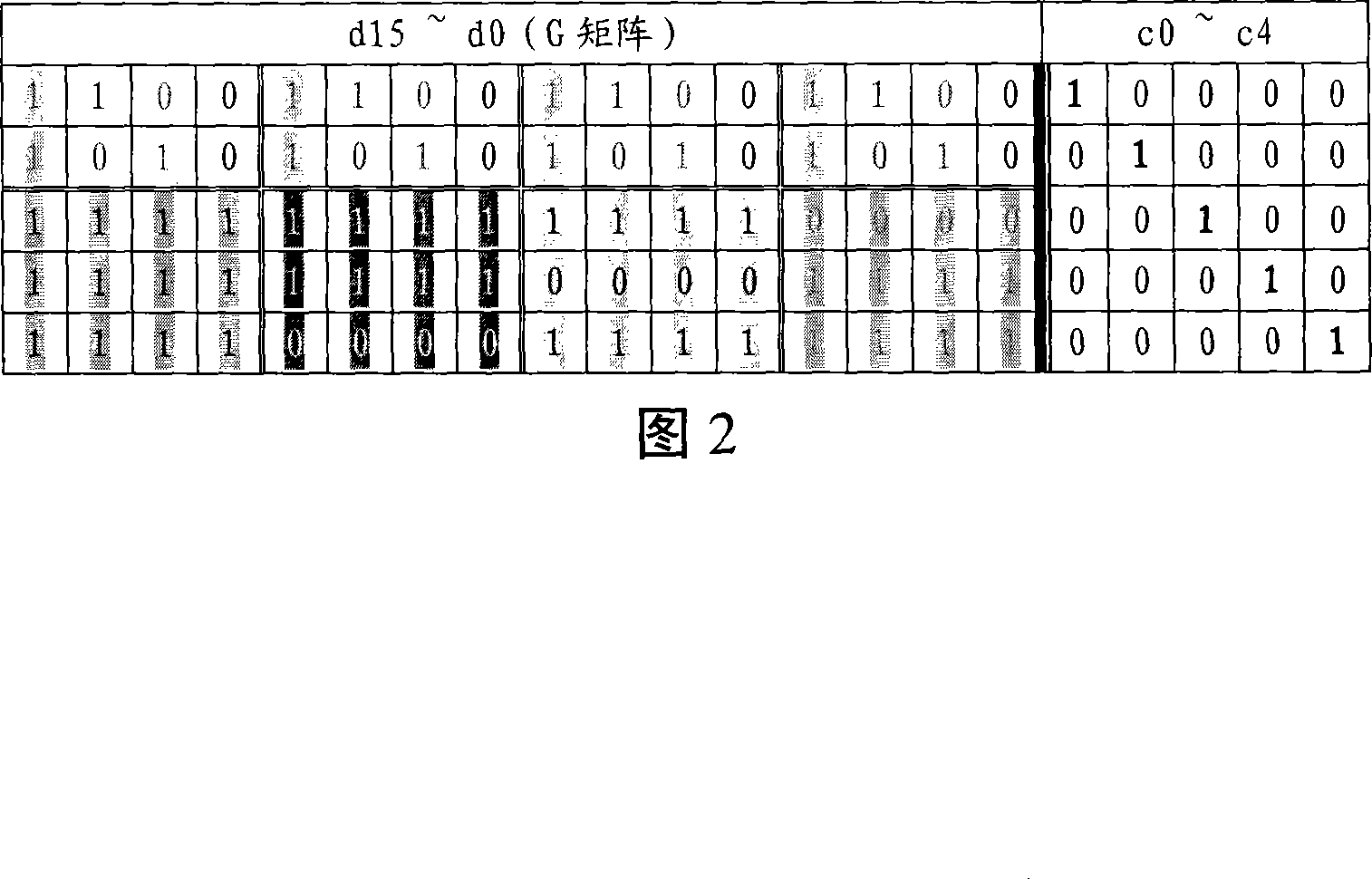

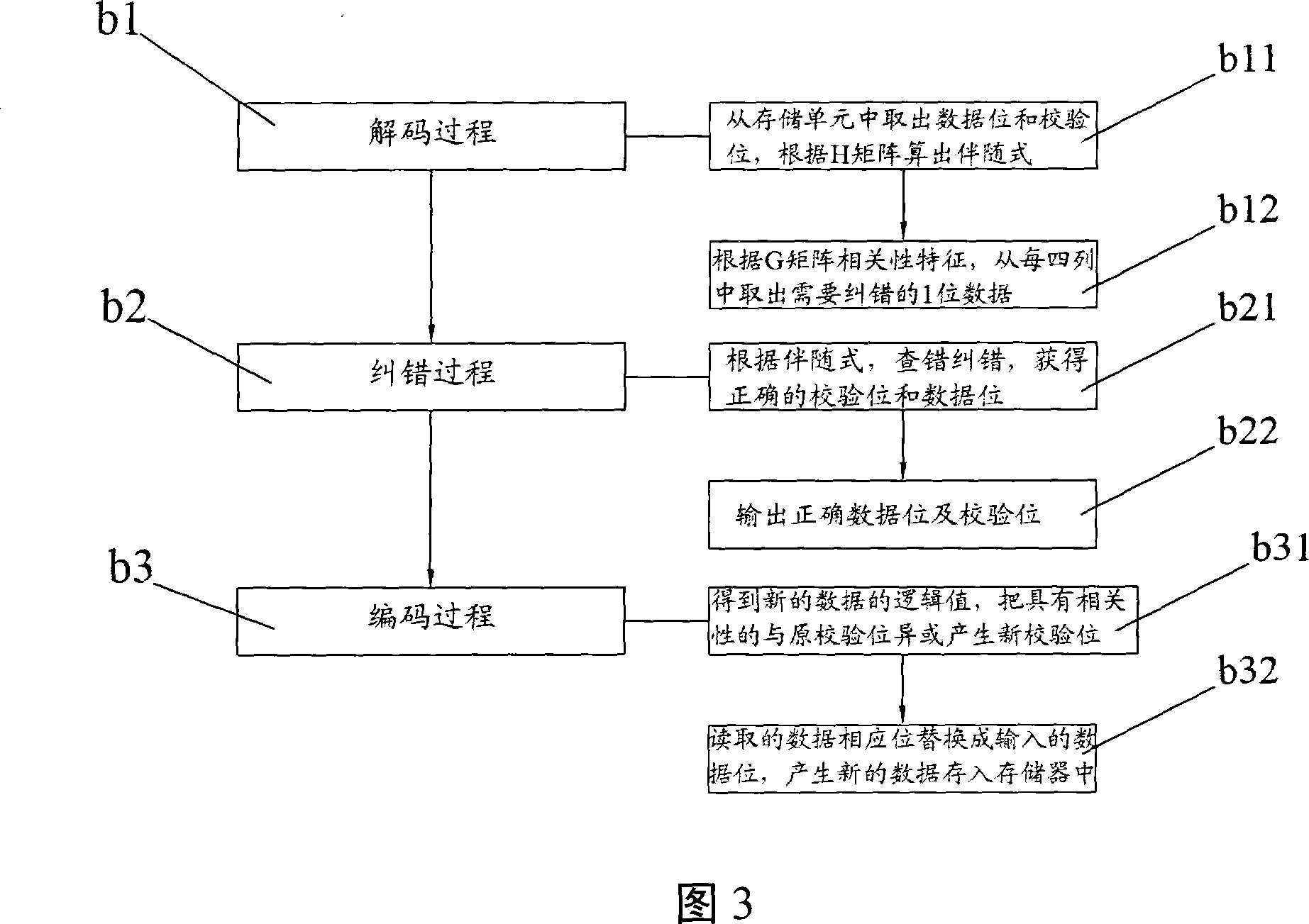

Memory error-detecting and error-correcting coding circuit and method for reading and writing data utilizing the same

ActiveCN101067972ASignificant simplificationImprove encoding rateStatic storageError checkComputer architecture

This invention relates to an error-check and error-correction code circuit for storages and a method for reading and writing data by it taking matrix G as a logic core including: a decoding process and a coding process and a method for writing in data by this method. Apart from a decoding process and an error correction process, it also includes a coding process, and finally puts forward an error check and correction and coding circuit for realizing said two methods including a decoder, an error-correction circuit, a coding circuit, an interface circuit and related data transmission circuit so as to simplify layout of bottom circuit and speed up operation speed of circuits.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Non-Volatile Memory and Method Having Efficient On-Chip Block-Copying with Controlled Error Rate

A non-volatile memory chip having SLC blocks acting as a write cache for MLC blocks for high density storage requires constant copying or folding of SLC blocks into MLC blocks. To avoid the time-consuming toggling out and in of the pages of the entire SLC block for ECC checking by a controller chip, only a small sample is checked. An optimal read point for reading the memory cells in the sample of the SLC block is dynamically determined by trying different read points so that the data is read within an error budget. Once the optimal read point is determined, it is used to read the entire SLC block without further error checking. Then the SLC block can be copied (blind folded) to the MLC block with the confidence of being within the error budget.

Owner:SANDISK TECH LLC

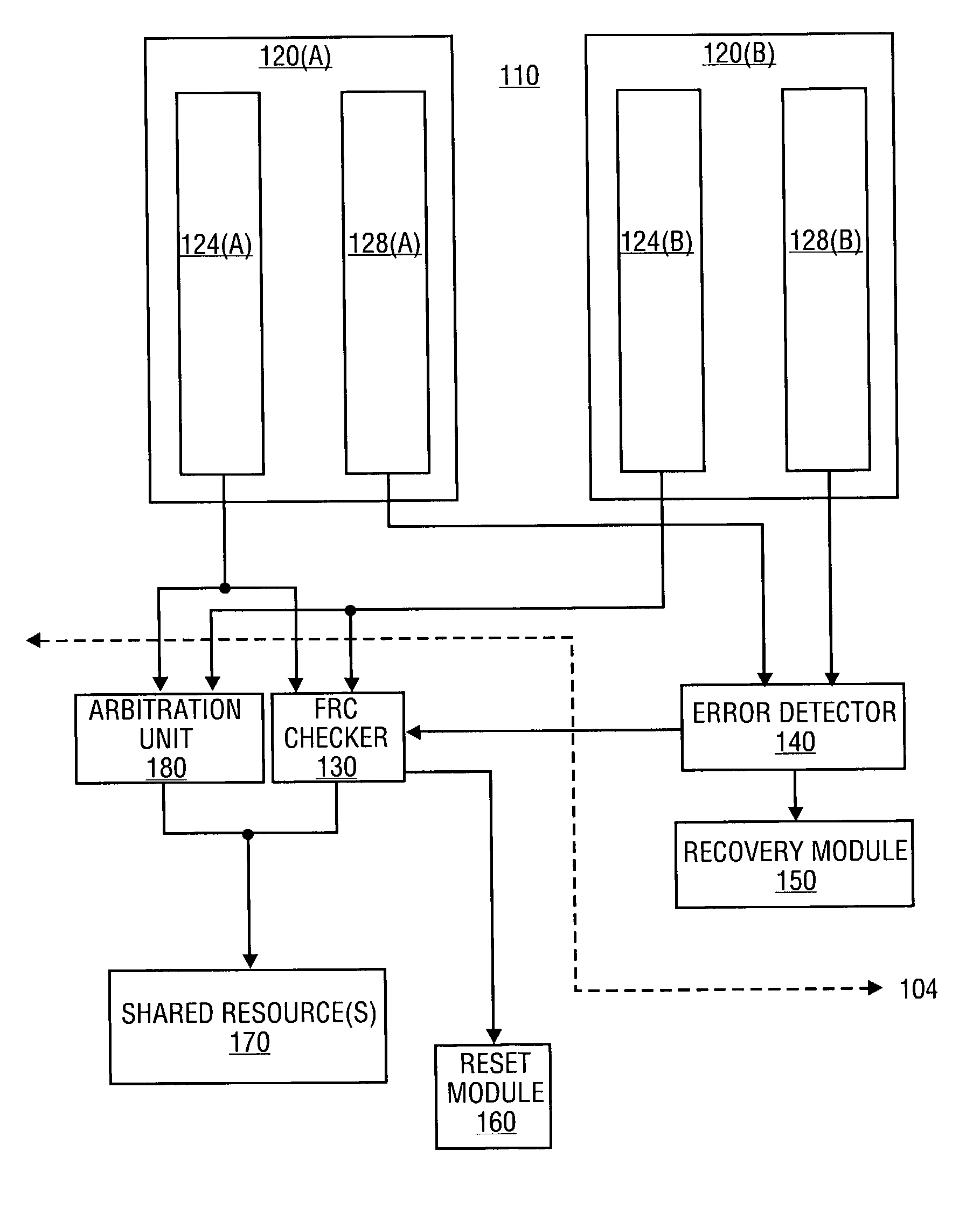

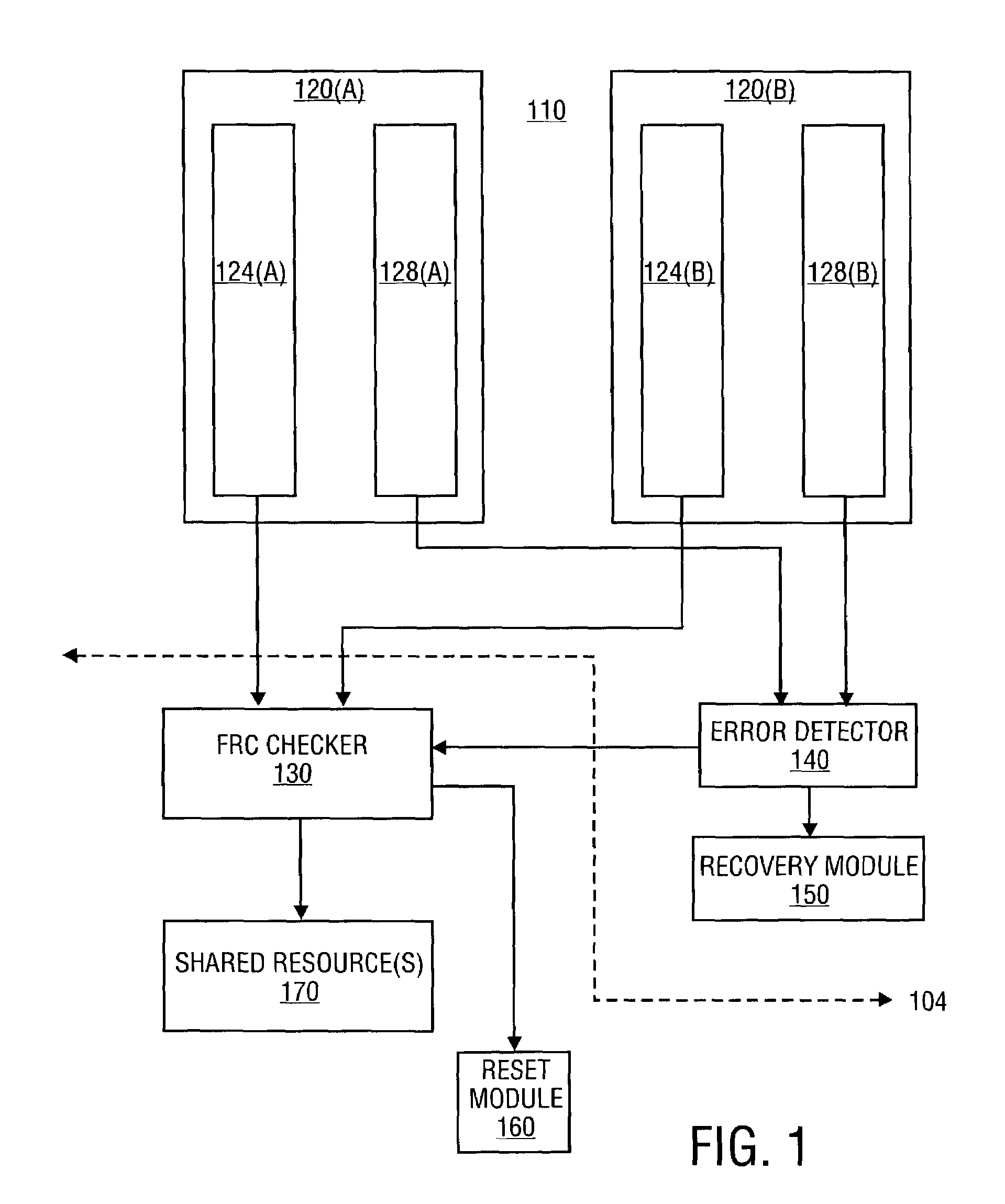

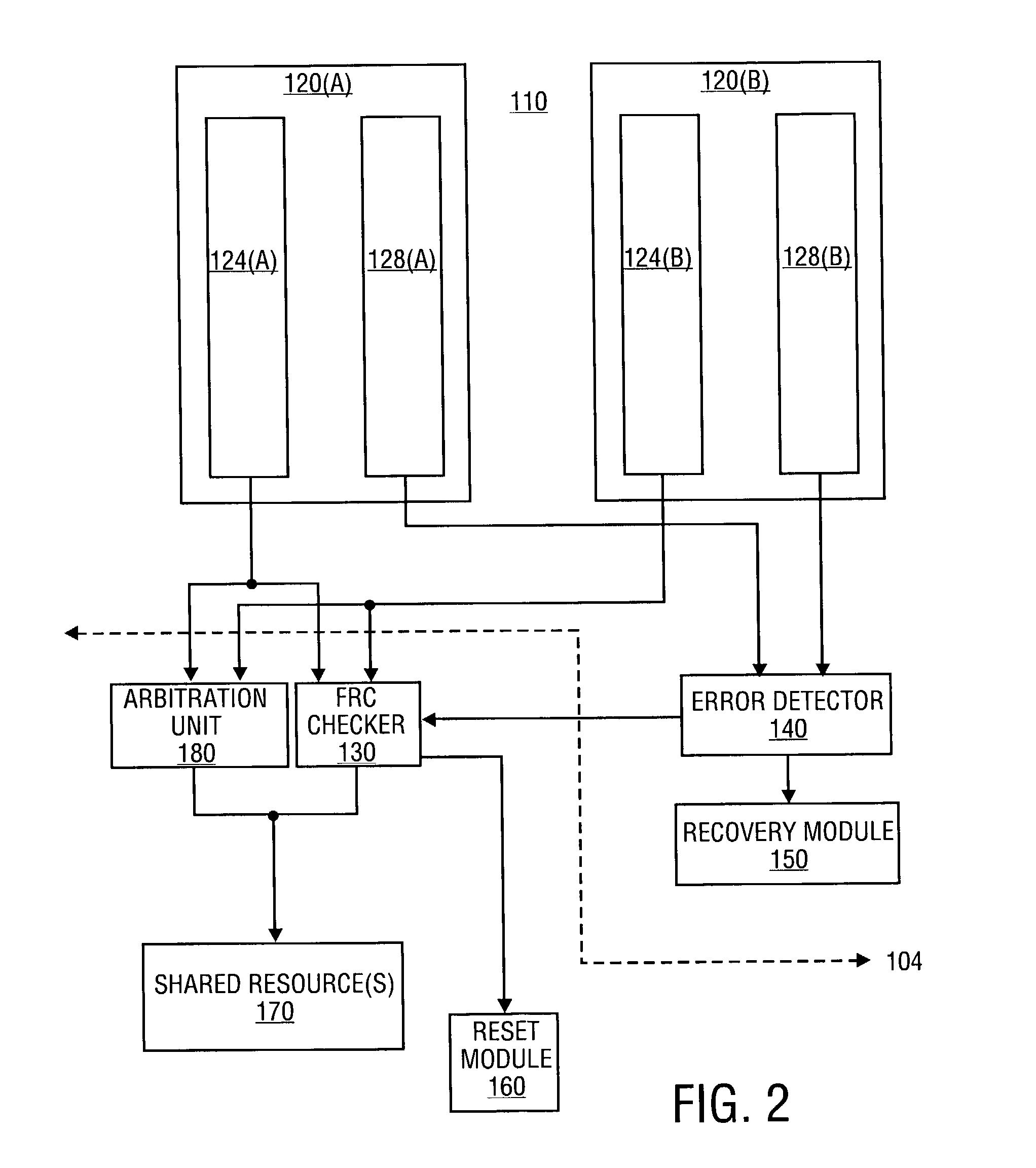

On-die mechanism for high-reliability processor

A processor includes first and second execution cores that operate in a redundant (FRC) mode, an FRC check unit to compare results from the first and second execution cores, and an error check unit to detect recoverable errors in the first and second cores. The error detector disables the FRC checker, responsive to detection of a recoverable error. A multi-mode embodiment of the processor implements a multi-core mode in addition to the FRC mode. An arbitration unit regulates access to resources shared by the first and second execution cores in multi-core mode. The FRC checker is located proximate to the arbitration unit in the multi-mode embodiment.

Owner:INTEL CORP

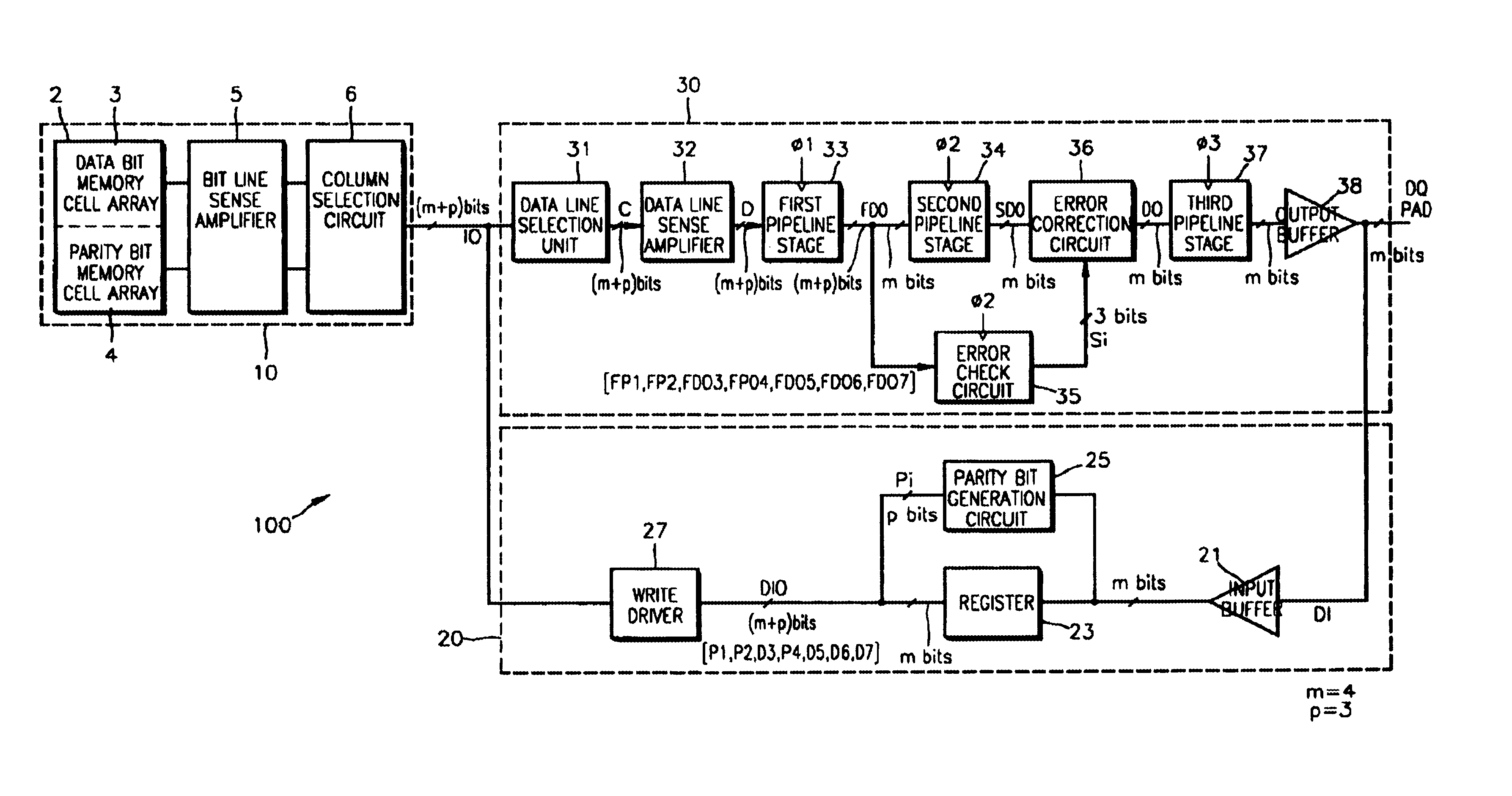

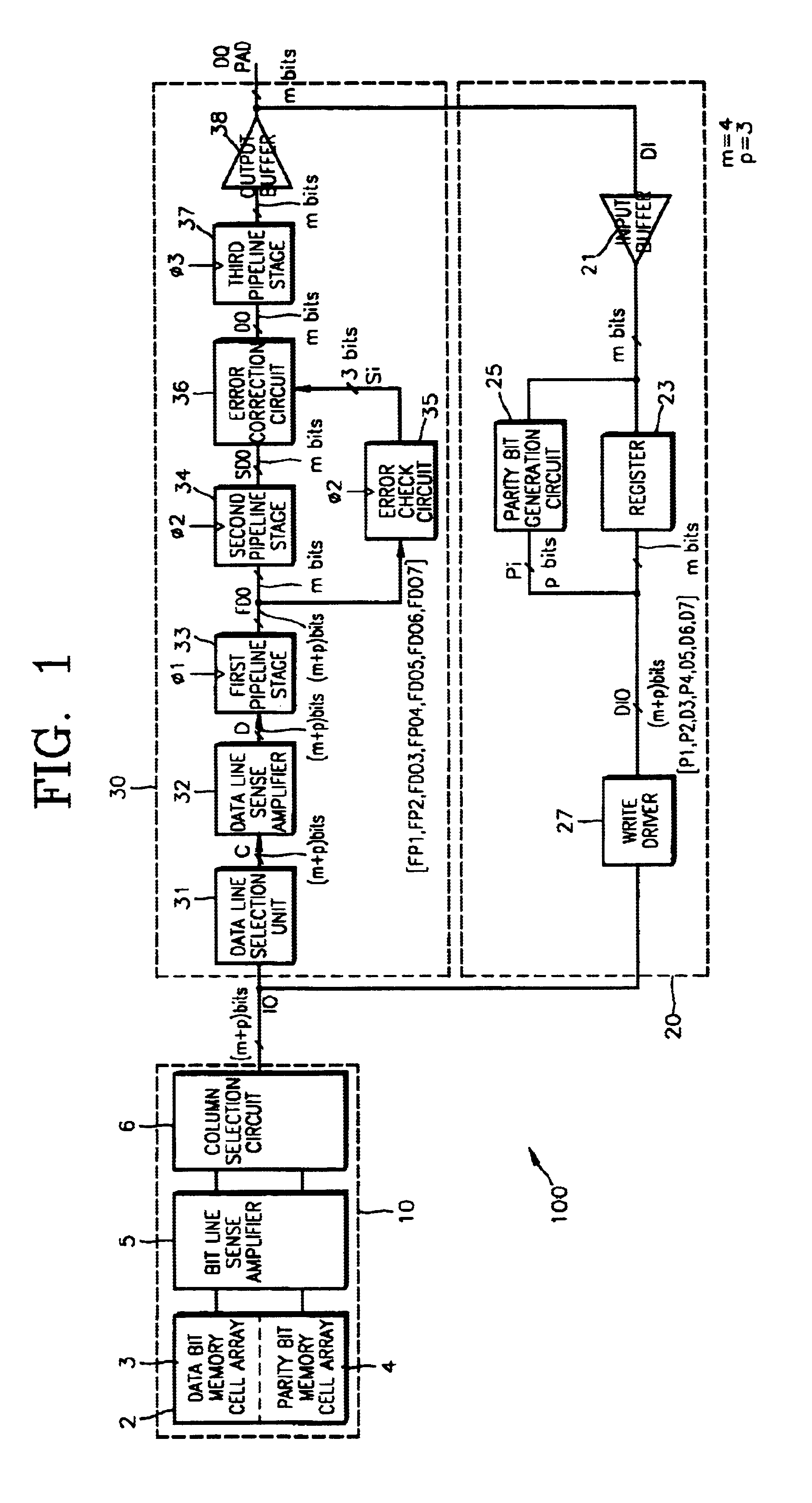

Integrated circuit memory devices having error checking and correction circuits therein and methods of operating same

Integrated circuit memory devices include a memory cell array having therein a plurality of stored data bits and a plurality of parity bits generated from a plurality of write data bits received by the memory device during a write operation. The plurality of stored data bits and the plurality of parity bits may collectively form a word having a length of m+p bits, where m and p are integers. An error check circuit is provided that converts the plurality of stored data bits and the plurality of parity bits into a plurality of syndrome bits (e.g., Si) that designate a location of a bit error in the plurality of stored data bits when compared against the original write data bits. An error correction circuit is provided that uses the plurality of syndrome bits to correct an error in the plurality of stored data bits and generate a plurality of read data bits that match the plurality of original write data bits.

Owner:SAMSUNG ELECTRONICS CO LTD

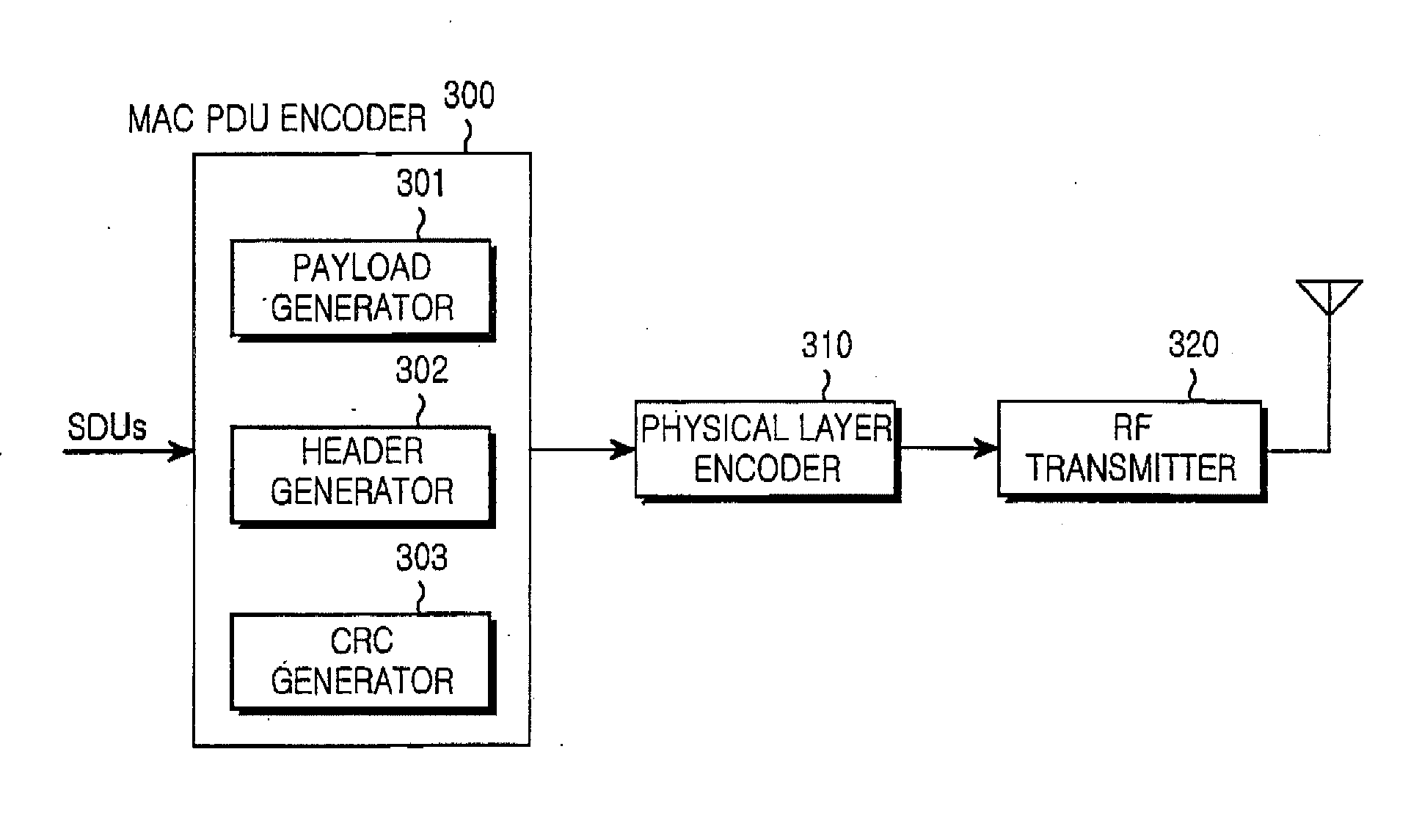

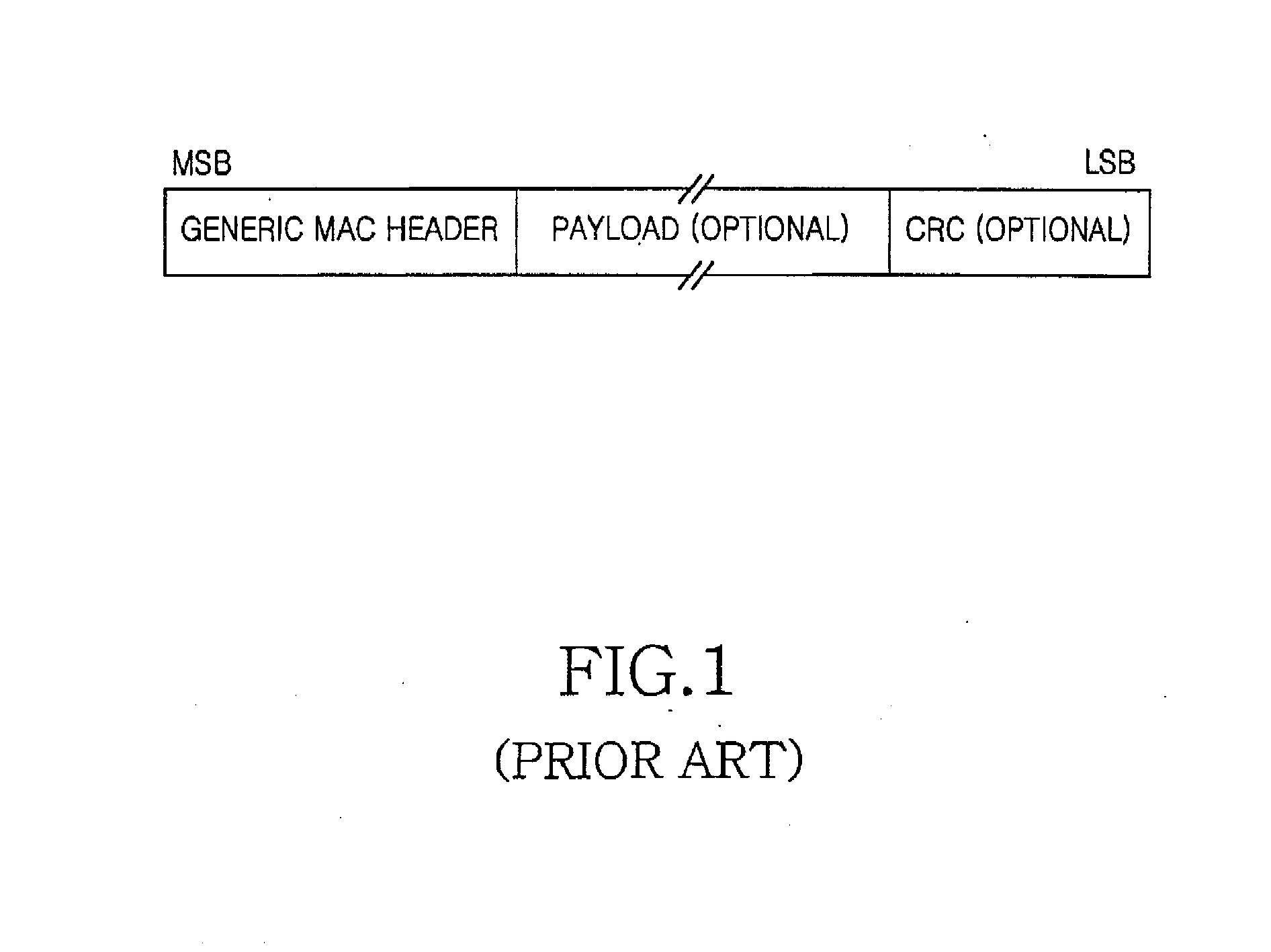

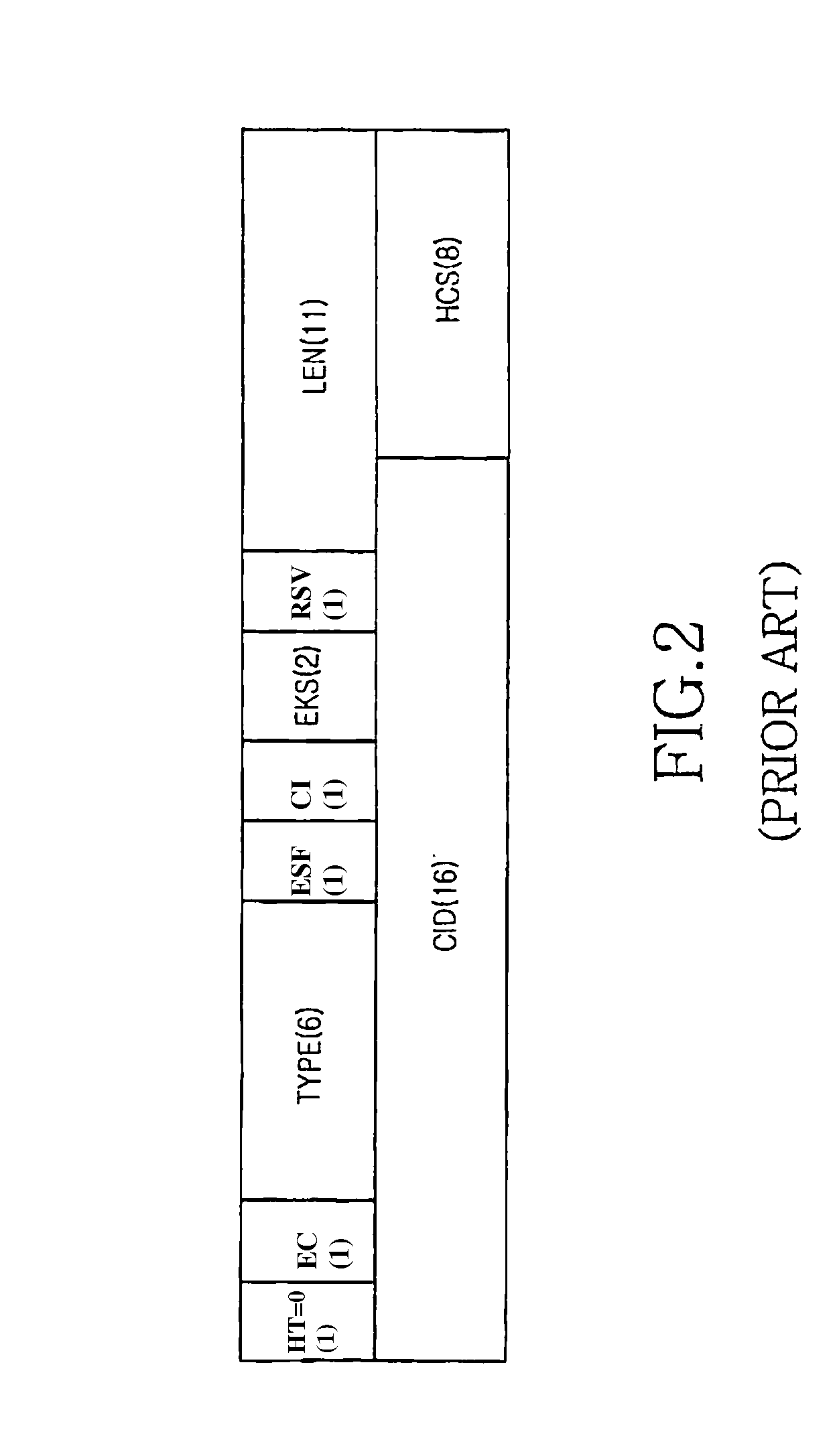

Apparatus and method for communicating mac layer data in broadband wireless communication system

Provided is an apparatus and method for varying the length of an error check code of a PDU according to the length of a payload in a broadband wireless communication system. A transmitting apparatus includes a first generator and a second generator. The first generator generates a payload of a PDU. The second generator selects the length of an error check code according to the length of the generated payload, generates an error check code according to the selected length, and suffixes the error check code to the payload.

Owner:SAMSUNG ELECTRONICS CO LTD

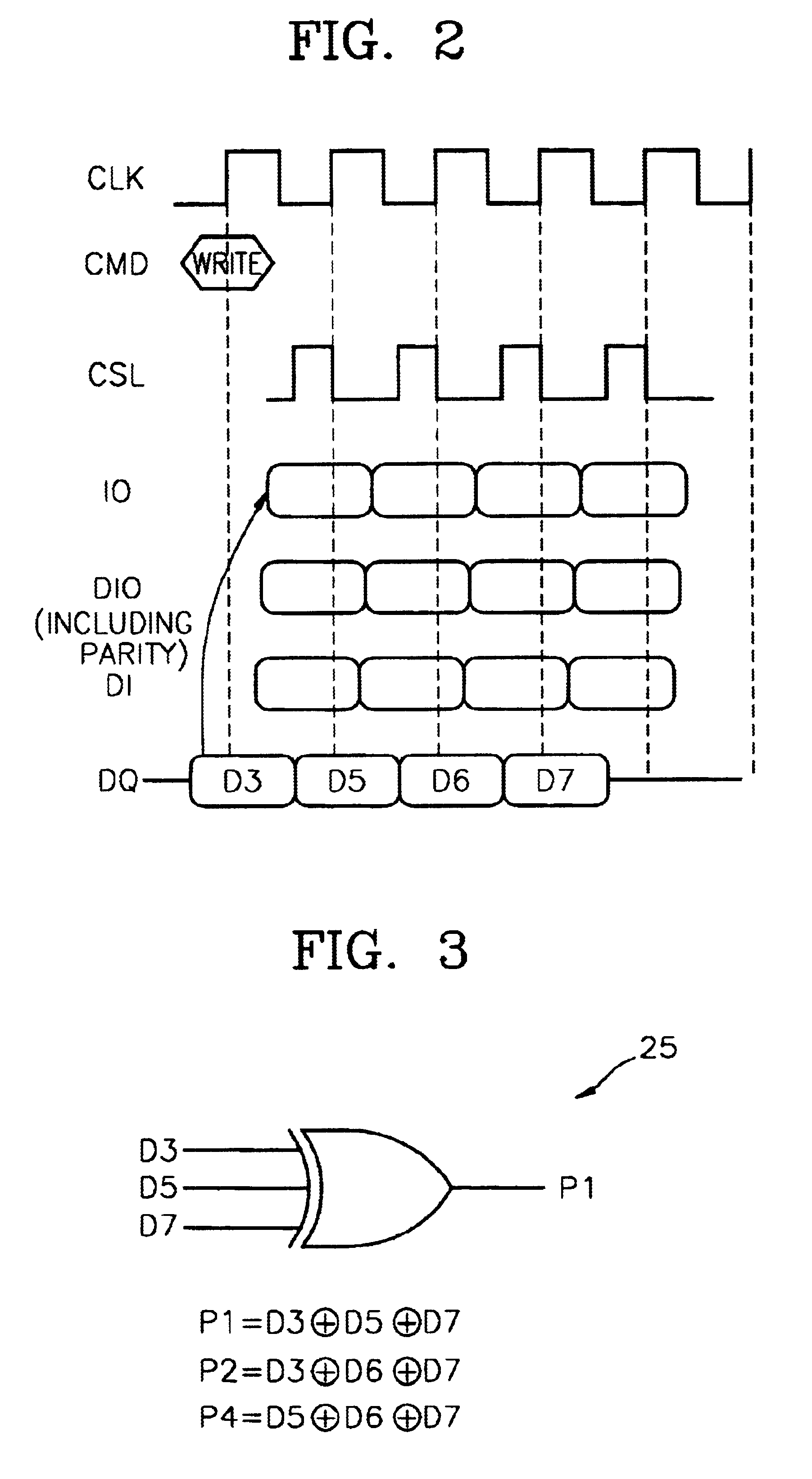

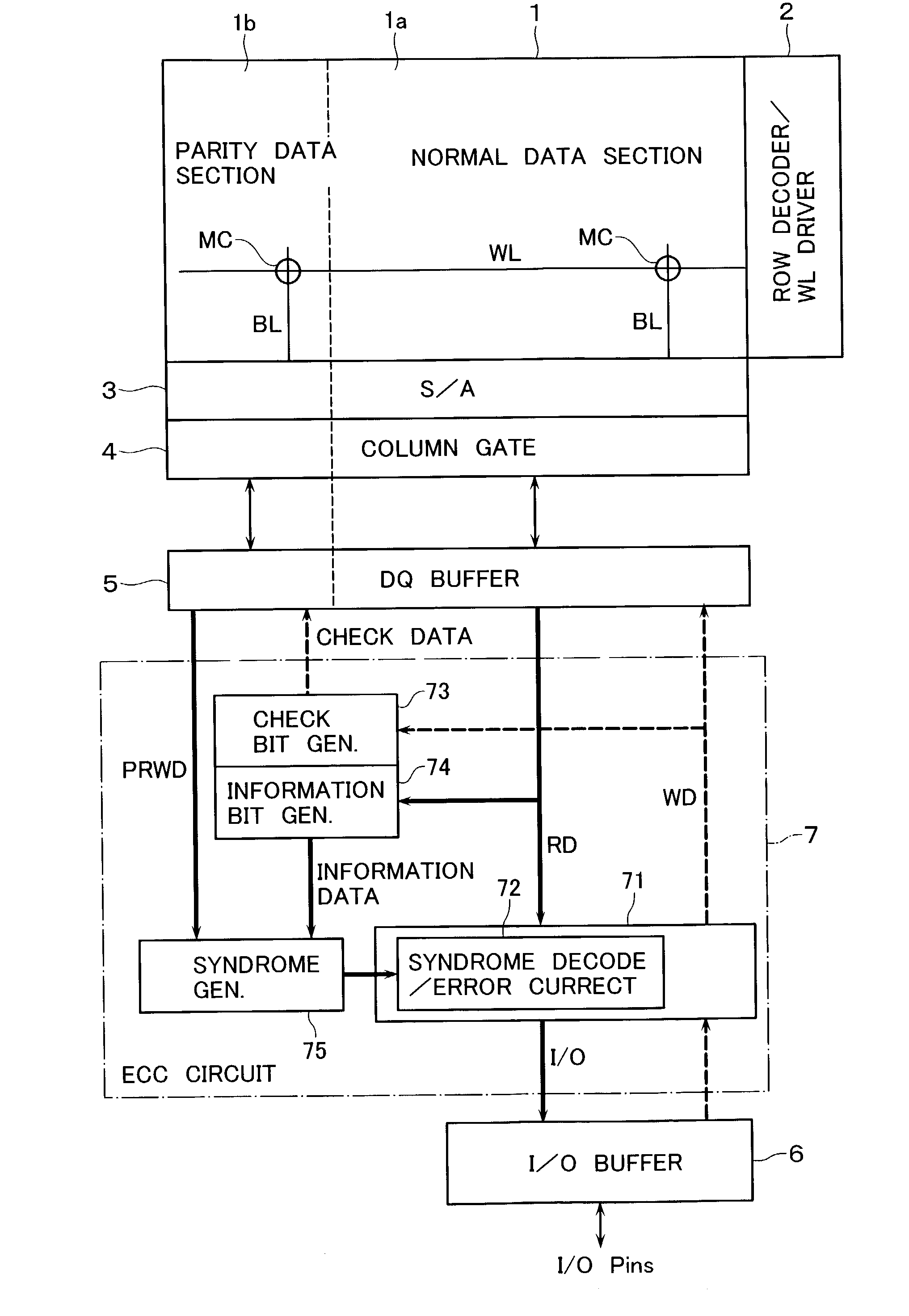

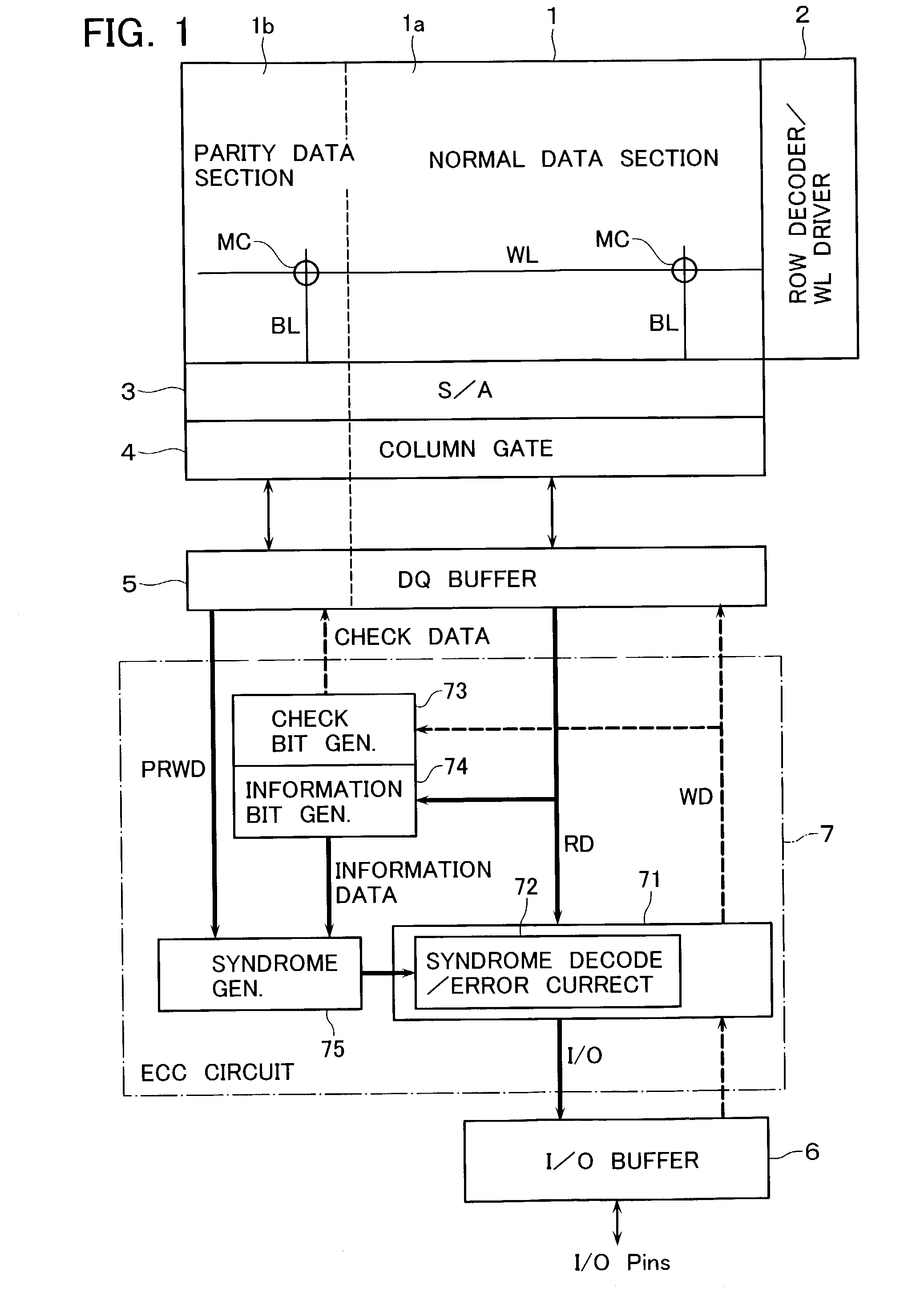

Semiconductor memory device

InactiveUS20020184592A1Reduce power consumptionCode conversionDigital storageError checkData transmission

A semiconductor memory device is disclosed which comprises a cell array including a normal data section used for normal data write and read and a parity data section used for check data write and read, the check data being for execution of error check of data as read out of the normal data section, a data buffer for temporal stage of read data from the cell array and write data into the cell array, and an ECC circuit for generating the check data to be stored in the parity data section from write data as input during data writing, and for performing error check and correction of data read out of the normal section based on the data read out of the normal data section and the check data read out of said parity data section during data reading. N-bit parallel data transfer is performed between the data buffer and normal data section whereas m-bit parallel data transfer is done between the data buffer and external input / output terminals (where m and n are integers satisfying m<n).

Owner:KK TOSHIBA

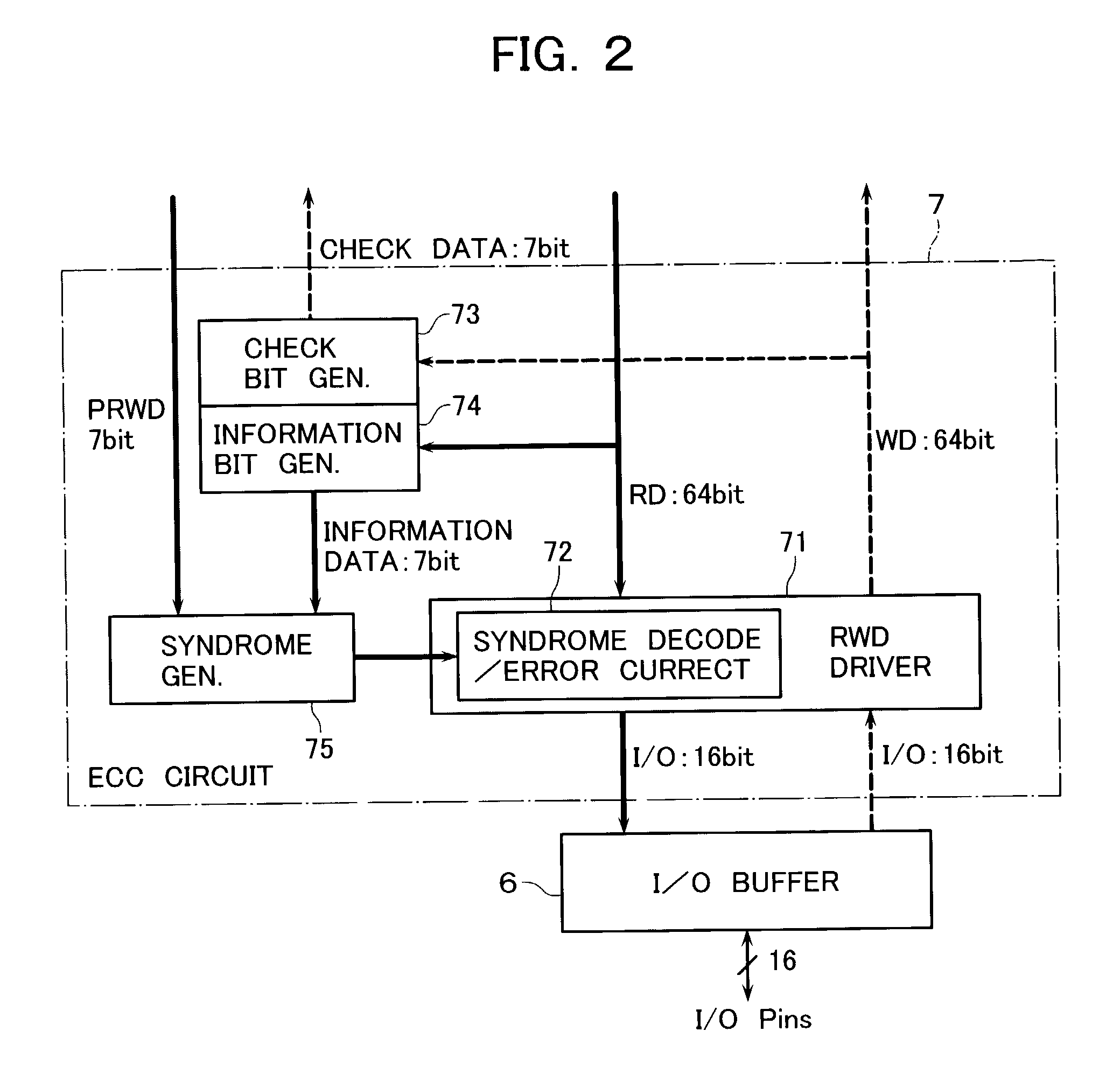

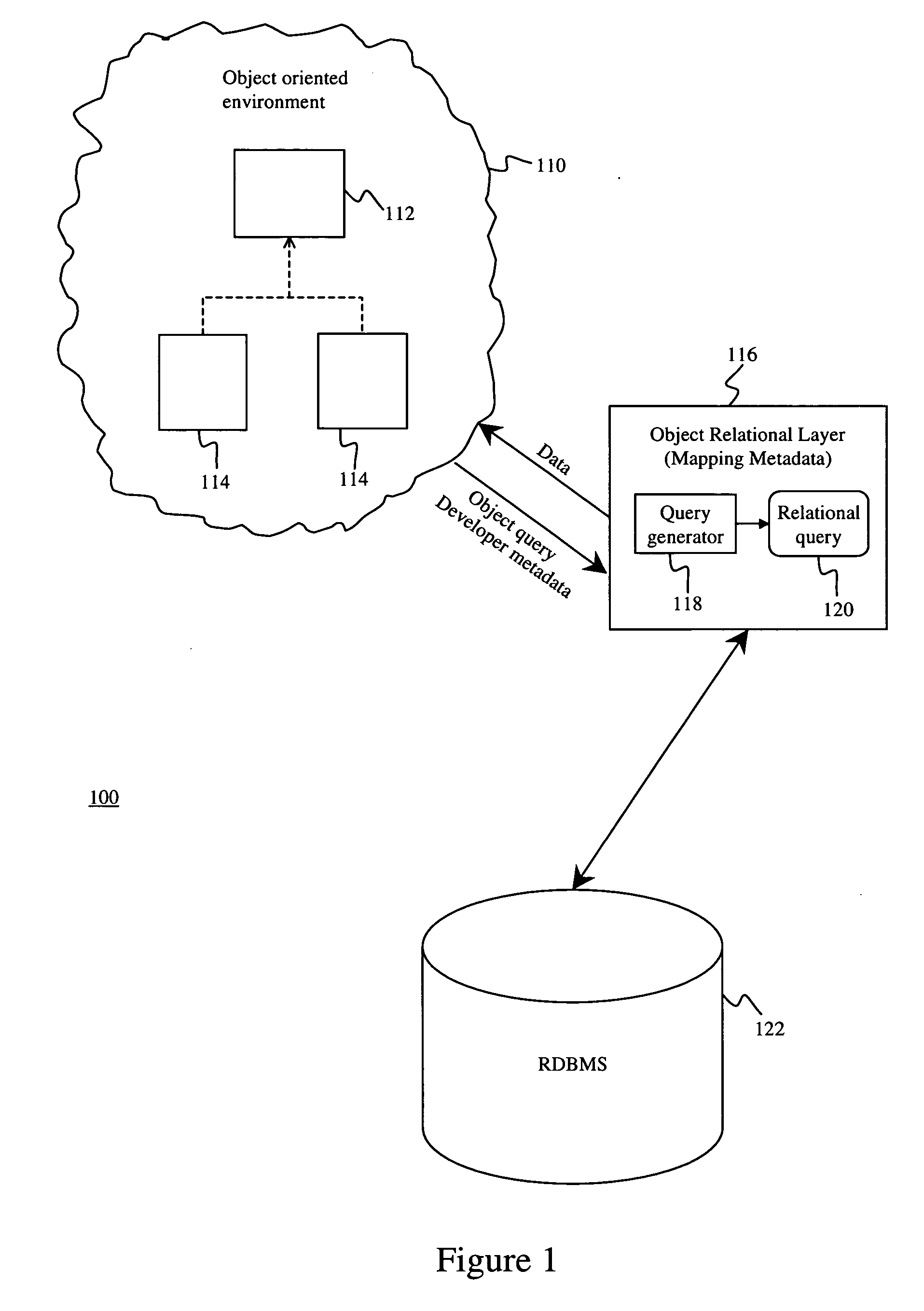

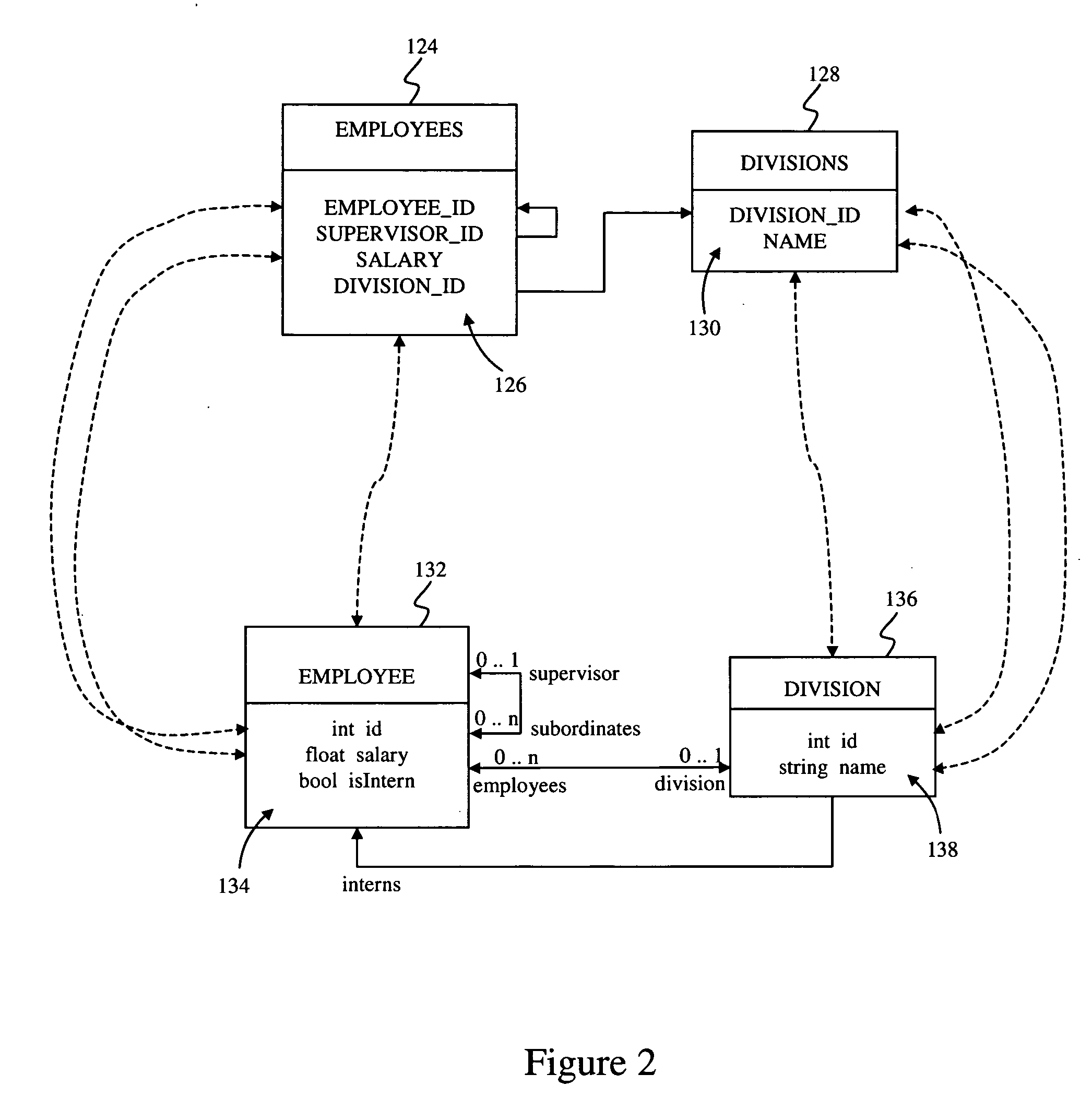

System and method for retrieving data from a relational database management system

InactiveUS20060200438A1Improve efficiencyGreat abstractionDigital data processing detailsRelational databasesError checkRelational database management system

As method is disclosed for retrieving data from a relational database management system (RDBMS). An object-oriented environment submits a query to an object relational layer to access data contained in the RDBMS. The object query can result in at least one logical object description that is defined using one or more predetermined expressions. The logical object descriptions are translated to corresponding relational descriptions, and a relational query is subsequently generated. The relational query is applied to the RDBMS in order to retrieve data satisfying the object query. Various error checks can be performed to detect correctness of the query. Additionally, the relational queries can be optimized to improve processing by the RDBMS.

Owner:RED HAT

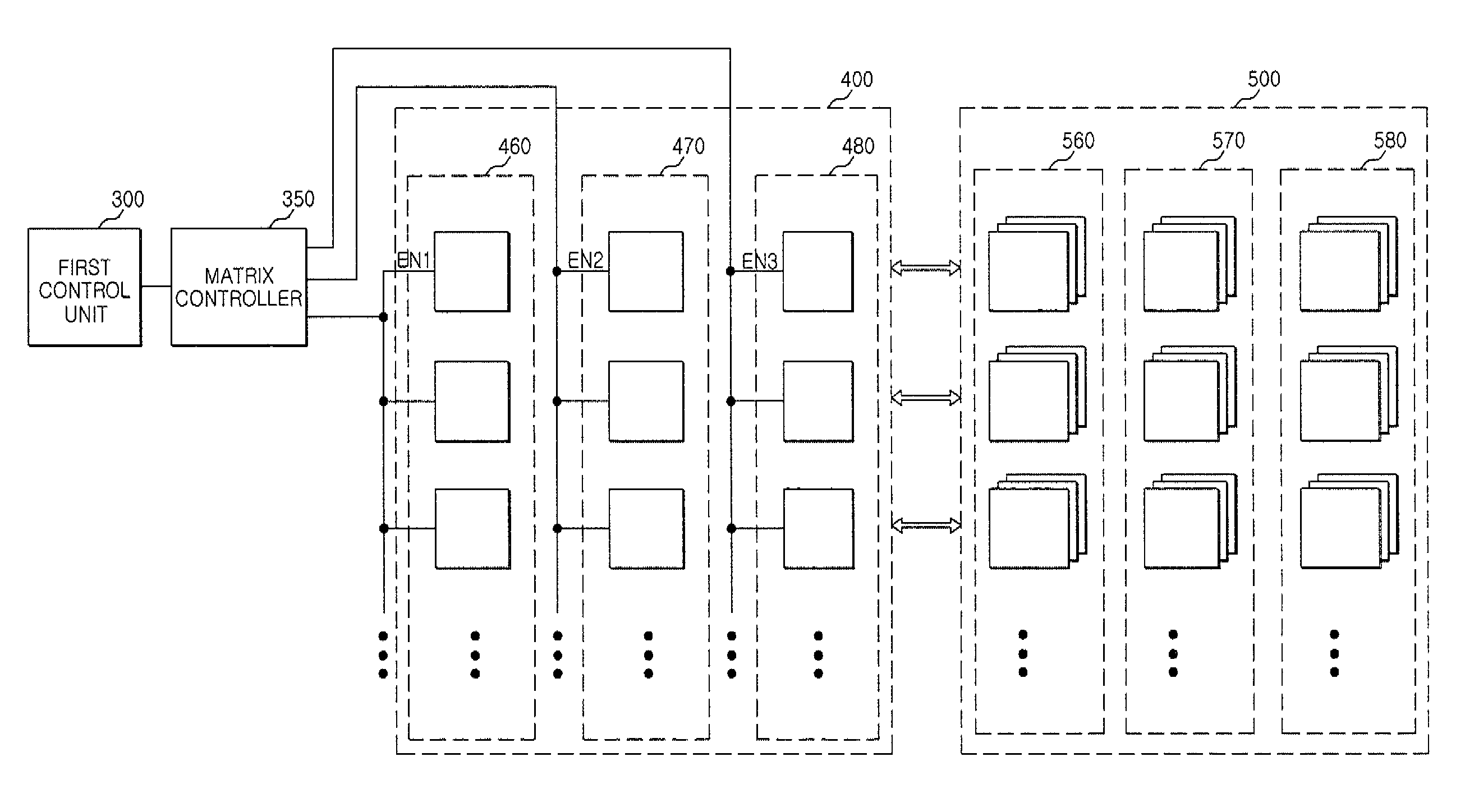

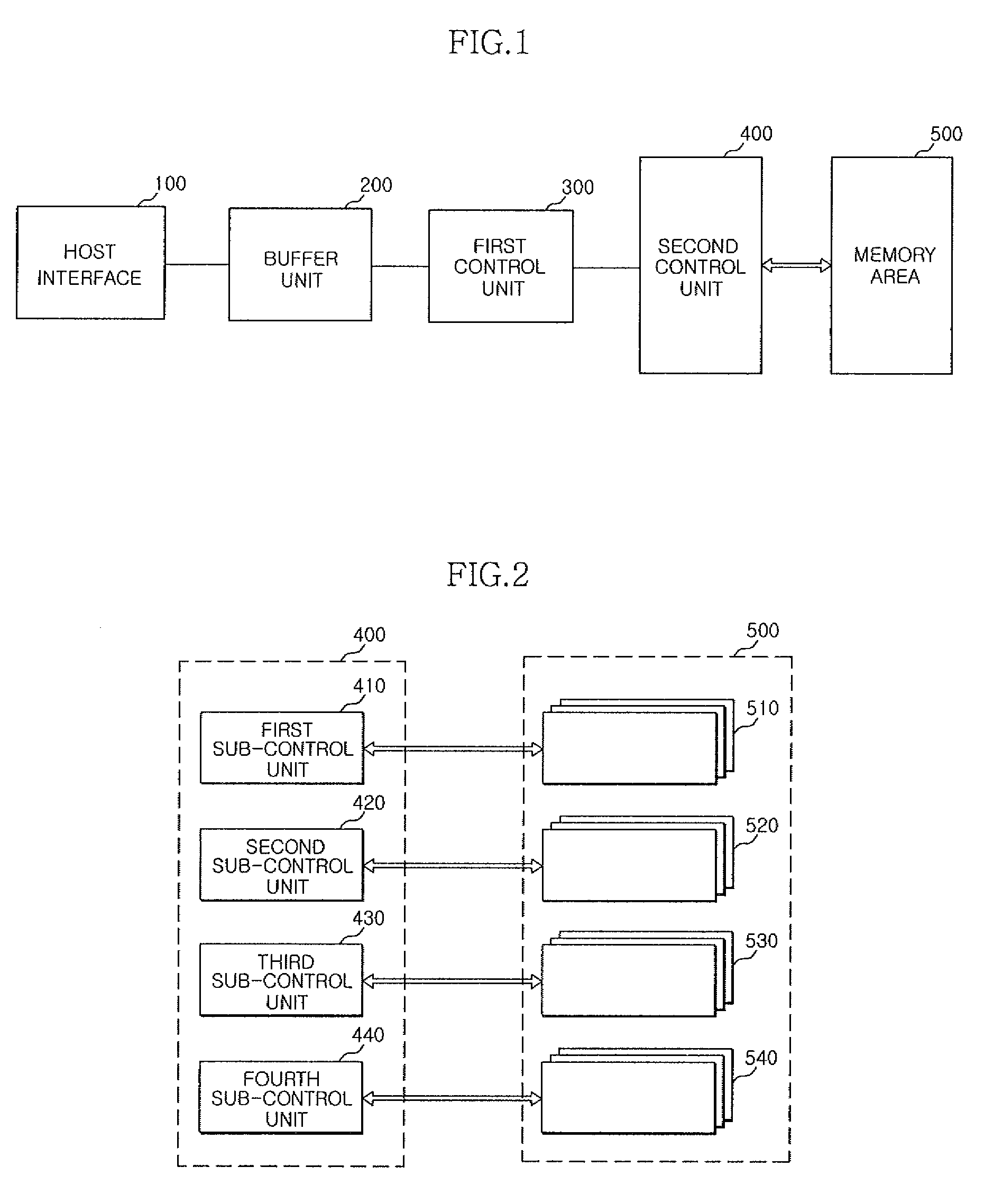

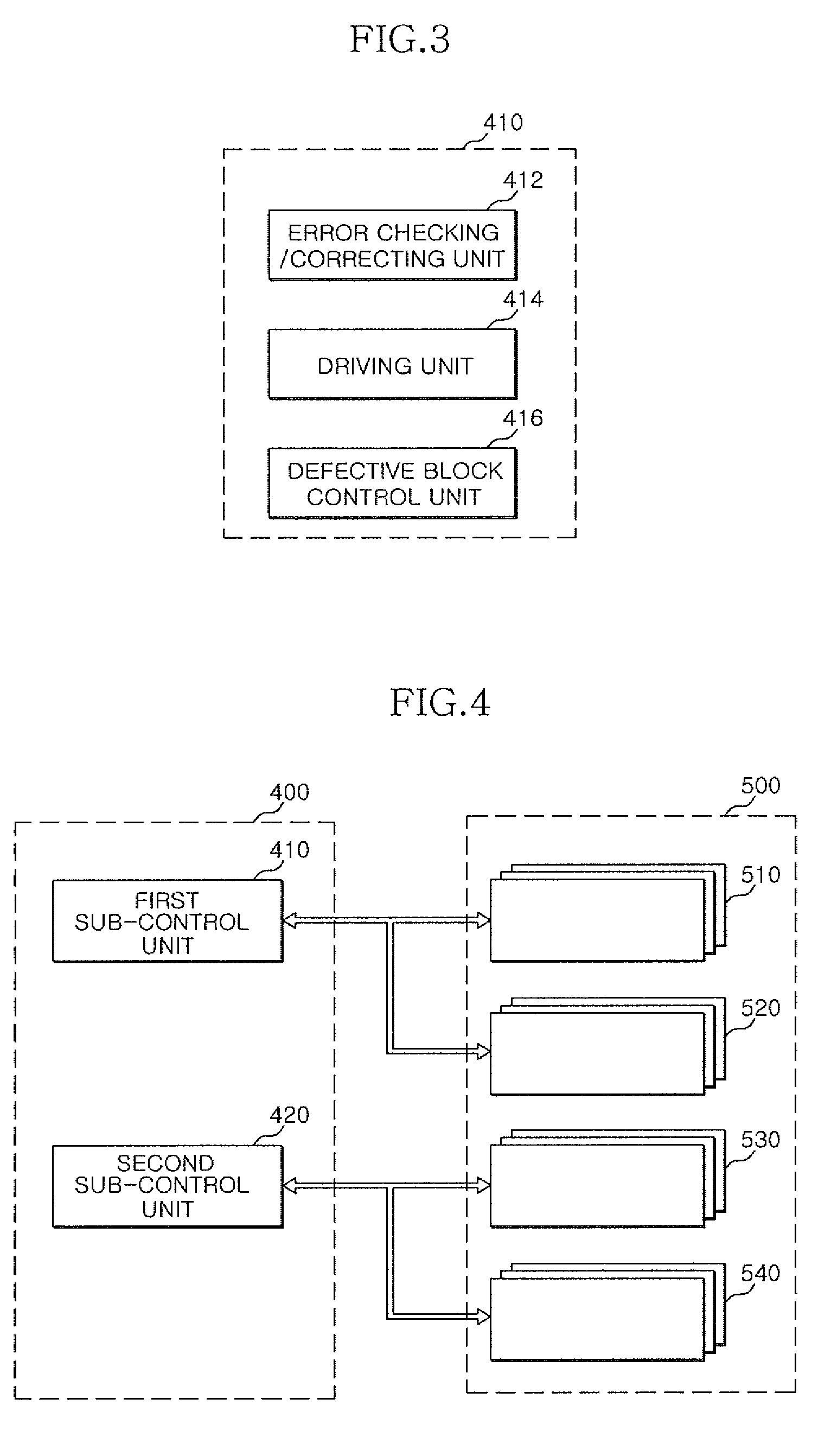

High-speed solid state storage system having a hierarchy of different control units that process data in a corresponding memory area and method of controlling the same

InactiveUS20090228637A1Run at high speedReduce system loadError detection/correctionMemory adressing/allocation/relocationSolid-state storageError check

A solid state storage system having a hierarchy of different control units that systematically process data in a corresponding memory area is disclosed. The solid state storage system includesa first control unit and at least one second control unit. The first control unit distributes and transmits external command signals that are provided from a host interface. The second control unit is controlled by the first control unit and performs an address mapping operation, an error checking / correcting operation, an ad defective block managing operation on a corresponding plurality of memory chips in the memory area.

Owner:PAXDISK +1

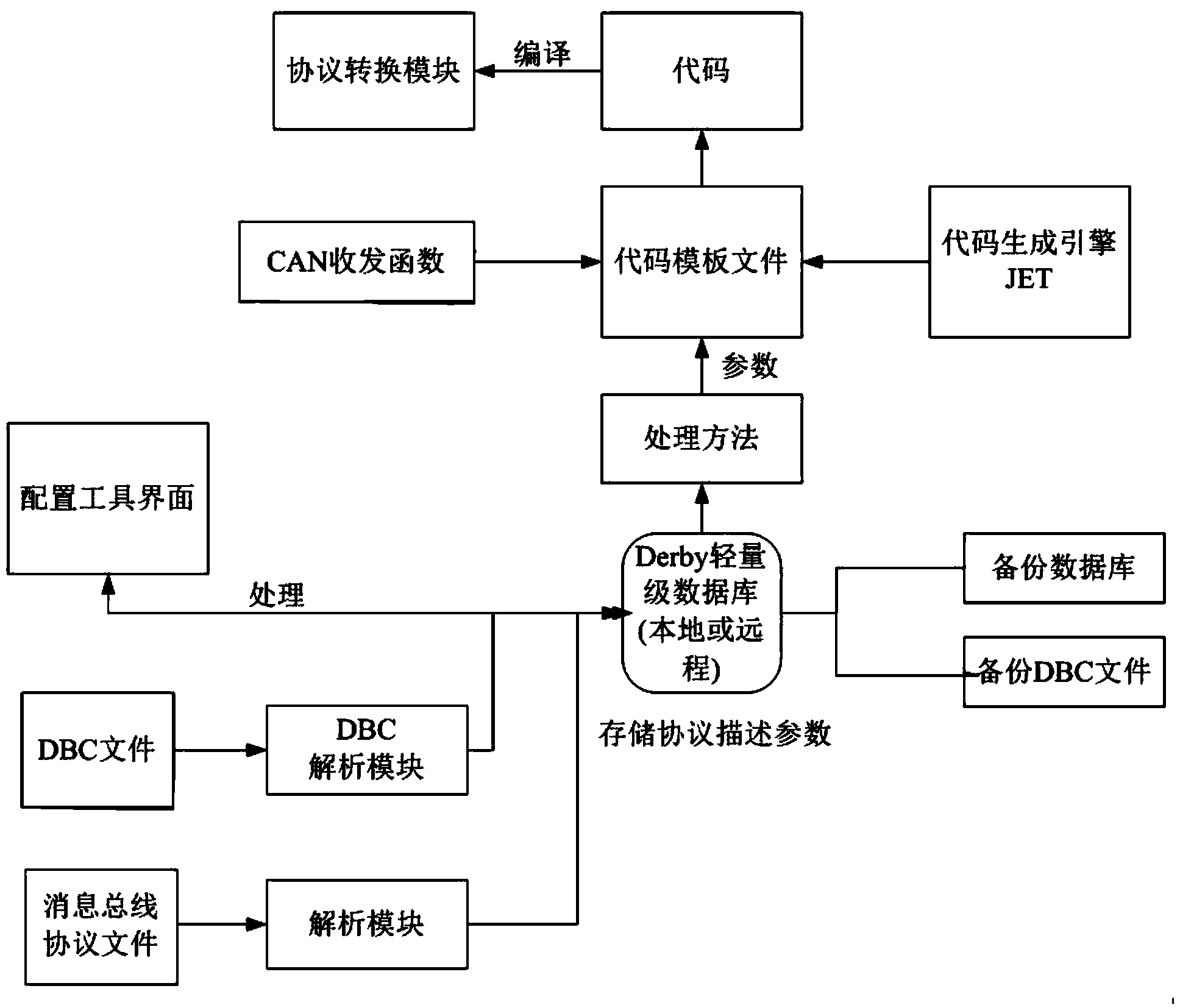

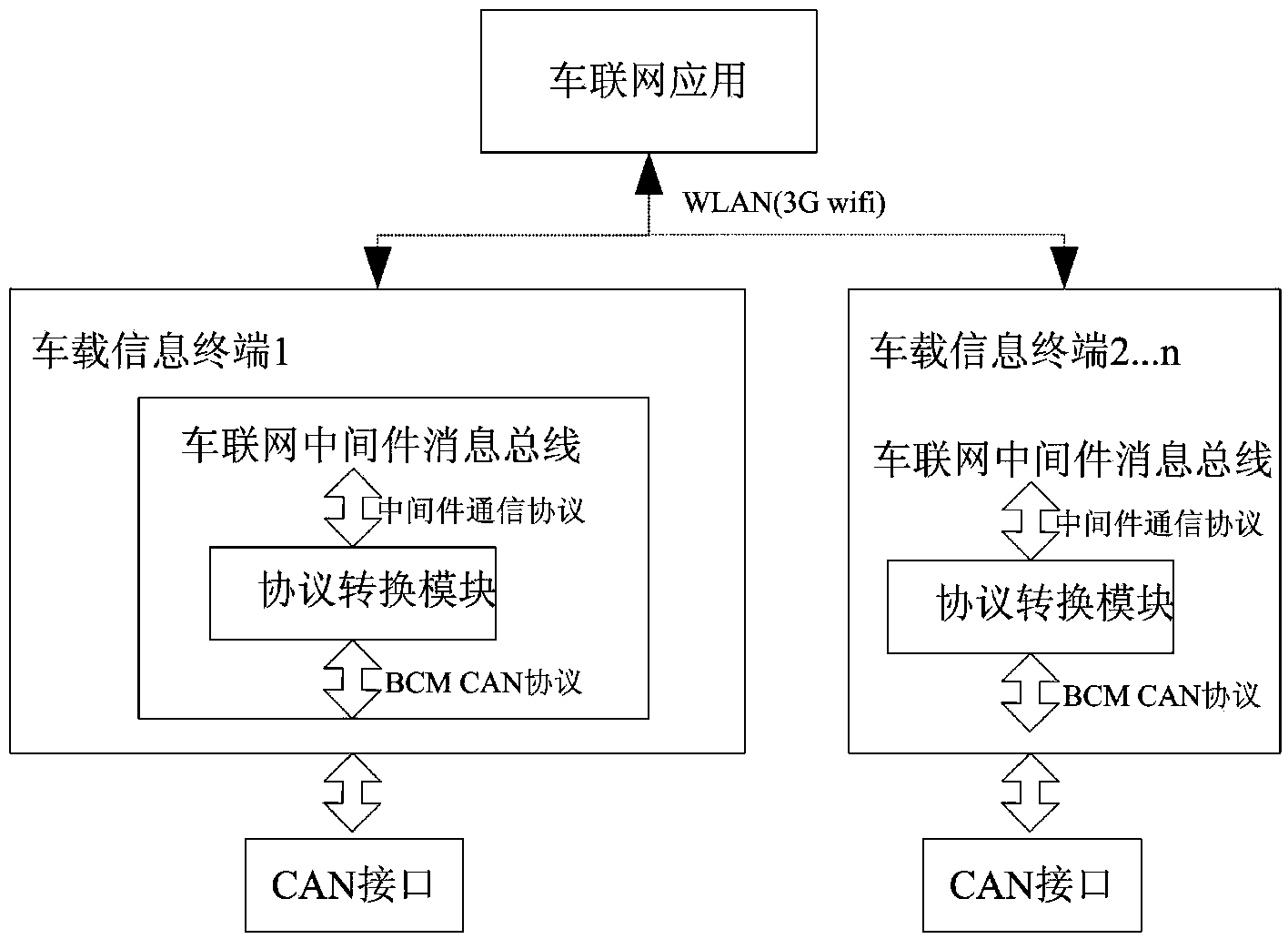

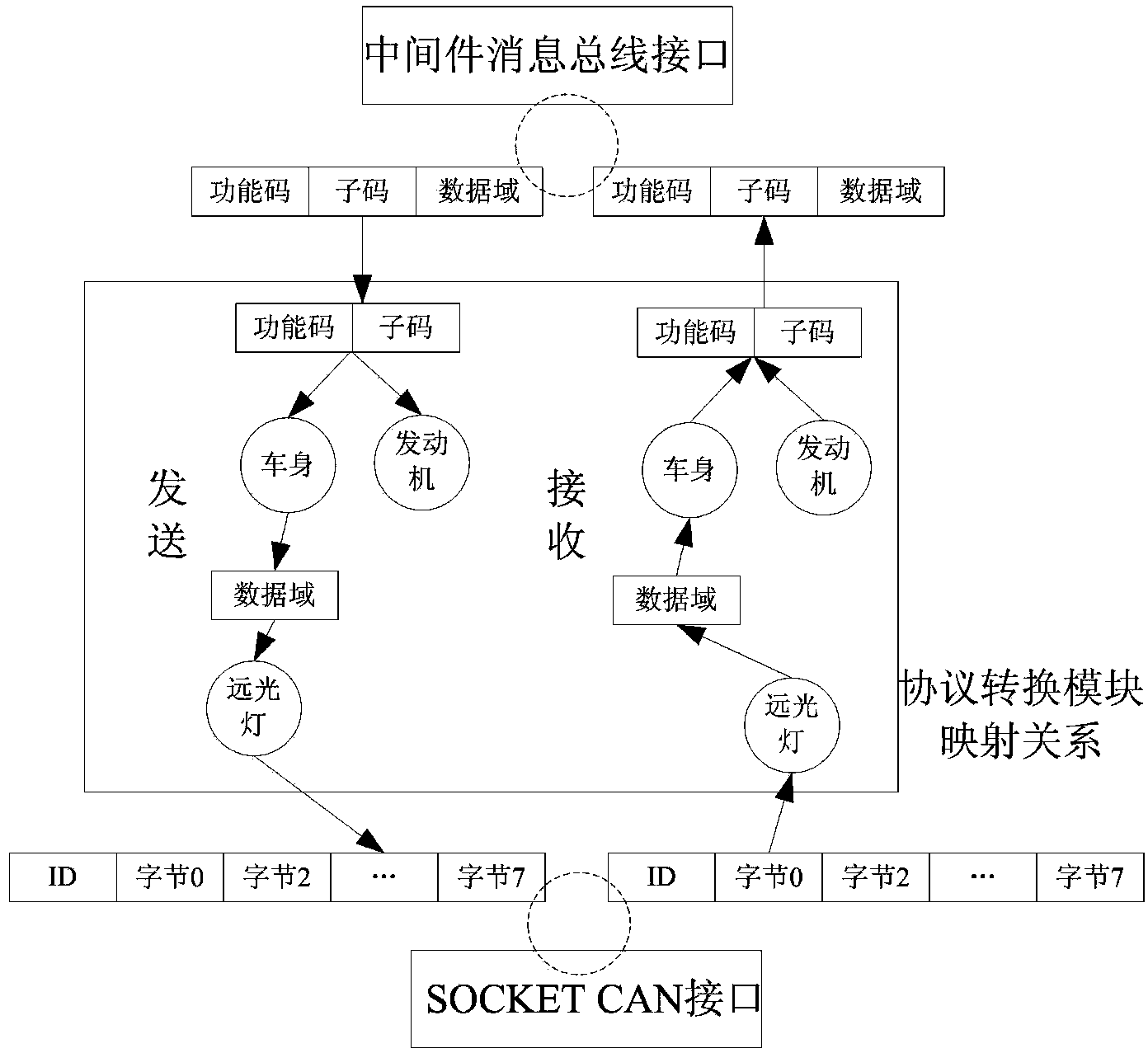

Method for generating configuration for middleware protocol conversion of Internet of vehicles

ActiveCN104331292AAvoid interventionImprove stabilitySpecific program execution arrangementsError checkDBc

The invention discloses a method for generating configuration for middleware protocol conversion of the Internet of vehicles. According to the method, the rapid development of a protocol conversion module is realized through configuration, vehicle enterprise communication protocol conversion parameters are added into a configuration tool through reading DBC (DataBase Commander) file description information which is compiled according to the communication protocol of the Internet of vehicles, configuration information is stored in a database, and middleware protocol conversion module codes of the Internet of vehicles are automatically generated by using protocol conversion template files; a vehicle body network is rapidly integrated with other networks, so as to realize the communication of the Internet of vehicles; the configuration tool can automatically generate configuration files and an application framework and carries out error check on the configuration of a user, worker involvement is avoided as much as possible, and the error rate is lowered, so that the stability of the protocol conversion module can be actively improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Catheter with serially connected sensing structures and methods of calibration and detection

ActiveUS20140187917A1Minimize breakageMinimizing failureDiagnostic signal processingCatheterError checkPressure sense

A catheter is responsive to external and internal magnetic field generators for generating signals representing position and pressure data, with a reduced number of sensing coil leads for minimizing lead breakage and failure. The catheter includes a flexible joint with pressure sensing and position coils, at least pair of a pressure sensing coil and a position coil are serially connected. Methods of calibrating a catheter for position and pressure sensing, and detecting magnetic field interference with one catheter by another catheter or other metal or ferrous object advantageously use signals between two sets of sensors as a “back up” or “error check”.

Owner:BIOSENSE WEBSTER (ISRAEL) LTD

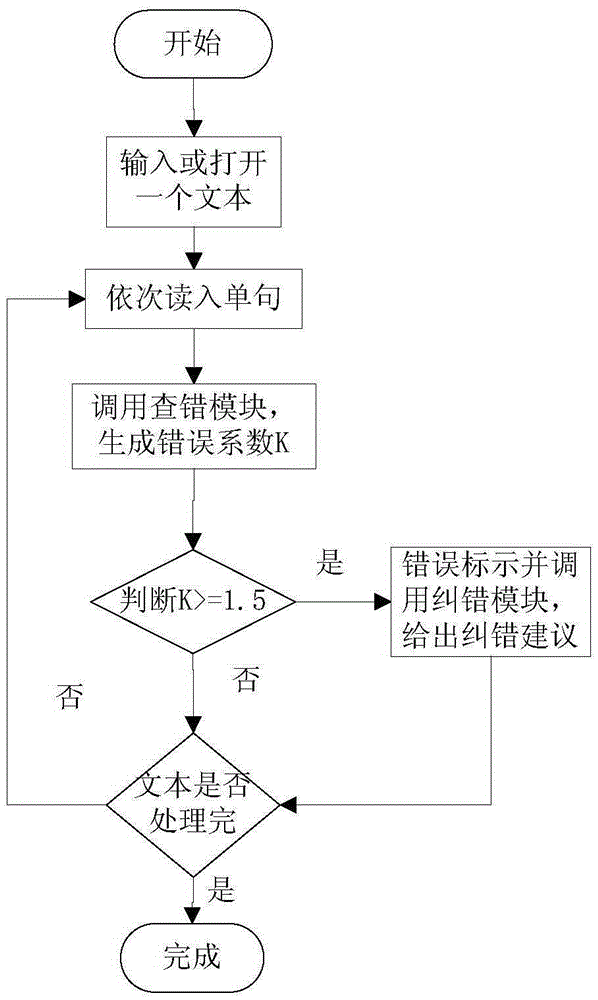

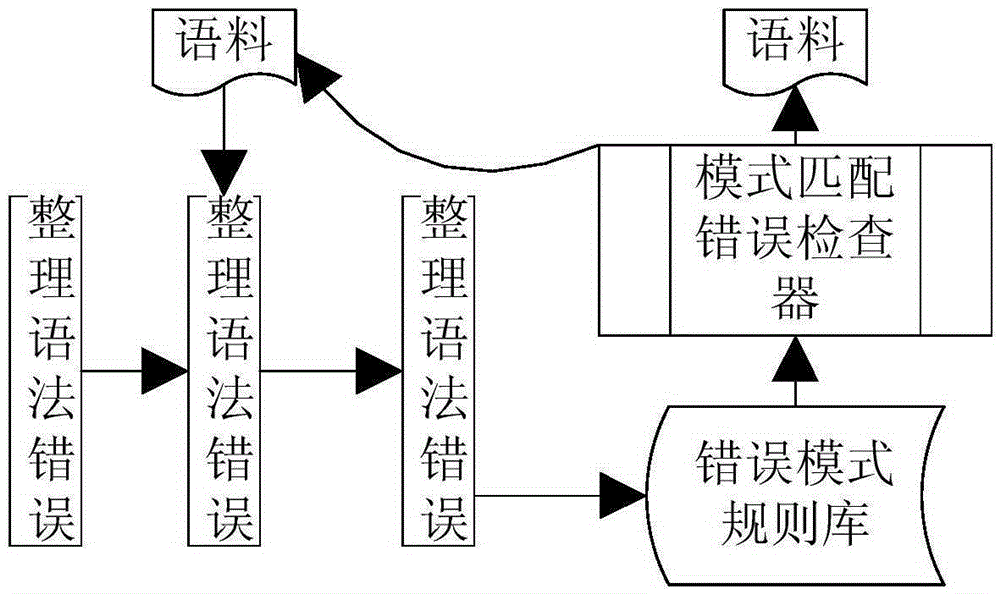

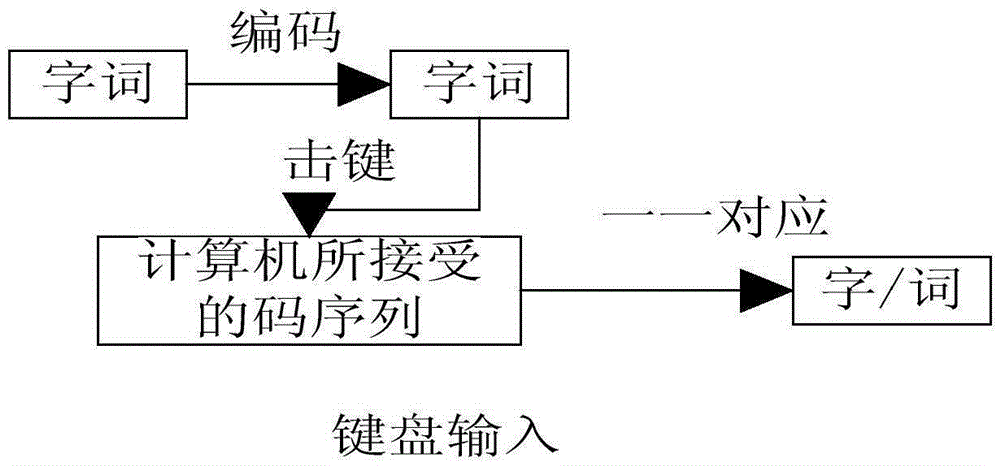

Chinese text automatic correction method

InactiveCN105279149AFast troubleshootingImprove error correction efficiencySpecial data processing applicationsError checkAutocorrection

The invention discloses a Chinese text automatic correction method. The method comprises the following steps of: a) inputting a to-be-corrected Chinese text, and performing word segmentation preprocessing on the Chinese text sentence by sentence; b) searching for one-character words, two-character words or disperse strings of three or more than three characters occurring in the text subjected to word segmentation sentence by sentence; c) performing continuous determination on the disperse strings occurring in the text subjected to word segmentation by adopting an N-gram model, and checking text word level errors for each single sentence in combination with a word forming probability of separate characters; and d) constructing an error correction knowledge base to generate an error correction candidate text. According to the Chinese text automatic correction method provided by the invention, the one-character words, two-character words or disperse strings of three or more than three characters occurring in the text subjected to word segmentation are searched for sentence by sentence, the disperse strings occurring in the text subjected to word segmentation are subjected to continuous determination by adopting the N-gram model to determine identification errors, and the error correction knowledge base is constructed to generate the error correction candidate text, so that error checking and correcting processes are combined very well, and the method has the characteristics of high error checking speed and high error correcting efficiency.

Owner:SHANGHAI INST OF TECH

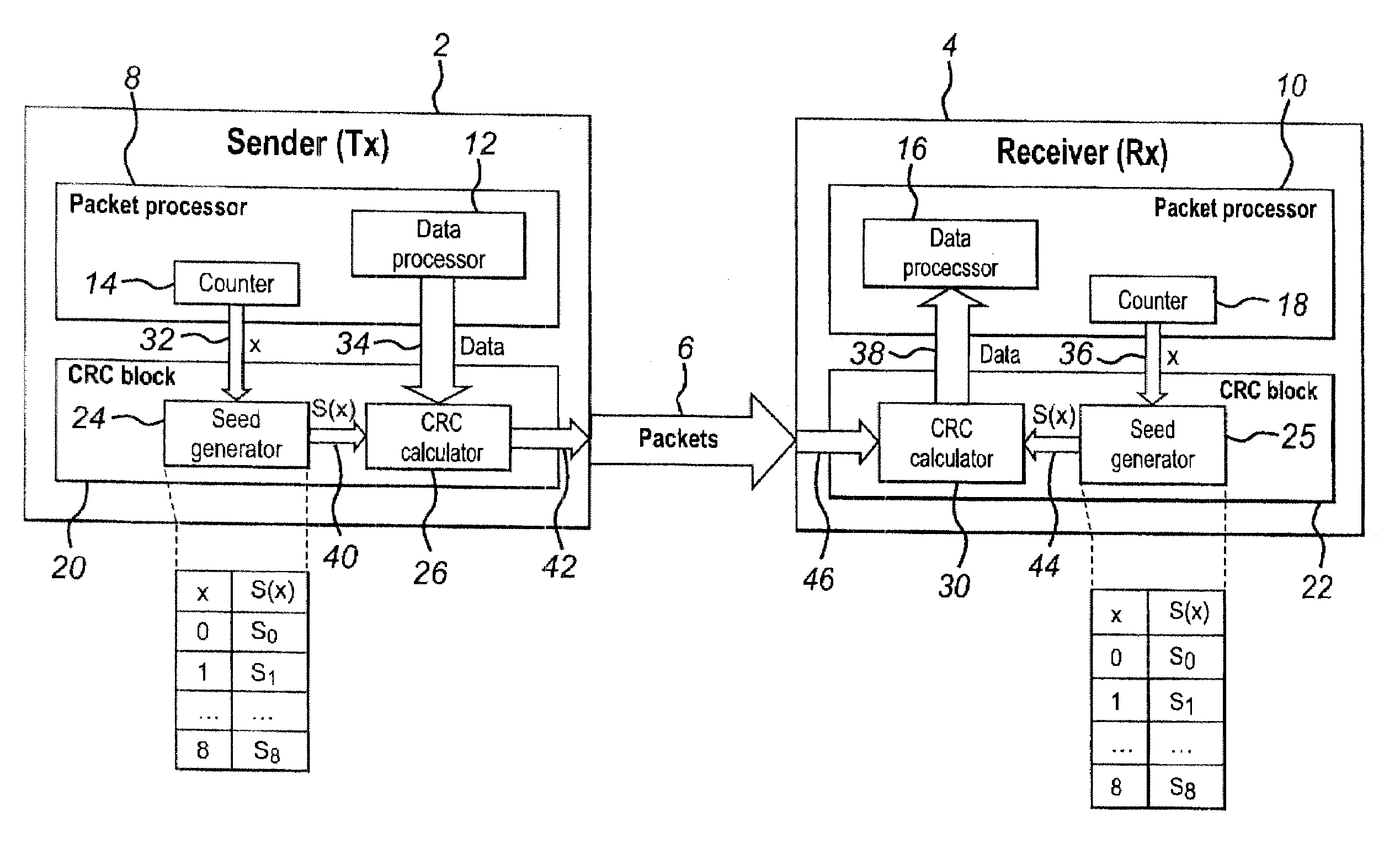

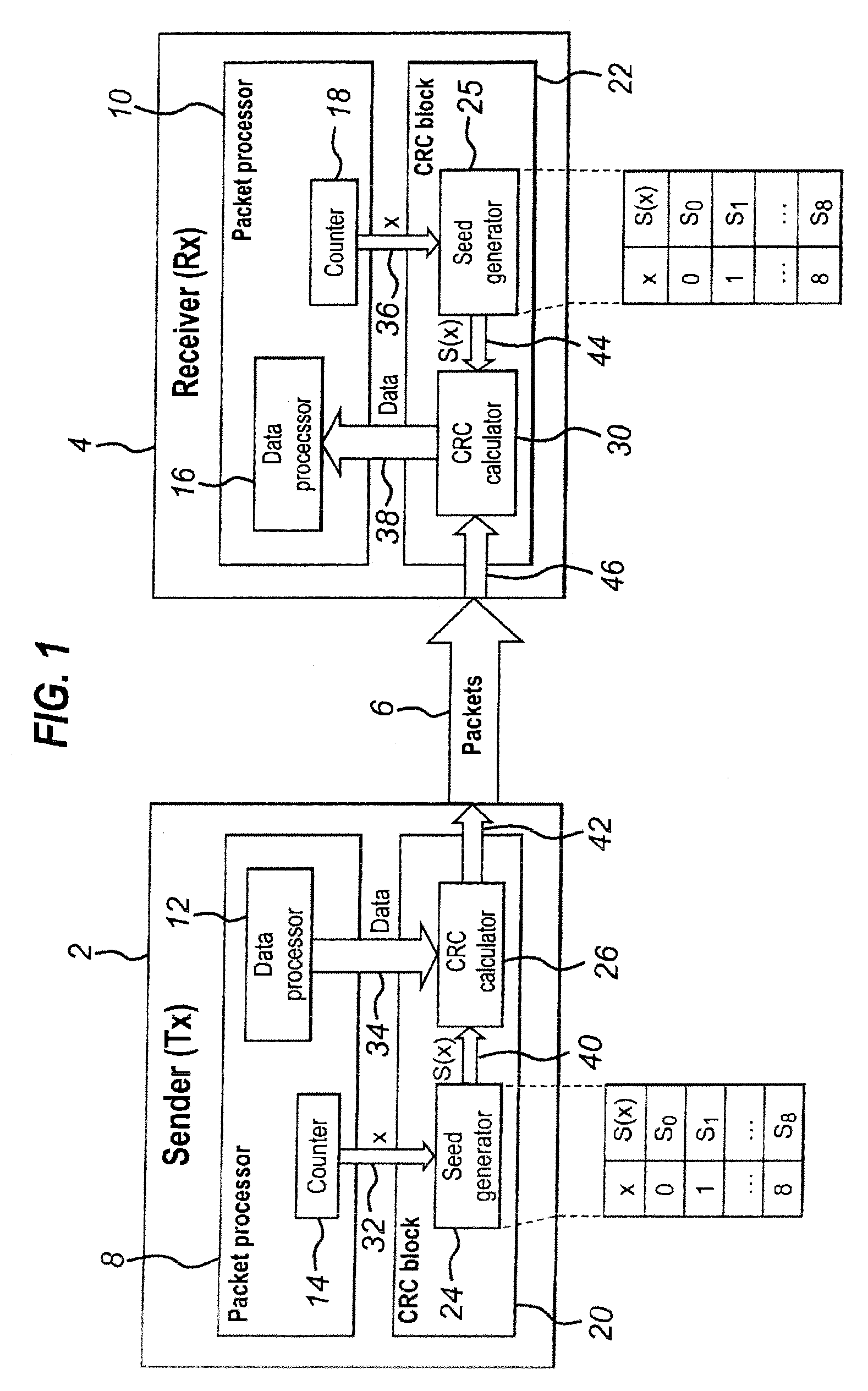

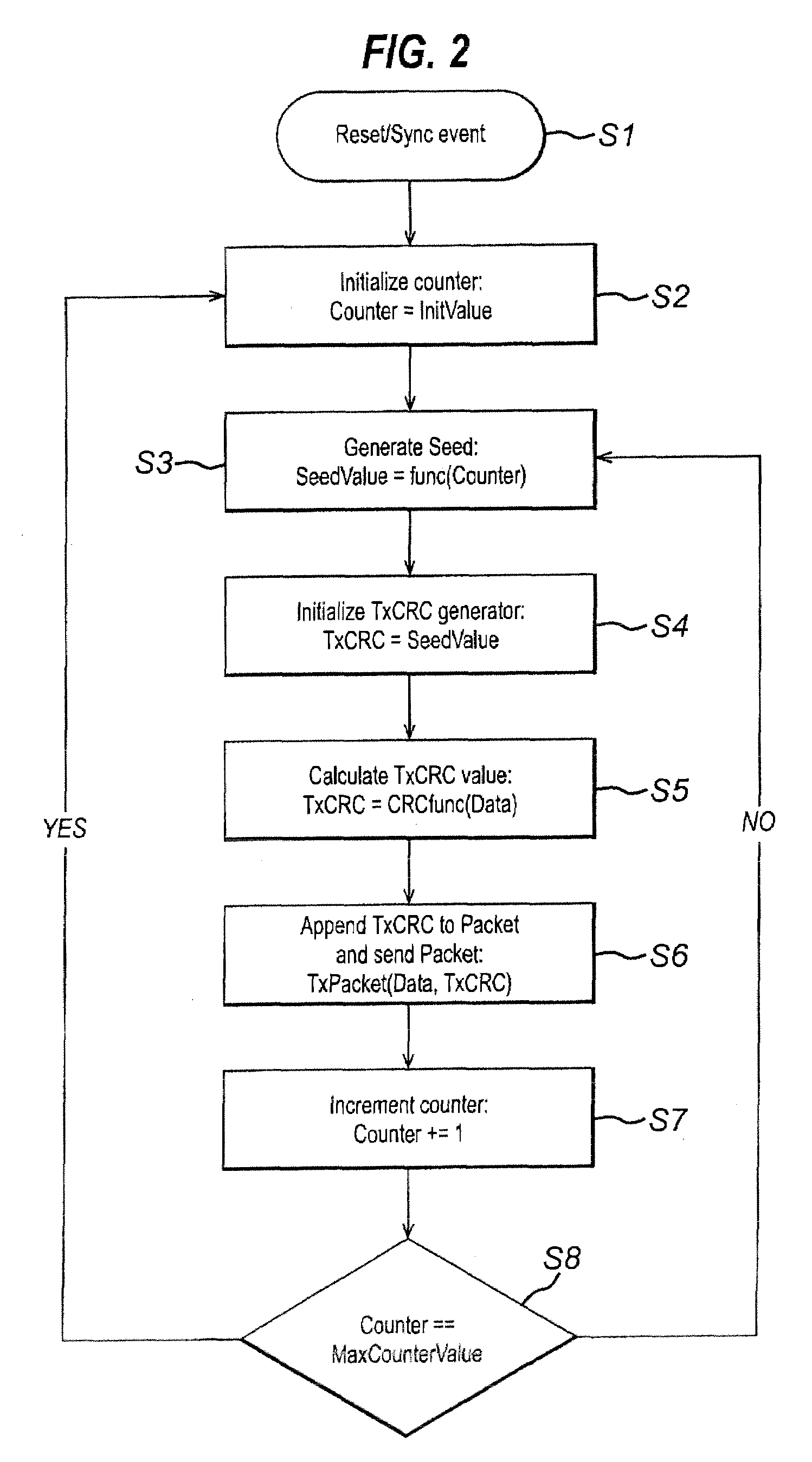

Method of communicatoin

A sending node comprising a processor configured to generate an error checking message, said error checking message being generated from data, said error checking message providing order information; and a transmitter configured to transmit said error checking message and said data.

Owner:NOKIA CORP

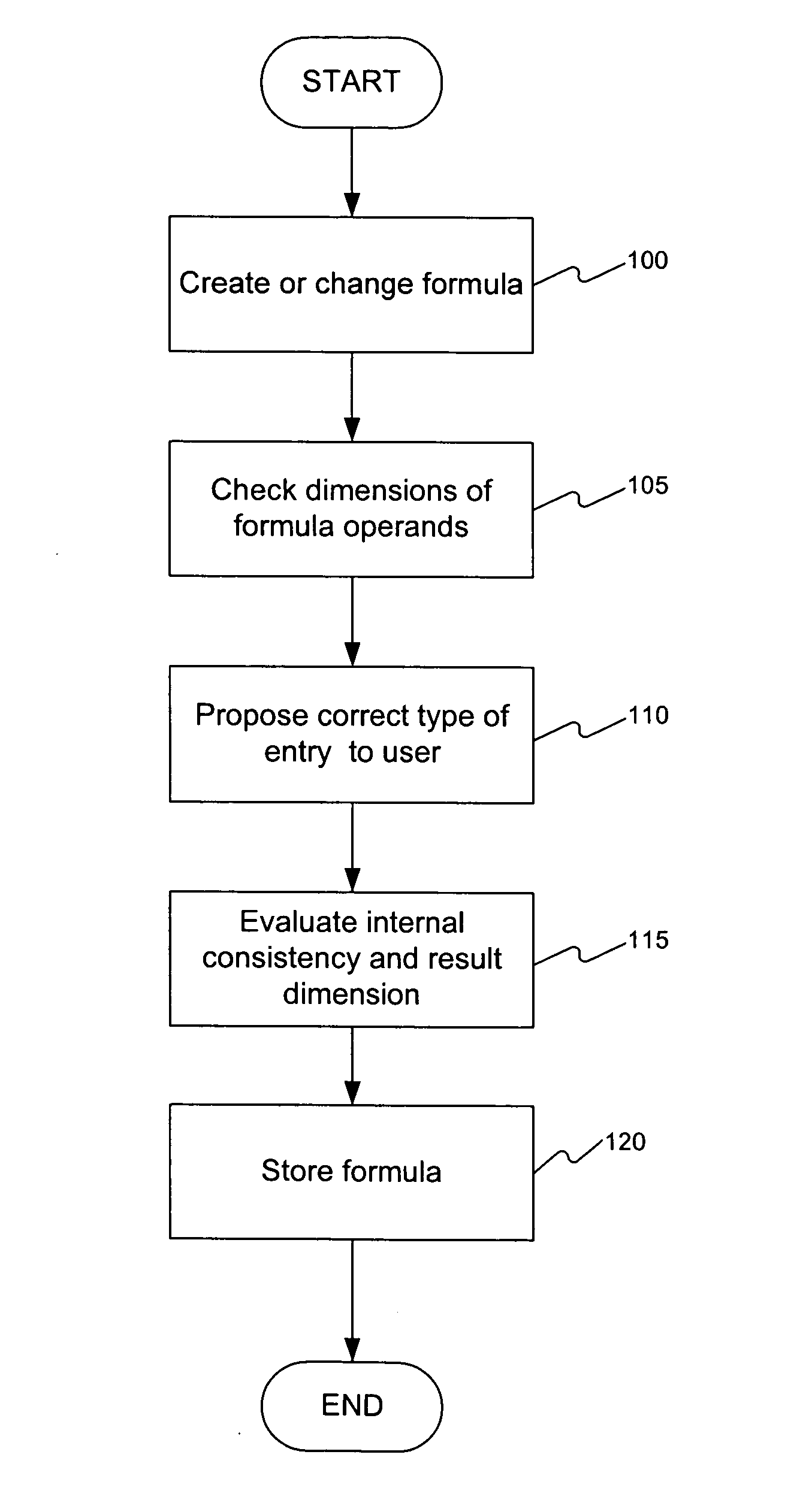

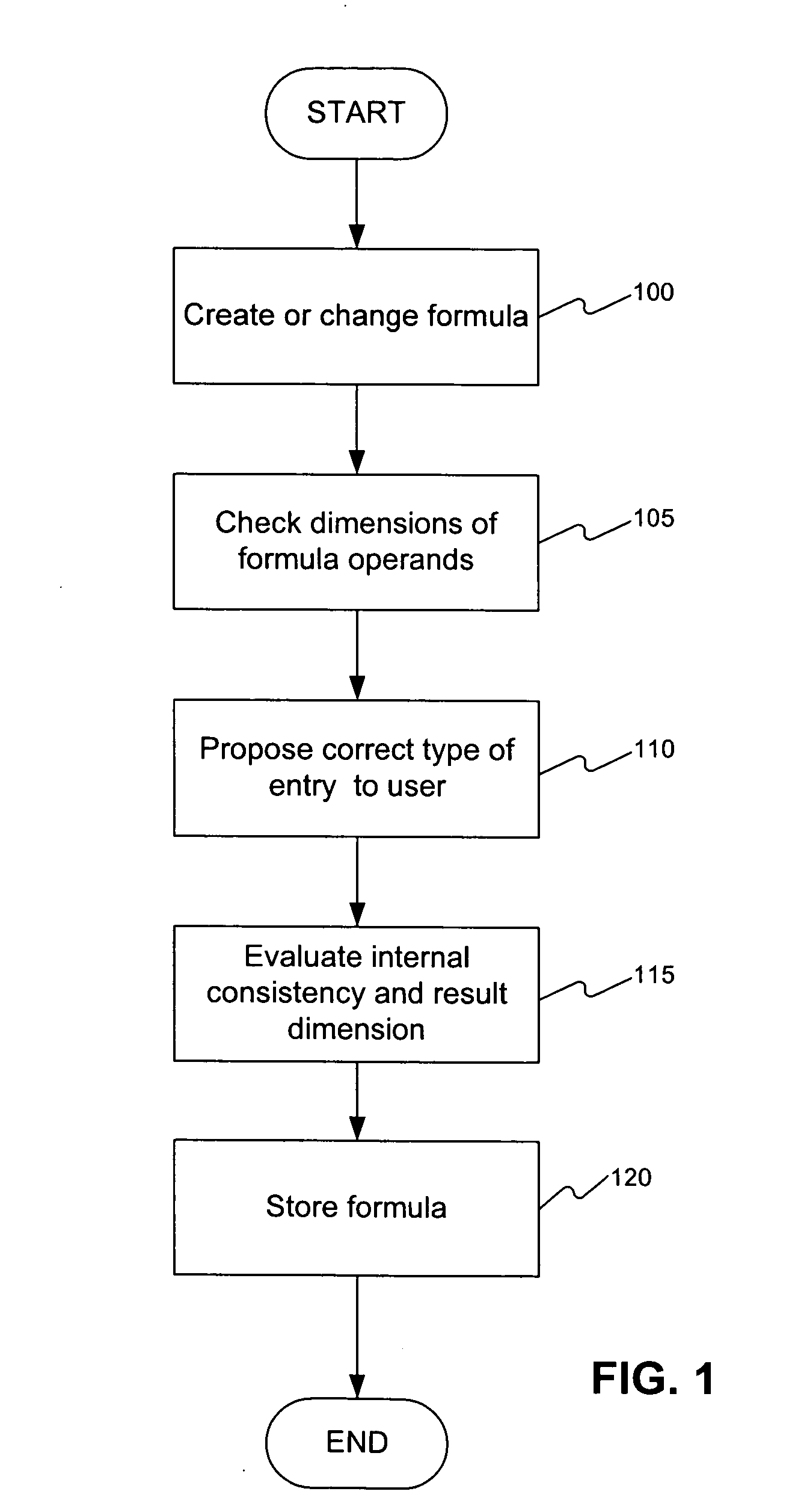

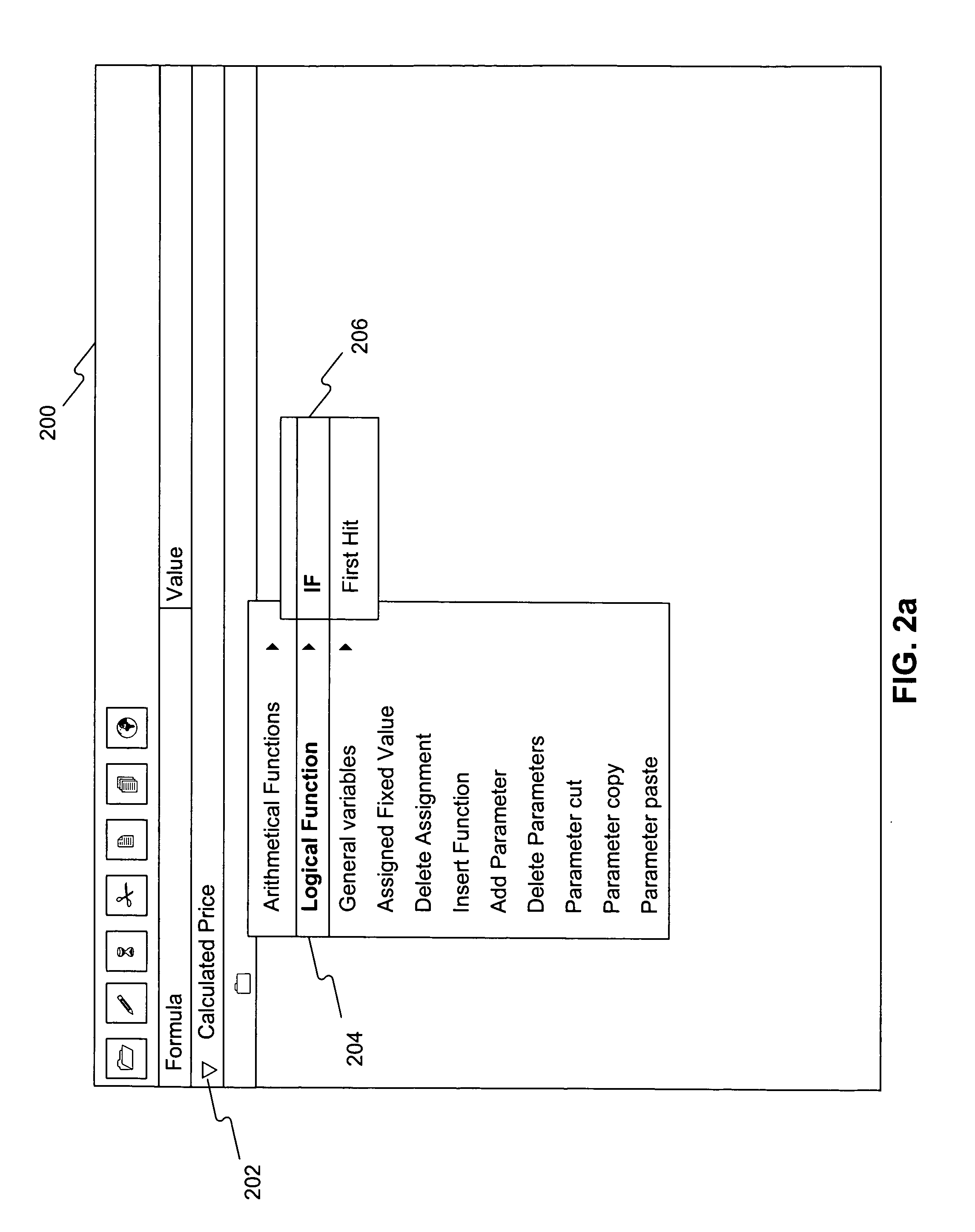

Systems and methods for implementing formulas

Systems and methods are provided for building and implementing formulas. The systems and methods may treat operands in a formula as having a value and a unit type or dimension and may recognize the compatibility of unit types among operands. One embodiment performs automatic error checking of a formula based on the value and dimension of the operands and the expected result. The automatic error checking may be performed to assist a user in defining and building a formula. Another embodiment performs automatic unit conversion based on the value and unit type of the formula's operands. The automatic unit conversion may be performed when applying data to the formula during runtime or execution of an application program.

Owner:SAP AG

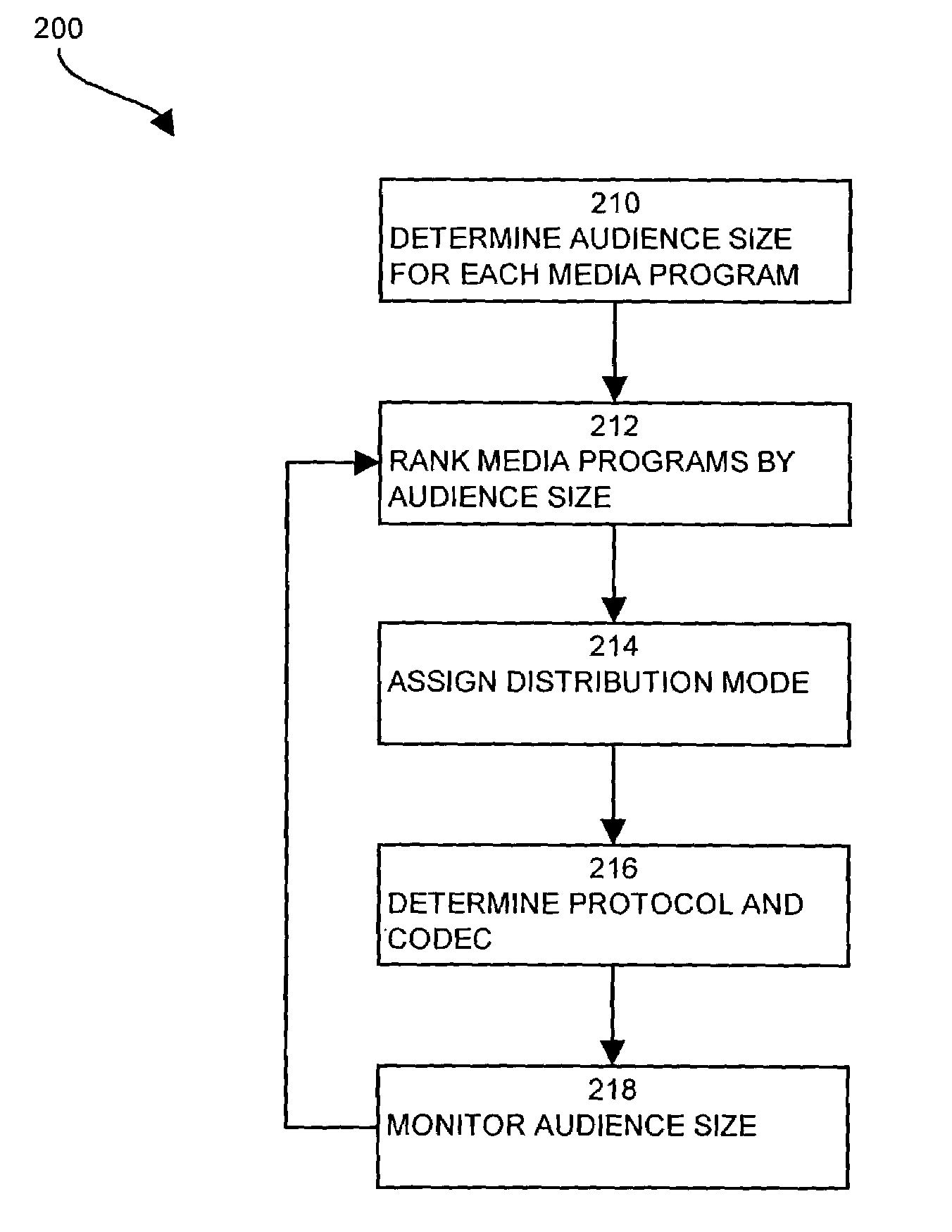

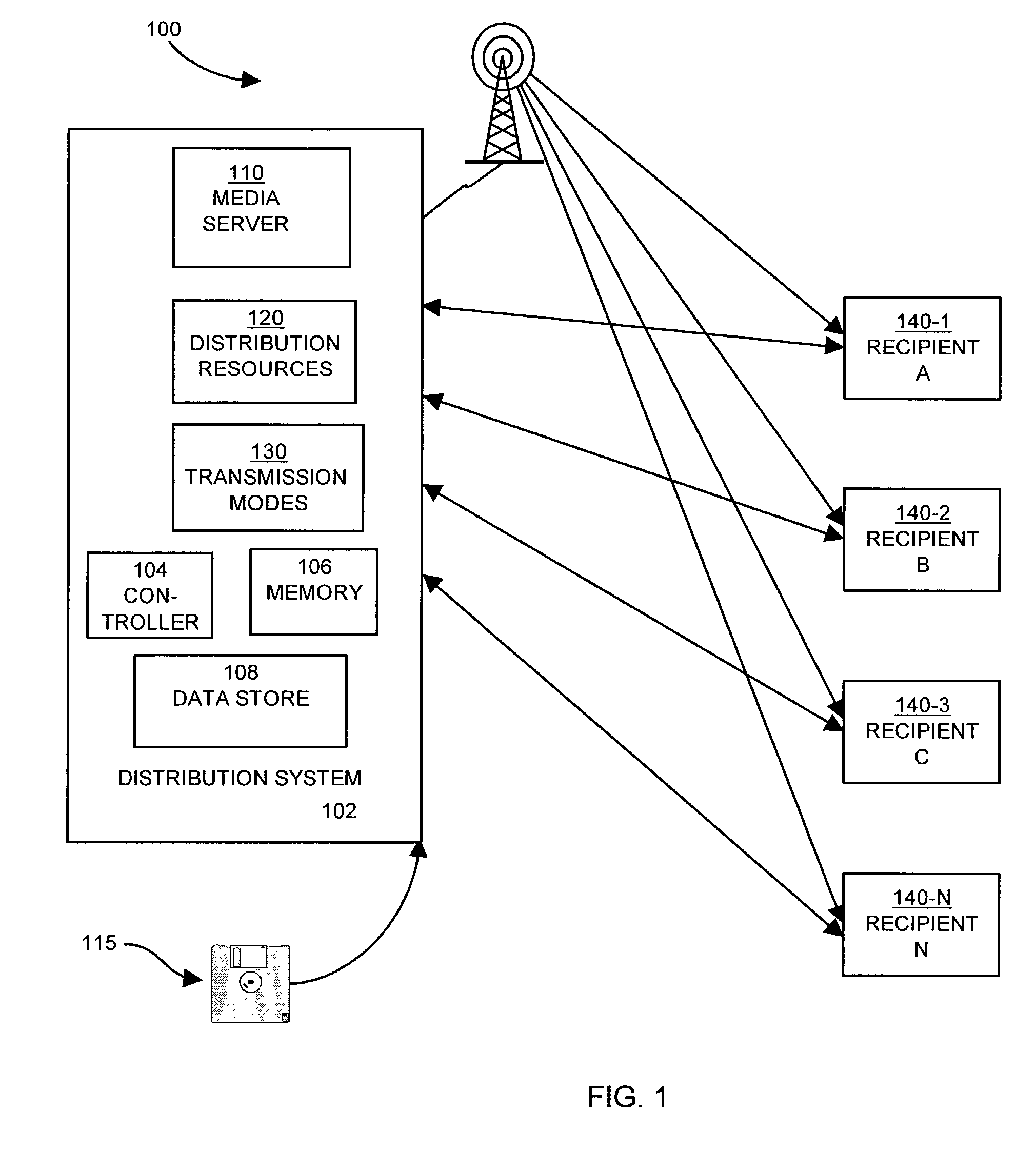

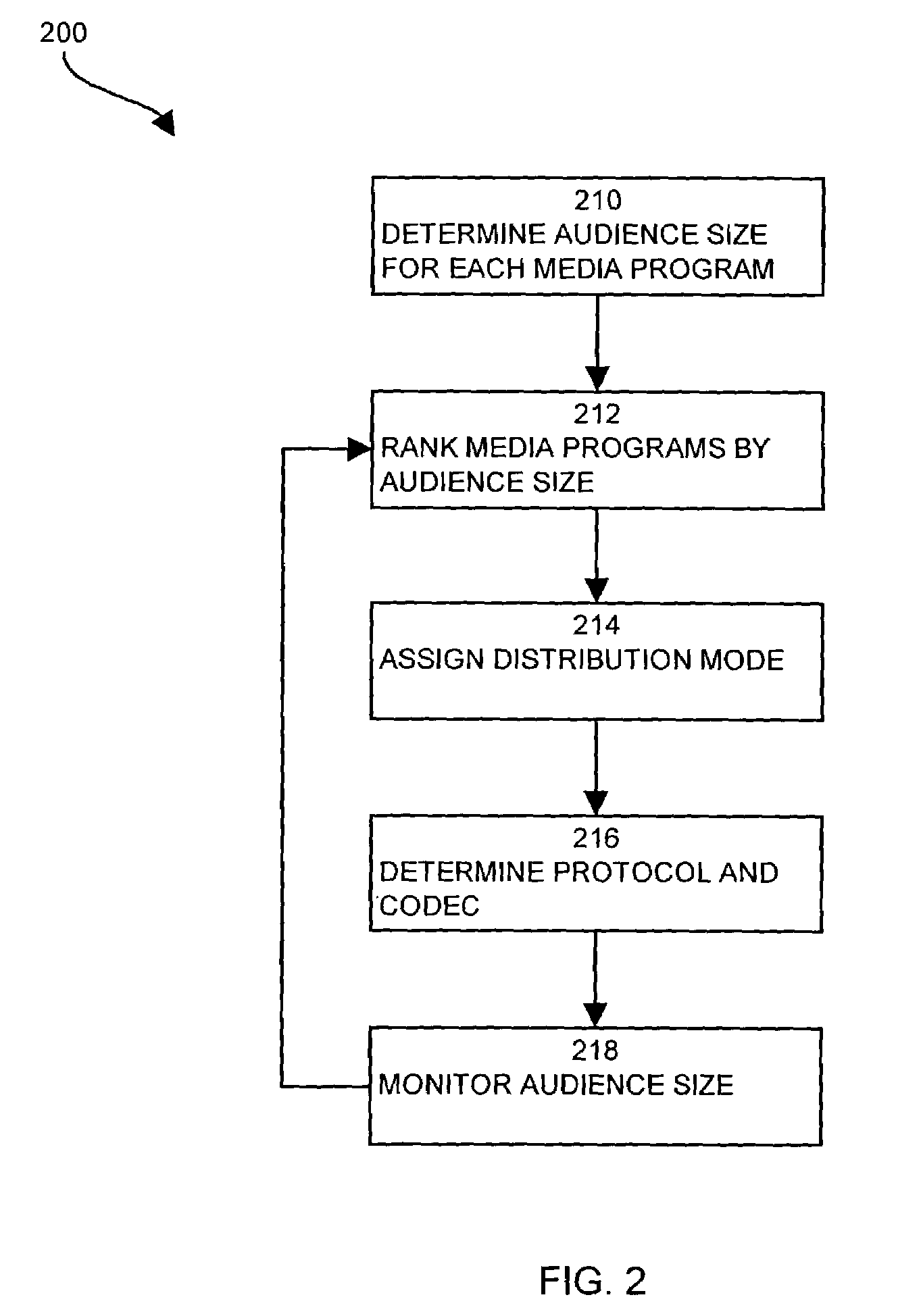

Methods and apparatus for transmitting media programs

ActiveUS7260601B1Valid choiceError preventionFrequency-division multiplex detailsError checkBroadcast channels

A system transmits a plurality of media programs in a network. In one embodiment of the invention, a media program distribution system determines a first resource attribute of a first media program and a second resource attribute of a second media program. The distribution system compares the first resource attribute with the second resource attribute to determine a relative value. In turn, the media server assigns a first distribution resource to the first media program and a second distribution resource to the second media program in response to the relative value and applies one of a plurality of transmission modes to each media program in response to the resource attribute and distribution resource type. Examples of distribution resources include unicast, multicast and broadcast channels. Examples of transmission modes include various protocols such as error checking protocols and encoding mechanisms such as codecs.

Owner:CISCO TECH INC

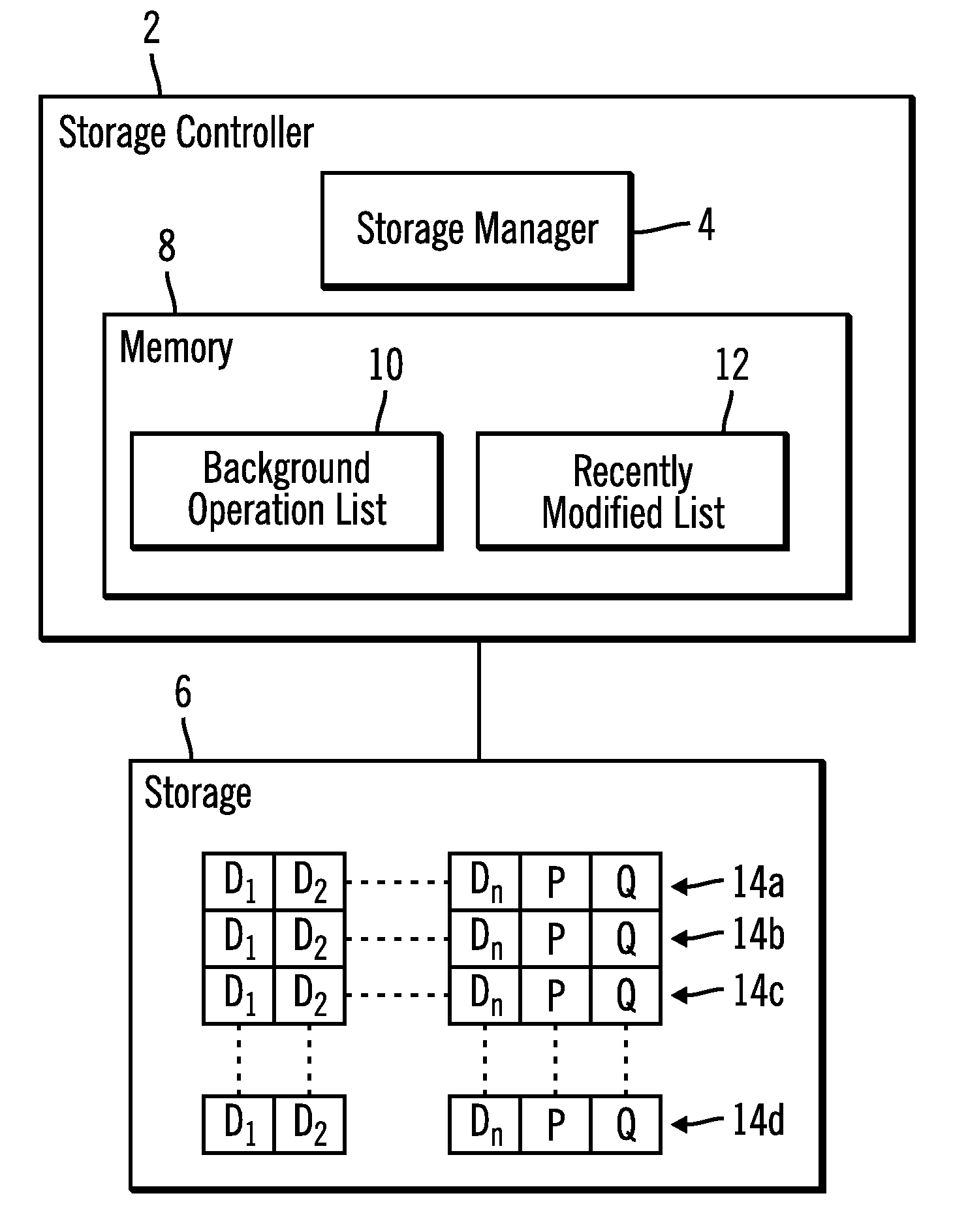

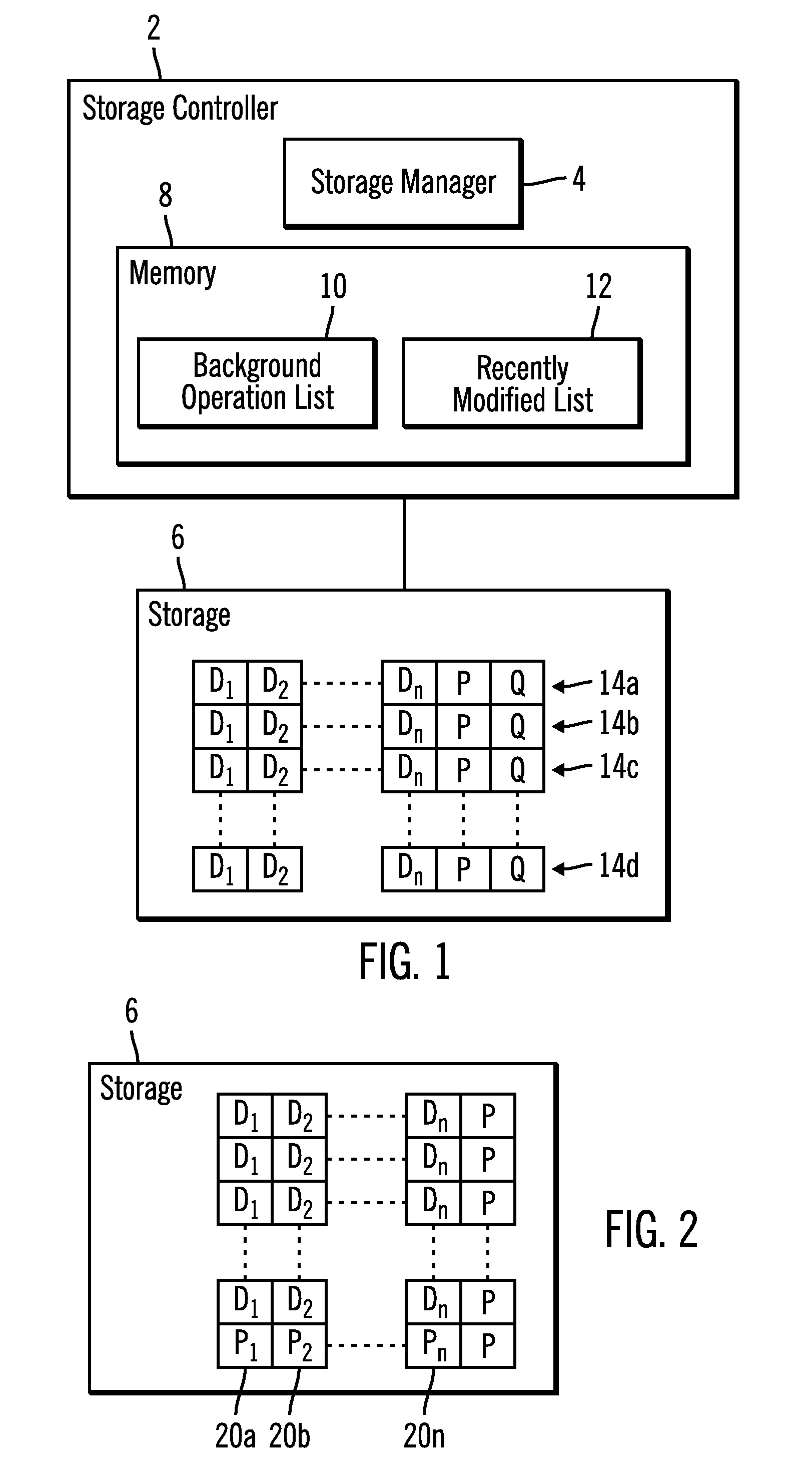

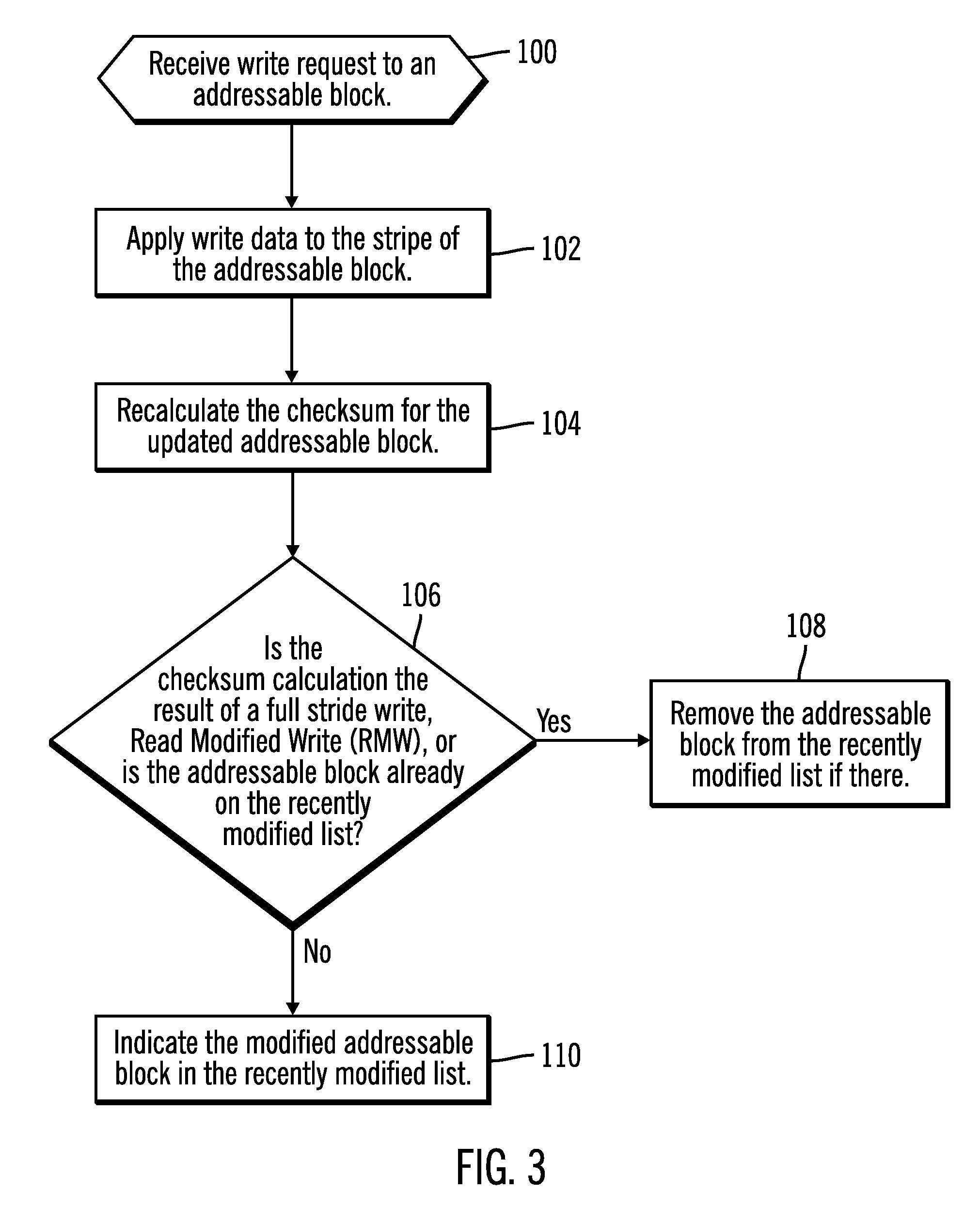

Error checking addressable blocks in storage

Provided are a method, system, and article of manufacture for error checking addressable blocks in storage. Addressable blocks of data are stored in a storage in stripes, wherein each stripe includes a plurality of data blocks for one of the addressable blocks and at least one checksum block including checksum data derived from the data blocks for the addressable block. A write request is received to modify data in one of the addressable blocks. The write and updating the checksum are performed in the stripe having the modified addressable block. An indication is made to perform an error checking operation on the stripe for the modified addressable block in response to the write request, wherein the error checking operation reads the data blocks and the checksum in the stripe to determine if the checksum data is accurate. An error handling operation is initiated in response to determining that the checksum data is not accurate.

Owner:GLOBALFOUNDRIES INC