Patents

Literature

91 results about "Type error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

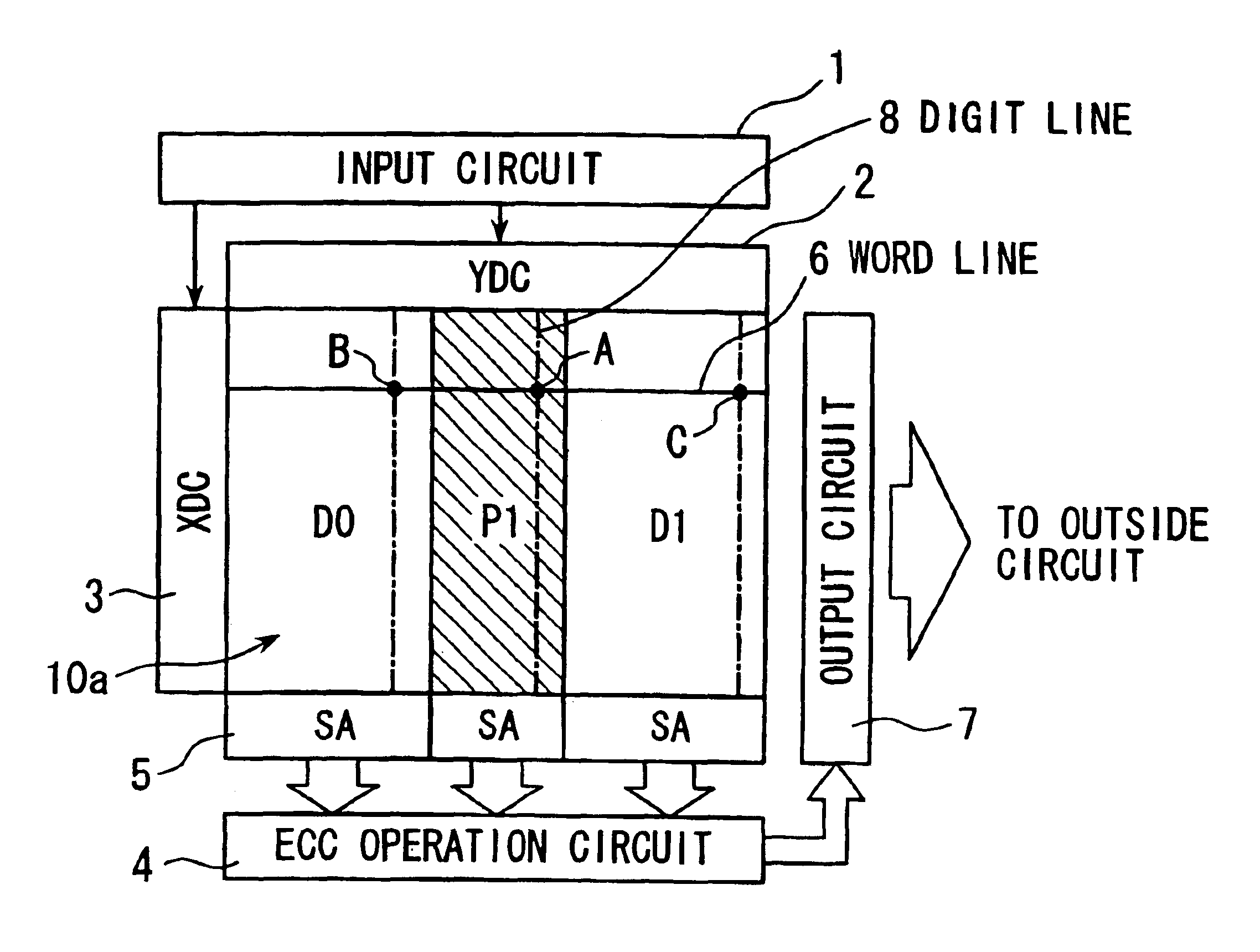

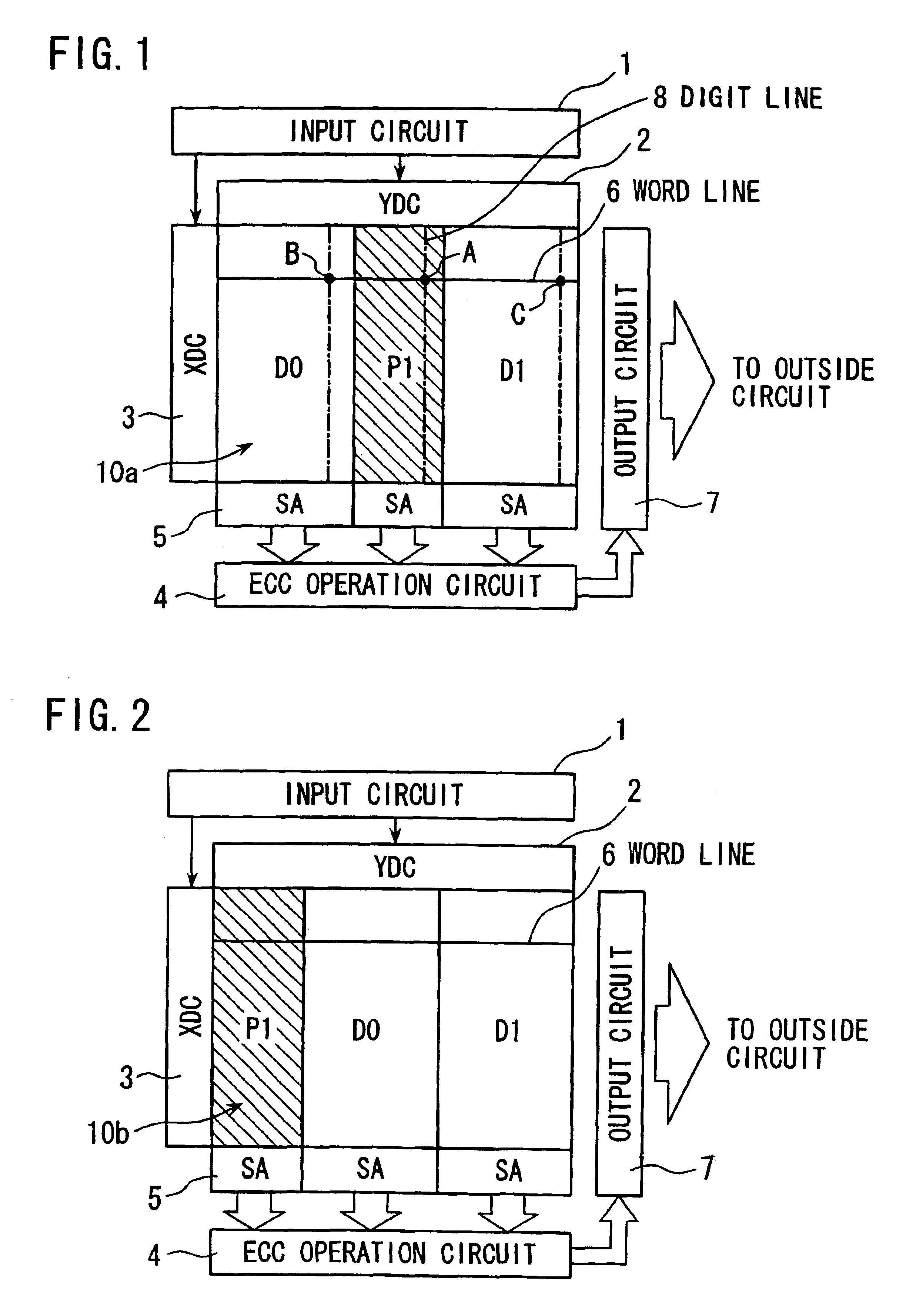

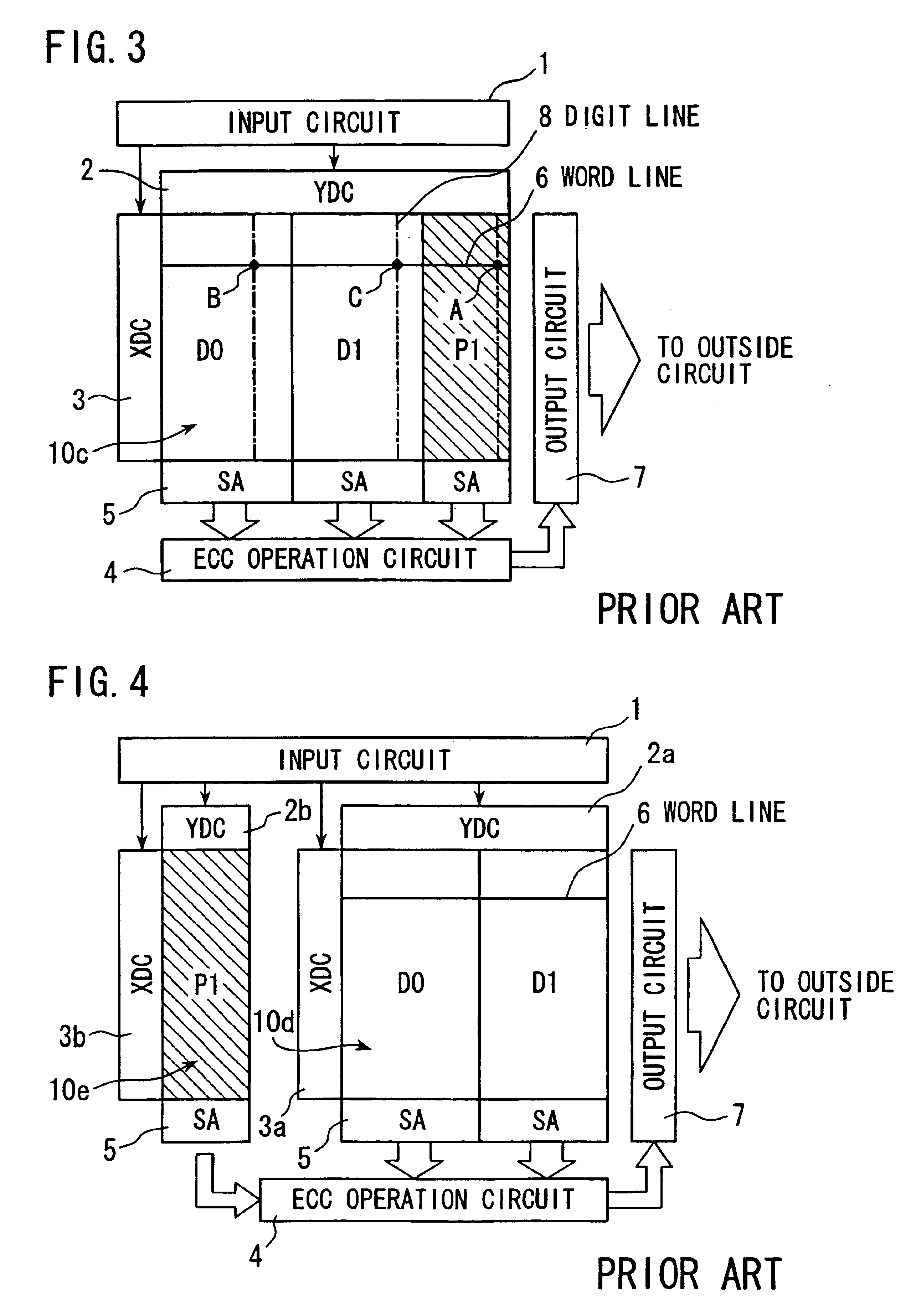

Semiconductor memory device having ECC type error recovery circuit

InactiveUS6851081B2Easy to measureEasy to readMemory loss protectionEmergency protective arrangements for automatic disconnectionType errorError check

A semiconductor memory device having an error check and correction (ECC) type error recovery circuit in which disposition of ECC cells is improved. The memory device comprises: a memory cell array including a plurality of normal cell array portions and an ECC cell array portion; an X decoder for selecting one of word lines in the memory cell array, the word lines extending from the X decoder to the memory cell array; an ECC operation circuit for performing error check and correction based on cell data read out from a selected word line, the cell data including data from normal cells and ECC cells of the selected word line. The ECC memory cell array portion is disposed at a location other than the far end of the word lines from the X decoder, that is, the ECC cell array portion is disposed at a location in which read out speed of data from ECC cell or cells does not become the worst speed in the memory device. Therefore, the worst data read out speed can be measured from outside.

Owner:RENESAS ELECTRONICS CORP

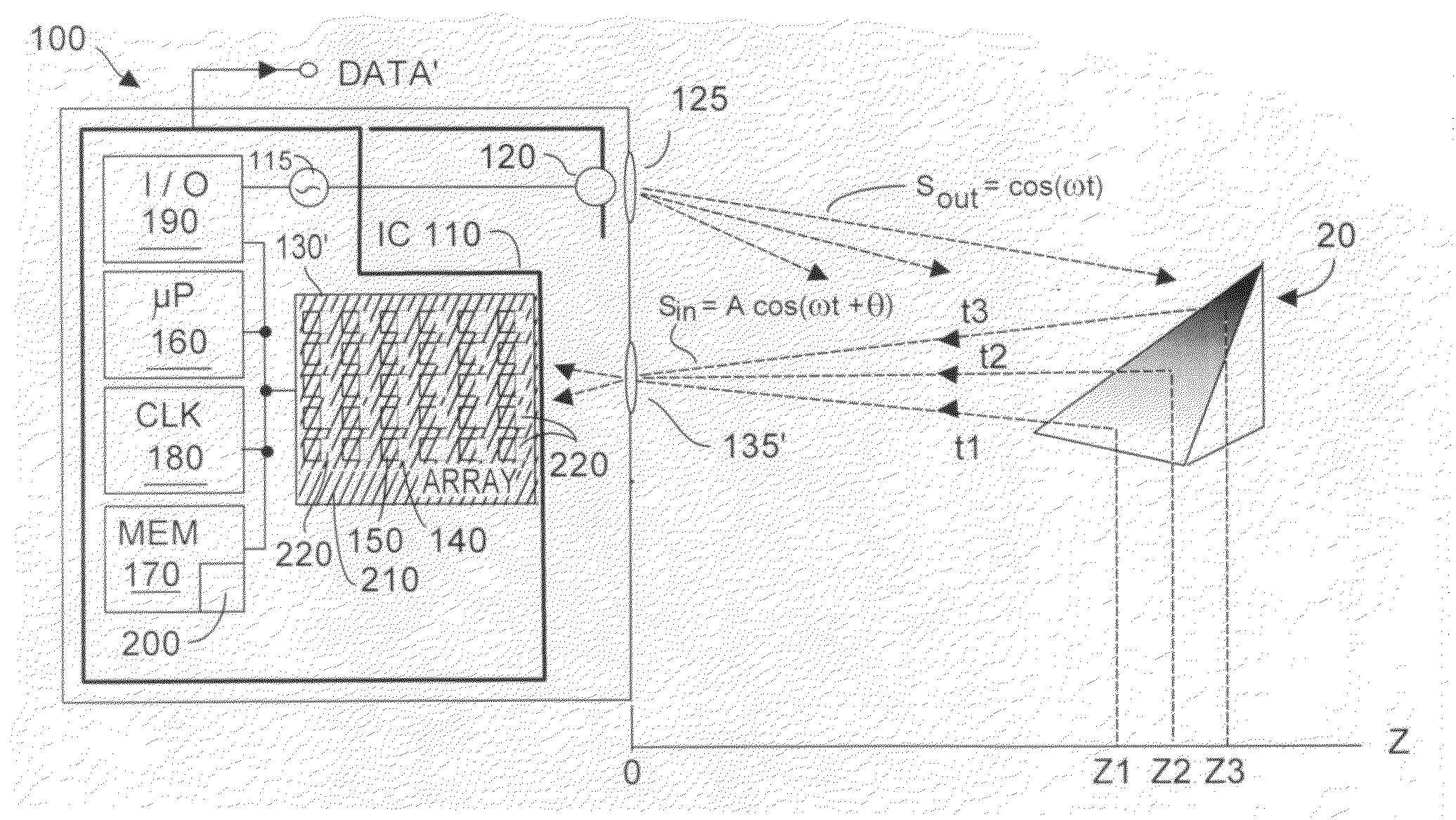

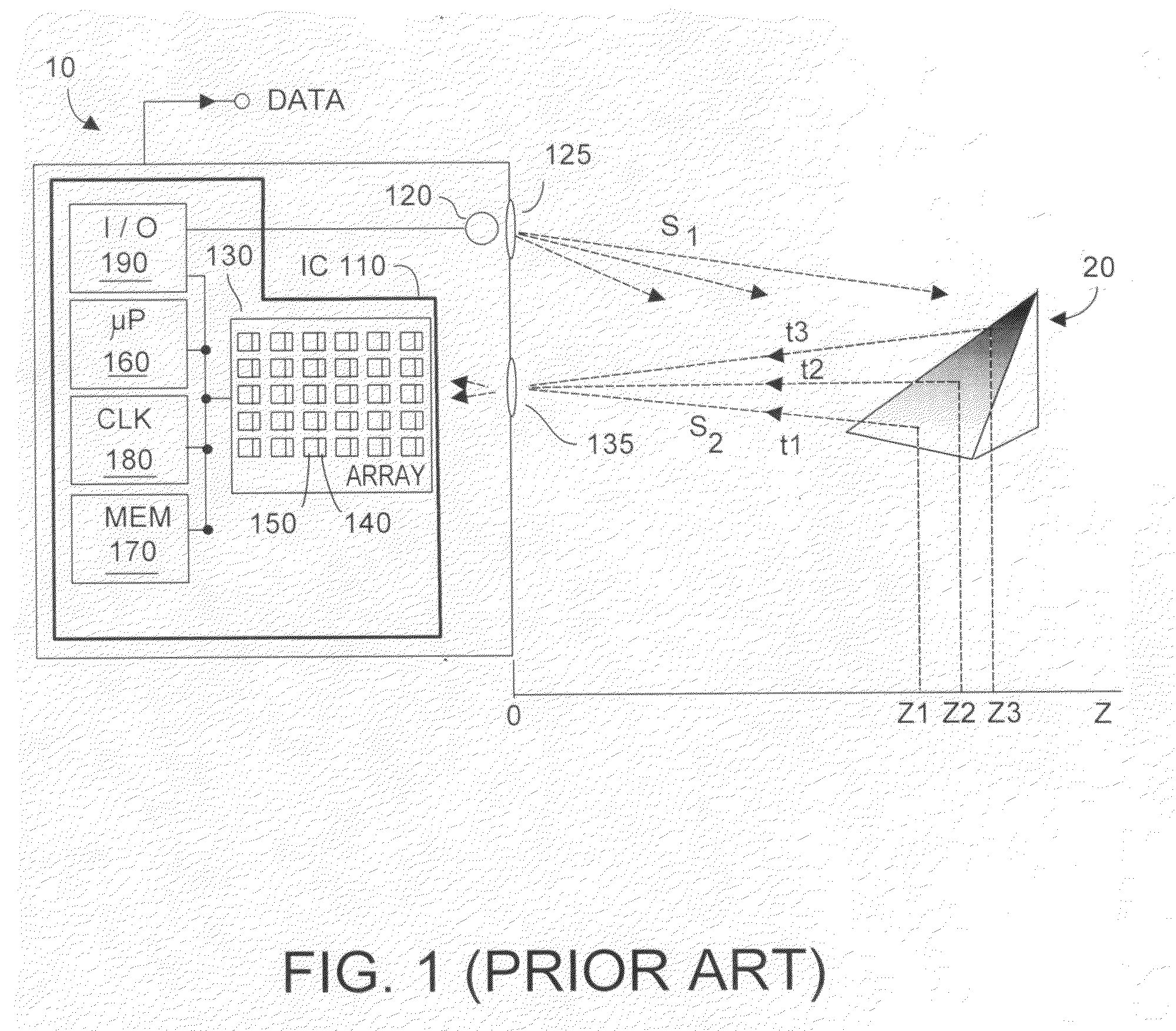

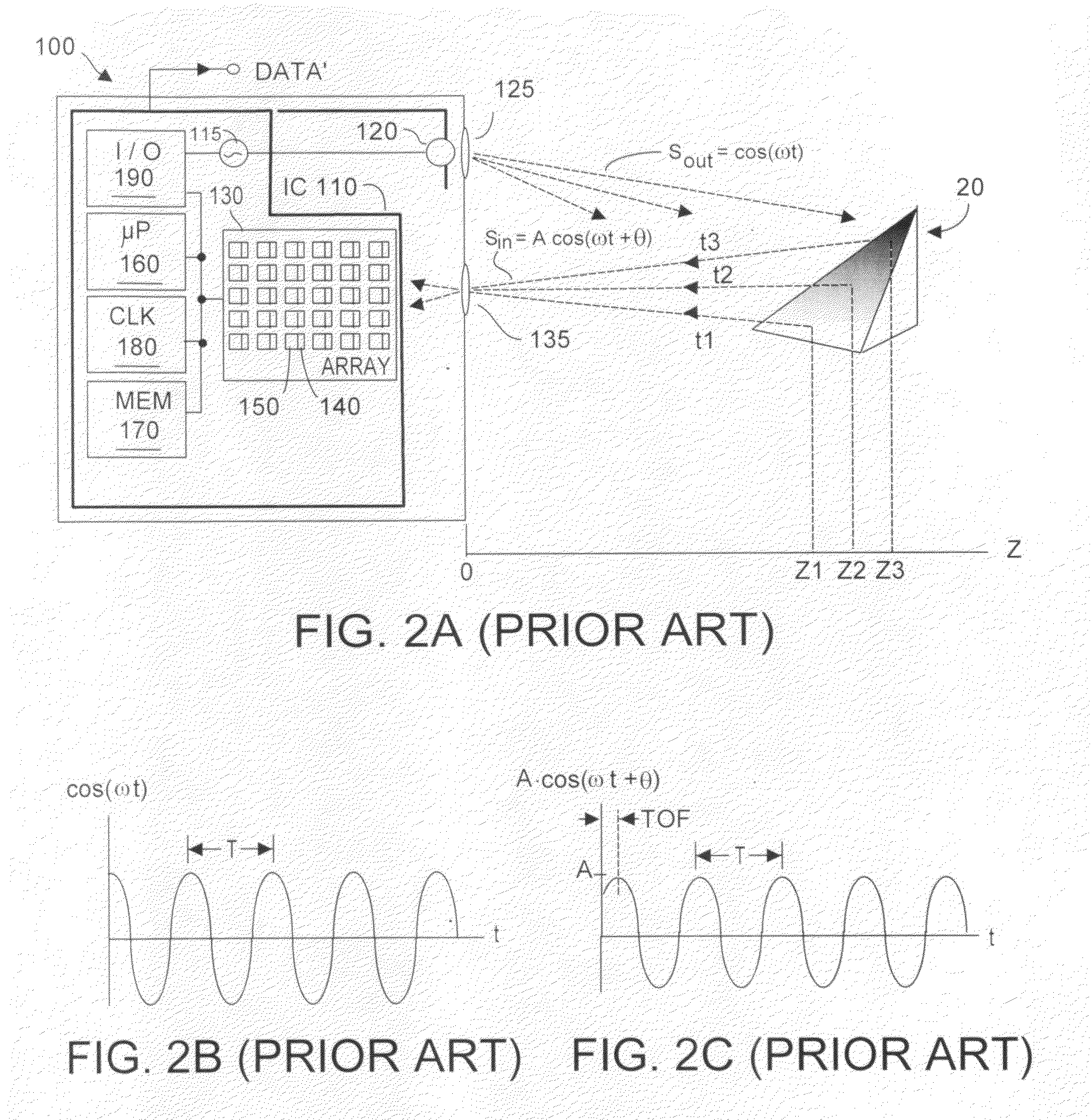

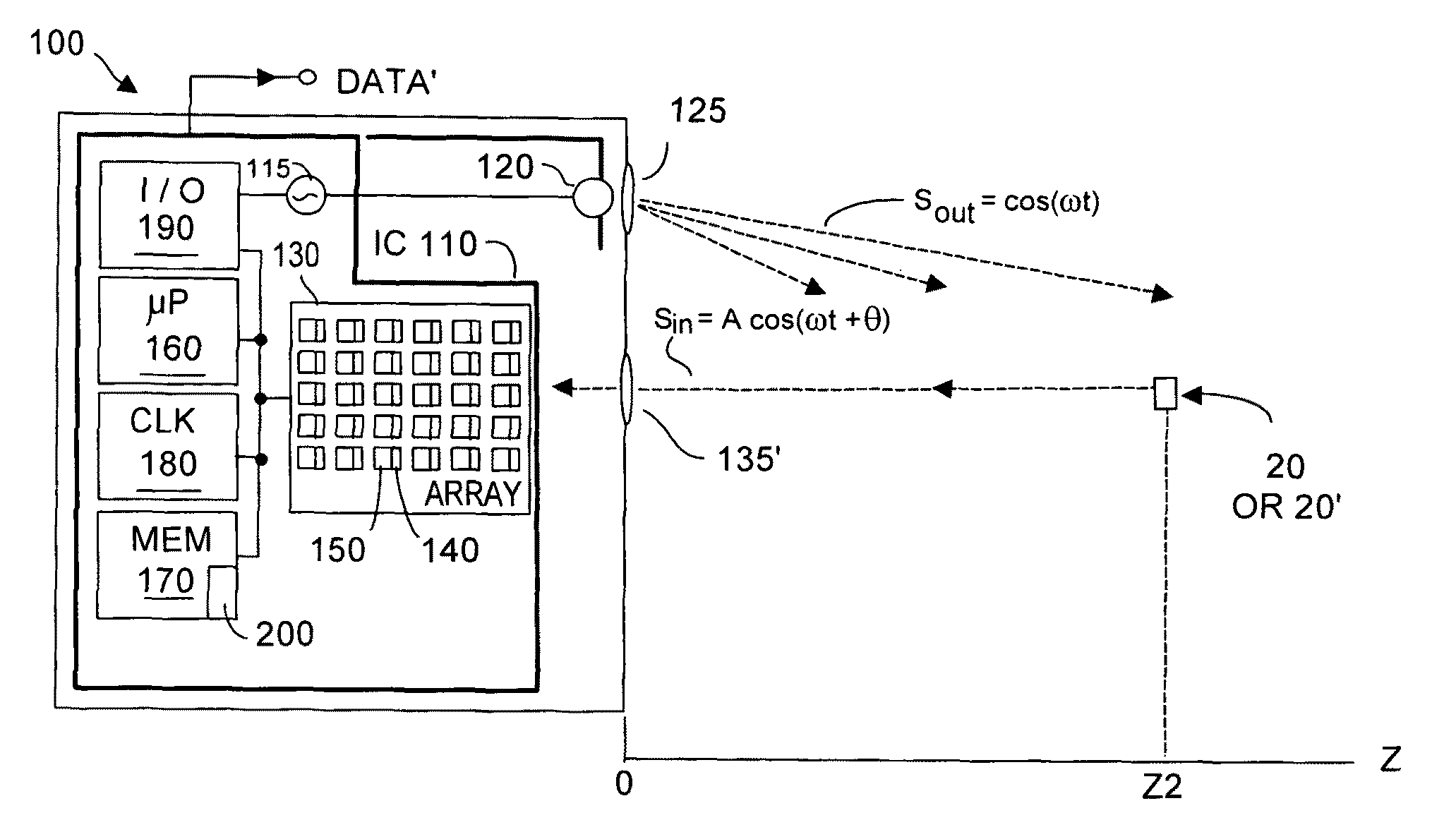

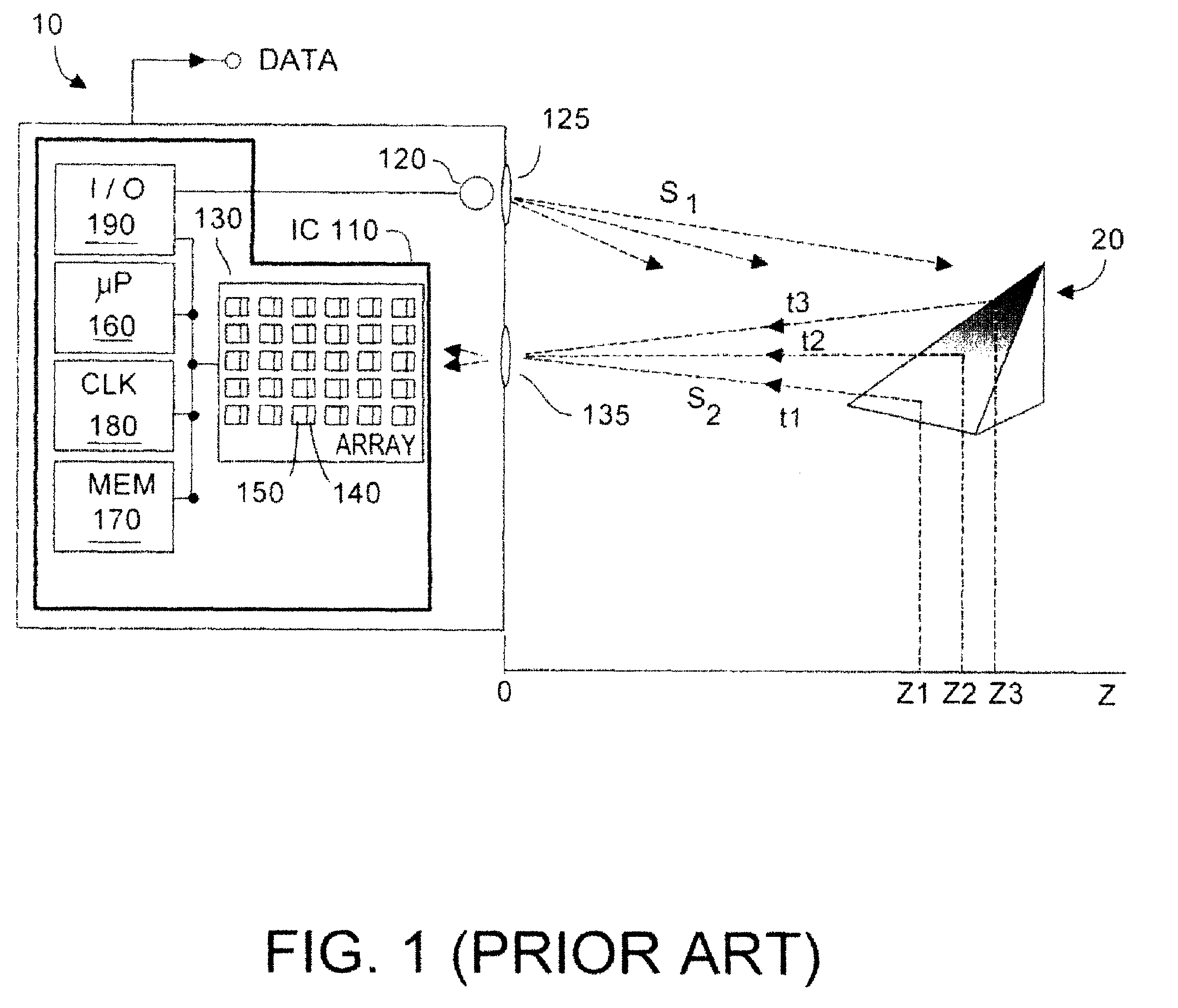

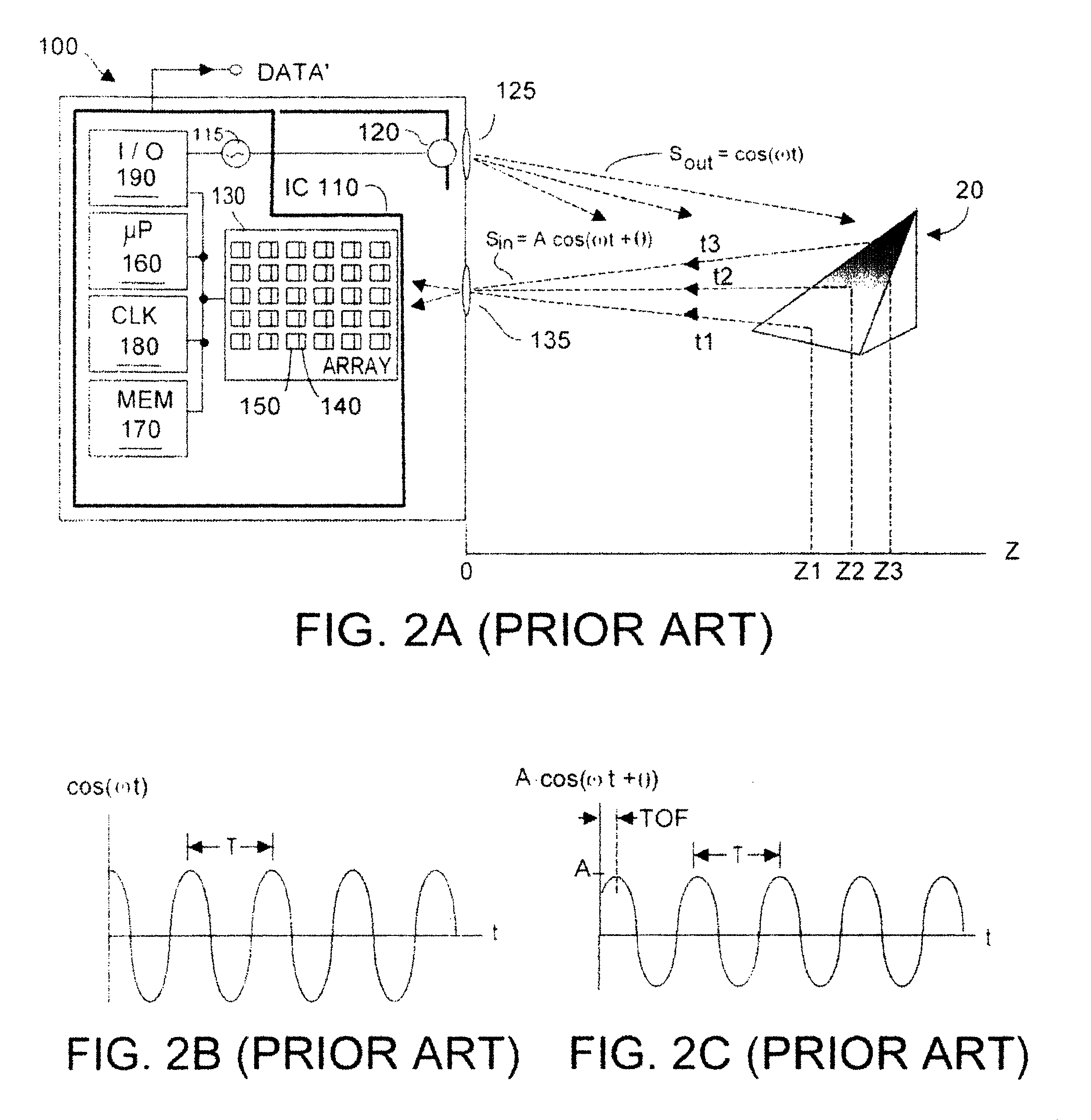

Method and system to reduce stray light reflection error in time-of-flight sensor arrays

ActiveUS20120008128A1Weakening rangeReduce surface reflectivityOptical rangefindersElectromagnetic wave reradiationSensor arrayType error

Haze-type phase shift error due to stray light reflections in a phase-type TOF system is reduced by providing a windowed opaque coating on the sensor array surface, the windows permitting optical energy to reach light sensitive regions of the pixels, and by reducing optical path stray reflection. Further haze-type error reduction is obtained by acquiring values for a plurality (but not necessarily all) of pixel sensors in the TOF system pixel sensor array. Next, a correction term for the value (differential or other) acquired for each pixel in the plurality of pixel sensors is computed and stored. Modeling response may be made dependent upon pixel (row,column) location within the sensor array. During actual TOF system runtime operation, detection data for each pixel, or pixel groups (super pixels) is corrected using the stored data. Good optical system design accounts for correction, enabling a simple correction model.

Owner:MICROSOFT TECH LICENSING LLC

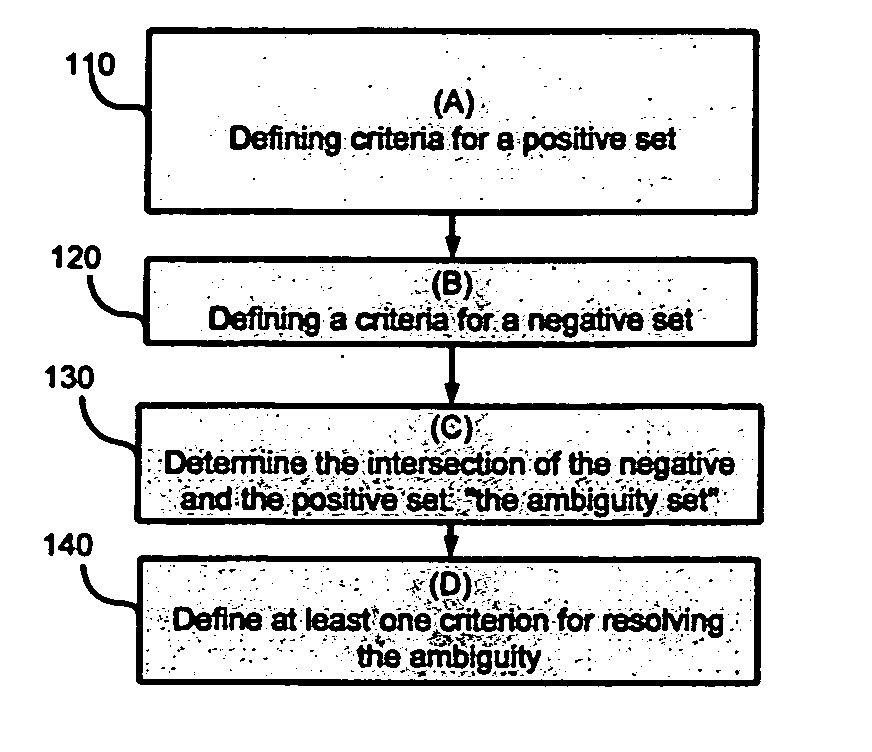

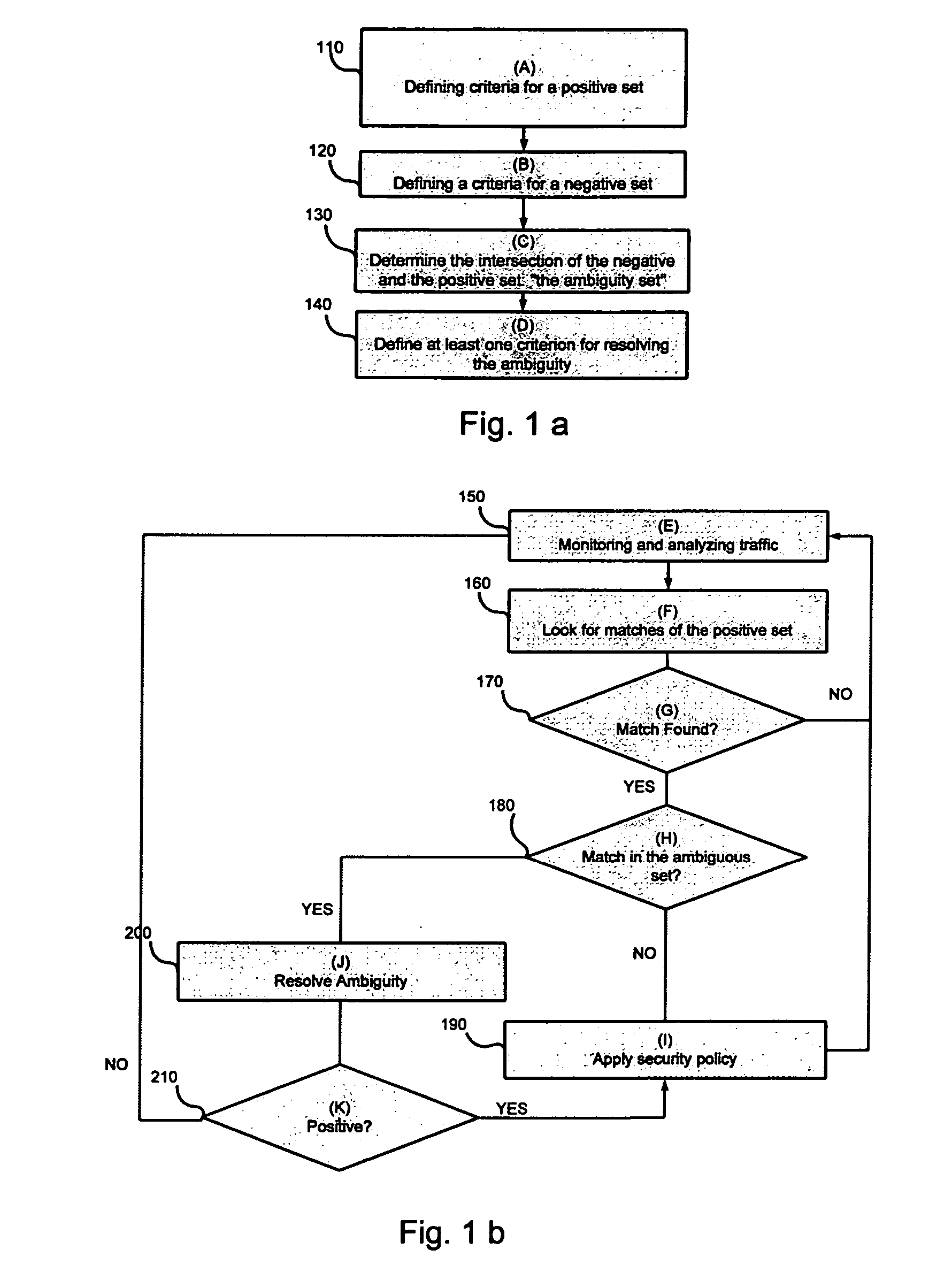

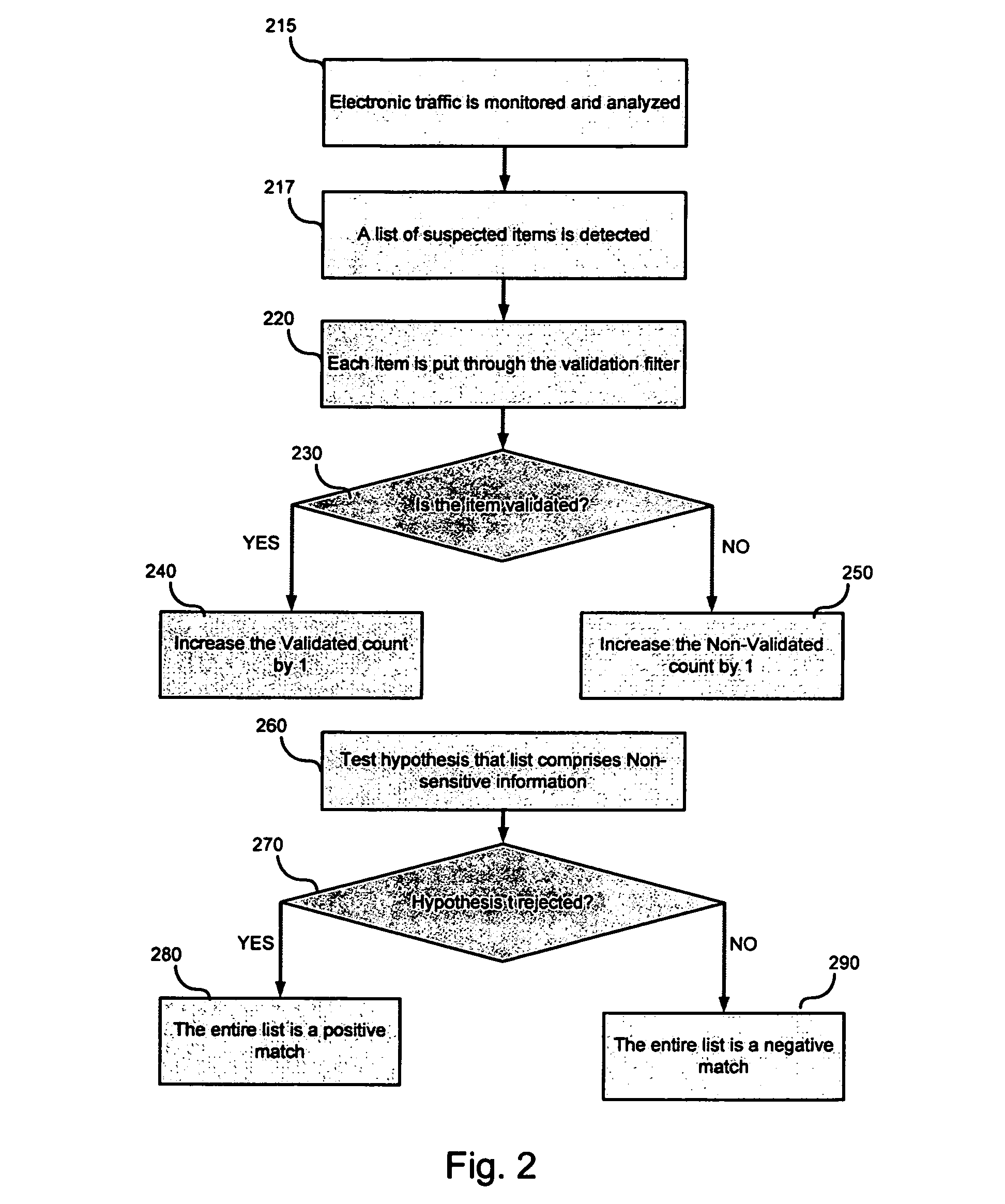

Method and system for information leak prevention

ActiveUS20070028297A1Efficient and cost-effective mitigationReduce errorsDigital data processing detailsUser identity/authority verificationType errorPositive type

A method for mitigating false positive type errors while applying an information leak prevention policy, the method comprising the computer implemented steps of: defining at least one positive criterion for a positive set, wherein the positive criterion comprises at least one indicator of a possible breach of the information leak prevention policy; defining at least one negative criterion for a negative set, wherein the negative criterion comprises at least one indicator of benign traffic; establishing an ambiguity set in association with an intersection between the positive set and the negative set, such that information items in the intersection enter the ambiguity set; defining at least one ambiguity resolution criterion for resolving the ambiguity; monitoring and analyzing electronic traffic, where each information item in the traffic is searched for matches with the positive set; checking for membership of each item in the positive set in the ambiguity set; resolving ambiguities using one of the ambiguity resolution criterion for each member of the ambiguity set and removing items from the positive set accordingly, and applying information leak prevention policy for all items remaining in the positive set following the removal of items using ones of the ambiguity resolution criteria.

Owner:FORCEPOINT LLC

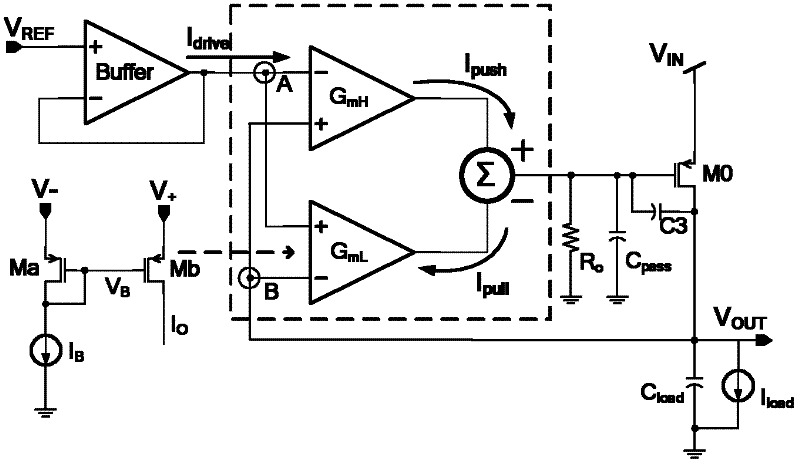

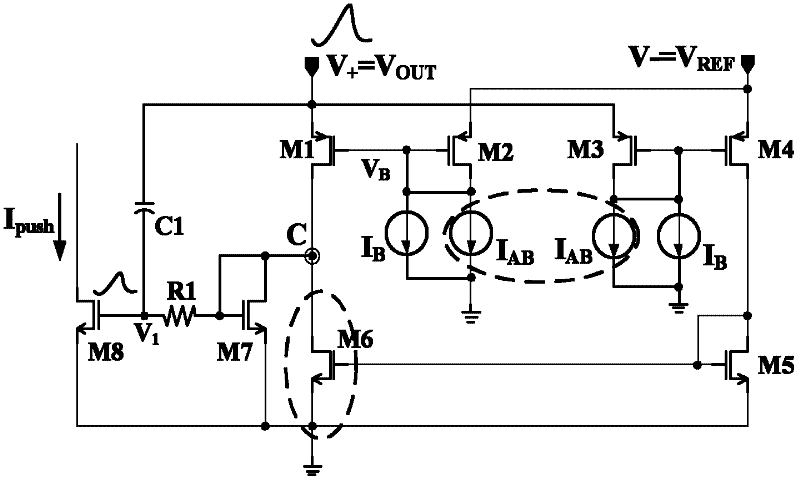

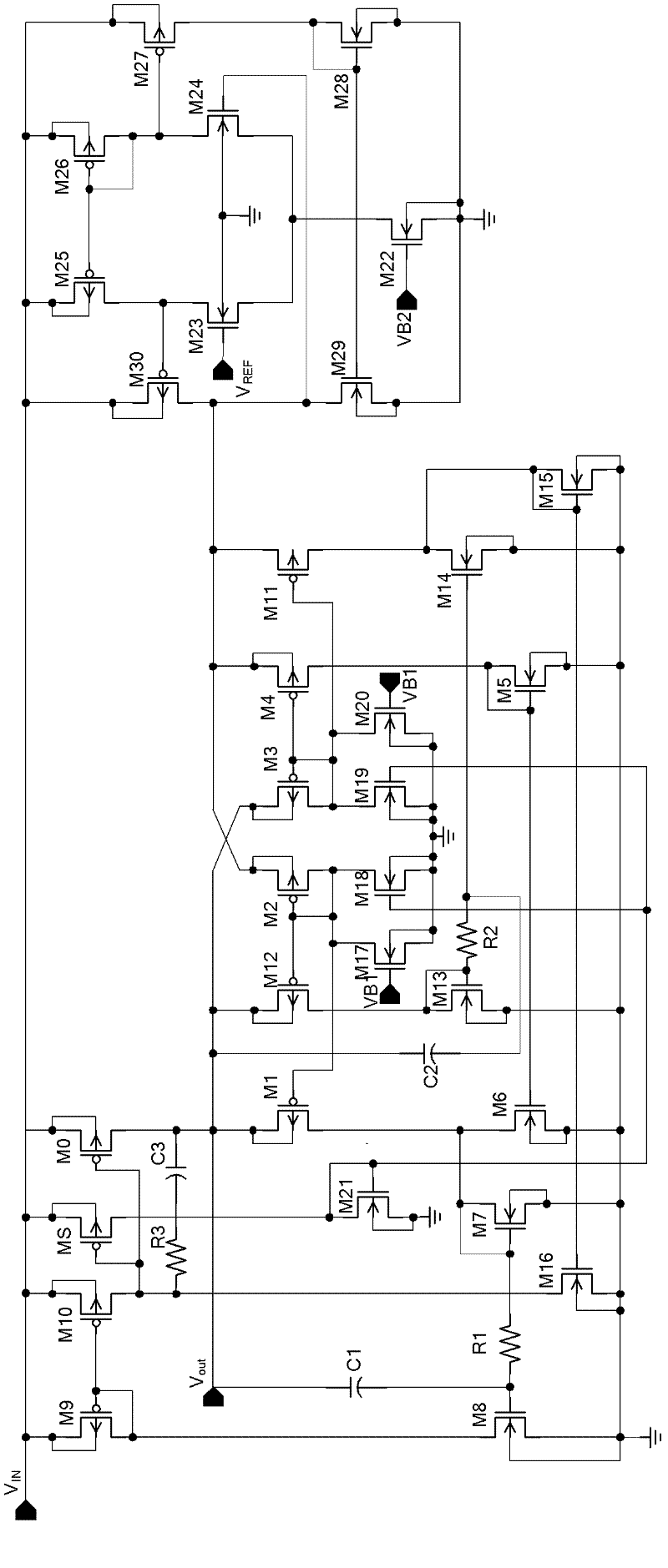

Low dropout linear voltage regulator

InactiveCN102385408AIncrease slew rateHigh bandwidthElectric variable regulationLinear regulatorCapacitance

The invention, belonging to the technical field of power supply management, discloses a low dropout linear voltage regulator, which comprises a power tube, a buffer, a first transconductance amplifier, a second transconductance amplifier, a current subtractor and a Miller compensation capacitor. The low dropout linear voltage regulator can remarkably increase slew rate and bandwidth of a common grid type error amplifier and enlarge the scope of the input common-mode voltage by three techniques of adaptive current bias, the current subtractor and capacitance coupling type dynamic charge and discharge, so that transient response speed of the linear voltage regulator is greatly increased and amplitude of the output voltage peak is reduced, meanwhile, good stability of a loop circuit is ensured.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

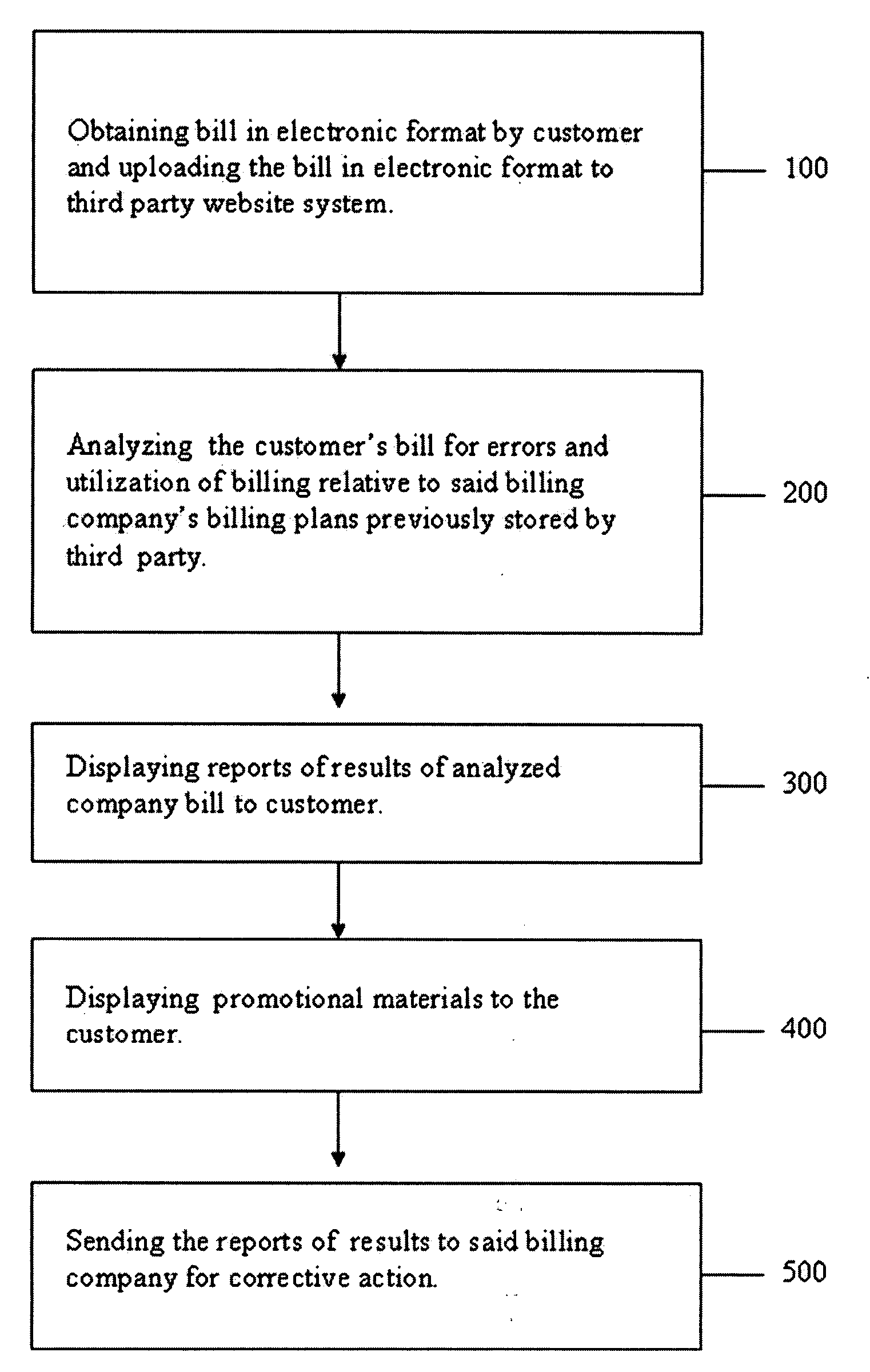

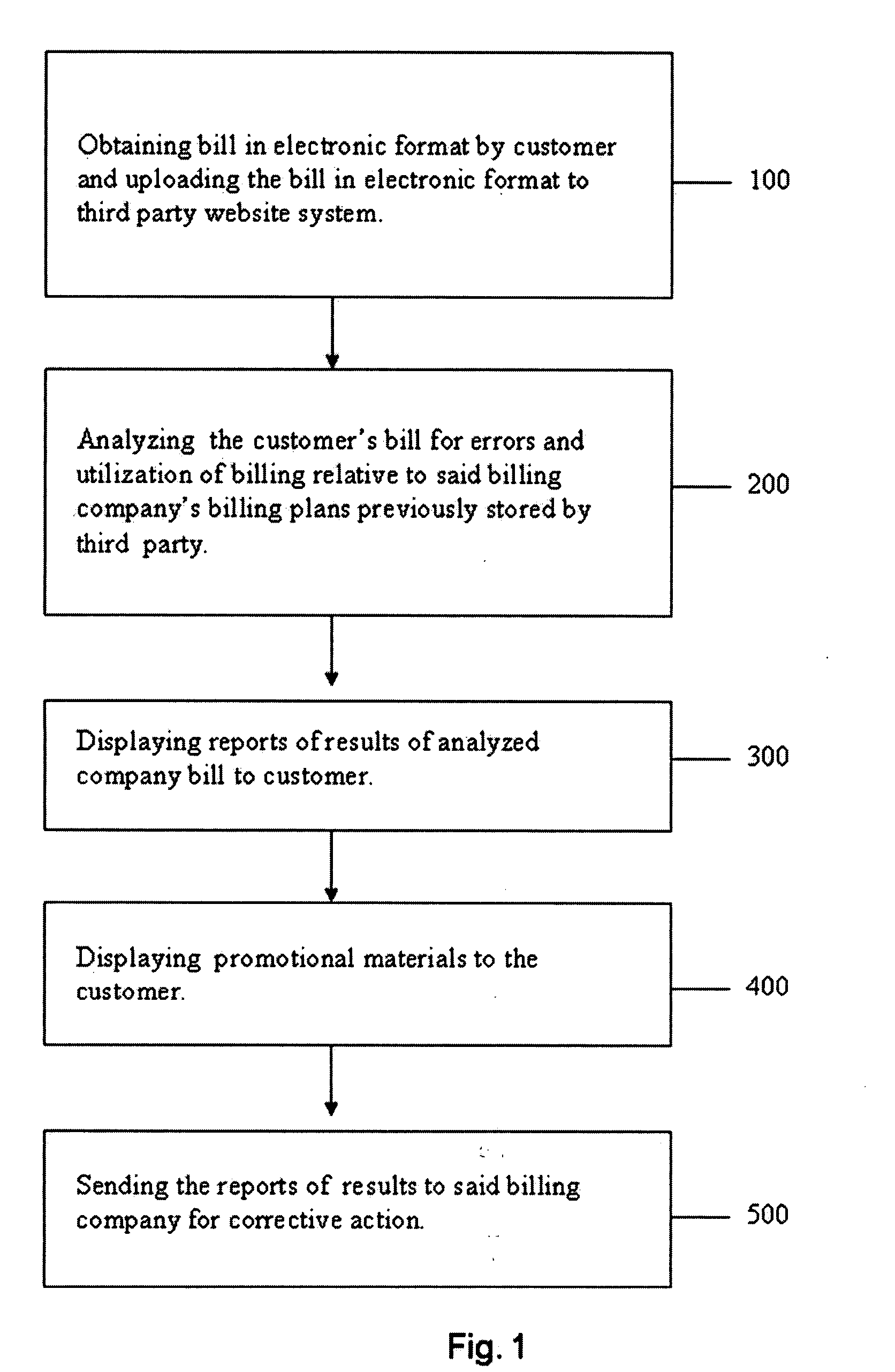

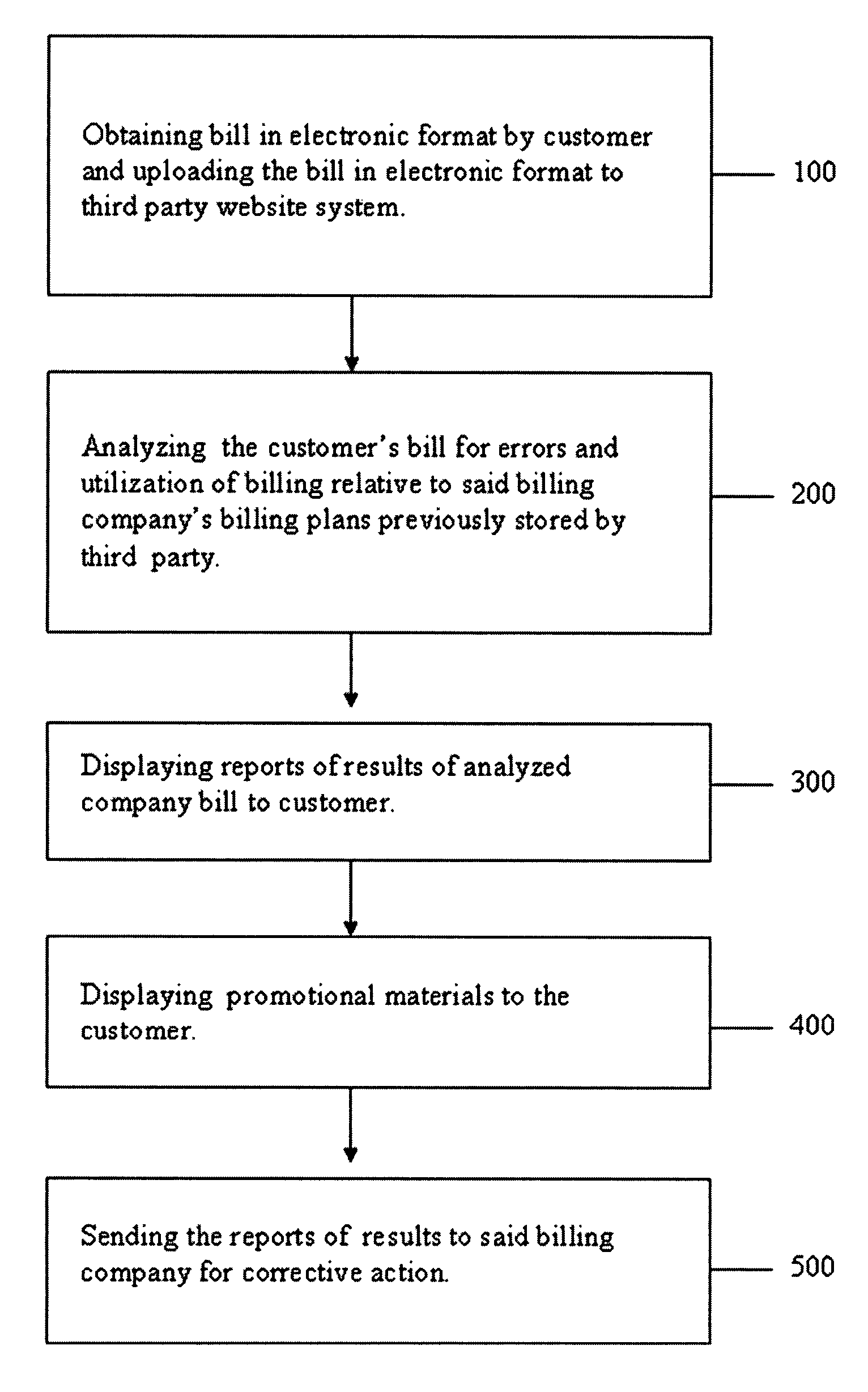

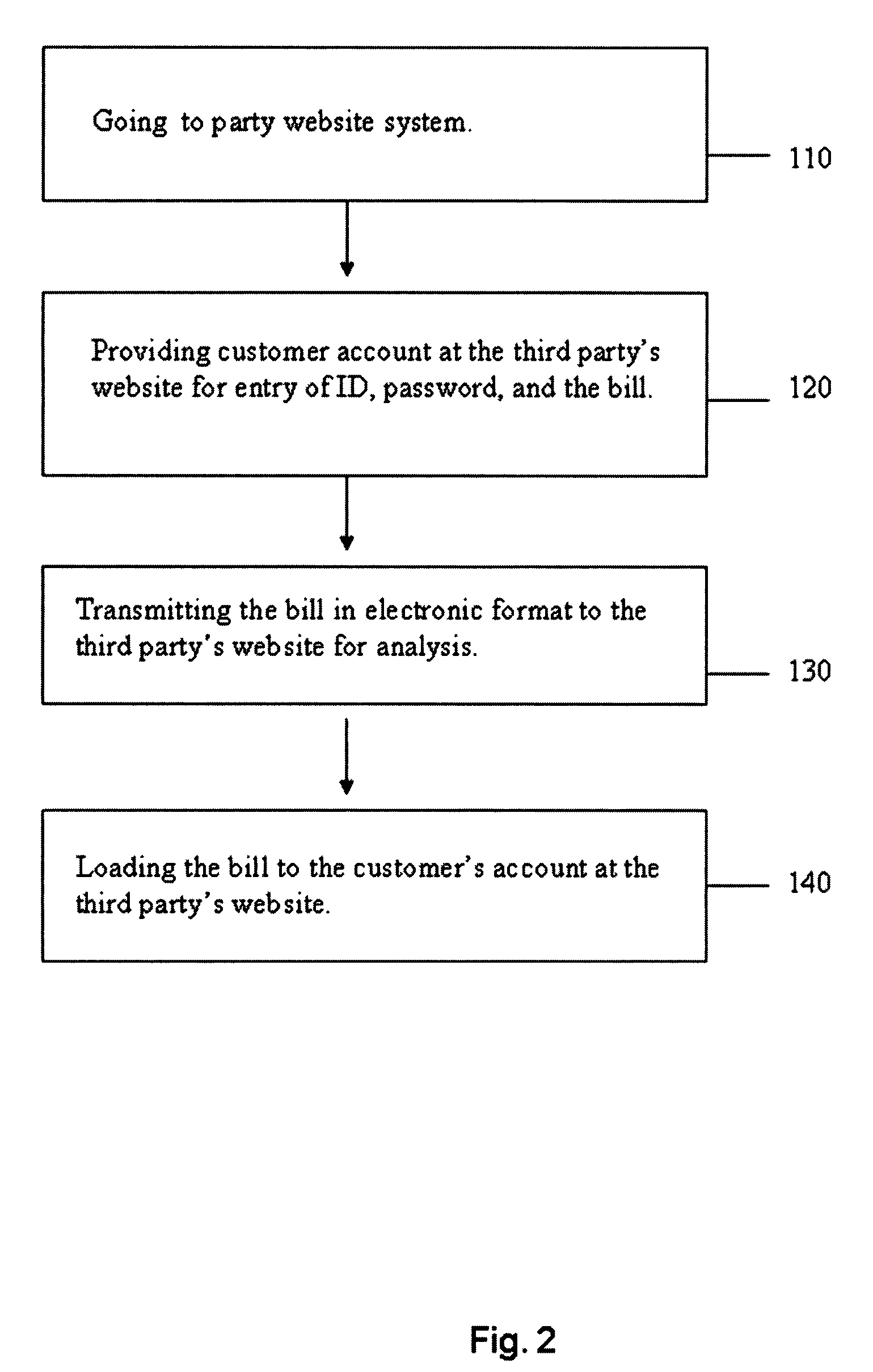

Web based auto bill analysis method

Method for automatically analyzing customer's bill, such as cell phone bill, received in electronic format for errors and utilization against company's published plan by third-party on third-party's website for customer. The company's published plan is previously stored on third-party's website. Third-party advises customer of results, in real-time, and provides blind feedback to billing company by type error and utilization. Results and feedback are specific to each customer and billing company, and also provides security for both. Promotional materials are provided to customer for revenue to third-party.

Owner:VALIDAS LLC

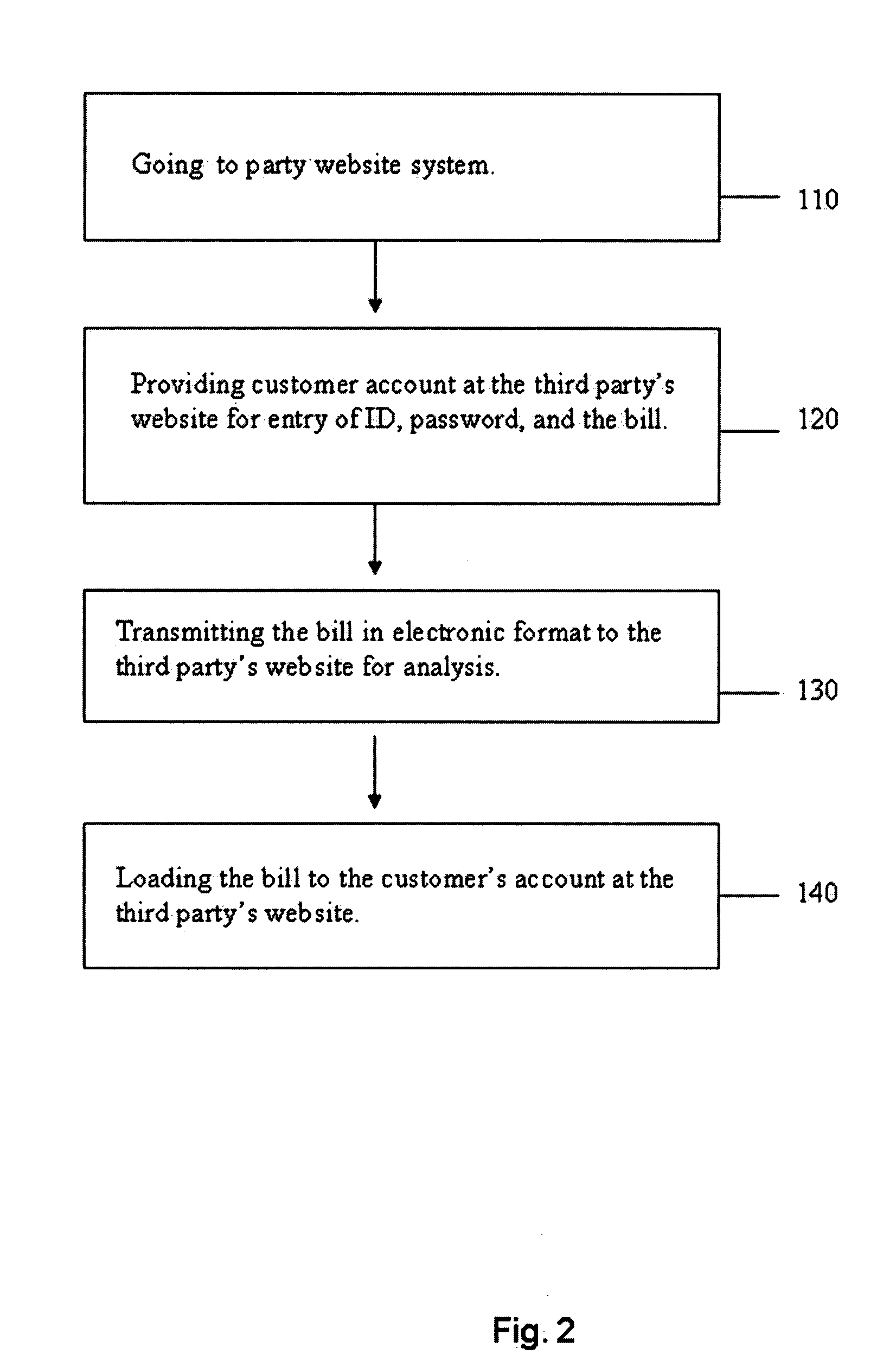

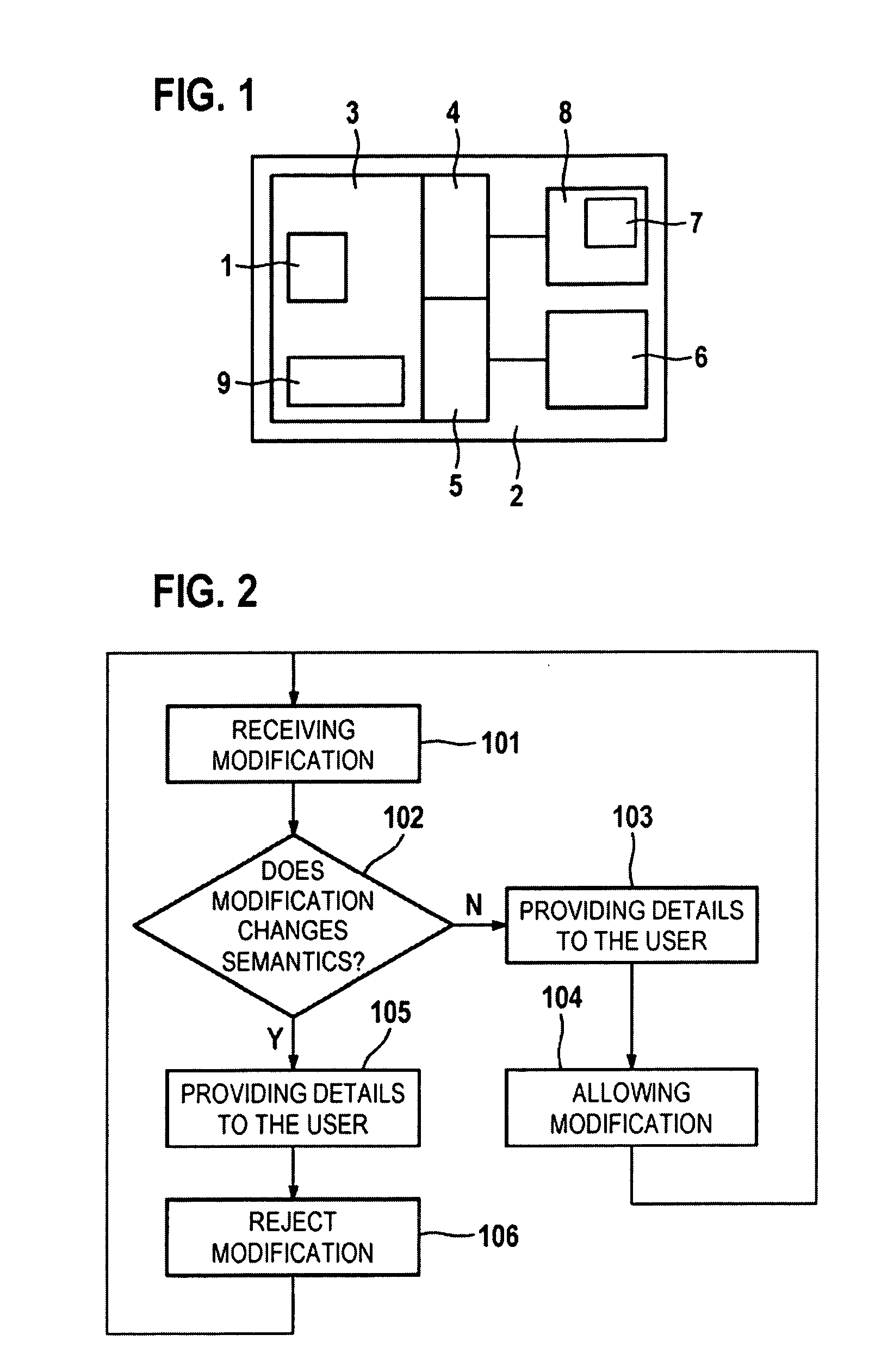

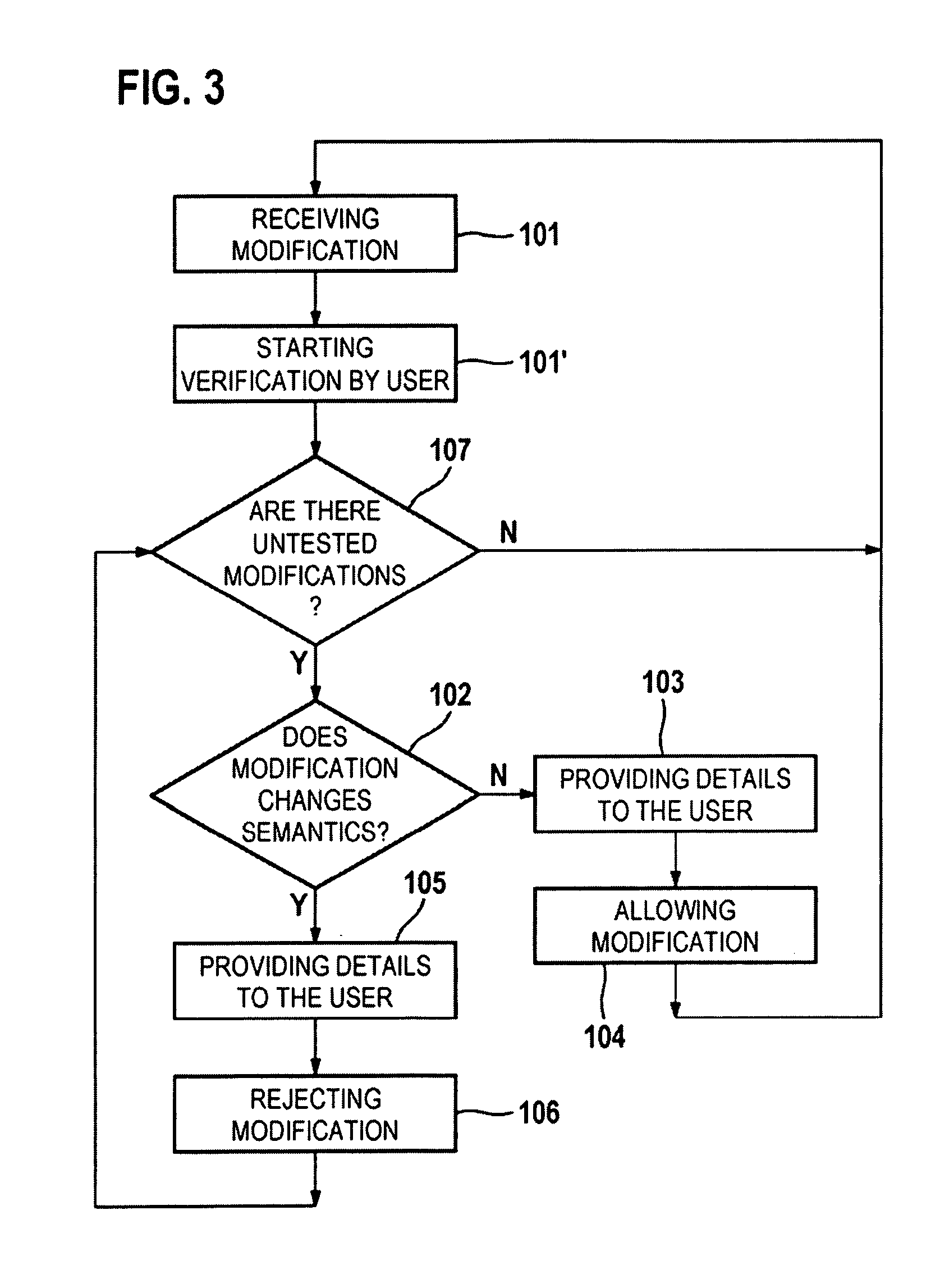

Method and System for Editing Source Code

InactiveUS20080172660A1Low system requirementsIncrease the number ofSoftware designIntelligent editorsData processing systemType error

The present invention relates to the field of computer programming. More specifically the invention relates to a method and a data processing system for editing the source code of a computer program. It is an object of the present invention to provide an easy source code editing technique, by which programming errors and type errors can reliably be avoided in cases where changes to the program are supposed not to change the semantics of the program. This object is achieved according to the invention by a method for editing source code, the method comprising the steps of: receiving a modification to the source code, said modification being made by a user, determining whether the modification would change the semantics of the source code, and handling the modification depending on the result of the determining step.

Owner:IBM CORP

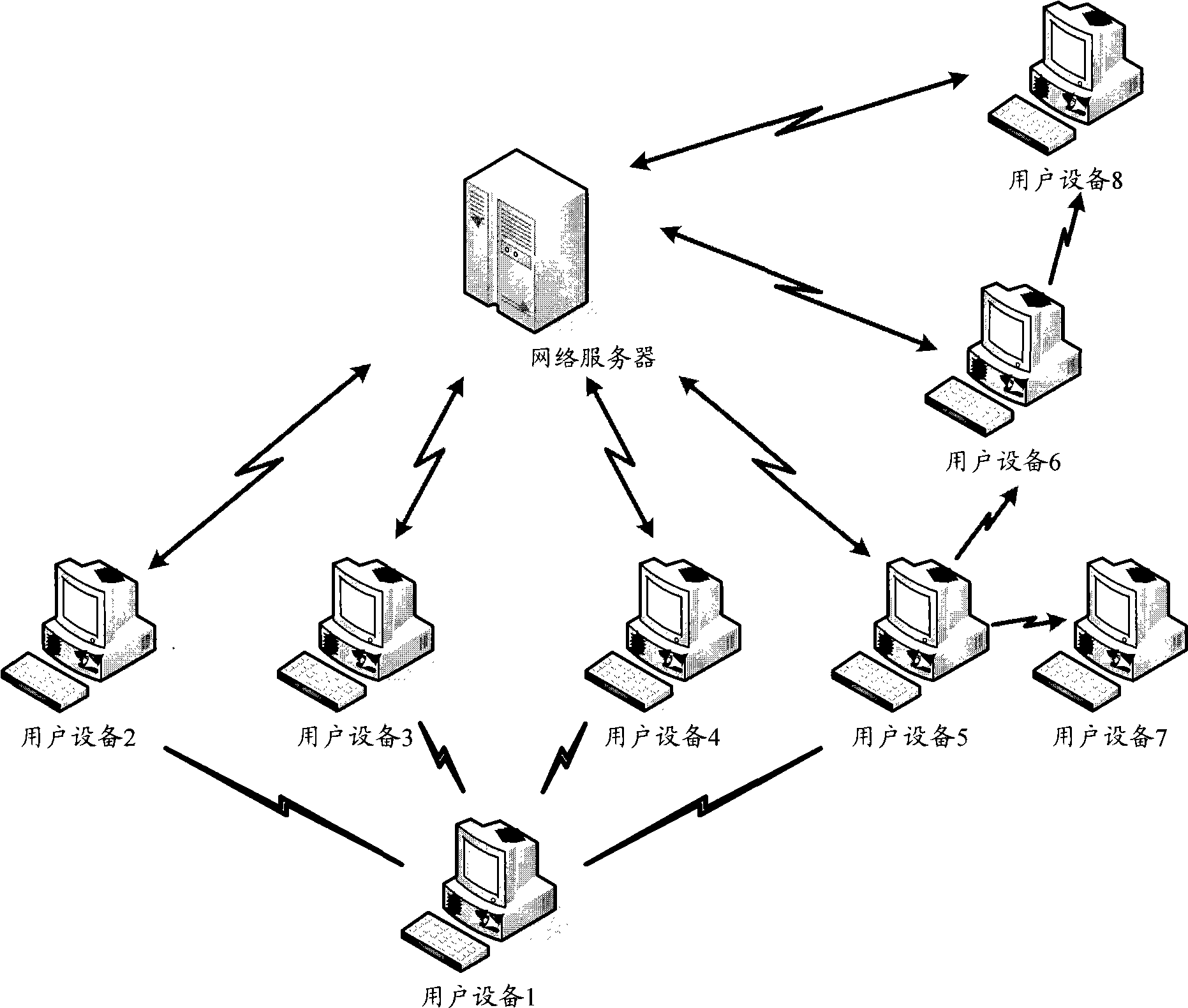

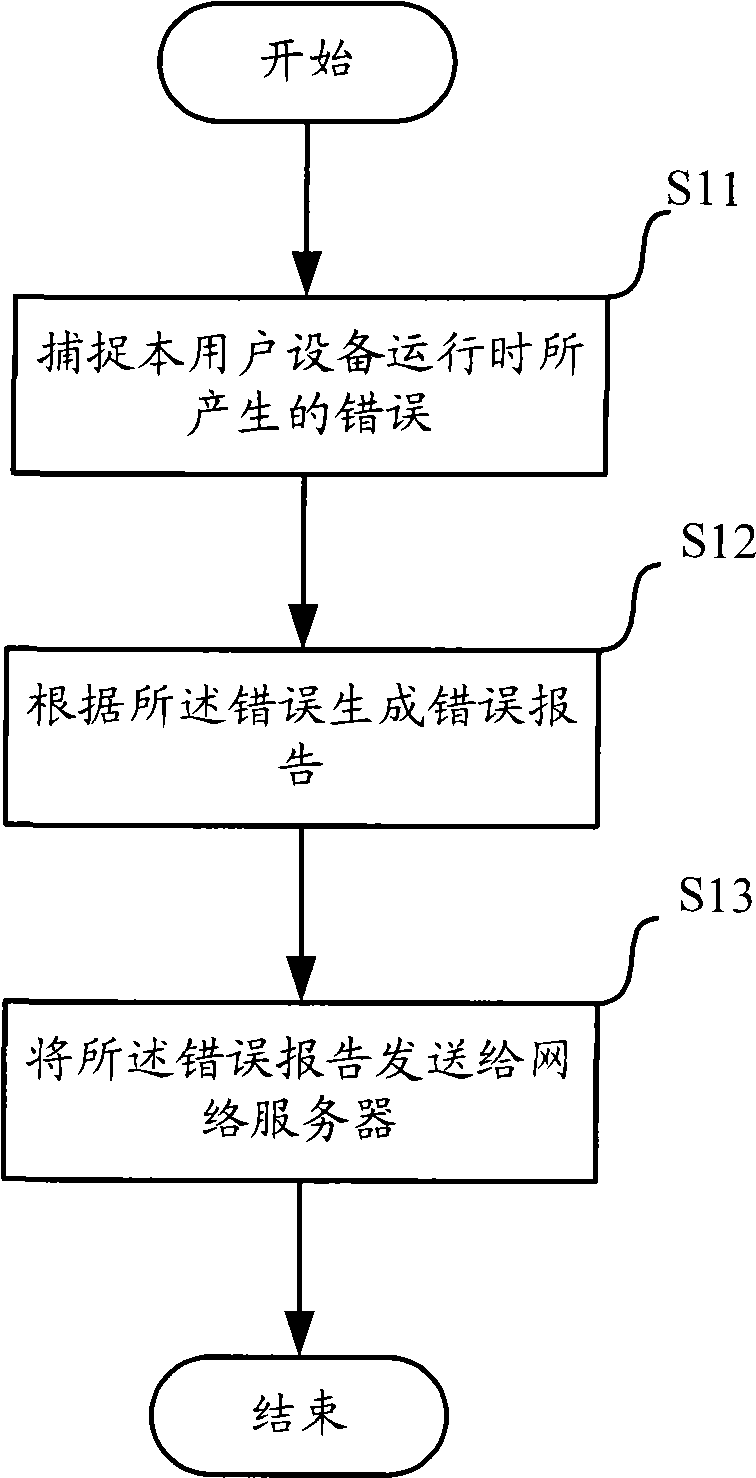

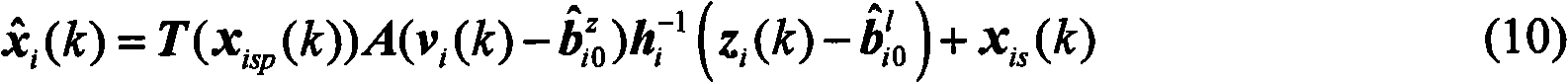

Method and apparatus for error control in network system

The invention provides a technical proposal for controlling errors in network systems. The technical proposal comprises the following steps: an user device captures the error generated in the operation of the user device to generate an error report which is sent to a network server through the user device; the network server collects the errors of a plurality of user devices and carries out analysis of the errors; and if the occurrence times of a same type errors reach to a preset threshold value, a corresponding processing can be executed. Through adopting the method and the device of the invention, the network server can know the errors generated by a plurality of user devices, and the cause of the errors can be found out through carrying out a statistical analysis of the errors and a corresponding processing measure can be adopted in time. The user device can also carry out analysis to the captured errors, sets the type of the errors and adopts a corresponding processing measure to deal with the errors in time.

Owner:SYNACAST COMP SYST SHANGHAI

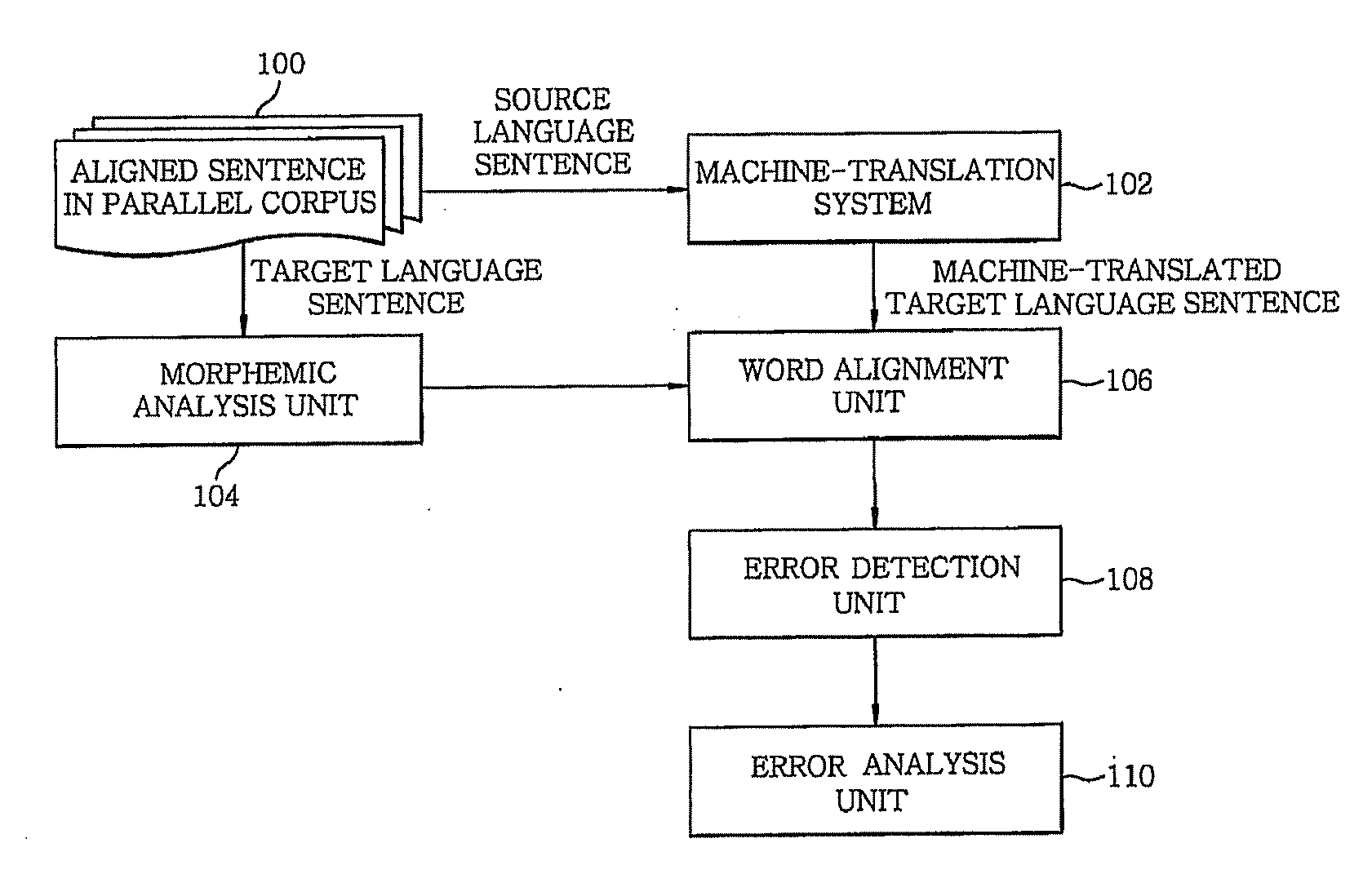

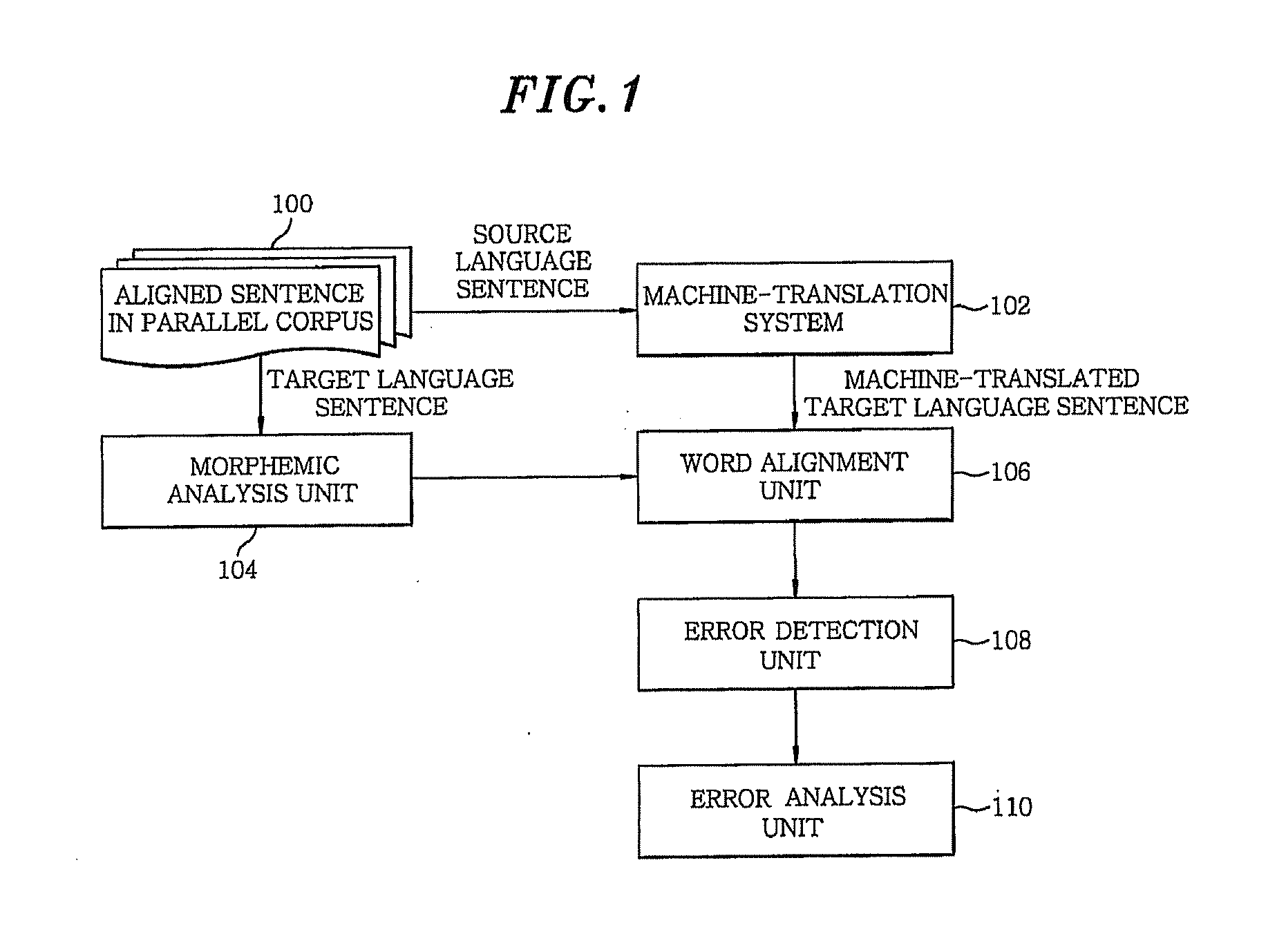

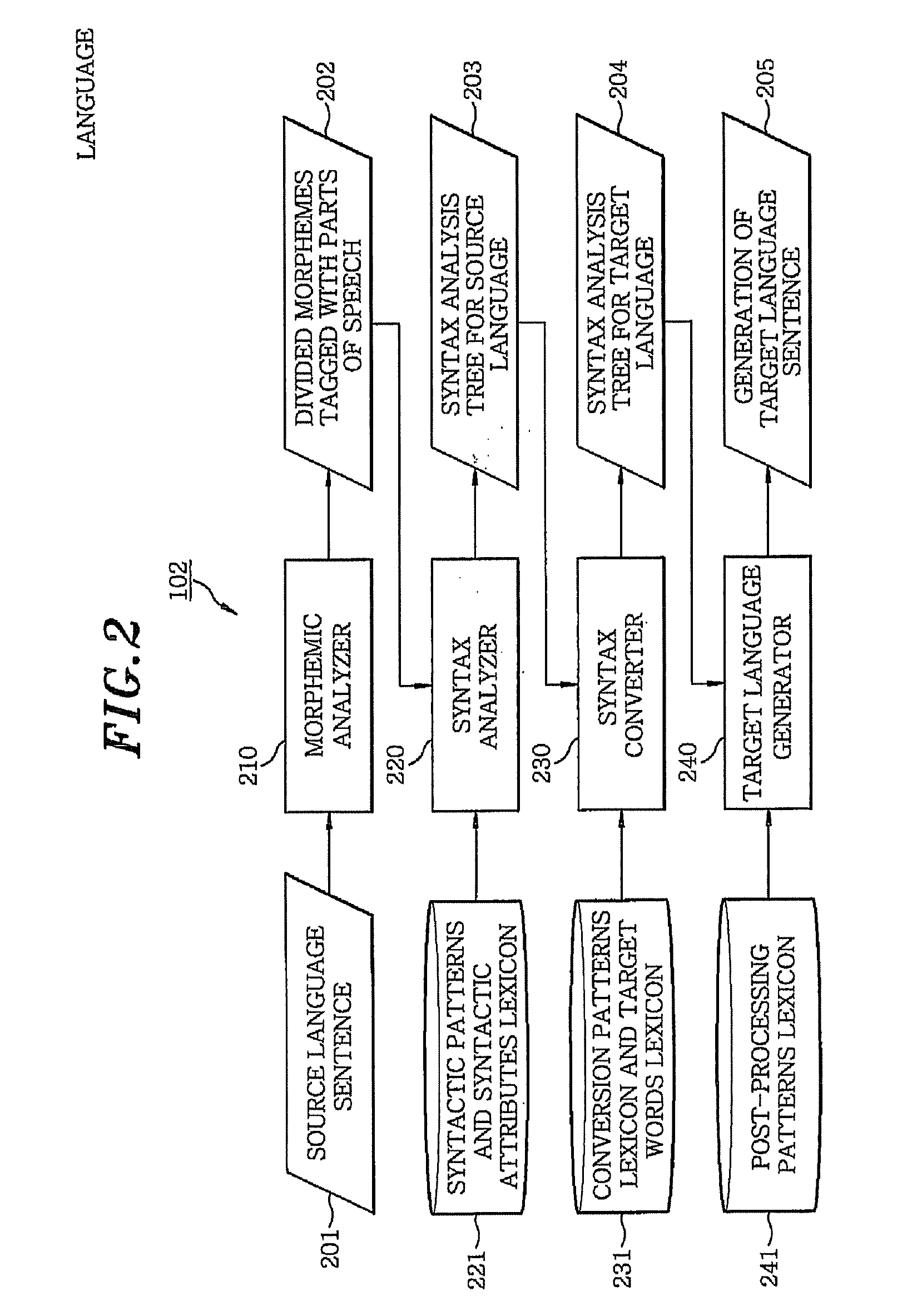

Method and apparatus for detecting errors in machine translation using parallel corpus

ActiveUS20100070261A1Improve performanceNatural language translationSpecial data processing applicationsType errorMorpheme

A method for automatically detecting errors in machine translation using a parallel corpus includes analyzing morphemes of a target language sentence in the parallel corpus and a machine-translated target language sentence, corresponding to a source language sentence, to classify the morphemes into words; aligning by words and decoding, respectively, a group of the source language sentence and the machine-translated target language sentence, and a group of the source language sentence and the target language sentence in the parallel corpus; classifying by types errors in the machine-translated target language sentence by making a comparison, word by word, between the decoded target language sentence in the parallel corpus and the decoded machine-translated target language sentence; and computing error information in the machine-translated target language sentence by examining a frequency of occurrence of the classified error types.

Owner:ELECTRONICS & TELECOMM RES INST

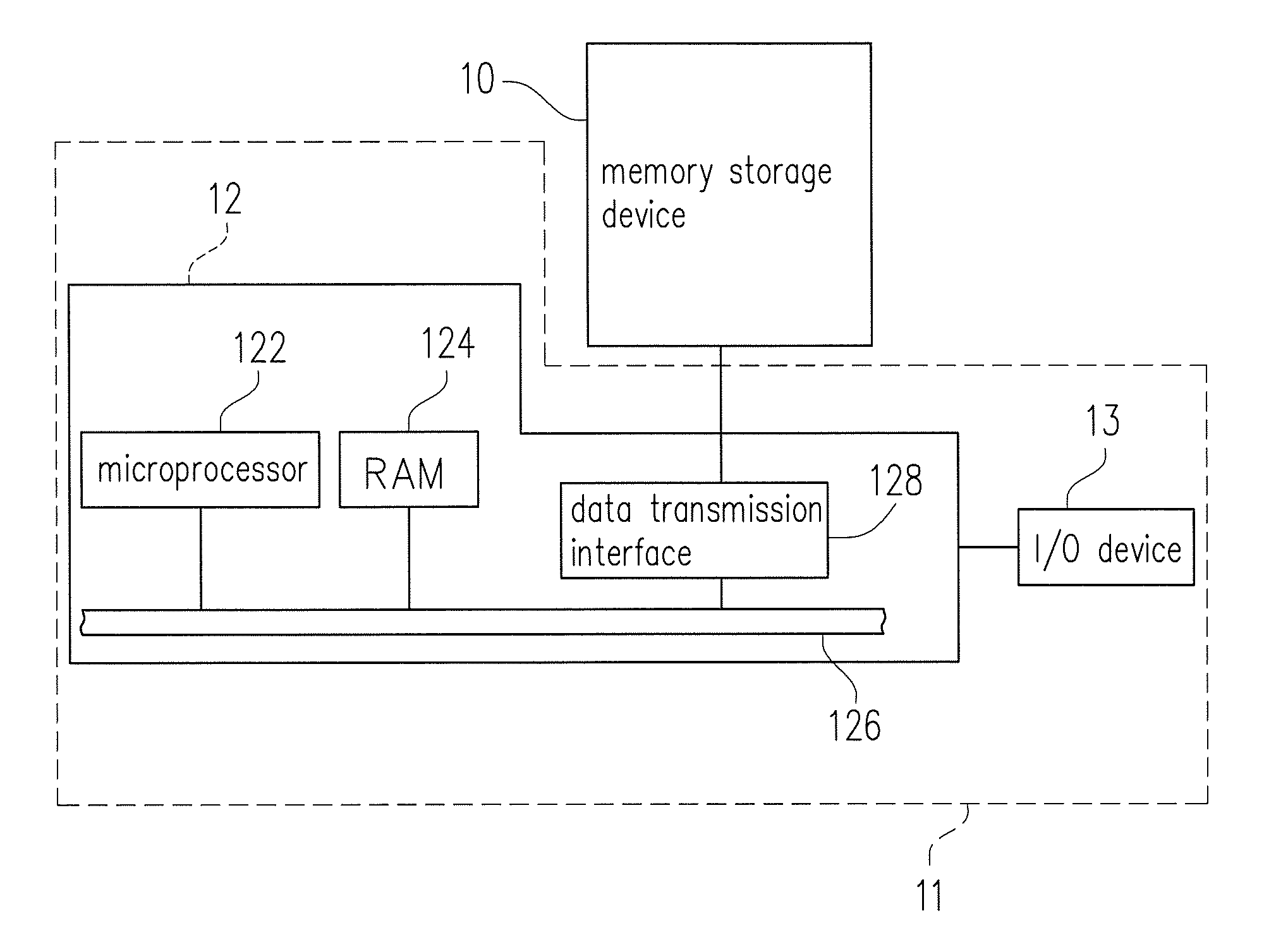

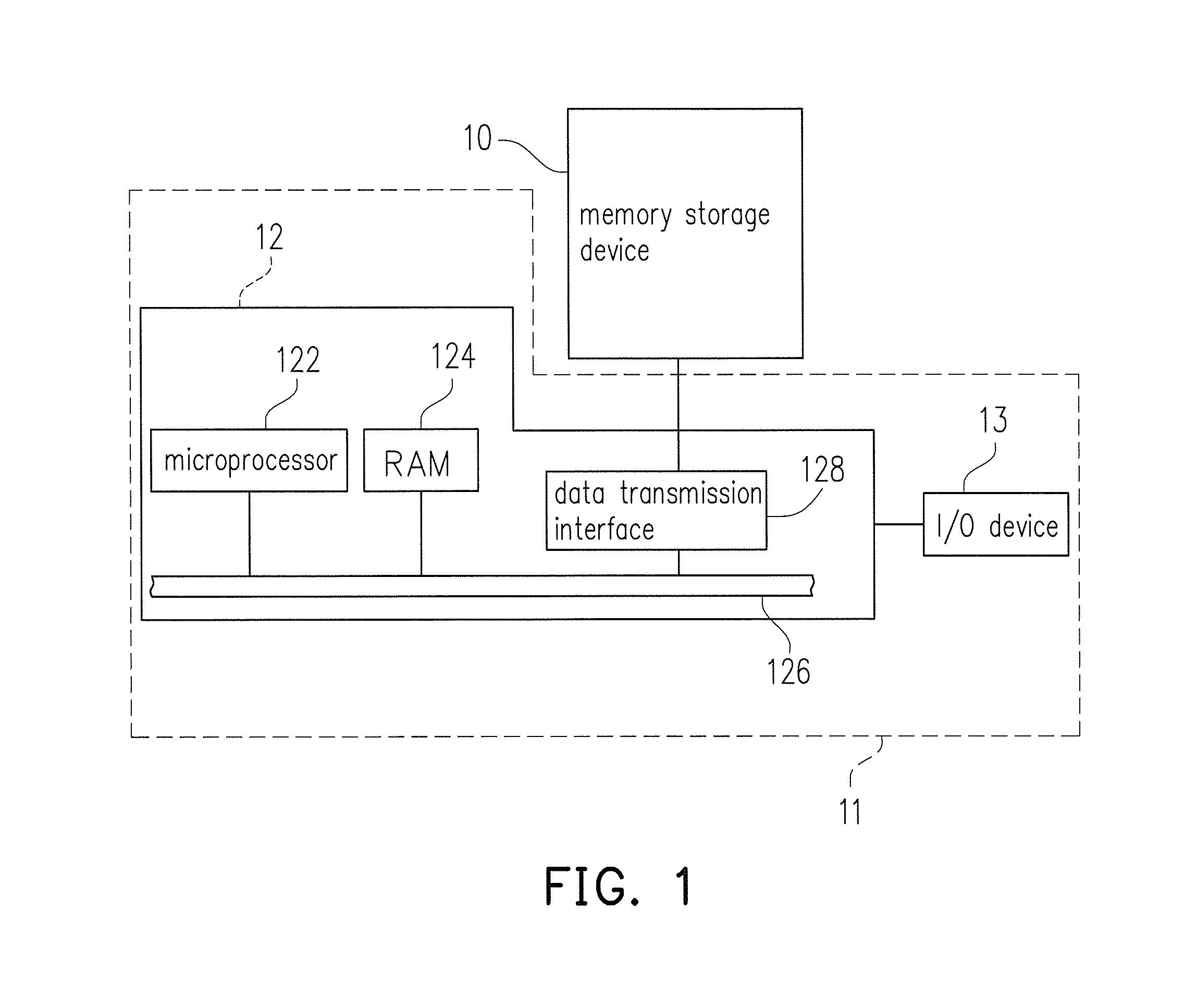

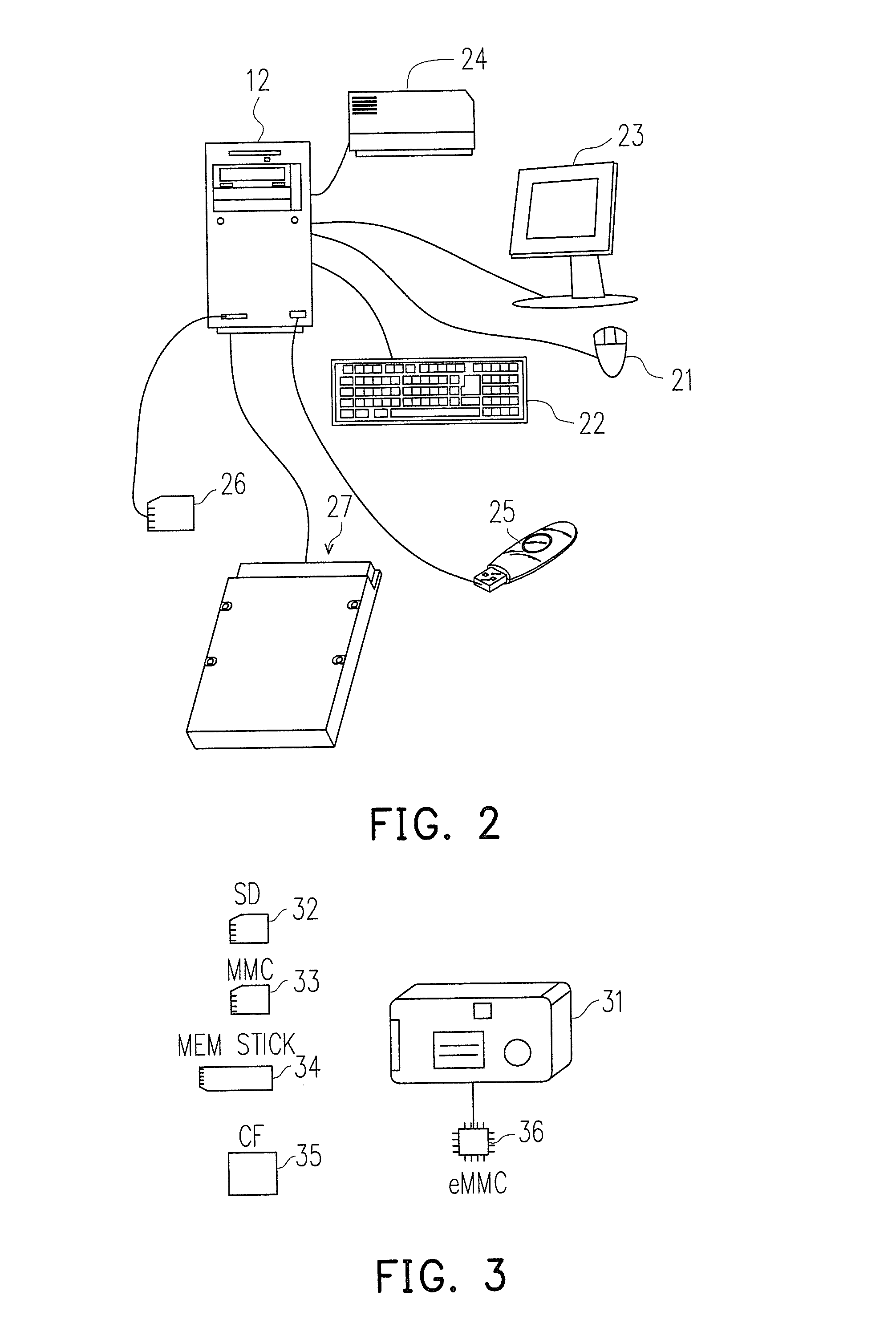

Error processing method, memory storage device and memory controlling circuit unit

An error processing method for a rewritable non-volatile memory module, a memory storage device and a memory controlling circuit unit are provided. The rewritable non-volatile memory module includes a plurality of memory cells. The error processing method includes: sending a first read command sequence for reading a plurality of bits from the memory cells; performing a first decoding on the bits; determining whether each error belongs to a first type error or a second type error if the bits have at least one error; recording related information of a first error in the at least one error if the first error belongs to the first type error; and not recording the related information of the first error if the first error belongs to the second type error. Accordingly, errors with particular type may be processed suitably.

Owner:PHISON ELECTRONICS

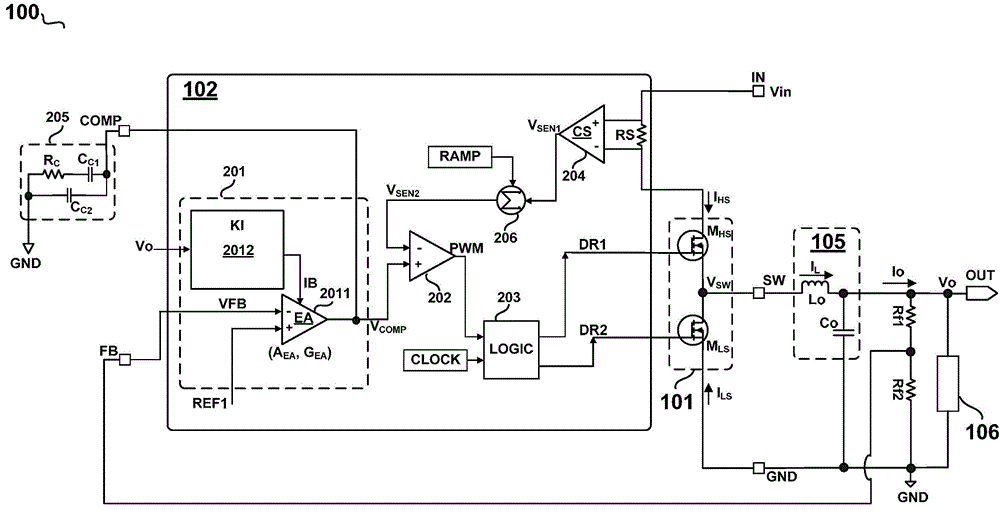

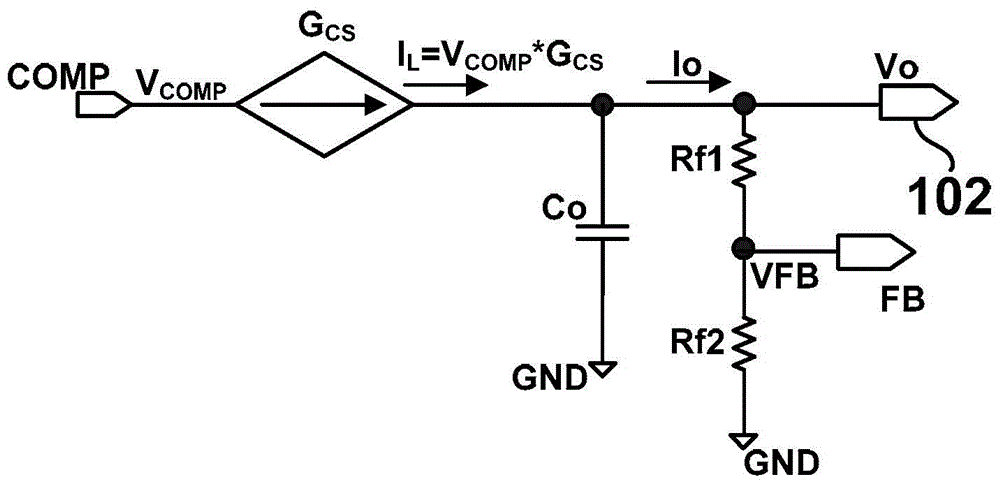

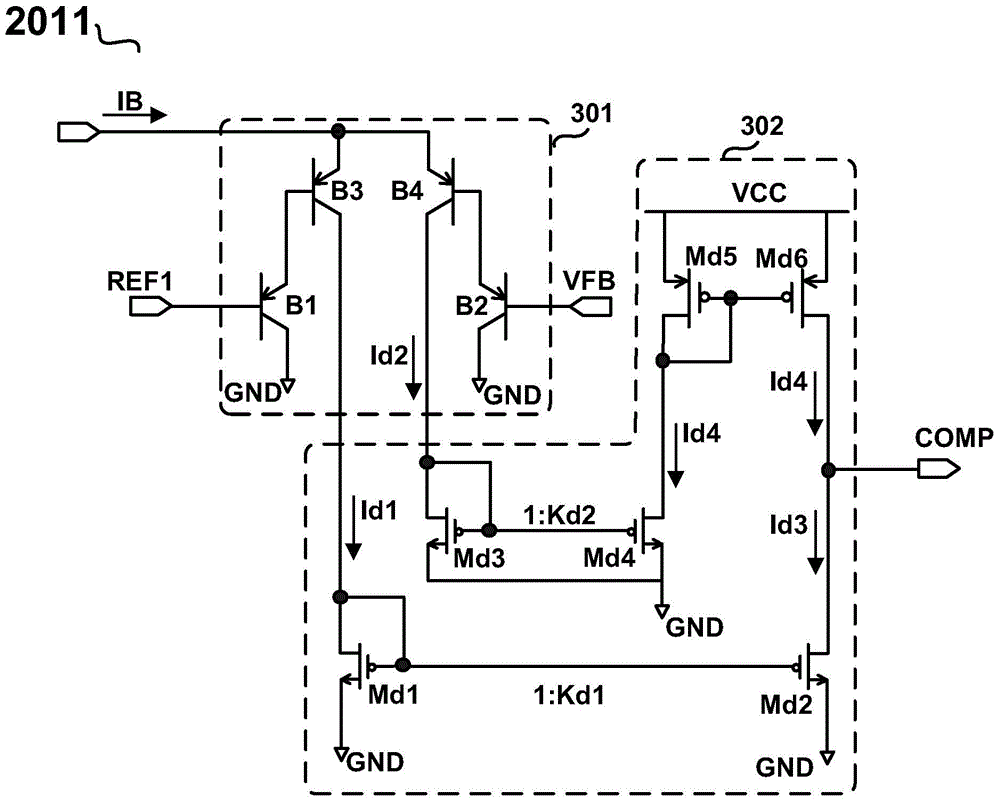

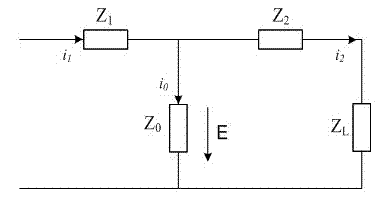

Transconductance adjustment circuit, transconductance type error amplification unit and switching type power converter

ActiveCN104092360AStable bandwidthNegative-feedback-circuit arrangementsDc-dc conversionNegative feedbackType error

Disclosed are a transconductance adjustment circuit, a transconductance type error amplification unit and a switching type power converter. The transconductance adjustment circuit is at least partially based on the output voltage of the switching type power converter to generate a bias current directly proportional to the output voltage, the bias current is provided for a transconductance type error amplifier in the transconductance type error amplification unit, and therefore transconductance of the transconductance type error amplifier is directly proportional to the output voltage. A negative feedback loop is adopted by the switching type power converter to adjust the output voltage of the power converter, the transconductance adjustment circuit and the transconductance type error amplification unit enable the bandwidth of the negative feedback loop to be basically stable, and the bandwidth is not affected by changes of the expected value of the output voltage.

Owner:CHENGDU MONOLITHIC POWER SYST

Web based auto bill analysis method

Method for automatically analyzing customer's bill, such as cell phone bill, received in electronic format for errors and utilization against company's published plan by third-party on third-party's website for customer. The company's published plan is previously stored on third-party's website. Third-party advises customer of results, in real-time, and provides blind feedback to billing company by type error and utilization. Results and feedback are specific to each customer and billing company, and also provides security for both. Promotional materials are provided to customer for revenue to third-party.

Owner:VALIDAS LLC

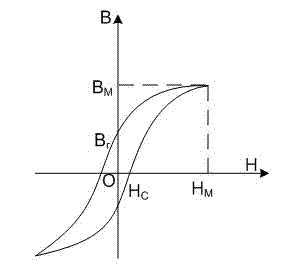

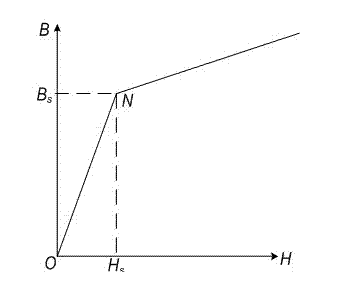

Method and device for measuring direct current magnetic bias error characteristics of current transformer

ActiveCN103207379AEasy to adjustSolve the traceability problemElectrical measurementsType errorComputed tomography

The invention discloses a method and device for measuring direct current magnetic bias error characteristics of a current transformer. Current is simulated into a power frequency current source and a direct-current current source according to an equal ampere-turn principle, wherein the power frequency current source and the direct-current current source are independent, the standard computed tomography CT is used for detecting variation of error characteristics of the measured CT influenced by direct current magnetic bias, a method and device for measuring current comparison type error characteristics or voltage comparison type error characteristics is included, data can be compared in a whole process, and the method and device is suitable for measurement of error characteristics of during direct current magnetic bias of a straight through current transformer and also suitable for checking direct current magnetic bias error characteristics of current transformer coils made of different iron core materials.

Owner:CHINA ELECTRIC POWER RES INST

Method and system to reduce stray light reflection error in time-of-flight sensor arrays

ActiveUS8194233B2Weakening rangeReduce surface reflectivityOptical rangefindersElectromagnetic wave reradiationSensor arrayType error

Haze-type phase shift error due to stray light reflections in a phase-type TOF system is reduced by providing a windowed opaque coating on the sensor array surface, the windows permitting optical energy to reach light sensitive regions of the pixels, and by reducing optical path stray reflection. Further haze-type error reduction is obtained by acquiring values for a plurality (but not necessarily all) of pixel sensors in the TOF system pixel sensor array. Next, a correction term for the value (differential or other) acquired for each pixel in the plurality of pixel sensors is computed and stored. Modeling response may be made dependent upon pixel (row, column) location within the sensor array. During actual TOF system runtime operation, detection data for each pixel, or pixel groups (super pixels) is corrected using the stored data. Good optical system design accounts for correction, enabling a simple correction model.

Owner:MICROSOFT TECH LICENSING LLC

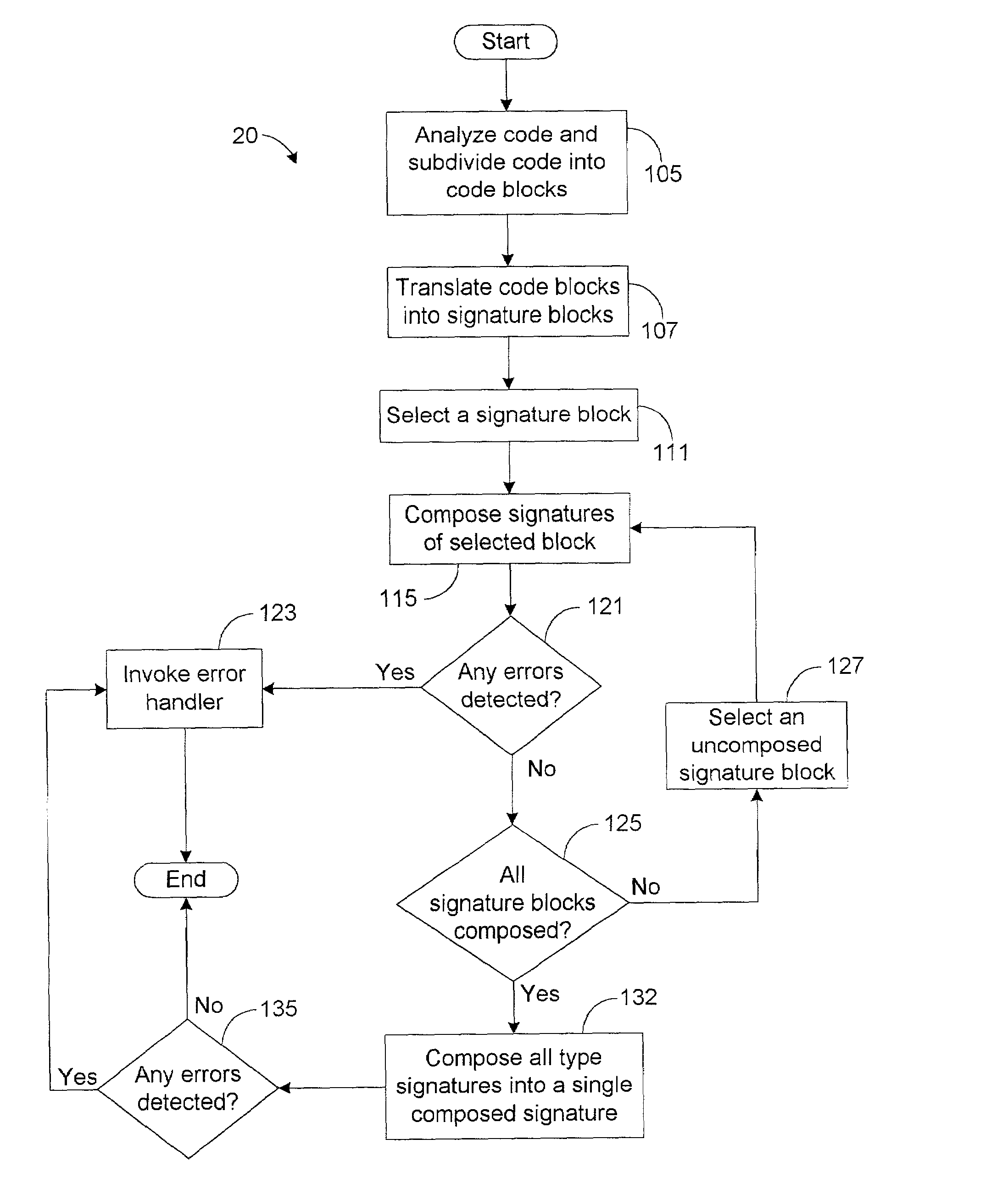

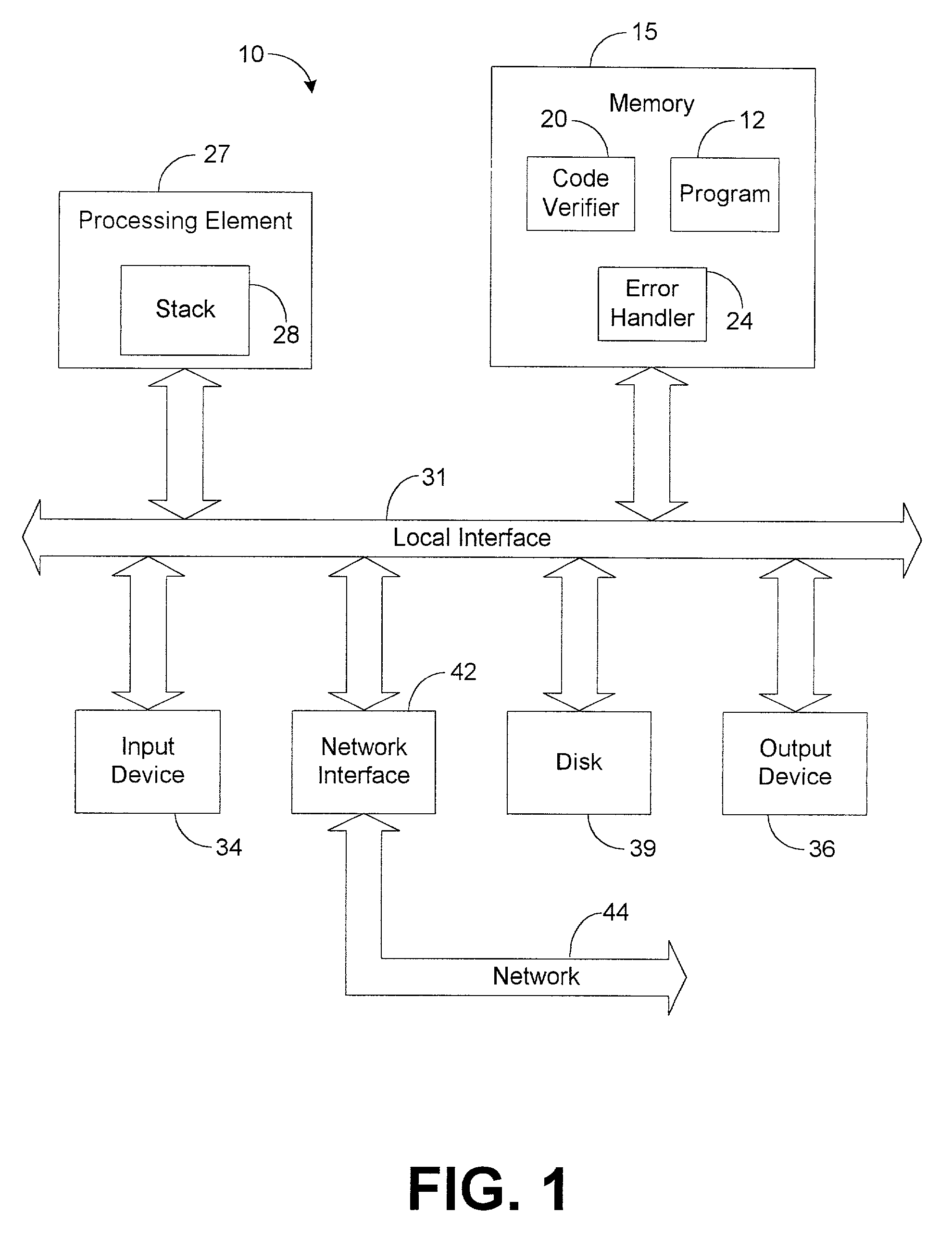

Code verification system and method

A code verification system is utilized to type check compiled code. The code verification system includes memory and a code verifier. The memory is utilized to store a compiled program. The code verifier analyzes instructions of the program and generates a plurality of type signatures based on the instructions The type signatures indicate the input type constraints and the output type descriptions of the instructions, and the code verifier analyzes the type signatures to detect a type error.

Owner:HTC CORP

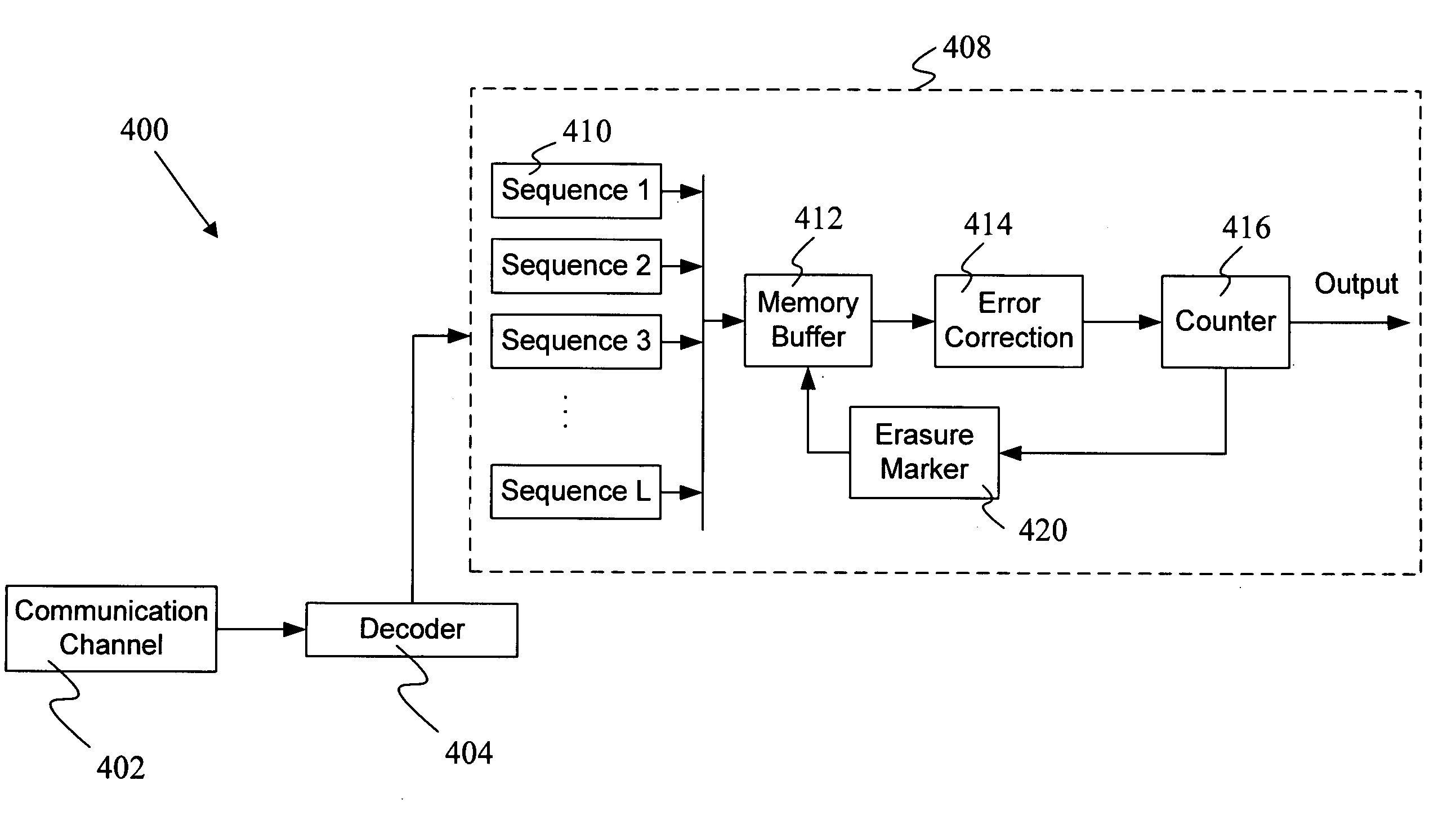

Enhanced interleave type error correction method and apparatus

An enhanced interleave type error correction method is provided in which decoding of an enhanced interleave block is done. Subsequently the decoding may be done by decoding the estimated codewords multiple times using a single error correction code. In addition, a decoder and a digital communication system for implementing the enhanced interleave type error correction method are provided.

Owner:SEAGATE TECH HDD HLDG +3

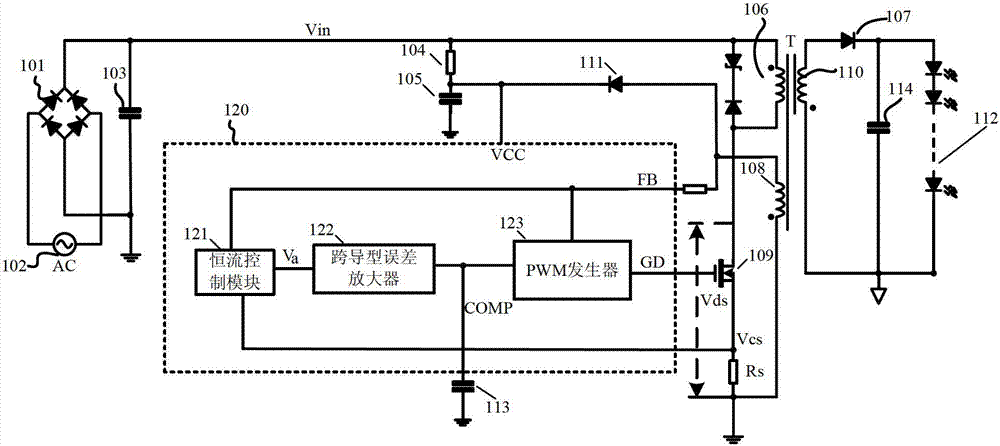

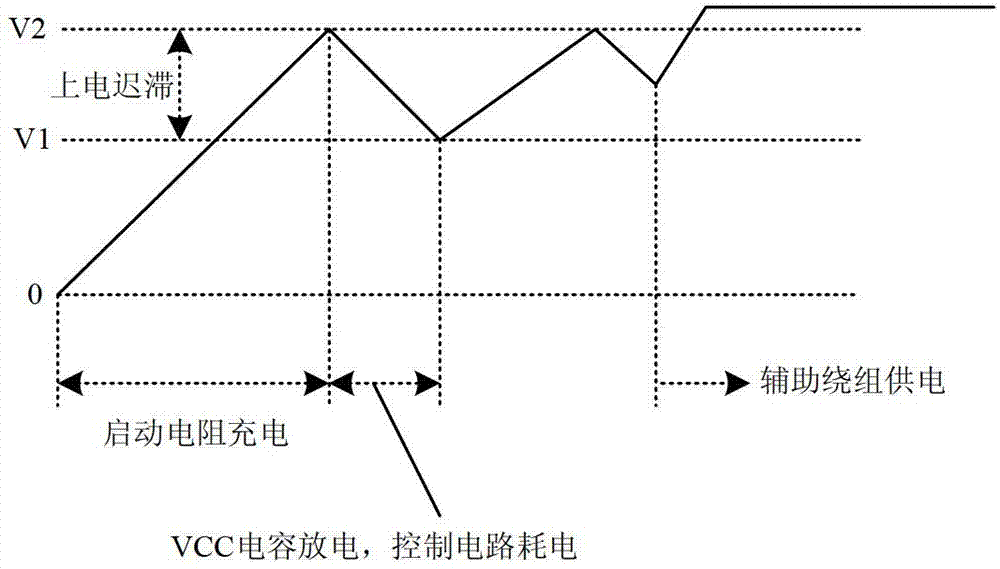

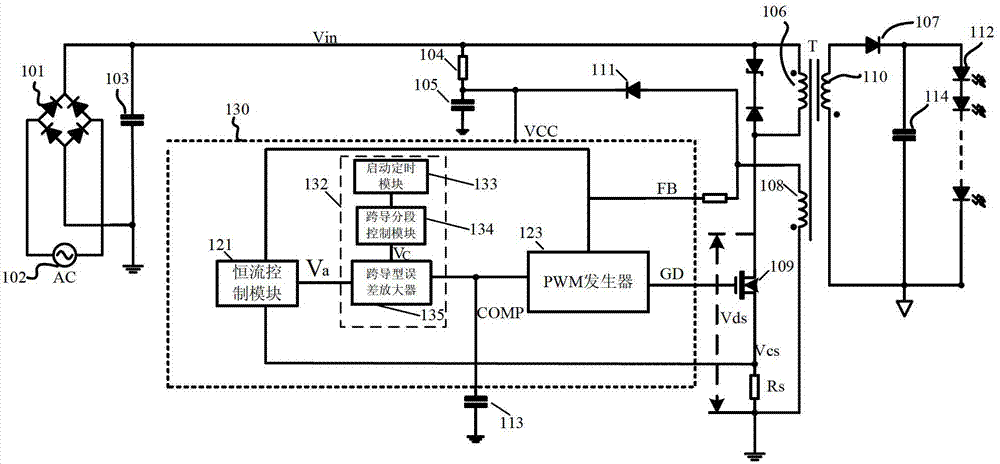

Switching power supply and controller thereof

ActiveCN103051220AQuick responsePrevent bad startupAc-dc conversion without reversalApparatus with intermediate ac conversionCapacitanceType error

The invention provides a switching power supply and a controller thereof. The controller comprises a constant current / constant voltage control module, a subdivision control type error amplifier and a PWM (pulse-width modulation) generator, wherein the constant current / constant voltage control module is used for detecting an output constant current value / an output constant voltage value of the switching power supply, and converting the output constant current value / the output constant voltage value into an equivalent value; the subdivision control type error amplifier is connected with the constant current / constant voltage control module to carry out error amplification on the equivalent value and a preset reference value, and the trans-conductance or the magnification time of the subdivision control type error amplifier are gradually reduced within two or more continuous time buckets after a circuit is started; and the PWM generator is connected with an output end of the subdivision control type error amplifier, the duty ratio of a driving signal is confirmed according to an output signal of the subdivision control type error amplifier, and the driving signal is used for driving a power tube of the switching power supply. According to the witching power supply and the controller, the quick start of the circuit can be realized, the overshoot of output voltage / current can be avoided, and the characteristic of the circuit can not be influenced when the circuit stably works on the premise that the VCC (virtual channel connection) capacitance power supply time is not prolonged.

Owner:HANGZHOU SILAN MICROELECTRONICS

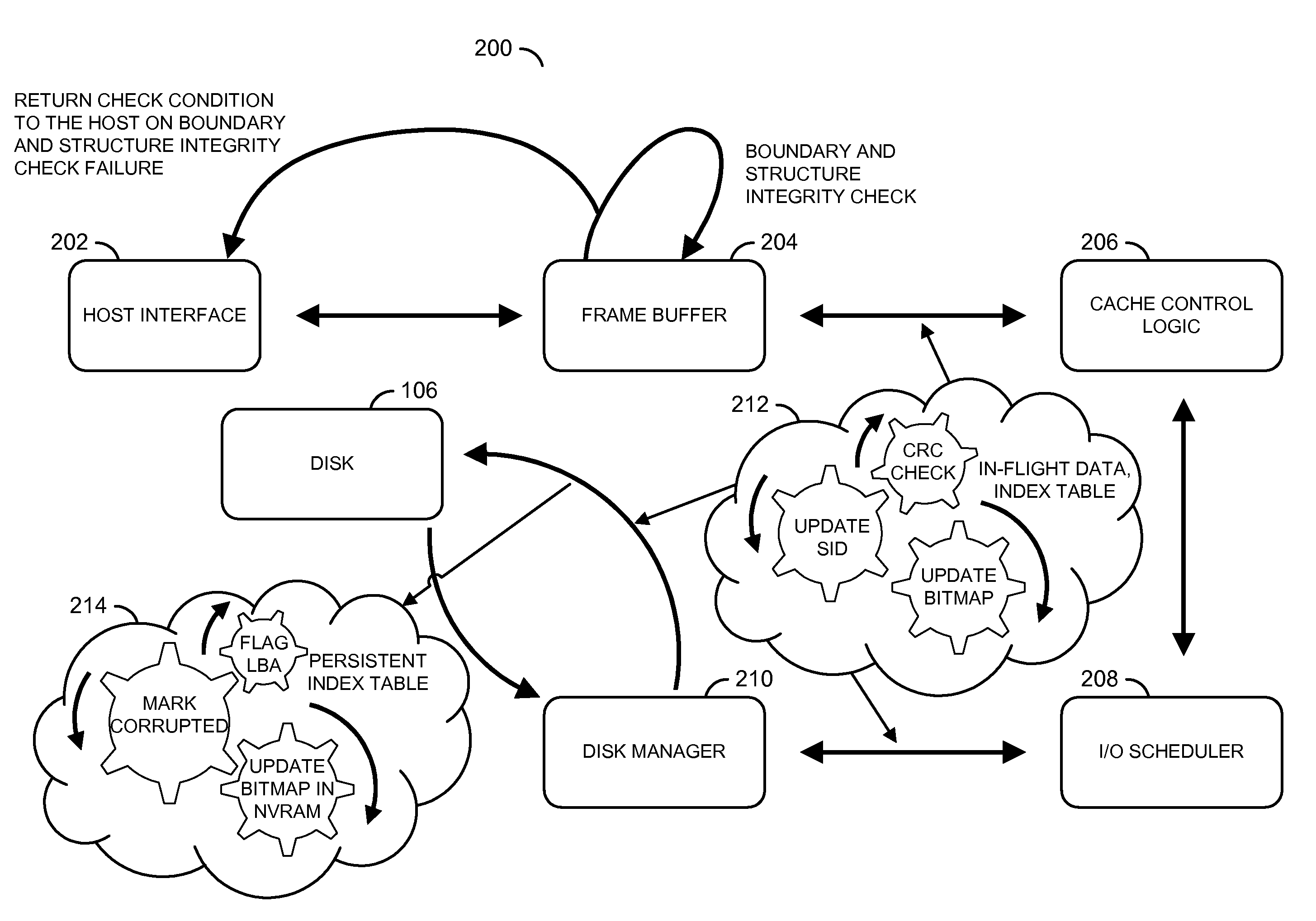

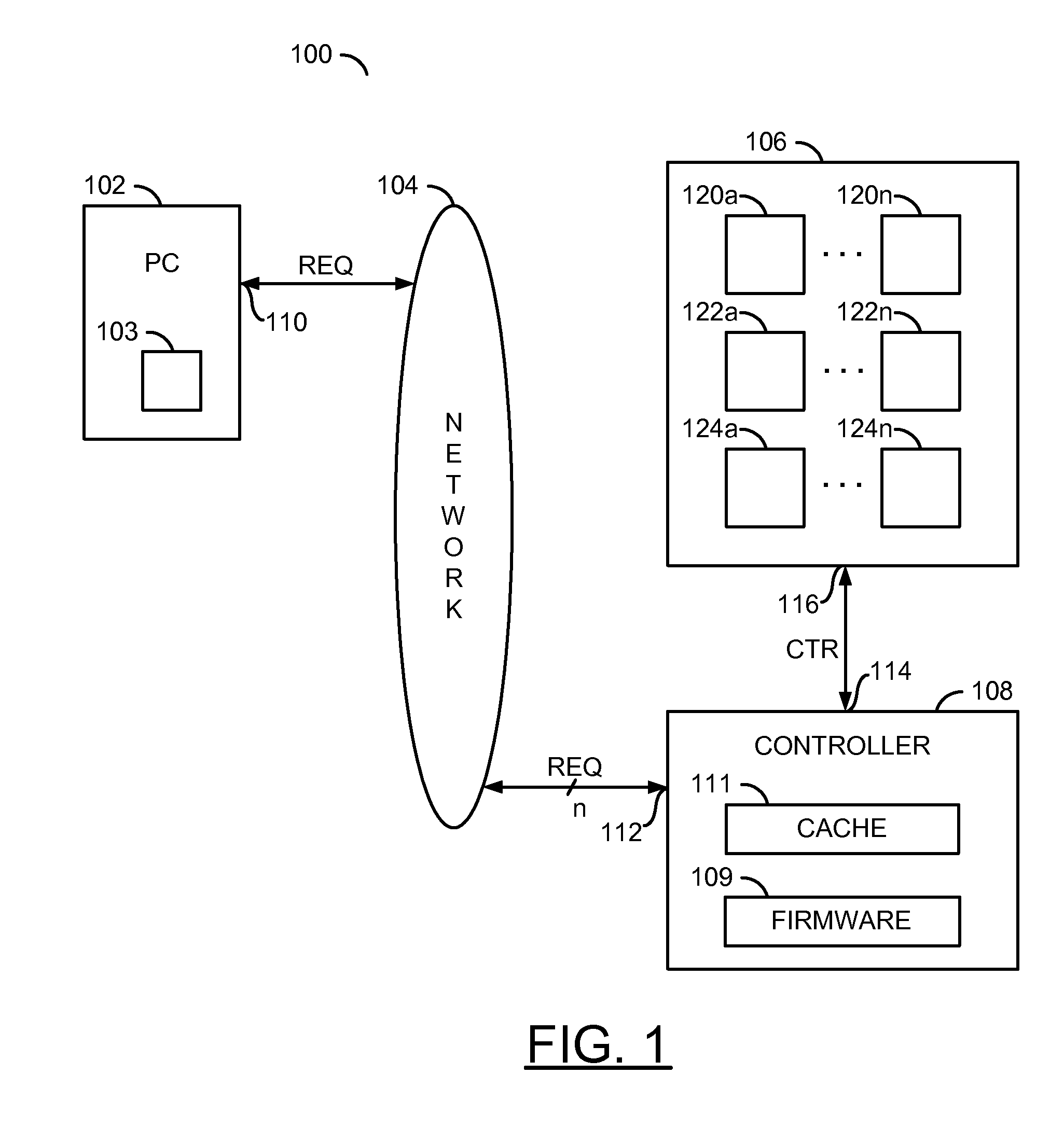

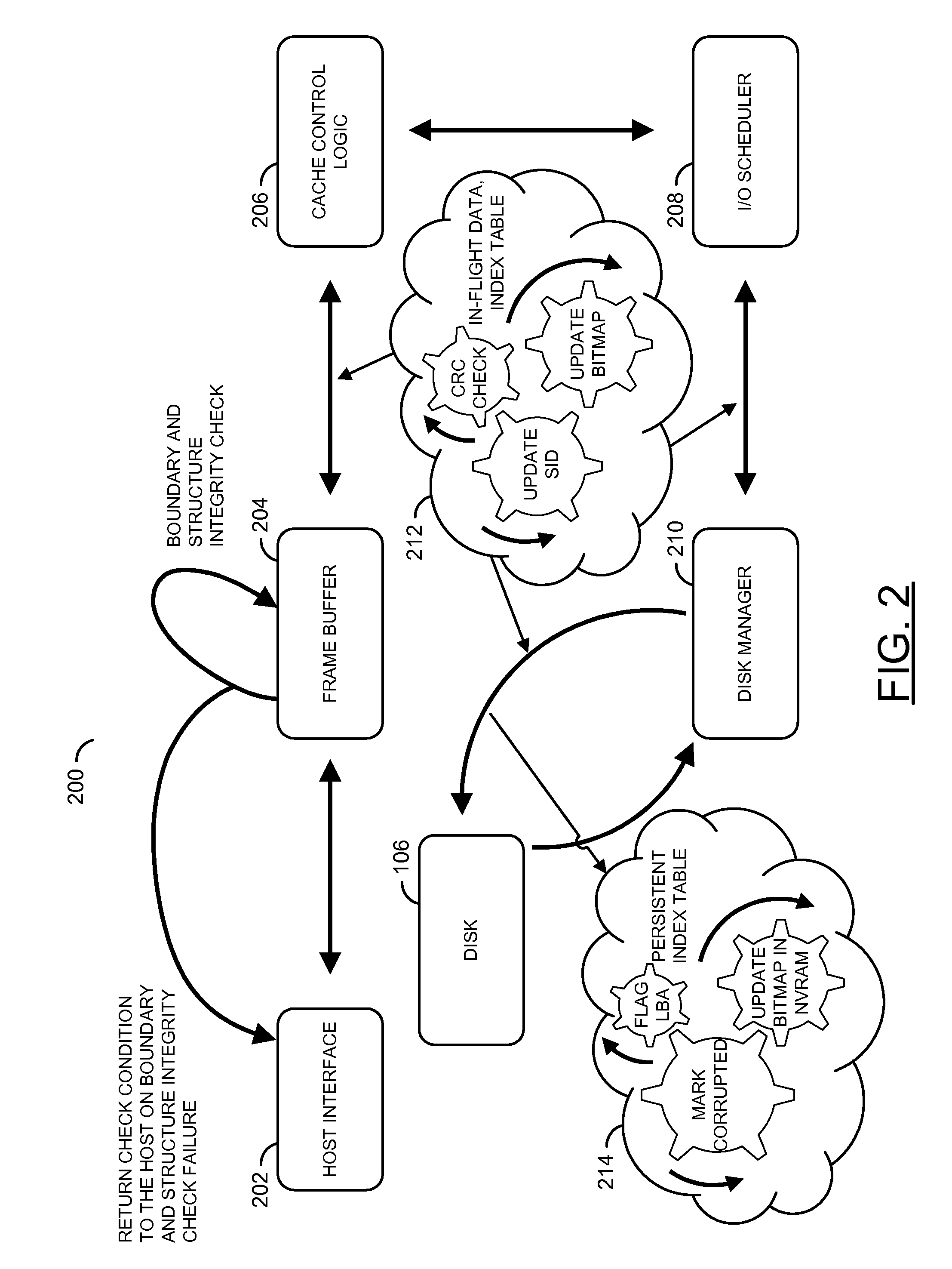

System and method to flag a source of data corruption in a storage subsystem using persistent source identifier bits

An apparatus comprising an array controller and a frame buffer. The array controller may be configured to read / write data to / from a drive array in response to one or more input / output requests. The frame buffer may be implemented within the array controller and may be configured to perform (i) a first data integrity check to determine a first type of data error and (ii) a second data integrity check to determine a second type of data error. The frame buffer may log occurrences of the first type of error and the second type of error in a field transmitted with the data. The field may be used to determine a source of possible corruption of the data.

Owner:AVAGO TECH INT SALES PTE LTD

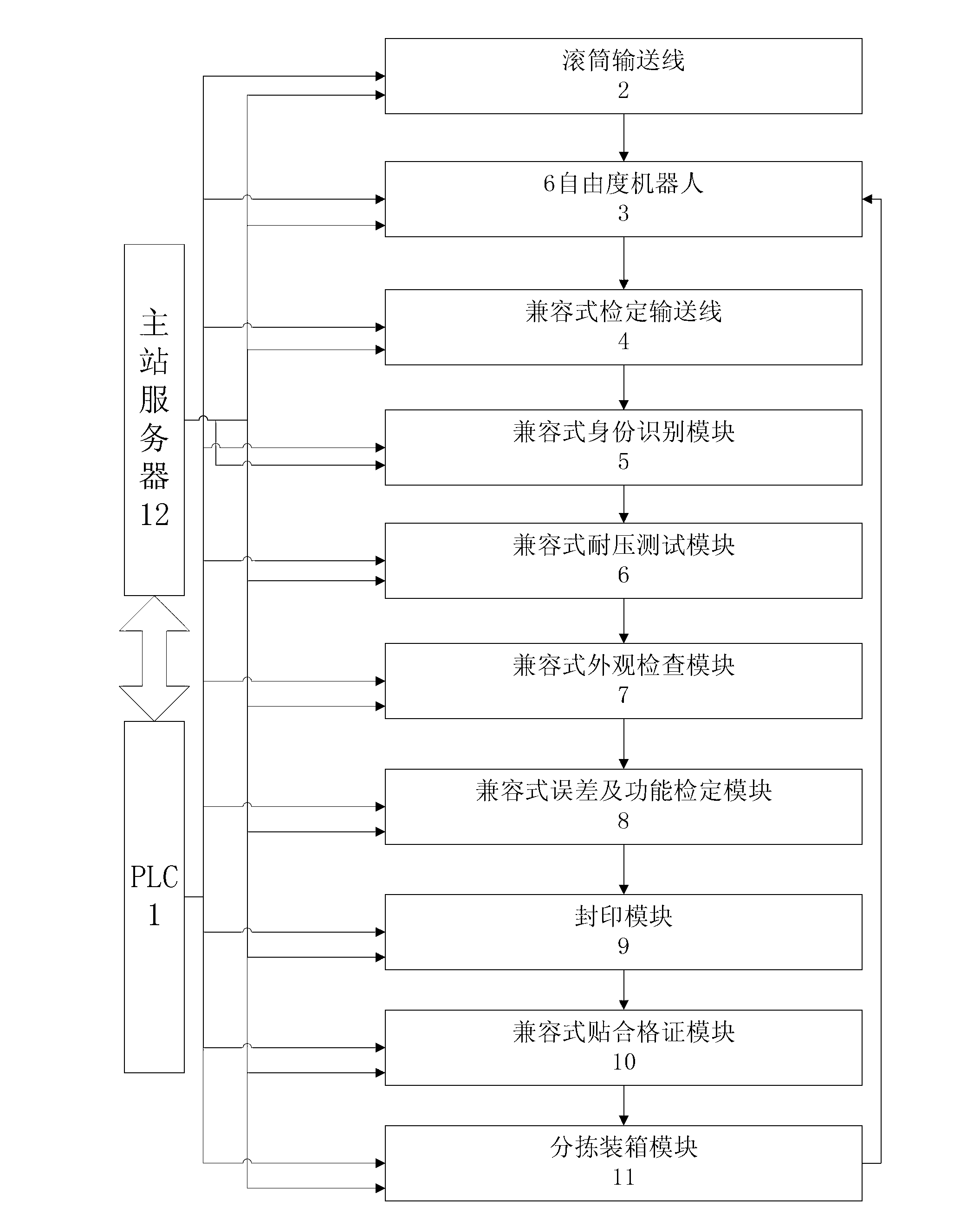

Single phase intelligent electric energy meter collector compatibility type automation verification system and method

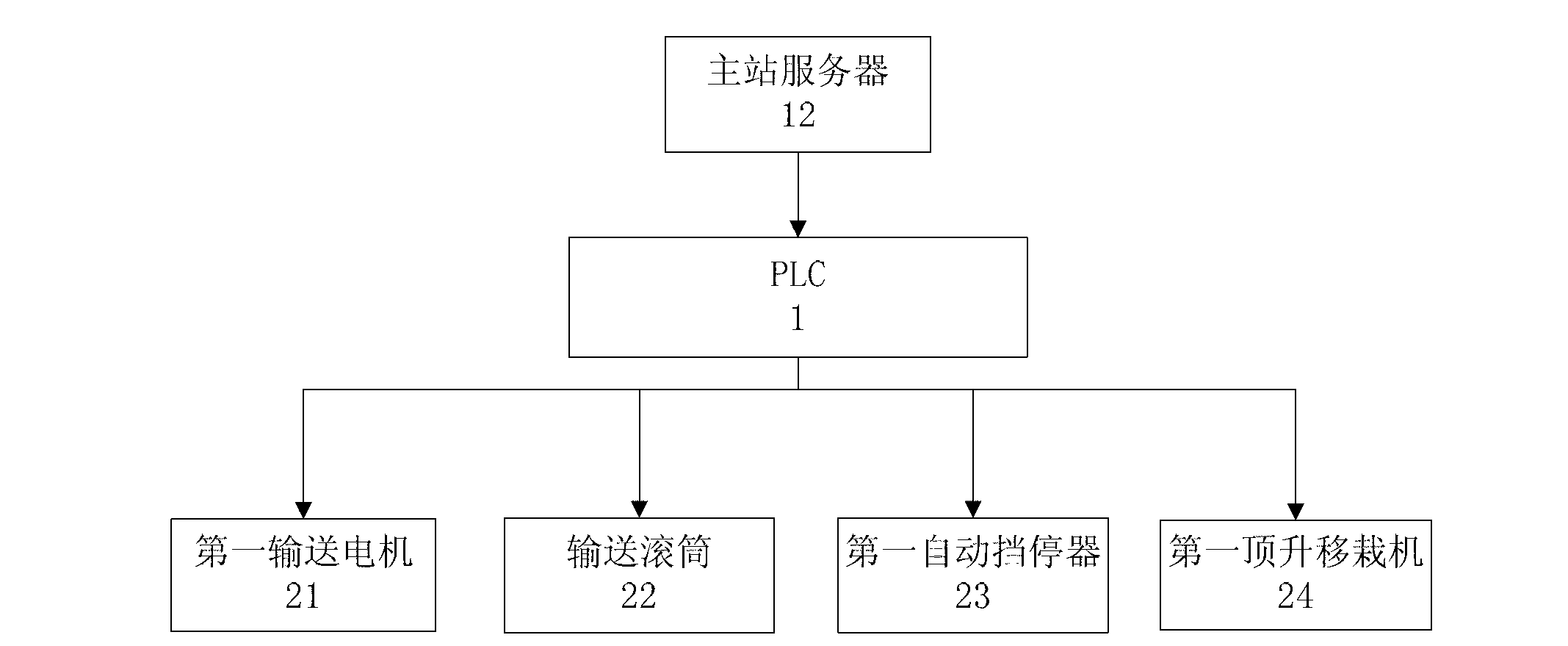

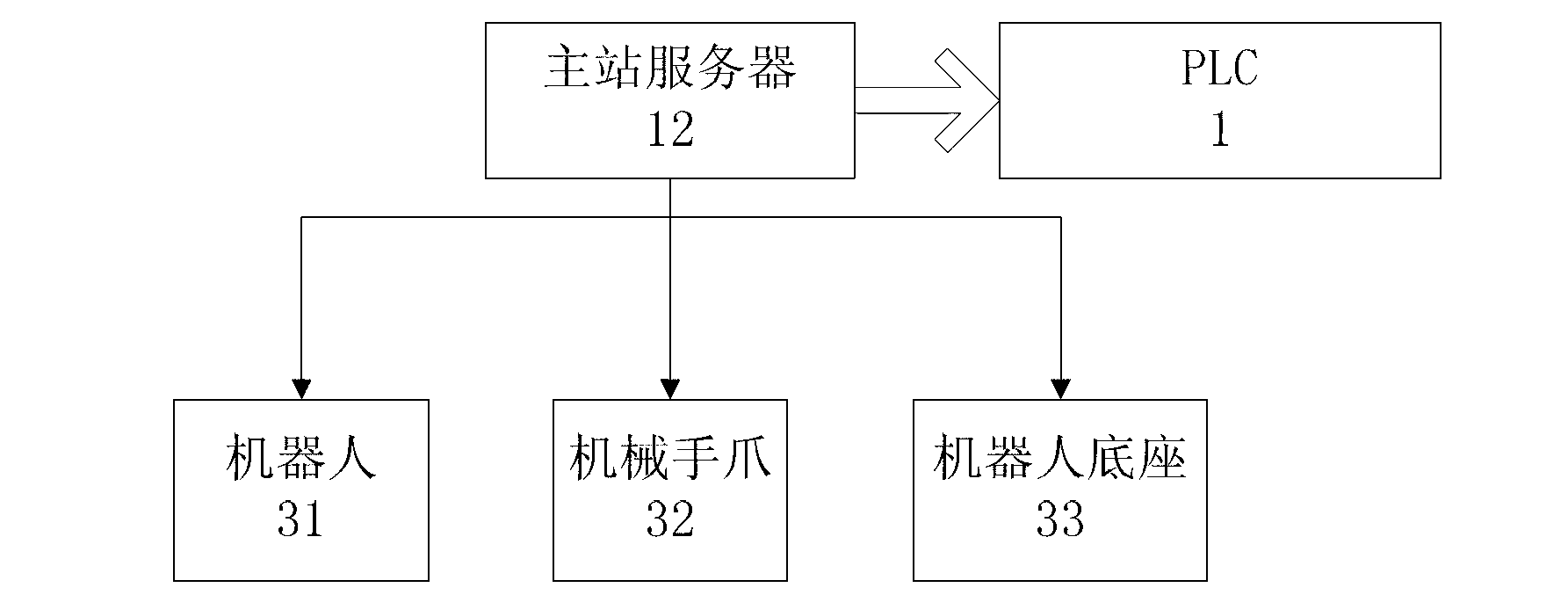

InactiveCN103064055ACompatible with automated checksNo manual operationElectrical measurementsType errorPrimary station

The invention relates to a single phase intelligent electric energy meter collector compatibility type automation verification system and a method. The verification system comprises a programmable logic controller (PLC) and a rolling barrel conveyor line connected with the PLC, 6 degrees of freedom robots, a compatibility type verification conveyor line, a compatibility type identification module, a compatibility type pressure-proof testing module, a compatibility type appearance checking module, a compatibility type error and function verification module, a sealing module, a compatibility sticking certification module and a sorting module. The verification method is the identification, the pressure-proof testing, the appearance checking, the error and the function verification, the sealing, the sticking certification, the sorting and enchasing of a to-be check list of a primary station server, the PLC controlling rolling barrel conveyor line, the 6 degrees of freedom robots, a compatibility type verification delivering module, the compatibility type identification module, the compatibility type pressure-proof testing module and the like. Compared with the prior art, the single phase intelligent electric energy meter collector compatibility type automation verification system and the method have the advantages of being capable of holding the automatic verification of the single phase intelligent electric energy meter and the collector at the same time, capable of improving working efficiency and the like.

Owner:SHANGHAI MUNICIPAL ELECTRIC POWER CO +2

Method and device for securing the memory of a computer against errors due to radiation

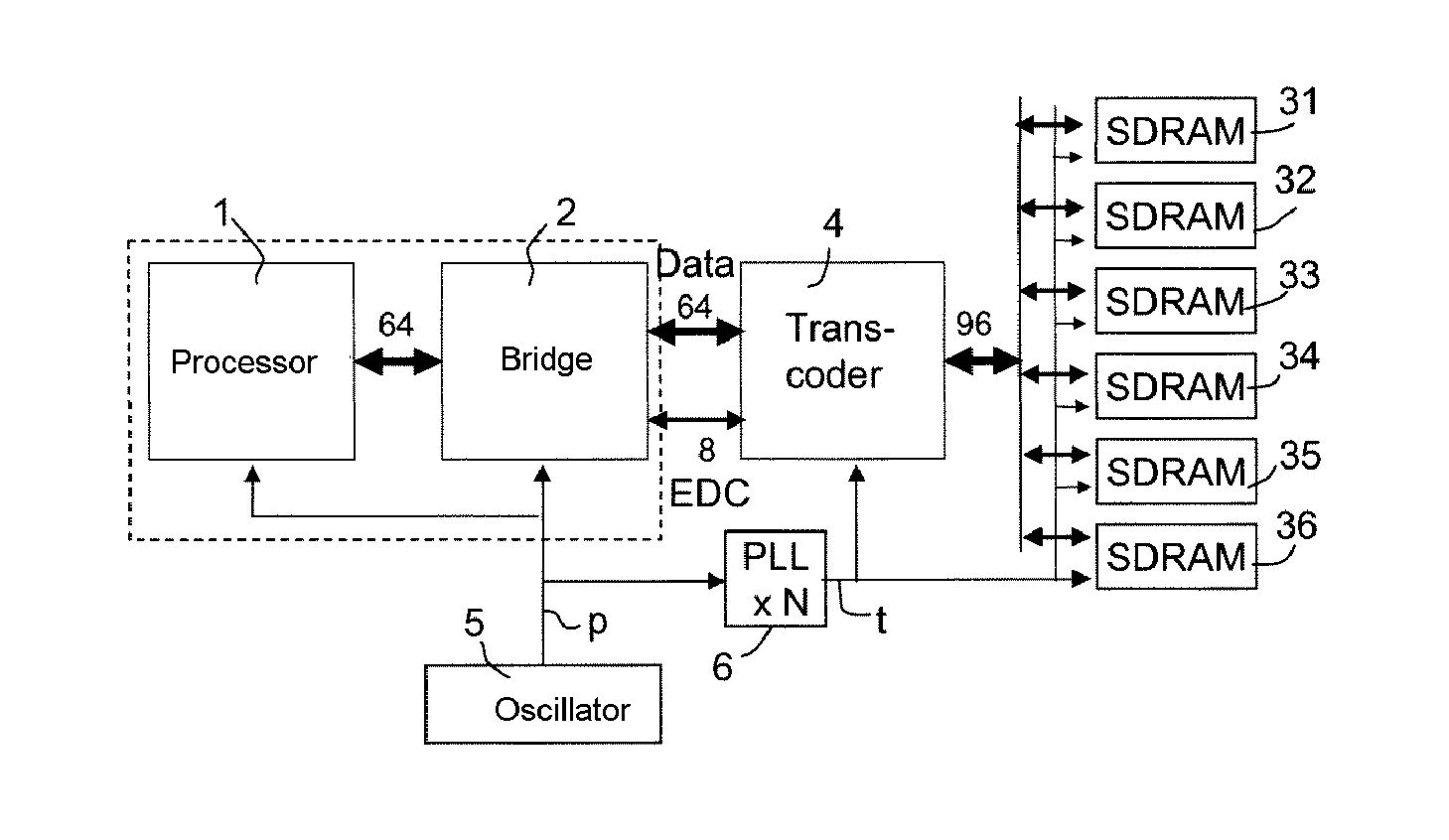

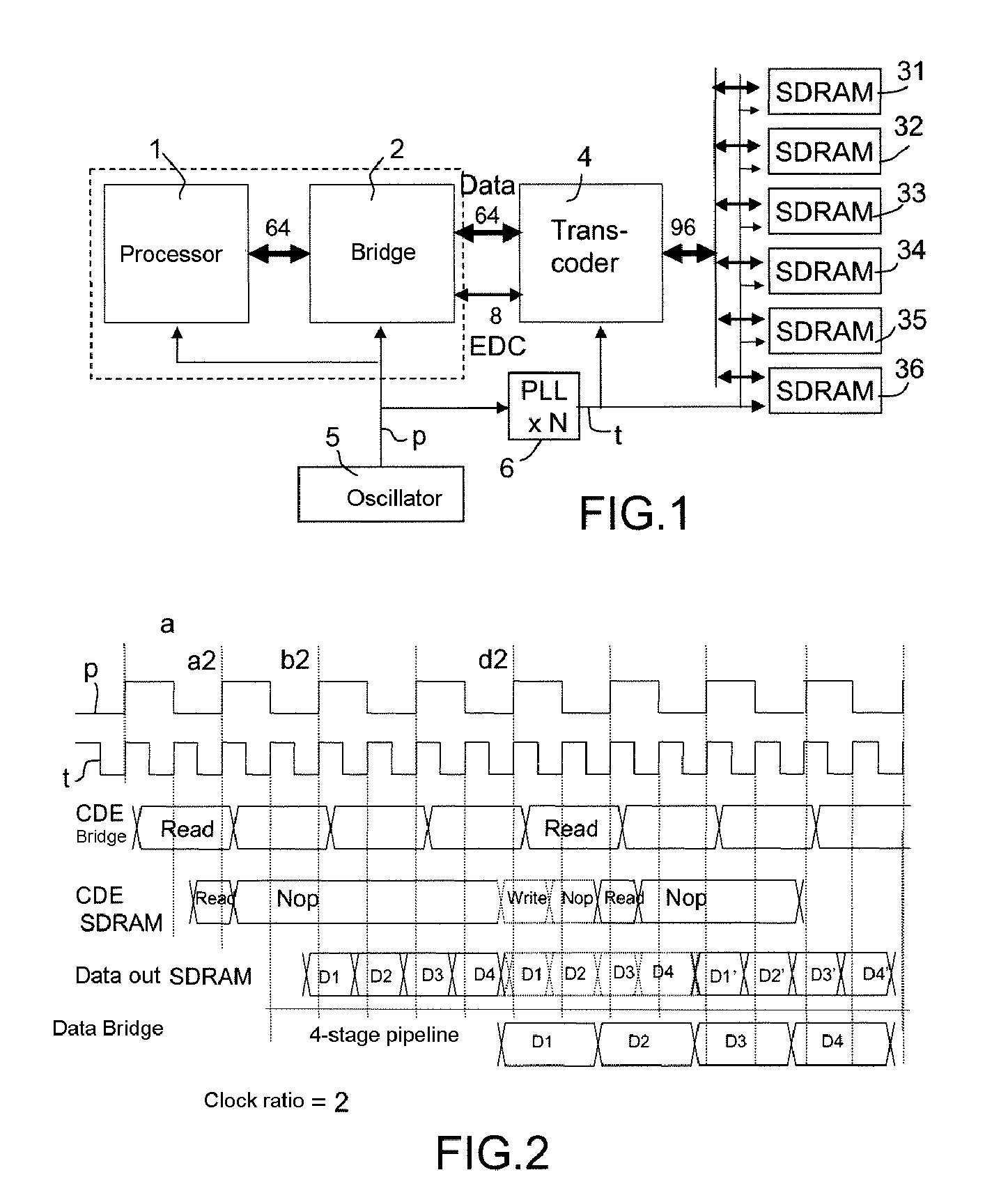

InactiveUS8151169B2Correction capabilityDigital data processing detailsError detection/correctionType errorOff the shelf

The method is for hardening a computer based on off-the-shelf components so that it resists bombardment by particles of cosmic origin encountered at high altitude and near the poles. It relates more particularly to a computer comprising a processor / bridge pair, the bridge ensuring auxiliary functions for controlling the data exchanges between the processor and a random-access memory incorporating a Hamming-type error corrector code into the information exchanged and consists in inserting between the processor / bridge pair and the random-access memory an interface device carrying out a two-way transcoding between the Hamming-type error correction code incorporated into the information exchanged by the auxiliary functions for controlling the data exchanges of the processor / bridge pair and a Reed-Solomon-type error correction code adapted to the architecture of the random-access memory.

Owner:THALES SA

Memory storage device, memory controller and data writing method

ActiveCN102890645AImprove stabilityRaise the number of error bitsInput/output to record carriersRedundant data error correctionType errorMemory chip

The invention discloses a memory storage device, a memory controller and a data writing method. The memory storage device is coupled to a host computer system; and the memory storage device comprises an error check and correction circuit and a reproducible nonvolatile memory chip. The method comprises a step of judging whether written data belong to a specific type when the written data are to be written into the reproducible nonvolatile memory chip, and also comprises the steps of generating at least one first type error check and correction code according with the first length by the error check and correction circuit according to the written data if the written data belong to the specific type, and generating at least one second type error check and correction code according with the second length by the error check and correction circuit according to the written data if the written data do not belong to the specific type, wherein the first length is larger than the second length.

Owner:PHISON ELECTRONICS

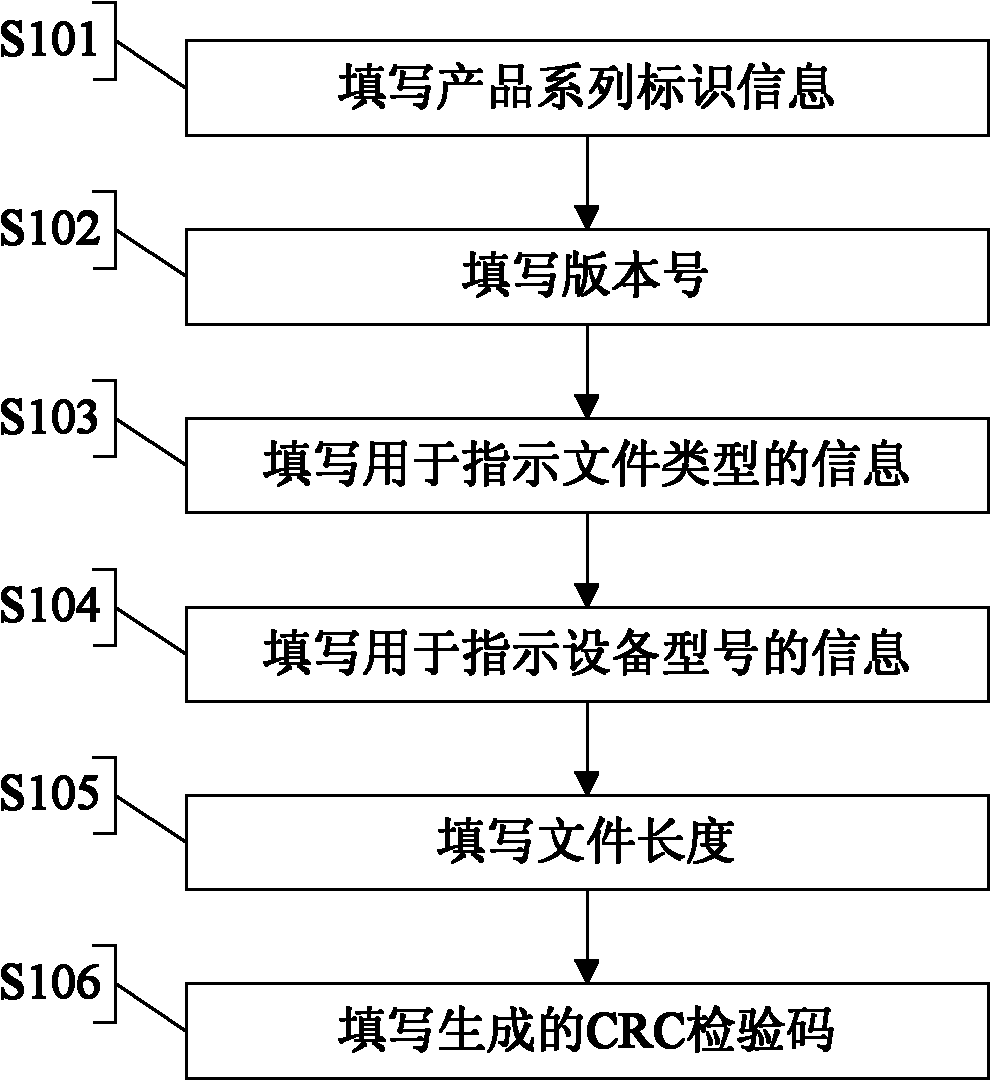

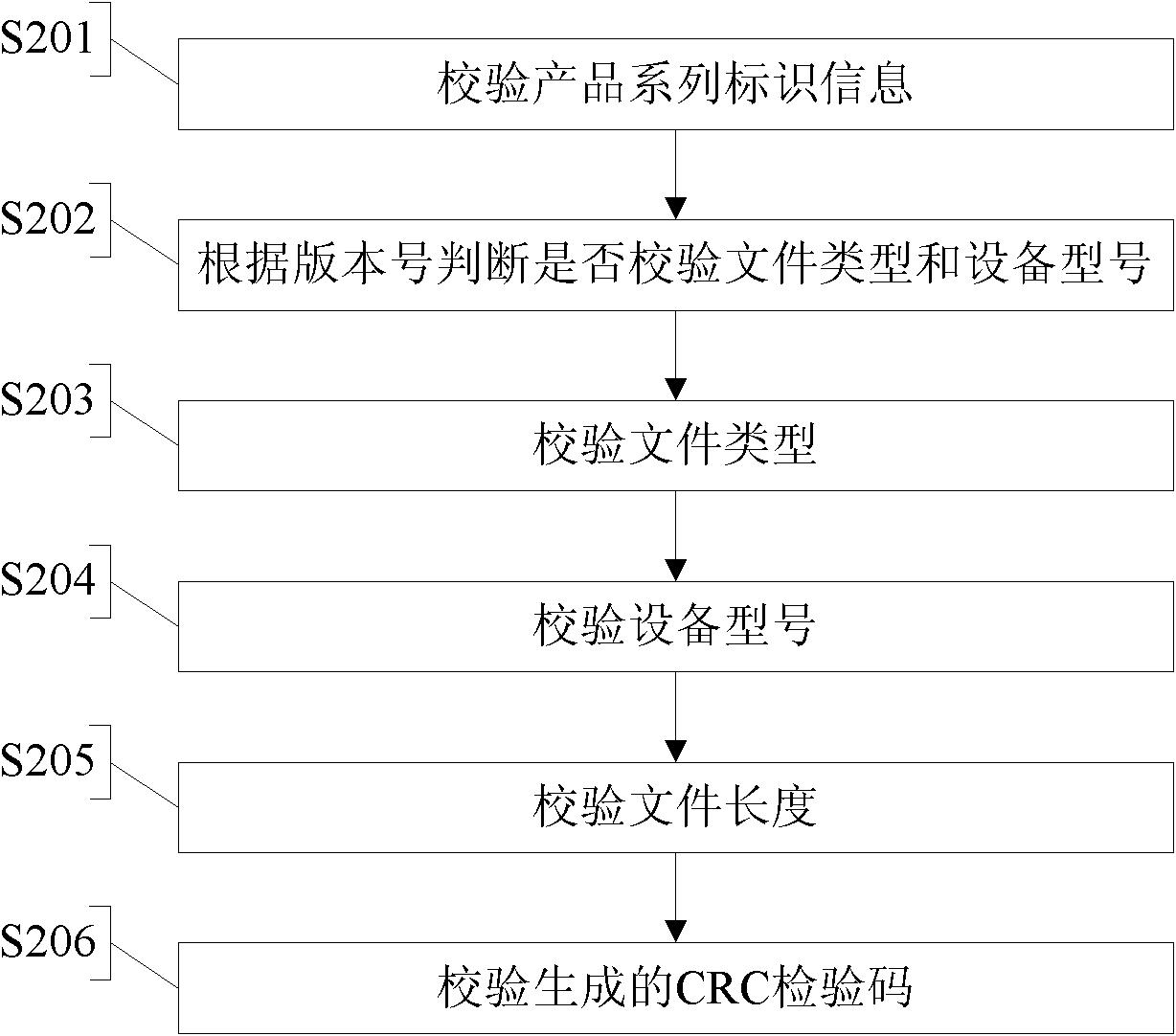

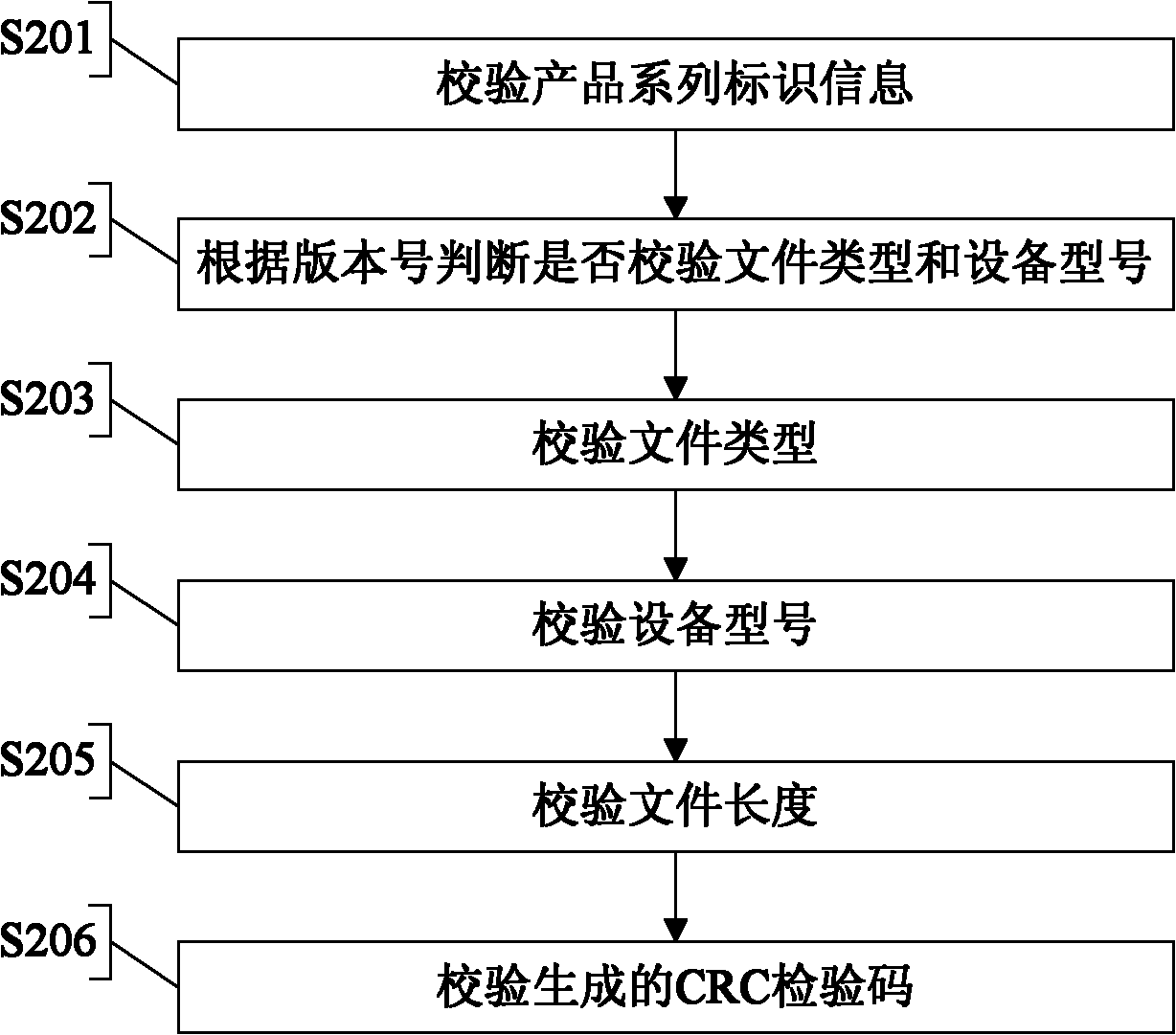

Automatic upgrading method and device of communication equipment

InactiveCN102082833AGuaranteed correctnessIntegrity guaranteedData switching networksType errorFile verification

The invention discloses an automatic upgrading method and an automatic upgrading device of communication equipment. The method comprises the following steps of: requiring a network side for downloading a required system file; verifying the system file according to file verification information carried in the downloaded system file and determining that verification passes if the file verification information is consistent with a requested system file, wherein the file verification information at least comprises information for indicating the file type and / or equipment model of the system file; and after the verification passes, replacing an original corresponding system file by the system file. Through the technical scheme, the correctness and completeness of a file downloaded during automatic upgrading of the communication equipment can be ensured, file type errors or equipment model errors can be avoided, and the situation of unavailable startup of the equipment after automatic upgrading due to a file error is avoided.

Owner:RAISECOM TECH

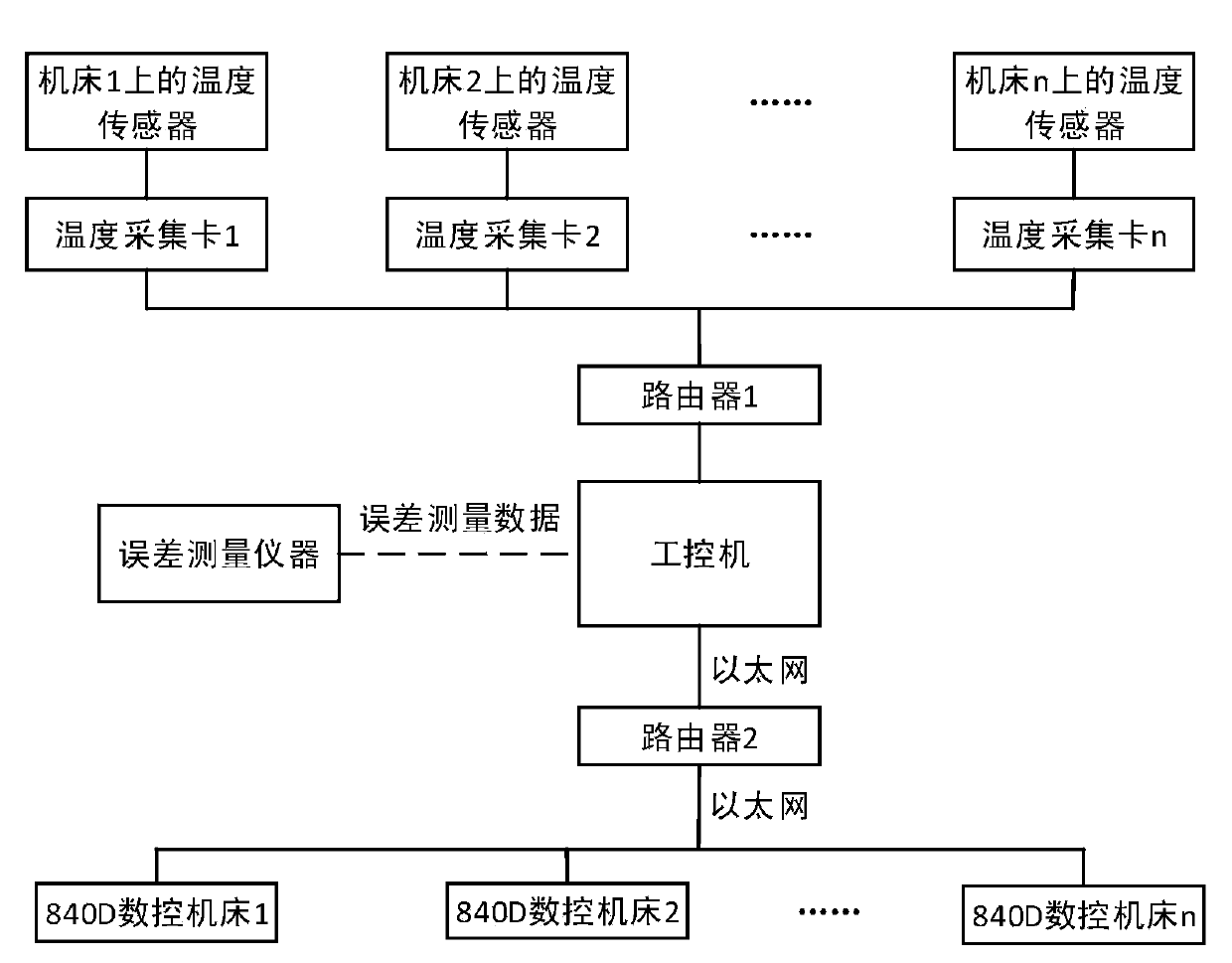

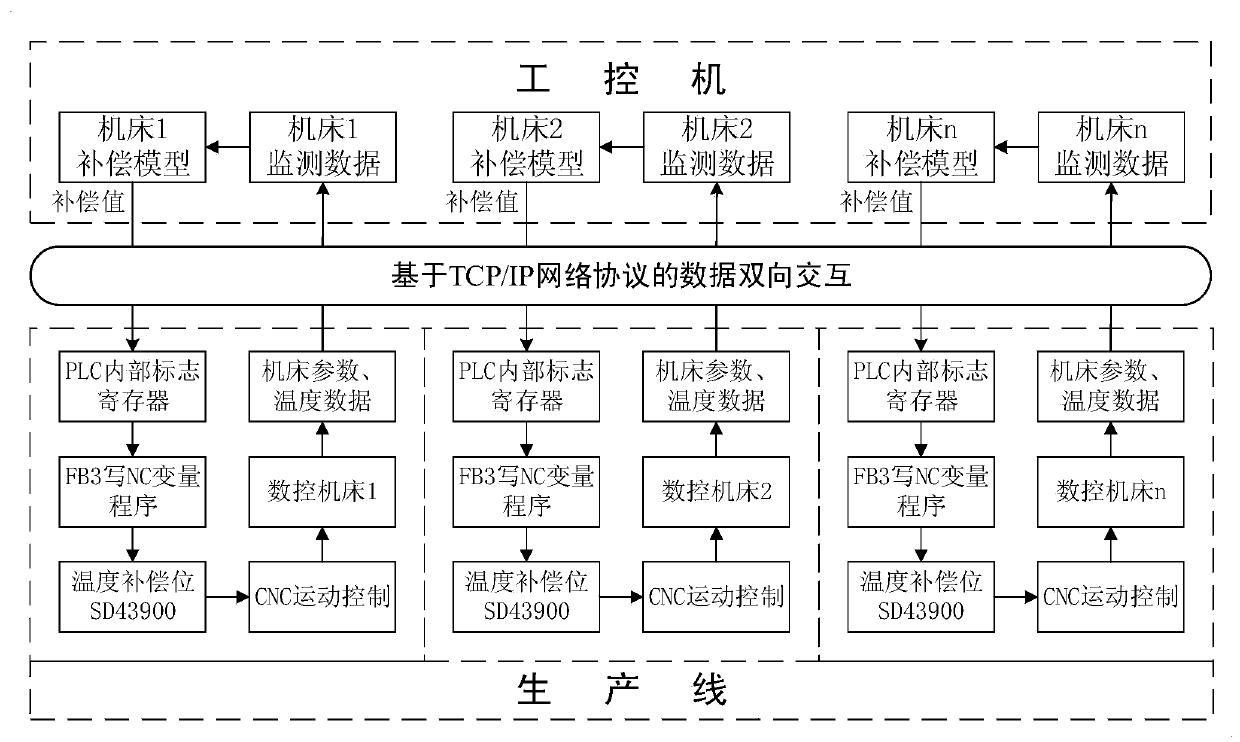

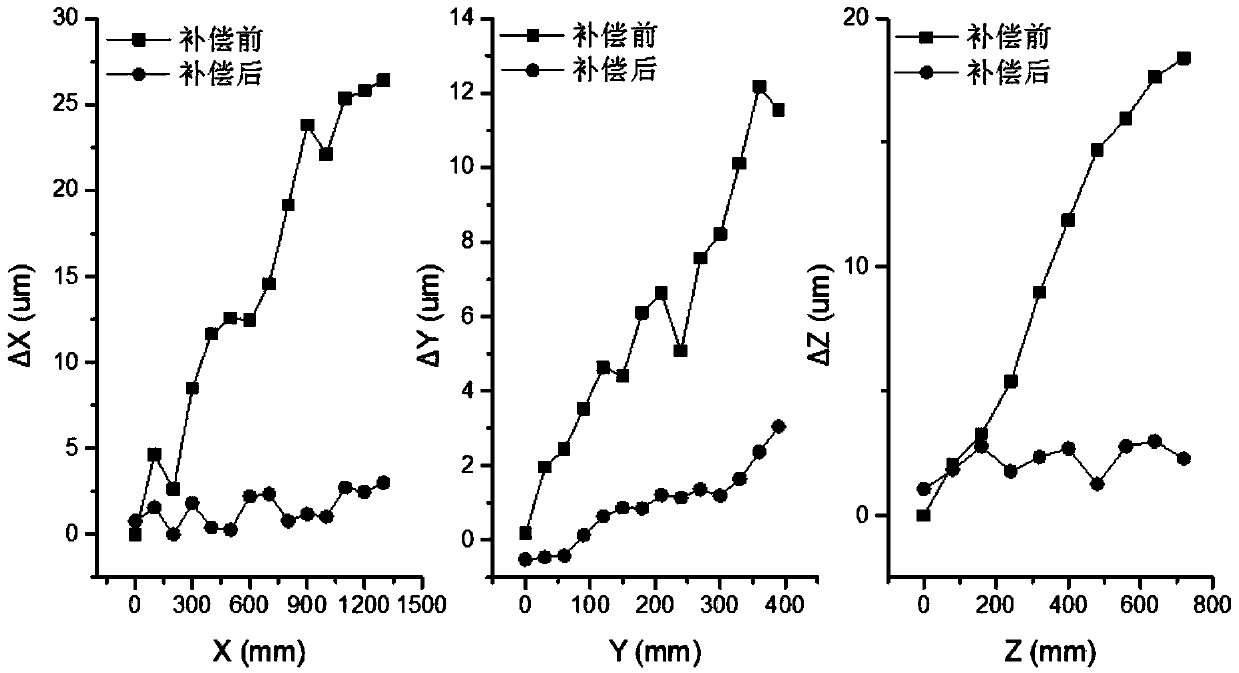

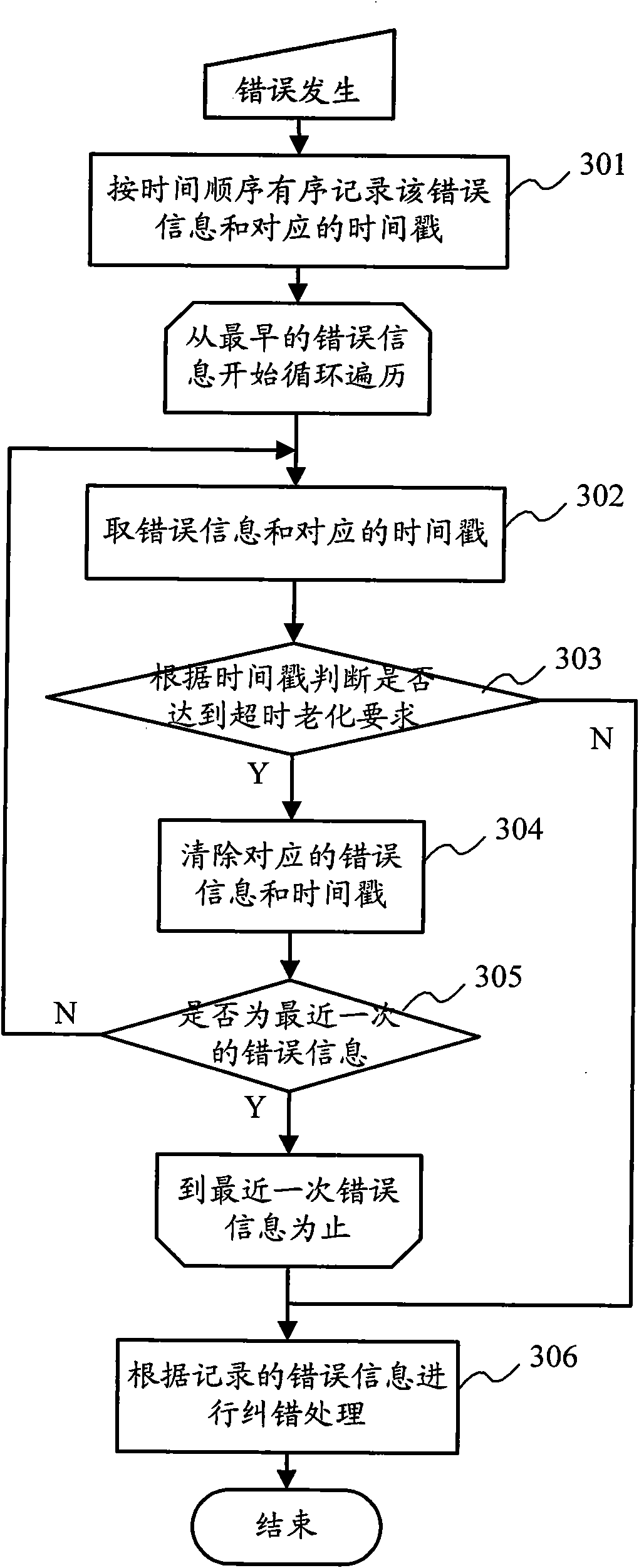

Network group control-type error dynamic compensation system of numerically-controlled machine tools

ActiveCN103792910ALow costEasy to handleTotal factory controlProgramme total factory controlNumerical controlType error

The invention relates to a network group control-type error dynamic compensation system of numerically-controlled machine tools. The network group control-type error dynamic compensation system includes a machine tool error measuring instrument, a temperature sensor, a temperature data acquisition card, a first router, an industrial personal computer and a second router; a group control error compensation and monitoring subsystem is embedded in the industrial personal computer and includes an error modeling module, a state monitoring module and an error compensation module; and a secondary interface subsystems is embedded in each numerically-controlled machine tool and includes a communication module, a machine tool parameter access module and an error compensation implementing module. Compared with the prior art, and according to the network group control-type error dynamic compensation system of the invention, each module is matched with each other, such that error dynamic compensation and state information monitoring of a plurality of numerically-controlled machine tools can be realized on one industrial personal computer, and therefore, the machining accuracy of the numerically-controlled machine tools can be improved in a batched manner. The network group control-type error dynamic compensation system has the advantages of high compensation efficiency, high compensation precision and low implementation cost.

Owner:SHANGHAI JIAO TONG UNIV

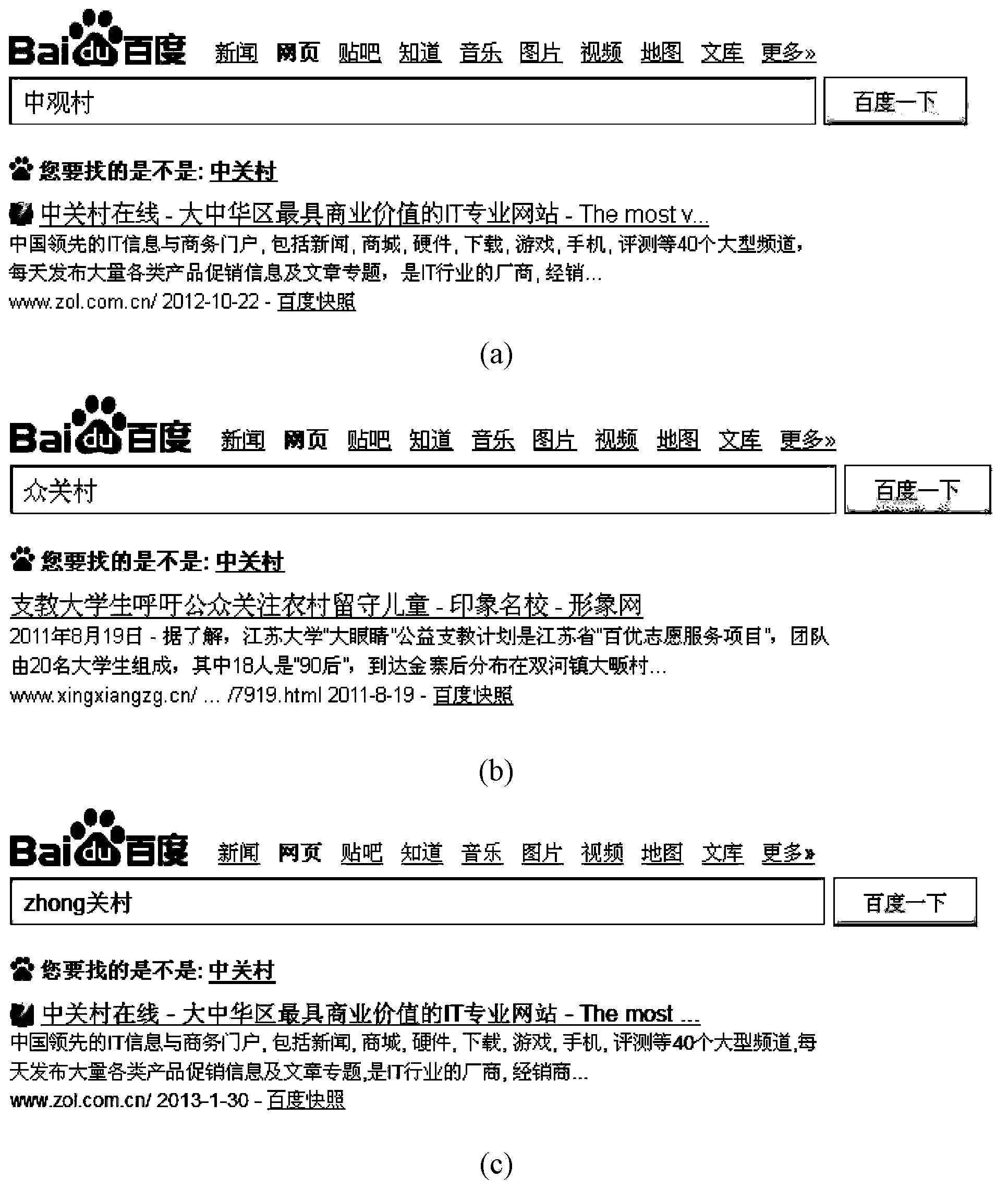

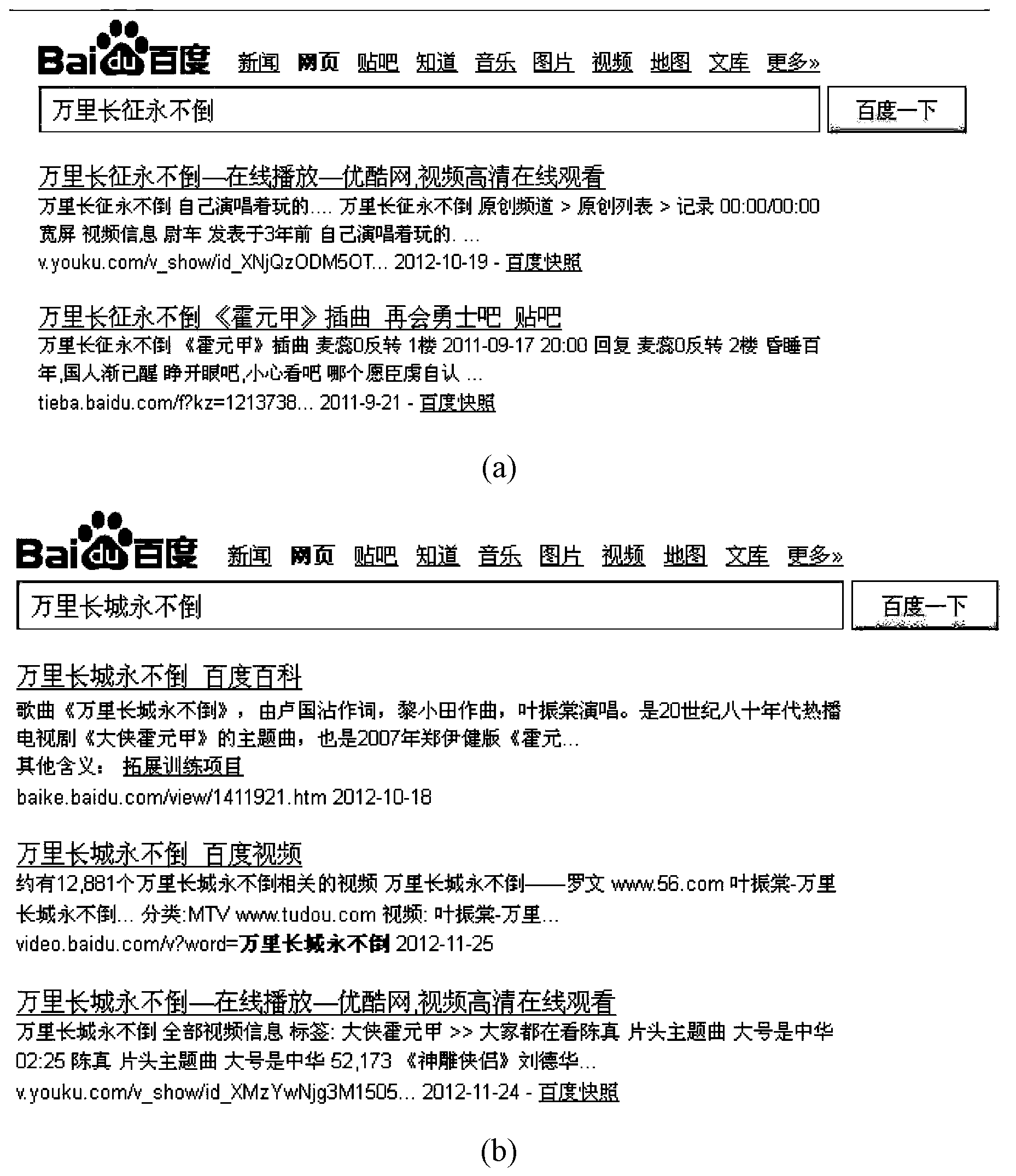

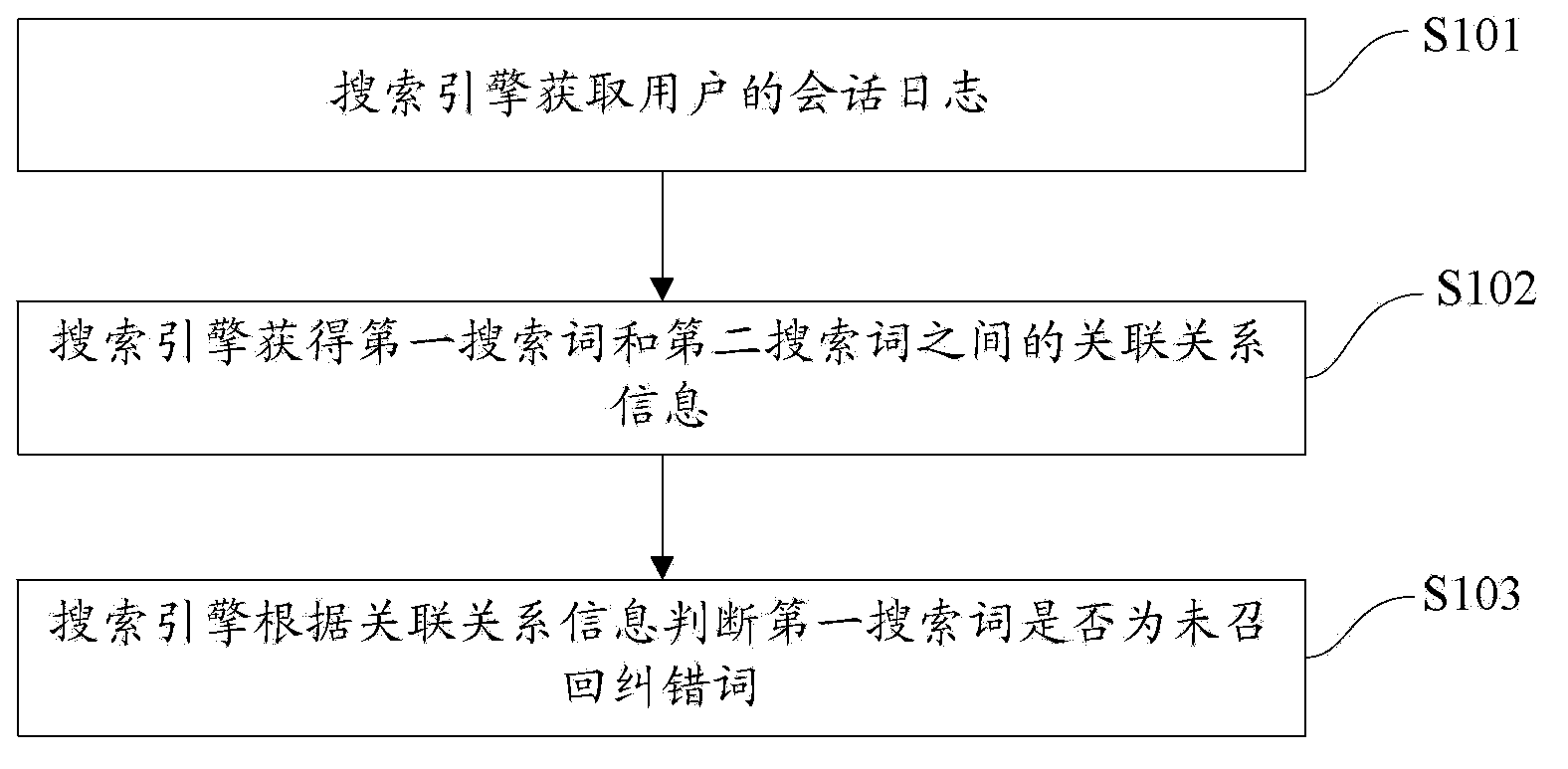

Method and method for digging non-recalled type error correction word of searching engine

InactiveCN104102633AAutomatic discoverySave human effortSpecial data processing applicationsType errorSearch words

The invention provides a method for digging a non-recalled type error correction word of a searching engine. The method comprises the following steps: the searching engine obtains a conversation log of a user, wherein the conversation log at least comprises a first conversation and a second conversation, and the first conversation and the second conversation respectively comprise a first searching word and a second searching word; the searching engine obtains related relation information between the first searching word and the second searching word; the searching engine judges whether the first searching word is the non-recalled type error correction word or not according to the related relation information. The invention further provides a device for digging the non-recalled type error correction word of the searching engine. According to the method and the device, modeling analysis on a user searching word sequence and a searching result is carried out so that the non-recalled type error correction word can be automatically found, and the recalling efficiency is considerably higher than that of manual searching; the manpower cost for finding out the non-recalled type error correction word is greatly reduced.

Owner:BAIDU ONLINE NETWORK TECH (BEIJIBG) CO LTD

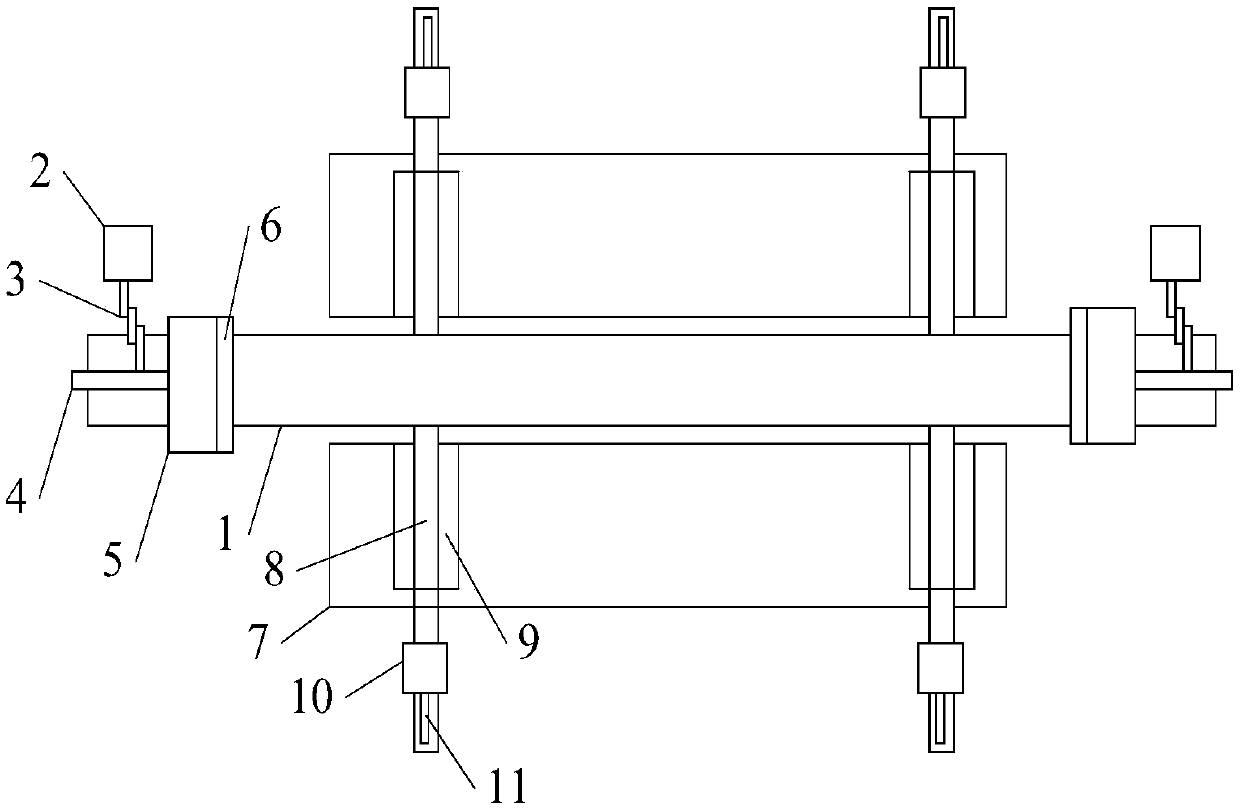

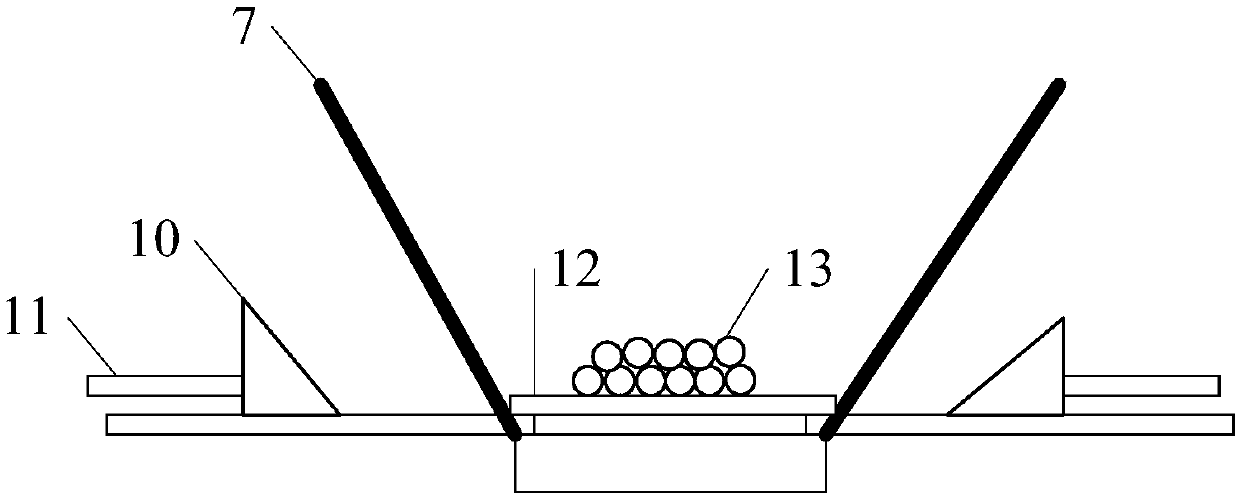

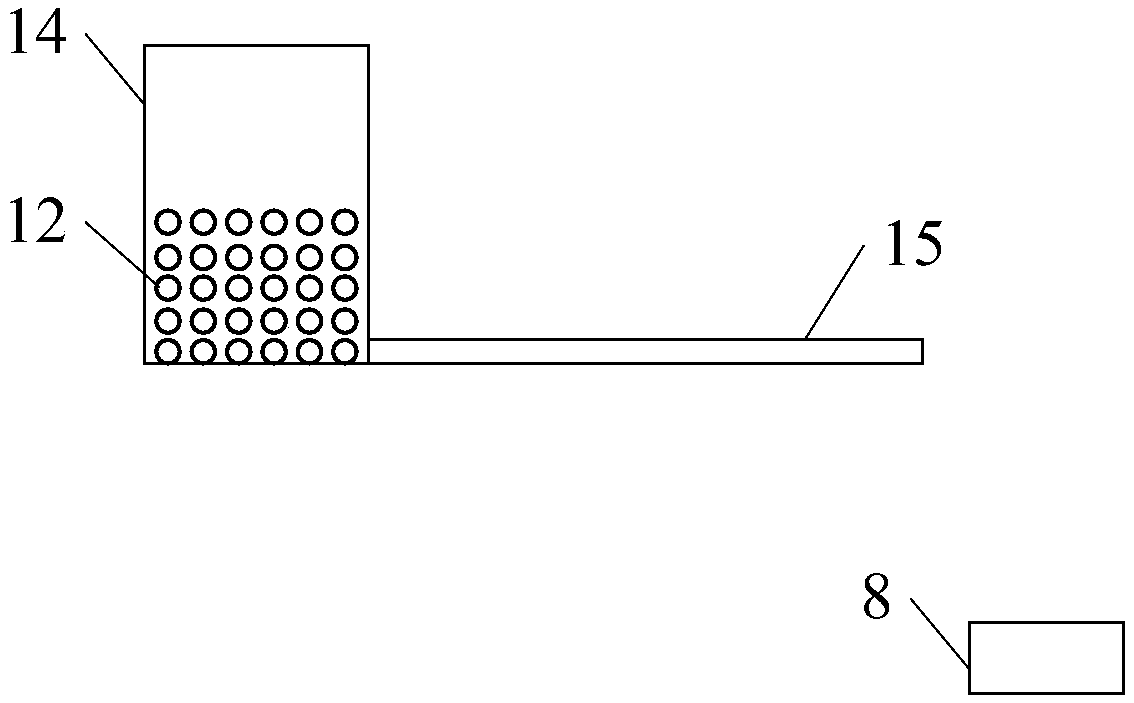

Reinforcement binding alignment device

InactiveCN109094845AAchieving end-face alignmentAchieving processing powerPackaging automatic controlBundling machine detailsType errorEngineering

The invention discloses a reinforcement binding alignment device. The reinforcement binding alignment device comprises a first guiding rail, end surface alignment structures are symmetrically arrangedat the two ends of the first guiding rail, and each end surface alignment structure comprises a first motor, a gear set, a rack, a pushing block, a flat plate, a plurality of pressure sensors and a first processor. First binding structures are symmetrically disposed on the left and right sides of the first guiding rail, and each first binding structure comprises a slanting plate, a second guidingrail, an extrusion block, a telescopic rod and a first controller. The reinforcement binding alignment device further includes a second binding structure, and the second binding structure comprises abase, a mechanical arm, a second controller, a second motor, a connecting rod and an electric clamping jaw. The technical problems of the recognition quantity and type errors of an existing reinforcement recognition system are solved, the end face alignment and binding processing of the reinforcement is realized, the acquisition of accurate images is facilitated, and the technical effect of improving the accuracy of the reinforcement recognition system is achieved.

Owner:四川知创知识产权运营有限公司

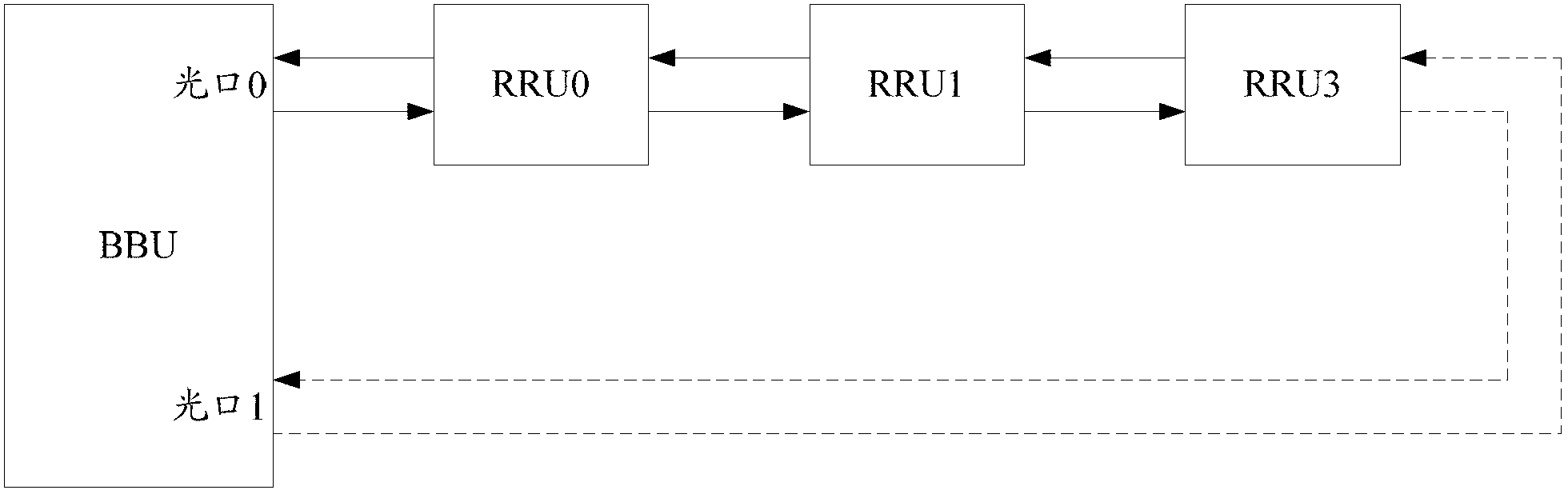

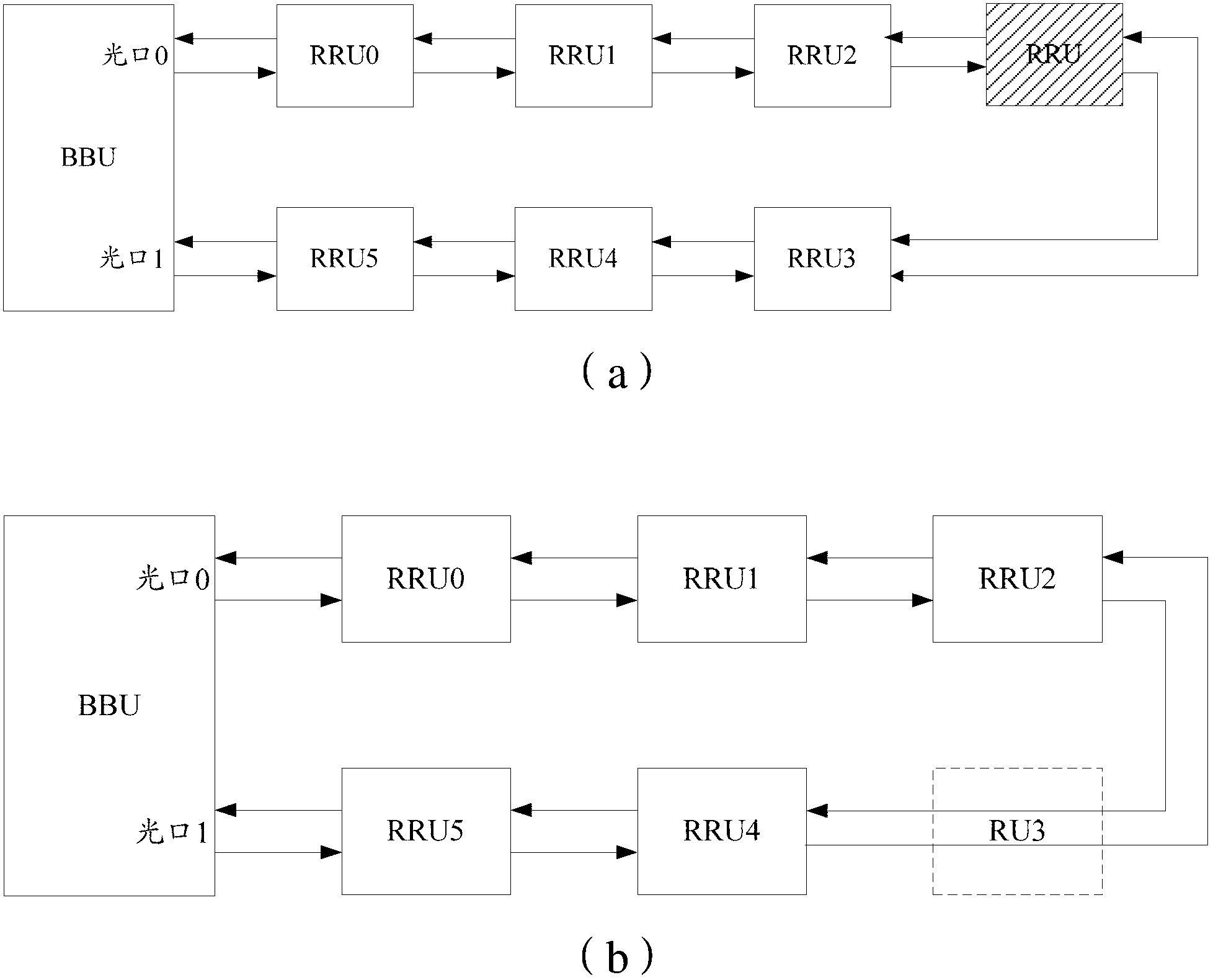

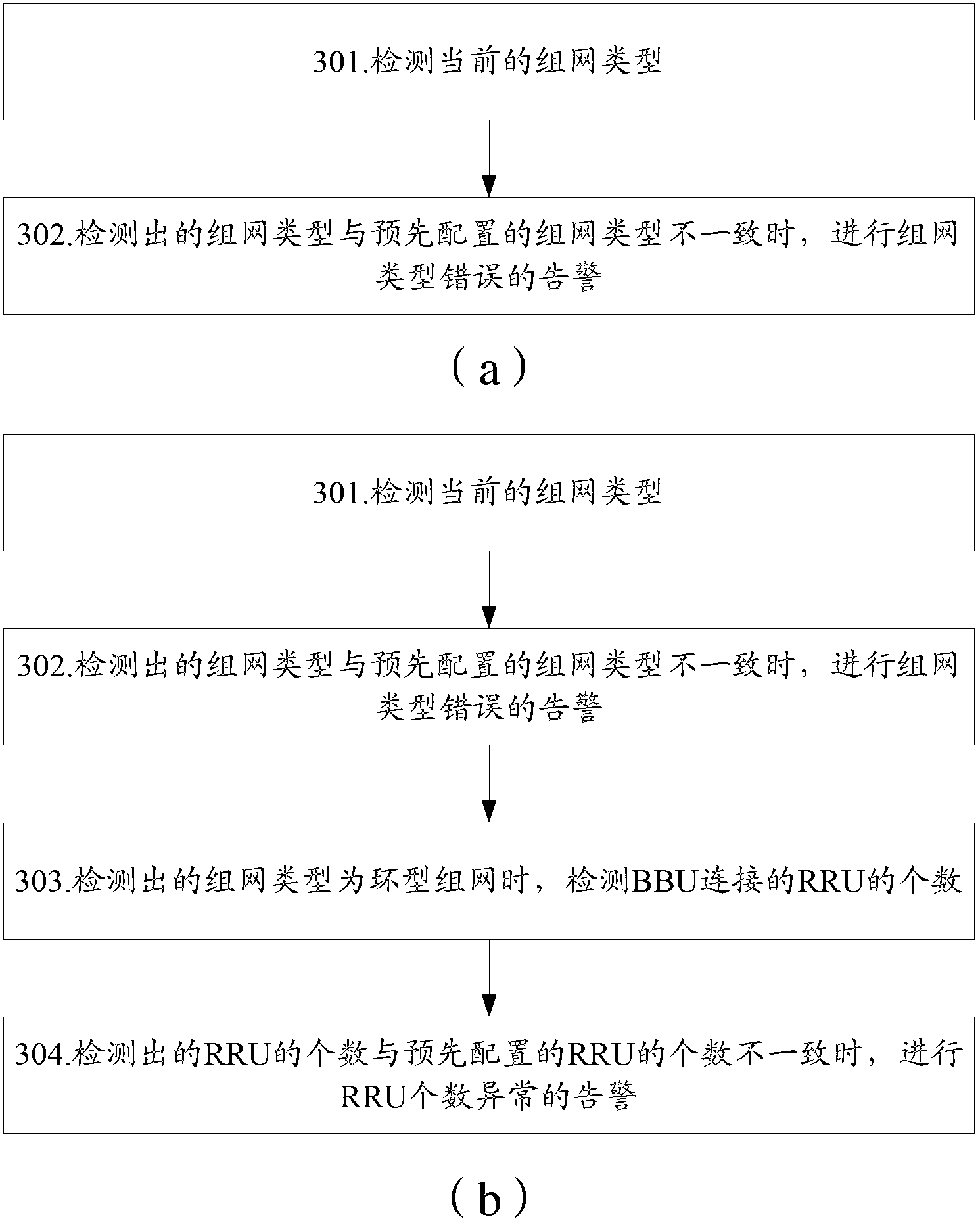

Method and system for detecting physical topological link

ActiveCN102802181ARapid positioningImprove work efficiencyWireless communicationType errorRadio frequency

The invention discloses a method for detecting a physical topological link. The method comprises the following steps of: detecting a current networking type; and if the detected networking type is different from a pre-configured networking type, carrying out alarming on a networking type error. The invention further provides a system for detecting the physical topological link. According to the technical scheme provided by the invention, an abnormal condition that an RRU (Remote Radio-Frequency Unit) which is actually connected under a BBU (Base Band Unit) is different from an RRU which is pre-configured by a background can be detected.

Owner:苏州医疗器械产业发展集团有限公司

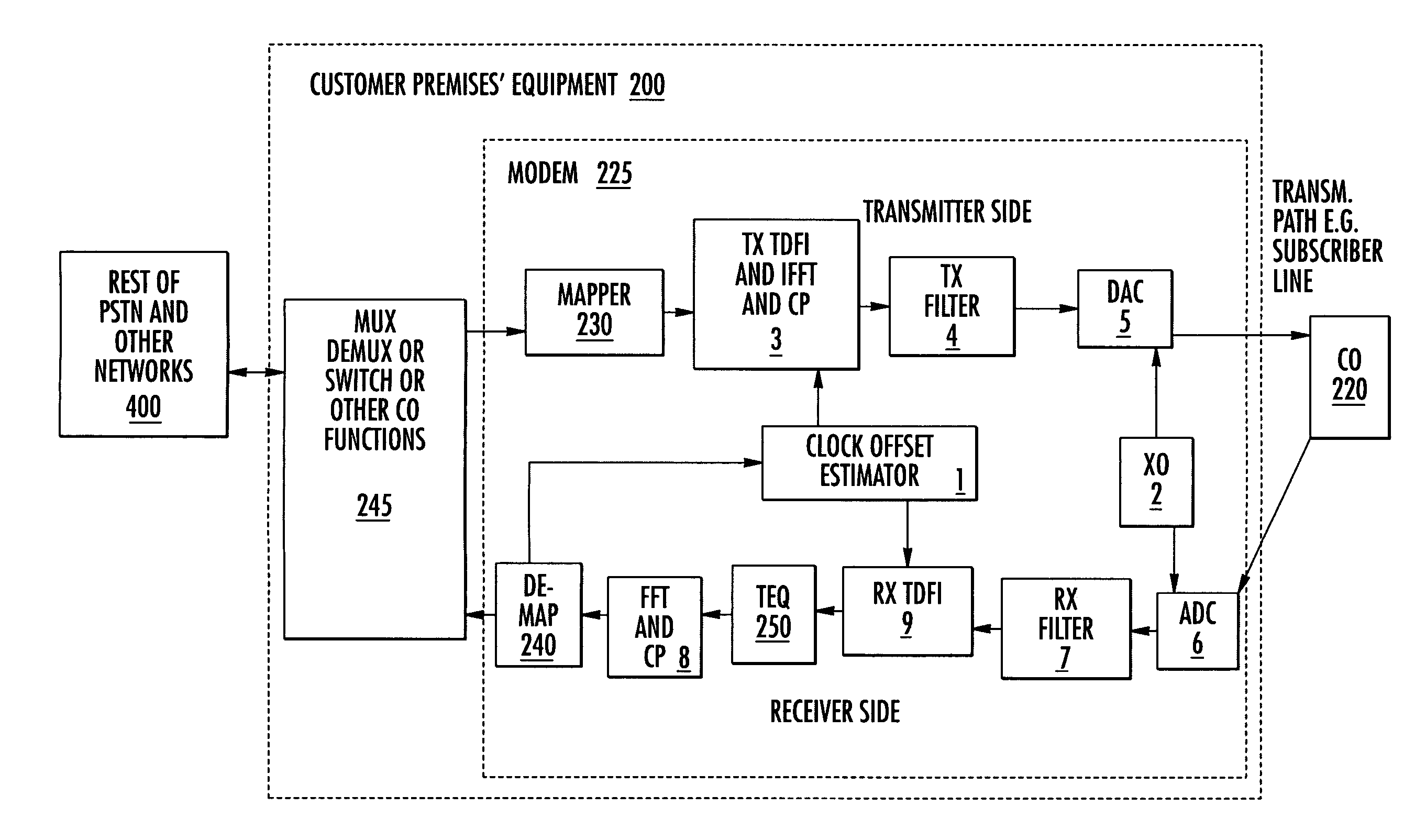

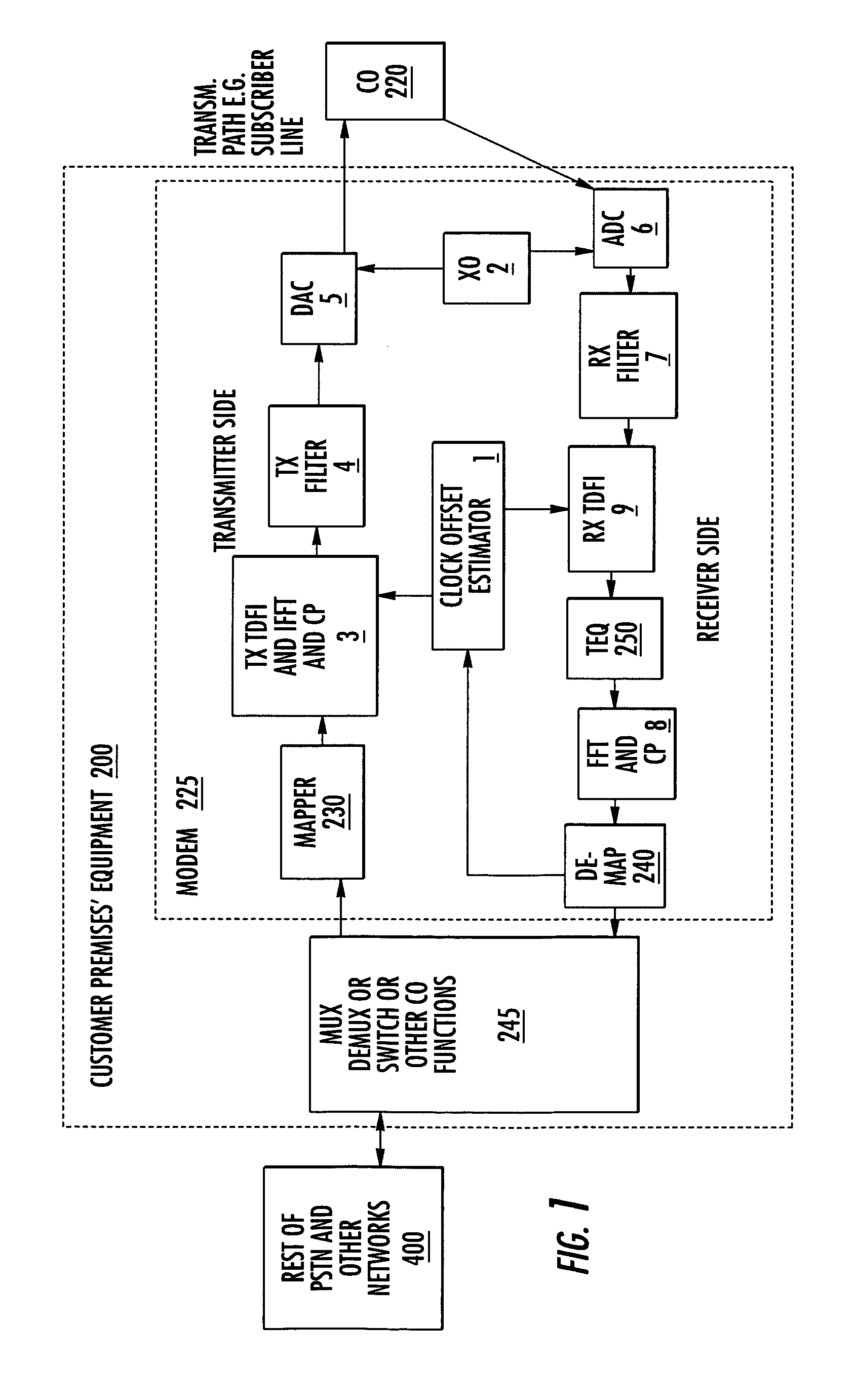

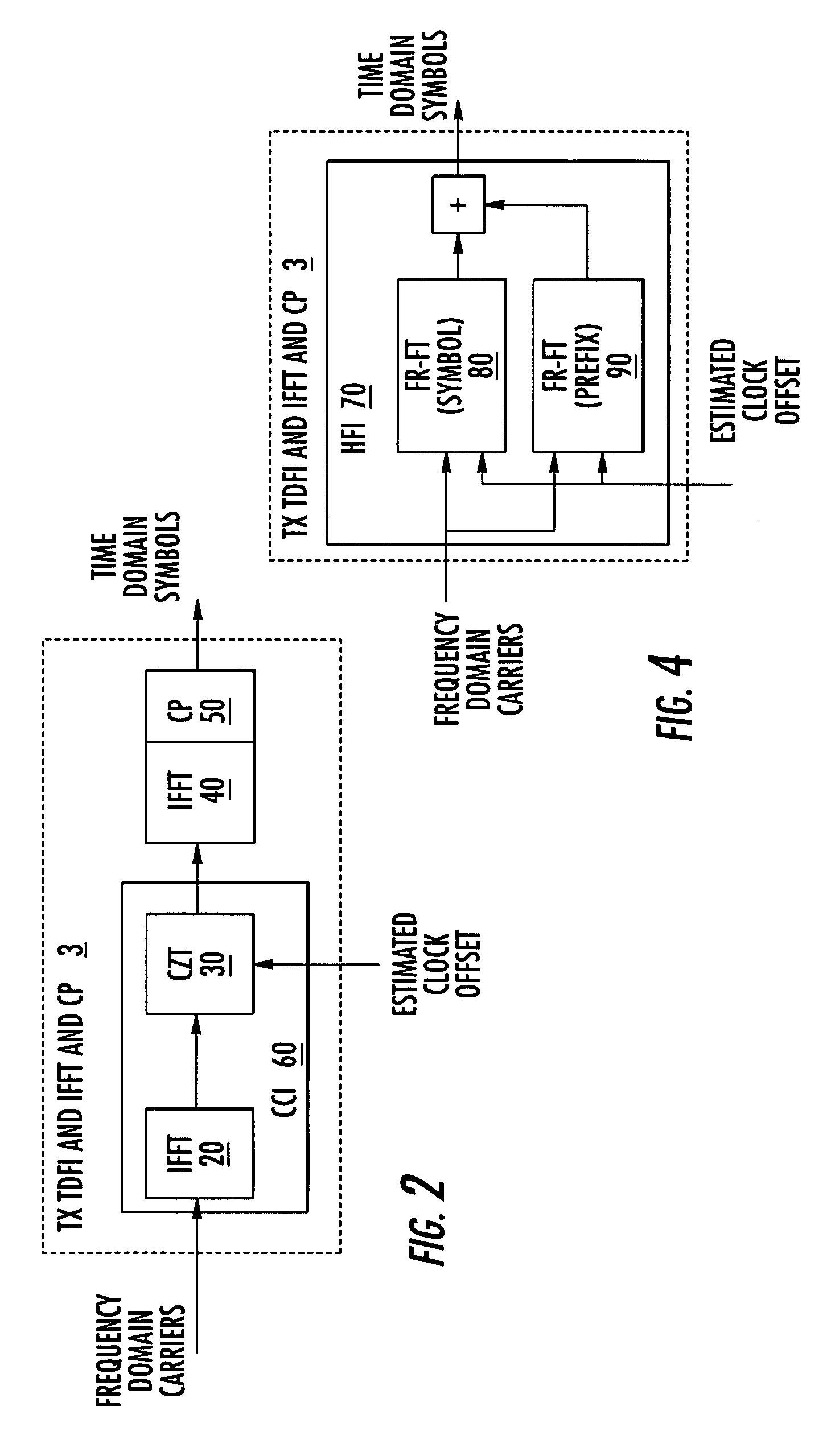

Electronic circuit for performing fractional time domain interpolation and related devices and methods

ActiveUS7460587B2Good clock offset compensationReduce the amount of processingDigital technique networkDigital computer detailsType errorTime domain

A clock offset compensation arrangement may include a fractional interpolator for applying a trigonometric interpolation to a sampled input signal according to a clock offset signal. It uses transform-based processing in the frequency domain. Compared to a polynomial type interpolation it may be easier to implement, and may achieve a closer approximation to an ideal interpolation. It may reduce the effects of non-linear type errors introduced by truncation of higher powers. The arrangement may be applied to receivers or transmitters of multi-carrier modems, as well as other applications which use rate adaptation or synchronization.

Owner:PROTON WORLD INT +1

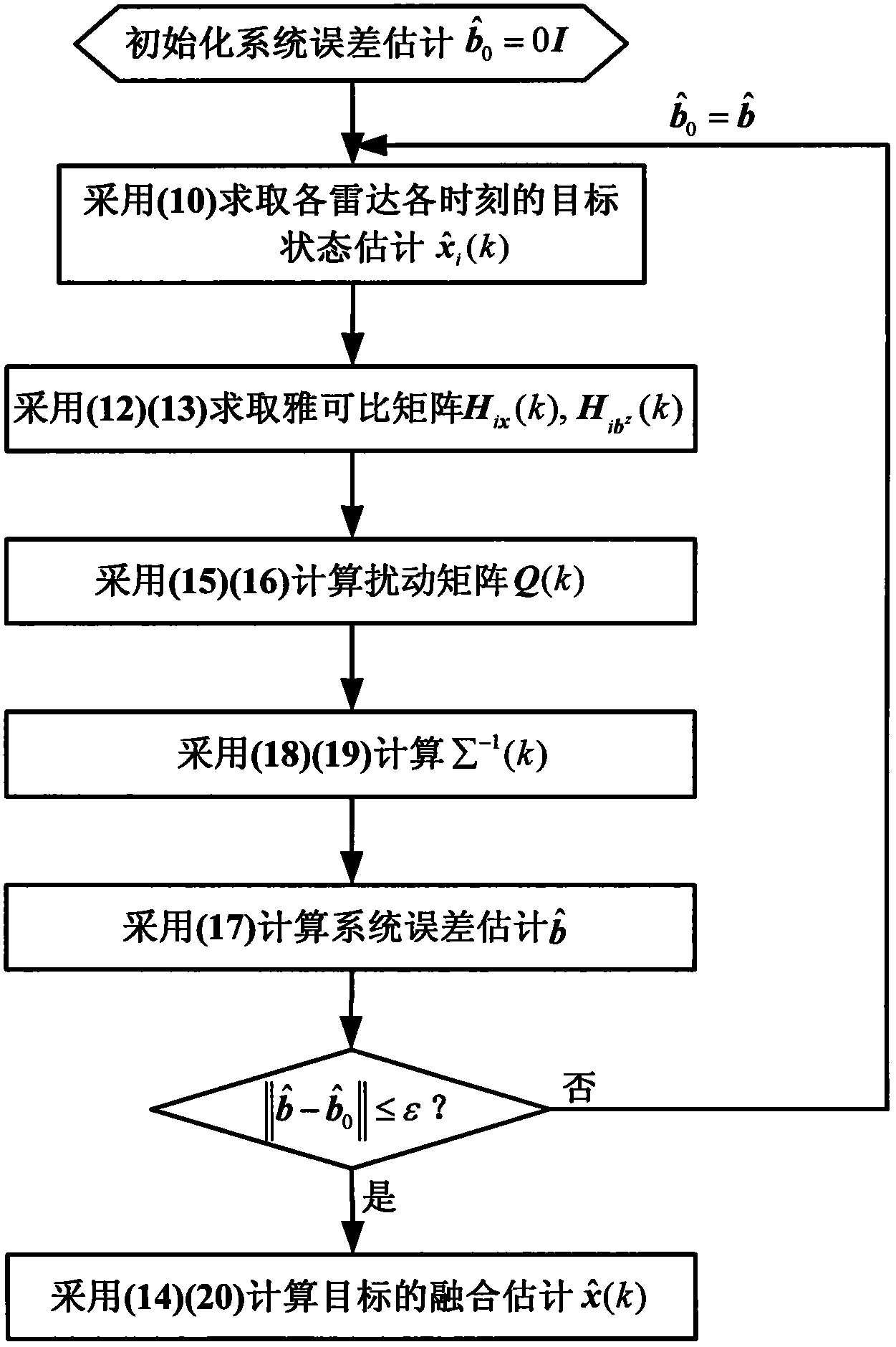

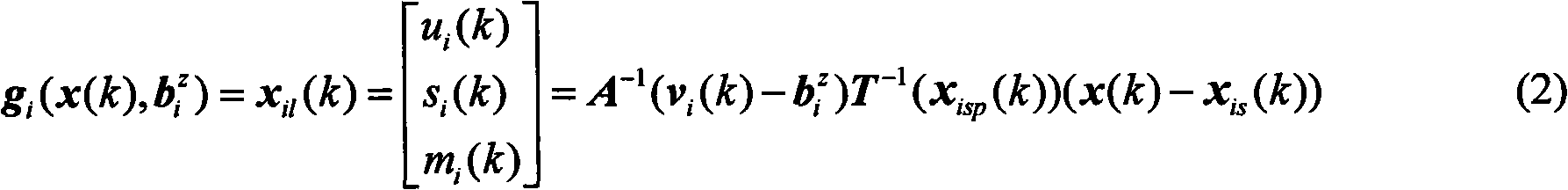

Movable radar networking batch-processing type error register

InactiveCN102707268AImprove estimation accuracyFast convergenceWave based measurement systemsType errorBatch processing

The invention discloses a movable radar networking batch-processing type error register and belongs to the field of radar data processing. According to the conventional movable radar network error registration technology, supposed and constructed models do not meet actual engineering background requirements, the problem about movable radar network error registration is not systematically and comprehensively modeled and solved, and availability is low. The invention relates to a batch-processing algorithm for measurement. According to the algorithm, converged system error estimation is finally realized by recursively optimizing system errors along the maximum gradient of disturbance. The distance between radars is not limited, the priori knowledge of fixed reference points is not required to be utilized, and the error register is high in convergence speed and high in accuracy and has popularization and application values.

Owner:NAVAL AERONAUTICAL & ASTRONAUTICAL UNIV PLA

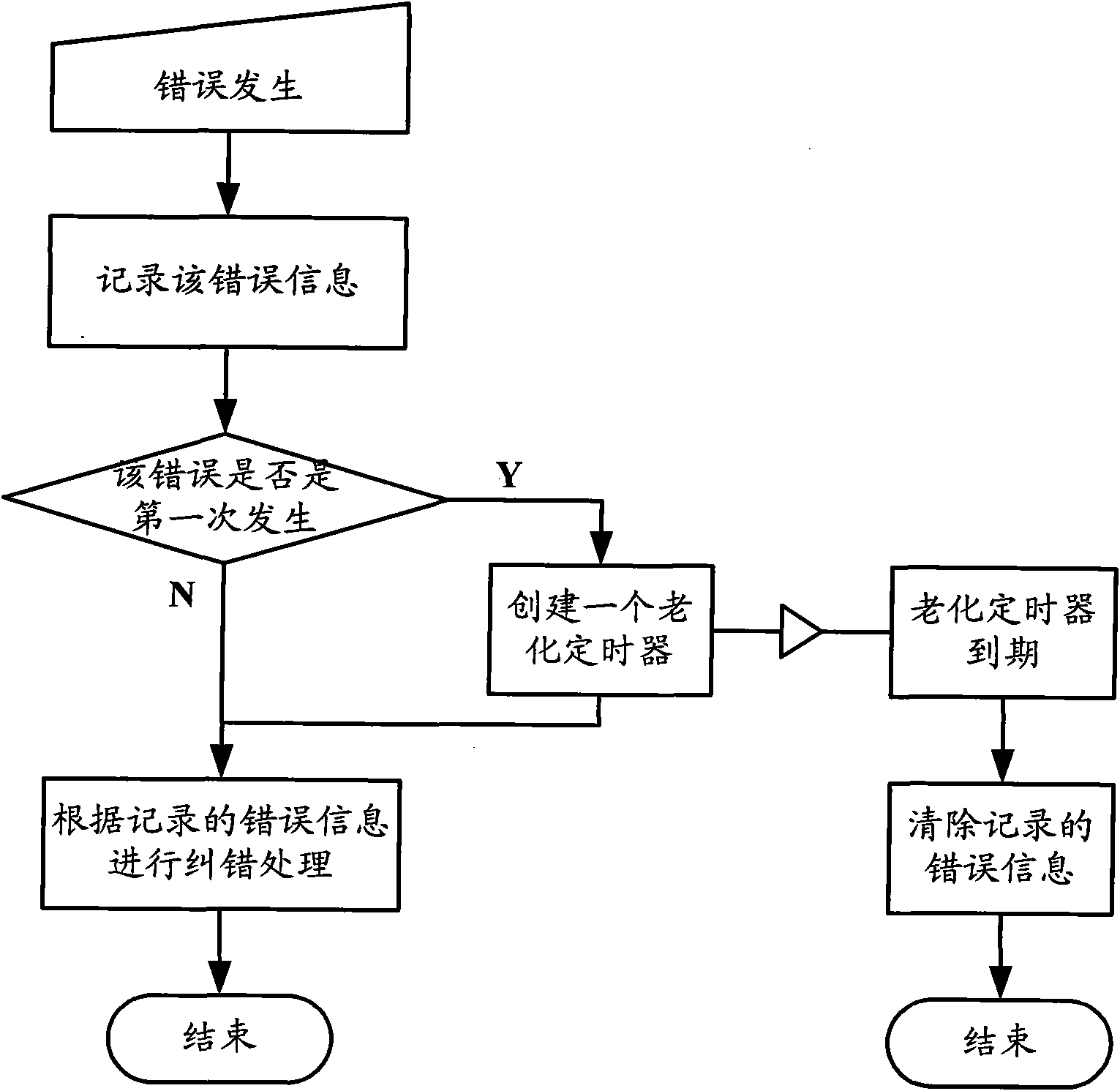

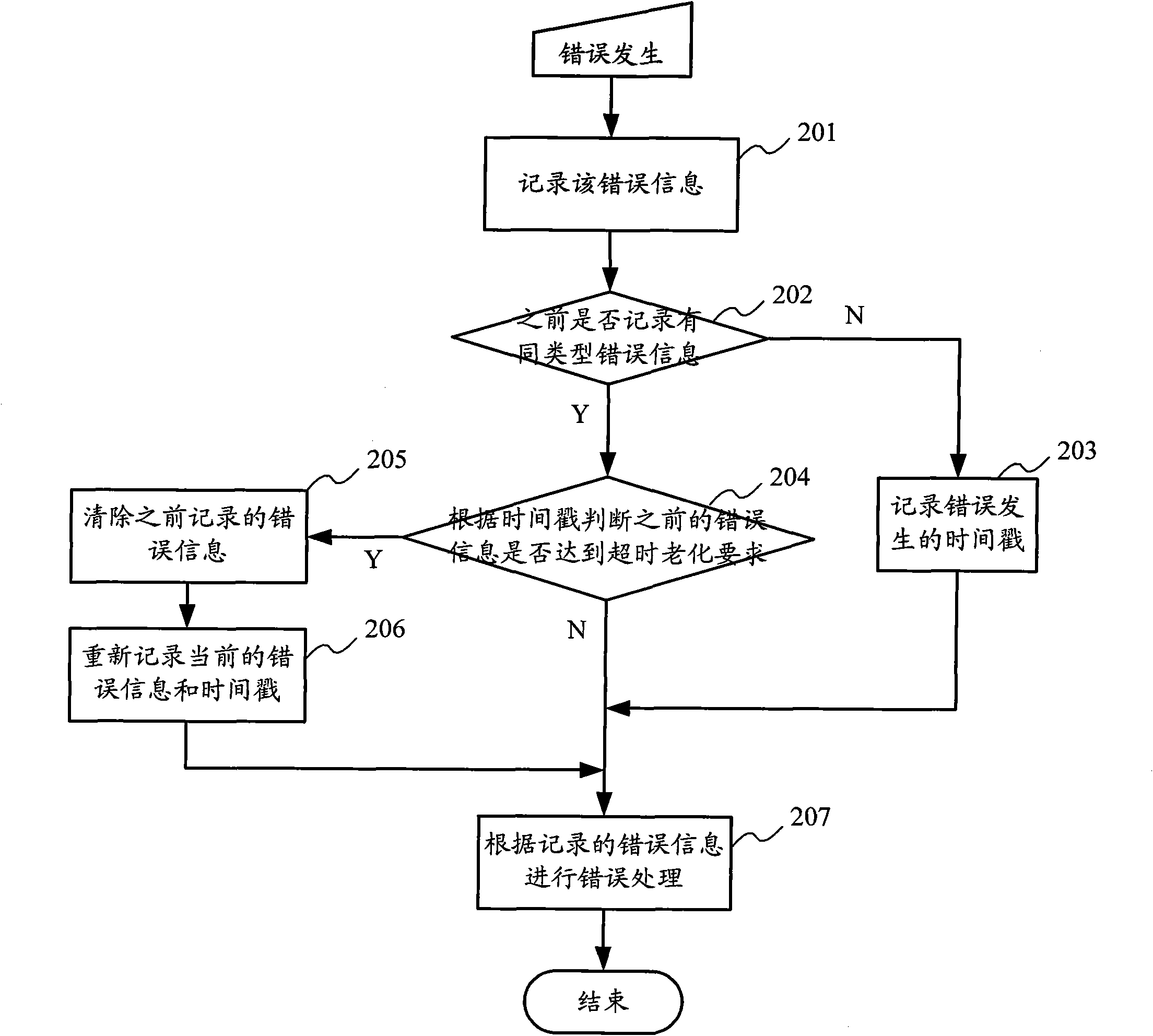

Method and device for data overtime aging processing

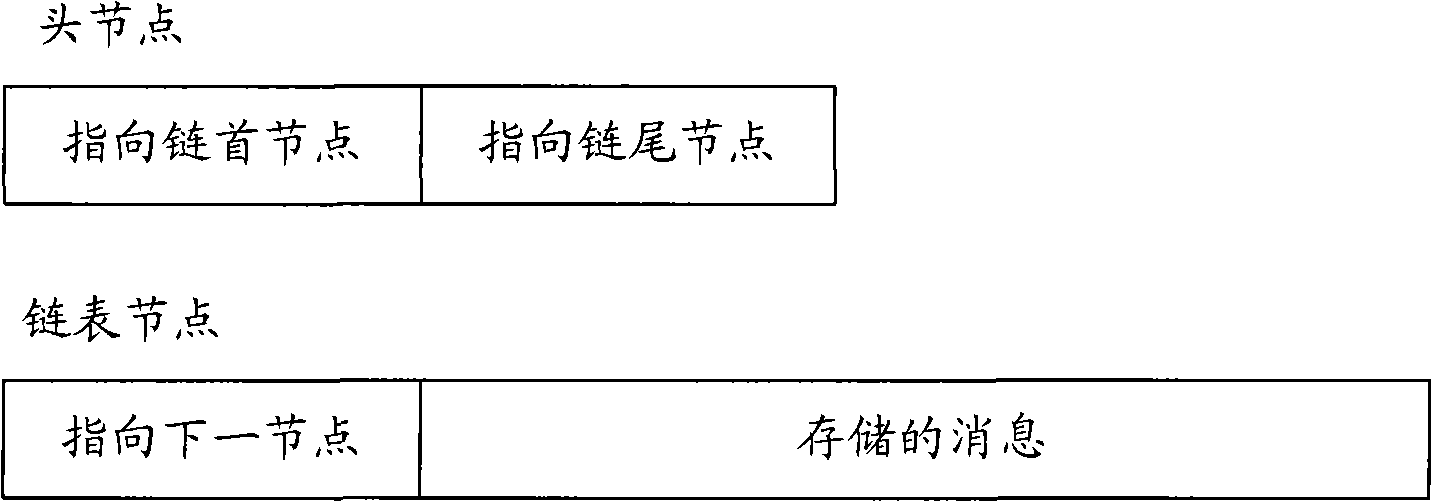

InactiveCN102023926AOvertime Aging Requirement ImplementationReduce overheadMemory adressing/allocation/relocationType errorSCSI

The invention discloses a method and device for data overtime aging processing, which are applied to a data storage system comprising a small computer system interface (SCSI) controller and an SCSI device. The method is as follows: the SCSI controller receives and stores error messages sent by the SCSI device; the SCSI controller judges whether corresponding error messages reaches overtime aging time or not according to the time stamps of same-type error messages stored in the SCSI controller and current time; and if yes, overtime aging processing is carried out on the corresponding error messages by the SCSI controller. By using the method and device disclosed in the invention, system source overhead is saved while realizing overtime aging of error messages.

Owner:NEW H3C TECH CO LTD

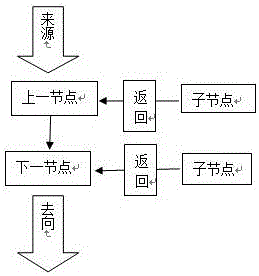

Logic node tree-shaped visual game editing engine

PendingCN105808260AImprove organizationEasy to readVisual/graphical programmingSpecific program execution arrangementsType errorLogic error

The invention relates to a logic node tree-shaped visual game editing engine. Different name lists are constructed by adopting tree-shaped programming, wherein the name lists of a logic set are arranged at the left side of a visual programming interface; the name lists correspond to the function lists in programming languages; a tree-shaped logic list is arranged at the right side of the visual programming interface; in a programming process, execution of the whole programming logic is started from a first line; the nodes are equipped with different icons for distinguishing different logic properties of the nodes; the part at the most right side of the visual programming interface is the attribute setting part of a single node; dynamical adjustment can be carried out according to the currently selected nodes; and the most lower part of the visual programming interface is equipped with a debugging operation interface. According to the method provided by the invention, logic errors resulting from typing errors can be reduced; the tree-shaped structure is clear in logic and is convenient for organizing and reading the logic; and the speed and efficiency of debugging the logic can be greatly improved.

Owner:成都神秘方块科技有限公司

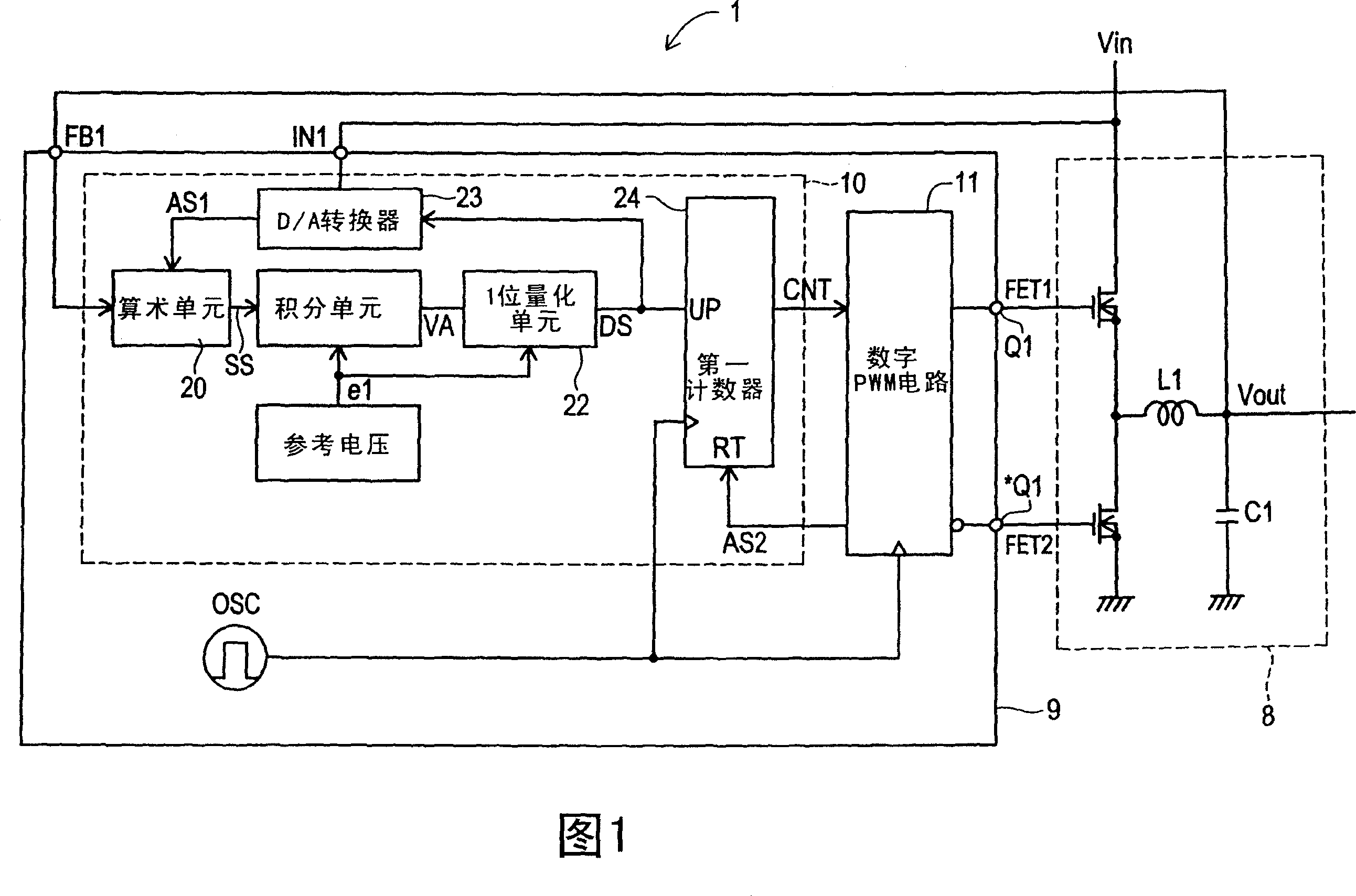

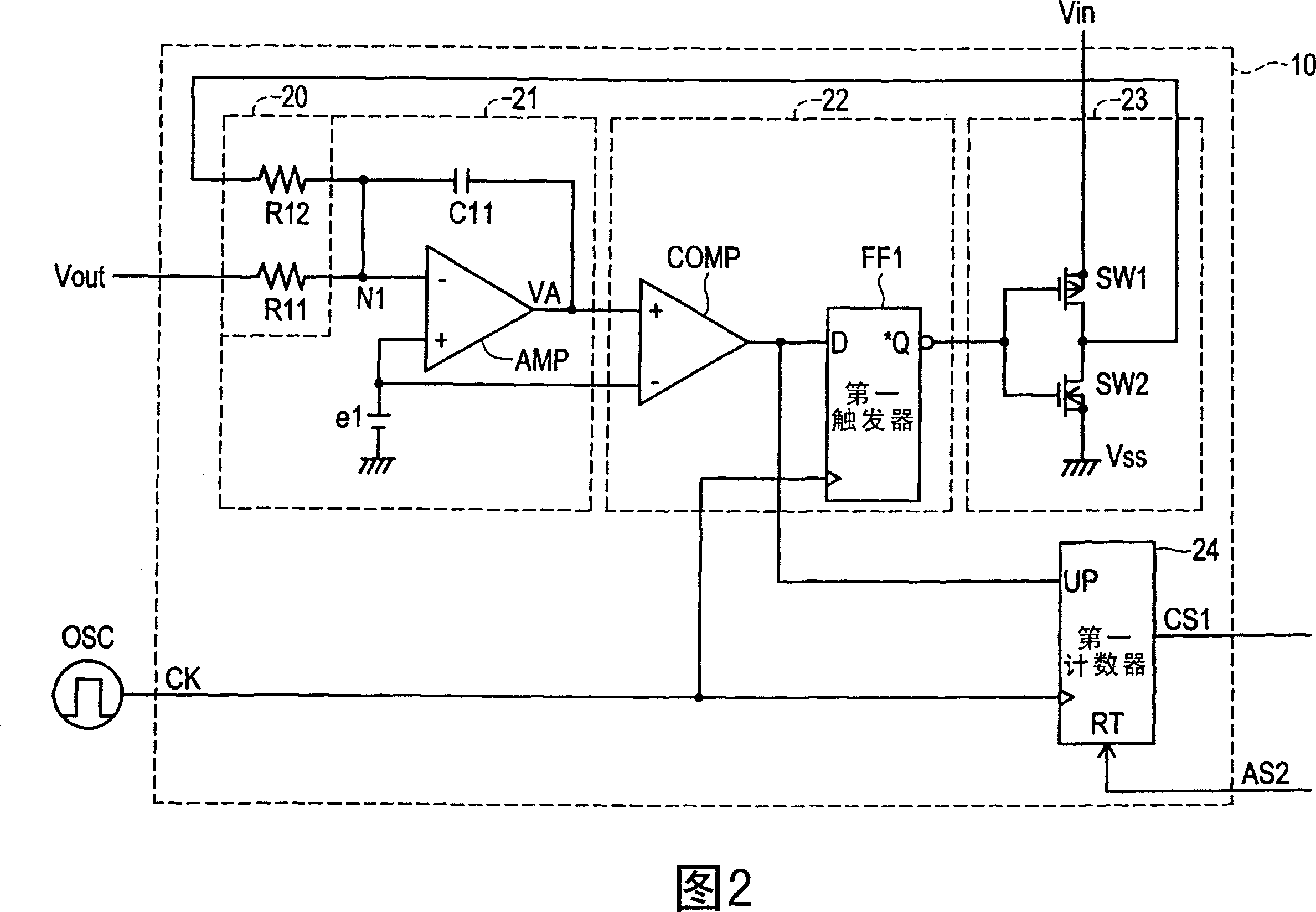

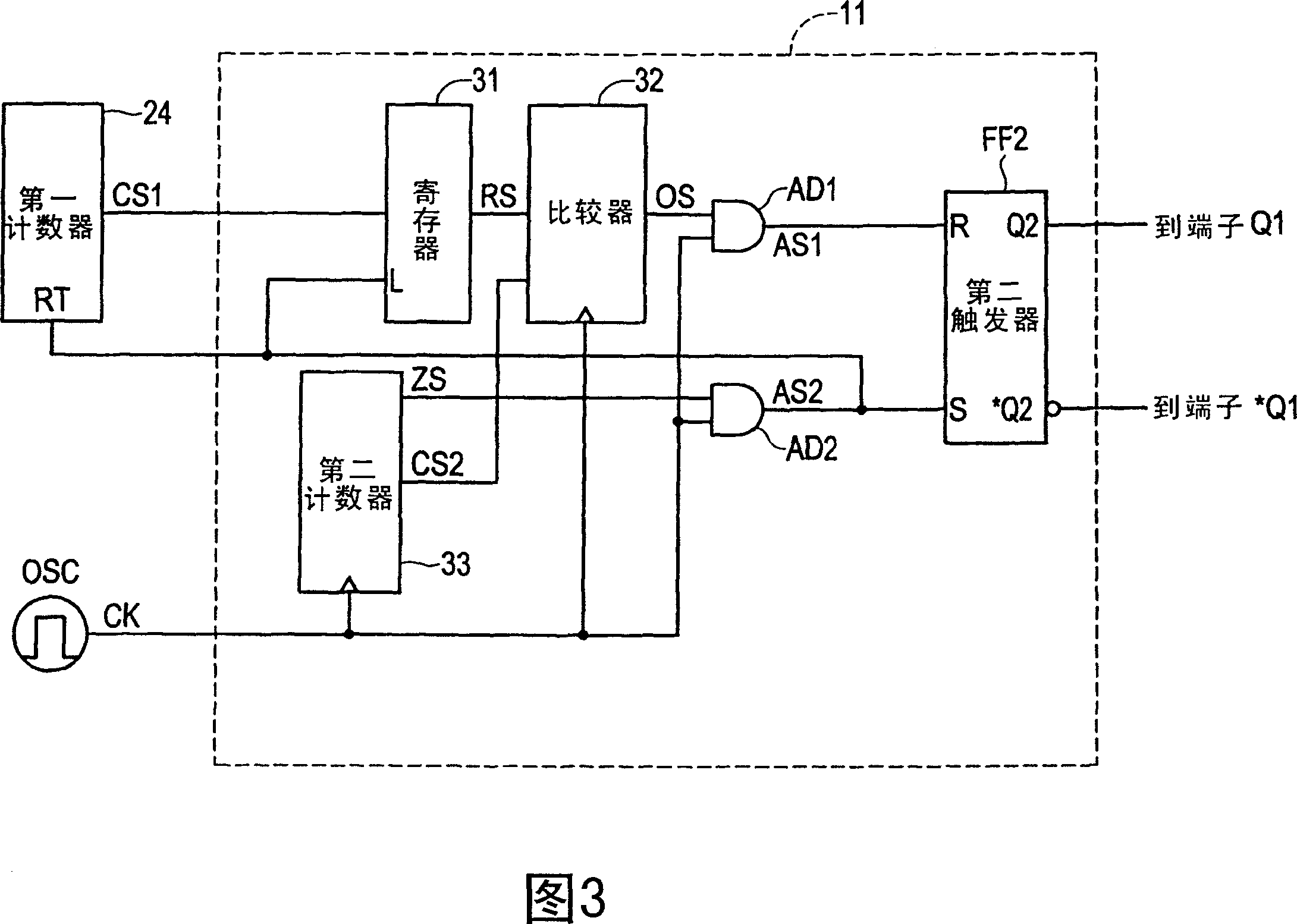

Control circuit of DC-DC converter and its control method

To present a control circuit of a DC-DC converter to be incorporated in a logic circuit, having a digital error amplifier capable of controlling the gain depending on an input voltage and an output voltage, without requiring a resistance or a capacitor of high precision used in a feedback circuit or the like. A SigmaDelta AD converter type error amplifier 10 includes an arithmetic unit 20 , an integrating unit 21 , a 1-bit quantizing unit 22 , a D / A converter 23 , and a first counter 24 . The arithmetic unit 20 outputs a differential signal of an output voltage Vout and an average output voltage AV. The integrating unit 21 outputs an integral signal by integrating the differential signal. The 1-bit quantizing unit 22 outputs a 1-bit digital signal by quantizing the integral signal. The D / A converter 23 converts from digital to analog depending on a 1-bit digital signal. A digital PWM circuit 11 determines the on-duty of the main switching element of the DC-DC converter depending on the pulse density of the D / A converter 23.

Owner:SOCIONEXT INC