Patents

Literature

130results about How to "Reduce surface reflectivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

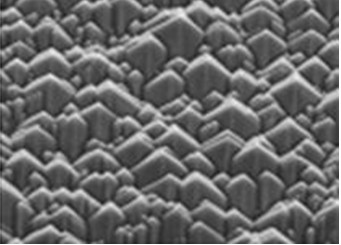

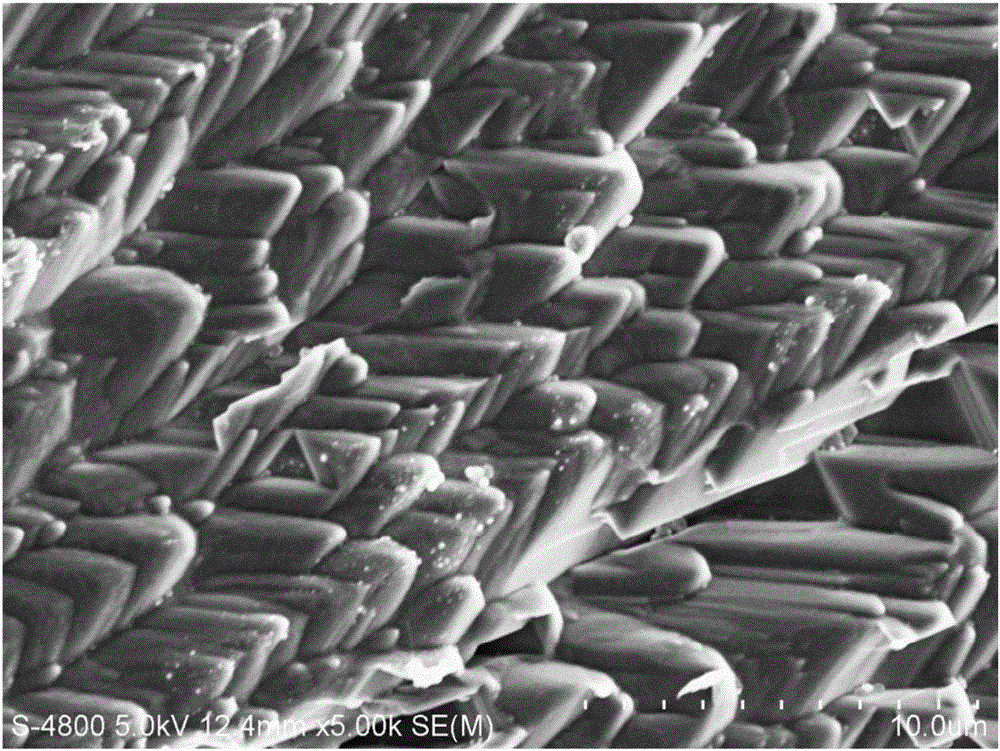

Method for forming inverted-pyramid porous surface nanometer texture on polycrystalline silicon and method for manufacturing short-wave reinforcing solar cell

InactiveCN103456804AExtend your lifeUniform and smooth microstructureFinal product manufacturePhotovoltaic energy generationCharge carrierSolar cell

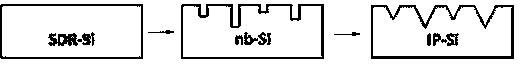

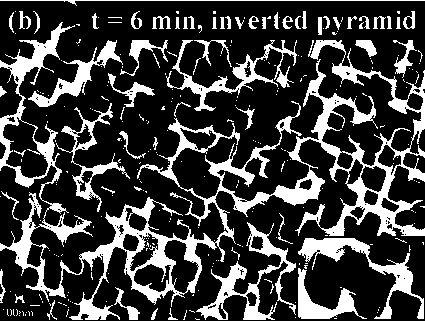

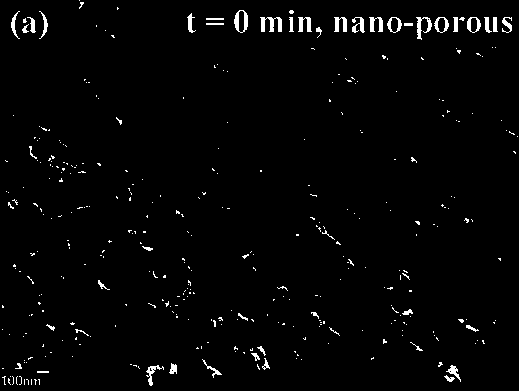

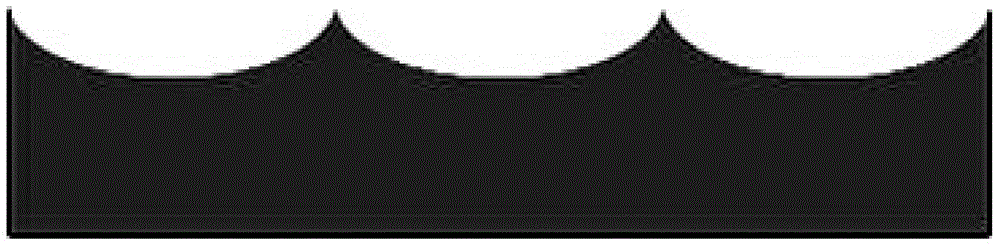

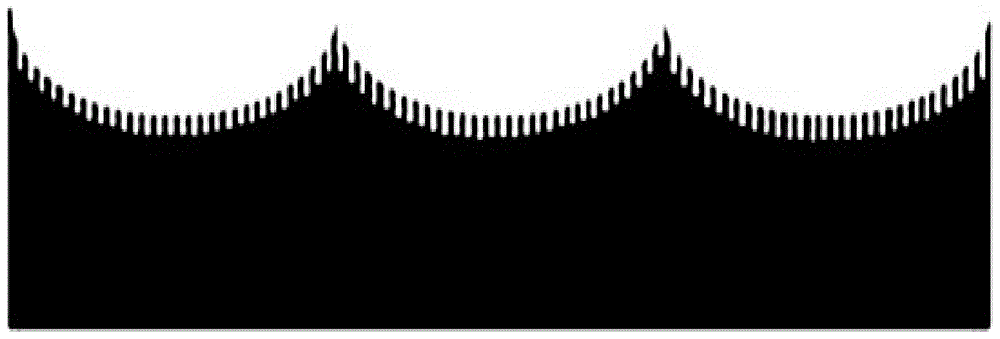

The invention discloses a method for forming an inverted-pyramid porous surface nanometer texture on polycrystalline silicon and a method for manufacturing a short-wave reinforcing solar cell. The method for forming the inverted-pyramid porous surface nanometer texture on the polycrystalline silicon and the method for manufacturing the short-wave reinforcing solar cell are suitable for the technical field of solar photovoltaic batteries. By means of a metal catalytic chemical corrosion method, a nanometer porous surface structure is formed on the polycrystalline silicon through HF, AgNO3, H2O2, HNO3 and other solutions, then partial samples are placed in a NaOH corrosive liquid with the concentration of 0.1-1% for surface modification of a nanometer inverted pyramid, a nanometer inverted pyramid silicon structure is formed, and the micro structure appearance of the nanometer inverted pyramid silicon structure is even and smooth, so that service life of a few effective charge carriers is greatly prolonged, and ultimately, in the nanometer texture surface structure, by means of changes of the thickness of a silicon nitride layer in the solar cell manufacturing process, a nanometer inverted pyramid silicon solar photovoltaic cell which is low in surface reflection rate and high in short wave spectrum response is prepared. The method for forming the inverted-pyramid porous surface nanometer texture on the polycrystalline silicon and the method for manufacturing the short-wave reinforcing solar cell are simple in process, convenient to operate, low in cost and suitable for industrial production.

Owner:SHANGHAI UNIV

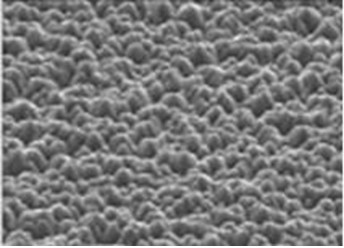

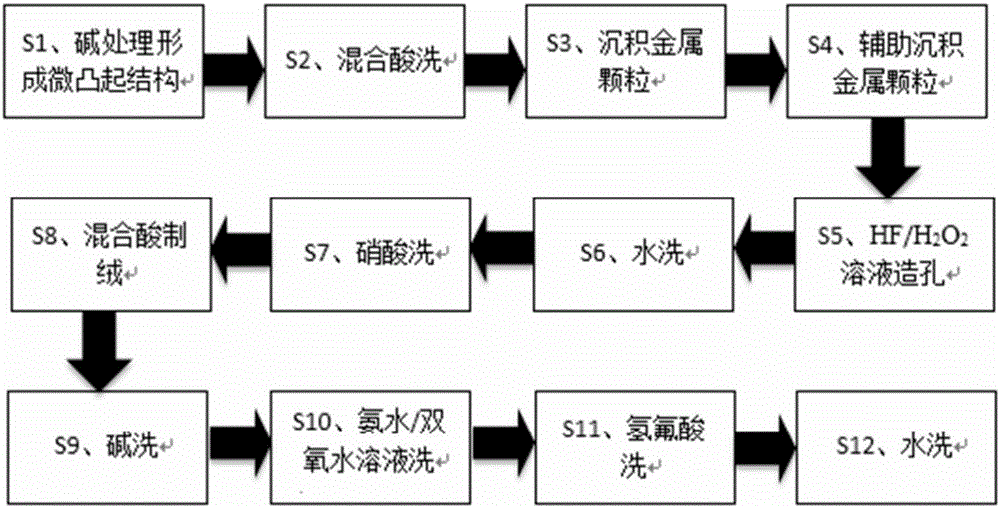

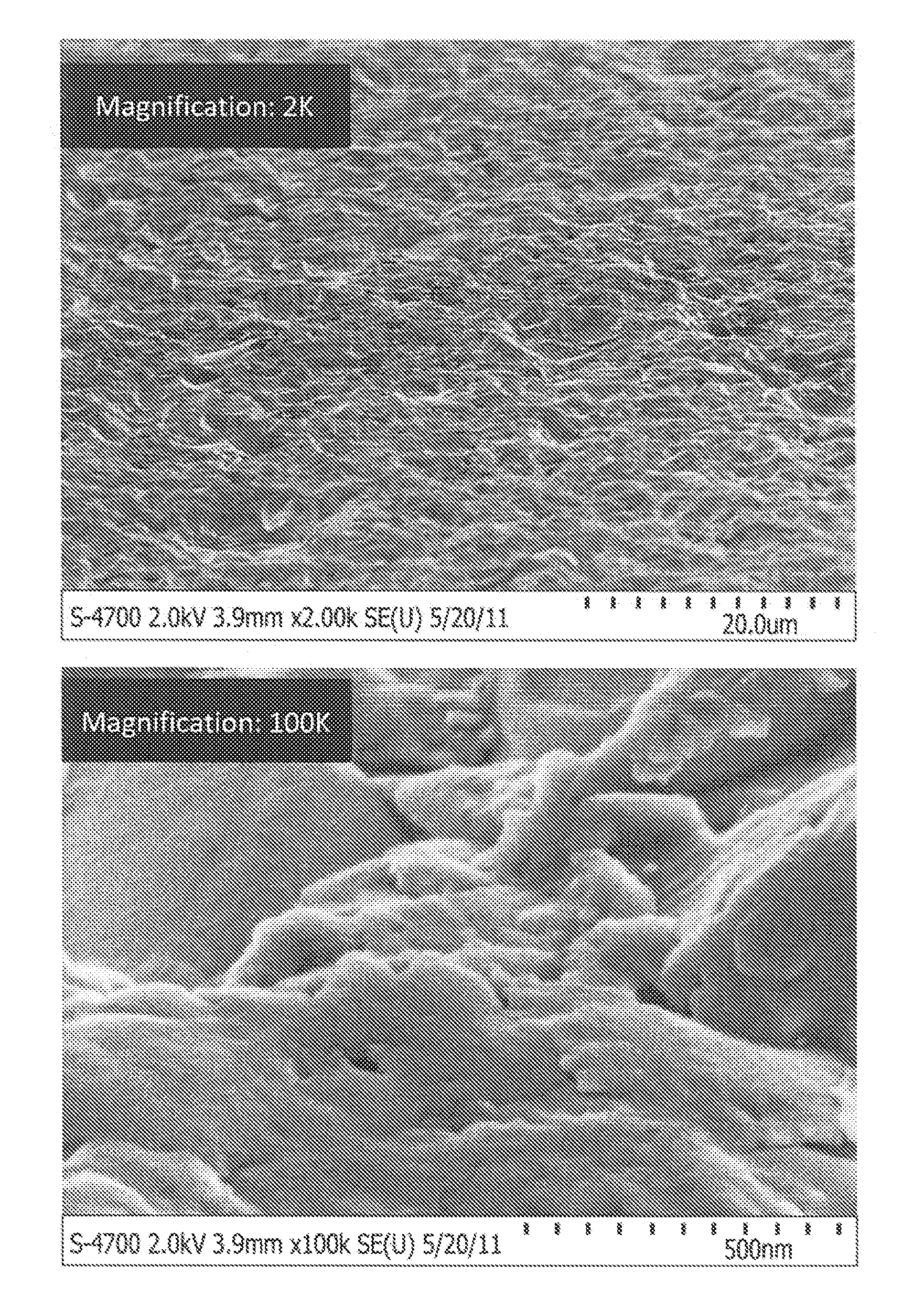

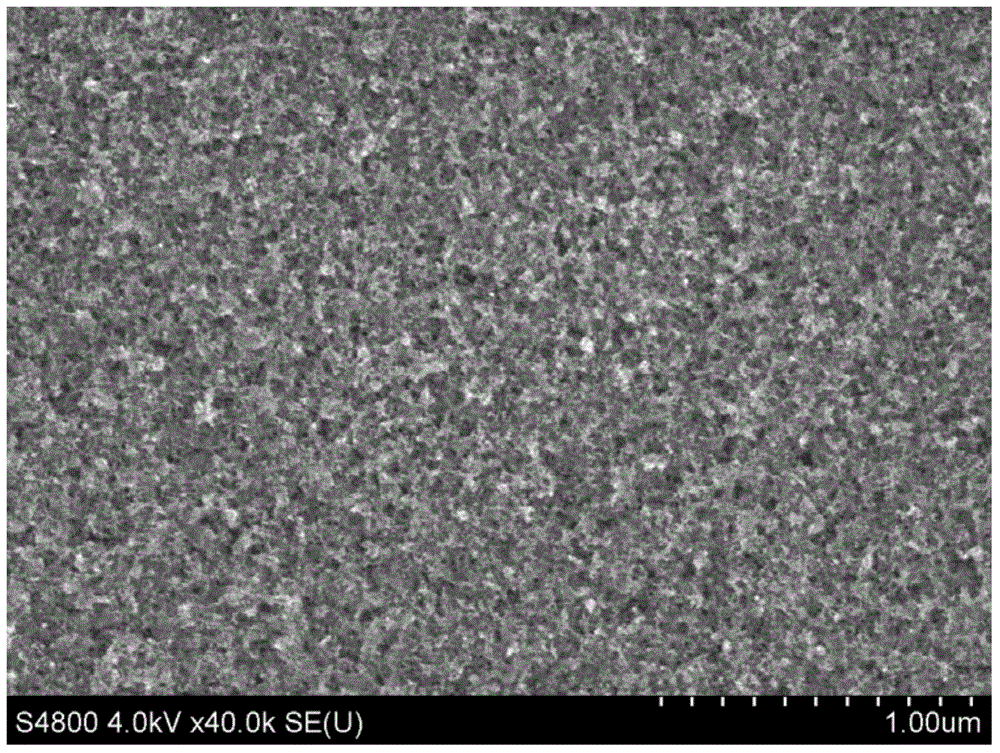

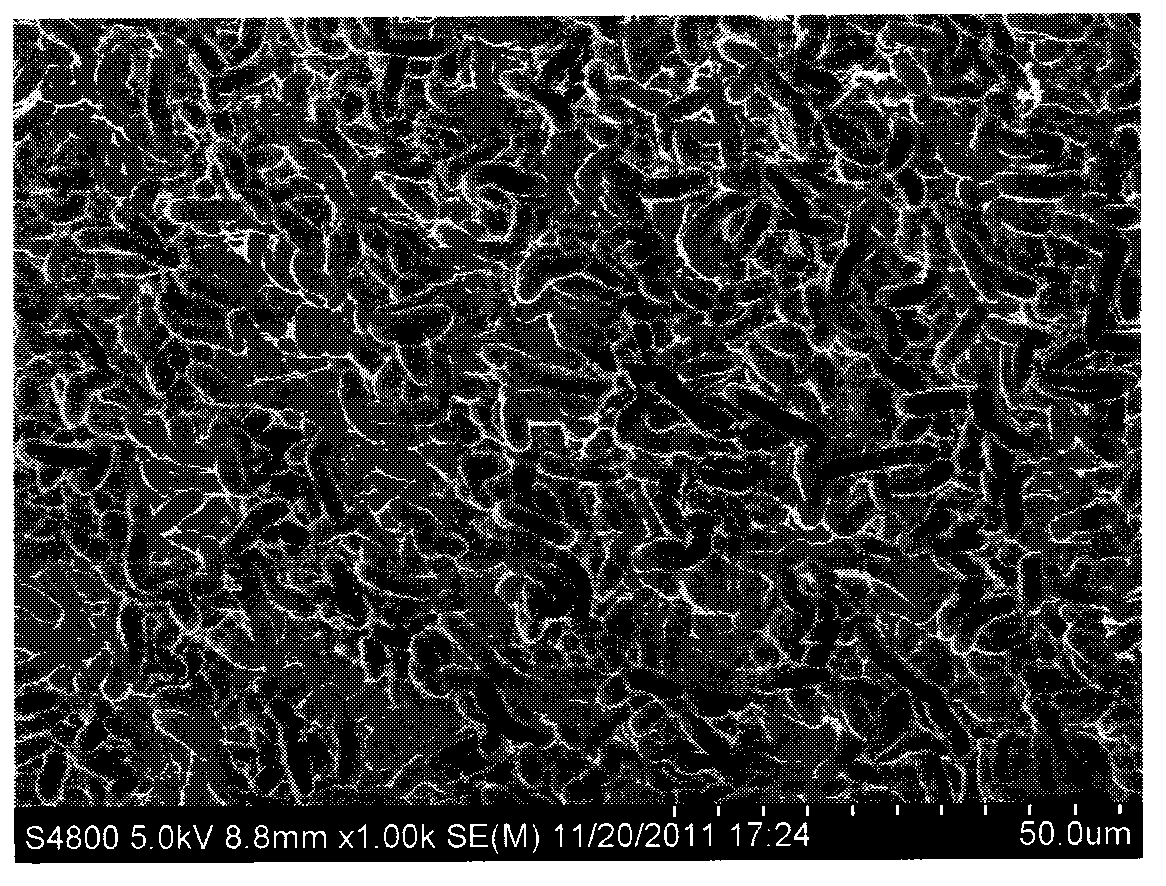

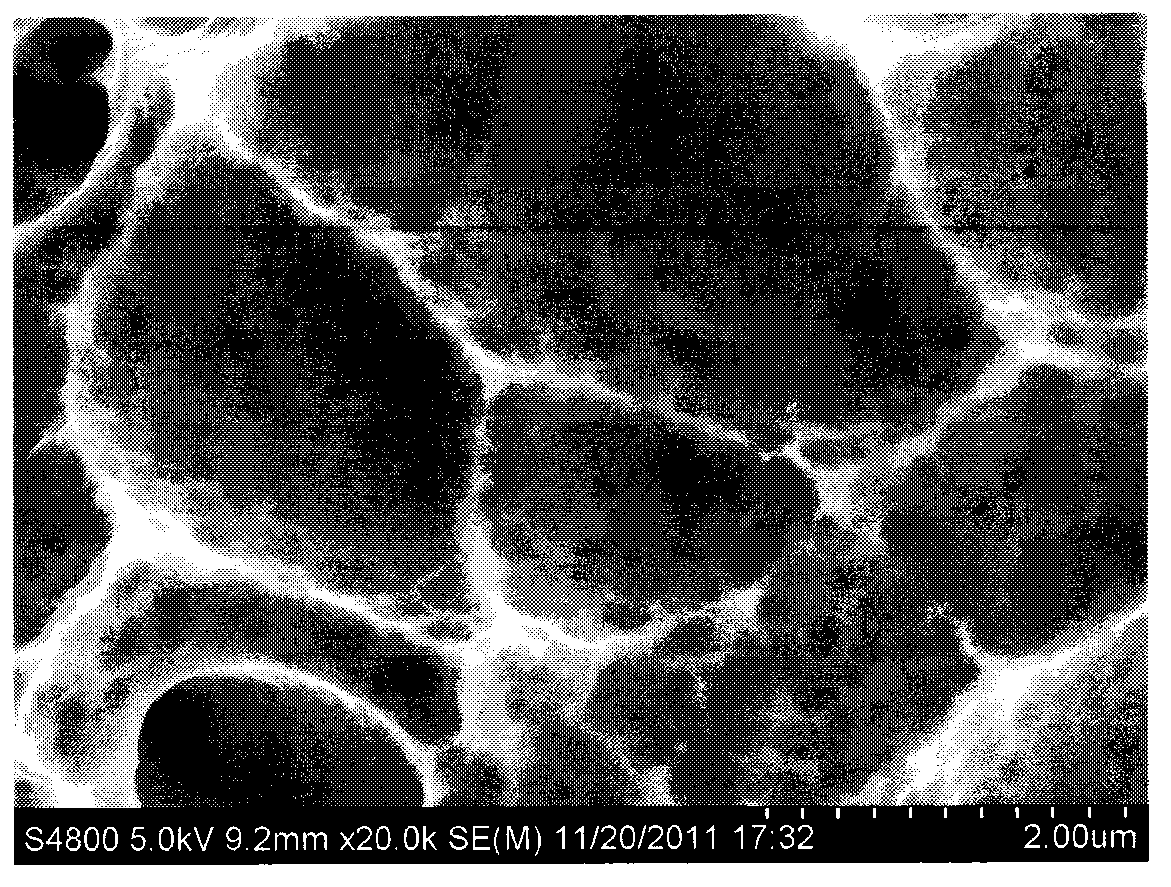

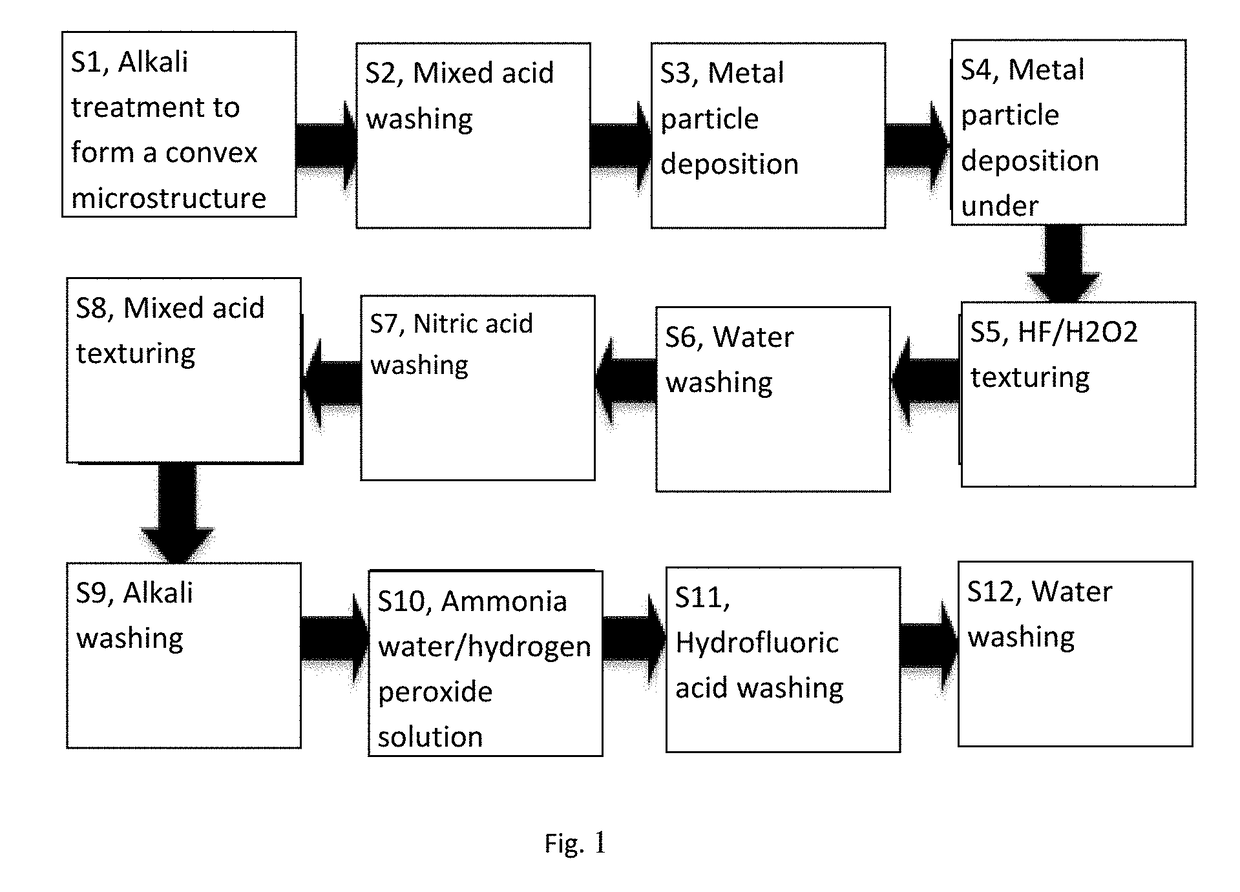

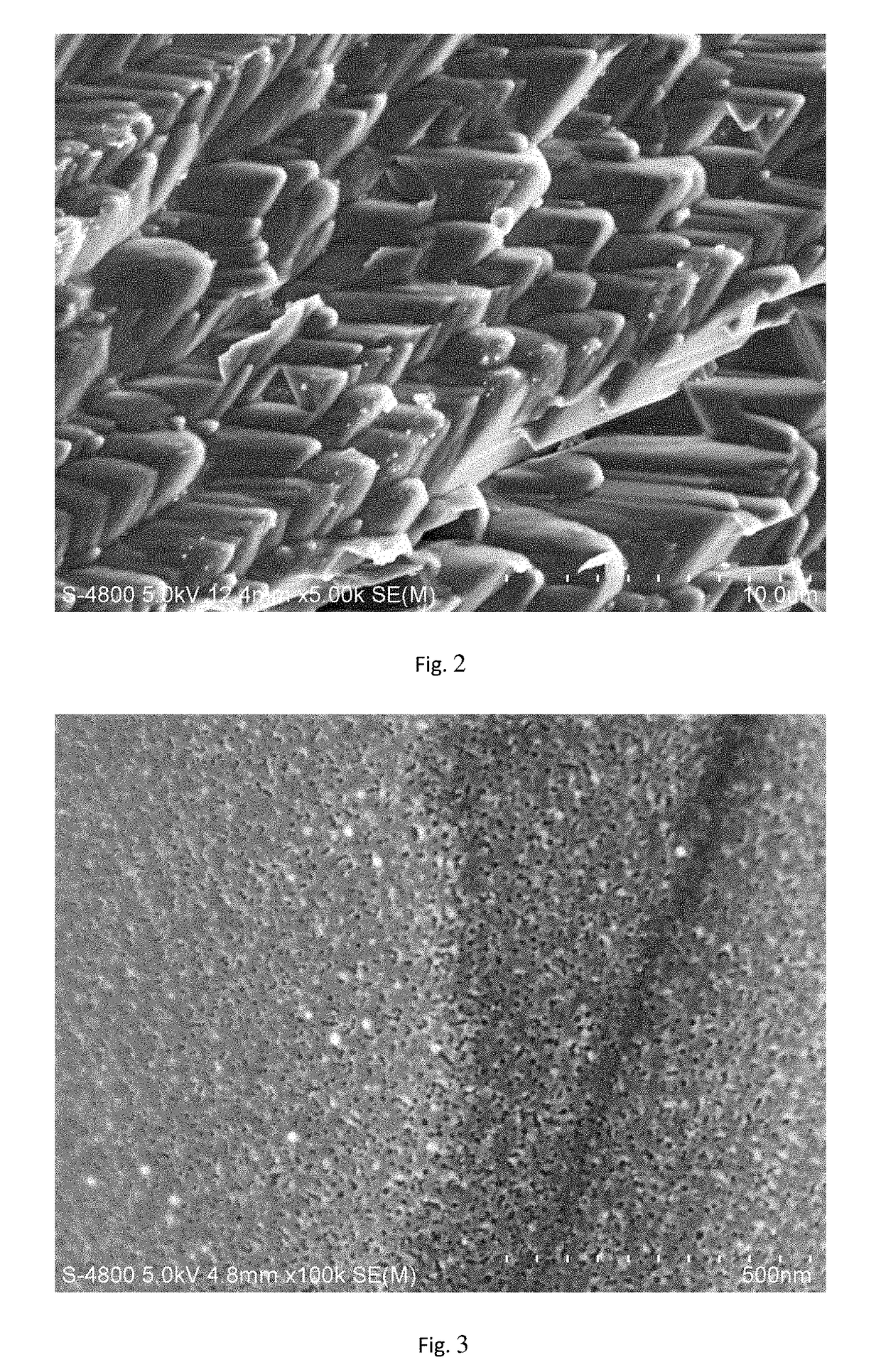

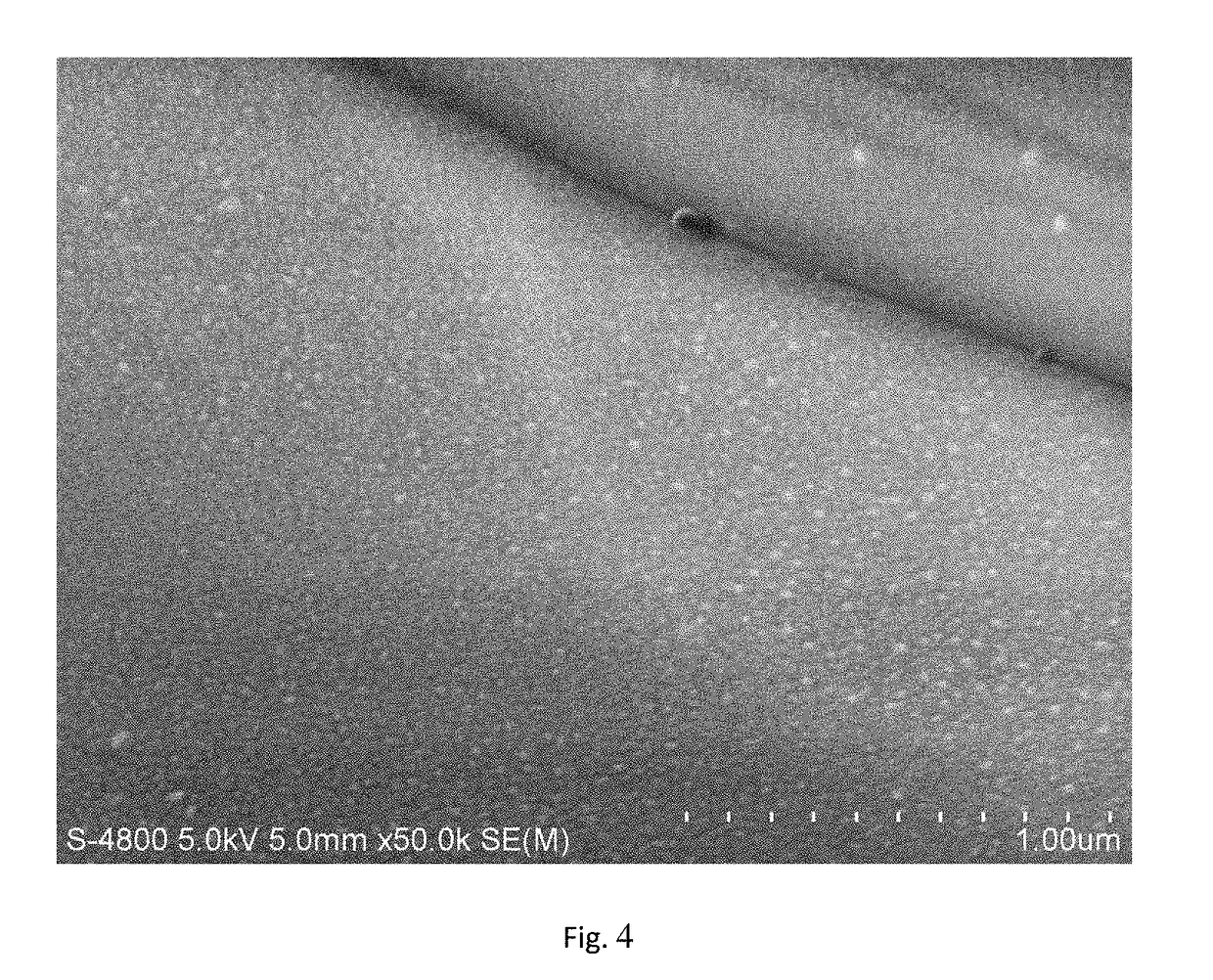

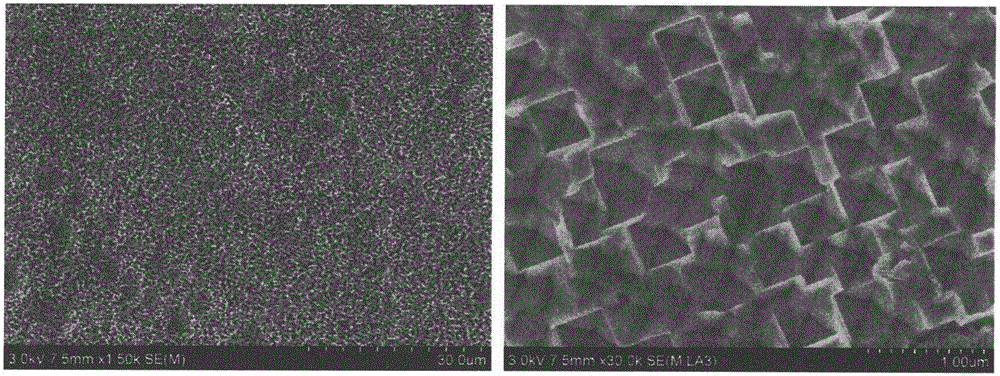

Preparation method of polycrystalline black silicon of micro-nano composite suede structure

InactiveCN104393114AReduce surface reflectivityConducive to removalAfter-treatment detailsFinal product manufactureIonMicro nano

The invention discloses a preparation method of polycrystalline black silicon of a micro-nano composite suede structure. The method comprises the following steps: imbedding polycrystalline silicon chips into etchant solution to obtain polycrystalline silicon chips with micro-meter suede structures; transferring the polycrystalline silicon chips with the micro-meter suede structures into a metal ion compound solution to deposit metal nanoparticles on the micro-meter suede; transferring into an etching solution to etch so as to obtain the polycrystalline silicon chips with the micro-nano composite suede structures; washing to remove metal particles residual on the surface; feeding into an alkaline solution to modify and etch the micro-nano composite suede structure; then drying to obtain the product. According to the method, the wet chemical etching method is carried out to prepare the micro-nano composite suede structure on the surface of the polycrystalline black silicone; such structure is extremely low in reflectivity; meanwhile, the preparation method is highly compatible with the general polycrystalline silicon suede preparation process; therefore, the preparation method can be quickly applied to the current general polycrystalline black silicon solar cell industry; the light absorbing efficiency can be obviously raised, and as a result, the efficiency of a solar cell is increased.

Owner:48TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

Hardcoat film, antireflection film and equipment for display

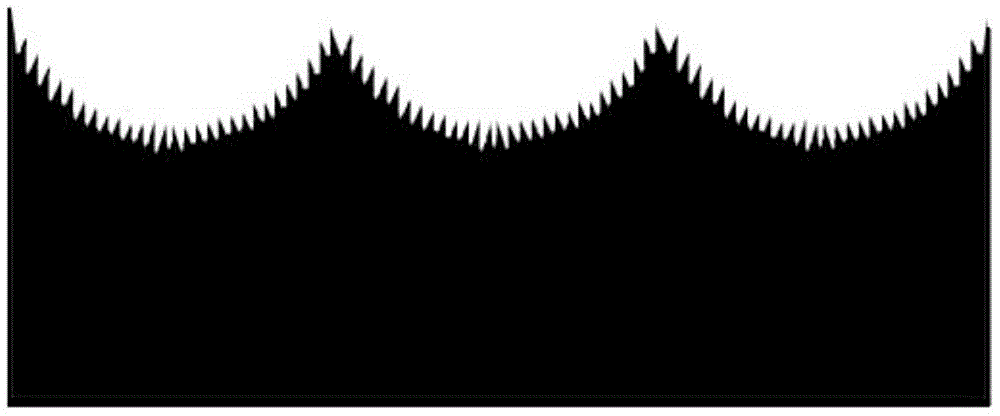

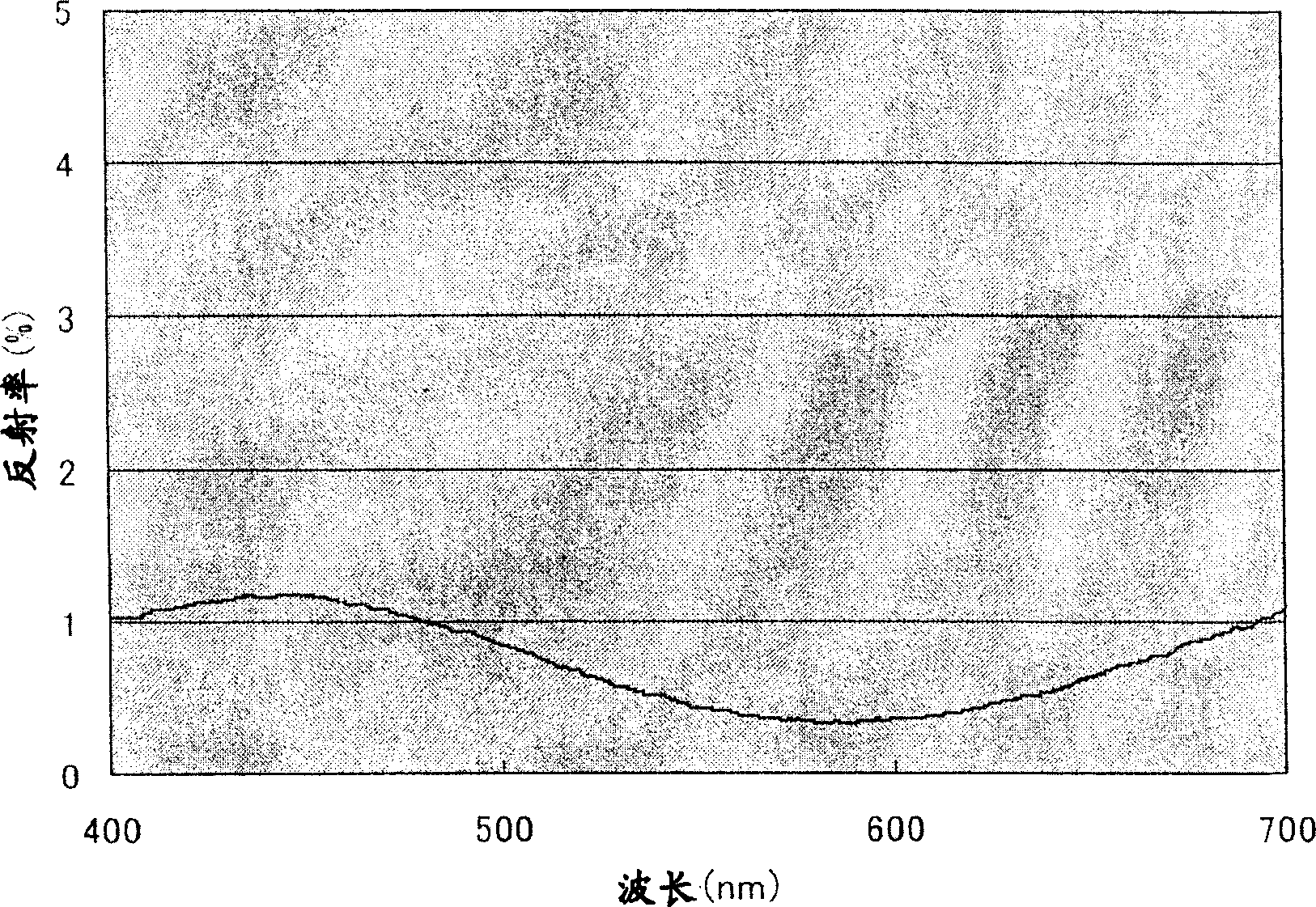

InactiveCN1575970AInhibitionGood visual effectSynthetic resin layered productsCoatingsThin membraneEngineering

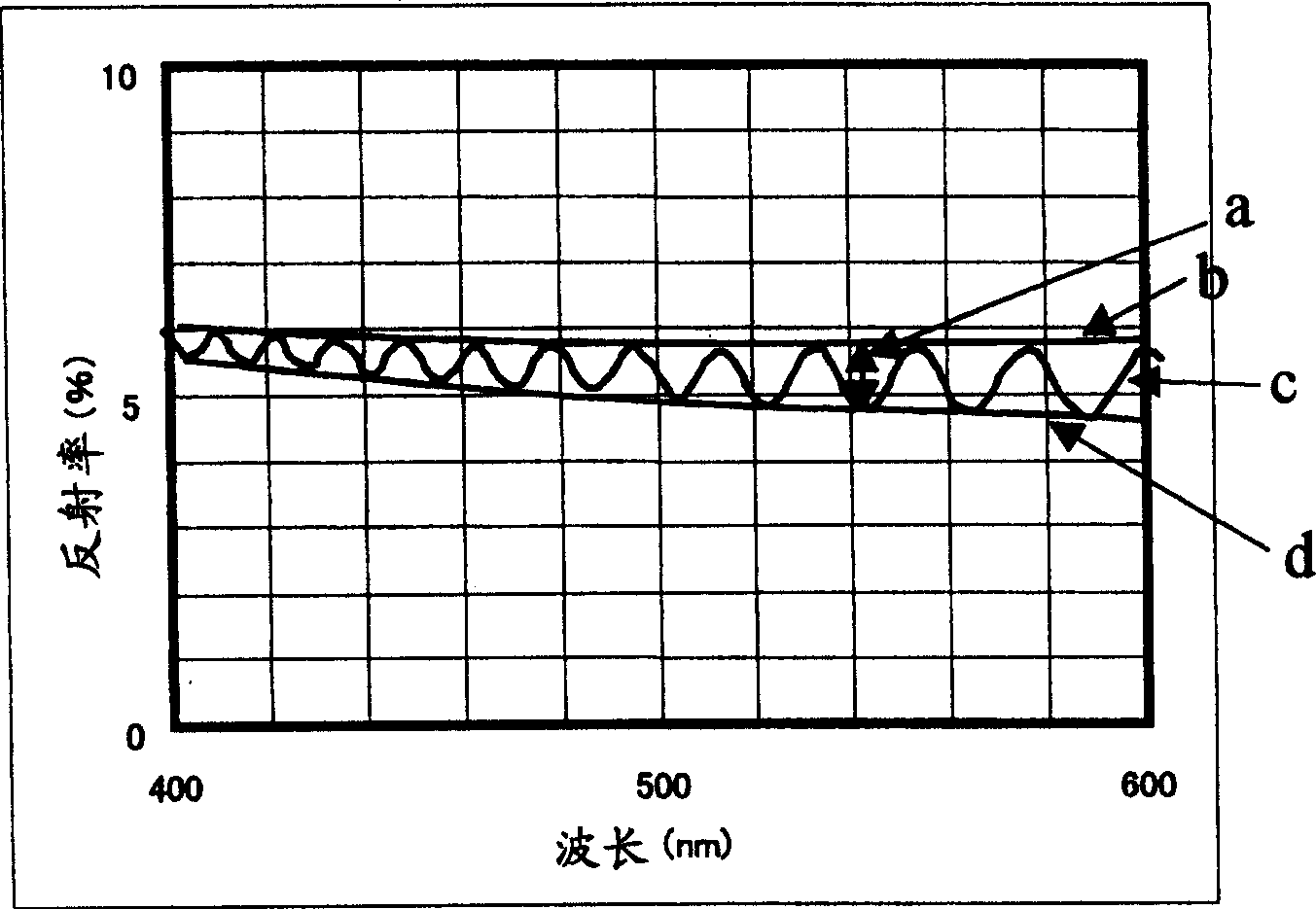

A hardcoat film comprises a substrate film, and a hardcoat layer laminated on at least one side of the substrate film, wherein a reflectance of the hardcoat layer at a wavelength within 400 to 600 nm has a mean ripple amplitude of 1% or less. The hardcoat film has decreased iris patterns. There is also provided an antireflection film having a low surface reflectance and a neutral tone of color, and an equipment for display including the film.

Owner:TORAY IND INC

Single crystal silicon texture-making additive and single crystal silicon texture-making technology

InactiveCN102115915AIncrease productivityIncrease production capacityAfter-treatment detailsFinal product manufactureActive agentPotassium hydroxide

The invention relates to a single crystal silicon texture-making additive and a single crystal silicon texture-making technology. The single crystal silicon texture-making additive consists of a wetting agent and a defoaming agent. The additive is characterized in that the wetting agent is a nonionic surfactant. The single crystal silicon texture-making technology comprises the following steps: heating deionized water to 70-80 DEG C, adding sodium hydroxide or potassium hydroxide to obtain a single crystal silicon texture-making corrosive liquid, wherein the mass percentage of sodium hydroxide or potassium hydroxide is 1%-2%; adding the single crystal silicon texture-making additive in the single crystal silicon texture-making corrosive liquid to obtain a mixed solution, wherein the volume percentage of the additive is 0.3%-2%; and placing a precleaned raw silicon chip in the mixed solution for 600-1200s for texture-making. By adopting the additive and technology in the invention, the texture-making quality can be greatly increased, the cost is greatly reduced, the technological operation can be easier and the automatic solution preparation can be realized.

Owner:百力达太阳能股份有限公司

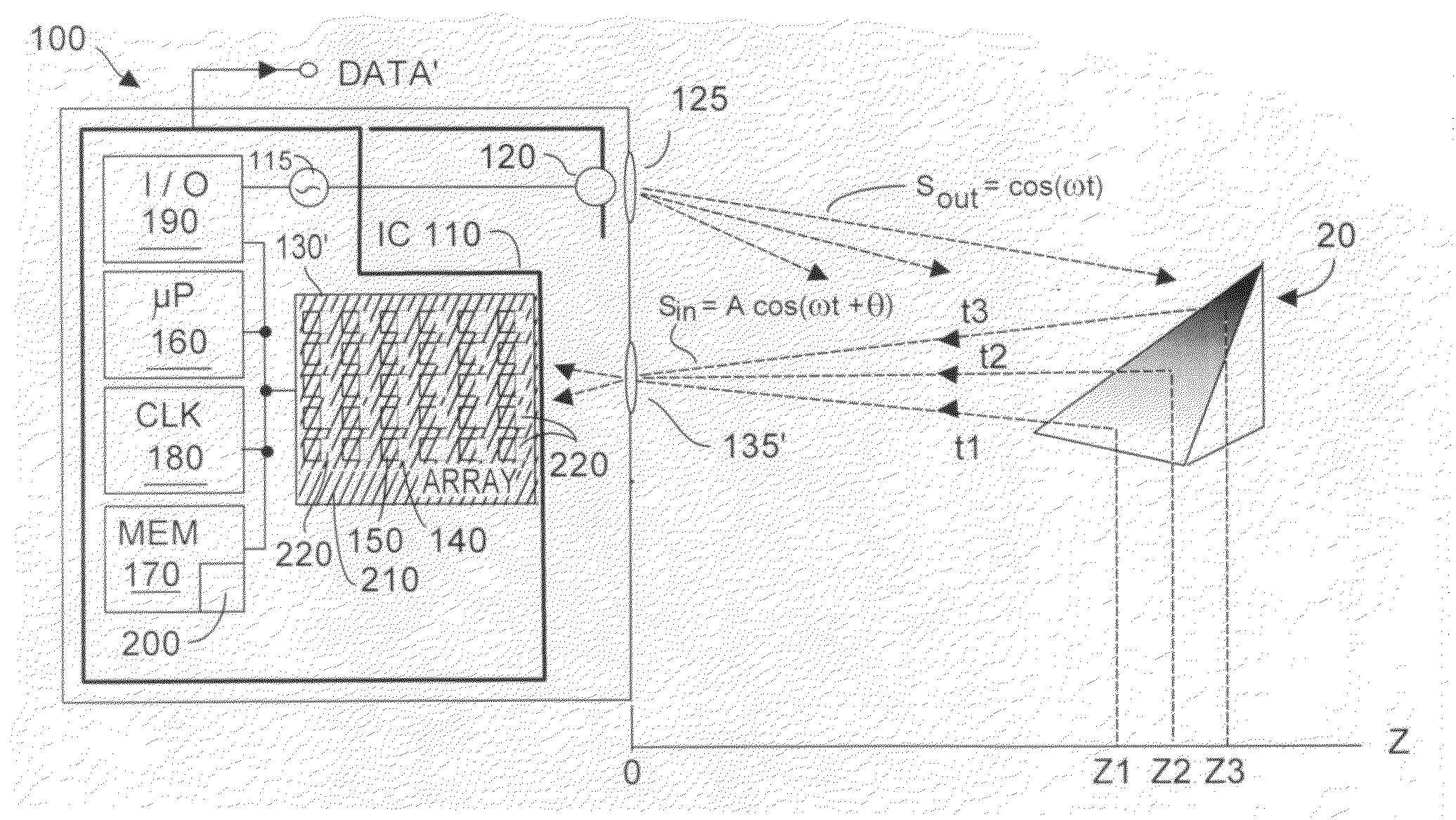

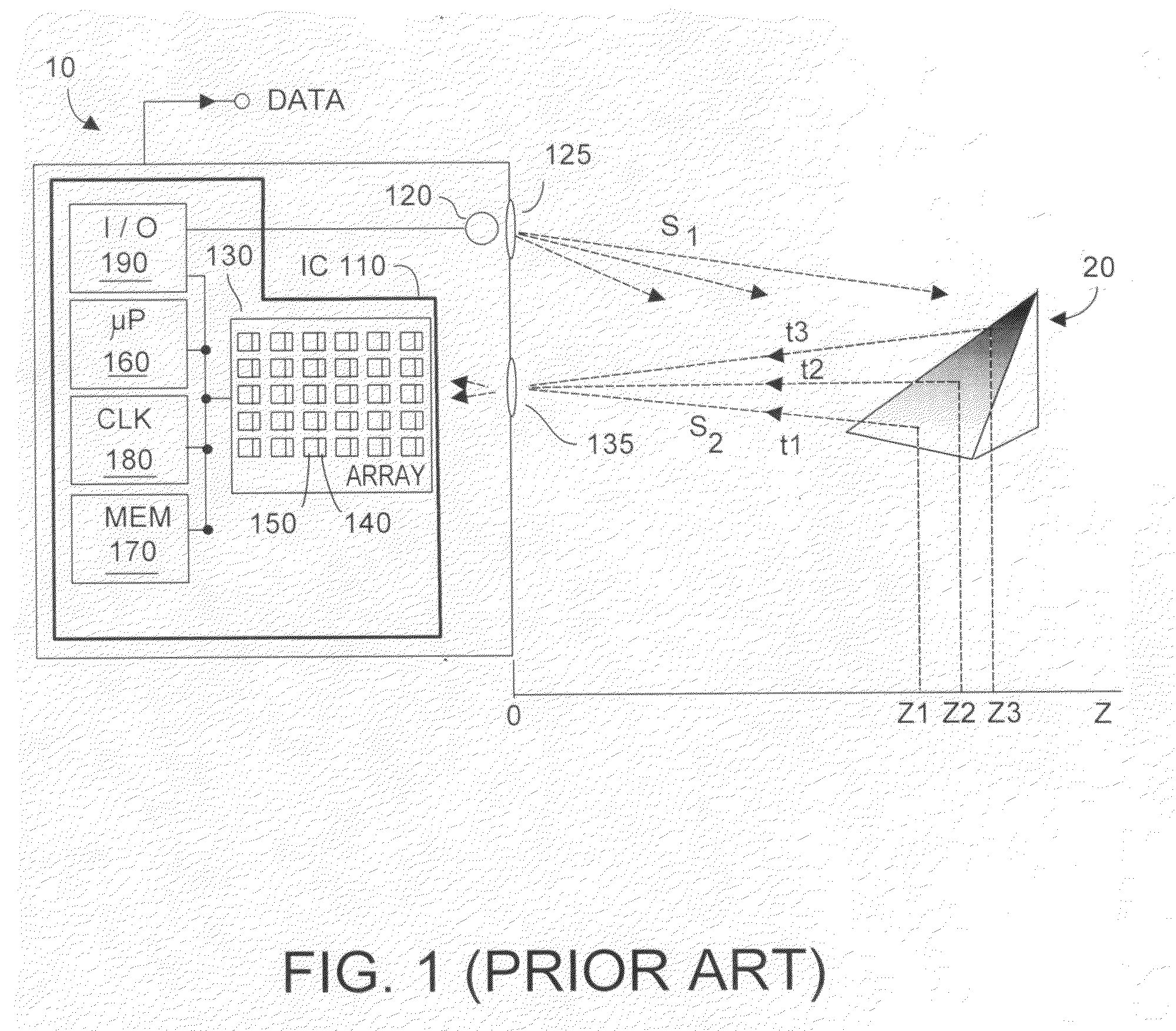

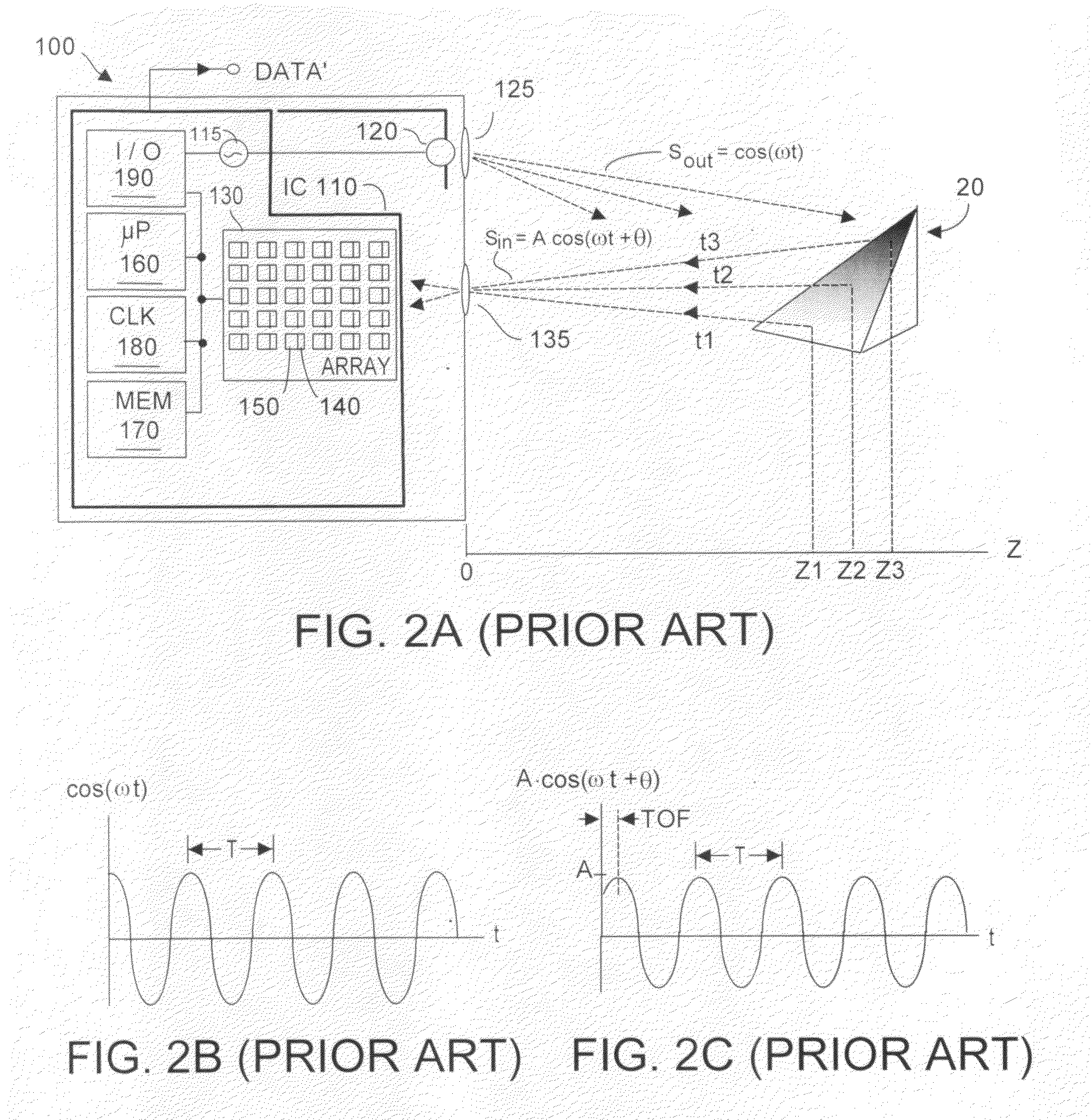

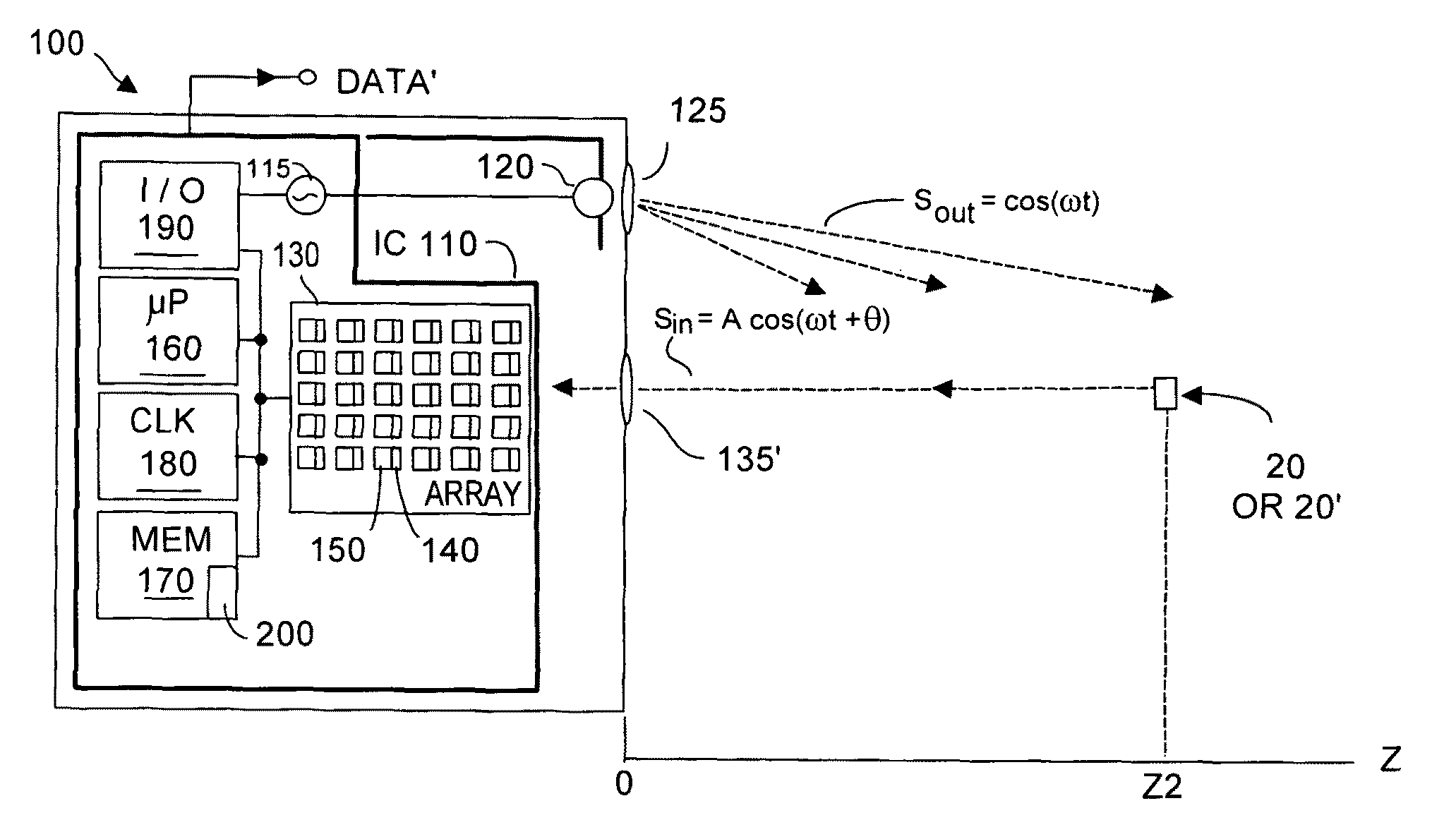

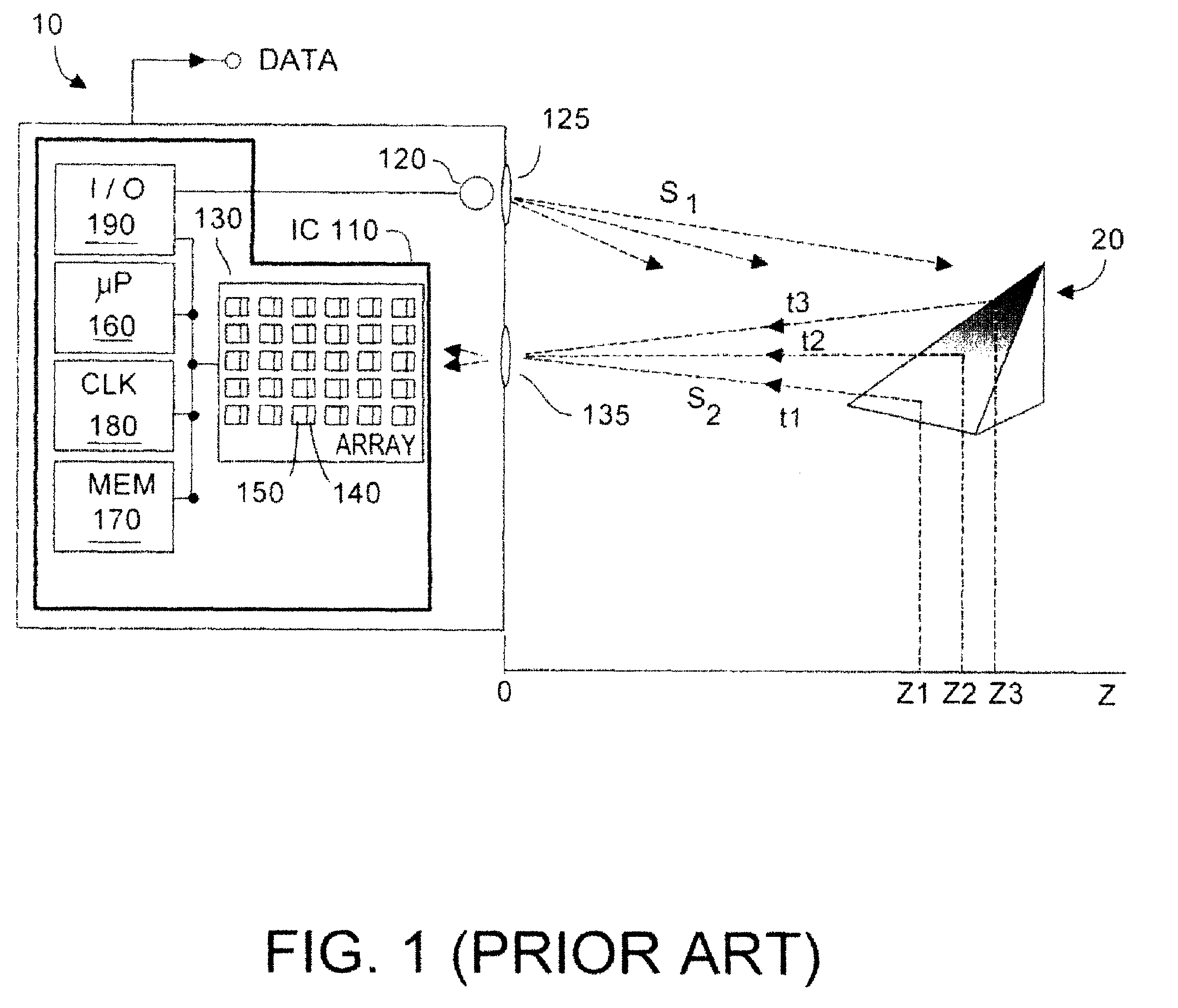

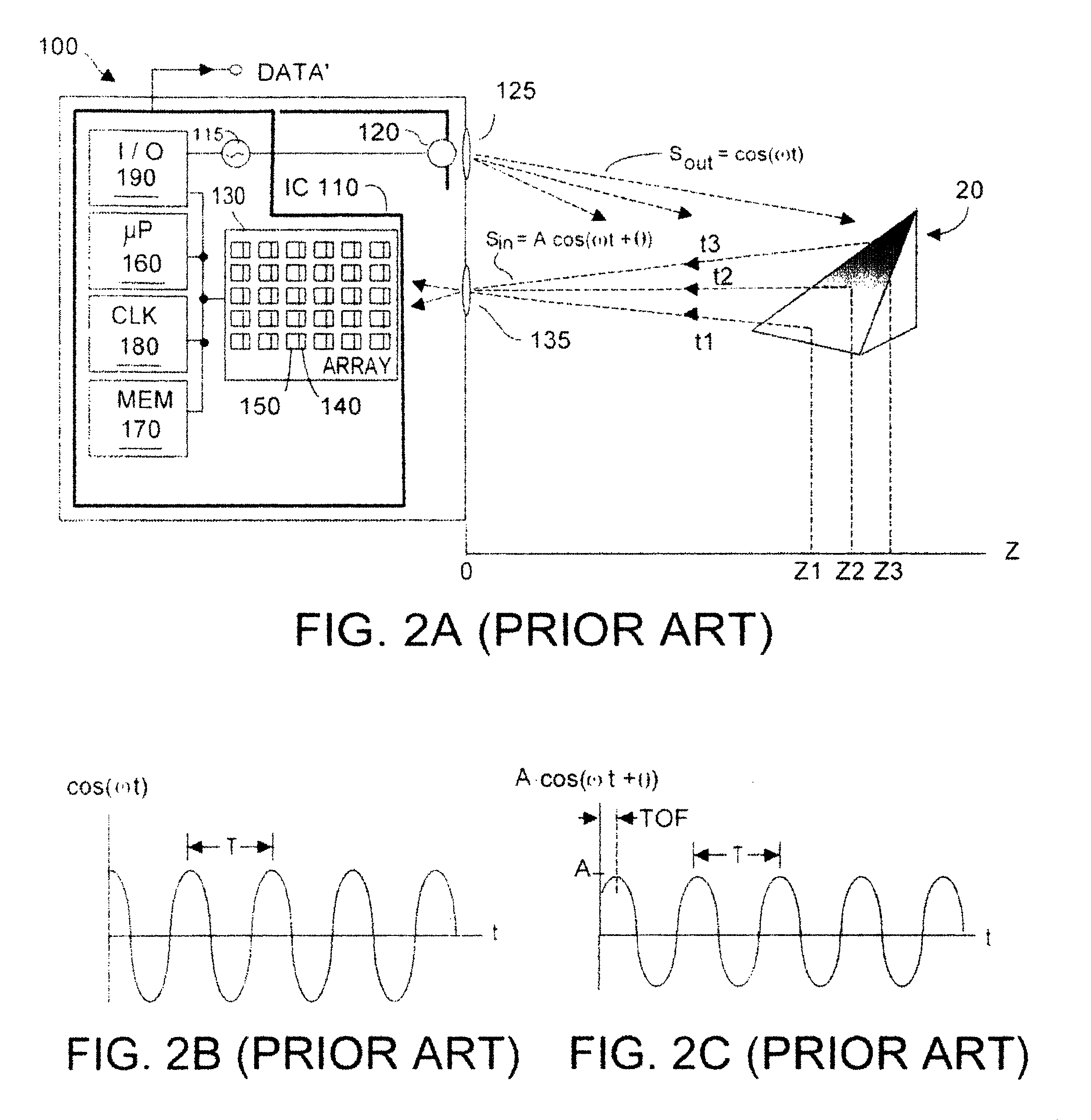

Method and system to reduce stray light reflection error in time-of-flight sensor arrays

ActiveUS20120008128A1Weakening rangeReduce surface reflectivityOptical rangefindersElectromagnetic wave reradiationSensor arrayType error

Haze-type phase shift error due to stray light reflections in a phase-type TOF system is reduced by providing a windowed opaque coating on the sensor array surface, the windows permitting optical energy to reach light sensitive regions of the pixels, and by reducing optical path stray reflection. Further haze-type error reduction is obtained by acquiring values for a plurality (but not necessarily all) of pixel sensors in the TOF system pixel sensor array. Next, a correction term for the value (differential or other) acquired for each pixel in the plurality of pixel sensors is computed and stored. Modeling response may be made dependent upon pixel (row,column) location within the sensor array. During actual TOF system runtime operation, detection data for each pixel, or pixel groups (super pixels) is corrected using the stored data. Good optical system design accounts for correction, enabling a simple correction model.

Owner:MICROSOFT TECH LICENSING LLC

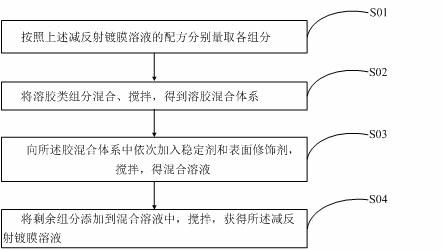

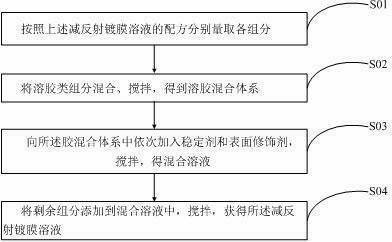

Antireflective coating solution and preparation method thereof, as well as photovoltaic glass and preparation method of photovoltaic glass

ActiveCN102531406AImprove transmittanceHigh spectral transmittanceAnti-reflective coatingsOptical elementsSurface finishPhysical chemistry

The invention relates to the technical field of solar photovoltaic glass and provides an antireflective coating solution, which comprises the following components in percentage by volume: 80.0-95.0% of silicon dioxide sol, 0.1-8.0% of titanium dioxide sol, 0.1-5.0% of zirconium dioxide sol, 0-3.0% of cerium dioxide and / or magnesium oxide and / or aluminum oxide sol, 0.1-3.6% of stabilizer, 0.1-3.8% of surface finishing agent, 0-8.0% of volatilization control agent, and 0.2-4.5% of processing assistants. The invention also provides a preparation method of the antireflective coating solution, photovoltaic glass prepared by adopting the antireflective coating solution, and a preparation method of the photovoltaic glass.

Owner:XINYI GLASS ENG (DONGGUAN) CO LTD

Method for preparing porous silicon dioxide antireflective film with controllable refractive index

The invention provides a method for preparing porous silicon dioxide antireflective film with controllable refractive index, which adopts the method of first base catalysis and then acid catalysis for preparing coating liquid and is suitable for dip coating or spraying process or spin-coating method. Porous silicon dioxide basement film layer is coated on a base plate; and the base plate with porous silicon dioxide basement film layer is processed under high temperature so as to obtain the silicon dioxide film layer. The film layer which is prepared by the invention has the advantages of high hardness, high chemical stability, good self-cleaning capability and broadband antireflection.

Owner:杭州光学精密机械研究所

Texturing method of polycrystalline silicon wafer cut by diamond wire

ActiveCN105810761AControl reaction rateImprove conversion efficiencyPolycrystalline material growthAfter-treatment detailsHydrofluoric acidInorganic ions

The invention discloses a texturing method of a polycrystalline silicon wafer cut by a diamond wire. The method comprises the following steps: firstly, immersing the polycrystalline silicon wafer cut by the diamond wire into a mixed water solution of an alkaline solution and an alkaline reaction control agent, removing a surface damage layer of the silicon wafer and immersing the polycrystalline silicon wafer into a hydrofluoric acid solution containing inorganic ions and organic molecules for reaction; secondly, carrying out pretreatment on the polycrystalline silicon surface by a mixed solution of a hydrofluoric acid and hydrogen peroxide and simultaneously adding a pore-forming regulator; and finally texturing the silicon wafer surface by a mixed acid solution of the hydrofluoric acid and a nitric acid. The texturing method has the advantages that the prepared polycrystalline textured wafer is uniform in suede, small in color difference and consistent in etching depth, and has low surface reflectivity and relatively high conversion efficiency; the preparation method is simple and feasible; the reagent cost is relatively low; the reaction conditions are easy to implement; and the texturing method is relatively good in compatibility with an existing industrial production procedure and is suitable for popularization and application.

Owner:NANJING TECH UNIV

Nanometer array and method for forming the same

InactiveCN101177237AReduce surface reflectivityImprove surface affinityIndividual molecule manipulationCoatingsNanometreMaterials science

The invention provides a method forming nanometer array, which comprises a template with a plurality of nanometer holes; which is characterized in that pressing art is performed on a macromolecule base material for the template; the template is stripped, thereby a plurality of bulges on the macromolecule base material are formed.

Owner:IND TECH RES INST

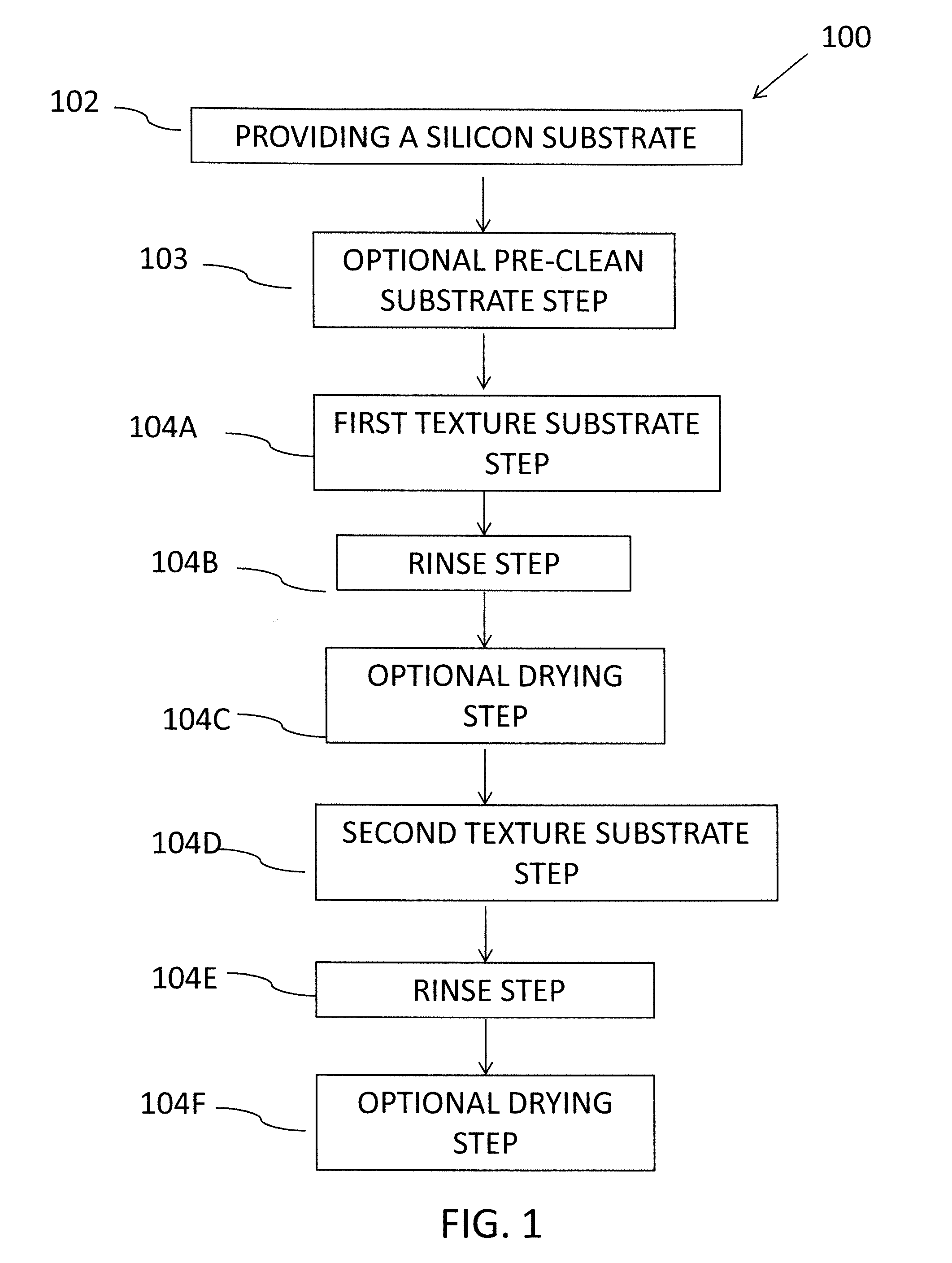

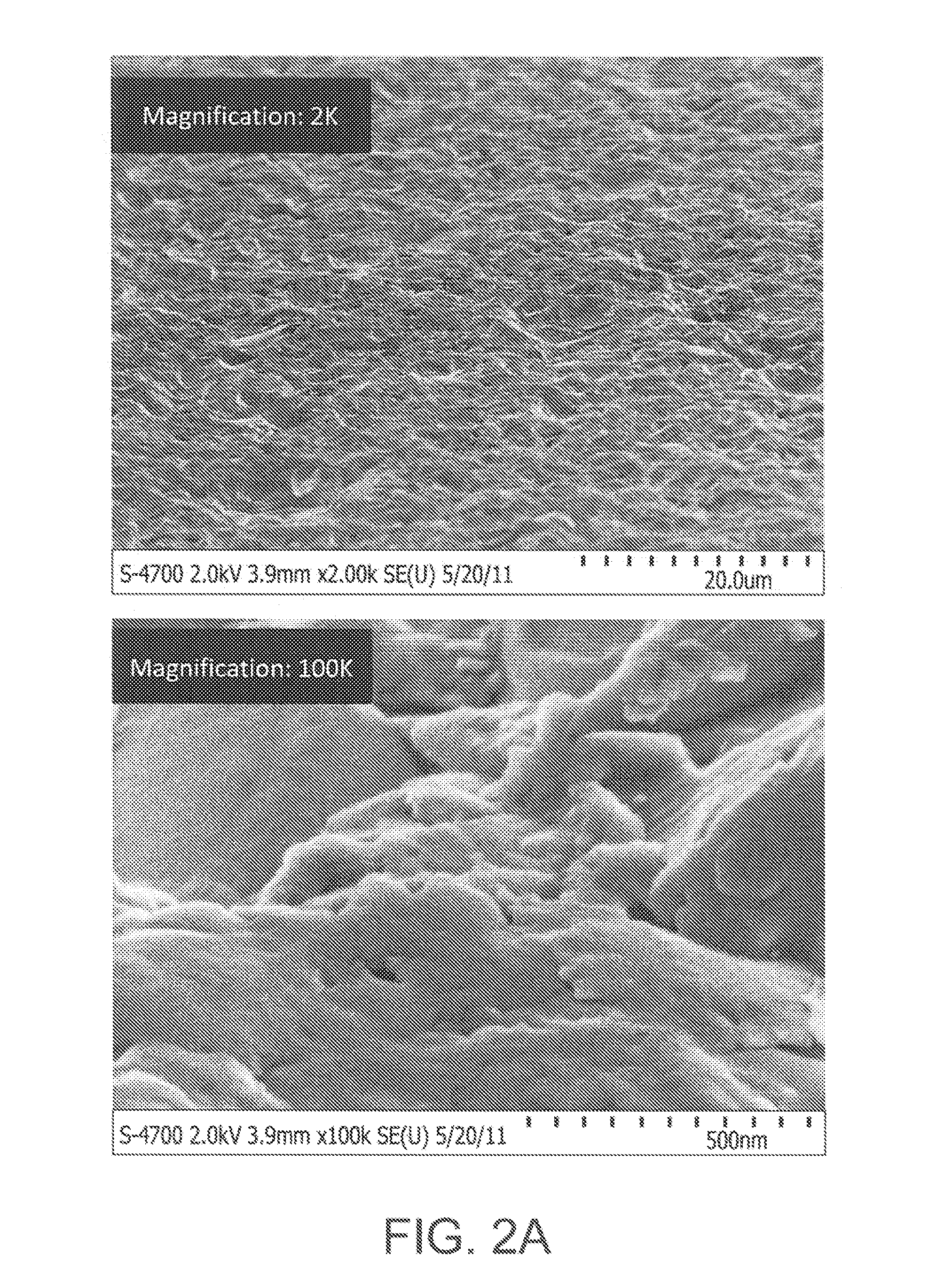

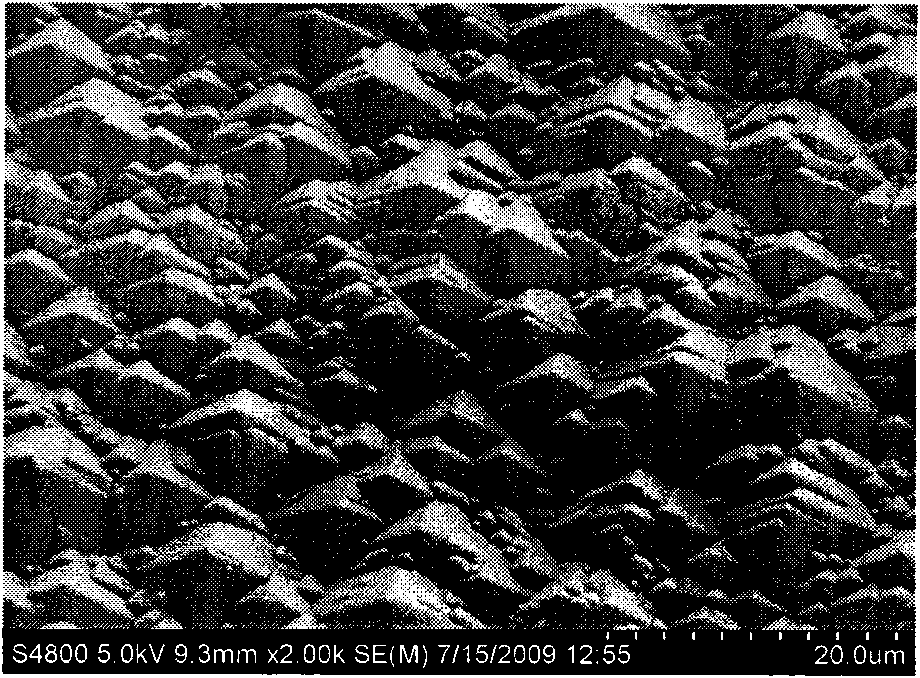

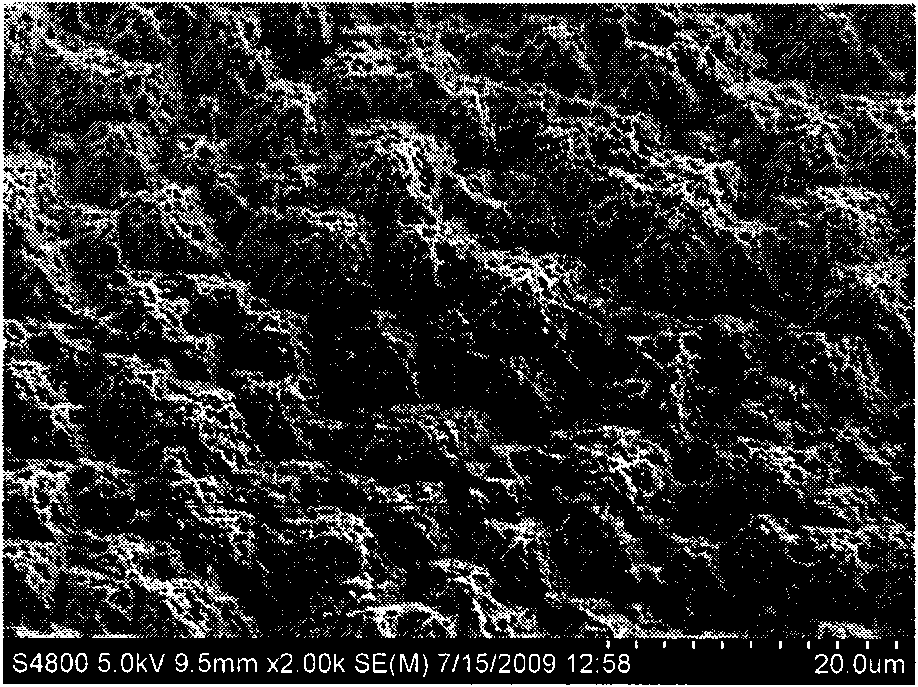

Compositions and Methods for Texturing of Silicon Wafers

InactiveUS20130130508A1Improve textureReduce reflectivitySemiconductor/solid-state device manufacturingPhotovoltaic energy generationWaferingSurface-active agents

Owner:VERSUM MATERIALS US LLC

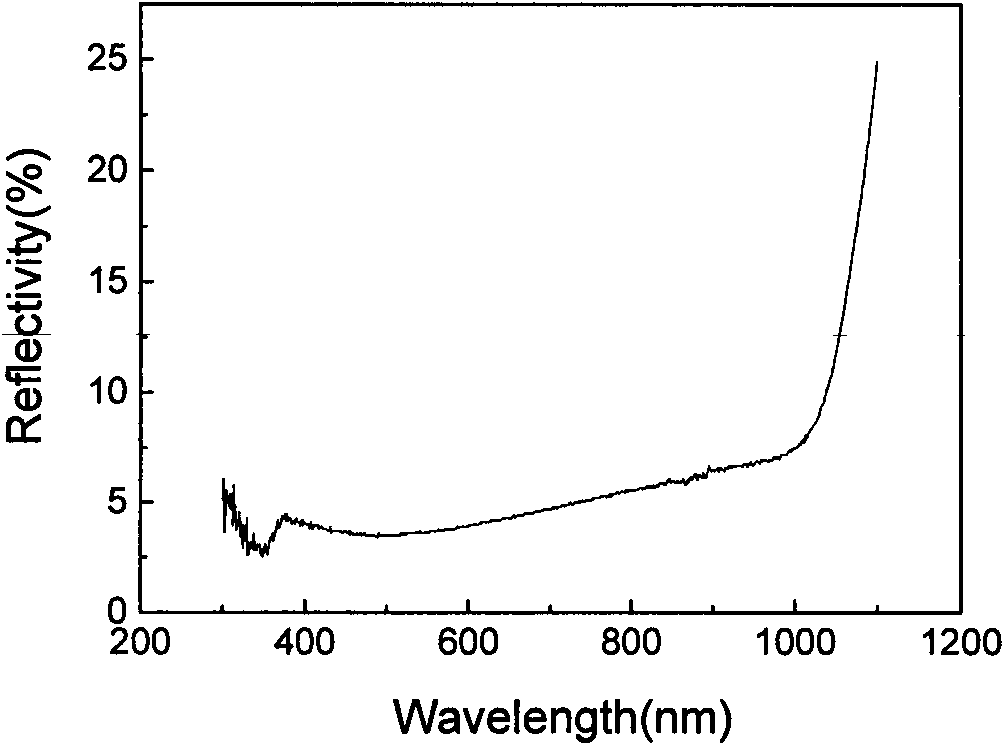

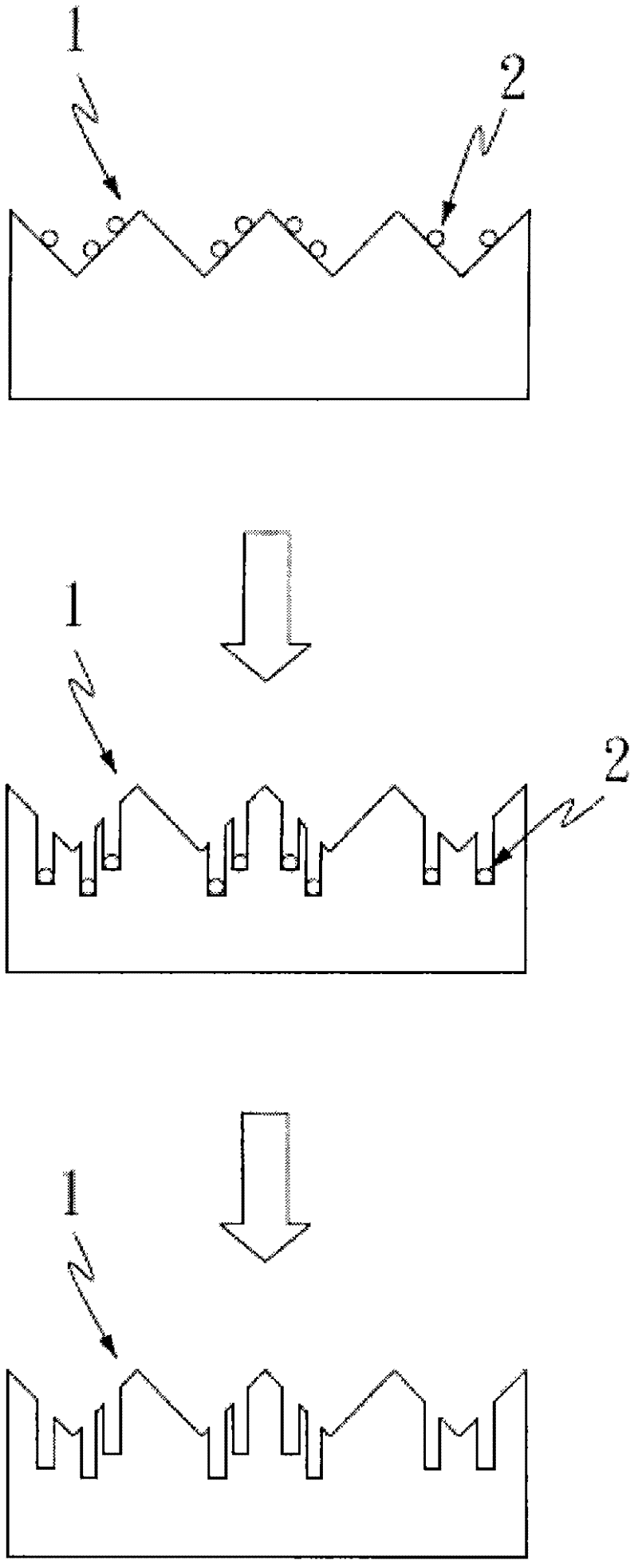

Process for manufacturing monocrystalline silicon solar cell texture with low surface reflectivity

ActiveCN101661972ALow priceReduce surface reflectivityFinal product manufactureSemiconductor devicesSolar cellPorous silicon

The invention discloses a process for manufacturing monocrystalline silicon solar cell texture with low surface reflectivity, comprising the steps of: washing silicon slices to remove damage on surfaces of the silicon slices; putting the washed silicon slices into a mixed solution formed by KOH and isopropanol to form a pyramid structure with equal size on the surfaces of the silicon slices; and putting the silicon slices with pyramid structure into the mixed solution formed by HF and Fe(NO3)3 for corrosion so as to form porous silicon on surface of the pyramid structure. The manufacturing process of the invention is simple, and the corrosion liquid is inexpensive; and the manufacturing process is compatible with the prior art and the surface reflectivity of the processed silicon slices islow, and can be less than 5 percent.

Owner:ZHEJIANG UNIV

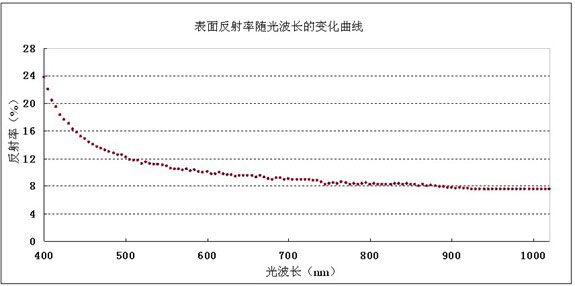

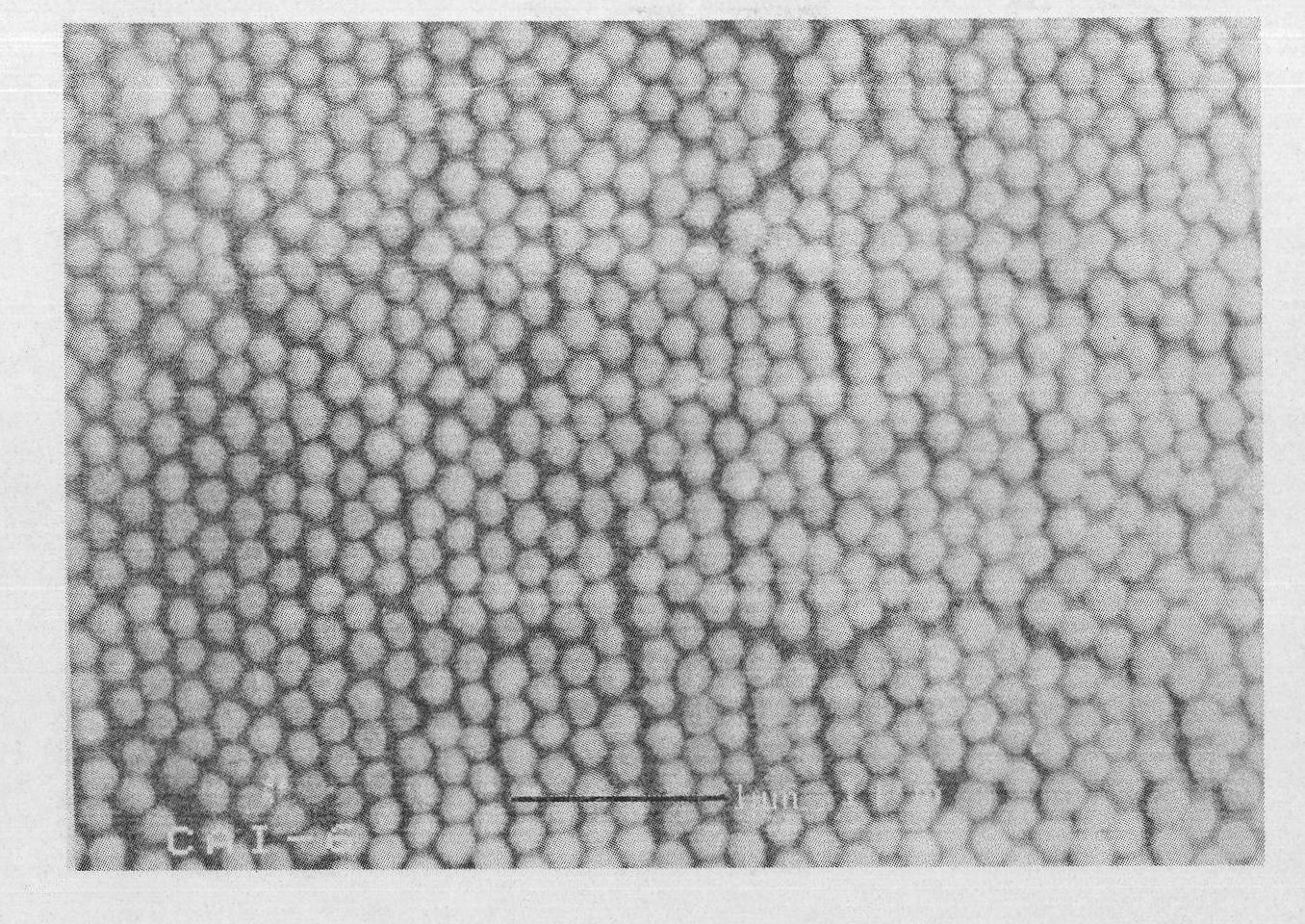

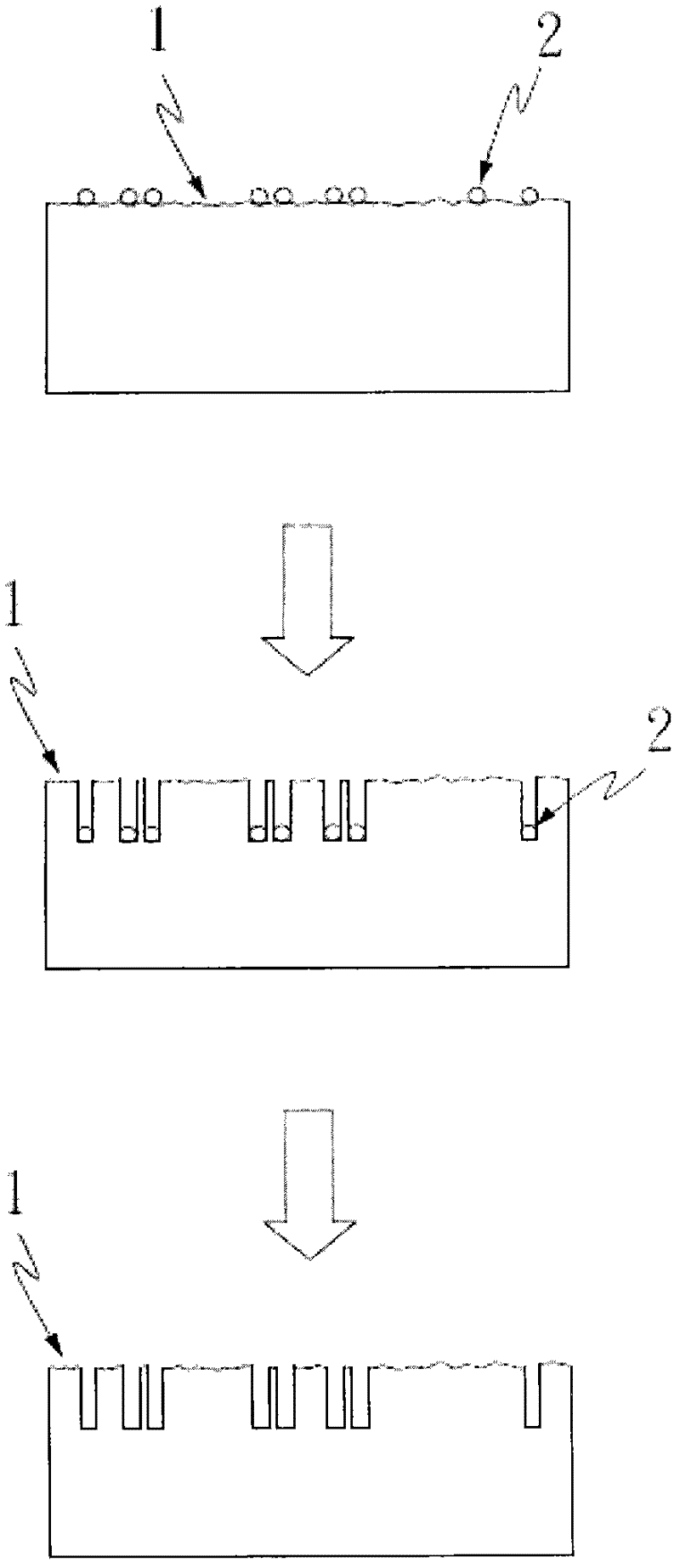

Polycrystalline silicon surface wool manufacturing method

InactiveCN101805929AReduce surface reflectivityEfficient collectionAfter-treatment detailsFinal product manufactureSolar batteryUltrasonic atomization

The invention relates to the manufacturing field of solar batteries, in particular to a polycrystalline silicon surface wool manufacturing method for solar batteries. The invention has the technical scheme that the polycrystalline silicon surface wool manufacturing method is characterized by successively adopting the following steps: 1) pre-cleaning a silicon wafer and removing an affected layer;2) adopting the ultrasonic atomization process or electrostatic spraying process to coat one layer of discontinuous plastic particle film on the surface of the silicon wafer to serve as a masking film; 3) putting the silicon wafer in acid solution and aqueous alkali for corrosion and wool manufacturing; and 4) cleaning the silicon wafer obtained in step 3) with acetone to remove plastic particle films, then cleaning with deionized water, and drying the silicon wafer. By adopting the scheme, the invention overcomes the defects and deficiencies in the prior art, and provides the polycrystallinesilicon surface wool manufacturing method. The method can be used for manufacturing high-performance polycrystalline silicon surface texture, has industrialization prospect and effectively lowers thesurface reflectivity of the silicon wafer.

Owner:SUN POWER PHOTOVOLTAIC SCI & TECH

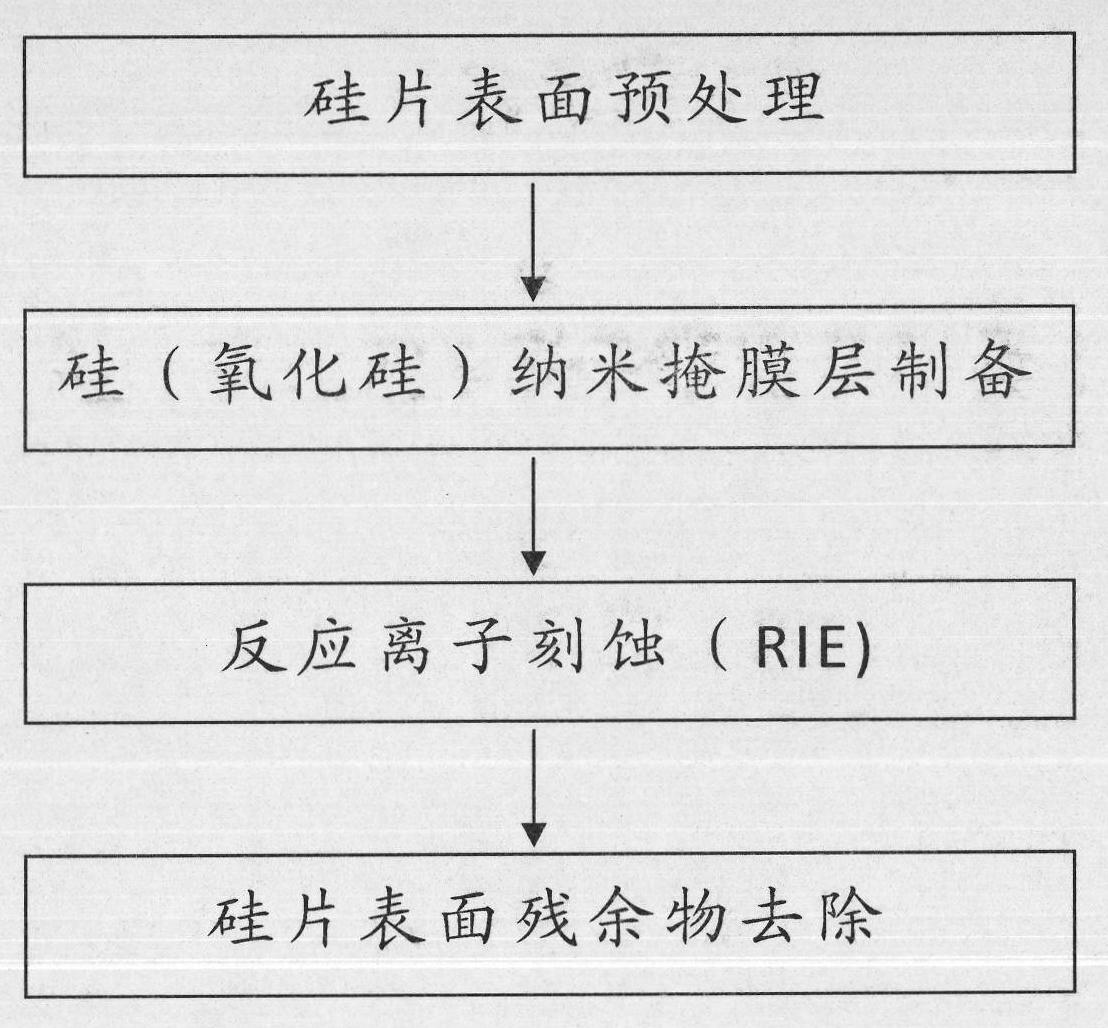

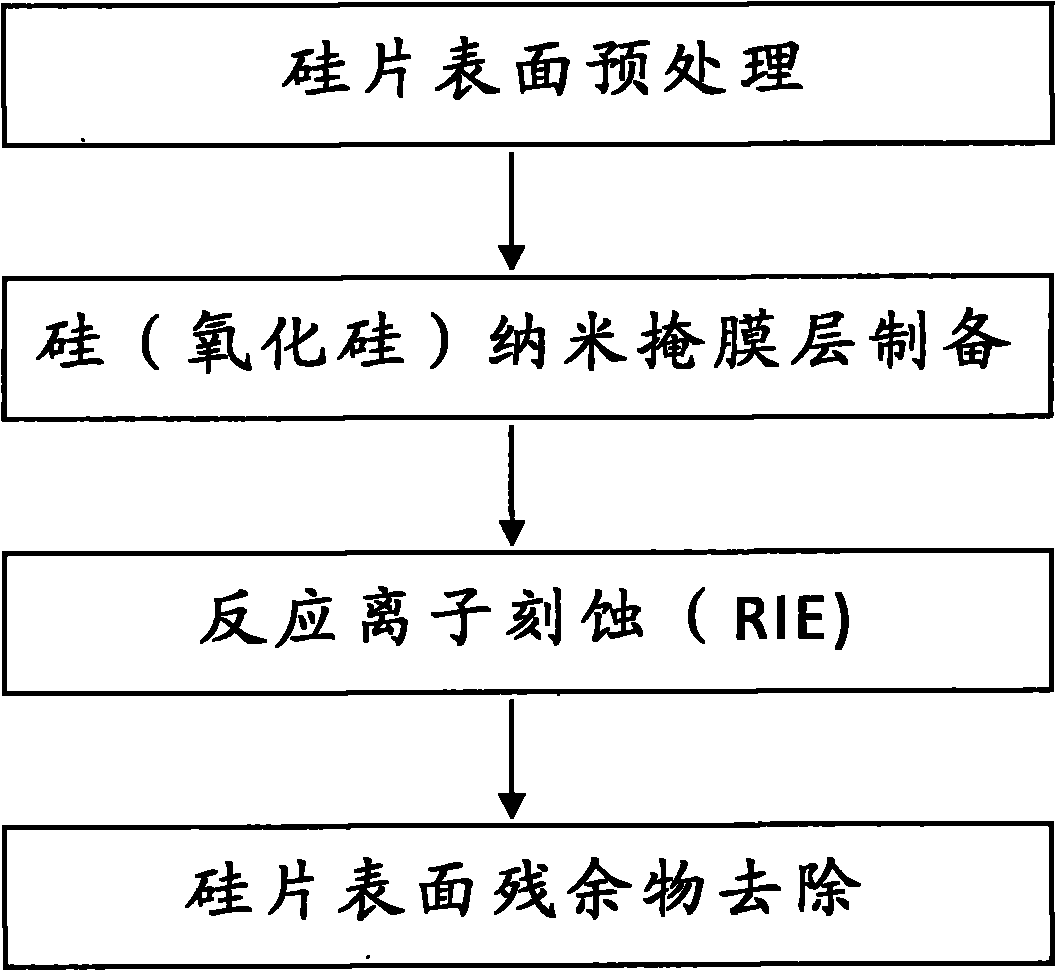

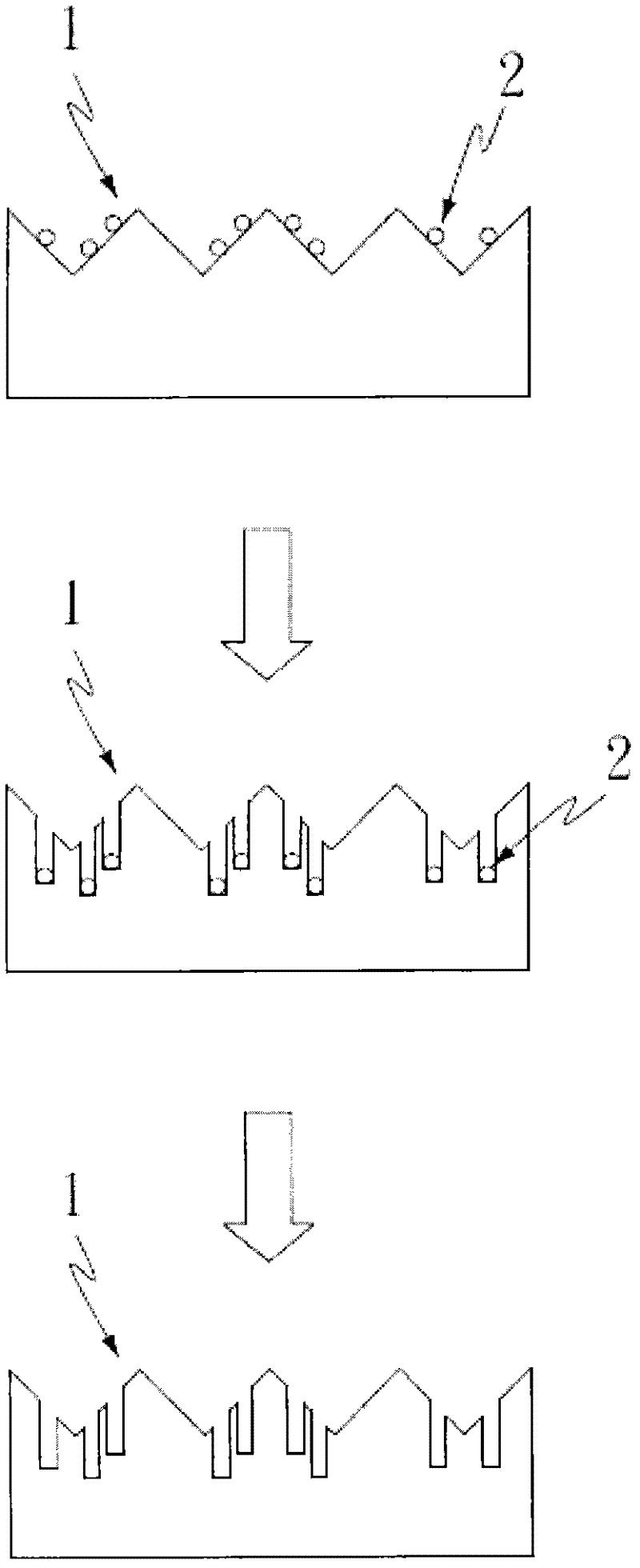

Process for texturing crystalline silicon solar cell by dry etching

InactiveCN101800264AReduce usageReduce pollutionFinal product manufacturePhotovoltaic energy generationSilicon solar cellPre treatment

The invention relates to a process for texturing a crystalline silicon solar cell by dry etching, belonging to the technical filed of the solar cell texturing. The process for texturing the crystalline silicon solar cell by dry etching comprises the following steps of pre-processing the surface of a silicon wafer, preparing a layer of nano masking film on the surface of the silicon wafer, carrying out the reactive ion etching (RIE) for the silicon wafer with the nano masking film, removing the residues on the surface of the silicon wafer and texturing the surface of the silicon wafer. After the surface of the silicon wafer is textured, the reflectivity of the surface of the silicon wafer can be reduced to less than 2 percent, and the light absorption rate can be improved. Compared with the traditional technology for texturing the crystalline silicon solar cell by wet chemical etching, the process for texturing the crystalline silicon solar cell by dry etching can ensure that crystalline silicon solar cell has higher photoelectric conversion efficiency and can reduce the environmental pollution caused by texturing the crystalline silicon solar cell and is suitable for the industrial production of the crystalline silicon solar cell.

Owner:山东力诺太阳能电力股份有限公司

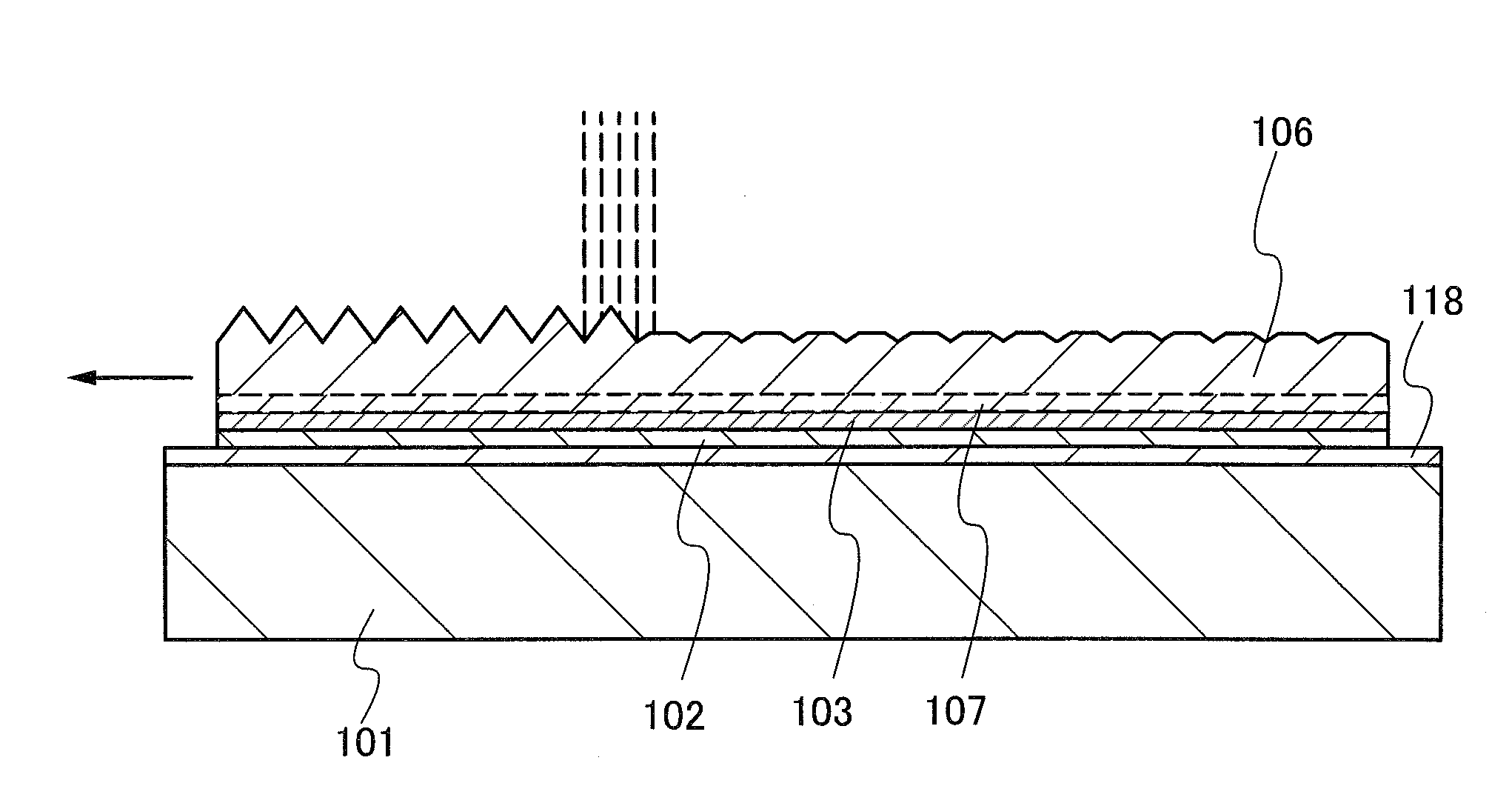

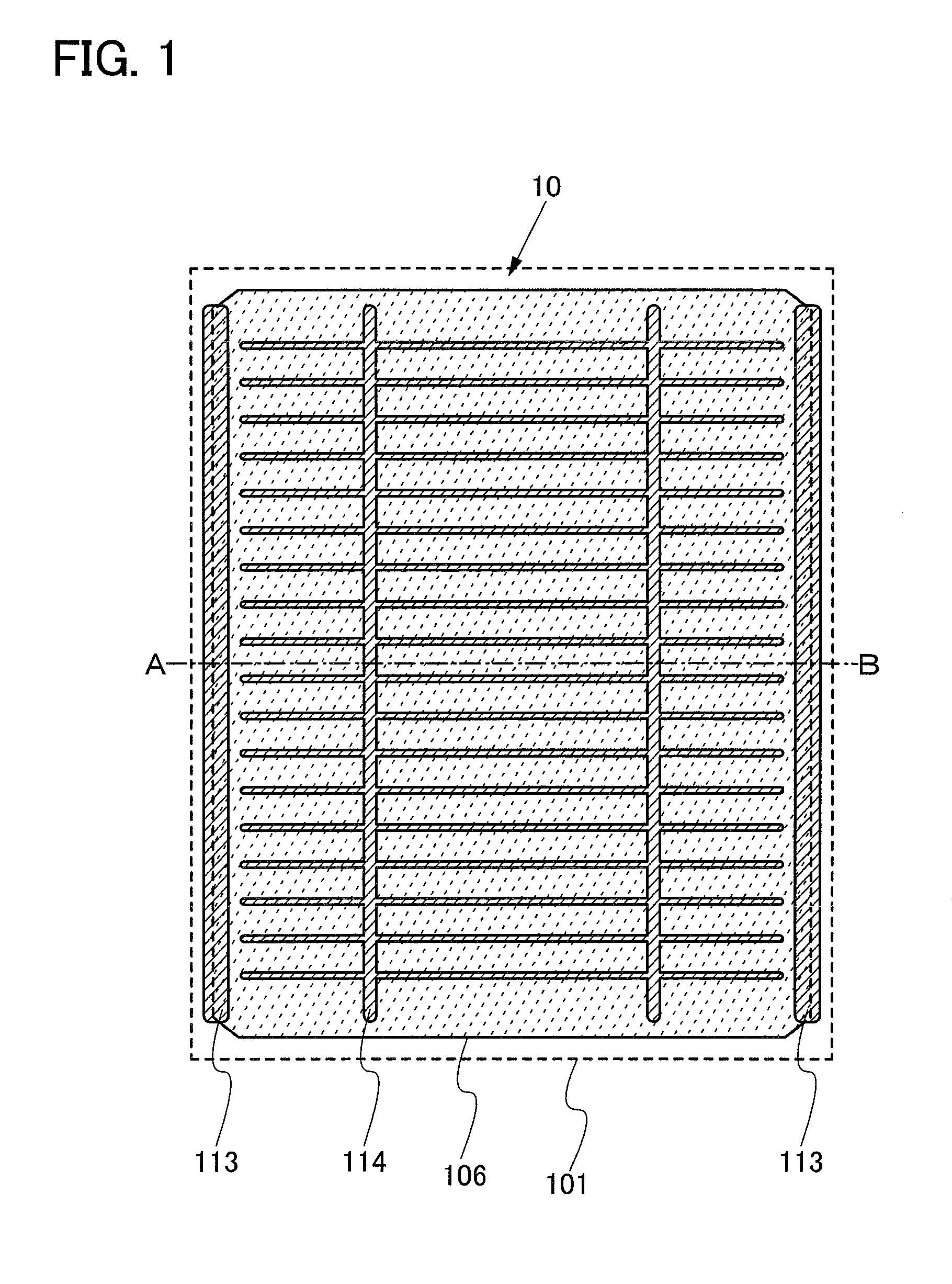

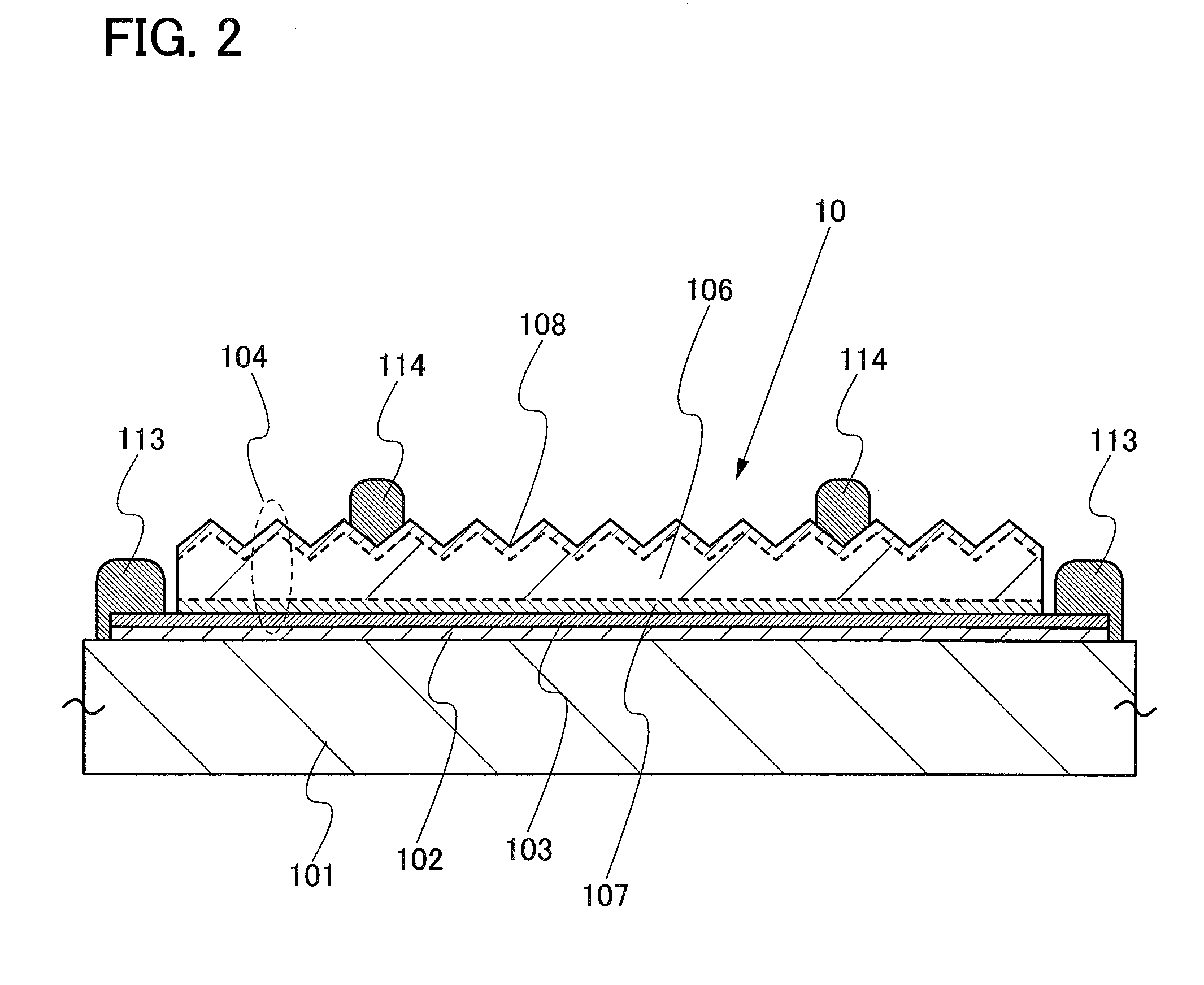

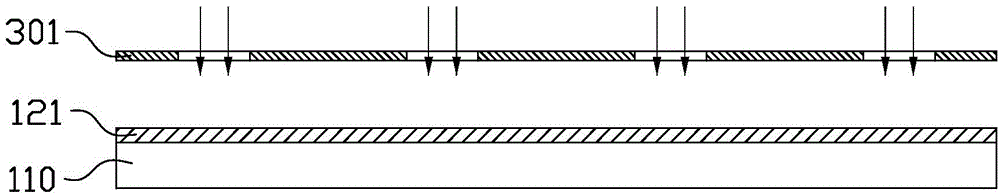

Method for manufacturing photoelectric conversion device

InactiveUS7674647B2Improve featuresEfficient use ofFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsPath length

Owner:SEMICON ENERGY LAB CO LTD

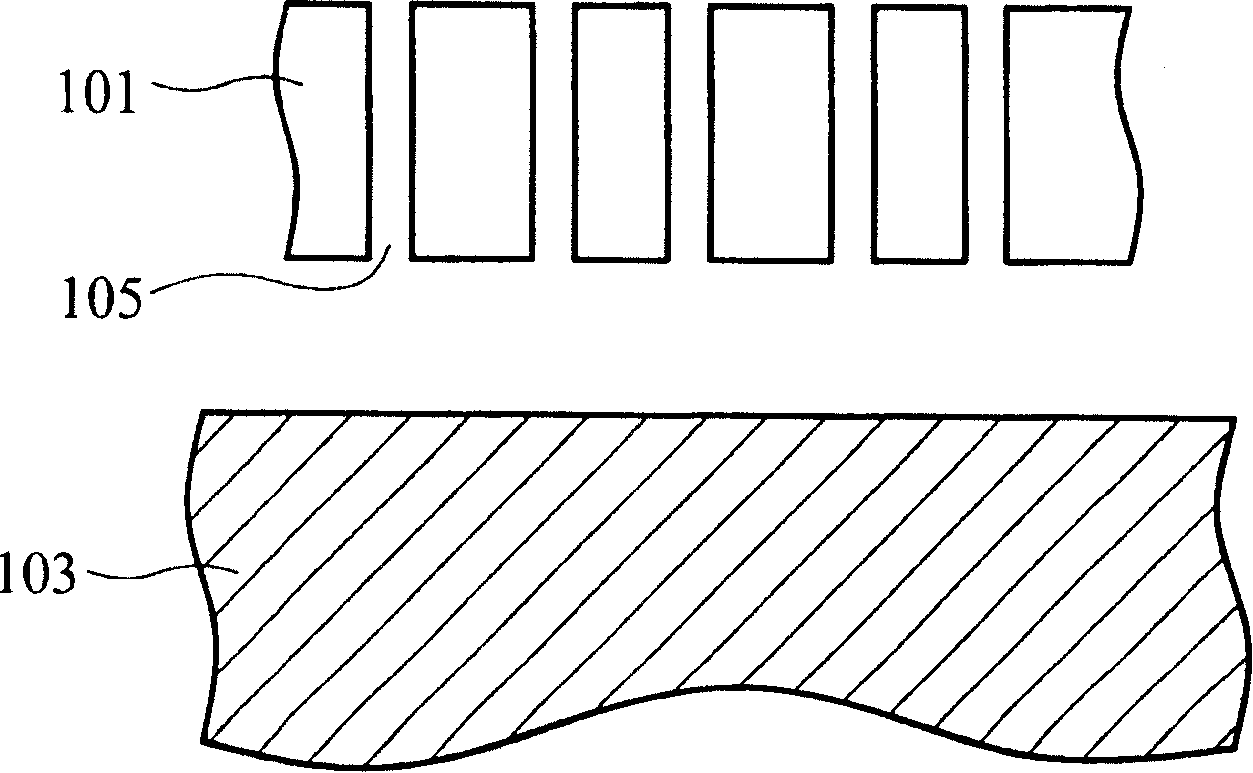

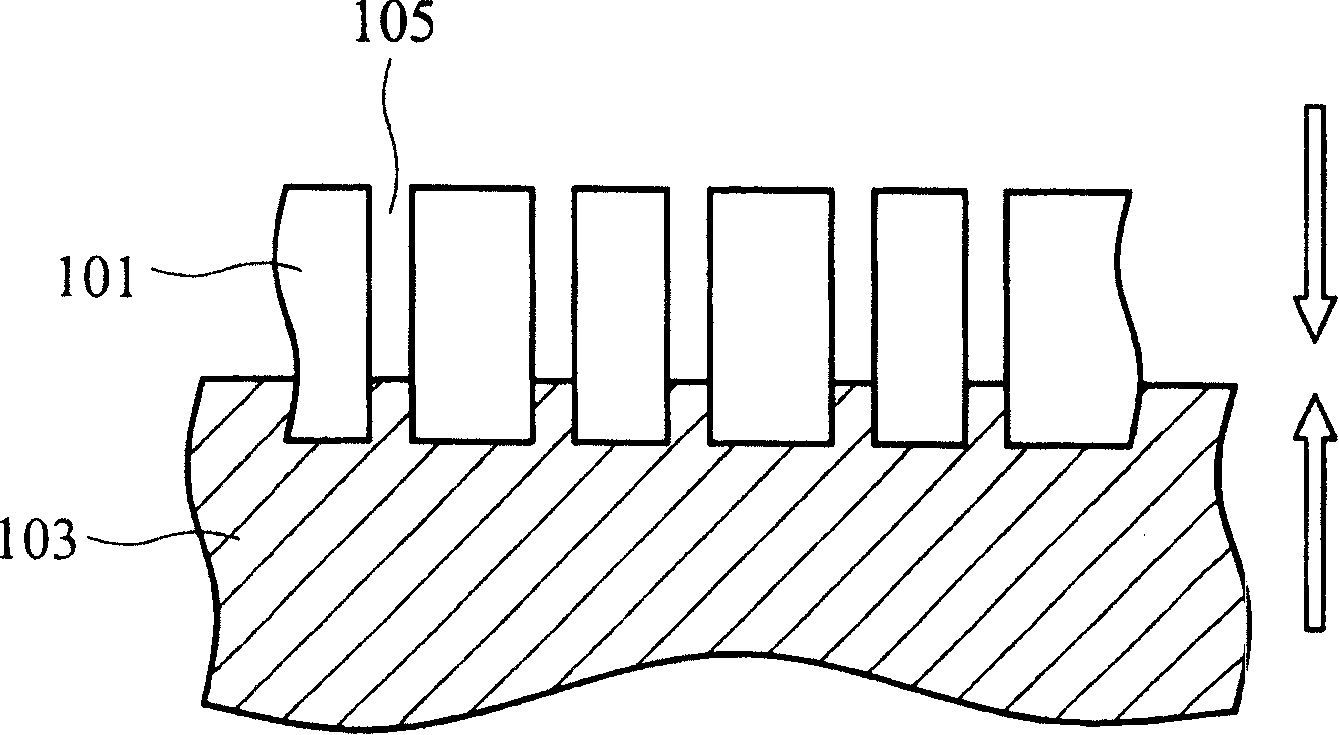

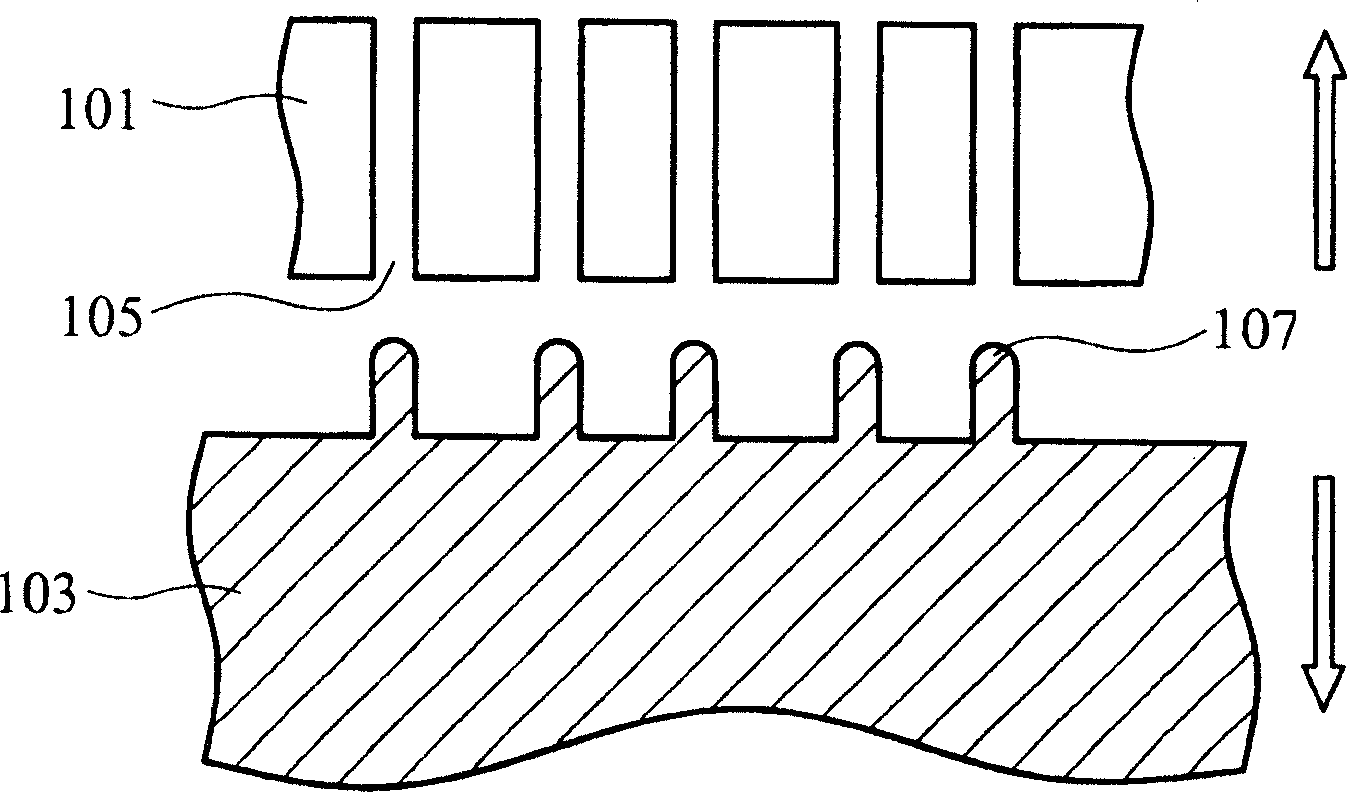

Method of forming micro-pore structures or trench structures on surface of silicon wafer substrate

InactiveCN102443801AReduce surface reflectivityImprove power generation efficiencySemiconductor/solid-state device manufacturingPhotovoltaic energy generationManufacturing cost reductionEtching

A method of forming micro-pore structures or trench structures on a surface of a silicon wafer substrate comprises (A) forming at least a noble-metal alloy particle on the surface of the silicon wafer substrate; and (B) then followed by employing a chemical wet etching on the surface of the silicon wafer substrate. During the processes, noble-metal alloy particle is used to catalyze the oxidation of the silicon wafer substrate surface in contact therewith, and an etchant is used to simultaneous etch the silicon dioxide to result in local micro-etching at the surface of the silicon wafer substrate, thereby forming micro-pore structures or trench structures on the surface of the silicon wafer substrate. Surface reflectivity of the silicon chip substrate can be effectively reduced. The method increases the power conversion efficiency of the solar cells and reduces the manufacturing costs so as to increase the production benefits of the solar cells.

Owner:纮泰科技股份有限公司

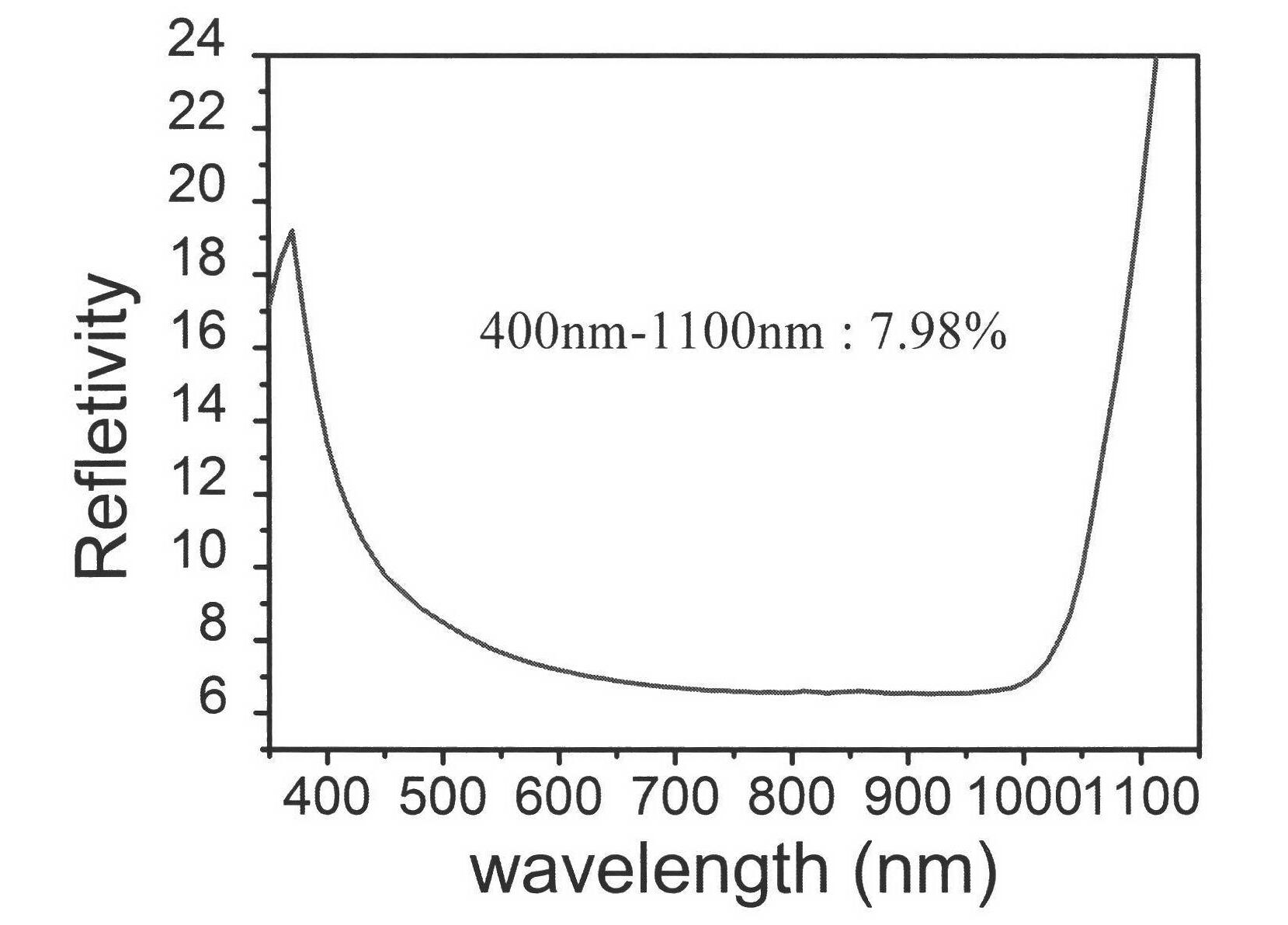

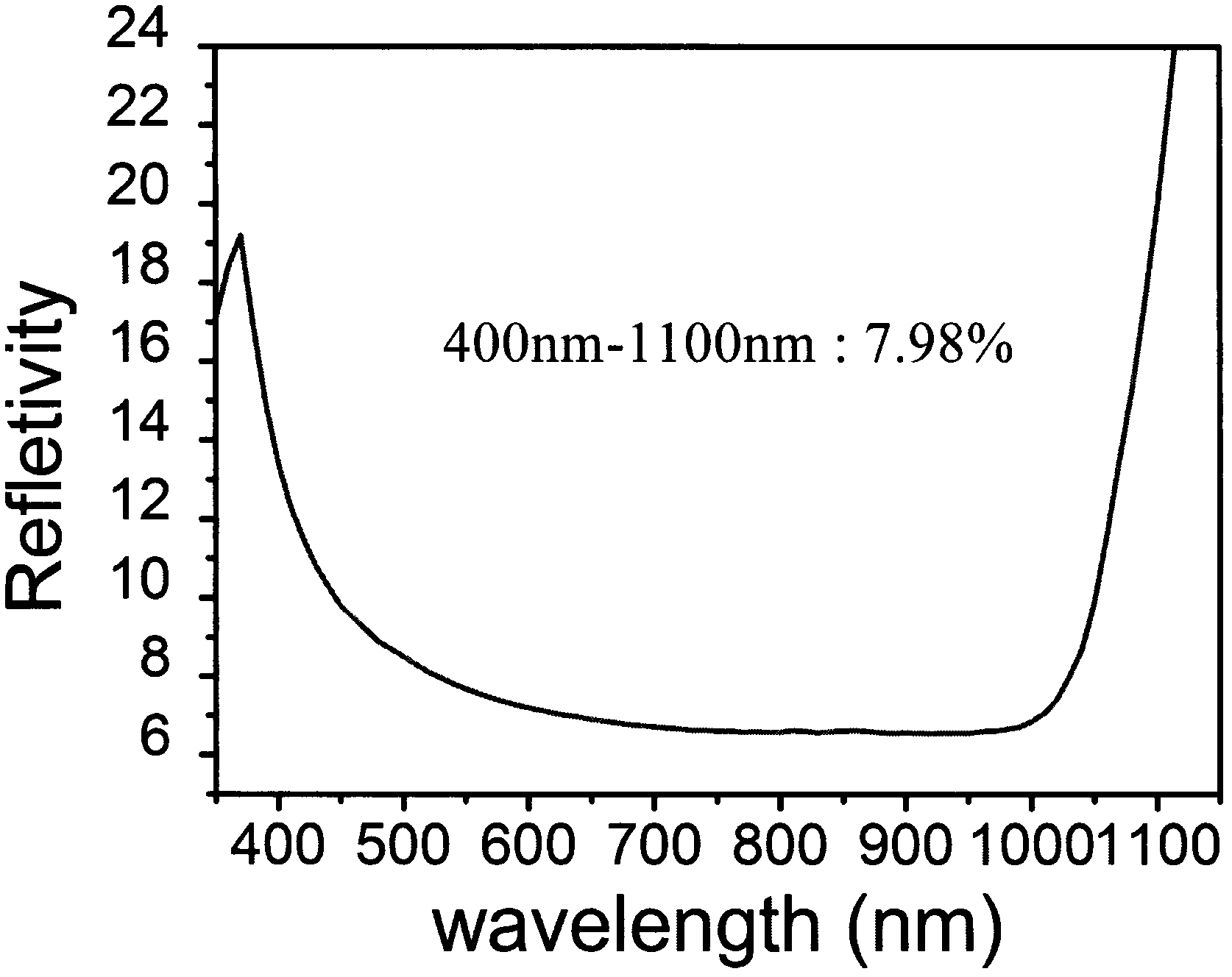

Suede-making additive for low-reflectivity monocrystalline silicon

InactiveCN102586887AIncrease densityReduce surface reflectivityPolycrystalline material growthAfter-treatment detailsAlbedoCrystalline silicon

The invention relates to the technical field of crystalline silicon solar cell production, in particular to a suede-making additive for low-reflectivity monocrystalline silicon. Formula components comprise sodium tripolyphosphate, butyl naphthalenesulfoni and deionized water. When the additive is used for suede-making of the monocrystalline silicon, average value of surface albedo of a monocrystalline silicon sheet in a wavelength range of 400 nm to 1100 nm can be reduced to below 8% from current 10%, and an even, small and dense suede pyramid can be obtained. The suede-making additive can improve photoelectric conversion efficiency of a crystalline silicon solar cell, is favorable for stabilizing technology of the crystalline silicon solar cell, and has good practical value.

Owner:苏州先拓光伏科技有限公司

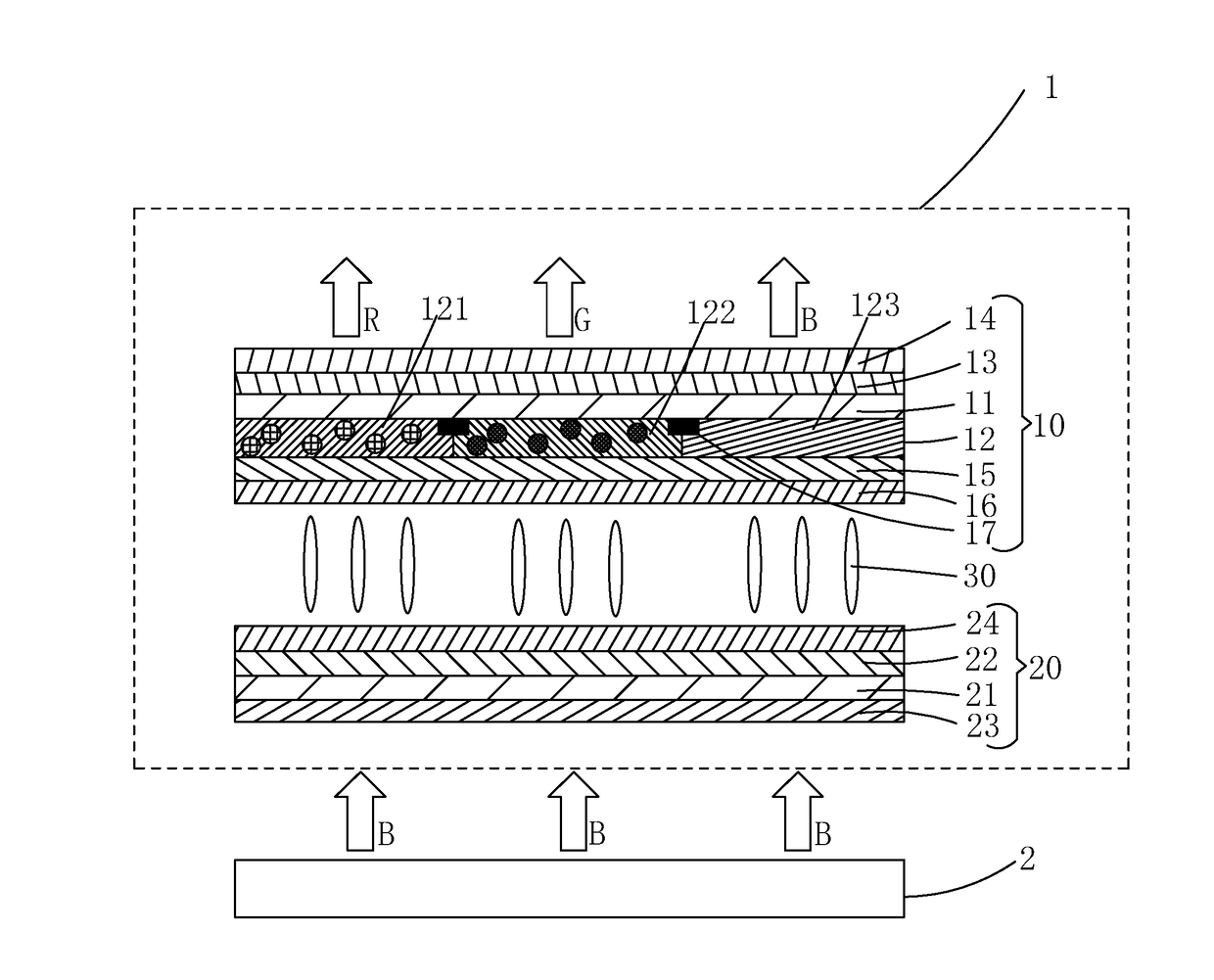

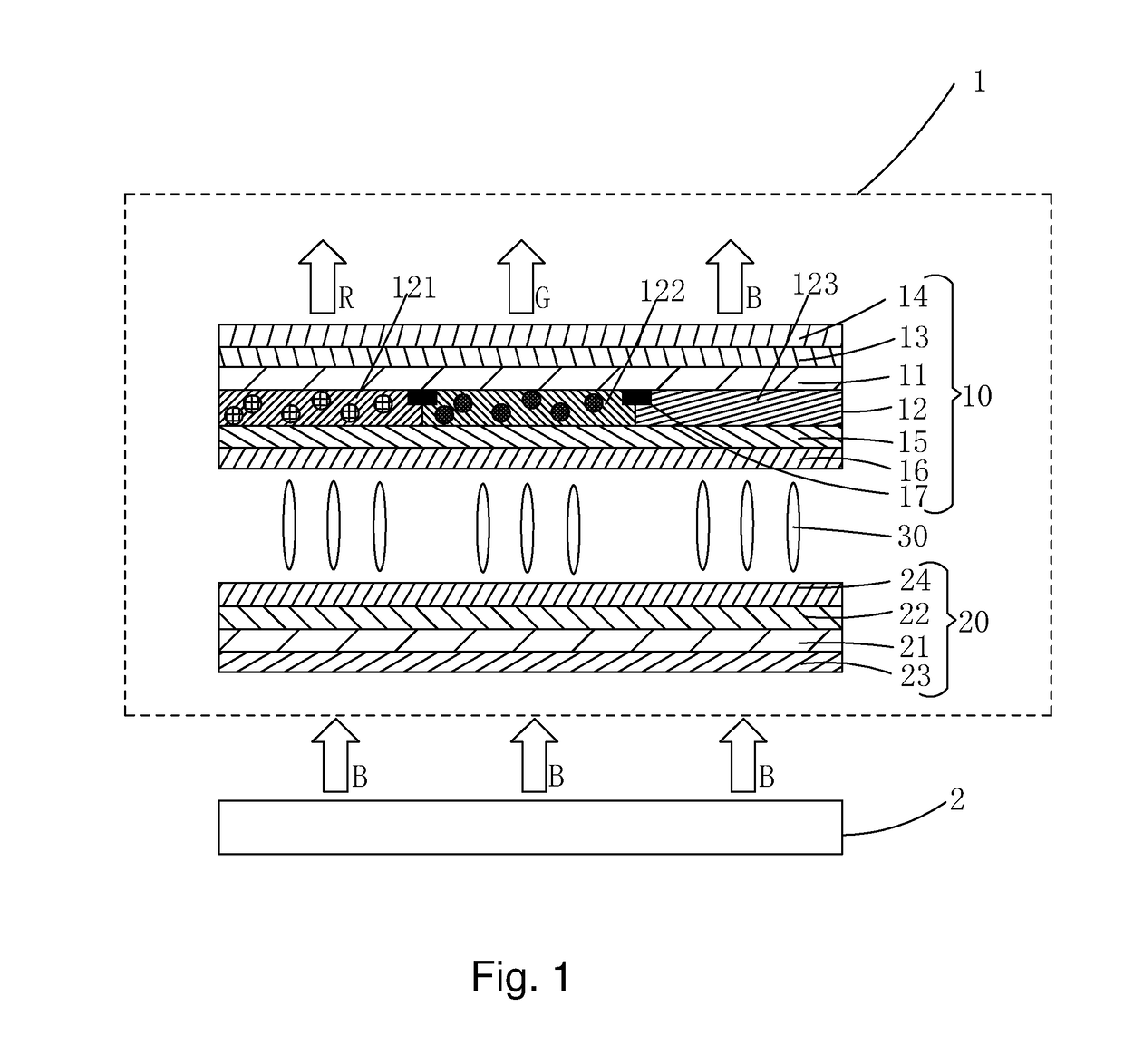

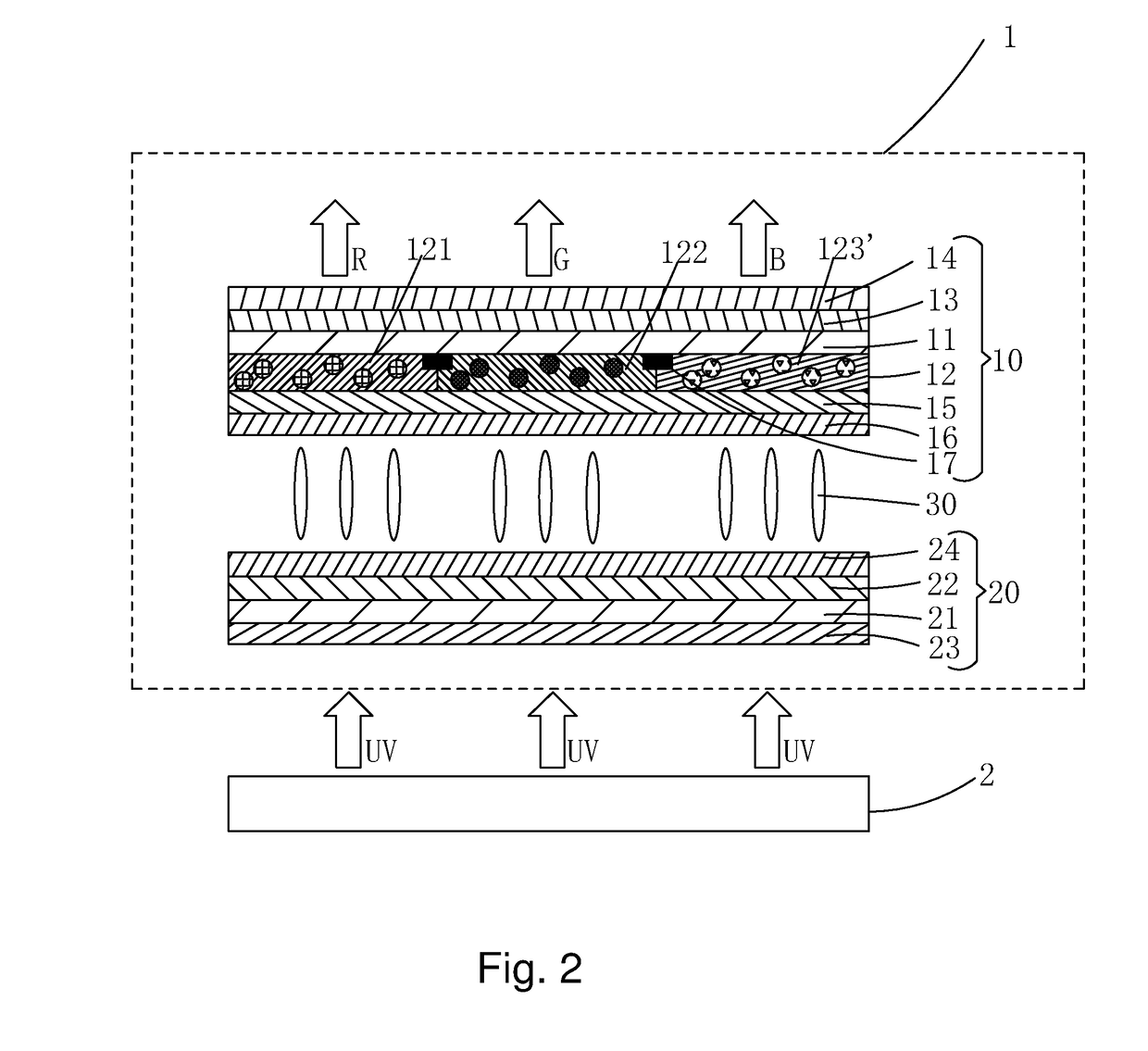

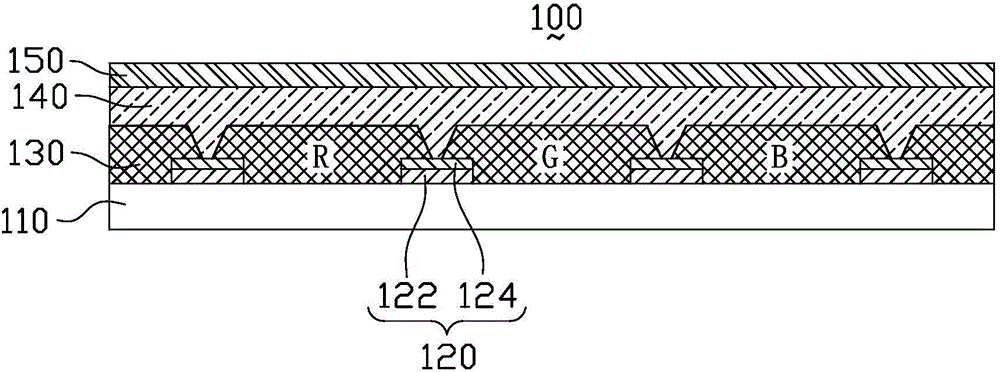

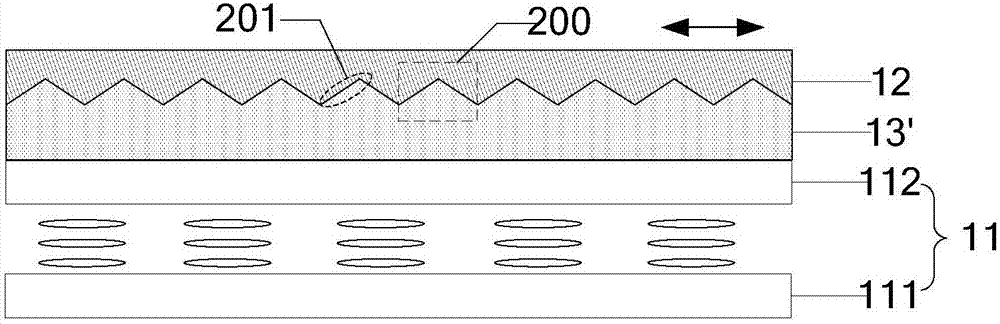

Quantum dot liquid crystal display device

InactiveUS20170255055A1Increase contrastReduce surface reflectivityNon-linear opticsLight guideColor gel

The present invention provides a quantum dot liquid crystal display device. The quantum dot liquid crystal display device has a color filter substrate (10) that includes a first base plate (11), a quantum dot color filter (12) arranged on one side of the first base plate (11) that is adjacent to a liquid crystal layer (30), a one-way light guide film (13) arranged on one side of the first base plate (11) that is distant from the liquid crystal layer (30), and an anti-reflection transmission-enhancing film (14) arranged on the one-way light guide film (13). The one-way light guide film (13) prevents light from getting incident into the interior of the liquid crystal display device to excite quantum dots so as to overcome the issues of contrast lowering and color shifting caused by external natural light exciting the quantum dots. The anti-reflection transmission-enhancing film (14) helps overcome the issues of glare and reflection light image of the liquid crystal display panel, thereby improving comfortableness of viewing of the viewers. Thus, the quantum dot liquid crystal display device has high contrast and low surface reflectance and does not induce image doubling and eye harshness caused by glare so as to provide enhanced comfortableness of viewing.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Method and system to reduce stray light reflection error in time-of-flight sensor arrays

ActiveUS8194233B2Weakening rangeReduce surface reflectivityOptical rangefindersElectromagnetic wave reradiationSensor arrayType error

Haze-type phase shift error due to stray light reflections in a phase-type TOF system is reduced by providing a windowed opaque coating on the sensor array surface, the windows permitting optical energy to reach light sensitive regions of the pixels, and by reducing optical path stray reflection. Further haze-type error reduction is obtained by acquiring values for a plurality (but not necessarily all) of pixel sensors in the TOF system pixel sensor array. Next, a correction term for the value (differential or other) acquired for each pixel in the plurality of pixel sensors is computed and stored. Modeling response may be made dependent upon pixel (row, column) location within the sensor array. During actual TOF system runtime operation, detection data for each pixel, or pixel groups (super pixels) is corrected using the stored data. Good optical system design accounts for correction, enabling a simple correction model.

Owner:MICROSOFT TECH LICENSING LLC

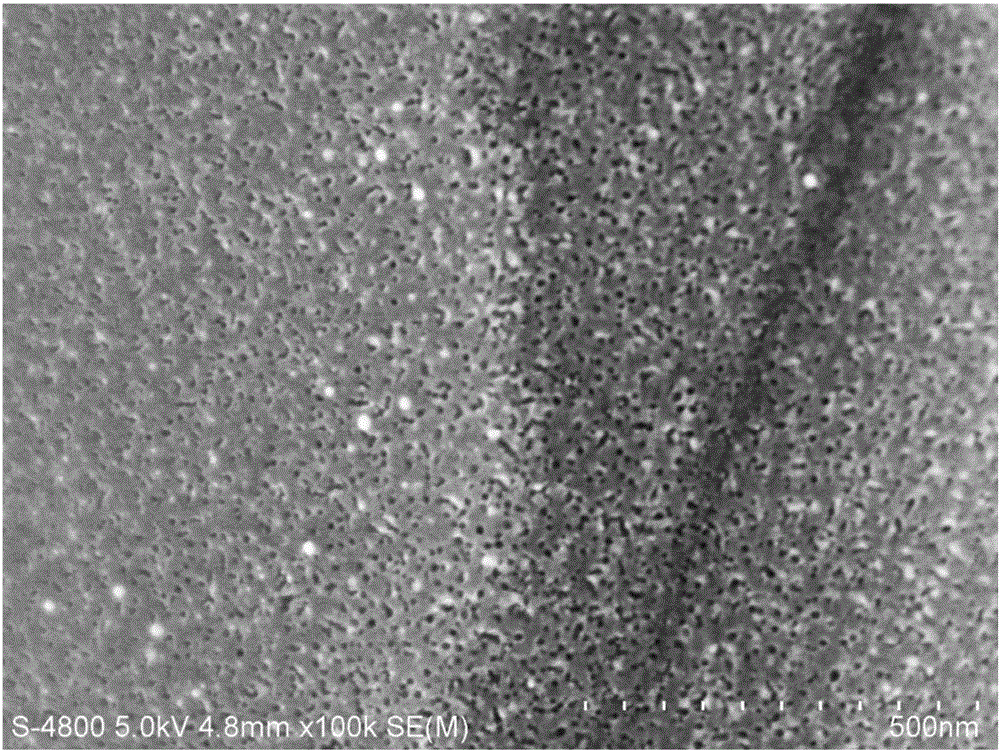

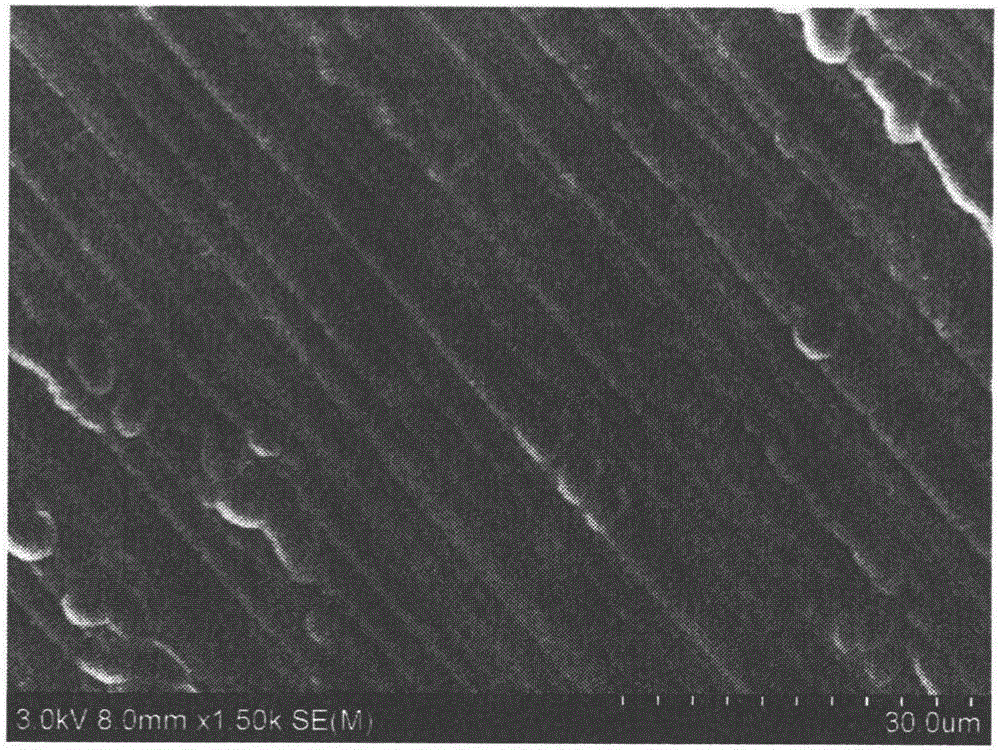

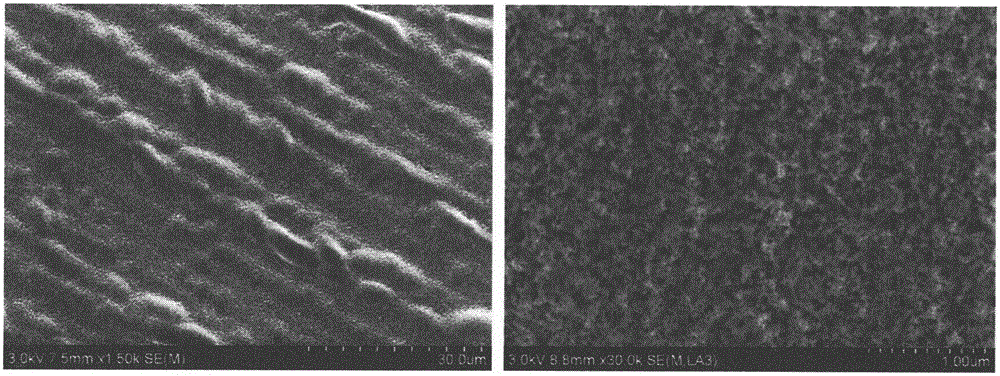

Diamond wire cutting-based silicon wafer texturing pretreatment method and silicon wafer texturing method

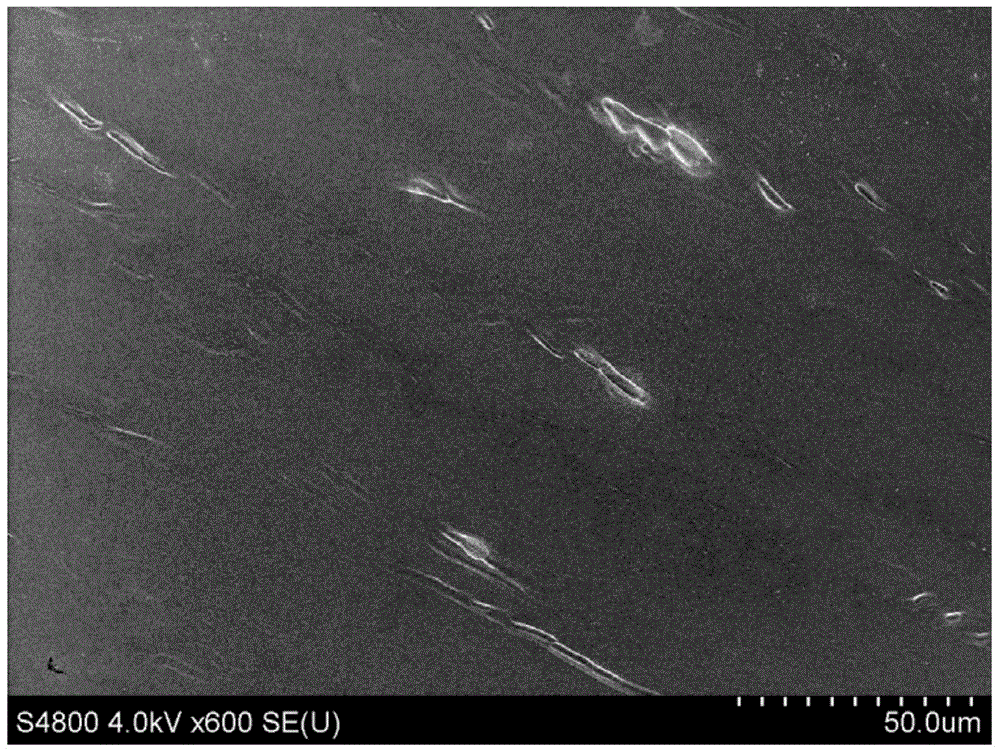

InactiveCN104962998AEffective cutting patternEffectively remove cut linesAfter-treatment detailsFinal product manufactureHydrofluoric acidNano structuring

The invention provides a diamond wire cutting-based silicon wafer texturing pretreatment method. The method comprises the following steps: a, mixing a hydrofluoric acid solution, a hydrogen dioxide solution, metal salt and water to obtain pretreatment liquid; b, putting a silicon wafer cut by a diamond wire into the pretreatment liquid and performing pretreatment A, until cutting lines on the silicon wafer are basically removed; c, cleaning the silicon wafer subjected to pretreatment A by an acid solution, so as to remove metal particles on the silicon wafer; d, putting the silicon wafer cleaned by the acid solution into the pretreatment liquid and performing pretreatment B, and forming a pretreatment texturing surface with a uniform micro / nano structure on the silicon wafer. The invention also provides a diamond wire cutting-based silicon wafer texturing method.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

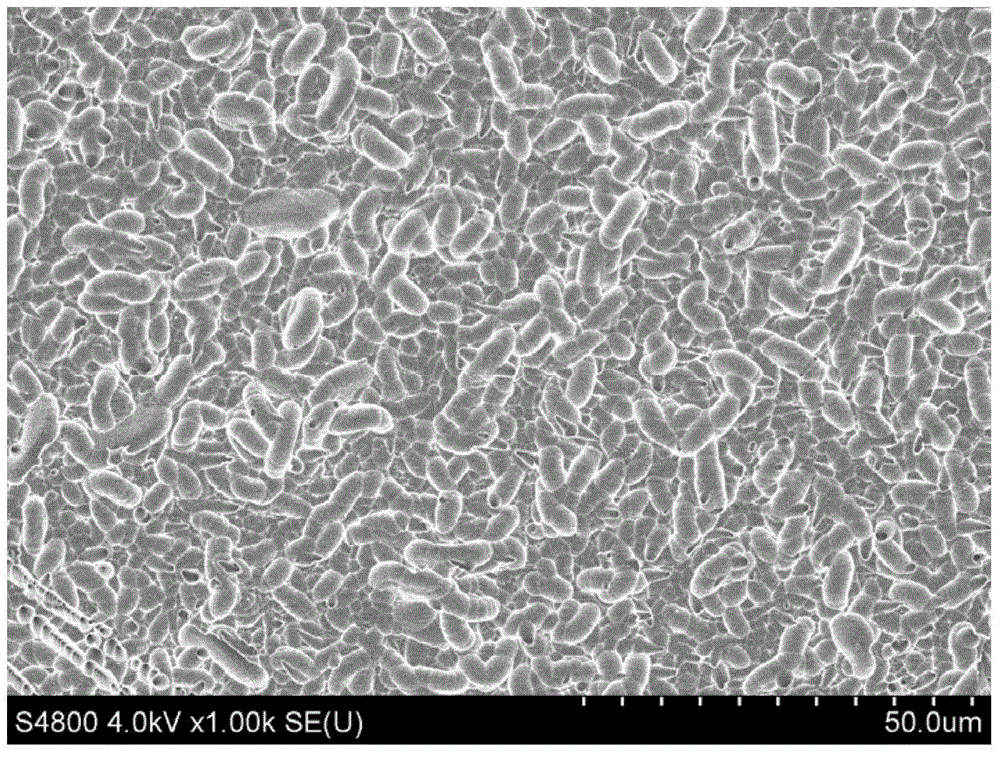

Method for preparing silicon solar battery pile face in magnetic field

InactiveCN101409313AControl the direction of motionUniform movementFinal product manufactureSemiconductor/solid-state device manufacturingPhosphoric acidSilicon solar cell

The invention discloses a method for preparing a texture of a silicon solar cell under a magnetic field. The method comprises the following technological steps: firstly, a polysilicon wafer is put into a texture preparation reactor with prepared acid reaction solution for reaction, and the texture preparation reactor is put in the magnetic field, wherein, the reaction solution is made from 0.05%-15% of nitric acid or chromic acid by mass, 1%-30% of hydrofluoric acid by mass and 1%-30% of phosphoric acid or acetic acid by mass; the temperature of the reaction solution is kept at 0-30 DEG C, and the polysilicon wafer is washed in 0.5%-3% sodium hydroxide solution for 1-5 minutes after reaction in the acid solution; secondly, the magnetic field is applied in the whole course of preparing the texture of the silicon solar cell, the magnetic field strength is kept at 0-10T, and the texture preparation time is 1-45 minutes. A compact and even texture can be grown on the surface of the polysilicon wafer by the method, thus realizing the high-efficiency and even production of the silicon solar cell texture by acid oxidants under the magnetic field.

Owner:张根发

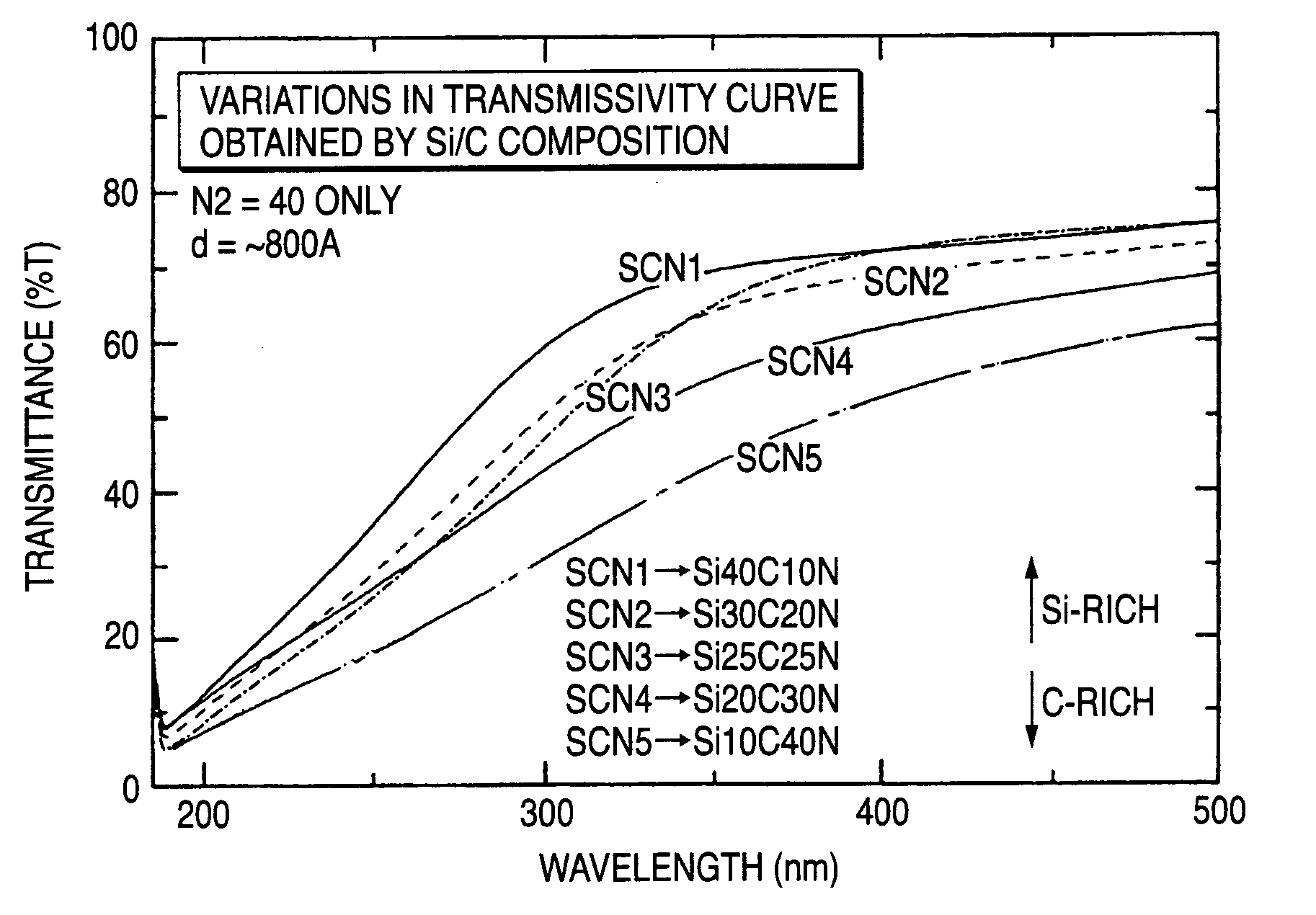

Halftone-type phase-shift mask blank, and halftone-type phase-shift mask

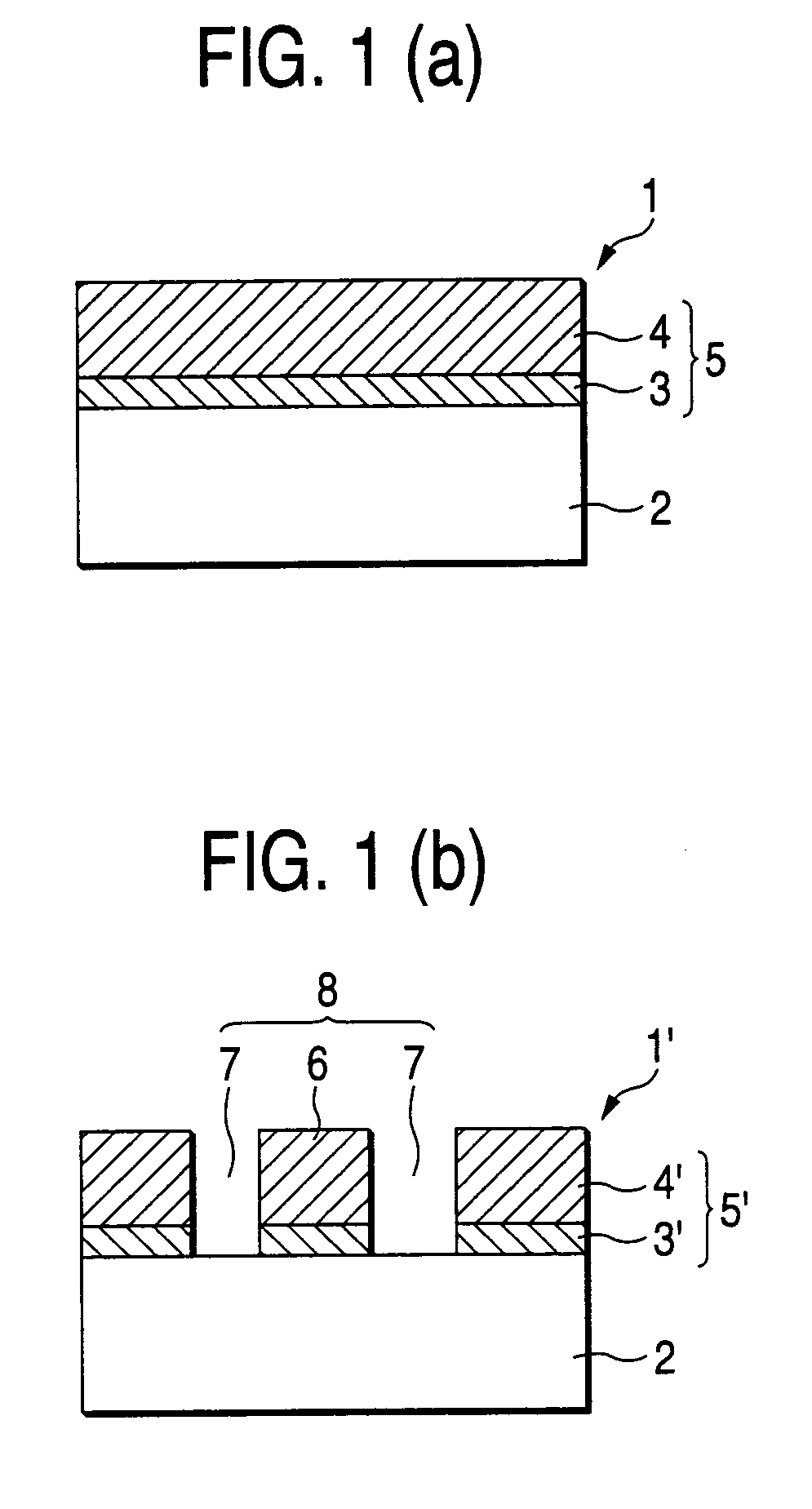

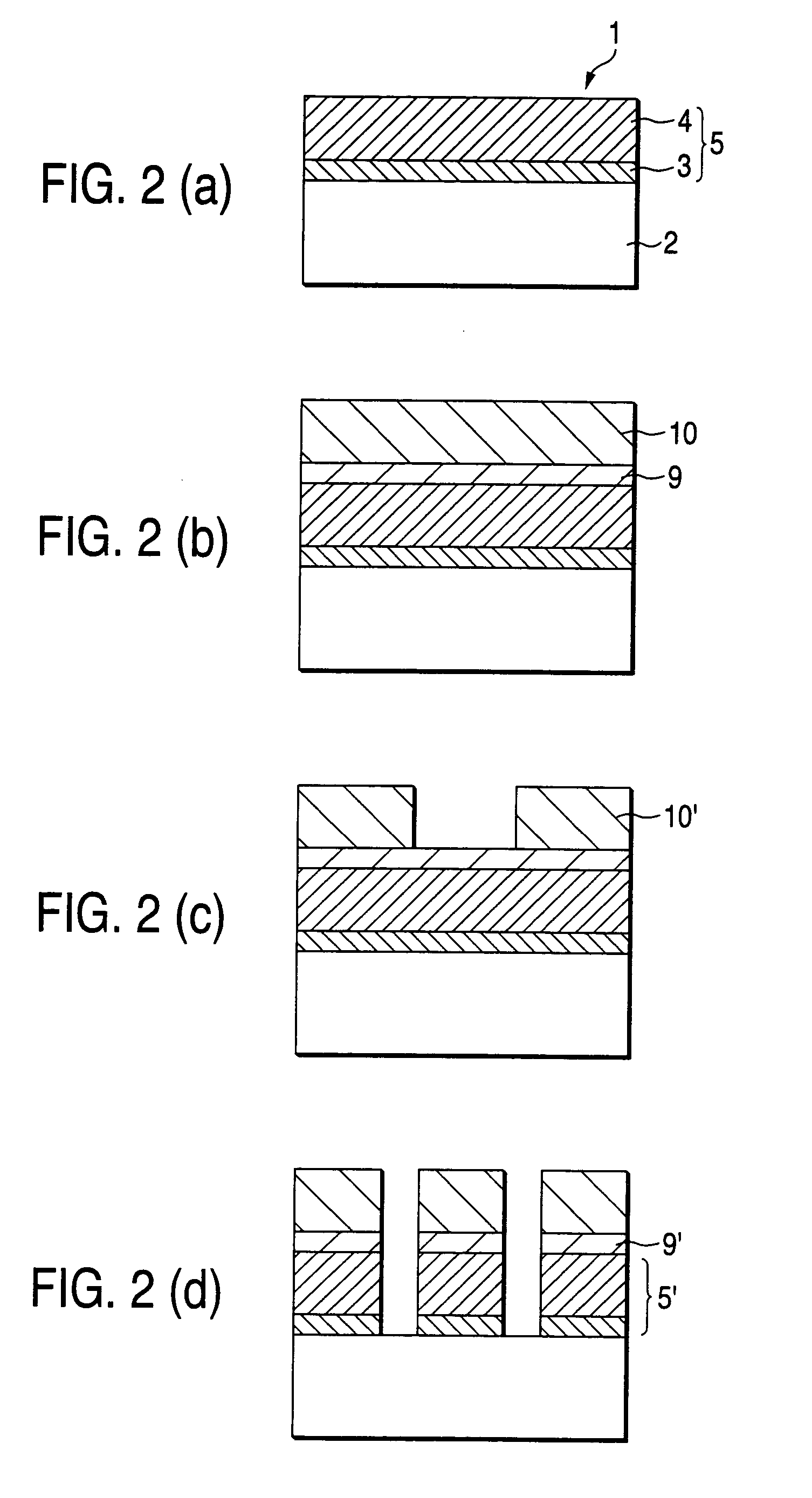

ActiveUS7011910B2Highly-accurate CD (critical-dimension) controlReduce surface reflectivitySemiconductor/solid-state device manufacturingPolarising elementsTransmittancePhase-shift mask

In a halftone-type phase-shift mask blank having a phase shifter film 5, the phase shifter film 5 has a phase adjustment layer 4 for primarily controlling the phase of exposure light, and a transmissivity adjustment layer 3 which is formed between a transparent substrate 2 and the phase adjustment layer 4 and primarily controls the transmissivity of exposure light. The transmissivity adjustment layer 3 has a thickness of 90 angstroms or less.

Owner:HOYA CORP

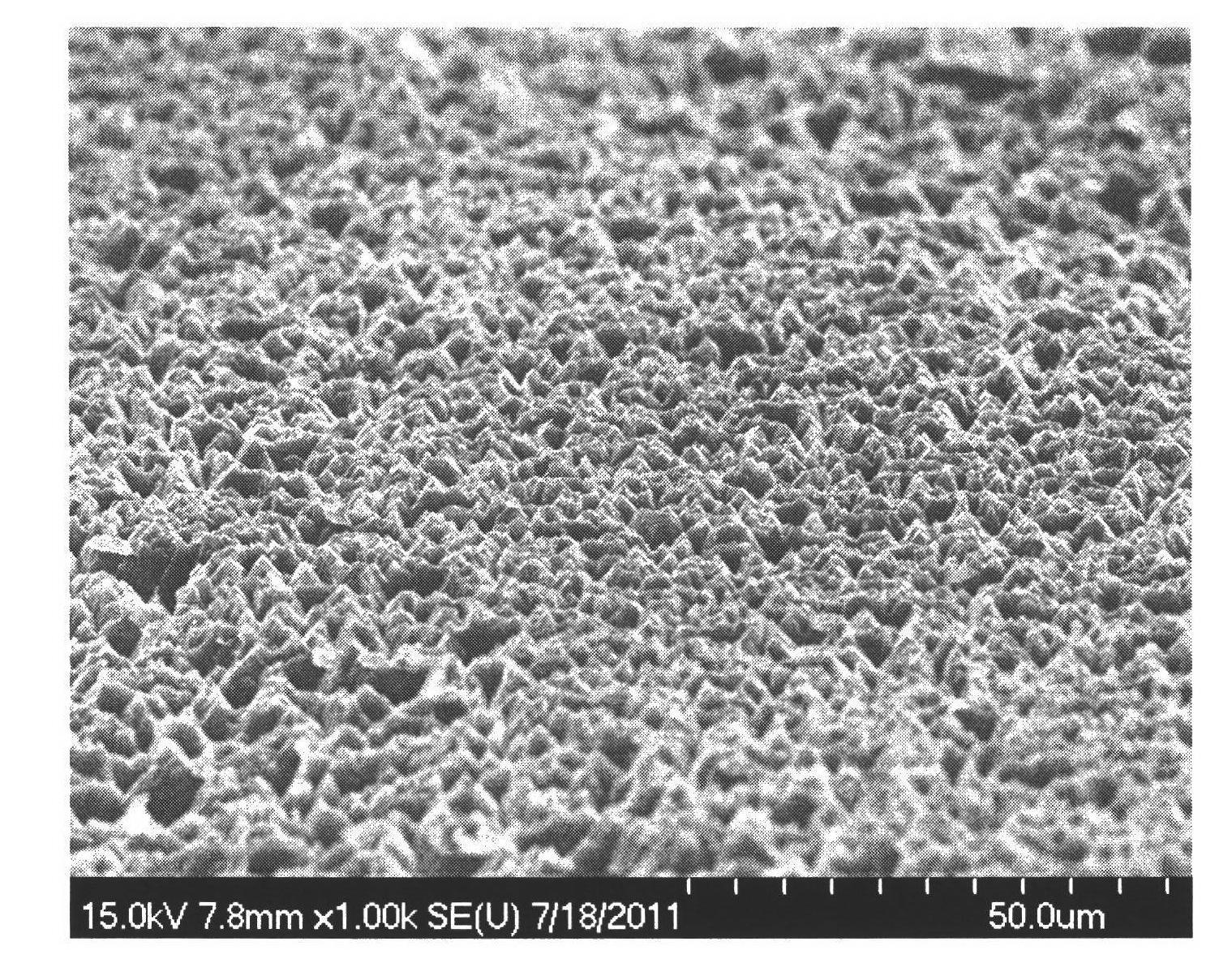

Silicon solar cell surface light trapping structure and preparation method thereof

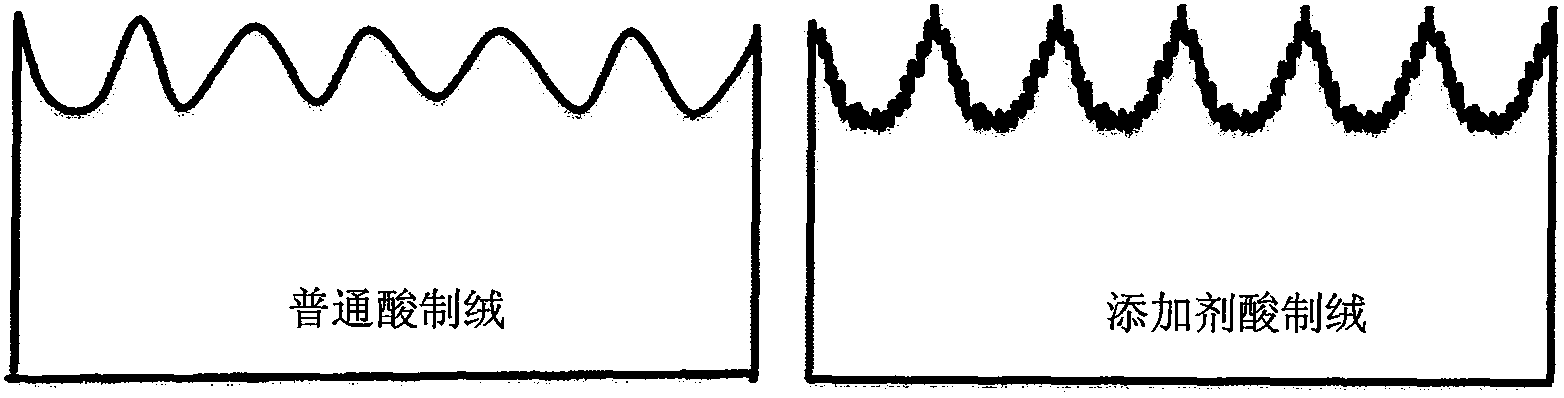

InactiveCN102978710AMeet cutting requirementsNon-toxicAfter-treatment detailsTrappingSilicon solar cell

The present invention provides a silicon solar cell surface light trapping structure and a preparation method thereof, and relates to a novel polycrystalline silicon acid texturing process, wherein addition of a certain proportion of an organosilicon surfactant is adopted, the whole acid texturing process can be controlled with citric acid, a textured structure having a specific structure is formed, and a large amount of micro corrosion pits are generated inside the ordinary worm-like structure of the textured structure, wherein a length of the large corrosion pit is 2-10 mum, a width of the large corrosion pit is 1-5 mum, a depth of the large corrosion pit is 0.5-2 mum, a length of the small corrosion pit is 100-500 nm, a width of the small corrosion pit is 100-500 nm, and a depth of the small corrosion pit is 0.2-0.5 mum. With the present invention, texturing reflectivity can be reduced by 2-3%.

Owner:HANGZHOU DAOLE SOLOR ENERGY TECH CO LTD

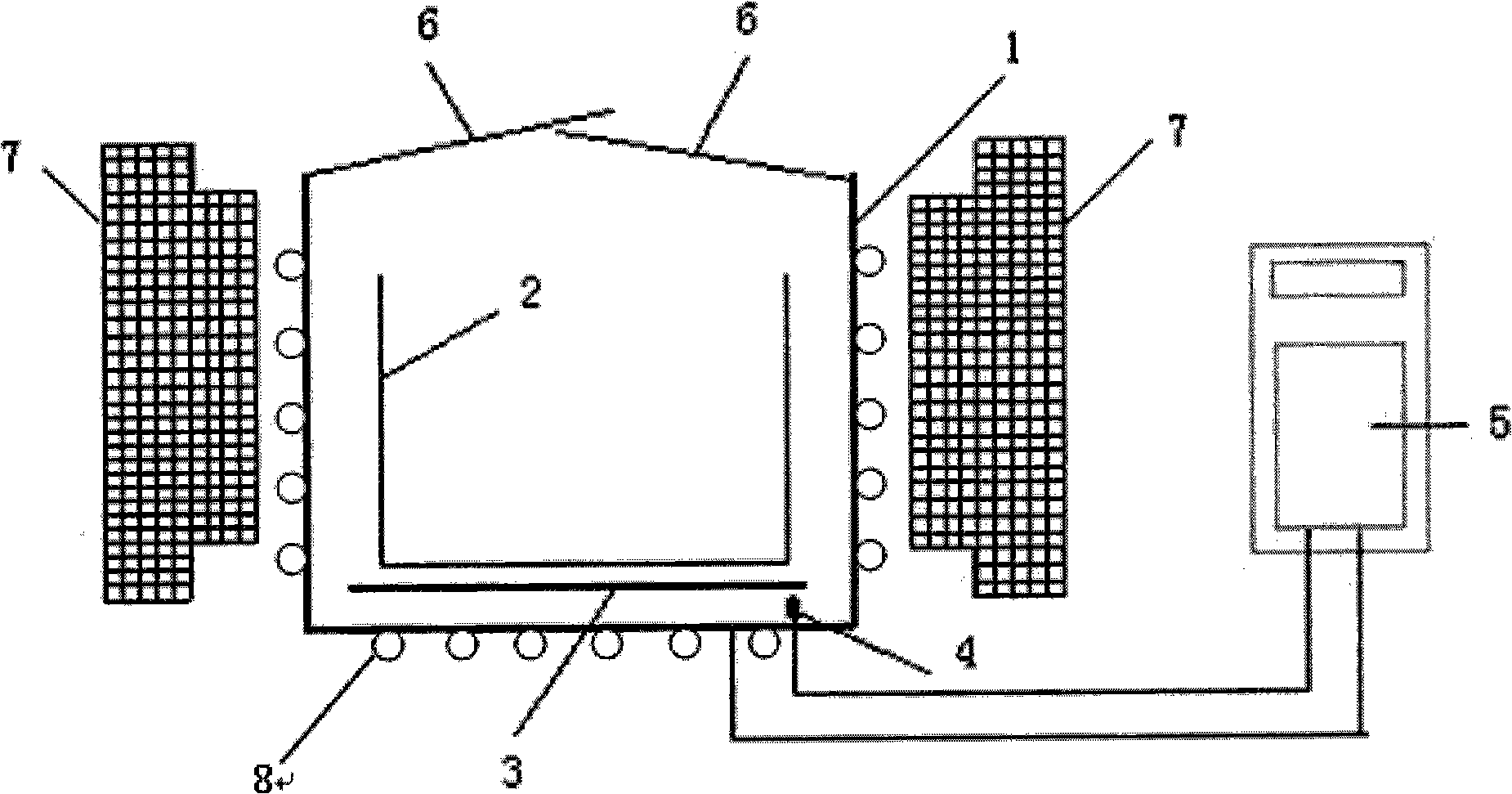

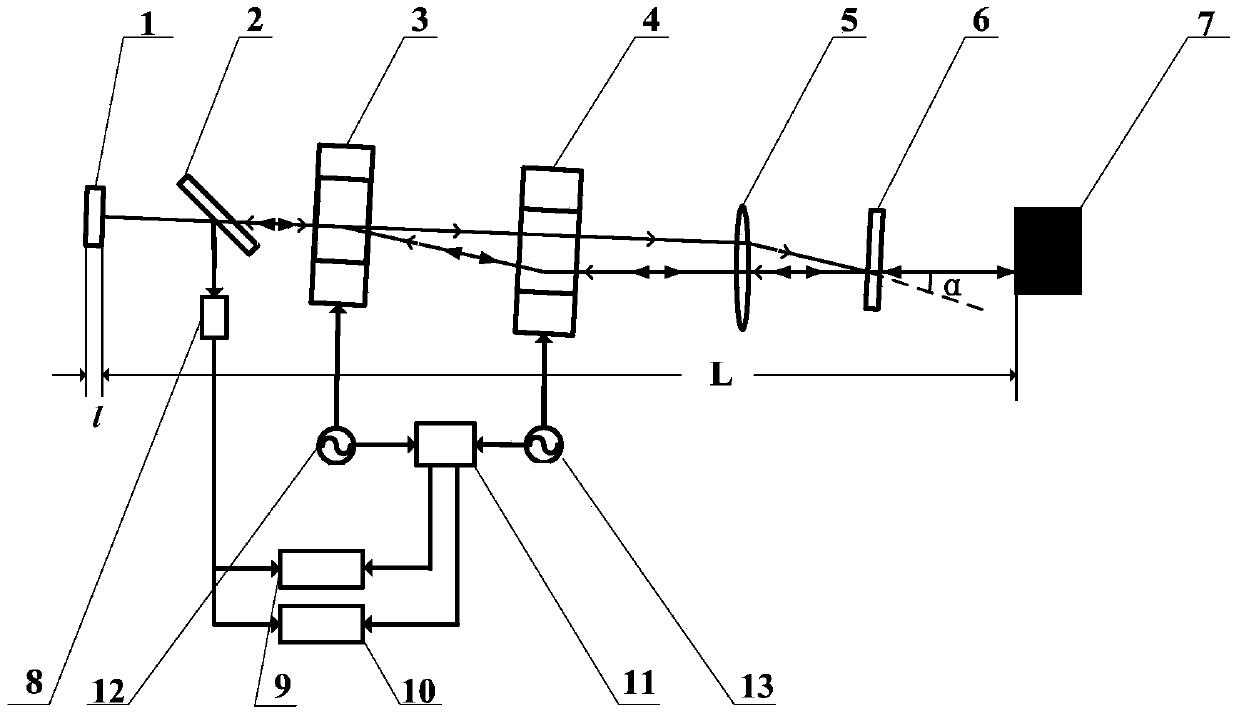

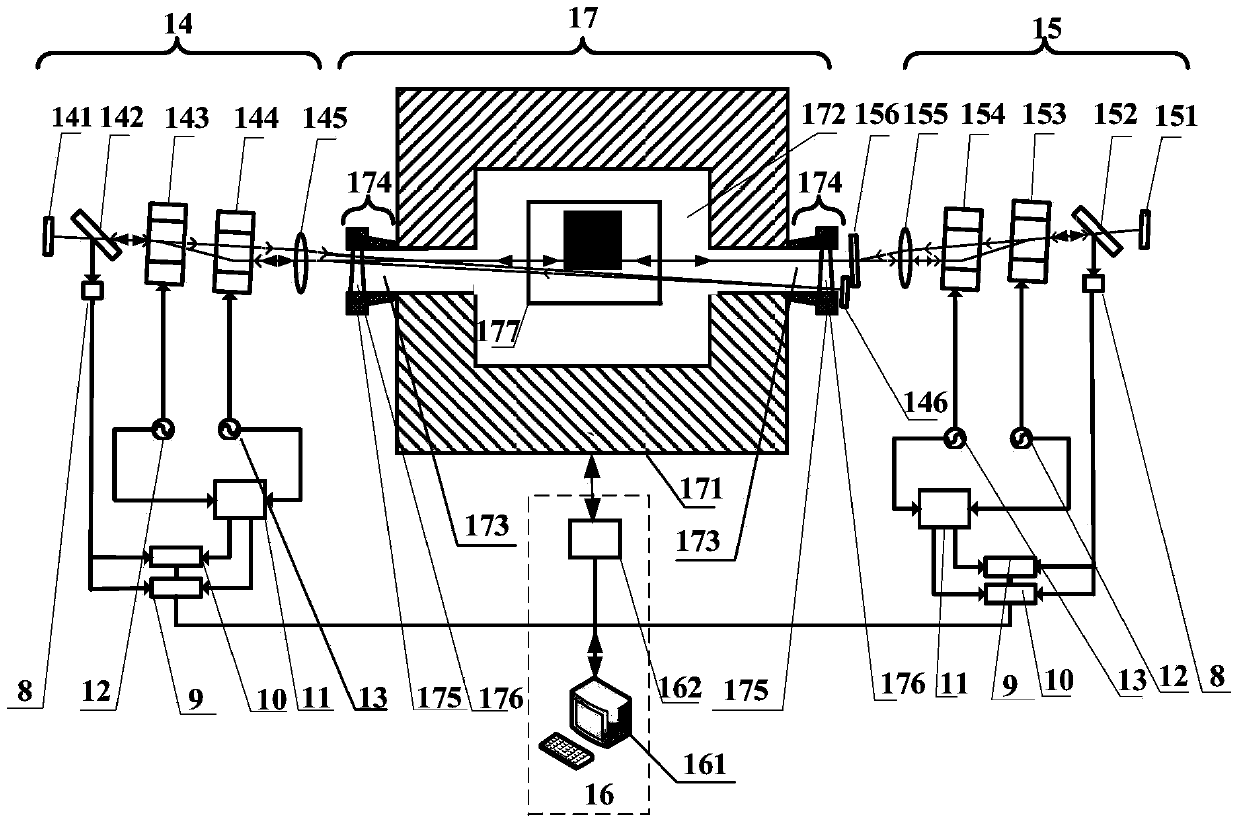

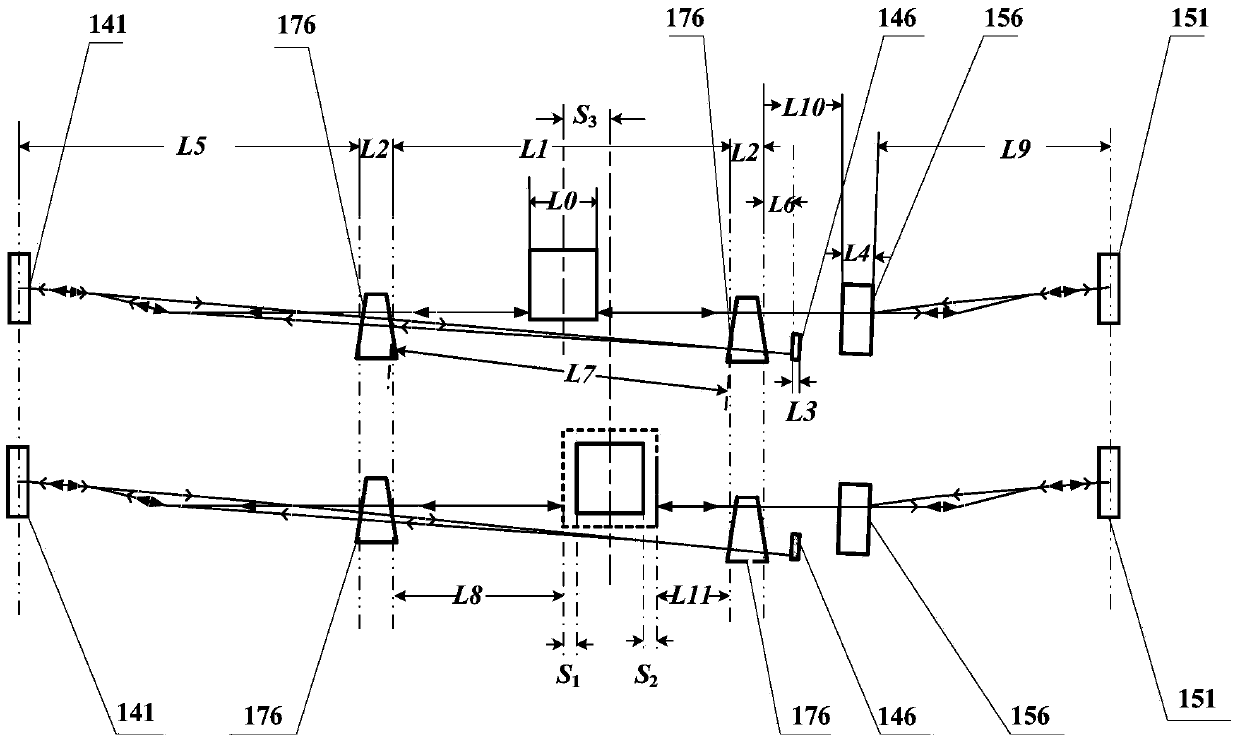

Measuring system for expansion coefficient of material

InactiveCN104198438AEliminate displacementAccurate measurementMaterial thermal coefficient of expansionPhase-affecting property measurementsElectricityHigh resistance

The invention relates to a measuring system for the expansion coefficient of a material. The measuring system is characterized by comprising two solid microchip laser feedback interferometer optical systems and an electrical logging and electric control system, wherein a heating furnace is arranged between the two solid microchip laser feedback interferometer optical systems and comprises a furnace chamber; a cavity is formed in the furnace chamber; a perforating hole is symmetrically formed in the two opposite sides of the cavity outward respectively; a perforating hole packaging structure is fixedly arranged at the outer end part of each perforating hole; a window plate is fixed outside each perforating hole packaging structure through a window plate clamping seat; a sample table device capable of accommodating a sample to be measured is further arranged in the cavity body; a heating element and a temperature sensor are fixedly arranged on the inner wall of the furnace chamber in a suspended mode. The measuring system for coefficient of liner expansion has the advantages of complete non-contact, high precision, large temperature measuring range and high resistance to shock, and is particularly suitable for a relatively low surface reflecting material. The measuring system can be widely applied to large temperature range and high precision measurement of expansion coefficient of various materials.

Owner:TSINGHUA UNIV

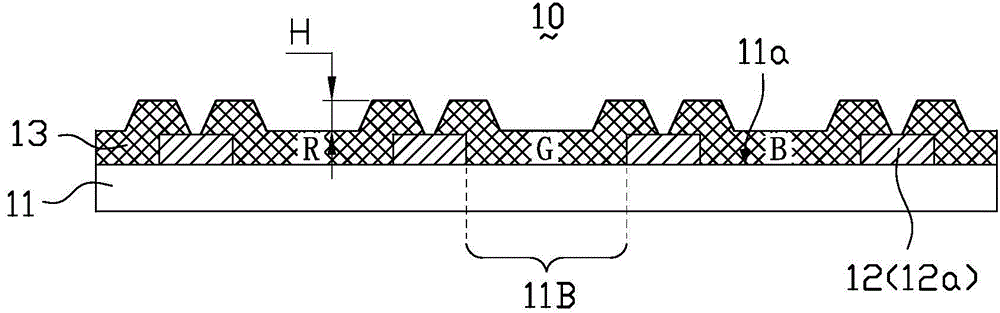

Color filter sheet, manufacturing method for color filter sheet and liquid crystal display device

ActiveCN104698521AReduce surface reflectivityHigh optical densityOptical filtersPhotomechanical apparatusLayer thicknessOptical density

The invention provides a color filter sheet. The color filter sheet comprises a transparent substrate, a black matrix layer and a color filter film layer. The black matrix layer is disposed on the transparent substrate, the thickness of the black matrix layer is smaller than or equal to 0.7 microns, the black matrix layer comprises a first shading layer and a second shading layer. The second shading layer is disposed on the first shading layer and is a black metal layer, and the color filter film layer is disposed on the transparent substrate and the second shading layer of the black matrix layer. The light density of the black matrix layer of the color filter sheet is high, the layer thickness is small, the angle segment difference of the color filter film layer is reduced effectively, the poor dark-state light leakage of the liquid crystal display device is reduced, and the liquid crystal display device display quality is improved. The invention further relates to a manufacturing method for the color filter sheet and a liquid crystal display device comprising the color filter sheet.

Owner:KUSN INFOVISION OPTOELECTRONICS

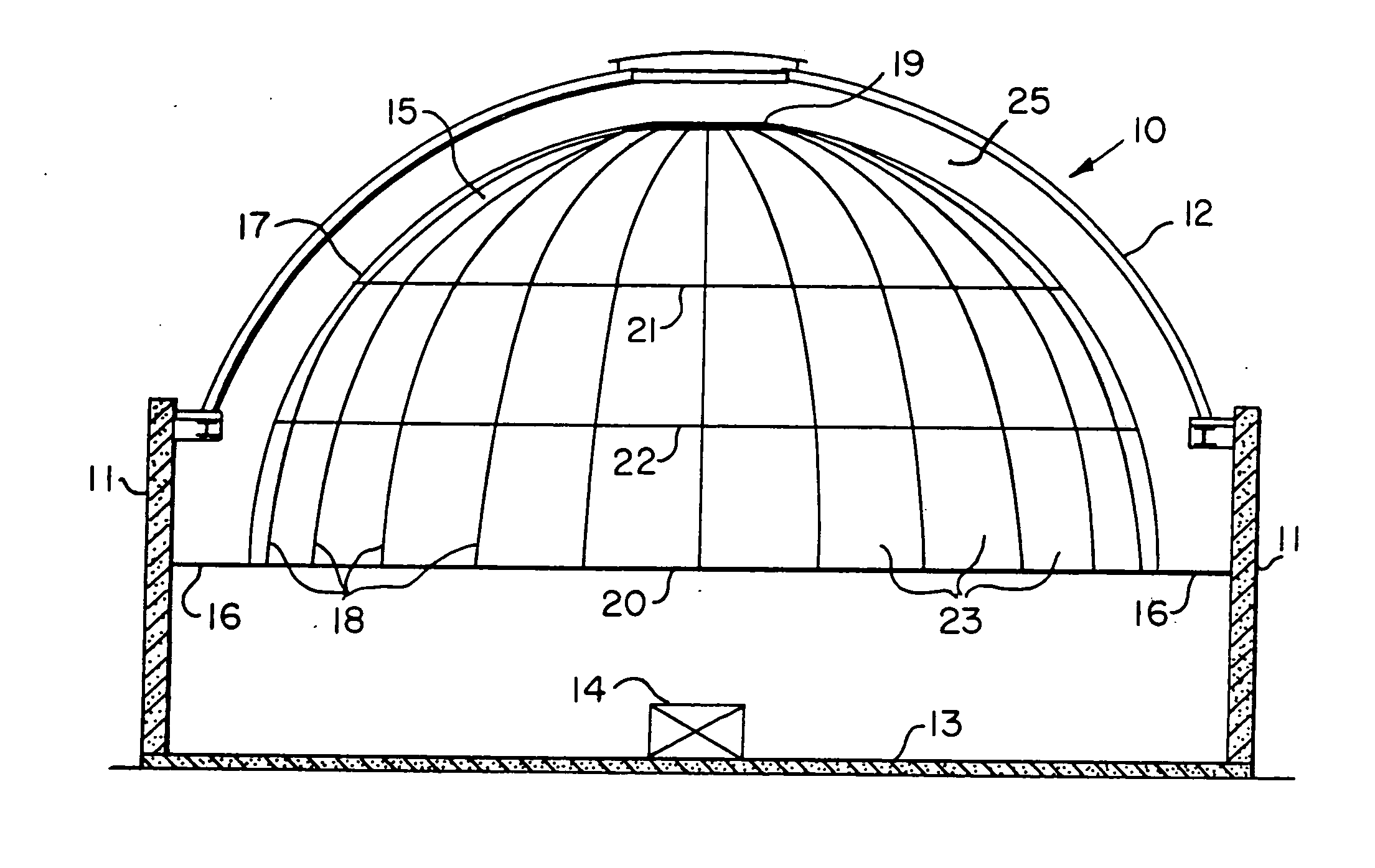

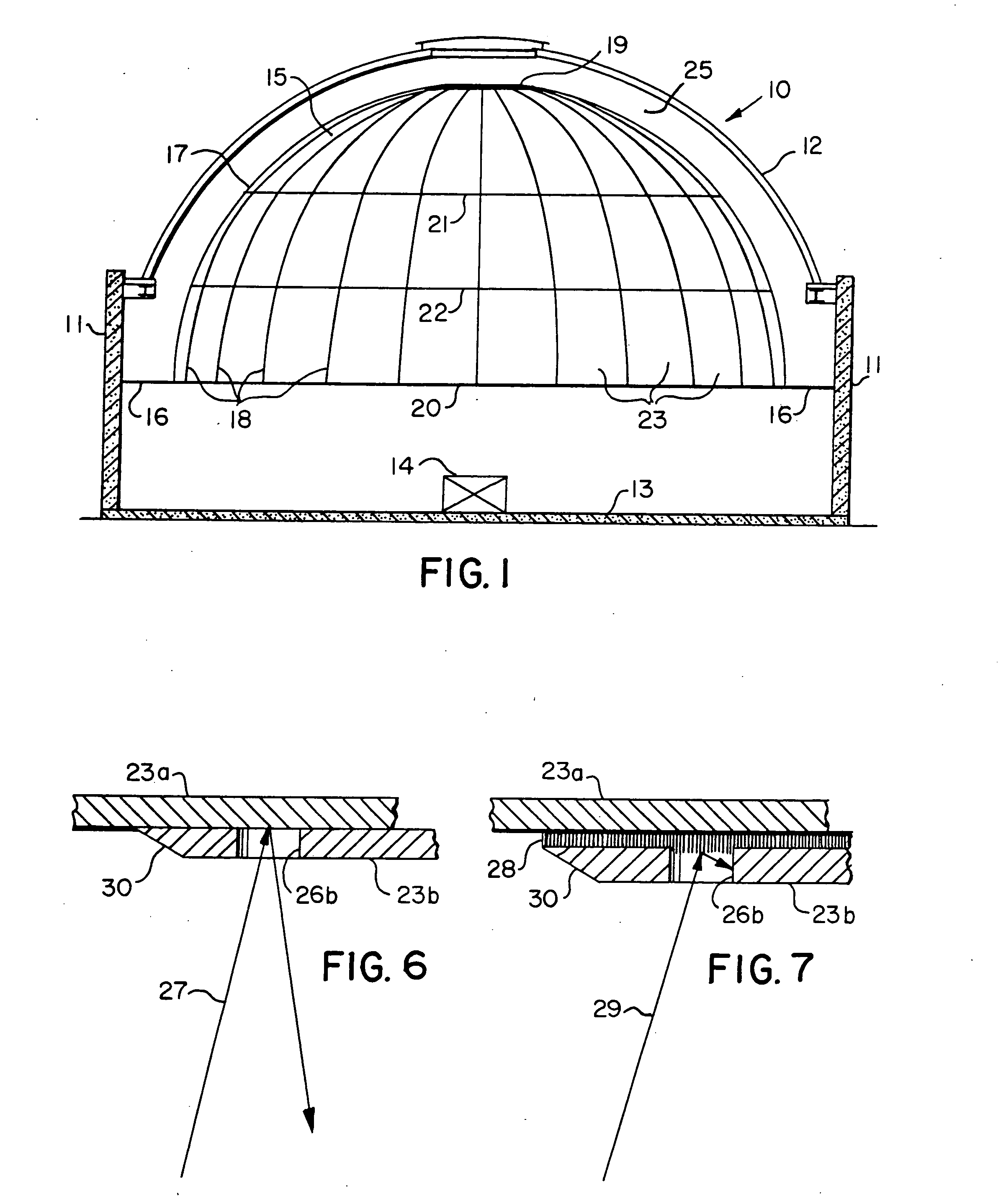

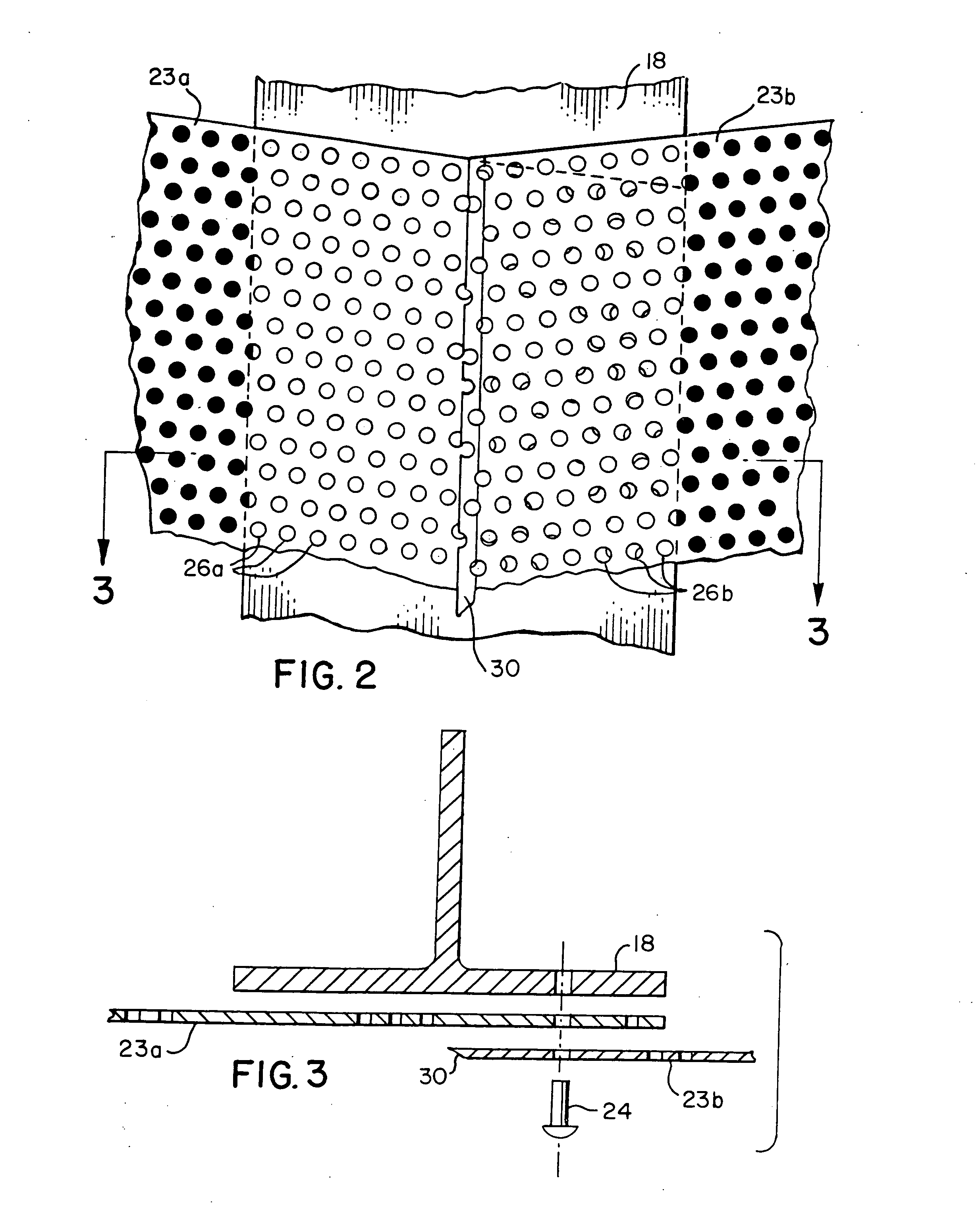

Perforate projection screen with inconspicuous seams

InactiveUS20060274413A1Simple and inexpensive solutionSimple and inexpensiveBuilding roofsProjectorsFiberProjection screen

A perforate projection screen for movies, planetariums and the like having inconspicuous seams and uniform reflectivity throughout its visible surface. The screen is made from a plurality of perforate panels and is mounted, when in use, with a dark non-reflective chamber behind the screen. Any overlapped areas of the panels and any frame members or other objects, in close proximity to the back of the panels are covered with a black velour type material having vertically extending fibers to absorb the light rays entering the holes in those areas of the panels and thereby prevent light reflection from such holes which would cause undesirable light strips or areas to be visible in the overlapped portions of the screen or in the area of the screen where frame members or other objects are in close proximity to the back of the panel. The edges of adjacent panels overlap to form seams with the overlapped edges of the panels being crimped to form recesses to receive the overlapping edge strip of an adjacent panel, thereby hiding the overlapping panel edge to reduce shadow lines on the screen and make the panel edges inconspicuous to seated viewers of the screen.

Owner:ASTRO TEC MFG

Display panel and display device

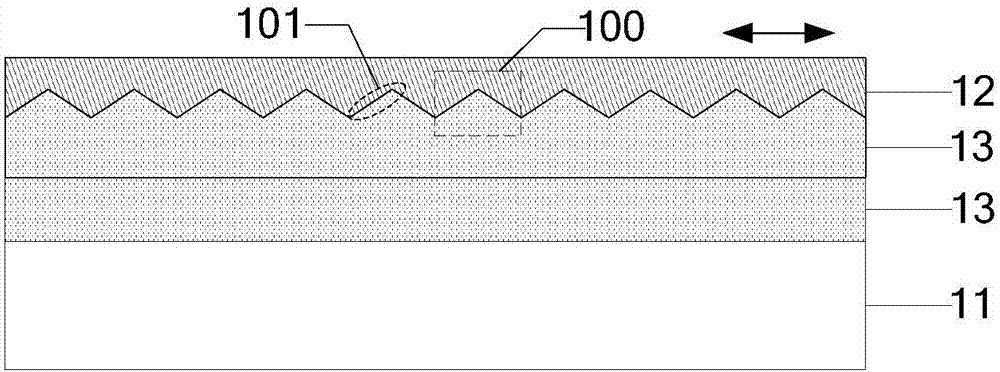

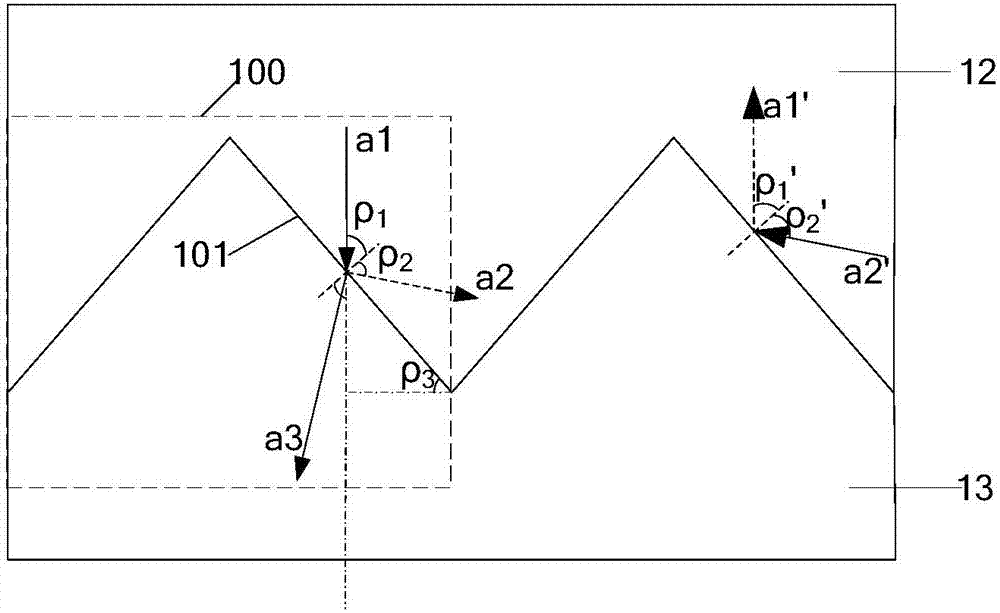

ActiveCN107272250AReduce surface reflectivityEliminate reflected lightNon-linear opticsDisplay deviceComputer science

The invention discloses a display panel and a display device. The display panel includes a display substrate, a first polarization layer positioned on a light going-out side of the display substrate, and at least one functional film layer positioned between the first polarization layer and the display substrate; at least one interface of each film layer is an uneven interface having a plurality of bar-shaped concave-convex edges which are arranged in parallel; the direction of the bar-shaped concave-convex edges of the outmost uneven interface is perpendicular to the polarization direction of the first polarization layer, the bar-shaped concave-convex edges have slopes extending in the direction of edges, and an included angle between the slopes and a flat surface is a Brewster angle that light enters the uneven interface. When environment light perpendicularly enters the display panel, the environment light can enter the display panel at the Brewster angle, the environment light passing through the first polarization layer is converted into linear polarized light, reflective light on the interface, of the perpendicularly incident environment light can be eliminated according to the Brewster law, and the surface reflectivity of the display panel is decreased.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Texturing Method for Diamond Wire Cut Polycrystalline Silicon Slice

ActiveUS20190067496A1Improve conversion efficiencyLight structurePolycrystalline material growthAfter-treatment detailsHydrofluoric acidInorganic ions

It discloses a texturing method for a diamond wire cut polycrystalline silicon slice, including the following steps: firstly, immersing the diamond wire cut polycrystalline silicon slice into a mixed aqueous solution of an alkali solution and an alkali reaction control agent, removing a damaged layer on a surface of the silicon slice, and then immersing the silicon slice into a hydrofluoric acid solution containing inorganic ions and organic molecules for reaction; secondly, pretreating the polycrystalline silicon surface by a mixed solution of hydrofluoric acid and hydrogen peroxide, adding a pore-forming regulator at the same time, and finally texturing the surface of the silicon slice by a mixed acid solution of hydrofluoric acid and nitric acid.

Owner:NANJING UNIV OF TECH

Method for removing surface line marks of diamond linear cutting polycrystalline silicon chip through wet method

ActiveCN106340446AGood repeatabilityReduce surface reflectivitySemiconductor/solid-state device manufacturingEtchingSolar battery

The invention discloses a method for removing cutting marks generated at the back surface of diamond linear cutting polycrystalline silicon. The method comprises the following steps: 1, pre-cleaning a silicon chip; 2, placing the cleaned silicon chip in an HF / HNO3 / H2O mixed solution for texturing processing; 3, placing the textured silicon chip in a mixed solution of H2O2 / HF / AgNO3 / Cu(NO3)2 and ultrapure water for corrosion so as to prepare a nanometer structure; and 4, performing expansion processing on the nanometer structure by use of a nanometer reconstruction solution, and performing anisotropic corrosion so as to remove the cutting marks at the surface of the polycrystalline silicon. According to the invention, on the basis that a black silicon anti-reflection structure is prepared based on MACE (metal-assisted chemical etching), the cutting marks at the surface of the diamond linear cutting polycrystalline silicon chip by use of anisotropy in a corrosion process, at the same time, the reflectivity of the surface of the silicon chip is also greatly reduced, and the method has important application potential in future preparation of low-cost high-conversion-efficiency diamond linear cutting polycrystalline silicon solar batteries.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Method for reducing surface reflectivity of texture mono-crystalline silicon chip

InactiveCN101609862AReduce surface reflectivityImprove conversion efficiencyFinal product manufactureSemiconductor devicesSolar cellAtmospheric pressure

The invention discloses a method for reducing the surface reflectivity of a texture mono-crystalline silicon chip, relating to the technical range and field of preparation of solar cells. A mono-crystalline silicon chip with a texture made by alkaline corrosion is put into a plasma etching device to implement non-mask plasma etching so as to further reduce the surface reflectivity of the texture mono-crystalline silicon chip. Gas used for etching is a mixed gas of CF4 and O2 with the flow portion ranging from 10:1 to 1:3, and the pressure in the treatment chamber ranges from 1Pa to 20Pa. The invention further reduces the surface reflectivity of the texture mono-crystalline silicon chip, and provides a feasible way to further improve the conversion efficiency of the solar cell. The method is characterized by simpleness, convenience, effectiveness, low cost, easy operation, no need of additional equipment and suitability for large-scale production.

Owner:EOPLLY NEW ENERGY TECH

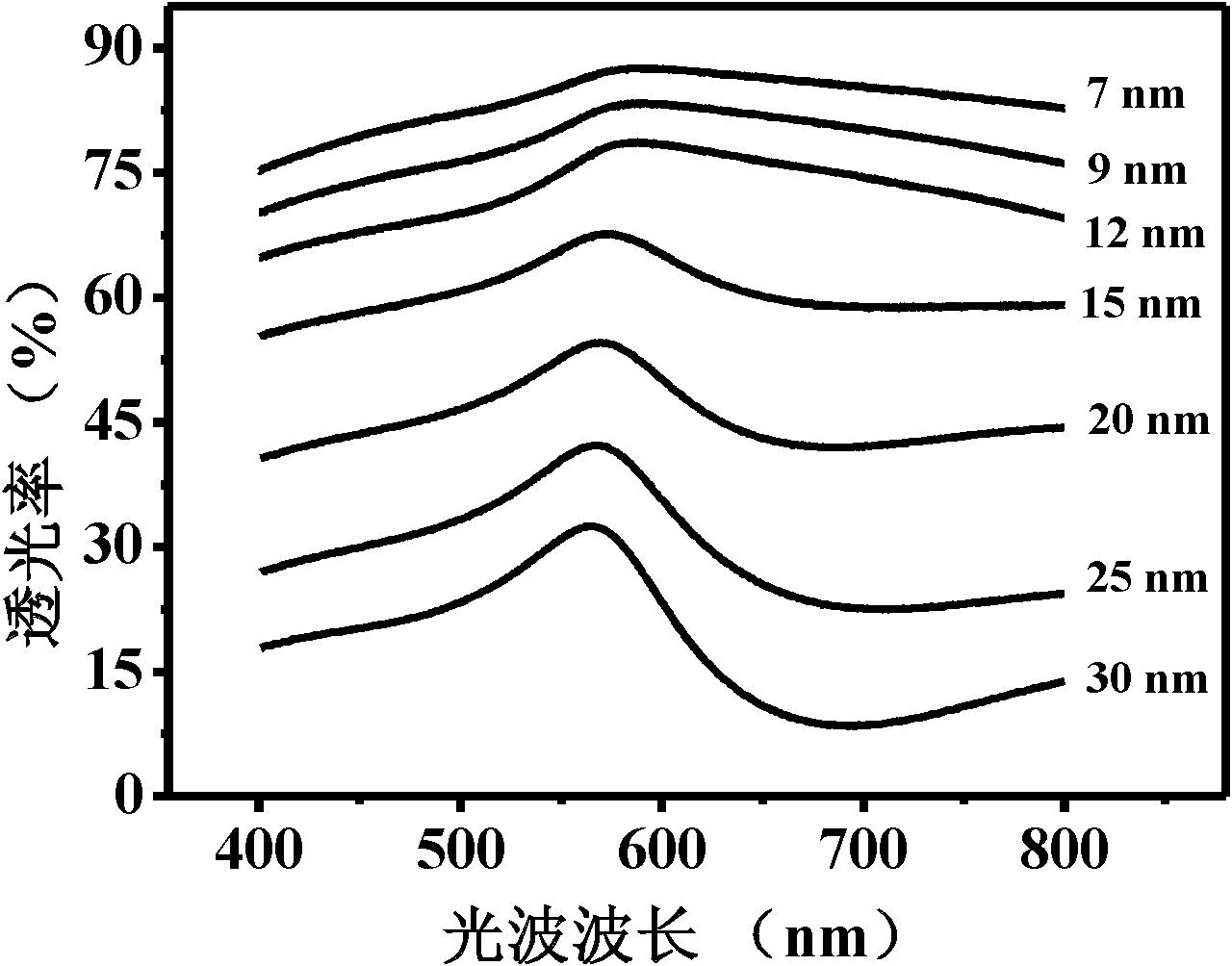

Transparent conductive metallic film and preparation method thereof

InactiveCN102051578ALow resistivitySimple preparation processVacuum evaporation coatingSputtering coatingLayered structureTransmittance

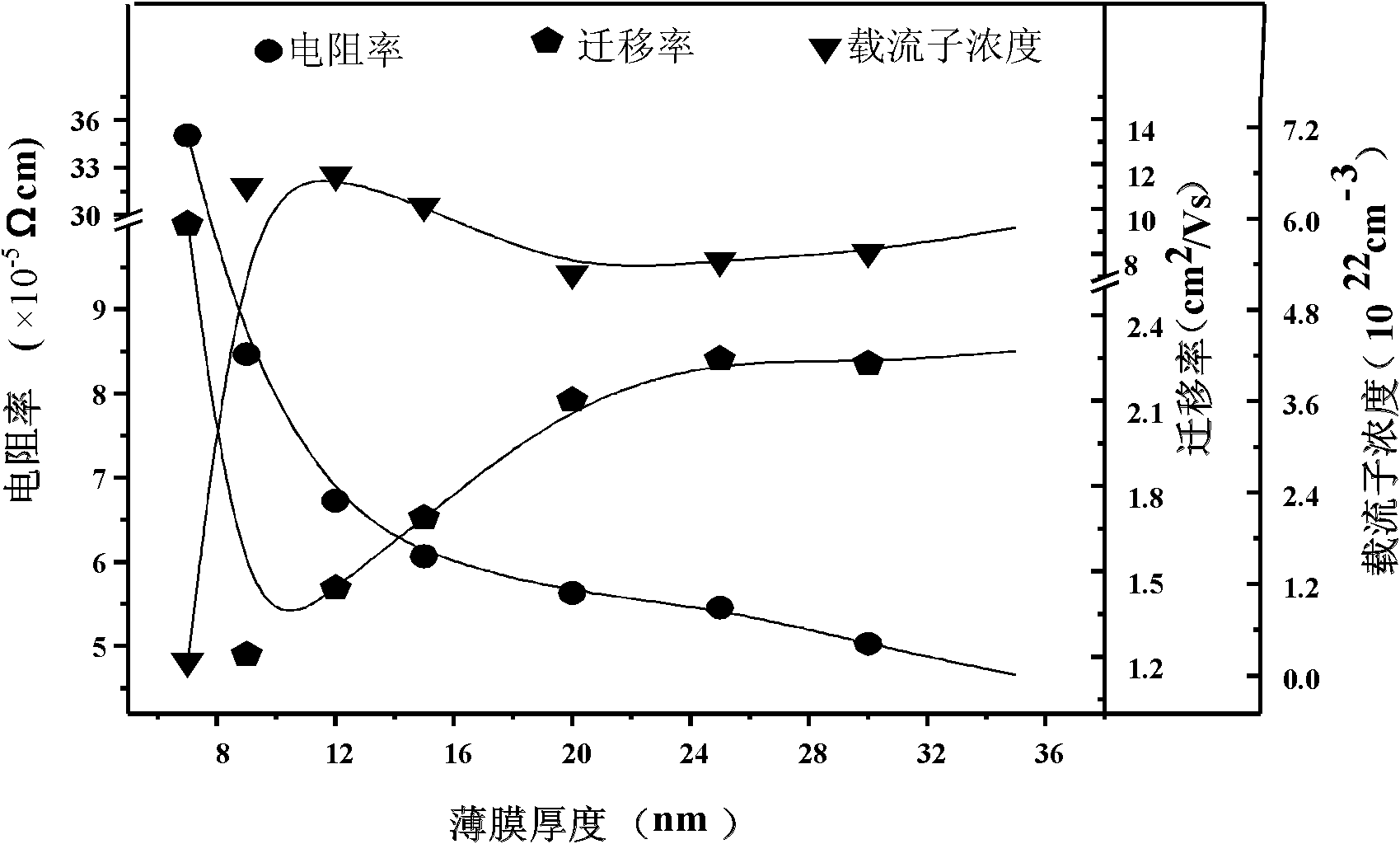

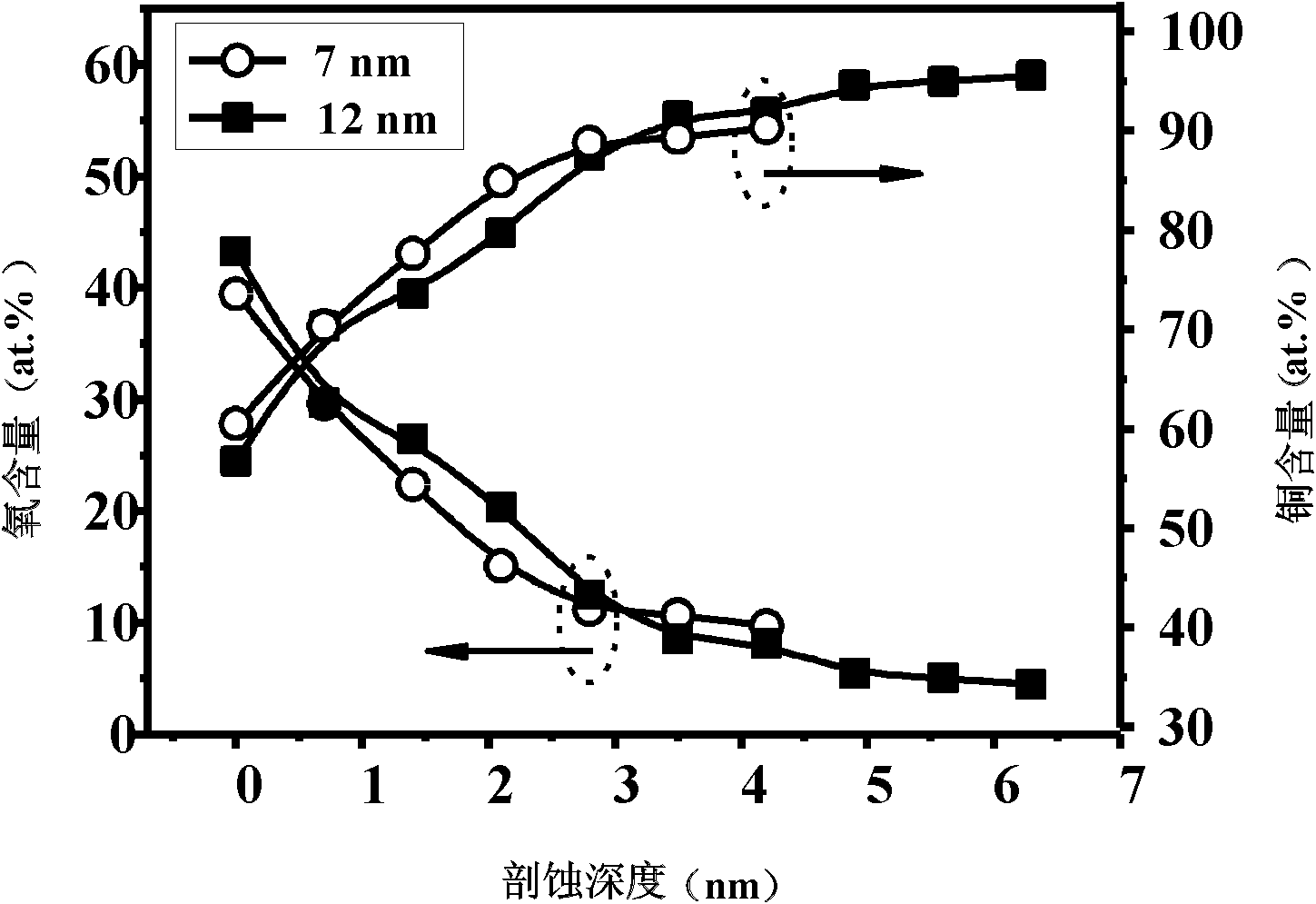

The invention provides a transparent conductive metallic film and a preparation method thereof. The film is prepared from amorphous metallic copper by using a magnetron sputtering method, wherein the transparent conductive metallic film has a thickness of 7-30nm and an electrical resistivity of 10-5 to 10-4 Ohm cm; when being preferably 7-12nm in thickness, the transparent conductive metallic film has the light transmittance of 78-85%; the transparent conductive metallic film has a double-layered structure, and the outermost layer is an oxygen absorbing layer with the thickness stabilized in the range of 3-5nm. The thickness of the oxygen absorbing layer is not increased following the increasing of the whole thickness of the transparent conductive metallic film, therefore, the transparent conductive metallic film has decreased reflectivity and increased light transmittance in the visible light range.

Owner:BEIHANG UNIV