Method of forming micro-pore structures or trench structures on surface of silicon wafer substrate

A substrate surface, microporous structure technology, applied in photovoltaic power generation, electrical components, circuits, etc., can solve the problem of high manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

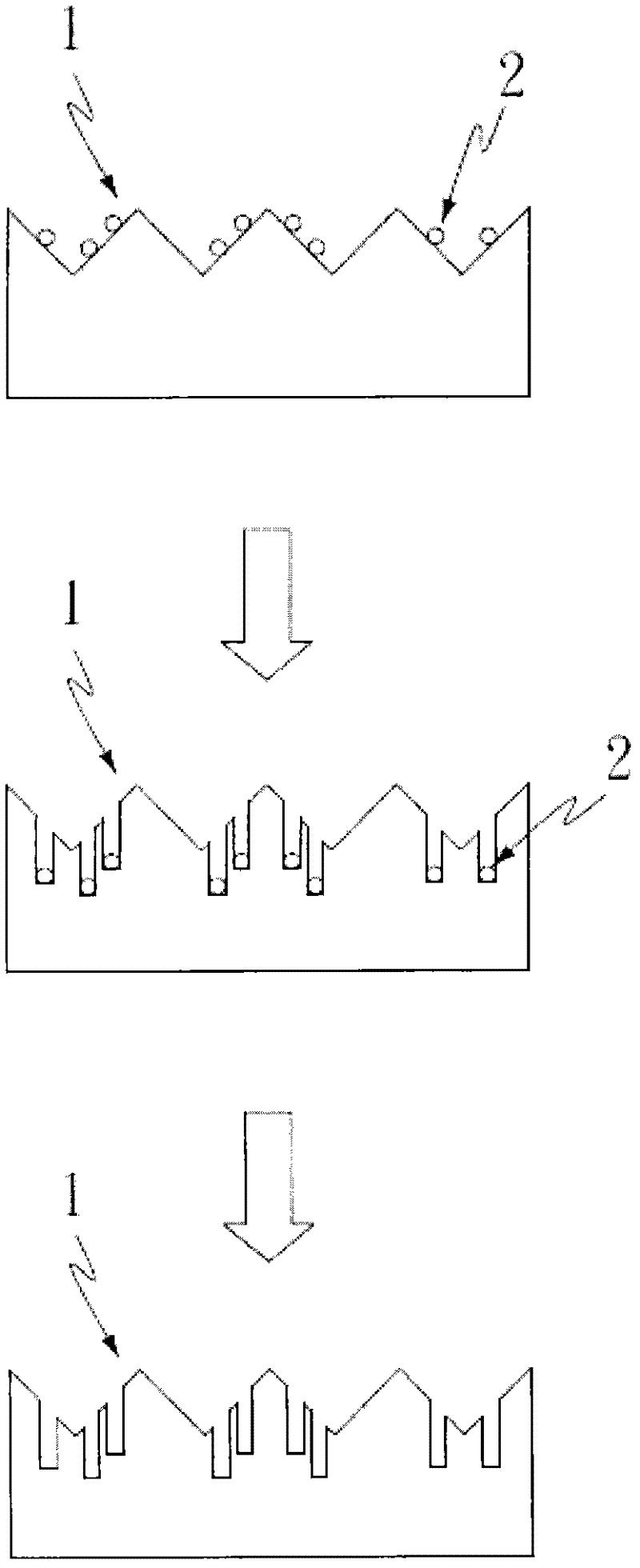

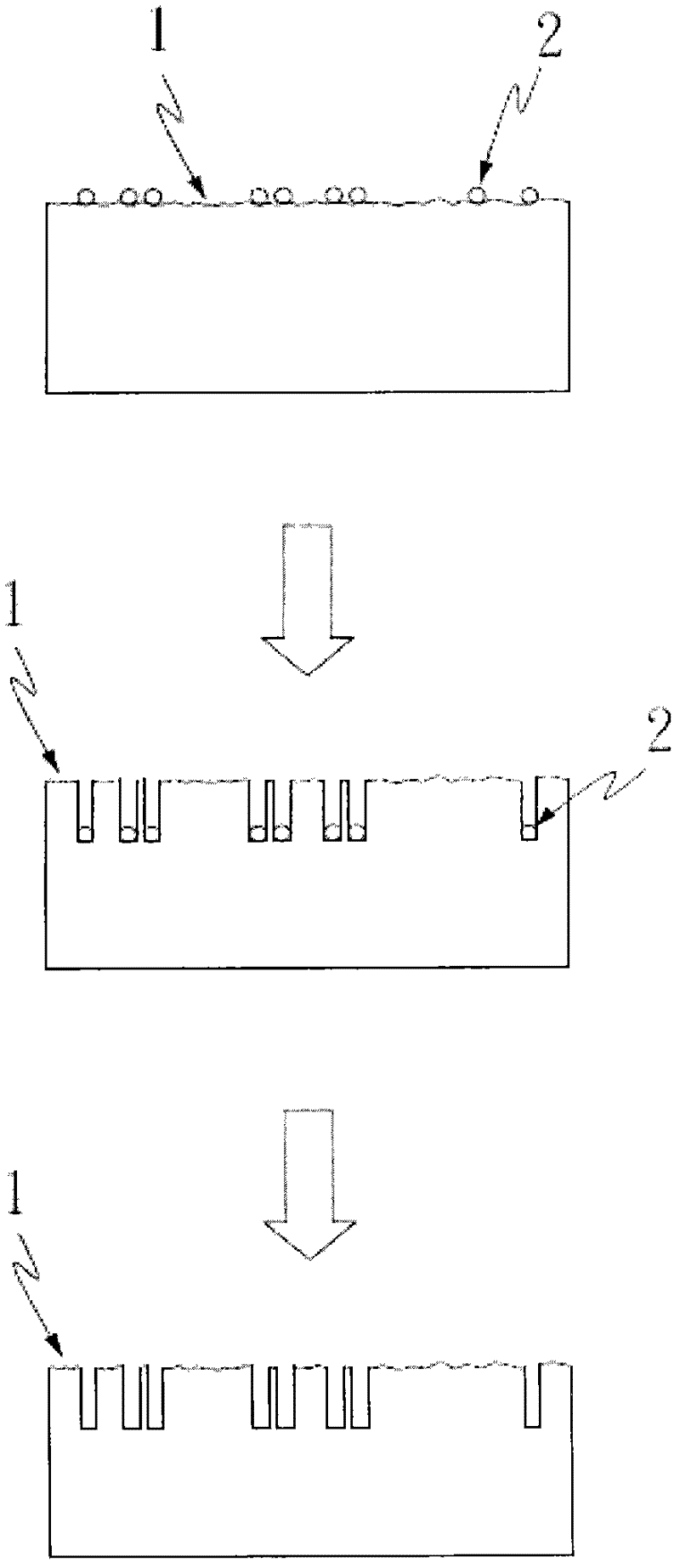

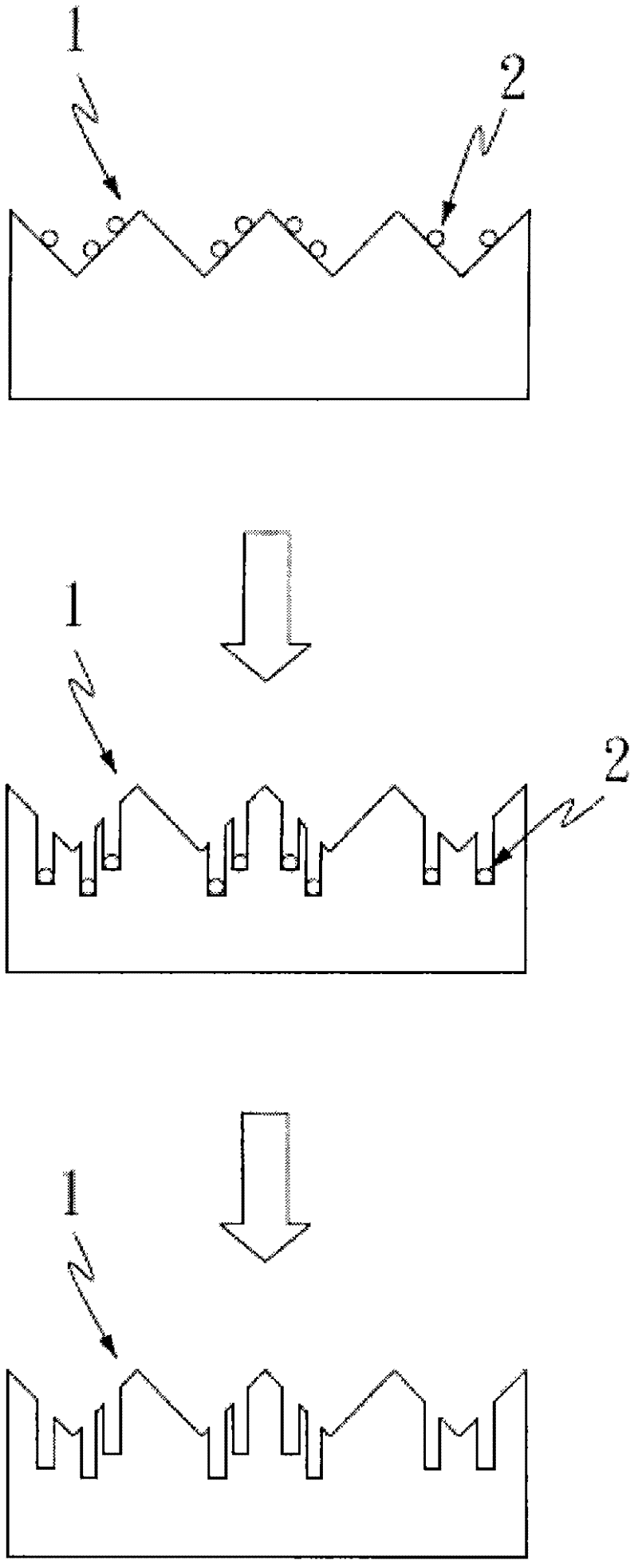

Method used

Image

Examples

Embodiment 1

[0063] A sliced, smooth-surfaced monocrystalline silicon chip (about 150 cm in size) was prepared, and the following aqueous solution was prepared.

[0064] Cleaning solution: an aqueous solution of 30% hydrogen peroxide and 98% concentrated sulfuric acid mixed at a ratio of 1:4 (volume ratio).

[0065] Electroless co-plating solution: containing 0.05mol / L silver nitrate (AgNO 3 ), 0.05mol / L zinc nitrate (Zn(NO 3 ) 2 ) and 1.0mol / L sodium hydroxide (NaOH) mixed aqueous solution.

[0066] Etching solution: an aqueous solution mixed with 10% hydrofluoric acid and 30% hydrogen peroxide at a ratio of 10:1 (volume ratio).

[0067]The chip was soaked in the cleaning solution for 10 minutes to clean the chip. Next, soak the chip in the electroless co-plating chemical solution for about 20 minutes, so that the alloy particles formed by silver and zinc are deposited on the surface of the chip. Second, soak the chip deposited with the silver-zinc alloy particles in the etching solu...

Embodiment 2

[0069] Except that the 0.05mol / L zinc nitrate of the electroless co-plating liquid in embodiment 1 is replaced by 0.02mol / L tin sulfate (SnSO 4 ), all the other implementation conditions and steps are the same as in Example 1.

Embodiment 3

[0071] Except that silver nitrate and zinc nitrate of the electroless co-plating liquid in embodiment 1 are replaced by silver sulfate (Ag 2 SO 4 ) and zinc sulfate (ZnSO 4 ), all the other implementation conditions and steps are the same as in Example 1.

PUM

| Property | Measurement | Unit |

|---|---|---|

| particle diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More