Patents

Literature

11590 results about "Noble metal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In chemistry, the noble metals are metals that are resistant to corrosion and oxidation in moist air (unlike most base metals). The short list of chemically noble metals (those elements upon which almost all chemists agree) comprises ruthenium (Ru), rhodium (Rh), palladium (Pd), silver (Ag), osmium (Os), iridium (Ir), platinum (Pt), and gold (Au).

Atomic layer deposition of noble metal oxides

Electrically conductive noble metal oxide films can be deposited by atomic layer deposition (ALD)-type processes. In preferred embodiments, Re, Ru, Os and Ir oxides are deposited by alternately and sequentially contacting a substrate with vapor phase pulses of a noble metal precursor and an oxygen source. The noble metal precursor is preferably a betadiketonate compound and the oxygen source is preferably ozone or oxygen plasma. The deposition temperature may be less than about 200° C.

Owner:ASM INTERNATIONAL

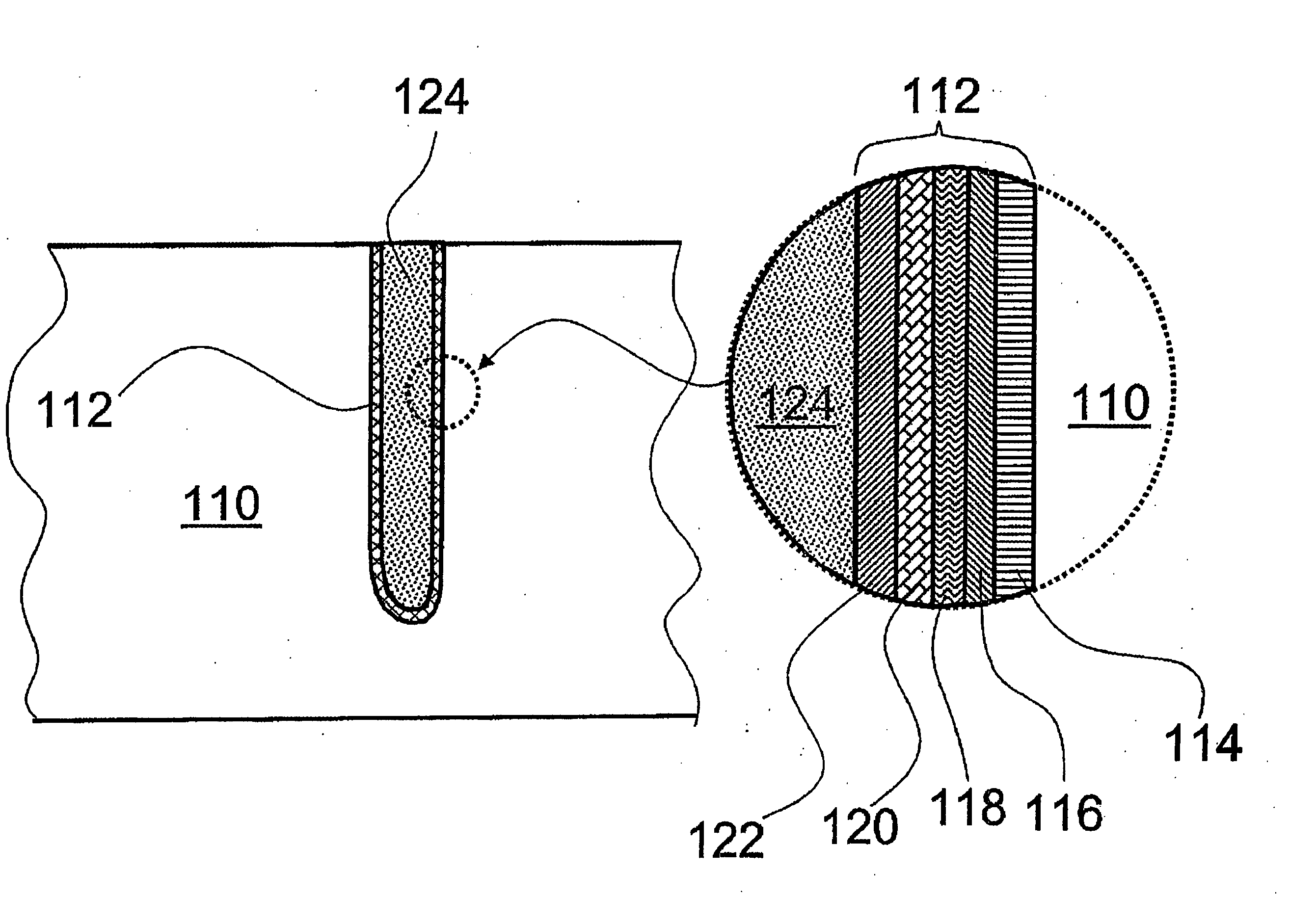

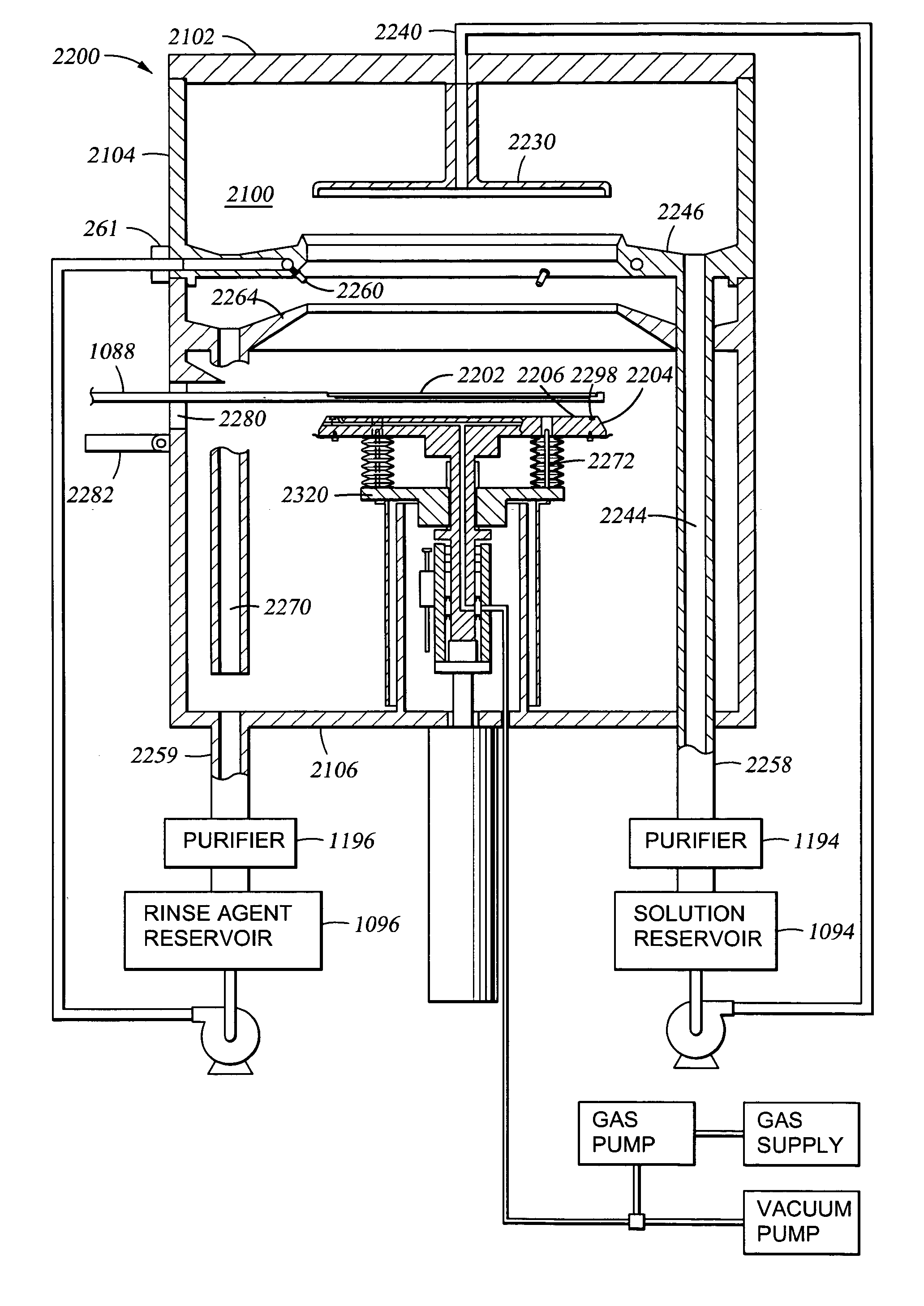

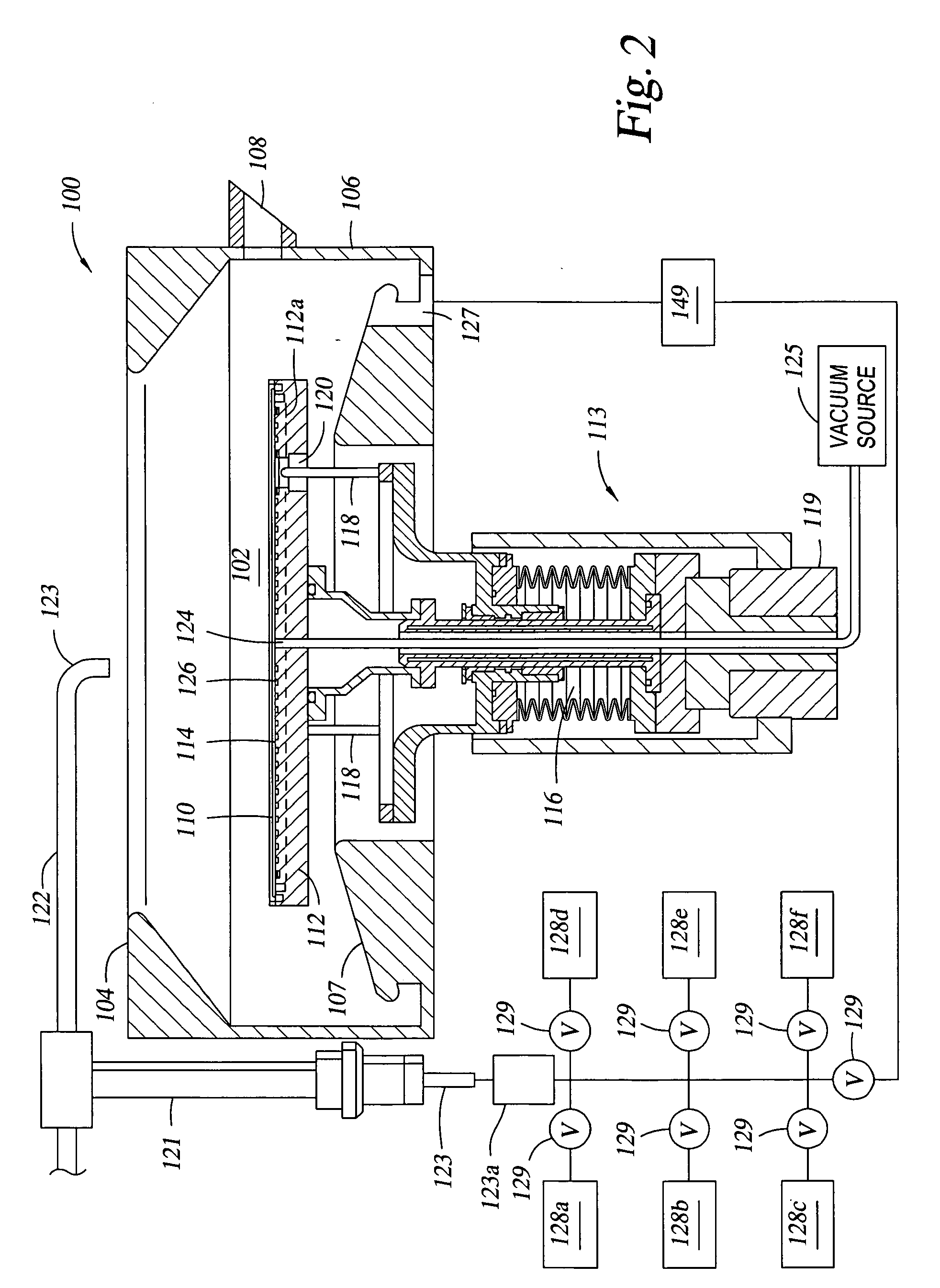

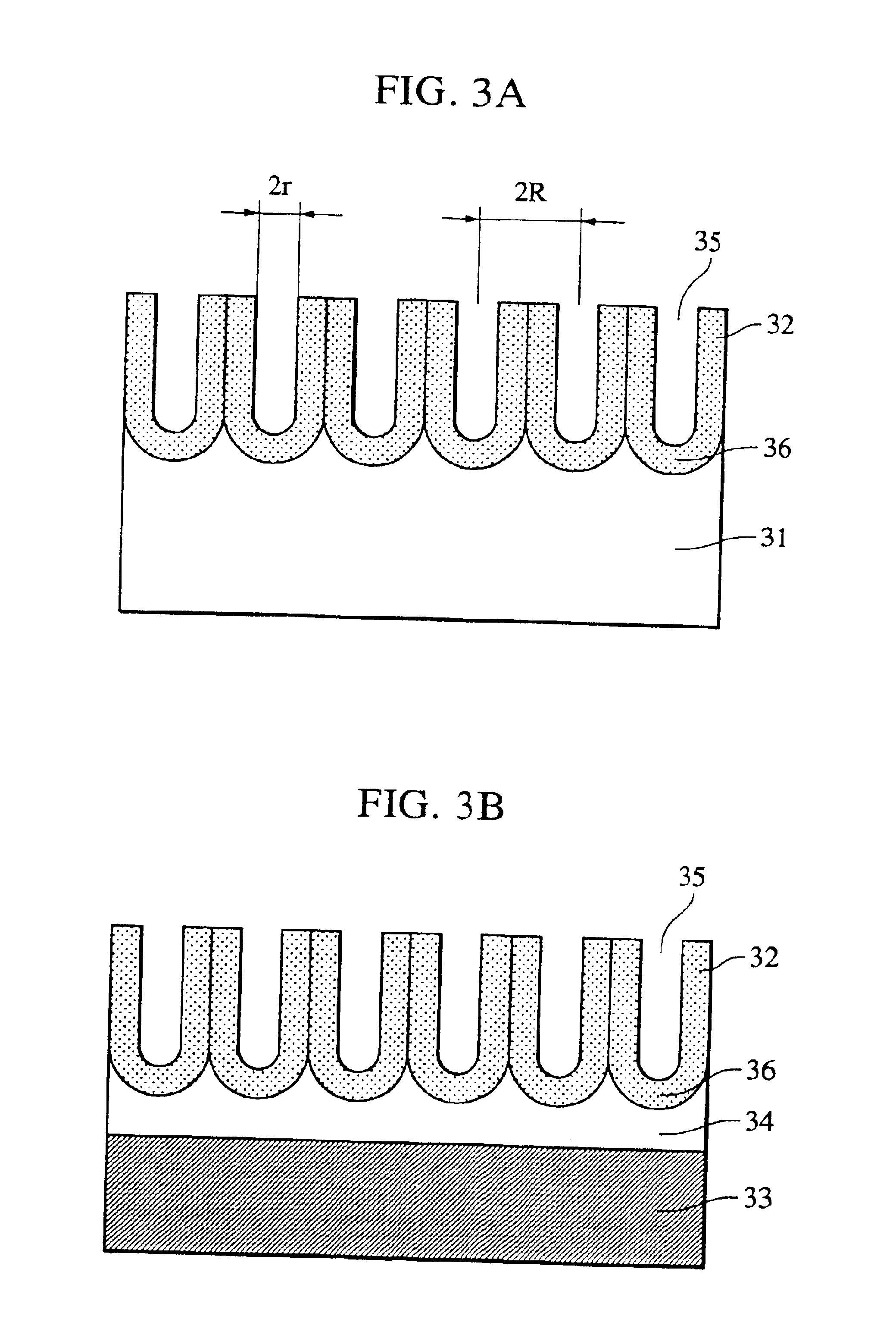

Electroless deposition apparatus

An apparatus and a method of depositing a catalytic layer comprising at least one metal selected from the group consisting of noble metals, semi-noble metals, alloys thereof, and combinations thereof in sub-micron features formed on a substrate. Examples of noble metals include palladium and platinum. Examples of semi-noble metals include cobalt, nickel, and tungsten. The catalytic layer may be deposited by electroless deposition, electroplating, or chemical vapor deposition. In one embodiment, the catalytic layer may be deposited in the feature to act as a barrier layer to a subsequently deposited conductive material. In another embodiment, the catalytic layer may be deposited over a barrier layer. In yet another embodiment, the catalytic layer may be deposited over a seed layer deposited over the barrier layer to act as a “patch” of any discontinuities in the seed layer. Once the catalytic layer has been deposited, a conductive material, such as copper, may be deposited over the catalytic layer. In one embodiment, the conductive material is deposited over the catalytic layer by electroless deposition. In another embodiment, the conductive material is deposited over the catalytic layer by electroless deposition followed by electroplating or followed by chemical vapor deposition. In still another embodiment, the conductive material is deposited over the catalytic layer by electroplating or by chemical vapor deposition.

Owner:APPLIED MATERIALS INC

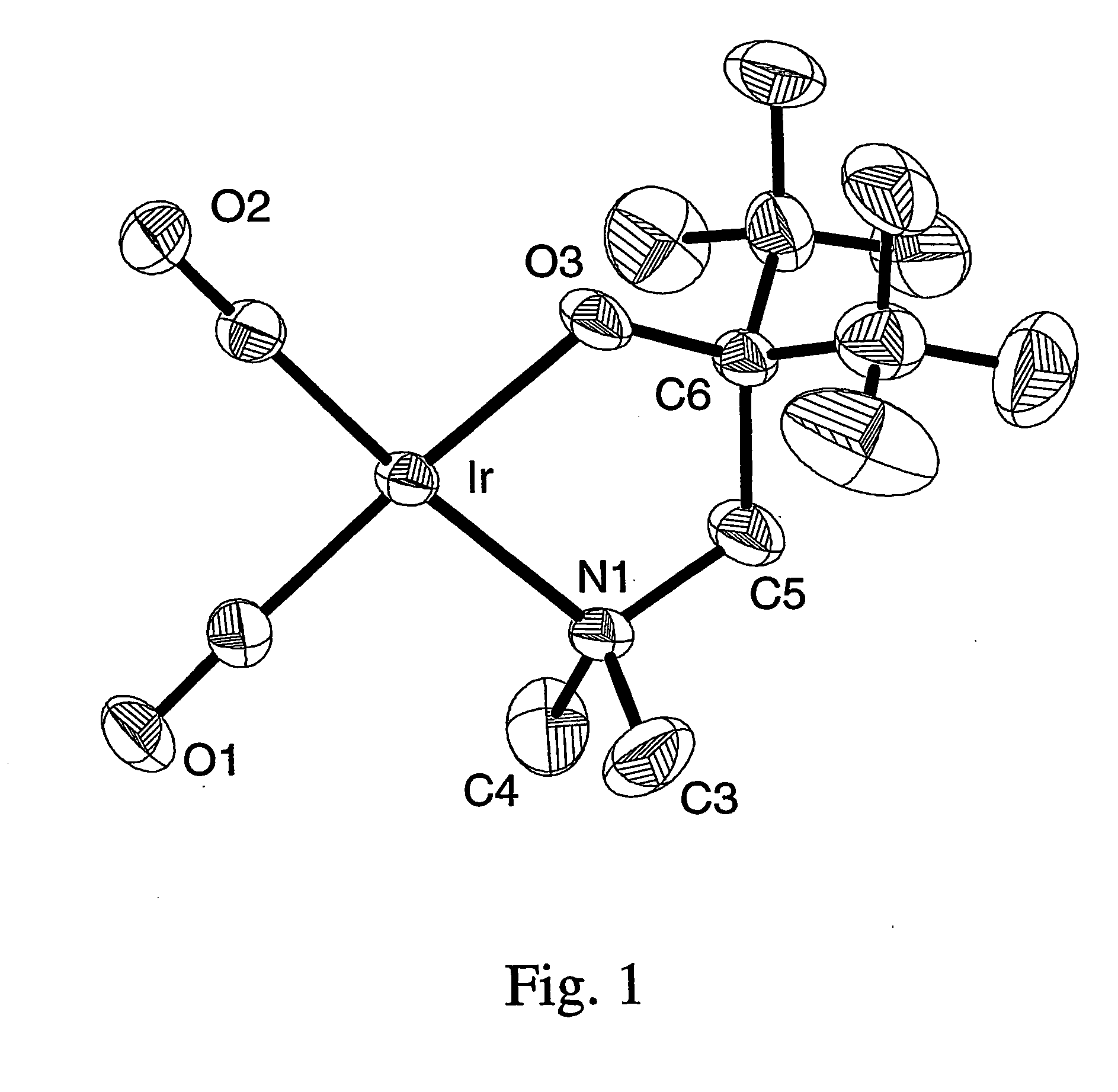

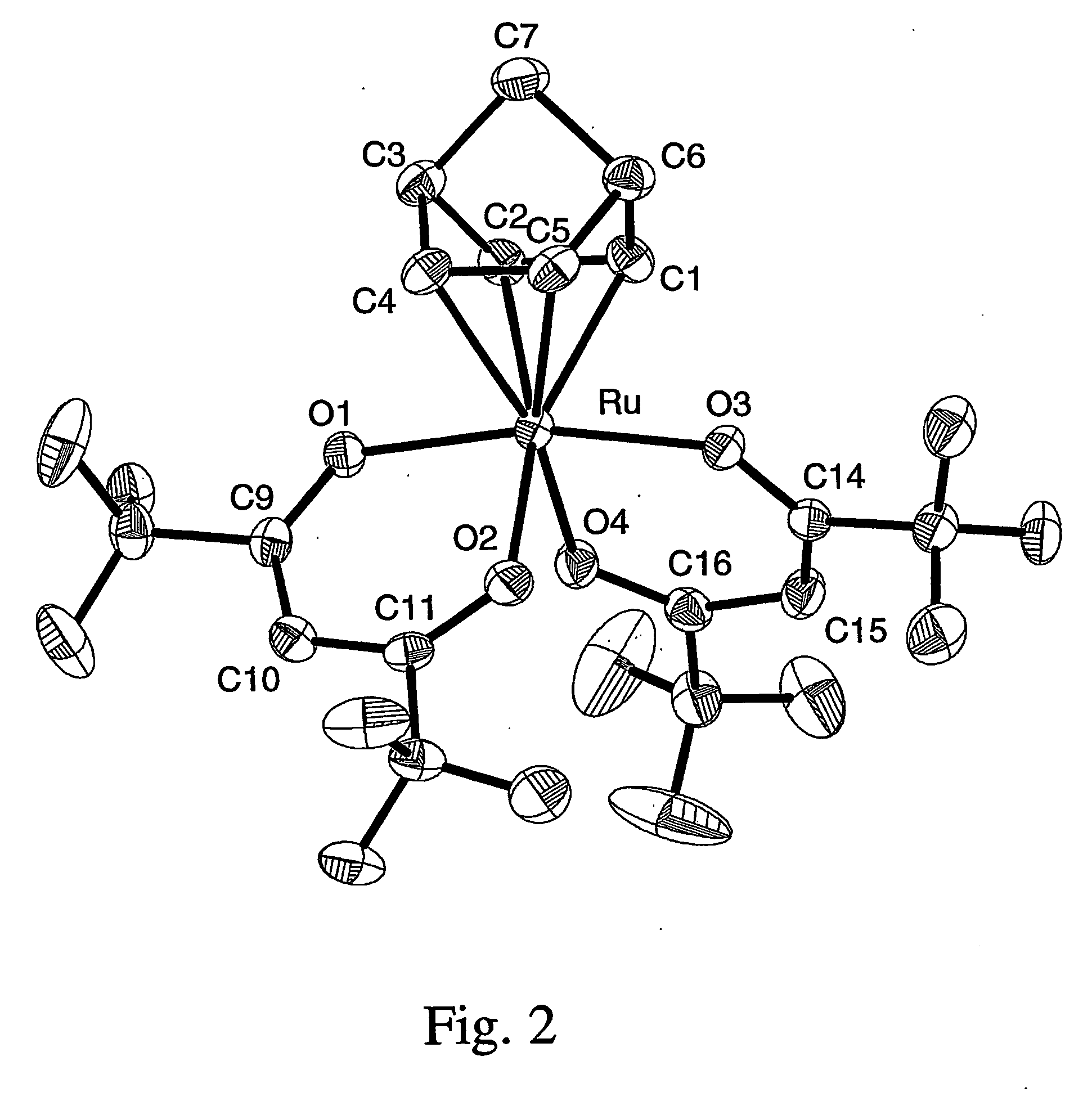

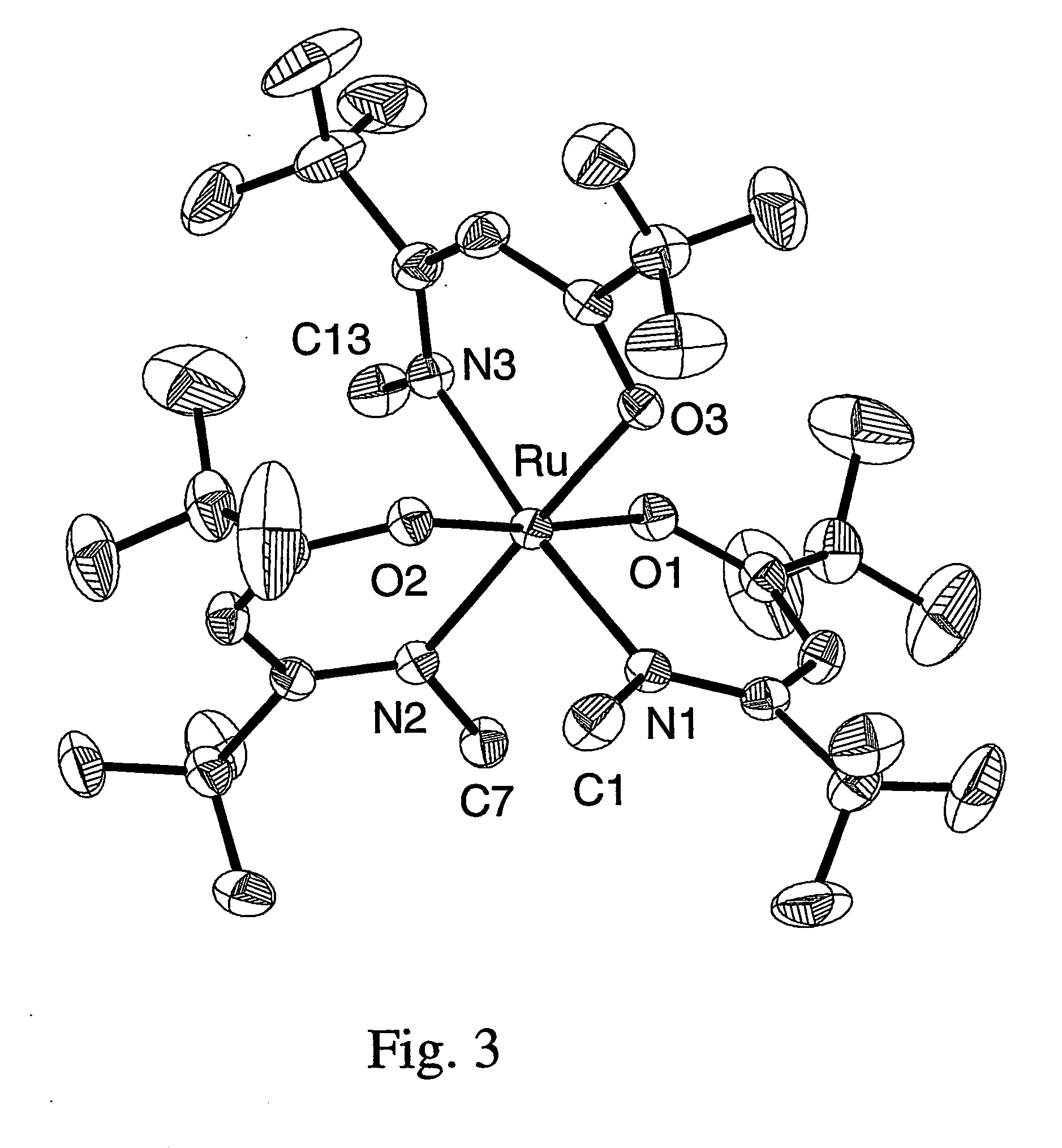

Volatile noble metal organometallic complexes

InactiveUS20050033075A1Reduce Van der Waals interactionBoiling and sublimation temperatureFurnaces without endless coreRuthenium organic compoundsIridiumIodide

A series of noble metal organometallic complexes of the general formula (I): MLaXb(FBC)c, wherein M is a noble metal such as iridium, ruthenium or osmium, and L is a neutral ligand such as carbonyl, alkene or diene; X is an anionic ligand such as chloride, bromide, iodide and trifluoroacetate group; and FBC is a fluorinated bidentate chelate ligand such as beta diketonate, beta-ketoiminate, amino-alcoholate and amino-alcoholate ligand, wherein a is an integer of from zero (0) to three (3), b is an integer of from zero (0) to one (1) and c is an 10 integer of from one (1) to three (3). The resulting noble metal complexes possess enhanced volatility and thermal stability characteristics, and are suitable for chemical vapor deposition(CVD) applications. The corresponding noble metal complex is formed by treatment of the FBC ligand with a less volatile metal halide. Also disclosed are CVD methods for using the noble metal complexes as source reagents for deposition of noble metal-containing films such as Ir, Ru and Os, or even metal oxide film materials IrO2, OsO2 and RuO2.

Owner:NATIONAL TSING HUA UNIVERSITY +1

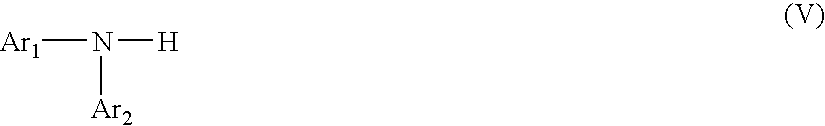

Method for producing aromatic amino compound

InactiveUS7250532B2High yieldEasy to eliminateOrganic compound preparationAmino compound preparationArylCompound a

A method for producing aromatic amino compound (V):by synthesizing intermediate compound (IV):by the reaction of compound (I): H2N—R1 with a mixture of halogenated aryl compounds (II): Ar1—X and (III): Ar2—X in the presence of a noble metal catalyst, followed by eliminating the substituent R1 from the nitrogen atom in compound (IV) under an acidic condition or an alkaline condition or by addition of a reducing agent or an oxidizing agent. (R1: a substituent having 2 to 50 carbon atoms; Ar1 and Ar2: a substituted or unsubstituted hydrocarbon group or heterocyclic group having 6 to 50 carbon atoms and the same with or different from each other; and X: a halogen group). The aromatic amino compound useful as the charge transporting material can be produced efficiently at a great yield without using highly toxic raw materials.

Owner:IDEMITSU KOSAN CO LTD

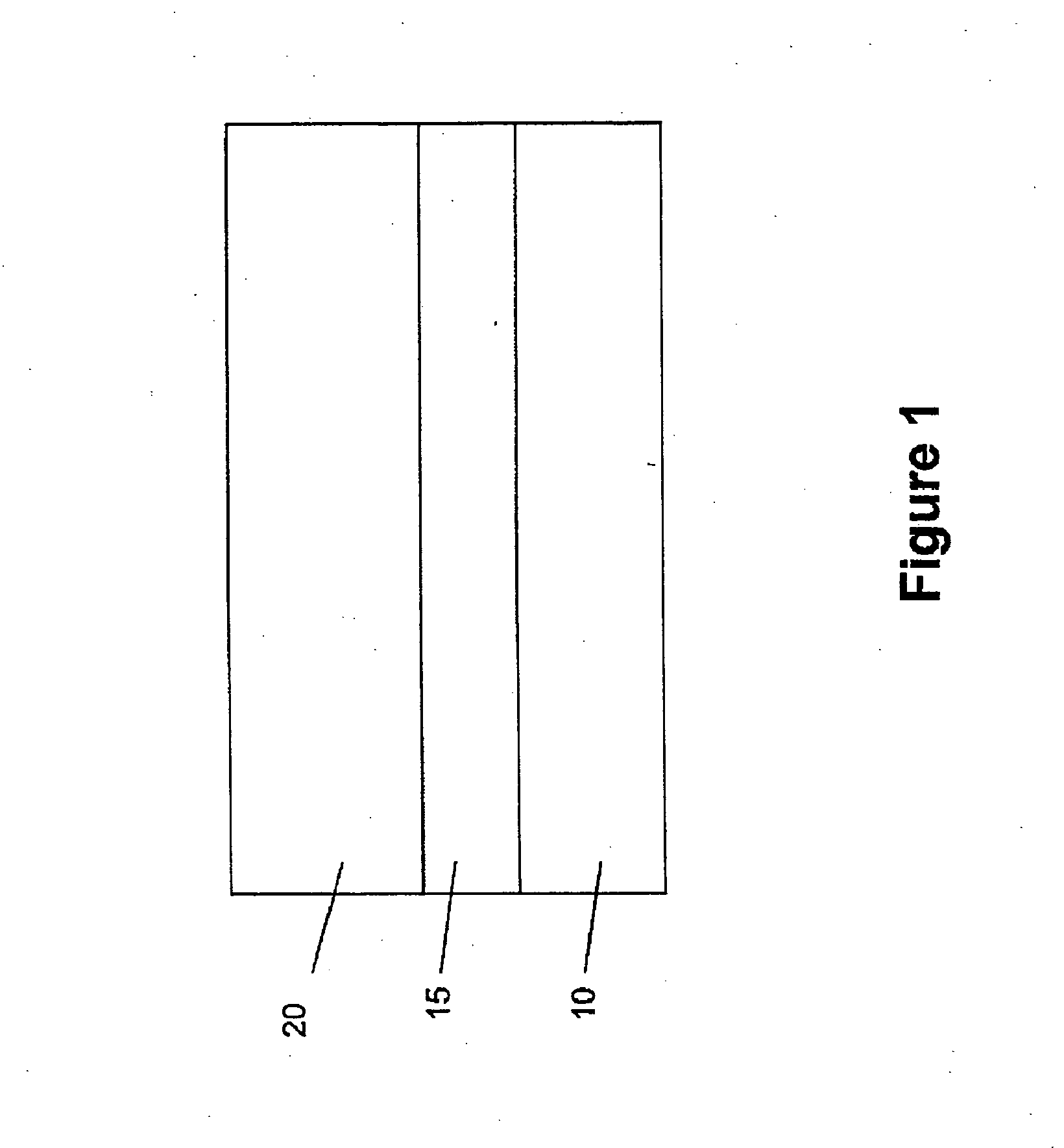

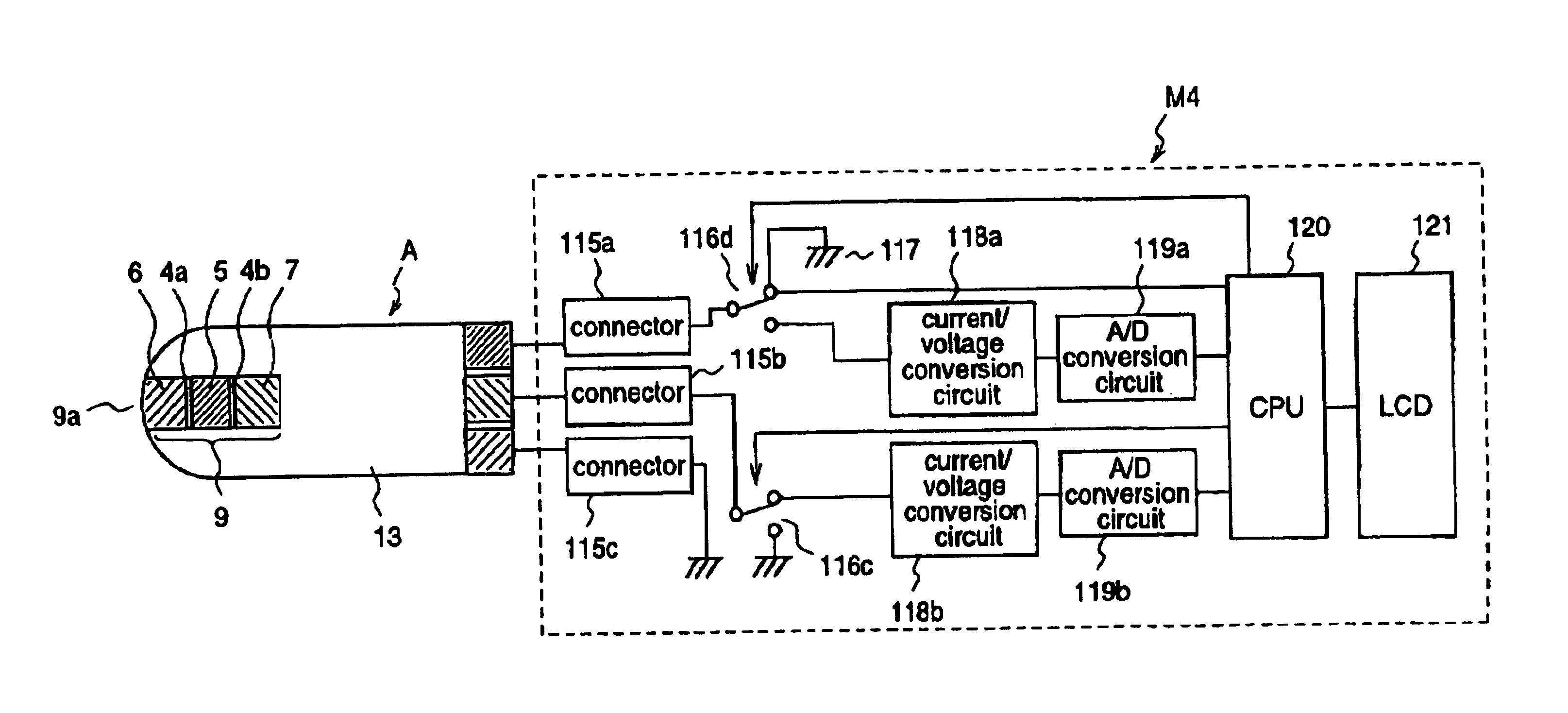

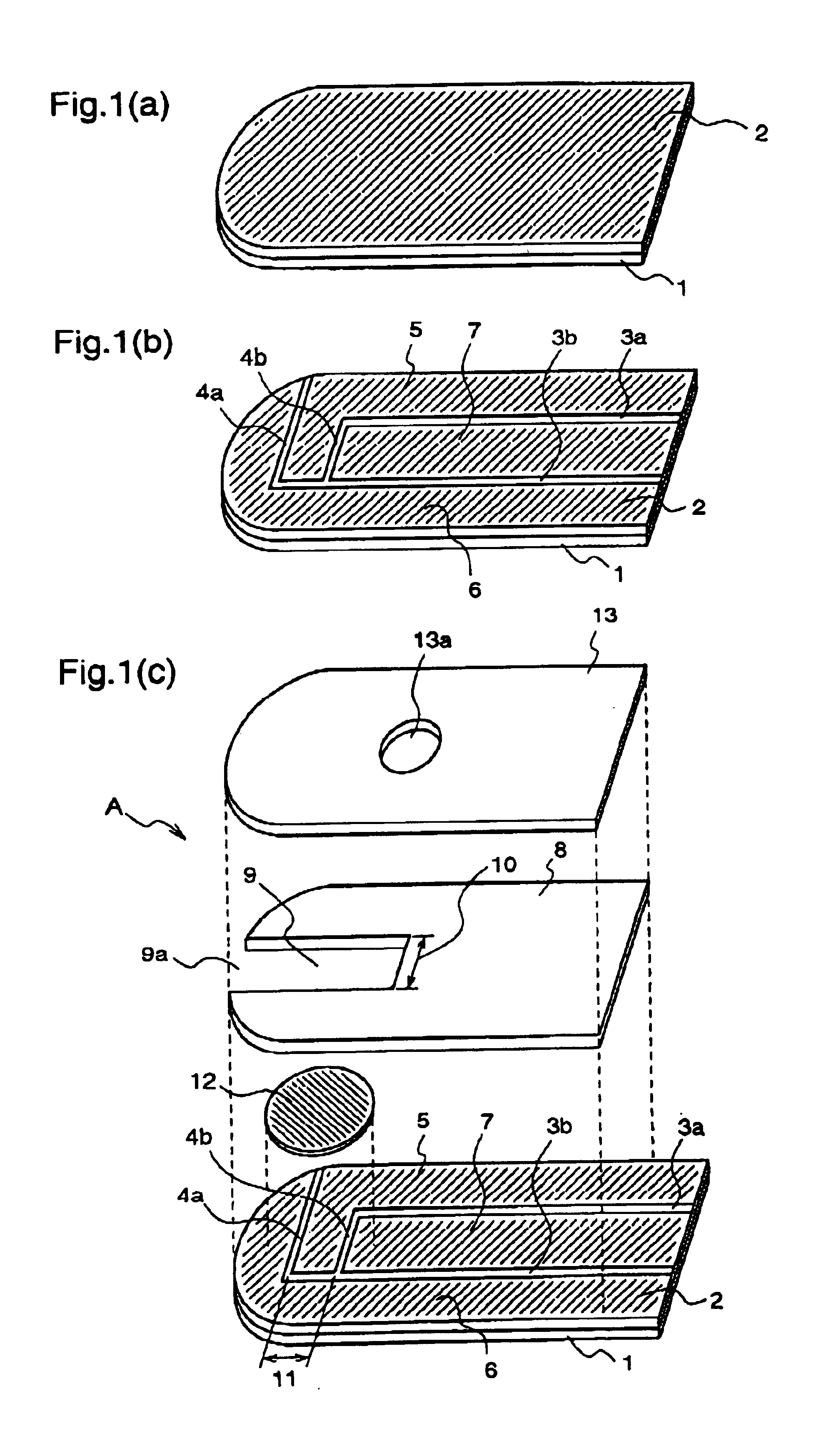

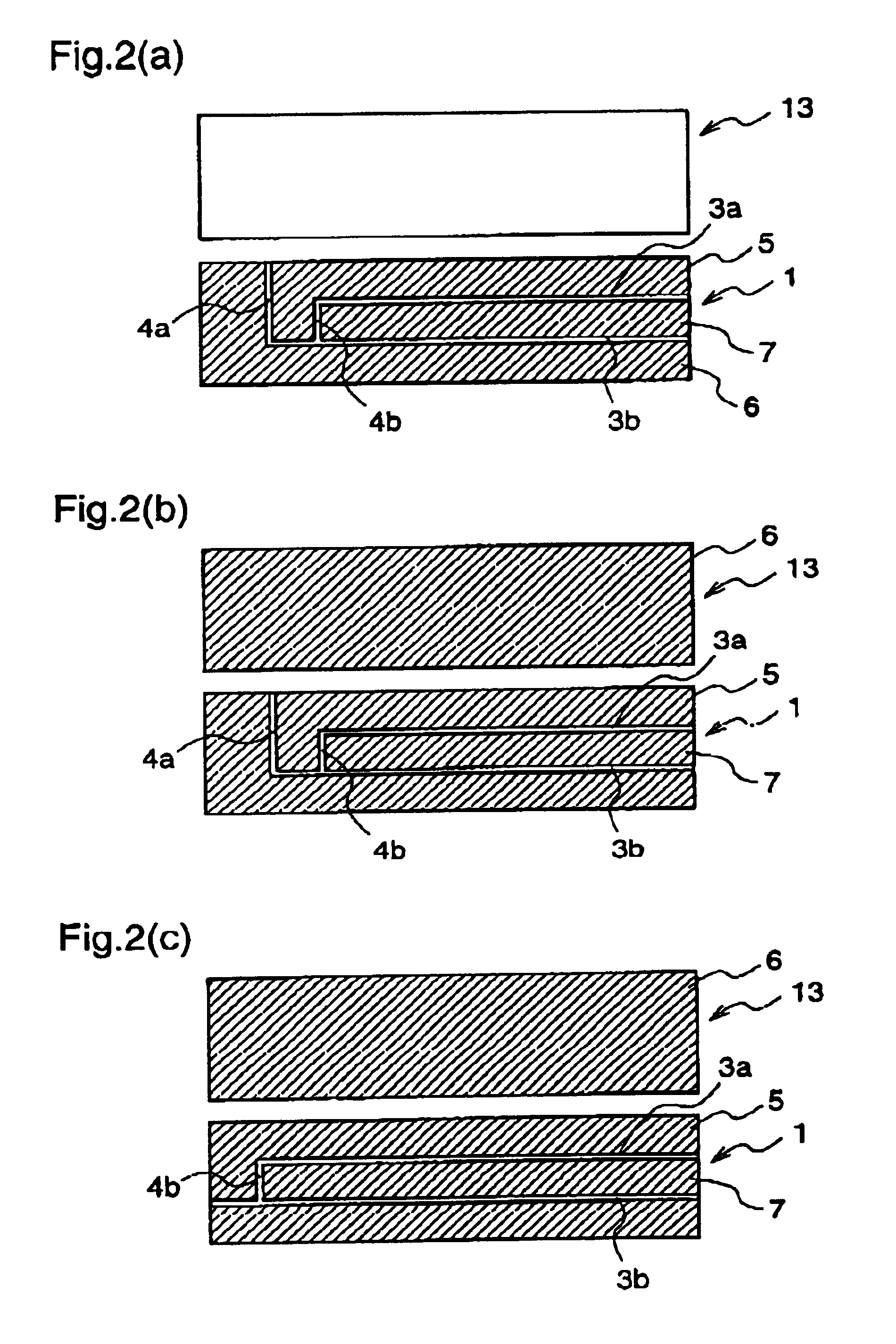

Biosensor, method of forming thin-film electrode, and method and apparatus for quantitative determination

InactiveUS6875327B1Improve convenienceImprove securityImmobilised enzymesBioreactor/fermenter combinationsThin film electrodeQuantitative determination

The invention provides a biosensor comprising a support; a conductive layer composed of a electrical conductive material such as a noble metal, for example gold or palladium, and carbon; slits parallel to and perpendicular to the side of the support; working, counter, and detecting electrodes; a spacer which covers the working, counter, and detecting electrodes on the support; a rectangular cutout in the spacer forming a specimen supply path; an inlet to the specimen supply path; a reagent layer formed by applying a reagent containing an enzyme to the working, counter, and detecting electrodes, which are exposed through the cutout in the spacer; and a cover over the spacer. The biosensor can be formed by a simple method, and provides a uniform reagent layer on the electrodes regardless of the reagent composition.

Owner:PHC HLDG CORP

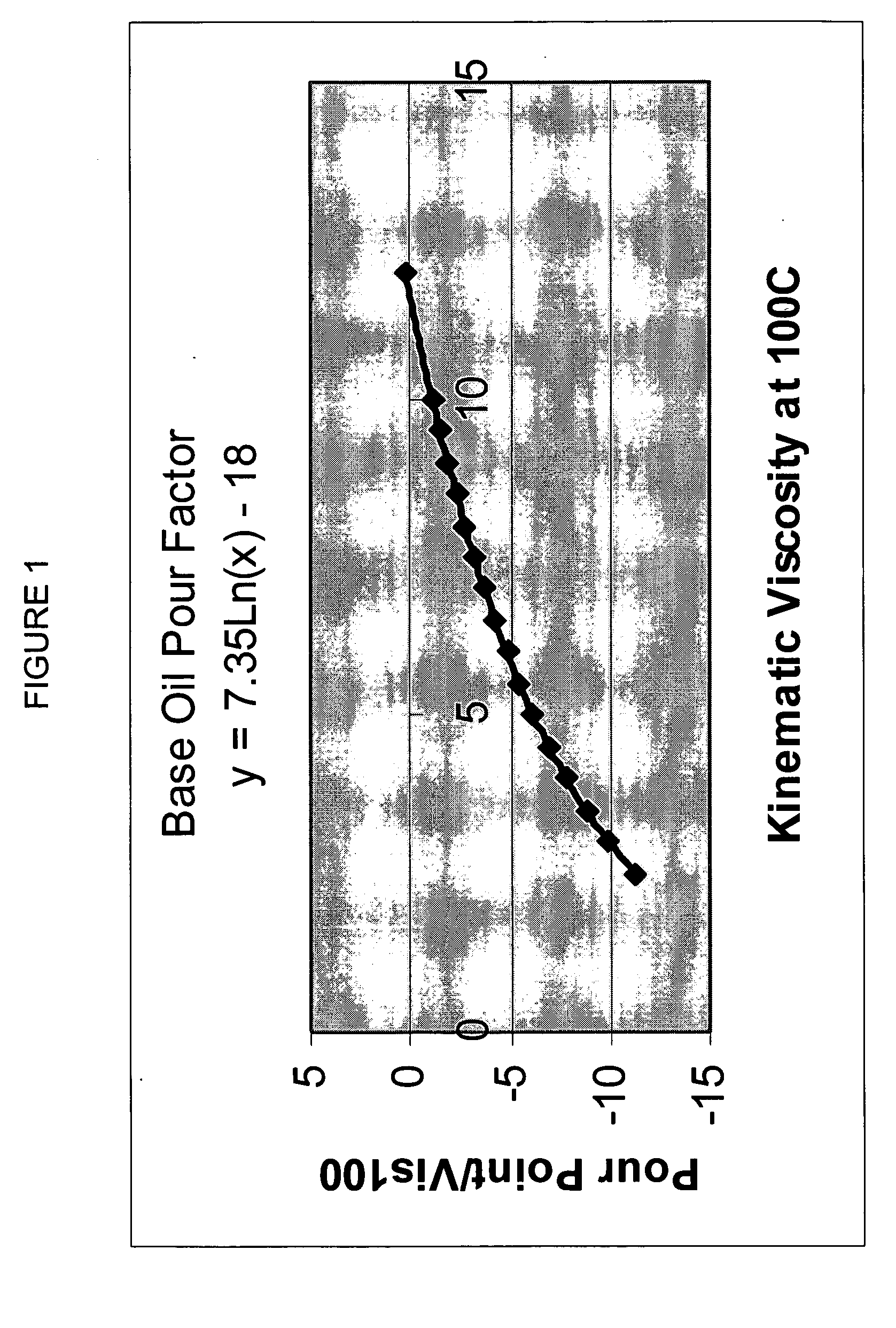

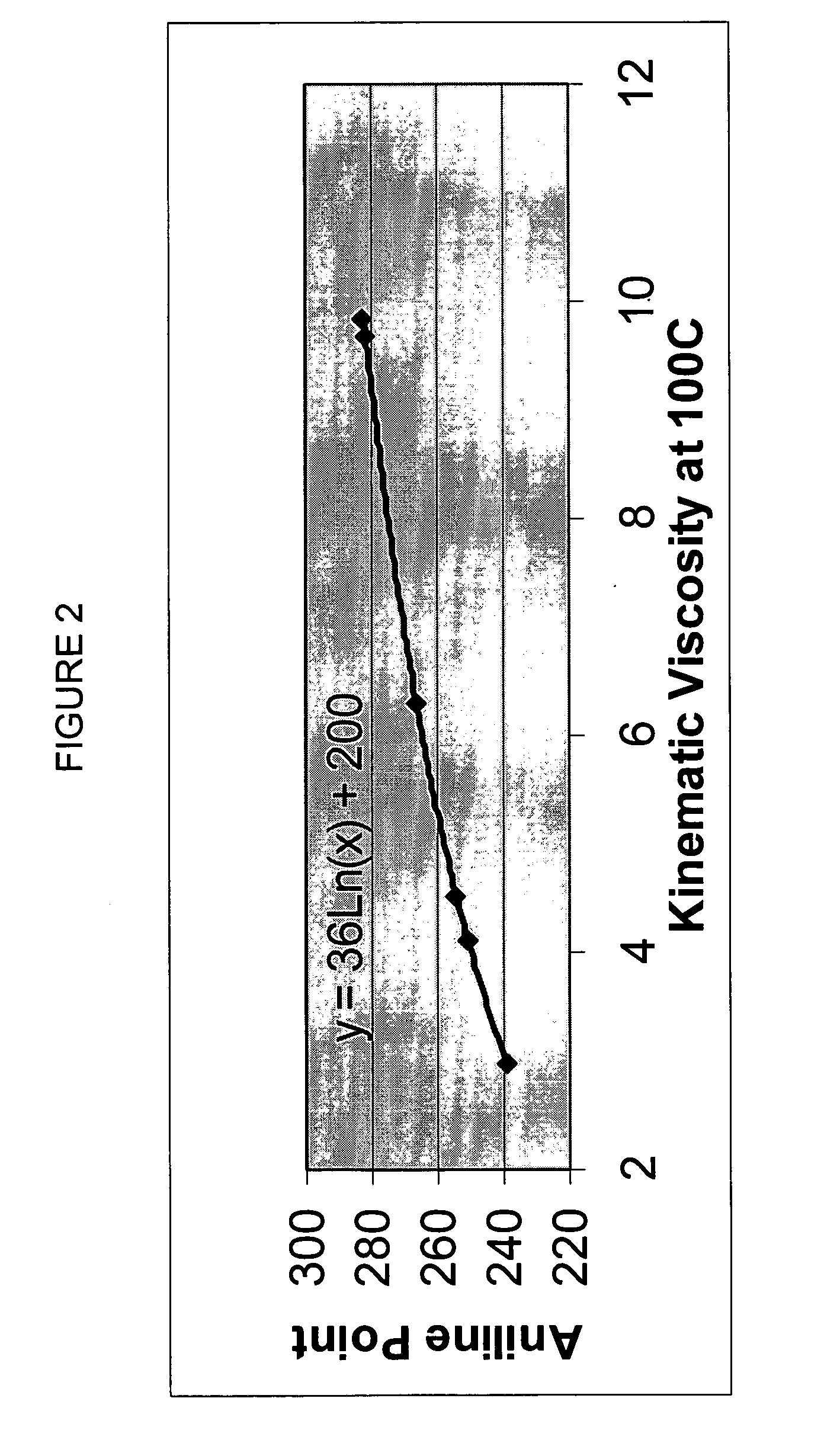

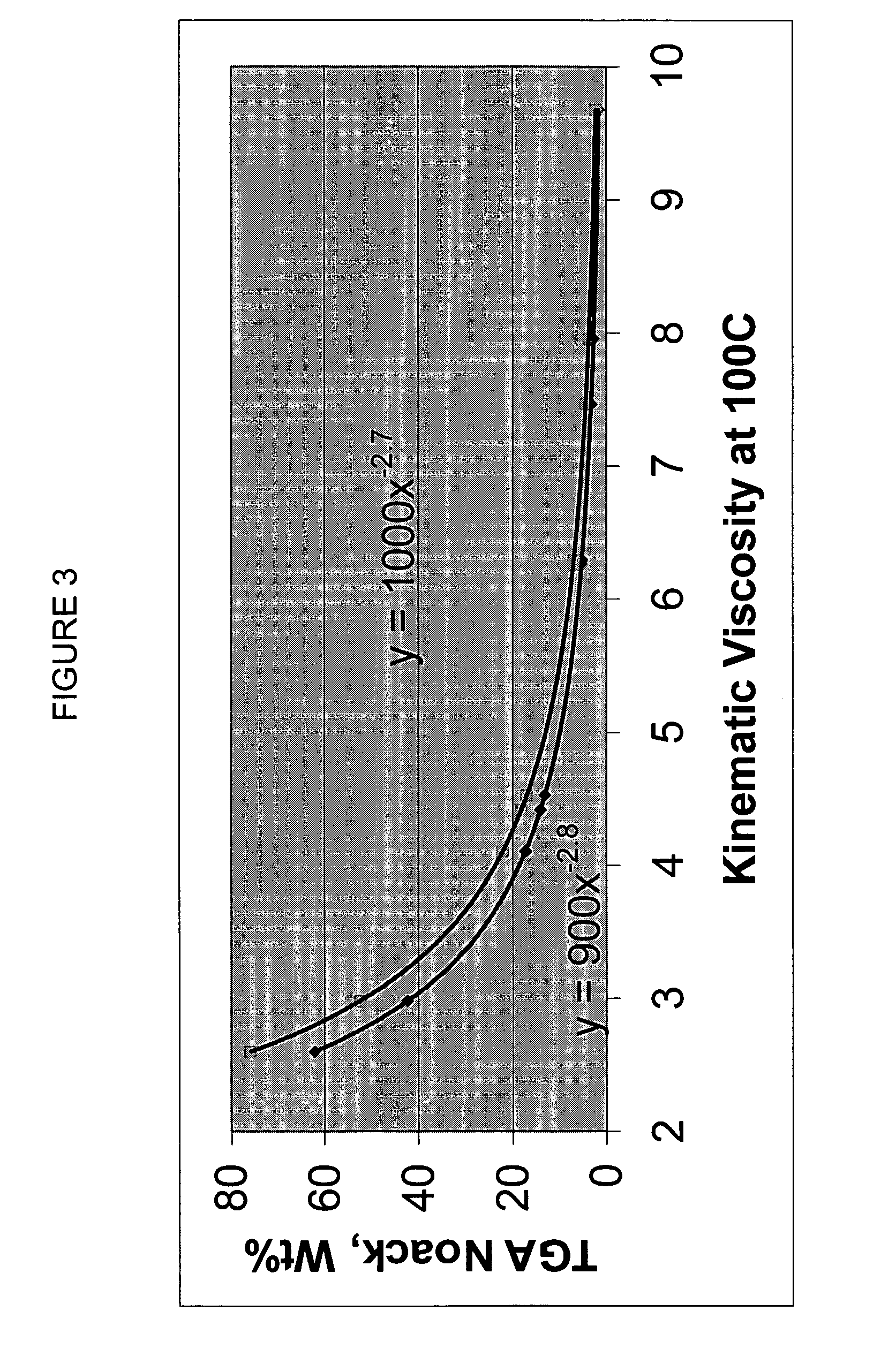

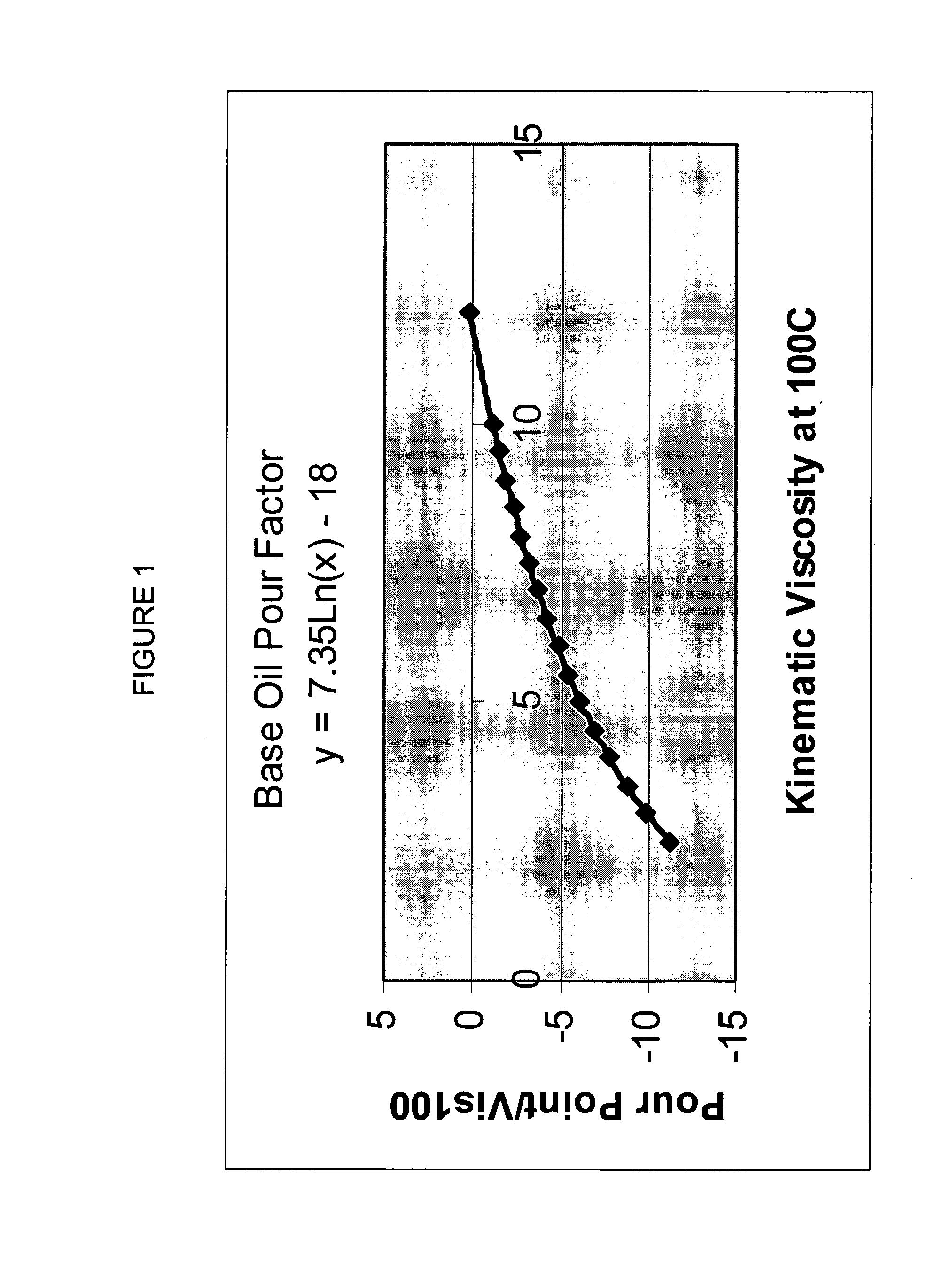

Process for manufacturing lubricating base oil with high monocycloparaffins and low multicycloparaffins

InactiveUS20050133409A1Improve Oxidation StabilityHigh viscosity indexTreatment with hydrotreatment processesAdditivesSyngasMolecular sieve

A process for manufacturing a lubricating base oil by: a) performing Fischer-Tropsch synthesis on syngas to provide a product stream; b) isolating from said product stream a substantially paraffinic wax feed having less than about 30 ppm total nitrogen and sulfur, and less than about 1 wt % oxygen; c) dewaxing said feed by hydroisomerization dewaxing using a shape selective intermediate pore size molecular sieve comprising a noble metal hydrogenation component, wherein the hydroisomerization temperature is between about 600° F. (315° C.) and about 750° F. (399° C.), to produce an is dimerized oil; and d) hydrofinishing said isomerized oil to produce a lubricating base oil having specific desired properties.

Owner:CHEVROU USA INC

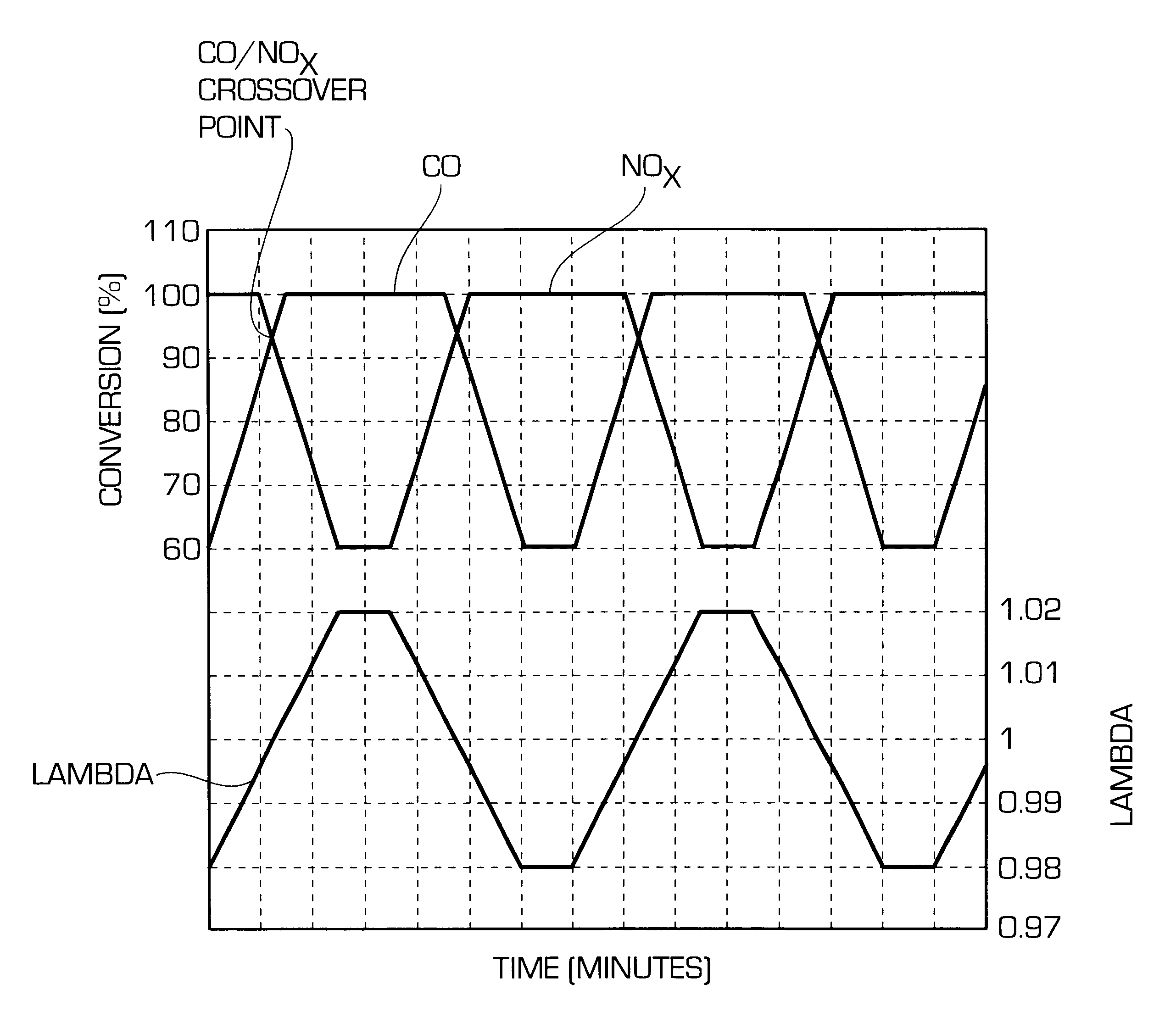

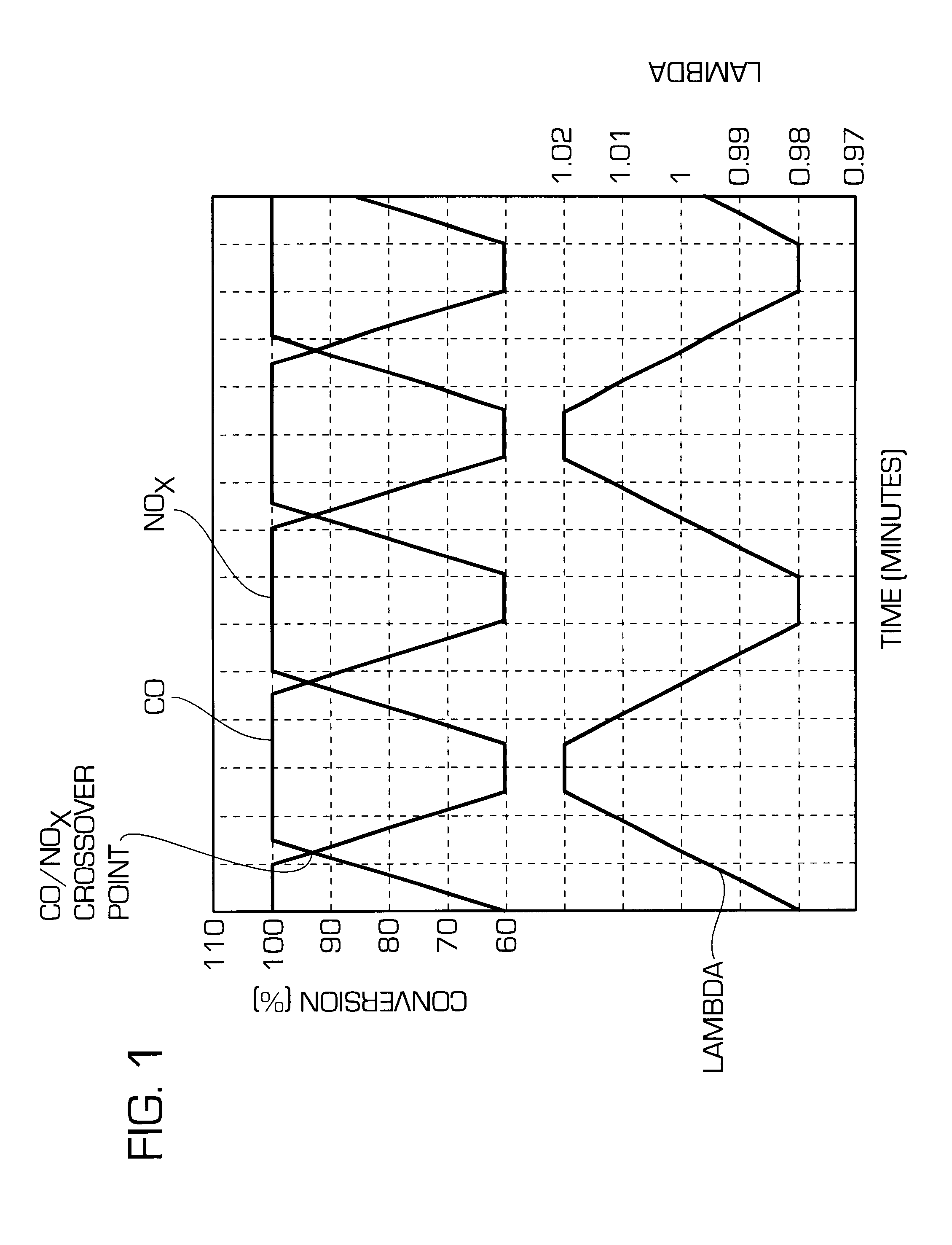

Layered noble metal-containing exhaust gas catalyst and its preparation

InactiveUS6294140B1Shorten recovery timeImprove conversion efficiencyOrganic chemistryNitrogen compoundsCerium(IV) oxideEngineering

A catalyst for treating exhaust gas from an internal combustion engine includes a carrier body coated with an inner layer and an outer layer. The inner layer includes platinum deposited on a first support material and on a first oxygen storage component, and the outer layer includes platinum and rhodium deposited on a second support material and on a second oxygen storage component. The first and second support materials may be the same or different, and may be selected from the group of: silica, alumina, titania, zirconia, mixed oxides or mixtures thereof, and zirconia-rich zirconia / ceria mixed oxide. The first and second oxygen storage components may include ceria-rich ceria / zirconia mixed oxide compounds, optionally including praseodymia, yttria, neodymia, lanthana or mixtures thereof.

Owner:DMC2 DEGUSSA METALS +1

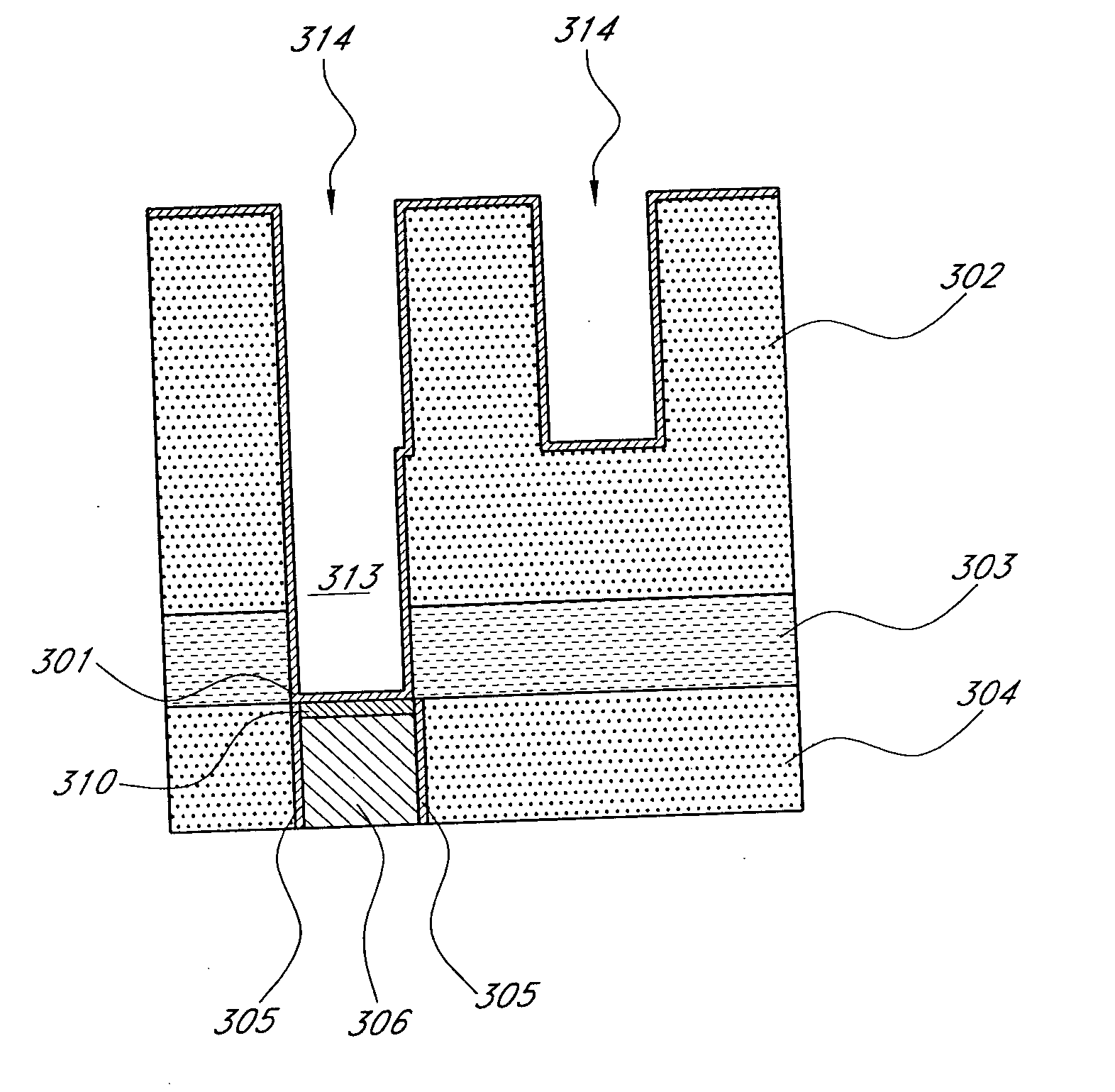

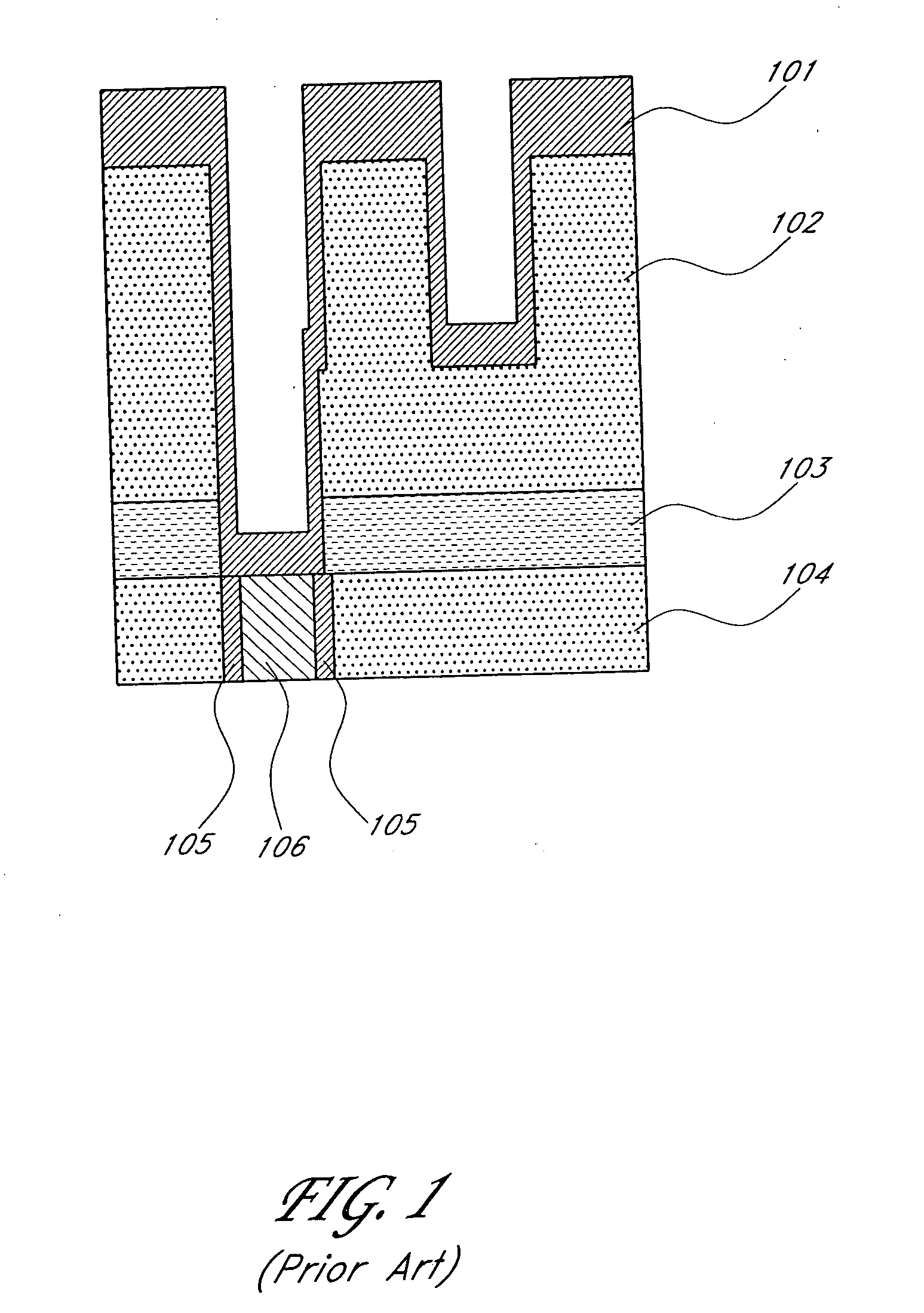

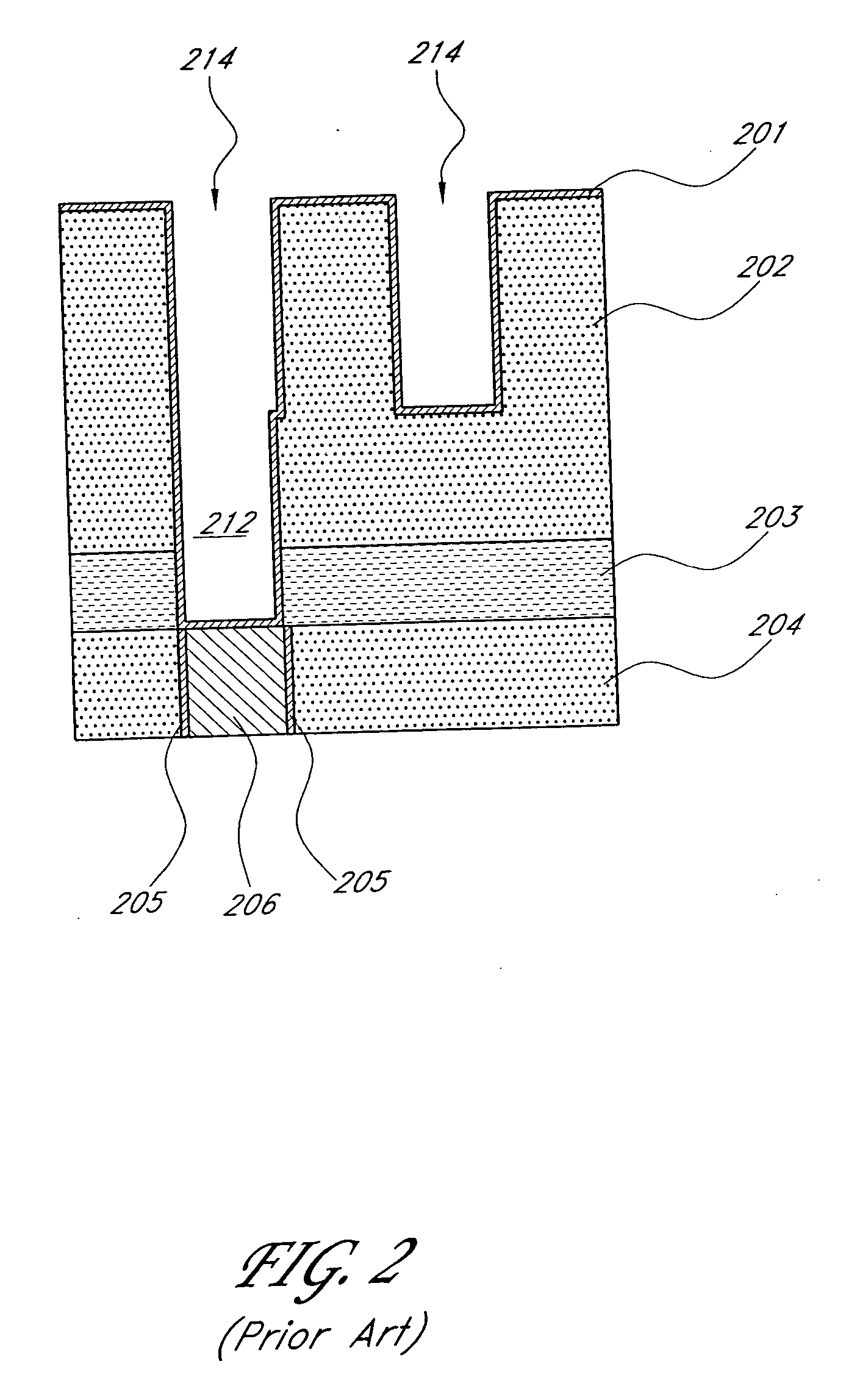

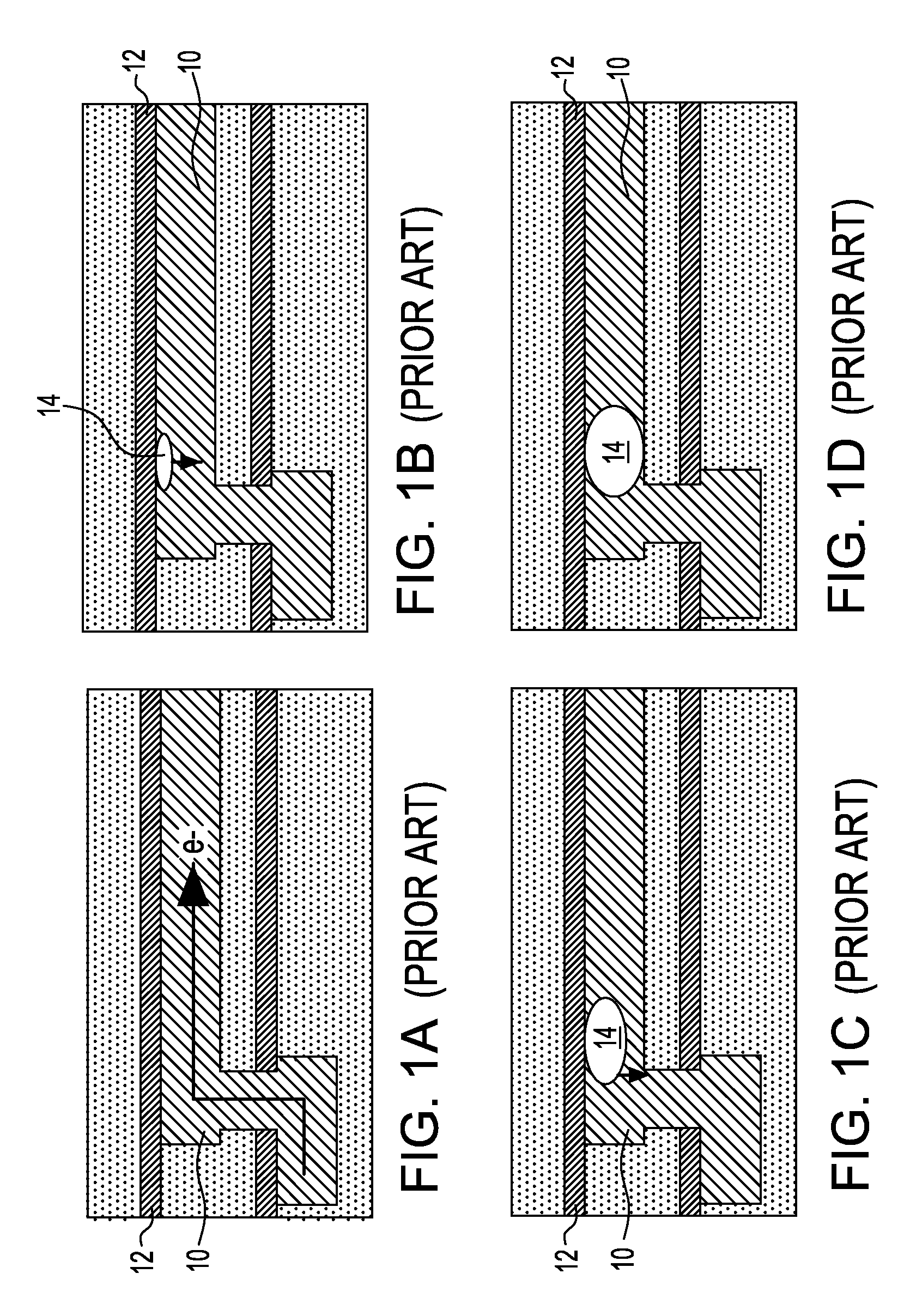

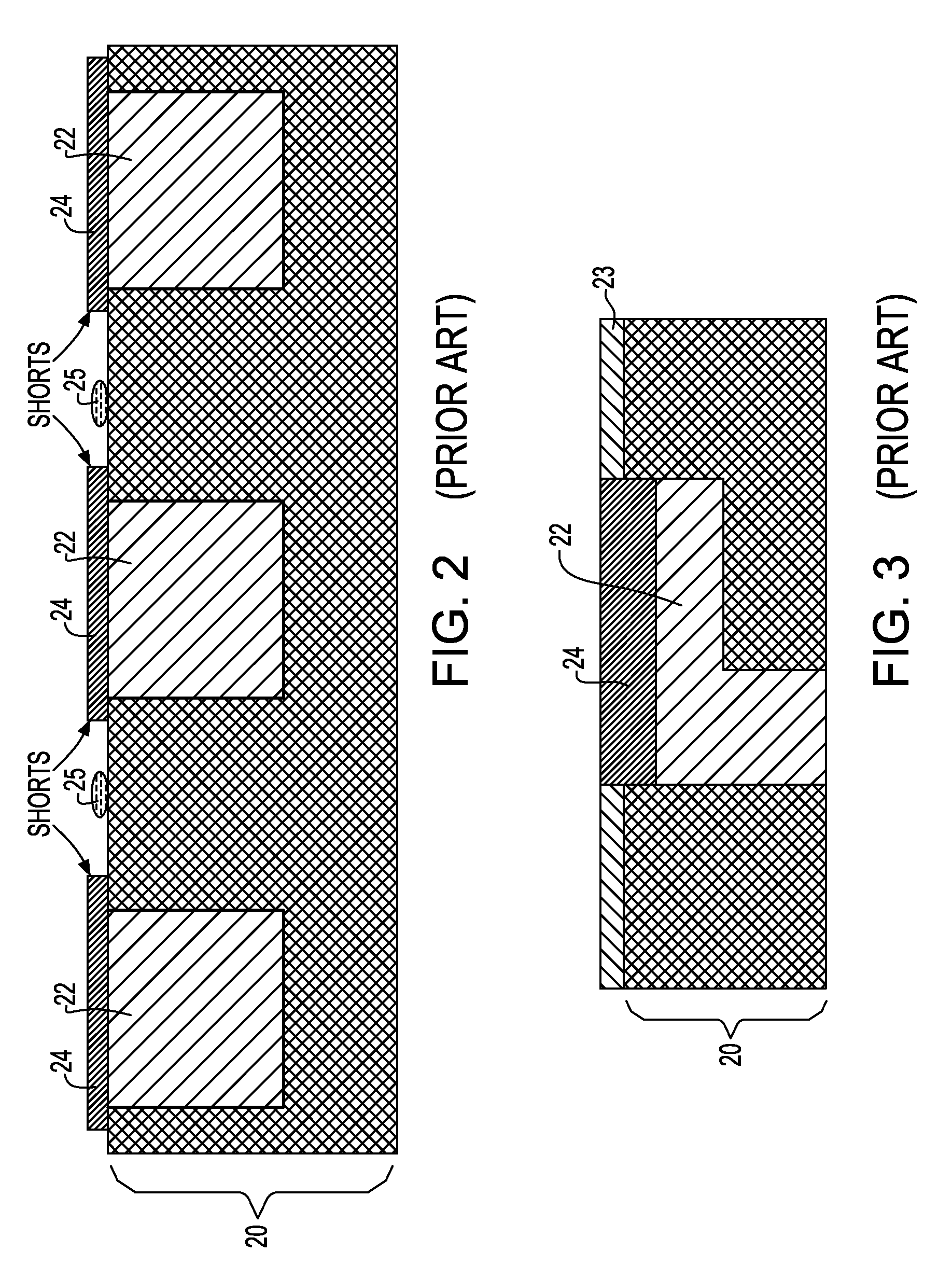

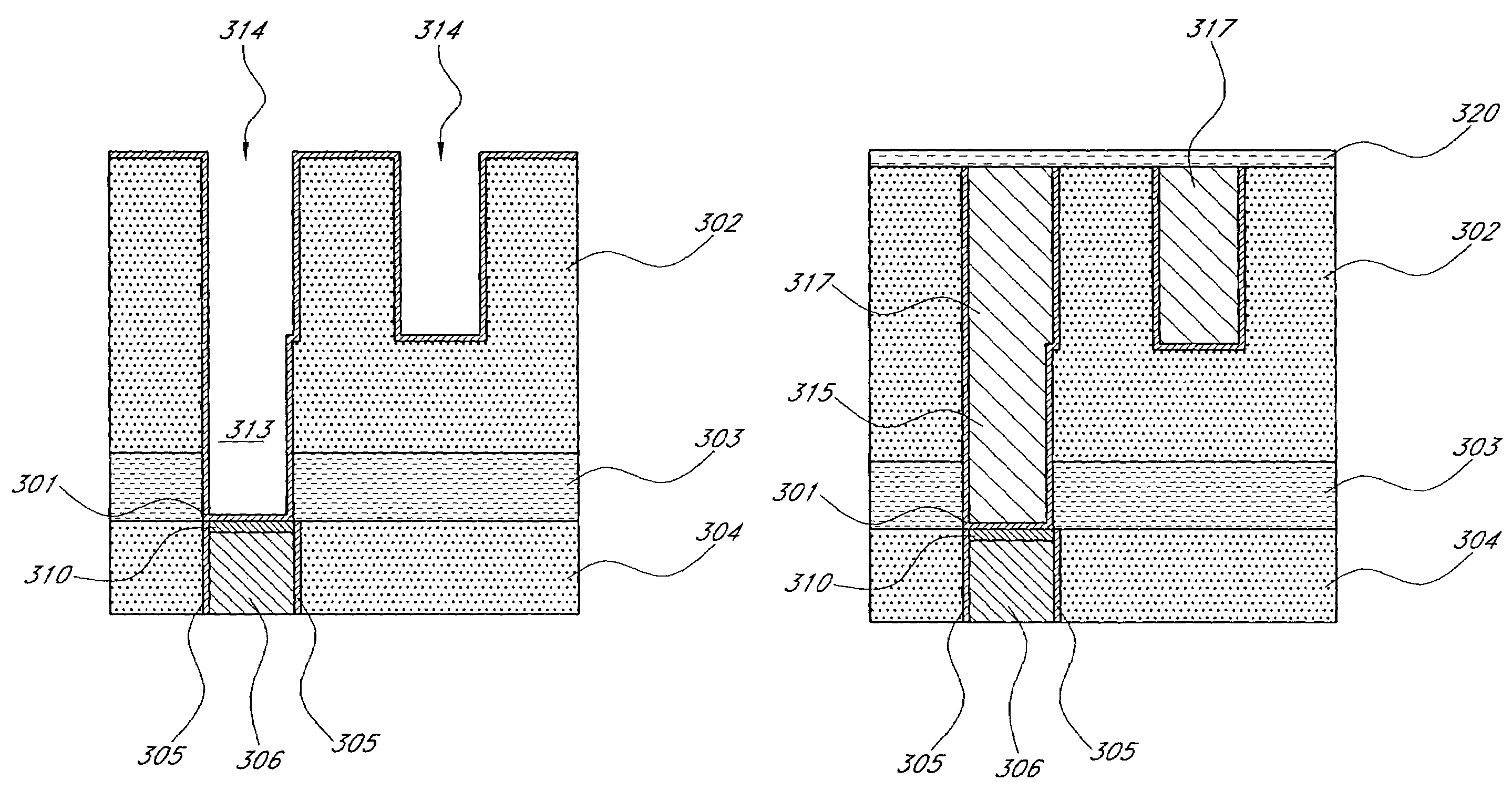

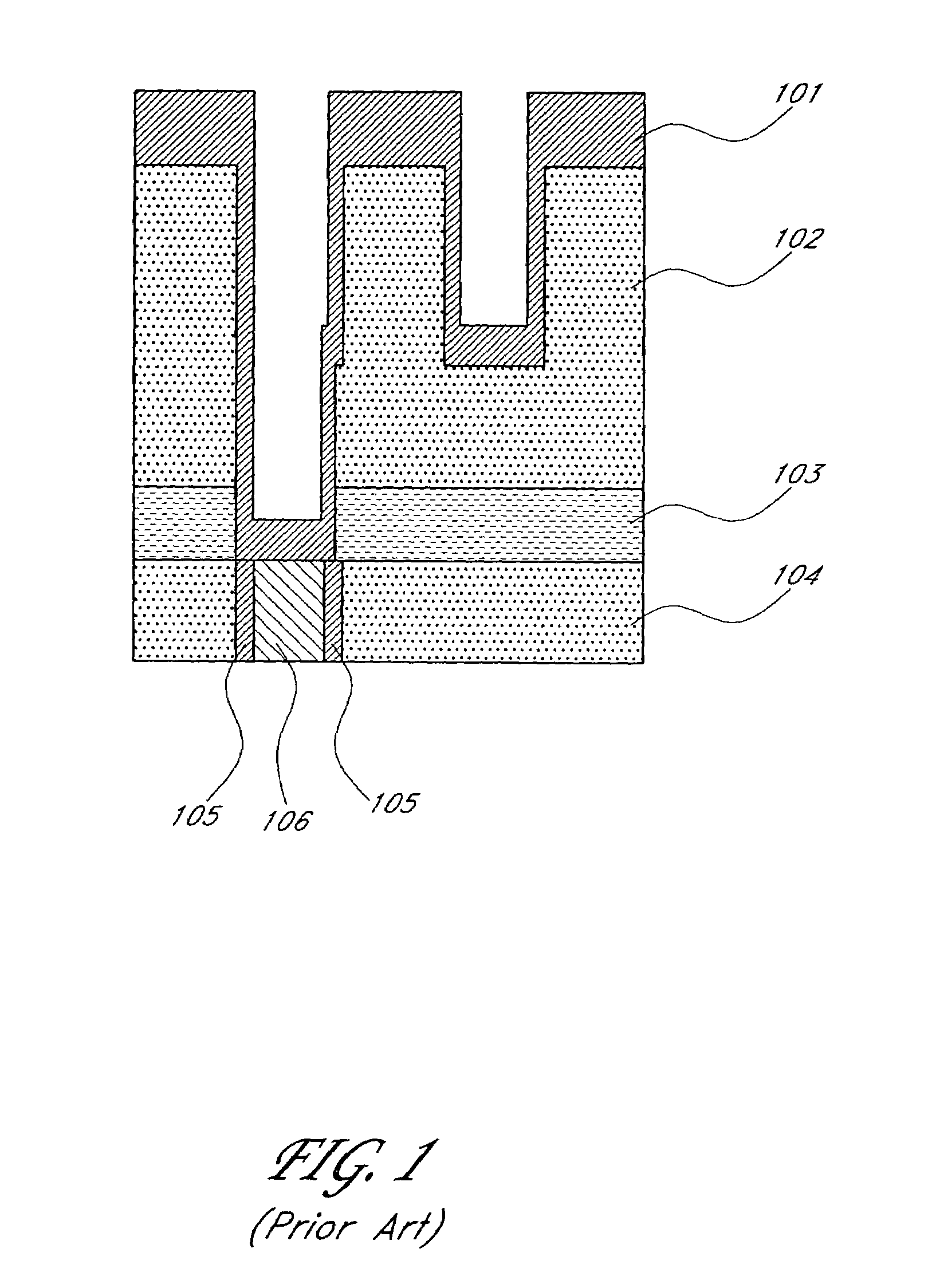

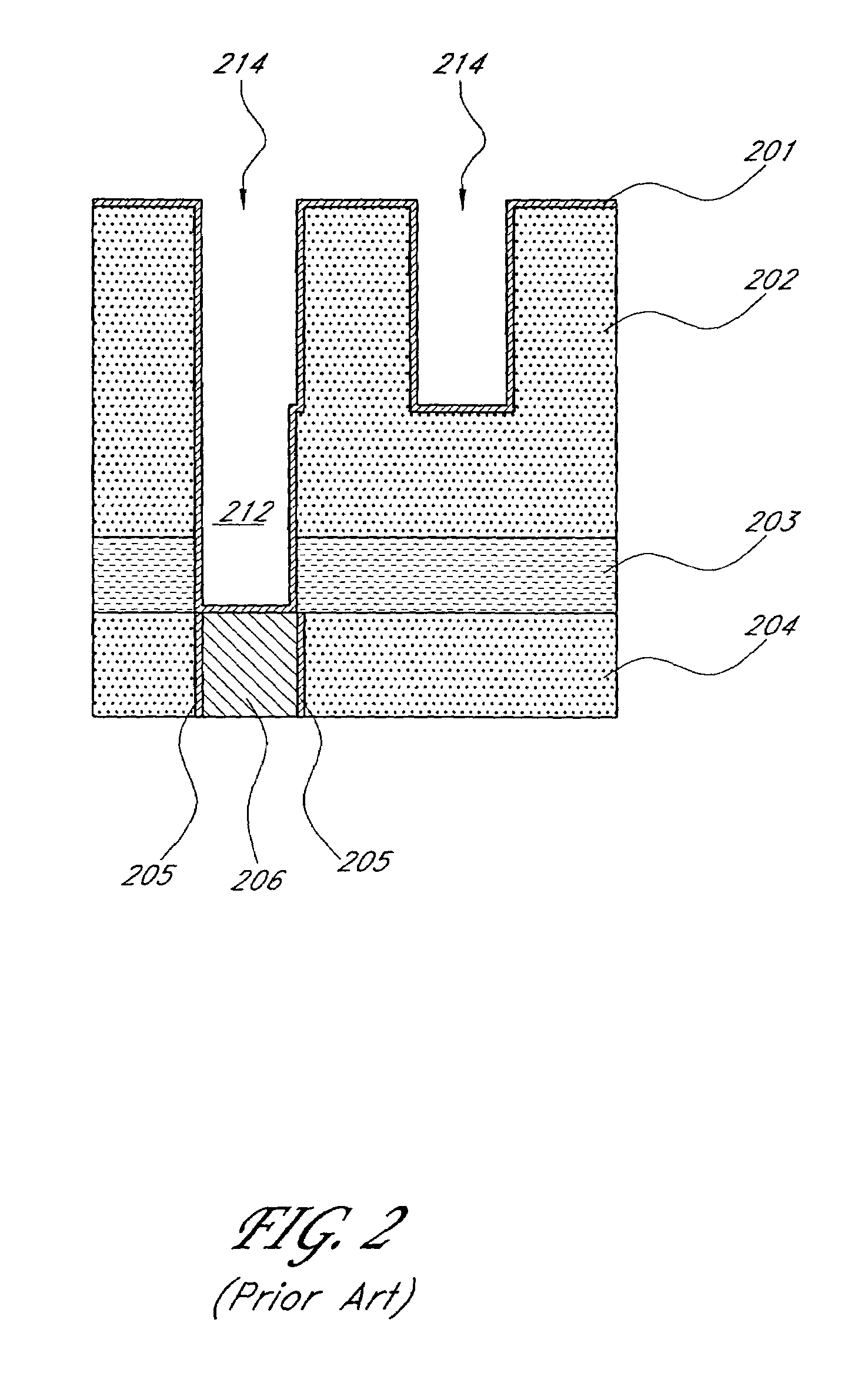

Selective formation of metal layers in an integrated circuit

ActiveUS20060121733A1Improve reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingCopper interconnectSelective deposition

A method for enhancing the reliability of copper interconnects and / or contacts, such as the bottom of vias exposing top surfaces of buried copper, or at the top of copper lines just after CMP. The method comprises contacting the exposed copper surface with a vapor phase compound of a noble metal and selectively forming a layer of the noble metal on the exposed copper surface, either by a copper replacement reaction or selective deposition (e.g., ALD or CVD) of the noble metal.

Owner:ASM JAPAN

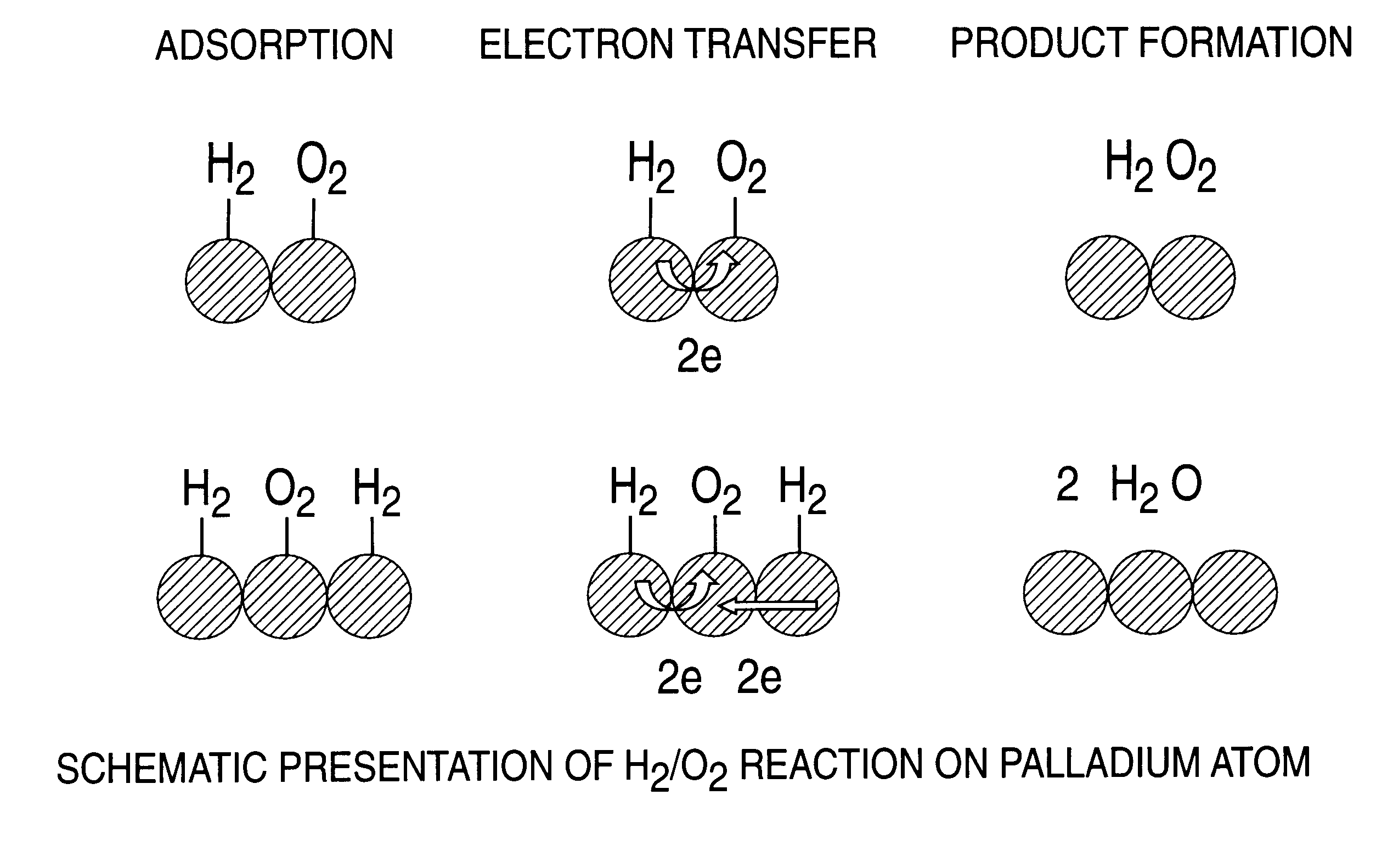

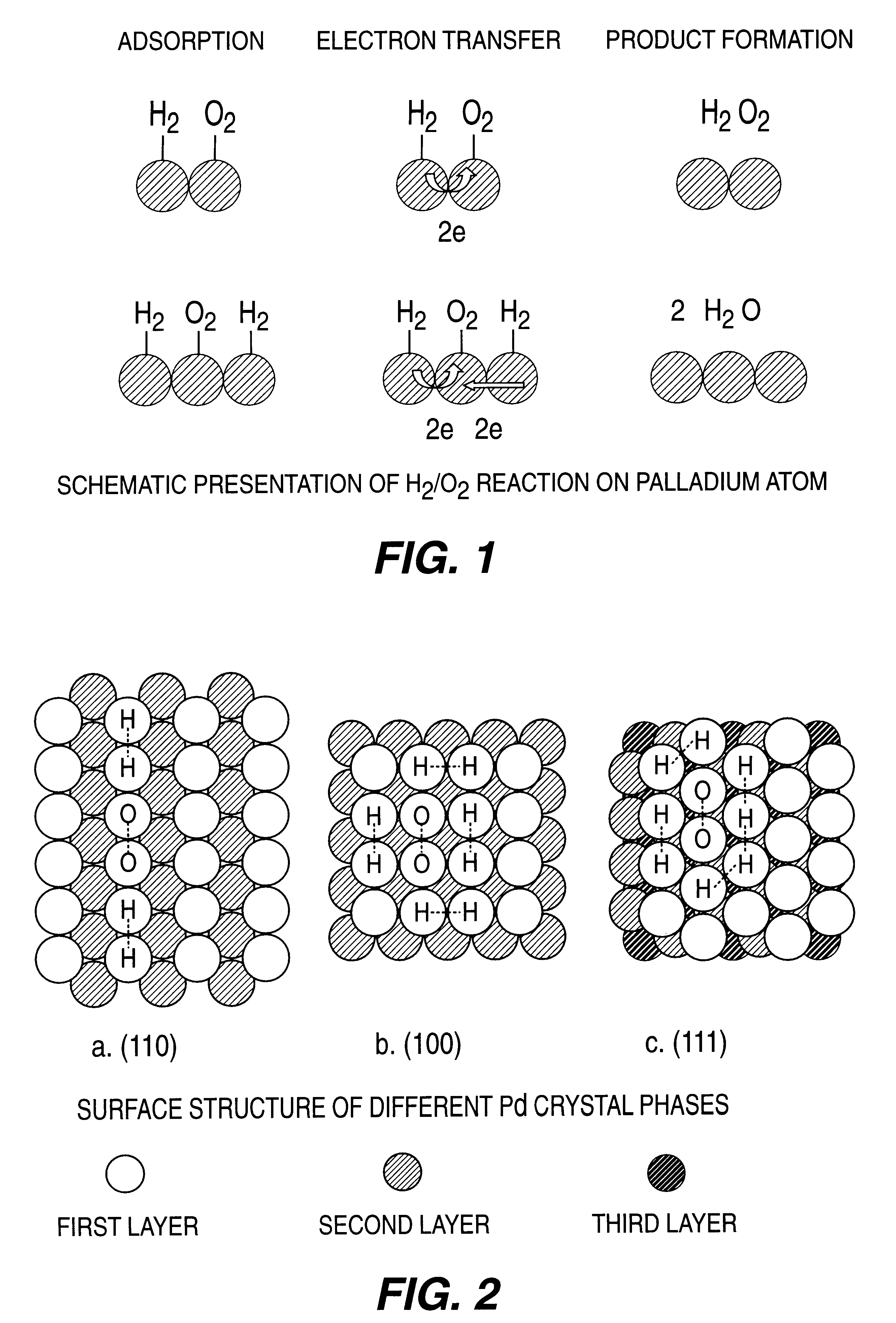

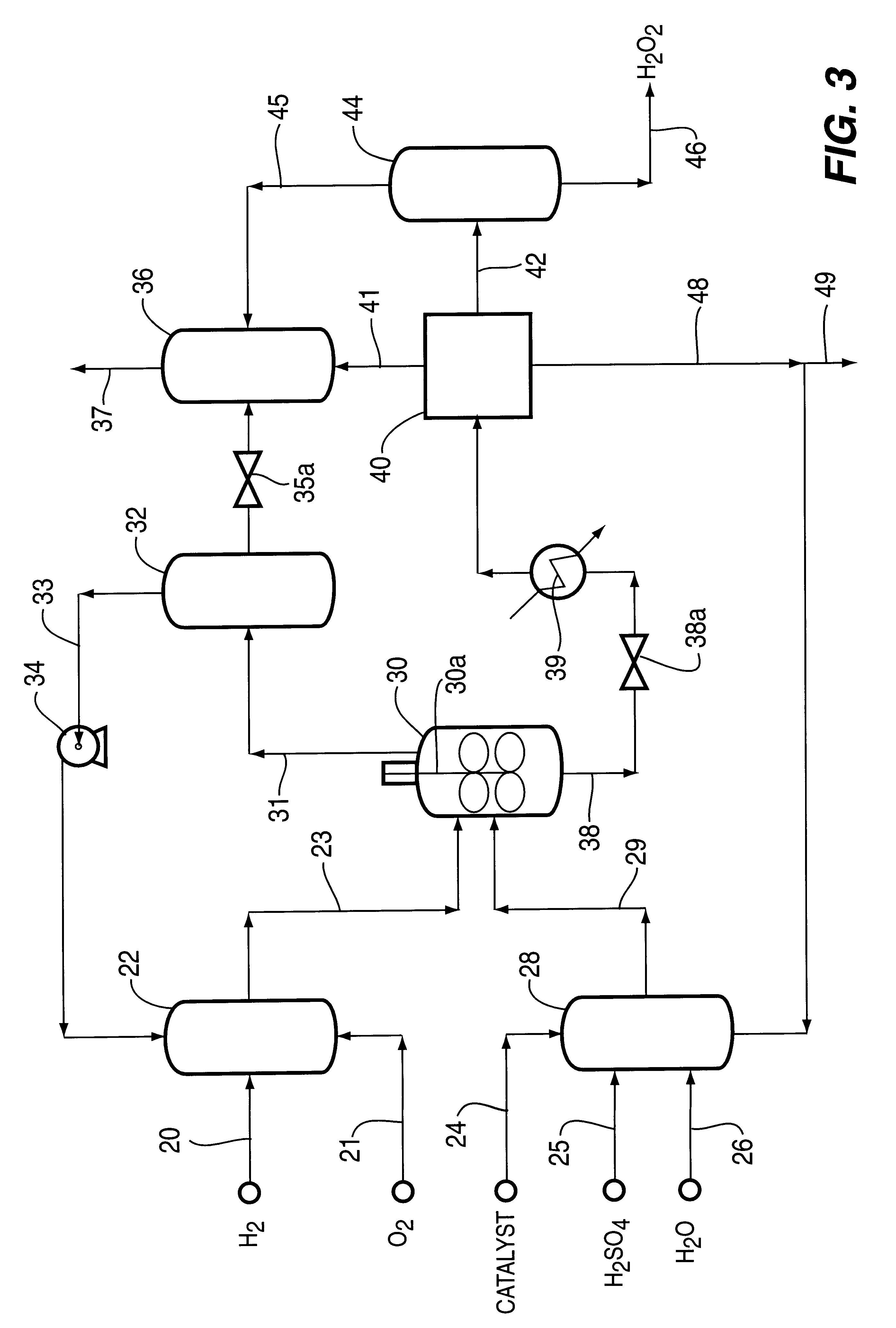

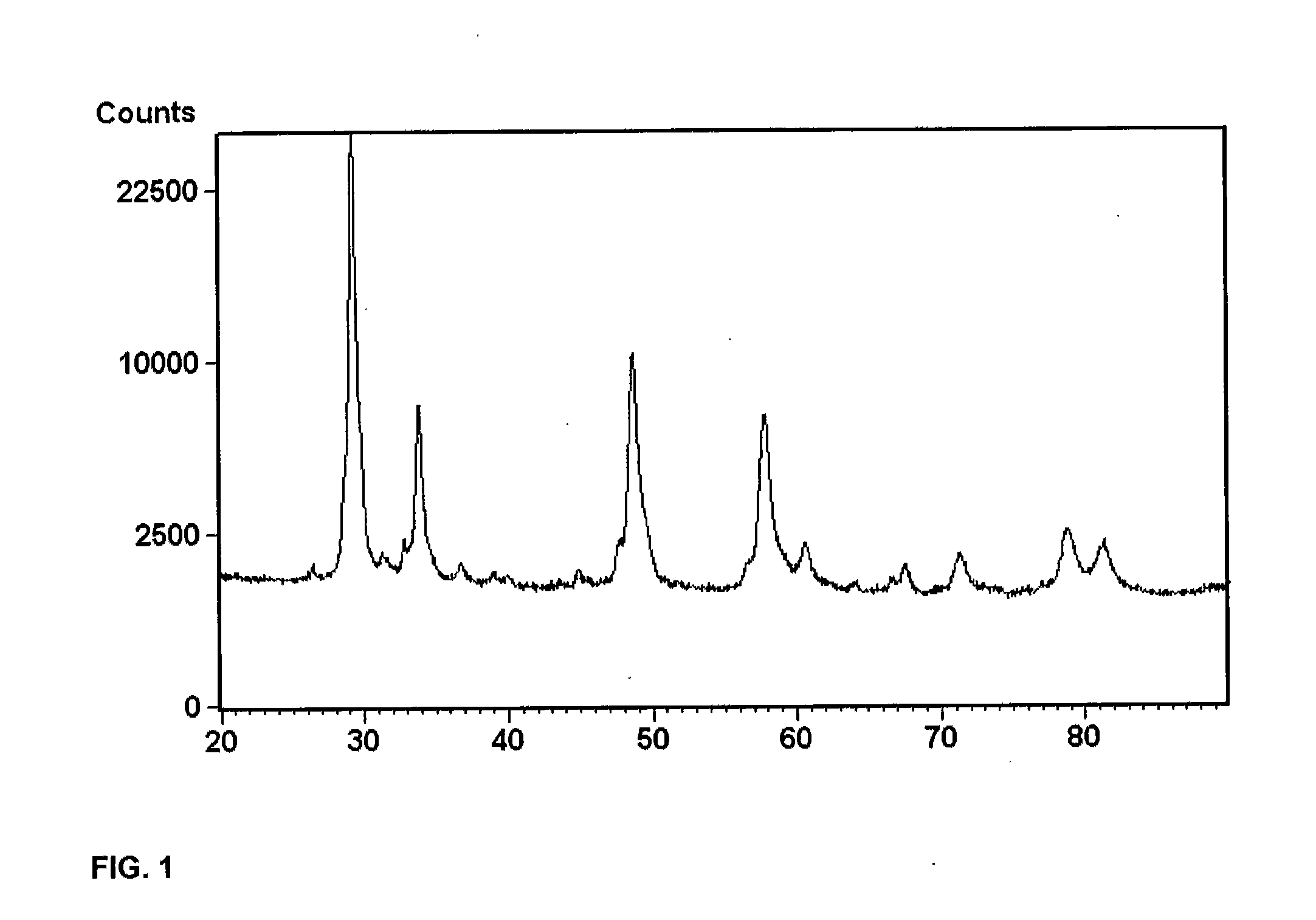

Catalyst and process for direct catalytic production of hydrogen peroxide, (H2O2)

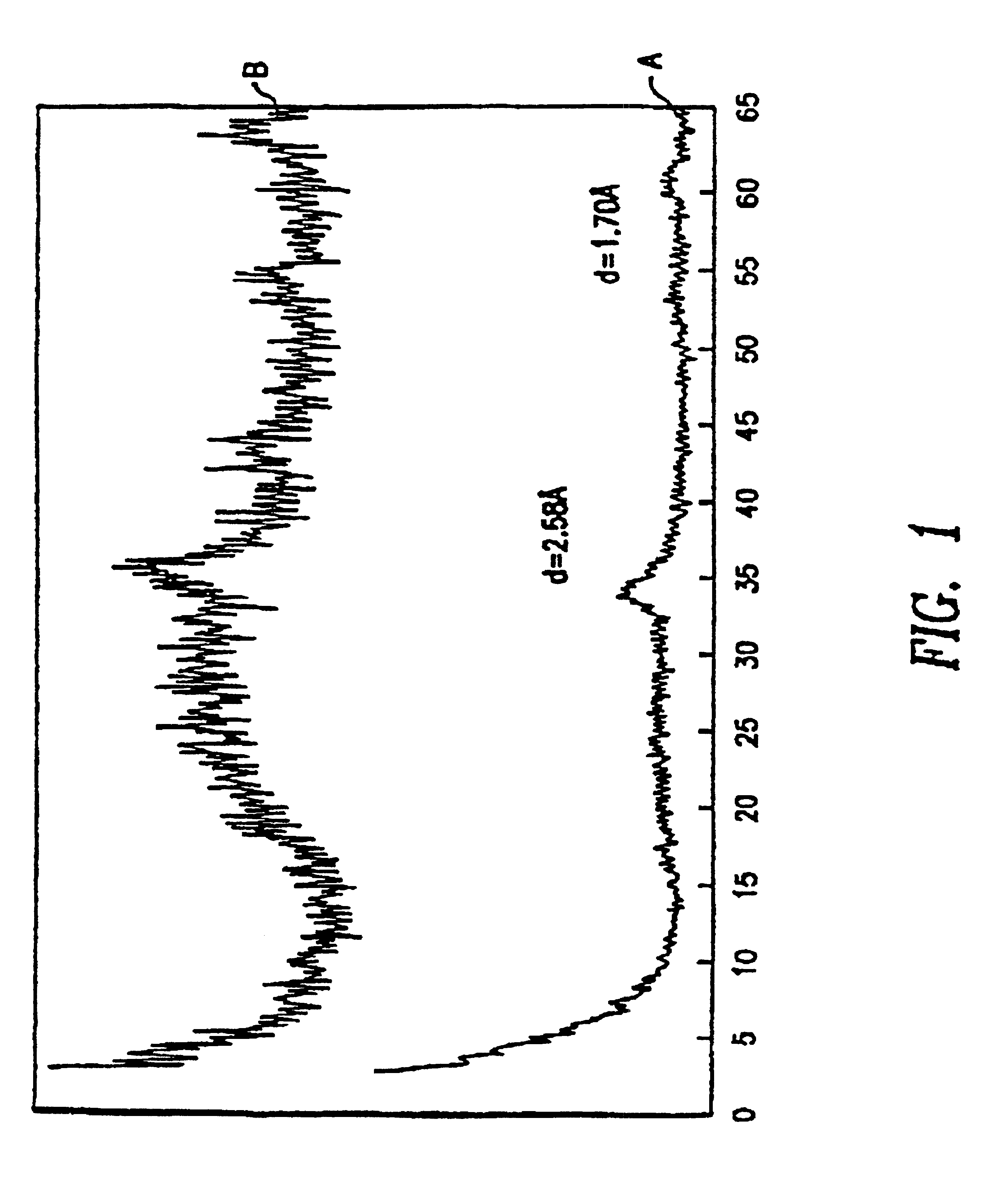

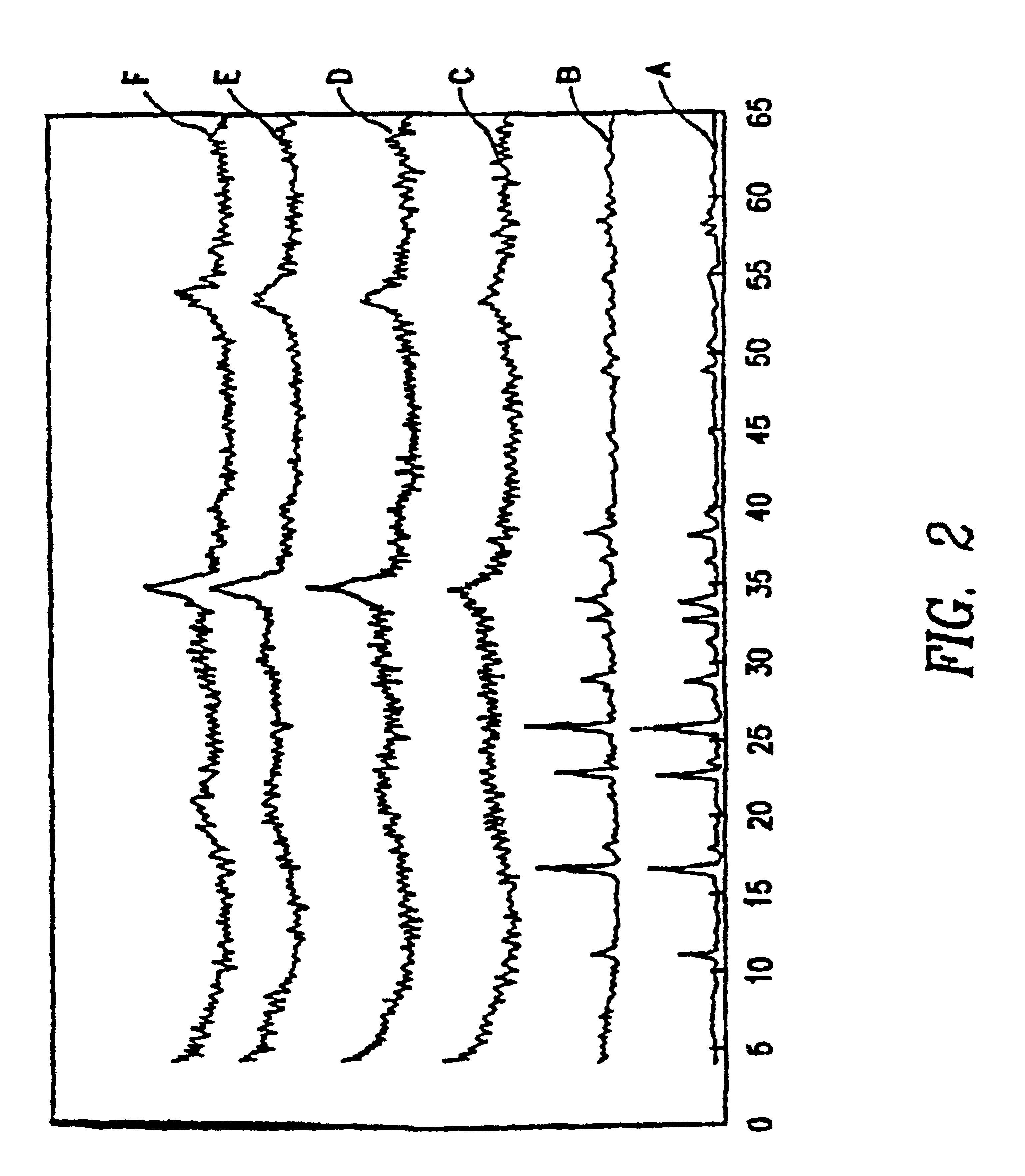

InactiveUS6168775B1High catalytic activityHigh activityHydrogen peroxideCatalyst activation/preparationParticulatesHydrogen

A particulate supported noble metal phase-controlled catalyst material having 5-1000 mum surface area of 50-500 m2 / gm is provided for use in direct catalytic production of hydrogen peroxide (H2O2) product from hydrogen and oxygen-containing feedstreams. The catalyst is made by depositing phase controlled crystals of a noble metal such as palladium on a suitable particulate support material such as carbon black, by utilizing a precursor solution of the metal and a suitable control ionic polymer having molecular weight of 300-8000 such as sodium polyacrylate in a selected metal to polymer molar ratio of 1:0.1 to 1:10, which procedure provides desired phase control of the noble metal atoms to form widely dispersed minute noble metal crystals on the support material. The invention includes methods for making the catalyst, and also a process for utilizing the catalyst to directly produce high yields of hydrogen peroxide (H2O2) product from hydrogen and oxygen-containing gaseous feedstreams.

Owner:BORAL IP HLDG

Finished lubricating comprising lubricating base oil with high monocycloparaffins and low multicycloparaffins

ActiveUS20050133407A1Improve Oxidation StabilityReduce wearRefining to change hydrocarbon structural skeletonLiquid hydrocarbon mixture productionMolecular sieveWax

A process for manufacturing a finished lubricant by: a) performing Fischer-Tropsch synthesis on syngas to provide a product stream; b) isolating from said product stream a substantially paraffinic wax feed having less than about 30 ppm total nitrogen and sulfur, and less than about 1 wt % oxygen; c) dewaxing said feed by hydroisomerization dewaxing using a shape selective intermediate pore size molecular sieve comprising a noble metal hydrogenation component, wherein the hydroisomerization temperature is between about 600° F. (315° C.) and about 750° F. (399° C.), to produce an isomerized oil; and d) hydrofinishing said isomerized oil, whereby a lubricating base oil is produced having specific desired properties; and e) blending the lubricating base oil with at least one lubricant additive.

Owner:CHEVROU USA INC

Two stage process for hydrodesulfurizing distillates using bulk multimetallic catalyst

InactiveUS6929738B1Preparation by oxo-reaction and reductionOrganic compound preparationLiquid productHydrogen

A two stage hydrodesulfurizing process for producing low sulfur distillates. A distillate boiling range feedstock containing in excess of about 3,000 wppm sulfur is hydrodesulfurized in a first hydrodesulfurizing stage containing one or more reaction zones in the presence of hydrogen and a hydrodesulfurizing catalyst. The liquid product stream thereof is passed to a first separation stage wherein a vapor phase product stream and a liquid product stream are produced. The liquid product stream, which has a substantially lower sulfur and nitrogen content then the original feedstream is passed to a second hydrodesulfurizing stage also containing one or more reaction zones where it is reacted in the presence of hydrogen and a second hydrodesulfurizing catalyst at hydrodesulfurizing conditions. The catalyst in any one or more reaction zones is a bulk multimetallic catalyst comprised of at least one Group VIII non-noble metal and at least two Group VIB metals.

Owner:EXXON RES & ENG CO

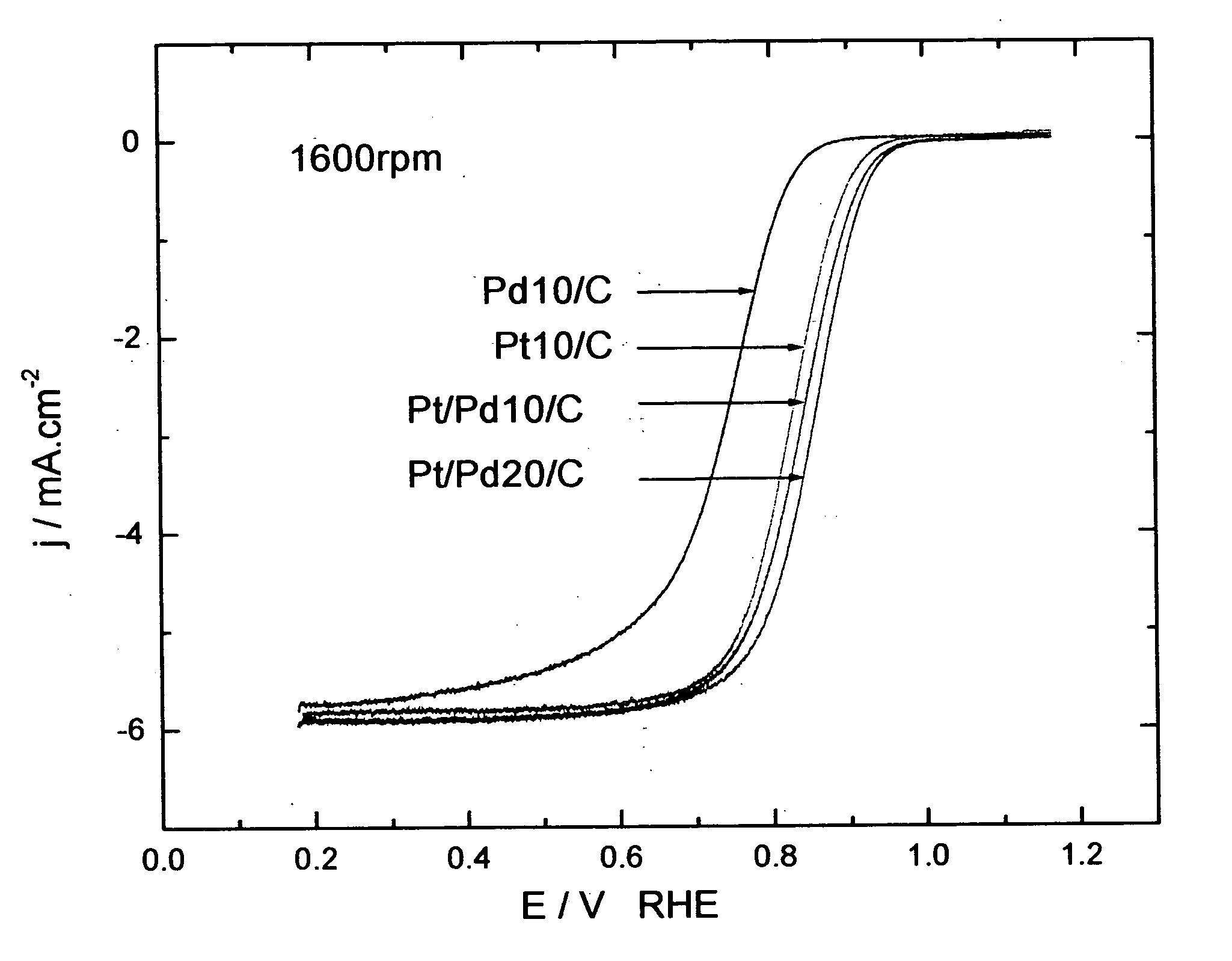

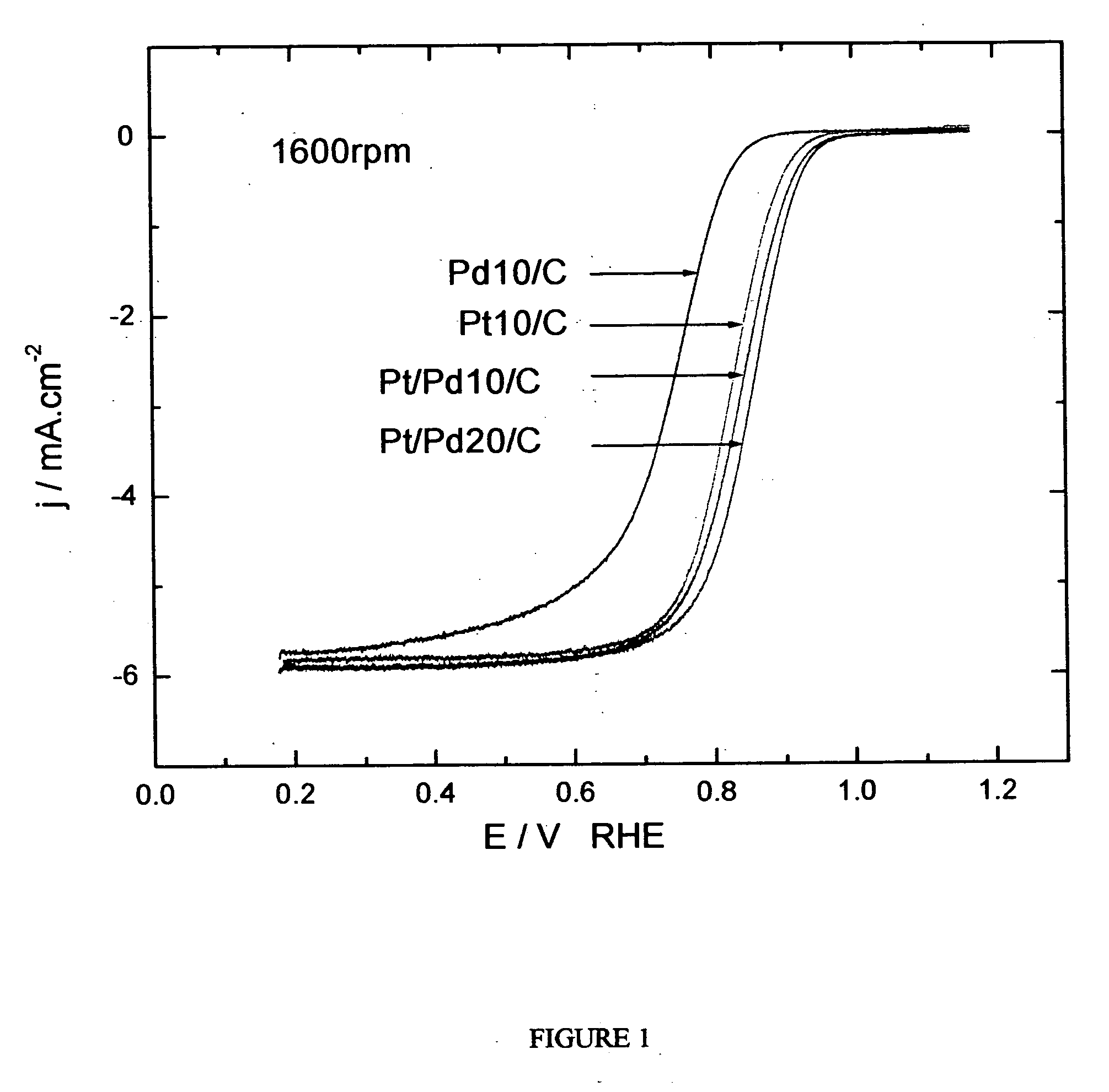

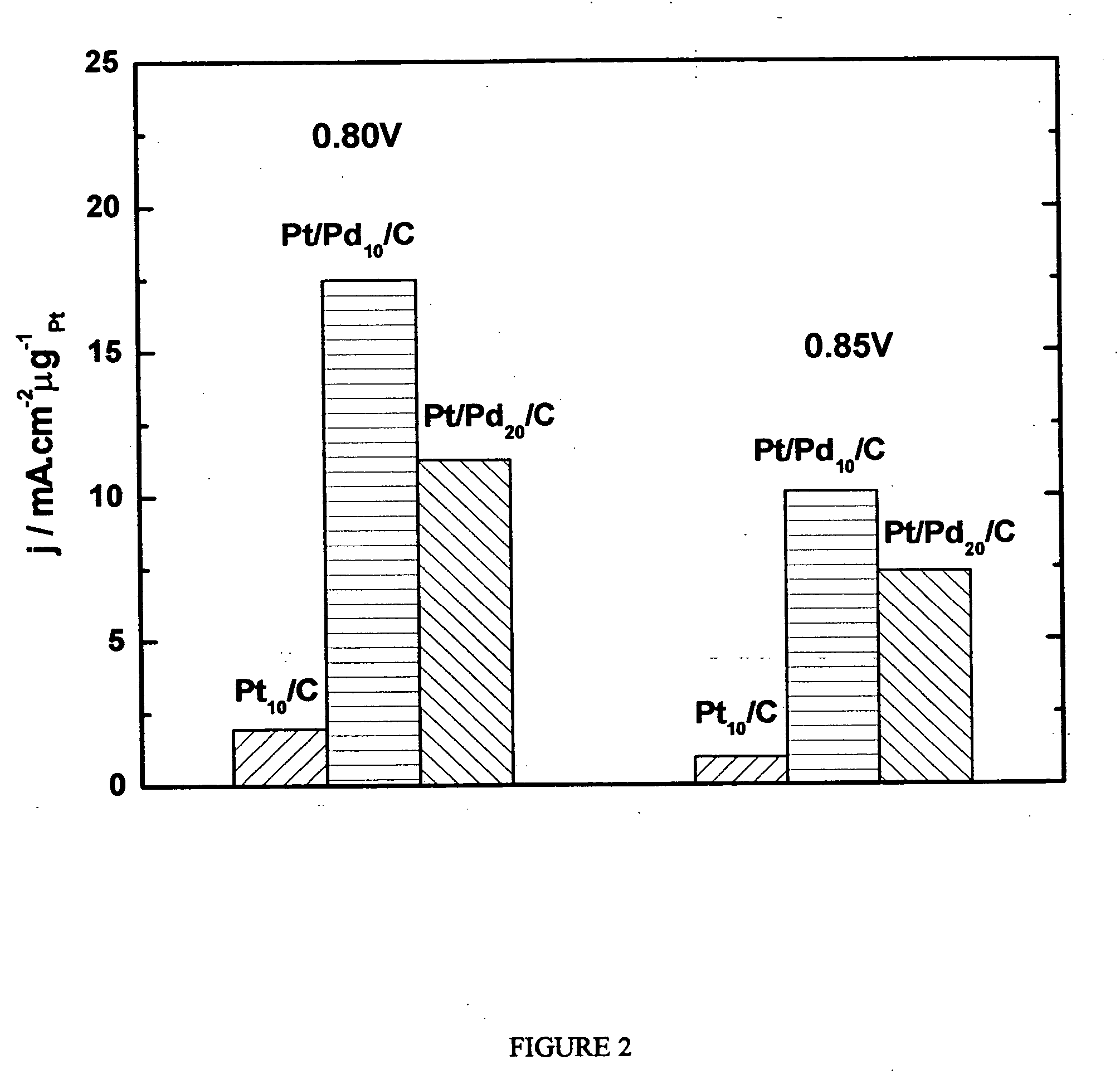

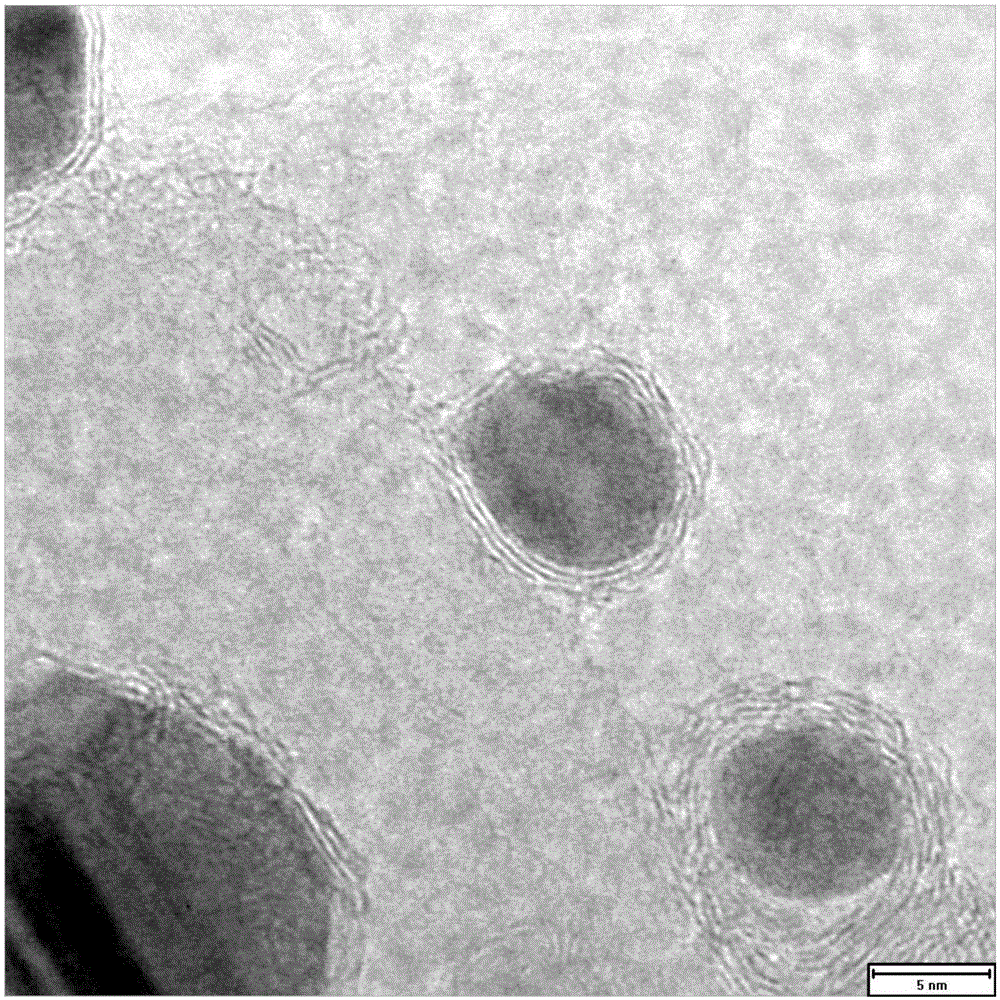

Electrocatalysts having platinum monolayers on palladium, palladium alloy, and gold alloy nanoparticle cores, and uses thereof

ActiveUS20070031722A1Improved oxygen-reducing catalytic activityLow platinum loadingMetal-working apparatusActive material electrodesRheniumGold alloys

The invention relates to platinum-coated particles useful as fuel cell electrocatalysts. The particles are composed of a noble metal or metal alloy core at least partially encapsulated by an atomically thin surface layer of platinum atoms. The invention particularly relates to such particles having a palladium, palladium alloy, gold alloy, or rhenium alloy core encapsulated by an atomic monolayer of platinum. In other embodiments, the invention relates to fuel cells containing these electrocatalysts and methods for generating electrical energy therefrom.

Owner:BROOKHAVEN SCI ASSOCS

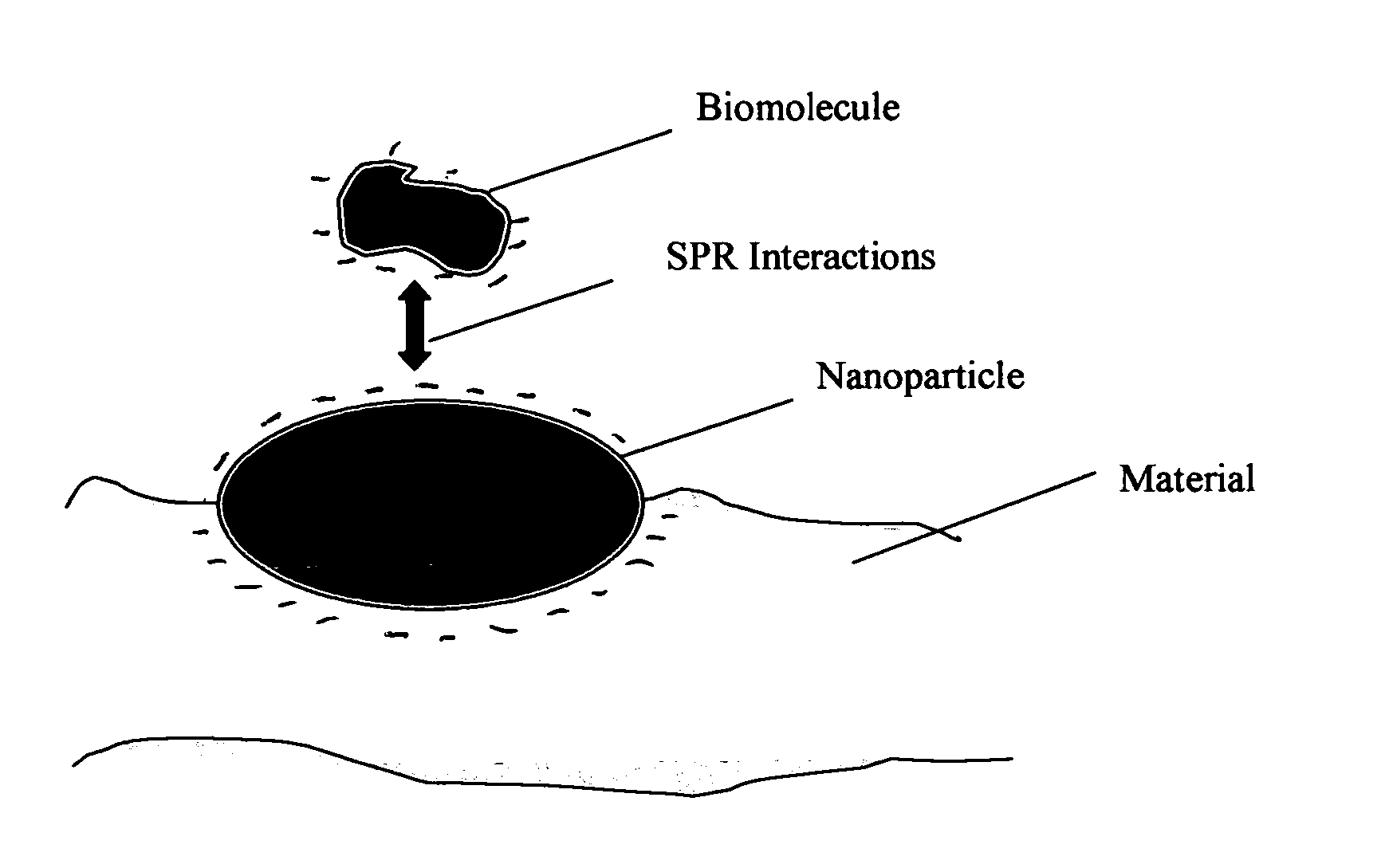

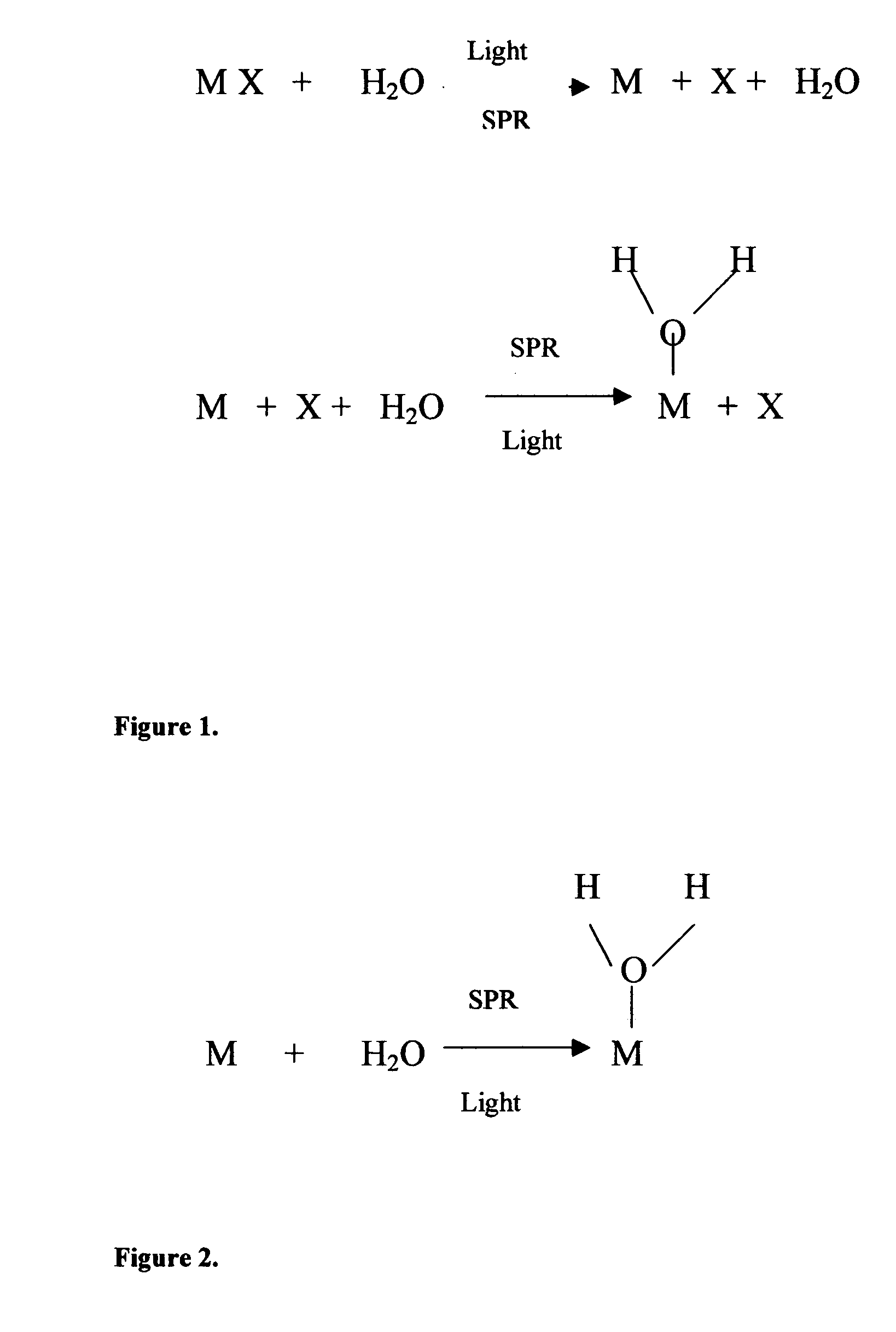

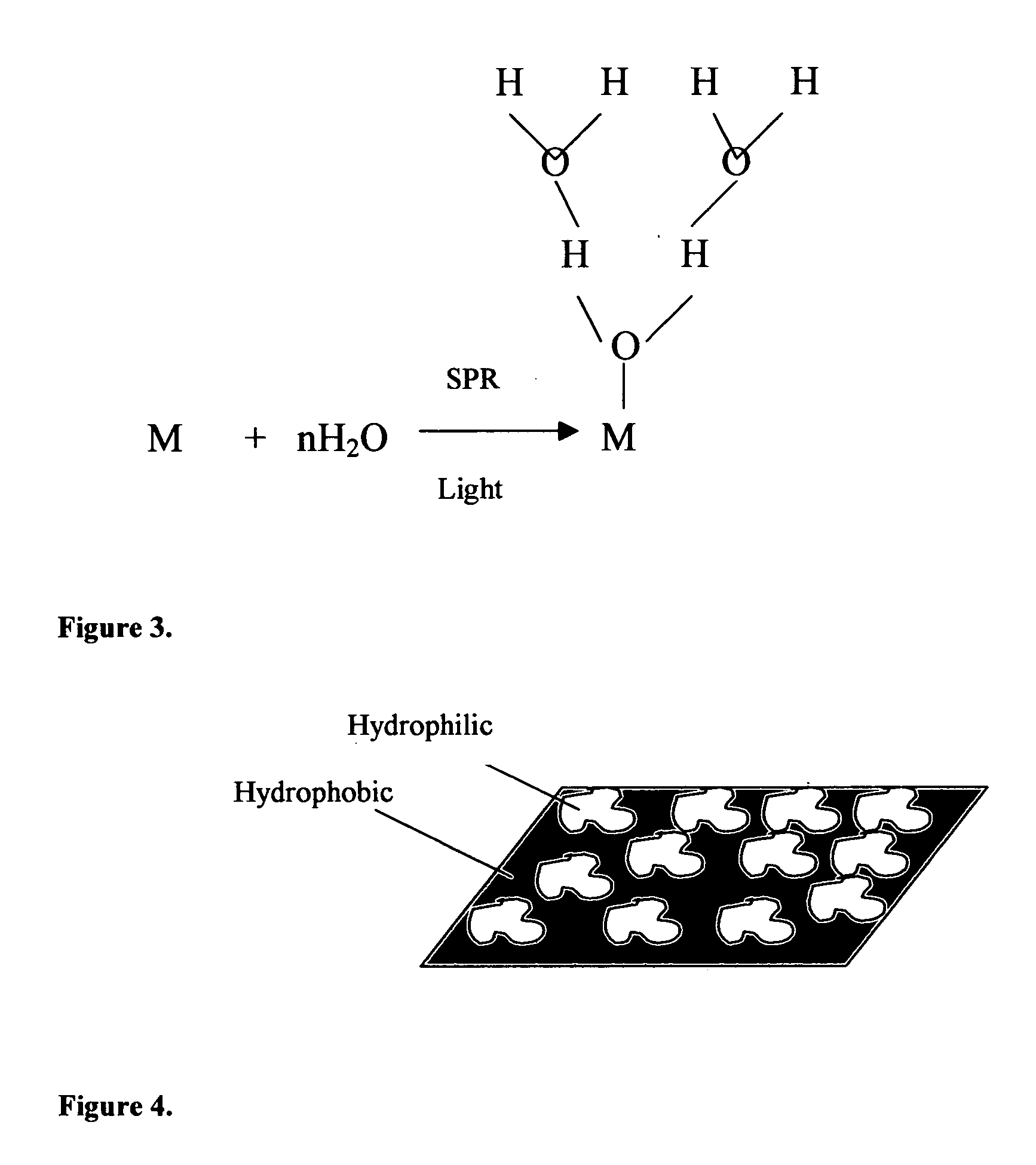

Method of plasmon-enhanced properties of materials and applications thereof

InactiveUS20050164169A1Bioreactor/fermenter combinationsMaterial nanotechnologyInfraredThermochromism

Methods and applications of surface plasmon resonance-enhanced antibacterial, anti-adhere, adhere, catalytic, hydrophilic, hydrophobic, spectral change, biological and chemical decomposition properties of materials with embedded nanoparticles are disclosed. A method of the nonlinear generation of surface plasmon resonance enables the use of light with wavelengths from X-Ray to IR to enhance properties of materials by several orders of magnitude. The nanoparticle size is crucial for the enhancement and their size is considered to be in the proposed methods and applications within a range of 0.1 nm to 200,000 nm. The nanoparticles preferably are made of noble metals and / or semiconductor oxides. The invention describes a very broad spectrum of applications of surface plasmon resonance-enhanced properties of materials with embedded nanoparticles, from environmental cleanup by road pavement and construction materials, self-cleaning processes of surface materials, thermochromic effects on heat blocking materials, corrosion preventing paint, to sanitization by antibacterial textile fabrics, filters, personal clothing, contact lenses and medical devices.

Owner:SPR ADVANCED TECH INC

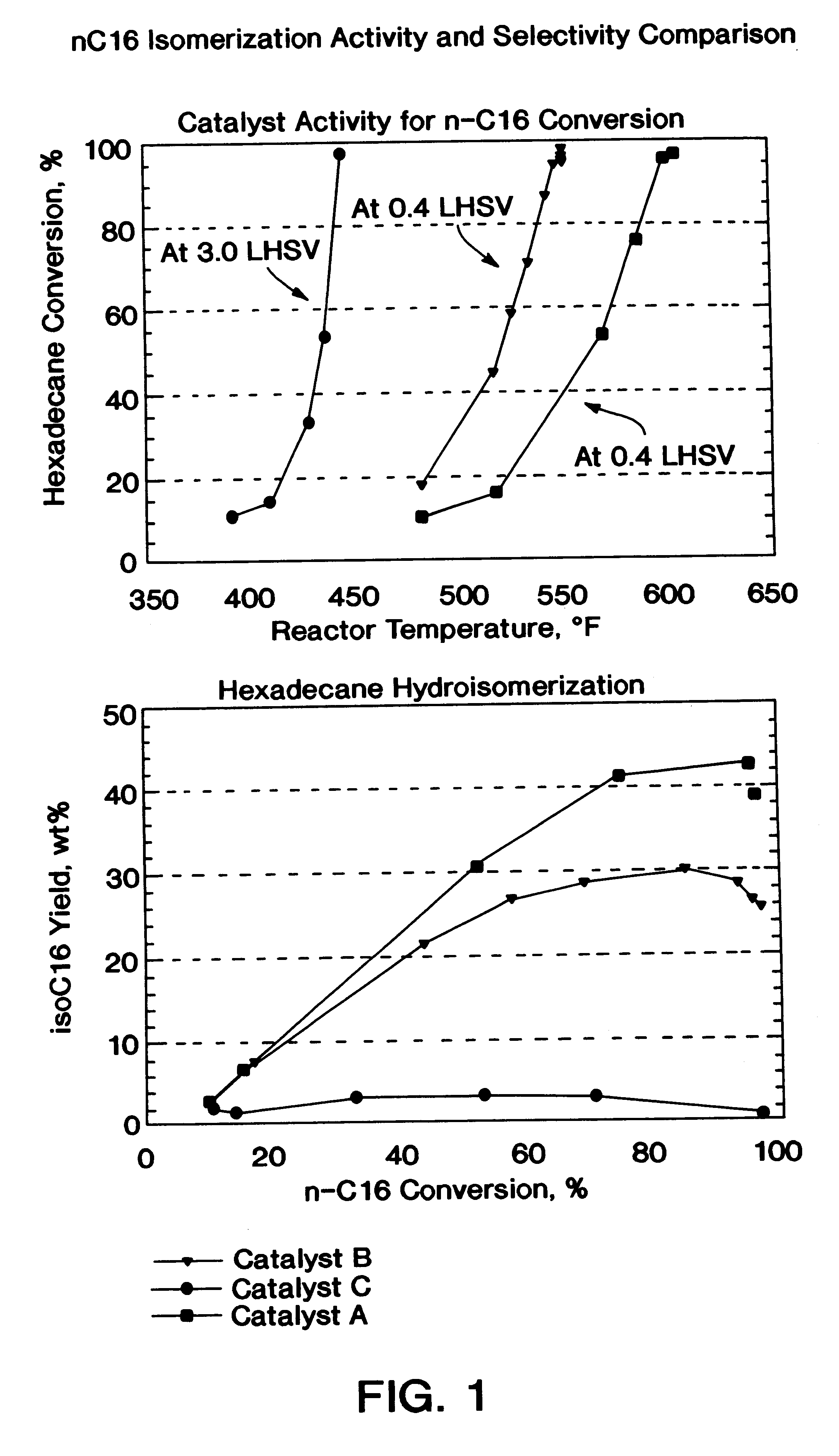

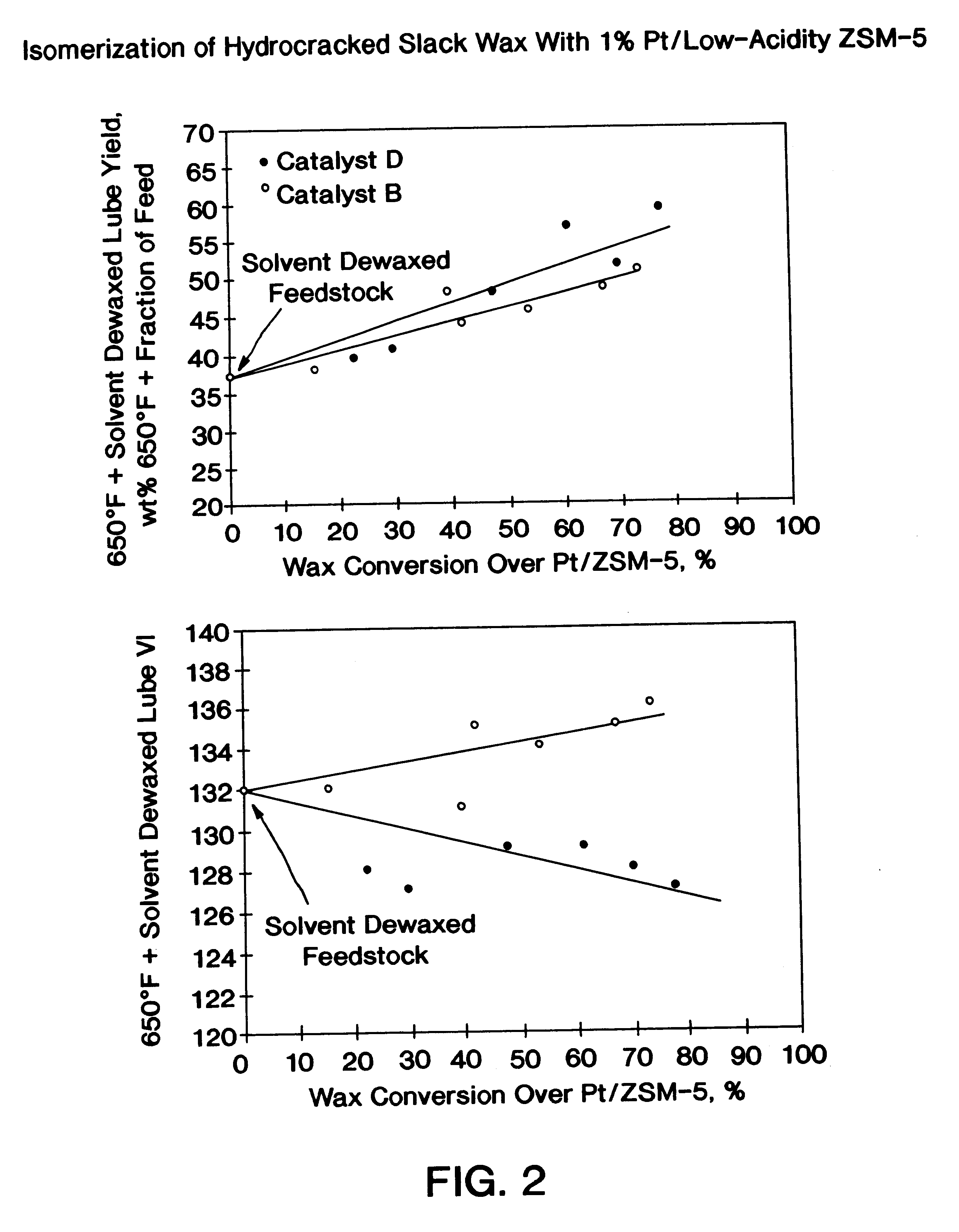

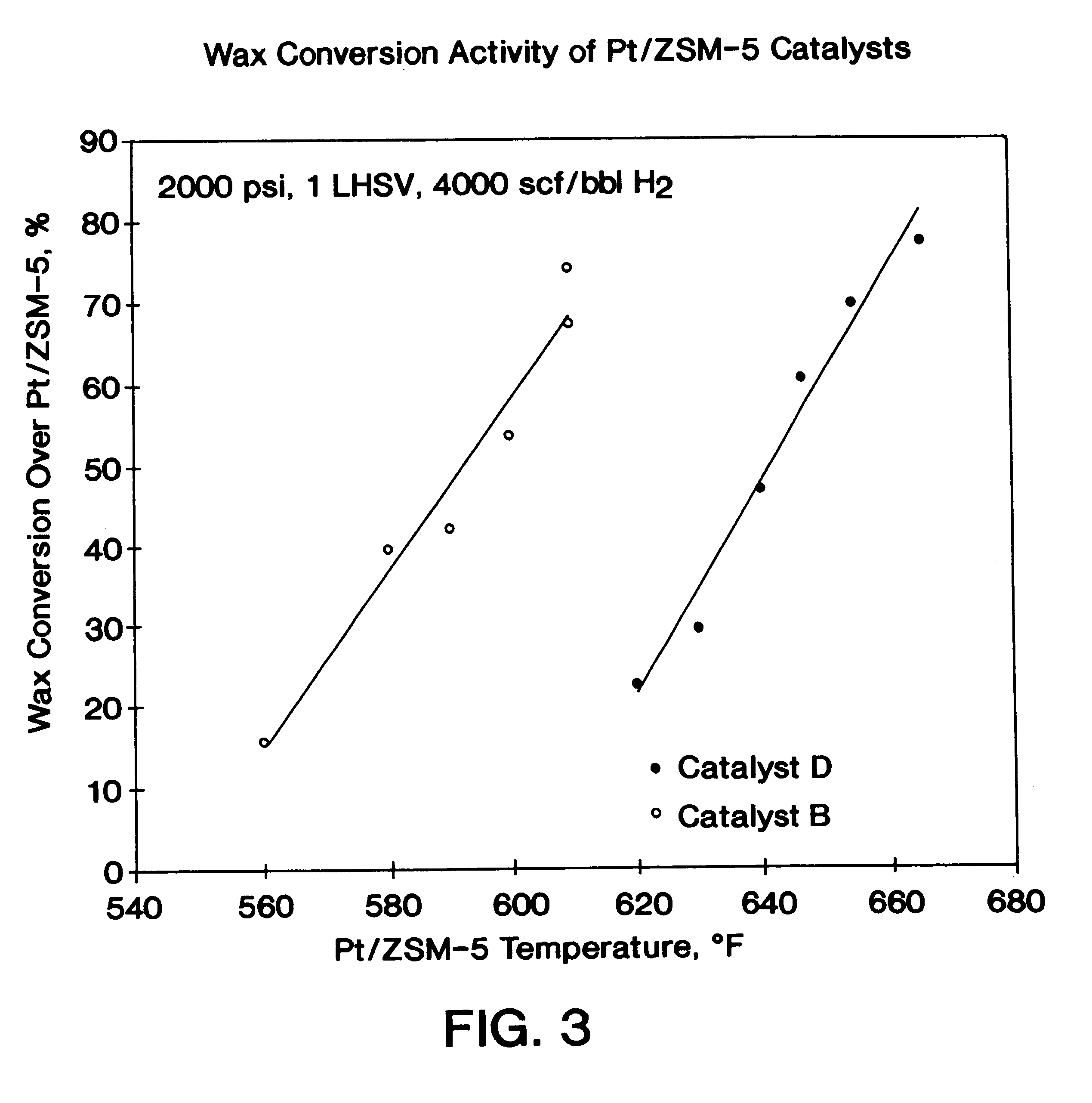

Production of high viscosity lubricating oil stock with improved ZSM-5 catalyst

InactiveUS6294077B1Low pour pointHigh viscosity indexMolecular sieve catalystsRefining to change hydrocarbon structural skeletonHydrogenParaffin oils

The present invention is a process for producing a high viscosity index and low pour point lubricating oil base stock which comprises catalytically converting a hydrotreated hydrocarbon lube oil feedstock containing waxy paraffins in the presence of hydrogen and in the presence of a low acidity ZSM-5 catalyst having a highly dispersed noble metal component. The ZSM-5 catalyst is subjected to controlled acidity reduction to an alpha value below 15 prior to incorporation of the noble metal component.

Owner:MOBIL OIL CORP

Hydrogenation process for hydrocarbon resins

InactiveUS20030150778A1Improve productivityIncrease volumePreparation by oxo-reaction and reductionCatalyst activation/preparationProduction rateHalogen

This invention provides a process for hydrotreating hydrocarbon resins, which process comprises contacting a feedstock comprising a hydrocarbon resin or rosin, under suitable hydrotreating conditions, with a bulk multimetallic catalyst comprised of at least one Group VIII non-noble metal and at least two Group VIB metals and wherein the ratio of Group VIB metal to Group VIII non-noble metal is from about 10:1 to about 1:10. The process accord invention can achieve increased hydrocarbon resin productivity through increase in throughput volumes and effective catalyst lifetimes. The process of the invention is desirably practiced with a bulk catalyst consisting of only the combination of the metal species with the active metal components. The absence of carrier substrates largely removes the possibility of halogen accumulation on substrate surfaces that, in turn, can acidify metal catalysts such that additional, progressive cracking of the hydrocarbon resin molecules occurs.

Owner:EXXONMOBIL CHEM PAT INC

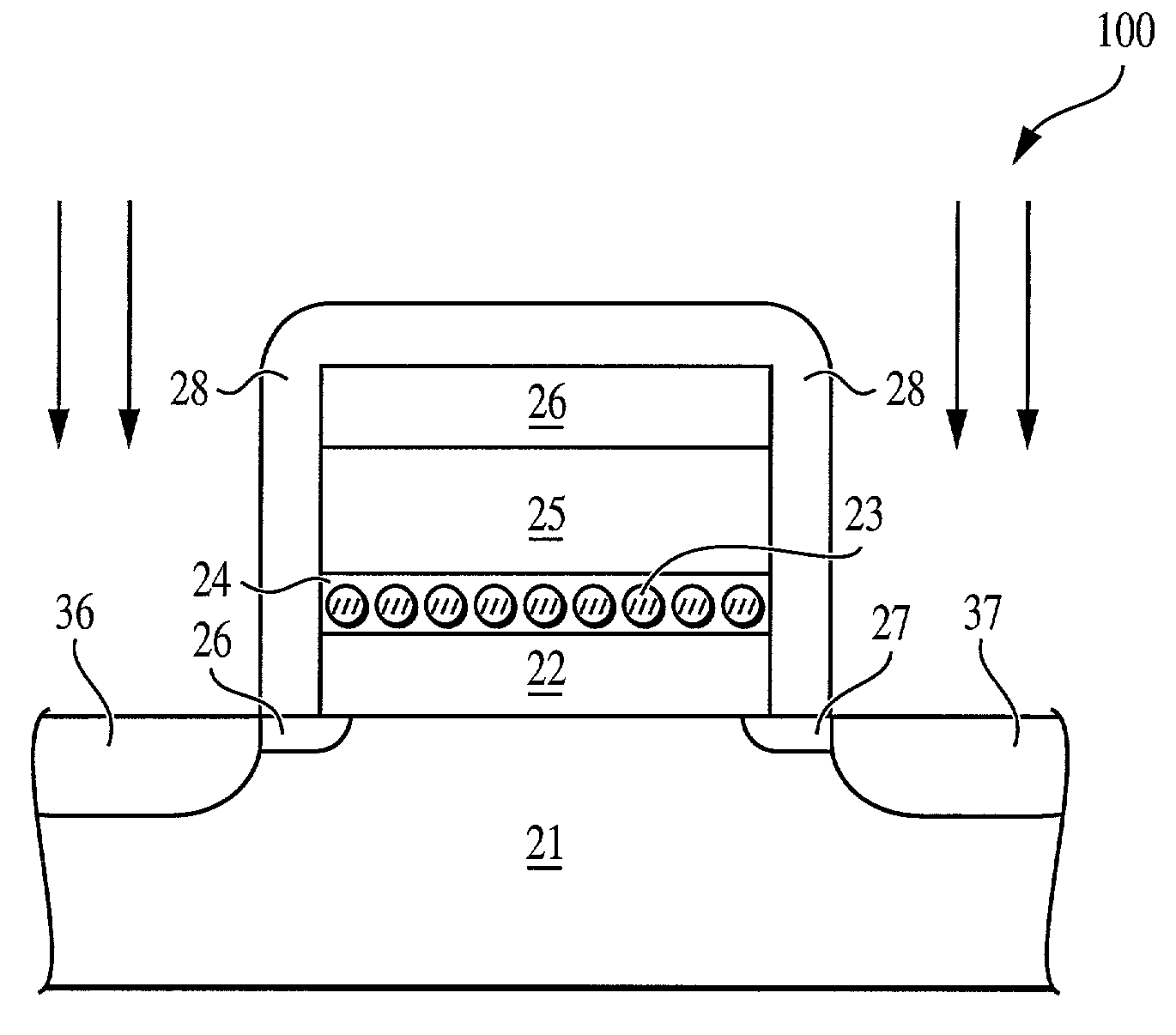

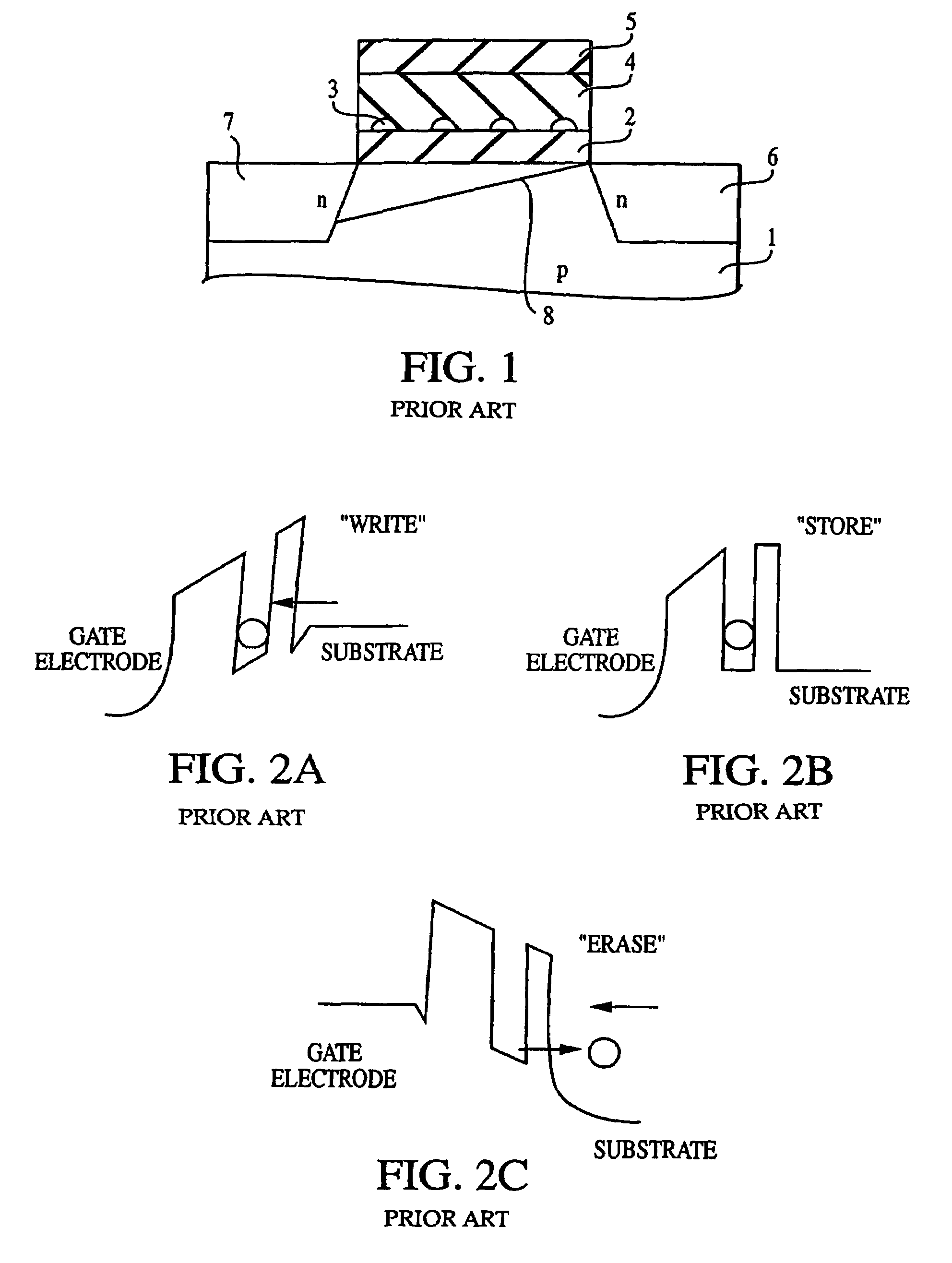

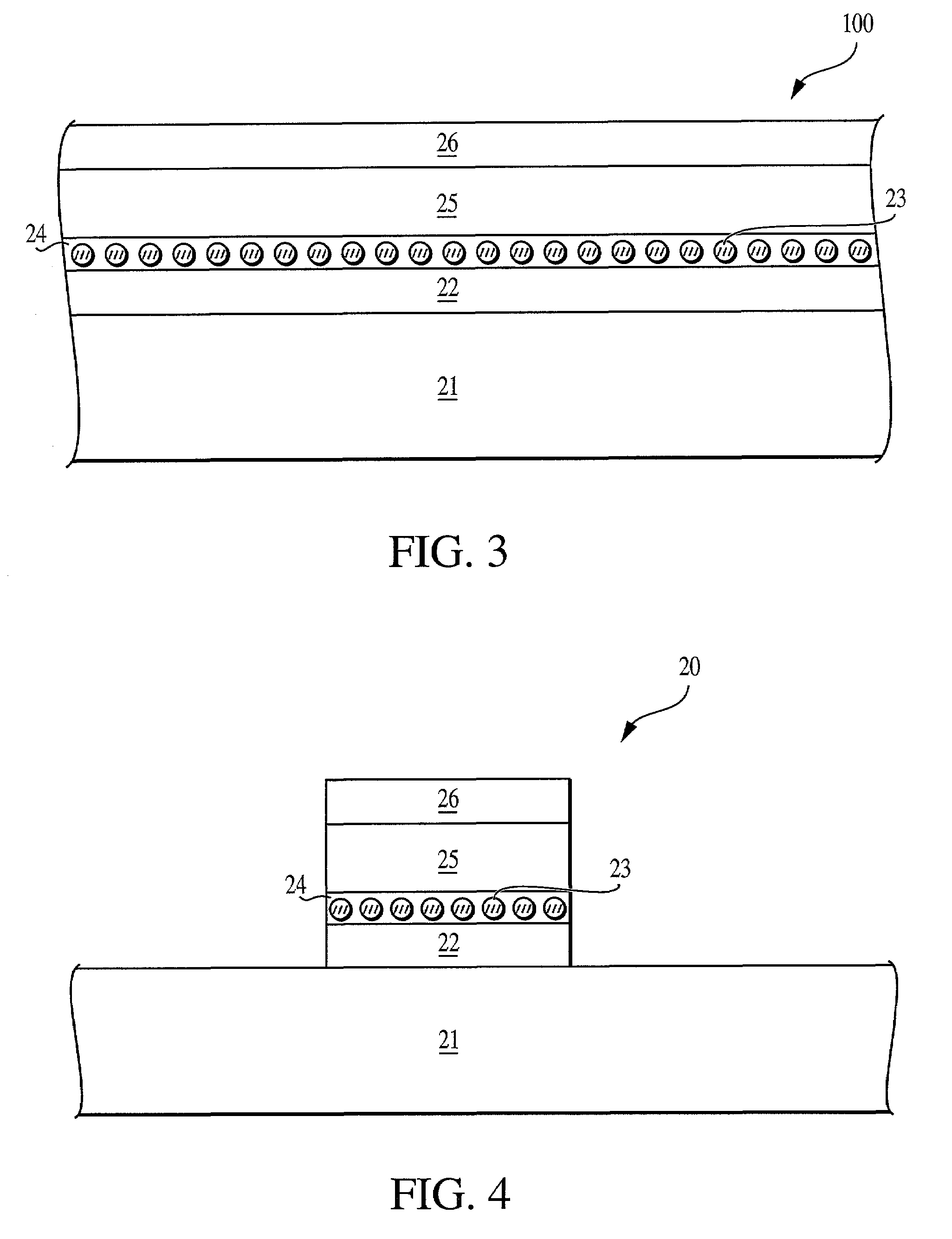

Method of forming a non-volatile electron storage memory and the resulting device

The invention provides a method of forming an electron memory storage device and the resulting device. The device comprises a gate structure which, in form, comprises a first gate insulating layer formed over a semiconductor substrate, a self-forming electron trapping layer of noble metal nano-crystals formed over the first gate insulating layer, a second gate insulating layer formed over the electron trapping layer, a gate electrode formed over the second gate insulating layer, and source and drain regions formed on opposite sides of the gate structure.

Owner:MICRON TECH INC

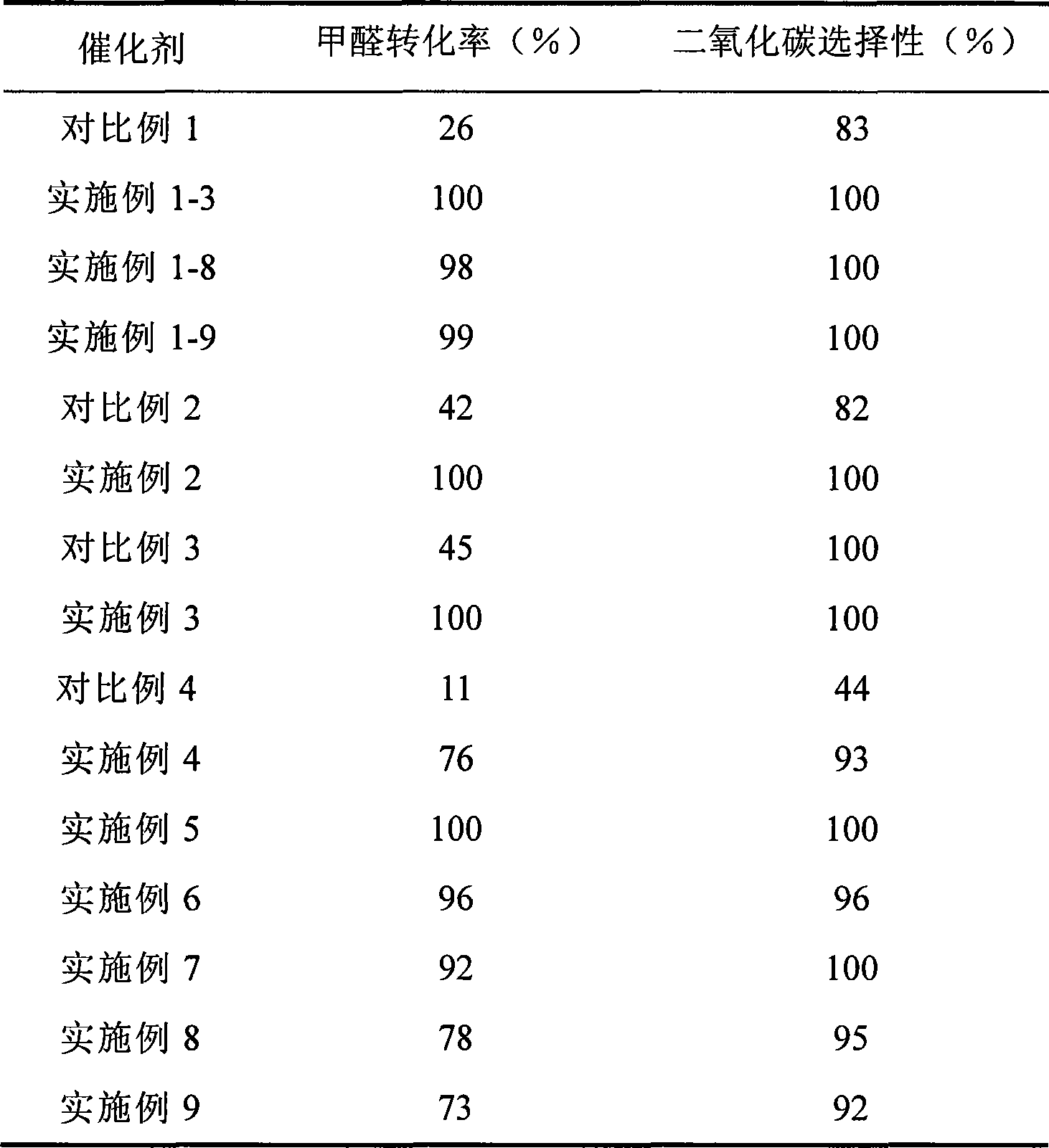

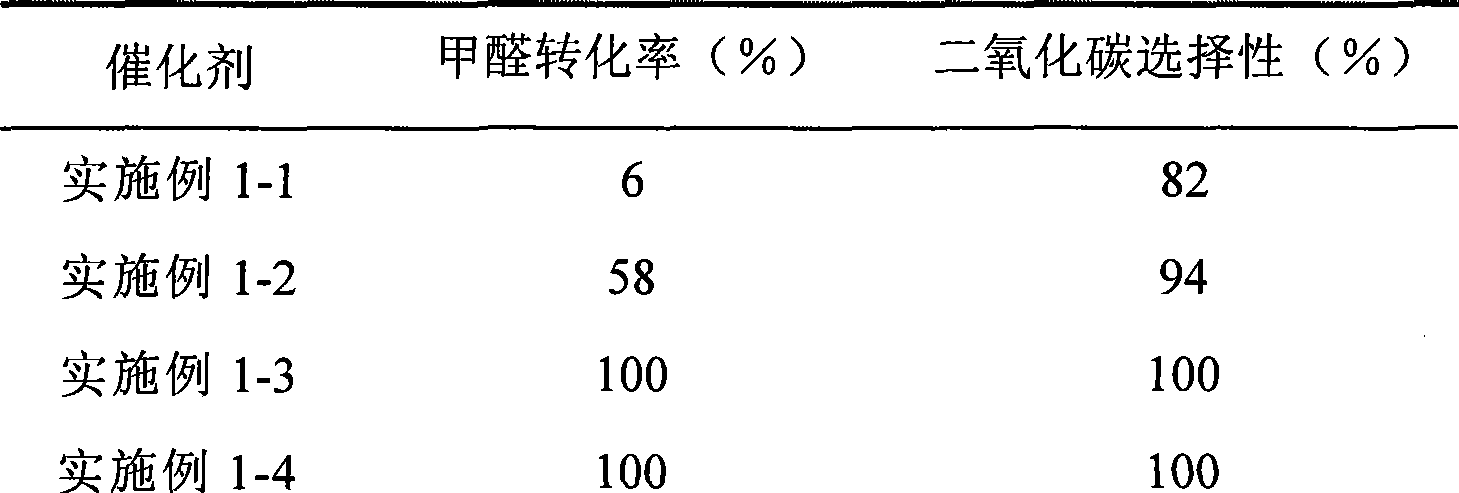

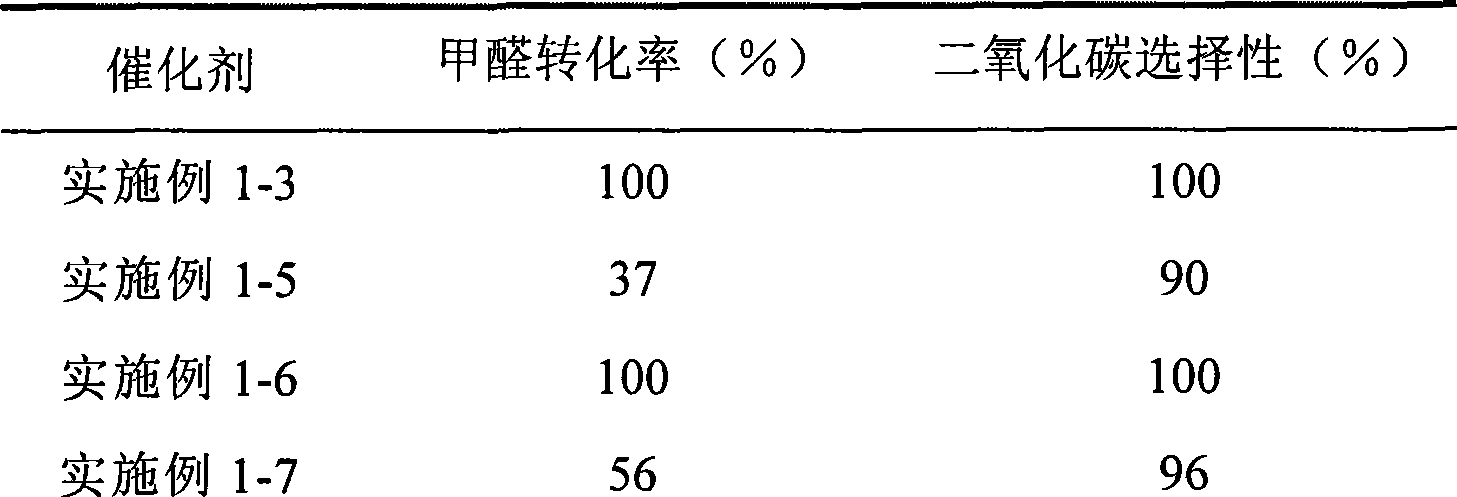

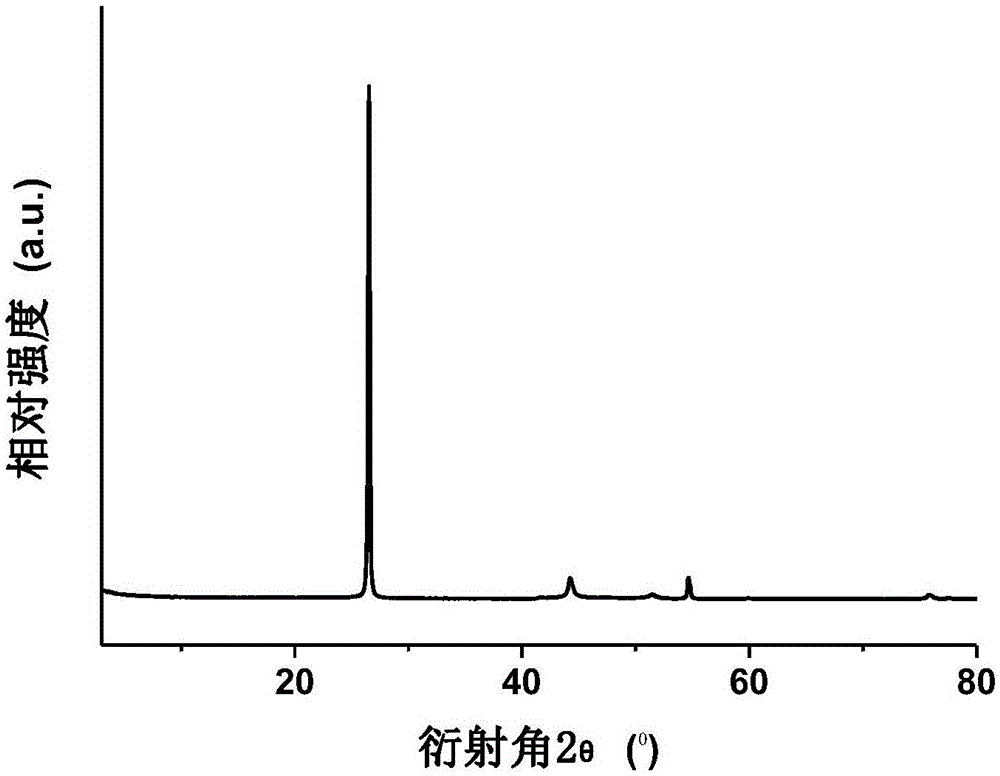

Catalyst for complete oxidation of formaldehyde at room temperature

ActiveCN101380574AEasy to makeEasy to operateDeodrantsMetal/metal-oxides/metal-hydroxide catalystsPorous carbonPt element

The invention provides a high selectivity catalyst used for catalyzing and completely oxidizing formaldehyde with low concentration at room temperature. The catalyst can catalyze formaldehyde completely so as to lead the formaldehyde to be converted into carbon dioxide and water at room temperature. In addition, the conversion rate of formaldehyde remains 100% within a long period of time, without complex auxiliary facilities such as light source, a heating oven and the like, and external conditions. The catalyst comprises three parts which are inorganic oxide carrier, noble metal component and auxiliary ingredient. Porous inorganic oxide carrier is one of cerium dioxide, zirconium dioxide, titanium dioxide, aluminium sesquioxide, tin dioxide, silicon dioxide, lanthanum sesquioxide, magnesium oxide and zinc oxide or the mixture thereof or composite oxide thereof, zeolite, sepiolite and porous carbon materials. The noble metal component of the catalyst is at least one of platinum, rhodium, palladium, gold and silver. The auxiliary ingredient is at least one of the alkali metals of lithium, sodium, kalium, rubidium and cesium. The loading of the noble metal component used in the catalyst of the invention is 0.1 to 10% according to weight converter of metal elements and the selective preference is 0.3 to 2%. The loading of the auxiliary ingredient is 0.2 to 30% according to weight converter of metal elements and the selective preference is 1 to 10%. When the loading of the auxiliary ingredient is lower than 0.2% or higher than 30%, the activity of the catalyst for catalyzing and oxidizing formaldehyde at room temperature is decreased remarkably.

Owner:广东顺德中科鸿图环境材料有限公司

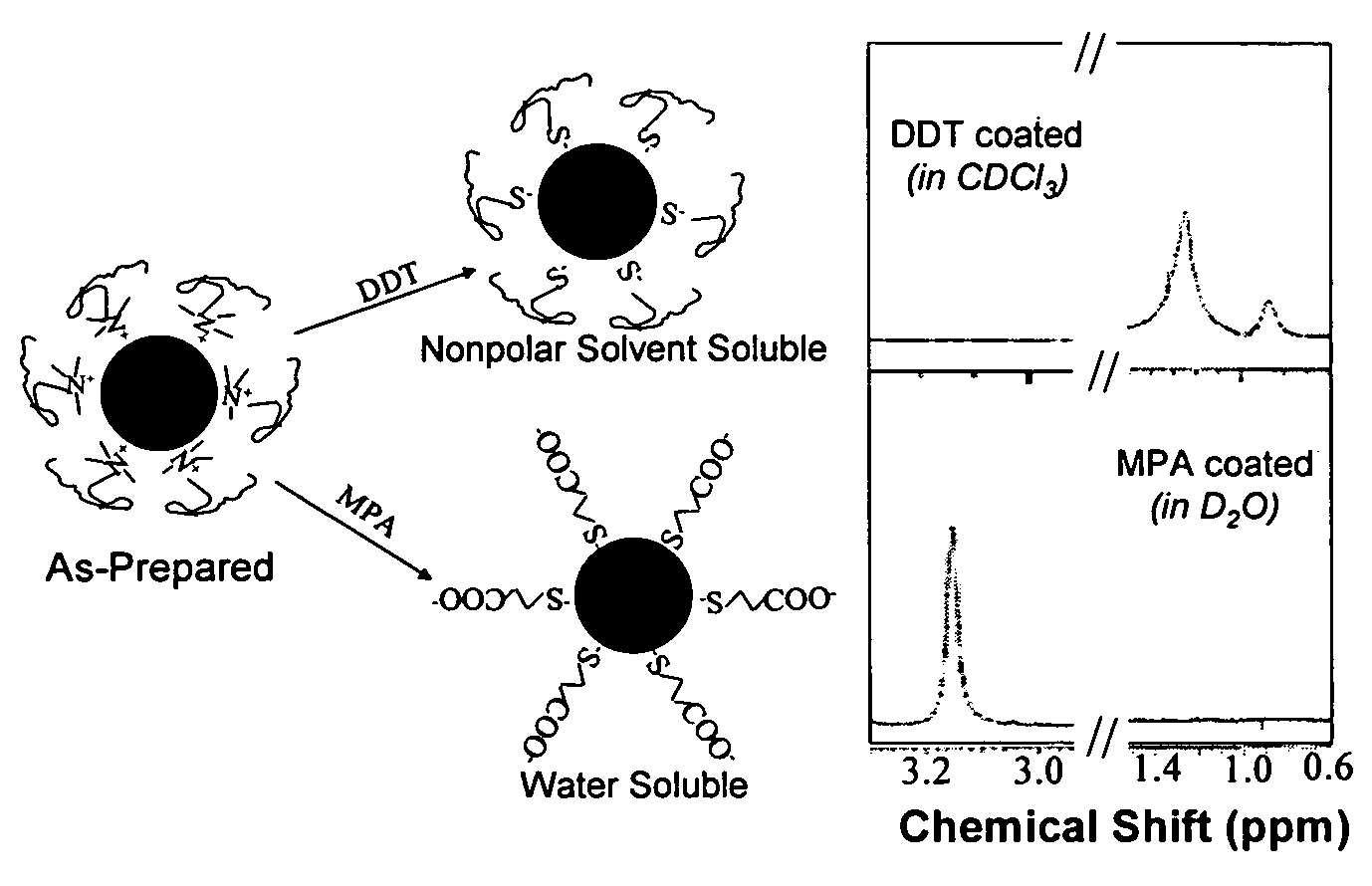

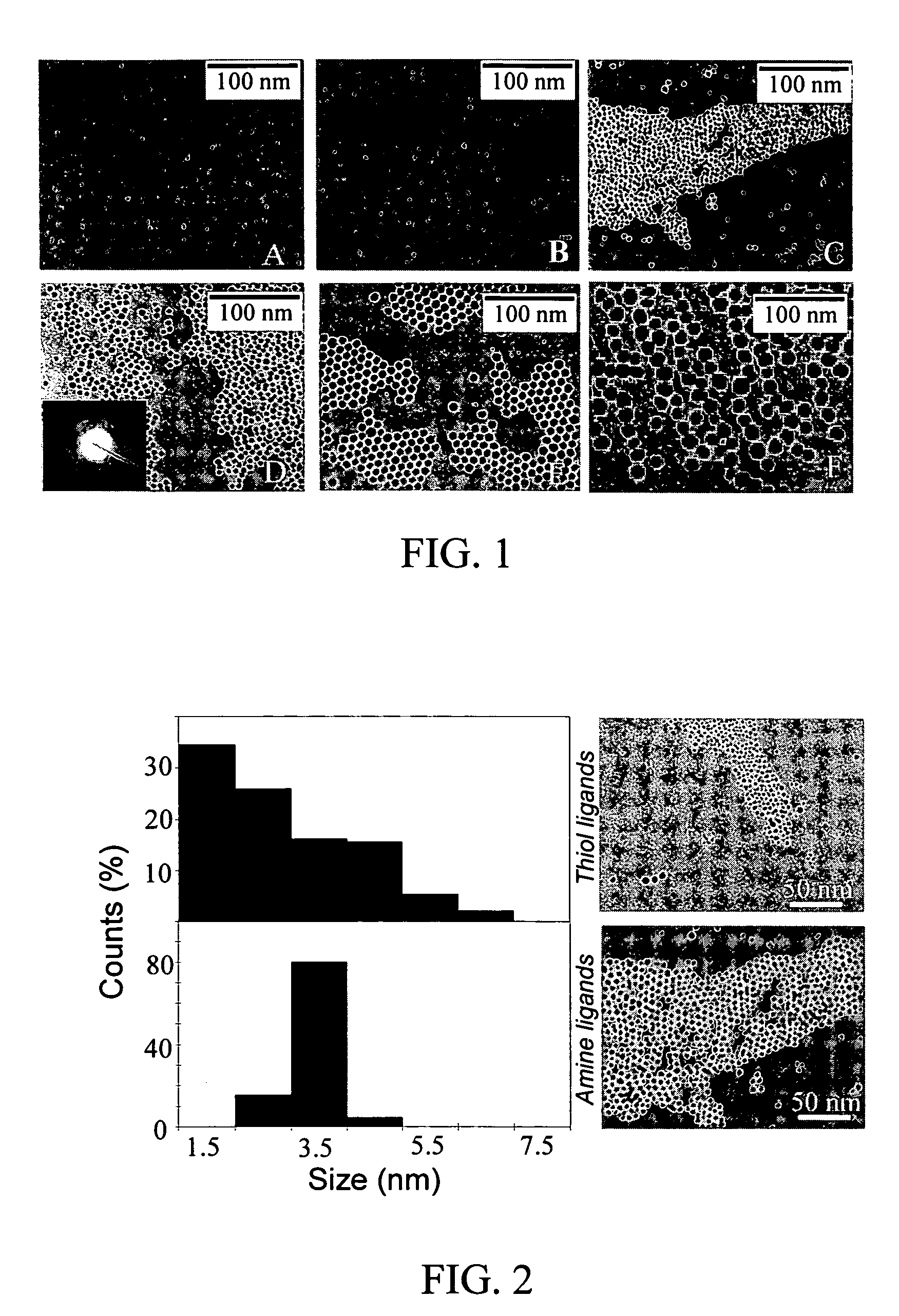

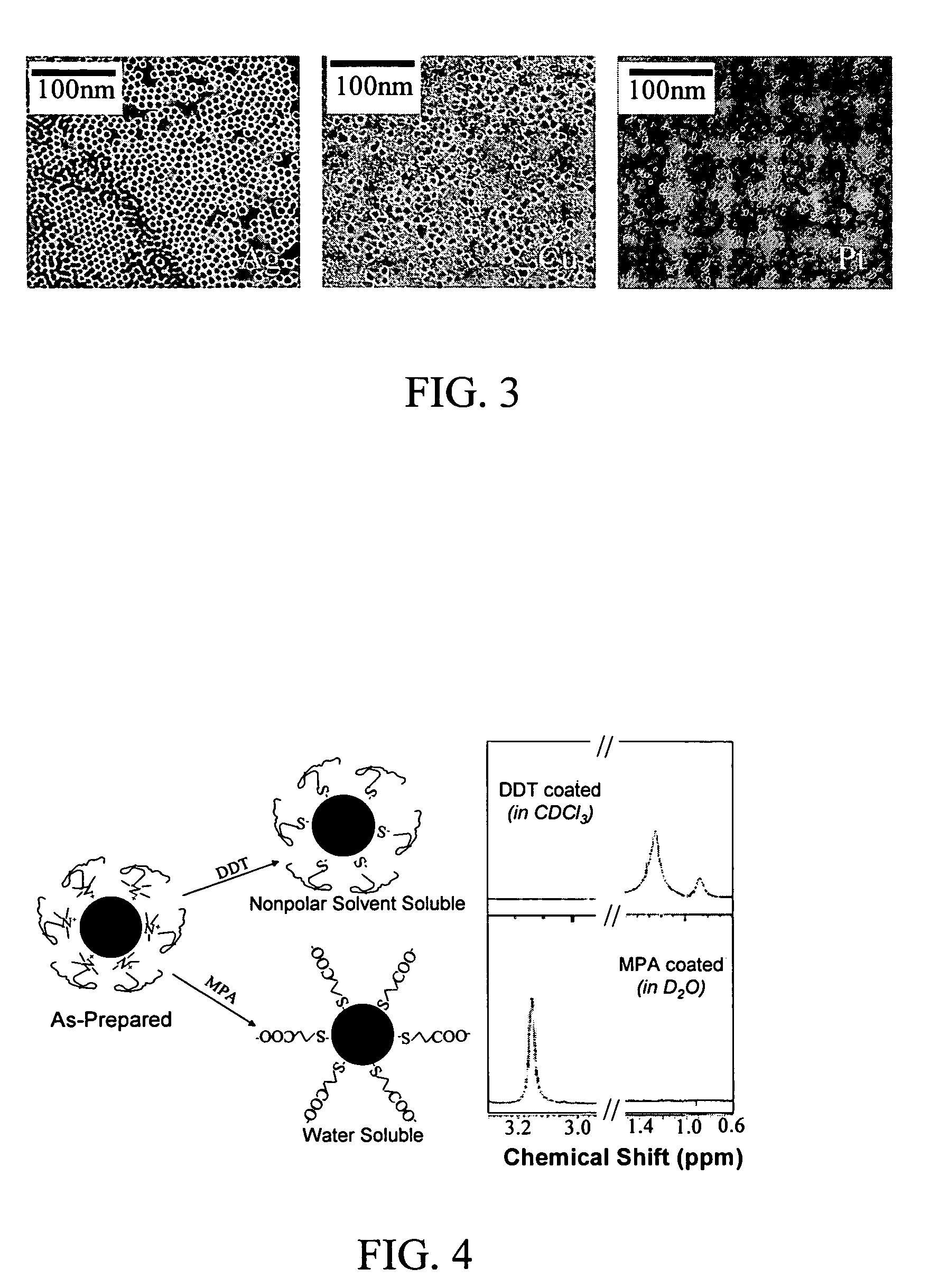

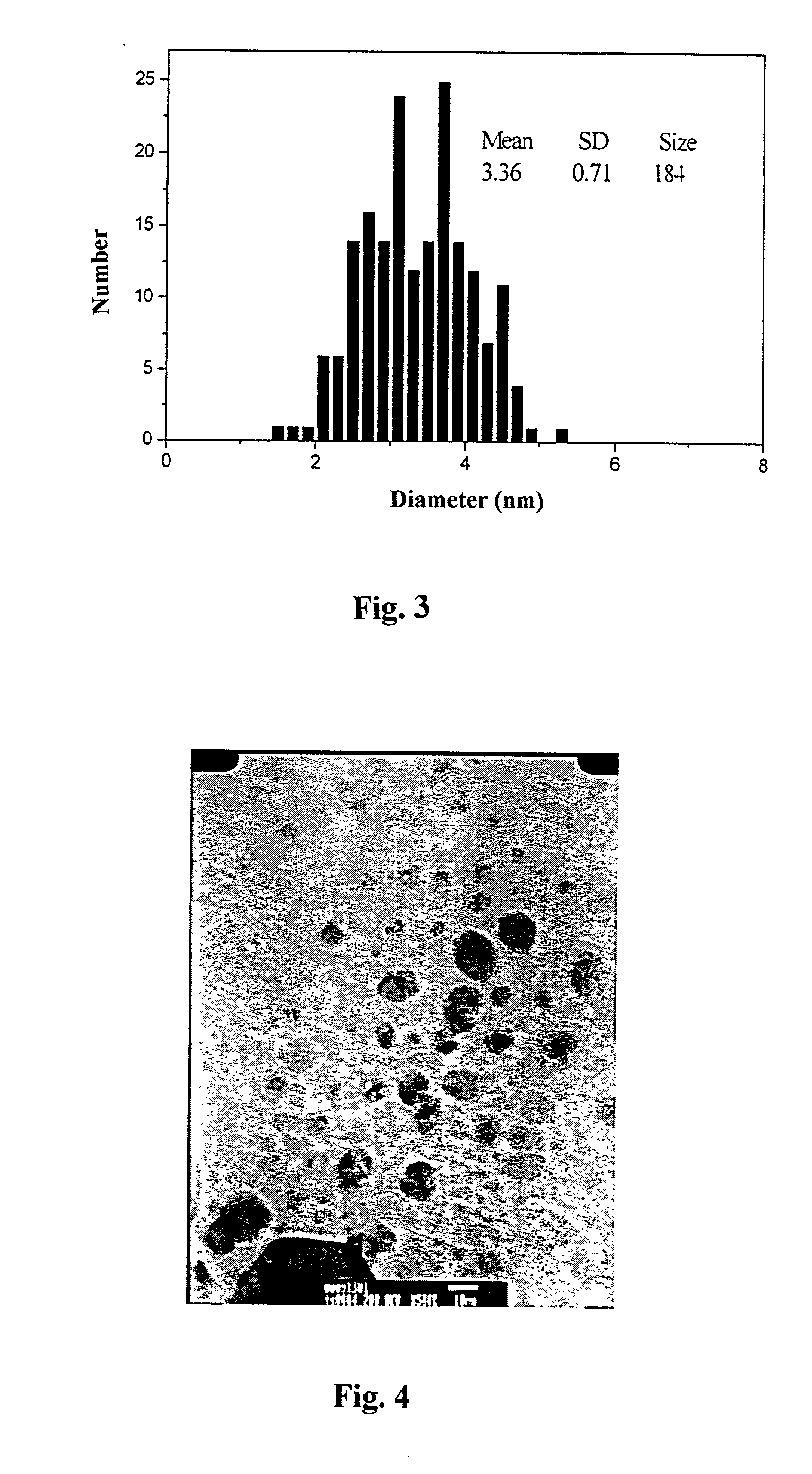

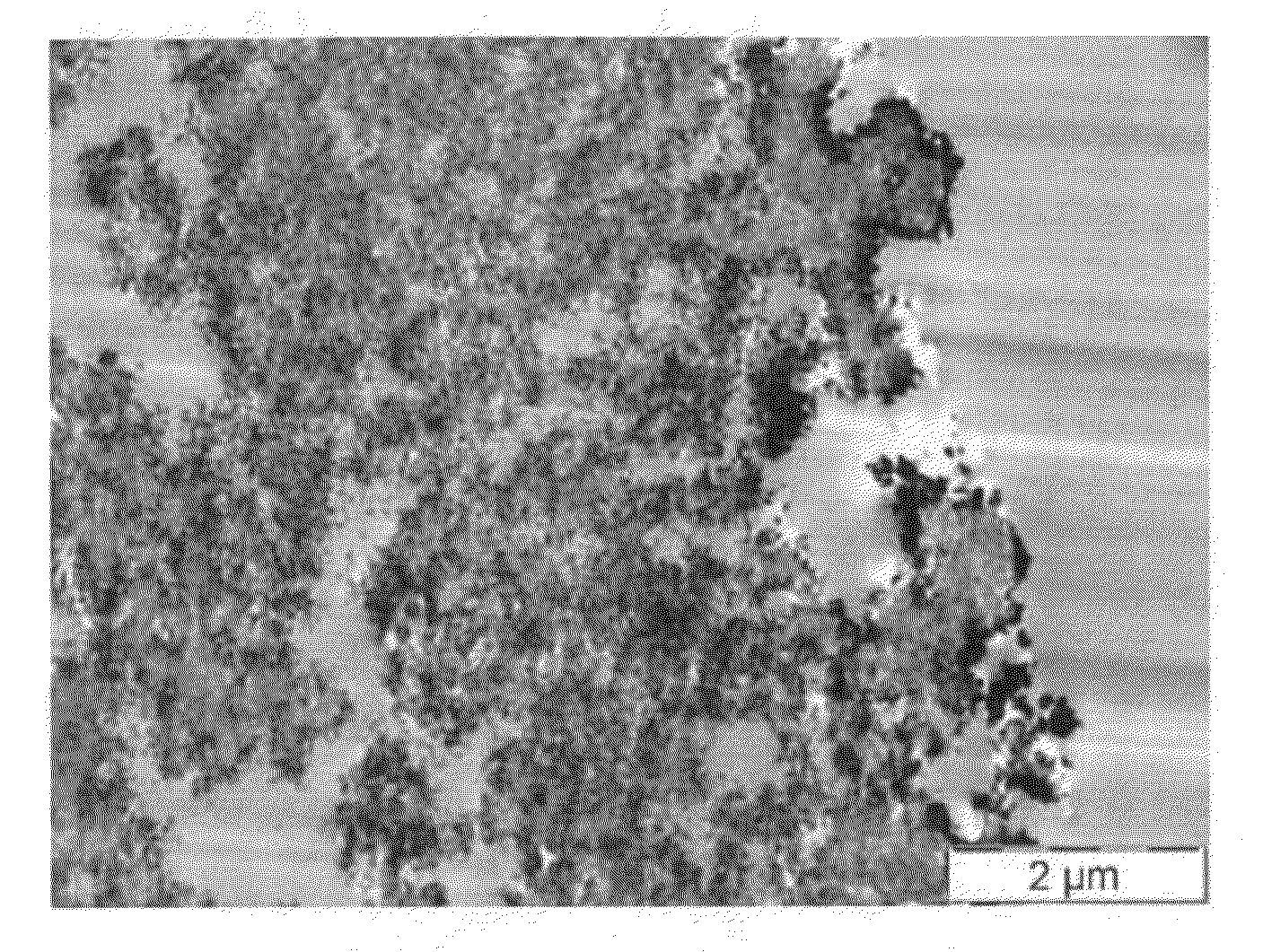

Monodisperse noble metal nanocrystals

Nanoparticle compositions of noble metals, and methods of making them, are described. The nanoparticle compositions are made by reacting a salt or complex of a noble metal, such as Au, Ag, Cu or Pt, with a weak ligand, and a reducing agent, in a single liquid phase. The noble metal is typically provided as a halide or carboxylate. The ligand is preferably a fatty acid or aliphatic amine. The reducing agent is preferably a borohydride reagent, hydrazine, or a mixture thereof. Nanocrystals in the size range of 1 nm to 20 nm are produced, and can be made in substantially monodisperse form.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

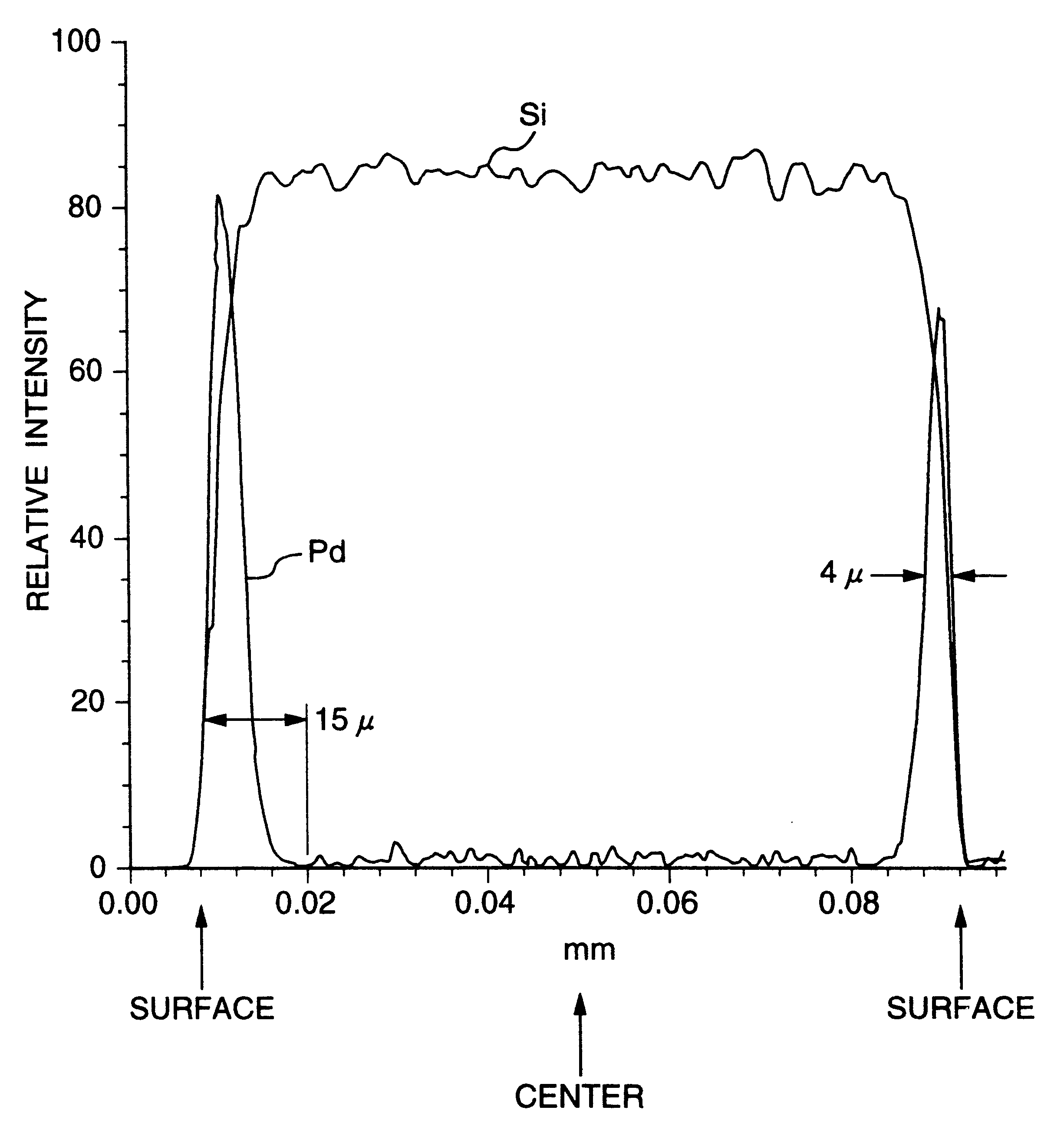

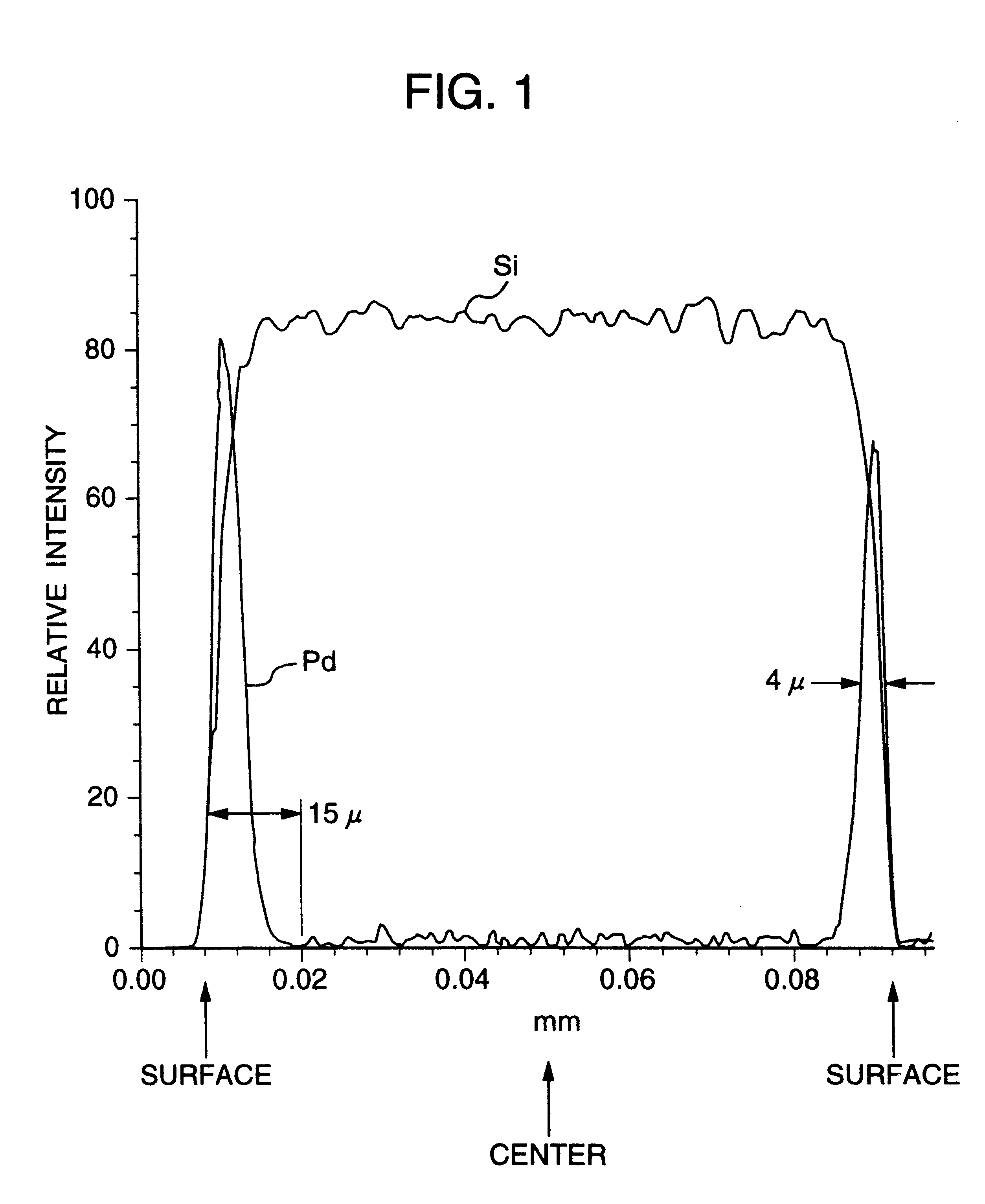

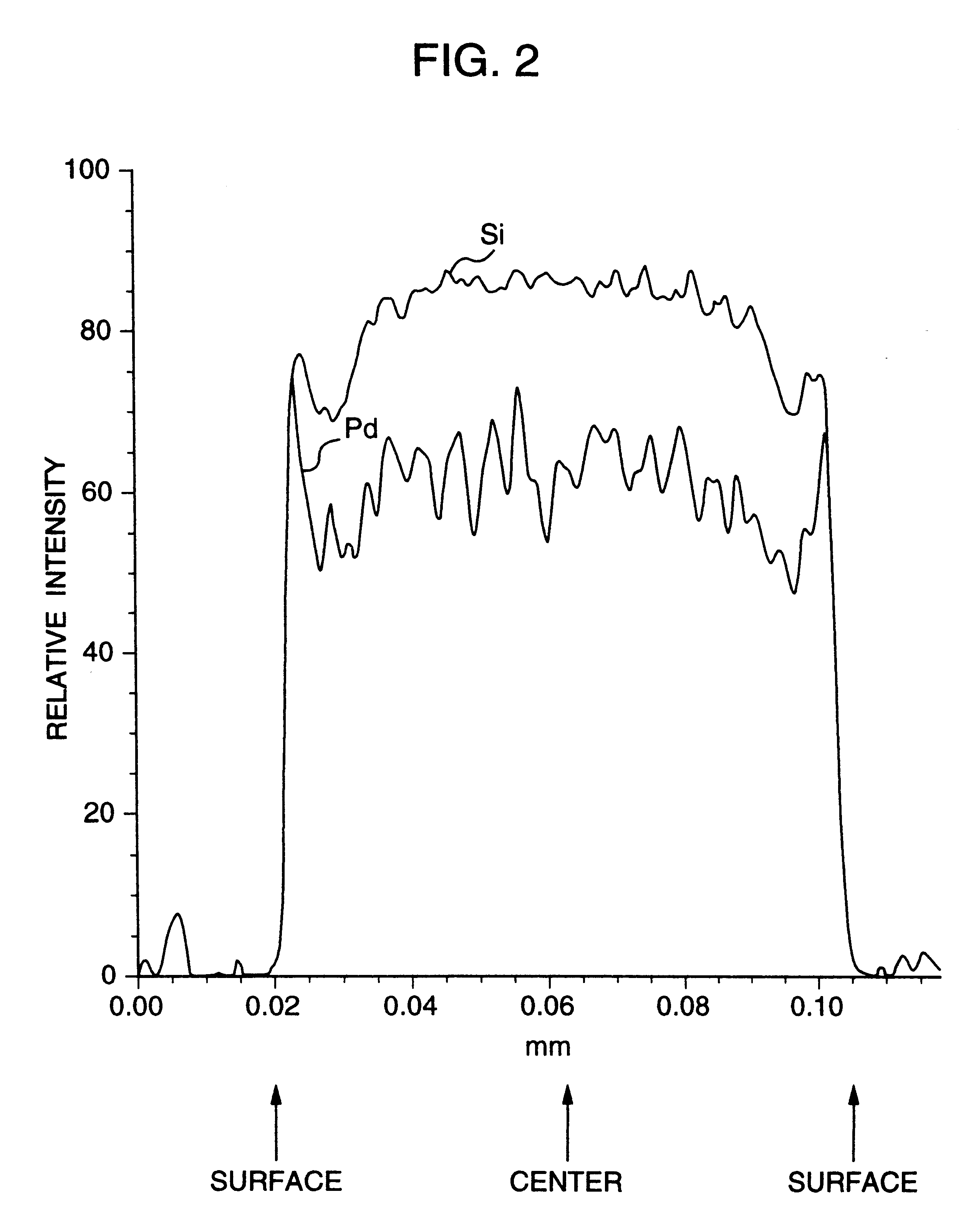

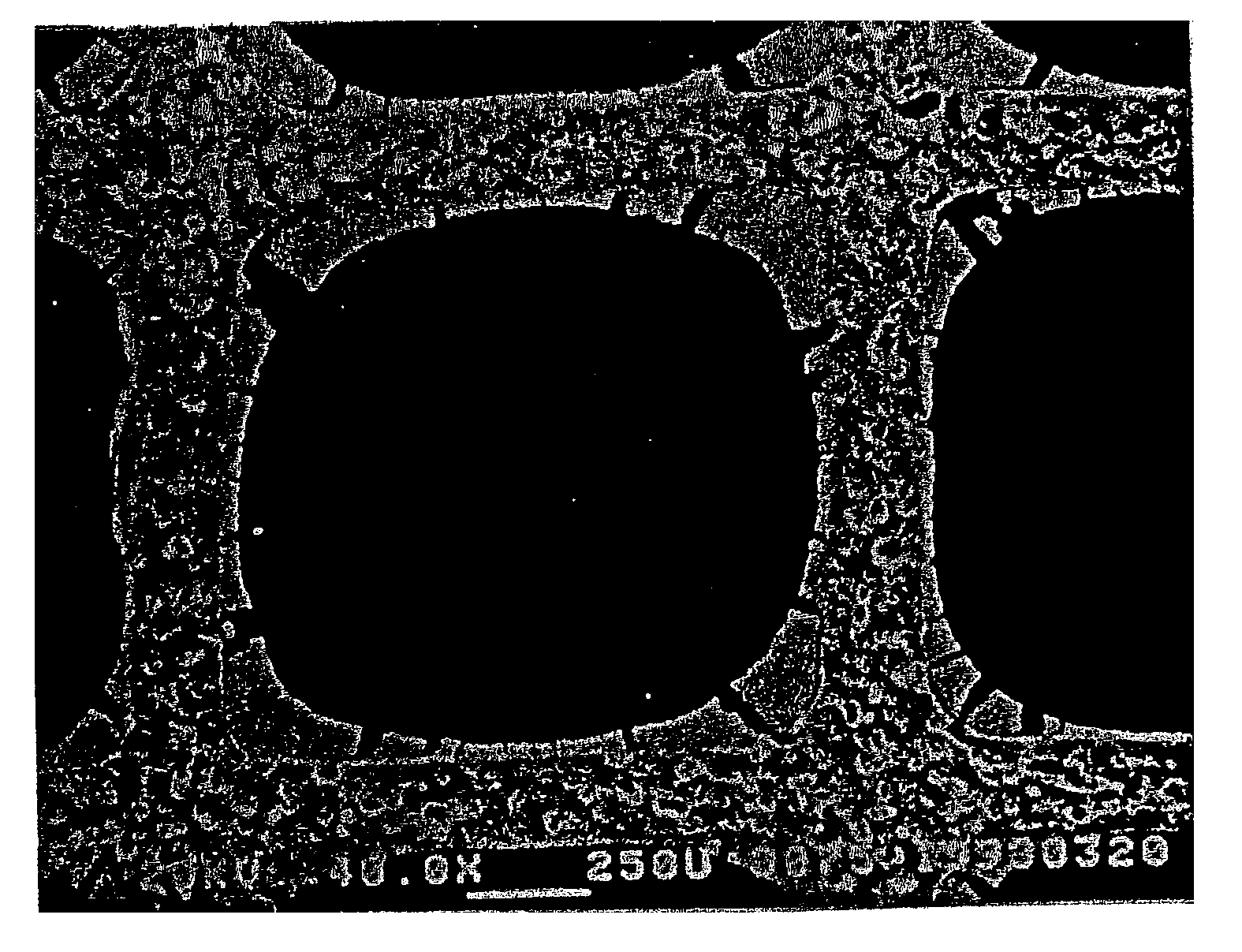

Noble metal support

InactiveUS6228800B1Efficient use ofLong catalyst lifeOrganic compound preparationCatalyst activation/preparationPalladiumChemistry

A noble metal-supported article which comprises a carrier and a palladium-containing metal component supported on the carrier, which article has (A) a layer in which substantially no palladium is supported in the interior of the carrier and (B) a layer in which palladium is supported in the region from the outer surface to a depth of less than 100 mum of the carrier.

Owner:ASAHI KASEI KK

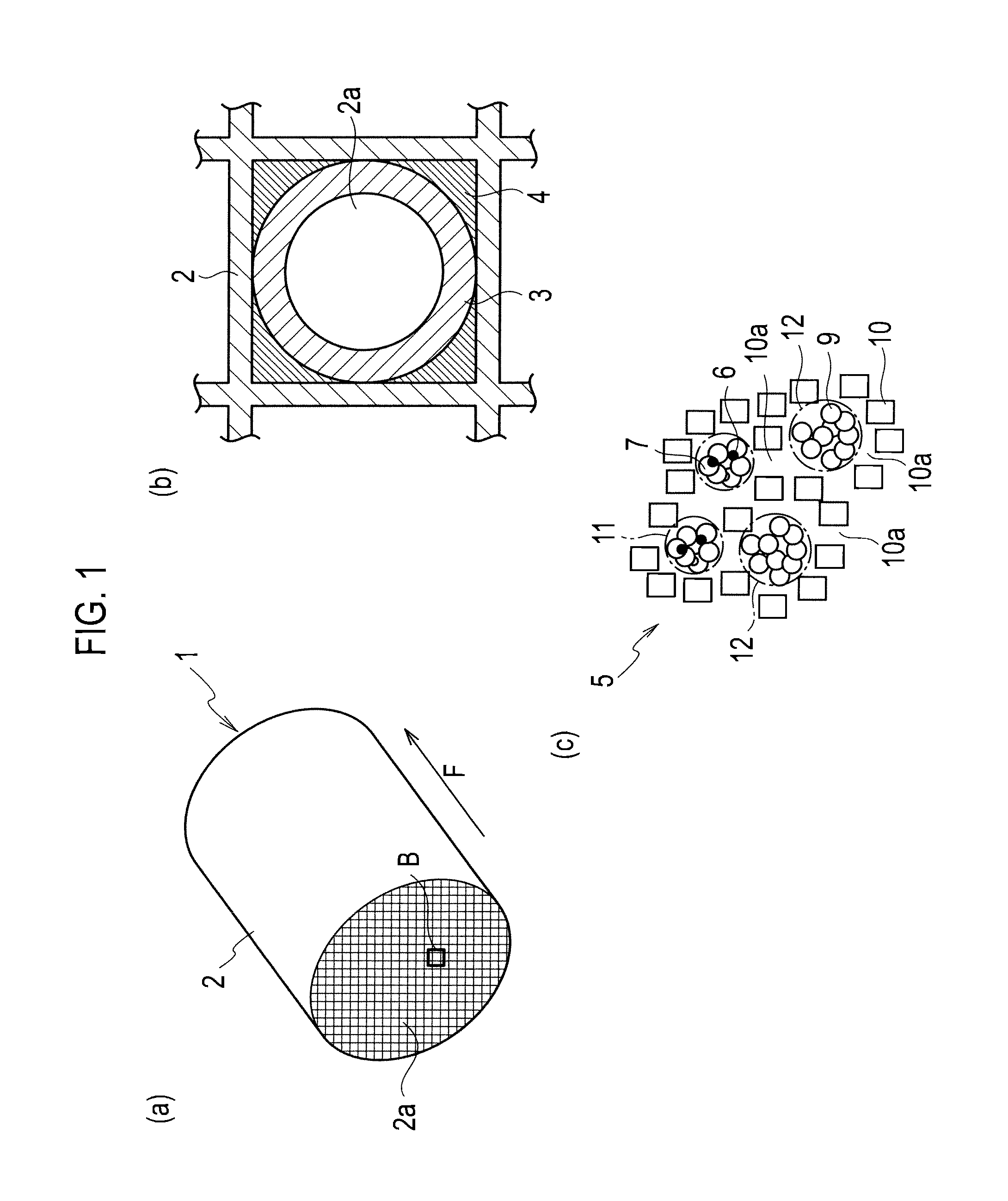

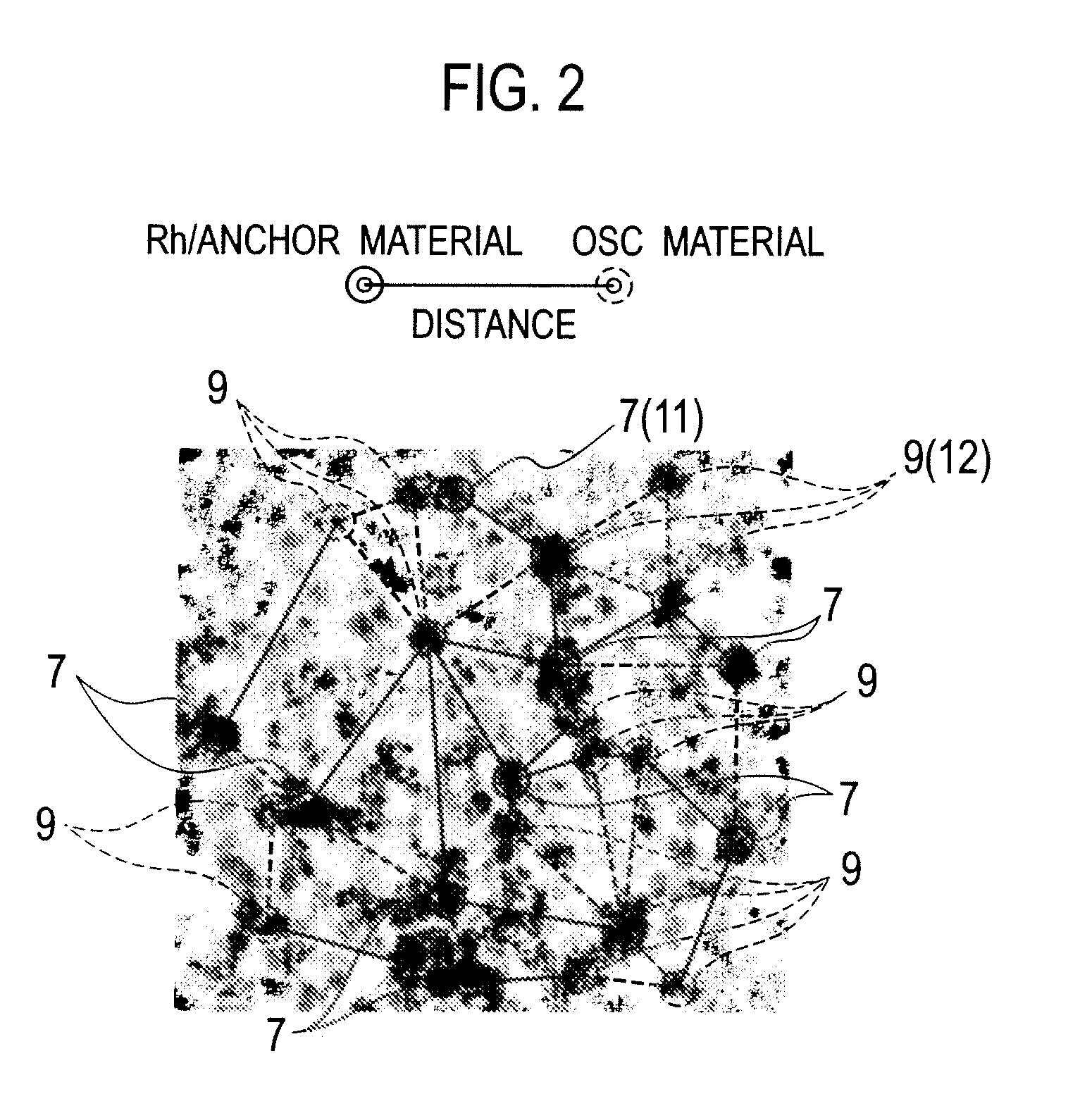

Catalyst for purifying exhaust gas

InactiveUS6335305B1Internal combustion piston enginesDispersed particle separationComposite oxideExhaust gas

A catalyst for purifying an exhaust gas includes a support and a noble metal loaded on the support. The support includes a mixture containing a porous oxide and a composite oxide. The composite oxide is expressed by the following formula:in which the values "a" and "b" are molar ratios and the value "a" falls in a range of from 0.4 to 2.5 and the value "b" falls in a range of from 0.2 to 0.7. The support includes a particle having a particle diameter of 5 mum or more in an amount of 30% by volume or more. With the thus arranged support, even when the catalyst is subjected to such a severe durability test that it is heated at 1,000° C. for 10 to 20 hours, it exhibits a high purifying activity, and its coating layer is inhibited from cracking or coming off.

Owner:TOYOTA CENT RES & DEV LAB INC

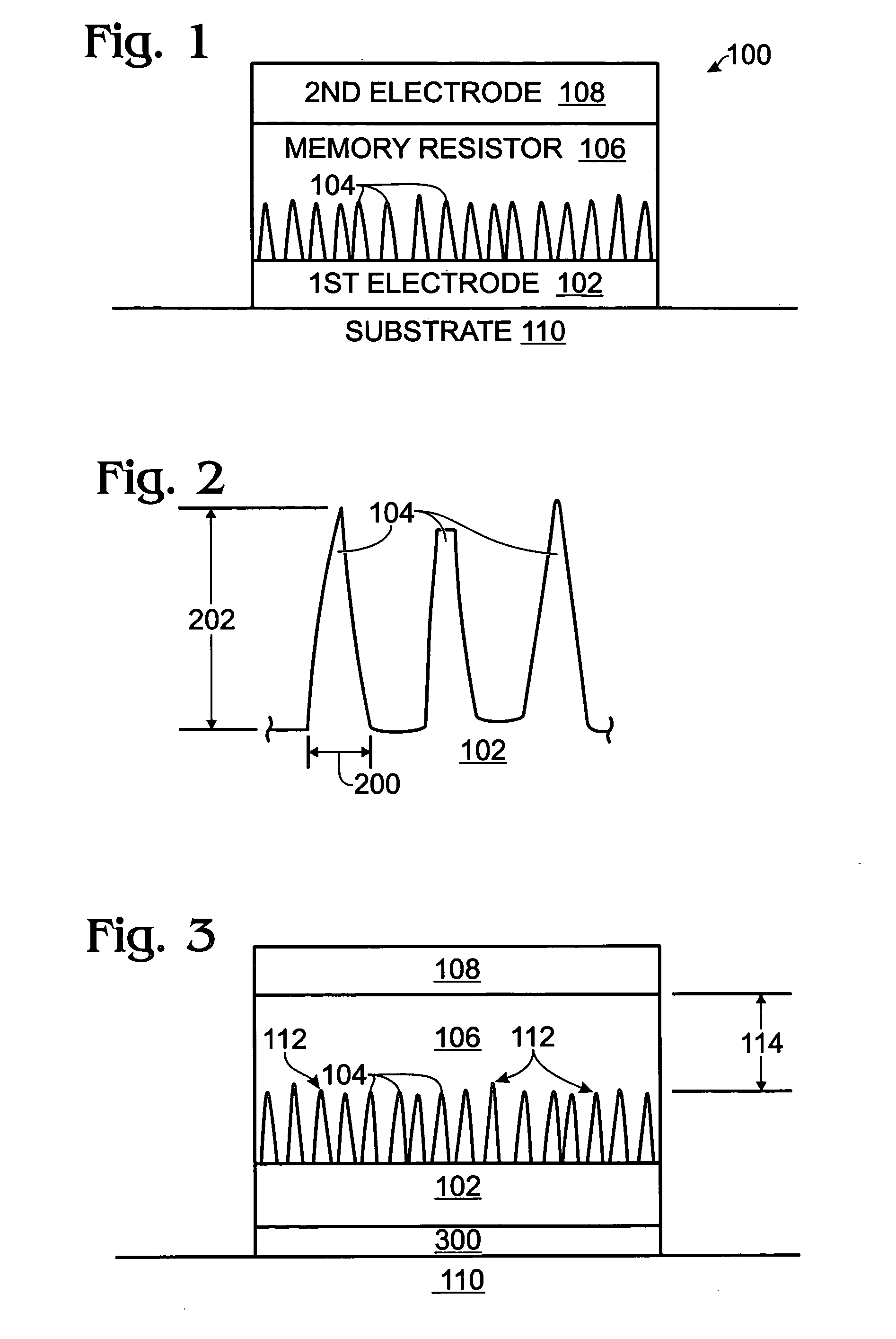

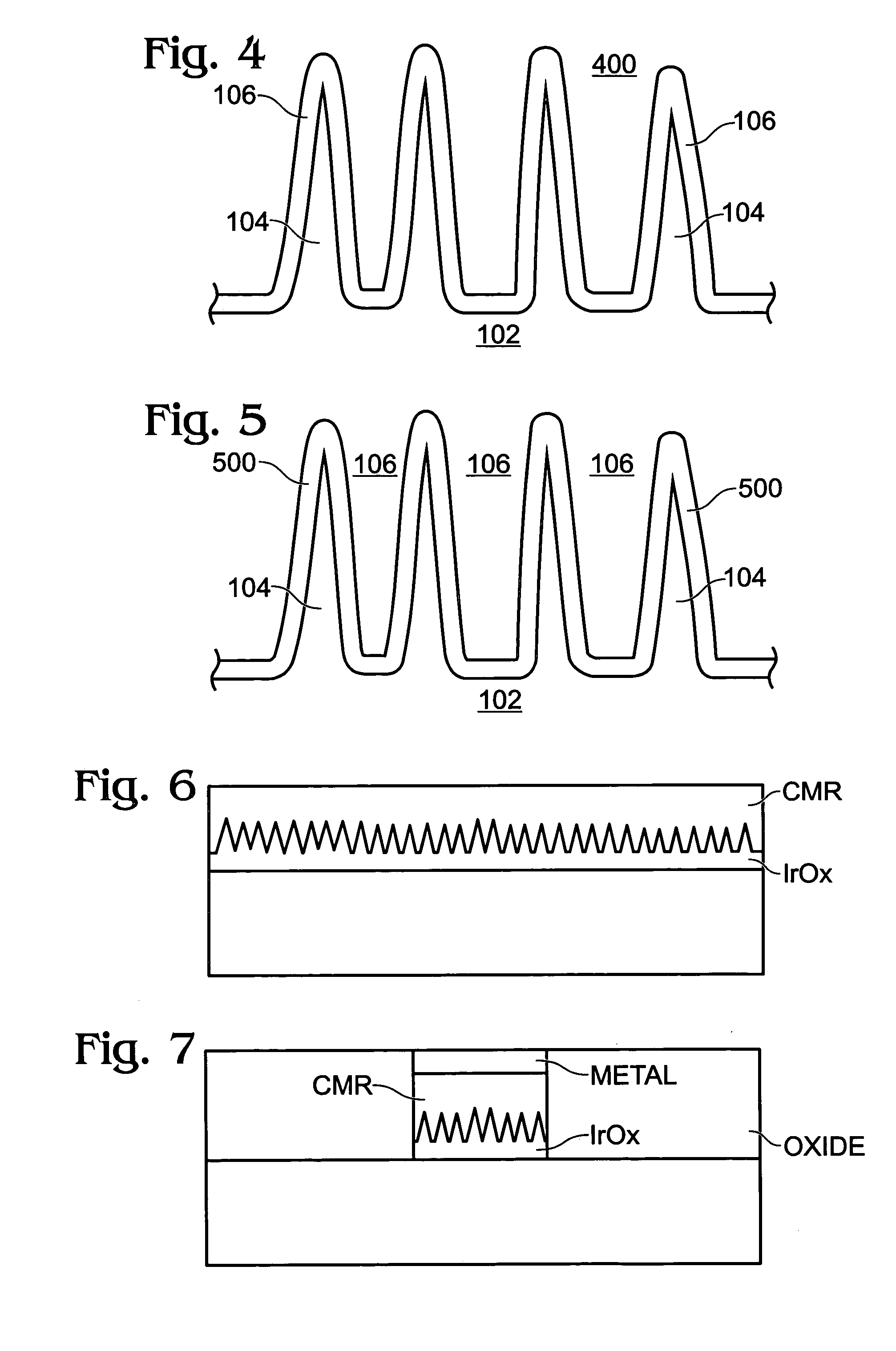

Non-volatile memory resistor cell with nanotip electrode

InactiveUS20060160304A1Promote bipolar switching characteristicReduce voltageSolid-state devicesSemiconductor/solid-state device manufacturingGas phaseEngineering

A non-volatile memory resistor cell with a nanotip electrode, and corresponding fabrication method are provided. The method comprises: forming a first electrode with nanotips; forming a memory resistor material adjacent the nanotips; and, forming a second electrode adjacent the memory resistor material, where the memory resistor material is interposed between the first and second electrodes. Typically, the nanotips are iridium oxide (IrOx) and have a tip base size of about 50 nanometers, or less, a tip height in the range of 5 to 50 nm, and a nanotip density of greater than 100 nanotips per square micrometer. In one aspect, the substrate material can be silicon, silicon oxide, silicon nitride, or a noble metal. A metalorganic chemical vapor deposition (MOCVD) process is used to deposit Ir. The IrOx nanotips are grown from the deposited Ir.

Owner:SHARP KK

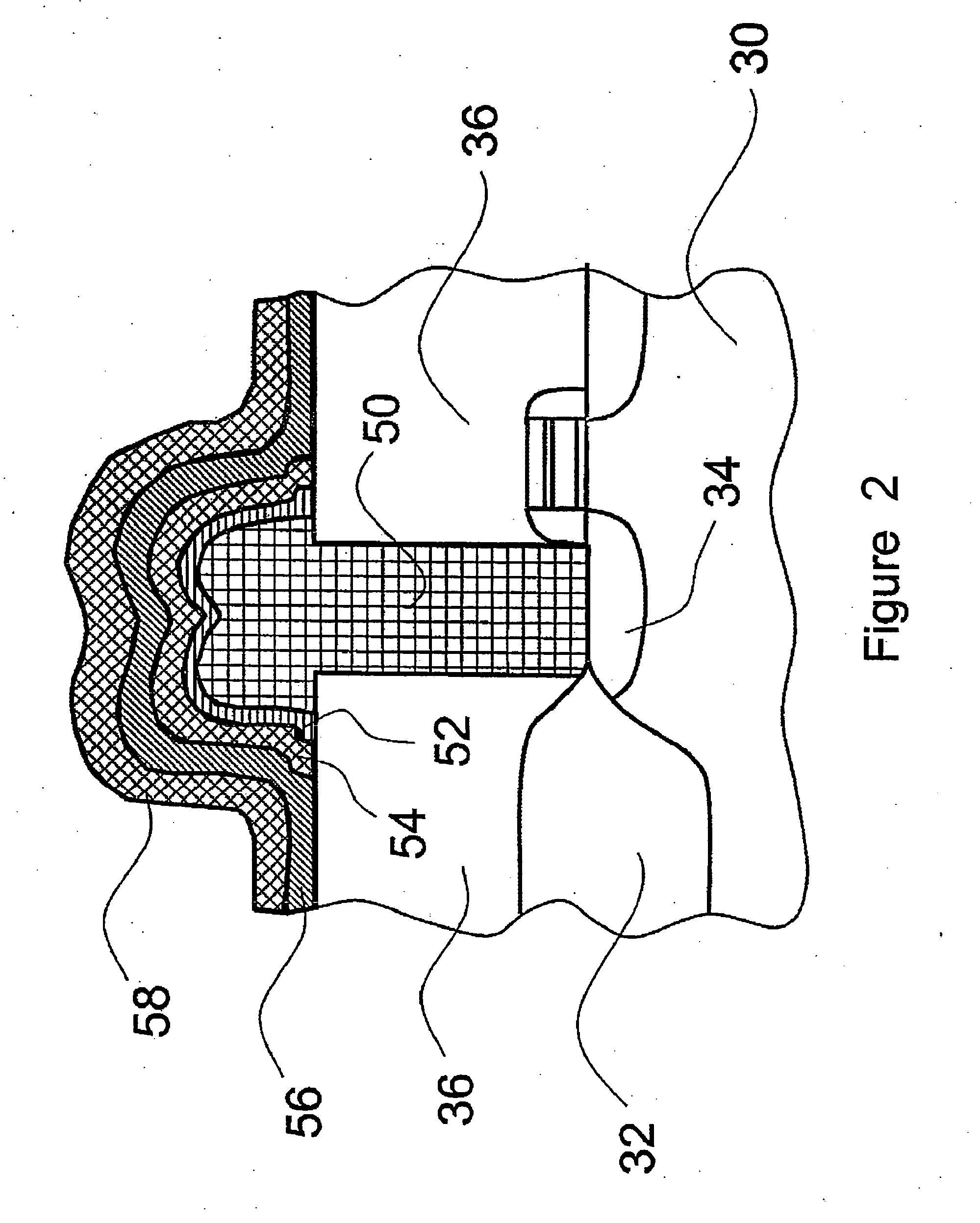

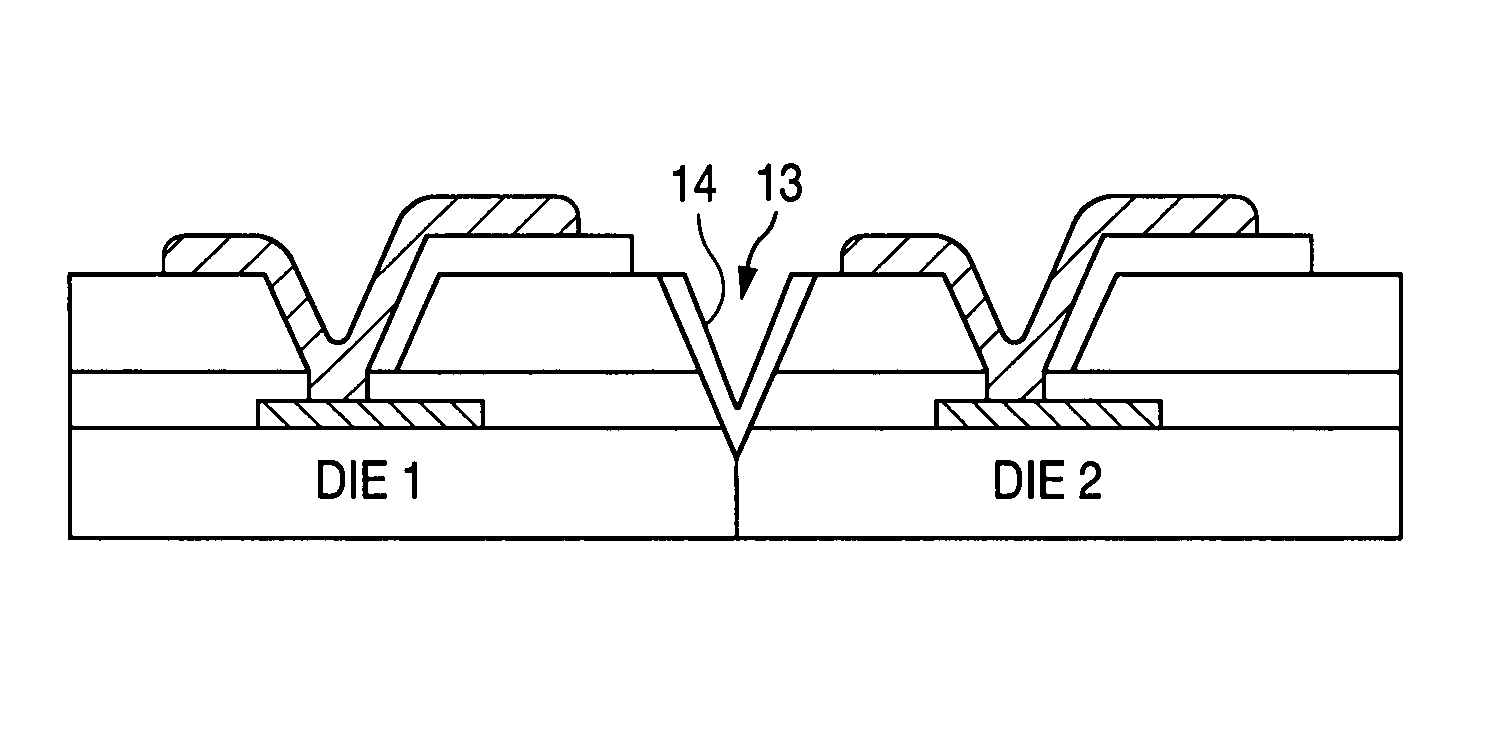

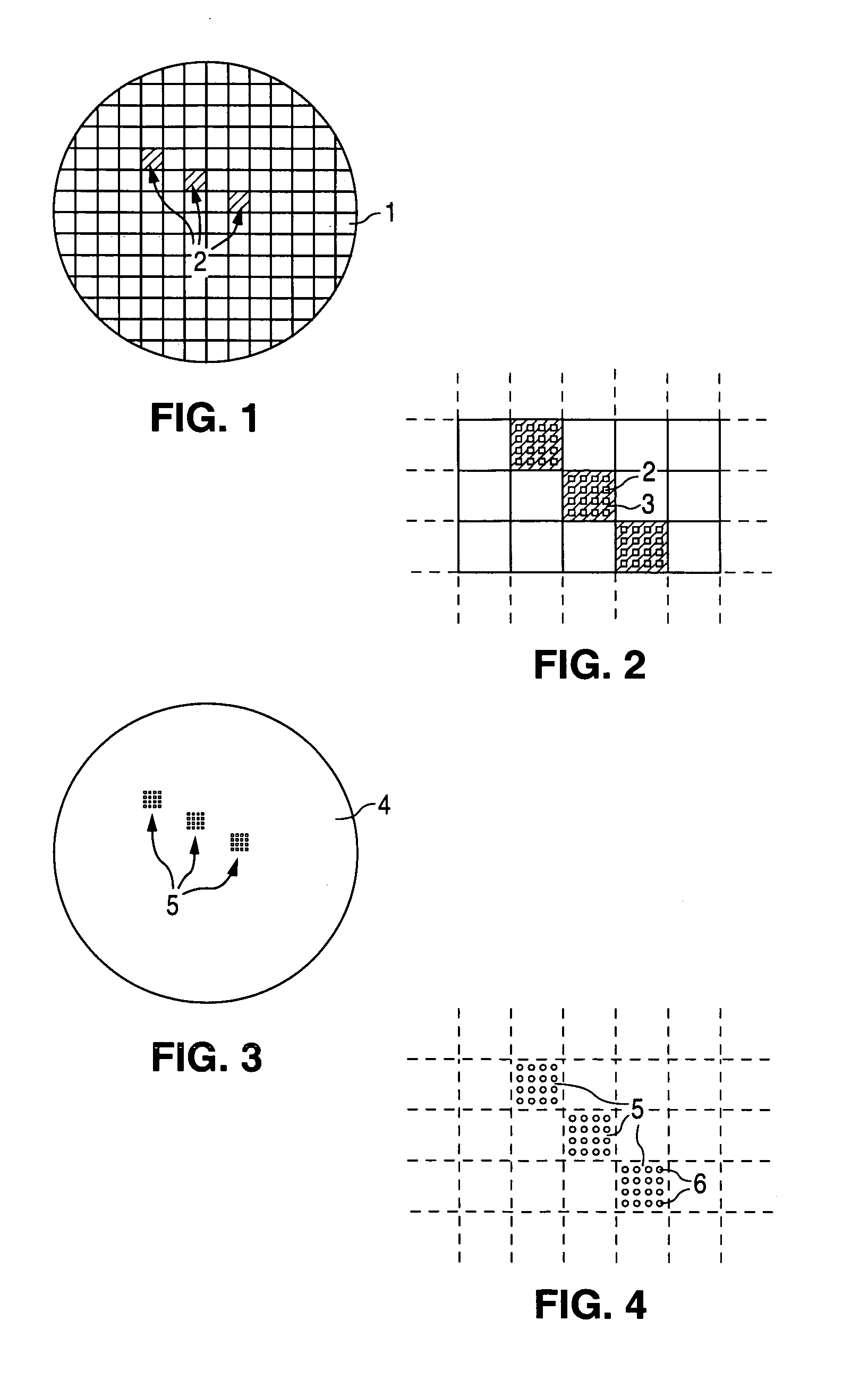

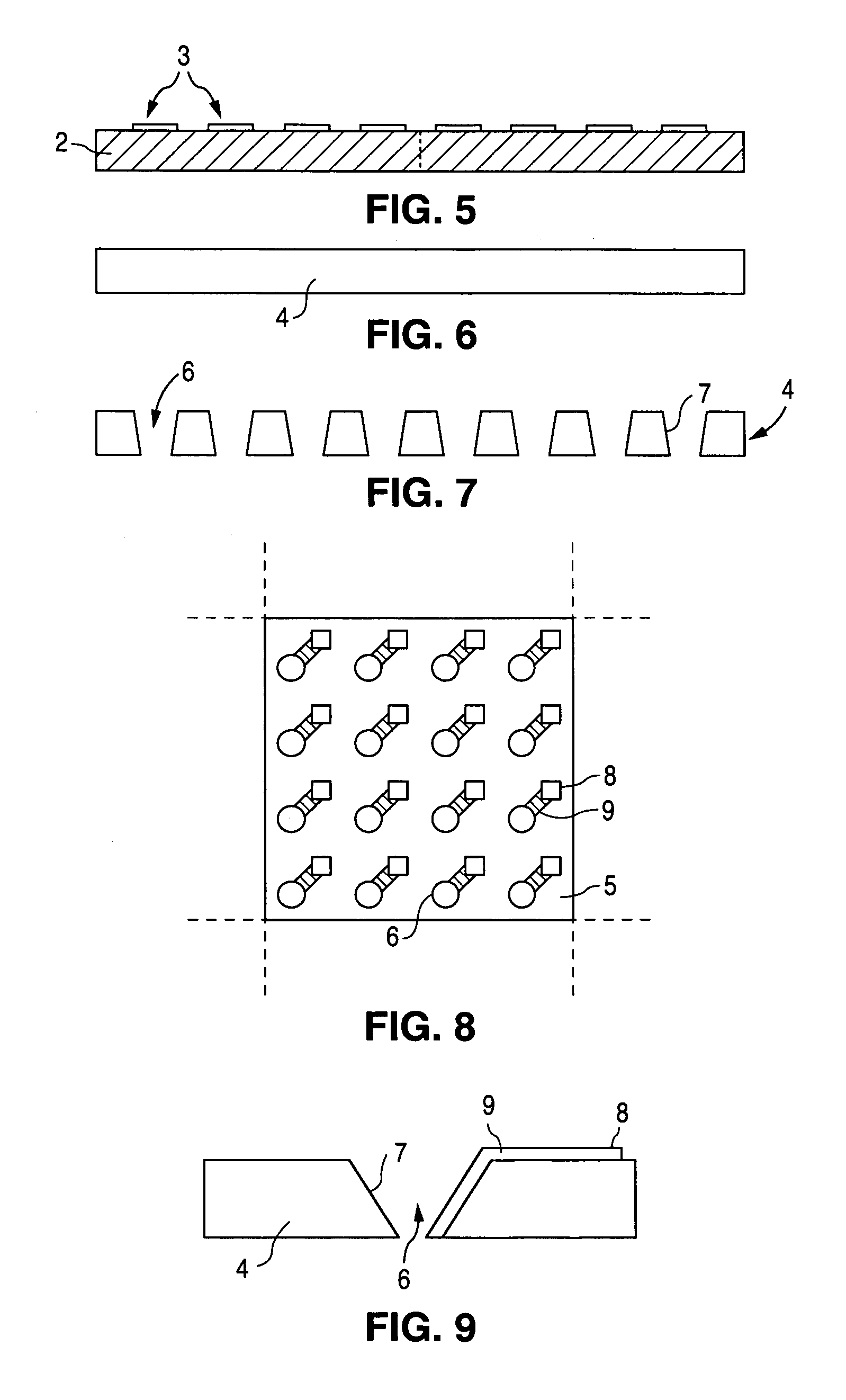

Hermetic wafer scale integrated circuit structure

InactiveUS6982475B1Prevent surfaceDamaged and destroyedSemiconductor/solid-state device detailsSolid-state devicesScale structureHermetic seal

A wafer scale semiconductor integrated circuit packaging technique provides a hermetic seal for the individual integrated circuit die formed as part of the wafer scale structure. A semiconductor wafer is manufactured to include a number of individual semiconductor die. Each individual die formed on the wafer includes a number of bond pads that are exposed on the die surface in various locations to provide electrical connections to the circuitry created on the die. The wafer further includes a planar glass sheet that is substantially the same size as the wafer, the glass sheet being adhered to the wafer using a suitable adhesive. The glass sheet has a number of pre-formed holes in it, the arrangement of the pre-formed holes corresponding to the location of the bond pads at each of the individual semiconductor die formed as part of the wafer structure. Following adherence of the glass sheet to the semiconductor wafer utilizing the intermediate adhesive material, metal connections are made between pads formed on the glass sheet and the bond pads formed on the integrated circuit die. Solder balls are then attached to the pads on the glass sheet to provide a conductive flow between the solder balls and the bond pads. After the solder balls are attached, trenches are cut around each of the individual die on the wafer. The trenches are cut at an angle and extend through the glass sheet and the intermediate adhesive material and into the semiconductor substrate in which the integrated circuits are formed. After the trenches are cut around each individual semiconductor die, a noble metal is deposited on the sidewalls of the trench to extend over the interface between the glass sheet, the adhesive material and the semiconductor die. The wafer is then cut along the noble metal lined trenches to provide individual, hermetically sealed packaged integrated circuit die.

Owner:MICRO CHIP SCALE PACKAGING

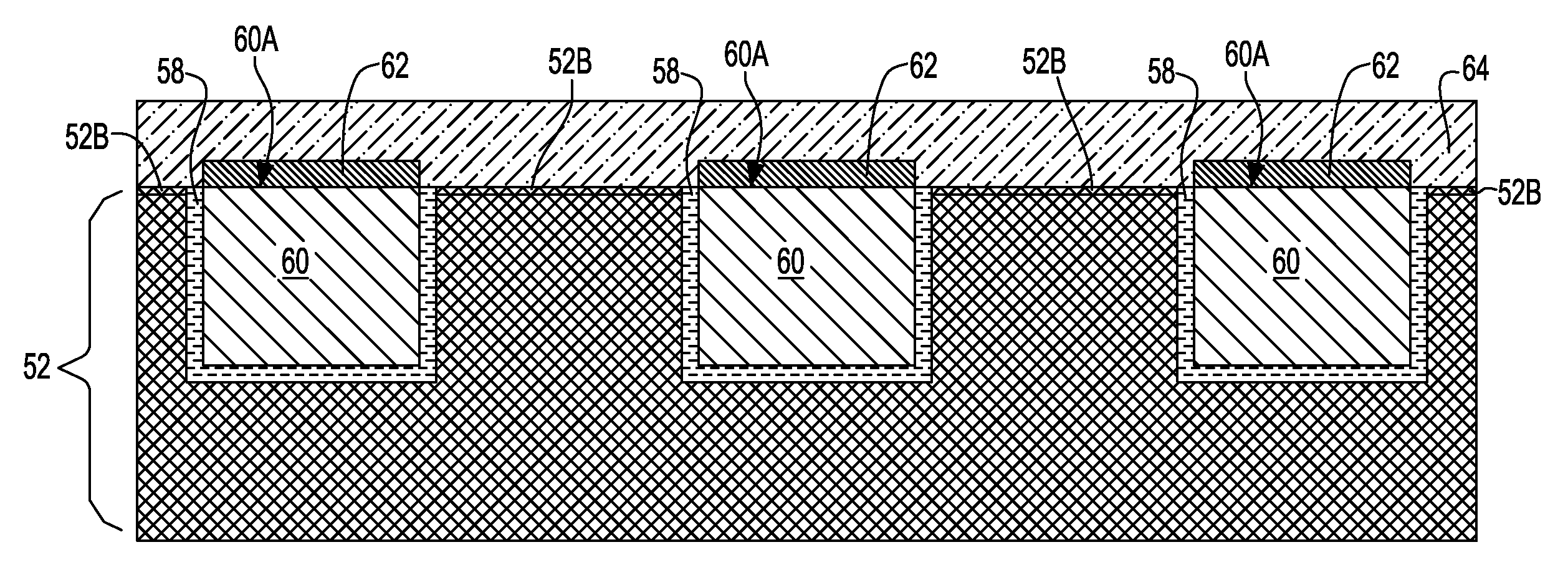

Noble metal cap for interconnect structures

InactiveUS20090189287A1Improved EM reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSurface layerDielectric surface

An interconnect structure that includes a dielectric material having a dielectric constant of about 3.0 or less is provided. This low k dielectric material has at least one conductive material having an upper surface embedded therein. The dielectric material also has a surface layer that is made hydrophobic prior to the formation of the noble metal cap. The noble metal cap is located directly on the upper surface of the at least one conductive material. Because of the presence of the hydrophobic surface layer on the dielectric material, the noble metal cap does not substantially extend onto the hydrophobic surface layer of the dielectric material that is adjacent to the at least one conductive material and no metal residues from the noble metal cap deposition form on this hydrophobic dielectric surface.

Owner:GLOBALFOUNDRIES INC

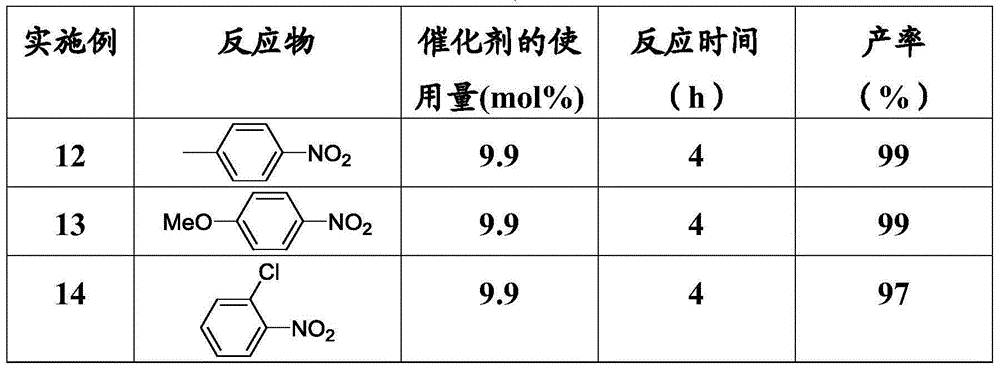

Catalyst for selective hydrogenation reaction of aromatic nitrocompound and preparation method of catalyst

InactiveCN105032424AEasy to storeLow costCarboxylic acid nitrile preparationOrganic compound preparationNitro compoundAlcohol

The invention relates to a catalyst for selective hydrogenation reaction of an aromatic nitrocompound and a preparation method of the catalyst. The catalyst consists of a catalyst carrier and active metal coated with carbon, wherein the catalyst carrier includes a carbon-base carrier, SiO2, TiO2 or Al2O3; the active metal is selected from Co, Fe, Ni or Cu and other poor and noble metals. The catalyst is prepared by adopting a Pechini type sol-gel process which comprises the steps of dispersing an active metal precursor to water containing a coordination compound, adding a polyhydric alcohol solution and a macromolecule auxiliary, then adding the carrier, stirring for dispersion, carrying out hydrothermal reaction, separating out solid on the lower layer, and calcining in the inert atmosphere to obtain the catalyst in which carbon coats the active metal. Compared with the prior art, the catalyst can realize the hydrogenation reaction of a substituted aromatic nitrocompound in the mild condition; substrate conversion rate and production selectivity are high; the catalyst has recyclable economy and good application prospect.

Owner:INST OF CHEM CHINESE ACAD OF SCI

Selective formation of metal layers in an integrated circuit

ActiveUS7476618B2Improve reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingCopper interconnectSelective deposition

A method for enhancing the reliability of copper interconnects and / or contacts, such as the bottom of vias exposing top surfaces of buried copper, or at the top of copper lines just after CMP. The method comprises contacting the exposed copper surface with a vapor phase compound of a noble metal and selectively forming a layer of the noble metal on the exposed copper surface, either by a copper replacement reaction or selective deposition (e.g., ALD or CVD) of the noble metal.

Owner:ASM JAPAN

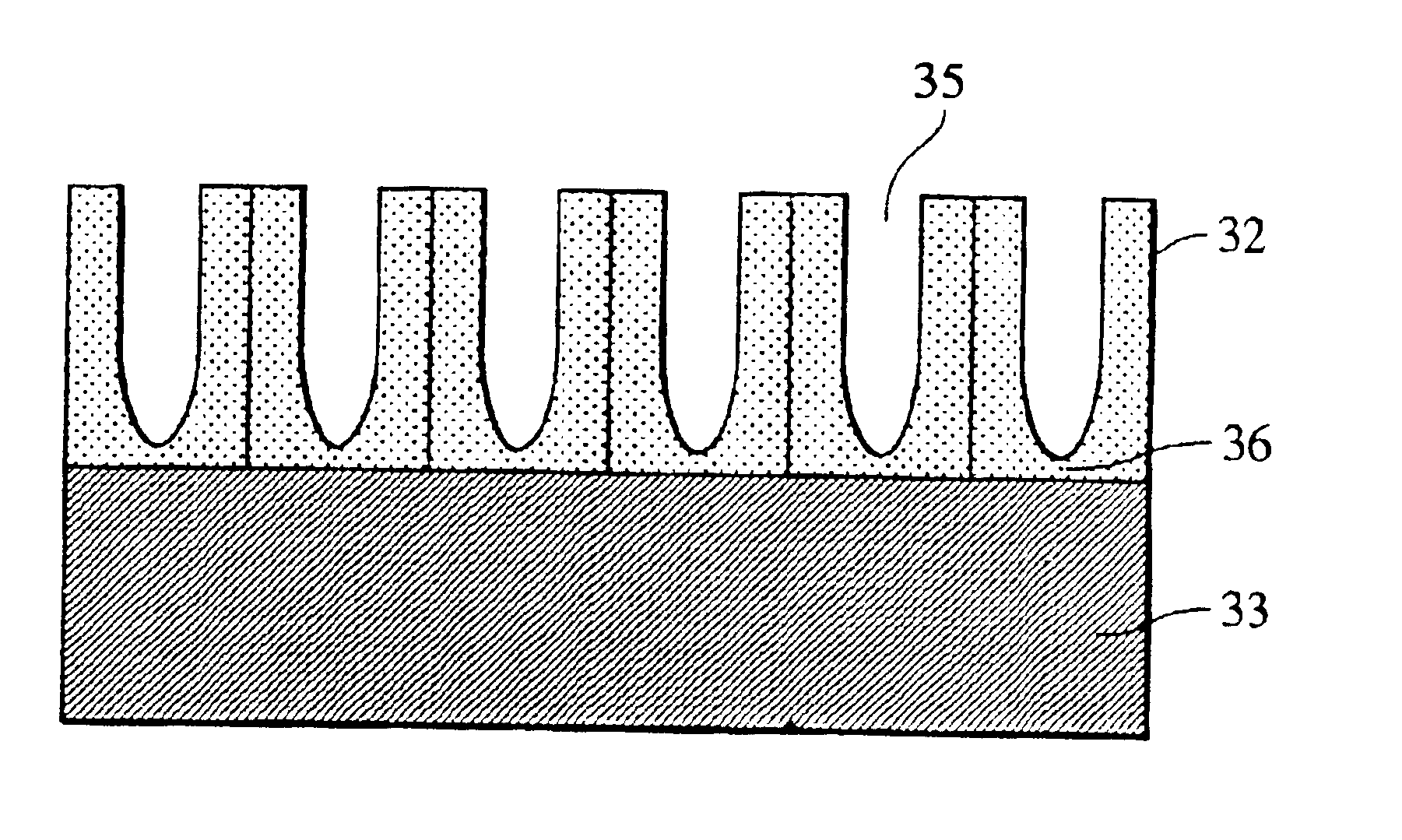

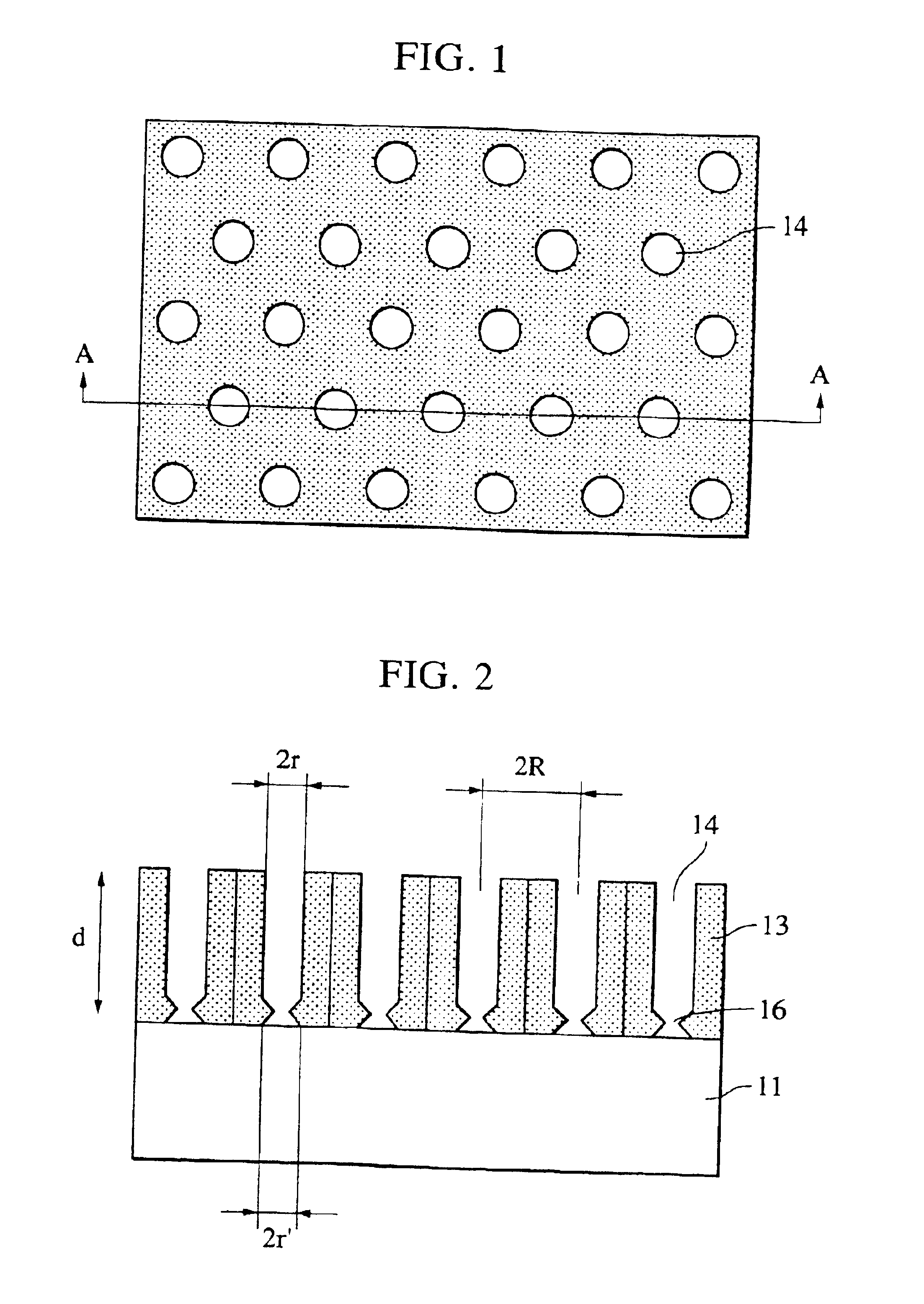

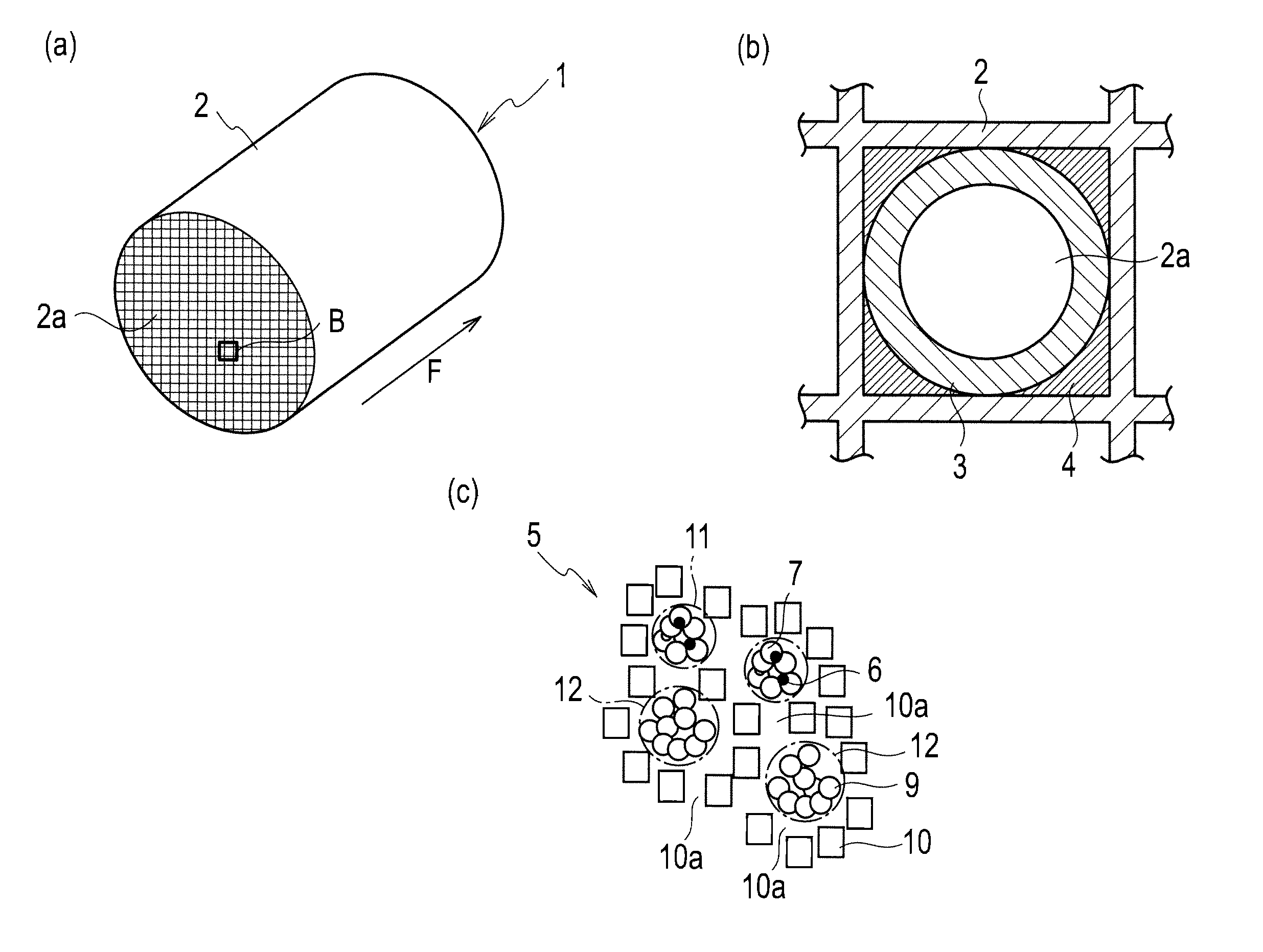

Nanostructure, electron emitting device, carbon nanotube device, and method of producing the same

InactiveUS6838297B2Good shape uniformityReliably producedNanostructure manufactureNanomagnetismNanoholeCarbon nanotube

Owner:CANON KK

Exhaust gas purifying catalyst and method for manufacturing the same

ActiveUS8486853B2Increased durabilityImprove performanceInternal combustion piston enginesOther chemical processesExhaust fumesExhaust gas

Owner:NISSAN MOTOR CO LTD

Process for preparing noble metal nanoparticles

A process for preparing metal nanoparticles, comprising reacting suitable metal salts and anionic surfactant containing an anionic group of carboxylic group (COO-), sulfate group (SO42-) or sulfonate group (SO32-) as reducing agent in water under reflux at a temperature of 50-140° C., such that under the reducing power of said anionic surfactant itself, the metal salts can be effectively reduced into metal nanoparticles having a uniform particle size and that the reaction will be not too fast, no large microparticle will be formed, the yield will not be lowered, and the nanoparticle thus prepared can be dispersed stably in polar and non-polar solvent.

Owner:CHANG CHUN PETROCHEMICAL CO LTD

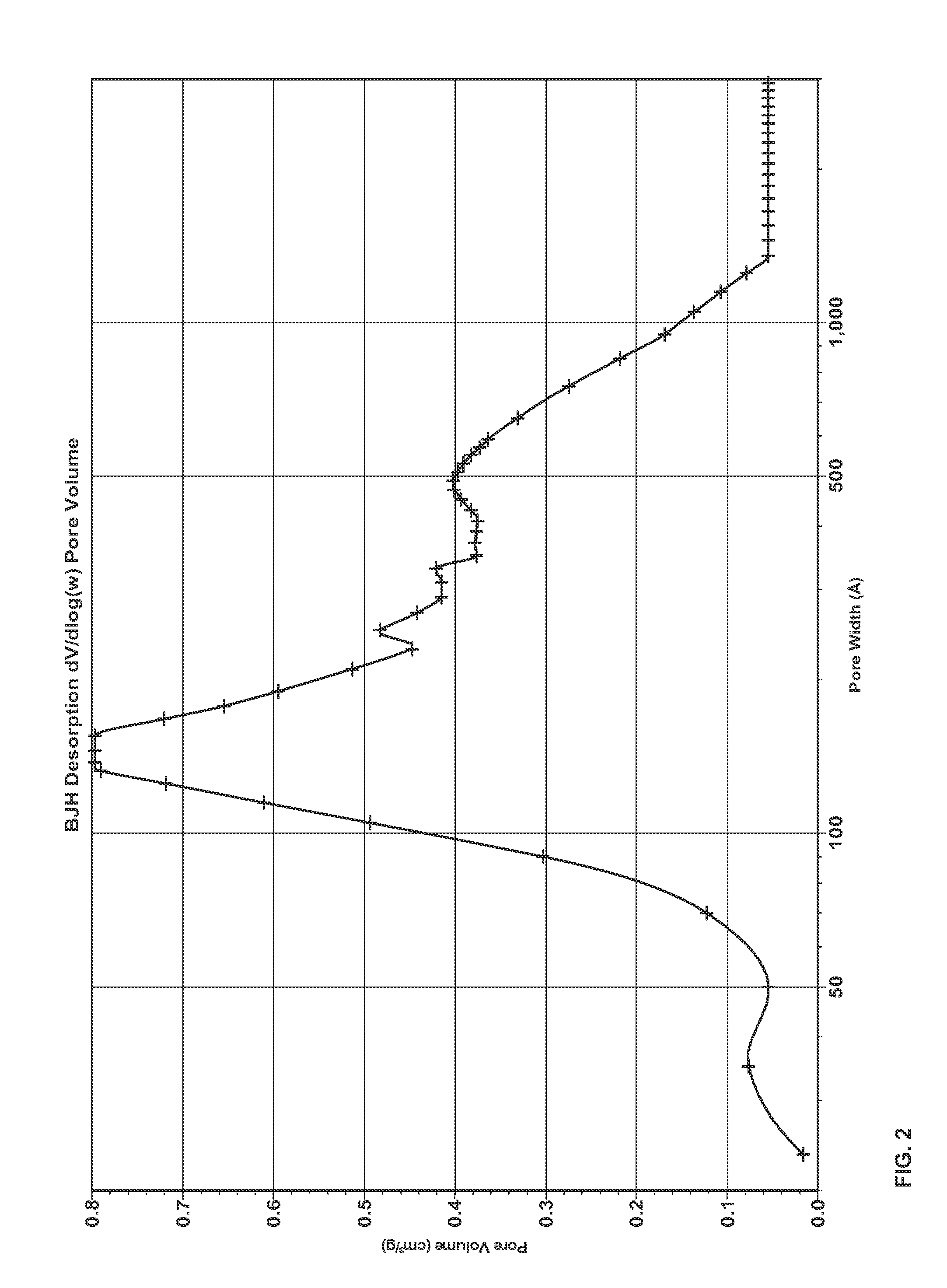

Porous inorganic composite oxide

ActiveUS20120129690A1Improve thermal stabilityHigh pore volumeHeat treatmentsInternal combustion piston enginesPtru catalystCerium

A porous inorganic composite oxide containing oxides of aluminum and of cerium and / or zirconium, and, optionally, oxides of one or more dopants selected from transition metals, rare earths, and mixtures thereof, and having a specific surface area, in m2 / g, after calcining at 1100° C. for 5 hours, of ≧0.8235[Al]+11.157 and a total pore volume, in cm3 / g, after calcining at 900° C. for 2 hours, of ≧0.0097[Al]+0.0647, wherein [Al] is the amount of oxides of aluminum, expressed as pbw Al2O3 per 100 pbw of the composite oxide; a catalyst containing one or more noble metals dispersed on the porous inorganic composite oxide; and a method for making the porous inorganic composite oxide.

Owner:RHODIA OPERATIONS SAS

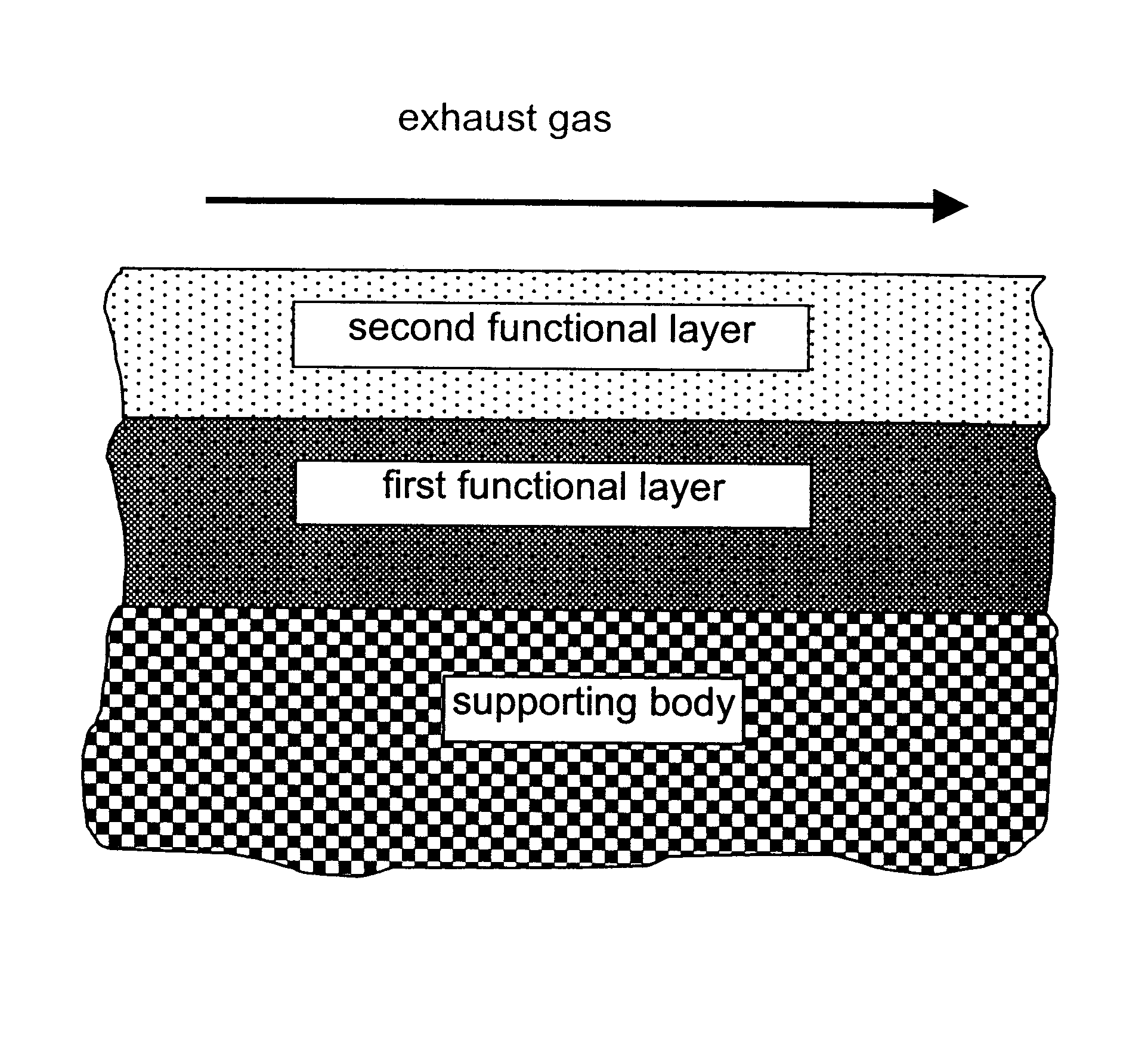

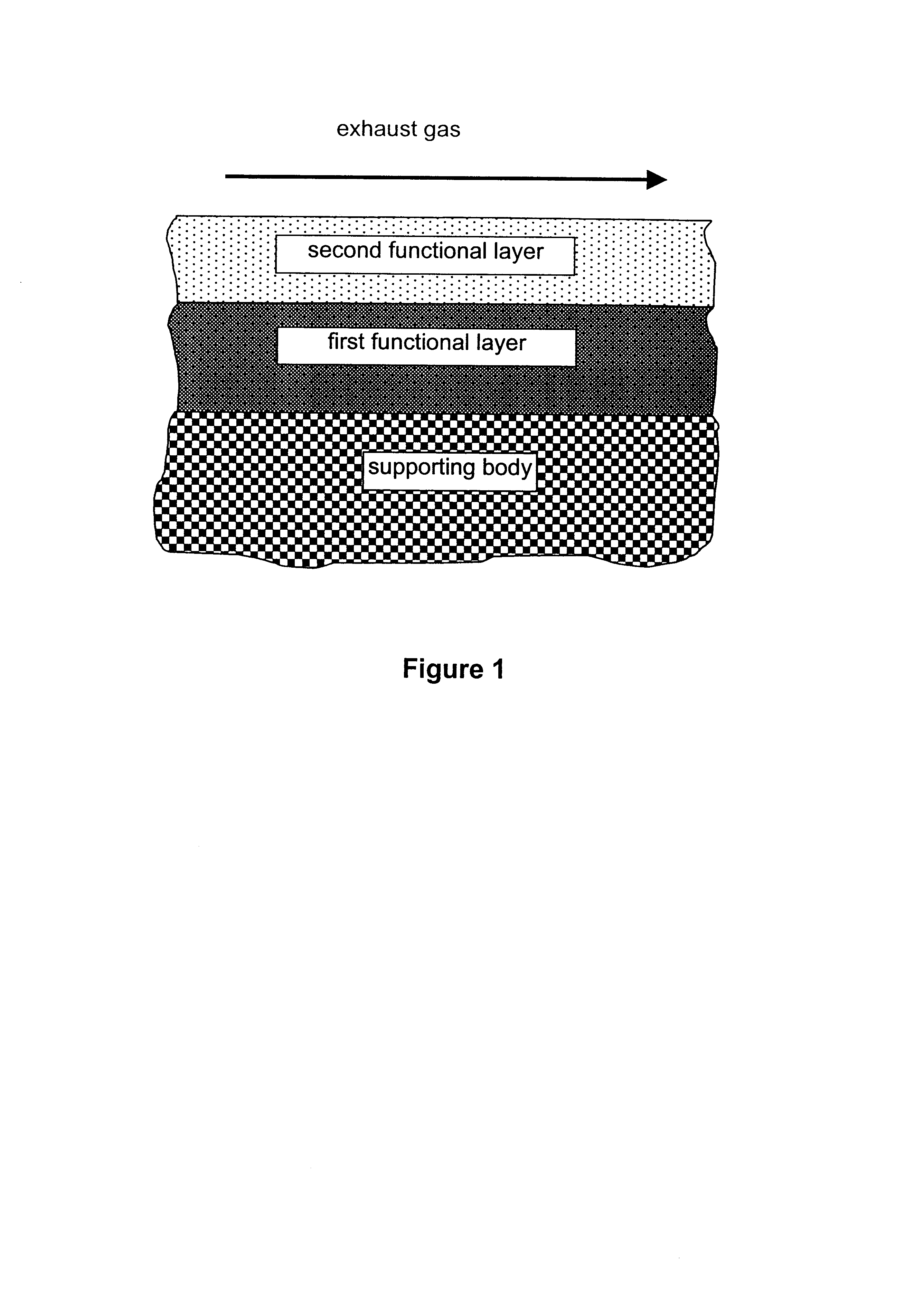

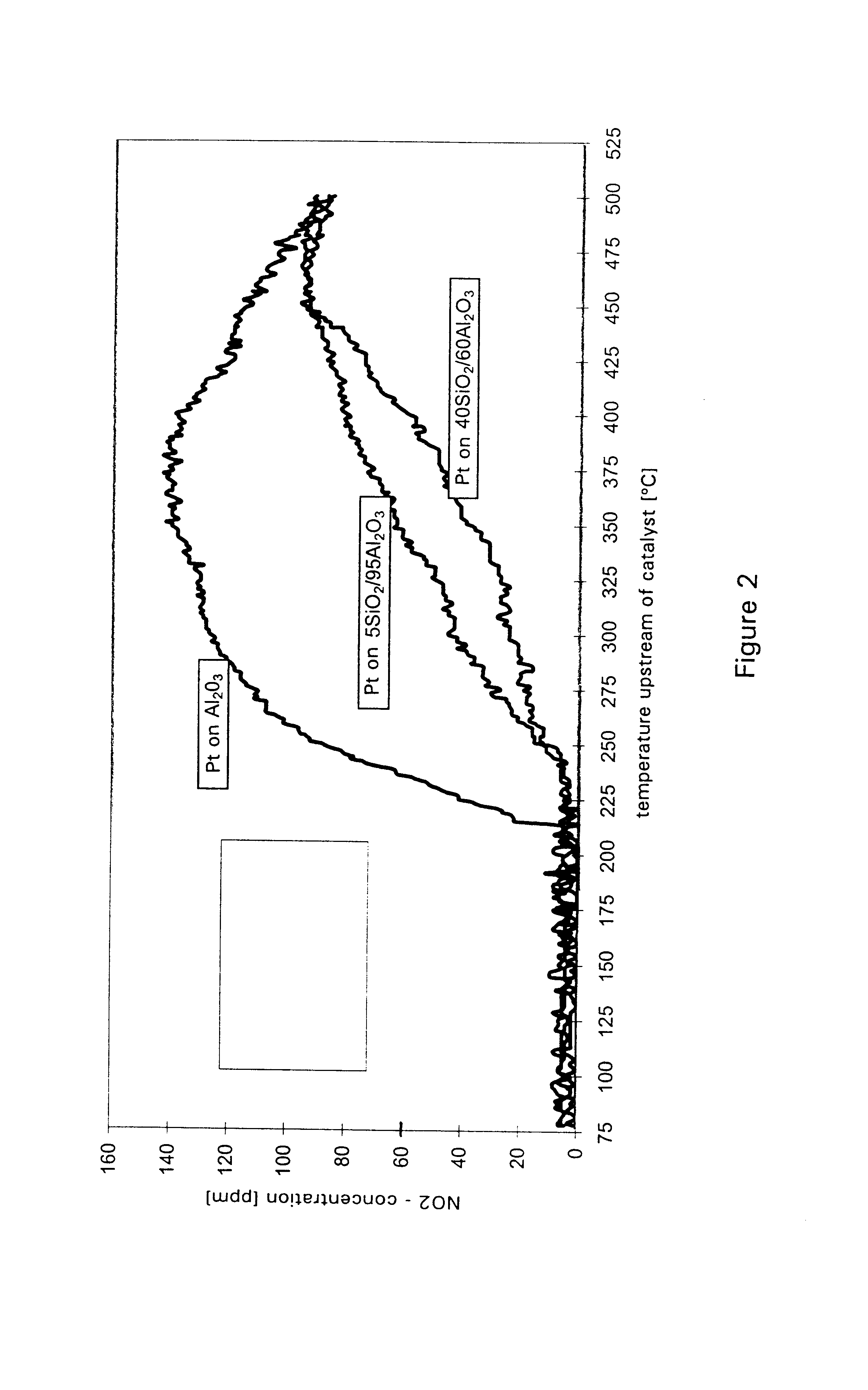

Catalyst for cleaning up the exhaust gases of a diesel engine

InactiveUS6677264B1Reduced activityReduce componentsMolecular sieve catalystsInternal combustion piston enginesCatalytic functionComponents of crude oil

A catalyst for purifying exhaust gases of a diesel engine. The catalyst contains two functional layers superimposed on an inert supporting body, whereby the first layer, which is situated directly on the supporting body, has a nitrogen oxide storage function and the second layer, which is in direct contact with the exhaust gas, has a catalytic function. The second functional layer additionally has a hydrocarbon-storage function and its catalytic function is provided by catalytically active noble metals of the platinum group which are deposited in highly dispersed form on finely divided, acidic carrier materials. Nitrogen oxides in the oxygen-rich exhaust gas of a diesel engine can be converted with optimal utilization of the reductive constituents contained in the exhaust gas. For this purpose, no reducing agents going beyond the reductive components (carbon monoxide and hydrocarbons) which are contained as a consequence of incomplete combustion need to be added to the exhaust gas. Nevertheless, rates of conversion in respect of the nitrogen oxides are obtained, averaged over practical driving cycles, which lie distinctly above the rates of conversion of conventional reduction catalysts.

Owner:UMICORE AG & CO KG +1