Patents

Literature

952 results about "Deposition temperature" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

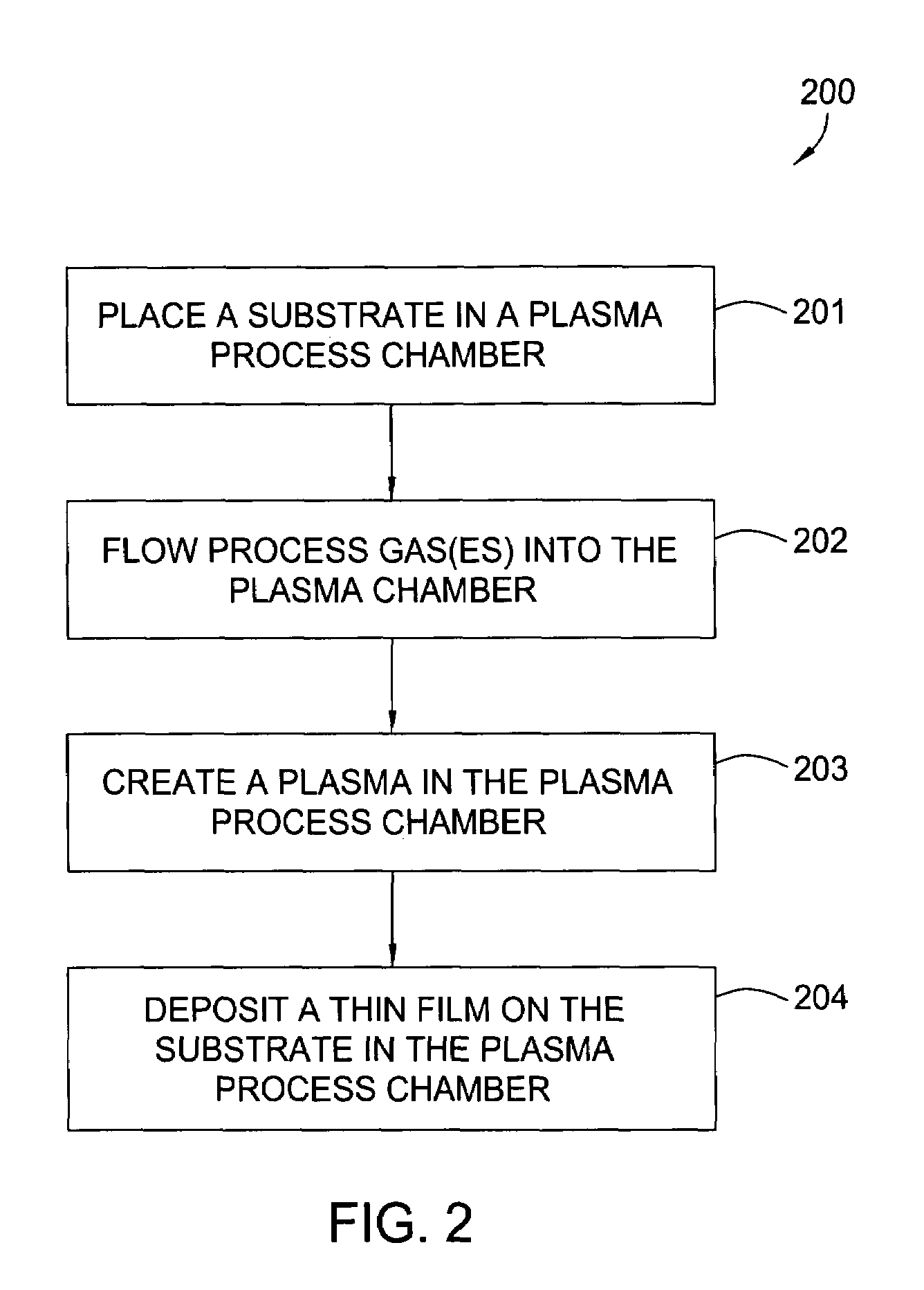

Plasma enhanced chemical vapor deposition. is a chemical vapor deposition technology that utilizes a plasma to provide some of the energy for the deposition reaction to take place. This provides an advantage of lower temperature processing compared with purely thermal processing methods like low pressure chemical vapor deposition (LPCVD).

Doping of dielectric layers

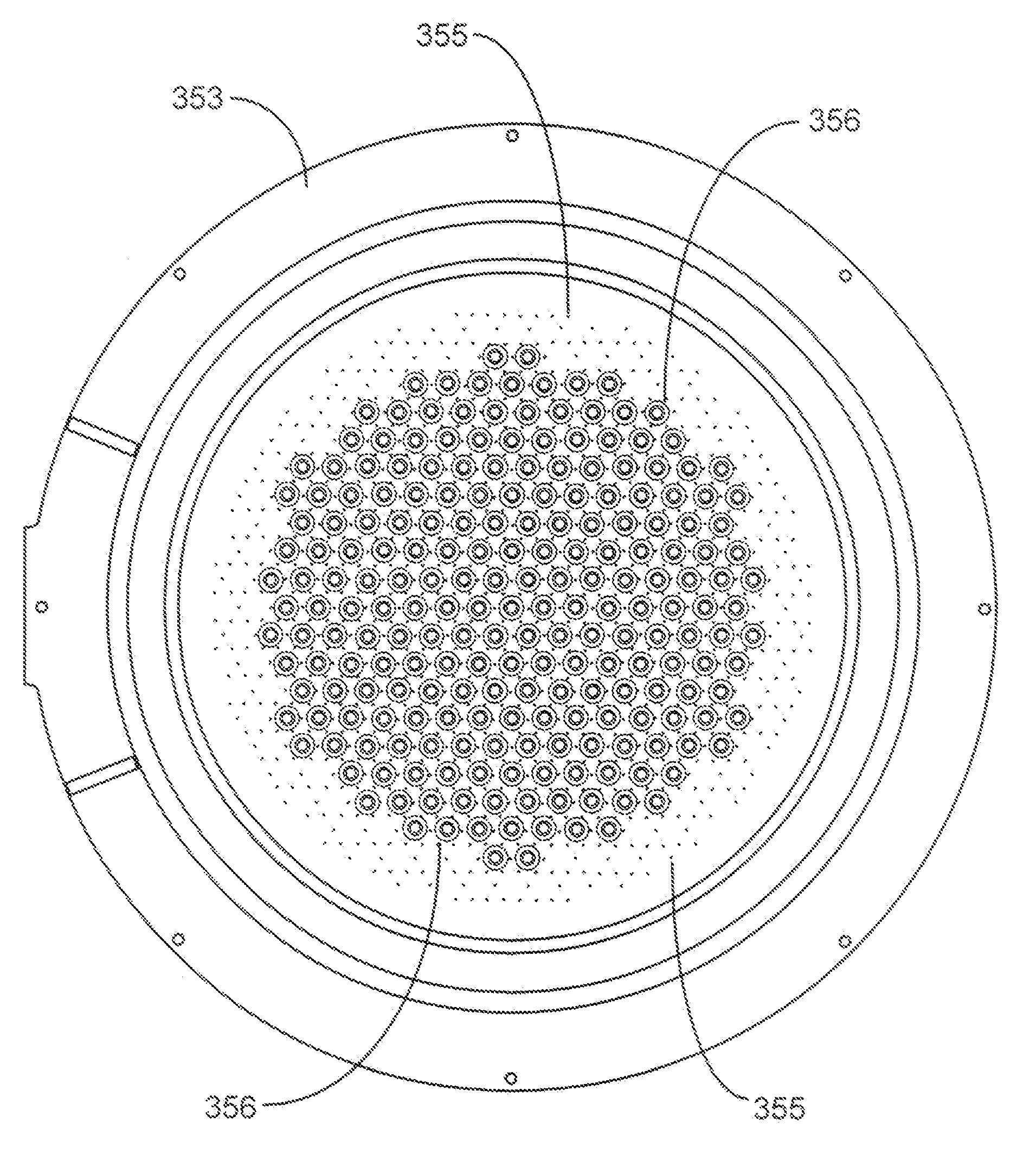

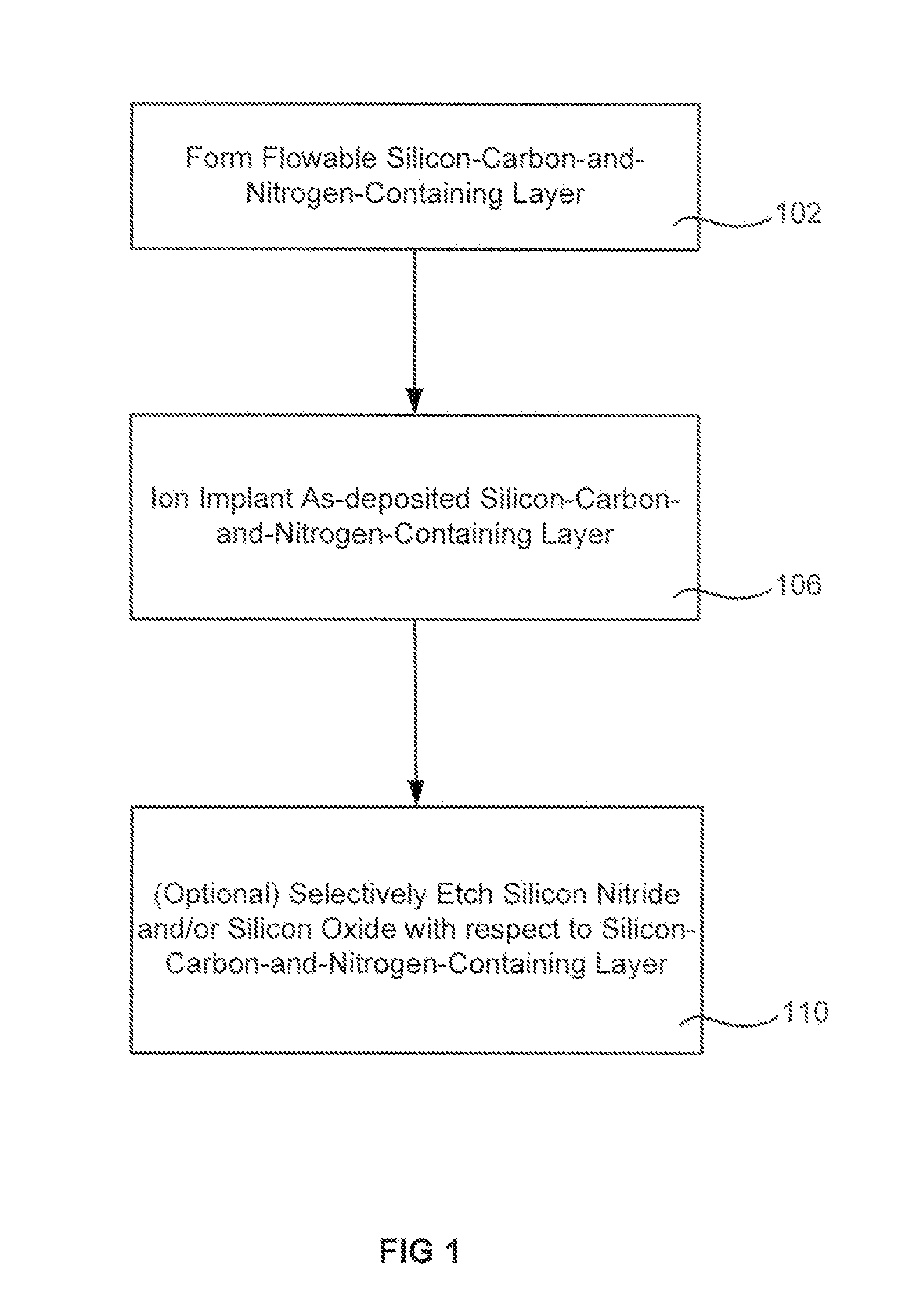

InactiveUS20130217243A1Increase etch tolerancePrevent shrinkageSemiconductor/solid-state device manufacturingDeposition temperaturePhysical chemistry

Methods are described for forming and treating a flowable silicon-carbon-and-nitrogen-containing layer on a semiconductor substrate. The silicon and carbon constituents may come from a silicon-and-carbon-containing precursor while the nitrogen may come from a nitrogen-containing precursor that has been activated to speed the reaction of the nitrogen with the silicon-and-carbon-containing precursor at lower deposition temperatures. The initially-flowable silicon-carbon-and-nitrogen-containing layer is ion implanted to increase etch tolerance, prevent shrinkage, adjust film tension and / or adjust electrical characteristics. Ion implantation may also remove components which enabled the flowability, but are no longer needed after deposition. Some treatments using ion implantation have been found to decrease the evolution of properties of the film upon exposure to atmosphere.

Owner:APPLIED MATERIALS INC

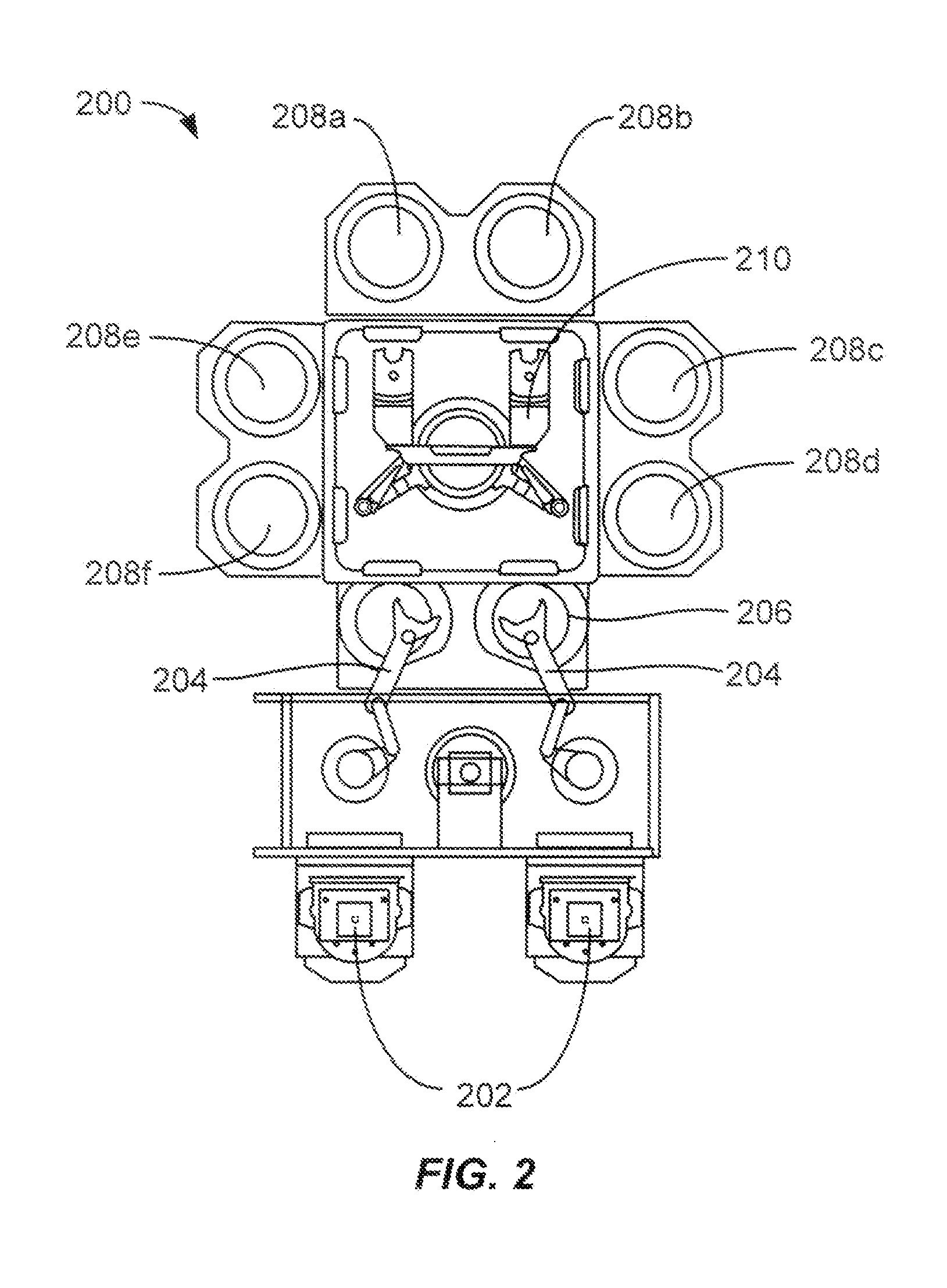

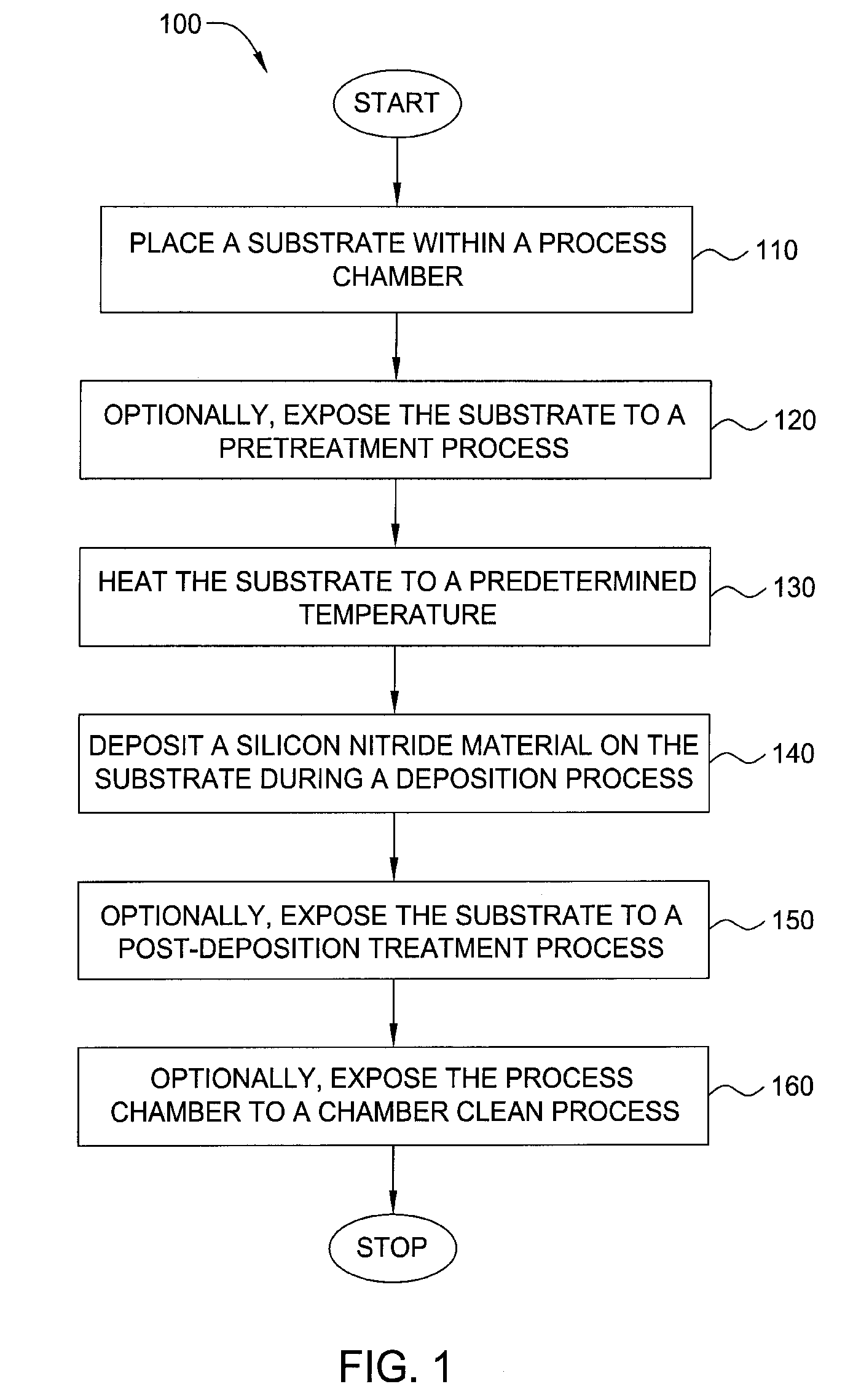

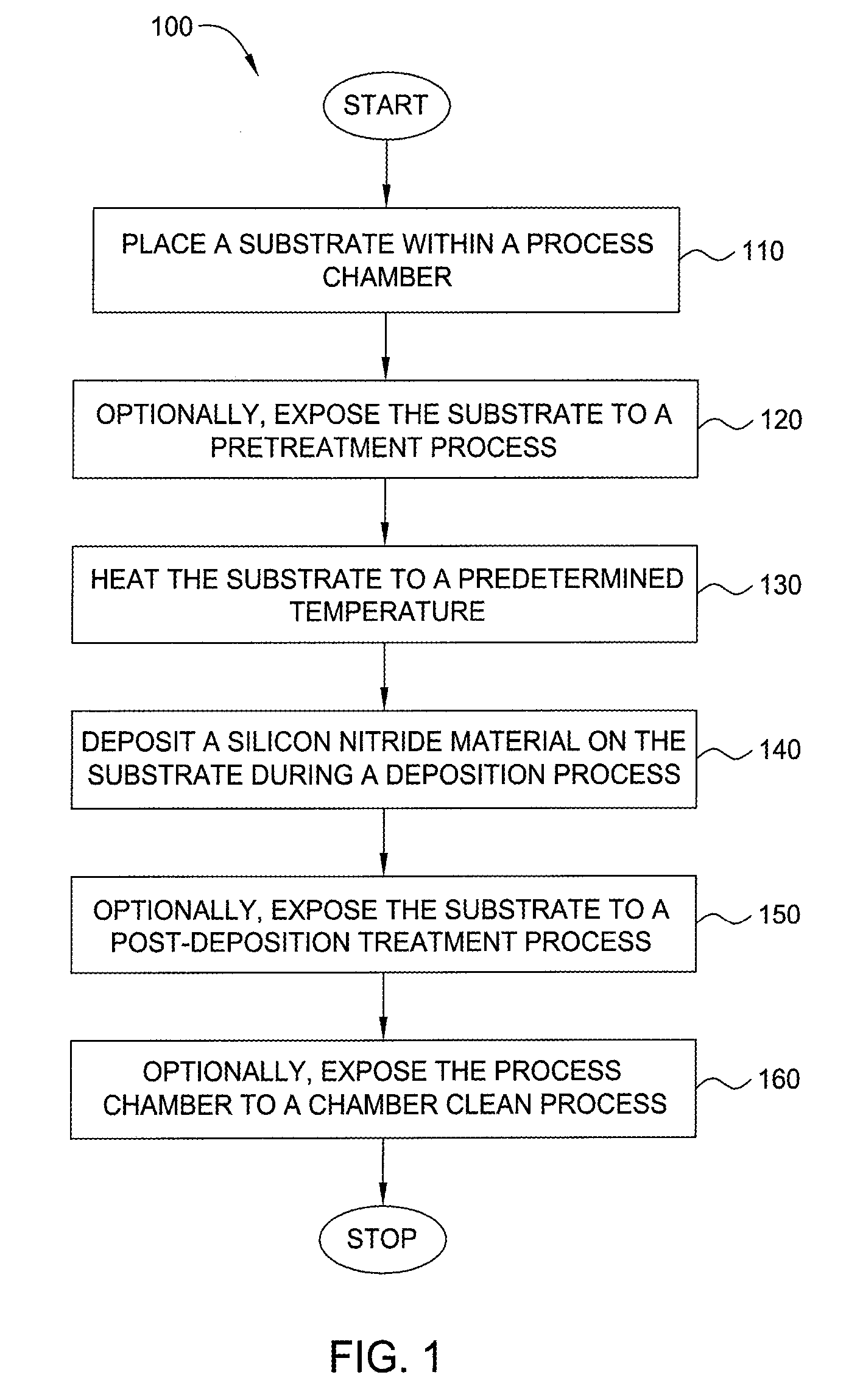

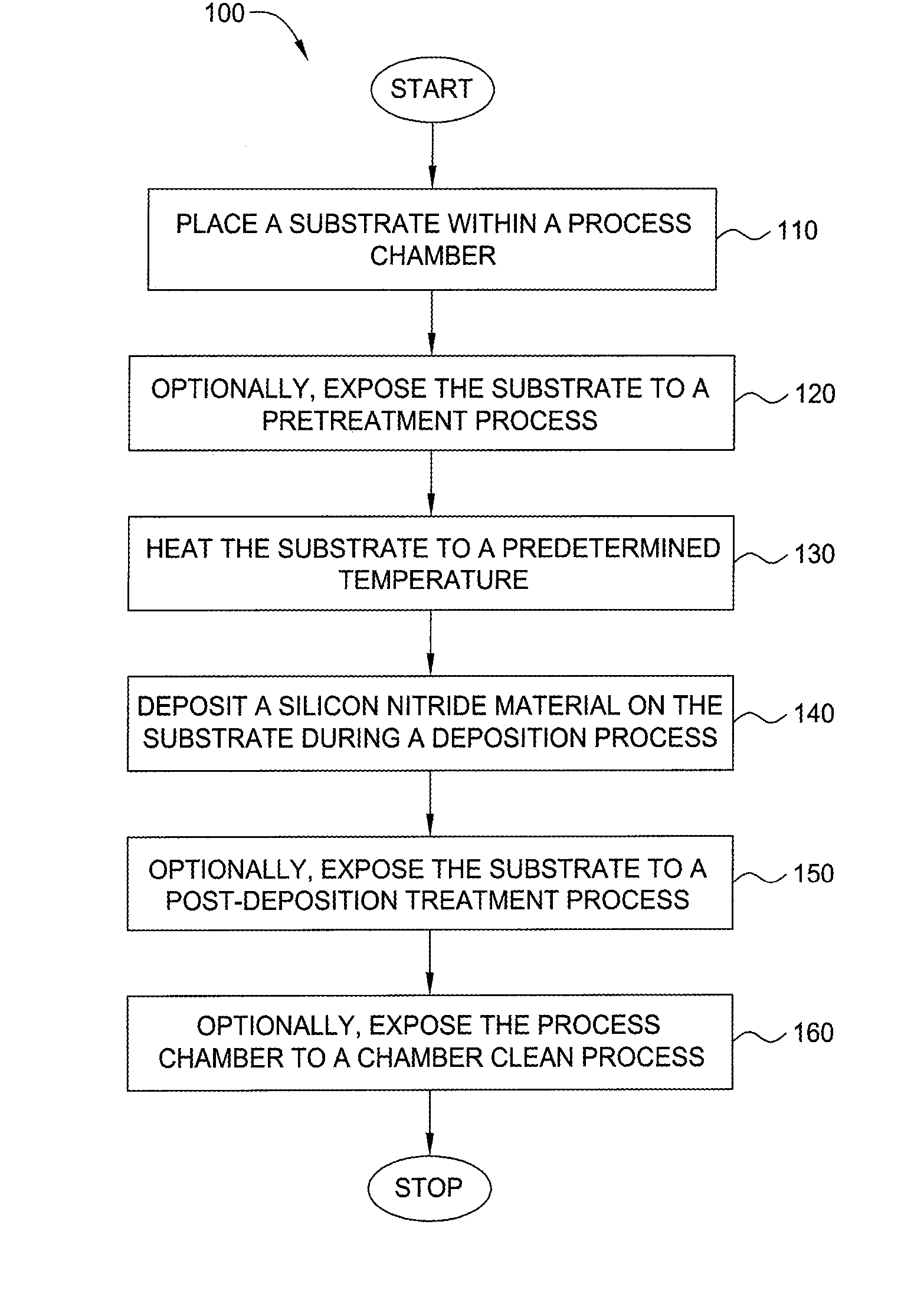

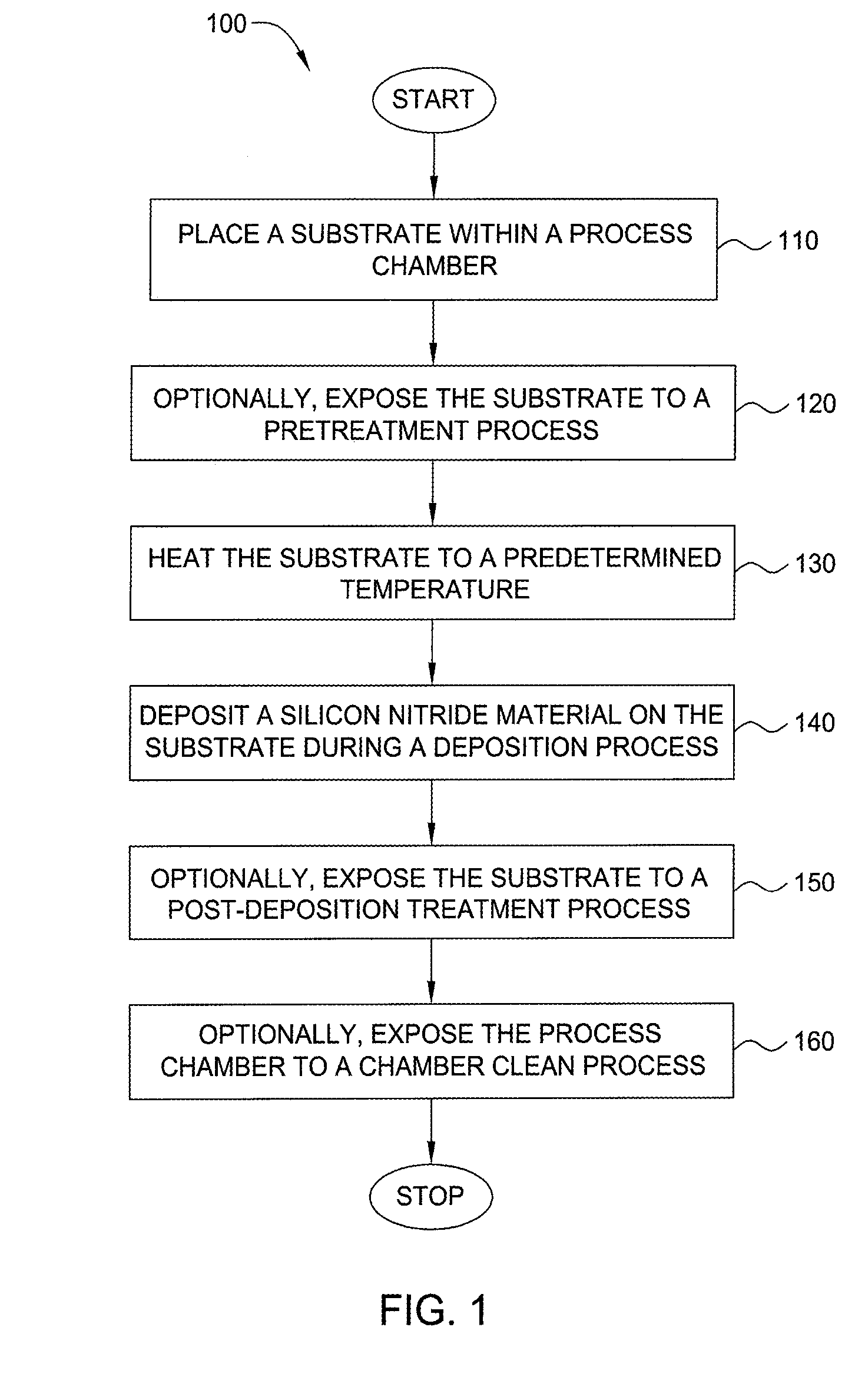

Method for forming silicon-containing materials during a photoexcitation deposition process

InactiveUS20060286774A1Enhance chamber cleaning processHigh surface energyPolycrystalline material growthSemiconductor/solid-state device manufacturingVolatilesSilicon oxide

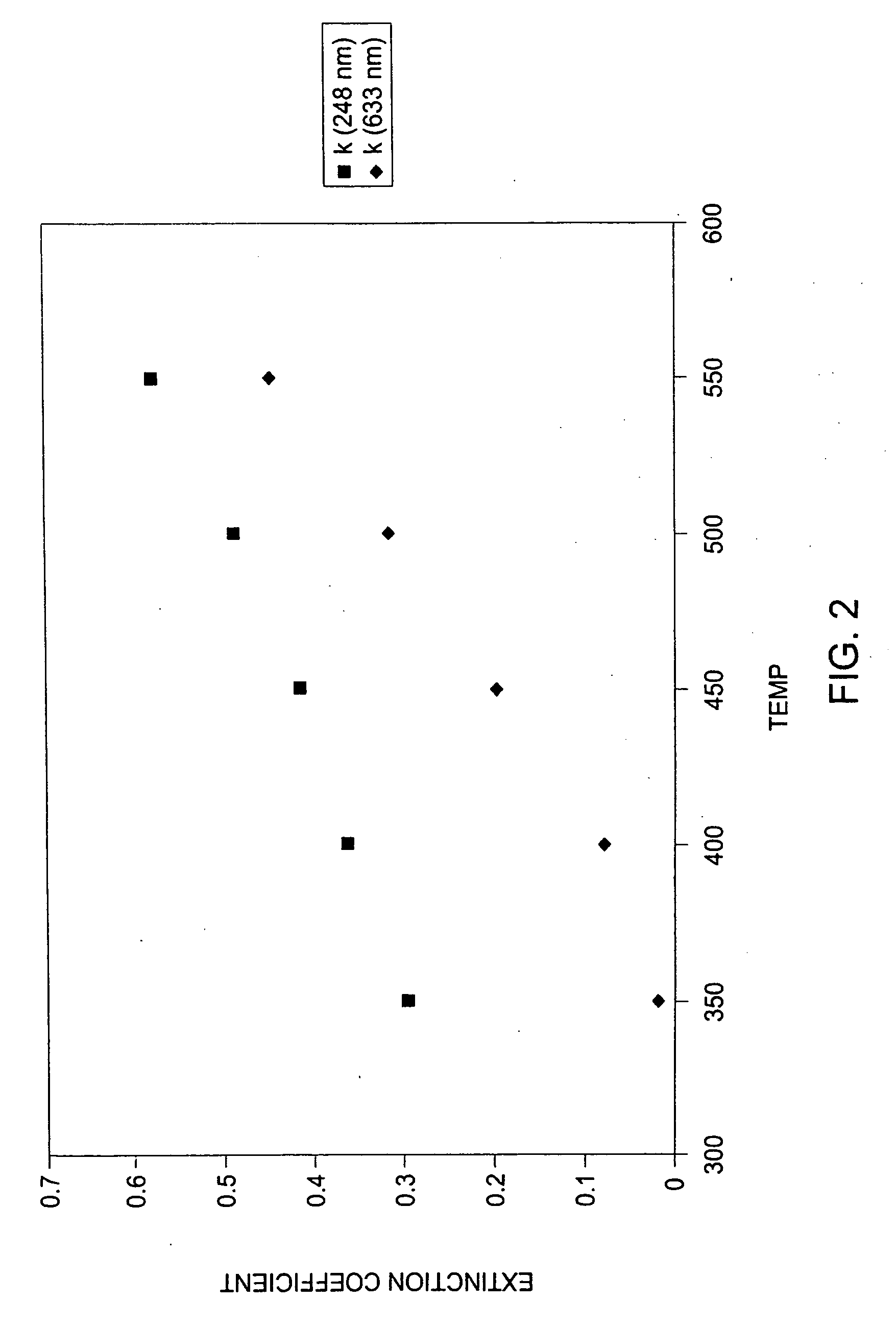

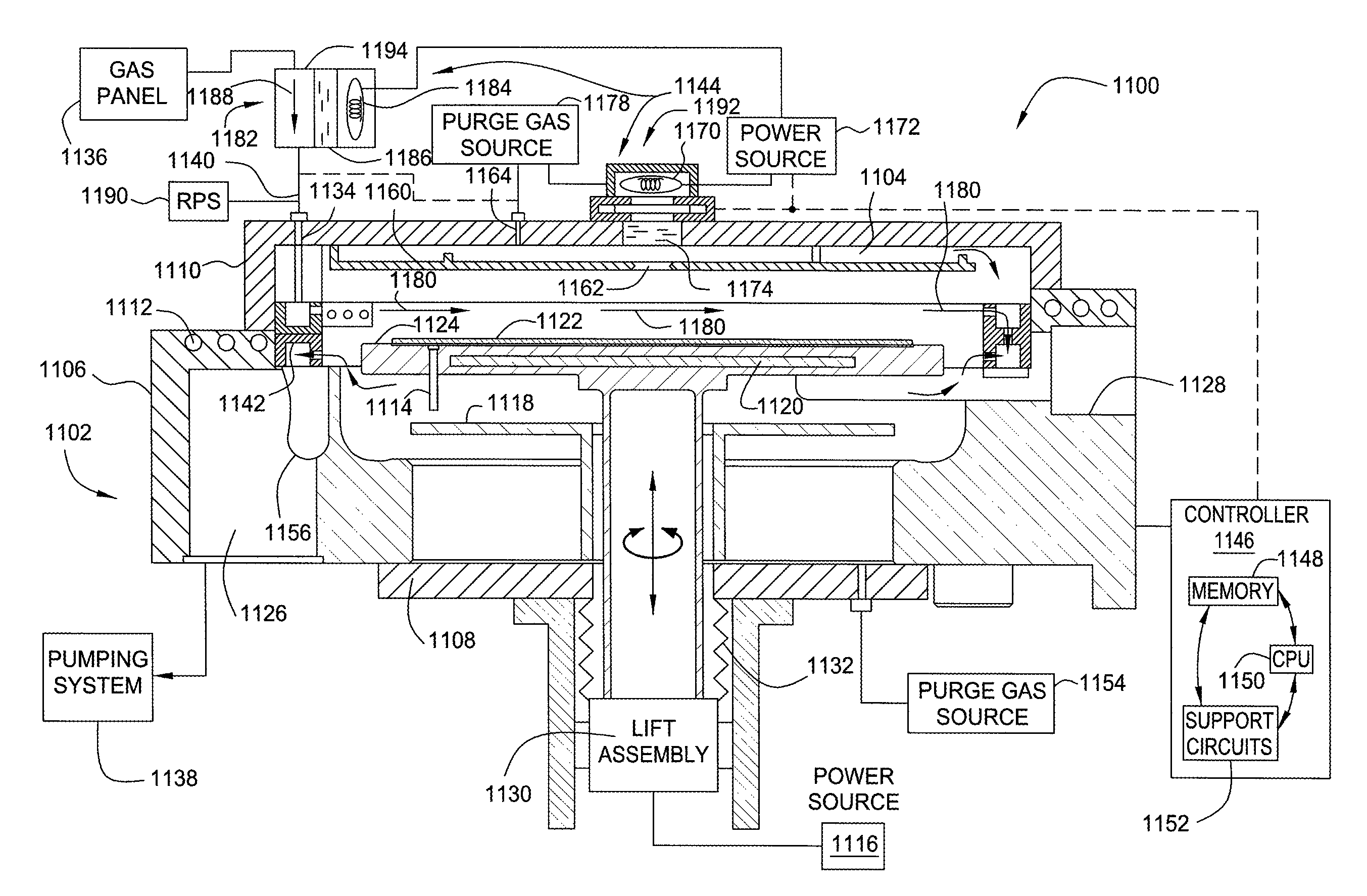

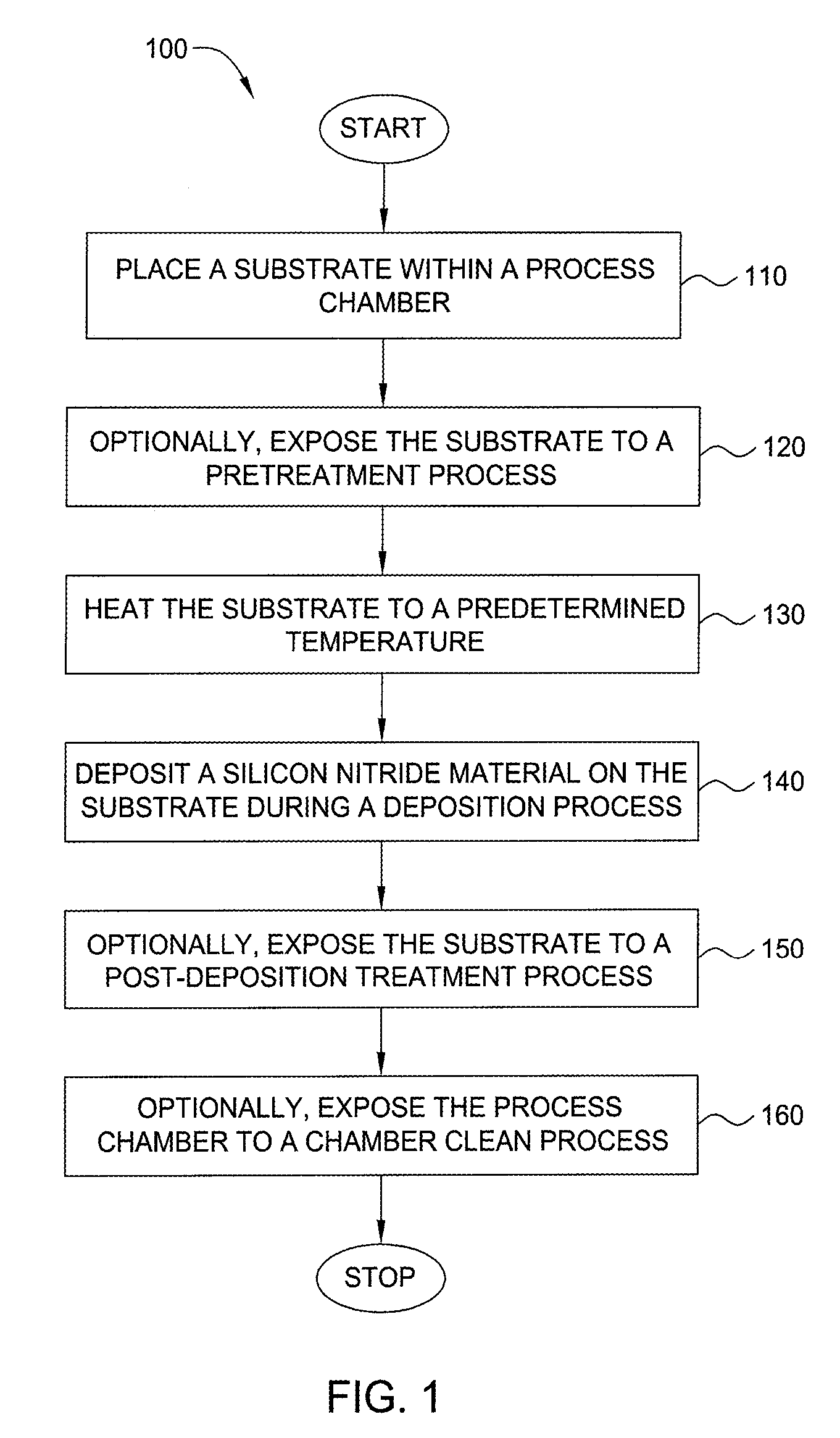

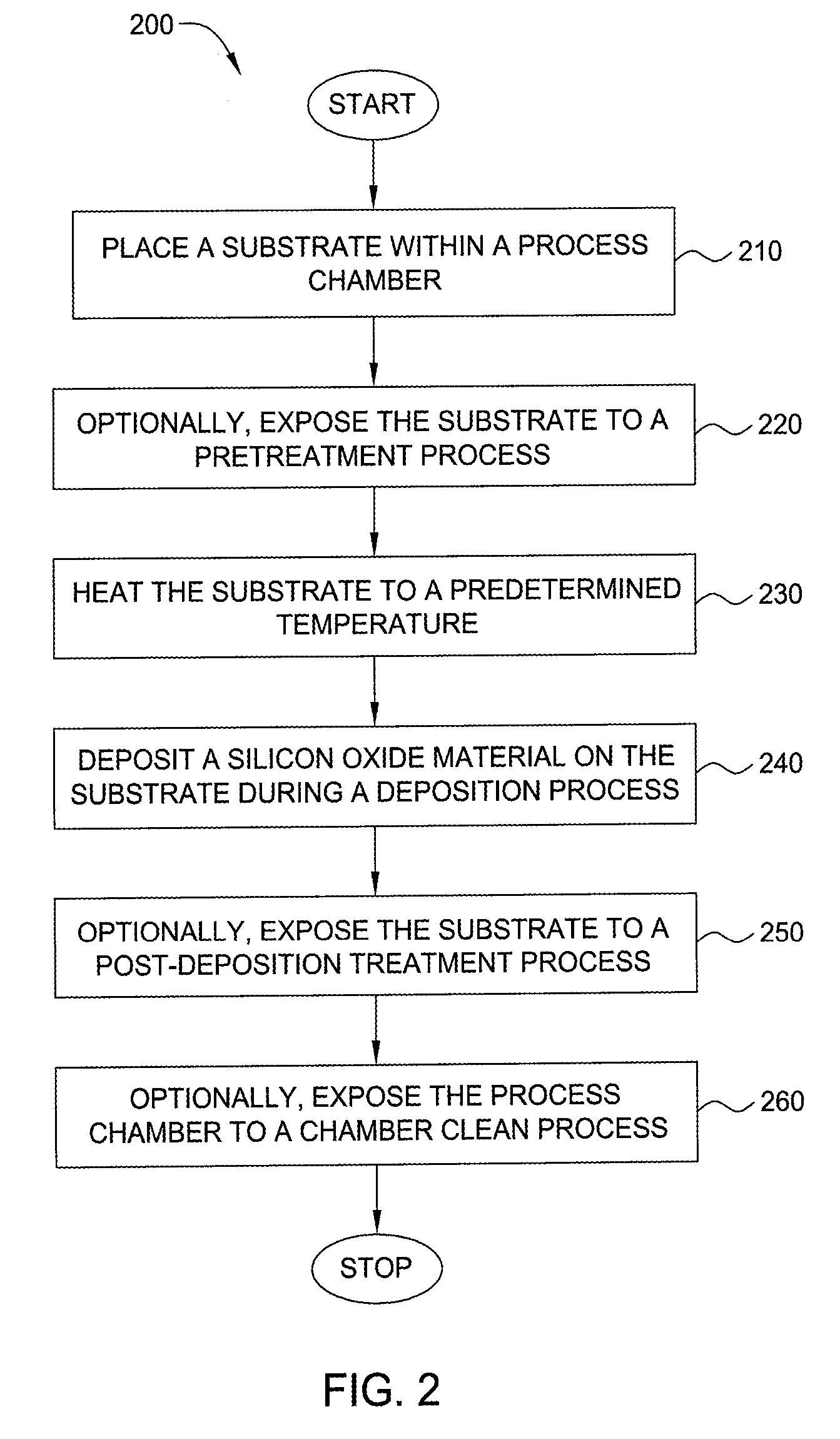

Embodiments of the invention generally provide a method for depositing films or layers using a UV source during a photoexcitation process. The films are deposited on a substrate and usually contain a material, such as silicon (e.g., epitaxy, crystalline, microcrystalline, polysilicon, or amorphous), silicon oxide, silicon nitride, silicon oxynitride, or other silicon-containing materials. The photoexcitation process may expose the substrate and / or gases to an energy beam or flux prior to, during, or subsequent a deposition process. Therefore, the photoexcitation process may be used to pre-treat or post-treat the substrate or material, to deposit the silicon-containing material, and to enhance chamber cleaning processes. Attributes of the method that are enhanced by the UV photoexcitation process include removing native oxides prior to deposition, removing volatiles from deposited films, increasing surface energy of the deposited films, increasing the excitation energy of precursors, reducing deposition time, and reducing deposition temperature.

Owner:APPLIED MATERIALS INC

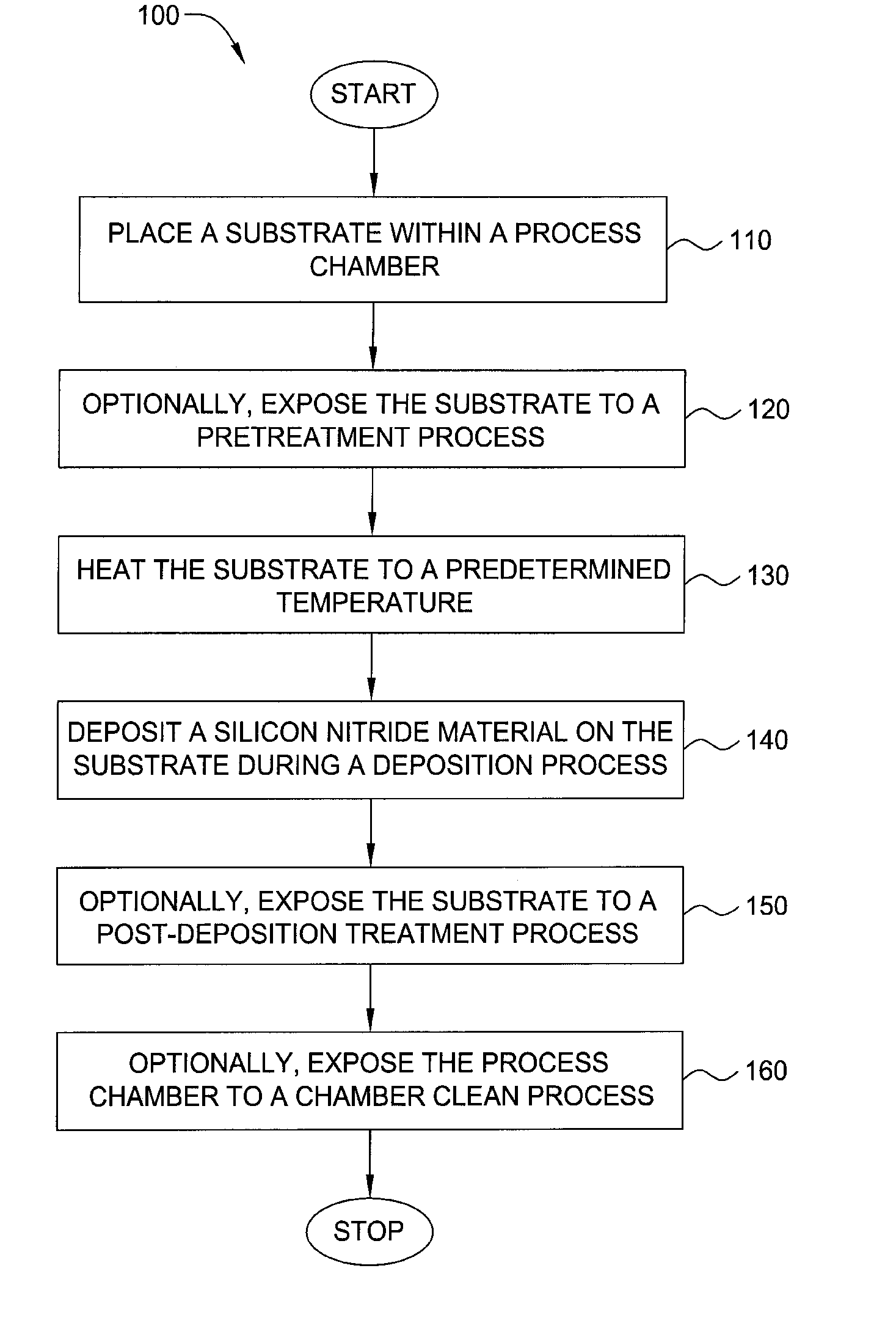

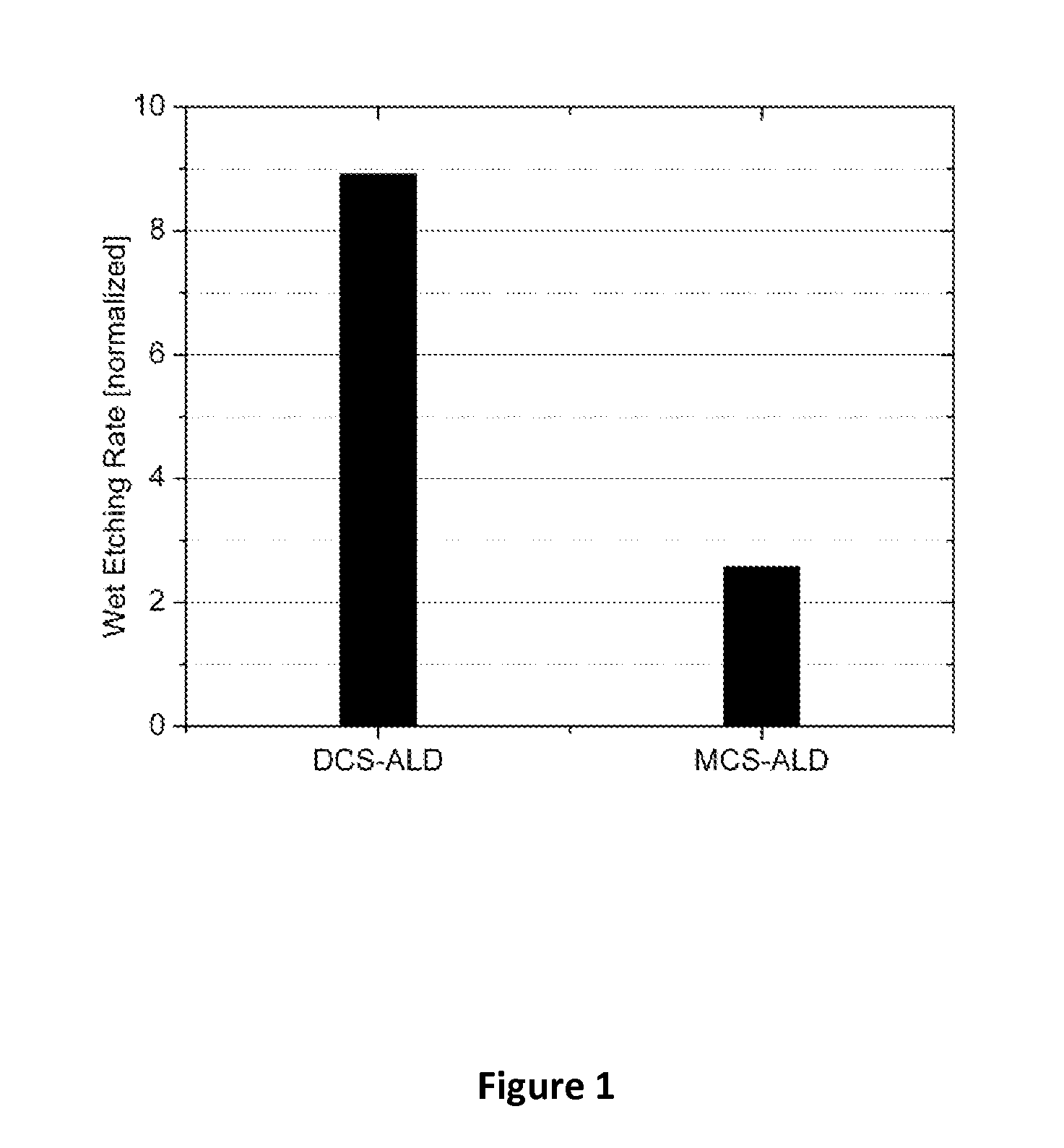

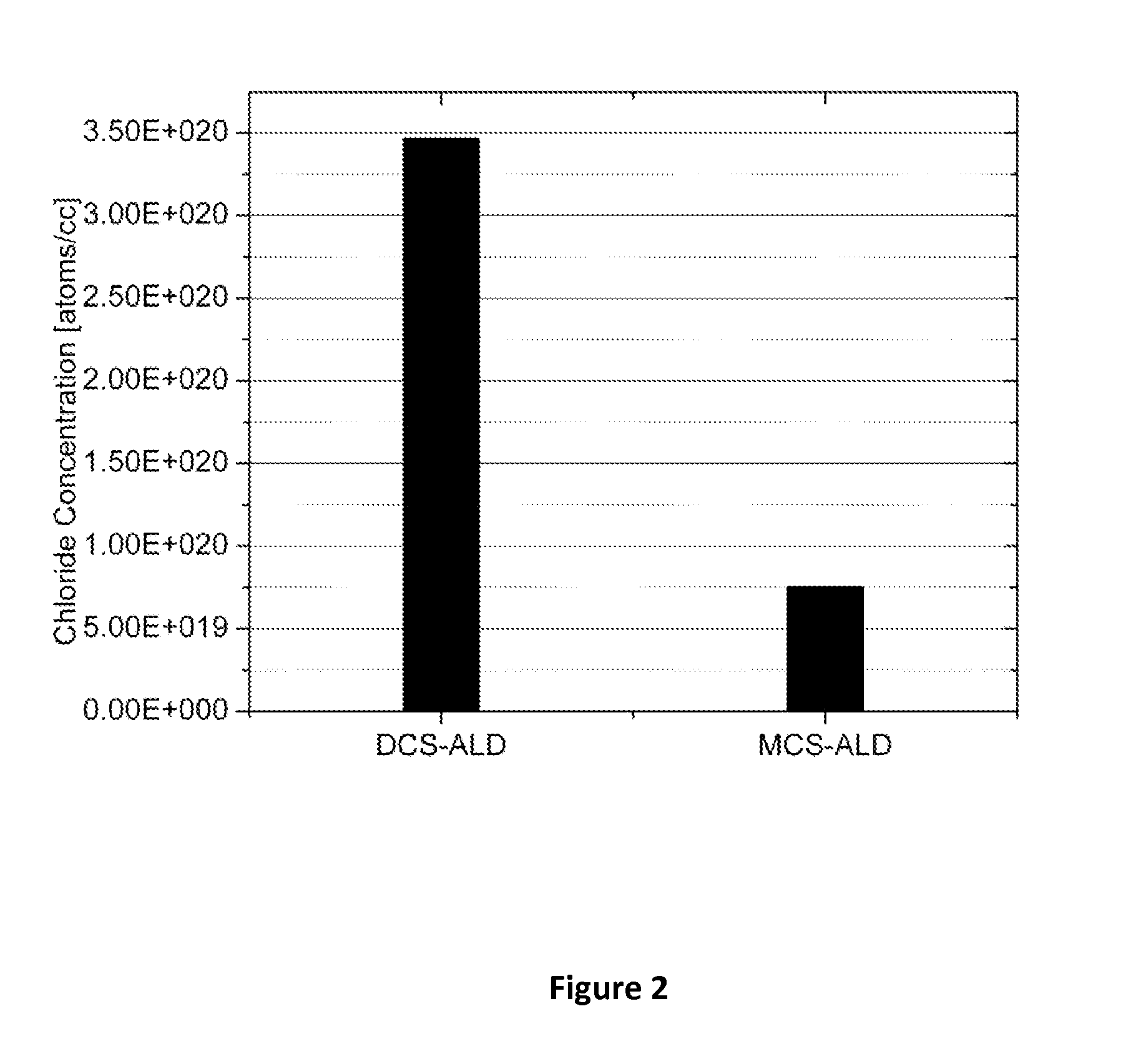

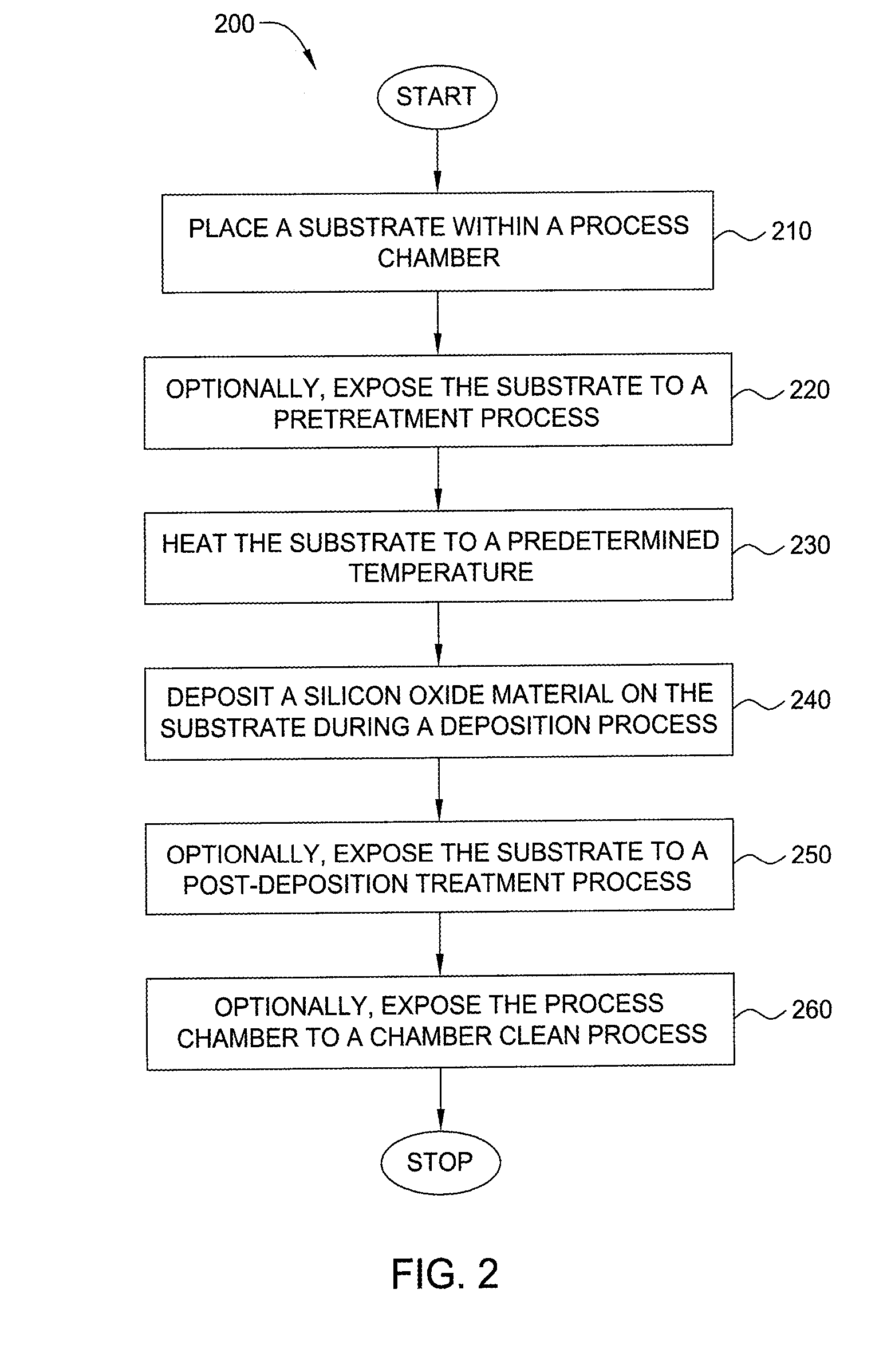

Low Temperature Deposition of Silicon-Containing Films

ActiveUS20100304047A1Low deposition temperatureSemiconductor/solid-state device manufacturingSpecial surfacesLow temperature depositionDeposition temperature

This invention discloses the method of forming silicon nitride, silicon oxynitride, silicon oxide, carbon-doped silicon nitride, carbon-doped silicon oxide and carbon-doped oxynitride films at low deposition temperatures. The silicon containing precursors used for the deposition are monochlorosilane (MCS) and monochloroalkylsilanes. The method is preferably carried out by using plasma enhanced atomic layer deposition, plasma enhanced chemical vapor deposition, and plasma enhanced cyclic chemical vapor deposition.

Owner:TOKYO ELECTRON LTD +1

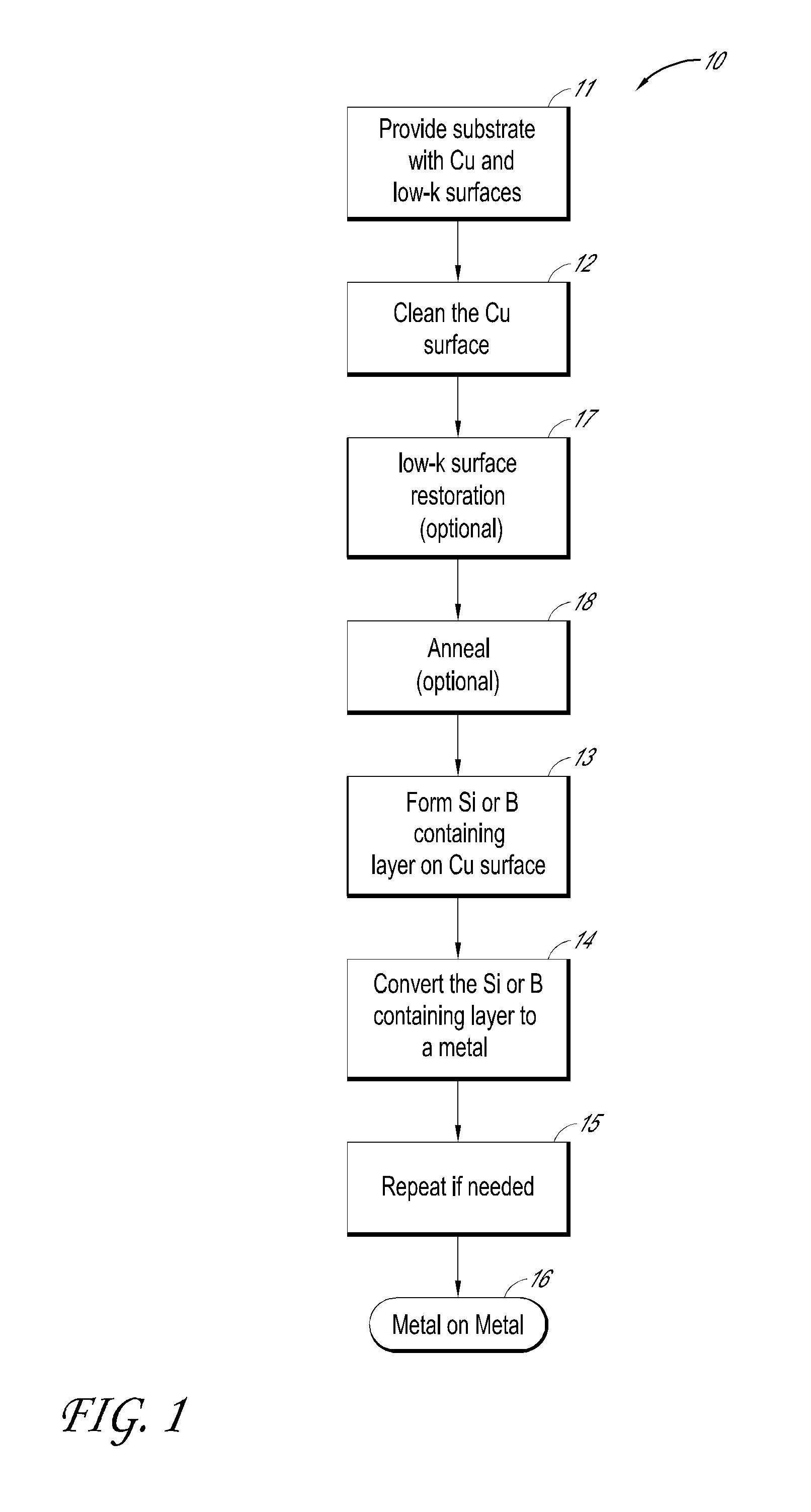

Selective formation of metallic films on metallic surfaces

ActiveUS8956971B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDeposition temperatureCopper

Owner:ASM INTERNATIONAL

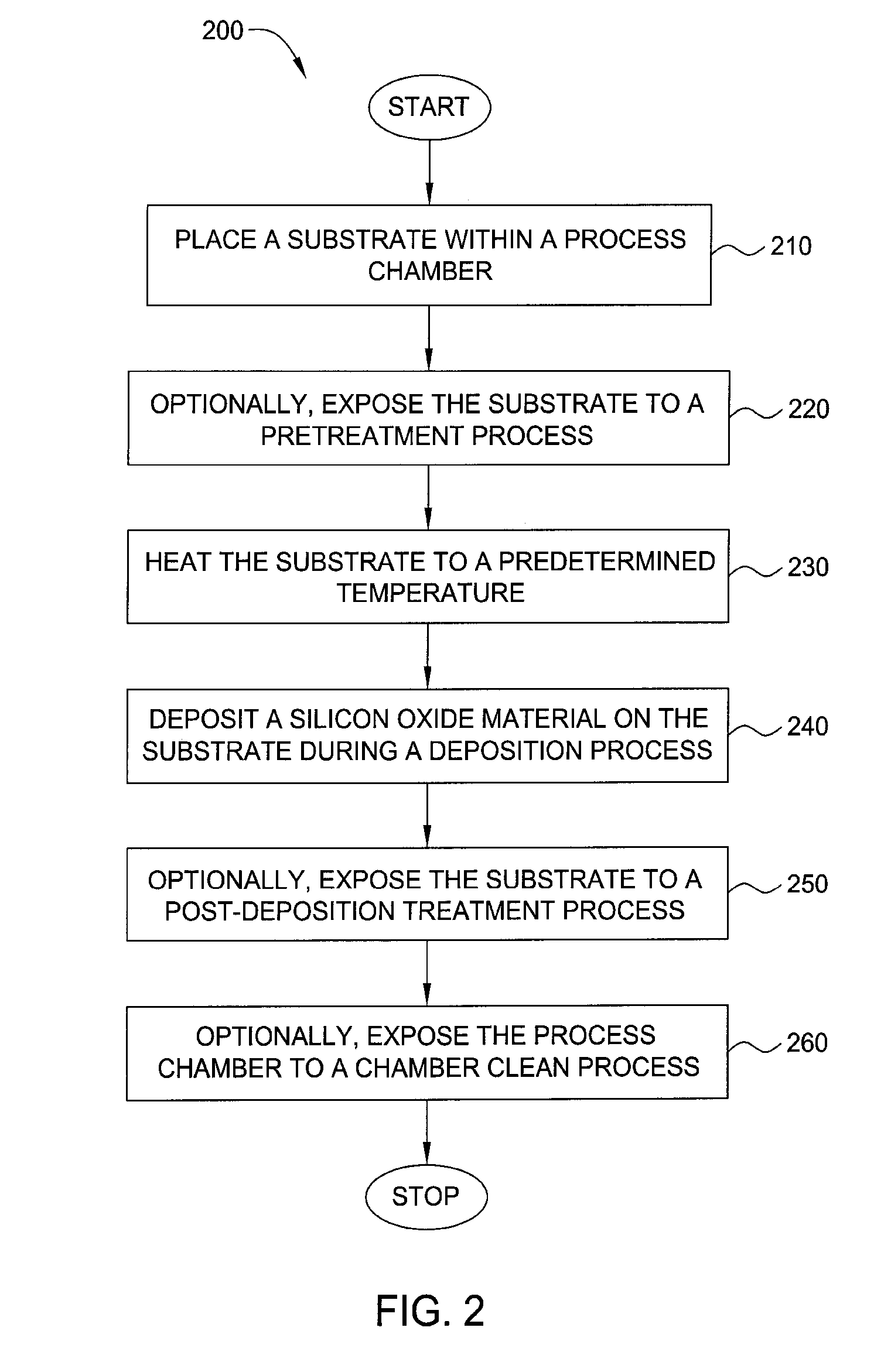

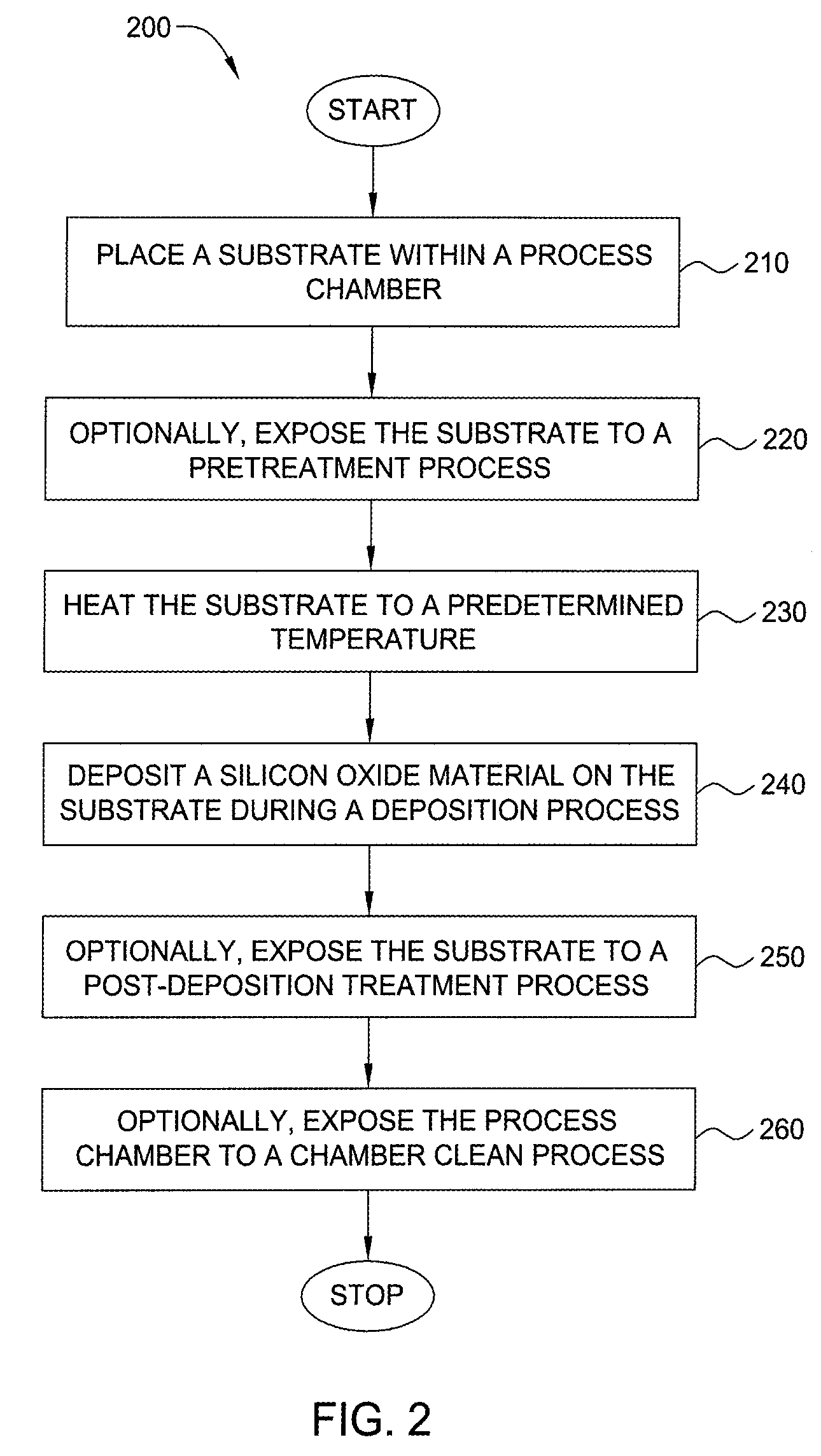

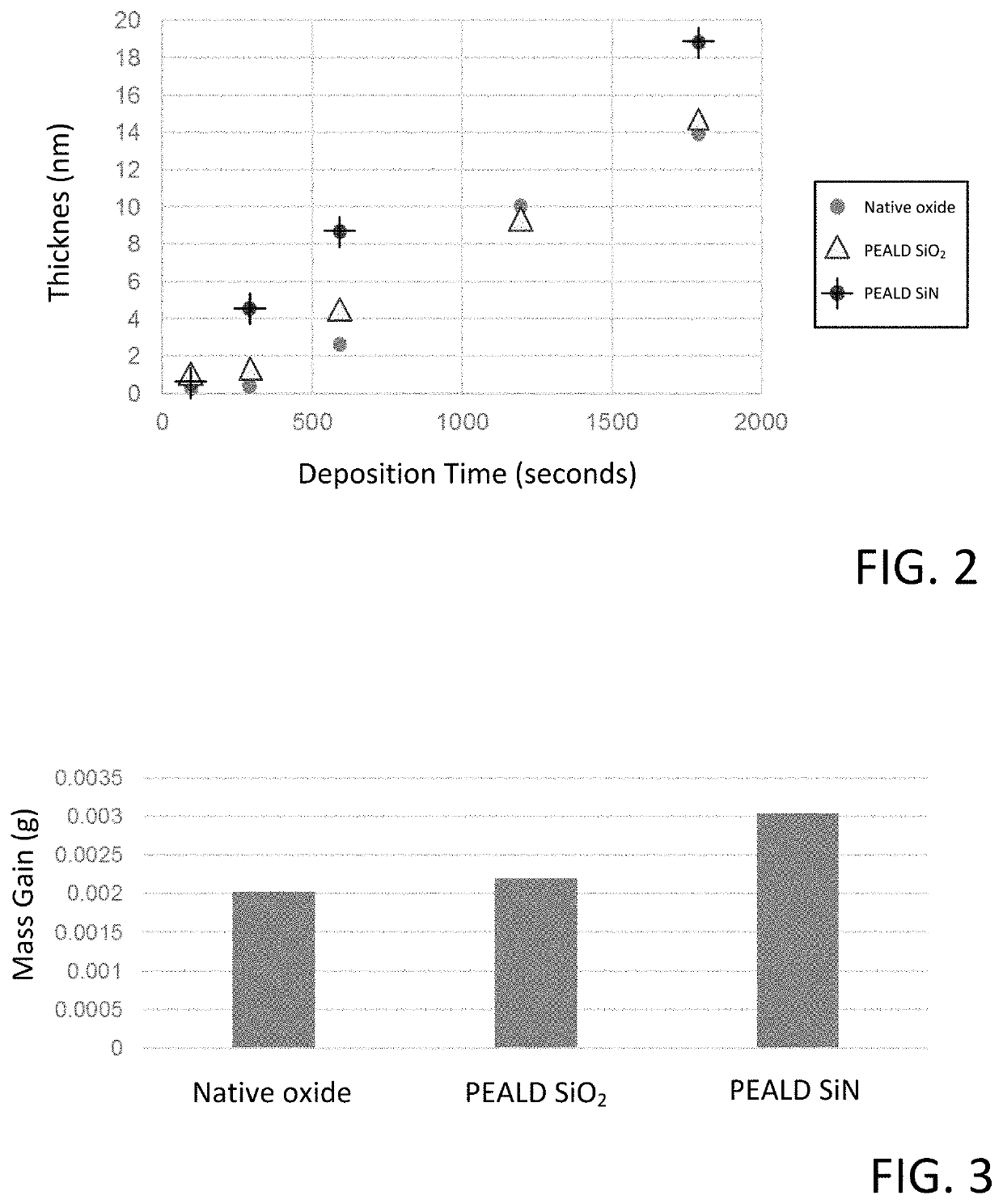

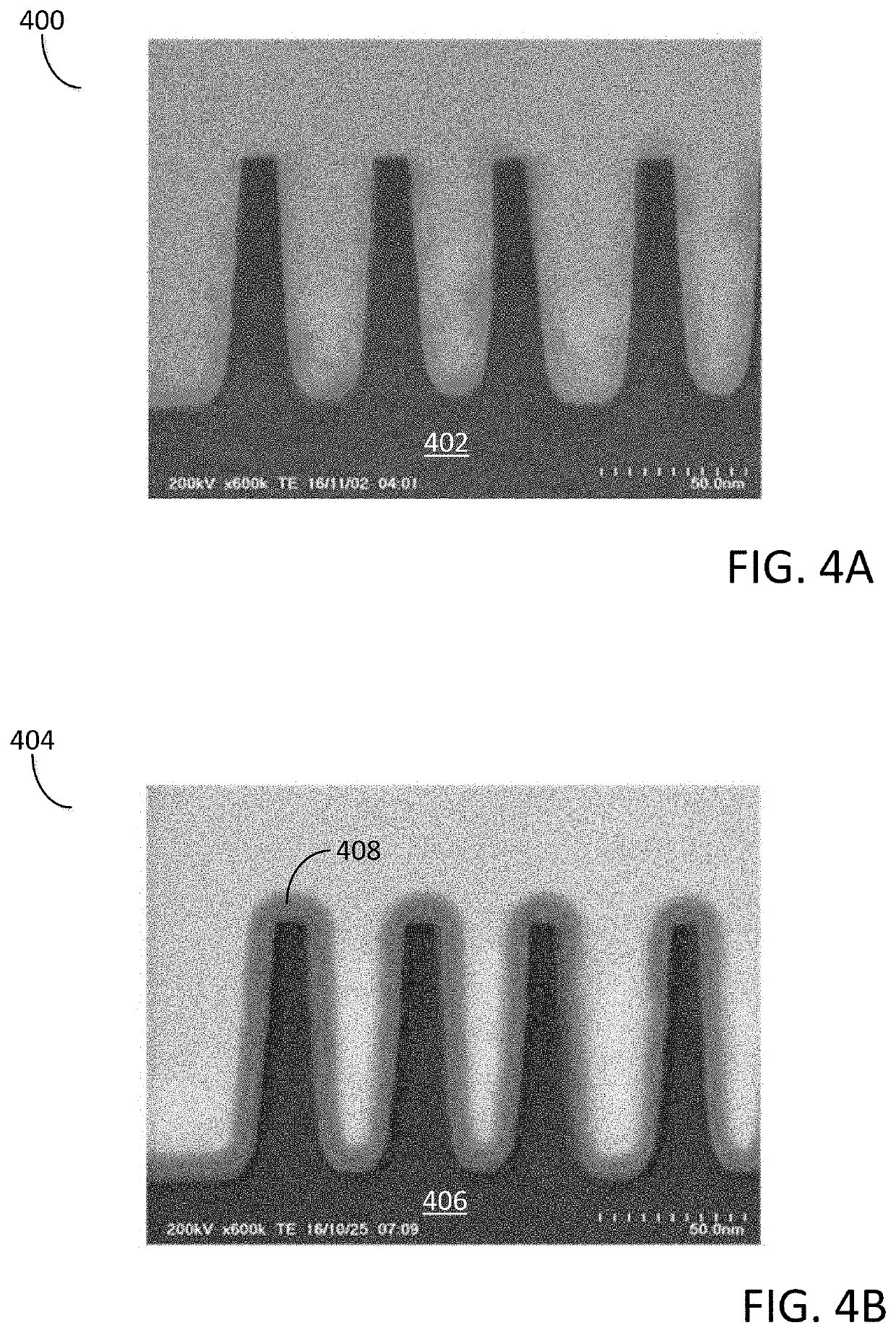

Method of depositing silicon oxide film by plasma enhanced atomic layer deposition at low temperature

ActiveUS8197915B2Increase deposition rateInhibition is effectiveSemiconductor/solid-state device manufacturingPhotosensitive material processingResistDeposition temperature

Owner:ASM JAPAN

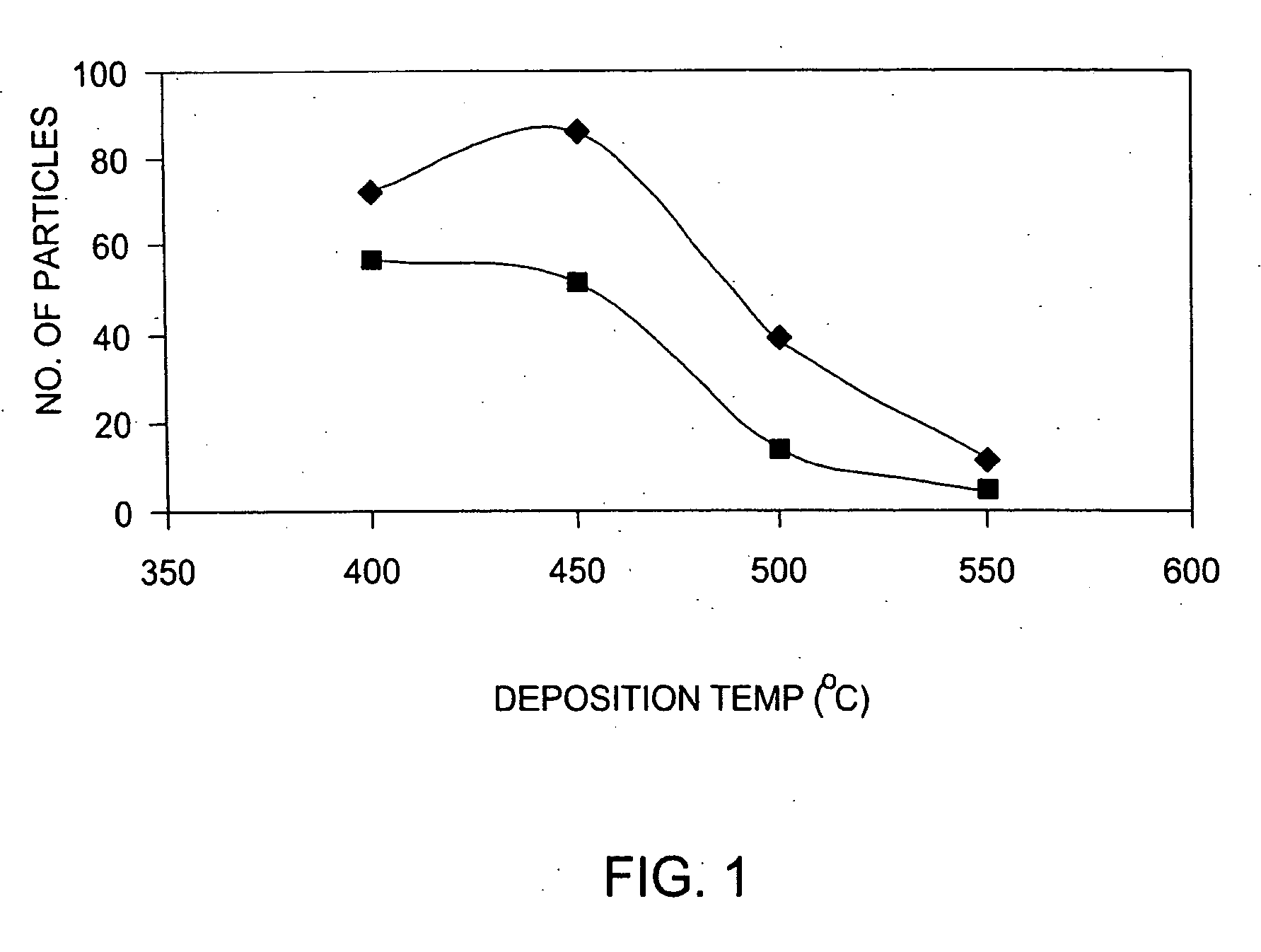

Methods for the reduction and elimination of particulate contamination with CVD of amorphous carbon

InactiveUS20060014397A1Minimal defect formationReduce particle pollutionSemiconductor/solid-state device manufacturingSpecial surfacesVariable thicknessMicroparticle

A method is provided for forming an amorphous carbon layer, deposited on a dielectric material such as oxide, nitride, silicon carbide, carbon doped oxide, etc., or a metal layer such as tungsten, aluminum or poly-silicon. The method includes the use of chamber seasoning, variable thickness of seasoning film, wider spacing, variable process gas flows, post-deposition purge with inert gas, and post-deposition plasma purge, among others, to make the deposition of an amorphous carbon film at low deposition temperatures possible without any defects or particle contamination.

Owner:APPLIED MATERIALS INC +1

Method for forming silicon-containing materials during a photoexcitation deposition process

InactiveUS7651955B2Easy to cleanHigh surface energyPolycrystalline material growthSemiconductor/solid-state device manufacturingAutoxidationDeposition temperature

Embodiments of the invention generally provide a method for depositing films or layers using a UV source during a photoexcitation process. The films are deposited on a substrate and usually contain a material, such as silicon (e.g., epitaxy, crystalline, microcrystalline, polysilicon, or amorphous), silicon oxide, silicon nitride, silicon oxynitride, or other silicon-containing materials. The photoexcitation process may expose the substrate and / or gases to an energy beam or flux prior to, during, or subsequent a deposition process. Therefore, the photoexcitation process may be used to pre-treat or post-treat the substrate or material, to deposit the silicon-containing material, and to enhance chamber cleaning processes. Attributes of the method that are enhanced by the UV photoexcitation process include removing native oxides prior to deposition, removing volatiles from deposited films, increasing surface energy of the deposited films, increasing the excitation energy of precursors, reducing deposition time, and reducing deposition temperature.

Owner:APPLIED MATERIALS INC

Method of Depositing Silicon Oxide Film by Plasma Enhanced Atomic Layer Deposition at Low Temperature

ActiveUS20100255218A1Increase deposition rateInhibition is effectiveLiquid surface applicatorsSemiconductor/solid-state device manufacturingResistDeposition temperature

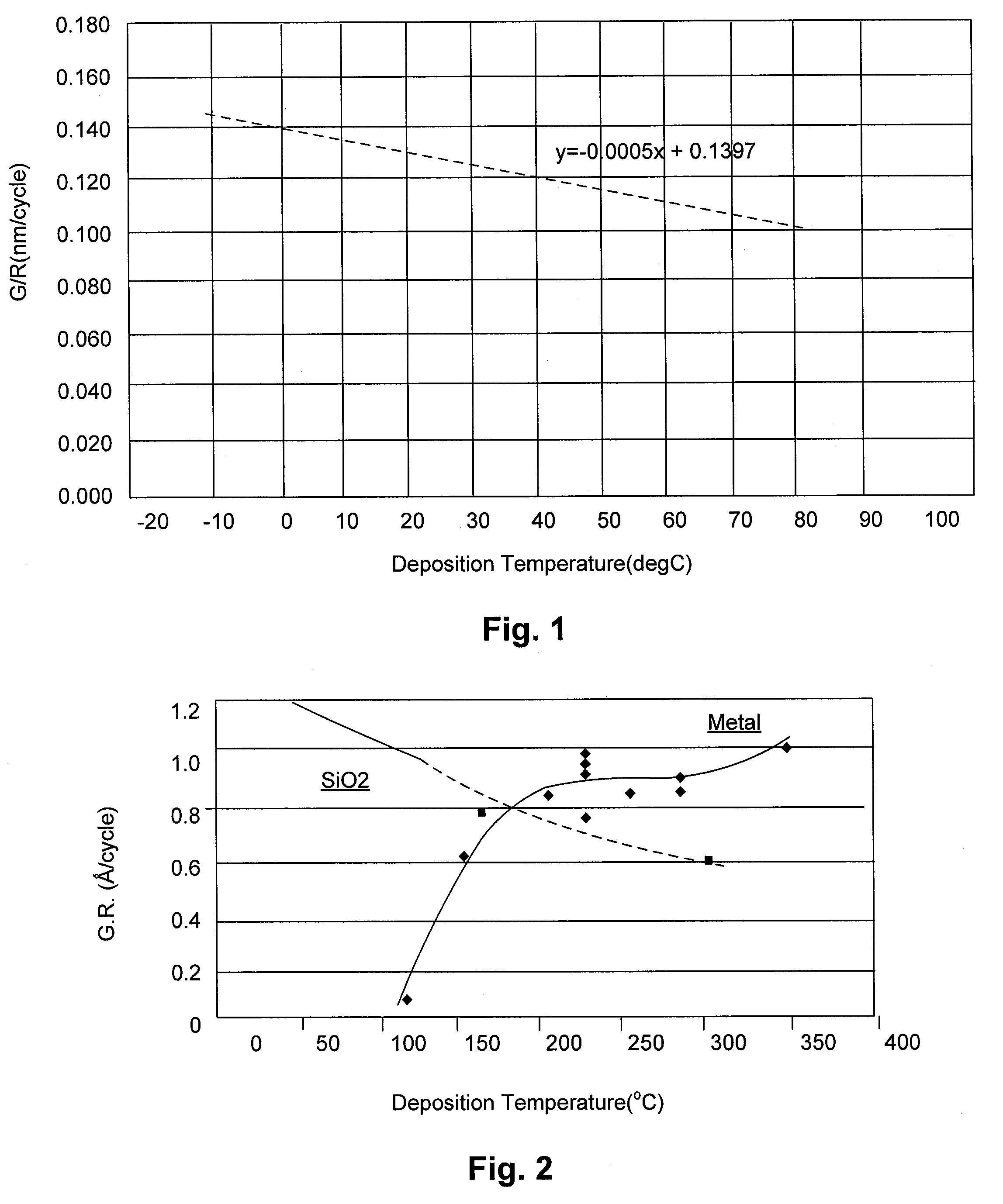

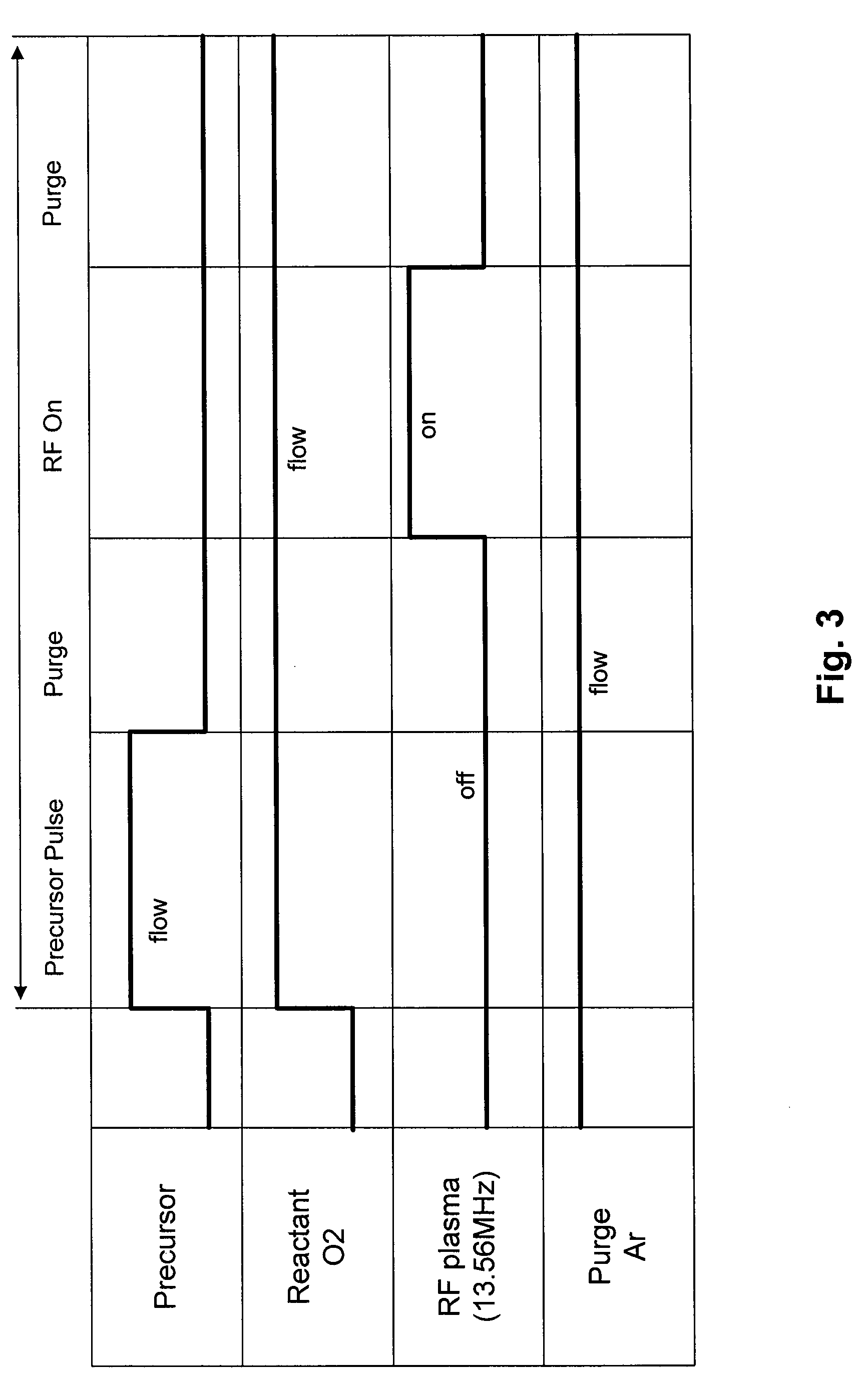

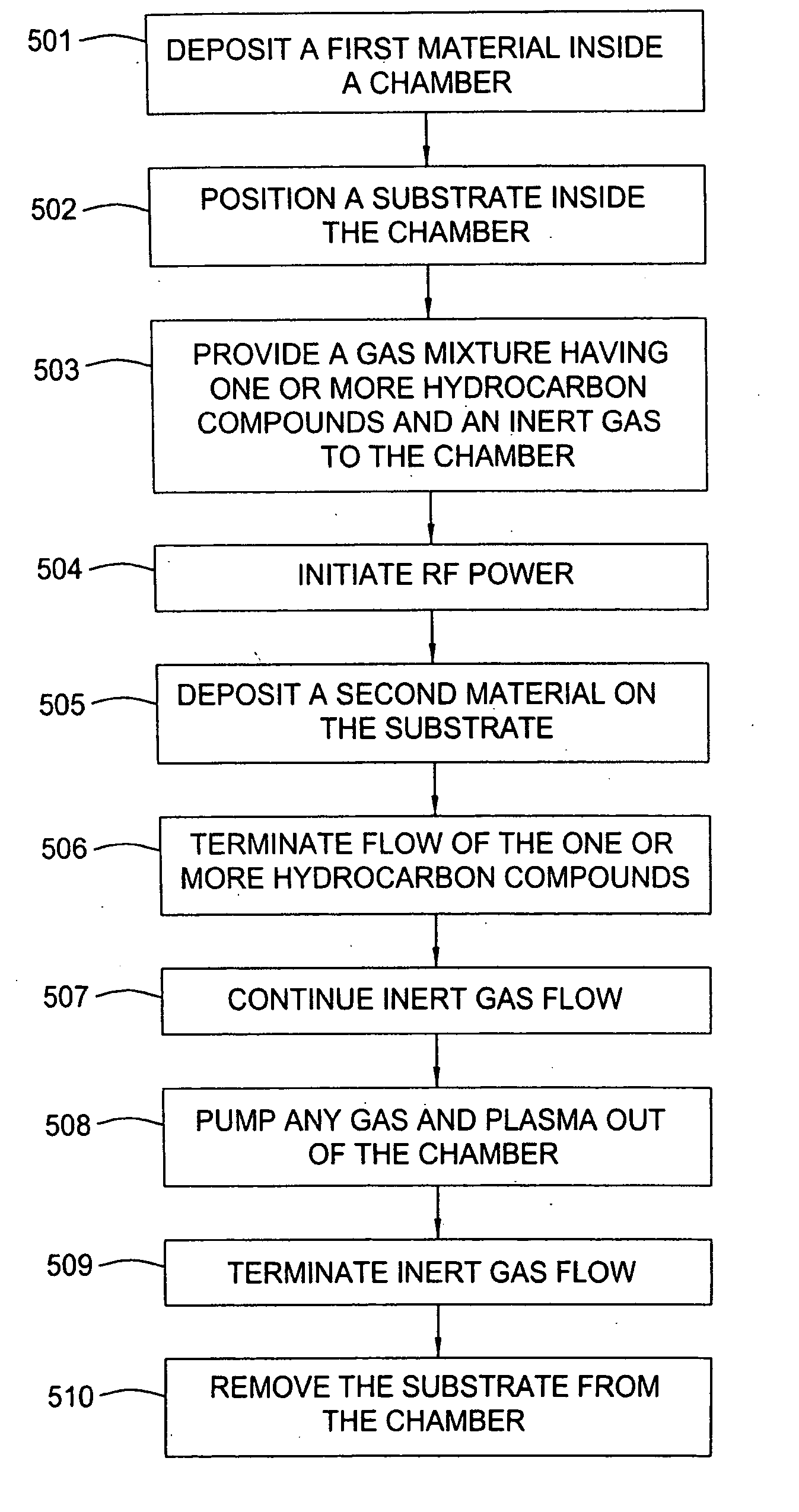

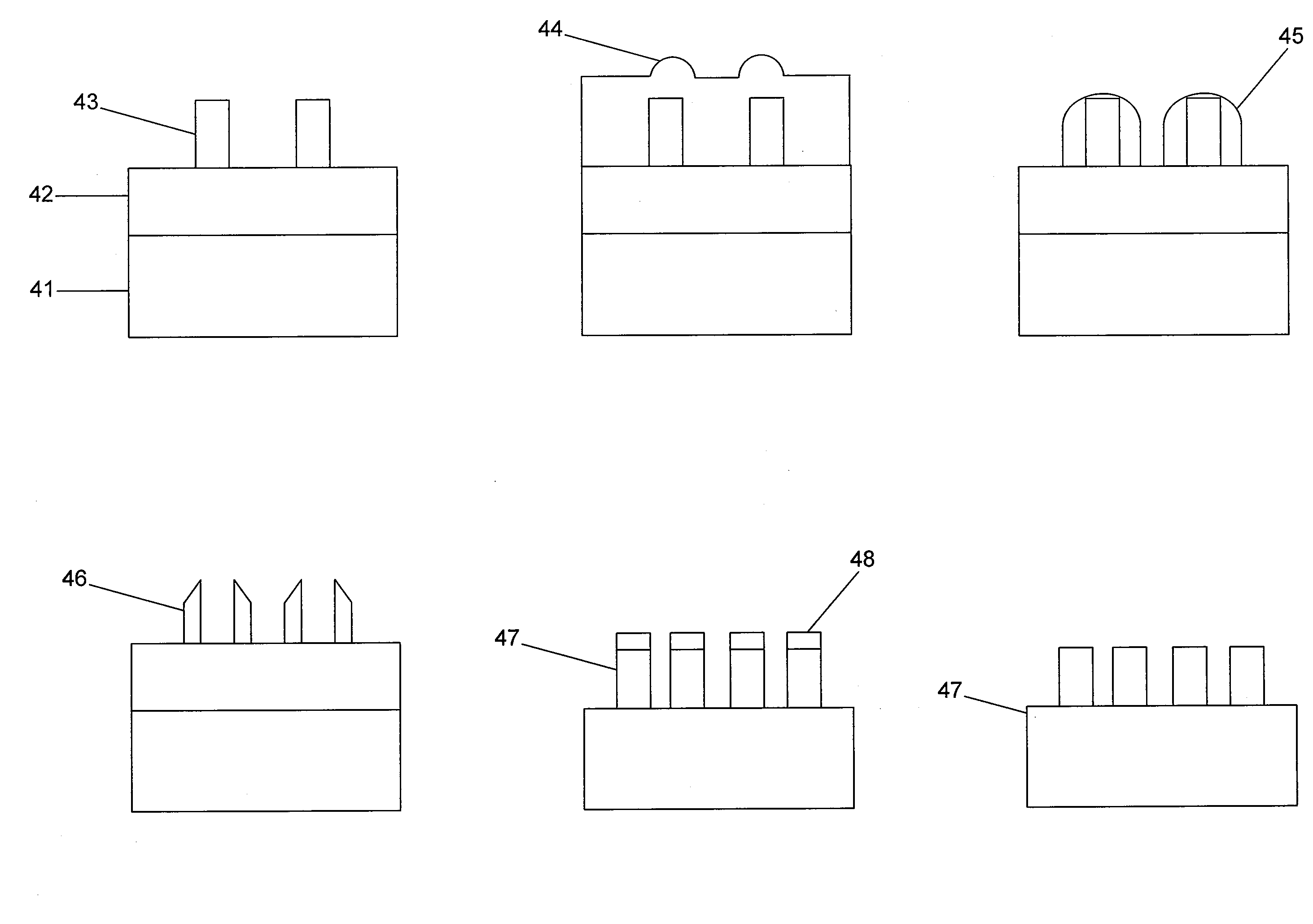

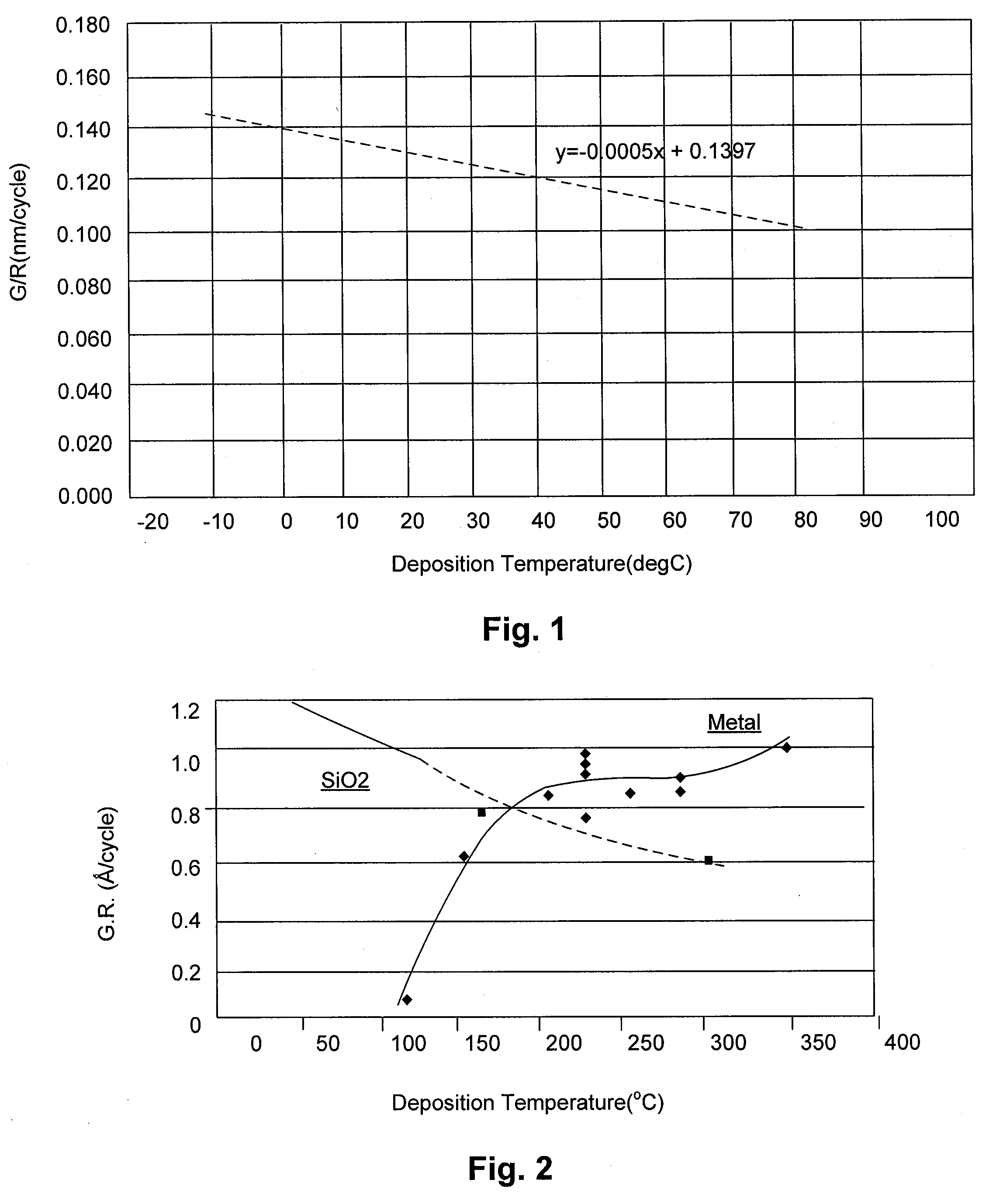

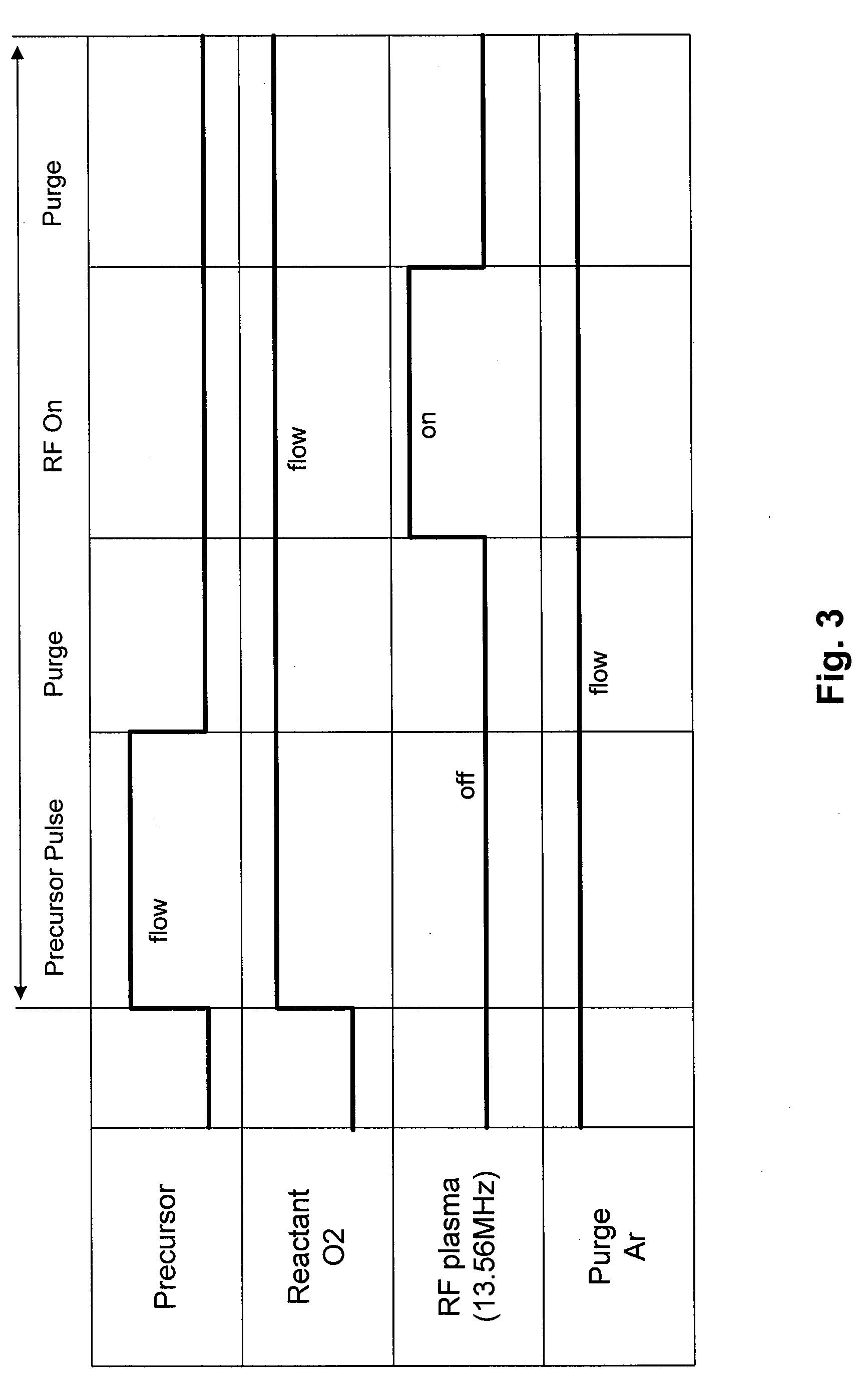

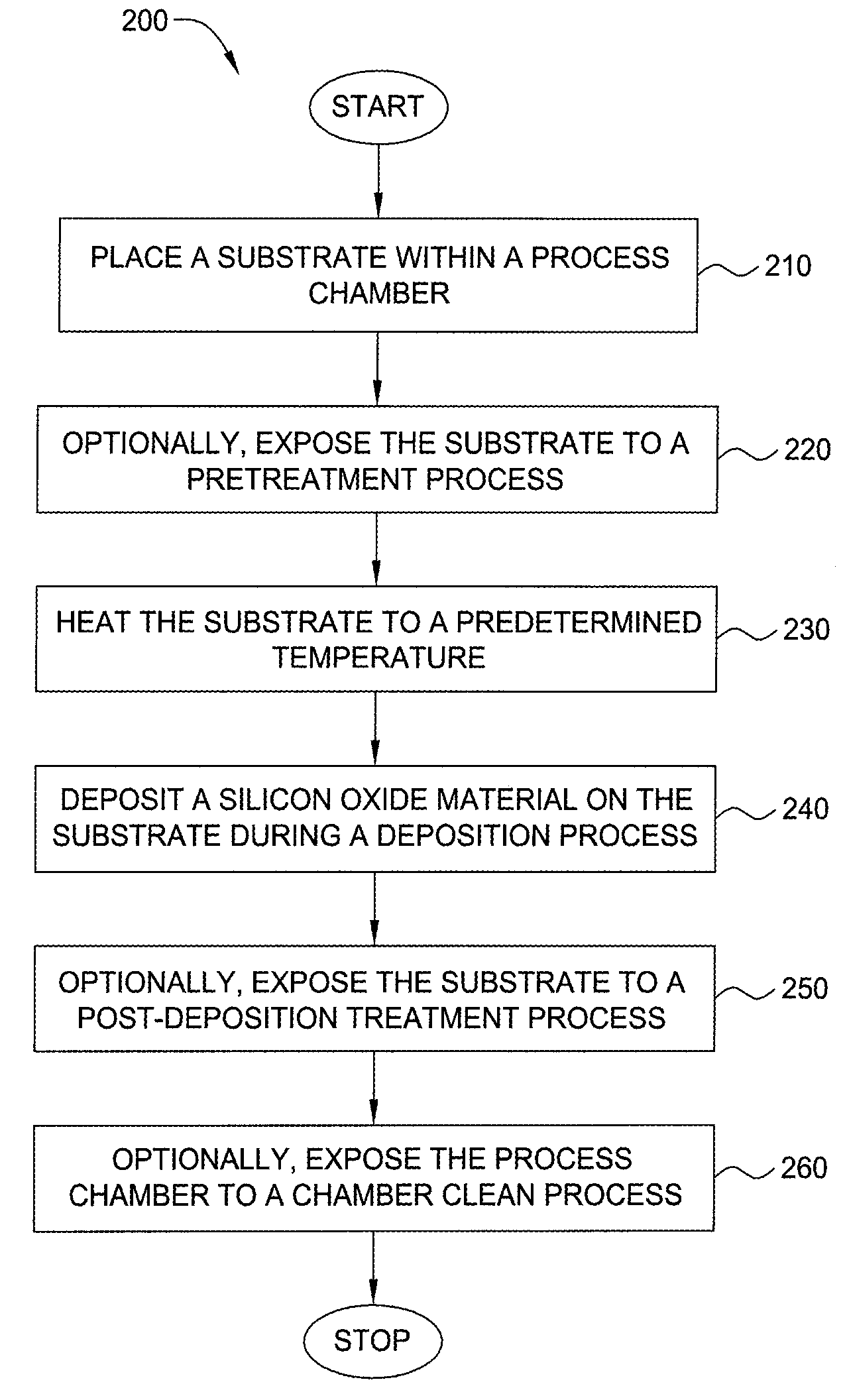

A method of depositing a silicon oxide film on a resist pattern or etched lines formed on a substrate by plasma enhanced atomic layer deposition (PEALD) includes: providing a substrate on which a resist pattern or etched lines are formed in a PEALD reactor; controlling a temperature of a susceptor on which the substrate is placed at less than 50° C. as a deposition temperature; introducing a silicon-containing precursor and an oxygen-supplying reactant to the PEALD reactor and applying RF power therein in a cycle, while the deposition temperature is controlled substantially or nearly at a constant temperature of less than 50° C., thereby depositing a silicon oxide atomic layer on the resist pattern or etched lines; and repeating the cycle multiple times substantially or nearly at the constant temperature to deposit a silicon oxide atomic film on the resist pattern or etched lines.

Owner:ASM JAPAN

Method for forming silicon-containing materials during a photoexcitation deposition process

InactiveUS7648927B2Easy to cleanHigh surface energyPolycrystalline material growthSemiconductor/solid-state device manufacturingAutoxidationDeposition temperature

Embodiments of the invention generally provide a method for depositing films or layers using a UV source during a photoexcitation process. The films are deposited on a substrate and usually contain a material, such as silicon (e.g., epitaxy, crystalline, microcrystalline, polysilicon, or amorphous), silicon oxide, silicon nitride, silicon oxynitride, or other silicon-containing materials. The photoexcitation process may expose the substrate and / or gases to an energy beam or flux prior to, during, or subsequent a deposition process. Therefore, the photoexcitation process may be used to pre-treat or post-treat the substrate or material, to deposit the silicon-containing material, and to enhance chamber cleaning processes. Attributes of the method that are enhanced by the UV photoexcitation process include removing native oxides prior to deposition, removing volatiles from deposited films, increasing surface energy of the deposited films, increasing the excitation energy of precursors, reducing deposition time, and reducing deposition temperature.

Owner:APPLIED MATERIALS INC

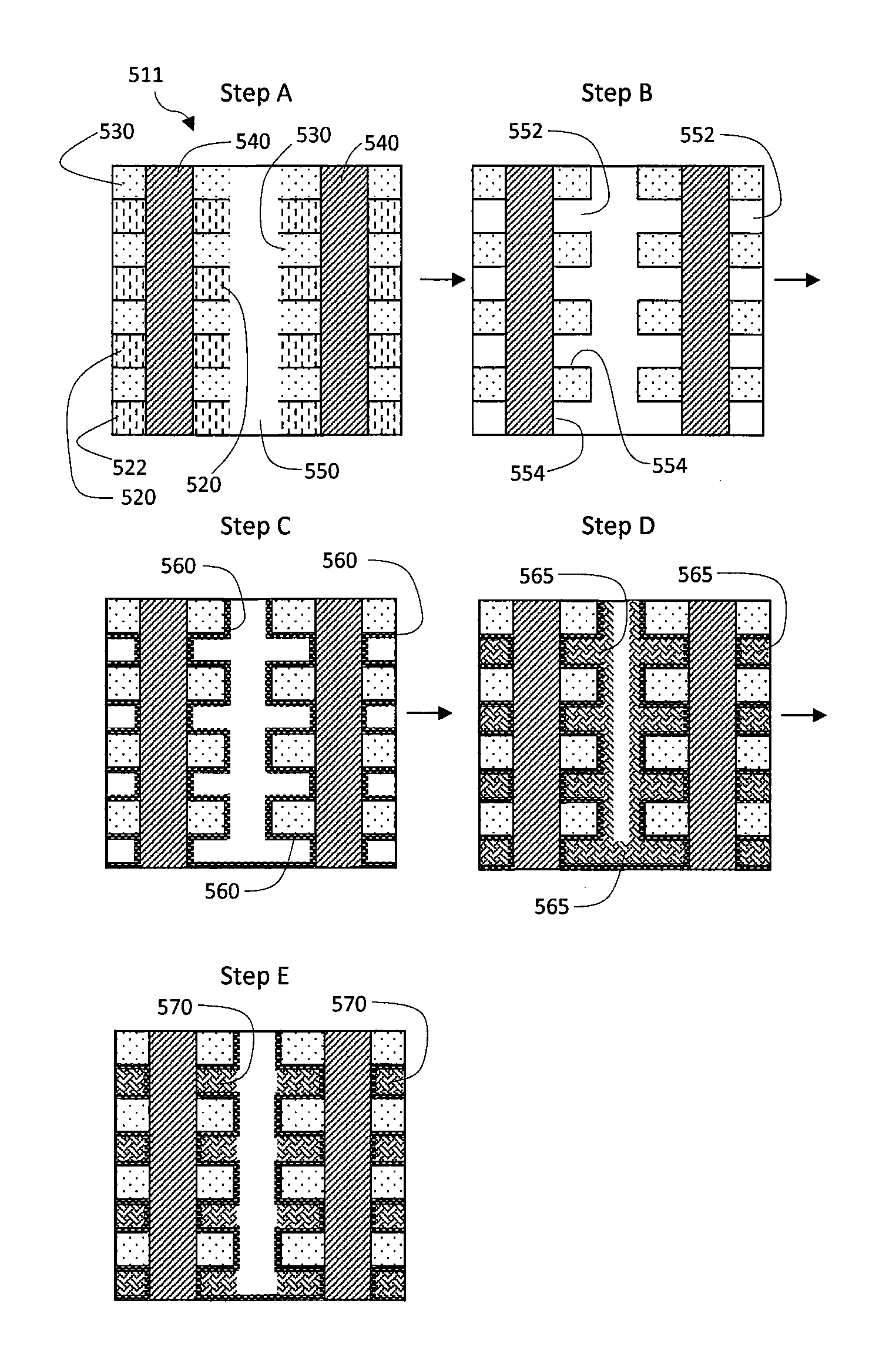

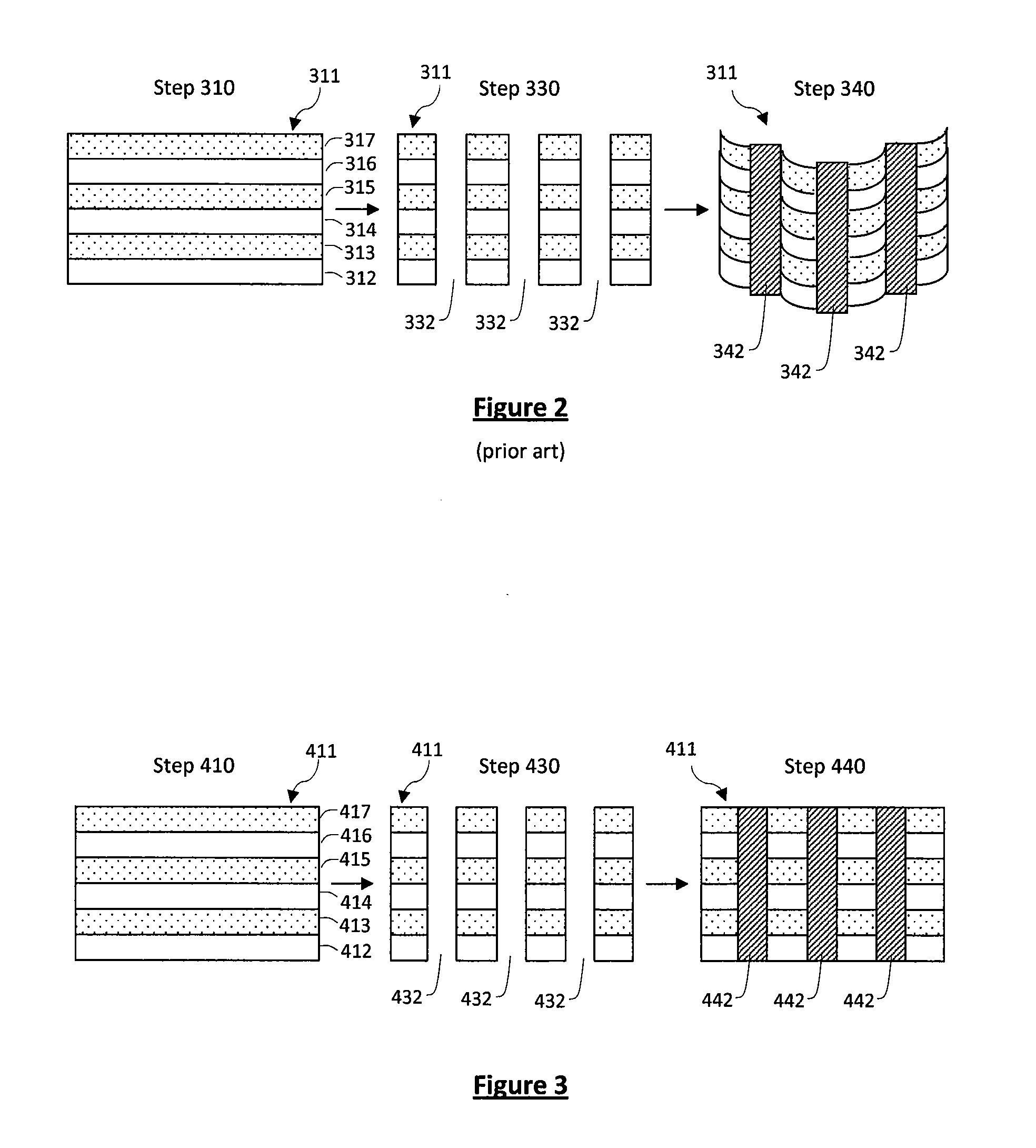

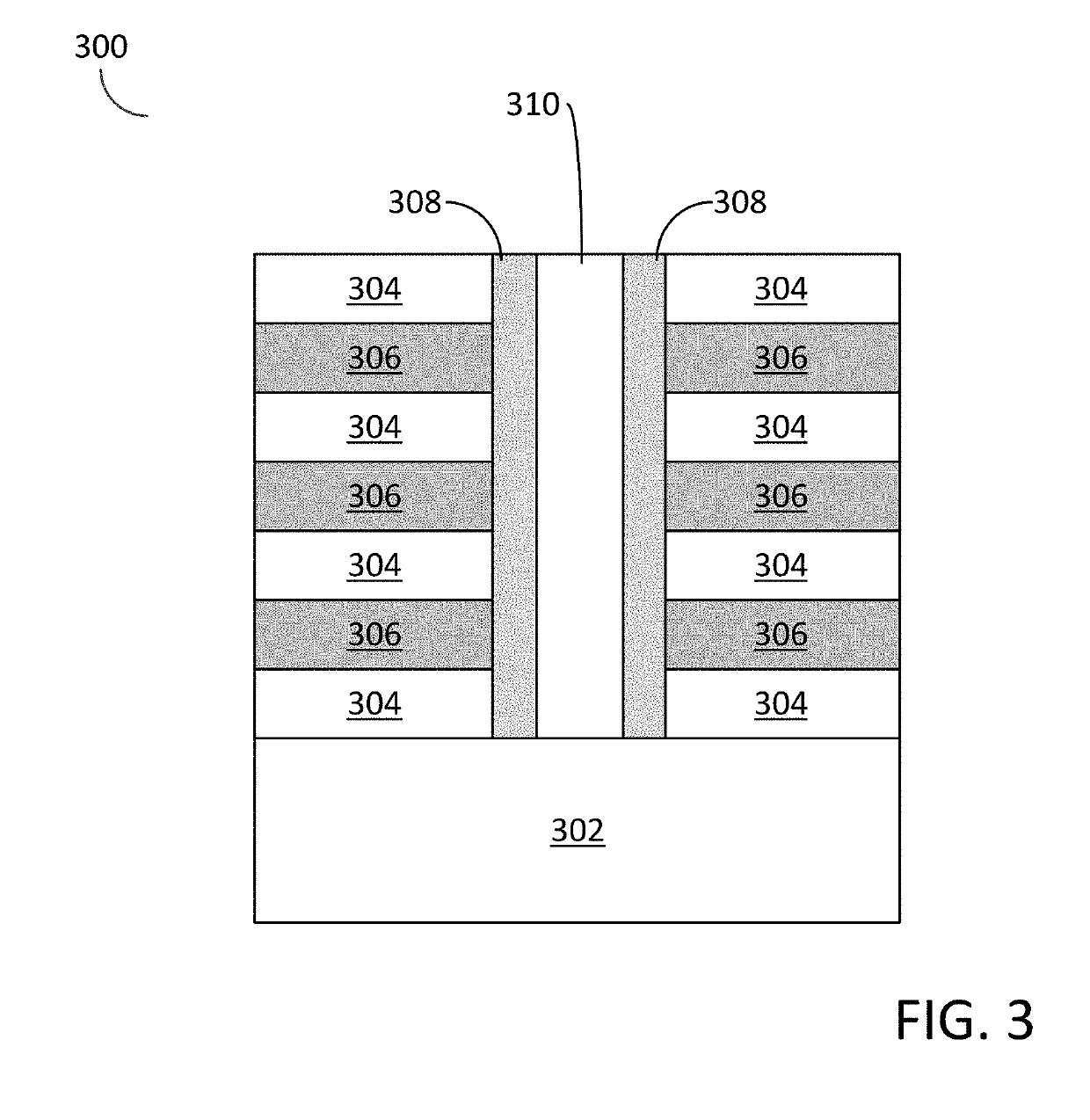

Zero shrinkage smooth interface oxy-nitride and oxy-amorphous-silicon stacks for 3D memory vertical gate application

InactiveUS20130161629A1Reduce AlFx depositReduce AlFx buildingSolid-state devicesSemiconductor/solid-state device manufacturingDeposition temperatureAmorphous silicon

Methods are provided for depositing a stack of film layers for use in vertical gates for 3D memory devices, by depositing a sacrificial nitride film layer at a sacrificial film deposition temperature greater than about 550° C.; depositing an oxide film layer over the nitride film layer, at an oxide deposition temperature of about 600° C. or greater; repeating the above steps to deposit a film stack having alternating layers of the sacrificial films and the oxide films; forming a plurality of holes in the film stack; and depositing polysilicon in the plurality of holes in the film stack at a polysilicon process temperature of about 700° C. or greater, wherein the sacrificial film layers and the oxide film layers experience near zero shrinkage during the polysilicon deposition. Flash drive memory devices may also be made by these methods.

Owner:APPLIED MATERIALS INC

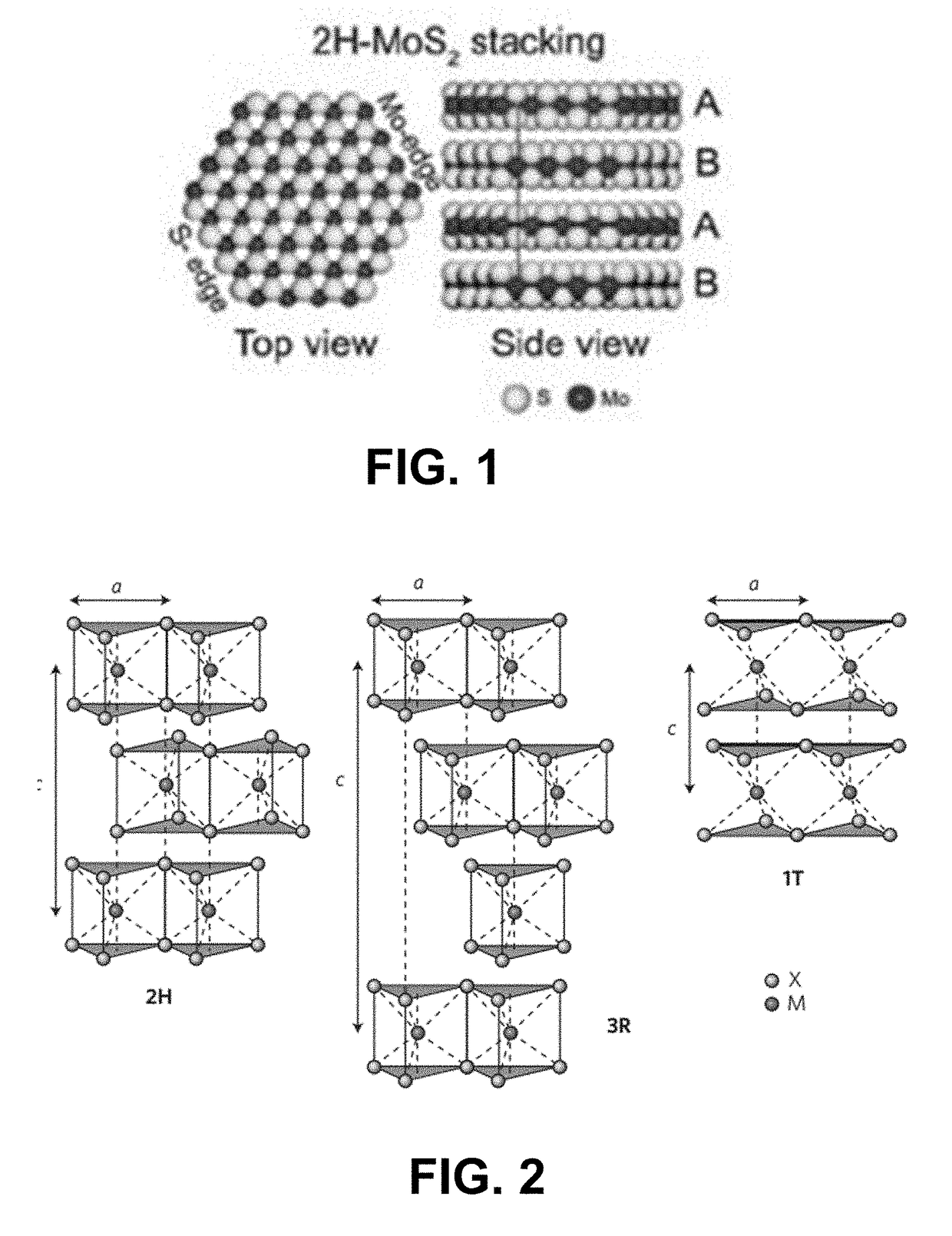

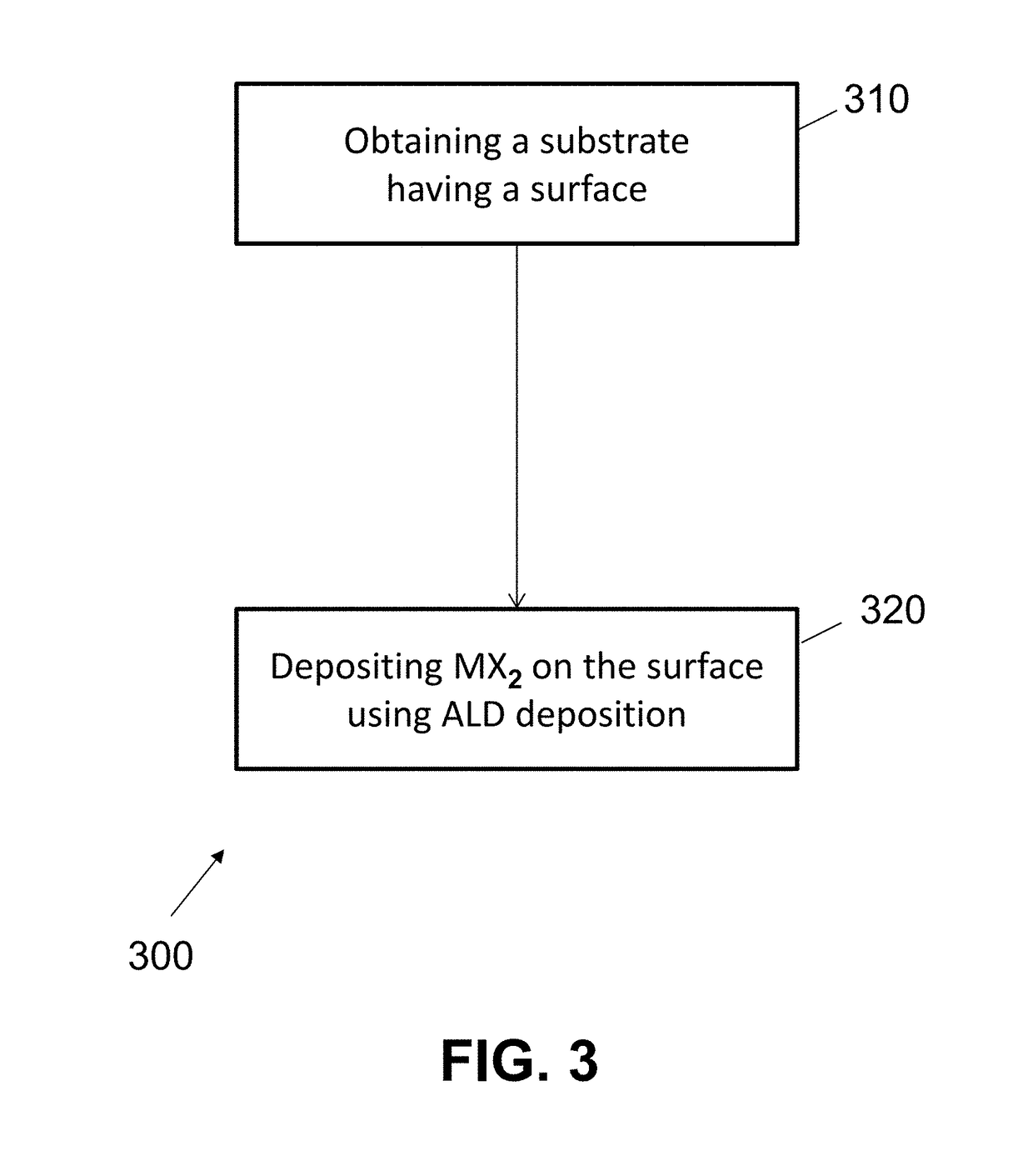

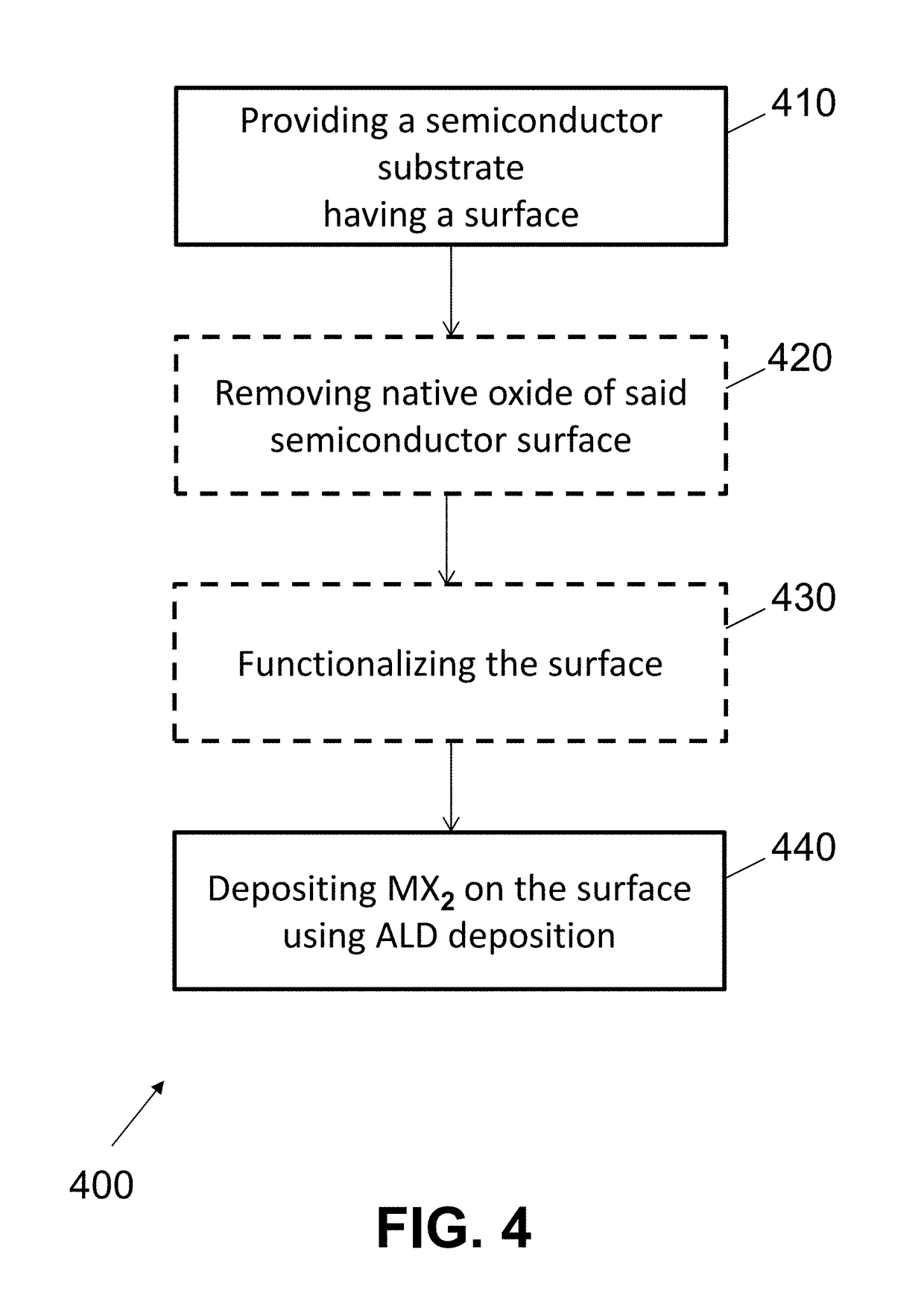

Method of Producing Transition Metal Dichalcogenide Layer

ActiveUS20170250075A1Advantageously producedSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDeposition temperatureChalcogen

Method of producing one or more transition metal dichalcogenide (MX2) layers on a substrate, comprising the steps of: obtaining a substrate having a surface and depositing MX2 on the surface using ALD deposition, starting from a metal halide precursor and a chalcogen source (H2X), at a deposition temperature of about 300° C. Suitable metals are Mo and W, suitable chalcogenides are S, Se and Te. The substrate may be (111) oriented. Also mixtures of two or more MX2 layers of different compositions can be deposited on the substrate, by repeating at least some of the steps of the method.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

Atomic layer deposition of noble metal oxides

Electrically conductive noble metal oxide films can be deposited by atomic layer deposition (ALD)-type processes. In preferred embodiments, Re, Ru, Os and Ir oxides are deposited by alternately and sequentially contacting a substrate with vapor phase pulses of a noble metal precursor and an oxygen source. The noble metal precursor is preferably a betadiketonate compound and the oxygen source is preferably ozone or oxygen plasma. The deposition temperature may be less than about 200° C.

Owner:ASM INTERNATIONAL

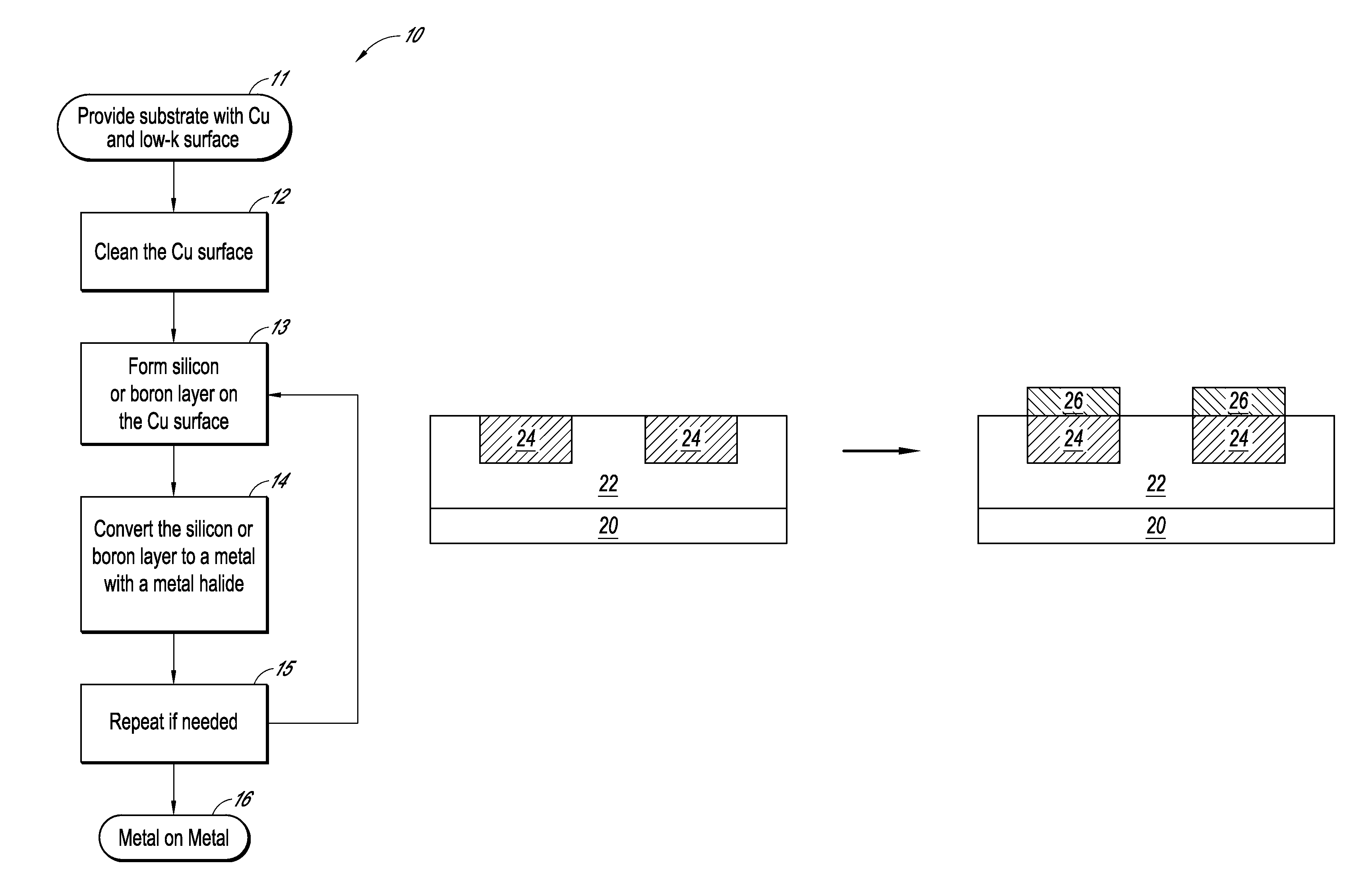

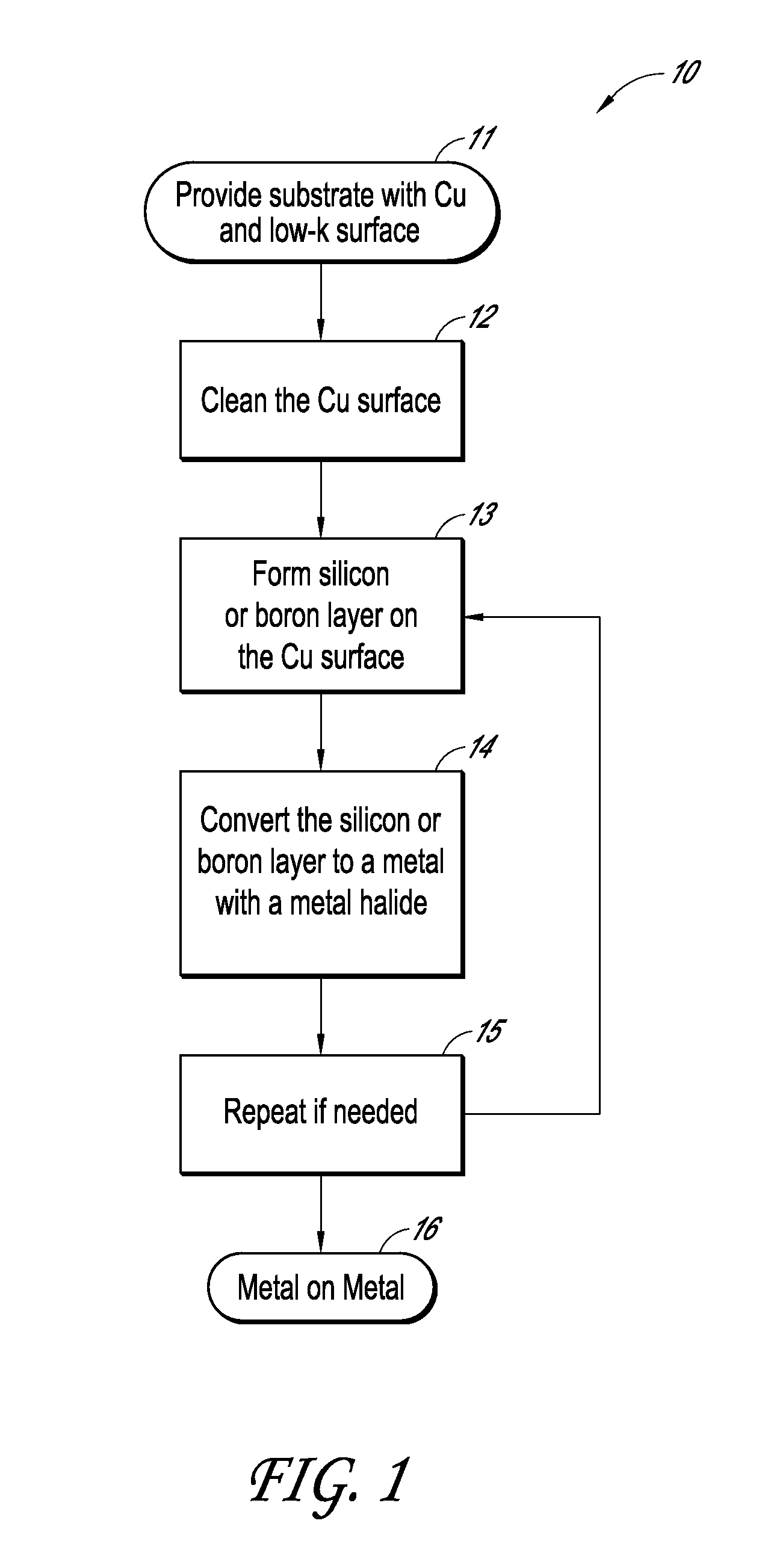

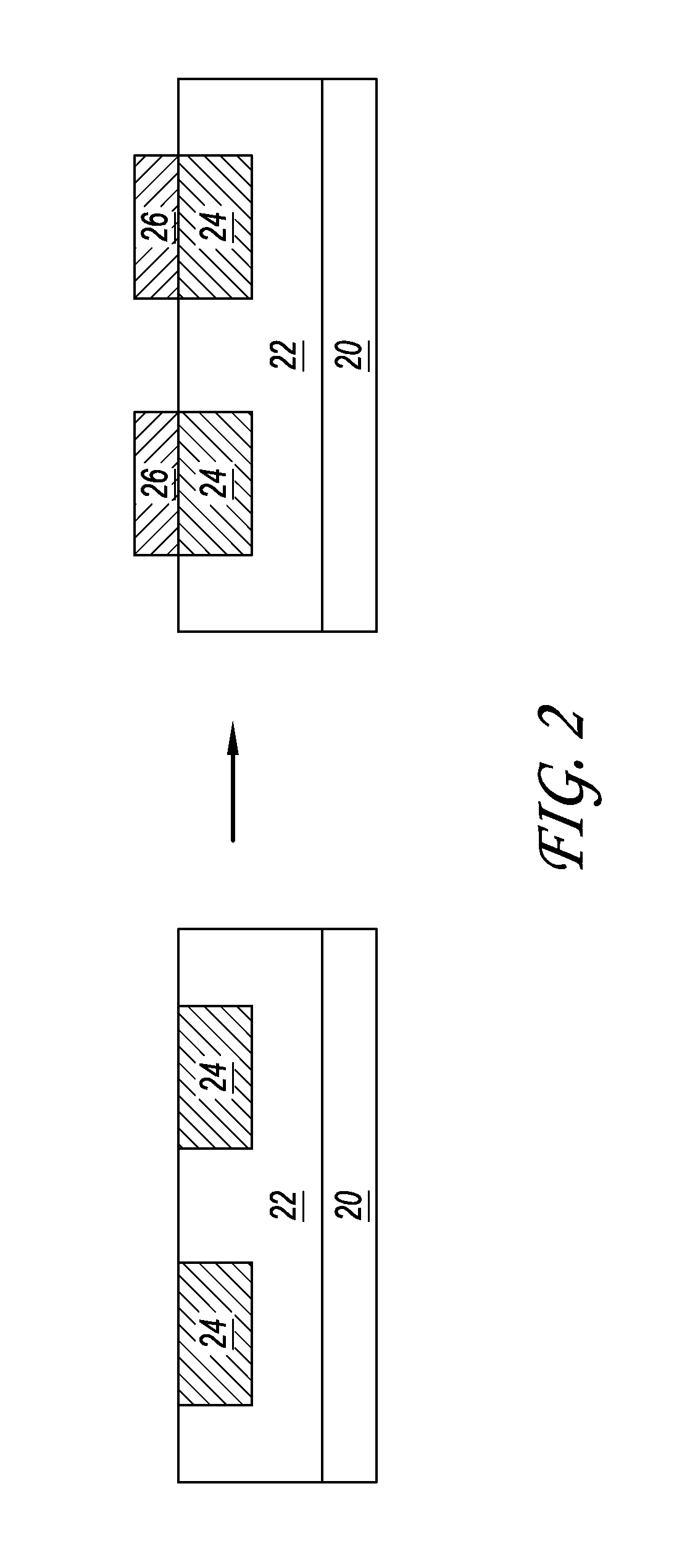

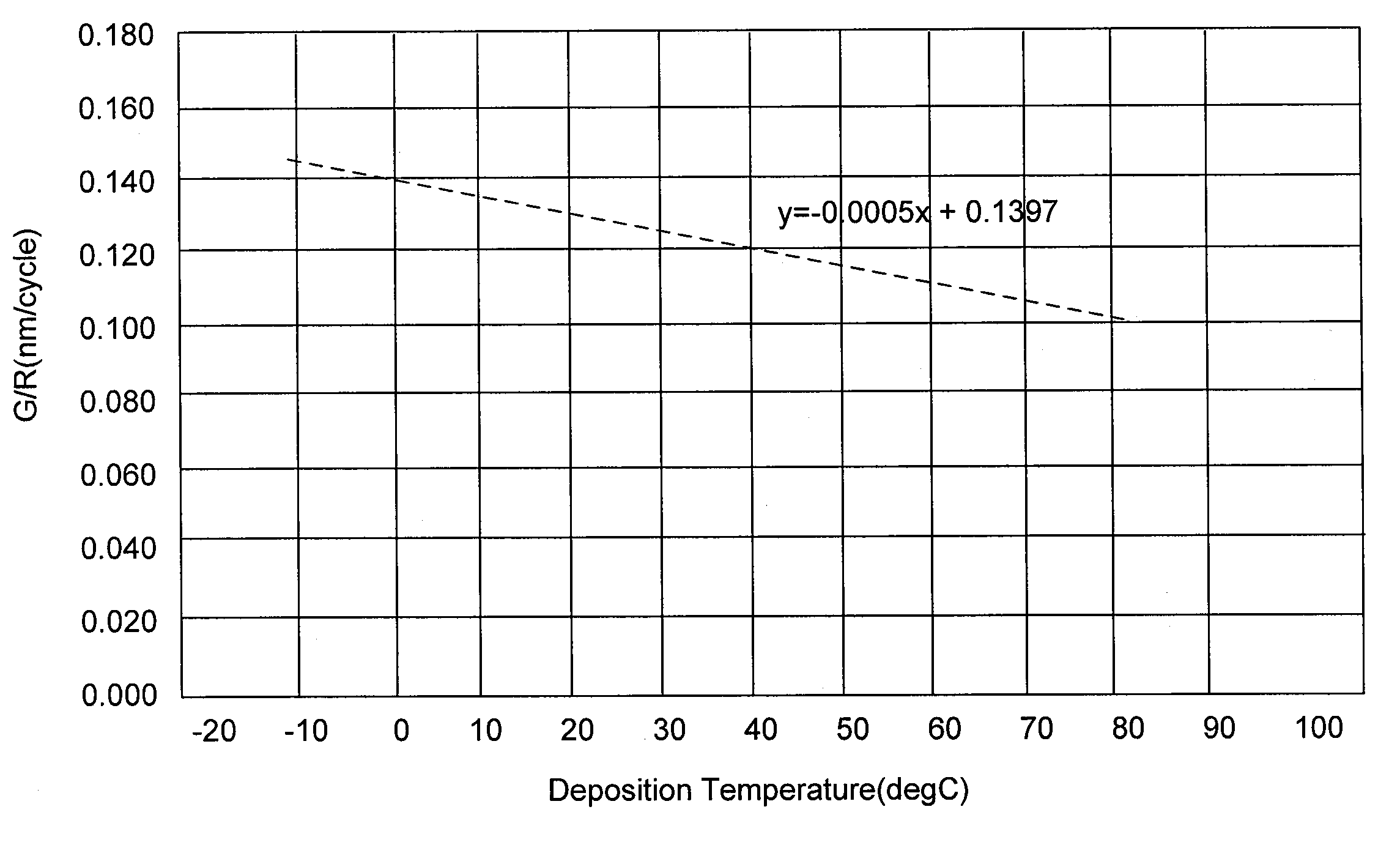

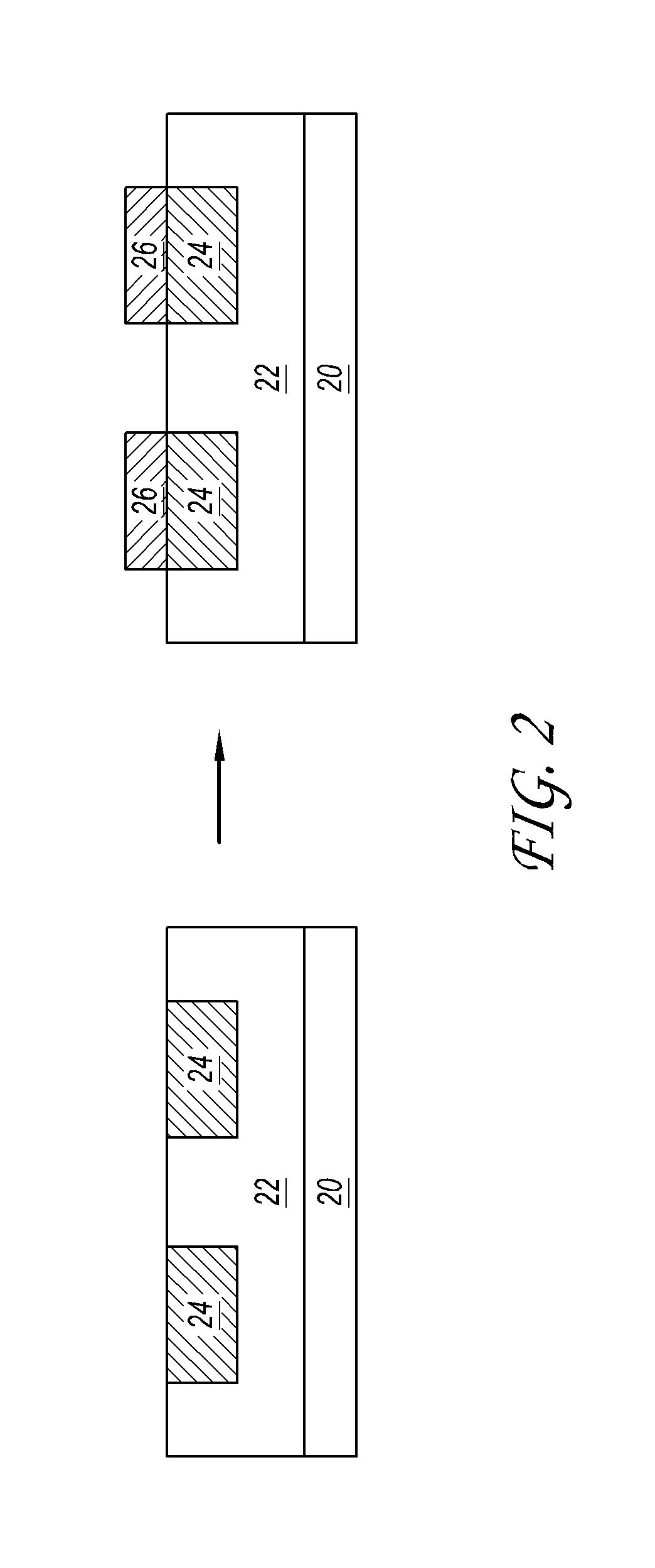

Selective formation of metallic films on metallic surfaces

ActiveUS20130196502A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingDeposition temperatureCopper

Metallic layers can be selectively deposited on one surface of a substrate relative to a second surface of the substrate. In some embodiments, the metallic layers are selectively deposited on copper instead of insulating or dielectric materials. In some embodiments, a first precursor forms a layer on the first surface and is subsequently reacted or converted to form a metallic layer. The deposition temperature may be selected such that a selectivity of above about 50% or even about 90% is achieved.

Owner:ASM INTERNATIONAL

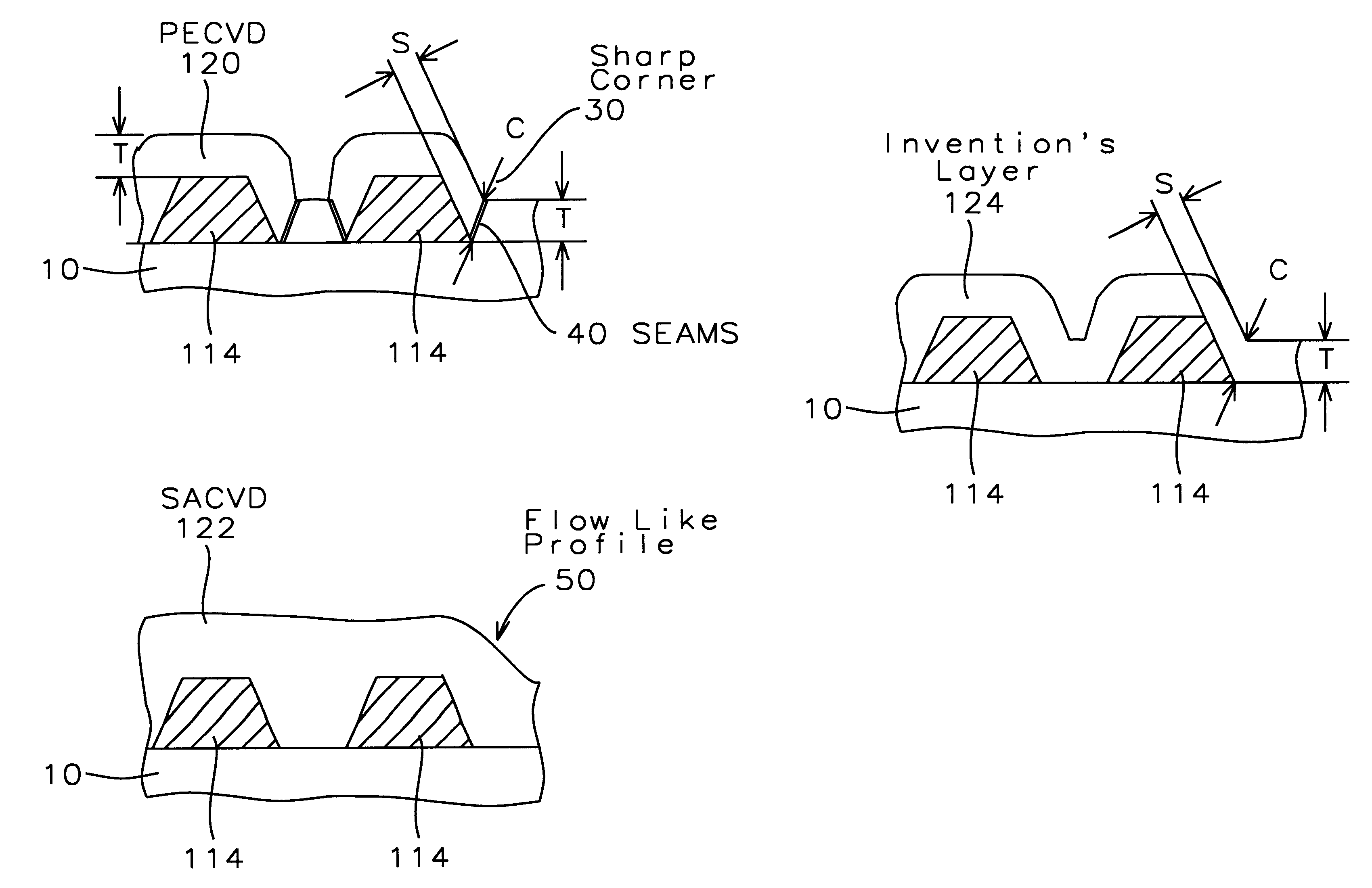

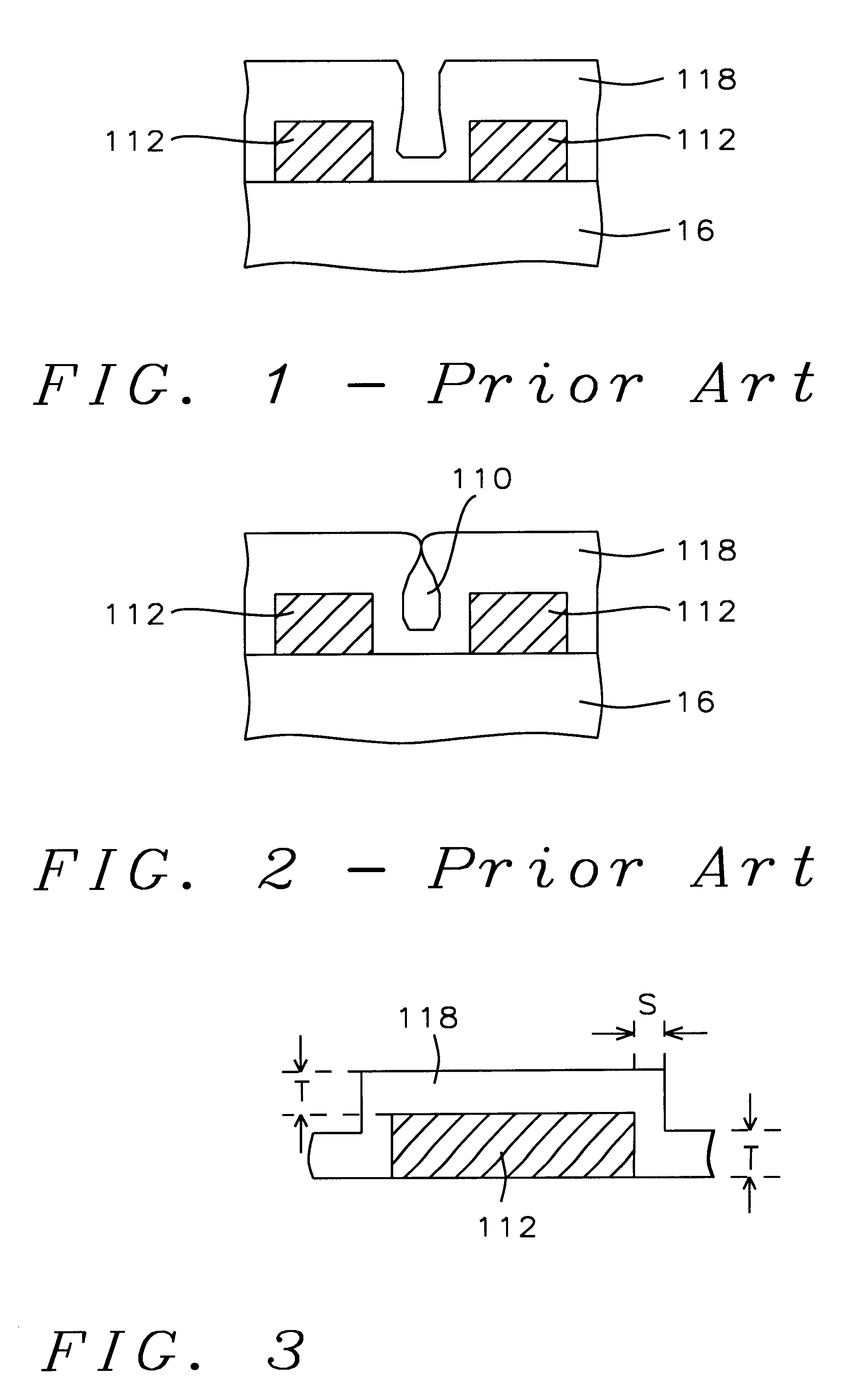

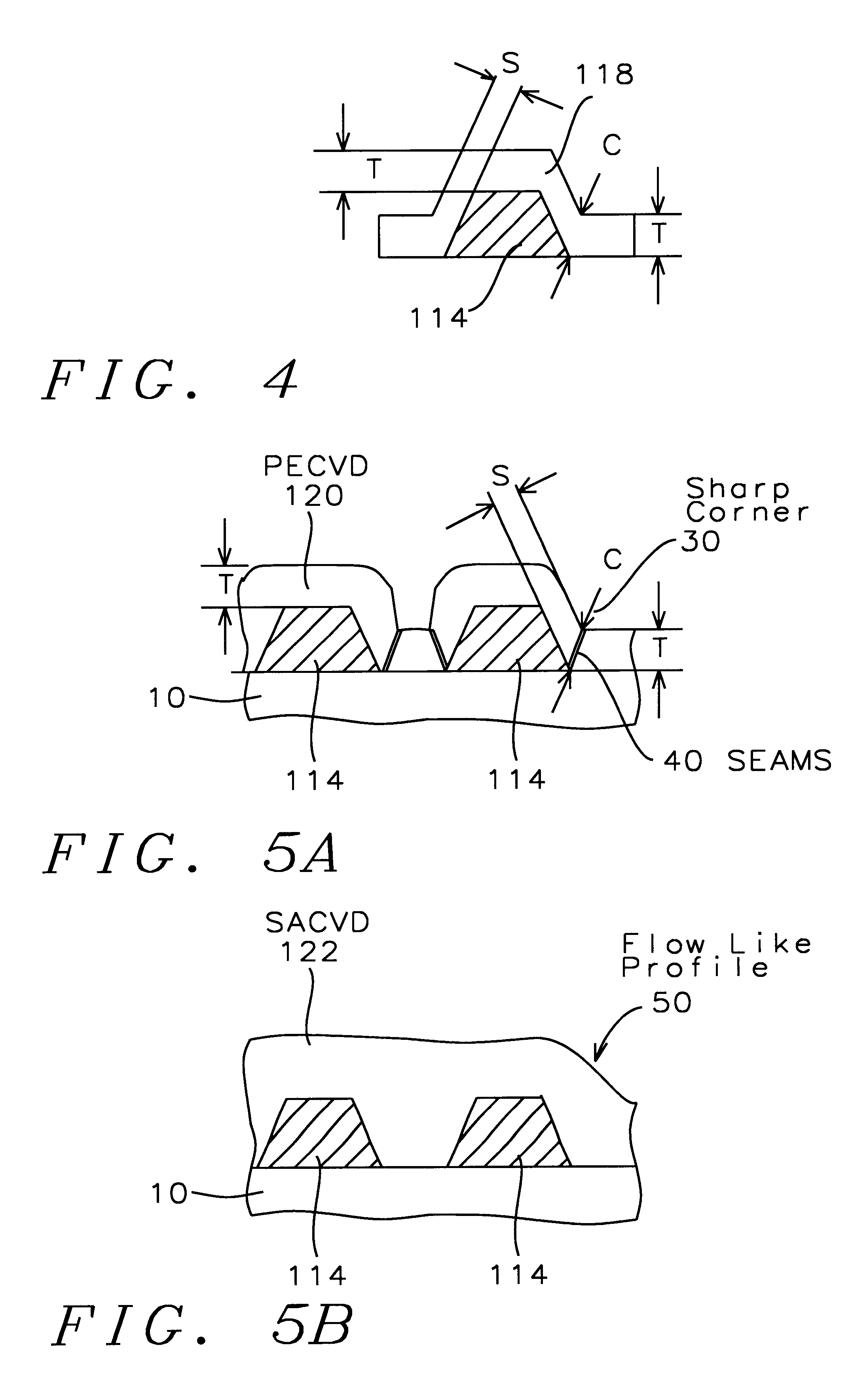

Method of silicon oxide and silicon glass films deposition

InactiveUS6197705B1Good step coverageImprove integrityPretreated surfacesSemiconductor/solid-state device manufacturingDielectricPlasma density

A method for fabricating a silicon oxide and silicon glass layers at low temperature using soft power-optimized Plasma-Activated CVD with a TEOS-ozone-oxygen reaction gas mixture (TEOS O3 / O2 PACVD) is described. It combines advantages of both low temperature Plasma-Enhanced Chemical Vapor Deposition (PECVD) and TEOS-ozone Sub-Atmospheric Chemical Vapor Deposition (SACVD) and yields a coating of silicon oxide with stable and high deposition rate, no surface sensitivity, good film properties, conformal step coverage and good gap-fill. Key features of the invention's O3 / O2 PACVD process are: a plasma is maintain throughout the entire deposition step in a parallel plate type reactor chamber, the precise RF plasma density, ozone concentration in oxygen and the deposition temperature. These features provide the reaction conditions for the proper O3 / O2 reaction mechanism that deposits a conformal silicon oxide layer. The process has significant implication for semiconductor device manufacturing involving the deposition of a dielectric over a conducting non-planar surface.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

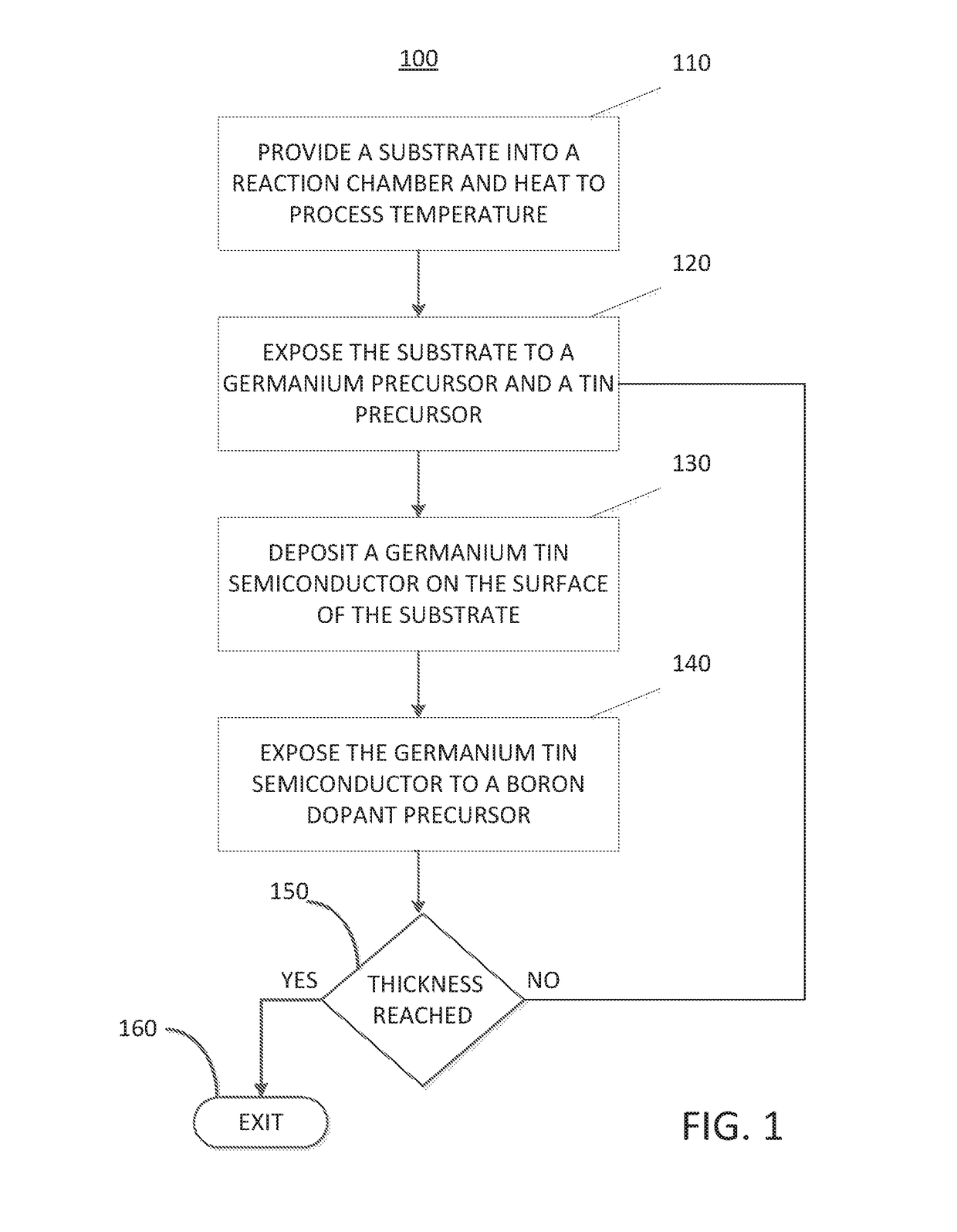

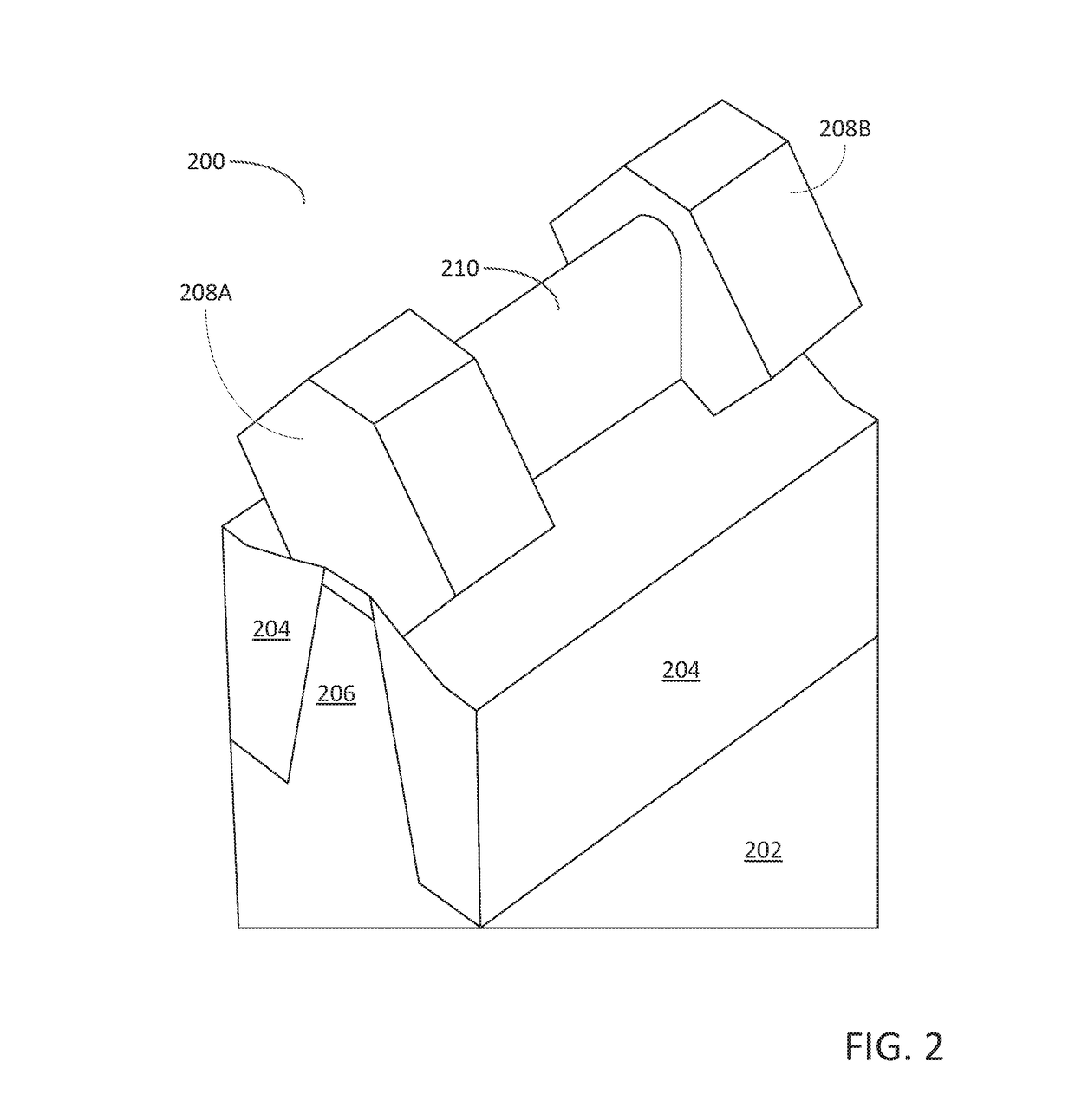

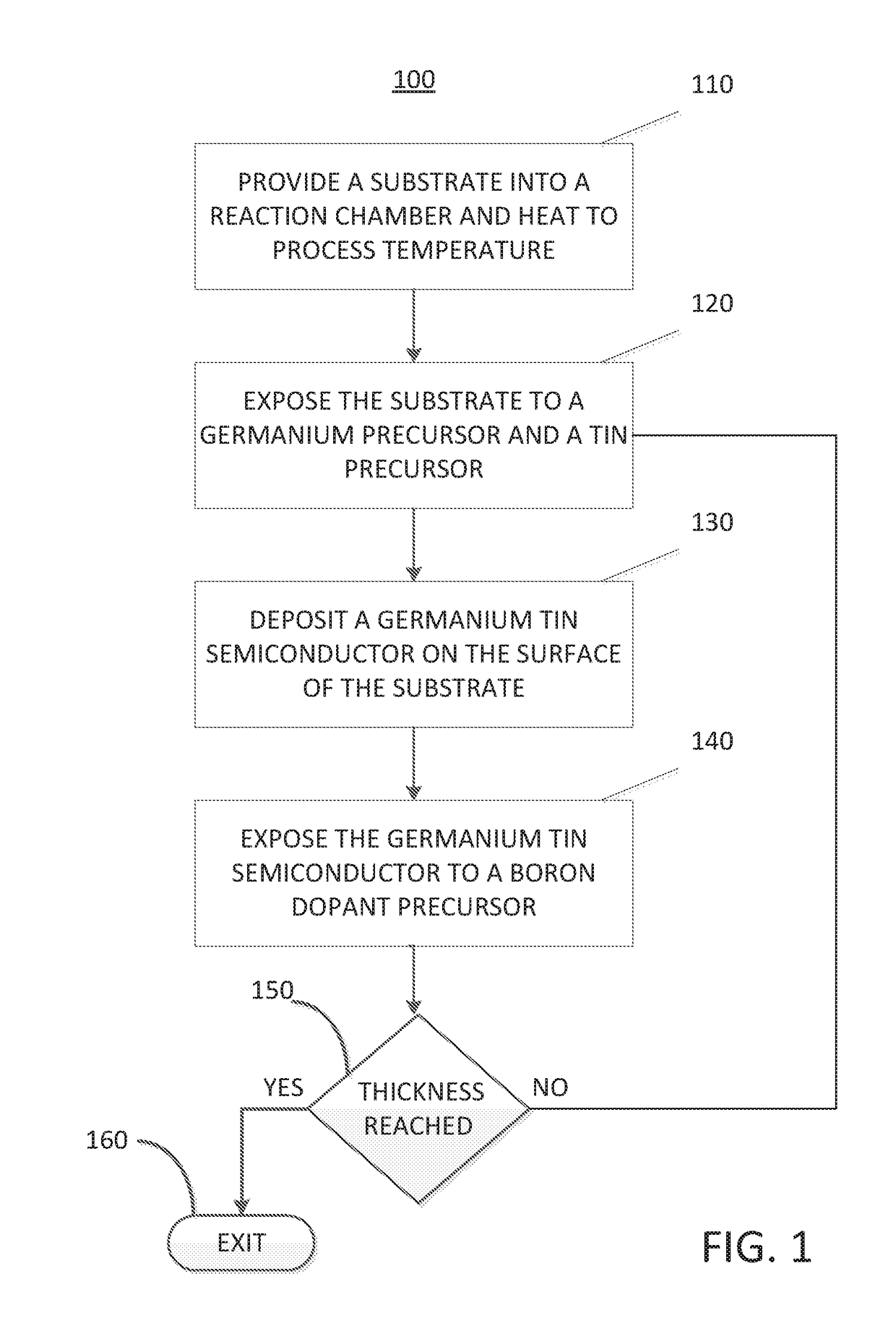

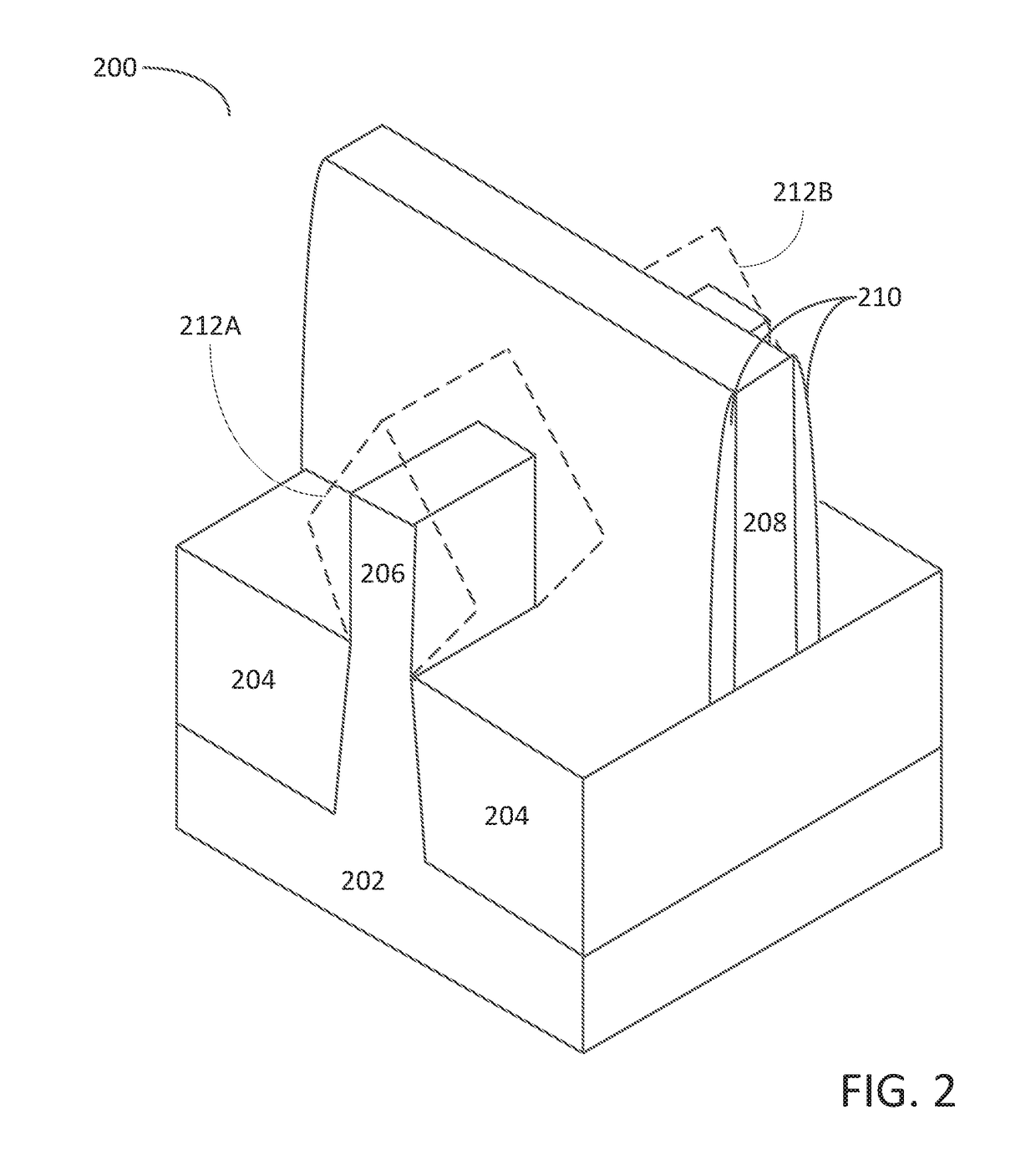

Methods for depositing a doped germanium tin semiconductor and related semiconductor device structures

ActiveUS10236177B1Polycrystalline material growthAfter-treatment detailsDopantDeposition temperature

A method for depositing a germanium tin (Ge1-xSnx) semiconductor is disclosed. The method may include; providing a substrate within a reaction chamber, heating the substrate to a deposition temperature and exposing the substrate to a germanium precursor and a tin precursor. The method may further include; depositing a germanium tin (Ge1-xSnx) semiconductor on the surface of the substrate, and exposing the germanium tin (Ge1-xSnx) semiconductor to a boron dopant precursor. Semiconductor device structures including a germanium tin (Ge1-xSnx) semiconductor formed by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

Methods for depositing a doped germanium tin semiconductor and related semiconductor device structures

ActiveUS20190067004A1Polycrystalline material growthAfter-treatment detailsDopantDeposition temperature

A method for depositing a germanium tin (Ge1-xSnx) semiconductor is disclosed. The method may include; providing a substrate within a reaction chamber, heating the substrate to a deposition temperature and exposing the substrate to a germanium precursor and a tin precursor. The method may further include; depositing a germanium tin (Ge1-xSnx) semiconductor on the surface of the substrate, and exposing the germanium tin (Ge1-xSnx) semiconductor to a boron dopant precursor. Semiconductor device structures including a germanium tin (Ge1-xSnx) semiconductor formed by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

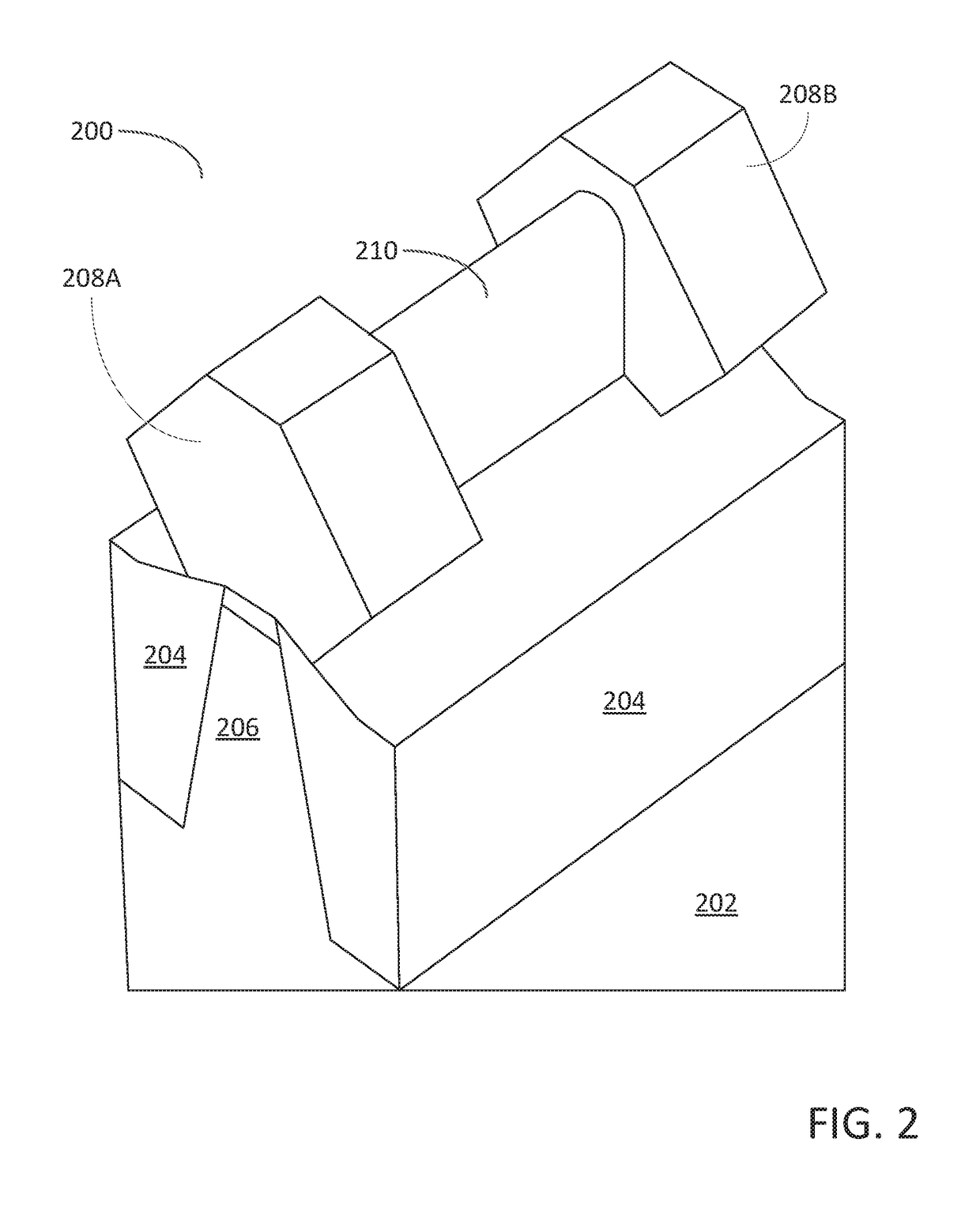

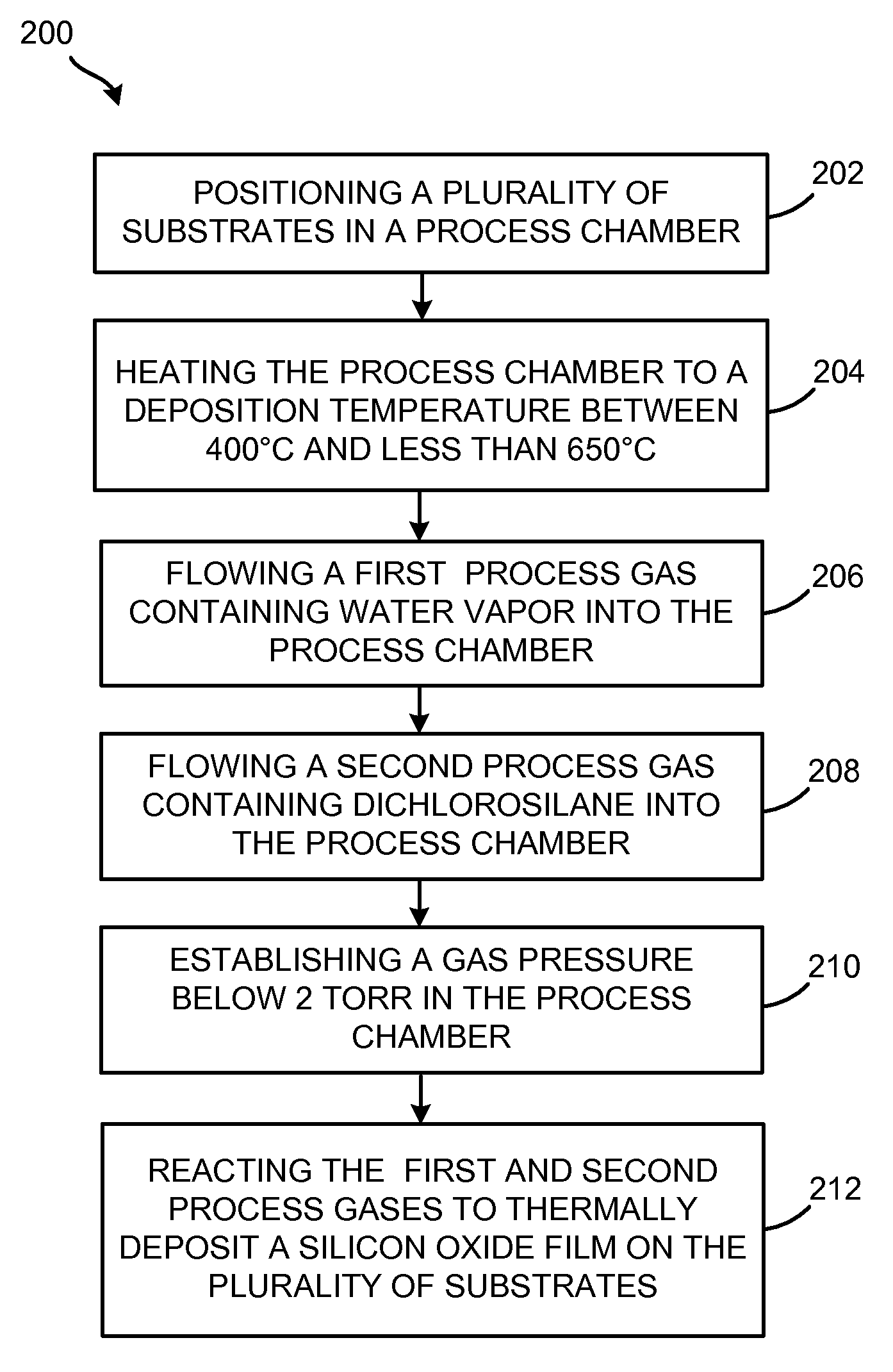

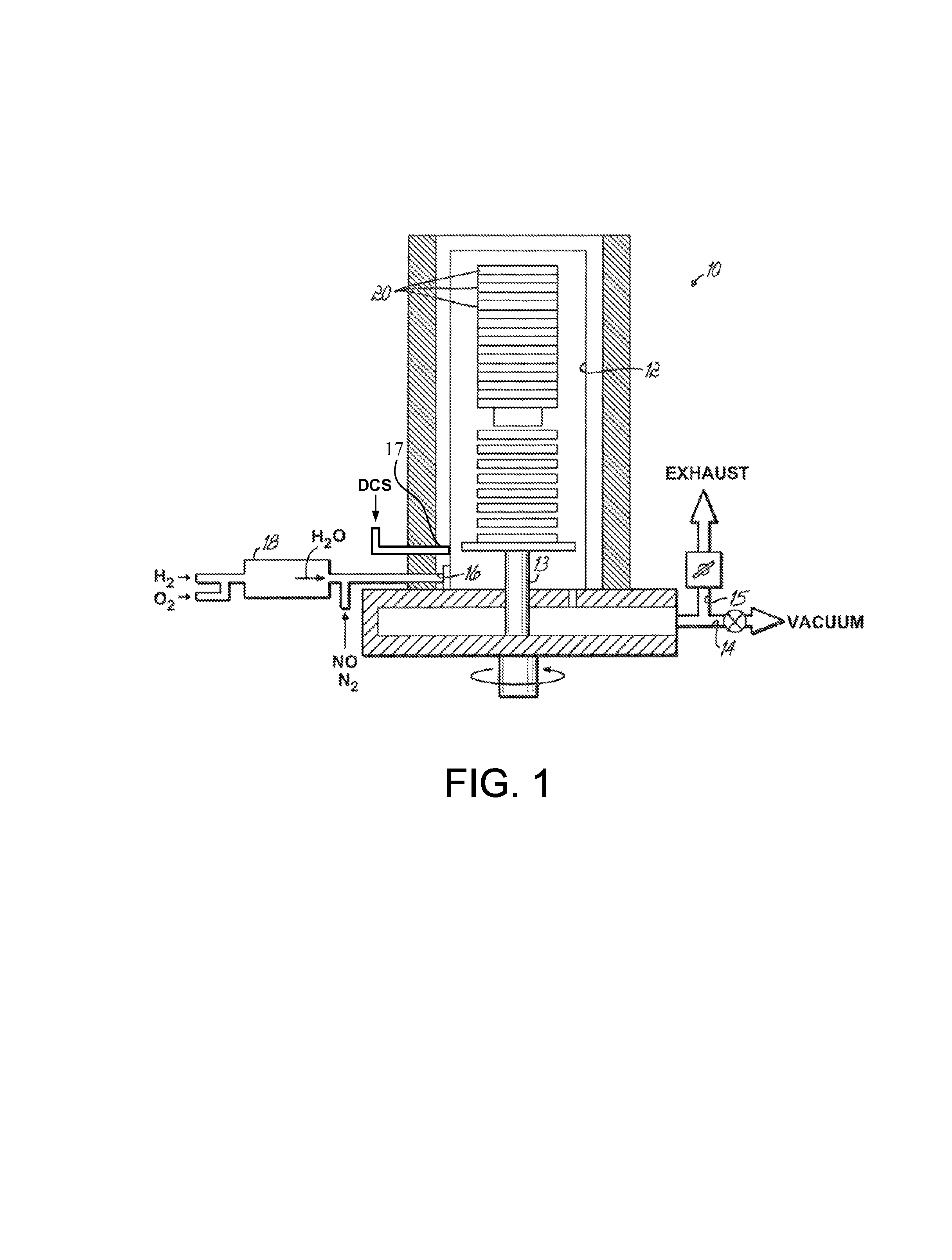

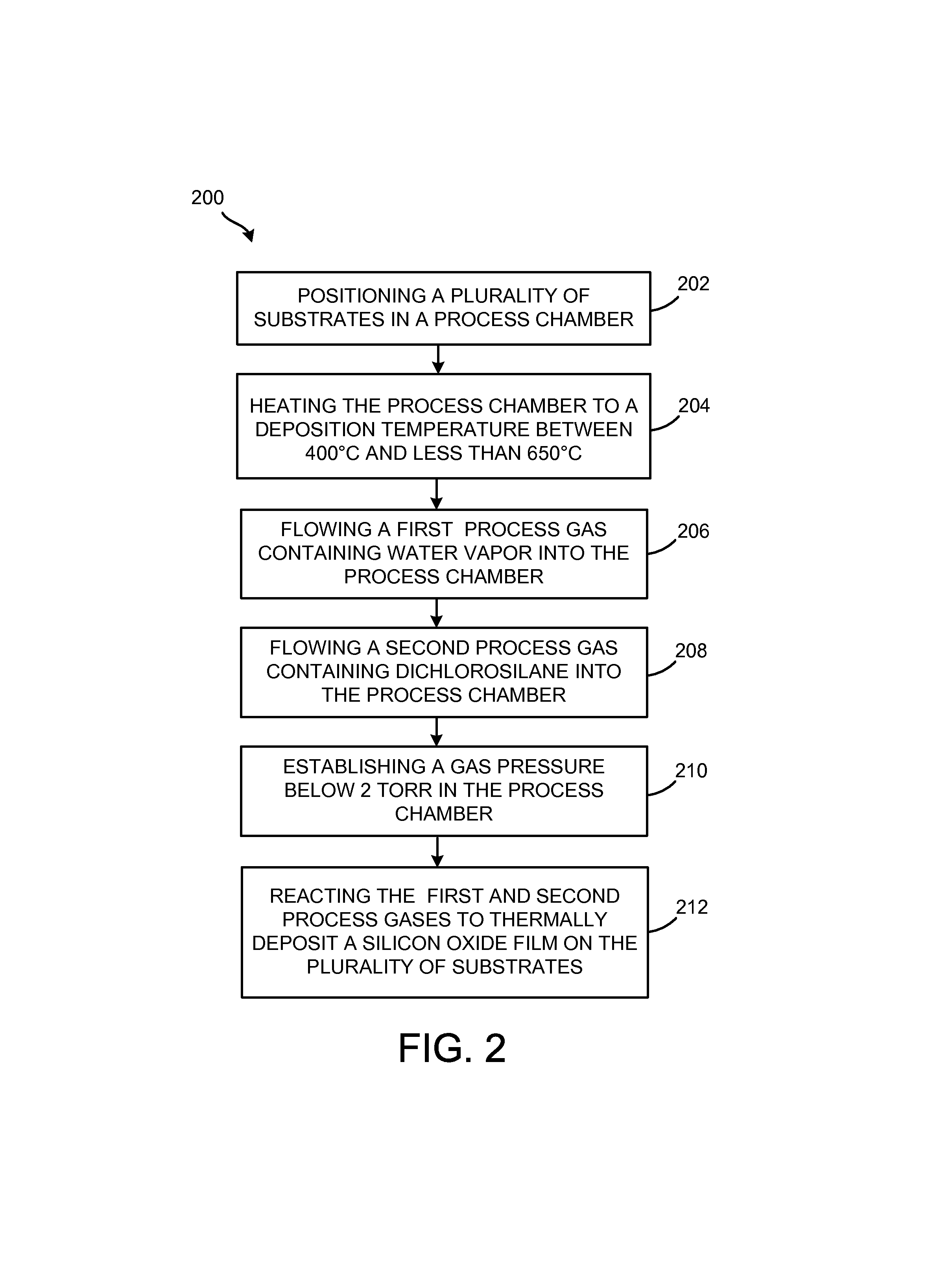

Low-temperature dielectric film formation by chemical vapor deposition

InactiveUS7994070B1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricWater vapor

A method for depositing a dielectric film on a substrate includes positioning a plurality of substrates in a process chamber, heating the process chamber to a deposition temperature between 400° C. and less than 650° C., flowing a first process gas comprising water vapor into the process chamber, flowing a second process gas comprising dichlorosilane (DCS) into the process chamber, establishing a gas pressure of less than 2 Torr, and reacting the first and second process gases to thermally deposit a silicon oxide film on the plurality of substrates. One embodiment further includes flowing a third process gas comprising nitric oxide (NO) gas into the process chamber while flowing the first process gas and the second process gas; and reacting the oxide film with the third process gas to form a silicon oxynitride film on the substrate.

Owner:TOKYO ELECTRON LTD

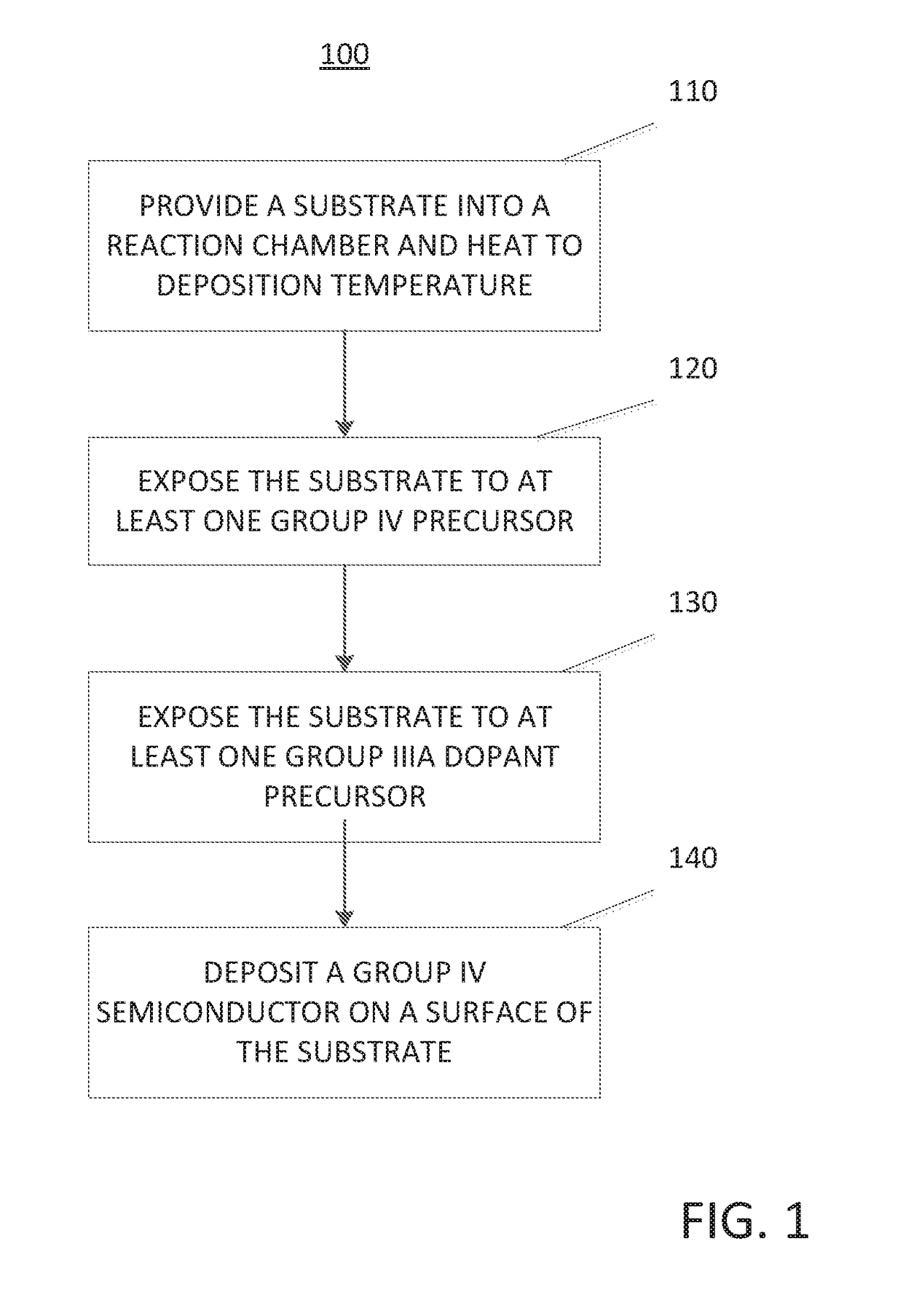

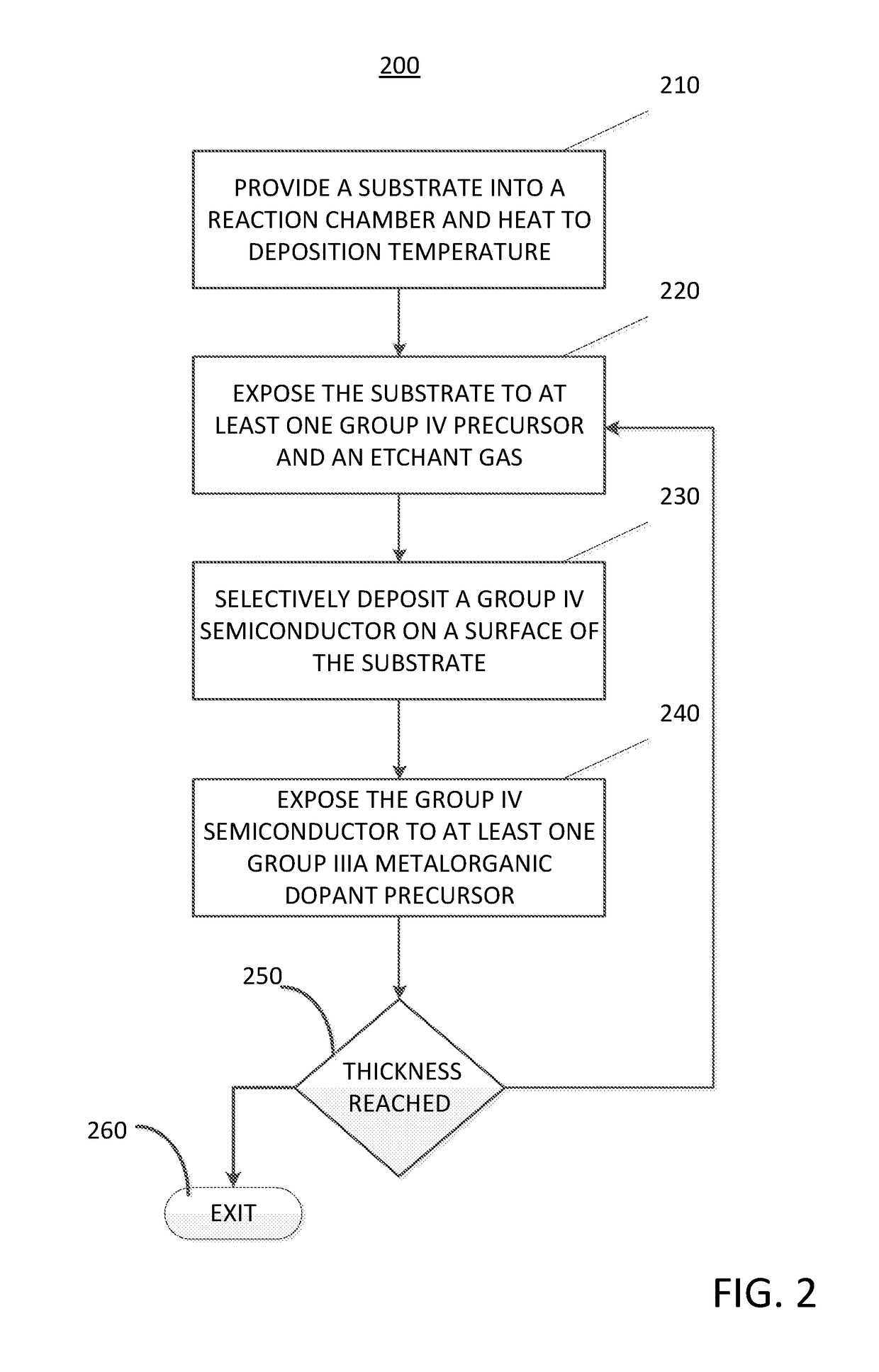

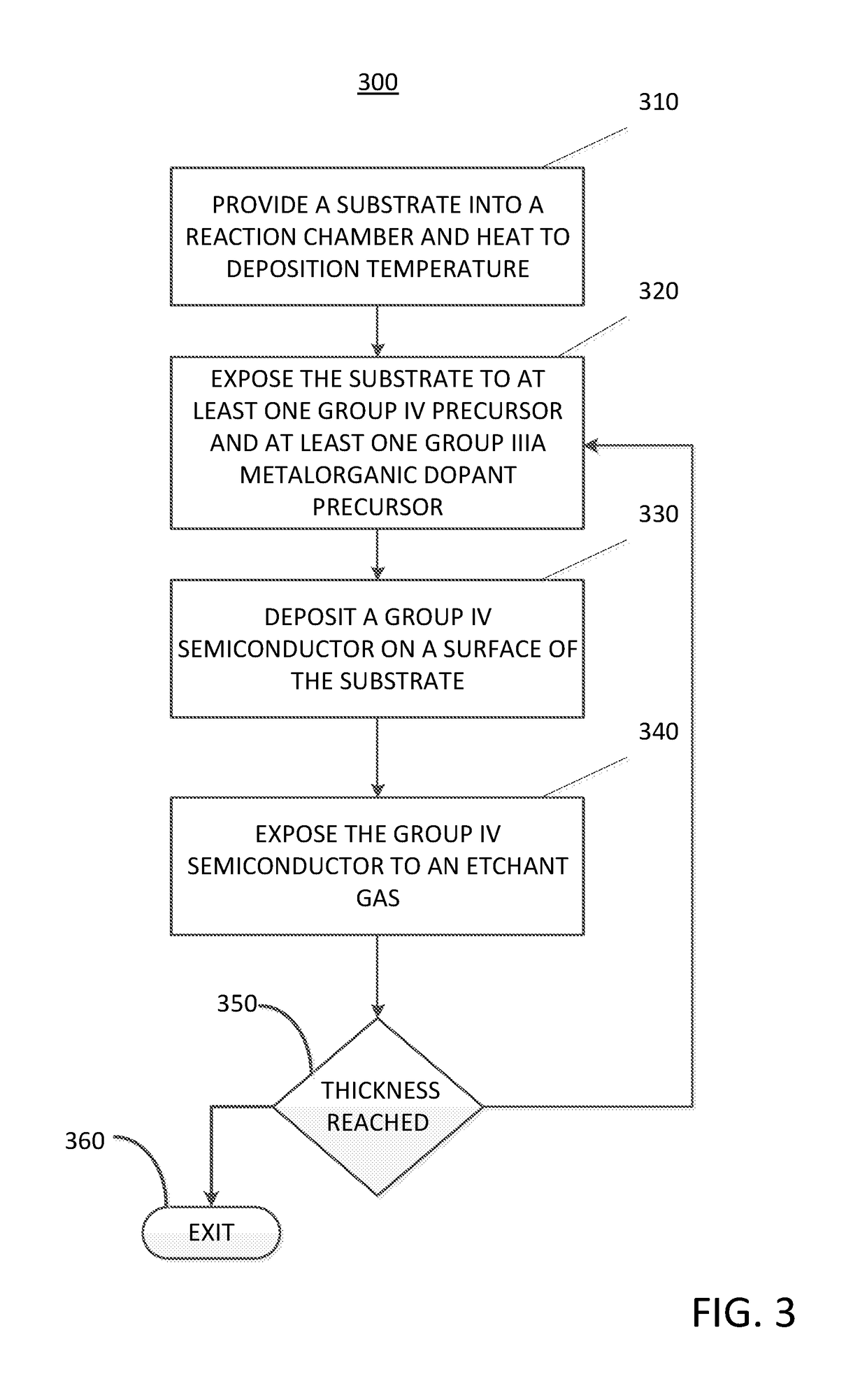

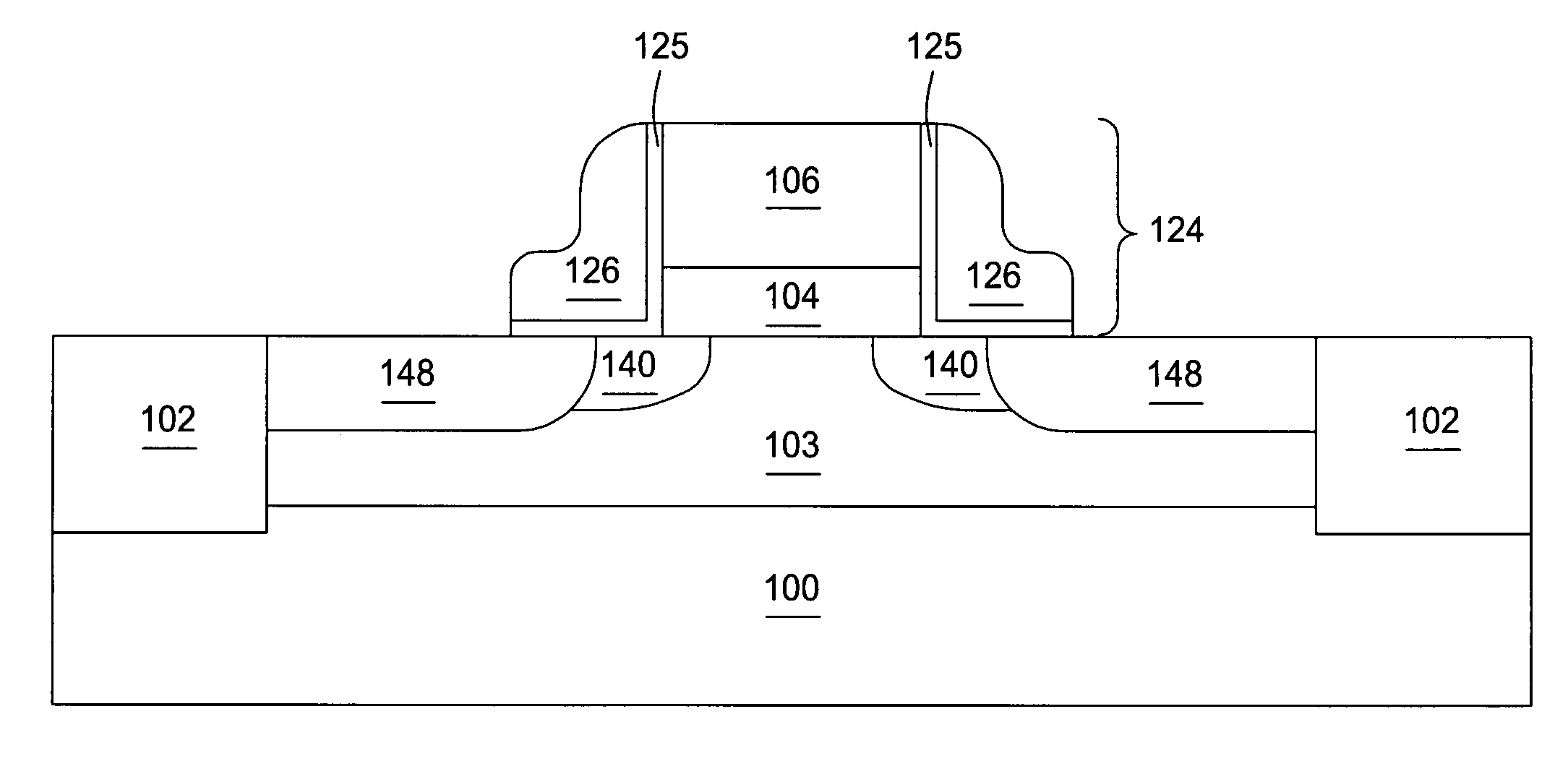

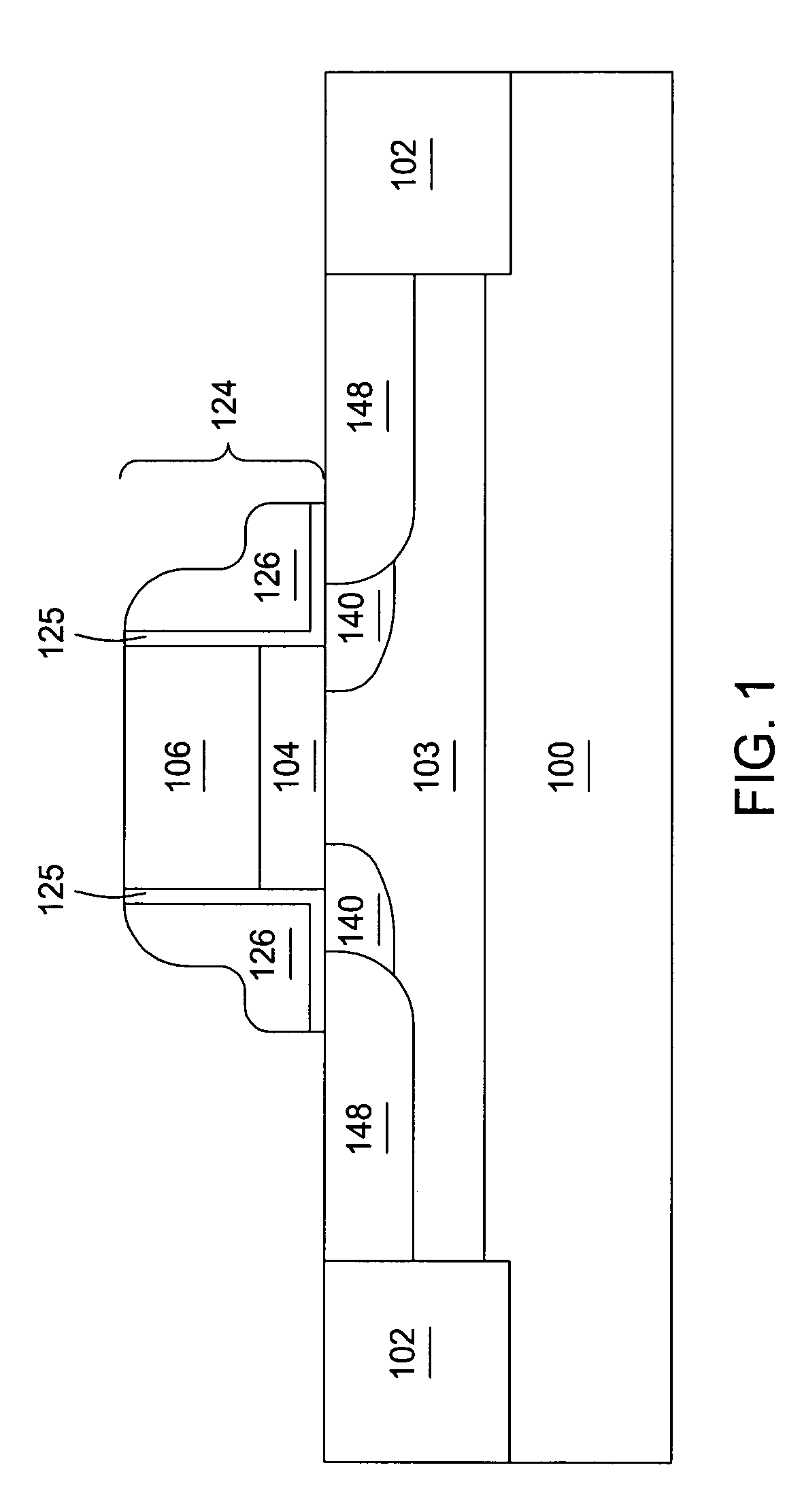

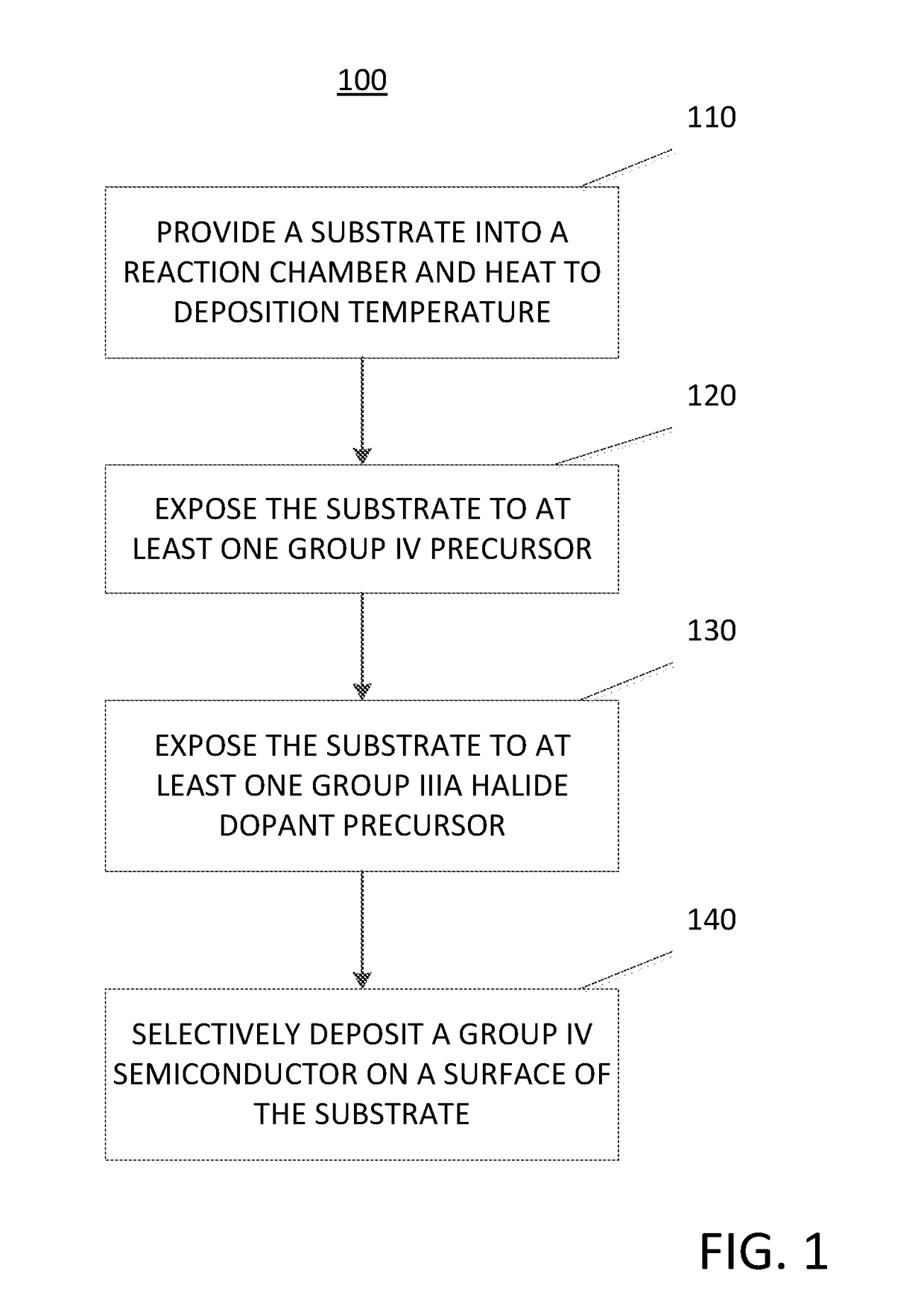

Method for depositing a group iv semiconductor and related semiconductor device structures

ActiveUS20190027605A1TransistorSemiconductor/solid-state device manufacturingDopantDeposition temperature

A method for depositing a Group IV semiconductor on a surface of a substrate is disclosed. The method may include: providing a substrate within a reaction chamber and heating the substrate to a deposition temperature. The methods may further include: exposing the substrate to at least one Group IV precursor and exposing the substrate to at least one Group IIIA dopant precursor; wherein the at least one Group IIIA dopant precursor comprises a borohydride, an organic borohydride, a halide, or an organohalide. Semiconductor device structures including a Group IV semiconductor deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

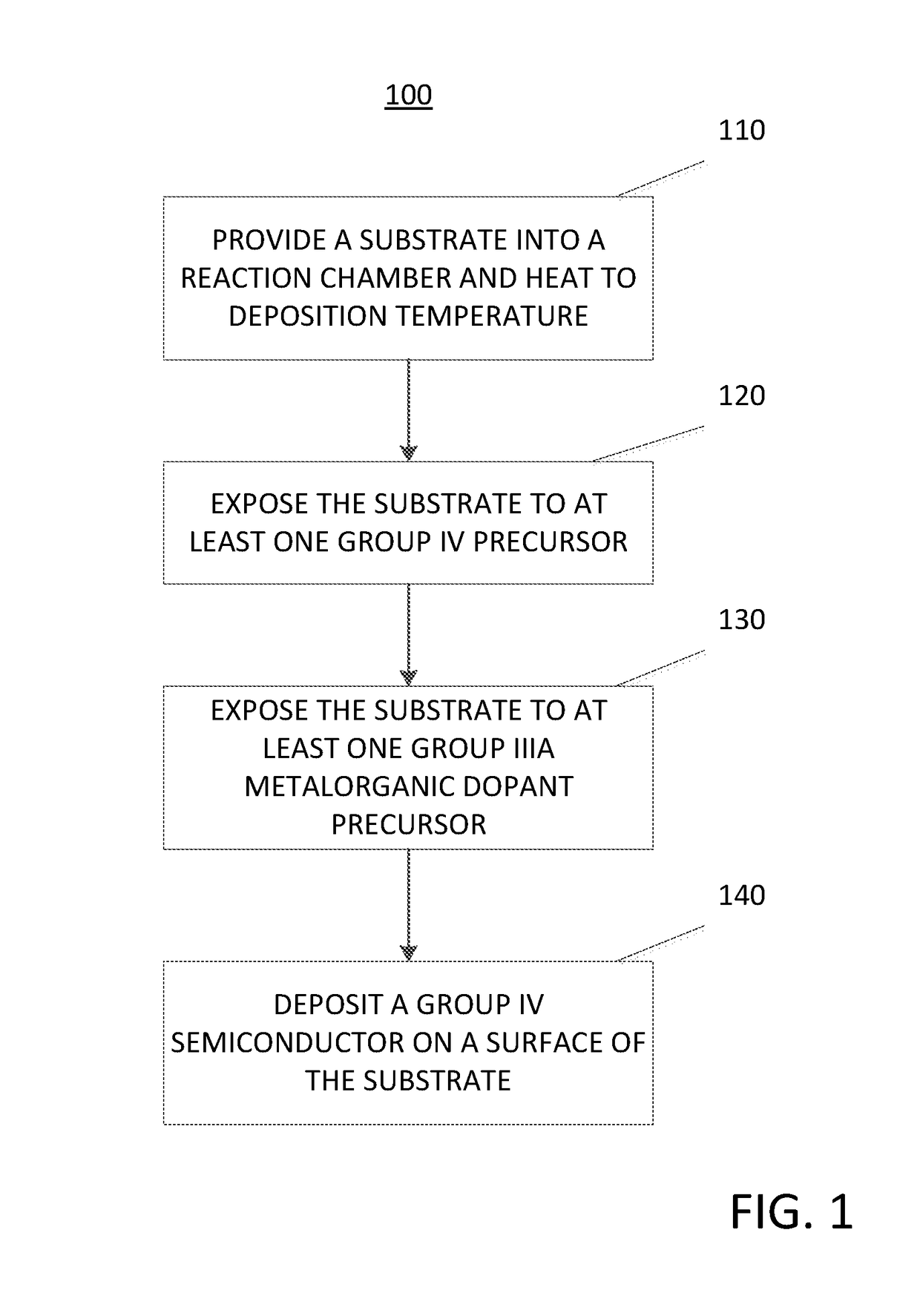

Method for depositing a group iv semiconductor and related semiconductor device structures

ActiveUS20190027583A1Semiconductor/solid-state device detailsSolid-state devicesDopantDeposition temperature

A method for depositing a Group IV semiconductor is disclosed. The method may include, providing a substrate within a reaction chamber and heating the substrate to a deposition temperature. The methods may further include, exposing the substrate to at least one Group IV precursor and exposing the substrate to at least one Group IIIA metalorganic dopant precursor. The methods may further include depositing a Group IV semiconductor on a surface of the substrate. Semiconductor device structures including a Group IV semiconductor deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

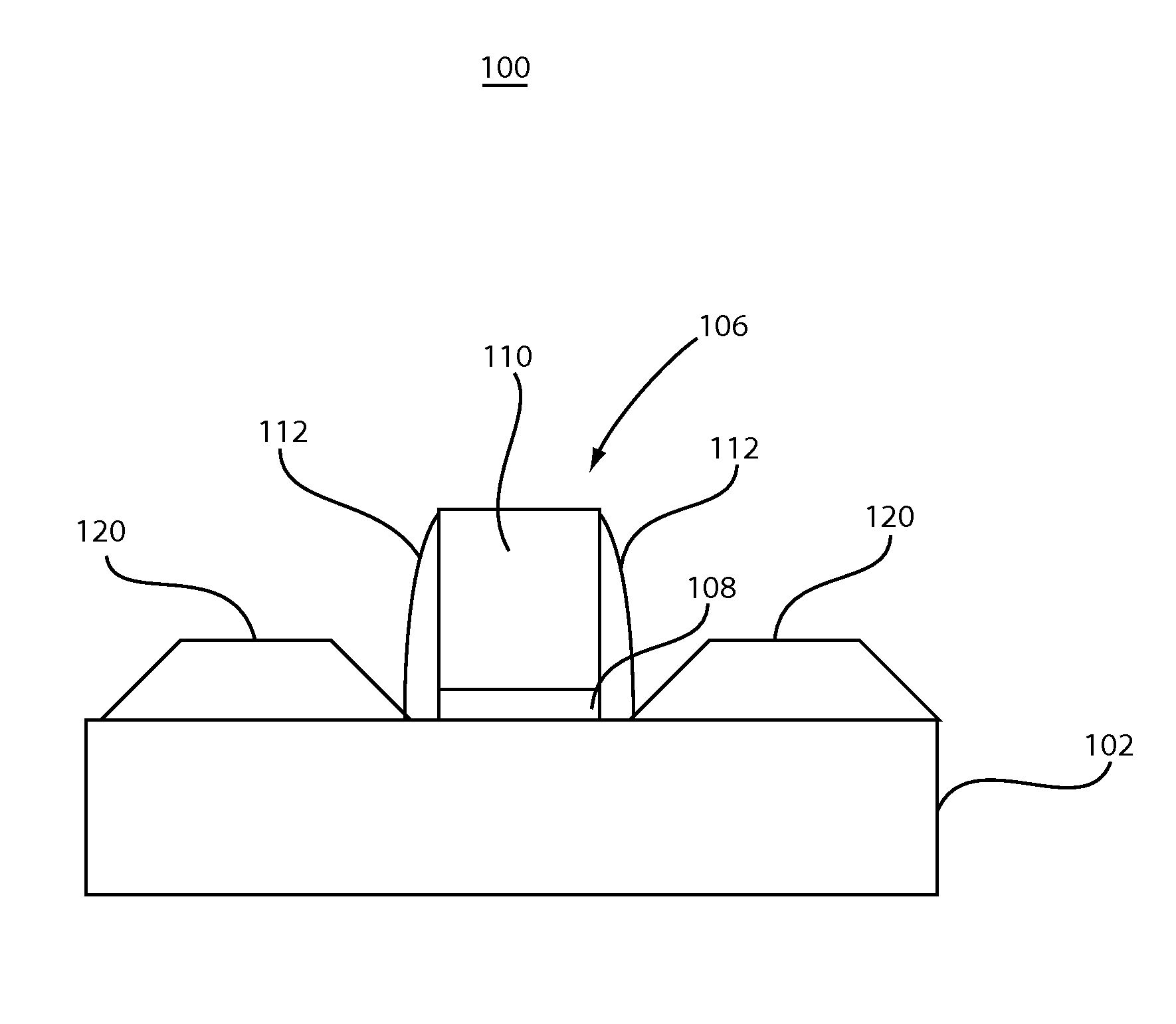

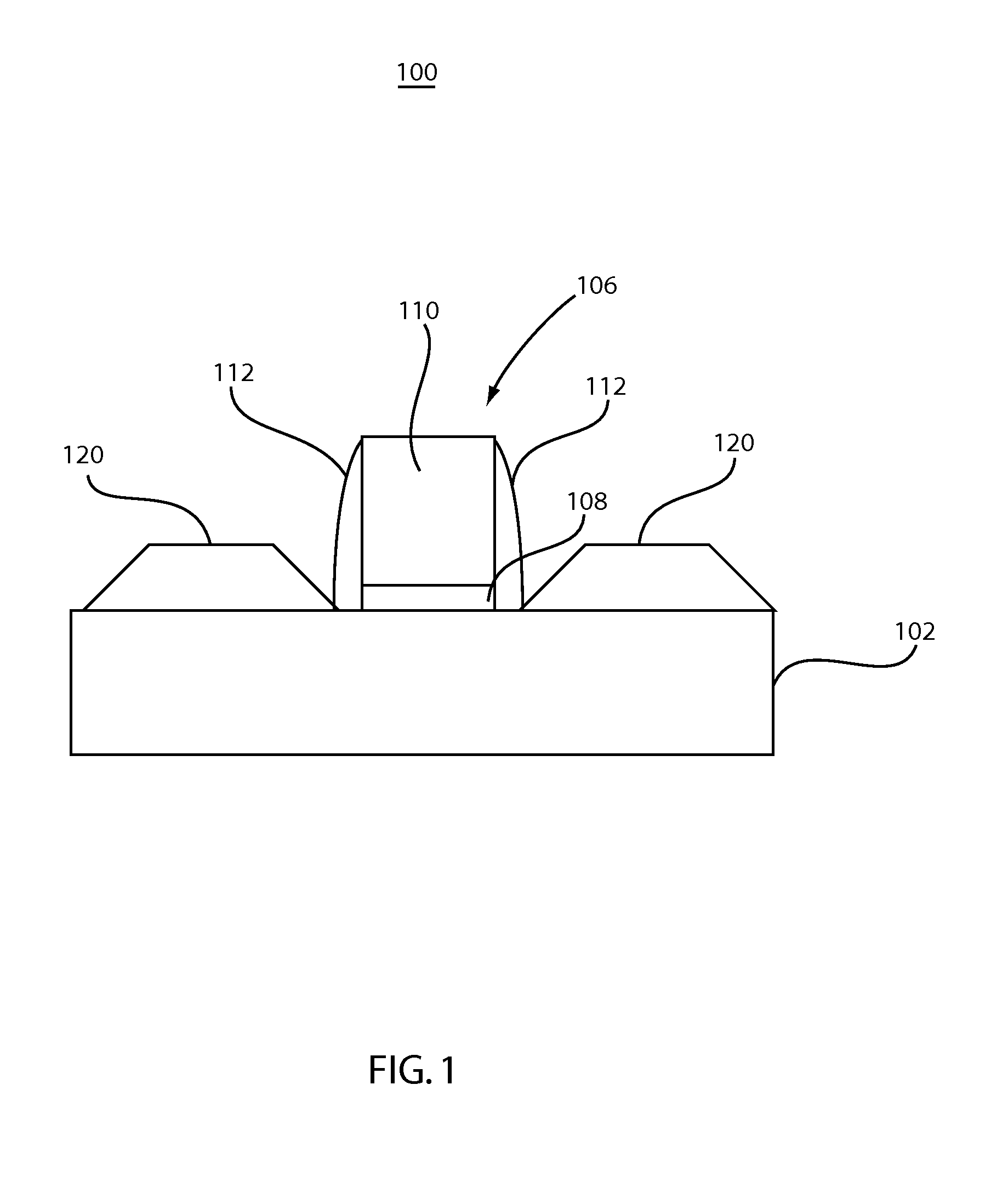

Method for producing gate stack sidewall spacers

A method for forming sidewall spacers on a gate stack by depositing one or more layers of silicon containing materials using PECVD process(es) on a gate structure to produce a spacer having an overall k value of about 3.0 to about 5.0. The silicon containing materials may be silicon carbide, oxygen doped silicon carbide, nitrogen doped silicon carbide, carbon doped silicon nitride, nitrogen doped silicon oxycarbide, or combinations thereof. The deposition is performed in a plasma enhanced chemical vapor deposition chamber and the deposition temperature is less than 450° C. The sidewall spacers so produced provide good capacity resistance, as well as excellent structural stability and hermeticity.

Owner:APPLIED MATERIALS INC

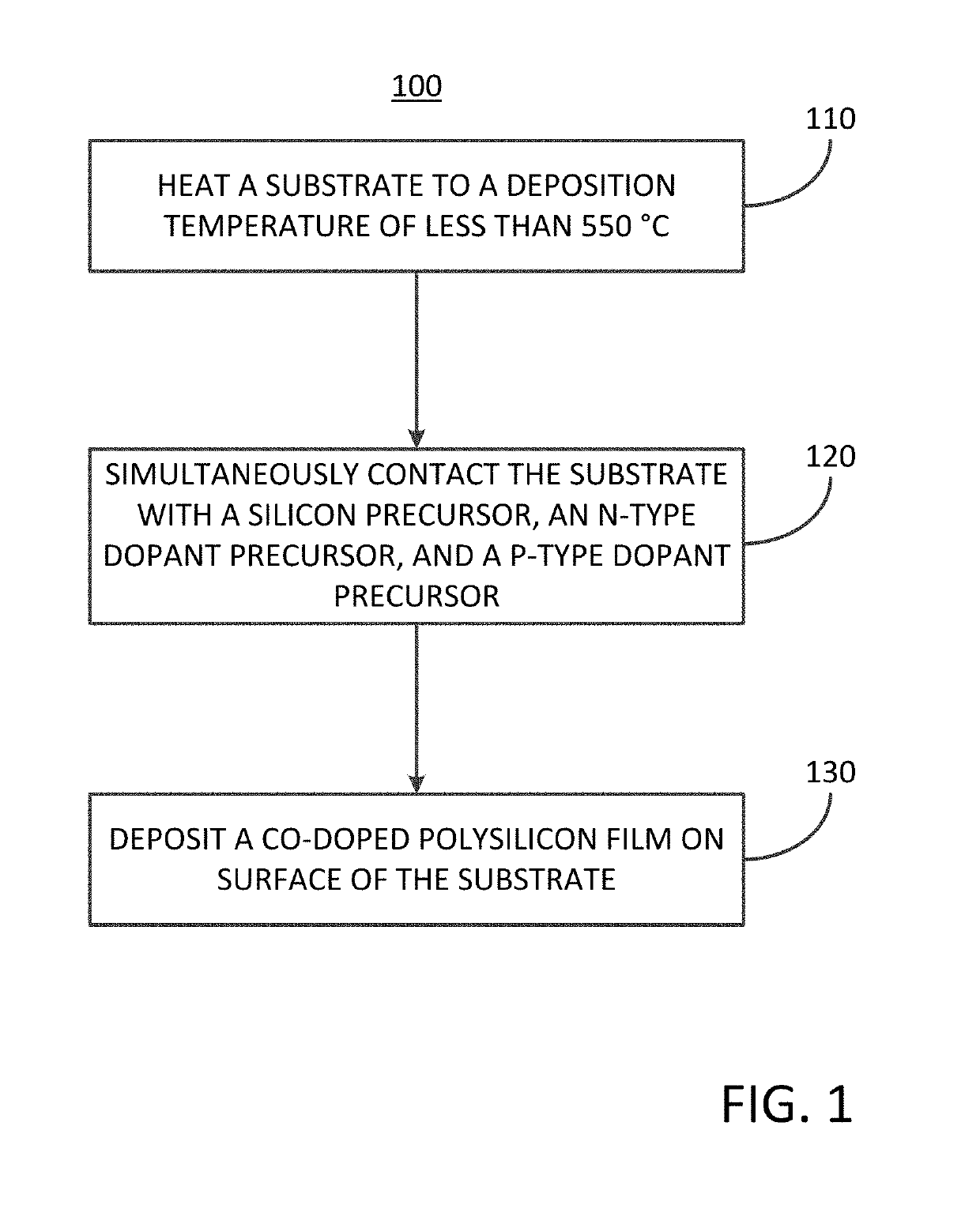

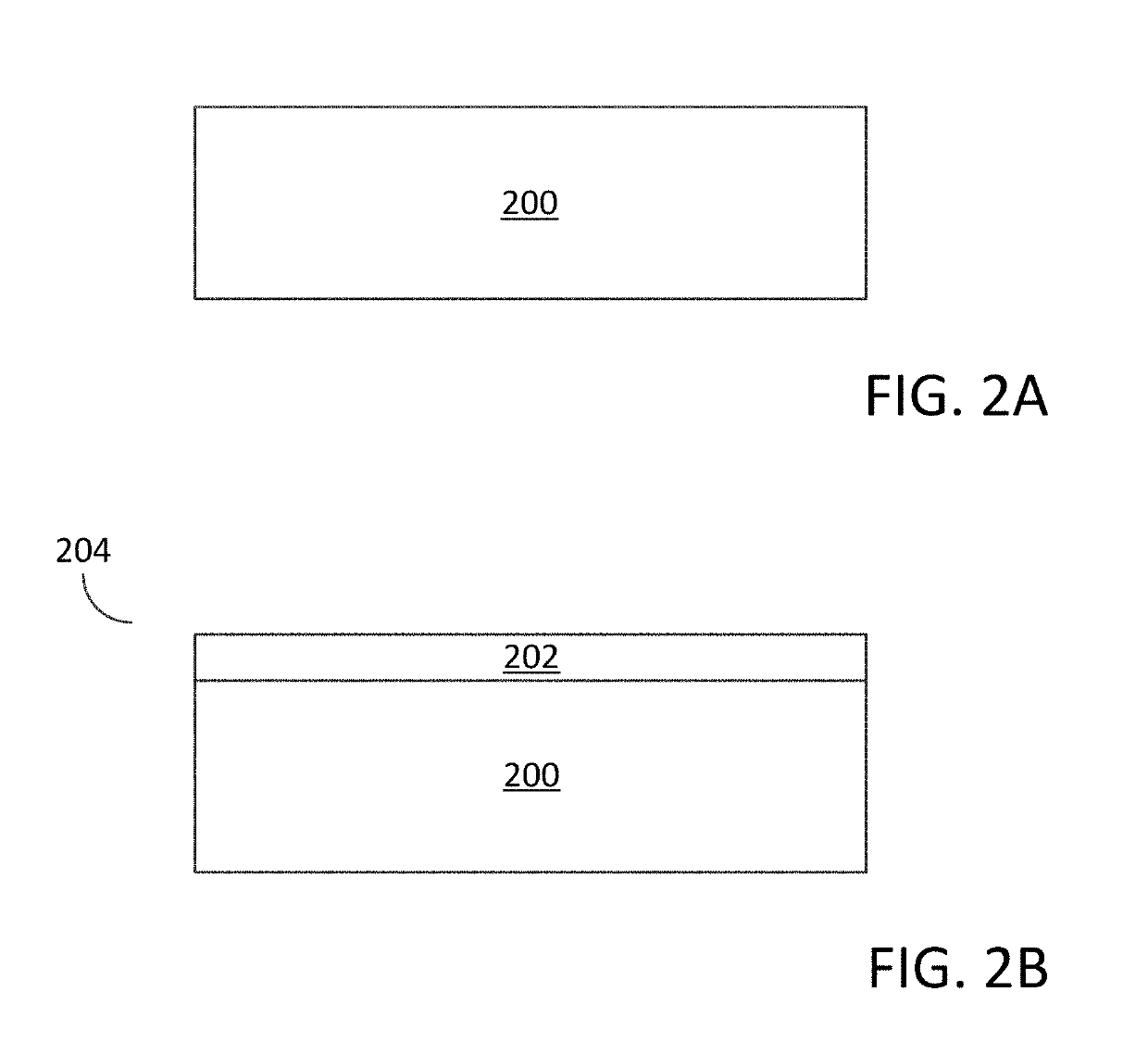

Method of depositing a co-doped polysilicon film on a surface of a substrate within a reaction chamber

ActiveUS20190304780A1Semiconductor/solid-state device detailsSolid-state devicesDeposition temperatureSemiconductor structure

Methods for depositing a co-doped polysilicon film on a surface of a substrate within a reaction chamber are provided. The method may include: heating the substrate to a deposition temperature of less than 550° C.; simultaneously contacting the substrate with a silicon precursor, a n-type dopant precursor, and a p-type dopant precursor; and depositing the co-doped polysilicon film on the surface of the substrate. Related semiconductor structures are also disclosed.

Owner:ASM IP HLDG BV

Method for selectively depositing a group iv semiconductor and related semiconductor device structures

ActiveUS20190027584A1Semiconductor/solid-state device detailsSolid-state devicesDeposition temperatureDopant

A method for selectively depositing a Group IV semiconductor on a surface of a substrate is disclosed. The method may include, providing a substrate within a reaction chamber and heating the substrate to a deposition temperature. The method may further include, exposing the substrate to at least one Group IV precursor, and exposing the substrate to at least one Group IIIA halide dopant precursor. Semiconductor device structures including a Group IV semiconductor deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

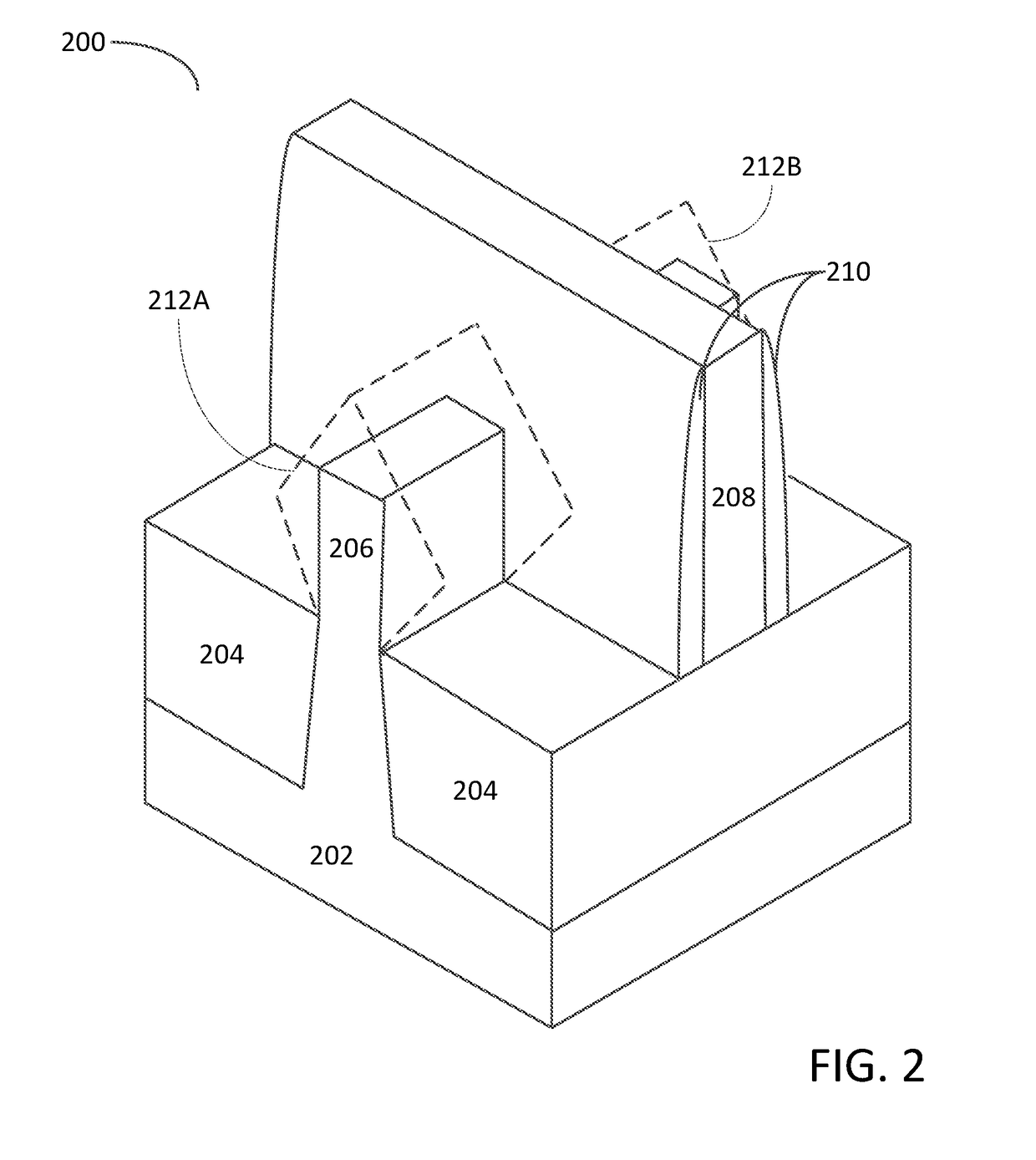

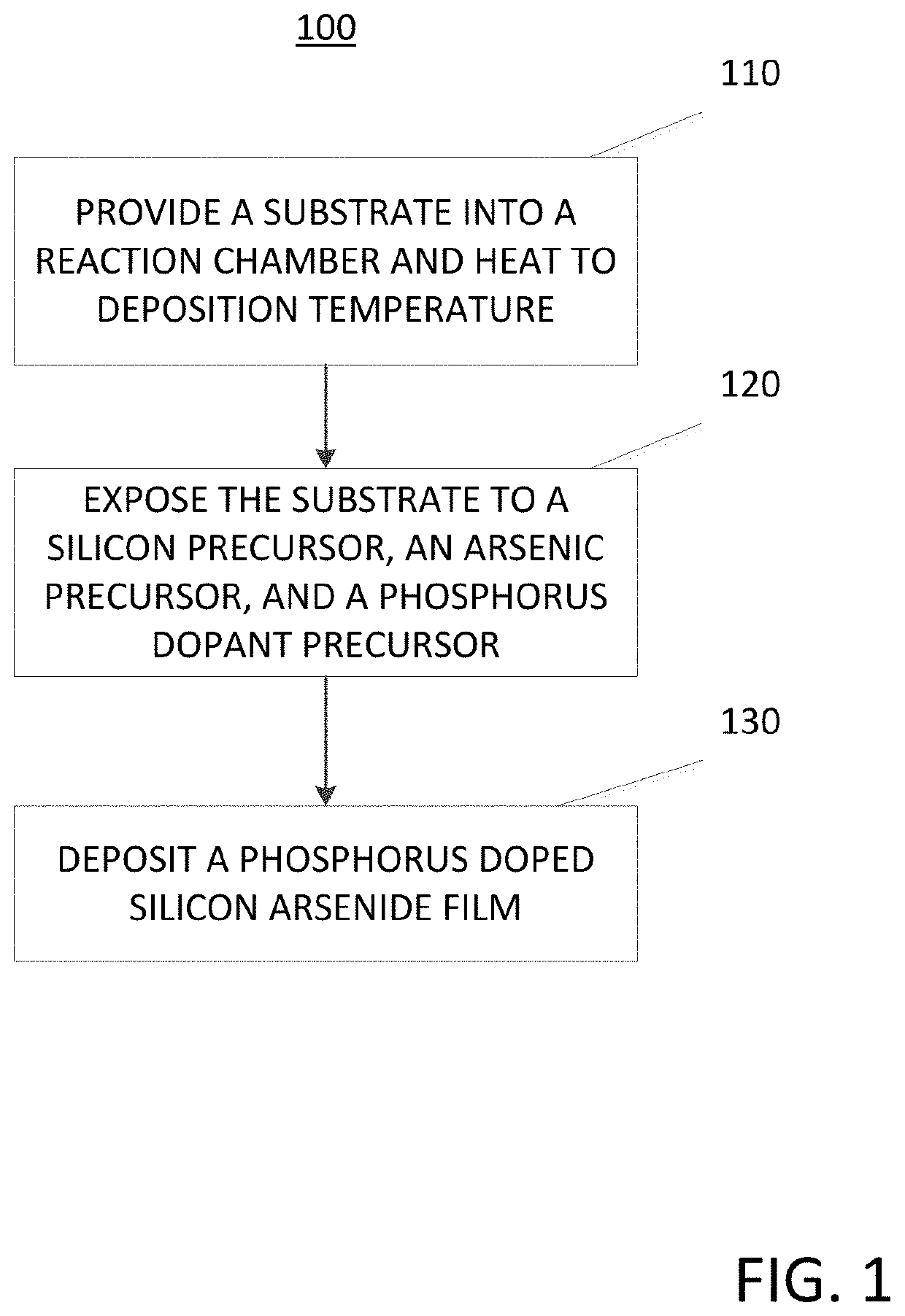

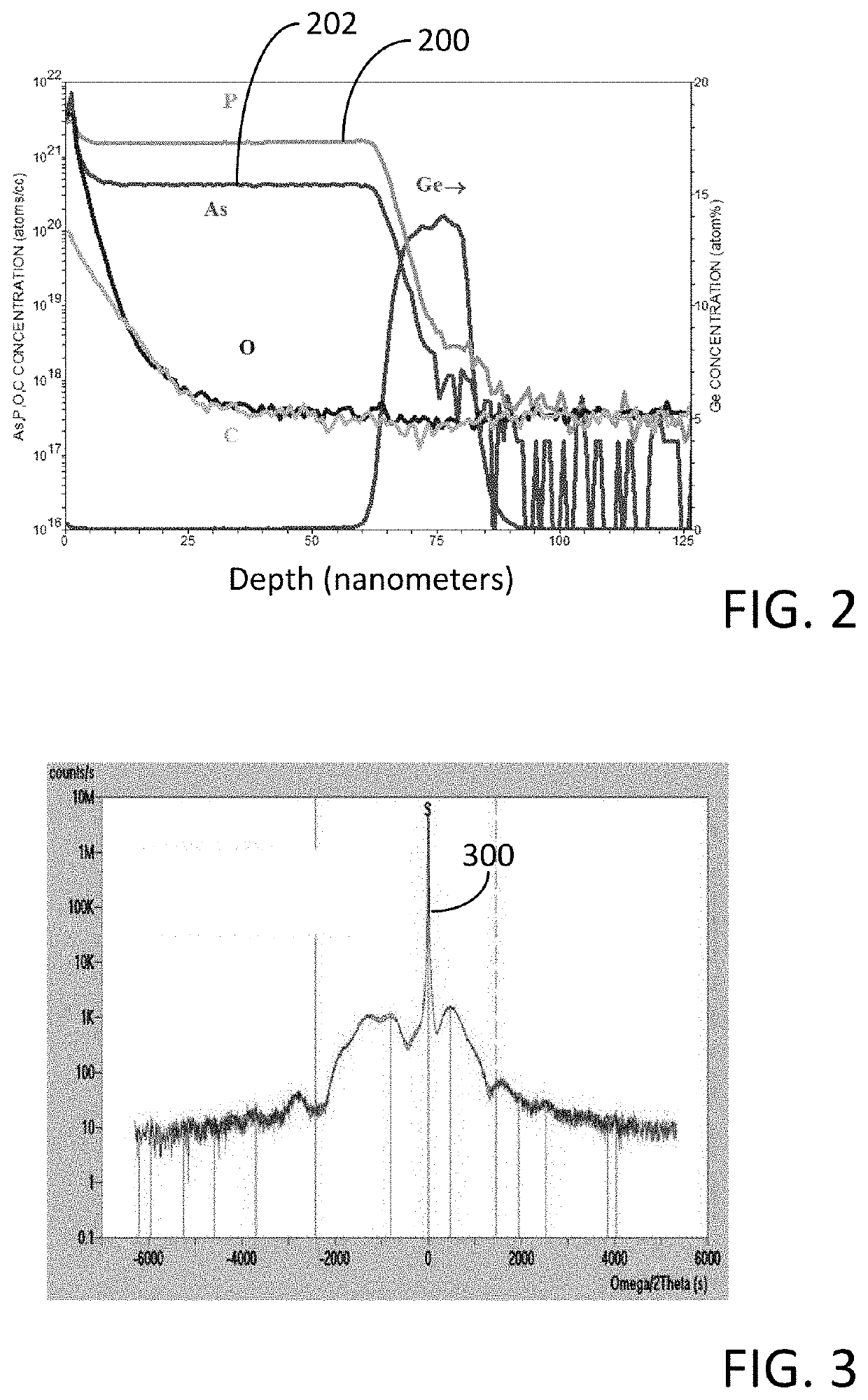

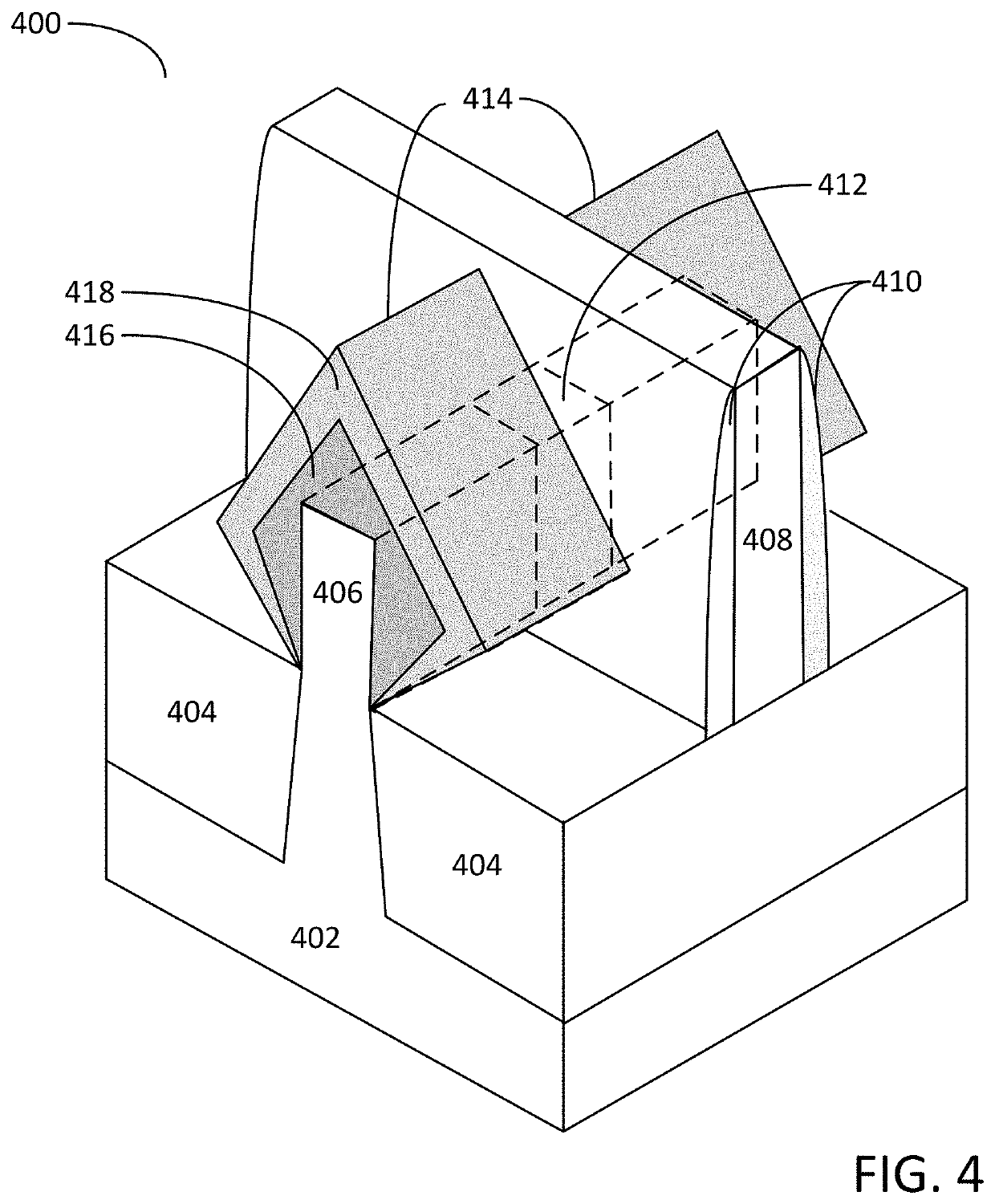

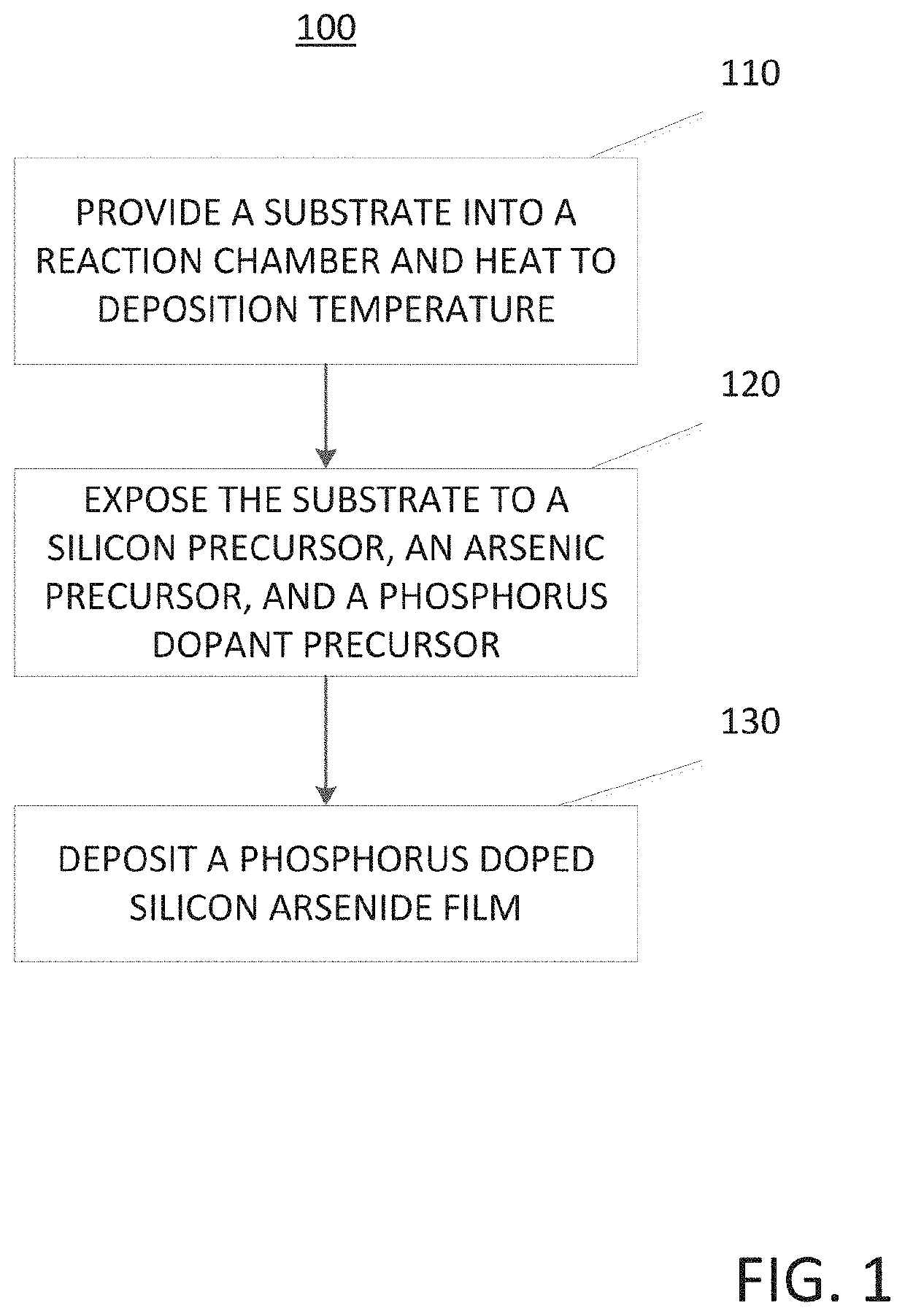

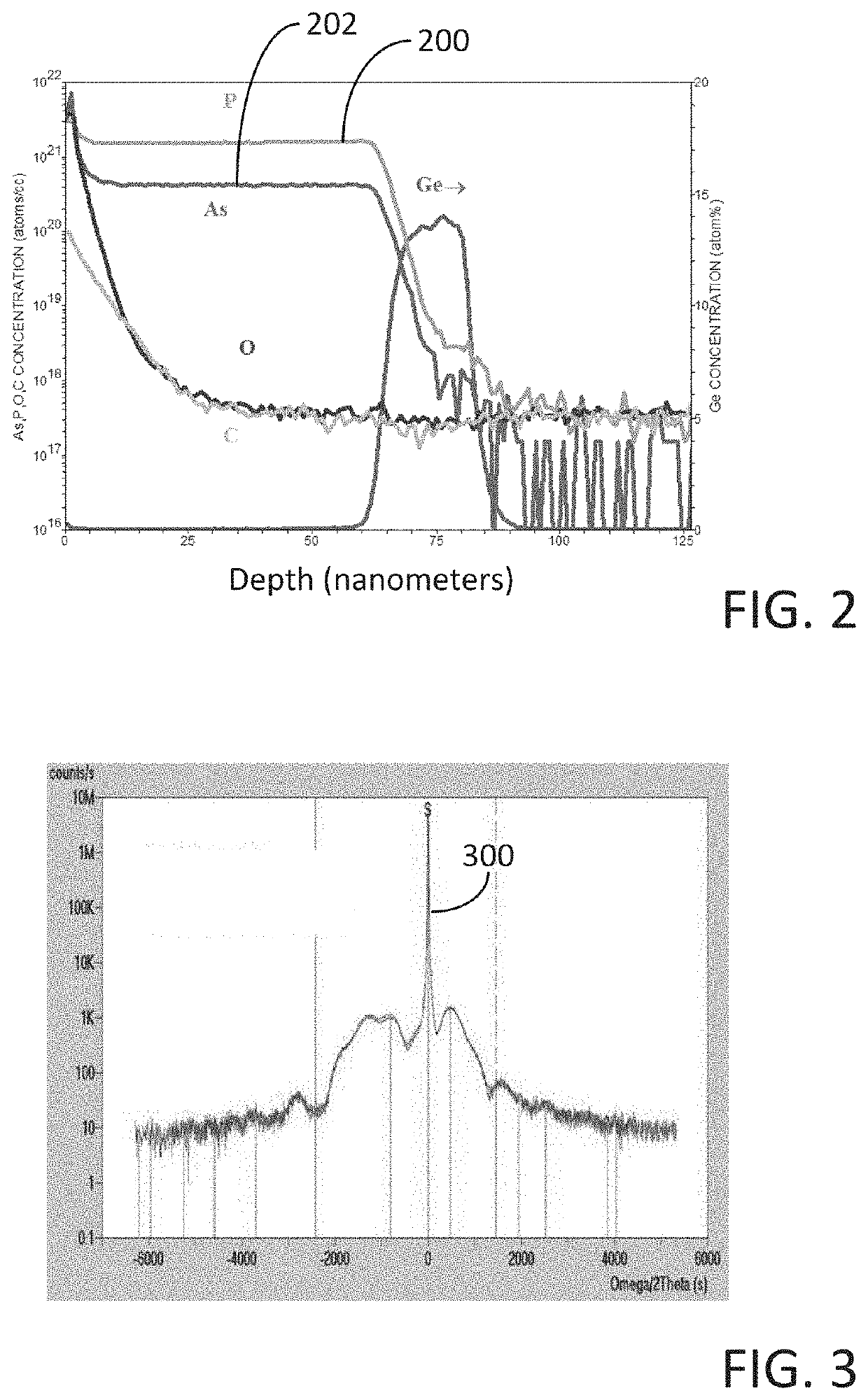

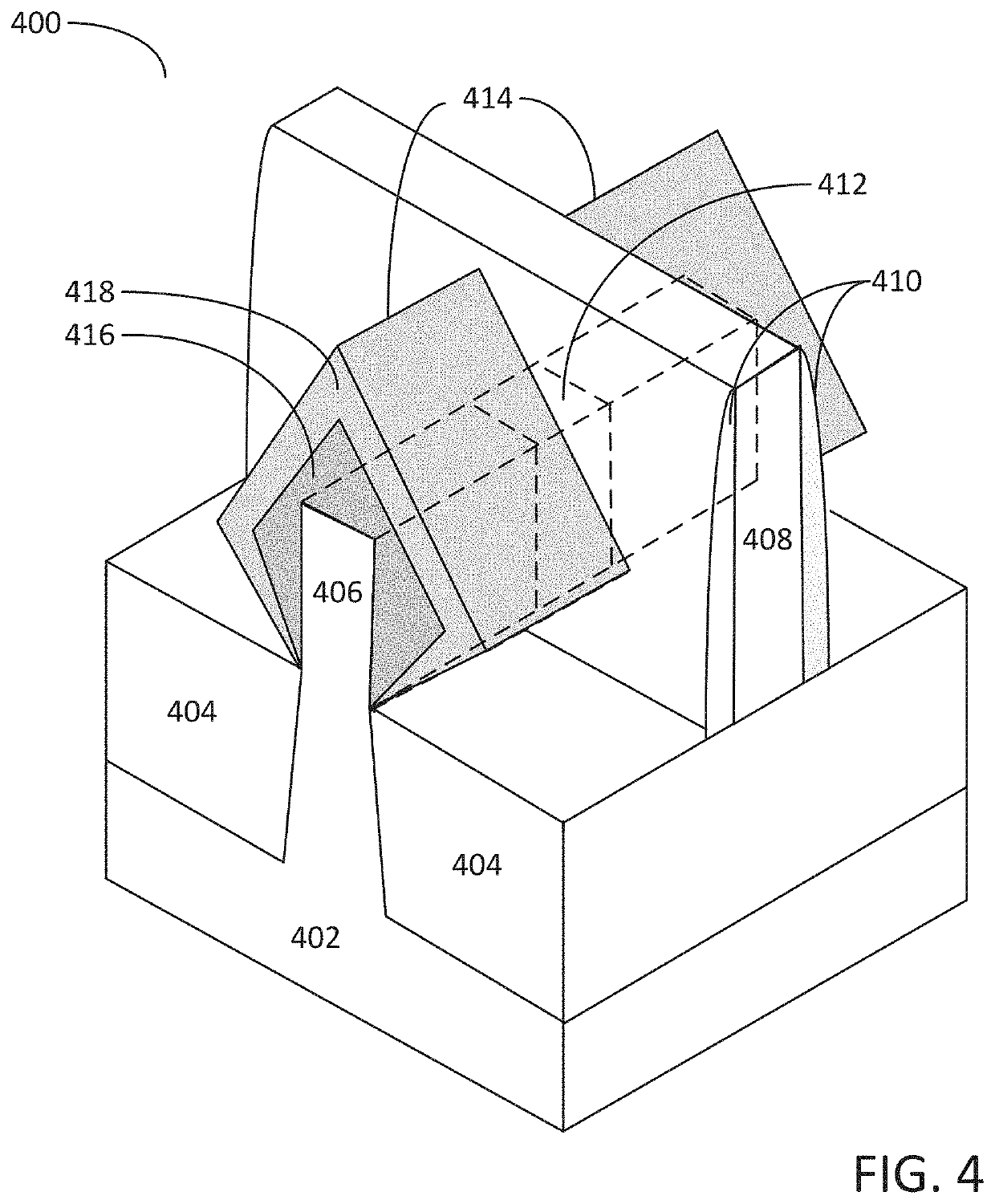

Method for depositing a phosphorus doped silicon arsenide film and related semiconductor device structures

ActiveUS20190393308A1Inhibited DiffusionTransistorPolycrystalline material growthDopantDeposition temperature

A method for depositing a phosphorus doped silicon arsenide film is disclosed. The method may include, providing a substrate within a reaction chamber, heating the substrate to a deposition temperature, exposing the substrate to a silicon precursor, an arsenic precursor, and a phosphorus dopant precursor, and depositing the phosphorus doped silicon arsenide film over a surface of the substrate. Semiconductor device structures including a phosphorus doped silicon arsenide film deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

Method for depositing a phosphorus doped silicon arsenide film and related semiconductor device structures

ActiveUS20200395444A1Inhibited DiffusionTransistorPolycrystalline material growthDevice materialSilicon thin film

A method for depositing a phosphorus doped silicon arsenide film is disclosed. The method may include, providing a substrate within a reaction chamber, heating the substrate to a deposition temperature, exposing the substrate to a silicon precursor, an arsenic precursor, and a phosphorus dopant precursor, and depositing the phosphorus doped silicon arsenide film over a surface of the substrate. Semiconductor device structures including a phosphorus doped silicon arsenide film deposited by the methods of the disclosure are also provided.

Owner:ASM IP HLDG BV

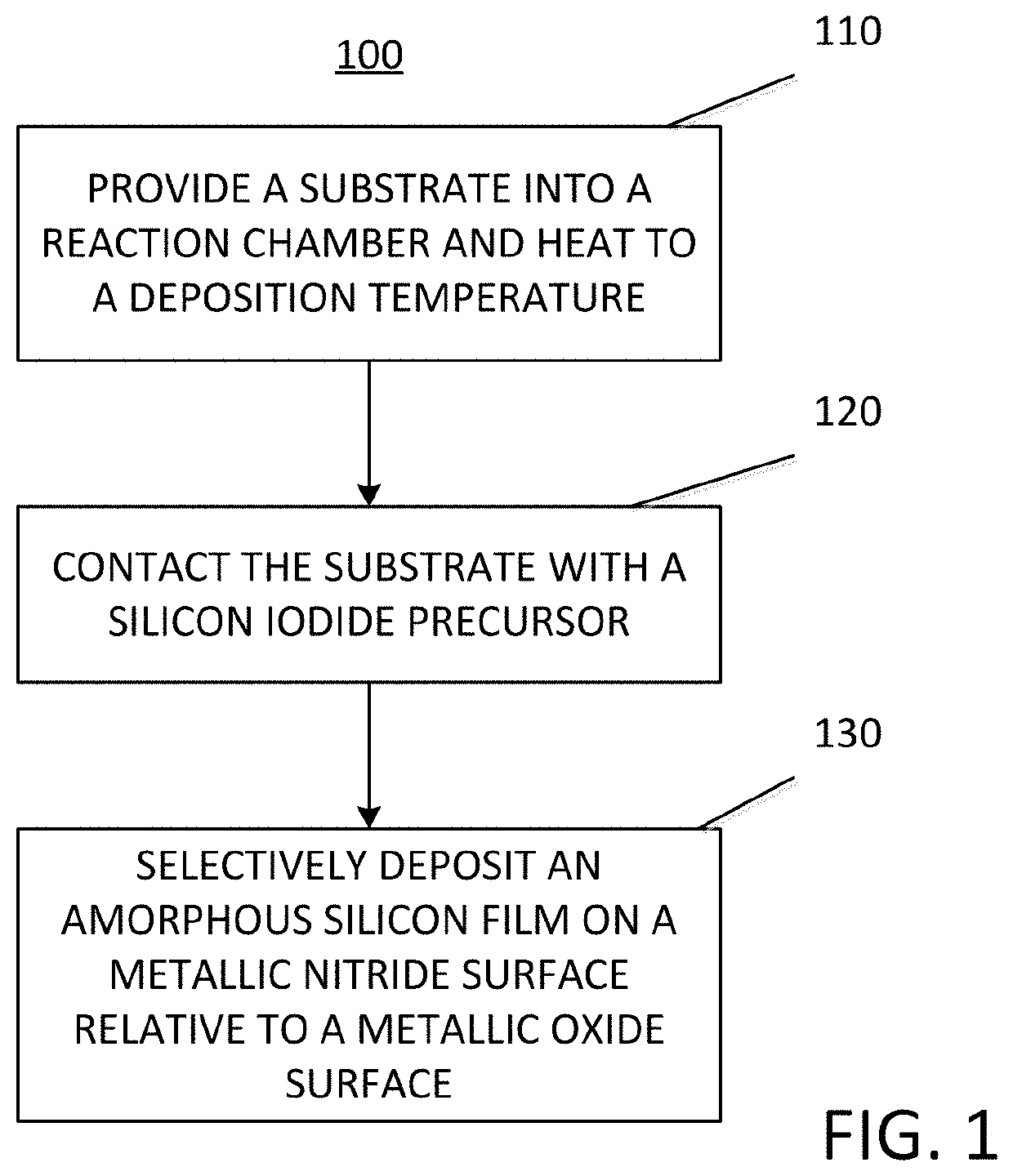

Methods for selectively depositing an amorphous silicon film on a substrate

ActiveUS20200140995A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDeposition temperatureDevice material

A method for selectively depositing an amorphous silicon film on a substrate comprising a metallic nitride surface and a metallic oxide surface is disclosed. The method may include; providing a substrate within a reaction chamber, heating the substrate to a deposition temperature, contacting the substrate with silicon iodide precursor, and selectively depositing the amorphous silicon film on the metallic nitride surface relative to the metallic oxide surface. Semiconductor device structures including an amorphous silicon film deposited by selective deposition methods are also disclosed.

Owner:ASM IP HLDG BV

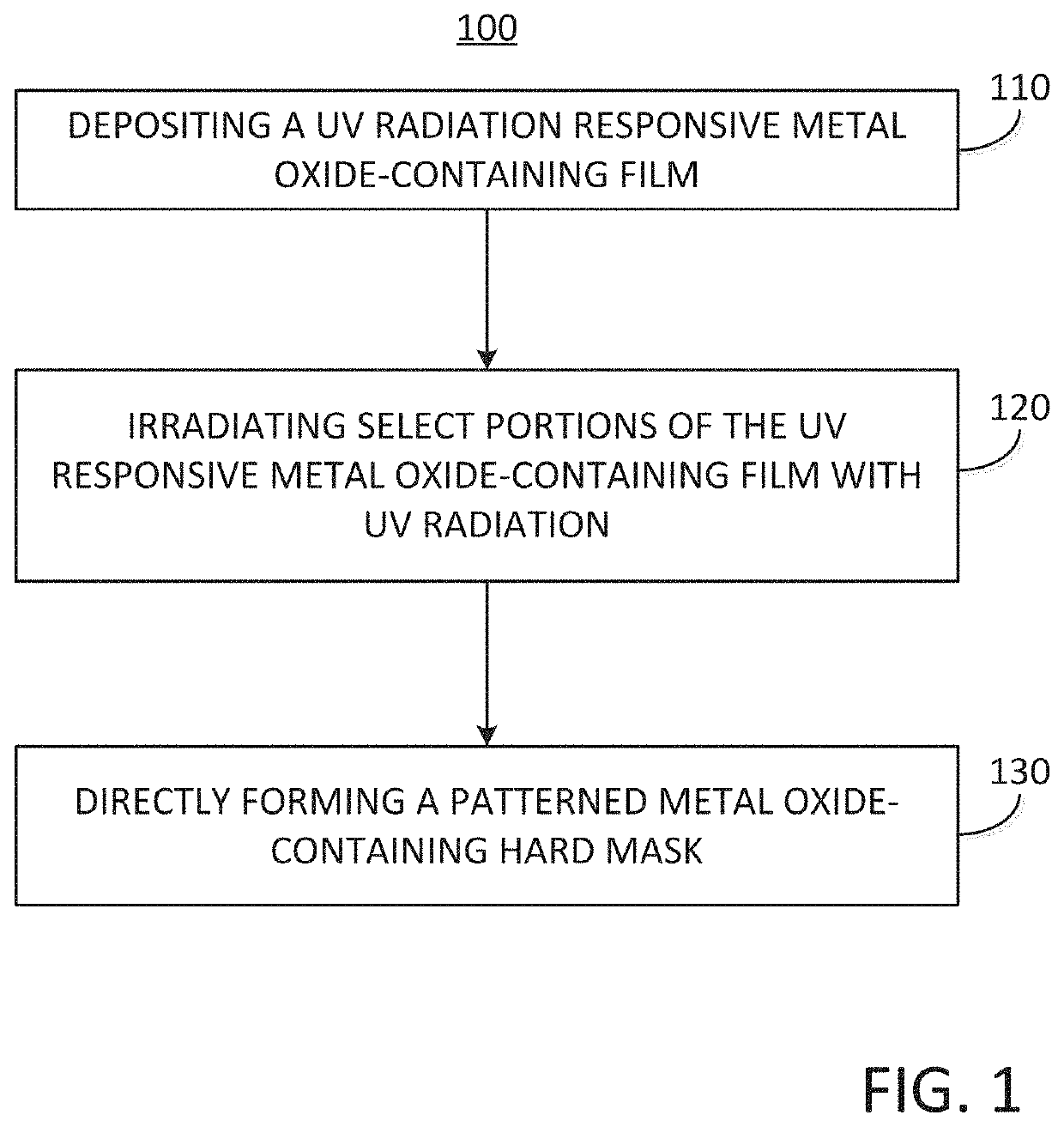

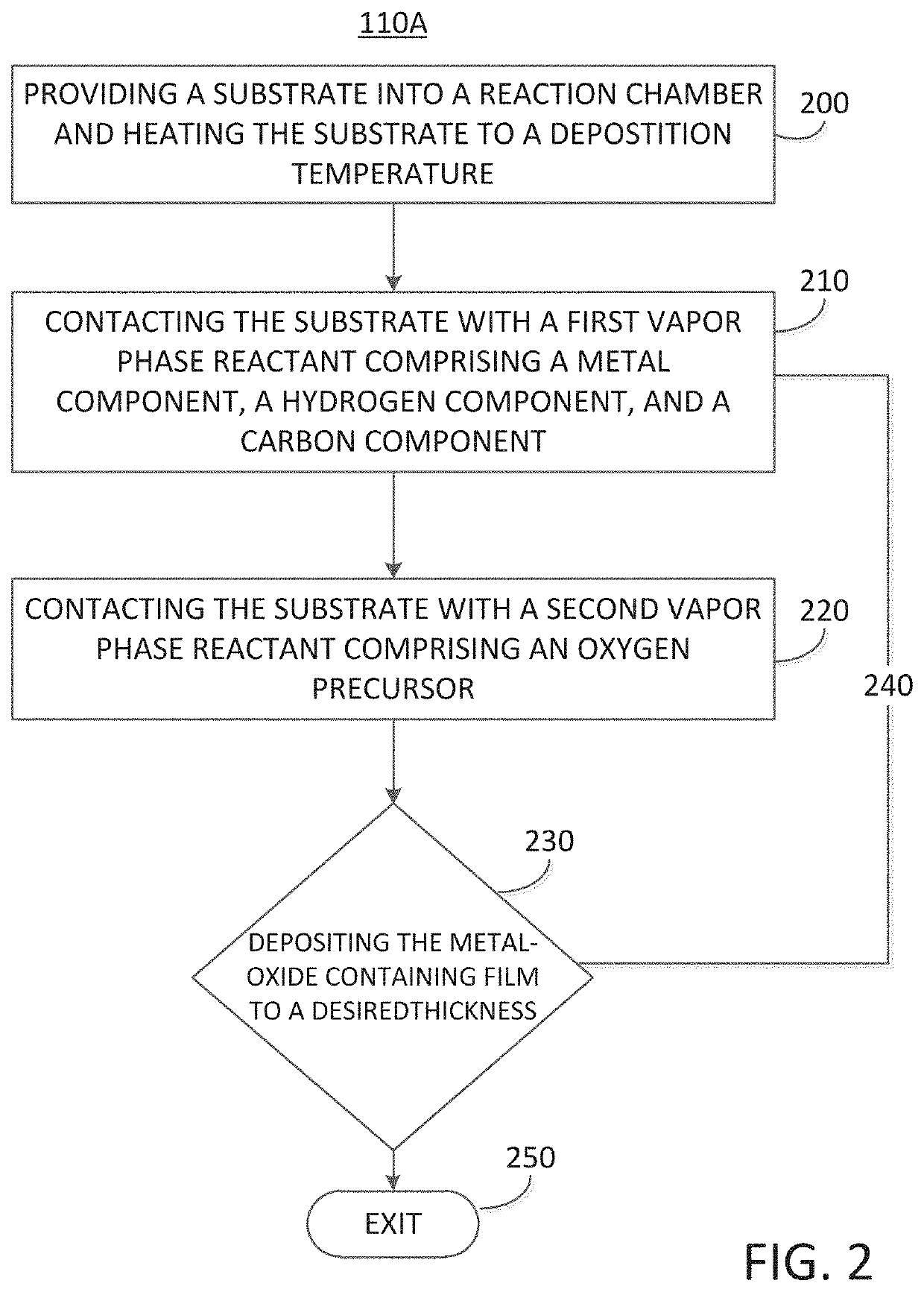

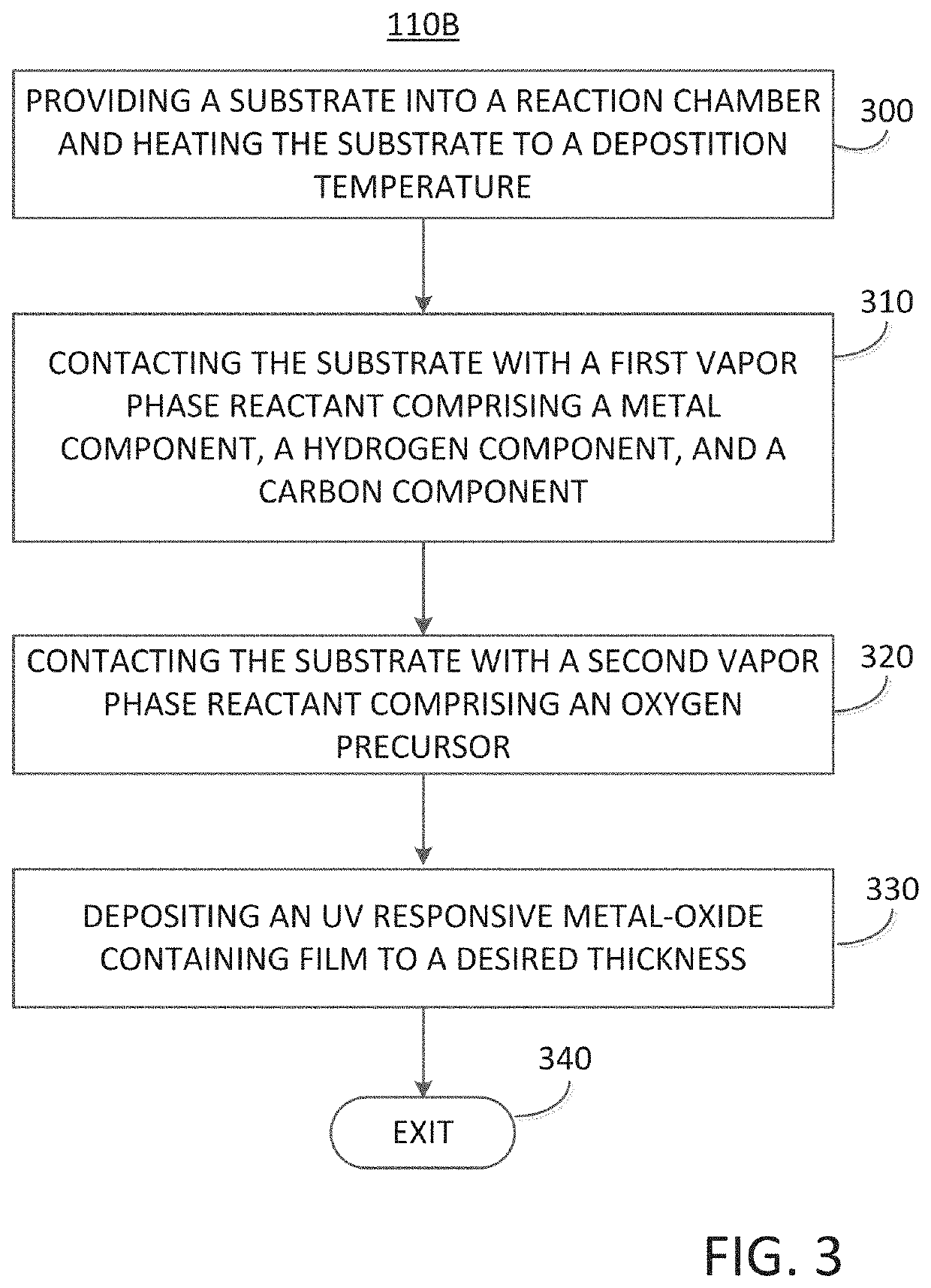

Method for forming an ultraviolet radiation responsive metal oxide-containing film

ActiveUS20200176246A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDeposition temperatureRadiation exposure

A method for forming ultraviolet (UV) radiation responsive metal-oxide containing film is disclosed. The method may include, depositing an UV radiation responsive metal oxide-containing film over a substrate by, heating the substrate to a deposition temperature of less than 400° C., contacting the substrate with a first vapor phase reactant comprising a metal component, a hydrogen component, and a carbon component, and contacting the substrate with a second vapor phase reactant comprising an oxygen containing precursor, wherein regions of the UV radiation responsive metal oxide-containing film have a first etch rate after UV irradiation and regions of the UV radiation responsive metal oxide-containing film not irradiated with UV radiation have a second etch rate, wherein the second etch rate is different from the first etch rate.

Owner:ASM IP HLDG BV

Method for forming silicon-containing materials during a photoexcitation deposition process

InactiveUS20060286776A1Enhance chamber cleaning processHigh surface energyPolycrystalline material growthSemiconductor/solid-state device manufacturingVolatilesSilicon oxide

Embodiments of the invention generally provide a method for depositing films or layers using a UV source during a photoexcitation process. The films are deposited on a substrate and usually contain a material, such as silicon (e.g., epitaxy, crystalline, microcrystalline, polysilicon, or amorphous), silicon oxide, silicon nitride, silicon oxynitride, or other silicon-containing materials. The photoexcitation process may expose the substrate and / or gases to an energy beam or flux prior to, during, or subsequent a deposition process. Therefore, the photoexcitation process may be used to pre-treat or post-treat the substrate or material, to deposit the silicon-containing material, and to enhance chamber cleaning processes. Attributes of the method that are enhanced by the UV photoexcitation process include removing native oxides prior to deposition, removing volatiles from deposited films, increasing surface energy of the deposited films, increasing the excitation energy of precursors, reducing deposition time, and reducing deposition temperature.

Owner:APPLIED MATERIALS INC

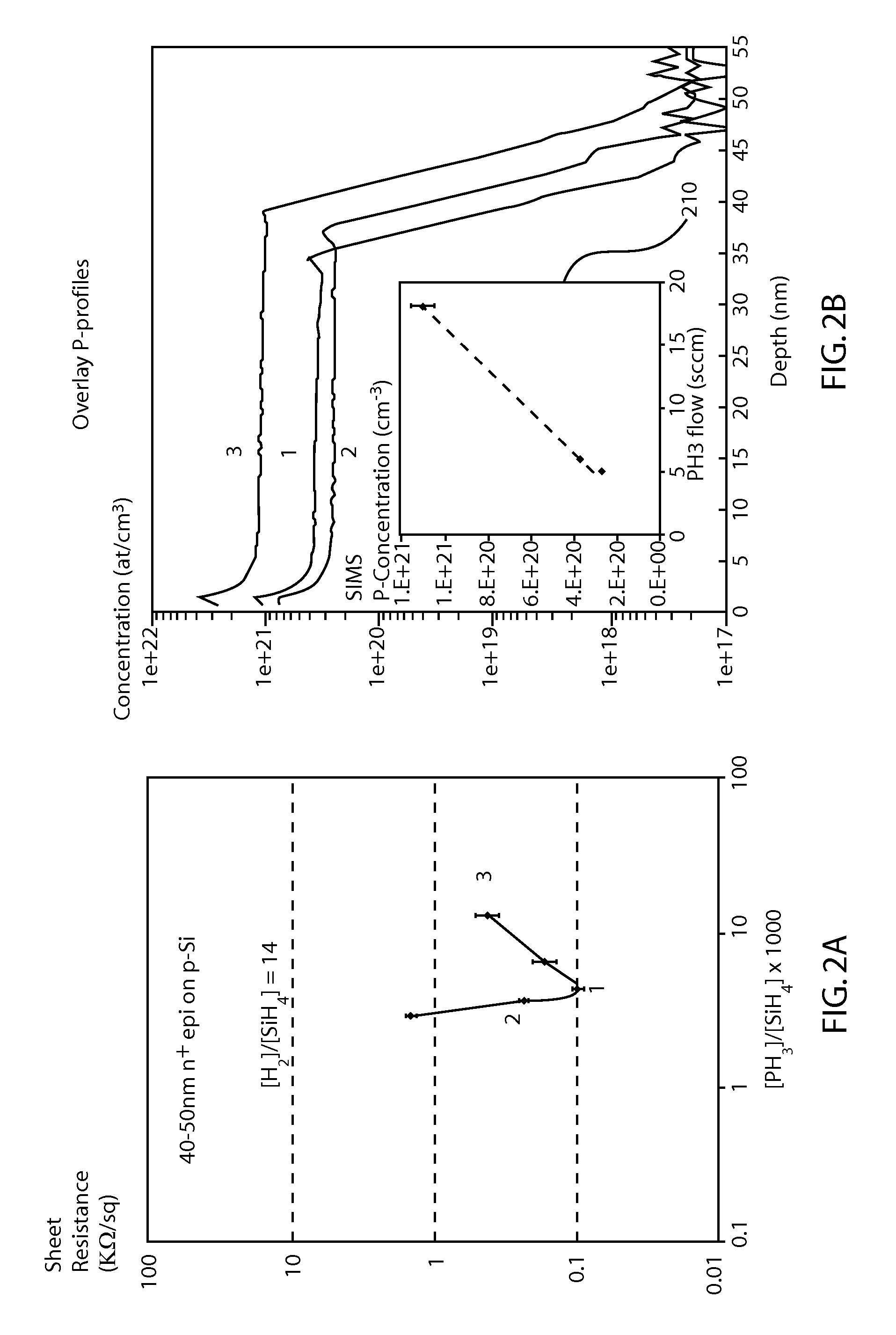

Low-temperature selective epitaxial growth of silicon for device integration

InactiveUS20150247259A1Polycrystalline material growthAfter-treatment detailsDeposition temperaturePhysical chemistry

An epitaxy method includes providing an exposed crystalline region of a substrate material. Silicon is epitaxially deposited on the substrate material in a low temperature process wherein a deposition temperature is less than 500 degrees Celsius. A source gas is diluted with a dilution gas with a gas ratio of dilution gas to source gas of less than 1000.

Owner:INT BUSINESS MASCH CORP

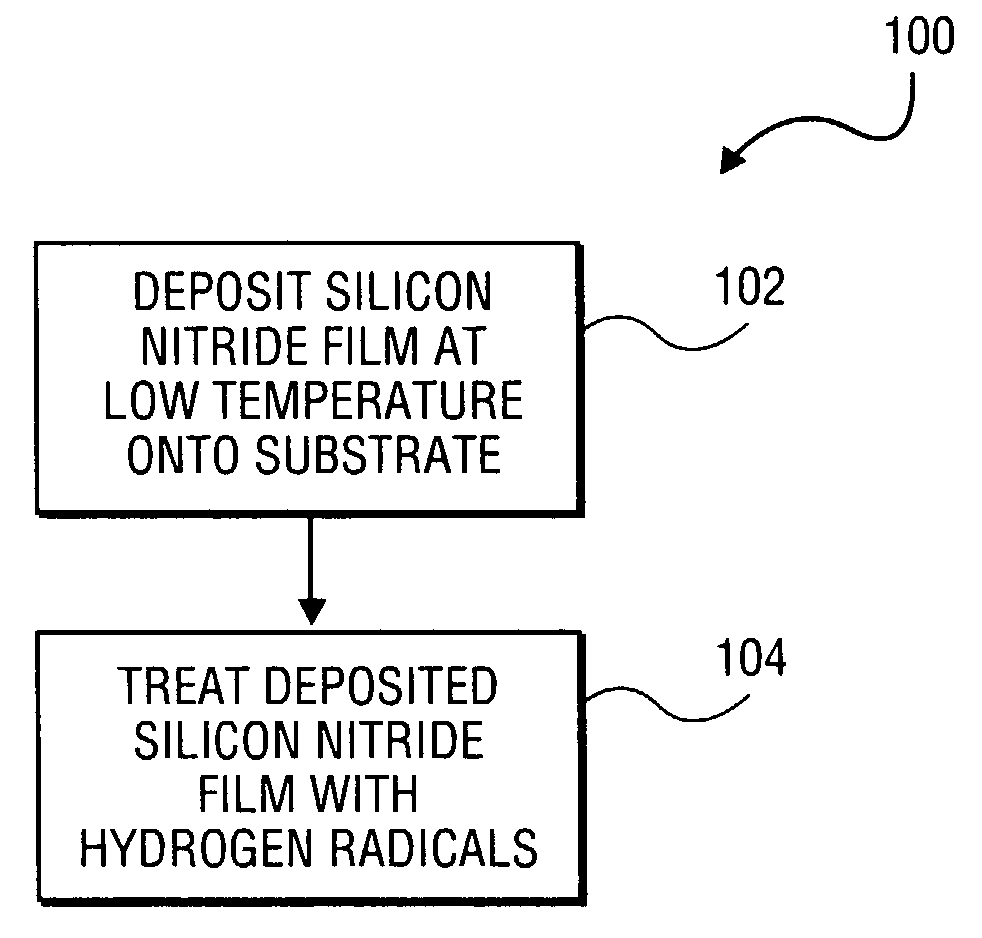

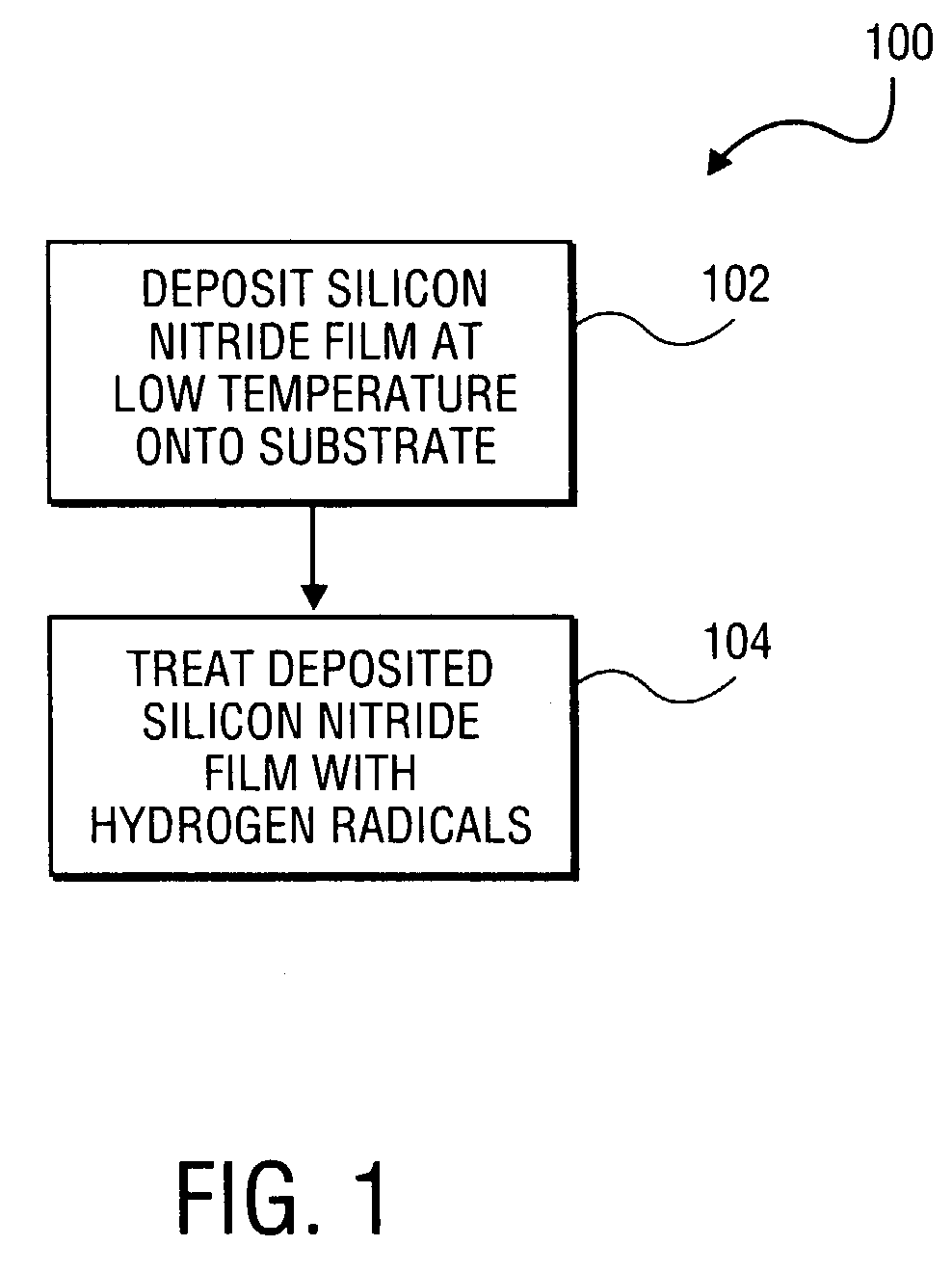

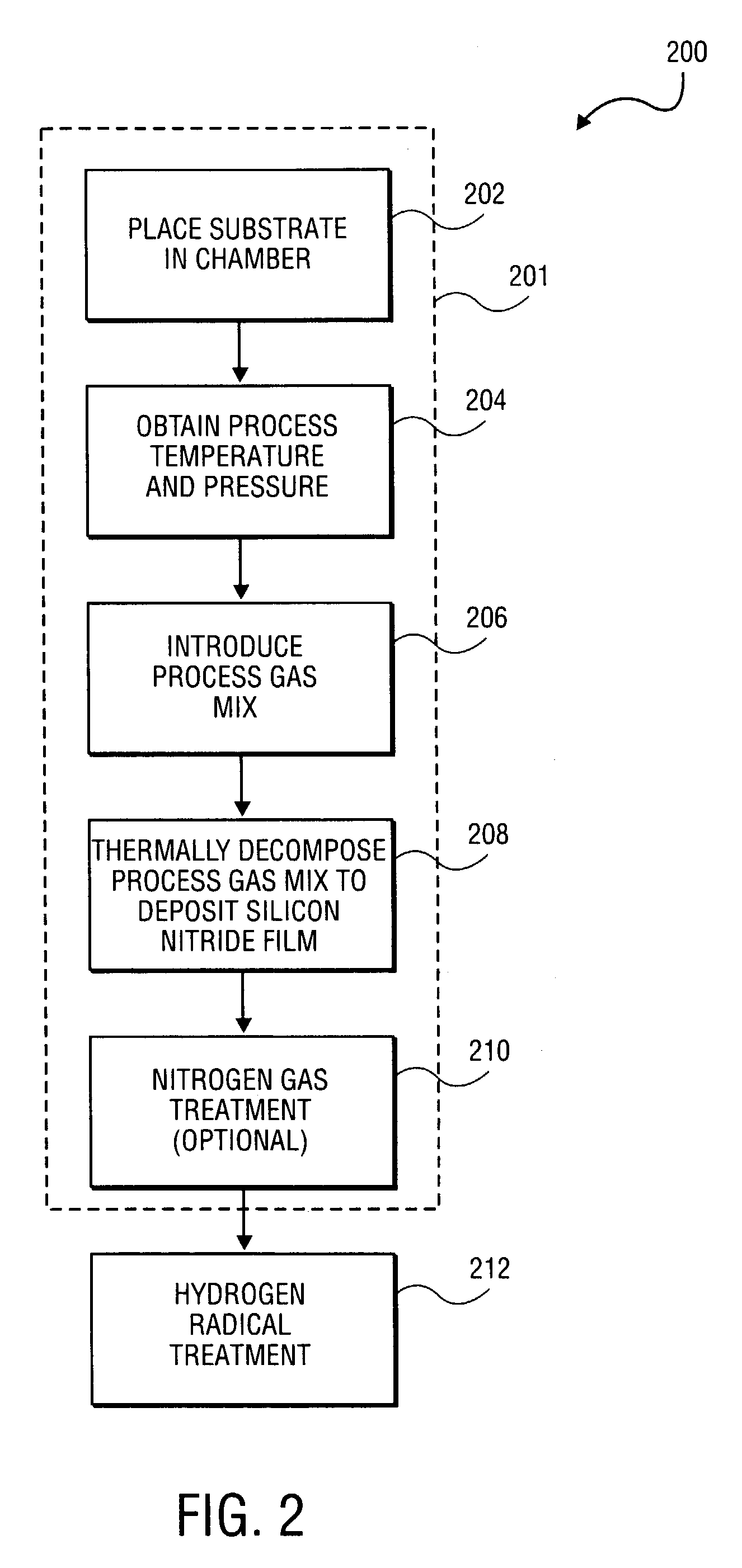

Method for forming a high quality low temperature silicon nitride film

InactiveUS7172792B2TransistorSemiconductor/solid-state device manufacturingDeposition temperatureNitrogen

A method of forming a silicon nitride film is described. According to the present invention, a silicon nitride film is deposited by thermally decomposing a silicon / nitrogen containing source gas or a silicon containing source gas and a nitrogen containing source gas at low deposition temperatures (e.g., less than 550° C.) to form a silicon nitride film. The thermally deposited silicon nitride film is then treated with hydrogen radicals to form a treated silicon nitride film.

Owner:APPLIED MATERIALS INC

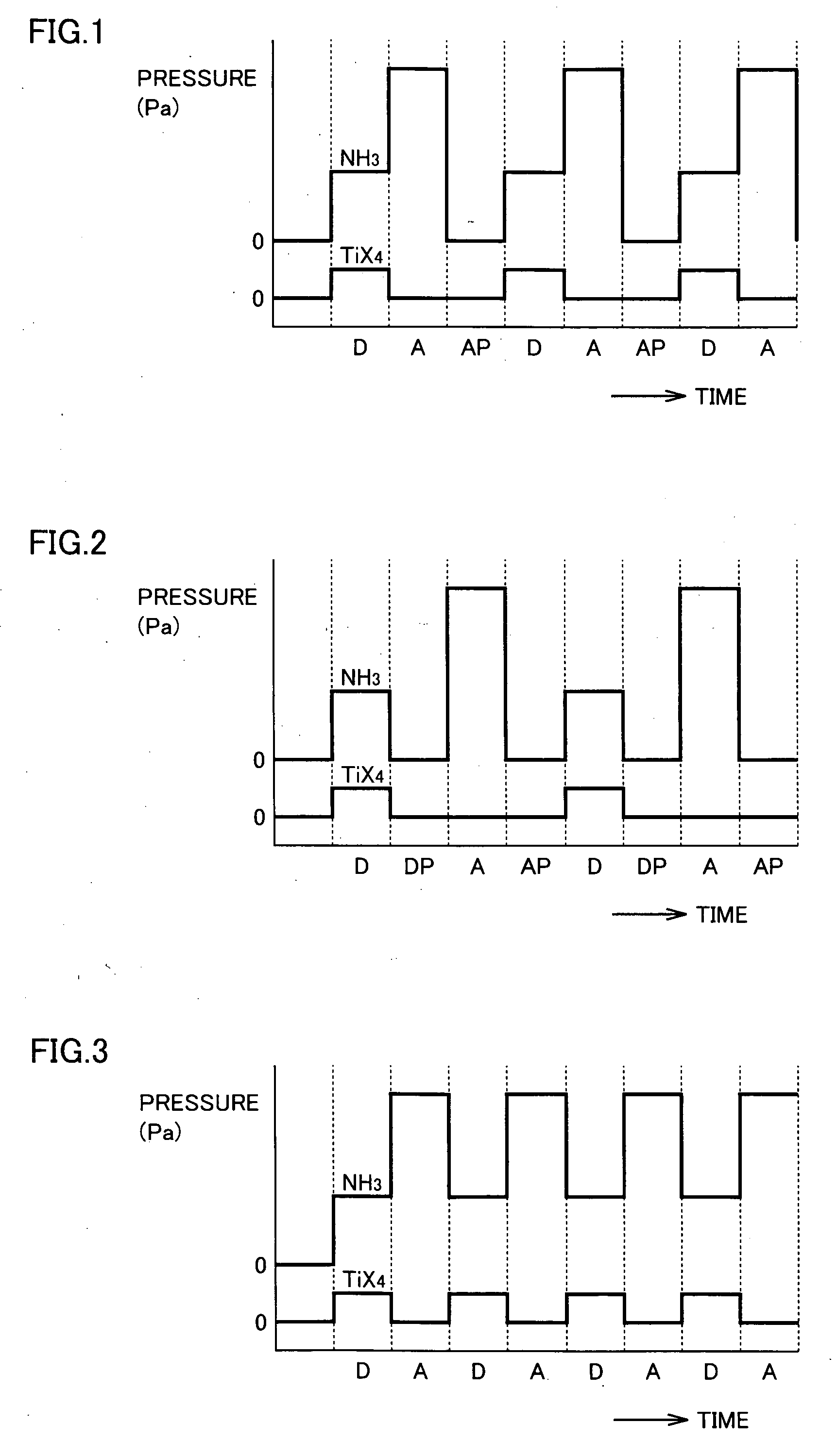

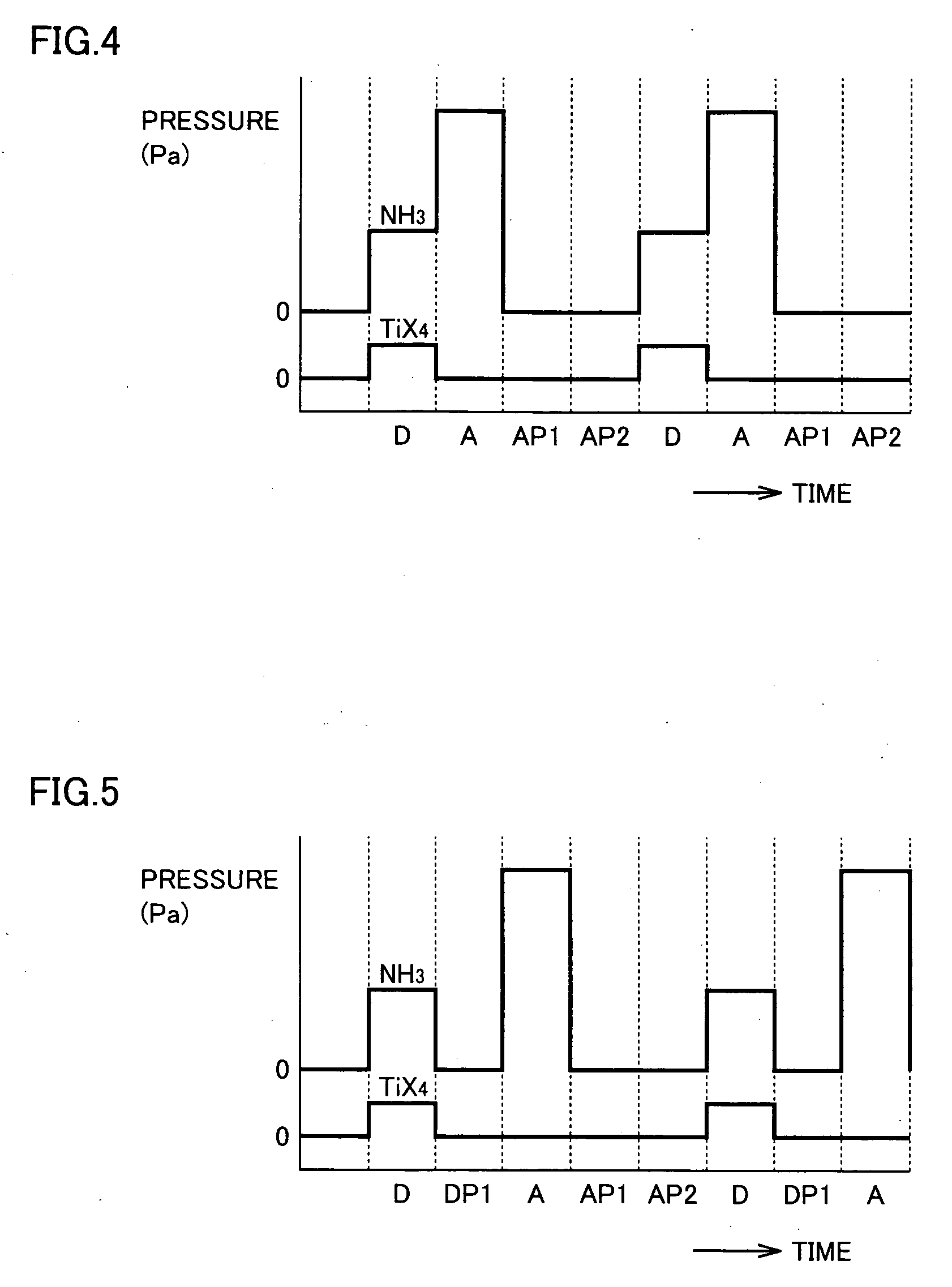

Semiconductor device and manufacturing method thereof

ActiveUS20050153573A1Suppress generationTransistorSolid-state devicesDeposition temperatureDevice material

A manufacturing method of a semiconductor device including a TiN film, including a deposition step of forming a TiN film by the CVD method, an anneal step of performing a heat treatment to the formed TiN film in an atmosphere of NH3 gas, an NH3 gas purge step of purging NH3 gas, and a step of further repeating the deposition step, the anneal step, and the NH3 gas purge step for at least one time. The deposition step is performed using titanium halide gas and NH3 gas as material gases and with a deposition temperature of 300° C.-450° C. to form the TiN film by a thickness of 1 nm-5 nm for each deposition step. Thus, a semiconductor device in which generation of irregularly grown objects in the TiN film is suppressed and a manufacturing method thereof can be provided.

Owner:RENESAS ELECTRONICS CORP +1