Patents

Literature

5154 results about "Low-k dielectric" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

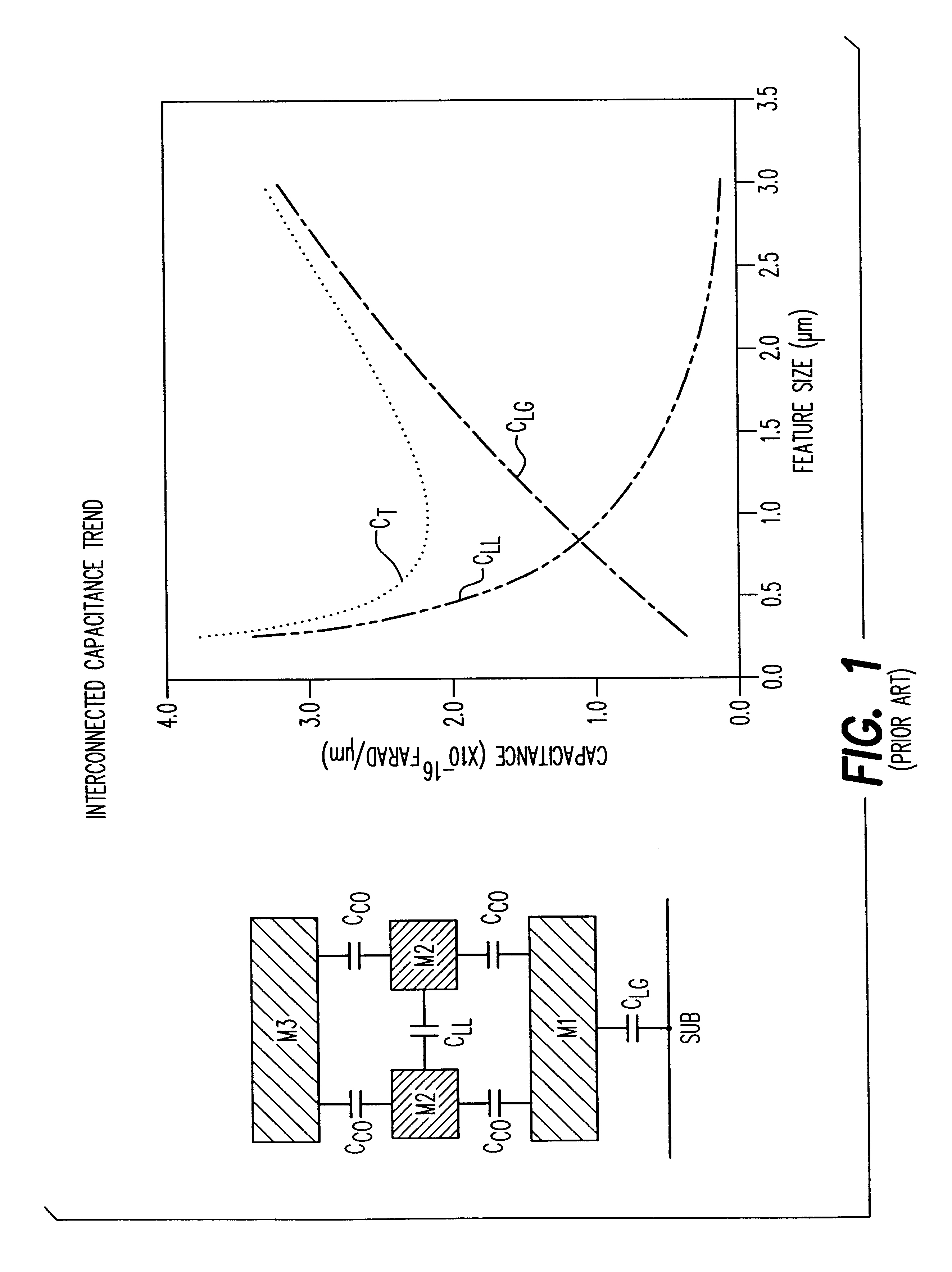

In semiconductor manufacturing, a low-κ is a material with a small relative dielectric constant relative to silicon dioxide. Although the proper symbol for the relative dielectric constant is the Greek letter κ (kappa), in conversation such materials are referred to as being "low-k" (low-kay) rather than "low-κ" (low-kappa). Low-κ dielectric material implementation is one of several strategies used to allow continued scaling of microelectronic devices, colloquially referred to as extending Moore's law. In digital circuits, insulating dielectrics separate the conducting parts (wire interconnects and transistors) from one another. As components have scaled and transistors have gotten closer together, the insulating dielectrics have thinned to the point where charge build up and crosstalk adversely affect the performance of the device. Replacing the silicon dioxide with a low-κ dielectric of the same thickness reduces parasitic capacitance, enabling faster switching speeds and lower heat dissipation.

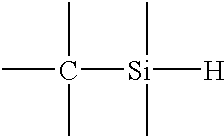

Method of depositing a low k dielectric with organo silane

InactiveUS6054379ASemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilane compoundsSilanes

A method and apparatus for depositing a low dielectric constant film by reaction of an organo silane compound and an oxidizing gas. The oxidized organo silane film has excellent barrier properties for use as a liner or cap layer adjacent other dielectric layers. The oxidized organo silane film can also be used as an etch stop or an intermetal dielectric layer for fabricating dual damascene structures. The oxidized organo silane films also provide excellent adhesion between different dielectric layers. A preferred oxidized organo silane film is produced by reaction of methyl silane, CH3SiH3, and N2O.

Owner:APPLIED MATERIALS INC

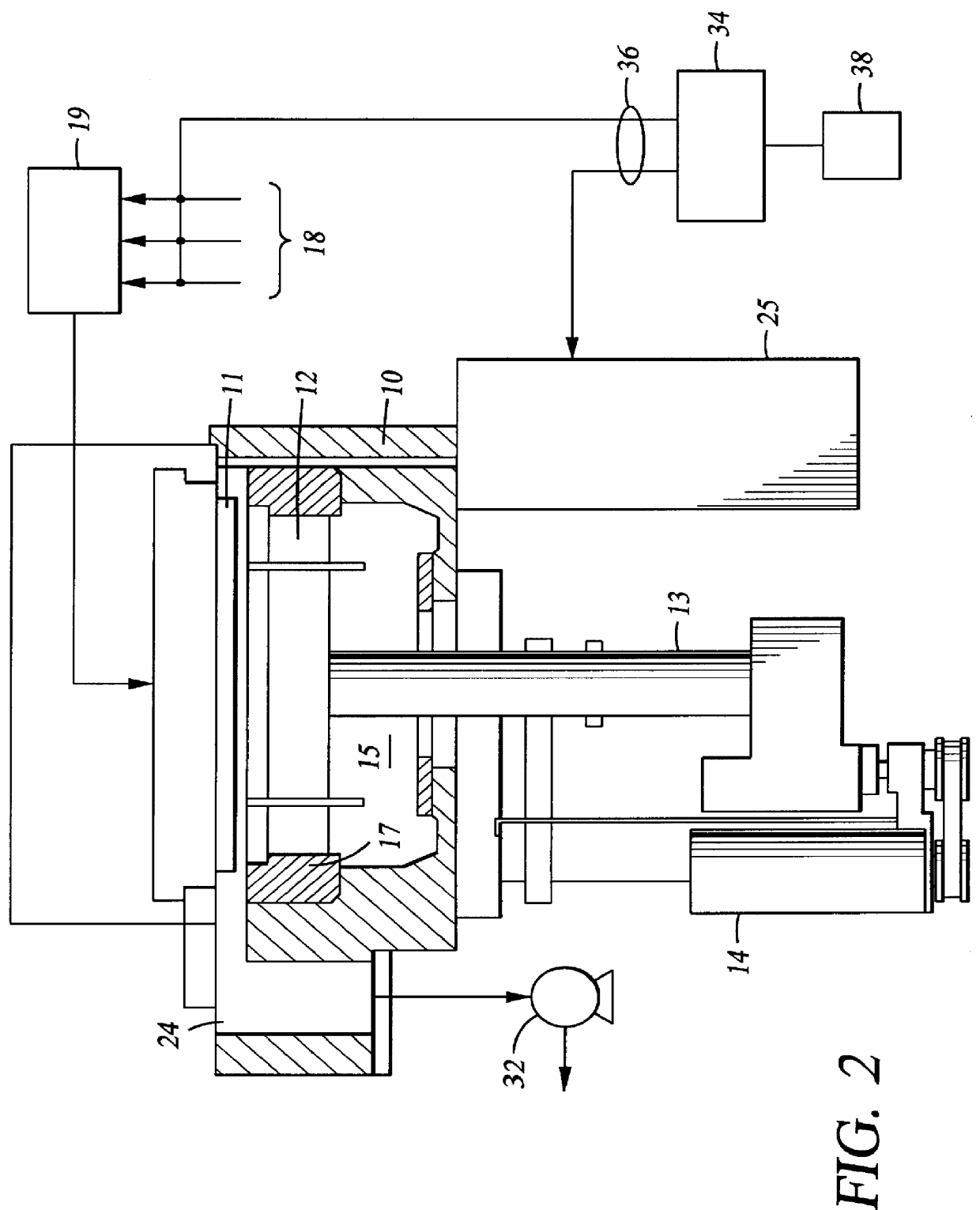

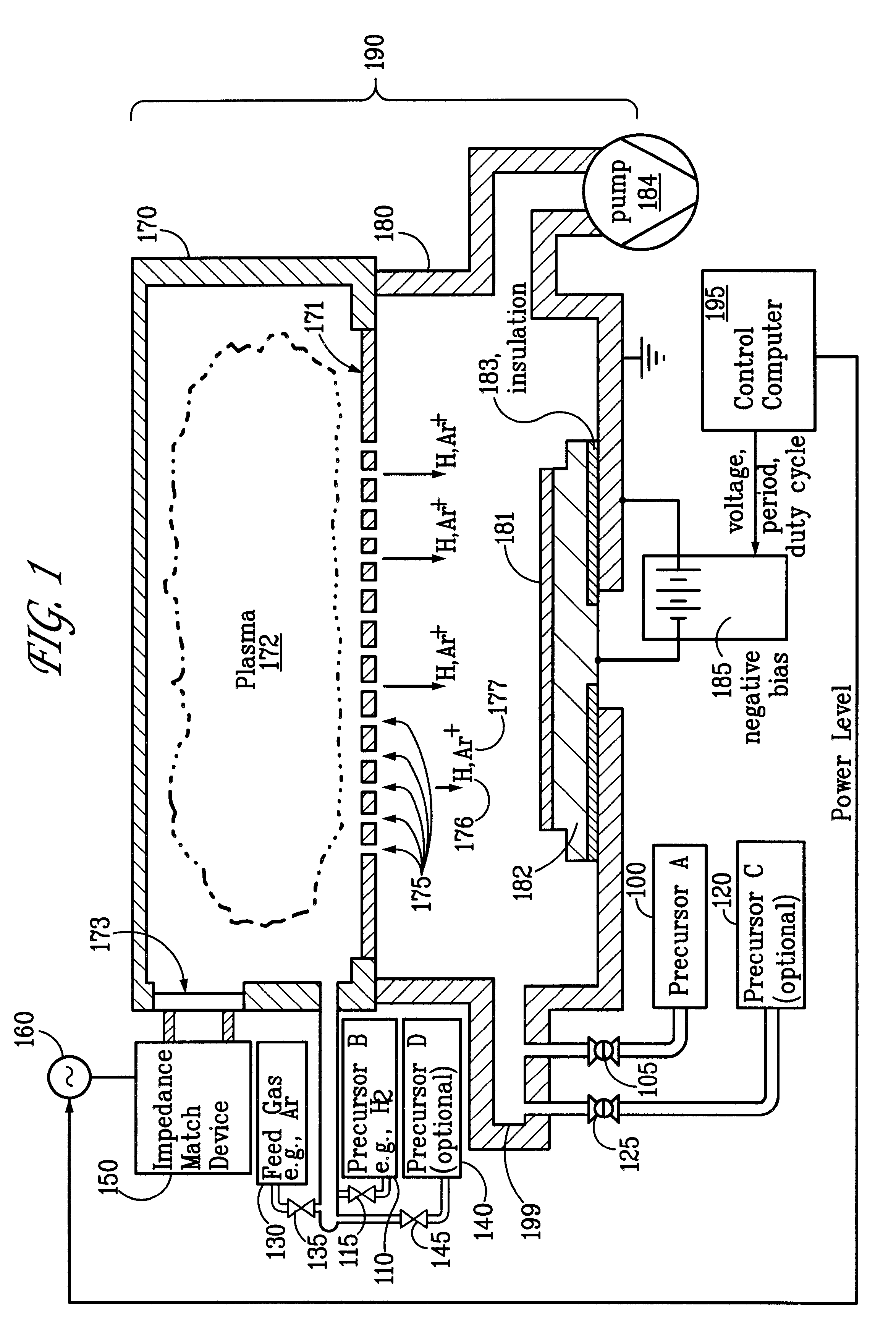

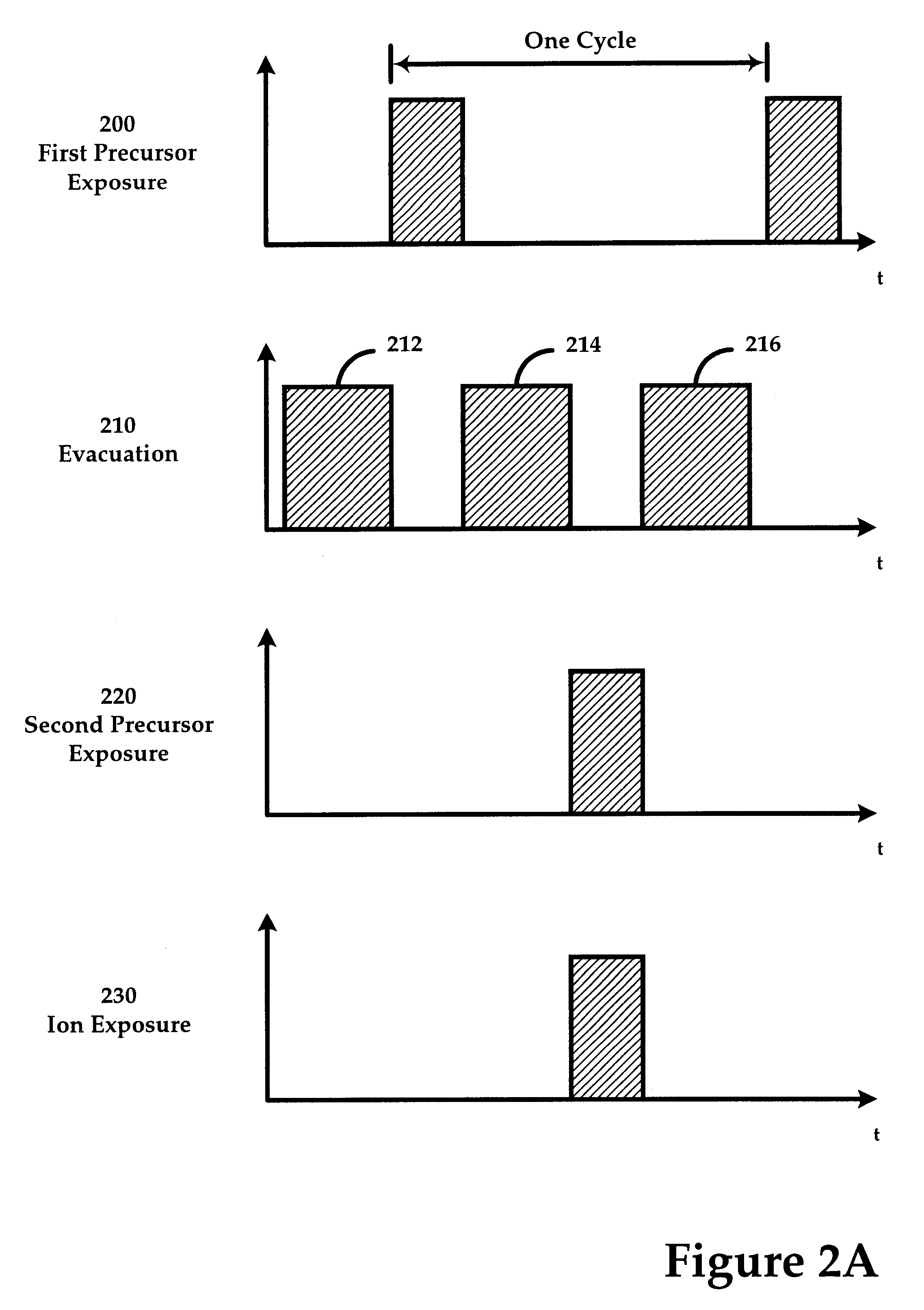

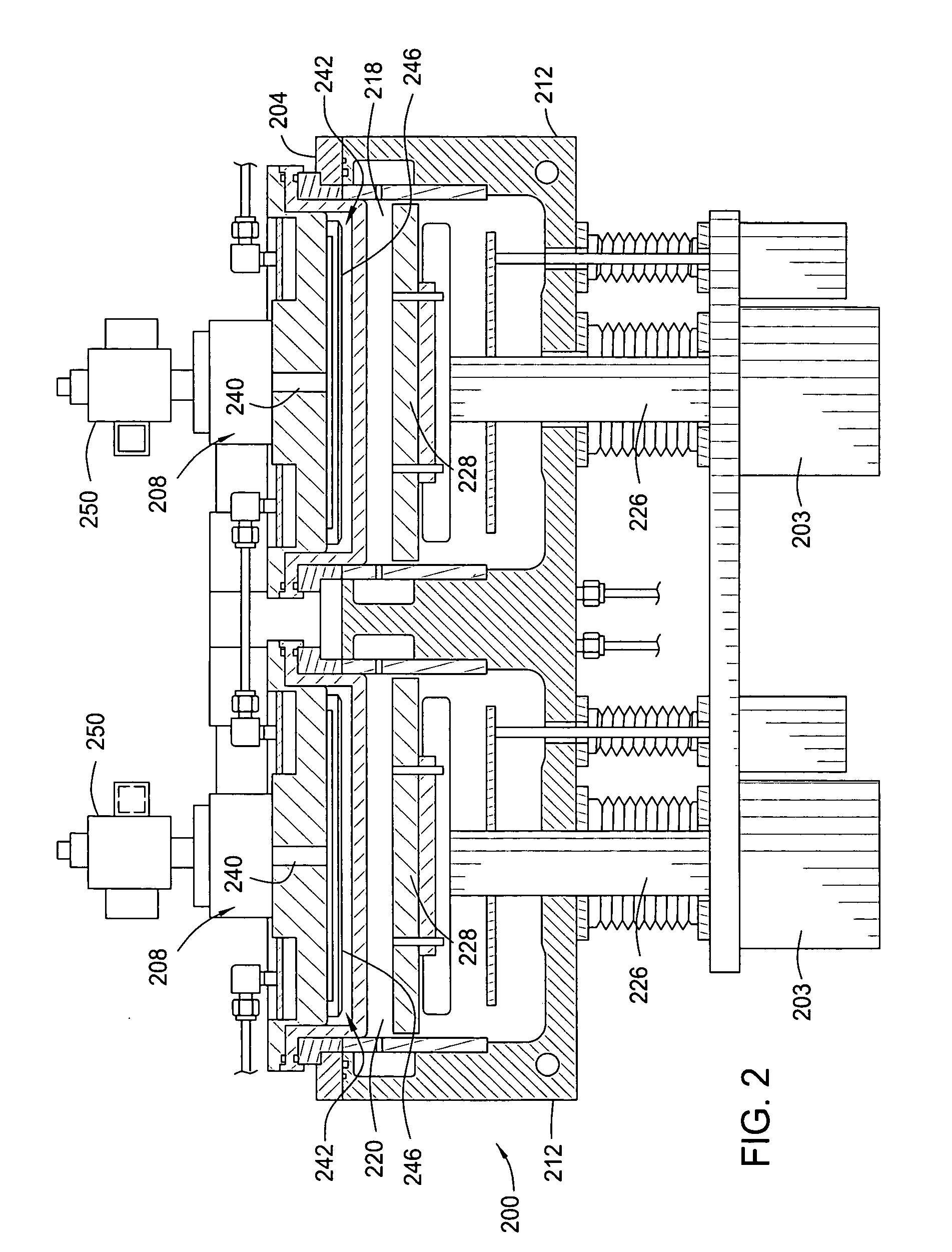

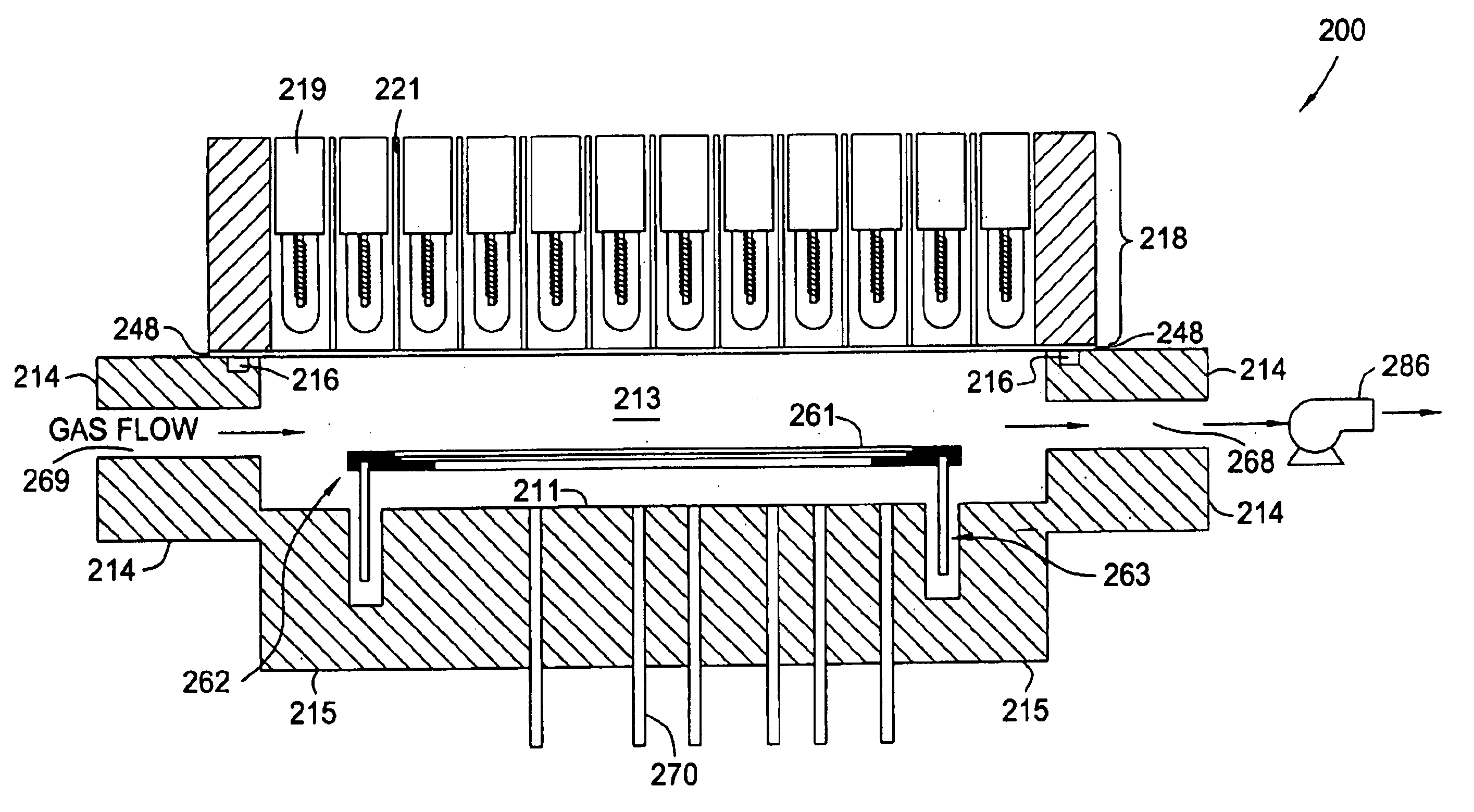

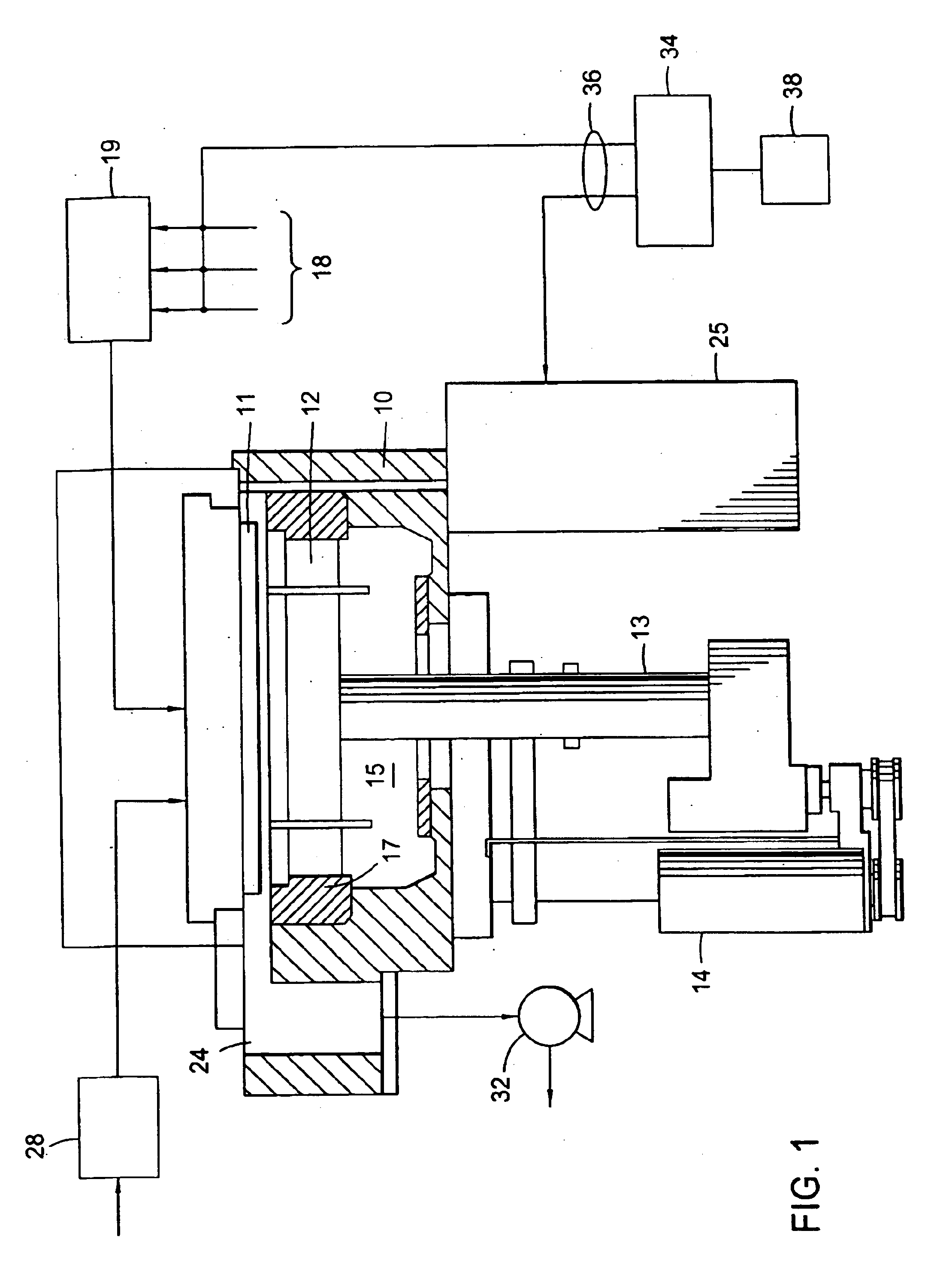

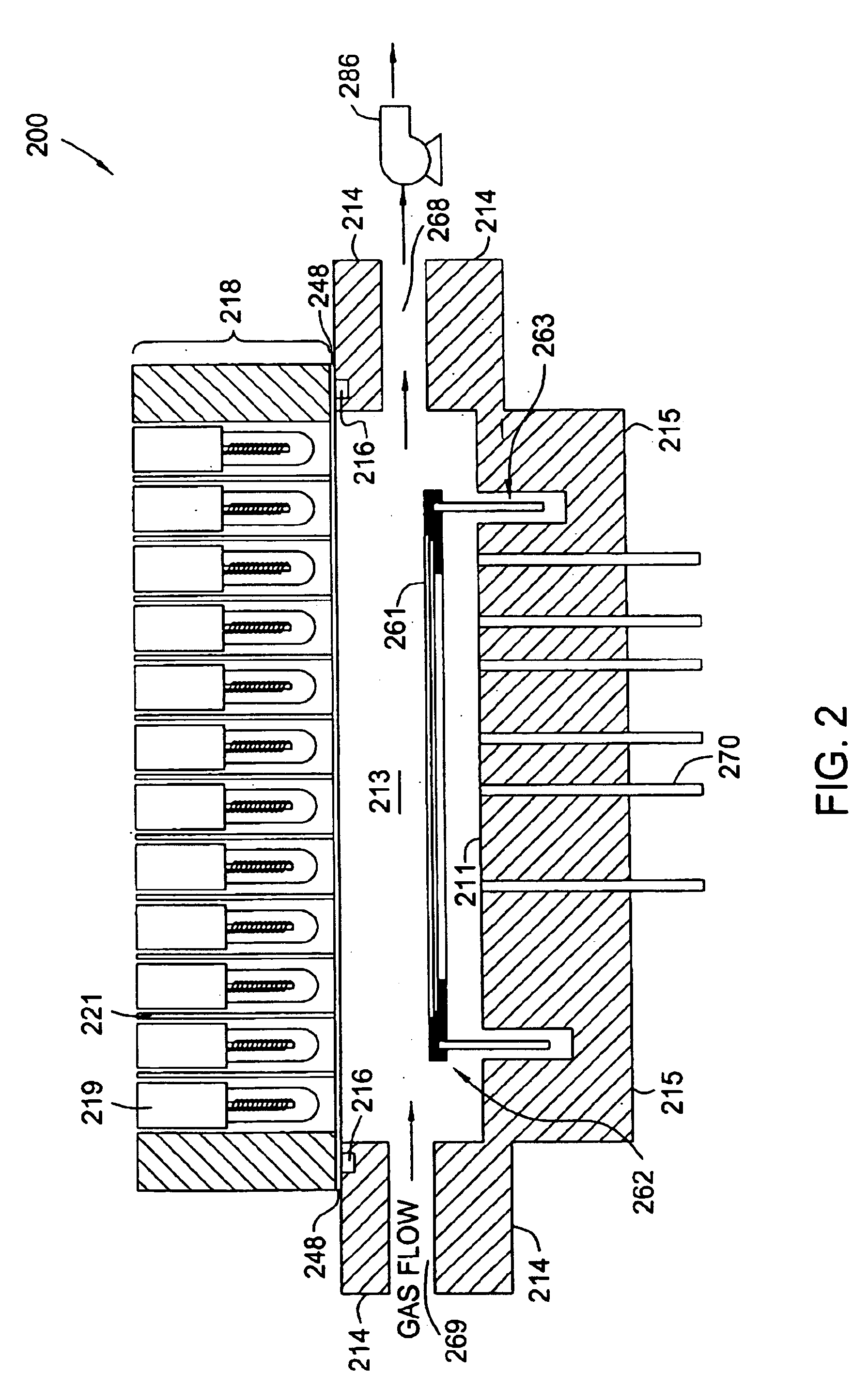

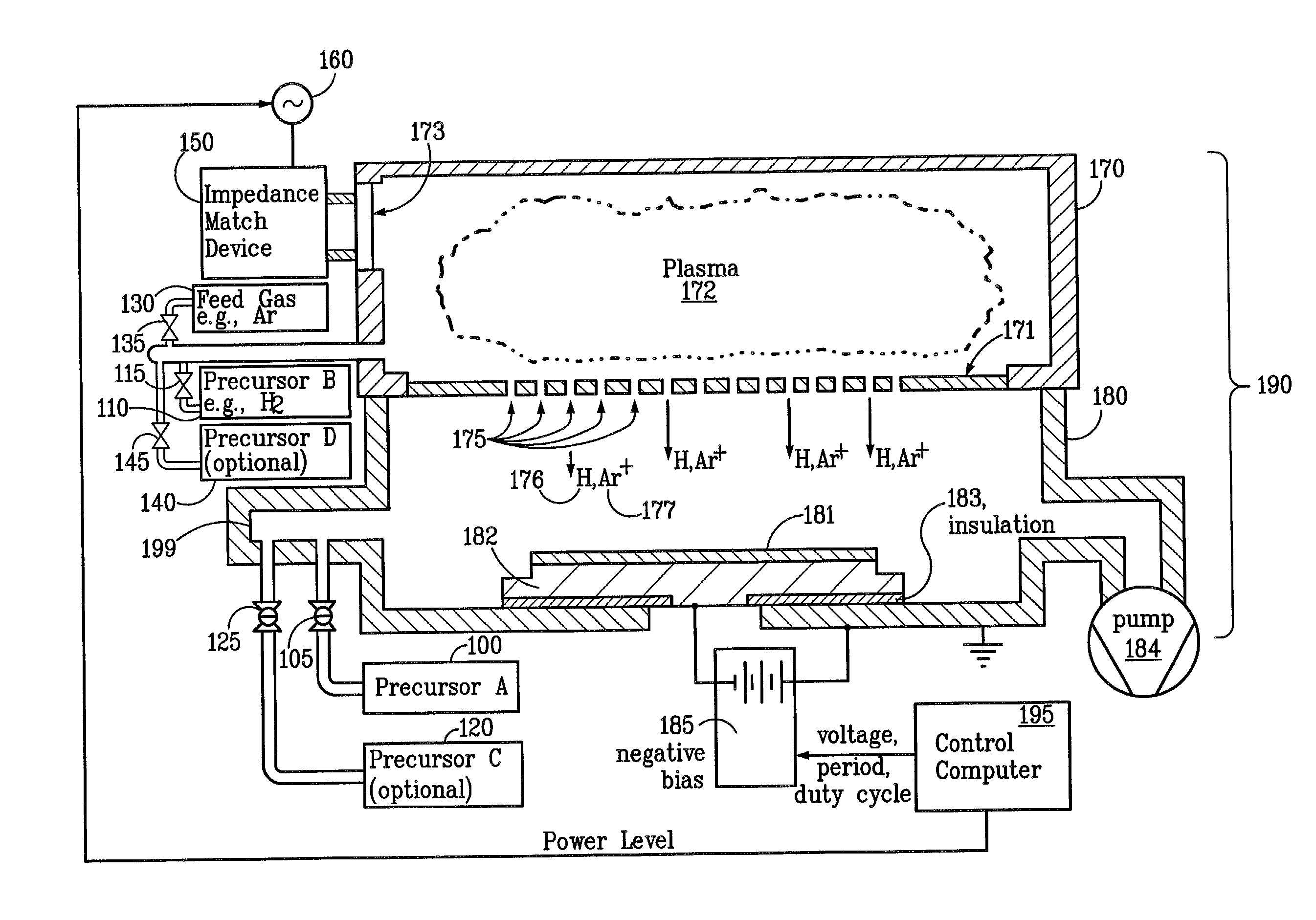

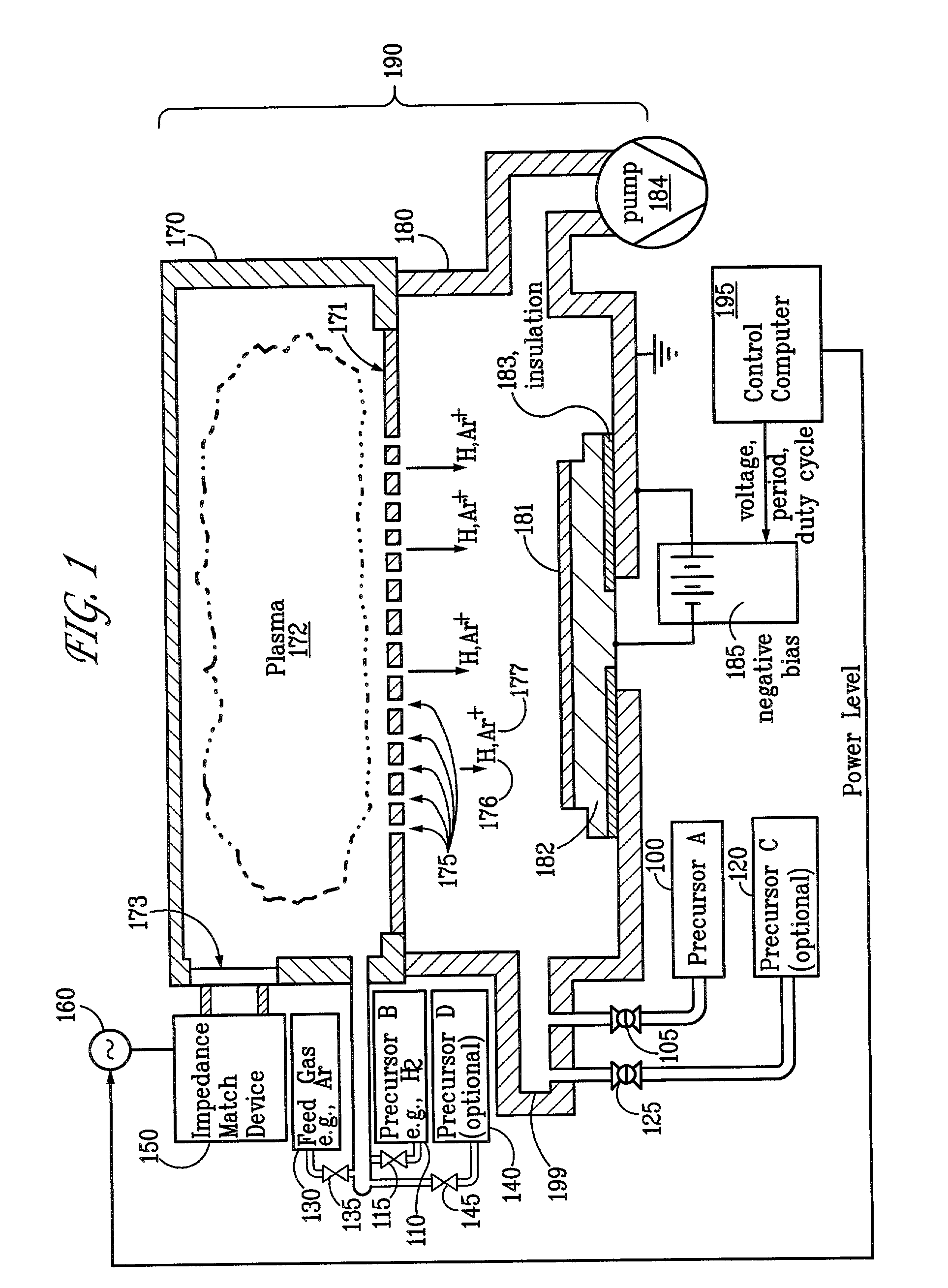

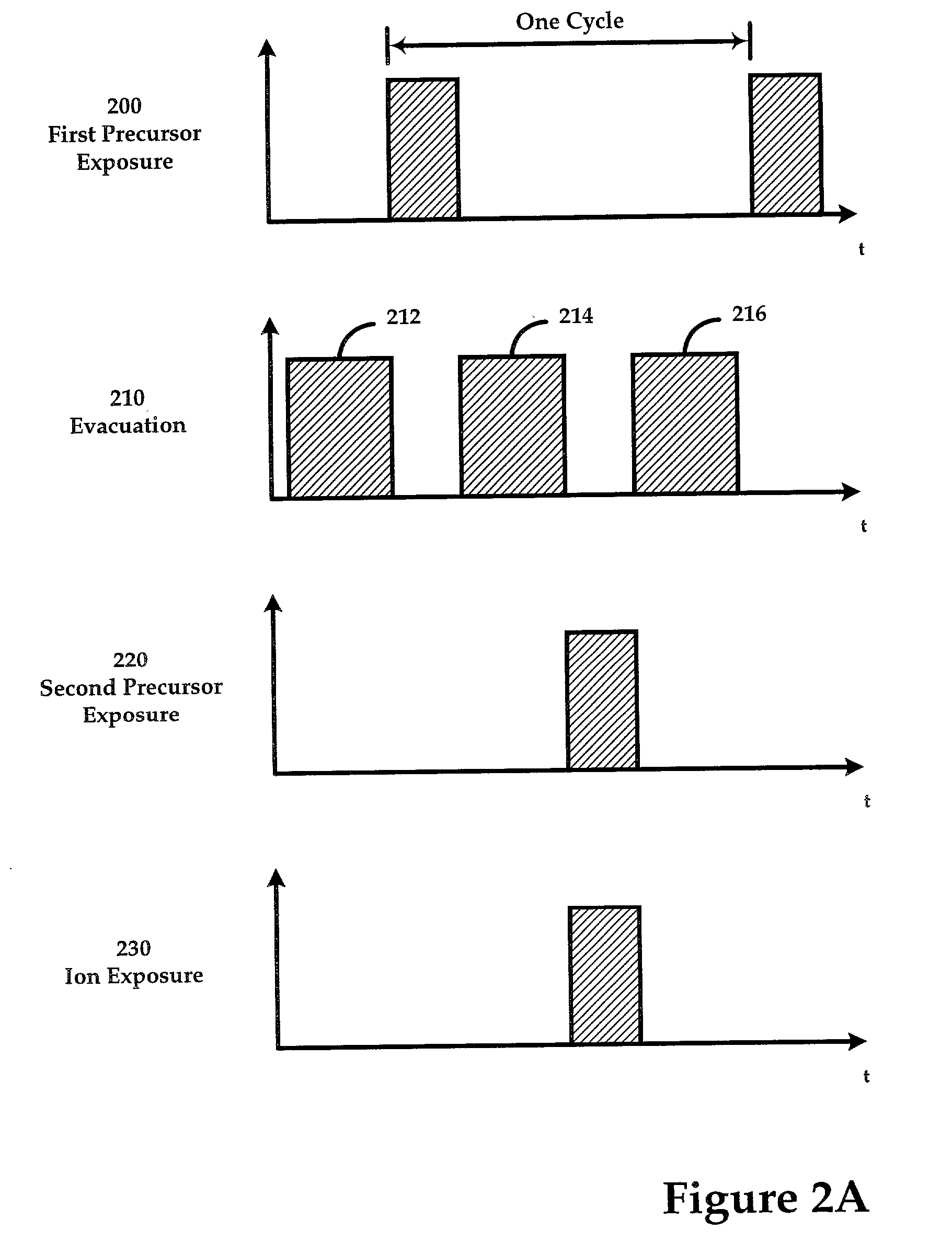

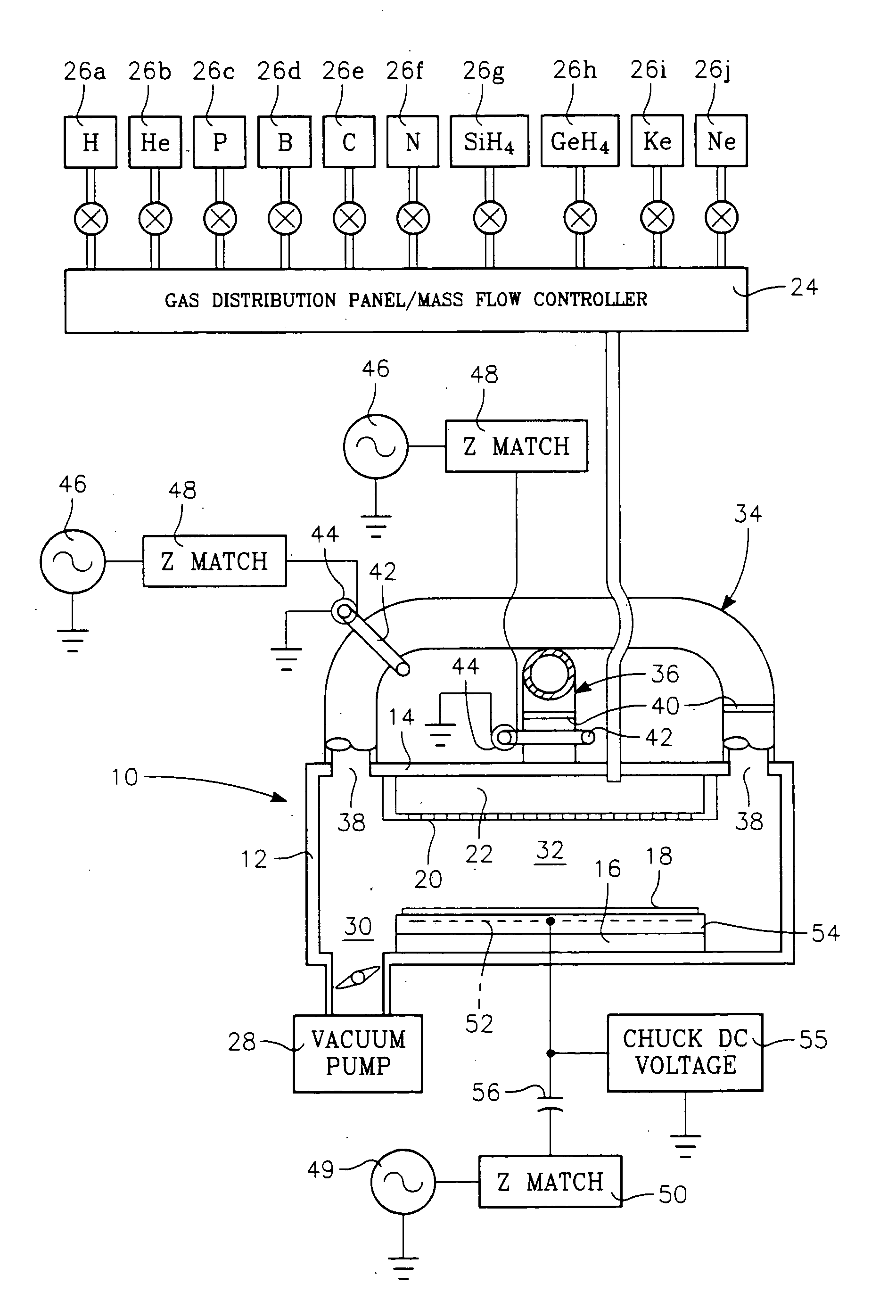

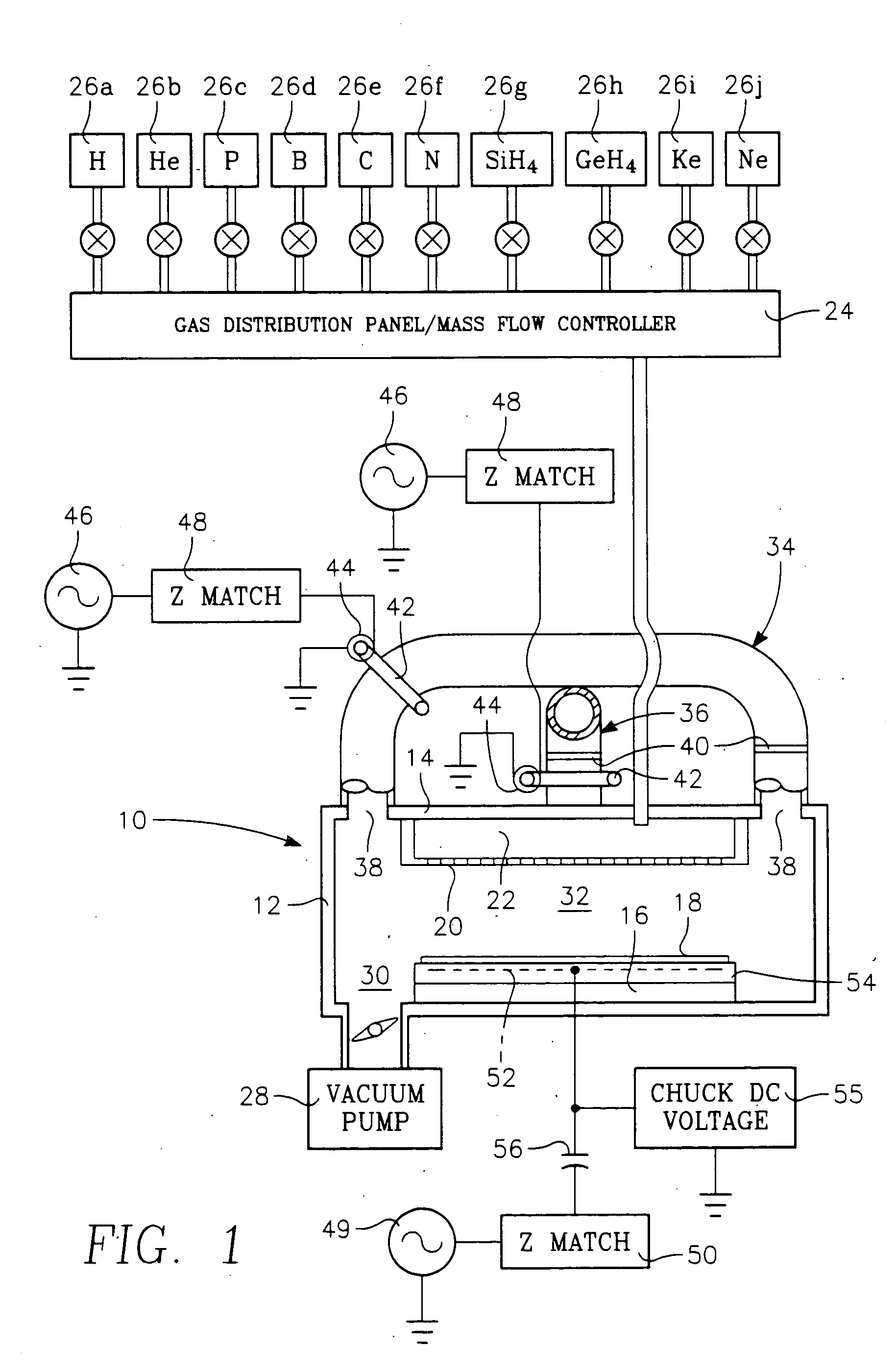

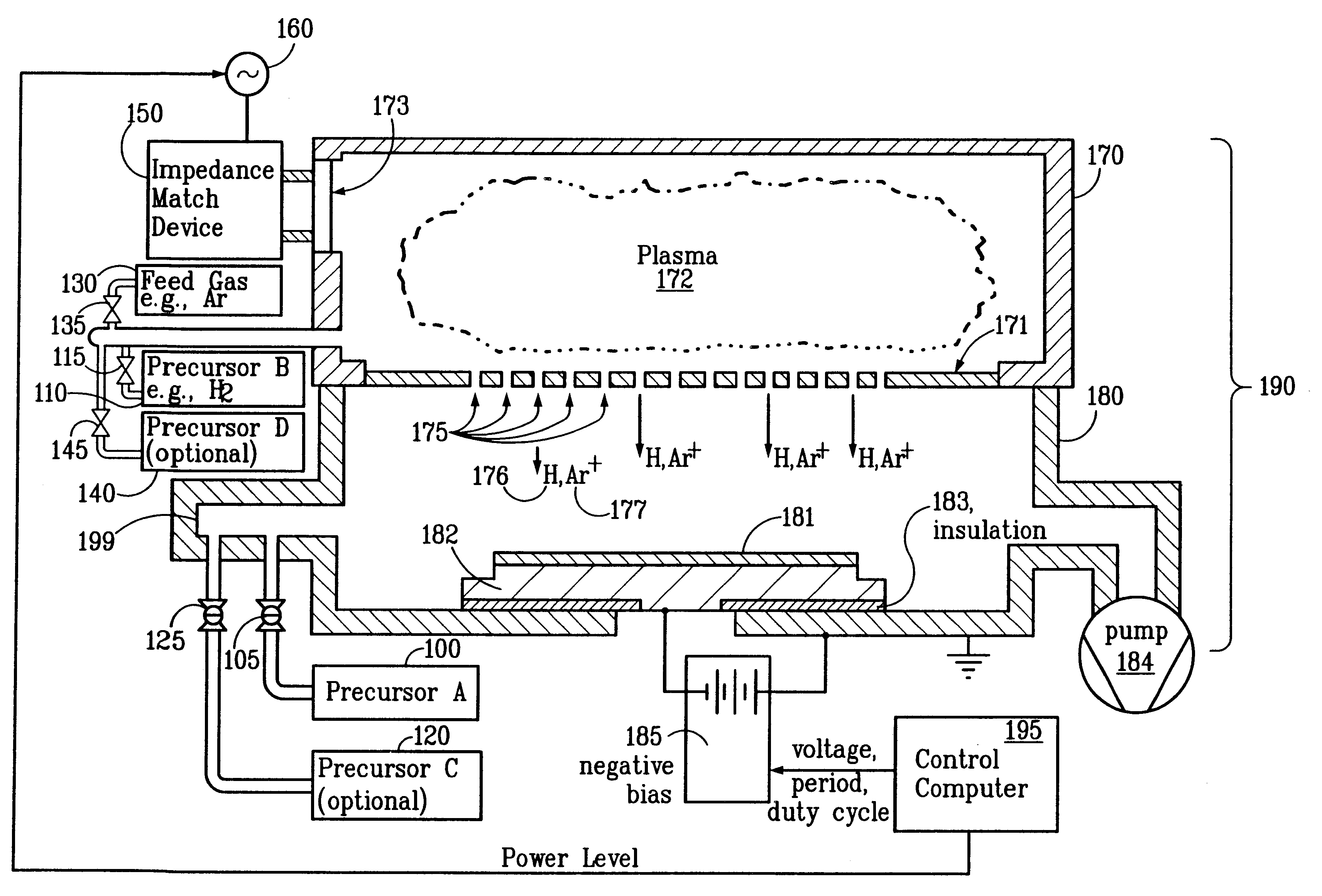

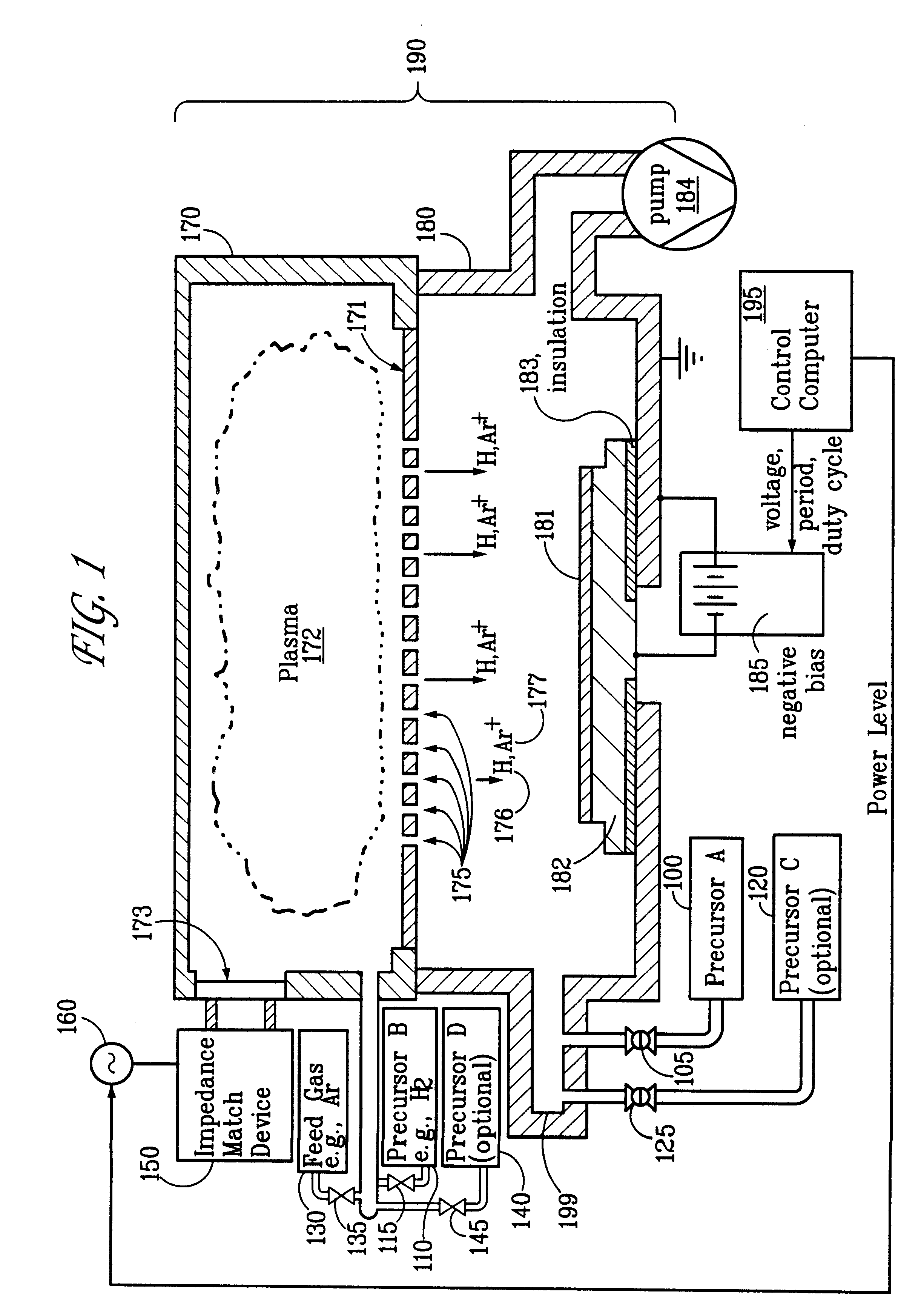

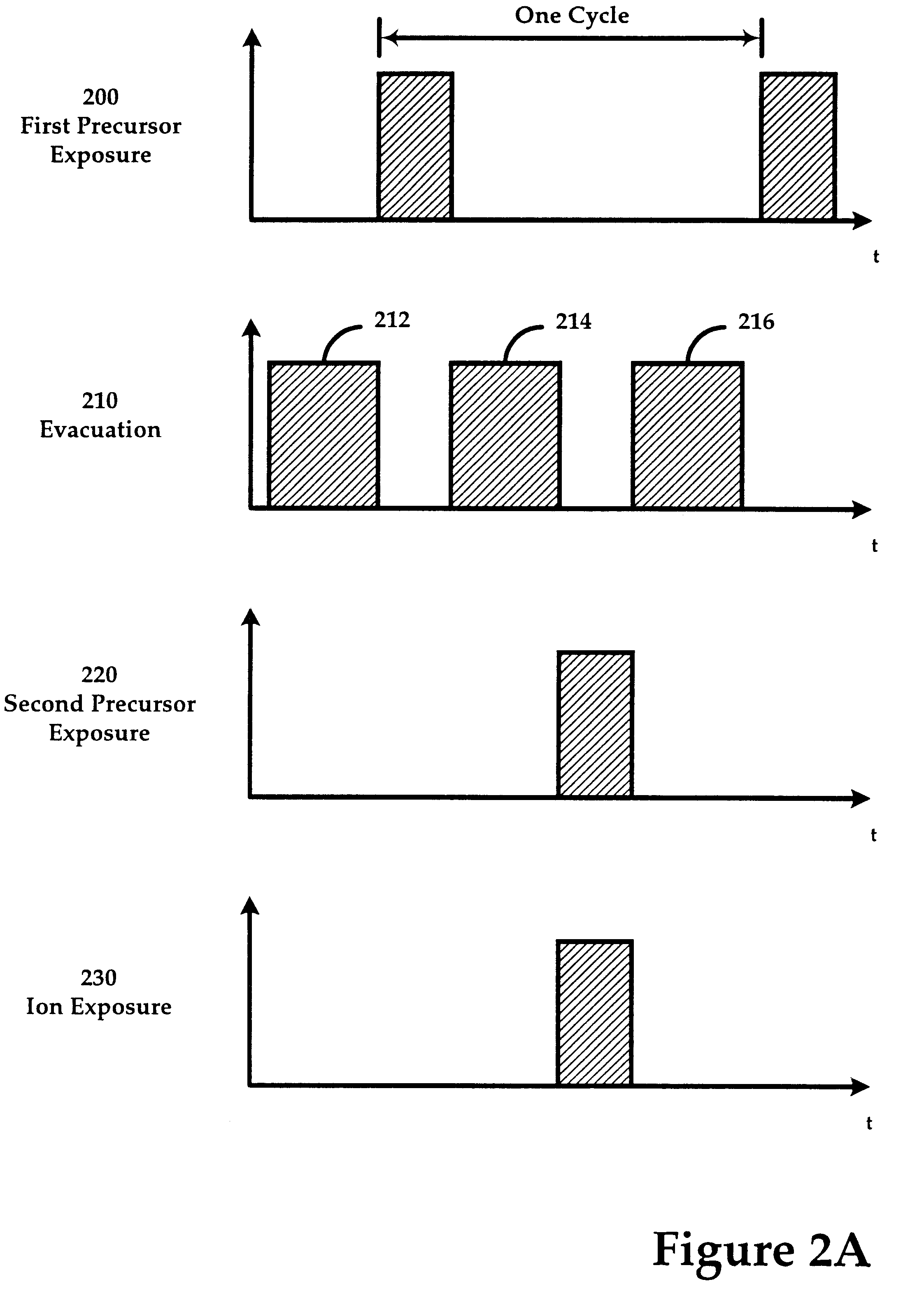

Sequential method for depositing a film by modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS6428859B1Faster efficient meanSimple methodVacuum evaporation coatingSputtering coatingSequential methodHigh density

The present invention relates to an enhanced sequential atomic layer deposition (ALD) technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; and, 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:NOVELLUS SYSTEMS

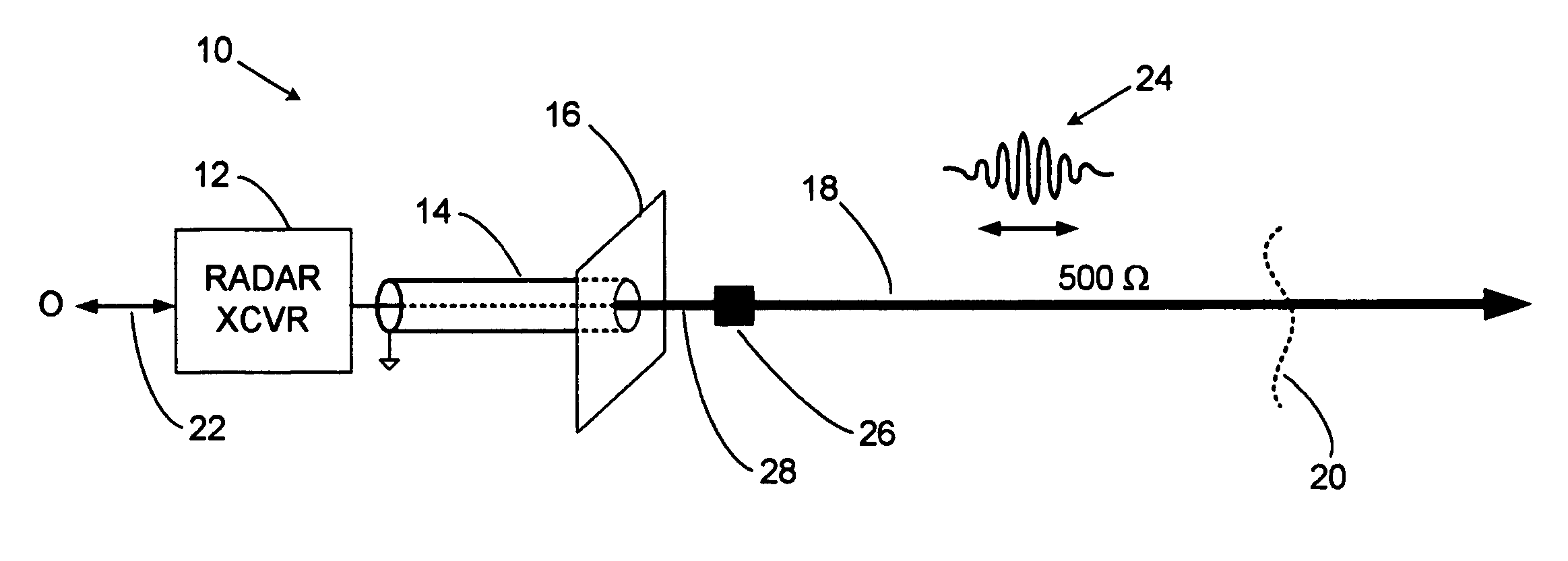

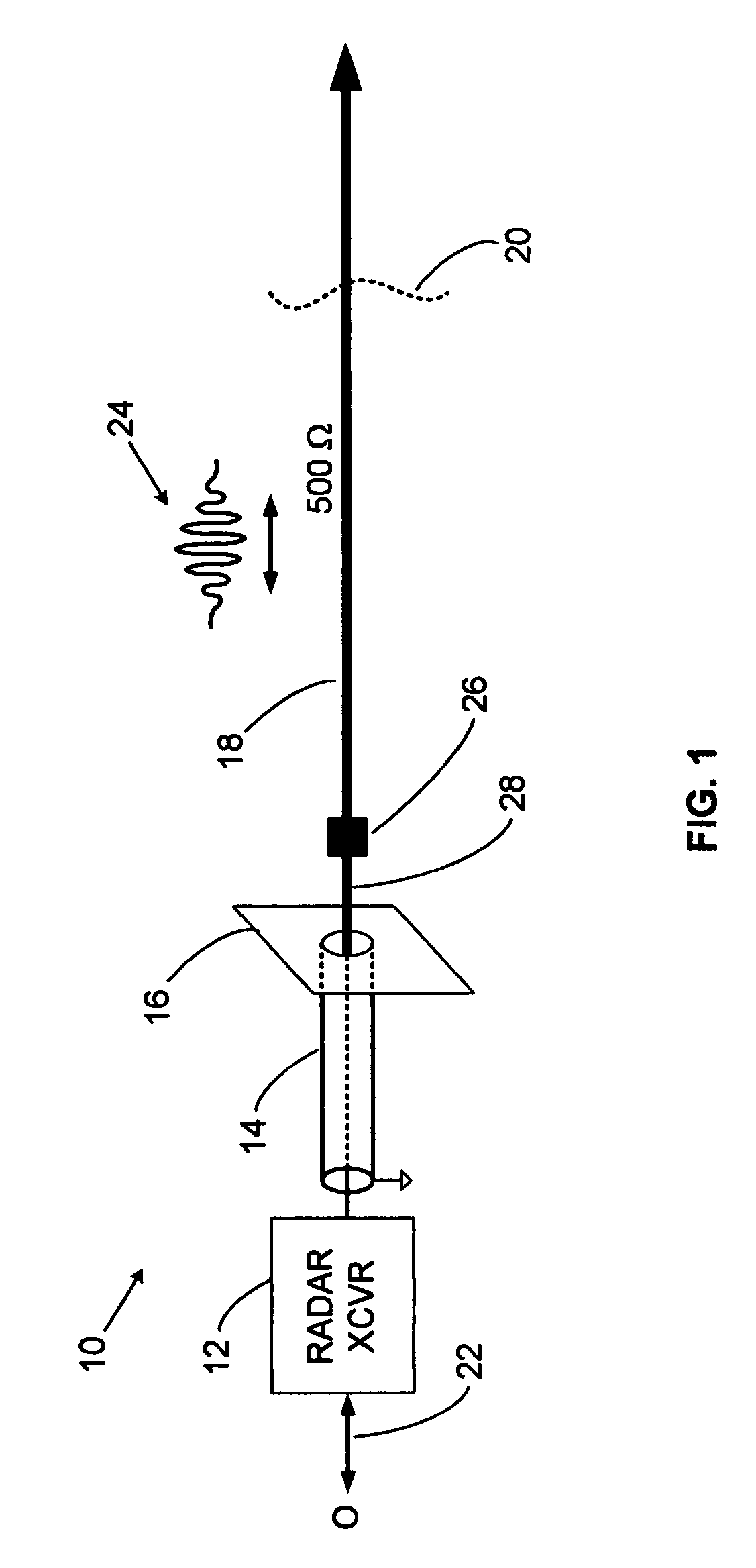

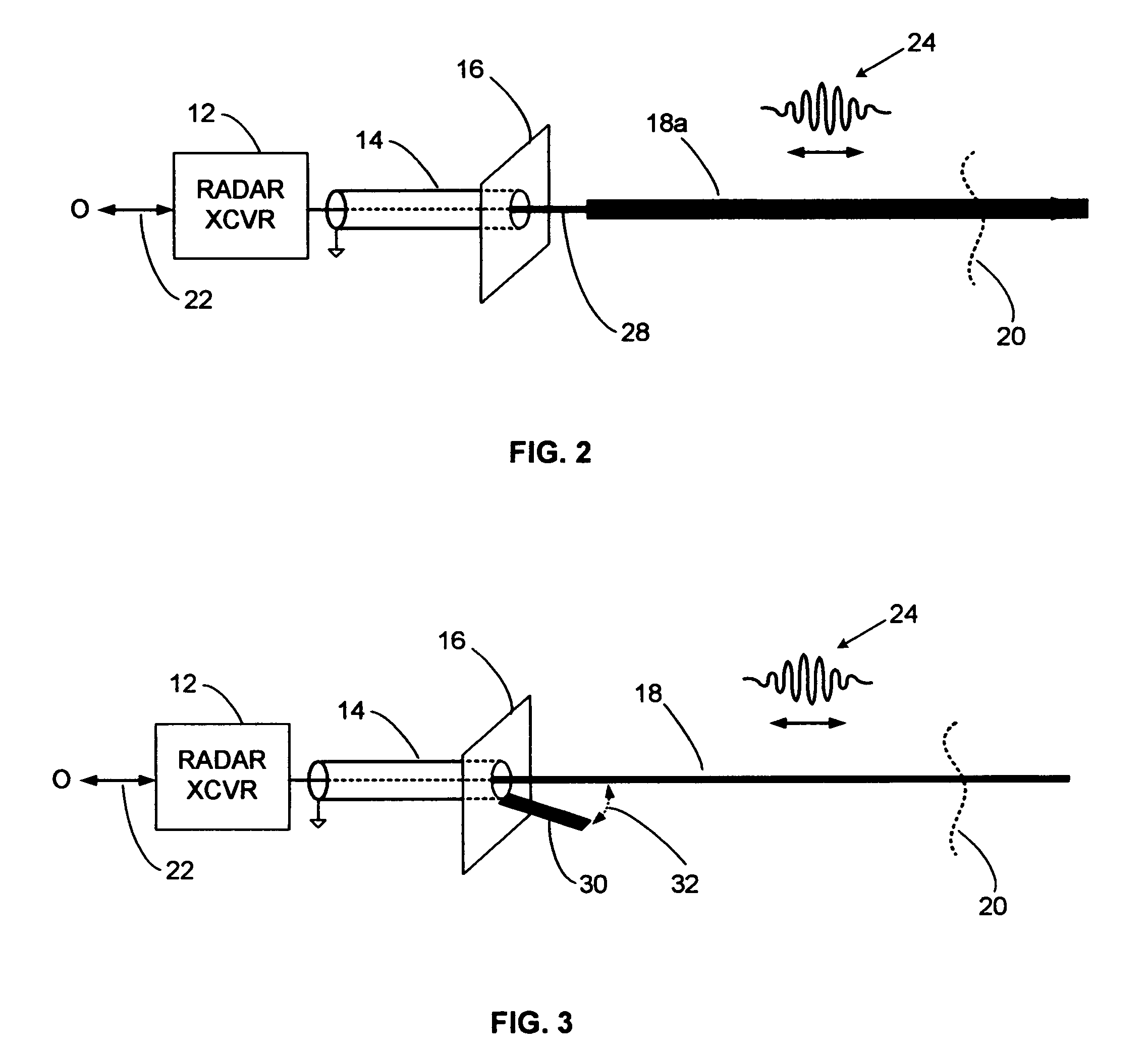

Reflection free launcher for electromagnetic guide wire

InactiveUS7345623B2Easy to measureSmall sizeMachines/enginesLevel indicatorsEngineeringImpedance matching

Guided wave radar (GWR) pulses are launched onto an electromagnetic guide wire using a compact launcher that includes an impedance matching element. The impedance matching element produces reflections that cancel launcher reflections. Short range echoes can be accurately detected after impedance matching. GWR operation in small tanks and in tanks containing low dielectric constant materials, such as propane, can be enhanced with the compact impedance-matched launcher.

Owner:MCEWAN TECH

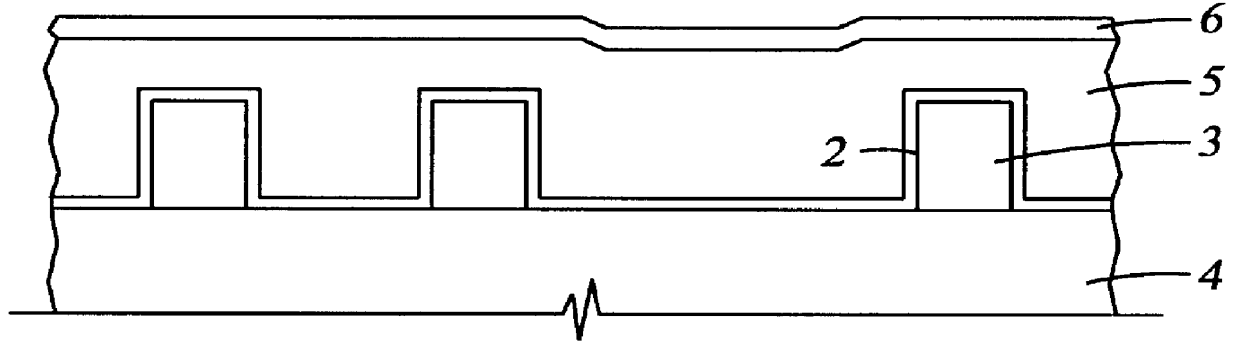

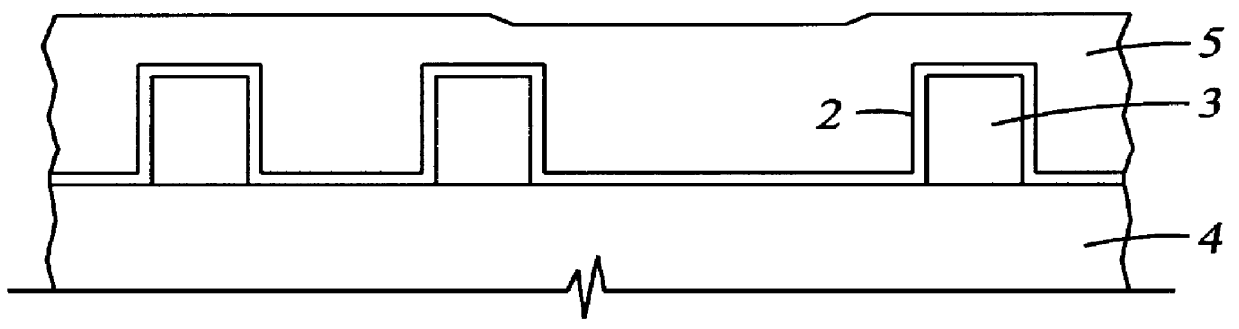

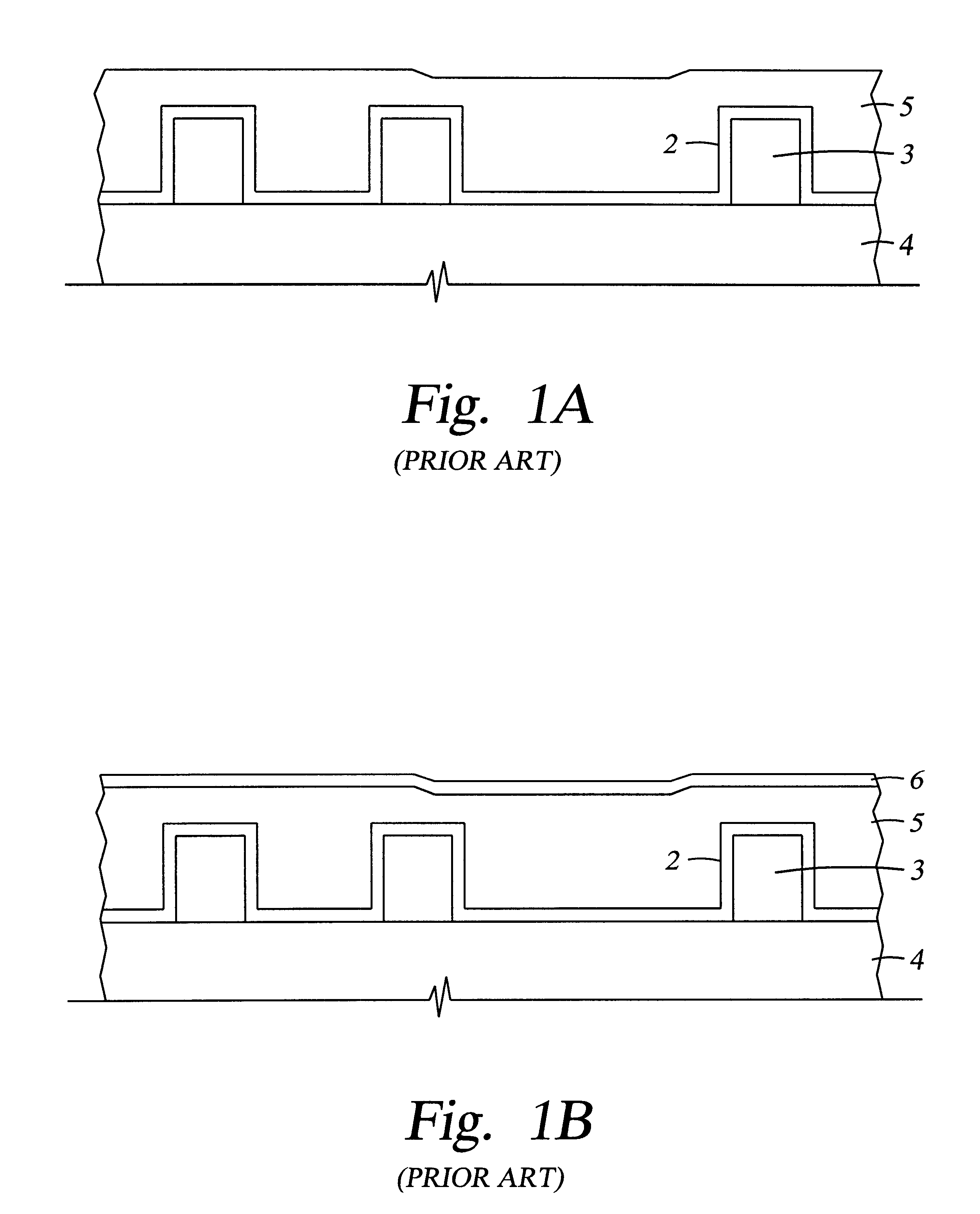

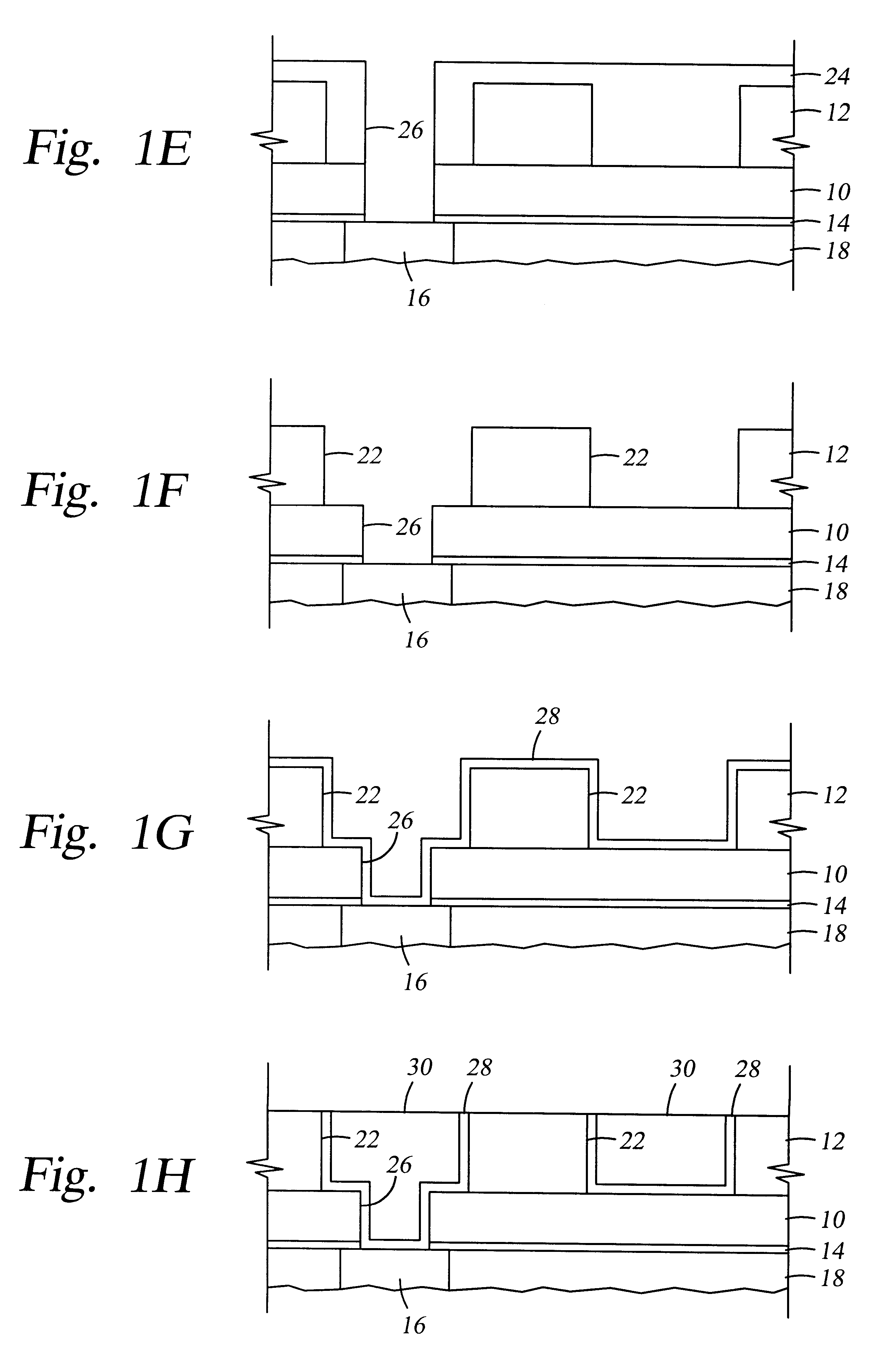

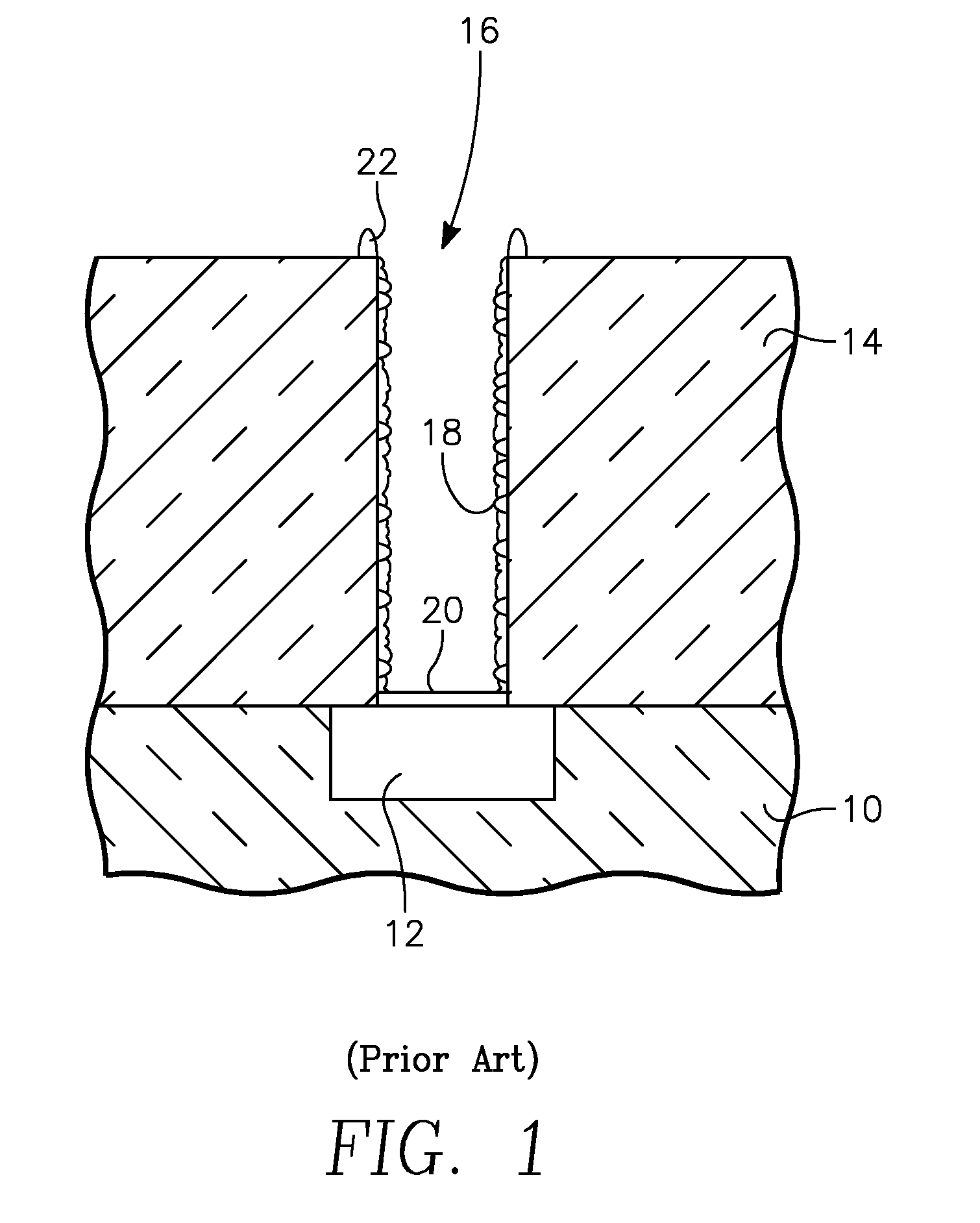

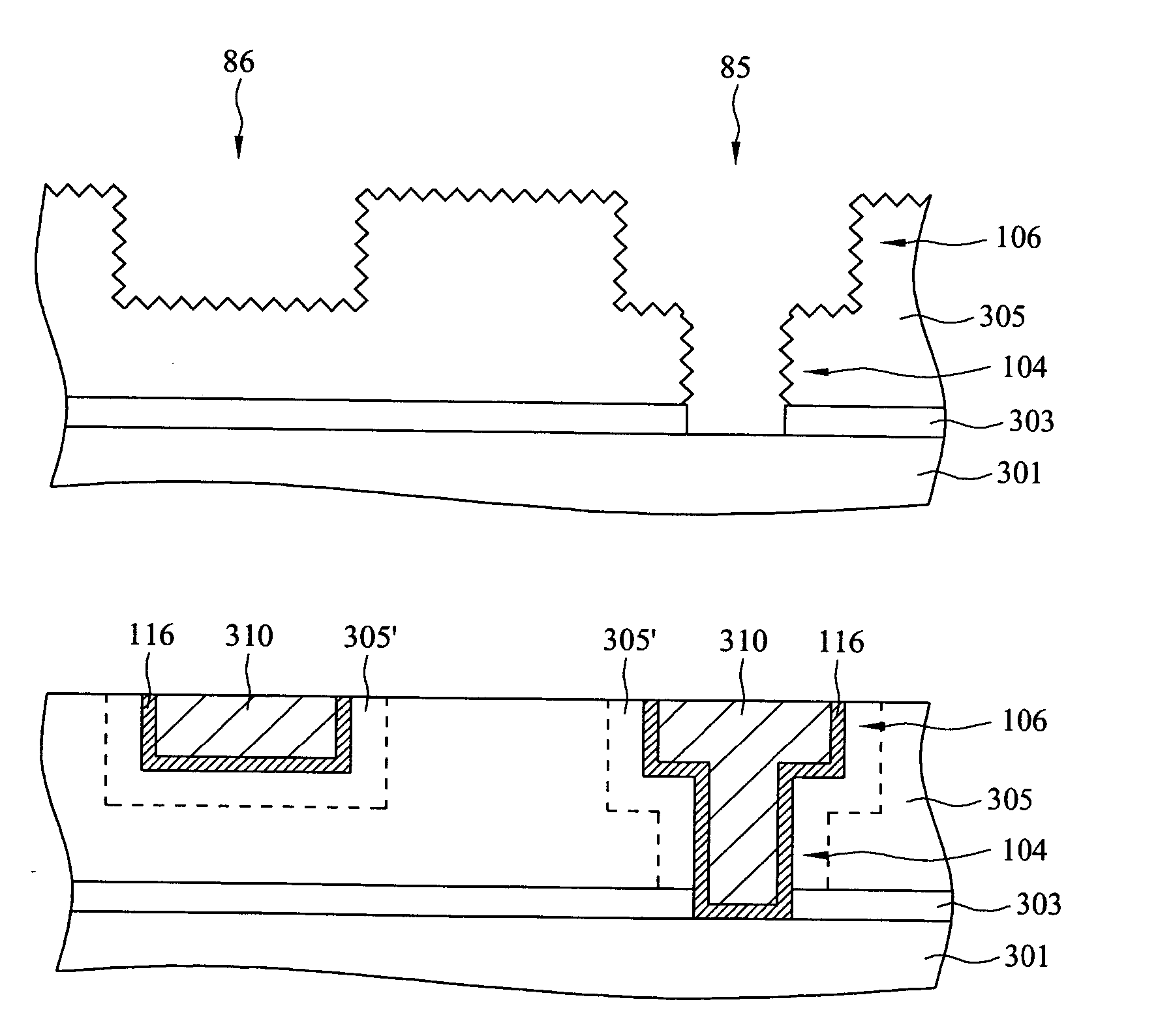

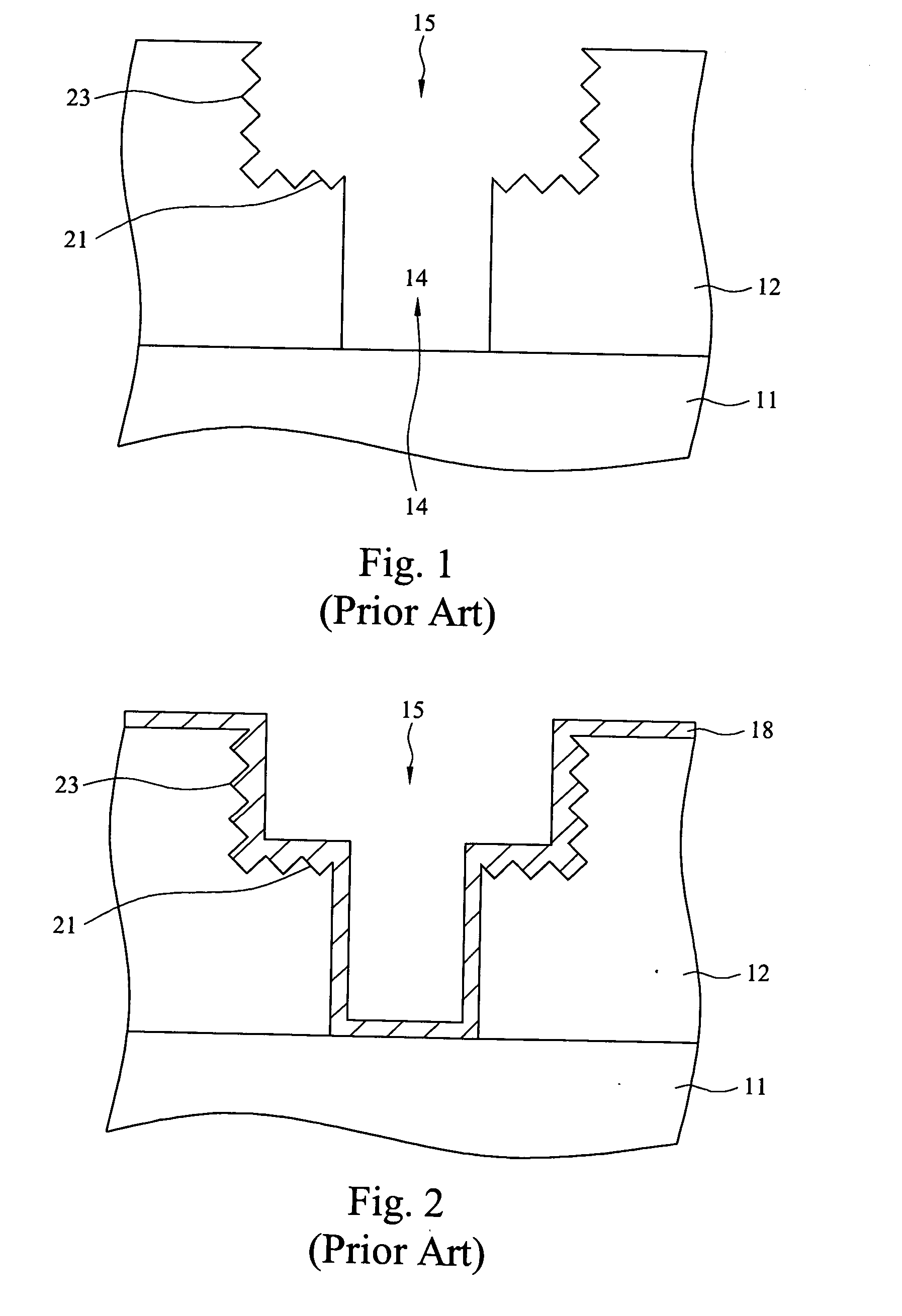

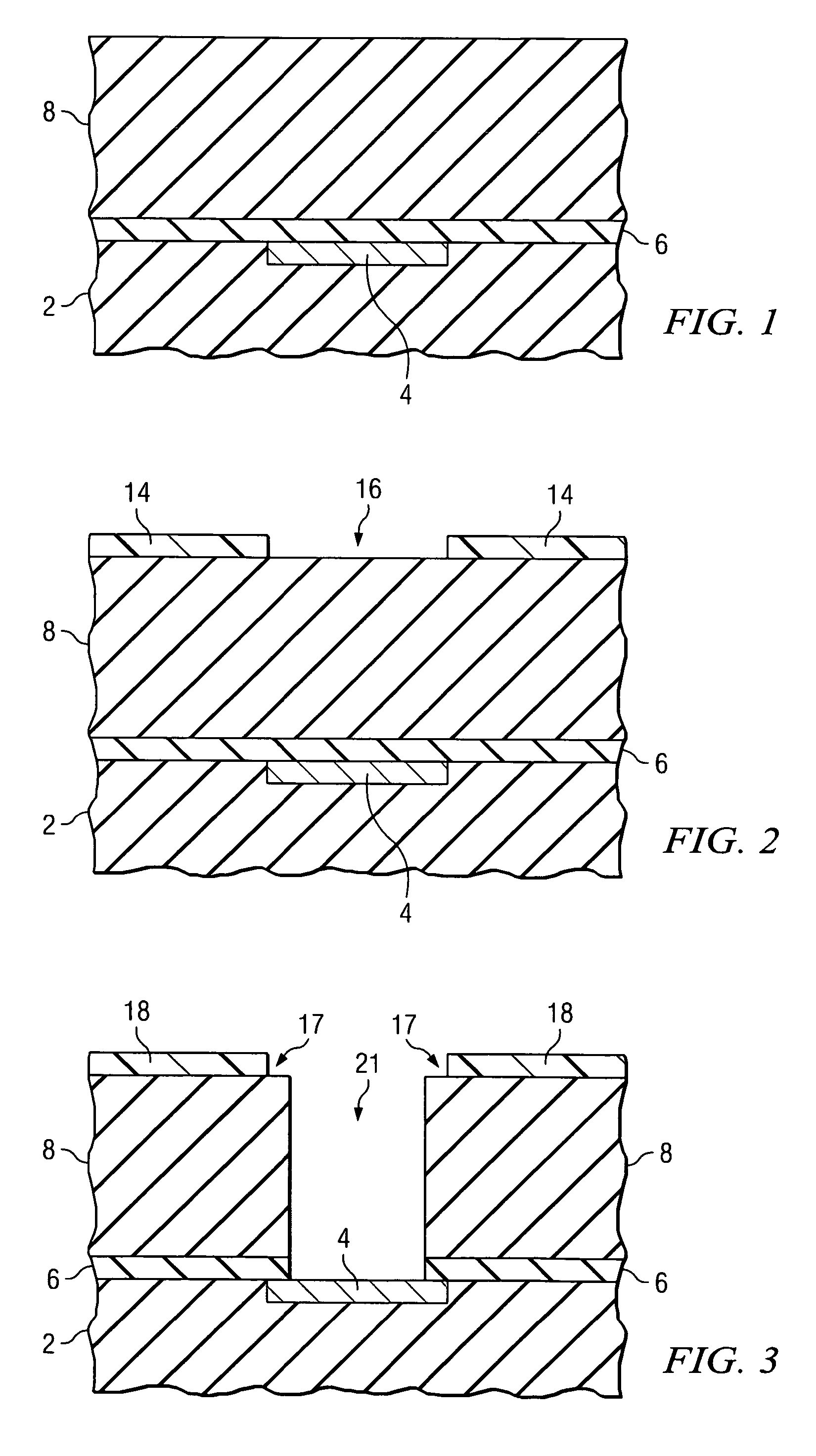

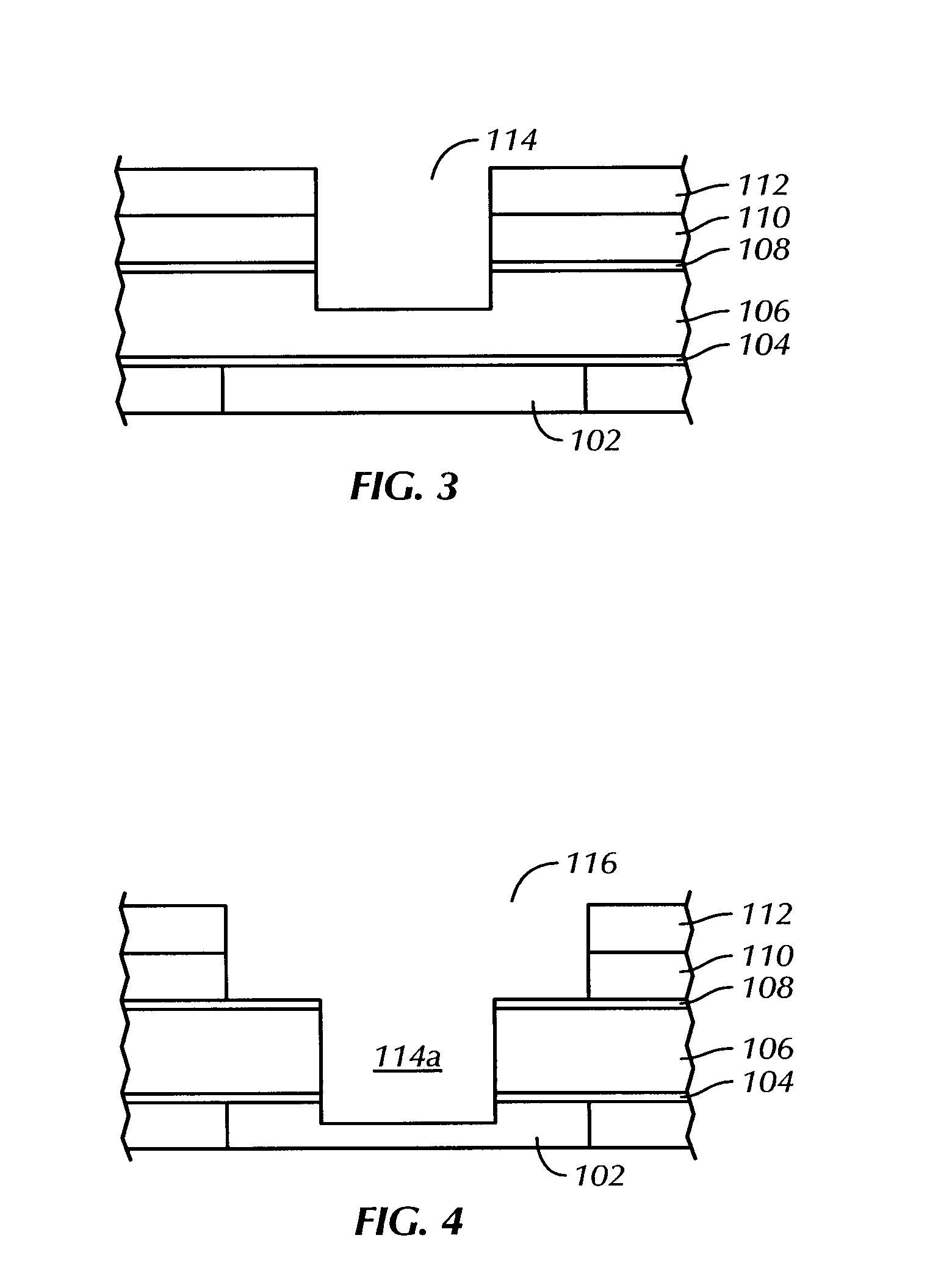

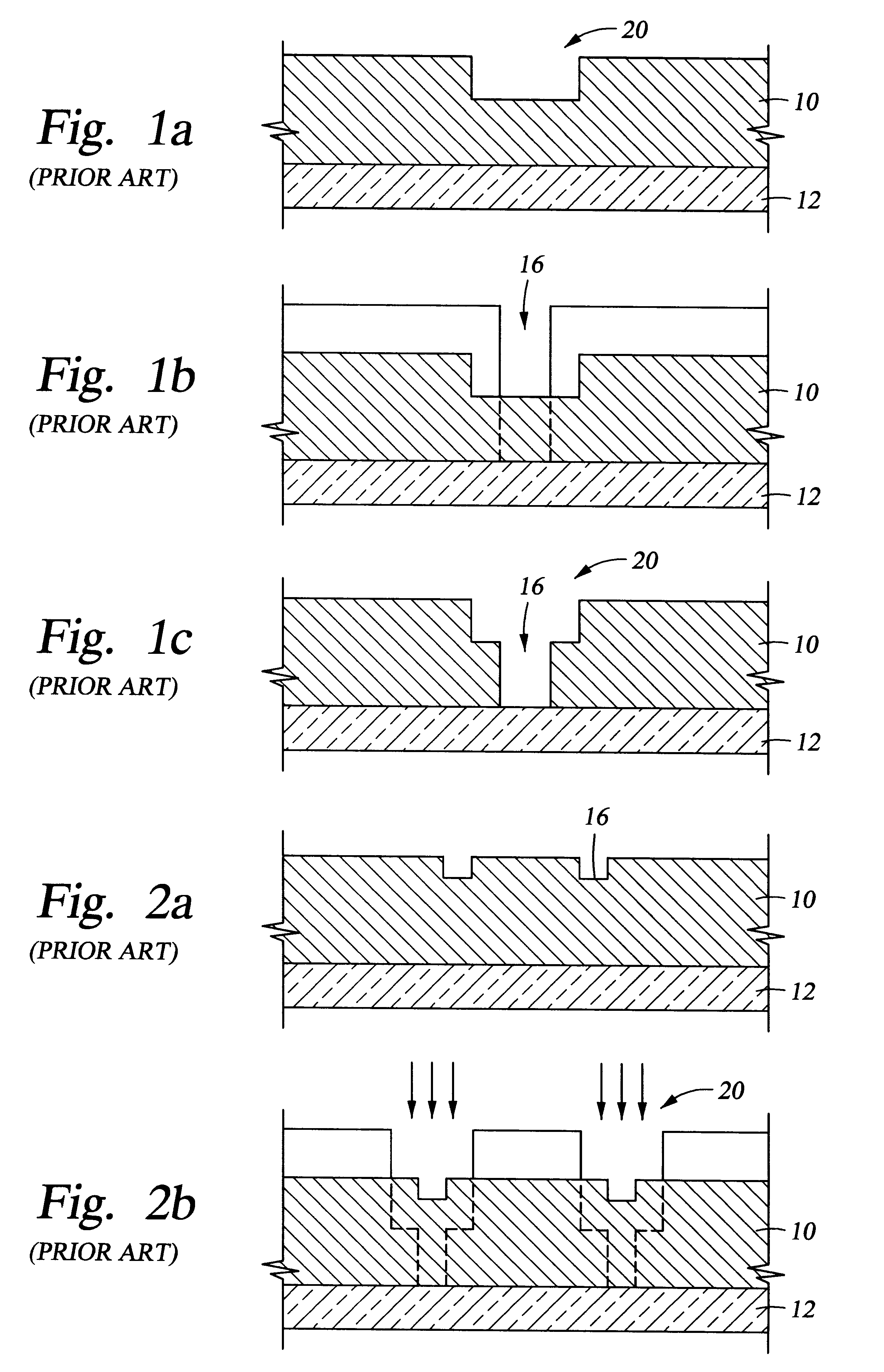

Method of etching patterned layers useful as masking during subsequent etching or for damascene structures

InactiveUS6080529APhotomechanical apparatusSemiconductor/solid-state device manufacturingConductive polymerOrganic base

A first embodiment of the present invention pertains to a method of patterning a semiconductor device conductive feature while permitting easy removal of any residual masking layer which remains after completion of the etching process. A multi-layered masking structure is used which includes a layer of high-temperature organic-based masking material overlaid by either a patterned layer of inorganic masking material or by a layer of patterned high-temperature imageable organic masking material. The inorganic masking material is used to transfer a pattern to the high-temperature organic-based masking material and is then removed. The high-temperature organic-based masking material is used to transfer the pattern and then may be removed if desired. This method is also useful in the pattern etching of aluminum, even though aluminum can be etched at lower temperatures. A second embodiment of the present invention pertains to a specialized etch chemistry useful in the patterning of organic polymeric layers such as low k dielectrics, or other organic polymeric interfacial layers. This etch chemistry is useful for mask opening during the etch of a conductive layer or is useful in etching damascene structures where a metal fill layer is applied over the surface of a patterned organic-based dielectric layer. The etch chemistry provides for the use of etchant plasma species which minimize oxygen, fluorine, chlorine, and bromine content.

Owner:APPLIED MATERIALS INC

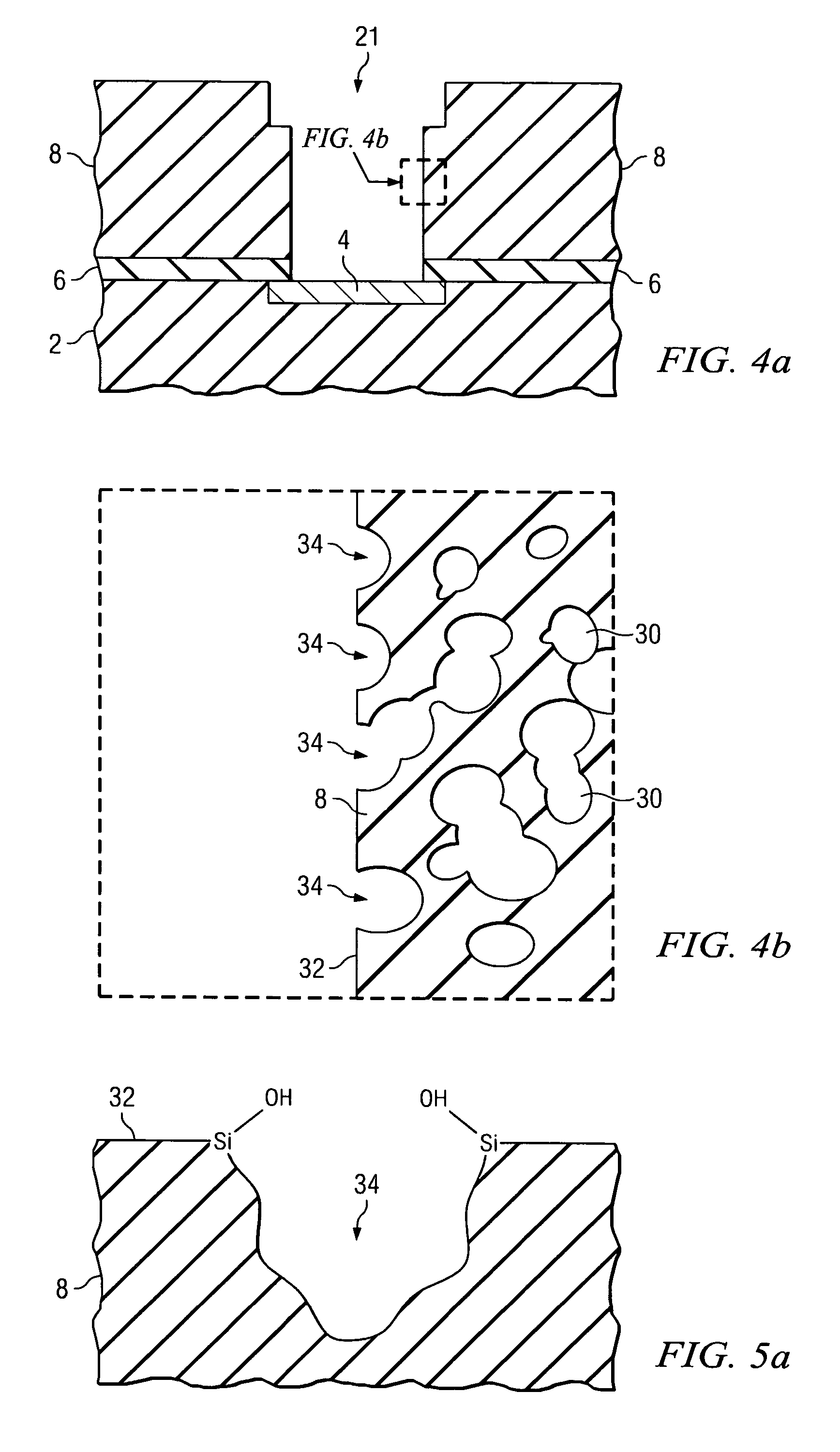

Formation of a liquid-like silica layer by reaction of an organosilicon compound and a hydroxyl forming compound

InactiveUS6413583B1Semiconductor/solid-state device detailsSolid-state devicesSilicon oxideSilicon dioxide

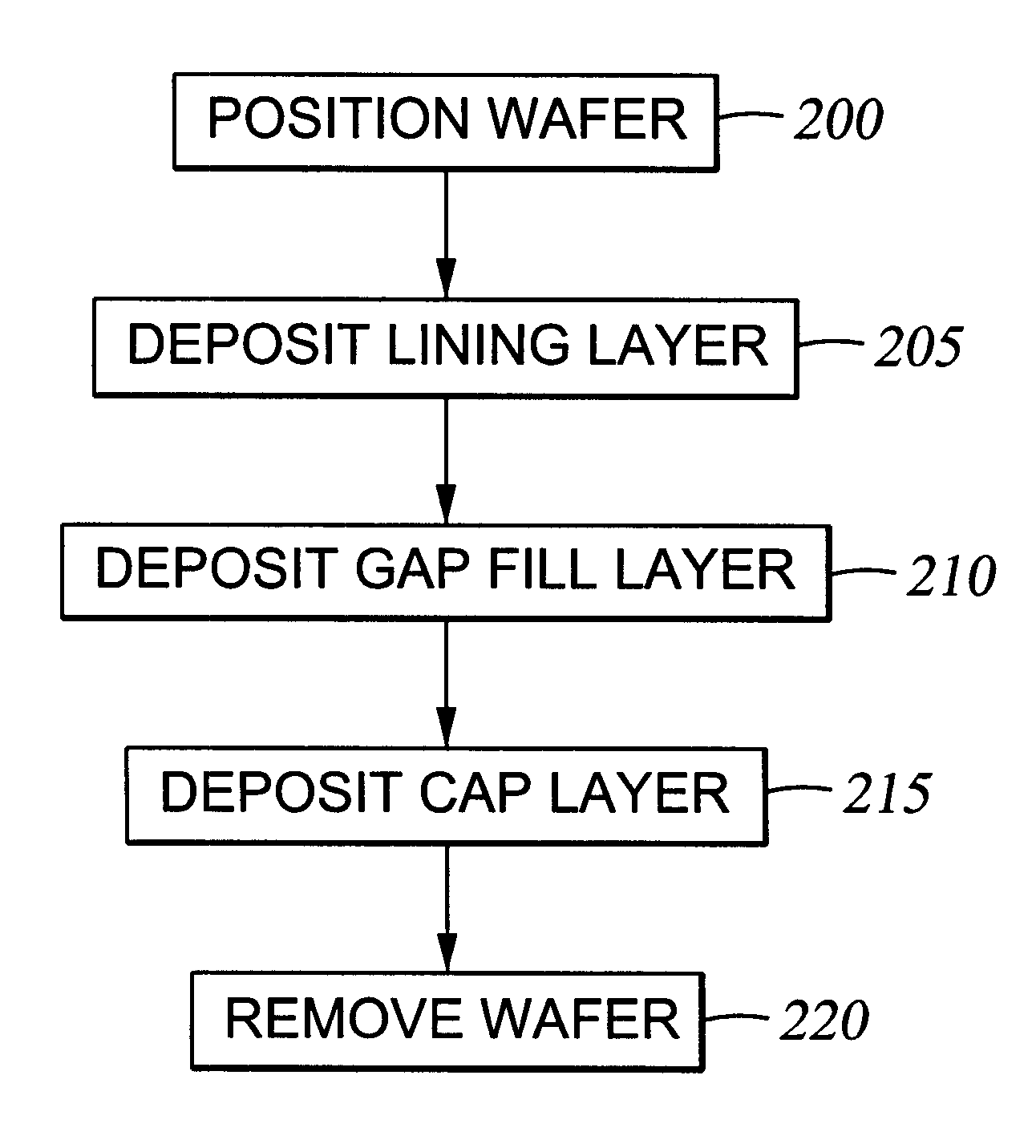

A method for depositing silicon oxide layers having a low dielectric constant by reaction of an organosilicon compound and a hydroxyl forming compound at a substrate temperature less than about 400° C. The low dielectric constant films contain residual carbon and are useful for gap fill layers, pre-metal dielectric layers, inter-metal dielectric layers, and shallow trench isolation dielectric layers in sub-micron devices. The hydroxyl compound can be prepared prior to deposition from water or an organic compound. The silicon oxide layers are preferably deposited at a substrate temperature less than about 40° C. onto a liner layer produced from the organosilicon compound to provide gap fill layers having a dielectric constant less than about 3.0.

Owner:APPLIED MATERIALS INC

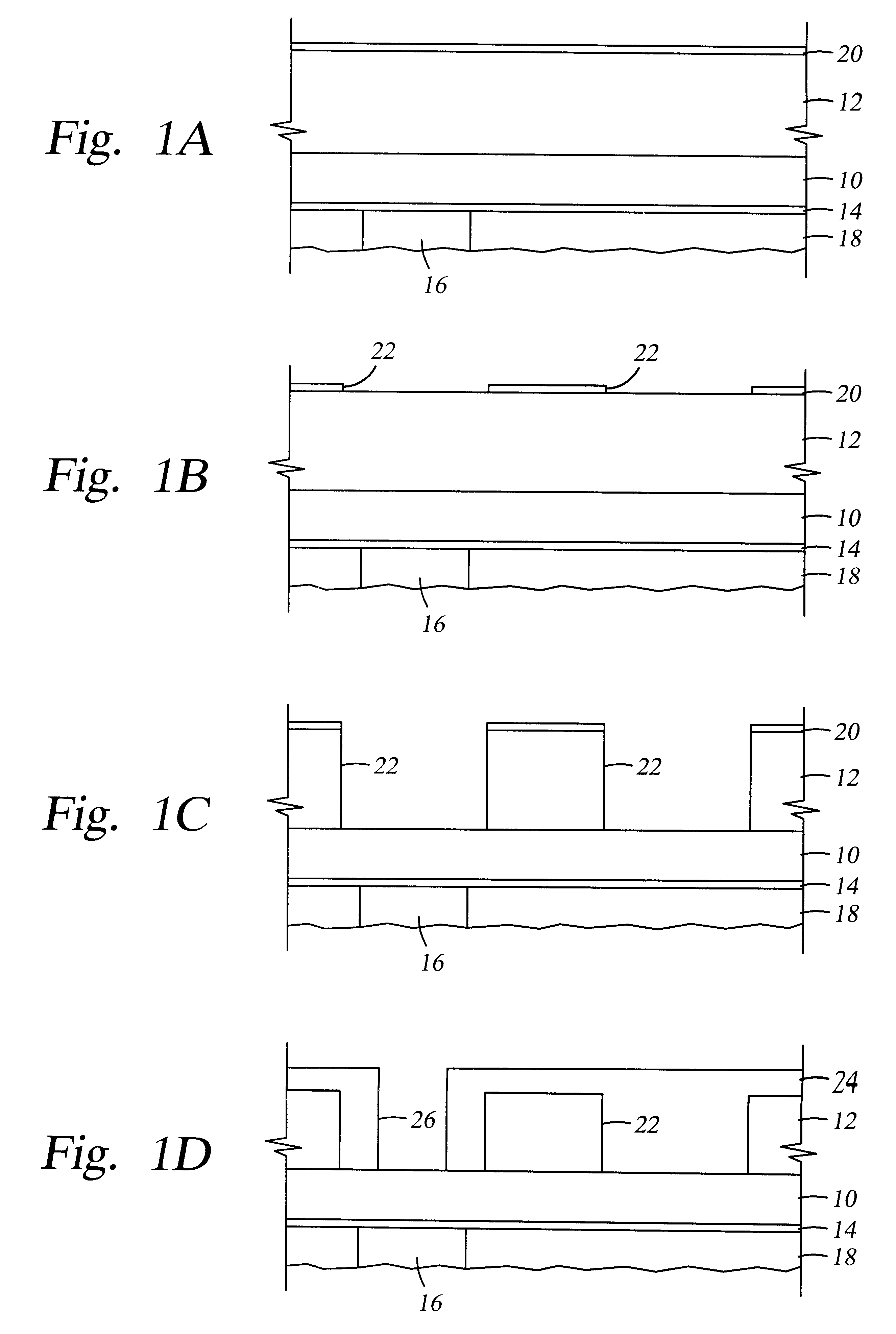

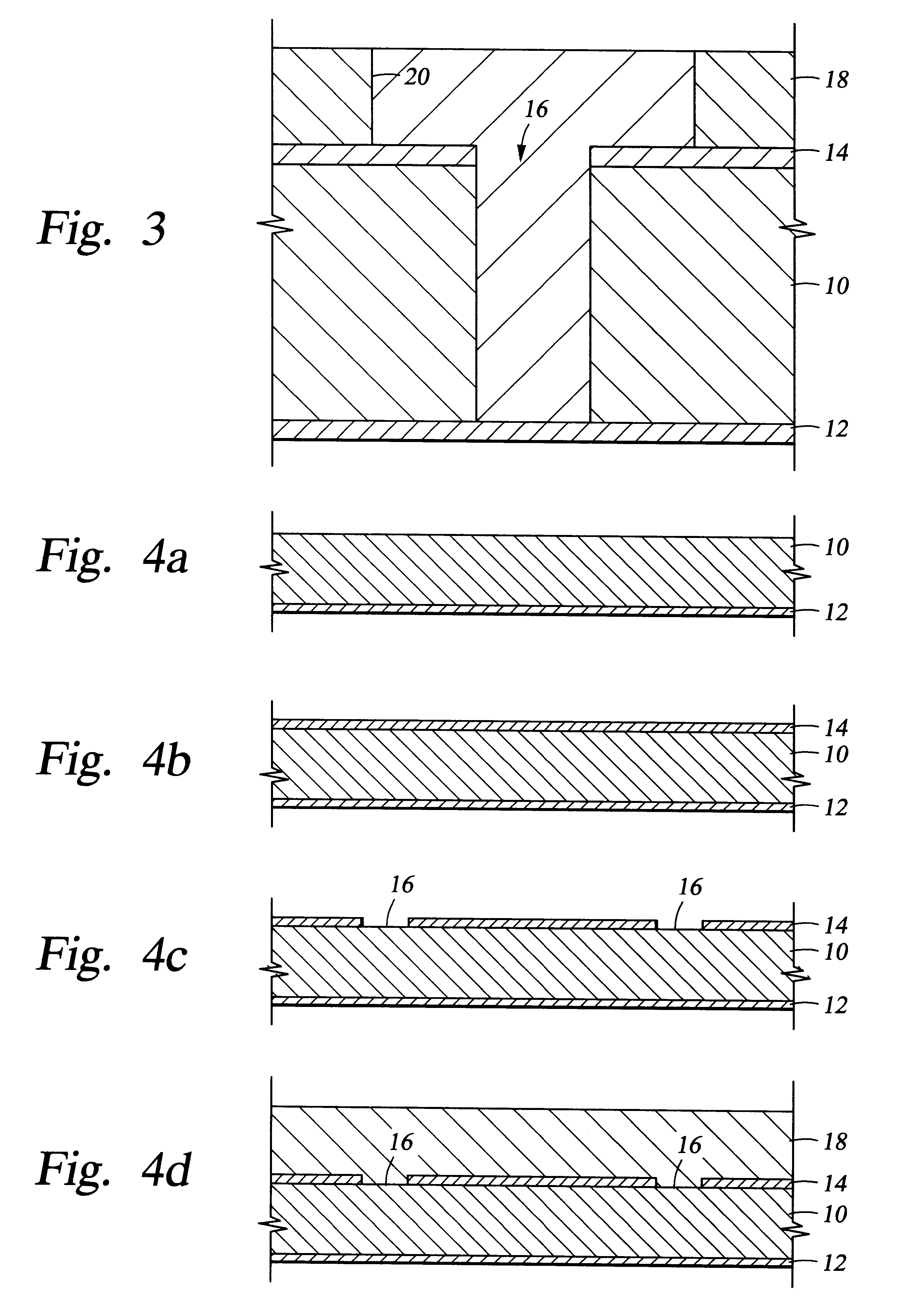

Integrated low K dielectrics and etch stops

InactiveUS6340435B1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenFluorocarbon

A method of depositing and etching dielectric layers having low dielectric constants and etch rates that vary by at least 3:1 for formation of horizontal interconnects. The amount of carbon or hydrogen in the dielectric layer is varied by changes in deposition conditions to provide low k dielectric layers that can replace etch stop layers or conventional dielectric layers in damascene applications. A dual damascene structure having two or more dielectric layers with dielectric constants lower than about 4 can be deposited in a single reactor and then etched to form vertical and horizontal interconnects by varying the concentration of a carbon:oxygen gas such as carbon monoxide. The etch gases for forming vertical interconnects preferably comprises CO and a fluorocarbon, and CO is preferably excluded from etch gases for forming horizontal interconnects.

Owner:APPLIED MATERIALS INC

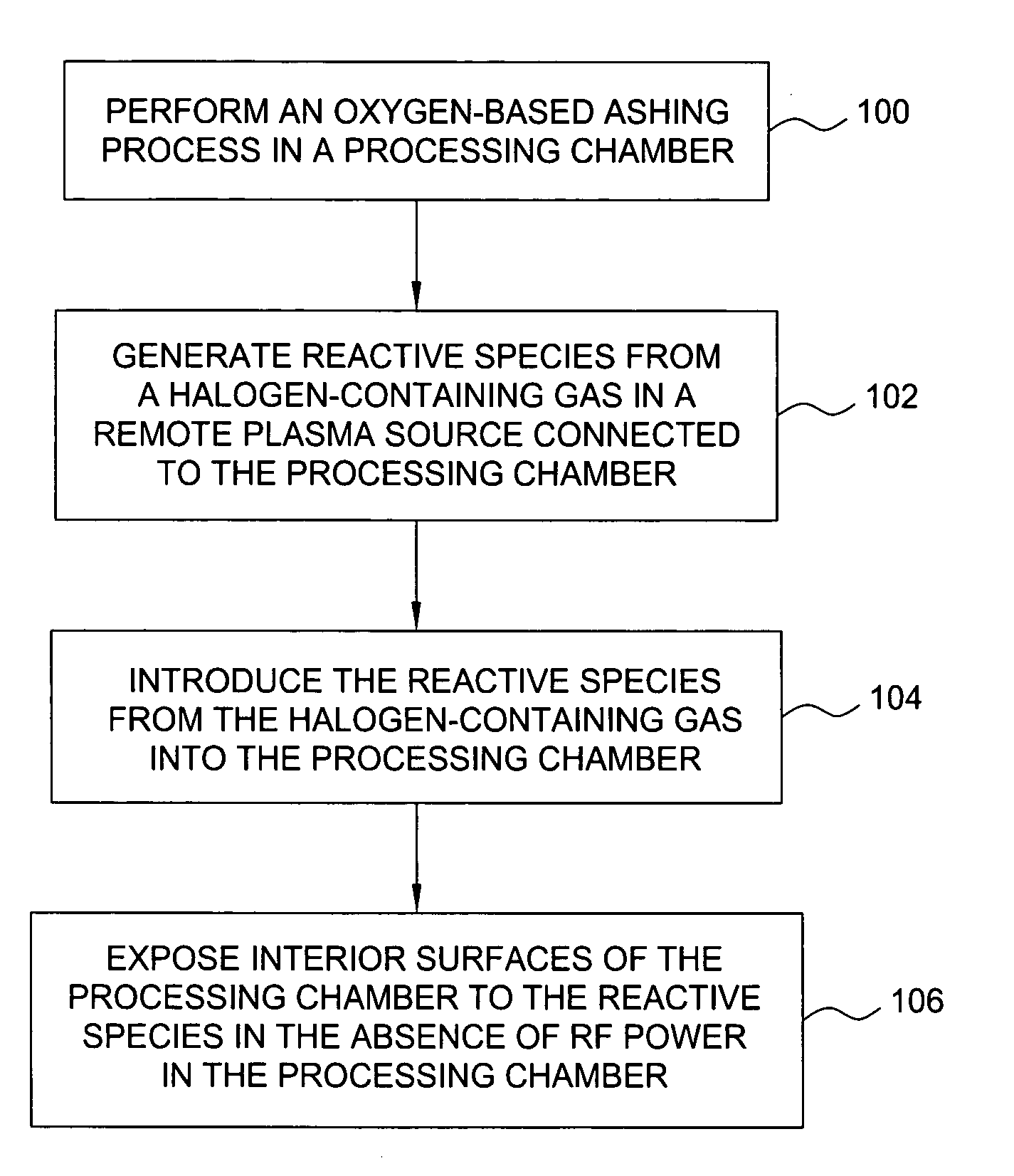

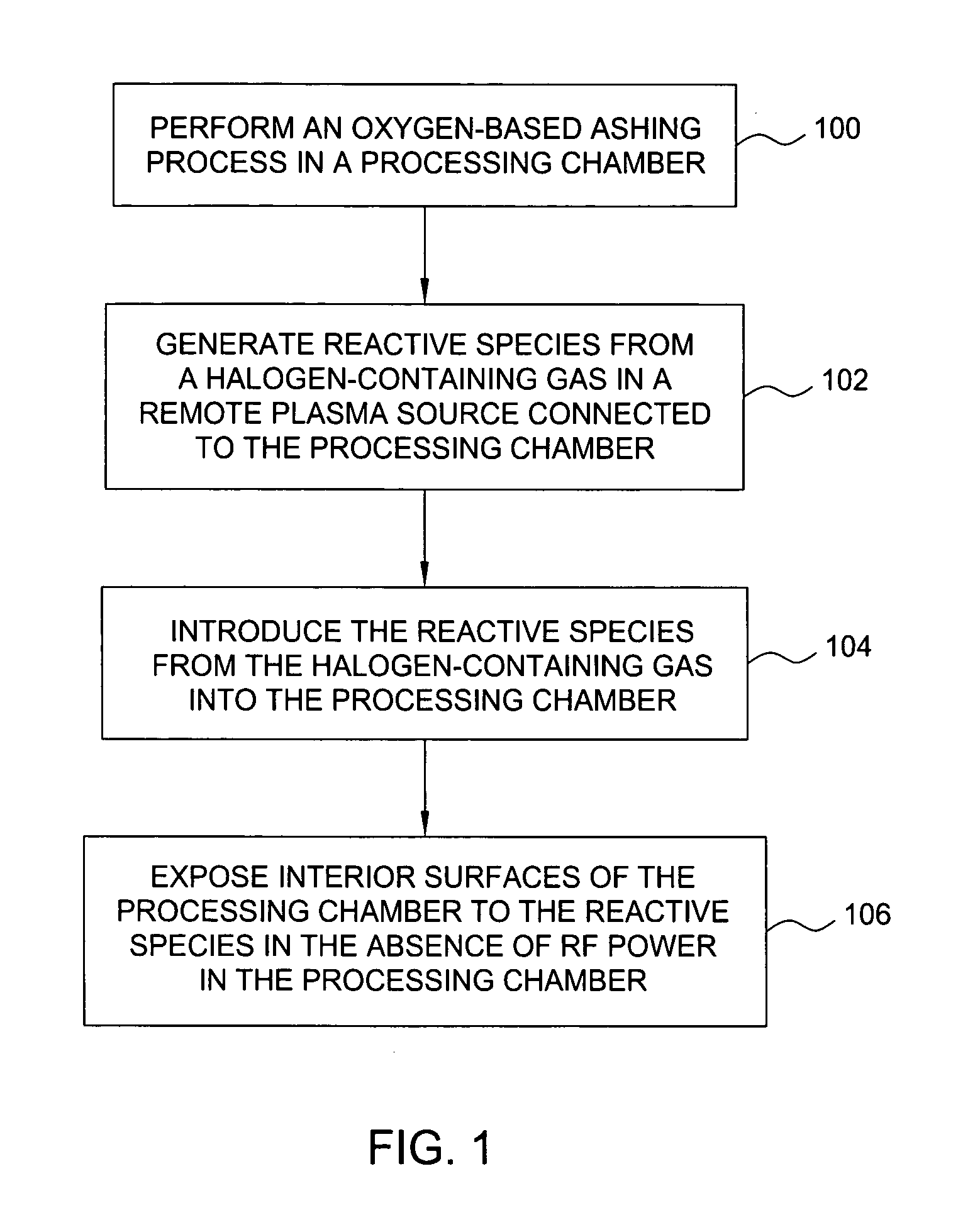

Enhancement of remote plasma source clean for dielectric films

Methods for cleaning semiconductor processing chambers used to process carbon-containing films, such as amorphous carbon films, barrier films comprising silicon and carbon, and low dielectric constant films including silicon, oxygen, and carbon are provided. The methods include using a remote plasma source to generate reactive species that clean interior surfaces of a processing chamber in the absence of RF power in the chamber. The reactive species are generated from an oxygen-containing gas, such as O2, and / or a halogen-containing gas, such as NF3. An oxygen-based ashing process may also be used to remove carbon deposits from the interior surfaces of the chamber before the chamber is exposed to the reactive species from the remote plasma source.

Owner:APPLIED MATERIALS INC

Post treatment of low k dielectric films

ActiveUS7018941B2Semiconductor/solid-state device manufacturingOptoelectronicsDielectric permittivity

A method of depositing a low dielectric constant film on a substrate and post-treating the low dielectric constant film is provided. The post-treatment includes rapidly heating the low dielectric constant film to a desired high temperature and then rapidly cooling the low dielectric constant film such that the low dielectric constant film is exposed to the desired high temperature for about five seconds or less. In one aspect, the post-treatment also includes exposing the low dielectric constant film to an electron beam treatment and / or UV radiation.

Owner:APPLIED MATERIALS INC

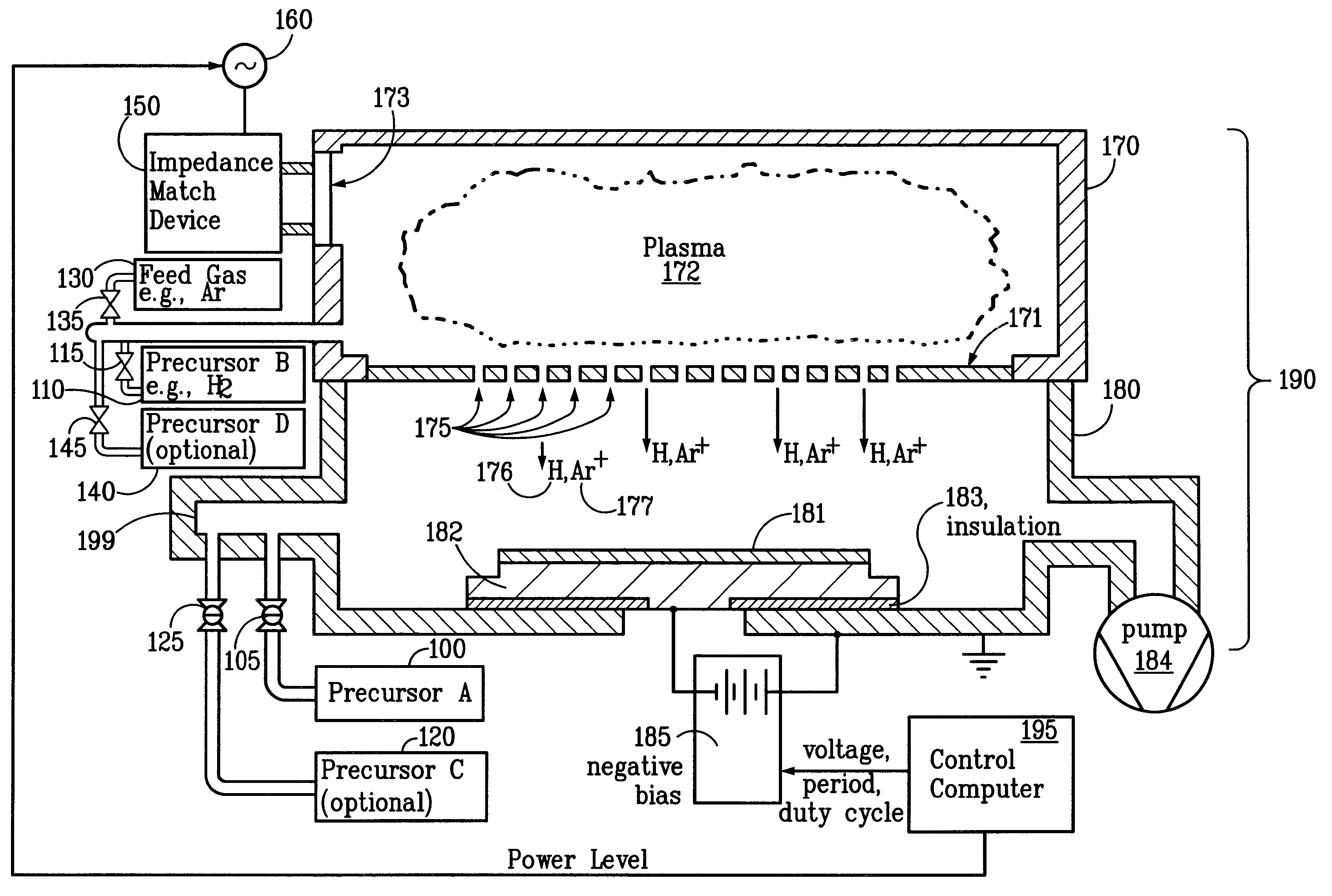

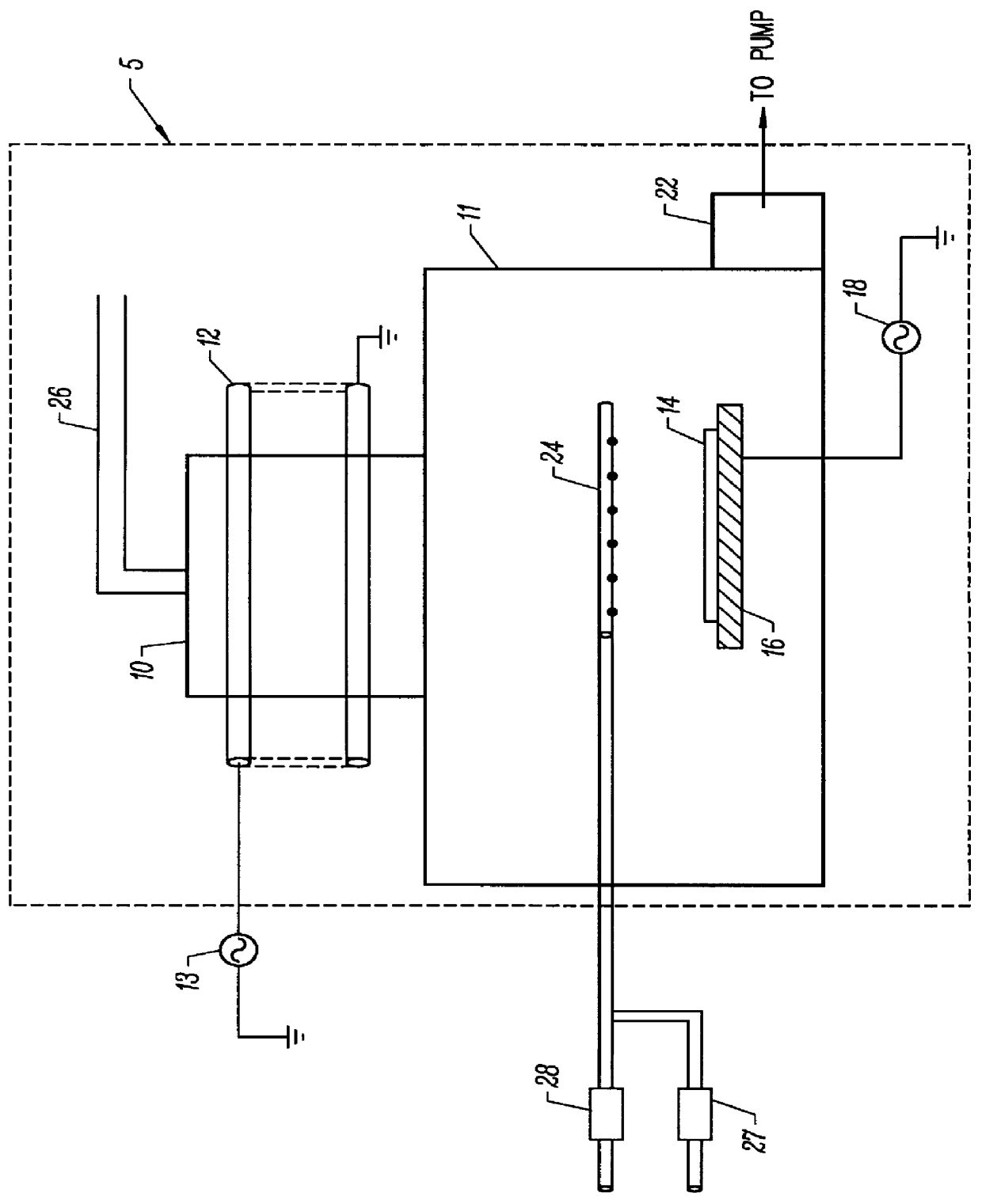

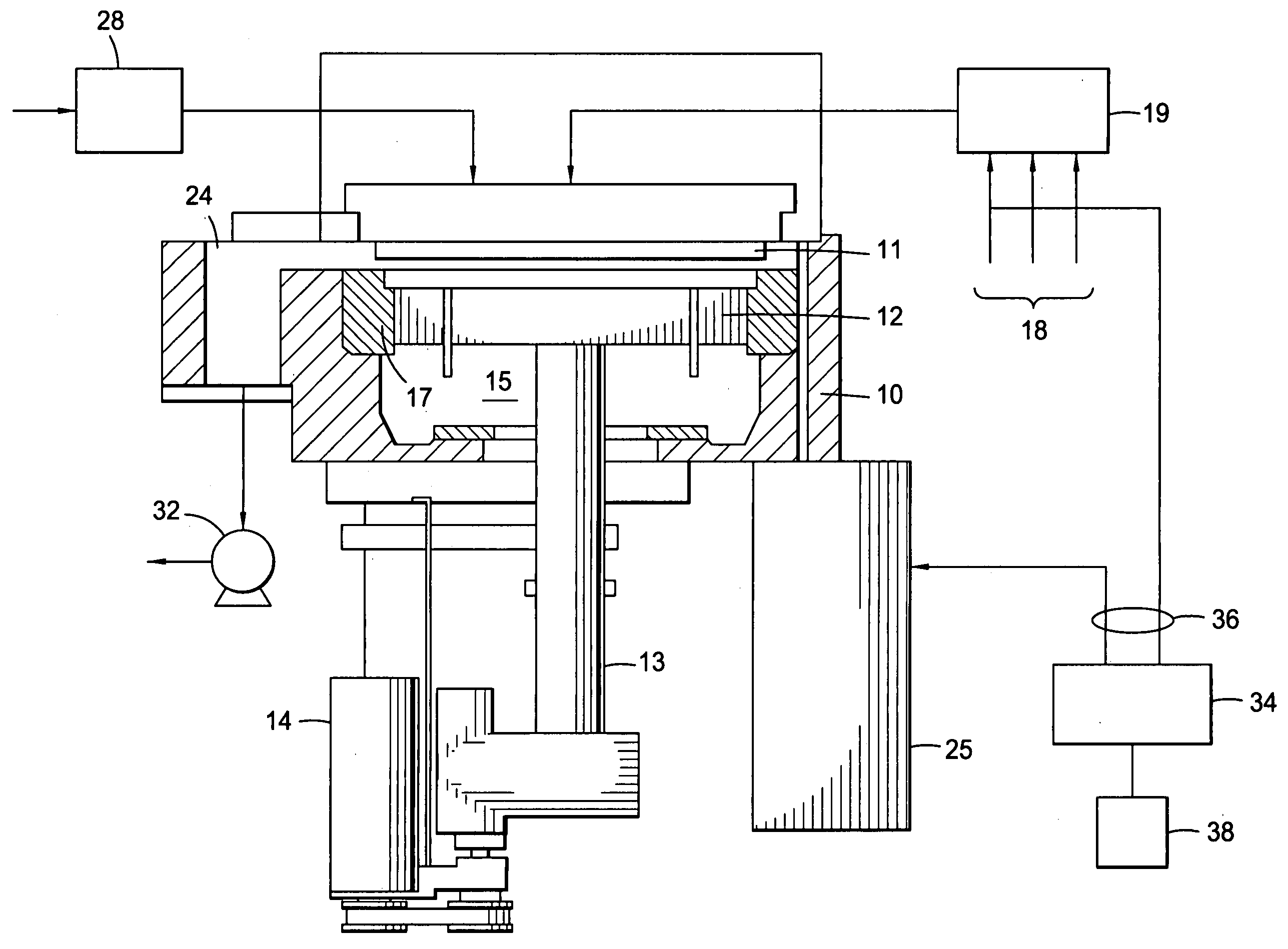

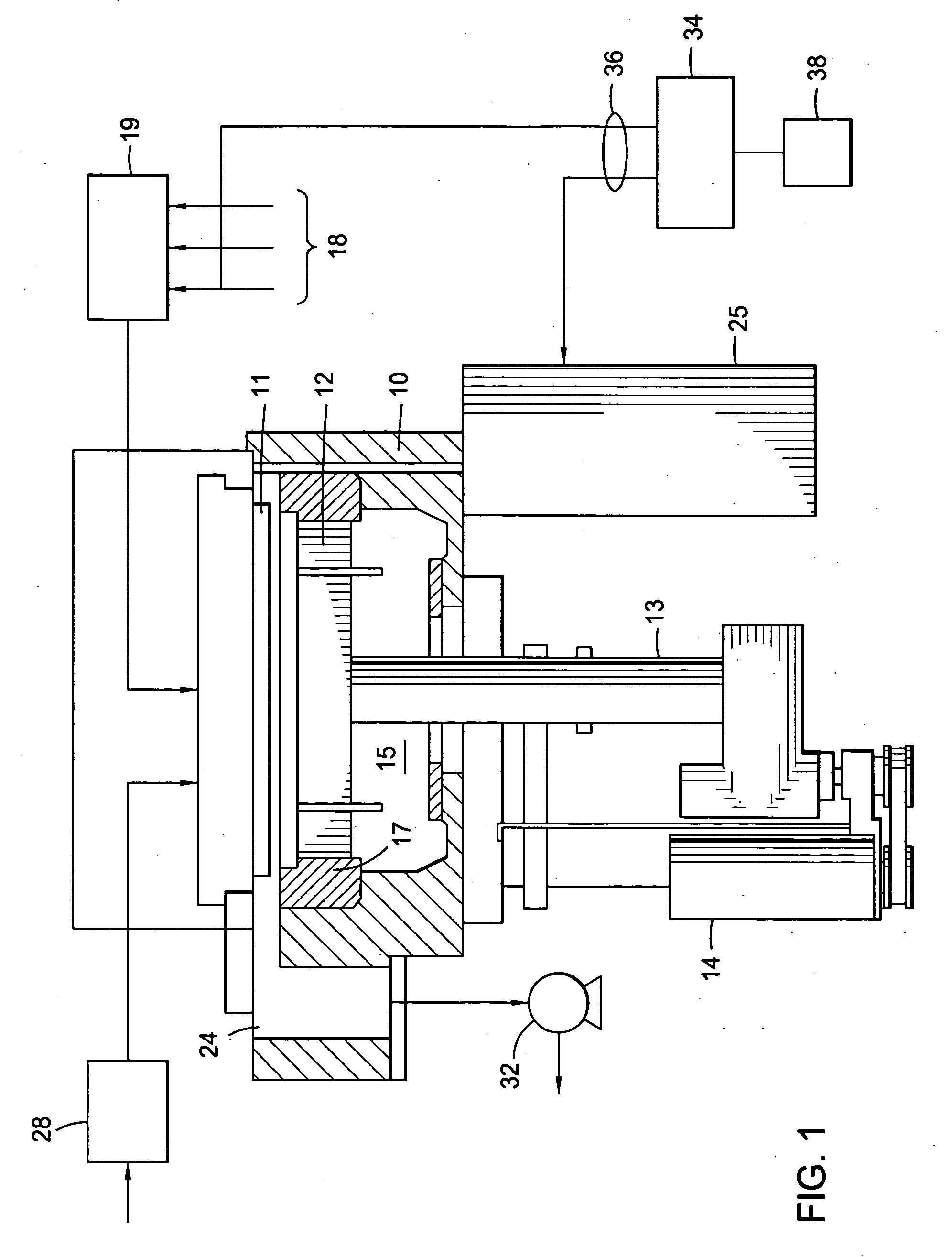

System and method for modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS20020104481A1Faster efficient meanSimple methodSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh densitySubject matter

The present invention relates to an enhanced sequential or non-sequential atomic layer deposition (ALD) apparatus and technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method; and, 4) providing a means of improved radical generation and delivery. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. [37 C.F.R. § 1.72(b)].

Owner:ANGSTRON SYST

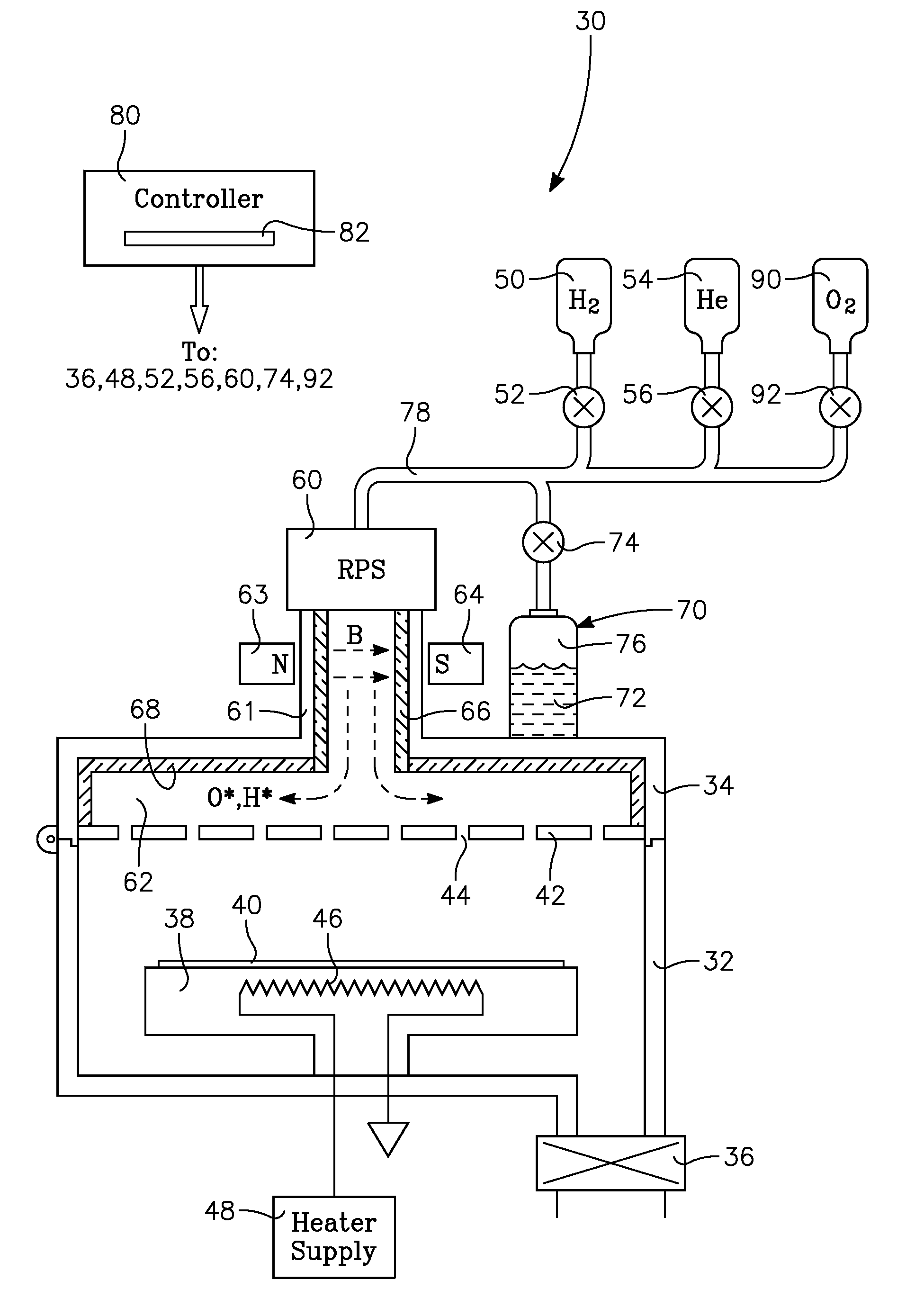

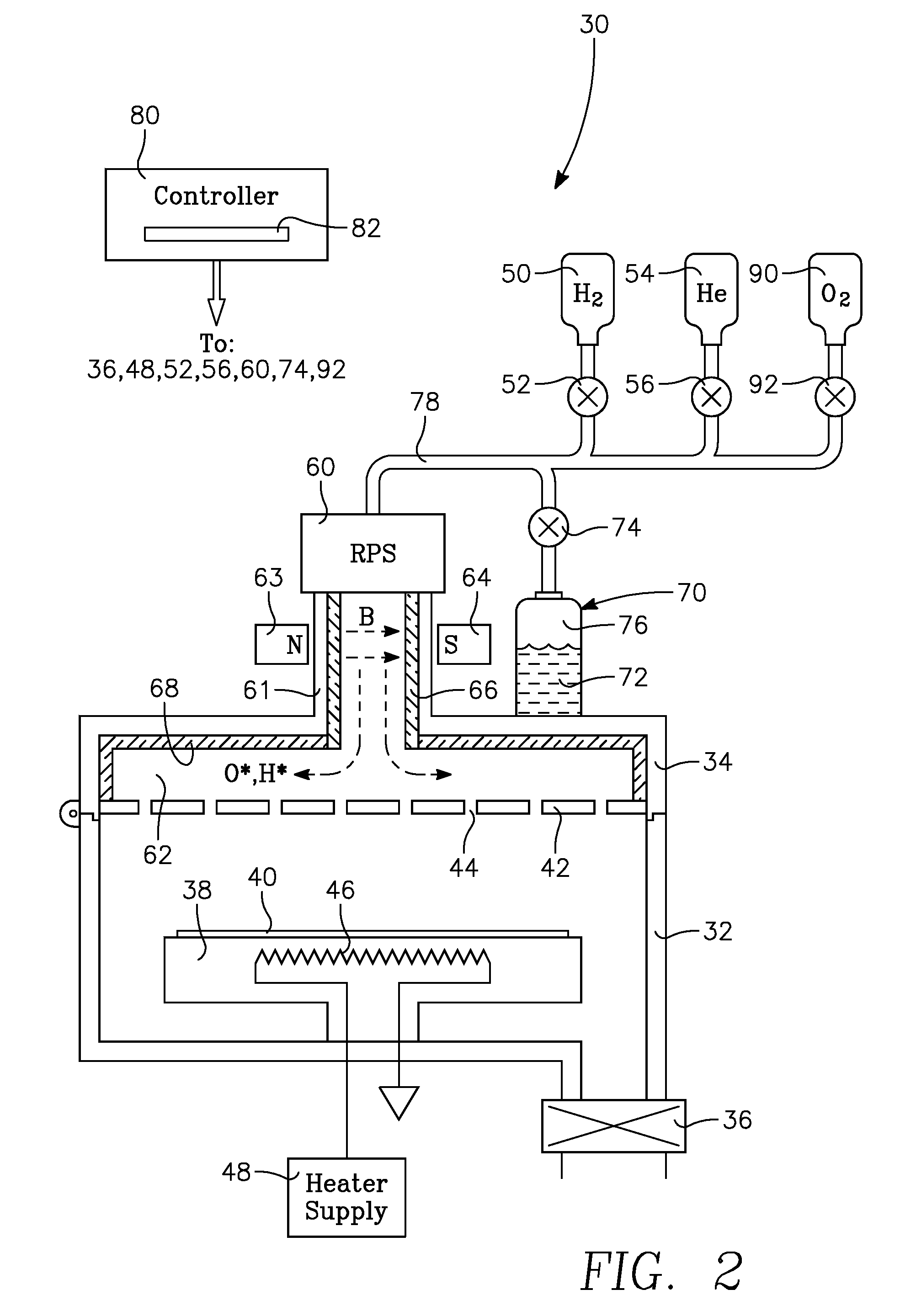

Remote Plasma Source for Pre-Treatment of Substrates Prior to Deposition

ActiveUS20090017227A1Electric discharge tubesSemiconductor/solid-state device manufacturingOxygenRefractory metals

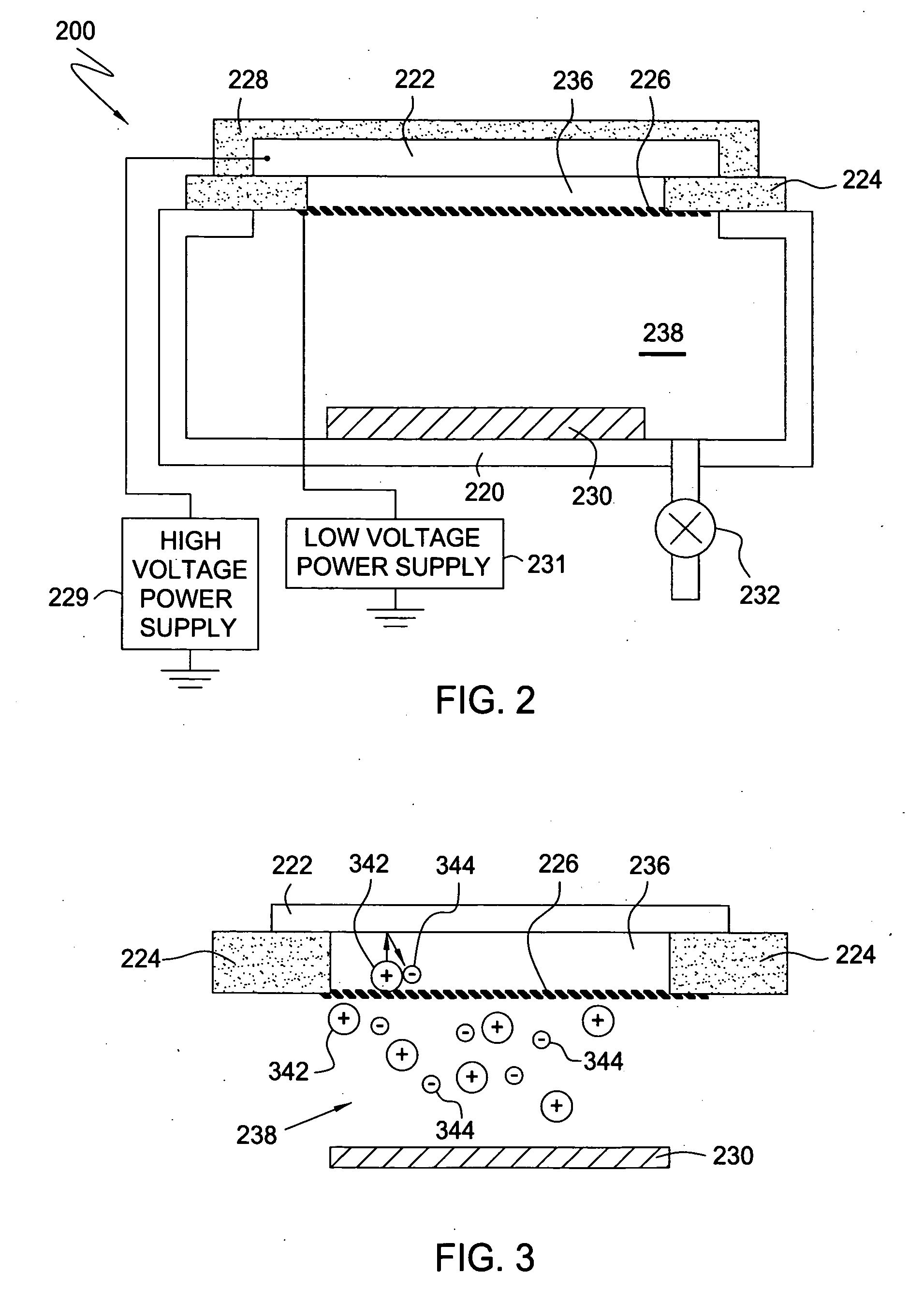

A plasma processing chamber particularly useful for pre-treating low-k dielectric films and refractory metal films subject to oxidation prior to deposition of other layers. A remote plasma source (RPS) excites a processing gas into a plasma and delivers it through a supply tube to a manifold in back of a showerhead faceplate. The chamber is configured for oxidizing and reducing plasmas in the same or different processes when oxygen and hydrogen are selectively supplied to the RPS. The supply tube and showerhead may be formed of dielectric oxides which may be passivated by a water vapor plasma from the remote plasma source. In one novel process, a protective hydroxide coating is formed on refractory metals by alternating neutral plasmas of hydrogen and oxygen.

Owner:APPLIED MATERIALS INC

Method for ion implanting insulator material to reduce dielectric constant

InactiveUS20050191828A1Low dielectric constantElectric discharge tubesSemiconductor/solid-state device manufacturingMicroelectronic circuitsIon implantation

An integrated microelectronic circuit has a multi-layer interconnect structure overlying the transistors consisting of stacked metal pattern layers and insulating layers separating adjacent ones of said metal pattern layers. Each of the insulating layers is a dielectric material with plural gas bubbles distributed within the volume of the dielectric material to reduce the dielectric constant of the material, the gas bubbles being formed by ion implantation of a gaseous species into the dielectric material.

Owner:APPLIED MATERIALS INC

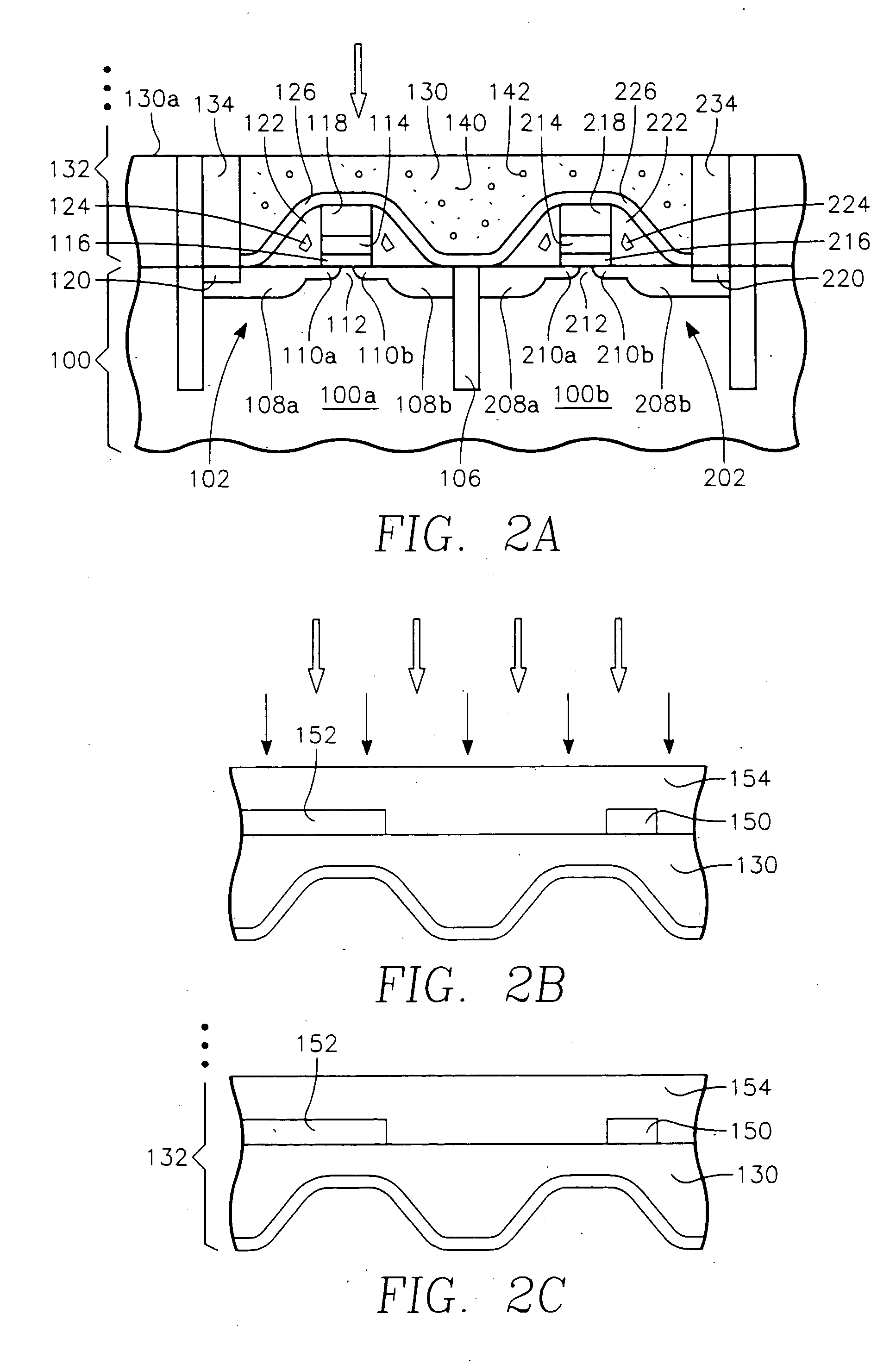

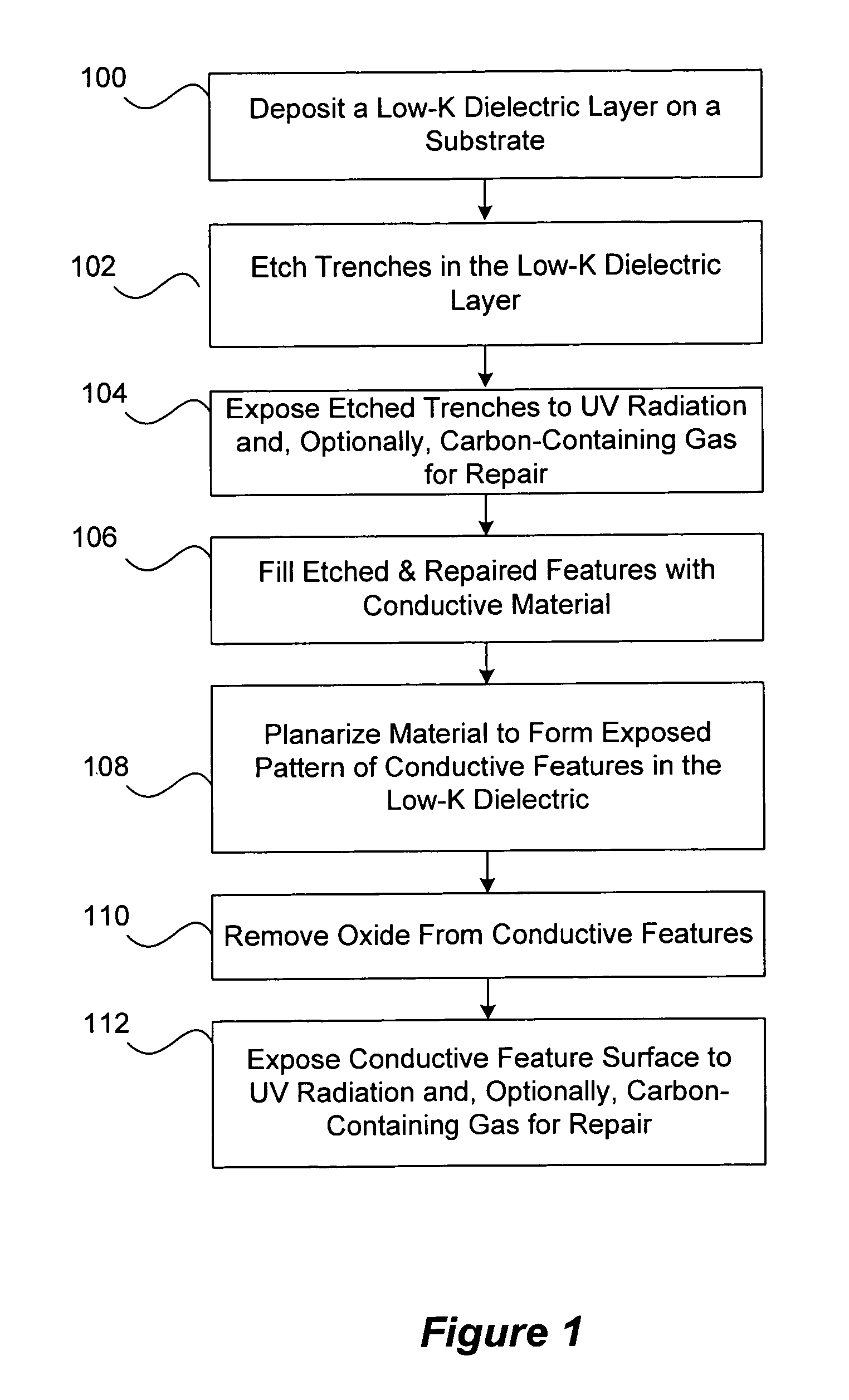

UV treatment for carbon-containing low-k dielectric repair in semiconductor processing

Owner:NOVELLUS SYSTEMS

Method to minimize wet etch undercuts and provide pore sealing of extreme low k (k<2.5) dielectrics

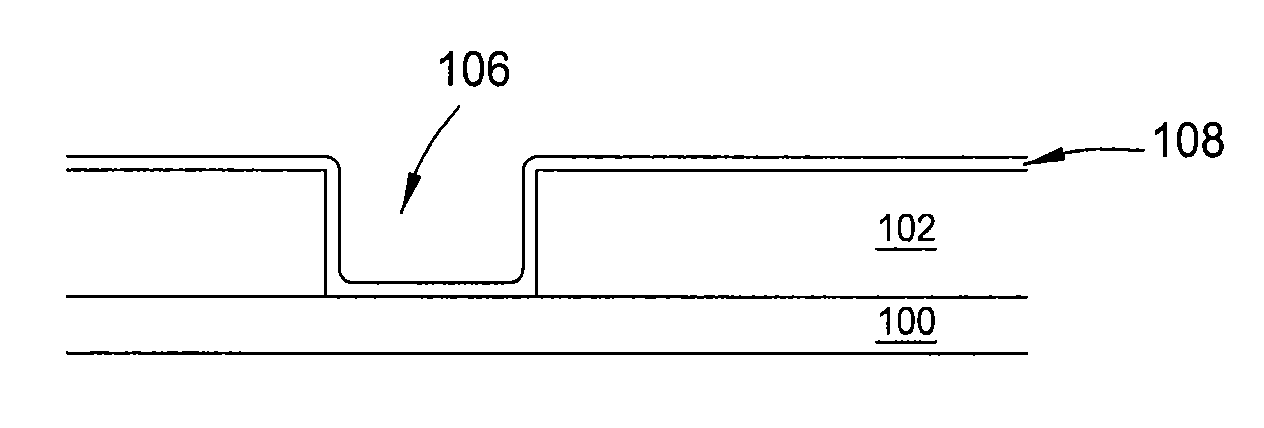

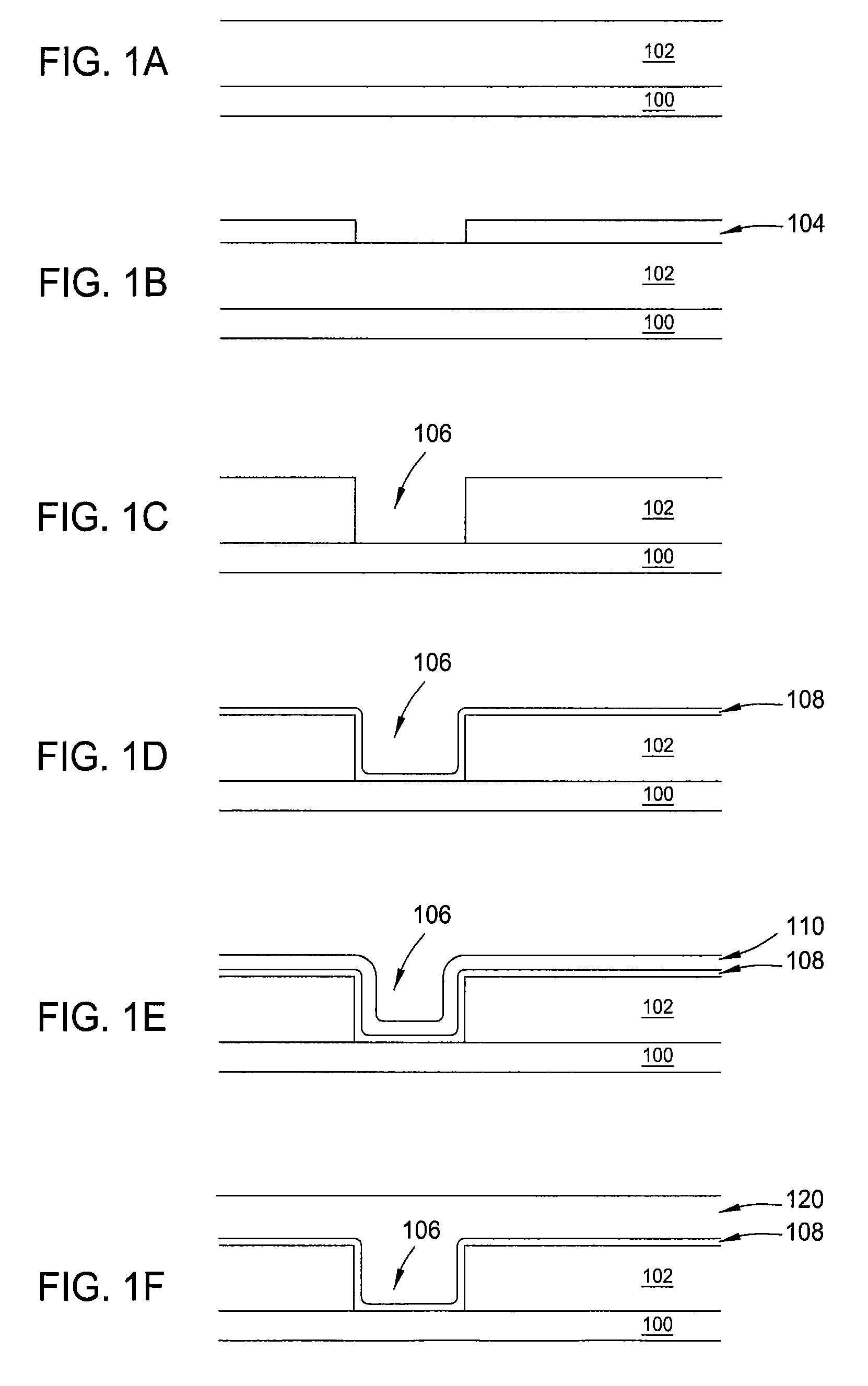

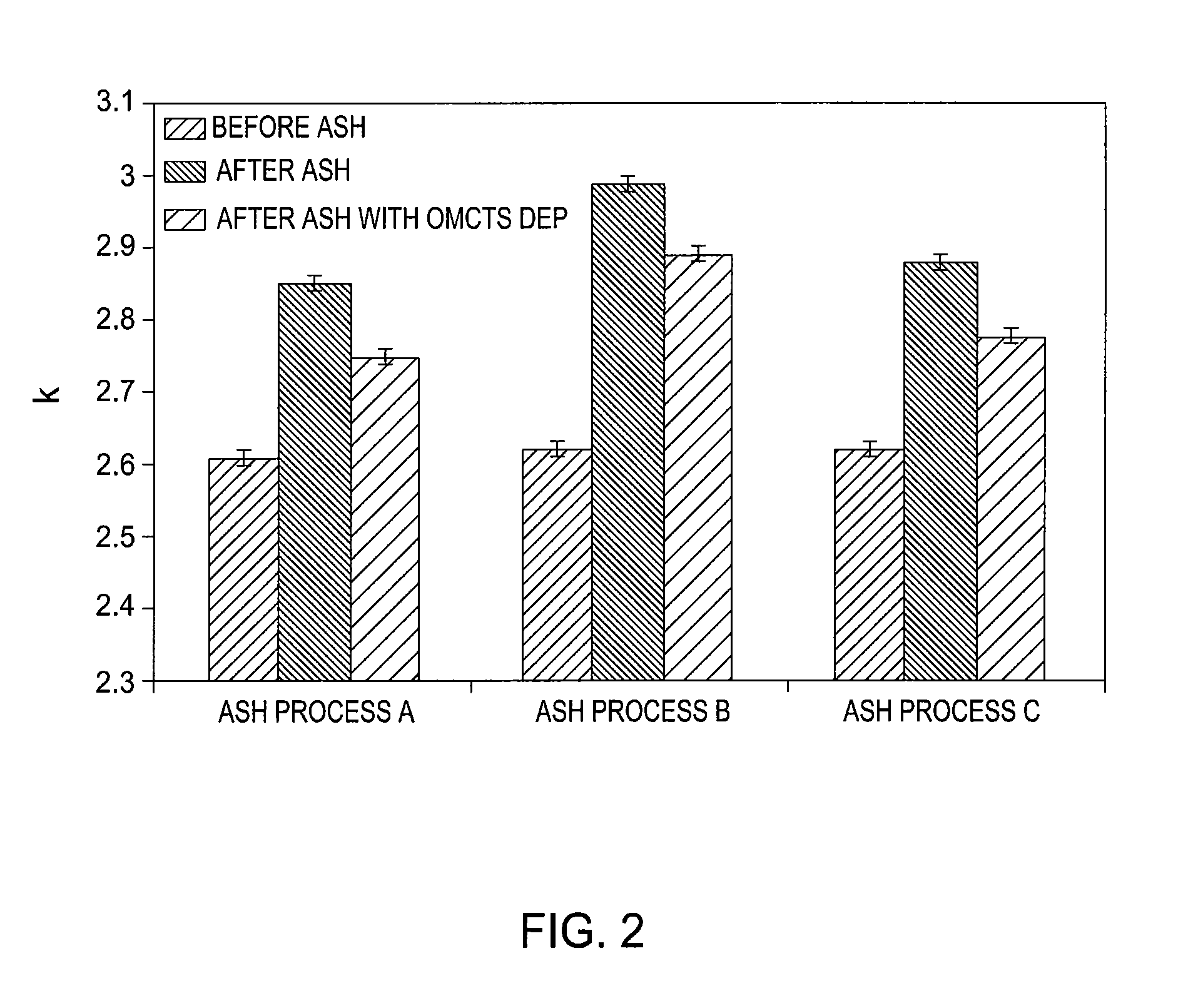

ActiveUS8445075B2Constant ratePrevents undercuts and CD lossVacuum evaporation coatingPretreated surfacesNitrogenThin layer

Methods of processing films on substrates are provided. In one aspect, the methods comprise treating a patterned low dielectric constant film after a photoresist is removed from the film by depositing a thin layer comprising silicon, carbon, and optionally oxygen and / or nitrogen on the film. The thin layer provides a carbon-rich, hydrophobic surface for the patterned low dielectric constant film. The thin layer also protects the low dielectric constant film from subsequent wet cleaning processes and penetration by precursors for layers that are subsequently deposited on the low dielectric constant film.

Owner:APPLIED MATERIALS INC

Plasma curing process for porous silica thin film

InactiveUS6558755B2Low dielectric constantHigh elastic modulusSilicaSemiconductor/solid-state device manufacturingSilicon dioxideHeat treated

Low dielectric constant films with improved elastic modulus. The method of making such coatings involves providing a porous network coating produced from a resin containing at least 2 Si-H groups and plasma curing the coating to convert the coating into porous silica. Plasma curing of the network coating yields a coating with improved modulus, but with a higher dielectric constant. The costing is plasma cured for between about 15 and about 120 seconds at a temperature less than or about 350° C. The plasma cured coating can optionally be annealed. Rapid thermal processing (RTP) of the plasma cured coating reduces the dielectric constant of the coating while maintaining an improved elastic modulus as compared to the plasma cured porous network coating. The annealing temperature is typically loss than or about 475° C., and the annealing time is typically no more than or about 180 seconds. The annealed, plasma cured coating has a dielectric constant in the range of from about 1.1 to about 2.4 and an improved elastic modulus.

Owner:AXCELIS TECHNOLOGIES +1

Method for fabricating an ultralow dielectric constant material as an intralevel or interlevel dielectric in a semiconductor device and electronic device made

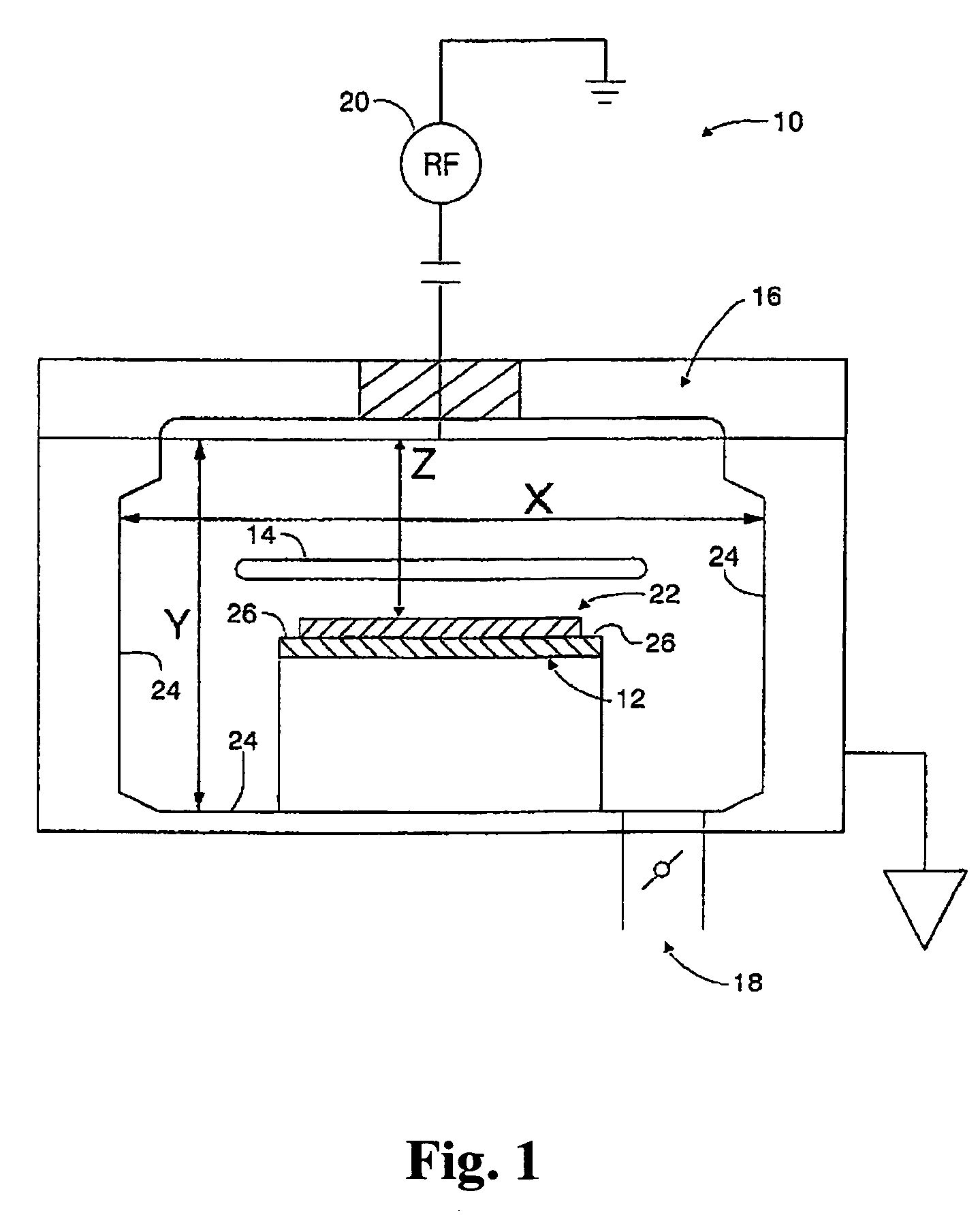

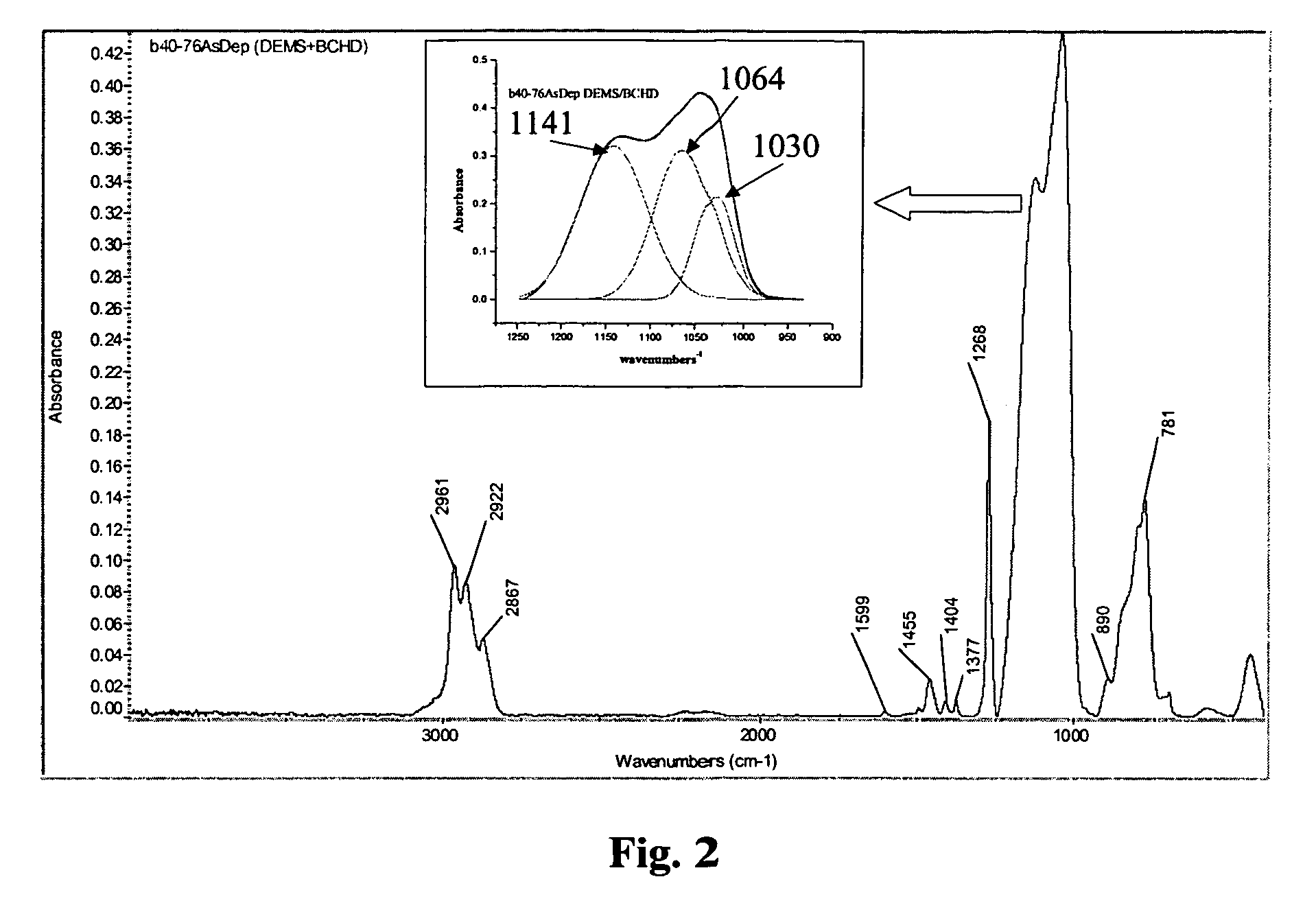

InactiveUS7049247B2Low costReduce tensile stressSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseParallel plate

A method for fabricating a thermally stable ultralow dielectric constant film comprising Si, C, O and H atoms in a parallel plate chemical vapor deposition process utilizing a plasma enhanced chemical vapor deposition (“PECVD”) process is disclosed. Electronic devices containing insulating layers of thermally stable ultralow dielectric constant materials that are prepared by the method are further disclosed. To enable the fabrication of a thermally stable ultralow dielectric constant film, specific precursor materials are used, such as, silane derivatives, for instance, diethoxymethylsilane (DEMS) and organic molecules, for instance, bicycloheptadiene and cyclopentene oxide.

Owner:INTEL CORP

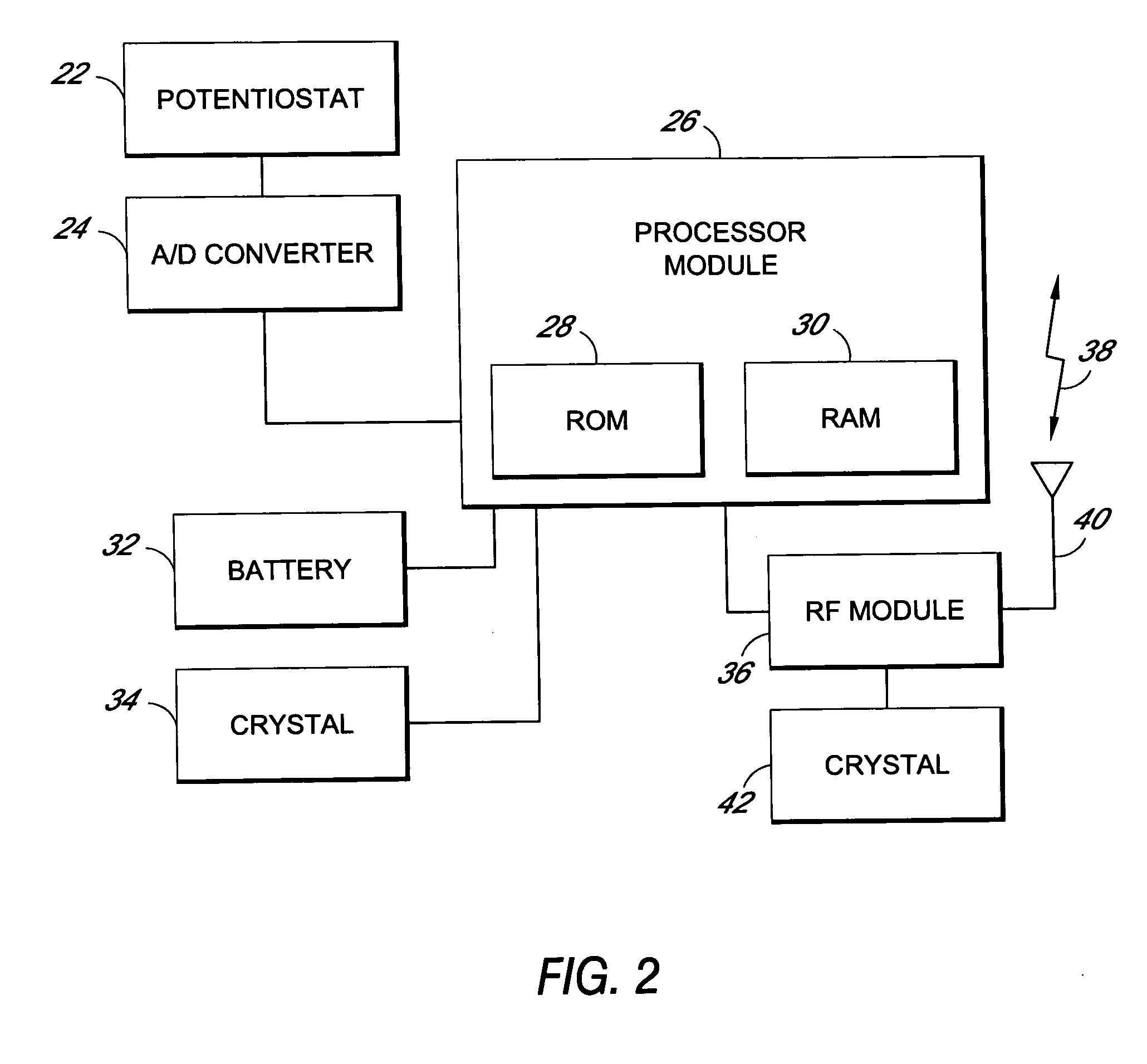

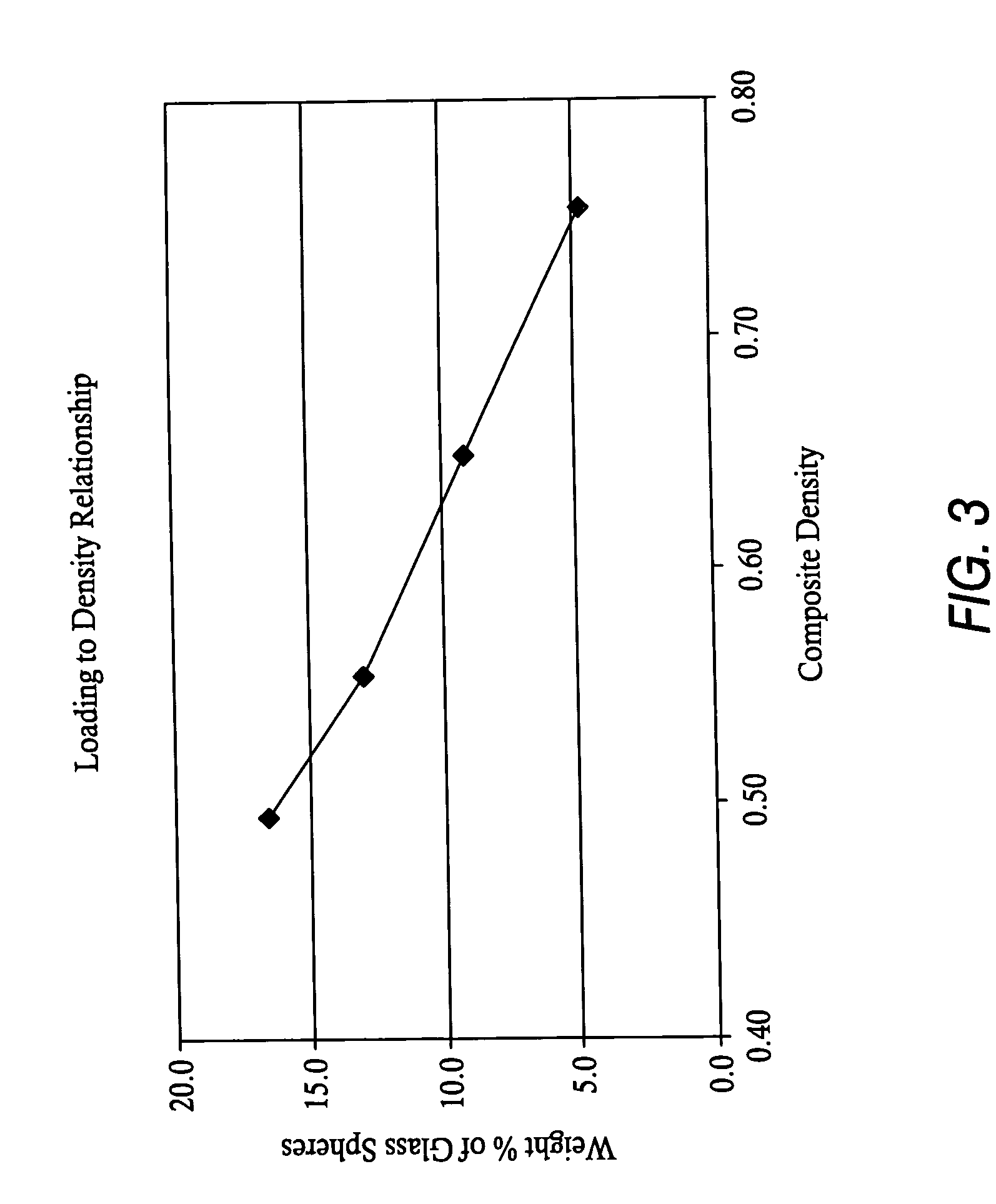

Composite material for implantable device

Devices suitable for implantation in a body of a host and systems and methods for their manufacture are provided. The implantable devices include a composite material formed at least from a matrix material and hollow gas-filled beads. In preferred embodiments, the composite material includes a polymeric matrix mixed with hollow air-filled glass beads, which are mixed and cured to form at least a portion of the body of the implantable device. Implantable devices including this composite material have decreased weight and / or overall density as compared to implantable devices without the beads incorporated therein, which is believed to improve the acceptance and function of the implantable device in vivo. Additionally, implantable devices concerned with transmitting and receiving via RF are believed to achieve improved RF performance due to a reduced dielectric constant provided by the incorporation of beads within the composite material.

Owner:DEXCOM

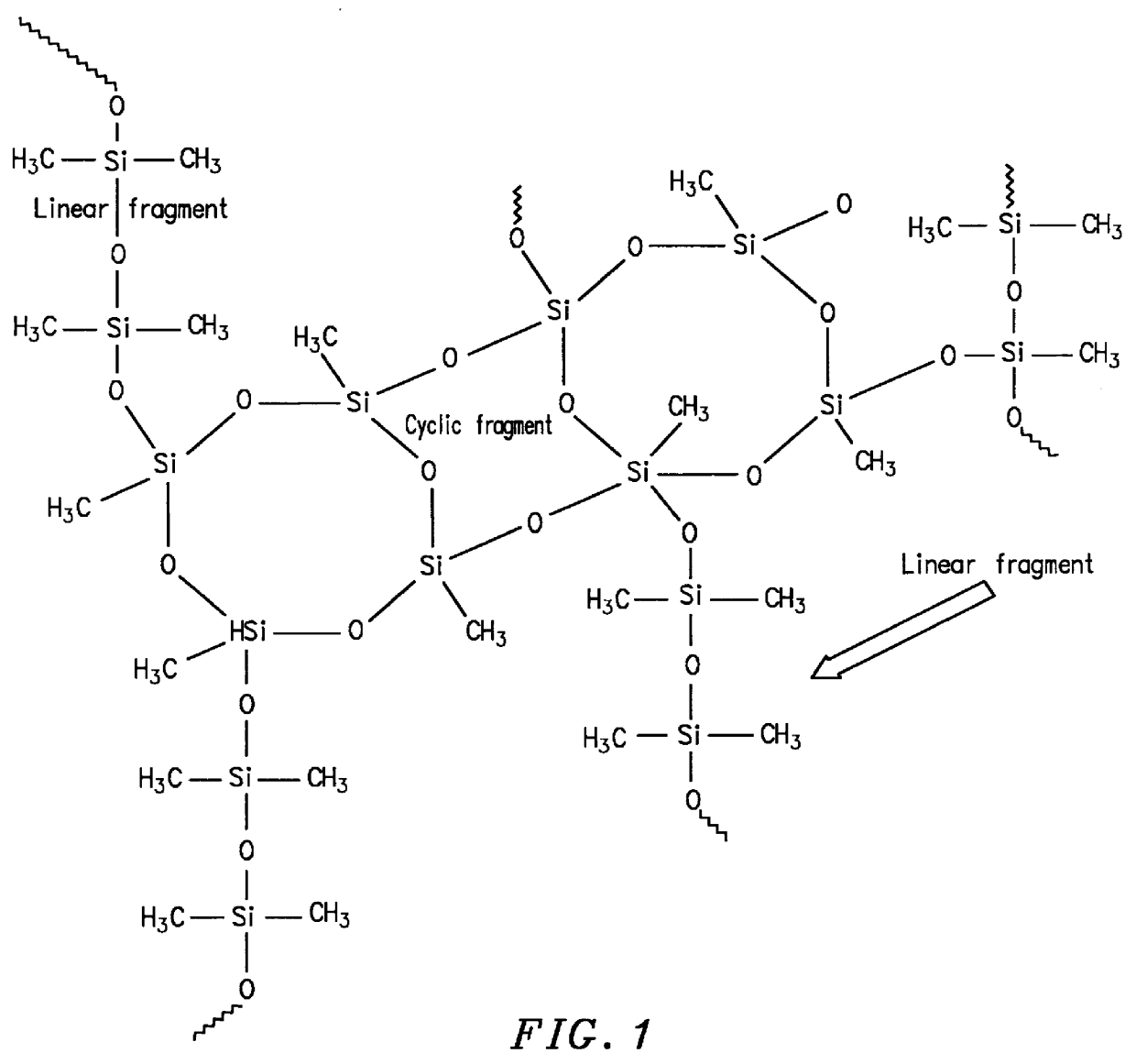

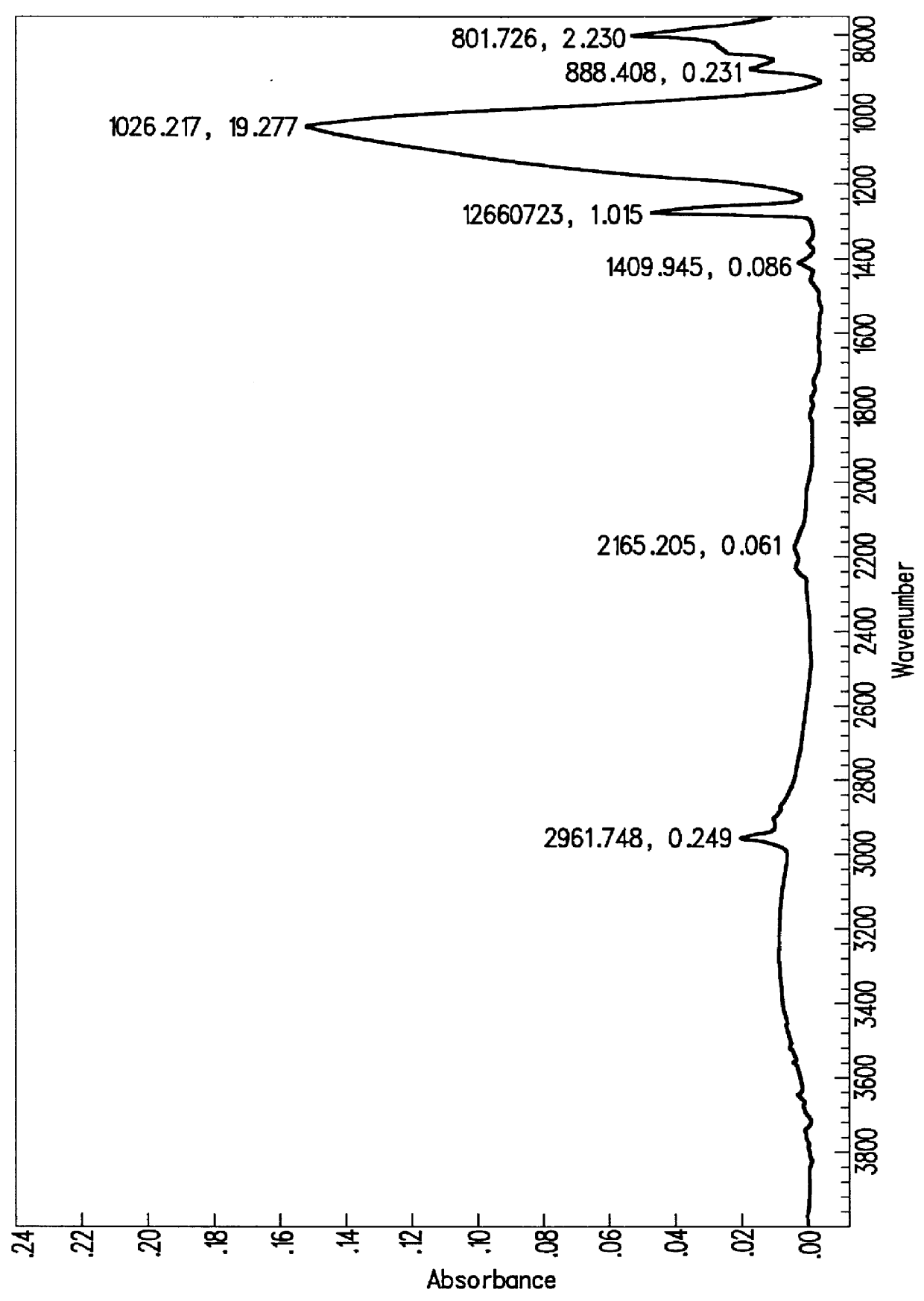

Method of making low kappa dielectric inorganic/organic hybrid films

InactiveUS6068884AImprove thermal stabilityLow dielectric constantLayered productsSemiconductor/solid-state device detailsThermal chemical vapor depositionSemiconductor

A method of depositing a dielectric film exhibiting a low dielectric constant in a semiconductor and / or integrated circuit by chemical vapor deposition (CVD) is provided. The film is deposited using an organosilicon precursor in a manner such that the film is comprised of a backbone made substantially of Si-O-Si or Si-N-Si groups with organic side groups attached to the backbone.

Owner:APPLIED MATERIALS INC

Continuous method for depositing a film by modulated ion-induced atomic layer deposition (MII-ALD)

InactiveUS6416822B1Faster efficient meanSimple methodPretreated surfacesSemiconductor/solid-state device manufacturingHigh densityVolumetric Mass Density

The present invention relates to an enhanced non-sequential atomic layer deposition (ALD) technique suitable for deposition of barrier layers, adhesion layers, seed layers, low dielectric constant (low-k) films, high dielectric constant (high-k) films, and other conductive, semi-conductive, and non-conductive films. This is accomplished by 1) providing a non-thermal or non-pyrolytic means of triggering the deposition reaction; 2) providing a means of depositing a purer film of higher density at lower temperatures; and, 3) providing a faster and more efficient means of modulating the deposition sequence and hence the overall process rate resulting in an improved deposition method.

Owner:NOVELLUS SYSTEMS

Sealing pores of low-k dielectrics using CxHy

A semiconductor method of manufacturing involving porous and / or carbon containing, low-k dielectrics is provided. The method includes forming a hydrocarbon of the general composition CxHy on the surface of the low-k dielectric. The hydrocarbon layer includes depositing a precursor material, preferably C2H4 or (CH3)2CHC6H6CH3. In accordance with embodiments of this invention, carbon diffuses into the low-k dielectric, thereby reducing carbon depletion damage caused by plasma processing or etching. Surface dielectric pores damaged by plasma processing are also repaired by sealing them with the CXHY layer. Embodiments include semiconductor devices, such as devices having damascene interconnect structures, manufacturing using methods provided.

Owner:TAIWAN SEMICON MFG CO LTD

Deposition of low dielectric constant films by N2O addition

InactiveUS20050214457A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingOxygenHydrocarbon

A method for depositing a low dielectric constant film includes providing a gas mixture including a cyclic organosiloxane and N2O as an oxidizing gas to a chamber and applying RF power to the gas mixture to deposit a low dielectric constant film. The gas mixture may also include oxygen and / or a linear hydrocarbon. In one aspect, the gas mixture includes N2O and oxygen as oxidizing gases, and a ratio of the flow rate of the N2O to a total flow rate of the N2O and the oxygen is between about 0.1 and about 0.5.

Owner:APPLIED MATERIALS INC

Ultraviolet assisted pore sealing of porous low k dielectric films

InactiveUS20060105566A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingAtmospheric airCarbonization

Processes for sealing porous low k dielectric film generally comprises exposing the porous surface of the porous low k dielectric film to ultraviolet (UV) radiation at intensities, times, wavelengths and in an atmosphere effective to seal the porous dielectric surface by means of carbonization, oxidation, and / or film densification. The surface of the surface of the porous low k material is sealed to a depth less than or equal to about 20 nanometers, wherein the surface is substantially free of pores after the UV exposure.

Owner:AXCELIS TECHNOLOGIES

Using polydentate ligands for sealing pores in low-k dielectrics

InactiveUS7163900B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingCross-linkDerivatization

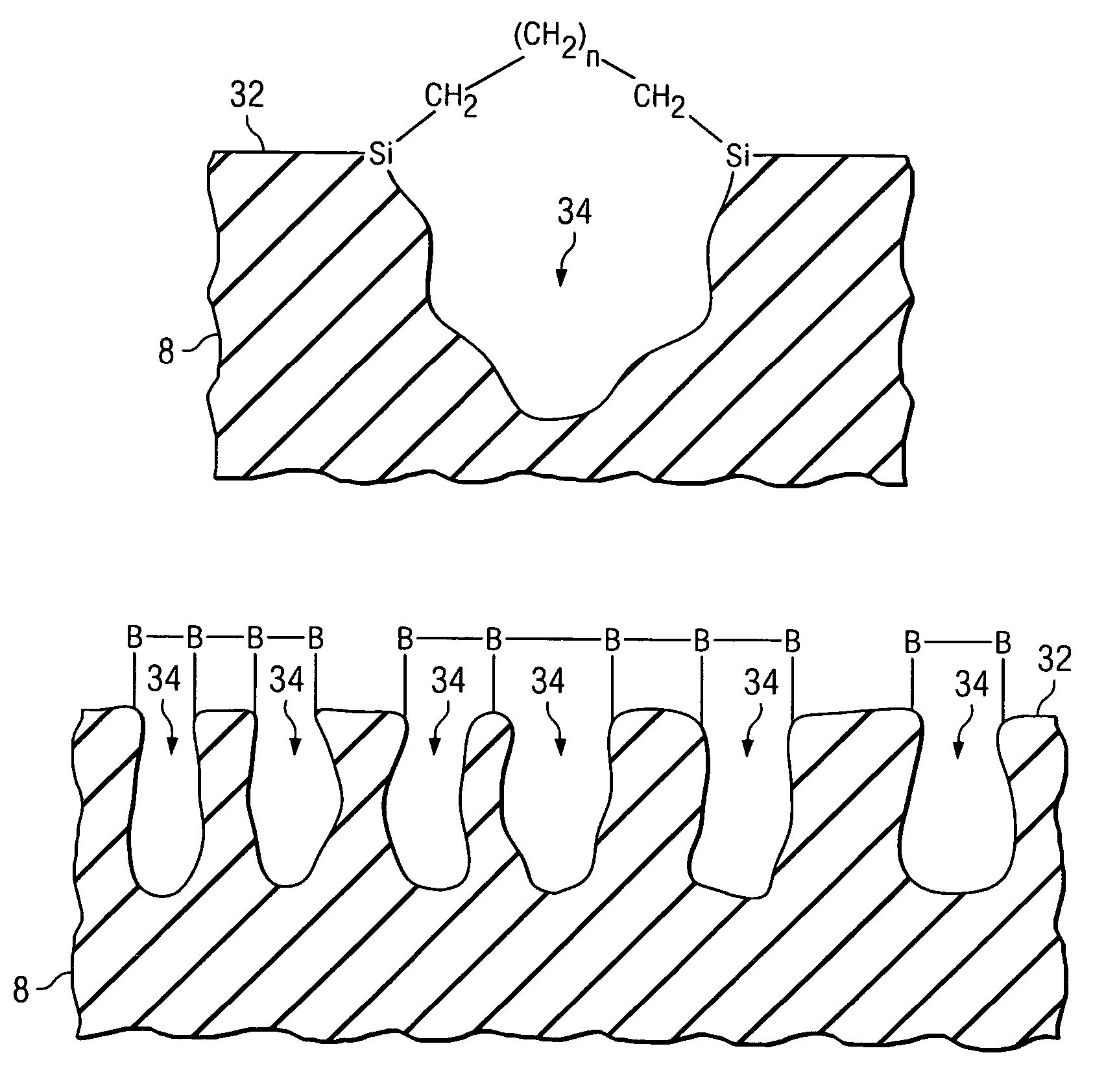

In preferred embodiments, a polydentate pore-sealing ligand is used to seal or repair pores damaged by plasma processing. The polydentate ligand includes bidentate ligands corresponding to the general formula X—CH2—(CH2)n—CH2—X or X—Si(CH3)2—(CH2)n—Si(CH3)2—X. The polydentate ligand also includes tridendate ligands corresponding to the general formula X—CH2—(CH2)m(CXH)(CH2)o—CH2—X or X—Si(CH3)2—(CH2)m(CXH)(CH2)o—Si(CH3)2—X. Alternative embodiments may include single or multiply branched polydentate ligands. Other embodiments include ligands that are cross-linked after attachment to the dielectric. Still other embodiments include a derivatization reaction wherein silanol groups formed by plasma damage are removed and favorable dielectric properties are restored.

Owner:INFINEON TECH AG

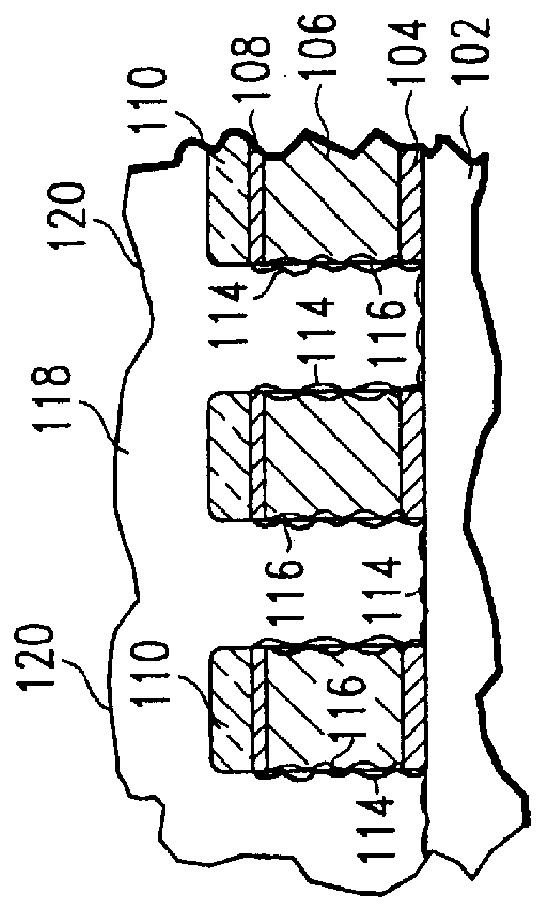

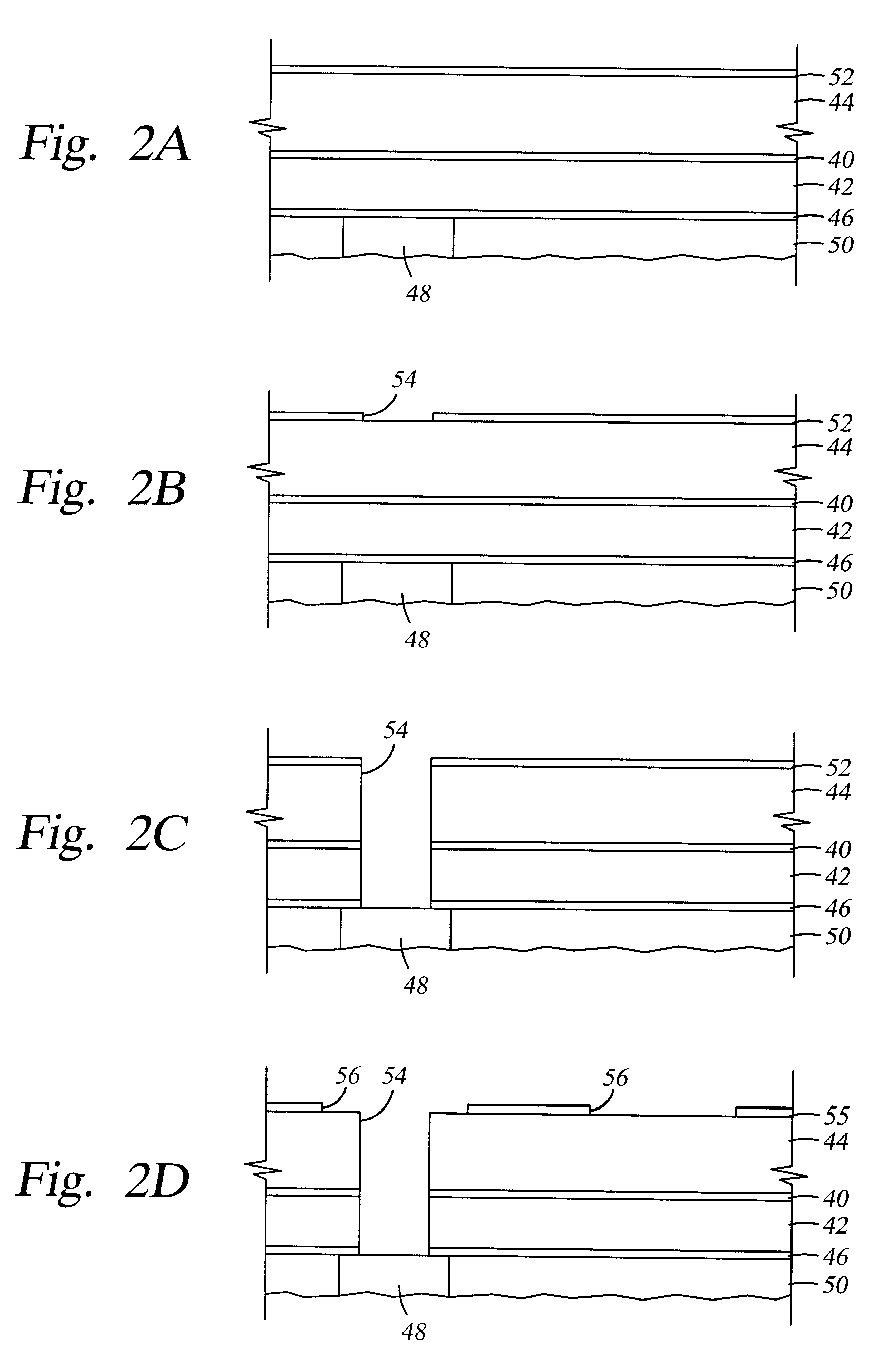

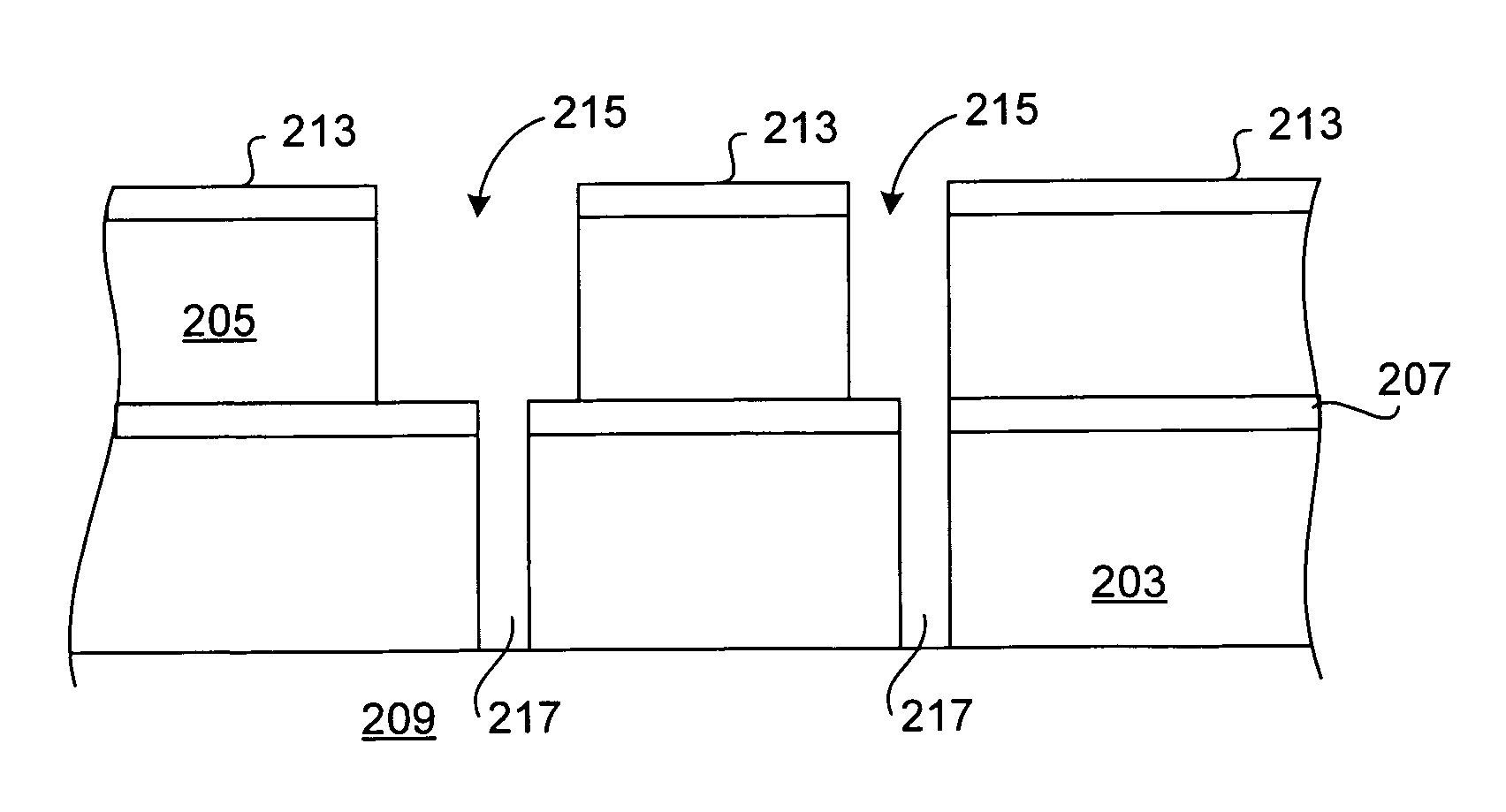

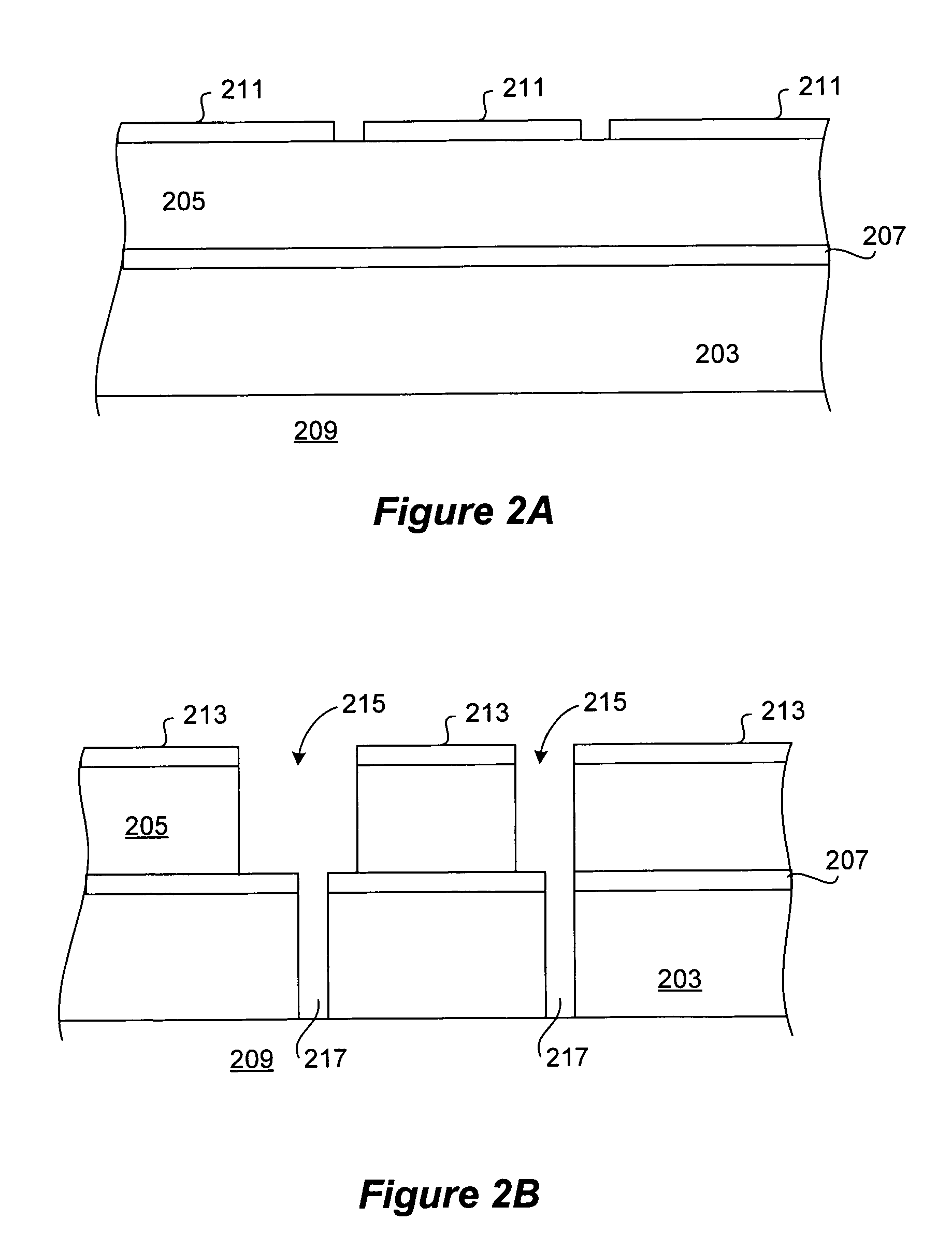

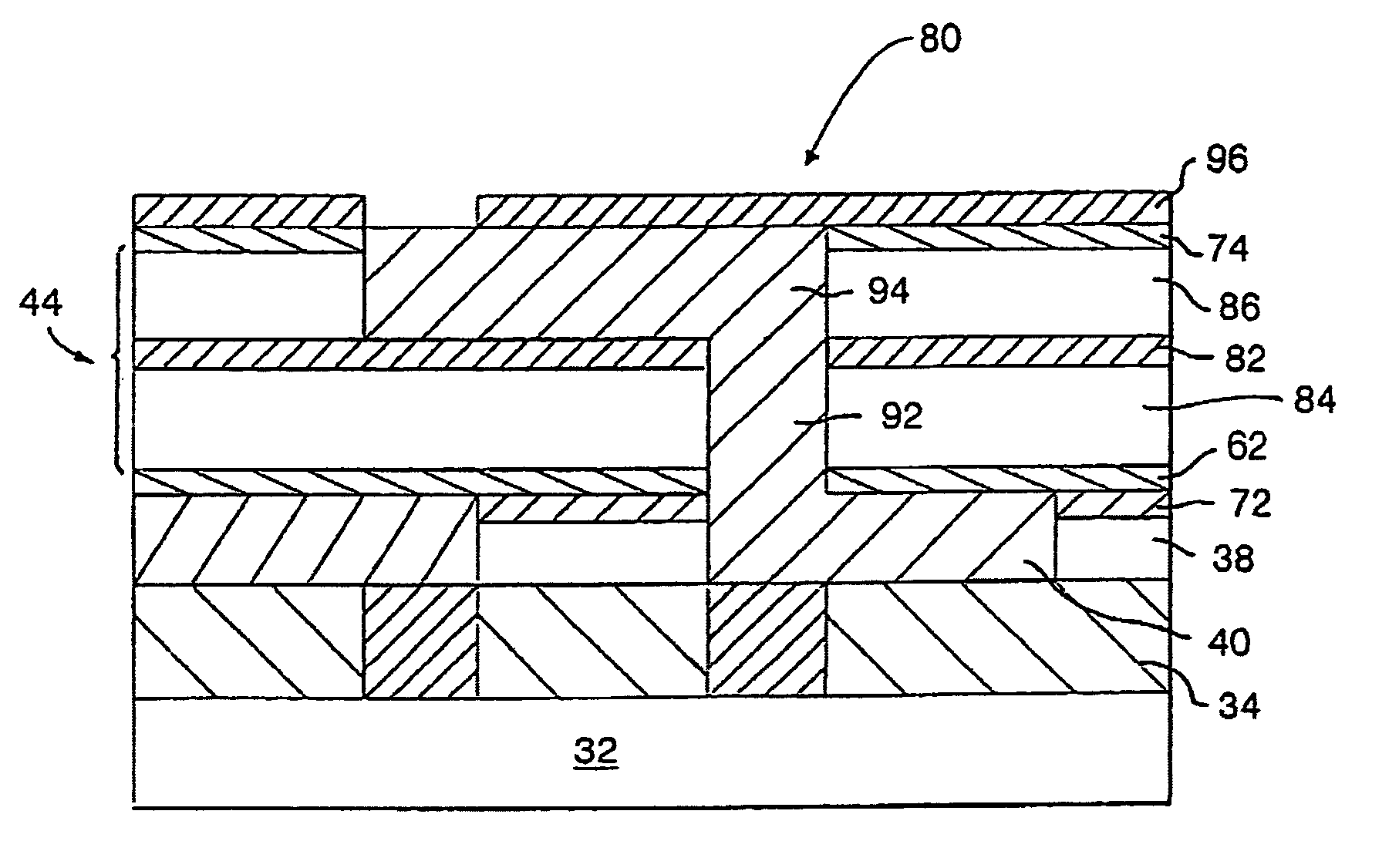

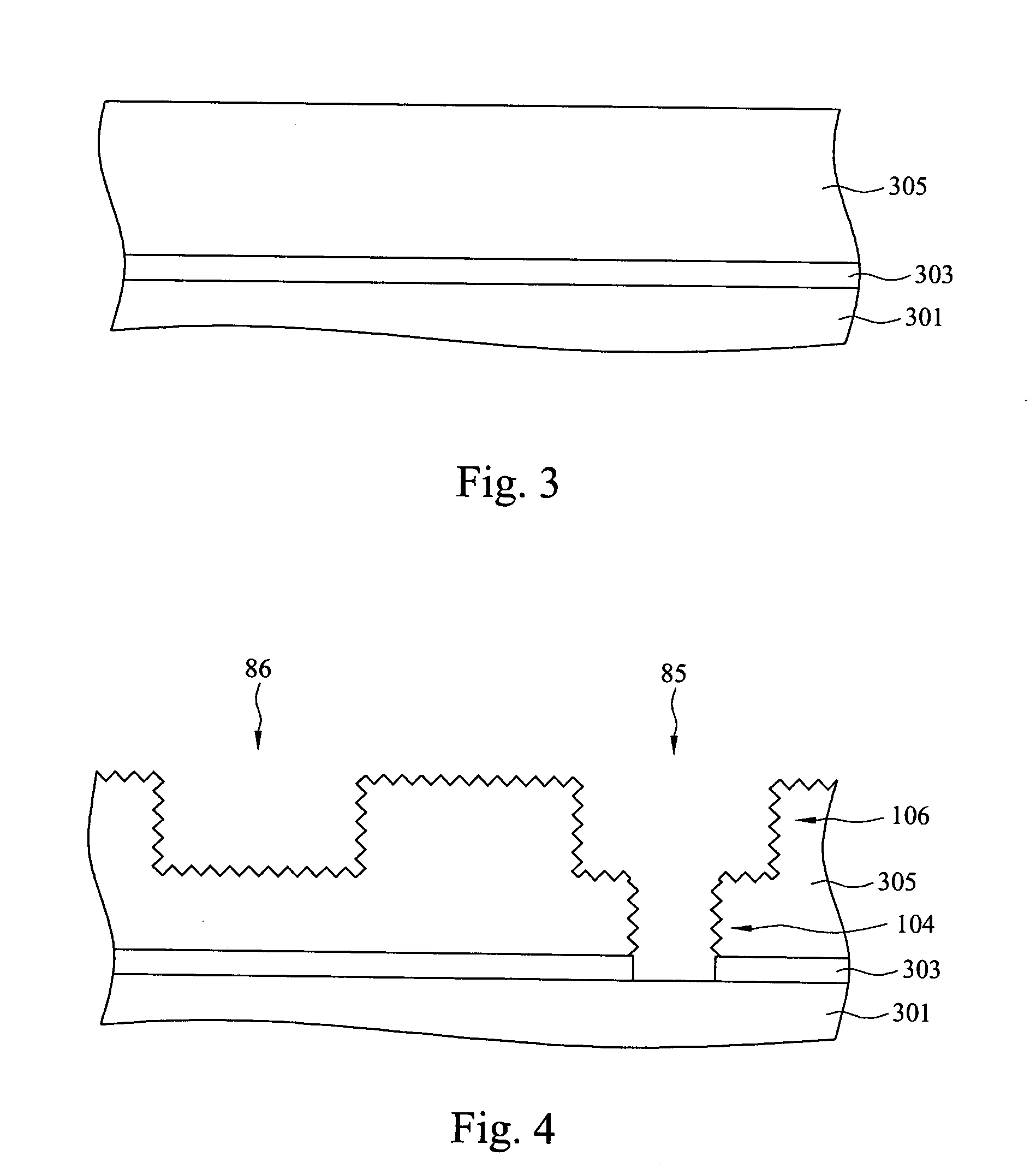

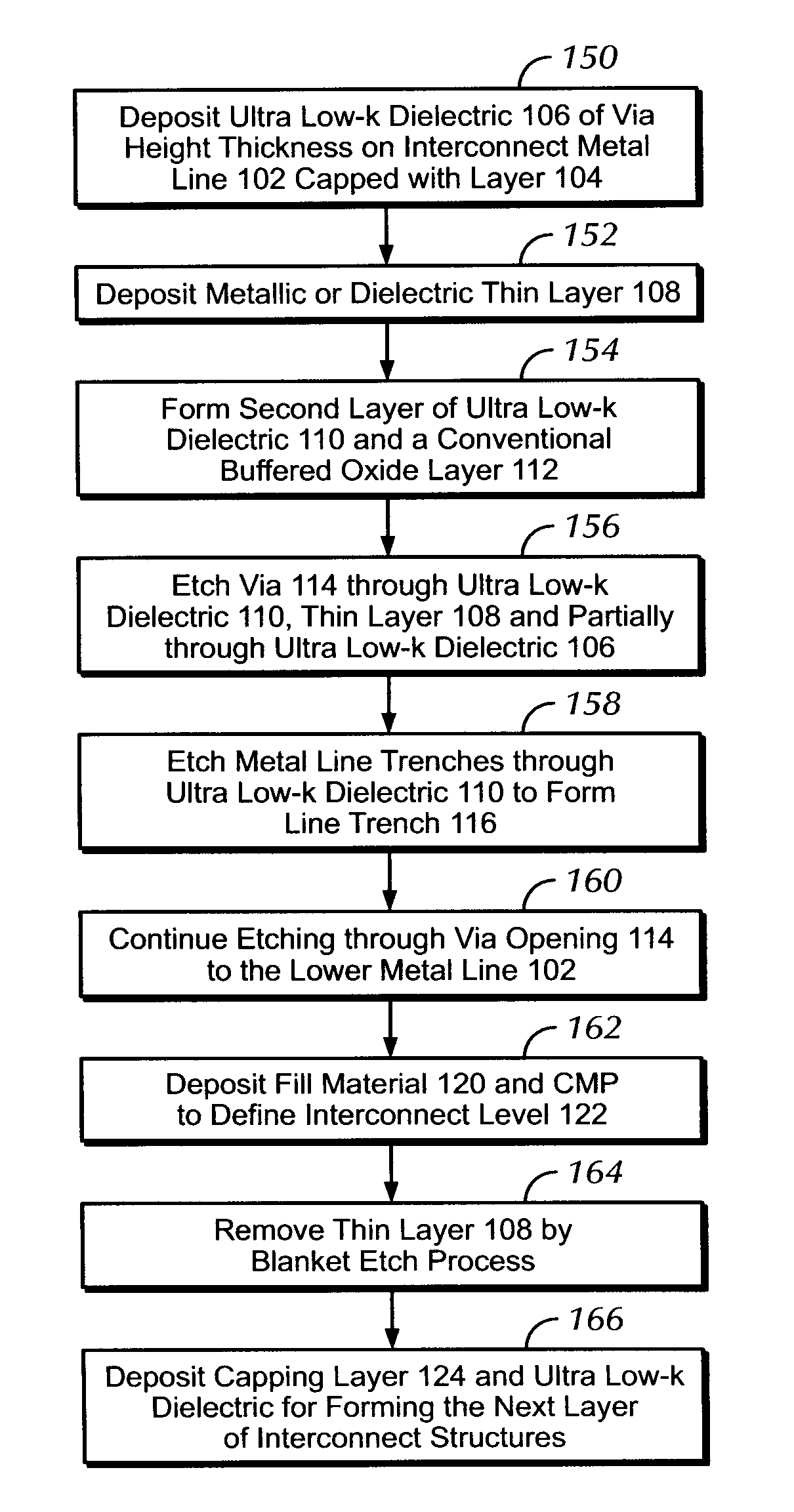

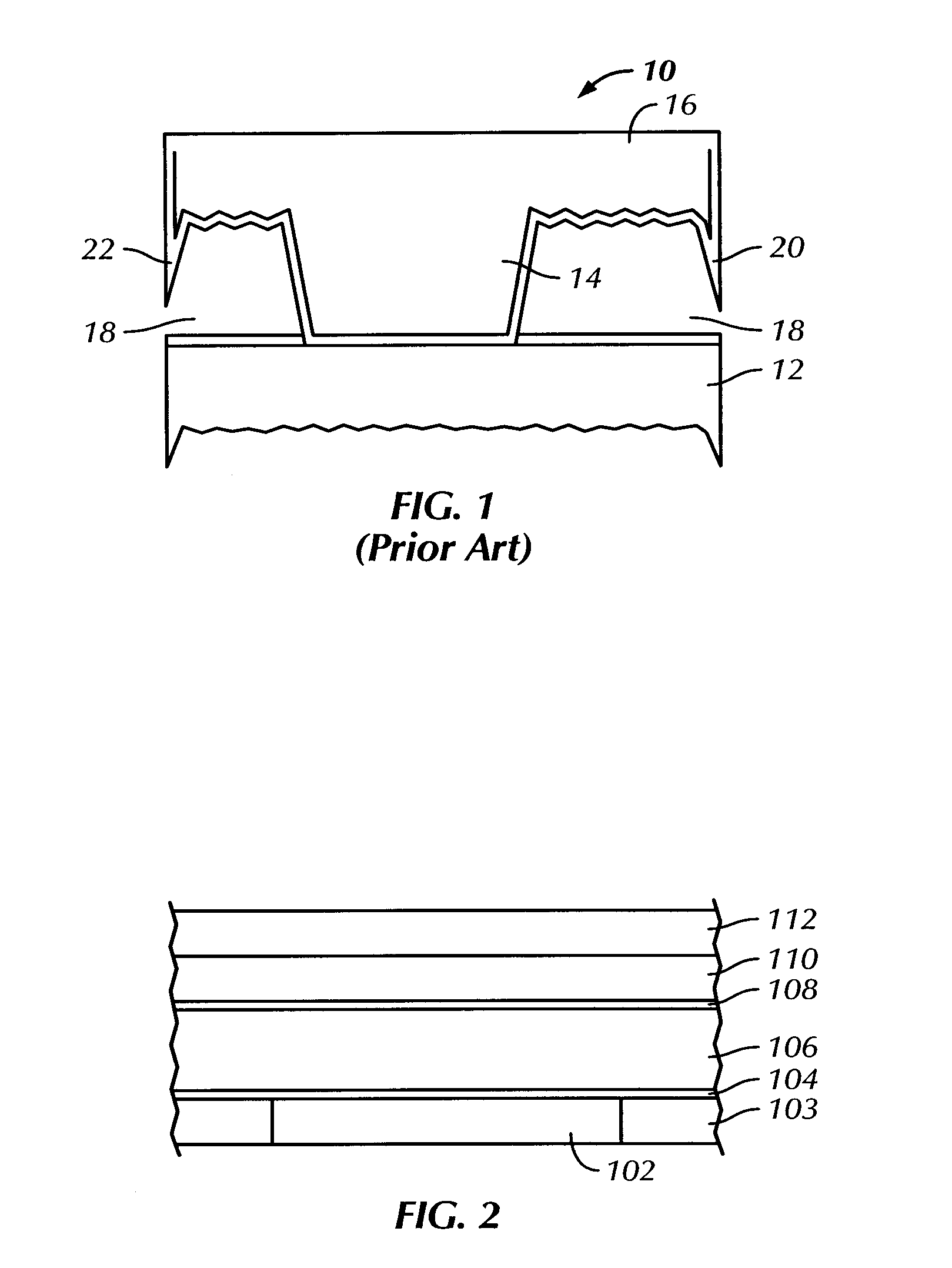

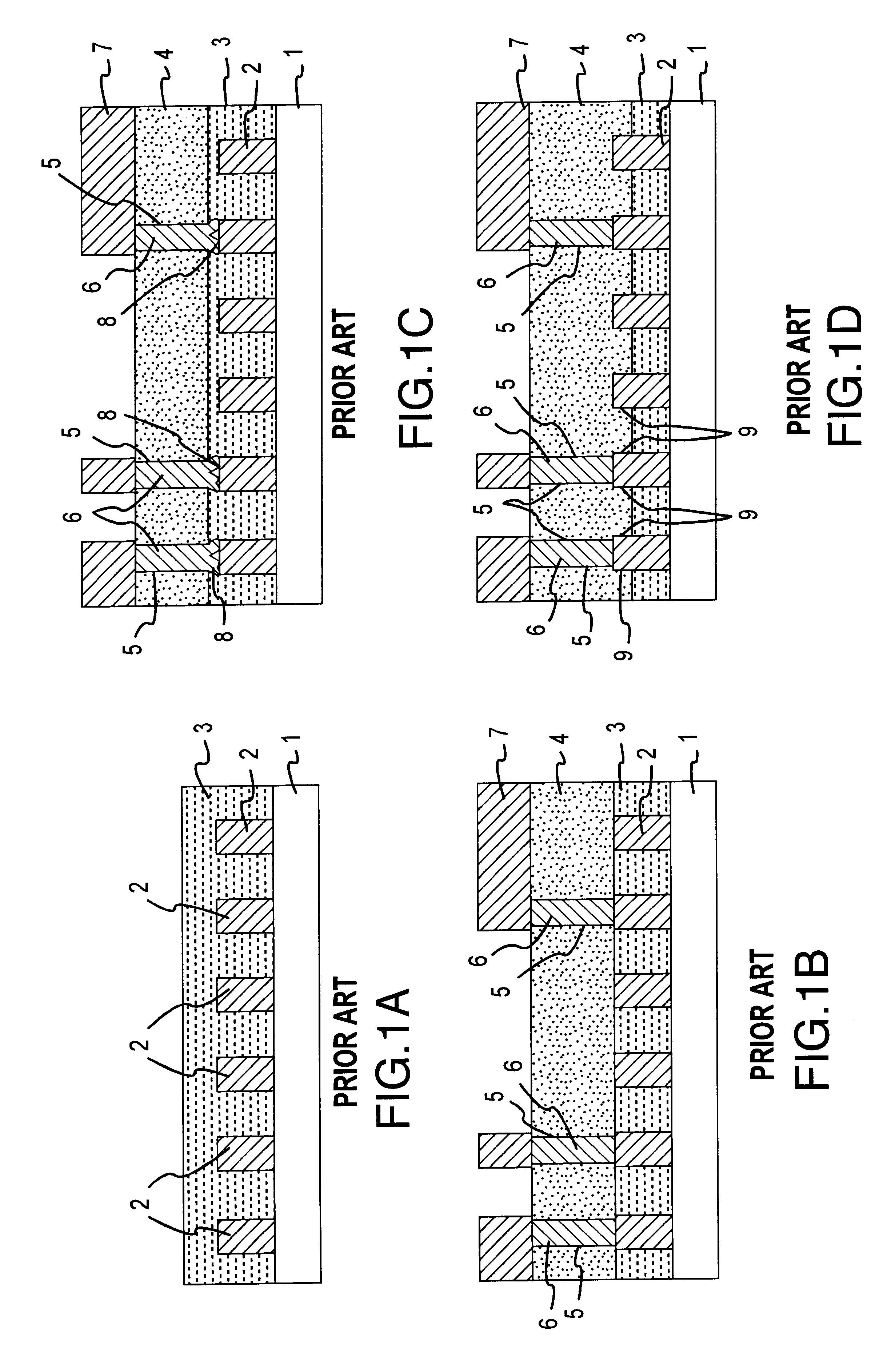

Method of Forming Metal Interconnect Structures in Ultra Low-K Dielectrics

ActiveUS20110117737A1Semiconductor/solid-state device manufacturingMetal interconnectConductive materials

A metal interconnect structure in ultra low-k dielectrics is described having a capped interconnect layer; an interconnect feature with a contact via and a contact line formed in a dielectric layer, where the via is partially embedded into the interconnect layer; and a thin film formed on the dielectric layer and separating the dielectric layer from the contact line. A method of fabricating the interconnect structure is also described and includes forming a first dielectric on a capped interconnect element; forming a thin film over the first dielectric; forming a second dielectric on the thin film; forming a via opening on the second dielectric, the thin film and extending into the first dielectric; forming a line trench on a portion of the second dielectric; and filling the via opening and the line trench with a conductive material for forming a contact via and a contact line, where the contact via is partially embedded in the interconnect element.

Owner:GLOBALFOUNDRIES US INC

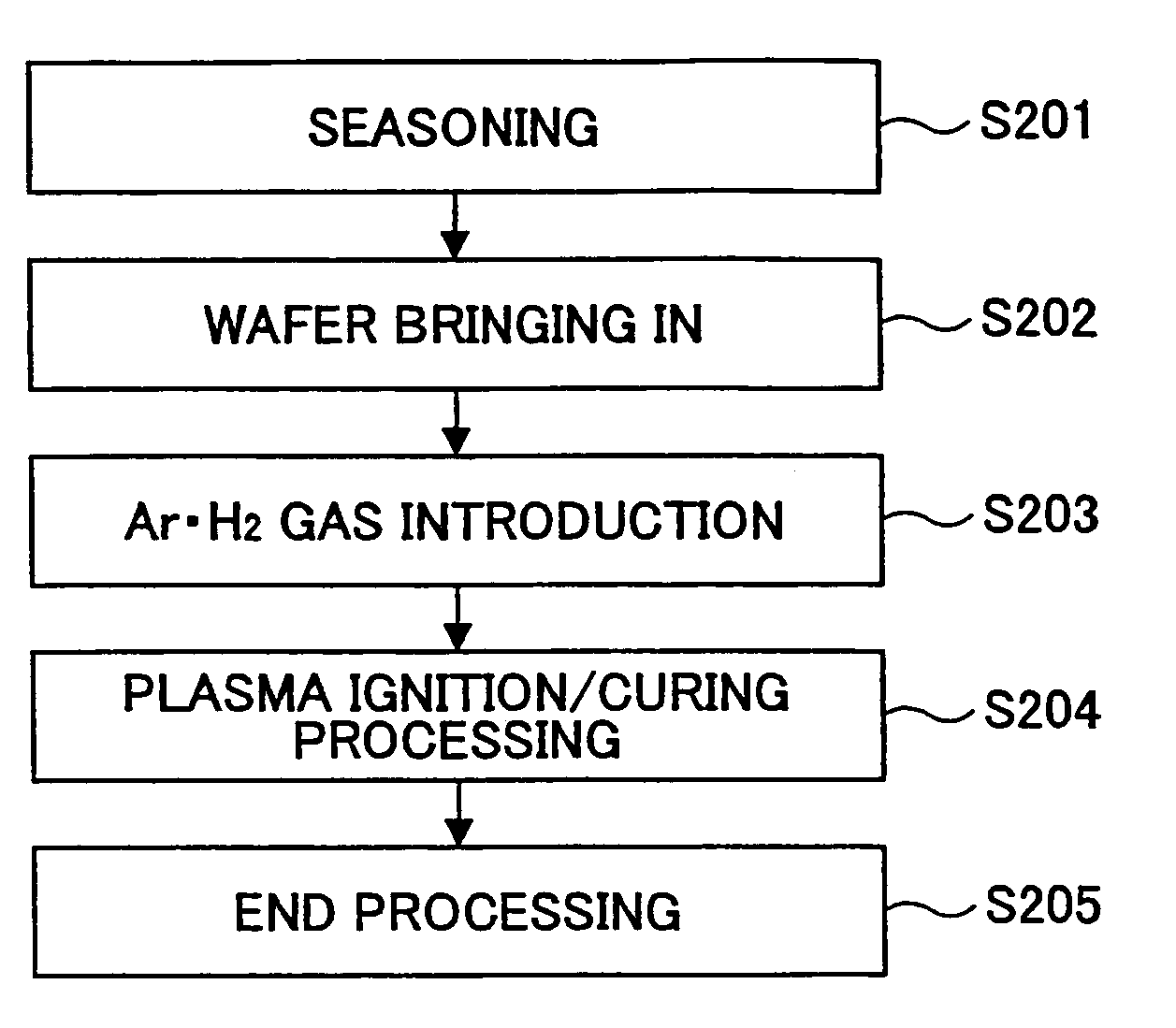

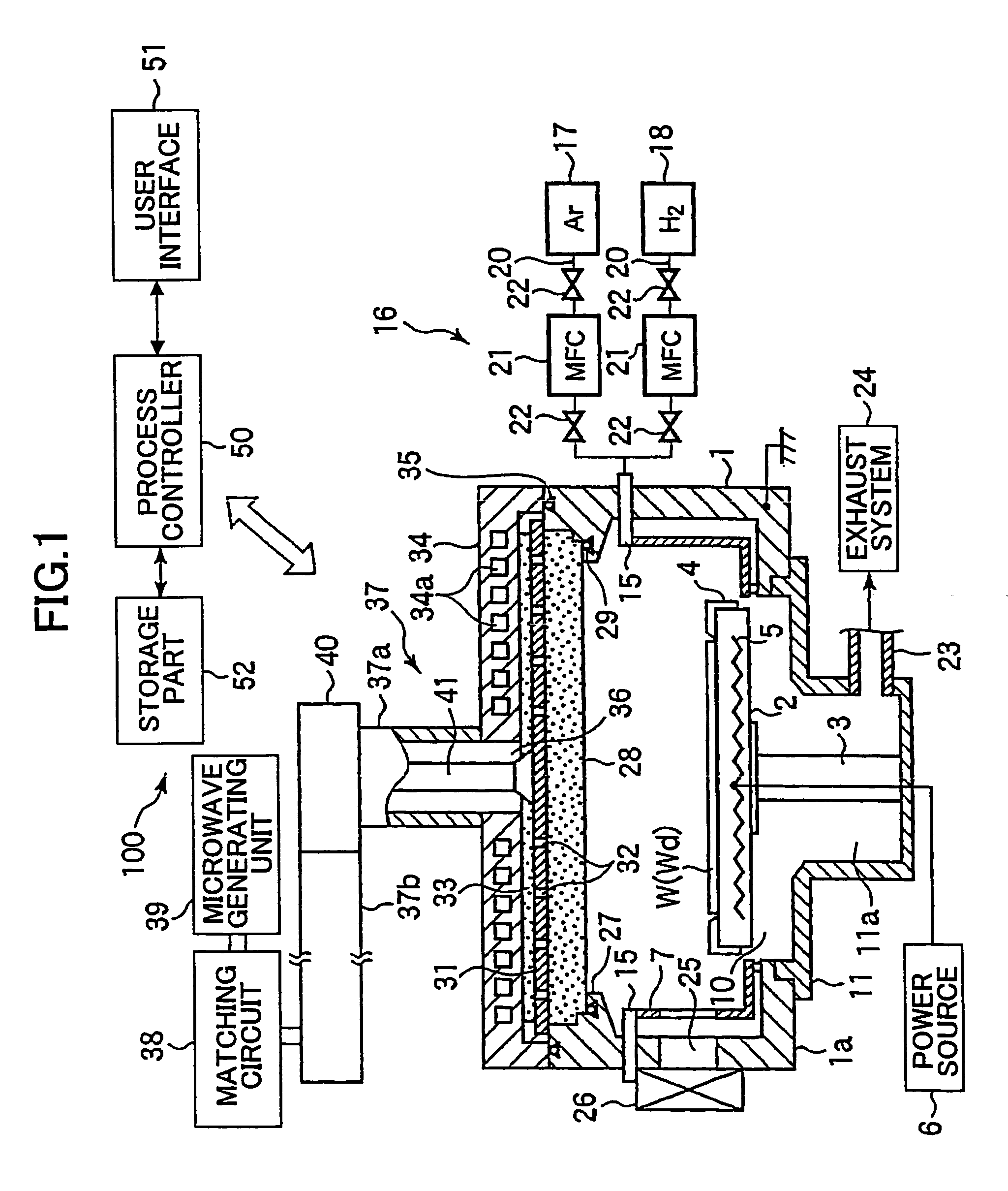

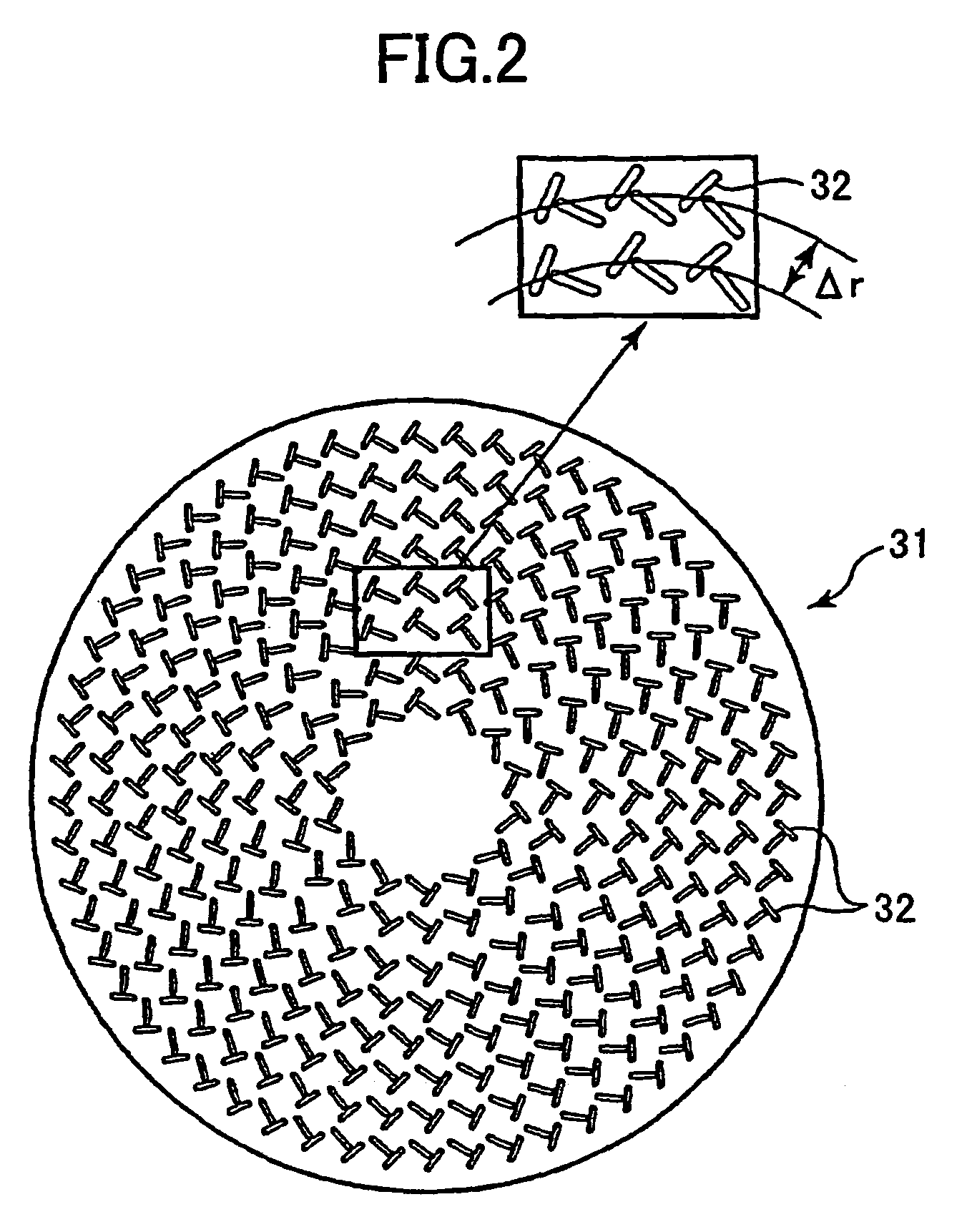

Plasma processing method and film forming method

InactiveUS7771796B2Low dielectric constantImprove adhesionElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenProduct gas

A plasma processing method of carrying out curing processing on a low dielectric constant film produced on a to-be-processed substrate by applying plasma thereto in a processing chamber of a plasma processing apparatus, includes the steps of: a) introducing, in the plasma processing chamber, a first gas having a function of stabilizing plasma and a second gas generating active hydrogen, and, after that; b) generating plasma, and carrying out curing processing on the low dielectric constant film.

Owner:TOKYO ELECTRON LTD

Plasma curing process for porous low-k materials

InactiveUS6913796B2Improving elastic modulusImproving material hardnessSilicaLayered productsHardnessMaterials science

Low dielectric constant porous materials with improved elastic modulus and hardness. The process of making such porous materials involves providing a porous dielectric material and plasma curing the porous dielectric material to produce a plasma cured porous dielectric material. Plasma curing of the porous dielectric material yields a material with improved modulus and hardness. The improvement in elastic modulus is typically greater than or about 50%, more typically greater than or about 100%, and more typically greater than or about 200%. The improvement in hardness is typically greater than or about 50%. The plasma cured porous dielectric material can optionally be post-plasma treated. The post-plasma treatment of the plasma cured porous dielectric material reduces the dielectric constant of the material while maintaining an improved elastic modulus and hardness as compared to the plasma cured porous dielectric material. The post-plasma treated, plasma cured porous dielectric material has a dielectric constant between about 1.1 and about 3.5 and an improved elastic modulus and hardness.

Owner:DOW CORNING CORP

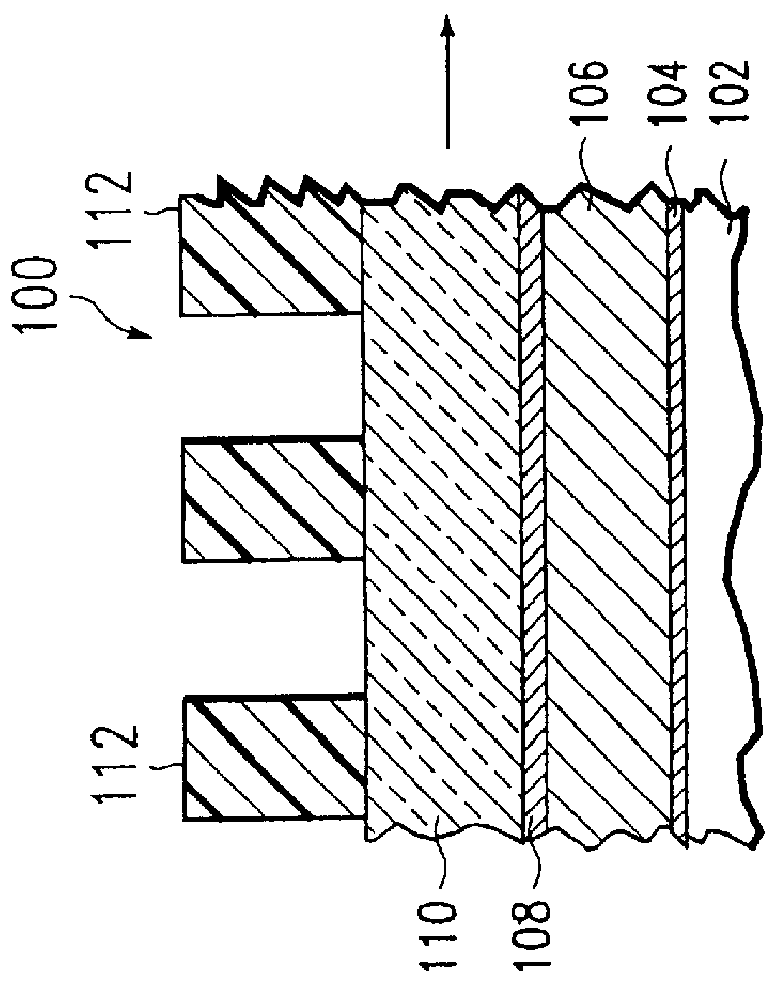

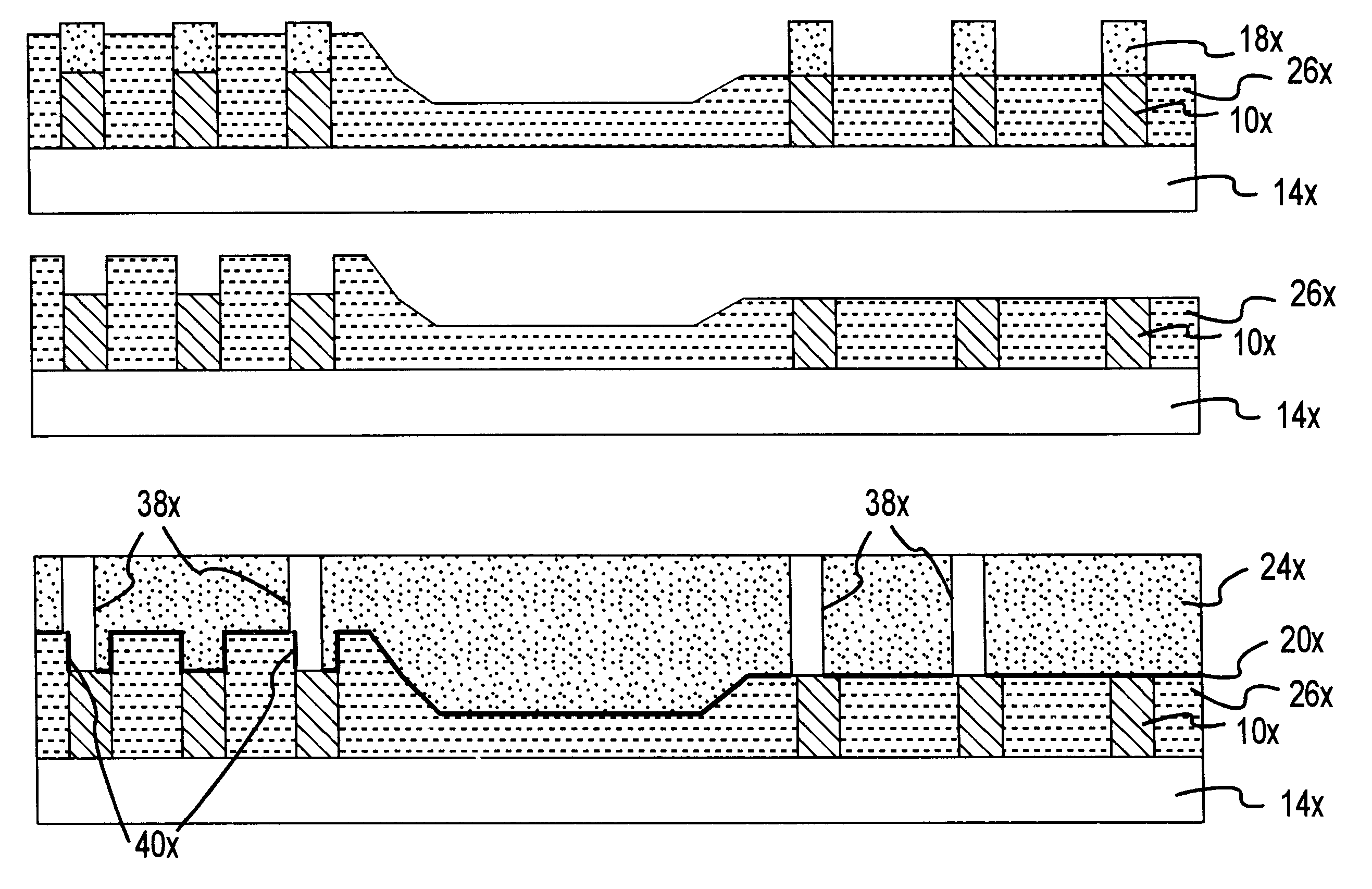

Chip interconnect wiring structure with low dielectric constant insulator and methods for fabricating the same

A method to achieve a very low effective dielectric constant in high performance back end of the line chip interconnect wiring and the resulting multilayer structure are disclosed. The process involves fabricating the multilayer interconnect wiring structure by methods and materials currently known in the state of the art of semiconductor processing; removing the intralevel dielectric between the adjacent metal features by a suitable etching process; applying a thin passivation coating over the exposed etched structure; annealing the etched structure to remove plasma damage; laminating an insulating cover layer to the top surface of the passivated metal features; optionally depositing an insulating environmental barrier layer on top of the cover layer; etching vias in the environmental barrier layer, cover layer and the thin passivation layer for terminal pad contacts; and completing the device by fabricating terminal input / output pads. The method obviates issues such as processability and thermal stability associated with low dielectric constant materials by avoiding their use. Since air, which has the lowest dielectric constant, is used as the intralevel dielectric the structure created by this method would possess a very low capacitance and hence fast propagation speeds. Such structure is ideally suitable for high density interconnects required in high performance microelectronic device chips.

Owner:GLOBALFOUNDRIES INC

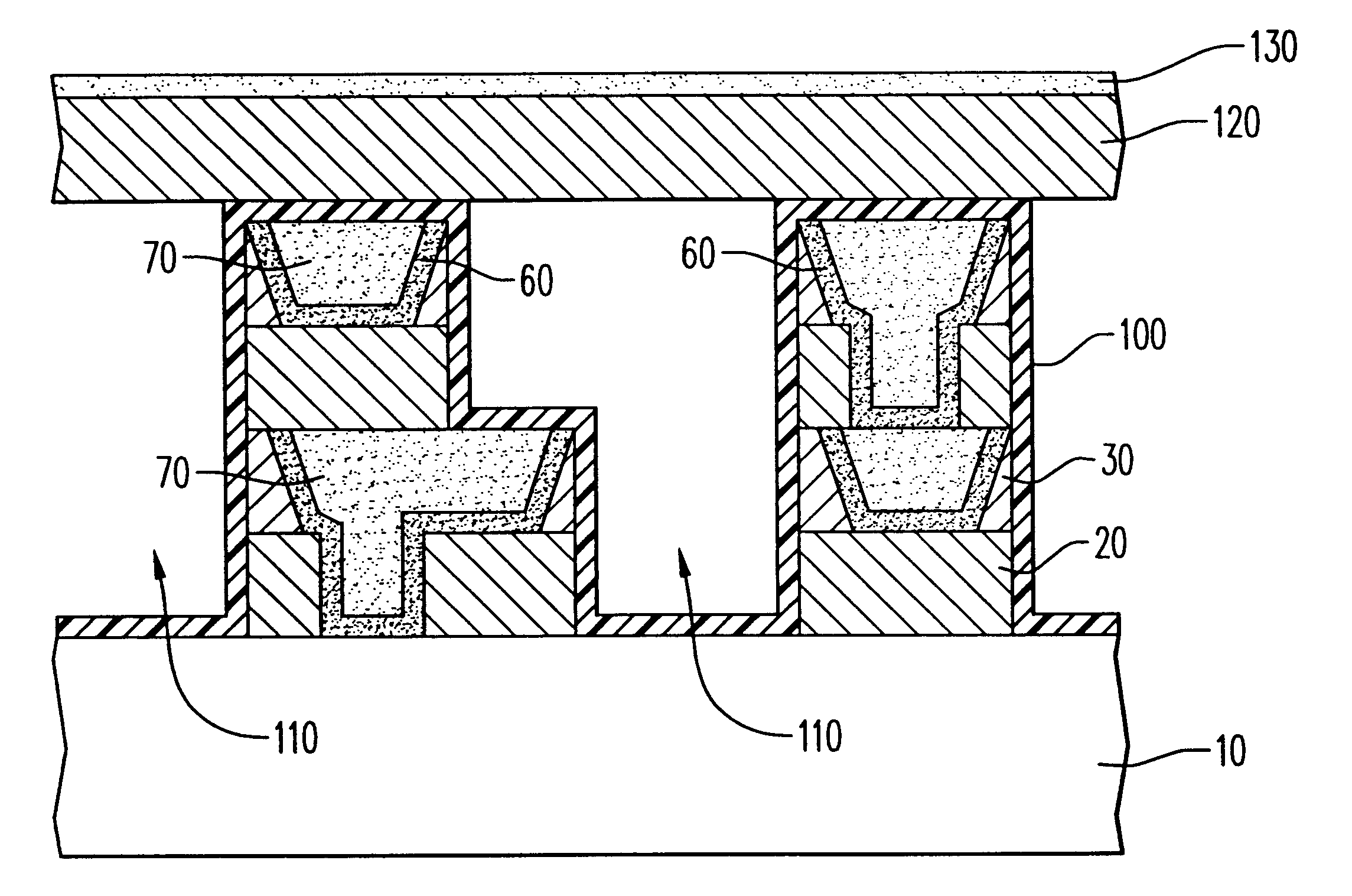

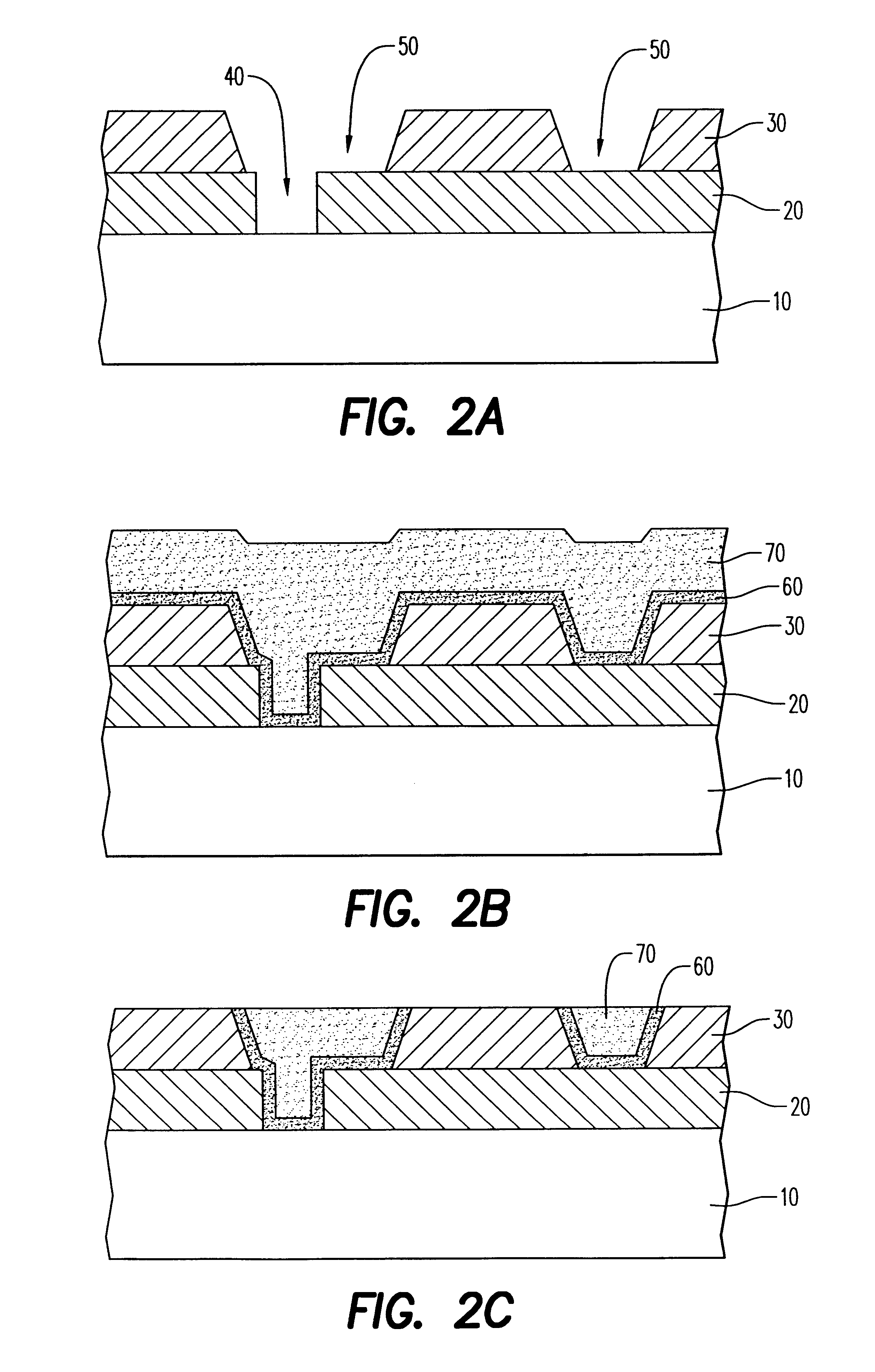

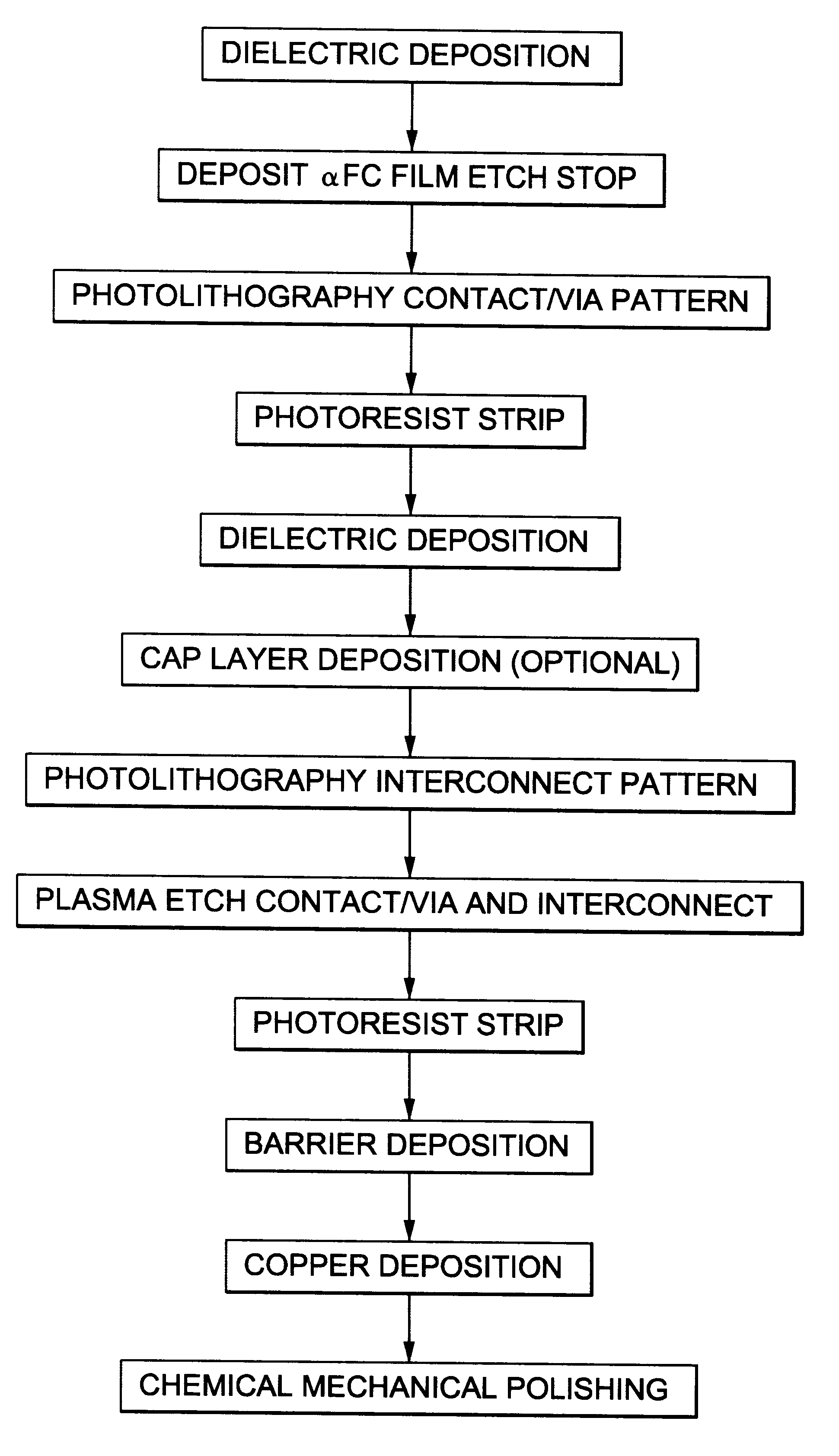

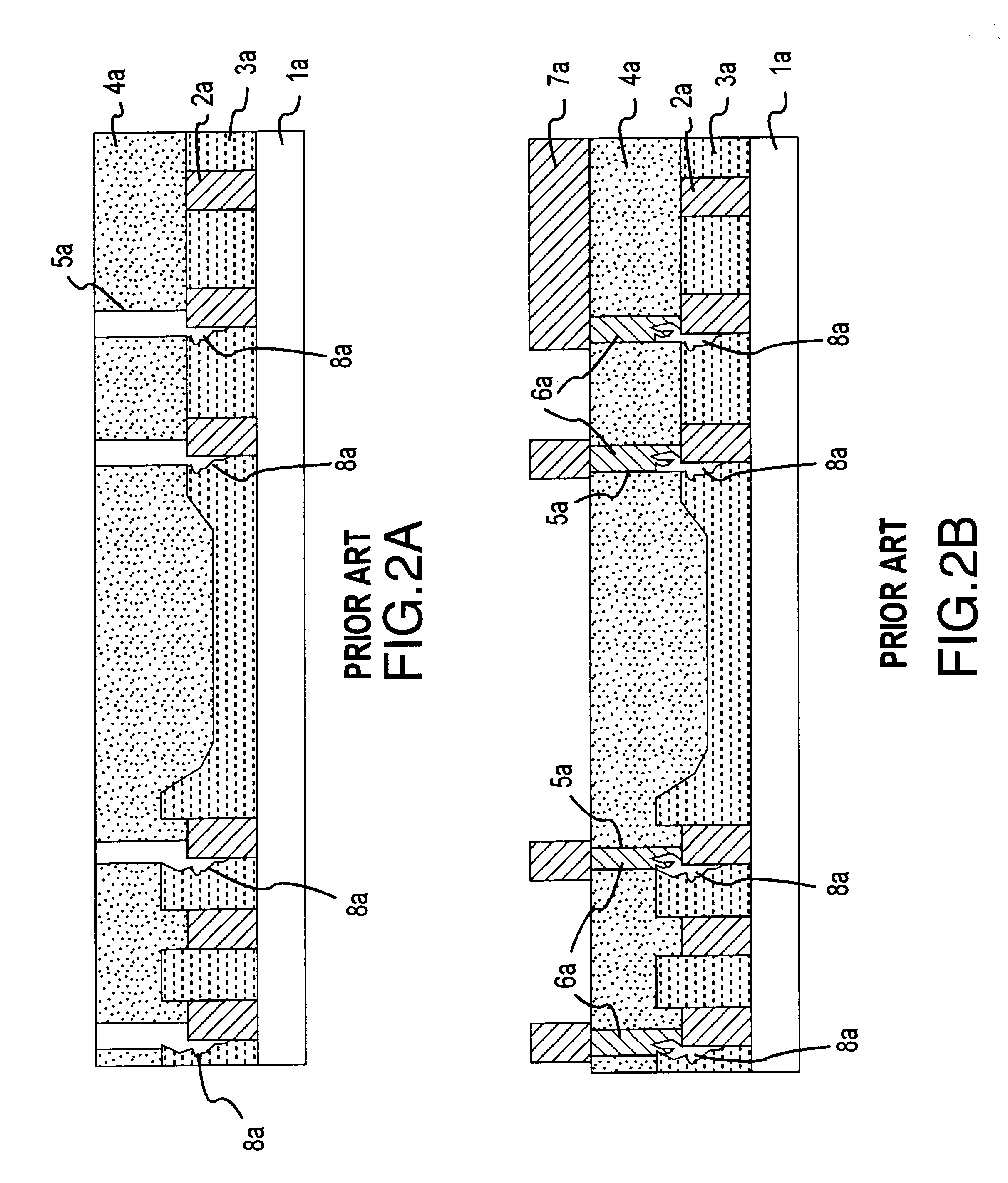

An etch stop layer for dual damascene process

The present invention provides a carbon based etch stop, such as a diamond like amorphous carbon, having a low dielectric constant and a method of forming a dual damascene structure. The low k etch stop is preferably deposited between two dielectric layers and patterned to define the underlying interlevel contacts / vias. The second or upper dielectric layer is formed over the etch stop and patterned to define the intralevel interconnects. The entire dual damascene structure is then etched in a single selective etch process which first etches the patterned interconnects, then etches the contact / vias past the patterned etch stop. The etch stop has a low dielectric constant relative to a conventional SiN etch stop, which minimizes the capacitive coupling between adjacent interconnect lines. The dual damascene structure is then filled with a suitable conductive material such as aluminum or copper and planarized using chemical mechanical polishing.

Owner:APPLIED MATERIALS INC

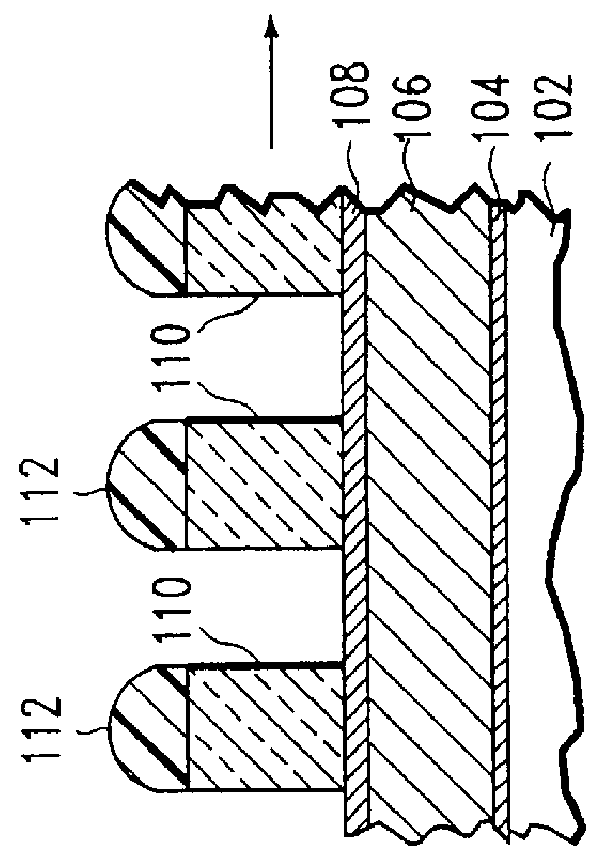

Interconnect with low dielectric constant insulators for semiconductor integrated circuit manufacturing

InactiveUS6187672B1Semiconductor/solid-state device manufacturingResistIntegrated circuit manufacturing

A method is provided for forming an improved interconnect structure on a semiconductor body. A first metal layer is deposited on the semiconductor body. A sacrificial layer having a height is deposited on the first metal layer. The sacrificial layer and the metal layer are patterned to form separate metal lines with the sacrificial layer remaining on said metal lines. A low-k material is then deposited to fill the gaps between metal lines and to cover the sacrificial layer. The low-k material is then removed to a level within the height of the sacrificial layer. The sacrificial layer is then removed. A protective layer is deposited on top of the metal lines and the low-k material. A dielectric layer is deposited over the protective layer. The protective layer protects the low-k material from attack by chemicals utilized by subsequent process steps to etch vias in the dielectric layer, to strip photo-resist, and to clean the vias. The protective layer is then selectively etched away to make contact between a via plug and the metal lines.

Owner:NEWPORT FAB

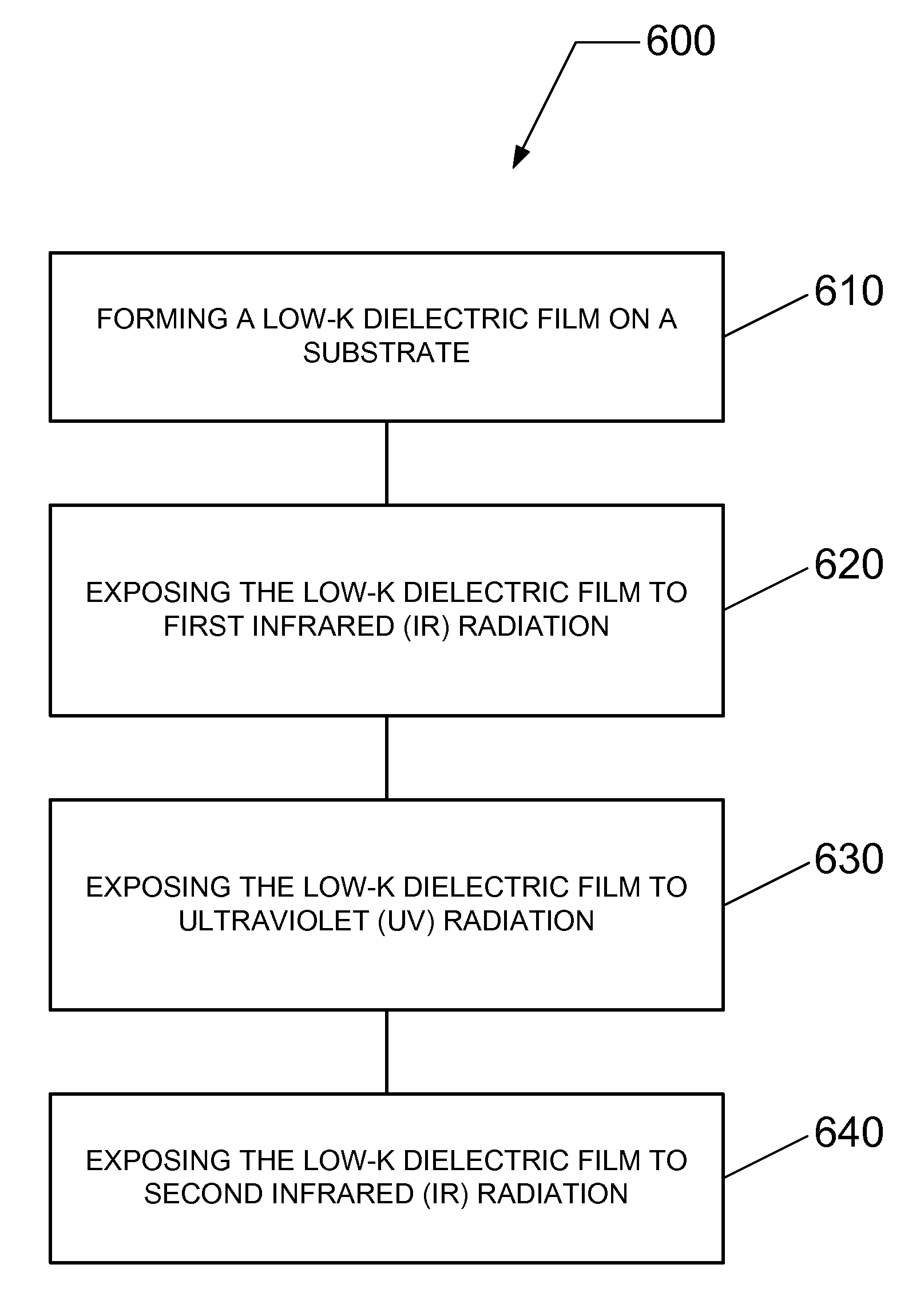

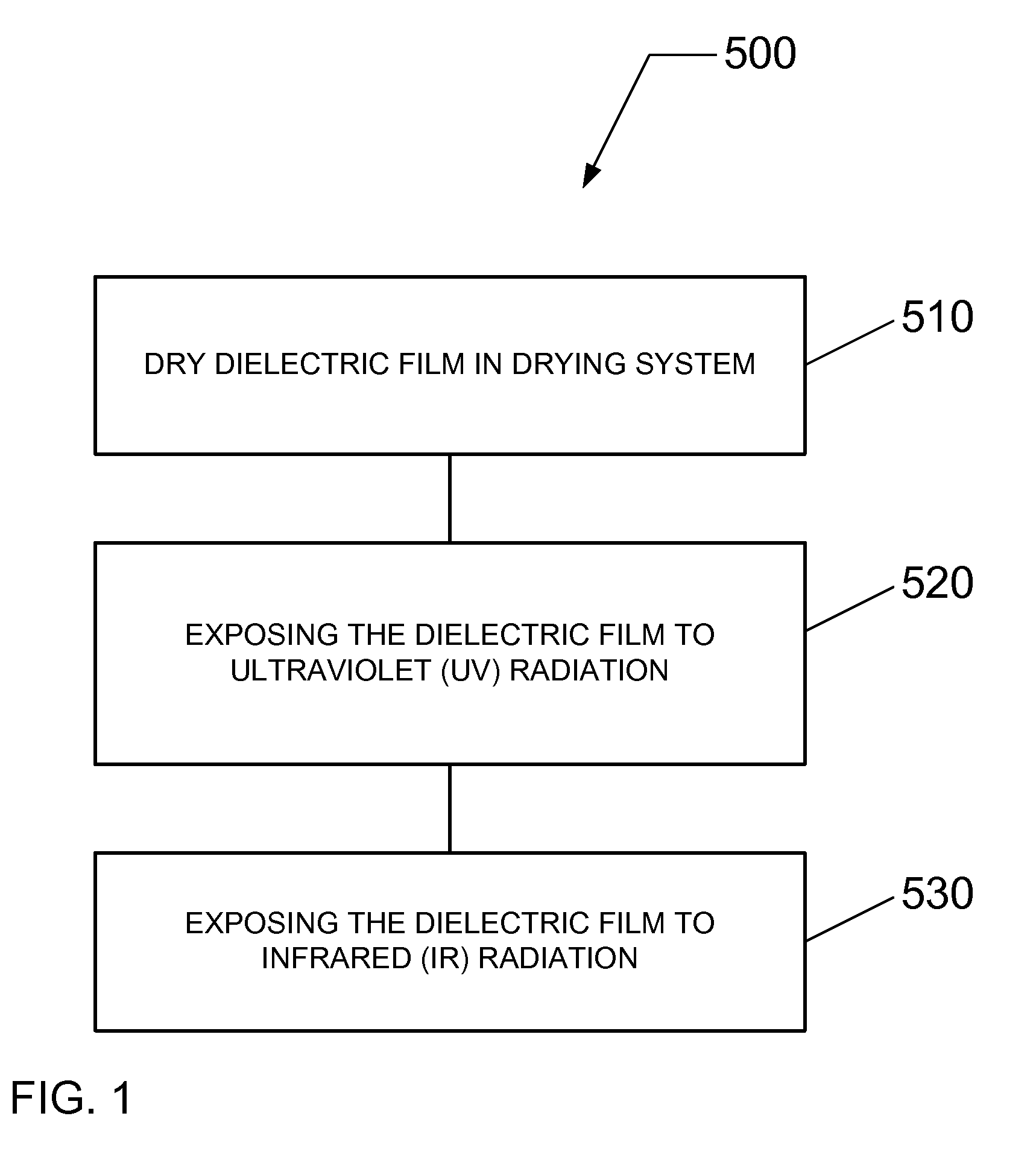

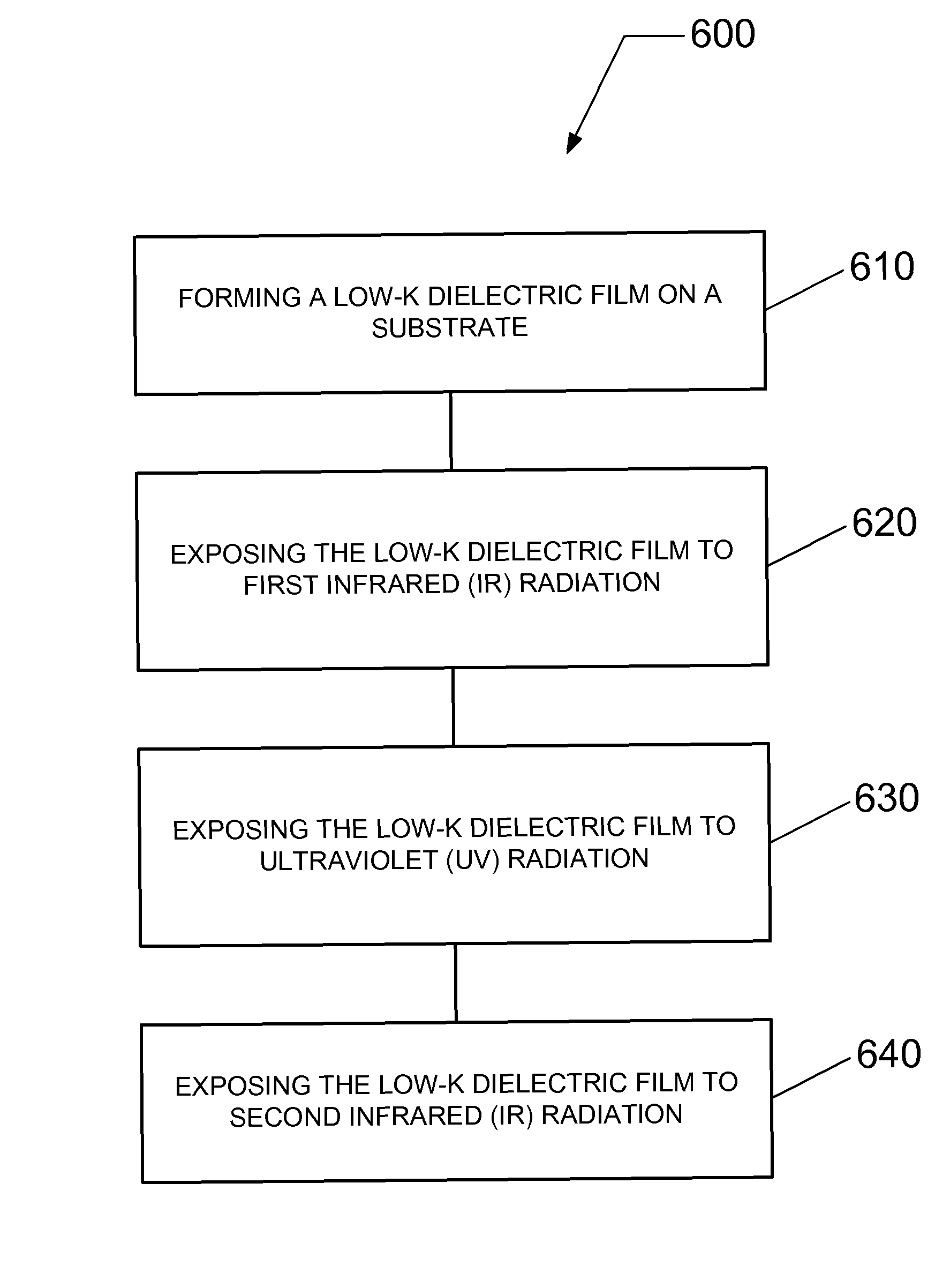

Method for curing a porous low dielectric constant dielectric film

A method of curing a low dielectric constant (low-k) dielectric film on a substrate is described, wherein the dielectric constant of the low-k dielectric film is less than a value of approximately 4. The method comprises exposing the low-k dielectric film to infrared (IR) radiation and ultraviolet (UV) radiation.

Owner:TOKYO ELECTRON LTD

Method for removing a pore-generating material from an uncured low-k dielectric film

A method of forming a porous low dielectric constant (low-k) dielectric film on a substrate is described, wherein the dielectric constant of the low-k dielectric film is less than a value of approximately 4. The method comprises exposing the low-k dielectric film to infrared (IR) radiation and adjusting a residual amount of cross-linking inhibitor, such as pore-generating material, within the low-k dielectric film.

Owner:TOKYO ELECTRON LTD