Patents

Literature

205 results about "Microelectronic circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

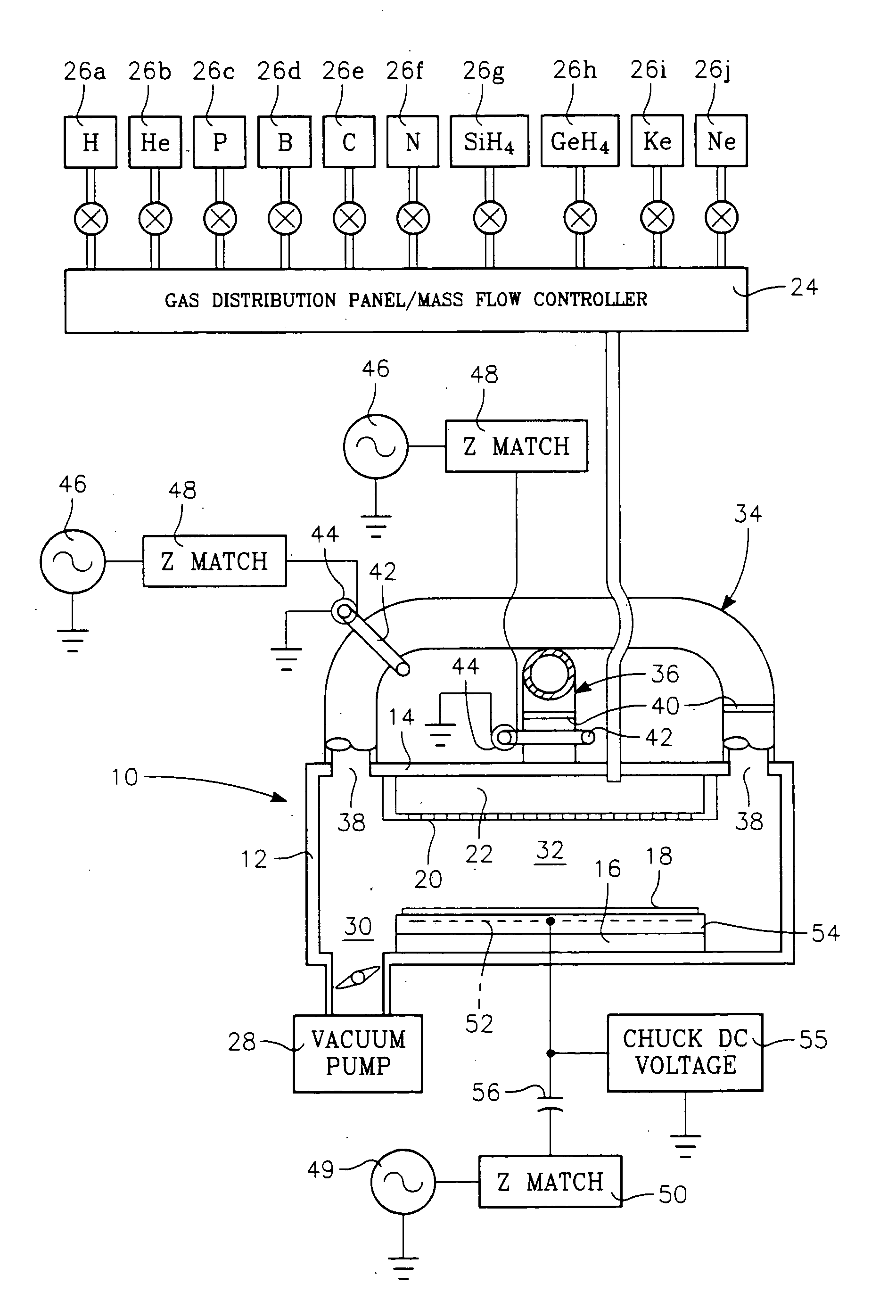

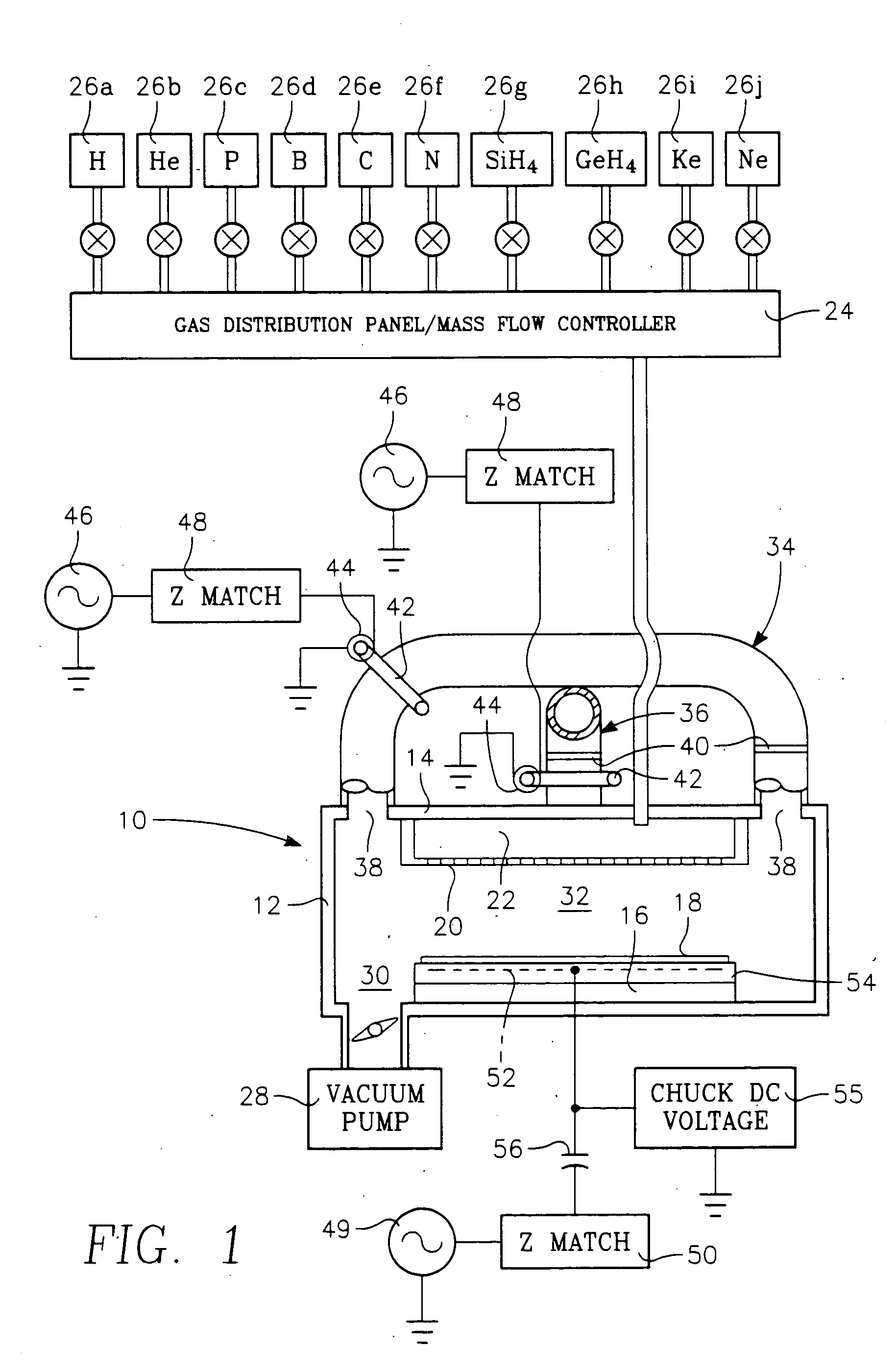

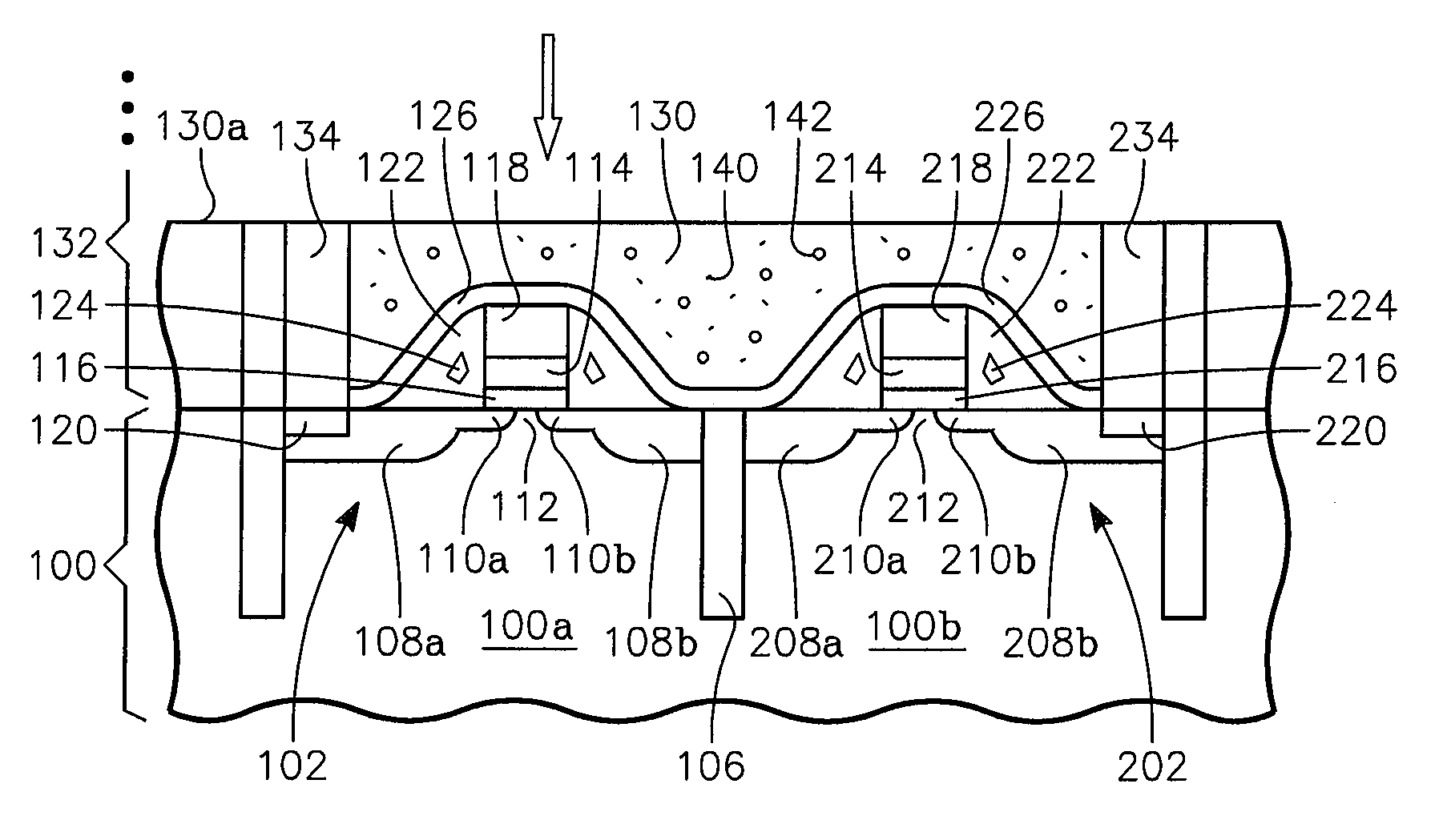

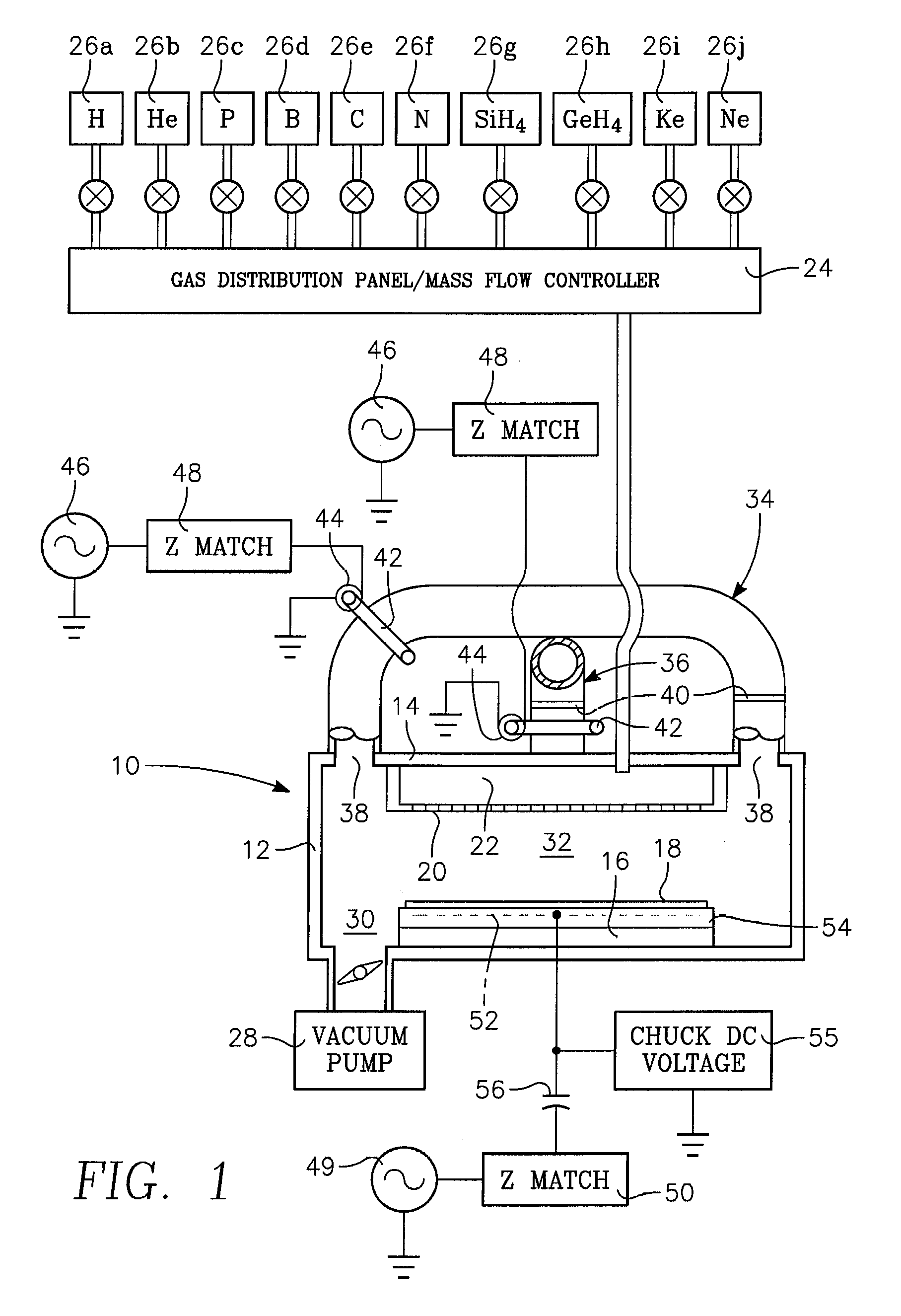

Method for ion implanting insulator material to reduce dielectric constant

InactiveUS20050191828A1Low dielectric constantElectric discharge tubesSemiconductor/solid-state device manufacturingMicroelectronic circuitsIon implantation

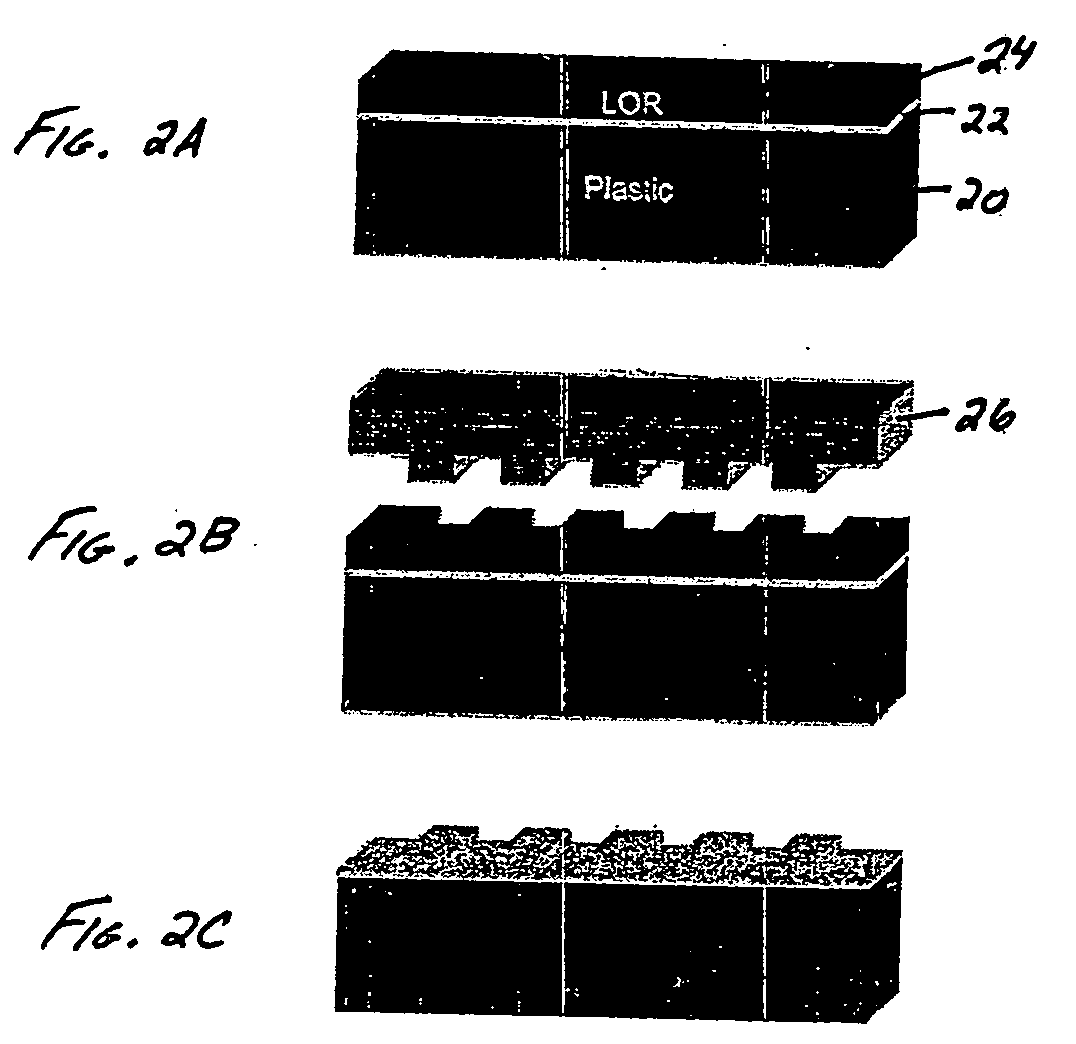

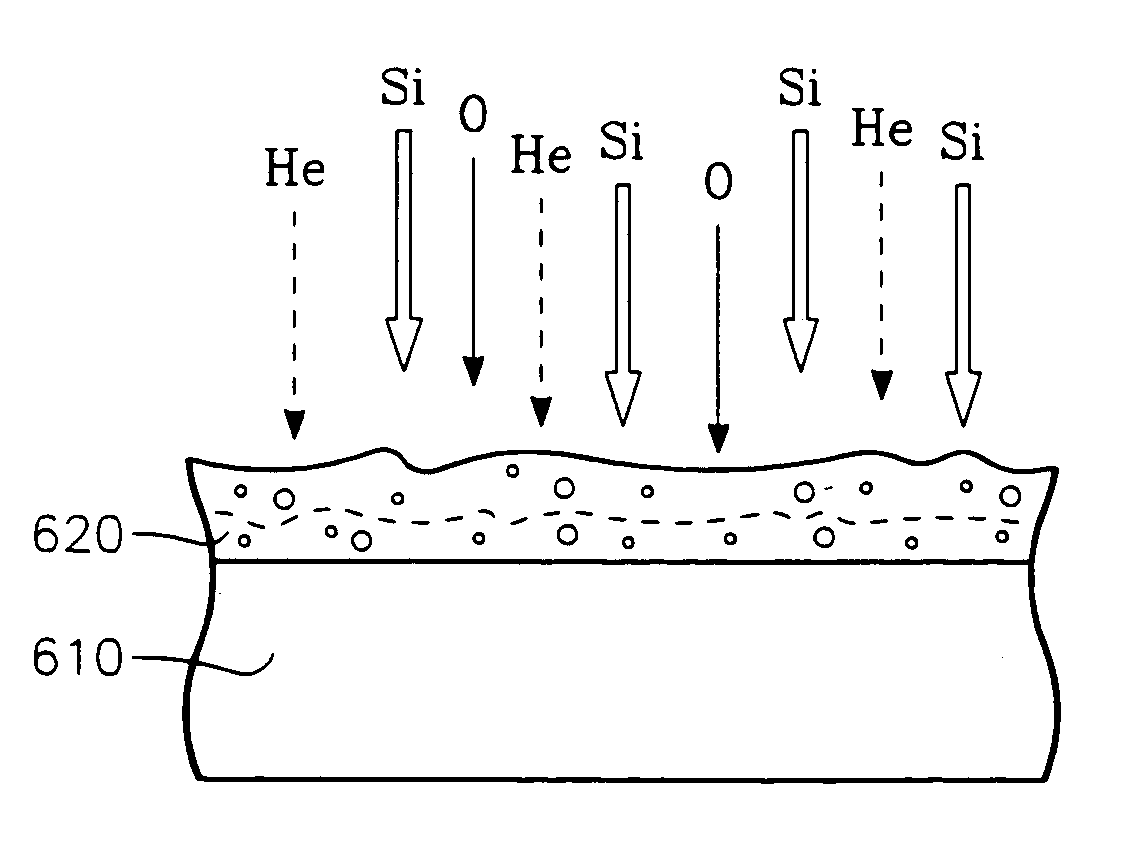

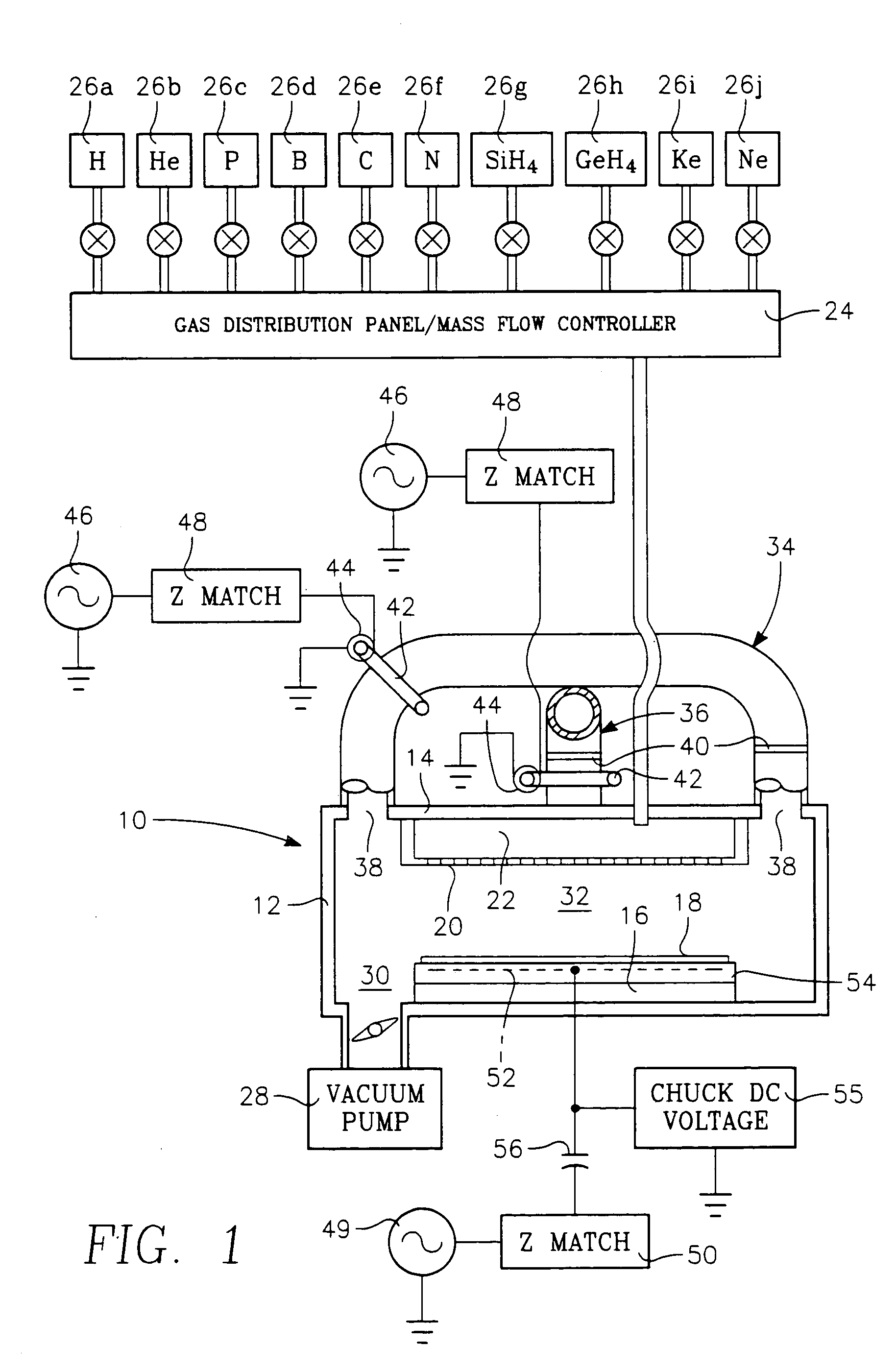

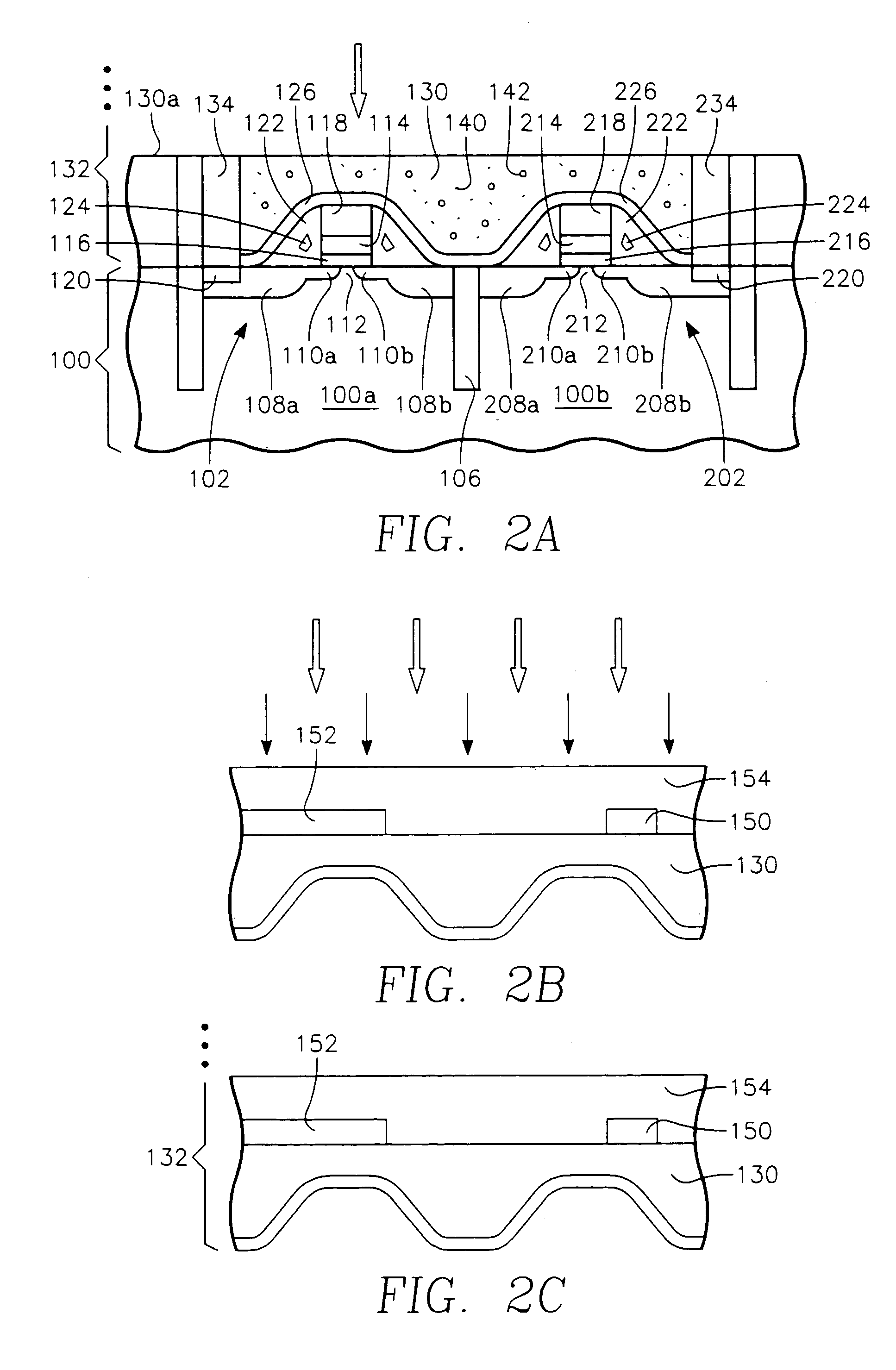

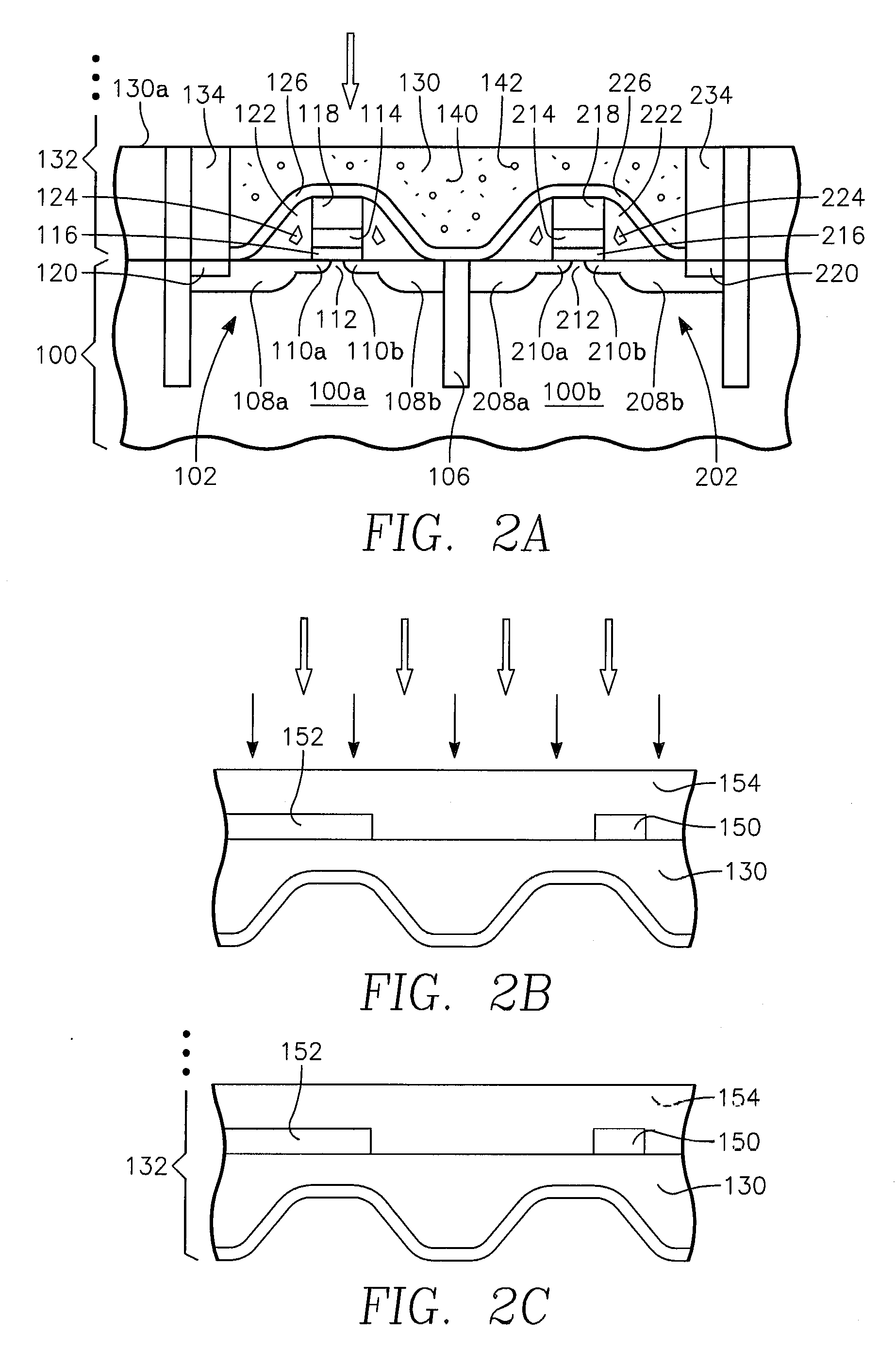

An integrated microelectronic circuit has a multi-layer interconnect structure overlying the transistors consisting of stacked metal pattern layers and insulating layers separating adjacent ones of said metal pattern layers. Each of the insulating layers is a dielectric material with plural gas bubbles distributed within the volume of the dielectric material to reduce the dielectric constant of the material, the gas bubbles being formed by ion implantation of a gaseous species into the dielectric material.

Owner:APPLIED MATERIALS INC

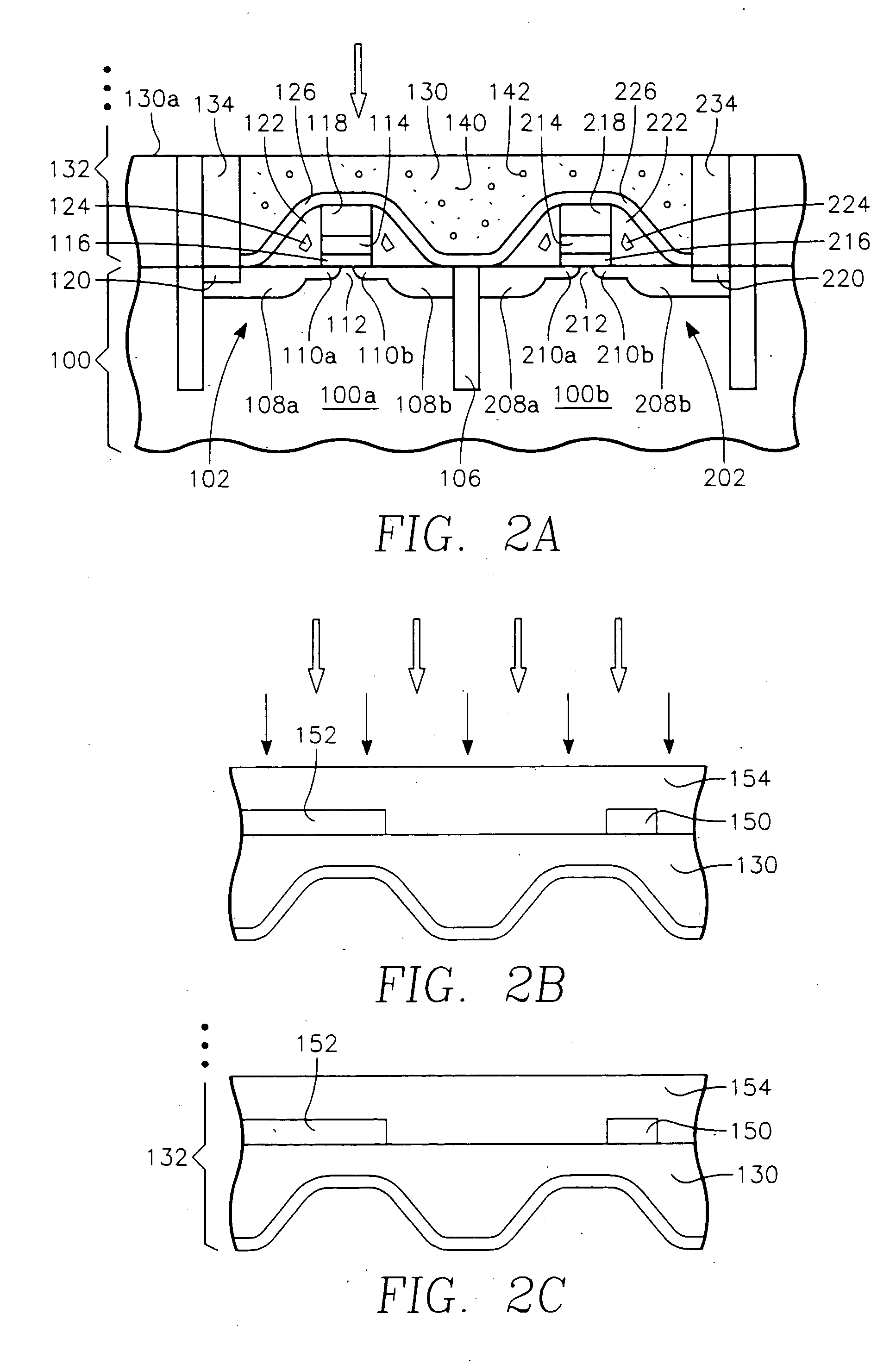

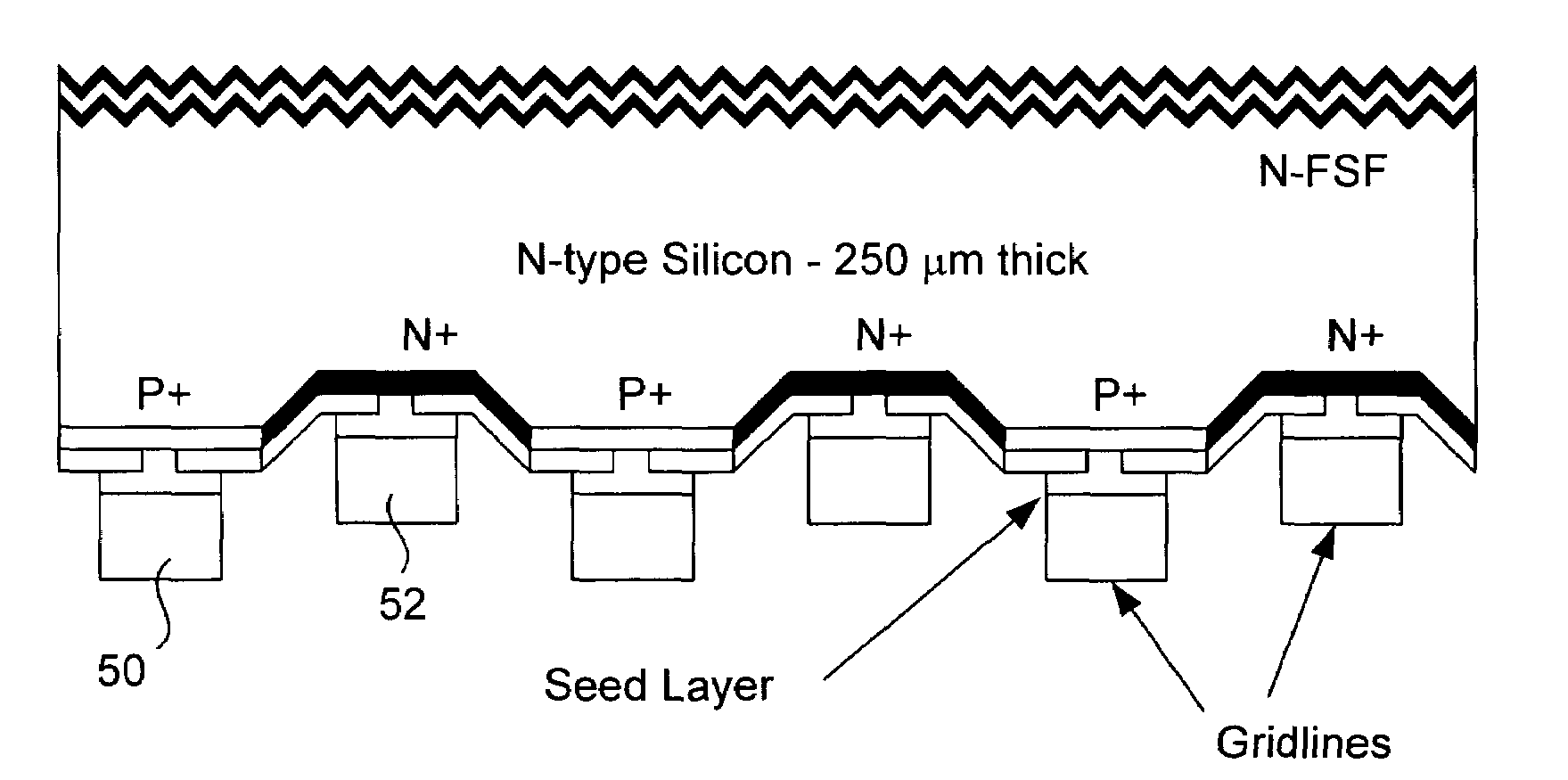

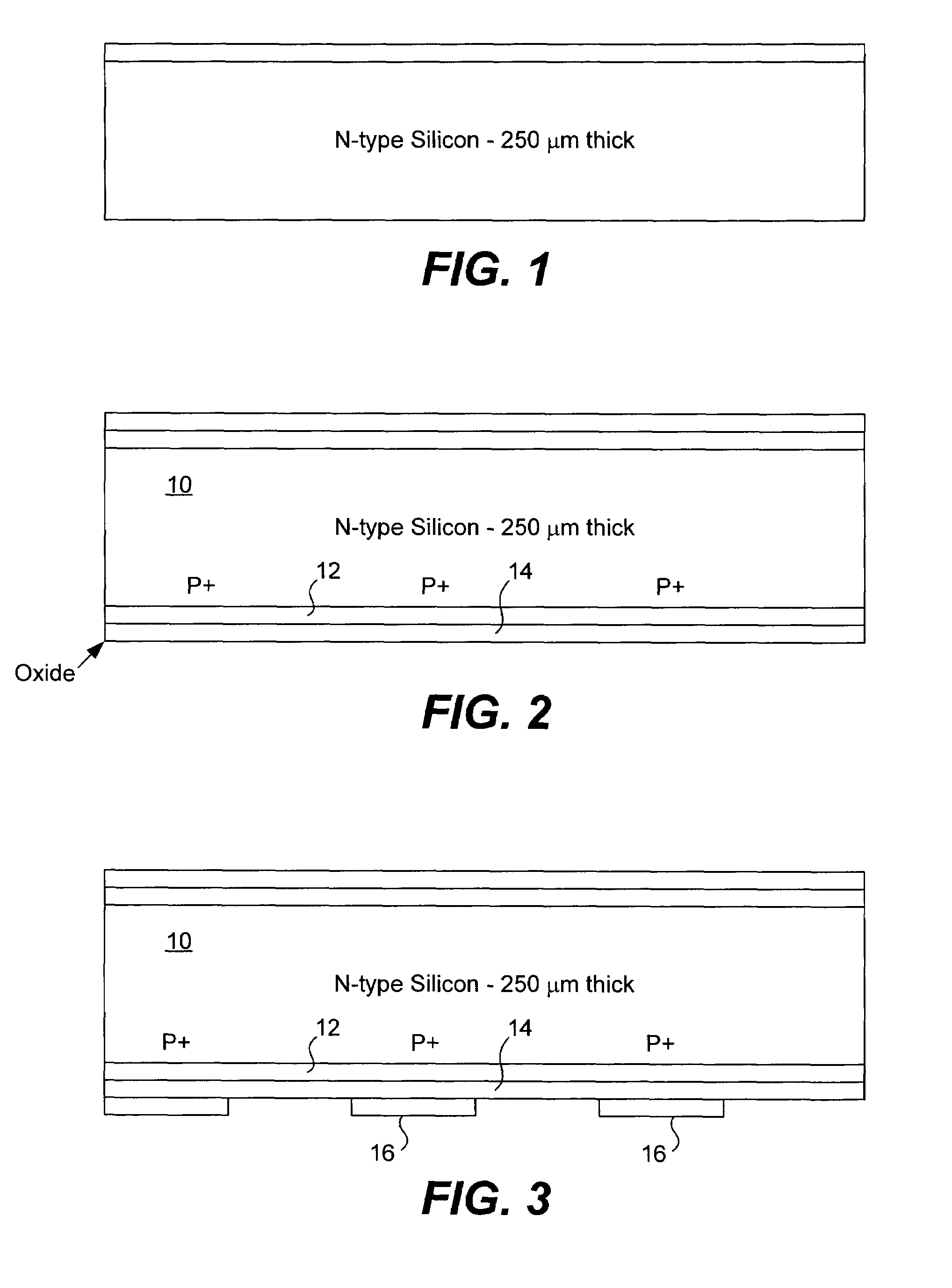

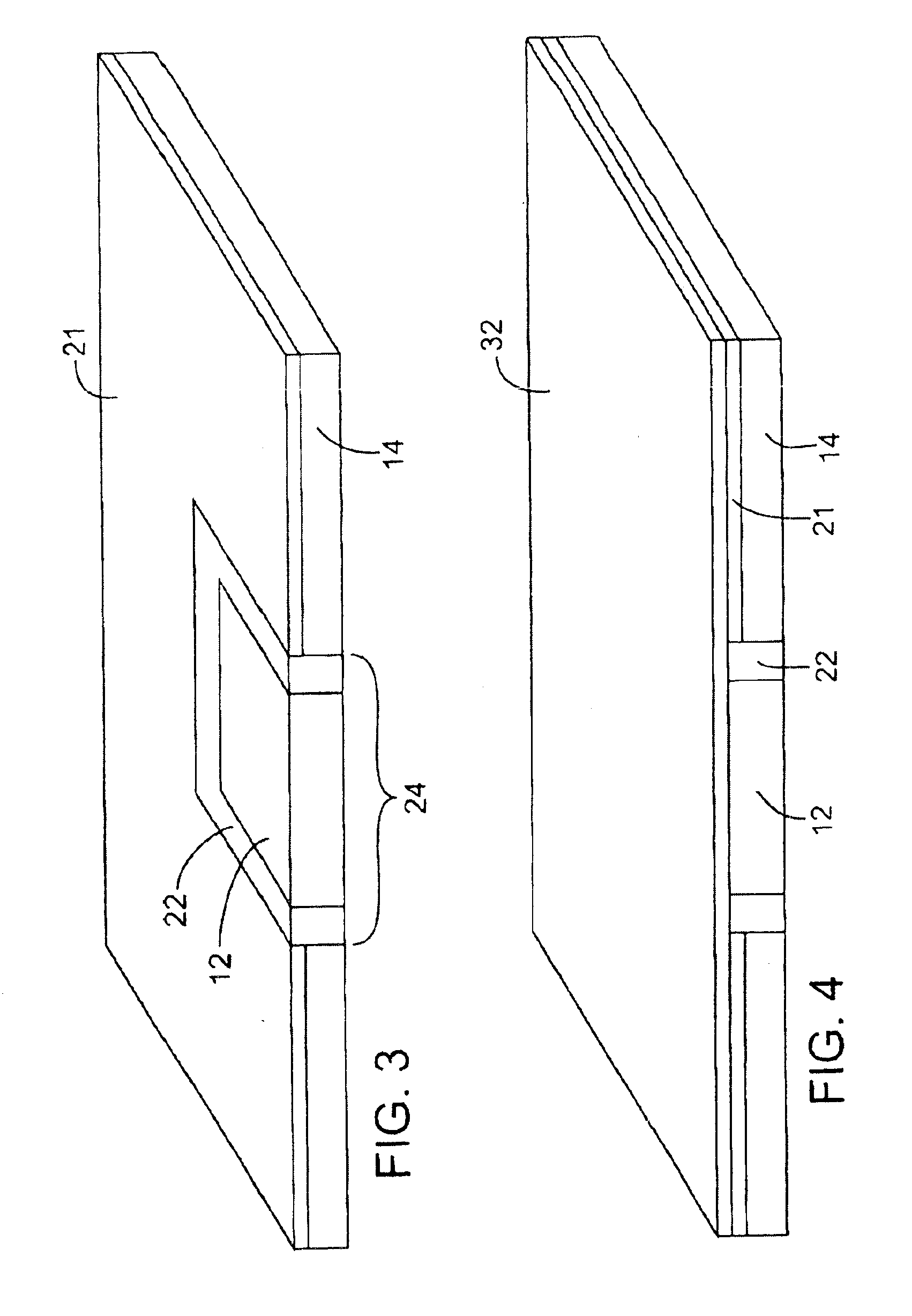

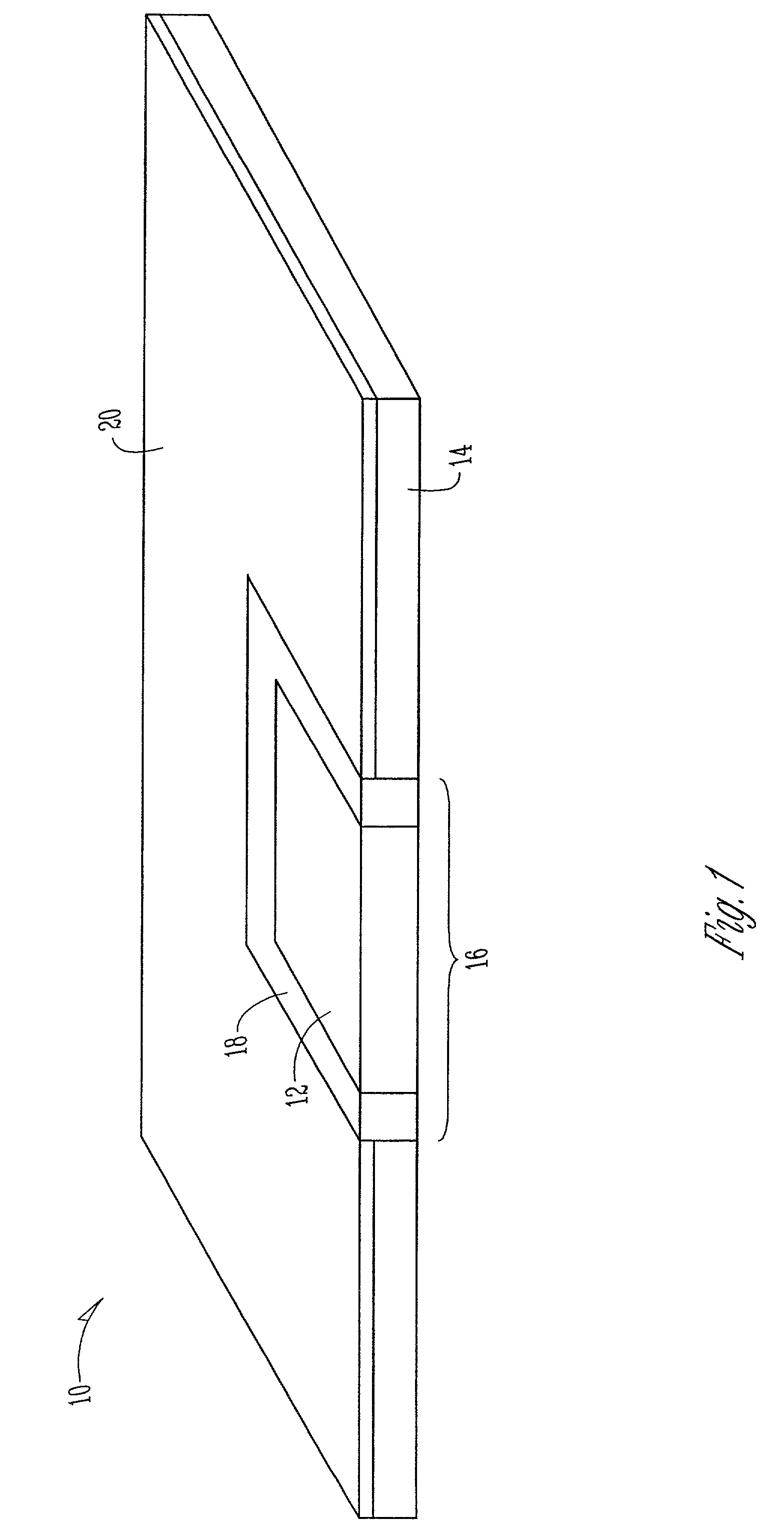

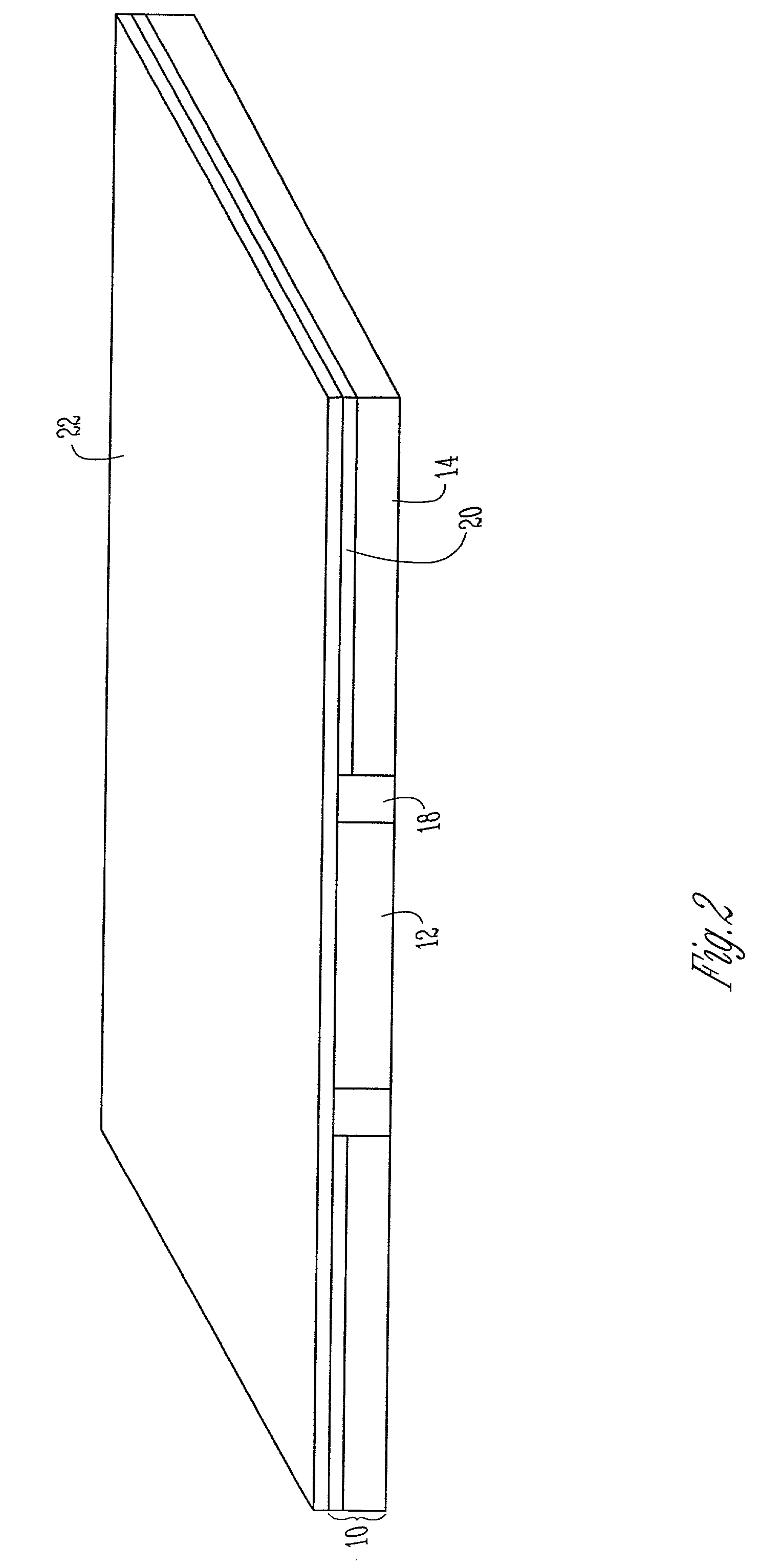

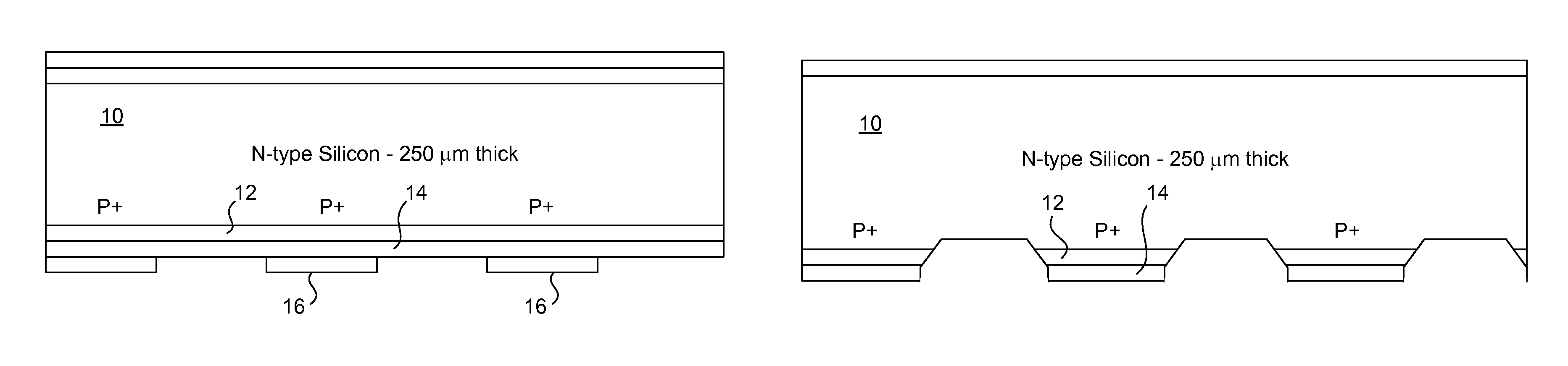

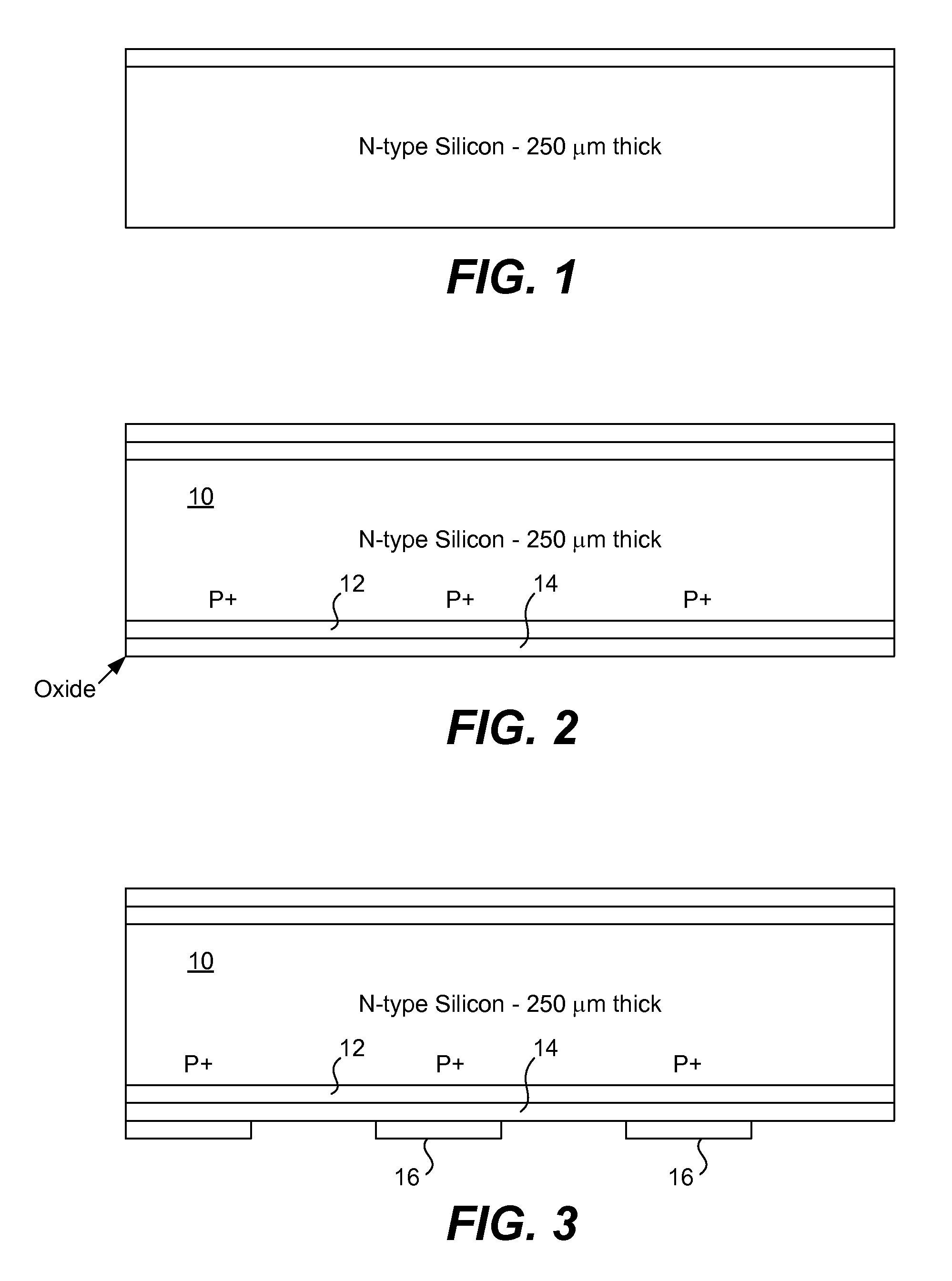

Solar cell and method of manufacture

ActiveUS7339110B1Easy to manufactureLess expensiveFinal product manufacturePhotovoltaic energy generationEngineeringSilicon oxide

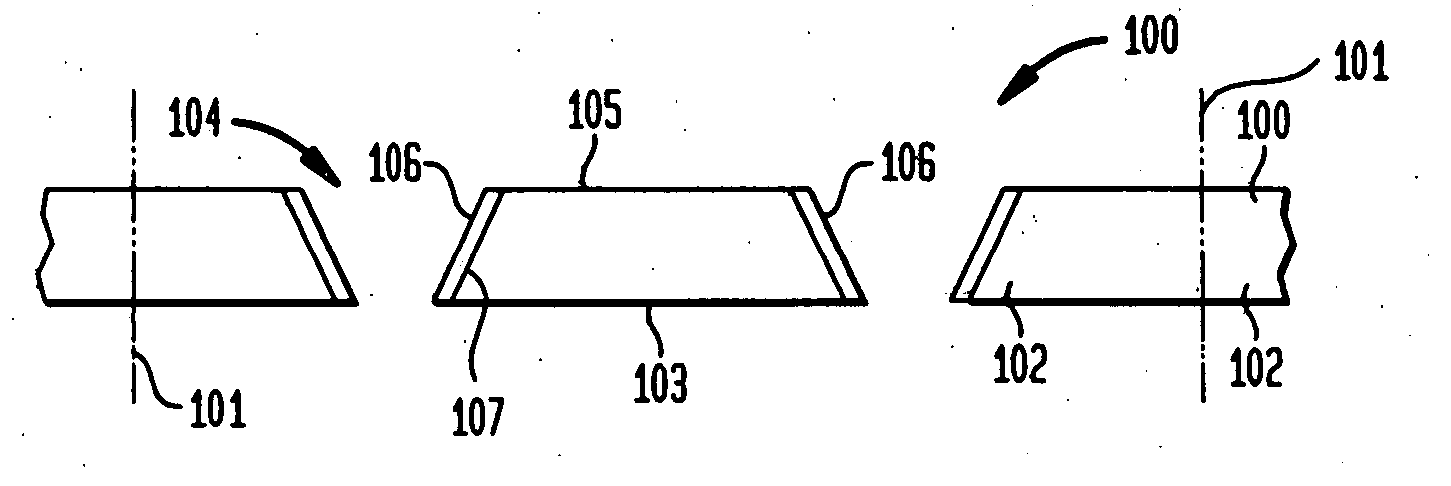

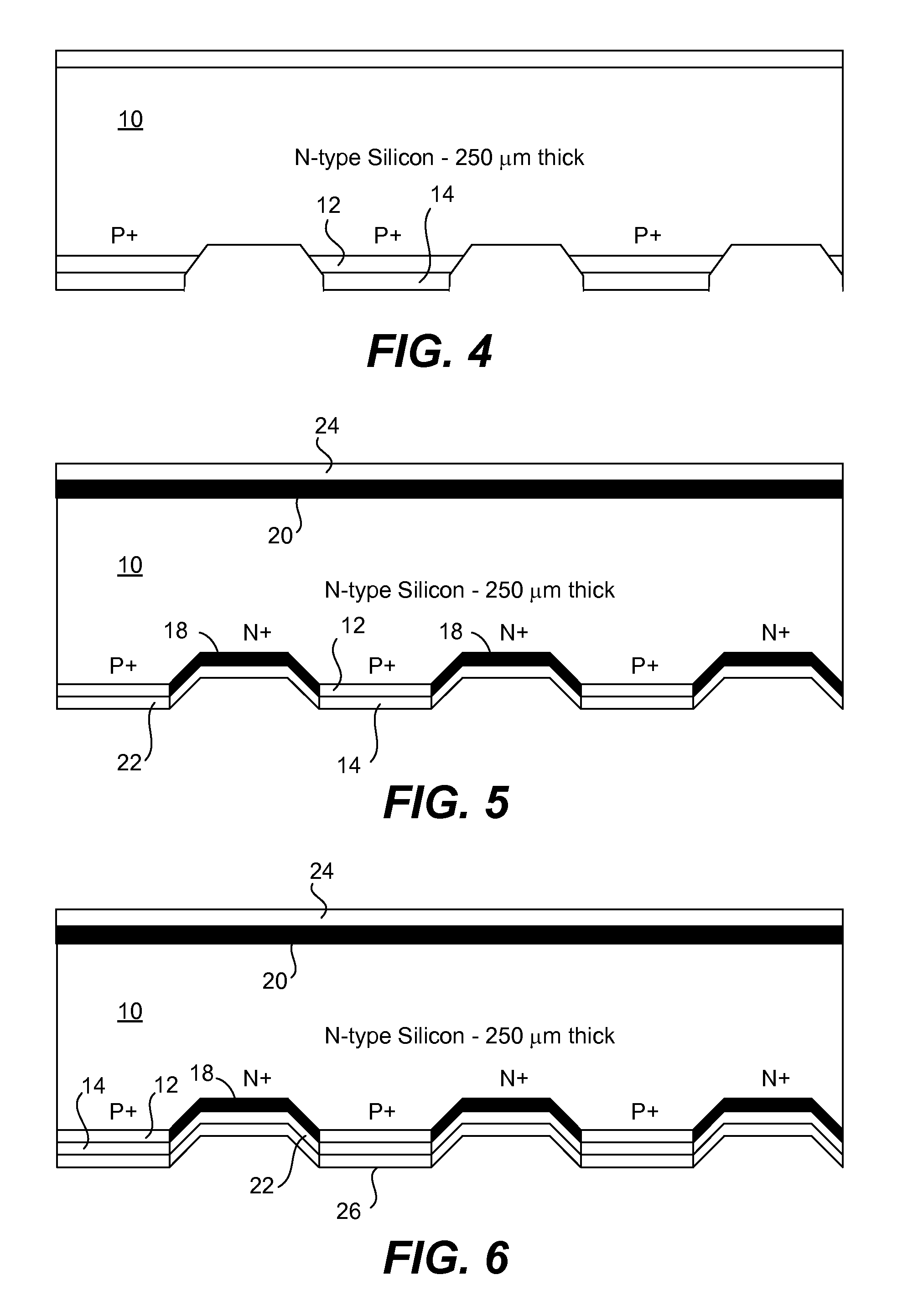

A solar cell that is readily manufactured using processing techniques which are less expensive than microelectronic circuit processing. In preferred embodiments, printing techniques are utilized in selectively forming masks for use in etching of silicon oxide and diffusing dopants and in forming metal contacts to diffused regions. In a preferred embodiment, p-doped regions and n-doped regions are alternately formed in a surface of the wafer in offset levels through use of masking and etching techniques. Metal contacts are made to the p-regions and n-regions by first forming a seed layer stack that comprises a first layer such as aluminum that contacts silicon and functions as an infrared reflector, second layer such titanium tungsten that acts as diffusion barrier, and a third layer functions as a plating base. A thick conductive layer such as copper is then plated over the seed layer, and the seed layer between plated lines is removed. A front surface of the wafer is preferably textured by etching or mechanical abrasion with an antireflection layer provided over the textured surface. A field layer can be provided in the textured surface with the combined effect being a very low surface recombination velocity.

Owner:MAXEON SOLAR PTE LTD +1

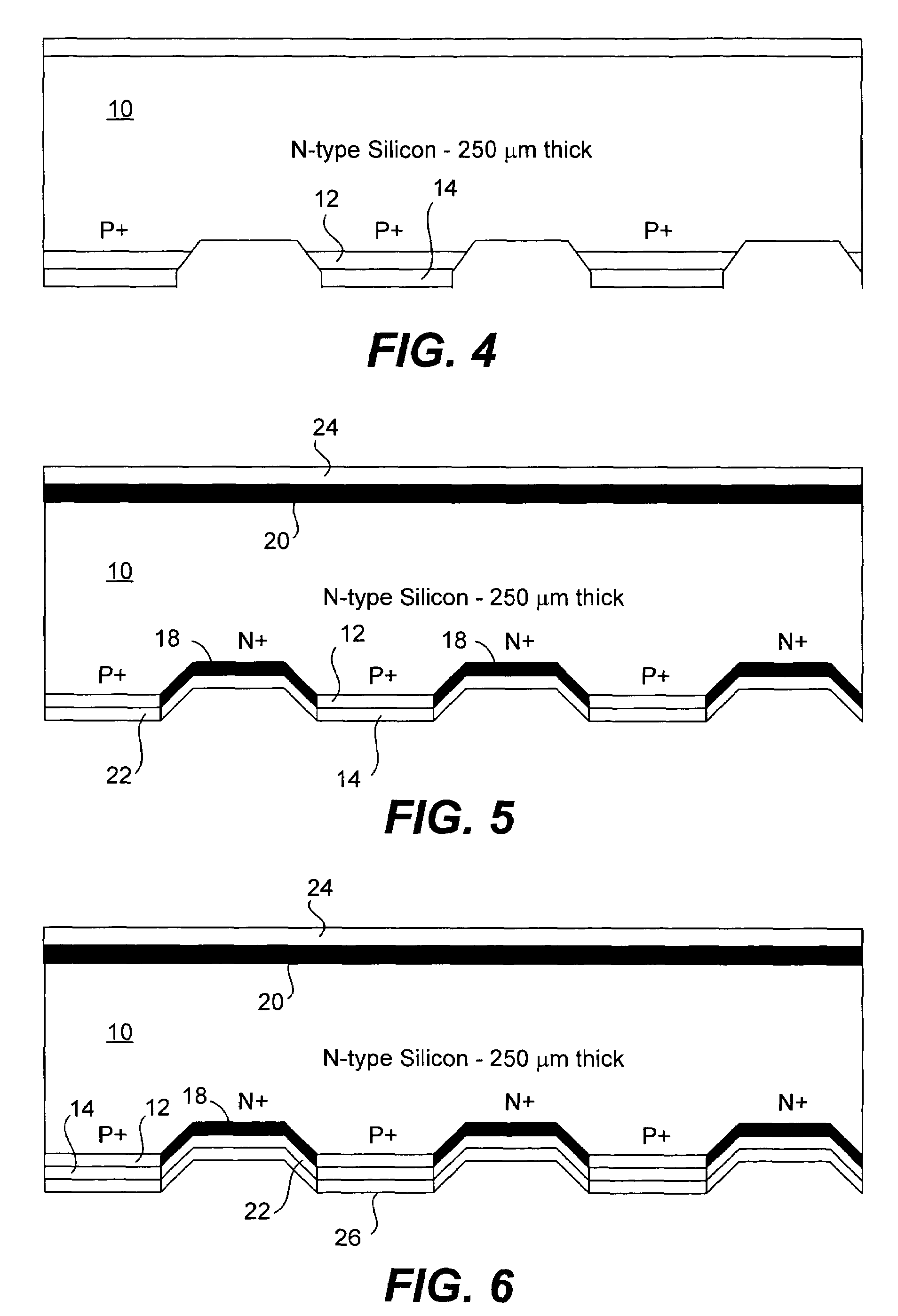

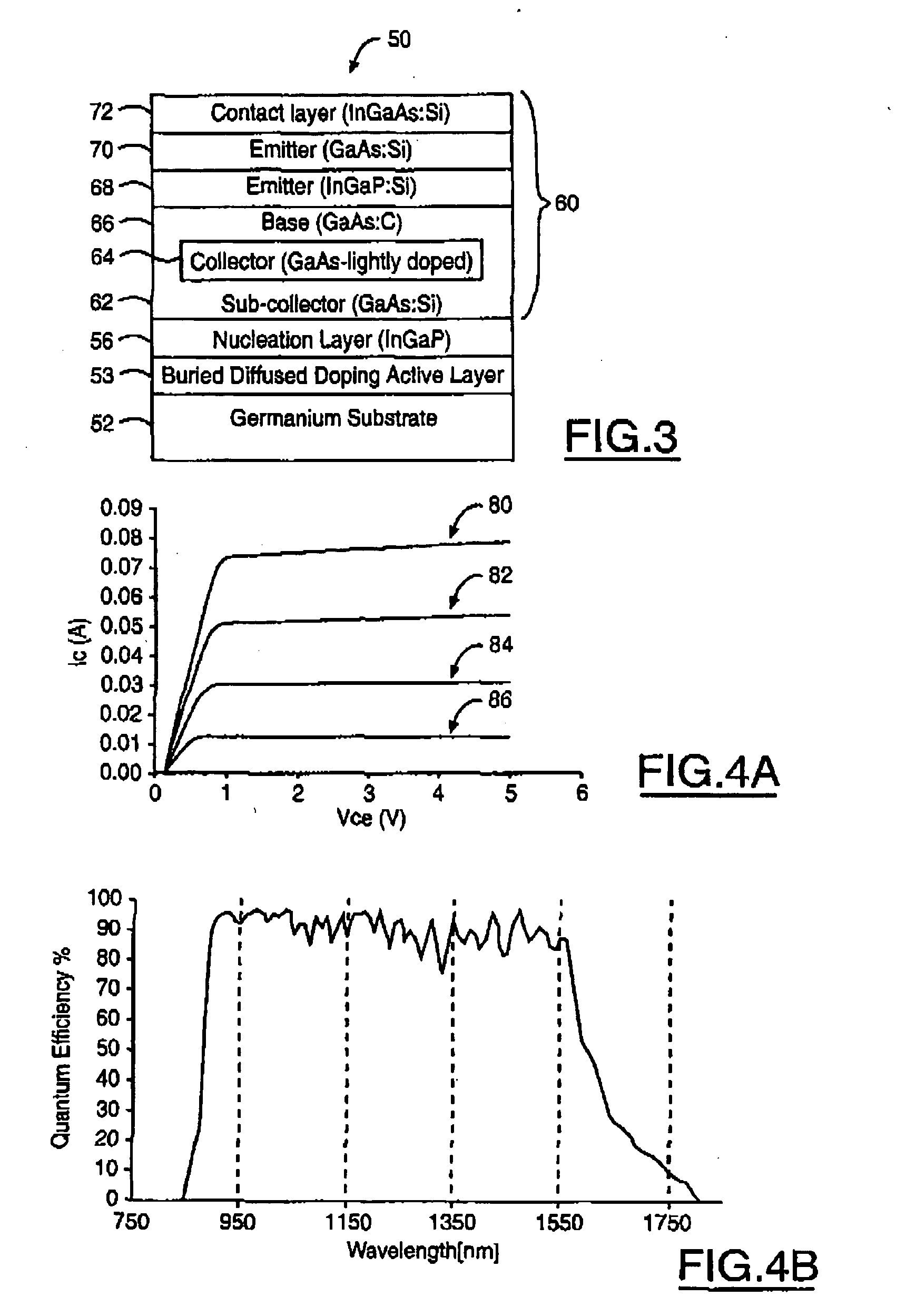

Integrated semiconductor circuits on photo-active Germanium substrates

InactiveUS20050110041A1Less expensiveSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSemiconductor materialsDevice material

A semiconductor device having at least one layer of a group III-V semiconductor material epitaxially deposited on a group III-V nucleation layer adjacent to a germanium substrate. By introducing electrical contacts on one or more layers of the semiconductor device, various optoelectronic and microelectronic circuits may be formed on the semiconductor device having similar quality to conventional group III-V substrates at a substantial cost savings. Alternatively, an active germanium device layer having electrical contacts may be introduced to a portion of the germanium substrate to form an optoelectronic integrated circuit or a dual optoelectronic and microelectronic device on a germanium substrate depending on whether the electrical contacts are coupled with electrical contacts on the germanium substrate and epitaxial layers, thereby increase the functionality of the semiconductor devices.

Owner:THE BOEING CO

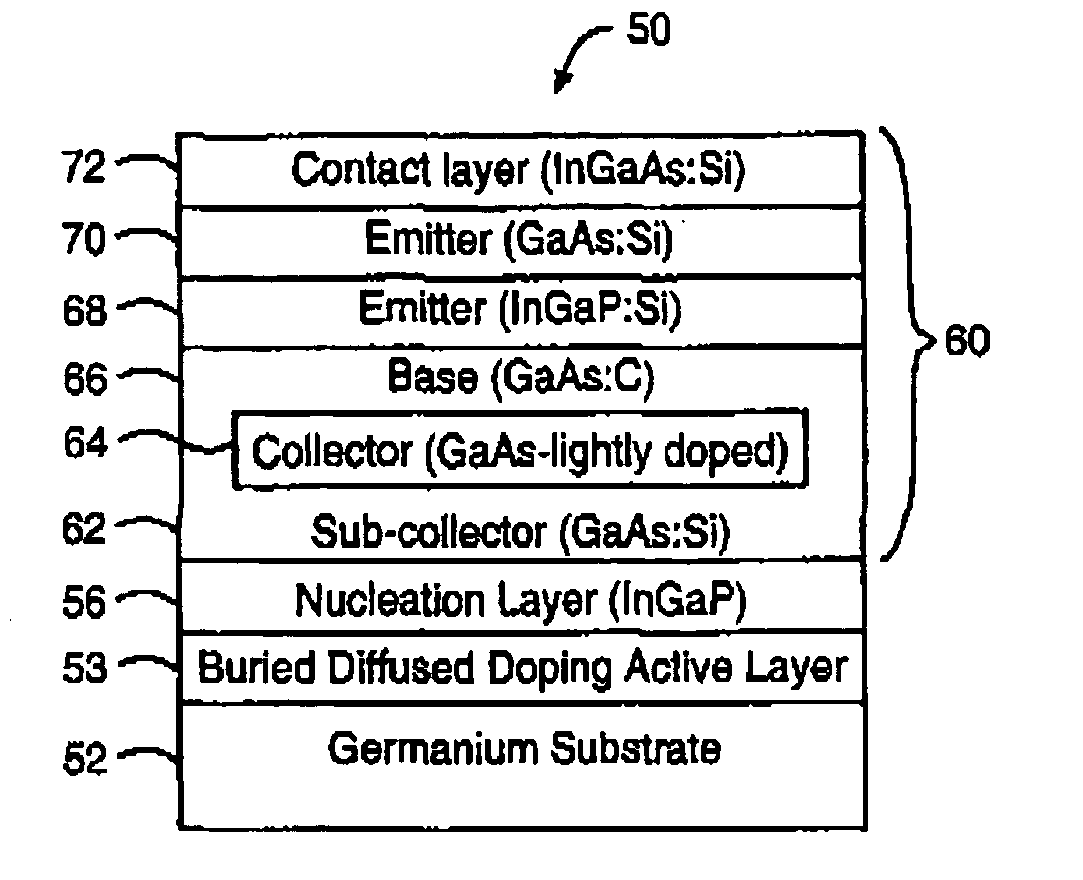

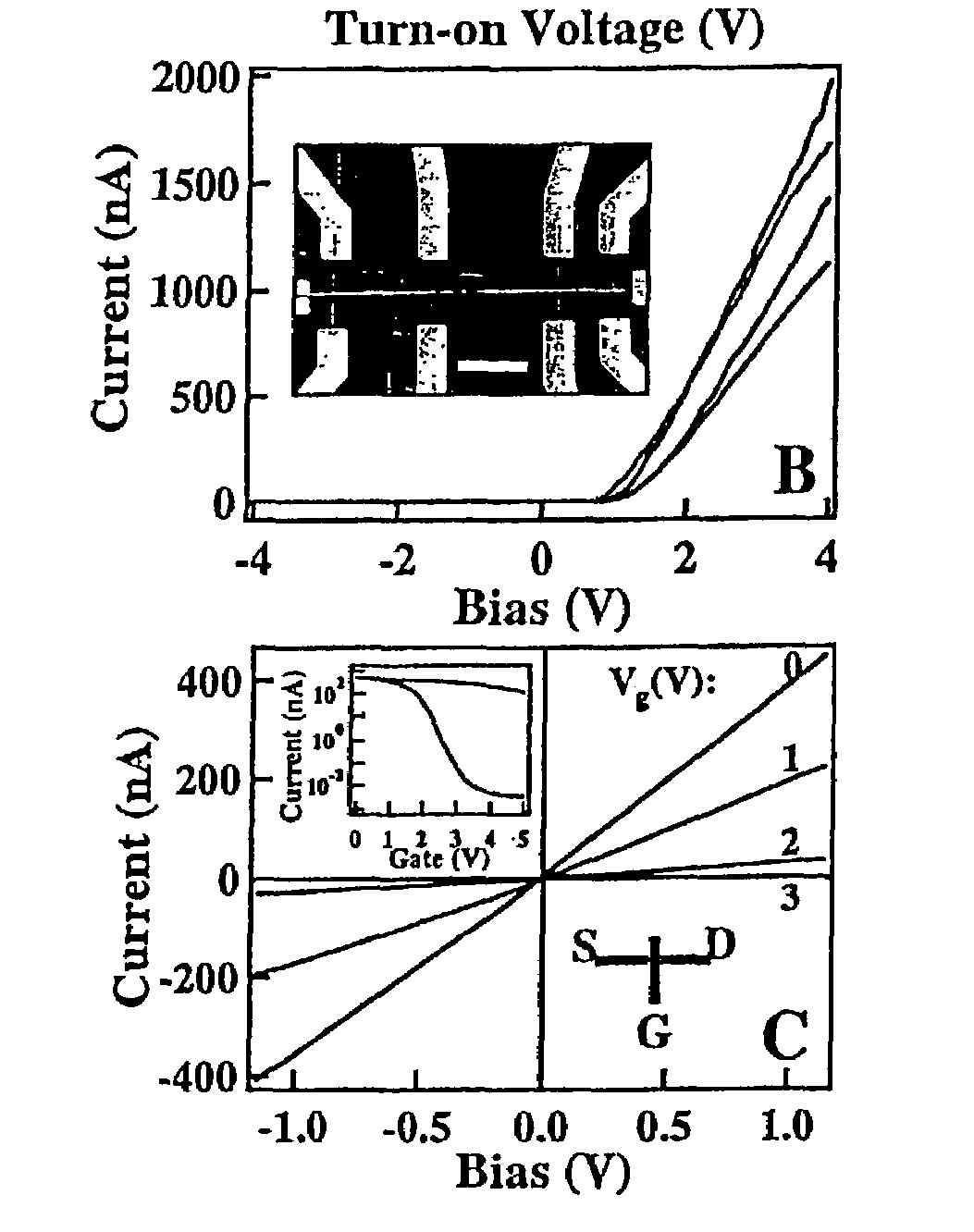

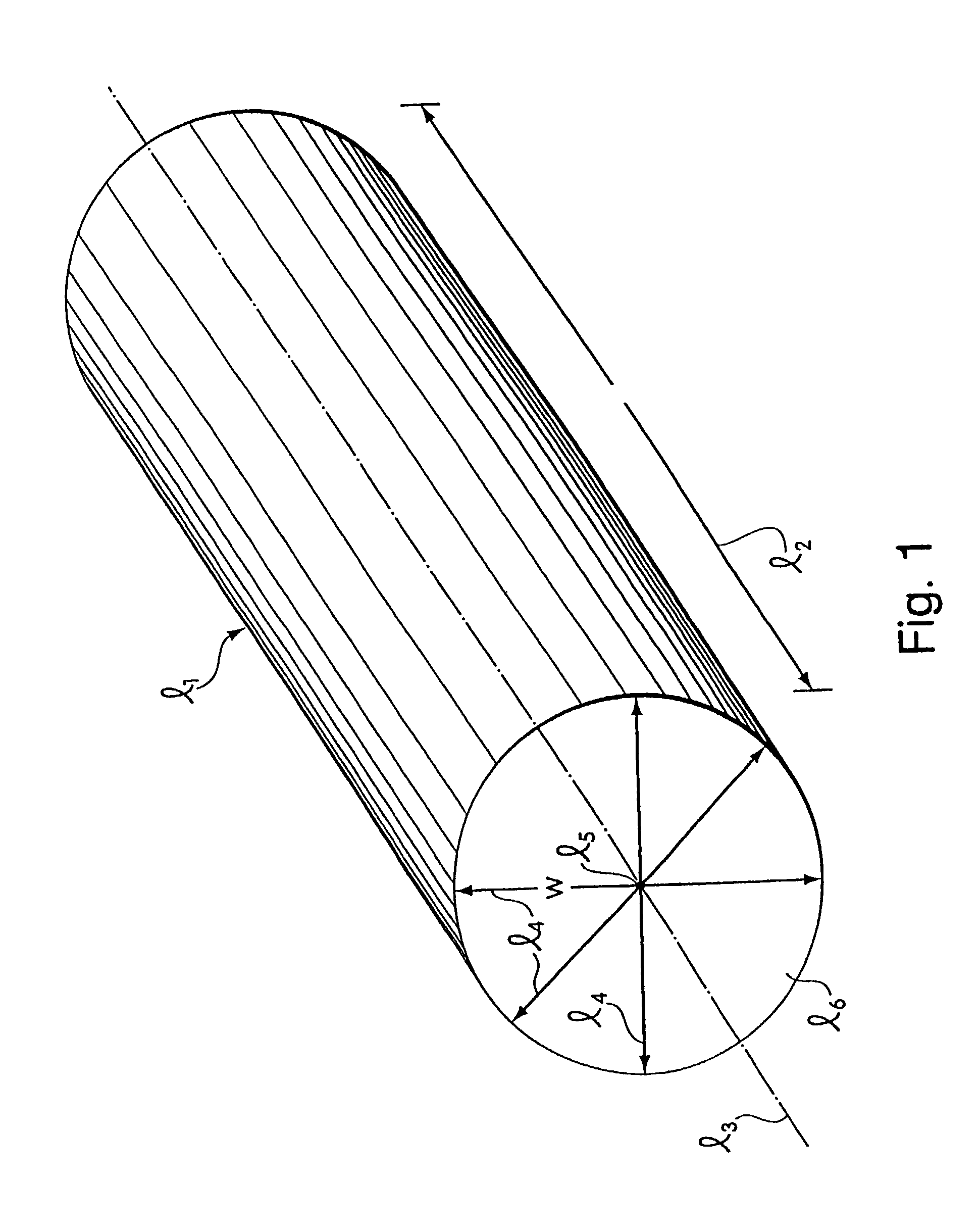

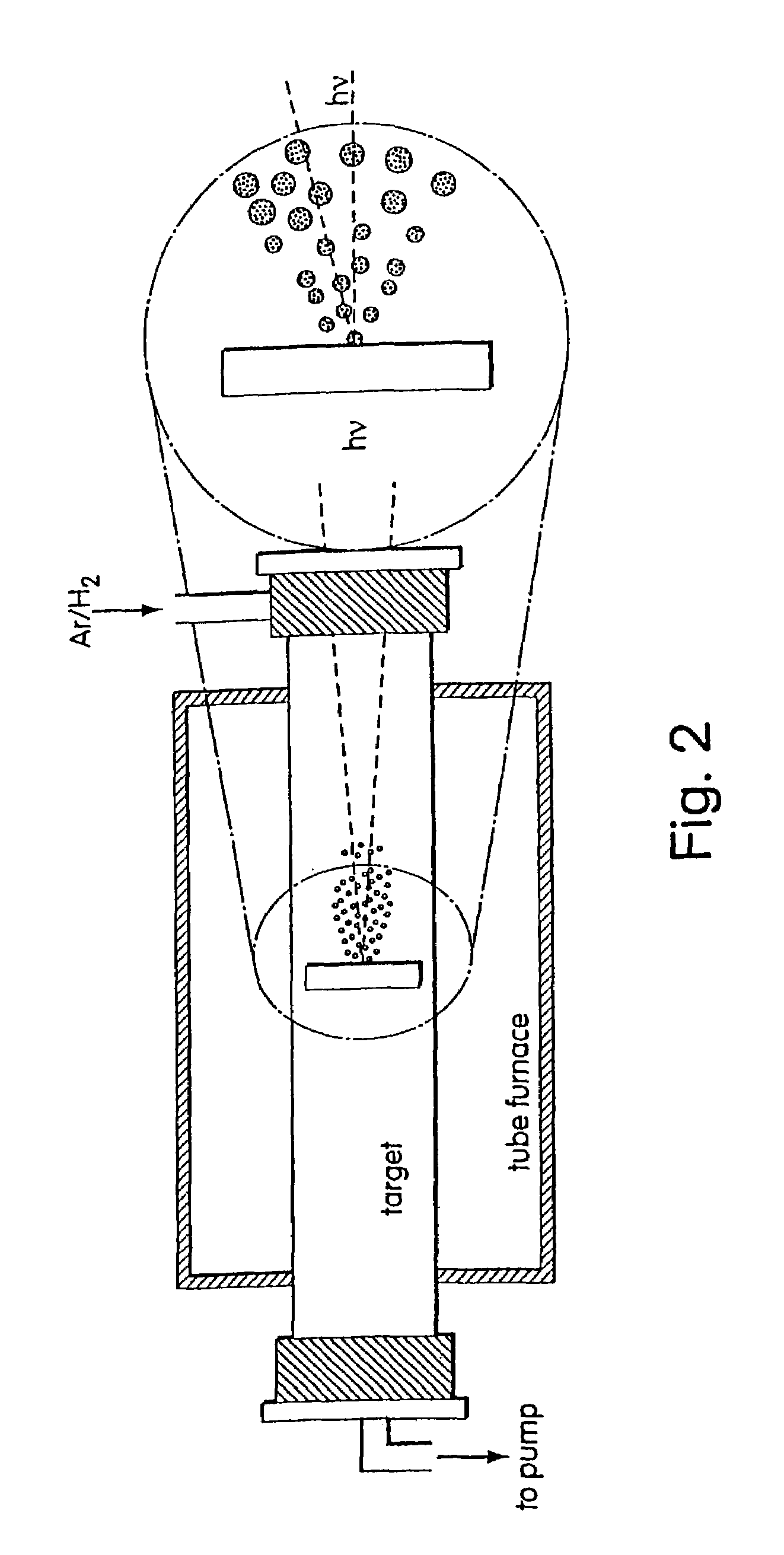

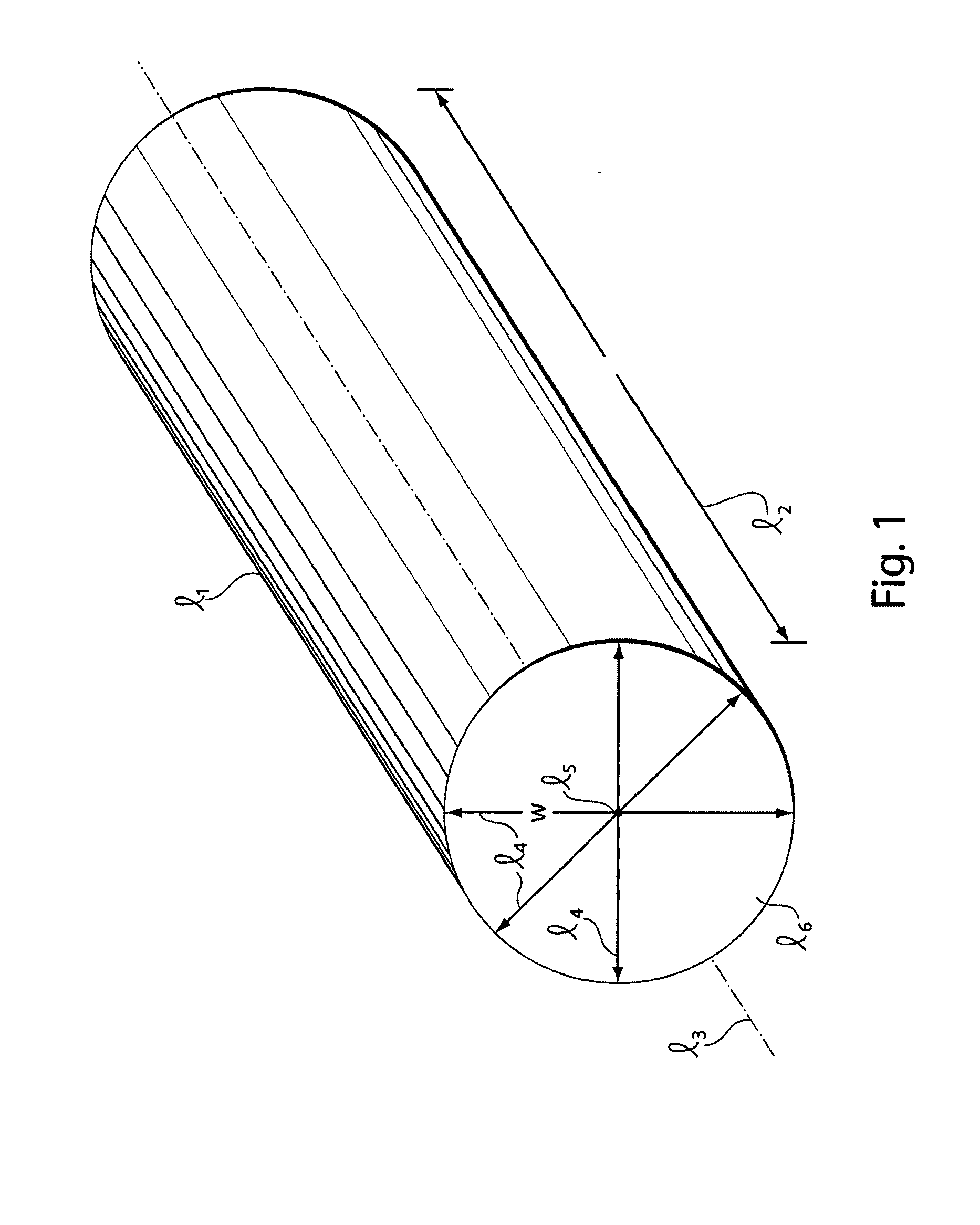

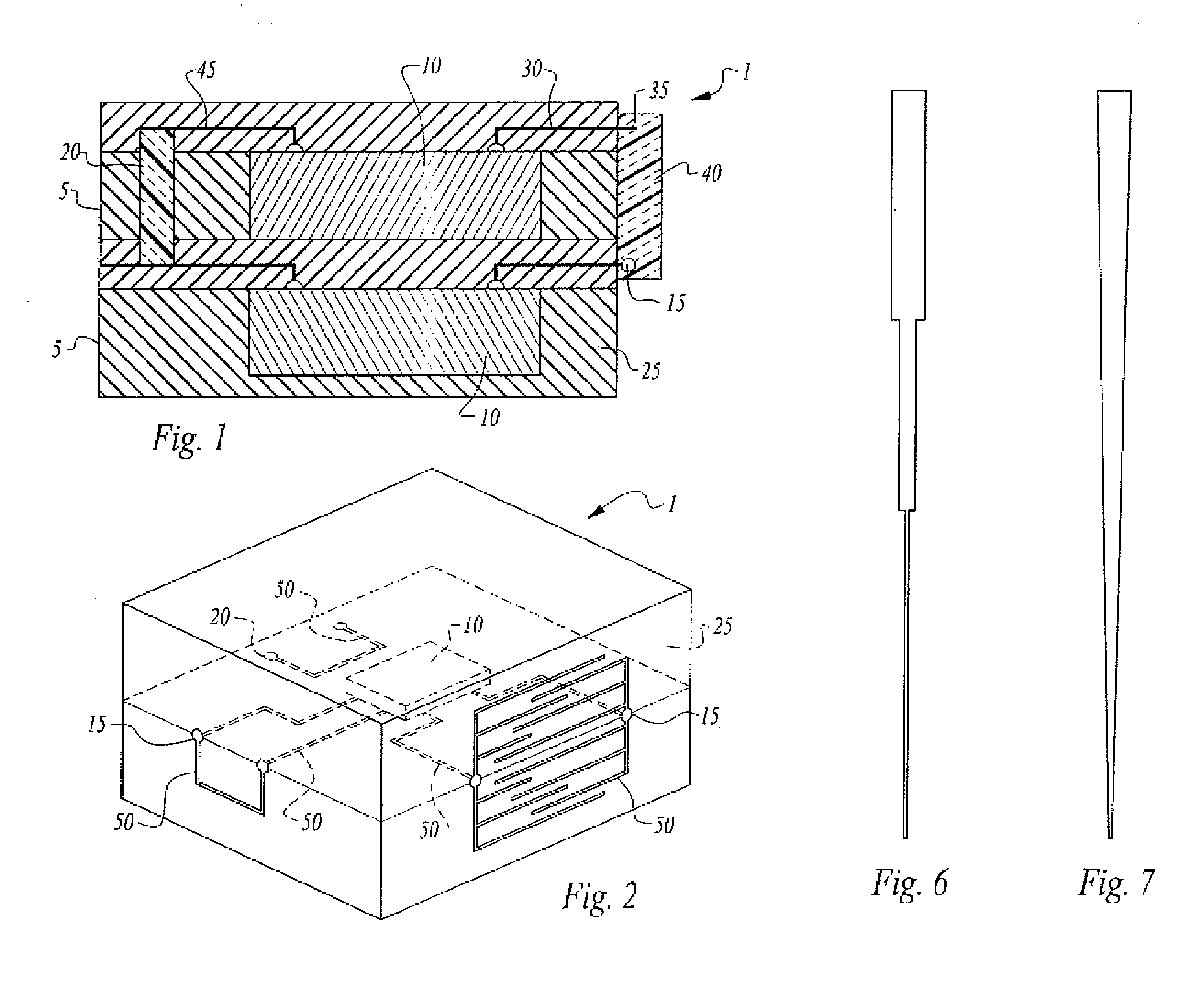

Nanoscale wires and related devices

InactiveUS7301199B2Material nanotechnologySemiconductor/solid-state device detailsDopantTunnel diode

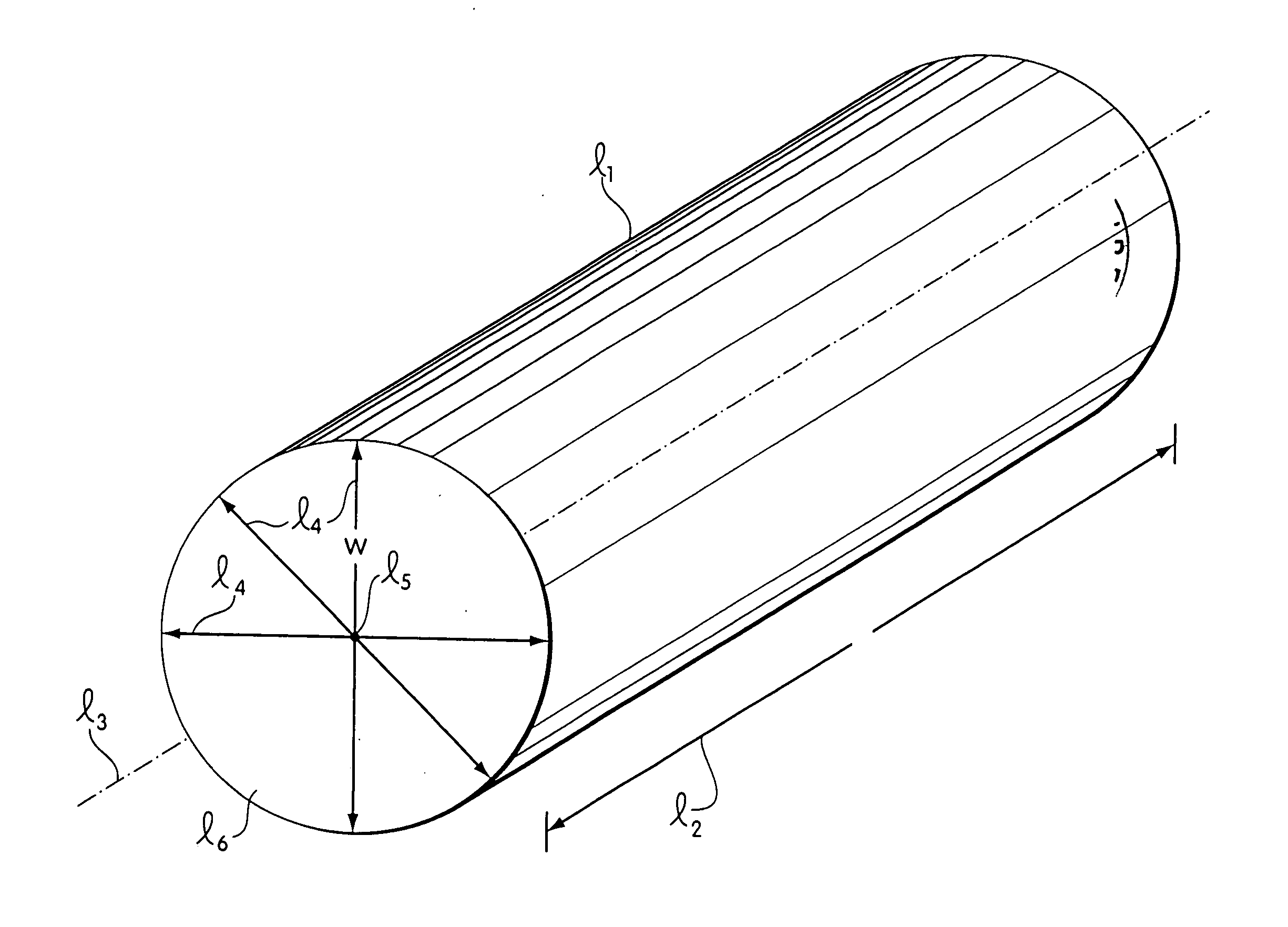

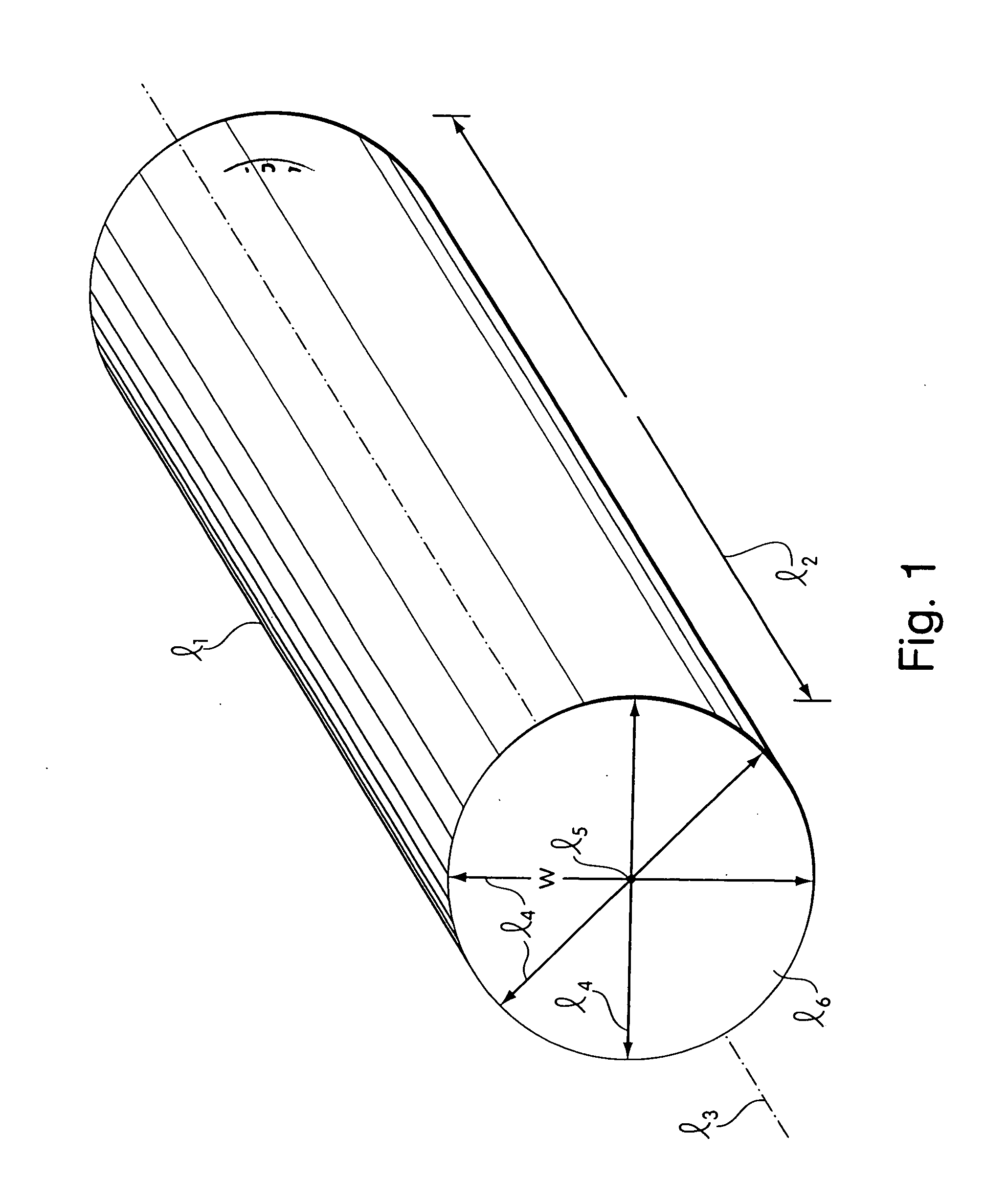

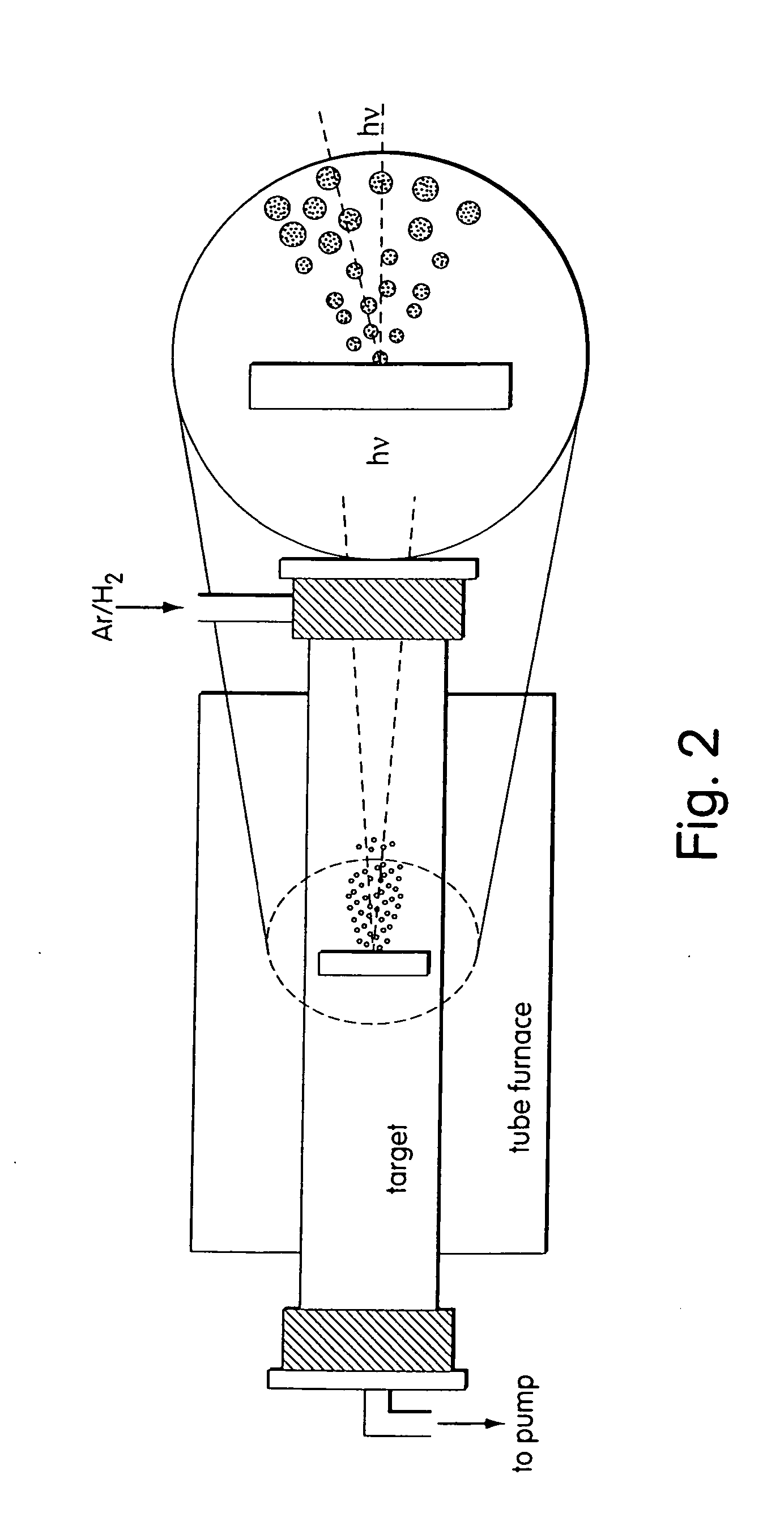

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Nanoscale wires and related devices

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

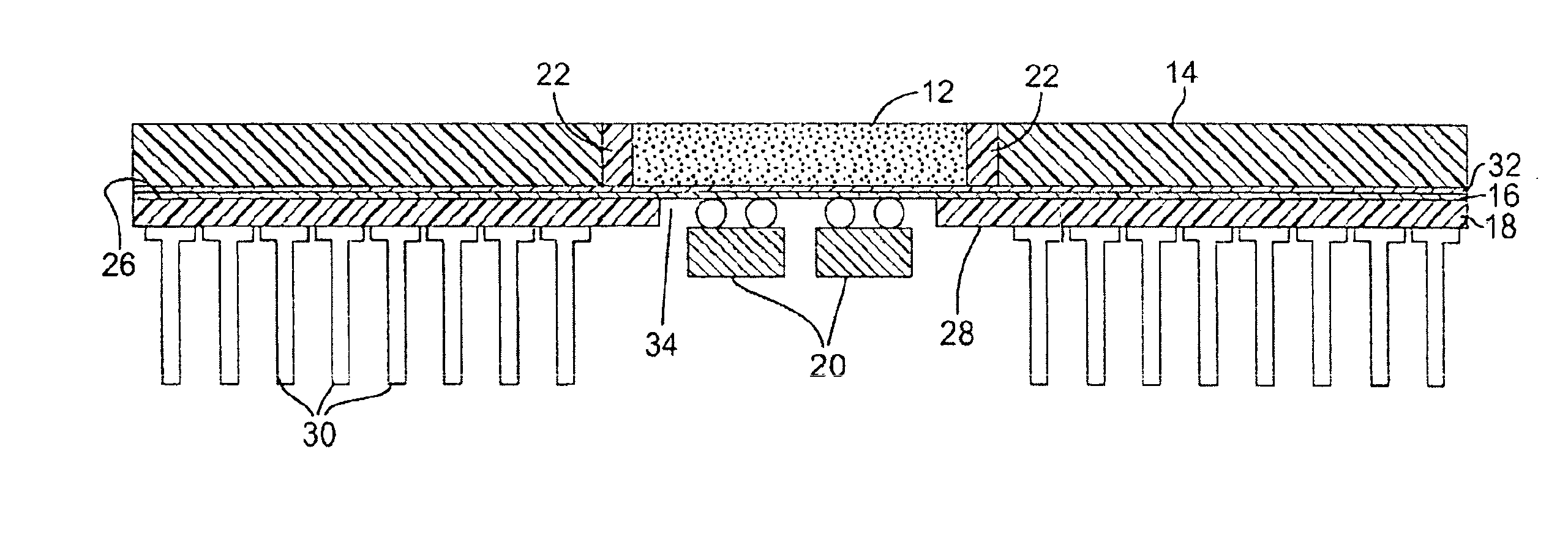

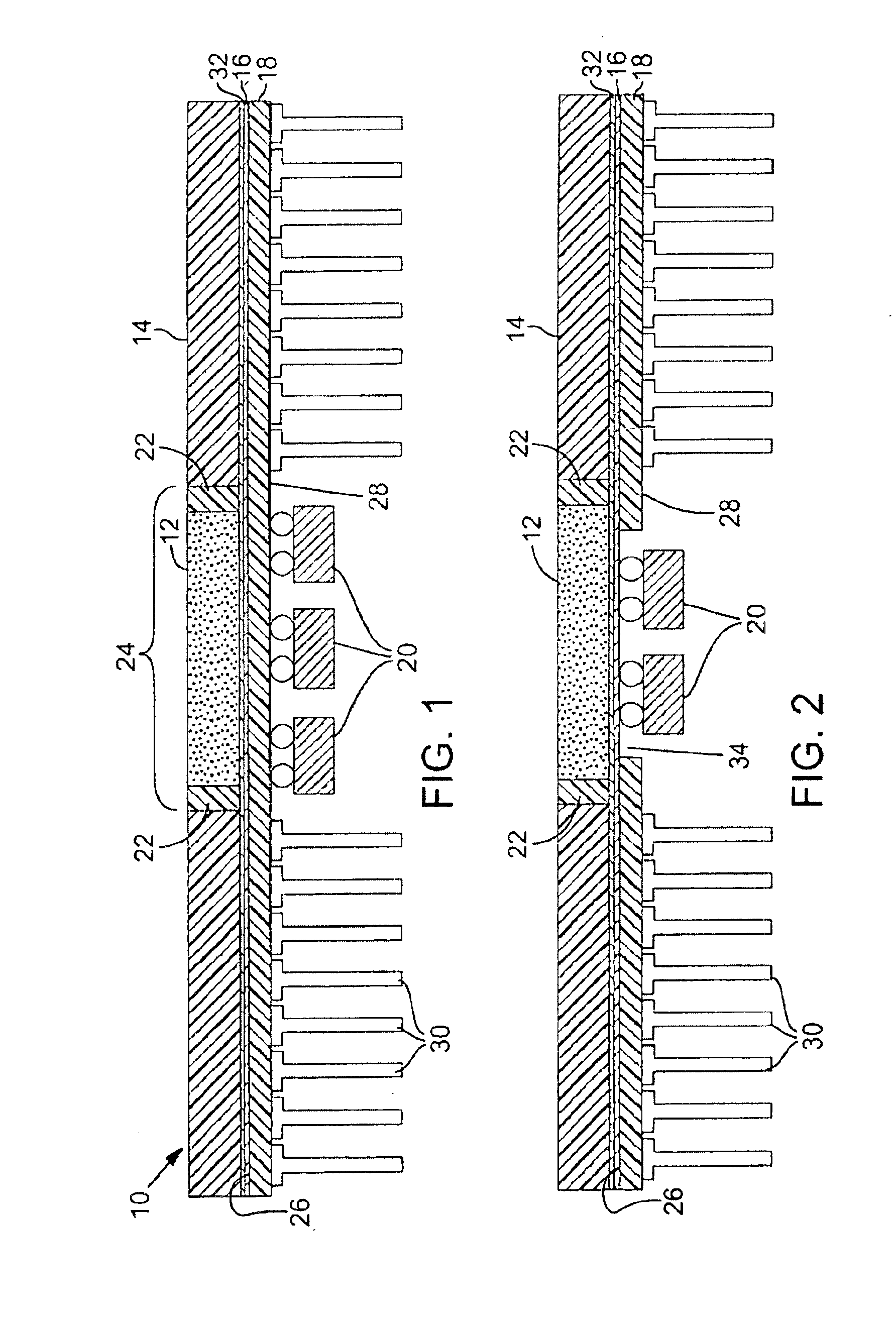

High performance, low cost microelectronic circuit package with interposer

InactiveUS6888240B2Semiconductor/solid-state device detailsSolid-state devicesPin grid arrayInterposer

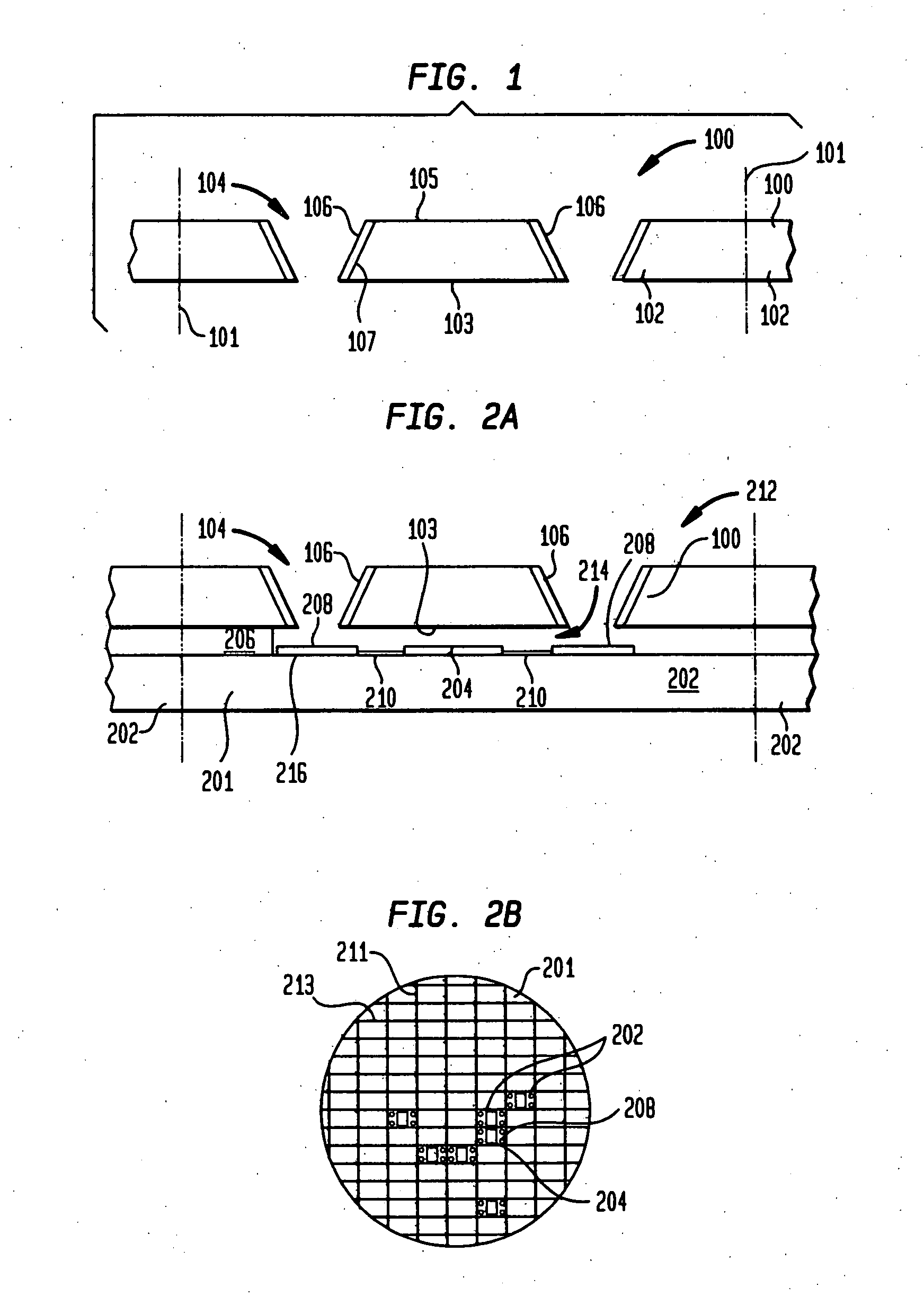

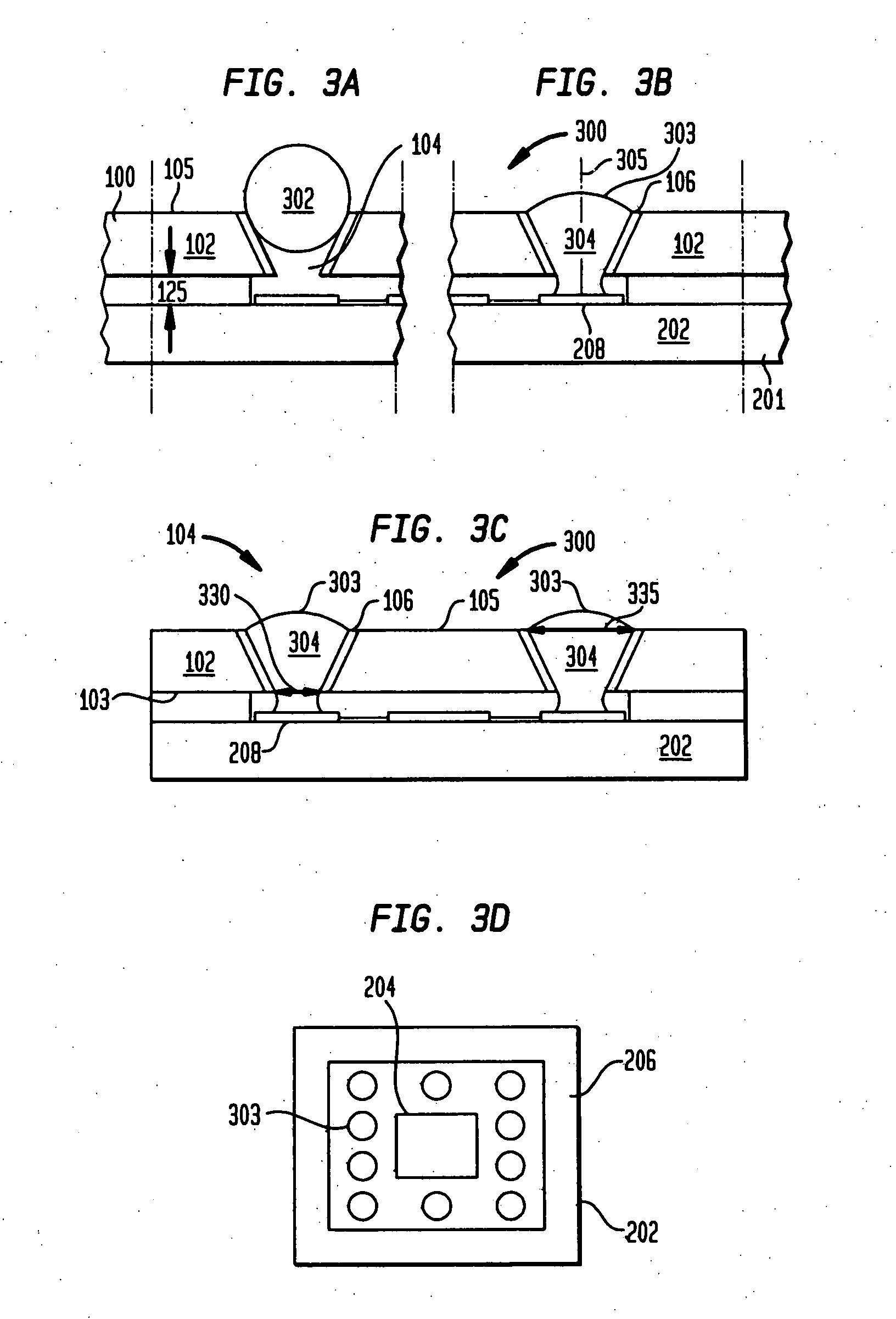

A low cost technique for packaging microelectronic circuit chips fixes a die within an opening in a package core. At least one metallic build up layer is then formed on the die / core assembly and a grid array interposer unit is laminated to the build up layer. The grid array interposer unit can then be mounted within an external circuit using any of a plurality of mounting technologies (e.g., ball grid array (BGA), land grid array (LGA), pin grid array (PGA), surface mount technology (SMT), and / or others). In one embodiment, a single build up layer is formed on the die / core assembly before lamination of the interposer.

Owner:INTEL CORP

Nanoscale arrays, robust nanostructures, and related devices

InactiveUS20050253137A1NanoinformaticsSolid-state devicesMicroelectronic circuitsElectronic component

The present invention relates generally to nanotechnology and sub-microelectronic circuitry, and more particularly to nanoelectronics. One aspect of the invention is directed to nanostructures on substrates. In some cases, the substrate may be or comprise glass and / or polymers, and in some cases, the substrate may be flexible and / or transparent. The present invention is also directed, according to another aspect, to techniques for fabricating nanostructures on substrates. For example, monolayers of nanoscale semiconductors may be etched, e.g. photolithographically, to yield discrete and / or predetermined arrays of nanoscale semiconductors and other articles on a substrate. In one embodiment, the array may include hundreds, thousands, or more of electronic components such as field-effect transistors. Such arrays may be connected to electrodes using photolithographic techniques, and in some cases, without the need for registering individual semiconductor-metal contacts.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Structure and method of making lidded chips

InactiveUS20080029879A1High mechanical strengthObstruct passageSemiconductor/solid-state device detailsSolid-state devicesMicroelectronic circuitsMaterials science

Lidded chip packages are provided in which an optoelectronic device chip has microelectronic circuits exposed at a surface of the chip with a lid mounted to overlie the optoelectronic device and the microelectronic circuits. An opaque film may be attached to the lid to overlie the microelectronic circuits while exposing the optoelectronic device. Lidded chip packages are also provided in which the lid overlies an active or passive device mounted to the chip. Wiring traces may be embedded within an adhesive between the lid and the chip.

Owner:TESSERA INC

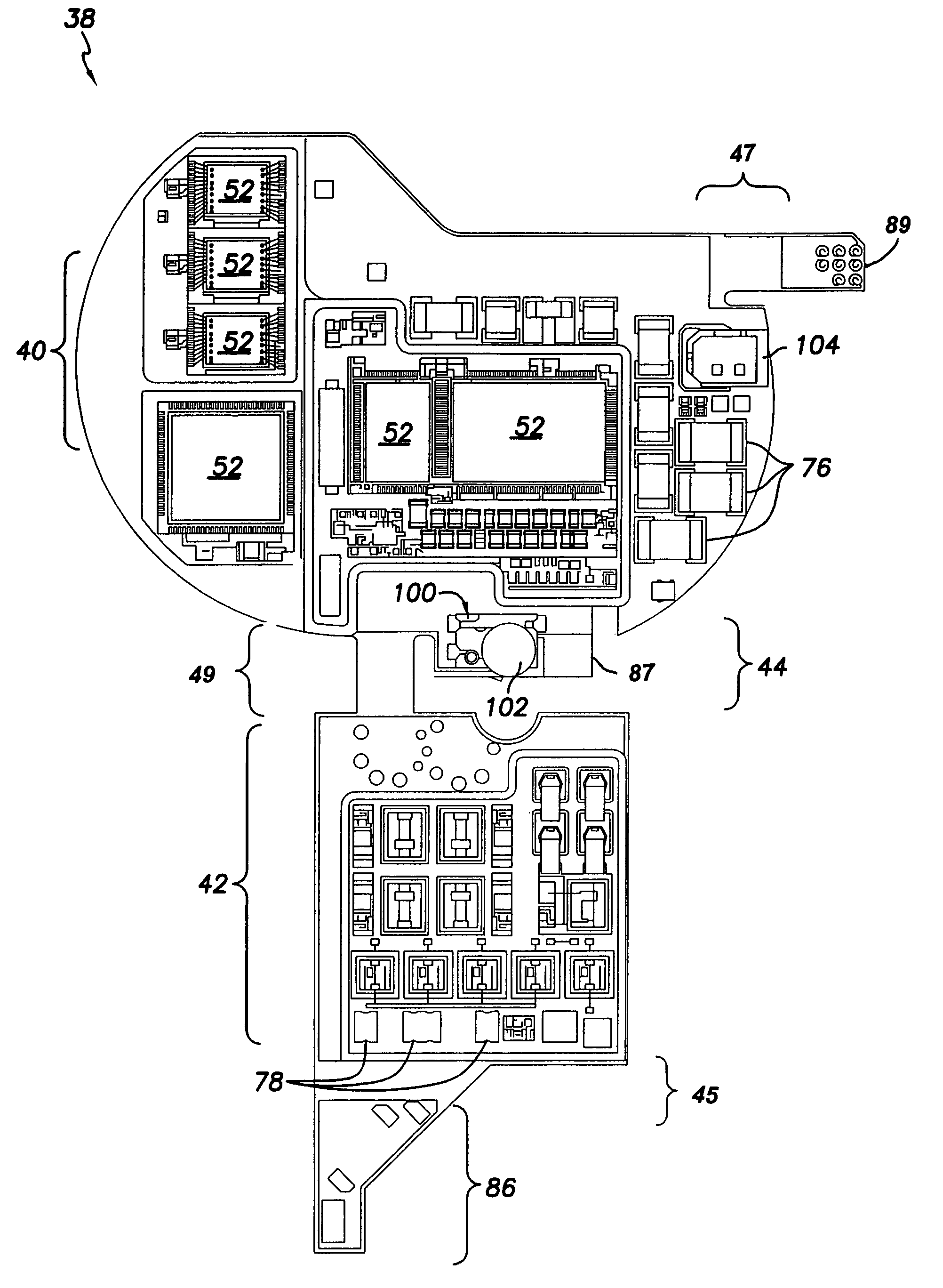

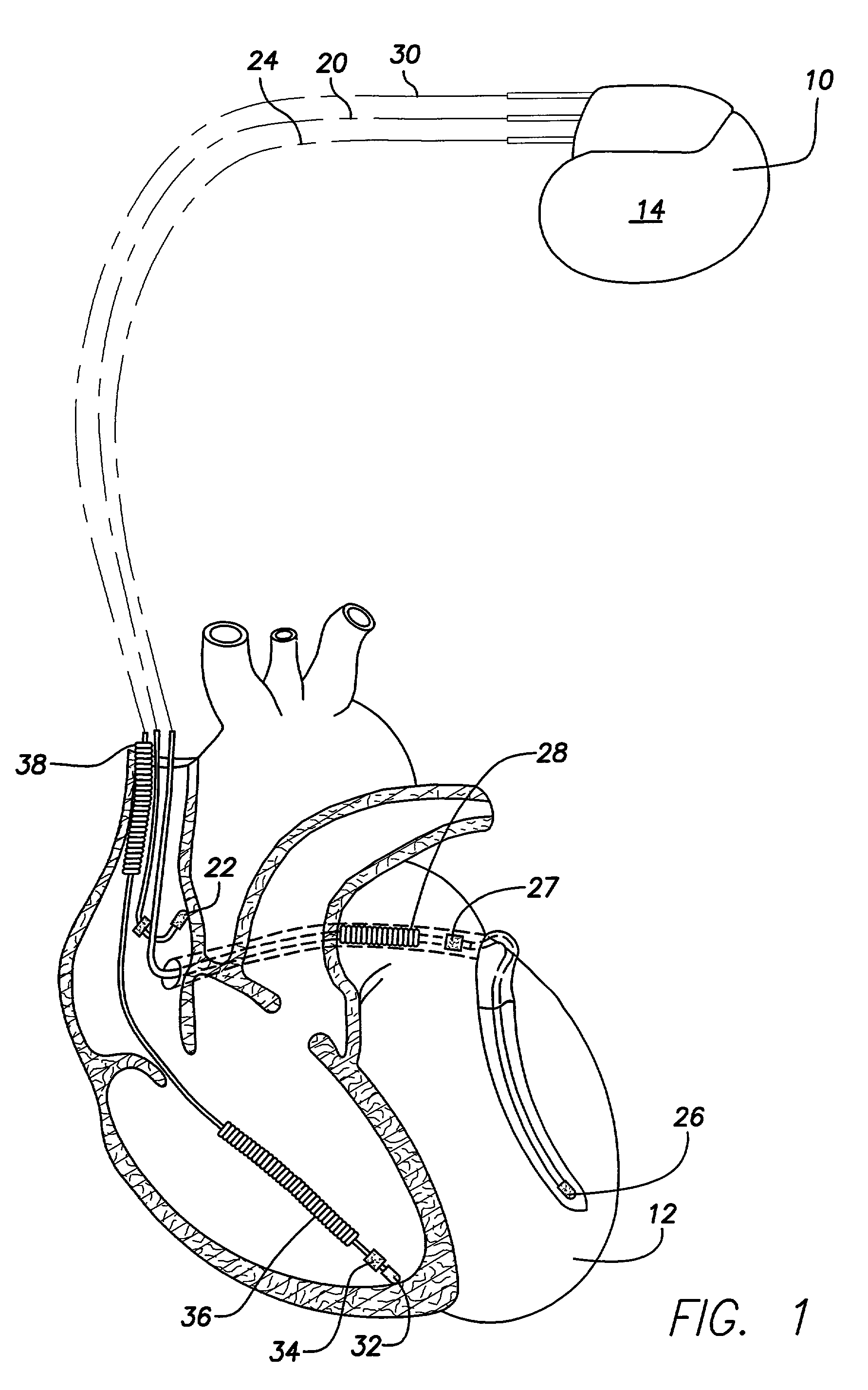

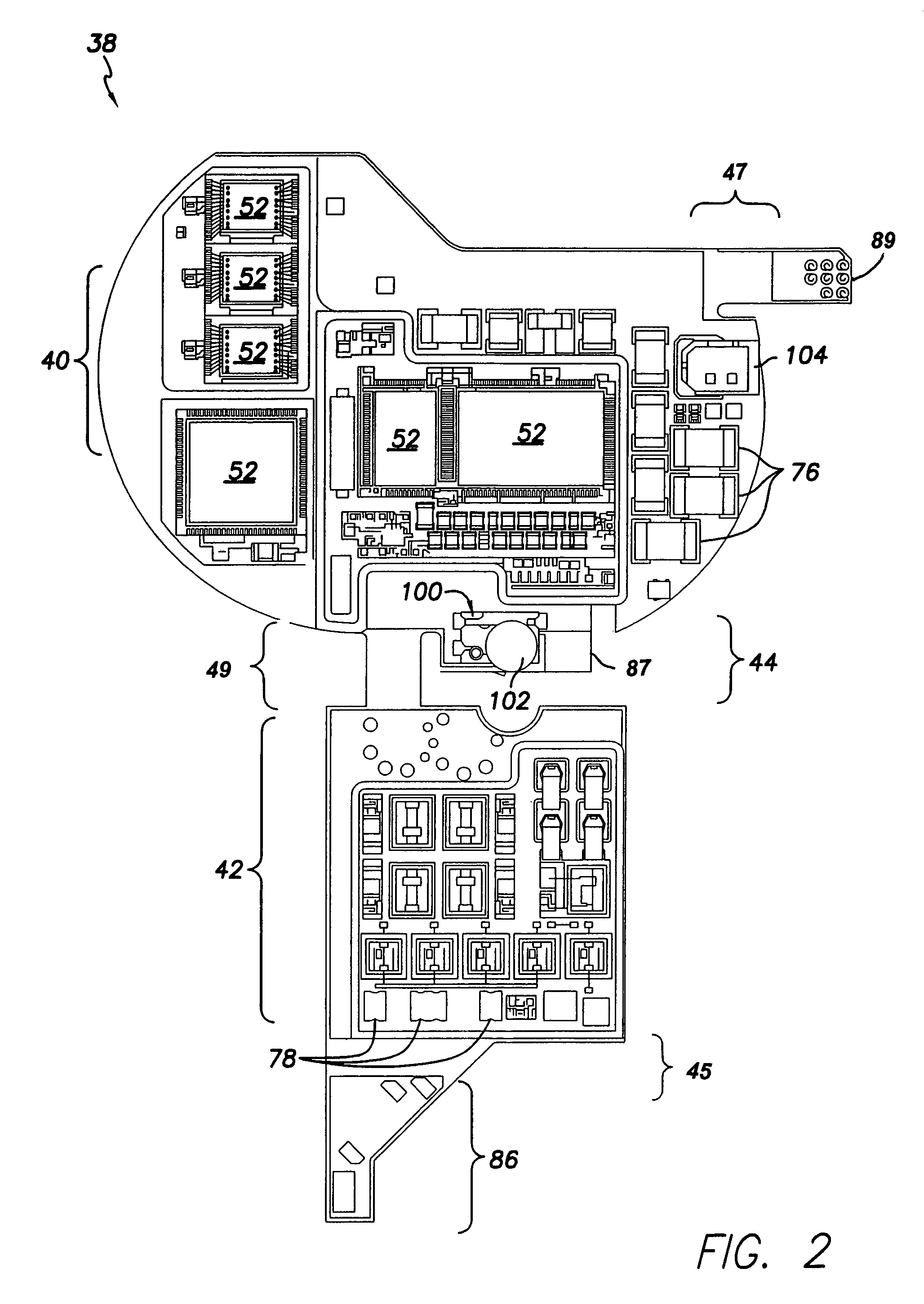

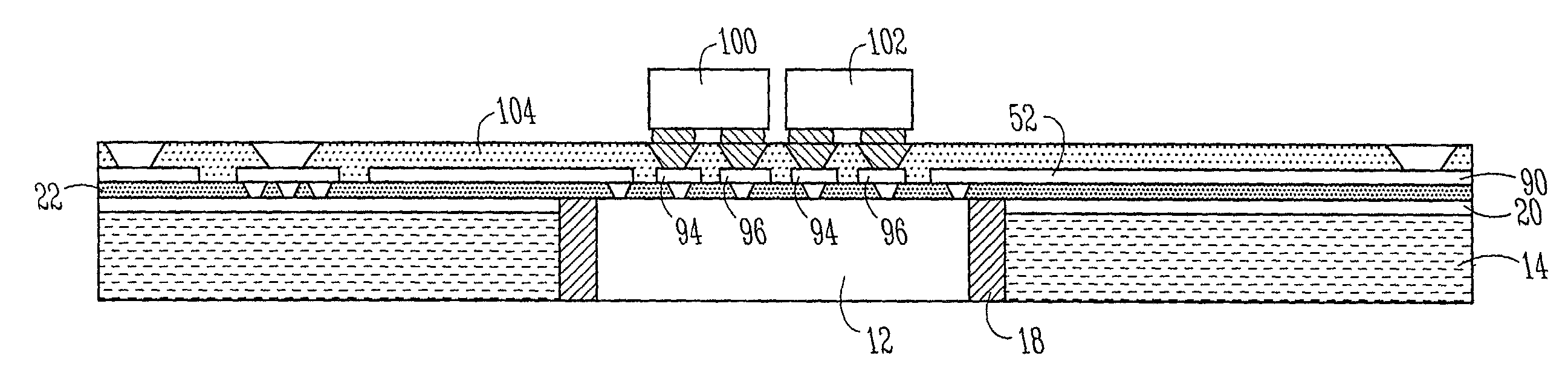

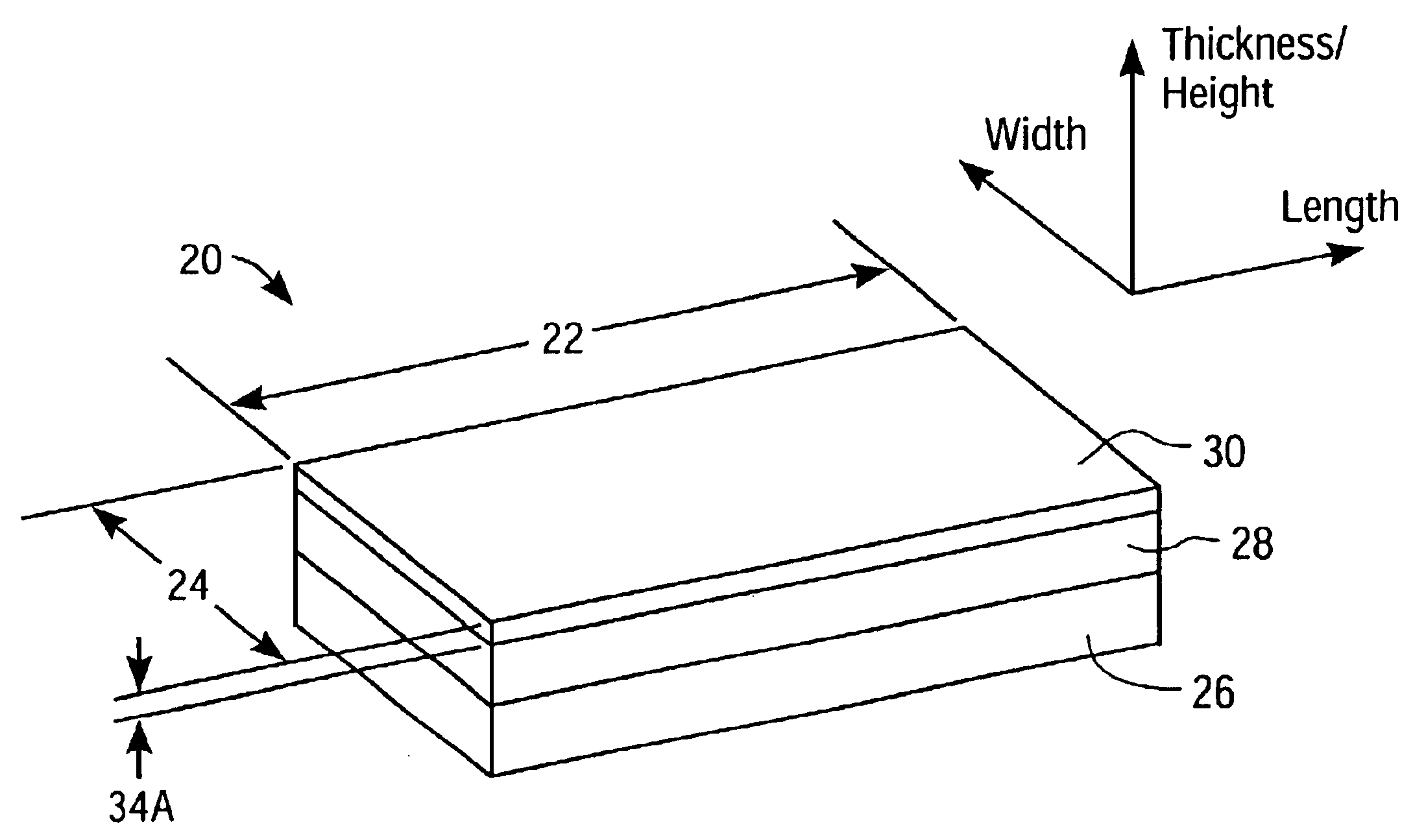

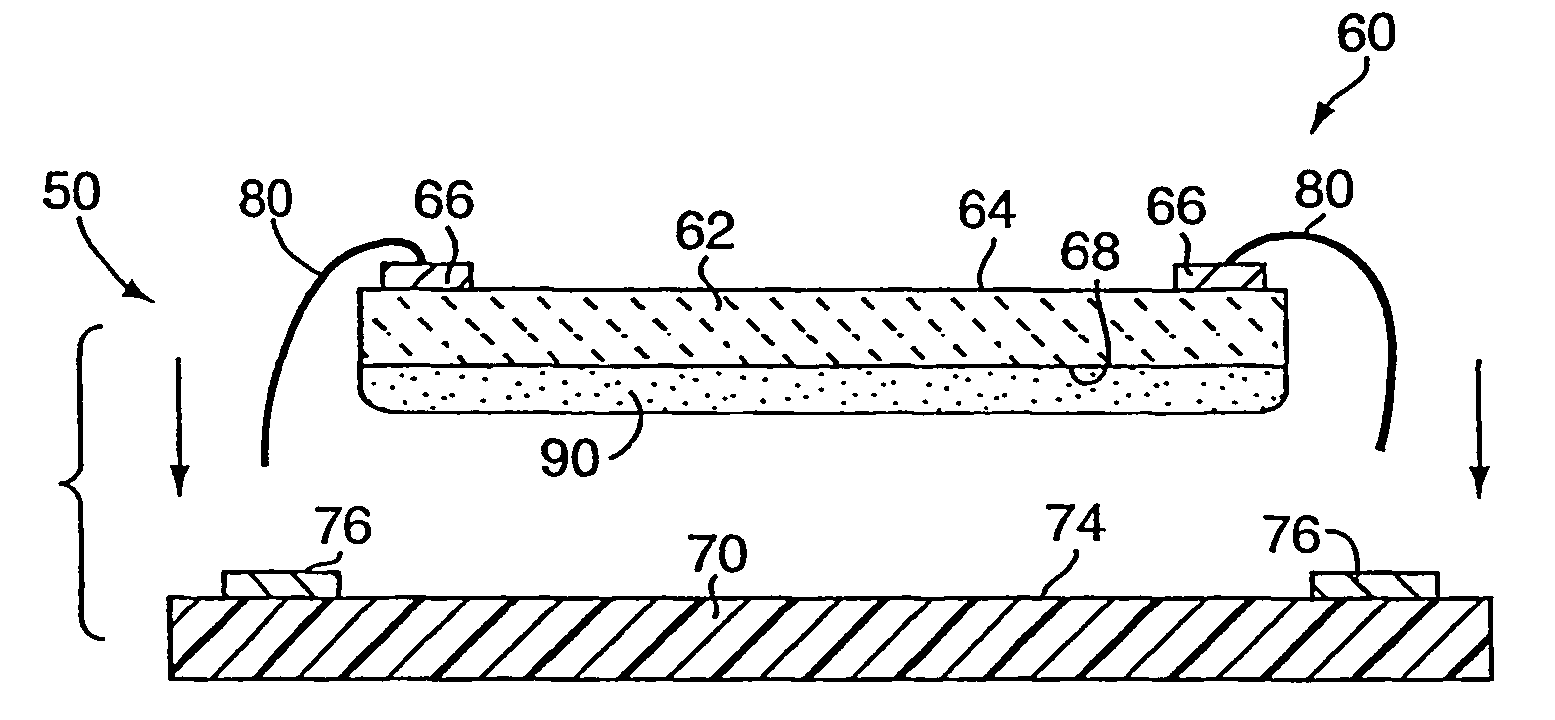

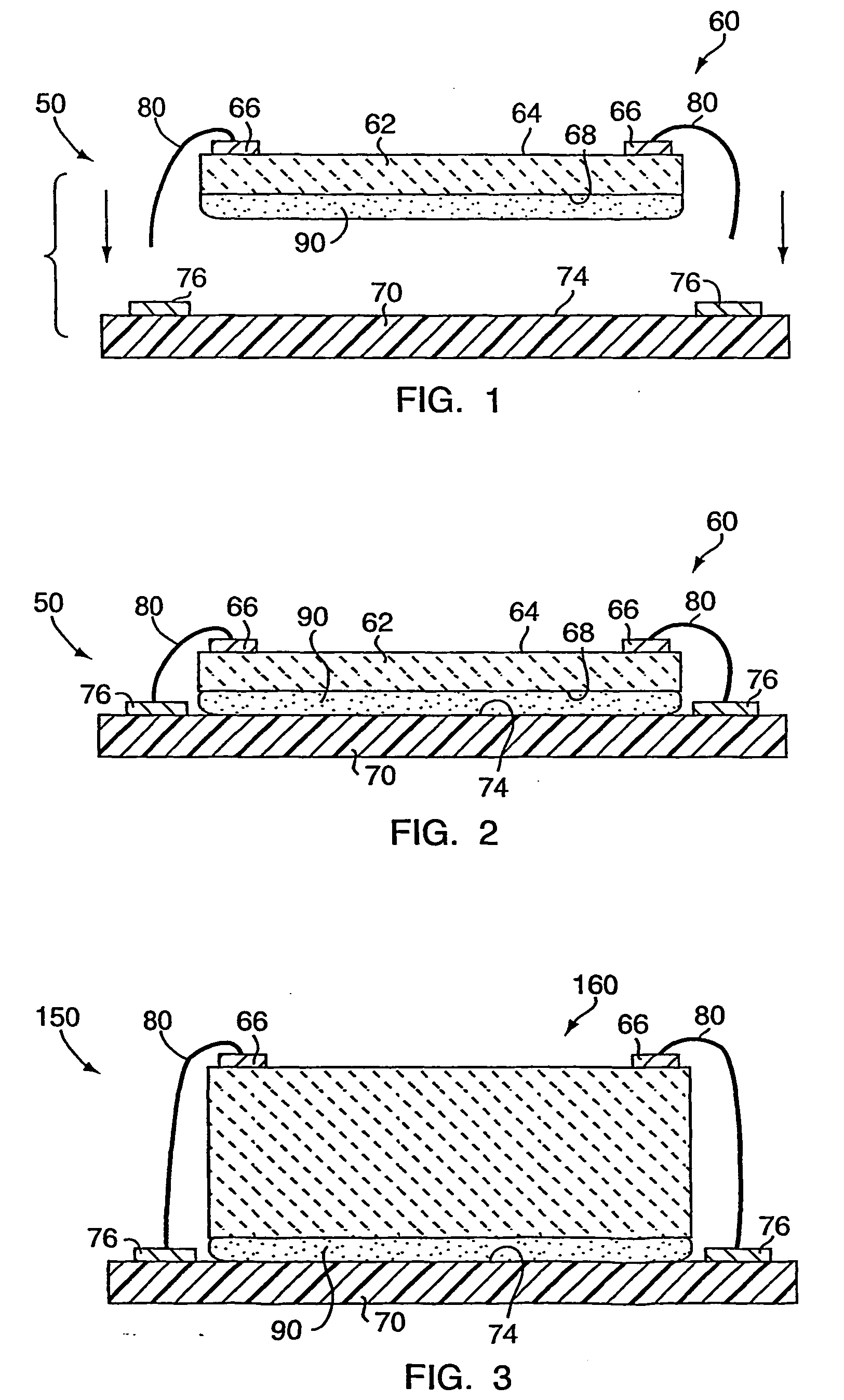

Implantable medical device construction using a flexible substrate

InactiveUS7211884B1Easy to manufactureLow costElectrotherapySemiconductor/solid-state device detailsEpoxyContact pad

A high density electronic circuit for use in an implantable stimulation device that comprises a flexible substrate that has the advantage of integrating “chip-and-wire” microelectronic circuits and flexible interconnections that are adapted to conform to the body compatible housing into a single structure. The flexible substrate has die attach pads, each die attach pad having a set of wire bond pads therearound, each wire bond pad being connected to conductors formed within the substrate according to circuit function. A plurality of chip-and-wire integrated circuit (IC) chips are mounted by epoxy die attachment on the die attach pads, each IC chip has a plurality of contact pads formed on a top surface thereof, and gold wire bonds electrically connect the plurality of contact pads to the wire bonds pads. The wire bonds include a primary bond and, optionally, a safety bond for reinforcement. Other techniques are disclosed to enable the use of the gold wire bonds on a flexible substrate.

Owner:PACESETTER INC

Low cost microelectronic circuit package

InactiveUS7183658B2Semiconductor/solid-state device detailsSolid-state devicesMicroelectronic circuitsExternal circuit

A low cost microelectronic circuit package includes a single build up metallization layer above a microelectronic die. At least one die is fixed within a package core using, for example, an encapsulation material. A single metallization layer is then built up over the die / core assembly. The metallization layer includes a number of landing pads having a pitch that allows the microelectronic device to be directly mounted to an external circuit board. In one embodiment, the metallization layer includes a number of signal landing pads within a peripheral region of the layer and at least one power landing pad and one ground landing pad toward a central region of the layer.

Owner:INTEL CORP

Method of manufacturing solar cell

ActiveUS7883343B1Easy to manufactureLess expensiveFinal product manufactureSemiconductor/solid-state device manufacturingIr reflectionEngineering

A solar cell that is readily manufactured using processing techniques which are less expensive than microelectronic circuit processing. In preferred embodiments, printing techniques are utilized in selectively forming masks for use in etching of silicon oxide and diffusing dopants and in forming metal contacts to diffused regions. In a preferred embodiment, p-doped regions and n-doped regions are alternately formed in a surface of the wafer through use of masking and etching techniques. Metal contacts are made to the p-regions and n-regions by first forming a seed layer stack that comprises a first layer such as aluminum that contacts silicon and functions as an infrared reflector, second layer such titanium tungsten that acts as diffusion barrier, and a third layer functions as a plating base. A thick conductive layer such as copper is then plated over the seed layer, and the seed layer between plated lines is removed. A front surface of the wafer is preferably textured by etching or mechanical abrasion with an IR reflection layer provided over the textured surface. A field layer can be provided in the textured surface with the combined effect being a very low surface recombination velocity.

Owner:MAXEON SOLAR PTE LTD

Nanoscale wires and related devices

The present invention relates generally to sub-microelectronic circuitry, and more particularly to nanometer-scale articles, including nanoscale wires which can be selectively doped at various locations and at various levels. In some cases, the articles may be single crystals. The nanoscale wires can be doped, for example, differentially along their length, or radially, and either in terms of identity of dopant, concentration of dopant, or both. This may be used to provide both n-type and p-type conductivity in a single item, or in different items in close proximity to each other, such as in a crossbar array. The fabrication and growth of such articles is described, and the arrangement of such articles to fabricate electronic, optoelectronic, or spintronic devices and components. For example, semiconductor materials can be doped to form n-type and p-type semiconductor regions for making a variety of devices such as field effect transistors, bipolar transistors, complementary inverters, tunnel diodes, light emitting diodes, sensors, and the like.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

Method for ion implanting insulator material to reduce dielectric constant

InactiveUS7166524B2Electric discharge tubesSemiconductor/solid-state device manufacturingMicroelectronic circuitsDielectric permittivity

An integrated microelectronic circuit has a multi-layer interconnect structure overlying the transistors consisting of stacked metal pattern layers and insulating layers separating adjacent ones of said metal pattern layers. Each of the insulating layers is a dielectric material with plural gas bubbles distributed within the volume of the dielectric material to reduce the dielectric constant of the material, the gas bubbles being formed by ion implantation of a gaseous species into the dielectric material.

Owner:APPLIED MATERIALS INC

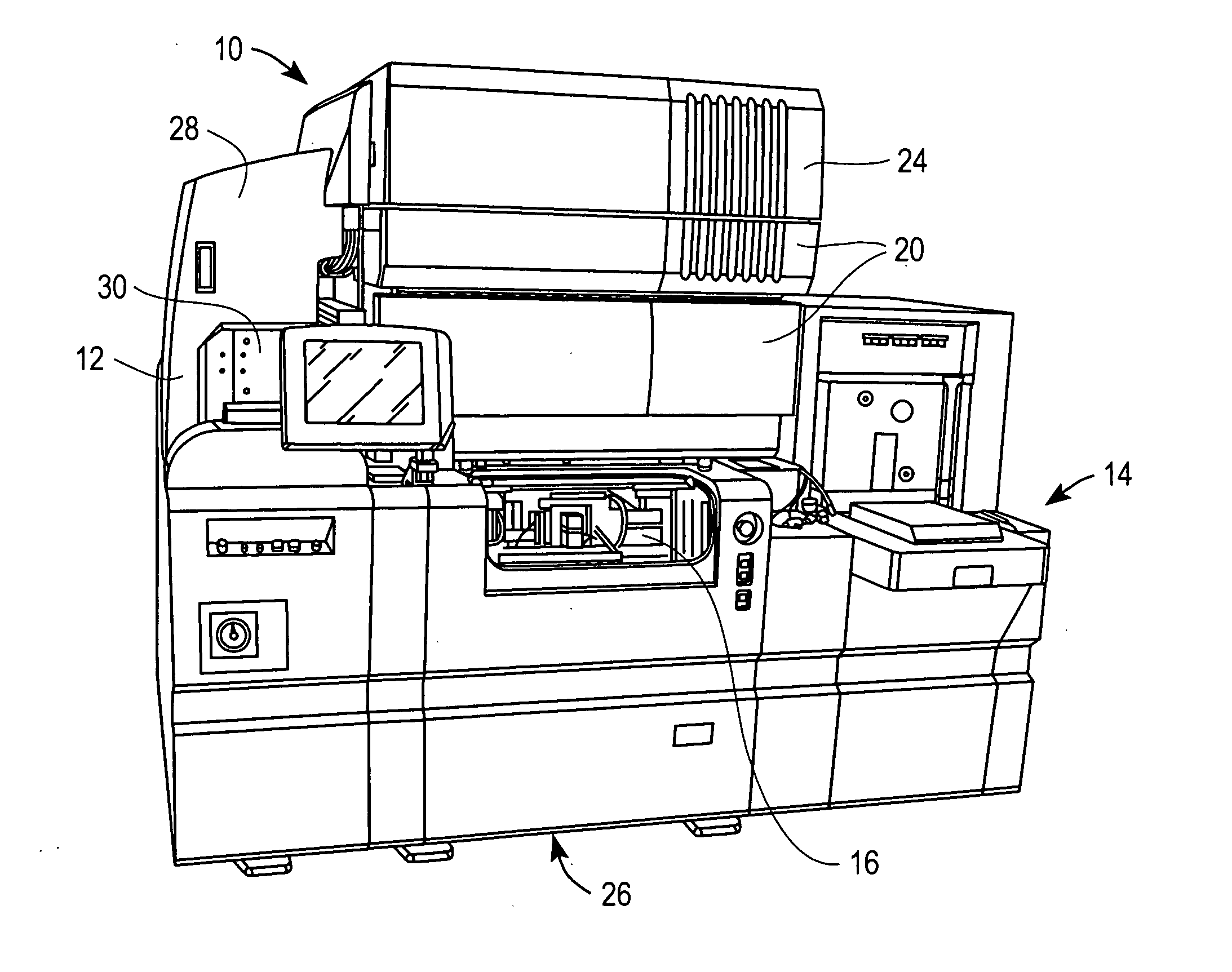

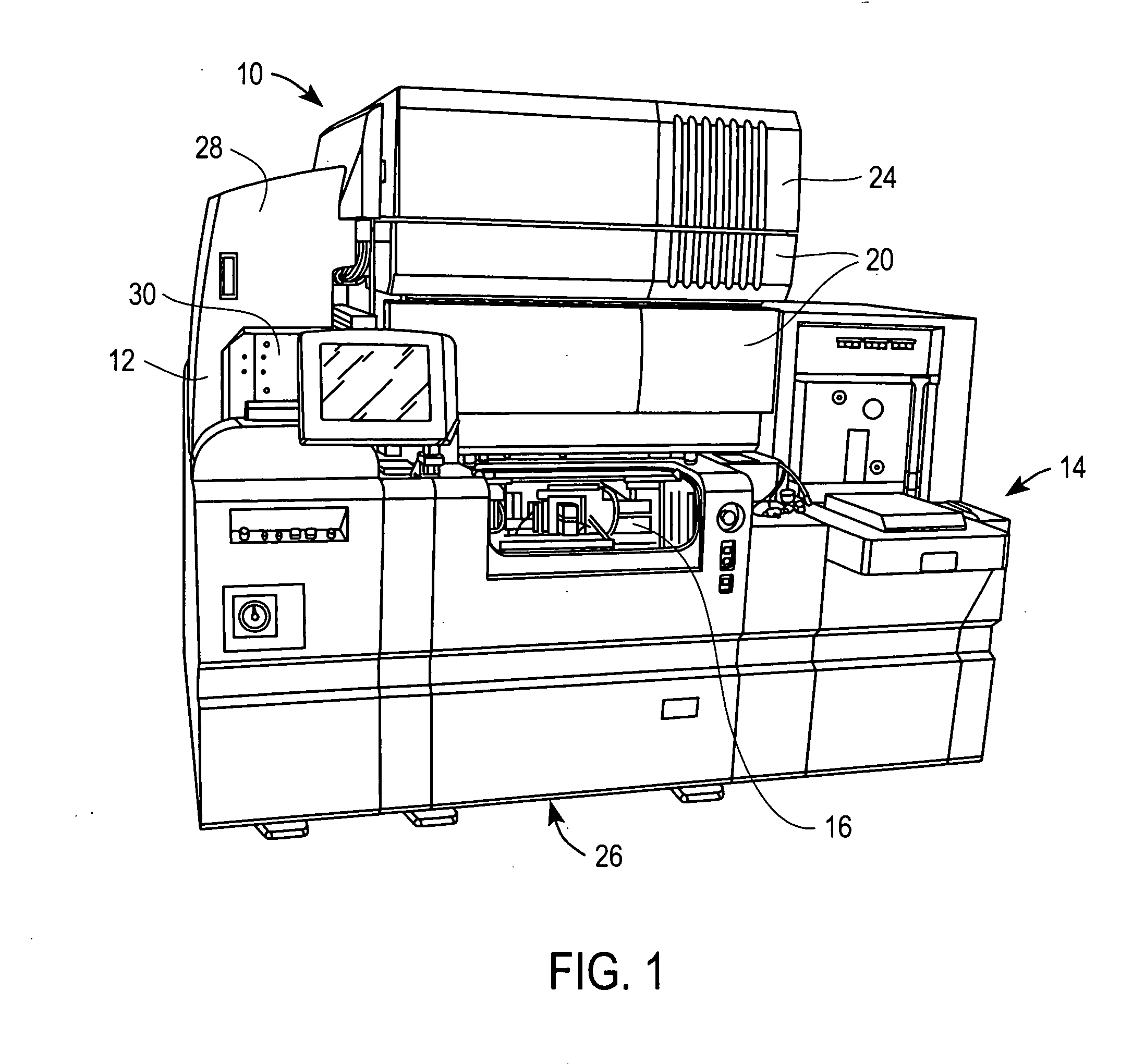

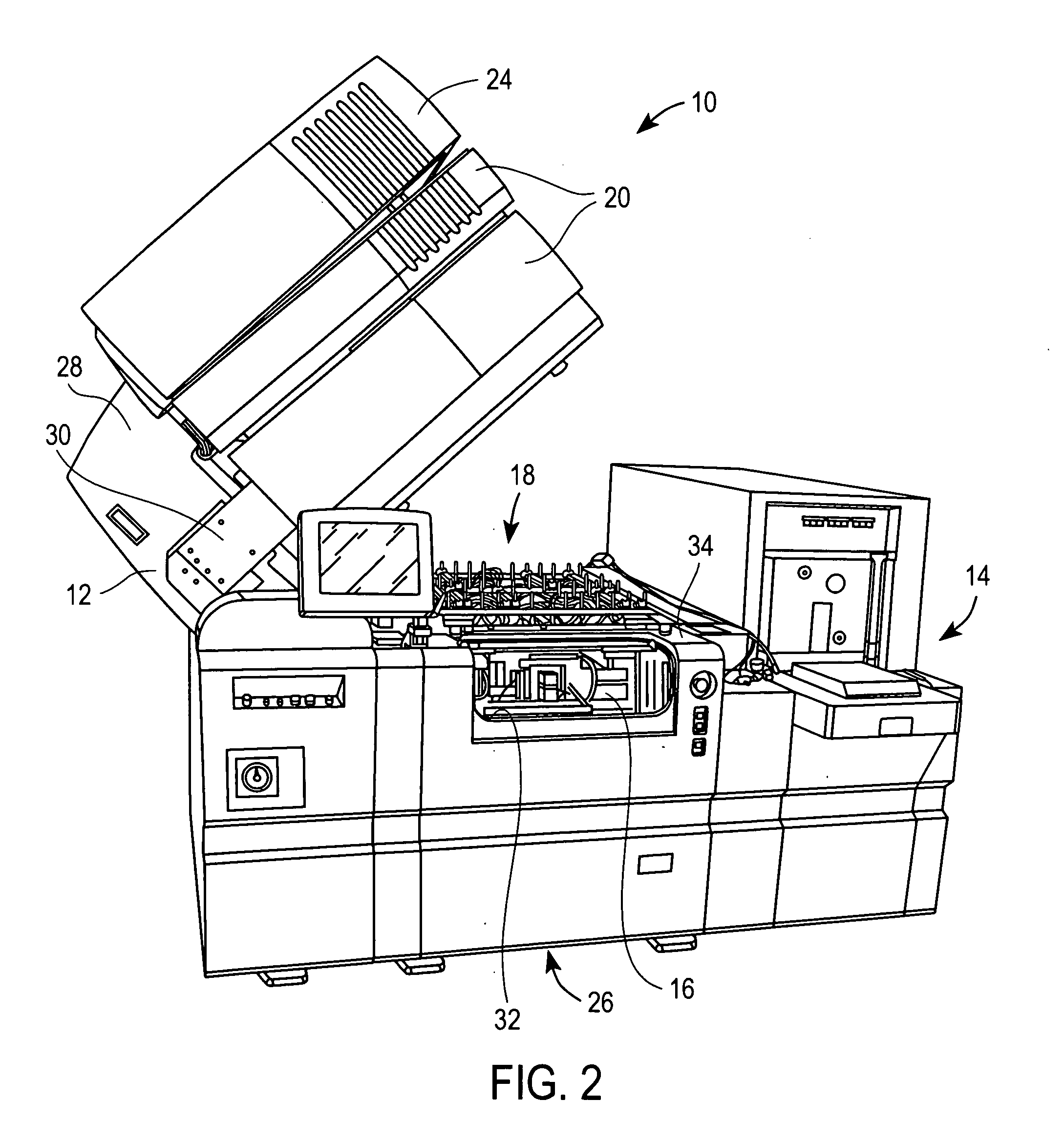

Apparatus for testing electronic devices

ActiveUS20070001790A1Semiconductor/solid-state device testing/measurementSemiconductor operation lifetime testingFunctional testingMicroelectronic circuits

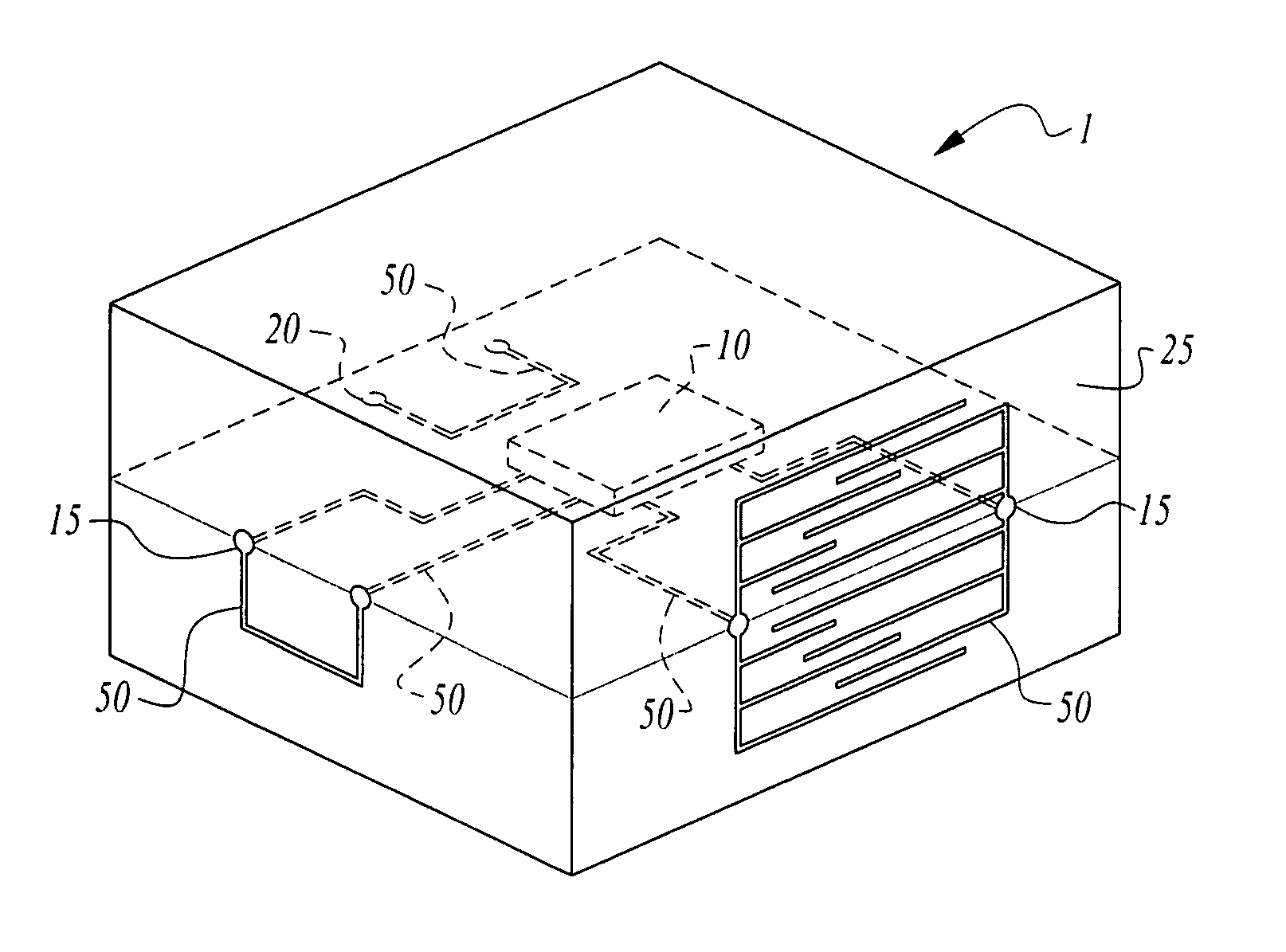

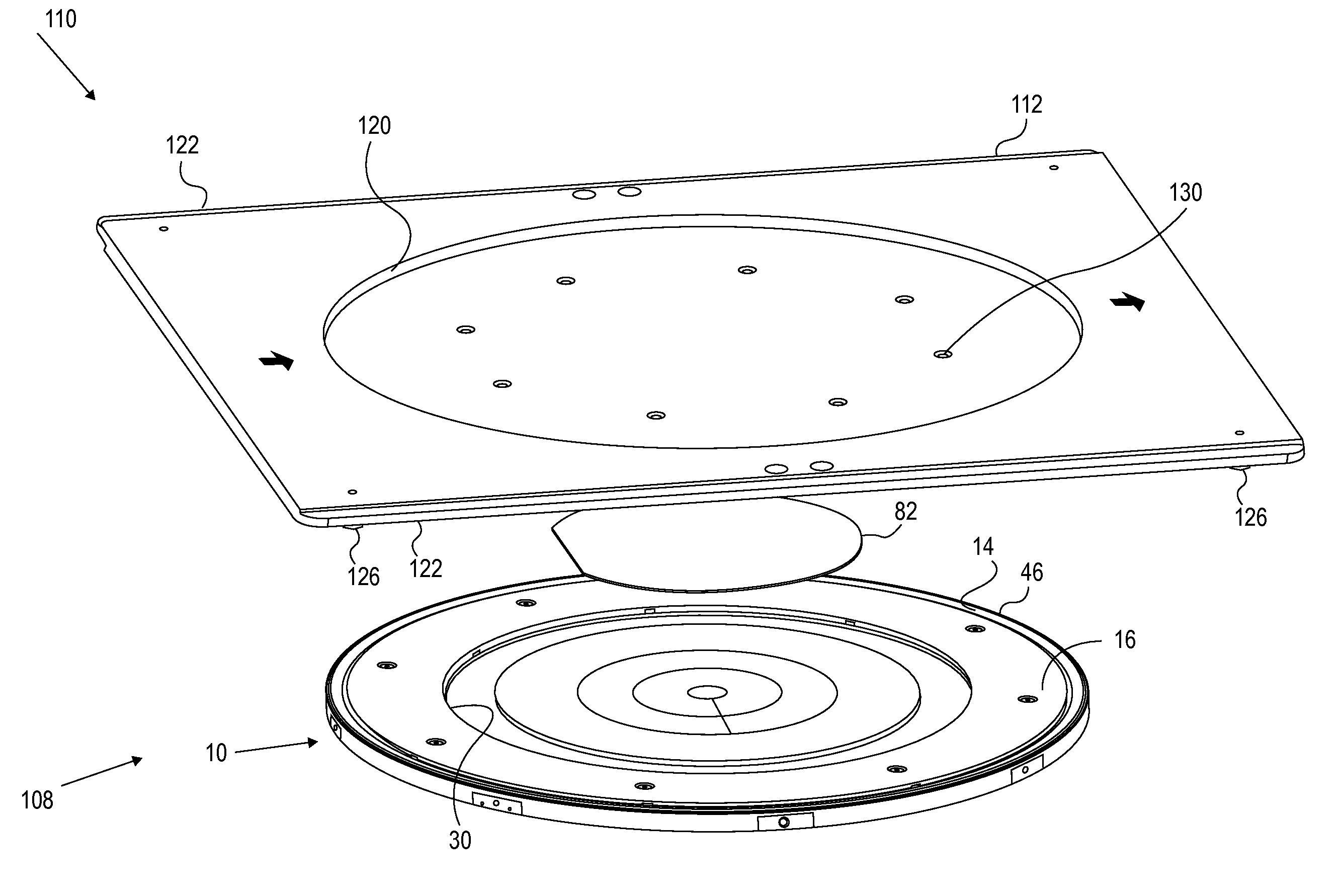

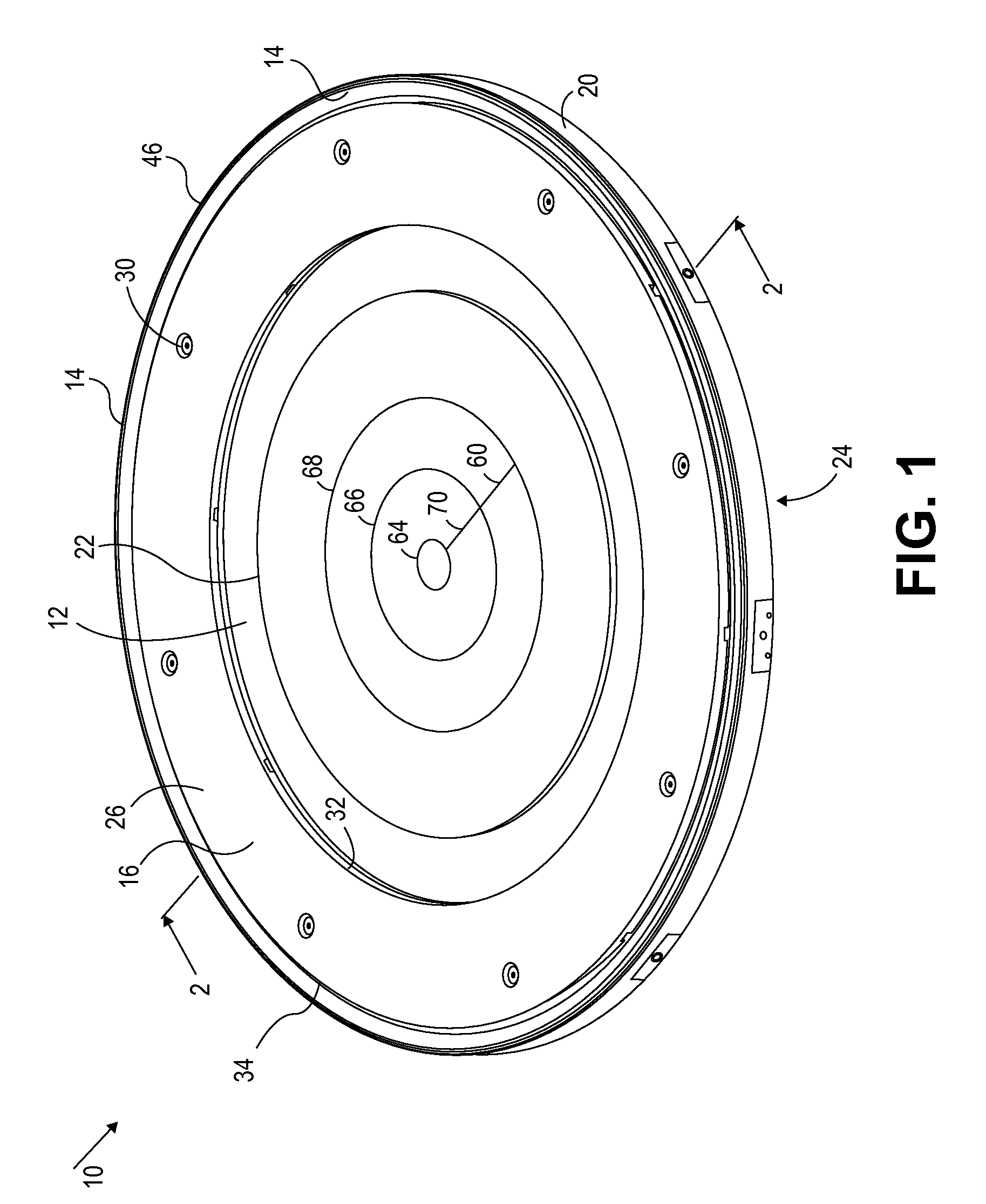

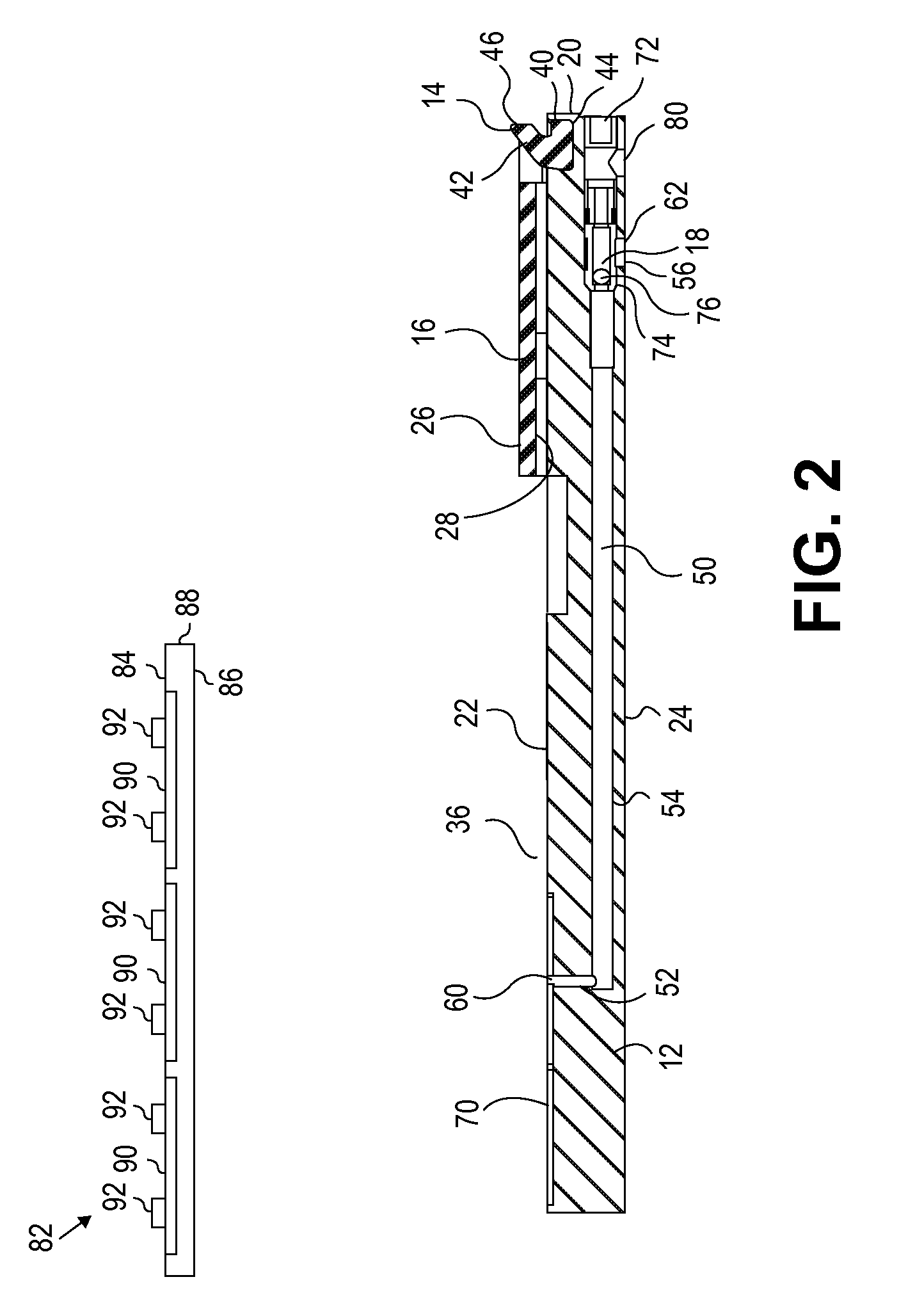

An apparatus is described for burn-in and / or functional testing of microelectronic circuits of unsingulated wafers. A large number of power, ground, and signal connections can be made to a large number of contacts on a wafer. The apparatus has a cartridge that allows for fanning-in of electric paths. A distribution board has a plurality of interfaces that are strategically positioned to provide a dense configuration. The interfaces are connected through flexible attachments to an array of first connector modules. Each one of the first connector modules can be independently connected to a respective one of a plurality of second connector modules, thereby reducing stresses on a frame of the apparatus. Further features include for example a piston that allows for tight control of forces exerted by terminals onto contacts of a wafer.

Owner:AEHR TEST SYST

Ion implanted insulator material with reduced dielectric constant

InactiveUS20070042580A1Low dielectric constantSemiconductor/solid-state device detailsSolid-state devicesDielectricMicroelectronic circuits

An integrated microelectronic circuit has a multi-layer interconnect structure overlying the transistors consisting of stacked metal pattern layers and insulating layers separating adjacent ones of said metal pattern layers. Each of the insulating layers is a dielectric material with plural gas bubbles distributed within the volume of the dielectric material to reduce the dielectric constant of the material, the gas bubbles being formed by ion implantation of a gaseous species into the dielectric material.

Owner:AL BAYATI AMIR +7

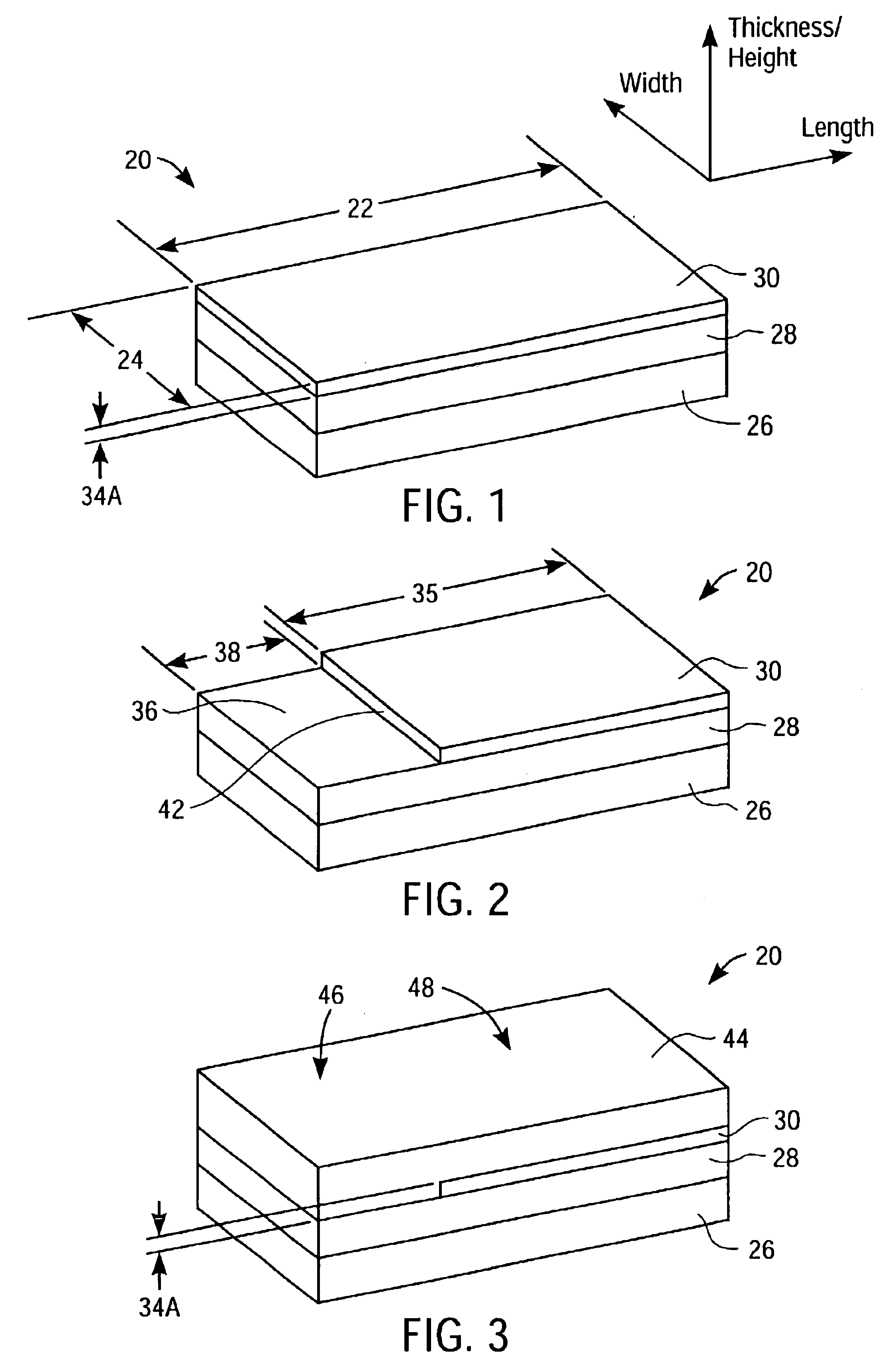

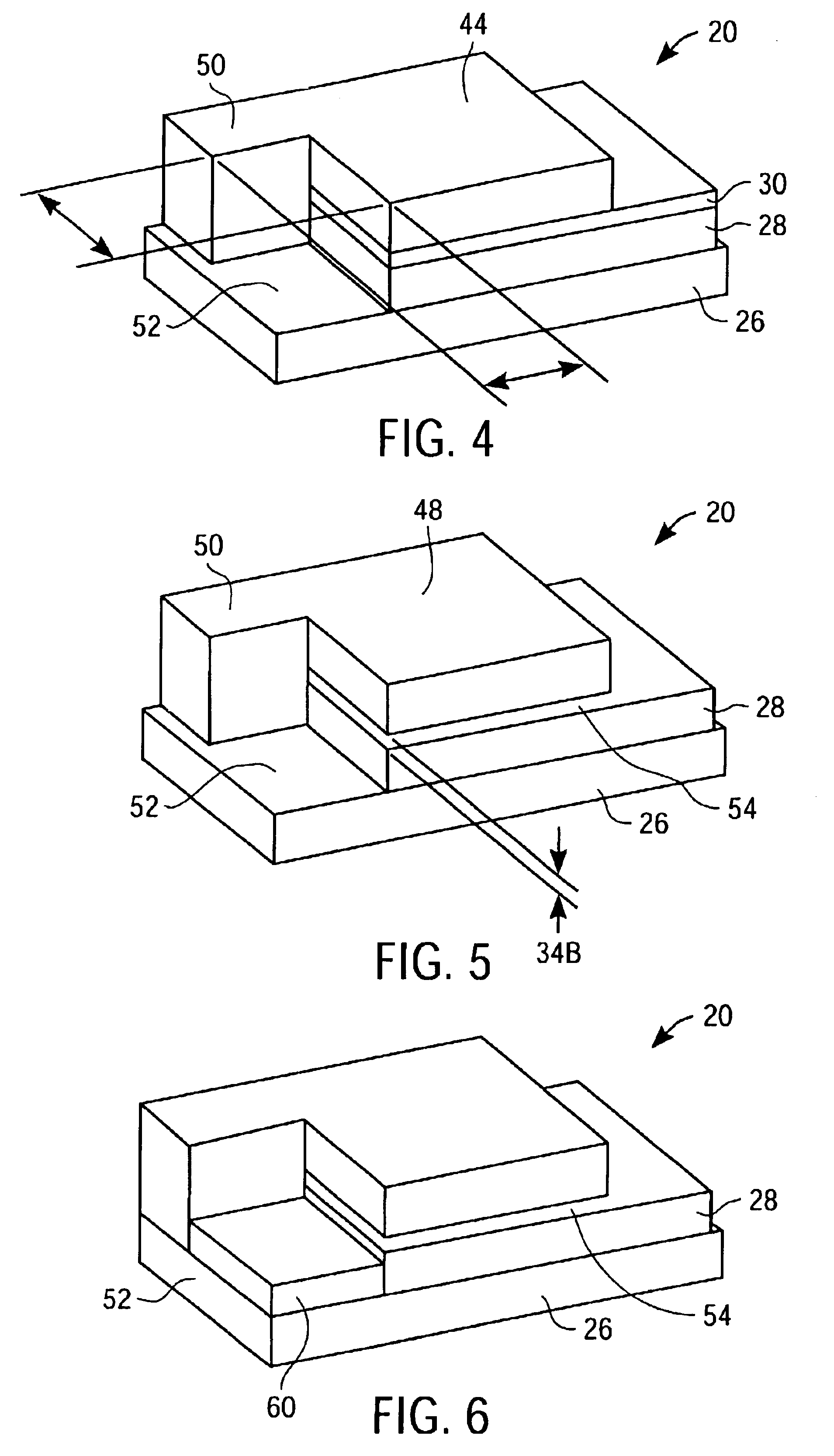

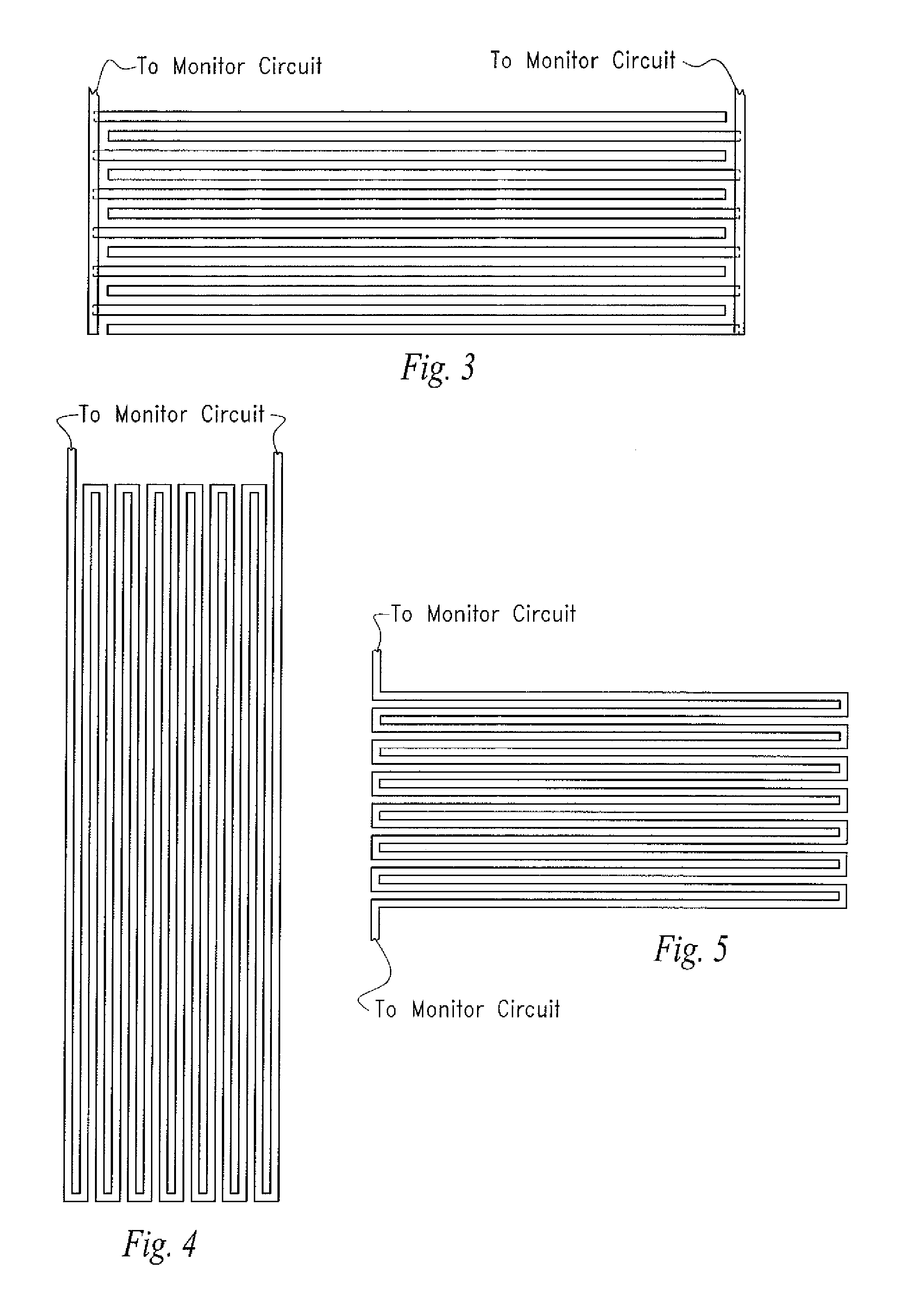

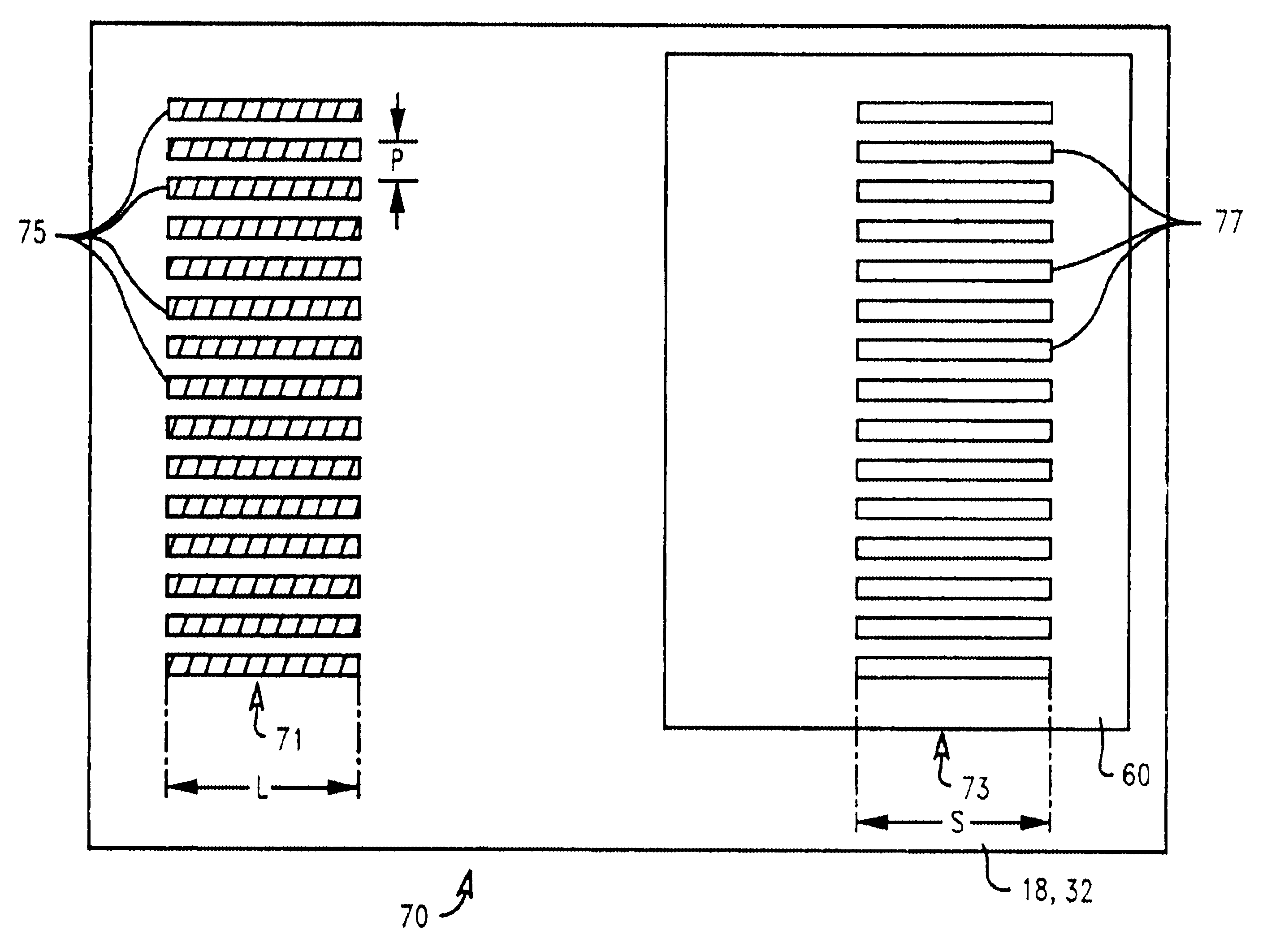

Tamper-resistant electronic circuit and module incorporating electrically conductive nano-structures

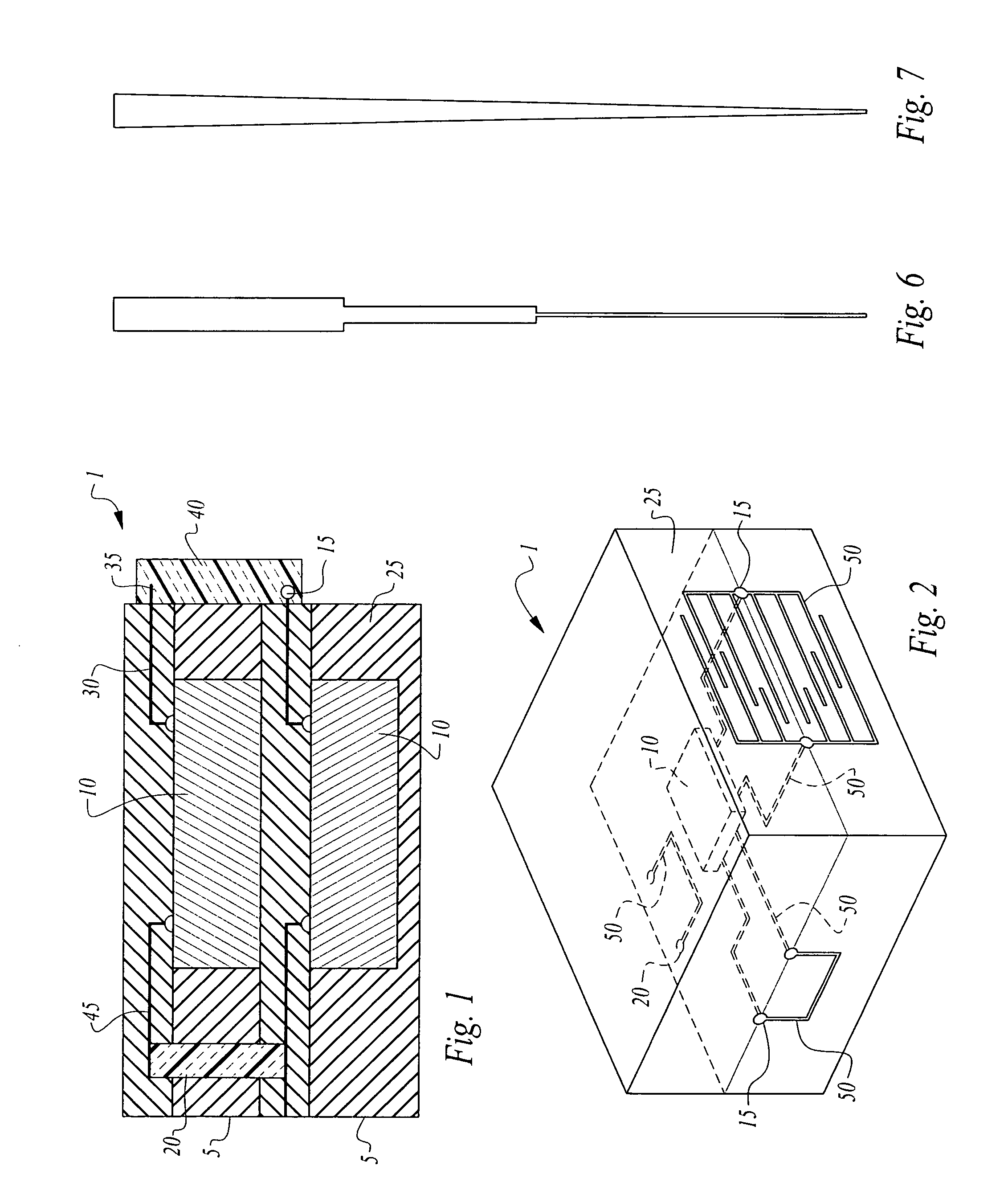

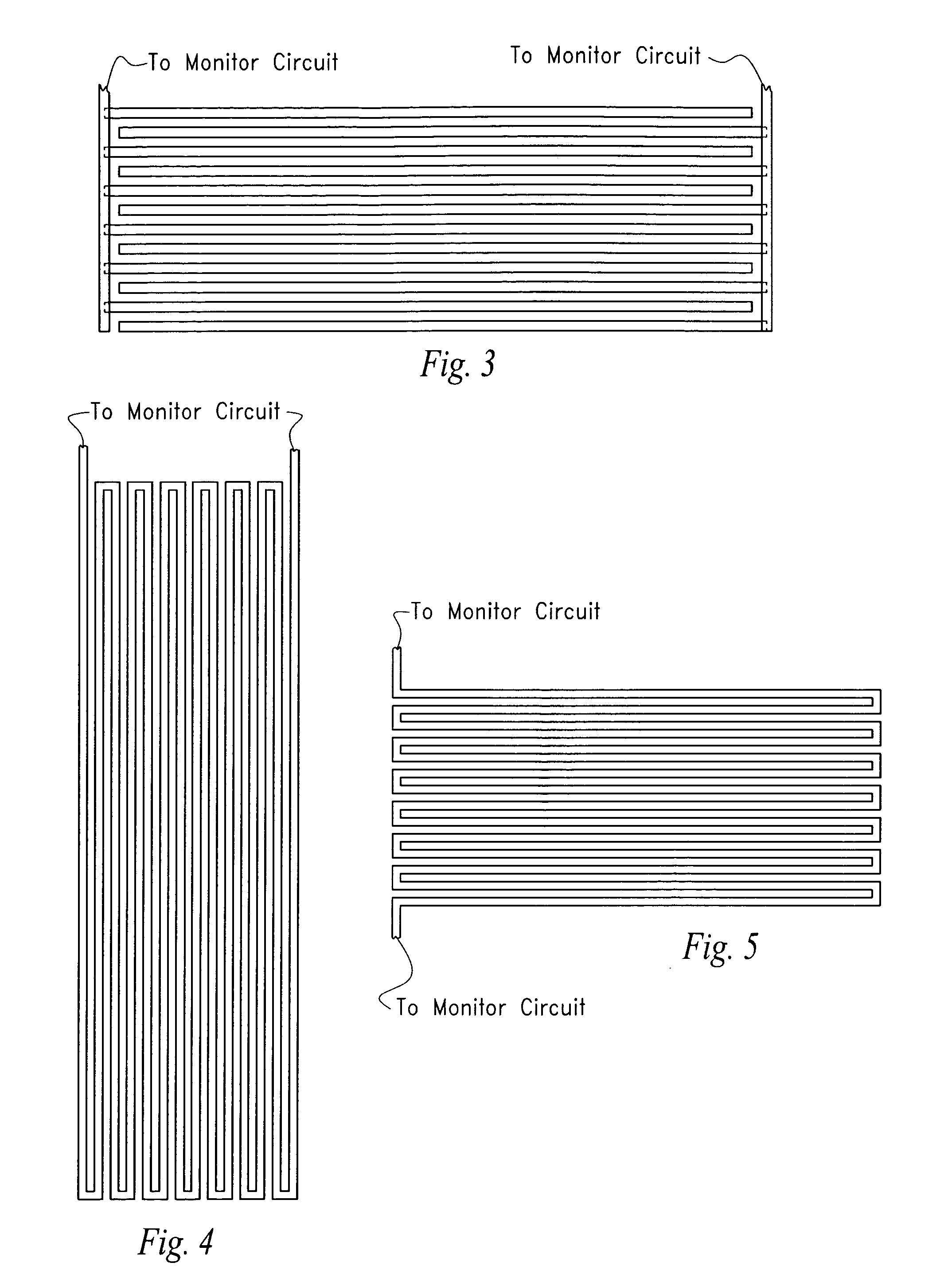

InactiveUS20110031982A1Resistance/reactance/impedenceSemiconductor/solid-state device detailsNano structuringX-ray

A device and method are disclosed comprising one or more electrically conductive nano-structures defined on one or more surfaces of a microelectronic circuit such as an integrated circuit die, microelectronic circuit package (such as a TSOP, BGA or other prepackaged IC) a stacked microelectronic circuit package, or on the surface of one or more layers in a stack of layers containing one or more ICs.In one embodiment, the electrically conductive nano-structure is in electrical connection with a monitoring circuit and acts as a “trip wire” to detect unauthorized tampering with the device or module. Such a monitoring circuit may include a power source such as an in-circuit or in-module battery and a “zeroization” circuit within the chip or package to erase the contents of a memory when the electrically conductive nano-structure is breached or altered. The device may be configured to blow one or more fuses or overcurrent protection devices when the electrically conductive nano-structure is breached or altered.In a further embodiment, one or more electrically conductive nano-structures are used to interconnect and reroute one or more electrical connections between one or more ICs (or dummy leads and vias) to create an “invisible” set of electrical connections on the chip or stack to obfuscate an attempt to reverse engineer the device, i.e., a set of connections that cannot be observed by standard test means such as by X-ray or conventional microscope.

Owner:PFG IP +1

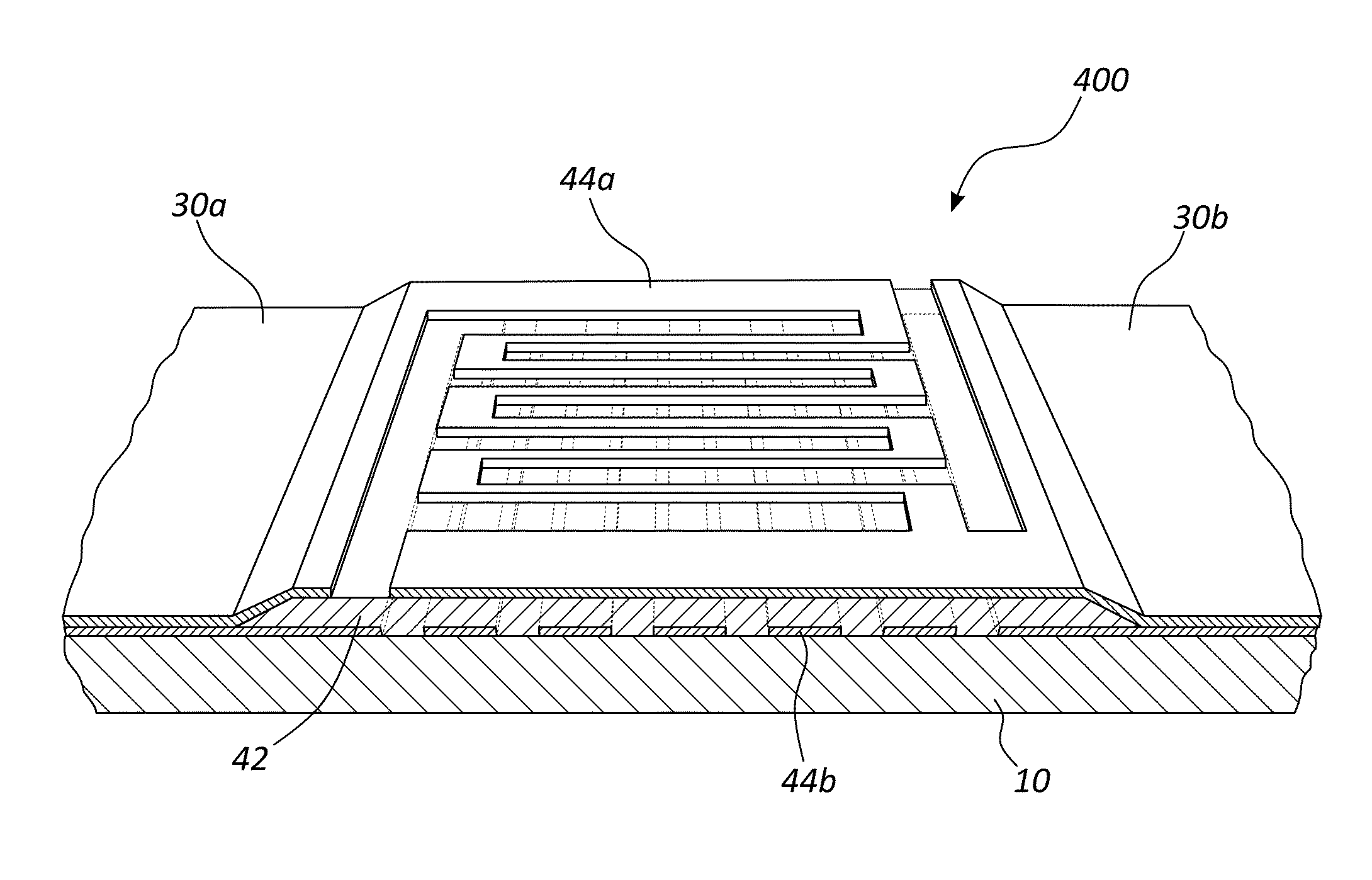

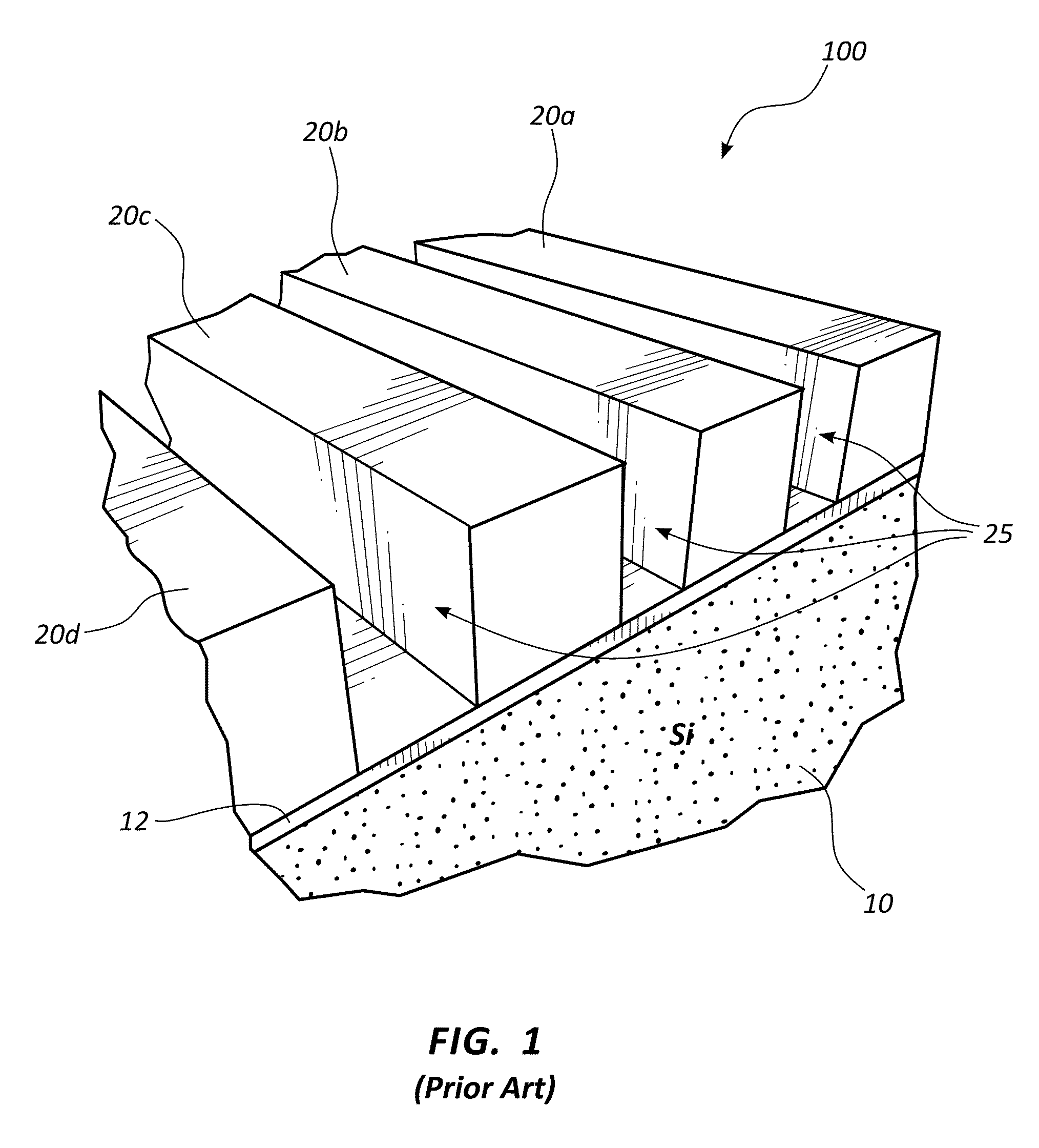

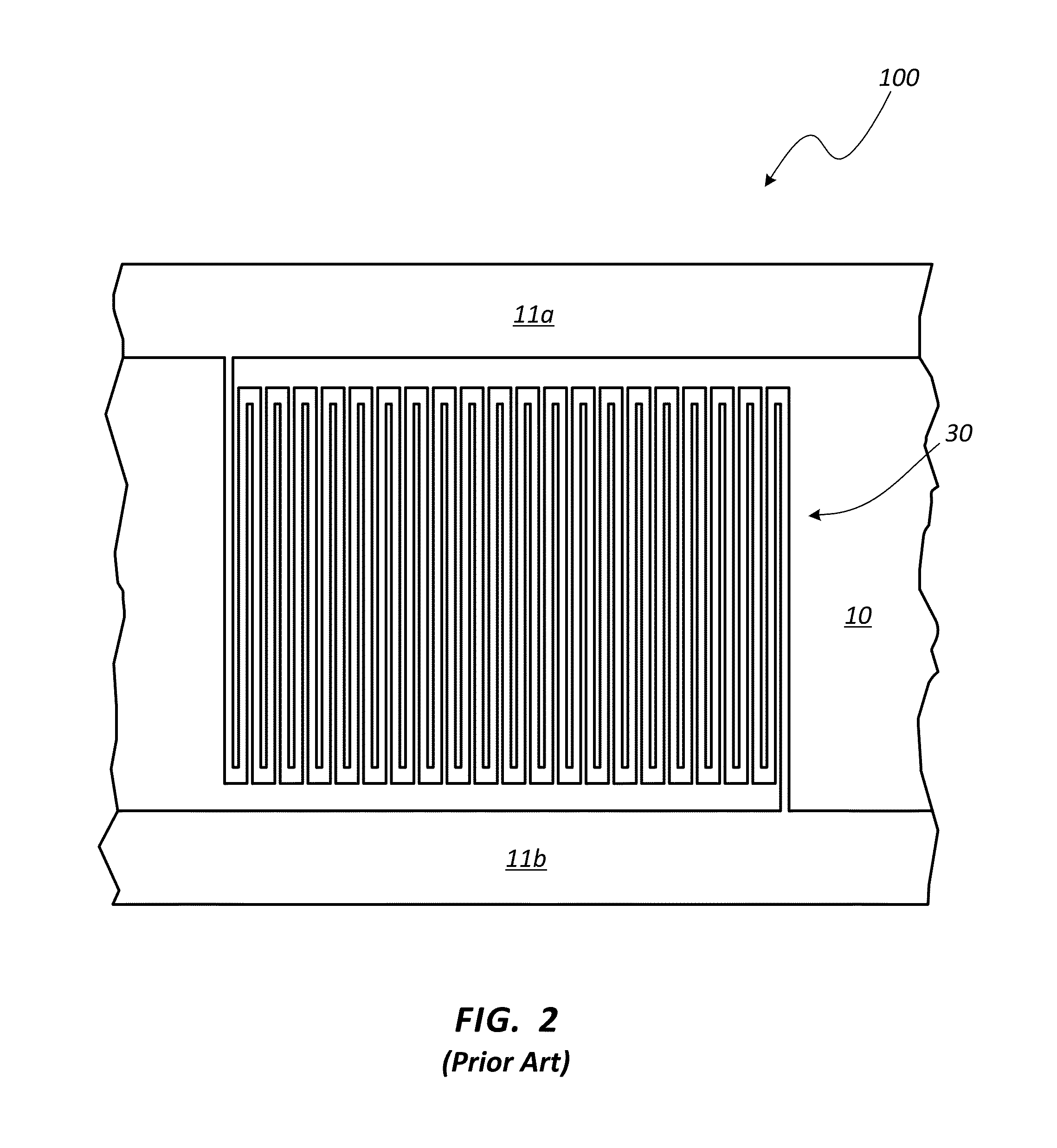

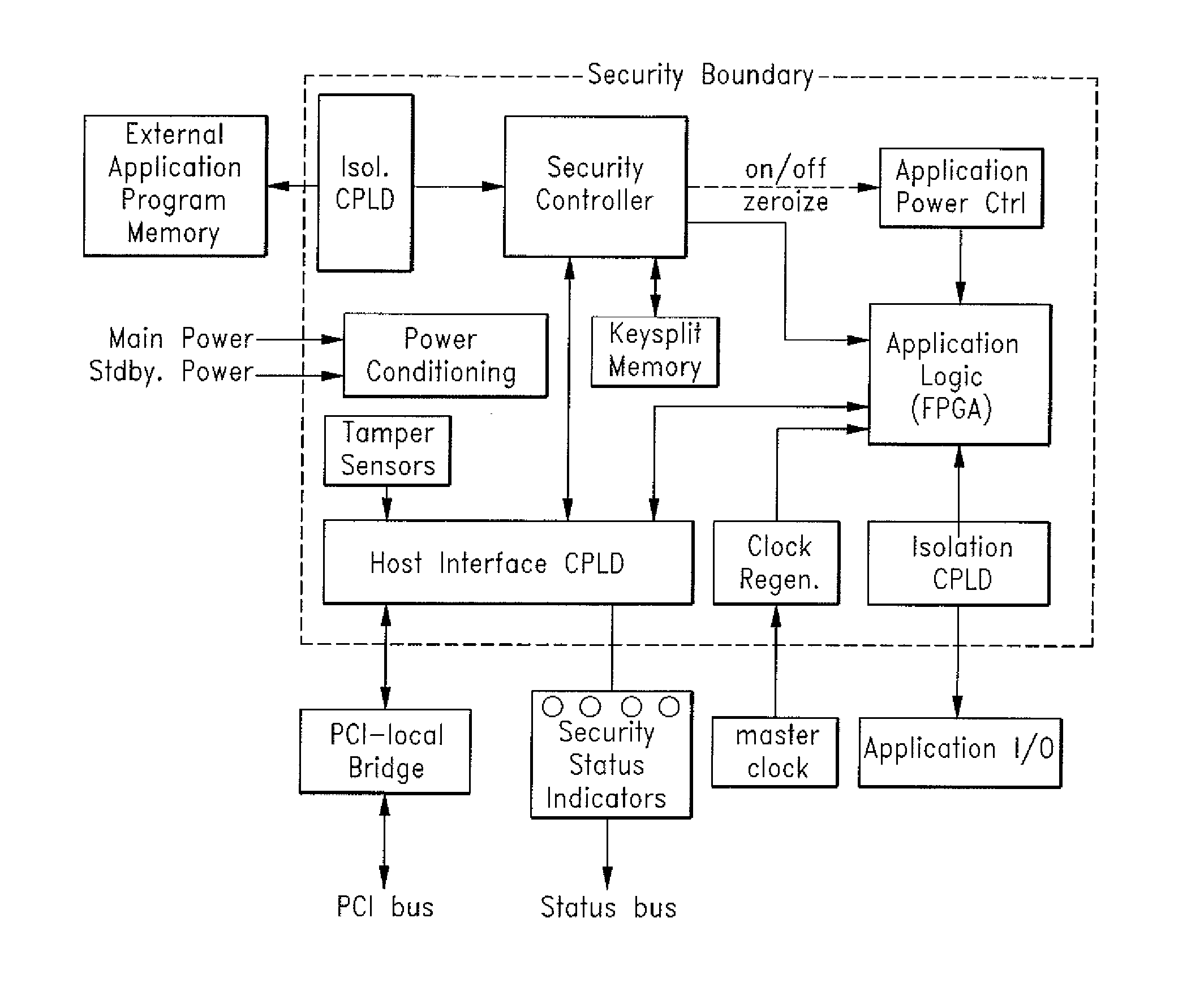

Efficient Polarization Independent Single Photon Detector

ActiveUS20140087952A1Improve quantum efficiencySuperconductors/hyperconductorsSemiconductor/solid-state device manufacturingQuantum efficiencyNanowire

A superconducting nanowire single photon detector (SN-SPD) microelectronic circuit is described which has higher quantum efficiency and signal-to-noise than any SN-SPD's known in the art. The material and configuration of the microelectronic circuit eliminates the polarization dependence and shows improved signal-to-noise over SN-SPD microelectronic circuits known in the art. The higher efficiency, polarization independence, and high signal-to-noise is achieved by vertically stacking two tungsten-silicide (TS) SN-SPDs and electrically connecting them in parallel. This structure forms a multilayer superconducting nanowire avalanche photo-detector (SNAP). A single photon detection device employing the multilayer (SNAP) microelectronic circuit demonstrates a peak system detection efficiency of 87.7% and a polarization dependence of less than 2%. This represents nearly an order of magnitude improvement in both system detection efficiency and reduction of polarization dependence compared to conventional SNSPDs.

Owner:GOVERNMENT OF THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SEC OF COMMERCE THE NAT INST OF STANDARDS & TEHCNOLOGY

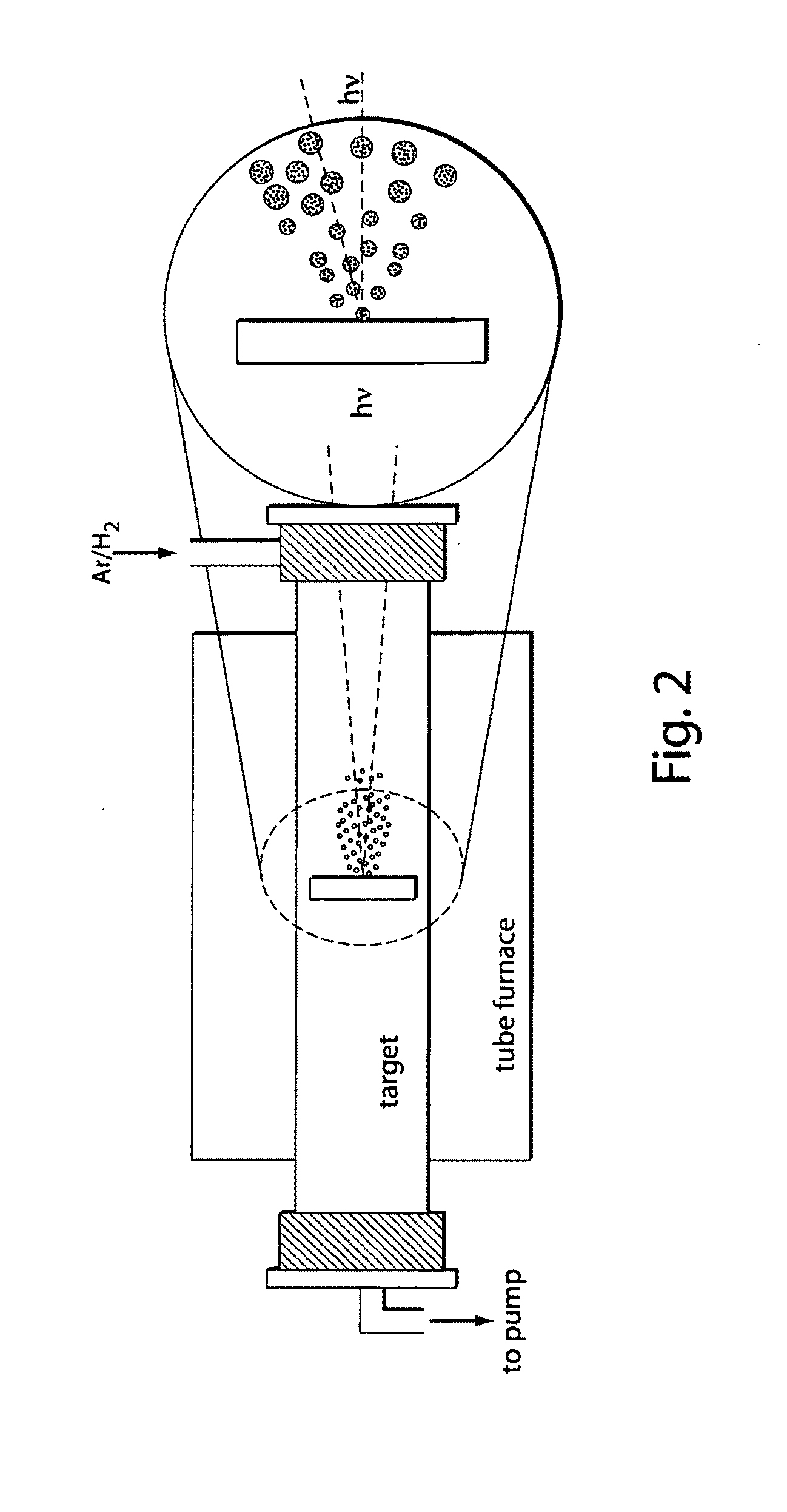

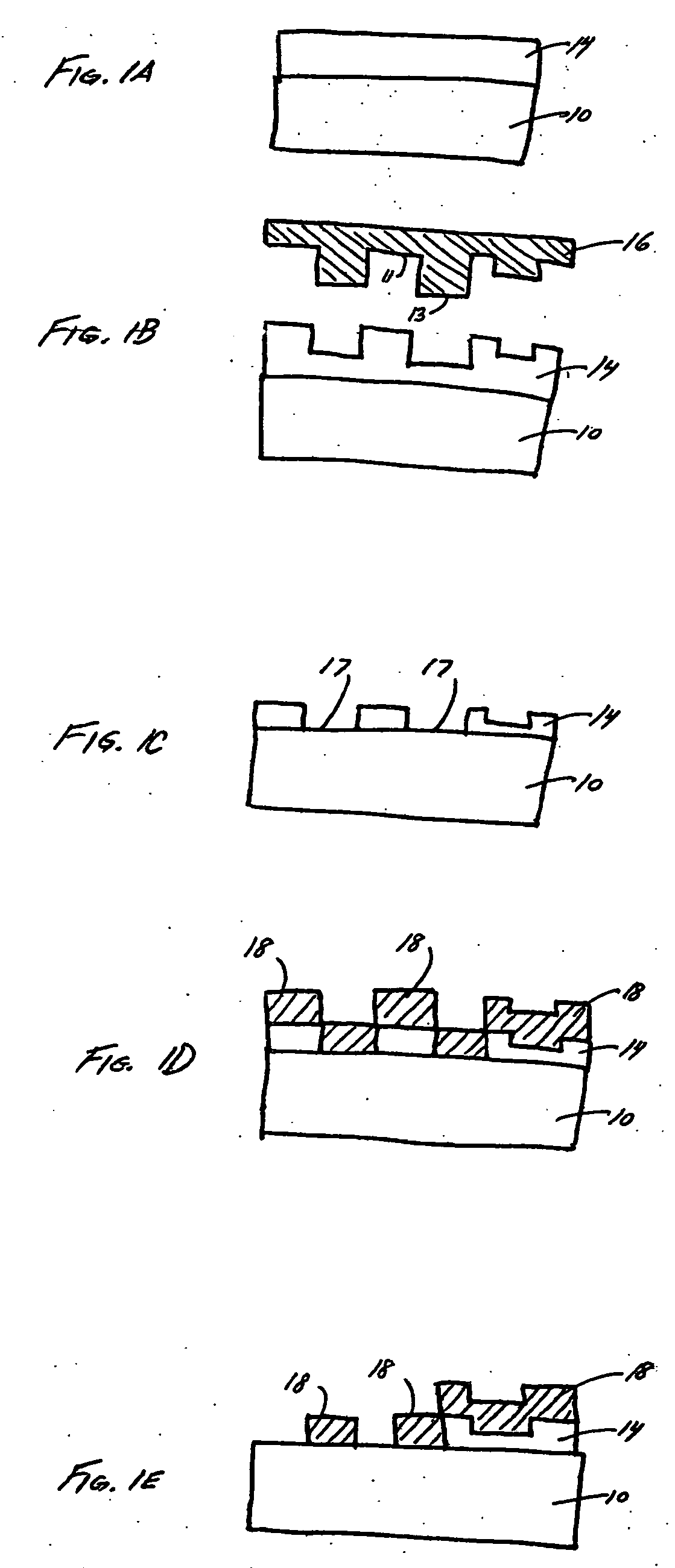

Method of forming an element of a microelectronic circuit

InactiveUS6972228B2Laser active region structureNanoinformaticsSemiconductor materialsMicroelectronic circuits

A method is described for forming an element of a microelectronic circuit. A sacrificial layer is formed on an upper surface of a support layer. The sacrificial layer is extremely thin and uniform. A height-defining layer is then formed on the sacrificial layer, whereafter the sacrificial layer is etched away so that a well-defined gap is left between an upper surface of the support layer and a lower surface of the height-defining layer. A monocrystalline semiconductor material is then selectively grown from a nucleation silicon site through the gap. The monocrystalline semiconductor material forms a monocrystalline layer having a thickness corresponding to the thickness of the original sacrificial layer.

Owner:INTEL CORP

Secure Anti-Tamper Integrated Layer Security Device Comprising Nano-Structures

InactiveUS20110227603A1Resistance/reactance/impedenceSemiconductor/solid-state device detailsElectricityNano structuring

A device and method using one or more electrically conductive nano-structures defined on one or more surfaces of a microelectronic circuit such as an integrated circuit die, microelectronic circuit package a stacked microelectronic circuit package, or on the surface of one or more layers in a stack of layers containing one or more ICs. The nano-structure is in connection with a monitoring circuit and acts as a “trip wire” to detect unauthorized tampering with the device or module. Such a monitoring circuit may include a power source such as an in-circuit or in-module battery and a “zeroization” circuit within the chip or package to erase the contents of a memory when the nano-structure is breached or altered. One or more electrically conductive nano-structures interconnect and reroute one or more electrical connections between one or more ICs to create an “invisible” set of electrical connections on the chip or stack to obfuscate an attempt to reverse engineer the device. microscope.

Owner:PFG IP +1

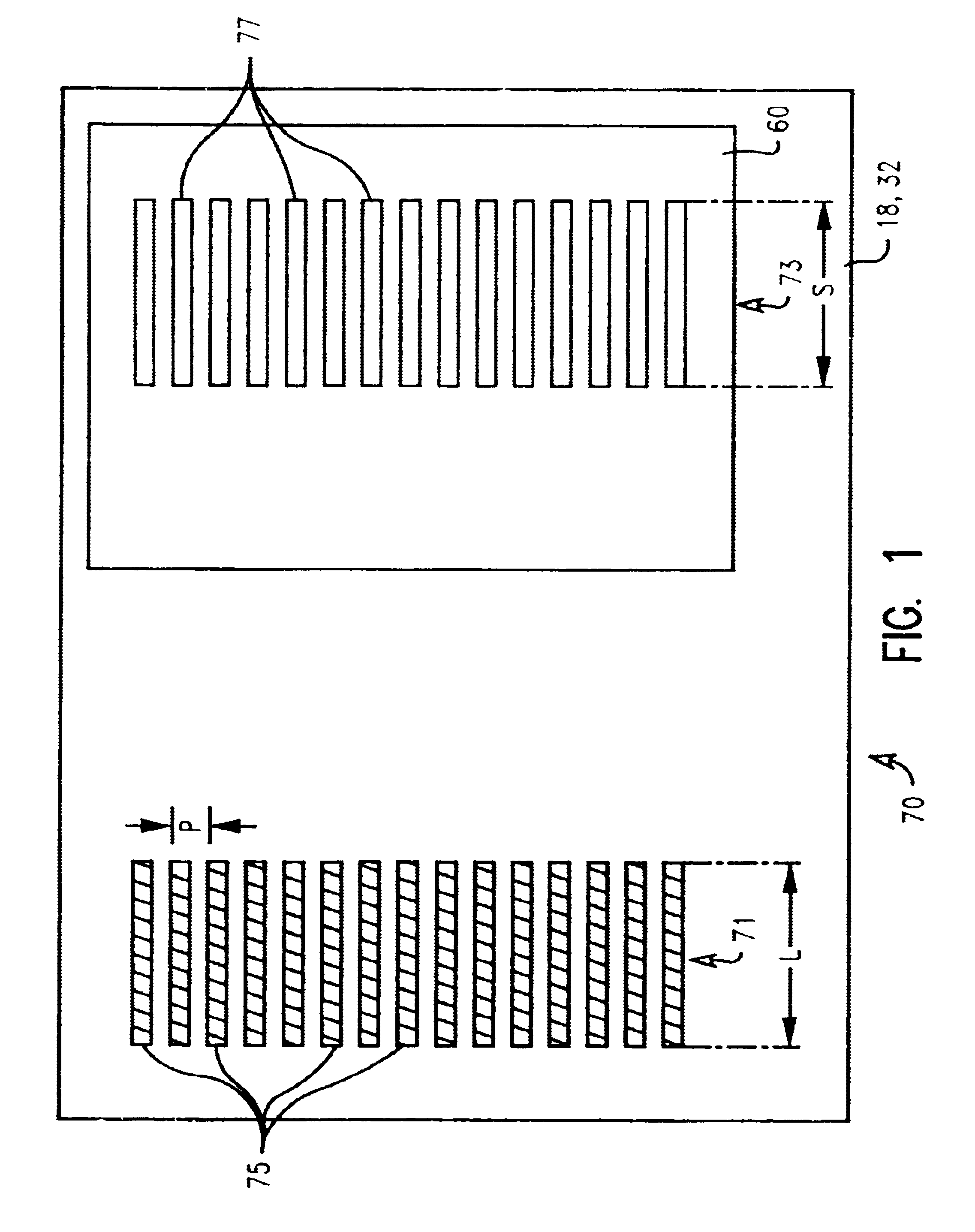

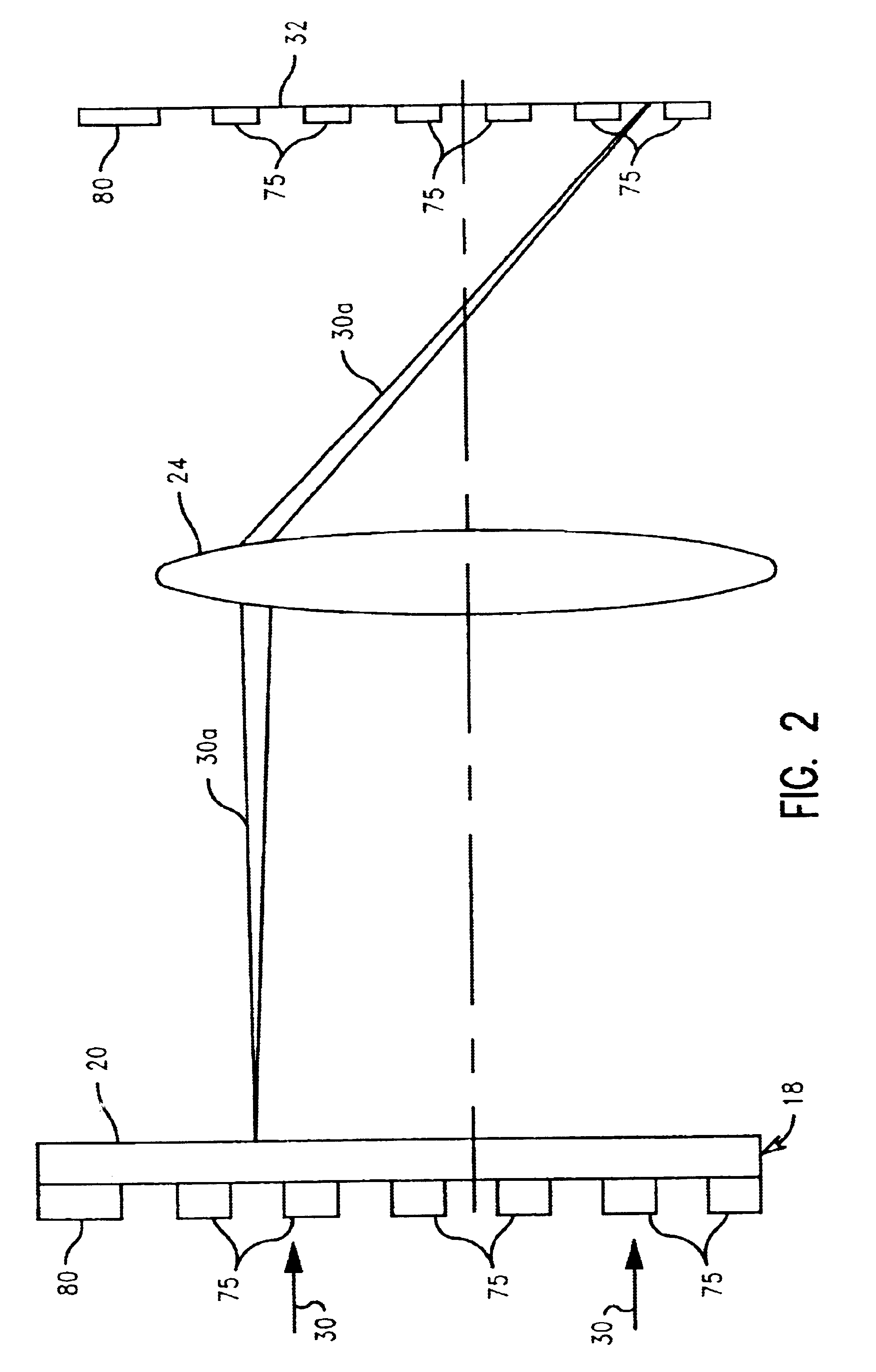

Focus control system

InactiveUS6803995B2Photography auxillary processesUsing optical meansControl systemMicroelectronic circuits

A process for controlling focus parameters in a lithographic process used in manufacture of microelectronic circuits. The process comprises initially providing a lithographic mask having a target mask portion containing a measurable dimension sensitive to defocus, projecting an energy beam through the target mask portion onto a first location of a substrate at a first focus setting, and lithographically forming a first target on the substrate corresponding to the first focus setting, the first target containing a measurable dimension sensitive to defocus. The process then includes projecting an energy beam through the target mask portion onto a second location of the substrate at a second focus setting, lithographically forming a second target on the substrate corresponding to the second focus setting, the second target containing a measurable dimension sensitive to defocus, and measuring the defocus sensitive dimension for each of the first and second targets on the substrate. The defocus sensitive dimension of the first and second targets are then compared and there is determined a desired focus setting of the energy beam based on the comparison of the dimensions of the first and second target. The process may be used to form focus setting targets on a semiconductor wafer for use in manufacture of microelectronic circuits.

Owner:GLOBALFOUNDRIES INC

Electronics tester with a signal distribution board and a wafer chuck having different coefficients of thermal expansion

ActiveUS20090015282A1Reduce pressureElectrical measurement instrument detailsElectrical testingThermal dilatationWafering

Owner:AEHR TEST SYST

Flexible diode package and method of manufacturing

InactiveUS20100136748A1Simple packagingLow production costSemiconductor/solid-state device detailsSolid-state devicesAdhesiveExtreme temperature

A single step packaging process that both melts a solder and also cures an adhesive about a microelectronic circuit. The process finds technical advantages by simplifying packaging of a die that may be coupled to a planar flexible lead, which leads to a lower production cost and quicker manufacturing time. The planar flexible lead may be adapted to bend and flex during mechanical stress and during extreme temperature cycling, and allow direct mounting of the device to a member by easily welding or soldering. The invention may comprise a flexible solar cell diode that can be closely positioned on solar panels at an extremely low cost.

Owner:MICROSEMI

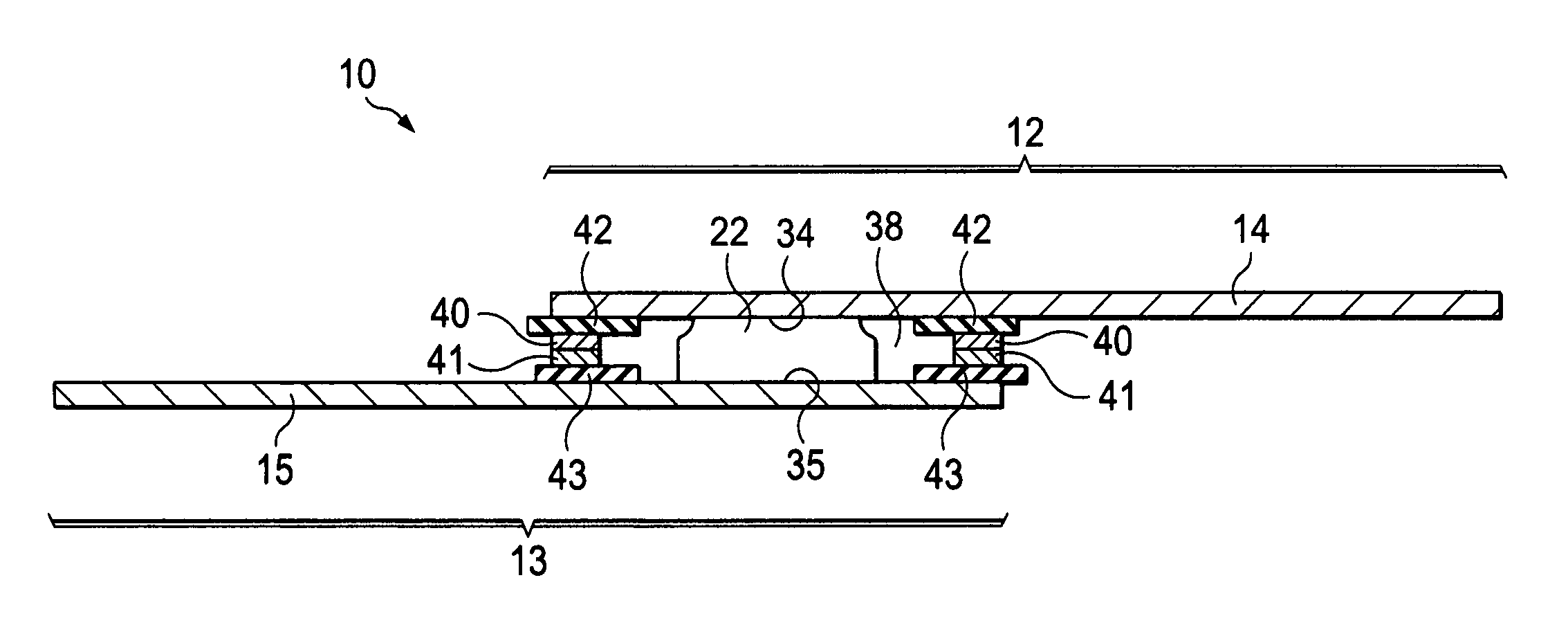

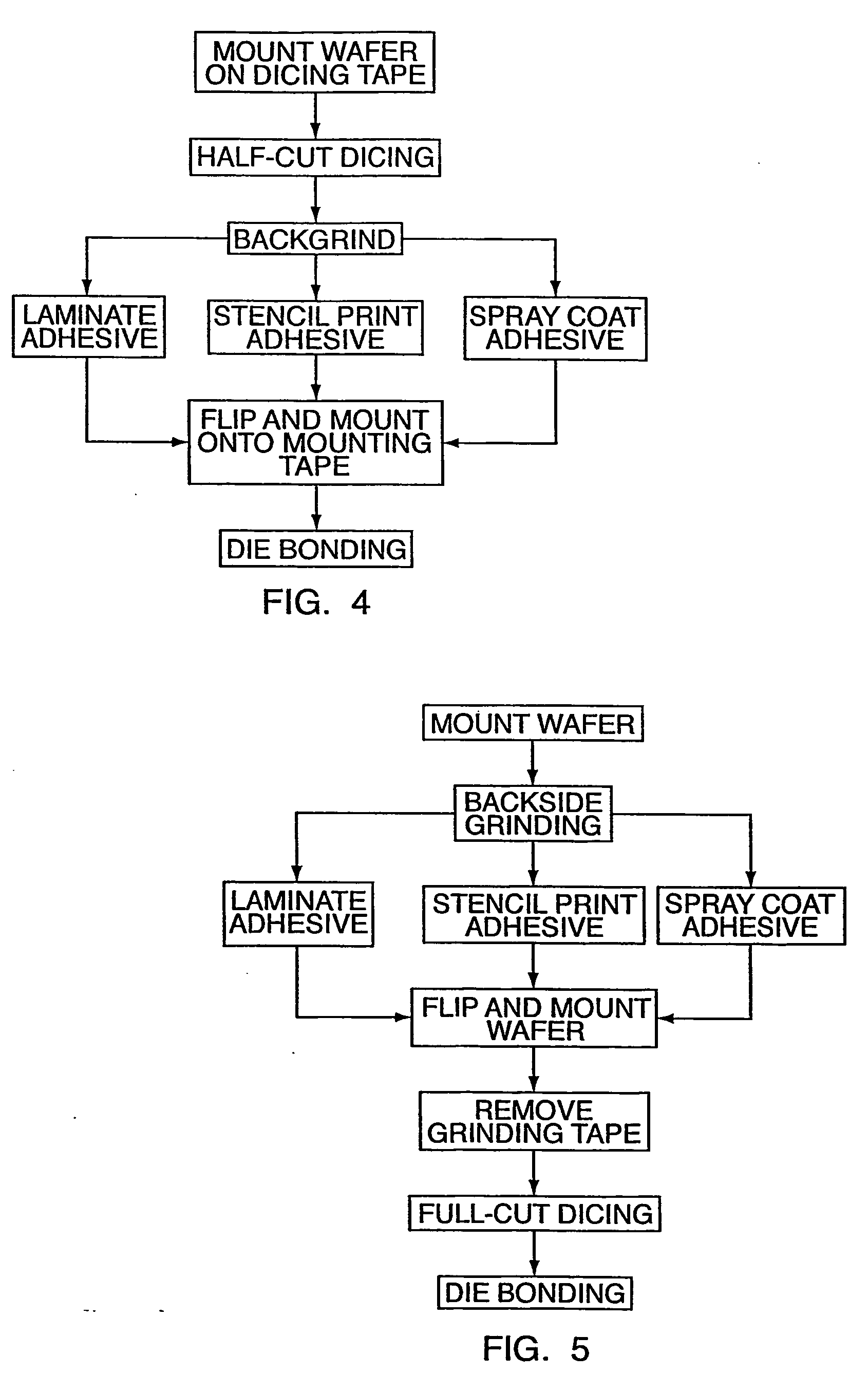

Interlayer dielectric and pre-applied die attach adhesive materials

InactiveUS20050008832A1Avoidance of dispensingAvoid handlingNon-macromolecular adhesive additivesSemiconductor/solid-state device detailsSemiconductor chipMicroelectronic circuits

The present invention relates to interlayer dielectric materials and pre-applied die attach adhesives, more specifically pre-applied die attach adhesives (such as wafer and other substrate-applied die attach adhesives), methods of applying the interlayer dielectric materials onto substrates to prepare low K dielectric semiconductor chips, methods of applying the pre-applied die attach adhesives onto wafer and other substrate surfaces, and assemblies prepared therewith for connecting microelectronic circuitry.

Owner:HENKEL CORP

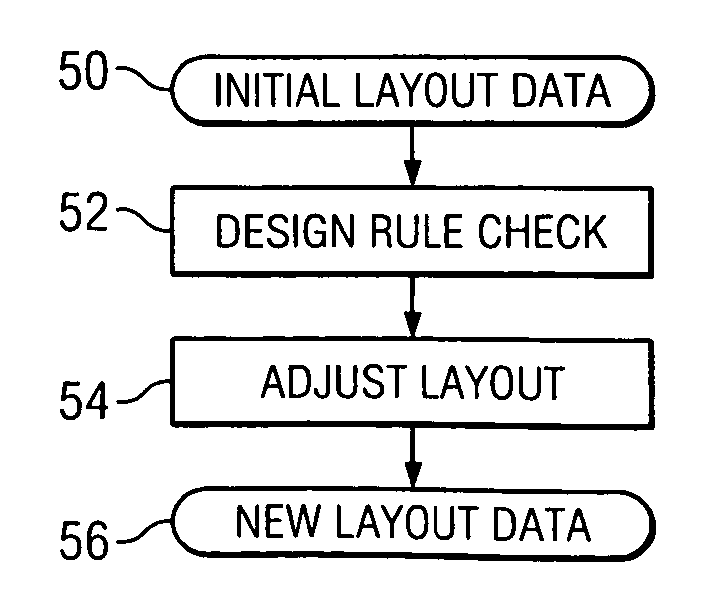

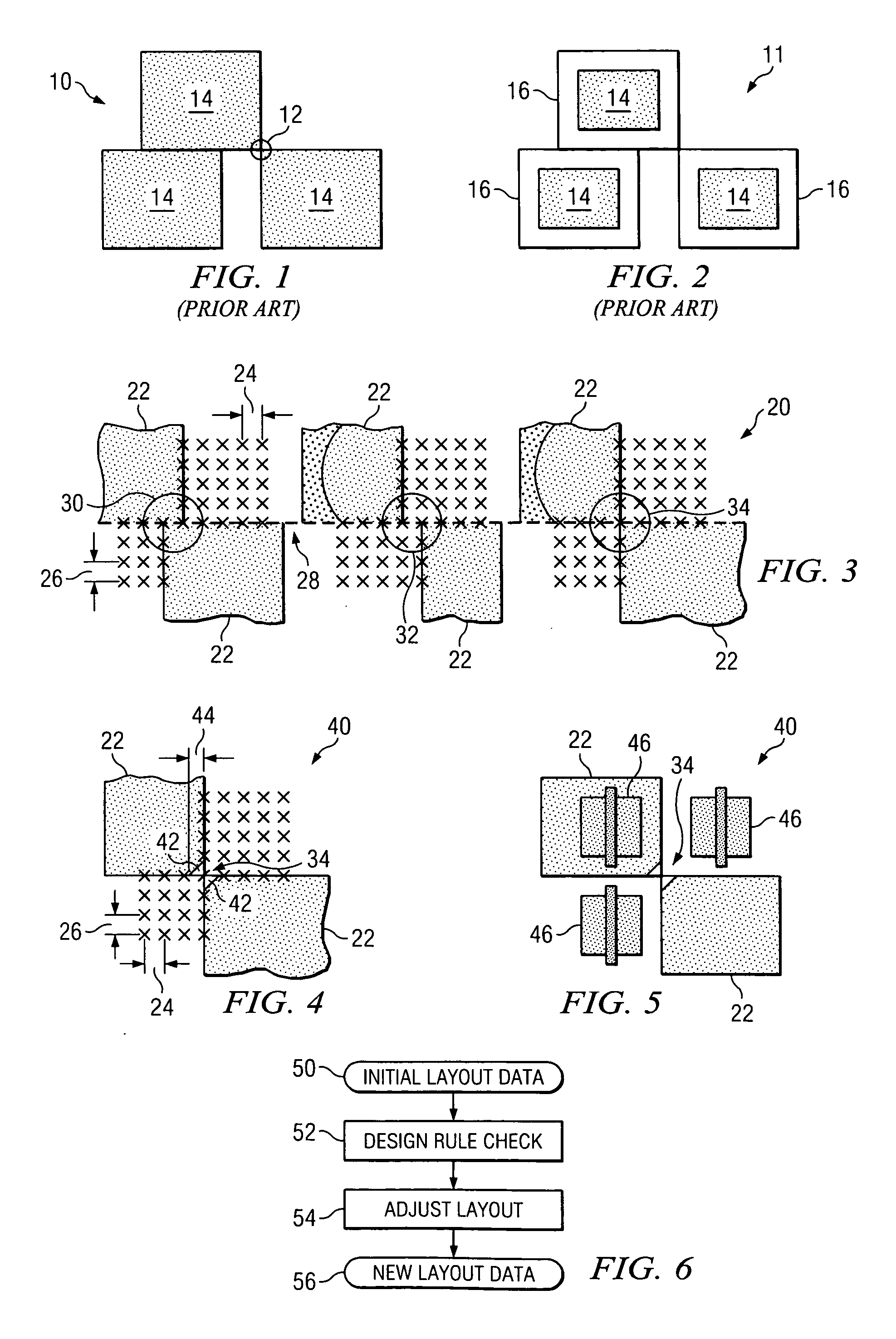

Placement methods for standard cell library

ActiveUS20070011639A1Originals for photomechanical treatmentComputer aided designEngineeringMicroelectronic circuits

Methods are disclosed for the layout and manufacture of microelectronic circuits. The methods employ the monitoring of the placement of macros within circuit layouts for design rule compliance. Upon detection of noncompliance, the macros associated with noncompliance are adapted to bring the layout within the design rules. In a preferred embodiment of the invention monitoring the relative positions of macros includes identifying instances of coinciding macro (x, y) coordinates. Adapting noncompliant macros further includes steps for maintaining minimum (x, y) distances between adjacent macro corners.

Owner:TEXAS INSTR INC

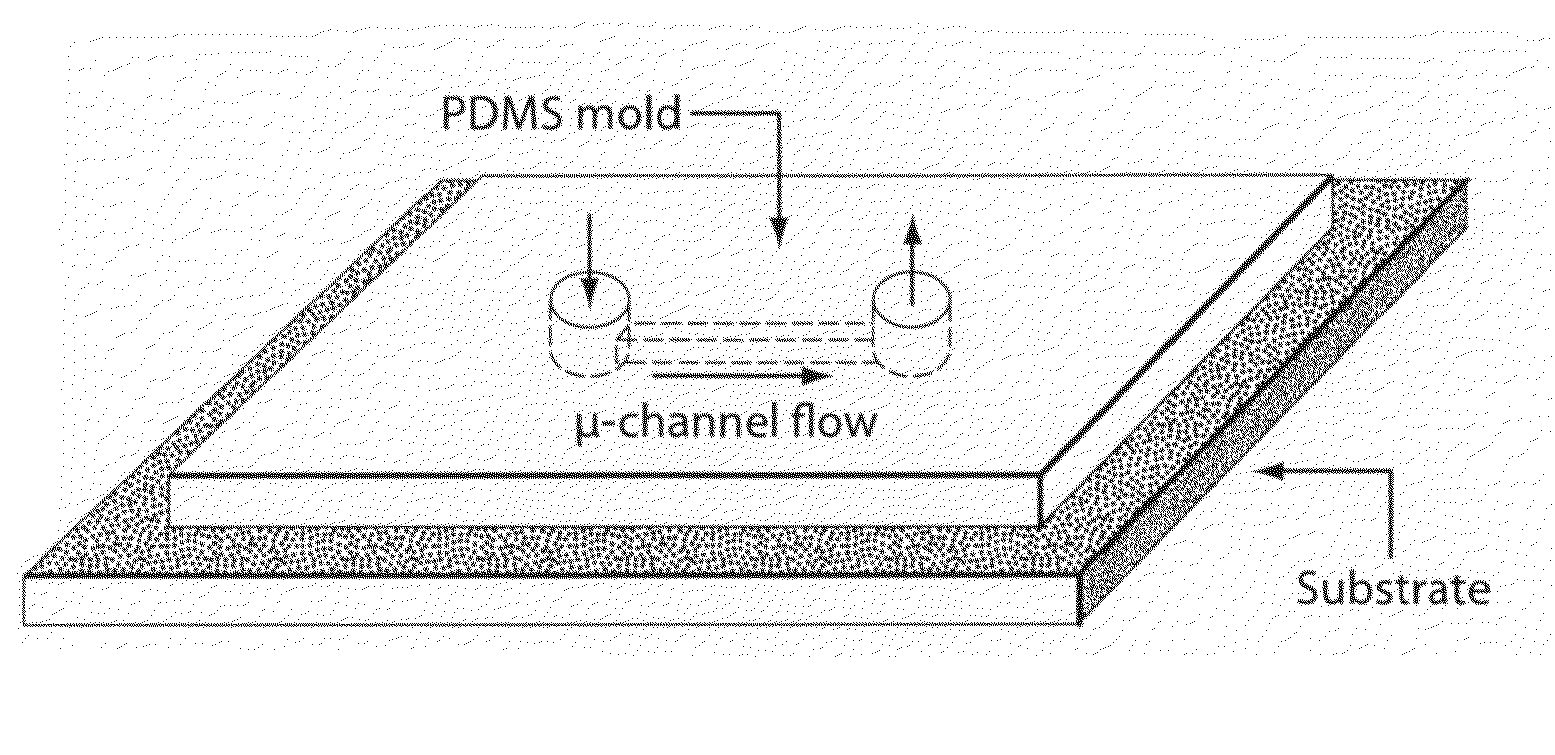

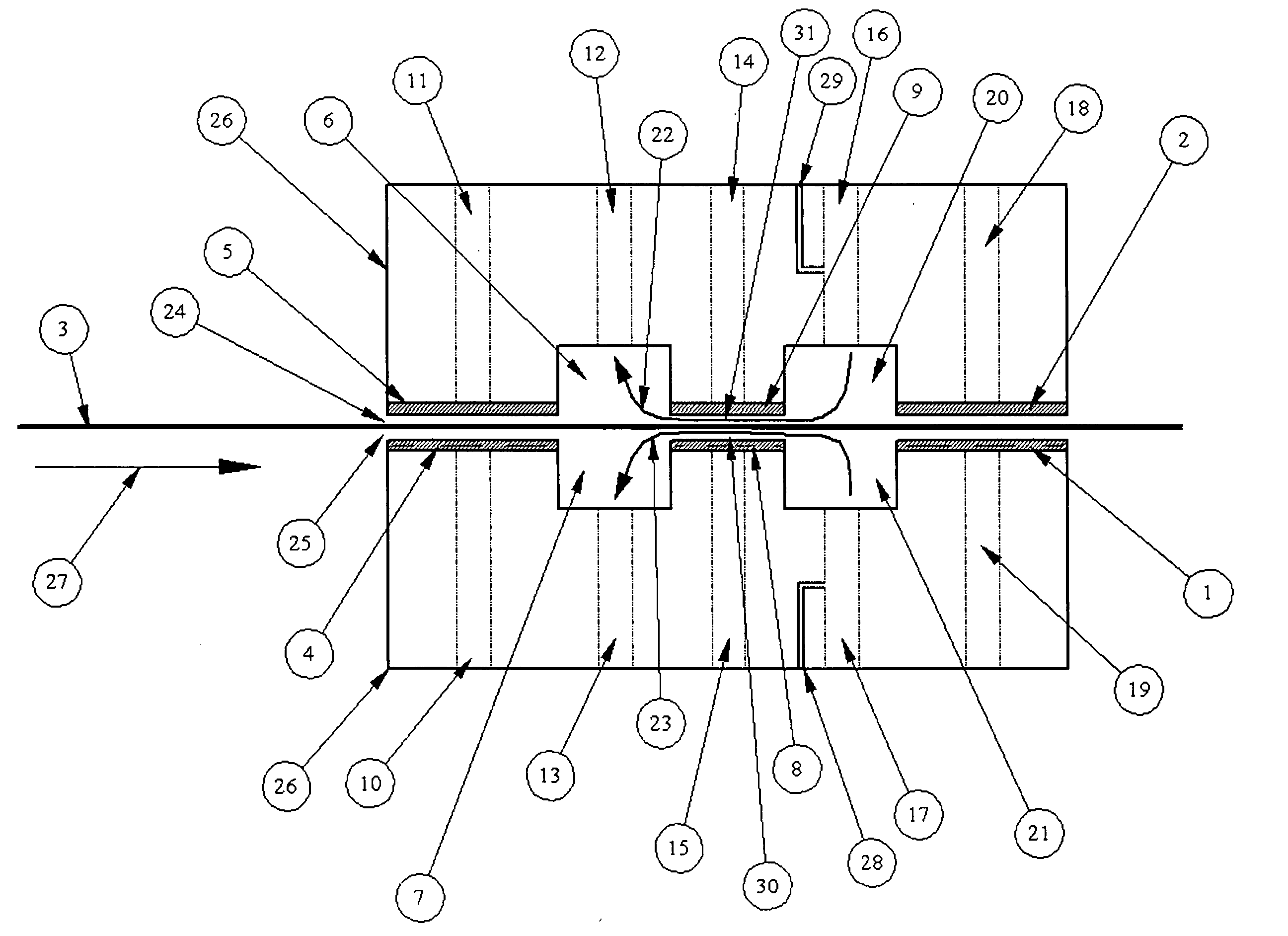

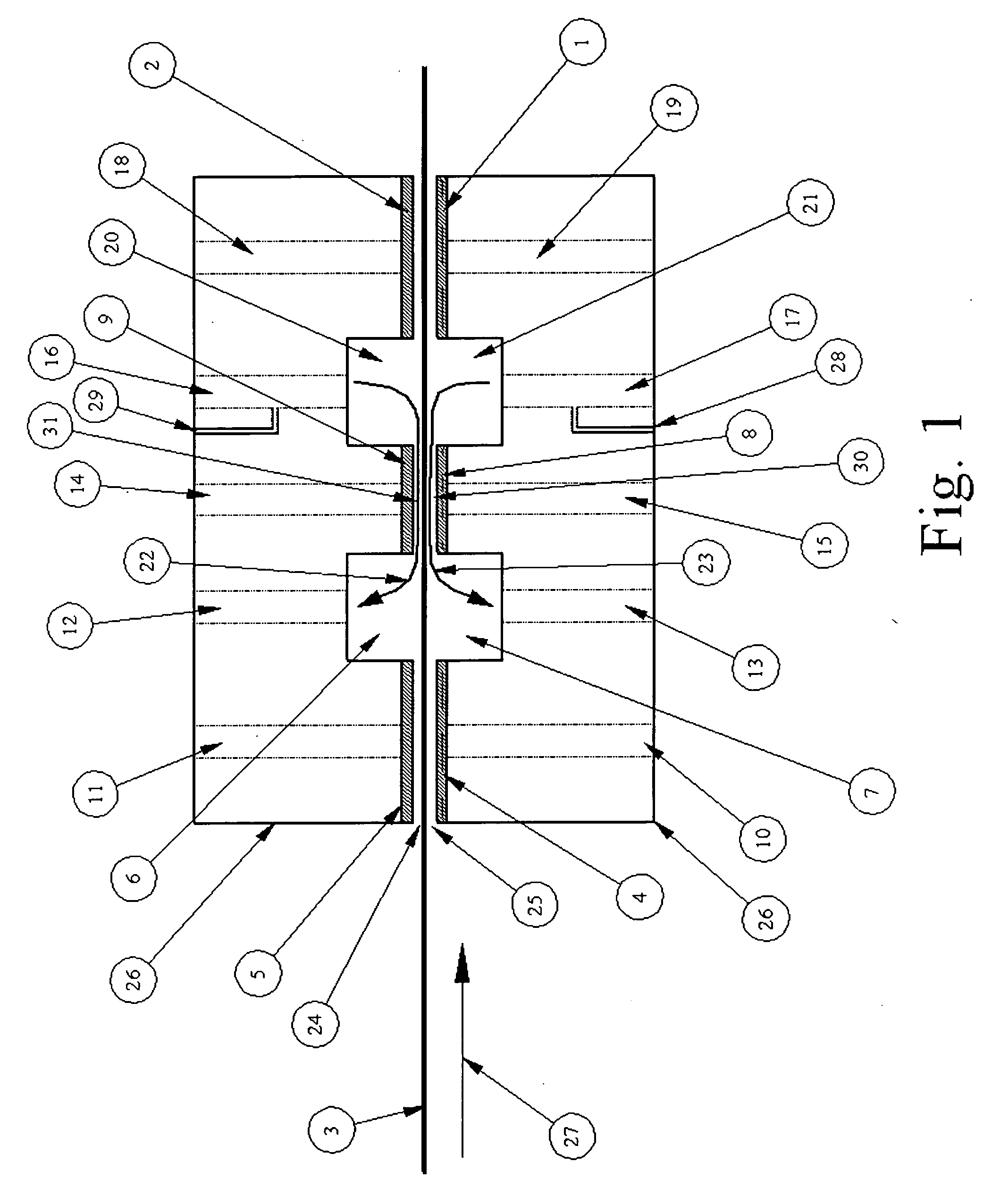

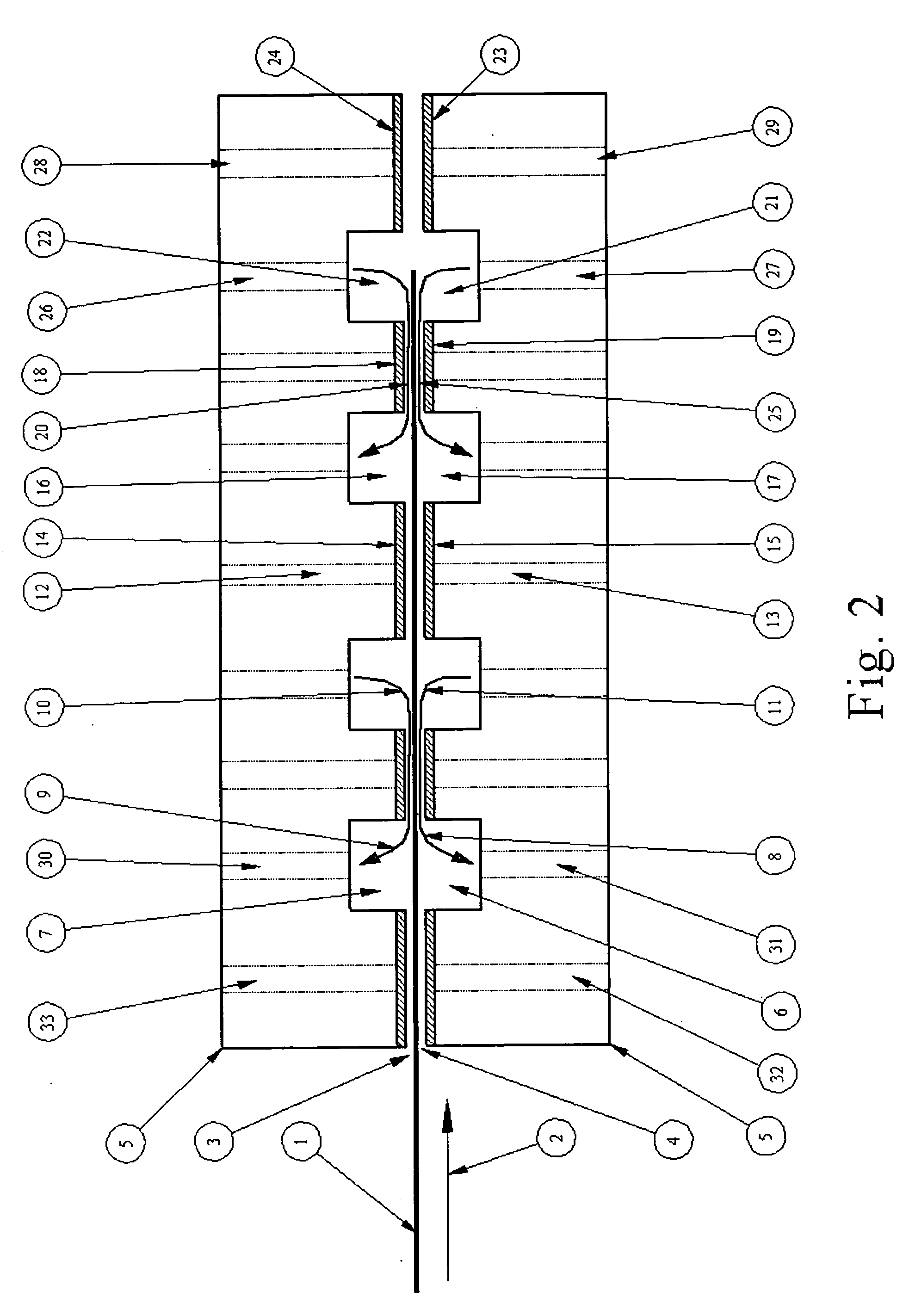

Method and apparatus for in-line processing and immediately sequential or simultaneous processing of flat and flexible substrates through viscous shear in thin cross section gaps for the manufacture of micro-electronic circuits or displays

InactiveUS20070034228A1Thin thicknessTransportation safetyVacuum evaporation coatingGlass transportation apparatusViscous shearPorous medium

A method and apparatus for cleaning, drying, coating, baking etching and deposition of surfaces on glass substrate as it transitions thru and between small gaps between hydro-static porous media bearings. Due to the non-contact nature of the device extremely high pressures can be induced upon the work piece through various fluids without damage to the substrate, allowing the system to utilize the viscous nature of fluids to accomplish the desired cleaning, drying, coating, etching or baking. The process also allows for simultaneous and immediately sequential ordering of processes.

Owner:NEW WAY MACHINE COMPONENTS

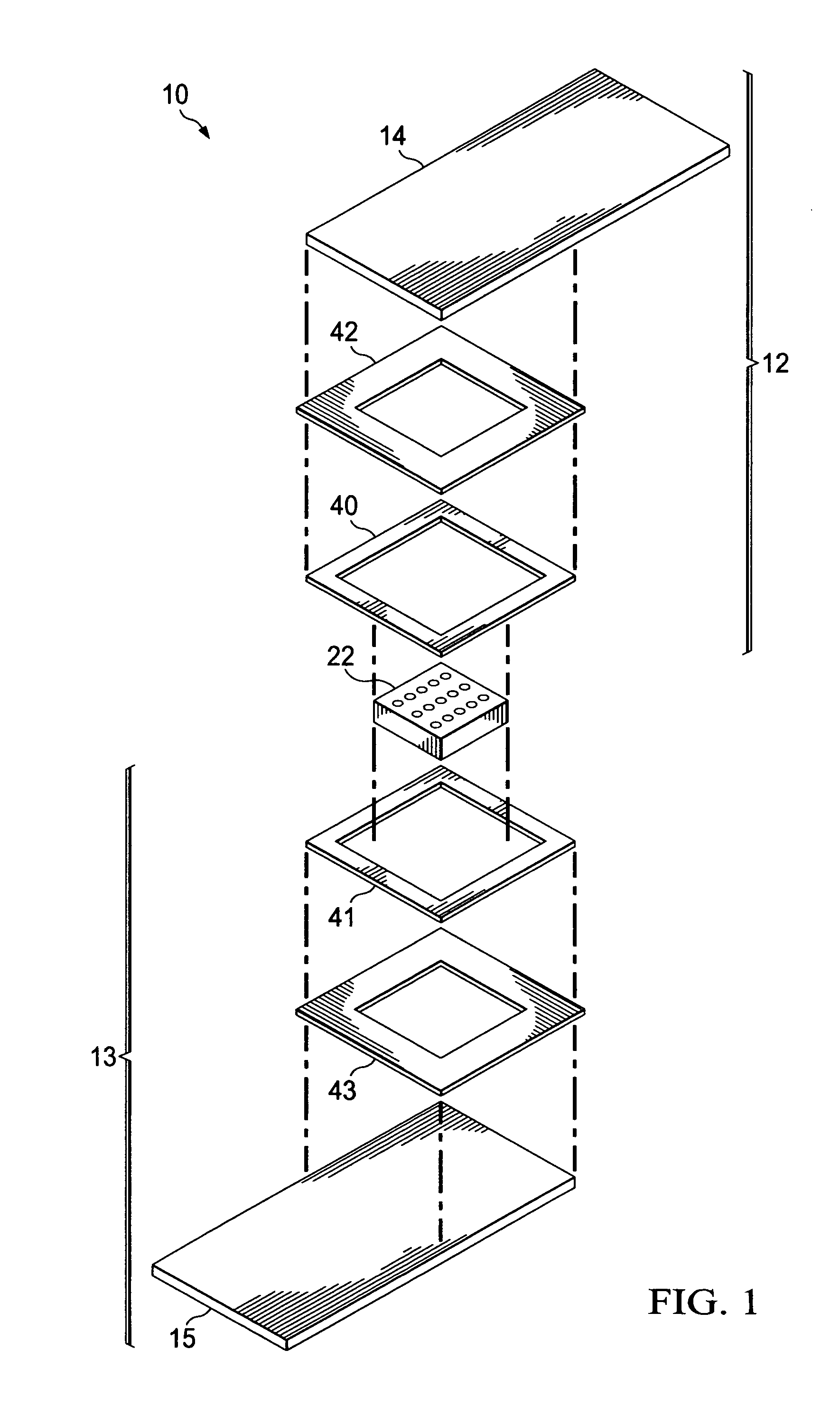

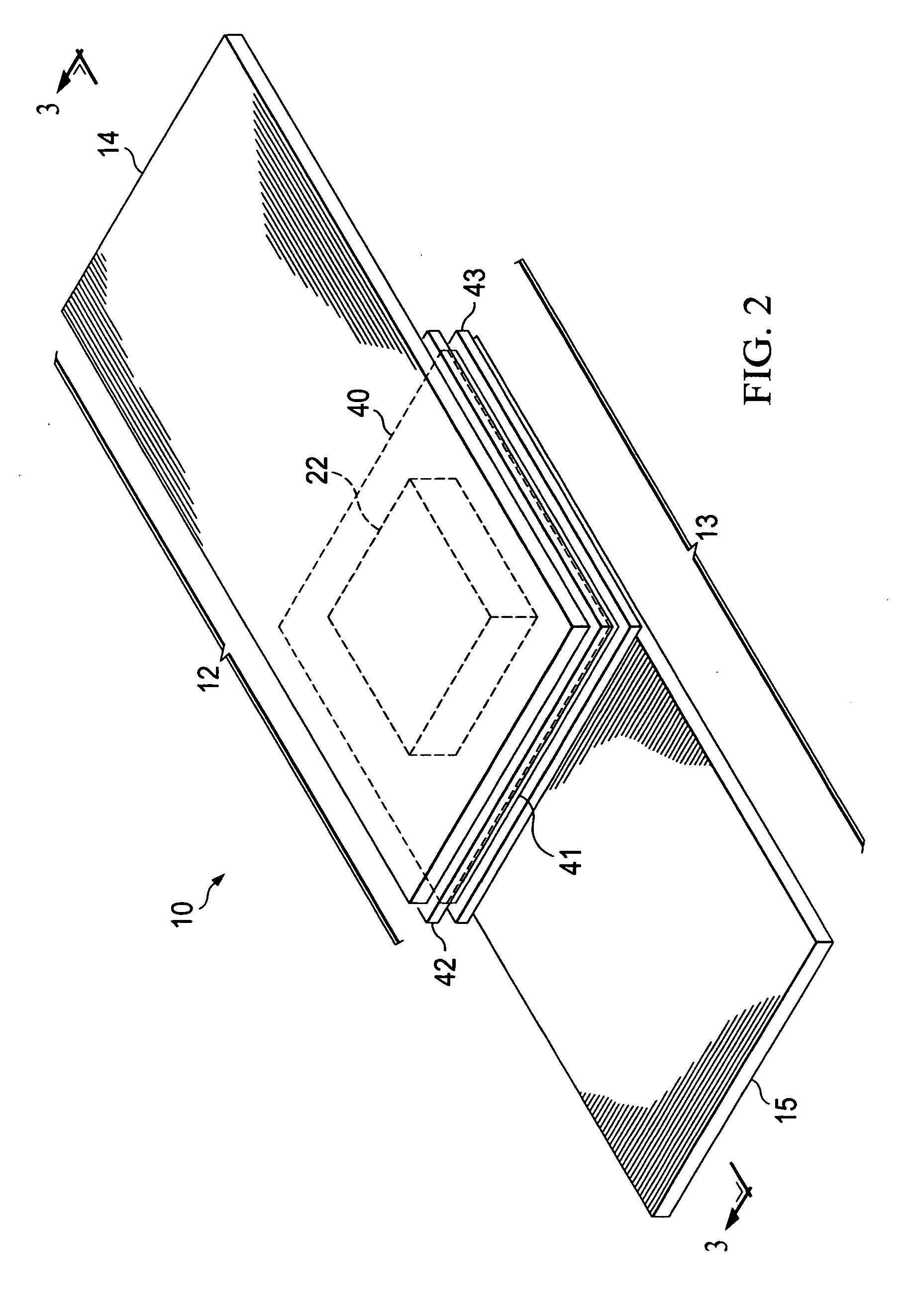

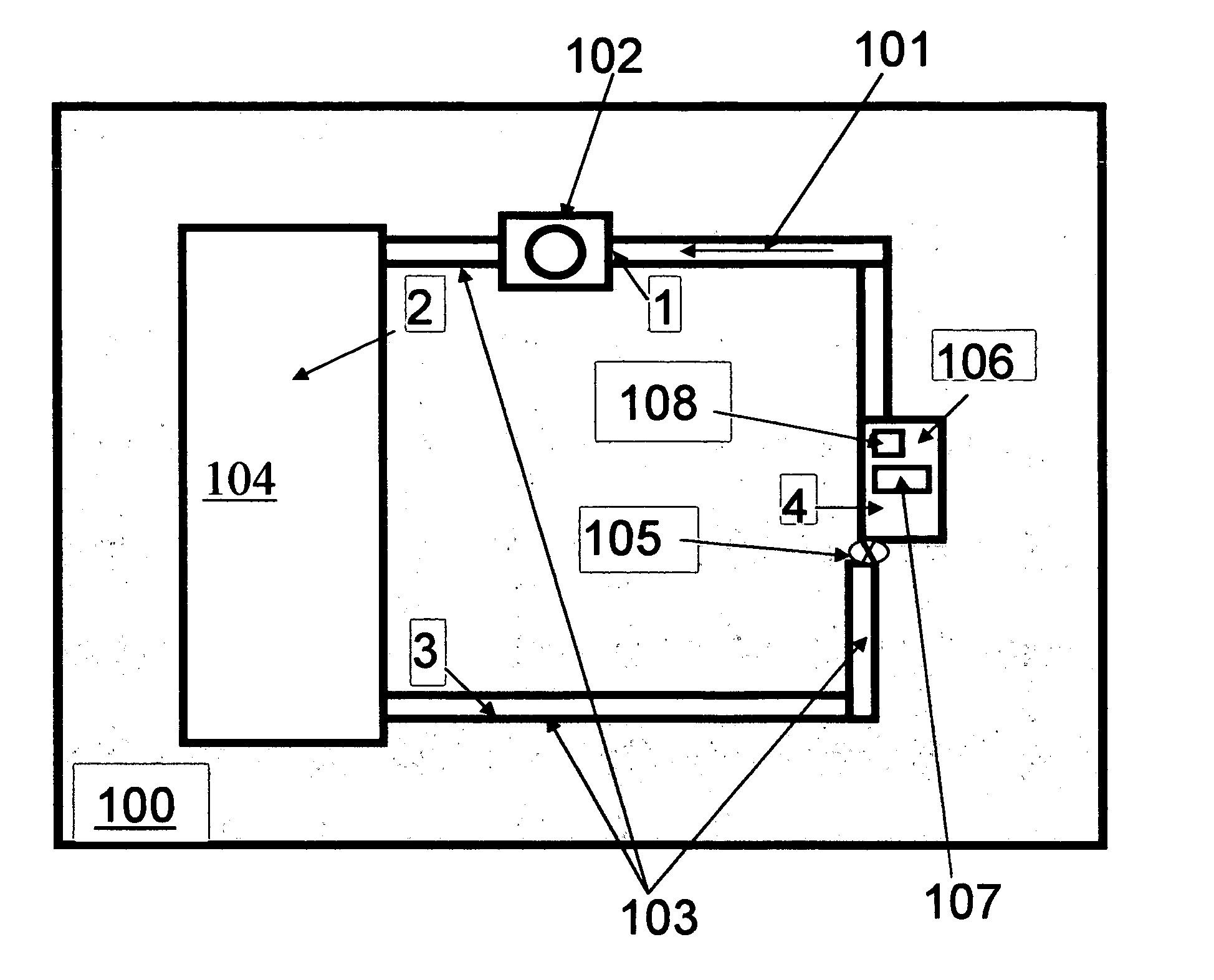

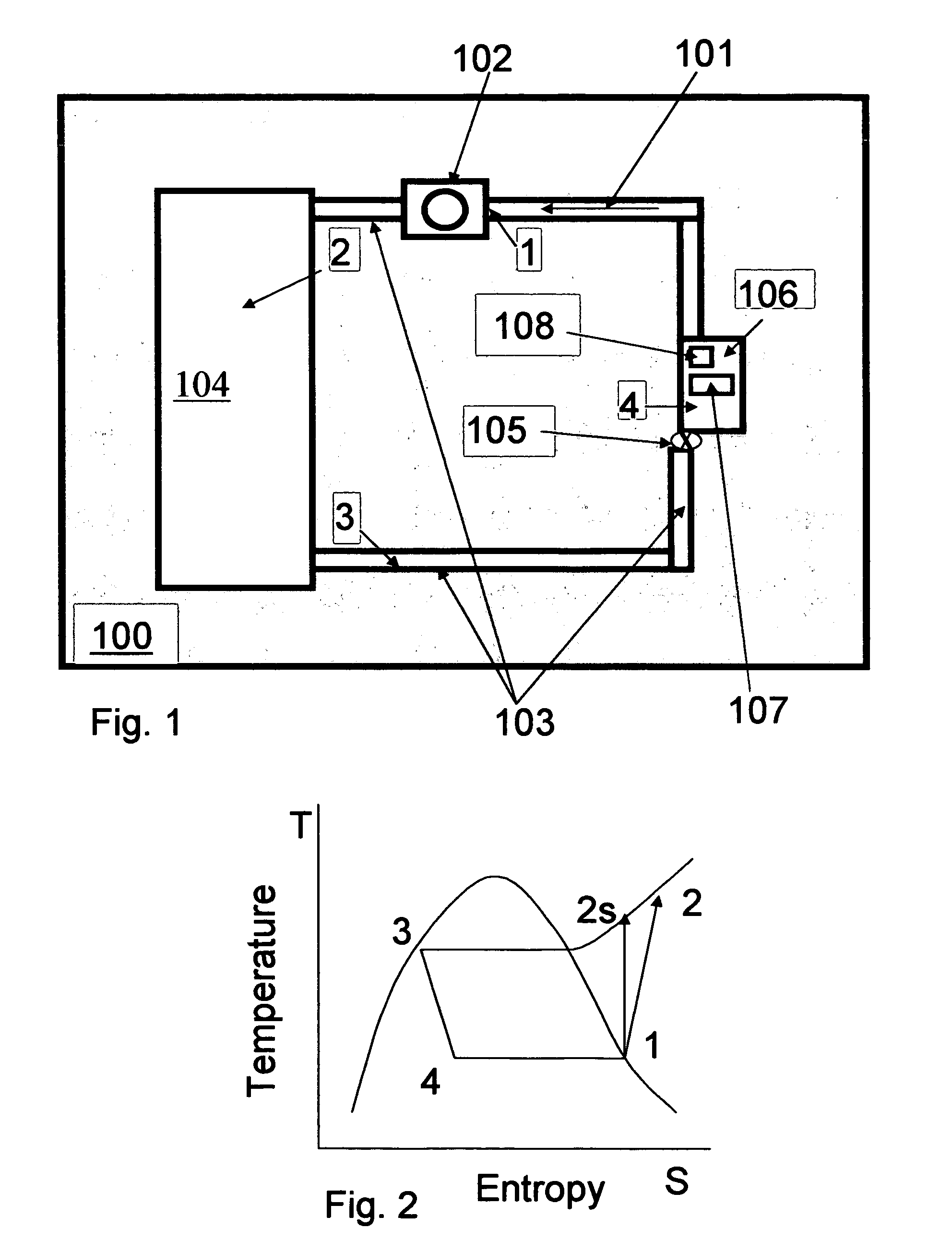

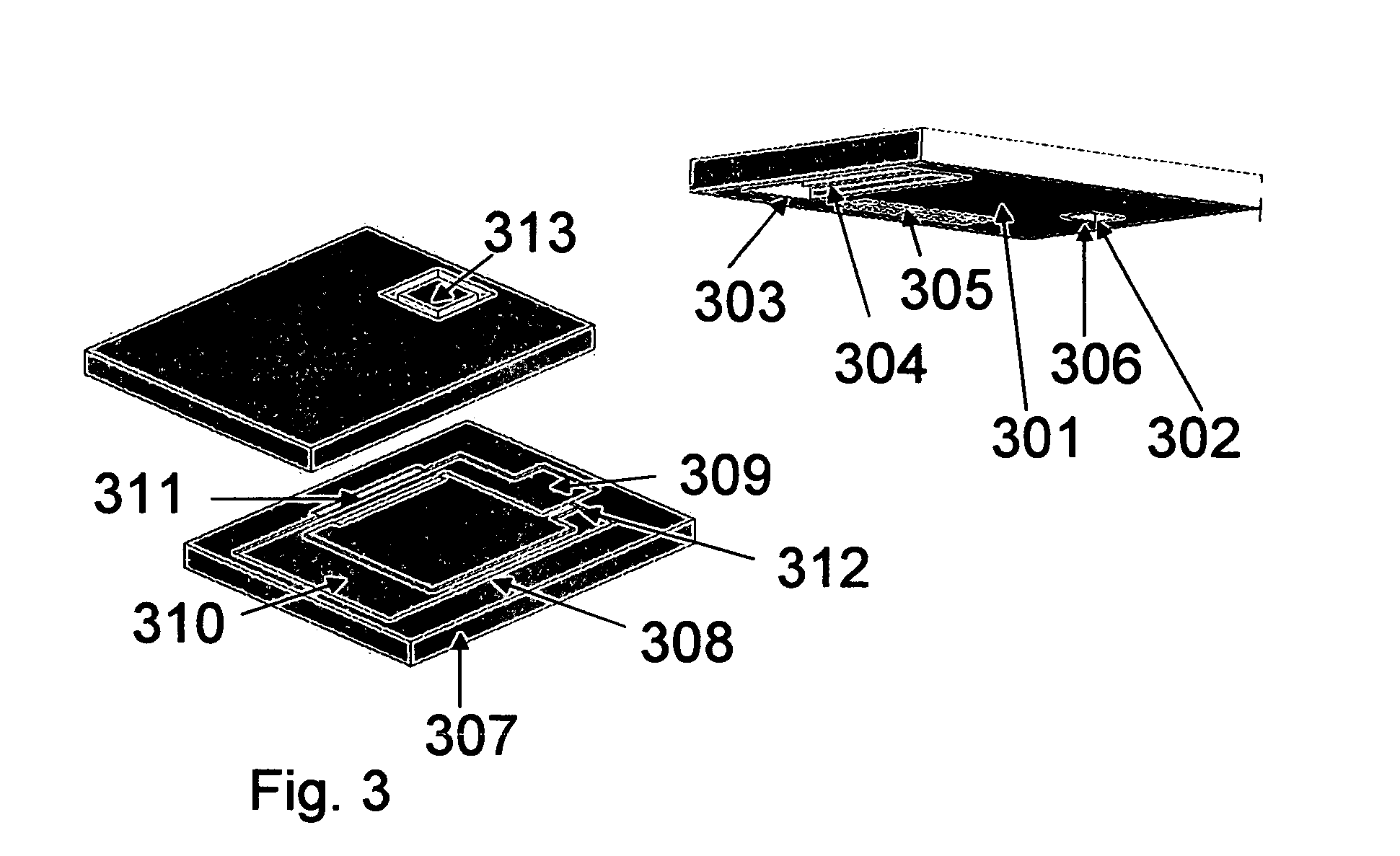

MEMS based micro vapor compression refrigeration system for microelectronic and photonic thermal control

InactiveUS20050144968A1Compression machines with non-reversible cycleRefrigeration devicesThermoelectric coolingVolumetric Mass Density

A micro-refrigerator is fabricated using Micro-Electro Mechanical Systems processing and is used to thermally control photonic or microelectronic circuits. Temperatures below local ambient are possible due to the refrigeration capability of the device and unwanted parasitic heat such as from the walls or lid of an enclosure is minimized due to the small size of the cooled mounting area for the integrated circuit. Localized cooling is provided by jets of vapor droplet mixture controlled to impinge directly onto the hottest regions of a microelectronic or photonic integrated circuit allowing greater circuit density and thermal dissipation at isolated regions within the integrated circuit and advantageously improving performance. Methods of manufacturing micro-scale refrigerator elements including the compressor, evaporator and condenser are defined. This device is a direct improvement over the commonly used thermoelectric cooler for thermal control of microelectronic or photonic devices.

Owner:SHAKESPEARE WALTER JEFFREY

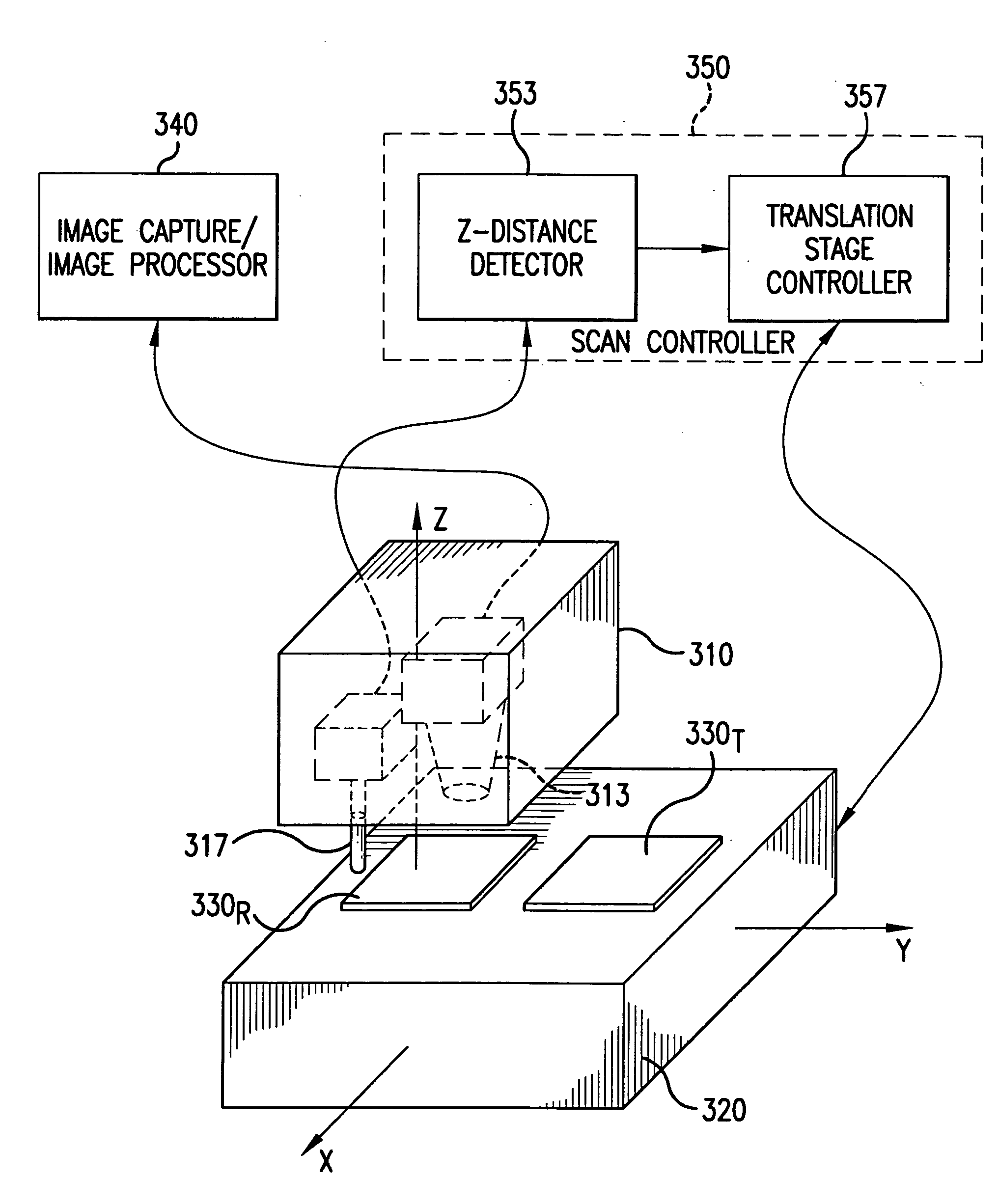

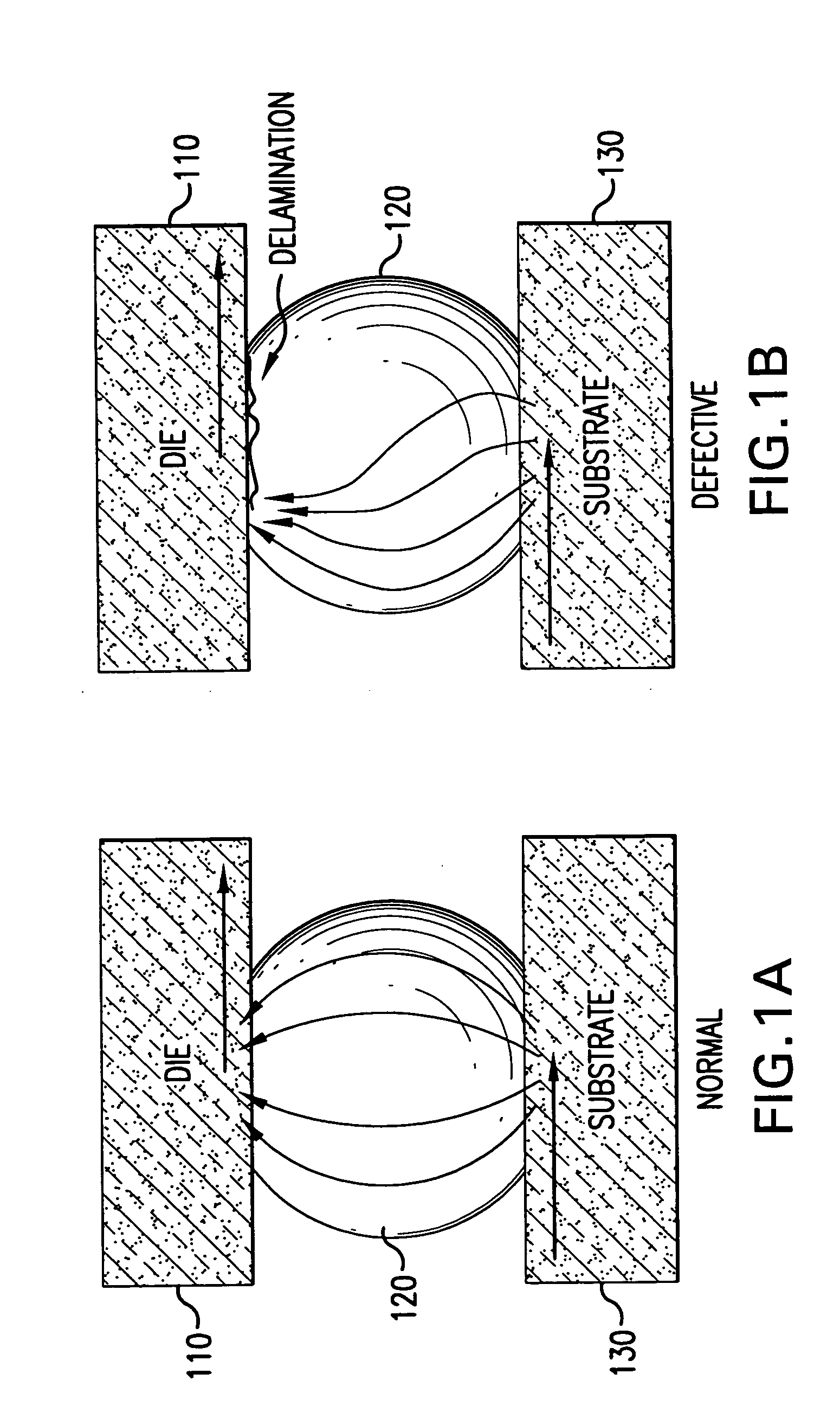

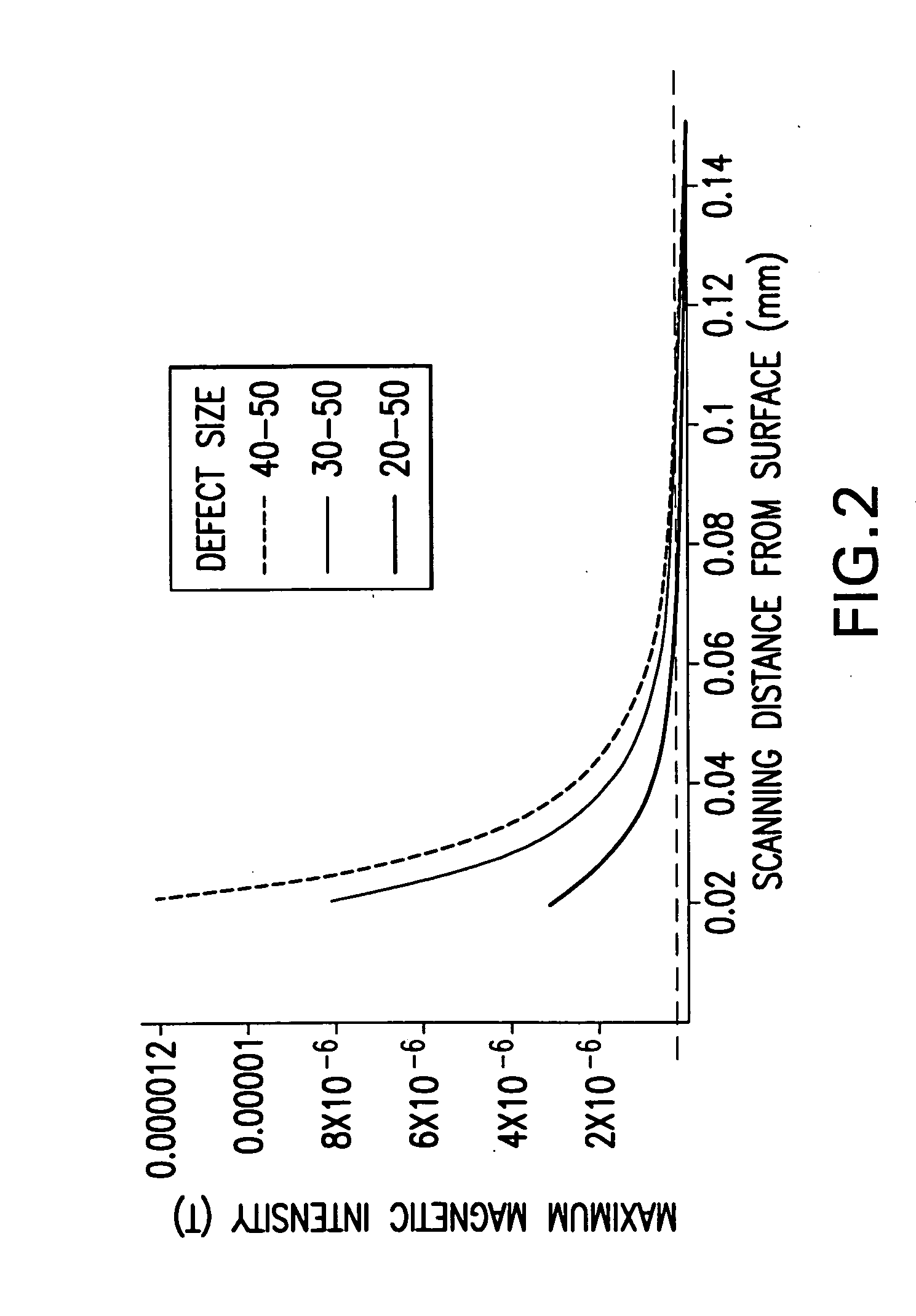

Fault isolation of circuit defects using comparative magnetic field imaging

ActiveUS20050057246A1Magnetic property measurementsElectrographic process apparatusHigh resistanceAmpere

Circuit flaws in microelectronic circuitry present regions of high resistance in which a current distribution deviates from that of a defect-free circuit. The altered current distribution emits a correspondingly altered magnetic field in accordance with Ampere's Law. When compared with the magnetic field of a defect-free circuit, the anomaly in the magnetic field of the defective device is detected and the location of the circuit flaw may be determined therefrom. As the anomaly in the magnetic field is very small in magnitude, a sensitive magnetic microscope is utilized to obtain images of the magnetic fields of a defect-free reference device and a device-under-test. The distance between the magnetic sensor and the devices being scanned is precisely controlled to minimize influences of scanning distance on the difference in measured magnetic field strength. Comparative image analysis reveals the location of the circuit flaw. Maximal image registration through image interpolation, displacement and resampling optimizes the comparative image analysis.

Owner:NEOCERA

Lead-free solder paste

InactiveUS20060180245A1Inspection/indentification of circuitsPrinted circuit manufactureMicroelectronic circuitsColor changes

A lead-free solder paste suitable for soldering components in electronic or microelectronic circuitry including a solder powder and a flux medium. The flux medium includes at least one colored dye material and at least one fluorescent dye material. The solder paste upon melting undergoes a color change from a colored state to a colorless metallic state and the melted solder paste fluoresces under black light.

Owner:QUALITEK INT

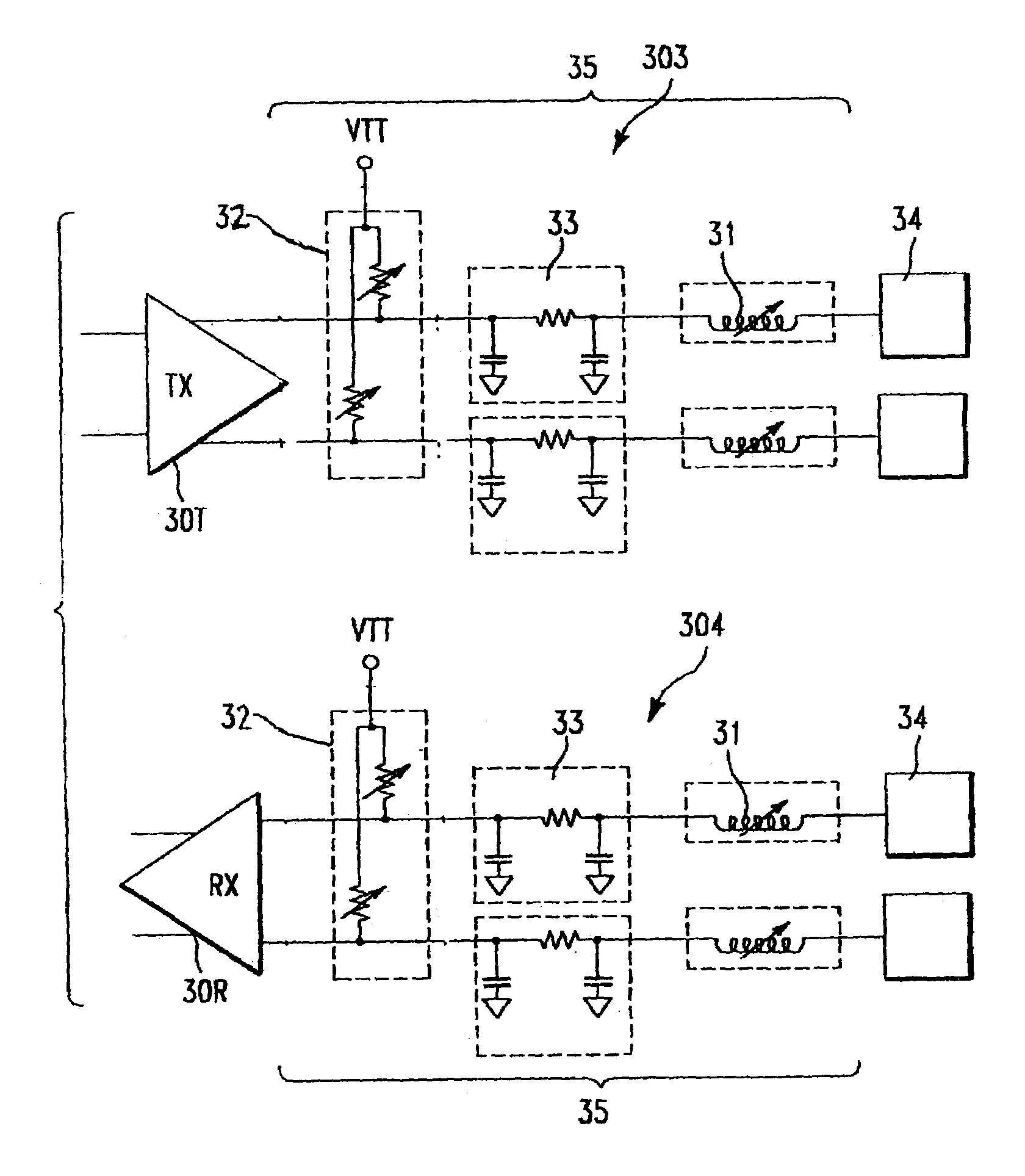

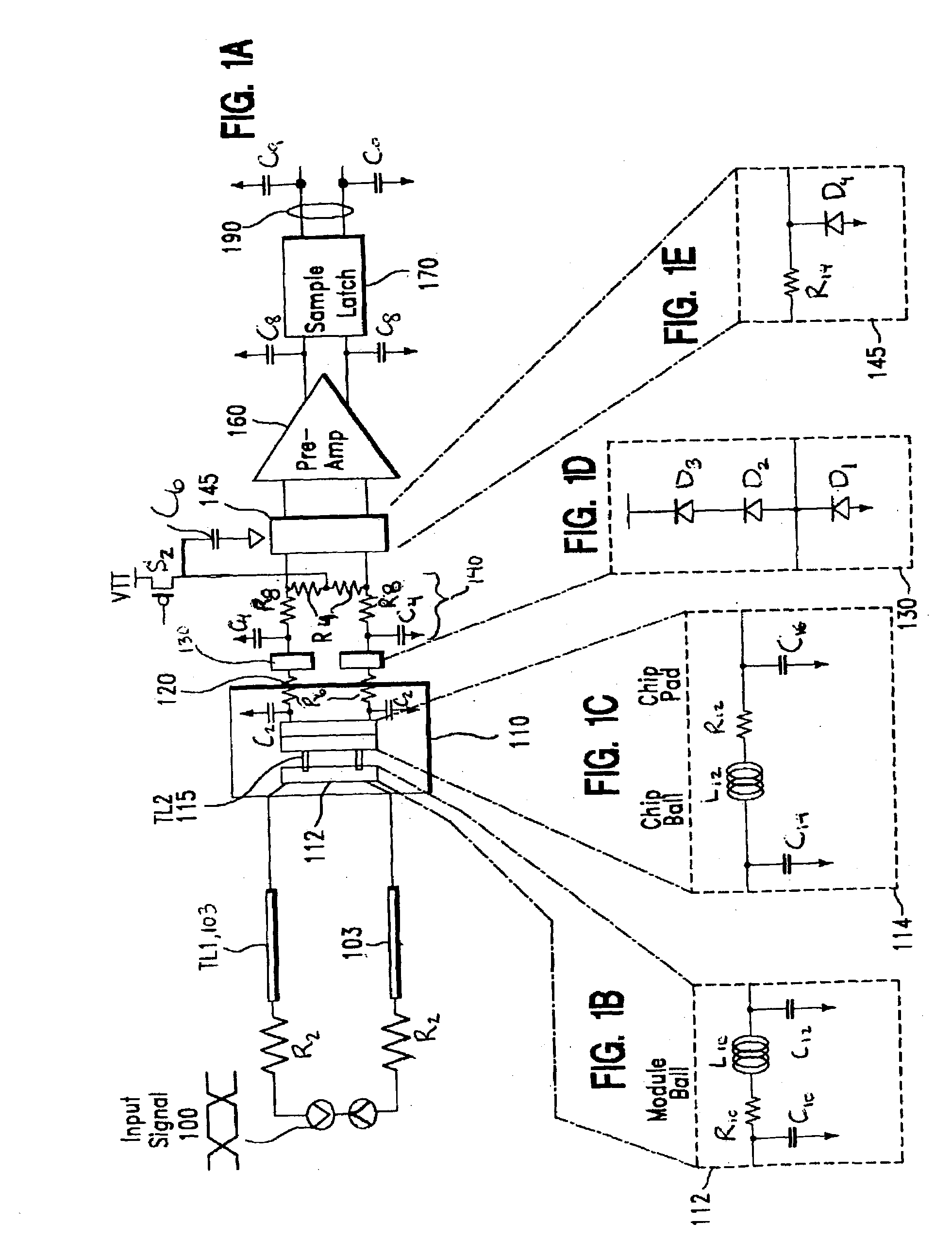

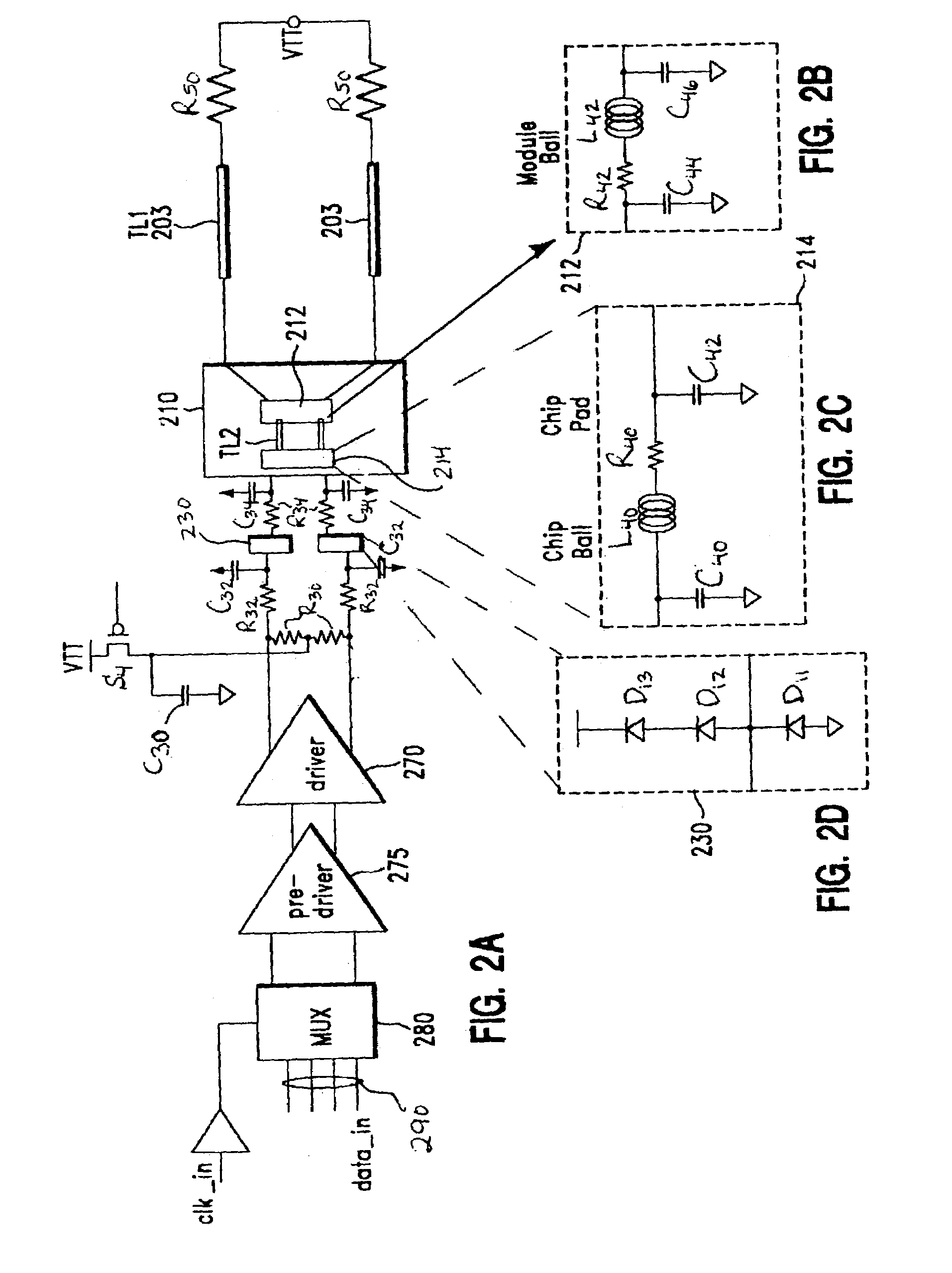

Programmable impedance matching circuit and method

InactiveUS7145413B2Improve signal integrityMultiple-port networksResonant long antennasInductorMicroelectronic circuits

As disclosed herein, a microelectronic circuit and method are provided for improving signal integrity at a transmission line. The circuit includes a programmably adjustable impedance matching circuit which is coupled to a transmission line which includes a programmably adjustable inductive element. The programmably adjustable impedance matching circuit is desirably provided on the same chip as a receiver or transmitter to which the transmission line is coupled, or alternatively, on an element packaged together with the chip that includes the receiver or transmitter. The impedance of the programmably adjustable impedance matching circuit is adjustable in response to control input to improve signal integrity at the transmission line.

Owner:IBM CORP

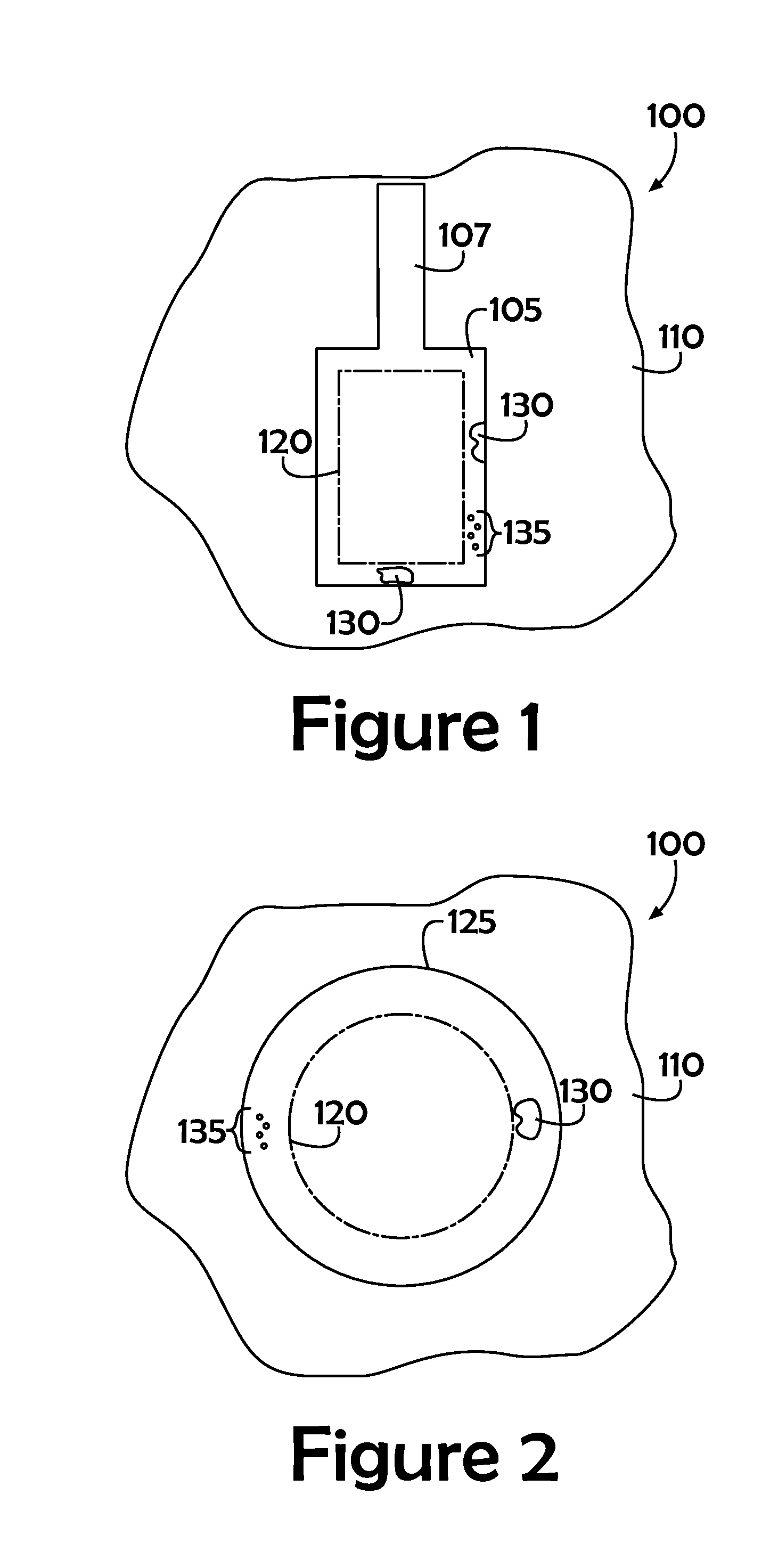

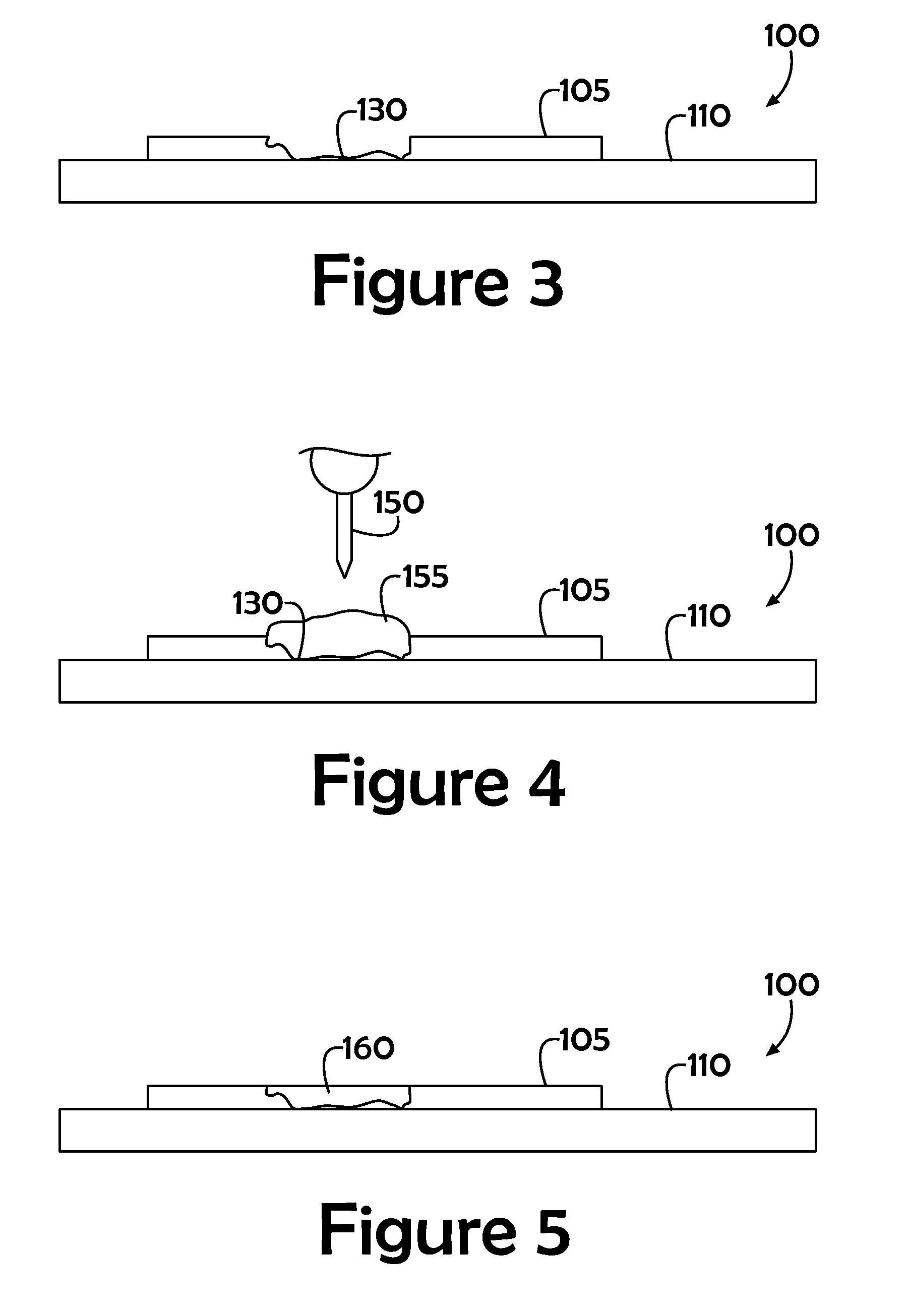

Defective conductive surface pad repair for microelectronic circuit cards

An electrically conductive adhesive (ECA) for repairing electrically conductive pad and trace interconnects and a method of repairing interconnect locations. The method of repairing at least one defect within the area of electrically conductive circuitized substrate traces and pads outside of a pristine center area incorporates an ECA and a forming gas plasma. The ECA contains a mixture of components that allow the adhesive to be adapted to specific requirements. Curing the adhesive results in effective electrical connections being formed between the adhesive and the base pad so that the metallurgies of the conductors and of the ECA are effectively combined to engage and repair the conductor defect.

Owner:I3 ELECTRONICS