Patents

Literature

459results about How to "Improve signal integrity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

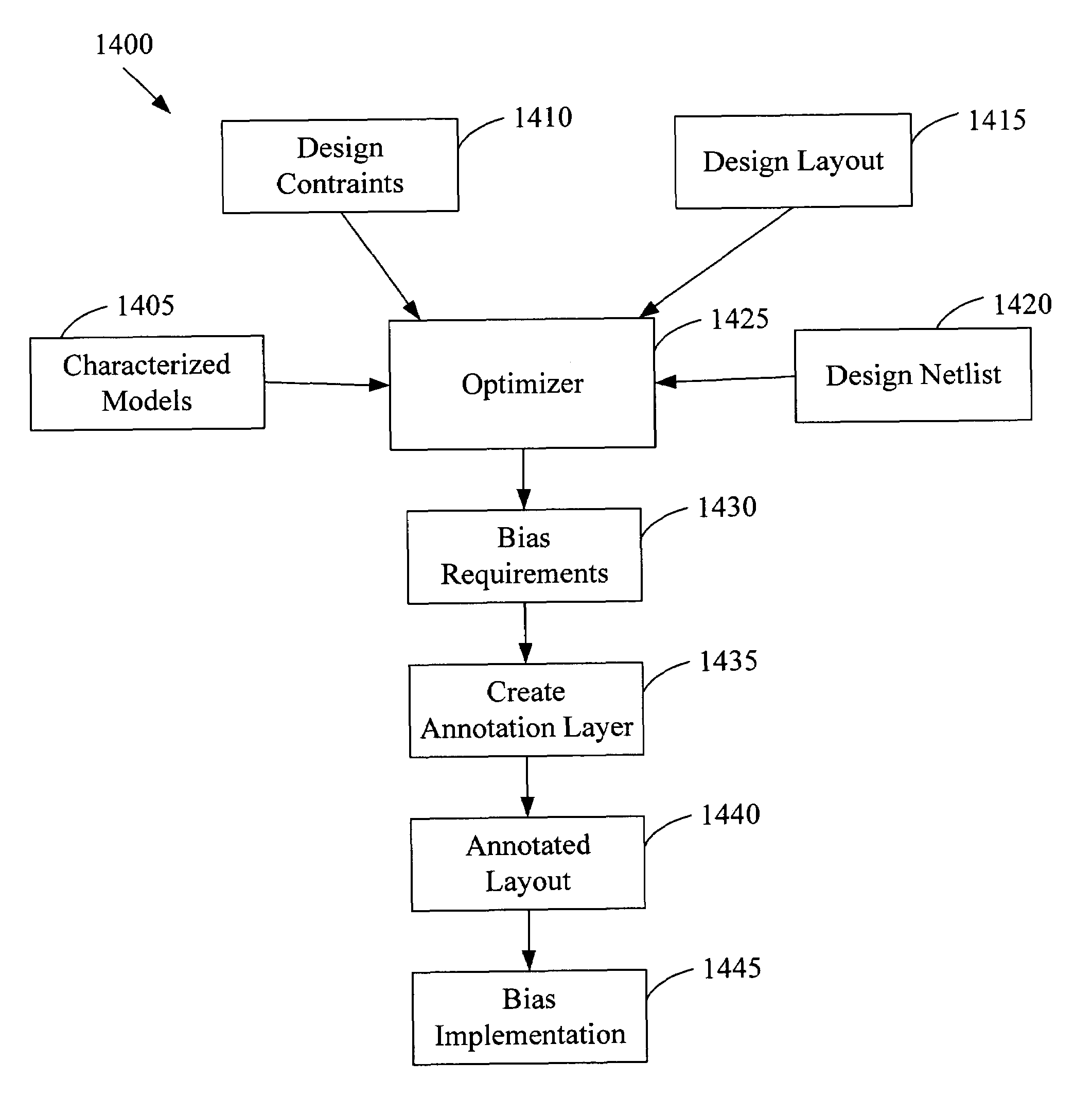

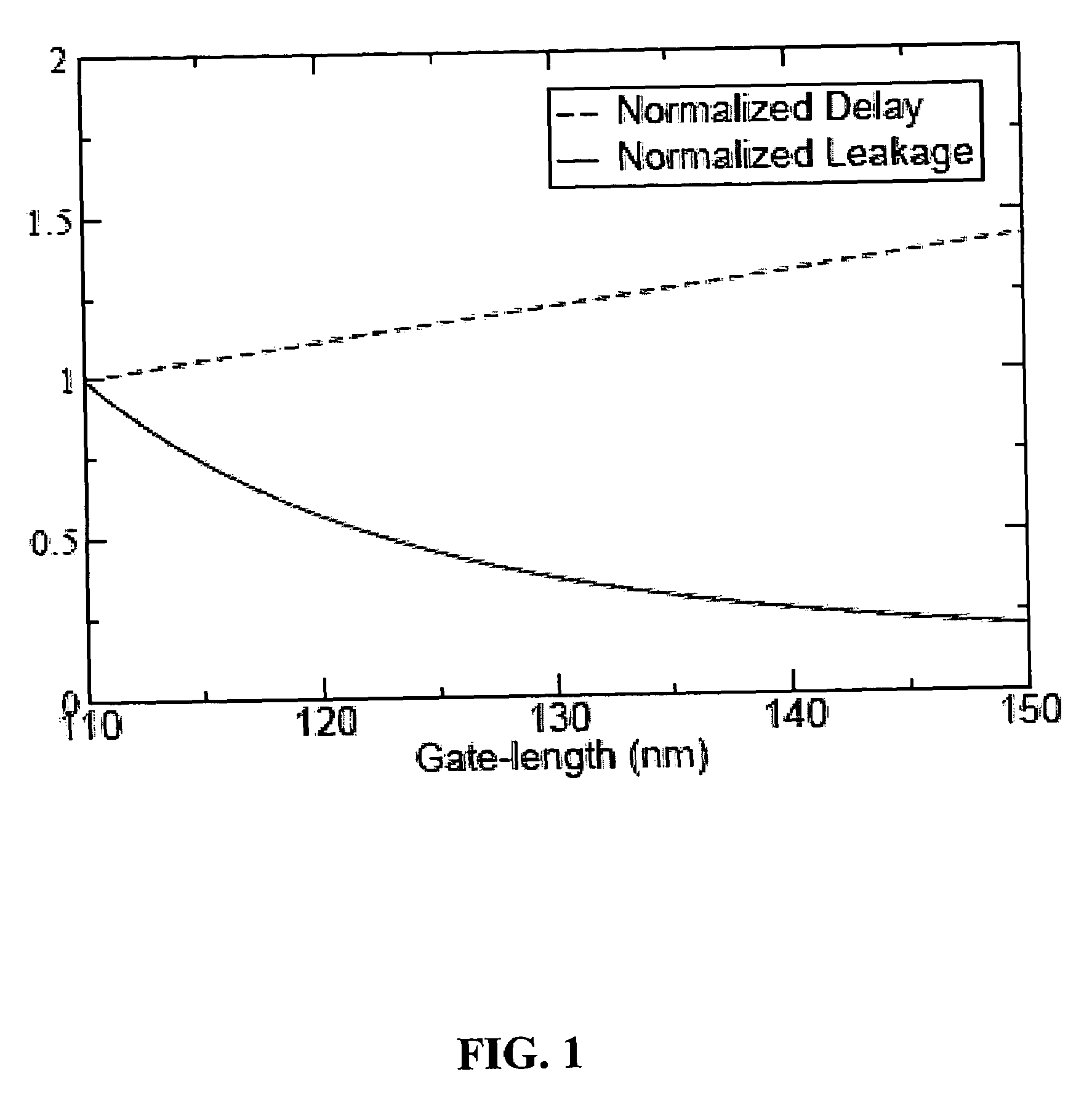

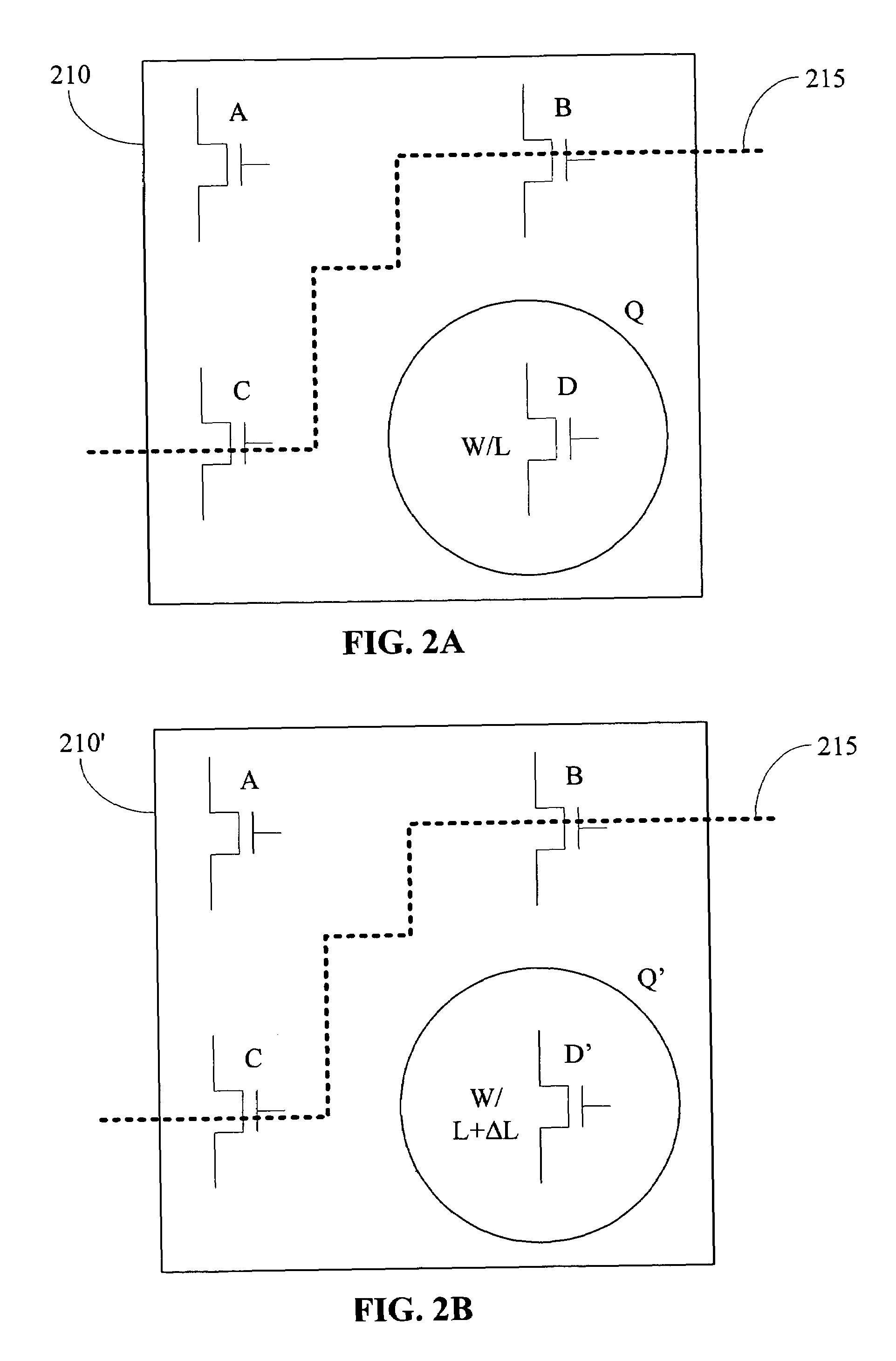

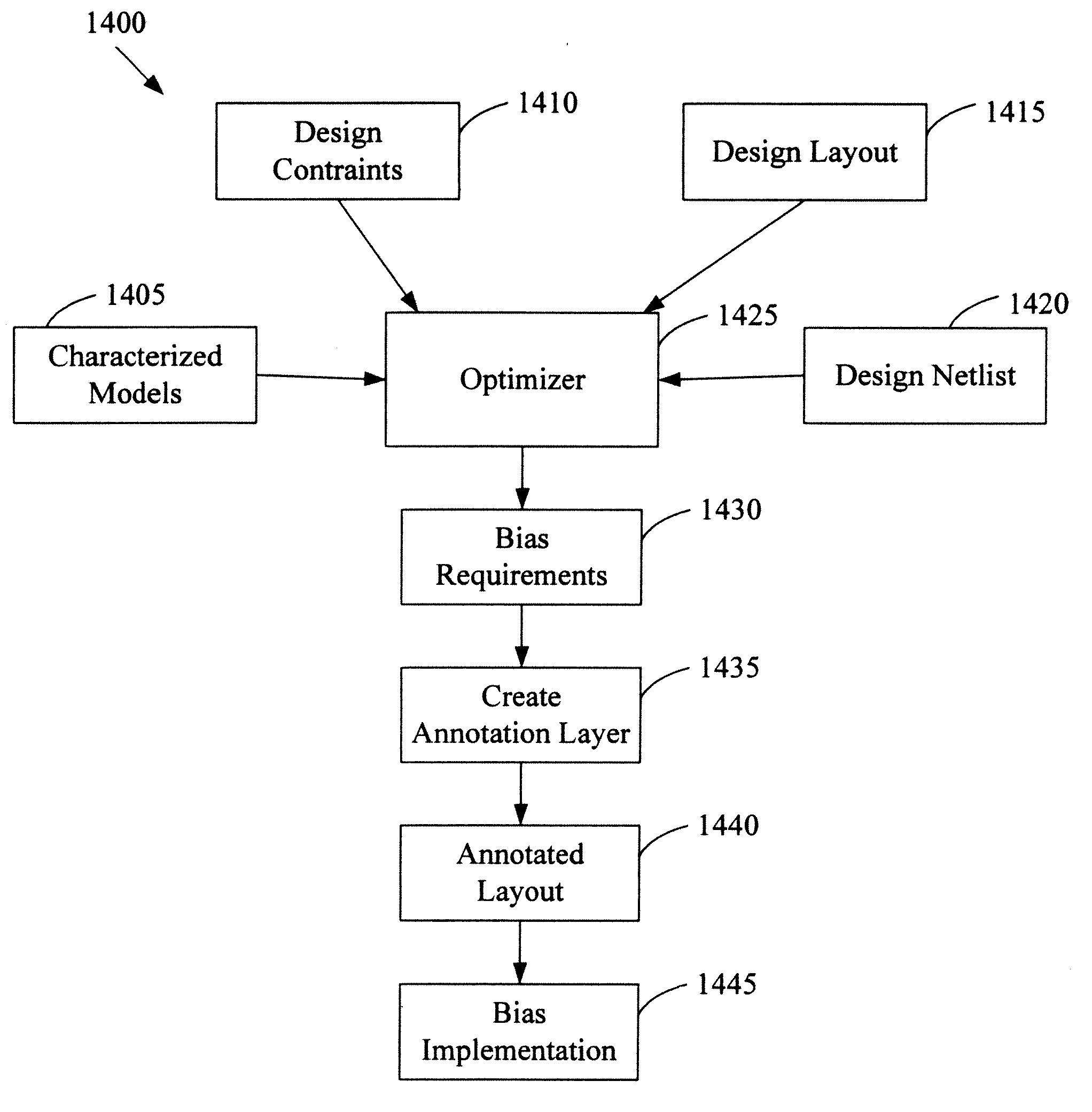

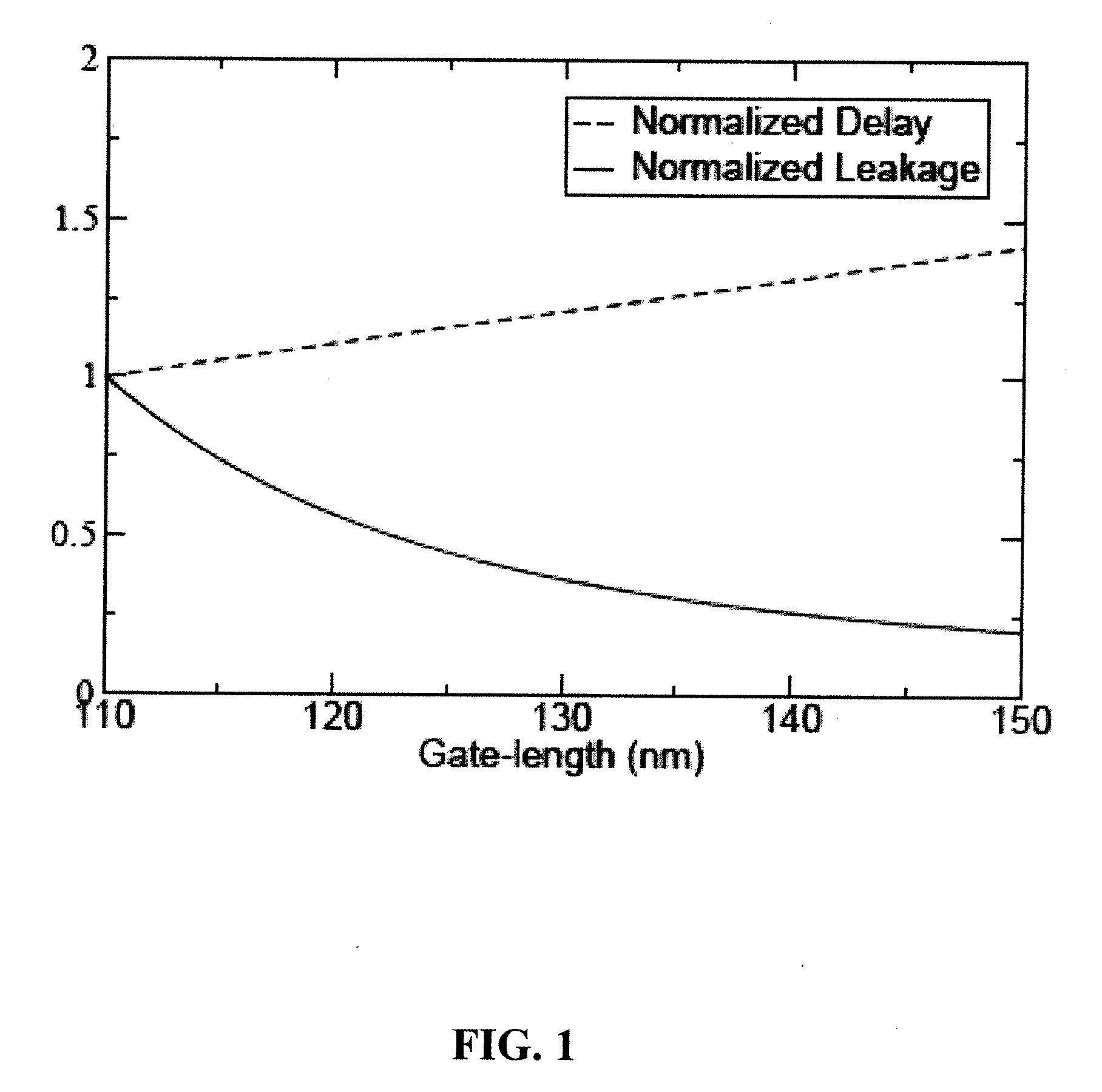

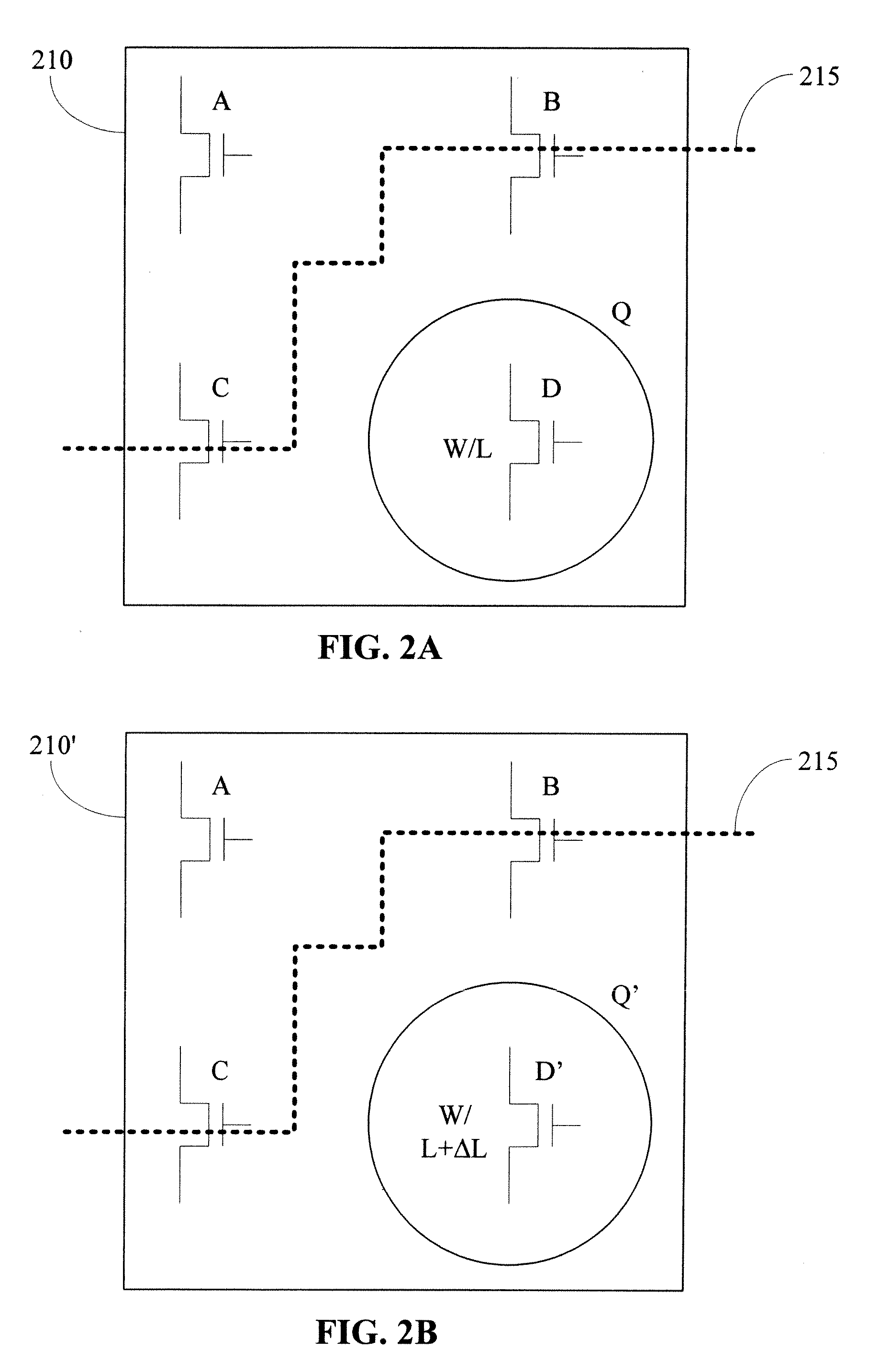

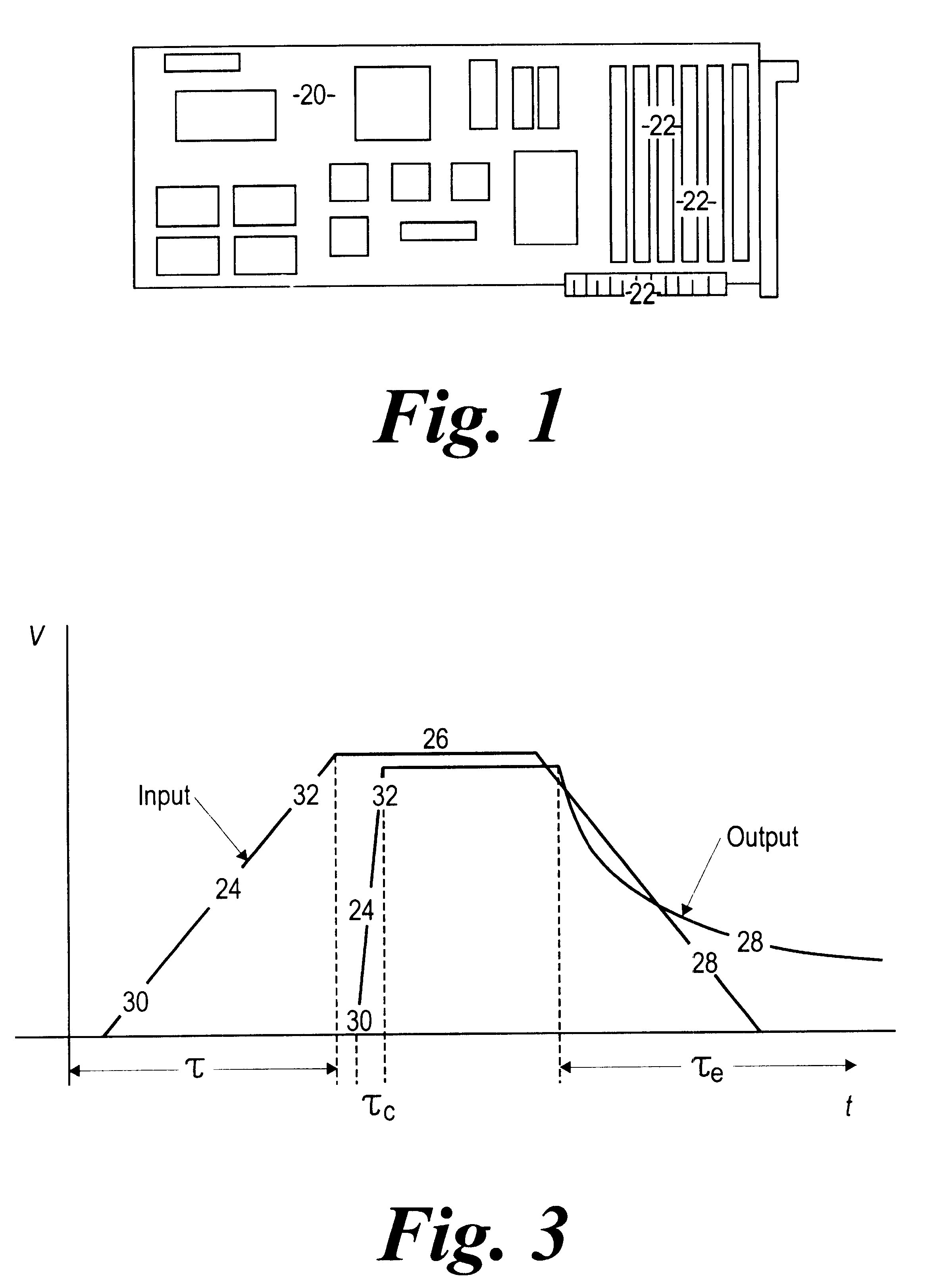

Gate-length biasing for digital circuit optimization

InactiveUS7441211B1Reduce impactImpairing time delay performance only linearlySolid-state devicesCAD circuit designEngineeringDigital electronics

Methods and apparatus for a gate-length biasing methodology for optimizing integrated digital circuits are described. The gate-length biasing methodology replaces a nominal gate-length of a transistor with a biased gate-length, where the biased gate-length includes a bias length that is small compared to the nominal gate-length. In an exemplary embodiment, the bias length is less than 10% of the nominal gate-length.

Owner:RPX CORP

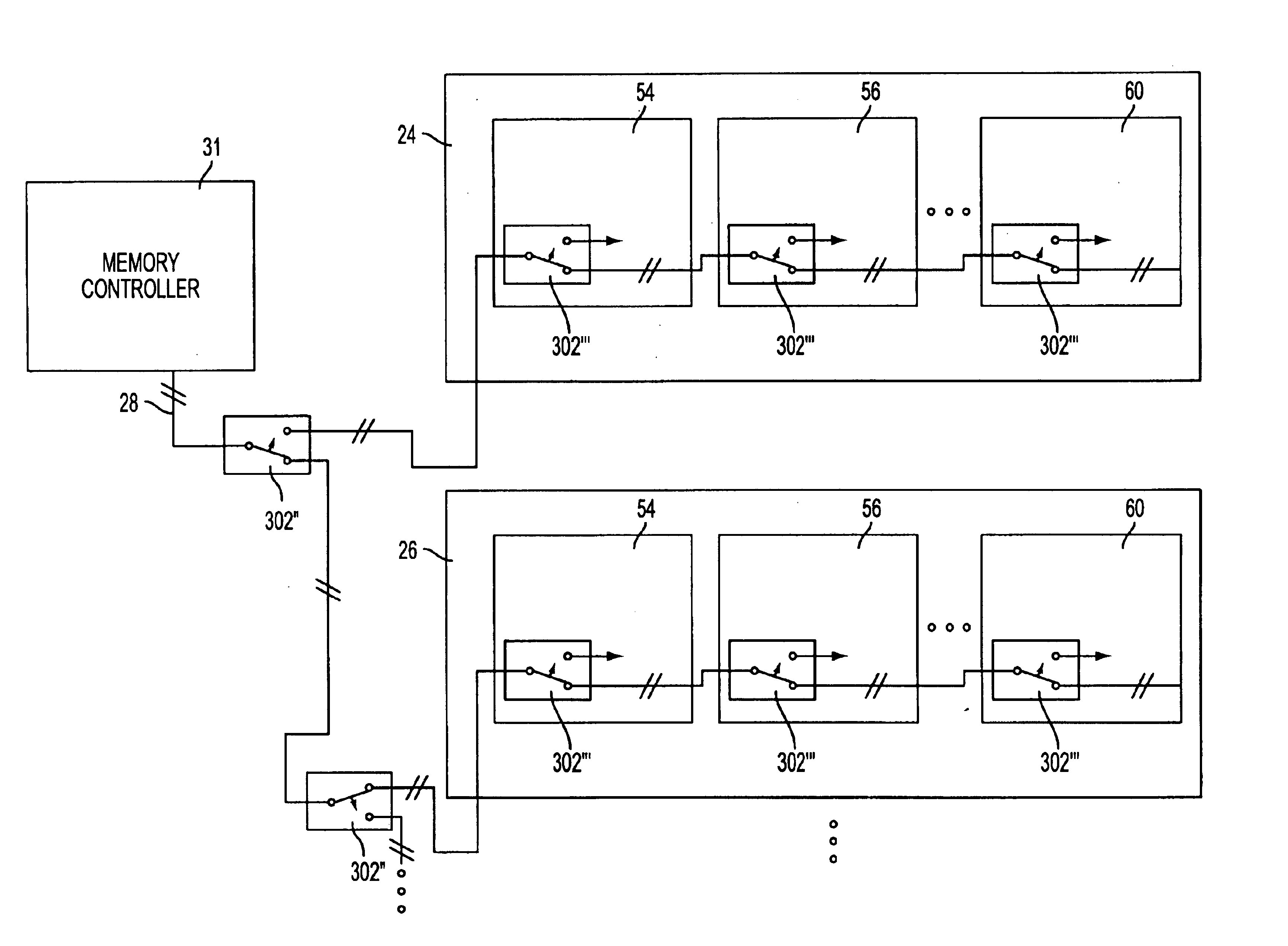

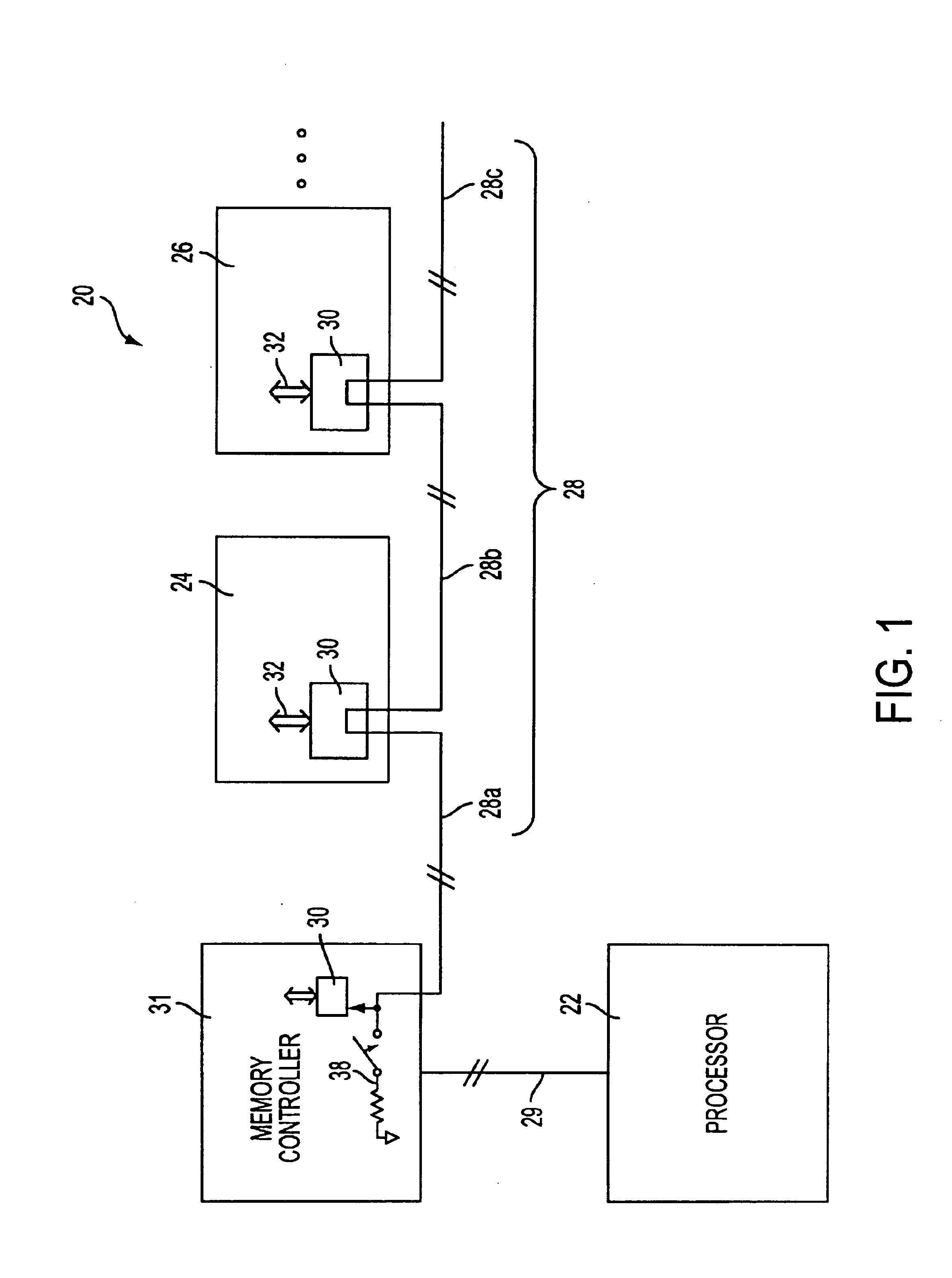

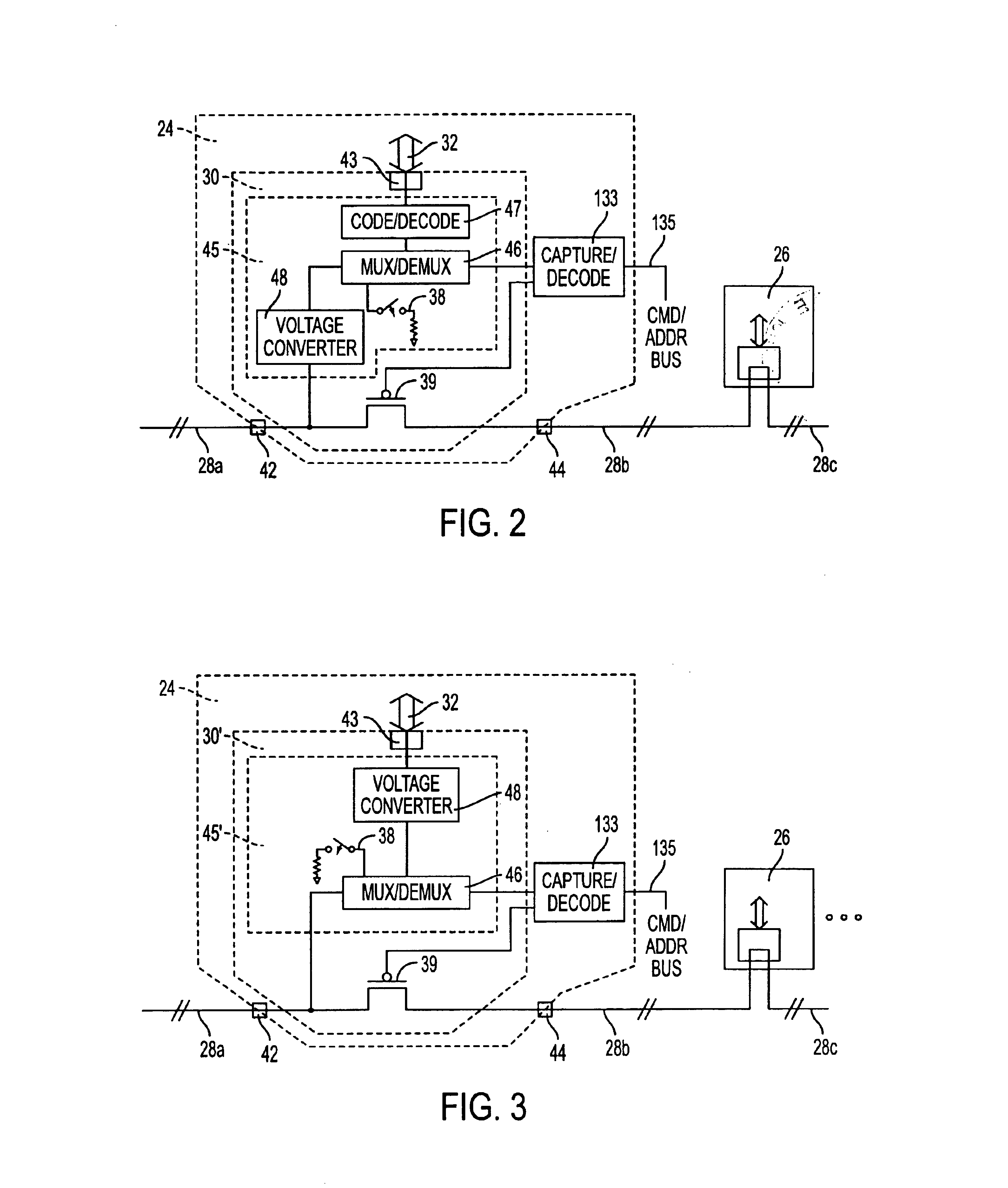

Data transmission circuit for memory subsystem, has switching circuit that selectively connects or disconnects two data bus segments to respectively enable data transmission or I/O circuit connection

InactiveUS6871253B2Improve acceleration performanceReduce reflectionEnergy efficient ICTDigital data processing detailsElectricityHigh speed memory

A method and associated apparatus is provided for improving the performance of a high speed memory bus using switches. Bus reflections caused by electrical stubs are substantially eliminated by connecting system components in a substantially stubless configuration using a segmented bus wherein bus segments are connected through switches. The switches disconnect unused bus segments during operations so that communicating devices are connected in an substantially point-to-point communication path.

Owner:MICRON TECH INC

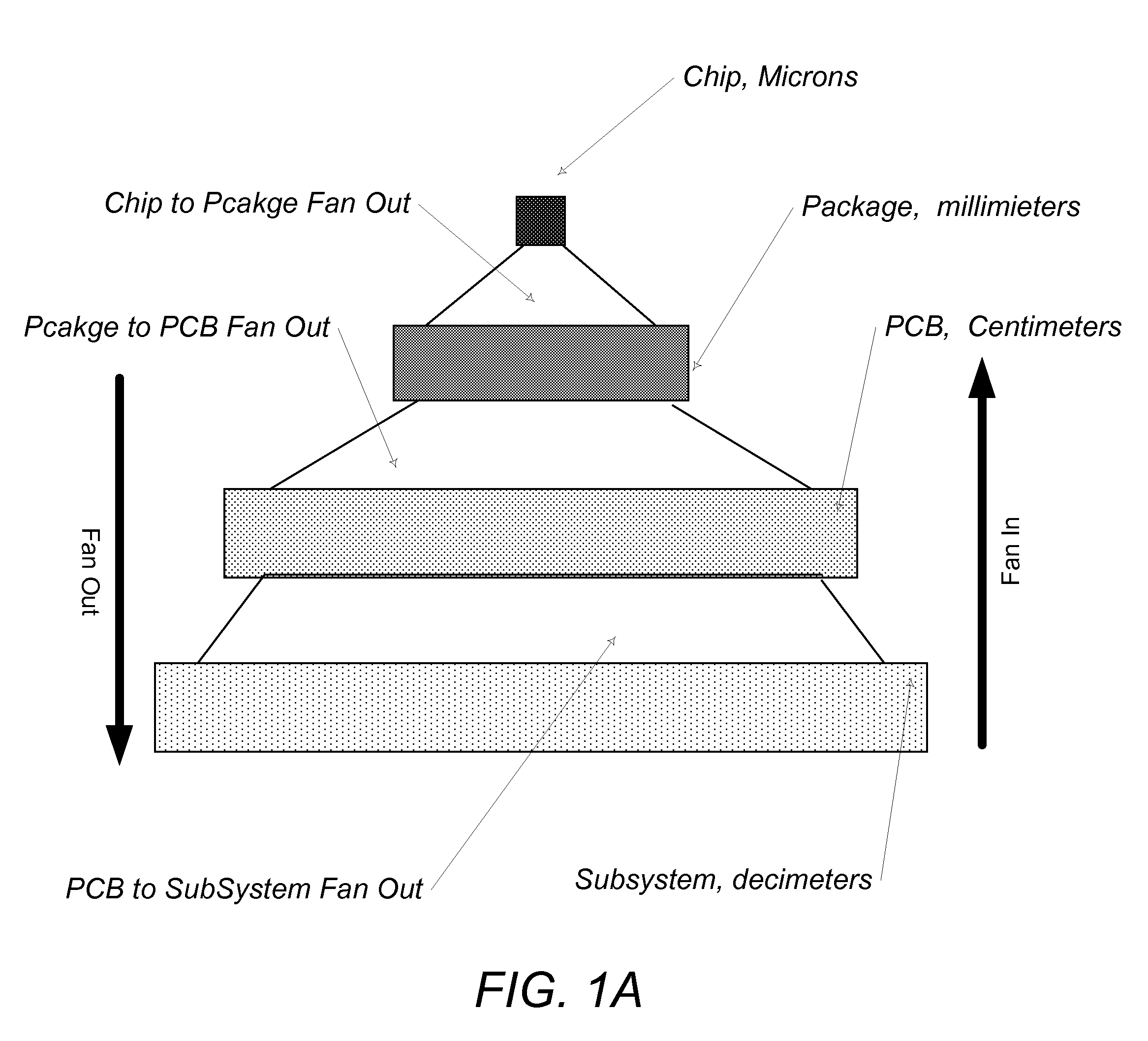

Unified scalable high speed interconnects technologies

InactiveUS20100307798A1Improve performanceIncreasing signal speedSemiconductor/solid-state device detailsHigh frequency circuit adaptationsCMOSHigh bandwidth

Traditional High Speed Electronic Systems Interconnect experience several bandwidth bottlenecks along the multiplicity of signal paths that limits the information throughput. Here we build upon the cellular interconnect concept of PMTL, the Periodic Micro Transmission Line which was introduced in an earlier patent application, and provide a new type of transmission line VMPL, as the Vertical Micro Transmission Line approach to make all the elements of a high speed interconnect wideband, unified, scalable, and practical for high volume manufacturing. This provides total connectivity improvements from end-to-end of electronic systems that demands higher bandwidth, and increased information throughput, thermal management, and impeccable signal integrity. The technologies introduced here provide solutions for any level of the fan out from chips to systems, in CMOS, or Packages, and PCB's.

Owner:WAYMO LLC

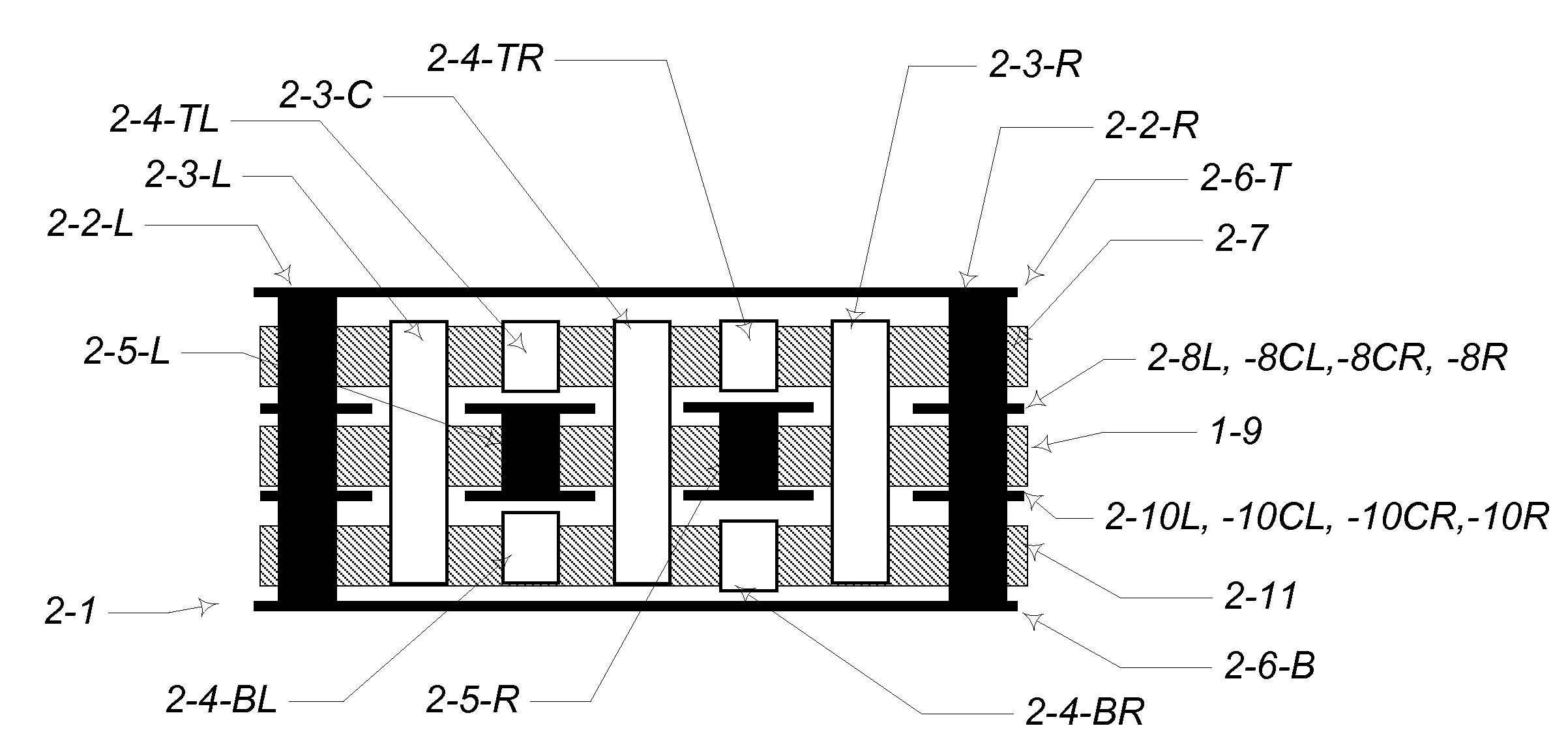

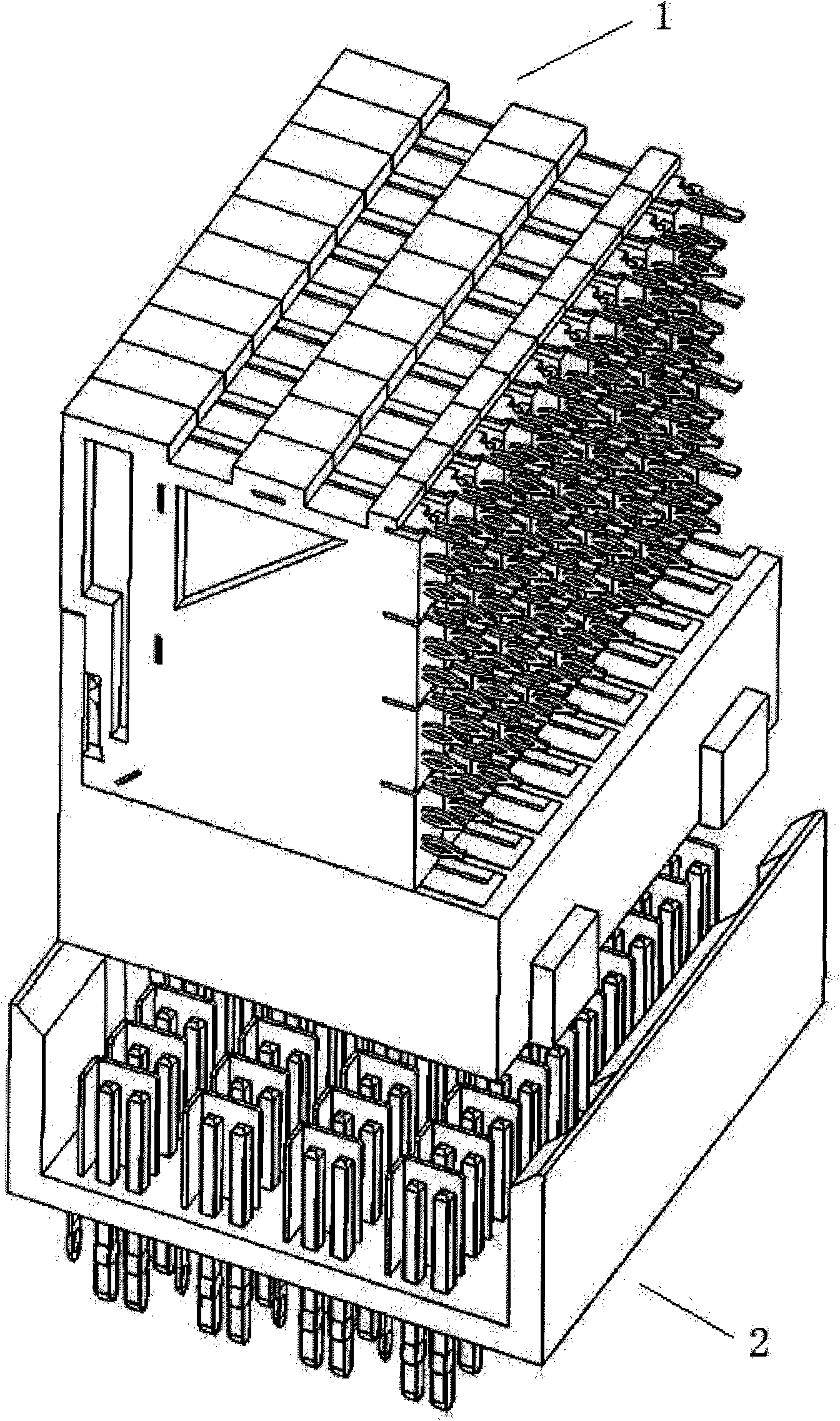

Electrical connector with complementary conductive elements

ActiveUS7794240B2Improve signal integrityDesirable electrical propertyPrinted circuit assemblingCoupling device detailsElectrical connectorElectrical interconnect

Owner:AMPHENOL CORP

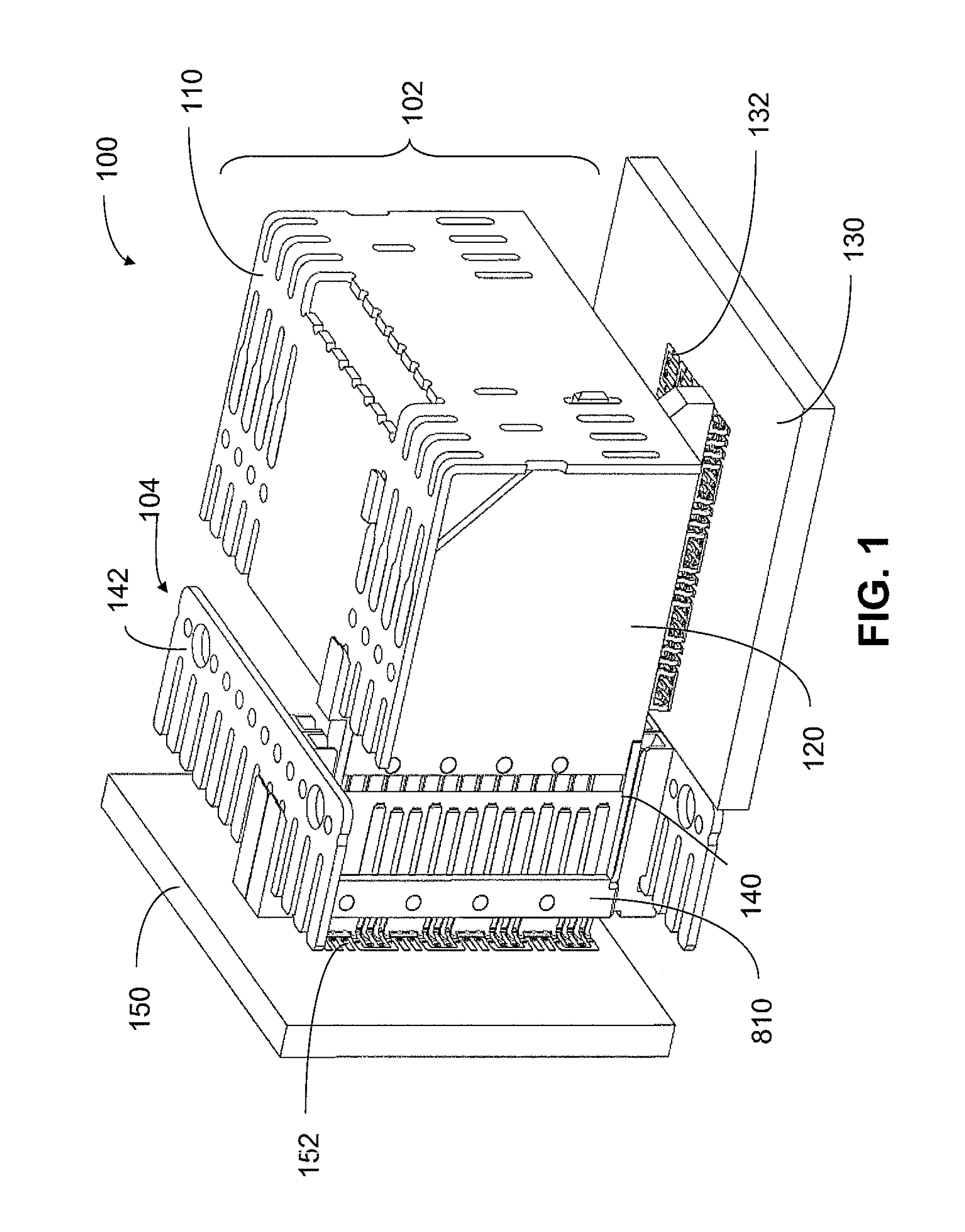

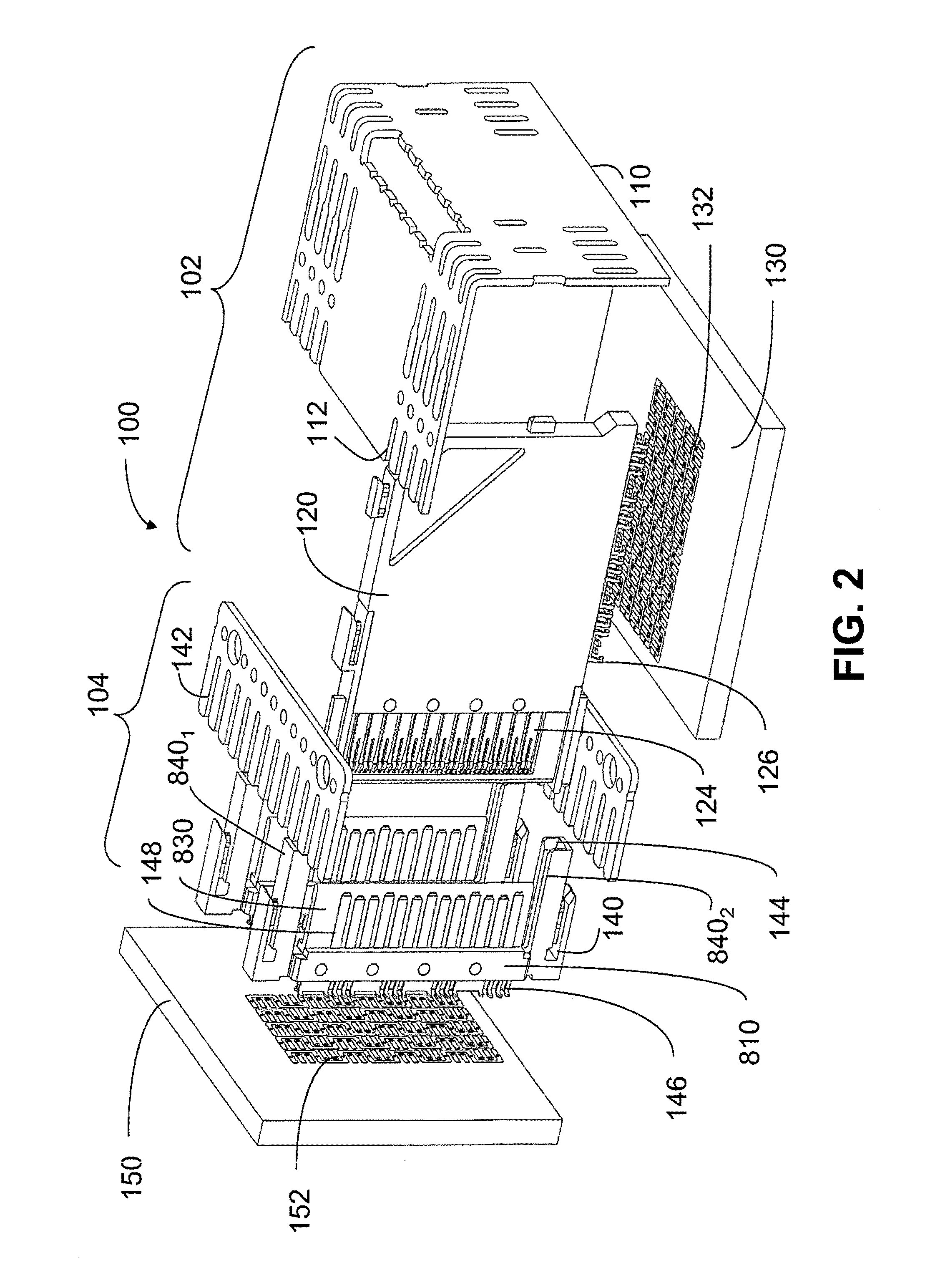

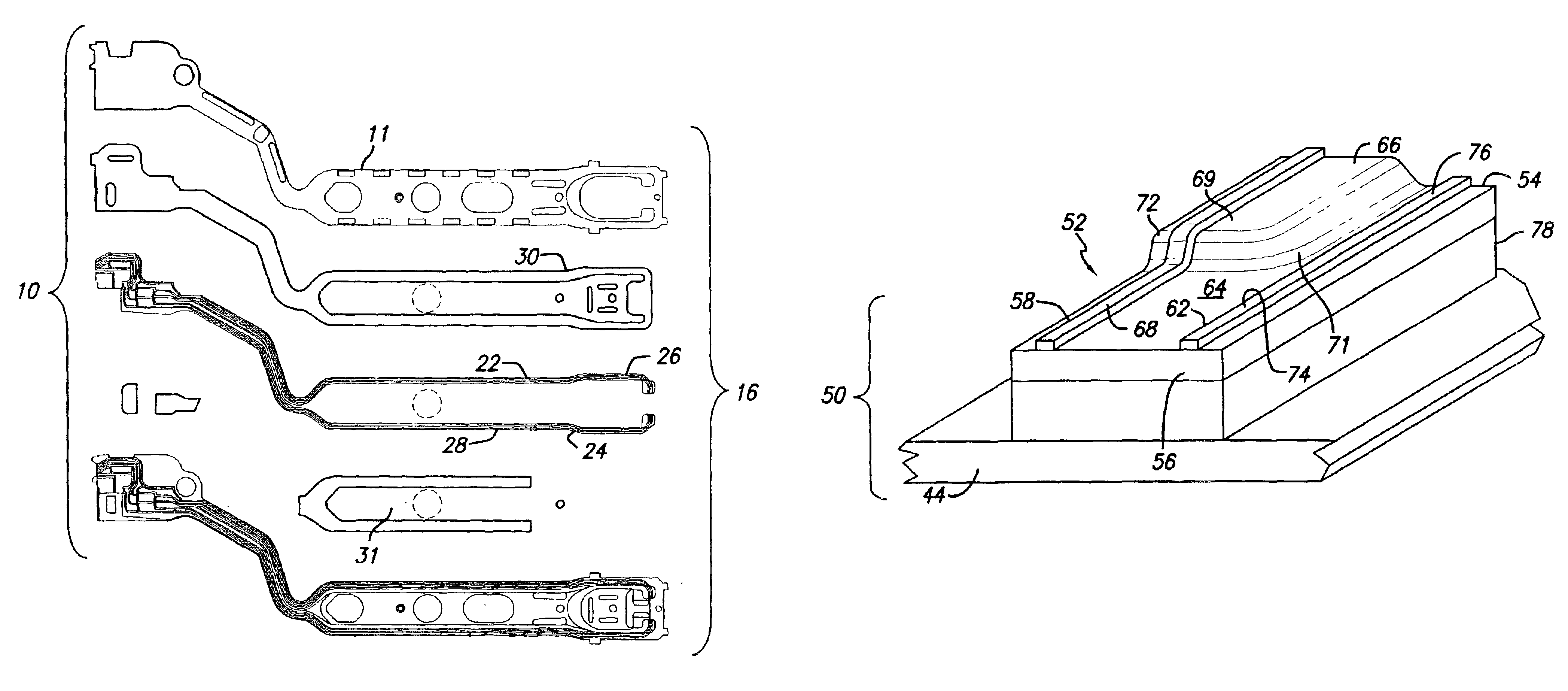

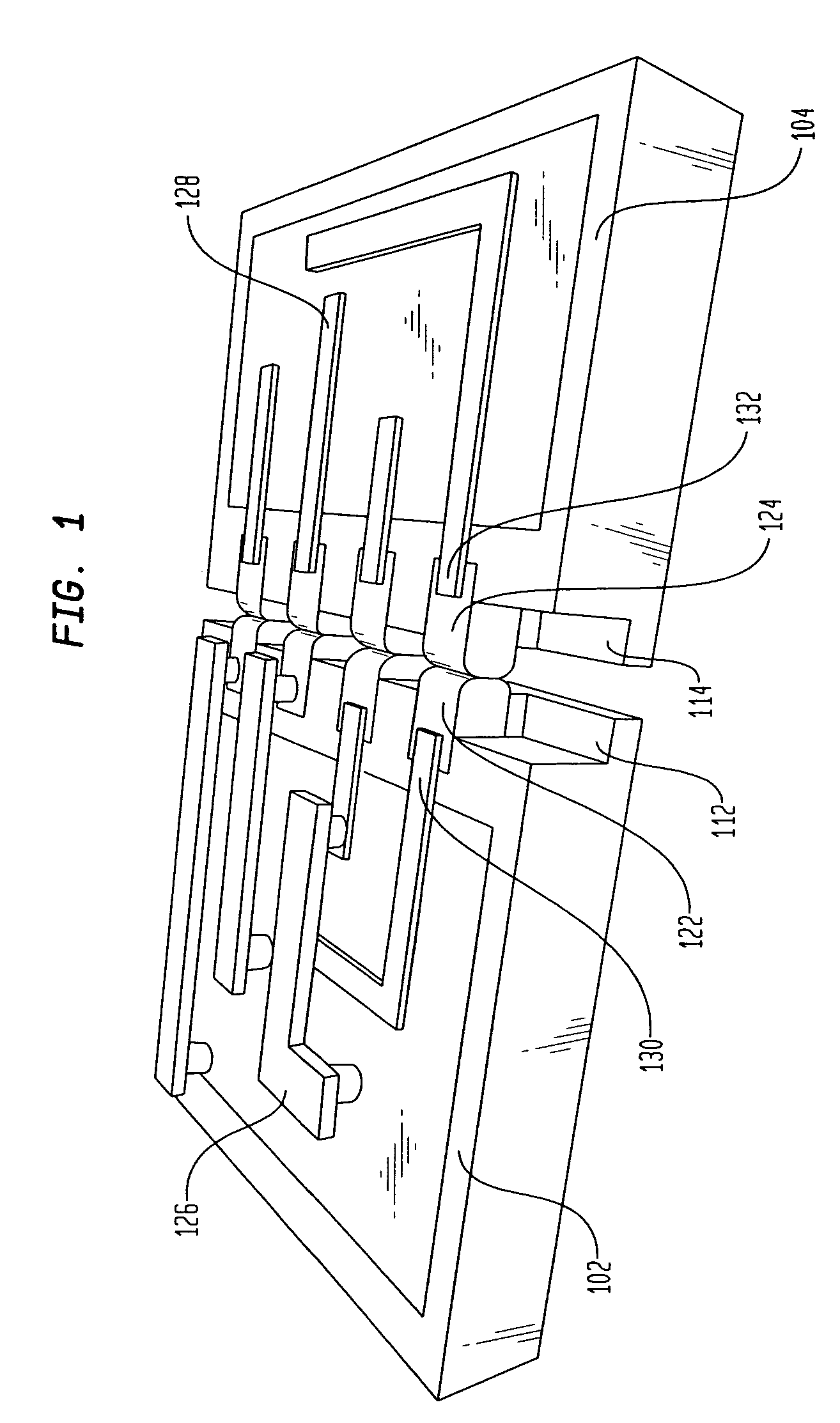

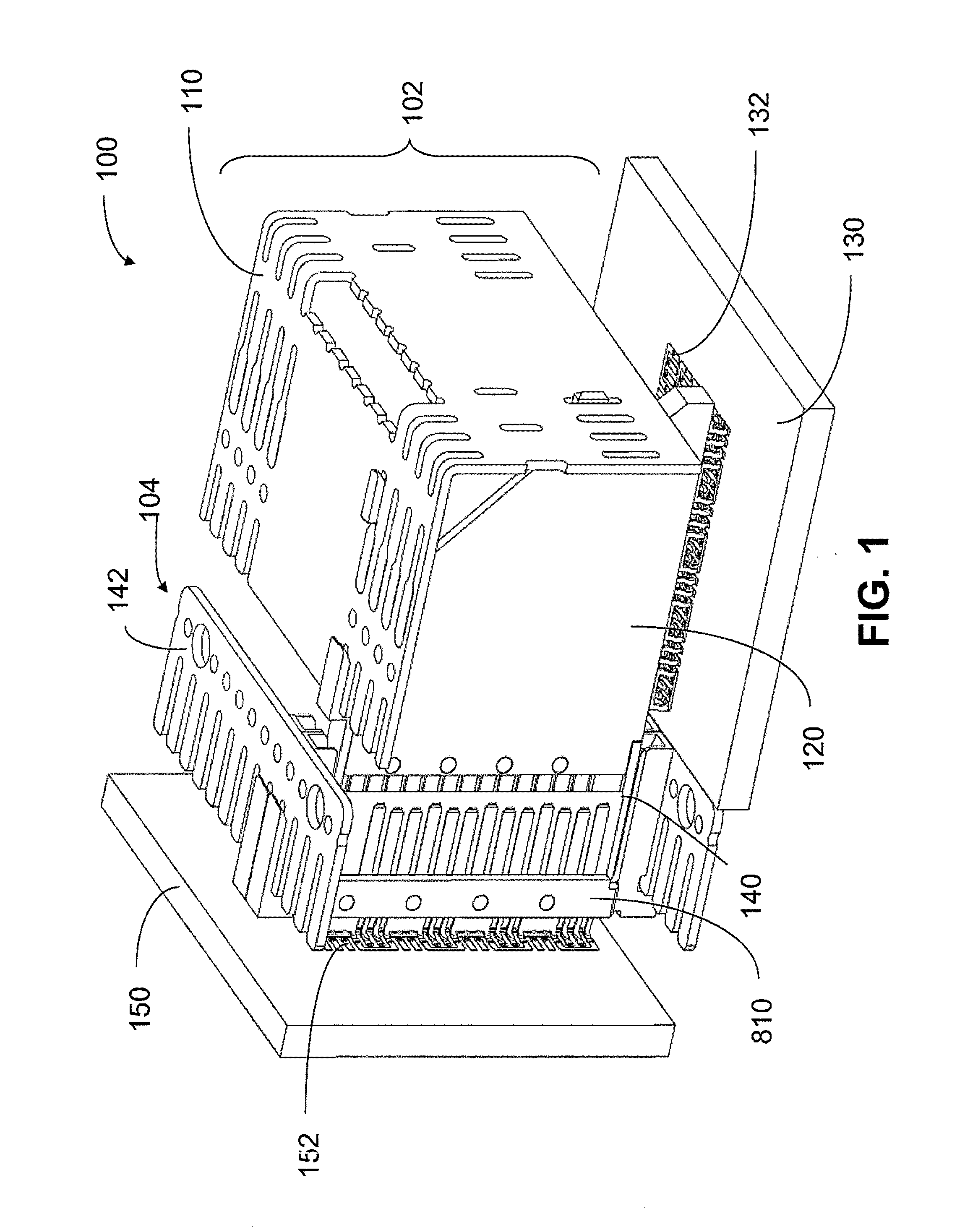

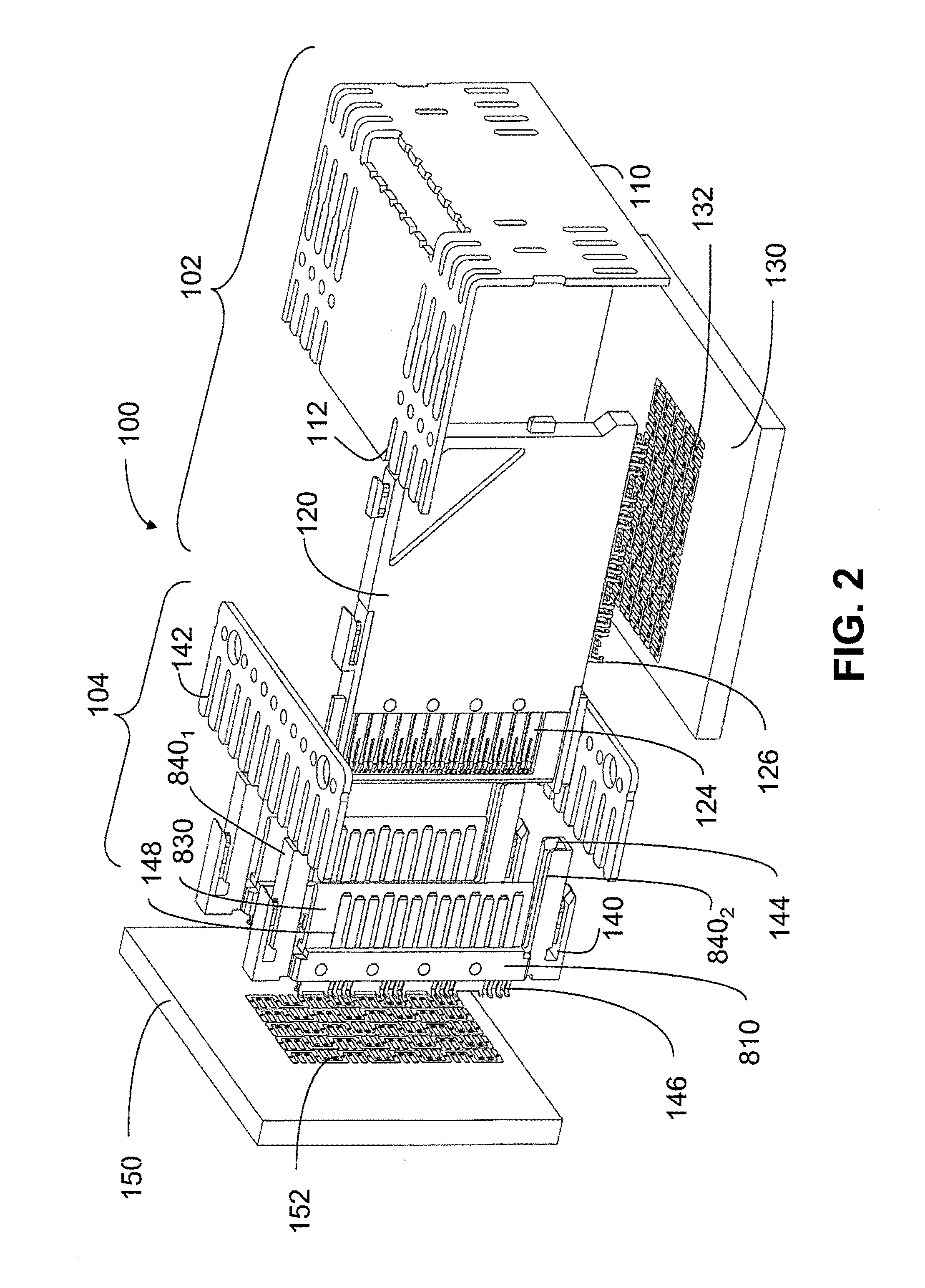

High density electrical connector with variable insertion and retention force

ActiveUS8182289B2Lower insertion forceImprove retentionTwo-part coupling devicesCoupling protective earth/shielding arrangementsElectricityHigh density

An interconnection system that includes a daughter card and backplane electrical connectors mounted to printed circuit boards at connector footprints. The spring rate of beam-shaped contacts in the daughter card connector increases while mating with the backplane connector so that the retention force may be greater than the insertion force. Such a change in spring rate may be achieved by positioning the beam-shaped contacts adjacent a surface of a connector housing. That surface may include a projection that aligns with the beam-shaped contact. When the connectors are unmated, the beam-shaped contact may be spaced from the projection. As the connectors begin to mate, a central portion of the beam-shaped contact may be pressed against the projection, which has the effect of shortening the beam length and increasing its stiffness.

Owner:AMPHENOL CORP

High density electrical connector with variable insertion and retention force

ActiveUS20110212649A1High retention forceHigh spring rateTwo-part coupling devicesCoupling protective earth/shielding arrangementsElectricityBackplane

An interconnection system that includes a daughter card and backplane electrical connectors mounted to printed circuit boards at connector footprints. The spring rate of beam-shaped contacts in the daughter card connector increases while mating with the backplane connector so that the retention force may be greater than the insertion force. Such a change in spring rate may be achieved by positioning the beam-shaped contacts adjacent a surface of a connector housing. That surface may include a projection that aligns with the beam-shaped contact. When the connectors are unmated, the beam-shaped contact may be spaced from the projection. As the connectors begin to mate, a central portion of the beam-shaped contact may be pressed against the projection, which has the effect of shortening the beam length and increasing its stiffness.

Owner:AMPHENOL CORP

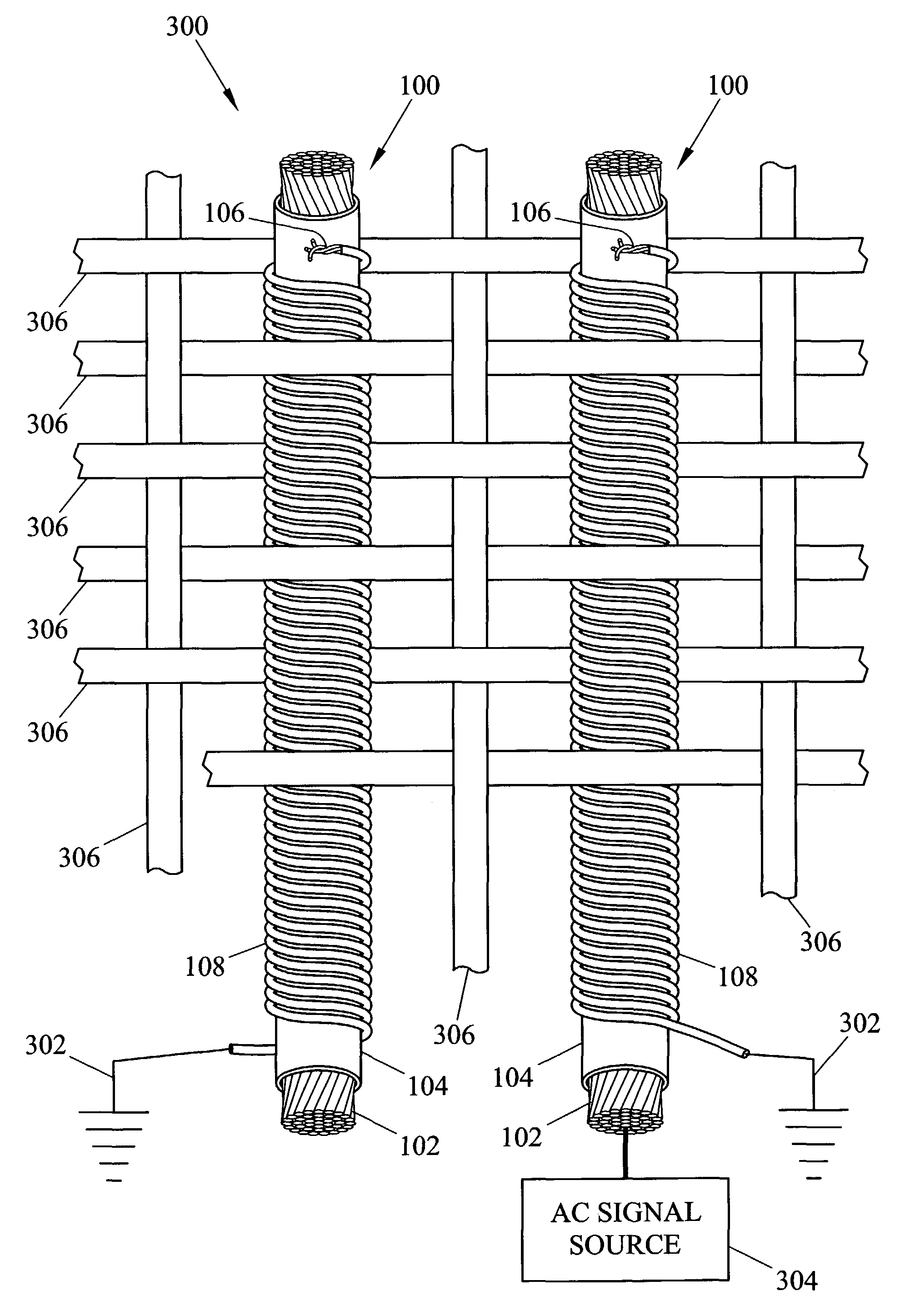

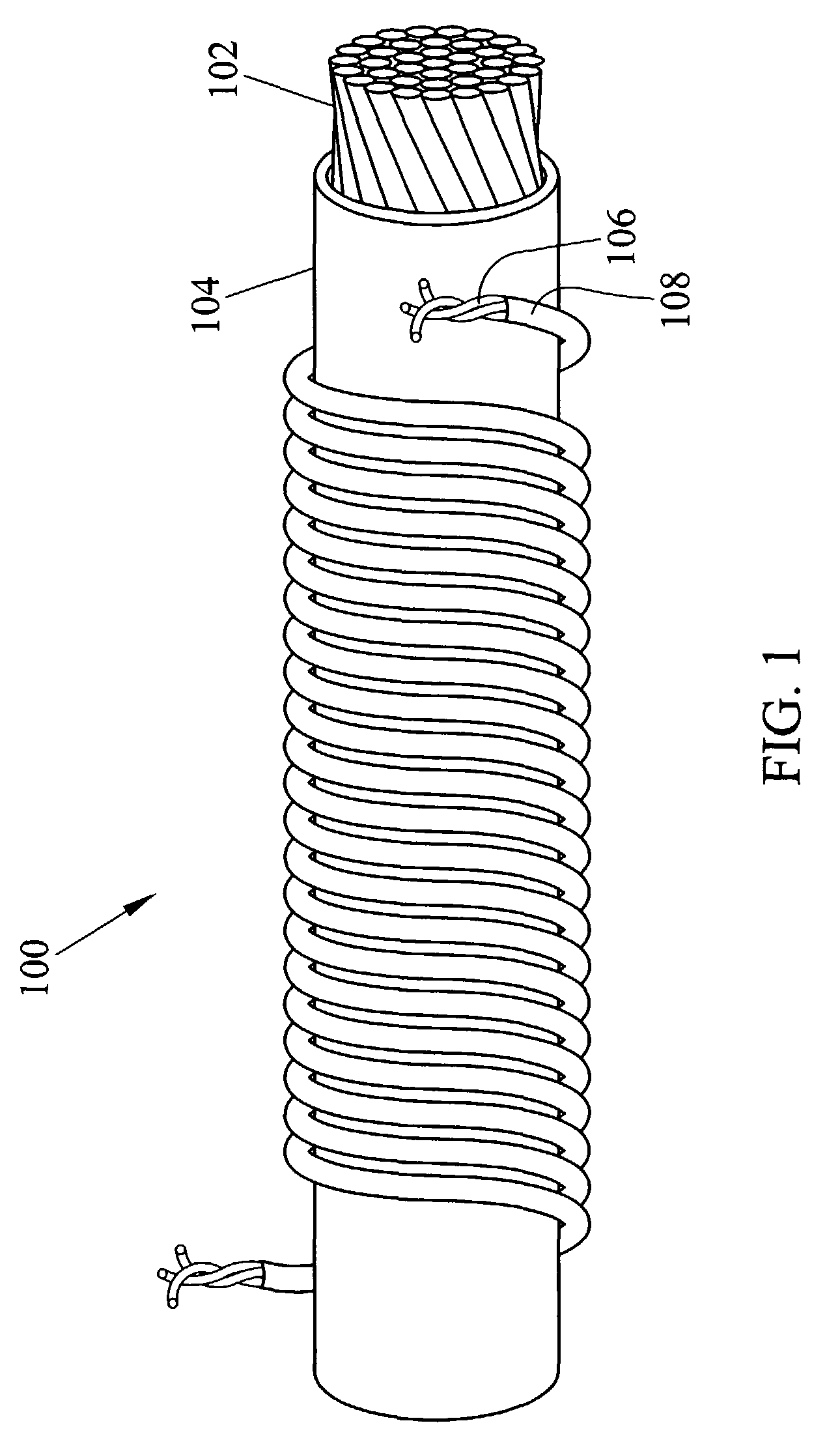

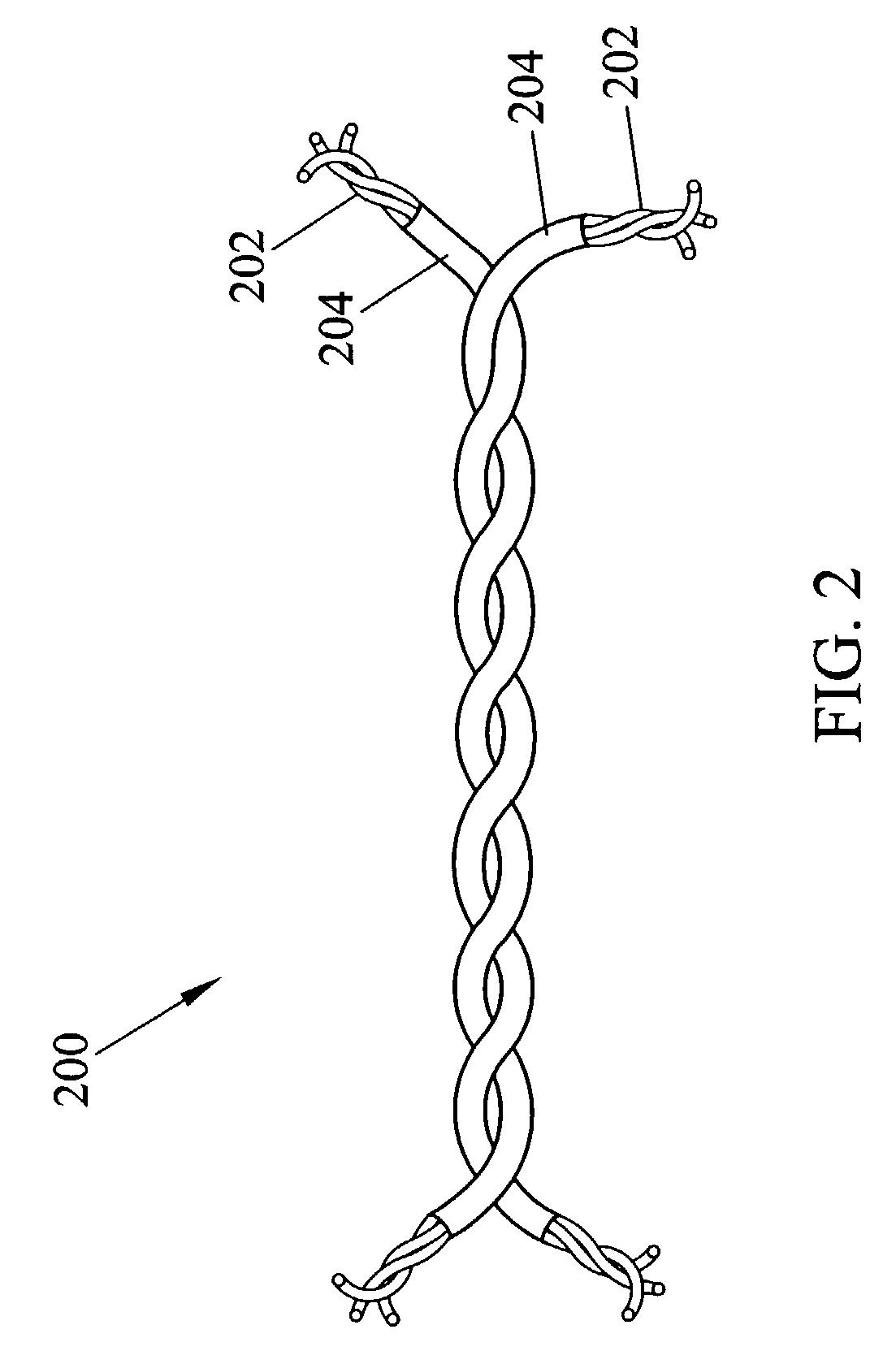

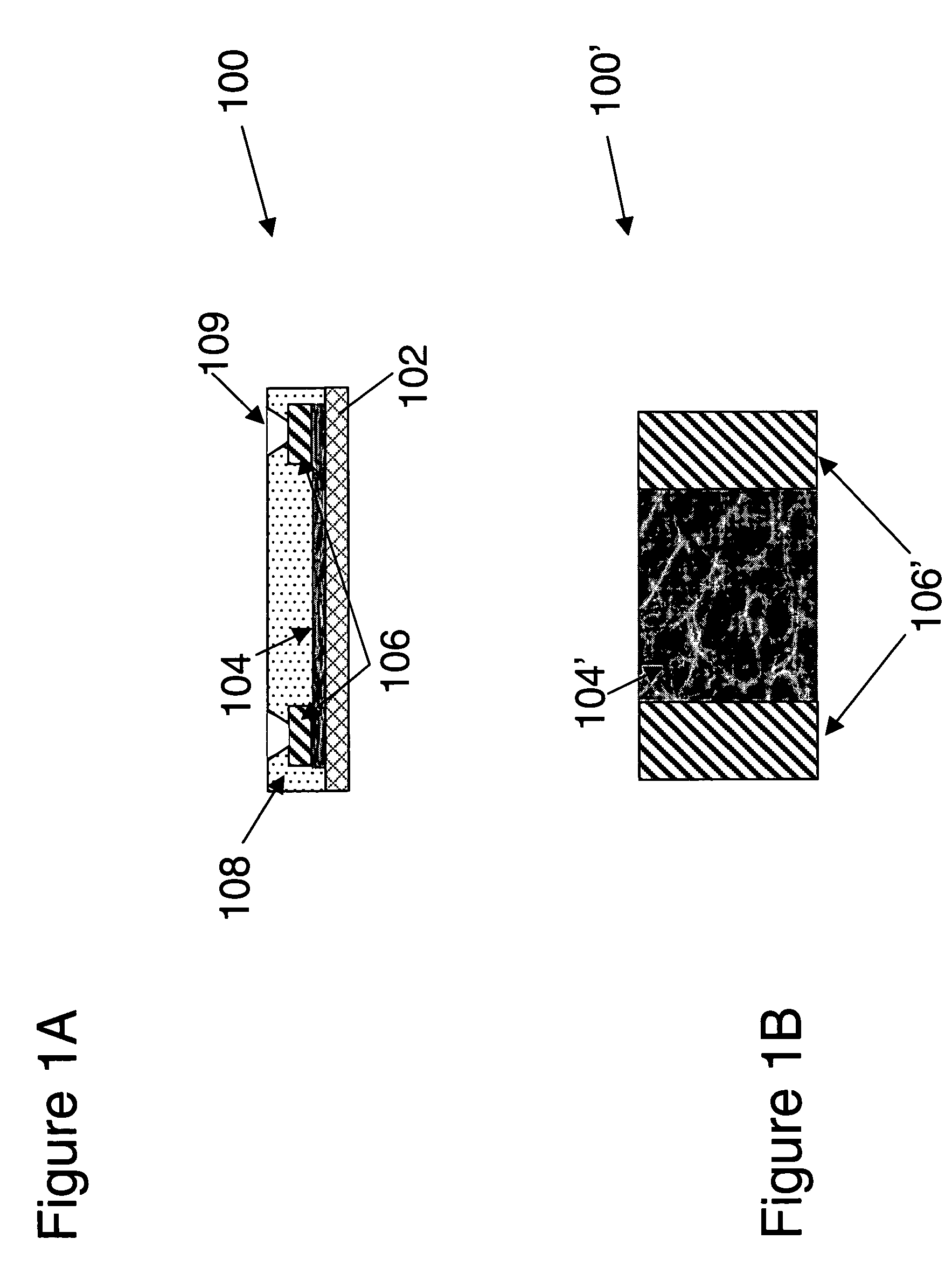

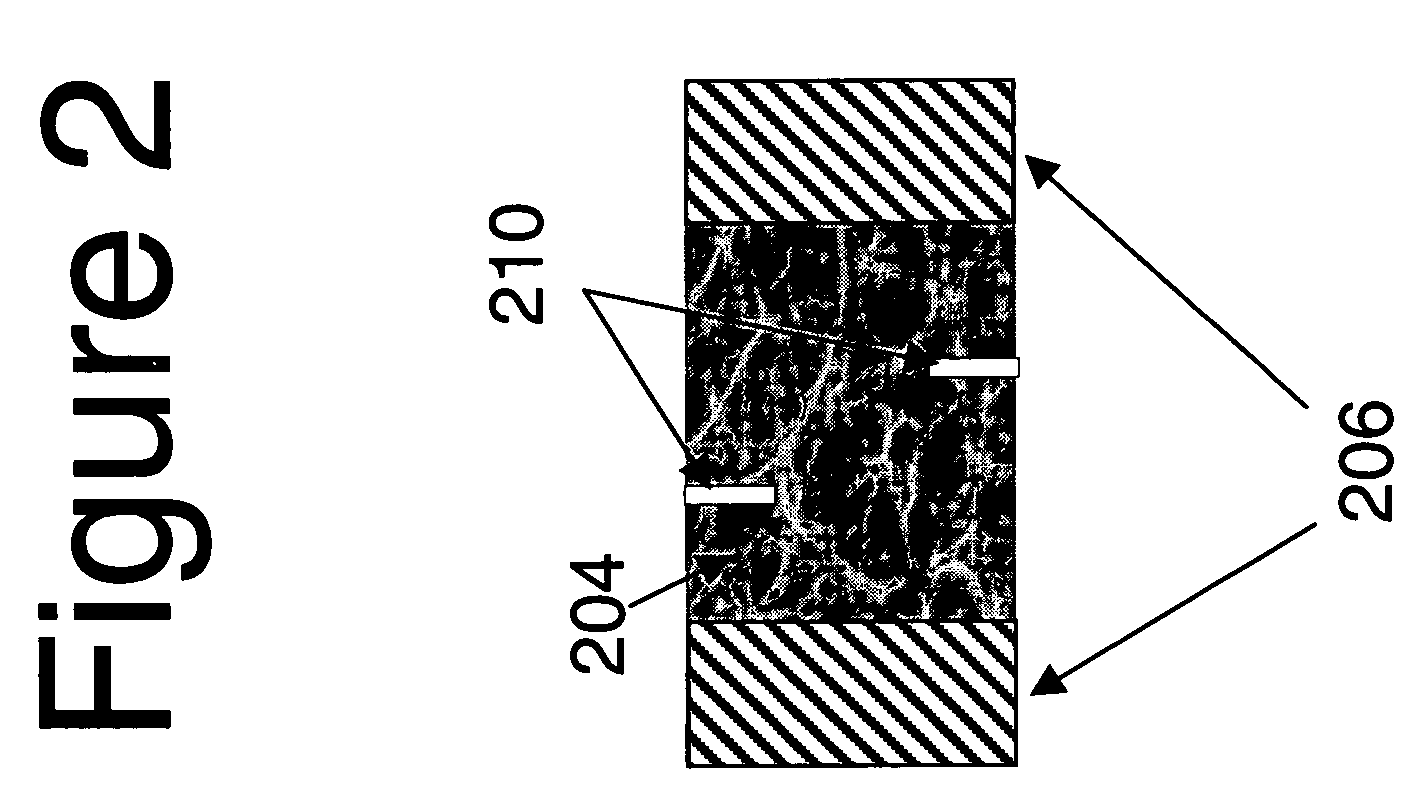

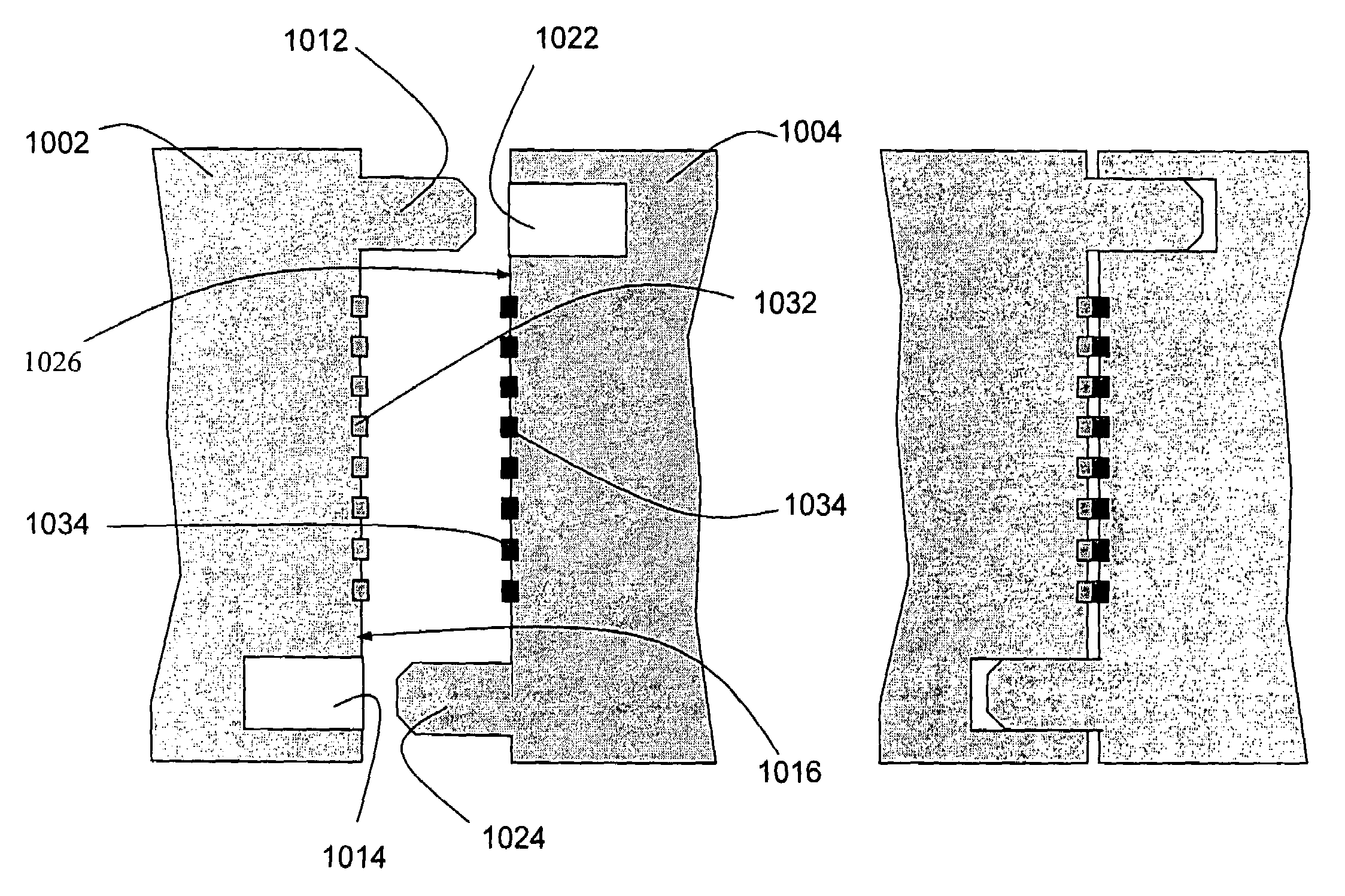

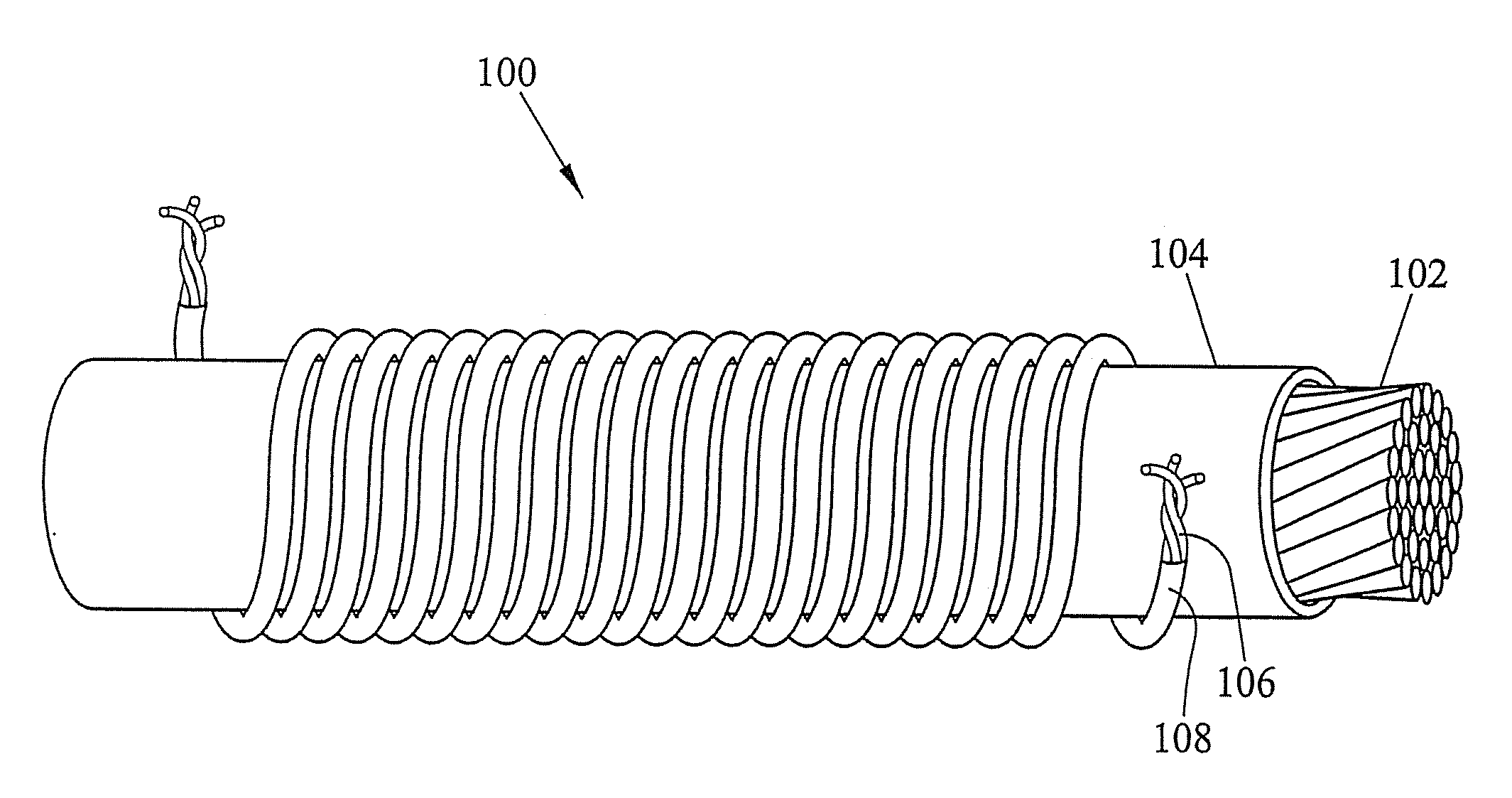

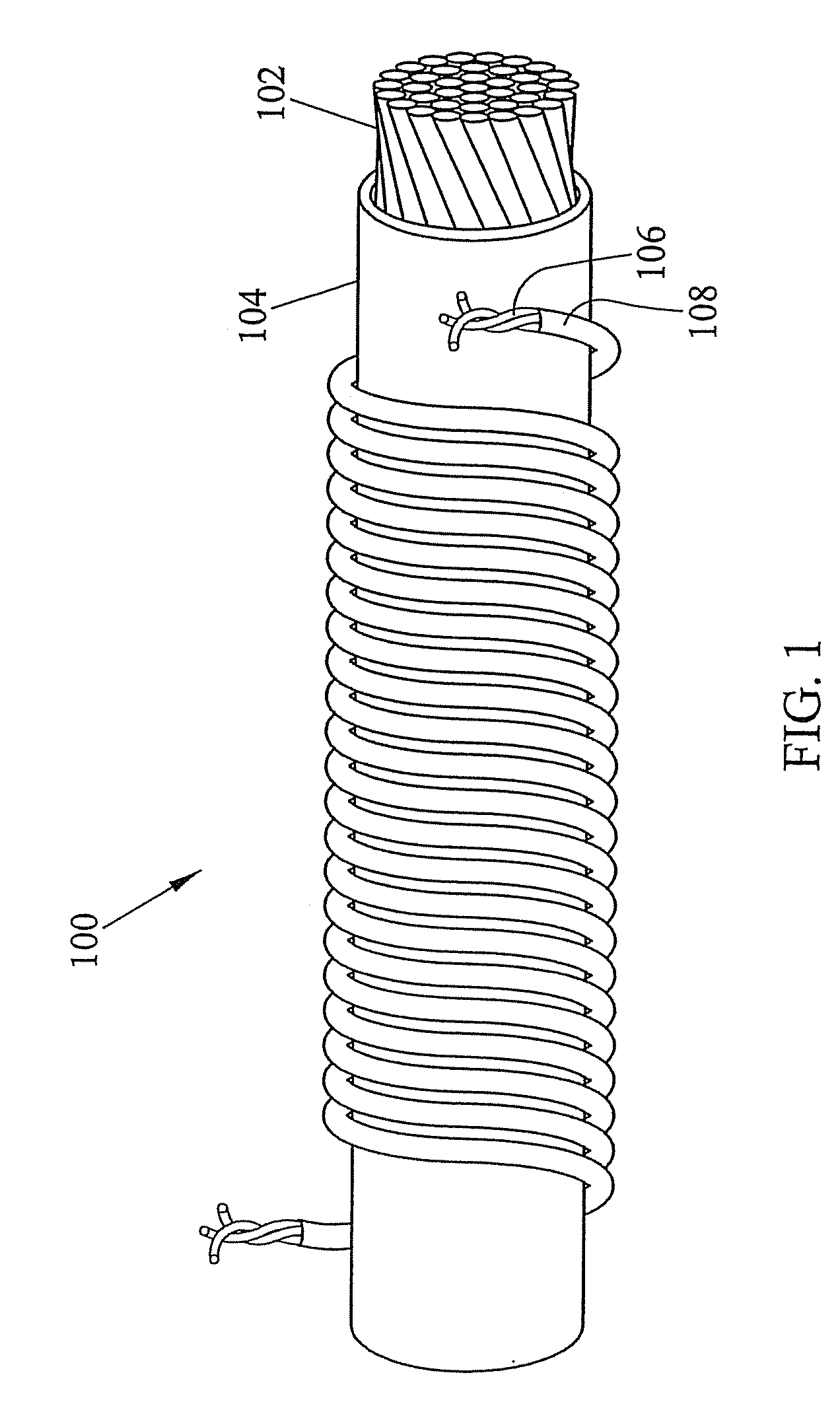

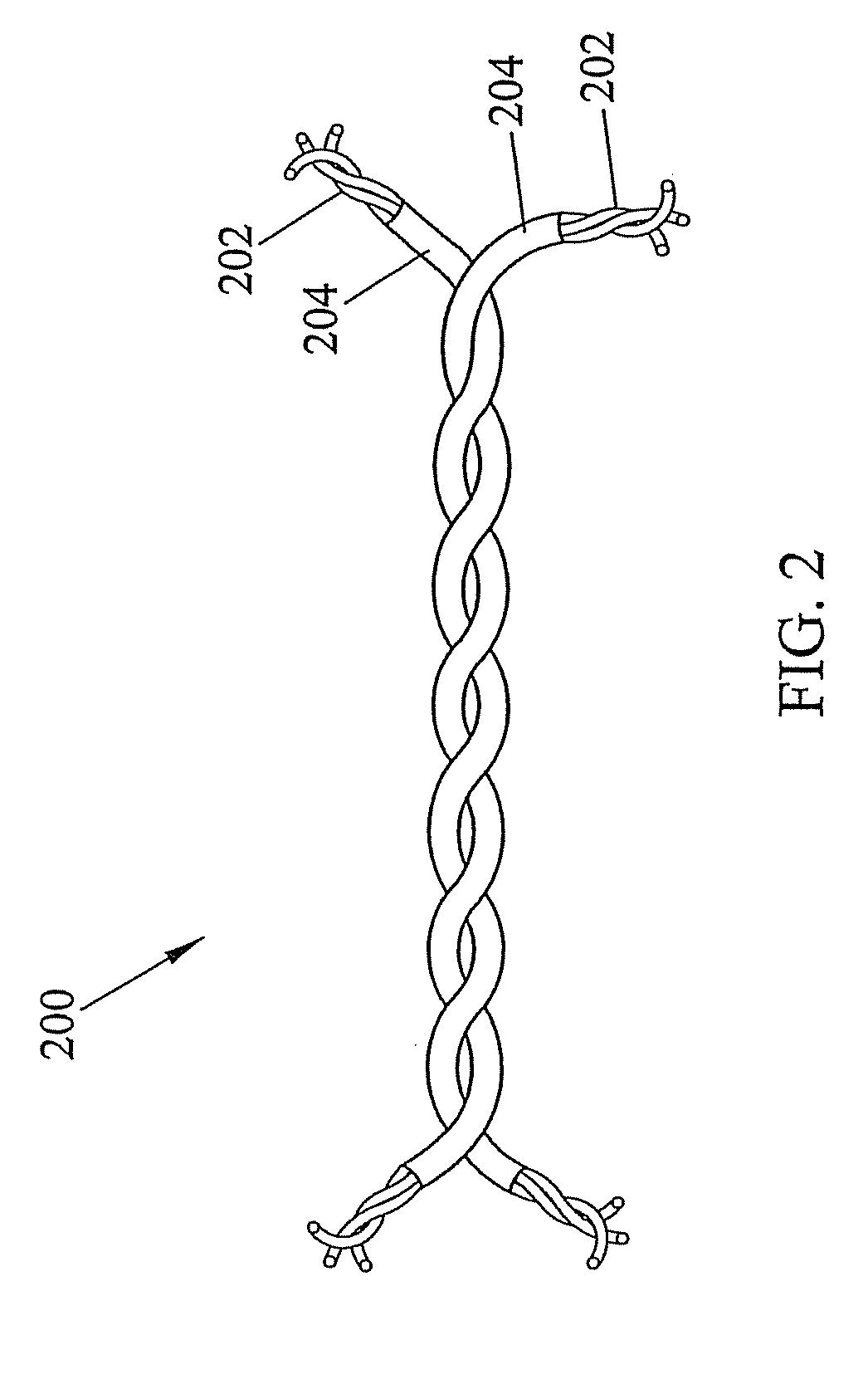

Fabric and yarn structures for improving signal integrity in fabric-based electrical circuits

InactiveUS7348285B2Reduce crosstalkImprove signal integrityAlcoholic beverage preparationPower cables with screens/conductive layersPower gridTwisted pair

Coaxial and twisted pair conductive yarn structures reduce signal crosstalk between adjacent lines in woven electrical networks. A coaxial conductive yarn structure includes an inner conductive yarn having a plurality of conductive strands twisted together. An outer conductive yarn is wrapped around the inner conductive yarn. An insulating layer separates the inner and outer yarns. A twisted pair conductive yarn structure includes first and second conductive yarns, each including a plurality of conductive strands being twisted together. The first and second conductive yarns are twisted together to form a helical structure. In a woven electrical network, at least one conductor of adjacent conductive yarn structures is connected to ground to reduce signal crosstalk. Coaxial and twisted pair yarn structures may also be formed simultaneously with weaving or knitting the threads that make up the structures into a fabric.

Owner:NORTH CAROLINA STATE UNIV

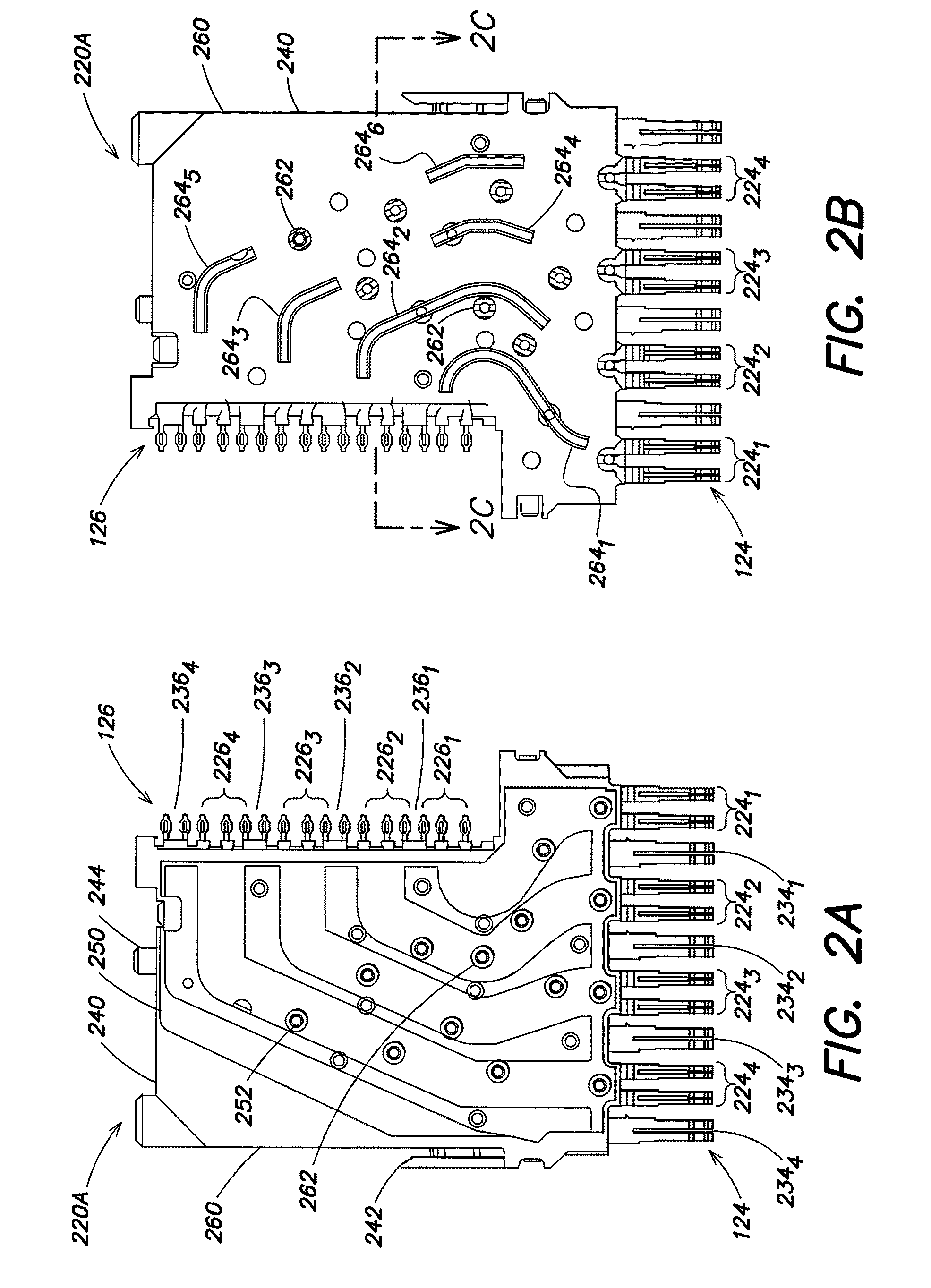

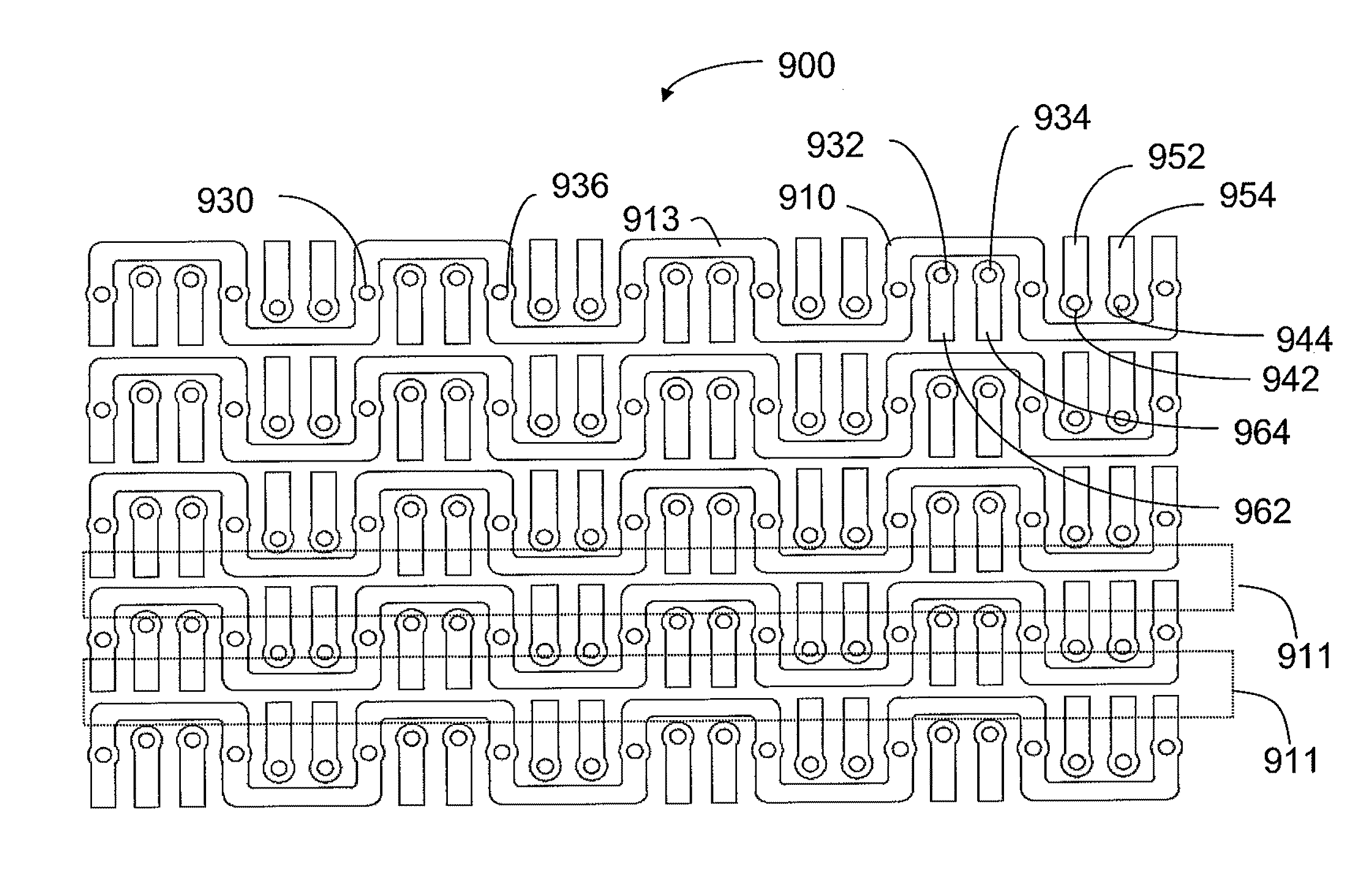

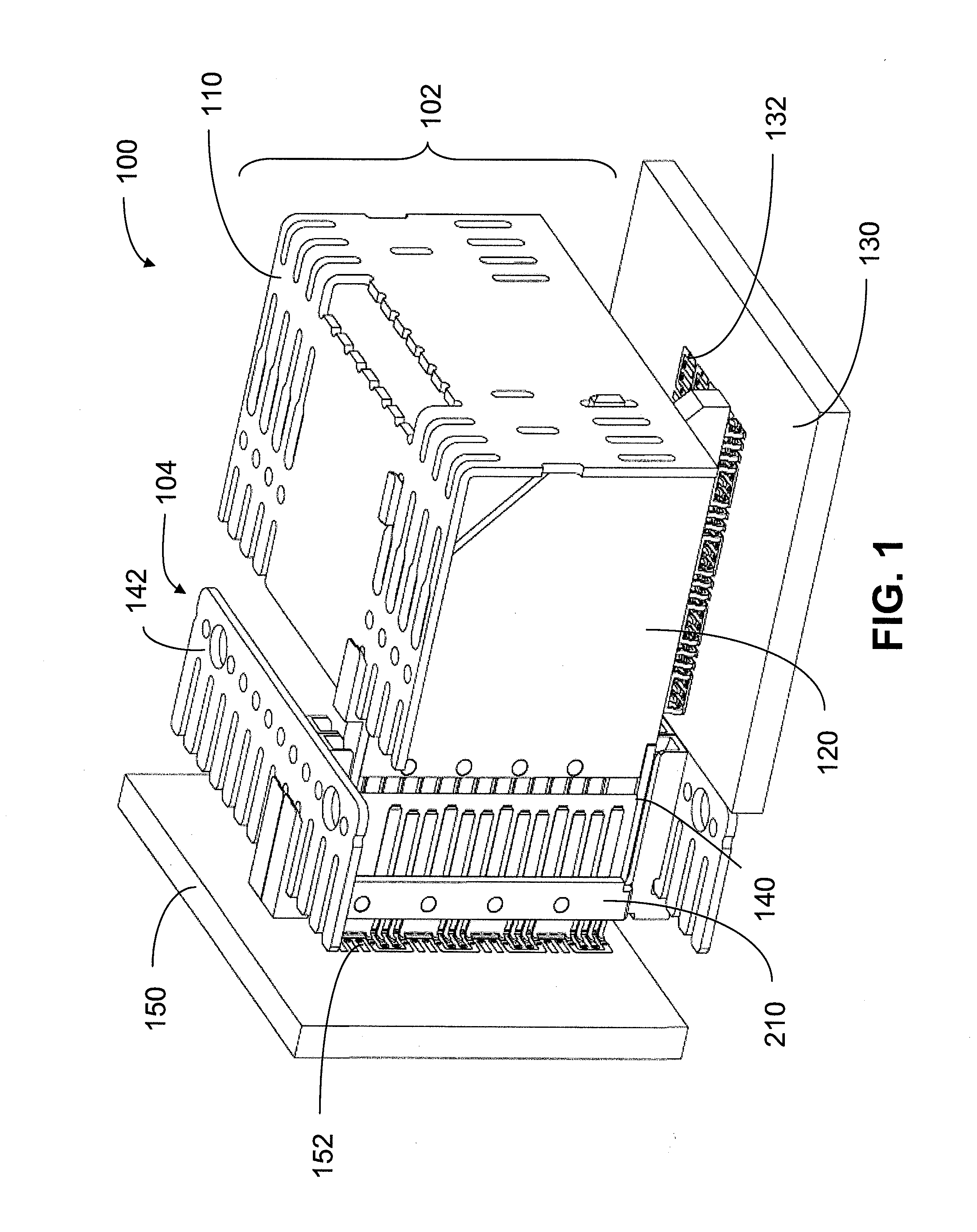

High density electrical connector and PCB footprint

ActiveUS8272877B2Reduces instanceImprove signal integrityTwo-part coupling devicesElectrical connection printed elementsHigh densityElectrical conductor

An interconnection system that includes a daughter card and backplane electrical connectors, each mounted to a printed circuit board at a connector footprint. The backplane connector has conductive elements with transition regions that allow the mating contact portions to be positioned on a uniform pitch while contact tail portions can be shaped to improve signal integrity or to provide a more compact and / or mechanically robust footprint. The conductive elements in both connectors are configured such that the contact tails of the ground conductors align from column to column, but the planar portions of the ground conductors in one column align with a pair of signal conductors in the other column, which improves mechanical and signal integrity. Mechanical integrity may be improved by forming the connector footprints with pads for the ground conductors that span multiple columns.

Owner:AMPHENOL CORP

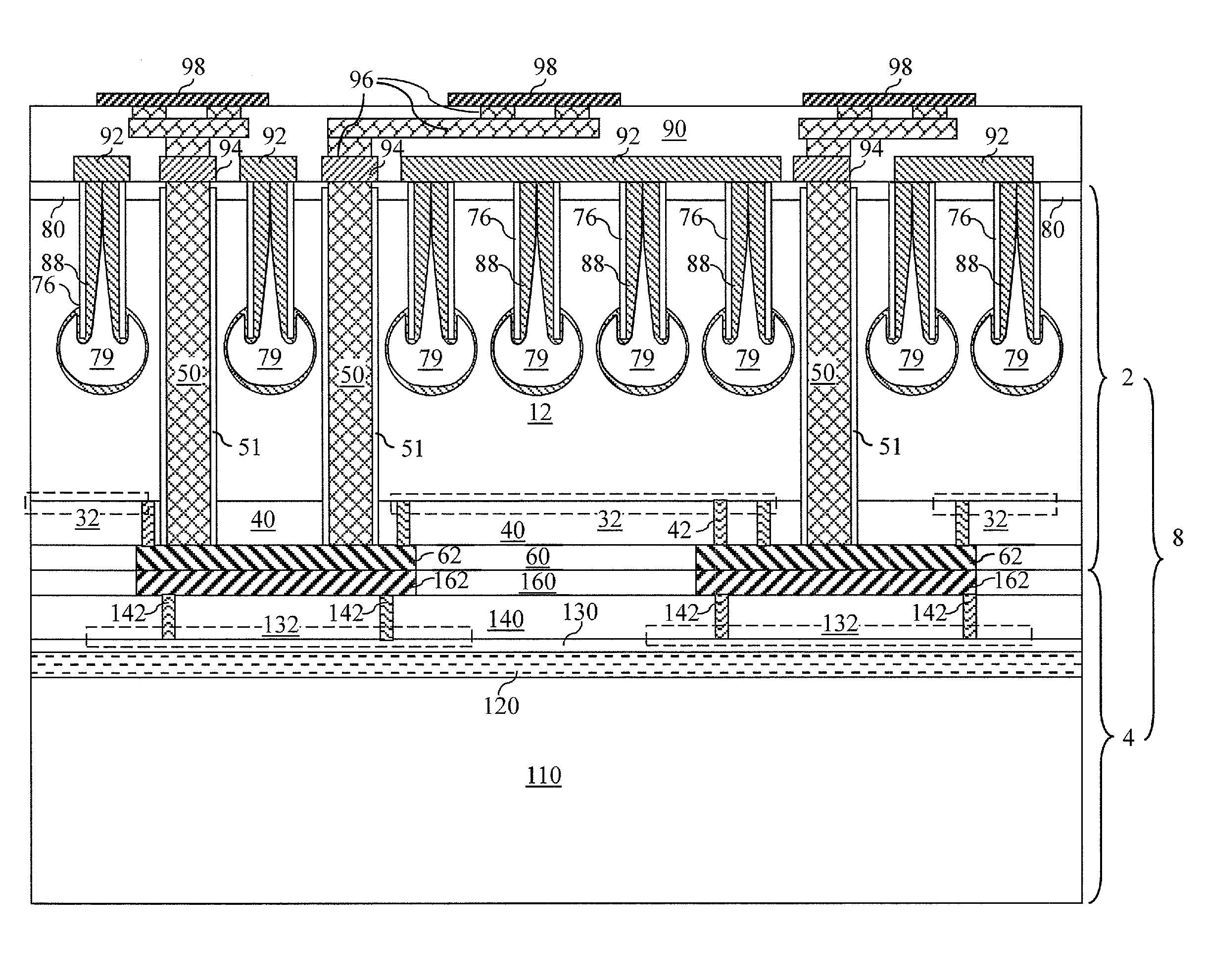

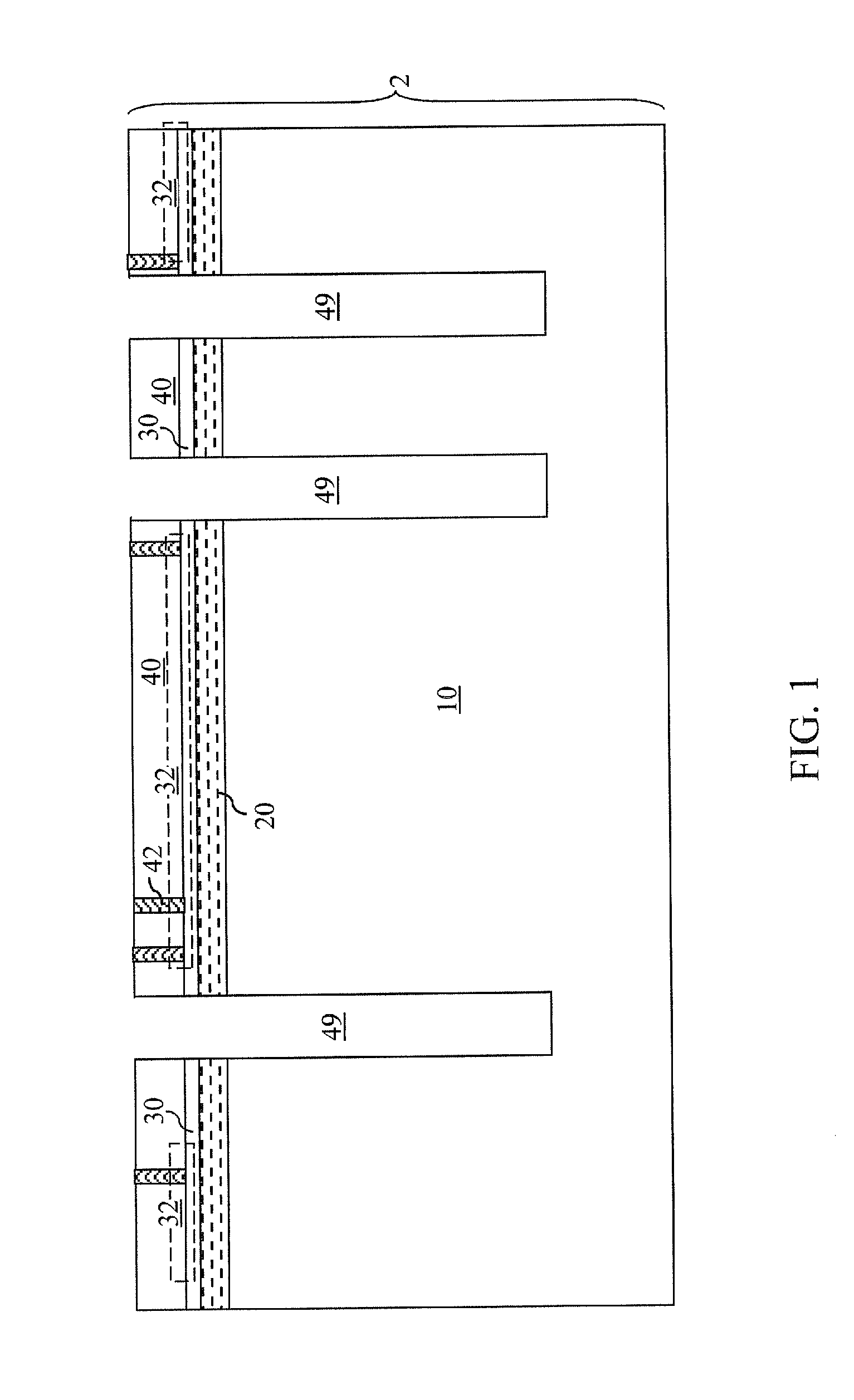

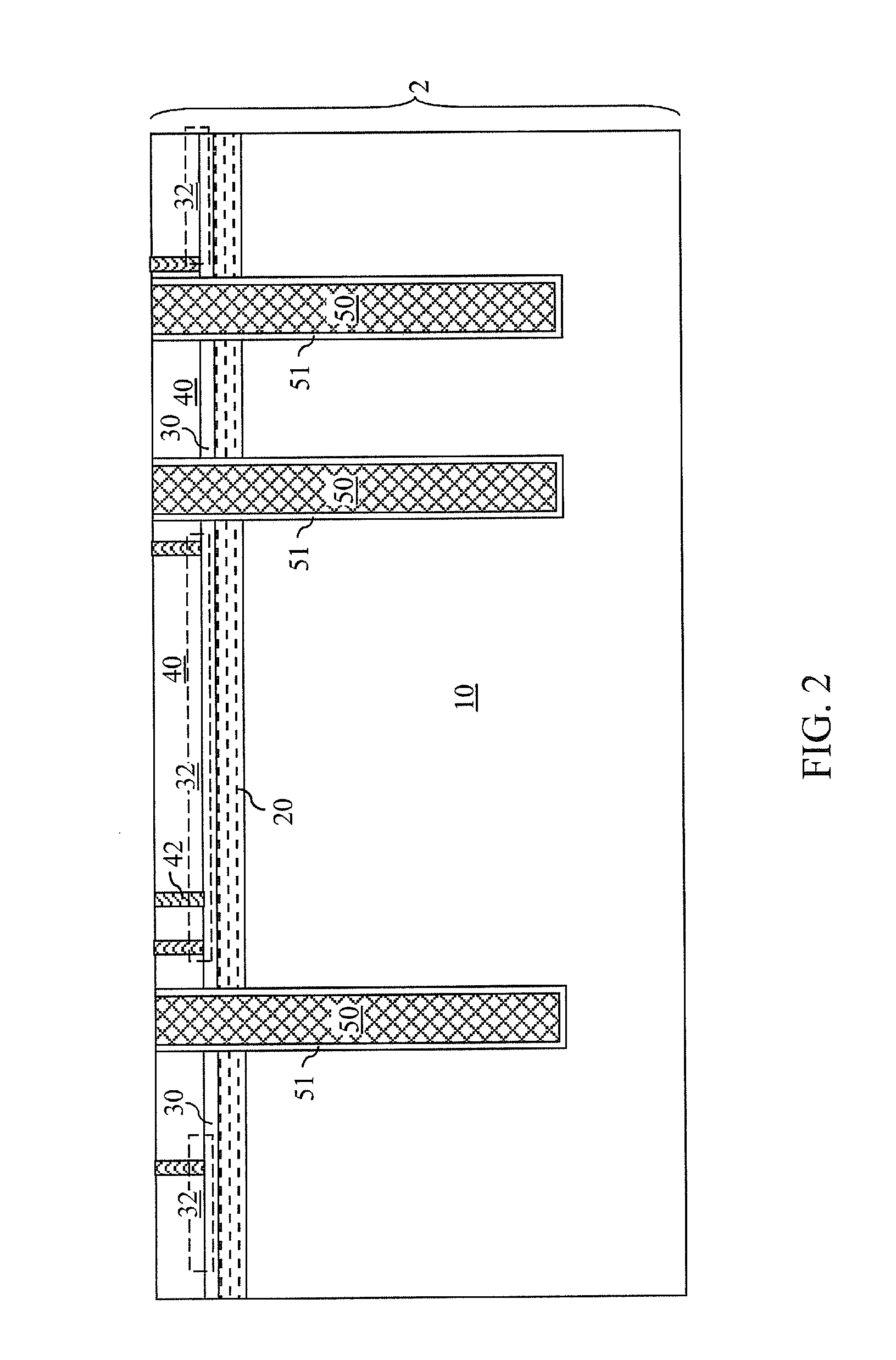

Backside dummy plugs for 3D integration

ActiveUS20110233785A1Enhances vertical thermal conductivityReduce mechanical stressSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureSemiconductor chip

A semiconductor structure includes backside dummy plugs embedded in a substrate. The backside dummy plugs can be a conductive structure that enhances vertical thermal conductivity of the semiconductor structure and provides electrical decoupling of signals in through-substrate vias (TSVs) in the substrate. The backside dummy plug can include a cavity to accommodate volume changes in other components in the substrate, thereby alleviating mechanical stress in the substrate during thermal cycling and operation of the semiconductor chip. The backside dummy plug including the cavity can be composed of an insulator material or a conductive material. The inventive structures can be employed to form three-dimensional structures having vertical chip integration, in which inter-wafer thermal conductivity is enhanced, cross-talk between signals through TSVs is reduced, and / or mechanical stress to the TSVs is reduced.

Owner:GLOBALFOUNDRIES US INC

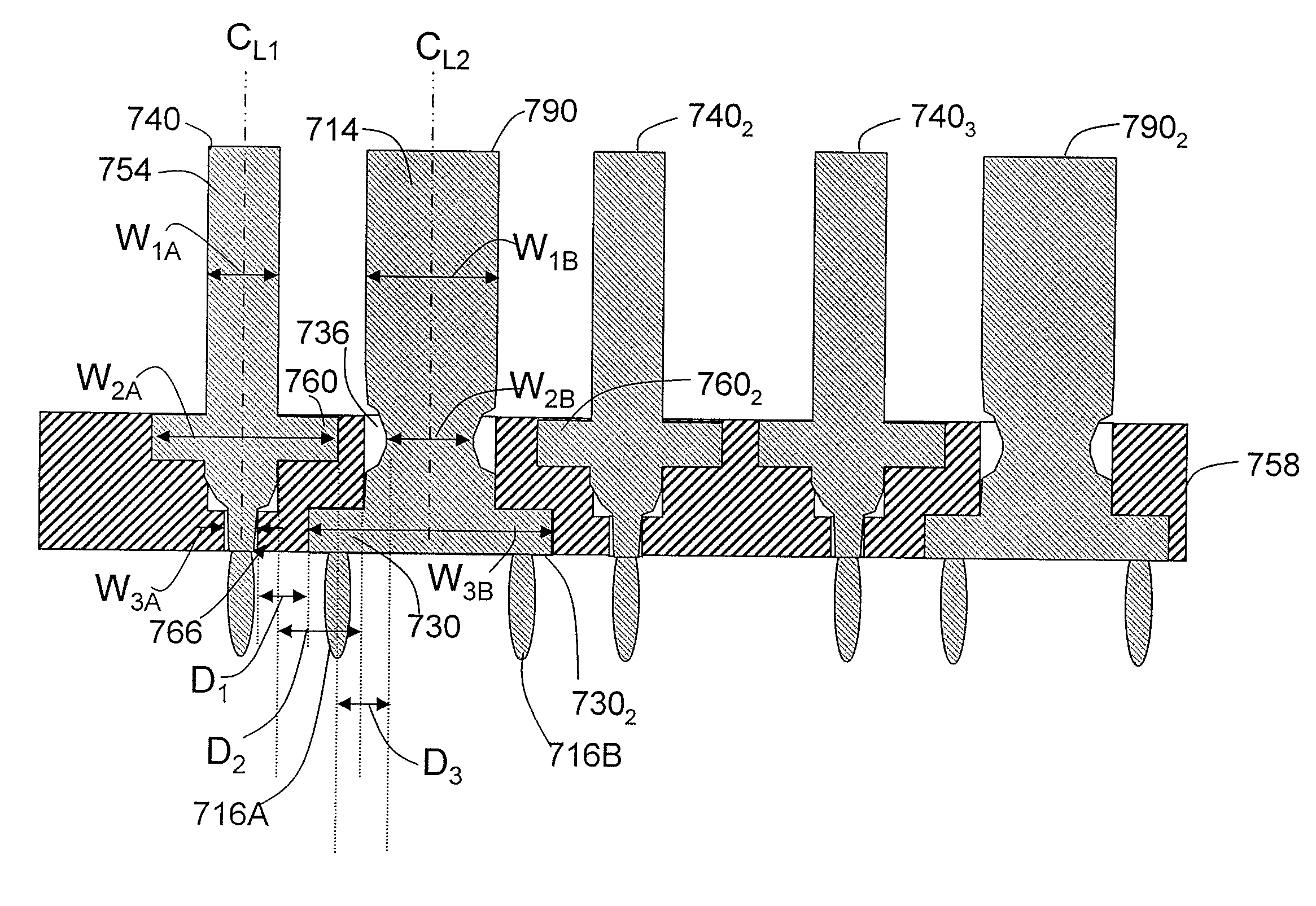

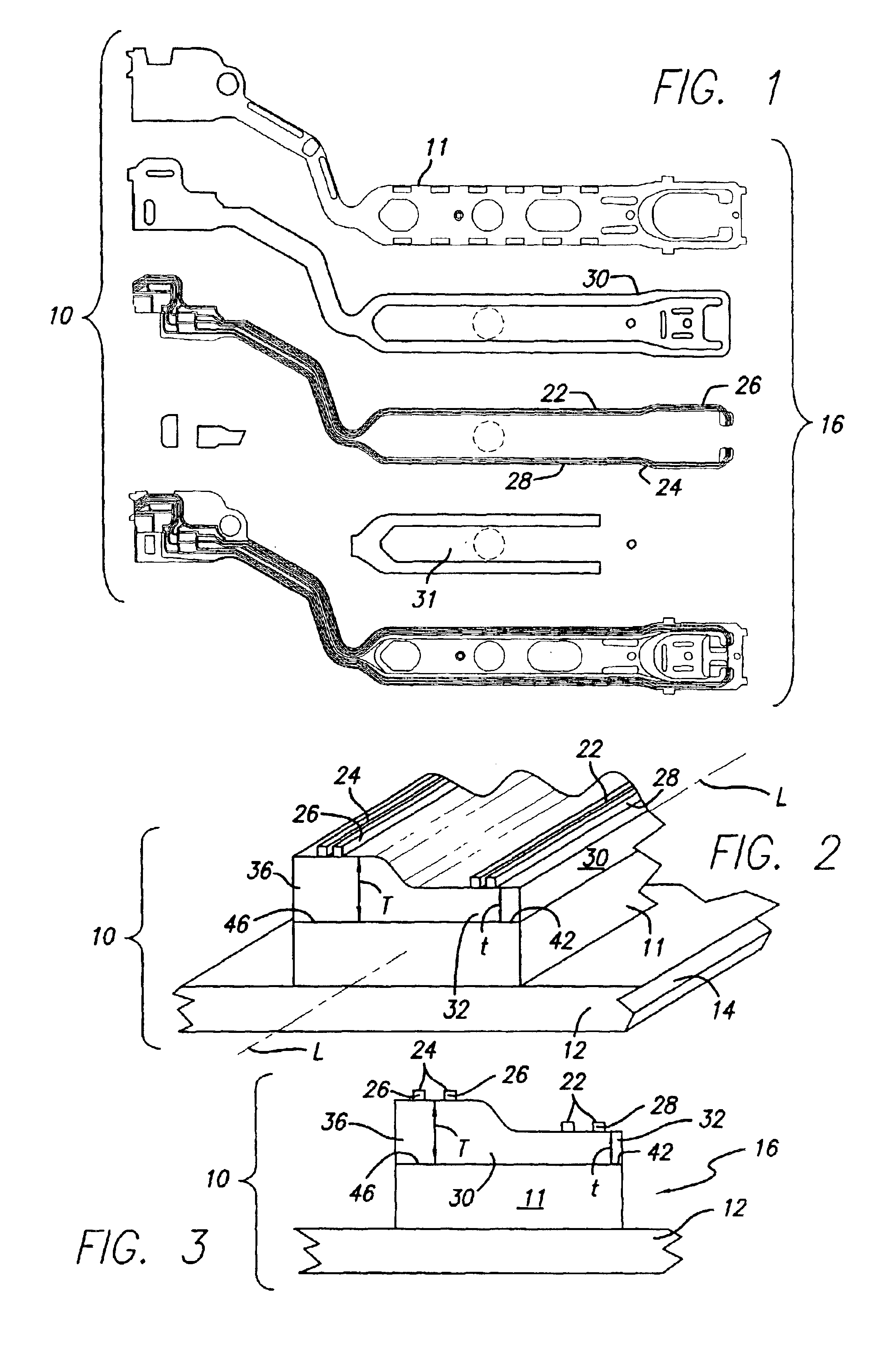

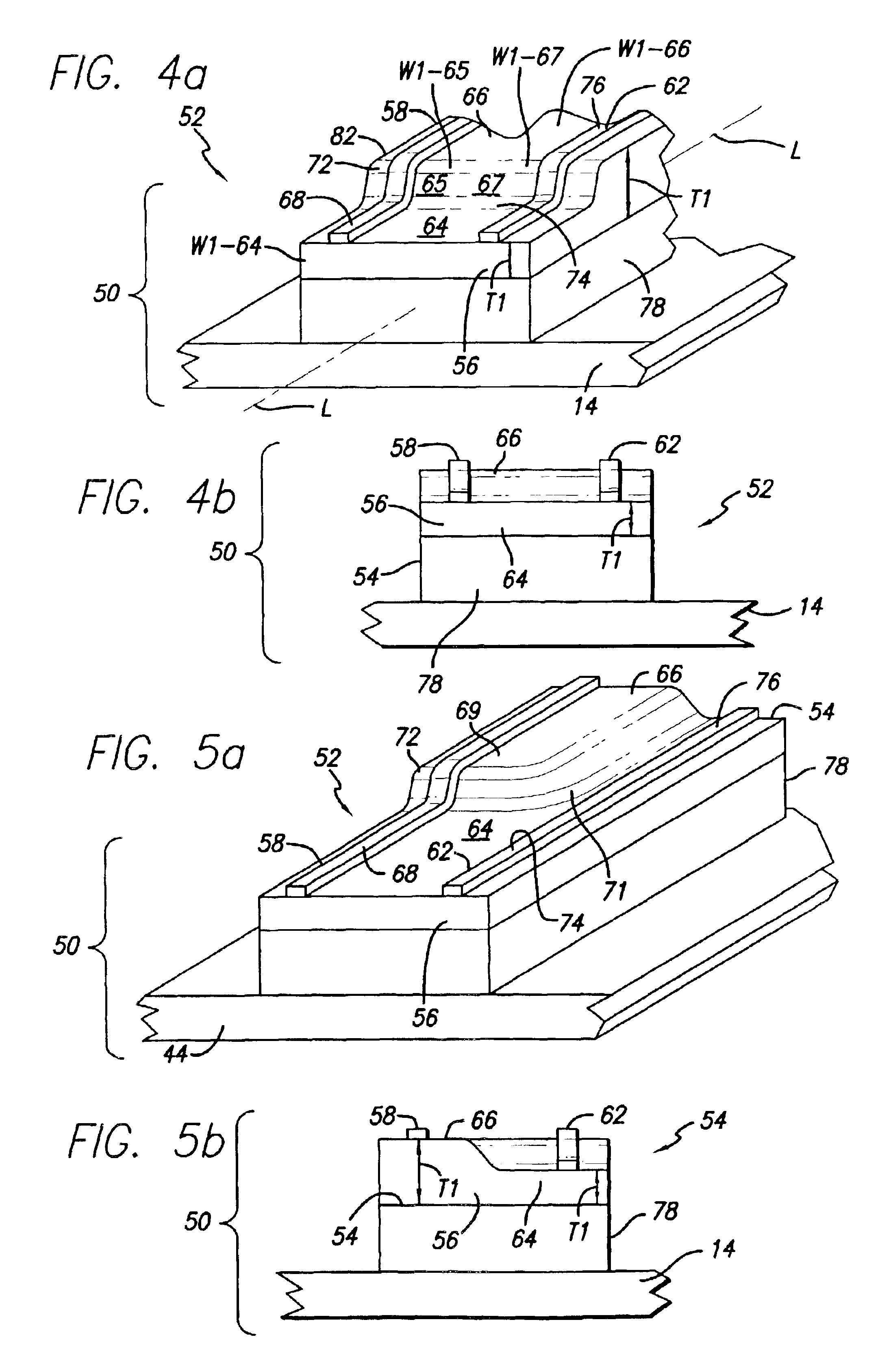

Trace flexure suspension with differential insulator and trace structures for locally tailoring impedance

InactiveUS6900967B1Easy to controlUniform impedanceRecord information storageRecording/reproducing/erasing methodsCapacitanceElectrical conductor

A novel flexure or interconnect for a disk drive suspension having a locally different thickness and / or width of insulative layer and a locally different thickness, width and / or relative spacing in its trace conductors to vary capacitance and circuit impedance values accordingly to locally desirable different and optimum values for the type of circuit and the suspension features.

Owner:MAGNECOMP

Surface mount footprint in-line capacitance

ActiveUS20110104948A1Improved routabilityImprove signal integrityPrinted circuit assemblingPrinted electric component incorporationCapacitanceSurface mounting

An interconnection system with capacitors integrated into a printed circuit board footprint of an electrical connector. One end of each capacitor shares a pad on the printed circuit board with a contact tail of a conductive element in a connector. The shared pads are not connected through vias to internal circuit structures. Rather, a via, such as which would conventionally be formed as part of the connector mounting pad, is formed as part of a separate, adjacent pad. A second end of the capacitor is attached to the adjacent pad, forming an electrical connection between the conductive element and the via through the capacitor. Incorporating capacitors into the footprint reduces the number of vias required, which improves signal integrity. The capacitors may be placed on the printed circuit board separately from the connector or may be incorporated into the connector, allowing the connector and capacitors to be placed in one operation.

Owner:AMPHENOL CORP

Resistive elements using carbon nanotubes

ActiveUS7365632B2Function increaseEasy parameter controlCurrent responsive resistorsSolid-state devicesBulk resistanceCarbon nanotube

Resistive elements include a patterned region of nanofabric having a predetermined area, where the nanofabric has a selected sheet resistance; and first and second electrical contacts contacting the patterned region of nanofabric and in spaced relation to each other. The resistance of the element between the first and second electrical contacts is determined by the selected sheet resistance of the nanofabric, the area of nanofabric, and the spaced relation of the first and second electrical contacts. The bulk resistance is tunable.

Owner:NANTERO

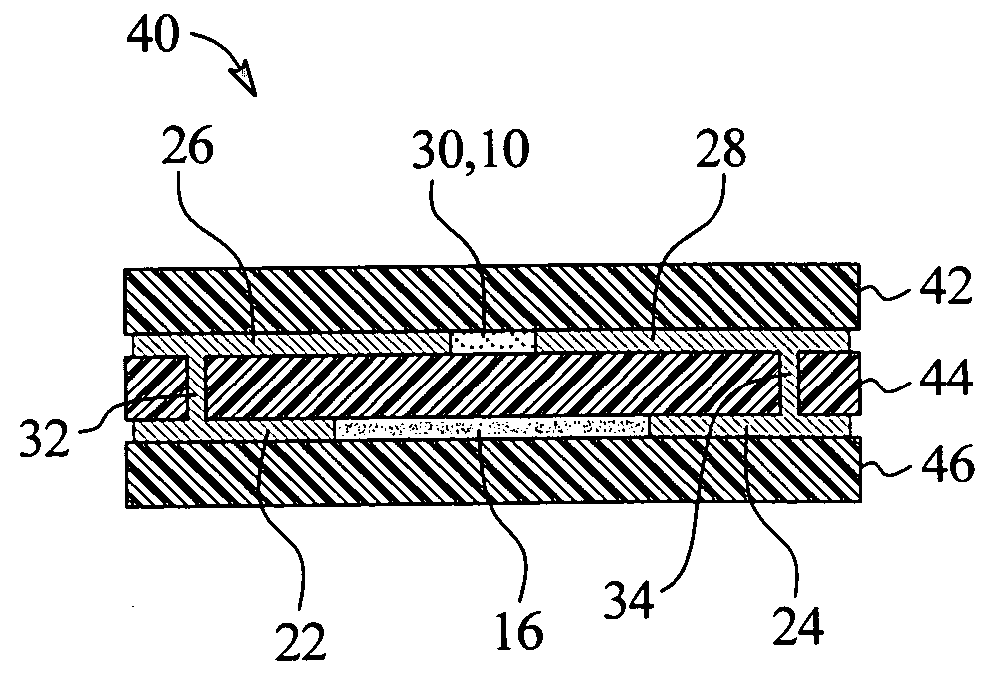

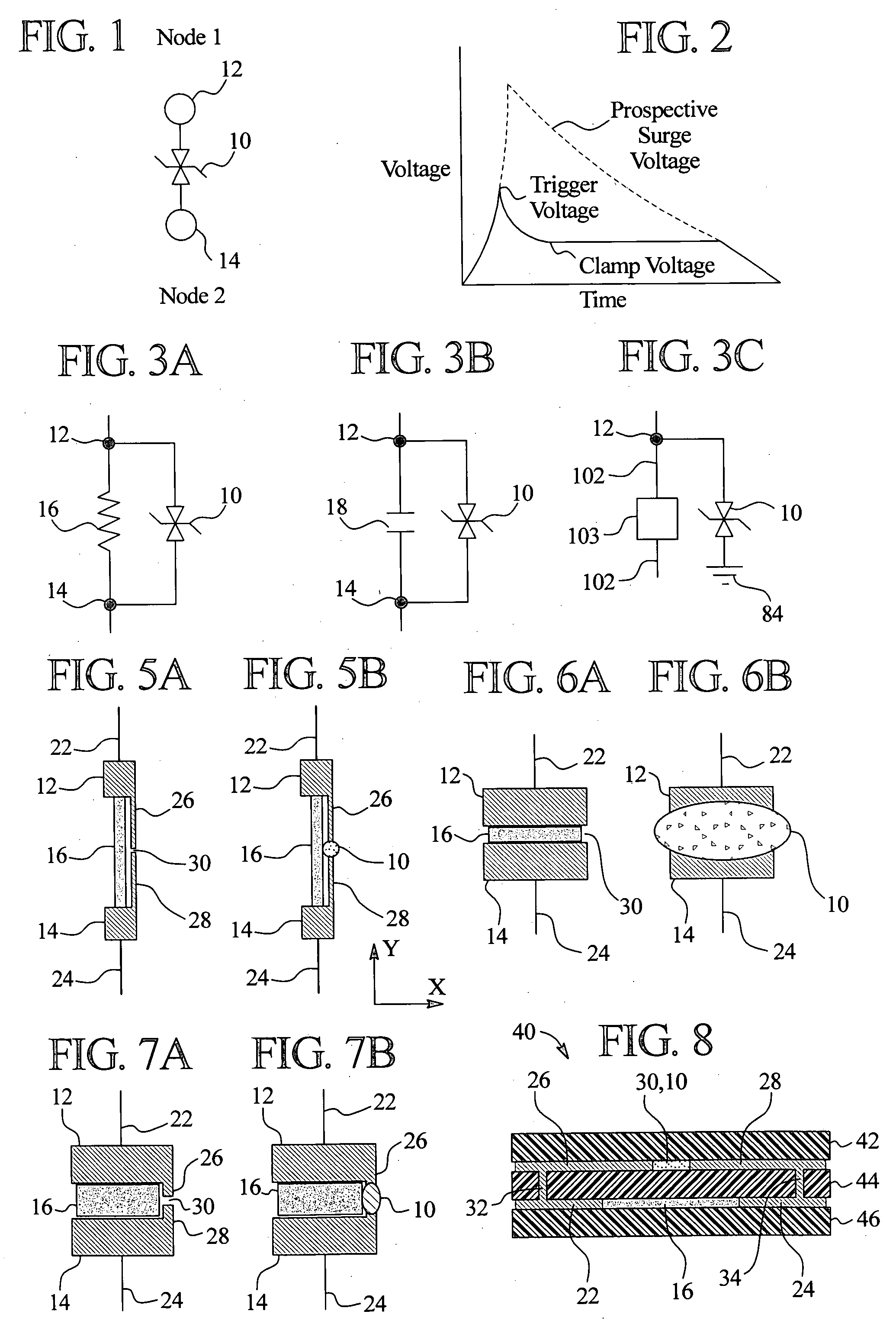

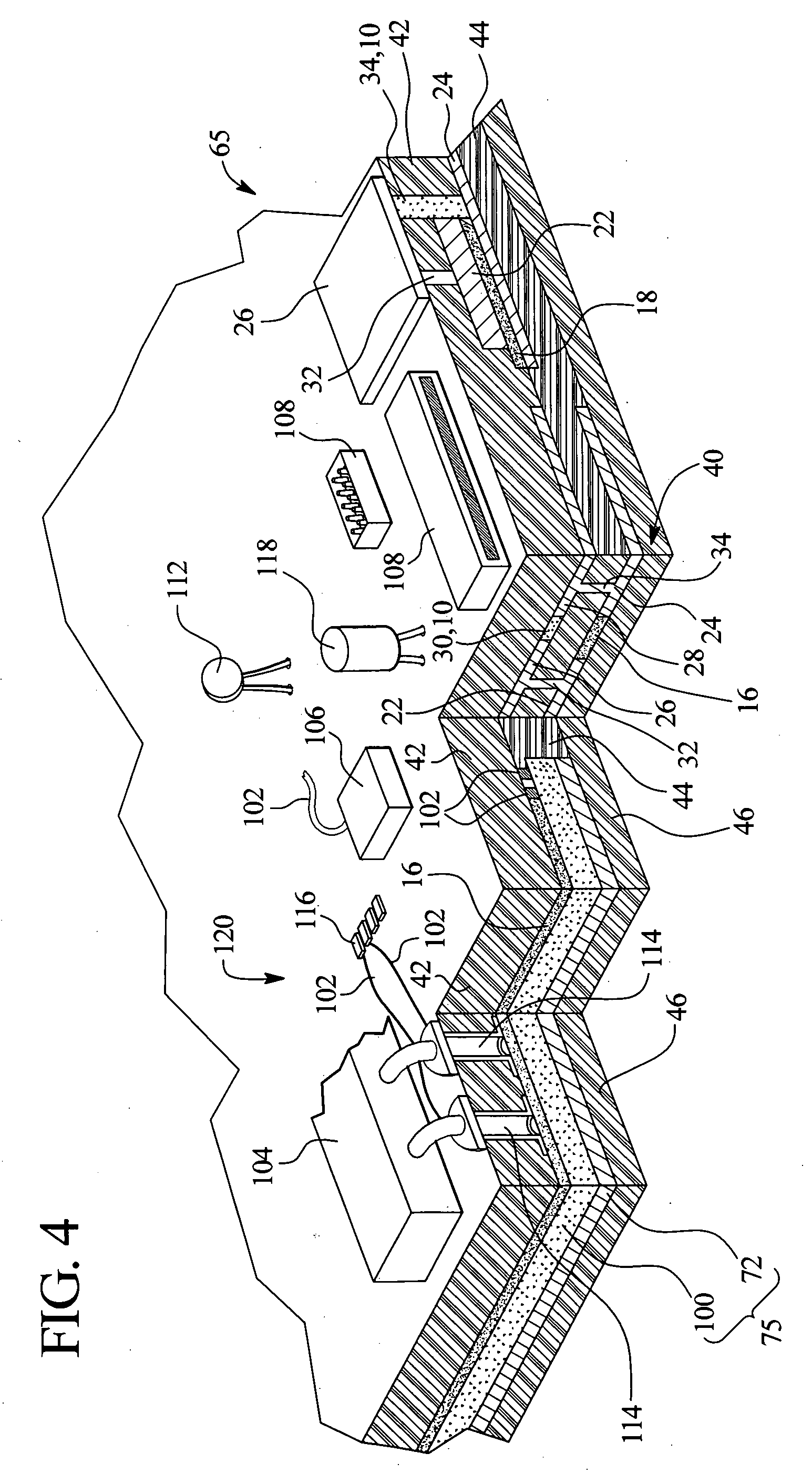

Electrostatic discharge protection for embedded components

InactiveUS20060152334A1Protection elementLow costPrinted circuit aspectsHigh voltage circuit adaptationsCapacitanceElectrical resistance and conductance

An improved electrical circuit that includes an embedded electrical component and an embedded voltage variable material (“VVM”) is provided. In one embodiment, the embedded VVM is provided as a voltage variable substrate, which is used in combination with an embedded electrical component, such as an embedded resistive material or an embedded capacitive material.

Owner:LITTELFUSE INC

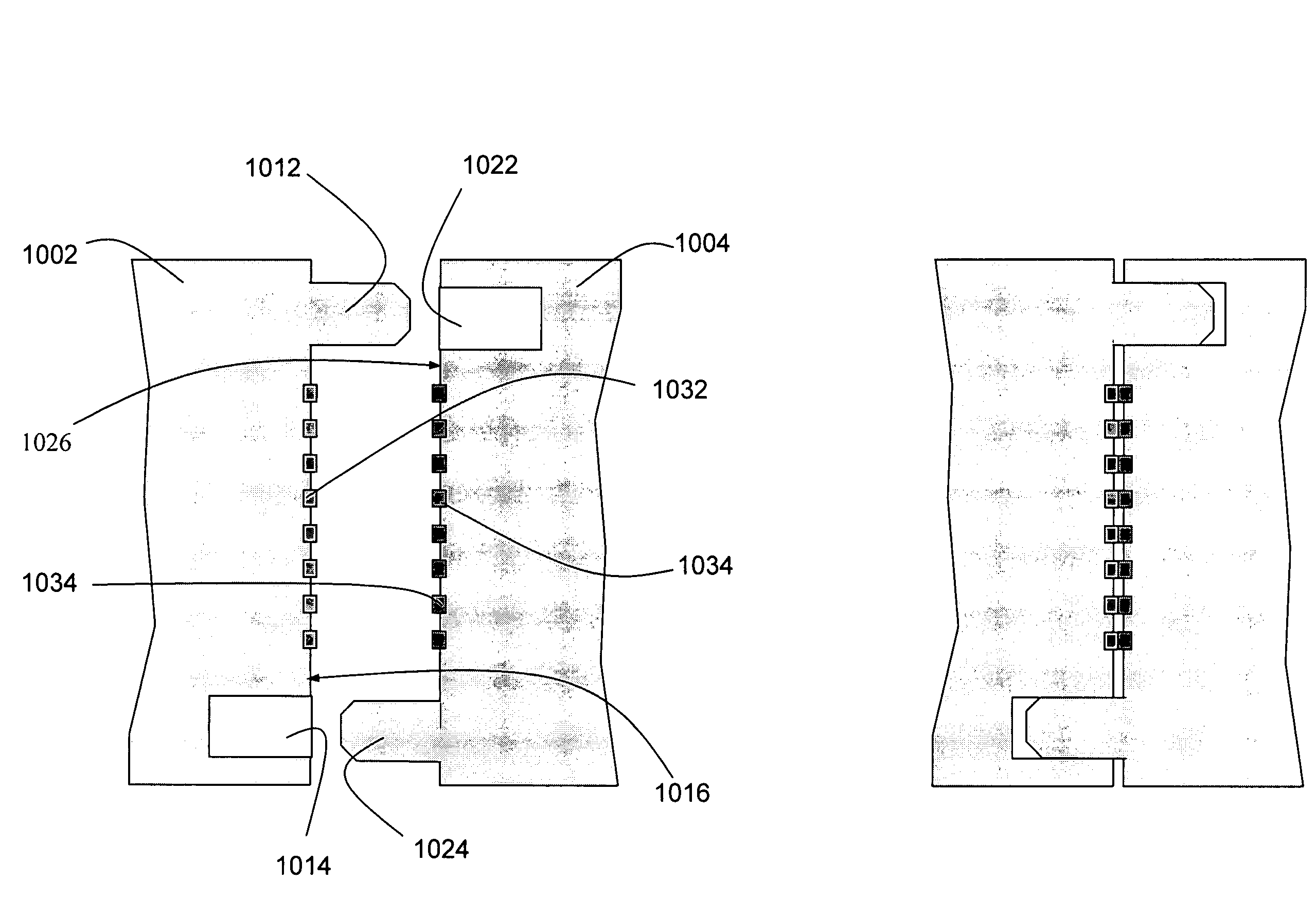

Inter-chip communication

ActiveUS7612443B1Reduce power consumptionEliminate capacitanceFinal product manufactureSemiconductor/solid-state device detailsEngineeringQuilt packaging

Owner:UNIV OF NOTRE DAME DU LAC

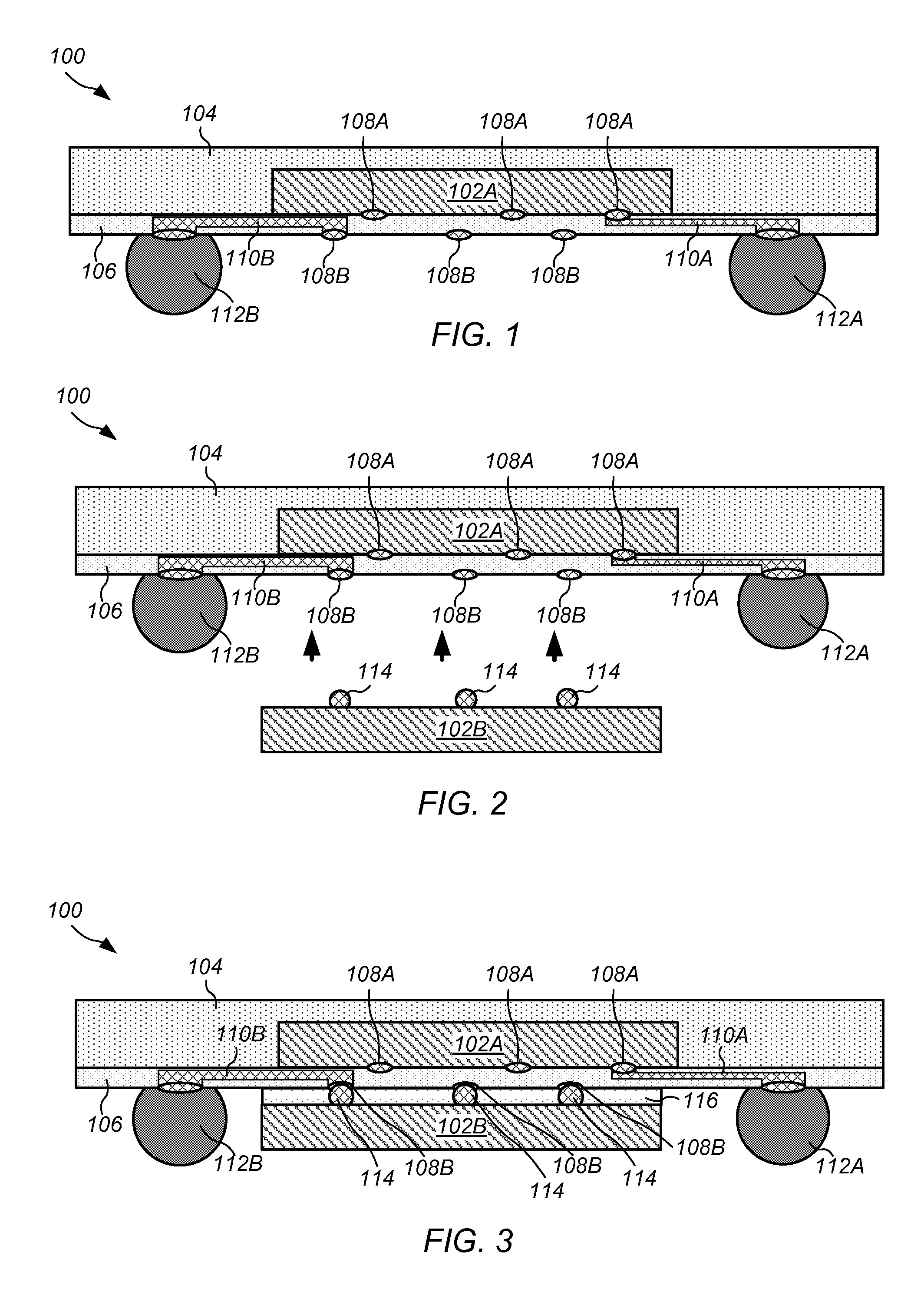

Interconnect packaging systems

ActiveUS7608919B1Reduce power consumptionEliminate capacitanceFinal product manufactureSemiconductor/solid-state device detailsQuilt packagingElectrical and Electronics engineering

Owner:UNIV OF NOTRE DAME DU LAC

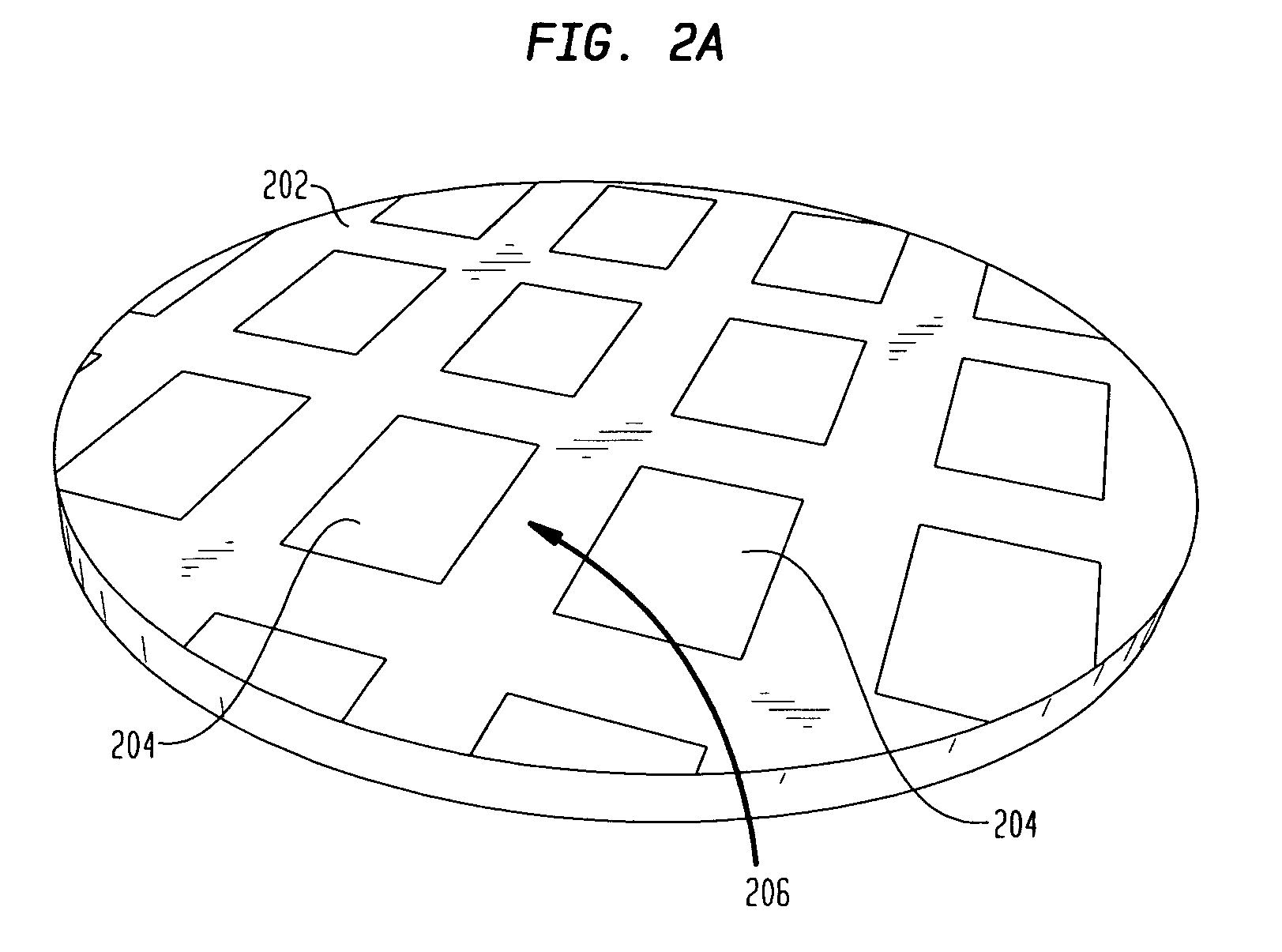

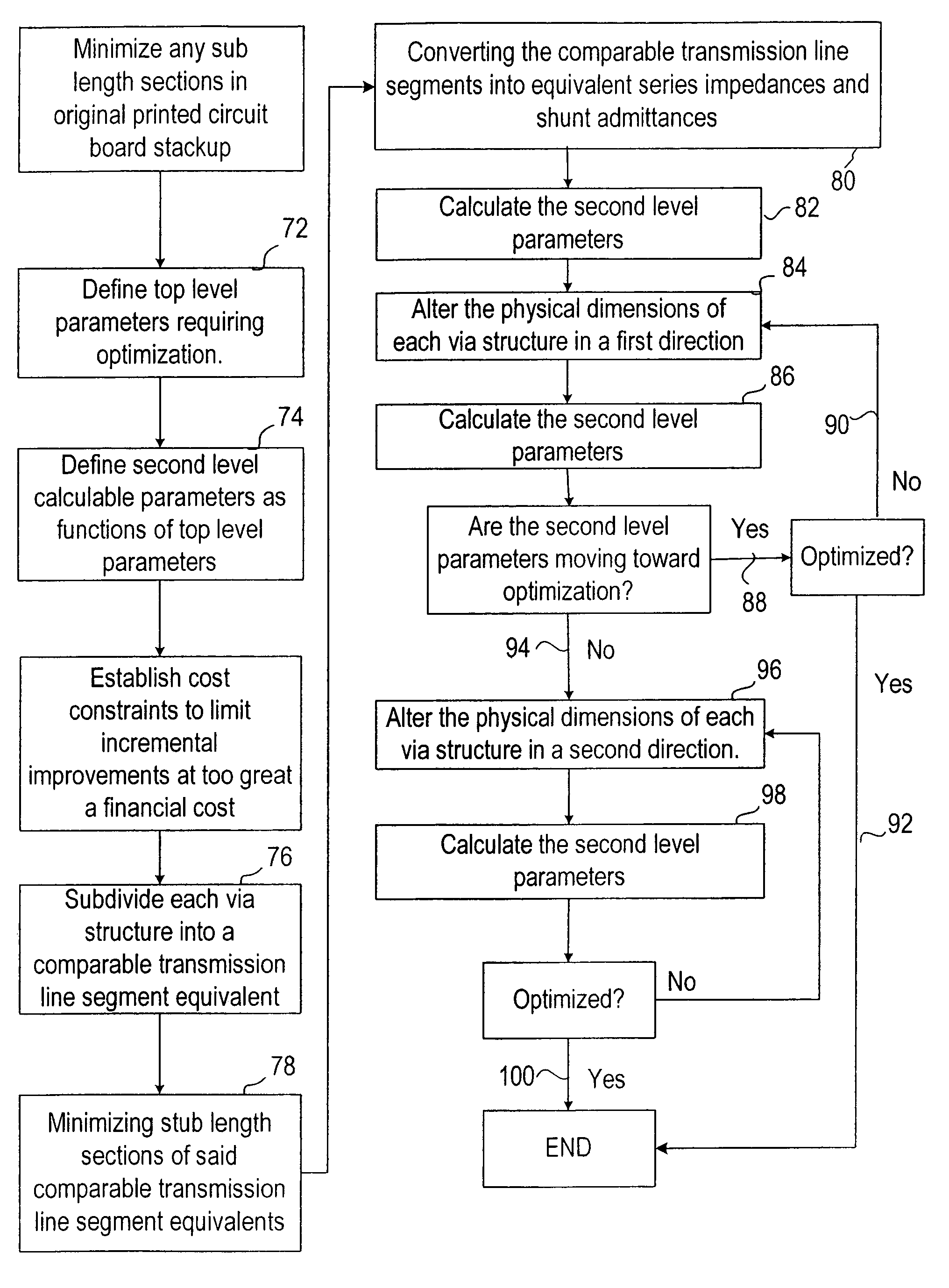

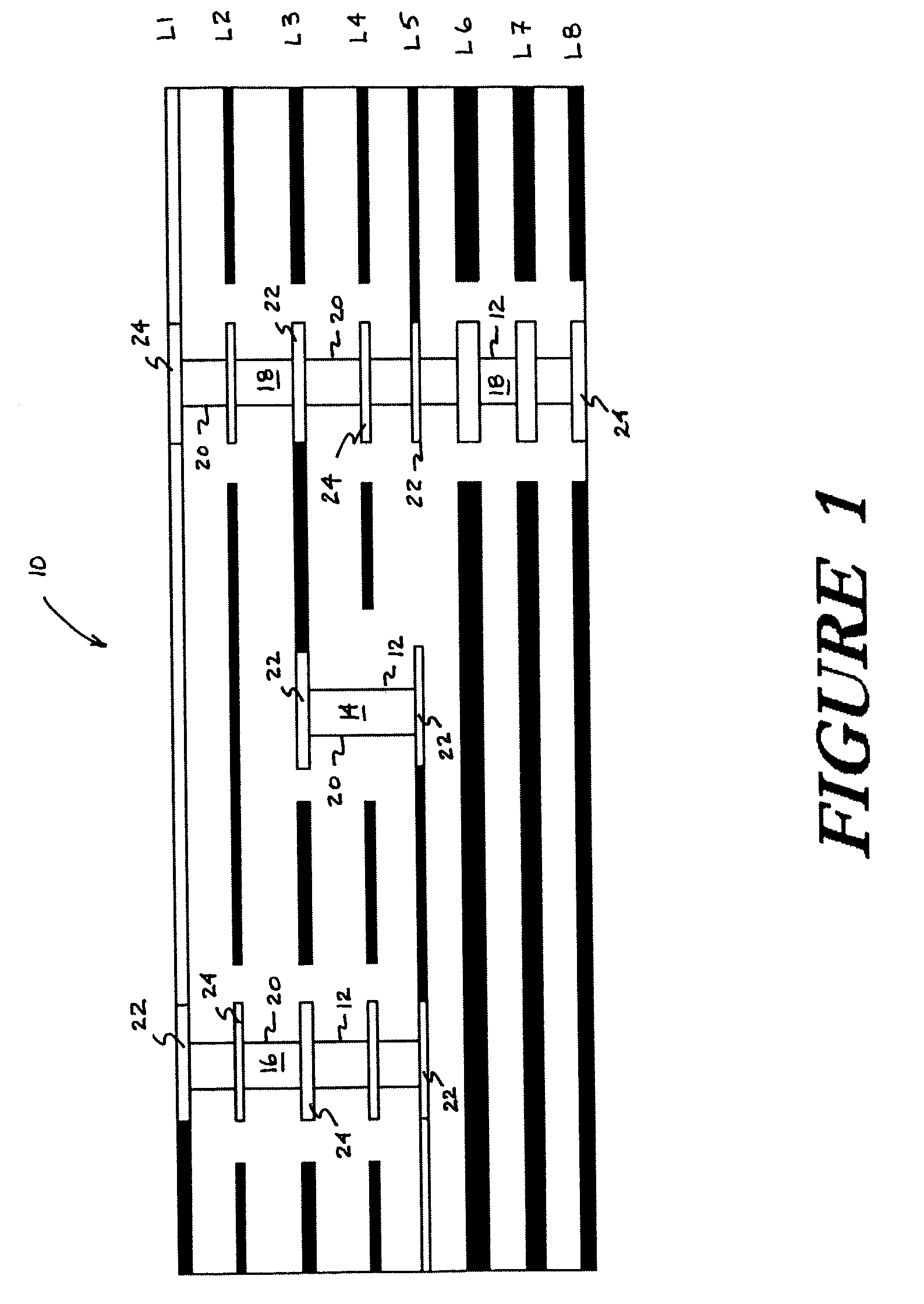

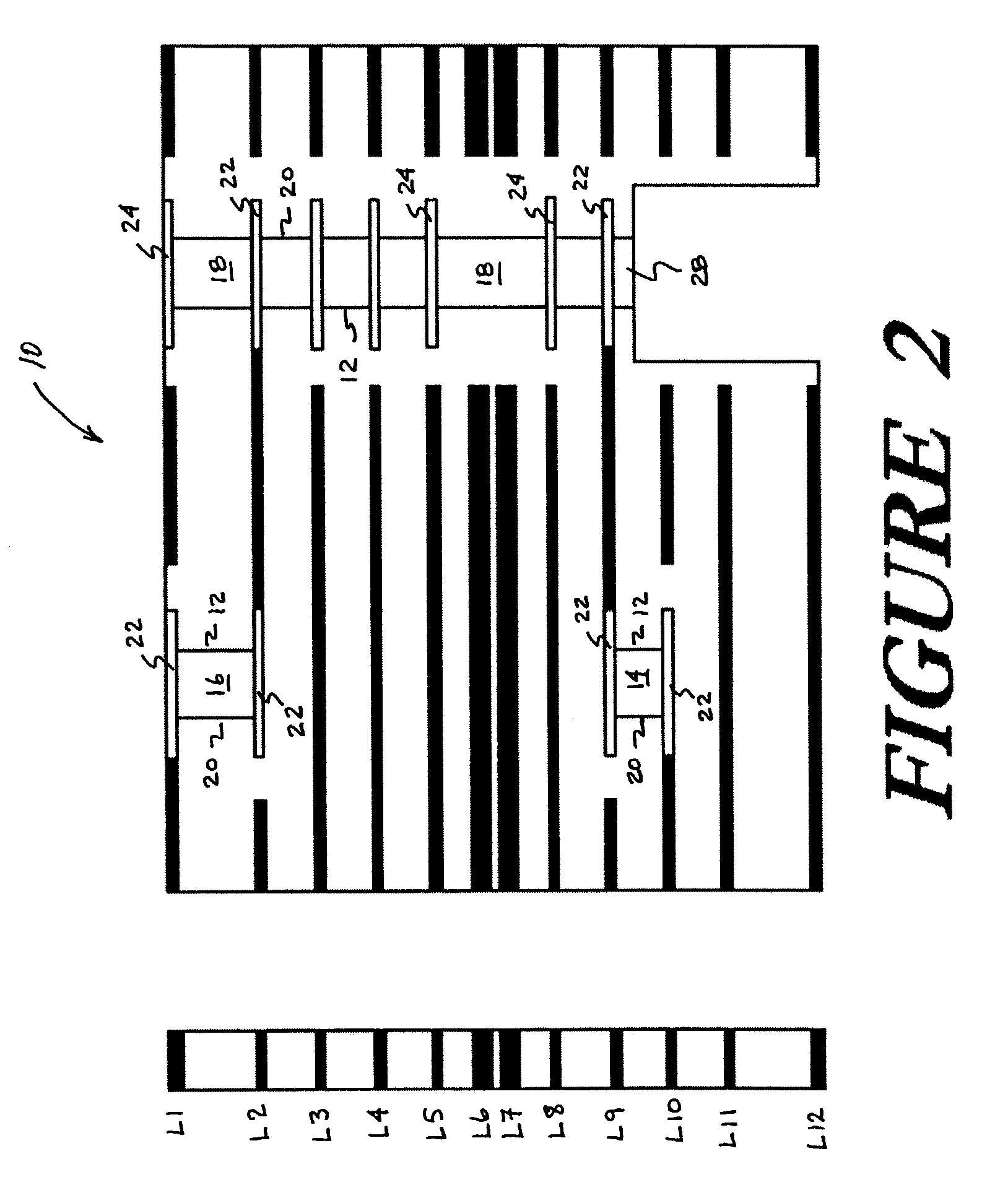

Method for optimizing high frequency performance of via structures

ActiveUS7249337B2Improve performanceImproving signal integrity performance of high-frequencySubstation/switching arrangement detailsSemiconductor/solid-state device detailsCapacitancePrinted circuit board

A method for enhancing the high frequency signal integrity performance of a printed circuit board (PCB) or backplane is provided. According to one embodiment of the present invention, the method involves the use of S-parameters as the primary cost factors associated with an iterative process to optimize the physical dimensions and shape of a single or a collection of vias within the PCB or backplane. In certain embodiments, the process involves the representation of the via components as equivalent lumped series admittances and impedances, as well as, RLGC sub-circuits upon which basic circuit analysis is performed to optimize secondary characteristics, for example, the maximization of the sub-circuit's resistance and / or the minimization of the sub-circuit's capacitance. The iterative process involves the alteration of physical dimensions and the shape of the via components such that the secondary characteristics are optimized.

Owner:SANMINA-SCI CORPORATION

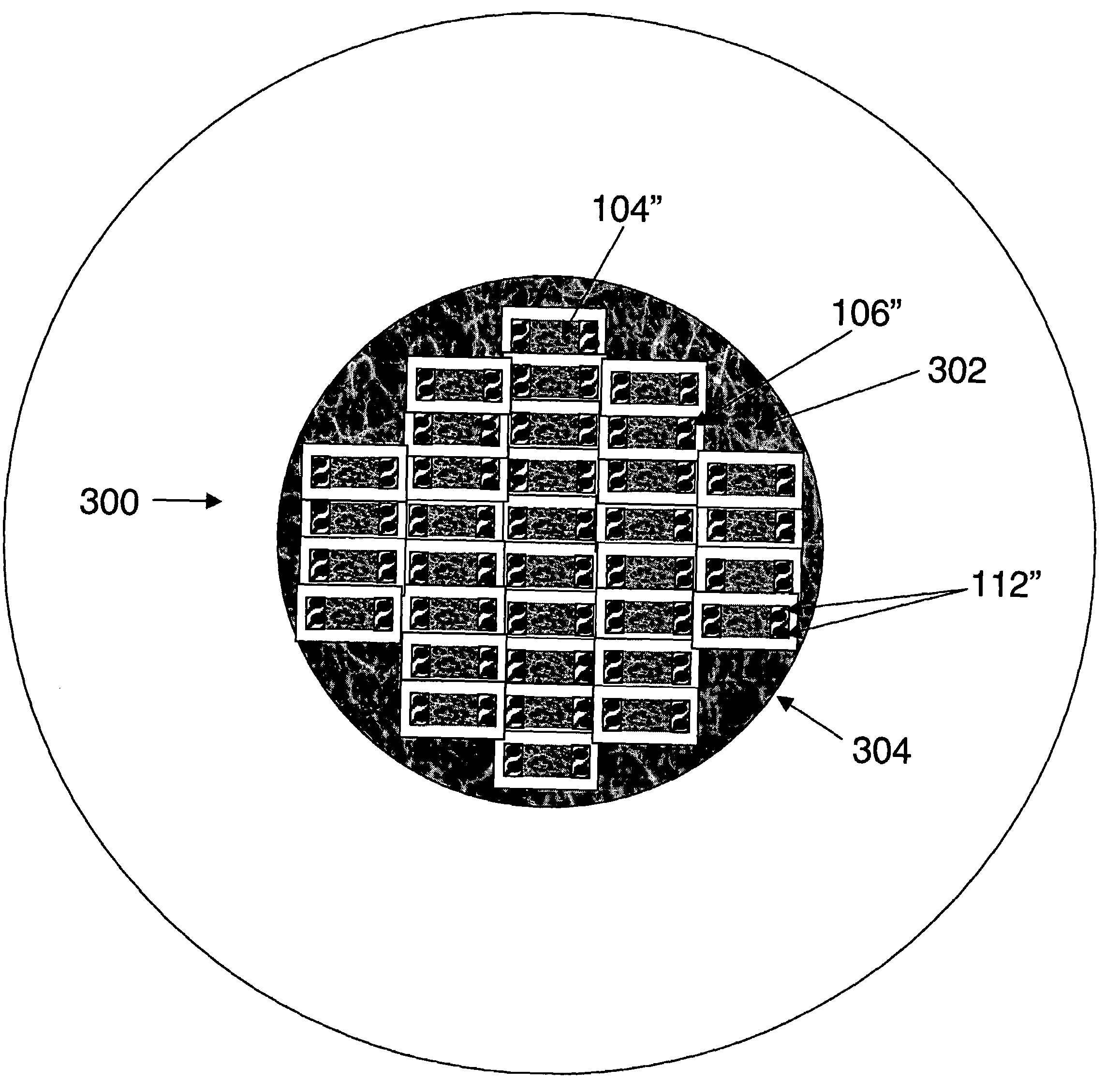

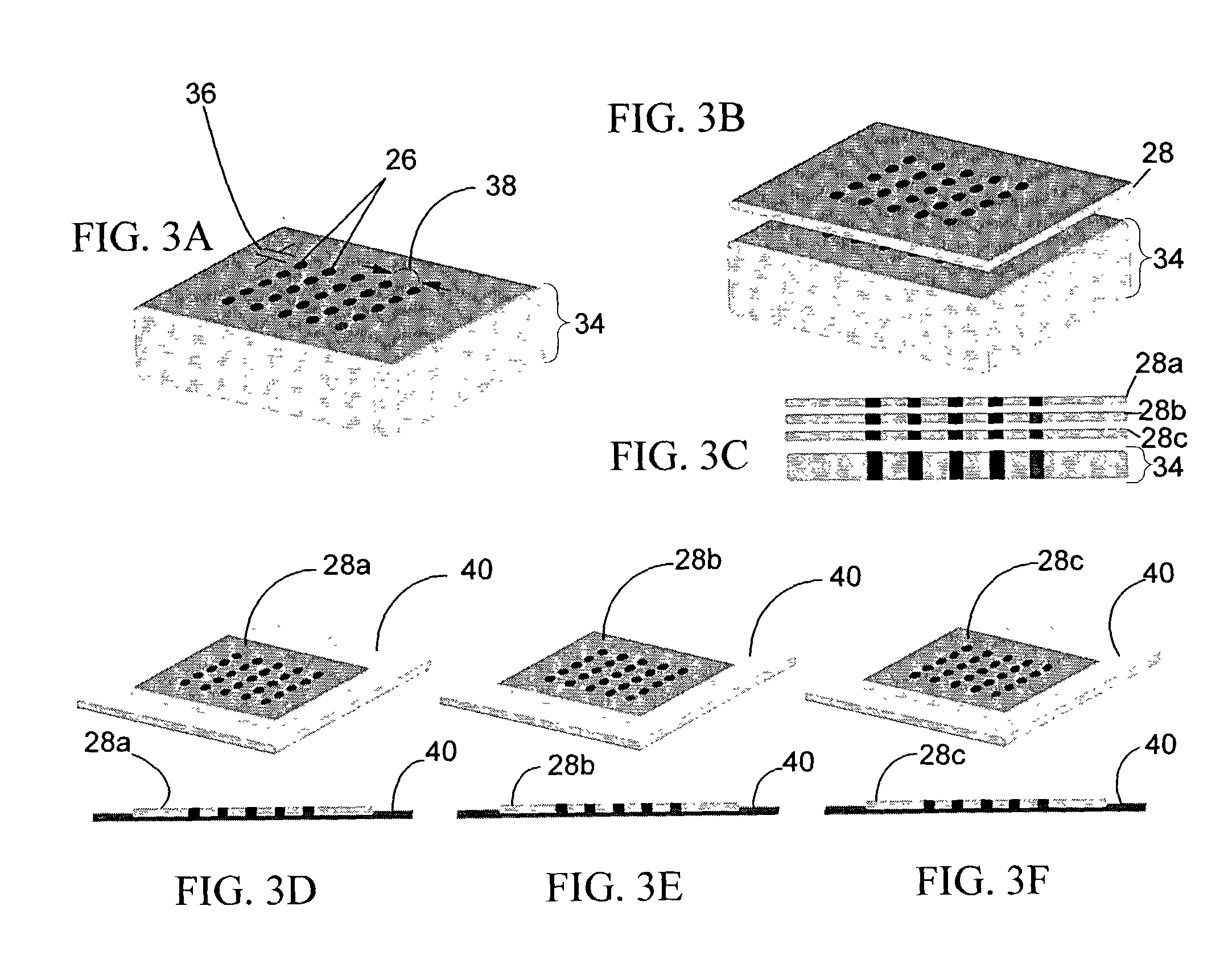

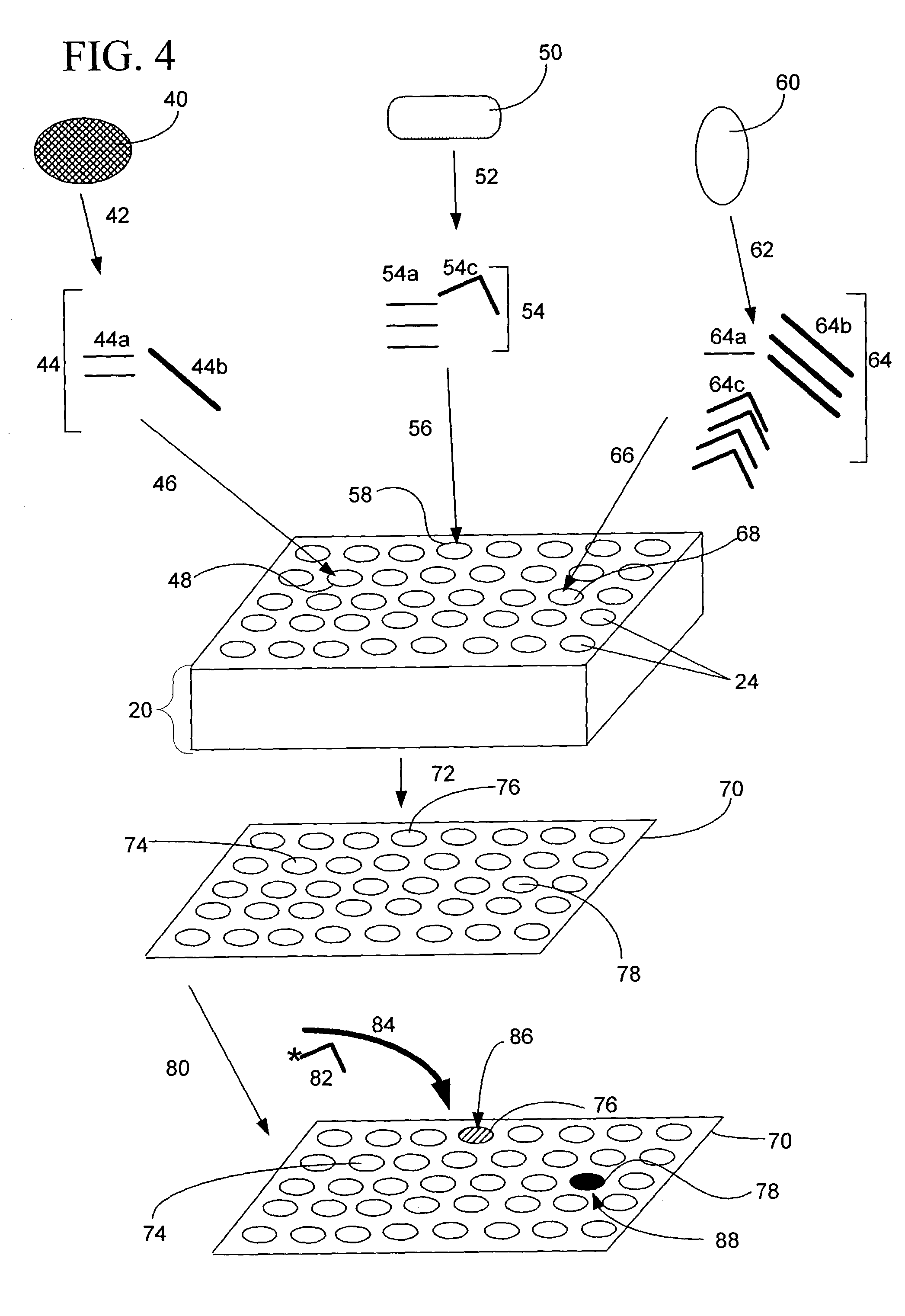

Measurements of multiple molecules using a cryoarray

InactiveUS20030054342A1Maintained in placeMore productiveBioreactor/fermenter combinationsSequential/parallel process reactionsBiologyVirus

This disclosure relates to CryoArrays, which permit the analysis of samples (such as protein, nucleic acid, virus, or cell samples) in arrays that are prepared at low temperatures. Because CryoArrays are constructed as a block of substantially columnar samples, the block can be sliced to provide a plurality of identical or substantially identical individual arrays. The individual arrays can be used for parallel analysis of the same array feature set, for instance with different probes or under different conditions. Also provided are methods of making CryoArrays, devices for making CryoArrays, and kits.

Owner:DEPT OF HEALTH & HUMAN SERVICES THE GOVERNMENT OF THE US SEC THE

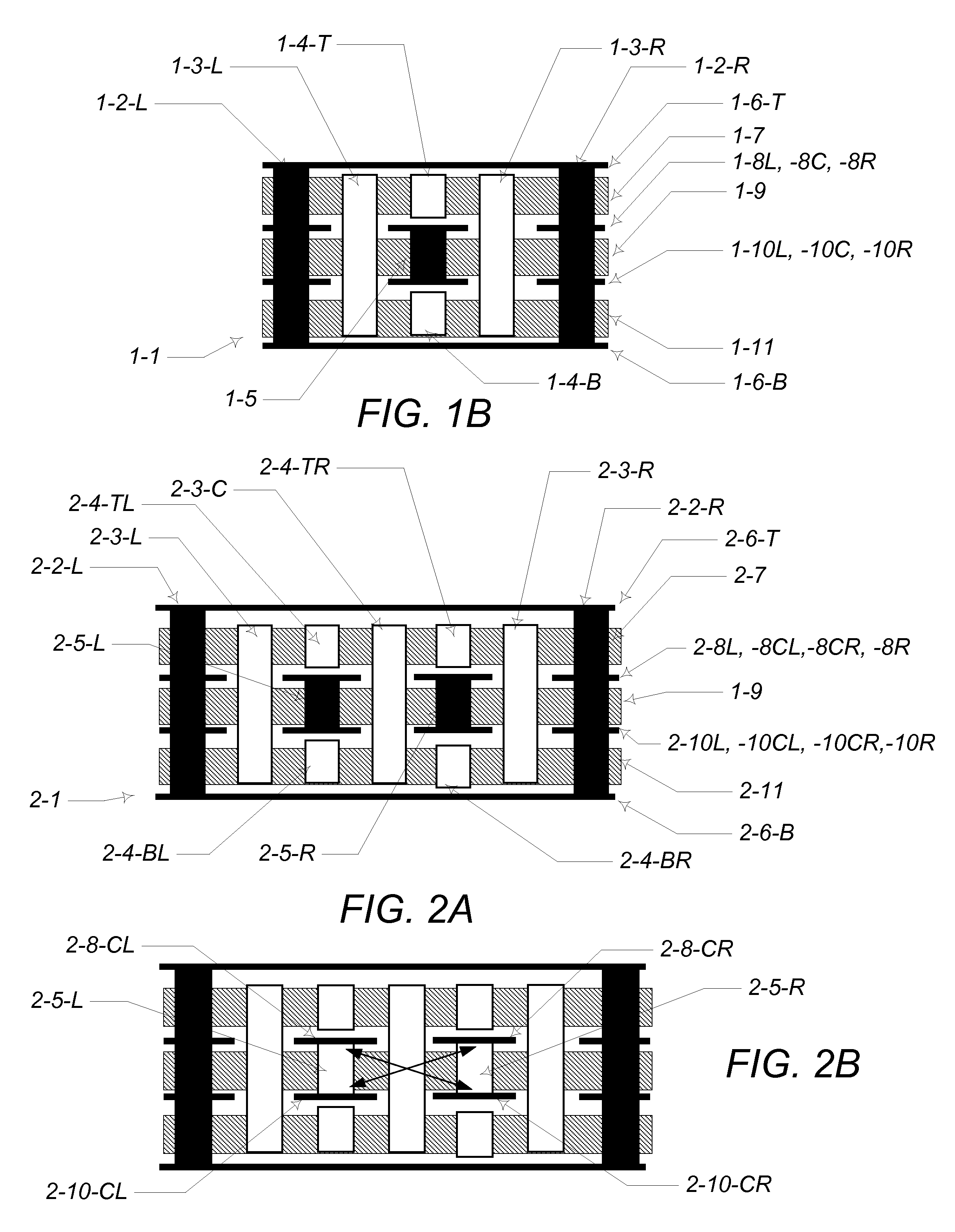

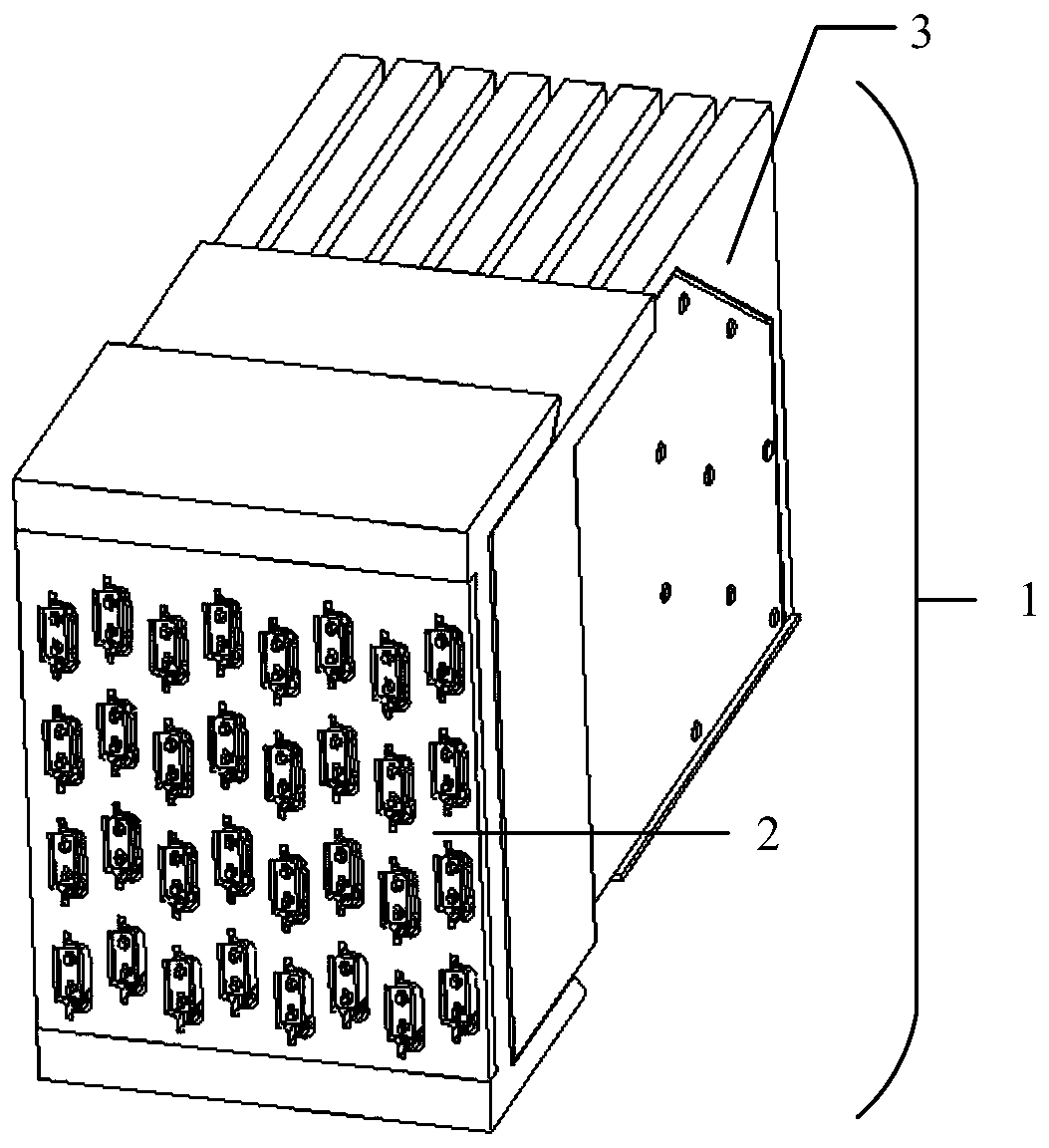

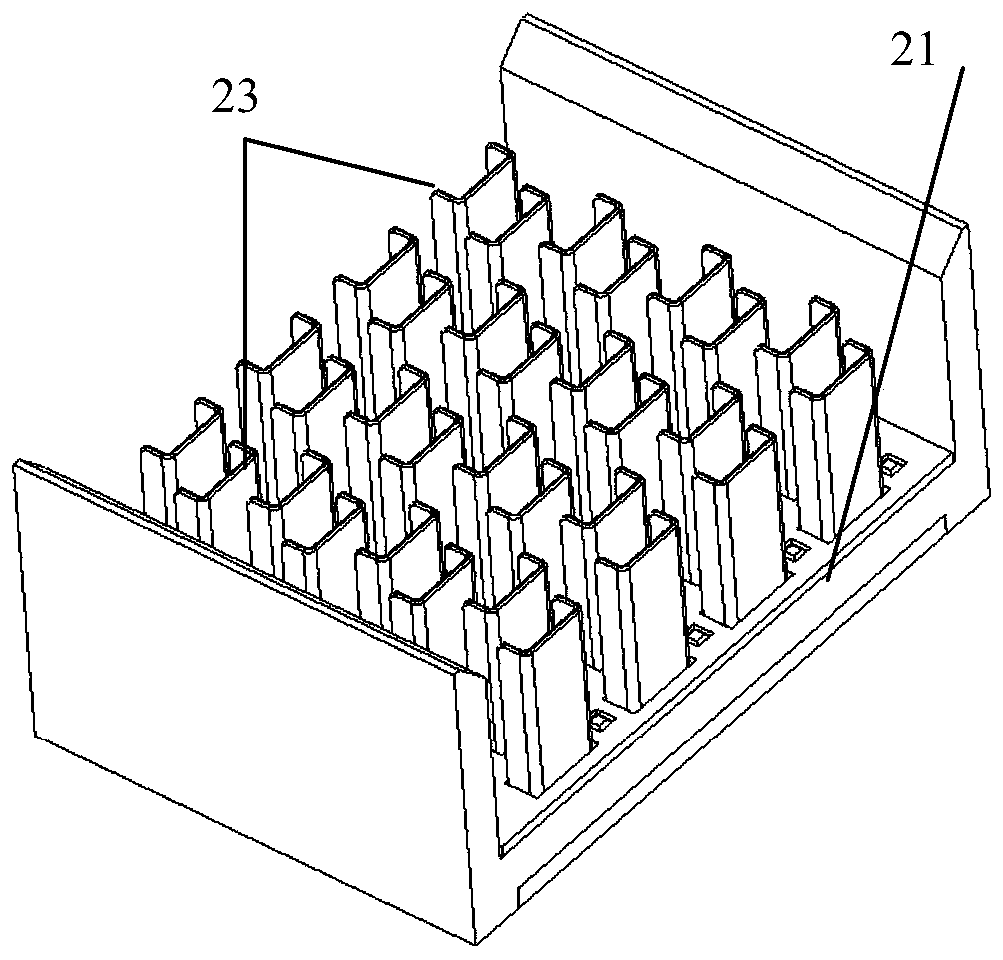

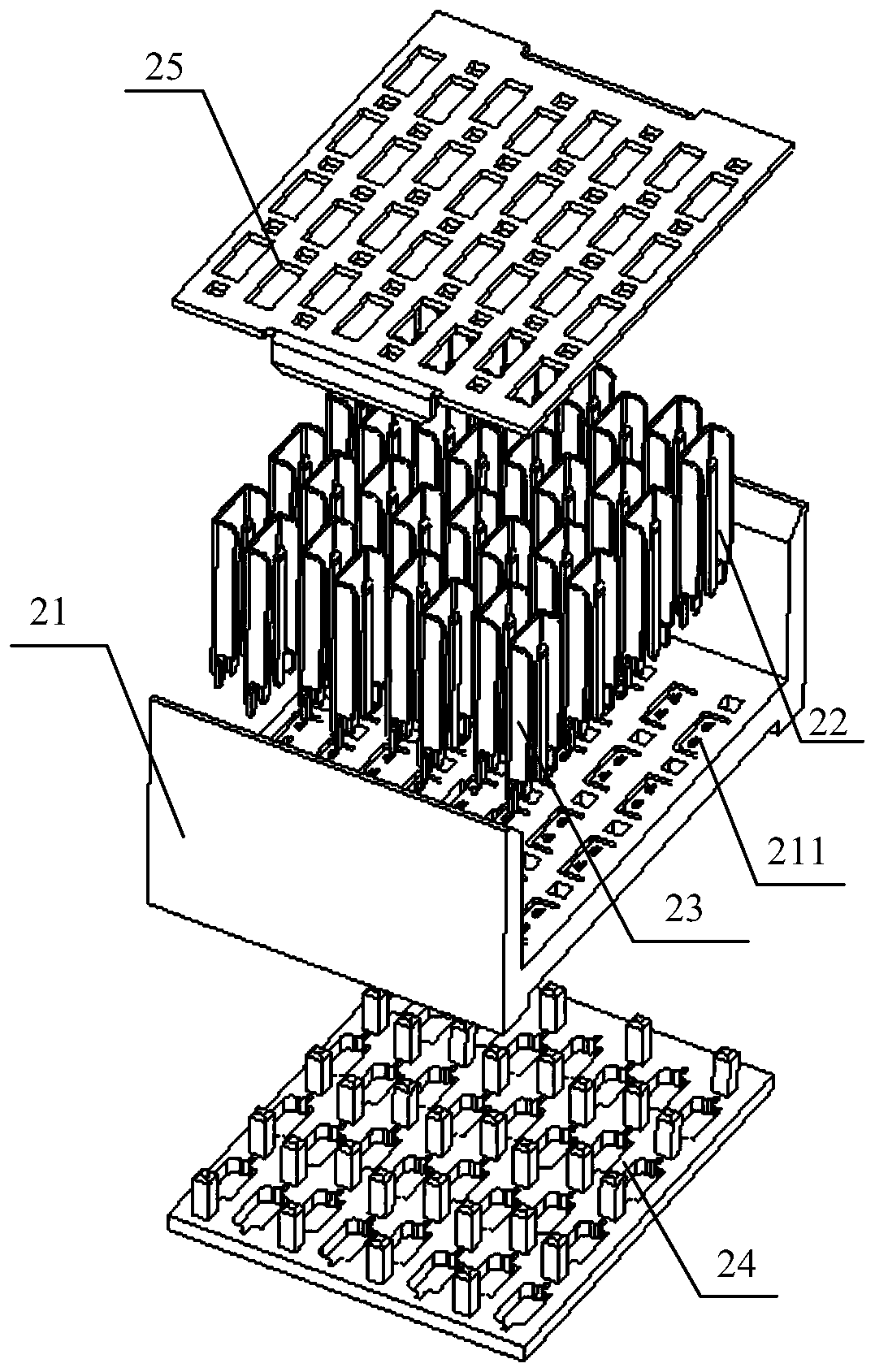

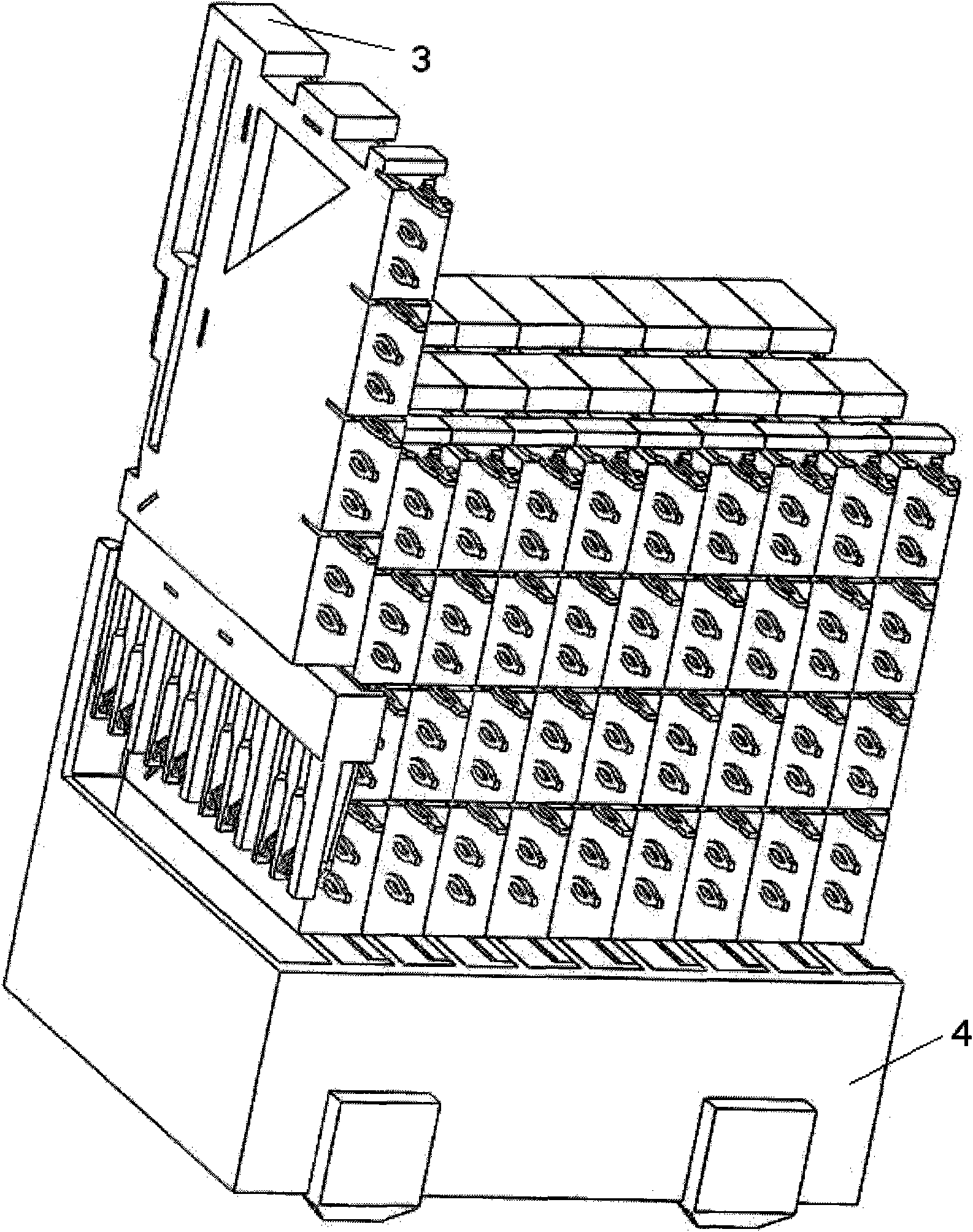

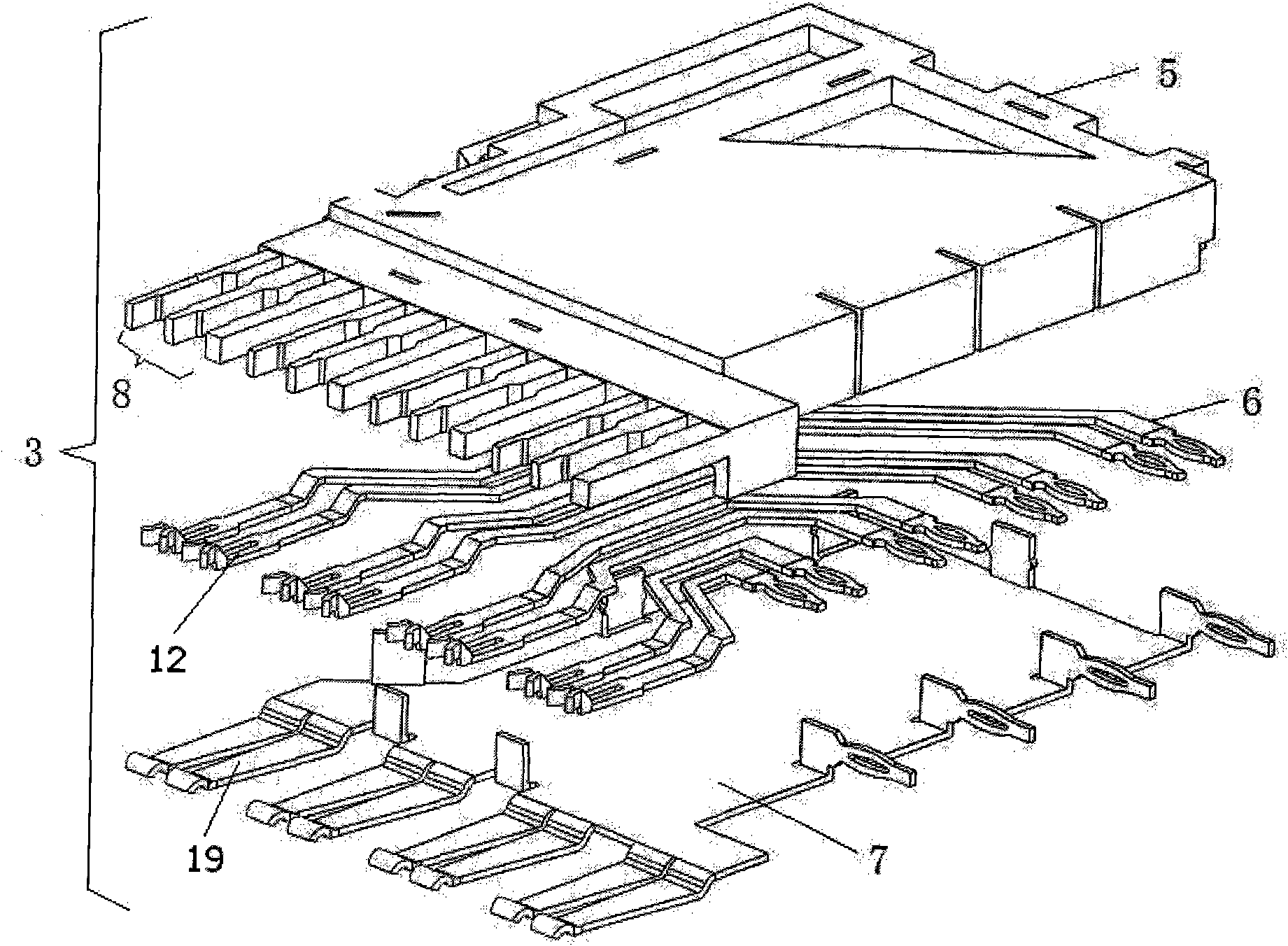

Signal connector

The invention provides a signal connector and relates to the field of data transmission. The signal connector includes a backplane connection portion and a daughter card connection unit. The backplaneconnection portion is provided with a first signal terminal pair and a first shielding sheet, and the daughter card connection unit is provided with a second signal terminal pair and a second shielding sheet. When the backplane connecting portion and the daughter card connecting unit cooperate with each other, the first signal terminal pair and the second signal terminal pair are joined one by one, and the first shielding sheet and the second shielding sheet can form a shielding cavity which coats the first signal terminal pair and the second signal terminal. Through the signal connector provided by the invention, the better shielding structure can be formed between transmission signals, the signal crosstalk can be reduced, and the signal integrity can be improved.

Owner:HUAWEI TECH CO LTD

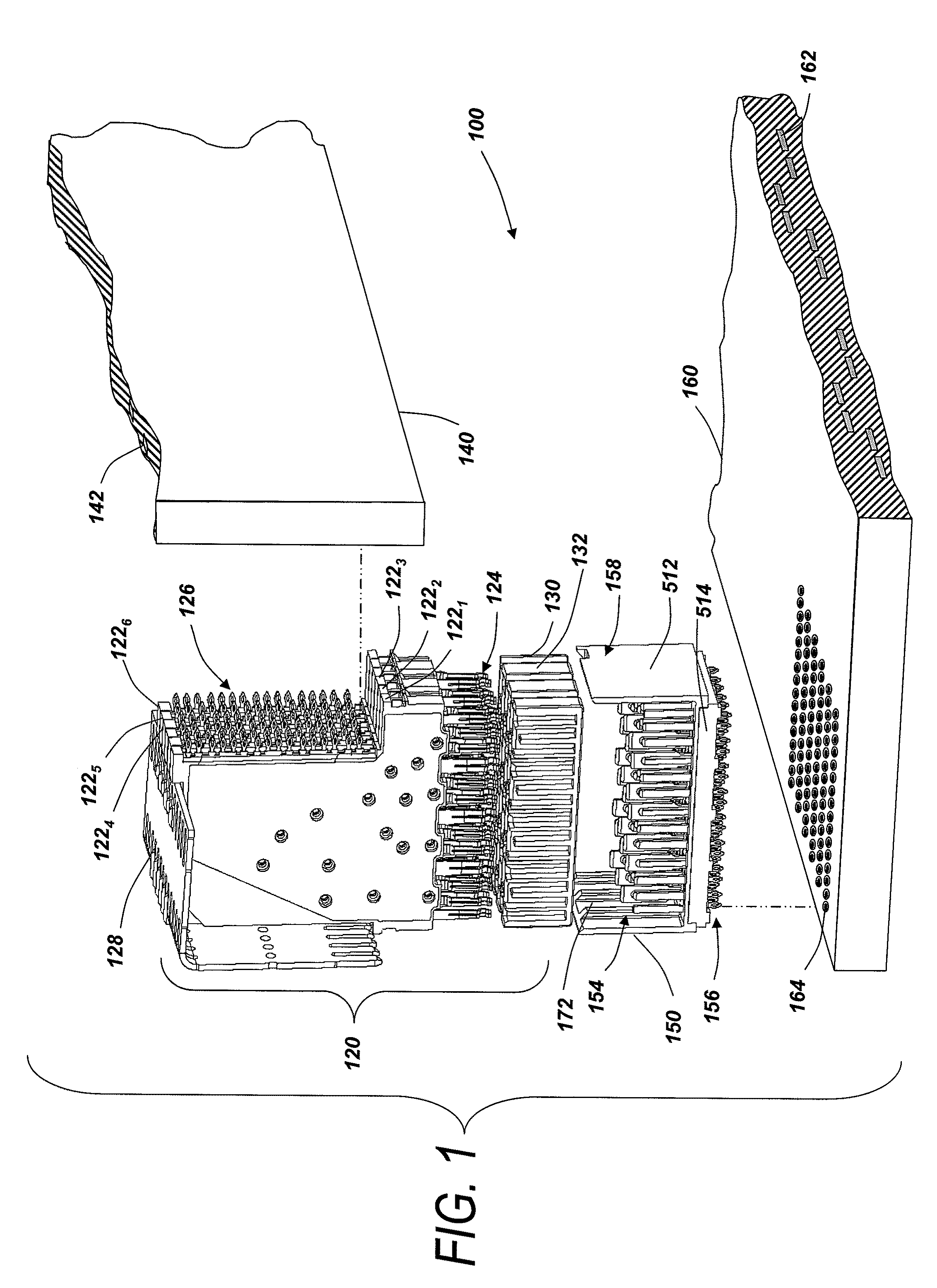

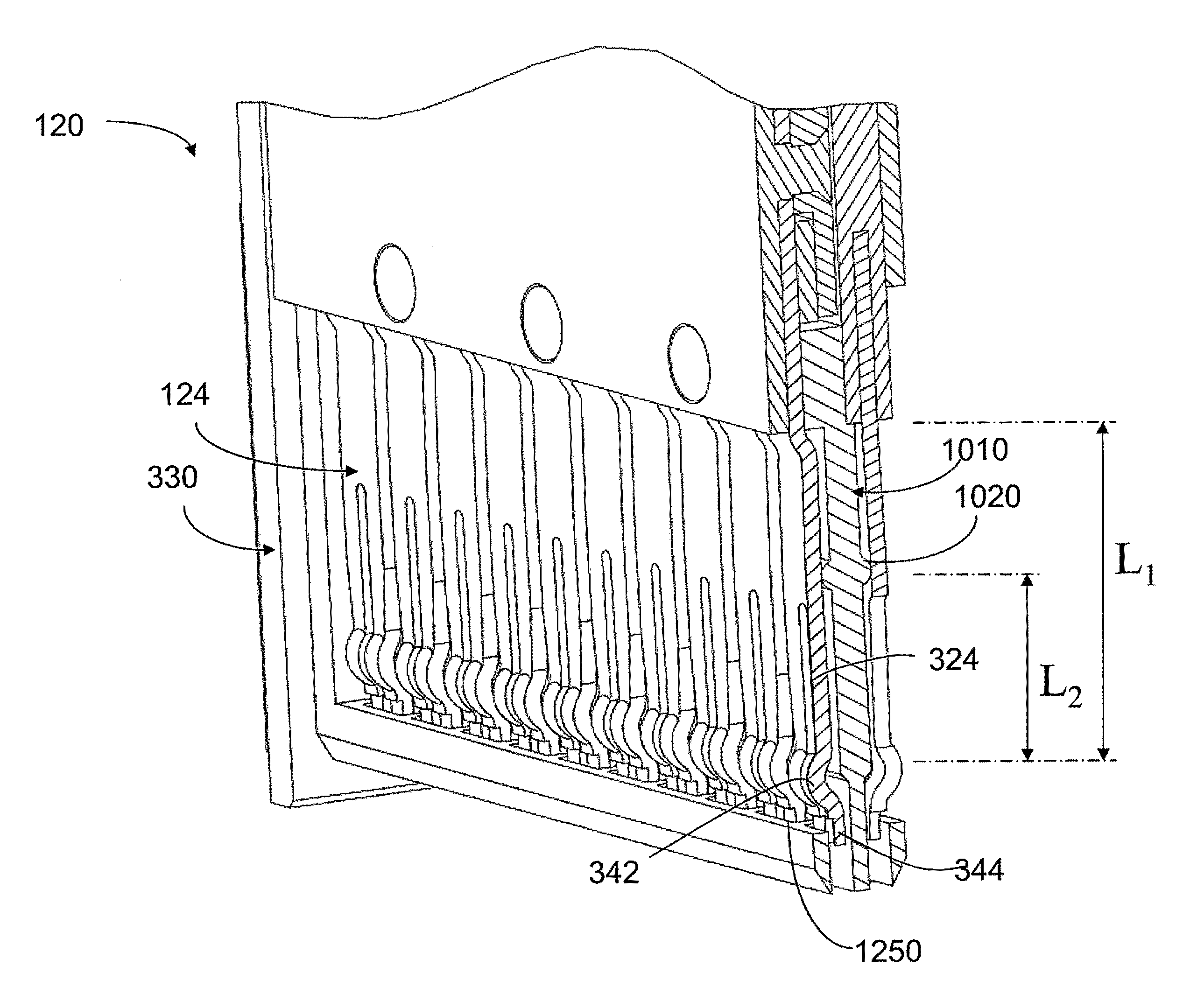

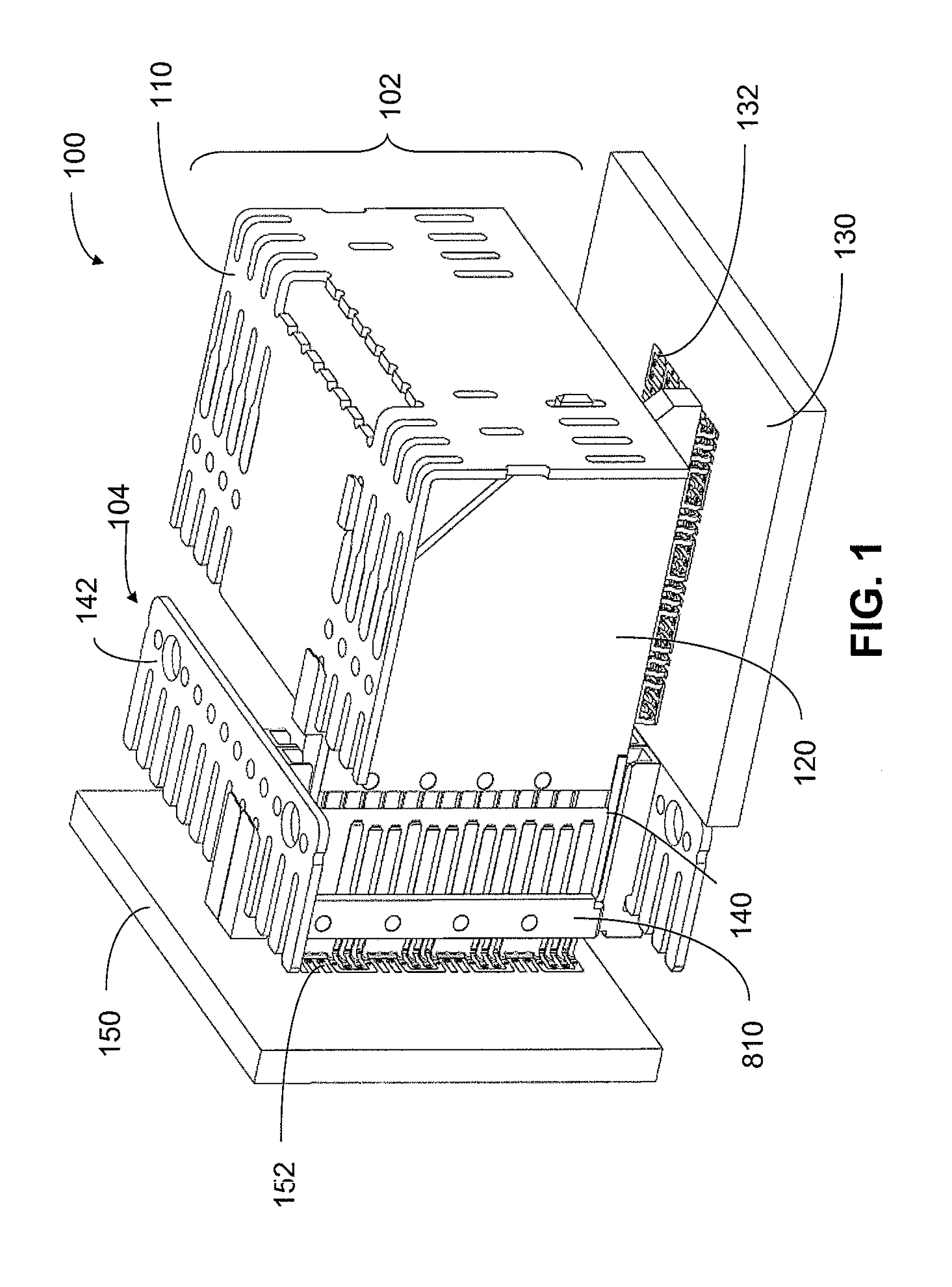

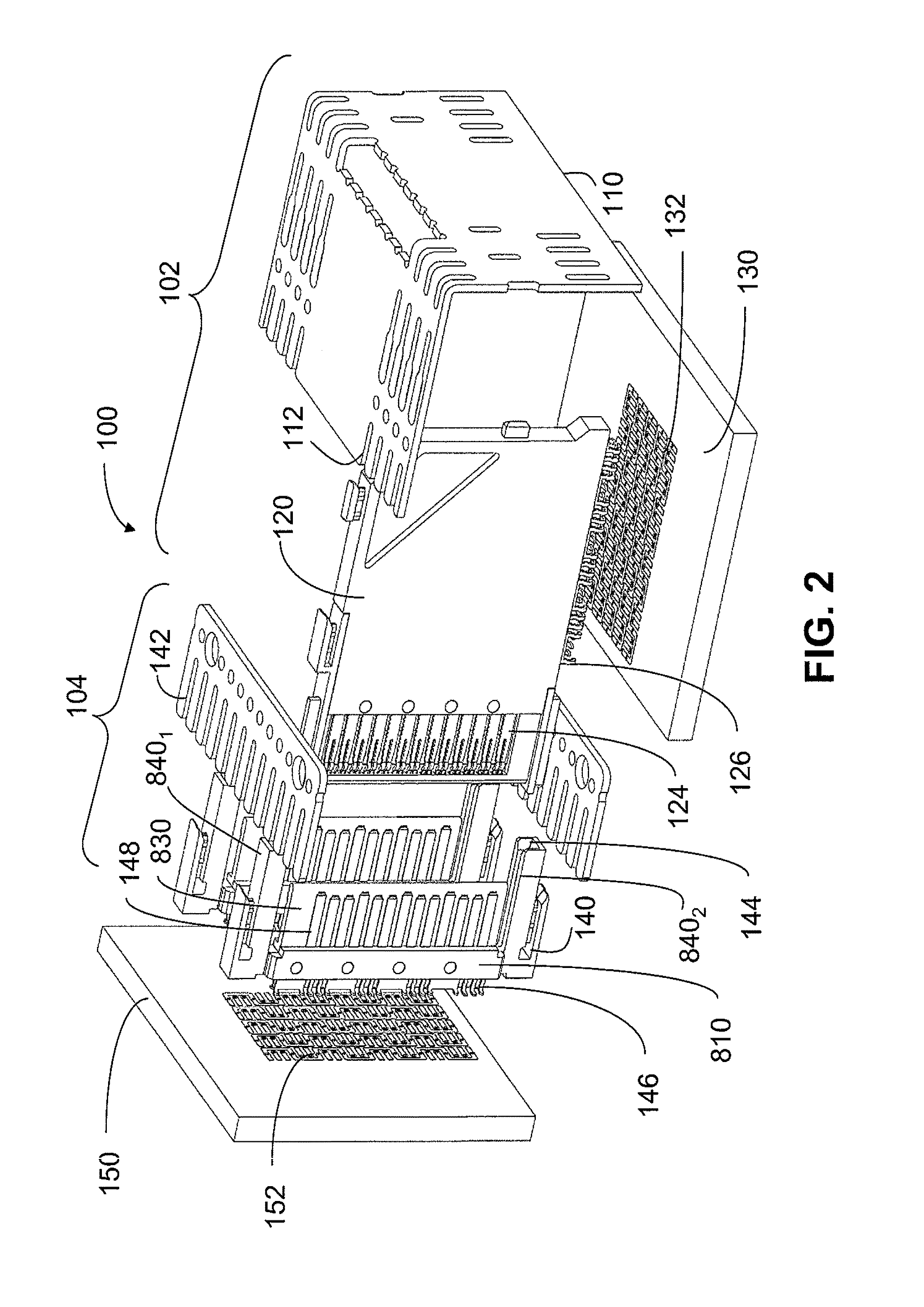

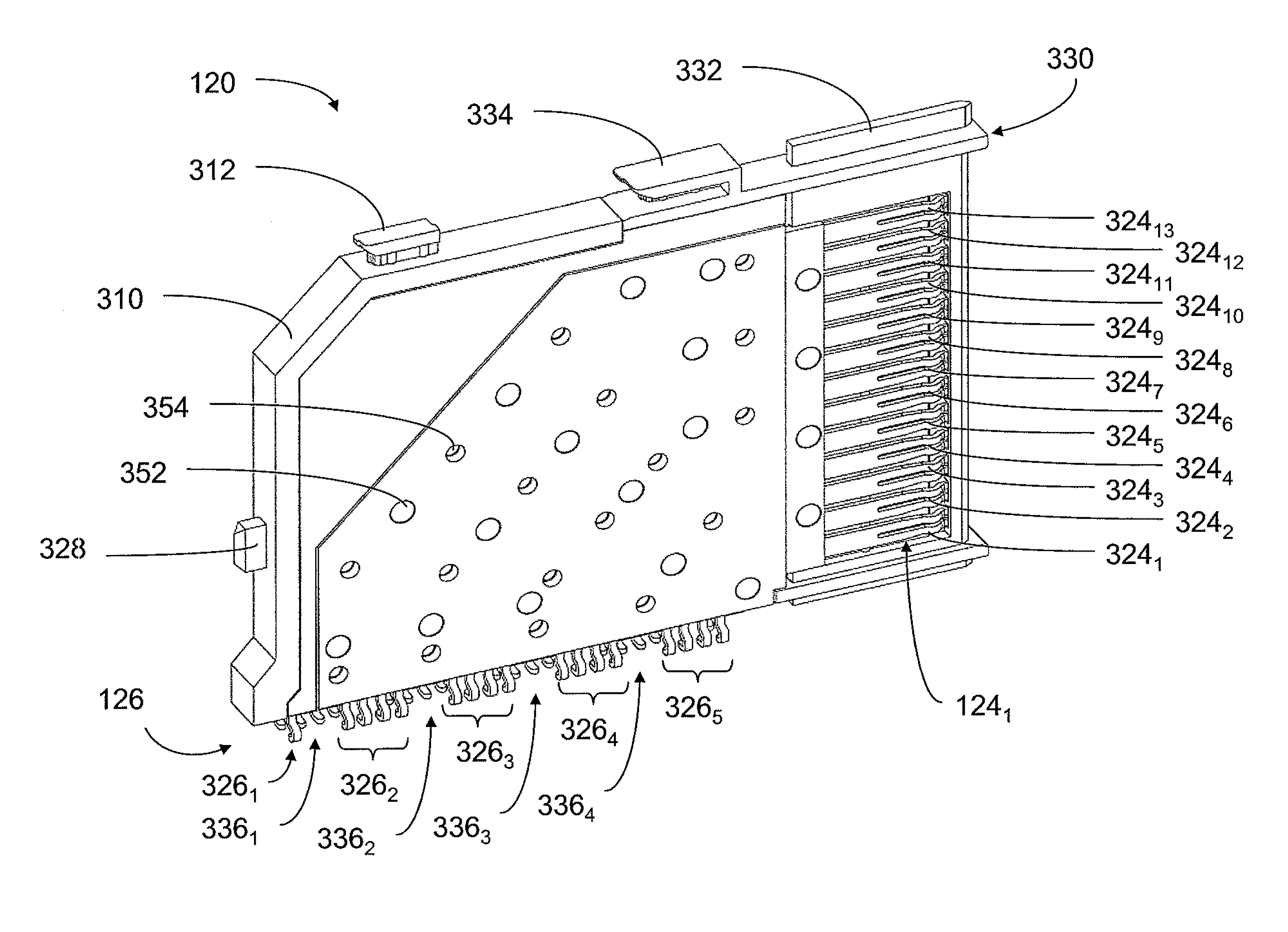

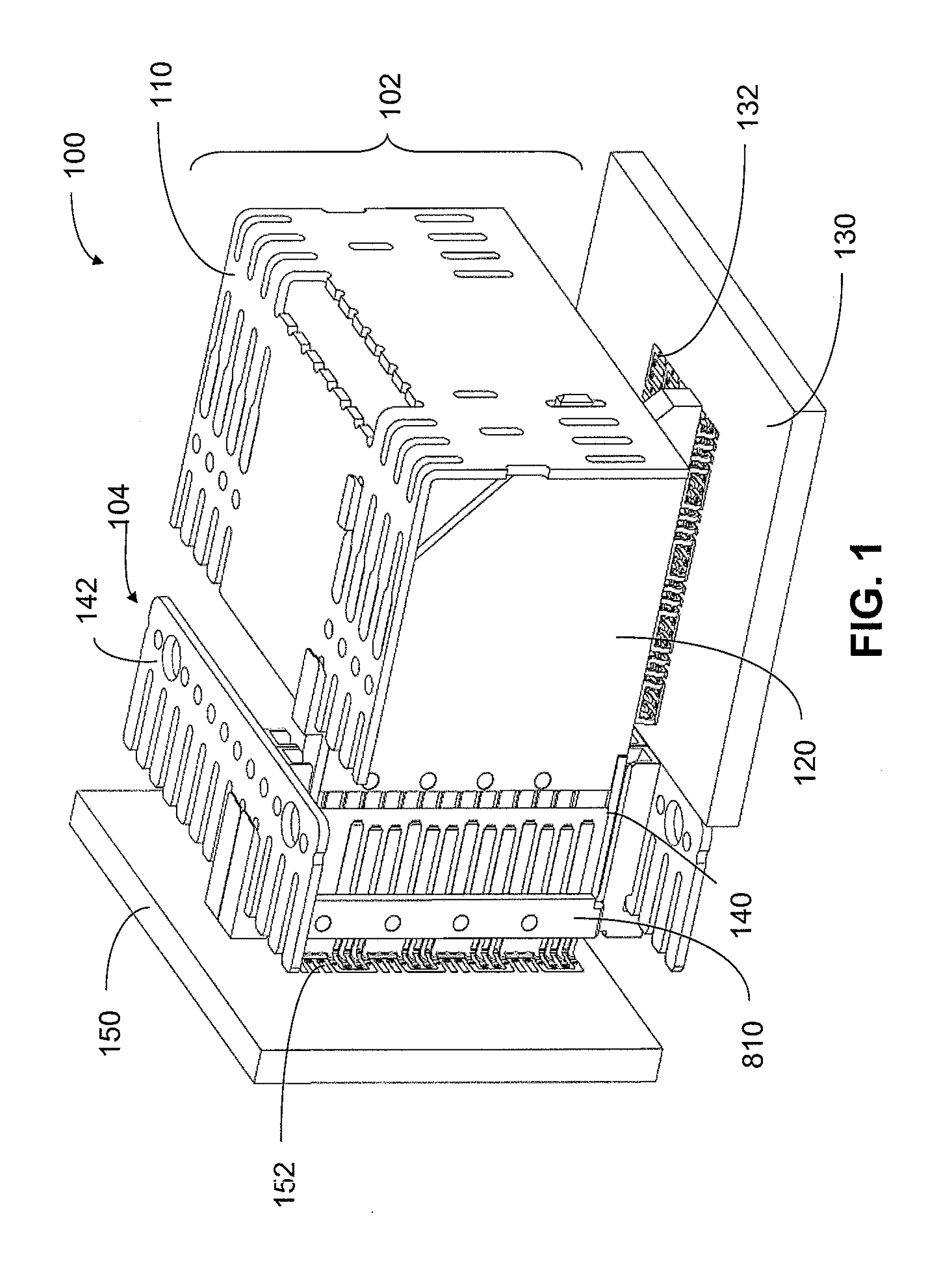

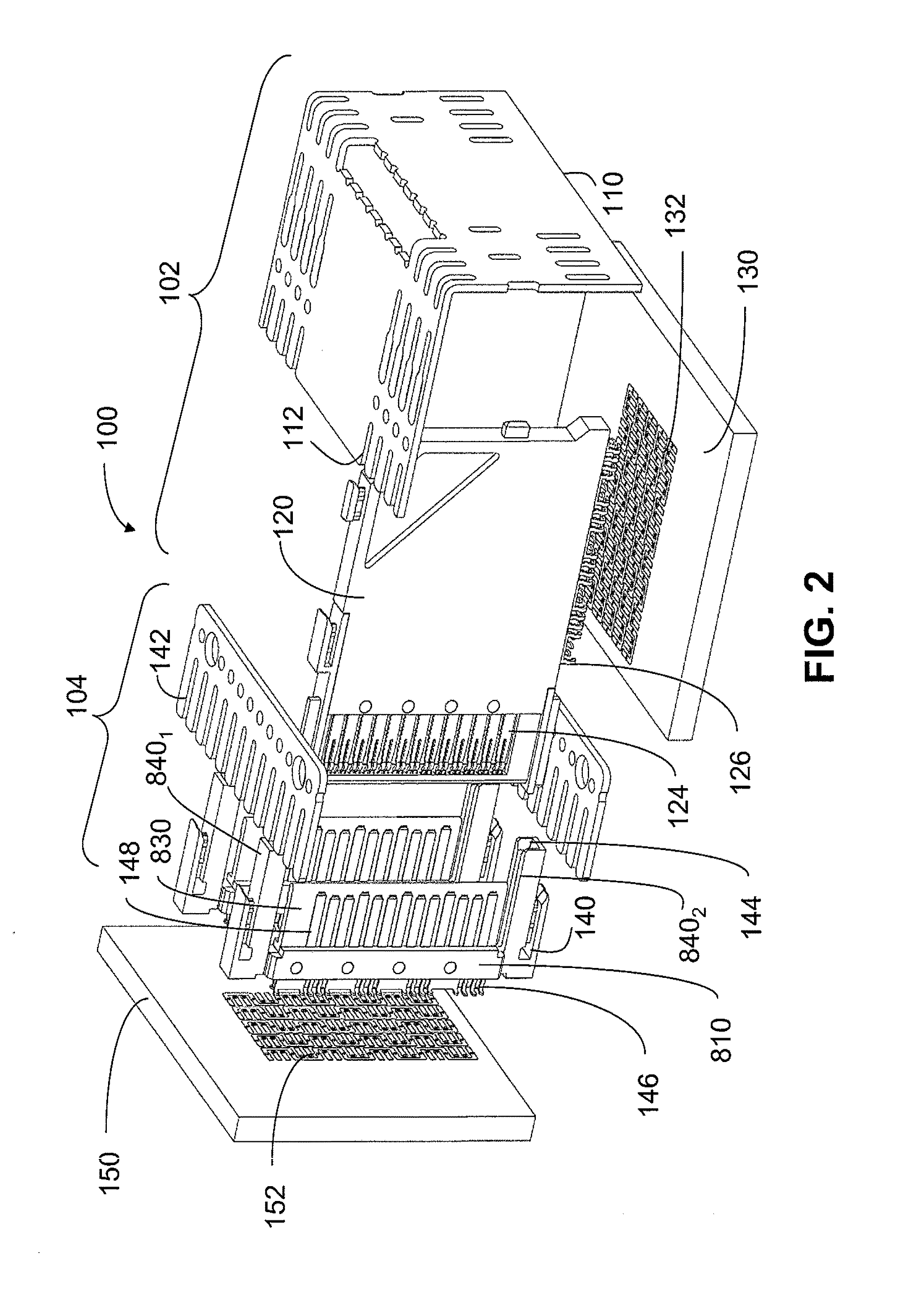

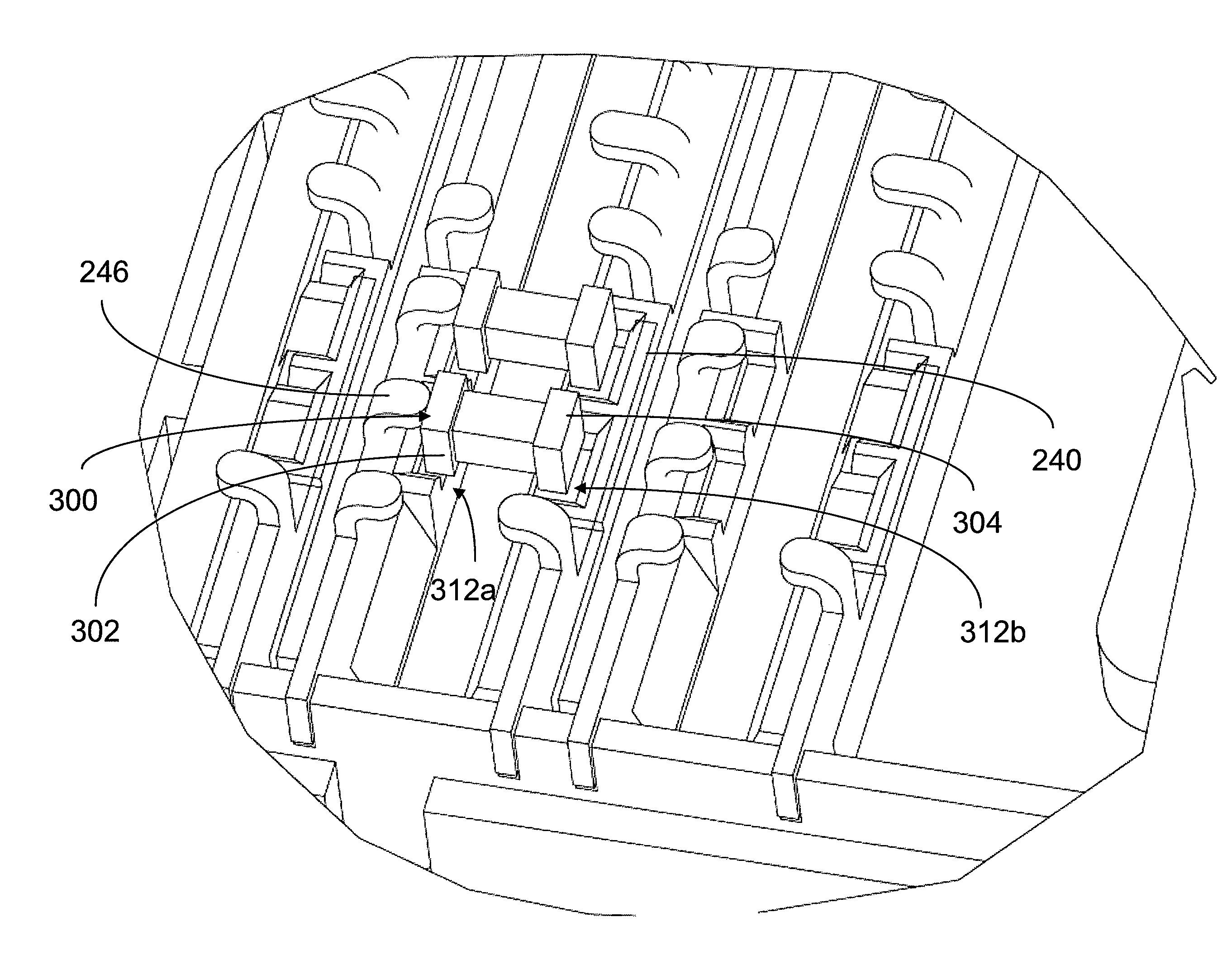

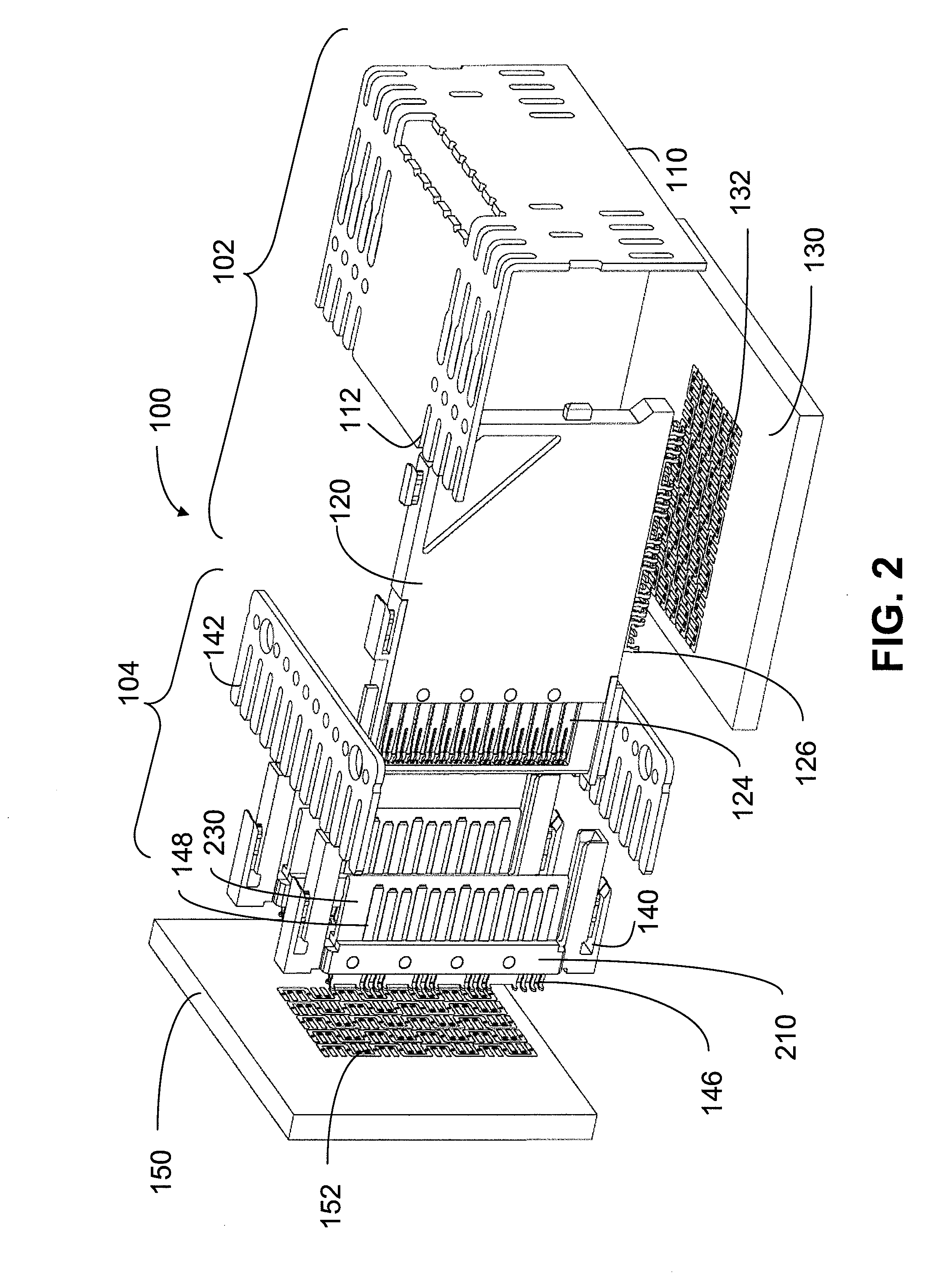

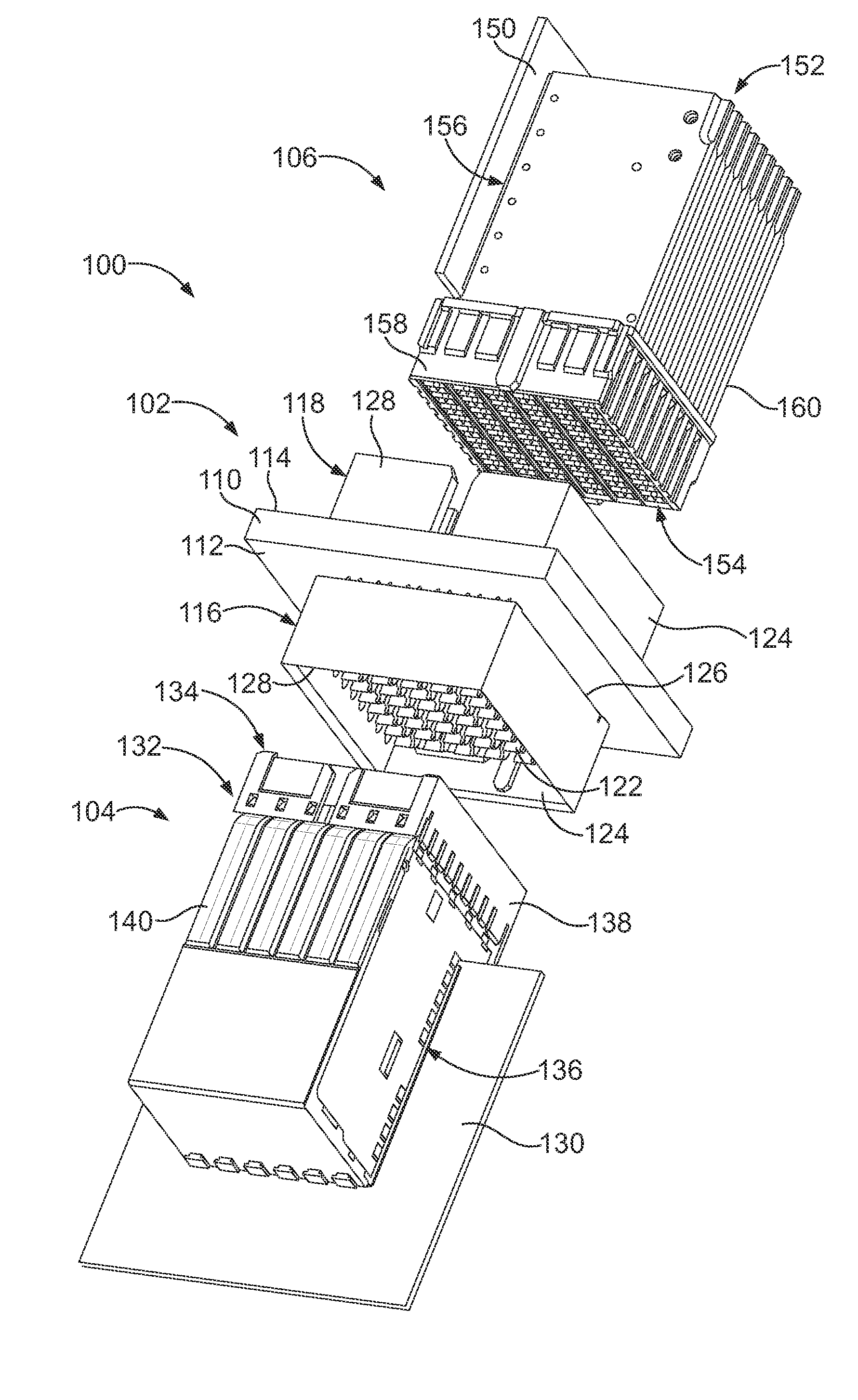

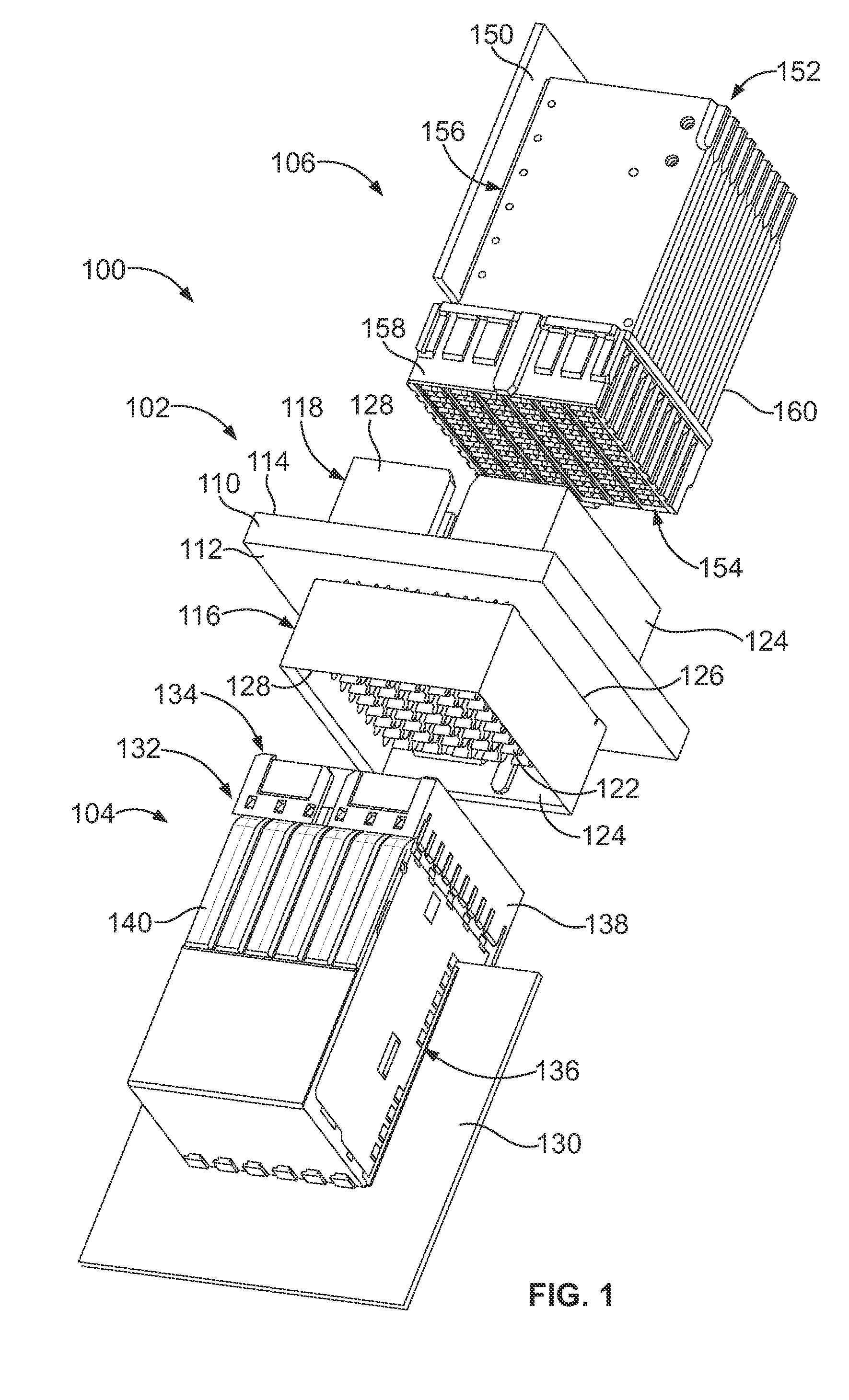

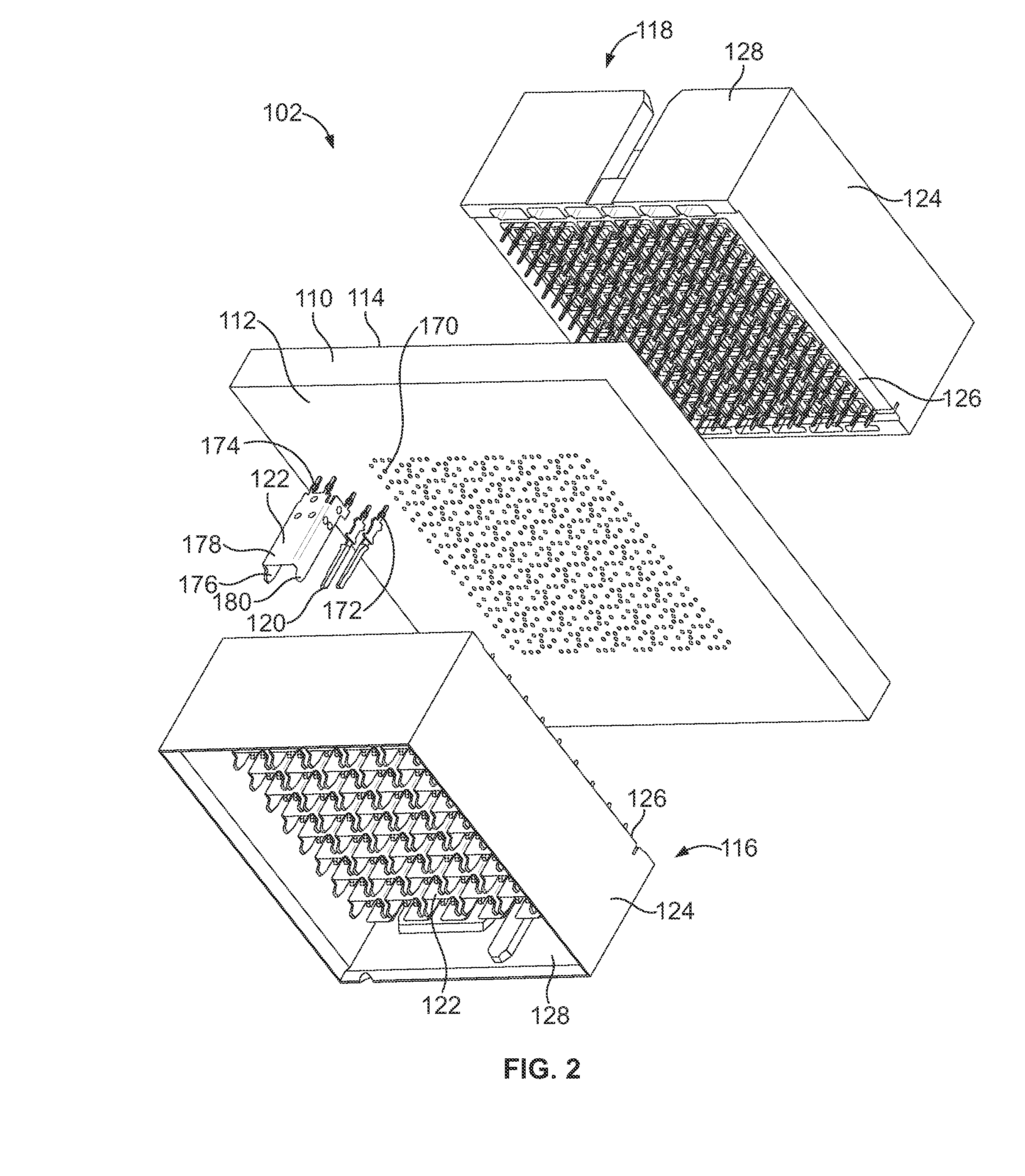

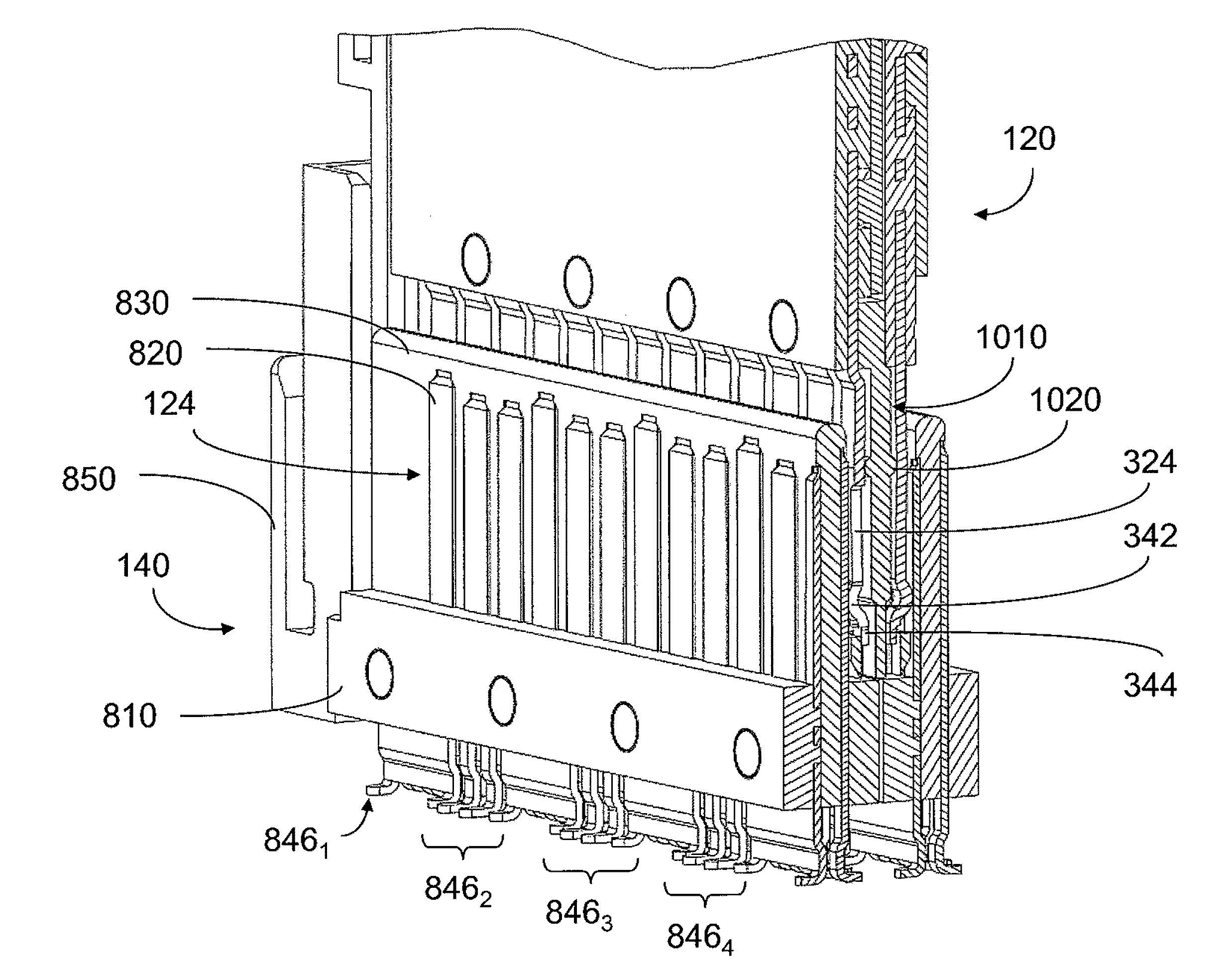

Receptacle assembly for a midplane connector system

ActiveUS20130288539A1High contact densityImprove signal integrityElectrically conductive connectionsCoupling device detailsEngineeringMechanical engineering

A receptacle assembly includes a contact module having a conductive holder and a frame assembly received in the conductive holder. The frame assembly includes a first frame and a second frame, each frame having at least two frame members each supporting a differential pair of receptacle signal contacts and being separated by a gap. The first and second frames are interested such that at least one frame member of the first frame is received in a corresponding gap of the second frame between frame members of the second frame and such that at least one frame member of the second frame is received in a corresponding gap of the first frame between frame members of the first frame.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

Standard cells having transistors annotated for gate-length biasing

InactiveUS20100169847A1Reduce impactImpairing time delay performance only linearlyCAD circuit designSpecial data processing applicationsSemiconductor chipAnnotation

A standard cell library is disclosed. The standard cell library contains cells wherein at least one transistor in at least one cell is annotated for gate length biasing. Gate length biasing includes the modification of the gate length, so as to change the speed or power consumption of the modified gate length. The standard cell library is one used in the manufacturing of semiconductor devices (e.g., that result as semiconductor chips), by way of fabricating features defined on one or more layouts of geometric shapes. The annotations serve to identify which ones of the transistor gate features are to be modified before using the geometric shapes for manufacturing the semiconductor device.

Owner:RPX CORP

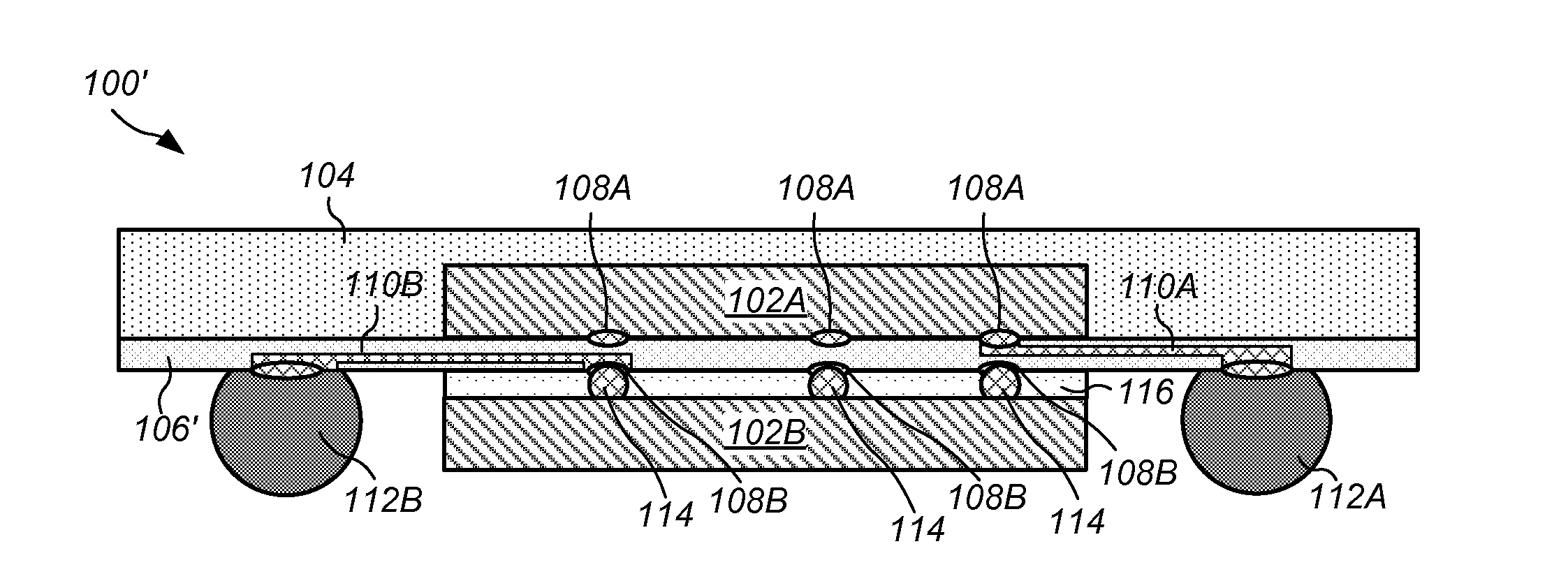

Stacked wafer DDR package

ActiveUS20140210107A1Reduce thicknessImprove power integritySemiconductor/solid-state device detailsSolid-state devicesConductive pasteRedistribution layer

A top package used in a PoP (package-on-package) package includes two memory die stacked with a redistribution layer (RDL) between the die. The first memory die is encapsulated in an encapsulant and coupled to a top surface of the RDL. A second memory die is coupled to a bottom surface of the RDL. The second memory die is coupled to the RDL with either a capillary underfill material or a non-conductive paste. The RDL includes routing between each of the memory die and one or more terminals coupled to the RDL on a periphery of the die.

Owner:APPLE INC

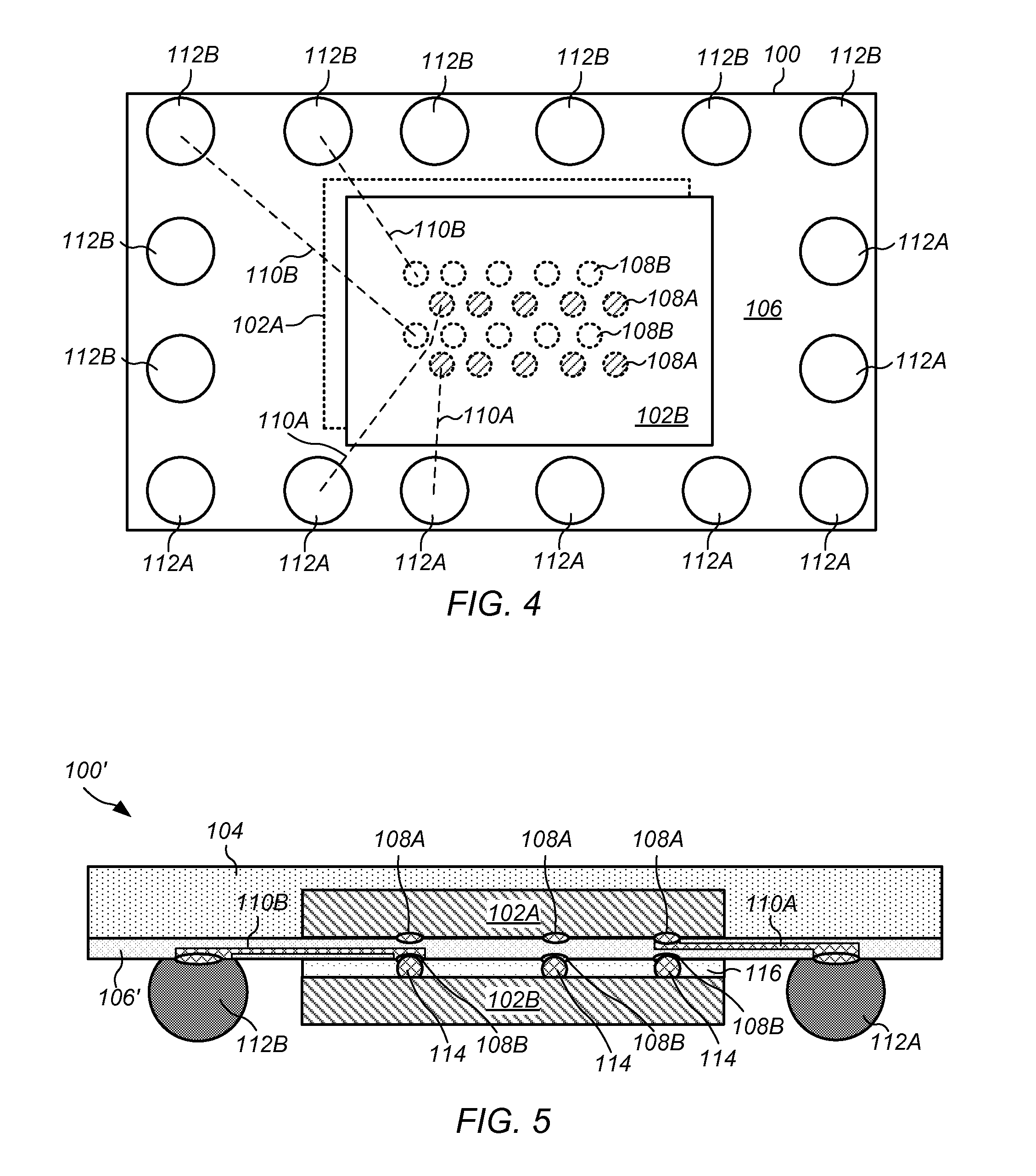

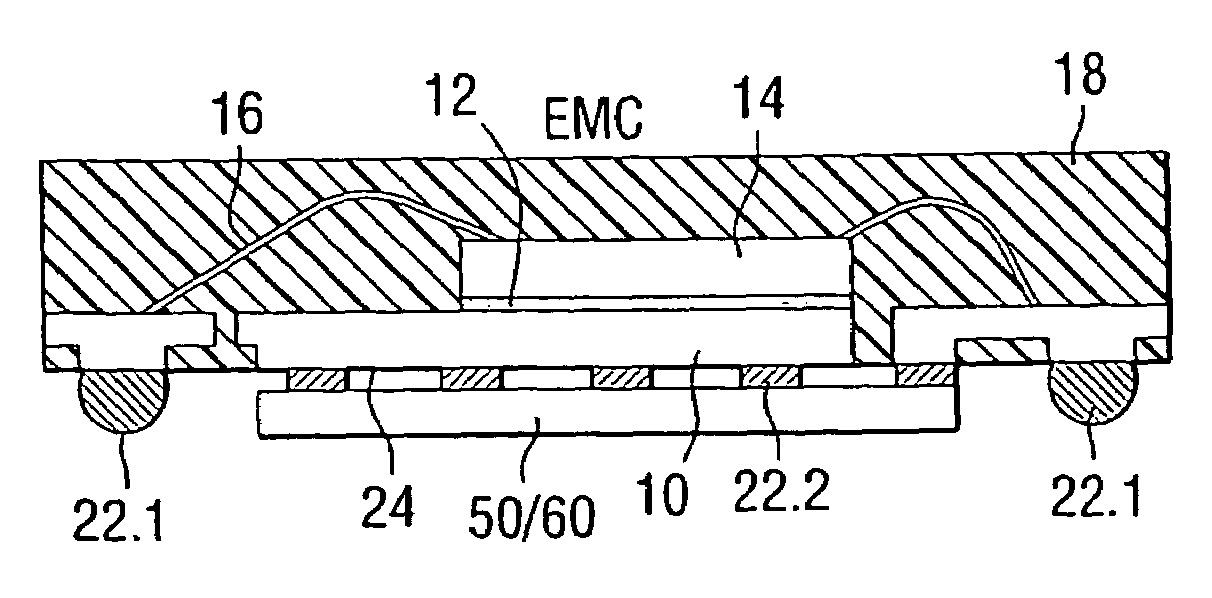

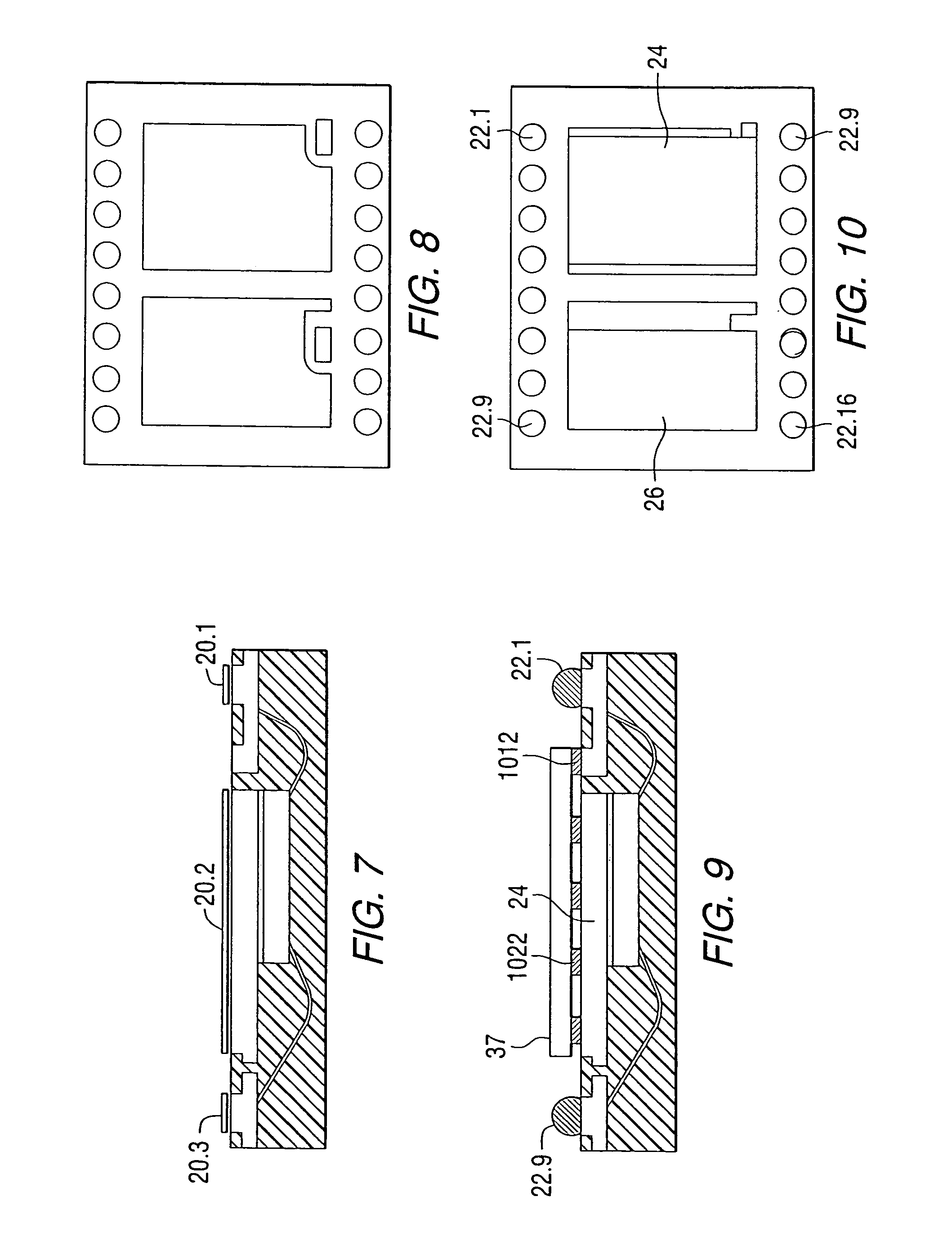

Multi-flip chip on lead frame on over molded IC package and method of assembly

InactiveUS7154186B2Improve signal integrityImprove interconnect densitySemiconductor/solid-state device detailsSolid-state devicesMOSFETIntegrated circuit

A multichip module package uses bond wire with plastic resin on one side of a lead frame to package an integrated circuit and flip chip techniques to attach one or more mosfets to the other side of the lead frame. The assembled multichip module 30 has an integrated circuit controller 14 on a central die pad. Wire bonds 16 extend from contact areas on the integrated circuit to outer leads 2.6 of the lead frame 10. On the opposite, lower side of the central die pad, the sources and gates of the mosfets 24, 26 are bump or stud attached to the half etched regions of the lead frame. The drains 36 of the mosfets and the ball contacts 22.1 on the outer leads are soldered to a printed circuit board.

Owner:SEMICON COMPONENTS IND LLC

High density electrical connector and PCB footprint

ActiveUS20110212632A1Good signal integrityMechanically robustTwo-part coupling devicesElectrical connection printed elementsMechanical integrityPrinted circuit board

An interconnection system that includes a daughter card and backplane electrical connectors, each mounted to a printed circuit board at a connector footprint. The backplane connector has conductive elements with transition regions that allow the mating contact portions to be positioned on a uniform pitch while contact tail portions can be shaped to improve signal integrity or to provide a more compact and / or mechanically robust footprint. The conductive elements in both connectors are configured such that the contact tails of the ground conductors align from column to column, but the planar portions of the ground conductors in one column align with a pair of signal conductors in the other column, which improves mechanical and signal integrity. Mechanical integrity may be improved by forming the connector footprints with pads for the ground conductors that span multiple columns.

Owner:AMPHENOL CORP

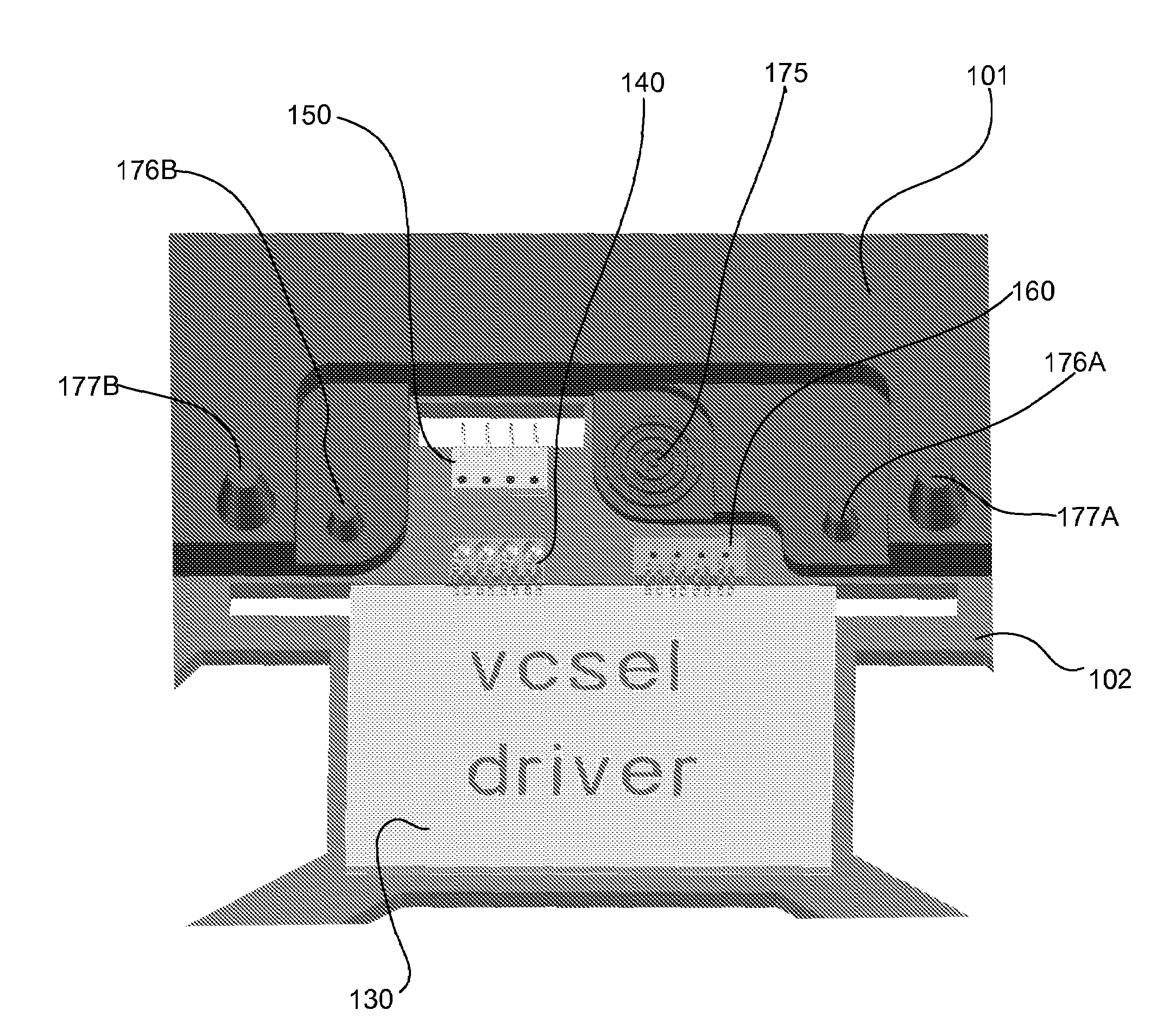

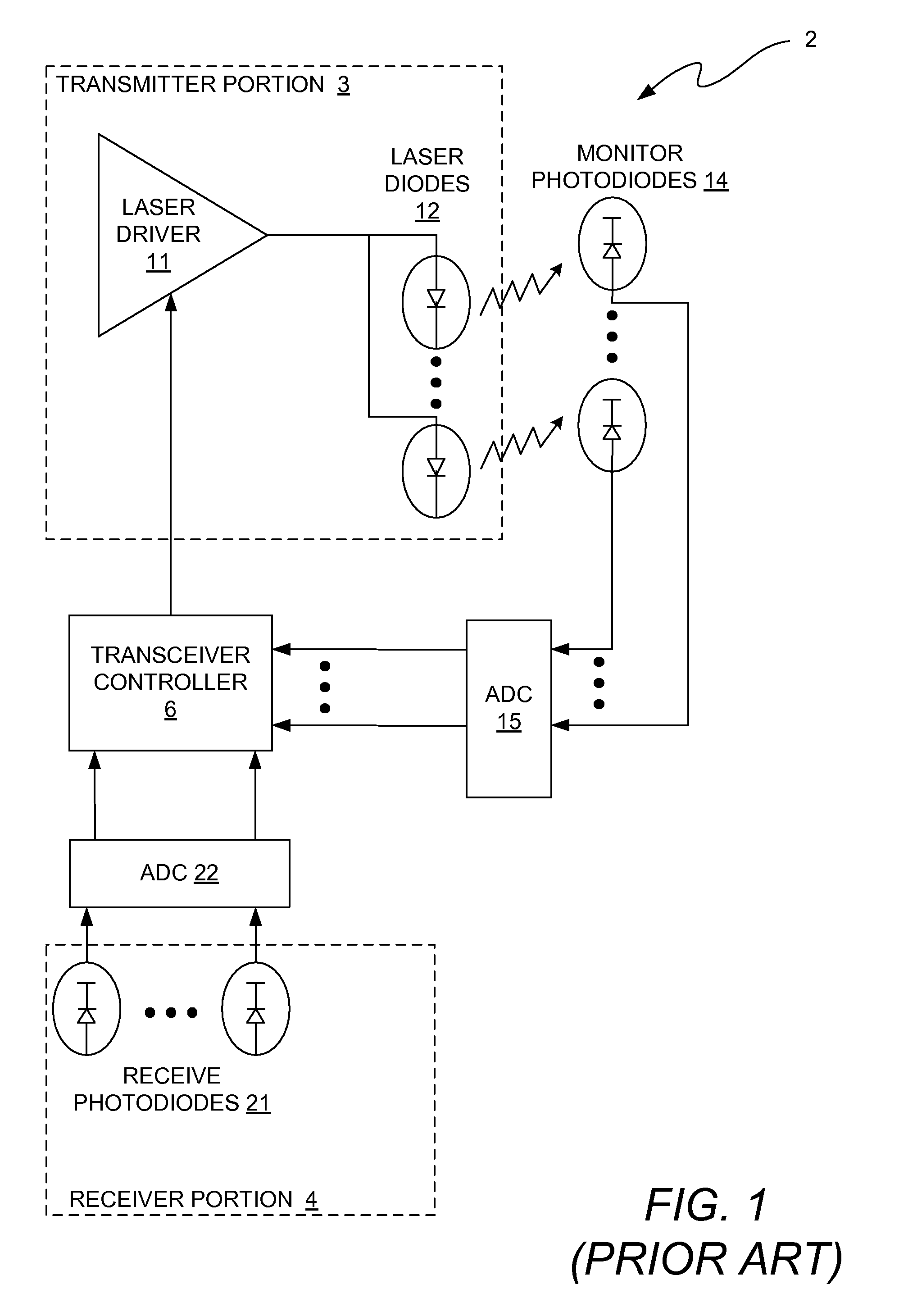

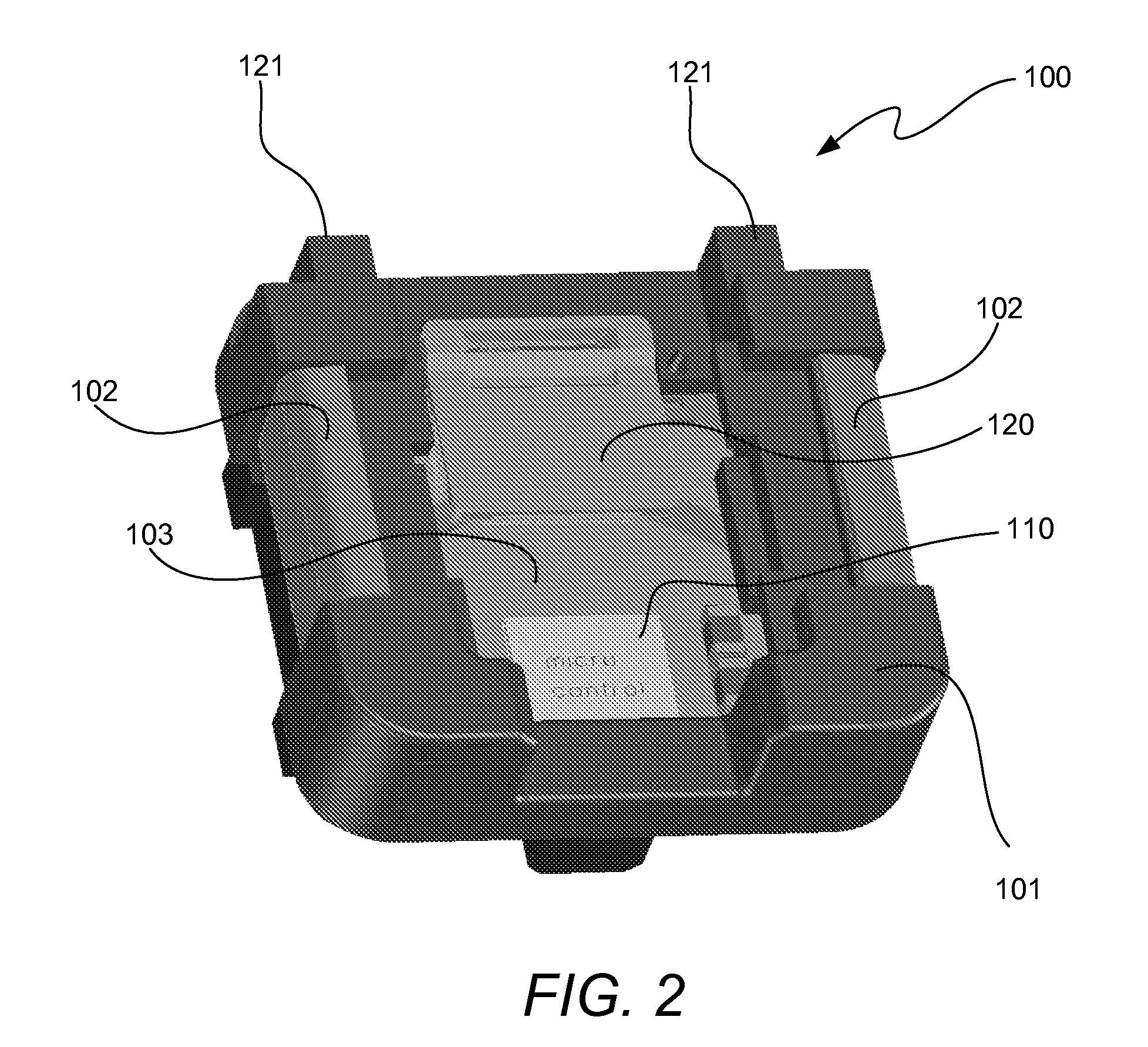

Transceiver module for optical communications and method for transmitting and receiving data

InactiveUS7331720B1Reduce inductanceImprove signal integrityCoupling light guidesMountingsTransceiverContact pad

A transceiver module for optical communications is provided in which the leadframe assembly includes at least first and second die attach regions to which the laser diode driver IC and the laser diode IC are secured, respectively. A slot formed in the leadframe between the first and second die attach regions provides an air gap that at least partially thermally isolates the laser diode IC from the laser diode driver IC. This air gap results prevents heat generated by the laser diode driver IC from appreciably affecting the temperature of the laser diode IC, and thus from detrimentally affecting the performance of the laser diode IC. This slot also allows contact pads of the laser diode IC to be directly connected by leads to contact pads of the laser diode driver IC, which reduces the lengths of the leads and thus their inductances, which prevents EMI problems from occurring.

Owner:AVAGO TECH INT SALES PTE LTD

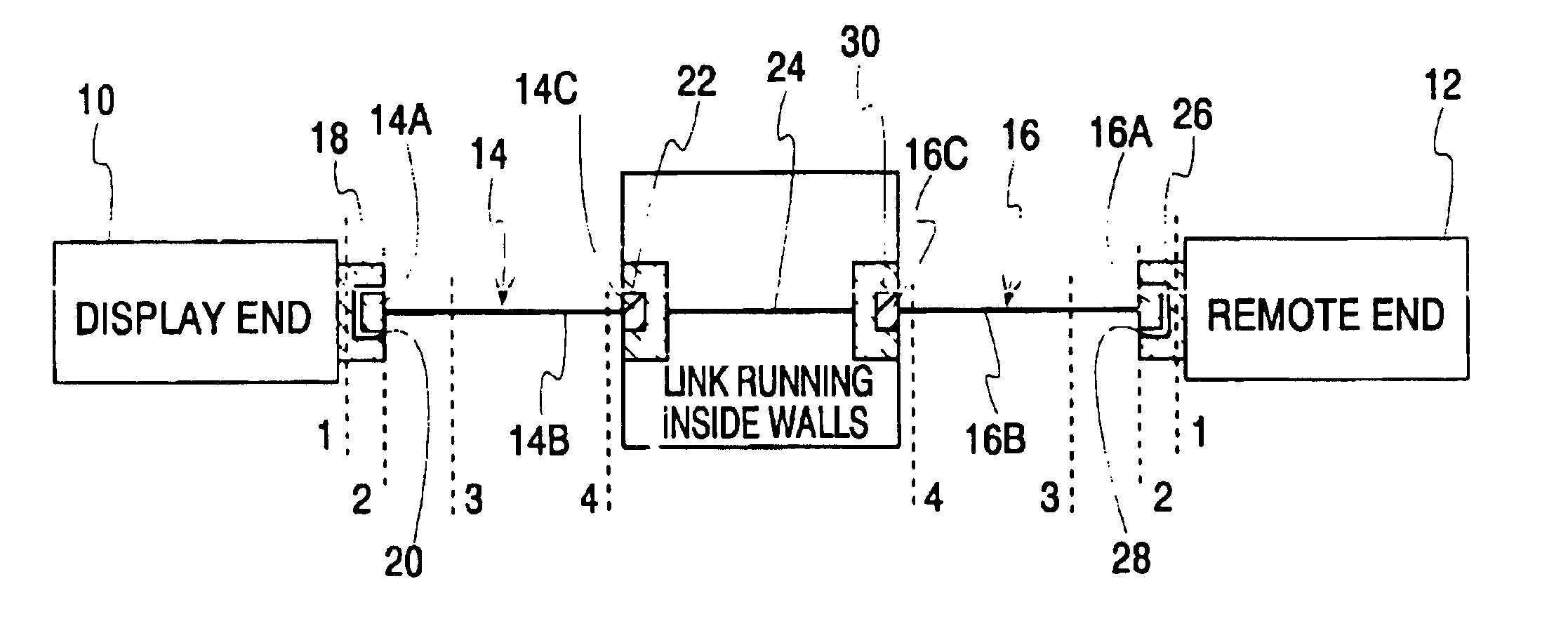

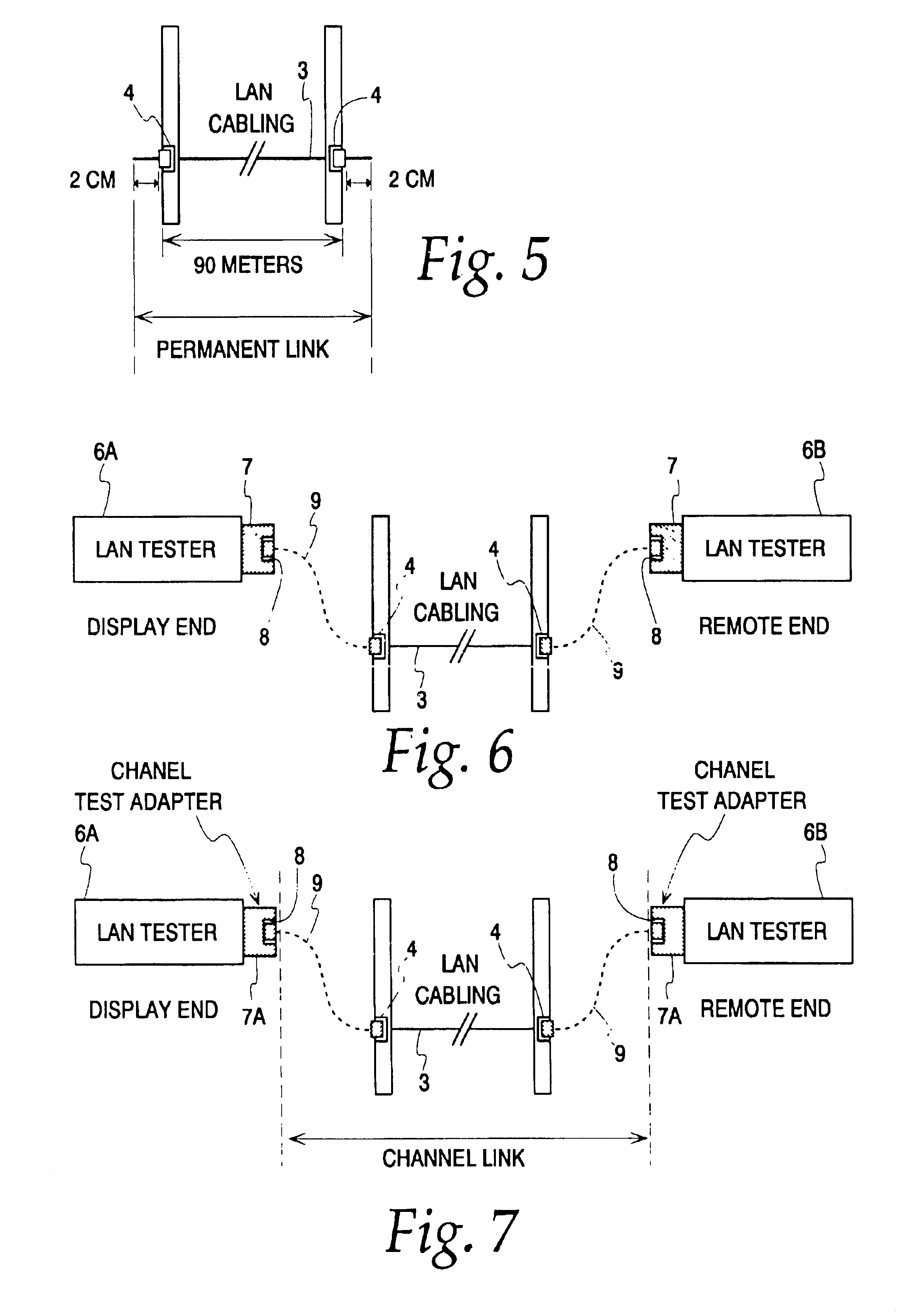

Hand-held tester and method for local area network cabling

InactiveUS6847213B2Low costReduce LAN measurement overhead support costsCurrent/voltage measurementResistance/reactance/impedenceTester deviceDisplay device

A LAN tester has display and remote units each having a connector jack attached to an adapter board for connection to the plug of a patch cord. Both the display and remote units have circuits which are capable of measuring the phase between a drive signal voltage and the corresponding coupled or reflected signal due to the drive signal. Scattering parameters for the mated connector pairs and the patch cord itself are measured during a field calibration. A computer in one or both of the tester units stores the measured scattering parameters and uses the scattering parameters to move the reference plane to any desired location along the patch cord. Channel link or permanent link tests can be conducted using the same equipment.

Owner:IDEAL IND NETWORKS LTD

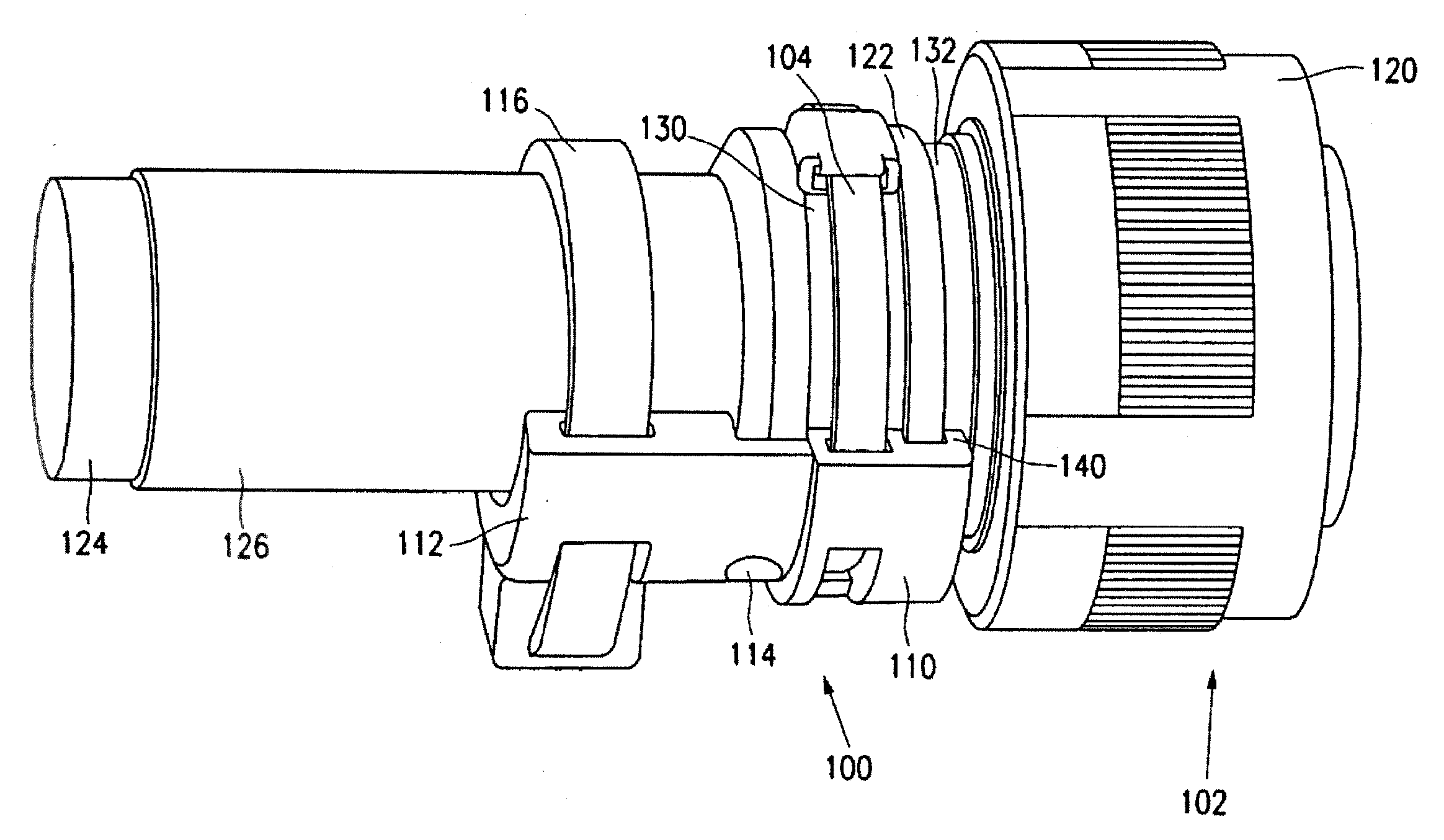

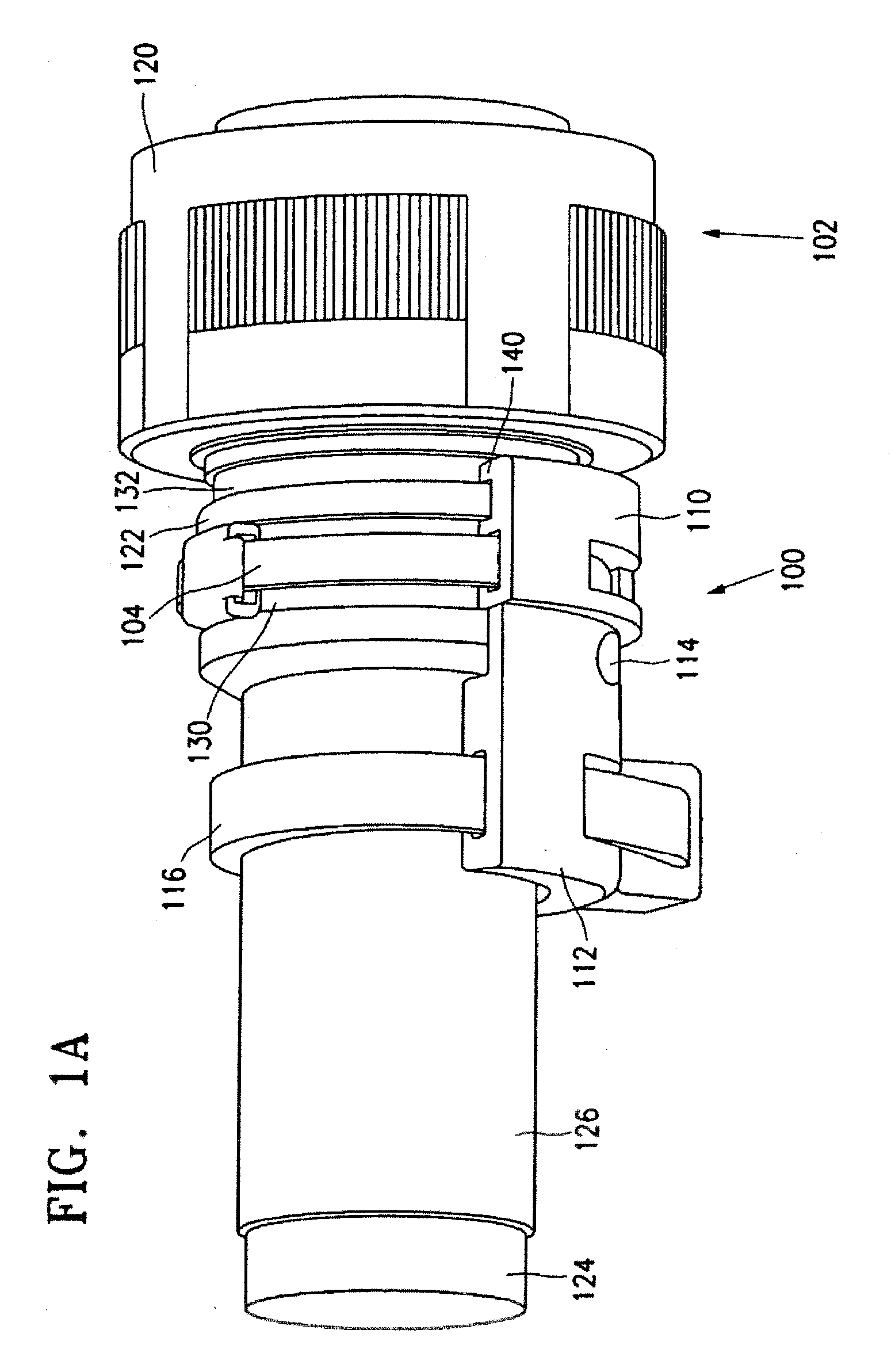

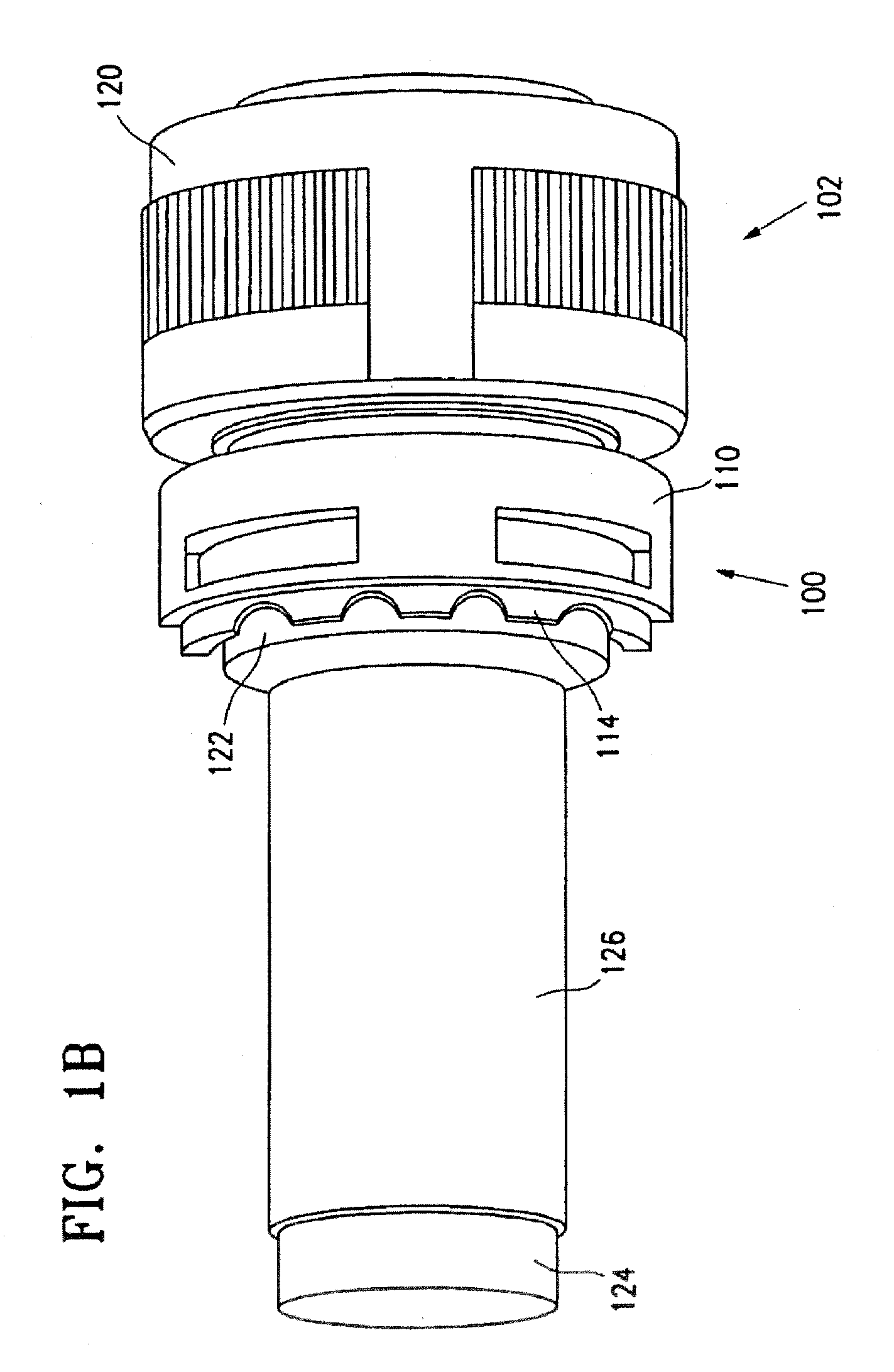

Backshell device for a connector

ActiveUS20080009173A1Strain relief to the wiring harnessProvide strain reliefRelieving strain on wire connectionCoupling contact membersEngineeringMechanical engineering

A backshell device and assembly are provided for achieved improved signal integrity, wherein the design of the backshell device is less complicated, more light weight, and easier to build and use than existing devices. In one embodiment, the backshell device can be coupled to adaptor which is coupled to a connector. The backshell device generally comprises a mounting section coupled to the adaptor, and an extension section extending from the mounting section. The extension section preferably comprises an increased-diameter section configured to accommodate a non-staggered or aligned arrangement of a plurality of solder sleeves of the wiring harness.

Owner:DEUT ENGINEERED CONNECTING DEVICES

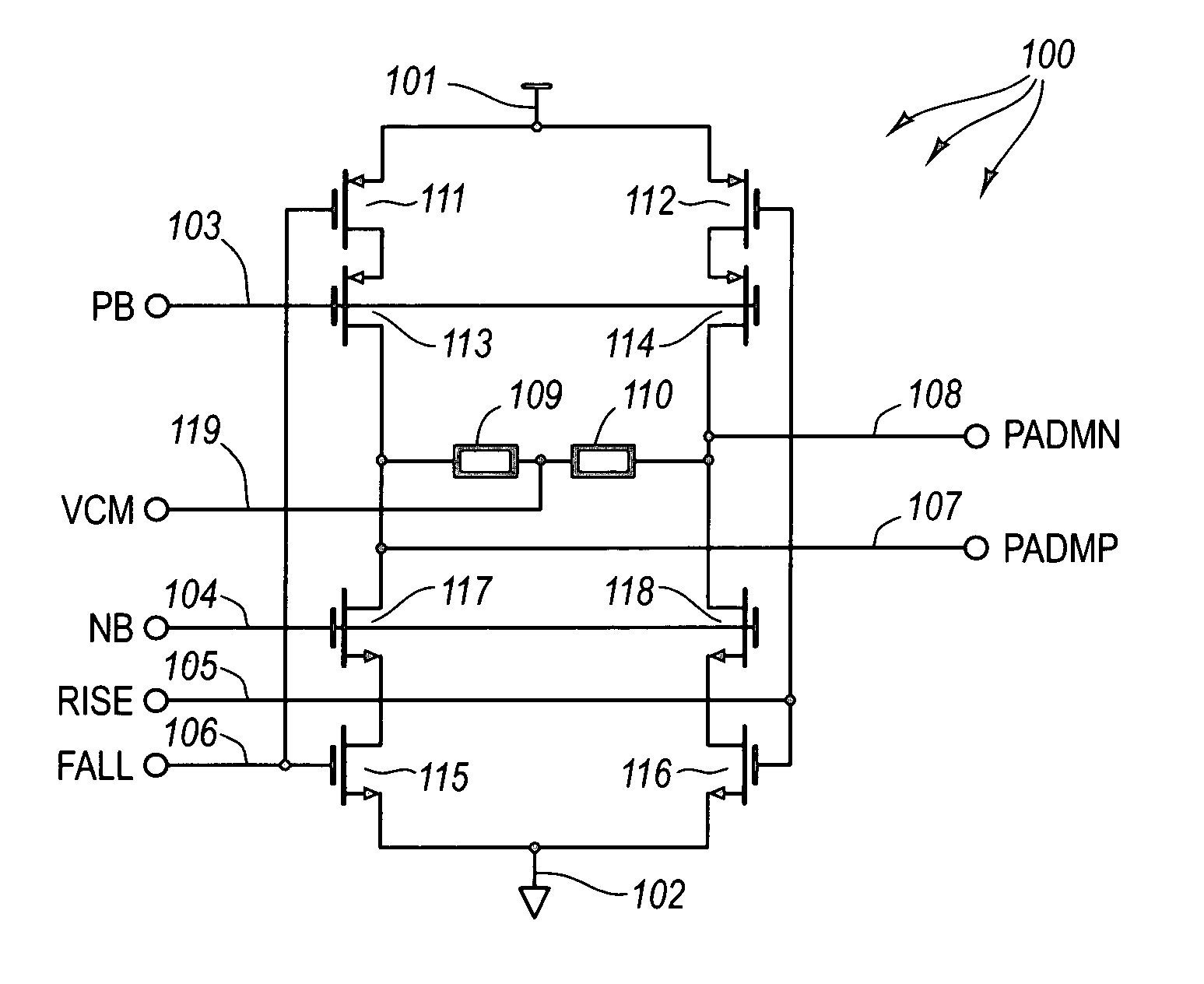

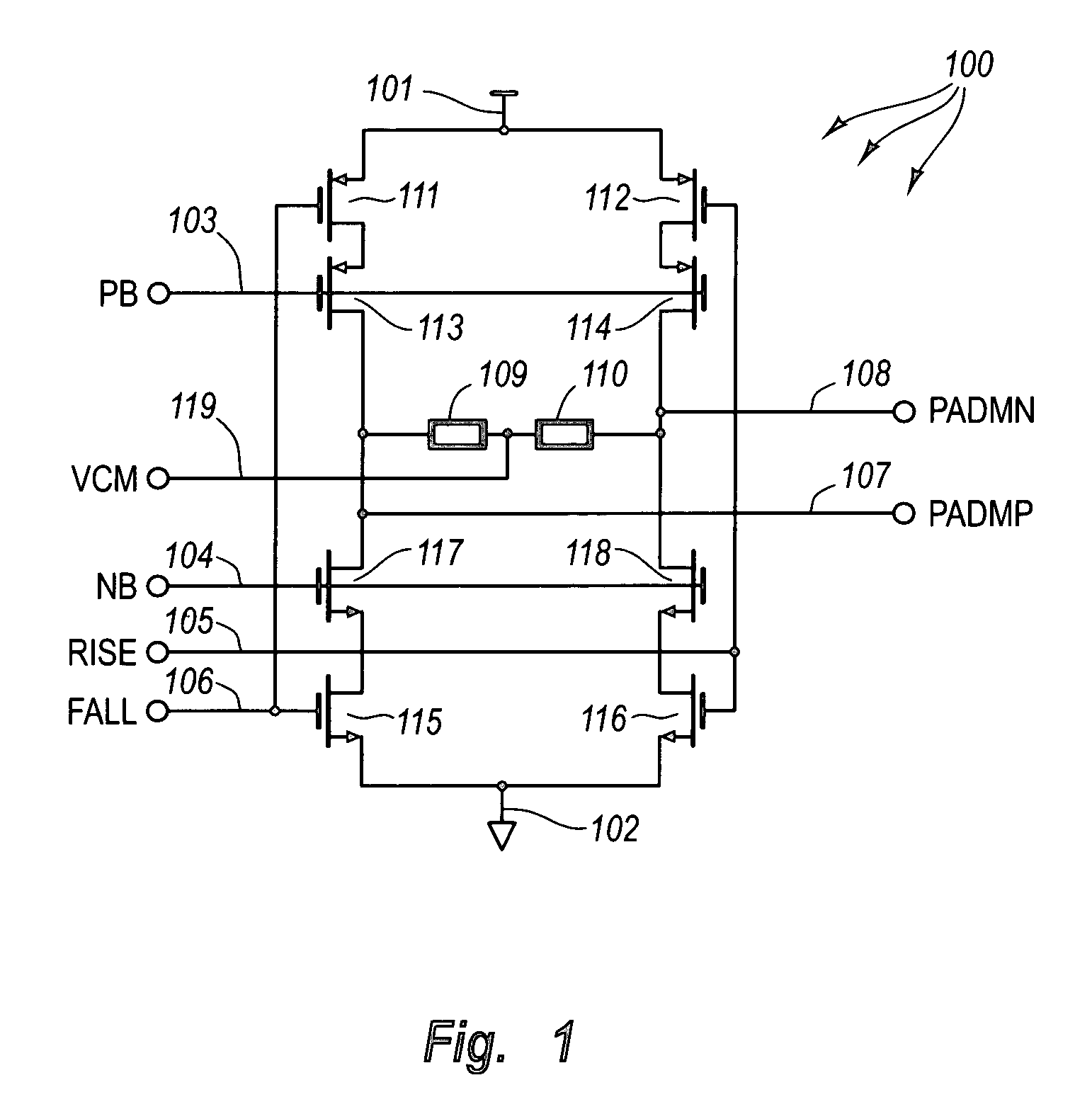

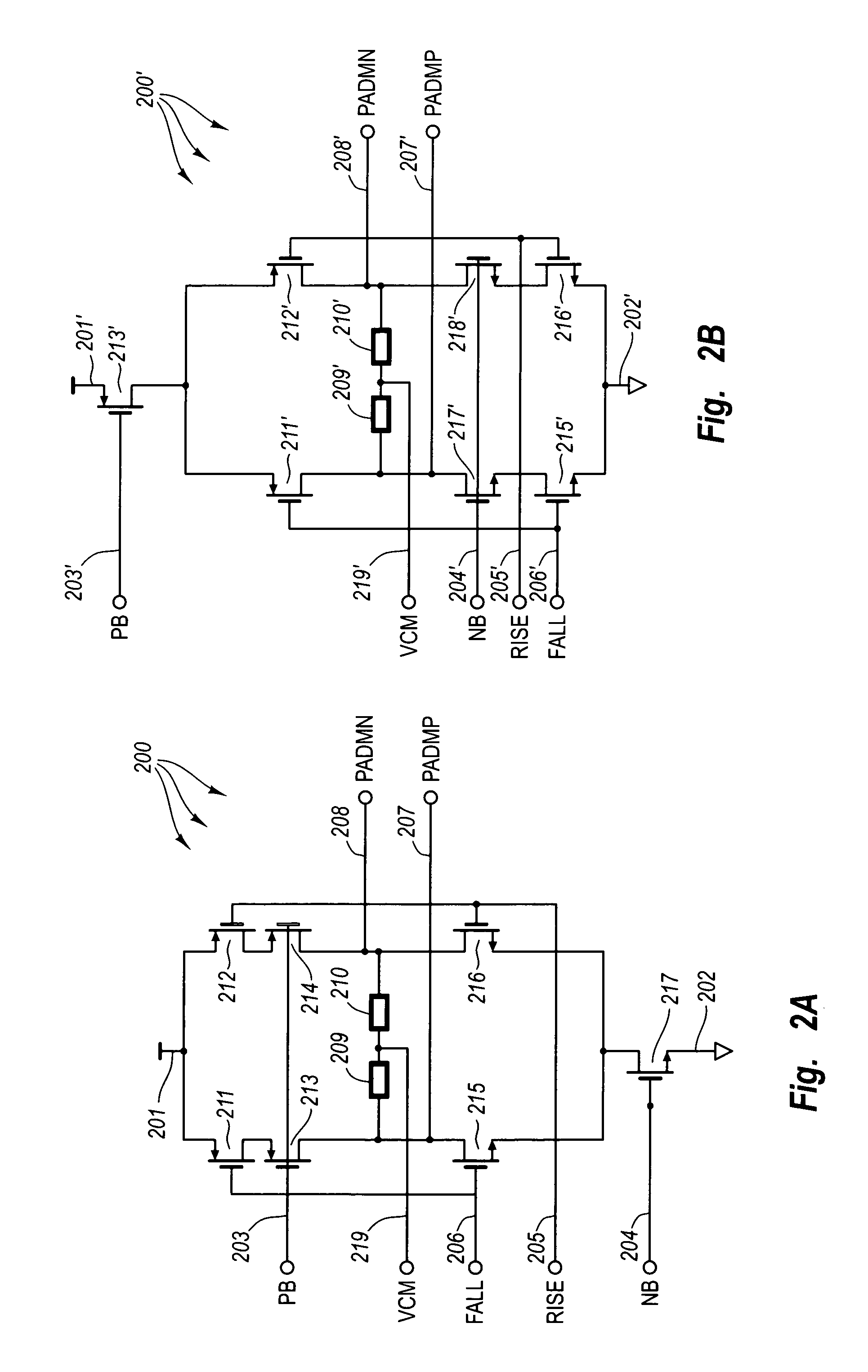

Low-voltage differential signal (LVDS) transmitter with high signal integrity

ActiveUS7034574B1Overcome problemsImprove signal integrityTransmission line coupling arrangementsLogic circuit coupling/interface arrangementsDriver circuitCapacitance

A differential signal output driver circuit having four switching transistors and having a bias transistor that shields each of the switching transistors from the corresponding output terminal thereby blocking the Miller capacitance of the switching capacitor from generating overshoot or undershoot in the output differential voltage. Also, the output driver circuit may be driven by a differential skew cancellation circuit that generates a balanced differential signal to drive the switching transistors to further improve signal integrity. The signal path for generating each signal in the differential signal goes through a similar structure thereby ensuring similar slew in each differential signal provided to the output driver circuit.

Owner:SEMICON COMPONENTS IND LLC

Connector socket capable of protecting jack terminal

InactiveCN102088148ASo as not to damageHigh strengthCoupling device detailsEngineeringMechanical engineering

The invention relates to a connector socket capable of protecting a jack terminal, wherein the socket comprises a module base and m jack modules, wherein the jack modules are composed of jack bases, jacks and jack shielding plates; one end of the jack base is provided with n plugs which are arranged in order; each plug is composed of two side columns and a central column disposed between the two side columns; the gaps formed among the two side columns and the central column are used for containing the jack terminal on the jack; and the outlines of the two side columns, the central column and the jack terminal within the plug are linear; the module base comprises n*m plug cavities which are used for installing n*m plugs and jack terminals contained in the plugs, wherein each plug cavity isinternally provided with a side wall and a central wall, and the plug and the jack terminal are arranged in the cavity between the side wall and the central wall. The connector socket capable of protecting a jack terminal provided by the invention has the advantages that the jack modules can be prevented from damaging while assembling by providing the plugs which are used for protecting the jacks, the jack bases and the jacks are integrated by means of injection molding, and the production and assembly efficiencies are improved.

Owner:CHINA AEROSPACE TIMES ELECTRONICS

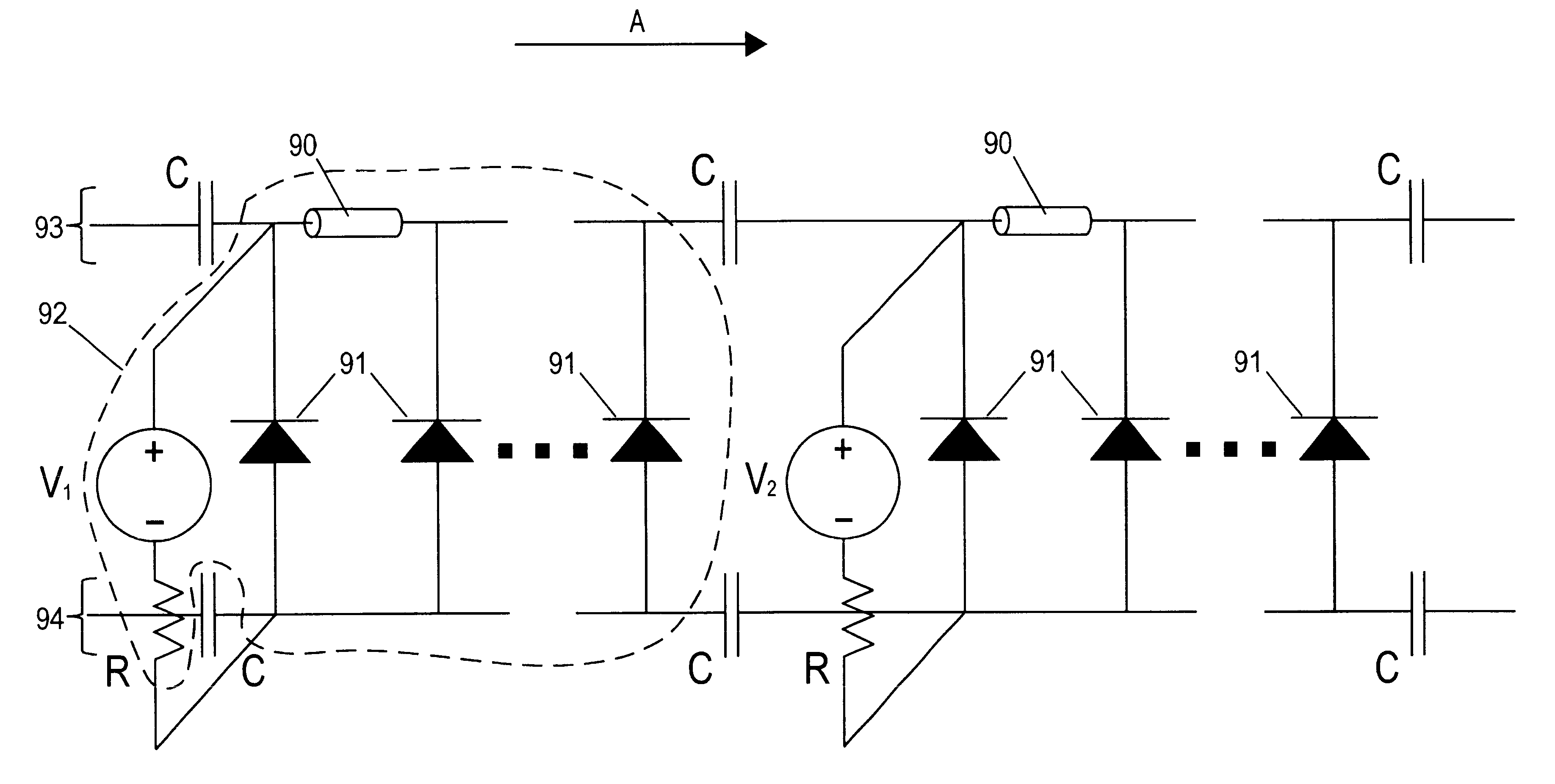

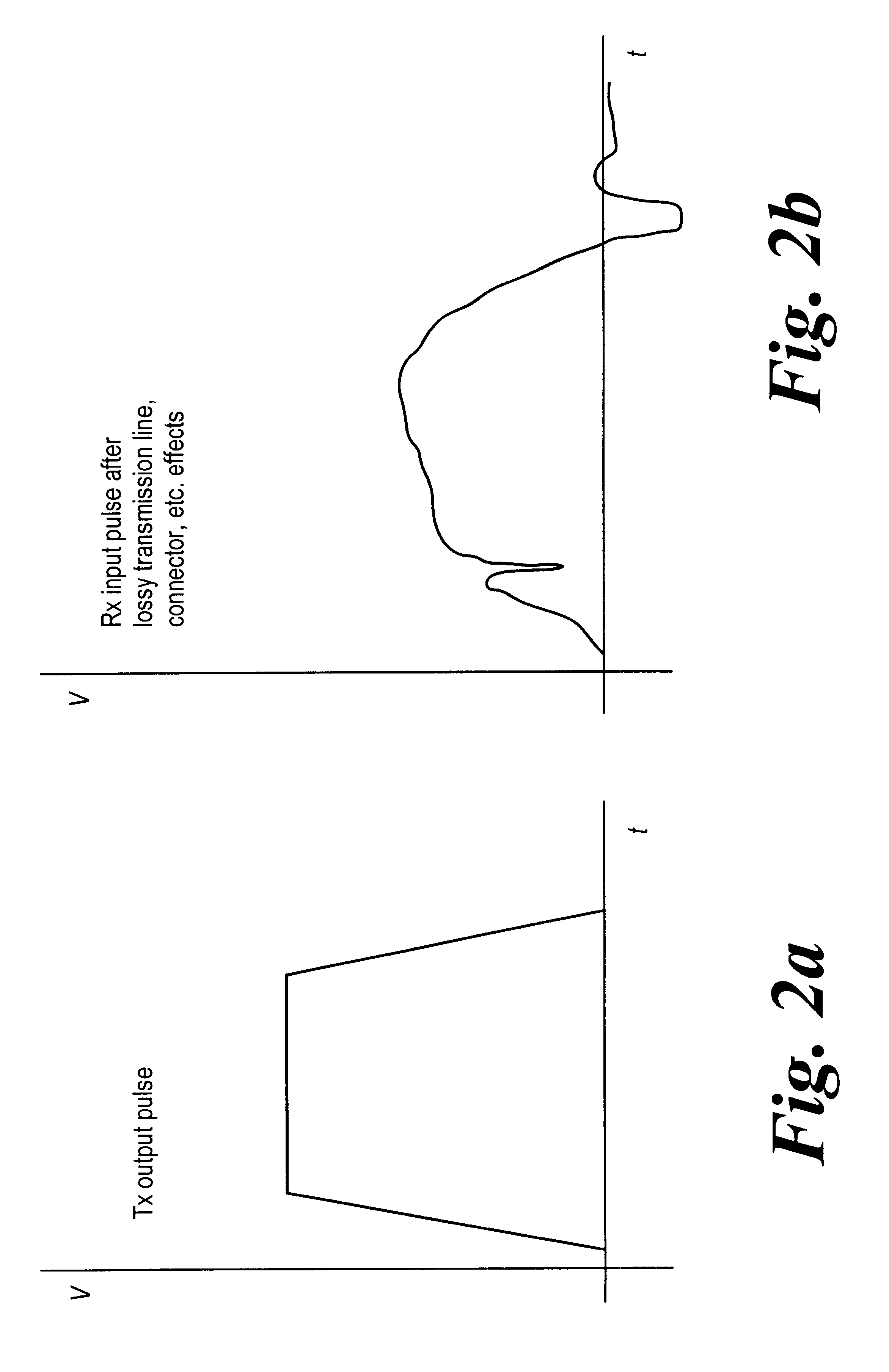

Voltage biased section of non-linear transmission line

InactiveUS6538525B1Reduce stub effectImprove signal integrityTransmission control/equlisationHigh frequency circuit adaptationsCapacitanceEngineering

The principal reason that commercially available 10 gigabits per second electrical interconnect has not previously been available is that such interconnect structures possess too high a level of parasitic inductance, capacitance, resistance and conductance. These result in signal degradation as a result of attenuation, harmonic distortion and dispersion and so sufficiently error-free transmission of data has been virtually impossible for high data rates such as those around 5 gigabits per second and above. By providing compensation mechanisms, signal integrity is improved thus enabling reliable data transmission at data rates of 5 gigabits per second, 10 gigabits per second and above. Non-linear transmission lines are used to form these compensation mechanisms. The non-linear transmission line may take the form of a distributed diode, for example, formed from a layer of N-doped silicon covered on its top surface by a layer of platinum and on its bottom surface by a layer of silicon dioxide. Advantageously, voltage biased sections of NLTL are used to perform compensation for different regions of a signal pulse according to the particular voltage biasing used. A plurality of such voltage biased sections of NLTL may be connected in series in order to obtain improved signal compensation.

Owner:RPX CLEARINGHOUSE

Fabric and yarn structures for improving signal integrity in fabric-based electrical circuits

InactiveUS20080287022A1Reduce crosstalkImprove the immunityJacquardsLeno shedding mechanismPower gridTwisted pair

Coaxial and twisted pair conductive yarn structures reduce signal crosstalk between adjacent lines in woven electrical networks. A coaxial conductive yarn structure includes an inner conductive yarn having a plurality of conductive strands twisted together. An outer conductive yarn is wrapped around the inner conductive yarn. An insulating layer separates the inner and outer yarns. A twisted pair conductive yarn structure includes first and second conductive yarns, each including a plurality of conductive strands being twisted together. The first and second conductive yarns are twisted together to form a helical structure. In a woven electrical network, at least one conductor of adjacent conductive yarn structures is connected to ground to reduce signal crosstalk. Coaxial and twisted pair yarn structures may also be formed simultaneously with weaving or knitting the threads that make up the structures into a fabric.

Owner:NORTH CAROLINA STATE UNIV