Patents

Literature

63results about How to "Eliminate capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

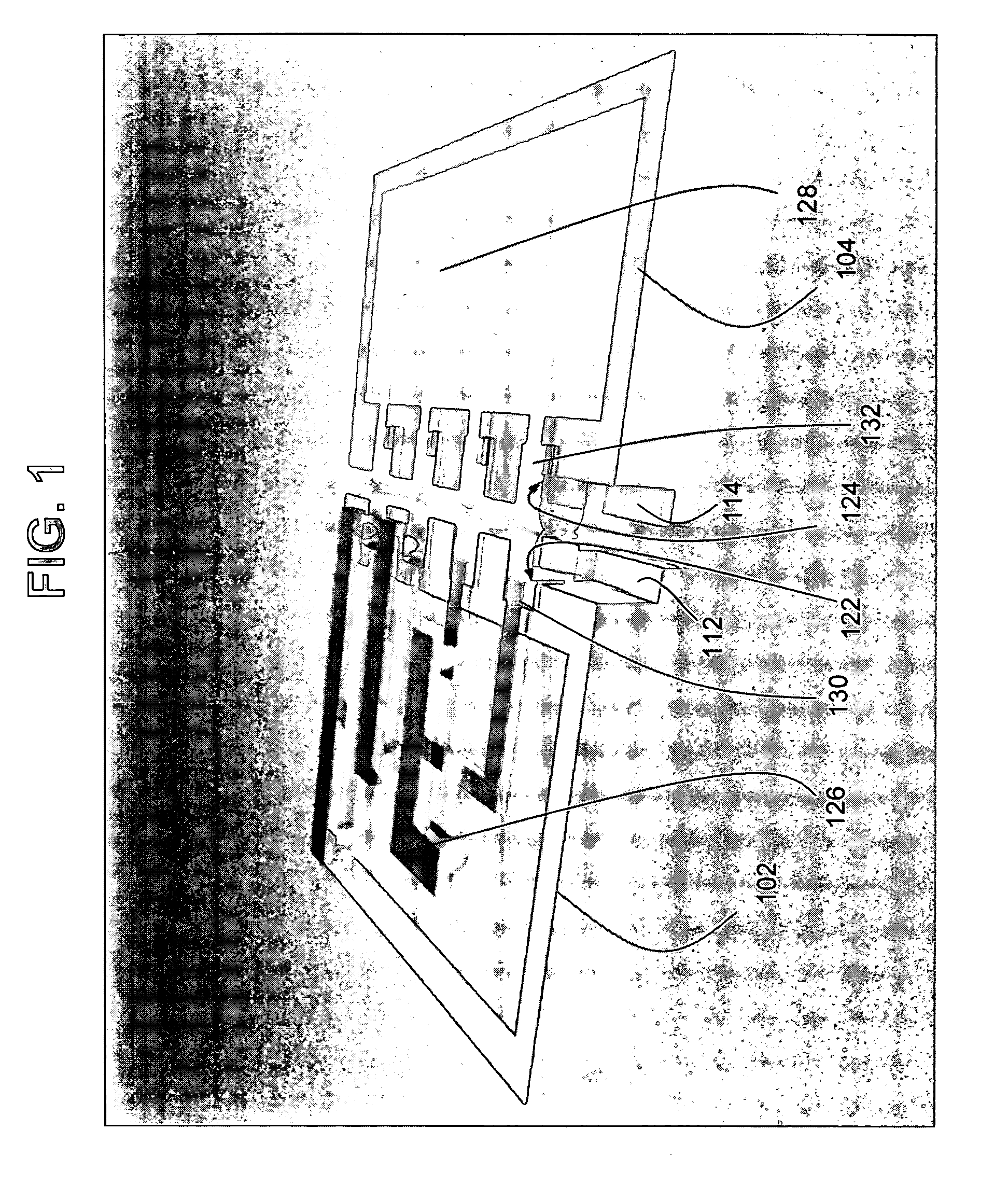

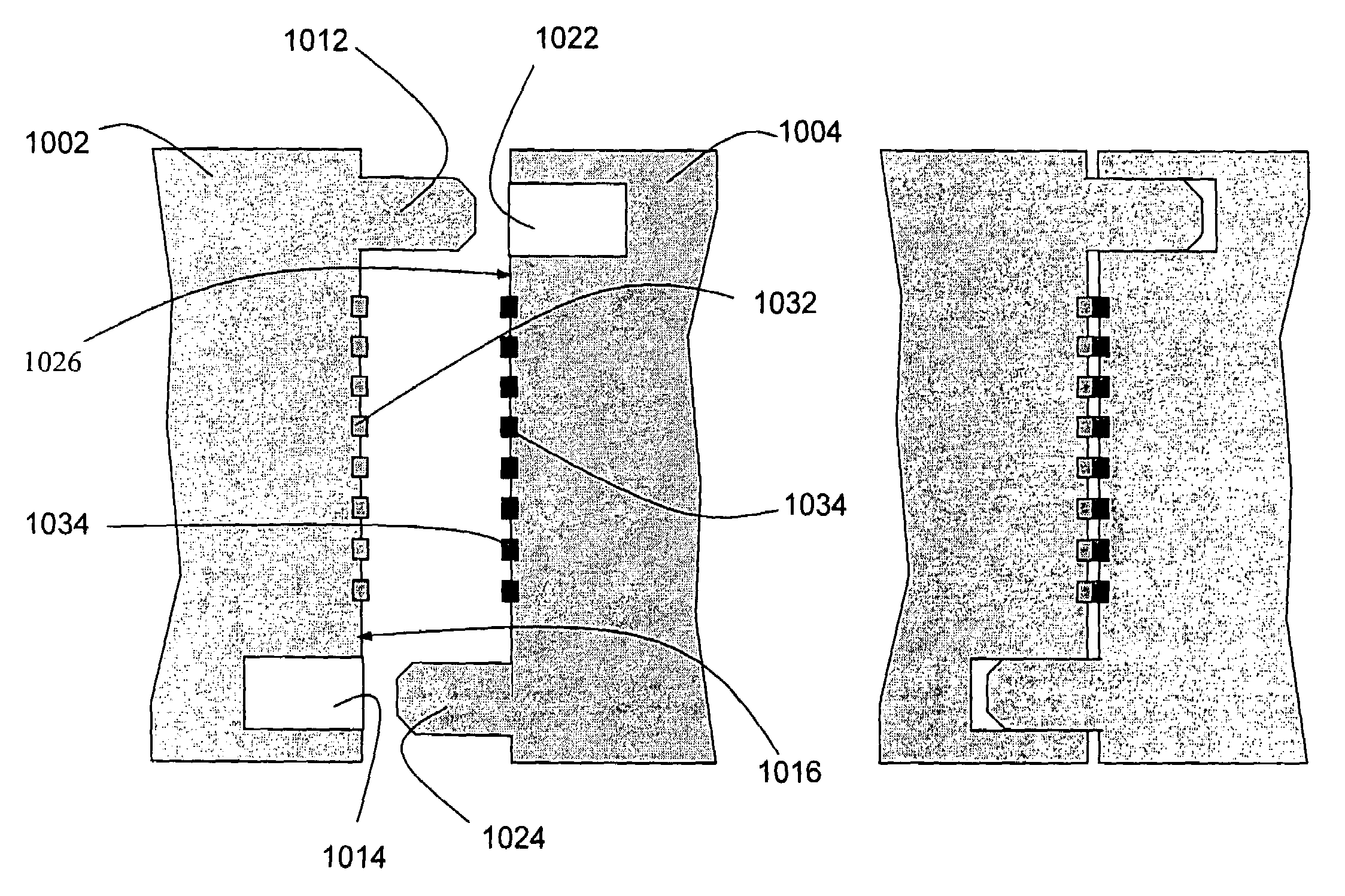

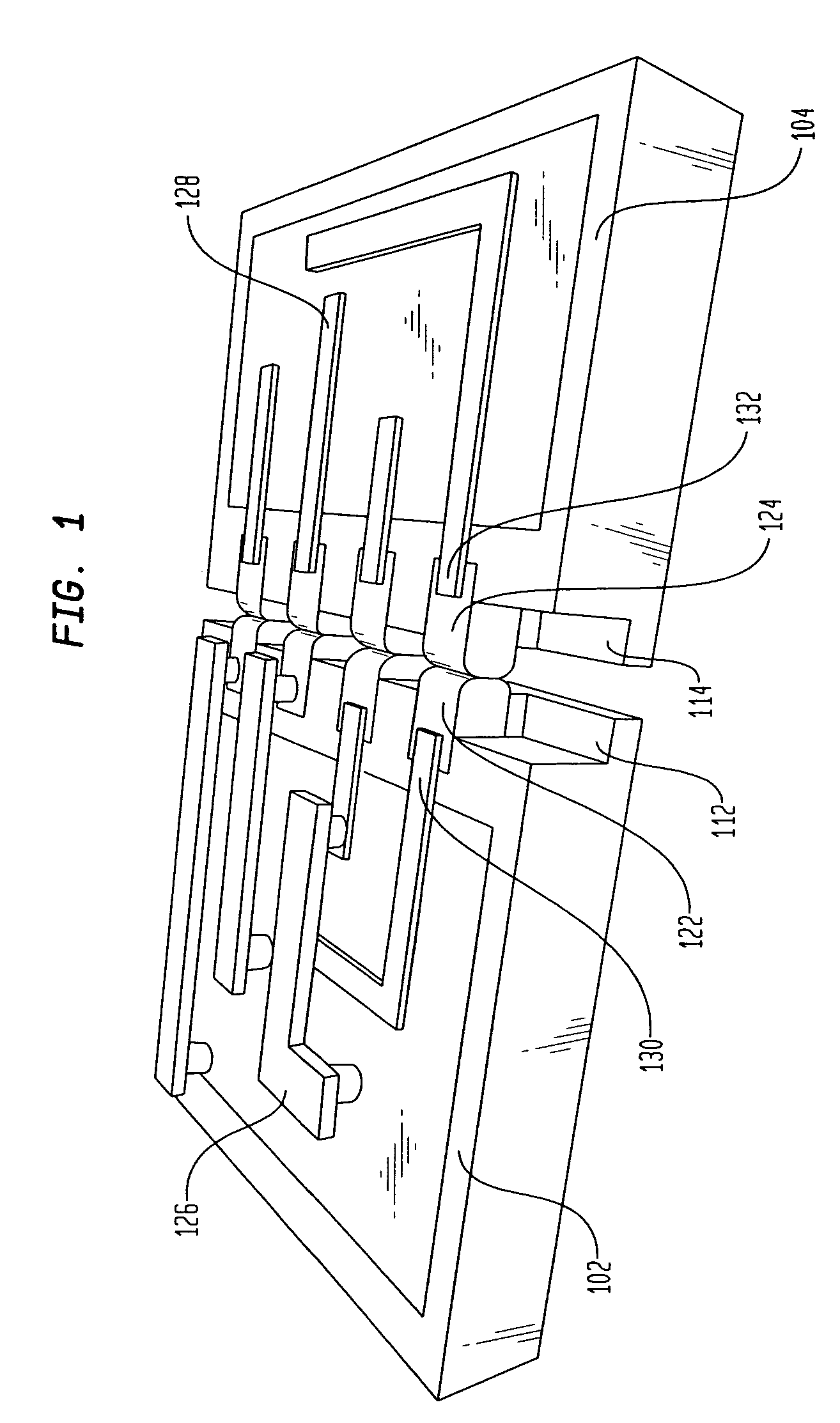

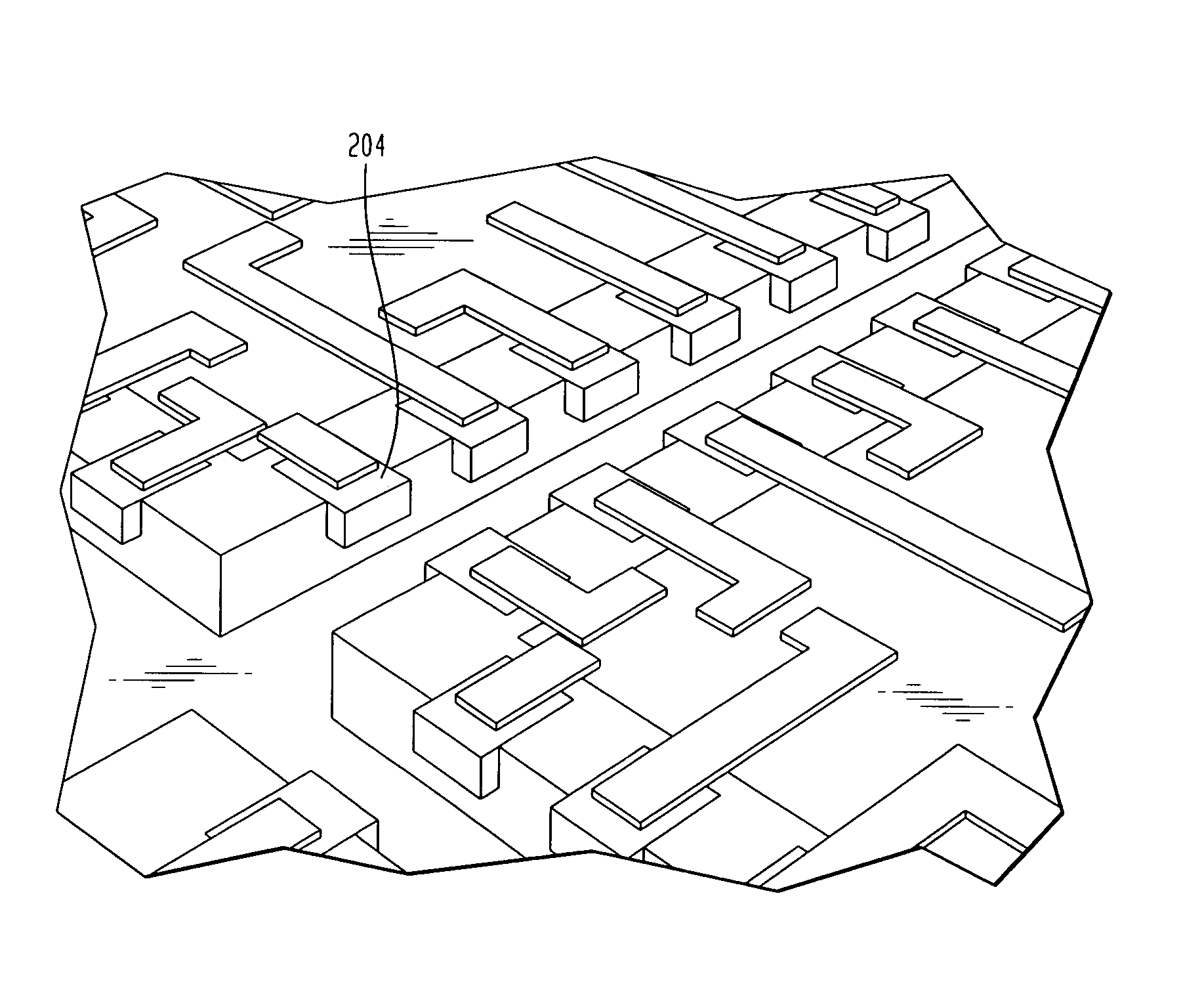

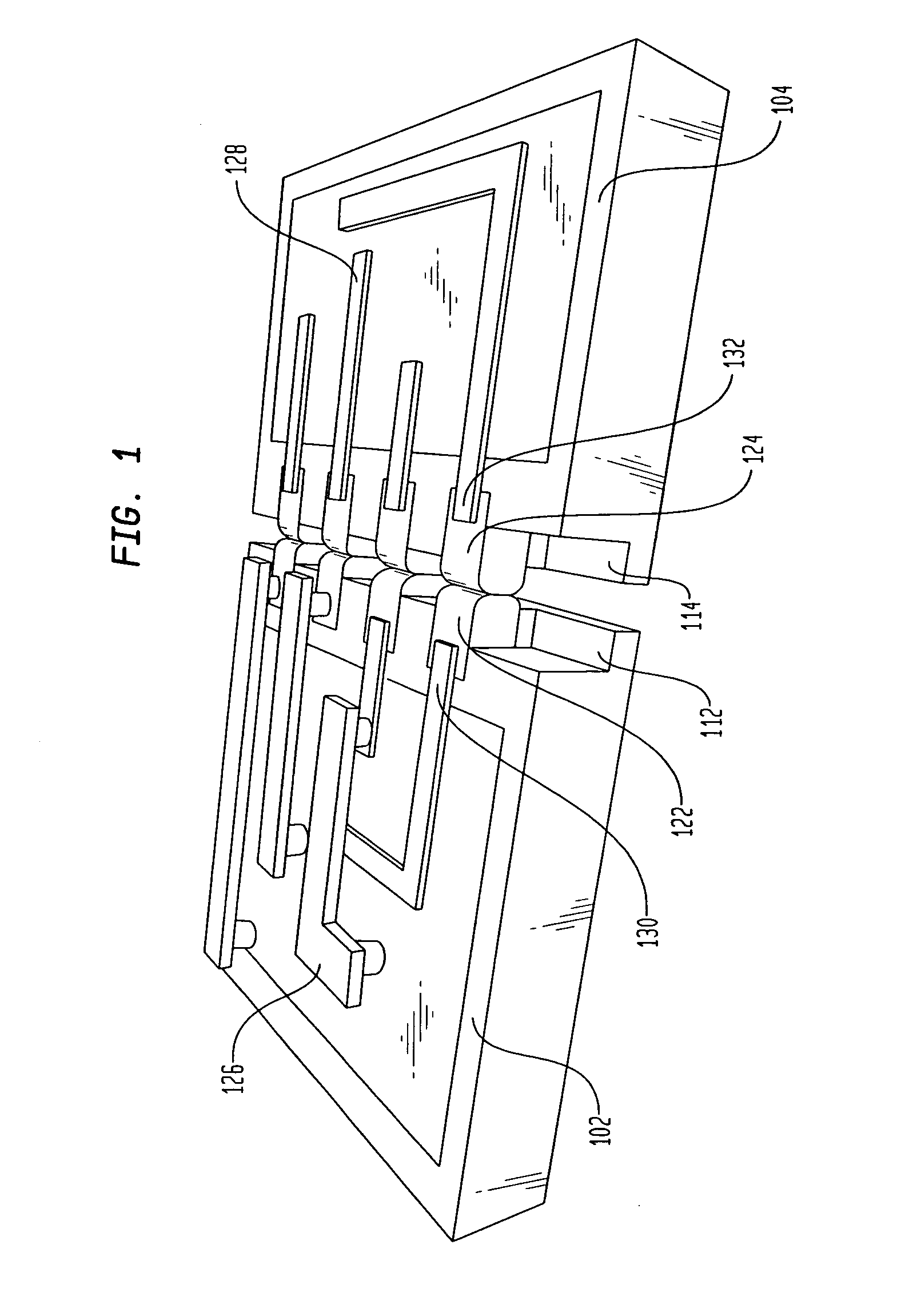

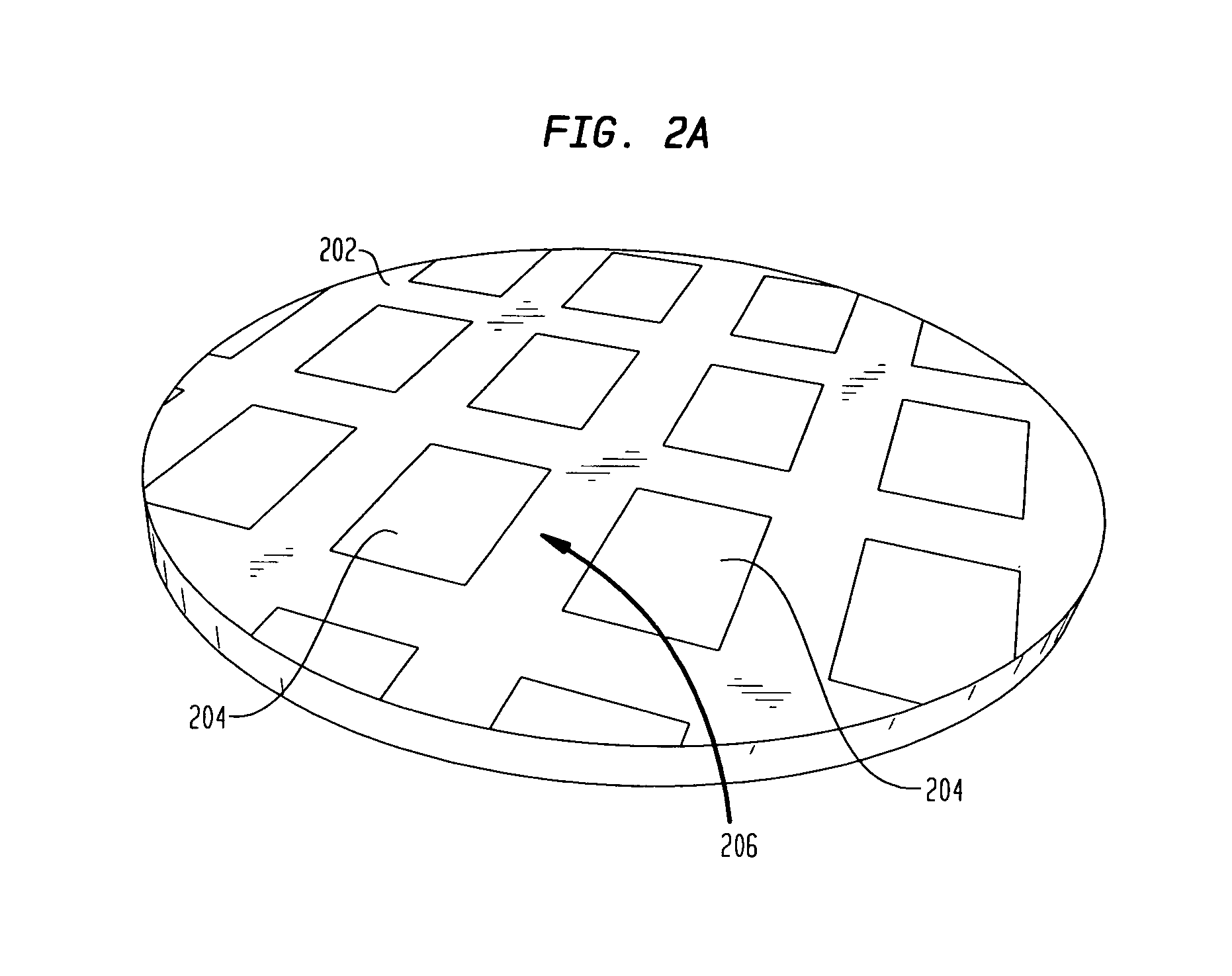

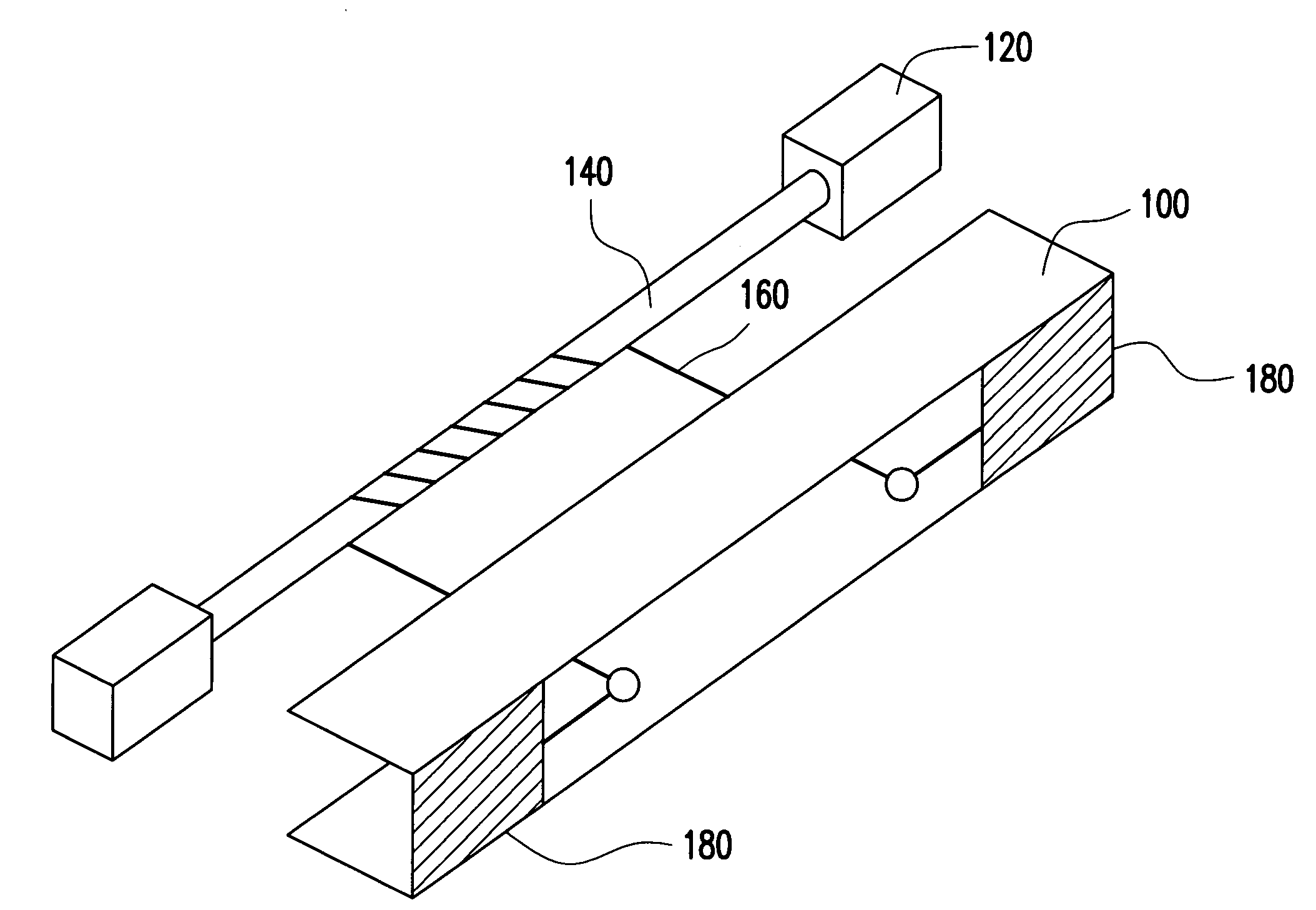

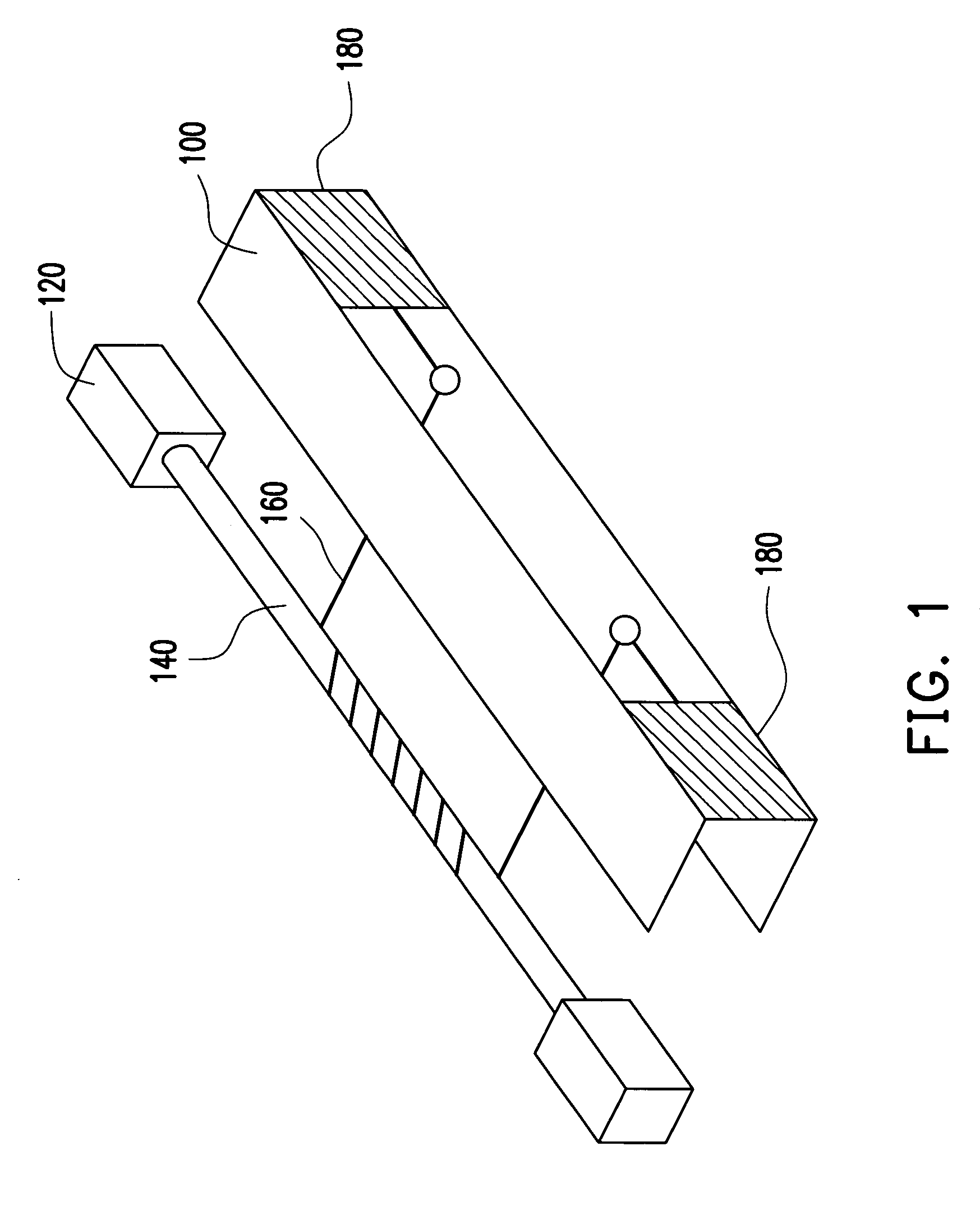

Inter-chip communication

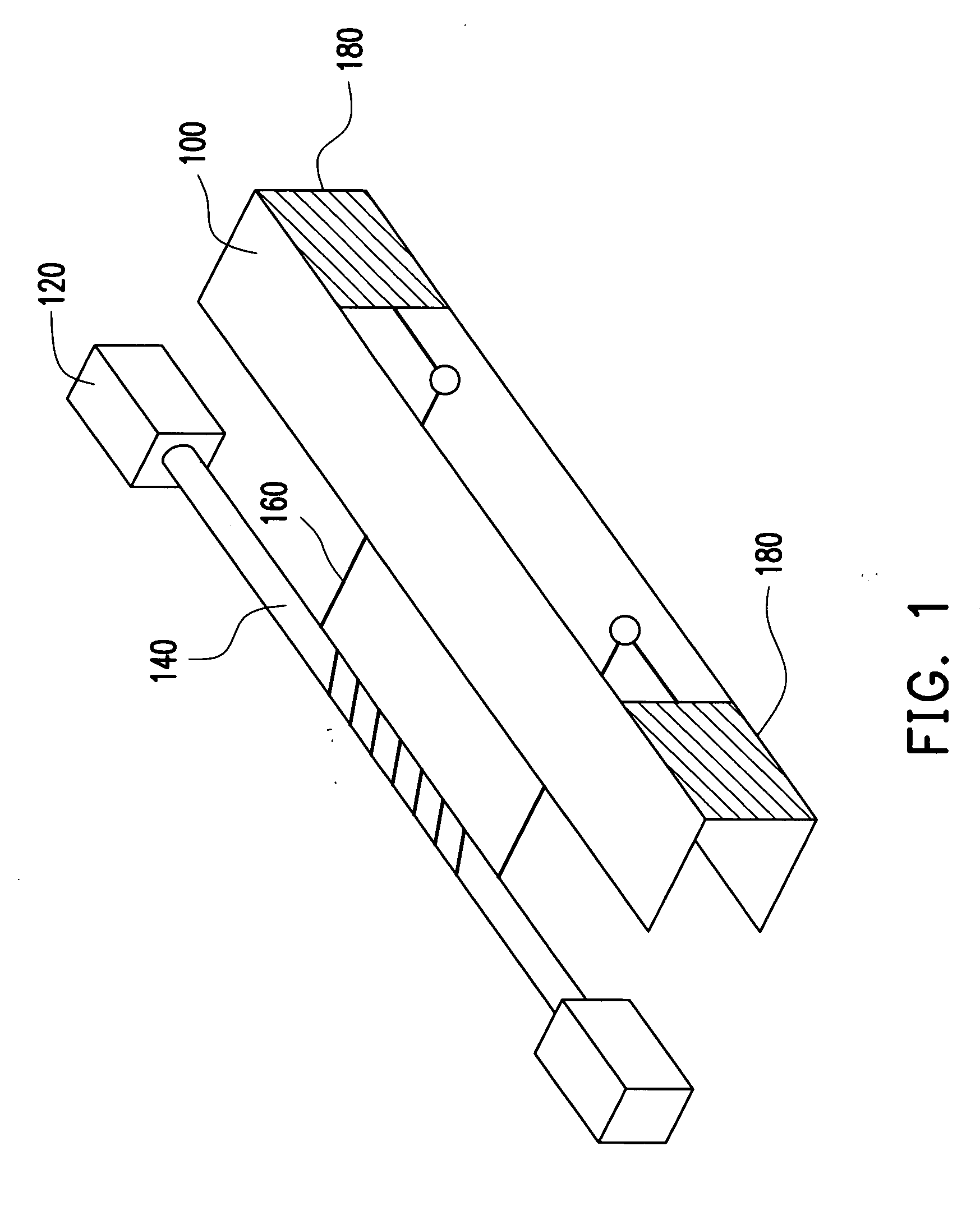

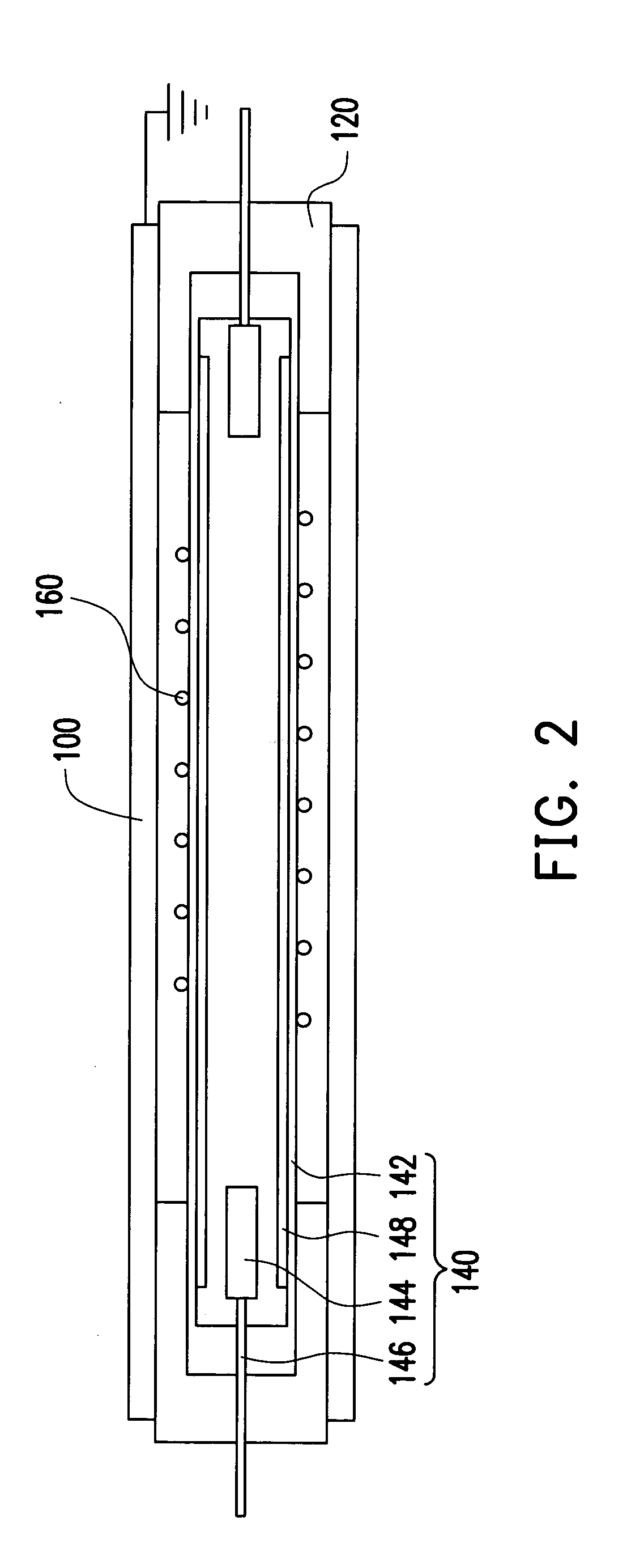

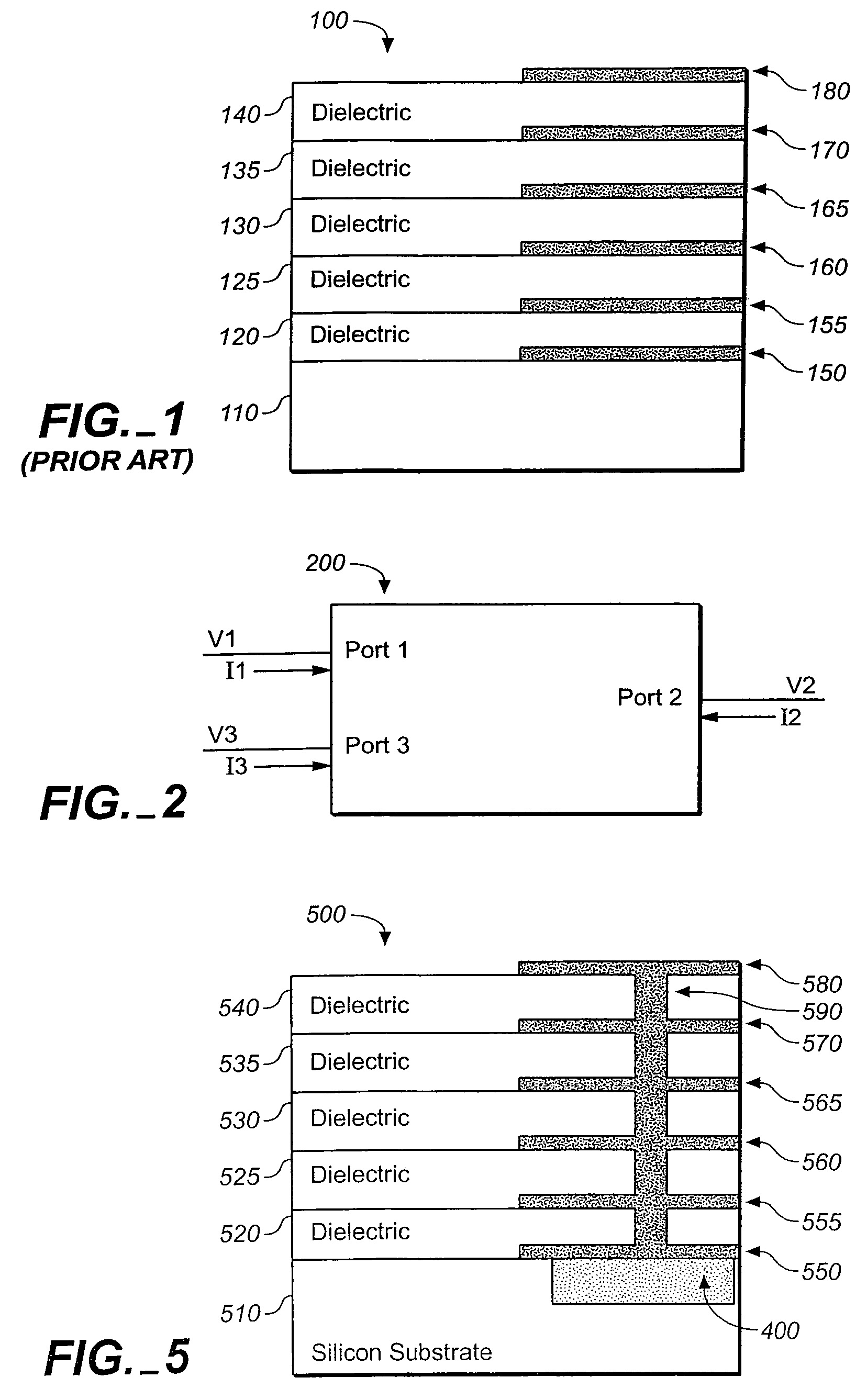

ActiveUS7612443B1Reduce power consumptionEliminate capacitanceFinal product manufactureSemiconductor/solid-state device detailsEngineeringQuilt packaging

Owner:UNIV OF NOTRE DAME DU LAC

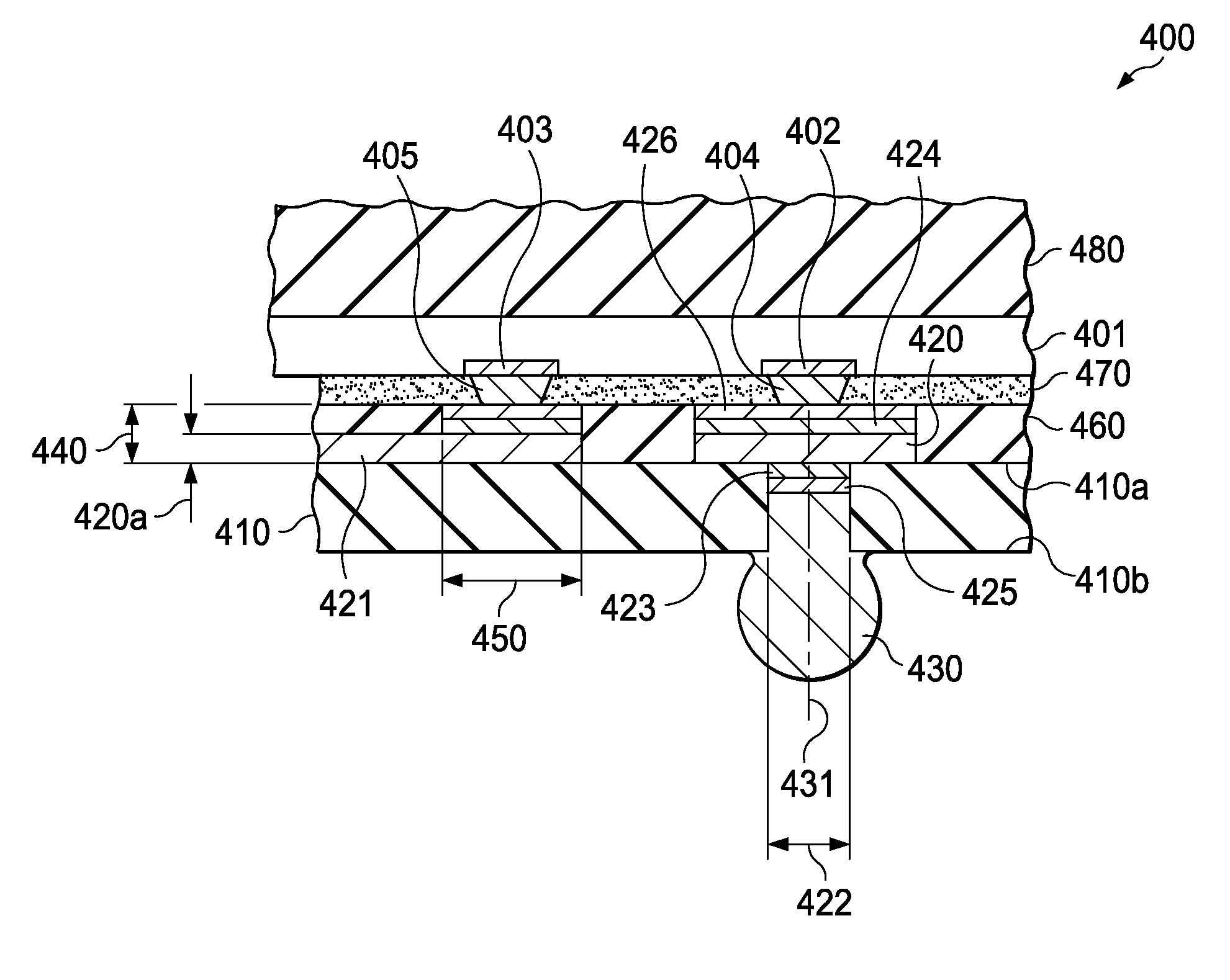

Interconnect packaging systems

ActiveUS7608919B1Reduce power consumptionEliminate capacitanceFinal product manufactureSemiconductor/solid-state device detailsQuilt packagingElectrical and Electronics engineering

Owner:UNIV OF NOTRE DAME DU LAC

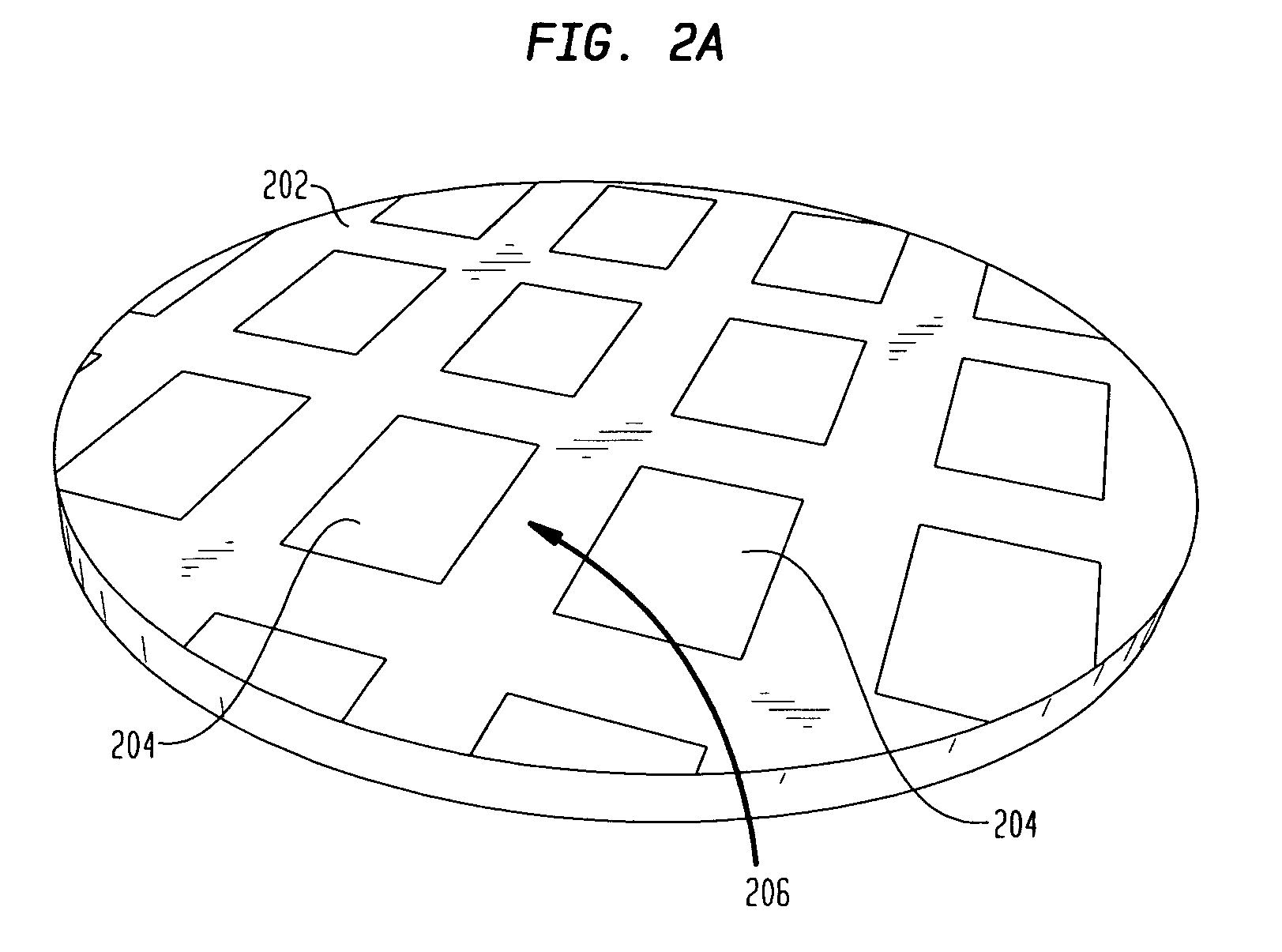

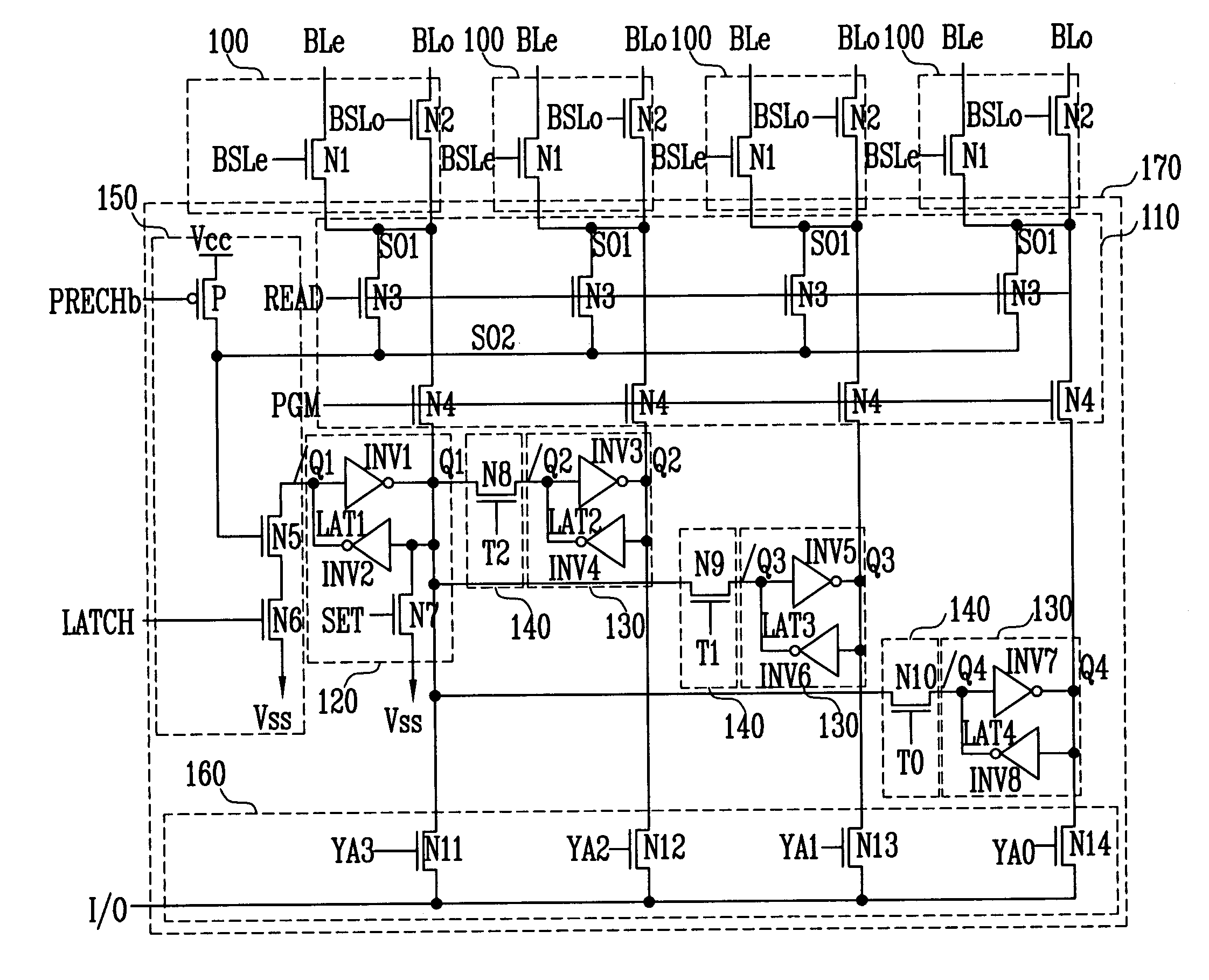

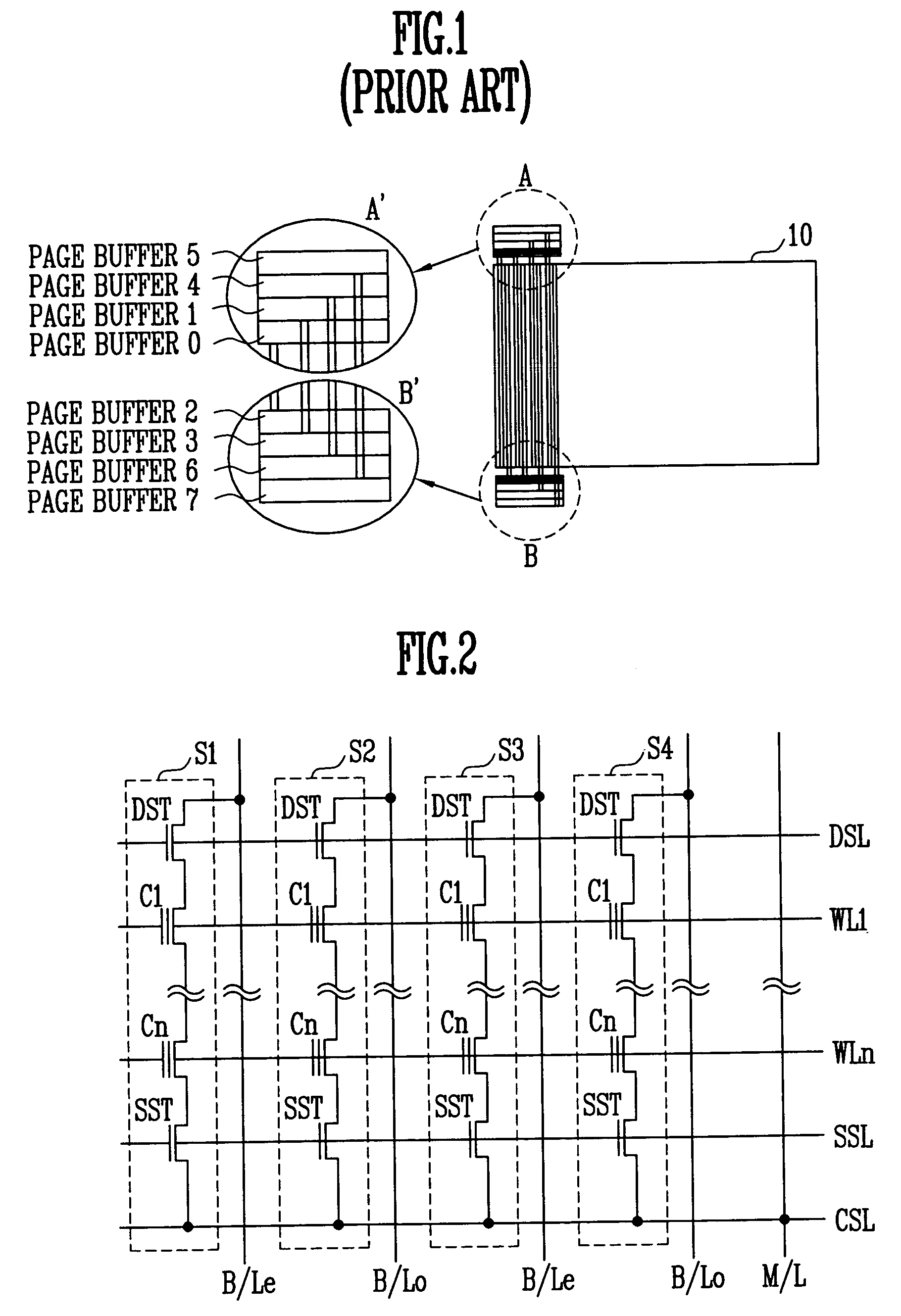

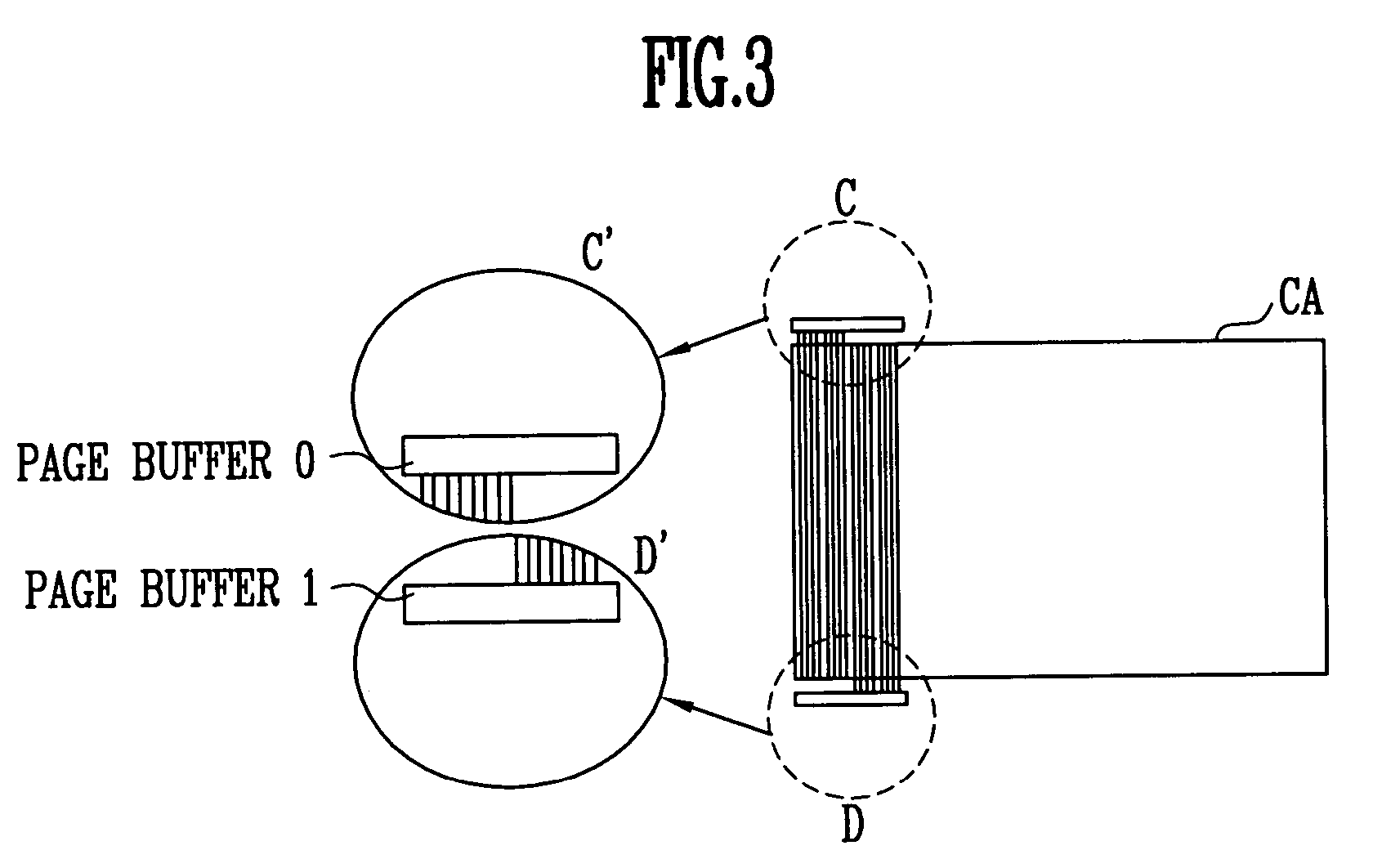

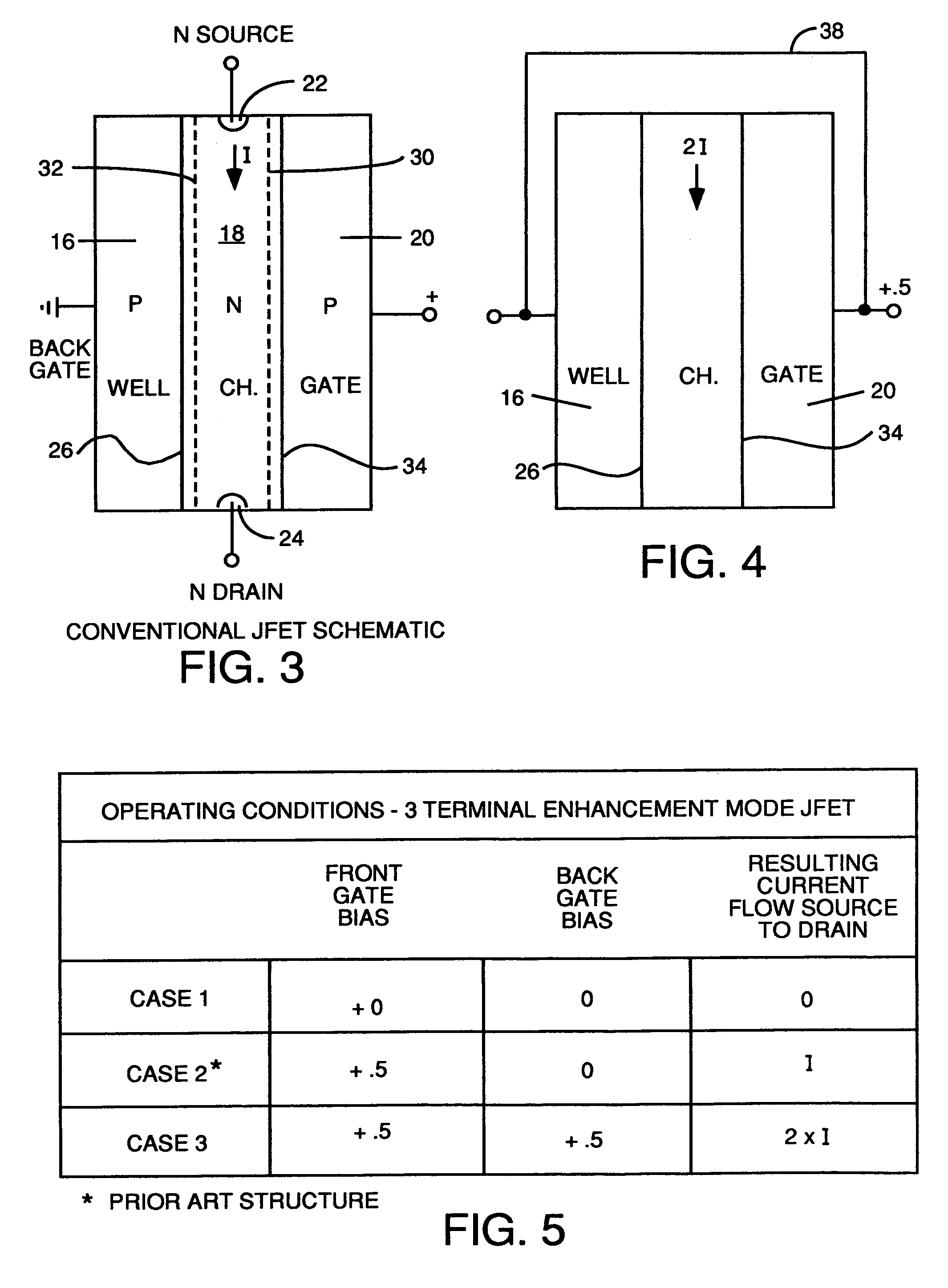

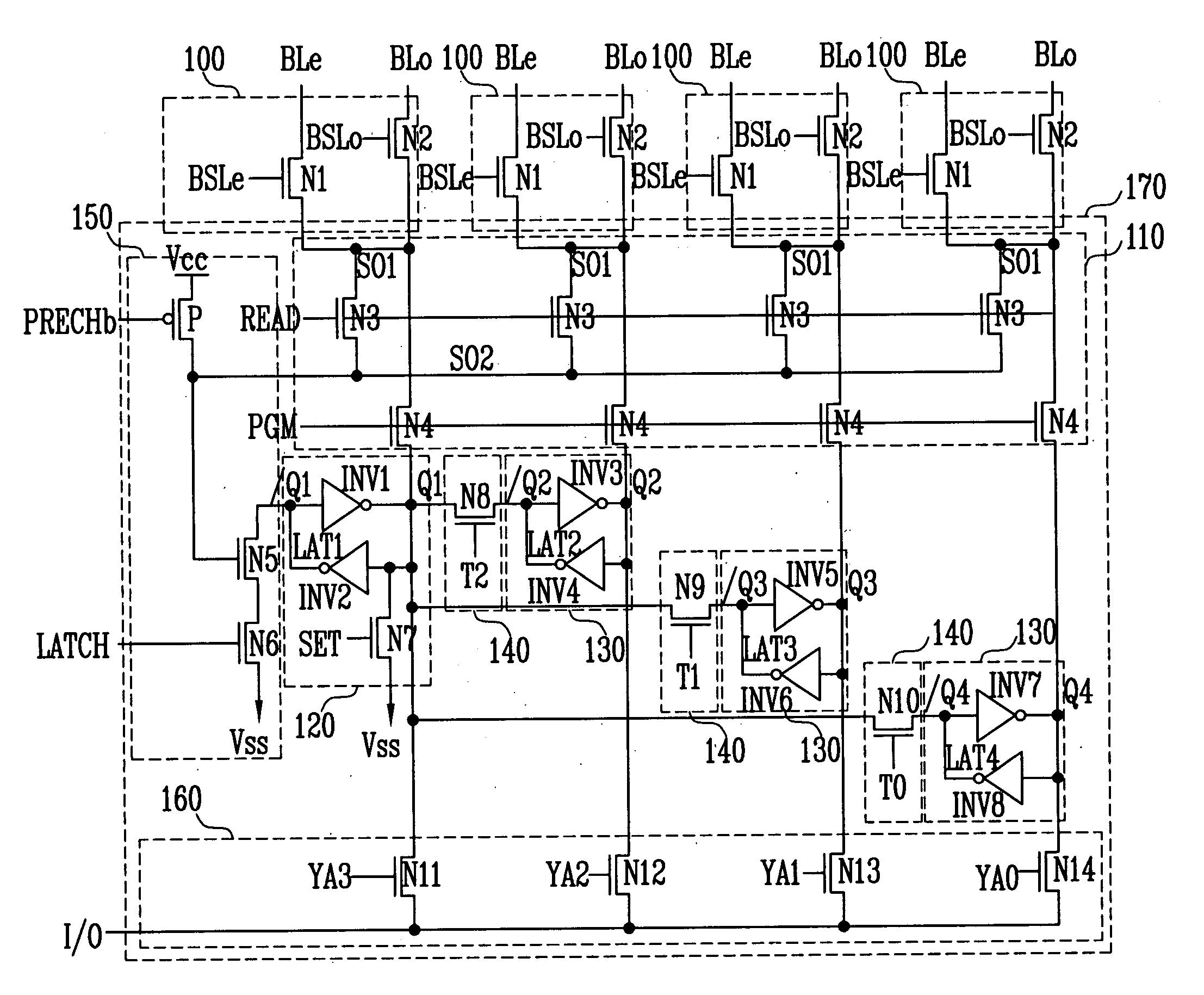

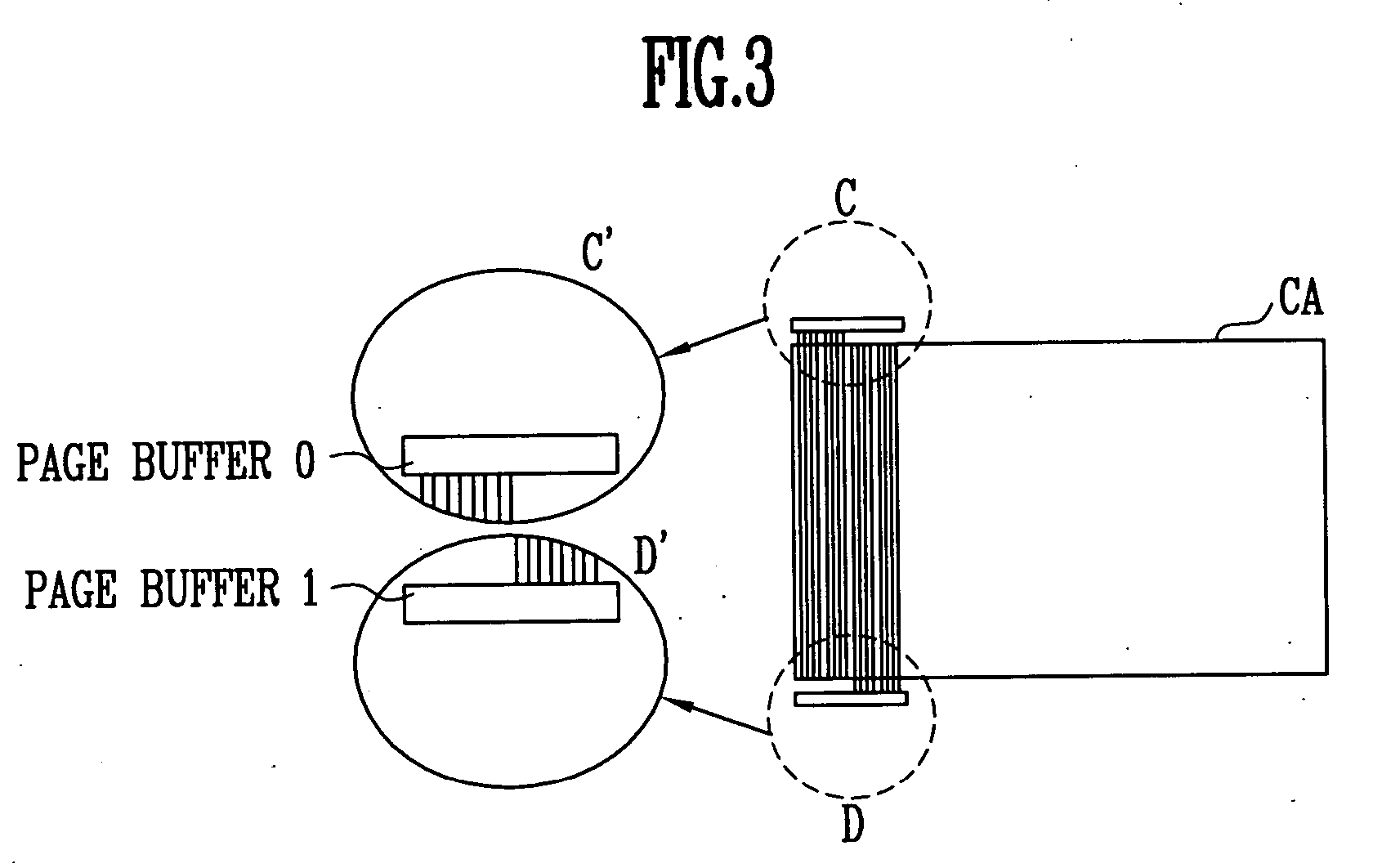

Page buffer of non-volatile memory device and method of programming and reading non-volatile memory device

A page buffer of a non-volatile memory device and a method for programming and reading the same is provided. The page buffer includes a first latch unit and one or more second latch units for storing data, transfer units connected between the first latch unit and the second latch units for transferring the data stored in the first latch unit to the second latch units, a path select unit that that senses data from bit lines and stores the sensed data in the first latch unit, and, in a program operation, transfers the data from the first and second latch units to the bit lines, a sensing unit for allowing the path select unit to sense data or the data received from the bit lines to be stored in the first latch unit, and a data I / O unit.

Owner:SK HYNIX INC +1

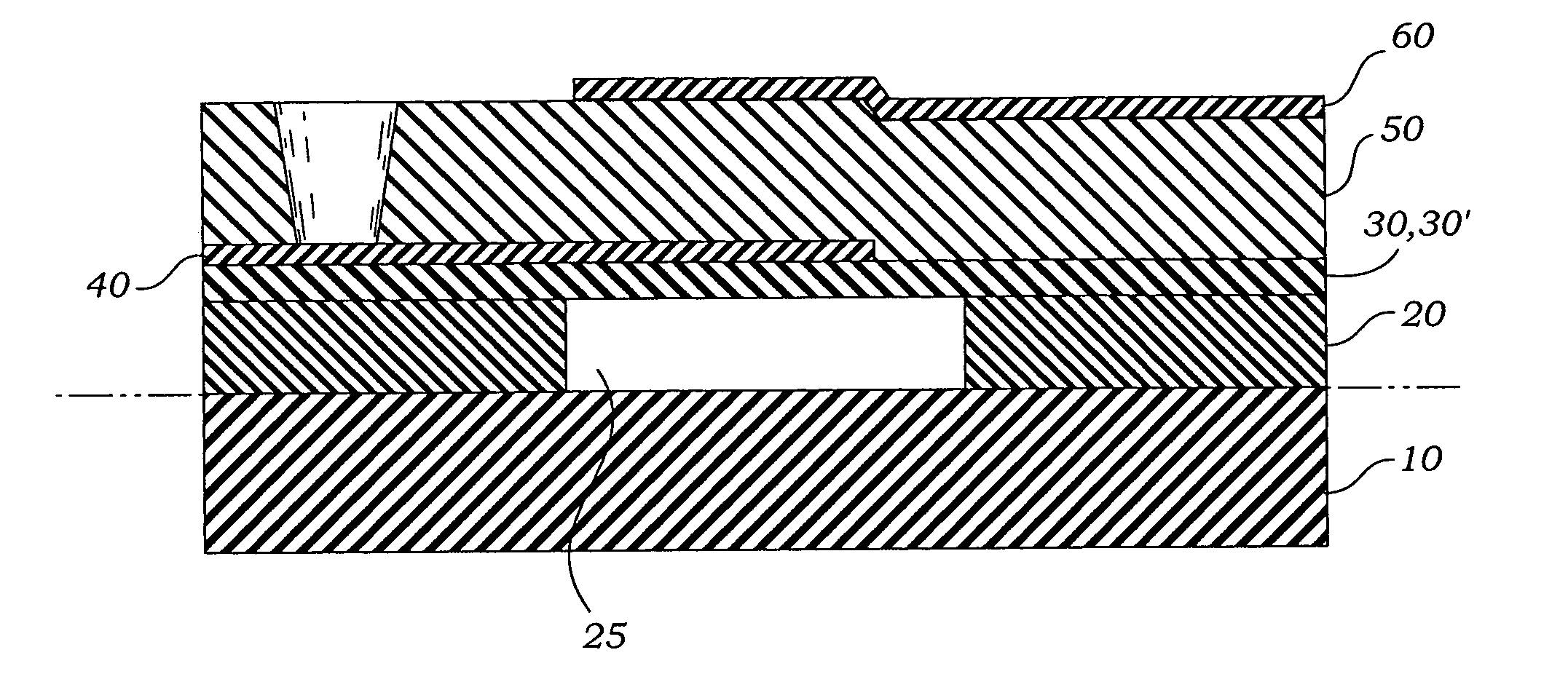

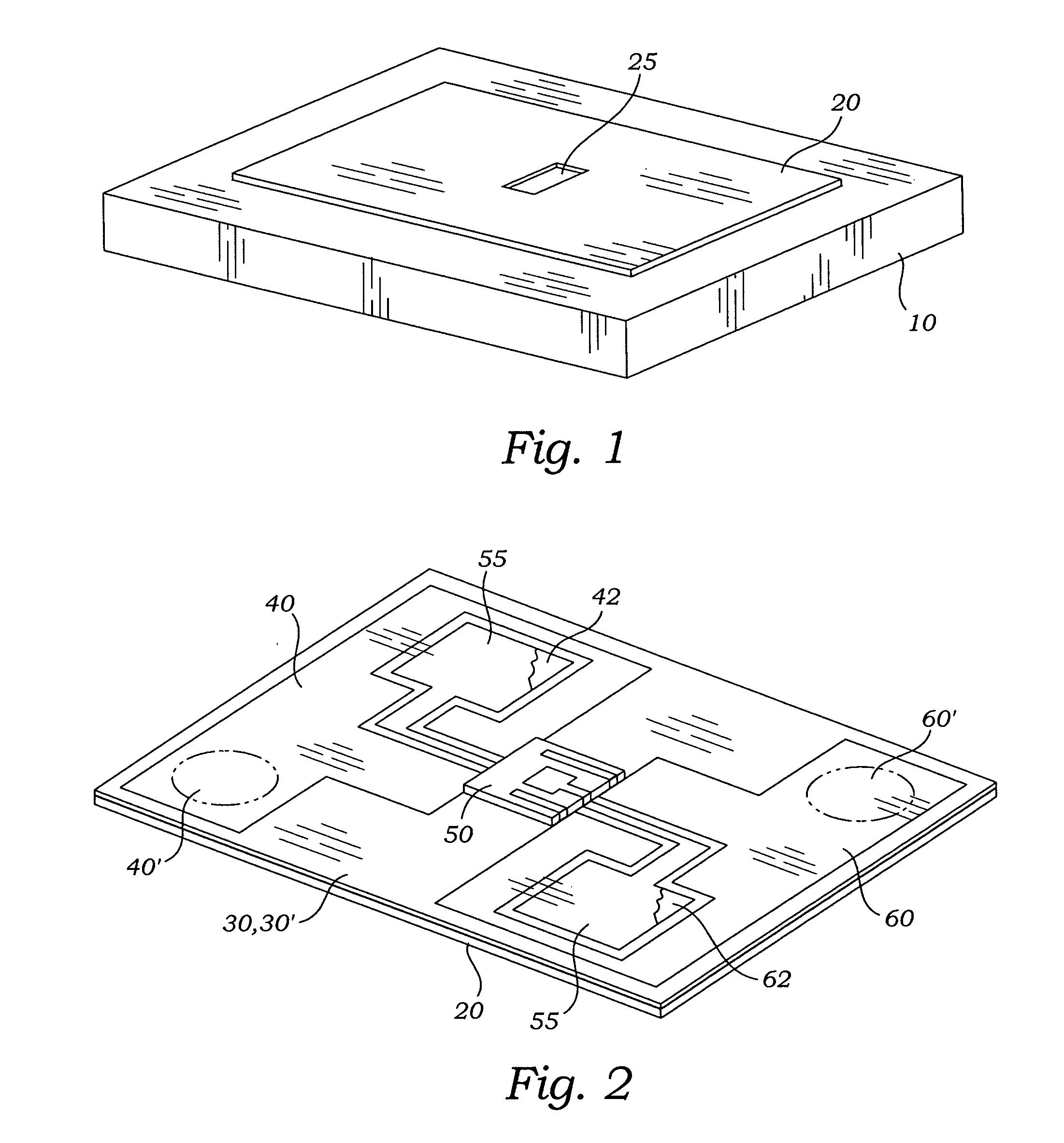

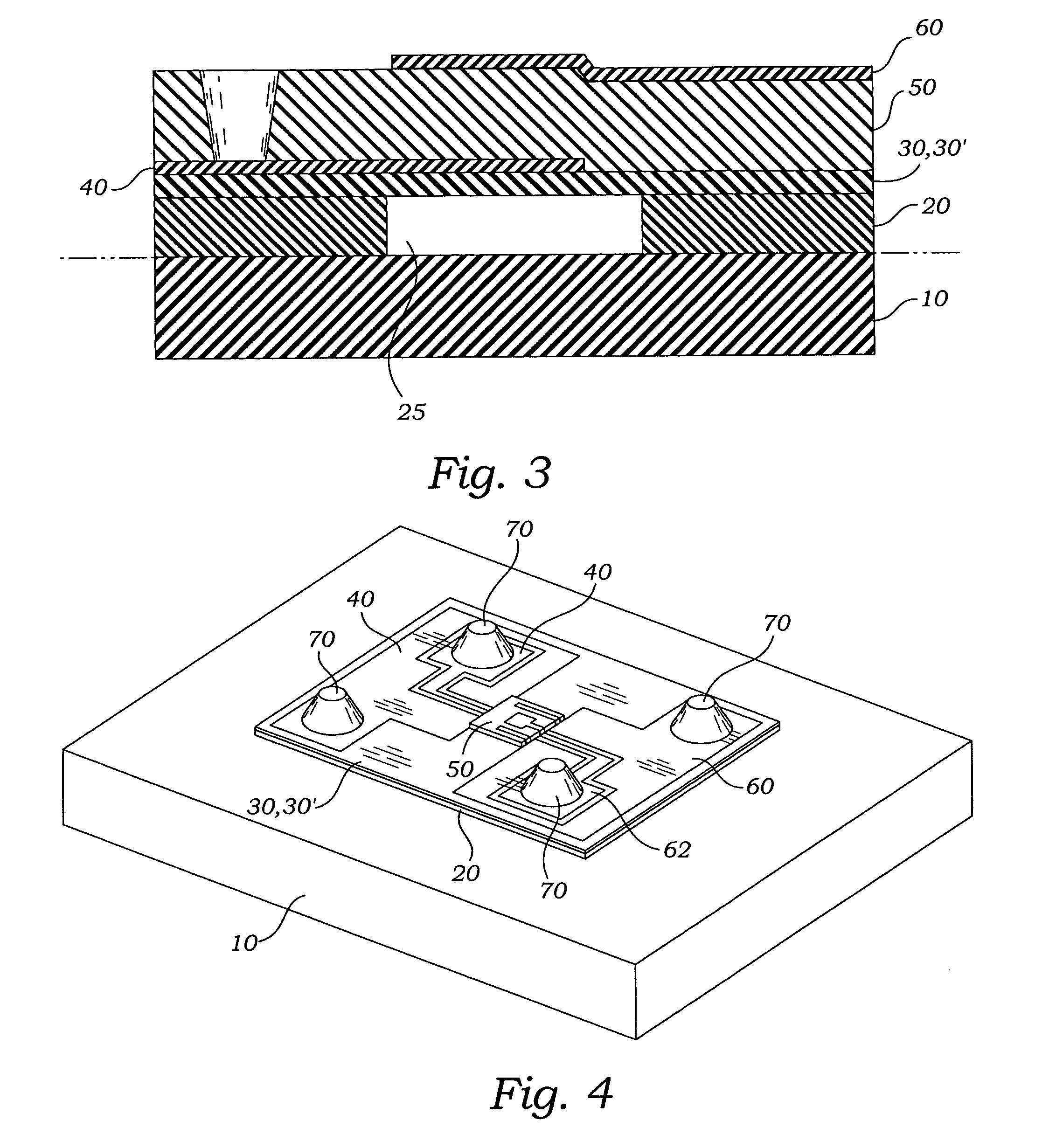

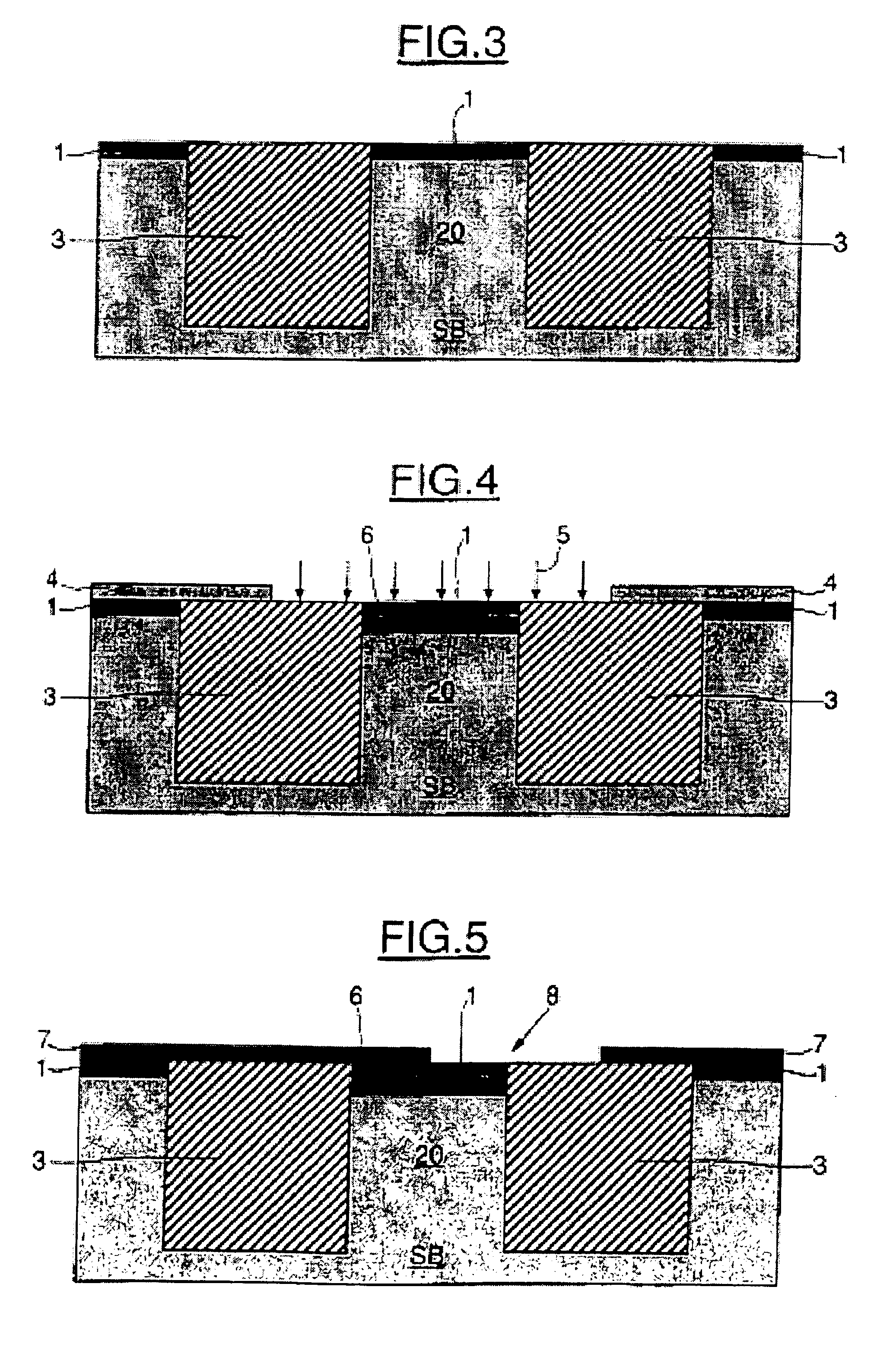

Thin device and method of fabrication

InactiveUS20060017352A1Improve performanceEasily etched awayImpedence networksPiezoelectric/electrostriction/magnetostriction machinesAir bridgeAcoustic wave

A method of fabricating air-bridge type FBAR devices provides for a piezoelectric material sandwiched between two electrodes with an air / crystal interface on each electrode to trap sound waves within the film structure. Copper is used as a sacrificial material deposited in cavities in the substrate. Following deposition of the electrodes and piezoelectric material, the copper is etched away leaving the bottom electrode suspended over a cavity void.

Owner:TOKO JAPANESE

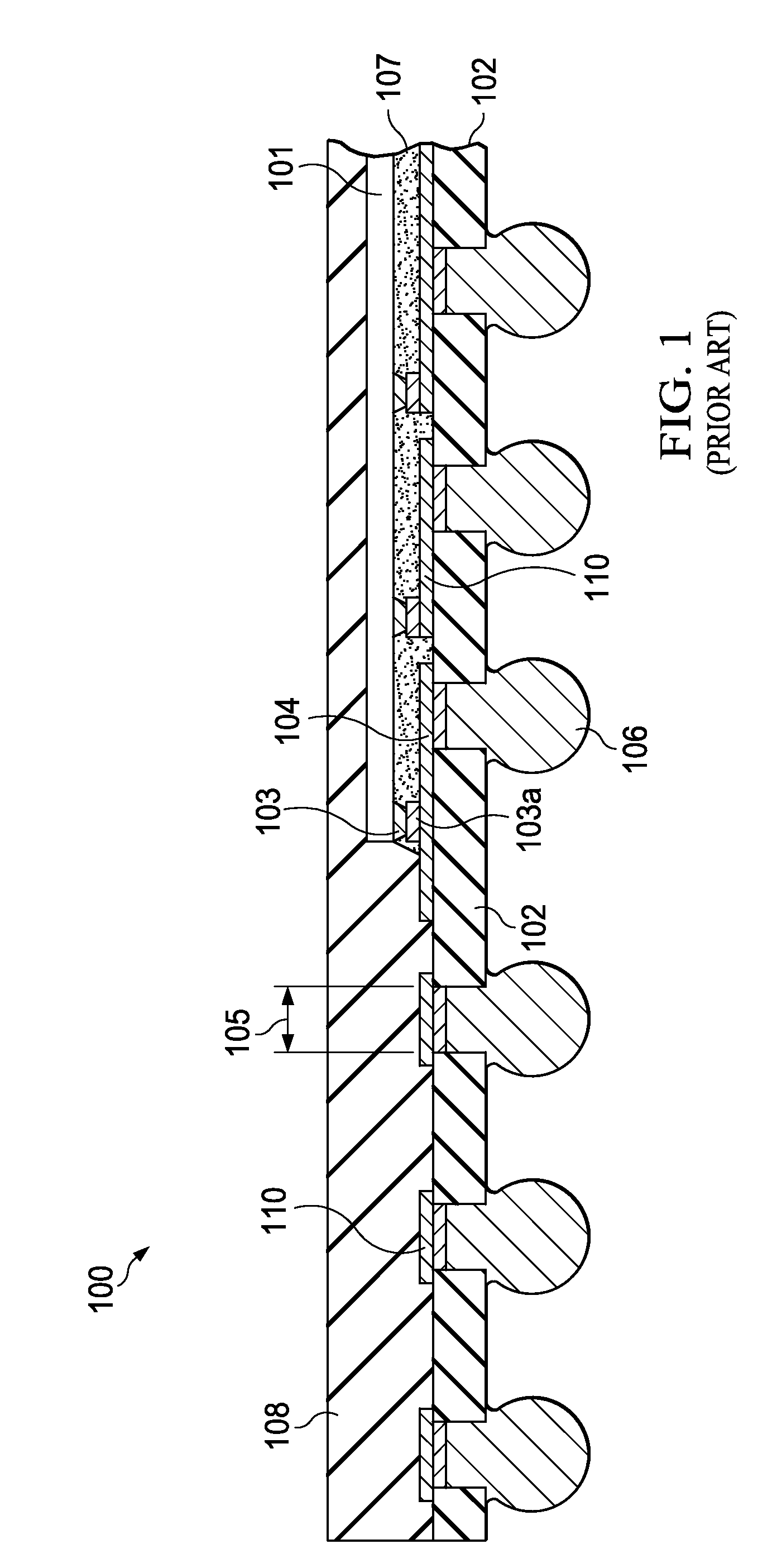

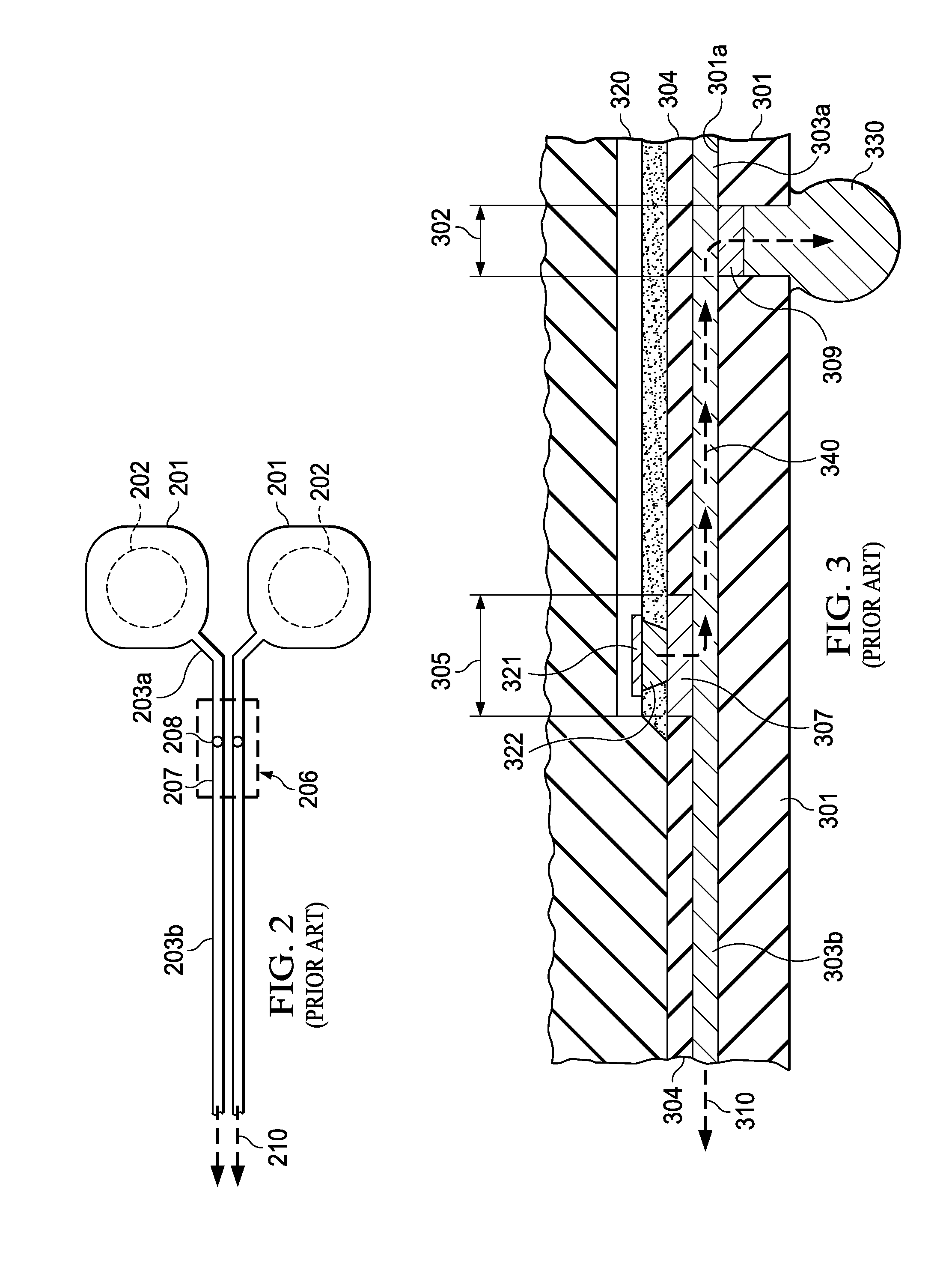

Low Inductance Ball Grid Array Device Having Chip Bumps on Substrate Vias

InactiveUS20090289362A1Eliminate couplingReduces bump-to-via current path inductanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceLow inductance

A high-frequency BGA device (500) with the chip (501) assembled by metal bumps (503) on an insulating substrate (502) with conductive vias (505) and metal traces (504). Chip bumps which serve the high frequency signal terminals are attached directly to the lands (510) on the vias in order to minimize parasitic electrical parameters such as inductance, resistance, and IR drops, thus achieving the required 0.1 nH inductance for each chip terminal. Chip bumps which serve the remaining chip terminals are attached to pads on certain substrate traces. In both cases, the bumps can be attached reliably because the lands on the vias and the pads on the traces are plated with additional metal layers (511, 512), which provide extra thickness as well as a metallurgically suitable surface.

Owner:TEXAS INSTR INC

On-chip capacitor

InactiveUS6897505B2Increases intralevel and “ sidewall ” capacitanceHigh dielectric materialTransistorSolid-state devicesCapacitanceMetal interconnect

An on-chip analog capacitor. Metal interconnect structures are used to form the capacitor, and the interdigitated fingers of like polarity within the interconnect structure are connected above and below to one another by metal vias to form a wall of metal which increases total capacitance by taking advantage of the via sidewall capacitance.

Owner:TEXAS INSTR INC

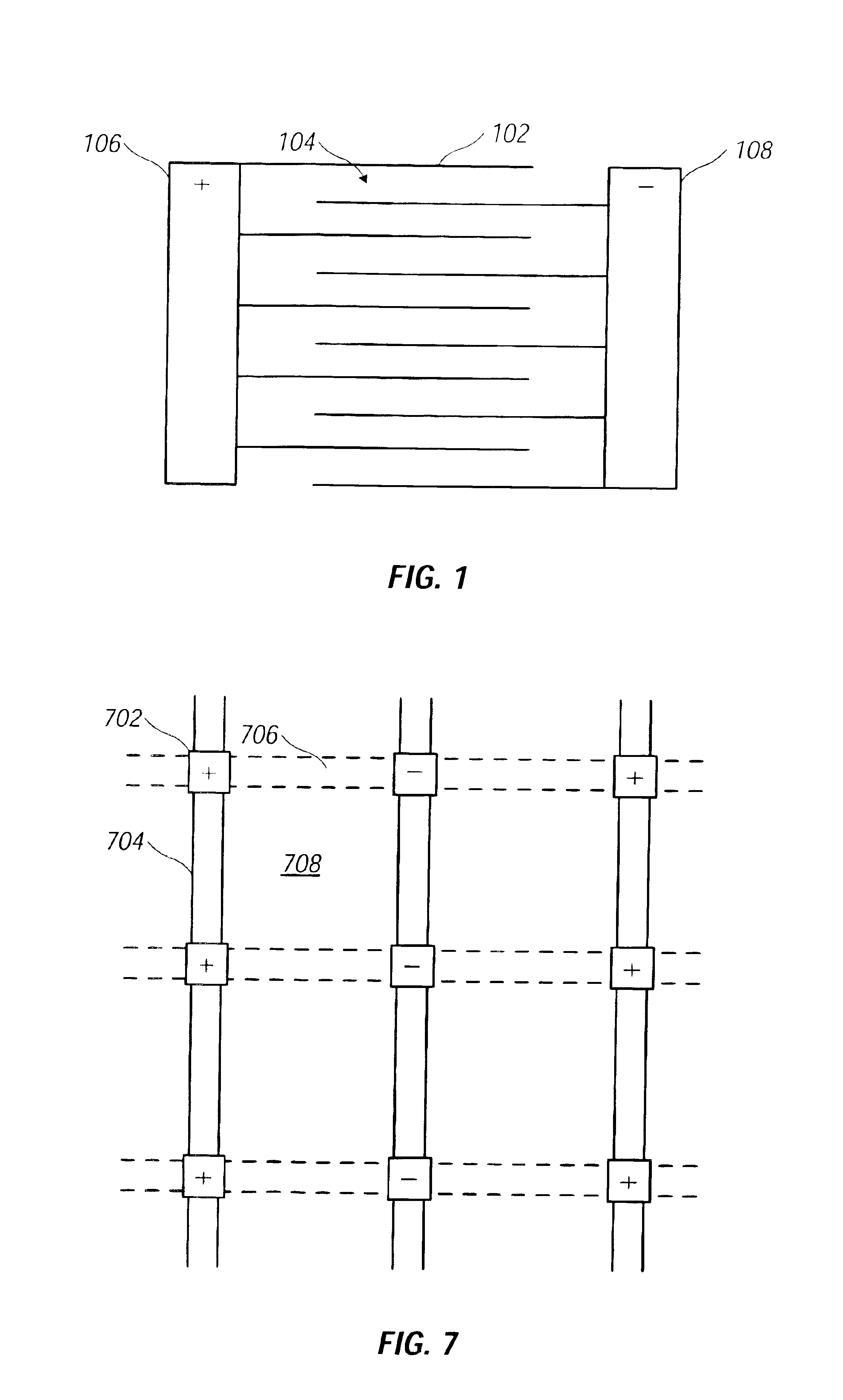

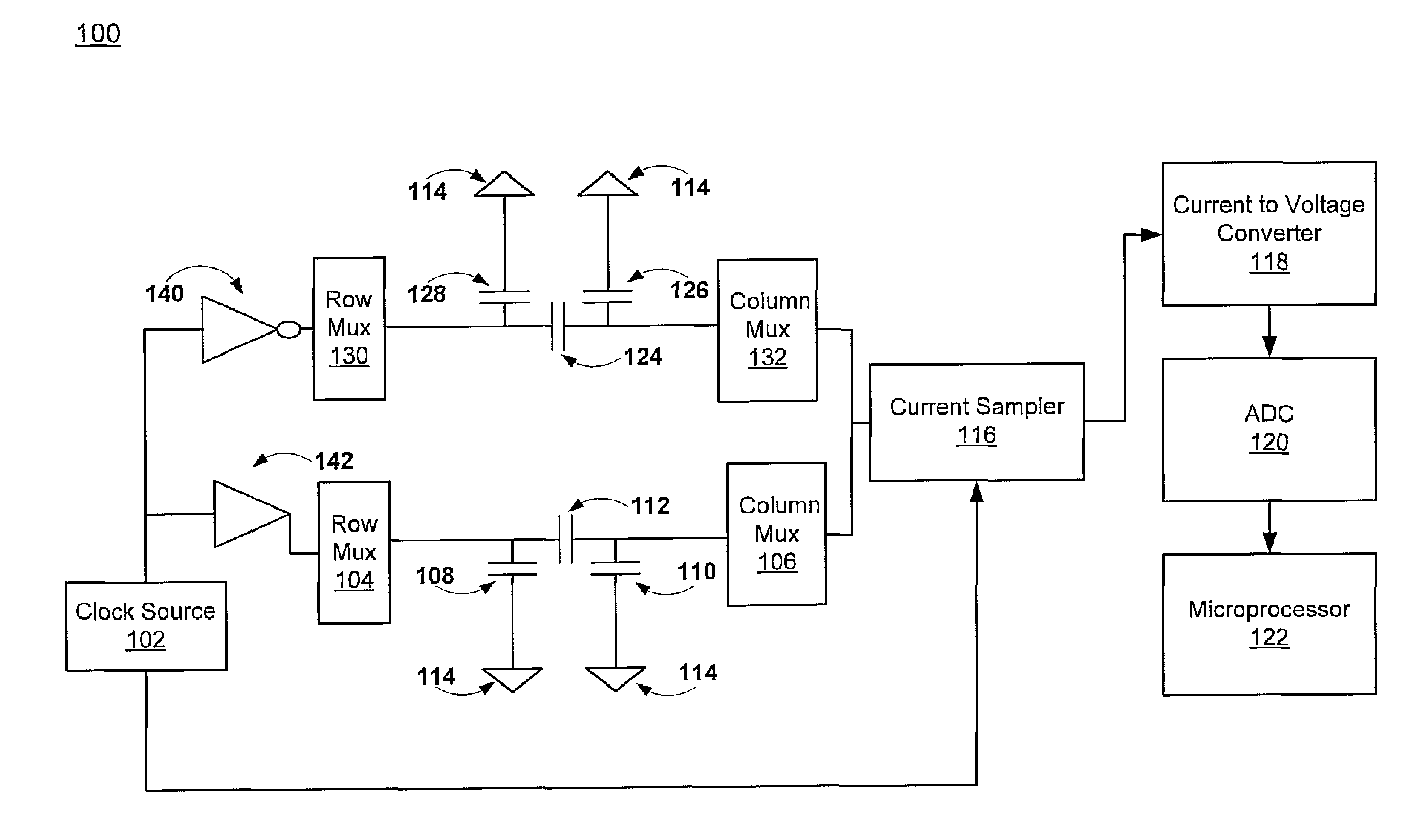

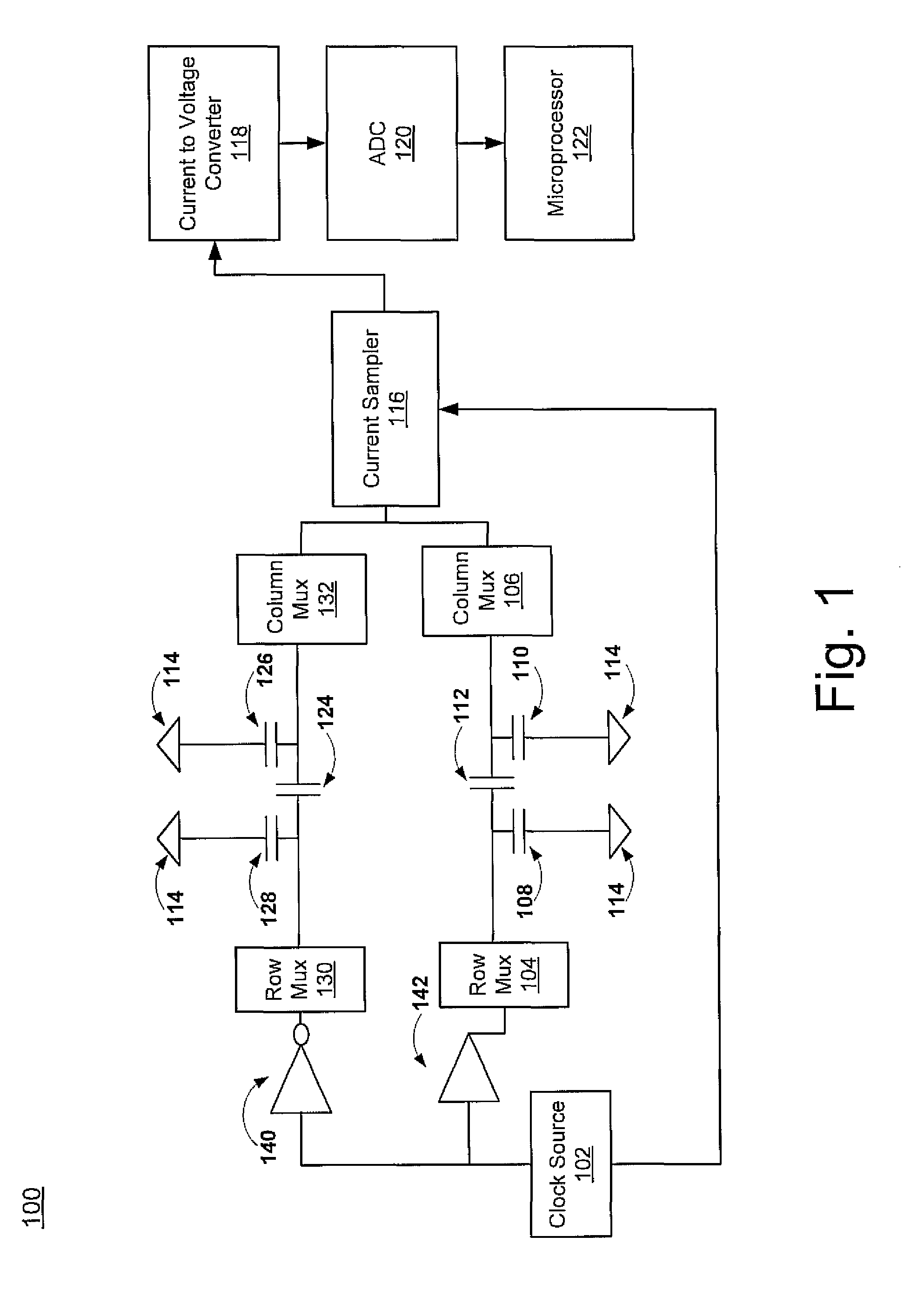

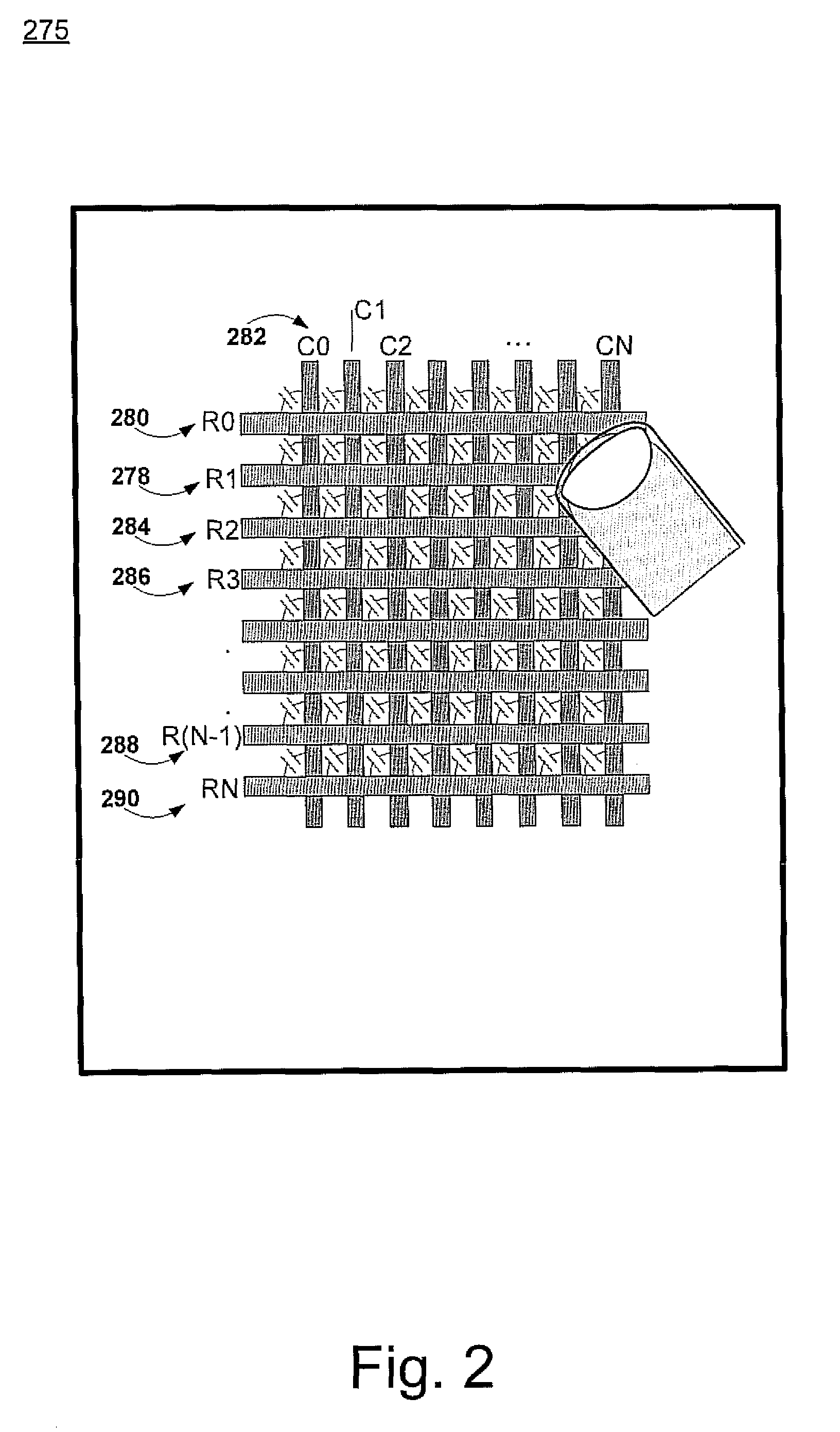

System and method to measure capacitance of capacitive sensor array

ActiveUS8321174B1Accelerated settlementFew measurementDigital computer detailsSpeed measurement using gyroscopic effectsSensor arrayEngineering

A system and method for measuring capacitance of a capacitive sensor array is disclosed. Upon measuring the capacitance, position information with respect to the sensor array may be determined. A column, a first row, and a second row of a capacitive sensor array may be selected. The first row and the second row intersect with the column of the capacitive sensor array. A differential capacitance between the first row and the second row may be measured. The differential capacitance may be utilized in determining a location of an object proximate to the capacitive sensor array.

Owner:CYPRESS SEMICON CORP

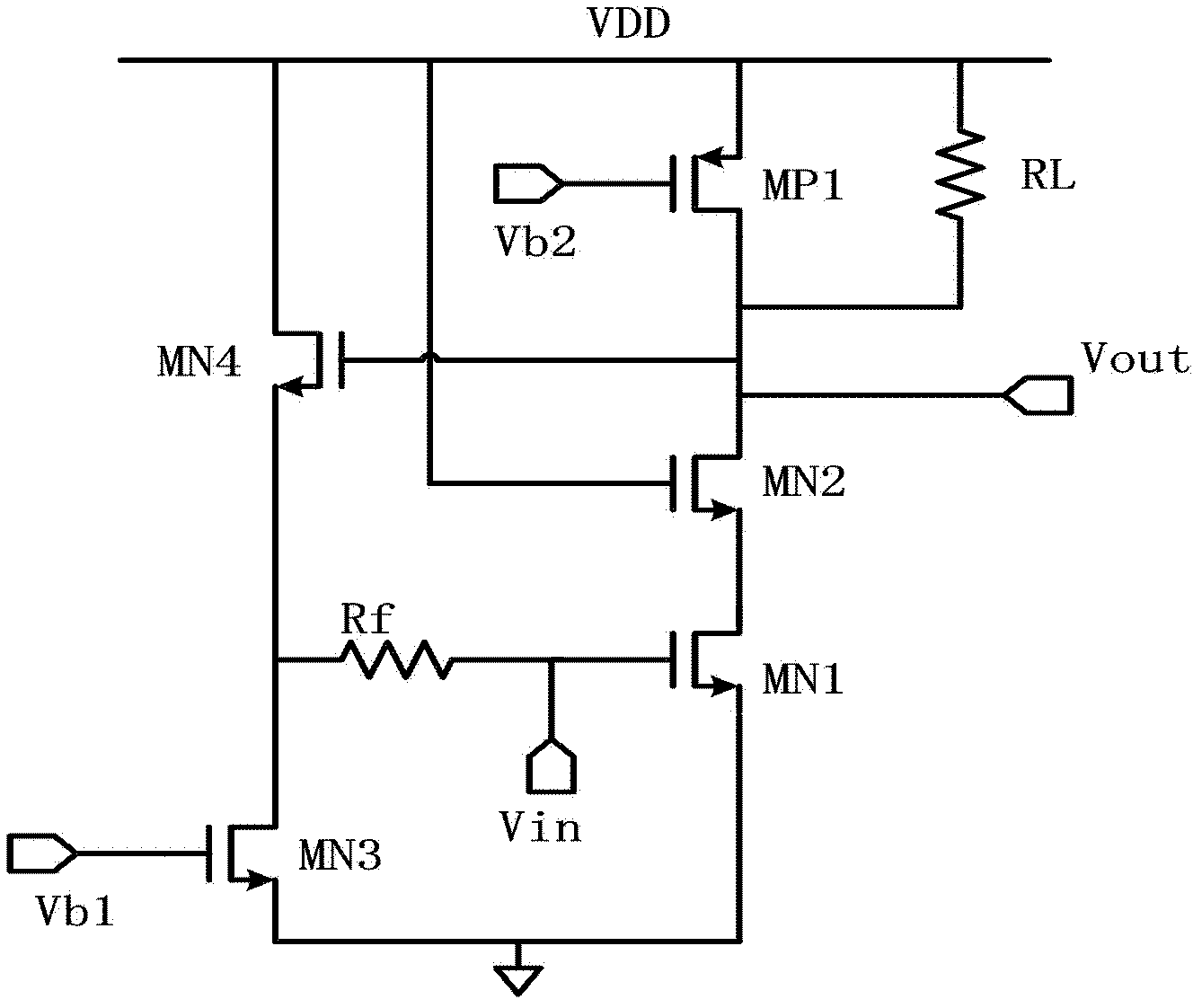

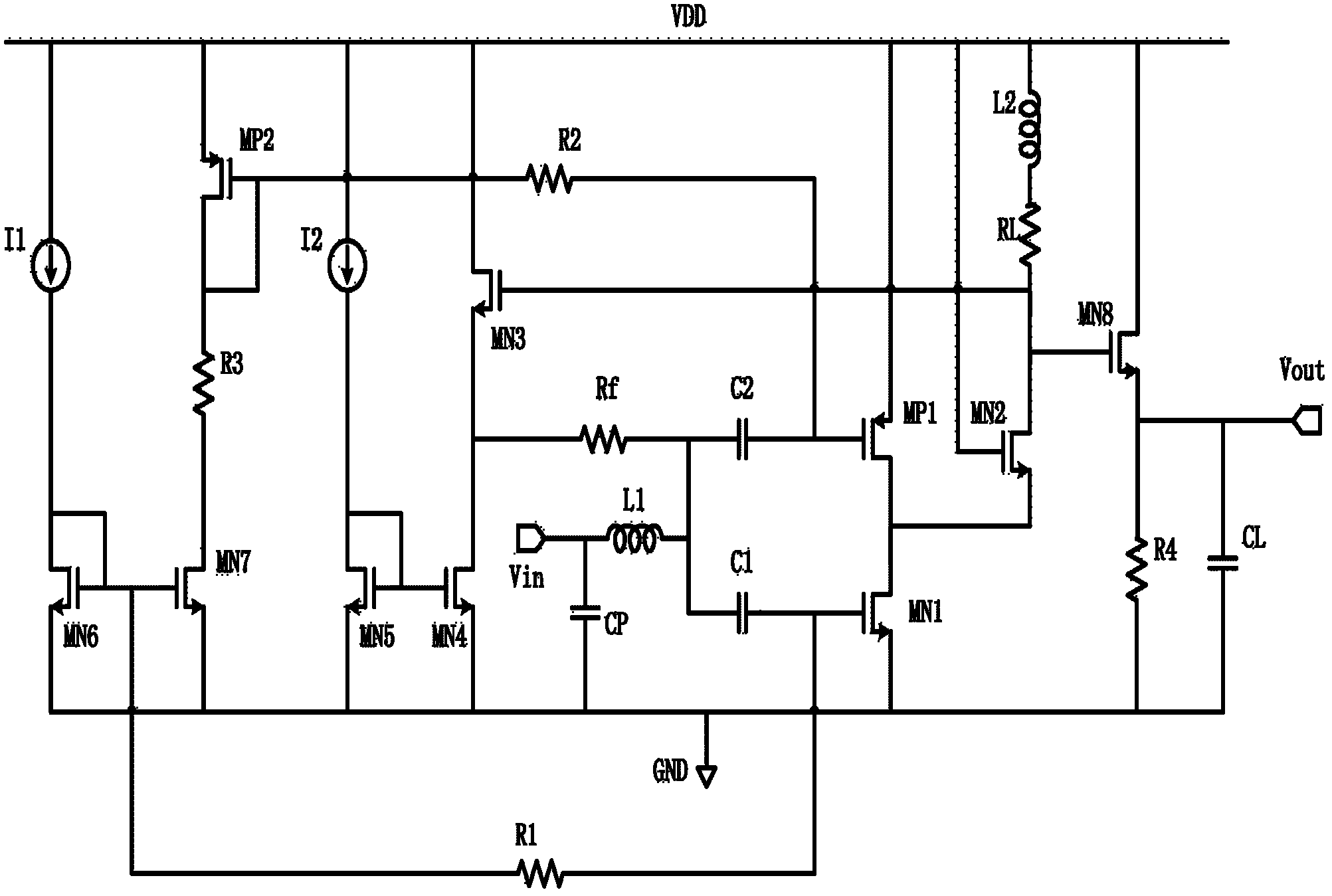

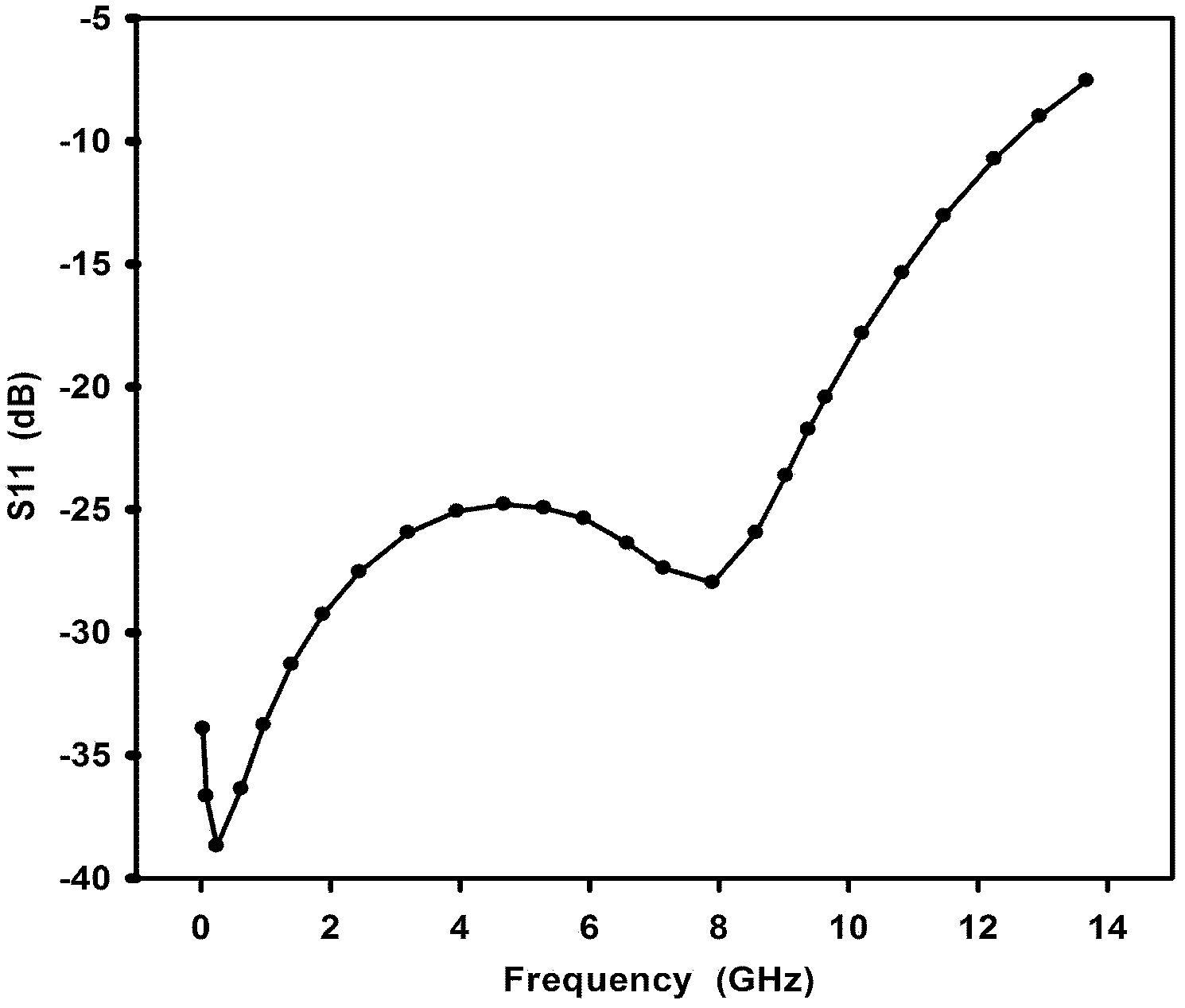

Radio-frequency ultra-wideband low-noise amplifier based on inductance compensation

InactiveCN102497167AImprove transconductanceHigh gainAmplifier modifications to reduce noise influenceHigh frequency amplifiersUltra-widebandTuned amplifier

The invention discloses a radio-frequency ultra-wideband low-noise amplifier based on inductance compensation, relating to a radio-frequency integrated circuit technology. The radio-frequency ultra-wideband low-noise amplifier mainly consists of an input amplification-stage circuit, a feedback-stage circuit, a matching-stage circuit, a load-stage circuit, a bias-stage circuit and an output buffering-stage circuit jointly. According to the radio-frequency ultra-wideband low-noise amplifier, both the input matching stage and the load stage are subjected to inductance compensation, and the sensitivity of the low-noise amplifier on the technology is reduced by adopting a current multiplexing technology with independent bias, so that the performance is more stable, the ultra-wideband is also realized, and the working frequency range is 0.1-12GHz; meanwhile, the radio-frequency ultra-wideband low-noise amplifier gets favorable indexes, such as noise, linearity, gain, power consumption and the like and is suitable for an ultra-wideband multi-standard wireless communication receiving system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

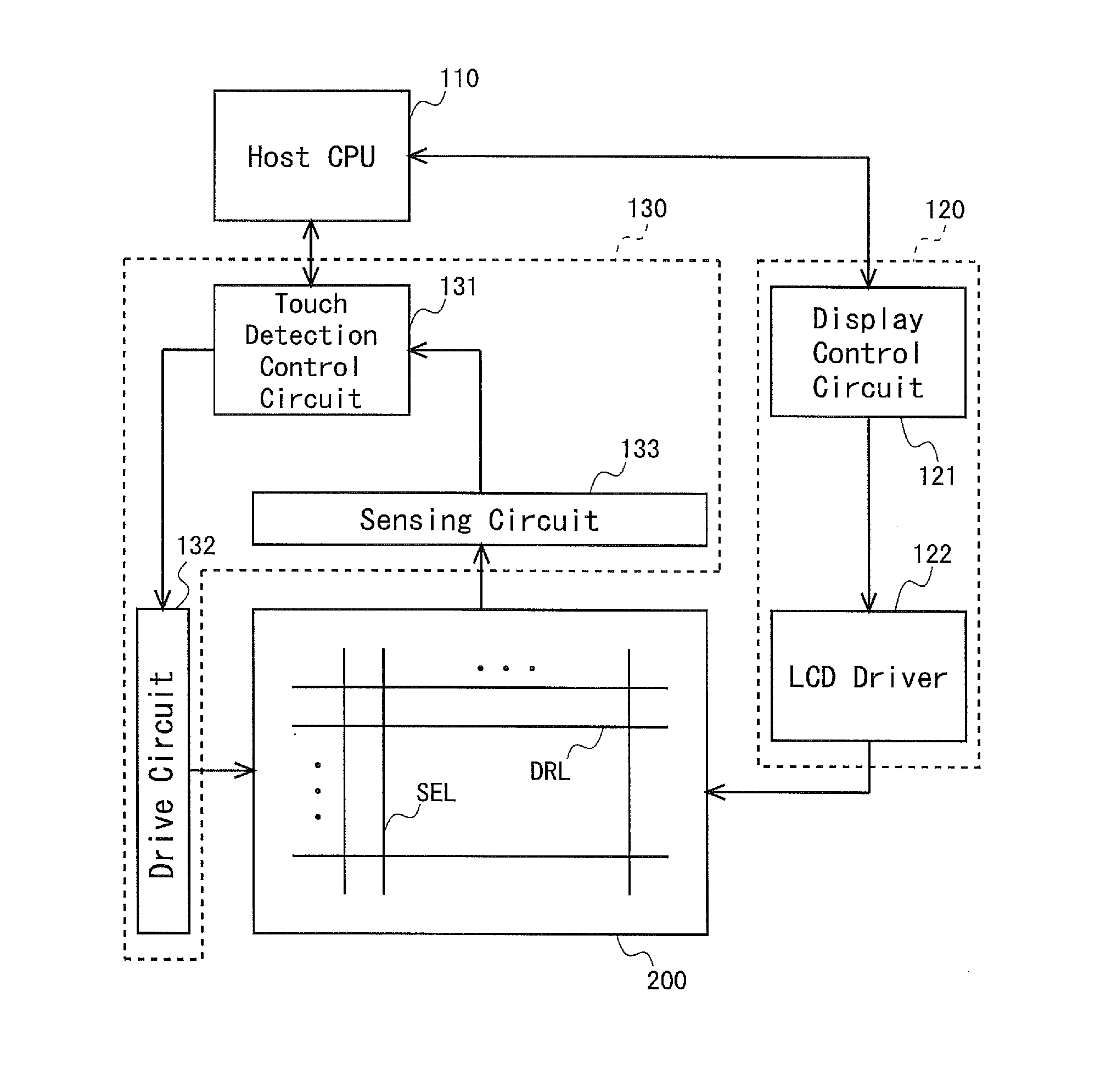

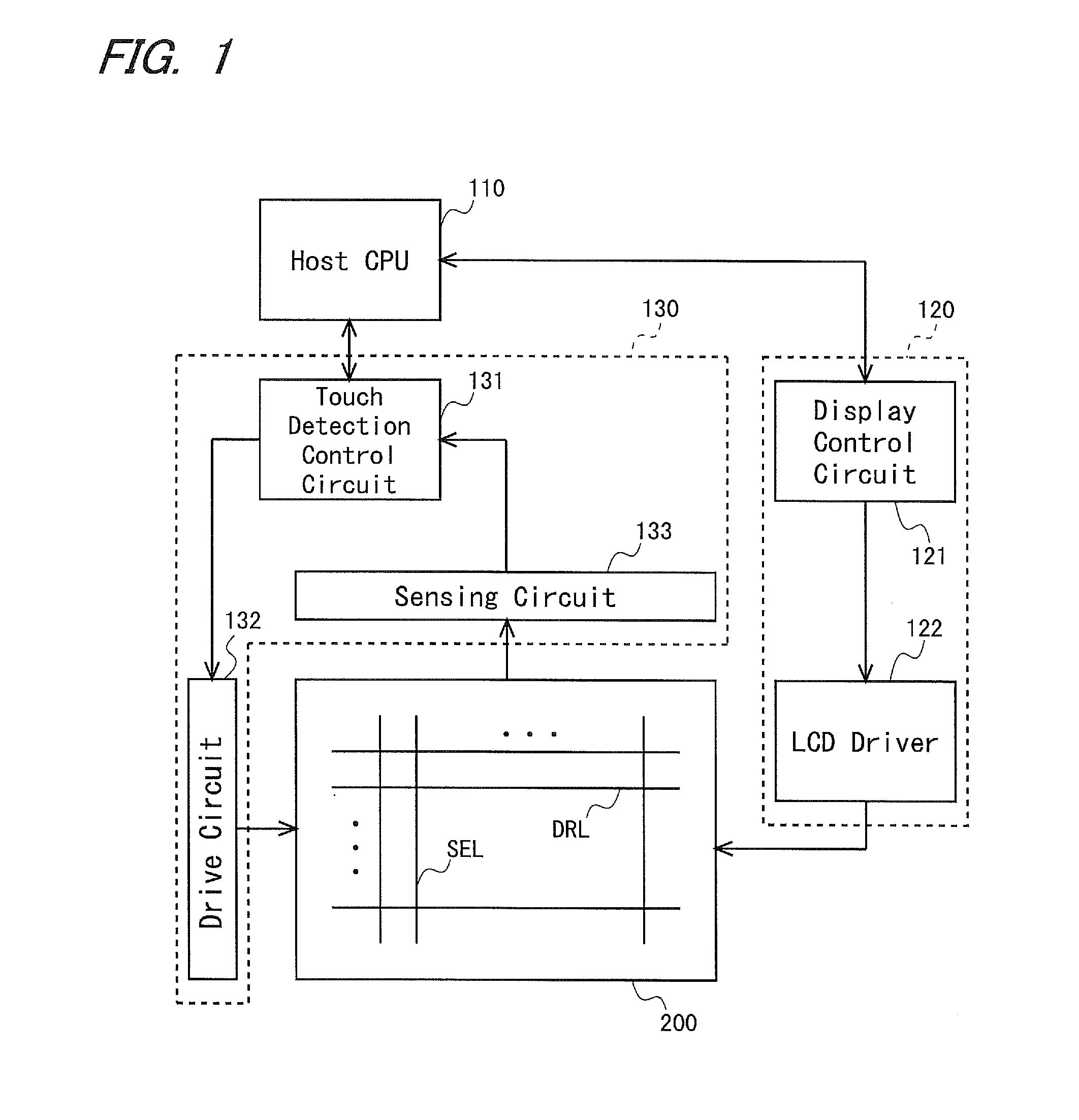

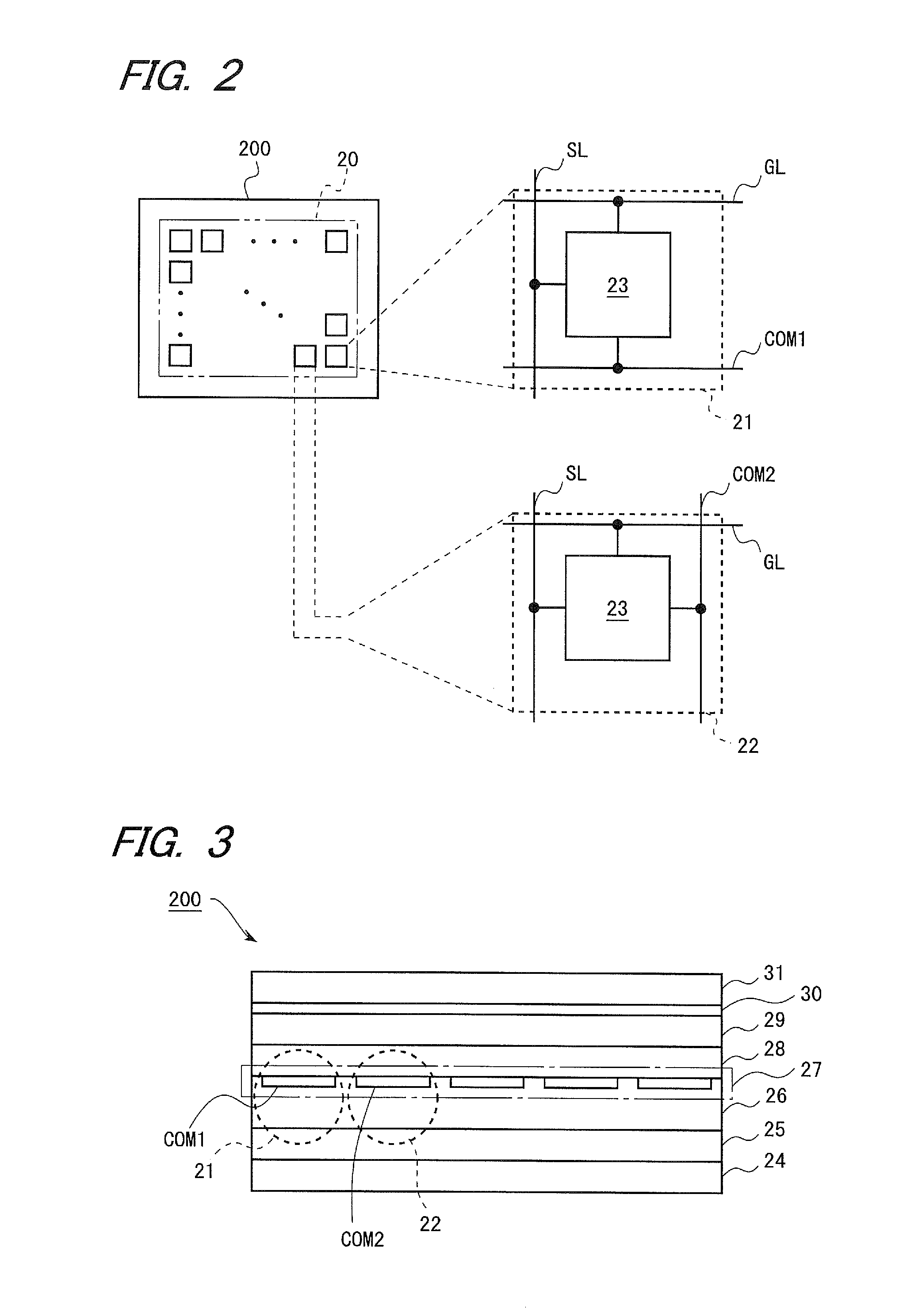

Touch-sensor-embedded display panel, display device provided therewith, and method for driving touch-sensor-embedded display panel

ActiveUS20140327654A1Eliminates auxiliary capacitanceReduce aperture ratioStatic indicating devicesNon-linear opticsCapacitanceDisplay device

There is provided a touch-sensor-embedded display panel with reduced decrease in aperture ratio and reduced increase in frame area, with lowered power consumption and improved operation performance.A driving pixel (21) is constituted by: a thin film transistor (T1); a pixel electrode (Epix1); a driving common electrode (COM1); and a liquid crystal capacitance (Clc1) which is formed between the pixel electrode (Epix1) and the driving common electrode (COM1). A sensing pixel (22) is constituted by a thin film transistor (T2), a pixel electrode (Epix2), a sensing common electrode (COM2), and a liquid crystal capacitance (Clc2) which is formed between the pixel electrode (Epix2) and the sensing common electrode (COM2). Neither the driving pixel (21) nor the sensing pixel (22) include an auxiliary capacitance. The thin film transistors (T1, T2) have their channel layers formed of IGZO.

Owner:SHARP KK

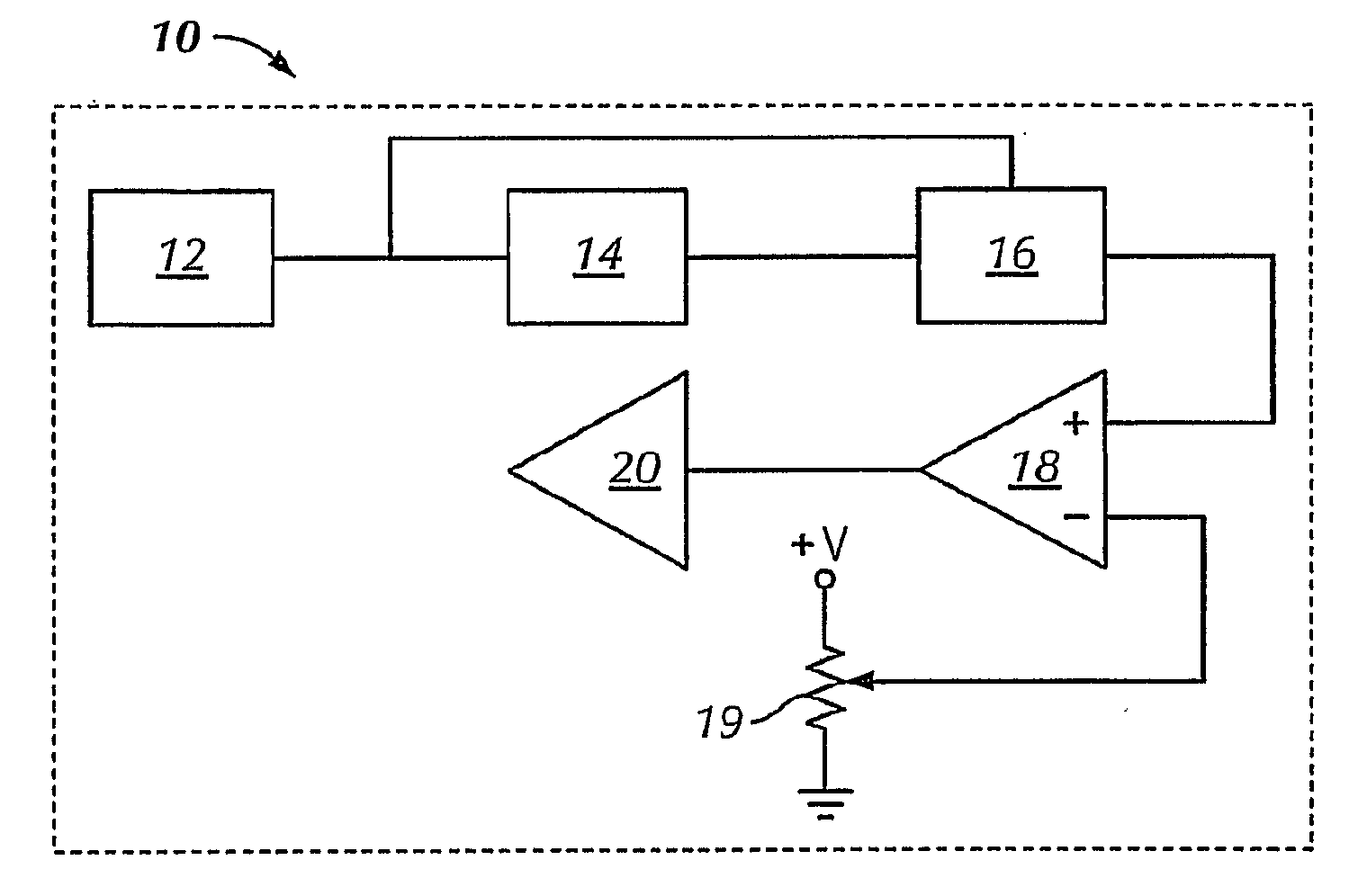

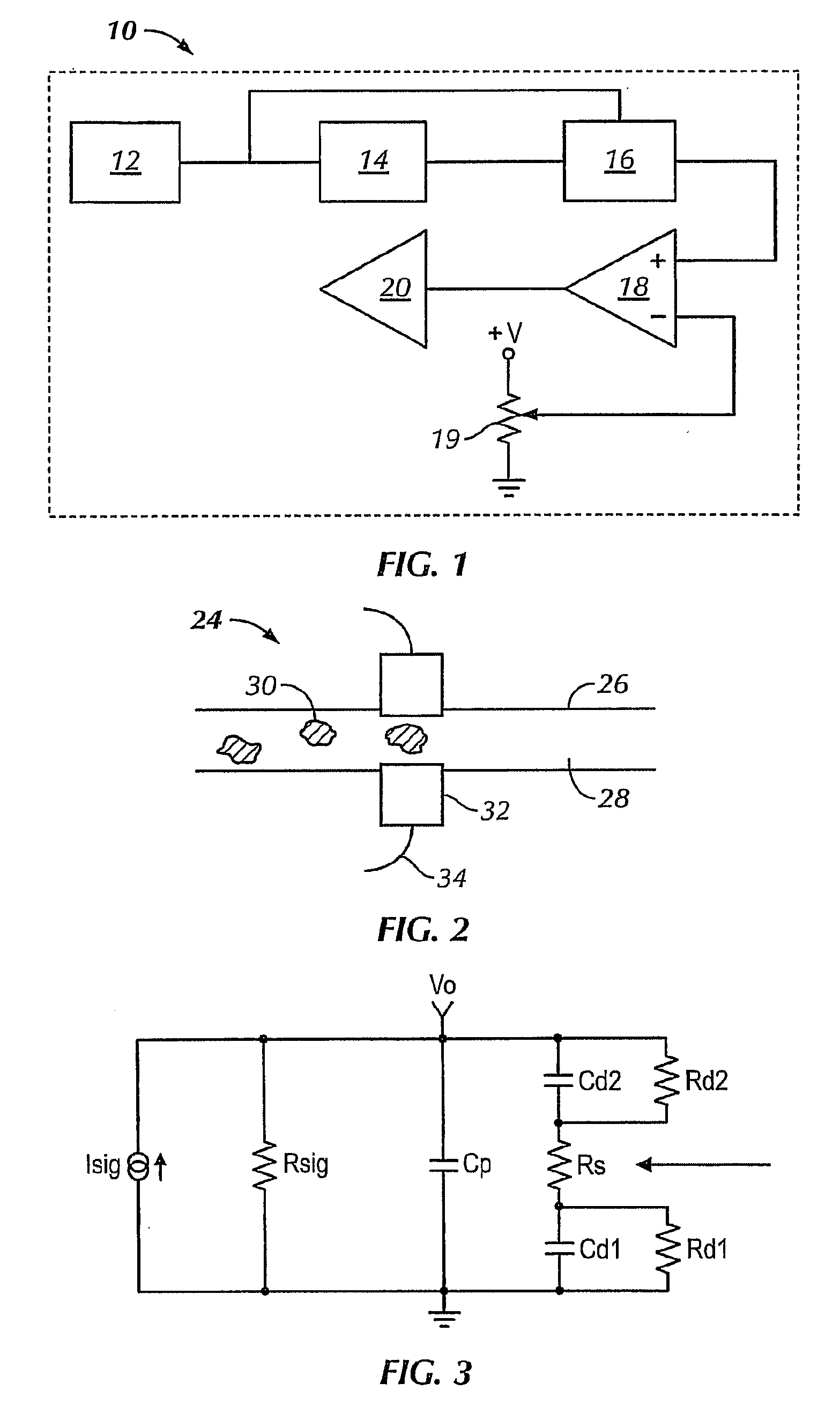

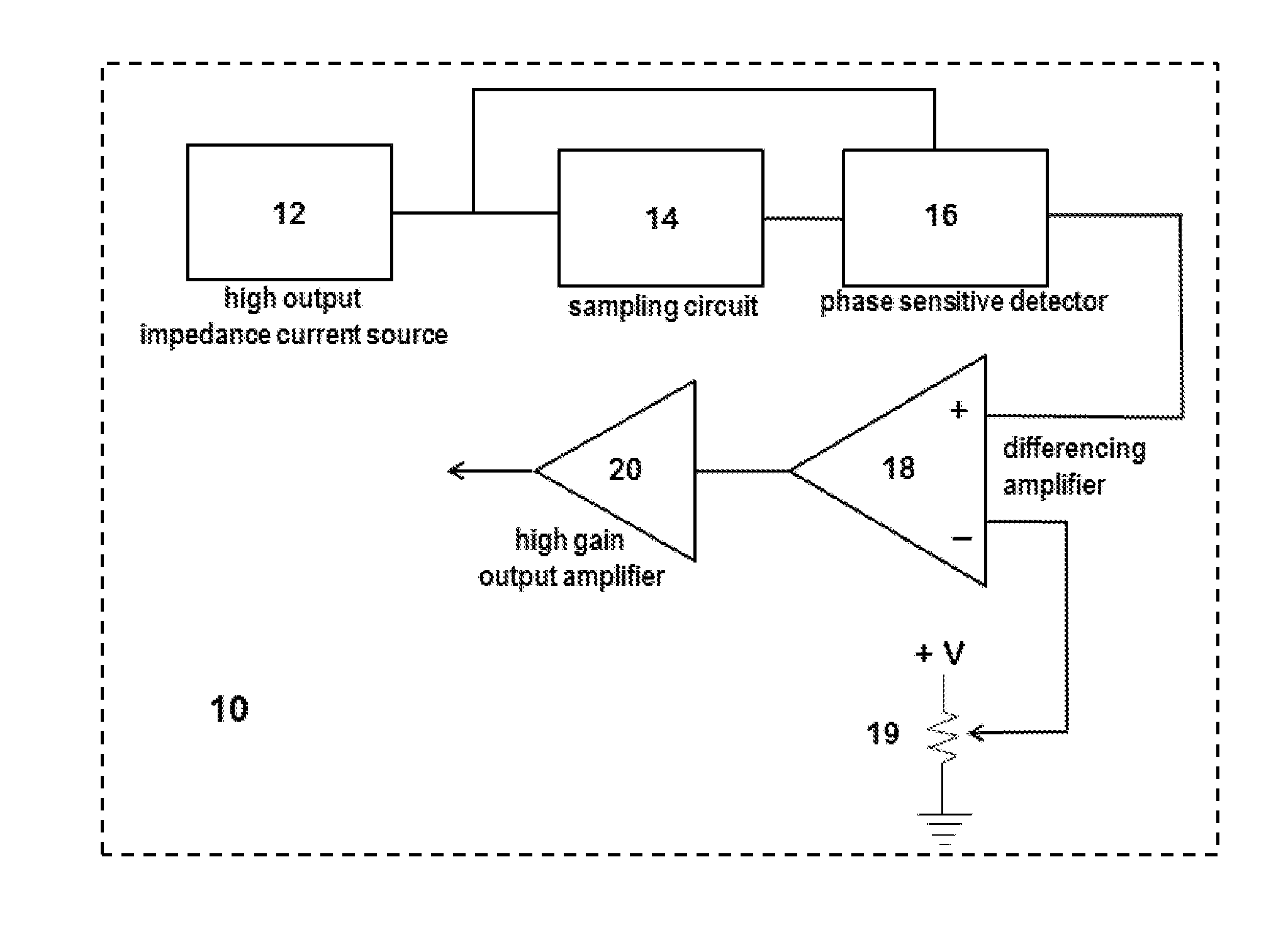

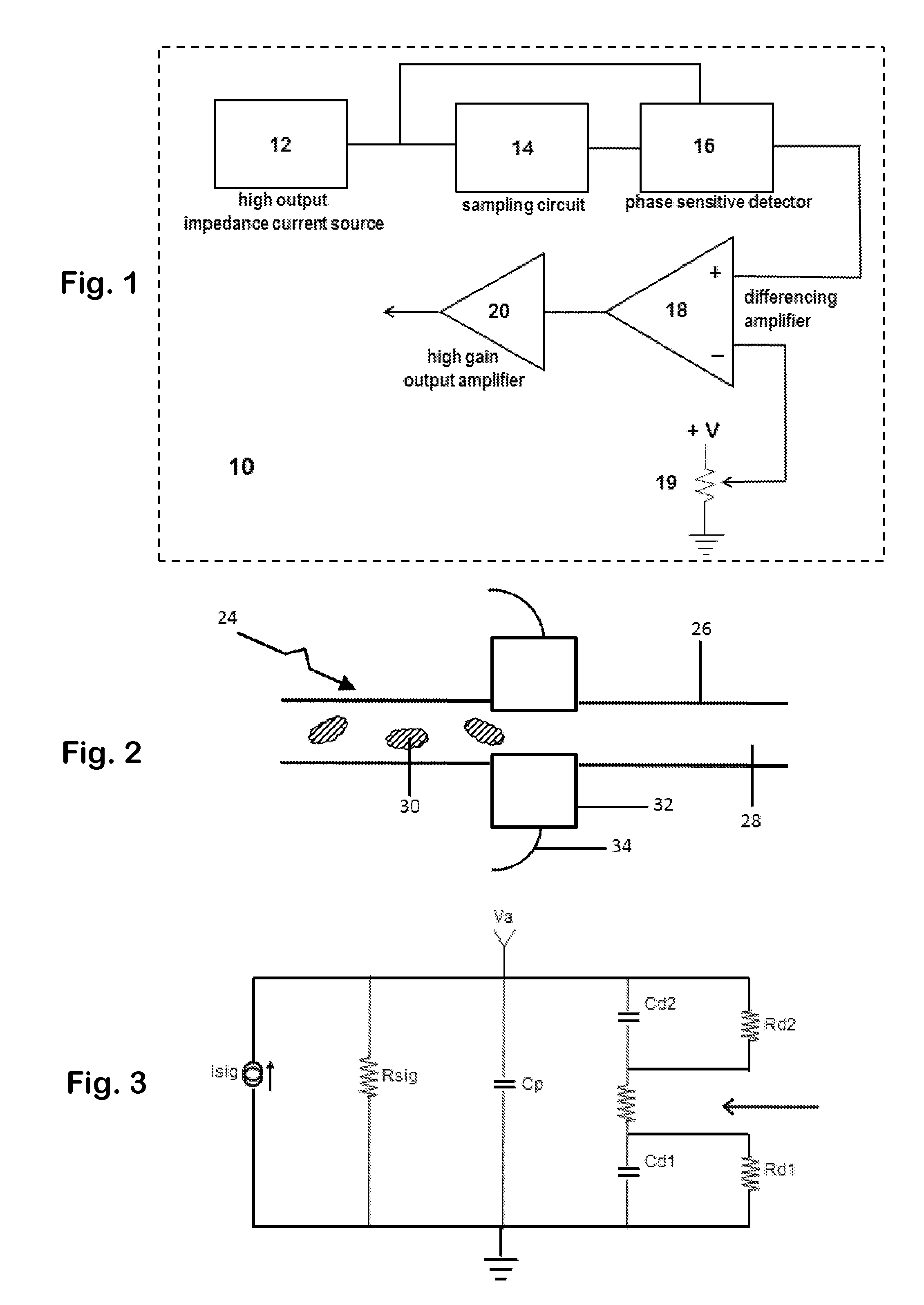

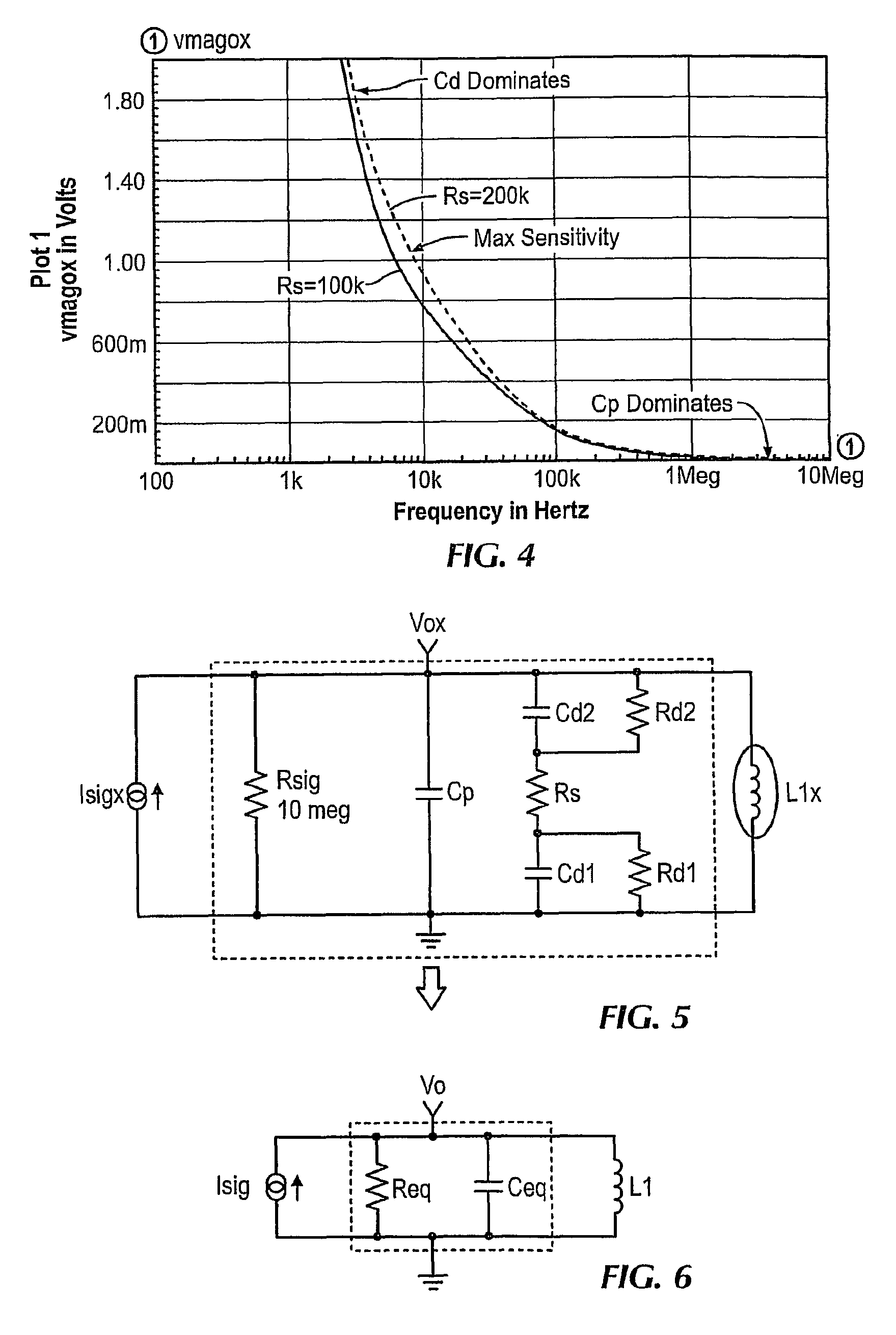

Conductivity Counter

ActiveUS20090212788A1Eliminate capacitanceImprove signal-to-noise ratioFluid resistance measurementsMaterial impedanceCapacitancePhase sensitive

A conductivity counter and method of determining conductivity of a fluid sample are disclosed. The counter is suitable for high-speed, accurate counting of discrete events or items, such as cancer cells, passing through a fluid sample cell. A variable frequency current source is used to supply an excitation current to a sample cell connected in parallel with an inductance or the electrical equivalence of an inductance. This configuration can be accurately modeled as a parallel RLC circuit when the system is operated at a stable frequency. The current source frequency is tuned to the resonance frequency of the equivalent RLC circuit, which effectively eliminates the capacitive and inductive components of the impedance, leaving only purely resistive components. The output of the equivalent RLC circuit is connected to a high input impedance buffer amplifier and then to a phase sensitive detector, which detects the phase shift resulting from the equivalent RLC circuit. The output is filtered and a differencing amplifier is used to zero out the output signal due to the system components and the sample cell buffer solution prior to taking active readings. The remaining output signal is due to perturbations in the fluid sample, such as passing cancer cells. This output is sent to a high-gain output amplifier and then supplied to a suitable signal processing device or system, such as a computer.

Owner:BOARD OF SUPERVISORS OF LOUISIANA STATE UNIV & AGRI & MECHANICAL COLLEGE

Inter-chip communication

ActiveUS8021965B1Reduce power consumptionEliminate capacitanceFinal product manufactureSemiconductor/solid-state device detailsEngineeringQuilt packaging

Owner:UNIV OF NOTRE DAME DU LAC

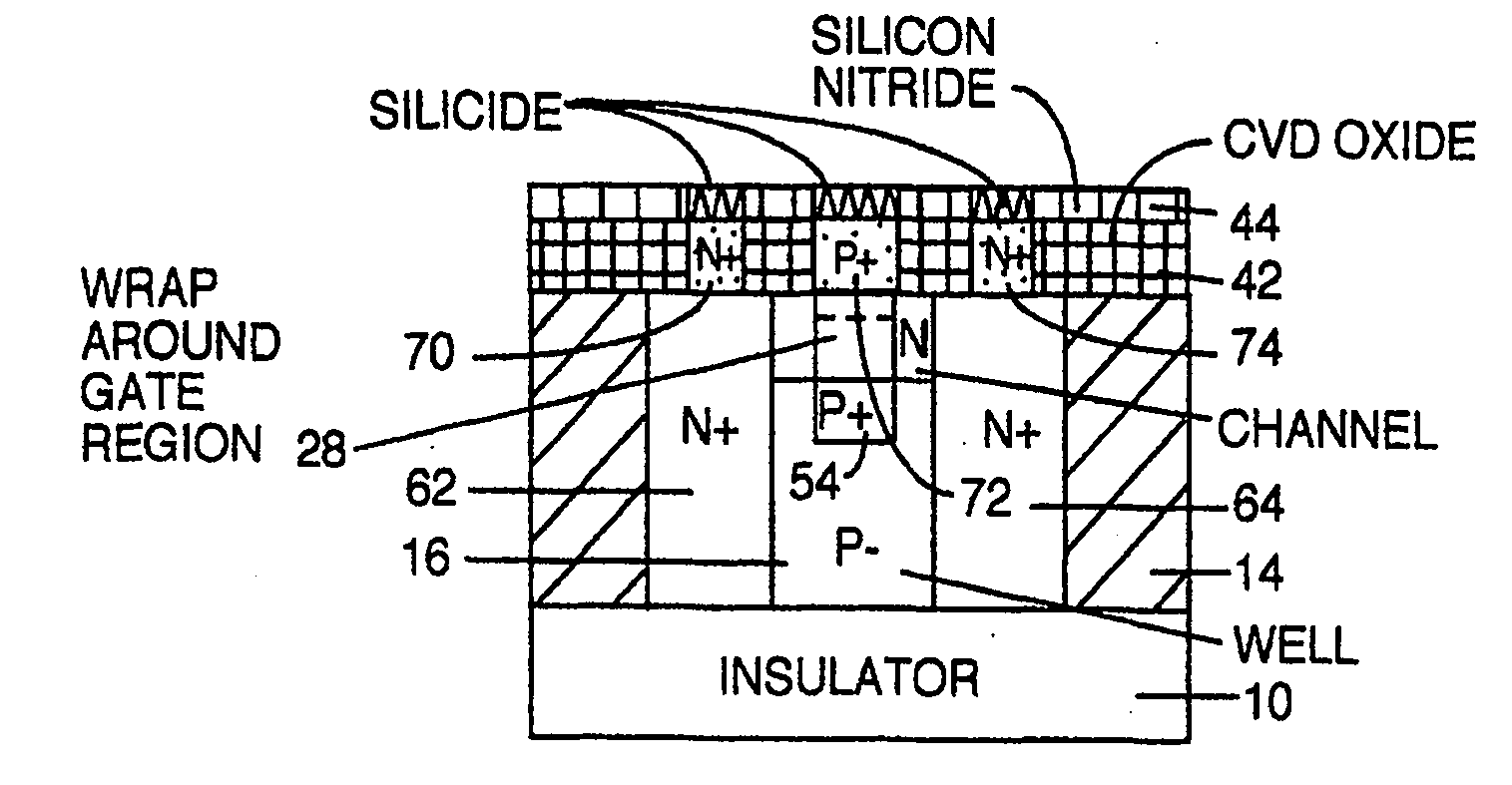

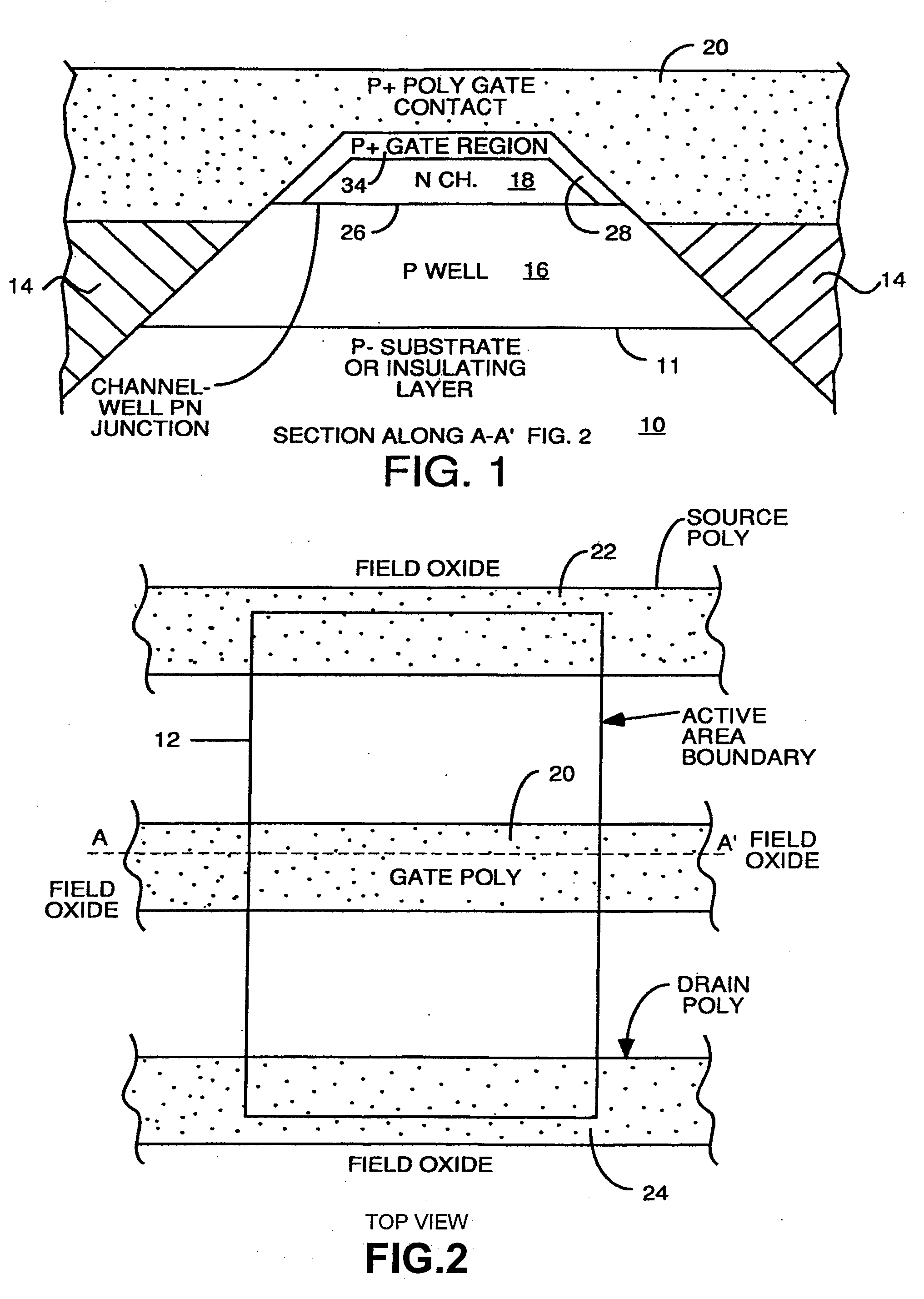

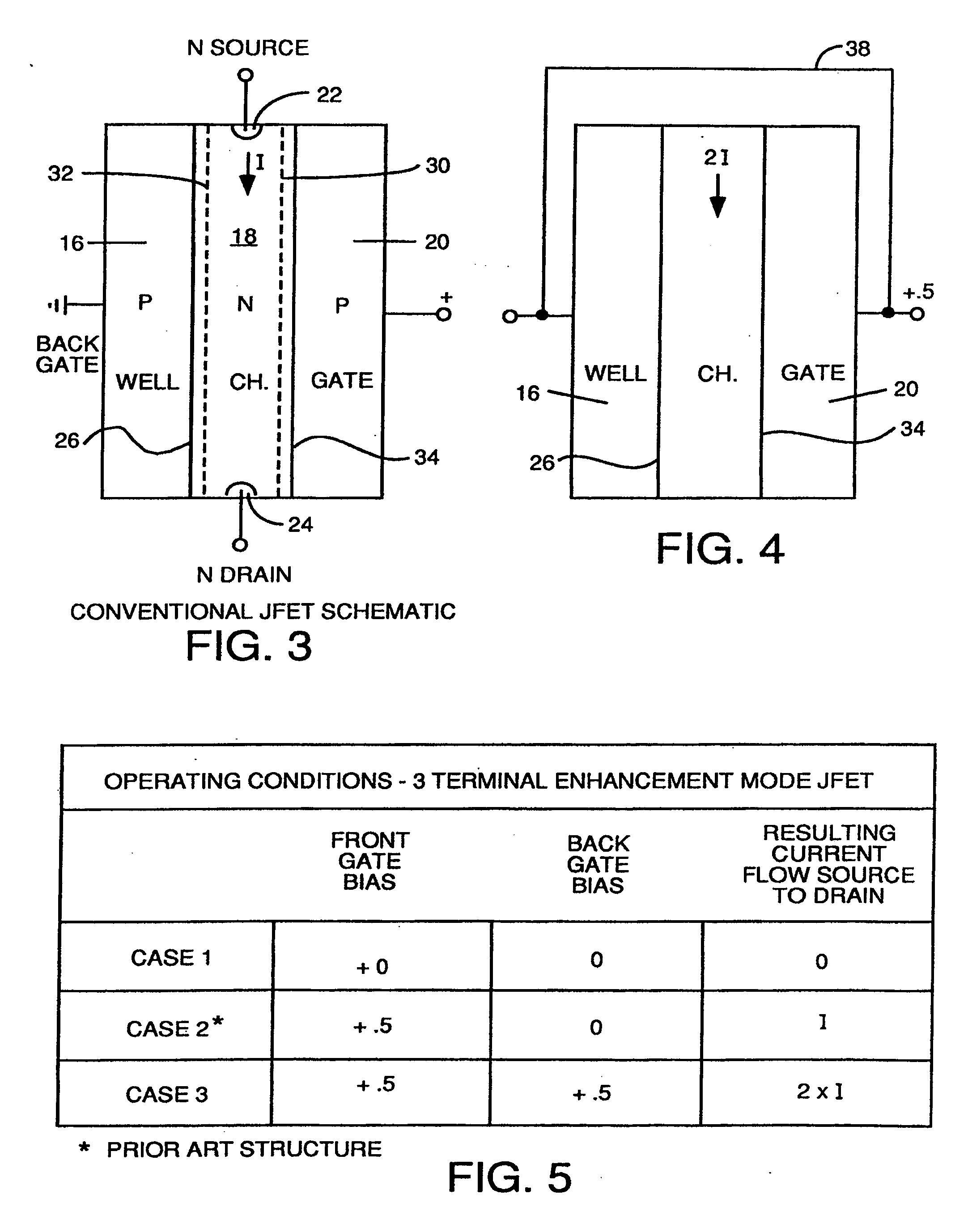

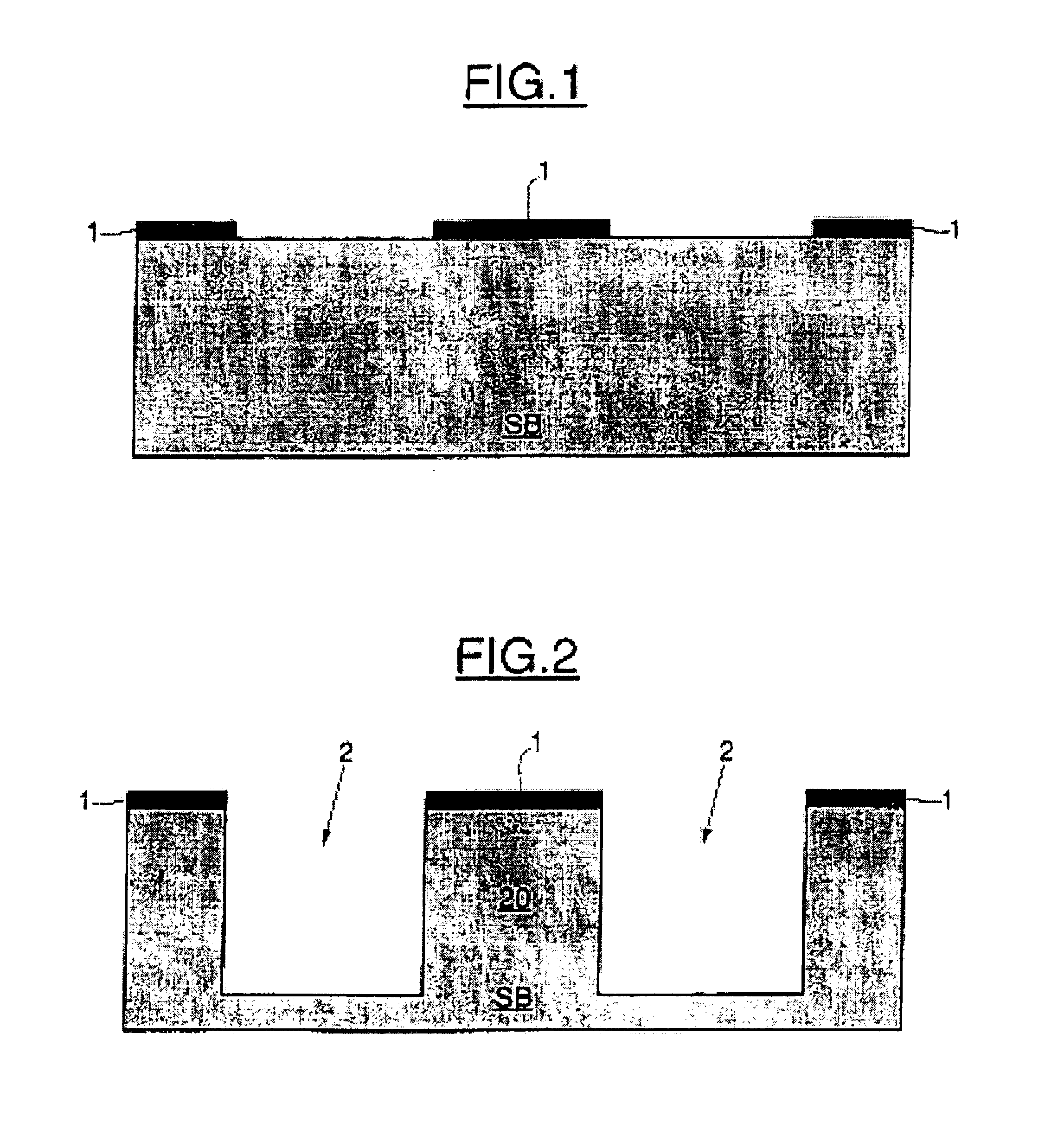

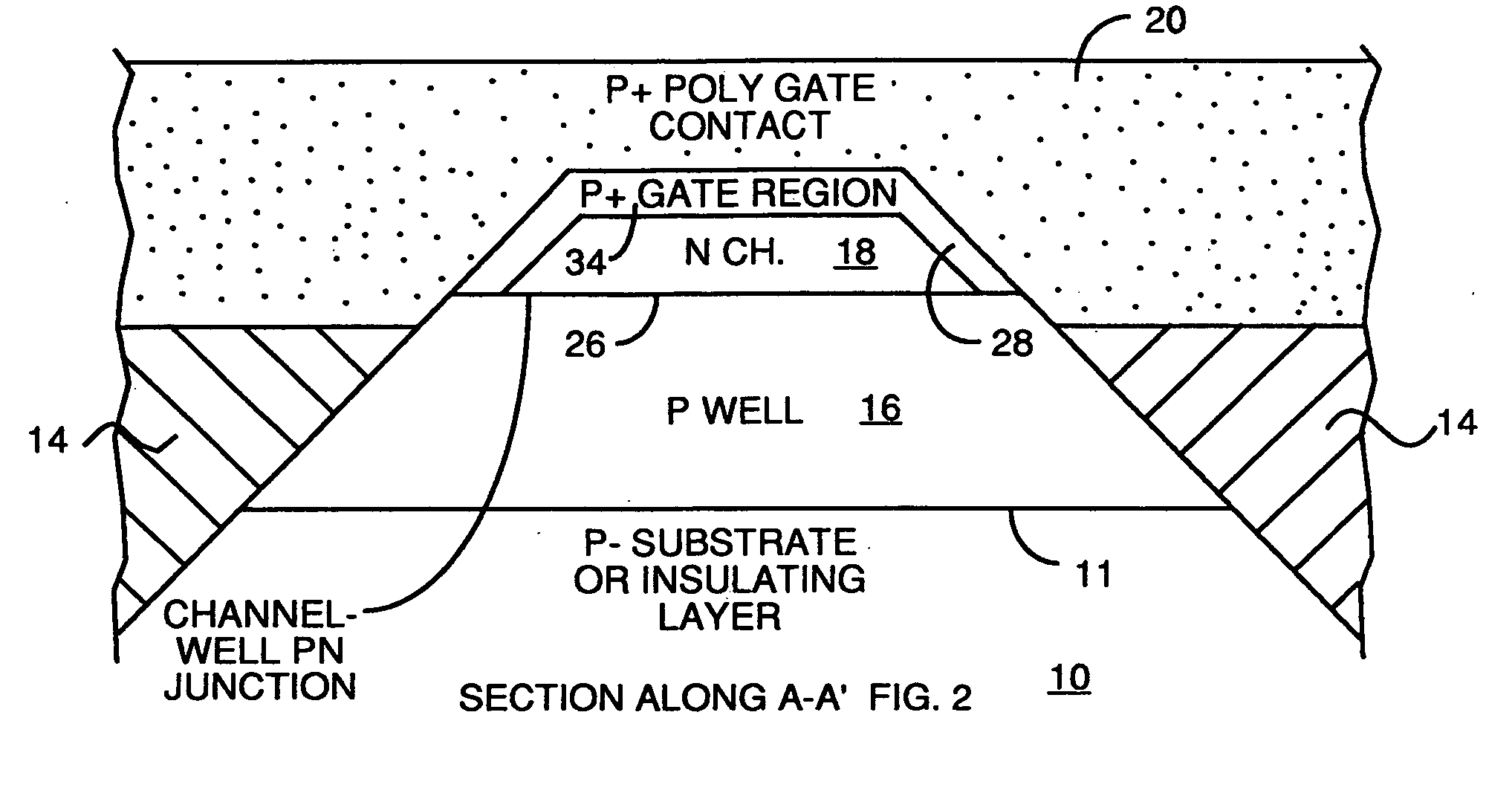

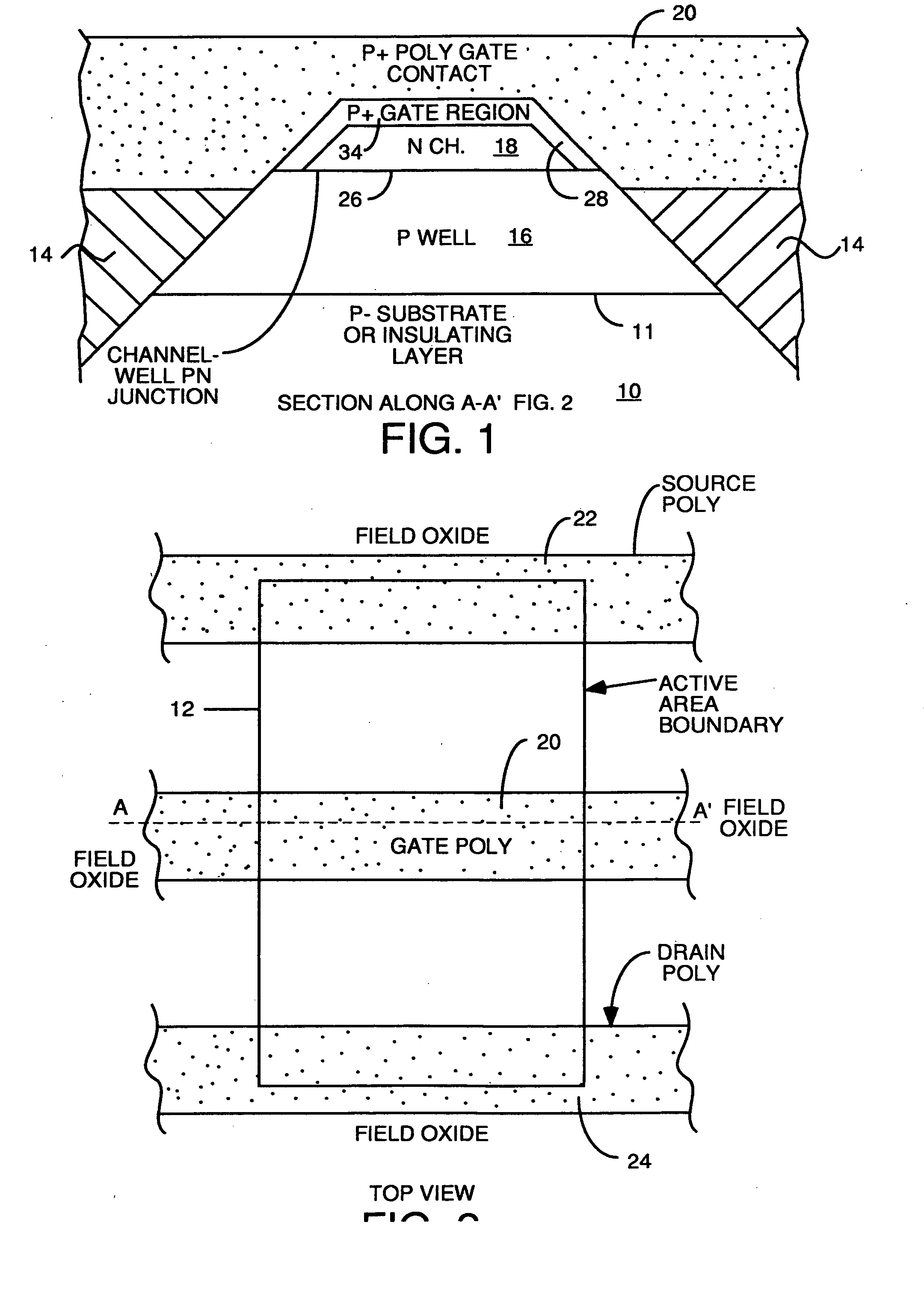

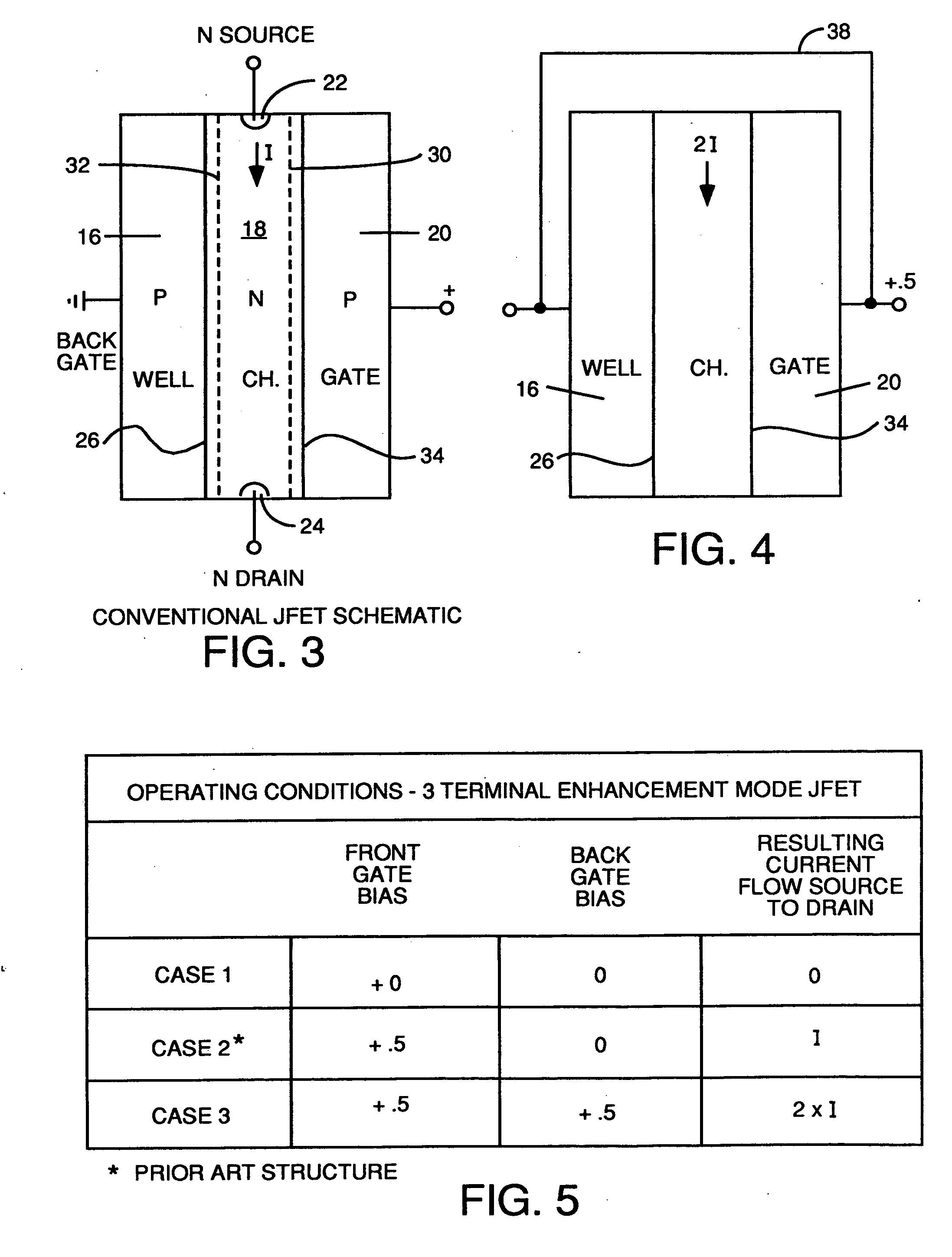

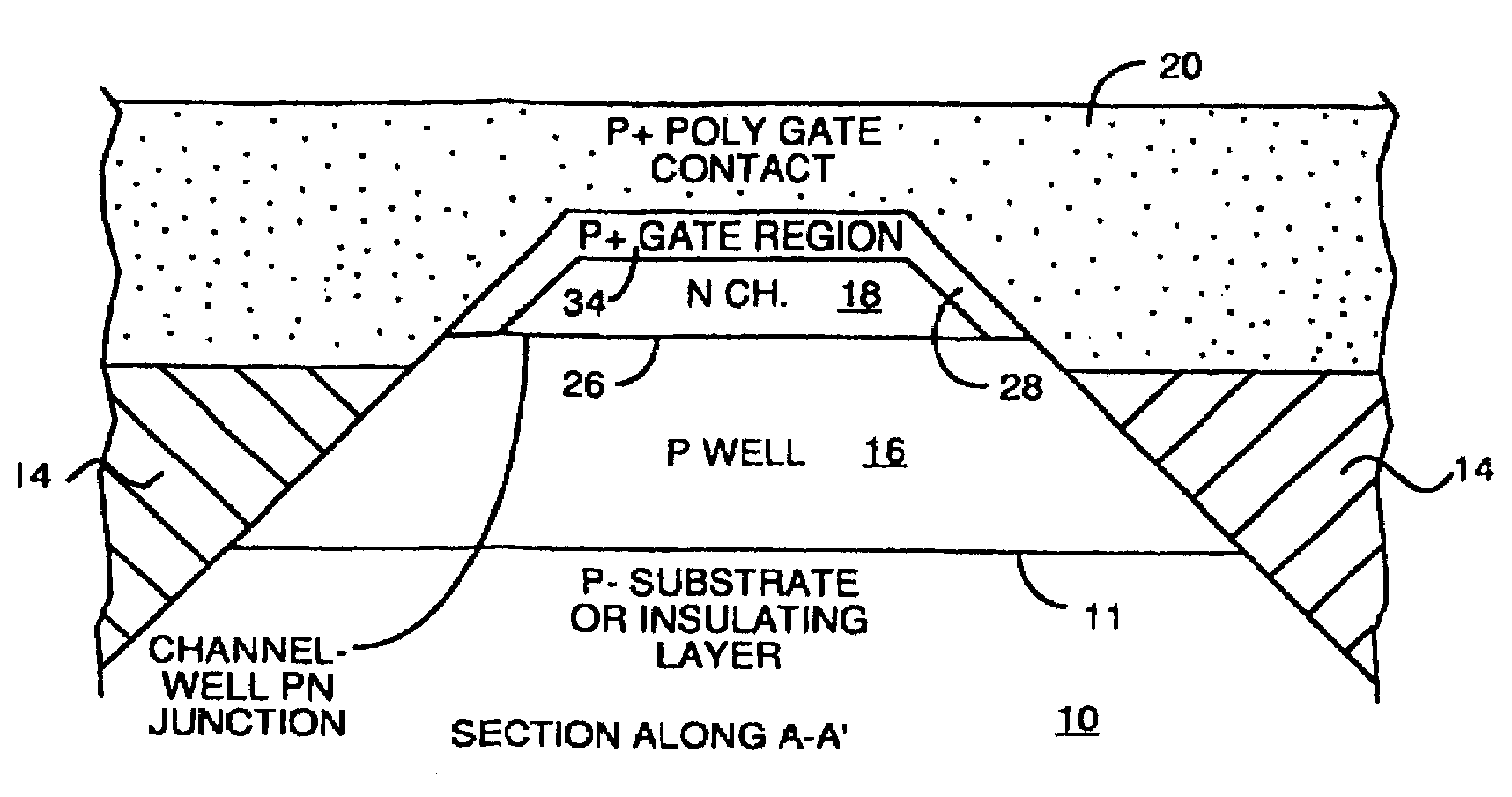

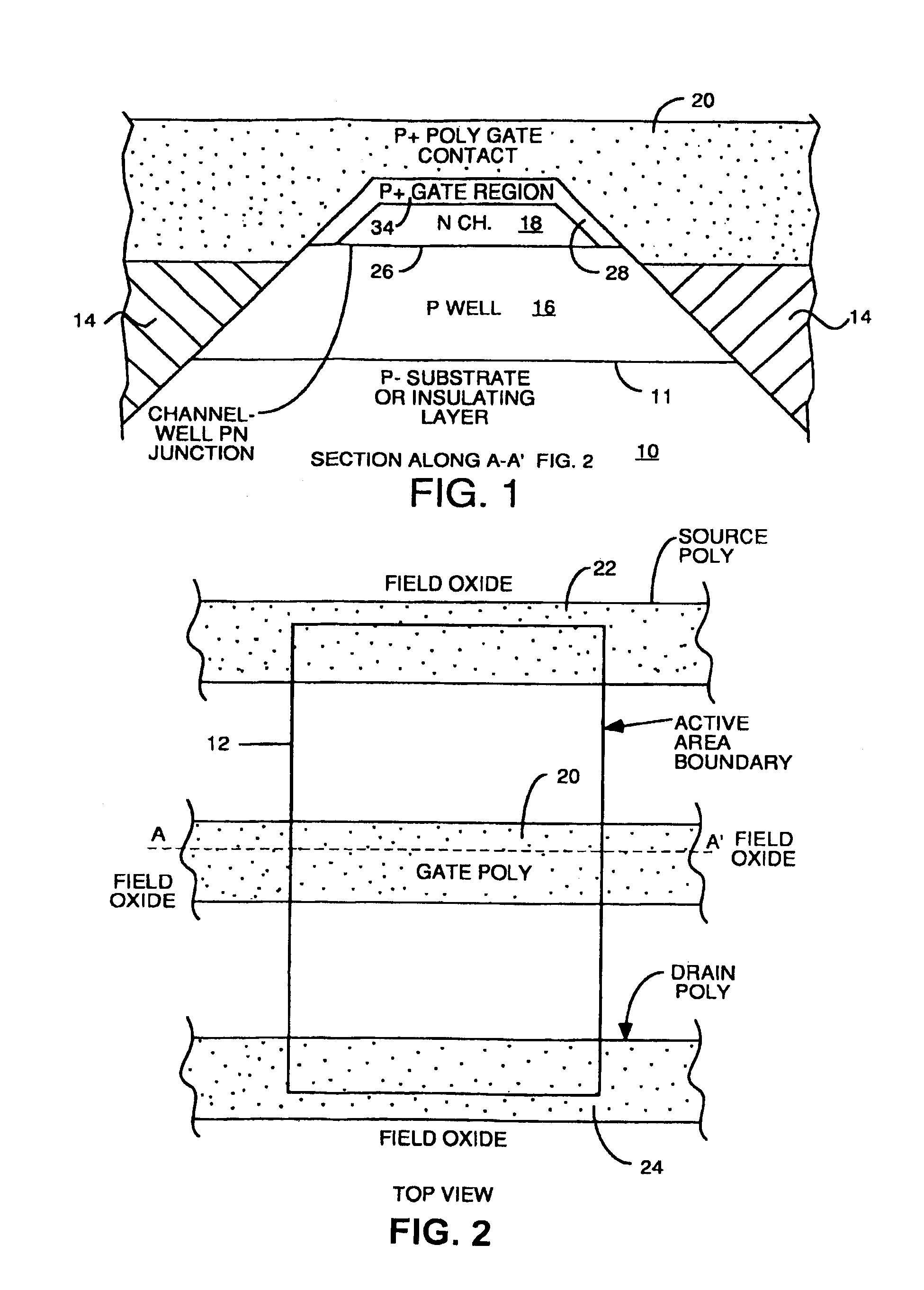

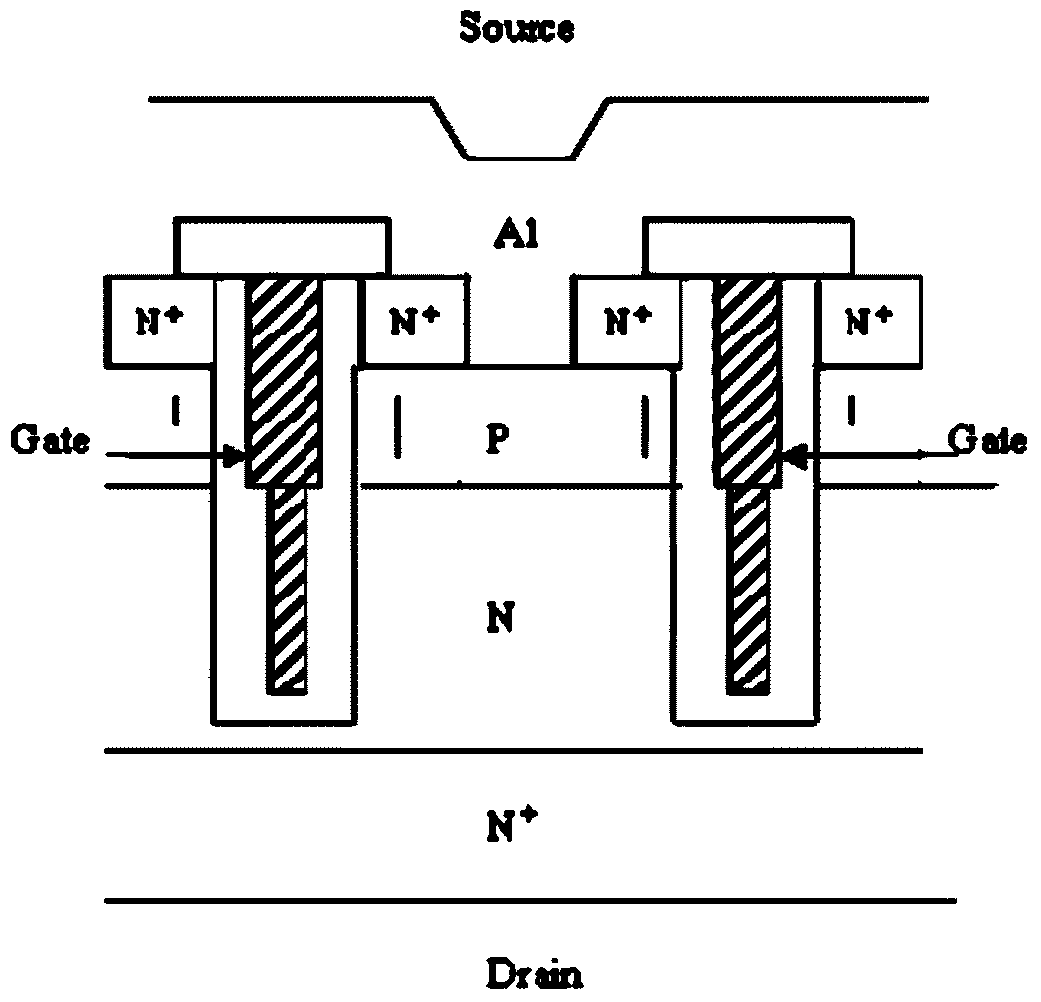

JFET With Built In Back Gate in Either SOI or Bulk Silicon

InactiveUS20090075435A1Disadvantages and reduced eliminatedProblems reduced eliminatedSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsEngineering

A process for manufacturing a Junction Field-Effect Transistor, comprises doping a semiconductor material formed on an insulating substrate with impurities of a first conductivity type to form a well region. The process continues by implanting impurities of a second conductivity type into said well region to form a channel region, and by implanting impurities of the first conductivity type in said well region to form a back gate region. The process continues by forming a trench to expose at least one sidewall of said channel region, wherein the trench extends far enough along the sidewall to expose at least a portion of said back gate region. The process continues by depositing polysilicon to fill said trench along the at least one sidewall of said channel region and at least a portion of said back gate region, wherein at least a portion of the polysilicon will form a gate contact. The polysilicon is then doped with impurities of a first conductivity type. The process concludes by annealing the polysilicon to activate the doped impurities and to cause the doped impurities to diffuse along the at least one sidewall of said channel region so as to form a top gate region. The top gate region extends far enough to make electrical contact with said back gate region.

Owner:MIE FUJITSU SEMICON

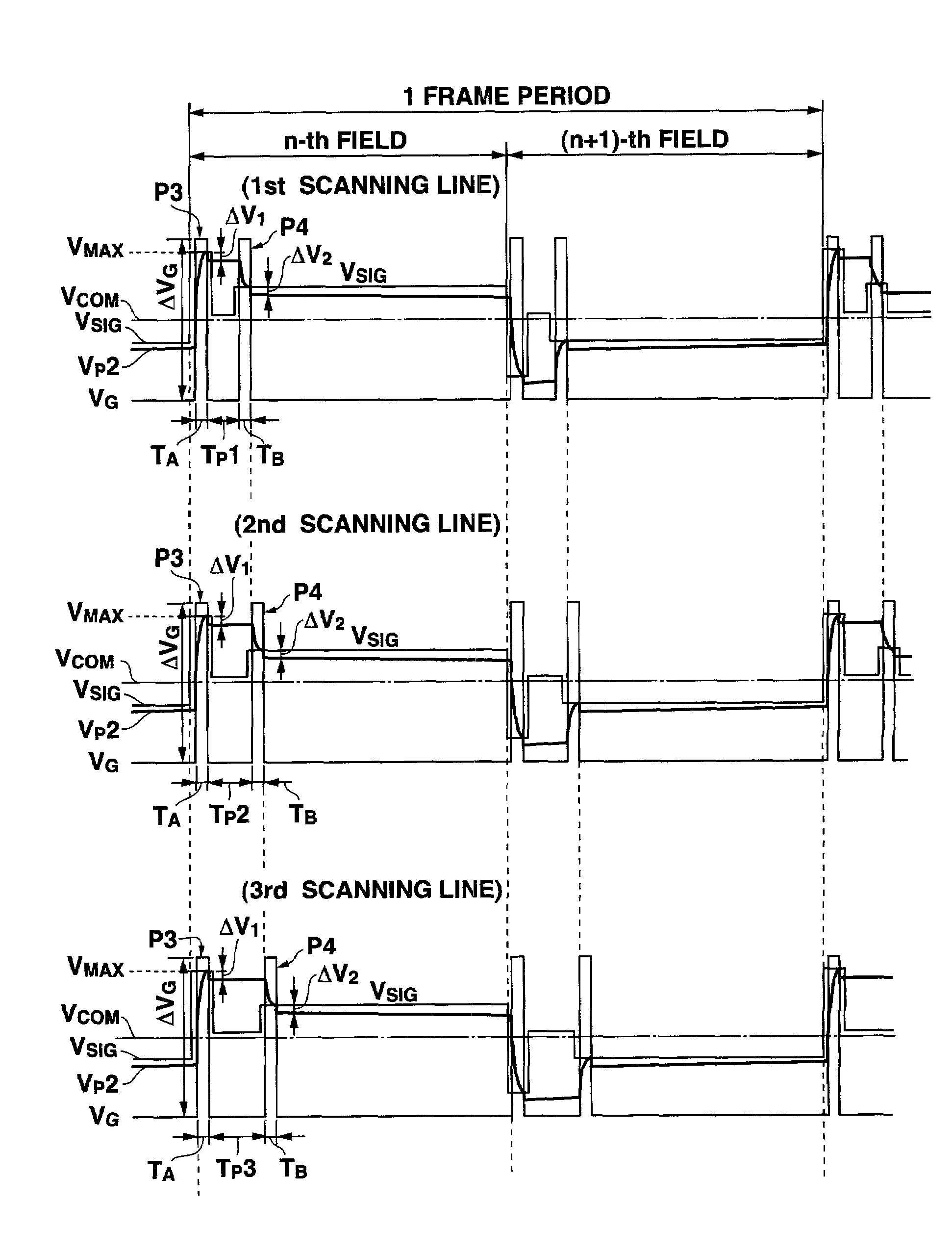

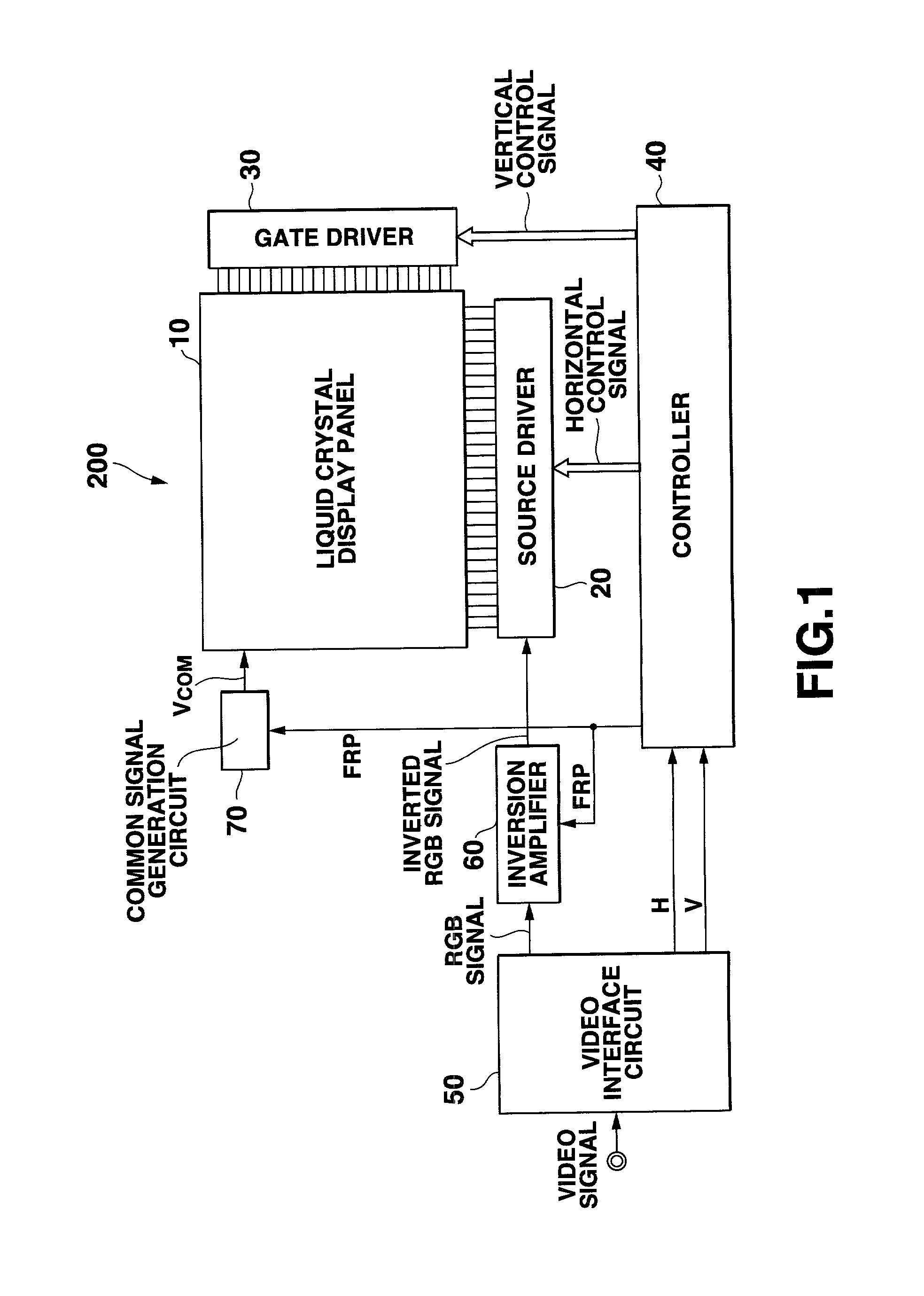

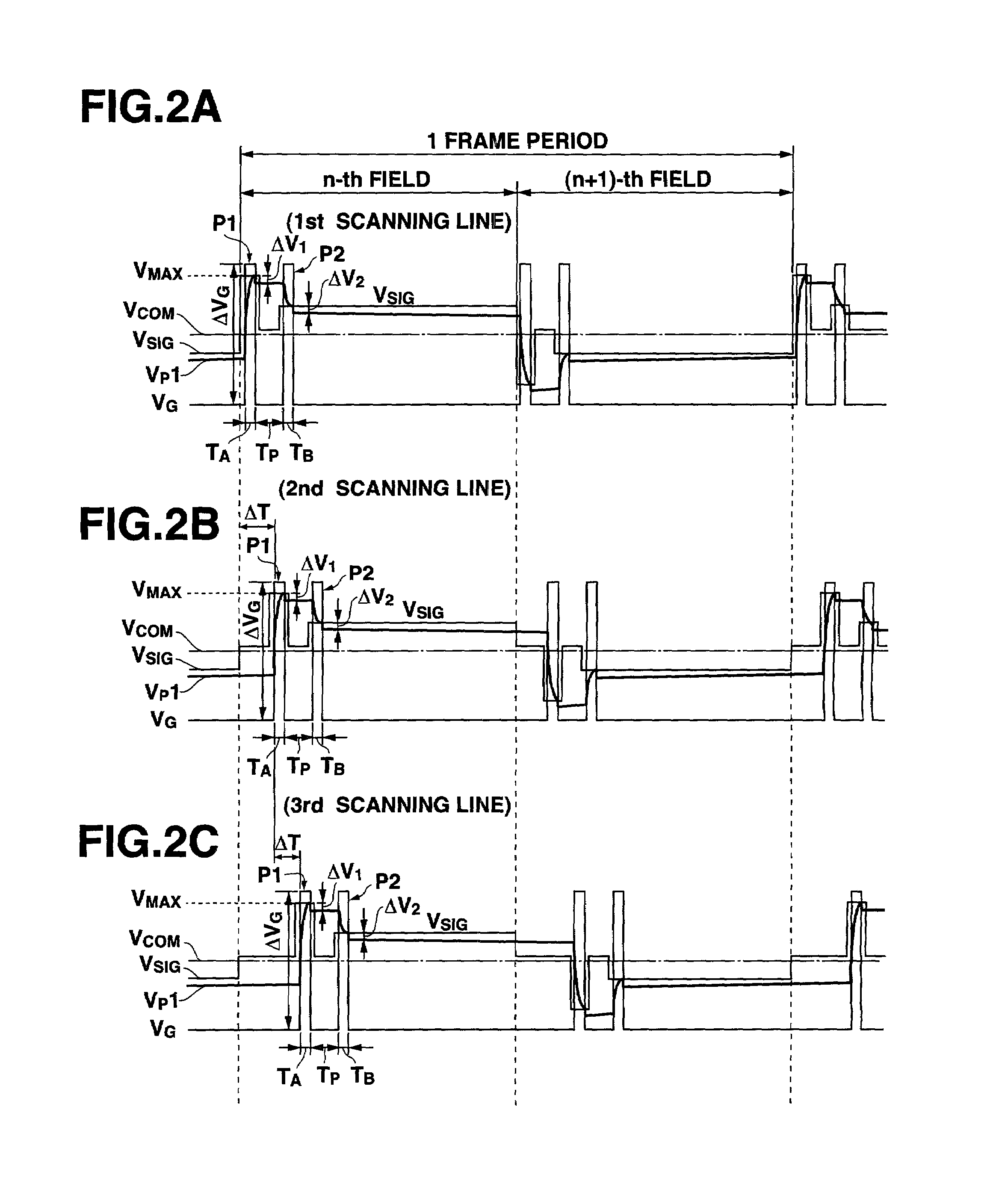

Liquid crystal display device and driving control method thereof

InactiveUS7221344B2Improve display qualityEliminate capacitanceCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayActive matrix

In a liquid crystal display device of an active matrix type, at first, an initialization signal voltage having a voltage value equal to or higher than the maximum voltage value of a display signal is applied to display pixels in a signal application period in a field period. The display signal is thereafter applied. As a result, the change amount of the voltage applied to liquid crystal due to the field-through voltage in relation to a gate pulse can be arranged to be substantially constant, and can always be cancelled by a common electrode voltage. Occurrence of flicker and seizure phenomena can be thereby restricted so that the display quality can be improved.

Owner:CASIO COMPUTER CO LTD

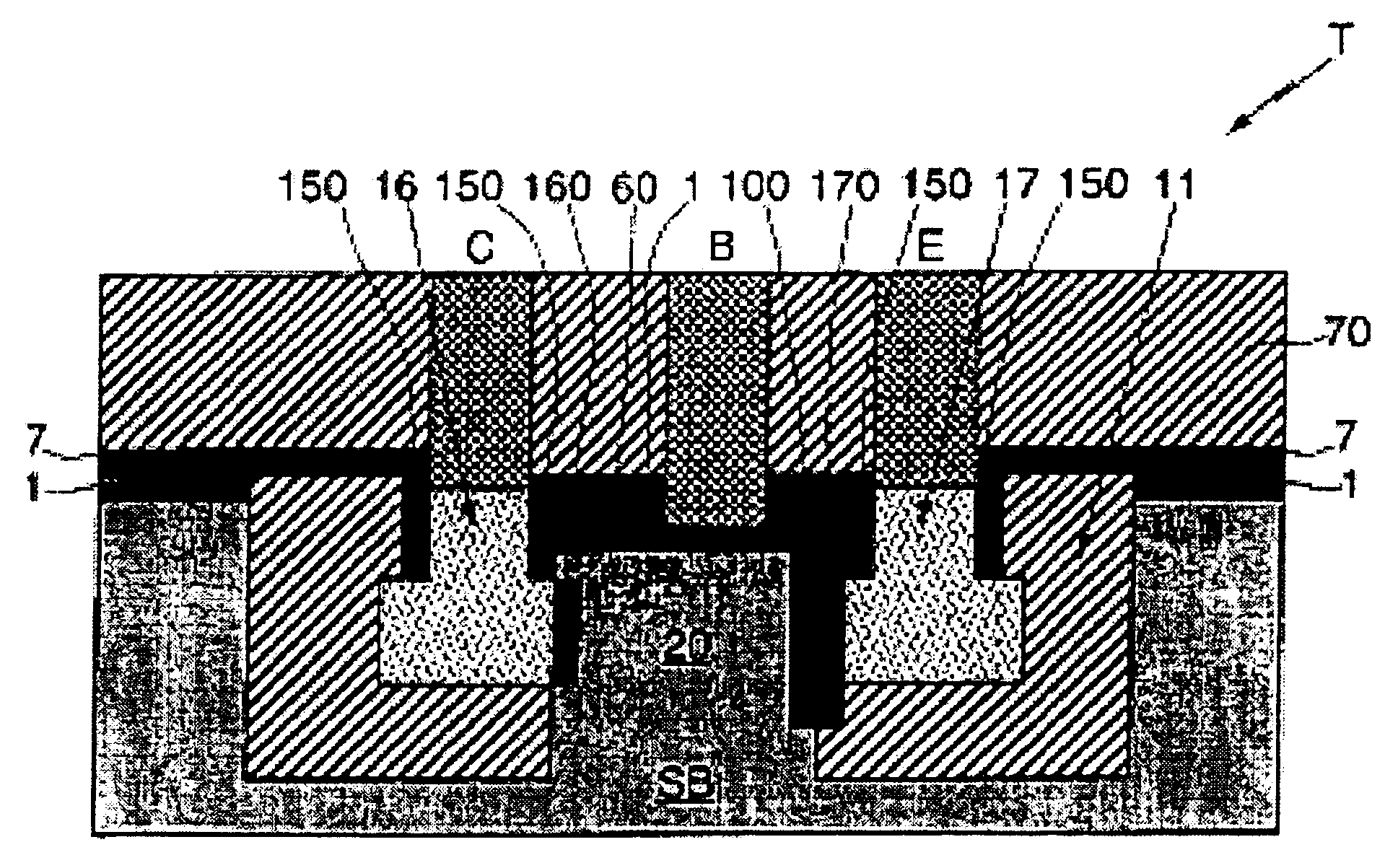

Lateral operation bipolar transistor and a corresponding fabrication process

The transistor includes an emitter region 17 disposed in a first isolating well 11, 150 formed in a semiconductor bulk. An extrinsic collector region 16 is disposed in a second isolating well 3, 150 formed in the semiconductor bulk SB and separated laterally from the first well by a bulk separator area 20. An intrinsic collector region is situated in the bulk separator area 20 in contact with the extrinsic collector region. An intrinsic base region 100 is formed which is thinner laterally than vertically and in contact with the intrinsic collector region and in contact with the emitter region through bearing on a vertical flank of the first isolating well facing a vertical flank of the second isolating well. An extrinsic base region 60 is formed which is substantially perpendicular to the intrinsic base region in the top part of the bulk separator area, and contact terminals C, B, E respectively in contact with the extrinsic collector region, the extrinsic base region, and the emitter region.

Owner:STMICROELECTRONICS SRL

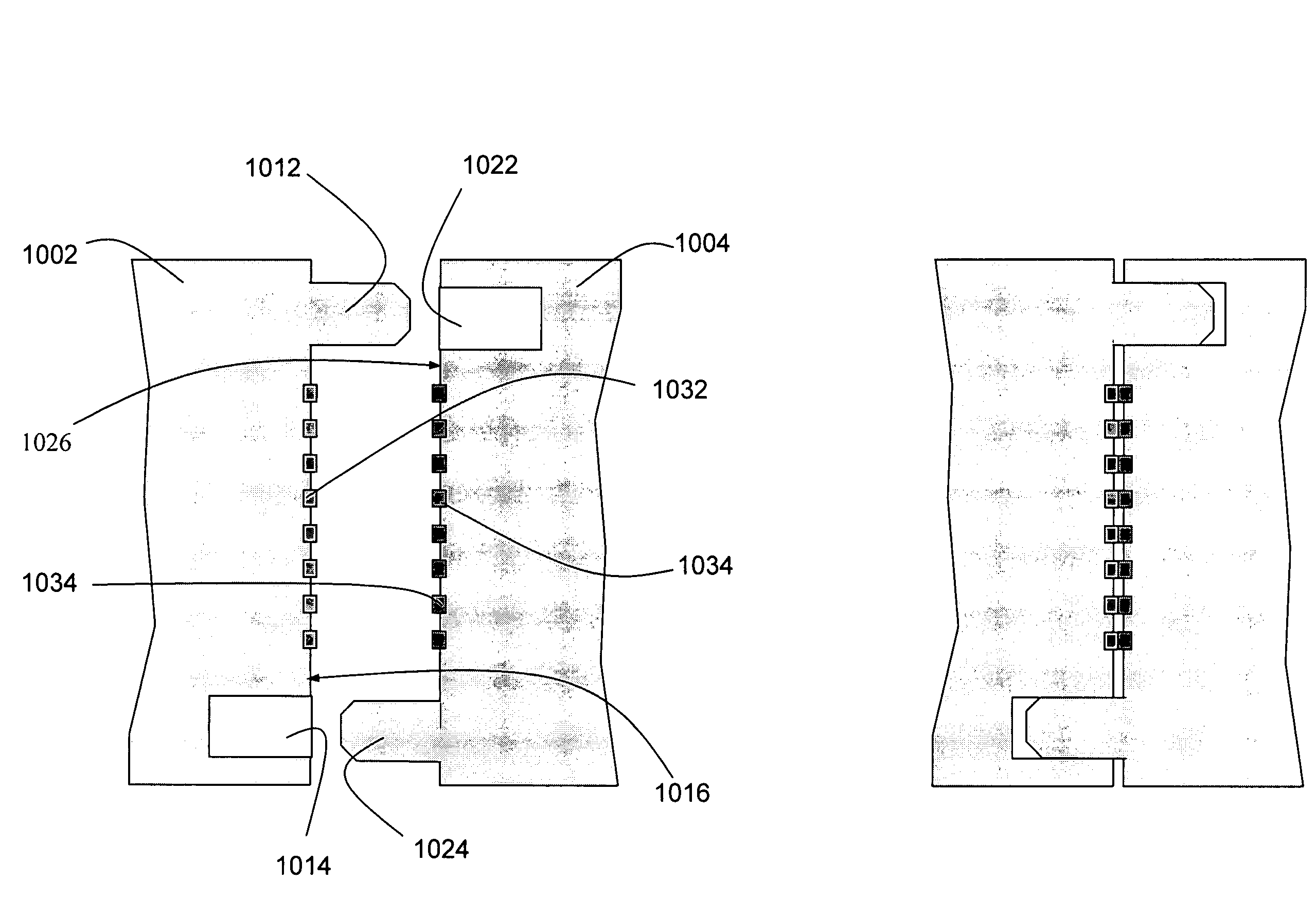

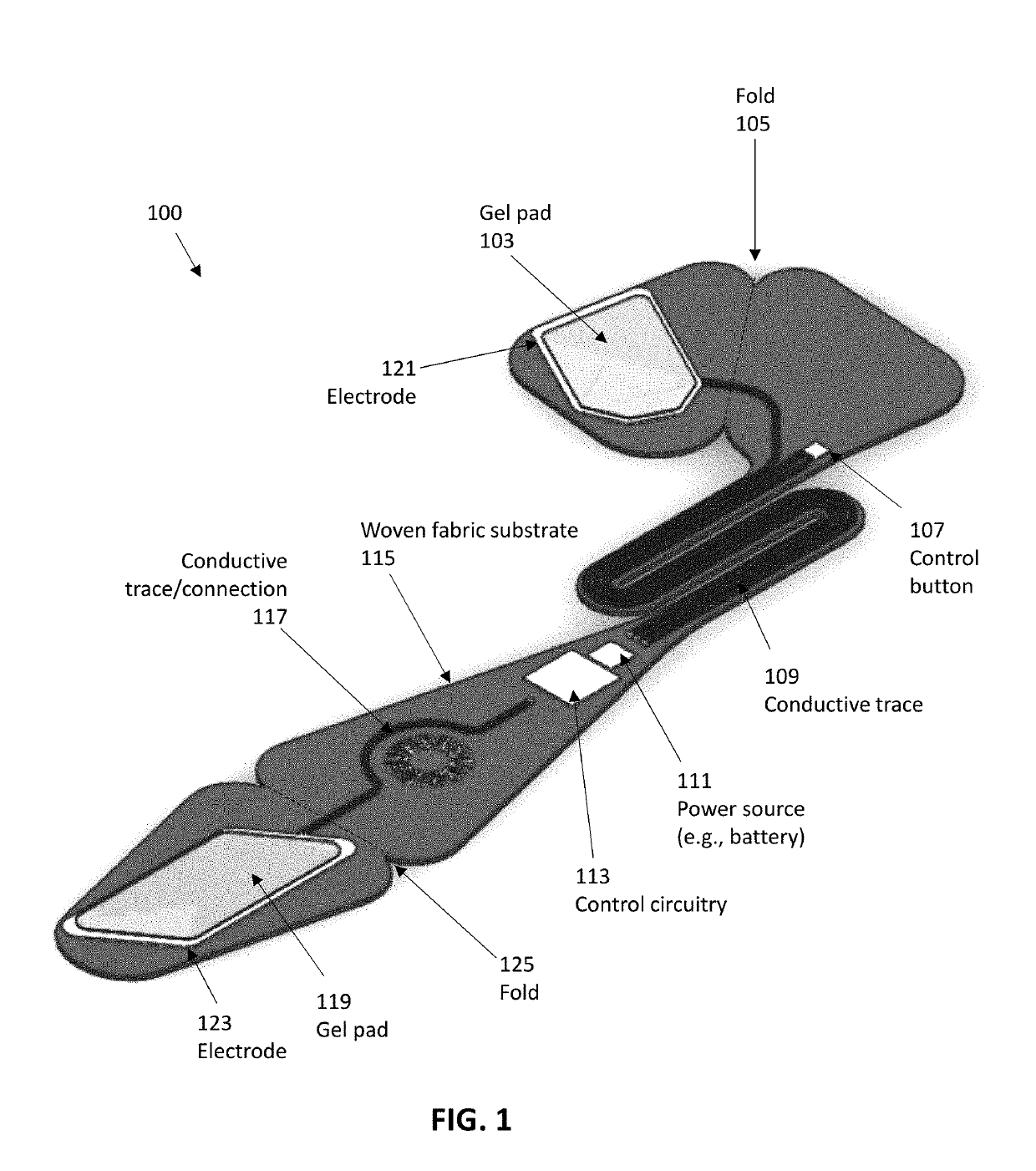

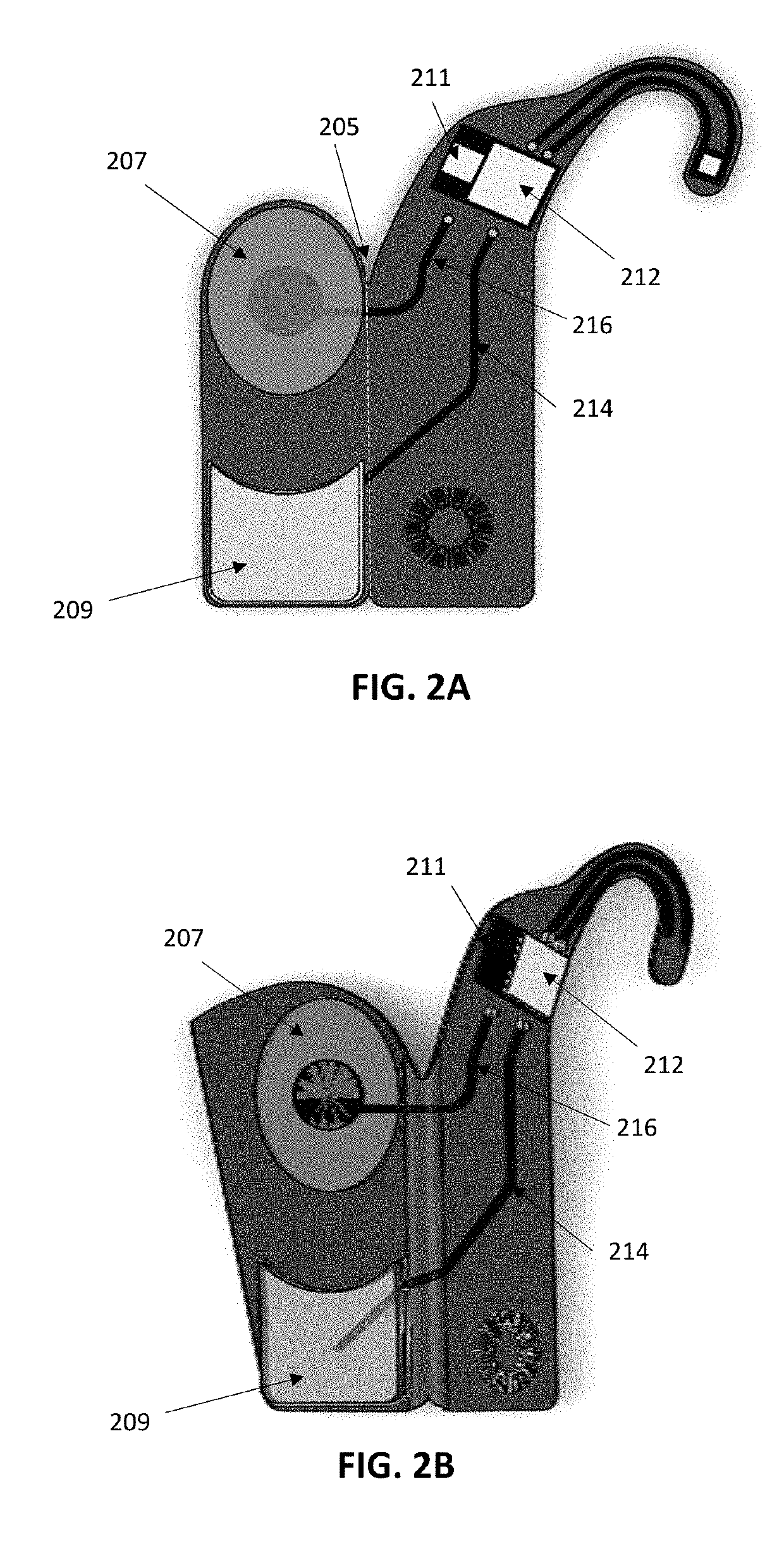

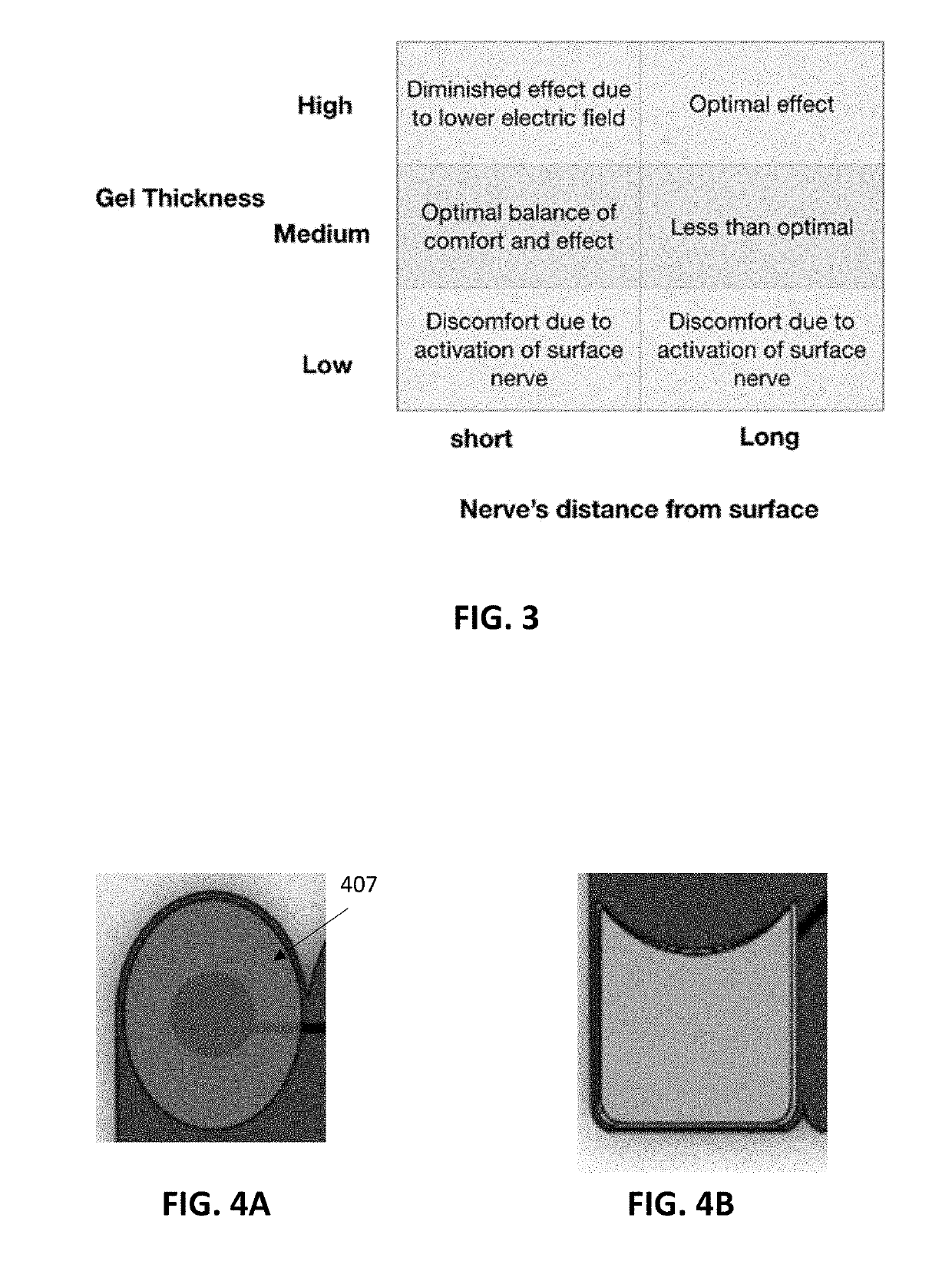

Streamlined and pre-set neuromodulators

ActiveUS20190321636A1Resist damageEasy to relaxExternal electrodesArtificial respirationElectricityEngineering

Limited-number-of-use neuromodulator apparatuses that may be comfortably worn on the skin of a user to non-invasively apply transdermal electrical stimulation (TES). The apparatuses described herein may be include a flexible / bendable substrate and an elastomeric cover (e.g., formed of an elastomeric fabric). These apparatuses may be simplified, to run autonomously. These apparatuses may also include improved power management features.

Owner:THYNC GLOBAL INC

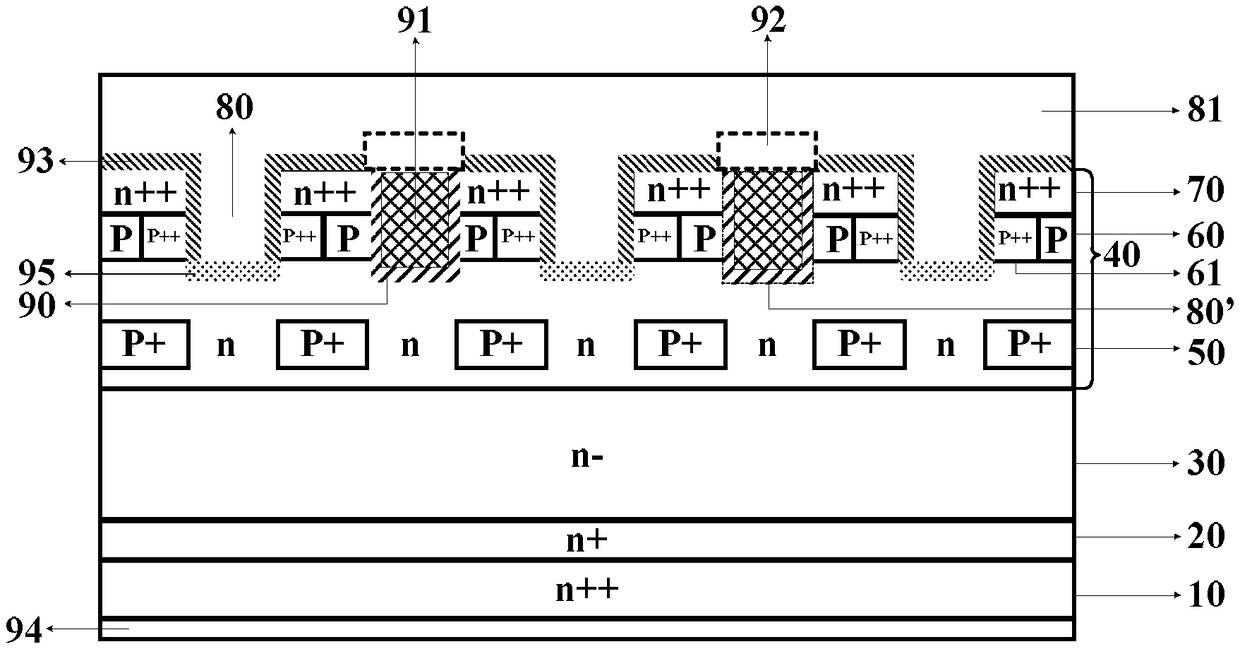

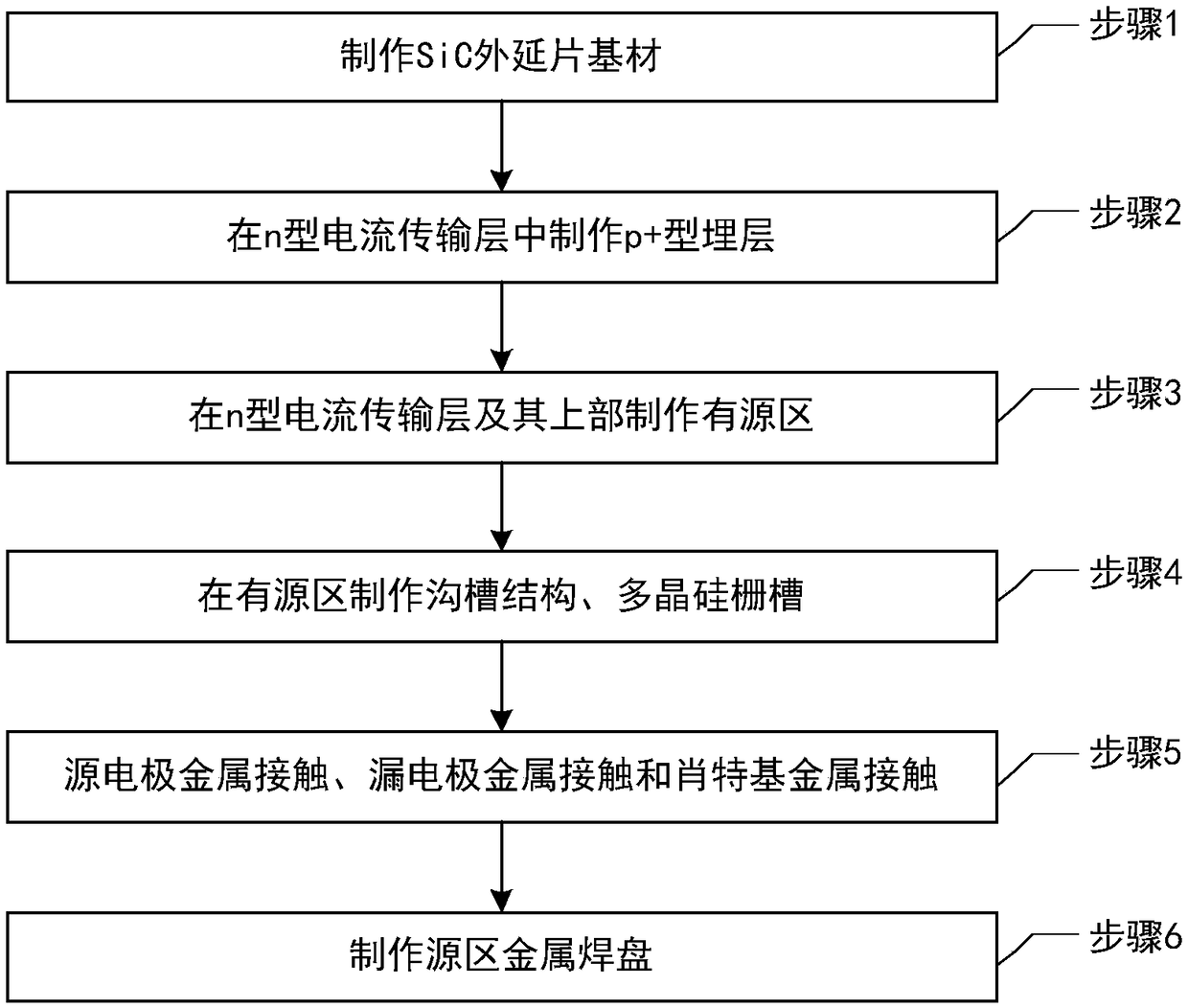

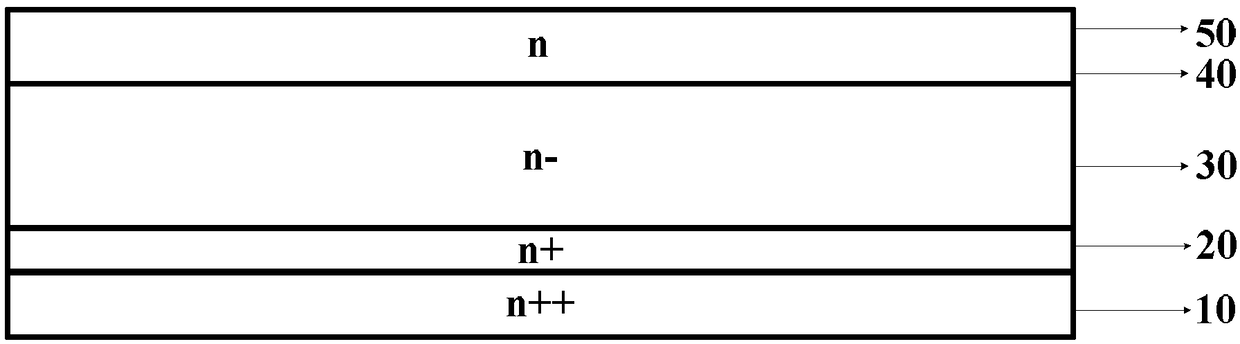

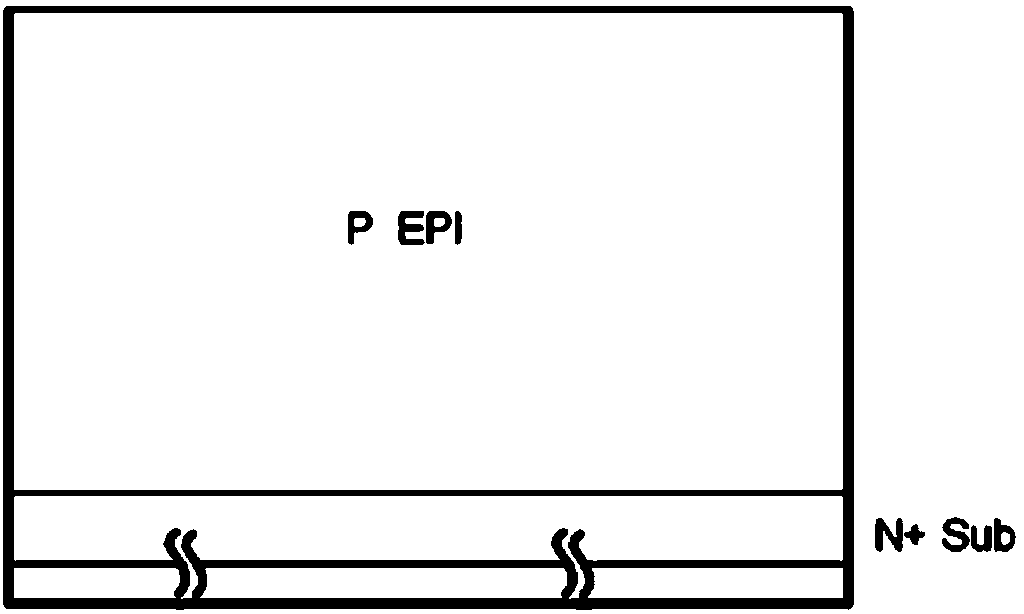

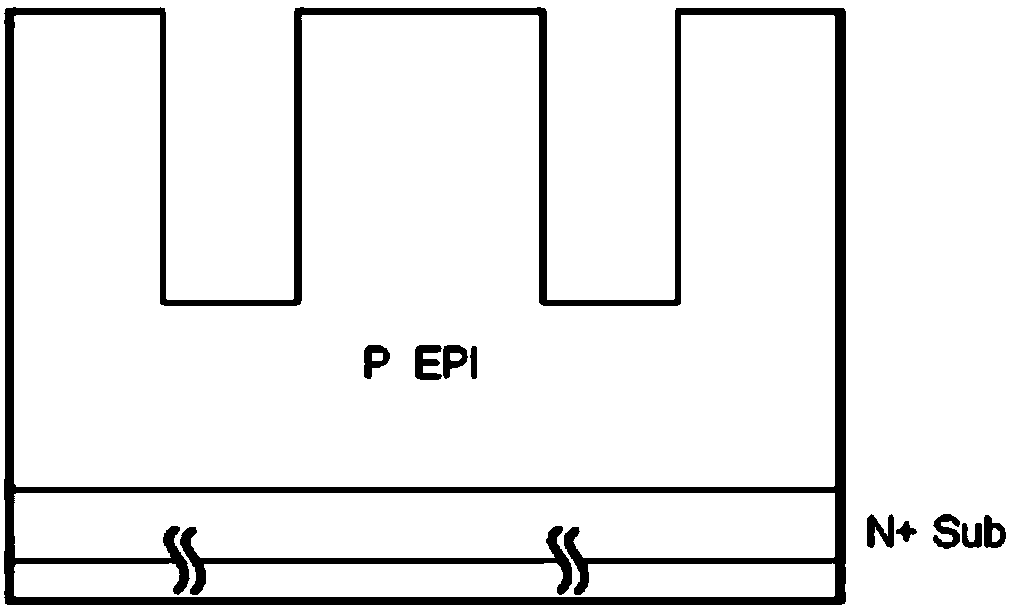

A structure of SiC UMOSFET integrated with SBD and a preparation method thereof

InactiveCN109065540AGood on-state characteristicsReduce dopingSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETField-effect transistor

The invention provides a silicon carbide trench gate metal oxide with semiconductor field effect transistor (SiC UMOSFET) structure integrated Schottky diode (SBD) and a method for manufacturing the same, The structure is characterized by, a p +-type bury layer (50) is formed on the n-type current transport layer (40) by implantation, and further an n-type current transport layer (40) is epitaxially formed so that the p +-type buried layer (50) floats, and the p +-type buried layer (50) can effectively reduce the electric field in the gate trench oxide and the electric field at the Schottky contact position in the blocking mode, so that the SBD integrated SiC UMOSFET has high blocking ability, and the high temperature and high field reliability of the device are greatly improved. At that same time, the relative position of the main trench (80), the main trench (80') and the p +-type buried layer (50) and the n-type current transport layer (40) are adjusted so that when the MOSFET is operated in the first quadrant, the conduction characteristic of the MOSFET does not degrade significantly; When the MOSFET is operated in the third quadrant, the conduction of the parasitic pn diode inthe MOSFET is effectively suppressed and the Schottky diode conduction mode is obtained. SiC UMOSFETs with integrated SBD have a lower total chip area than discrete SBD and MOSFET devices.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

JFET with built in back gate in either SOI or bulk silicon

A Junction Field-Effect transistor with no surface contact for the back gate and twice as much transconductance in the channel and with a higher switching speed is achieved by intentionally shorting the channel-well PN junction with the gate region. This is achieved by intentionally etching away field oxide outside the active area at least in the gate region so as to expose the sidewalls of the active area down to the channel-well PN junction or a buried gate which is in electrical contact with the well. Polysilicon is then deposited in the trench and doped heavily and an anneal step is used to drive impurities into the top and sidewalls of the channel region thereby creating a “wrap-around” gate region which reaches down the sidewalls of the channel region to the channel-well PN junction. This causes the bias applied to the gate terminal to also be applied to the well thereby modulating the channel transconductance with the depletion regions around both the gate-channel PN junction and the channel-well PN junction.

Owner:MIE FUJITSU SEMICON

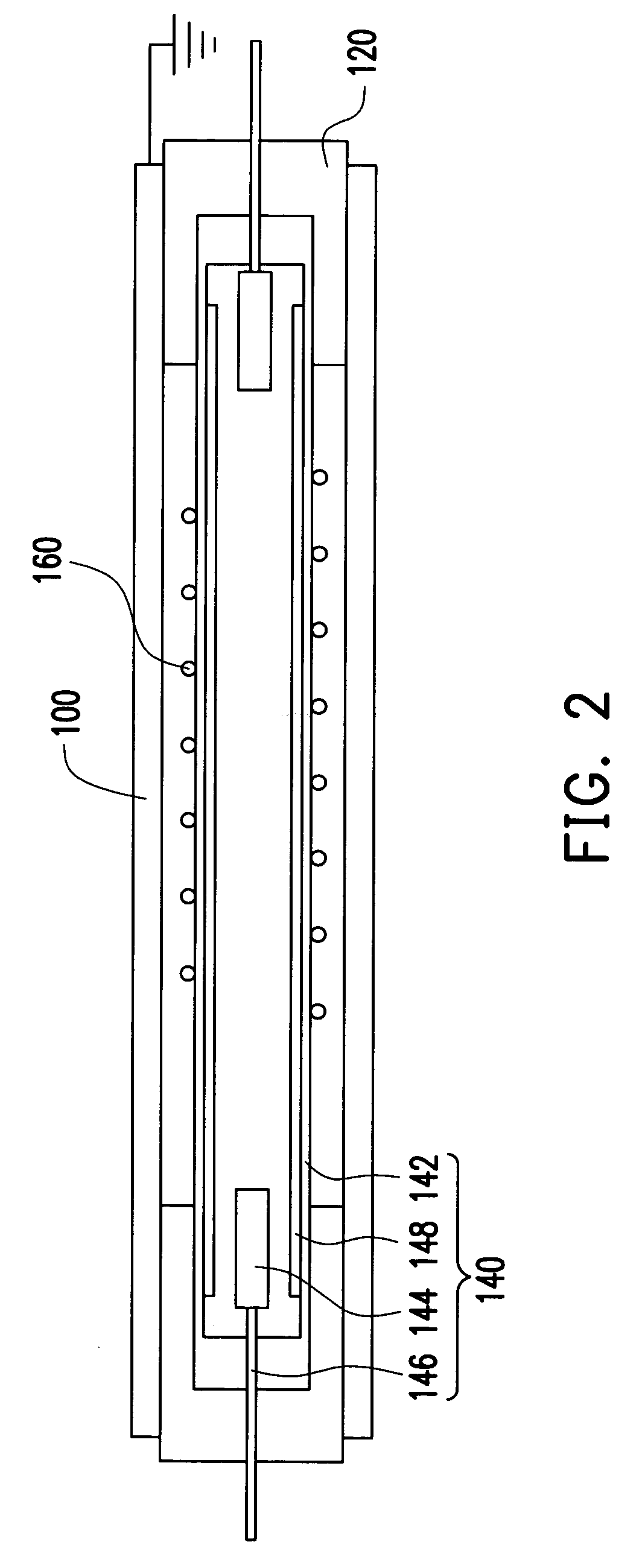

Light source module

InactiveUS7070298B2Preventing the lamp from flashingPrevent capacitance built-upIncadescent screens/filtersElectric discharge tubesCapacitanceElectricity

A light source module comprises a lamp cover, a lamp and at least a conductive wire. The lamp is fitted into the lamp cover. The conductive wire connects the lamp cover and the lamp to a ground. The conductive wire is wound around the lamp and the conductive wire has two ends connected to the lamp cover. The lamp cover includes at least a heat conductive plate connected with the conductive wire. The lamp cover, and the lamp are electrically connected to the ground through the conductive wire, so the capacitance there-between can be eliminated to improve the illumination performance of the light source module.

Owner:INNOLUX CORP

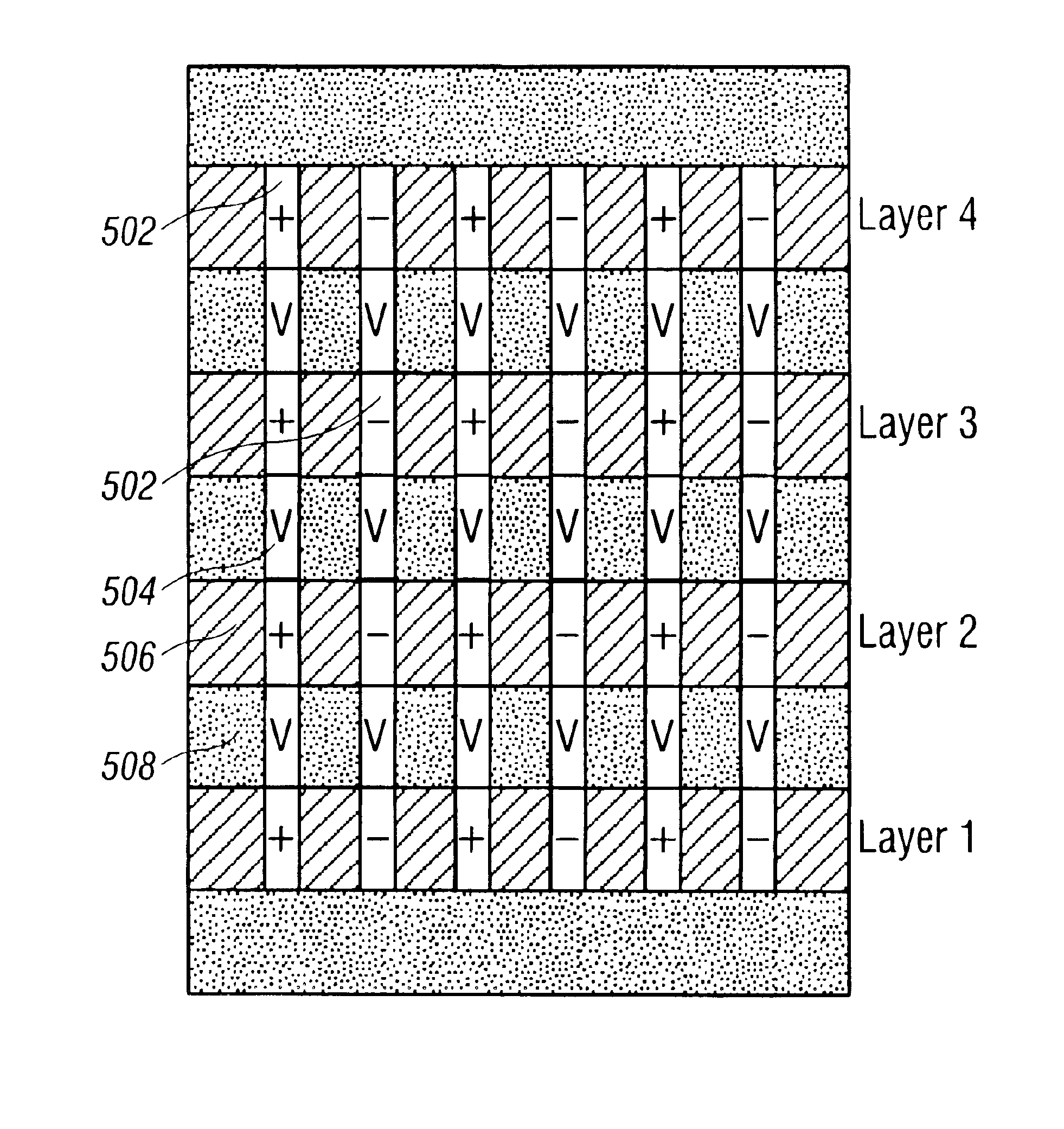

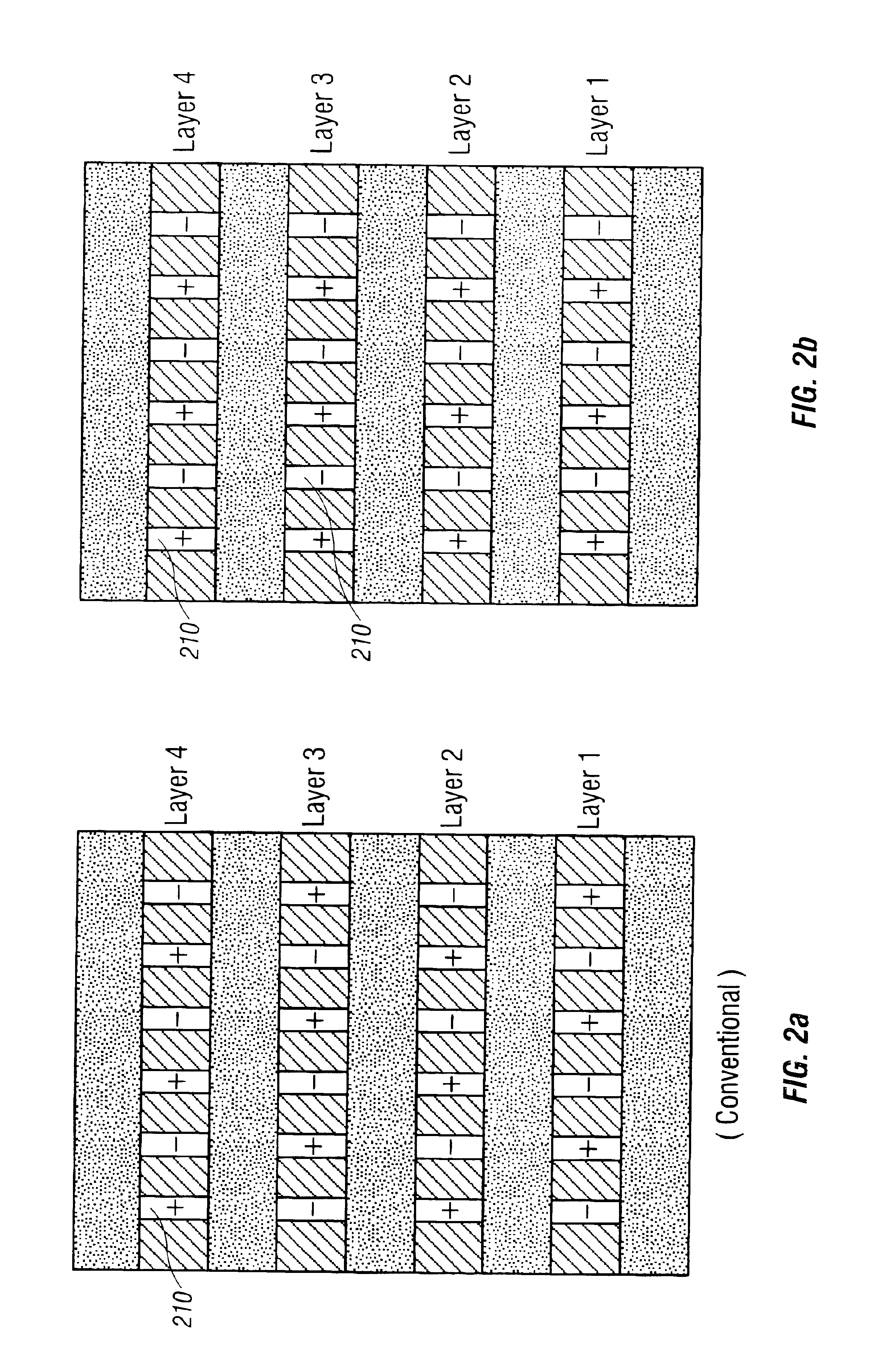

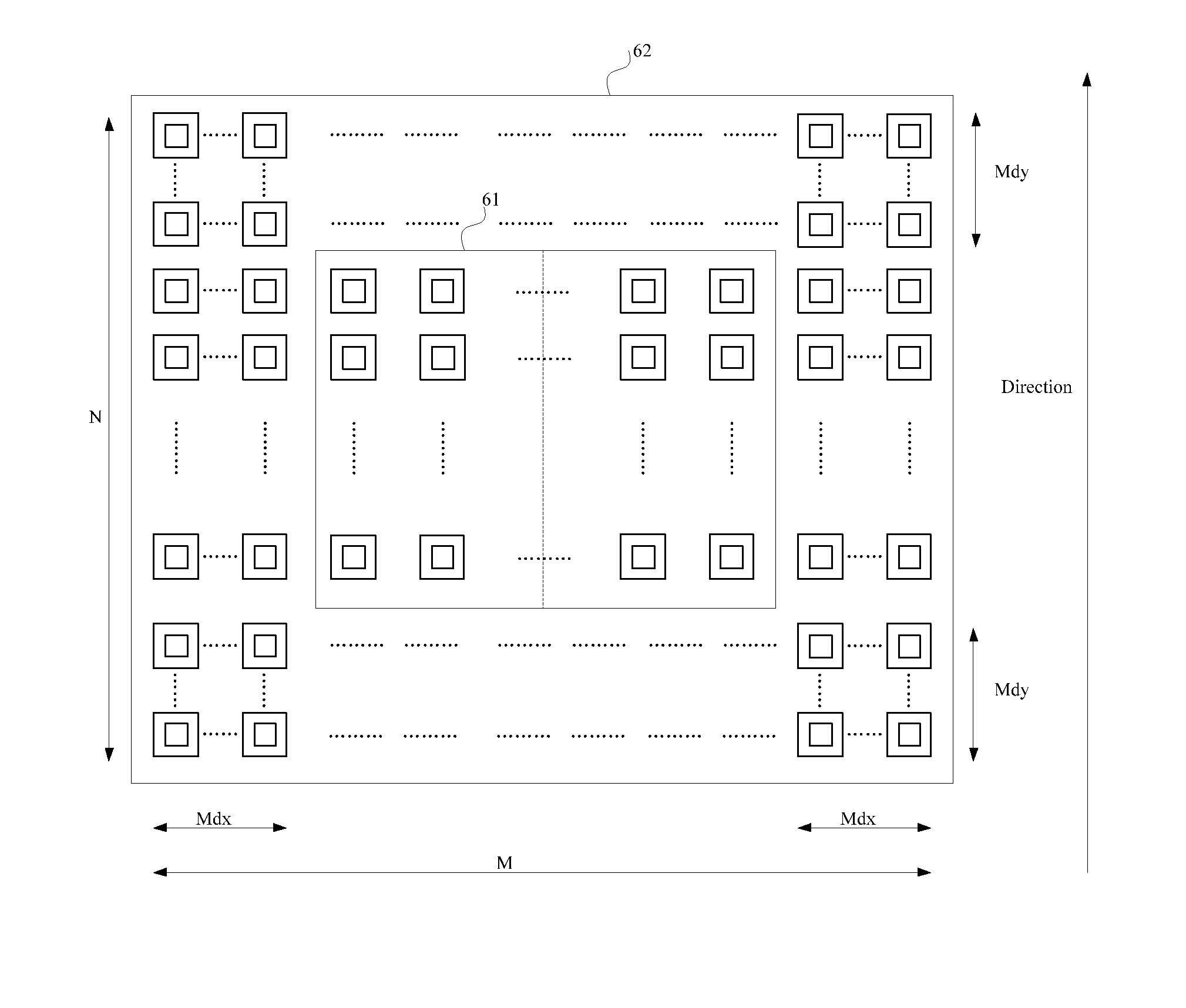

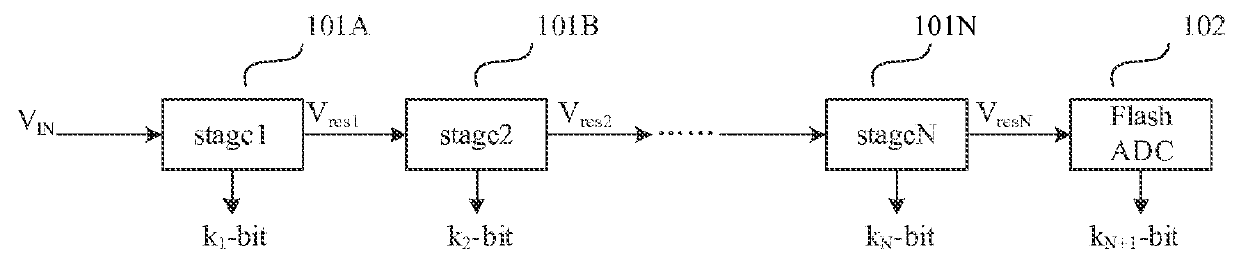

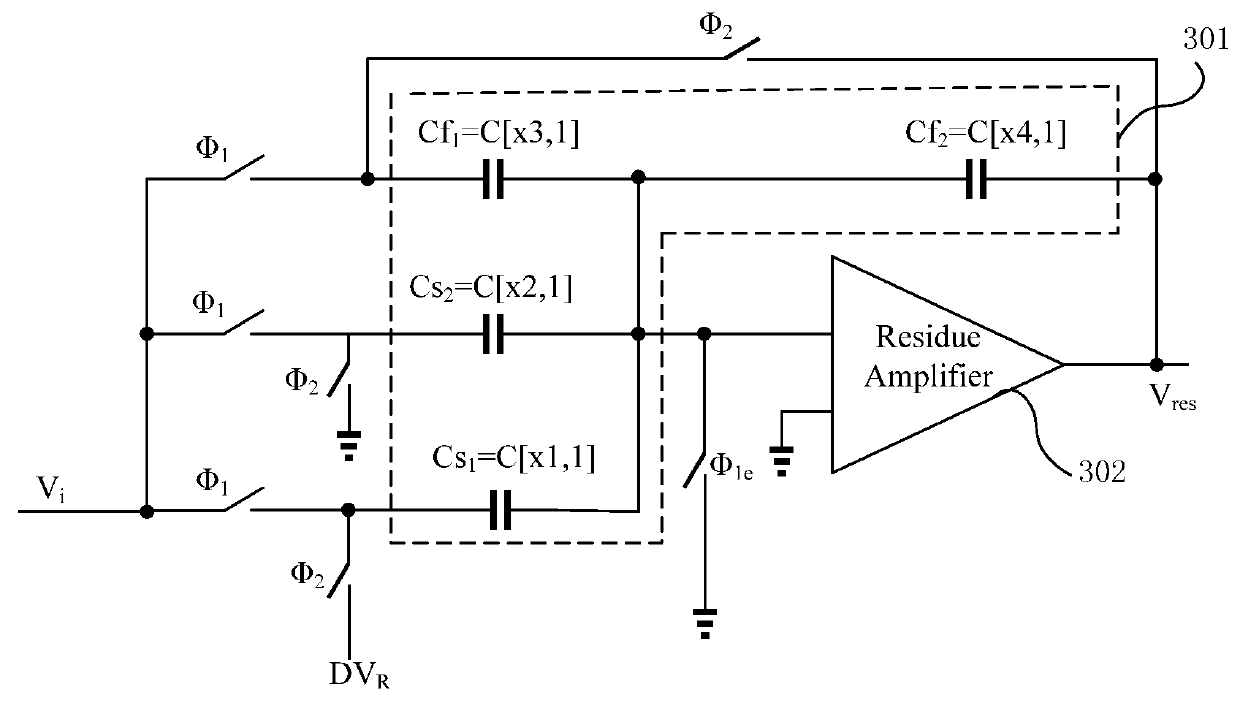

Capacitor array and layout design method thereof

ActiveUS20150370952A1Eliminate capacitance mismatching errorWell-matchedAnalogue/digital conversionMultiple fixed capacitorsParasitic capacitorCapacitance

A layout design method is provided for generating capacitor arrays being described in four steps: first, the wiring mode of unit capacitors is defined allowing the wire being connected to the upper plate to parallel that to the lower one, second, a capacitor array layout is designed with capacitors being distributed in Mh lines, Mh is the maximum of capacitors' lines, the line numbers of Class 1 to Class K capacitors are defined in the unilateral capacitor array, third, the wiring mode is set for capacitor array making sure the lengths of the wires to the upper and lower plates of unit capacitors are equal, at last, parasitic parameters are characterized in ways that verify the layout. A capacitor array is provided as well. By eliminating capacitance mismatching caused by parasitic capacitance, the method works to generate a well-matched capacitor array in an easy and efficient way.

Owner:CHONGQING GIGACHIP TECH CO LTD

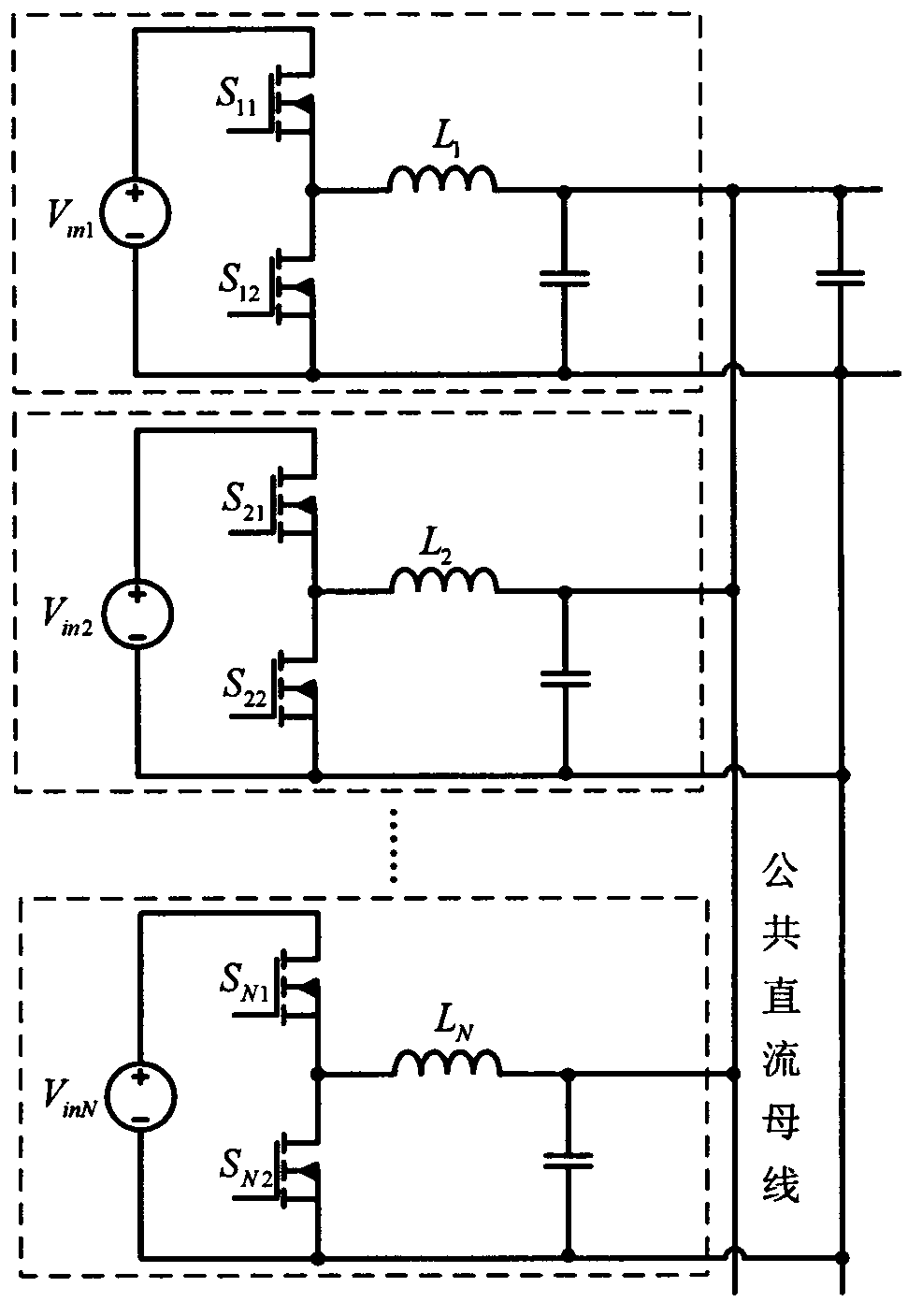

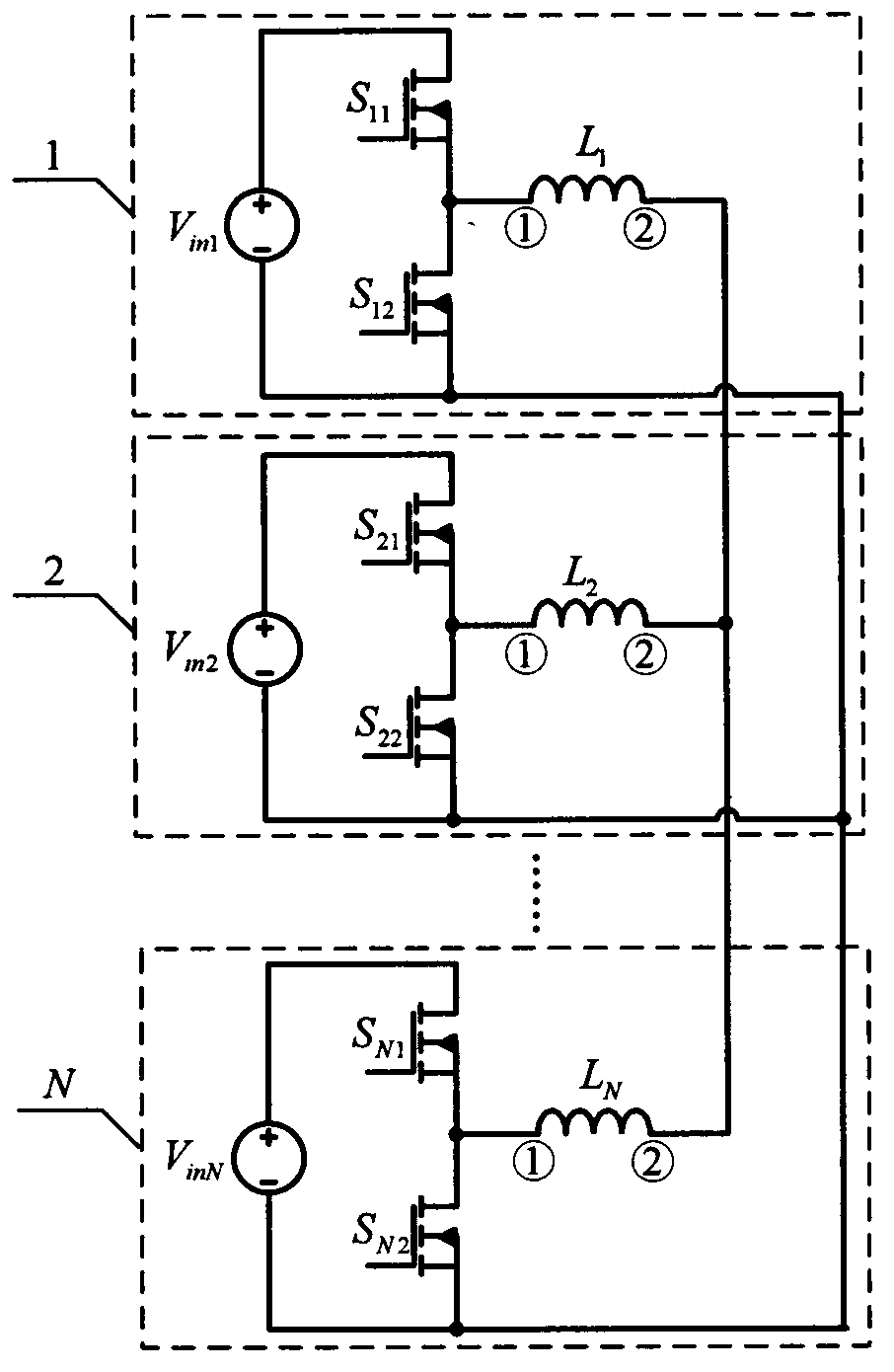

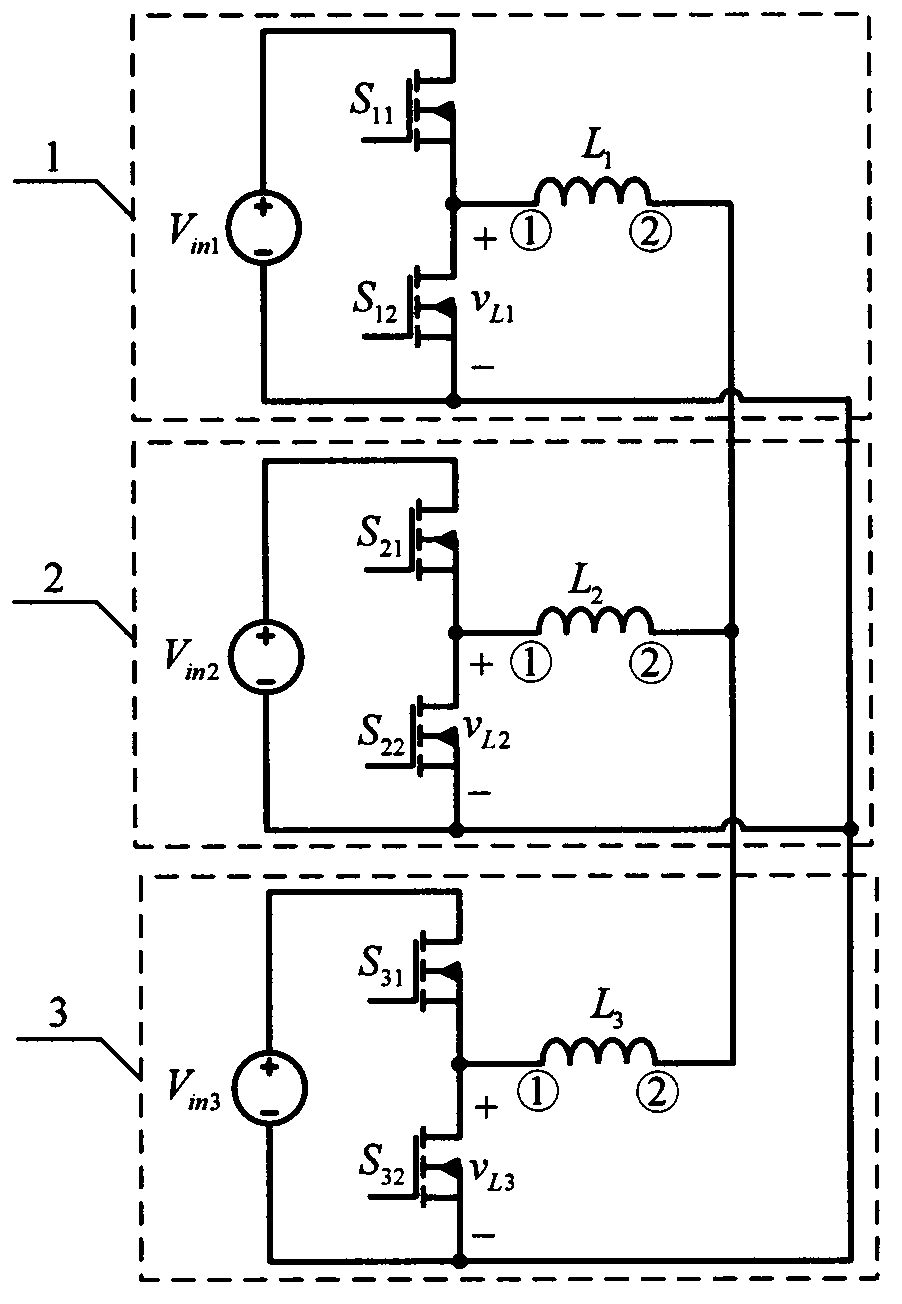

Non-isolated bidirectional multiport direct current (DC) converter

InactiveCN103199699AReduce the number of seriesImprove system efficiencyApparatus without intermediate ac conversionSingle stageInductor

The invention relates to a non-isolated bidirectional multiport direct current (DC) converter, and belongs to the technical field of power electronic converters. The converter is formed by N bidirectional input / output circuit units, wherein the N is a natural number bigger than 1. Each bidirectional input / output circuit unit is formed by an input source, two switching tubes and an inductor, the input sources of all the bidirectional input / output circuit units are in public ground connection, and one ends of the inductors of all the bidirectional input / output circuit units are connected together. The non-isolated bidirectional multiport DC converter has the advantages that all the input sources are in public ground connection, single-stage non-isolated switching is carried out among all the input sources, voltage ascending and descending switching is carried out among all the input sources, power can be transmitted mutually among all the input sources, a circuit topology is simple, power density is high, a switching rate is high, reliability is high, cost is low and the like, and the non-isolated bidirectional multiport DC converter settles key technology for a distributed DC supply system.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Light source module

InactiveUS20050111219A1Eliminating capacitance built-upEfficiently dissipatedIncadescent screens/filtersElectric discharge tubesCapacitanceEngineering

A light source module comprises a lamp cover, a lamp and at least a conductive wire. The lamp is fitted into the lamp cover. The conductive wire connects the lamp cover and the lamp to a ground. The conductive wire is wound around the lamp and the conductive wire has two ends connected to the lamp cover. The lamp cover includes at least a heat conductive plate connected with the conductive wire. The lamp cover, and the lamp are electrically connected to the ground through the conductive wire, so the capacitance there-between can be eliminated to improve the illumination performance of the light source module.

Owner:INNOLUX CORP

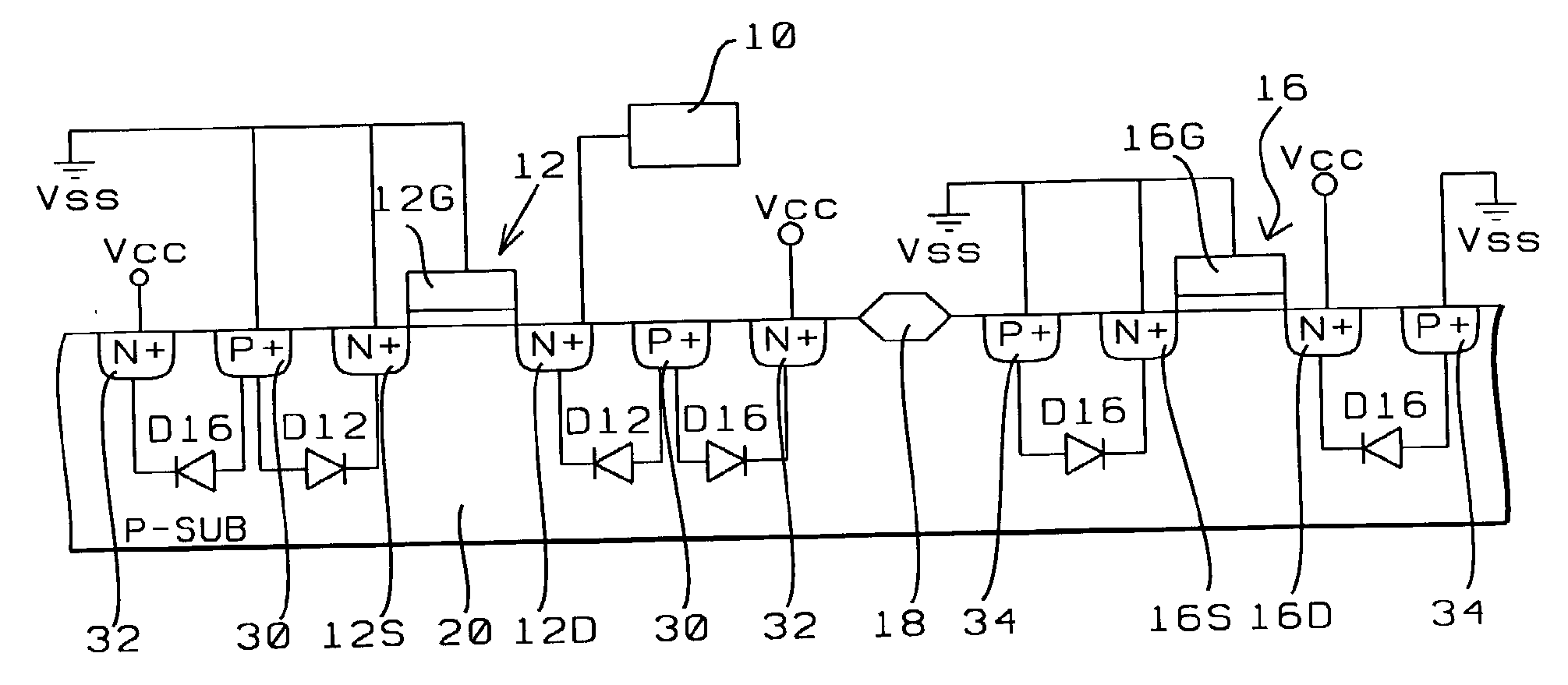

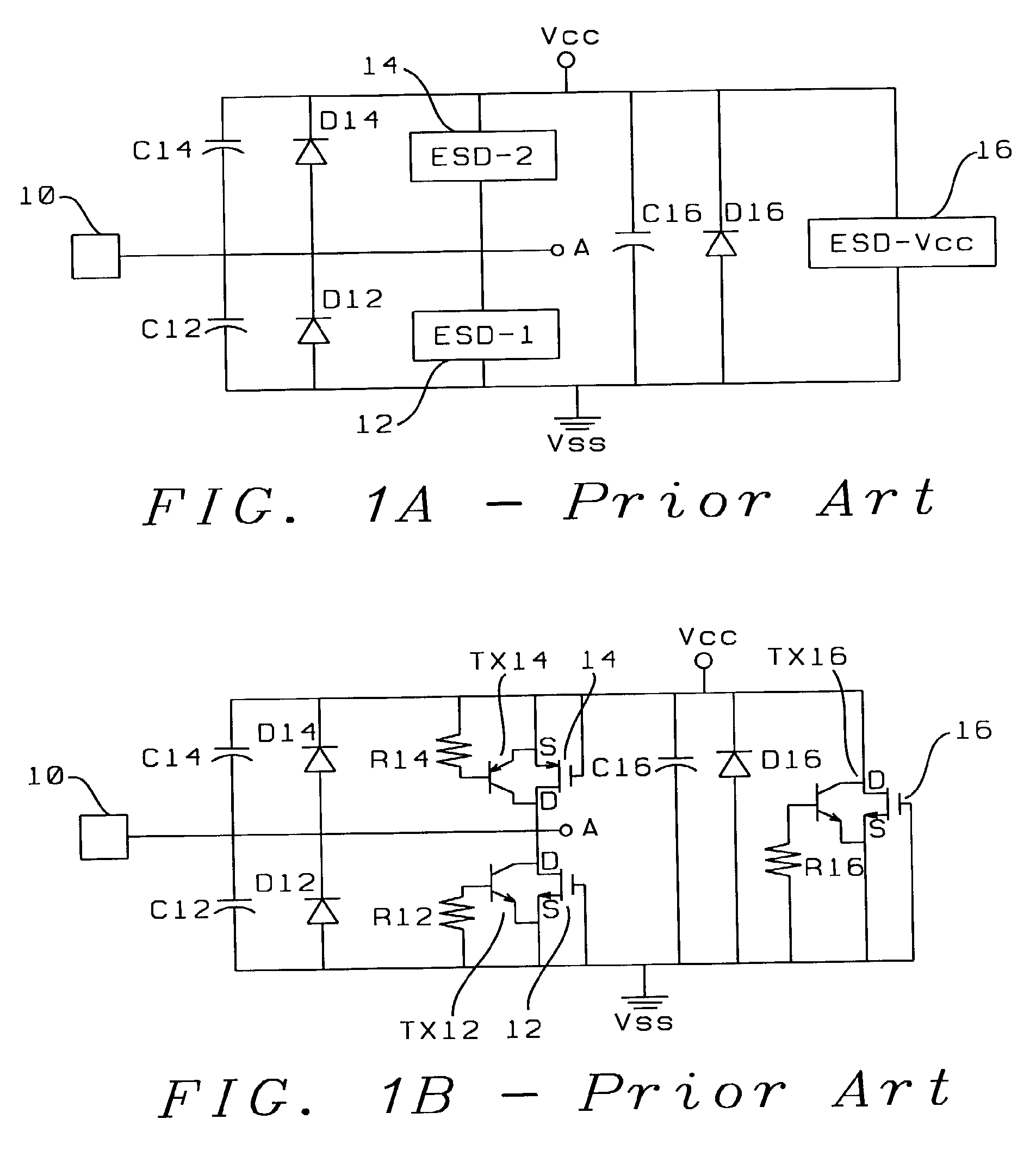

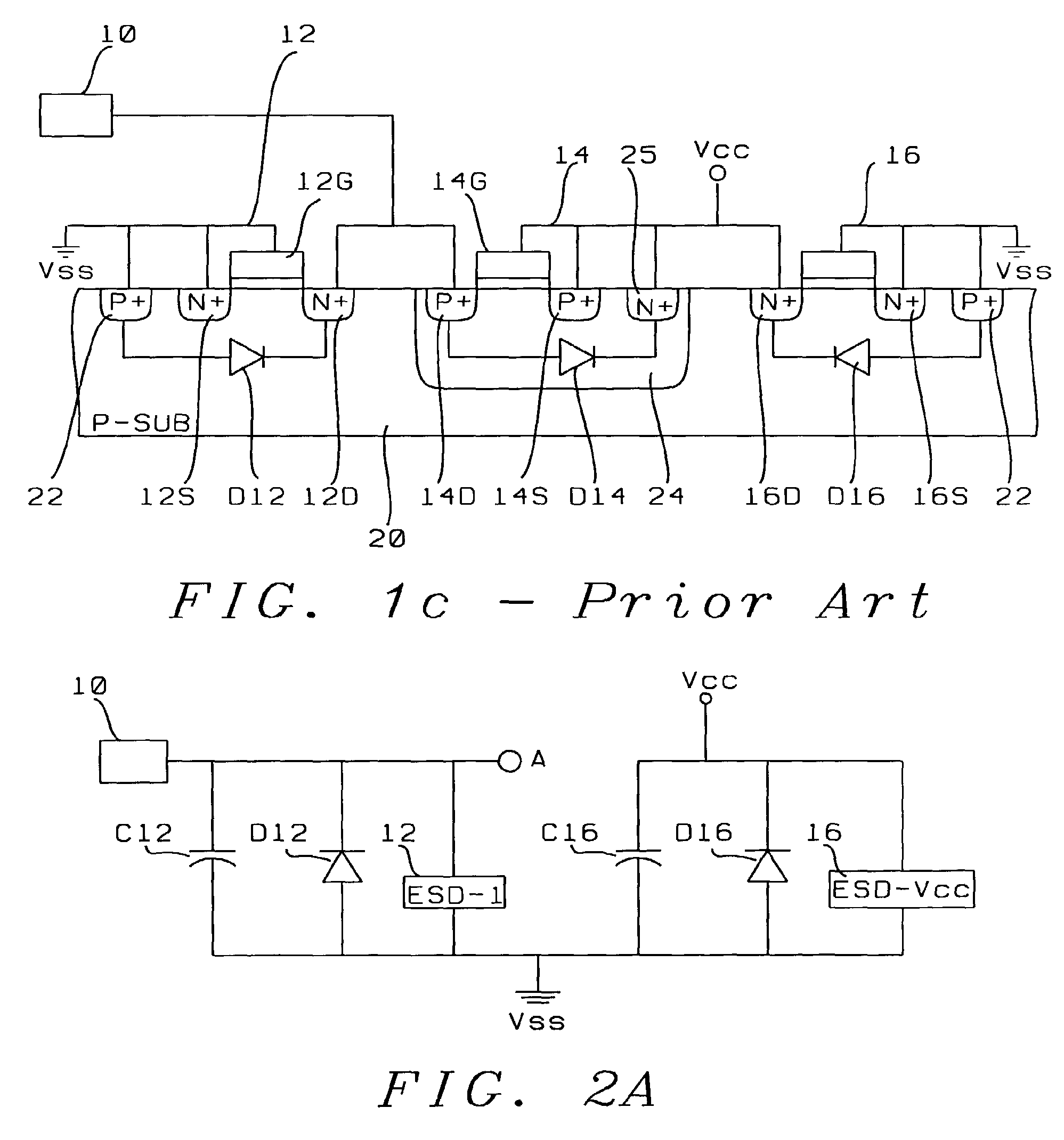

Novel method for four direction low capacitance ESD protection

InactiveUS20070108527A1Reduce capacitanceImprove protectionSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention describes a structure and a process for providing ESD semiconductor protection with reduced input capacitance. The structure consists of heavily doped P+ guard rings surrounding the I / O ESD protection device and the Vcc to Bss protection device. In addition, there is a heavily doped N+ guard ring surrounding the I / O protection device its P+ guard ring. The guard rings enhance structure diode elements providing enhanced ESD energy discharge path capability enabling the elimination of a specific conventional Vss to I / O pad ESD protection device. This reduces the capacitance seen by the I / O circuit while still providing adequate ESD protection for the active circuit devices.

Owner:TAIWAN SEMICON MFG CO LTD

Current feed circuit for sensor coils in coordinate input device

ActiveUS6987507B2Stable output voltageReduce outputTransmission systemsCathode-ray tube indicatorsElectrical currentTransistor

A current feed circuit for feeding a high-frequency current to a plurality of sensor coils in a coordinate input device includes a high-frequency signal transmitting circuit for generating a high-frequency current corresponding to a high-frequency signal input; a plurality of driver transistors, each being provided between the high-frequency signal transmitting circuit and each of a plurality of sensor coils for transmitting the high-frequency current to the corresponding sensor coil; and a plurality of switches, each being provided with respect to each of the plurality of driver transistors for turning on / off the corresponding driver transistor.

Owner:WACOM CO LTD

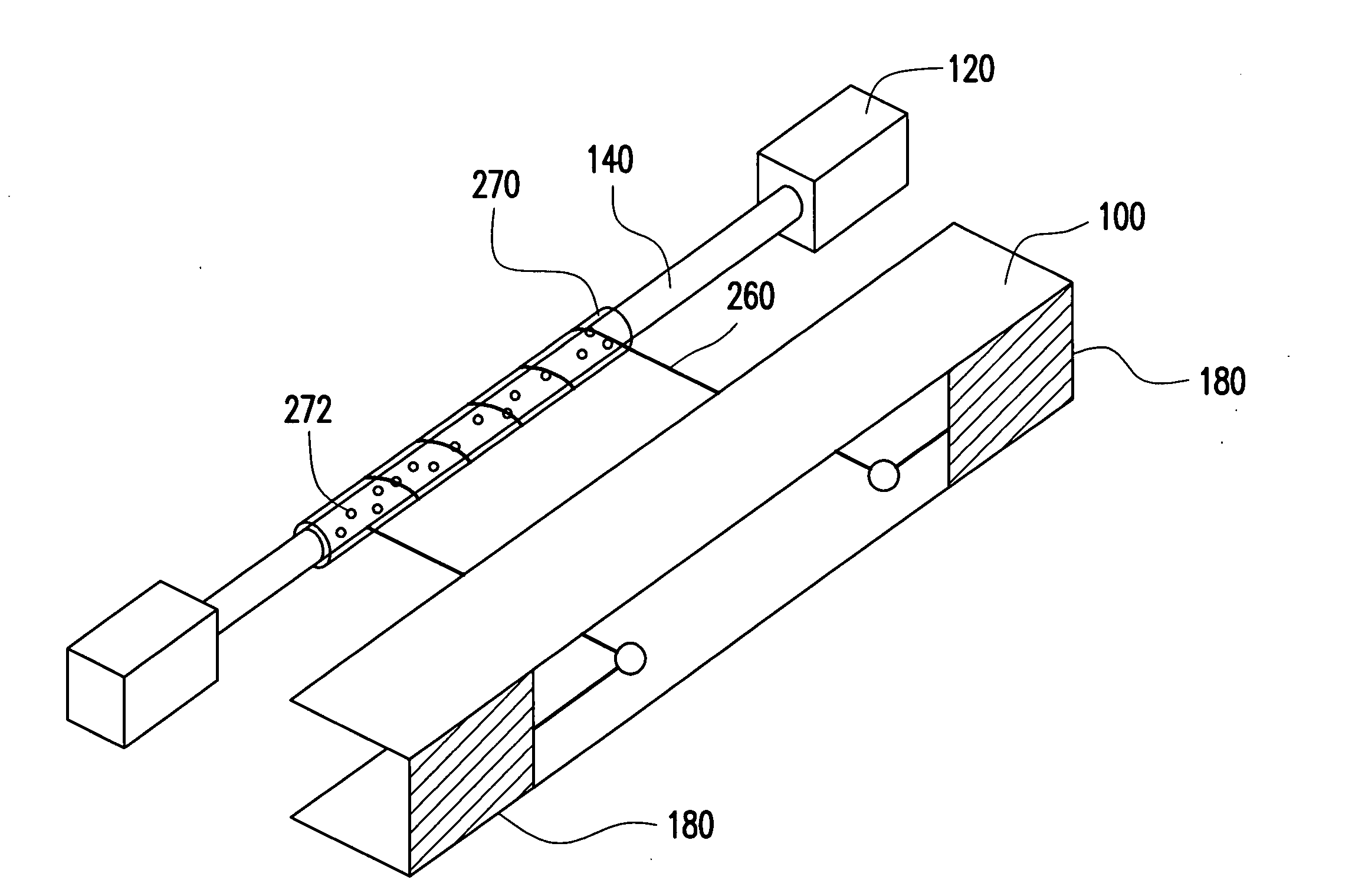

Electrical resonance detection of particles and analytes in microfluidic channels

ActiveUS8390304B2Eliminate capacitanceImprove signal-to-noise ratioMicrobiological testing/measurementFluid resistance measurementsCapacitanceCancer cell

A conductivity counter and method of determining conductivity of a fluid sample are disclosed. The counter is suitable for high-speed, accurate counting of discrete events or items, such as cancer cells, passing through a fluid sample cell. A variable frequency current source is used to supply an excitation current to a sample cell connected in parallel with an inductance or the electrical equivalence of an inductance. This configuration can be accurately modeled as a parallel RLC circuit when the system is operated at a stable frequency. The current source frequency is tuned to the resonance frequency of the equivalent RLC circuit, which effectively eliminates the capacitive and inductive components of the impedance, leaving only purely resistive components. The output of the equivalent RLC circuit is connected to a high input impedance buffer amplifier and then to a phase sensitive detector, which detects the phase shift resulting from the equivalent RLC circuit. The output is filtered and a differencing amplifier is used to zero out the output signal due to the system components and the sample cell buffer solution prior to taking active readings. The remaining output signal is due to perturbations in the fluid sample, such as passing cancer cells. This output is sent to a high-gain output amplifier and then supplied to a suitable signal processing device or system, such as a computer.

Owner:BOARD OF SUPERVISORS OF LOUISIANA STATE UNIV & AGRI & MECHANICAL COLLEGE

JFET with built in back gate in either SOI or bulk silicon

A Junction Field-Effect transistor with no surface contact for the back gate and twice as much transconductance in the channel and with a higher switching speed is achieved by intentionally shorting the channel-well PN junction with the gate region. This is achieved by intentionally etching away field oxide outside the active area at least in the gate region so as to expose the sidewalls of the active area down to the channel-well PN junction or a buried gate which is in electrical contact with the well. Polysilicon is then deposited in the trench and doped heavily and an anneal step is used to drive impurities into the top and sidewalls of the channel region thereby creating a “wrap-around” gate region which reaches down the sidewalls of the channel region to the channel-well PN junction. This causes the bias applied to the gate terminal to also be applied to the well thereby modulating the channel transconductance with the depletion regions around both the gate-channel PN junction and the channel-well PN junction.

Owner:MIE FUJITSU SEMICON

Page buffer of non-volatile memory device and method of programming and reading non-volatile memory device

A page buffer of a non-volatile memory device and a method for programming and reading the same is provided. The page buffer includes a first latch unit and one or more second latch units for storing data, transfer units connected between the first latch unit and the second latch units for transferring the data stored in the first latch unit to the second latch units, a path select unit that that senses data from bit lines and stores the sensed data in the first latch unit, and, in a program operation, transfers the data from the first and second latch units to the bit lines, a sensing unit for allowing the path select unit to sense data or the data received from the bit lines to be stored in the first latch unit, and a data I / O unit.

Owner:SK HYNIX INC +1

Channel voltage dividing field effect tube and production method based on high-energy ion implantation mode

ActiveCN103515245AIncrease the doping concentrationFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHigh energy

The invention discloses a channel voltage dividing field effect tube and production method based on a high-energy ion implantation mode. High-energy ion implantation equipment is used for carrying out gradual-deep implantation, an N-shaped channel is manufactured through diffusion for connecting a groove channel and a drain electrode, a similar-to-T-shaped structure formed by the N-shaped channel is of a 3D structure, a depletion zone formed between P and N is changed from a single vertical direction to a vertical direction and a horizontal direction, and accordingly the withstand voltage of the zone is greatly improved, the dosage concentration of the N channel can be increased, then the effect of lowering communicating resistance is achieved, and meanwhile P extends outwards and forms an obstruction between the bottom of a grid electrode and the drain electrode of the structure, and accordingly the capacitance between the bottom of the grid electrode and the drain electrode is nearly zero, the contacting part of the channel and the groove channel is small, so that the capacitance between the grid electrode and the drain electrode can be greatly removed, according to the two improvements, charging and discharging time during grid electrode opening and closing can be greatly shortened (Qgd can be greatly lowered), and accordingly opening and closing speed of an MOS tube is improved.

Owner:桂林斯壮桂微电子有限责任公司

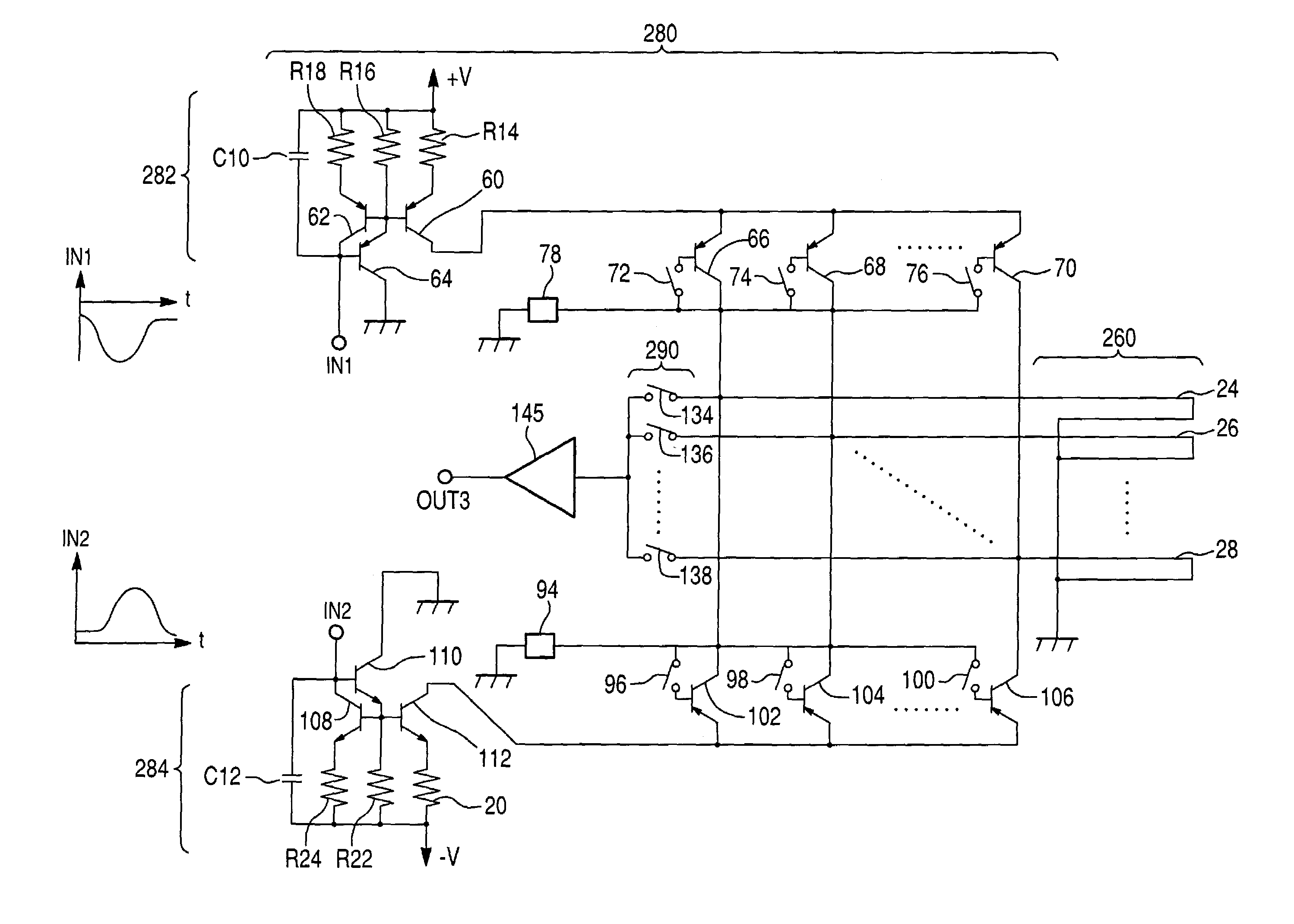

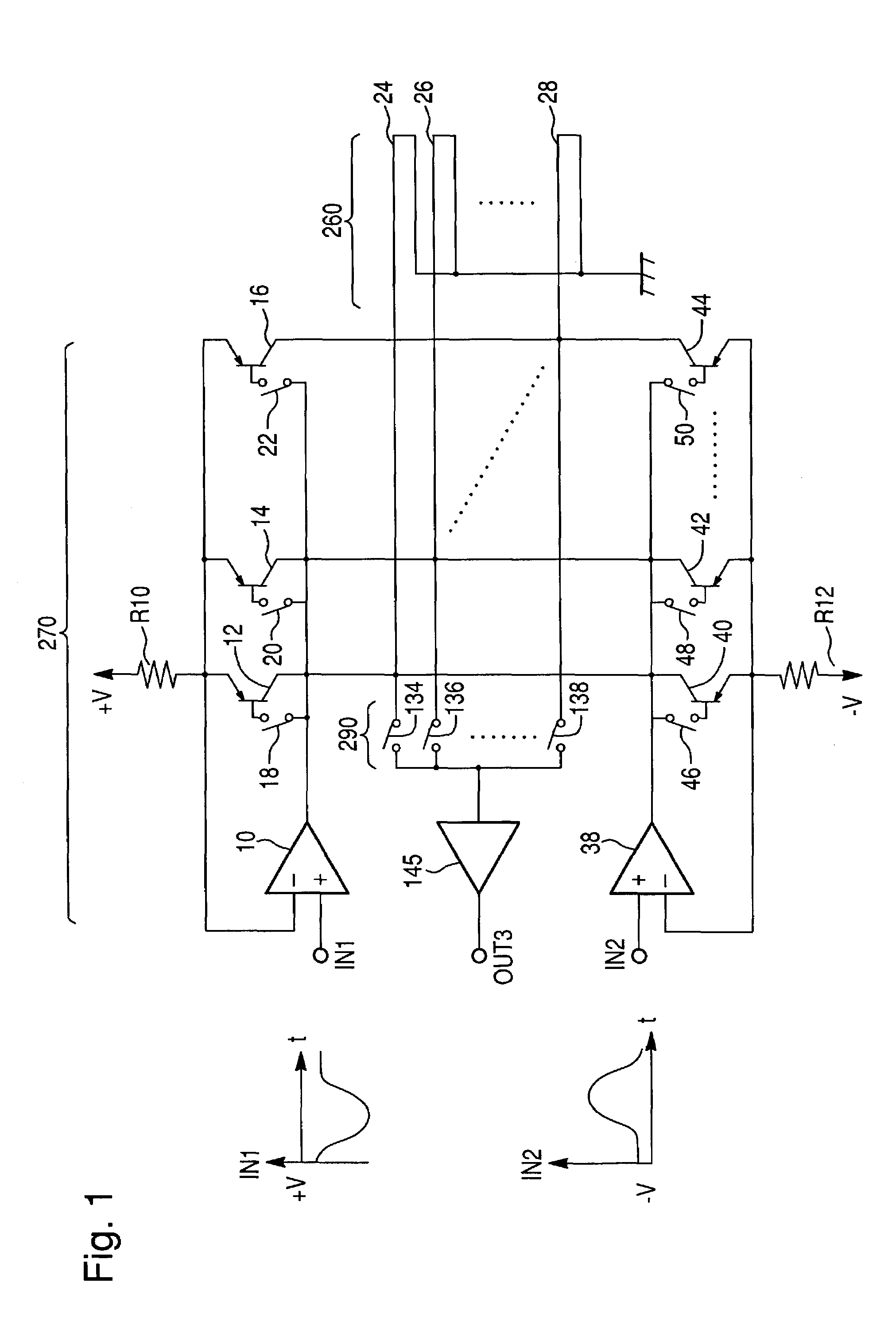

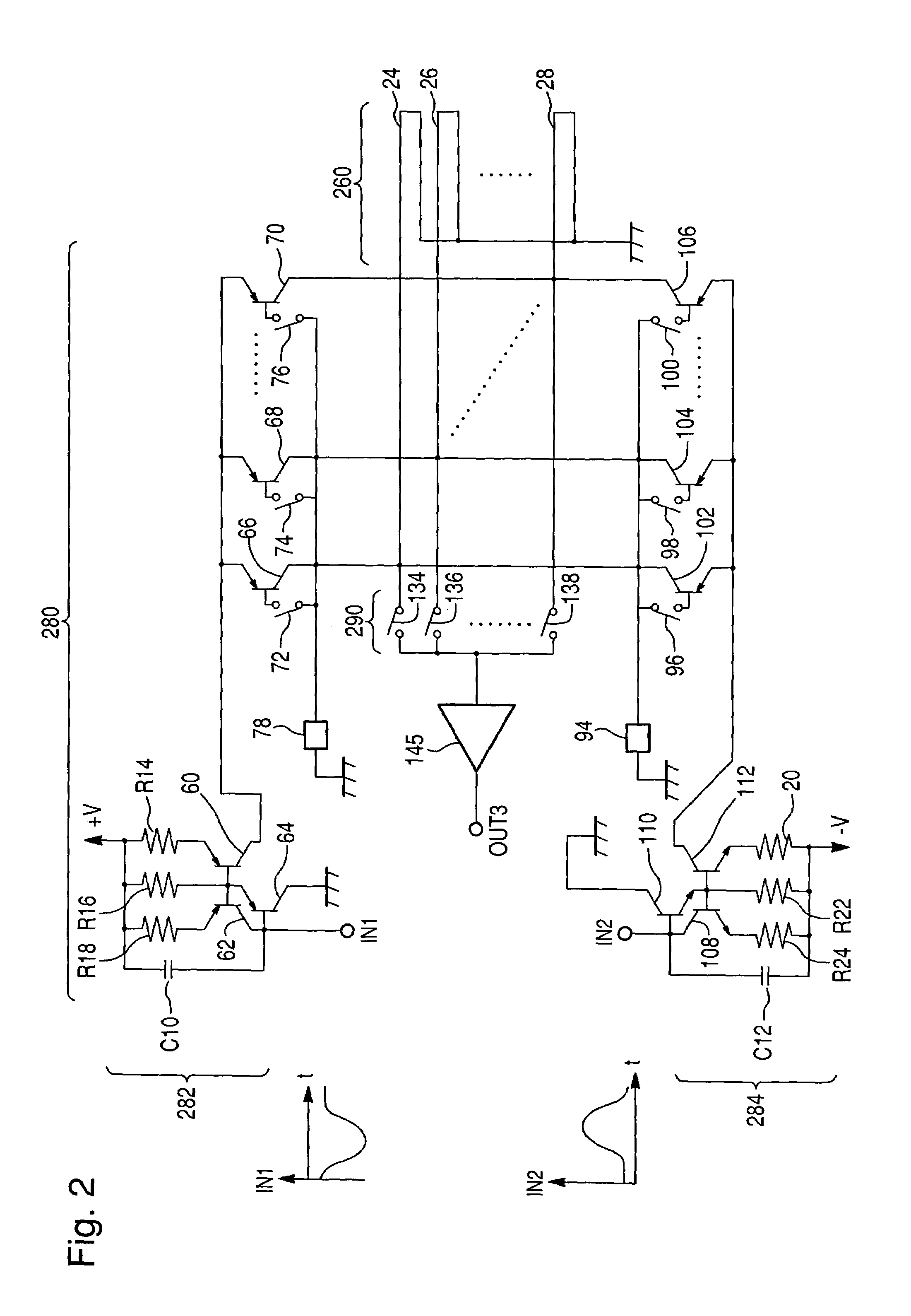

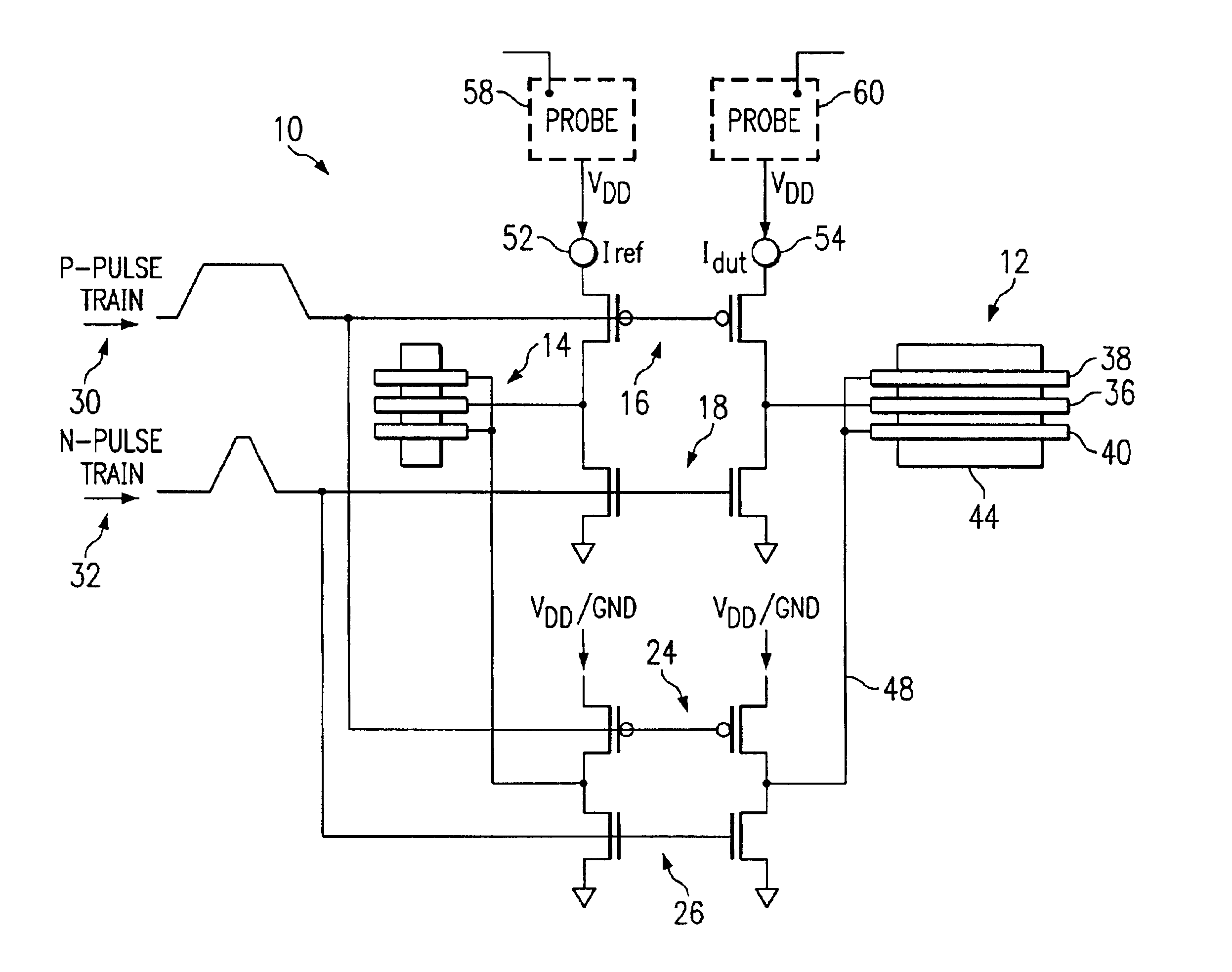

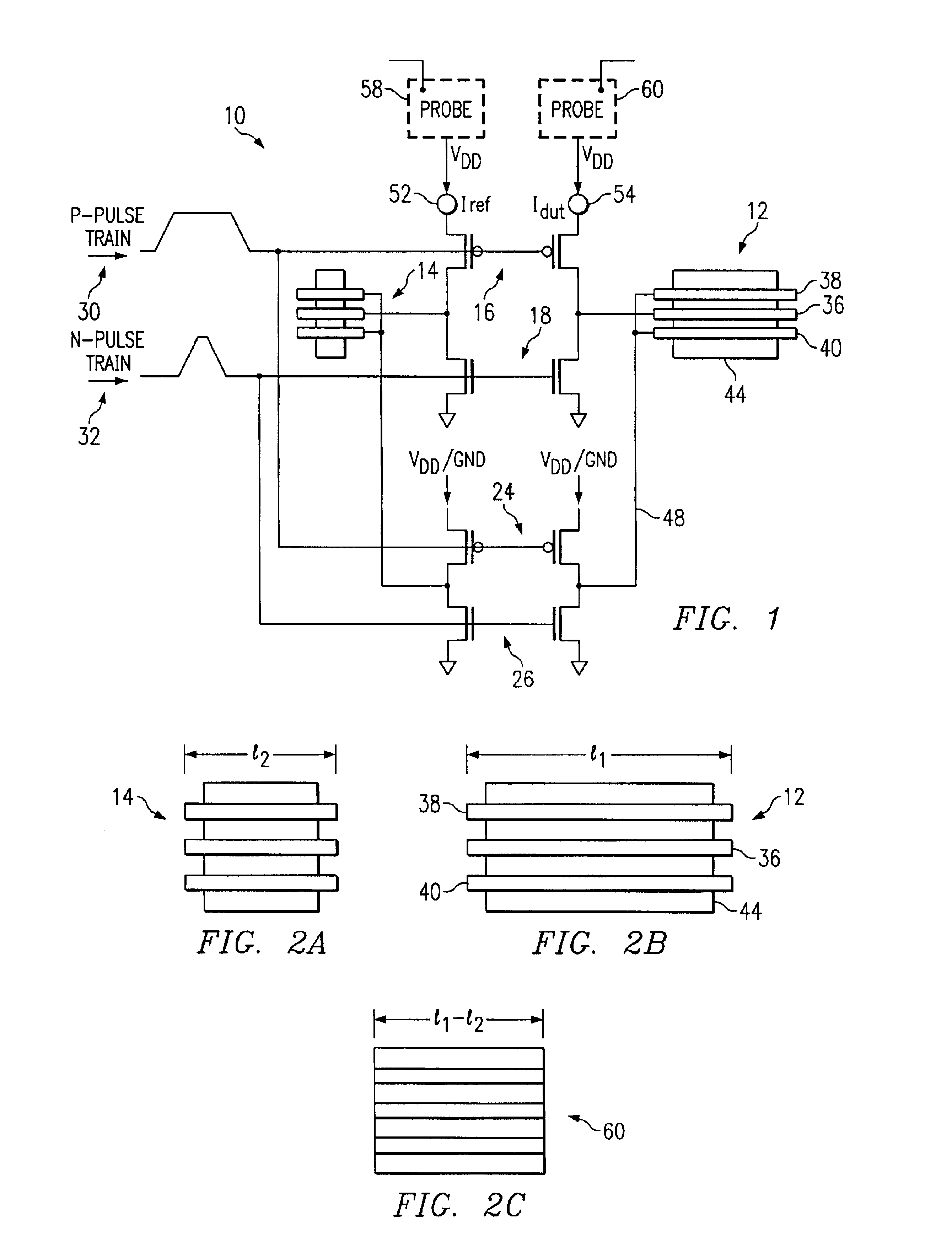

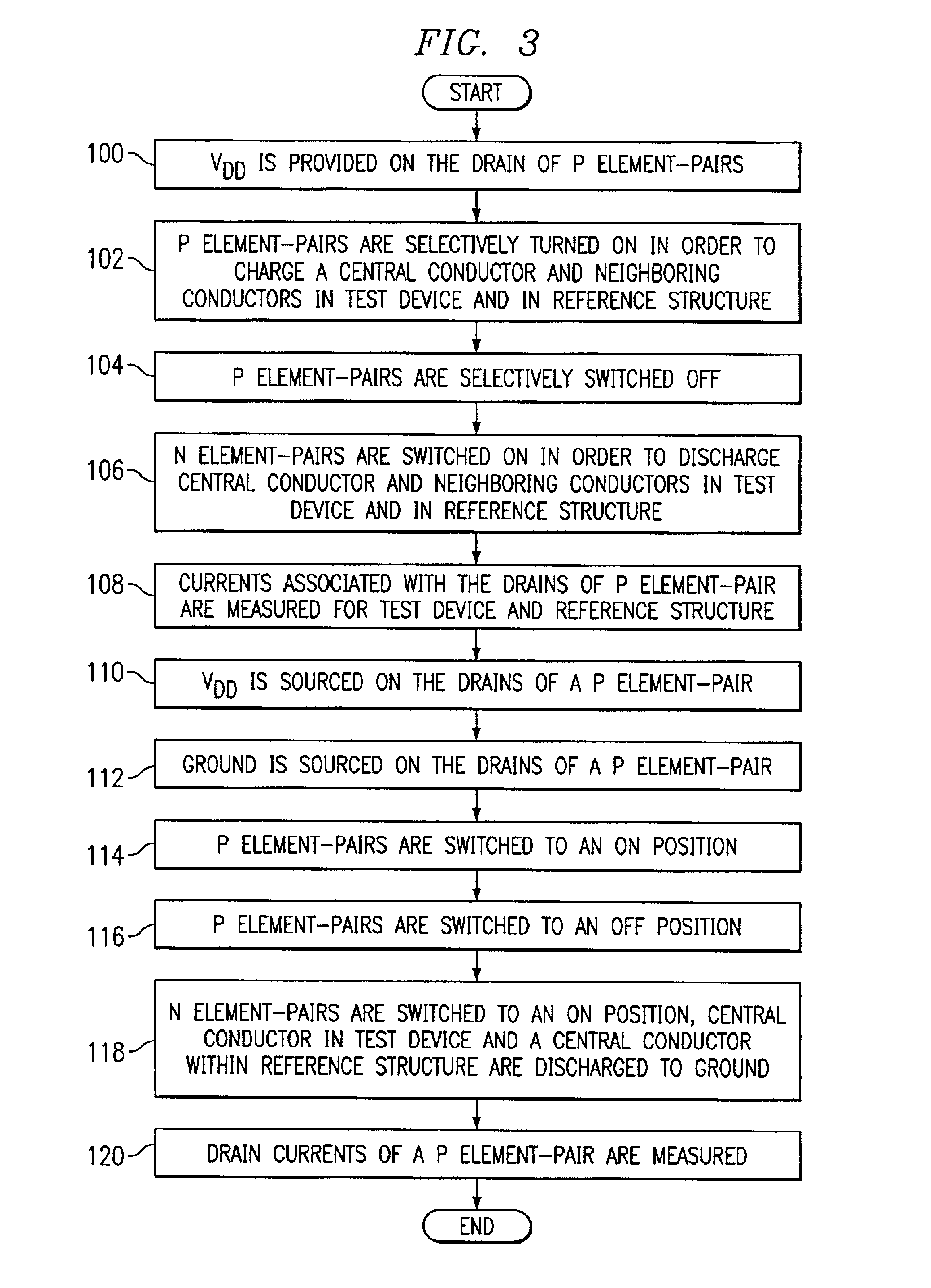

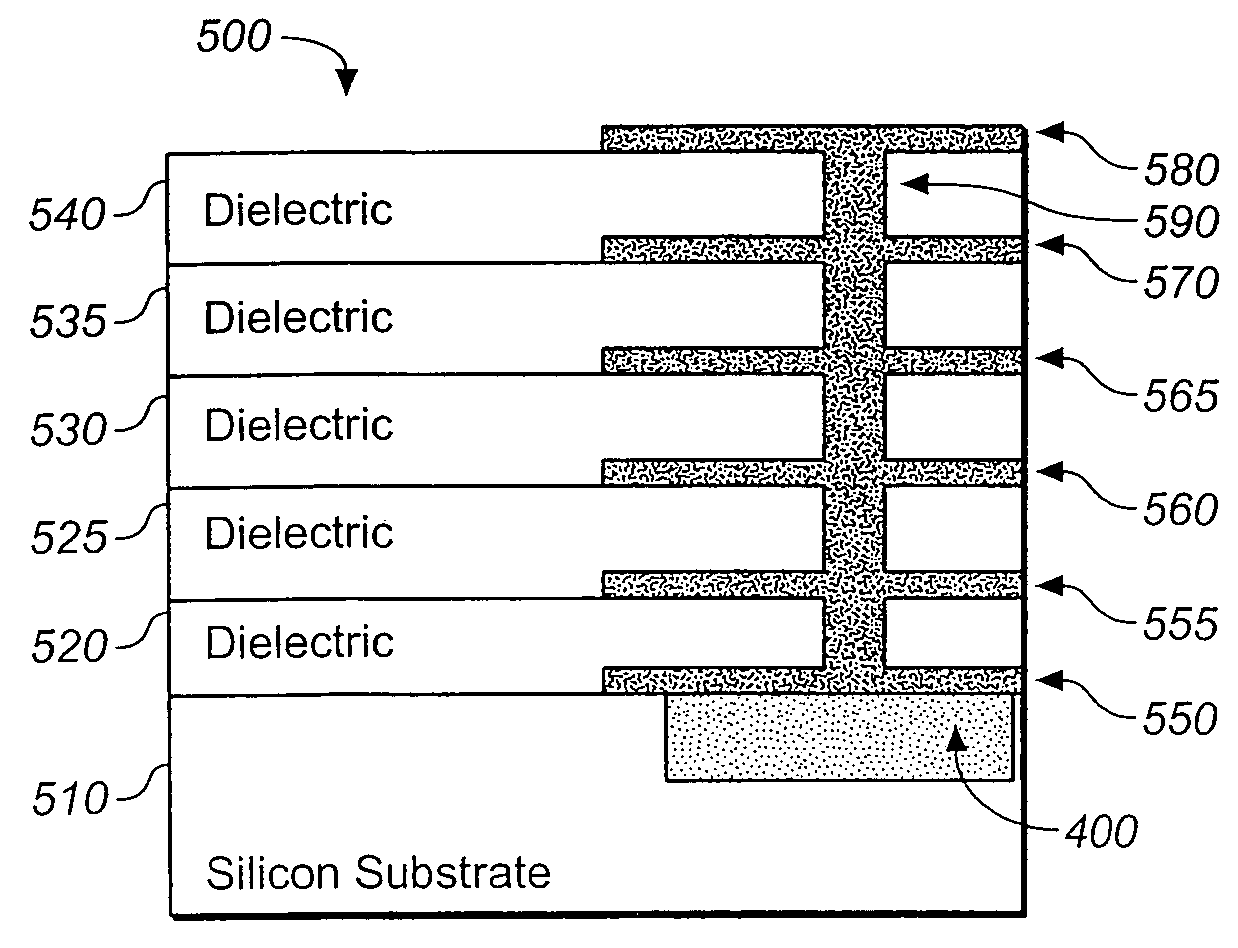

System and method for measuring a capacitance of a conductor

InactiveUS6856143B2High precision measurementEliminate capacitanceAnalog circuit testingCapacitance measurementsCapacitanceElectrical conductor

A method for measuring a capacitance of a device under test is provided that includes selectively charging and discharging a first conductor with a first set of p and n element-pairs in response to a voltage potential applied to the first set of p and n element-pairs. The method further includes selectively charging and discharging a second conductor with a second set of p and n element-pairs in response to a voltage potential applied to the second set of p and n element-pairs. Currents are measured at drains associated with the first set of p element-pairs as the first and second conductors charge and discharge such that a capacitance associated with the first conductor may be determined that is based on the drain currents.

Owner:TEXAS INSTR INC

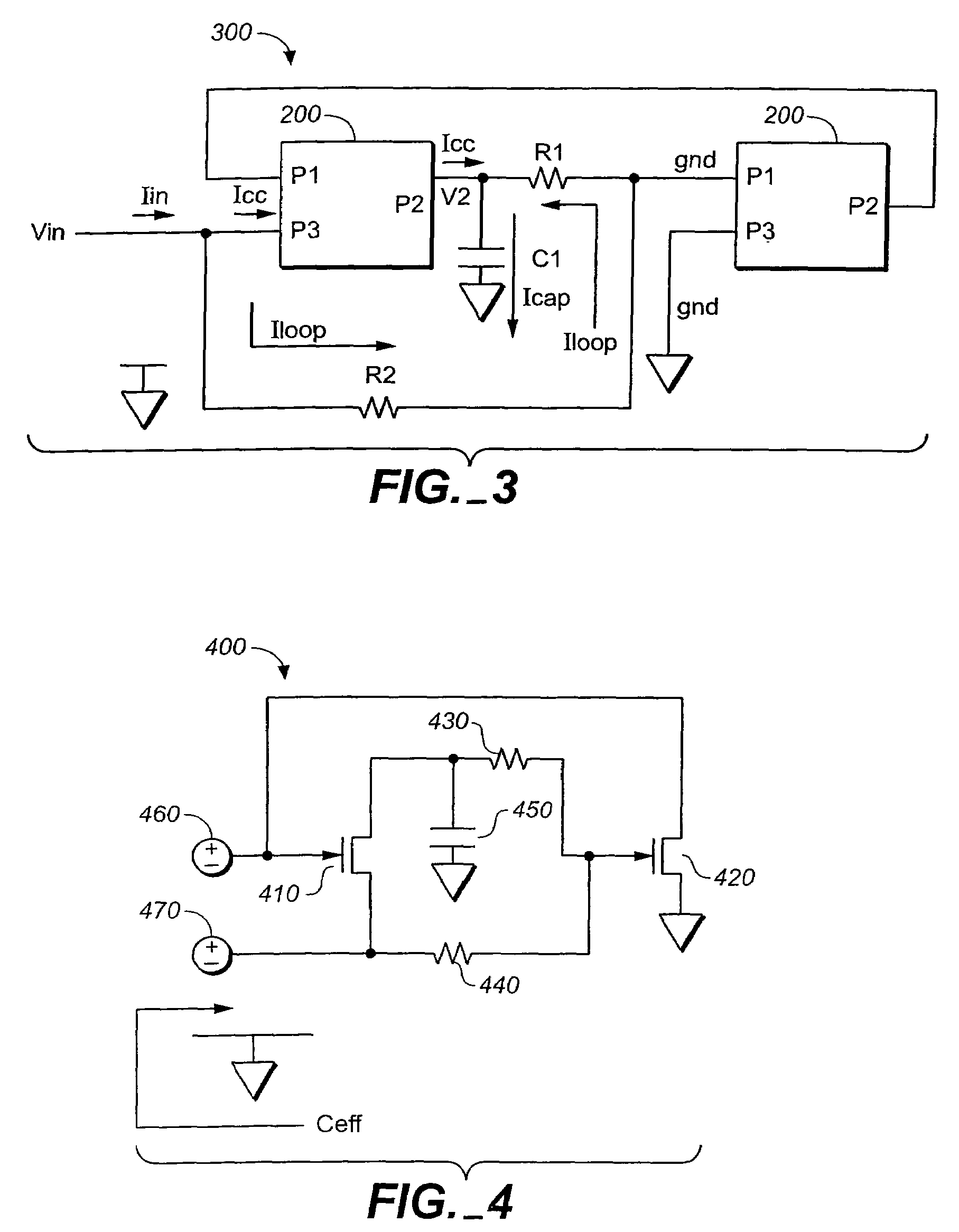

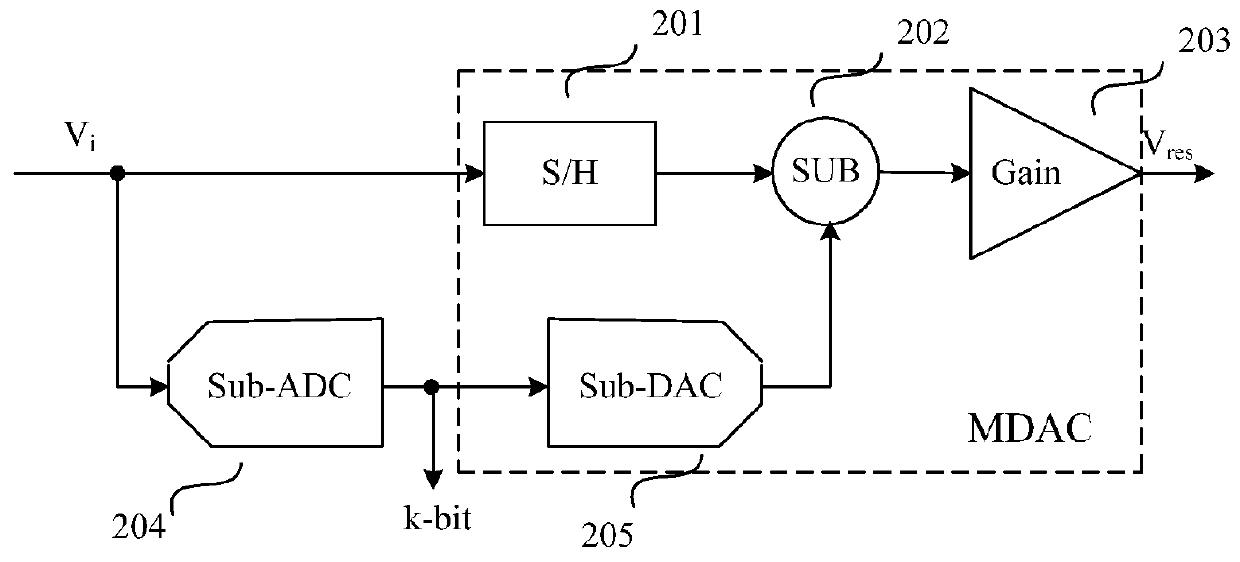

Zero capacitance bondpad utilizing active negative capacitance

ActiveUS7148535B2Reduce capacitanceEliminate capacitanceTransistorSemiconductor/solid-state device detailsCapacitanceCapacitor

The present invention is an apparatus and system for reducing bondpad capacitance of an integrated circuit. Circuitry of the present invention may produce a negative capacitance approximately equal in magnitude to the capacitance associated with the bondpad and thereby effectively eliminate the bondpad capacitance. Values of the components of the circuitry may be selectively and independently chosen to synthesize a variable range of negative capacitance and thus produce a negative capacitance approximately equal in magnitude to a unique capacitance associated with the bondpad of a variety of integrated circuits.

Owner:BELL SEMICON LLC

Capacitor array and layout design method thereof

ActiveUS9336347B2Eliminate capacitanceElectric signal transmission systemsMultiple fixed capacitorsParasitic capacitanceEngineering

A layout design method is provided for generating capacitor arrays being described in four steps: first, the wiring mode of unit capacitors is defined allowing the wire being connected to the upper plate to parallel that to the lower one, second, a capacitor array layout is designed with capacitors being distributed in Mh lines, Mh is the maximum of capacitors' lines, the line numbers of Class 1 to Class K capacitors are defined in the unilateral capacitor array, third, the wiring mode is set for capacitor array making sure the lengths of the wires to the upper and lower plates of unit capacitors are equal, at last, parasitic parameters are characterized in ways that verify the layout. A capacitor array is provided as well. By eliminating capacitance mismatching caused by parasitic capacitance, the method works to generate a well-matched capacitor array in an easy and efficient way.

Owner:CHONGQING GIGACHIP TECH CO LTD