Patents

Literature

418results about "Analog circuit testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

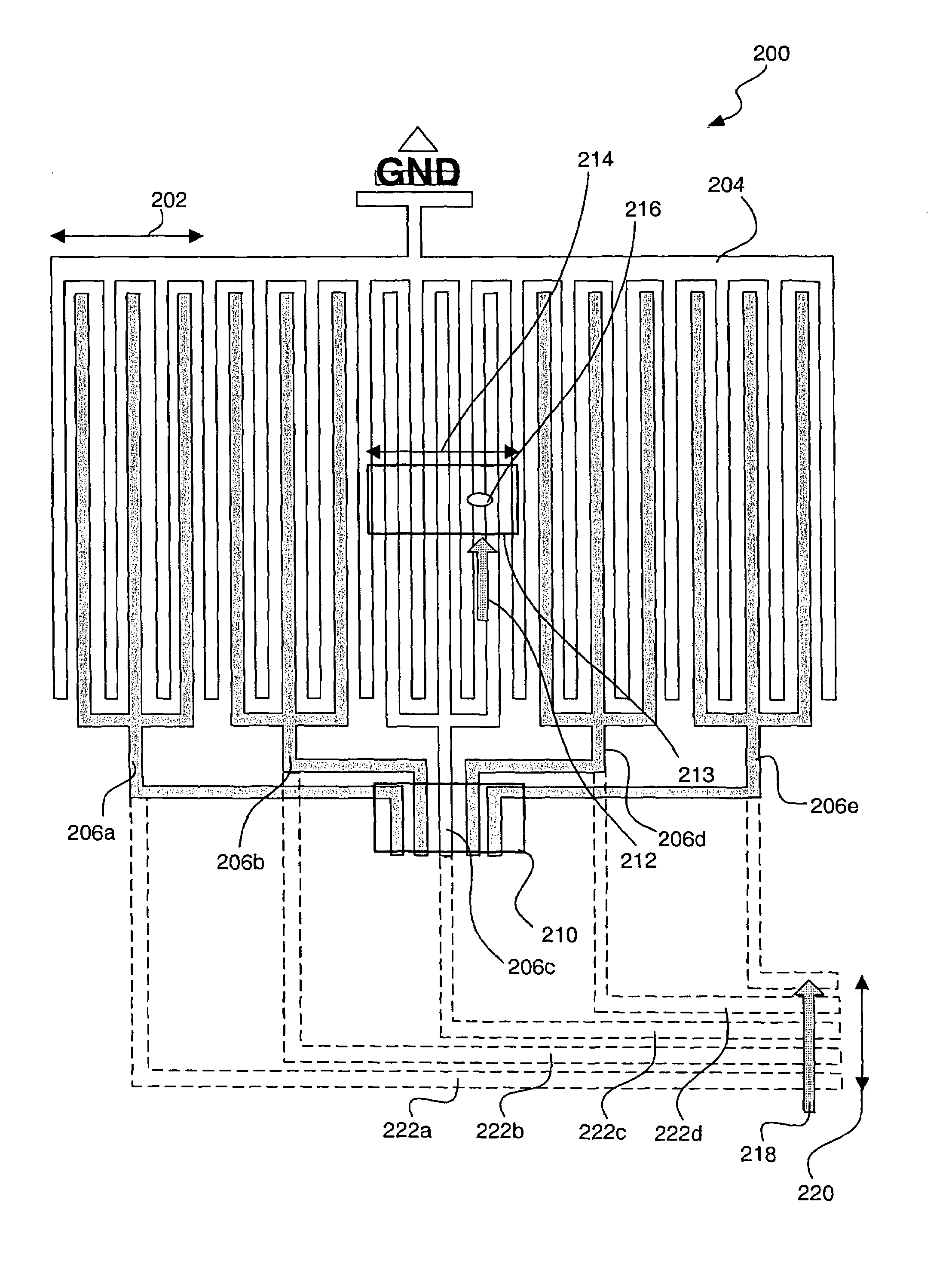

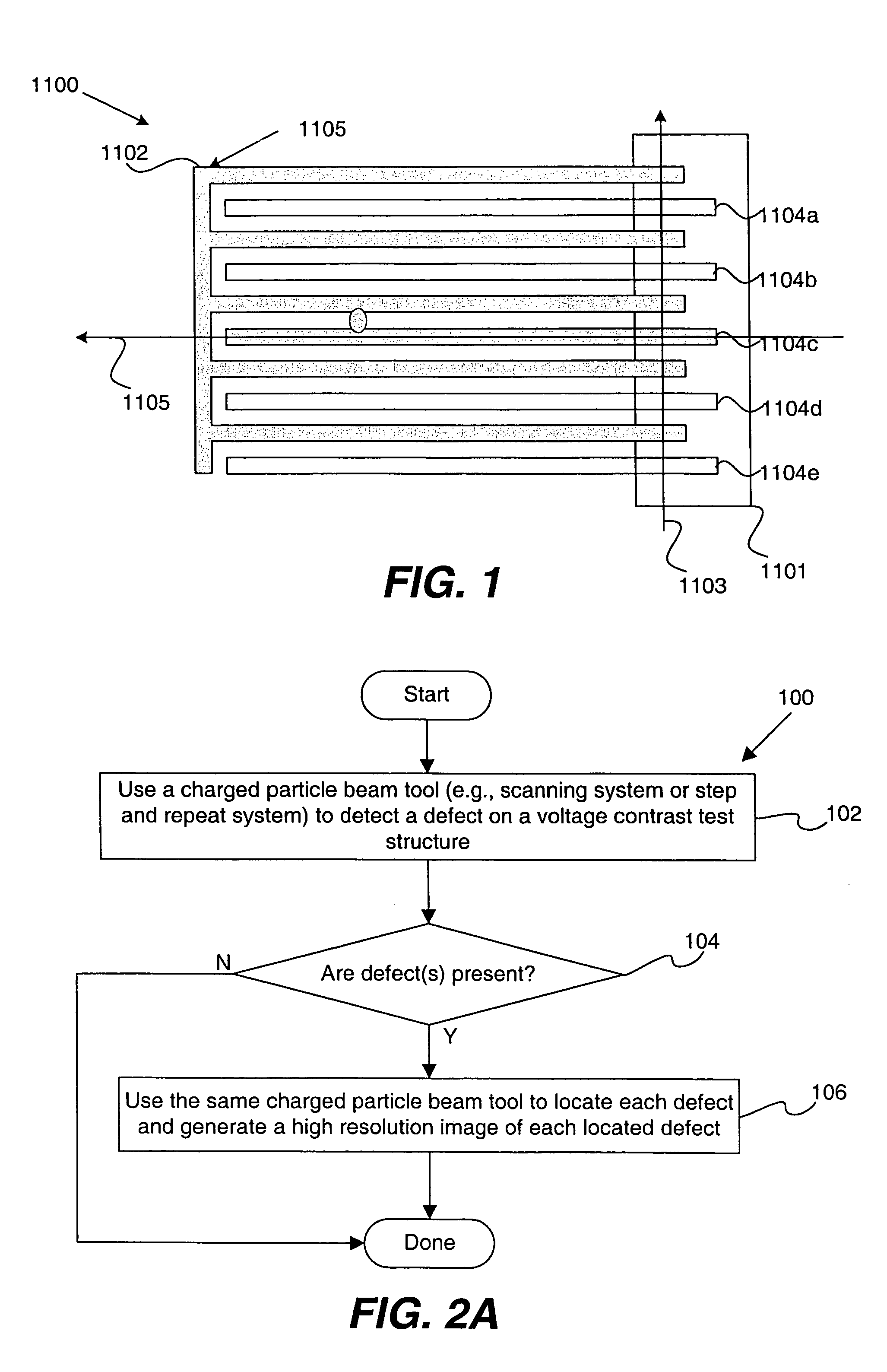

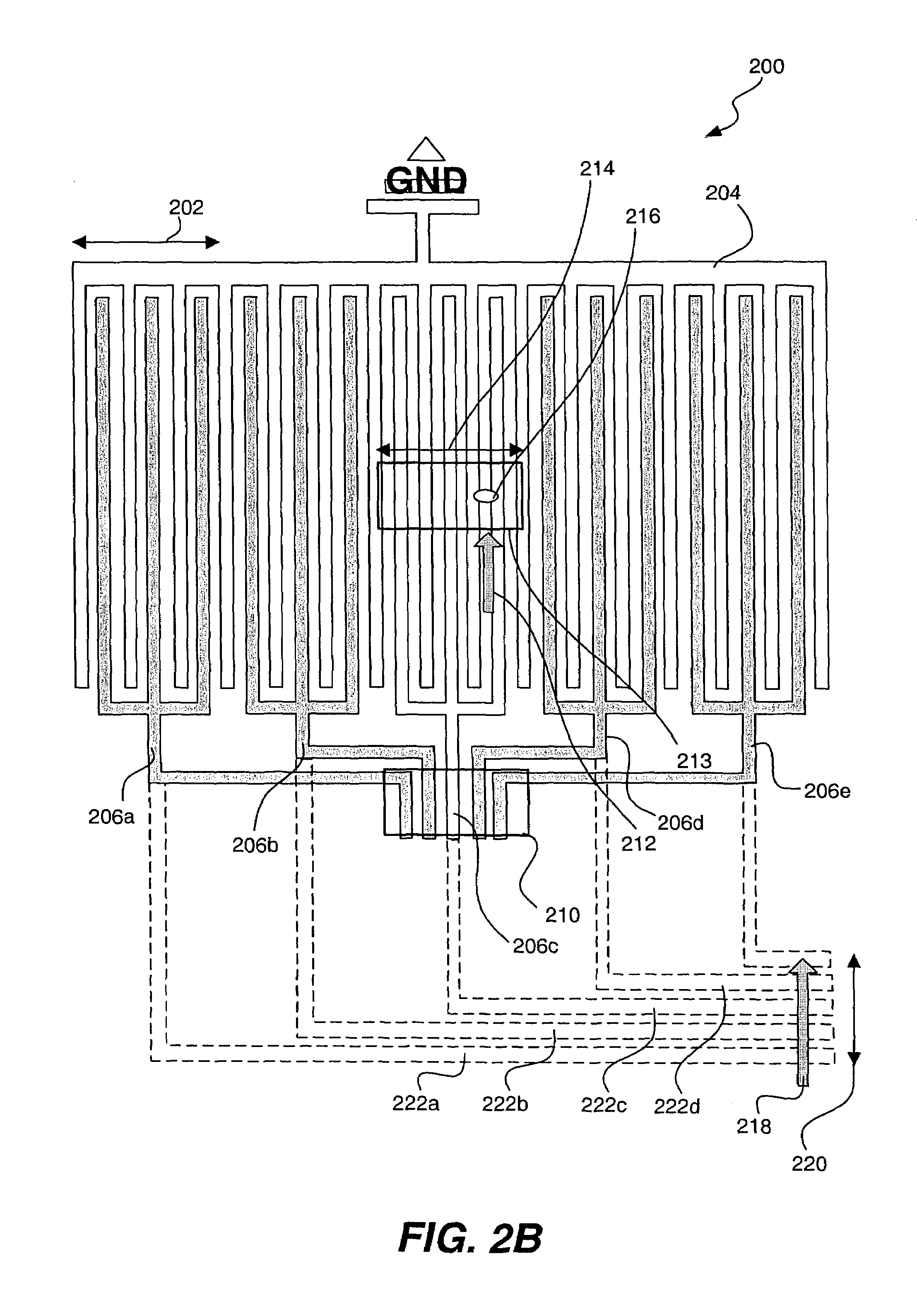

Methodologies for efficient inspection of test structures using electron beam scanning and step and repeat systems

ActiveUS7198963B2Analog circuit testingSemiconductor/solid-state device testing/measurementImage resolutionBeam scanning

Disclosed are techniques for efficiently inspecting defects on voltage contrast test. In one embodiment, methodologies and test structures allow inspection to occur entirely within a charged particle system. In a specific embodiment, a method of localizing and imaging defects in a semiconductor test structure suitable for voltage contrast inspection is disclosed. A charged particle beam based tool is used to determine whether there are any defects present within a voltage contrast test structure. The same charged particle beam based tool is then used to locate defects determined to be present within the voltage contrast test structure. Far each localized defect, the same charged particle beam based tool may then be used to generate a high resolution image of the localized defect whereby the high resolution image can later be used to classify the each defect. In one embodiment, the defect's presence and location are determined without rotating the test structure relative to the charged particle beam.

Owner:KLA TENCOR TECH CORP

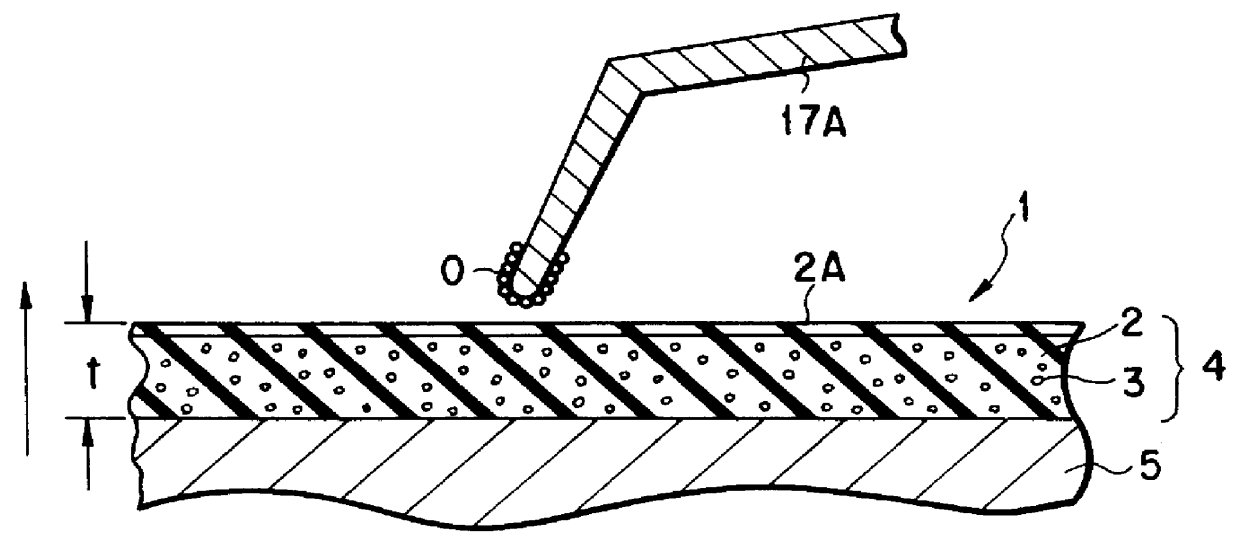

Cleaner for inspecting projections, and inspection apparatus and method for integrated circuits

InactiveUS6130104AImprove surface conditionAnalog circuit testingSemiconductor/solid-state device testing/measurementWaddingBiomedical engineering

A cleaner of this invention is a cleaner for inspecting projections and removes any substance, e.g., aluminum oxide, which attaches to needle points of probe needles, when the probe needles pierce into the cleaner. The cleaner has a cleaner layer and a substrate. The cleaner layer is constituted by an elastic material layer, and a filler having a surface state improving function of the inspecting projections and dispersed in the elastic material layer. As the filler having a surface state improving function, a powder including at least one of ceramic materials, e.g., sand, glass, alumina, Carborundum (trade name), and the like, or a fiber layer made of an inorganic fiber or organic fiber can be employed.

Owner:TOKYO ELECTRON LTD

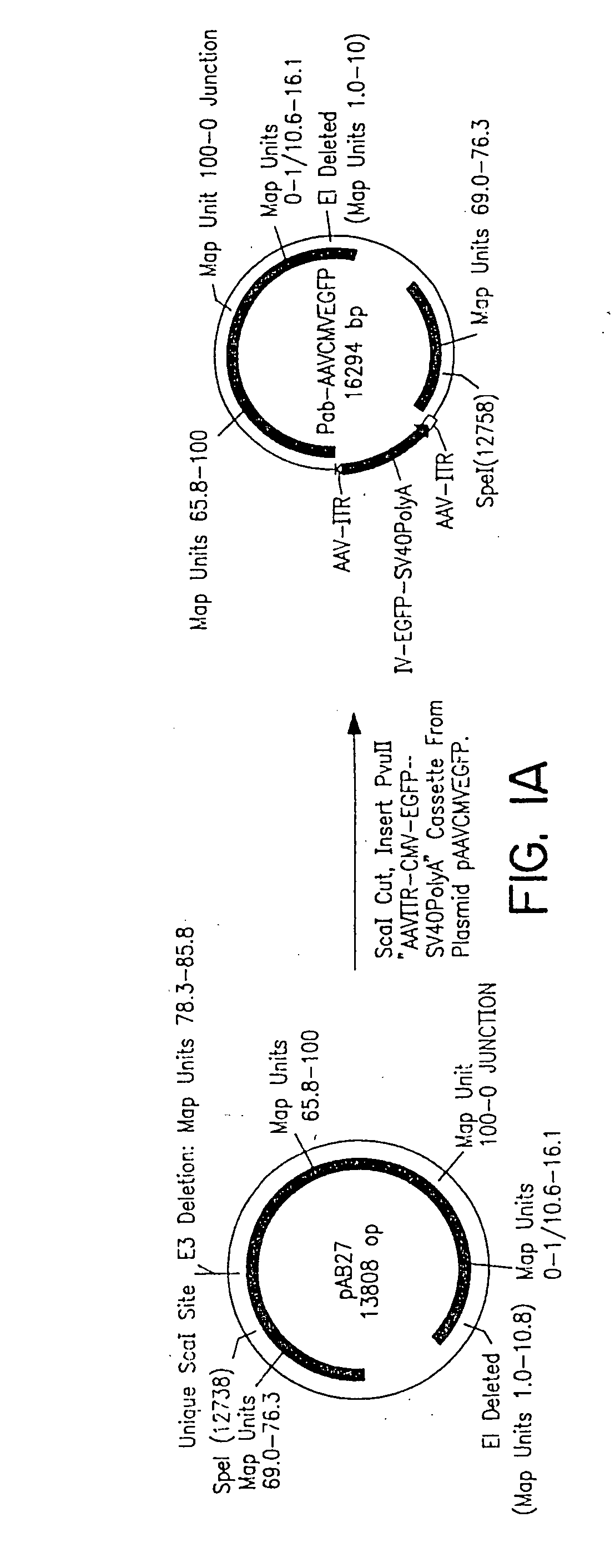

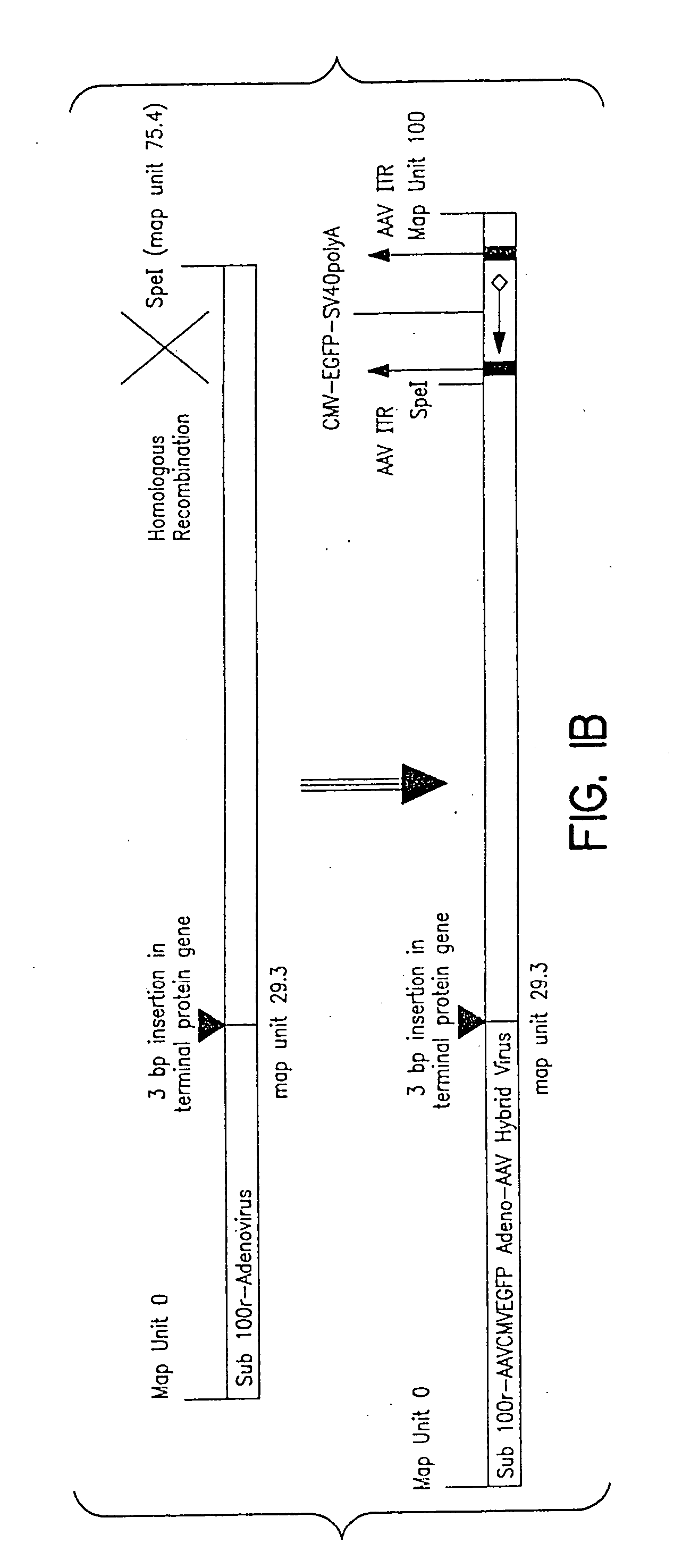

Compositions and methods for helper-free production of recombinant adeno-associated viruses

Owner:THE TRUSTEES OF THE UNIV OF PENNSYLVANIA

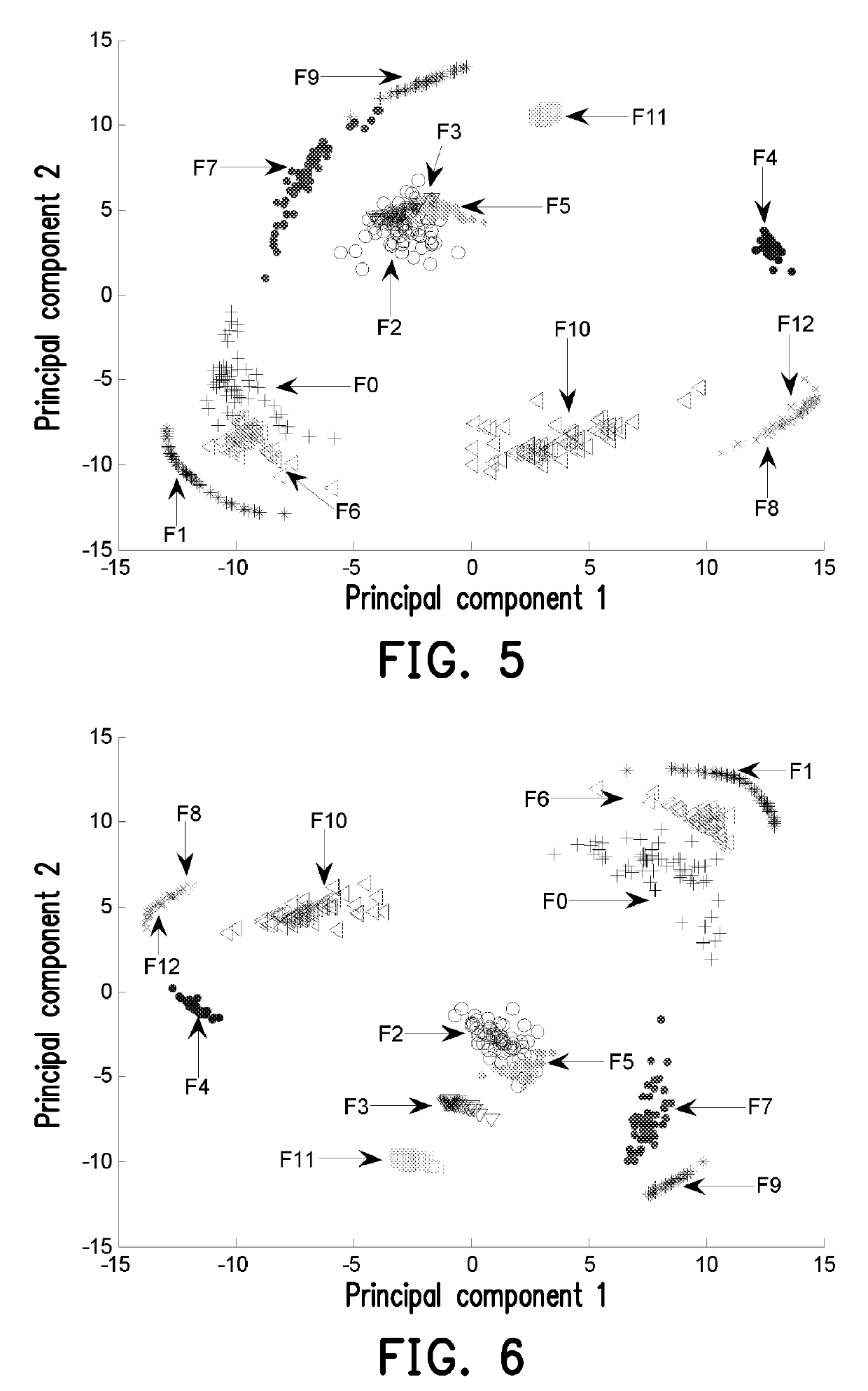

Analog circuit dynamic online failure diagnosing method based on GSD-SVDD

InactiveCN101907681AReflect the degree of separationHigh precisionAnalog circuit testingSpecial data processing applicationsClassification methodsDiagnostic system

The invention discloses an analog circuit dynamic online failure diagnosing method based on GSD-SVDD, belonging to the technical field of analog circuit failure diagnosis. In an offline test process, a KFCM algorithm is adopted to calculate a failure resolution value of each testable node and an optimal test node set is selected according to the failure resolution value. In an online diagnosis process, a failure diagnosis model is established by adopting an SVDD single classification approach based on a map spatial distance positive and negative sample weighting, test samples are diagnosed by a layered diagnosis method, and a failure class library and the diagnosis model are renewed dynamically. The method effectively reduces the drill and online diagnosis time of the diagnosis model, guarantees the real-time property of the online diagnosis and improves the precision of the failure diagnosis and can dynamically renew parameters of the diagnosis model so as to enable the a diagnosis system to have the self-adaption capability.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

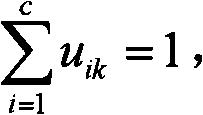

Deep belief network feature extraction-based analogue circuit fault diagnosis method

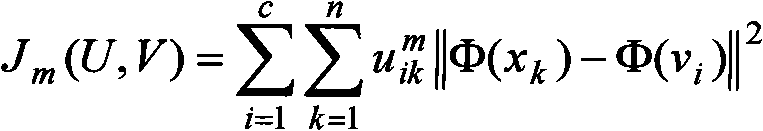

ActiveUS20190243735A1Improve feature extraction performanceImprove the extraction effectDetecting faulty hardware using neural networksAnalog circuit testingRestricted Boltzmann machineFeature extraction

A Deep Belief Network (DBN) feature extraction-based analogue circuit fault diagnosis method comprises the following steps: a time-domain response signal of a tested analogue circuit is acquired, where the acquired time-domain response signal is an output voltage signal of the tested analogue circuit; DBN-based feature extraction is performed on the acquired voltage signal, wherein learning rates of restricted Boltzmann machines in a DBN are optimized and acquired by virtue of a quantum-behaved particle swarm optimization (QPSO); a support vector machine (SVM)-based fault diagnosis model is constructed, wherein a penalty factor and a width factor of an SVM are optimized and acquired by virtue of the QPSO; and feature data of test data are input into the SVM-based fault diagnosis model, and a fault diagnosis result is output, where the feature data of the test data is generated by performing the DBN-based feature extraction on the test data.

Owner:WUHAN UNIV

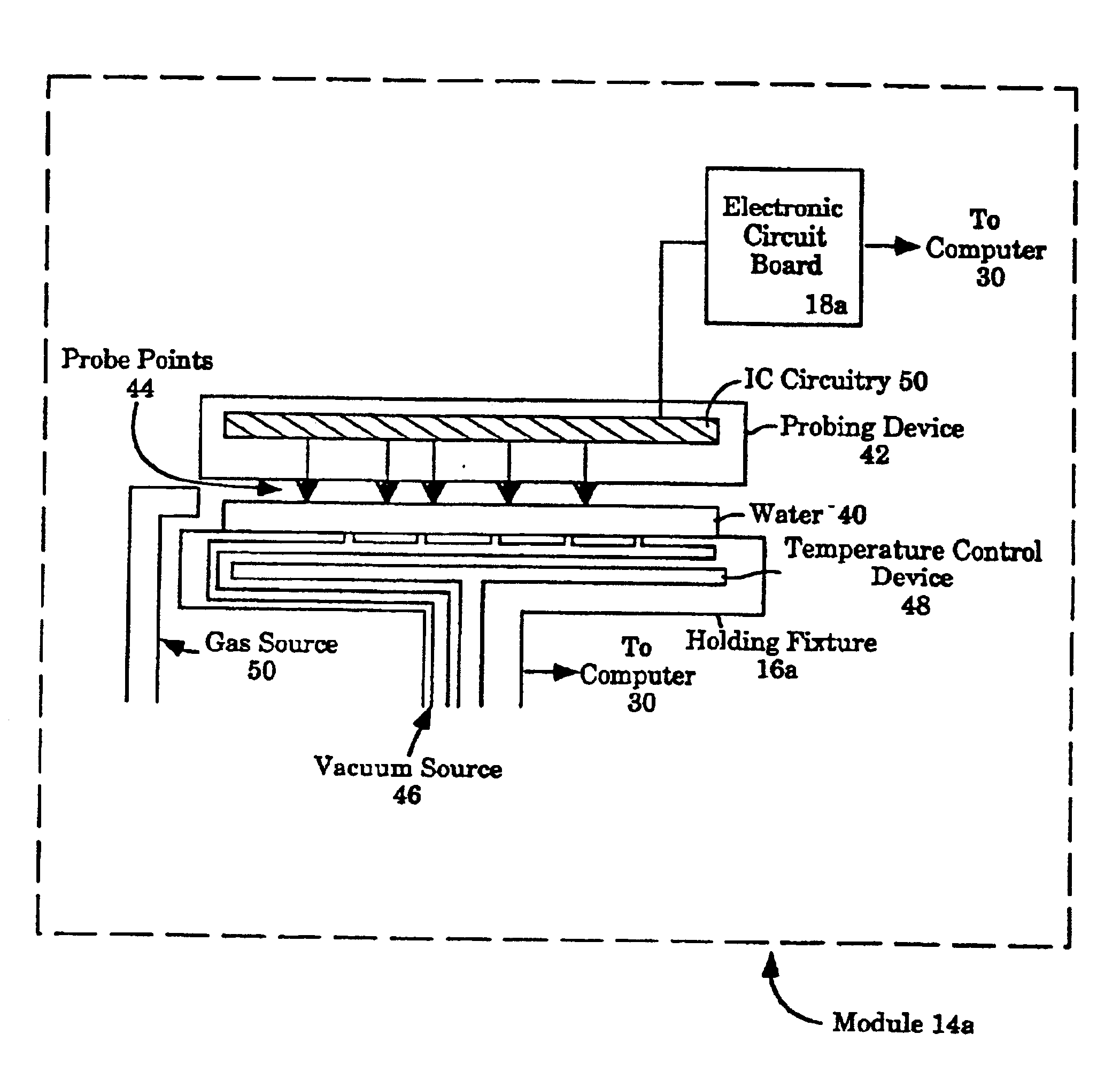

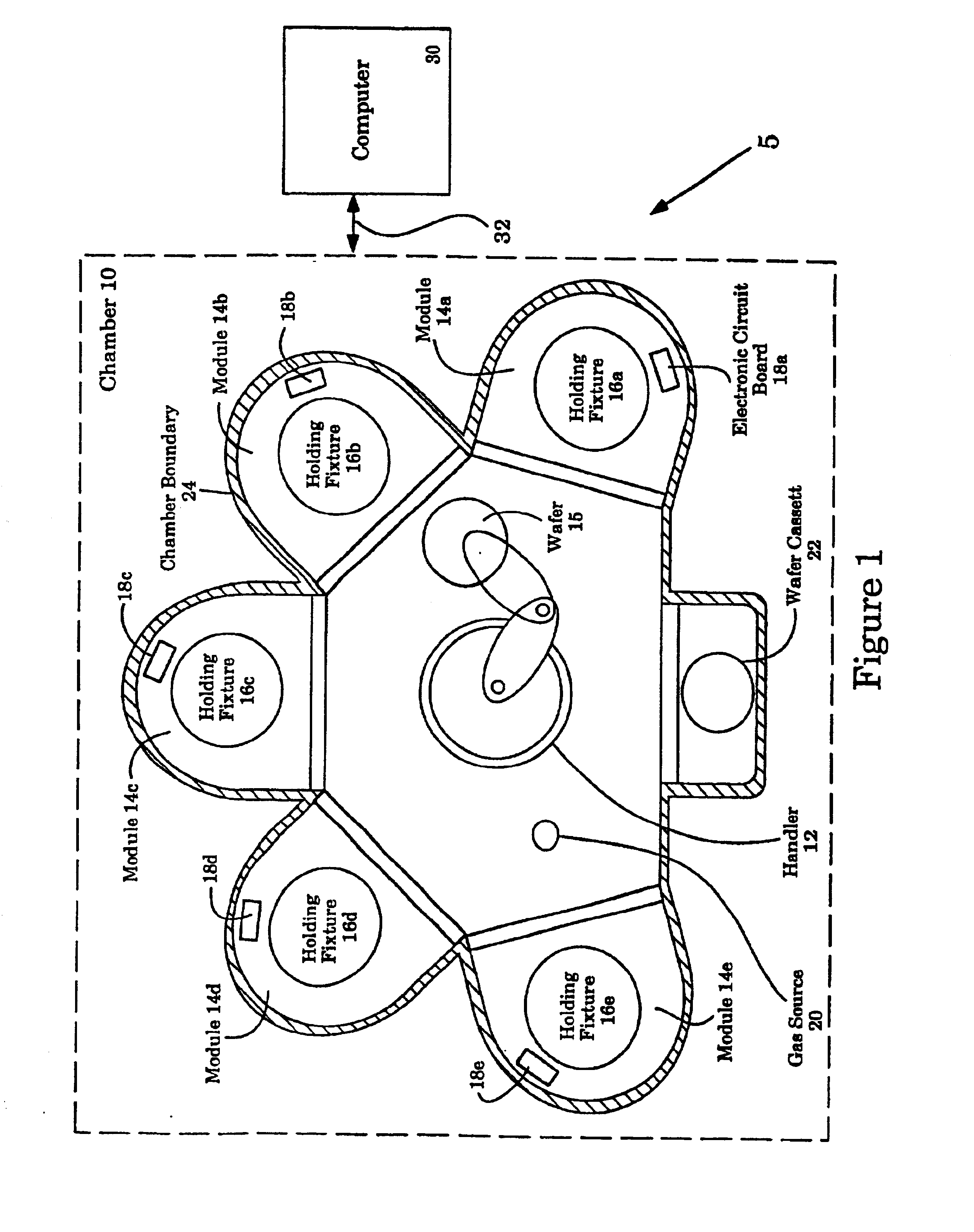

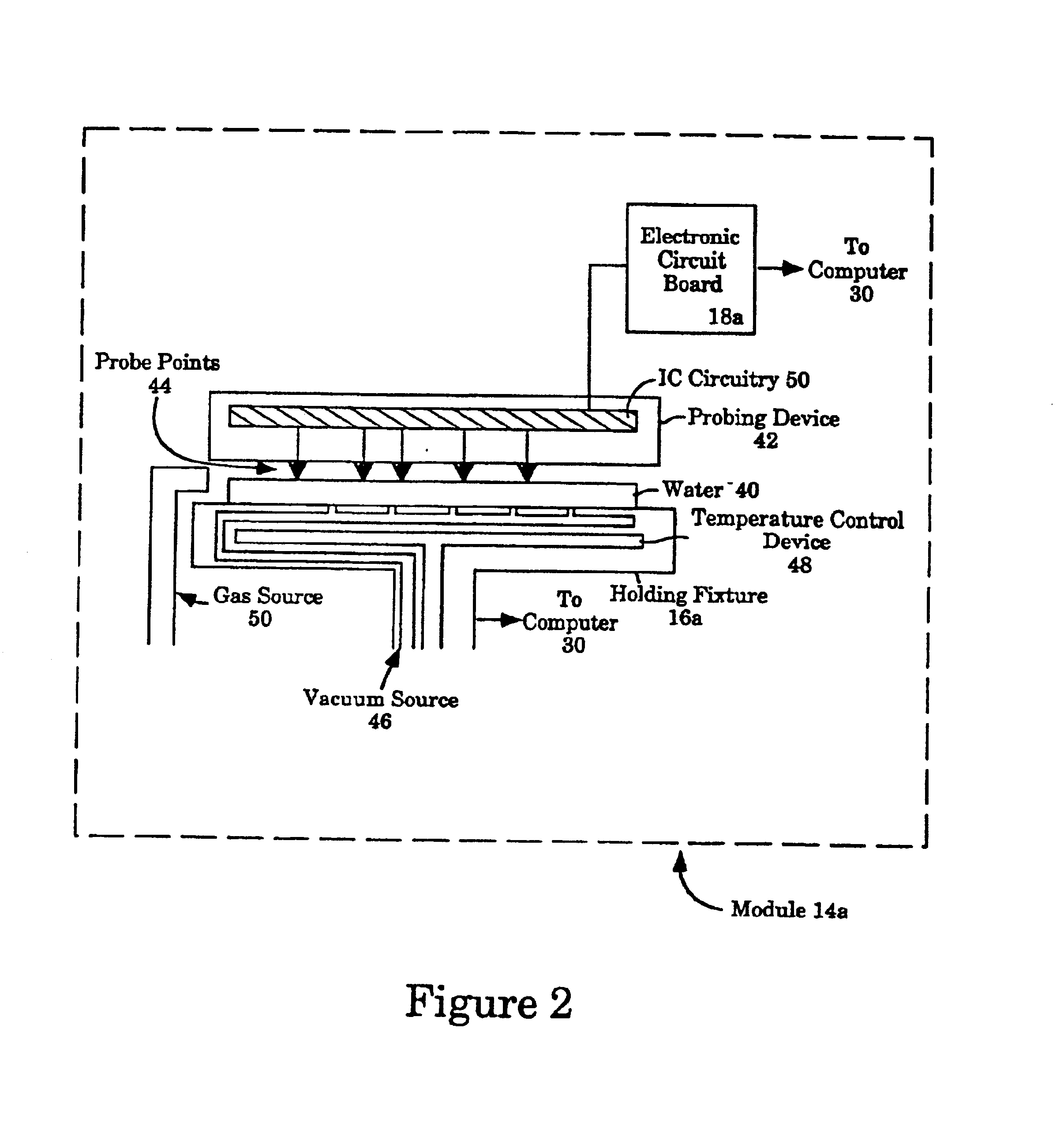

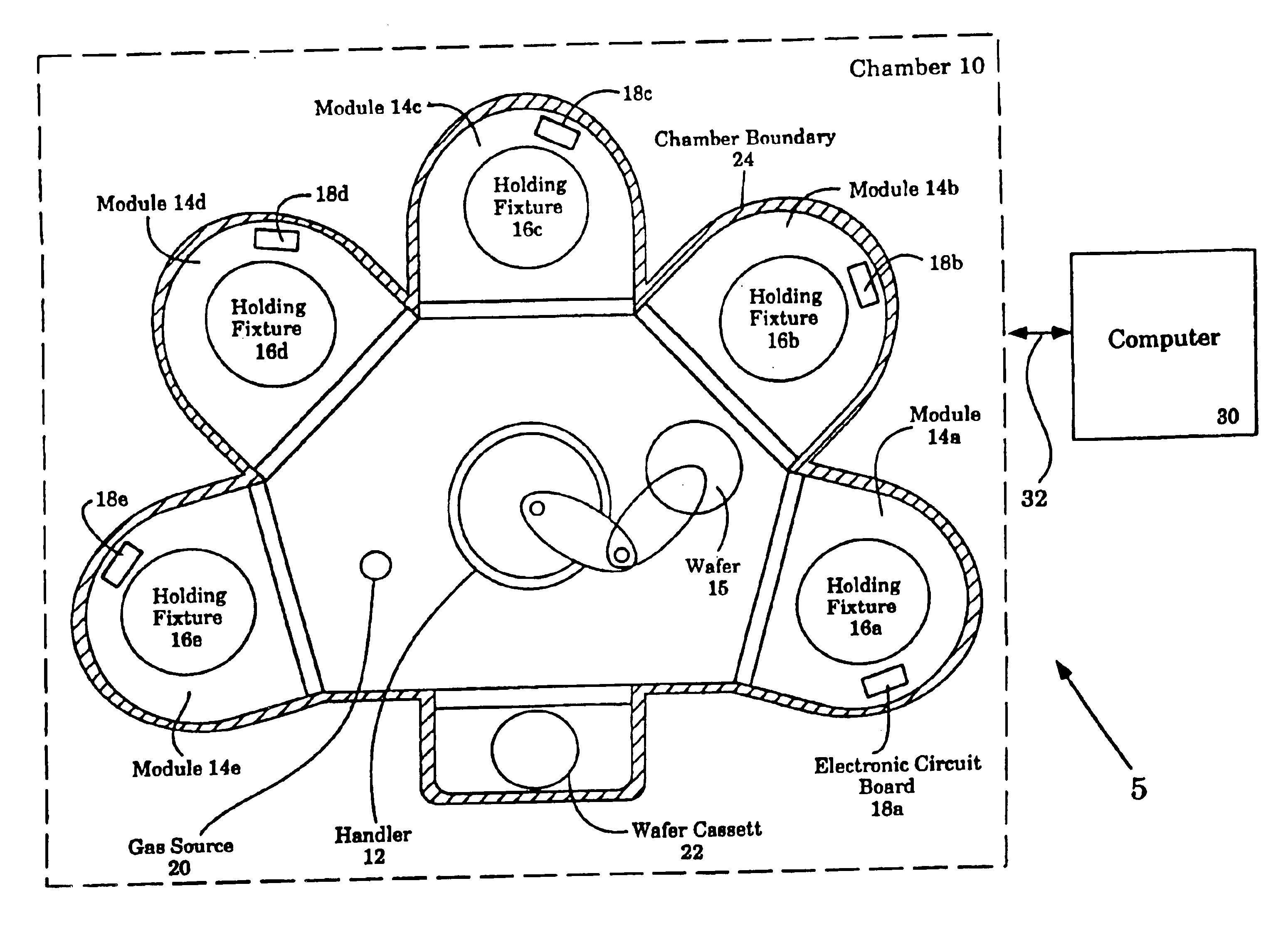

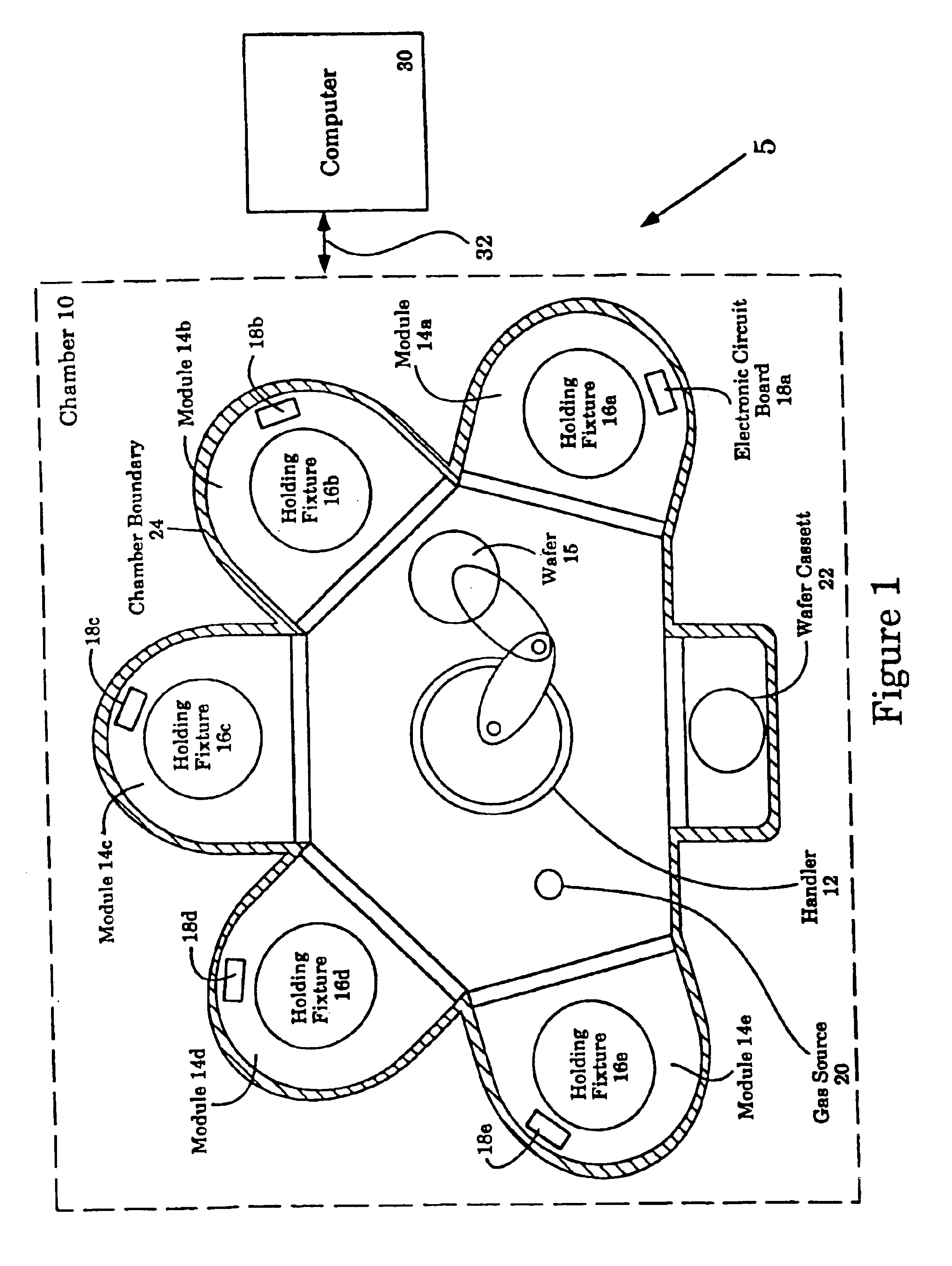

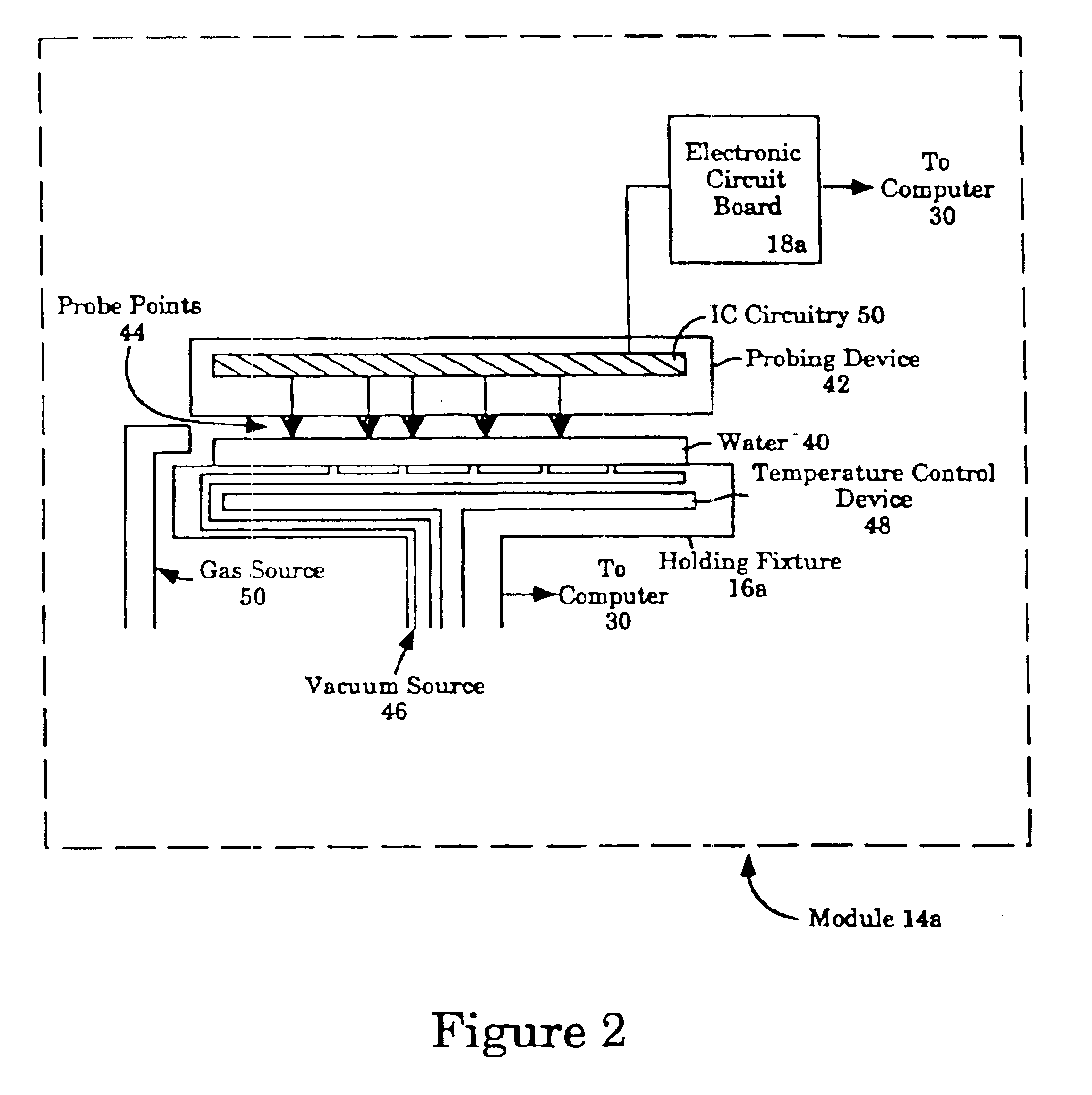

Method and system for probing, testing, burn-in, repairing and programming of integrated circuits in a closed environment using a single apparatus

InactiveUS6838896B2Reduce thicknessAnalog circuit testingDigital circuit testingTemperature controlContact pad

A single gas tight system may perform multi-functions including reducing the thickness of oxides on contact pads and probing, testing, burn-in, repairing, programming and binning of integrated circuits. A holding fixture holds a wafer having integrated circuits and aligns the wafer to a full-substrate probing device. A temperature control device is used to heat the wafer during an oxide reduction process or during burn-in of the wafer. During the oxide reduction process, hydrogen is introduced into the chamber, and the wafer is heated so that the oxides on the contact pads can combine with hydrogen to form water vapor, thus reducing the thickness of the oxides. A computer analyzes the test and / or burn-in data and provides control signals for repairing or programming the integrated circuits.

Owner:ELM TECH

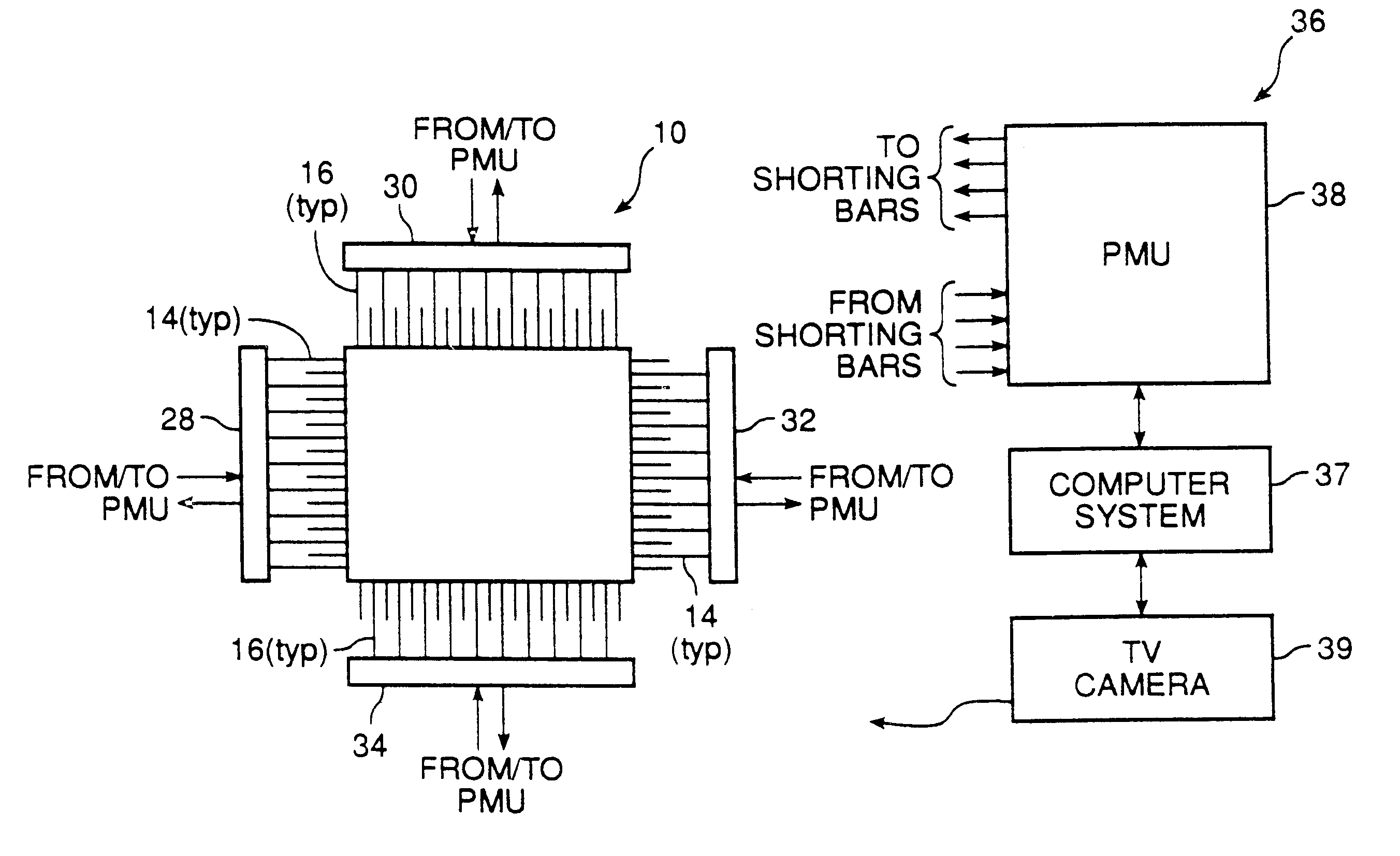

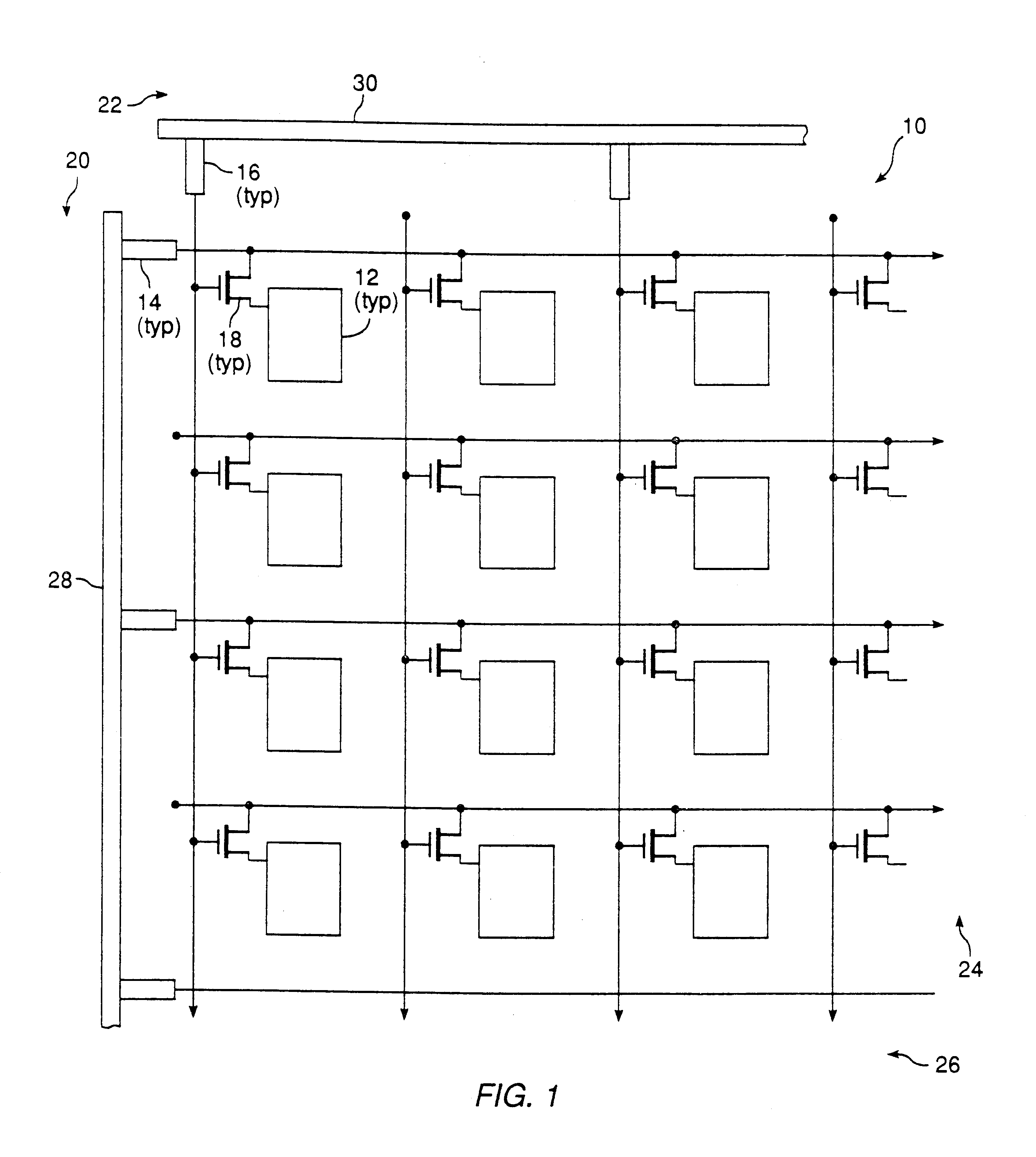

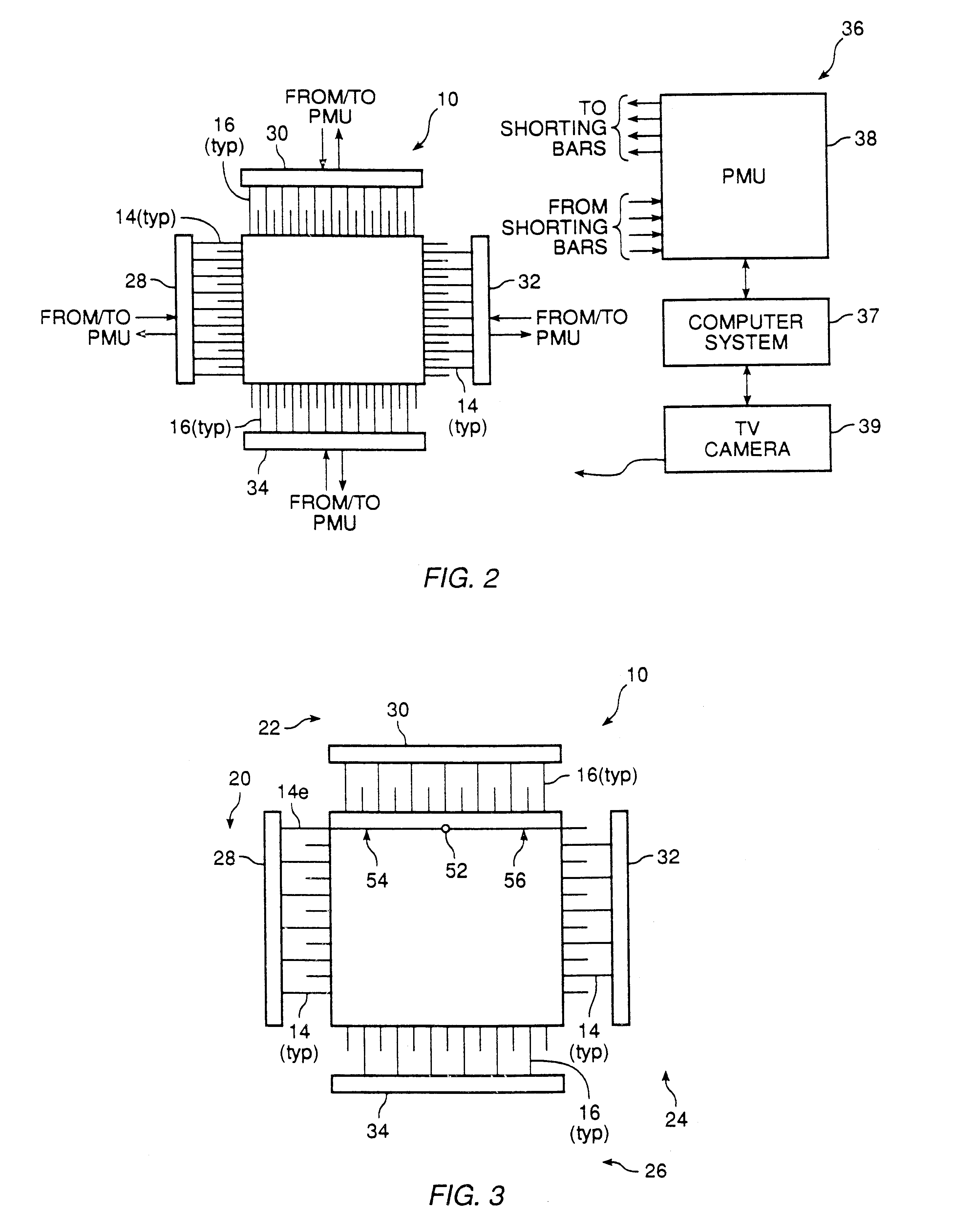

Method and apparatus for testing LCD panel array prior to shorting bar removal

Final testing of an LCD panel or the like is performed after preliminary testing for short circuit defects. During final testing, the panel is exposed to signals at the shorting bars and the resulting display pattern is imaged. The resulting image data then is processed at a computer system to determine whether the resulting display pattern differs from an expected display pattern. If differences are present then an open circuit or pixel defect is present. The applied test signals and the pattern or differences determine the type of defect present. For an open circuit defect along a gate line, a partial row (column) of the resulting display pattern does not activate. For an open circuit along a drive line, a partial column (row) of the resulting display does not activate. Pixel shorts are identified by applying test signals to the shorting bars during a first test cycle, then imaging the display during a second test cycle after at least one of the test signals is removed. Pixels which remain active that should be inactive have short circuit defects.

Owner:PHOTON DYNAMICS

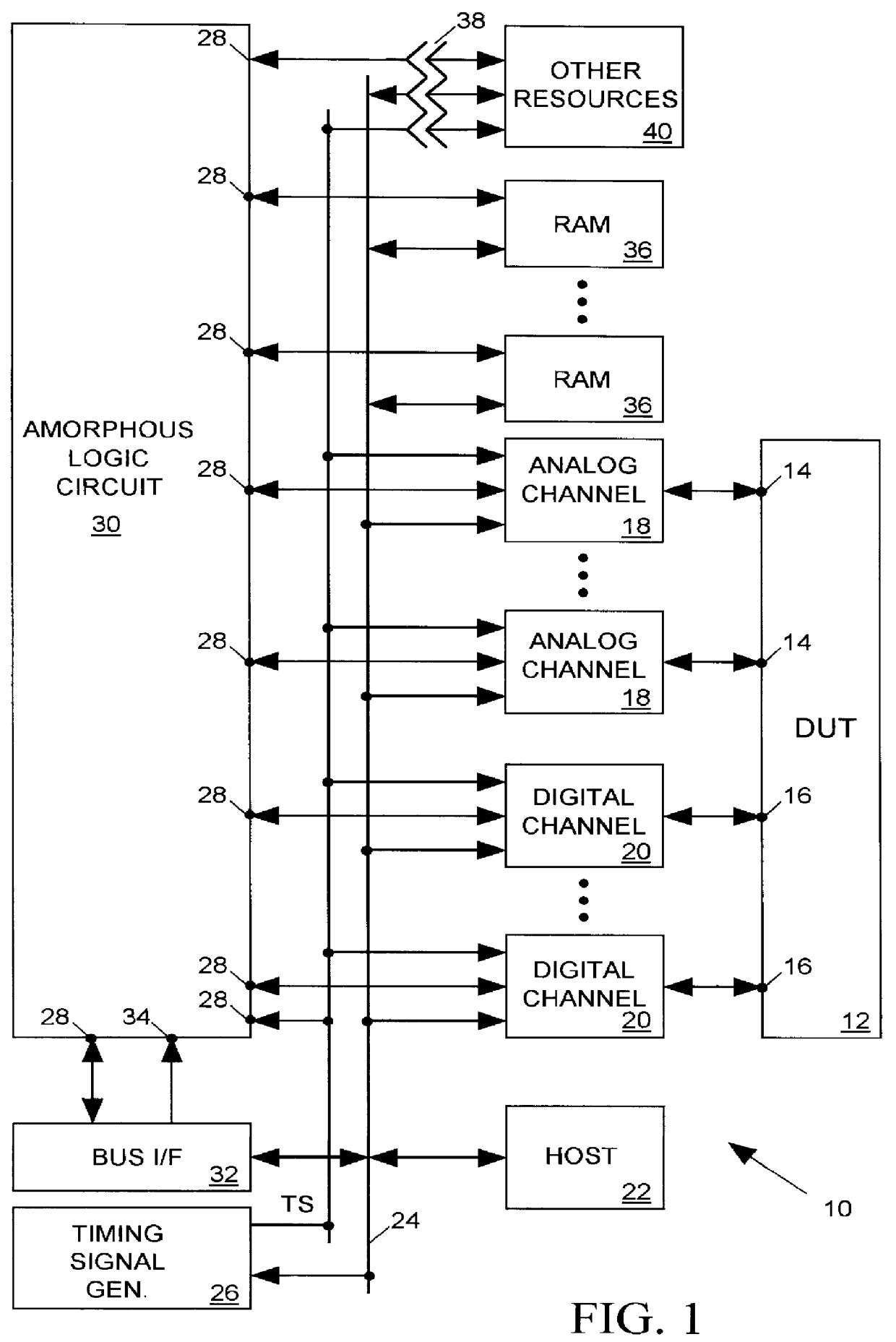

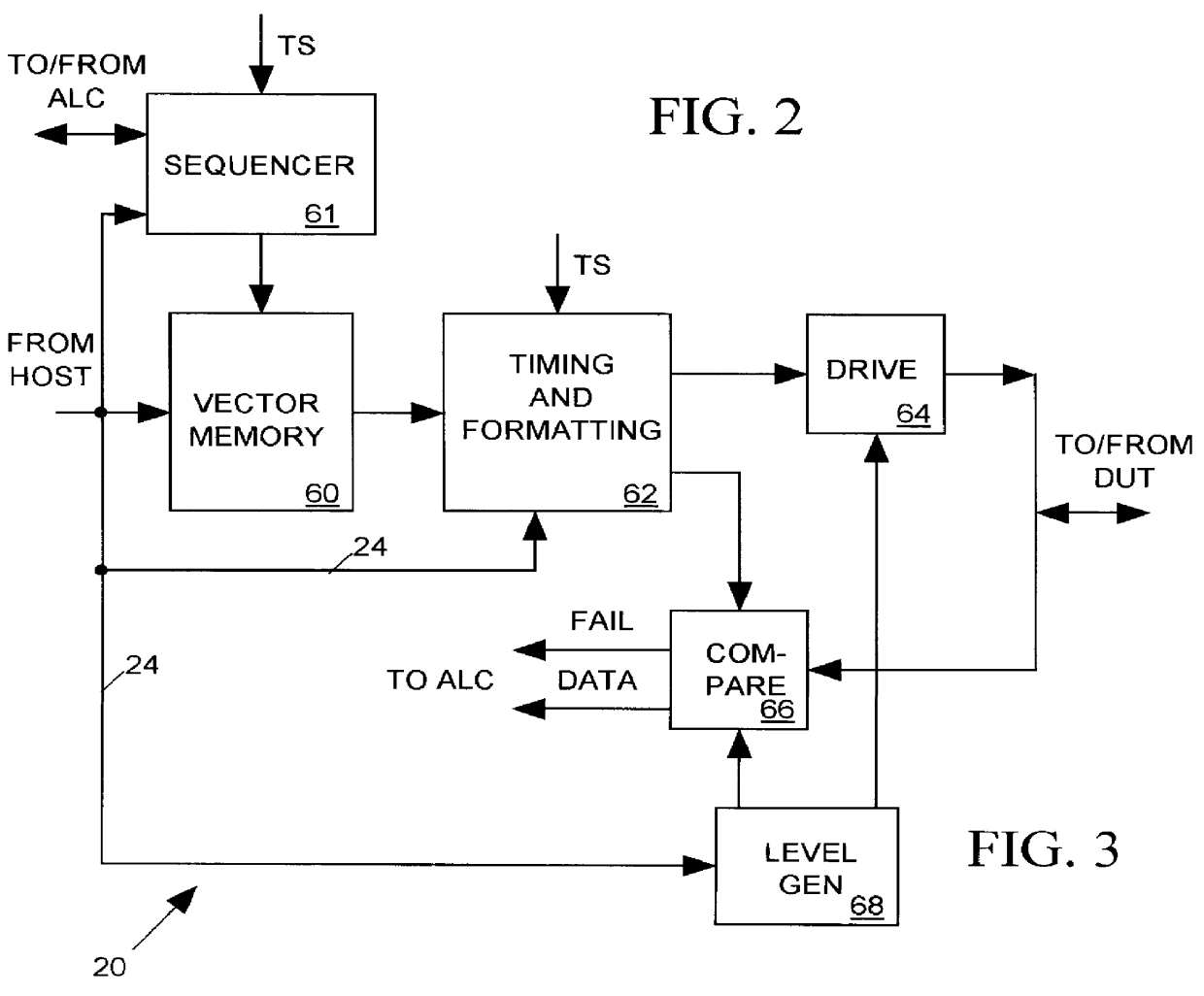

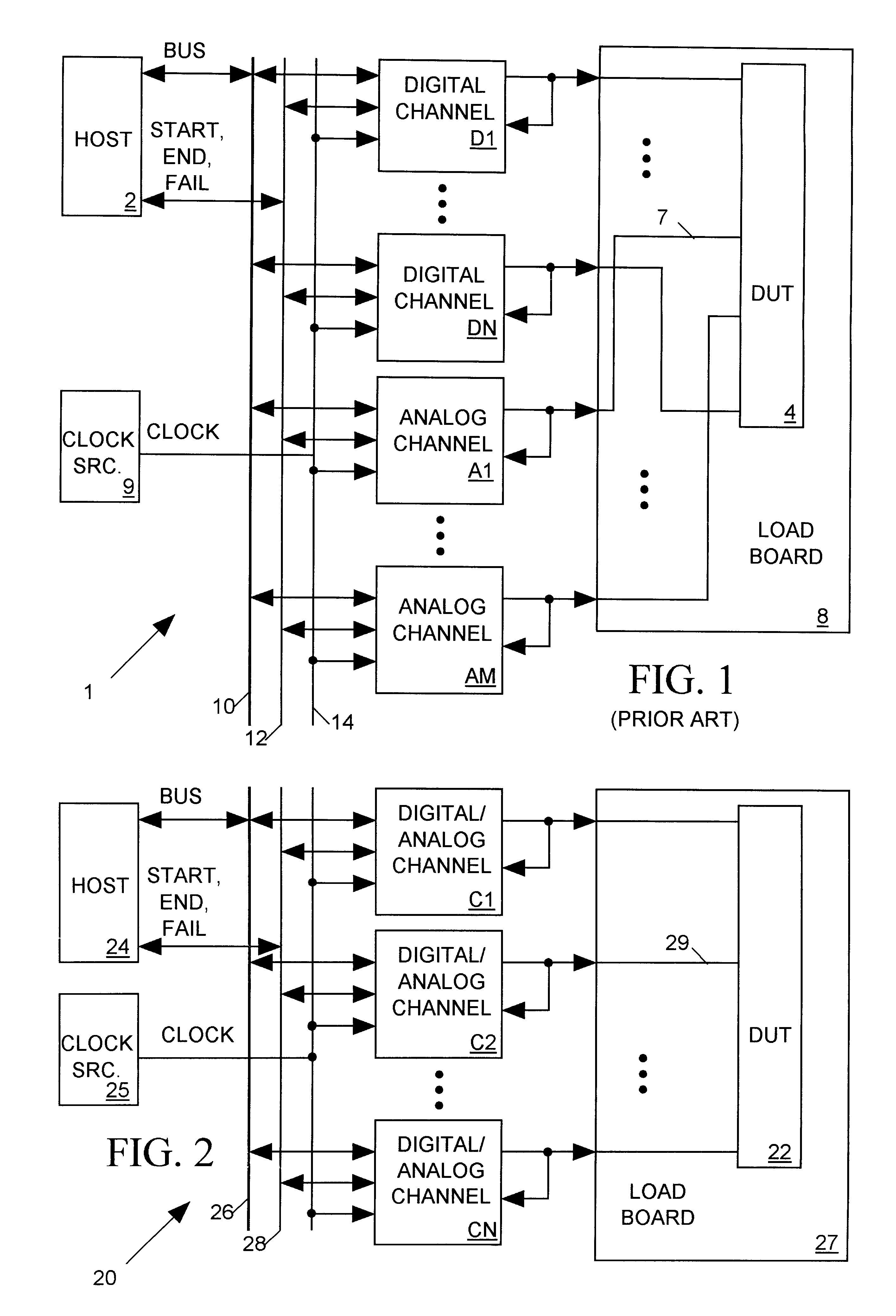

Integrated circuit tester having amorphous logic for real-time data analysis

InactiveUS6057679AAnalog circuit testingIndividual semiconductor device testingGeneral purposeReal-time data

A general purpose integrated circuit (IC) tester includes a set of channels, one for each input or output pin of an IC device under test (DUT). Each channel is programmed by a host computer to either supply a test signal to a DUT I / O pin or sample a DUT output signal appearing at the I / O pin and produce sample data representing its magnitude or logic state. The tester also includes an amorphous logic circuit (ALC) having a set of input and output terminals and a programmable logic circuit interconnecting the input and output terminals. Some of the ALC input and output terminals receive the sample data produced by each channel and other ALC terminals send control signals directly to each channel. Other ALC terminals transmit data to the host computer. When it programs the channels to perform a test, the host computer also programs the ALC to control various operations of the channels during the test, to perform a real-time analysis of the test data produced by the channels, and to communicate results of the analysis to the host.

Owner:CREDENCE SYSTEMS

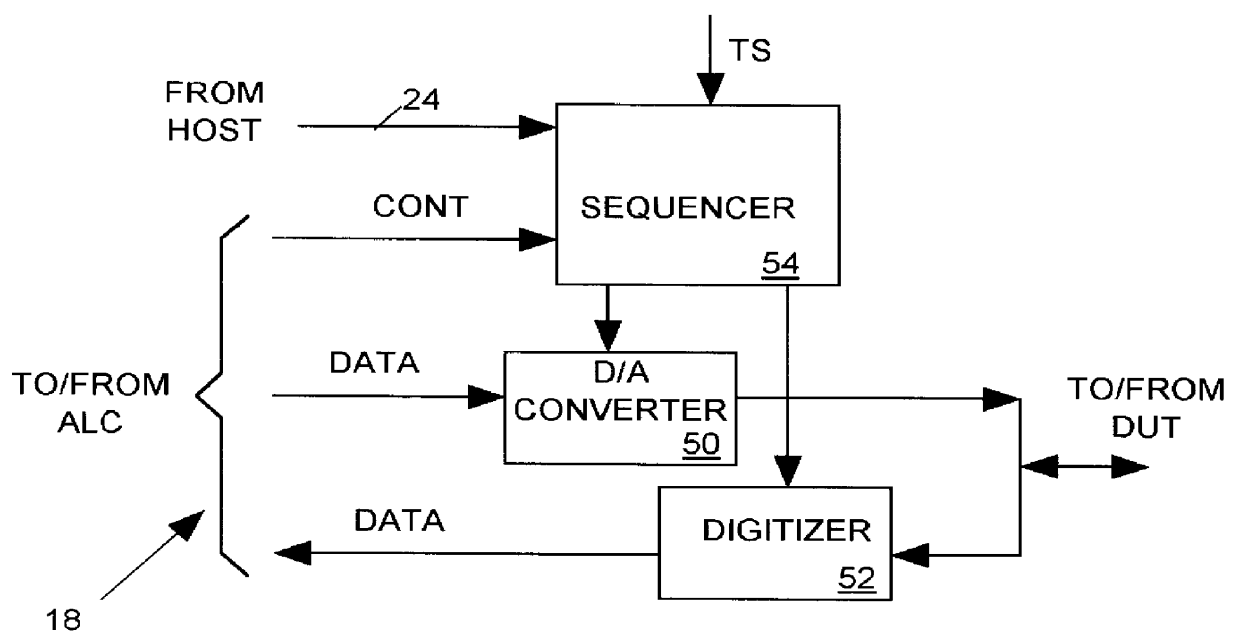

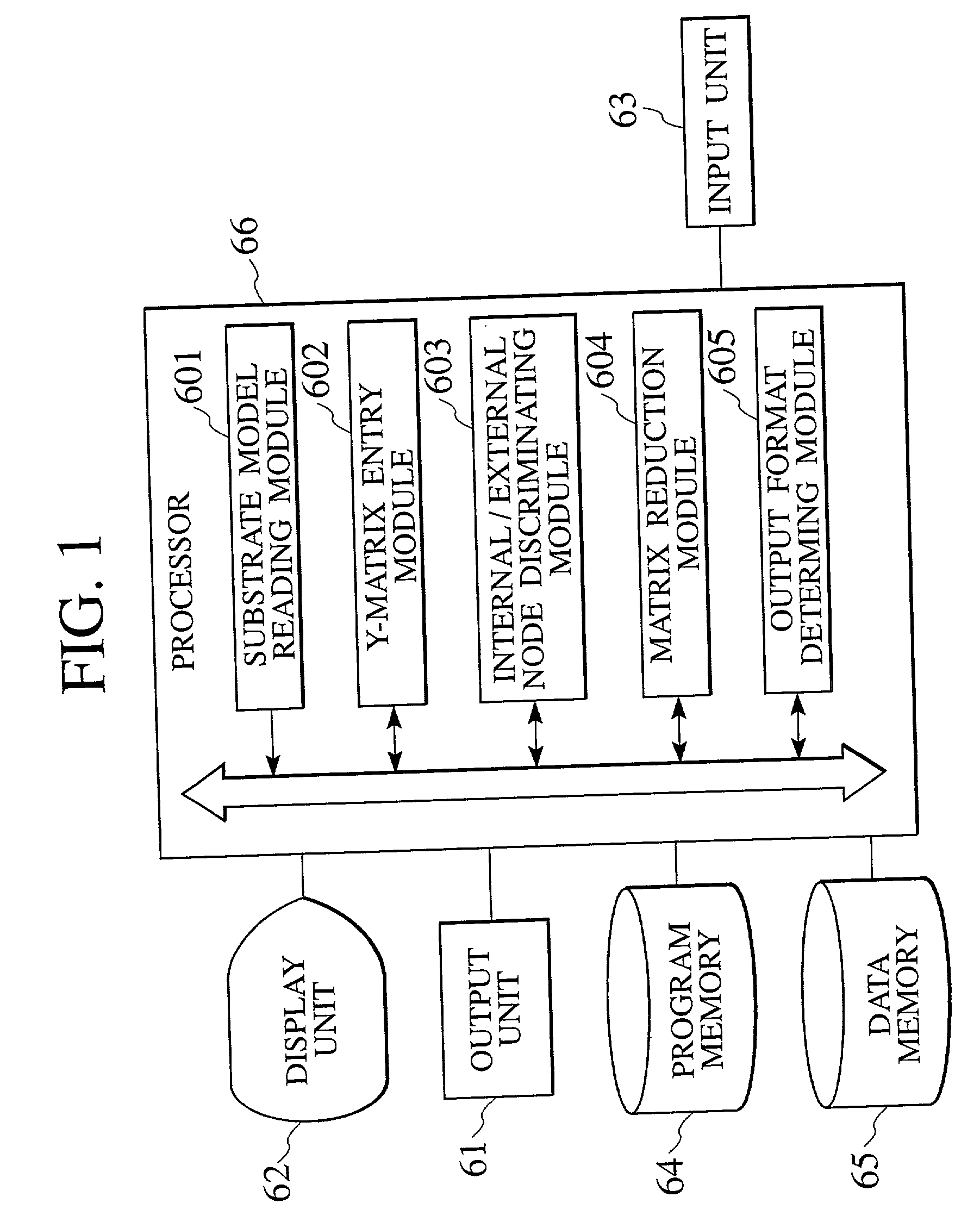

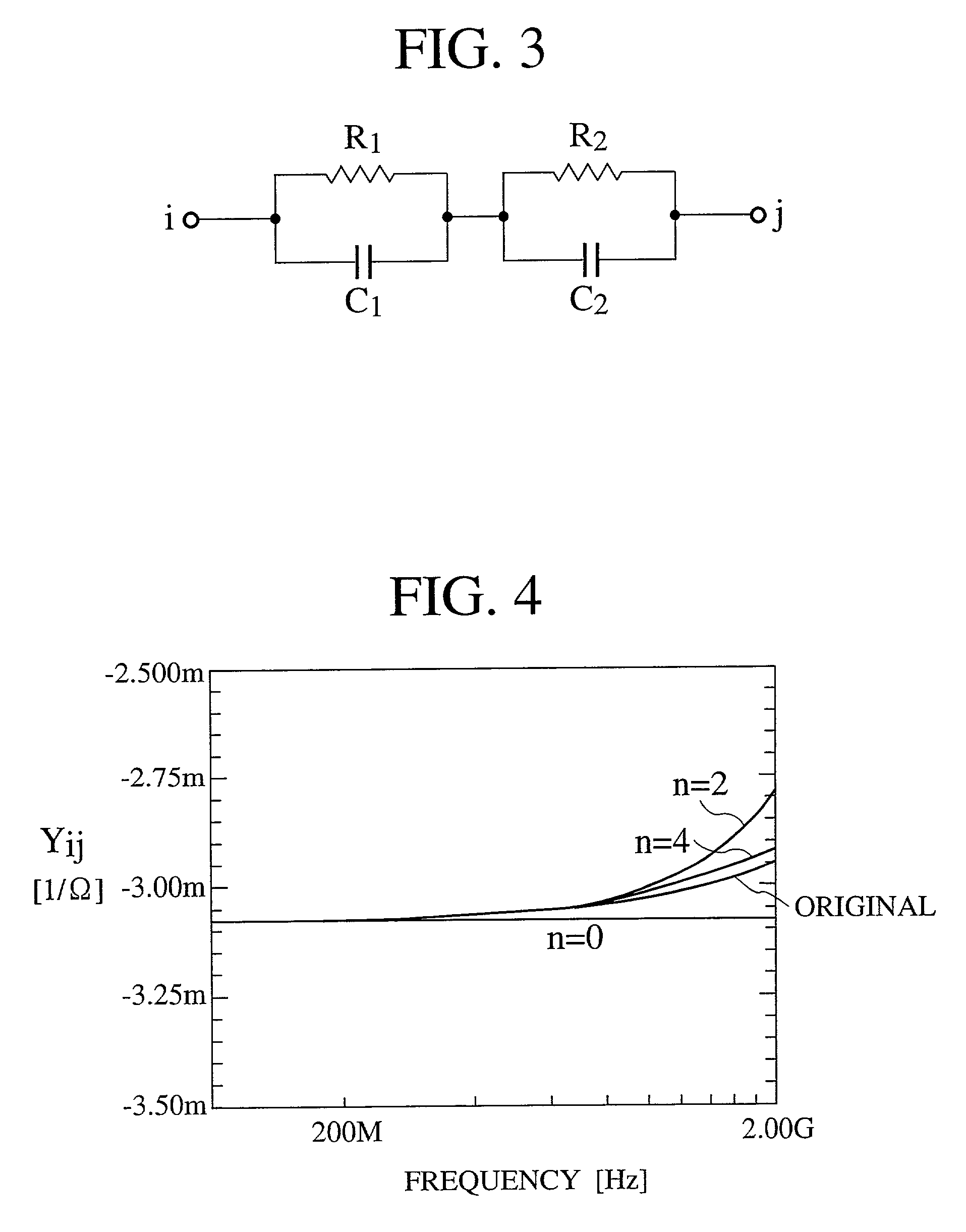

Semiconductor device analyzer, method for analyzing/manufacturing semiconductor device, and storage medium storing program for analyzing semiconductor device

InactiveUS20010029601A1Efficiently and correctly analyzingEfficiently influence of parasiticAnalog circuit testingDetecting faulty computer hardwareCapacitanceSubstrate network

A semiconductor device analyzer has a substrate model reading module, a Y-matrix entry module, a discriminating module, a matrix reduction module, and an output format discriminating module. The substrate model reading module reads a substrate network model of three-dimensional meshes representing the substrate of a semiconductor device. The substrate network model is a network of resistive and capacitive elements and is used for the simulation and analysis of the semiconductor substrate. The Y-matrix entry module prepares a Y-matrix from the substrate network model, each element of the Y-matrix being expressed with a polynomial of differential operator "s". The discriminating module discriminates internal nodes to be eliminated from external nodes to be left among the nodes of the substrate network model. The matrix reduction module eliminates the internal nodes, thereby reducing the Y-matrix. The output format determining module determines an output format for an operation result.

Owner:KK TOSHIBA

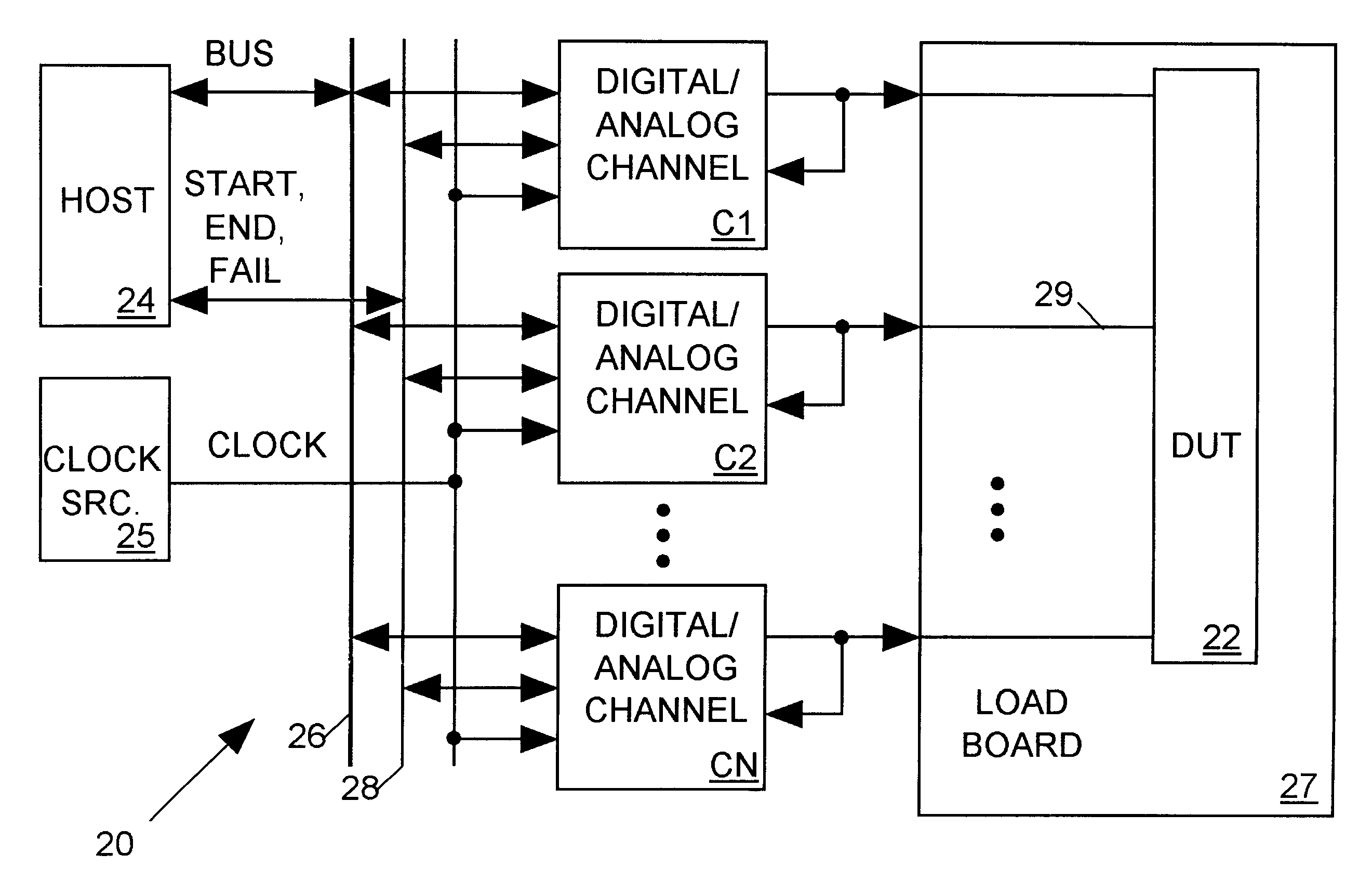

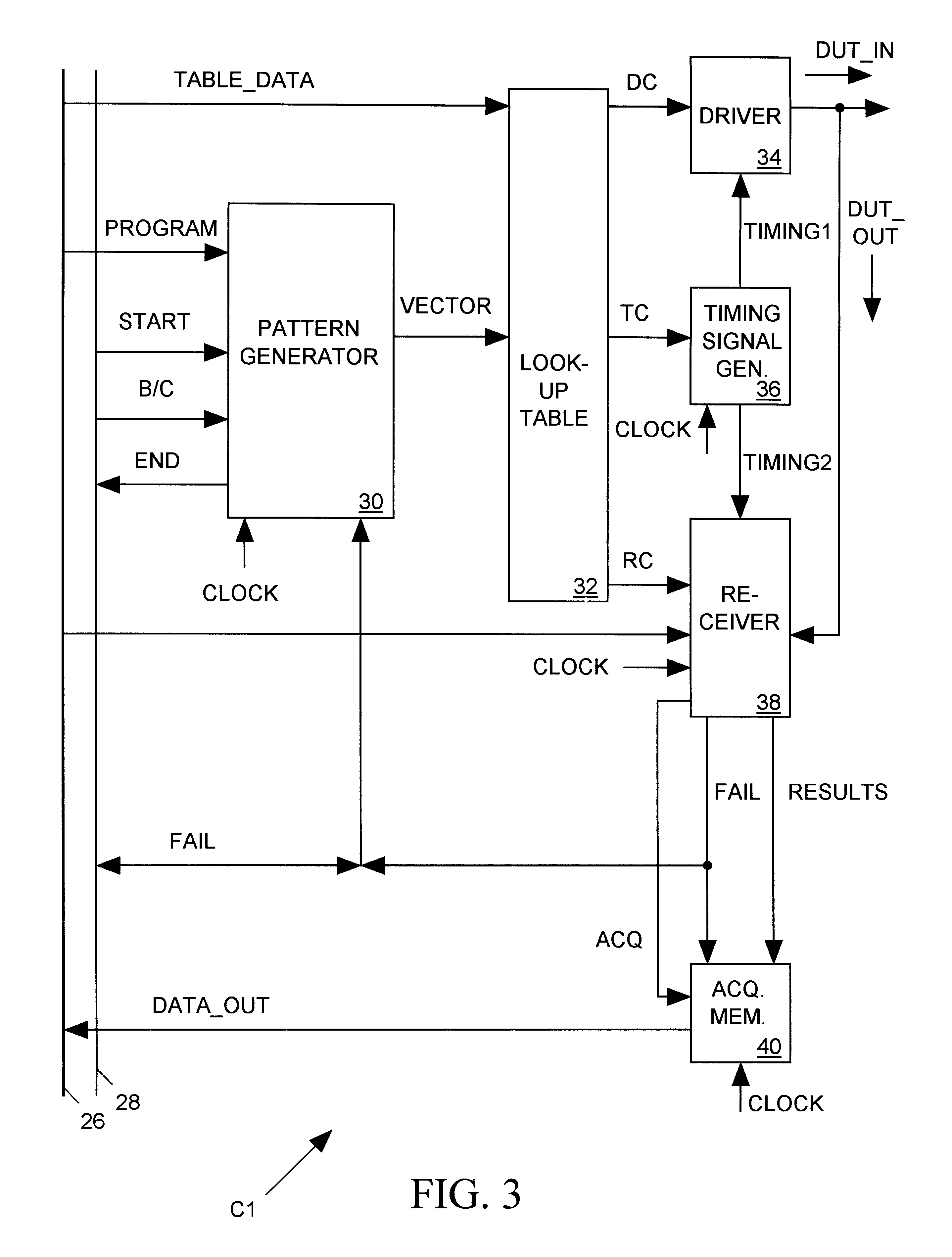

Integrated circuit testing device with dual purpose analog and digital channels

An integrated circuit (IC) tester includes a set of dual-purpose digital / analog channels. Each tester channel includes a driver capable of supplying either a digital or analog test signal input to an IC terminal and a receiver for digitizing and processing either an analog or digital IC output signal appearing at the DUT terminal to produce results data representing the behavior of that IC output signal during a test. A test is organized into a succession of test cycles, and before each test cycle a pattern generator within each channel produces data for controlling the behavior of the driver and receiver during the test cycle. The control data controls whether the driver is to produce an analog or a digital test signal, controls a magnitude or logic level to which the test signal is to be driven during the test cycle, and controls a time during the test cycle of any test signal state or magnitude changes. The control data also indicates how and when the receiver digitizes and processes an IC output signal during the test cycle.

Owner:CREDENCE SYSTEMS

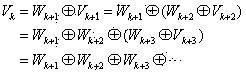

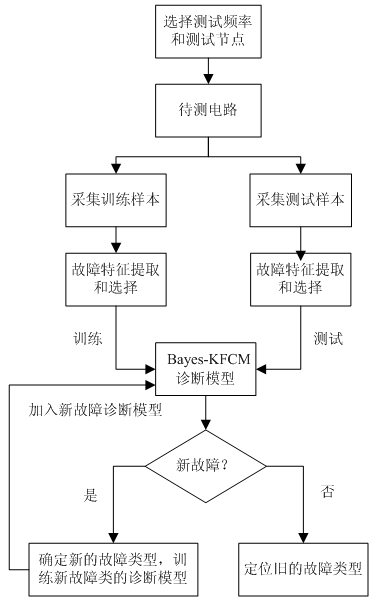

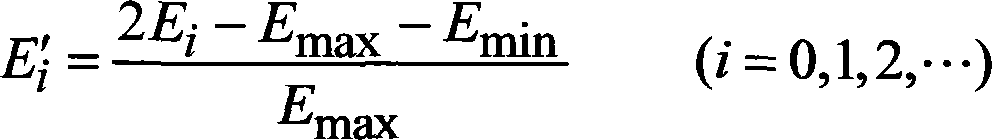

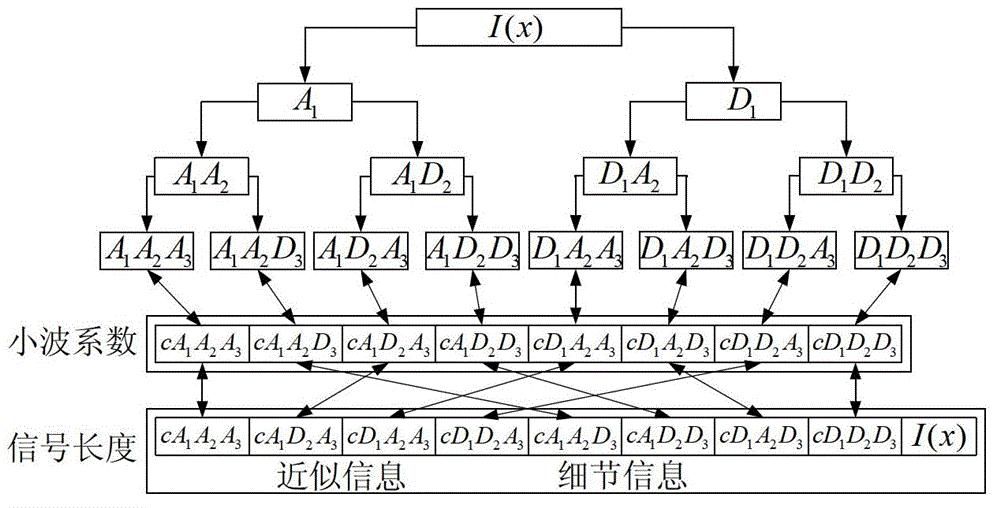

Novel analog circuit early fault diagnosis method

InactiveCN104198924AFacilitates early fault diagnosisImprove feature extractionAnalog circuit testingSpecial data processing applicationsFeature vectorLeast squares support vector machine

A novel analog circuit early fault diagnosis method includes the steps of (1) acquiring time domain response signals of an analog circuit and taking the time domain response signals as output voltage signals of the analog circuit; (2) performing wavelet transform to the acquired voltage signals; (3) performing fractal analysis to original signal patterns and wavelet sub patterns to generate wavelet fractal dimensions of different patterns; (4) performing kernel entropy component analysis to candidate feature vector data composed of the wavelet fractal dimensions to acquire low-dimension feature vector data; (5) creating a multi-class classifier of a least squares support vector machine, and optimally selecting penalty factor and width factor of the least squares support vector machine, which are used for distinguishing overlapped early fault categories, by a quantum-behaved particle swarm optimization algorithm; and (6) sending the low-dimension feature vector data into the multi-class classifier of the least squares support vector machine and then outputting early fault diagnosis results. The novel analog circuit early fault diagnosis method can effectively detect early faults of analog circuits.

Owner:HEFEI UNIV OF TECH

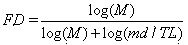

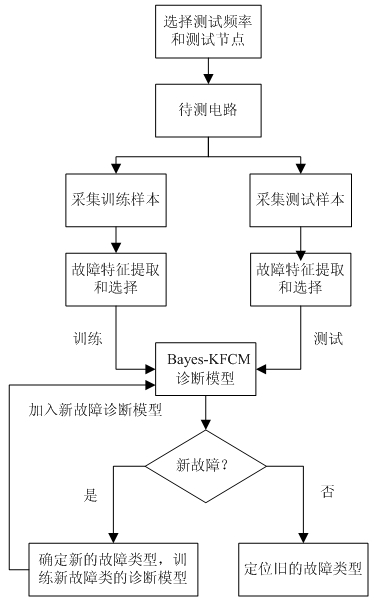

Analog circuit fault diagnosis method based on Bayes-KFCM (Kernelized Fuzzy C-Means) algorithm

InactiveCN102520341AComplementaryMake up for one-sidednessAnalog circuit testingCluster algorithmAlgorithm

The invention discloses an analog circuit fault diagnosis method based on a Bayes-KFCM (Kernelized Fuzzy C-Means) algorithm, which comprises the following steps of: carrying out fault diagnosis by adopting a kernelized fuzzy C-means clustering algorithm and firstly judging whether a new fault exits in a test sample, if YES, a diagnostic model of a new fault sample is trained to join a diagnosis system, or else, the fault positioning is carried out on the test sample according to a Bayes fault classification standard. In the invention, the wavelet transform pretreatment is carried out on the fault sample, and the multi-feature fusion is carried out on the wavelet coefficient energy value and the wavelet coefficient fractal dimension value of the sample to extract fault characteristics; and the frequency of an optimal measurable node and / or a test signal is selected through taking a maximum class inter-class distance as a basis. Compared with the prior art, the analog circuit fault diagnosis method realizes that the analog circuit fault diagnosis method, the new fault of an analog circuit can be effectively diagnosed, and the diagnosis accuracy can be improved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

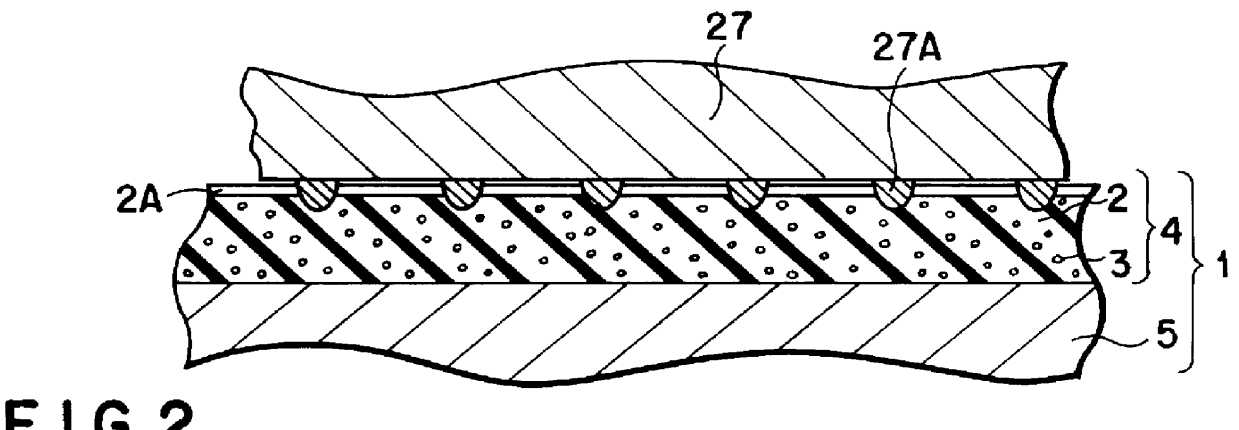

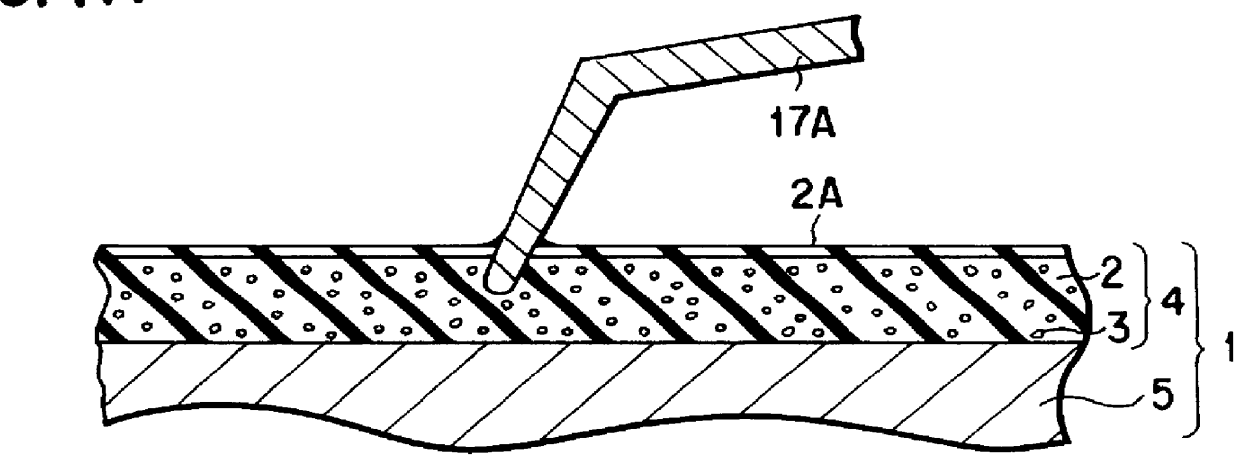

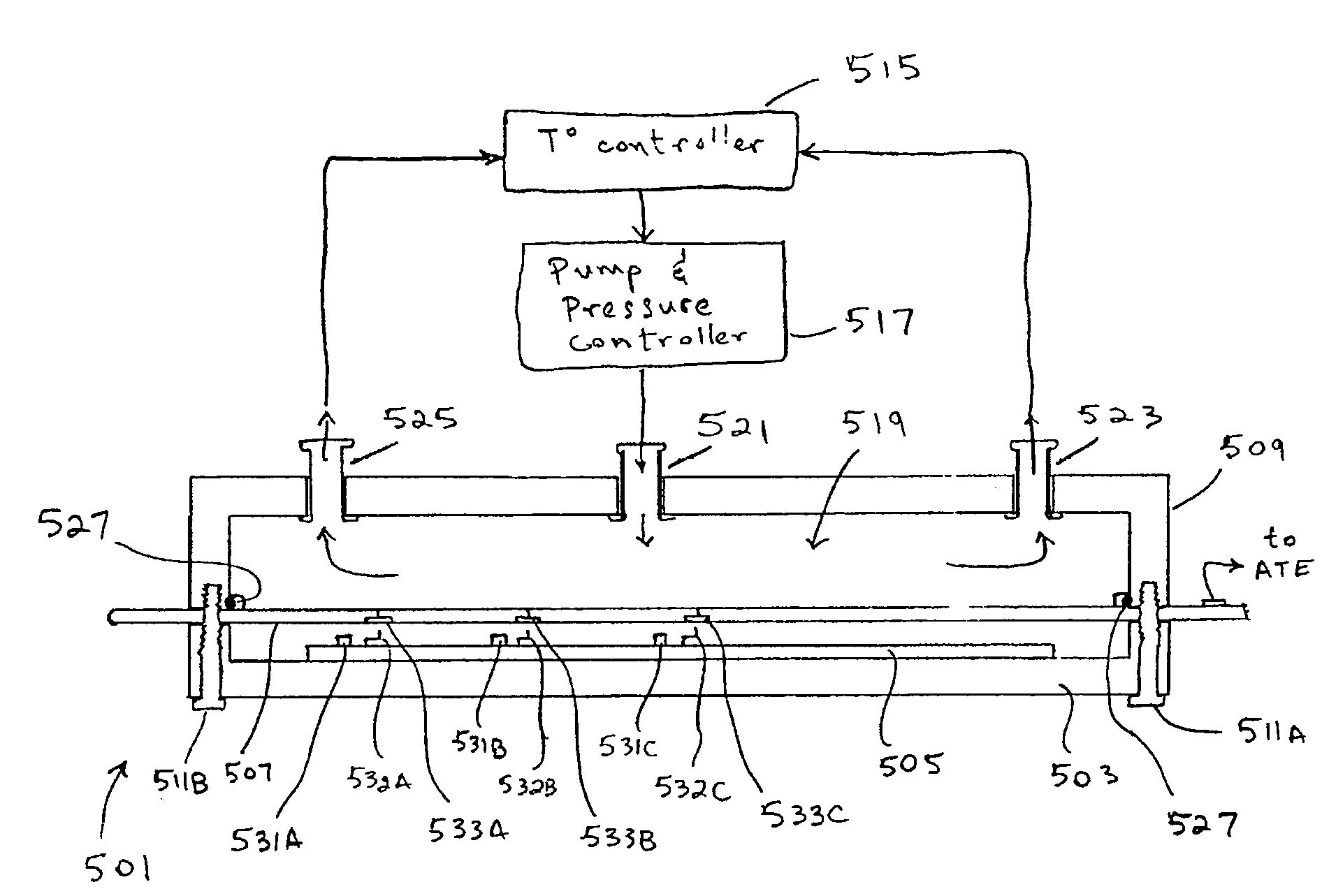

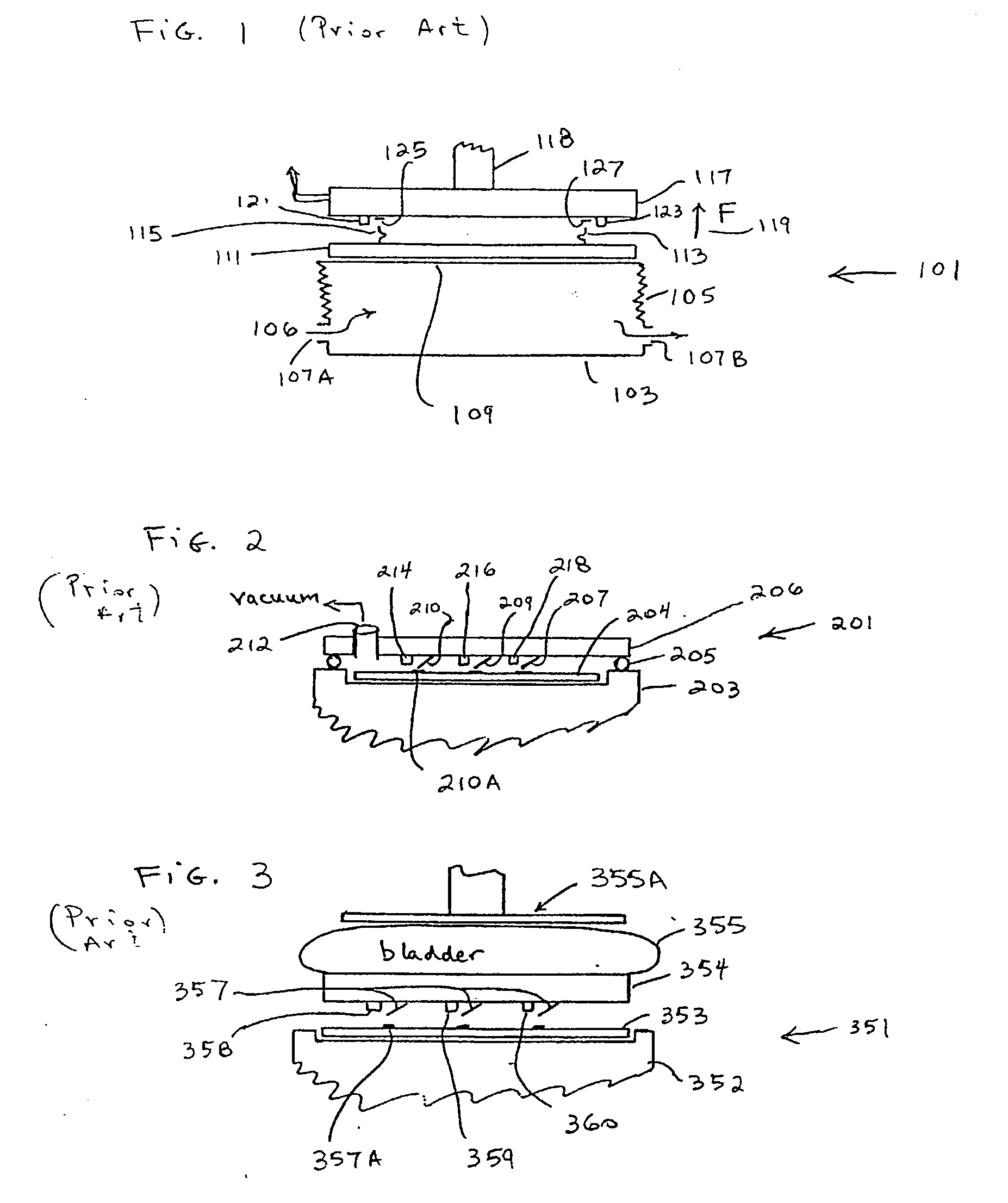

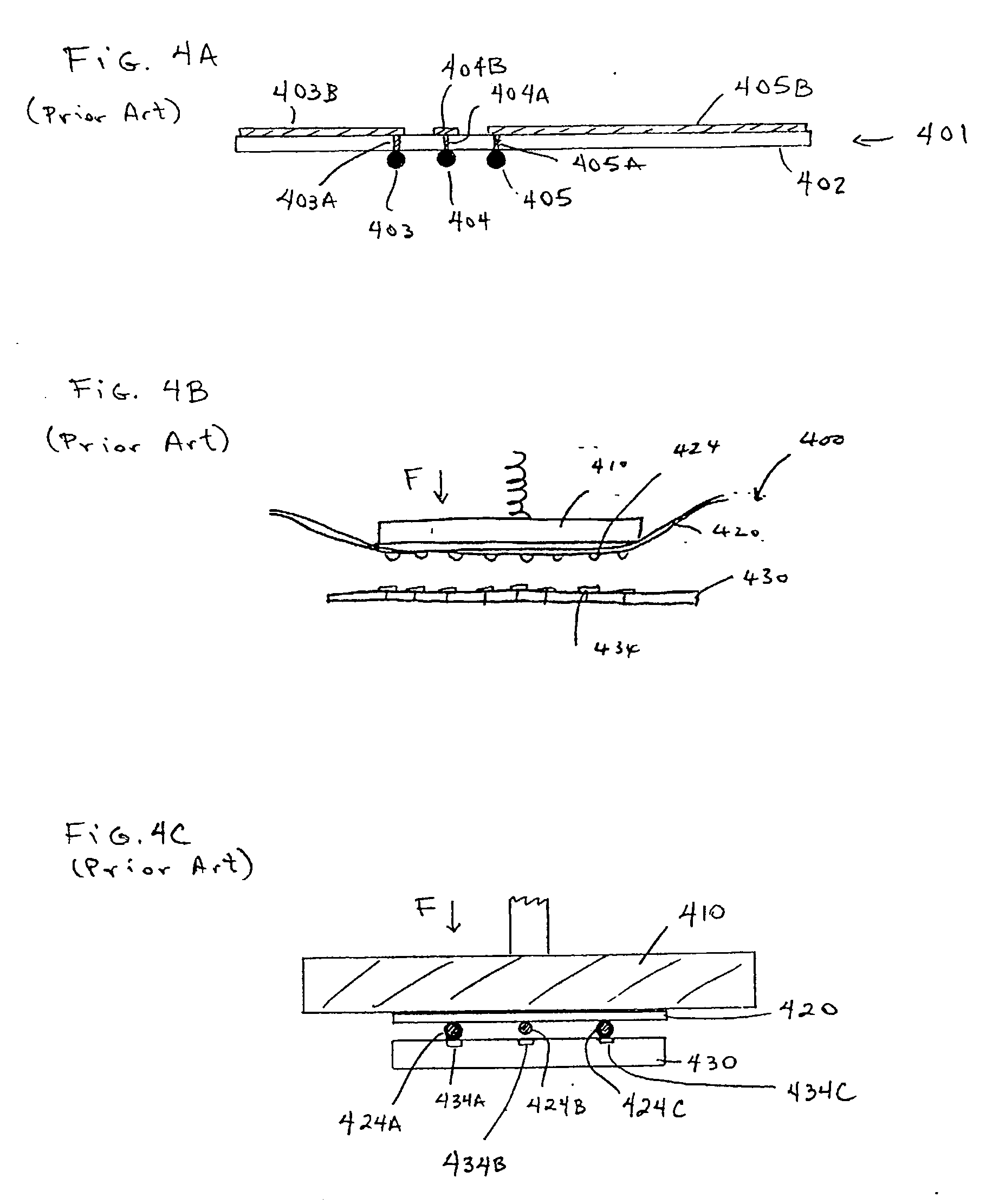

Electrical Contactor, Espcecially Wafer Level Contactor, Using Fluid Pressure

InactiveUS20070287304A1Analog circuit testingSemiconductor/solid-state device testing/measurementElectricityPressure difference

An electrical interconnect assembly and methods for making an electrical interconnect assembly. In one embodiment, an interconnect assembly includes a flexible wiring layer having a plurality of first contact elements and a fluid containing structure which is coupled to the flexible wiring layer. The fluid, when contained in the fluid containing structure, presses the flexible wiring layer towards a device under test to form electrical interconnections between the first contact elements and corresponding second contact elements on the device under test. In a further embodiment, an interconnect assembly includes a flexible wiring layer having a plurality of first contact terminals and a semiconductor substrate which includes a plurality of second contact terminals. A plurality of freestanding, resilient contact elements, in one embodiment, are mechanically coupled to one of the flexible wiring layers or the semiconductor substrate and make electrical contacts between corresponding ones of the first contact terminals and the second contact terminals. In another embodiment, a method of making electrical interconnections includes joining a flexible wiring layer and a substrate together in proximity and causing a pressure differential between a first side and a second side of the flexible wiring layer. The pressure differential deforms the flexible wiring layer and causes a plurality of first contact terminals on the flexible wiring layer to electrically connect with a corresponding plurality of second contact terminals on the substrate.

Owner:FORMFACTOR INC

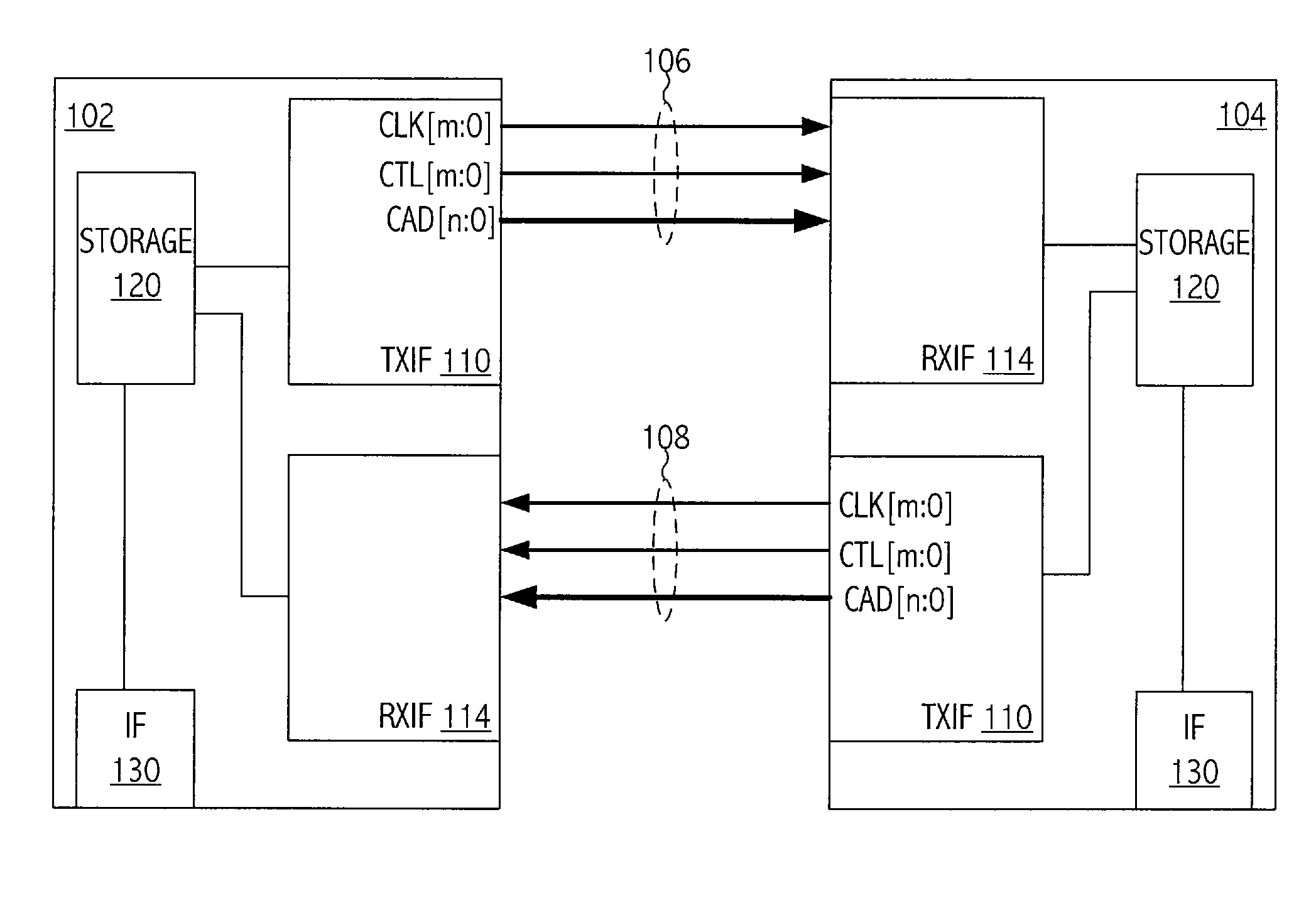

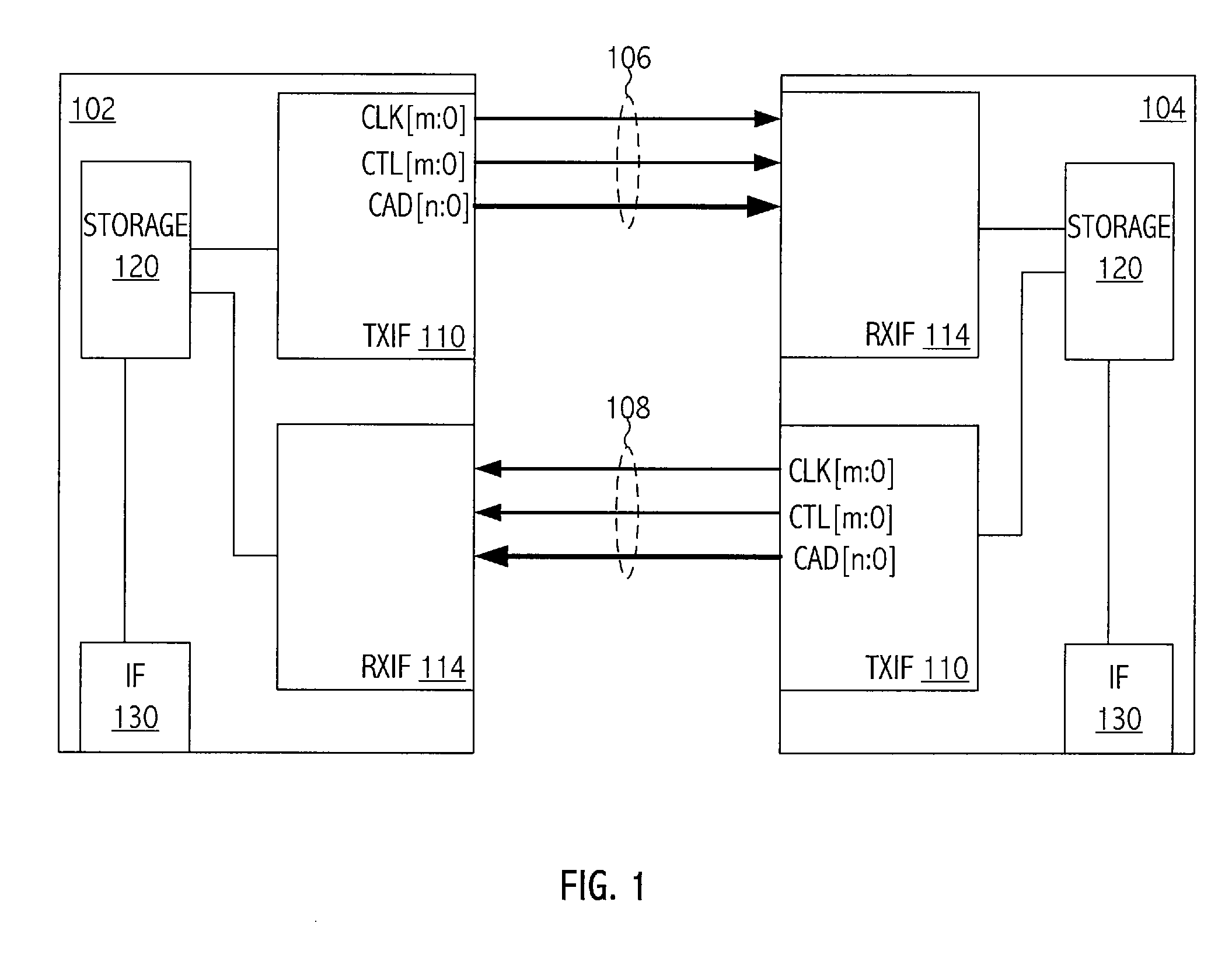

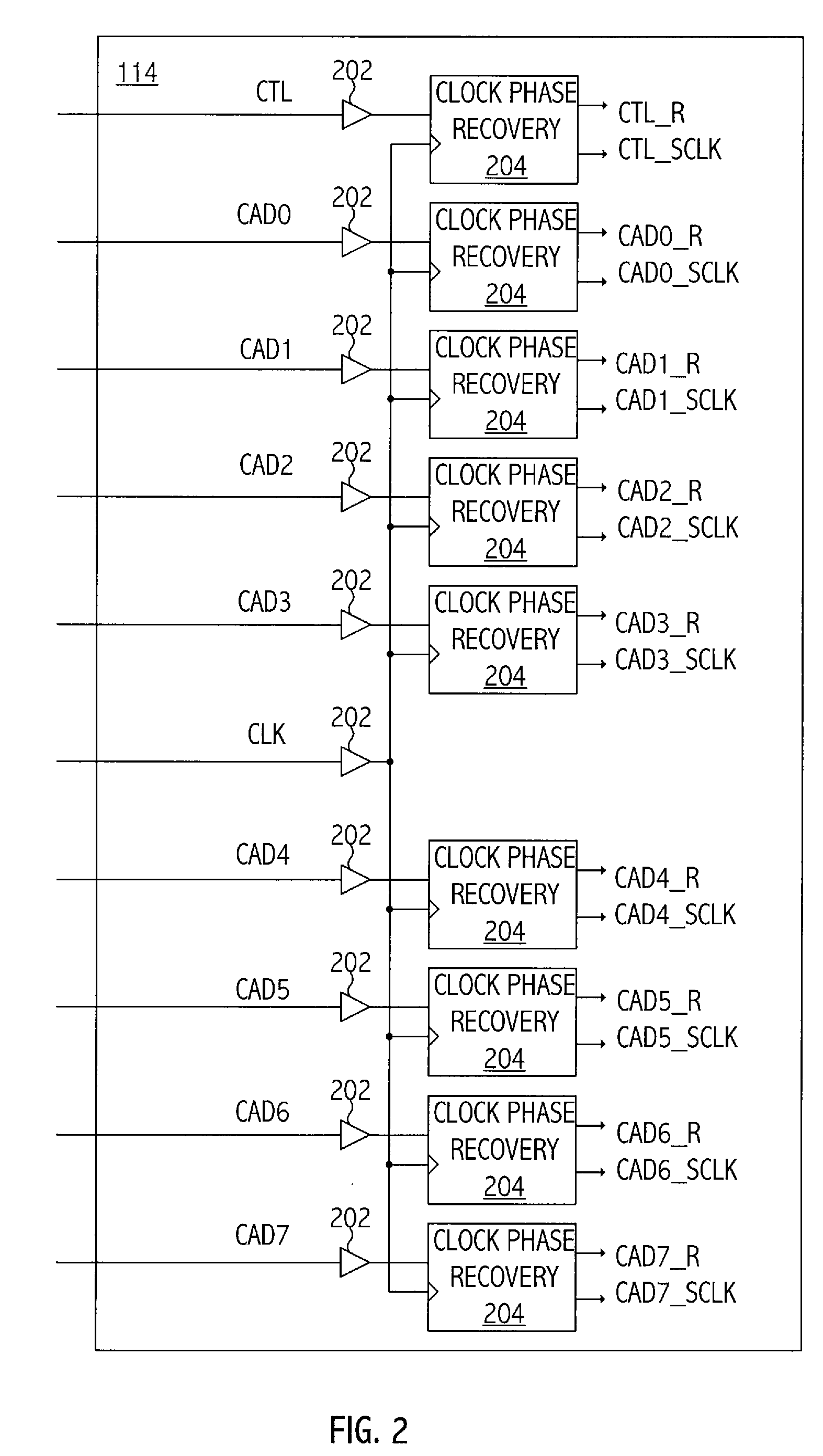

Transmitter voltage and receiver time margining

ActiveUS20070230513A1Analog circuit testingError detection/prevention using signal quality detectorCommunication interfaceTiming margin

A technique for characterizing a communications interface includes determining a voltage margin and a timing margin of the interface based on data sampled by a sampling device of a receiver of the interface. In at least one embodiment of the invention, a method for determining margin associated with a receiver circuit of an integrated circuit includes periodically sampling a signal over a time period by a receiver sampling circuit of the receiver circuit to generate a sampled version of the signal. The method includes incrementally varying a value of the parameter associated with the signal. The varying of the parameter is through a range of values of the parameter over the time period. The method includes determining a margin value of the receiver circuit associated with the parameter based, at least in part, on the sampled version of the signal.

Owner:ADVANCED MICRO DEVICES INC

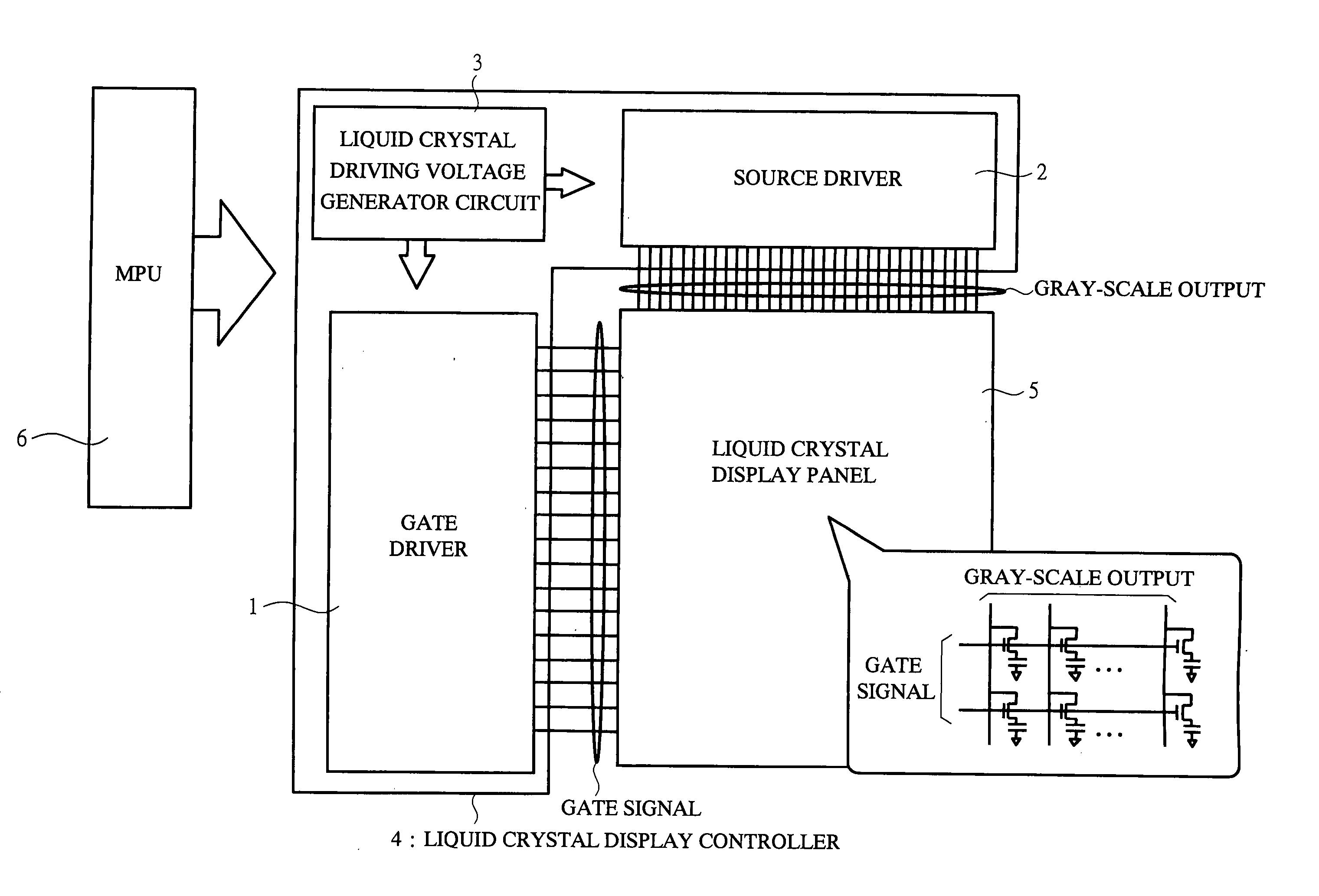

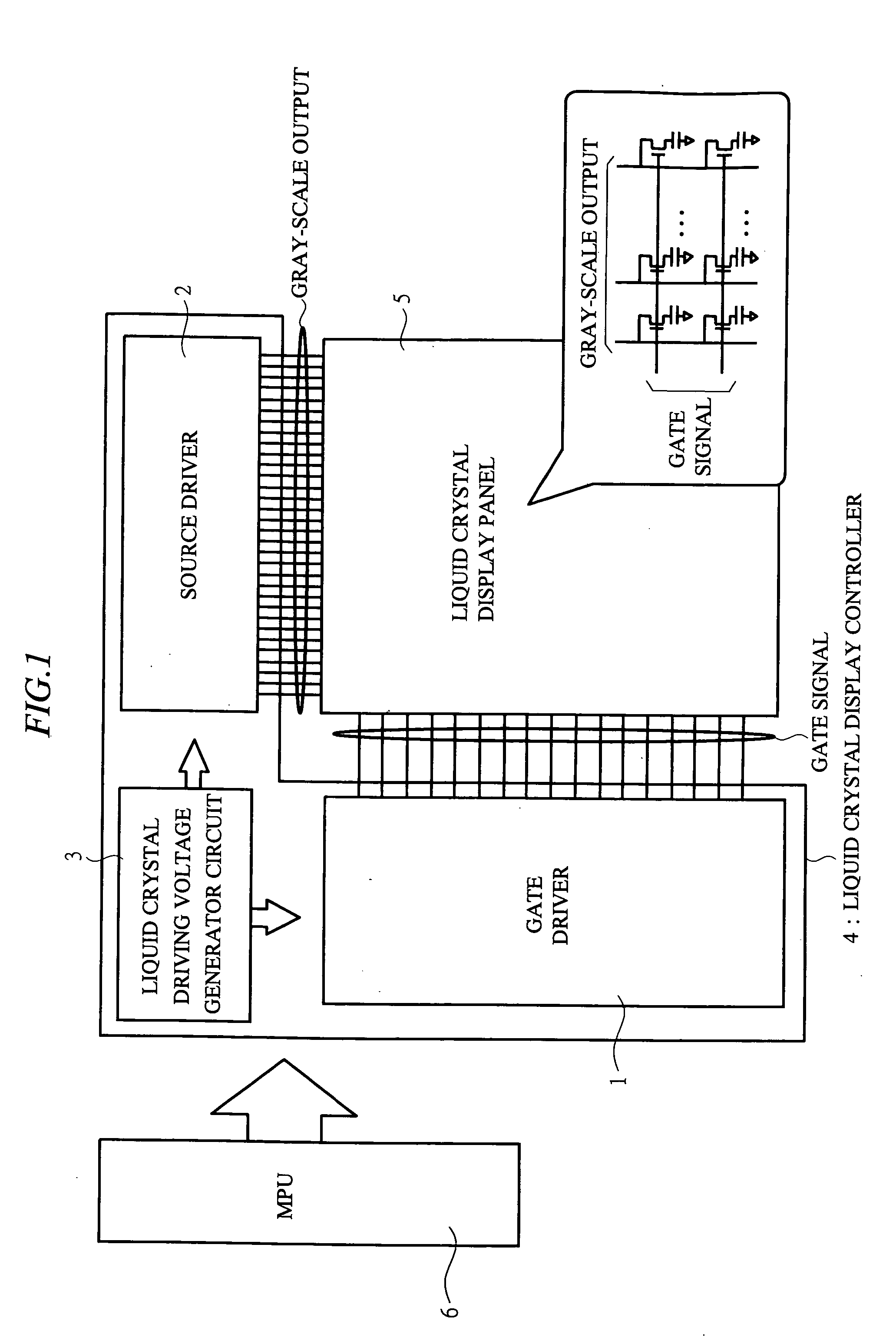

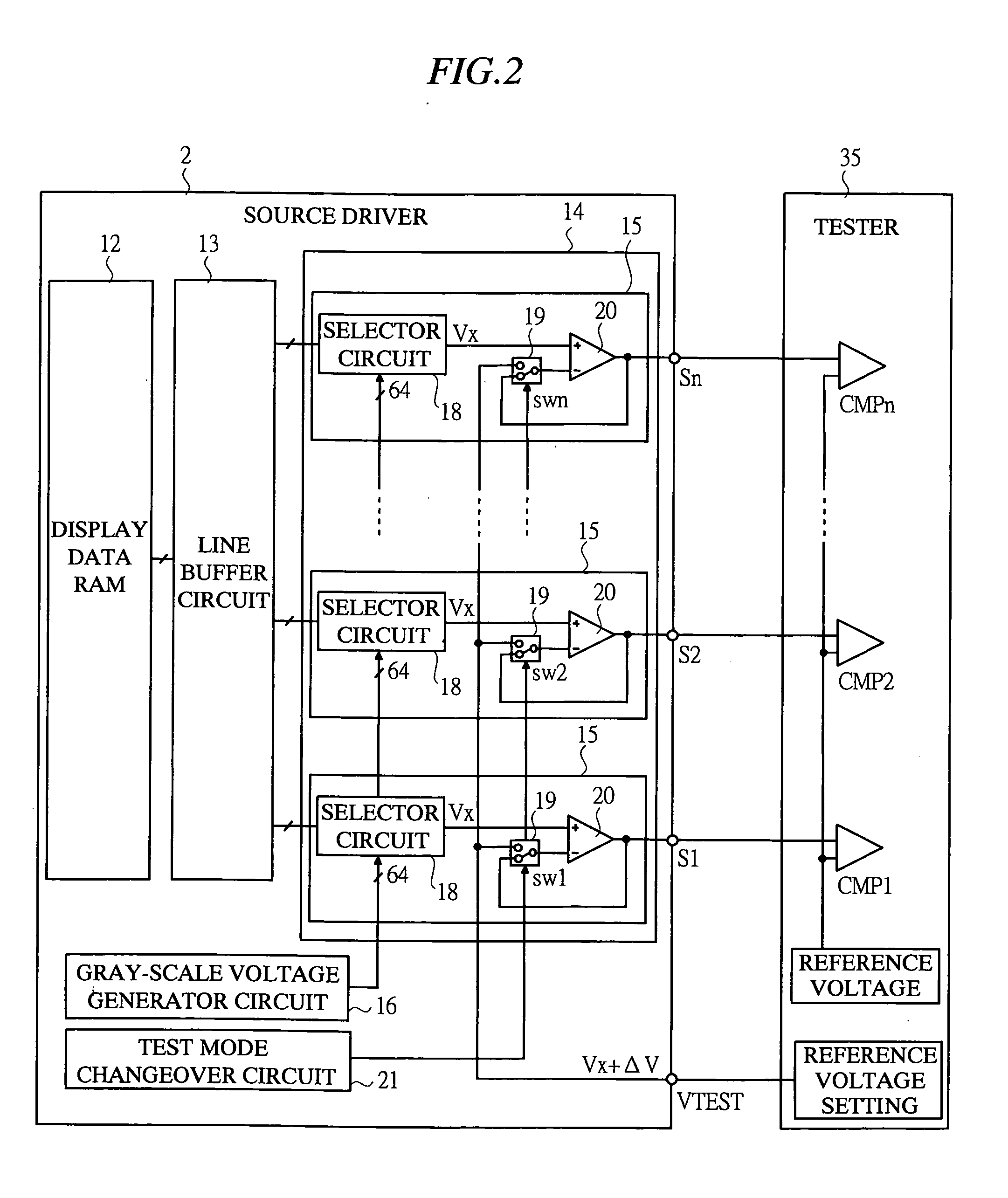

Semiconductor device and testing method thereof

InactiveUS20050122300A1Extended test timeShorten the timeAnalog circuit testingSolid-state devicesDriver circuitVoltage generator

A semiconductor device according to the present invention has a liquid crystal driver circuit, and when gray-scale voltage thereof is tested, the gray-scale voltage (Vx) generated in a gray-scale voltage generator circuit provided therein is compared with reference voltage (e.g., Vx+ΔV) generated for testing the gray-scale voltage and the test result is output as binarized voltage from external terminals of the semiconductor device. This can speed up the gray-scale voltage test even in the case of higher gray scale in the liquid crystal driver circuit or increased number of output terminals of the semiconductor device. Therefore, it becomes possible to reduce the time and cost required for the test.

Owner:RENESAS ELECTRONICS CORP

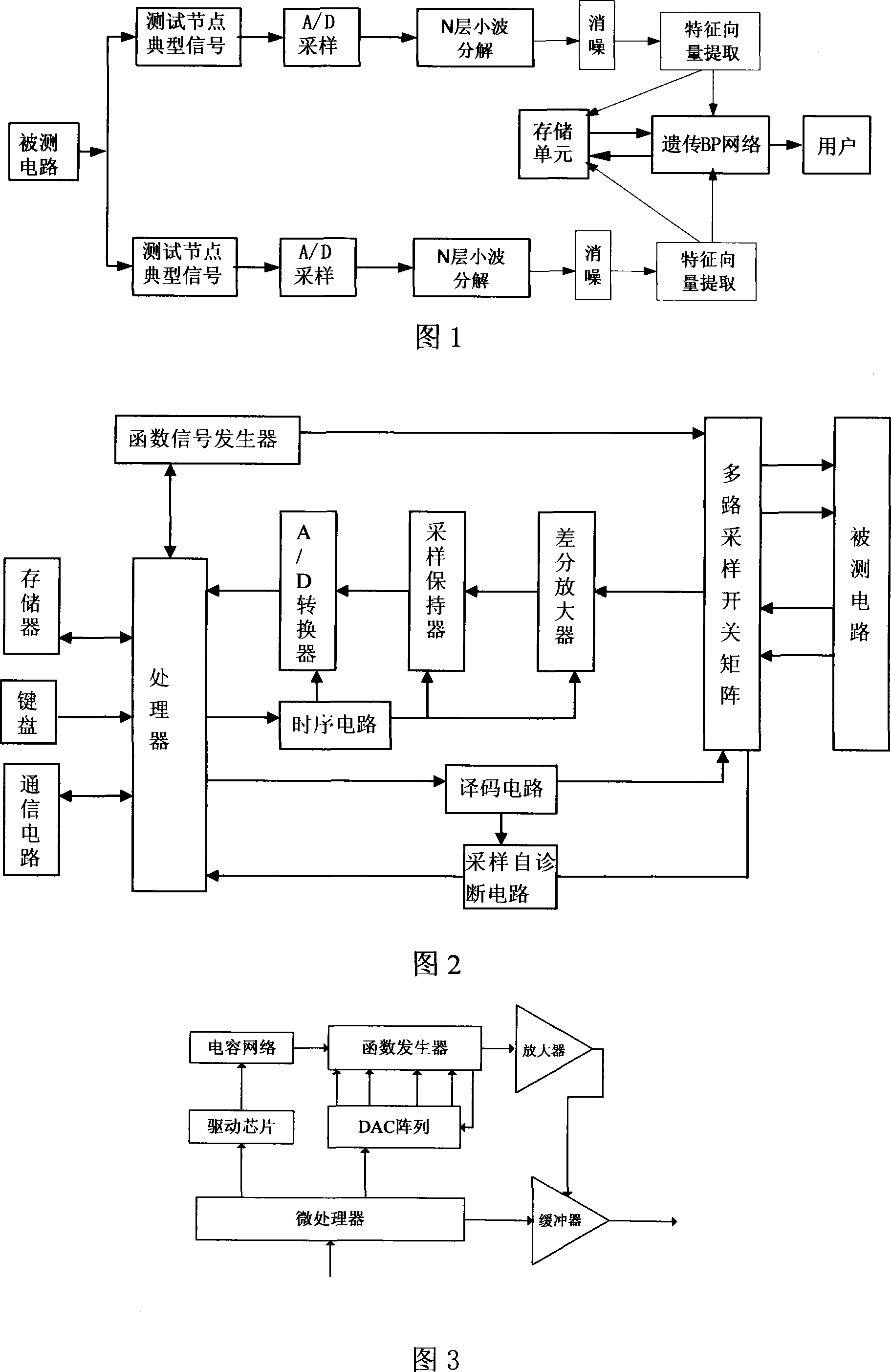

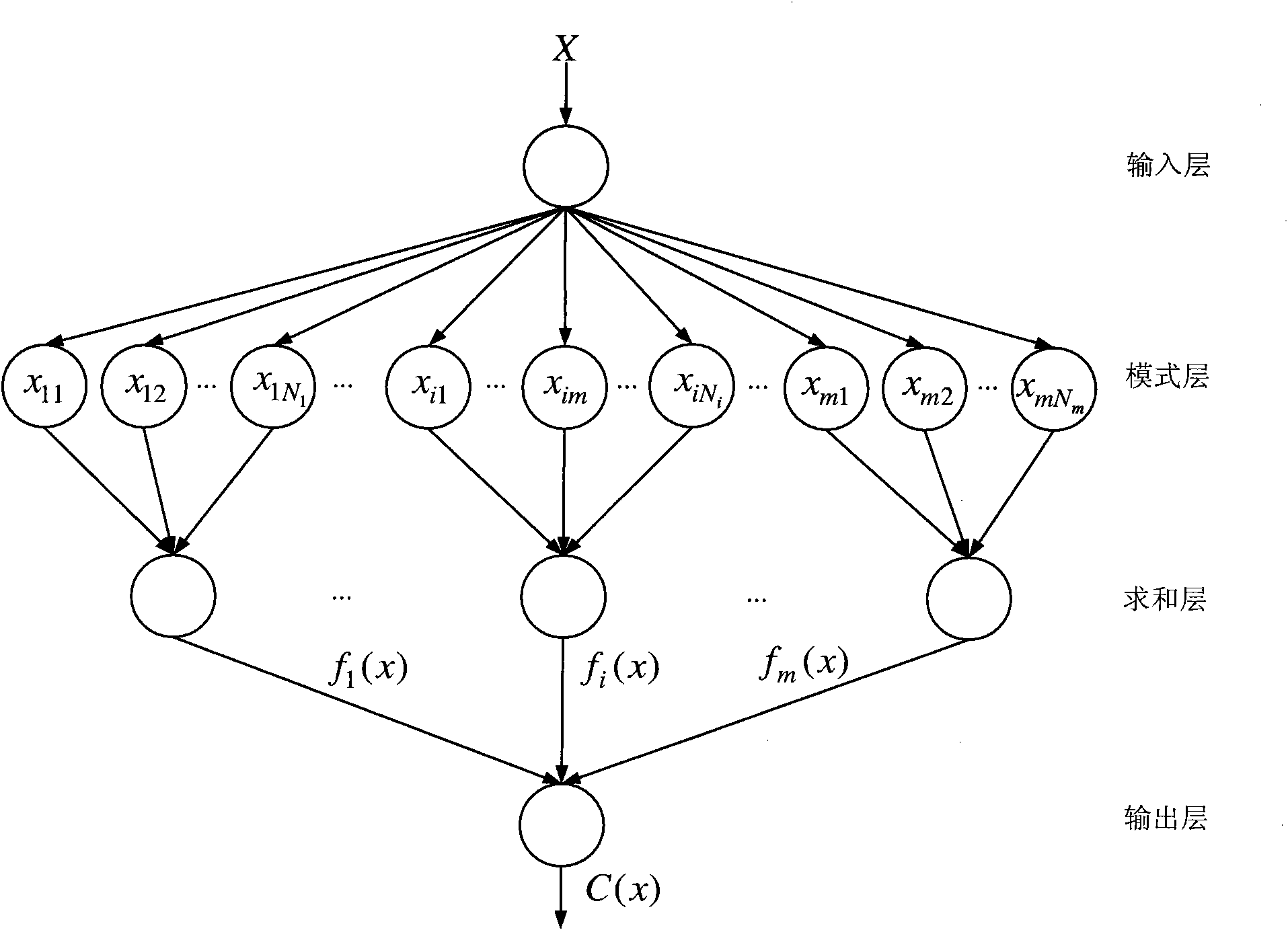

Analog PCB intelligent test system based on neural network

InactiveCN101246200ARealize acquisitionRealize transmissionAnalog circuit testingPhysical realisationNerve networkPrincipal component analysis

The invention discloses a simulating PCB intelligent test system which is based on nerve network, which includes main control PC machine, processor, storage, communication circuit, function signal generator, multi-channel sampling switch matrix, sequential circuit, decoding circuit, A / D converter, sampling retainer, differential amplifier, function signal generator under the control of processor outputs stimulating signal to the stimulating node of the tested circuit, the responding signal of the tested circuit is transmited to the processor by multi-channel sampling circuit, then is transmitted to the main control PC machine by communication circuit, the main control PC machine treats the sampling signal with wavelet packet transform de-noising treatment, and with principal component analysis and normalization processing for obtaining fault feature vector; the fault feature vector is inputted into the trained BP nerve network, the output of the BP nerve network is fault type. The invention can position the PCB test fault to the component level effectively, and improve the scalability of system greatly with the simple and effective test method of CMOS switch array.

Owner:HUNAN UNIV

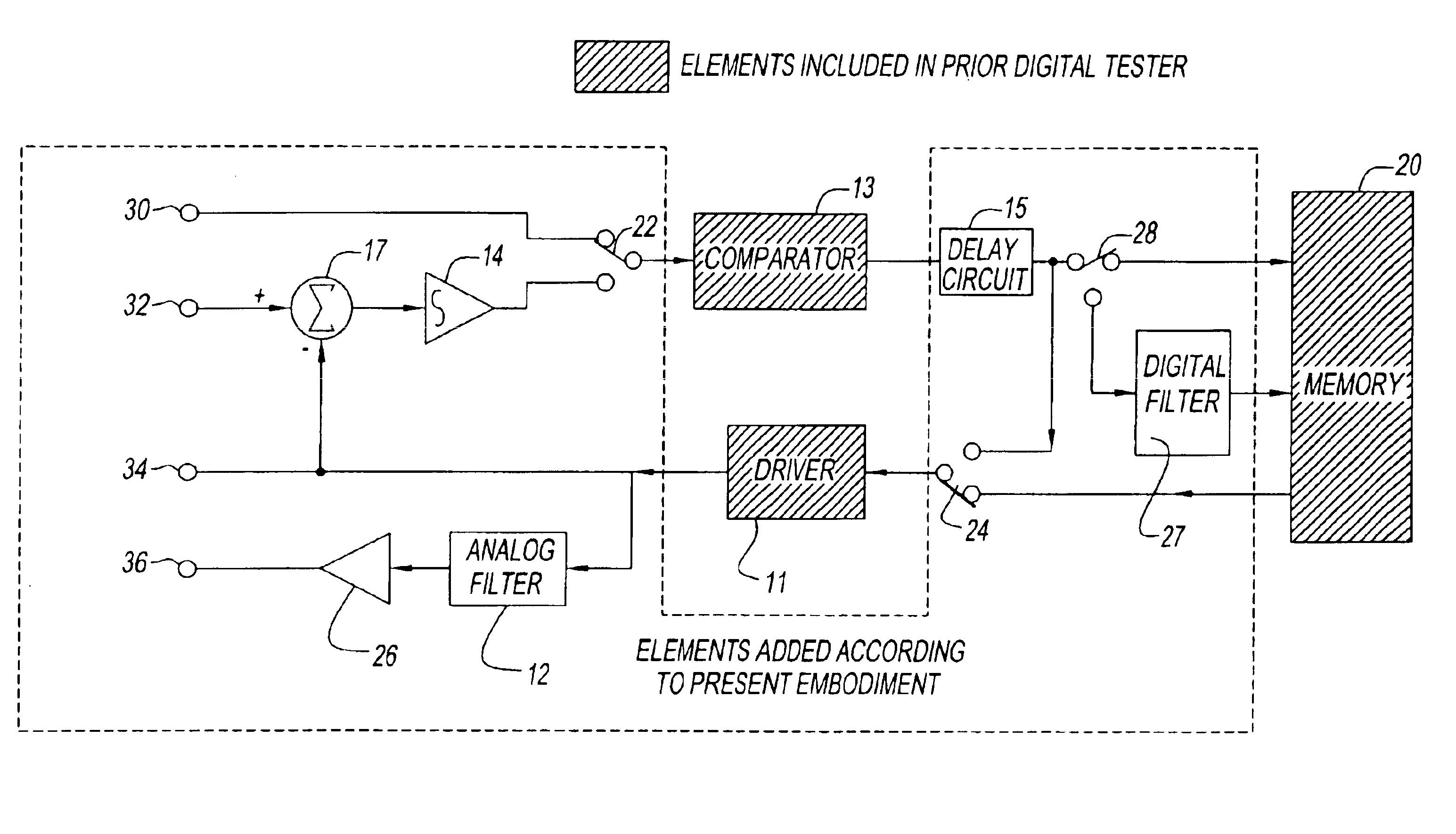

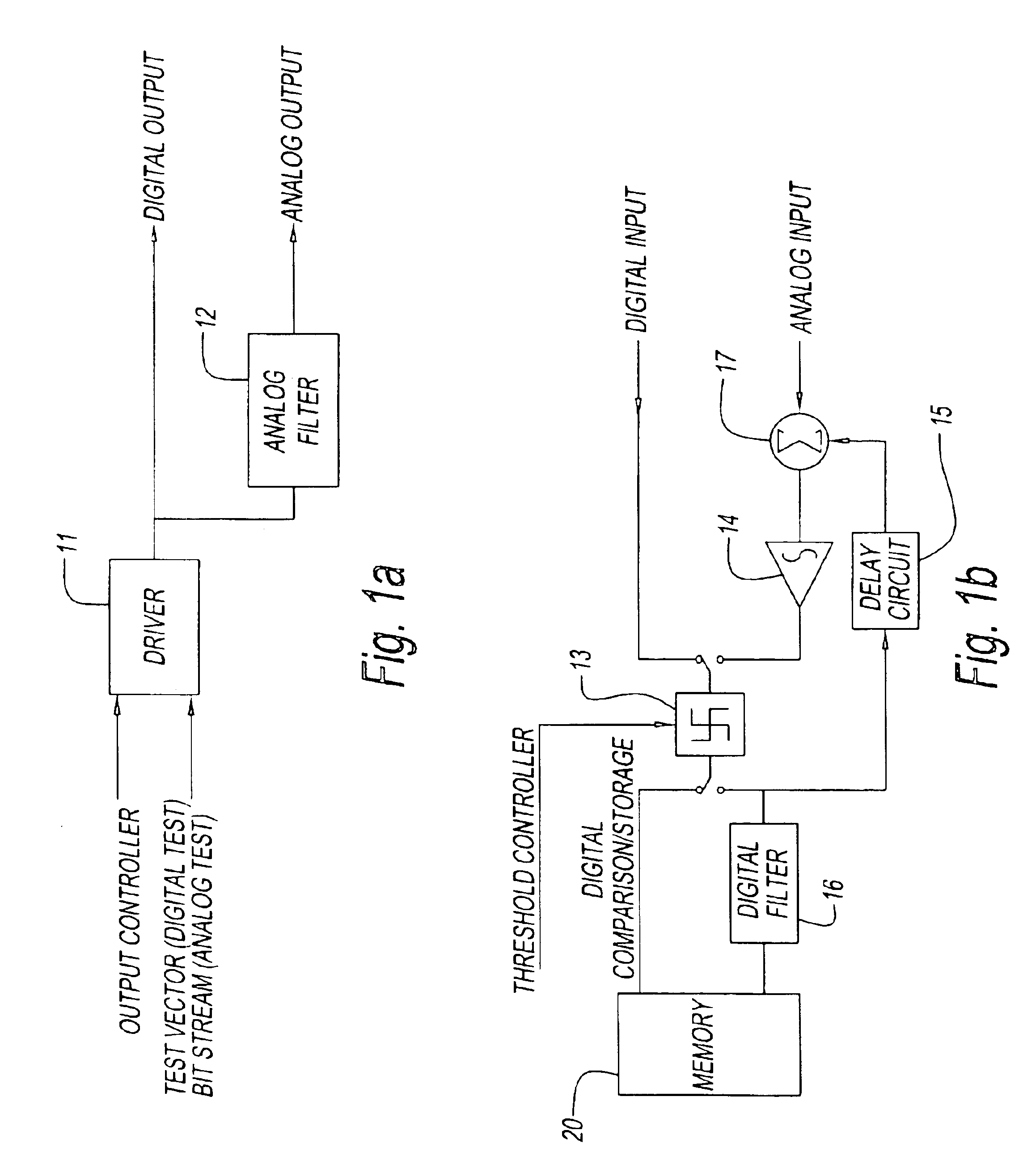

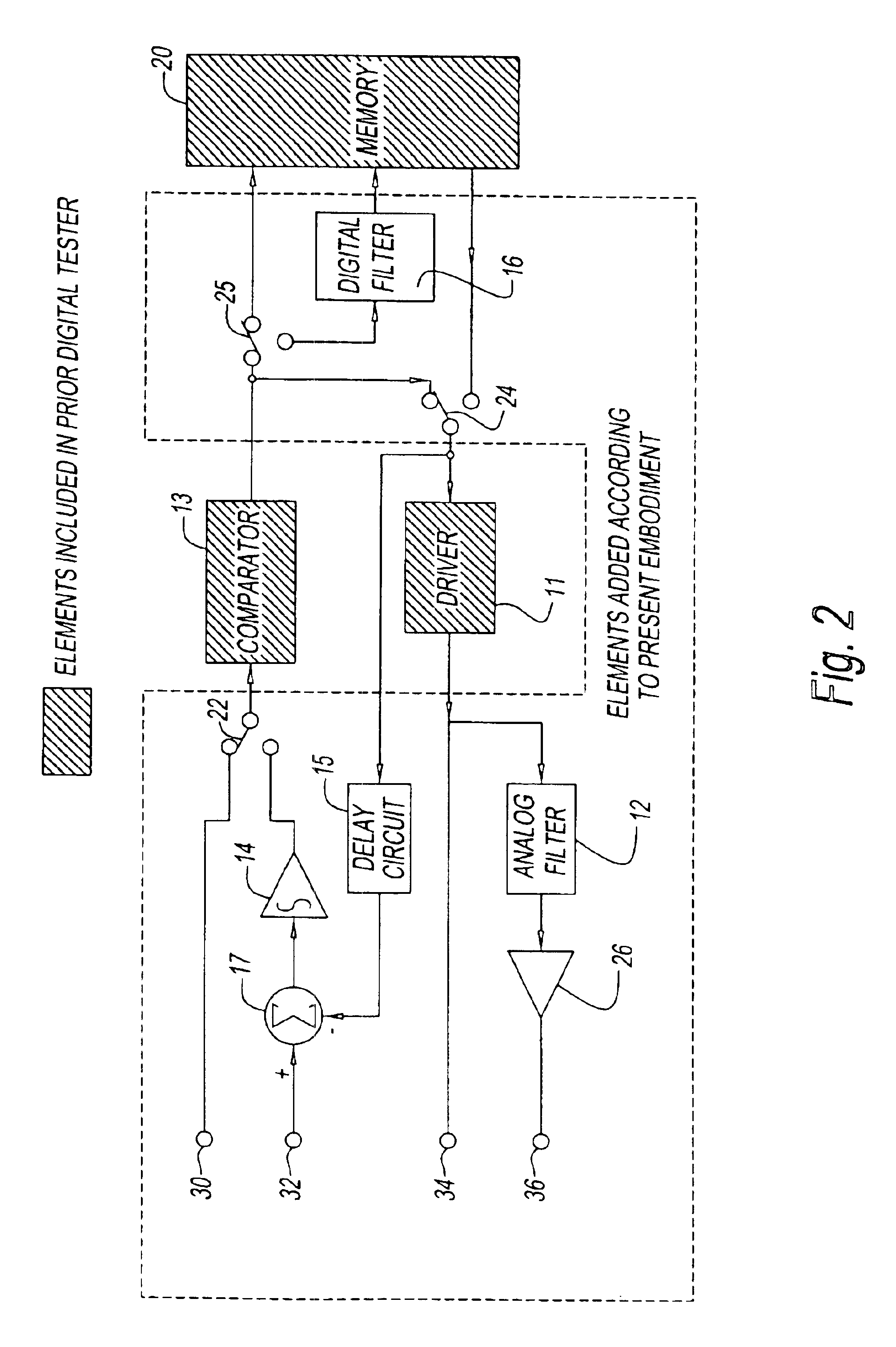

Apparatus for testing integrated circuits having an integrated unit for testing digital and analog signals

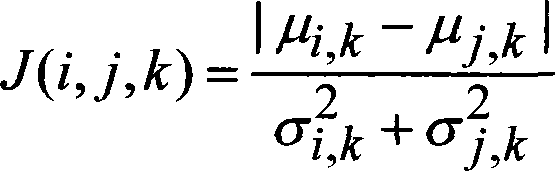

InactiveUS6864699B2Simple structureReduce testing costsAnalog circuit testingIndividual semiconductor device testingIntegratorIntegrated circuit layout

An apparatus for testing digital and analog signals from an integrated circuit includes an adder or subtractor 17 for being supplied with an analog signal outputted from the integrated circuit of a device under test and a signal outputted from a driver 11, an integrator 14 for being supplied with an analog signal outputted from the adder or subtractor 17, a switch 22 for selectively transmitting an analog signal outputted from the integrator 14 and a digital signal outputted from the integrated circuit to the comparator 13, and a switch 24 for selectively transmitting a signal outputted from a memory 20 and a signal outputted from a comparator 13 to the driver 11. At least one of the switches 22, 24 is operated depending on whether a signal to be tested is analog or digital.

Owner:ADVANTEST CORP

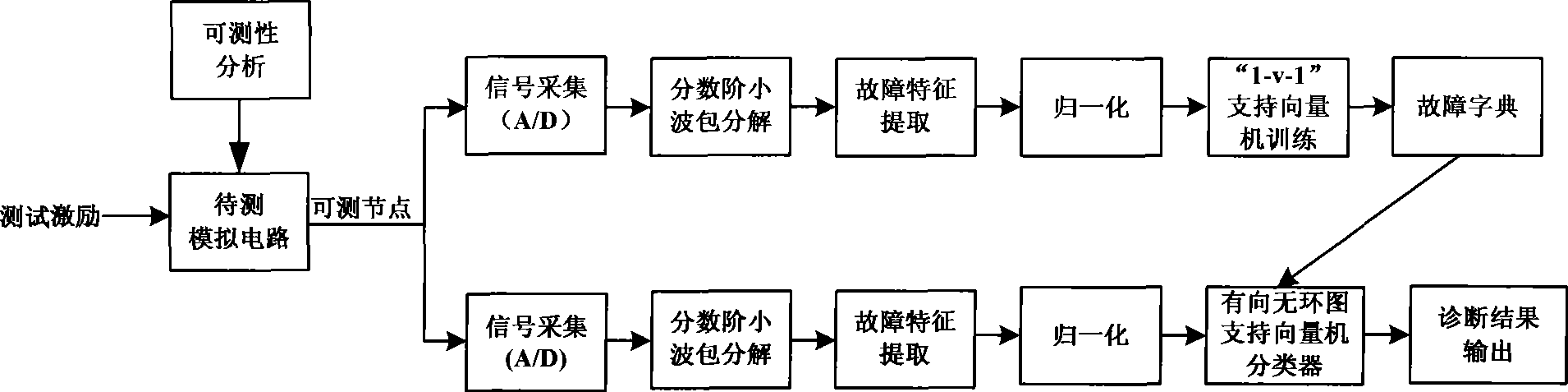

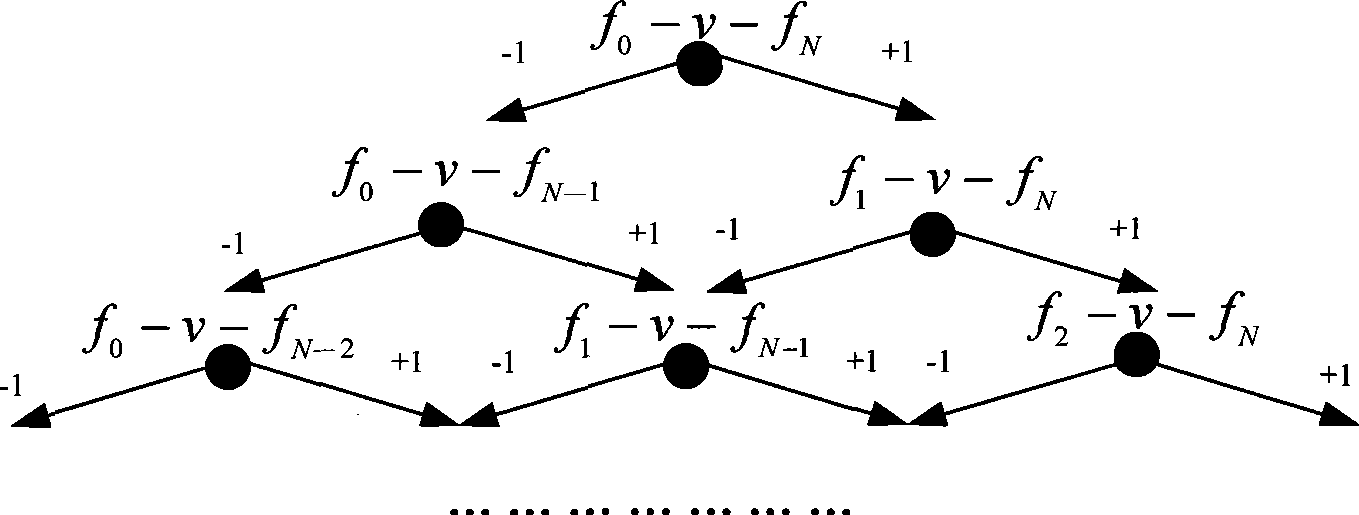

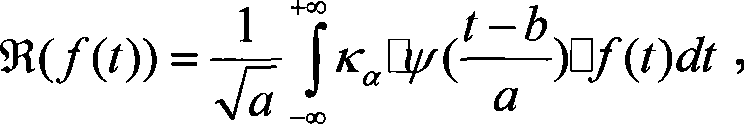

Analog-circuit fault diagnosis method based on DAGSVC

InactiveCN101533068AEfficient extractionSmall scaleAnalog circuit testingTest sampleImage resolution

The invention discloses an analog-circuit fault diagnosis method based on DAGSVC. The method comprises the following steps: applying certain test excitation to a analog circuit to be tested; acquiring circuit output response signals to be tested in a testable node of the circuit; performing multi-order fractional order wavelet packet (FRWPT) transformation on the acquired circuit output response signals and extracting fault characteristics so as to form a test sample; and performing calculation by utilizing fault-dictionary prestored information together with the DAGSVC to classify and position faults. The method has the advantages of global training optimality, fewer needed training samples, high fault-information resolution and the like, and can improve the precision and efficiency of diagnosing the faults of analog circuits.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

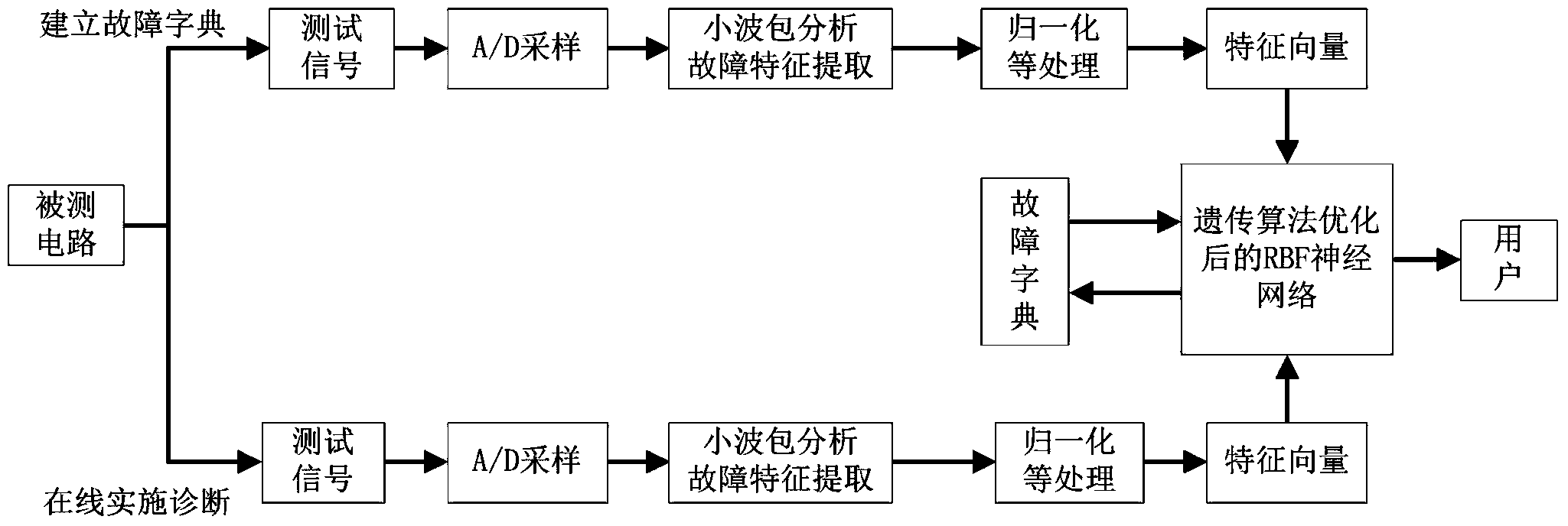

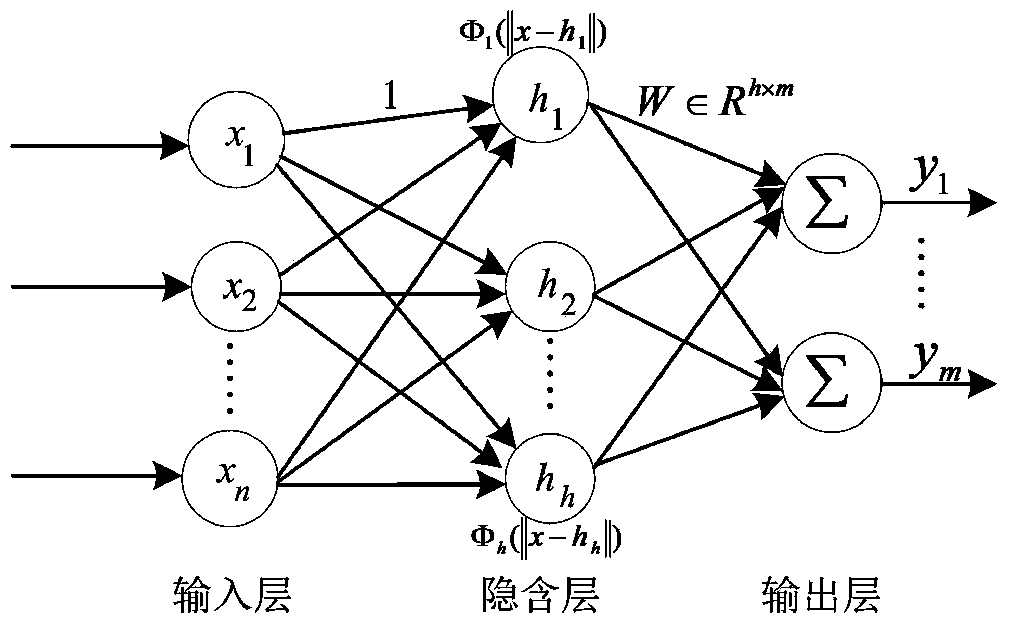

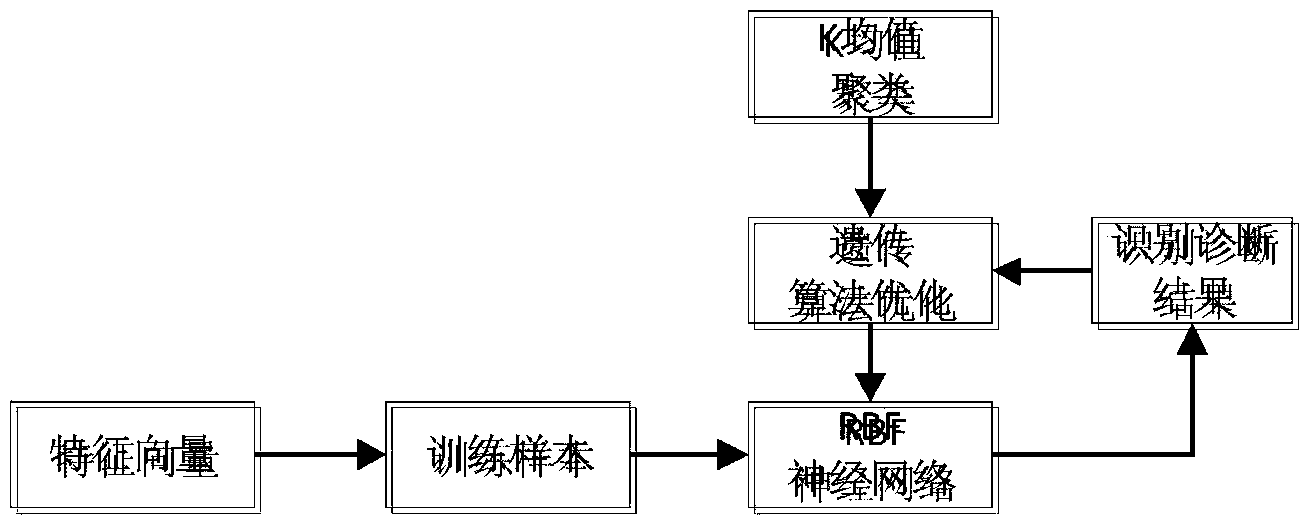

Analog circuit fault diagnosis method based on improved RBF neural network

InactiveCN103926526AReduce the number of iterationsImprove performanceAnalog circuit testingFeature vectorAlgorithm

The invention discloses an analog circuit fault diagnosis method based on an improved RBF neural network. The analog circuit fault diagnosis method includes the following steps that excitation is exerted on a circuit to be detected, and response signals are processed through improved wavelet packet transformation to extract fault characteristic signals; the extracted candidate characteristic signals are normalized to obtain fault characteristic vectors; the fault characteristic vectors serving as samples are input into the neural network and classified to obtain a result of fault diagnosis. Extraction of the fault characteristic vectors based on wavelet packet transformation is adopted, so that the distinguishability is improved; through normalization and other preprocessing, influences caused by different dimensions and too large numerical value difference on original variables are effectively eliminated; an LMS method in an RBF algorithm is replaced by a genetic optimization algorithm to train parameters of the neural network, so that the performance of the RBF algorithm is improved, an optimizing starting point of a genetic algorithm is set through a K average clustering learning algorithm, the iterations of the algorithm is effectively reduced, errors are reduced, diagnosis speed is increased, and the fault recognition rate is improved.

Owner:CHONGQING UNIV

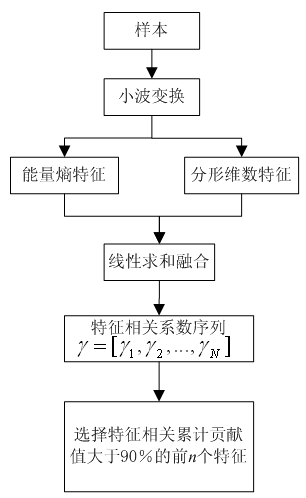

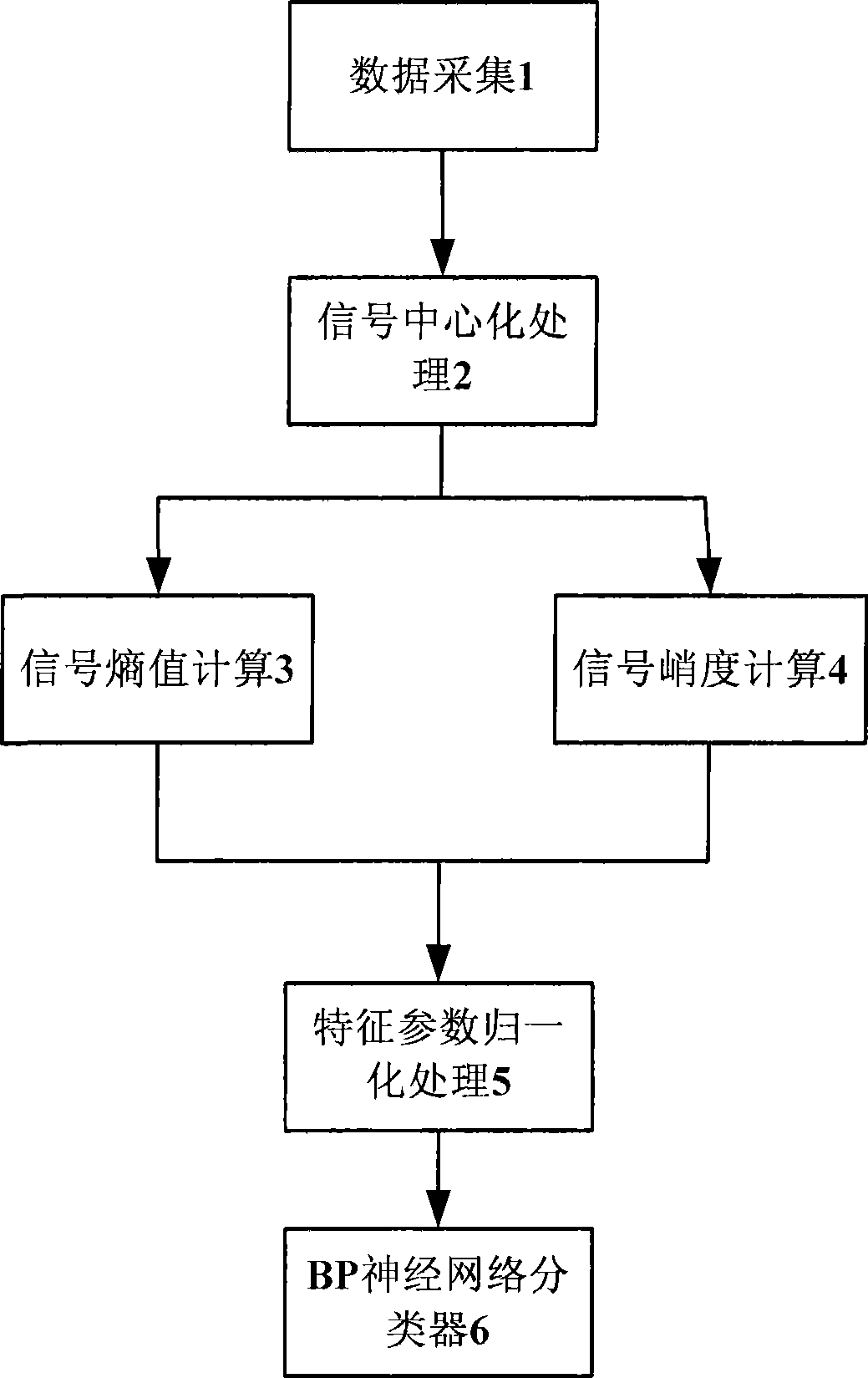

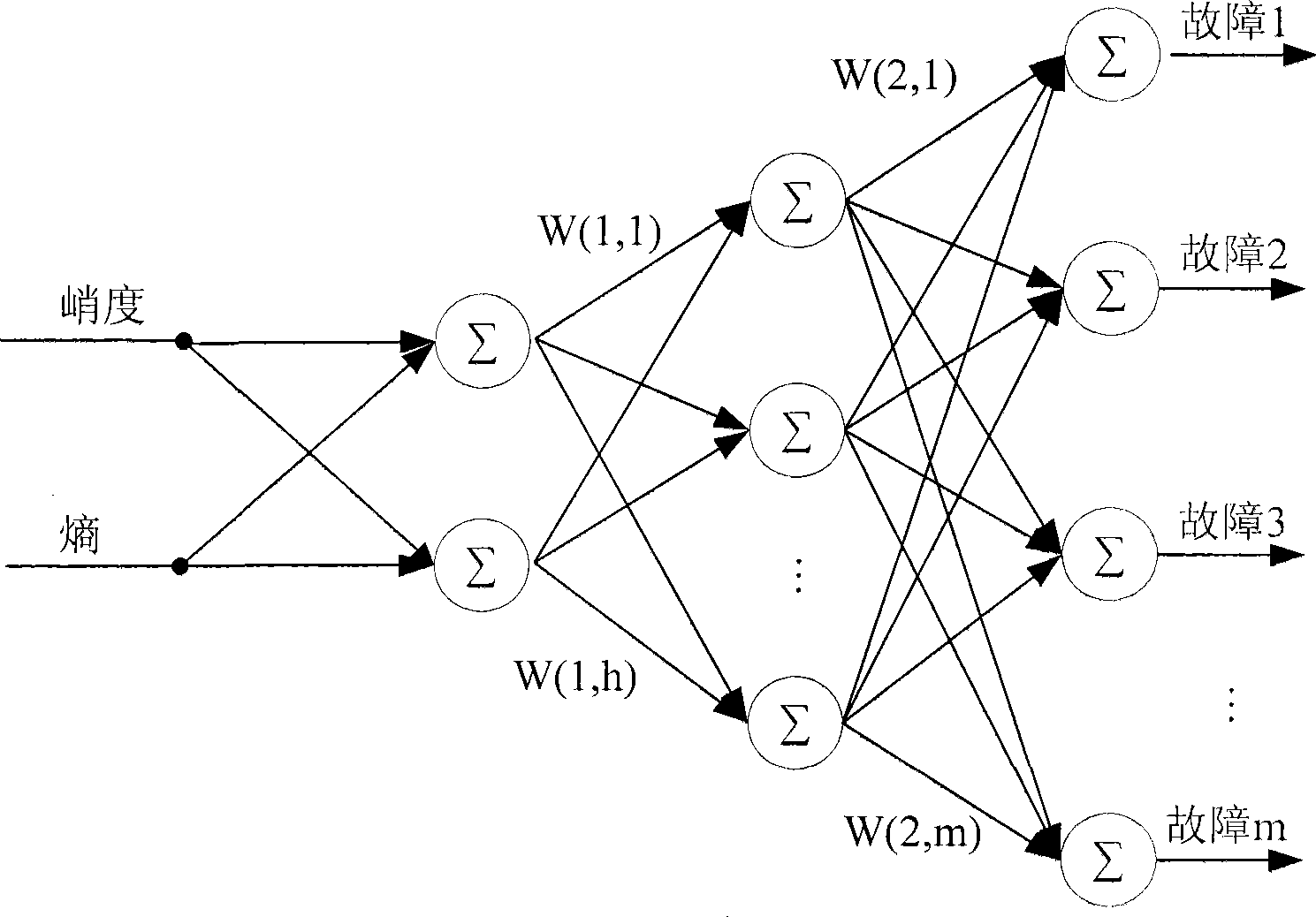

Analogue circuit fault diagnosis method based on neural network

InactiveCN101477172AReduce the numberSimple calculationAnalog circuit testingBiological neural network modelsNerve networkElectric signal

The invention discloses a method for diagnosing fault of an analog circuit based on a nerve network. The method is characterized in that the method comprises the following steps: (1) an electrical signal of the analog circuit is acquired; the electrical signal is testable node voltage of the analog circuit or a current signal of a branch circuit; (2) the acquired electrical signal is subjected to centralized processing; (3) signal entropy value and signal kurtosis of the electrical signal are calculated; and (4) the signal entropy value and the signal kurtosis are sent to a BP nerve network separator, and a fault diagnosis result is output by the BP nerve network separator. The method can be used for a real-time system and a nonreal-time system and can be also used for diagnosing hard fault and soft fault.

Owner:HUNAN UNIV

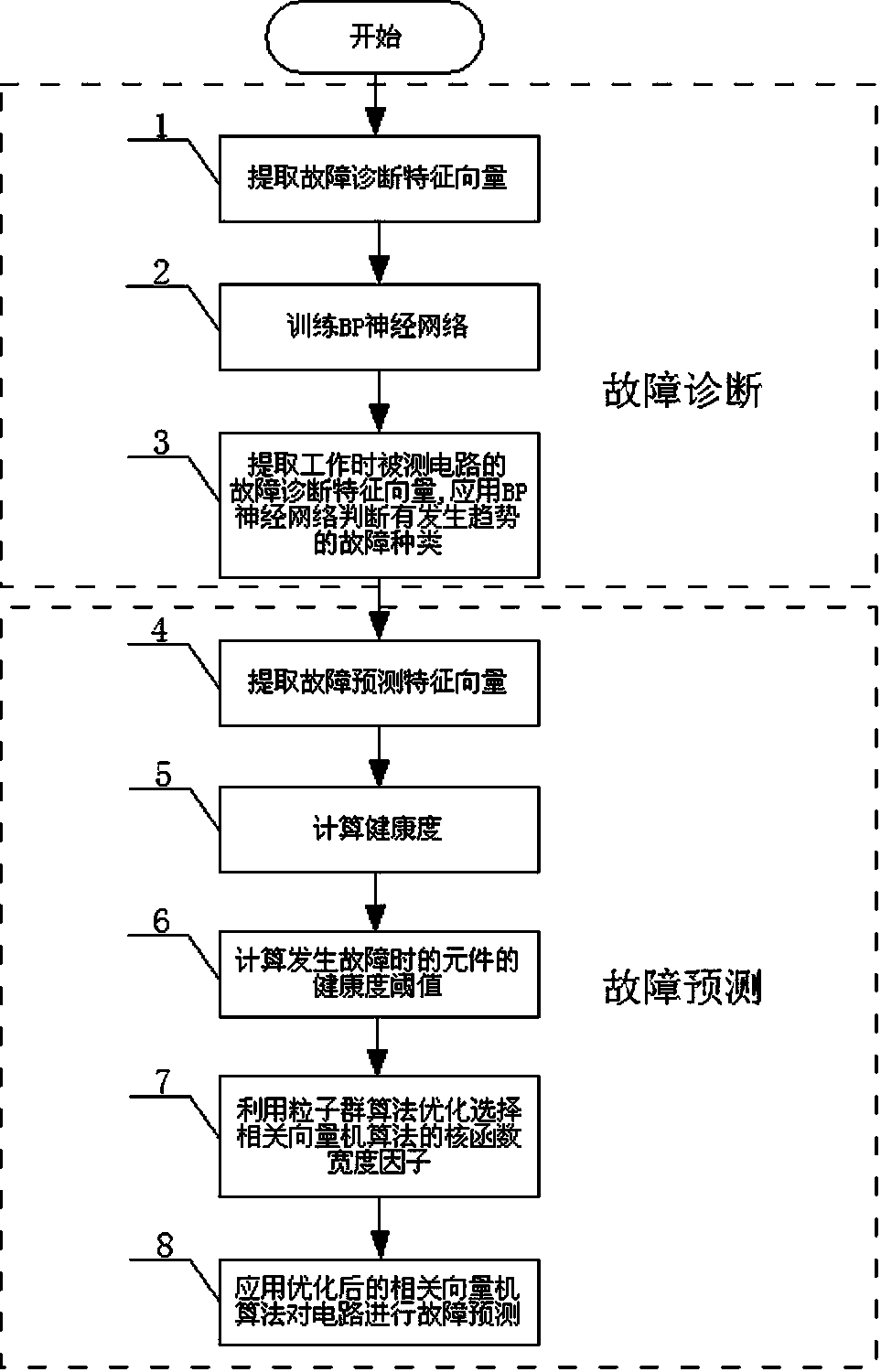

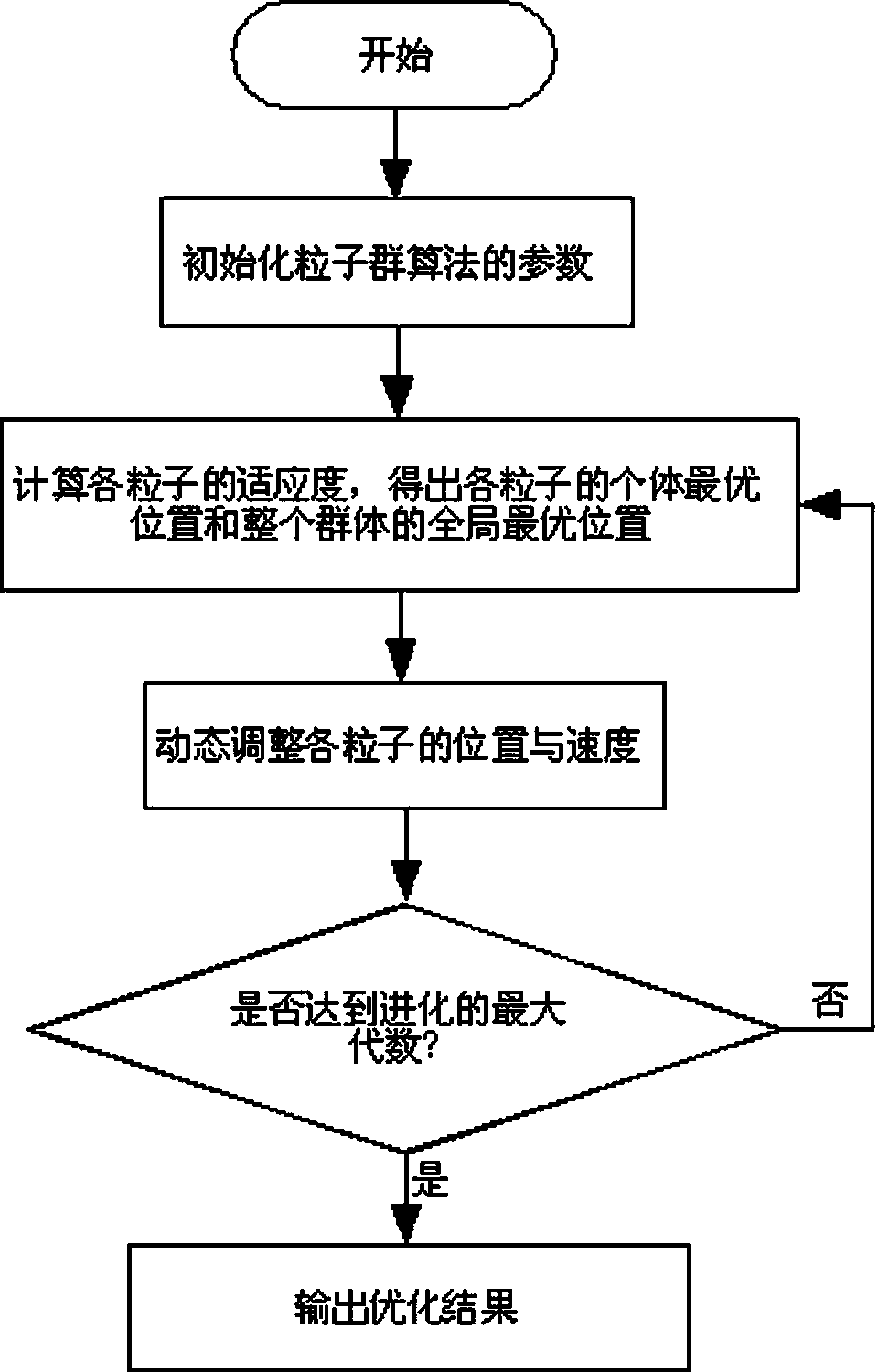

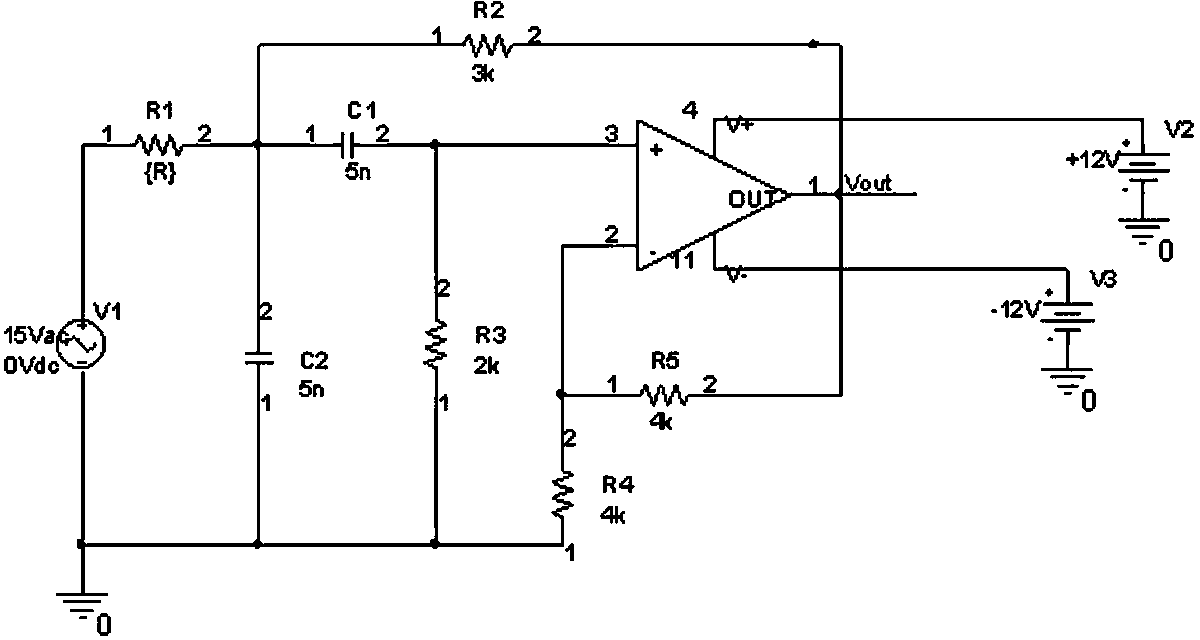

Analogue circuit failure prediction method

ActiveCN103824135ADecreased healthHigh precisionAnalog circuit testingForecastingCapacitanceTime system

The invention discloses an analogue circuit failure prediction method which comprises the following steps: performing Monte Carlo analysis on various elements of an analogue circuit in a failure-free section and extracting various frequency band signal energy, normalizing the extracted frequency band signal energy to obtain a feature vector; training a BP neural network; judging failure modes with occurrence trends, extracting a failure prediction feature vector when the element is at the initial value, extracting the failure prediction feature vector when a detected circuit is in work, computing the cosine angle distance to represent the health degree of the element, computing the health degree threshold value when the element is in failure, and optimally selecting a kernel function width factor of a relevance vector machine algorithm, and performing the failure prediction on the analogue circuit. The method can be used for a real-time system, and can be further used for a non-real-time system, a failure of the linear analogue circuit can be predicted, and a failure of the non-linear analogue circuit can be predicted, and failures of main elements such as resistor, inductor and the capacitor in the analogue circuit can be predicted.

Owner:HEFEI UNIV OF TECH

System for probing, testing, burn-in, repairing and programming of integrated circuits

InactiveUS6891387B2Reduce thicknessAnalog circuit testingDigital circuit testingContact padWater vapor

Owner:ELM TECH

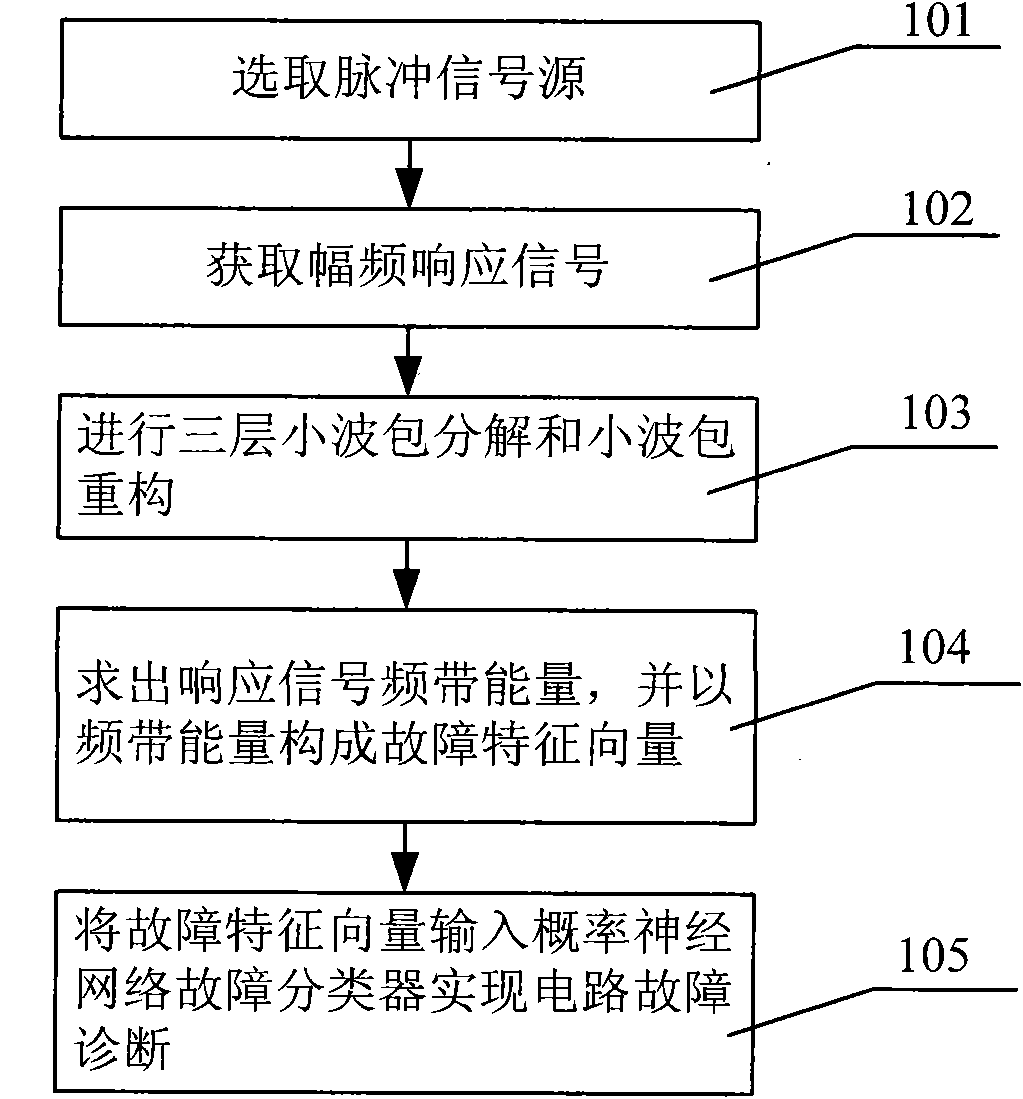

Probabilistic neural network-based tolerance-circuit fault diagnosis method

ActiveCN101819253AOvercome lossOvercoming structural complexityAnalog circuit testingBiological neural network modelsFault toleranceWavelet

Owner:HUNAN UNIV

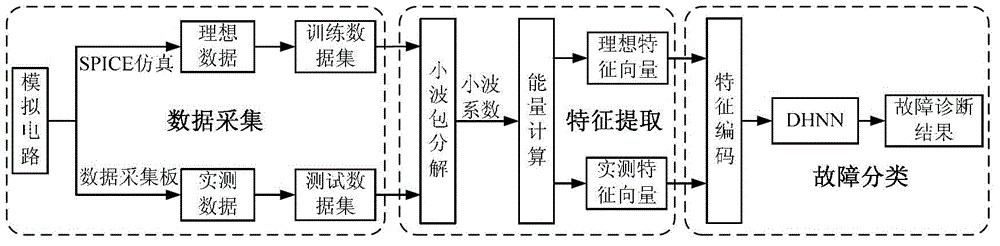

Analog circuit fault diagnosis method based on wavelet packet analysis and Hopfield network

InactiveCN102749573ADescribe the fault characteristicsFast and accurate fault classificationAnalog circuit testingHopfield networkData set

The invention provides an analog circuit fault diagnosis method based on wavelet packet analysis and the Hopfield network. The method includes data obtaining, feature extraction and fault classification, wherein data obtaining includes performing data sampling for output response of an analog circuit respectively through simulation program with integrated circuit emphasis (SPICE) simulation and a data collection plate connected at a practical circuit terminal so as to obtain an ideal output response data set and an actually-measured output response data set; feature extraction includes performing wavelet packet decomposition with ideal circuit output response and actually-measured output response respectively serving as a training data set and a test data set, and leading energy values obtained by decomposed wavelet coefficient through energy calculating to form feature vectors of corresponding faults; and fault classification includes leading the feature vectors of all samples to be subjected to Hopfield coding and then submitting the coded feature vectors to the Hopfield network to achieve accurate and fast fault classification. The analog circuit fault diagnosis method is good in fault feature pretreatment effect aiming at hard faults with weak amplitude response and soft faults with large amplitude response, and the newly defined energy function and the newly defined coding rule are remarkable in influence on fault diagnosis accuracy of the analog circuit.

Owner:CHONGQING UNIV

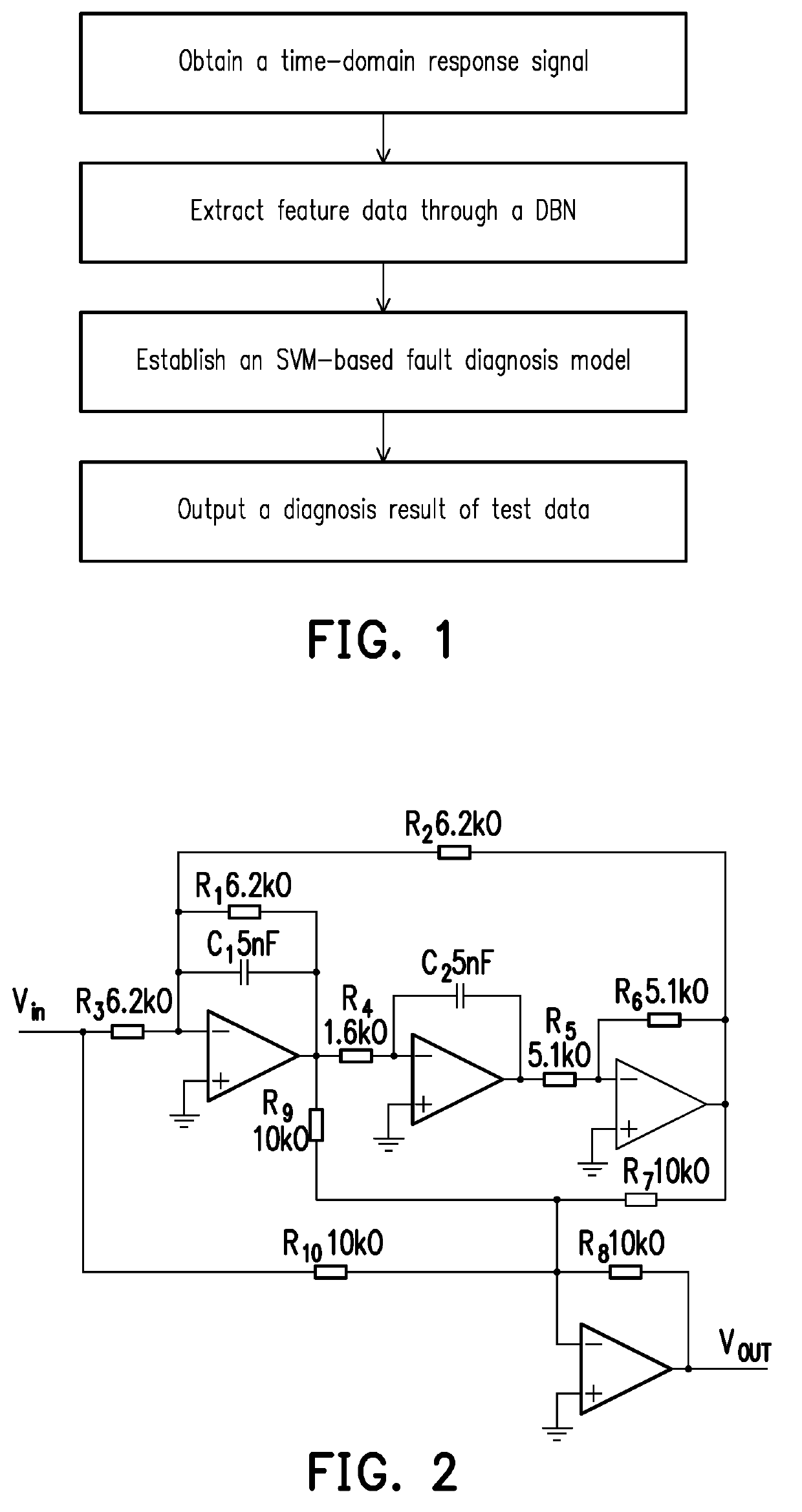

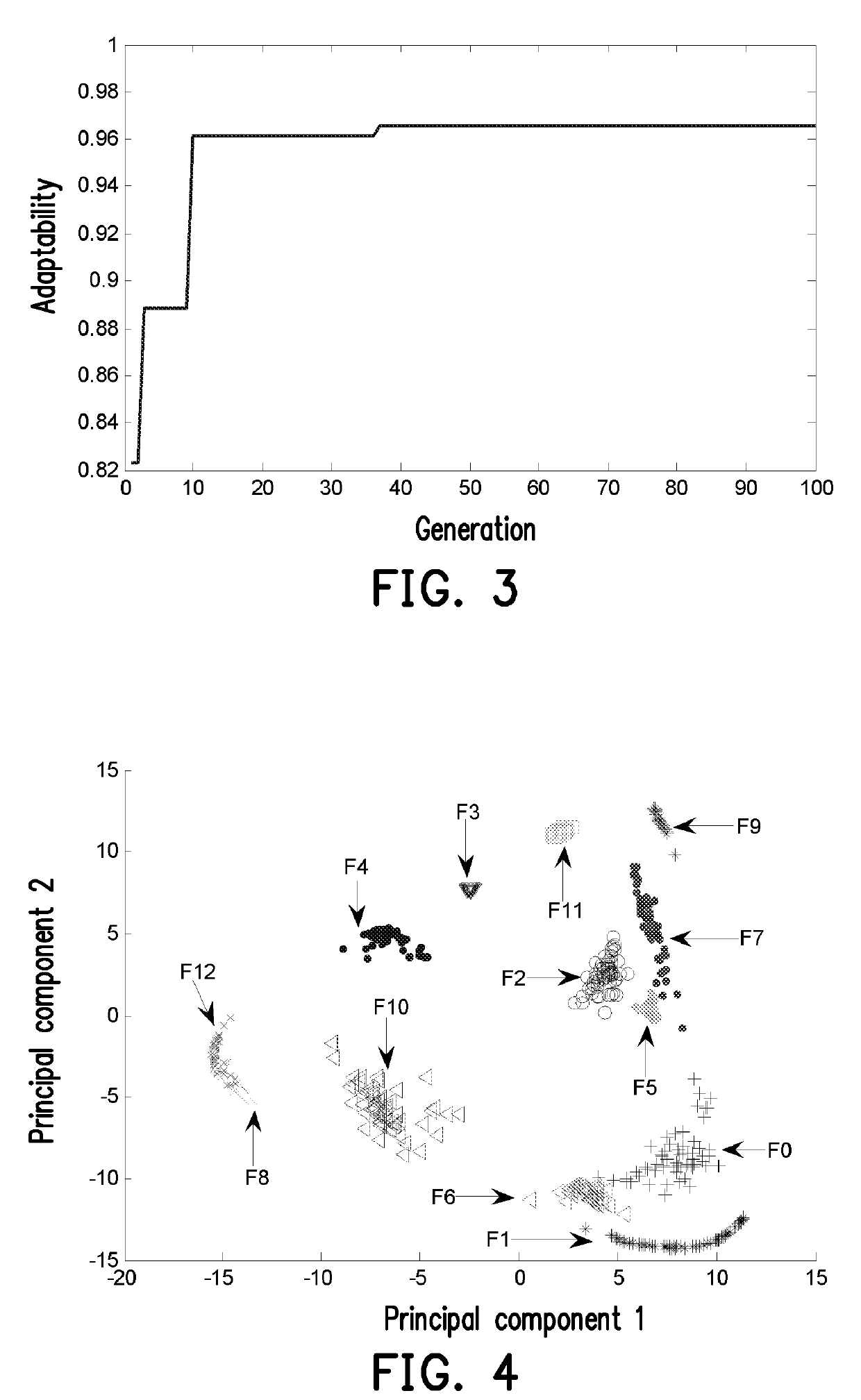

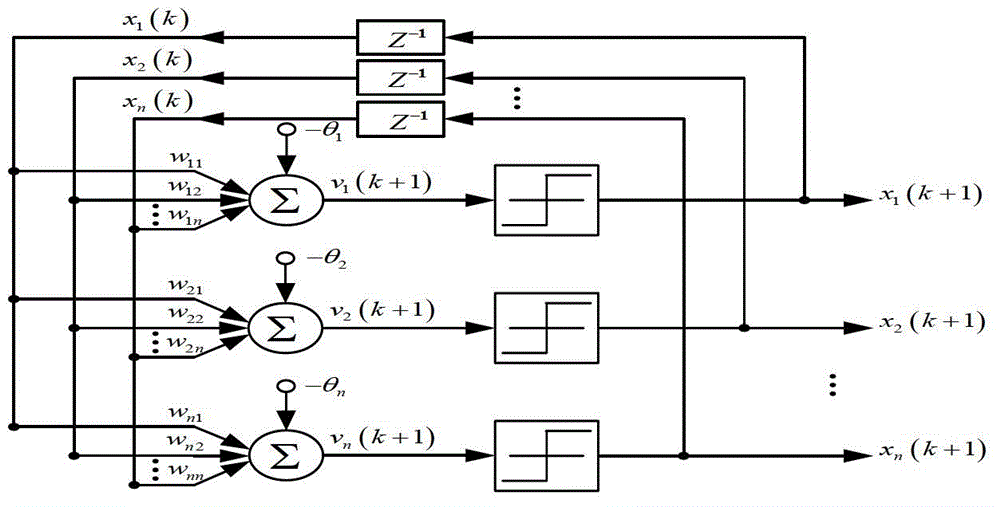

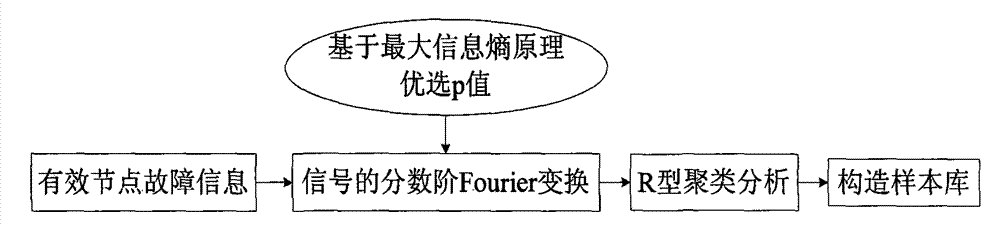

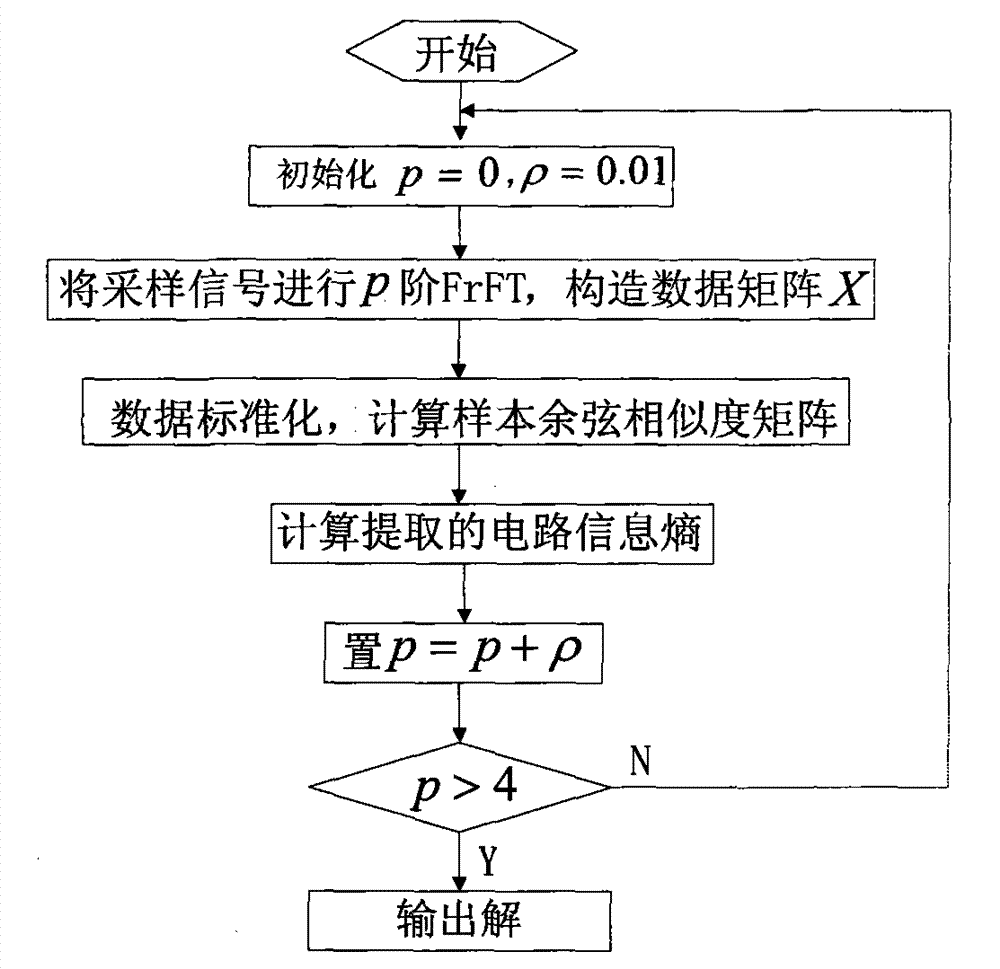

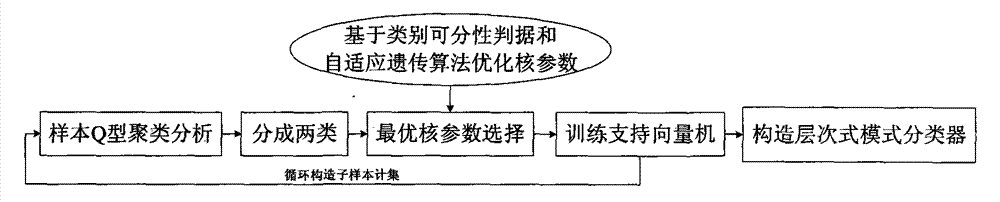

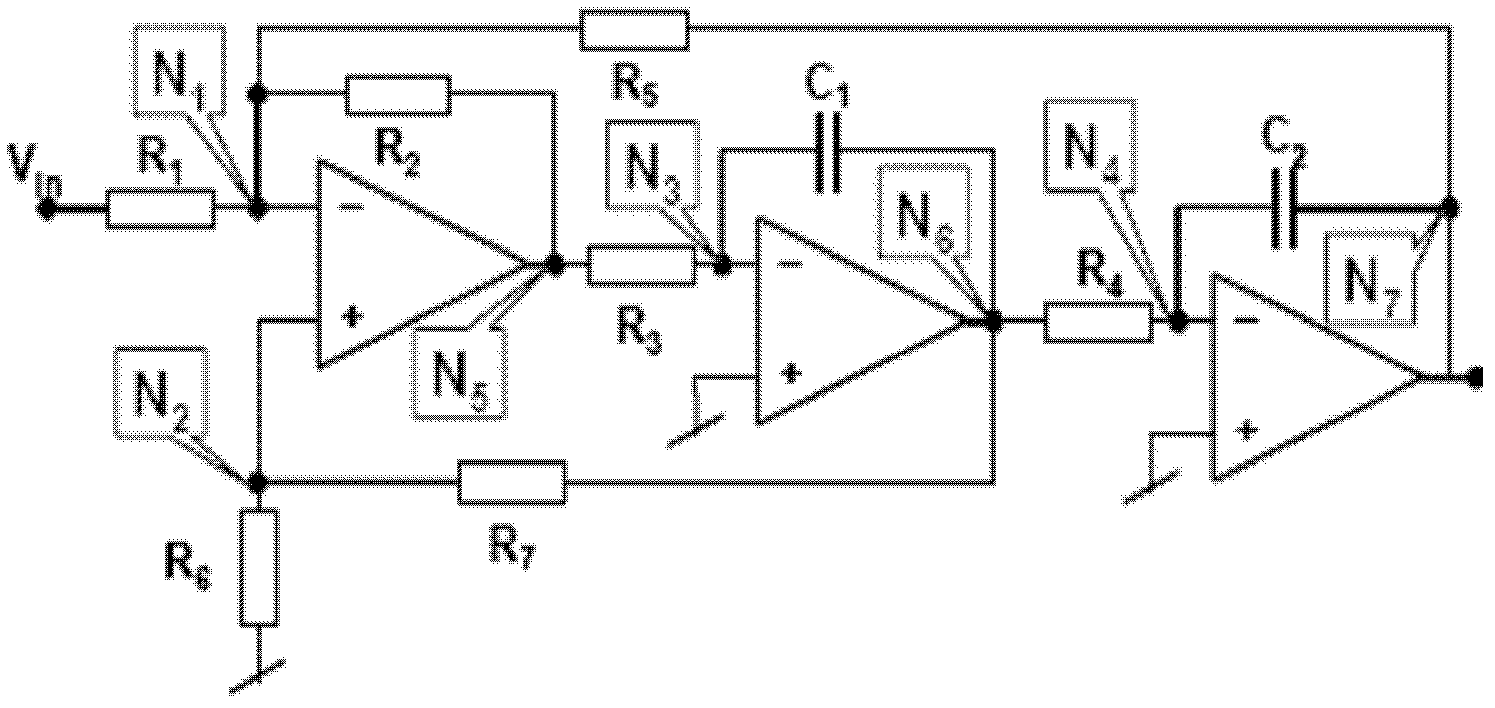

Artificial circuit fault diagnosis pattern sorting algorithm

The invention discloses an artificial circuit fault diagnosis pattern sorting algorithm based on signal characteristic space modeling. According to the method, signals collected by test nodes are utilized, optimal fractional Fourier transform (FrFT) and R type cluster analysis are performed on the signals on the basis of the maximum entropy principle (MEP) to describe the characteristics of fault samples, and different spatial distribution modeling of faults are conducted; according to the sort separability criterion of the characteristic evaluation of minimum-in-cluster-distance and maximum-between-cluster-distance, objective optimization functions of nuclear parameters are constructed, and on the basis of a self-adaption genetic algorithm, the objective functions are optimally solved, and the nuclear parameters are adjusted; in combination with Q type cluster analysis, a hierarchical support vector machine classifier (SVC) is constructed to find and separate the faults; and through the algorithm, sensitivity reflecting fault characteristics can be extracted from measurement signals, and higher fault diagnosis speed and higher fault diagnosis accuracy are achieved. The fault diagnosis examples of a Continuous-Time State-Variable Filter circuit and an ML-8 radar prove the speediness and effectiveness of the algorithm.

Owner:NAVAL AERONAUTICAL & ASTRONAUTICAL UNIV PLA

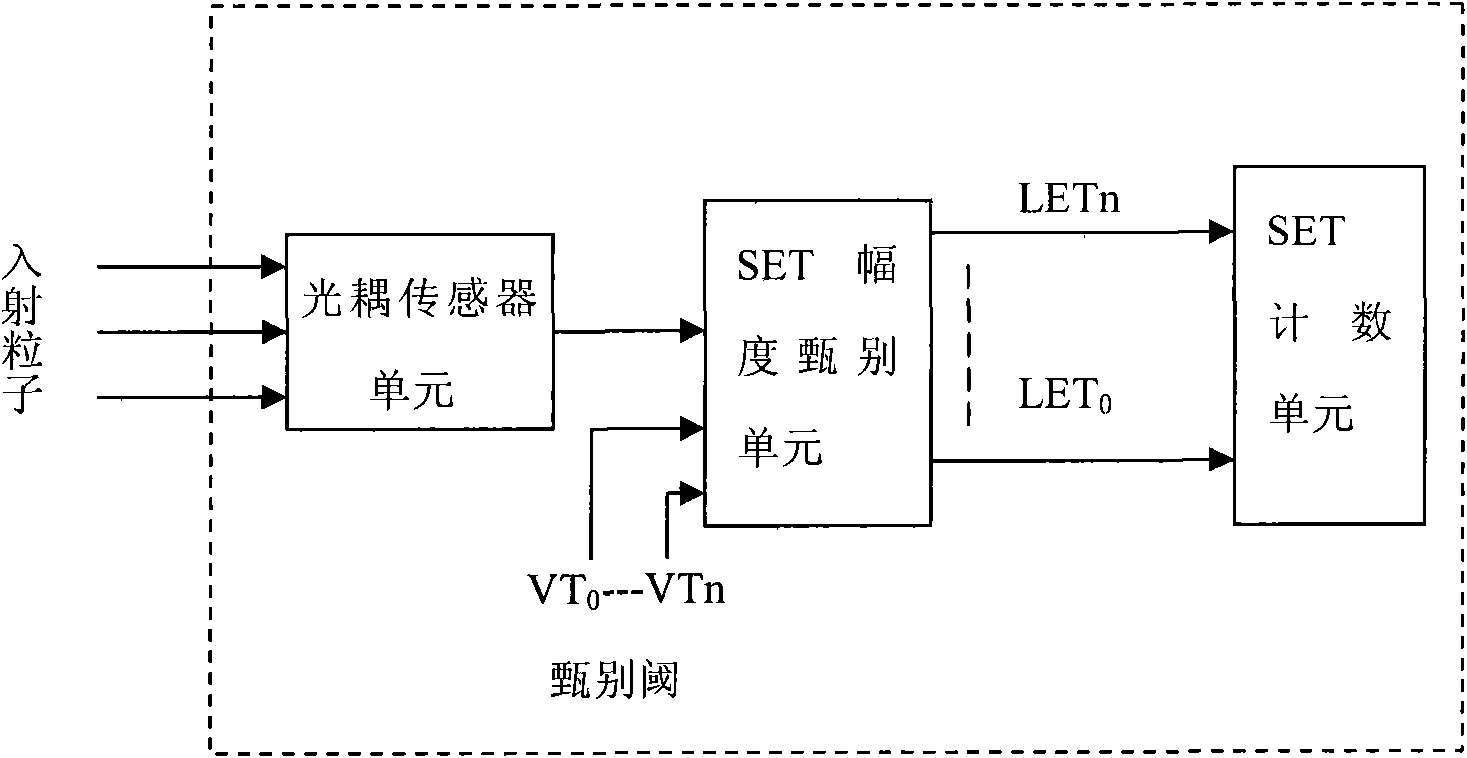

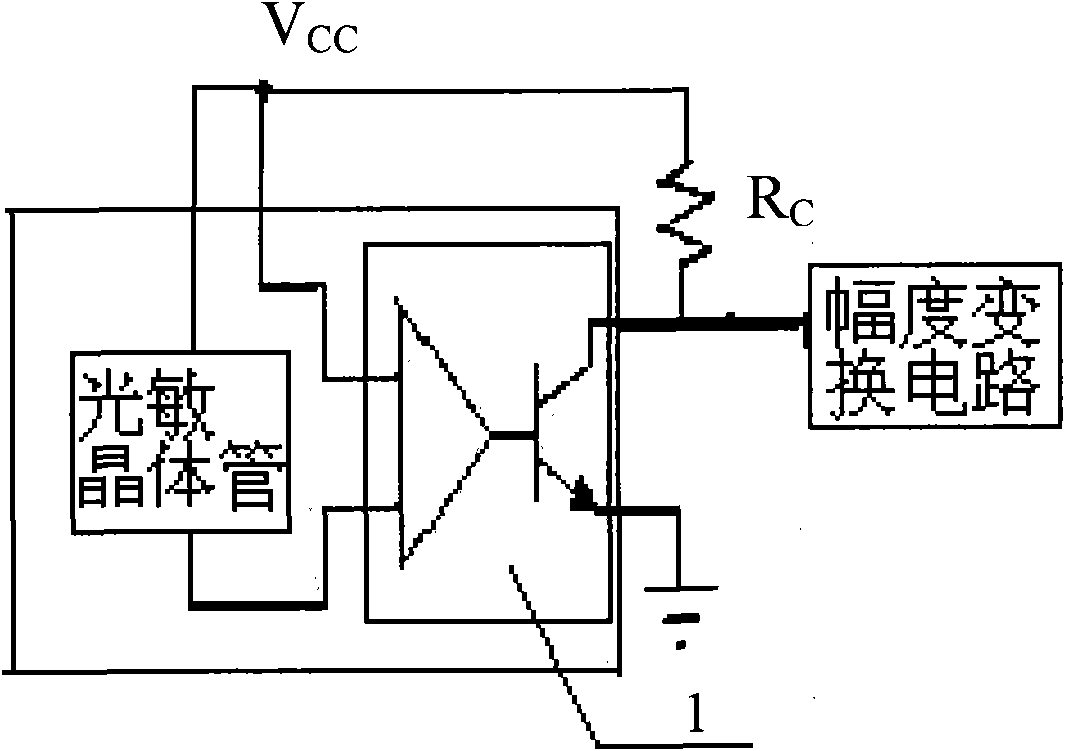

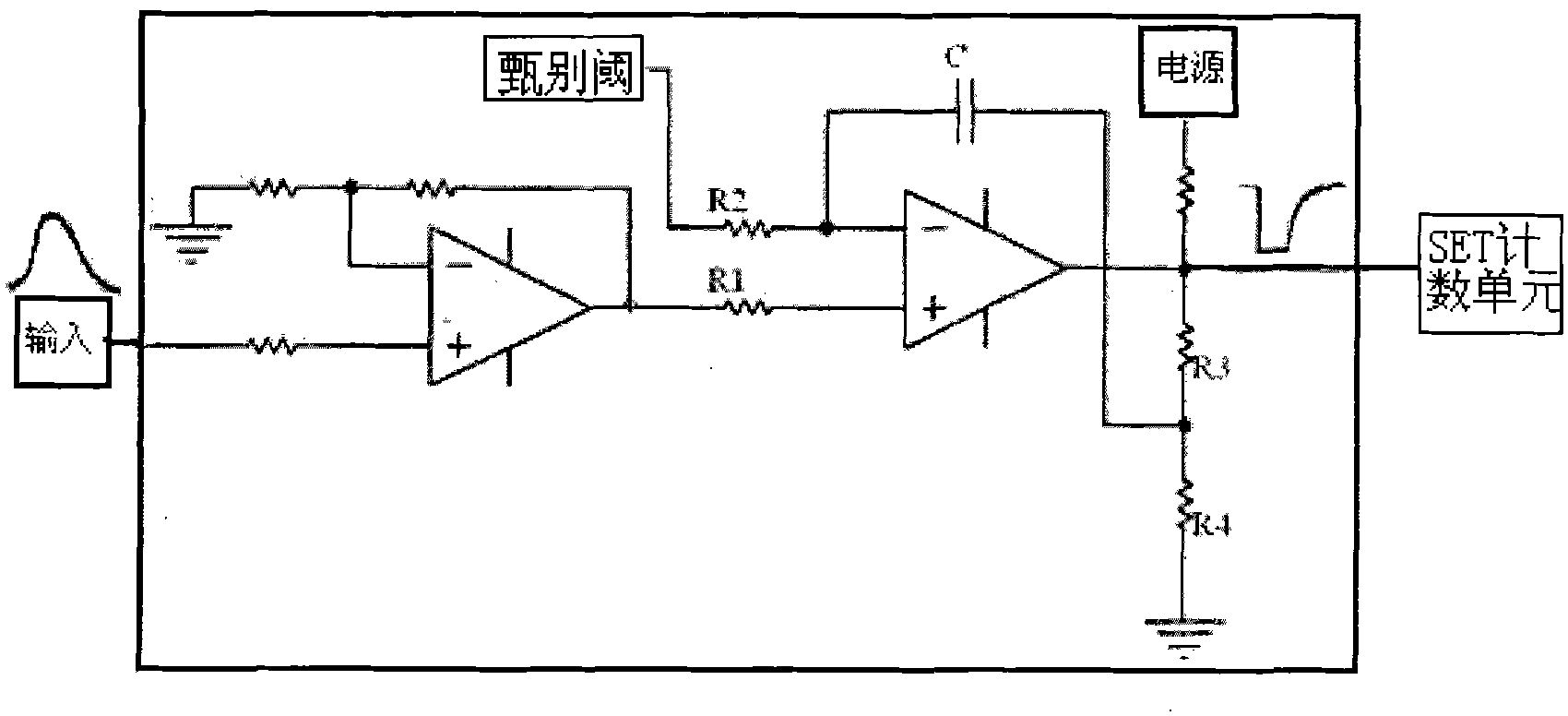

Single-event effect detection device and method

InactiveCN101907662ARealize measurementWide LET value quantitative measurement rangeAnalog circuit testingDiscriminatorMiniaturization

The invention provides a single-event effect detection device, which comprises a light-coupler sensor working unit, an SET amplitude discriminator unit and an SET counting unit, wherein the light-coupler sensor working unit is used for acquiring an SET signal from a radiation environment to be detected; the SET amplitude discriminator unit is used for comparing the SET signal amplitude obtained by the light-coupler sensor working unit with a threshold voltage to discriminate the amplitude ranges of different SET signals; and the SET counting unit is used for counting the number of the SET signals in each amplitude range. The device may also comprise a data mapping unit. The device and the method can realize the measurement of the values of several or tens of MeV.cm<2> / mg LETs and the measurement of the radiation environment of lower magnitudes and quantitatively measure the LET value for characterizing the single event effect of a specific micro electronic element, has a wider LET value quantitative measurement range. In addition, the used sensor has a small volume and small mass; the circuit structure is simple; and the lightening, miniaturization and low power consumption of the detection device can be realized easily.

Owner:CENT FOR SPACE SCI & APPLIED RES

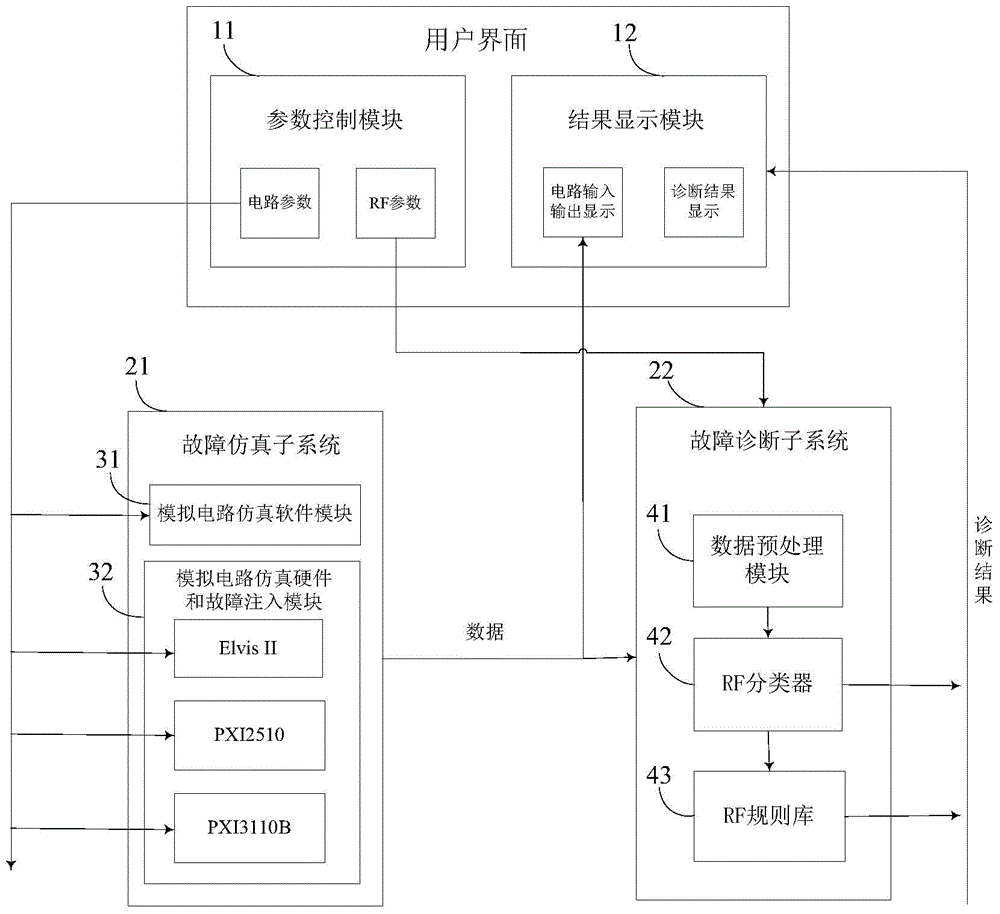

Artificial circuit fault diagnosis system based on random forest

ActiveCN104155596AAchieve transparencyVersatilityAnalog circuit testingNODALElectrical resistance and conductance

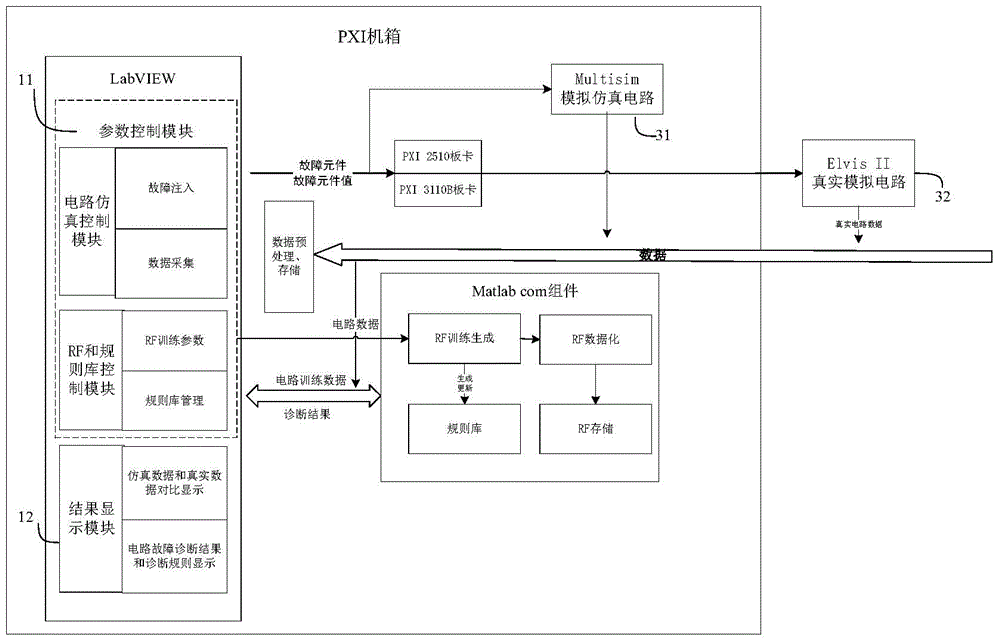

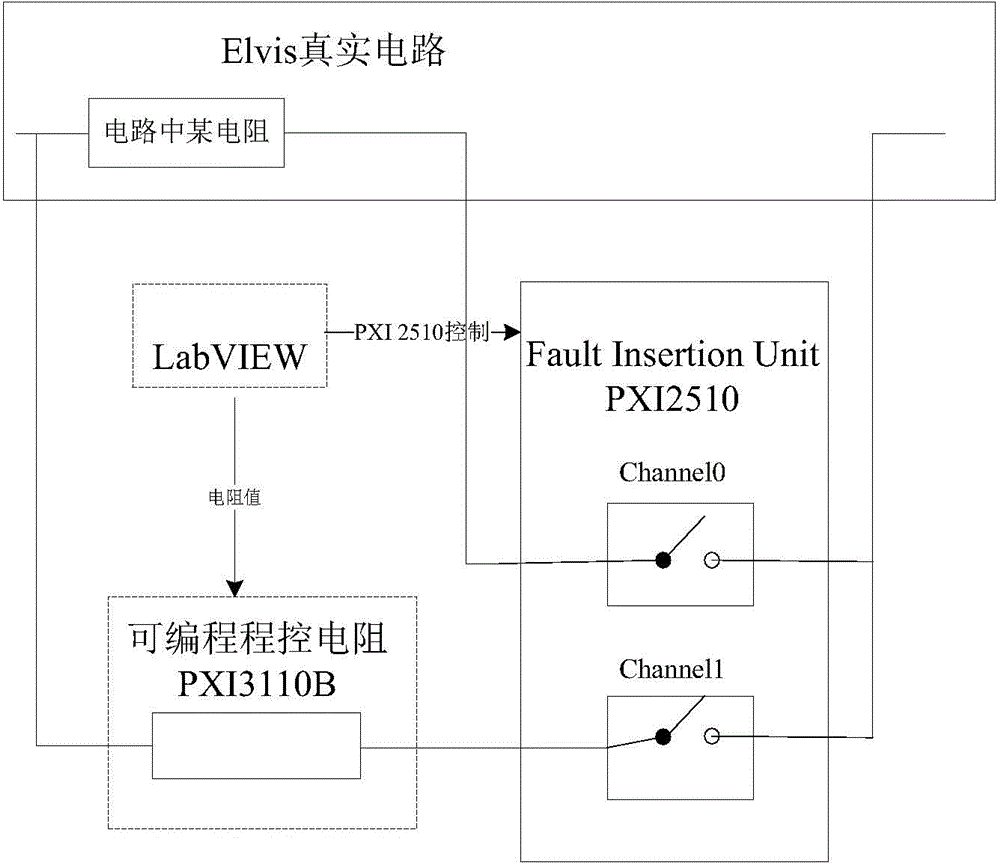

An artificial circuit fault diagnosis system based on a random forest of the present invention belongs to the fault diagnosis field, and comprises a fault simulation subsystem, a fault diagnosis subsystem and a man-machine interaction interface. The fault simulation subsystem is used to realize a simulation fault simulation circuit and a semi-physical fault simulation circuit, and output circuit data to the fault diagnosis subsystem. The fault diagnosis subsystem removes redundancy on the circuit data and then constructs an RF classifier and an RF rule base to diagnose faults. The semi-physical fault simulation circuit is characterized in that a programmable resistor card is added in a real circuit by a fault injection module to realize a resistor fault. When the RF classifier is used to diagnose faults, the reconstruction is carried out by the stored RF node data information, and the time of retraining the RF classifier is saved. According to the present invention, a plurality of fault mode simulation and fault diagnosis can be carried out on any resistor in any real circuit, the faults are diagnosed by completely using the circuit data, and the simulation circuit fault information is transparent.

Owner:BEIHANG UNIV

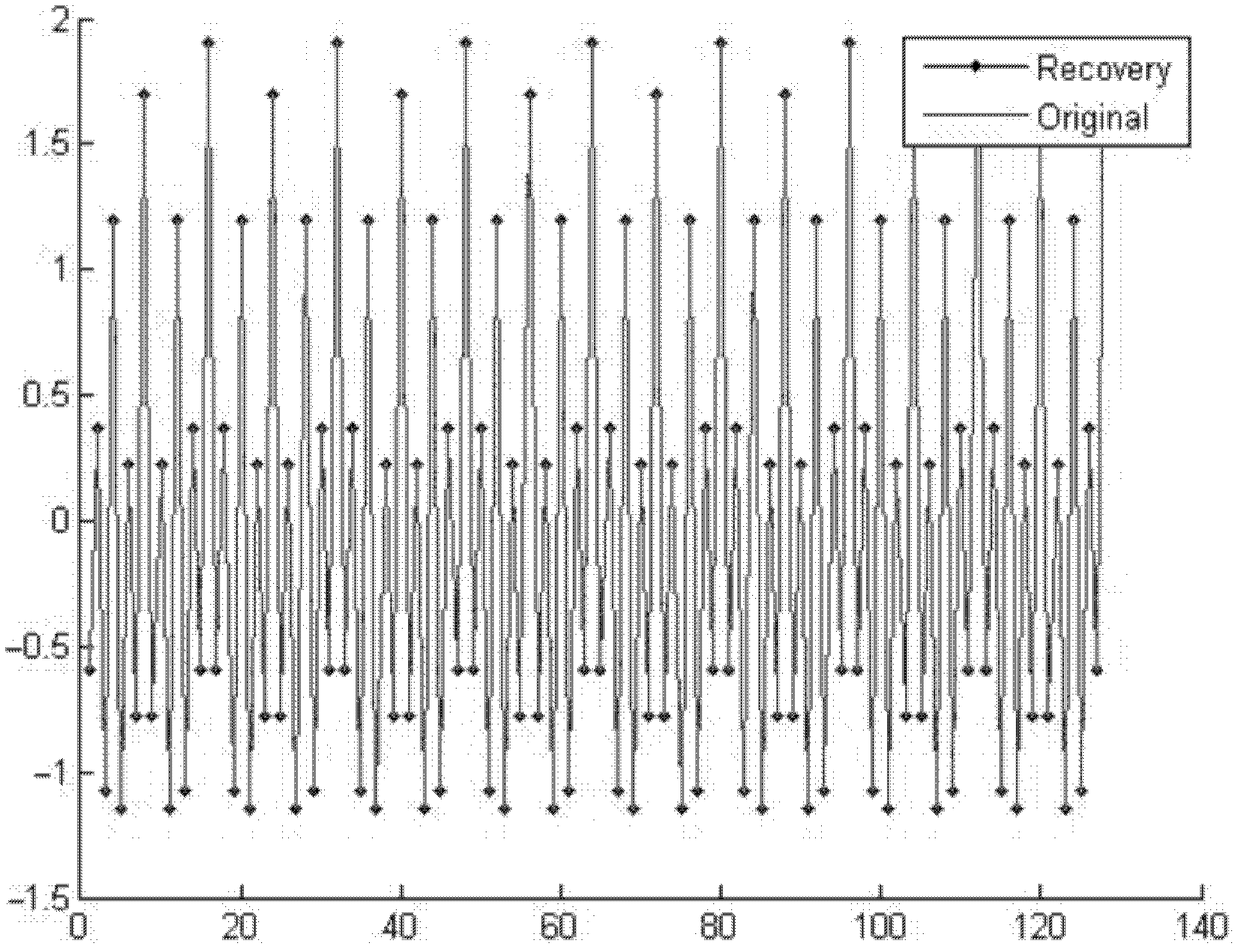

Random sampling analog circuit compressed sensing measurement and signal reconstruction method

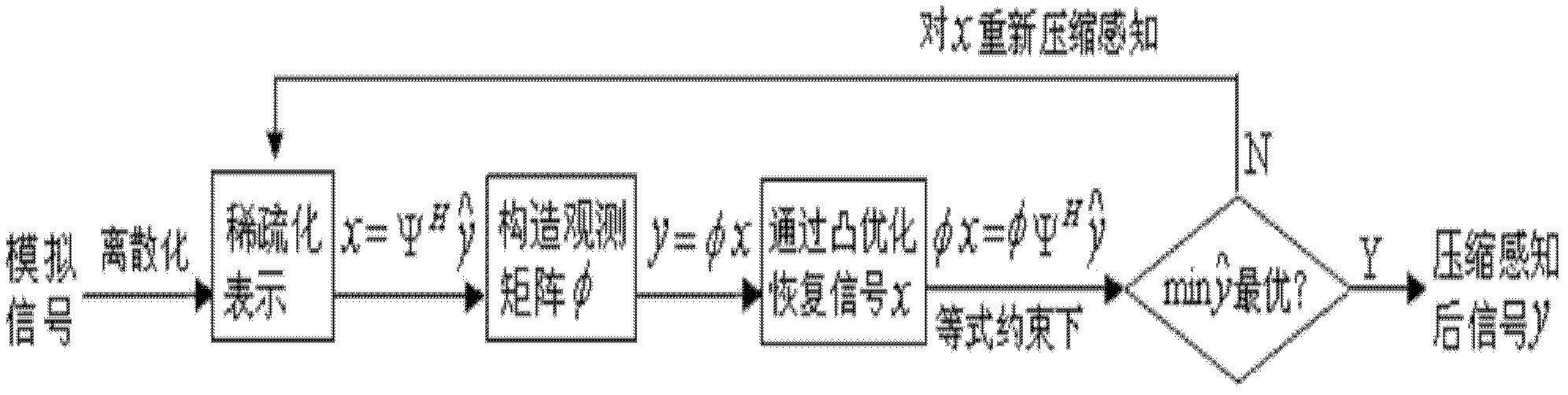

InactiveCN102435934AReduce In-Circuit Test CostsImplement fault diagnosisAnalog circuit testingElectronic systemsDistribution characteristic

The invention relates to a random sampling analog circuit compressed sensing measurement and signal reconstruction method, which belongs to the field of electronic system test and fault diagnosis. Aiming at a fault signal having a sparsity distribution characteristic per se or in an orthogonal space in an output response of an analog circuit, a test node is selected according to a circuit topology structure, circuit output responses are randomly sampled under a distributed sensor test network, response signals are expressed in a sparse way on a transform domain by utilizing discrete orthonormal basis, compressed sensing measurement of the sparse signals is completed under observability matrix projection, and when the recovery rate of signal reconstruction by randomly compressed sampling points reaches more than 80 percent, the compressed measurement values of the circuit output responses are effective, can form a characteristic set and can be used for analog circuit fault diagnosis. The method solves the problems that the traditional analog signal sampling occupies a large number of hardware resources, large signal reconstruction calculated amount and the like; and the random sampling compressed sensing measurement method is utilized to improve the efficiency of electronic system testing.

Owner:BEIJING UNIV OF TECH

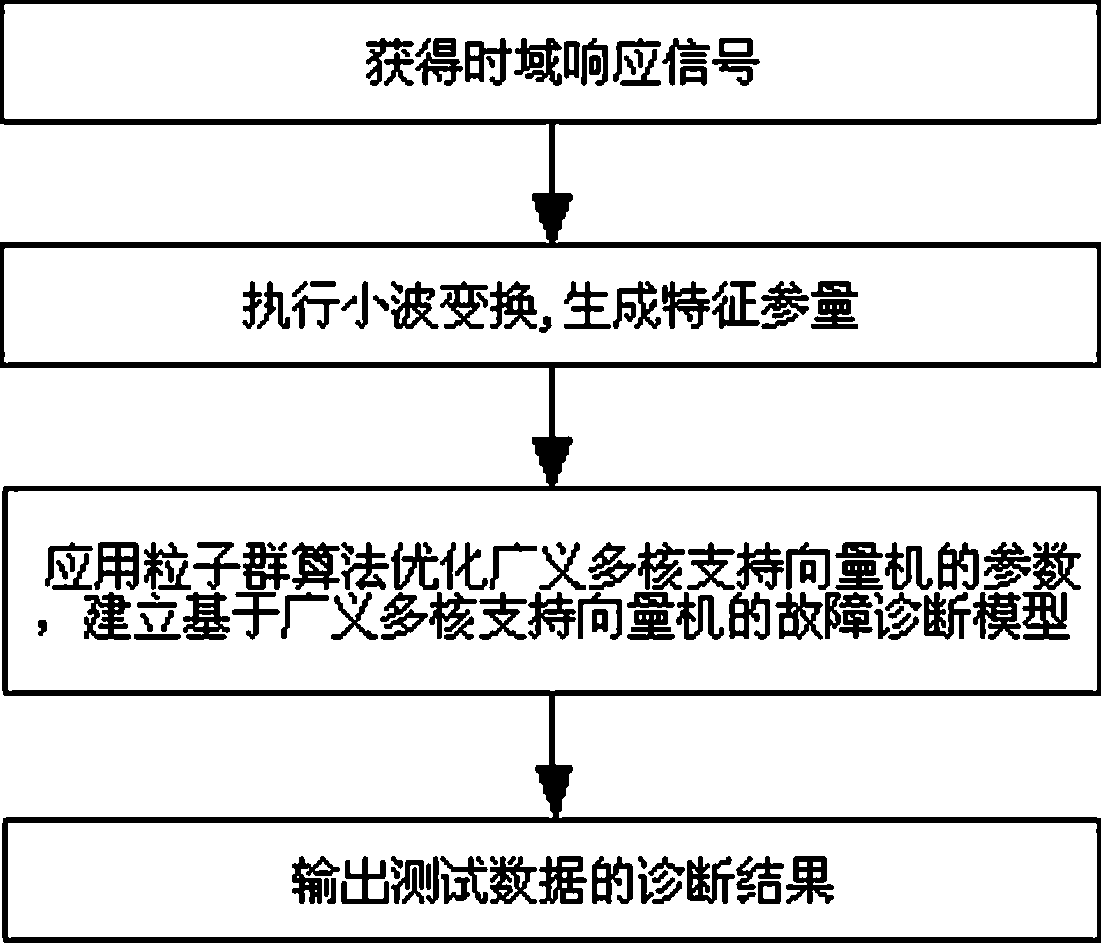

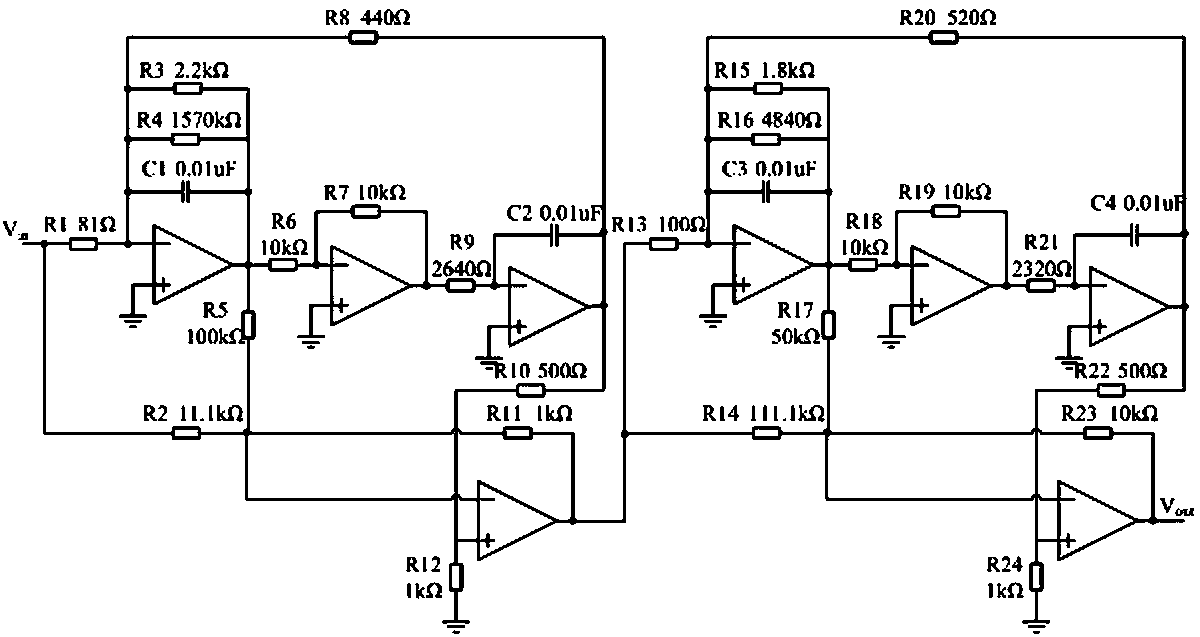

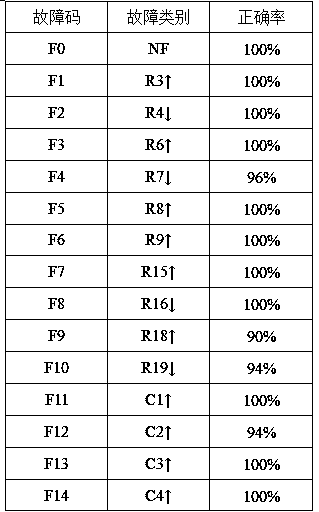

Simulation circuit fault diagnosis method on the basis of generalized multi-nuclear support vector machine

ActiveCN105548862AImprove classification accuracyEasy to classifyAnalog circuit testingCharacter and pattern recognitionSupport vector machineAlgorithm

The present invention provides a simulation circuit fault diagnosis method on the basis of a generalized multi-nuclear support vector machine. The method comprises the following steps: (1) collecting time domain response signals of a simulation circuit, namely collecting output voltage signals of a simulation circuit; (2) performing Wavelet Transform of collected voltage signals, taking energy used for calculating wavelet and coefficients as characteristic parameters, wherein the set of all the characteristic parameters is sample data; (3) applying regularization parameters and trade-off parameters of a PSO optimization generalized multi-nuclear support vector machine based on the sample data, and constructing a fault diagnosis model on the basis of GMKL-SVM; (4) taking the constructed fault diagnosis model on the basis of GMKL-SVM as a classifier, and performing fault diagnosis of the simulation circuit. The classification performance of the GMKL-SVM is better than other classification algorithms, and the method for optimization GMKL-SVM parameters by applying PSO is better than a traditional method for obtaining parameters so as to efficiently detect element faults of a simulation circuit.

Owner:HEFEI UNIV OF TECH

Method for testing analog circuits

InactiveUS6865500B1Easy to testAnalog circuit testingResistance/reactance/impedenceElectrical and Electronics engineeringEngineering

Owner:GEORGIA TECH RES CORP