Artificial circuit fault diagnosis pattern sorting algorithm

A technology for simulating circuit faults and circuit faults, which is applied in the field of fault diagnosis of analog circuits, can solve the problems of testing and fault diagnosis, the slow development of fault diagnosis research of analog circuits, and the complexity of structural models

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

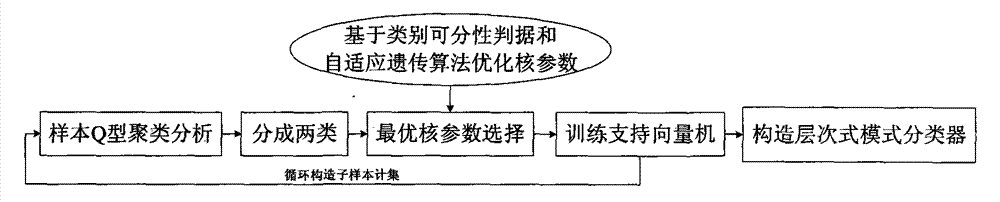

[0017] With the continuous development of artificial intelligence technology, analog circuit fault diagnosis technology based on machine learning has become a research hotspot. Fault diagnosis of analog circuits is essentially a pattern recognition and classification problem. Therefore, how to extract sensitive quantities that reflect fault characteristics is a key technology and an important part of analog circuit fault diagnosis. At the same time, the ultimate purpose of extracting features is to construct a classifier for test samples to realize the discovery and separation of different fault types.

[0018] In order to achieve the above object, method of the present invention is achieved like this:

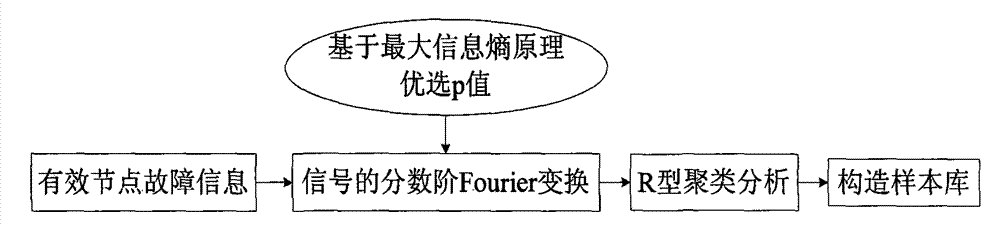

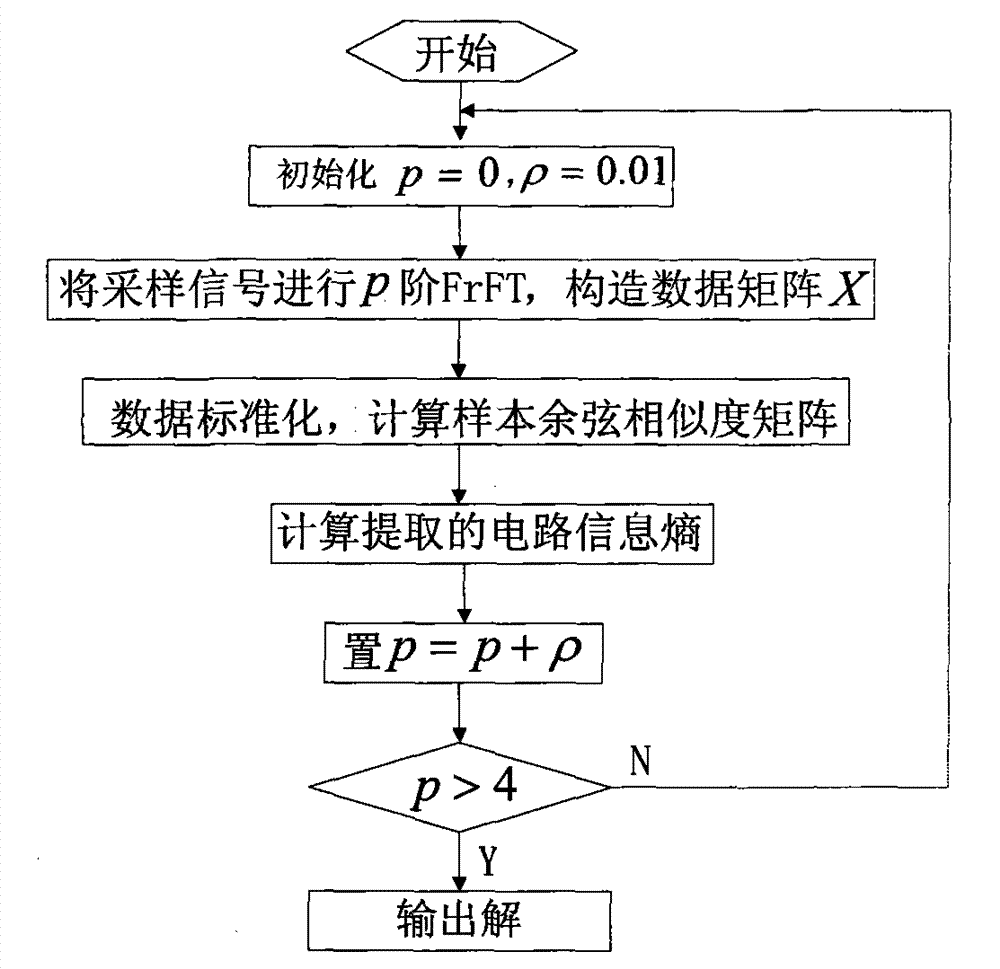

[0019] 1. Spatial modeling of analog circuit fault feature information

[0020] When a circuit fails, the signals of each effective node will change, and non-stationary signals often appear. If only the analysis methods in the time domain or frequency domain are used, the loc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More