Probabilistic neural network-based tolerance-circuit fault diagnosis method

A probabilistic neural network and circuit fault technology, applied in biological neural network models, analog circuit testing, electronic circuit testing, etc., can solve problems such as complex forward feedback neural network structure, low fault identification rate, and local optimum. It achieves the effects of high detection and positioning accuracy, improved identification accuracy, and strong extrapolation ability

Active Publication Date: 2010-09-01

HUNAN UNIV

View PDF5 Cites 27 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

In the usual fault diagnosis of analog electronic circuits, the conventional feedforward neural network (BP neural network) is used as the fault classifier, but for the diagnosis of multiple fault feature inputs, the conventional fe

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Login to View More

Login to View More PUM

Login to View More

Login to View More Abstract

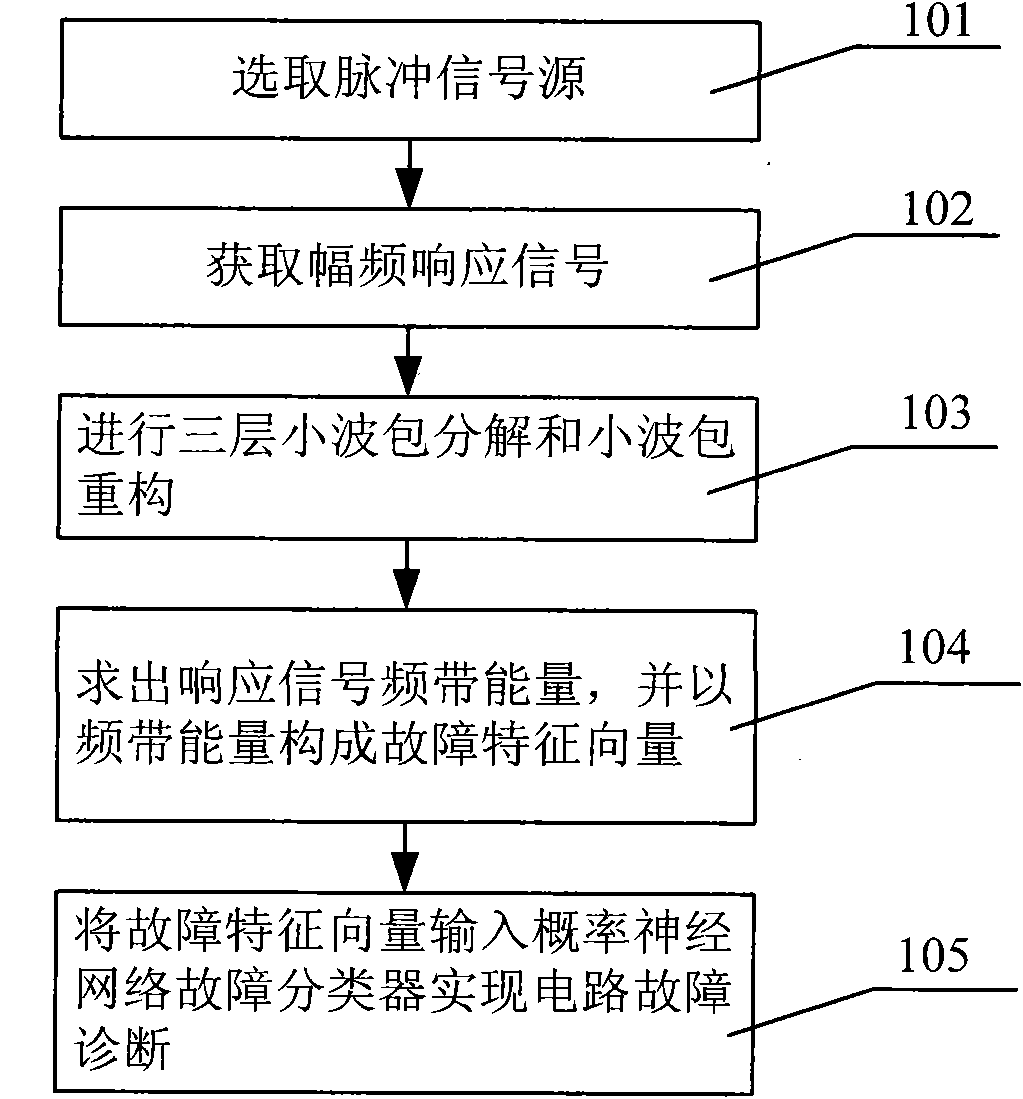

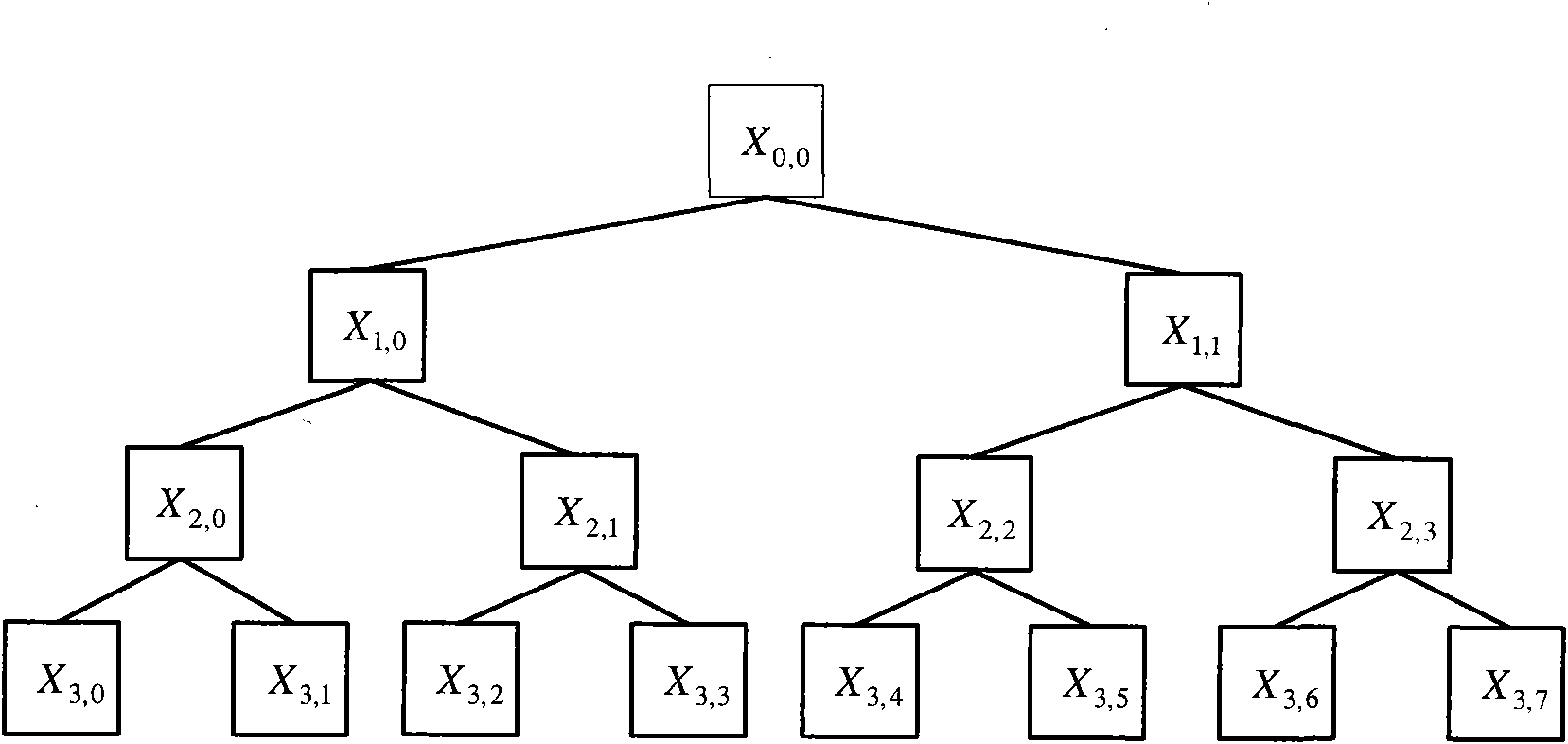

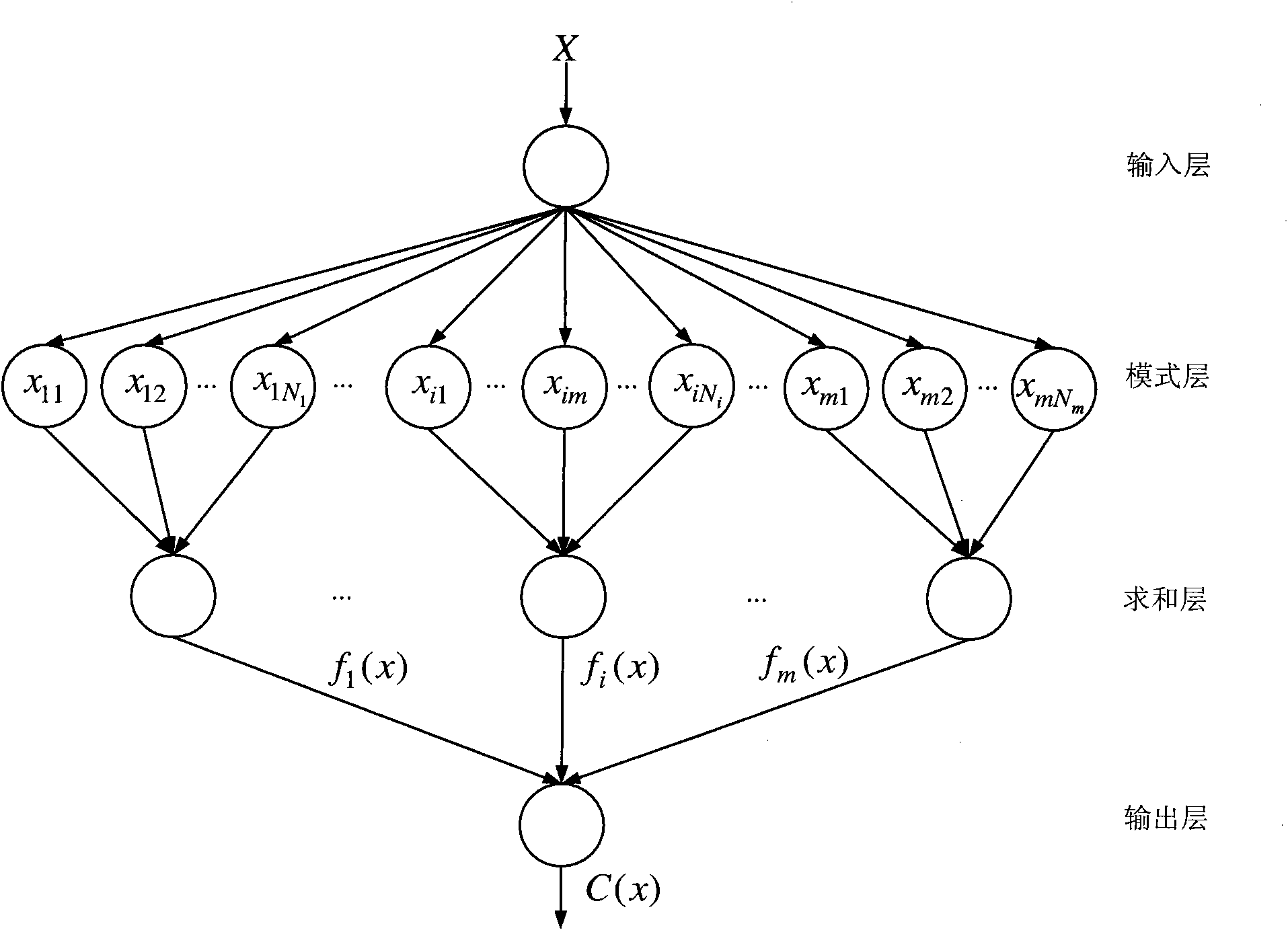

The invention discloses a probabilistic neural network-based tolerance-circuit fault diagnosis method, which comprises the following steps of: selecting a pulse signal source as the energization of a fault circuit to be detected; carrying out Monte Carlo analysis on the fault circuit so as to obtain an amplitude-frequency response signal of the fault circuit to be detected; carrying out three-layer wavelet packet decomposition on the amplitude-frequency response signal of the fault circuit so as to obtain low and high frequency coefficients of the amplitude-frequency response signal, carryingout threshold quantification on the wavelet packet decomposition coefficients, then carrying out wavelet packet reconstruction according to the lowest-layer low frequency wavelet packet decompositioncoefficients and the high frequency wavelet packet decomposition coefficients subjected to threshold quantification so as to complete the de-noising processing of the wavelet packet; calculating the band-gap energy of the response signal according to the low and high coefficients obtained after wavelet packet reconstruction, and constituting a fault characteristic vector by using the band-gap energy; and inputting the fault characteristic vector in a fault grader of the probabilistic neural network to realize circuit fault diagnosis. The method has the advantages of high right fault diagnosisrate, simple structure, short training time, high fault tolerance and strong extrapolation ability.

Description

technical field [0001] The invention relates to a tolerance circuit fault diagnosis method, in particular to a tolerance circuit fault diagnosis method based on a probability neural network. Background technique [0002] In the past few decades, the fault diagnosis theory and methods of digital electronic circuits have developed relatively maturely, while for analog electronic circuits, due to the tolerance of components and the widespread non-linear and noise problems in the circuit, the development is relatively slow . However, with the rapid development of science and technology, the degree of integration of electronic circuits is increasing day by day, the widespread use of analog electronic circuits and digital / analog mixed signal circuits, and the high reliability requirements for modern electronic systems have made analog electronic circuits Testing and fault diagnosis become an urgent problem to be solved. [0003] As a new time-frequency analysis method, wavelet a...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): G01R31/316G06N3/02

Inventor 何怡刚李目李晴方葛丰

Owner HUNAN UNIV