Patents

Literature

3431results about "Reliability increasing modifications" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

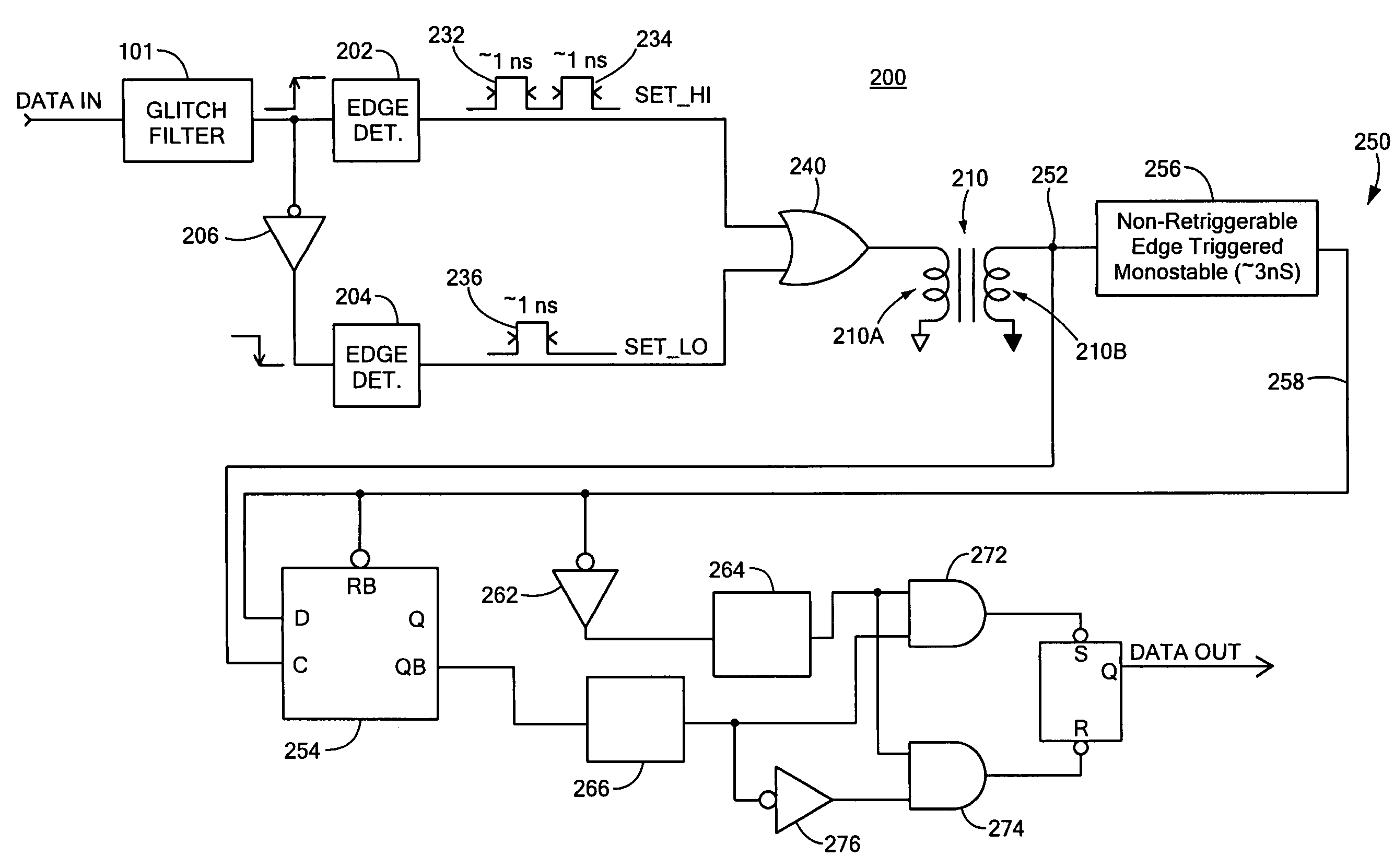

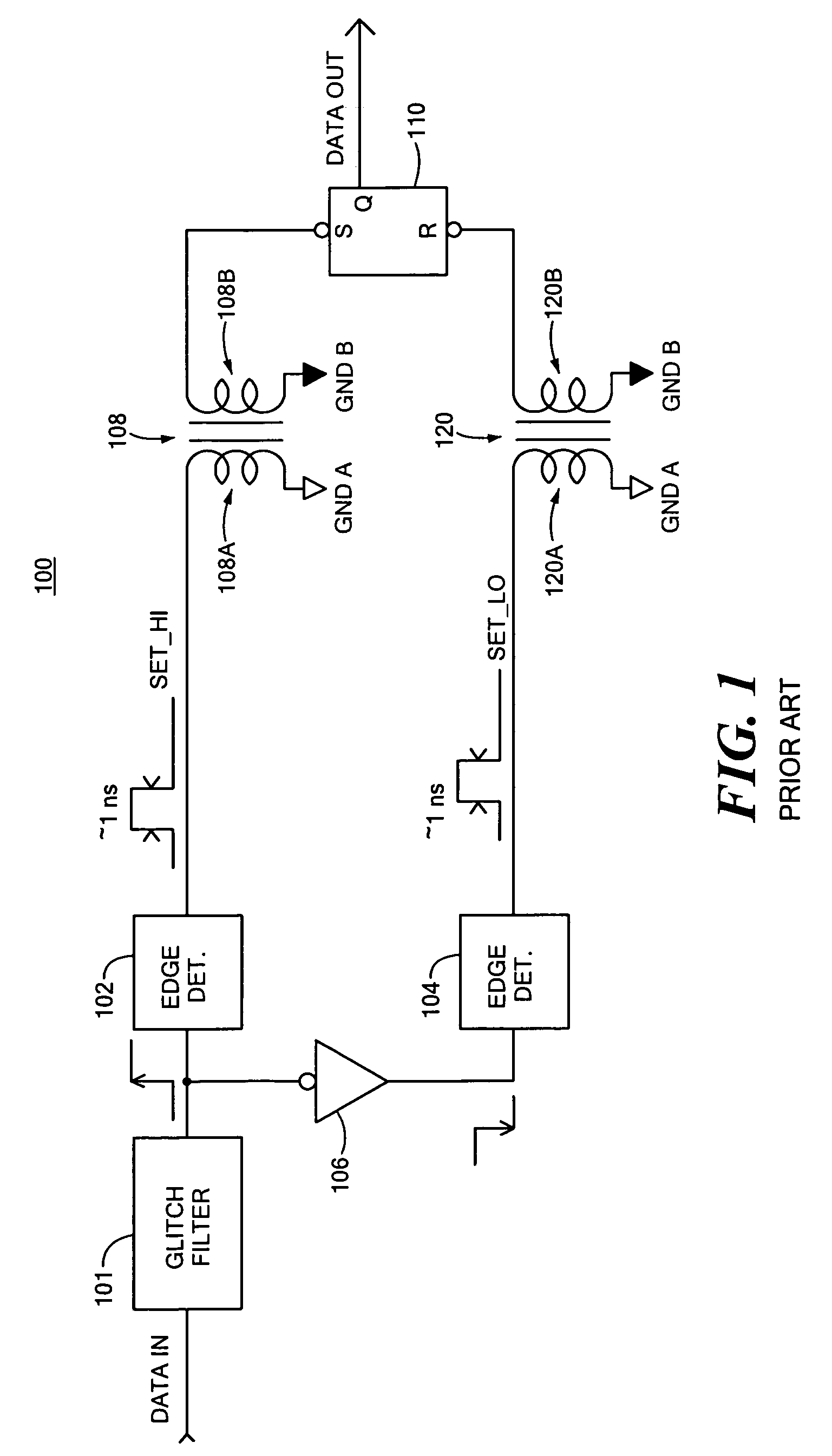

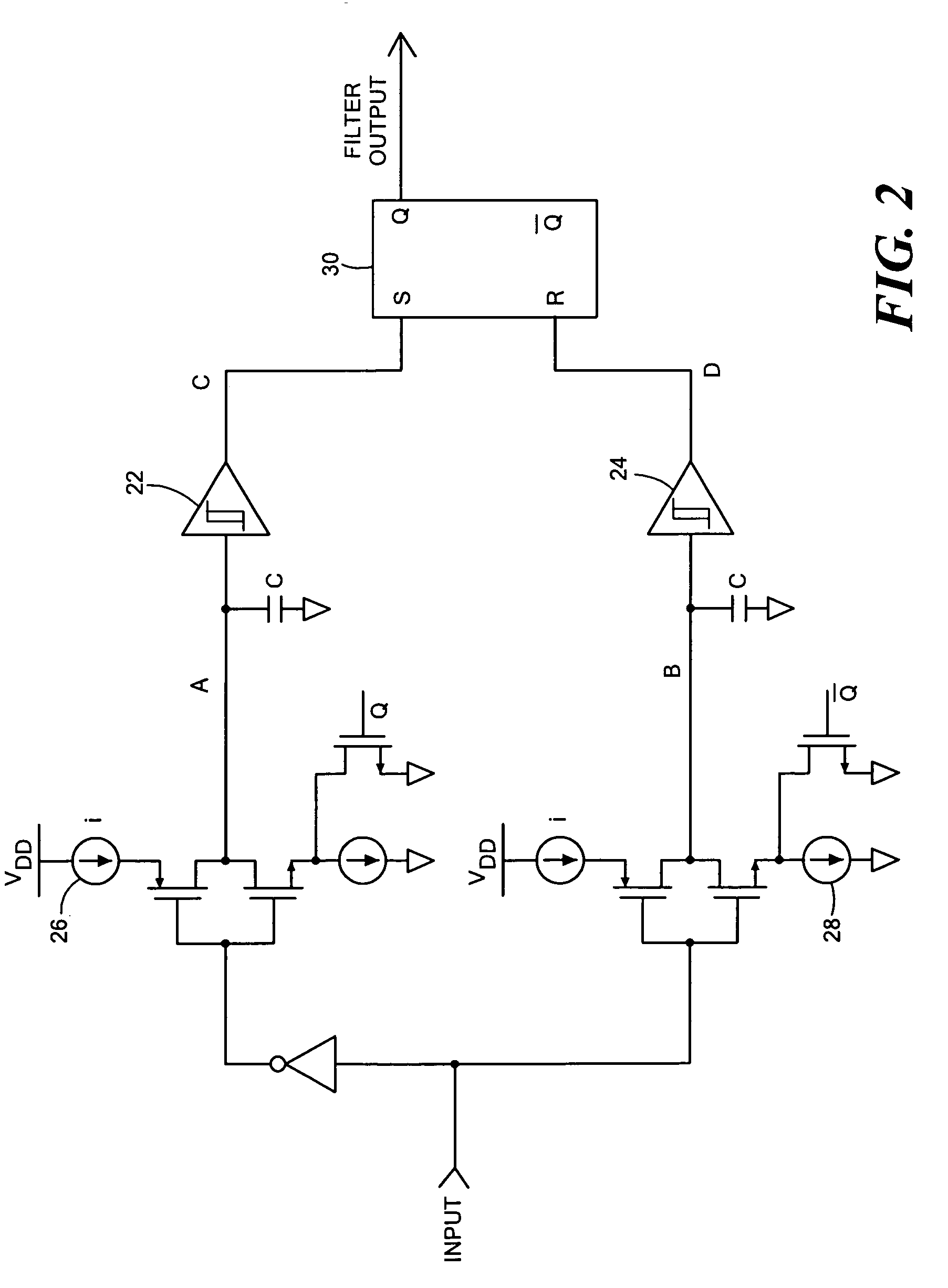

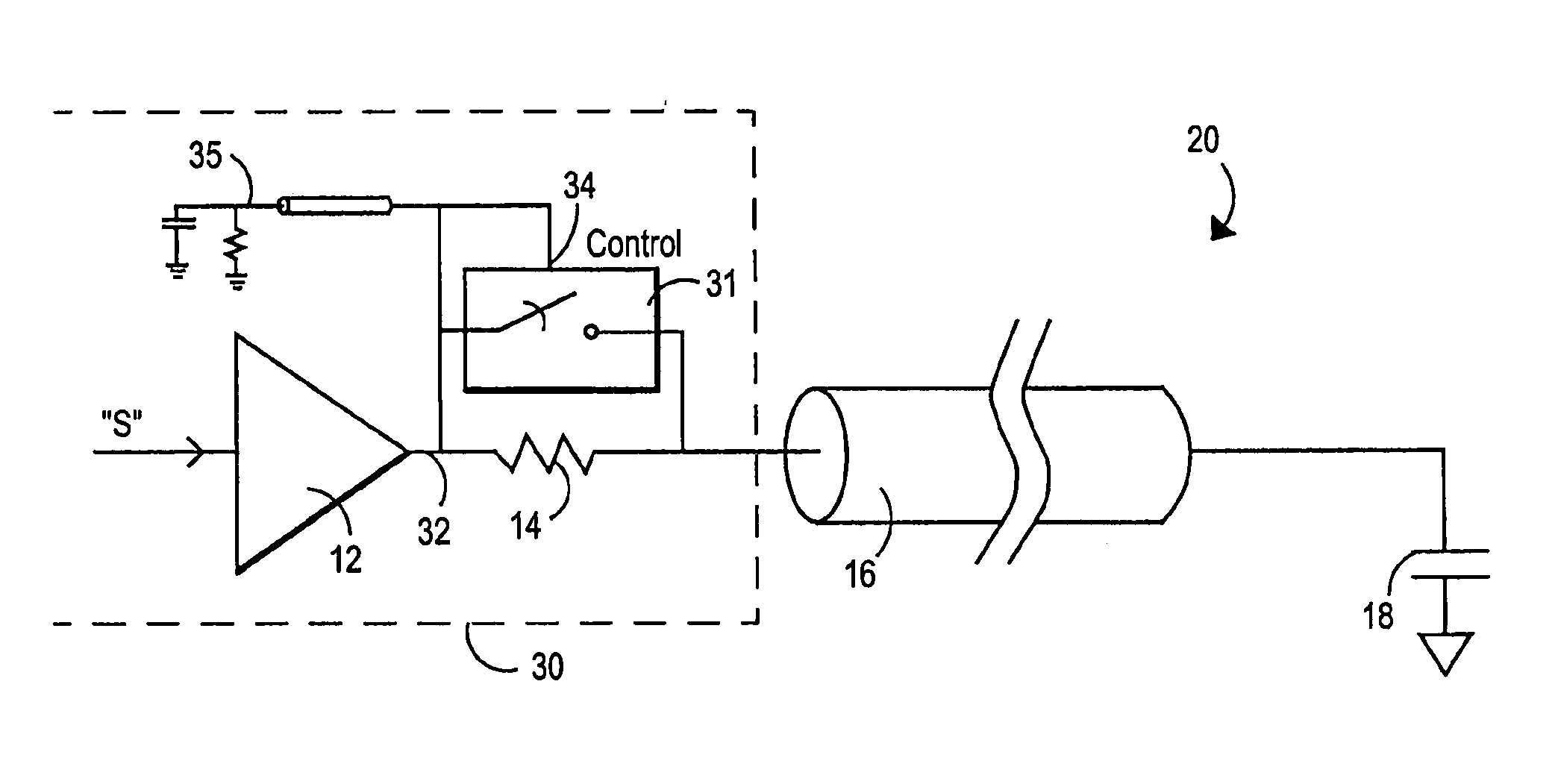

Signal isolators using micro-transformers

ActiveUS7075329B2Reliability increasing modificationsSemiconductor/solid-state device detailsTransformerEngineering

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

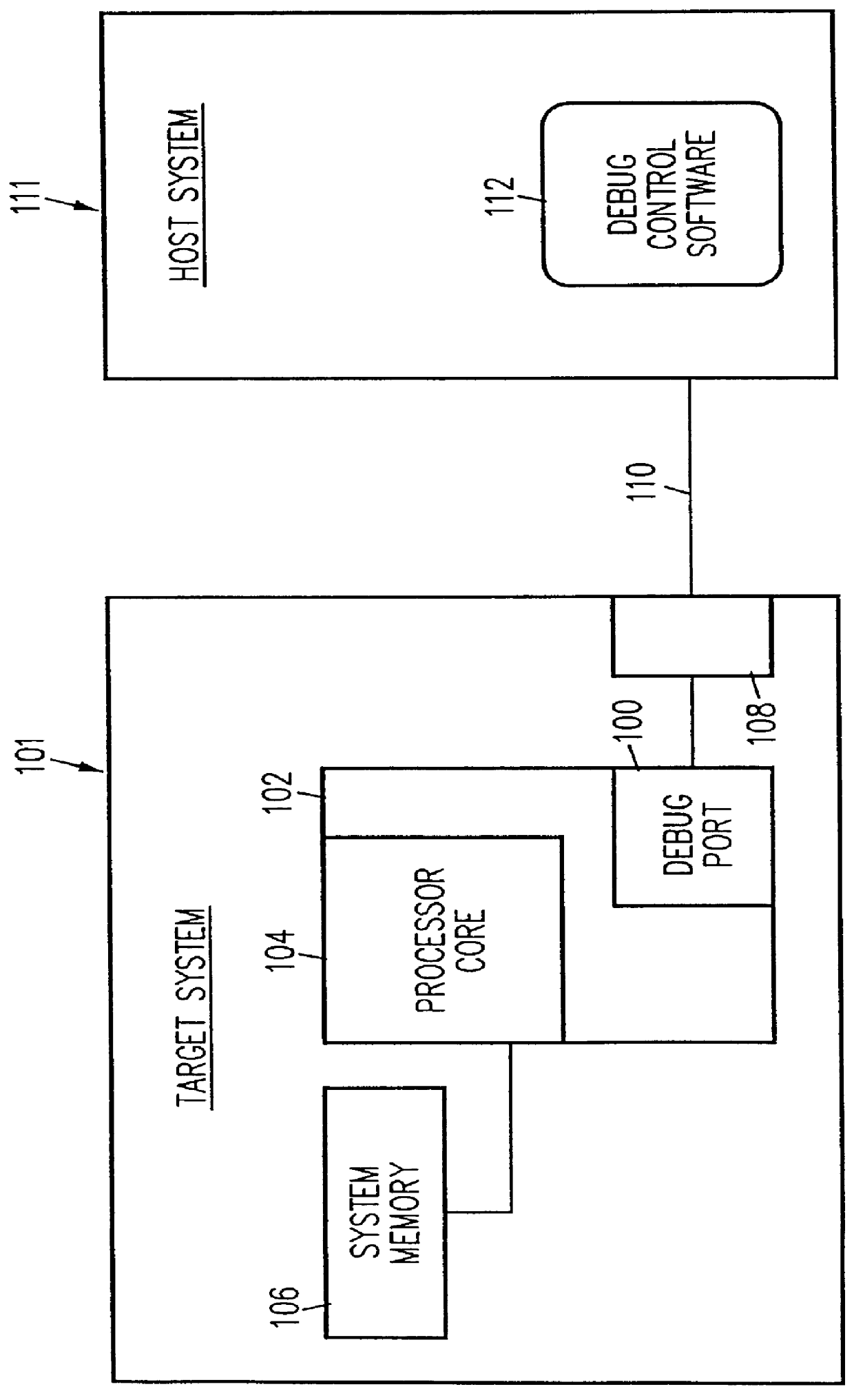

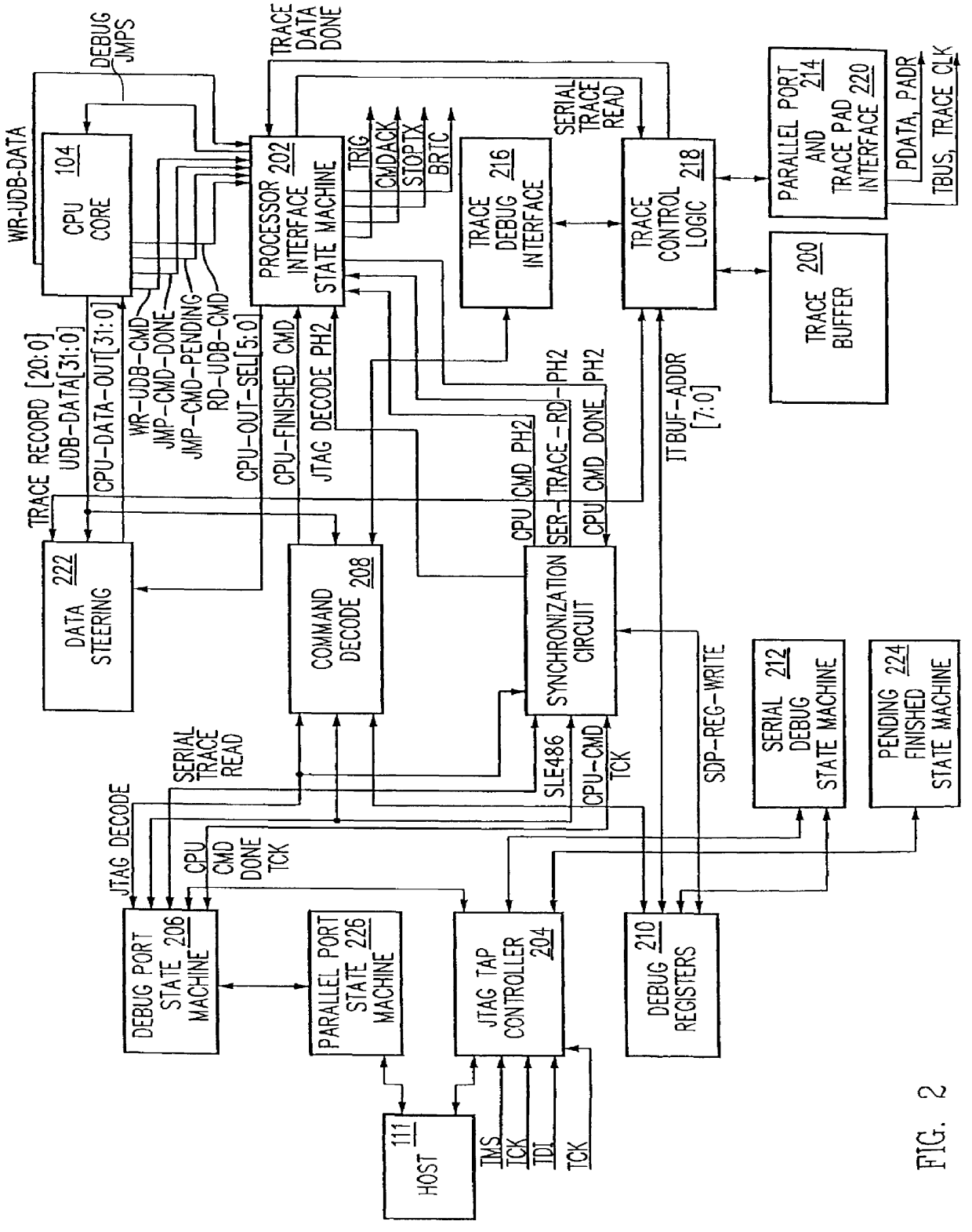

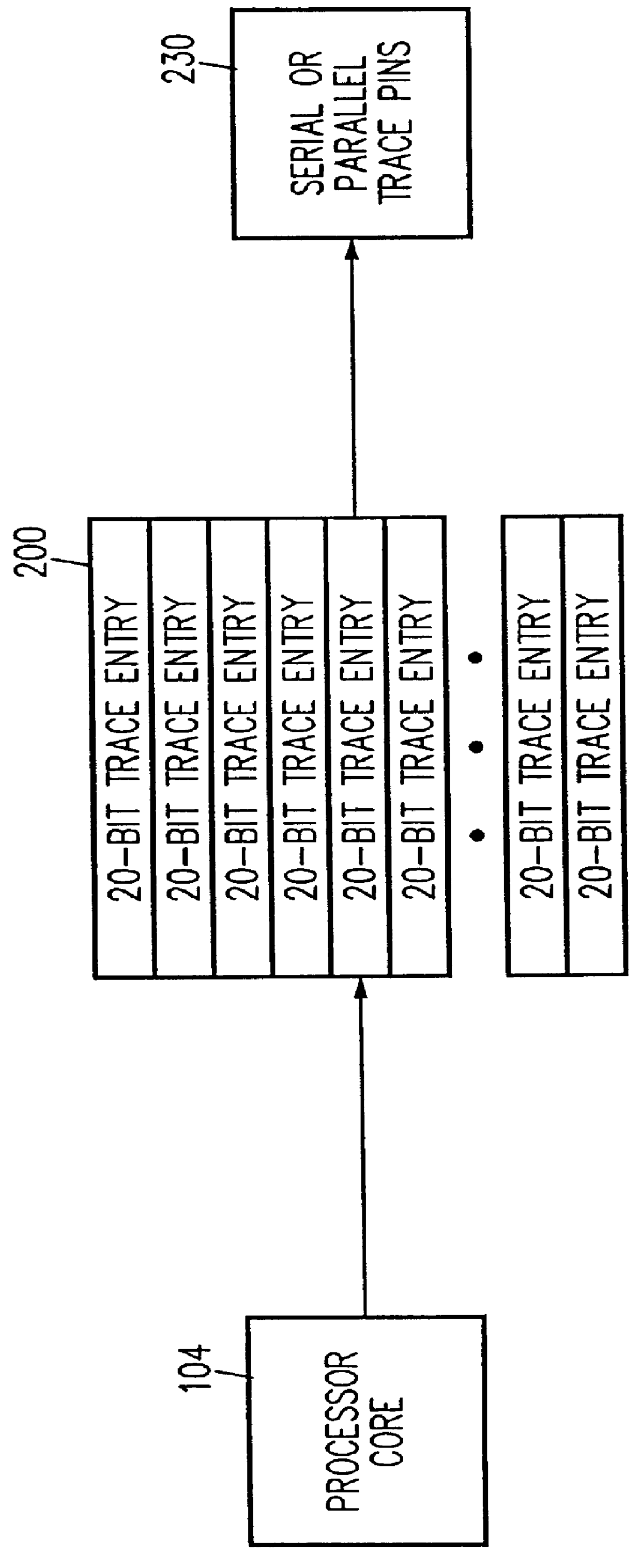

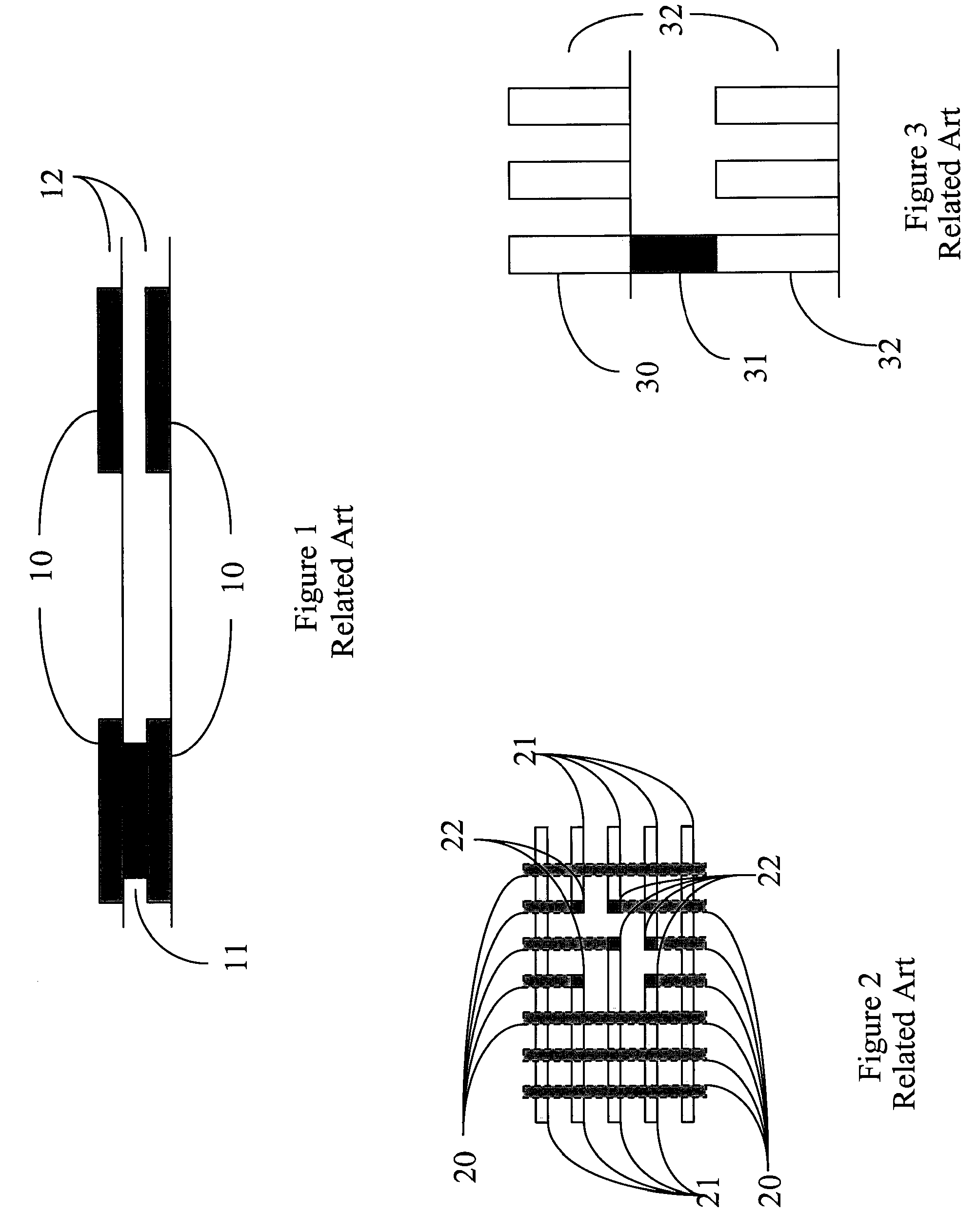

Debug interface including a compact trace record storage

InactiveUS6094729AReliability increasing modificationsHardware monitoringInformation typeParallel computing

In-circuit emulation (ICE) and software debug facilities are included in a processor via a debug interface that interfaces a target processor to a host system. The debug interface includes a trace controller that monitors signals produced by the target processor to detect specified conditions and produce a trace record of the specified conditions including a notification of the conditions are selected information relating to the conditions. The trace controller formats a trace information record and stores the trace information record in a trace buffer in a plurality of trace data storage elements. The trace data storage elements have a format that includes a trace code (TCODE) field indicative of a type of trace information and a trace data (TDATA) field indicative of a type of trace information data.

Owner:GLOBALFOUNDRIES INC

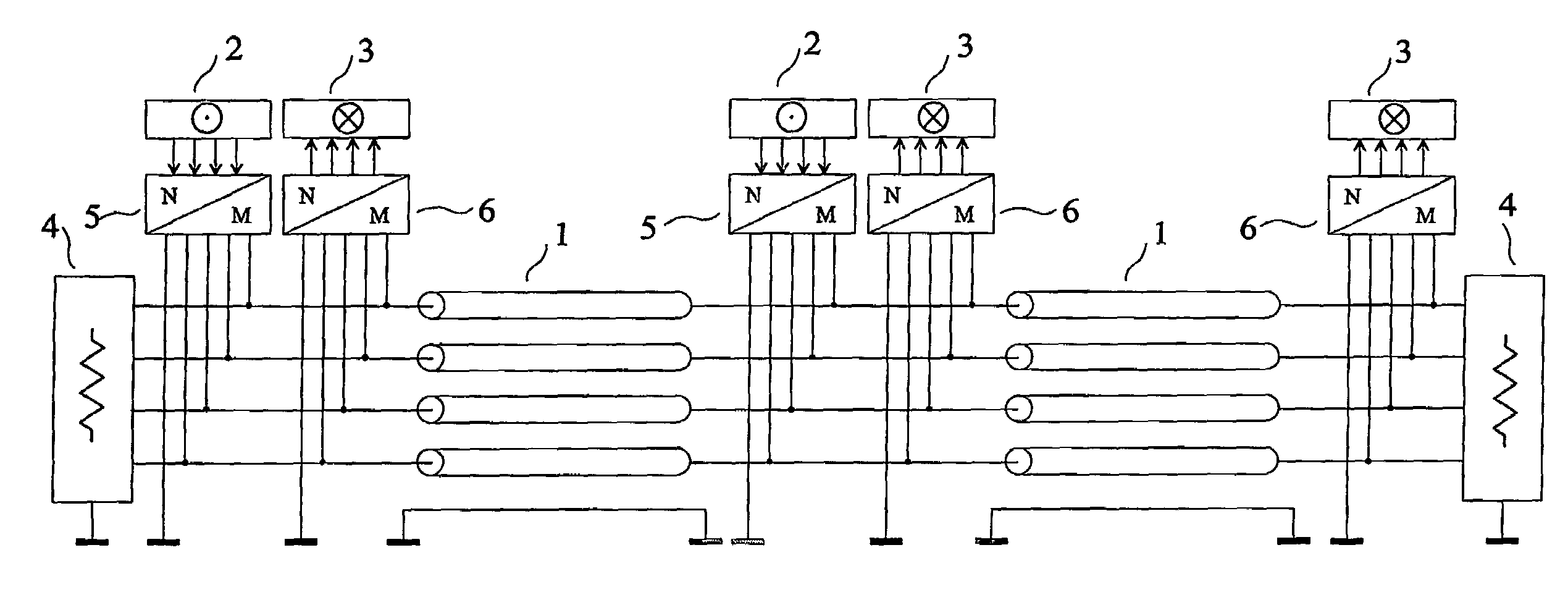

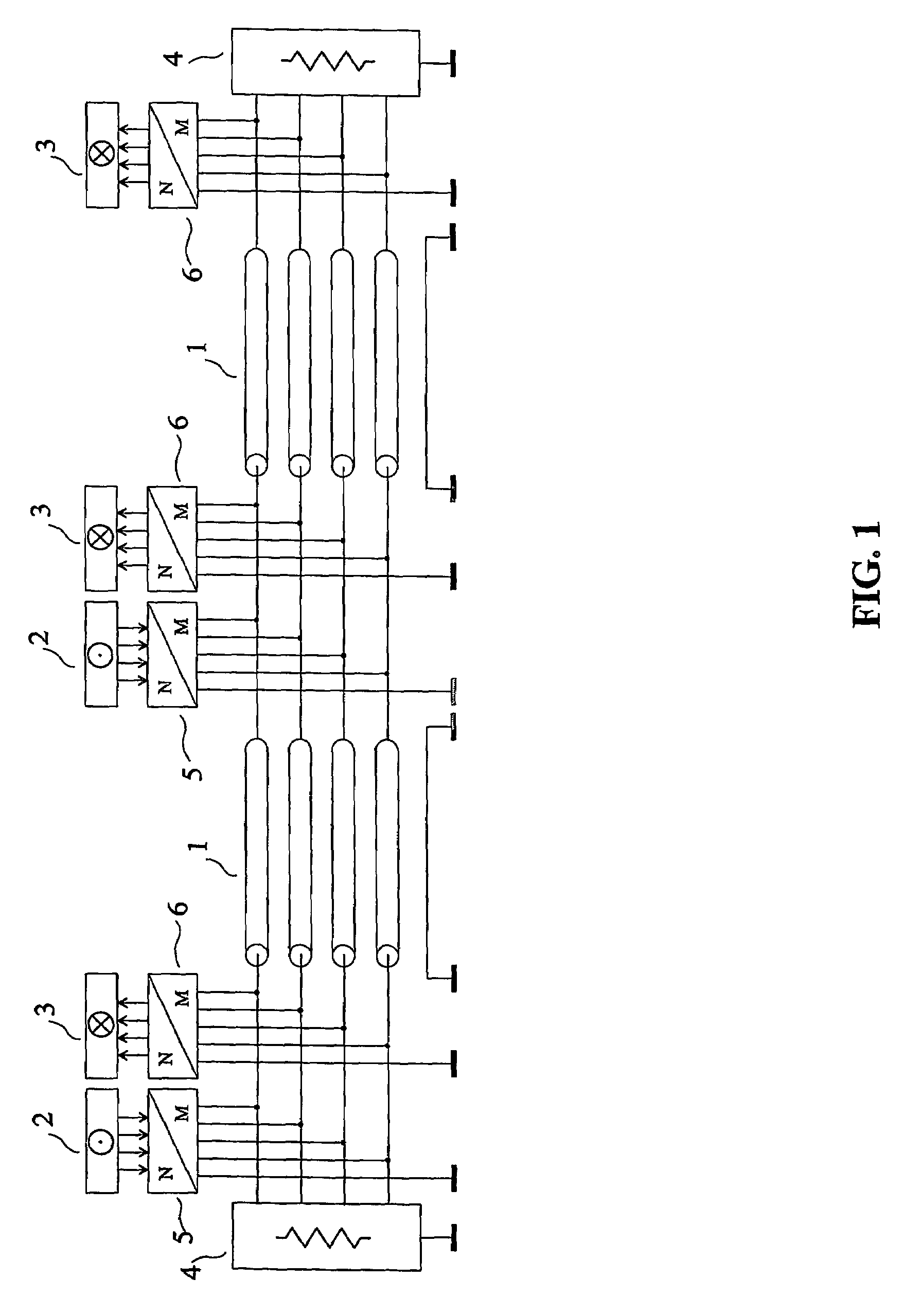

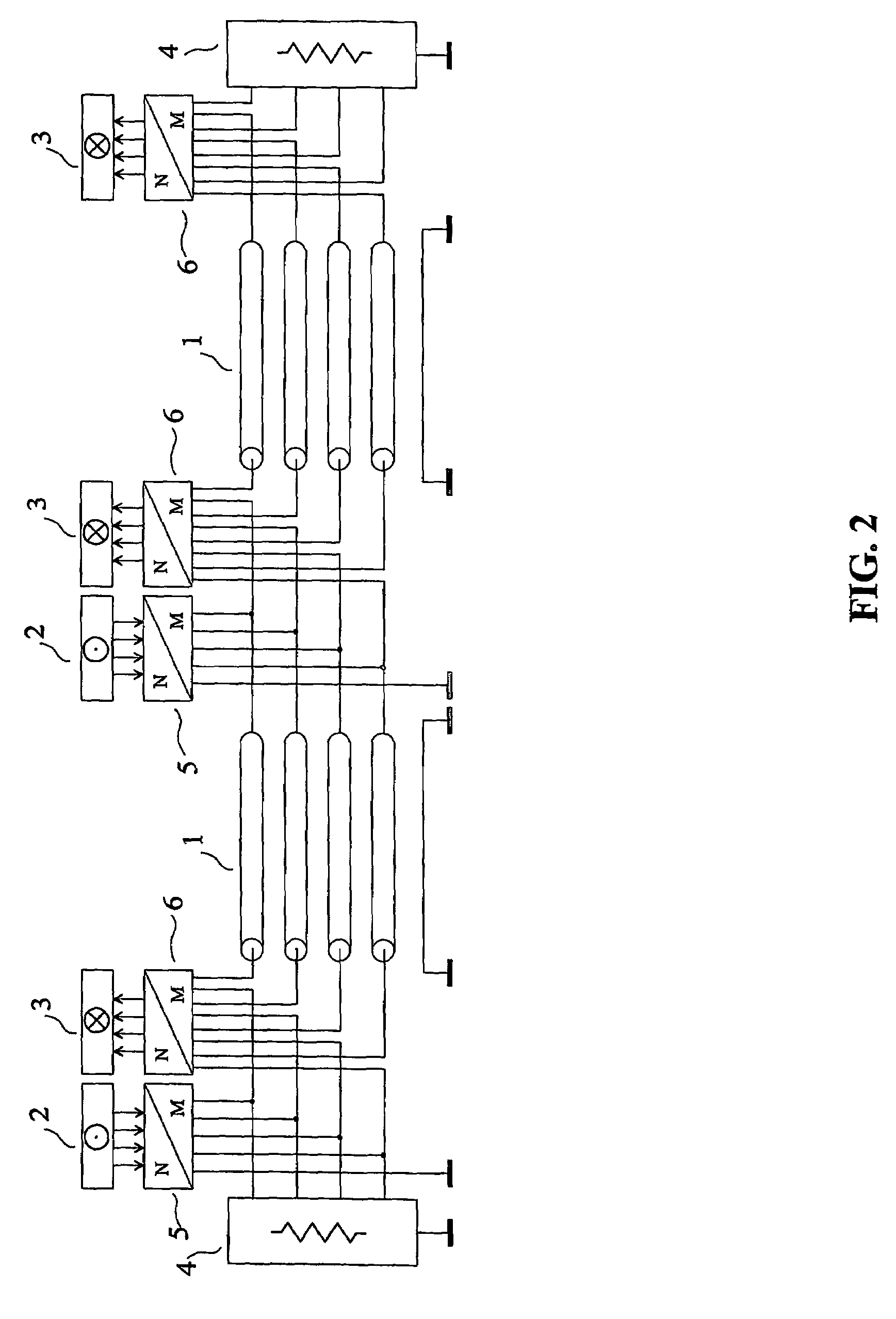

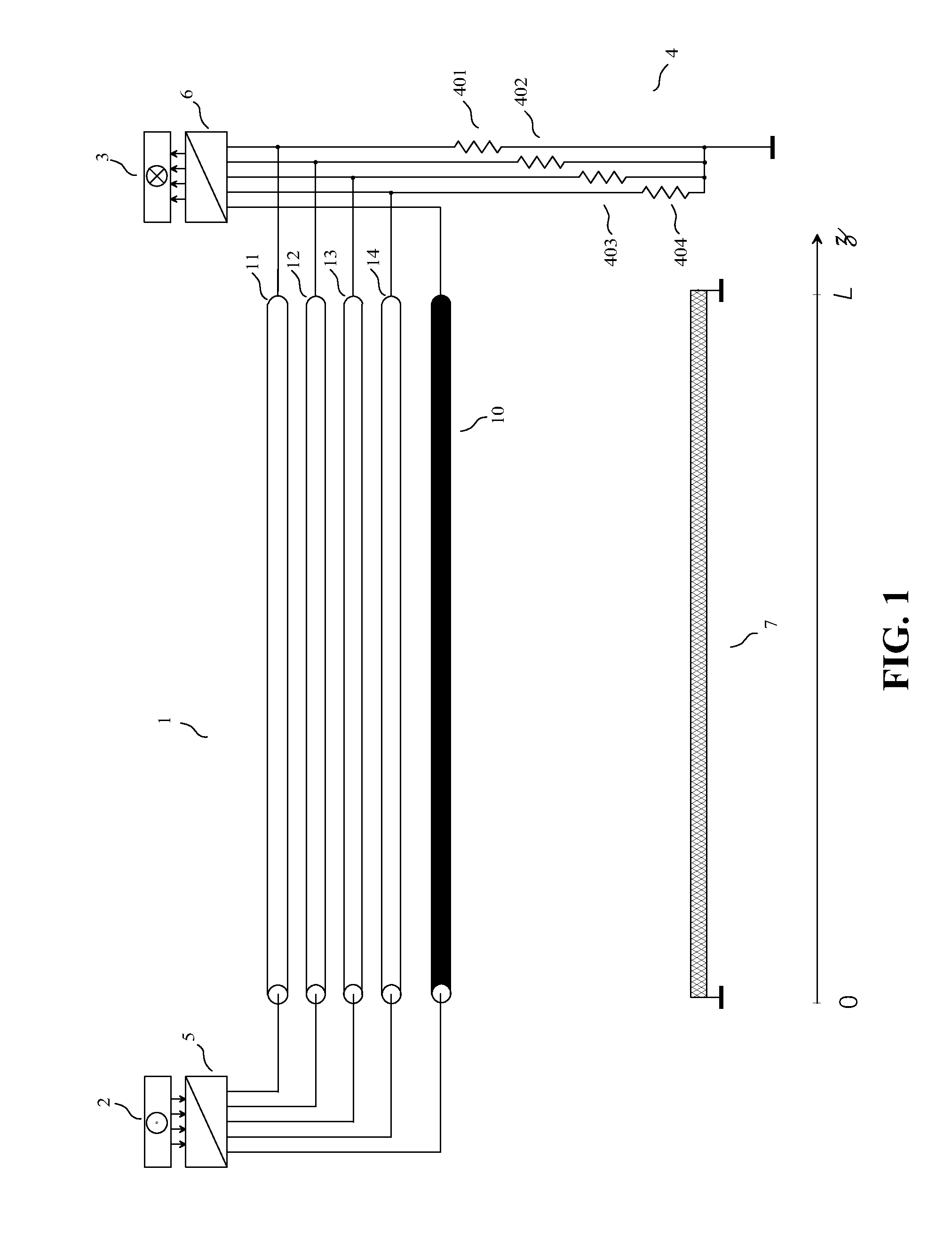

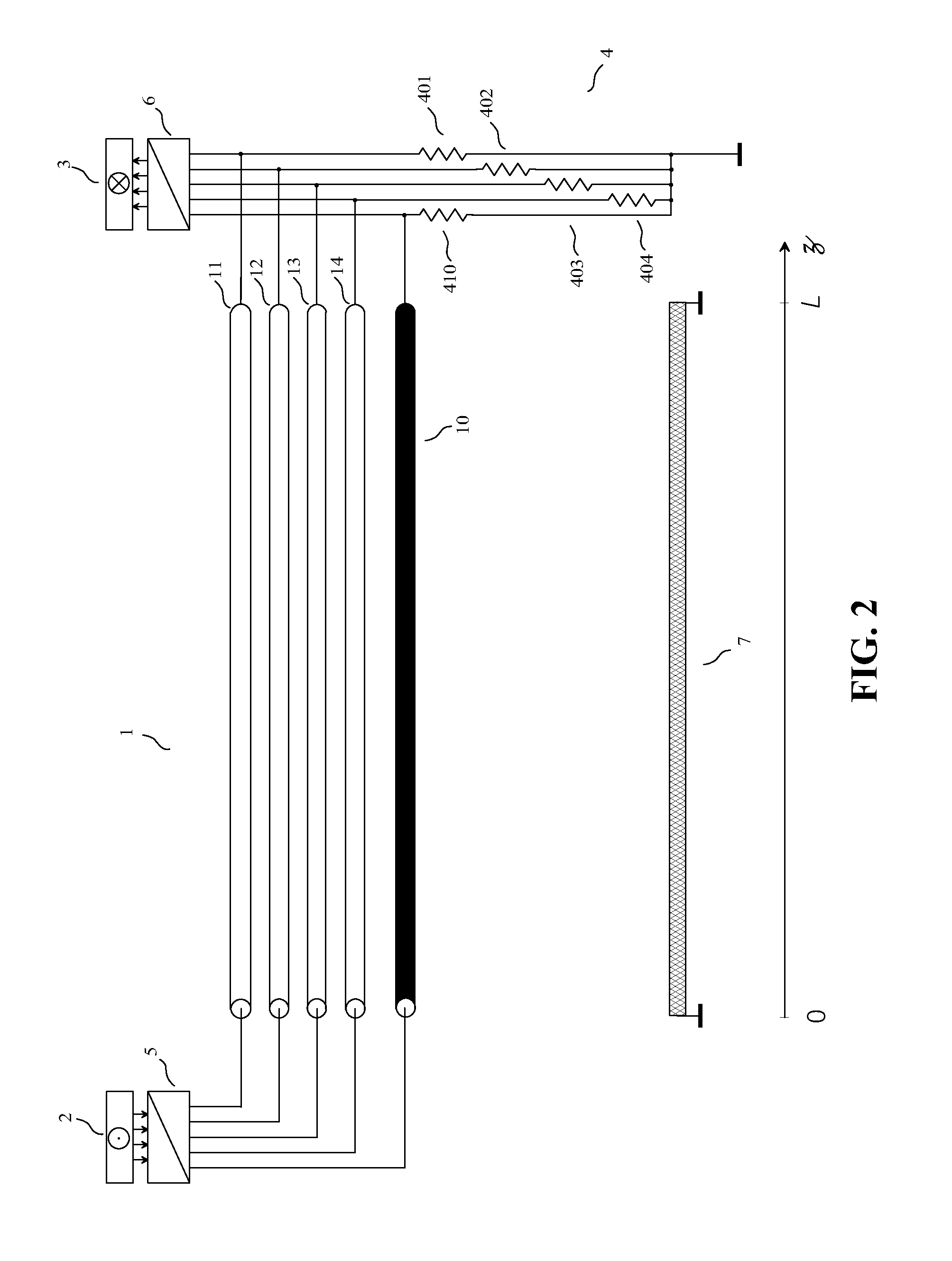

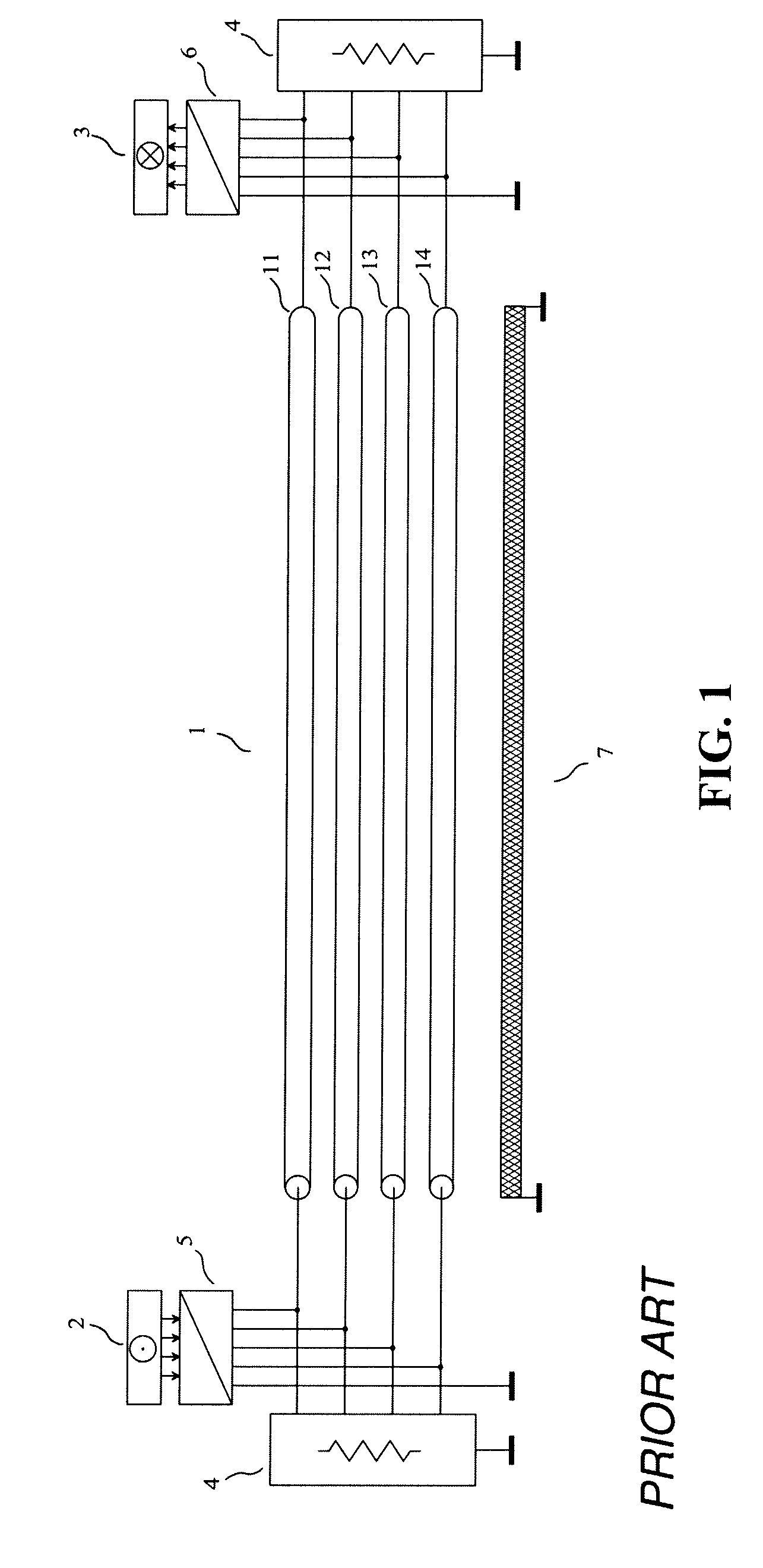

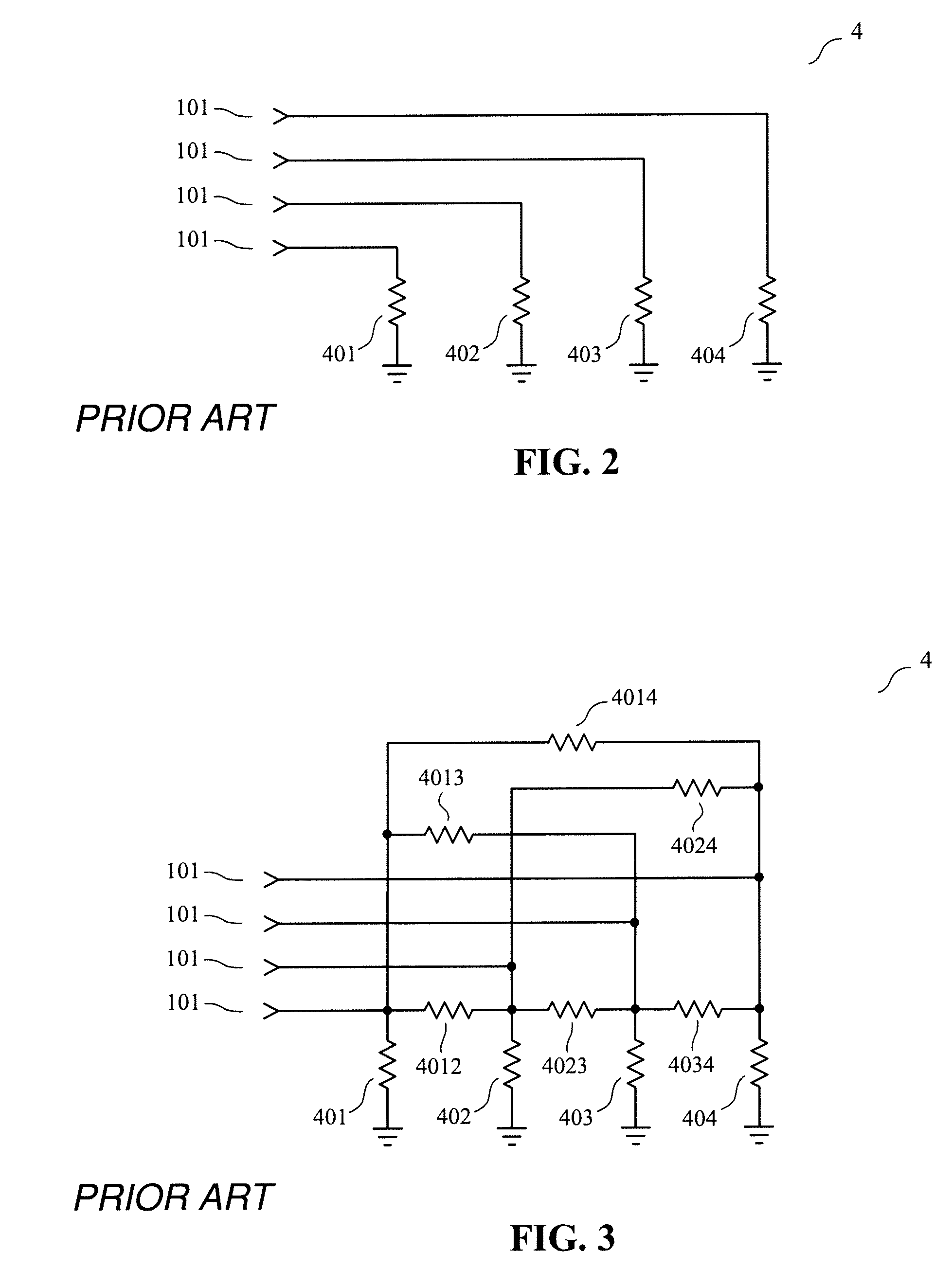

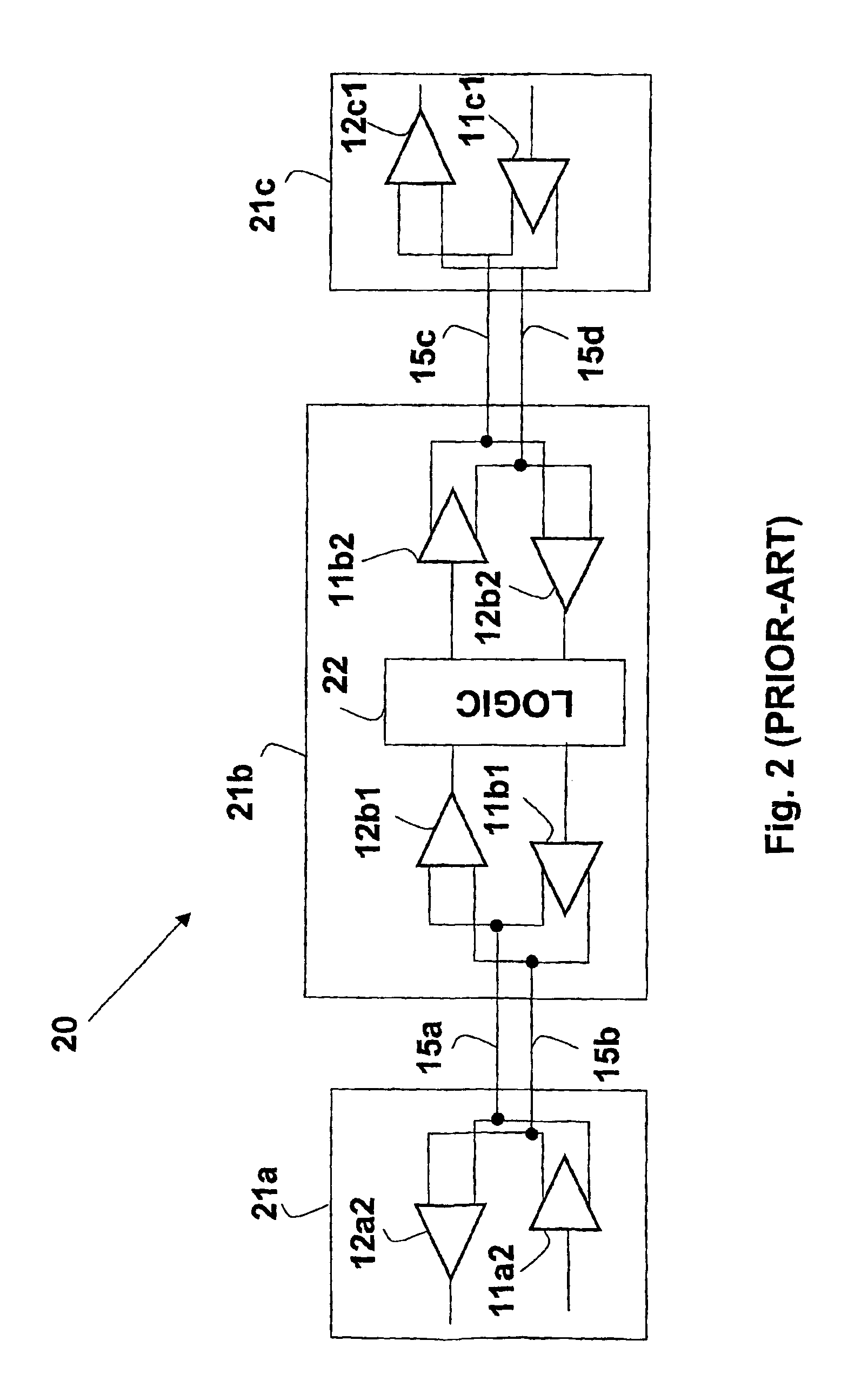

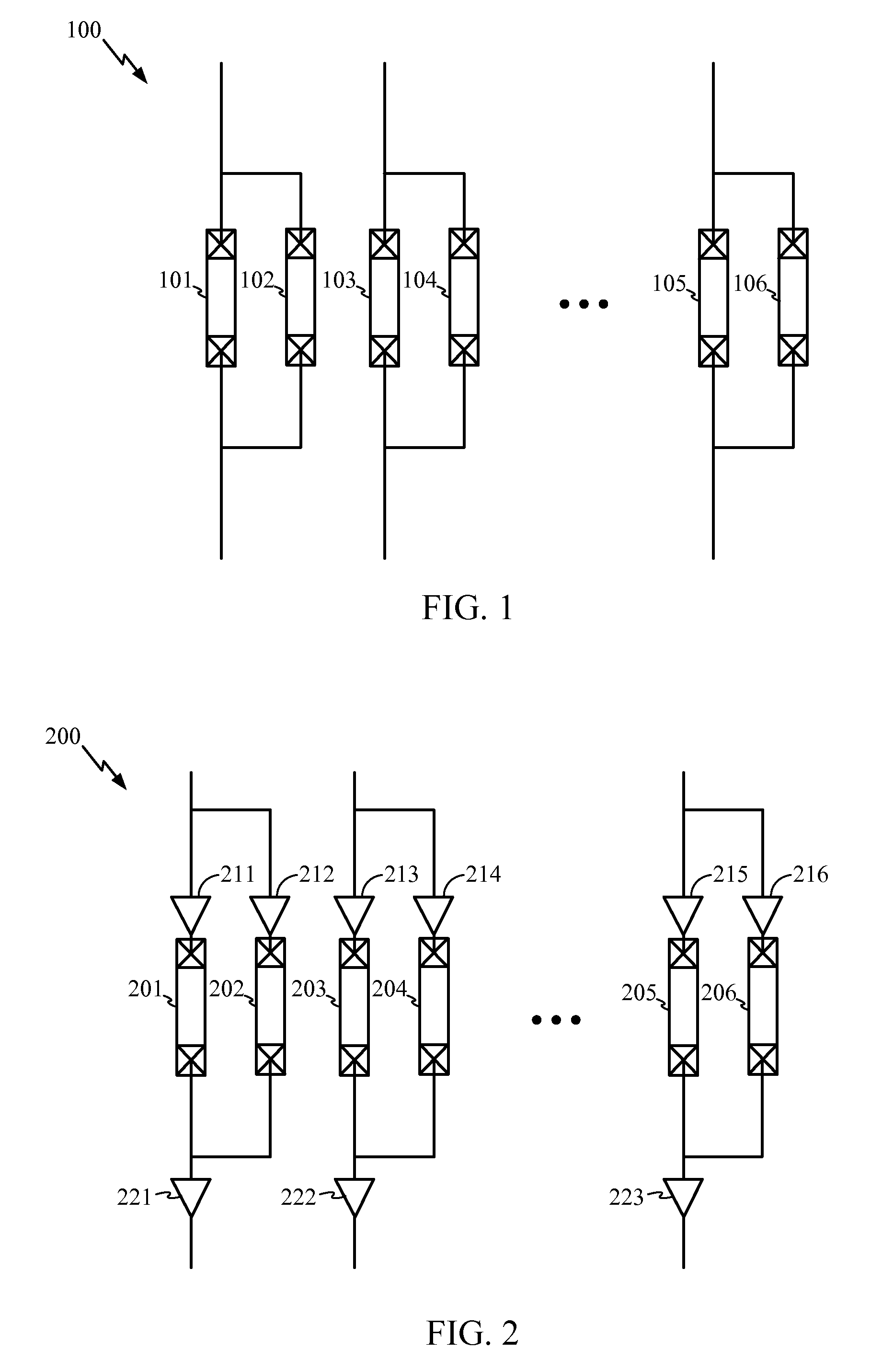

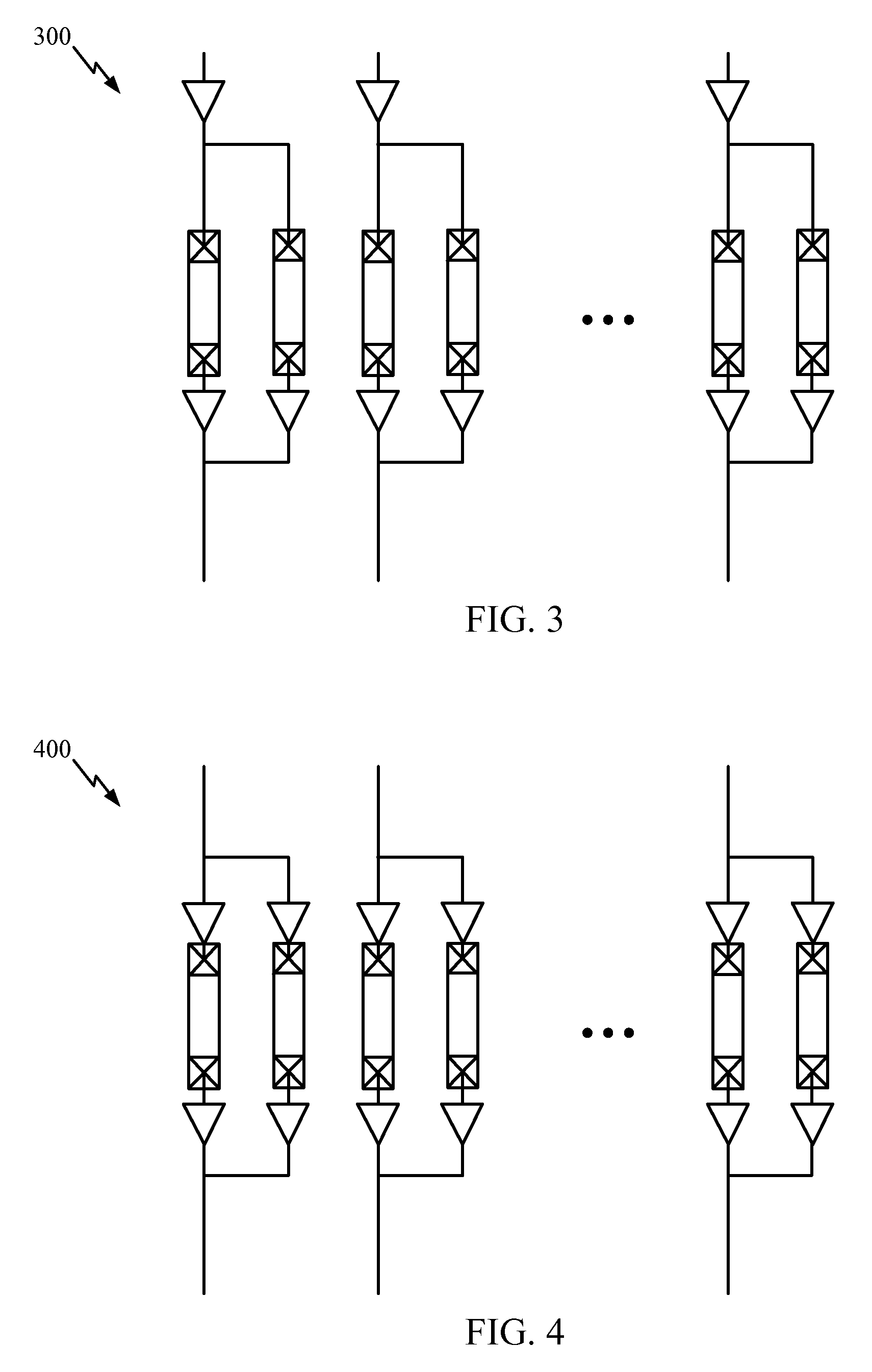

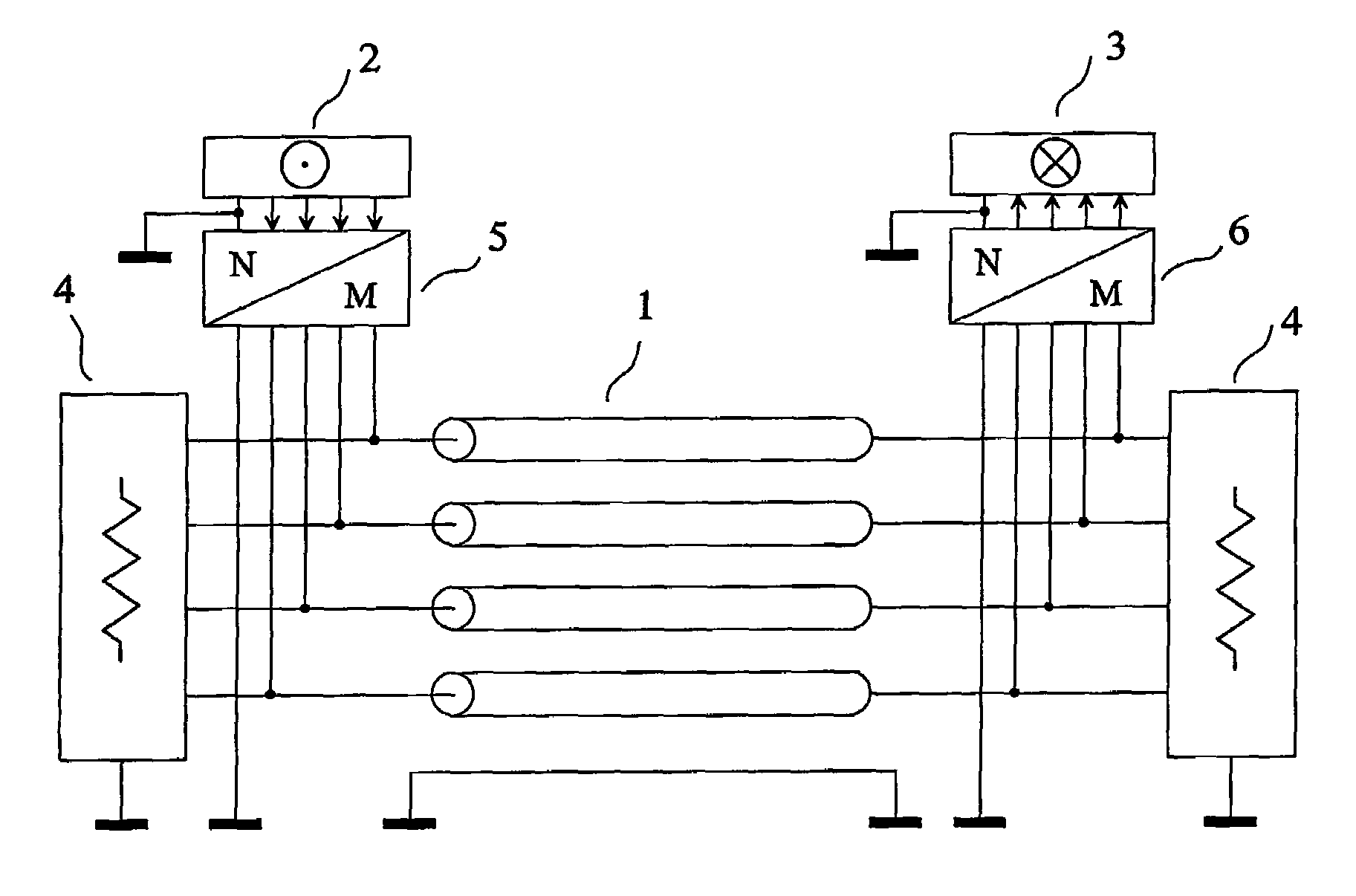

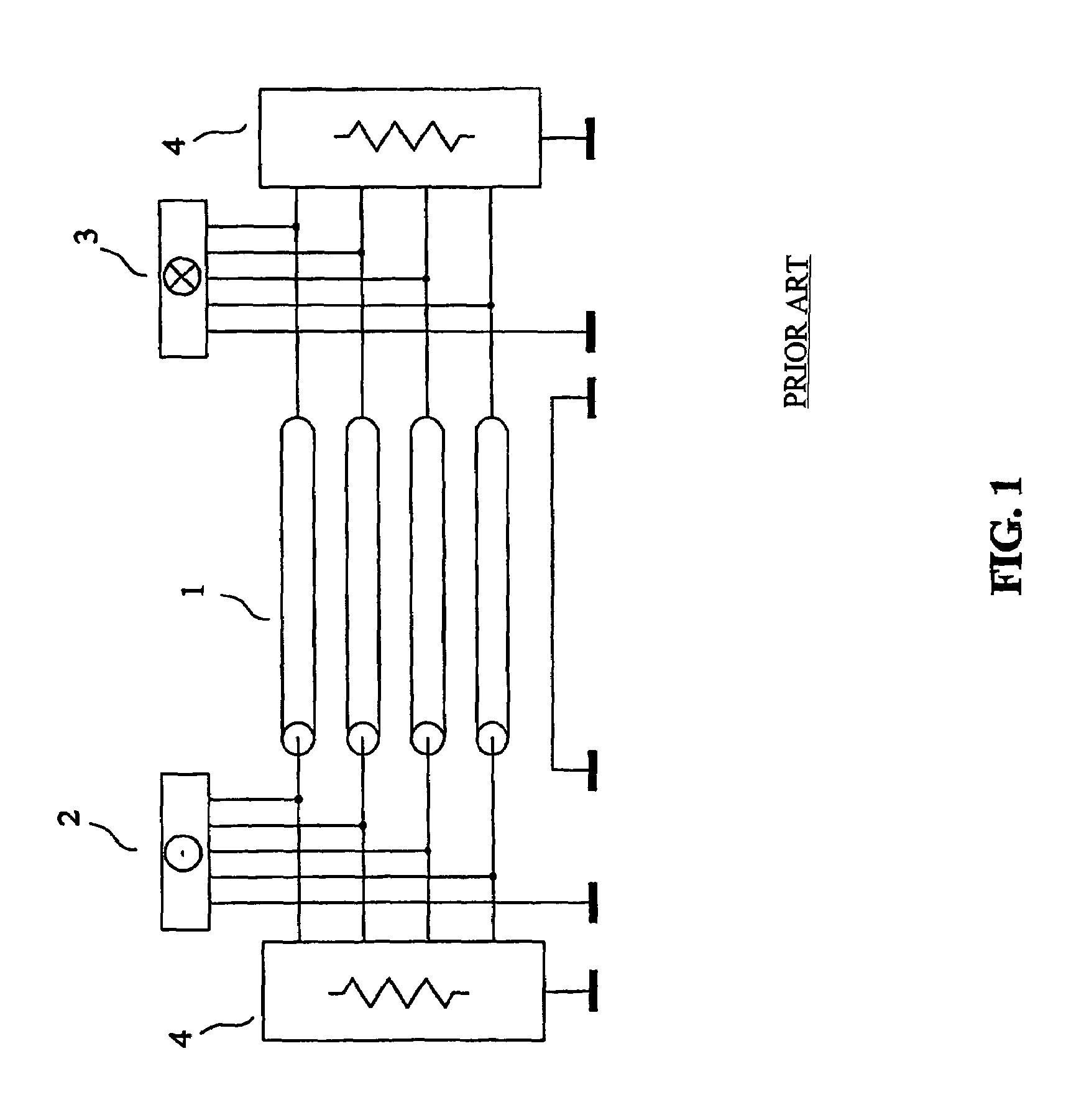

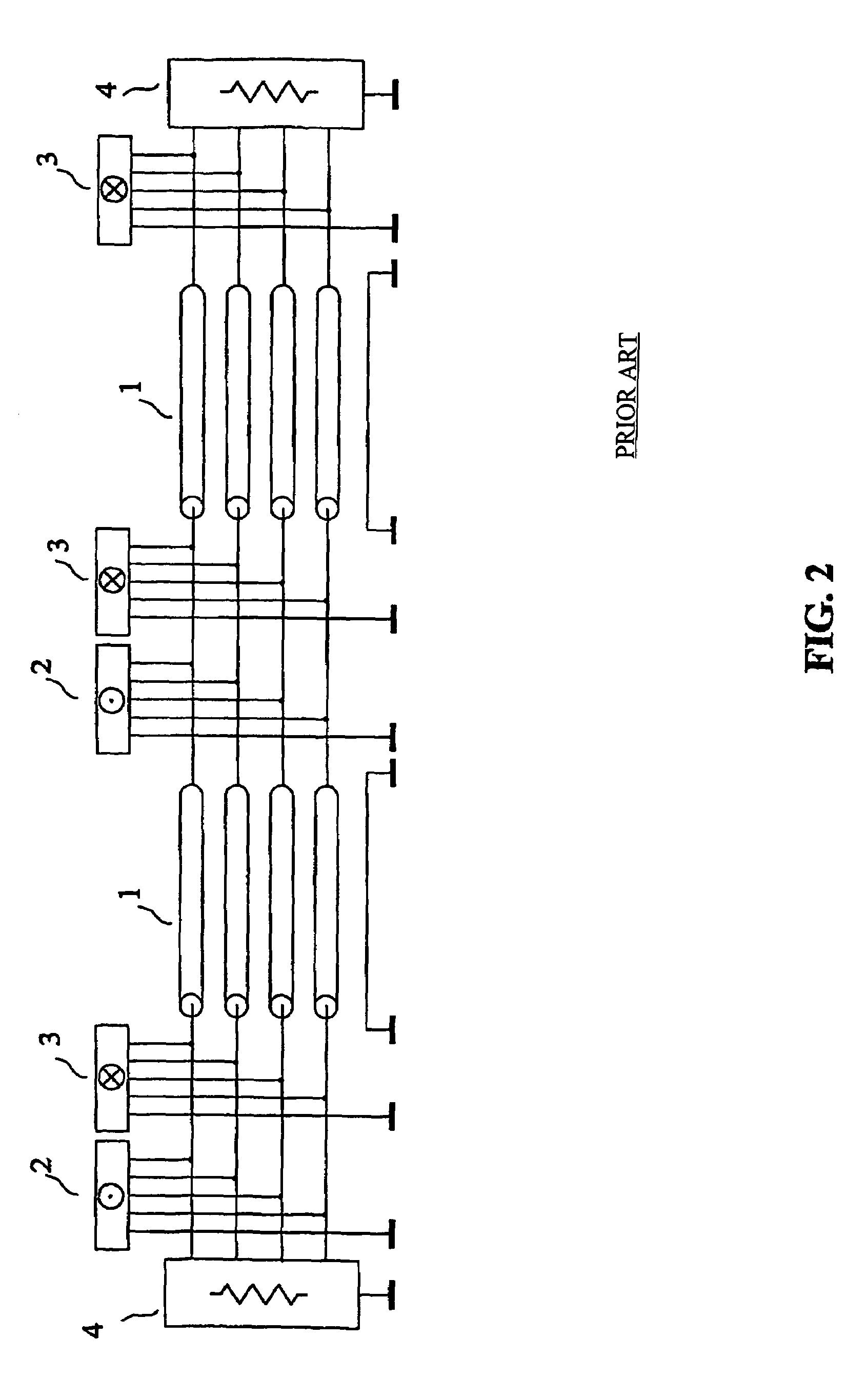

Method and device for transmission without crosstalk

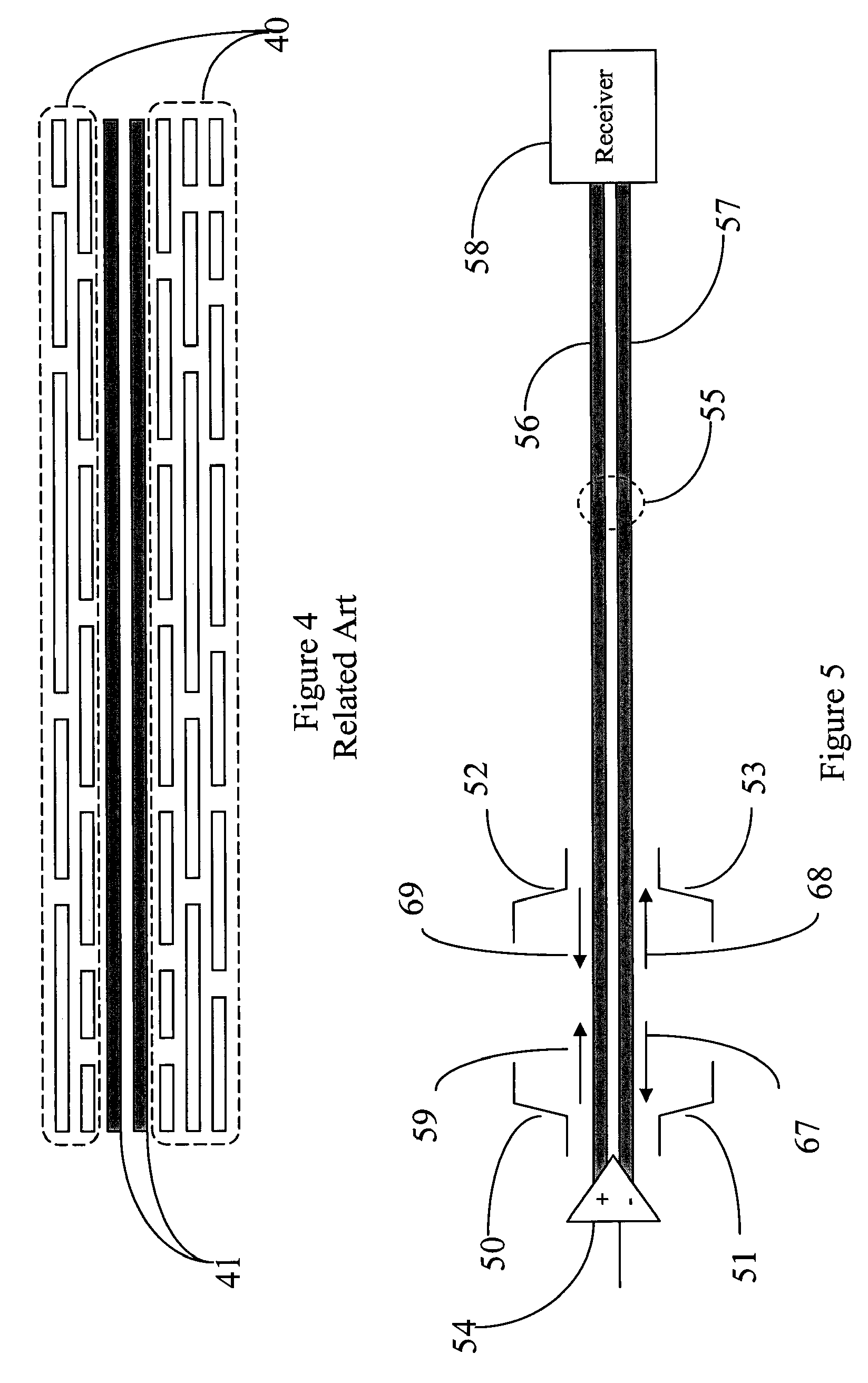

ActiveUS7408426B2Simplifying the transmitting circuits and/or the receiving circuitsSimplification of the transmitting circuits and/or the receiving circuitsReliability increasing modificationsDc network circuit arrangementsElectrical conductorInterconnection

The invention relates to a method and a device for transmission without crosstalk in interconnections used for sending a plurality of signals, such as the interconnections made with flat multiconductor cables, or with the tracks of a printed circuit board, or inside an integrated circuit. An interconnection with four parallel transmission conductors plus a reference conductor has each of its ends connected to a termination circuit. The transmitting circuit receives at its input the signals of the four channels of the source and its output terminals are connected to the conductors of the interconnection. The receiving circuit(s) input terminals are connected to the conductors of the interconnection, and its four output channels are connected to the destination. The signals of the four channels of an active source are sent to the four channels of the destination, without noticeable crosstalk.

Owner:S AQUA SEMICONDUCTOR LLC

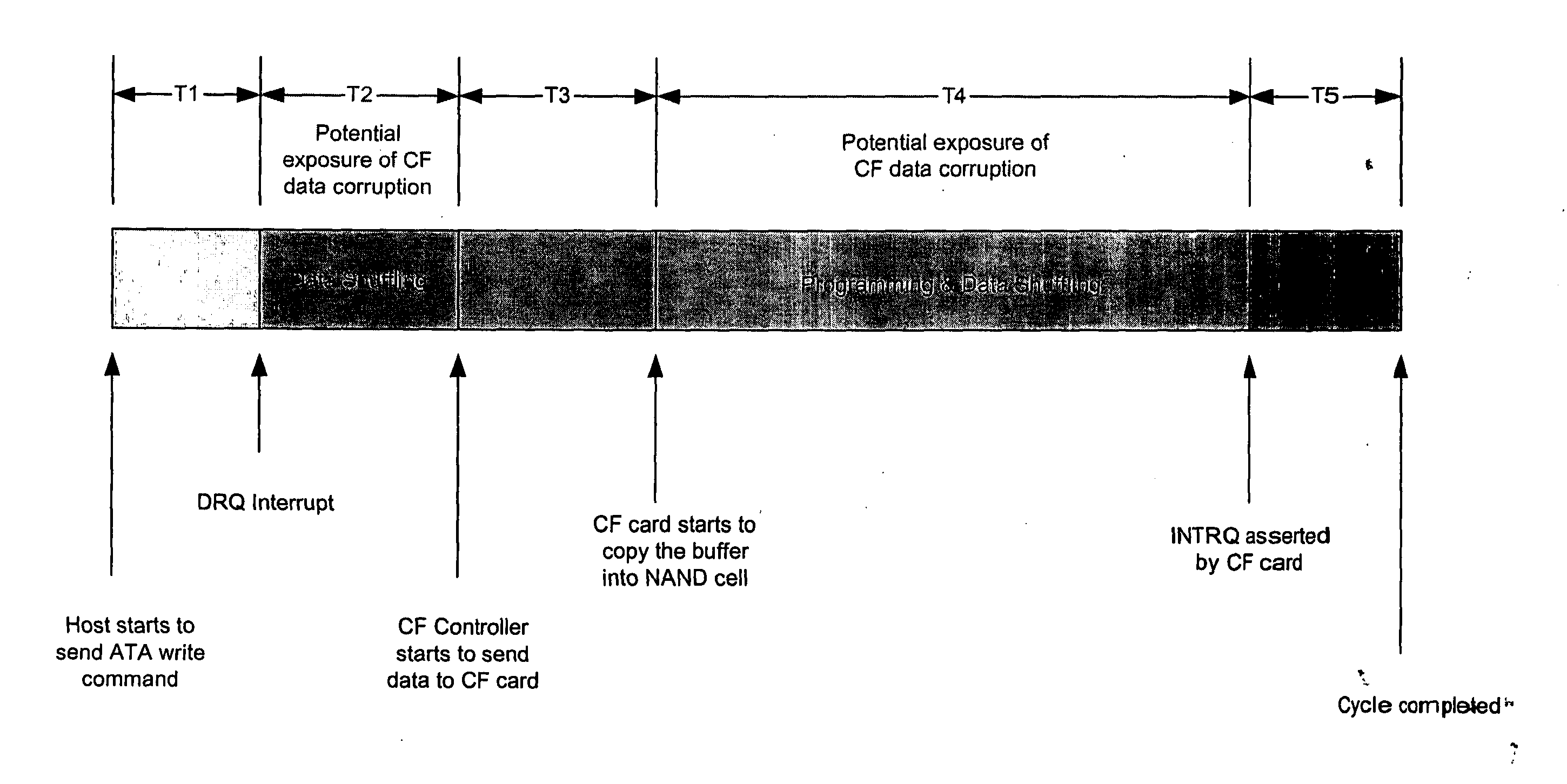

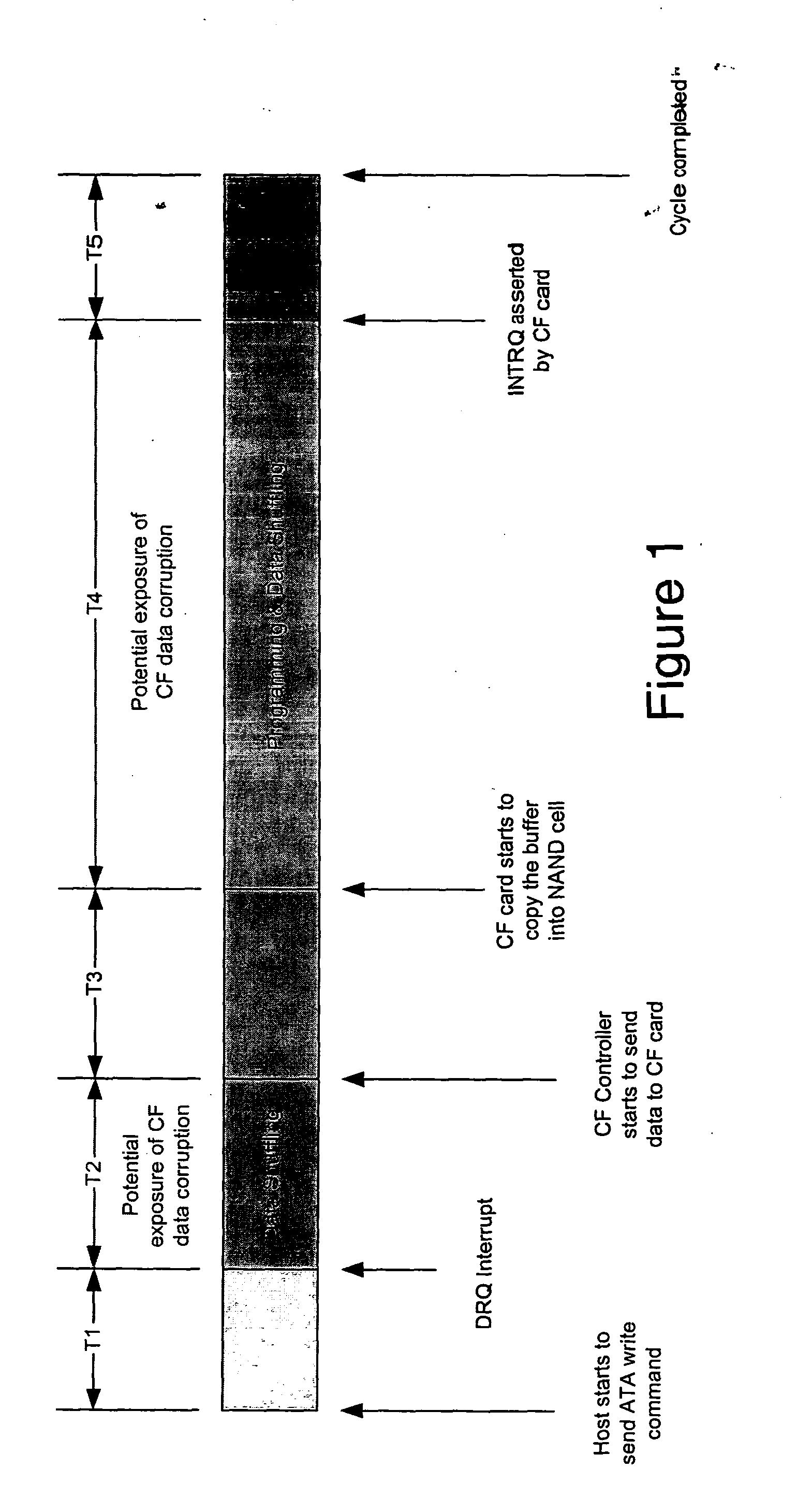

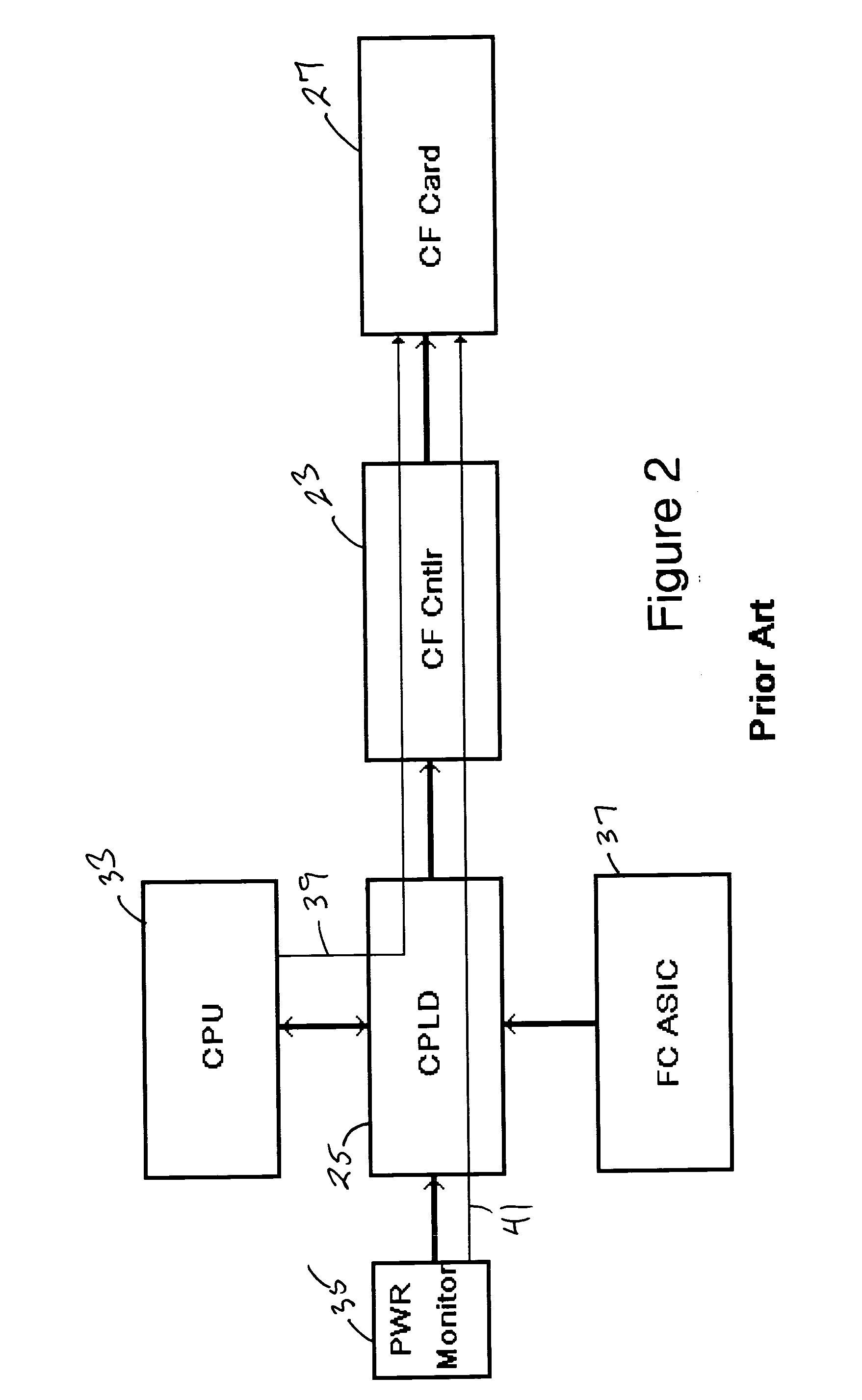

Apparatus for reducing data corruption in a non-volatile memory

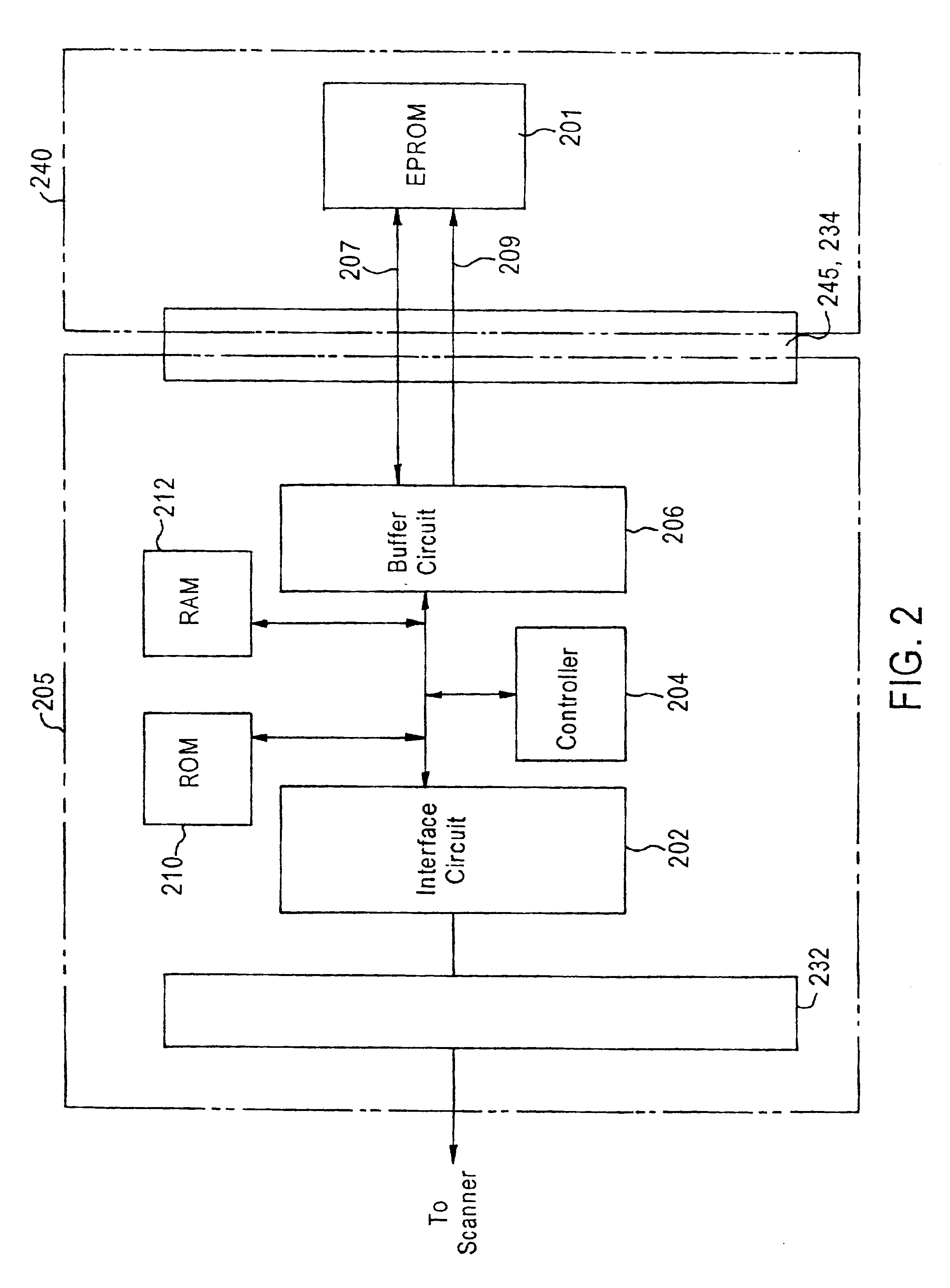

InactiveUS20050024968A1Loss and corruption can be preventedEliminate requirementsReliability increasing modificationsRead-only memoriesTime segmentData Corruption

The loss of data and / or the corruption of data that may occur in flash memory when a reset signal is received during a memory write cycle is prevented by delaying reset signals sent to the flash memory for a time period sufficient for a write cycle to be completed. The loss of data and / or the corruption of data that may occur in flash memory when the power supply is interrupted during a write cycle is prevented by providing a DC-to-DC converter with one or more large capacitors in parallel with its input as the power supply to the flash memory. If the system power supply fails or is interrupted, the discharge of the capacitor(s) delays the voltage decay at the input of the DC-to-DC converter such that the output of the DC-to-DC converter remains within tolerance for a time sufficient for the flash memory to complete a write cycle.

Owner:AVAGO TECH INT SALES PTE LTD

Pseudo-differential interfacing device having a switching circuit

InactiveUS7884648B2Reduce couplingReduced unwanted couplingReliability increasing modificationsElectronic switchingDifferential transmissionEngineering

The invention relates to an interfacing device for pseudo-differential transmission through interconnections used for sending a plurality of electrical signals. The interfacing device of the invention includes signal terminals and a common terminal. A transmitting circuit receives the input signals of the transmitting circuit coming from a source. The output of the transmitting circuit delivers, when the transmitting circuit is in the activated state, voltages between one of the signal terminals and the reference terminal (ground). A receiving circuit delivers, when the receiving circuit is in the activated state, output signals of the receiving circuit determined each by the voltage between one of the signal terminals and the common terminal, to the destination. In the closed state, the common terminal switching circuit is, for the common terminal, equivalent to a voltage source delivering a constant voltage, connected in series with a passive two-terminal circuit element presenting a low impedance.

Owner:ZXNOISE LLC

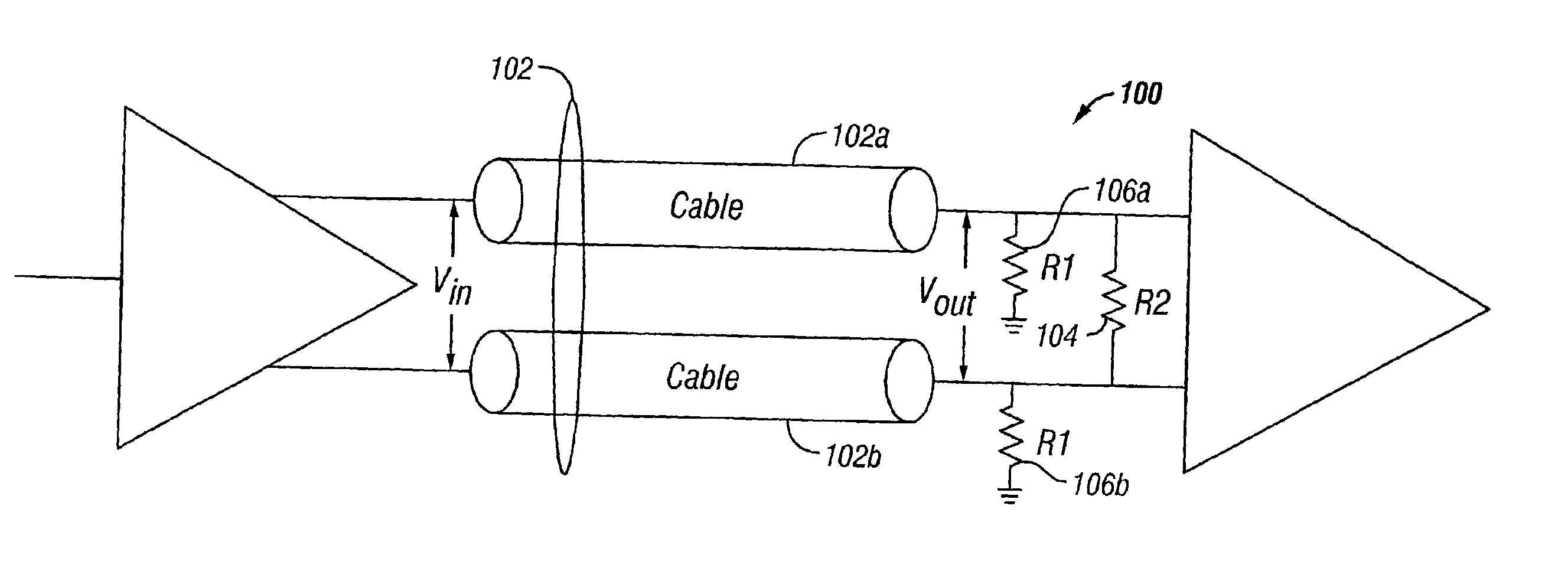

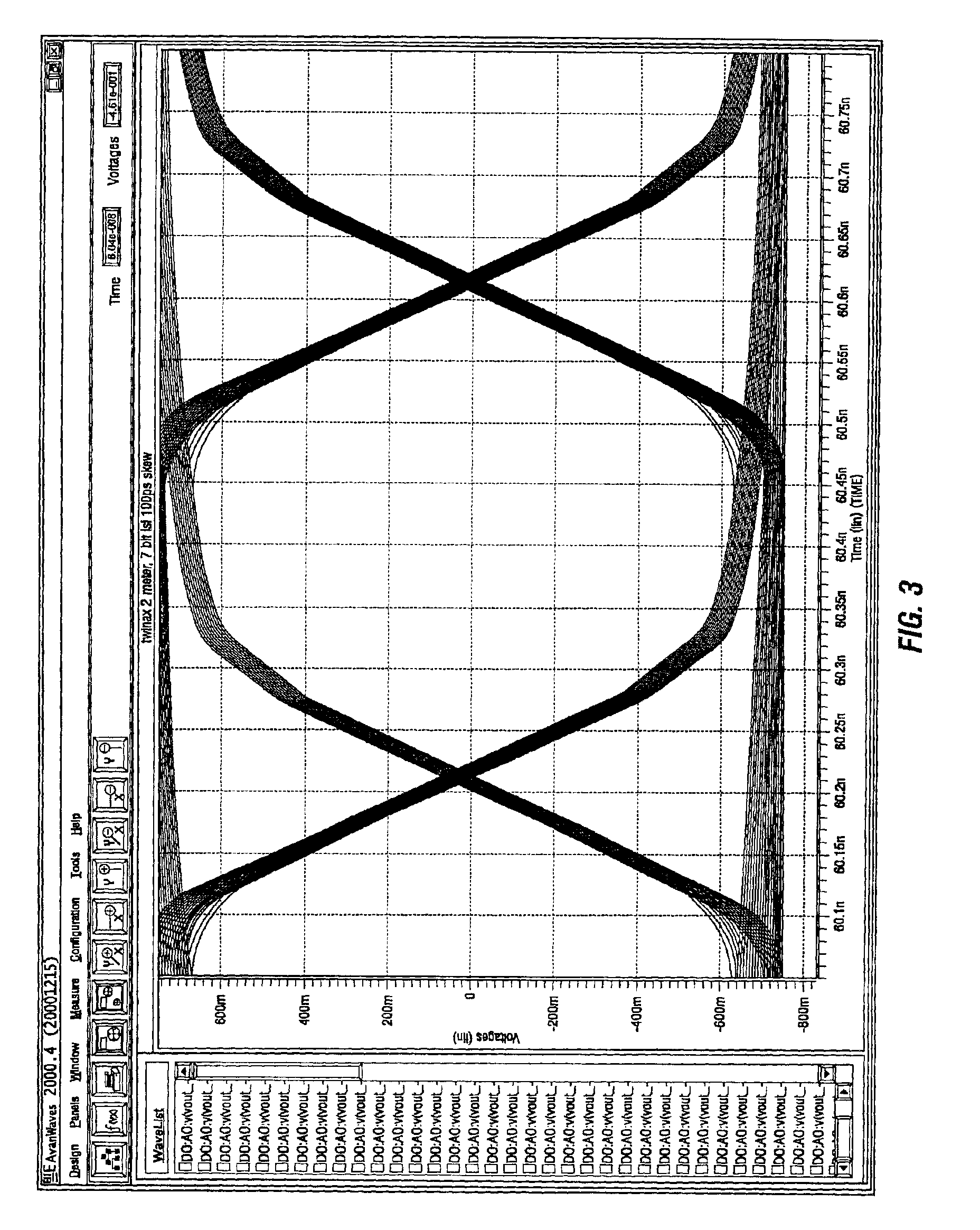

Improving signal integrity in differential signal systems

InactiveUS6886065B2Improves differential signal integrityEnhanced signalReliability increasing modificationsBaseband system detailsSignal qualityDifferential signaling

Over-terminating the differential mode impedance of a differential transmission line, such as an INFINIBAND™ cable, at the receiving end, improves the differential signal integrity for typical variations in termination network impedance component (e.g., resistor) and transmission line characteristics. Eye opening of the differential signal can be made larger with reduced attenuation but increased jitter compared to under-terminating the differential mode impedance. Because the differential signal quality (larger eye opening) is improved, data can be transmitted over a longer transmission line with the same transmitter and receiver.

Owner:VALTRUS INNOVATIONS LTD

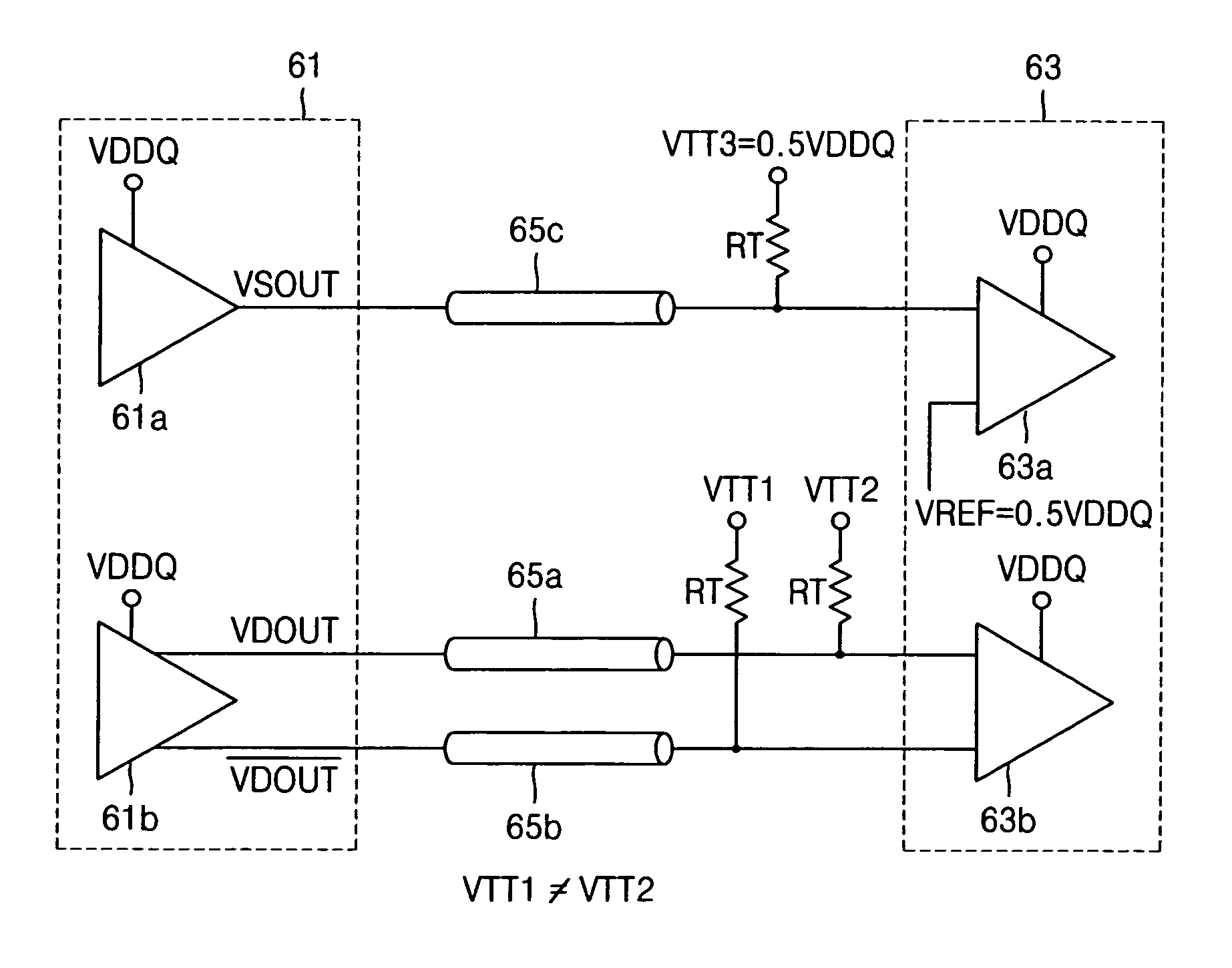

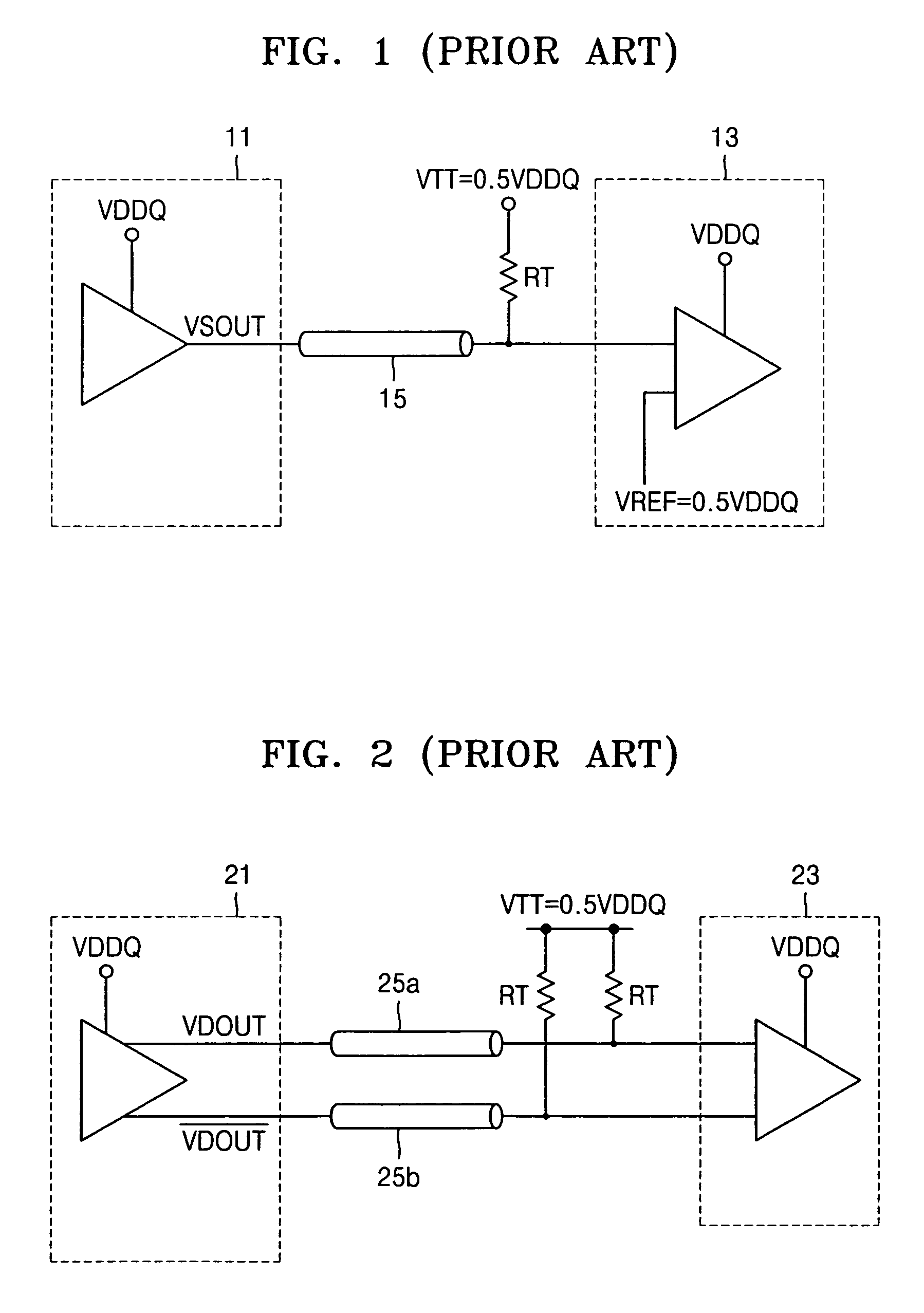

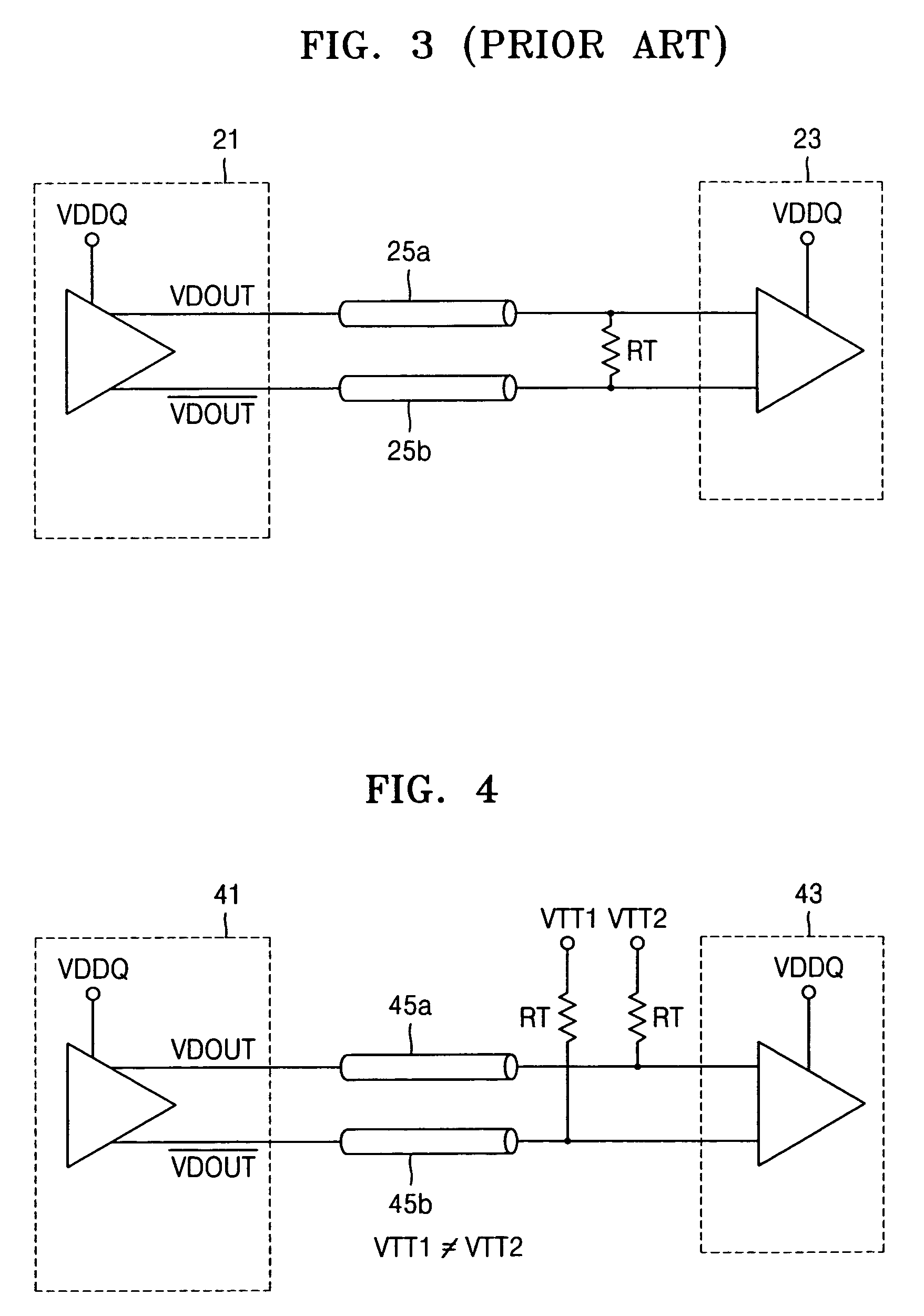

Memory system with stable termination of a pair of differential signals transmitted via a pair of transmission lines

InactiveUS7456650B2Avoid instabilityReliability increasing modificationsBaseband system detailsEngineeringTransmitter

Provided is a memory system in which a pair of differential signals transmitted via a pair of transmission lines are prevented from being terminated at the same voltage during a standby mode, thereby preventing a receiver from entering an unstable state. The memory system includes a pair of transmission lines, a transmitter that outputs a pair of differential signals to the pair of transmission lines, and a receiver that receives the pair of differential signals via the pair of transmission lines. A first termination voltage is applied to one of the pair of transmission lines, and a second termination voltage is applied to the other transmission line. The first termination voltage is determined to be different from the second termination voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

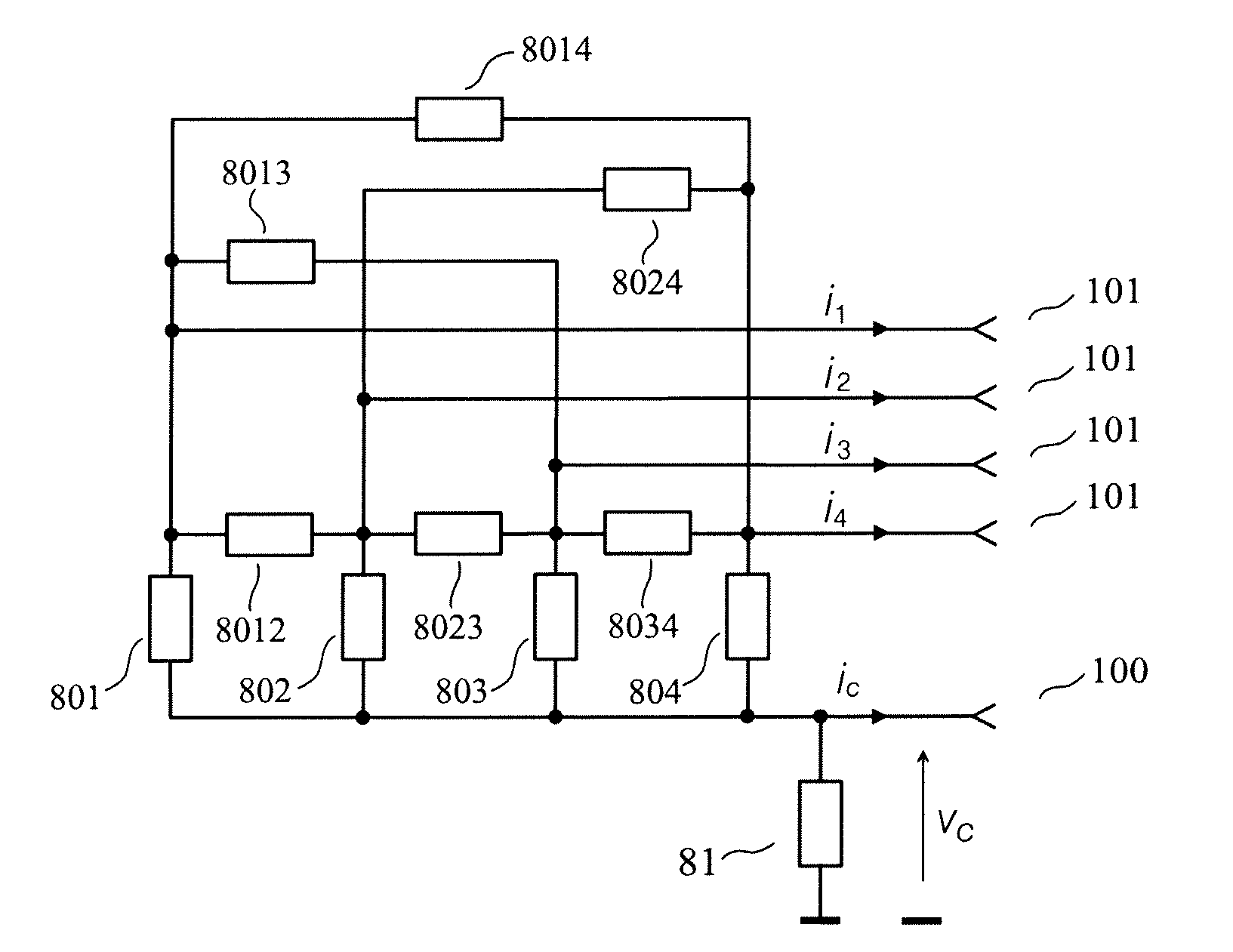

Multichannel interfacing device having a termination circuit

InactiveUS8222919B2Reduce reflectionReduce inductanceMultiple-port networksReliability increasing modificationsDiagonal matrixInterconnection

The invention relates to an interfacing device for transmission through interconnections used for sending a plurality of electrical signals.The interfacing device of the invention comprises signal terminals and a common terminal. A receiving circuit delivers, when the receiving circuit is in the activated state, “output signals of the receiving circuit” determined each by a linear combination of the voltages between one of the signal terminals and the common terminal, to the destination. A termination circuit is such that, when it is in the activated state, it is approximately equivalent, for the signal terminals and the common terminal, to a (m+1)-terminal network such that, for small signals, the impedance matrix, with respect to the common terminal, of the (m+1)-terminal network is equal to a wanted non-diagonal matrix of size m×m.

Owner:ZXNOISE LLC

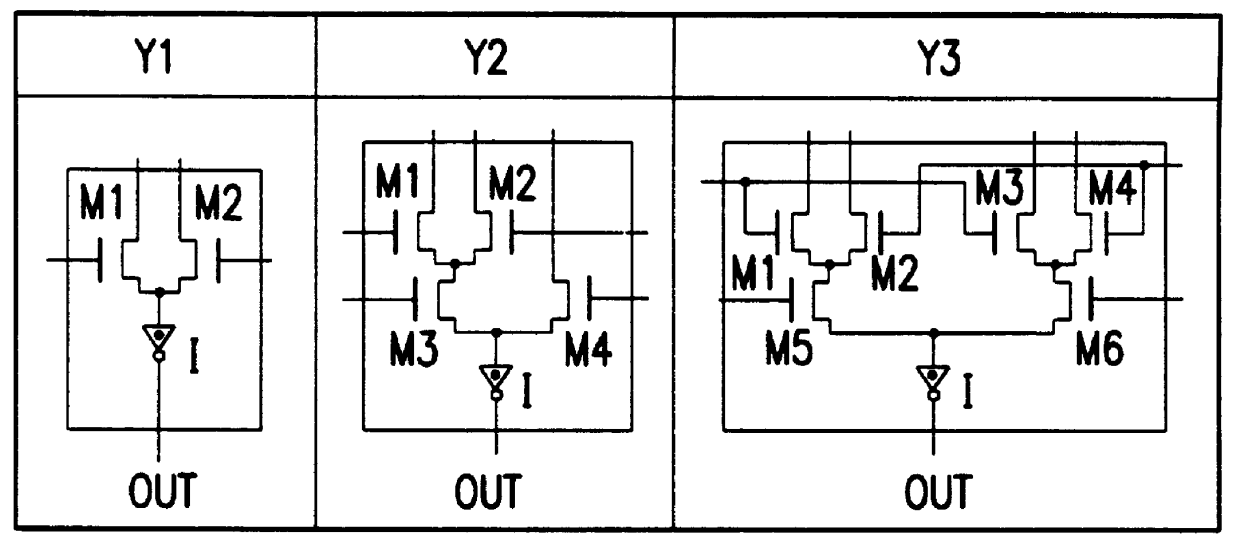

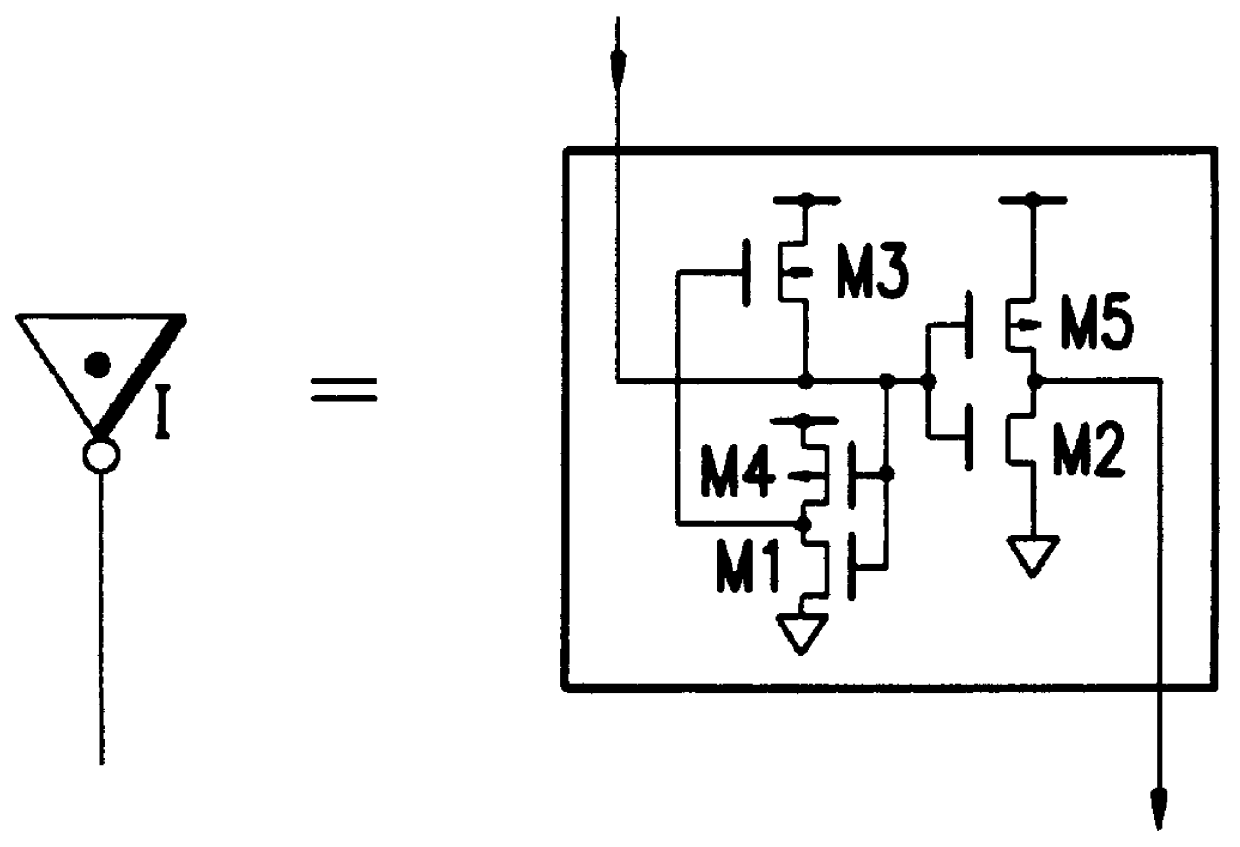

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

Integrated circuit communication techniques

ActiveUS7439773B2Reduce the required powerReduce power consumptionReliability increasing modificationsPower reduction by control/clock signalEngineeringSemiconductor

Owner:TAHOE RES LTD

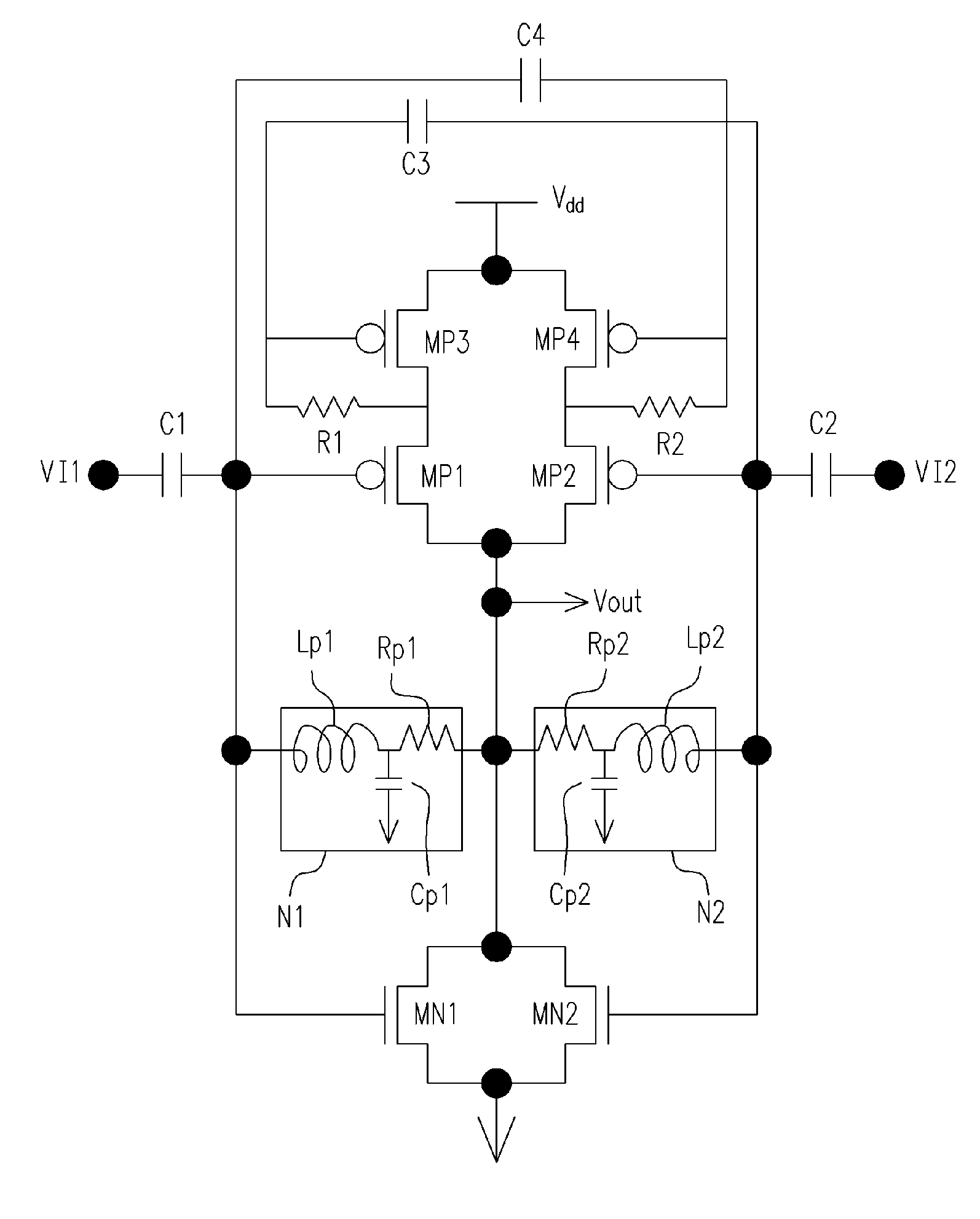

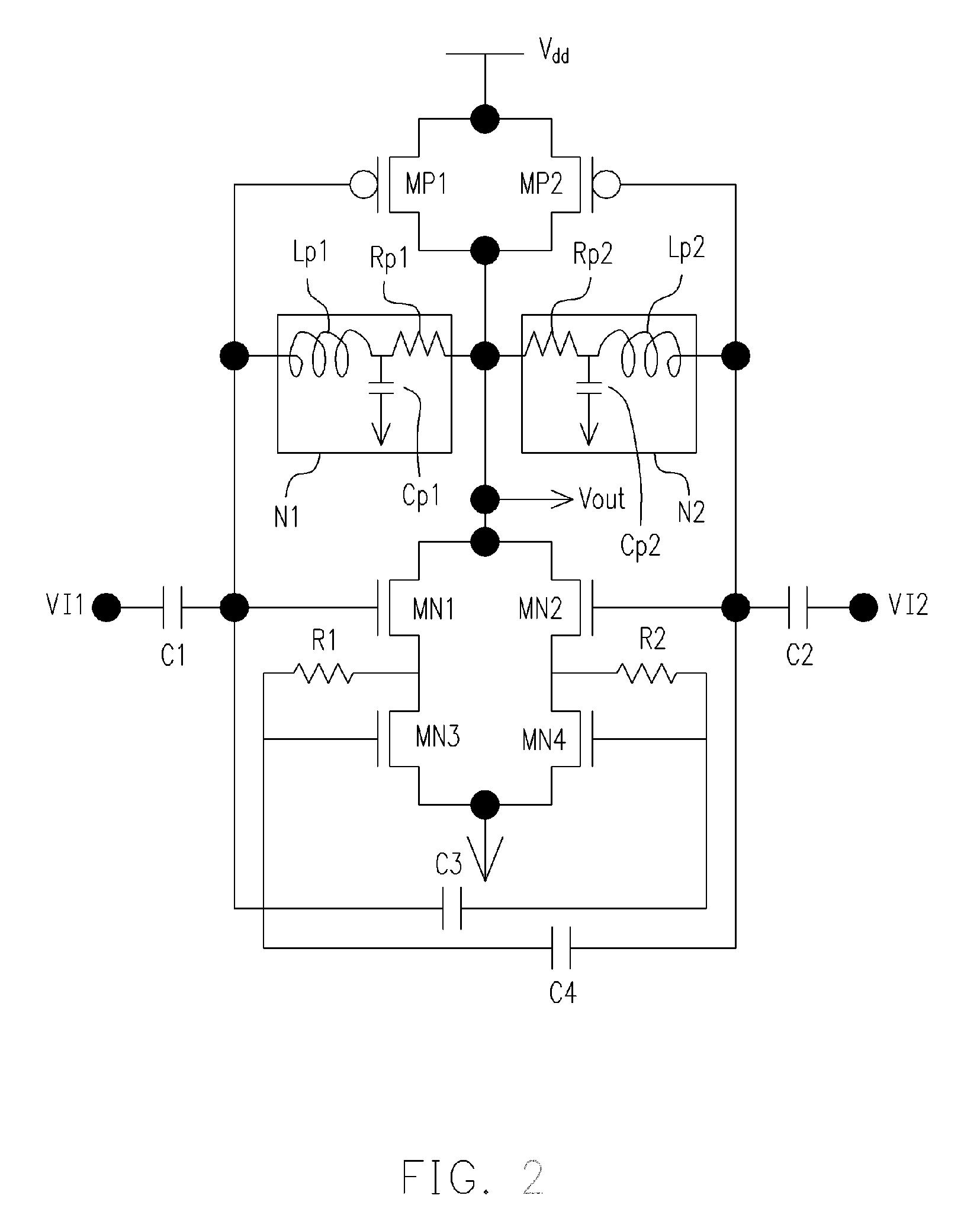

Self dc-bias high frequency logic gate, high frequency NAND gate and high frequency nor gate

InactiveUS20060197557A1Electric power will not be wastedNot to wasteReliability increasing modificationsMultiple input and output pulse circuitsNOR gateNAND gate

A self DC-bias high frequency logic gate is disclosed. The logic gate comprises at least one input terminal and one output terminal for performing Boolean operation on the high frequency input signals. The logic gate is characterized in that each transistor is coupled to an impedance matching network. The impedance matching network comprises a first terminal and a second terminal. Wherein, the first terminal is coupled to a gate of the transistor, and the second terminal is coupled to a drain of the transistor for providing an operation voltage to the transistor. When a gate of an N-type transistor and a gate of a P-type transistor are coupled with each other, and a drain of the N-type transistor and a drain of the P-type transistor are also coupled with each other, a common impedance matching network is shared with both the N-type transistor and the P-type transistor.

Owner:SUNPLUS TECH CO LTD

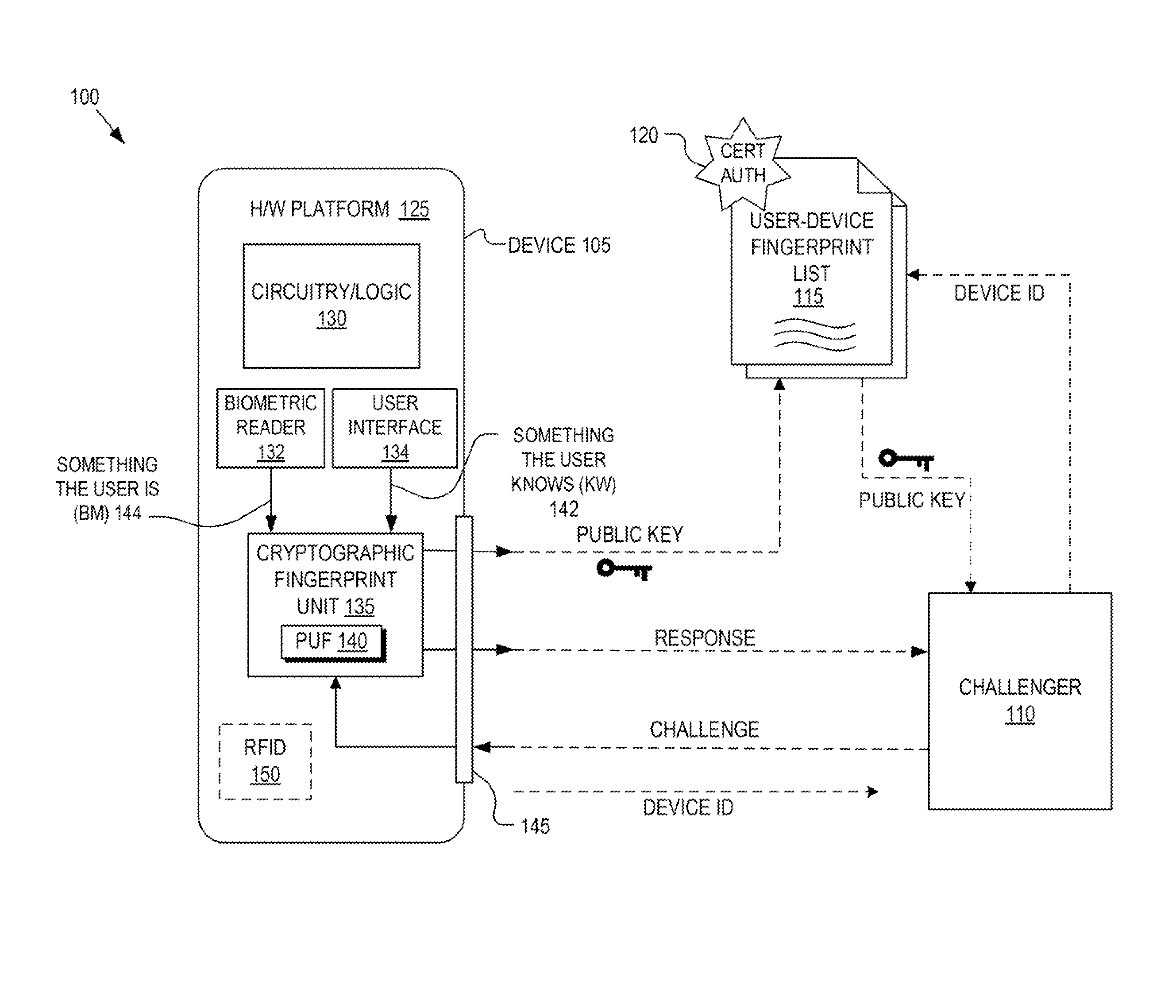

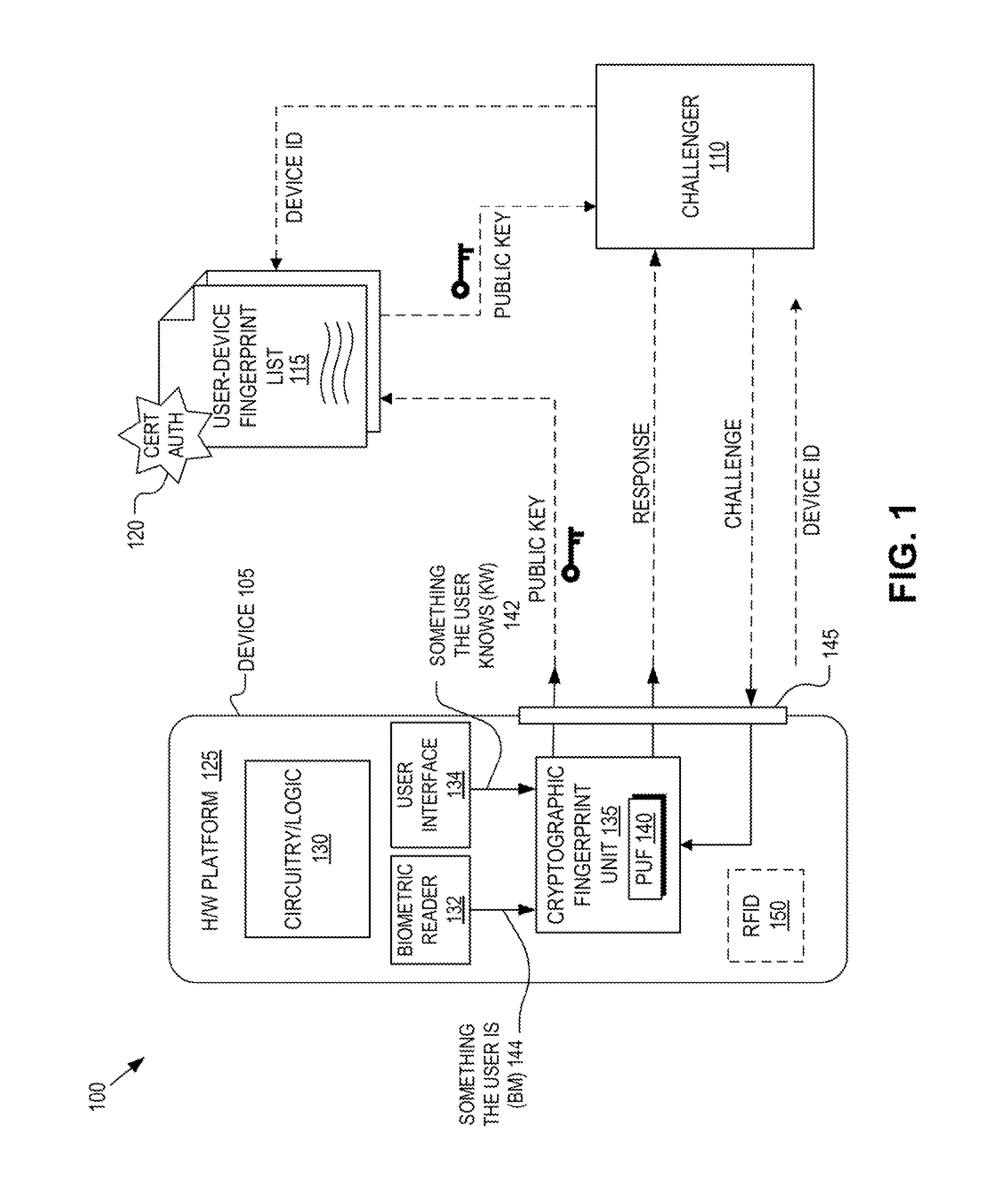

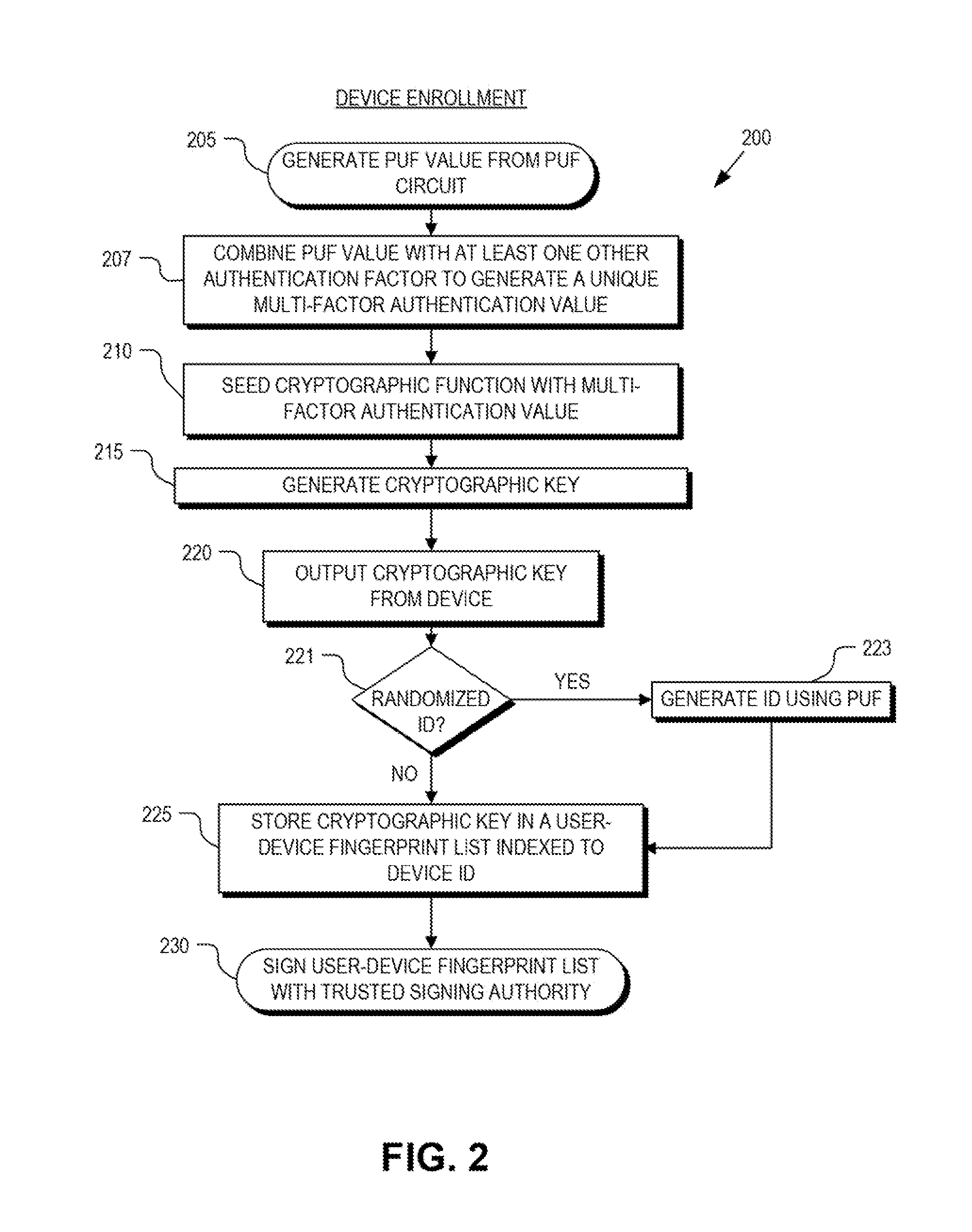

Multi-factor authentication

ActiveUS8868923B1Reliability increasing modificationsElectric signal transmission systemsPhysical unclonable functionUser authentication

Detection and deterrence of spoofing of user authentication may be achieved by including a cryptographic fingerprint unit within a hardware device for authenticating a user of the hardware device. The cryptographic fingerprint unit includes an internal physically unclonable function (“PUF”) circuit disposed in or on the hardware device, which generates a PUF value. Combining logic is coupled to receive the PUF value, combines the PUF value with one or more other authentication factors to generate a multi-factor authentication value. A key generator is coupled to generate a private key and a public key based on the multi-factor authentication value while a decryptor is coupled to receive an authentication challenge posed to the hardware device and encrypted with the public key and coupled to output a response to the authentication challenge decrypted with the private key.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

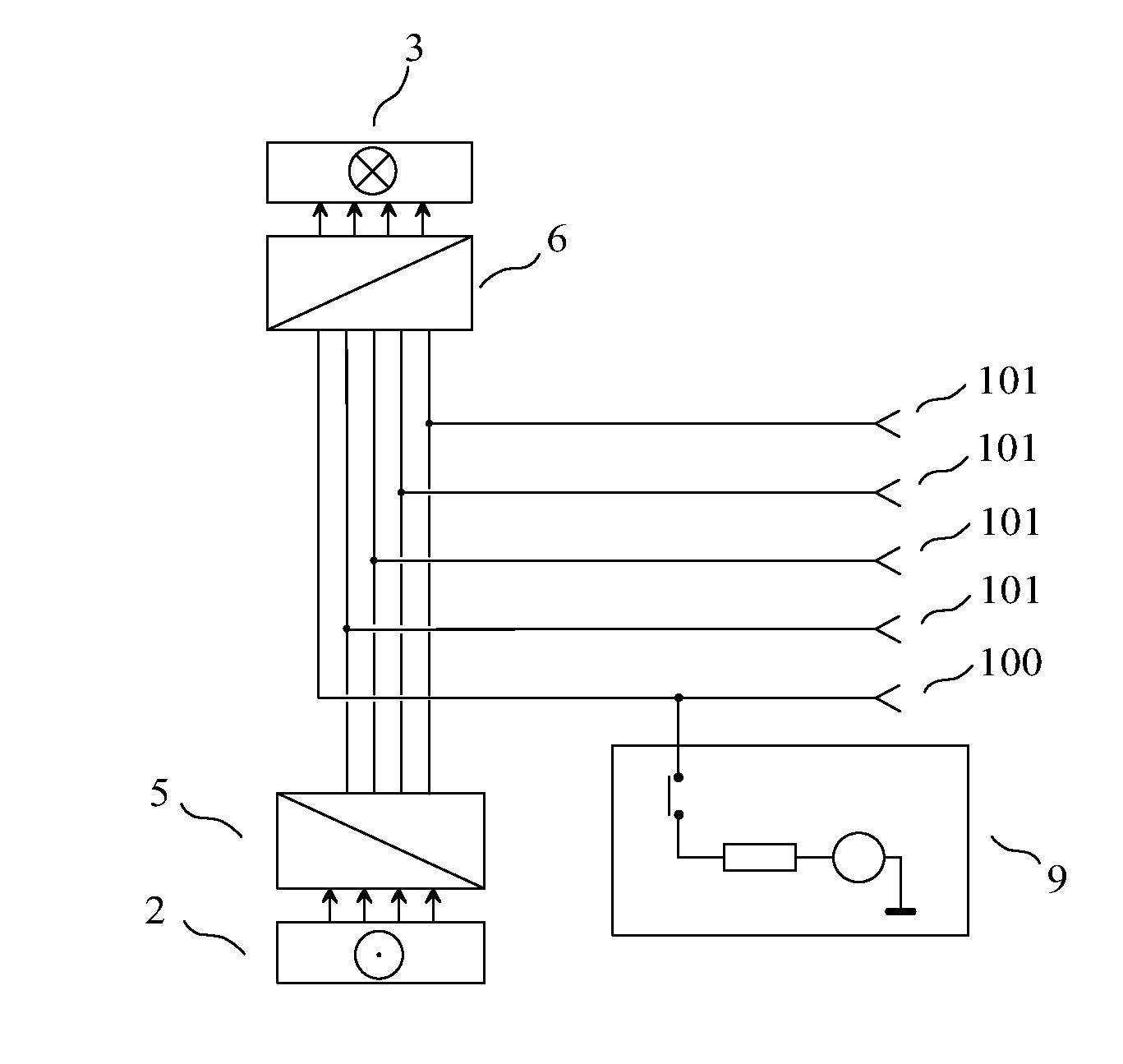

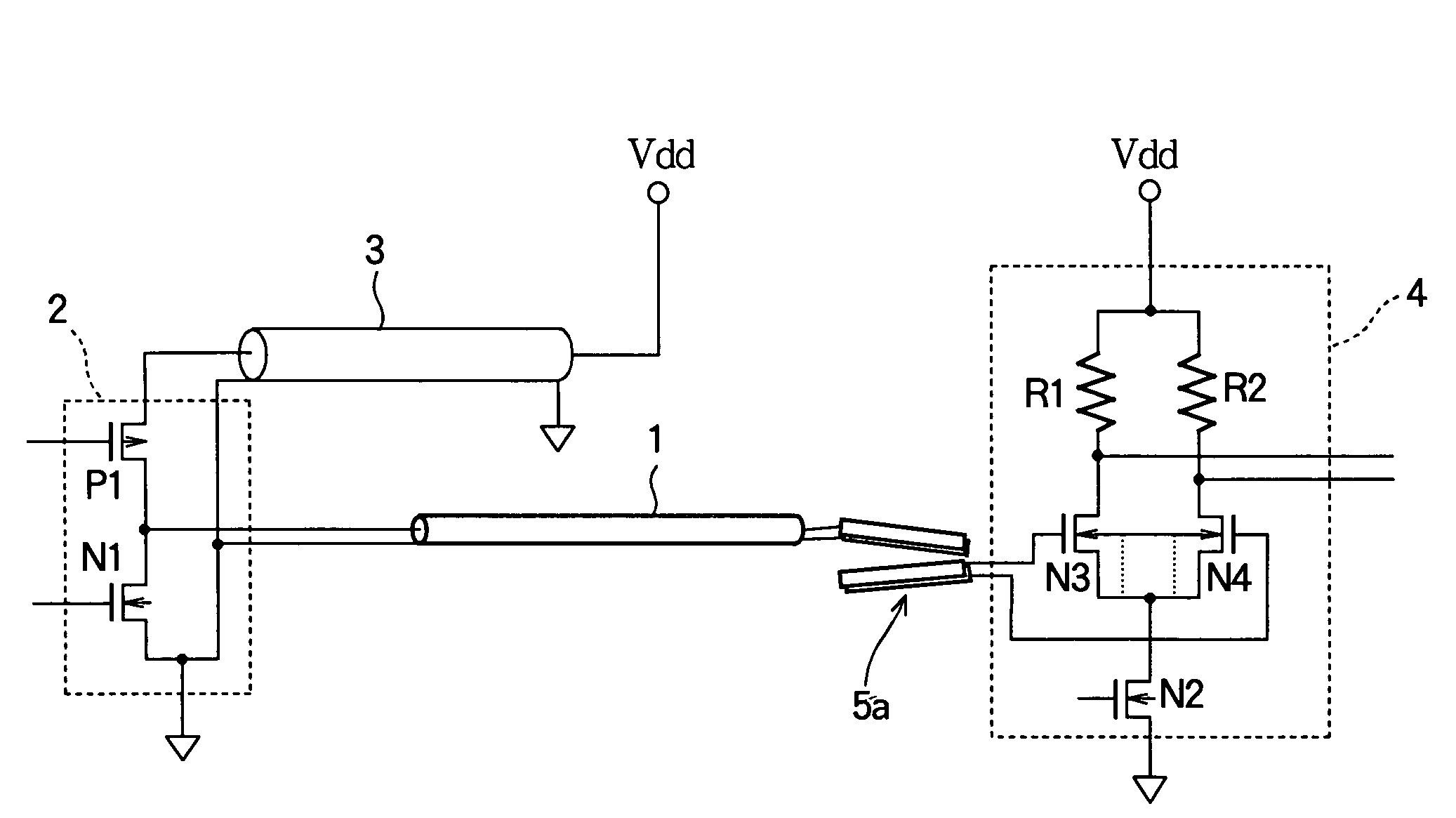

Signal transmission apparatus and interconnection structure

ActiveUS7446567B2Sufficient capabilitySimple and scalableReliability increasing modificationsBatteries circuit arrangementsLine pairHarmonic

Apparatus for transmitting a digital signal within, for example, an integrated circuit includes a signal transmission line with a directional coupler at one or both ends. The directional coupler blocks the direct-current component of the digital signal while transmitting the alternating-current component, including enough higher harmonics to transmit a well-defined pulse waveform. A suitable directional coupler consists of two adjacent line pairs in materials with different dielectric constants. The apparatus may also include a driver of the inverter type, a receiver of the differential amplifier type, a terminating resistor, and a power-ground transmission line pair for supplying power to the driver. An all-metallic transmission-line structure is preferably maintained from the output interconnections in the driver to the input interconnections in the receiver.

Owner:PANASONIC CORP +11

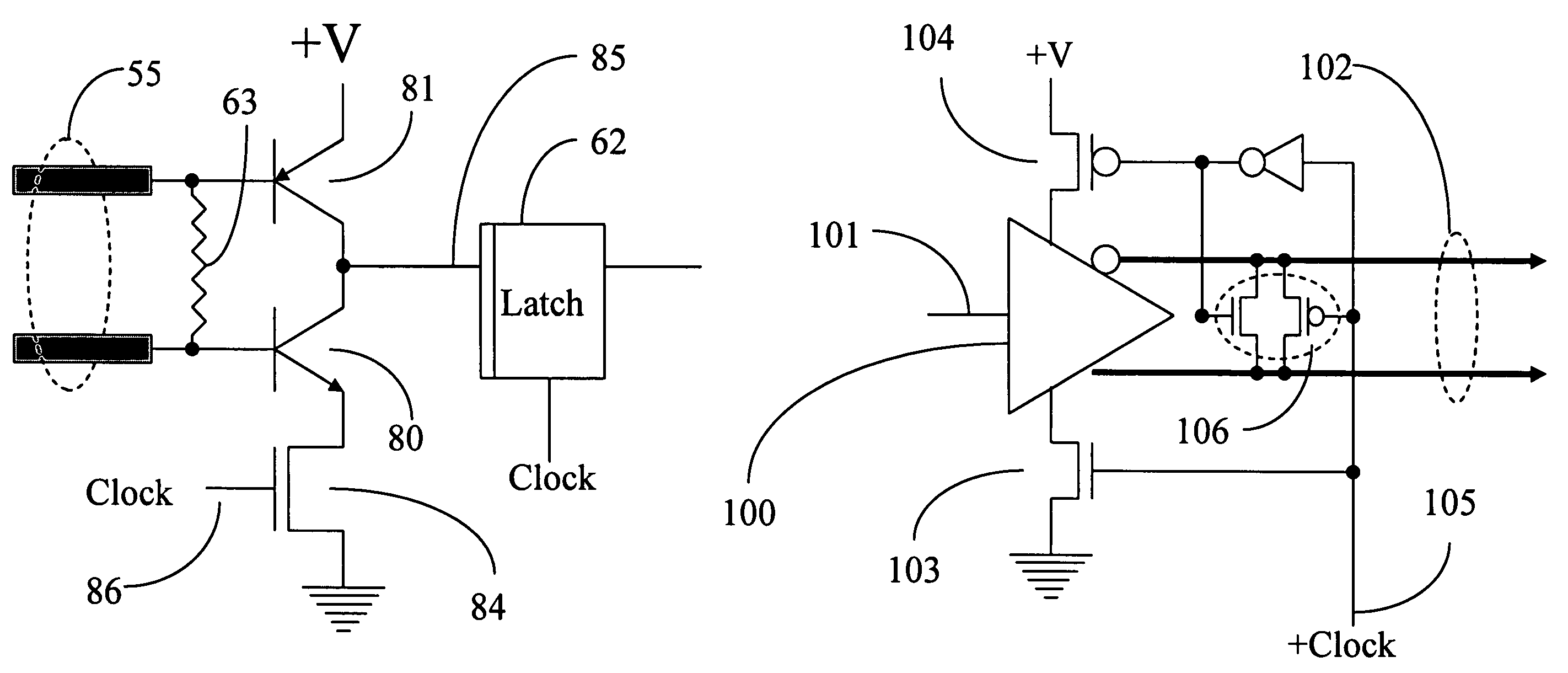

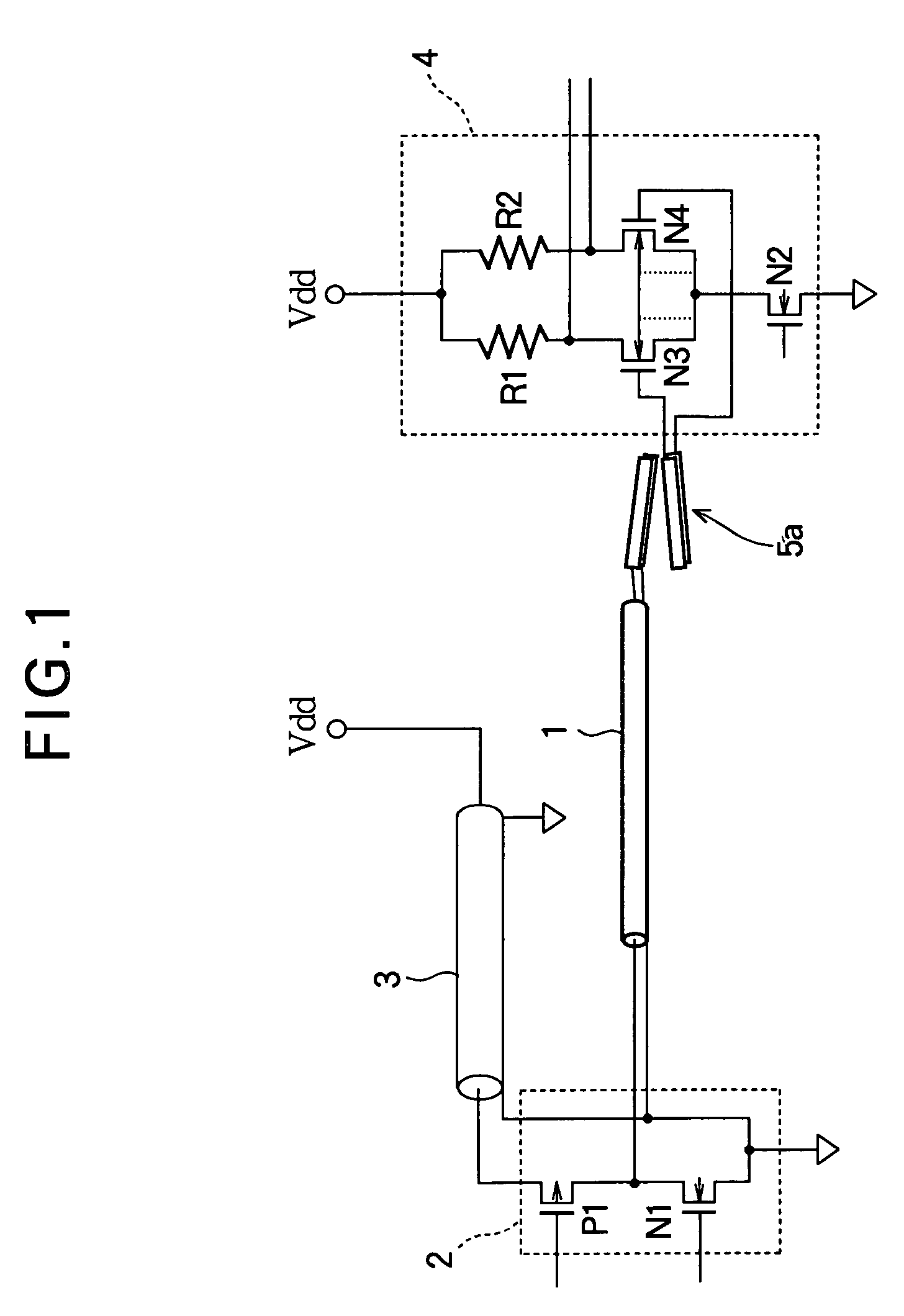

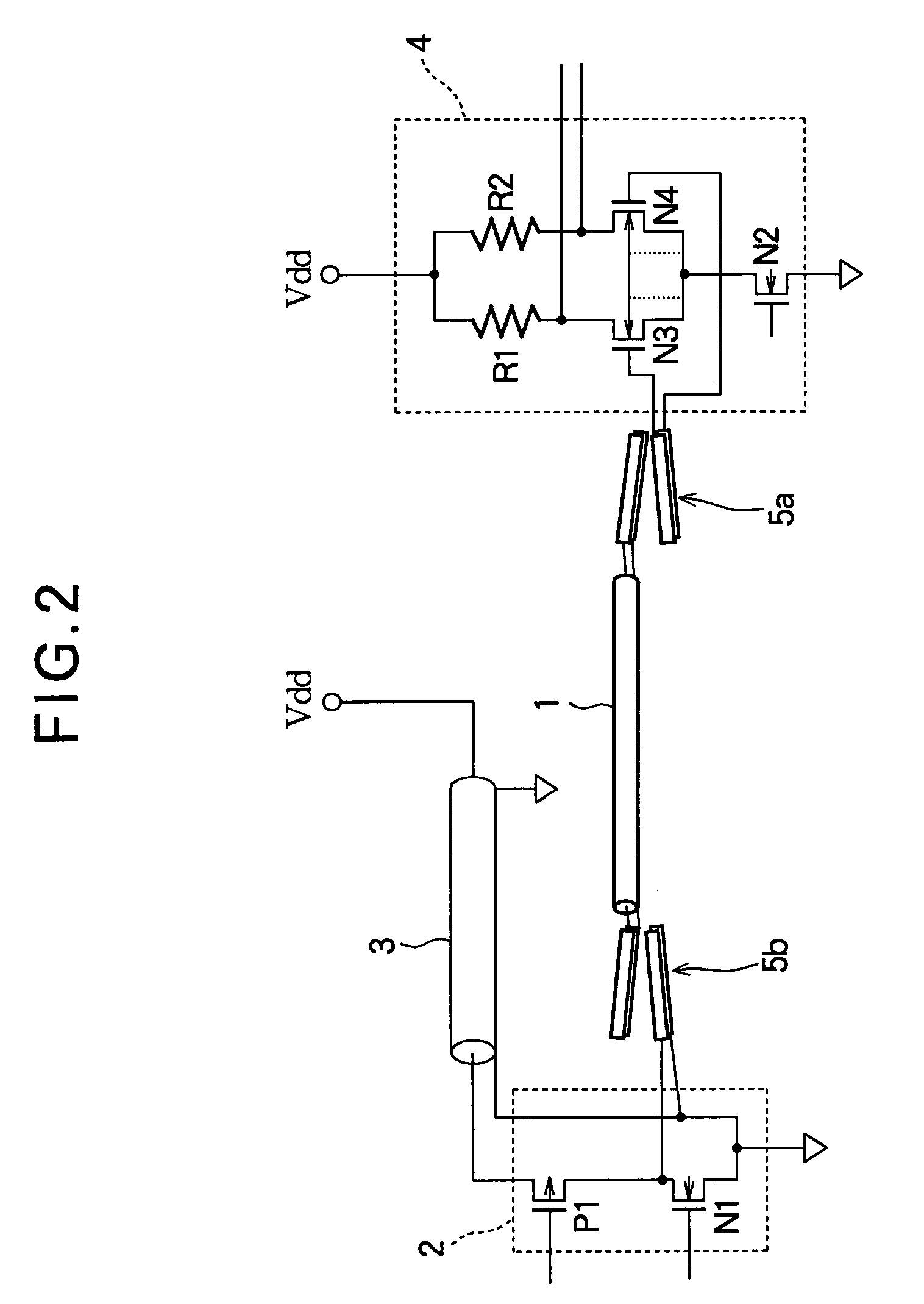

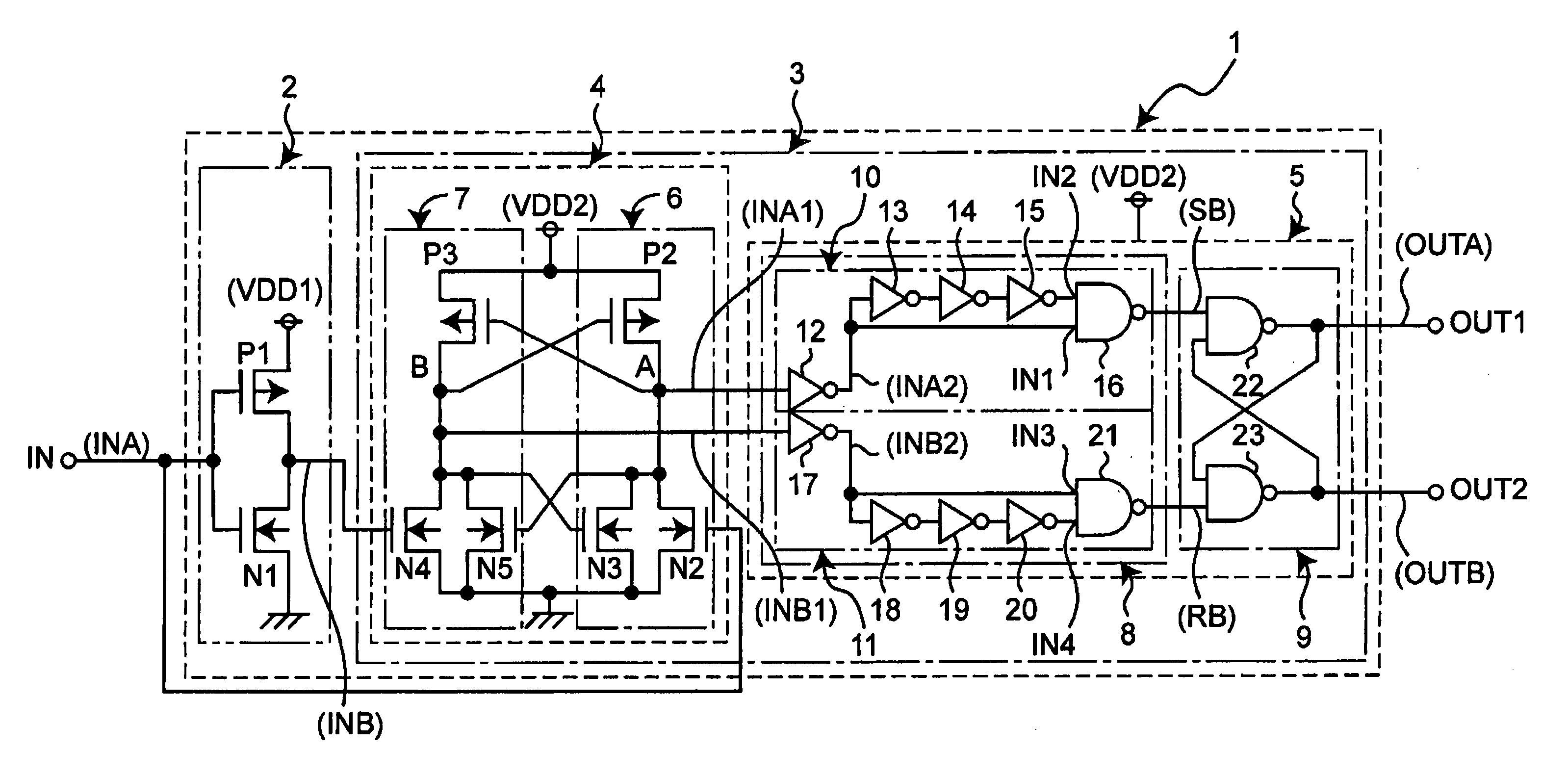

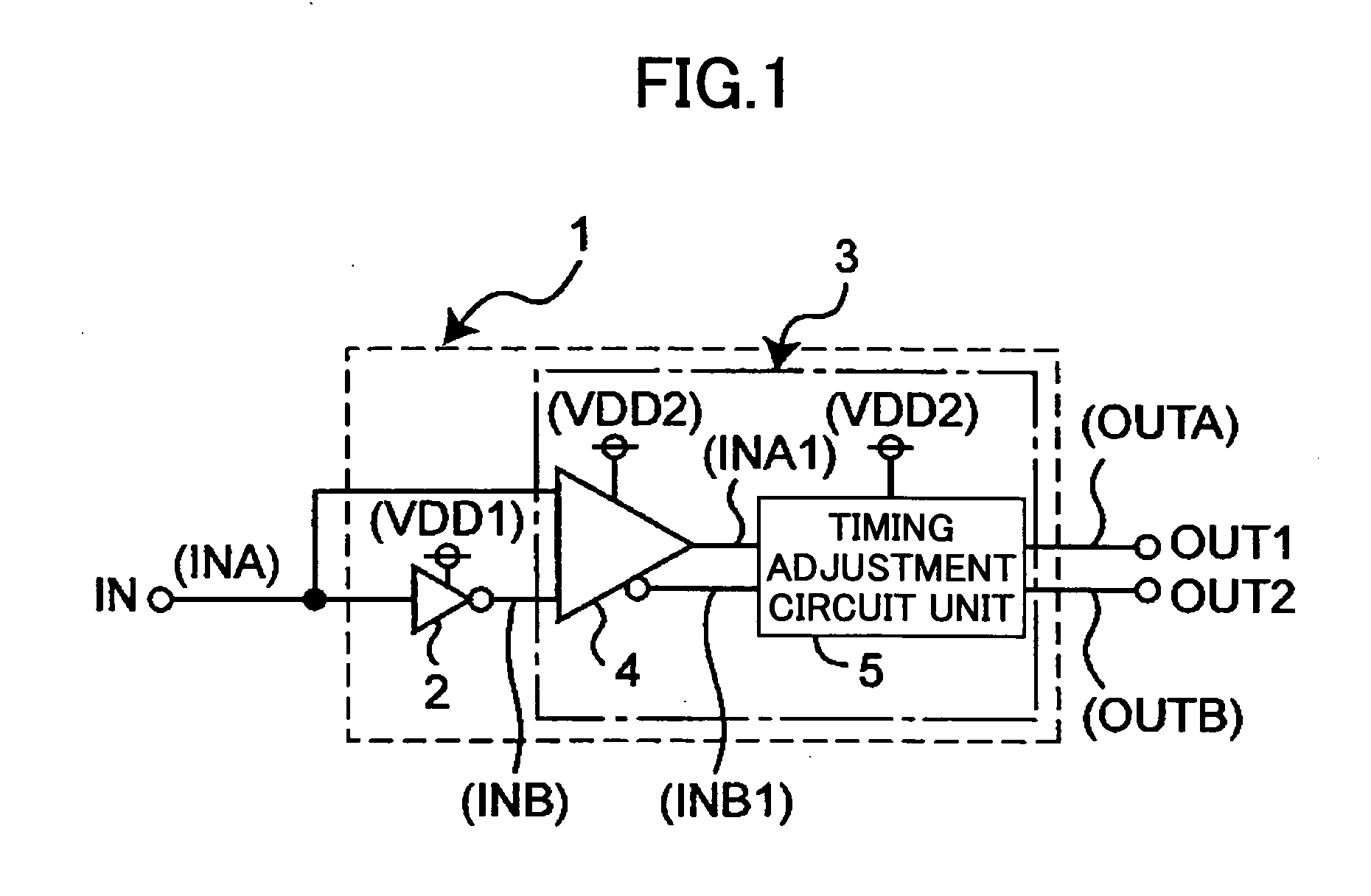

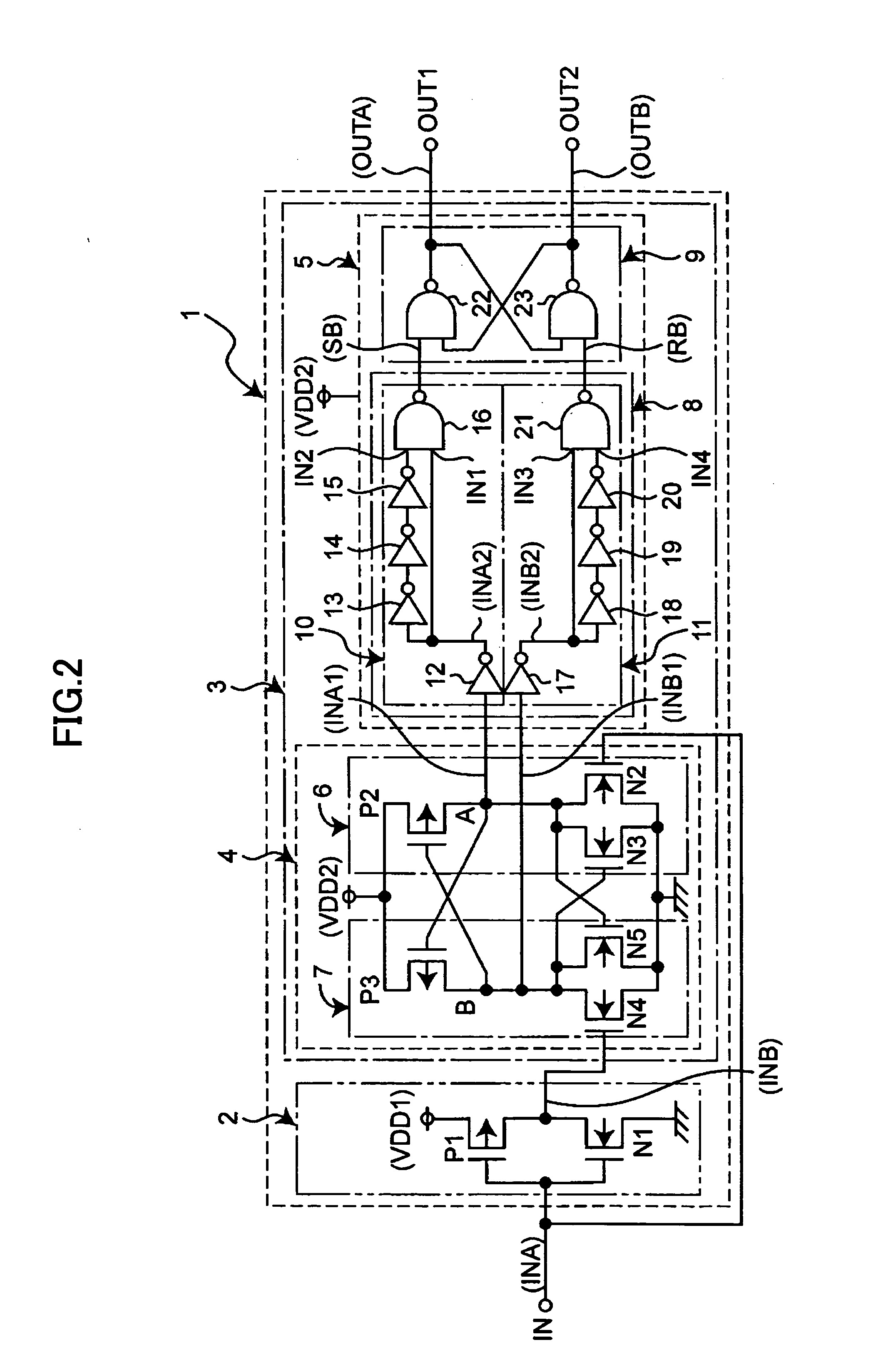

Level shift circuit having timing adjustment circuit for maintaining duty ratio

InactiveUS20060066349A1Accurate operationReliability increasing modificationsElectronic switchingEngineeringVoltage range

A level shift circuit for shifting levels of a pair of binary input signals having a first voltage range to produce a pair of binary output signals having a second voltage range includes a first circuit to shift a level of a first one of the binary input signals thereby to produce a first signal having the second voltage range, a second circuit to shift a level of a second one of the binary input signals thereby to produce a second signal having the second voltage range, and a timing adjustment circuit to produce the binary output signals by adjusting a pulse width thereof in response to the first and second signals such that the pulse width is equal to a time interval from when one of the first and second circuits stops level shift operation to when another one of the first and second circuits stops level shift operation.

Owner:RICOH ELECTRONIC DEVICES CO LTD

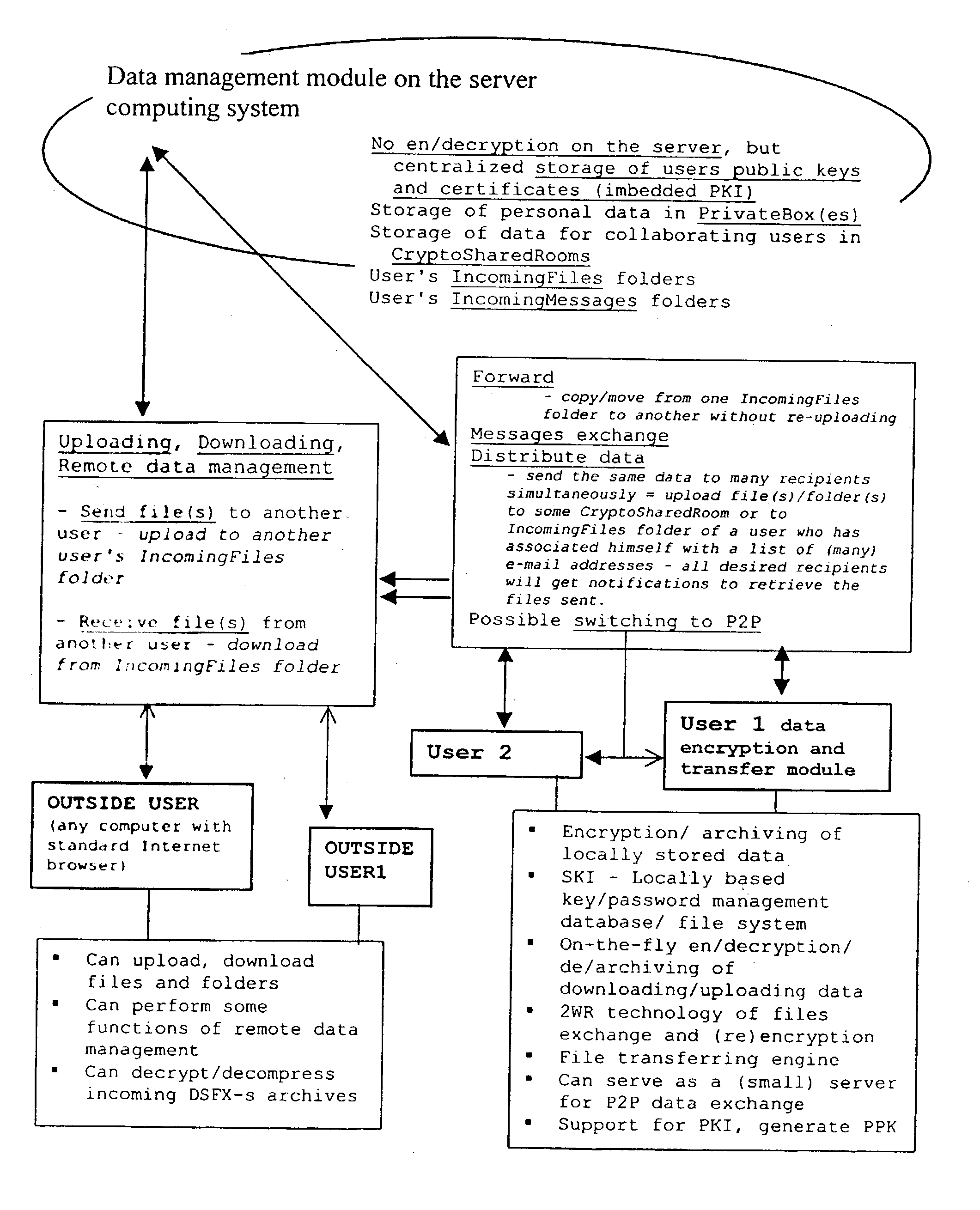

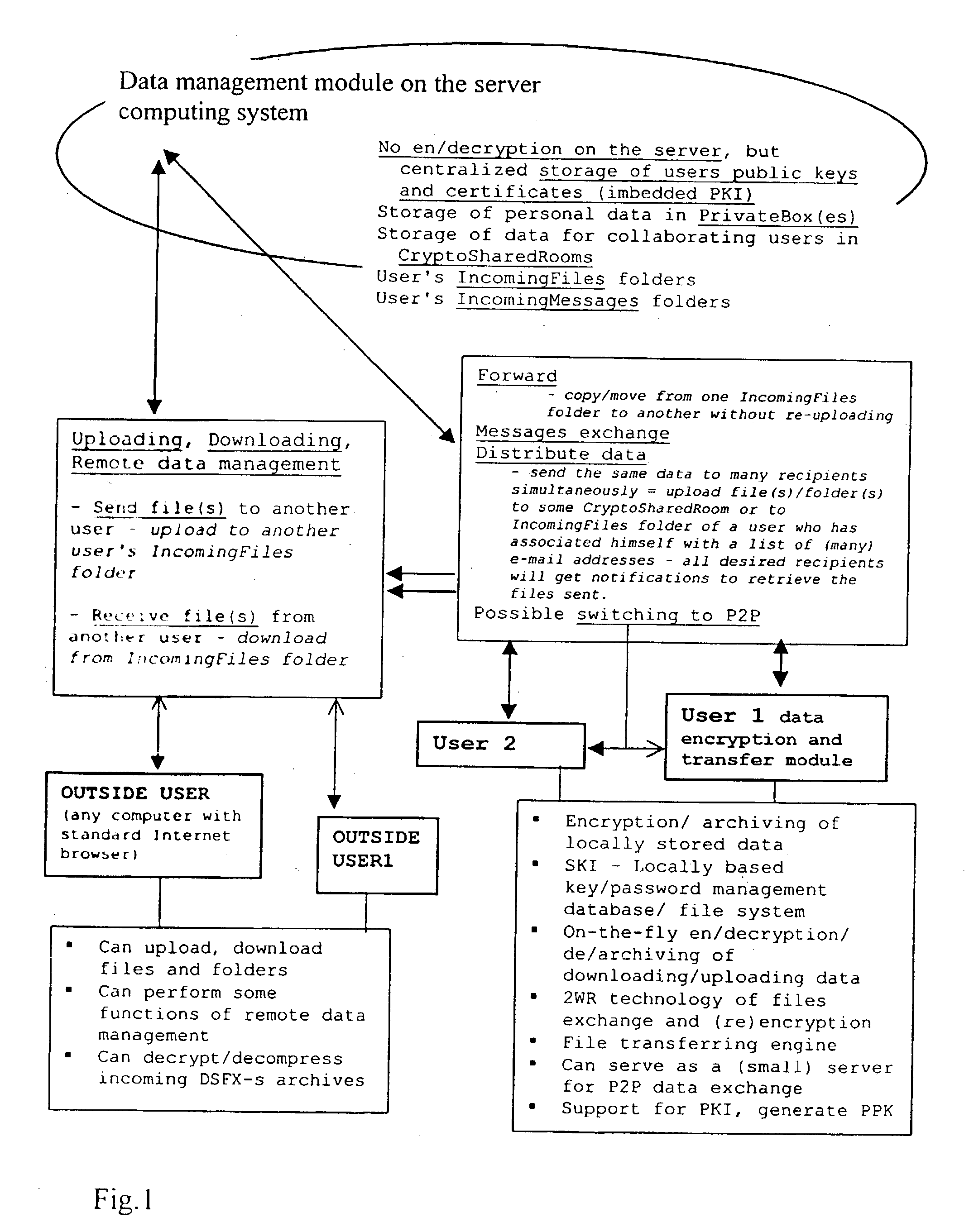

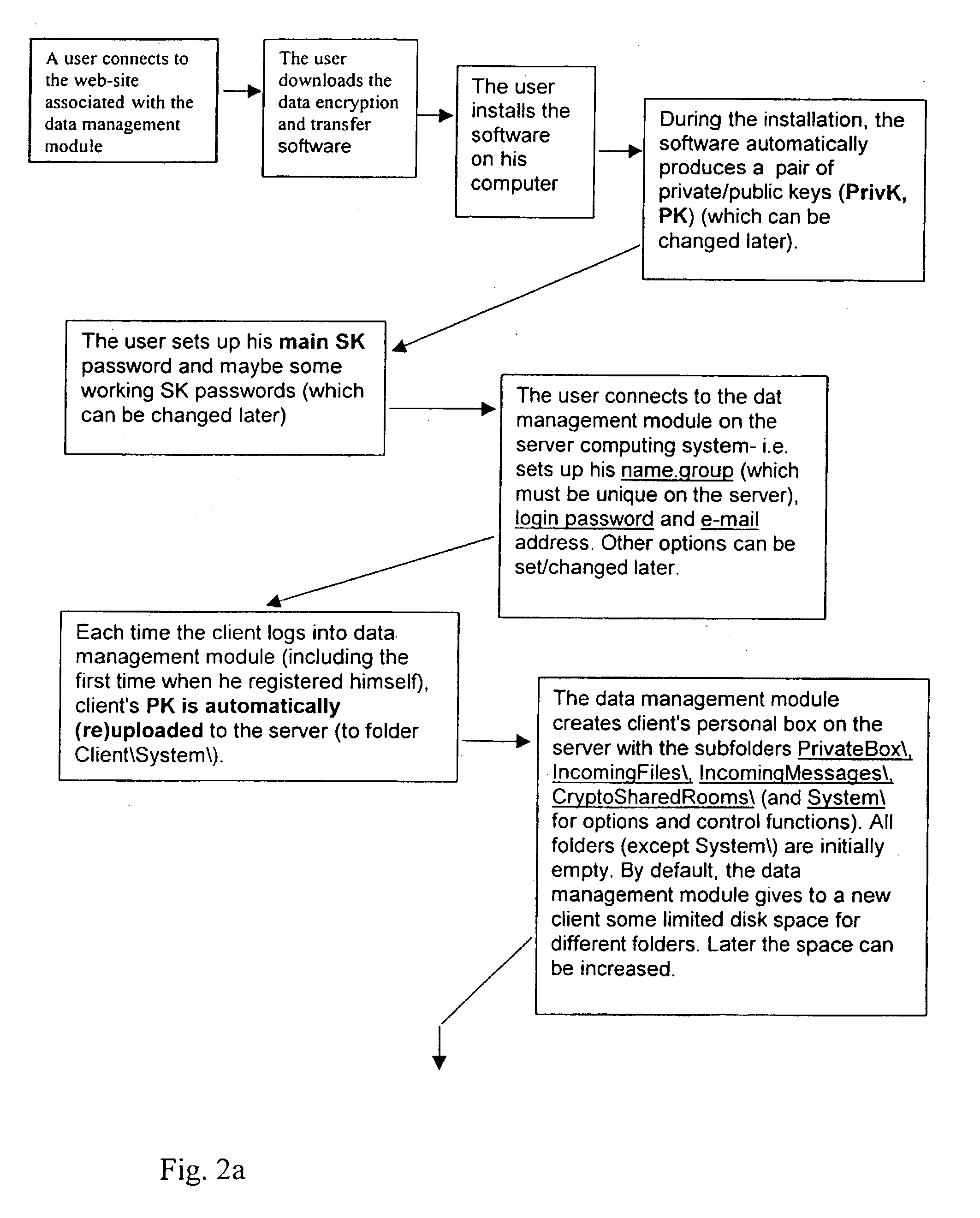

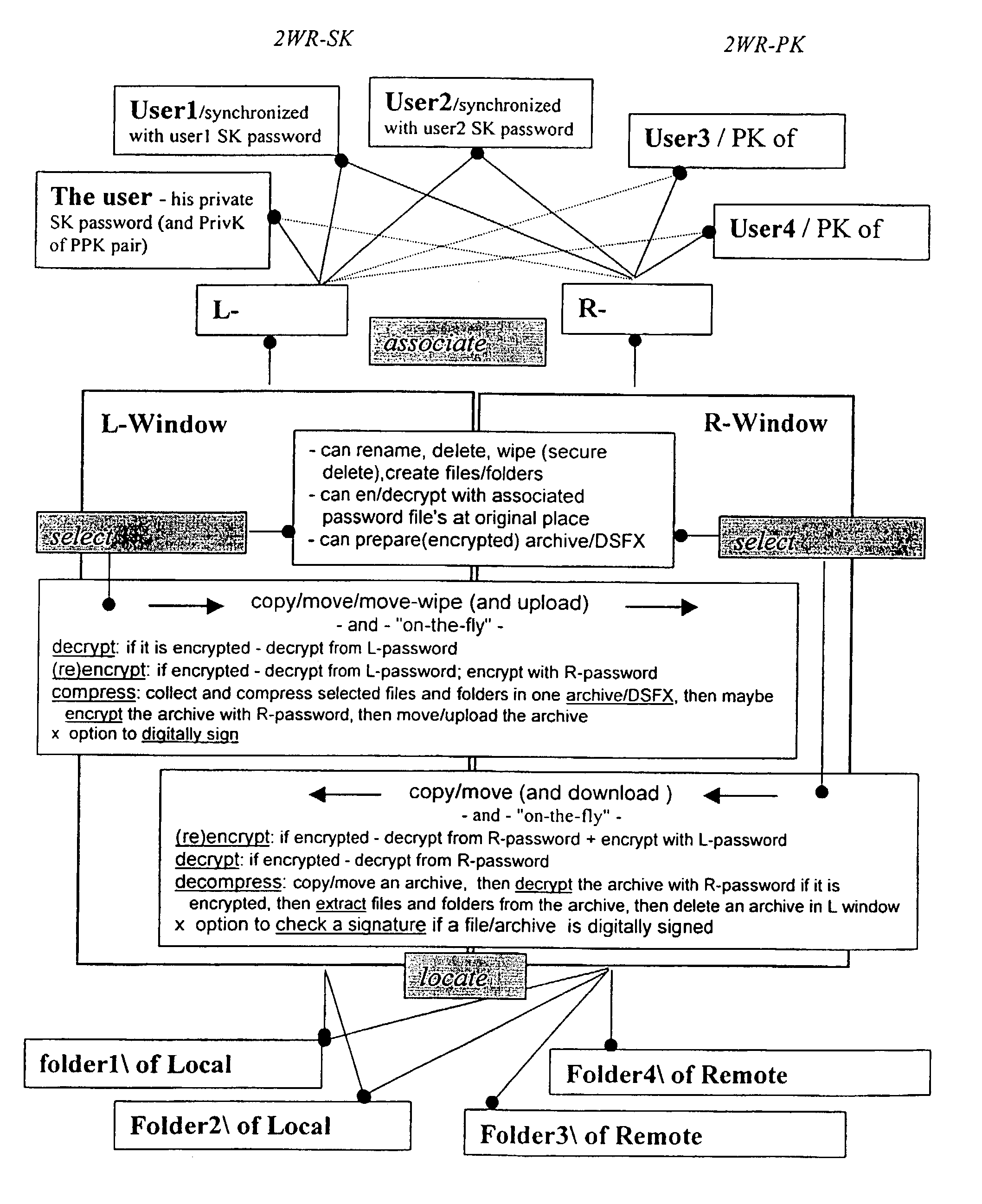

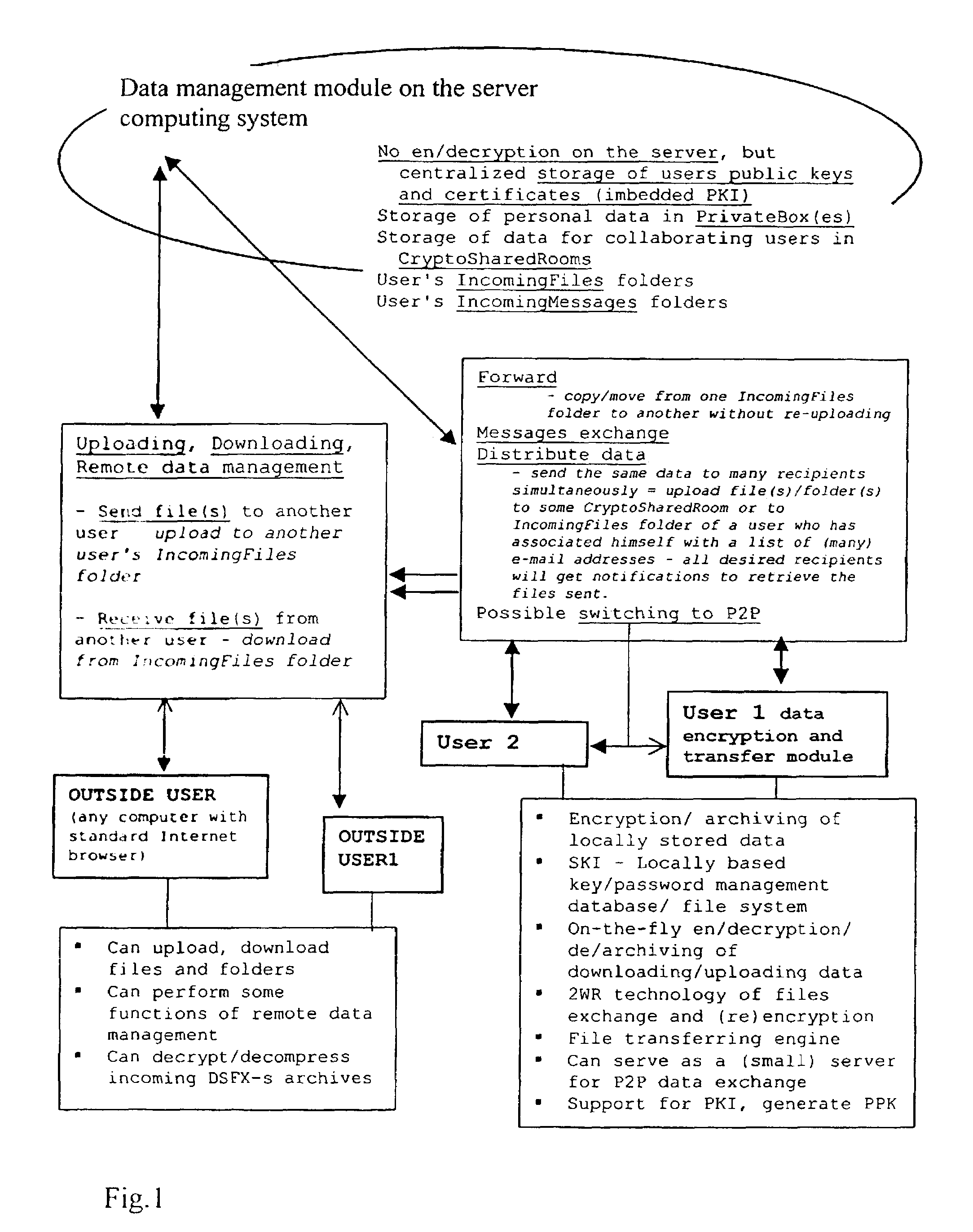

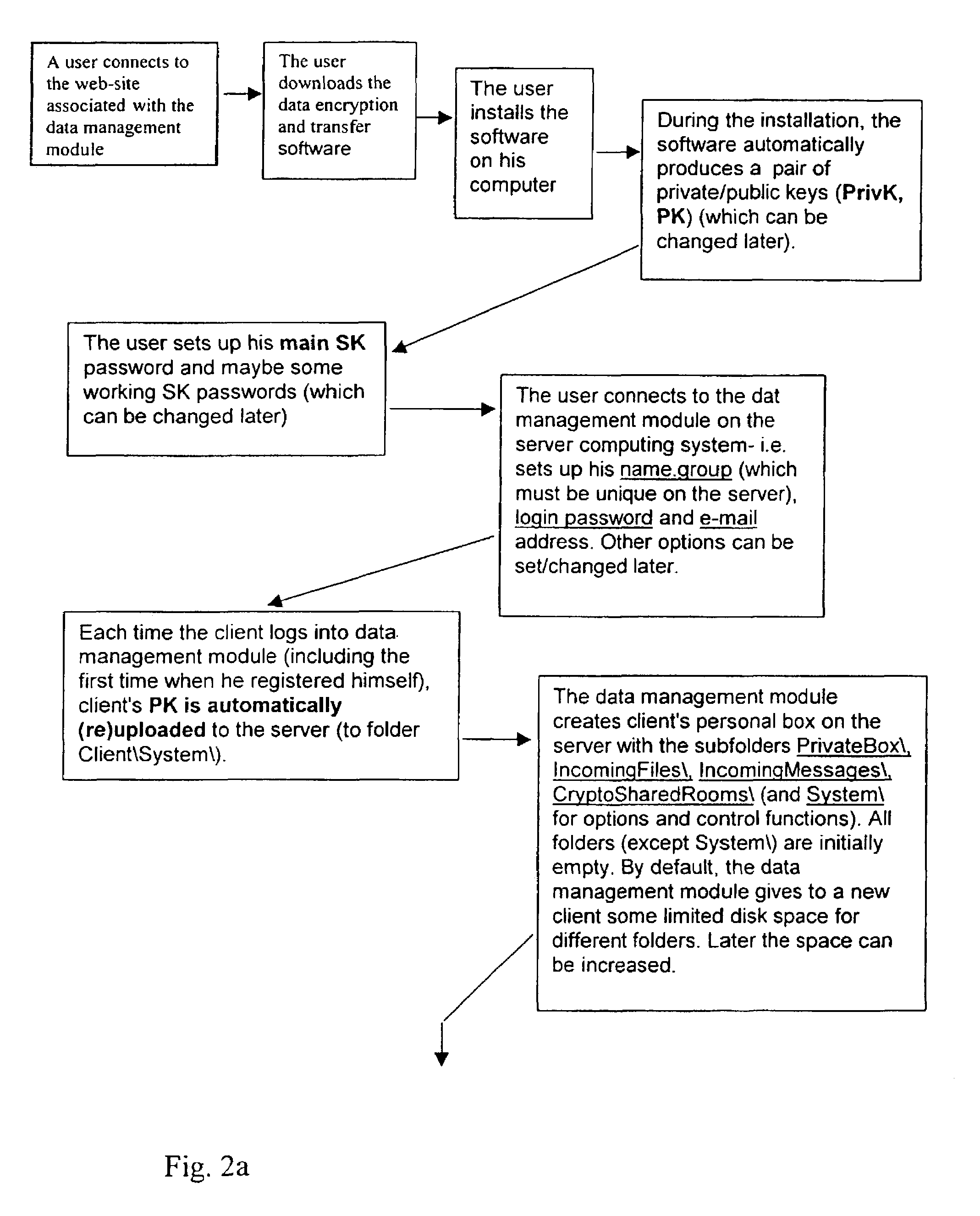

Data transfer and management system

InactiveUS20030177422A1Easily and securely managedEasily downloadableReliability increasing modificationsError preventionMegabyteData file

A system for the secure transfer of data and data management on the Internet has a data encryption and transfer module operable in a user computing system, a data management module operable in a server computing system, the transfer of data between the user and server computing systems being effected on the user computing system through use of the data encryption and transfer module, by moving the data to or from a first desktop window, associated with the user computing system, from or to a second desktop window, associated with the server computing system, each window being associated with a password, such that the step of moving the data from one window to the other causes the data to be encrypted / re-encrypted from one associated password to the other. The system also includes a password management module operable in the user computing system for managing the passwords, which are required to be used by a user of the system. The system uses symmetric key encryption coupled with file transfer protocol (FTP) data transfer and allows for the secure transfer of large data files of 100 megabytes or more.

Owner:HERBERT STREET TECH

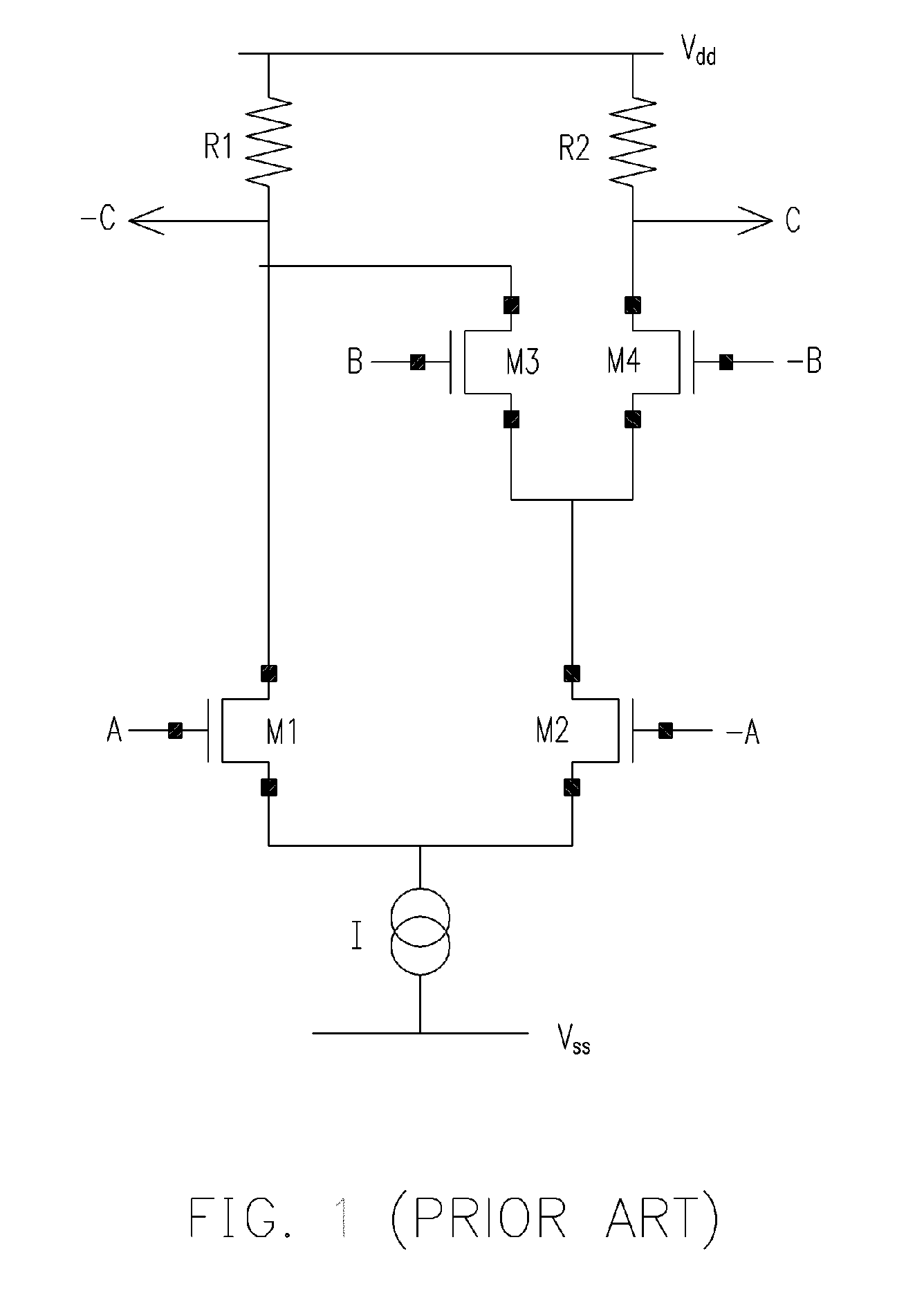

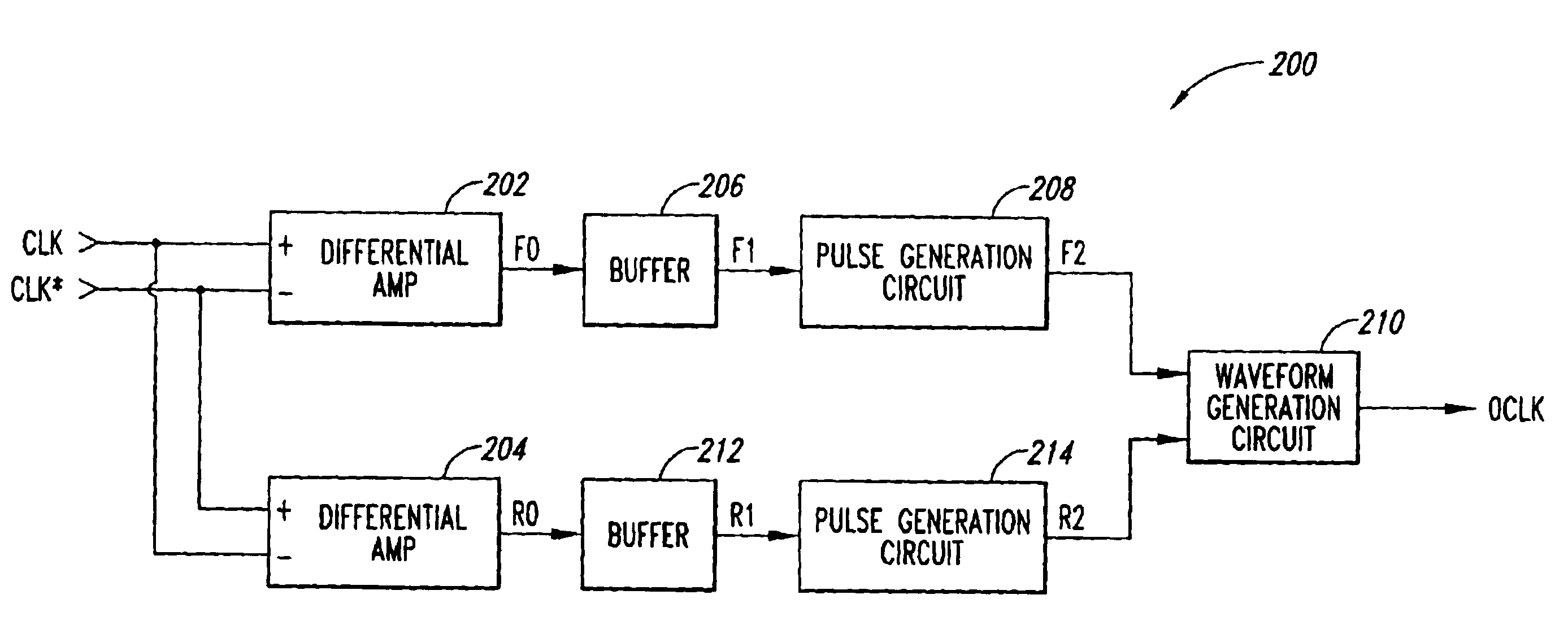

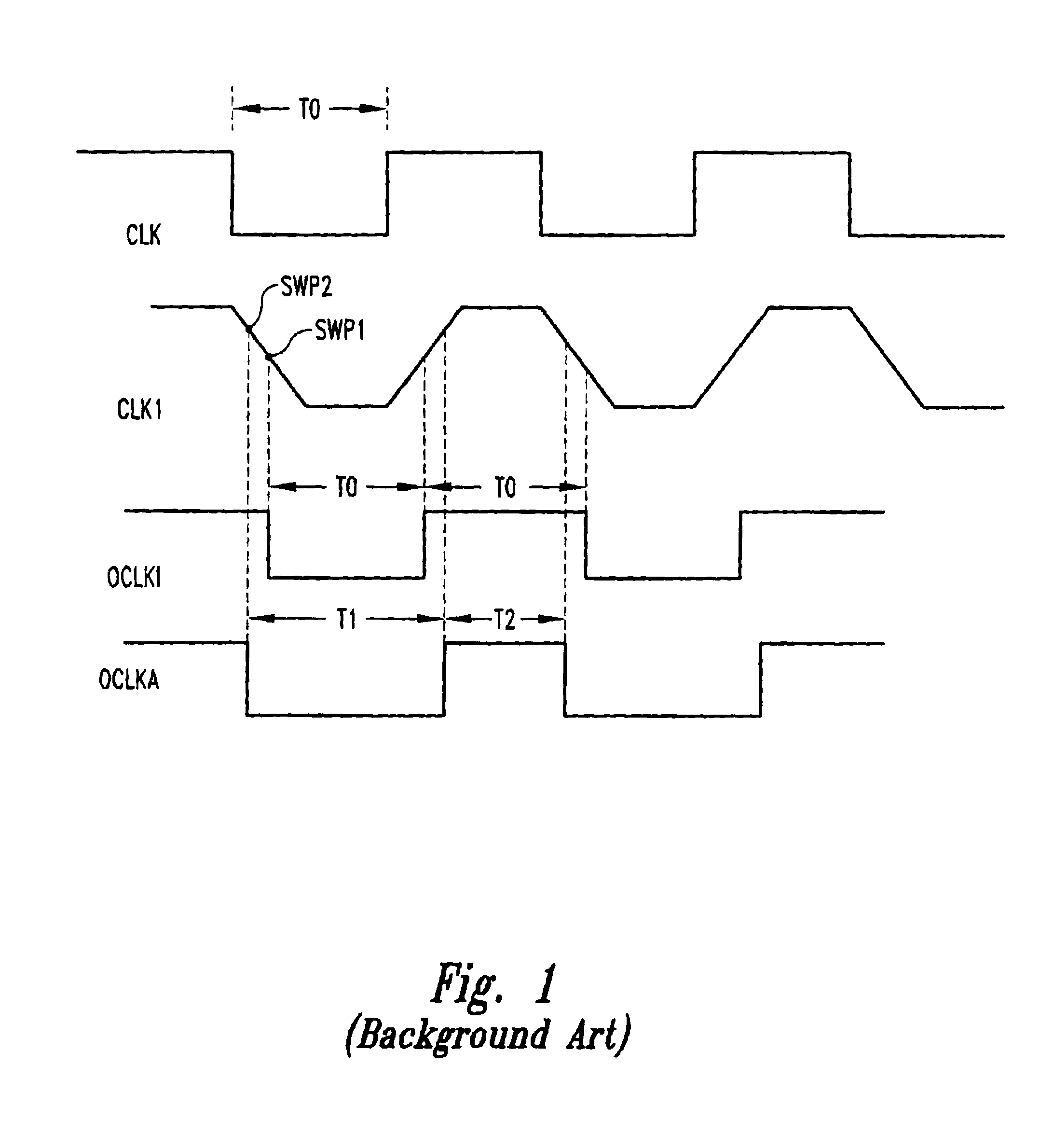

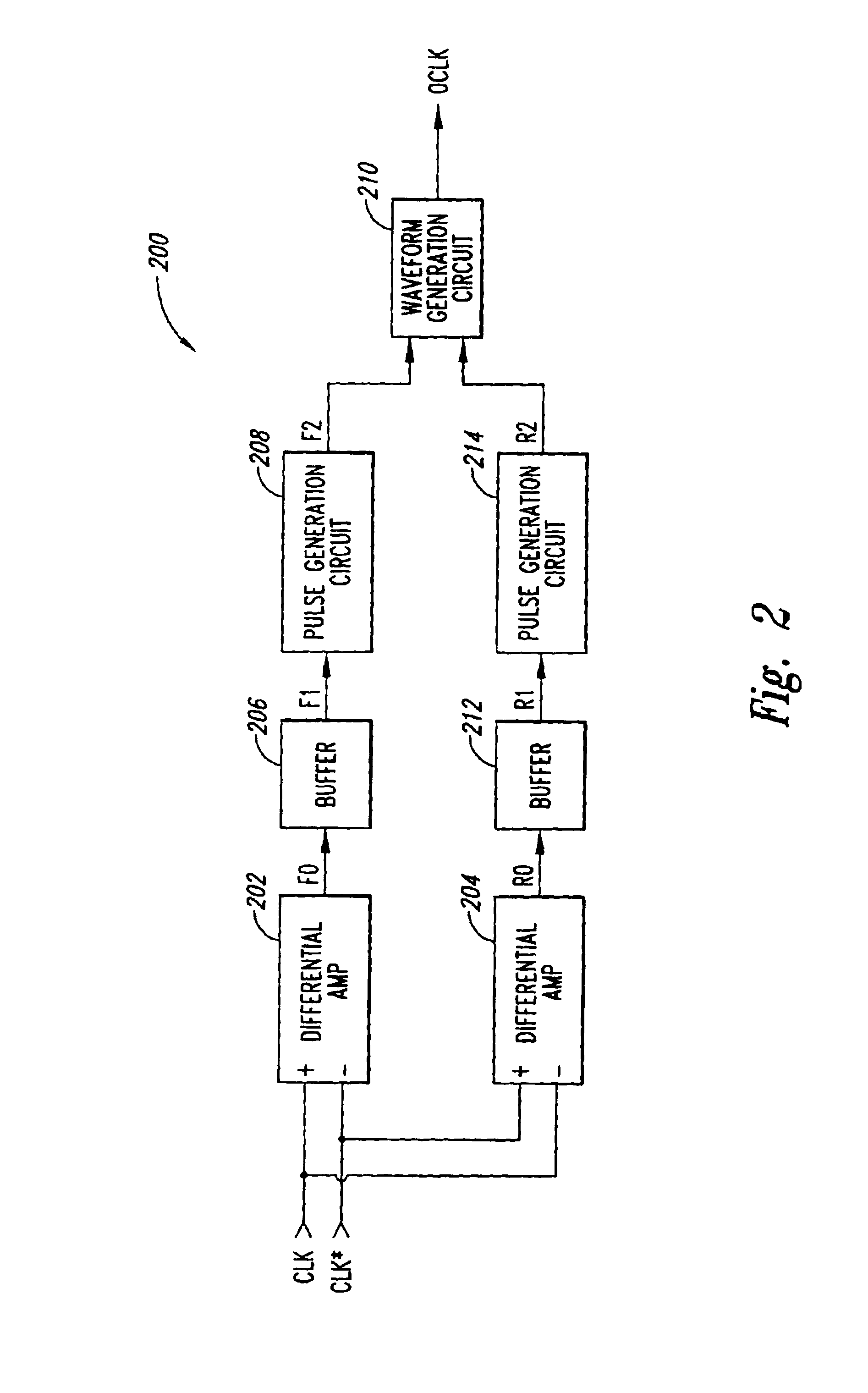

Low skew clock input buffer and method

InactiveUS6847582B2Reliability increasing modificationsDigital storageAudio power amplifierLogic state

An input buffer includes first and second cross-coupled differential amplifiers. Each amplifier drives a buffer signal from a first logic state to a second logic state at a first slew rate when input signal transitions from a first logic state to a second logic state and a complementary input signal transitions from the second logic state to the first logic state, and drives the buffer signal from the second logic state to the first logic state at a second slew rate when the signal transitions are the complement of these previous transitions. An output circuit generates a first edge of an output signal when the buffer signal from the first amplifier transitions from the first logic state to the second logic state and generates a second edged of the output signal when the buffer signal from the second amplifier transitions from the first to the second logic state.

Owner:MICRON TECH INC

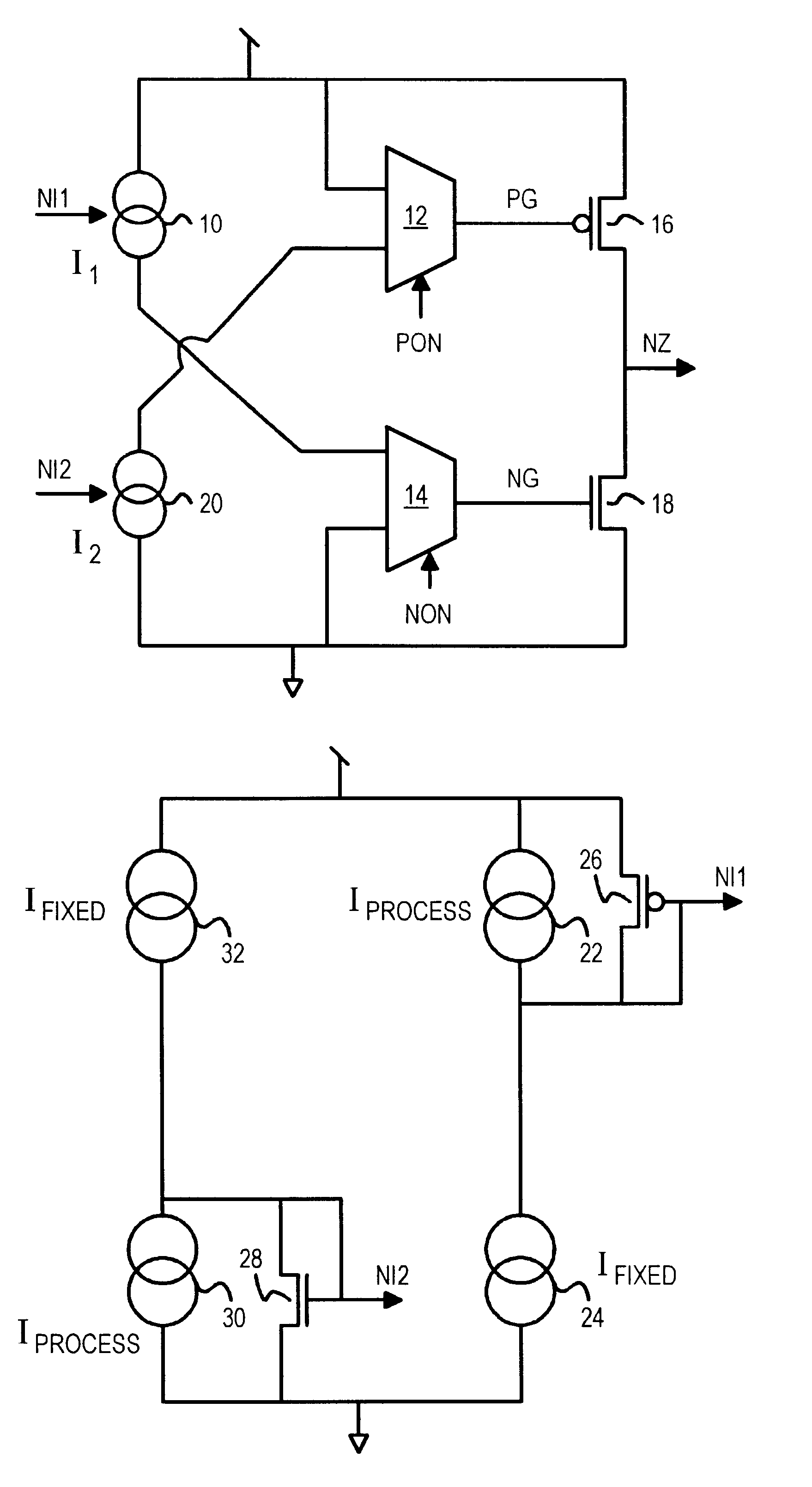

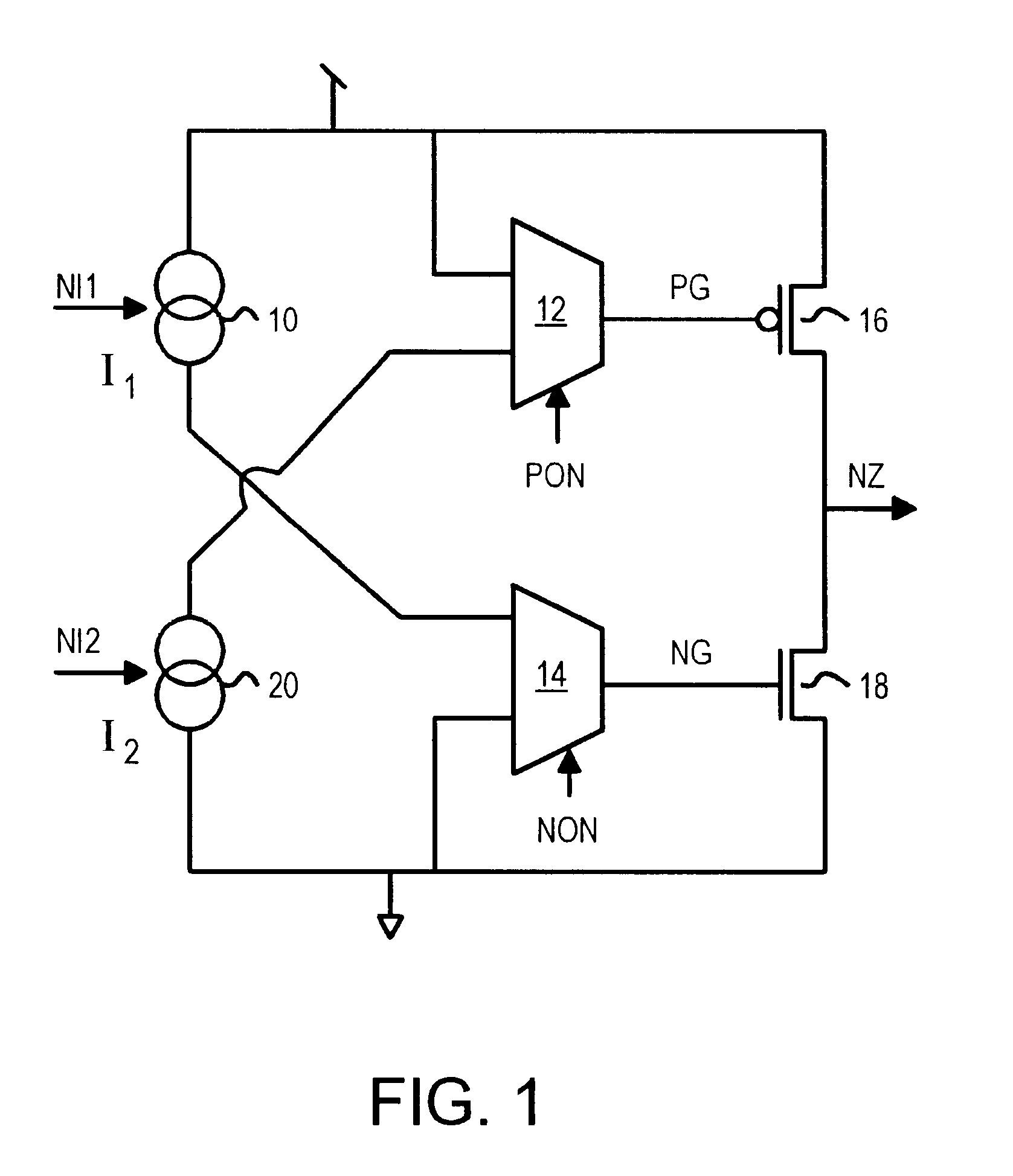

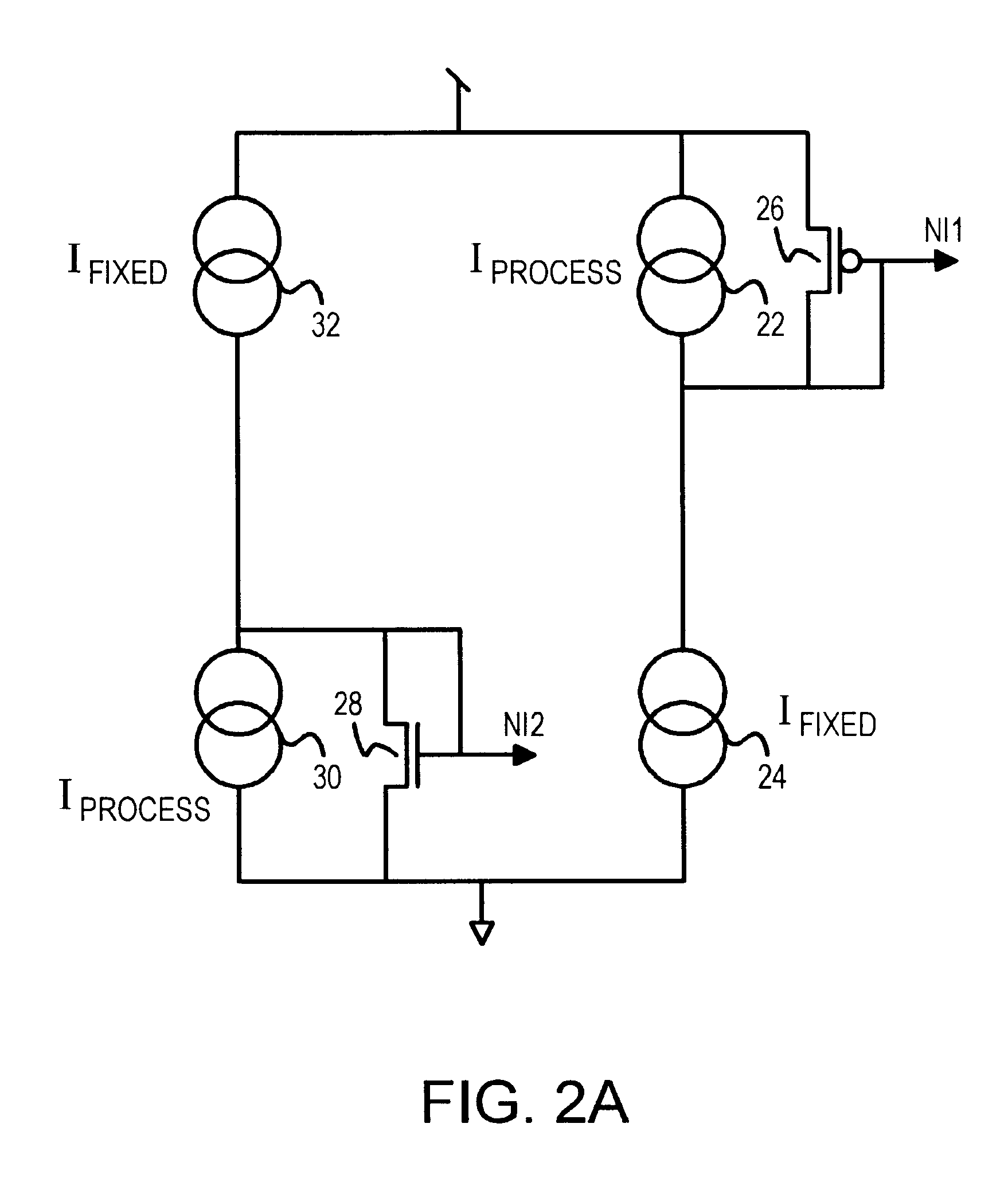

Current-compensated CMOS output buffer adjusting edge rate for process, temperature, and Vcc variations

Edge rates for output driver transistors are increased for slower conditions such as caused by supply-voltage, temperature, and process variations. The edge rates are increased by increasing charging and discharging currents to the gates of the driver transistors. Process-sensing transistors have gates tied to power or ground. Current through the process-sensing transistors changes with supply-voltage, temperature, and process variations. The currents through process-sensing transistors are used to generate process-compensated voltages that bias current sources and sinks to adjust process-dependent currents. Process-independent or fixed current sources and sinks use process-independent reference voltages ultimately generated from reference currents that are not sensitive to process variations. The process-dependent-currents are subtracted from the fixed currents to produce the charging and discharging currents.

Owner:DIODES INC

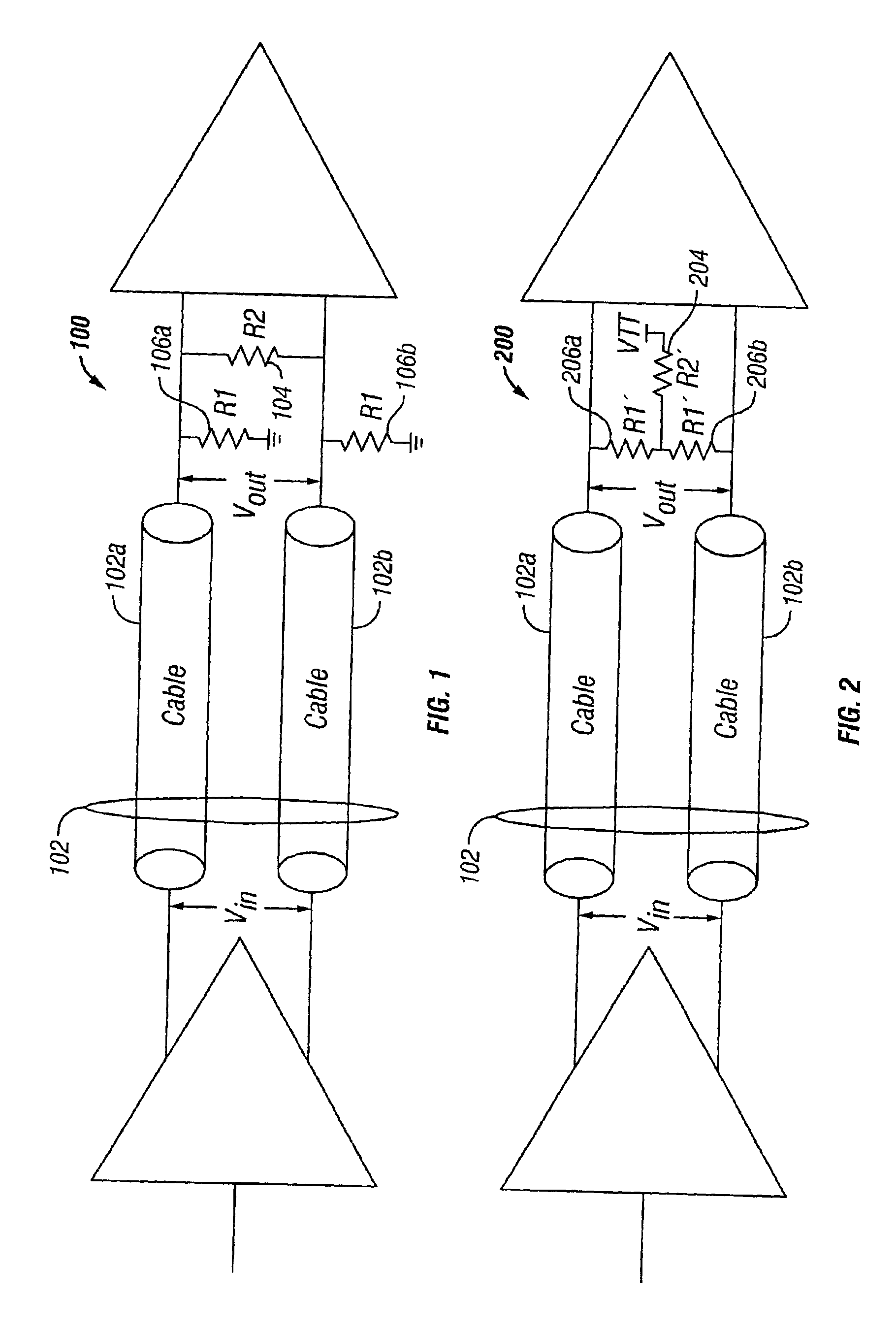

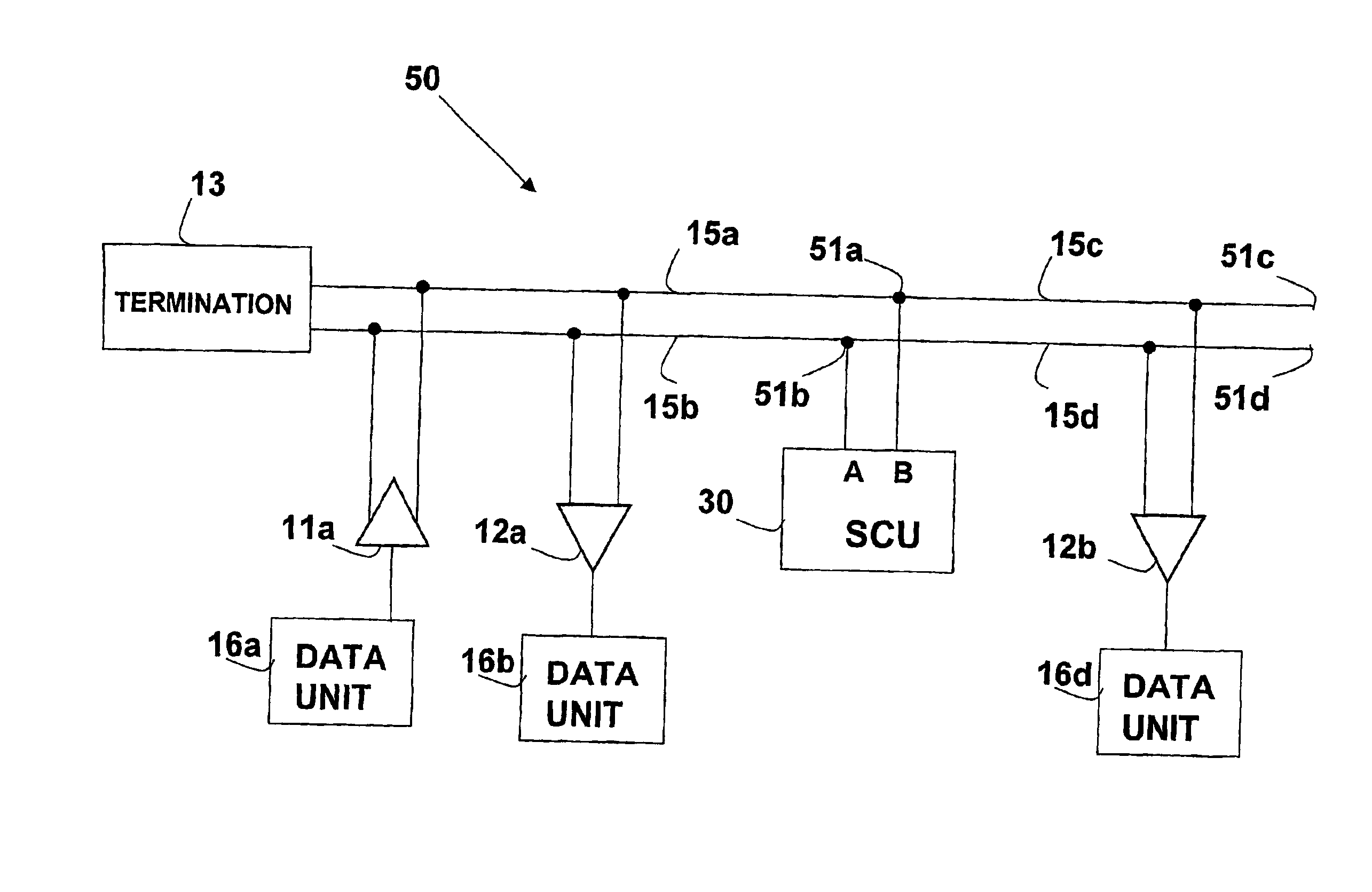

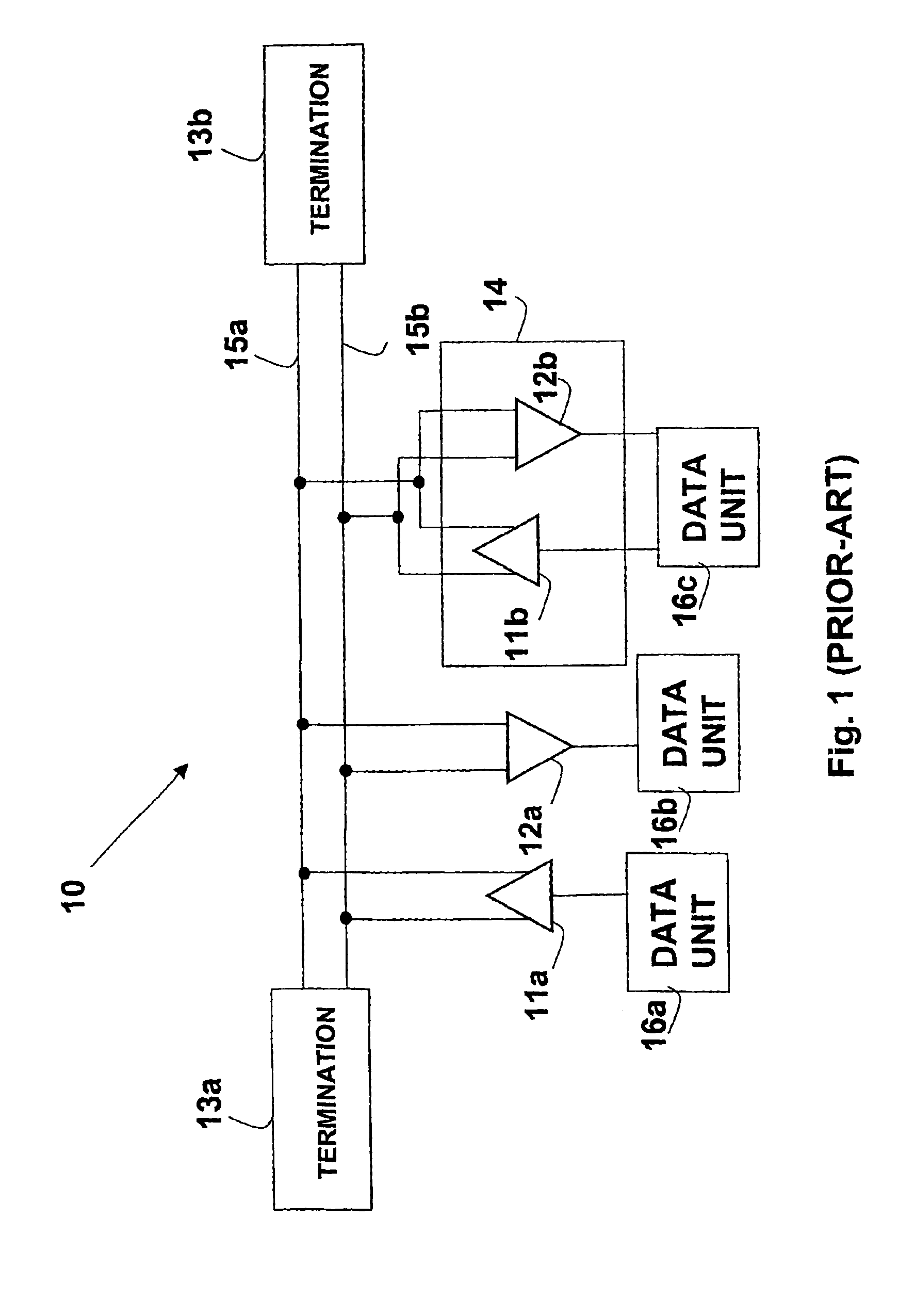

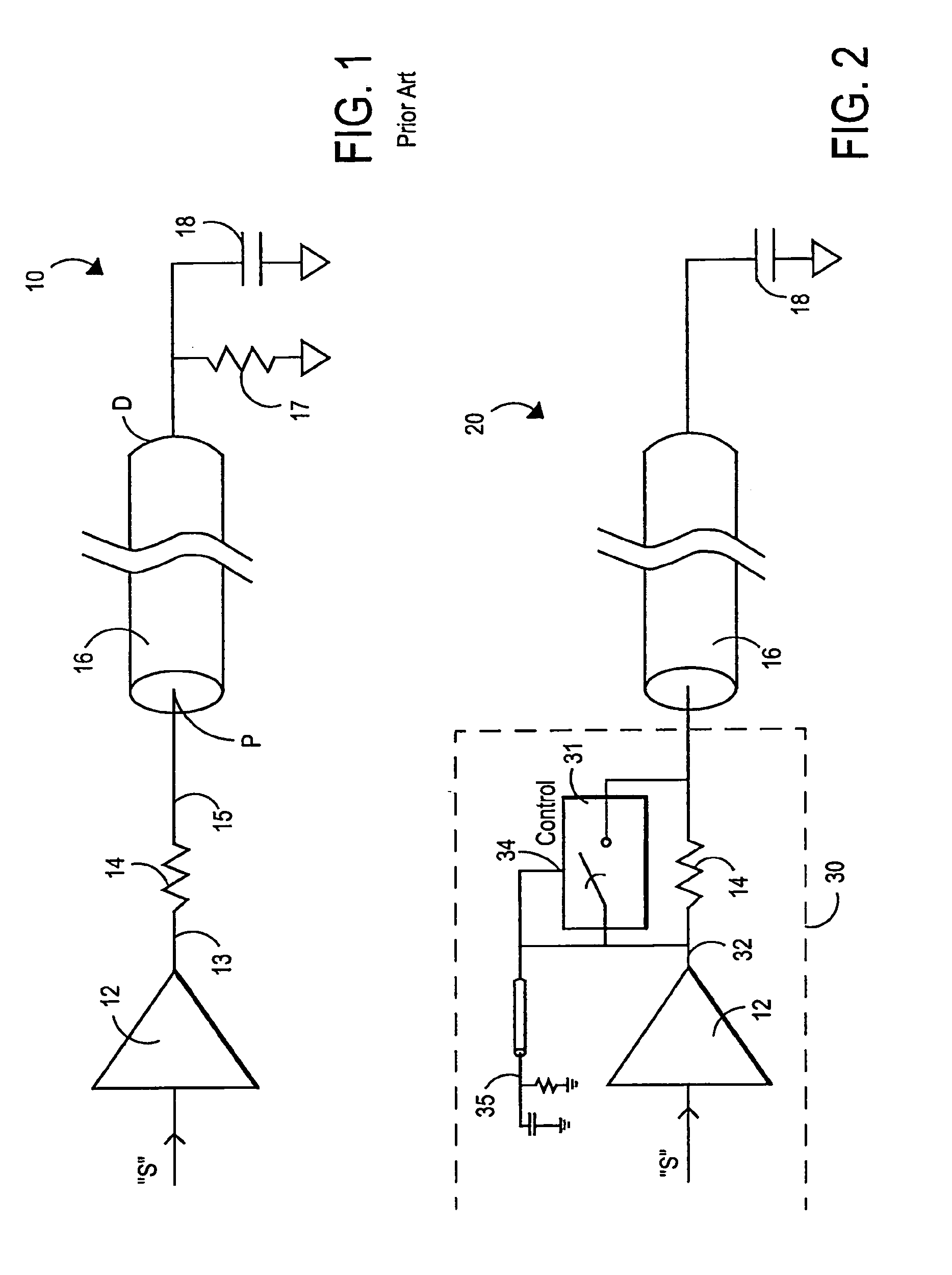

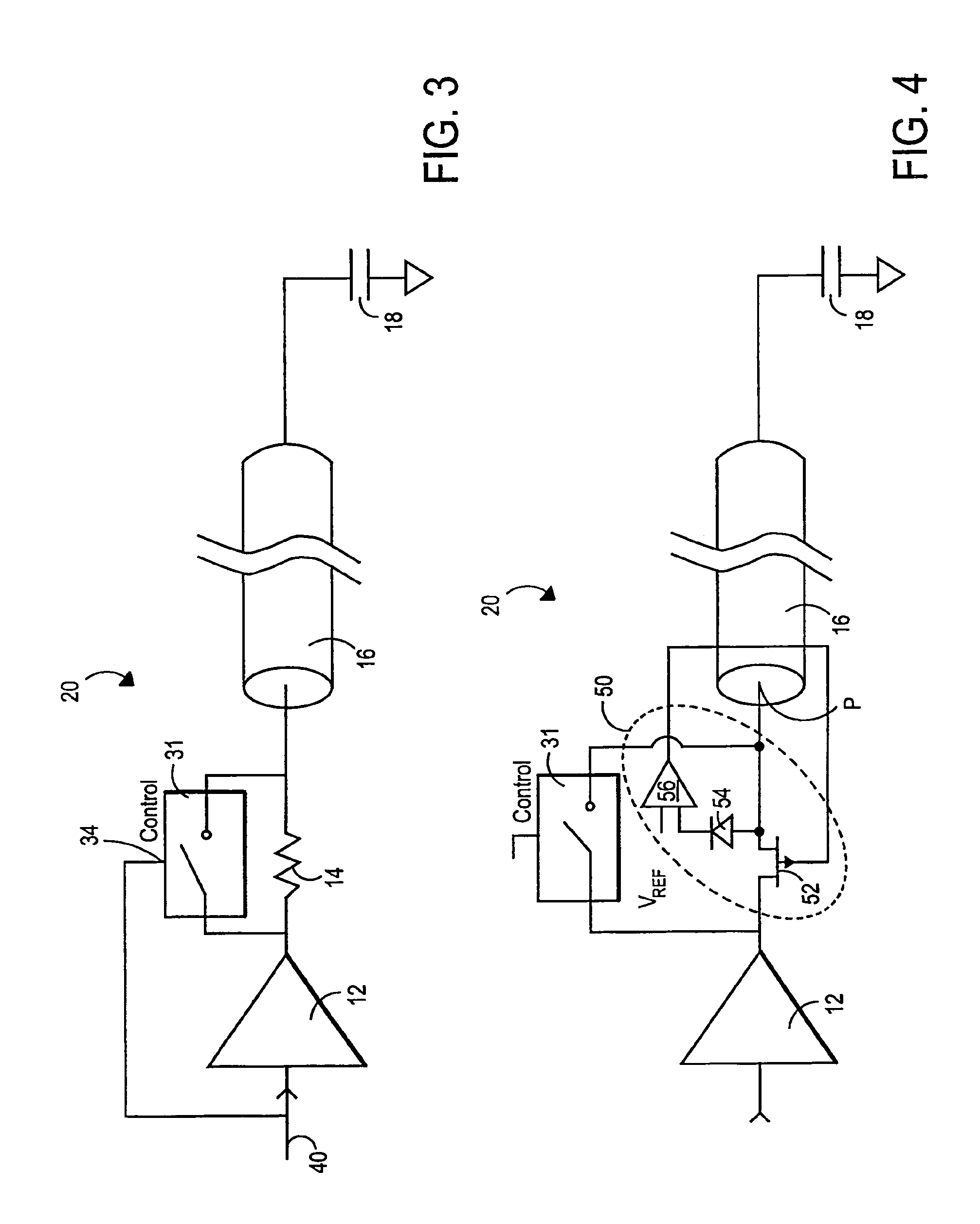

System and method for transmission-line termination by signal cancellation, and applications thereof

InactiveUS6937056B2Effective segmentationInput/output impedence modificationReliability increasing modificationsElectric power transmissionNetwork termination

An active terminating device (30) for an electrical transmission line with optional line-receiving and line-driving capabilities. The basic device is a two-terminal unit, denoted as a Signal Canceling Unit (SCU), which sensesthe signal available at its terminals (34a, 34b), and applies negative feedback in order to cancel and absorb the signal. When applied to the end of a transmission line (15a, 15b) as part of wired communication network, the SCU functions as a terminator. When connected in the middle of such wired transmission line, the SCU splits the transmission line into two separate and isolated segments. In such a configuration, the SCU can be used to isolate a portion of a network from signal degradation due to noise or bridge-tap. Furthermore, the two isolated segments may each employ independent communications, such that no interference exists between the segments. In another embodiment, line receiver functionality is integrated into the SCU, designated as a Signal Canceling and Receiving Unit (SCRU) (90). The SCRU can perform all the SCU functions, and also serves as a line receiver in the communication network. In yet another embodiment, line driver functionality is integrated into the SCRU, designated as a Signal Canceling, Receiving and Transmitting Unit (SCRTU) (120). The SCRTU can perform all the SCRU functions, and also serves as a line driver in the communication network. Upon connecting multiple SCRTU's to a continuous transmission line, terminated independent point-to-point communication segments are formed.

Owner:CONVERSANT INTPROP MANAGEMENT INC

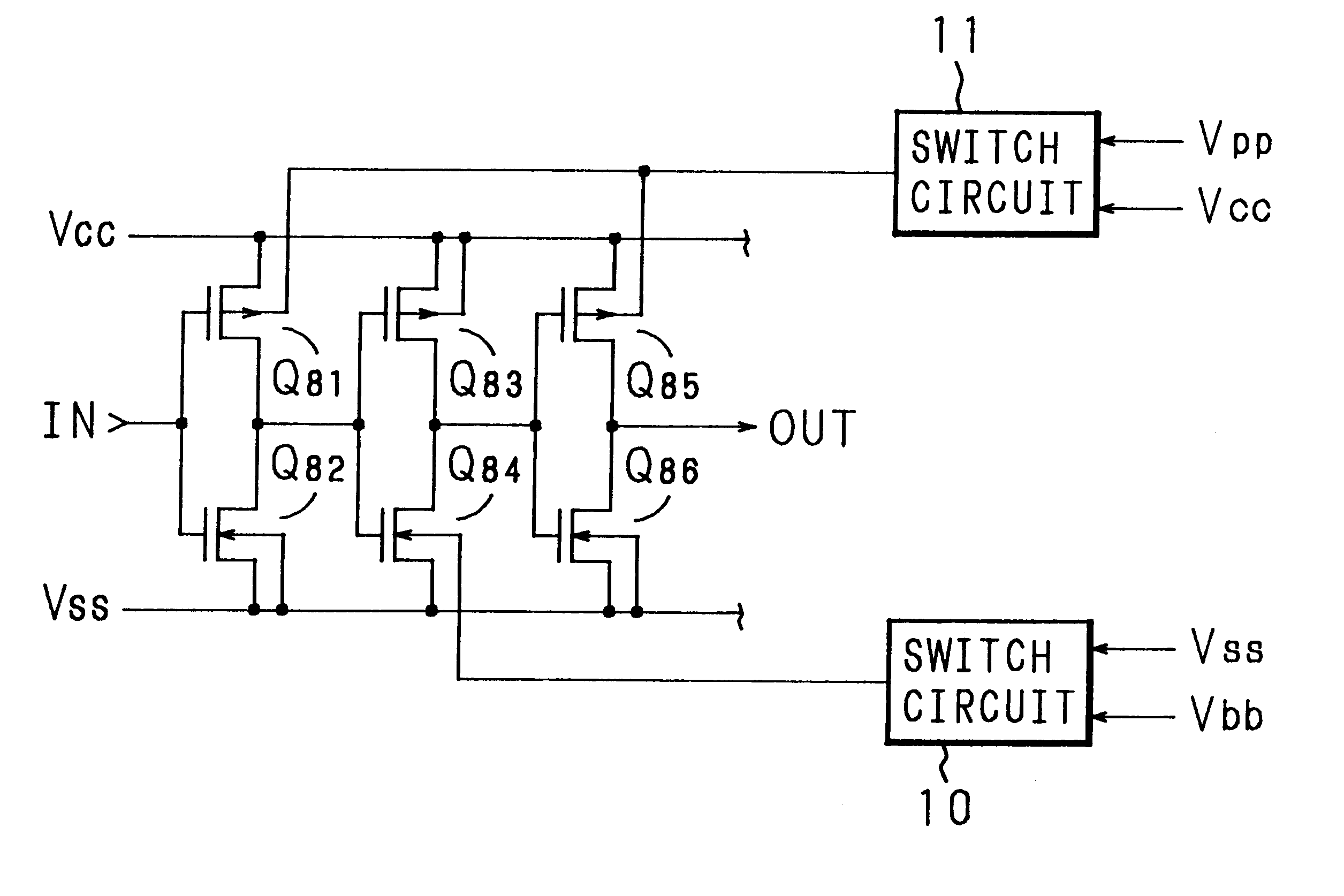

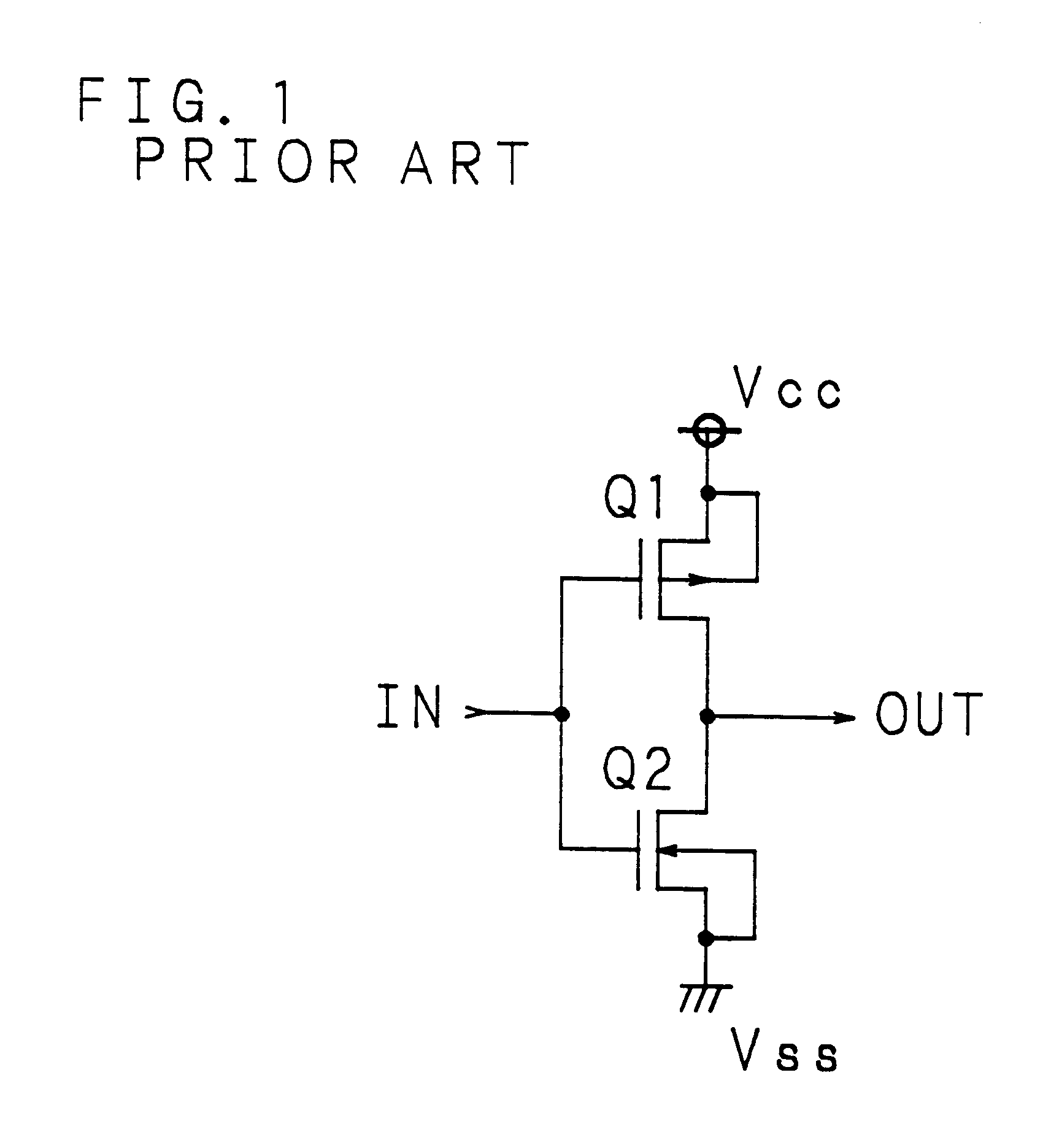

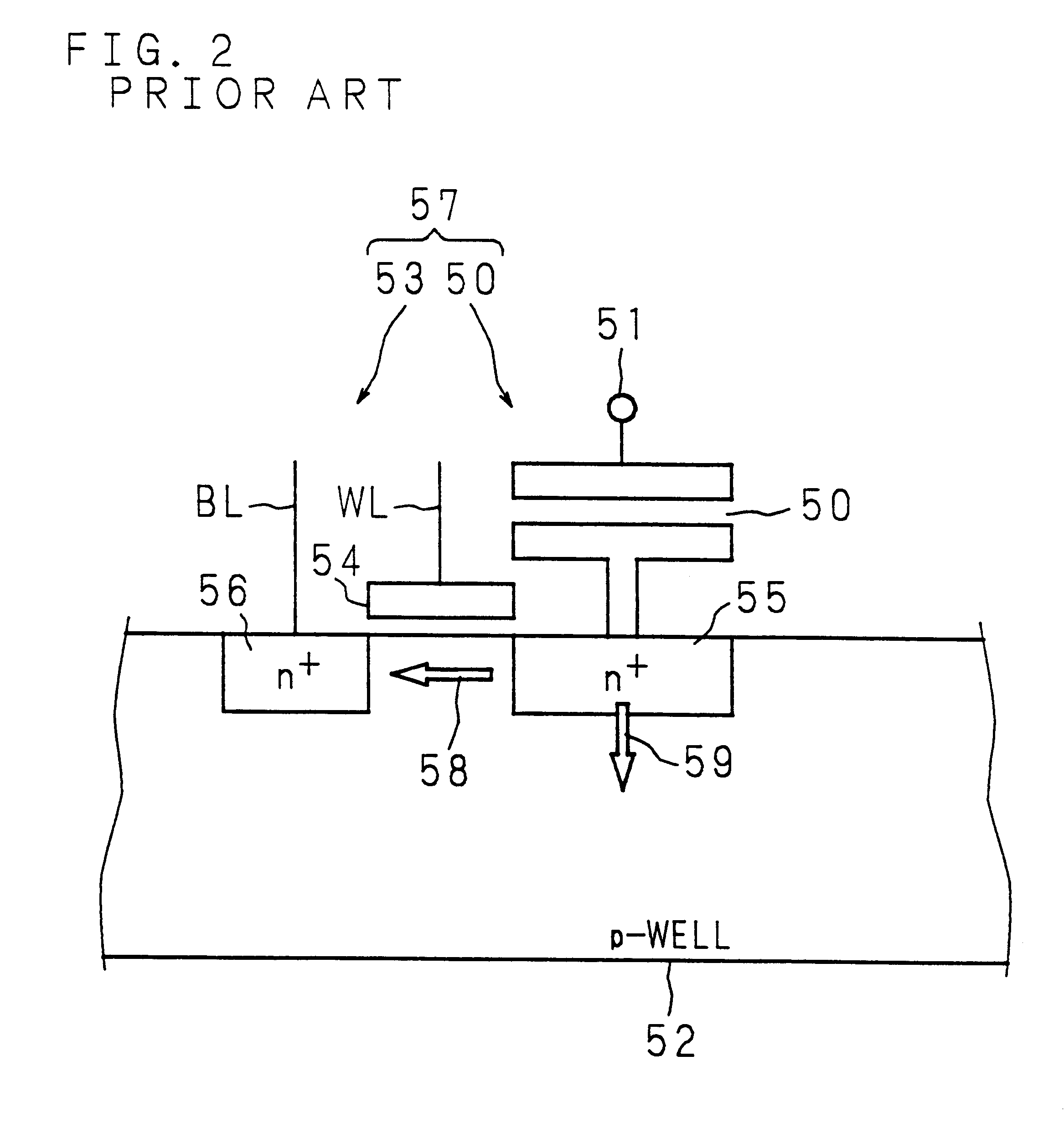

Switched backgate bias for FET

InactiveUS6232793B1Reliability increasing modificationsPower reduction by control/clock signalHemt circuitsEngineering

A semiconductor circuit or a MOS-DRAM wherein converting means is provided that converts substrate potential or body bias potential between two values for MOS-FETs in a logic circuit, memory cells, and operating circuit of the MOS-DRAM, thereby raising the threshold voltage of the MOS-FETs when in the standby state and lowering it when in active state. The converting means includes a level shift circuit and a switch circuit. The substrate potential or body bias potential is controlled only of the MOS-FETs which are nonconducting in the standby state; this configuration achieves a reduction in power consumption associated with the potential switching. Furthermore, in a structure where MOS-FETs of the same conductivity type are formed adjacent to each other, MOS-FETs of SOI structure are preferable for better results.

Owner:RENESAS ELECTRONICS CORP

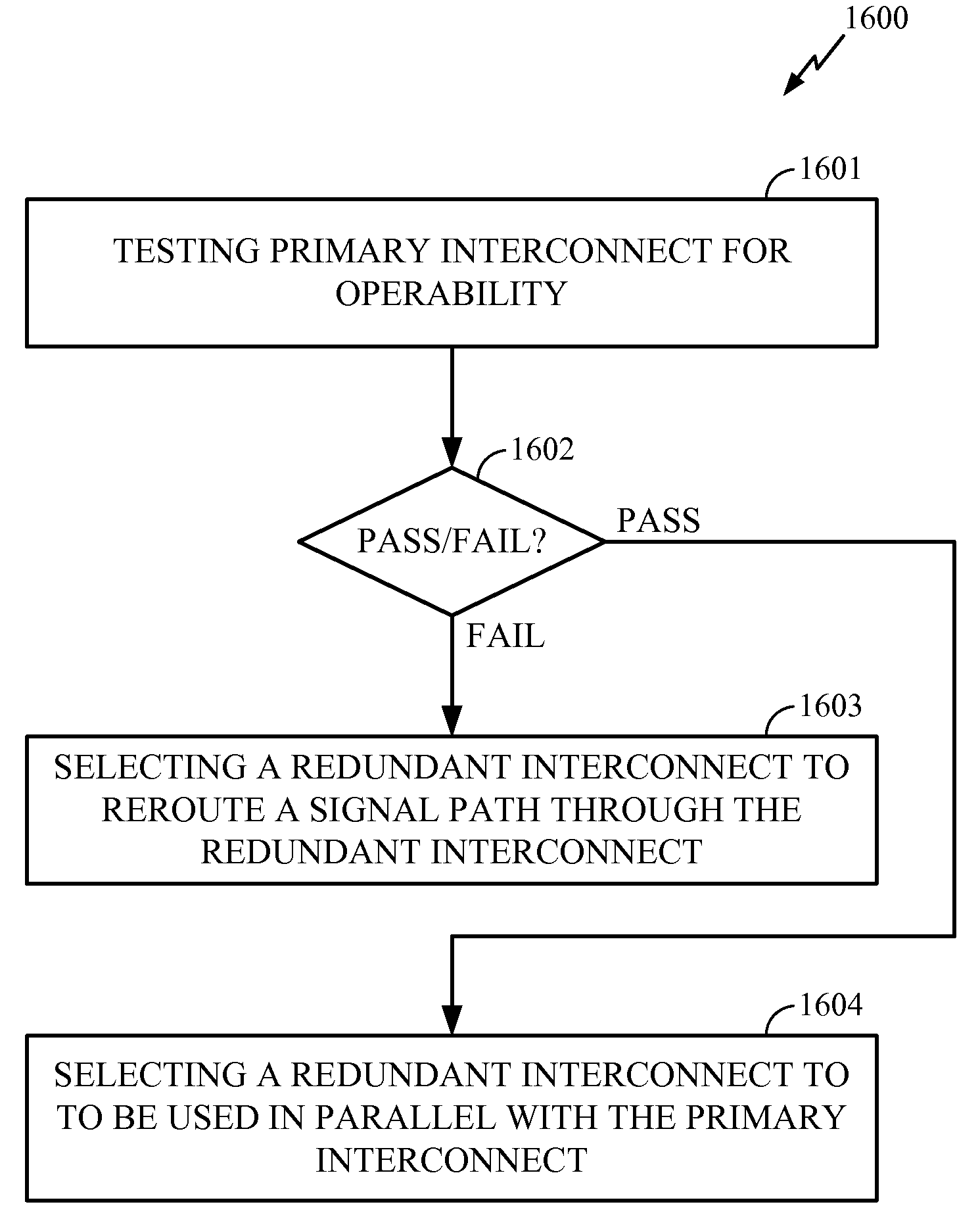

Systems and Methods Utilizing Redundancy in Semiconductor Chip Interconnects

ActiveUS20100060310A1Reliability increasing modificationsSemiconductor/solid-state device testing/measurementSemiconductor chipIntegrated circuit

An integrated circuit, or combination of integrated circuits, has a primary interconnect, a redundant interconnect, and circuitry connecting the primary and redundant interconnects allowing selection of the redundant interconnect to bypass the primary interconnect.

Owner:QUALCOMM INC

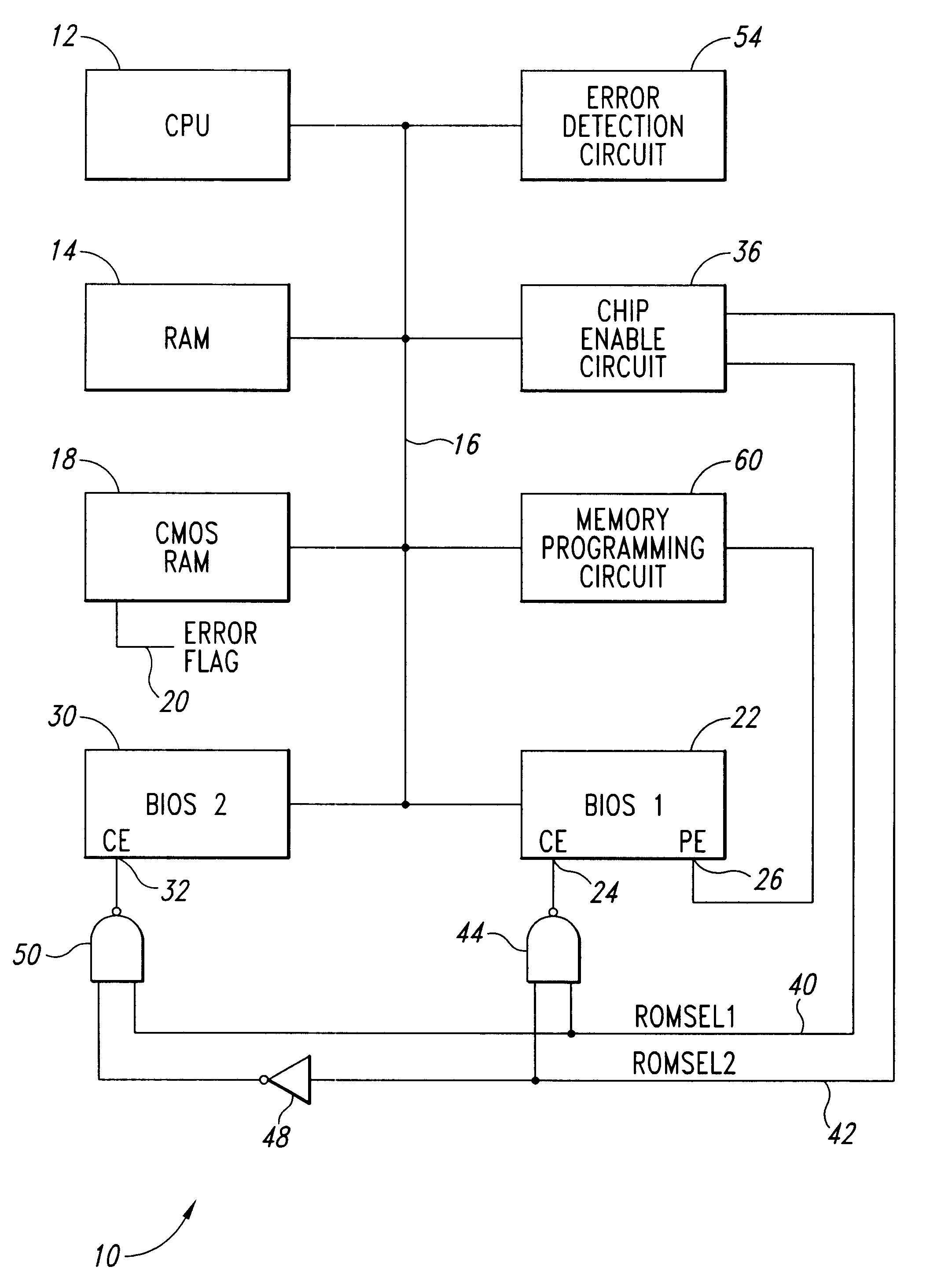

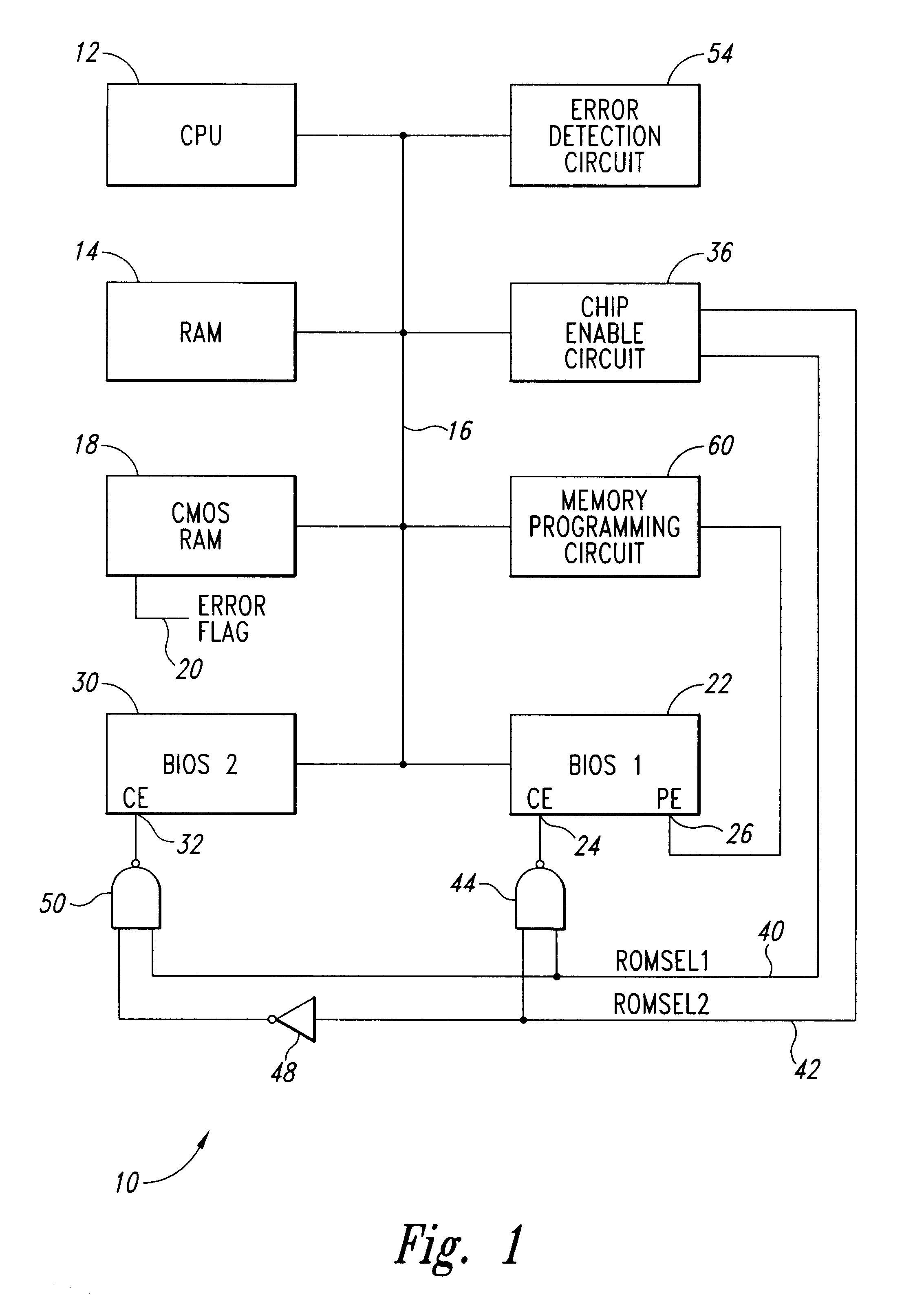

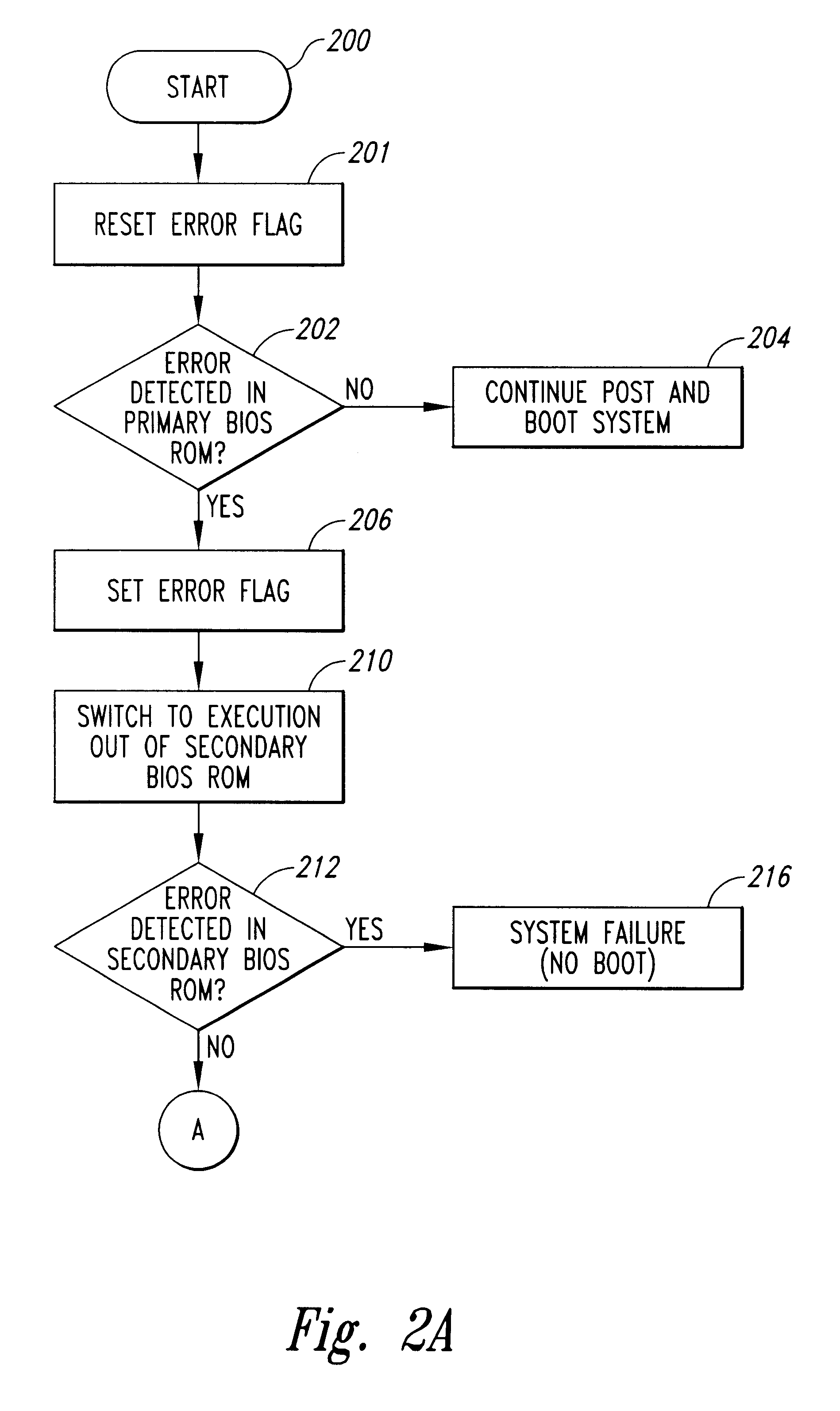

System for a primary BIOS ROM recovery in a dual BIOS ROM computer system

InactiveUS6185696B1Reliability increasing modificationsDetecting faulty hardware by power-on testRandom access memoryComputerized system

A computer system includes a dual basic input-output system (BIOS) read-only memory (ROM) system to initialize the computer. When the computer is first powered on or reset, the primary BIOS ROM is initially enabled. The computer analyzes the contents of the primary BIOS memory to detect data errors. If a data error is detected, a chip enable circuit disables the primary BIOS ROM and enables a secondary BIOS ROM containing essentially the same initialization instructions as the primary BIOS ROM. If no errors are detected in the secondary BIOS ROM, the initialization of the computer proceeds using the secondary BIOS ROM. As part of the initialization procedure, the contents of the secondary BIOS ROM are copied to a random access memory. The primary BIOS ROM can then be reprogrammed with the contents of the secondary BIOS ROM using the copy in random access memory, or from the secondary BIOS ROM itself.

Owner:MEI CALIFORNIA +1

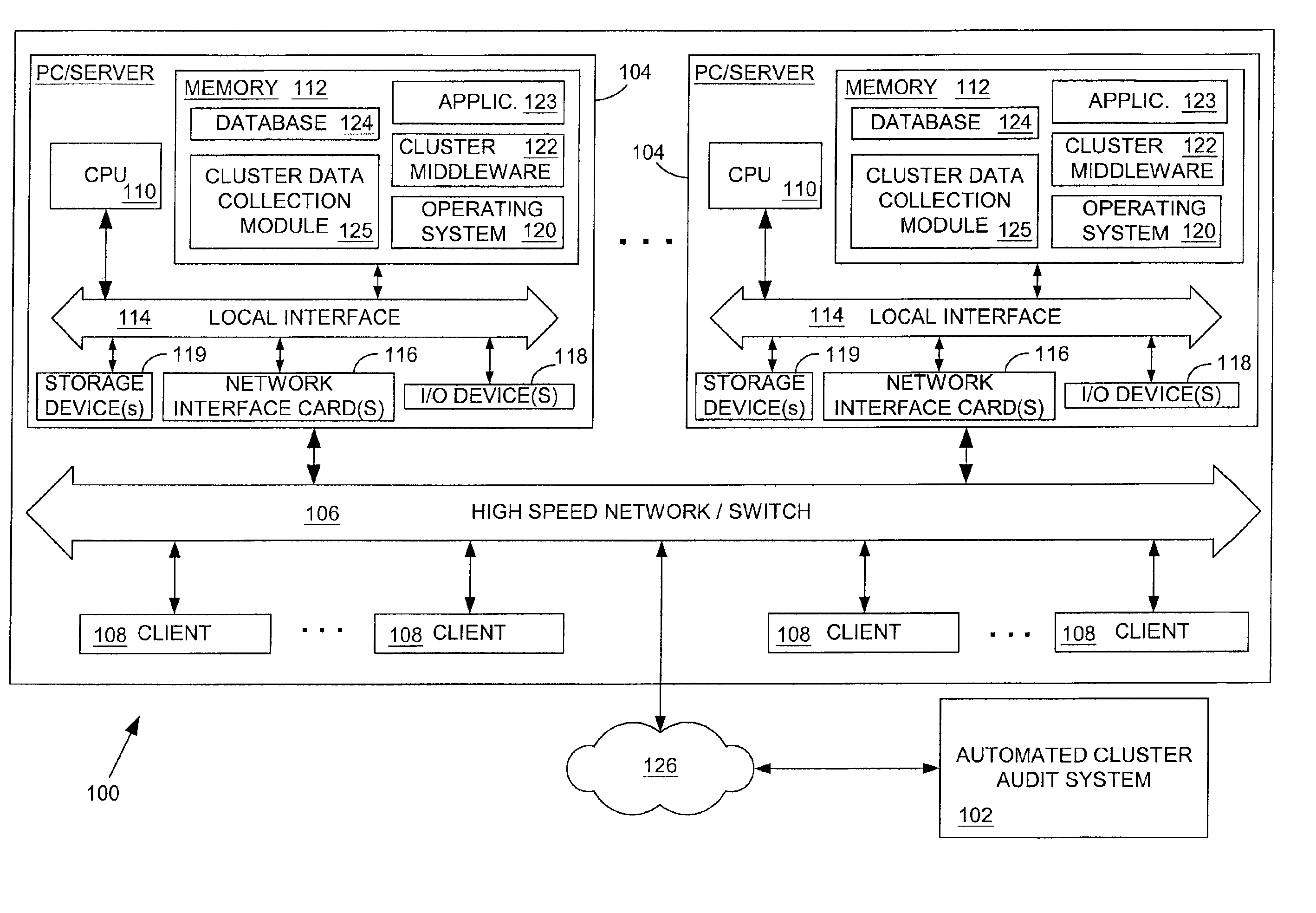

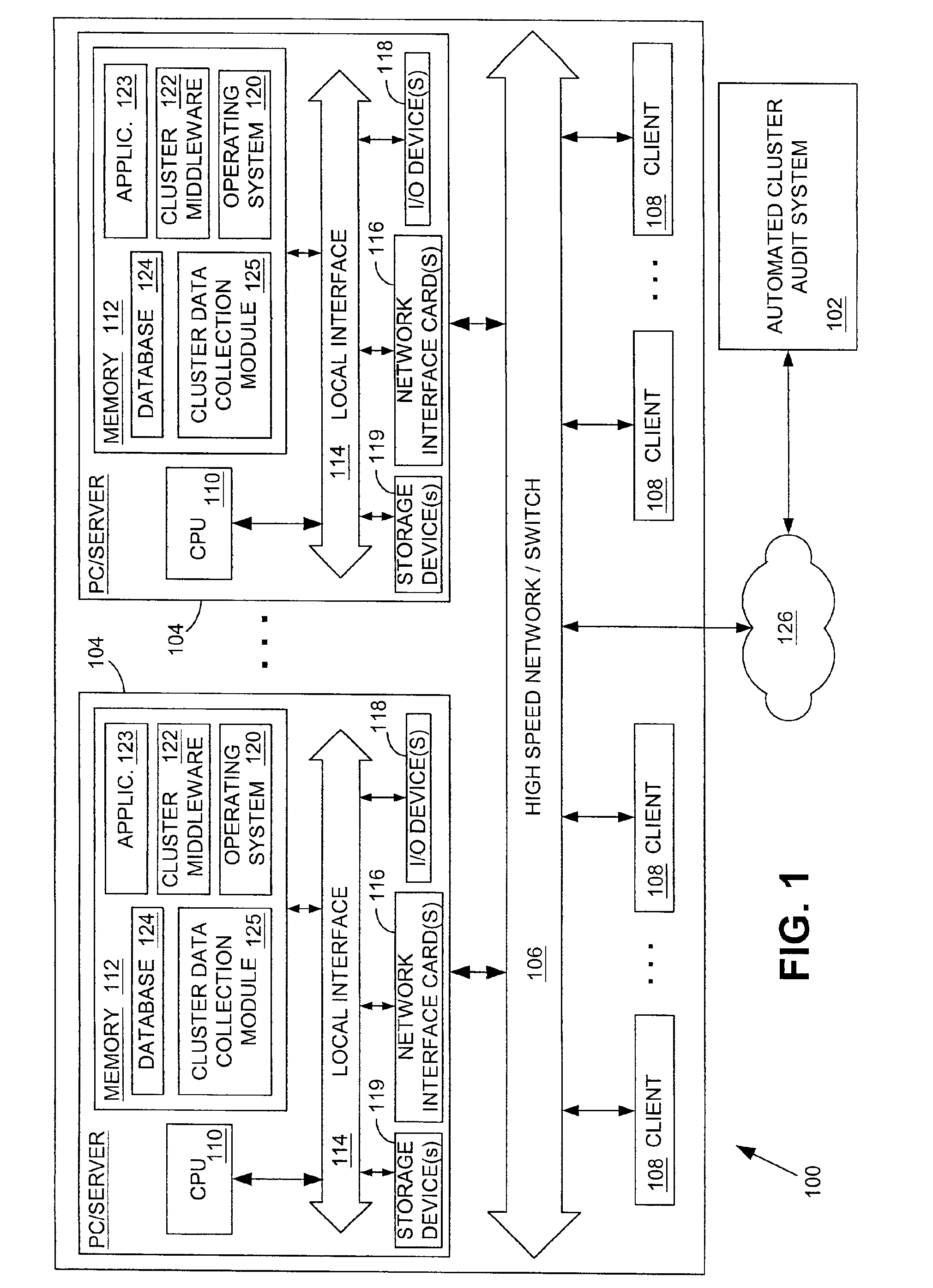

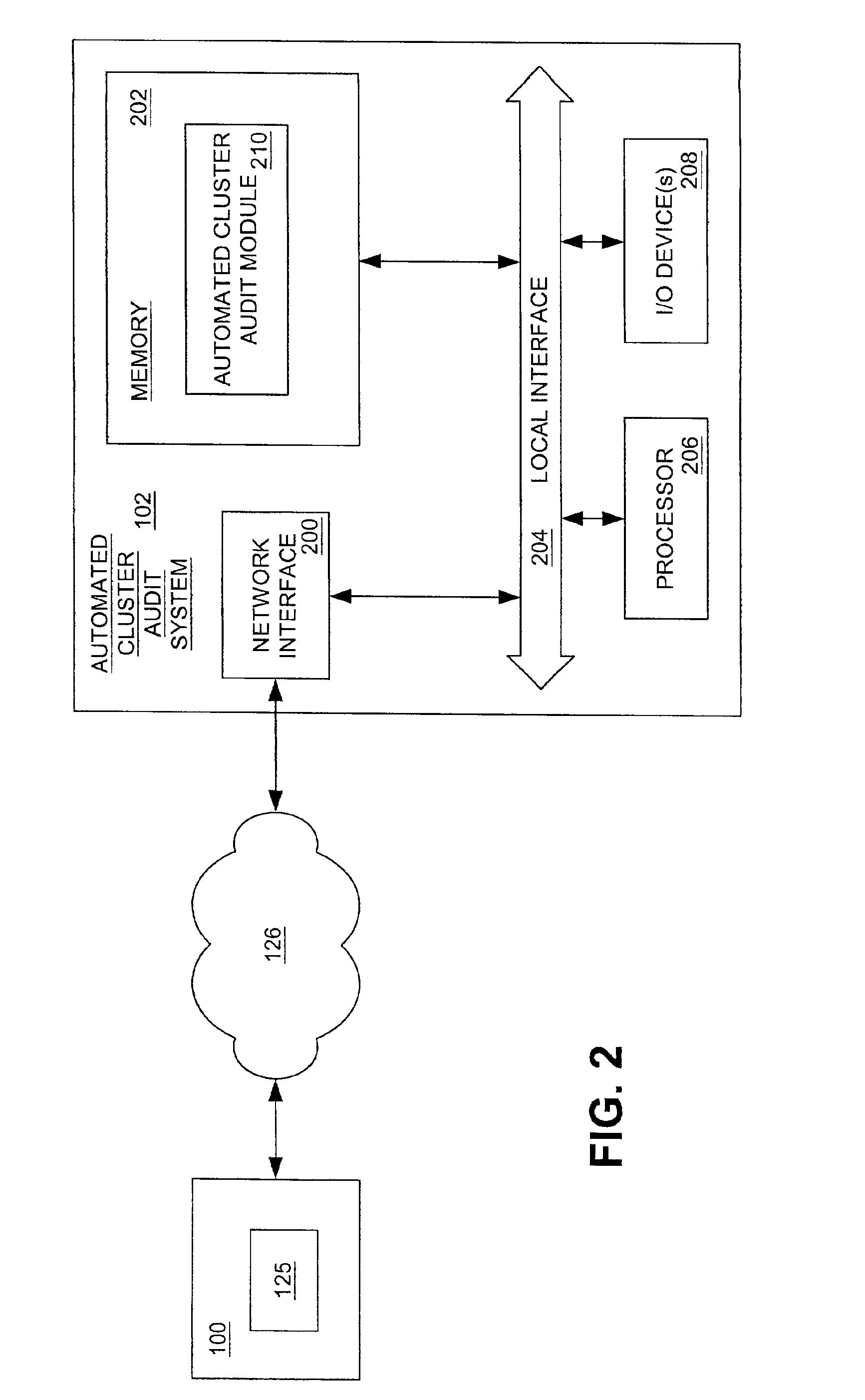

Systems and methods for providing automated diagnostic services for a cluster computer system

InactiveUS6895534B2Reliability increasing modificationsHardware monitoringMiddlewareNetwork parameter

Systems and methods for providing automated diagnostic services for a cluster computer system are provided. One embodiment is a method for providing automated diagnostic services for a cluster computer system comprising a plurality of nodes. Each of the plurality of nodes may provide an application to a plurality of clients. Briefly described, one such method comprises the steps of: receiving a current value of a network parameter related to cluster middleware associated with the cluster computer system; analyzing the current value of the network parameter relative to a predetermined reference value for the network parameter; and providing information based on the analysis of the current value relative to the predetermined reference value.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

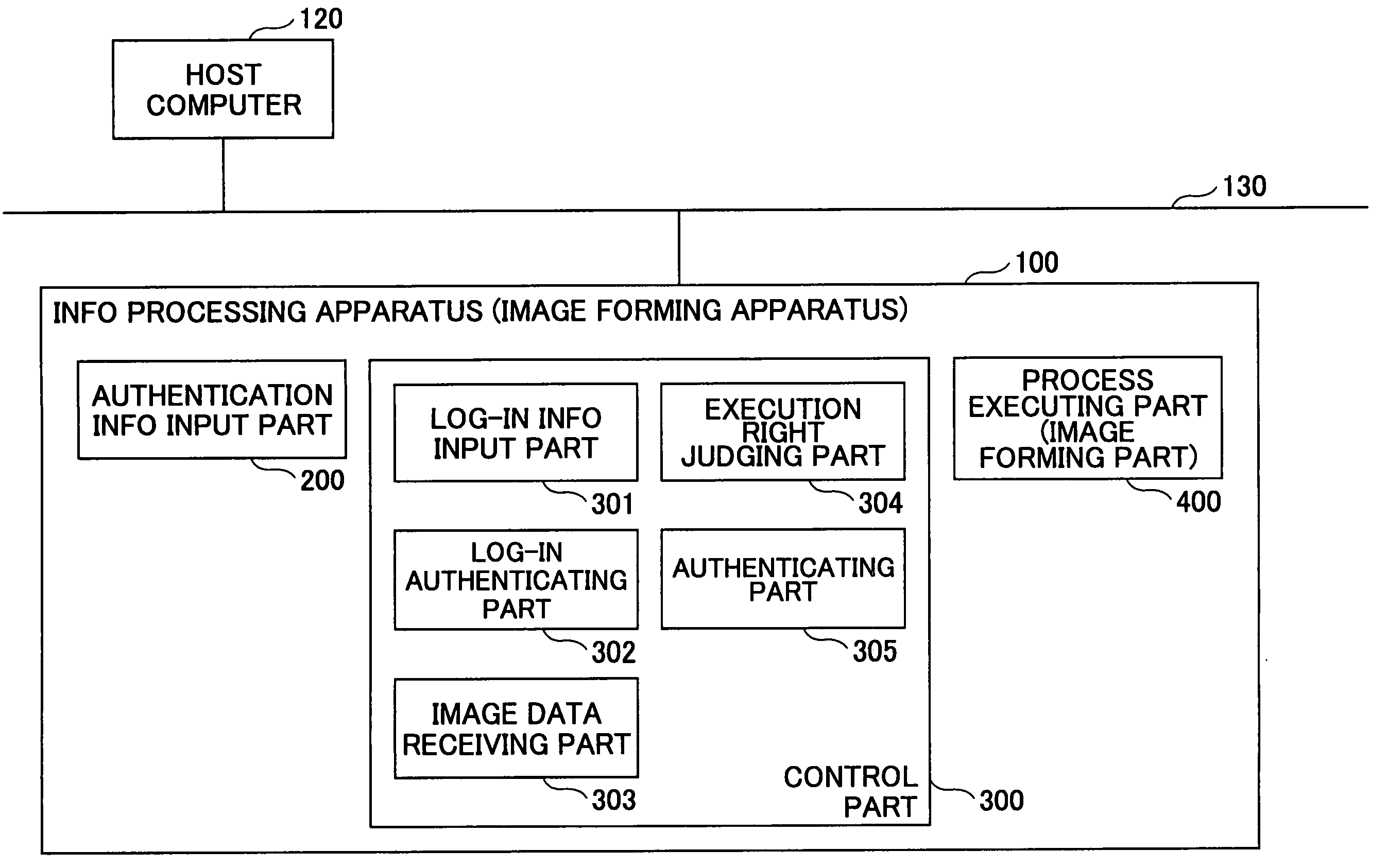

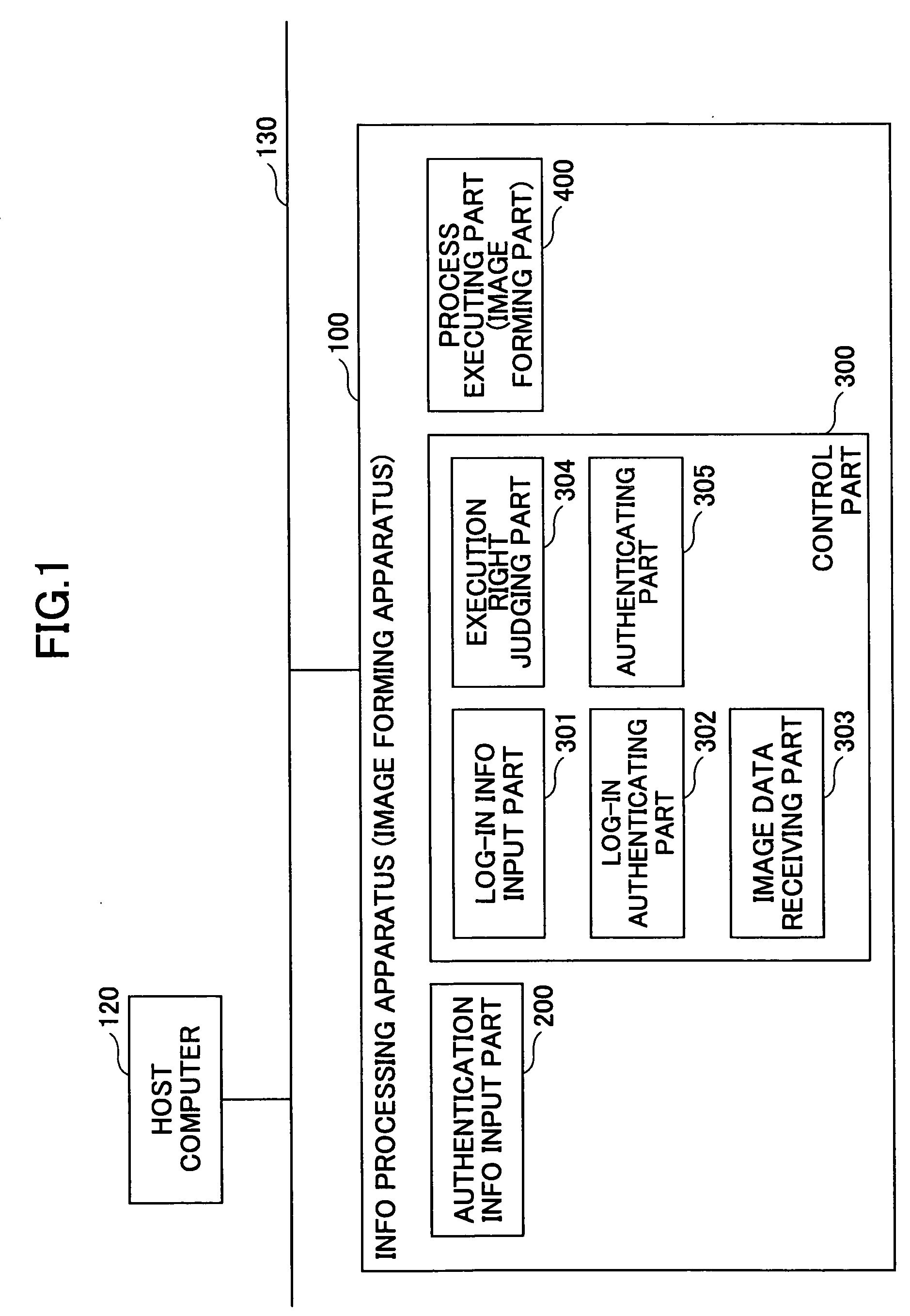

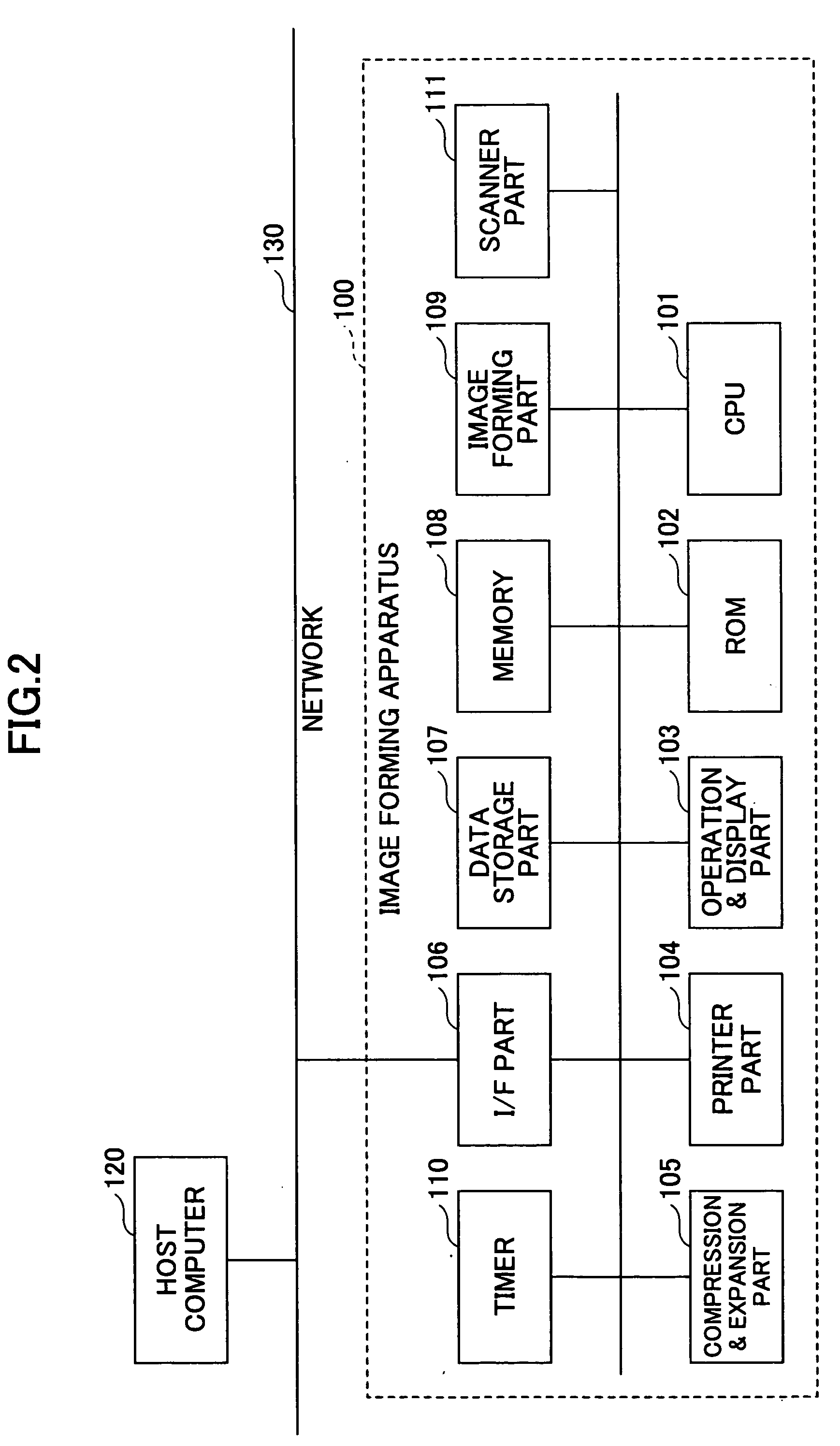

Image forming apparatus, information processing apparatus, information processing system, authentication method and computer-readable storage medium

ActiveUS20050183141A1Improve reliabilityReliable environmentReliability increasing modificationsMetering/charging/biilling arrangementsInformation handling systemInformation processing

An image forming apparatus includes an input part to input authentication information for authenticating a predetermined operation with respect to a registered printing job, an input part to input log-in authentication information for authenticating the predetermined operation from an operation part, an image forming part to form an image of the printing job, and a control part to request input of the authentication information for authenticating the predetermined operation with respect to a printing job that is being executed by the image forming part when the predetermined operation is made from the operation part in a logged in state, and authenticating the predetermined operation with respect to the printing job when authentication of the authentication information input by the input part is successful.

Owner:RICOH KK

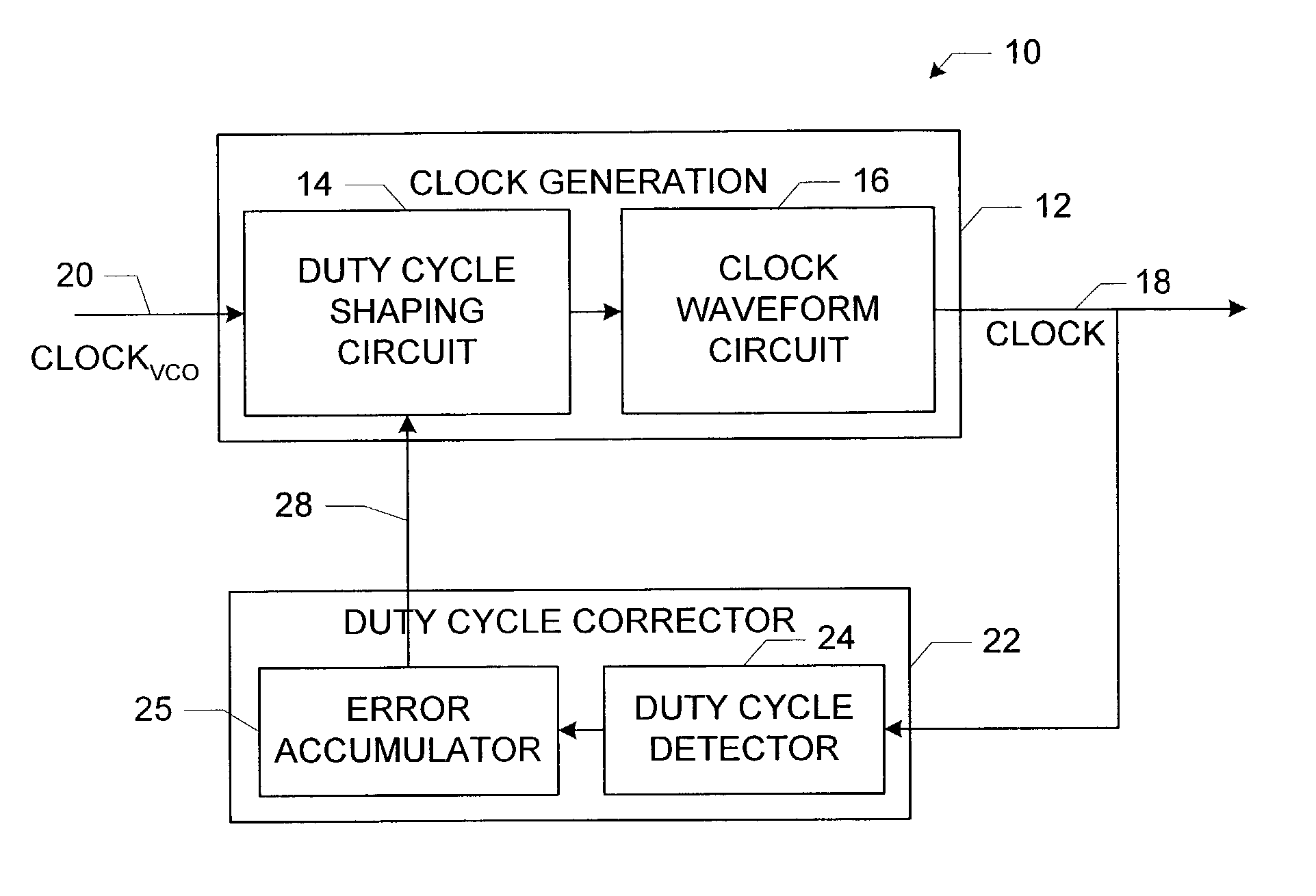

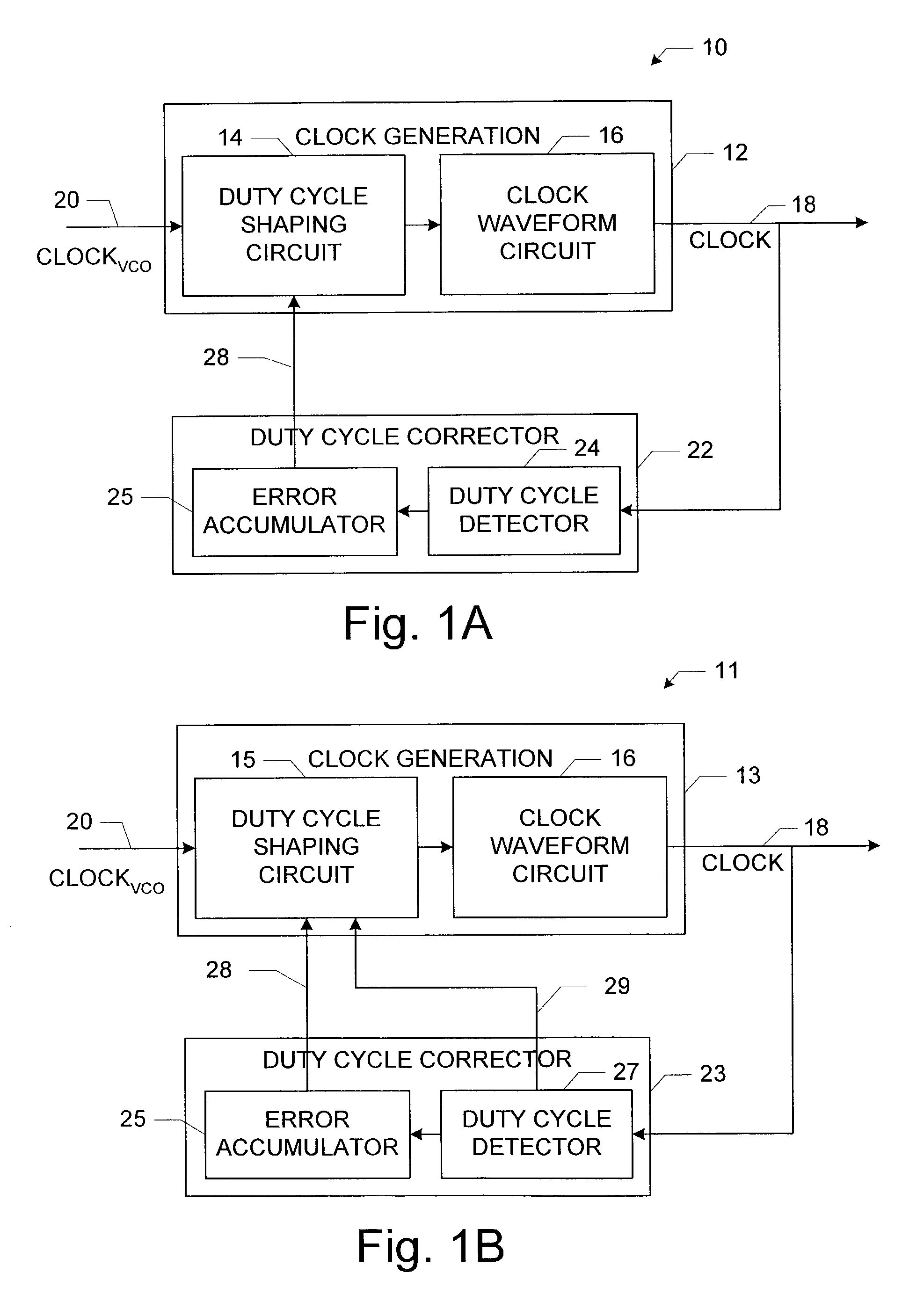

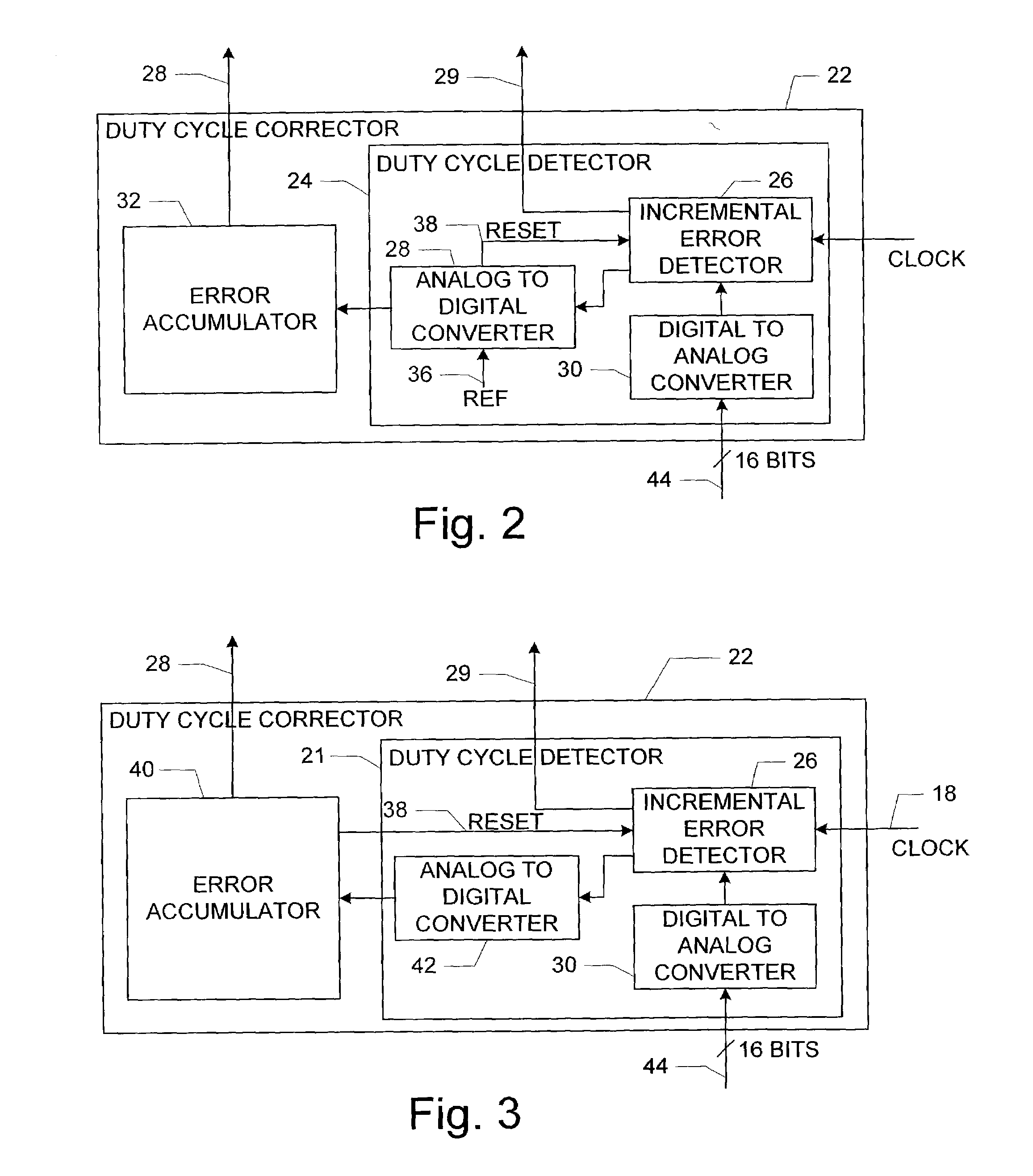

Method and apparatus for digital duty cycle adjustment

InactiveUS6967514B2Reliability increasing modificationsContinuous to patterned pulse manipulationError signalClock signal

Adjusting a clock duty cycle. An incremental error signal is generated in response to the clock signal. A cumulative error signal is generated in response to the incremental error signal. The incremental error signal is reset and the duty cycle of the clock signal is adjusted in response to the cumulative error signal.

Owner:RAMBUS INC

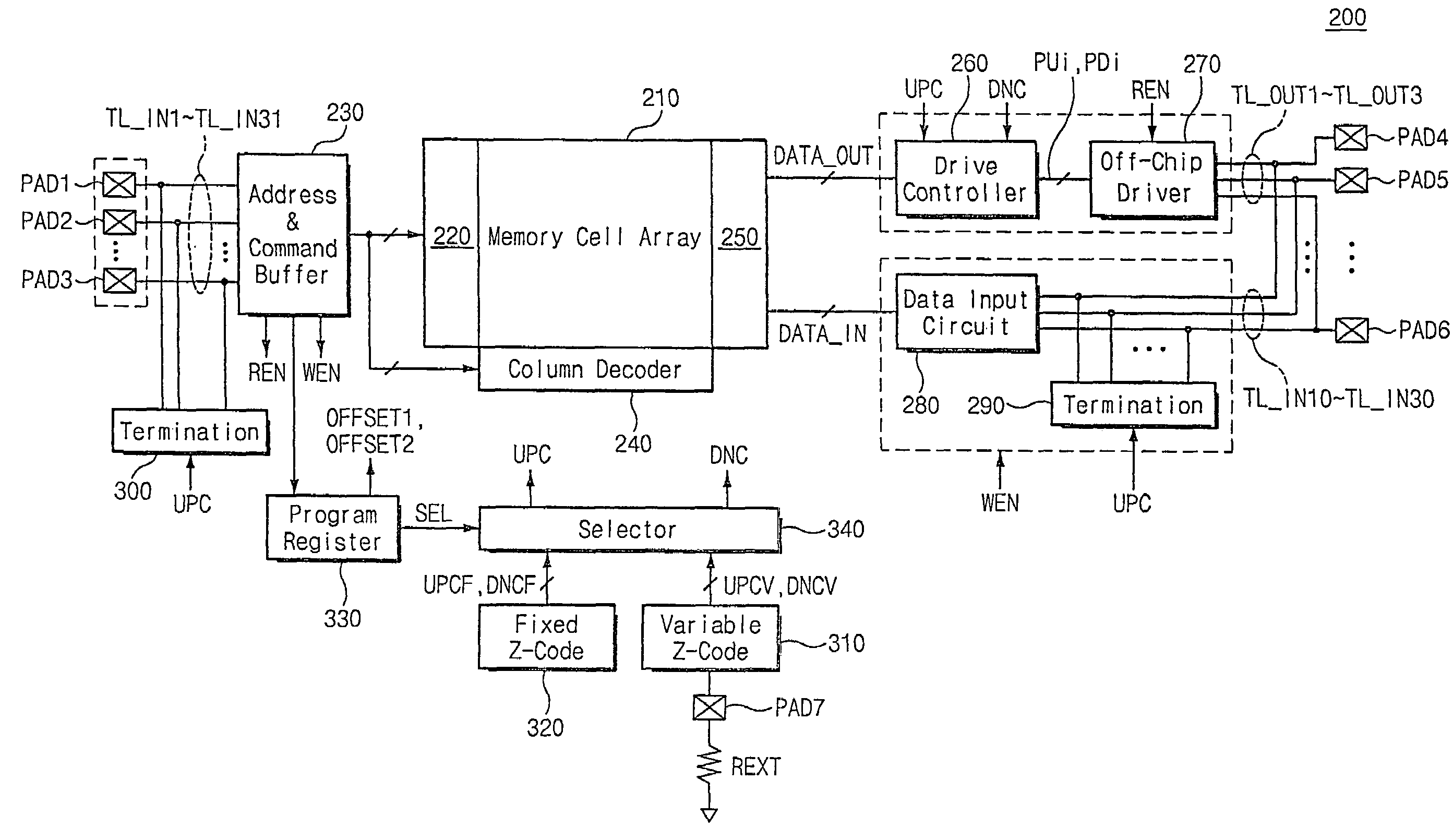

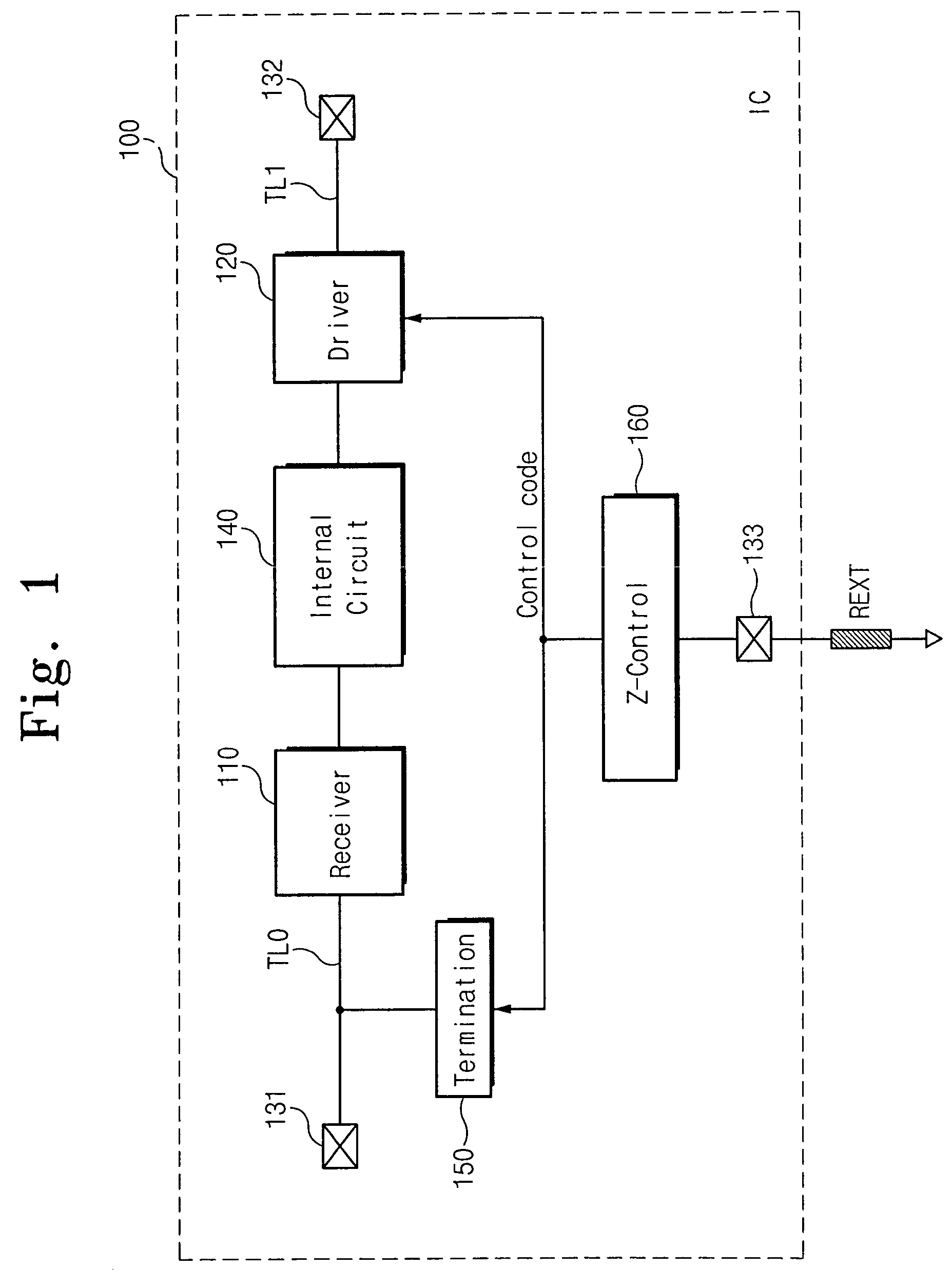

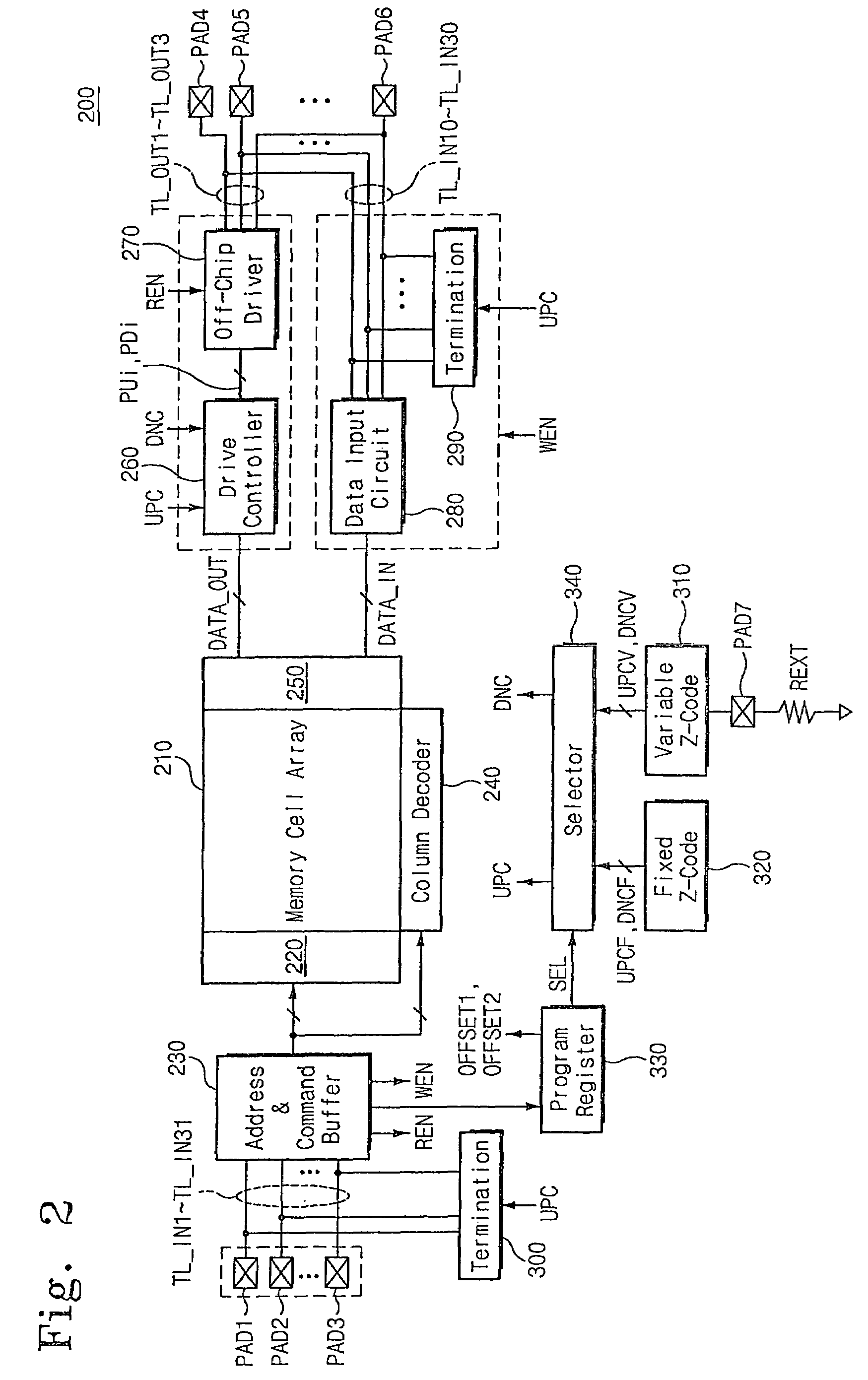

Semiconductor integrated circuit device capable of controlling impedance

ActiveUS7148721B2Input/output impedence modificationReliability increasing modificationsExternal referenceSemiconductor

A semiconductor integrated circuit device is connected to an external reference resistor, including an impedance control circuit for generating impedance control codes variable with impedances established by the external reference resistor. An input circuit receives an external signal through an input transfer line and forwards the external signal to an internal circuit. A termination circuit terminates the input transfer line in response to at least one of the impedance control code. An output circuit drives an output transfer line in accordance with an output signal. Impedance is variable with the control codes.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and device for transmission with reduced crosstalk

InactiveUS7167019B2Accurately determinedOptimize locationReliability increasing modificationsElectrically conductive connectionsElectrical conductorInterconnection

The invention relates to a method and a device for transmission with reduced crosstalk in interconnections used for sending a plurality of signals, such as the interconnections made with flat multiconductor cables, or with the tracks of a printed circuit board, or inside an integrated circuit. An interconnection with four parallel transmission conductors plus a reference conductor has each of its ends connected to a termination circuit. The transmitting circuit receives at its input the signals of the four channels of the source and its output terminals are connected to the conductors of the interconnection. The receiving circuit's input terminals are connected to the conductors of the interconnection, and its four output channels are connected to the destination. The signals of the four channels of the source are sent to the four channels of the destination, without noticeable crosstalk.

Owner:RAMBUS INC +1

Data transfer and management system

InactiveUS7406596B2Easy to manageEasily downloadableReliability increasing modificationsError preventionPasswordSecure transmission

A system for the secure transfer of data and data management on the Internet has a data encryption and transfer module operable in a user computing system, a data management module operable in a sewer computing system, the transfer of data between the user and the server computing systems being effected on the user computing system through use of the data encryption and transfer module, by moving the data to or from a first desktop window, associated with the user computing system, from or to a second desktop window, associated with the server computing system, each window being associated with a password, such that the step of moving the data from one window to the other causes the data to encrypted / re-encrypted from one associated password to the other.

Owner:HERBERT STREET TECH

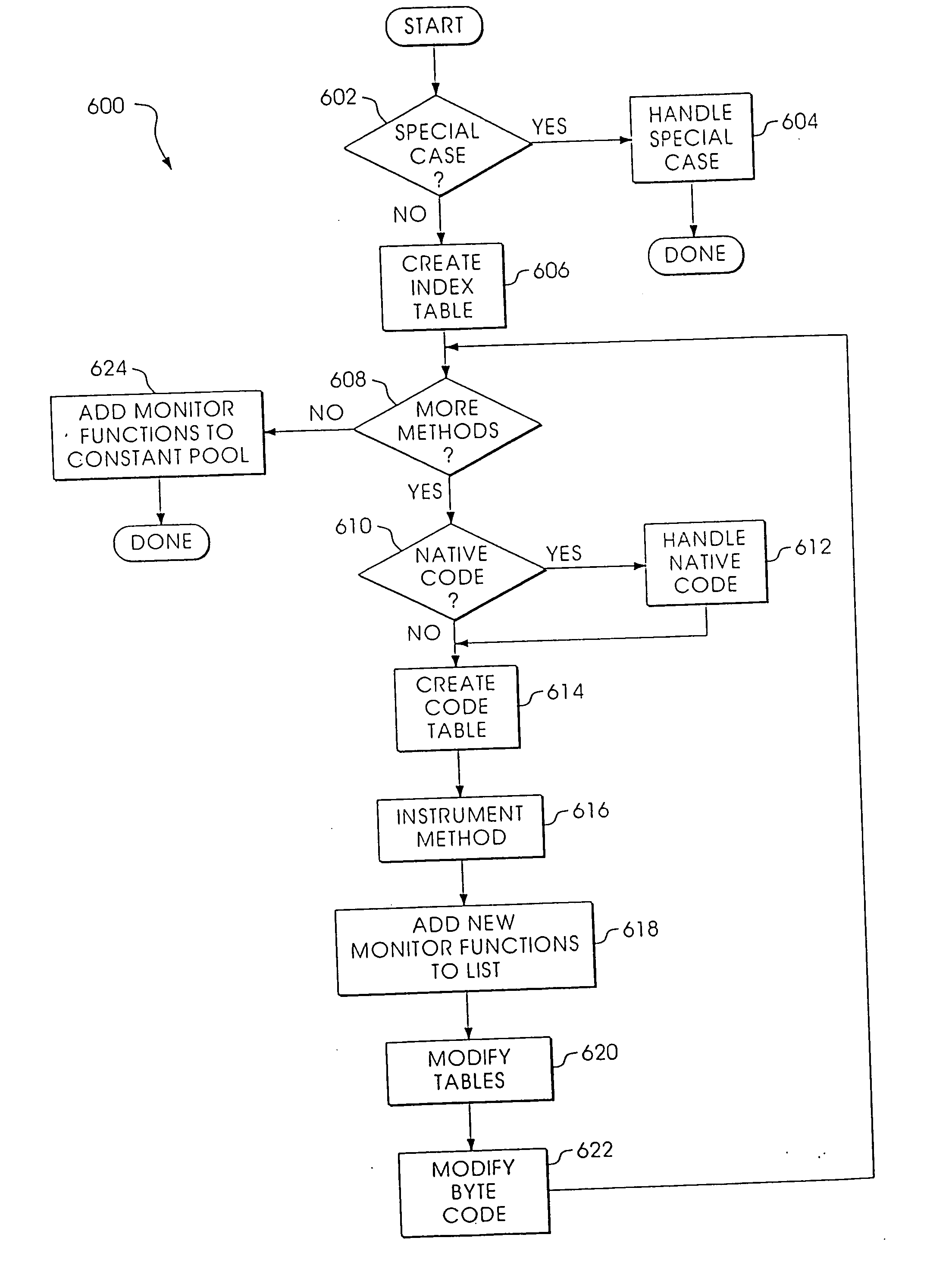

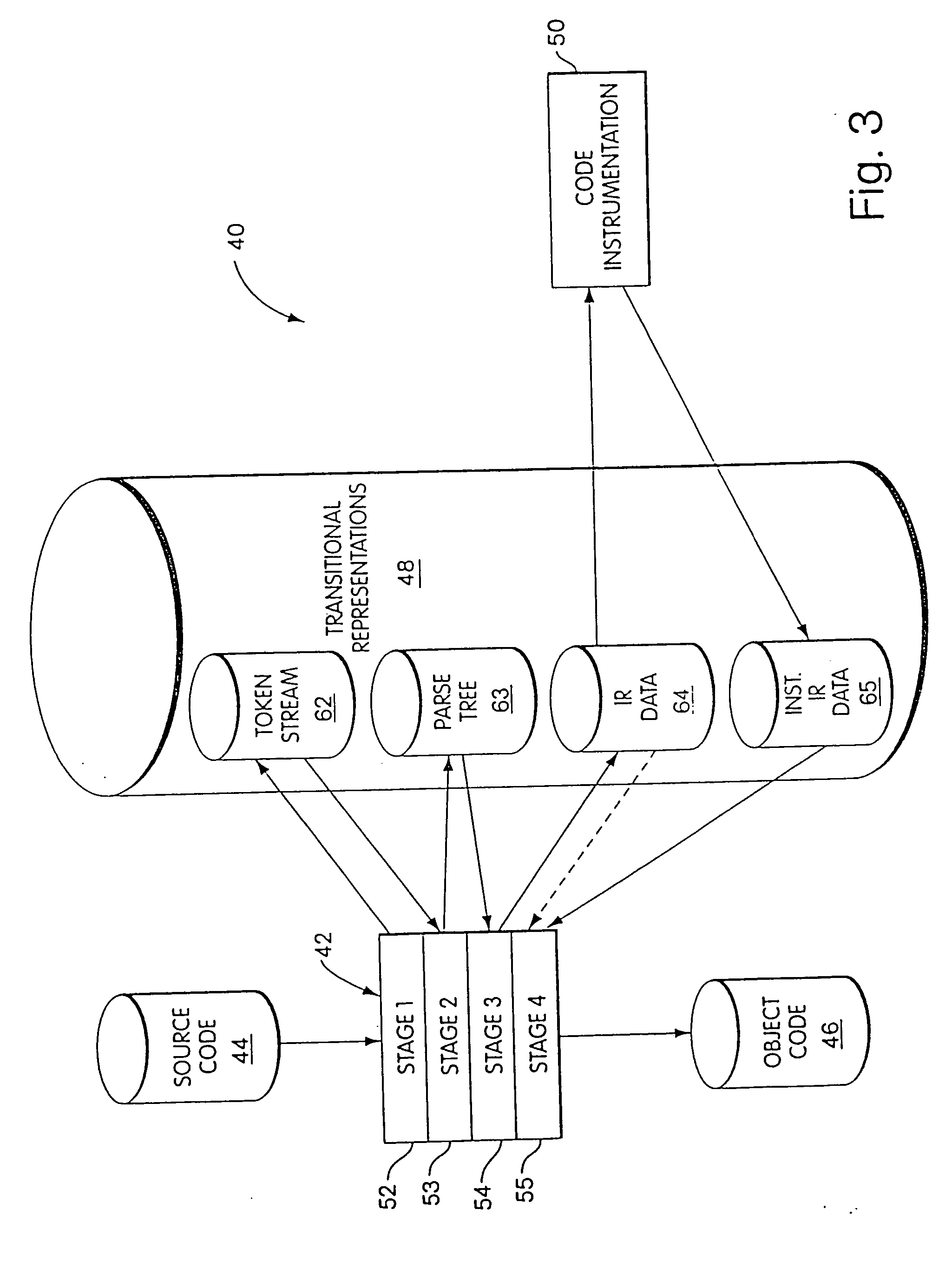

Byte code instrumentation

InactiveUS20040133882A1Reliability increasing modificationsSoftware testing/debuggingMessage flowParallel computing

Instrumenting a computer program to provide instrumented byte code includes examining the byte code, selecting portions of the byte code for instrumentation, and instrumenting the portions to provide instrumented byte code. Selecting the portions may include choosing portions of the byte code corresponding to method entry, method exit, a throw, a method call, or a new line number. Instrumenting a portion of the byte code corresponding to a method call may include instrumenting a local line number of source code corresponding to the byte code being instrumented. Instrumenting the portions may include adding calls to instrumentation runtime functions that pass parameters indicative of the portions being instrumented. At least one of the parameters that is passed may include a line number of the source code corresponding to the portion being instrumented or a thispointer for the method corresponding to the portion being instrumented. Data from instrumentation may be passed via a message stream that is viewed as the data is being generated and / or stored.

Owner:BORLAND

Reflection-control system and method

ActiveUS6992501B2Reliability increasing modificationsElectronic switchingControl systemElectrical impedance

Owner:TAMIRAS PER PTE LTD LLC

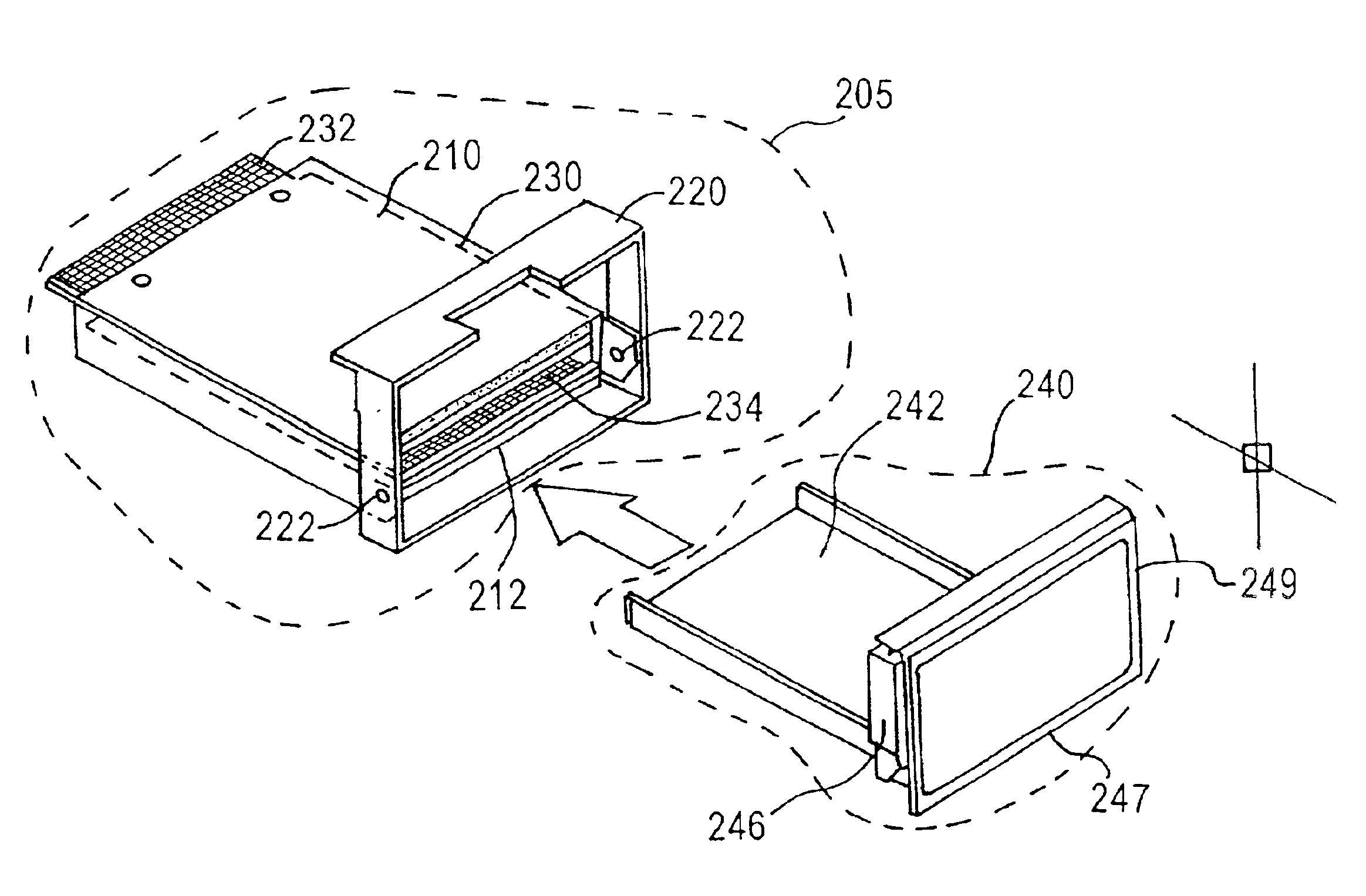

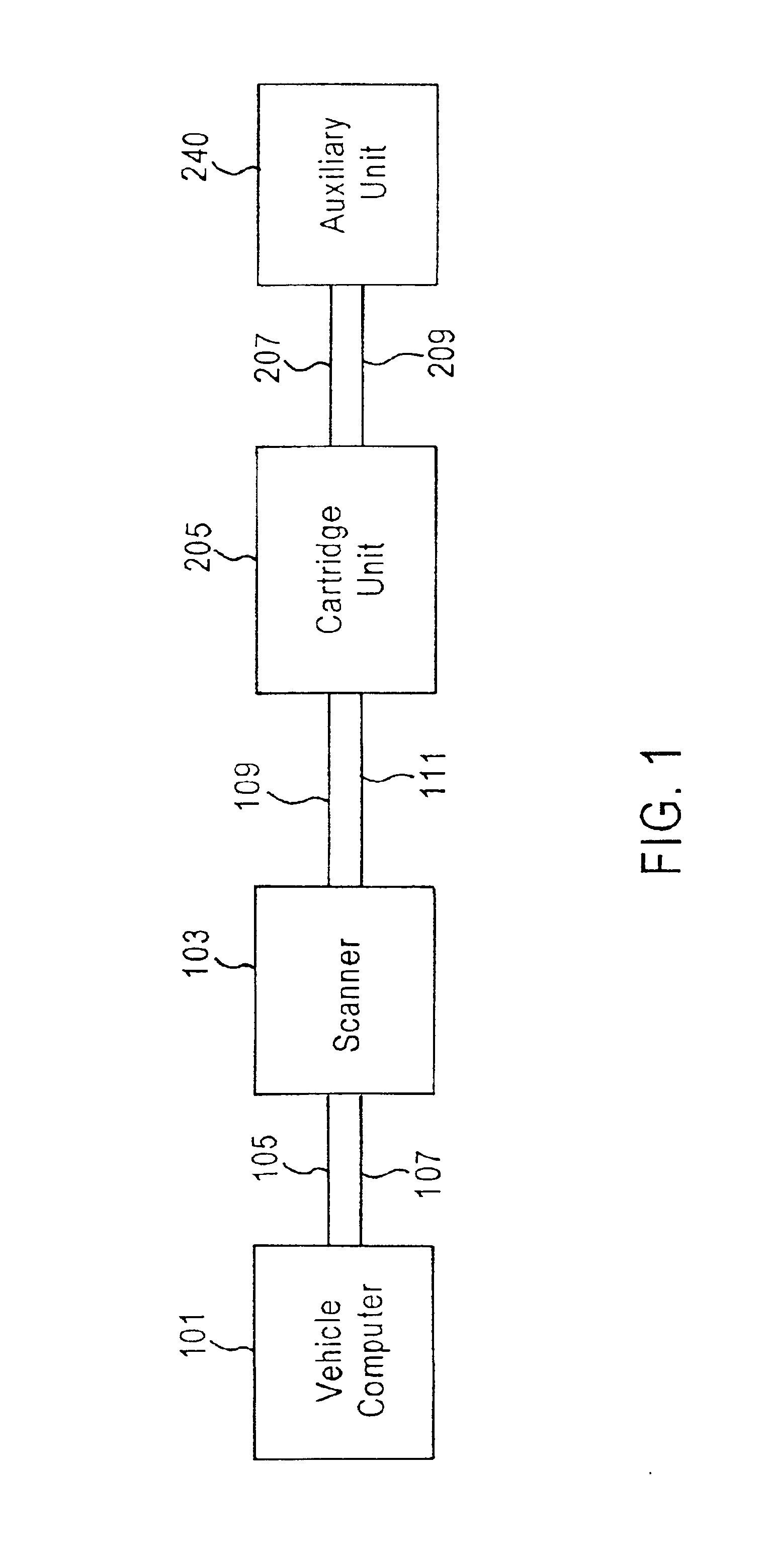

Detachable cartridge unit and auxiliary unit for function expansion of a data processing system

InactiveUS6859698B2Low costImprove protectionVehicle testingReliability increasing modificationsData processing systemEngineering

A detachable cartridge unit and an auxiliary unit combined forms a functional component for a data processing system. The cartridge unit is configured to receive a variety of auxiliary units in order to form different functional components and perform different functions. The circuit board of the cartridge unit contains circuits and components common to each functional component. The auxiliary unit contains components and circuits unique to the function that the auxiliary unit represents. The cartridge unit comprises a circuit board, a housing containing the circuit board, a first connector coupled to the circuit board for connecting to a data processing system, a second connector coupled to the circuit board, and a grip movably connected to the housing with a hinge. The auxiliary unit includes an auxiliary circuit board, an auxiliary connector coupled to the auxiliary circuit board for detachably connecting to the second connector, an auxiliary housing containing the auxiliary circuit board, a guide for guiding the auxiliary connector to connect to the second connector via a predetermined path, and an auxiliary grip movably connected to the auxiliary housing with a hinge.

Owner:SNAP ON INC