Patents

Literature

1365results about "Transmission line coupling arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

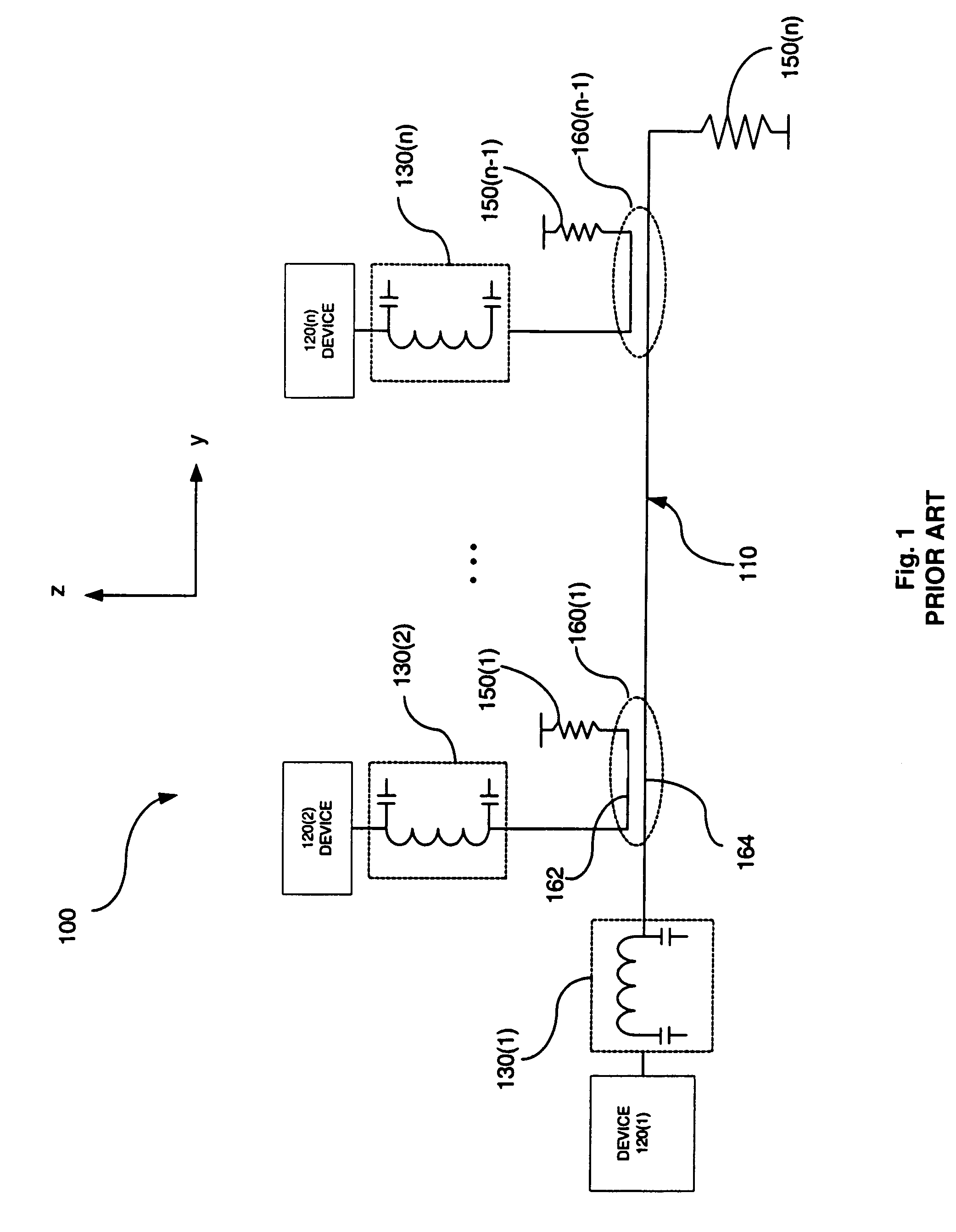

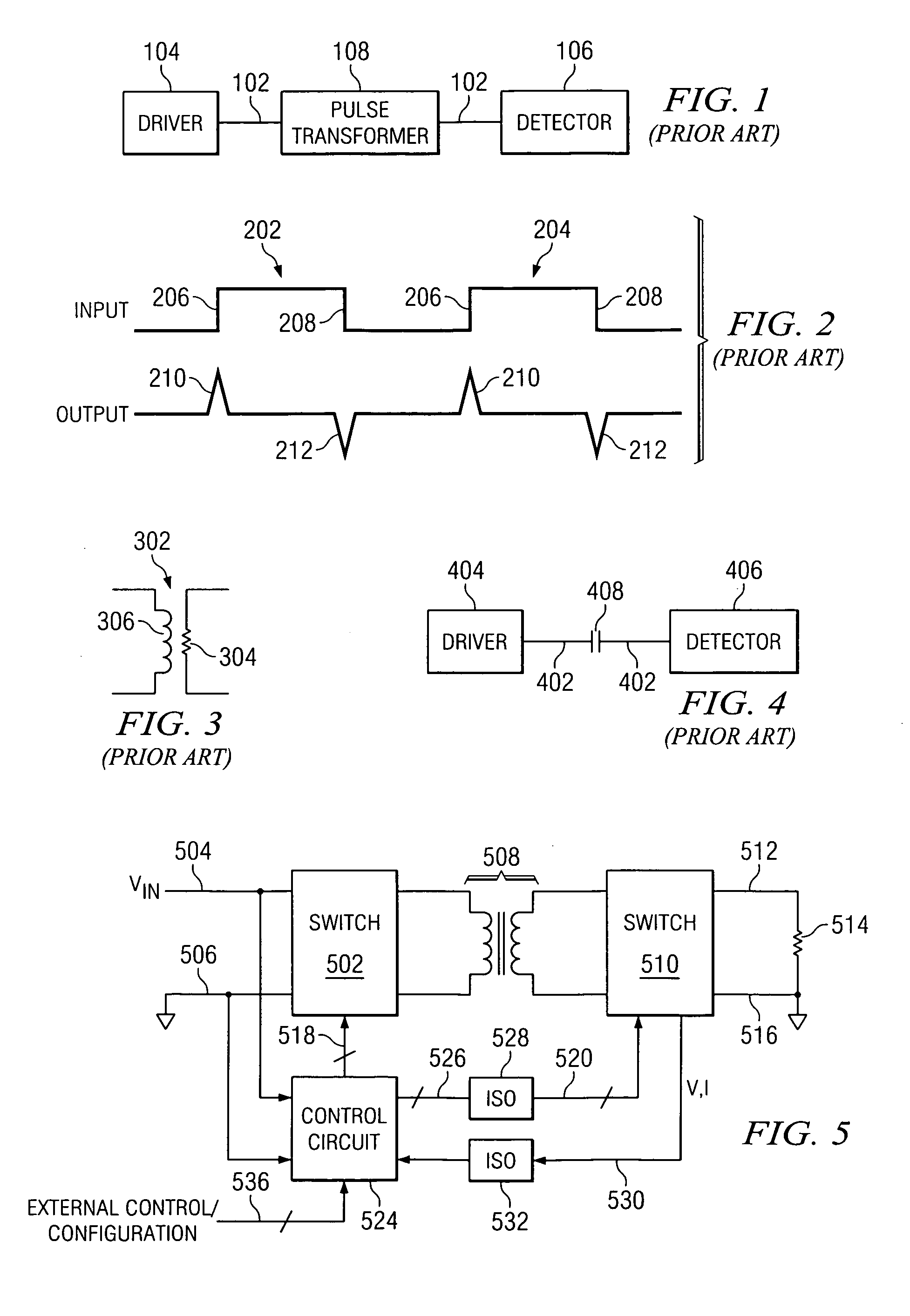

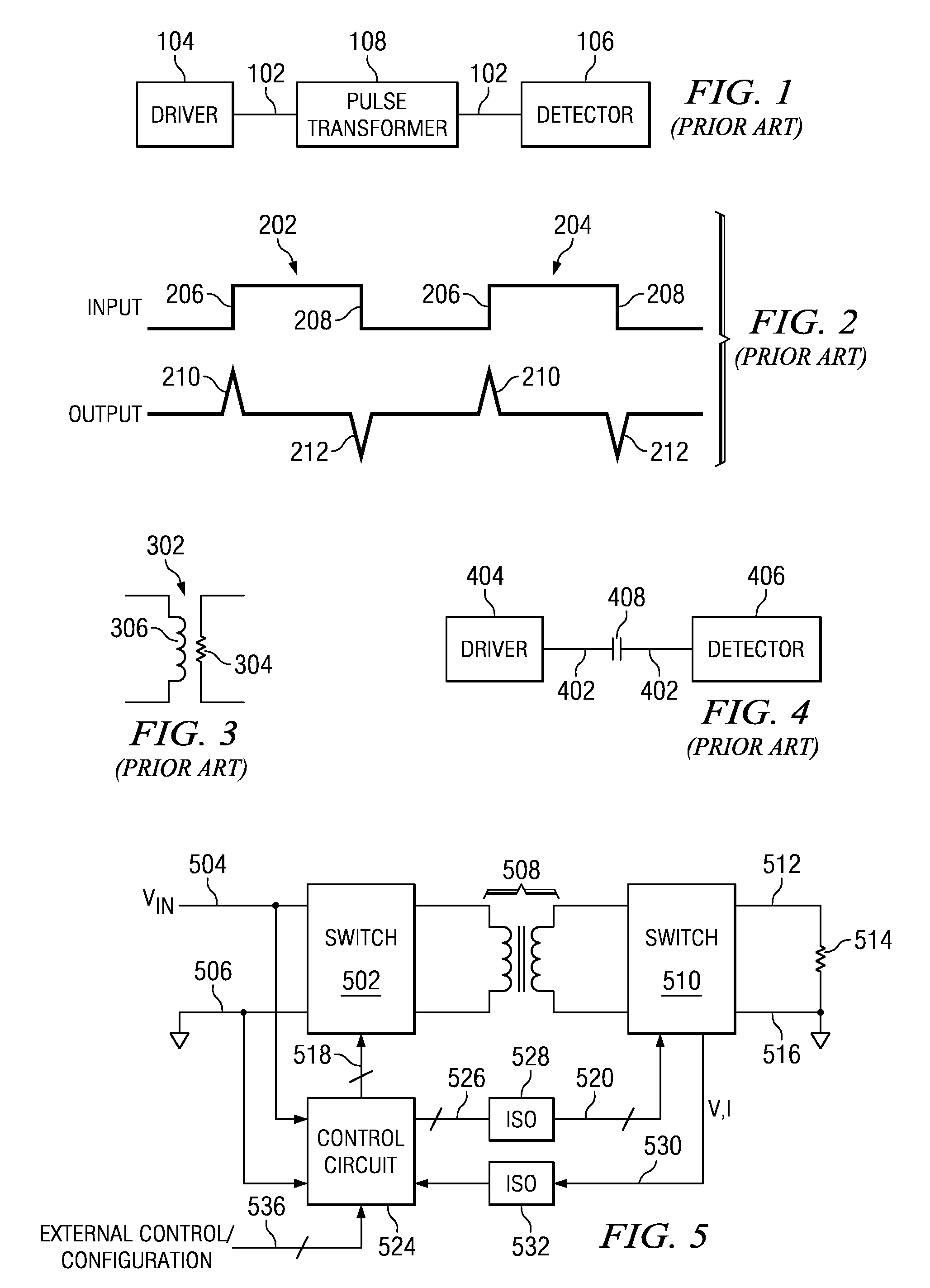

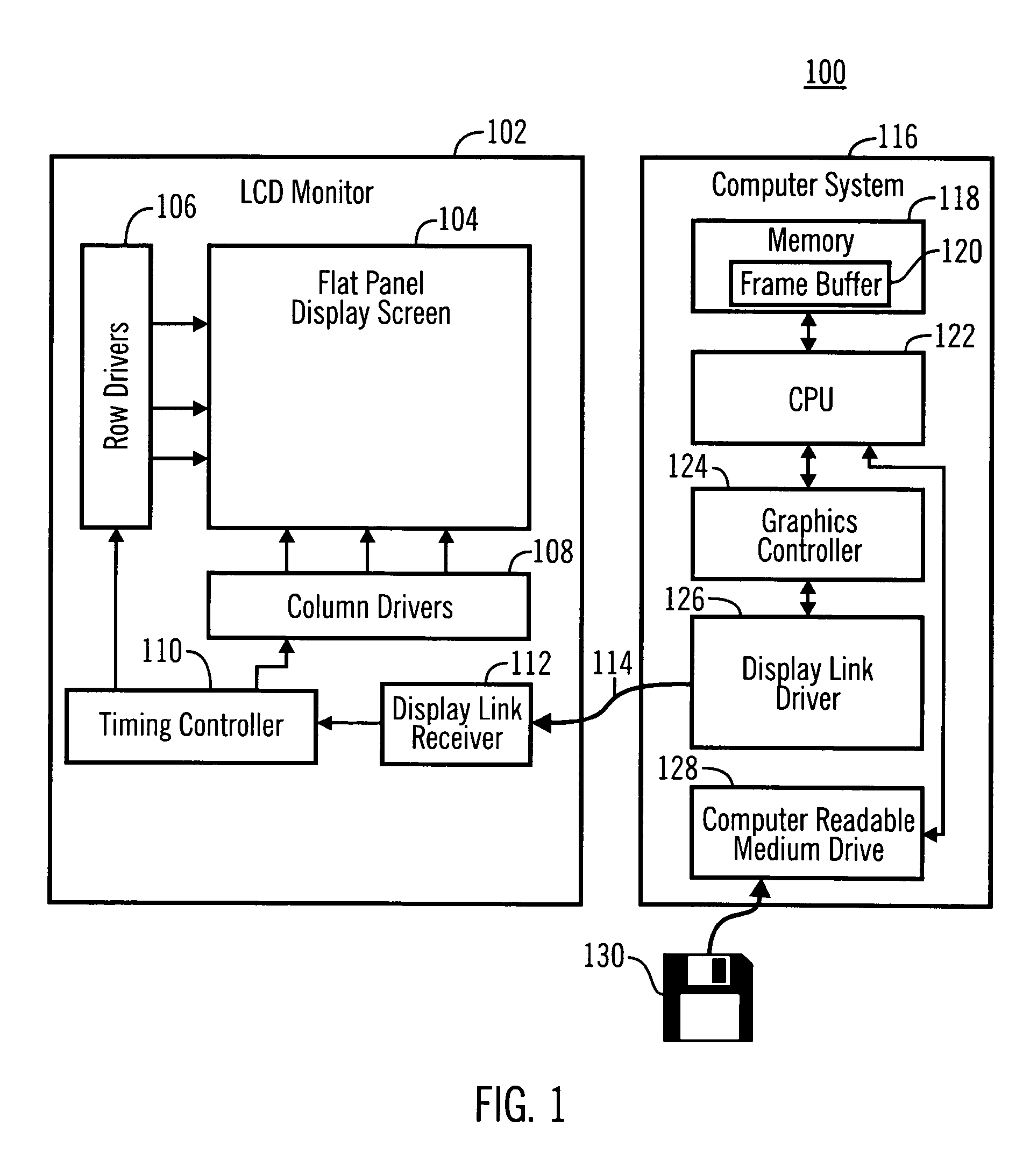

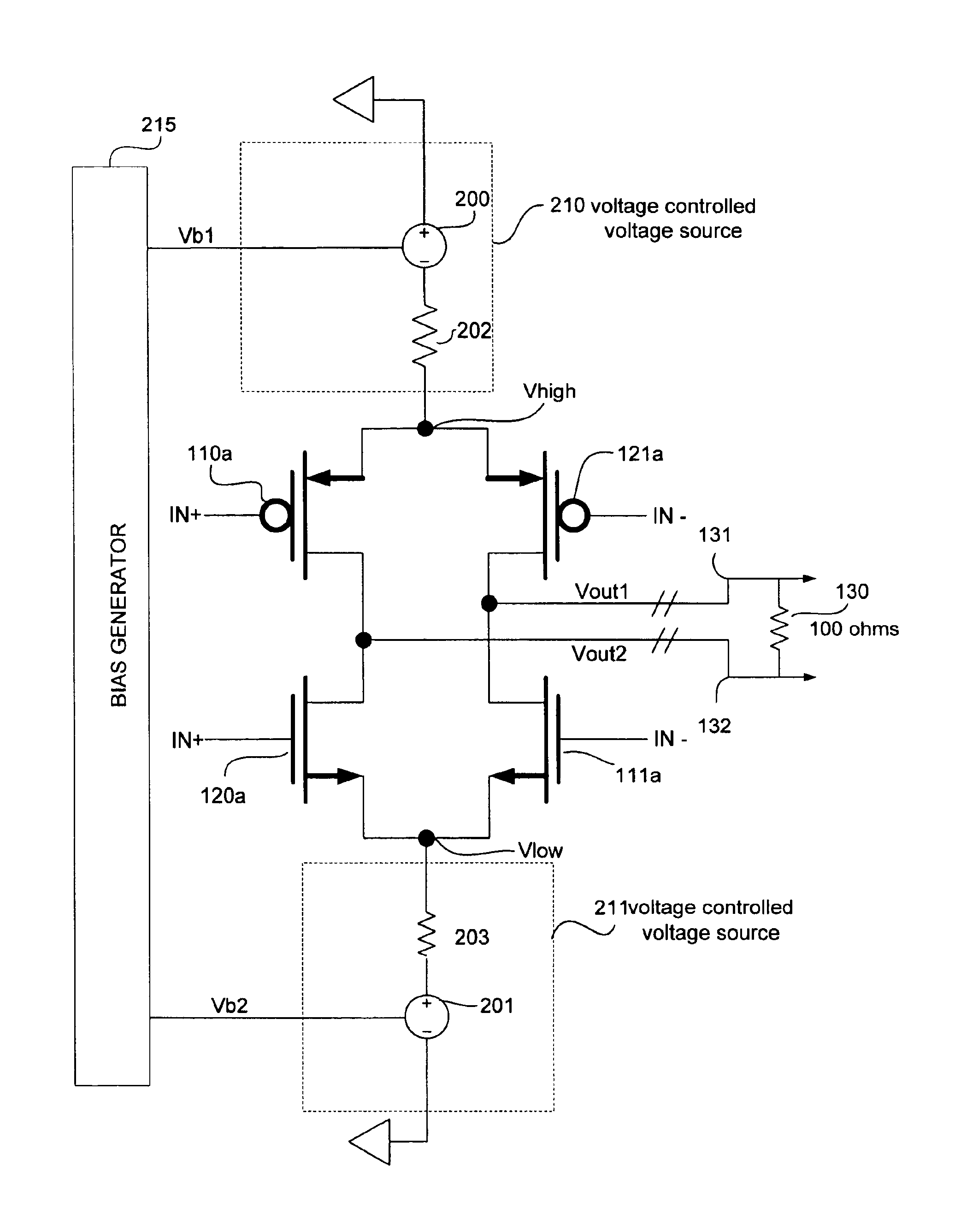

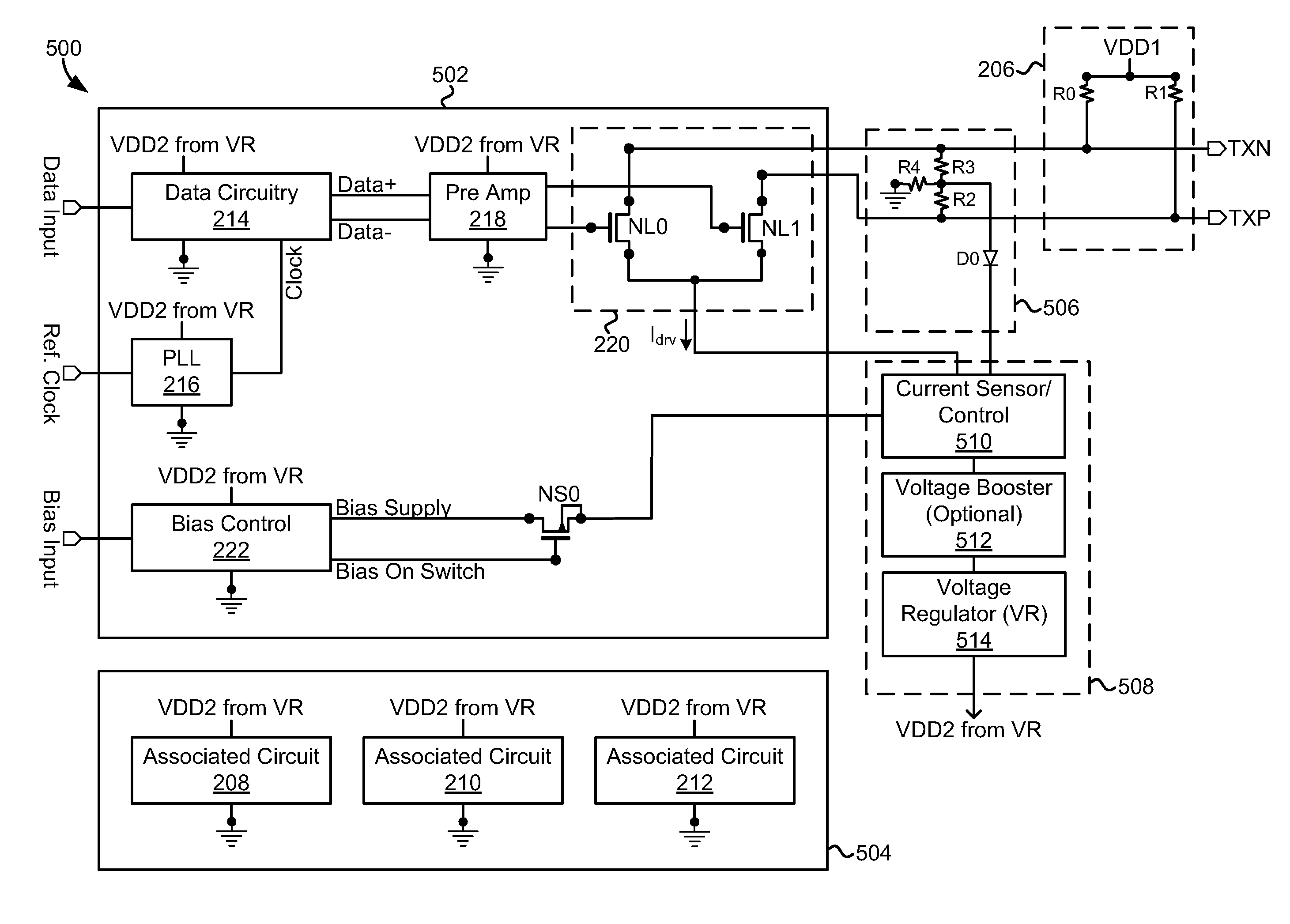

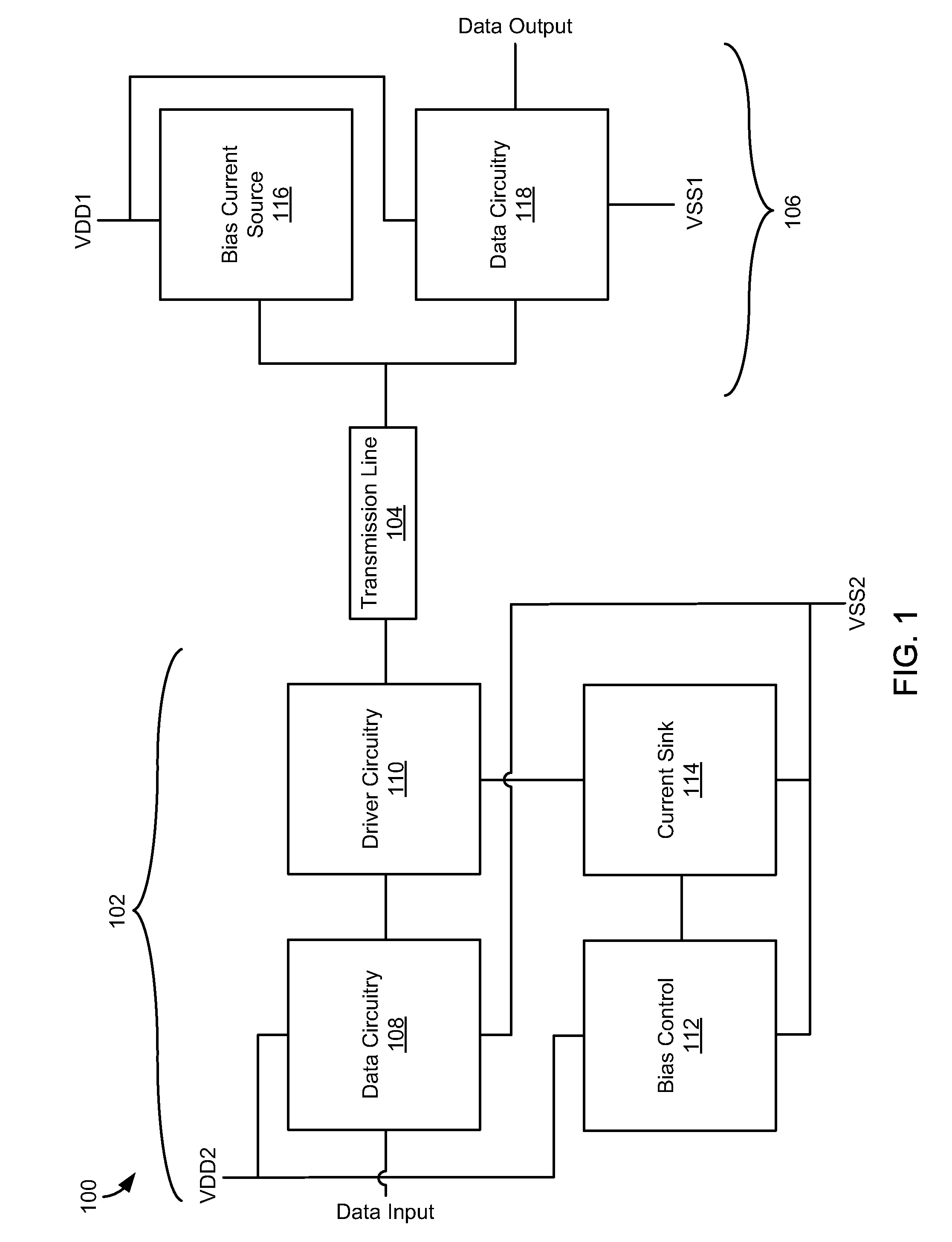

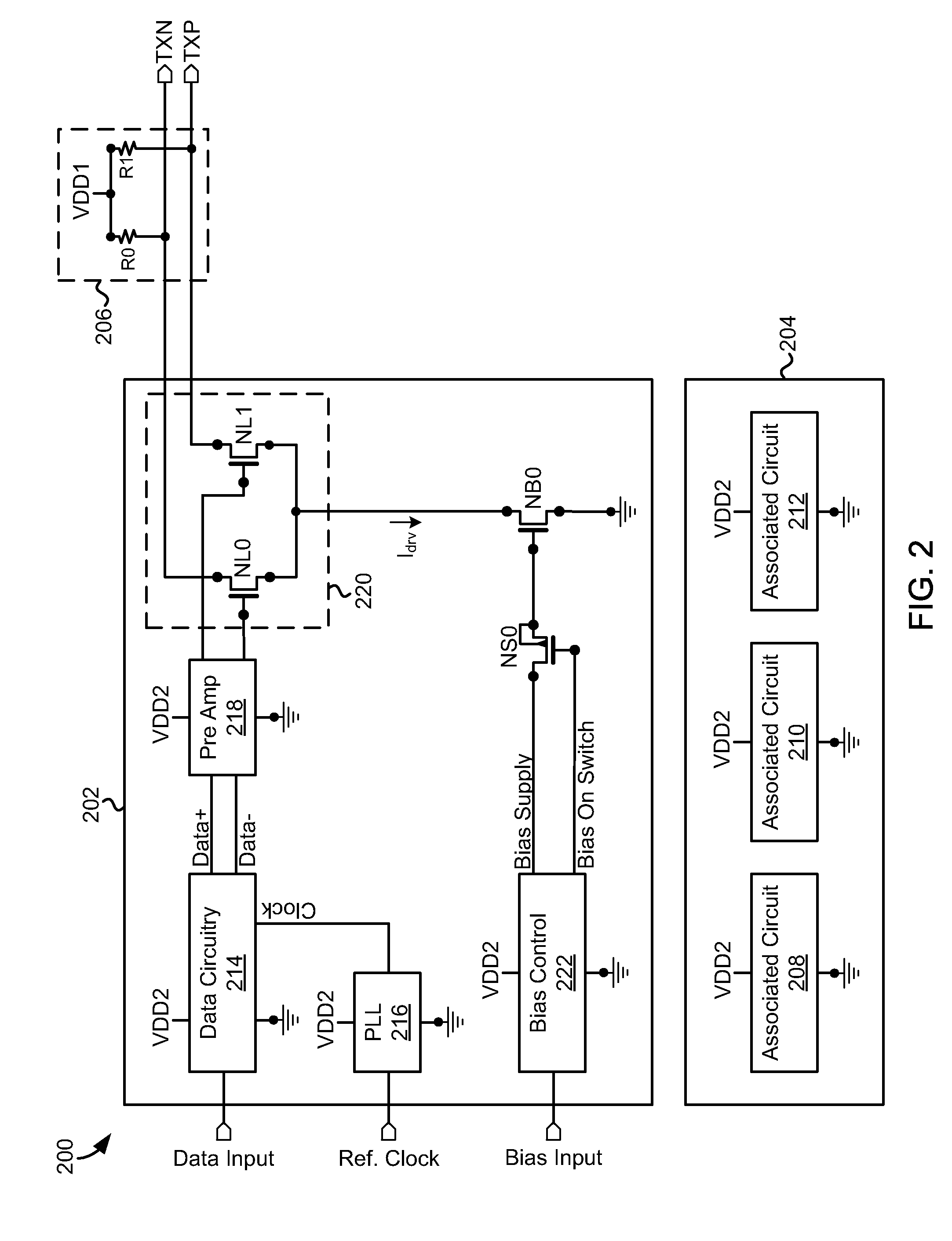

Non-optical signal isolator

InactiveUS6873065B2Magnetic/electric field screeningSemiconductor/solid-state device detailsDriver circuitOptical isolator

A non-optical isolator having a driver circuit for providing an input signal to one or more first passive components which are coupled across a galvanic isolation barrier to one or more corresponding second passive components, and an output circuit that converts the signal from the second passive components to an output signal corresponding to the input signal. The entire structure may be formed monolithically as an integrated circuit on one or two die substrates, for low cost, small size, and low power consumption. The passive components may be coils or capacitor plates, for example. When the first and second passive components are capacitor plates, a Faraday shield may be provided between them, with the first and second passive components being referenced to separate grounds and the Faraday shield referenced to the same ground as the second passive components.

Owner:ANALOG DEVICES INC

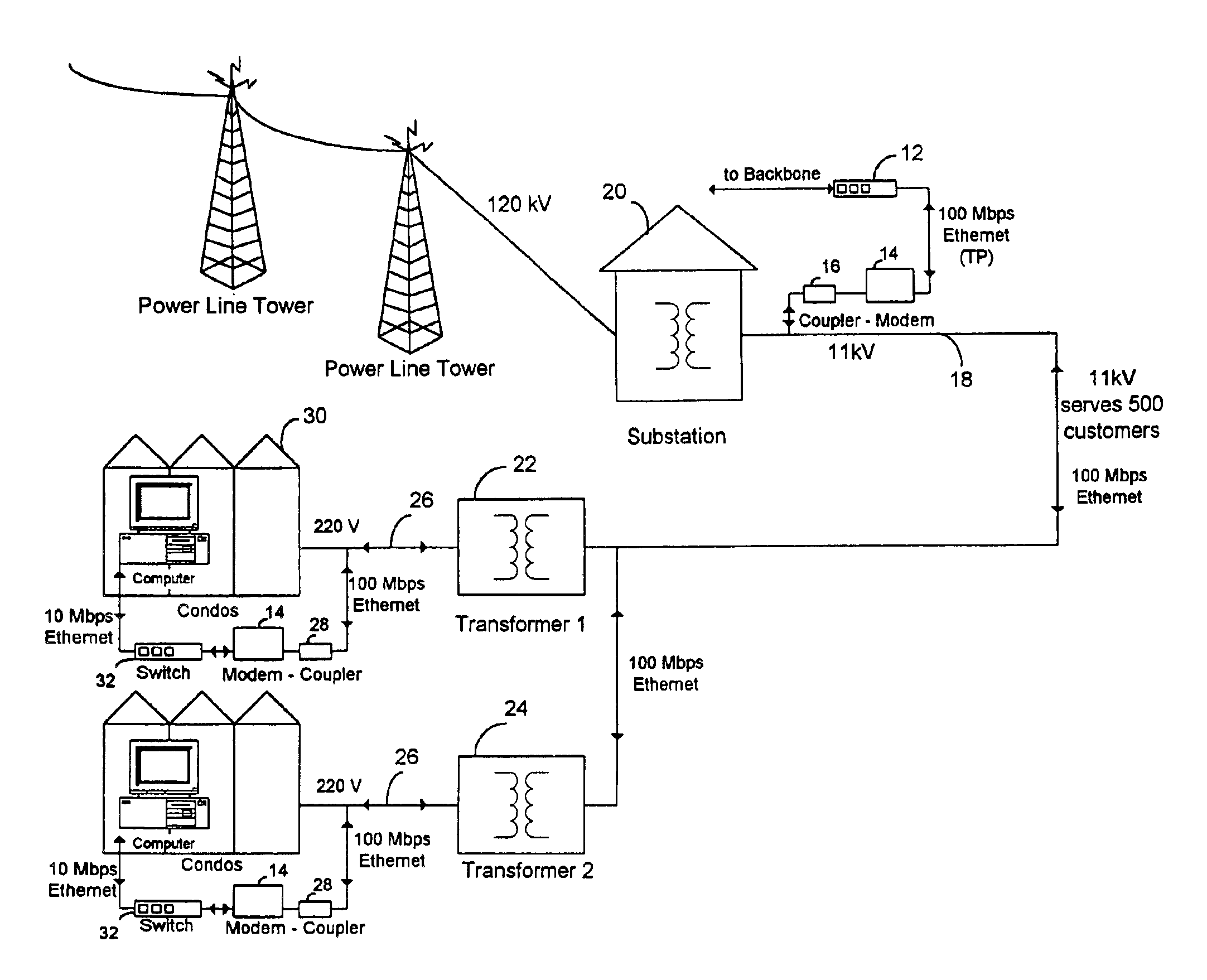

High frequency network multiplexed communications over various lines using multiple modulated carrier frequencies

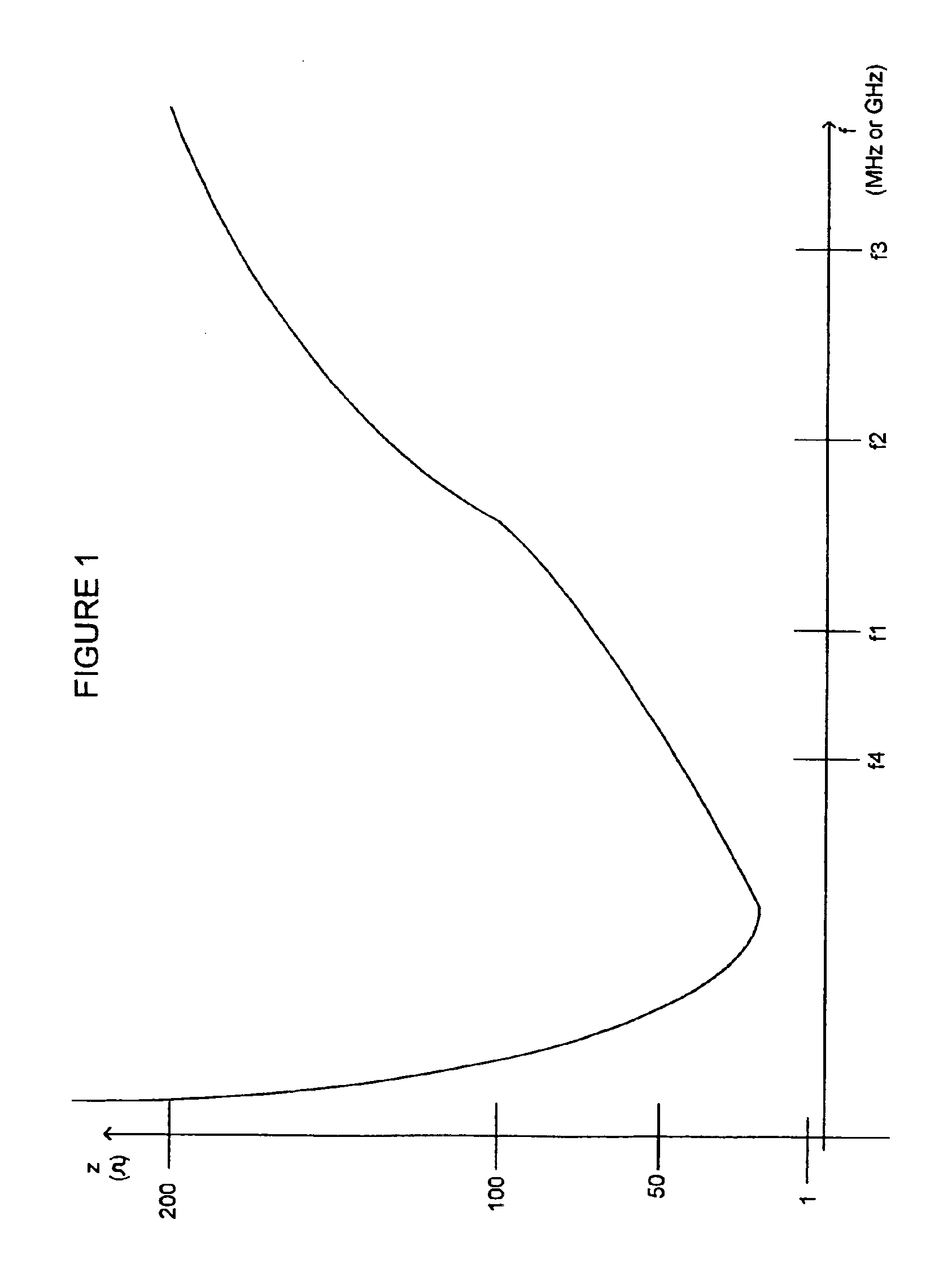

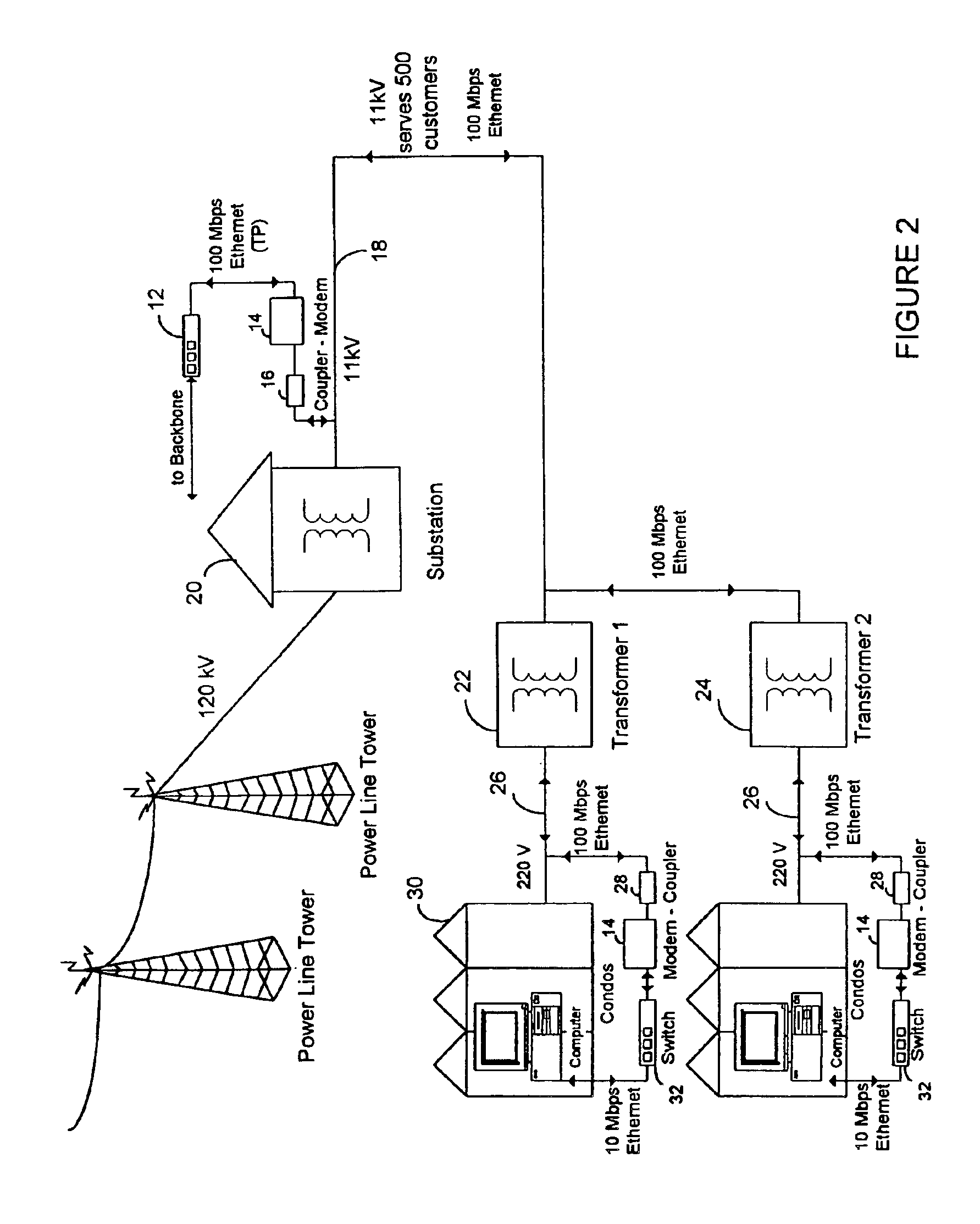

InactiveUS6922135B2Substantial phase distortionMultiple-port networksPowerline communication systemsCapacitanceModem device

An apparatus is provided for high frequency multiplexed electrical line communication for cable TV, telephone, internet, security and other control applications over the mid and low voltage power lines and directly through the transformers. The apparatus includes a transmitter, a receiver, a modem, a multiplexer and multiple couplers at each of two or more locations along an electrical line. The couplers have capacitive circuits serially connected with an air-core or dielectric-core transformer. The capacitive circuits resonate with the transformer at a preselected frequency. The coupler eliminates noise and is matched to the characteristic impedance of the line at the preselected frequency, which linearizes communication on the line and allows high speed data and voice communication over long distances. Multiple modulators and demodulators are used to produce multiple modulated carrier frequencies.

Owner:SATIUS

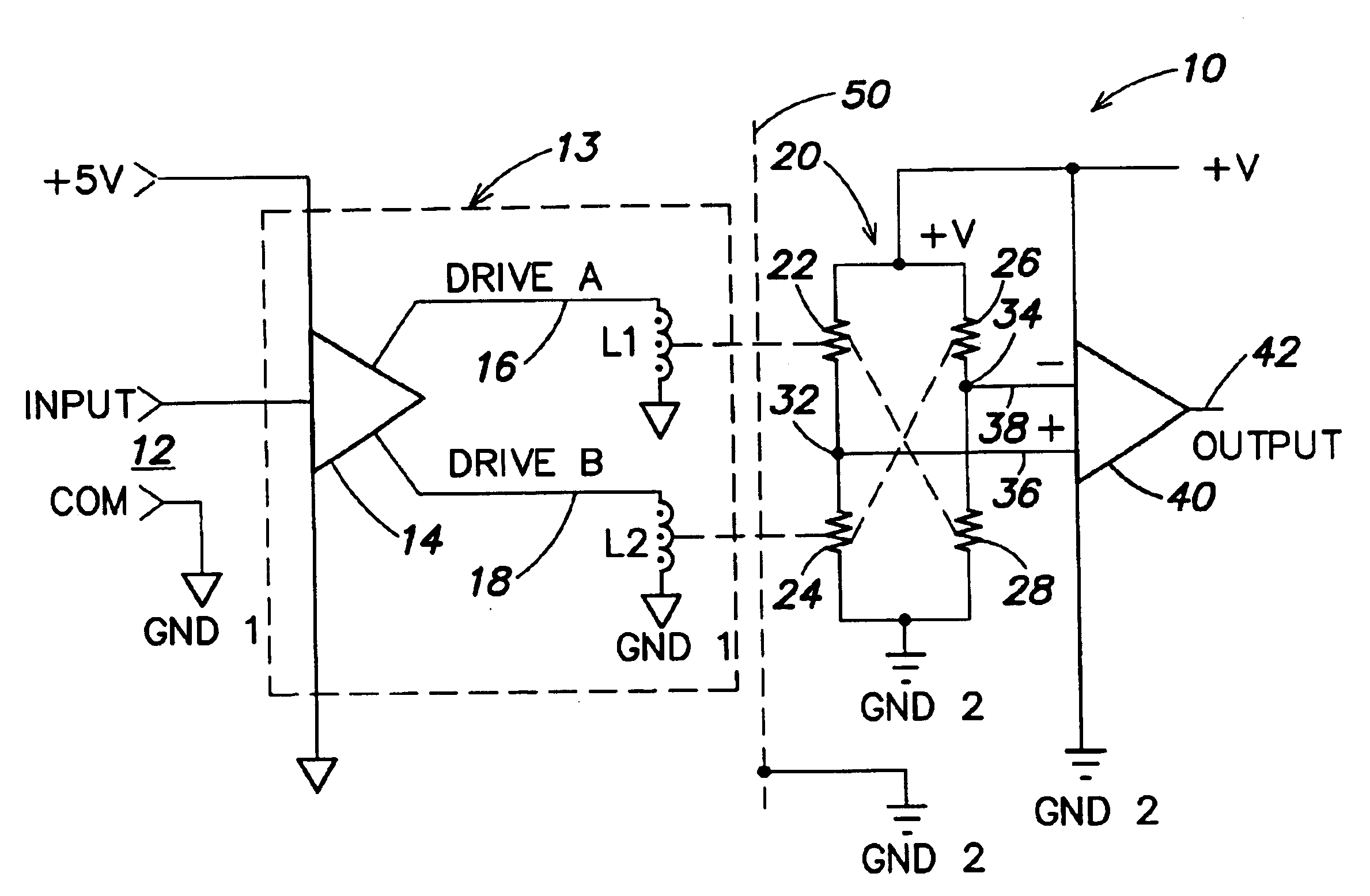

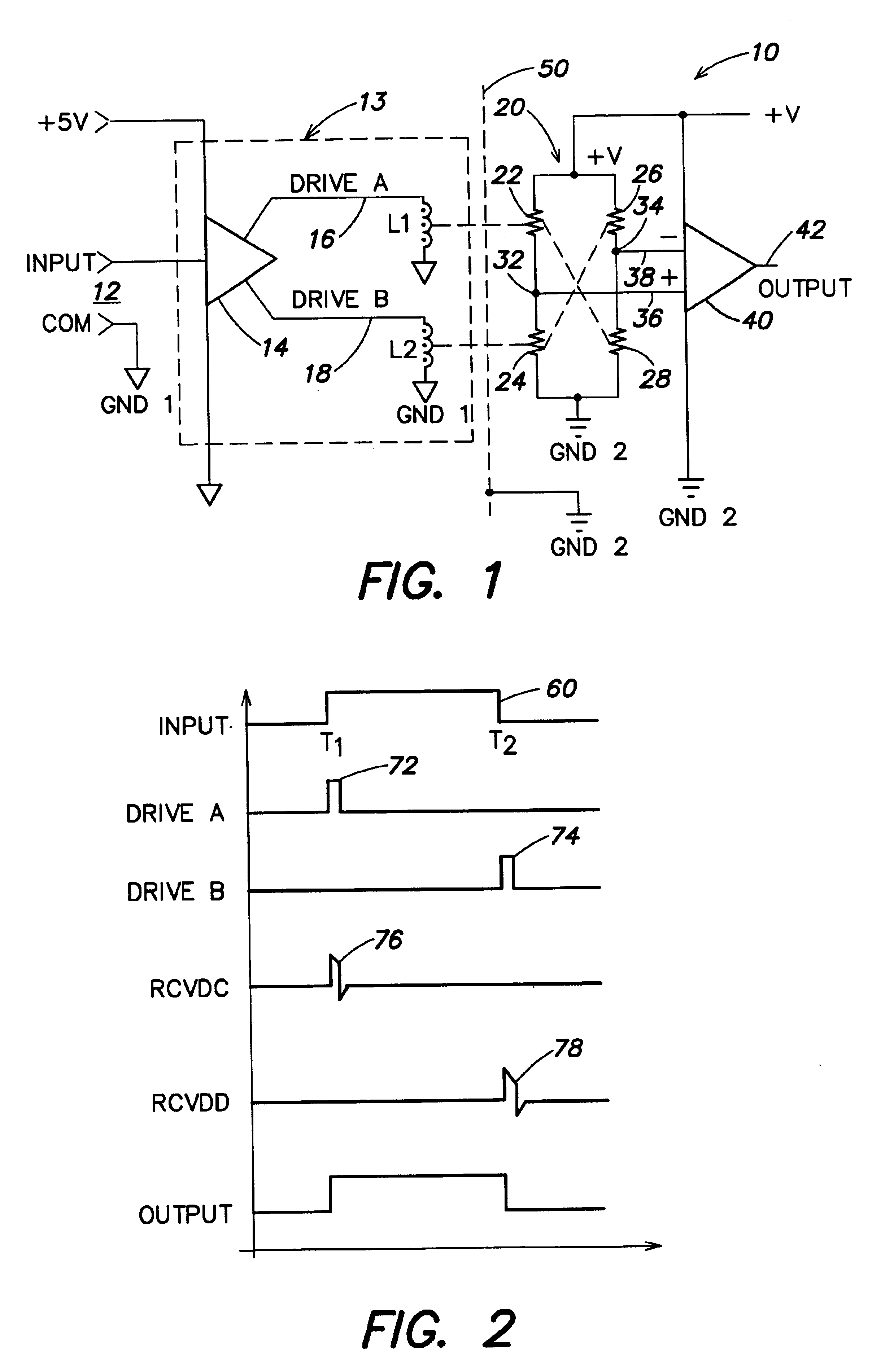

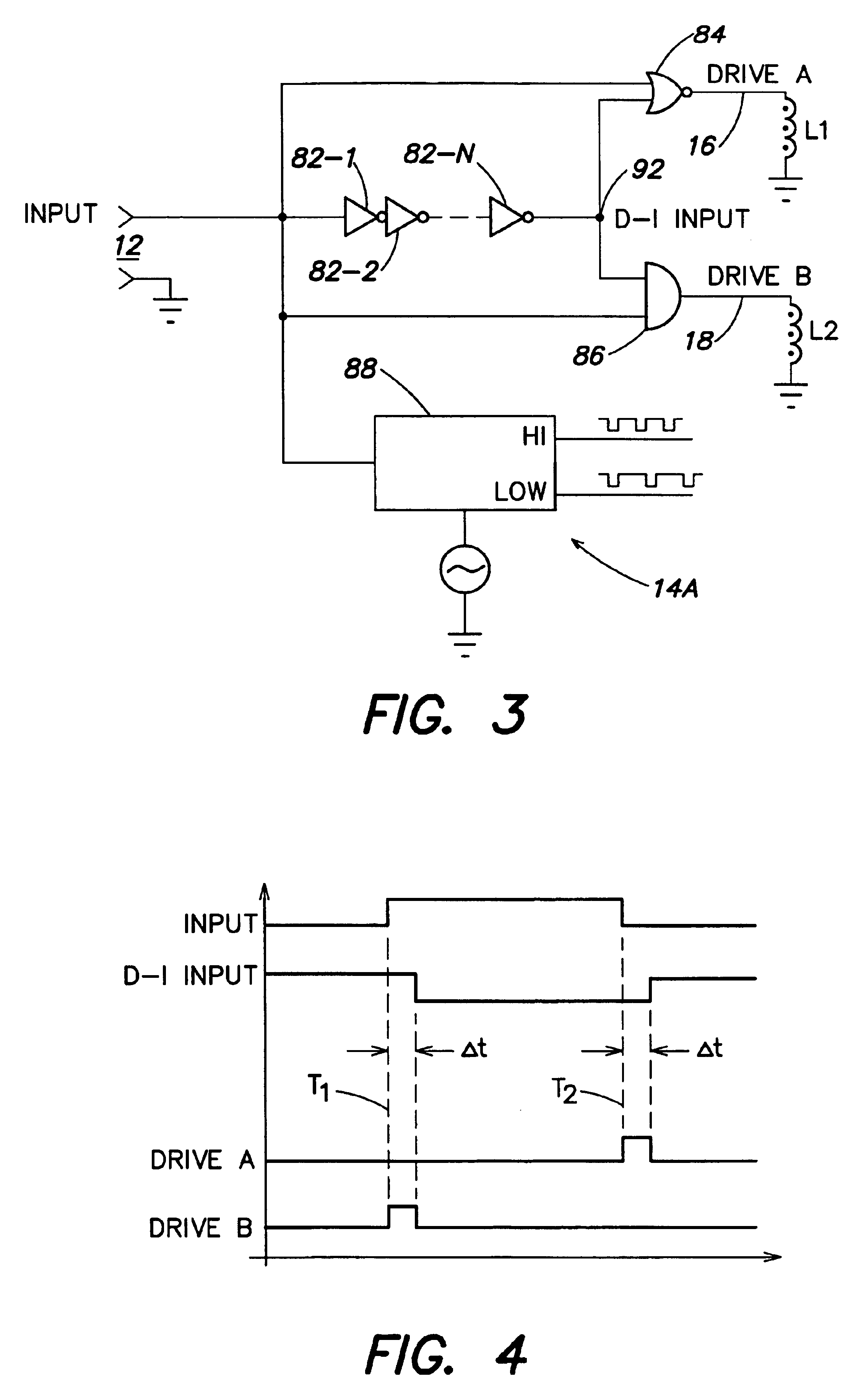

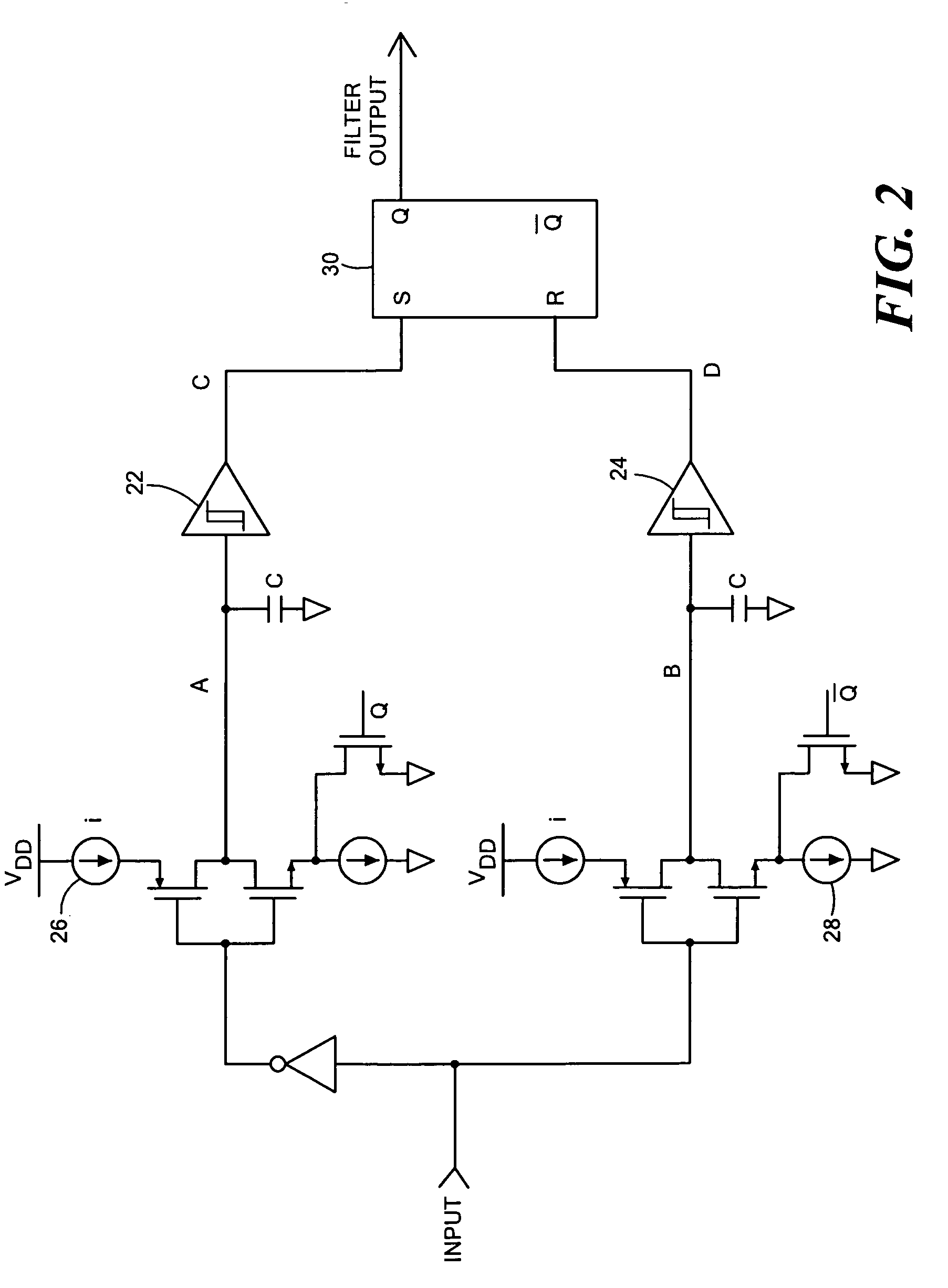

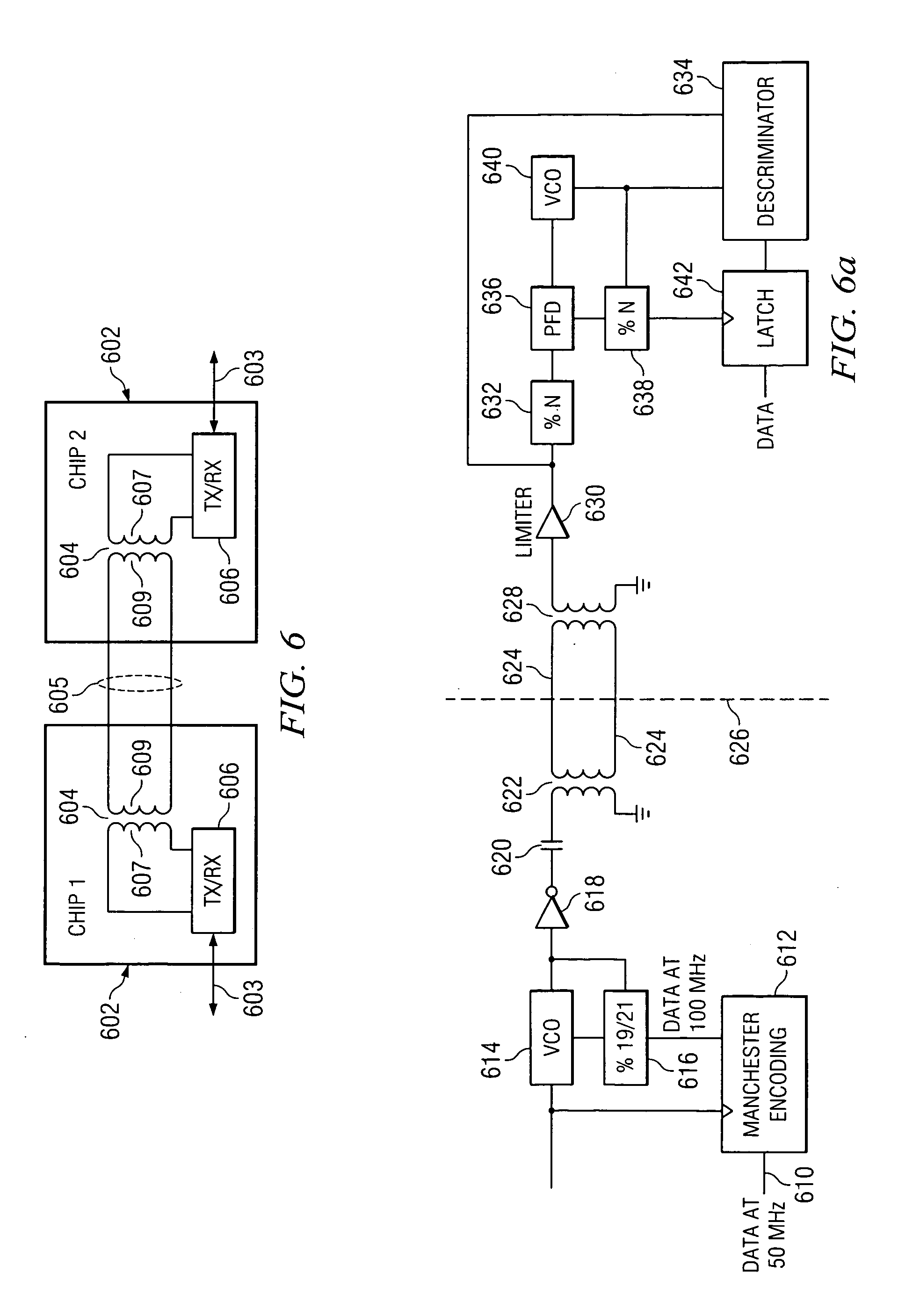

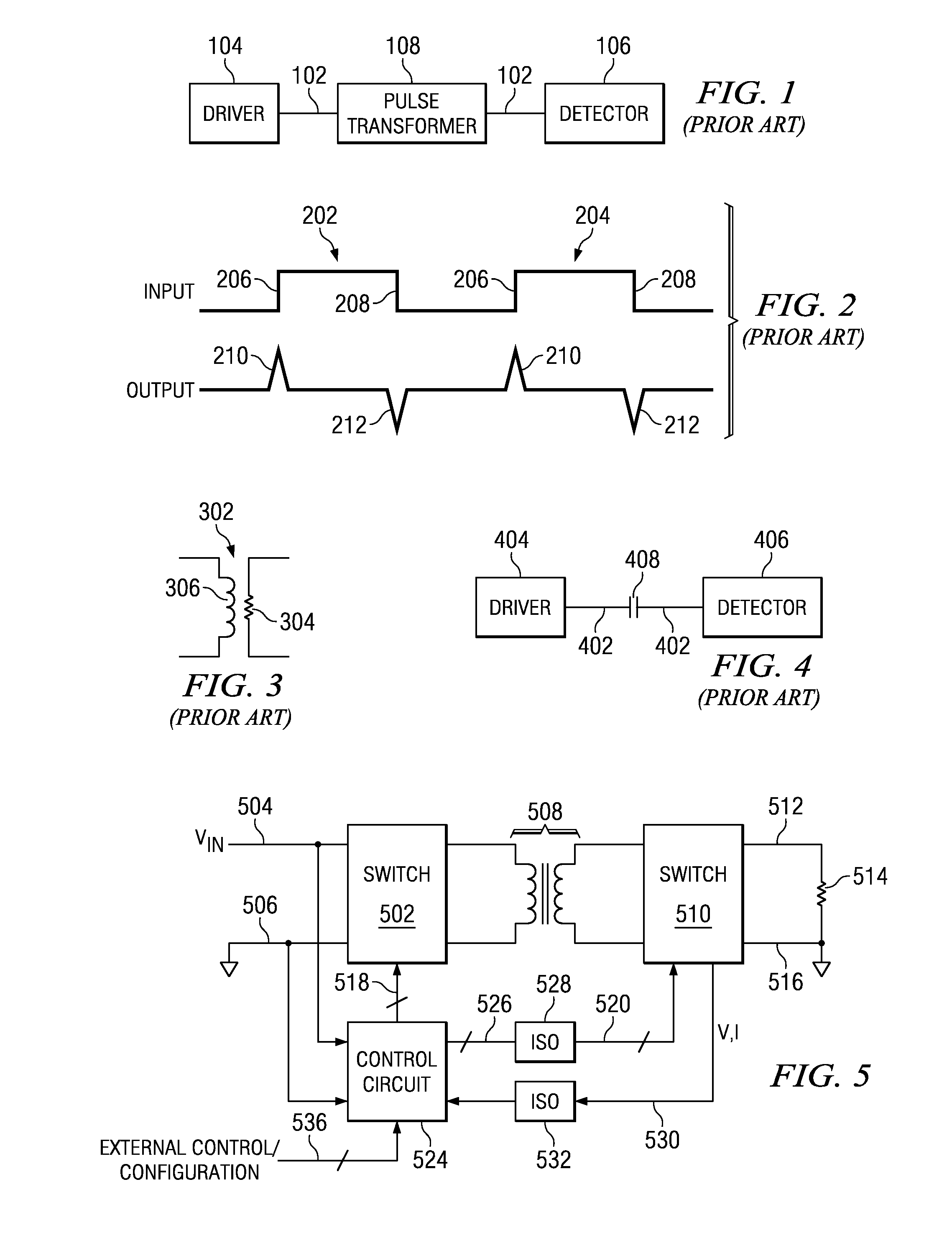

Signal isolators using micro-transformers

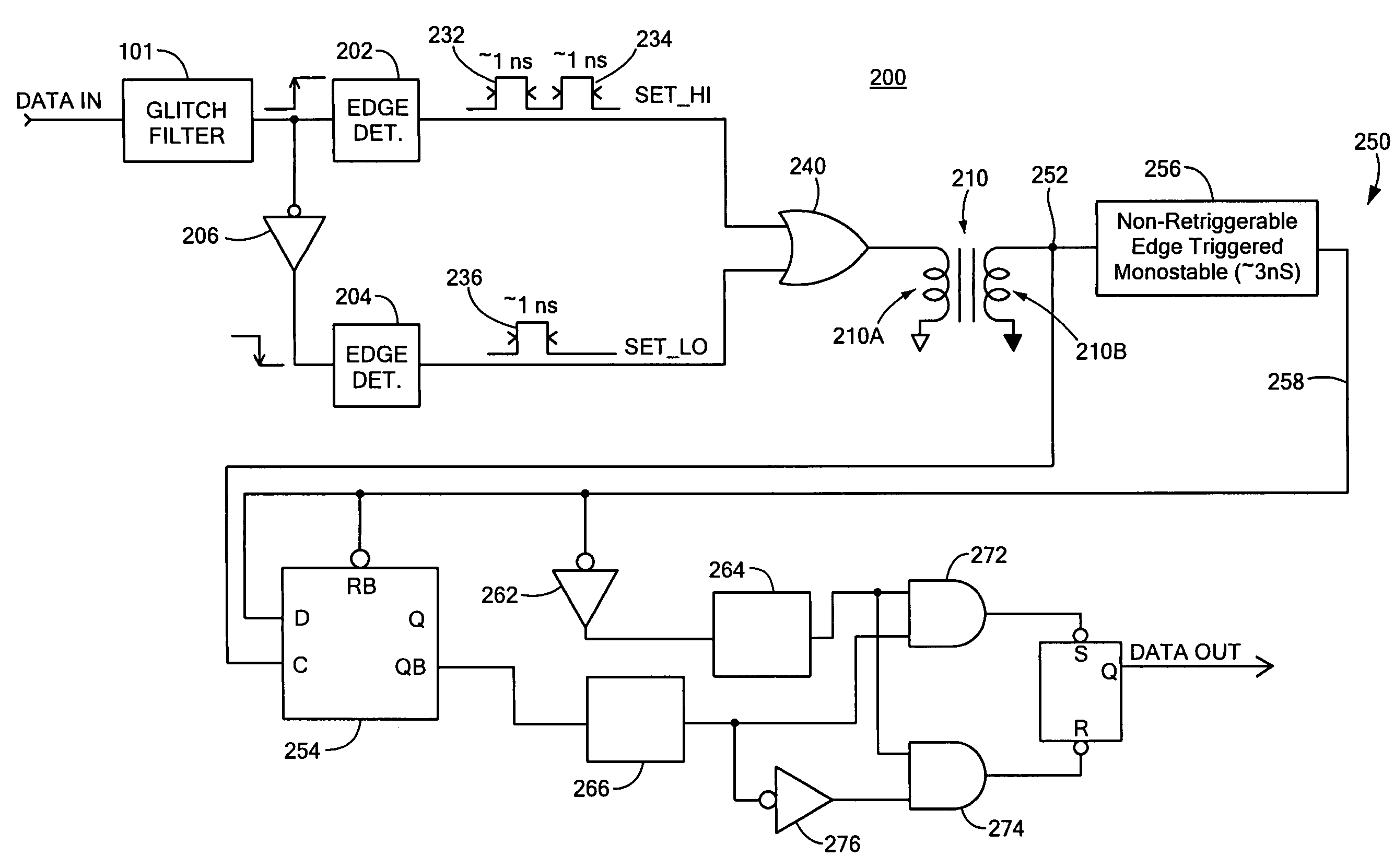

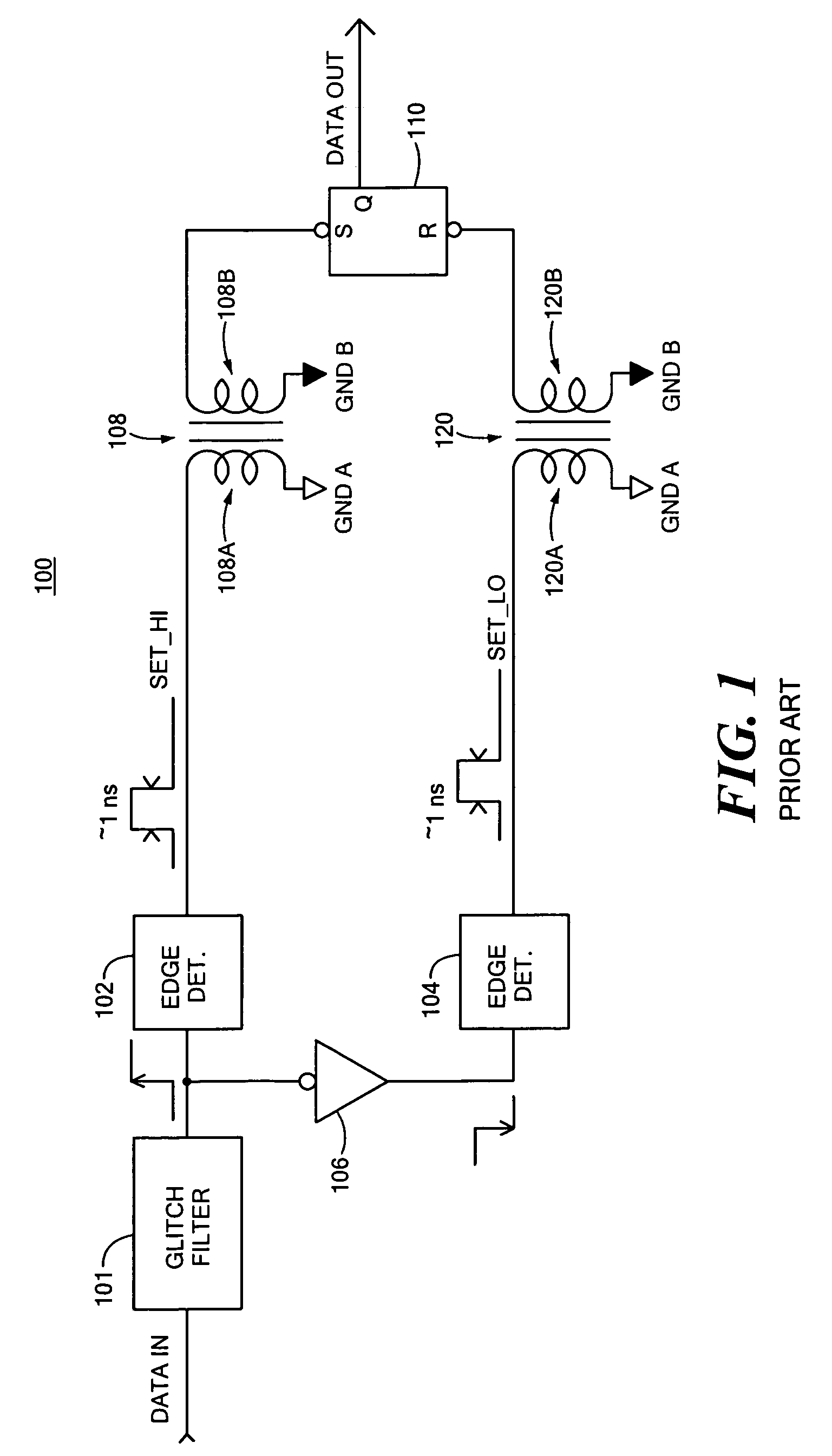

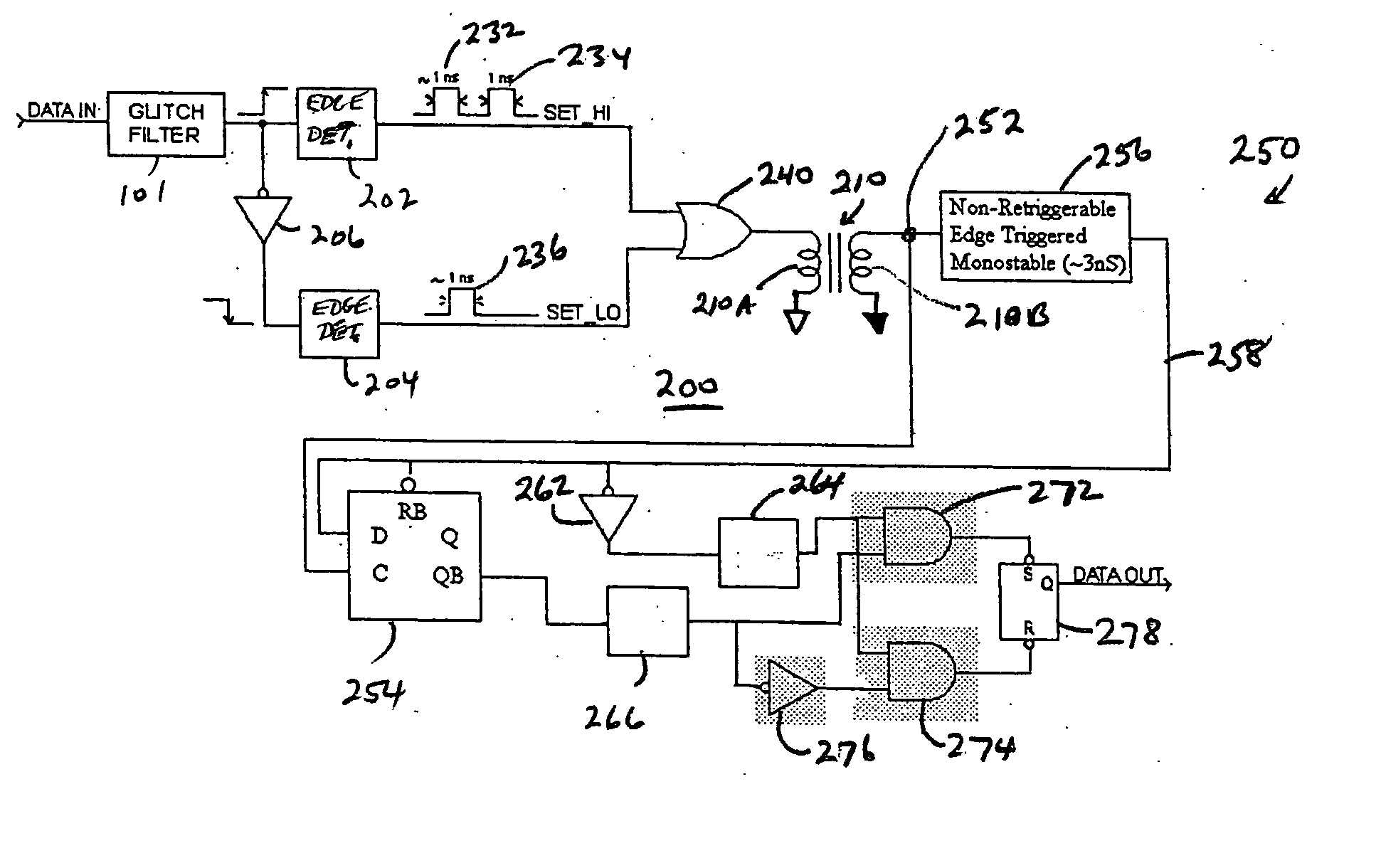

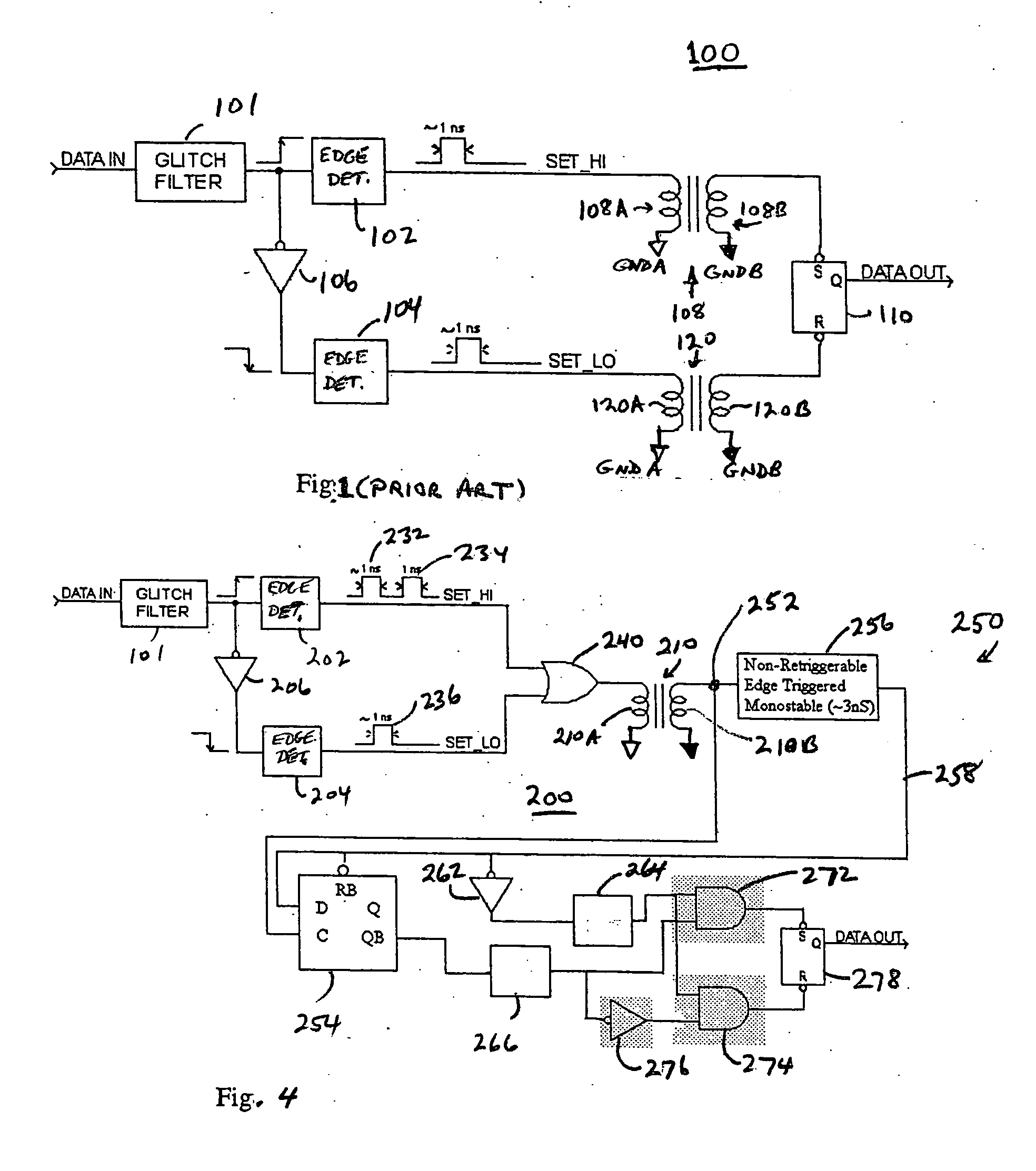

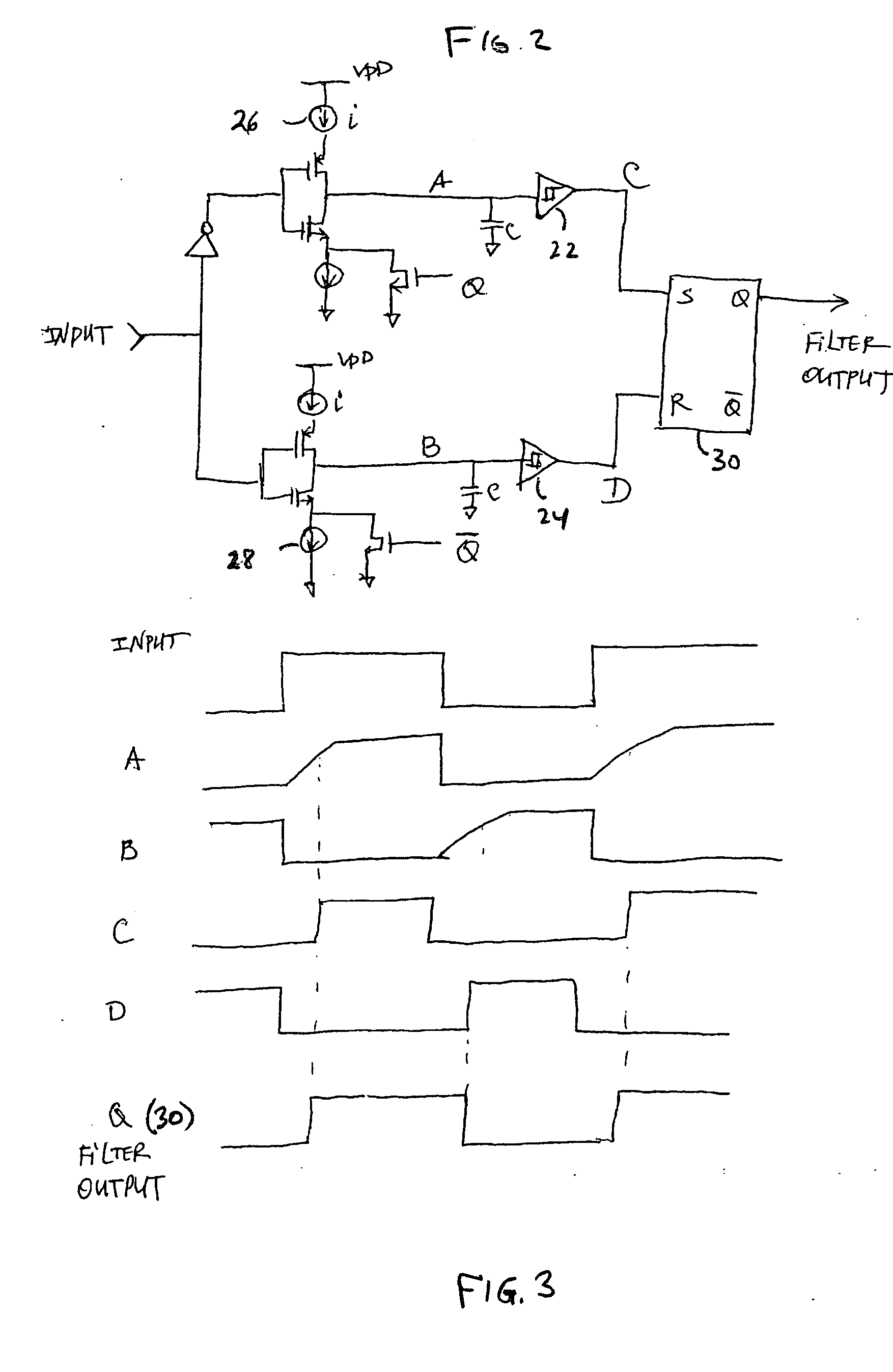

ActiveUS7075329B2Reliability increasing modificationsSemiconductor/solid-state device detailsTransformerEngineering

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

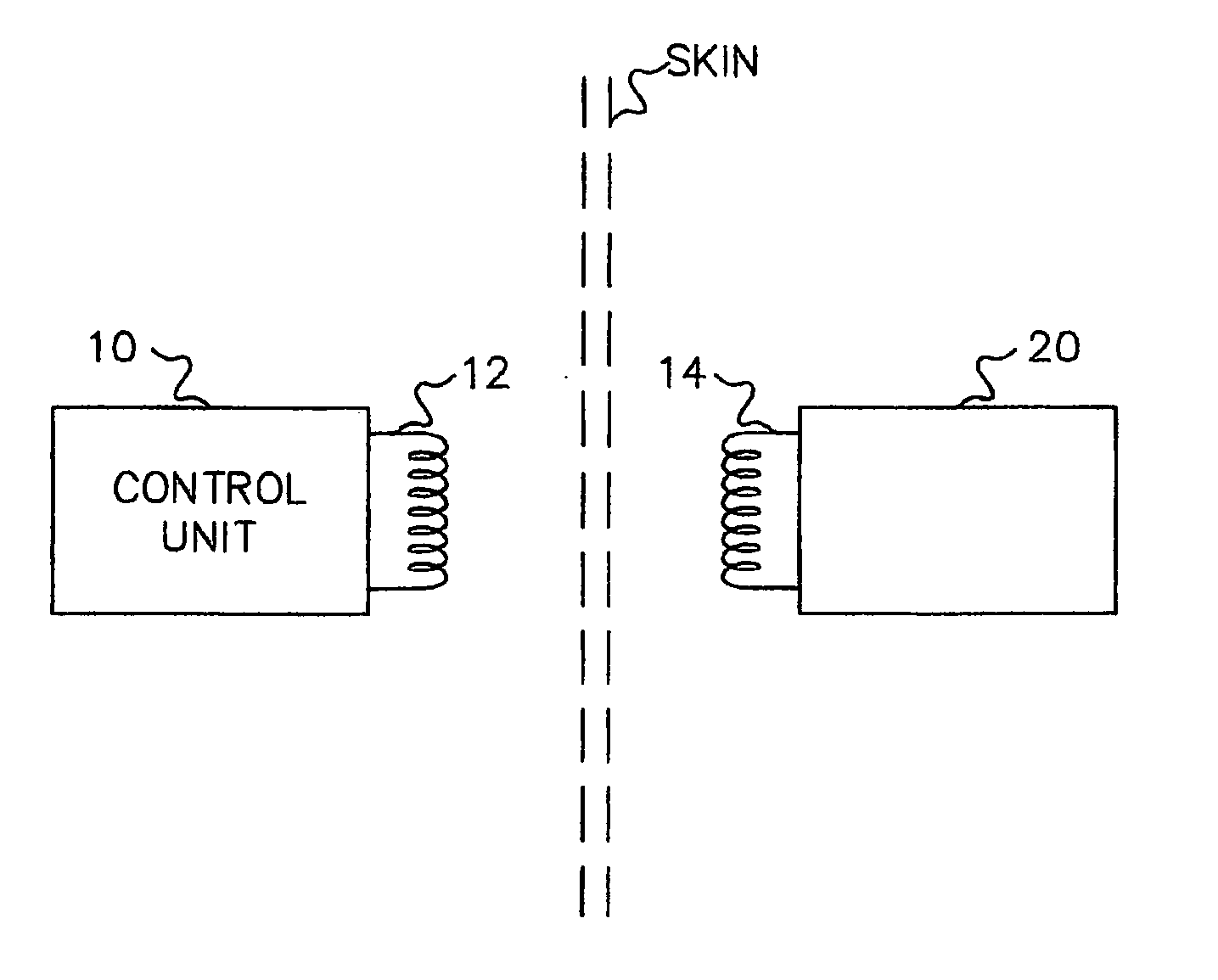

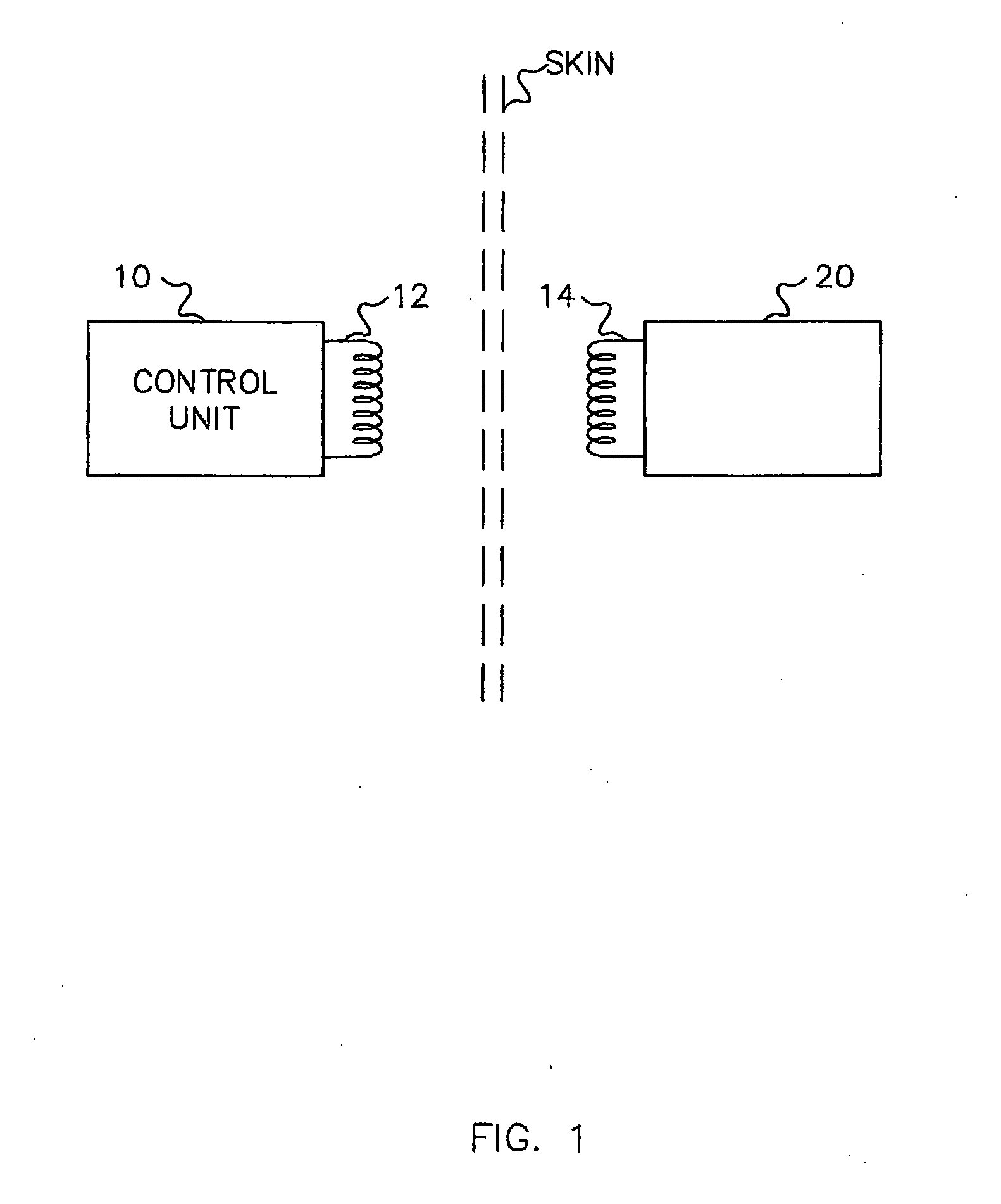

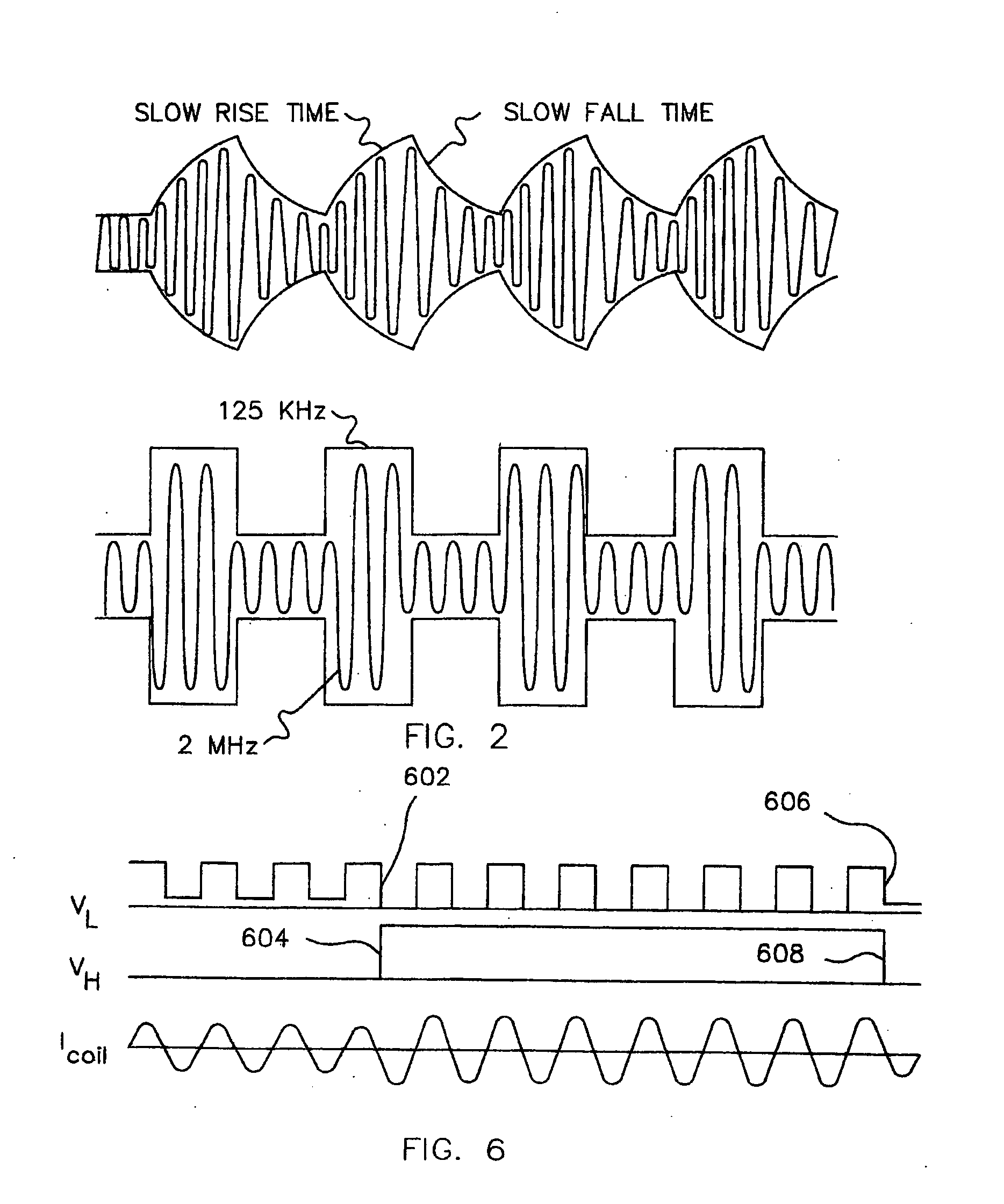

Method and apparatus for efficient power/data transmission

A system, method and power / data transmission device comprising a coil having a high Q, a low-voltage driver and a high-voltage driver switchably coupled to the coil. The low-voltage driver and the high-voltage driver are controlled by a microcontroller and switch at about the same time thereby providing a modulated data signal for transmission. Furthermore, the system includes at least one implantable microstimulator coupled to the transmission device.

Owner:ALFRED E MANN FOUND FOR SCI RES

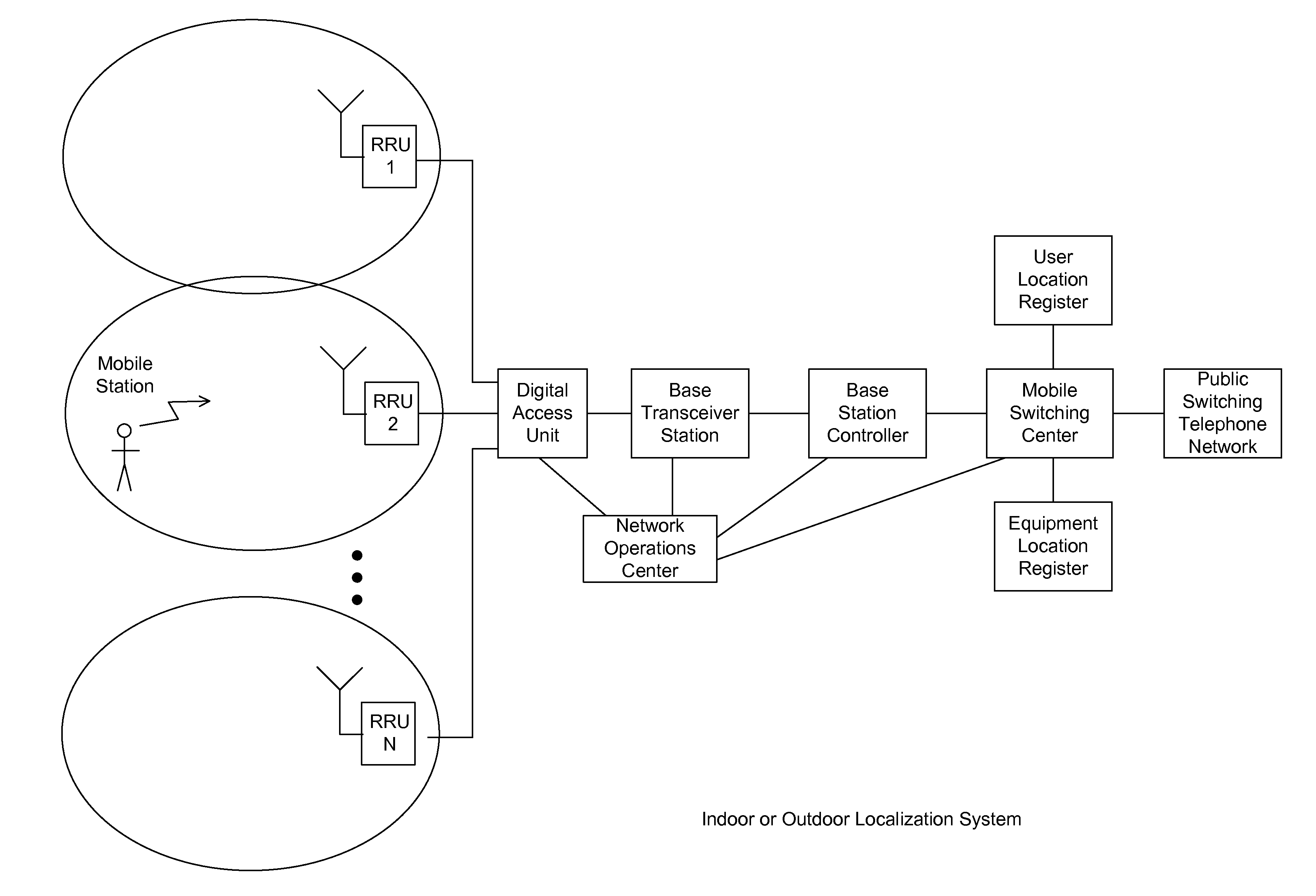

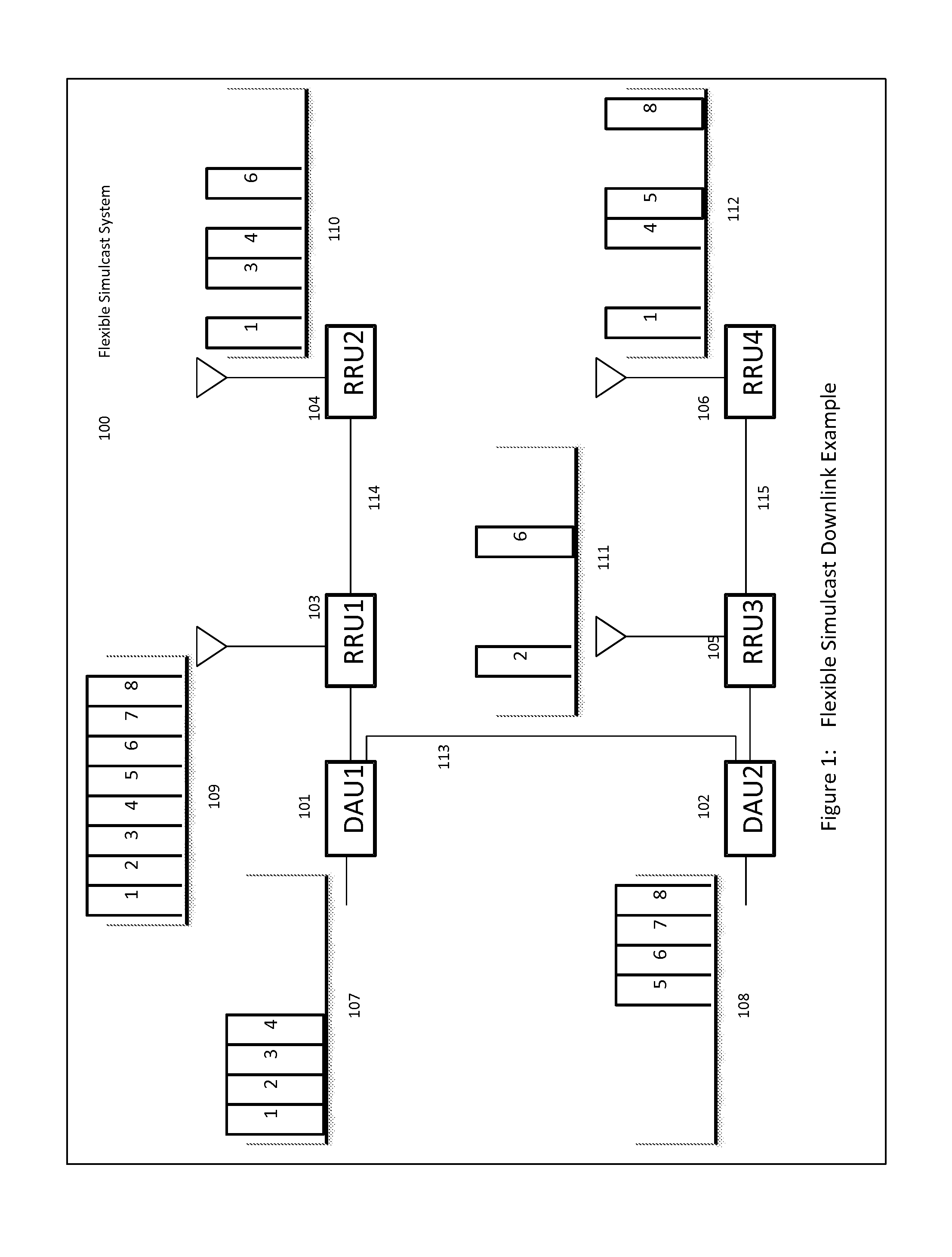

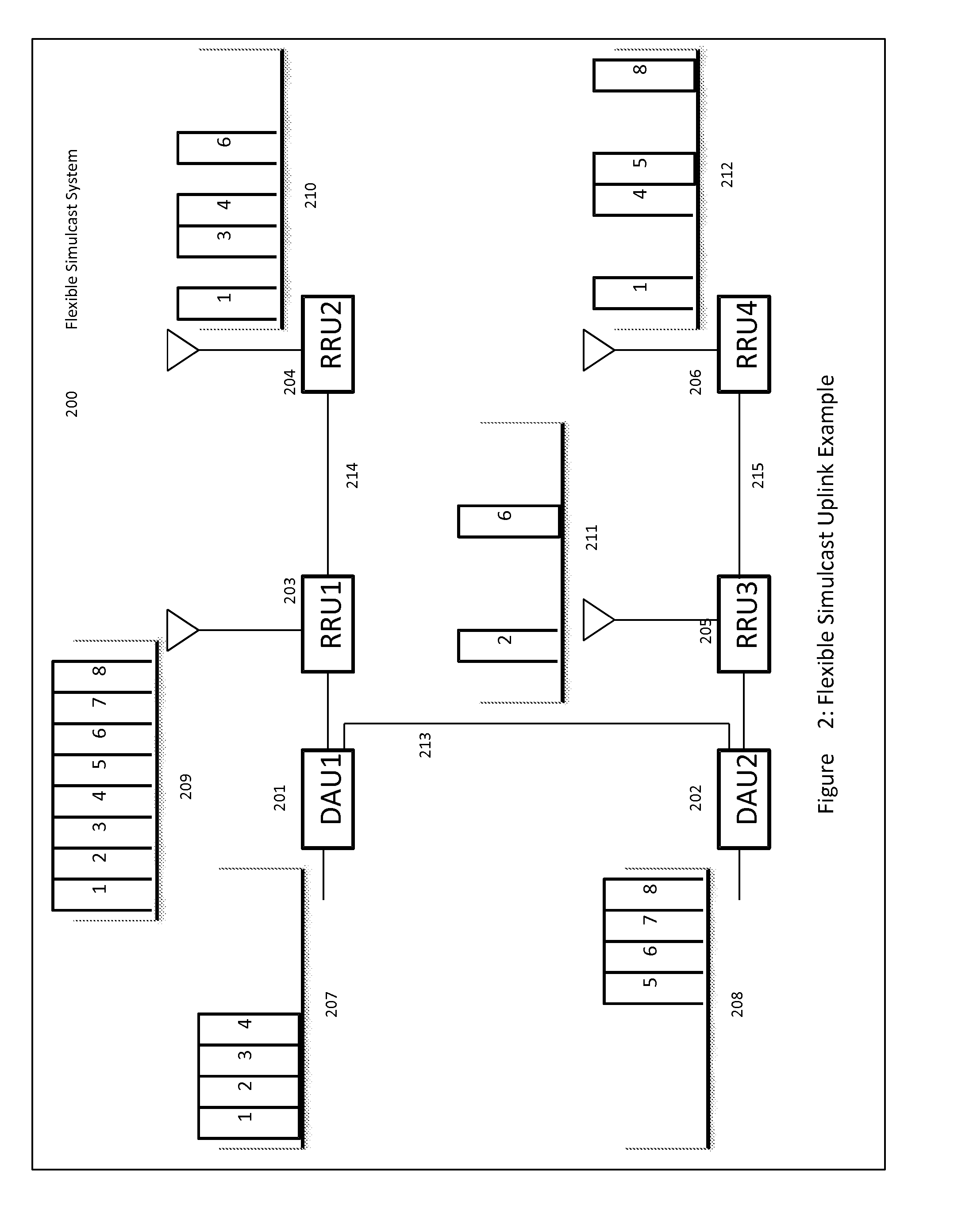

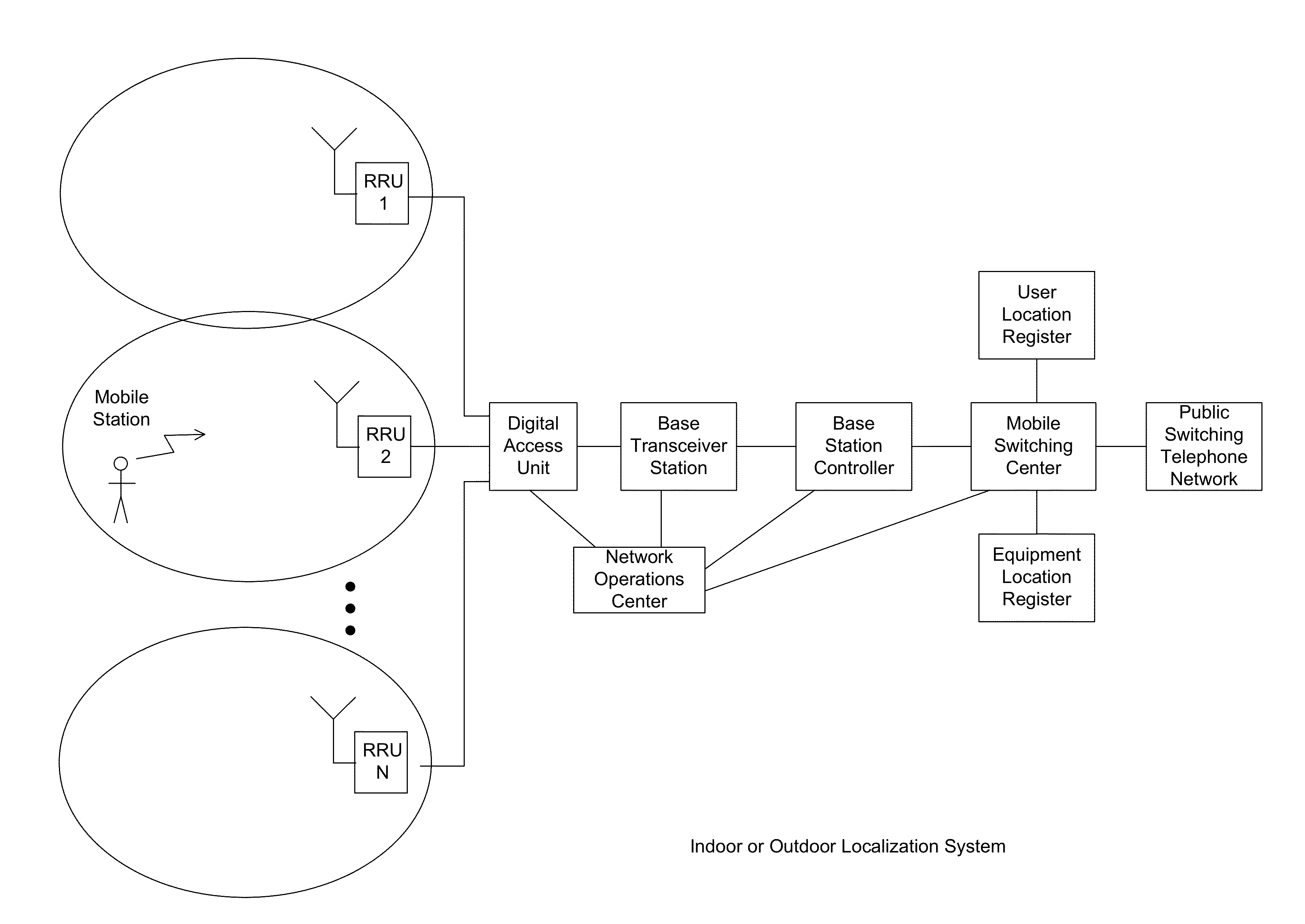

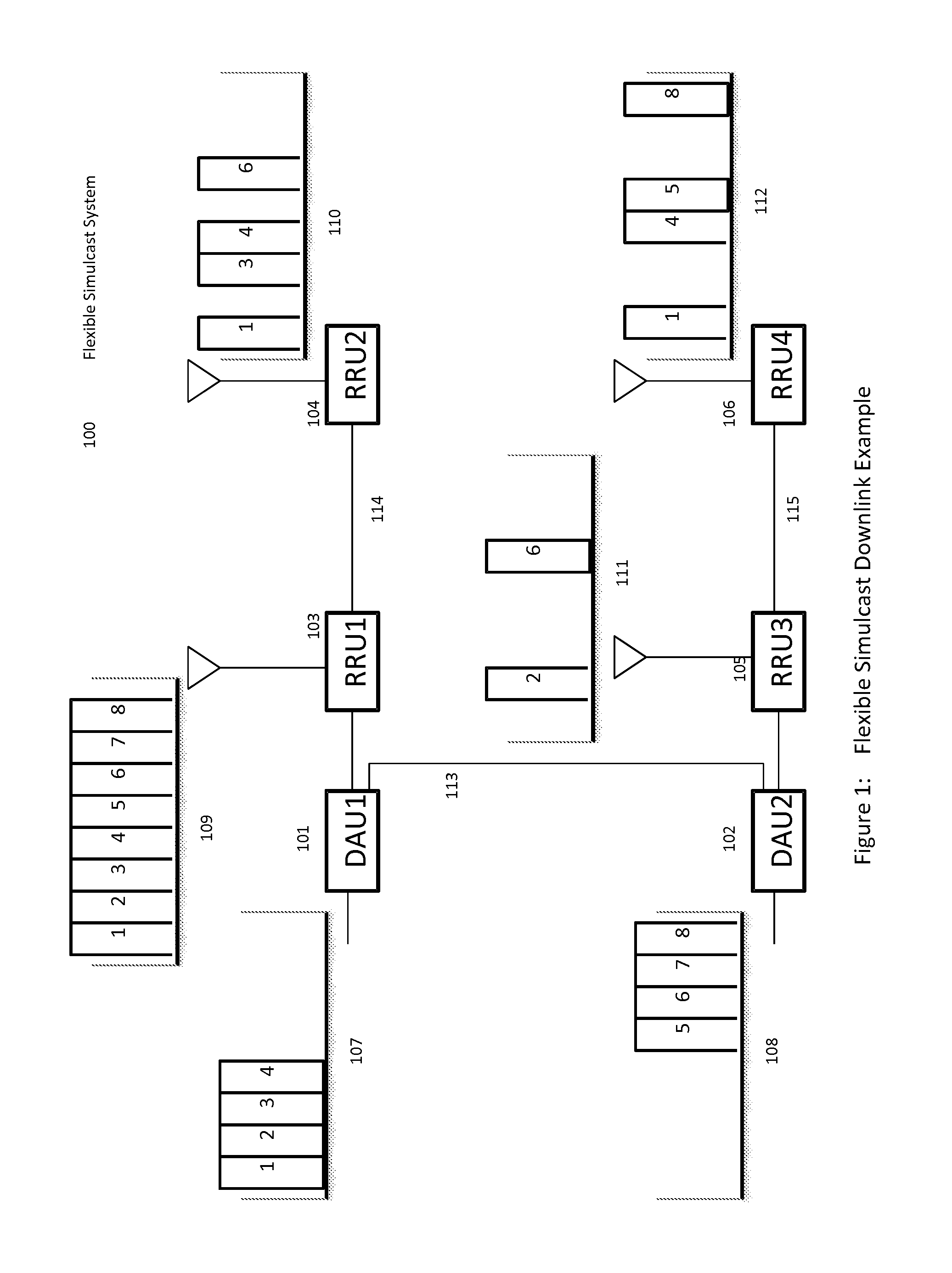

Remotely Reconfigurable Distributed Antenna System and Methods

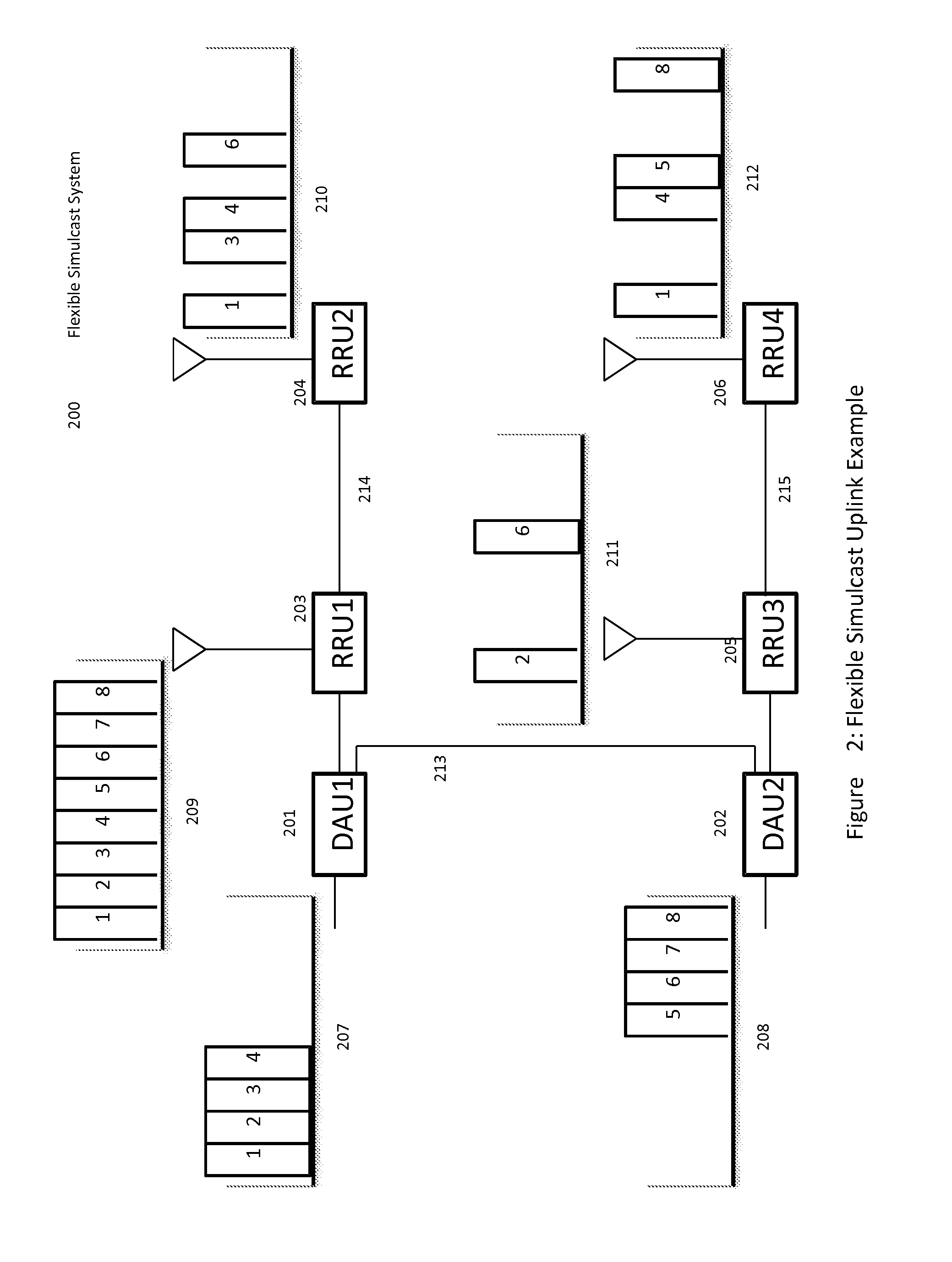

ActiveUS20120039320A1Improve efficiencyImprove traffic capacityMultiplex system selection arrangementsPower amplifiersDistributed antenna systemCarrier signal

The present disclosure is a novel utility of a software defined radio (SDR) based Distributed Antenna System (DAS) that is field reconfigurable and support multi-modulation schemes (modulation-independent), multi-carriers, multi-frequency bands and multi-channels. The present disclosure enables a high degree of flexibility to manage, control, enhance, facilitate the usage and performance of a distributed wireless network such as flexible simulcast, automatic traffic load-balancing, network and radio resource optimization, network calibration, autonomous / assisted commissioning, carrier pooling, automatic frequency selection, frequency carrier placement, traffic monitoring, traffic tagging, pilot beacon, etc. As a result, the SDR DAS can increase the efficiency and traffic capacity of the operators' wireless network.

Owner:DALI WIRELESS

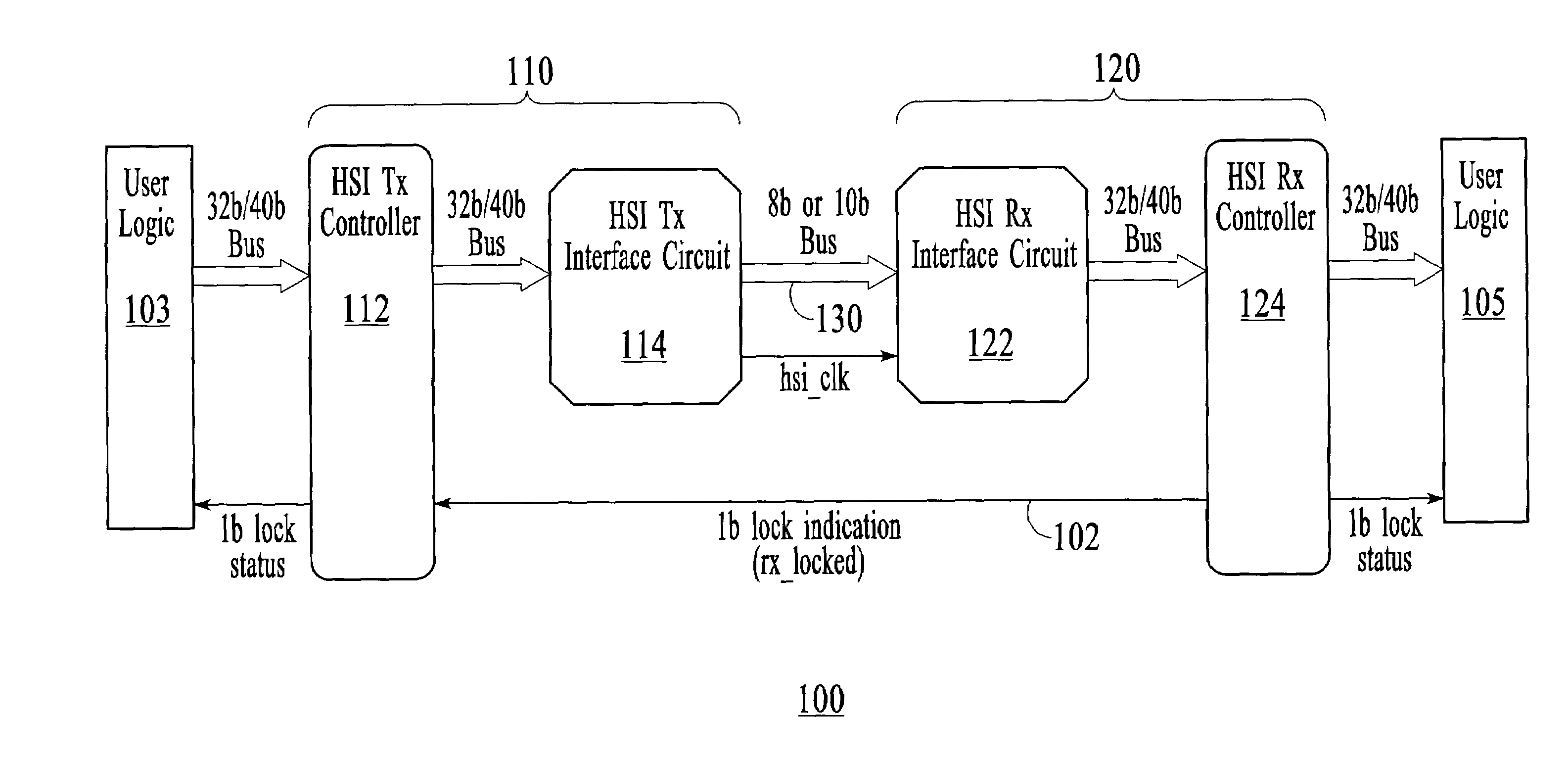

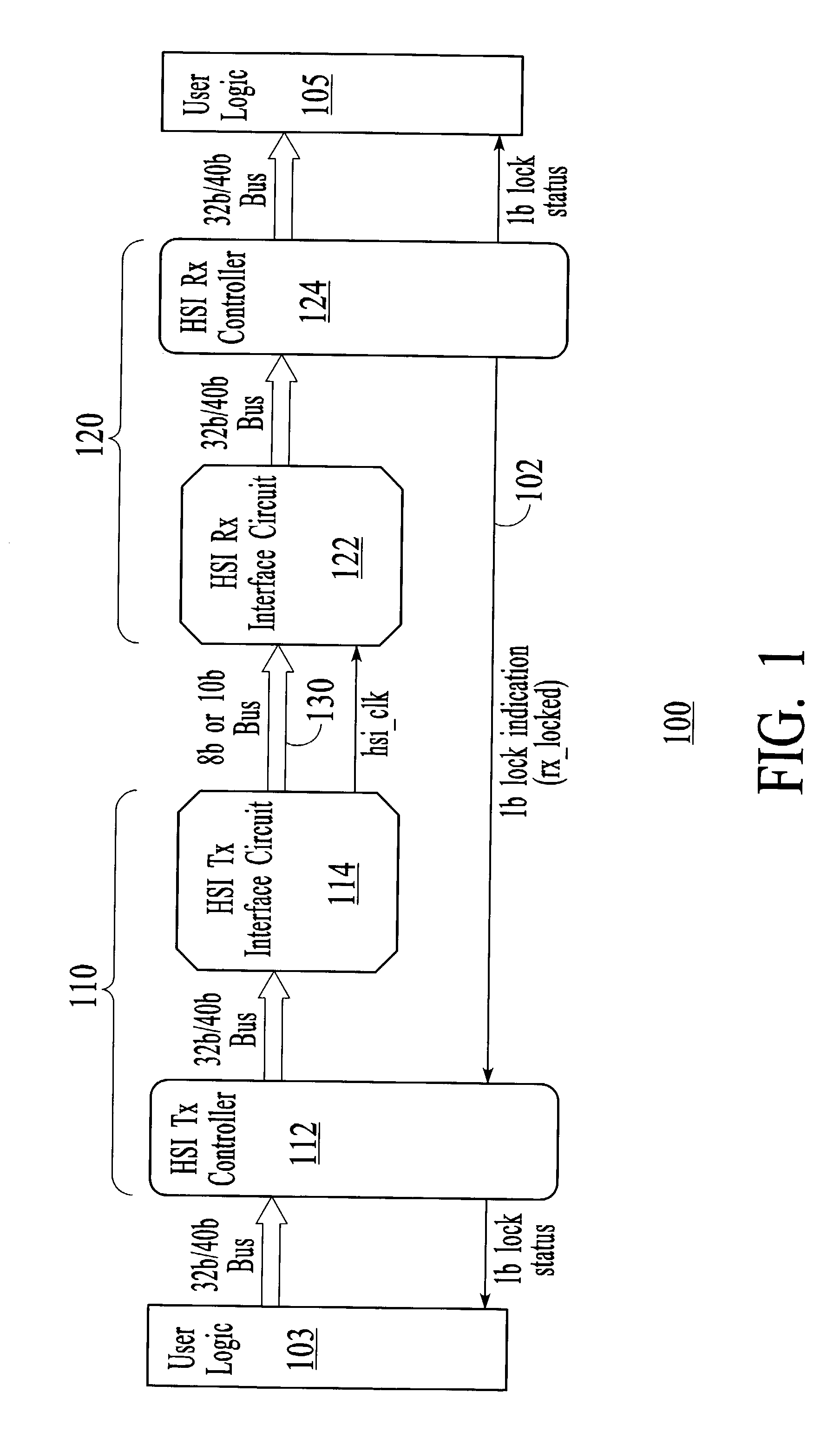

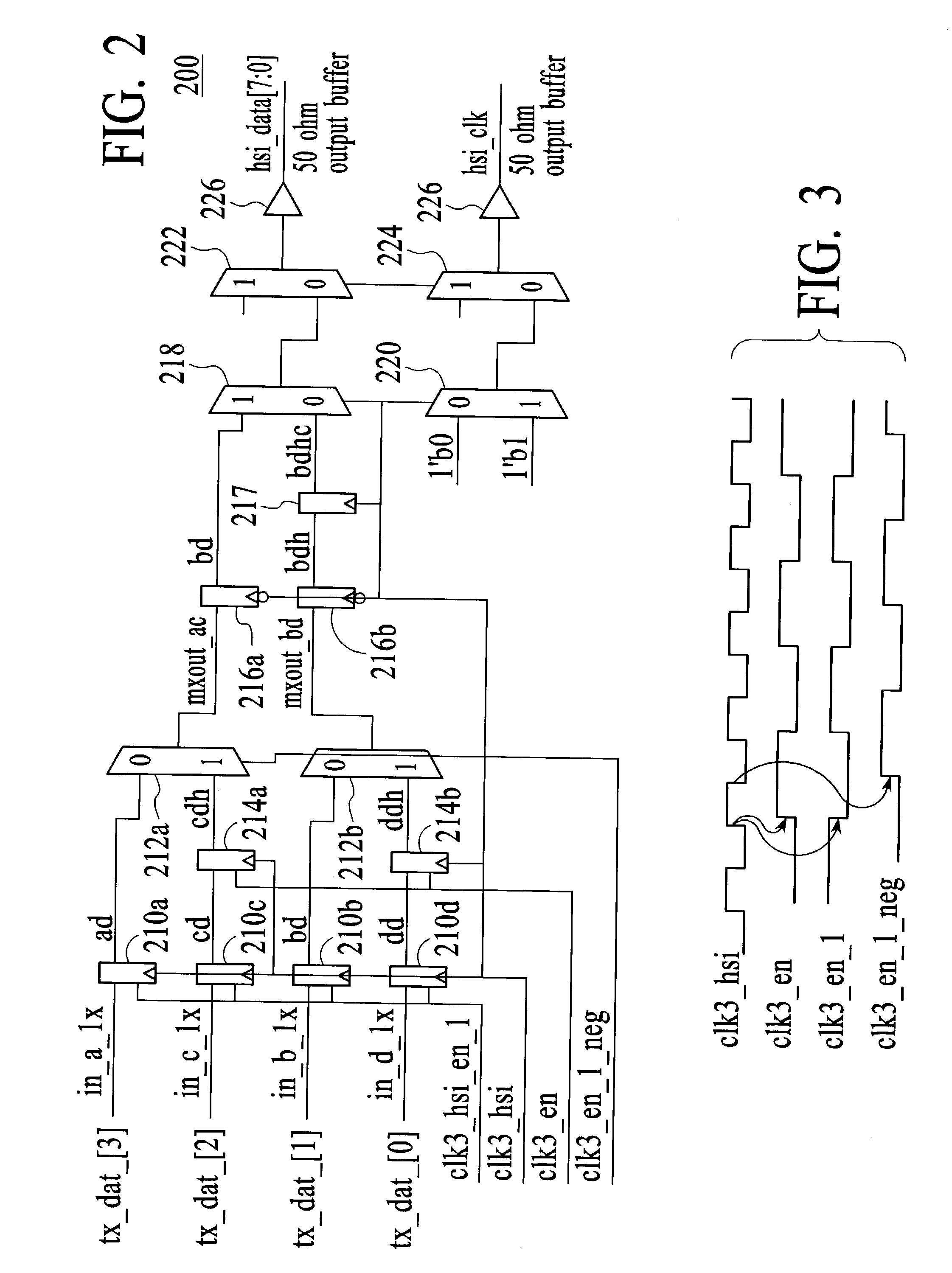

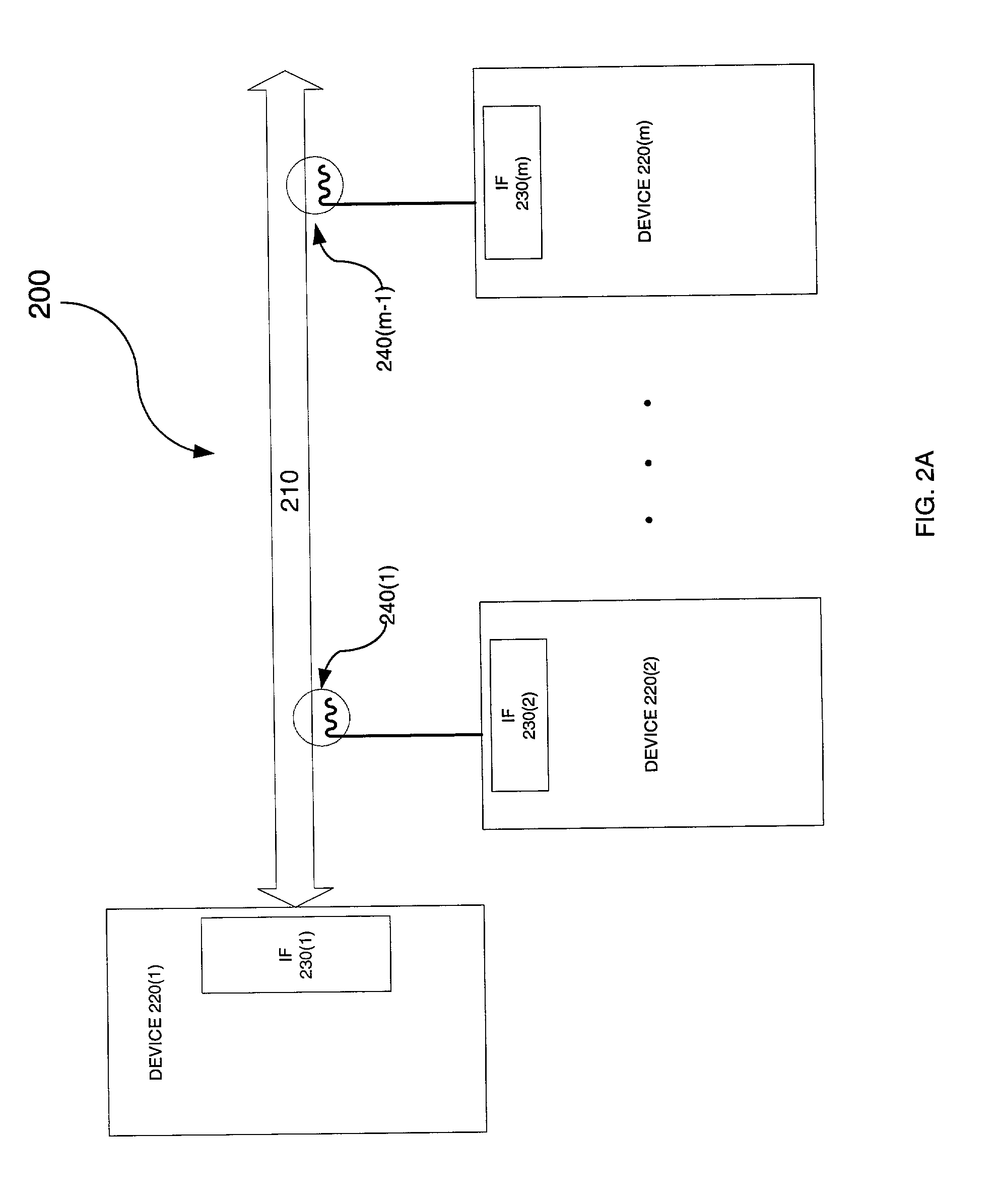

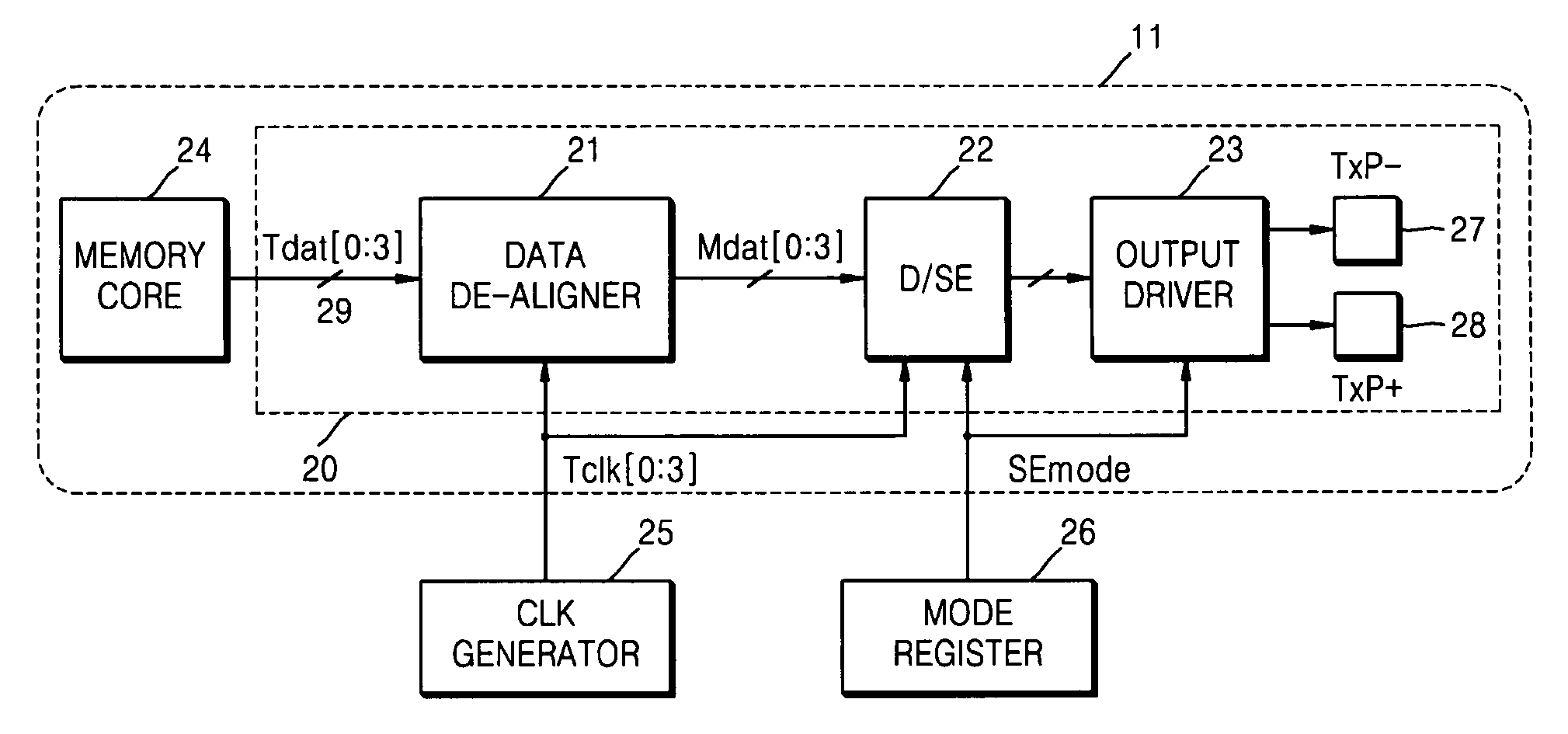

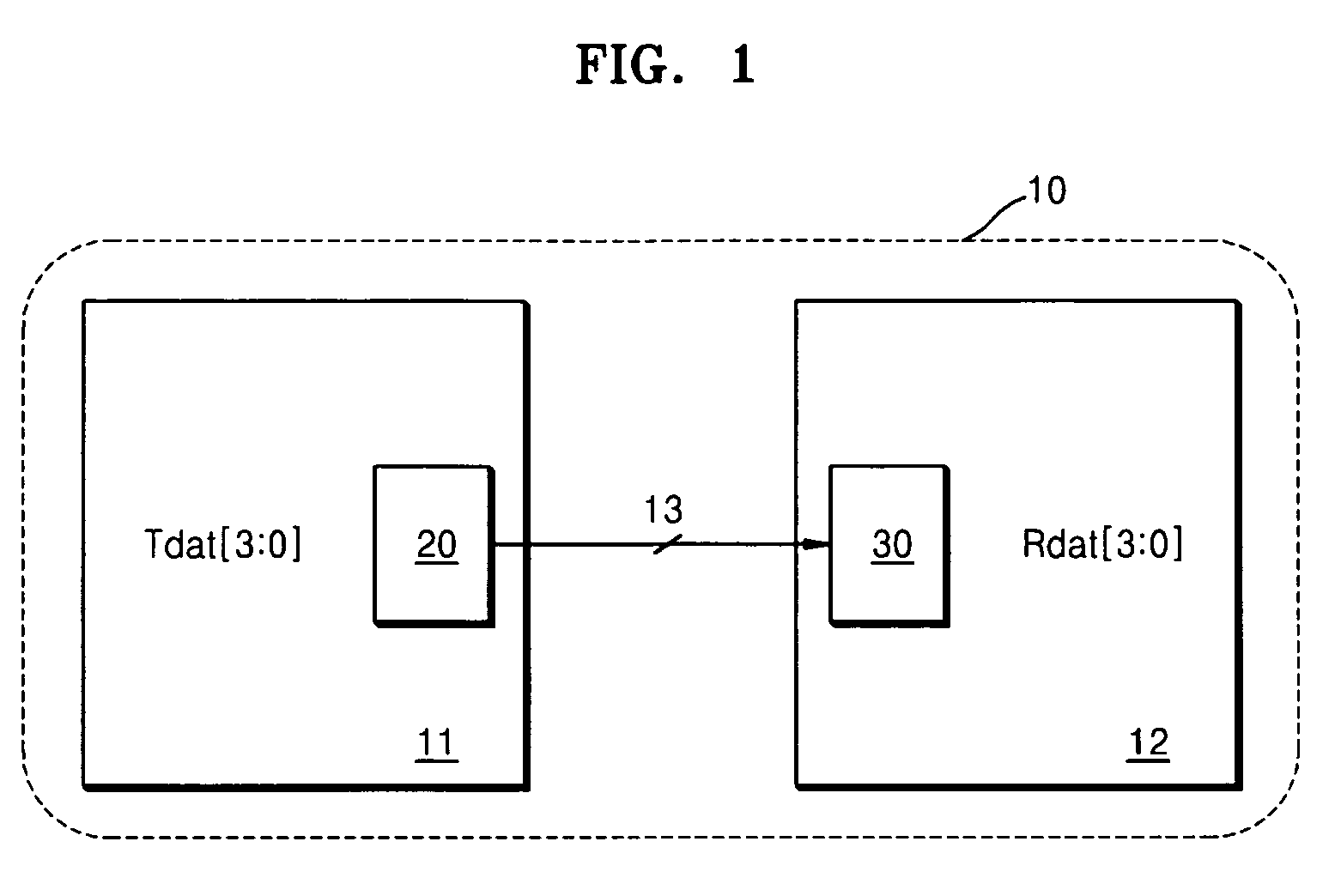

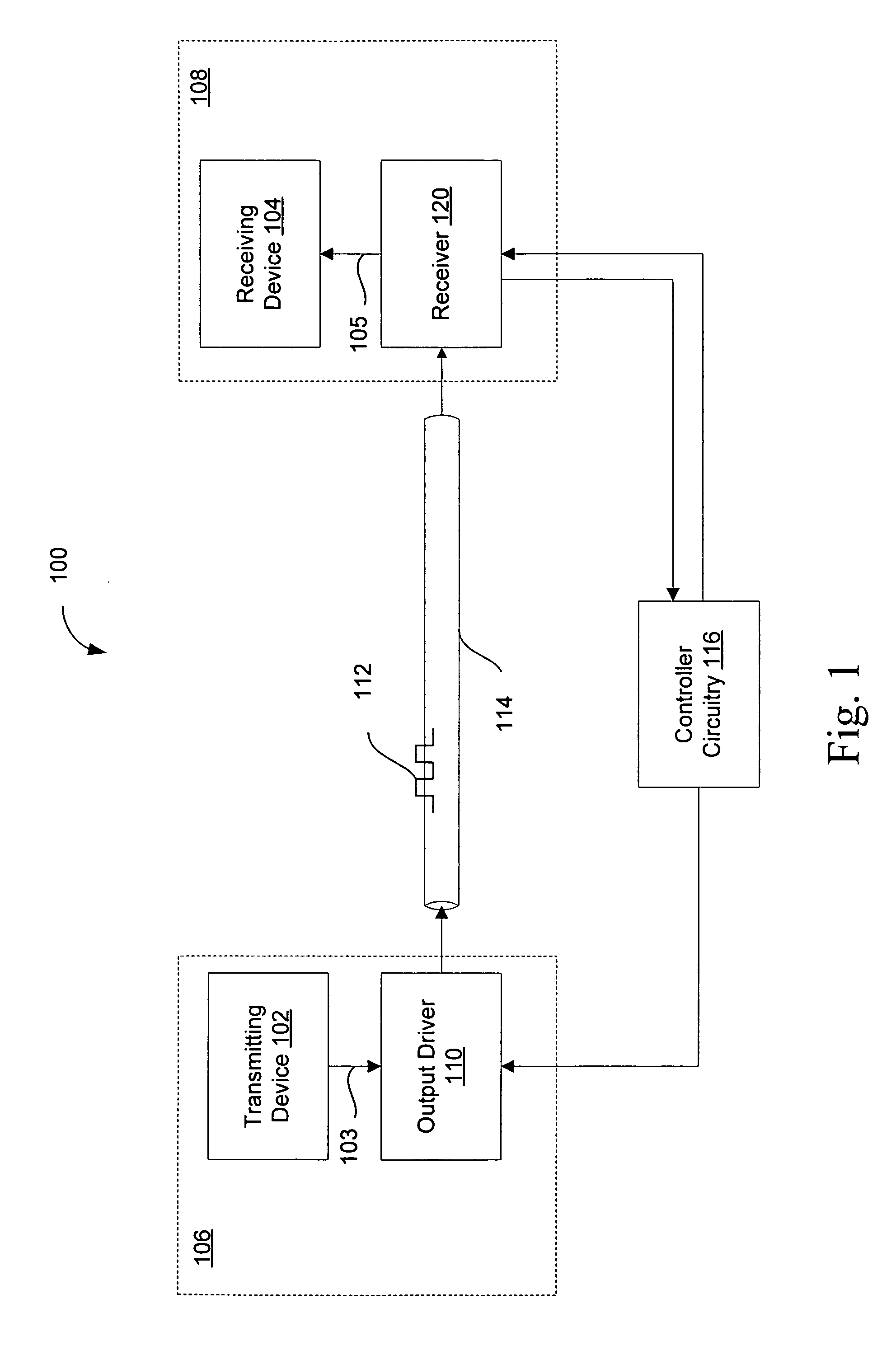

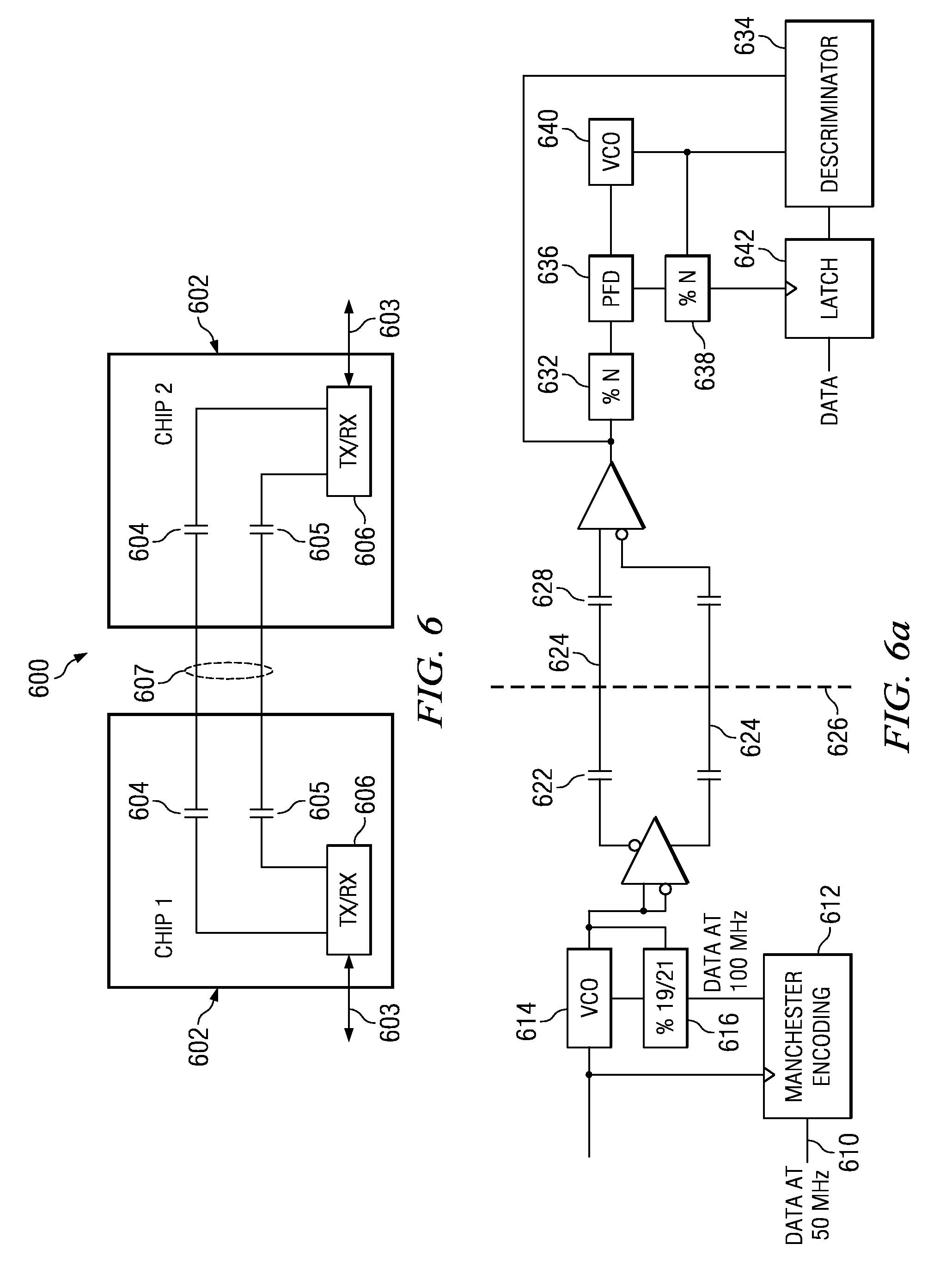

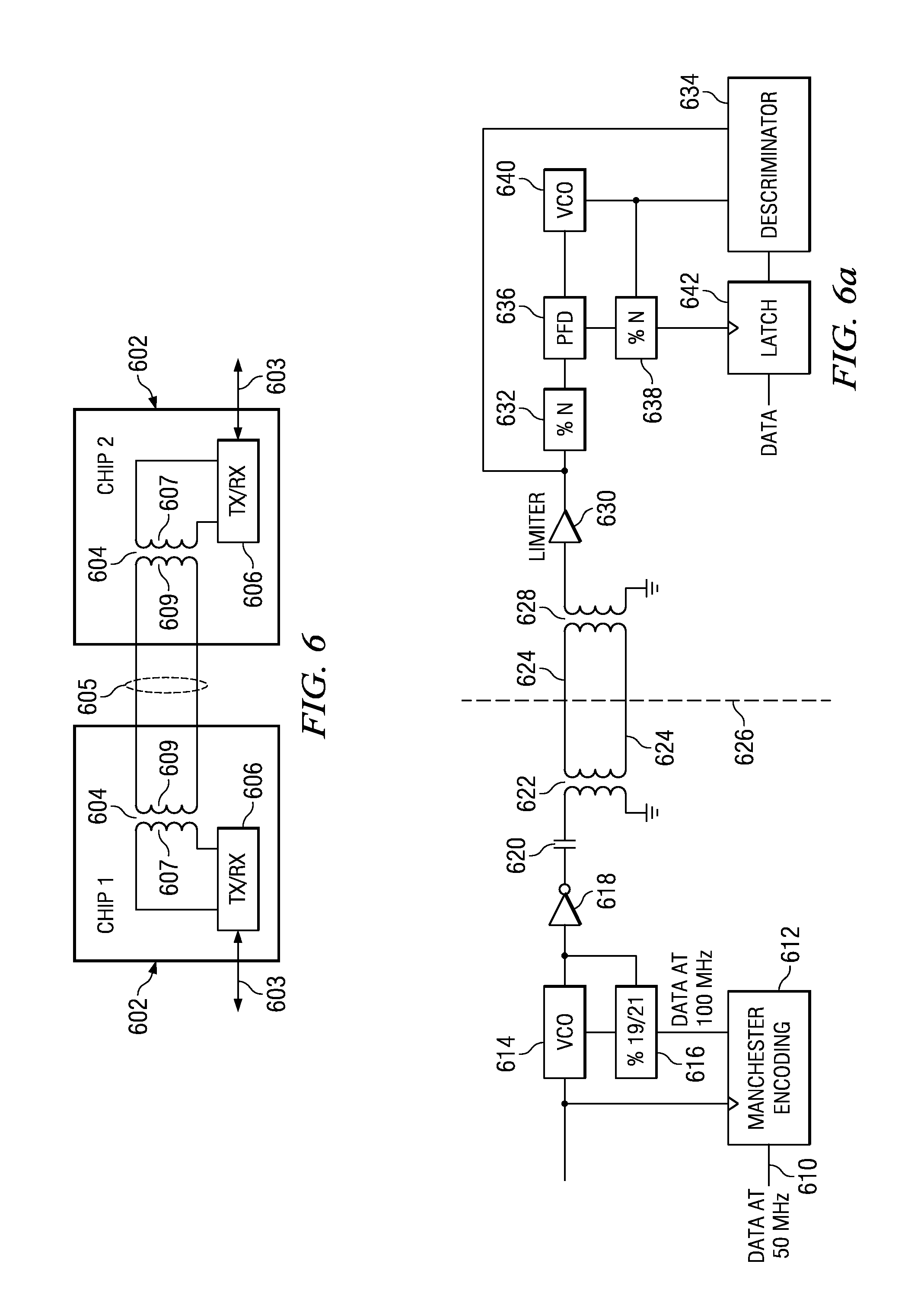

High-speed chip-to-chip communication interface

ActiveUS7180949B2Improve scalabilitySynchronisation information channelsModulated-carrier systemsCommunication interfaceCMOS

A high-speed parallel interface for communicating data between integrated circuits is disclosed. The interface is implemented by a transmitter and receiver pair and a single-ended parallel interconnect bus coupling to the transmitter and receiver pair. As opposed to transmitting small swing signals over differential signal lines, the transmitter transmits data to the receiver at full swing over the single-ended parallel interconnect bus. The invention can be implemented with simple CMOS circuitry that does not consume large die area. Accordingly, many link interfaces can be implemented on a single chip to provide a large data bandwidth.

Owner:RIVERSTONE NETWORKS +1

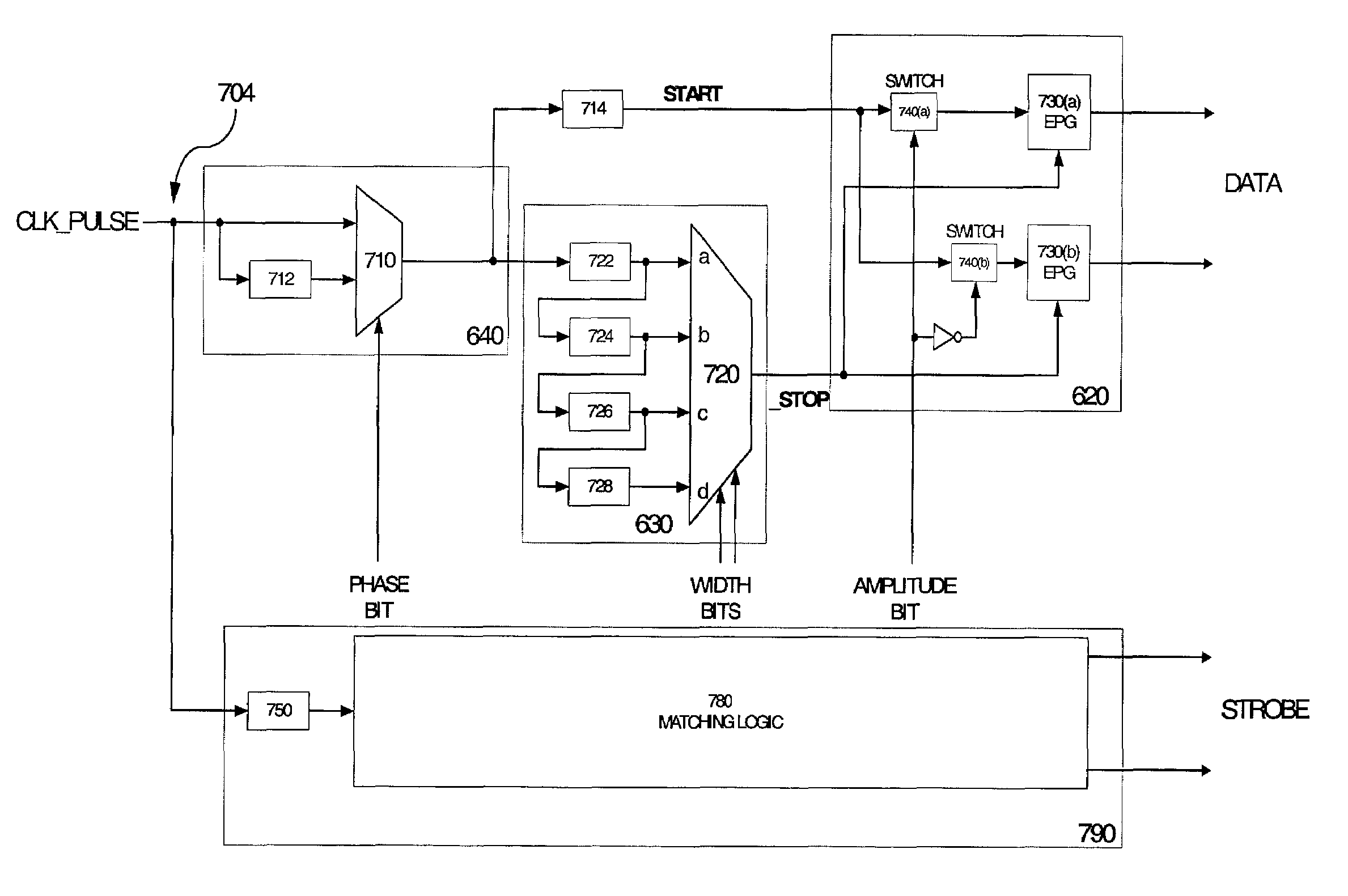

Symbol-based signaling device for an electromagnetically-coupled bus system

InactiveUS7075996B2Printed circuit assemblingLine impedence variation compensationComplementary pairChipset

The present invention provides a chipset for transferring data through an electromagnetically coupled bus system. The chipset includes a modulator, a matching circuit and a demodulator. The modulator modifies a clock to encode multiple bits in a complementary pair of symbols. The matching circuit modifies the clock signal to generate a complementary pair of reference signals that is transmitted with the complementary symbol pair, and the demodulator decodes a second set of bits from selected properties of a complementary pair of transferred symbols.

Owner:INTEL CORP

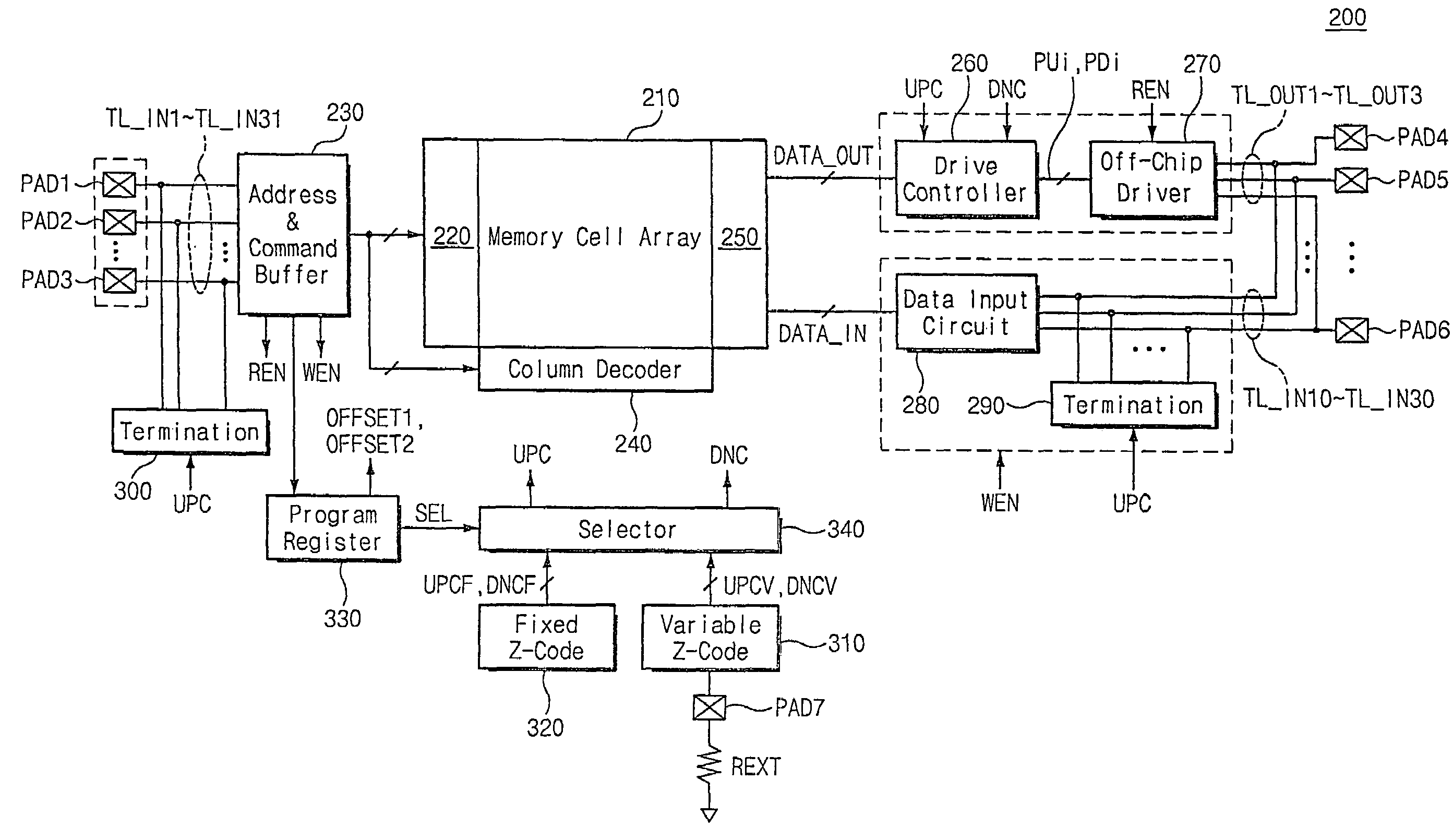

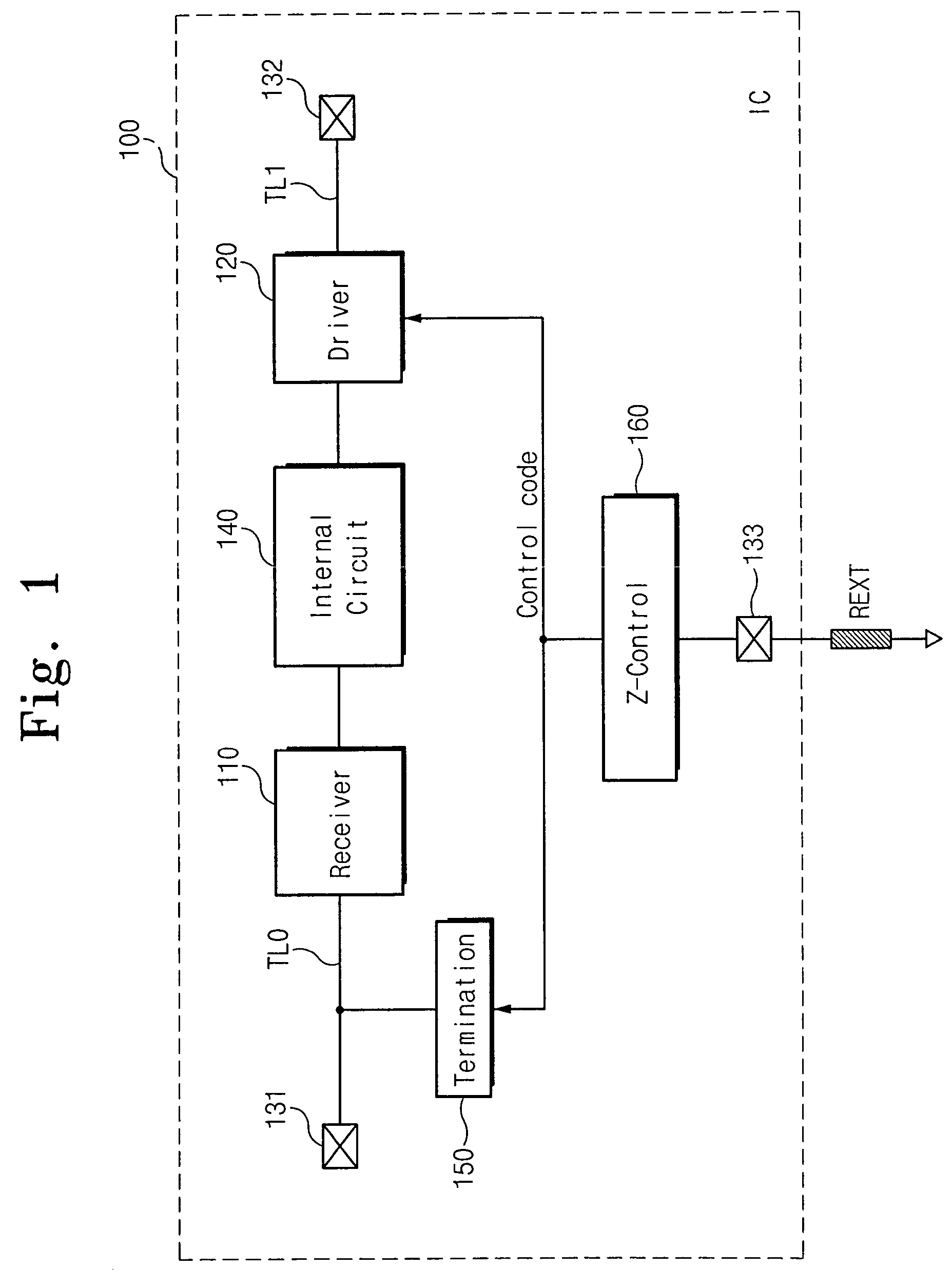

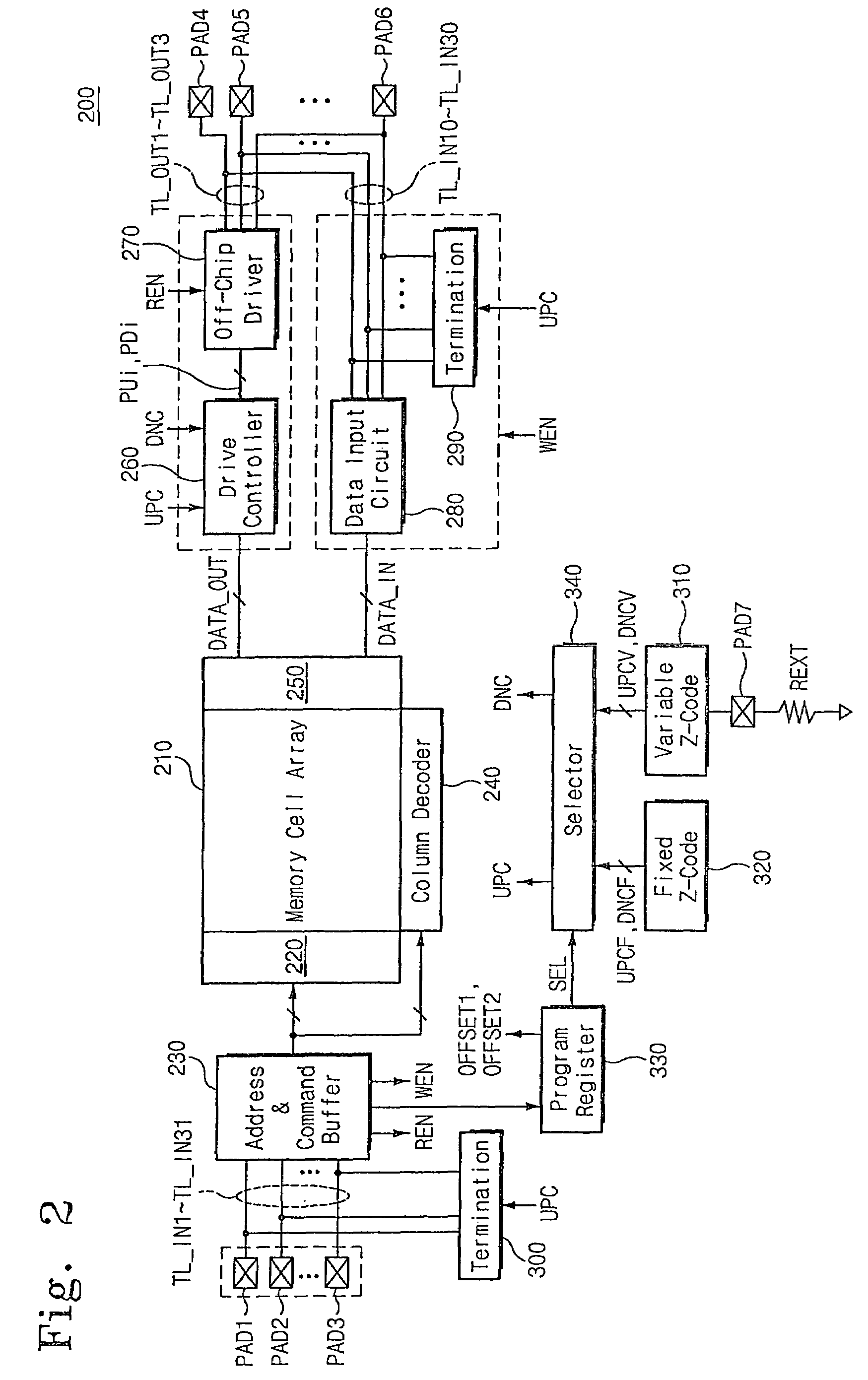

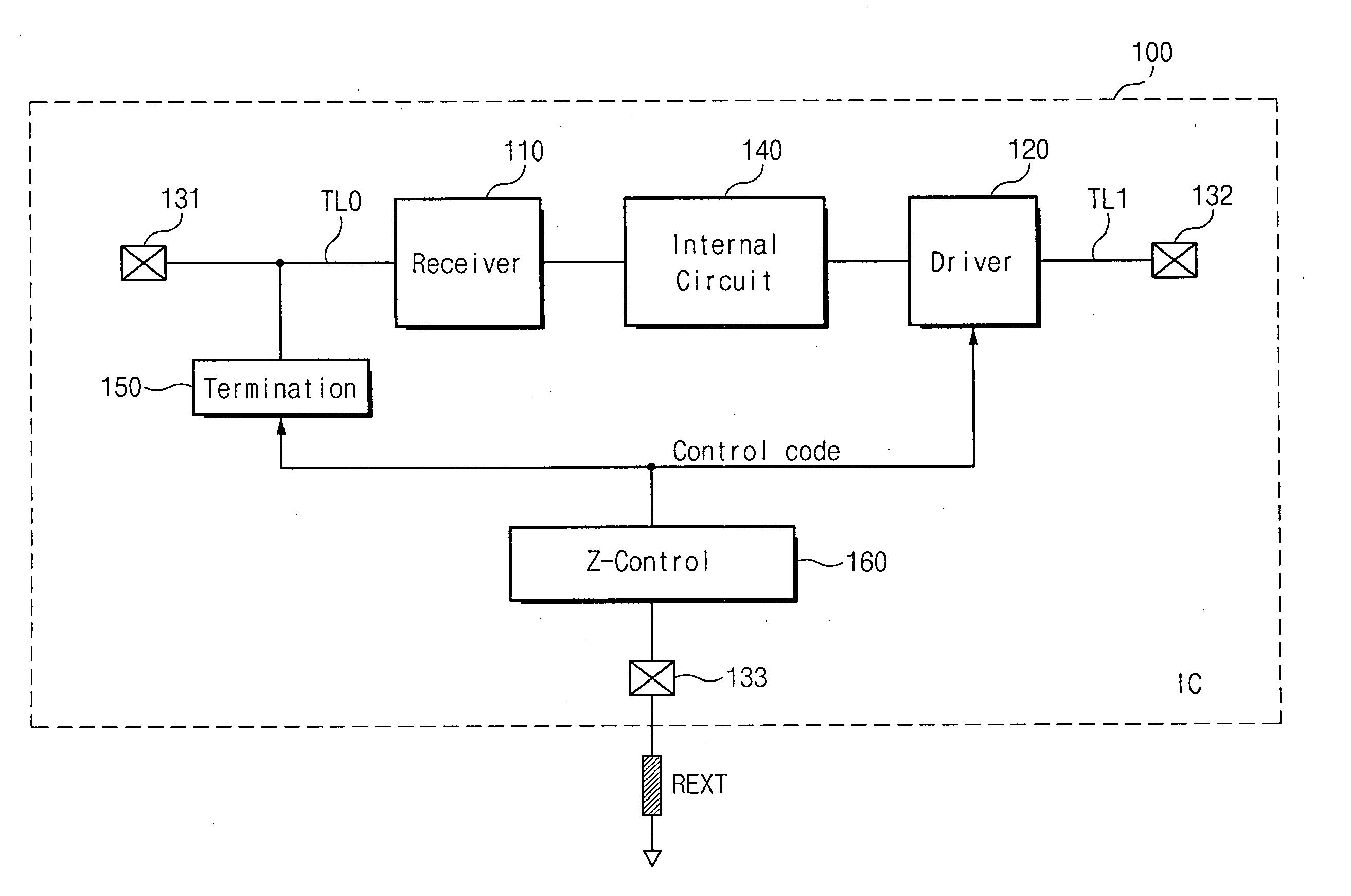

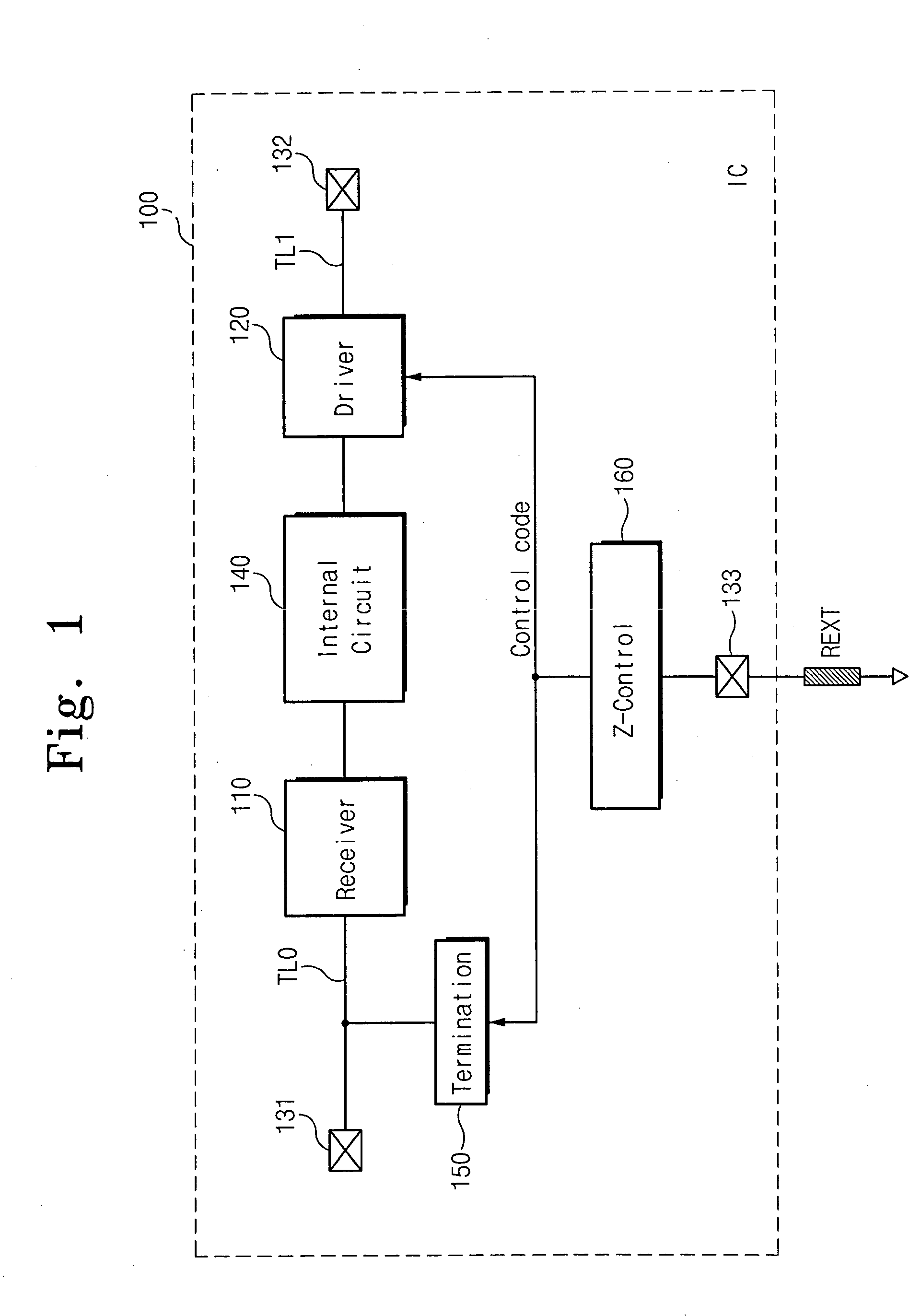

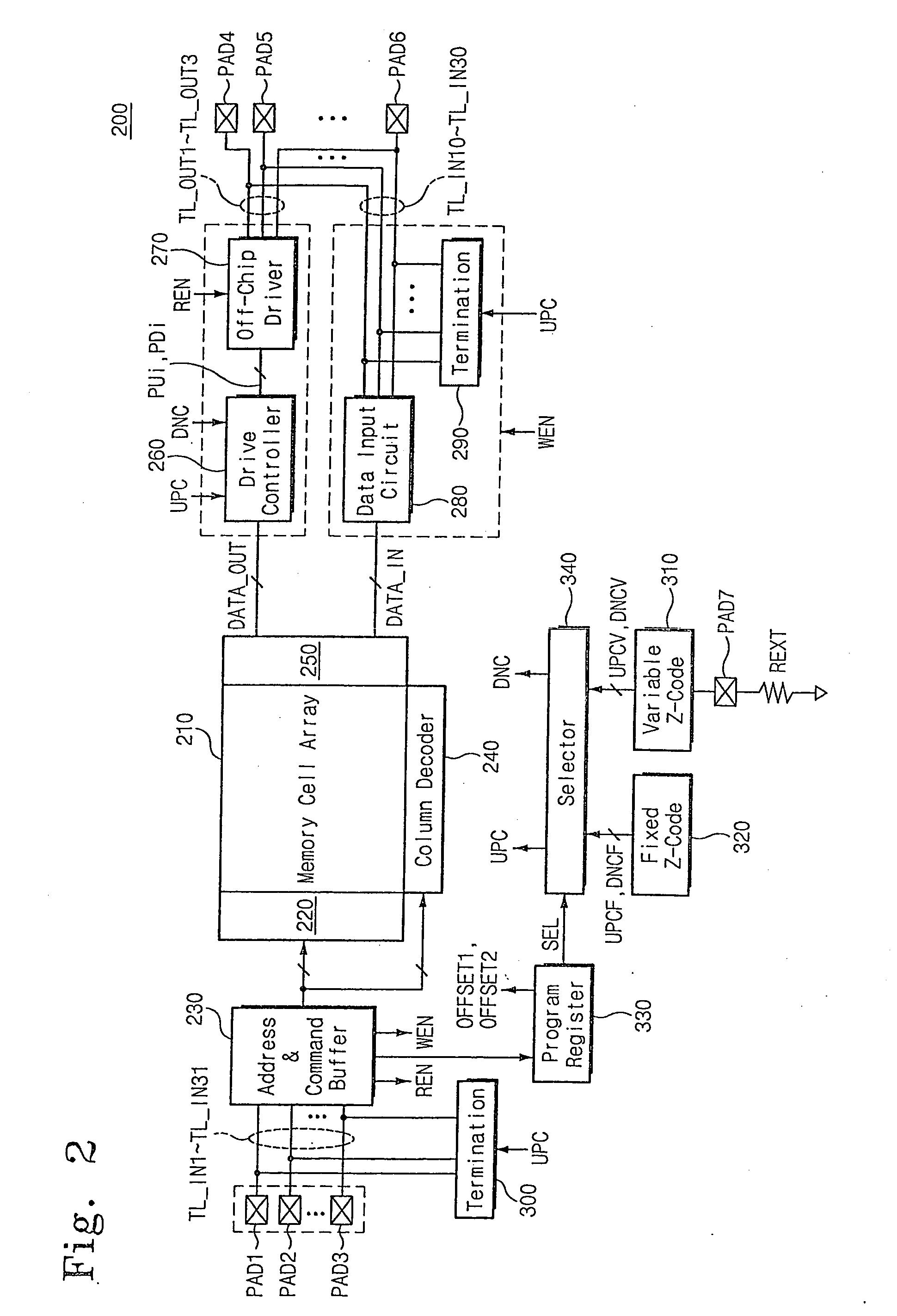

Semiconductor integrated circuit device capable of controlling impedance

ActiveUS7148721B2Input/output impedence modificationReliability increasing modificationsExternal referenceSemiconductor

A semiconductor integrated circuit device is connected to an external reference resistor, including an impedance control circuit for generating impedance control codes variable with impedances established by the external reference resistor. An input circuit receives an external signal through an input transfer line and forwards the external signal to an internal circuit. A termination circuit terminates the input transfer line in response to at least one of the impedance control code. An output circuit drives an output transfer line in accordance with an output signal. Impedance is variable with the control codes.

Owner:SAMSUNG ELECTRONICS CO LTD

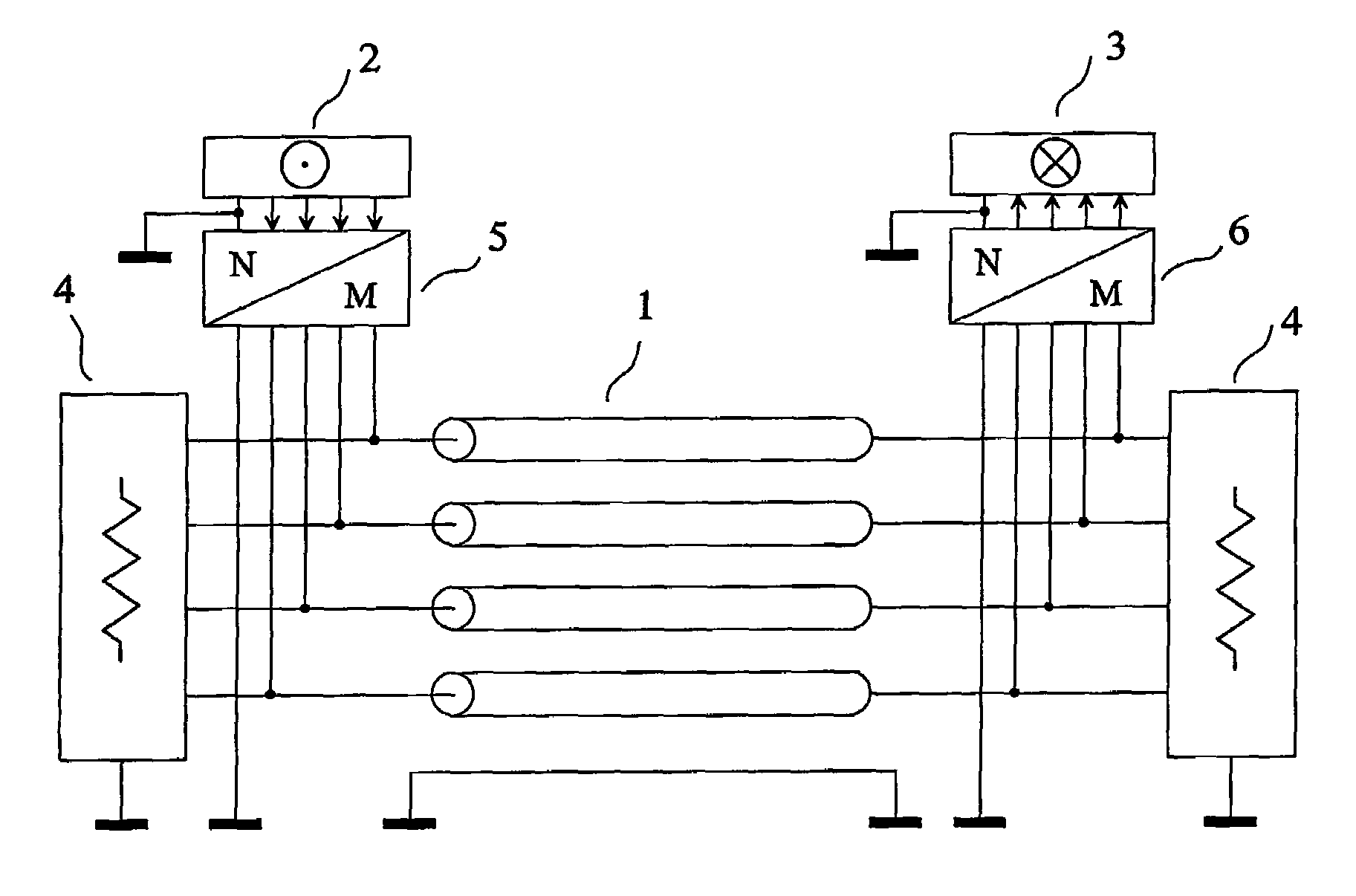

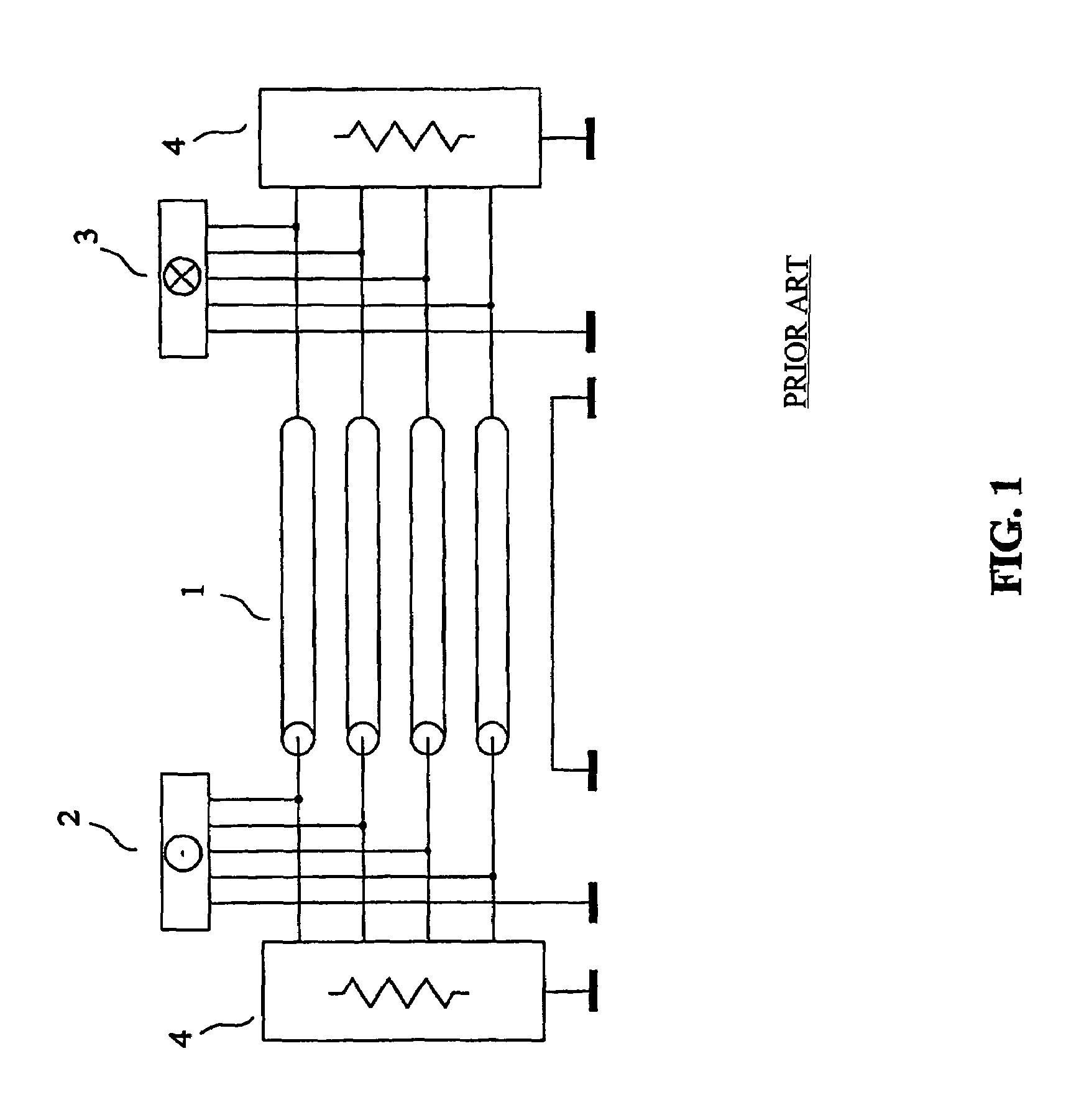

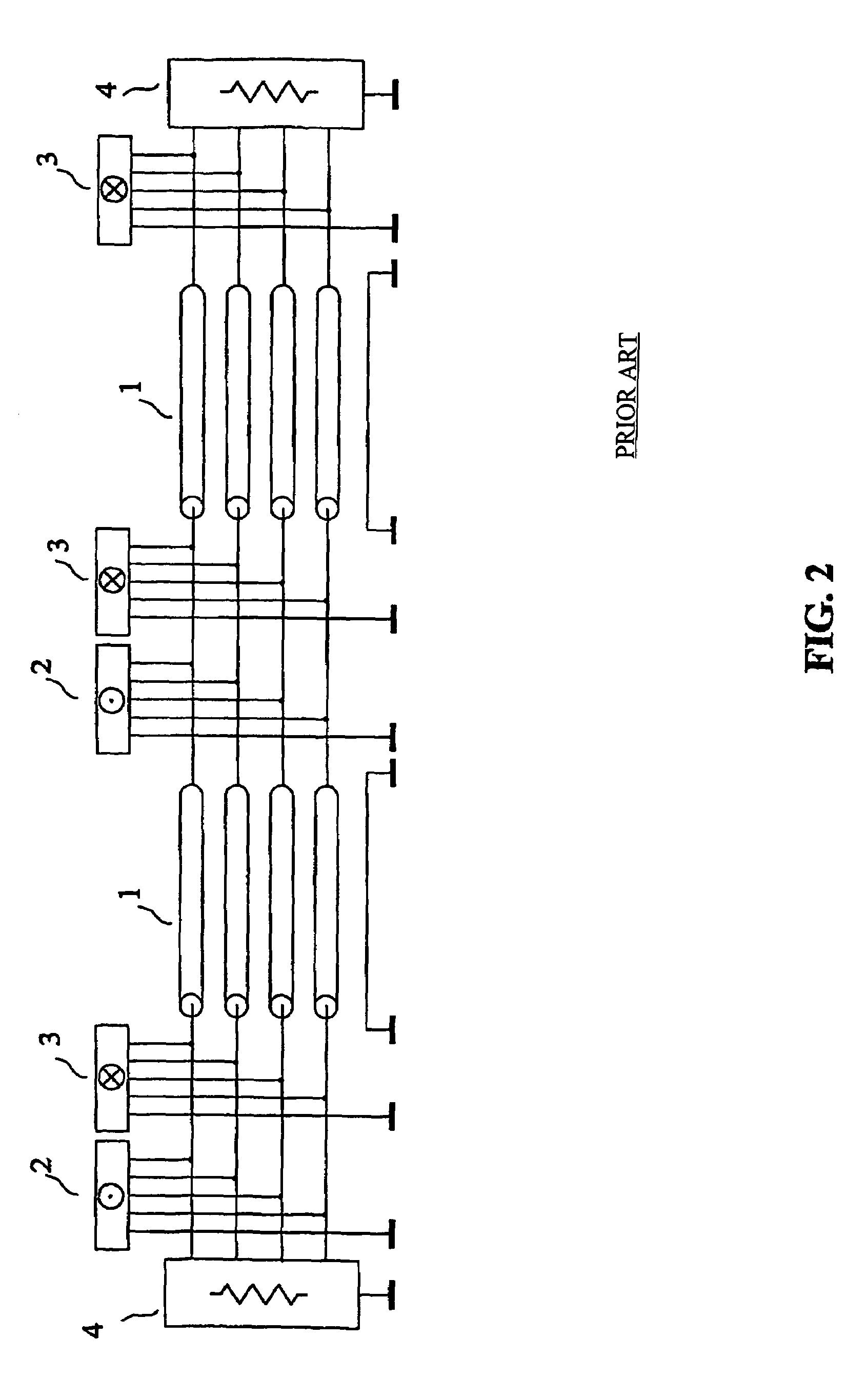

Method and device for transmission with reduced crosstalk

InactiveUS7167019B2Accurately determinedOptimize locationReliability increasing modificationsElectrically conductive connectionsElectrical conductorInterconnection

The invention relates to a method and a device for transmission with reduced crosstalk in interconnections used for sending a plurality of signals, such as the interconnections made with flat multiconductor cables, or with the tracks of a printed circuit board, or inside an integrated circuit. An interconnection with four parallel transmission conductors plus a reference conductor has each of its ends connected to a termination circuit. The transmitting circuit receives at its input the signals of the four channels of the source and its output terminals are connected to the conductors of the interconnection. The receiving circuit's input terminals are connected to the conductors of the interconnection, and its four output channels are connected to the destination. The signals of the four channels of the source are sent to the four channels of the destination, without noticeable crosstalk.

Owner:RAMBUS INC +1

System and method for selectively performing single-ended and differential signaling

In a communication system, data is selectively transmitted using single-ended or differential signaling. The data is transmitted in relation to a plurality of clock signals having different relative phases. When the data is transmitted using single-ended signaling, data on adjacent signal lines undergo logic transitions at different times in relation to the plurality of clock signals.

Owner:SAMSUNG ELECTRONICS CO LTD

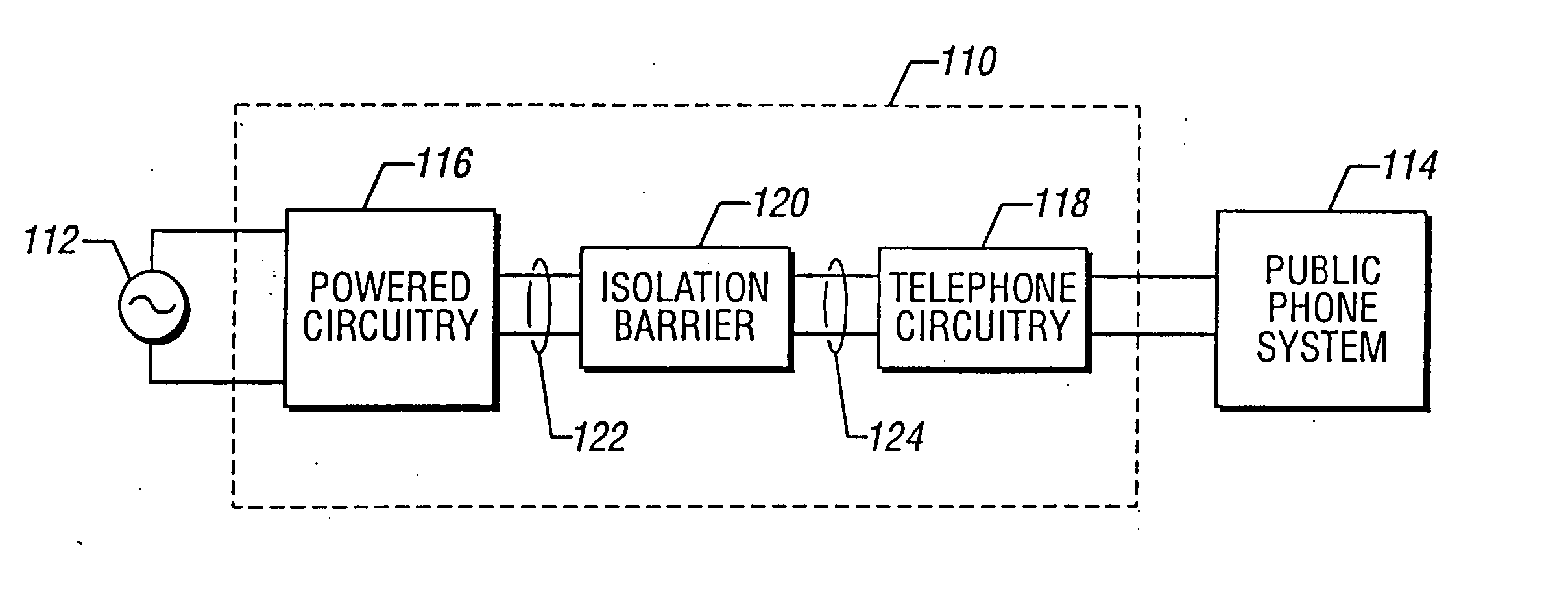

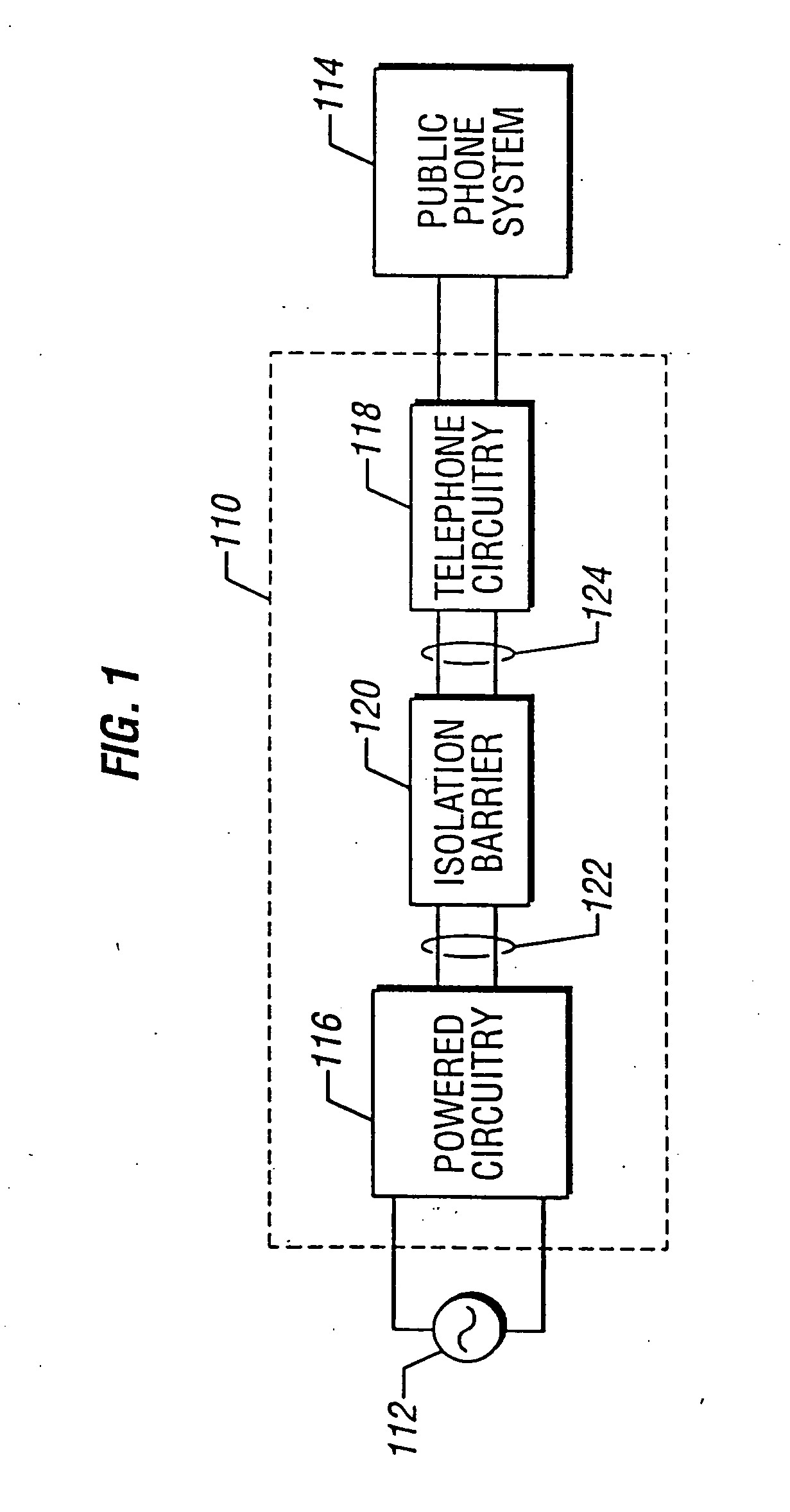

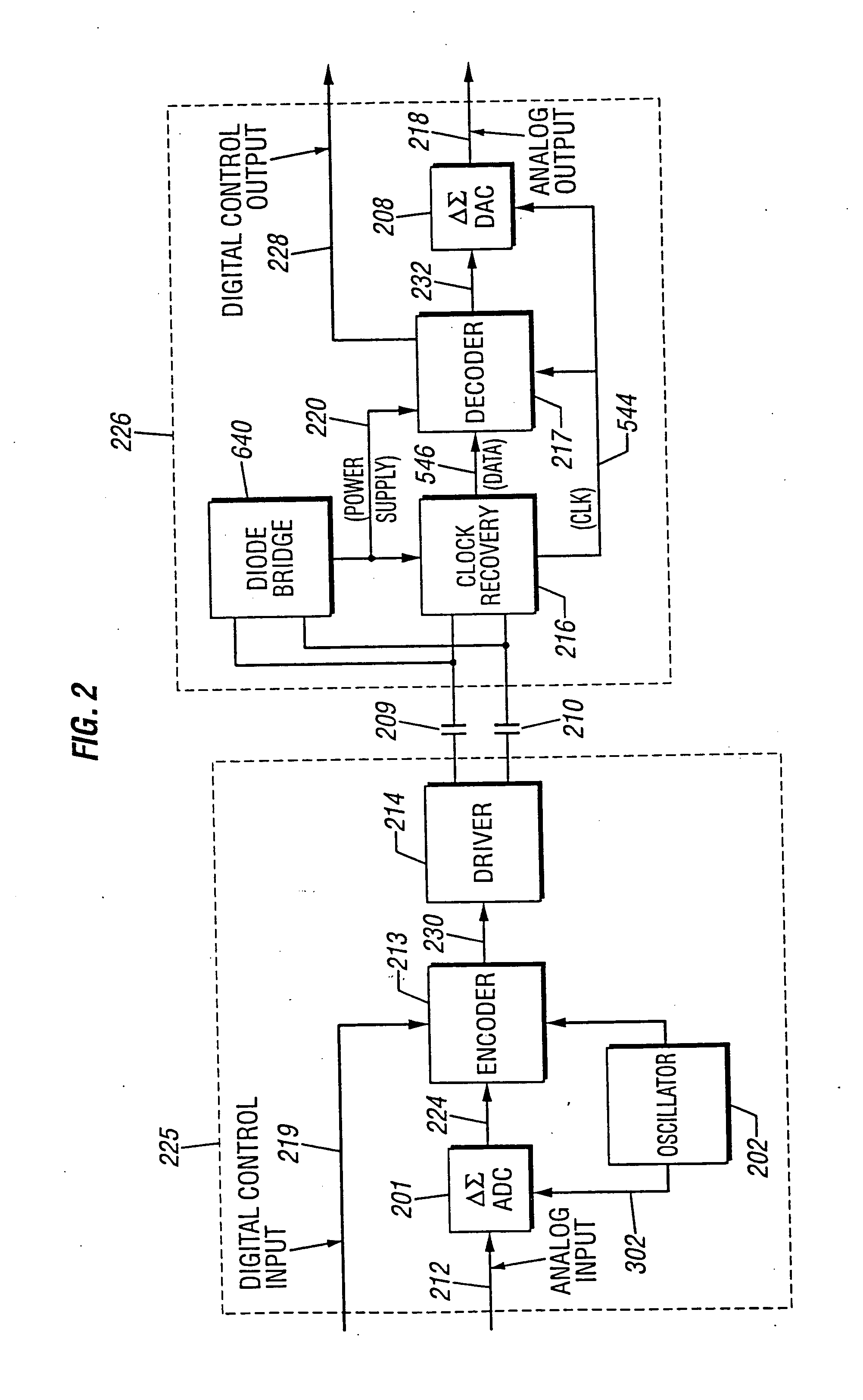

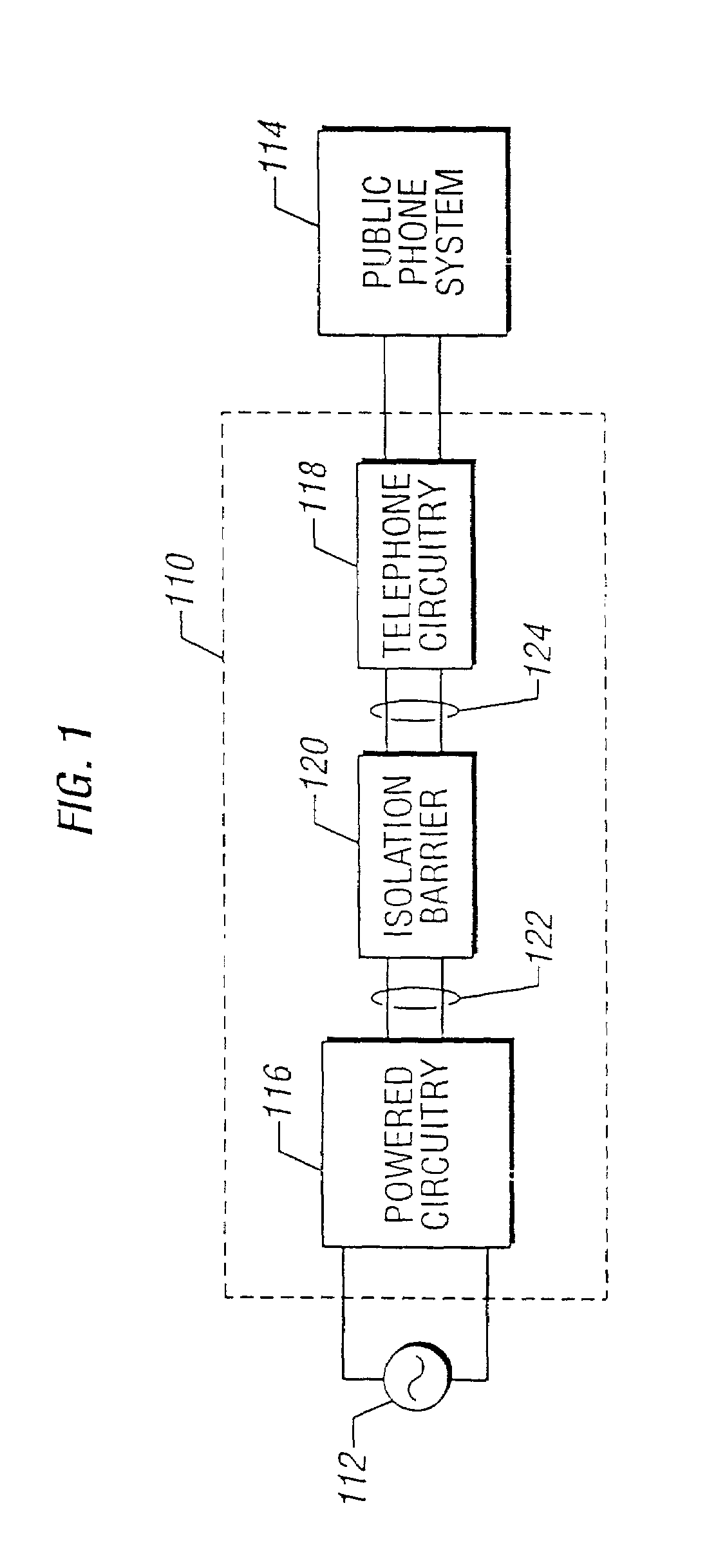

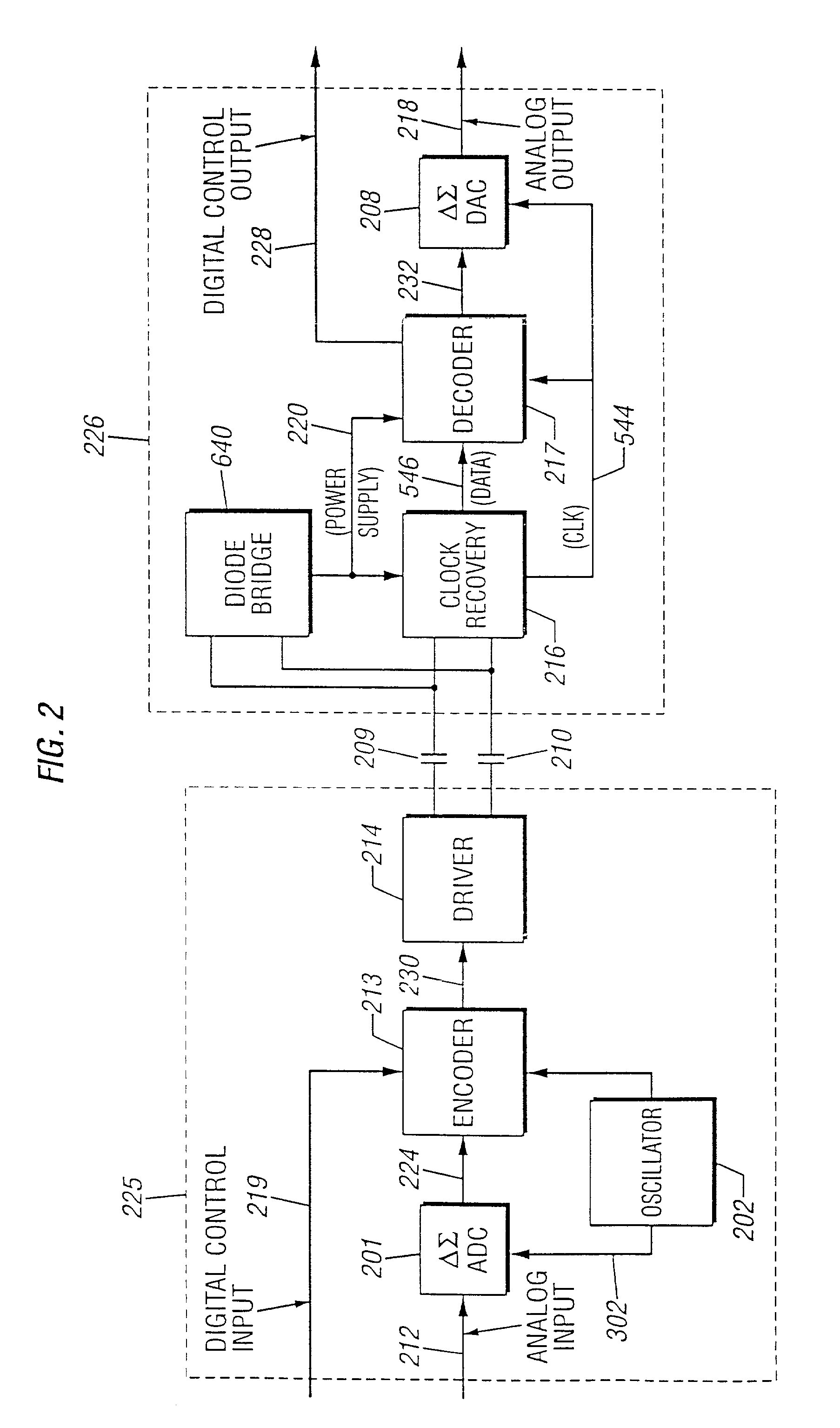

Direct digital access arrangement circuitry and method for connecting DSL circuitry to phone lines

InactiveUS20050036604A1Exact reproductionInterconnection arrangementsDc level restoring means or bias distort correctionCapacitanceDigital data

An isolation system is provided that is suitable for use in telephony, medical instrumentation, industrial process control and other applications. Preferred embodiments of the invention comprise a capacitive isolation barrier across which a digital signal is communicated. The system provides a means of communication across the isolation barrier that is highly immune to amplitude and phase noise interference. Clock recovery circuitry may be employed on one side of the isolation barrier to extract timing information from the digital signal communicated across the barrier, and to filter the effects of phase noise introduced at the barrier. Delta-sigma converters may be disposed on both sides of the isolation barrier to convert signals between analog and digital domains. An isolated power supply may also be provided on the isolated side of the barrier, whereby direct current is generated in response to the digital data received across the isolation barrier. A bidirectional isolation system is provided whereby bidirectional communication of digital signals is accomplished using a single pair of isolation capacitors. In preferred embodiments, the digital data communicated across the barrier consists of digital delta-sigma data signals multiplexed in time with other digital control, signaling and framing information. Finally, the isolation system may include a pulse transformer to accommodate ADSL circuitry, whereby power is transmitted through the pulse transformer.

Owner:SILICON LAB INC

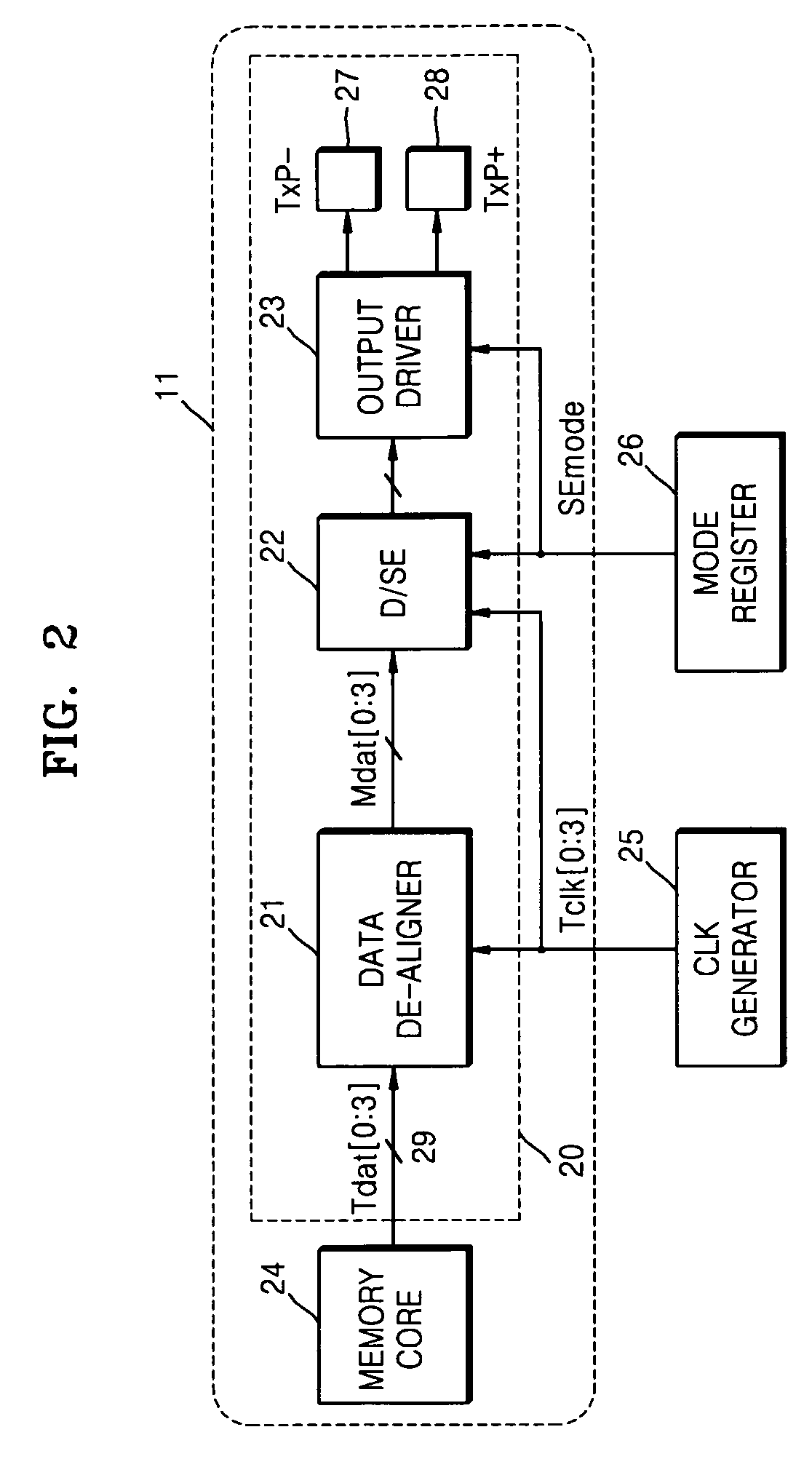

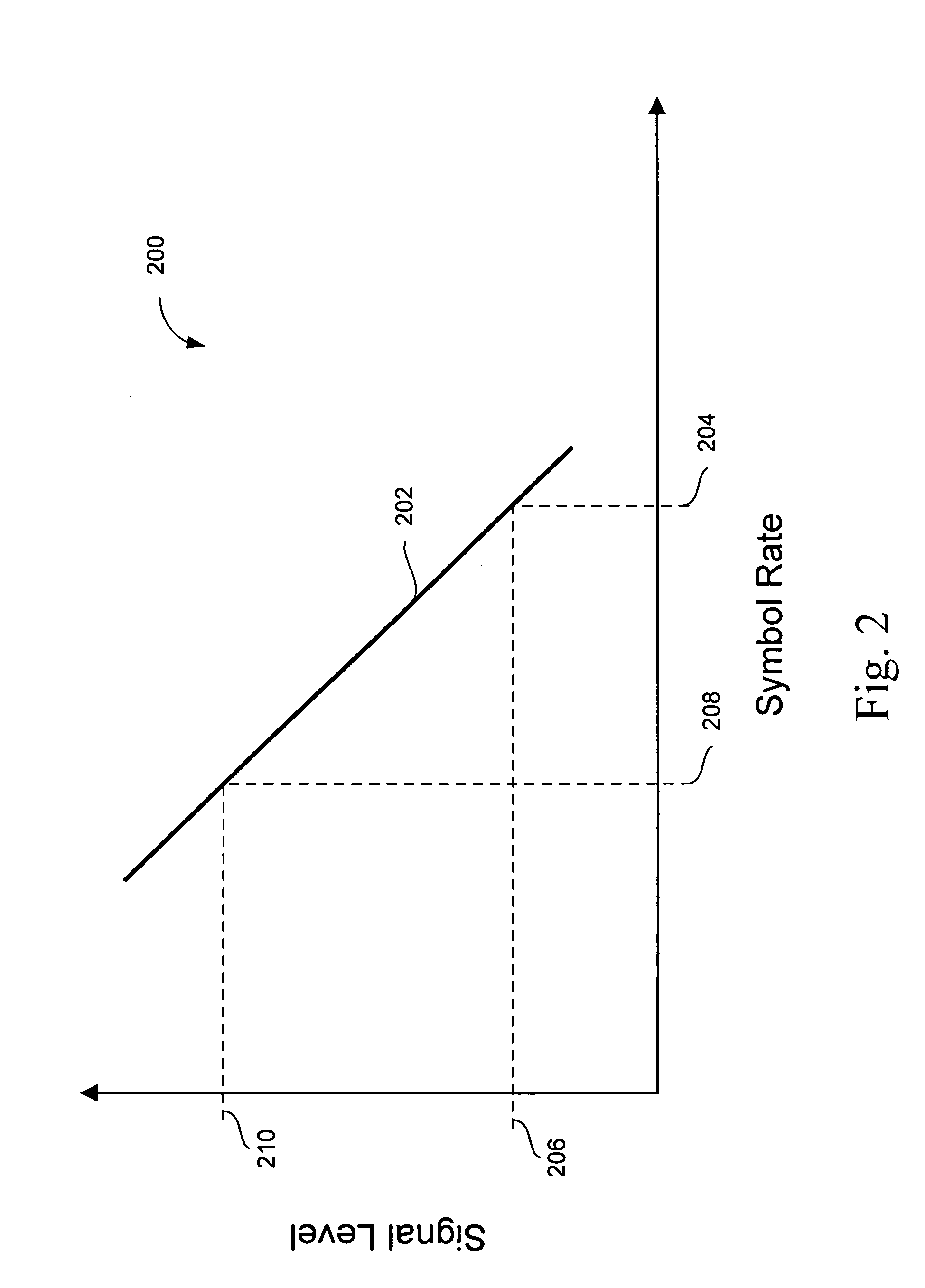

Transparent multi-mode PAM interface

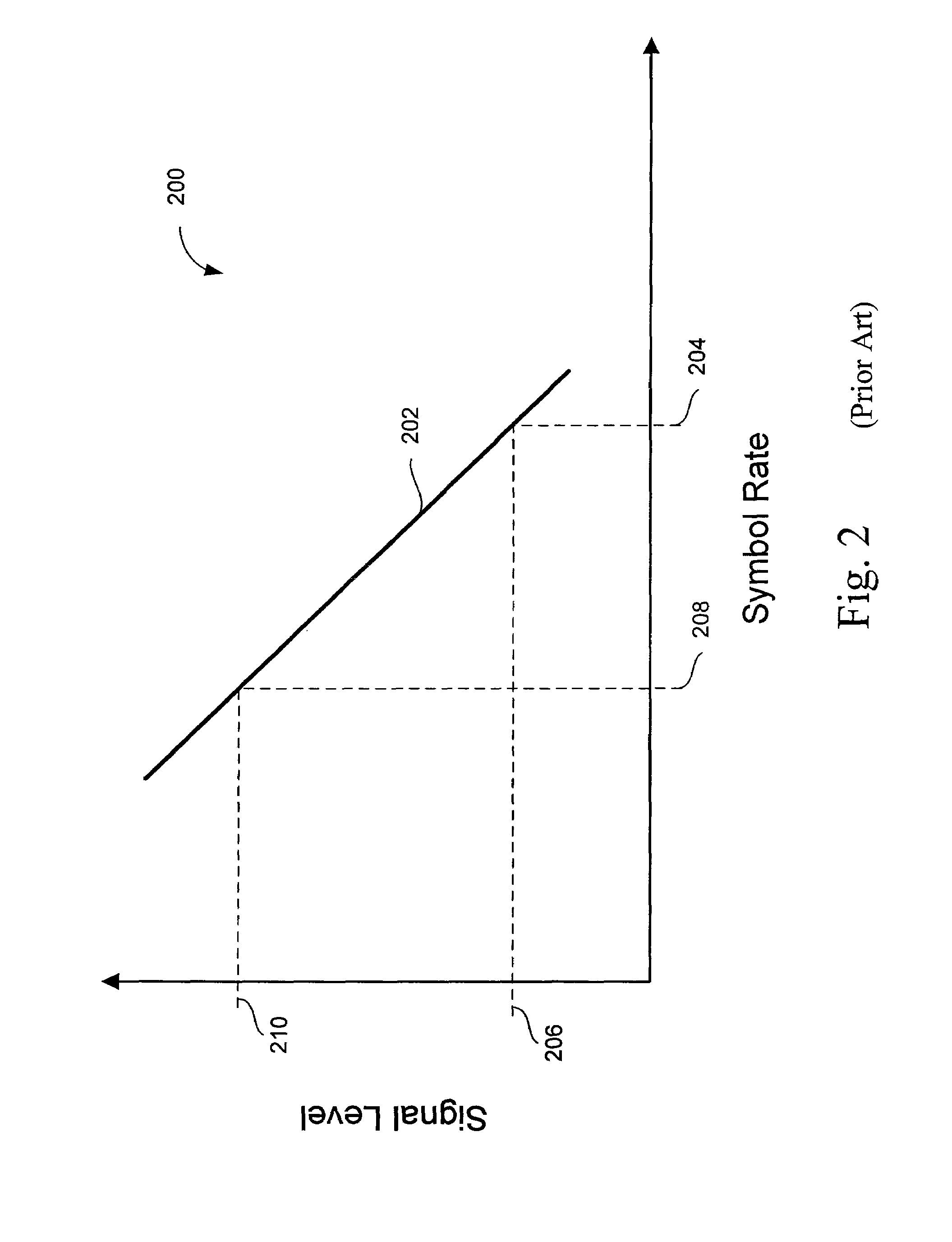

ActiveUS20050089126A1Amplitude-modulated carrier systemsAmplitude-modulated pulse demodulationState variationData rate

Provided are a method and apparatus for high-speed, multi-mode PAM symbol transmission. A multi-mode PAM output driver drives one or more symbols, the number of levels used in the PAM modulation of the one or more symbols depending on the state of a PAM mode signal. Additionally, the one or more symbols are driven at a symbol rate, the symbol rate selected in accordance with the PAM mode signal so that a data rate of the driven symbols in constant with respect to changes in the state of the PAM mode signal. Further provided are methods for determining the optimal number of PAM levels for symbol transmission and reception in a given physical environment.

Owner:RAMBUS INC

Transparent multi-mode PAM interface

ActiveUS7308058B2Amplitude-modulated carrier systemsAmplitude-modulated pulse demodulationData rateEngineering

Provided are a method and apparatus for high-speed, multi-mode PAM symbol transmission. A multi-mode PAM output driver drives one or more symbols, the number of levels used in the PAM modulation of the one or more symbols depending on the state of a PAM mode signal. Additionally, the one or more symbols are driven at a symbol rate, the symbol rate selected in accordance with the PAM mode signal so that a data rate of the driven symbols is constant with respect to changes in the state of the PAM mode signal. Further provided are methods for determining the optimal number of PAM levels for symbol transmission and reception in a given physical environment.

Owner:RAMBUS INC

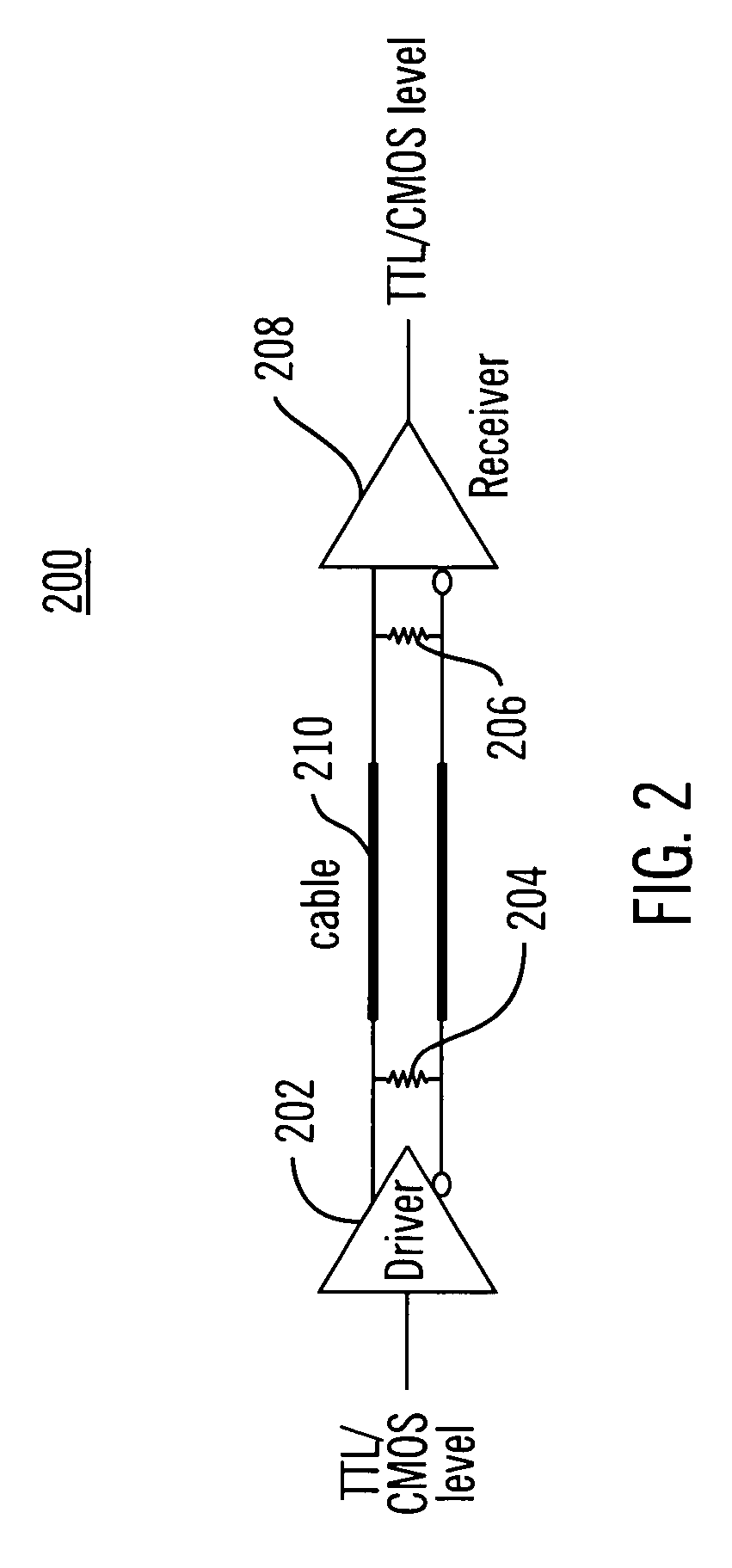

Low voltage differential signal driver circuit and method

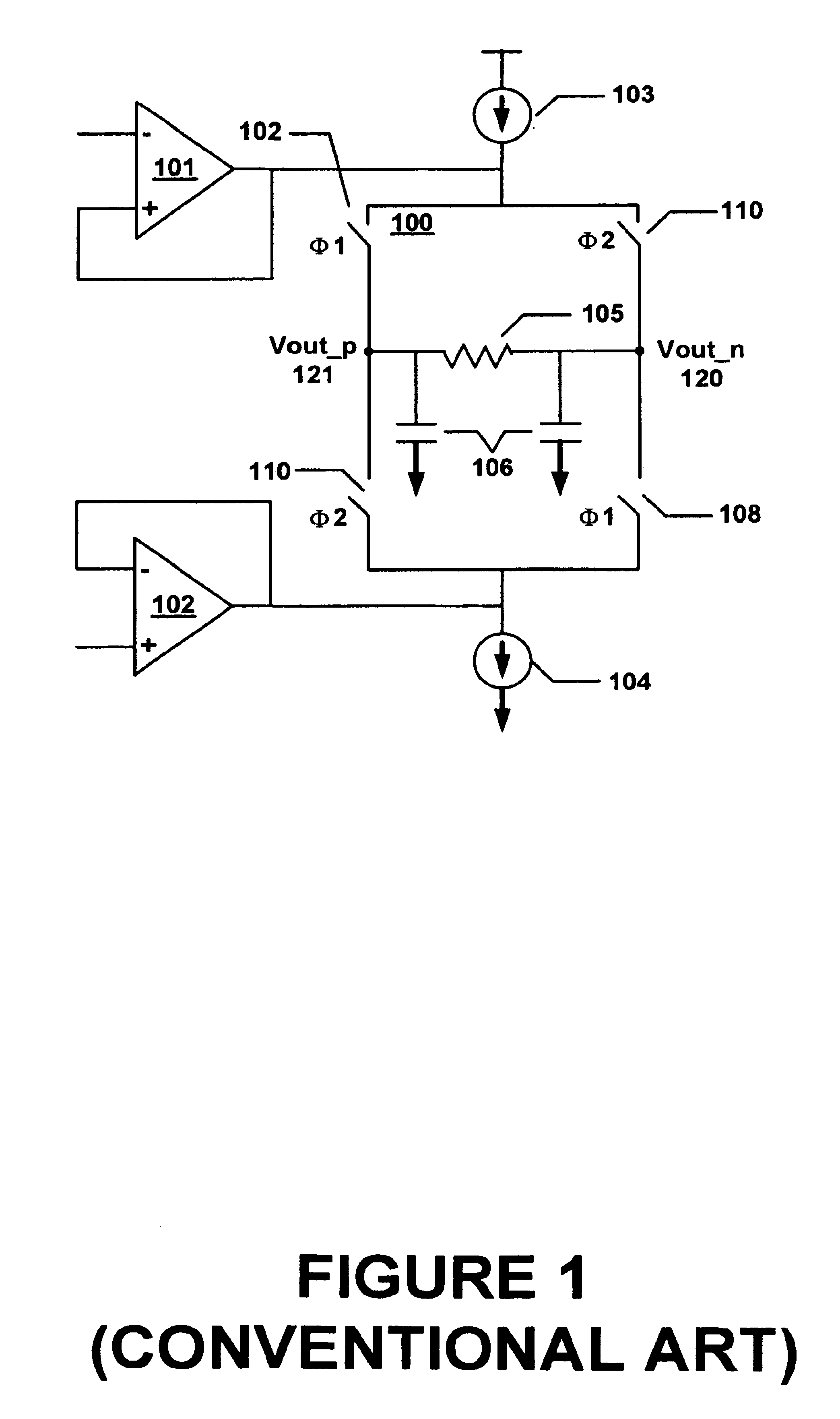

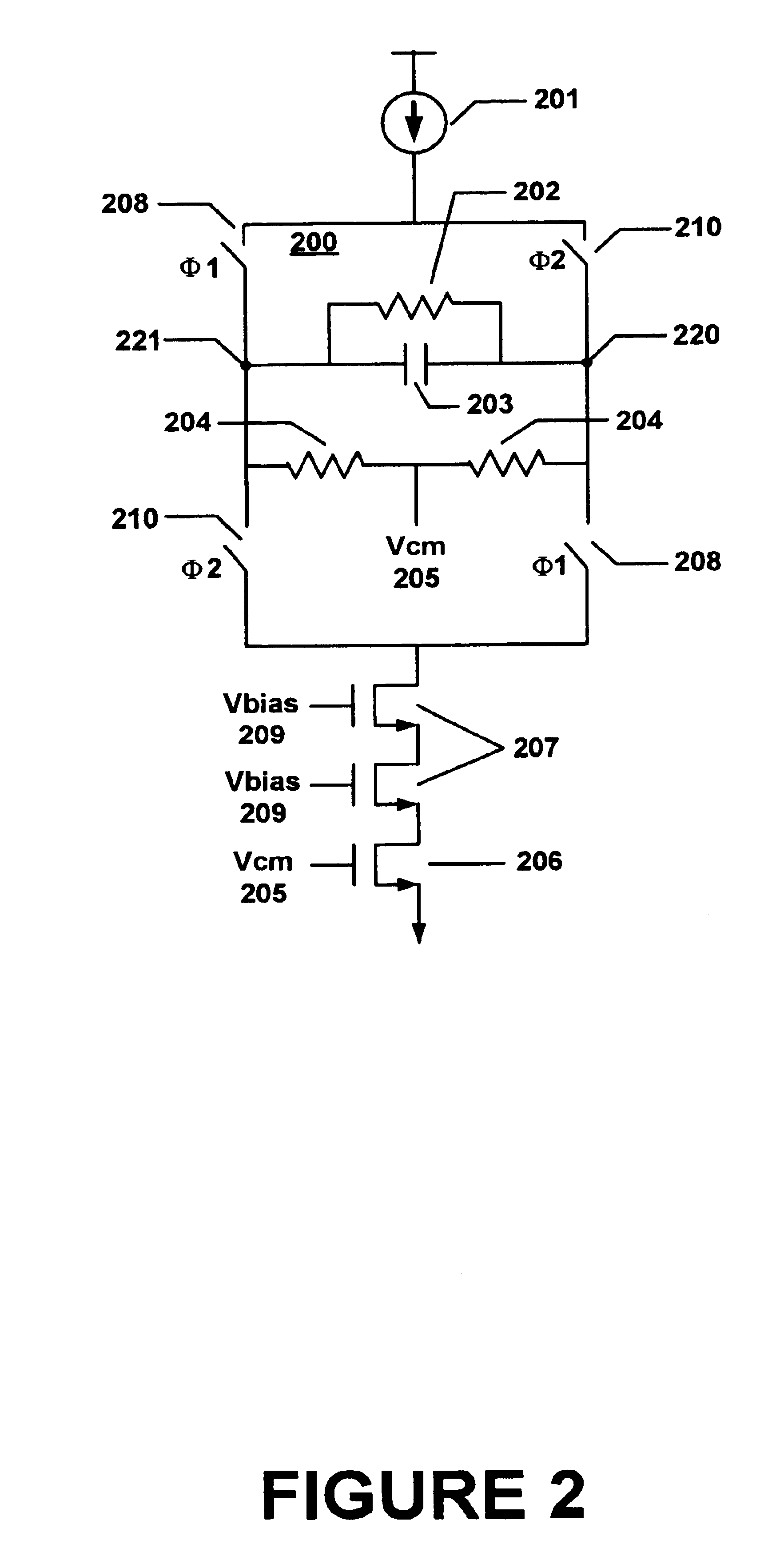

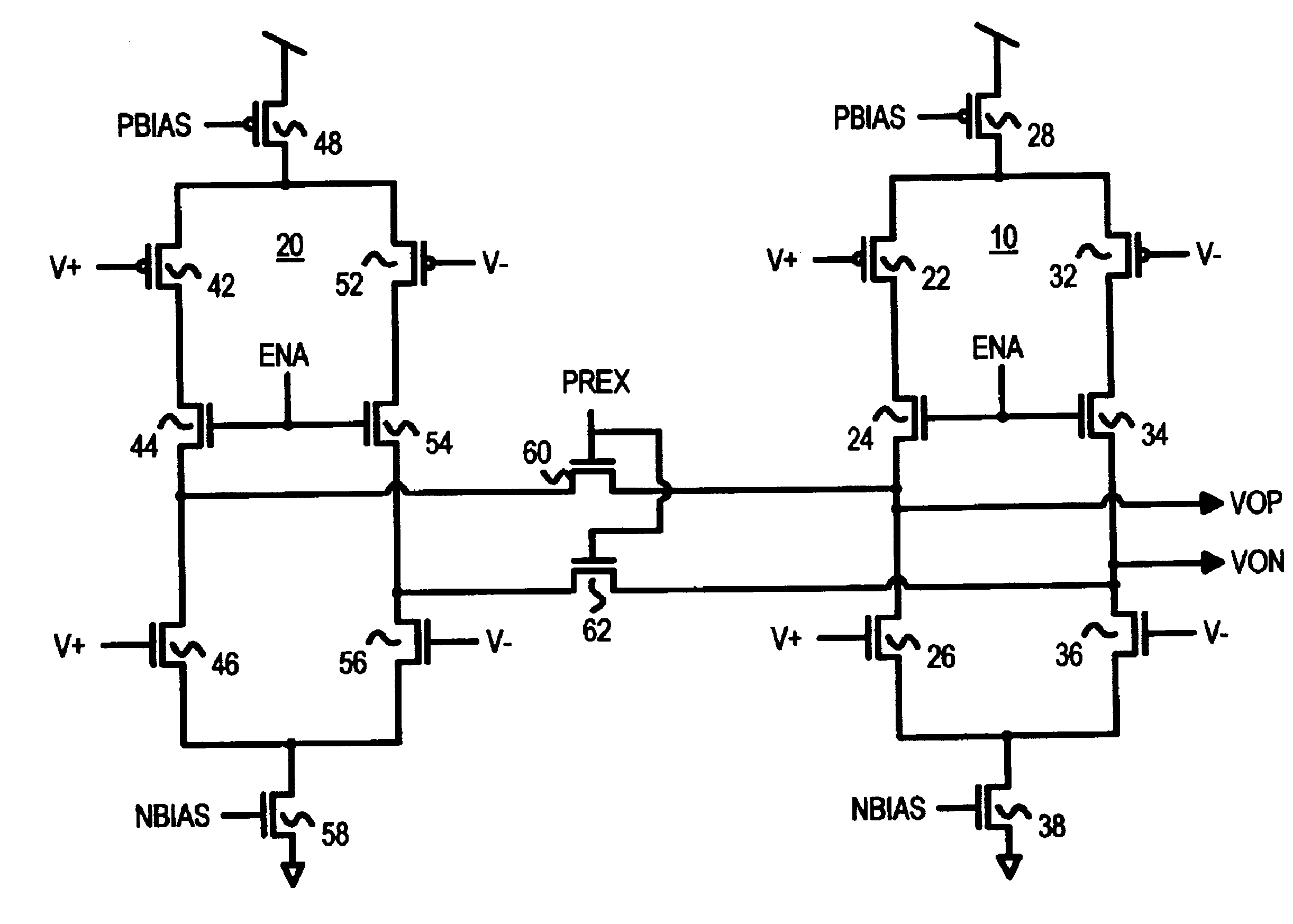

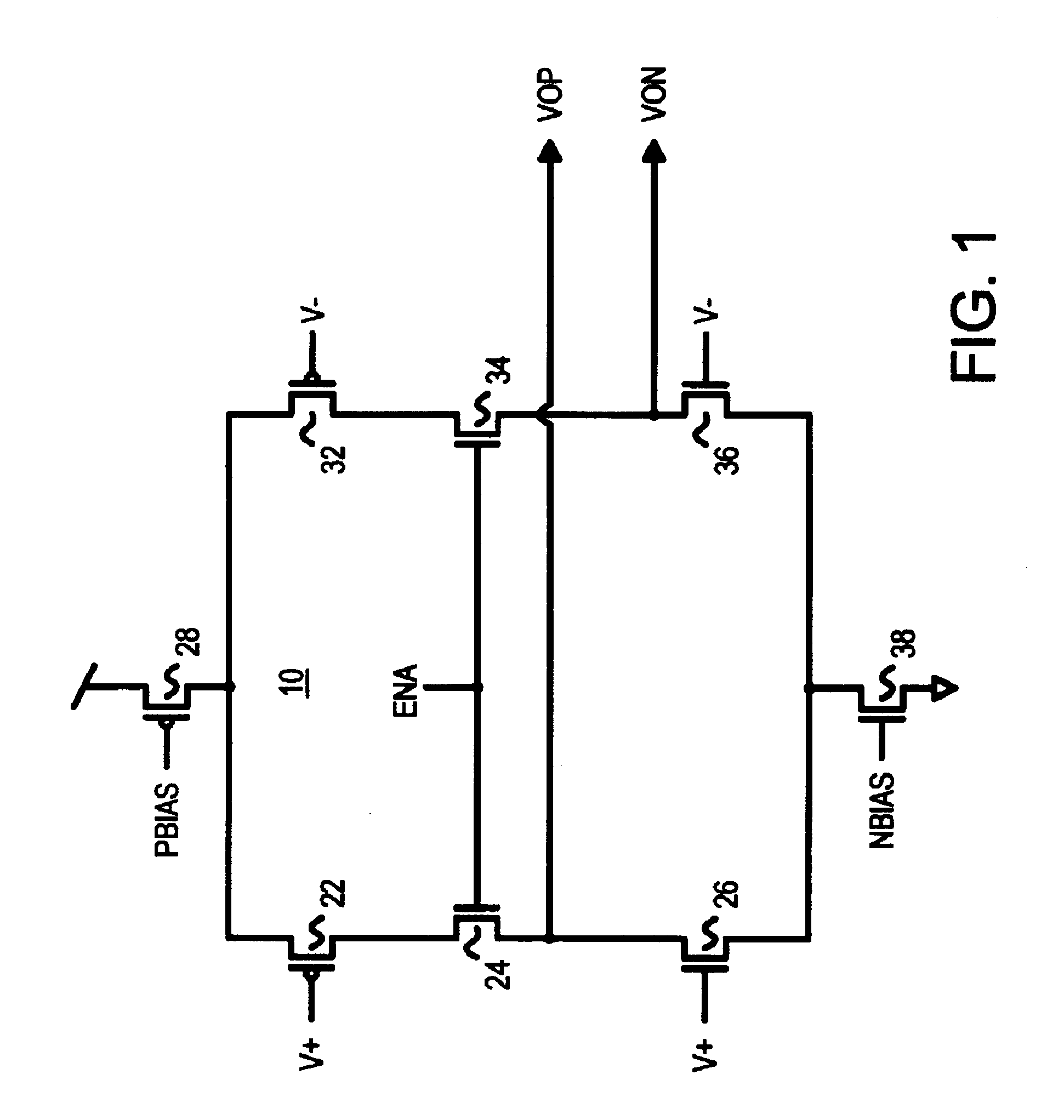

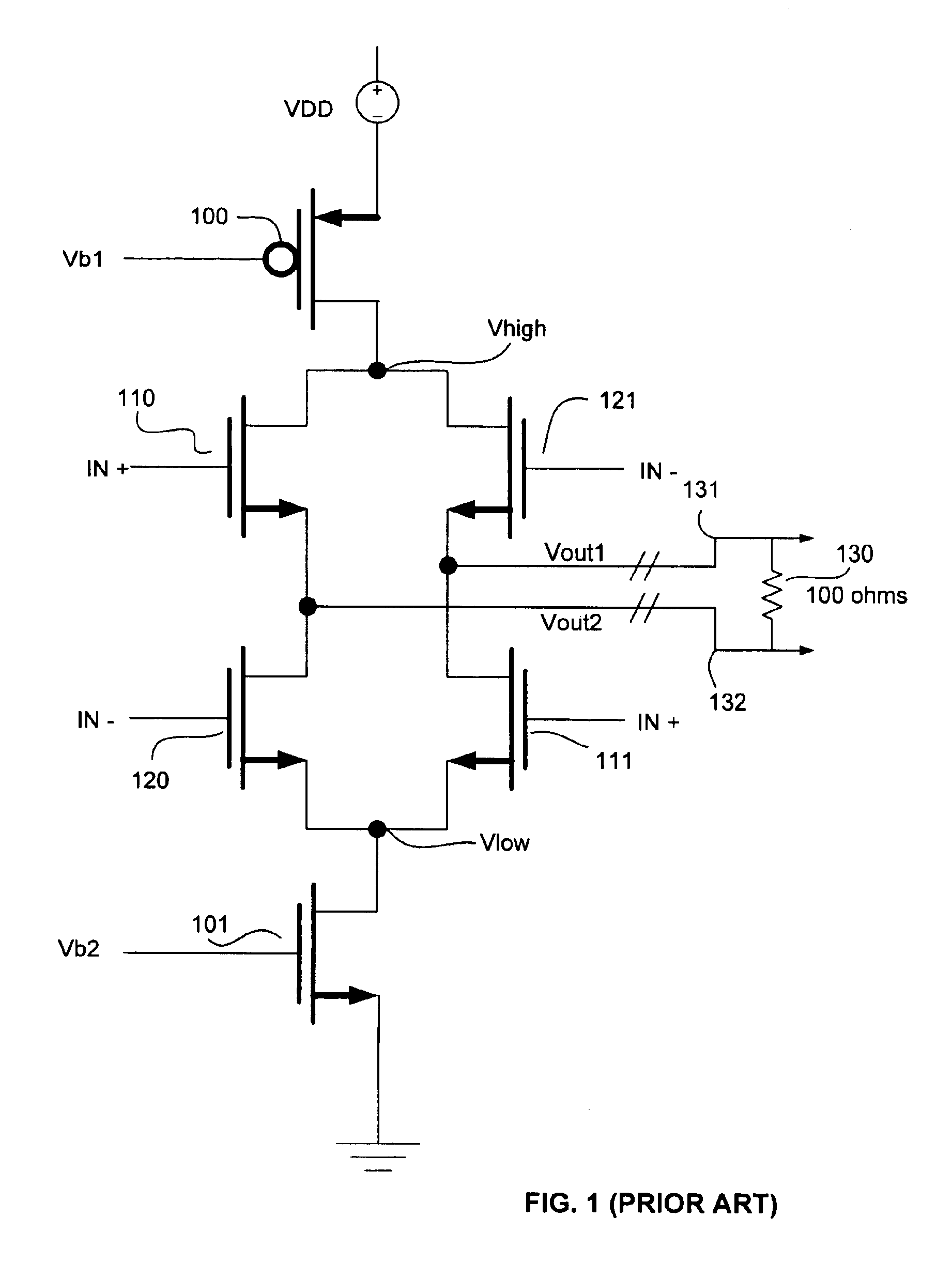

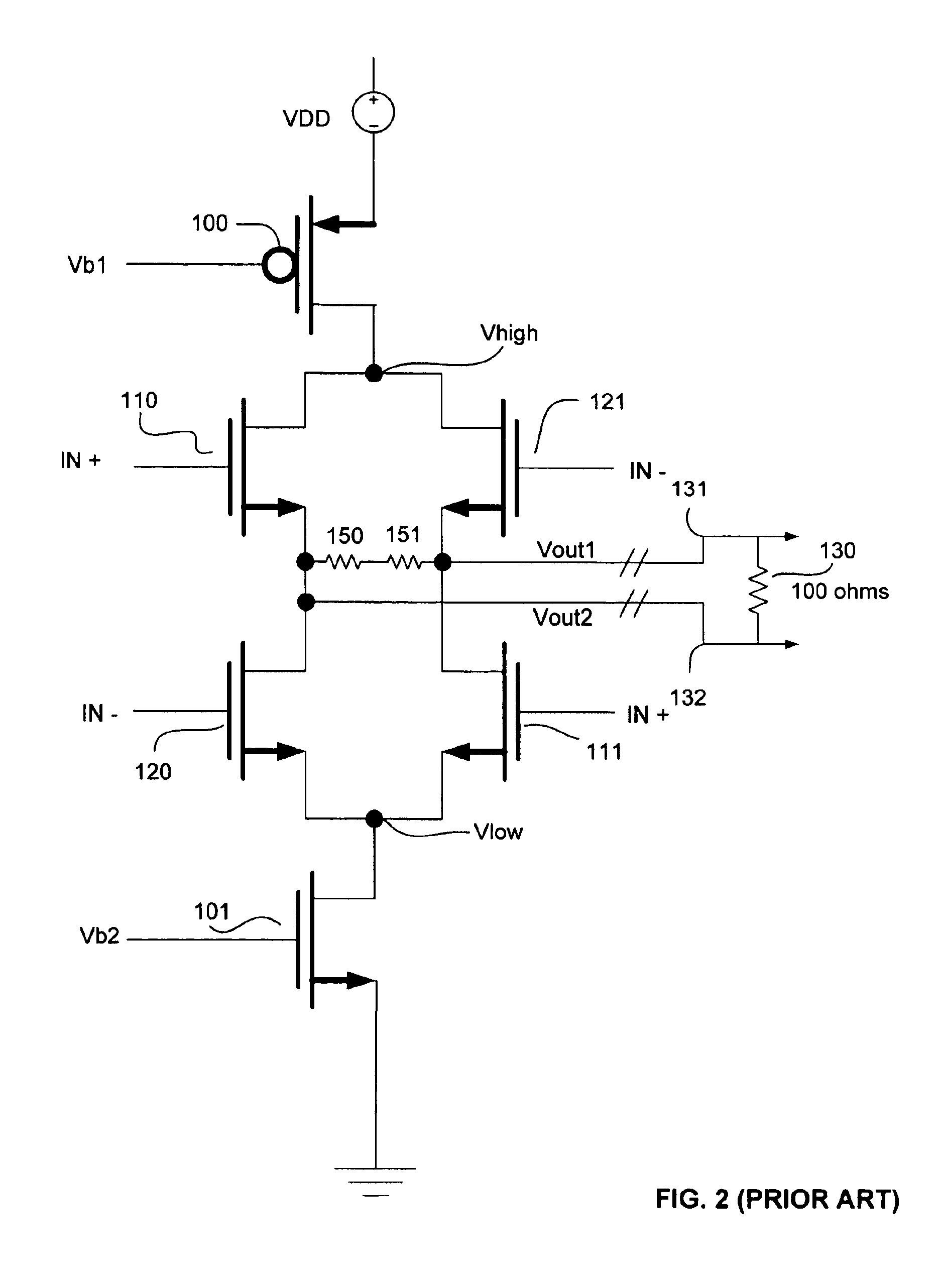

InactiveUS6900663B1Small RC-delaysSpeed maximizationTransmission line coupling arrangementsLogic circuit coupling/interface arrangementsDriver circuitElectronic load

Embodiments of the present invention relate to a low voltage differential signal driver (LVDS) circuit which comprises a current source, logic controlled switches for controlling the driver's output, an electronic load circuit coupled across the circuit, and a common-mode resistor feedback circuit coupled across the circuit, in parallel with the RC load, for tuning the driver's impedance. The driver is enabled to operate without op-amps and achieves optimum performance at 1.8 v supply voltages.

Owner:TAIWAN SEMICON MFG CO LTD

Remotely reconfigurable distributed antenna system and methods

ActiveUS8682338B2Increase capacityImprove efficiencyMultiplex system selection arrangementsPower amplifiersDistributed antenna systemCarrier signal

The present disclosure is a novel utility of a software defined radio (SDR) based Distributed Antenna System (DAS) that is field reconfigurable and support multi-modulation schemes (modulation-independent), multi-carriers, multi-frequency bands and multi-channels. The present disclosure enables a high degree of flexibility to manage, control, enhance, facilitate the usage and performance of a distributed wireless network such as flexible simulcast, automatic traffic load-balancing, network and radio resource optimization, network calibration, autonomous / assisted commissioning, carrier pooling, automatic frequency selection, frequency carrier placement, traffic monitoring, traffic tagging, pilot beacon, etc. As a result, the SDR DAS can increase the efficiency and traffic capacity of the operators' wireless network.

Owner:DALI WIRELESS

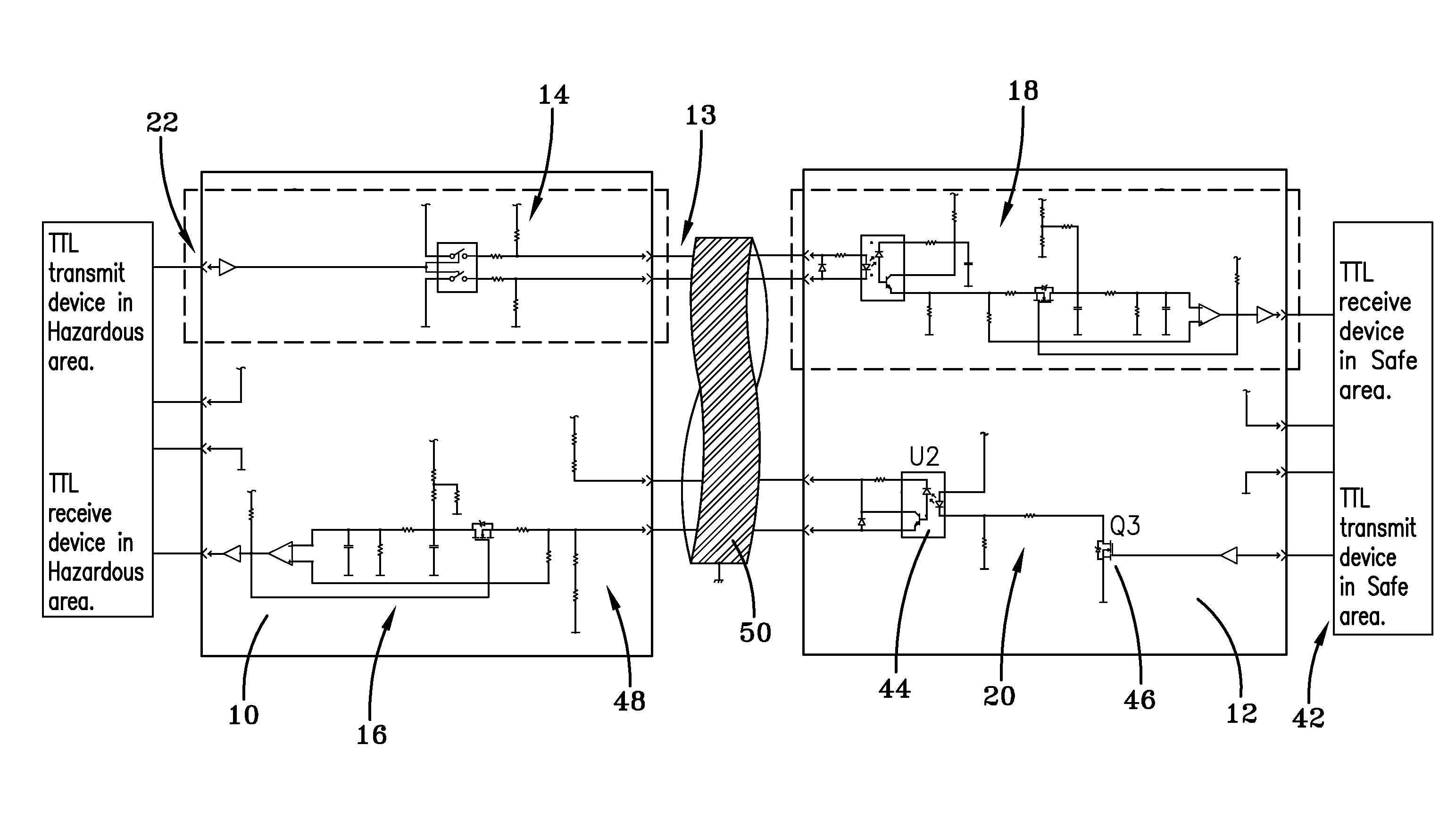

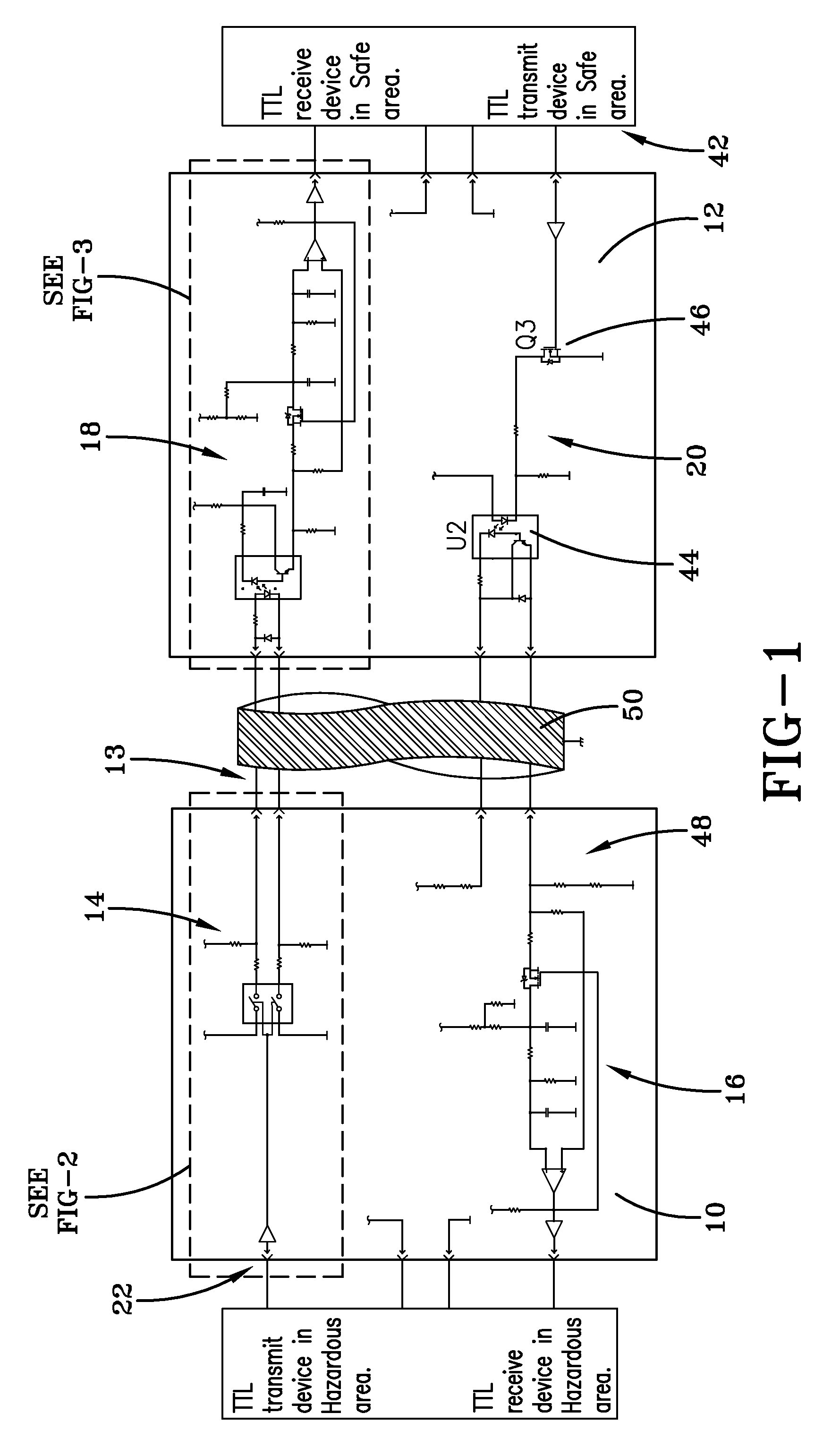

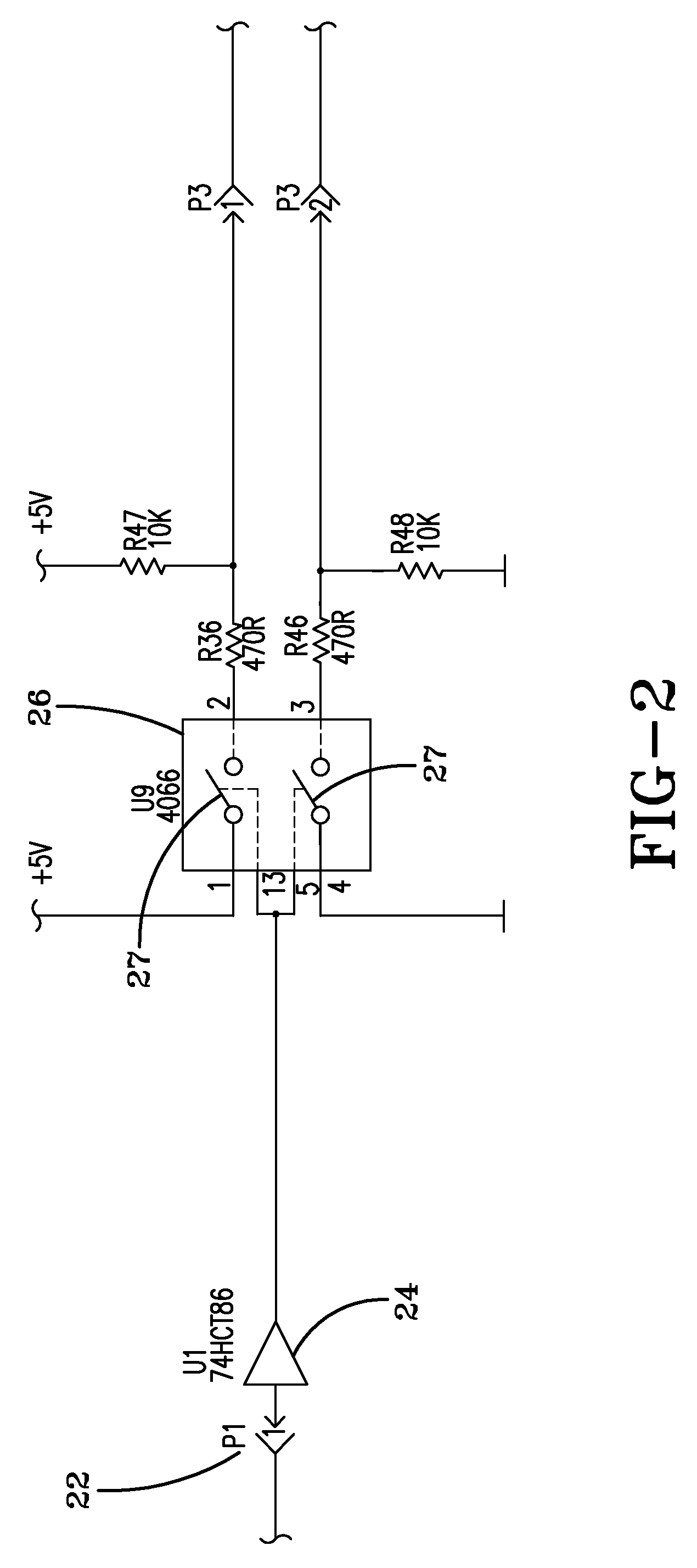

Low energy data communication circuit for hazardous or nonhazardous environments

The present invention relates to a data communication circuit and system for use in hazardous or nonhazardous environments. In the preferred embodiment, the system is a bi-directional, low energy, current loop data communication circuit primarily for high speed data communications via parallel or twisted pair conductors. The system of the present invention can safely transmit data across long distances (e.g., up to 1000 feet (300 meters)) in an explosive atmosphere.

Owner:METTLER TOLEDO INC

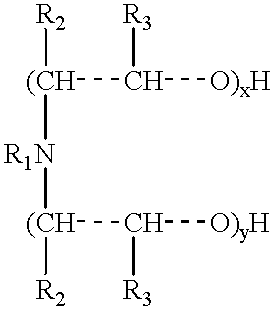

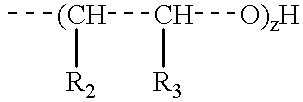

Oil and oil invert emulsion drilling fluids with improved anti-settling properties

InactiveUS6339048B1Dc level restoring means or bias distort correctionTelephonic communicationEmulsionOrganoclay

This invention is of a drilling fluid composition containing a liquid thixotrope, which thixotrope is free of solvents or any other diluent, and is in easily usable, liquid form, pourable at ambient temperatures, and which provides effective and efficient rheological properties when used at low levels in such compositions. In a specific aspect, the invention provides an oil or oil invert emulsion drilling fluid composition containing one or more organoclays, and in addition contains a additive which comprises the reaction product of an alkoxylated nitrogen containing compound or a diamine, and one or more polycarboxylic acids in a specified equivalent ratio.

Owner:ELEMENTIS SPECIALTIES INC

Spread spectrum isolator

A circuit package includes first and second units containing functional circuitry. At least one RF isolation link interconnects the first and second units and provides voltage isolation between the first and second units. The RF isolation link provides data between the first unit and the second unit using an RF carrier signal that sweeps between a first frequency and a second frequency.

Owner:SKYWORKS SOLUTIONS INC

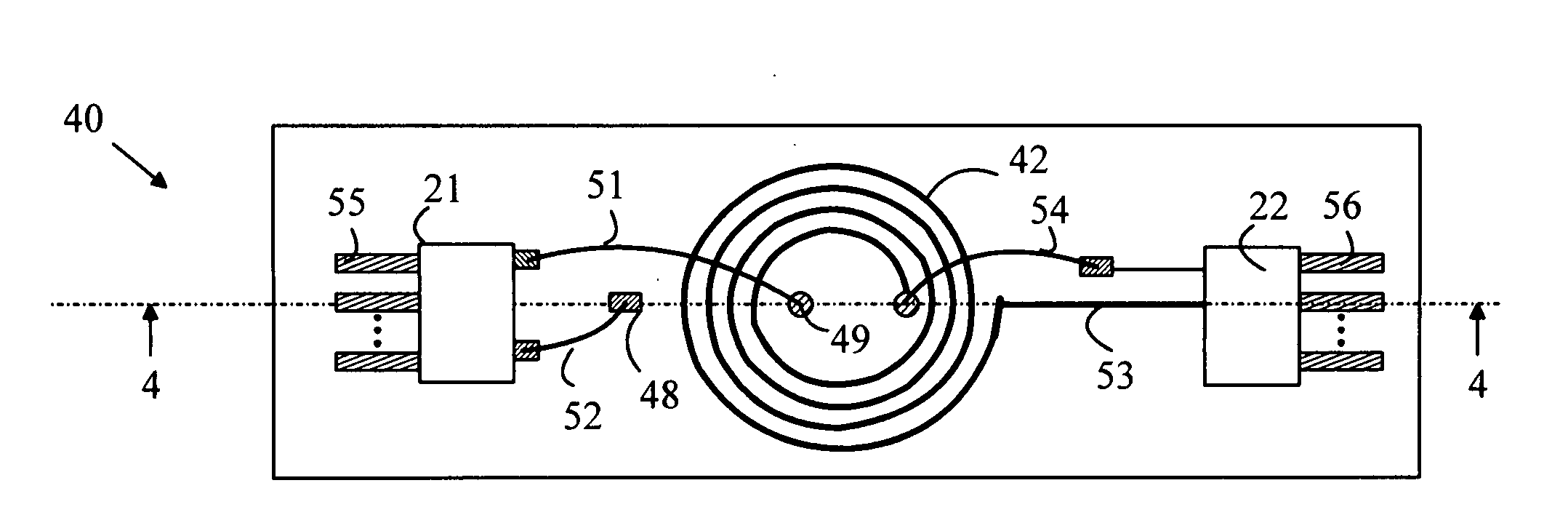

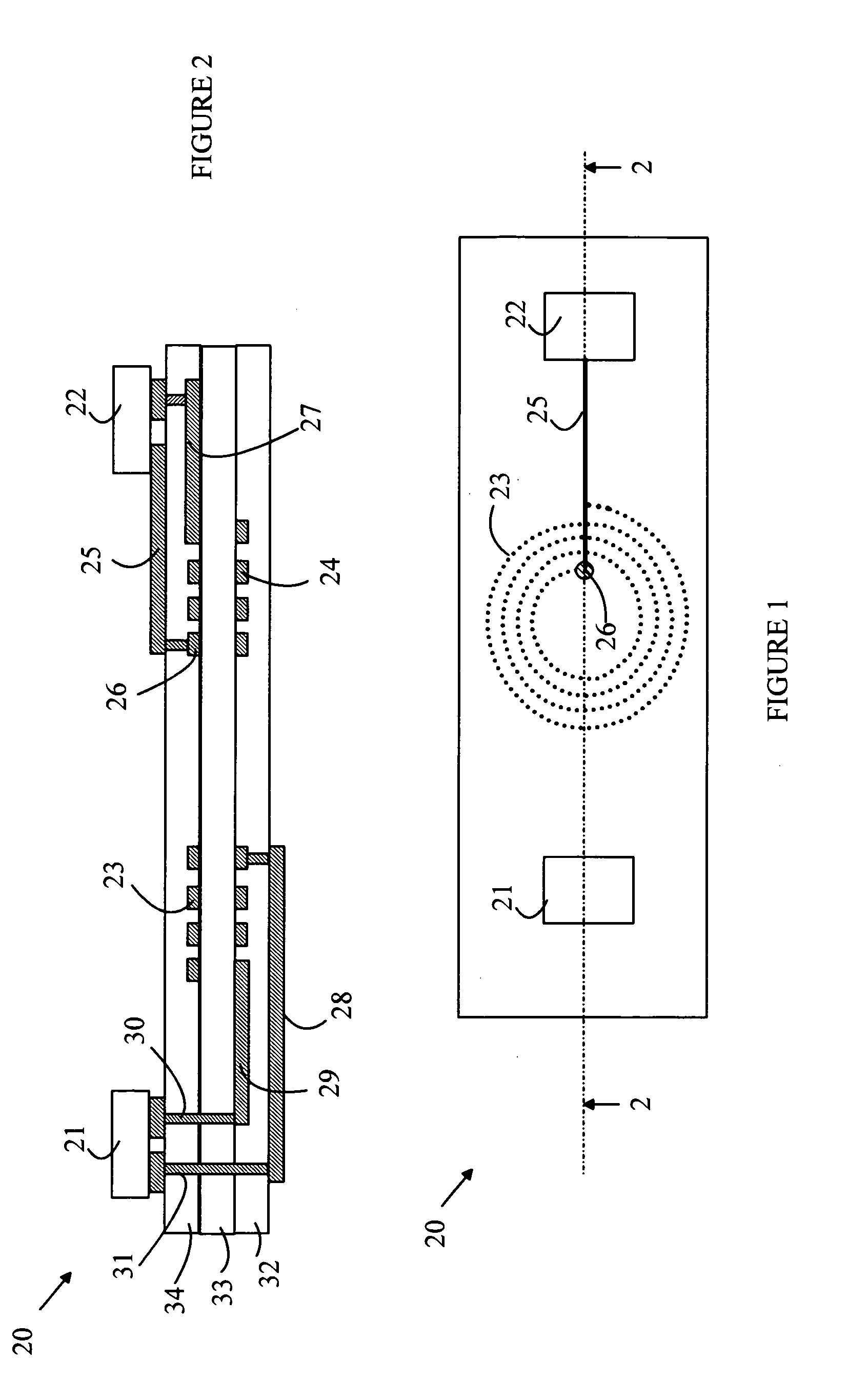

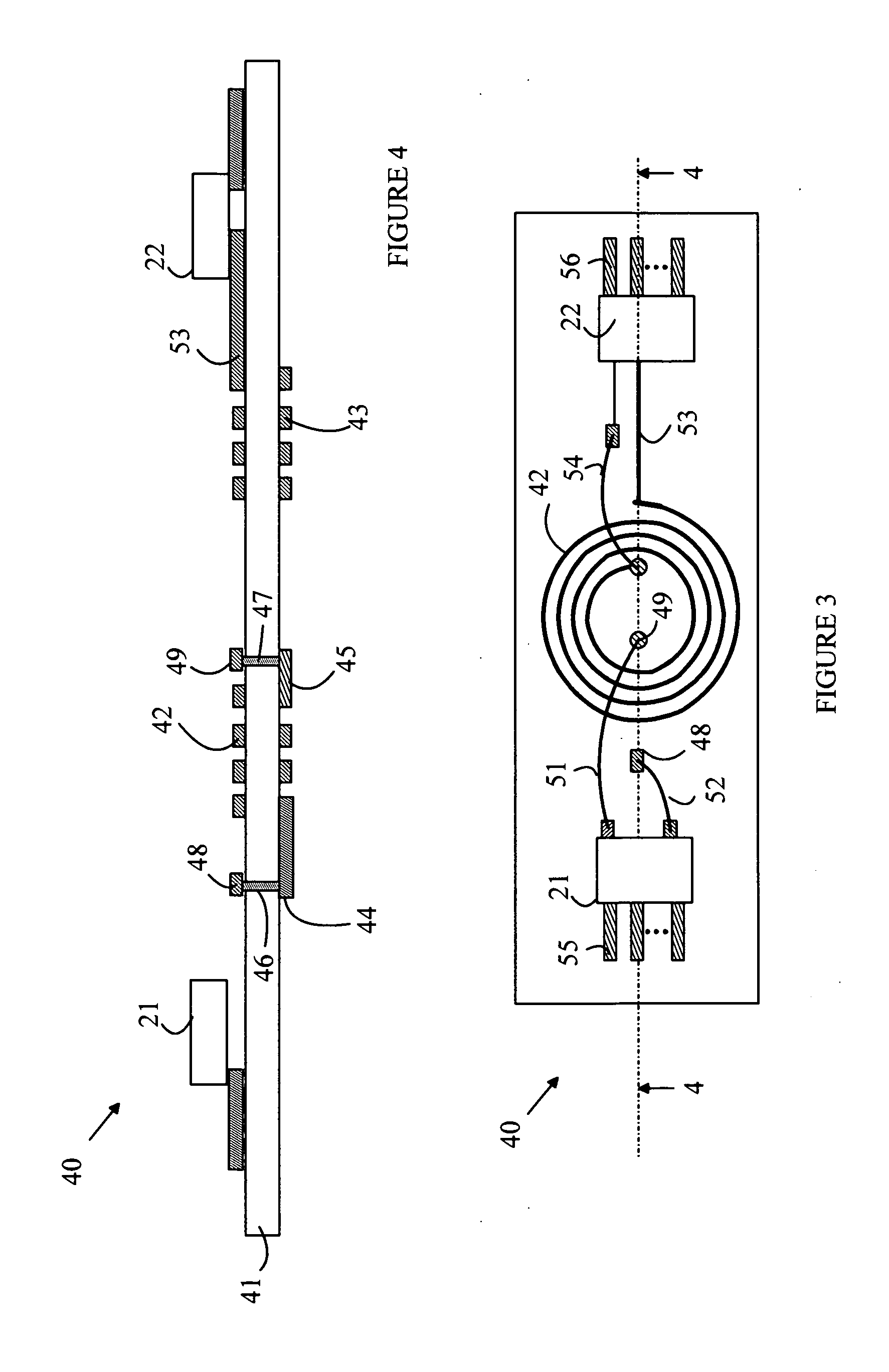

Galvanic isolator

InactiveUS20080061631A1Easy to understandAvoid insufficient thicknessMultiple-port networksNear-field transmissionFlexible circuitsEngineering

A galvanic isolator having a split circuit element, a polymeric substrate, a transmitter and receiver is disclosed. The split circuit element has first and second portions, the first portion being disposed on a first surface of the substrate and the second portion being disposed a second surface of the substrate. The transmitter receives an input signal and couples a signal derived from the input signal to the first portion. The receiver is connected to the second portion of the circuit element and generates an output signal that is coupled to an external circuit. The galvanic isolator can be economically fabricated on conventional printed circuit board substrates and flexible circuit substrates.

Owner:AVAGO TECH INT SALES PTE LTD

Semiconductor integrated circuit device capable of controlling impedance

ActiveUS20050040845A1Input/output impedence modificationReliability increasing modificationsExternal referenceEngineering

A semiconductor integrated circuit device is connected to an external reference resistor, including an impedance control circuit for generating impedance control codes variable with impedances established by the external reference resistor. An input circuit receives an external signal through an input transfer line and forwards the external signal to an internal circuit. A termination circuit terminates the input transfer line in response to at least one of the impedance control code. An output circuit drives an output transfer line in accordance with an output signal. Impedance is variable with the control codes.

Owner:SAMSUNG ELECTRONICS CO LTD

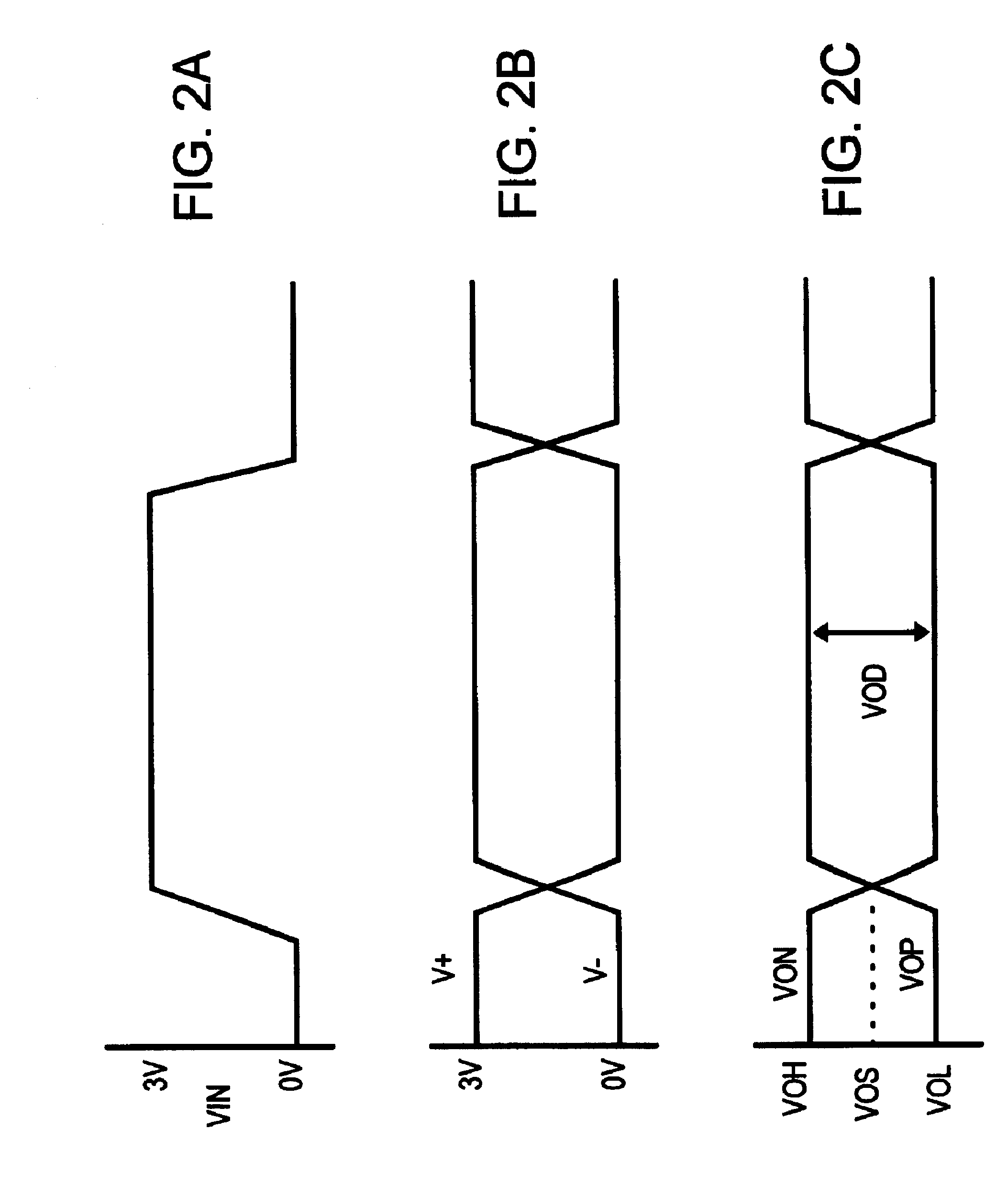

Low-voltage differential-signalling output buffer with pre-emphasis

InactiveUS6288581B1Multiple input and output pulse circuitsPulse automatic controlLow voltageEngineering

A low-voltage differential signaling (LVDS) output buffer has an improved eye pattern. The LVDS buffer has two parallel stages. A primary stage generates enough current to generate a first voltage drop across a load resistor. At higher frequencies, parasitic capacitive coupling reduces this first voltage drop, closing the eye pattern. A boost stage generates an additional boost current through the load resistor, adding to the voltage drop and opening the eye pattern. The boost stage is coupled to the outputs by link transistors that are enabled by a pre-emphasis signal generated by resetable pulse generators. When outputs switch, the pre-emphasis signal pulses the link transistors on, adding the boost current. At high frequencies, the pulse generators are reset before the pre-emphasis signal ends. The boost current is continuously added at high frequencies, but at low frequencies the boost current only occurs during the pre-emphasis period after outputs switch.

Owner:DIODES INC

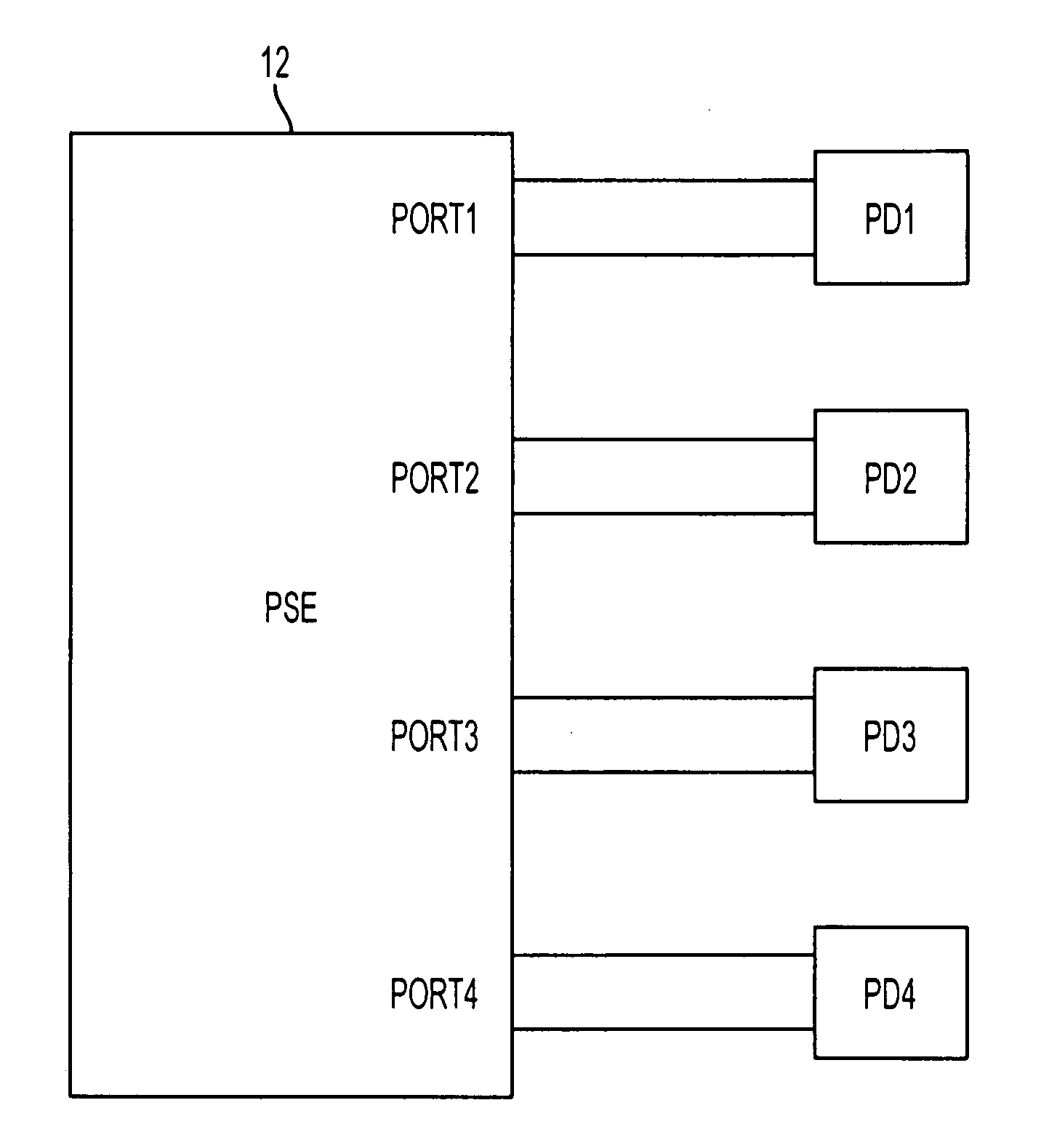

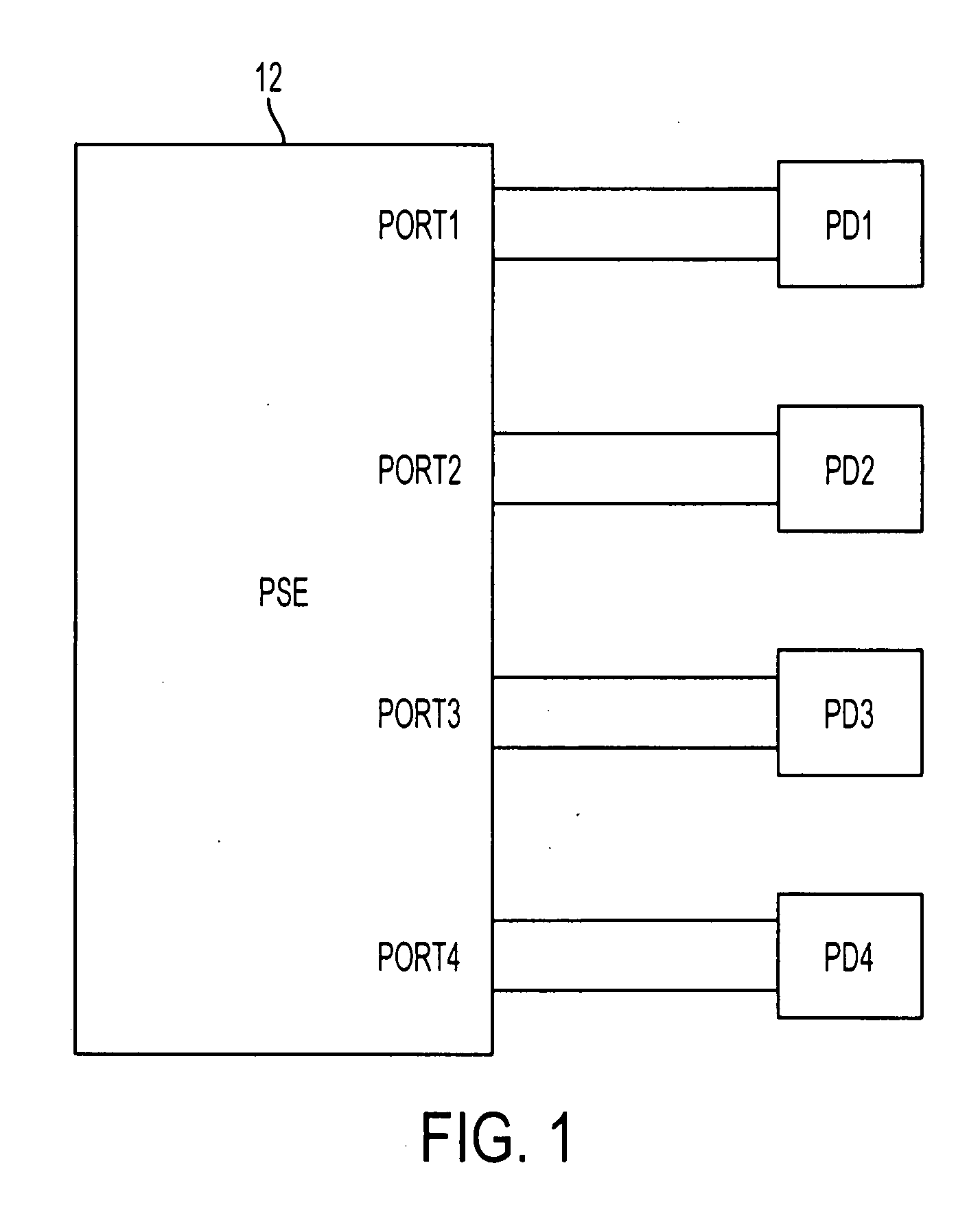

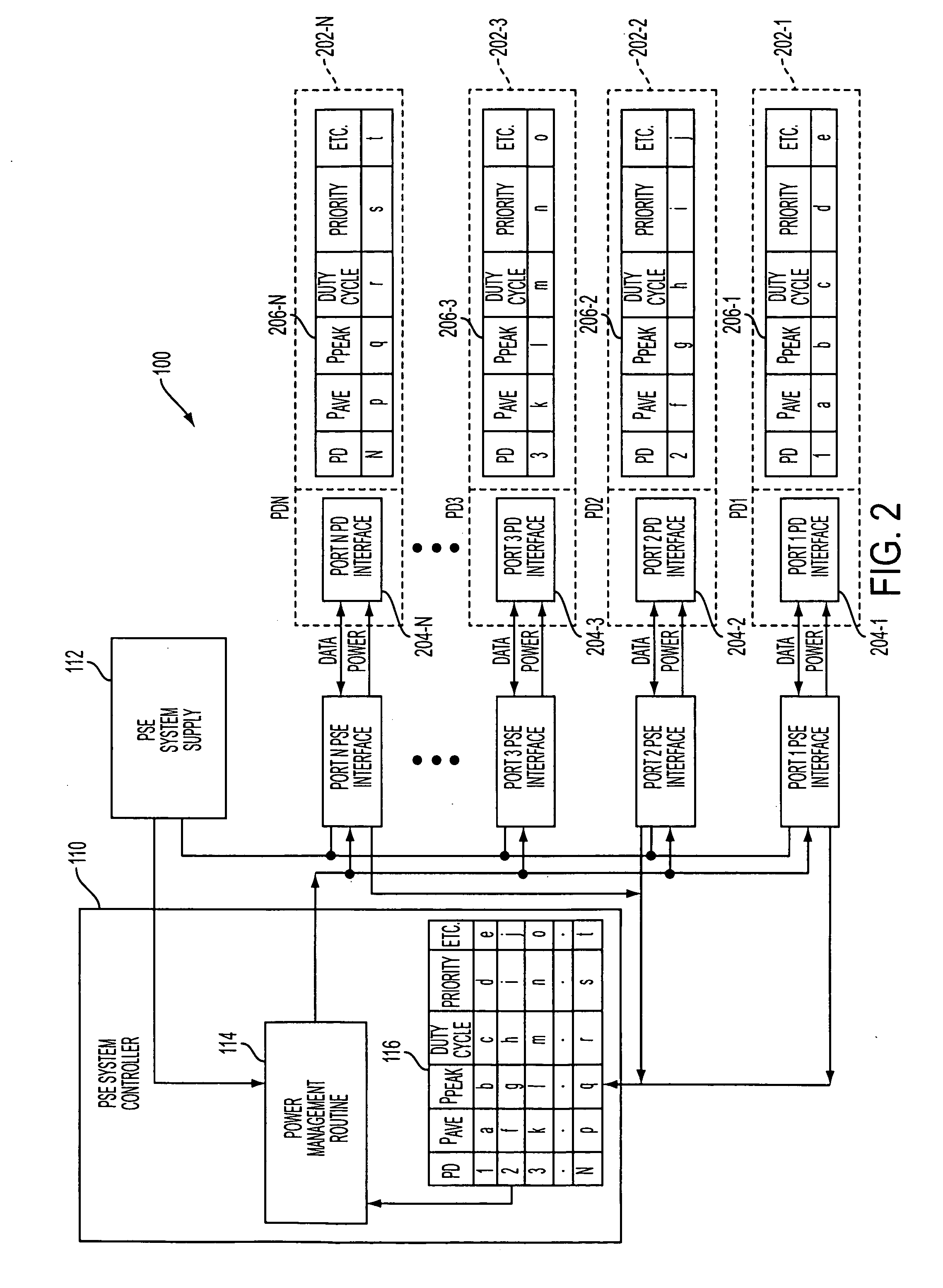

Providing detailed information on powered device in system for supplying power over communication link

InactiveUS20070135086A1Energy efficient ICTInterconnection arrangementsElectricityTelecommunications link

A powered device (PD) configured for receiving power over a communication link, such as an Ethernet link, has a power interface controller for implementing a power supply protocol. The power interface controller acquires multiple pieces of PD information representing multiple characteristics of the PD for transferring the PD information to a power supply device.

Owner:ANALOG DEVICES INT UNLTD

Capacitive isolator

ActiveUS8169108B2Systems using filtering and bypassingSemiconductor/solid-state device detailsCapacitanceHigh pressure

Owner:SKYWORKS SOLUTIONS INC

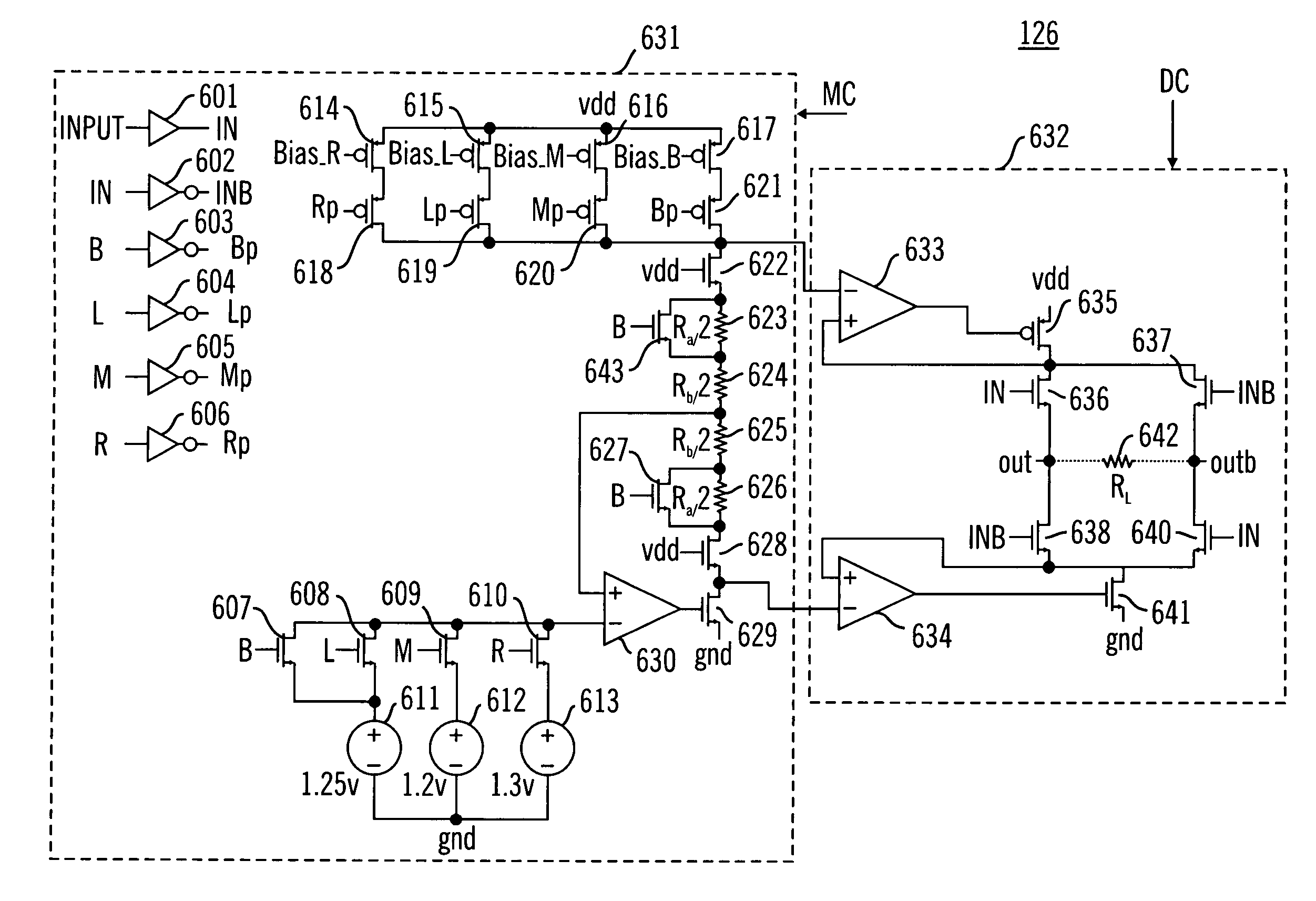

Versatile RSDS-LVDS-miniLVDS-BLVDS differential signal interface circuit

InactiveUS6992508B2Logic circuits coupling/interface using field-effect transistorsCathode-ray tube indicatorsDifferential signalingVoltage source

An electronic circuit includes a selectively configurable differential signal interface and a selection control input for selecting one of a plurality of standard differential signal interfaces for configuration of the differential signal interface. The selection control input selects one of the following plurality of standard differential signal interfaces: reduced swing differential signaling (RSDS), low voltage differential signaling (LVDS), mini low voltage differential signaling (mini-LVDS), and bussed low voltage differential signaling (BLVDS), for configuration of the differential signal interface. The electronic circuit may also include a plurality of selectable voltage sources (611, 612, 613) and a plurality of selectable current sources (614, 615, 616, 617), for selecting, in response to an input signal at the selection control input, at least one of an operating D.C. voltage, a standard differential signal voltage, and a standard differential signal current for the differential signal interface.

Owner:STMICROELECTRONICS SRL

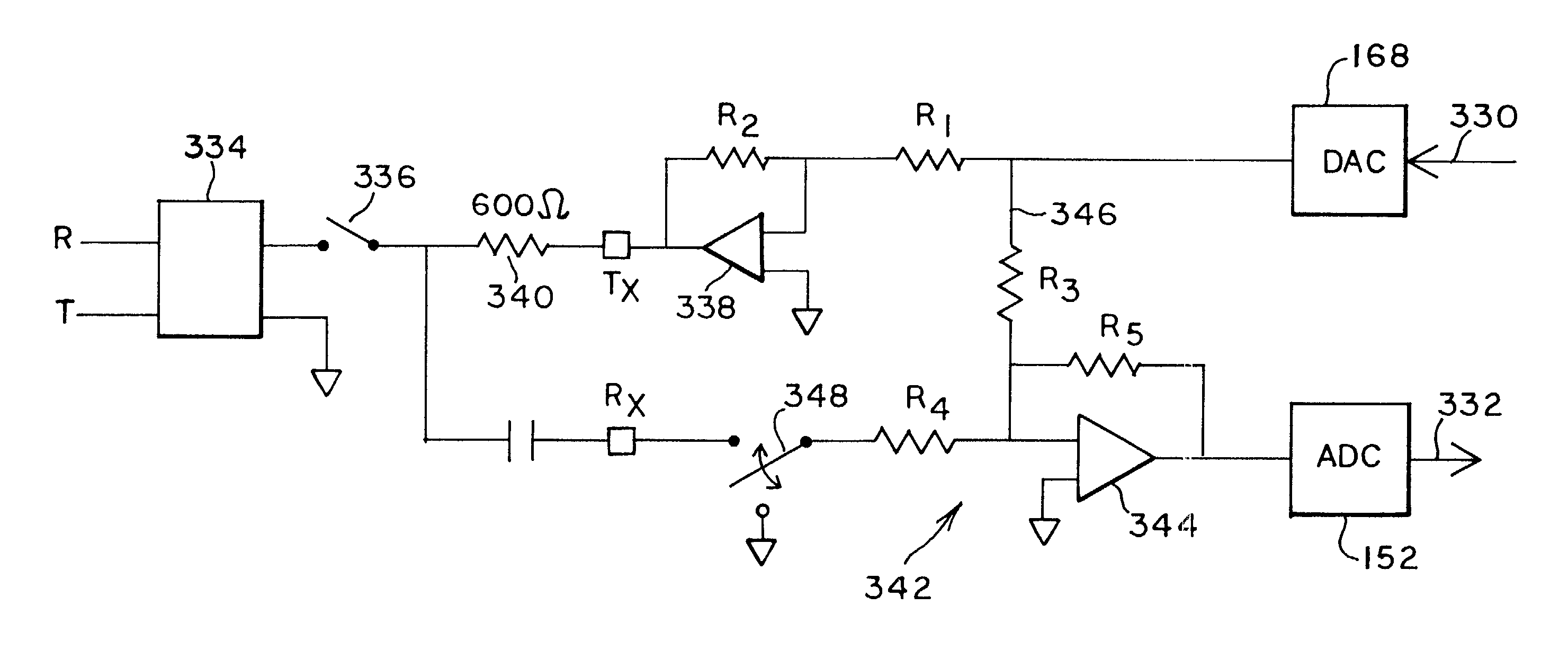

Digital isolation system with hybrid circuit in ADC calibration loop

InactiveUS7050509B2Analogue/digital conversionElectric signal transmission systemsCapacitanceModem device

An improved digital capacitive isolation barrier system is provided that is suitable for use in a telephone or modem where the locally powered circuits must be effectively isolated from the public telephone system, while permitting data transfer across the barrier. In particular, an automatic ADC offset calibration system is provided for determining the magnitude of the ADC offset signal required in the system during a calibration operation, and for providing the calibrated ADC offset signal during normal operation of the isolation barrier system. A modified hybrid circuit is provided for isolating the system input from the telephone line during calibration, and for completing the calibration loop. Fixed bias signals are also provided for the ADC and for a DAC in the system. In a preferred embodiment, the ADC is located on the isolated side of the isolation barrier, while the integrator and register that determine and hold the offset signal are located on the powered side of the isolation barrier.

Owner:SILICON LAB INC

Voltage mode differential driver and method

InactiveUS6867618B2Lower impedanceMultiple input and output pulse circuitsLogic circuits characterised by logic functionVoltage sourceVoltage control

Owner:AVAGO TECH INT SALES PTE LTD

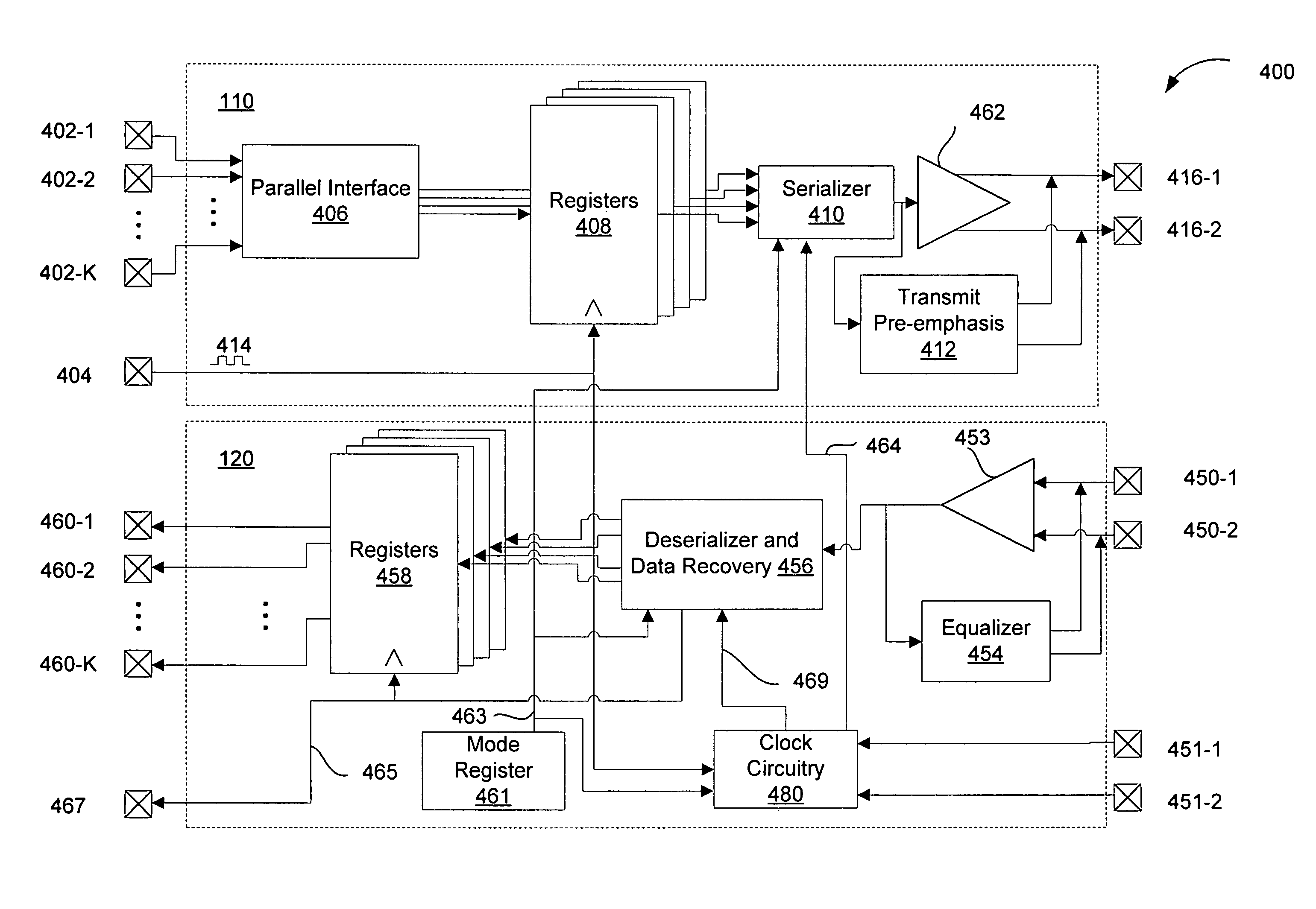

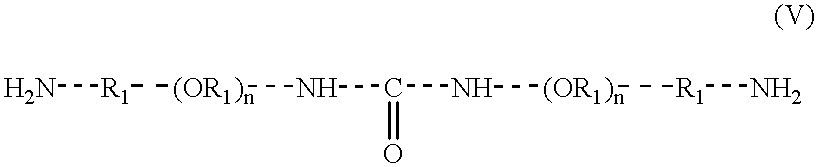

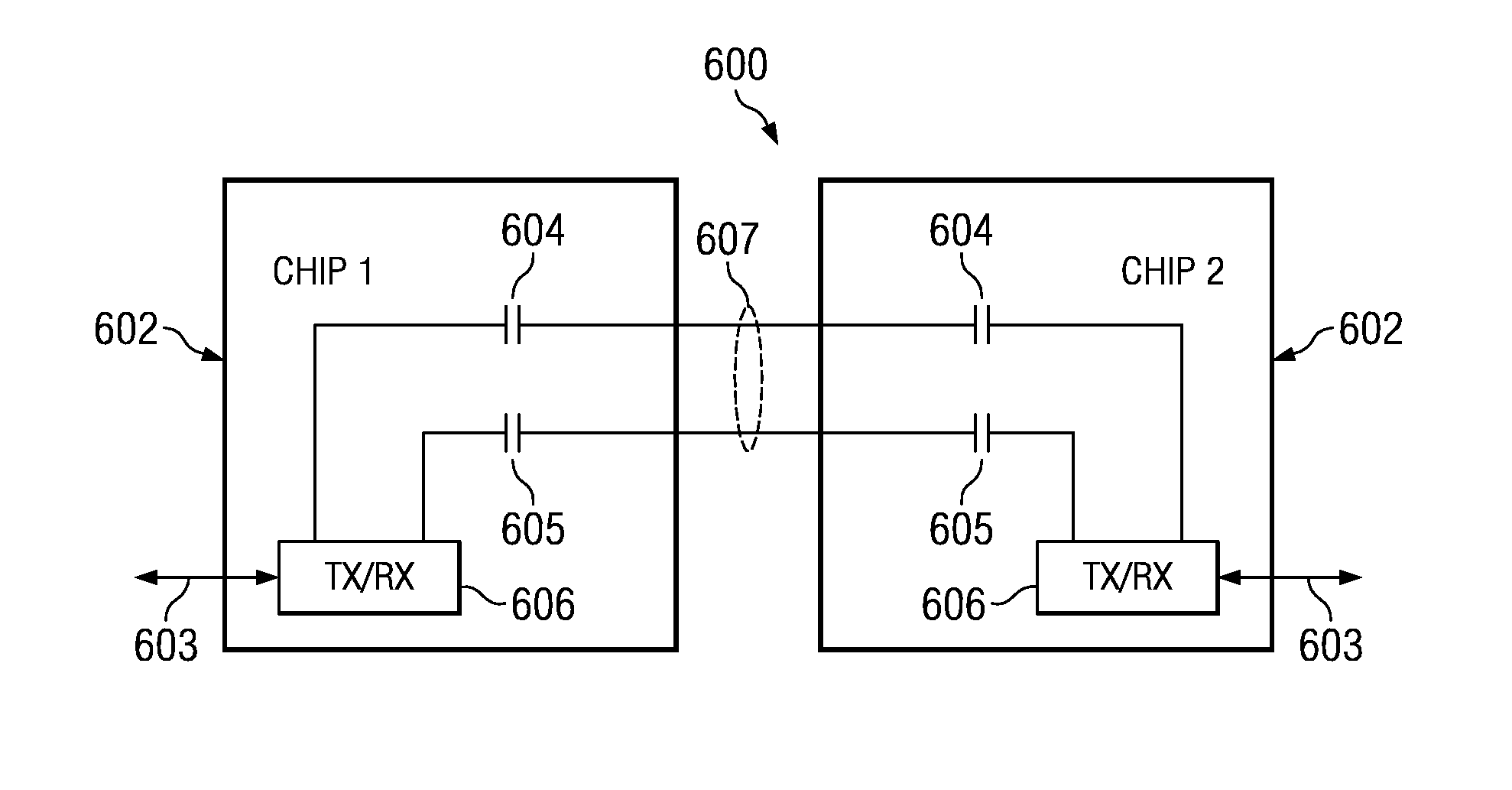

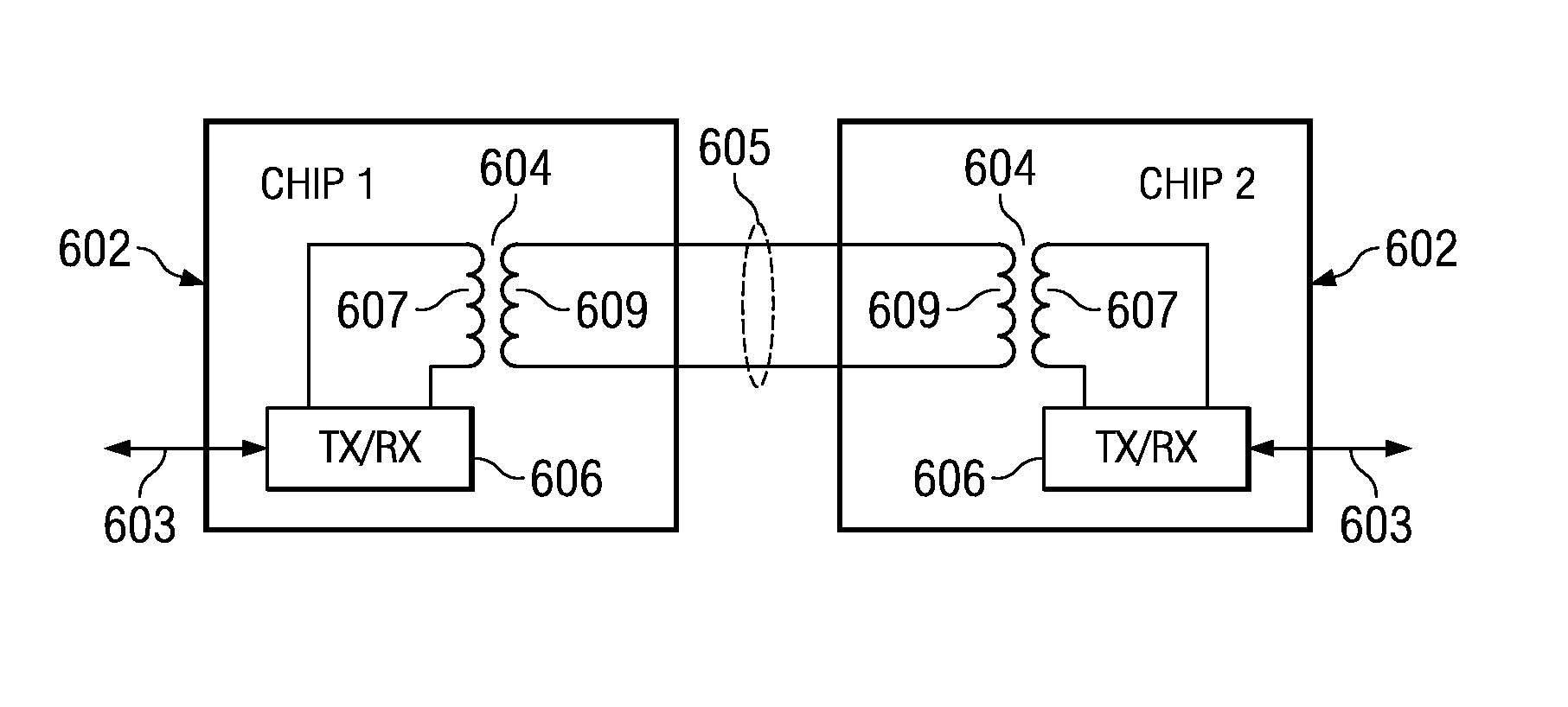

Bidirectional multiplexed RF isolator

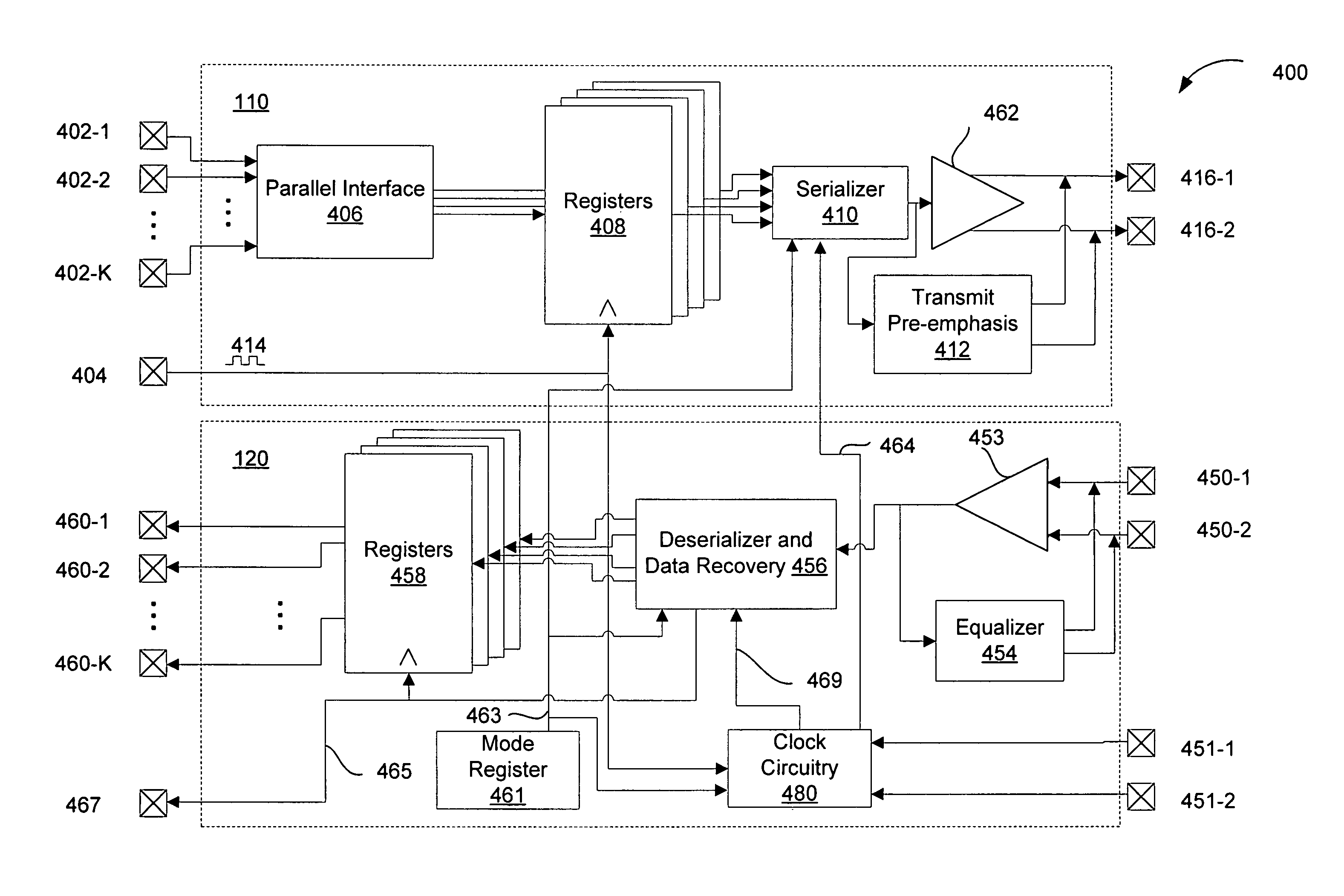

ActiveUS20080267301A1Parallel/series conversionPower distribution line transmissionDigital dataSingle chip

An integrated circuit single chip isolator provides bidirectional data transfer for a plurality of communications channels. A first and second dies are located on a first and second sides of a voltage isolation barrier in the chip and have a first and second plurality of digital data input / output pins associated therewith. First circuitry located on the first die on a first side of the voltage isolation barrier and third circuitry located on the second die on a second side of the voltage isolation barrier serializes a plurality of parallel digital data inputs from the associated plurality of digital data input / output pins onto a one link across the voltage isolation barrier and transmits synchronization clock signals associated with the plurality of digital data inputs over a another link across the voltage isolation barrier. Second circuitry located on the second die on a second side of the voltage isolation barrier and fourth circuitry located on the first die on a first side of the voltage isolation barrier de-serializes the first plurality of digital data inputs from the first link onto the second plurality of digital data input / output pins and receives the first synchronization clock signal associated with the plurality of digital data inputs on the second link. Switches associated with each of the plurality of input / output pins between transmit and receive circuitry.

Owner:SKYWORKS SOLUTIONS INC

Systems and methods for powering a charging circuit of a communications interface

ActiveUS20120229076A1Minimize power consumptionExtend battery lifeError prevention/detection by using return channelBatteries circuit arrangementsCommunication interfaceCoupling

Embodiments include systems and methods of powering a mobile device using a sink device. The method may include detecting a coupling of a mobile device to the sink device and transmitting an acknowledgement in response to a query, the acknowledgement confirming that the sink device has charging capability. Power may be selectively provided in response to the power request. According to some embodiments, the method includes transmitting a query by a communications transmitter to determine if a sink device has charging capability, and deactivating a driver for a power line and transmitting a power request using the communications transmitter in response to receiving an acknowledgement signal from the sink device. The method may further include selectively providing power received from the sink device to a charging circuit of the mobile device. The mobile device may include an HDMI transmitter for communicating through a transmission line to an HDMI sink device.

Owner:ANALOGIX SEMICON

Signal isolators using micro-transformer

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

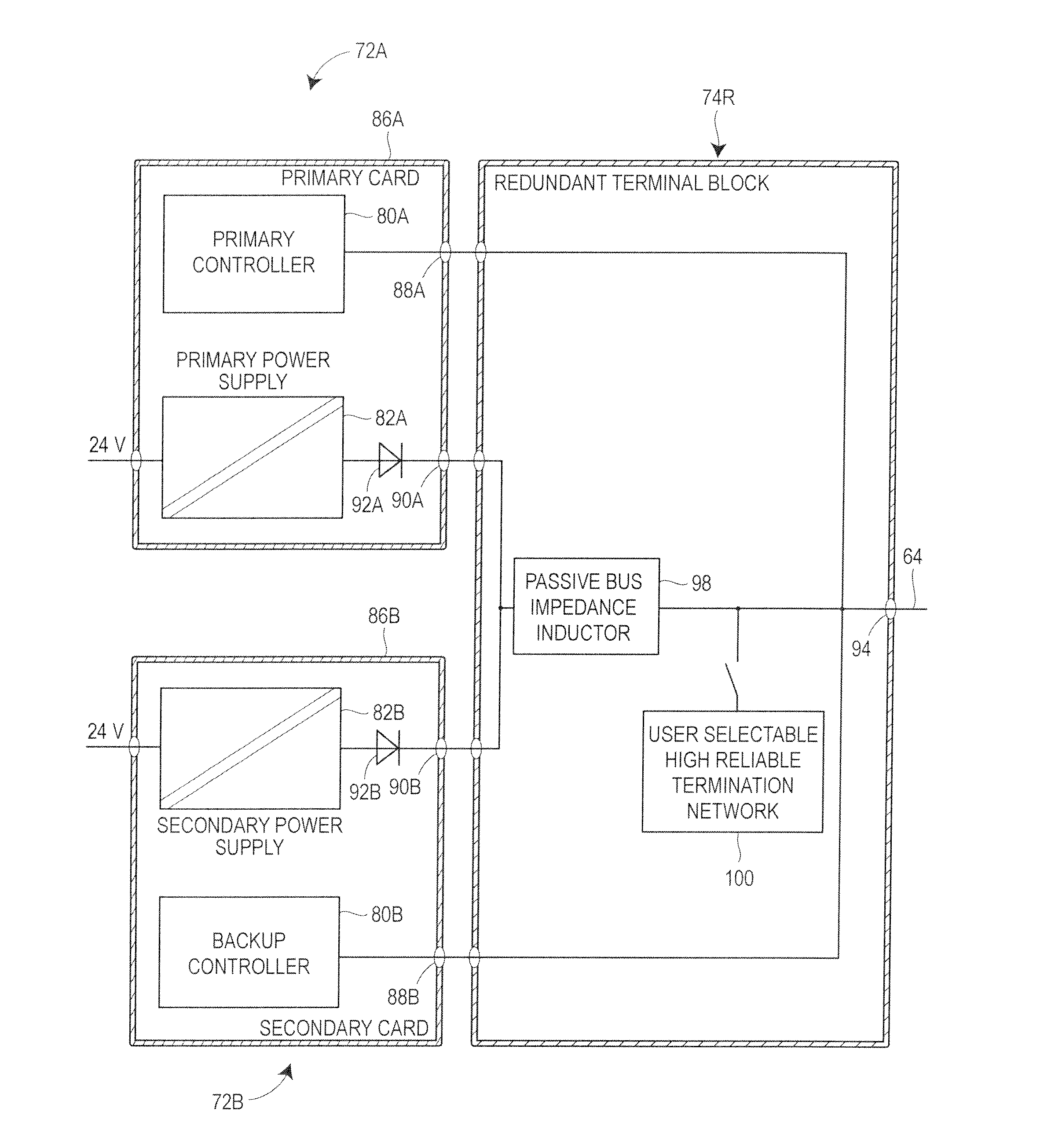

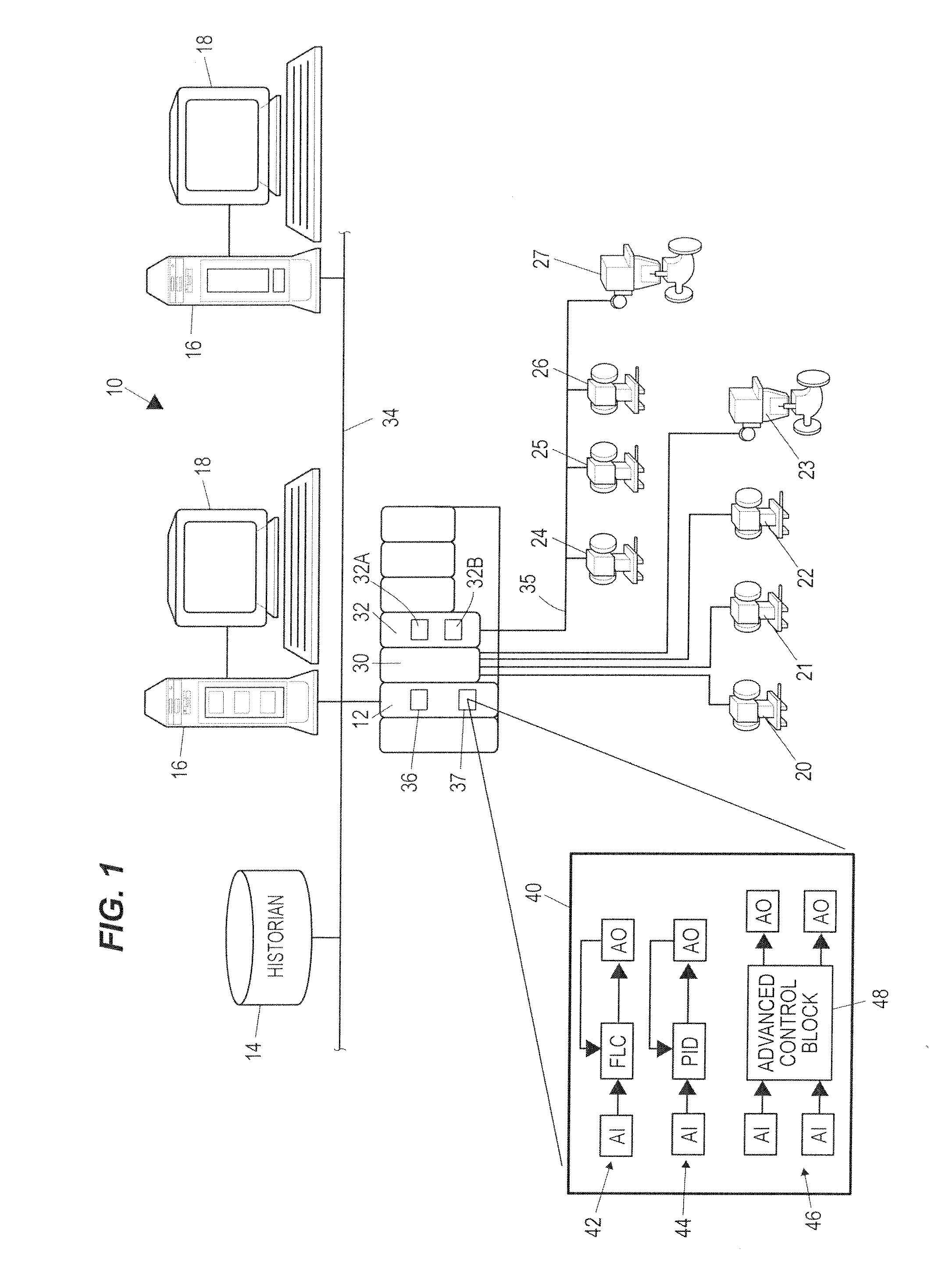

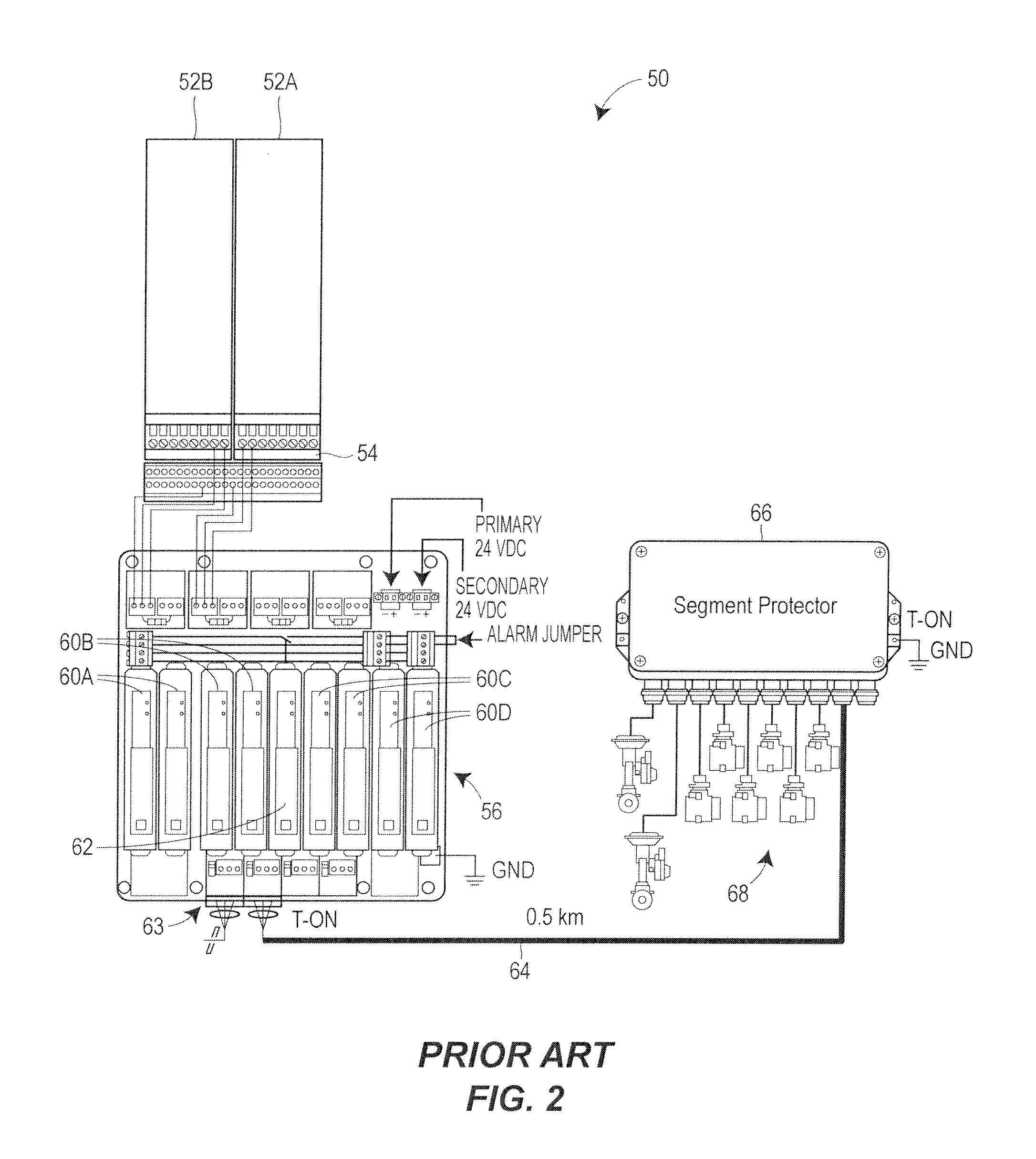

Integrated bus controller and power supply device for use in a process control system

ActiveUS20110131455A1Reducing wire neededReduce configurationProgramme controlVolume/mass flow measurementControl systemPower strip

An integrated bus controller and power supply device includes a typical or standard bus controller and a bus power supply disposed in a common housing, the size and external configuration of which may match a standard bus controller device associated with a typical I / O communication network. The bus controller may store and implement one or more control routines using one or more field devices connected to the I / O communication network while the bus power supply generates and provides the appropriate power signal to the bus of the I / O communication network, the power signal being used to power the field devices connected to the I / O communication network. The integrated bus controller and power supply device can be easily connected to the bus of the I / O communication network to provide both bus controller functionality and bus power supply functionality on the I / O communication network, without the need of configuring and attaching separate, dedicated bus controller and power supply devices to the bus and having to wire these devices together using multiple different terminal blocks.

Owner:FISHER-ROSEMOUNT SYST INC

Popular searches

Solid-state devices Transformers/inductances circuits Transmission noise suppression Line-transmission High level techniques Near-field systems with capacitive coupling Semiconductor devices Frequency-division multiplex details Plural information simultaneous broadcast Signal transmission/receiving via power distribution