Patents

Literature

2303 results about "Line structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Line structure definition, line structure meaning | English dictionary. [. a any straight one-dimensional geometrical element whose identity is determined by two points. a a white or coloured band indicating a boundary or division on a field, track, etc.

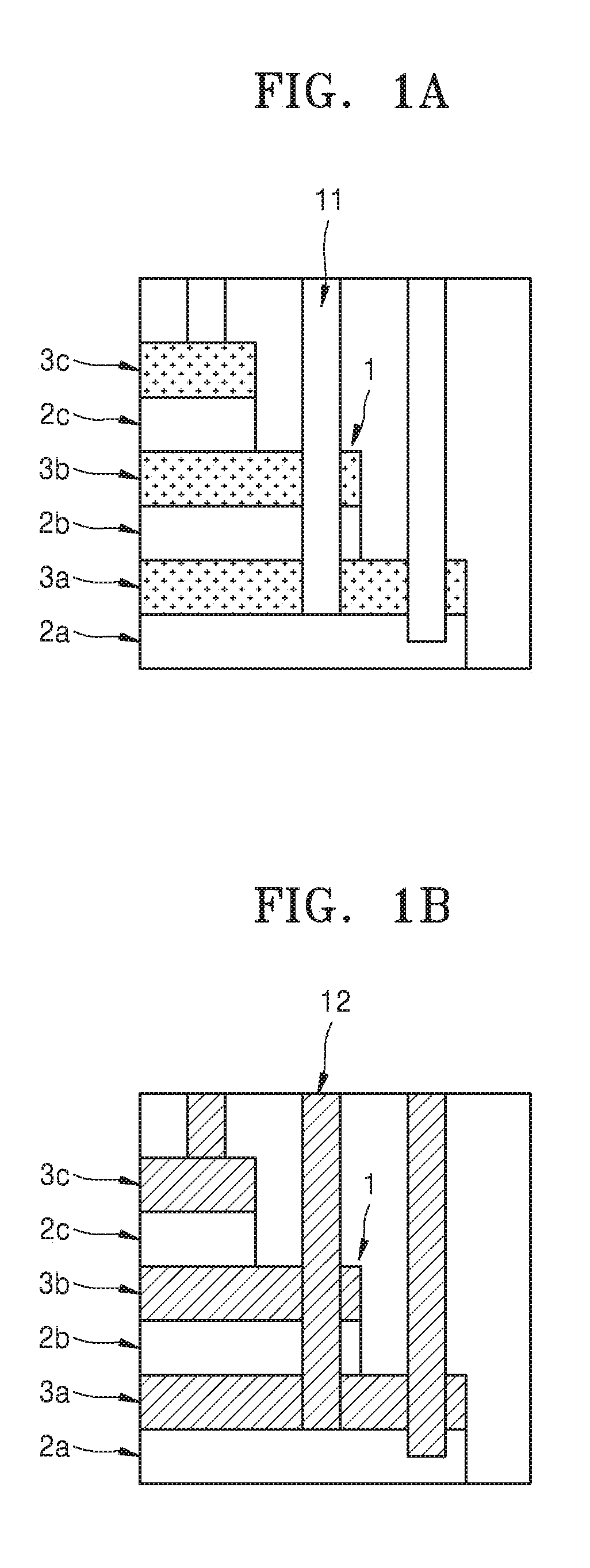

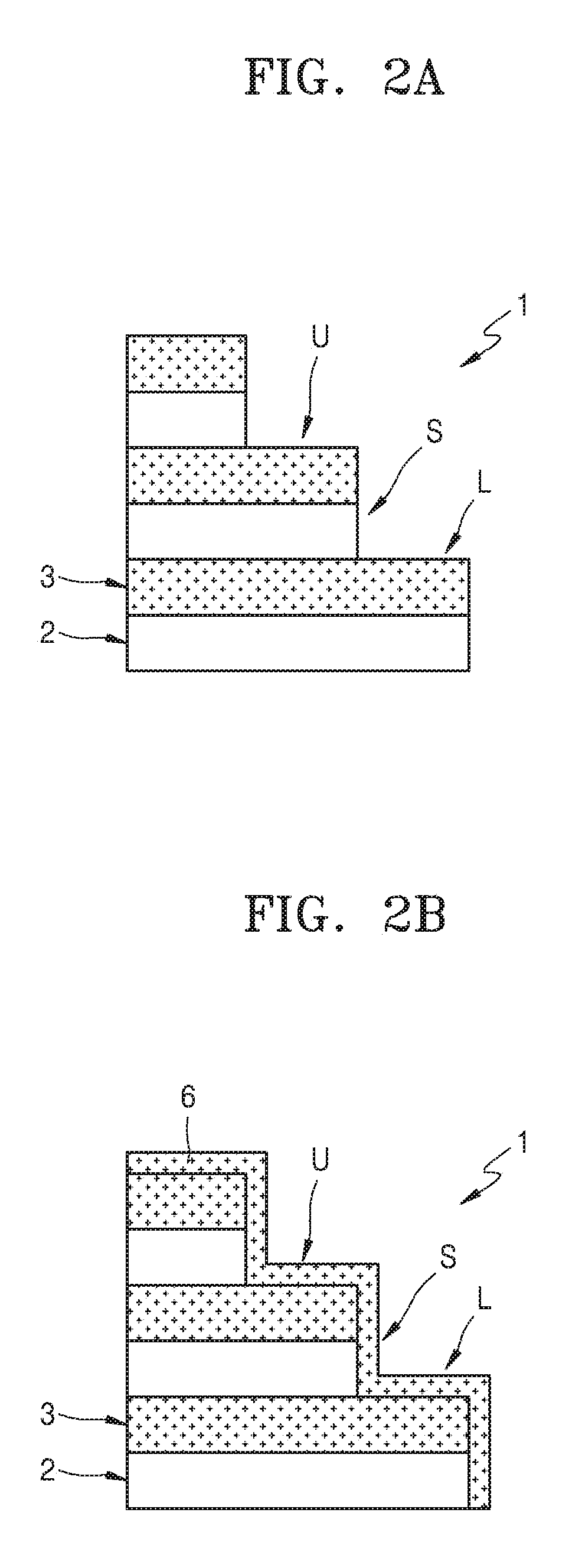

Method of processing a substrate and a device manufactured by the same

ActiveUS20190148398A1Prevent excessive etchingImprove the immunitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLine structure

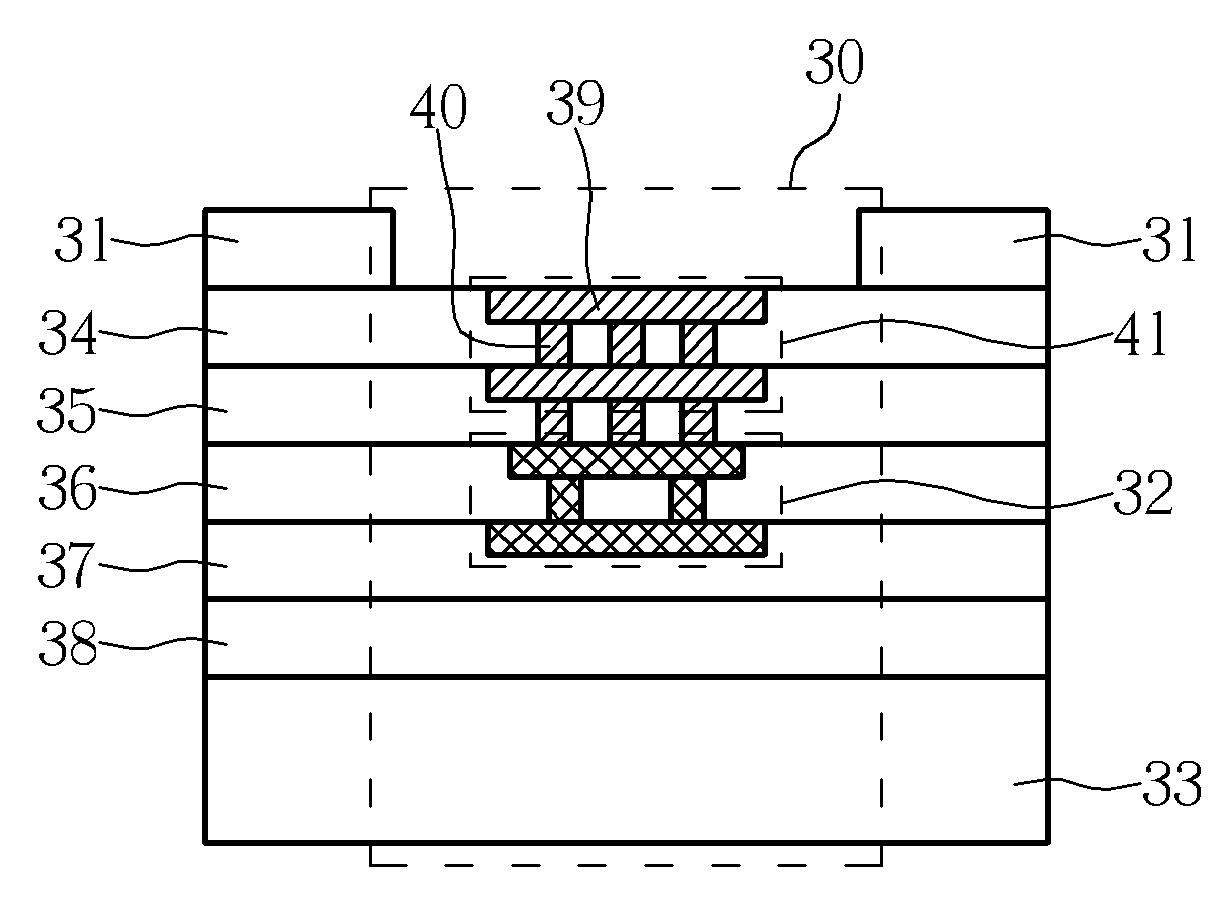

Provided is a substrate processing method capable of preventing over-etching of a part of a stair-case structure due to an etching solution, when a barrier layer is selectively formed on a VNAND device having the stair-case structure. The substrate processing method includes: alternately stacking a first insulating layer and a second insulating layer; forming a stepped structure having an upper surface, a lower surface, and a side surface connecting the upper surface to the lower surface by etching the first insulating layer and the second insulating layer that are stacked; densifying the stepped structure; forming a barrier layer on the densified second insulating layer; and performing isotropic etching on at least a part of a sacrificial word line structure including the second insulating layer and the barrier layer. During etching the barrier layer at the isotropic etching step, the second insulating layer is not etched or etched a little to an ignorable degree.

Owner:ASM IP HLDG BV

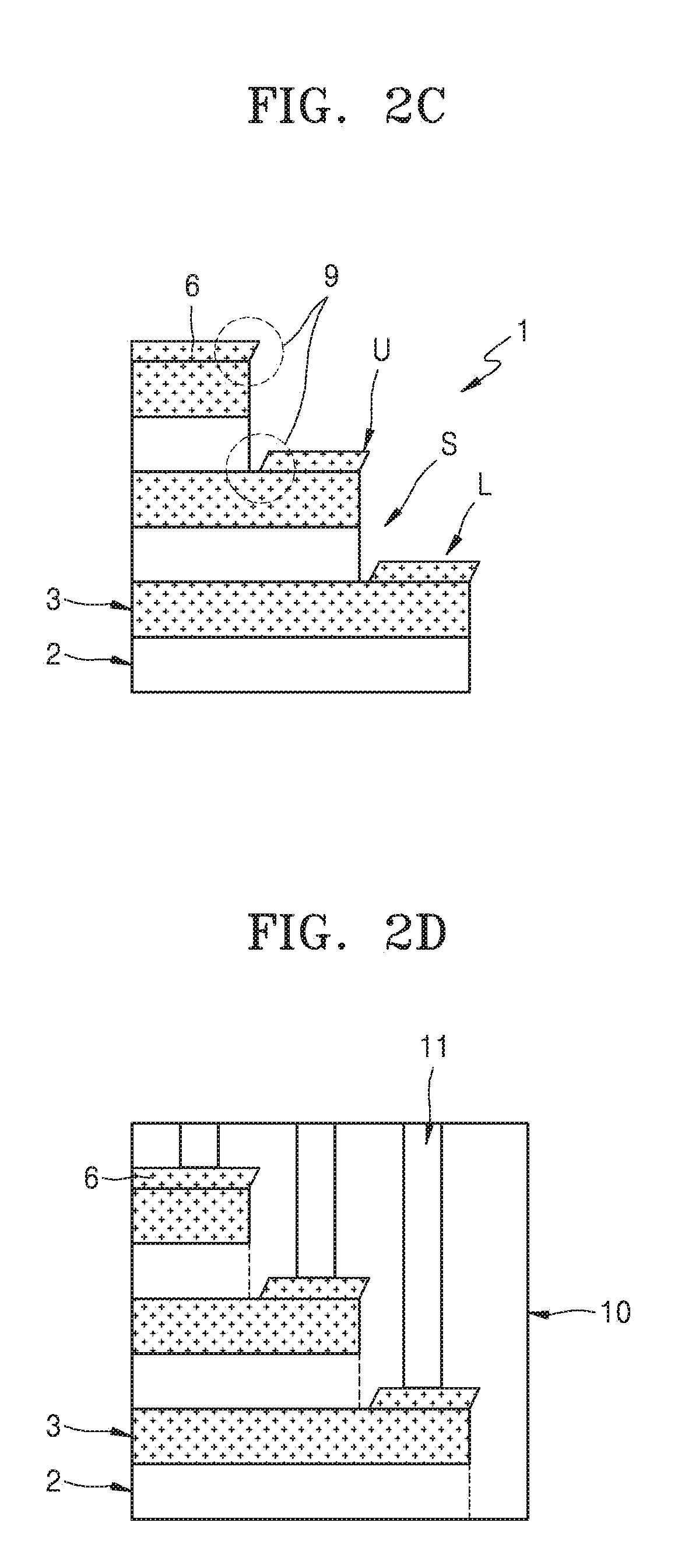

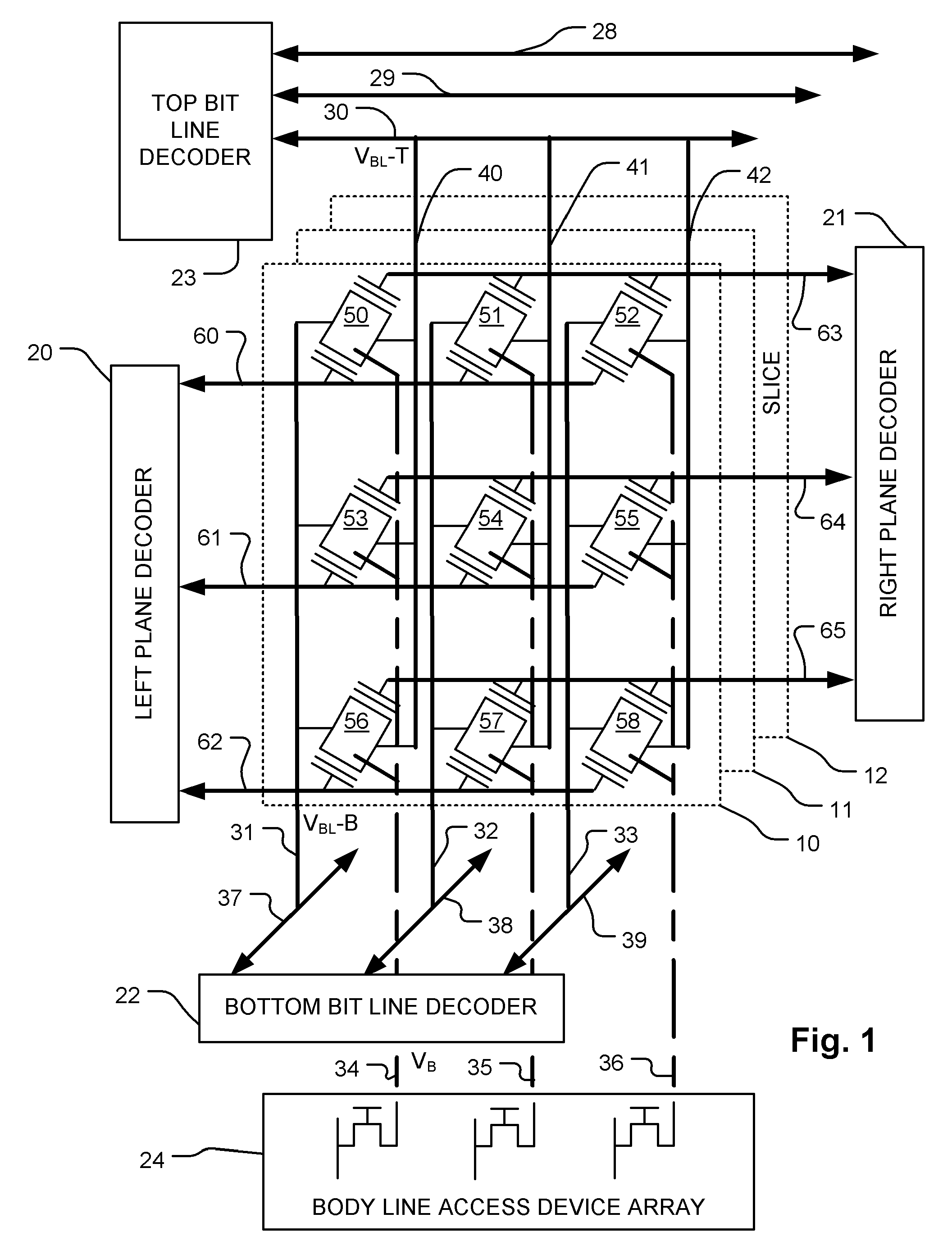

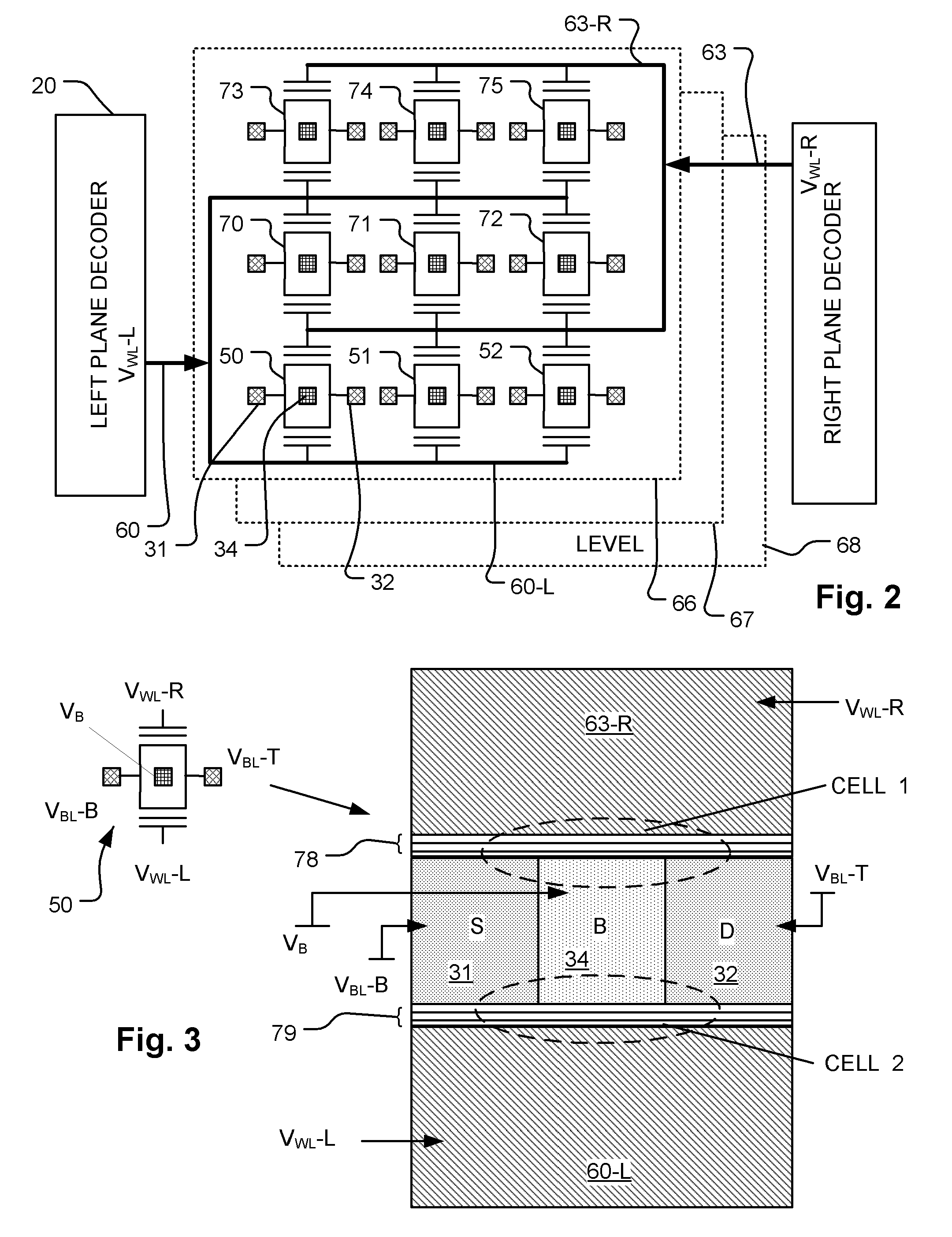

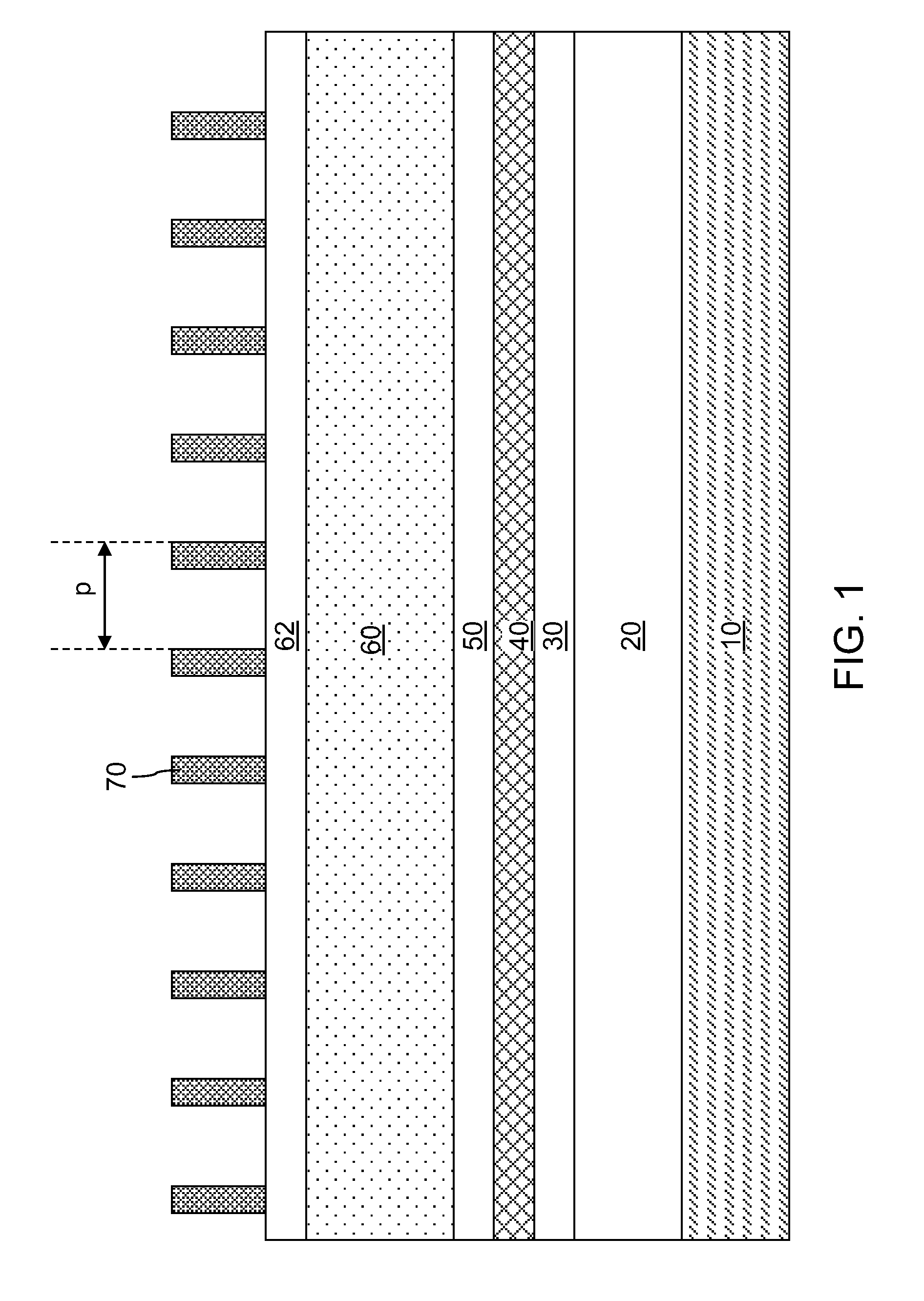

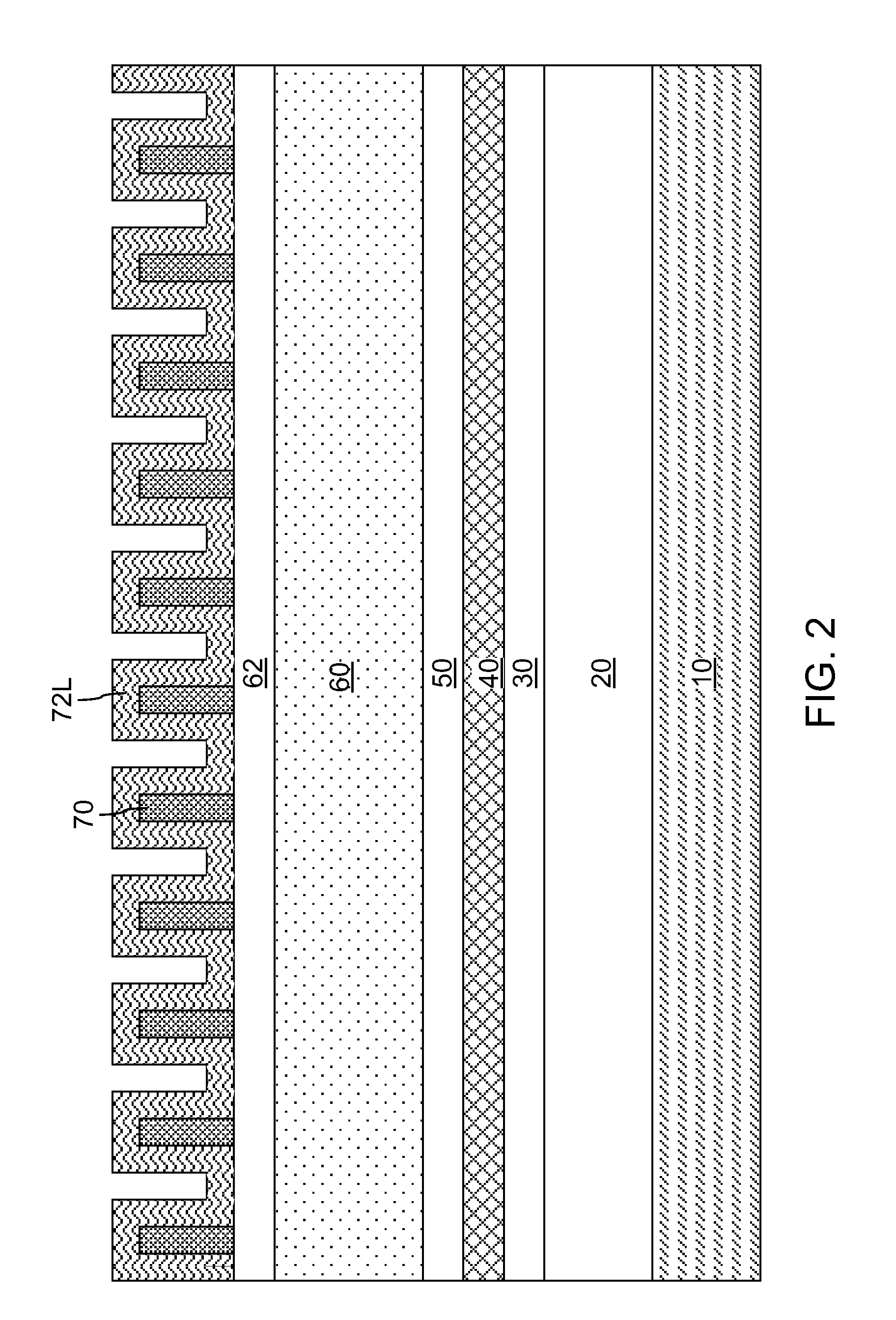

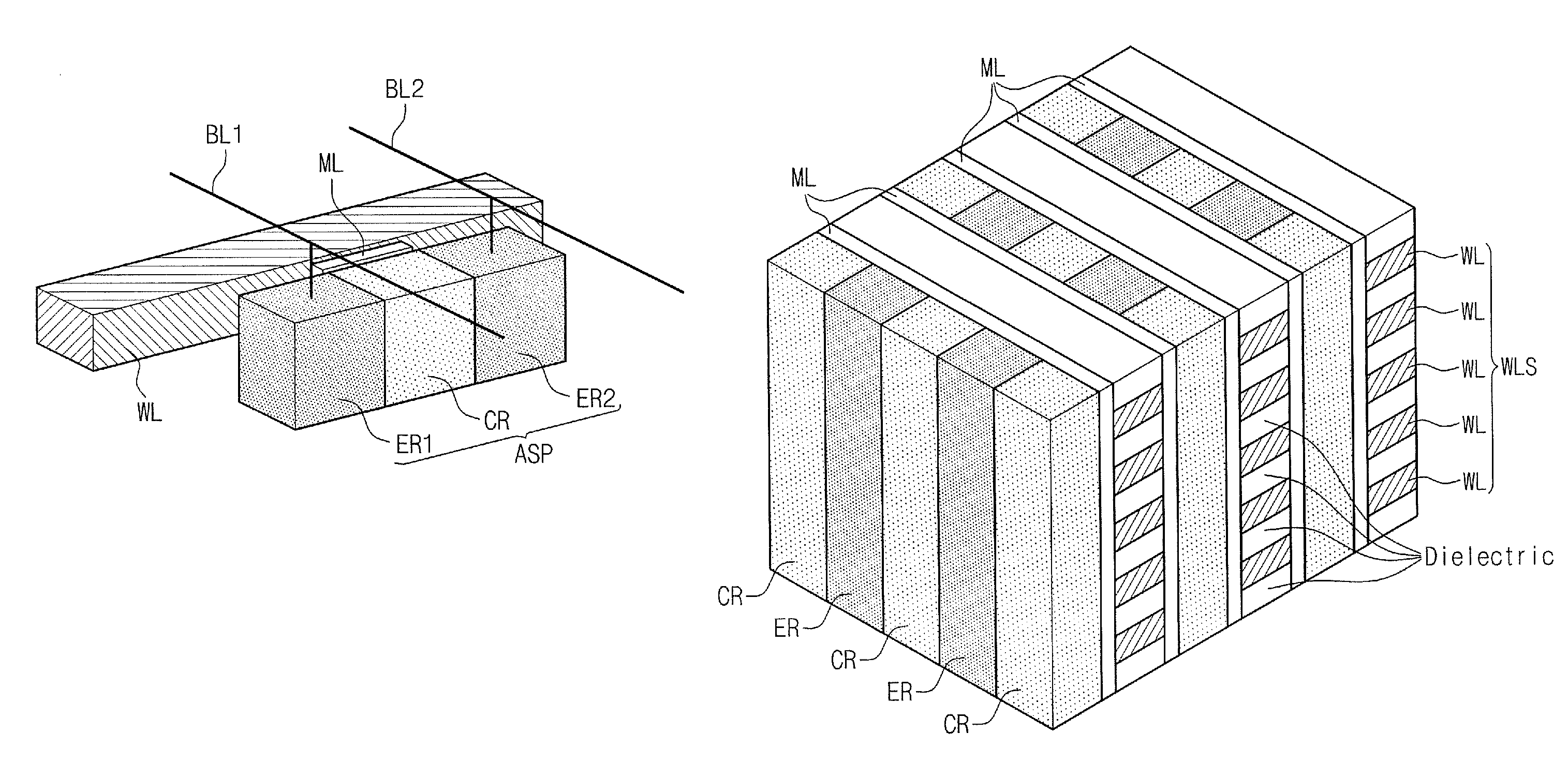

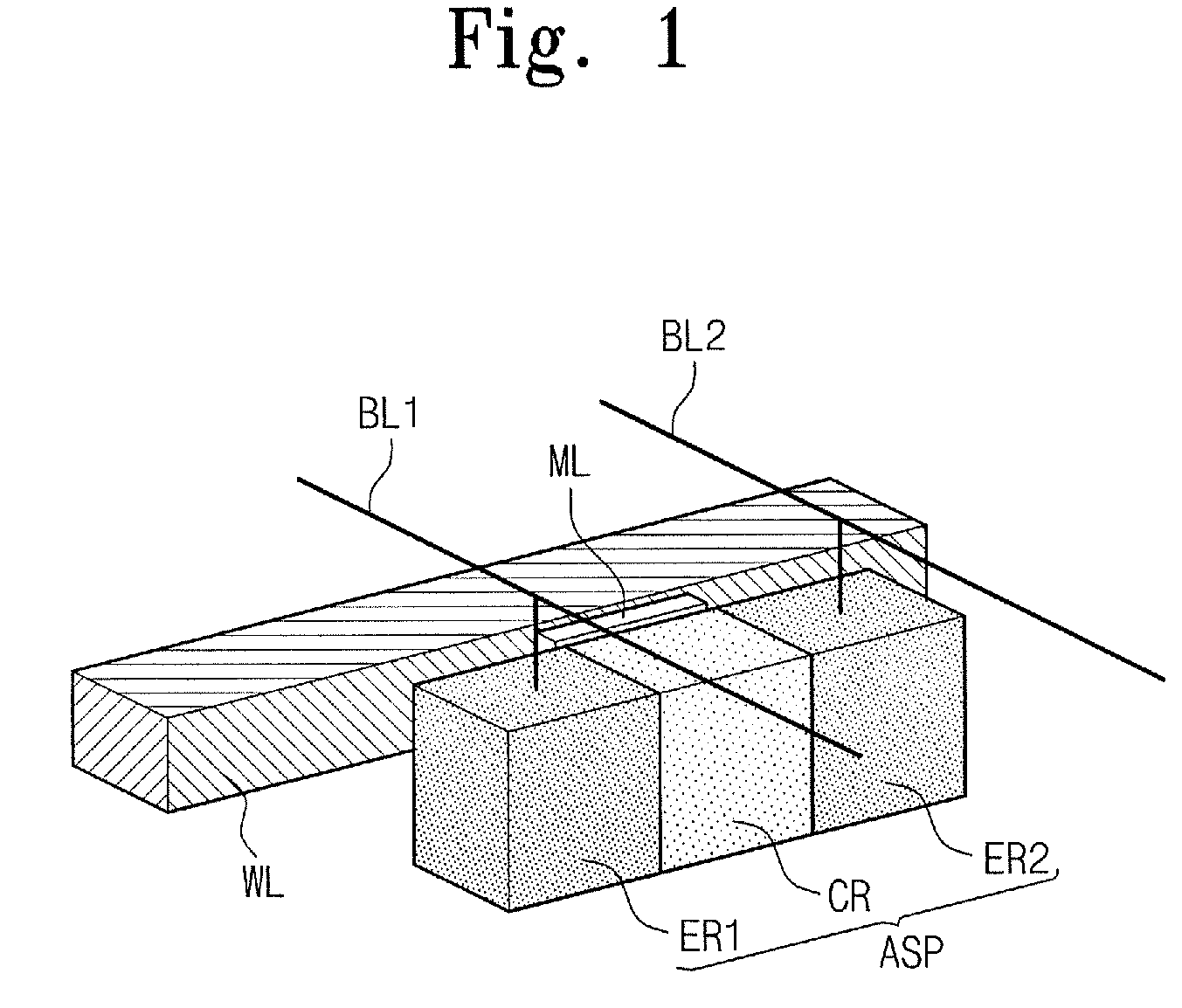

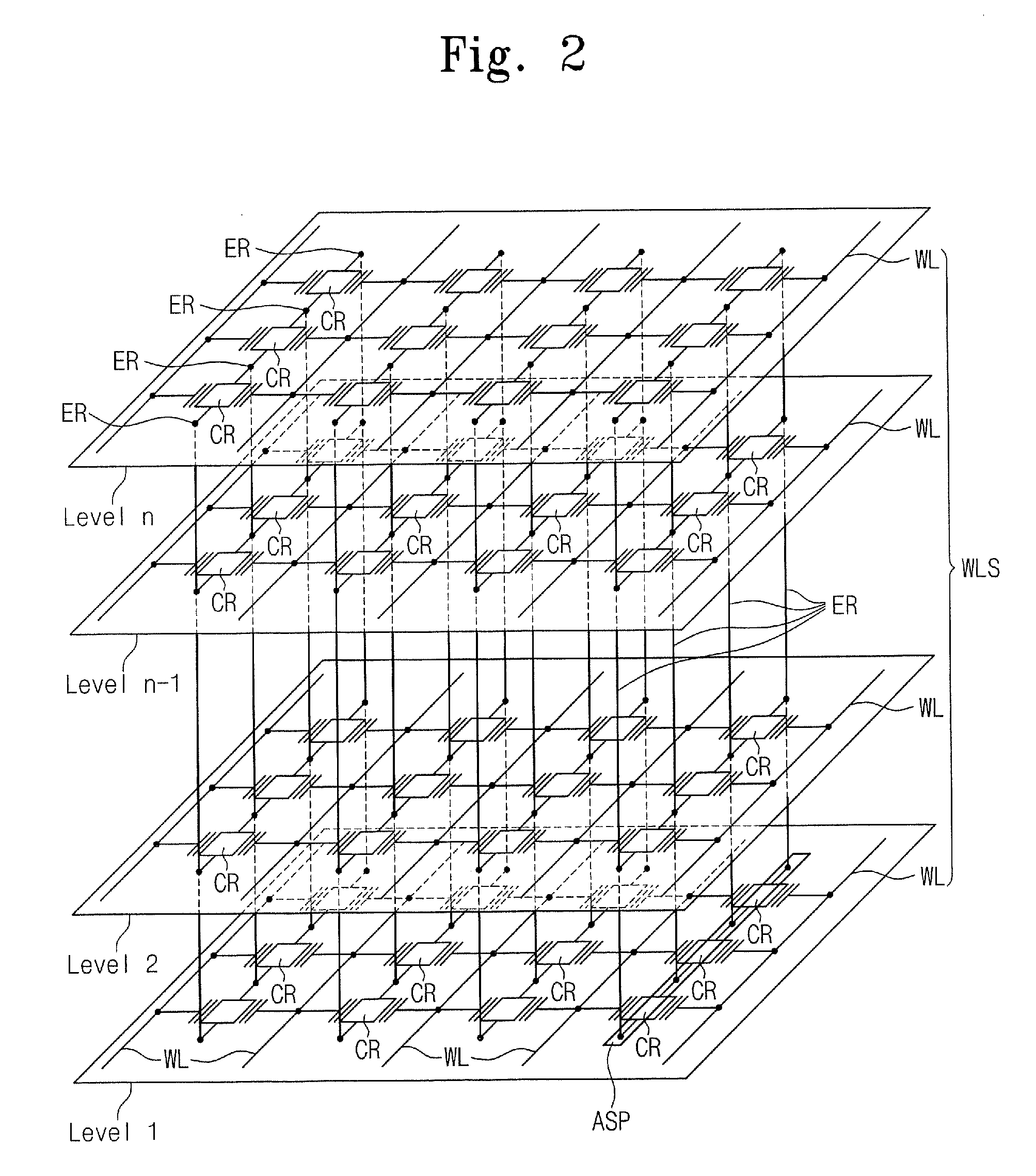

3D memory array arranged for FN tunneling program and erase

A 3D memory device includes an array of semiconductor body pillars and bit line pillars, dielectric charge trapping structures, and a plurality of levels of word line structures arranged orthogonally to the array of semiconductor body pillars and bit line pillars. The semiconductor body pillars have corresponding bit line pillars on opposing first and second sides, providing source and drain terminals. The semiconductor body pillars have first and second channel surfaces on opposing third and fourth sides. Dielectric charge trapping structures overlie the first and second channel surfaces, providing data storage sites on two sides of each semiconductor body pillar in each level of the 3D array. The device can be operated as a 3D AND-decoded flash memory.

Owner:MACRONIX INT CO LTD

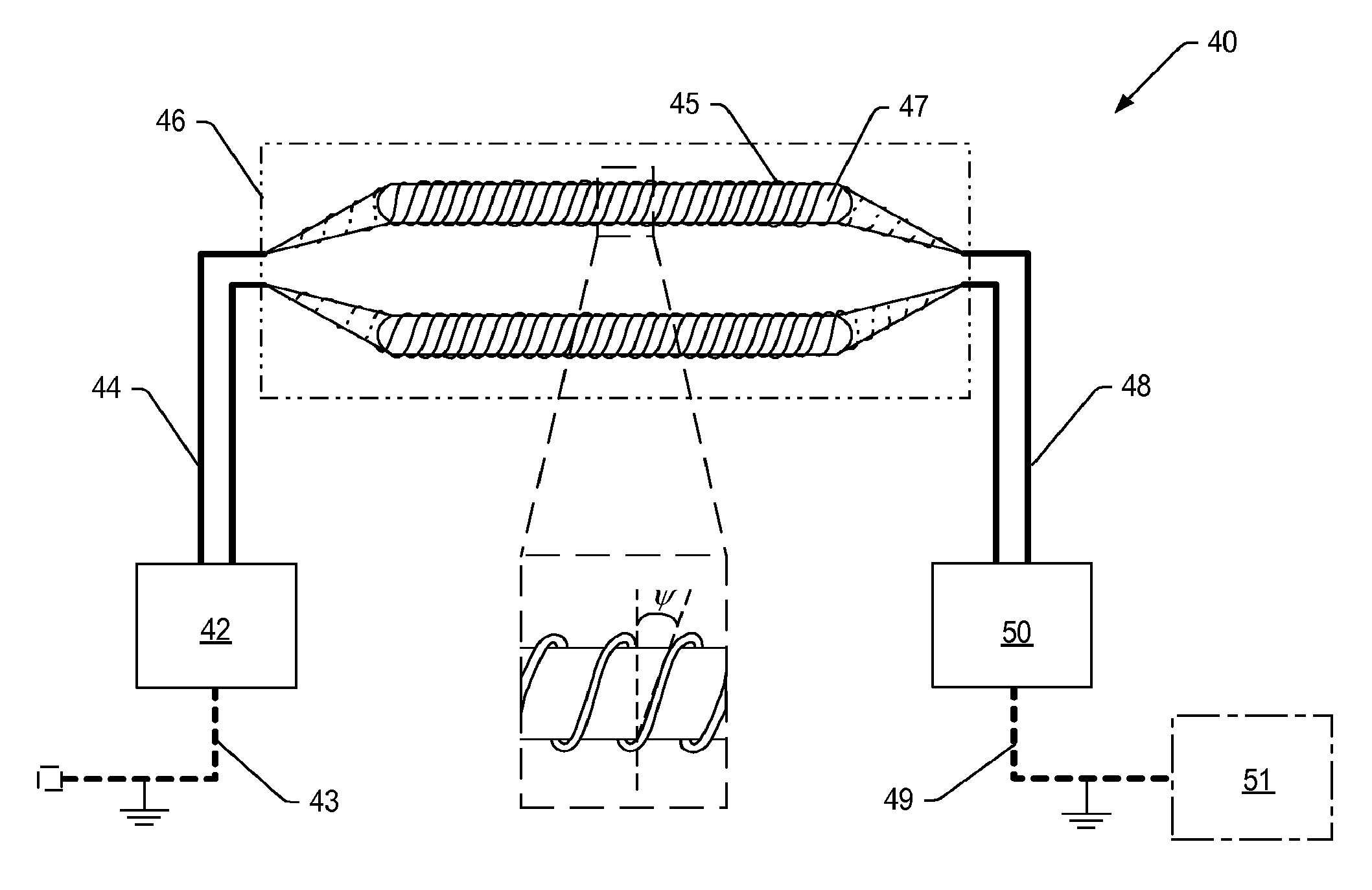

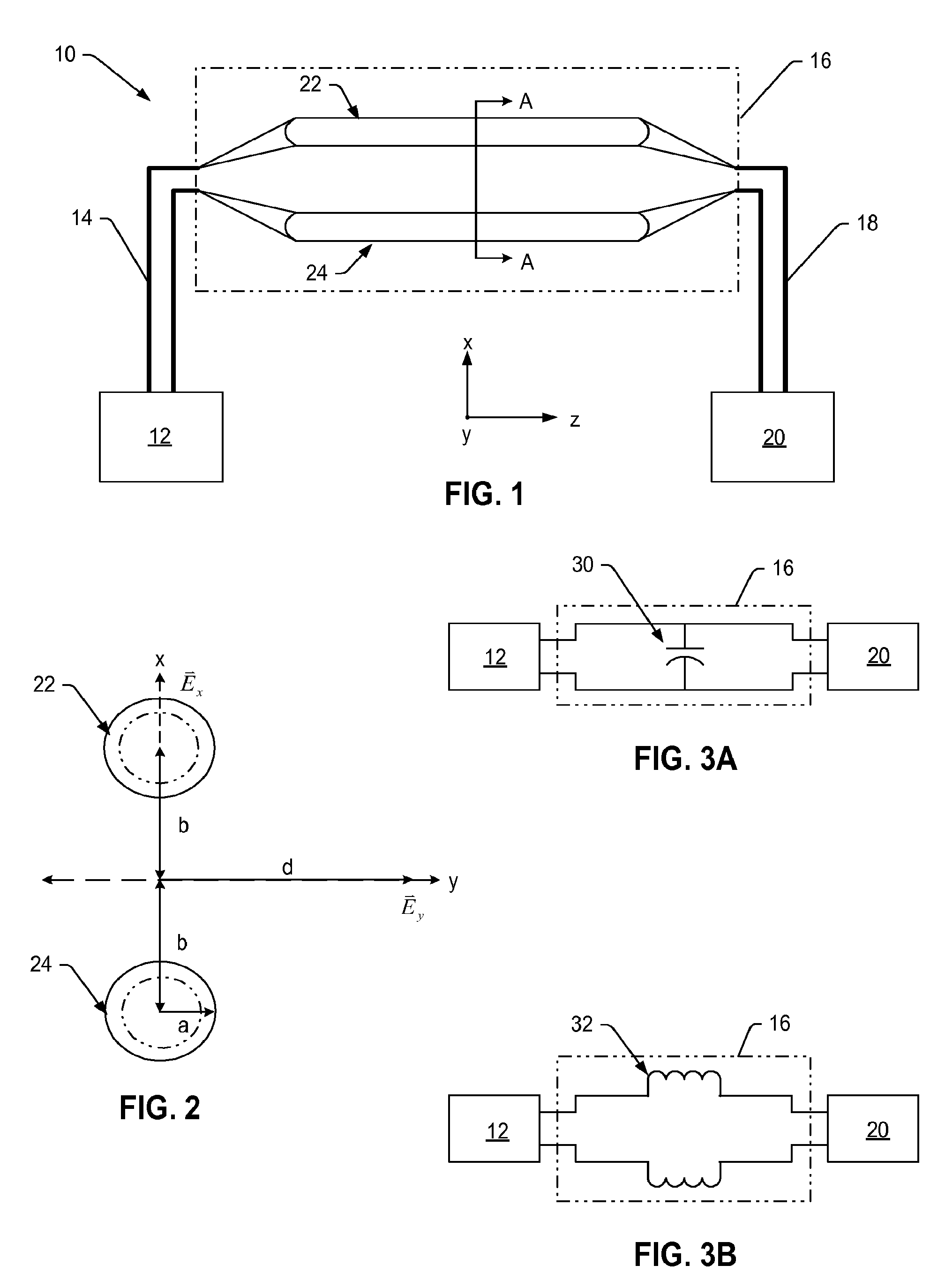

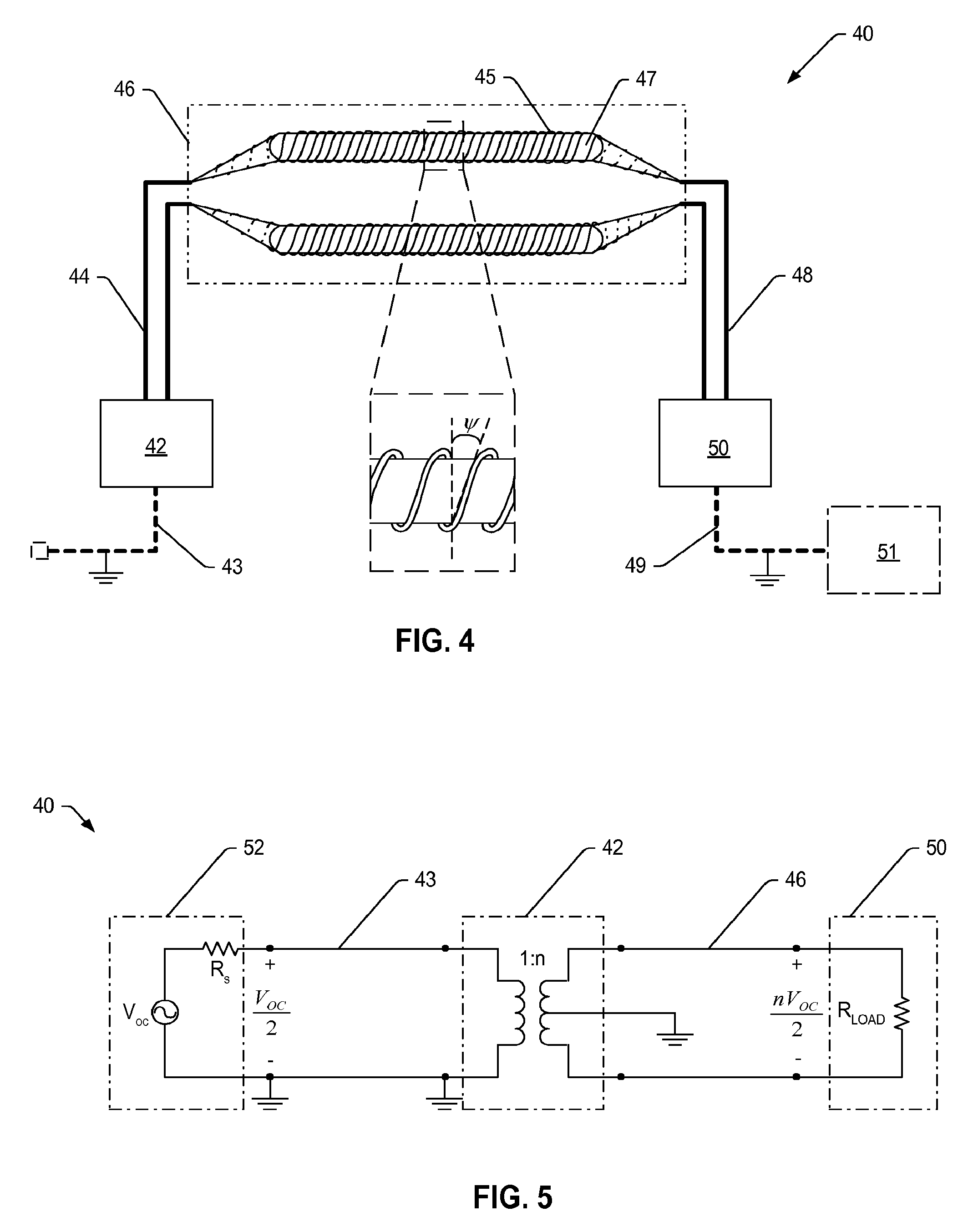

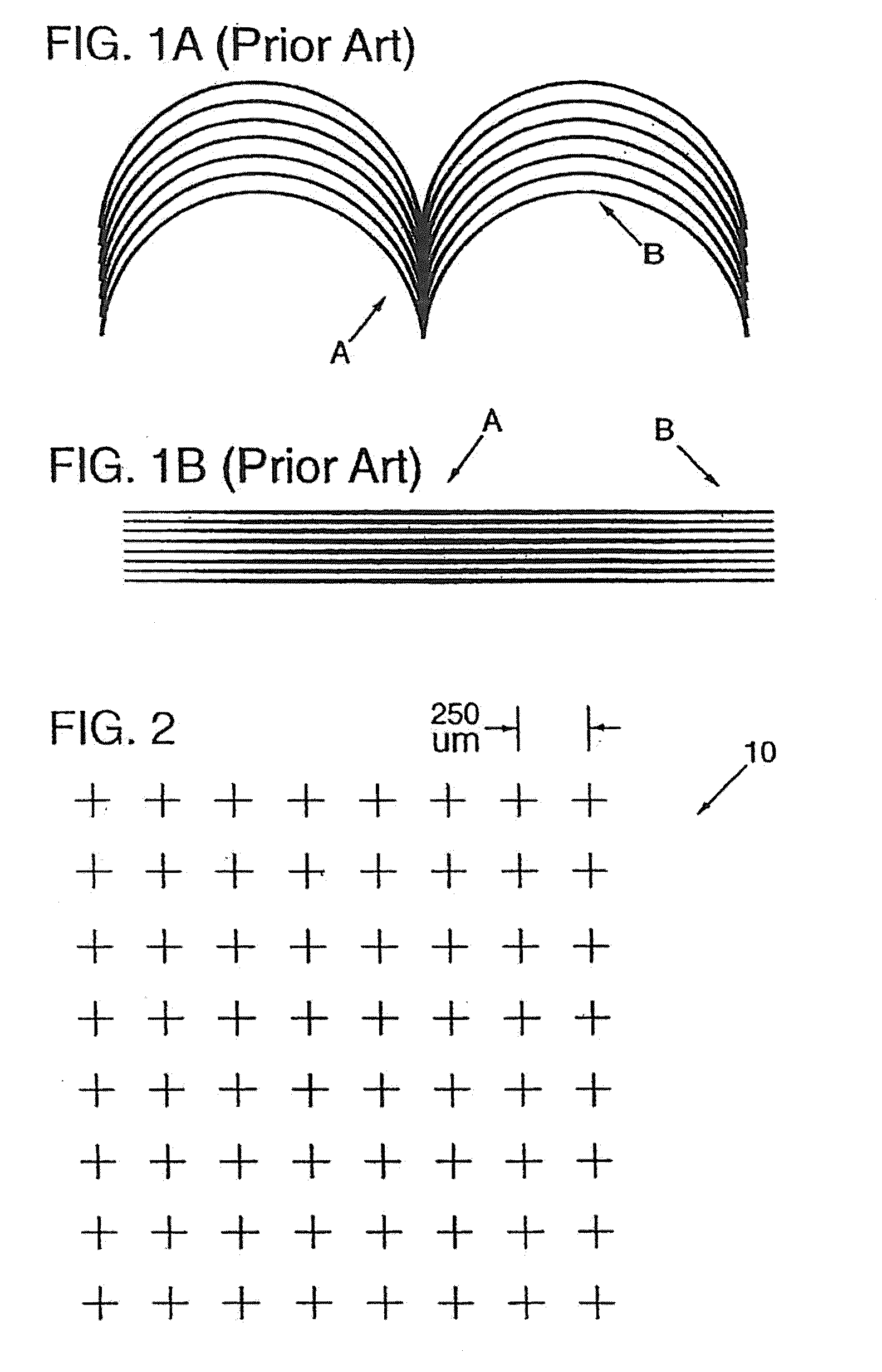

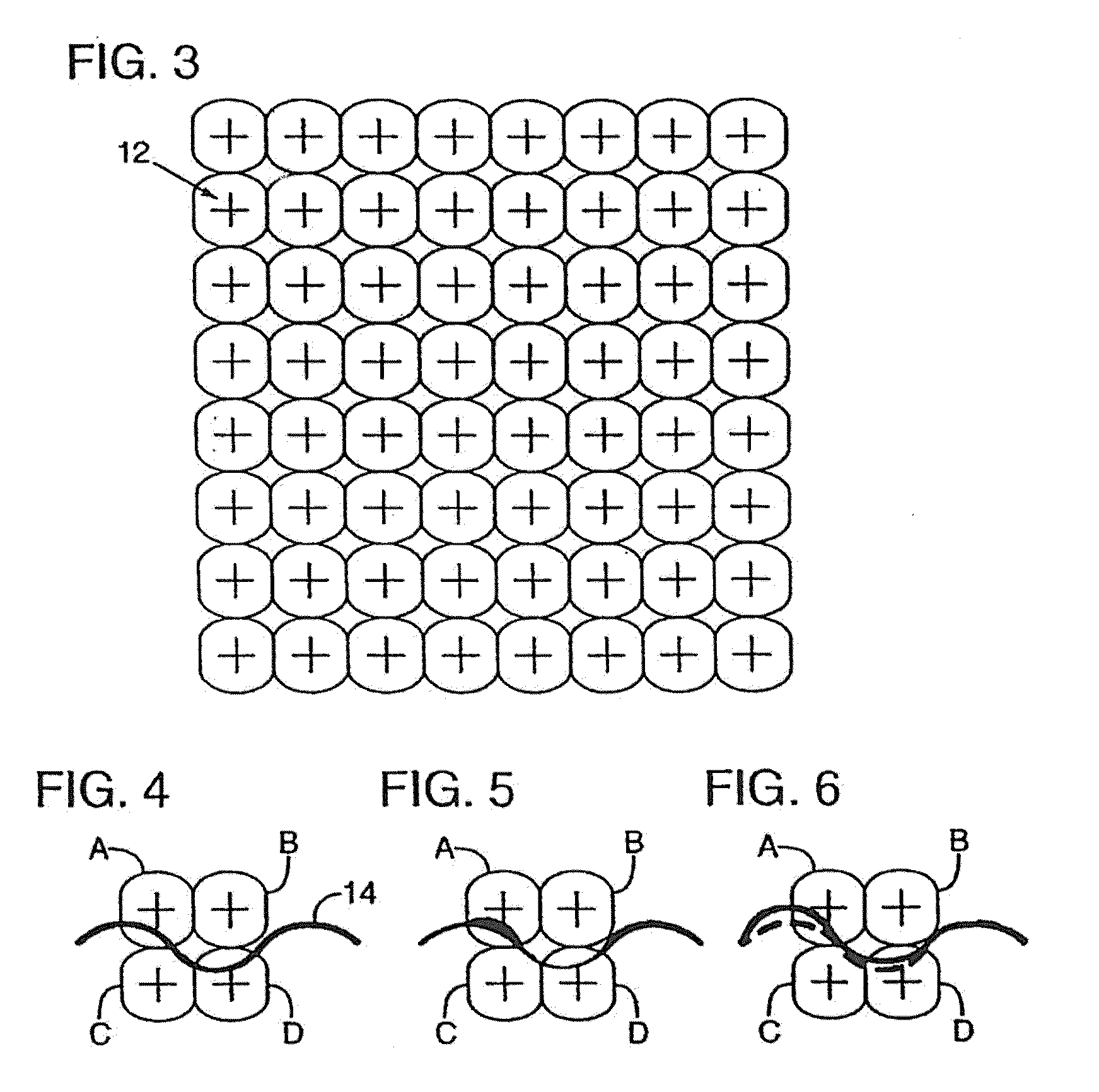

Electric field generator incorporating a slow-wave structure

InactiveUS7656167B1Increase the lengthReduced phase velocityResistance/reactance/impedenceDelay linesWave structureEngineering

An improved E-field generator including a slow-wave transmission line structure is provided herein. In some cases, the improved E-field generator may include an inductively-loaded slow-wave transmission line structure driven by a power source at one end of the structure and terminated by a load at the other end of the structure. In other cases, the improved E-field generator may include a capacitively-loaded slow-wave transmission line structure. In either case, the improved E-field generator provides a frequency-independent, significantly increased electric field at a distance spaced from the generator without altering the dimensions of the generator and / or the input power supplied to the generator. The increase in generated field intensity is achieved by decreasing the phase velocity of the electromagnetic wave propagating along the parallel elements of the generator.

Owner:TDK CORPARATION

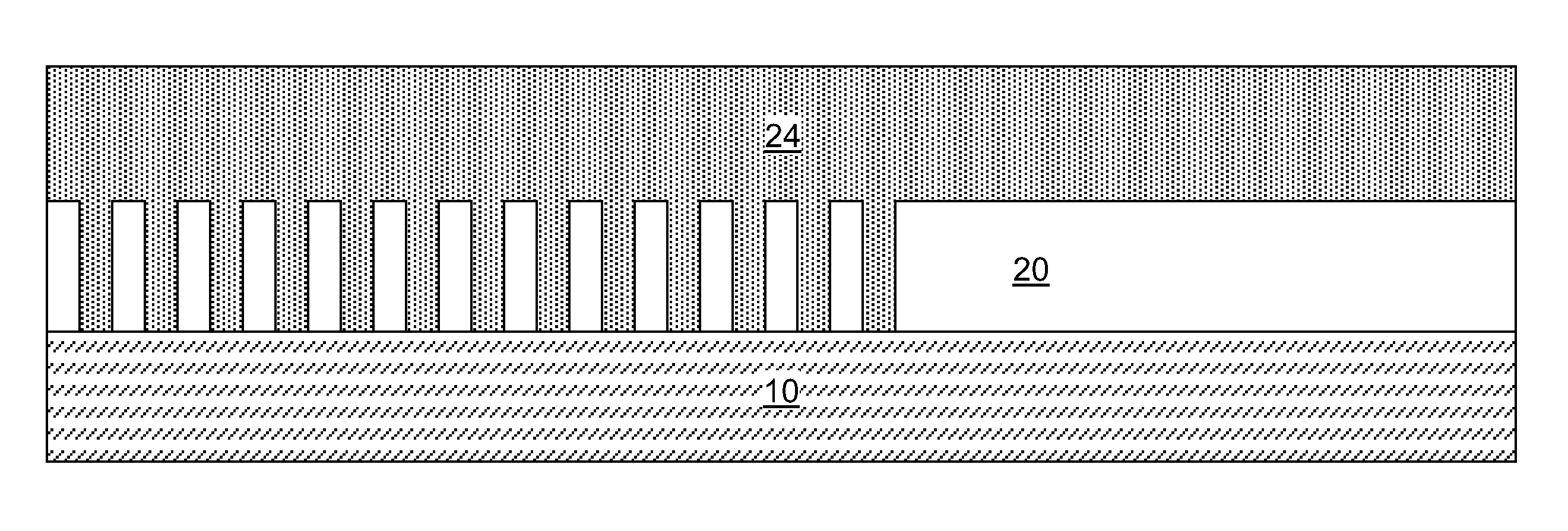

Sidewall image transfer process employing a cap material layer for a metal nitride layer

InactiveUS20120282779A1High fidelity reproductionSemiconductor/solid-state device manufacturingImage transferNitride

A cap material layer is deposited on a metal nitride layer. An antireflective coating (ARC) layer, an organic planarizing layer (OPL), and patterned line structures are formed upon the cap material layer. The pattern in the patterned line structures is transferred into the ARC layer and the OPL. Exposed portions of the cap material layer are etched simultaneously with the etch removal of the patterned line structures and the ARC layer. The OPL is employed to etch the metal nitride layer. The patterned cap material layer located over the metal nitride layer protects the top surface of the metal nitride layer, and enables high fidelity reproduction of the pattern in the metal nitride layer without pattern distortion. The metal nitride layer is subsequently employed as an etch mask for pattern transfer into an underlying layer.

Owner:INT BUSINESS MASCH CORP

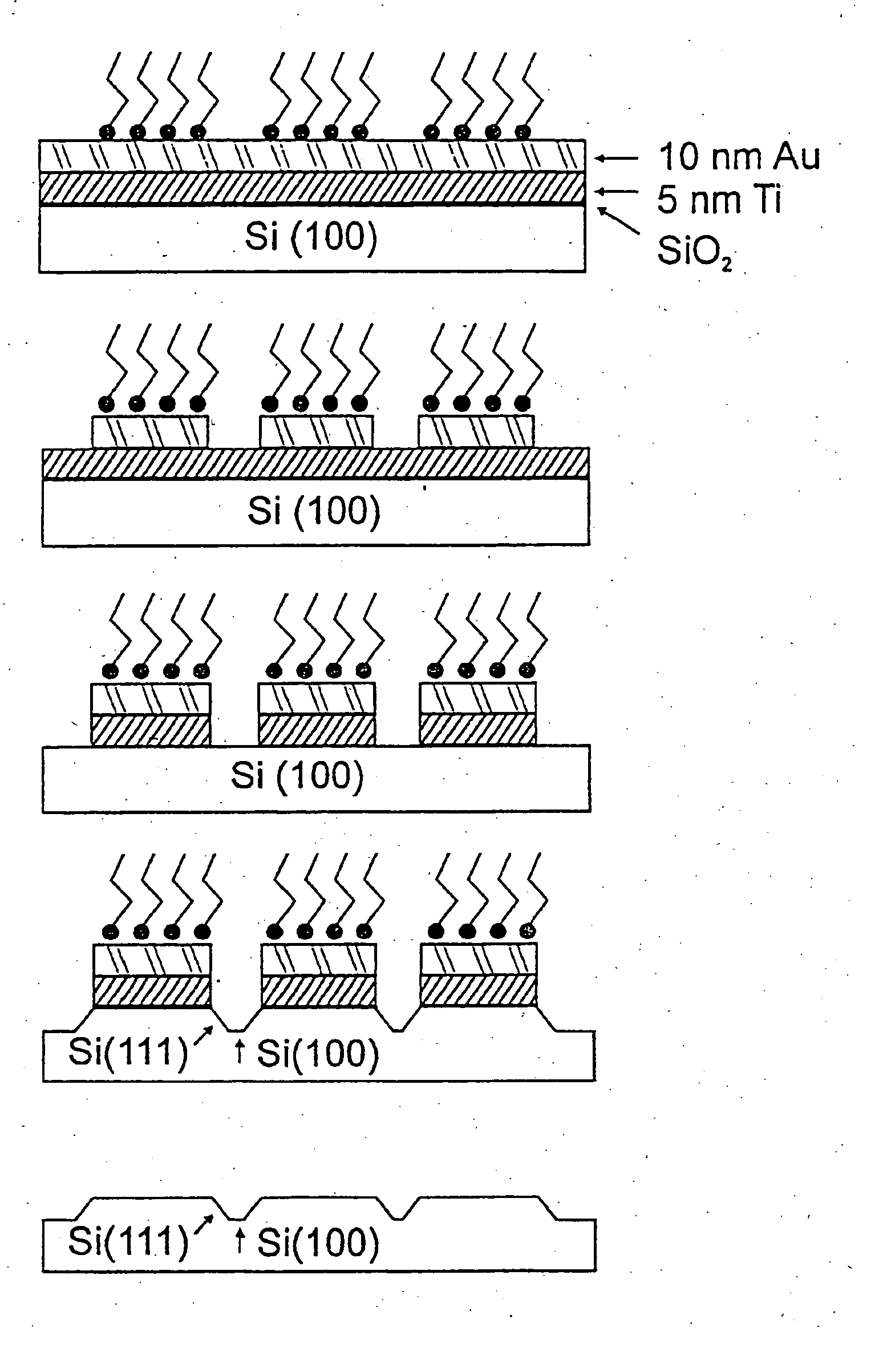

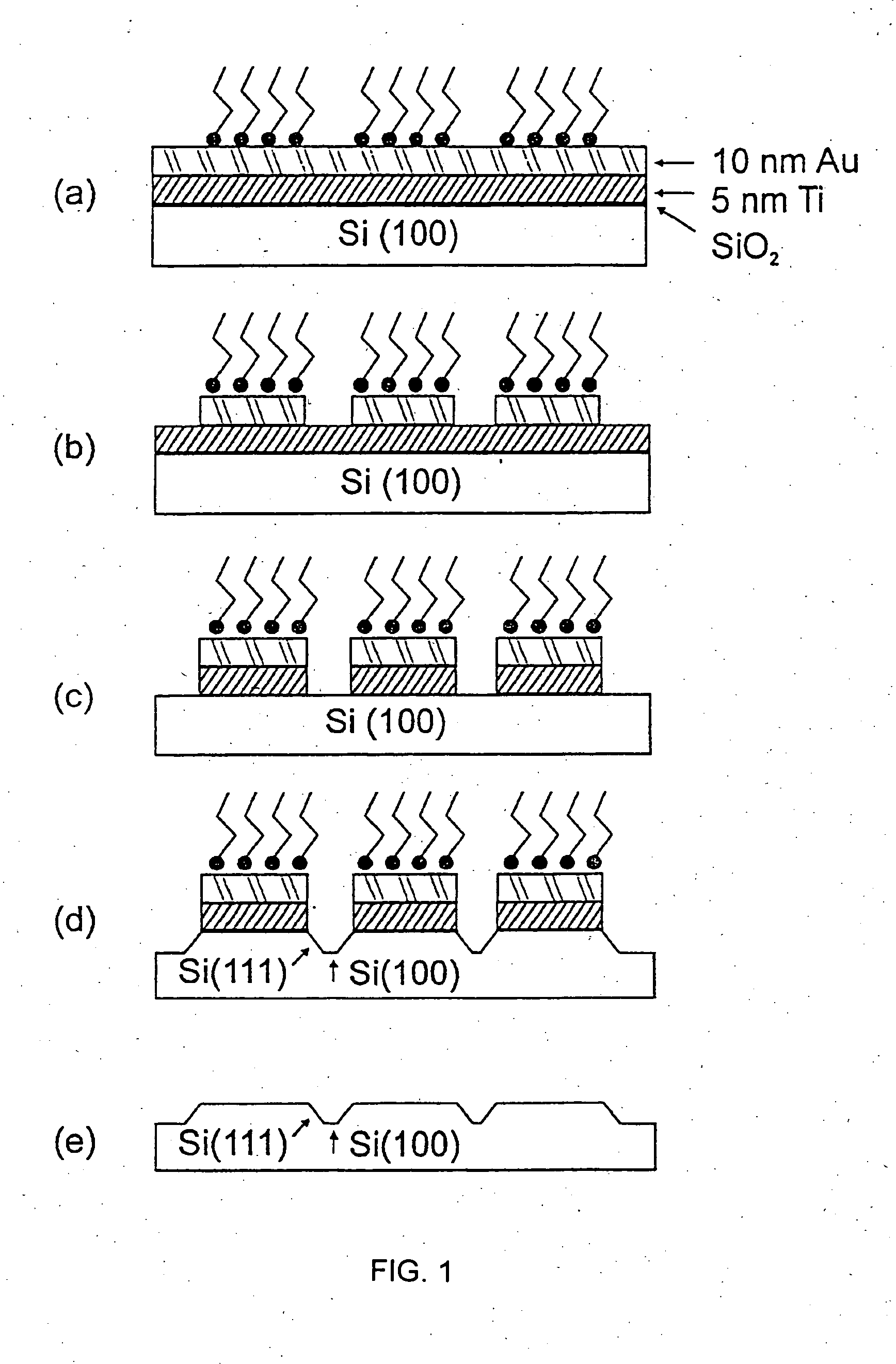

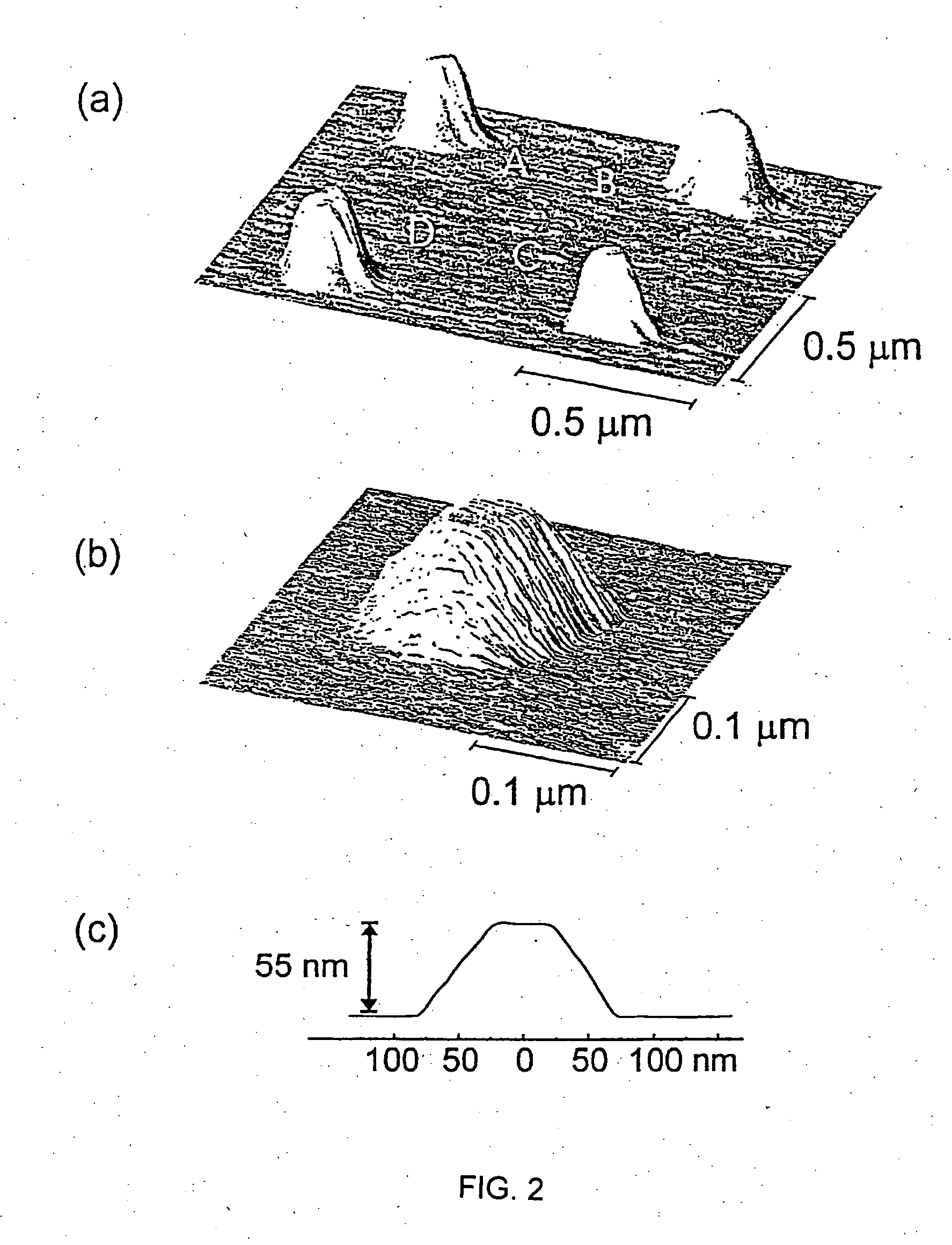

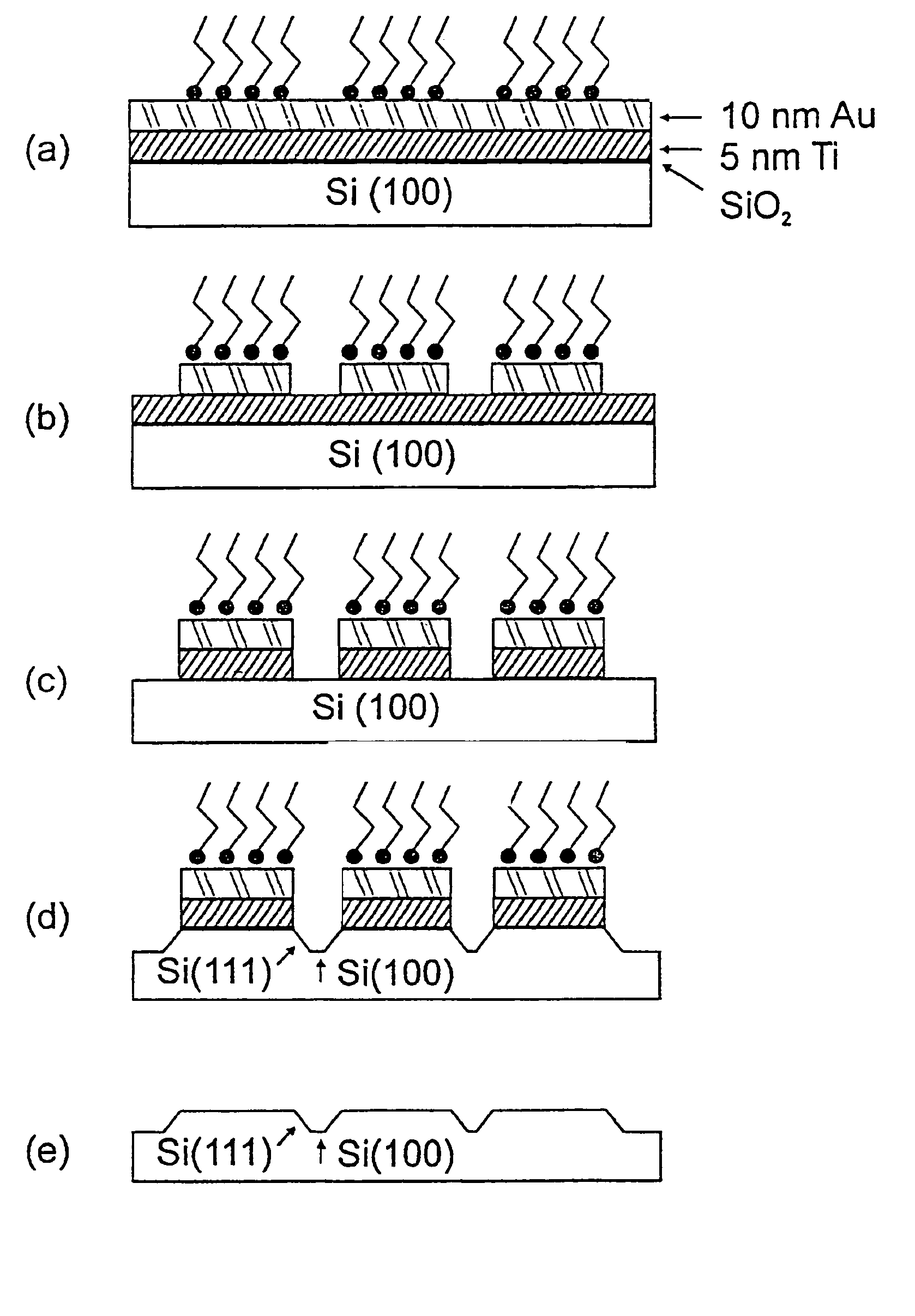

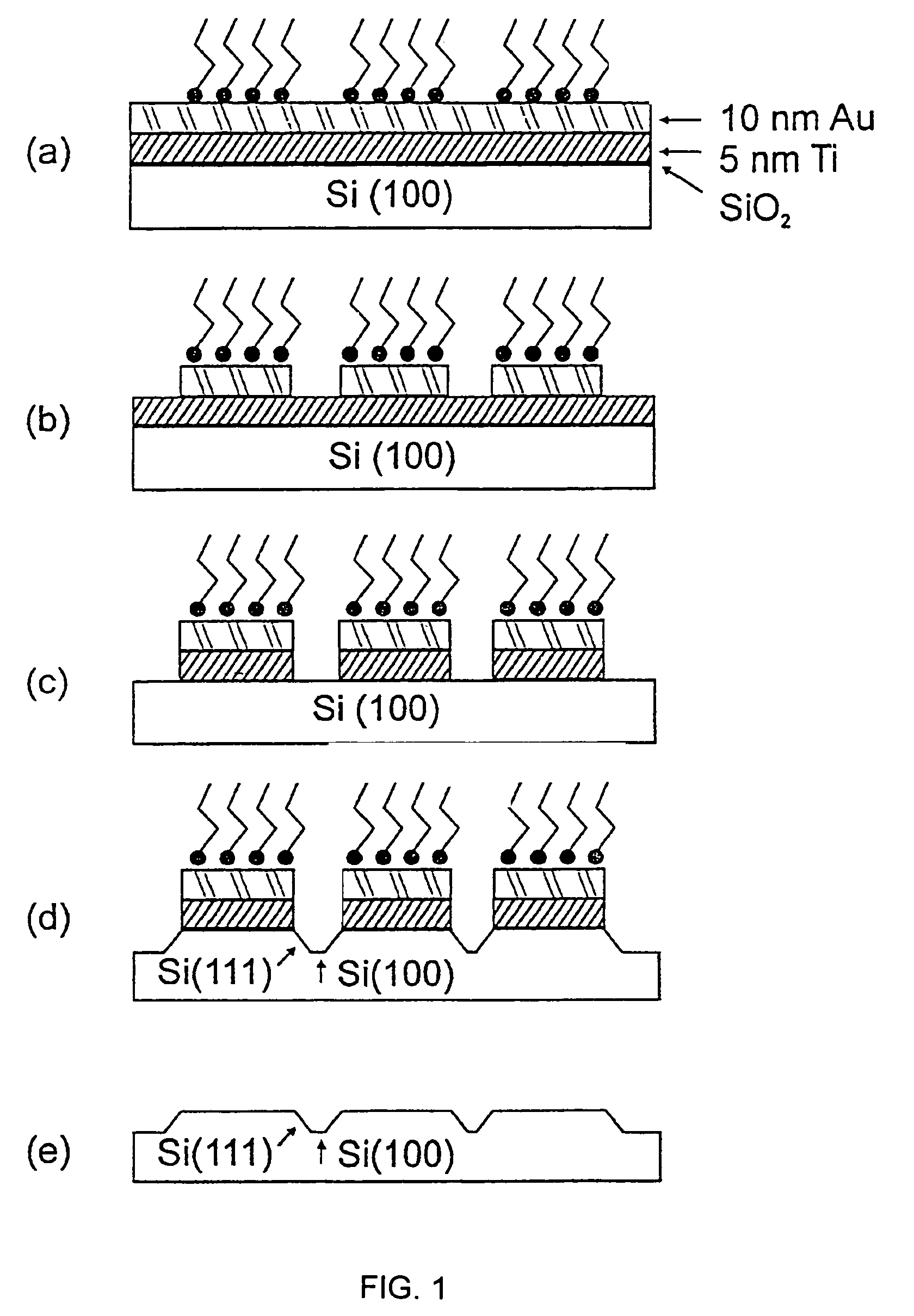

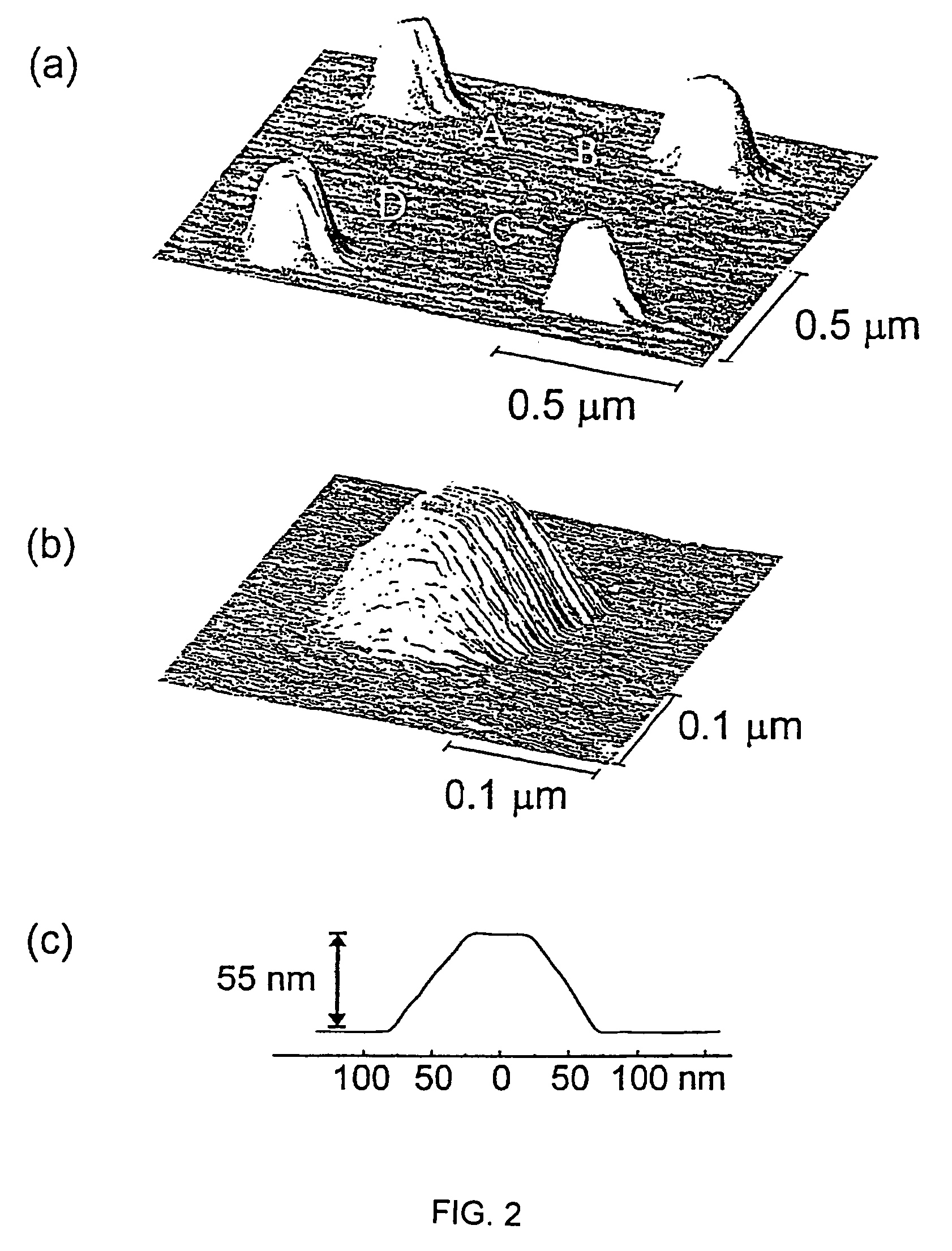

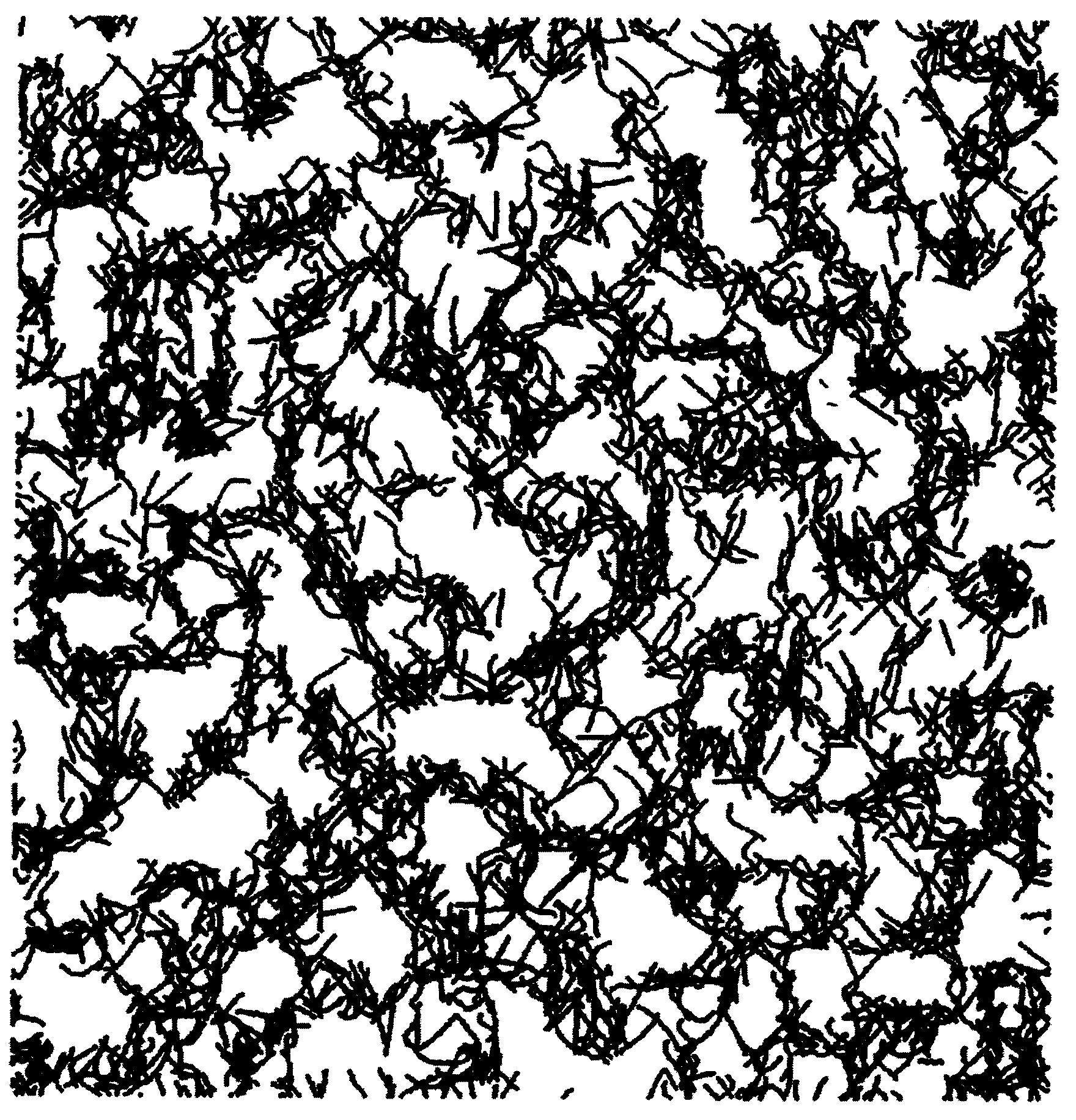

Fabrication of sub-50 nm solid-state nanostructures based on nanolithography

InactiveUS20060014001A1High resolutionMaterial nanotechnologyDecorative surface effectsResistDip-pen nanolithography

Combination of nanolithography and wet chemical etching including the fabrication of nanoarrays of sub-50 nm gold dots and line structures with deliberately designed approximately 12-100 nm gaps. These structures were made by initially using direct write nanolithography to pattern the etch resist, 16-mercaptohexadecanoic acid (MHA), on Au / Ti / SiOx / Si substrates and then wet chemical etching to remove the exposed gold. These are the smallest Au structures prepared by a wet chemical etching strategy. Also, Dip-Pen Nanolithography (DPN) has been used to generate resist layers on Au, Ag, and Pd that when combined with wet chemical etching can lead to nanostructures with deliberately designed shapes and sizes. Monolayers of mercaptohexadecanoic acid (MHA) or octadecanethiol (ODT), patterned by DPN, were explored as etch resists. They work comparably well on Au and Ag, but ODT is the superior material for Pd. MHA seems to attract the FeCl3 etchant and results in nonuniform etching of the underlying Pd substrate. Dots, lines, triangles and circles, ranging in size from sub-100 to several hundred nm have been fabricated on these substrates. These results show how one can use DPN as an alternative to more complex and costly procedures like electron beam lithography to generate nanostructures from inorganic materials.

Owner:NORTHWESTERN UNIV

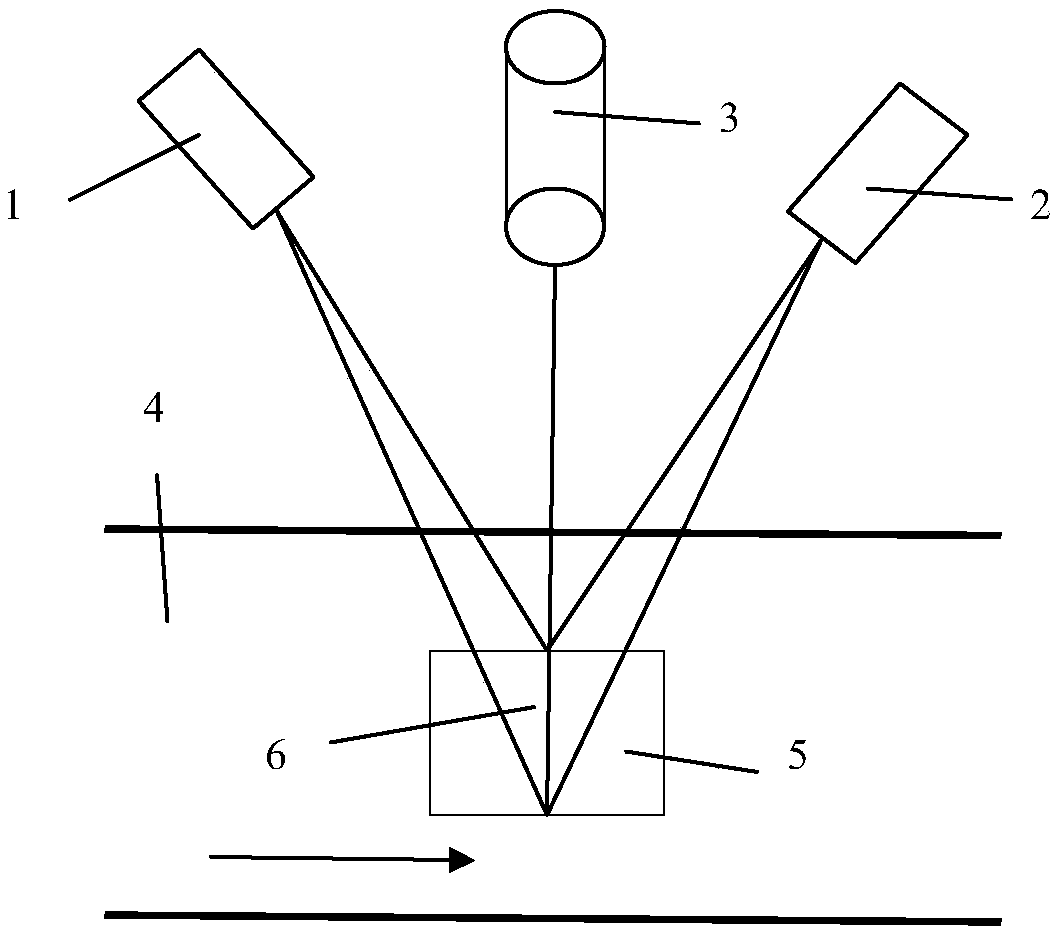

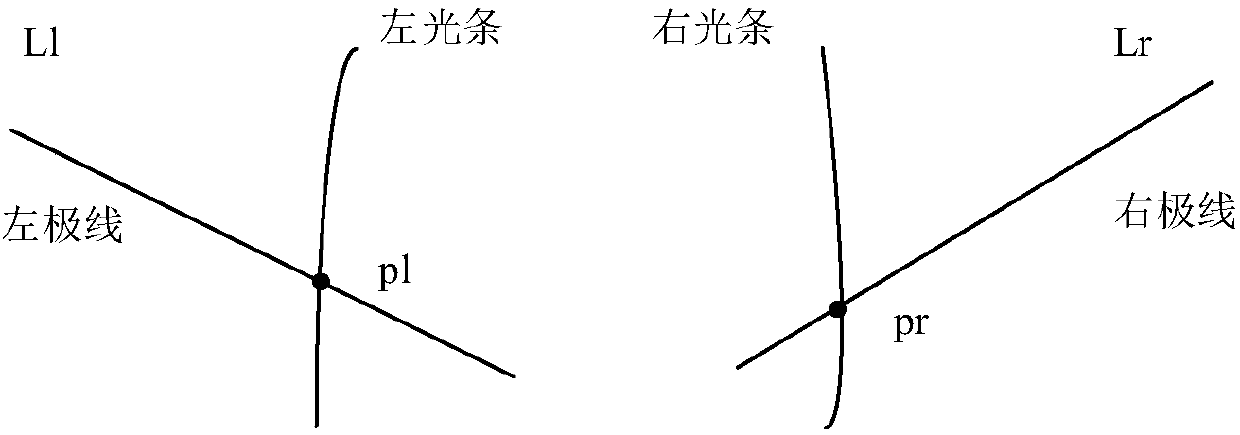

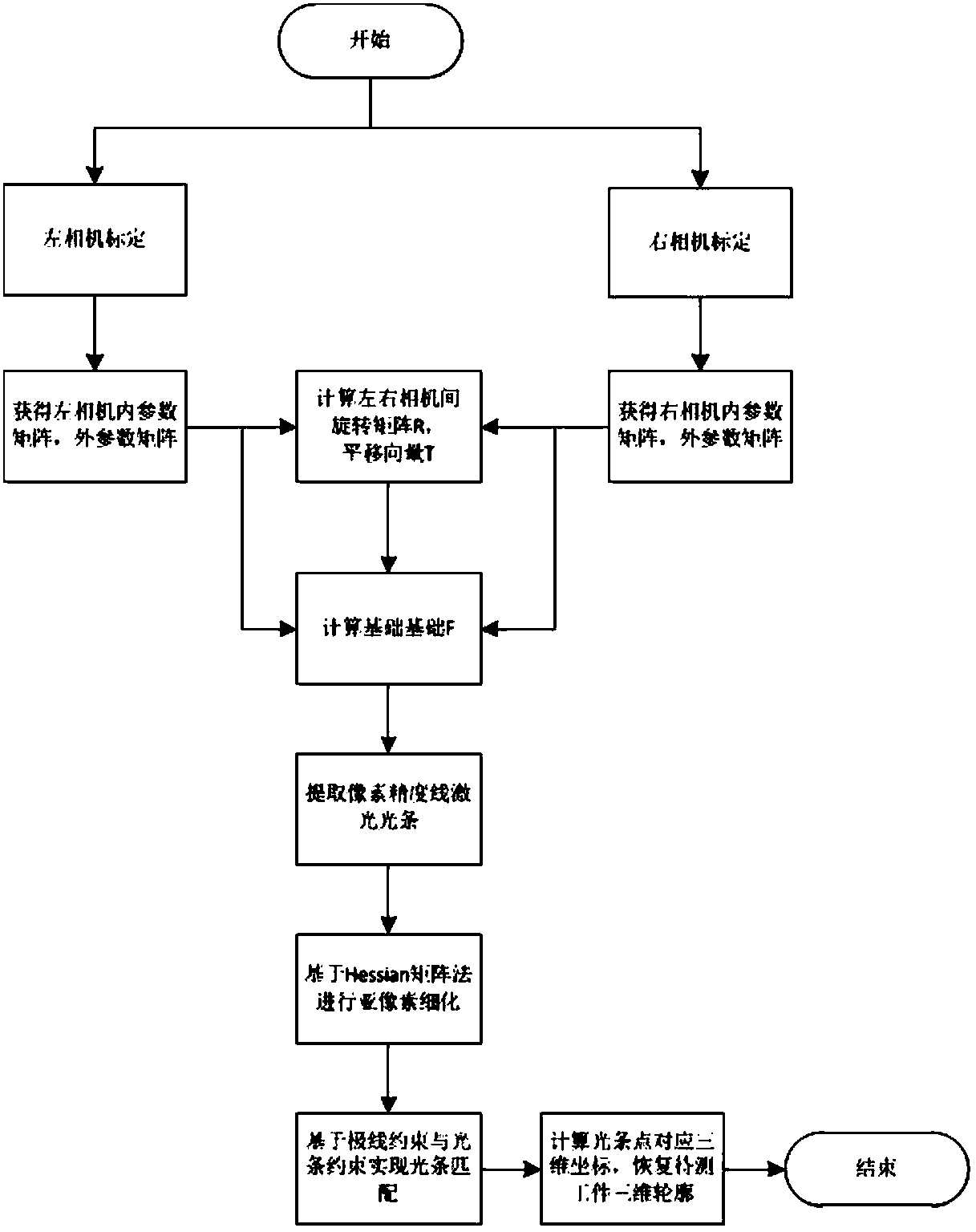

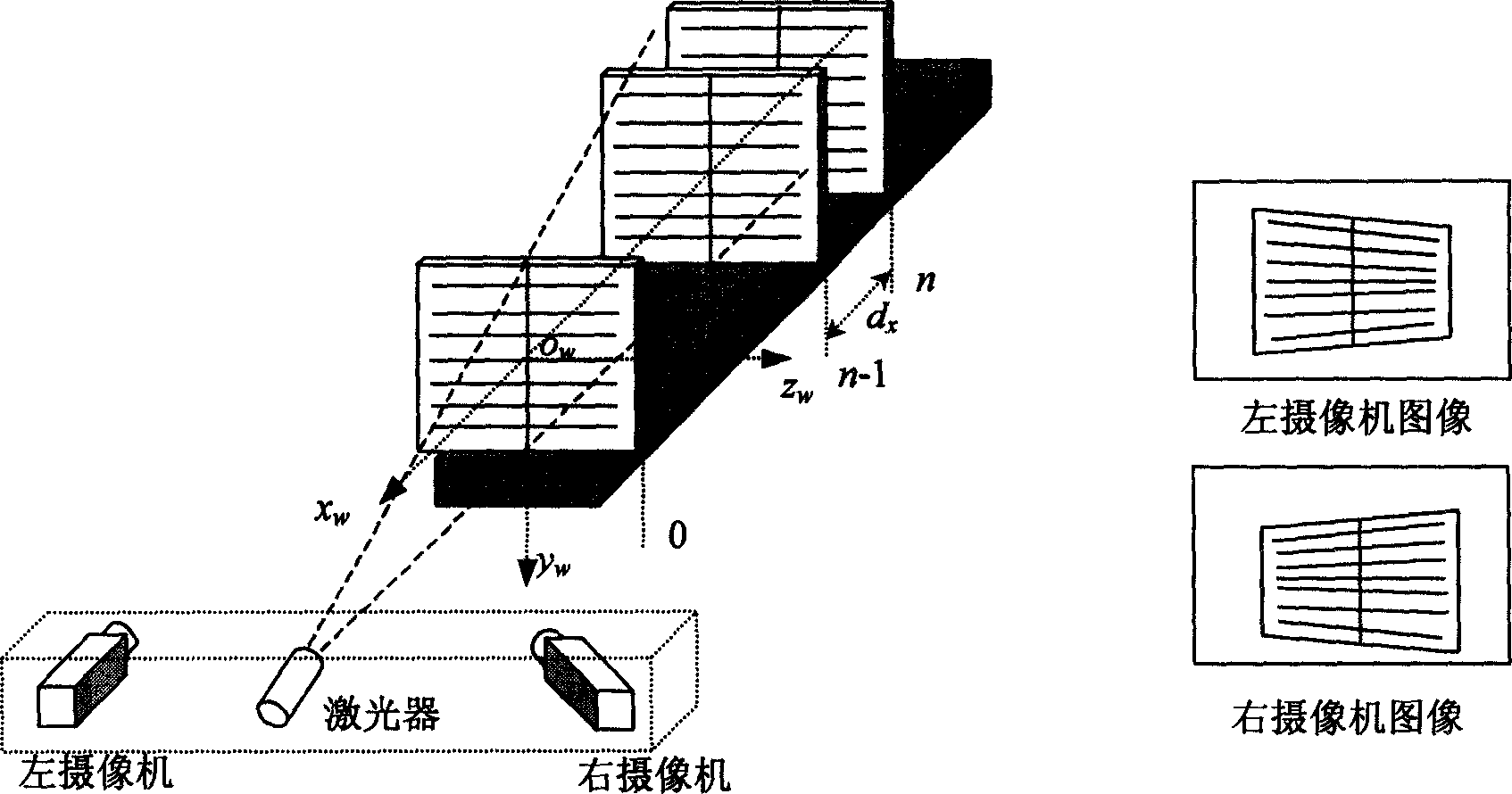

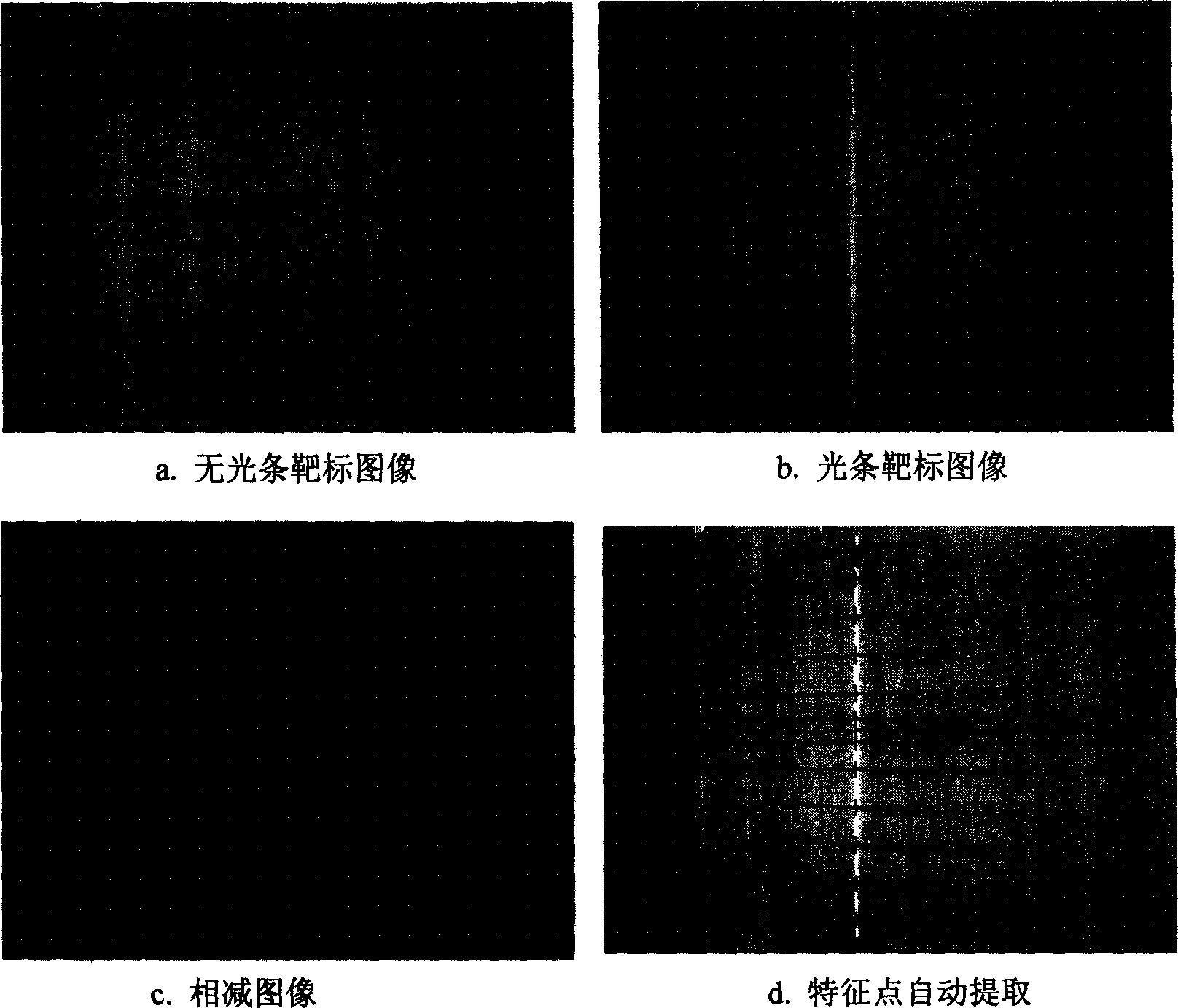

Binocular stereo vision three-dimensional measurement method based on line structured light scanning

InactiveCN107907048AReduce the difficulty of matchingImprove robustnessUsing optical meansThree dimensional measurementLaser scanning

The invention discloses a binocular stereo vision three-dimensional measurement method based on line structured light scanning, which comprises the steps of performing stereo calibration on binocularindustrial cameras, projecting laser light bars by using a line laser, respectively acquiring left and right laser light bar images, extracting light bar center coordinates with sub-pixel accuracy based on a Hessian matrix method, performing light bar matching according to an epipolar constraint principle, and calculating a laser plane equation; secondly, acquiring a line laser scanning image of aworkpiece to be measured, extracting coordinates of the image of the workpiece to be measured, calculating world coordinates of the workpiece to be measured by combining binocular camera calibrationparameters and the laser plane equation, and recovering the three-dimensional surface topography of the workpiece to be measured. Compared with a common three-dimensional measurement system combininga monocular camera and line structured light, the binocular stereo vision three-dimensional measurement method avoids complicated laser plane calibration. Compared with the traditional stereo vision method, the binocular stereo vision three-dimensional measurement method reduces the difficulty of stereo matching in binocular stereo vision while ensuring the measurement accuracy, and improves the robustness and the usability of a visual three-dimensional measurement system.

Owner:CHANGSHA XIANGJI HAIDUN TECH CO LTD

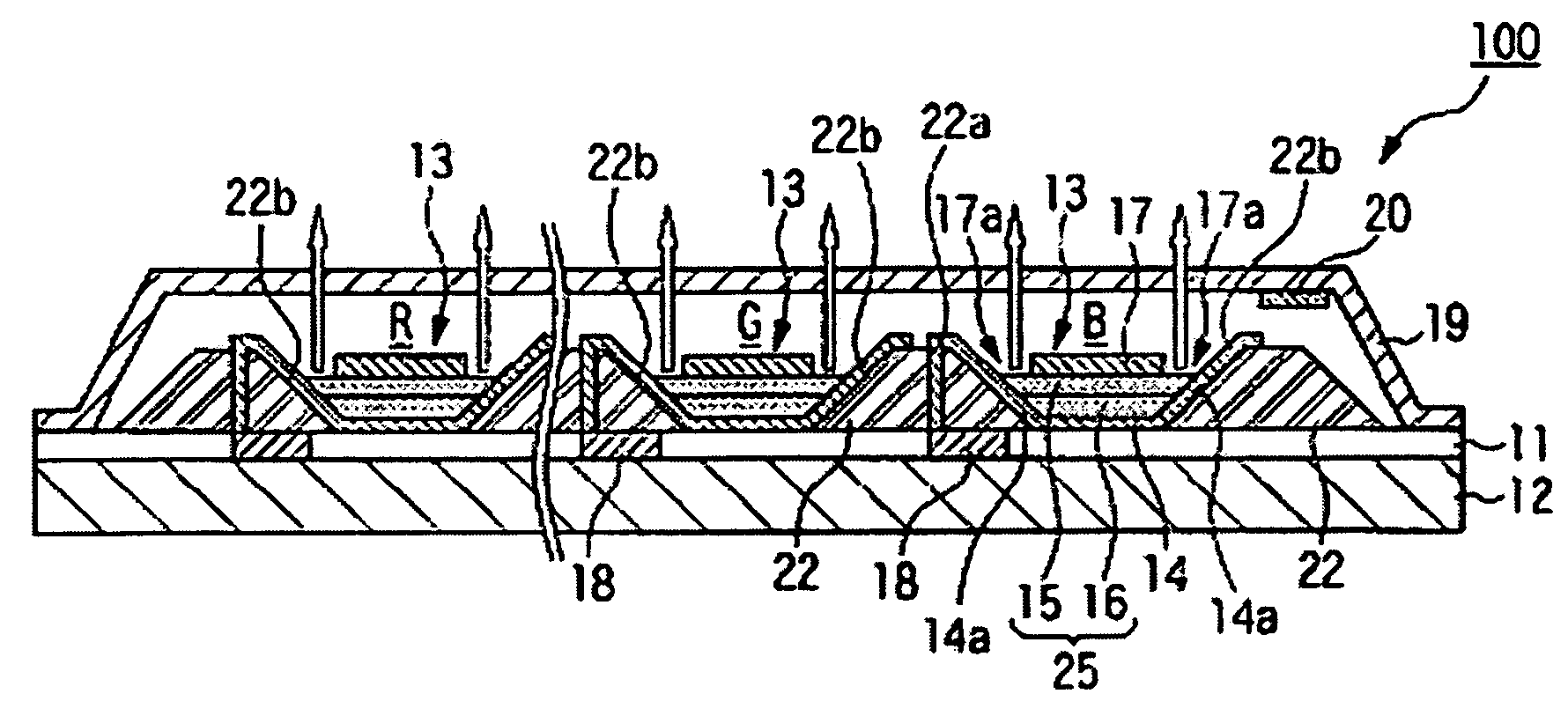

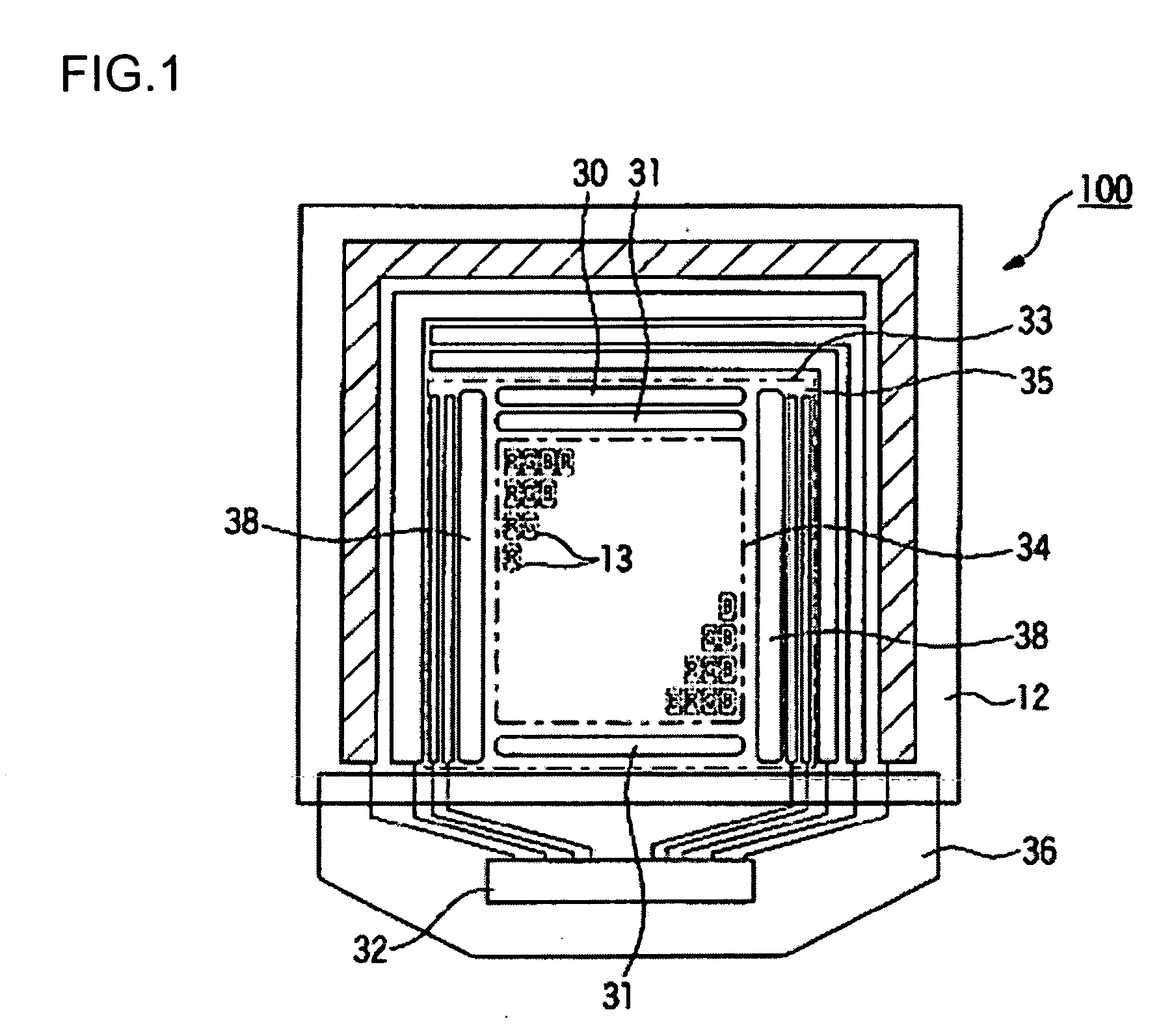

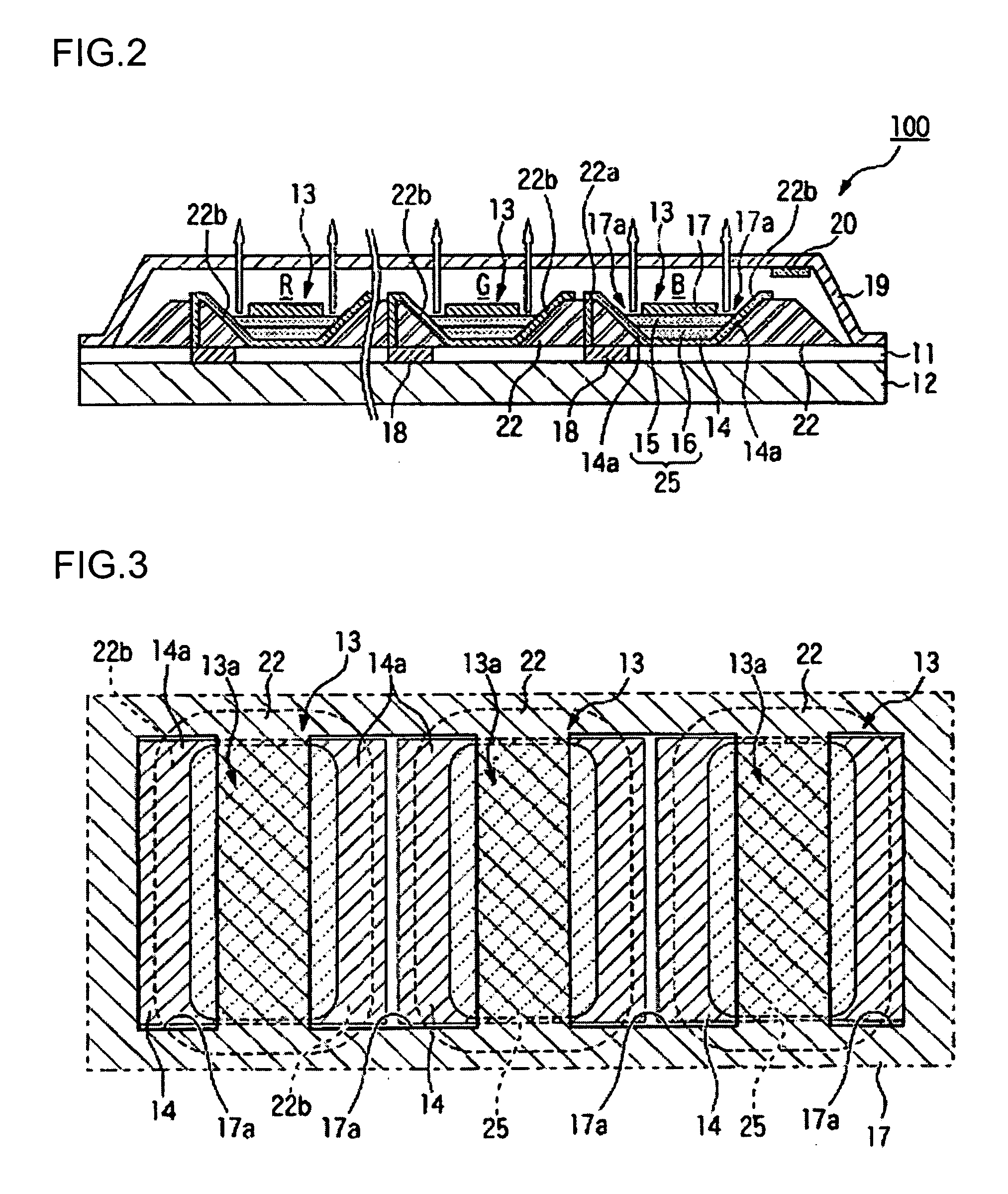

Light-emitting device, manufacturing method thereof, and electronic apparatus

ActiveUS20050116620A1Quality improvementImprove reliabilityDischarge tube luminescnet screensStatic indicating devicesEngineeringLarge screen

The invention provides a light-emitting device, a manufacturing method thereof, and an electronic apparatus which can improve the emission efficiency of light, obtain uniform brightness within a display surface in high reliability, in particular, and which can suppress lowering of the emission efficiency of light due to various wiring line structures, even though a large screen is performed. In a light-emitting device having a light-emitting element in which a first electrode on a base substrate, a functional layer having a light-emitting layer, and a second electrode are sequentially deposited, the first electrode and the second electrode are reflective, and the second electrode has an opening through which light from the light-emitting layer passes.

Owner:SEIKO EPSON CORP

Fabrication of sub-50 nm solid-state nanostructures based on nanolithography

Combination of nanolithography and wet chemical etching including the fabrication of nanoarrays of sub-50 nm gold dots and line structures with deliberately designed approximately 12-100 nm gaps. These structures were made by initially using direct write nanolithography to pattern the etch resist, 16-mercaptohexadecanoic acid (MHA), on Au / Ti / SiOx / Si substrates and then wet chemical etching to remove the exposed gold. These are the smallest Au structures prepared by a wet chemical etching strategy. Also, Dip-Pen Nanolithography (DPN) has been used to generate resist layers on Au, Ag, and Pd that when combined with wet chemical etching can lead to nanostructures with deliberately designed shapes and sizes. Monolayers of mercaptohexadecanoic acid (MHA) or octadecanethiol (ODT), patterned by DPN, were explored as etch resists. They work comparably well on Au and Ag, but ODT is the superior material for Pd. MHA seems to attract the FeCl3 etchant and results in nonuniform etching of the underlying Pd substrate. Dots, lines, triangles and circles, ranging in size from sub-100 to several hundred nm have been fabricated on these substrates. These results show how one can use DPN as an alternative to more complex and costly procedures like electron beam lithography to generate nanostructures from inorganic materials.

Owner:NORTHWESTERN UNIV

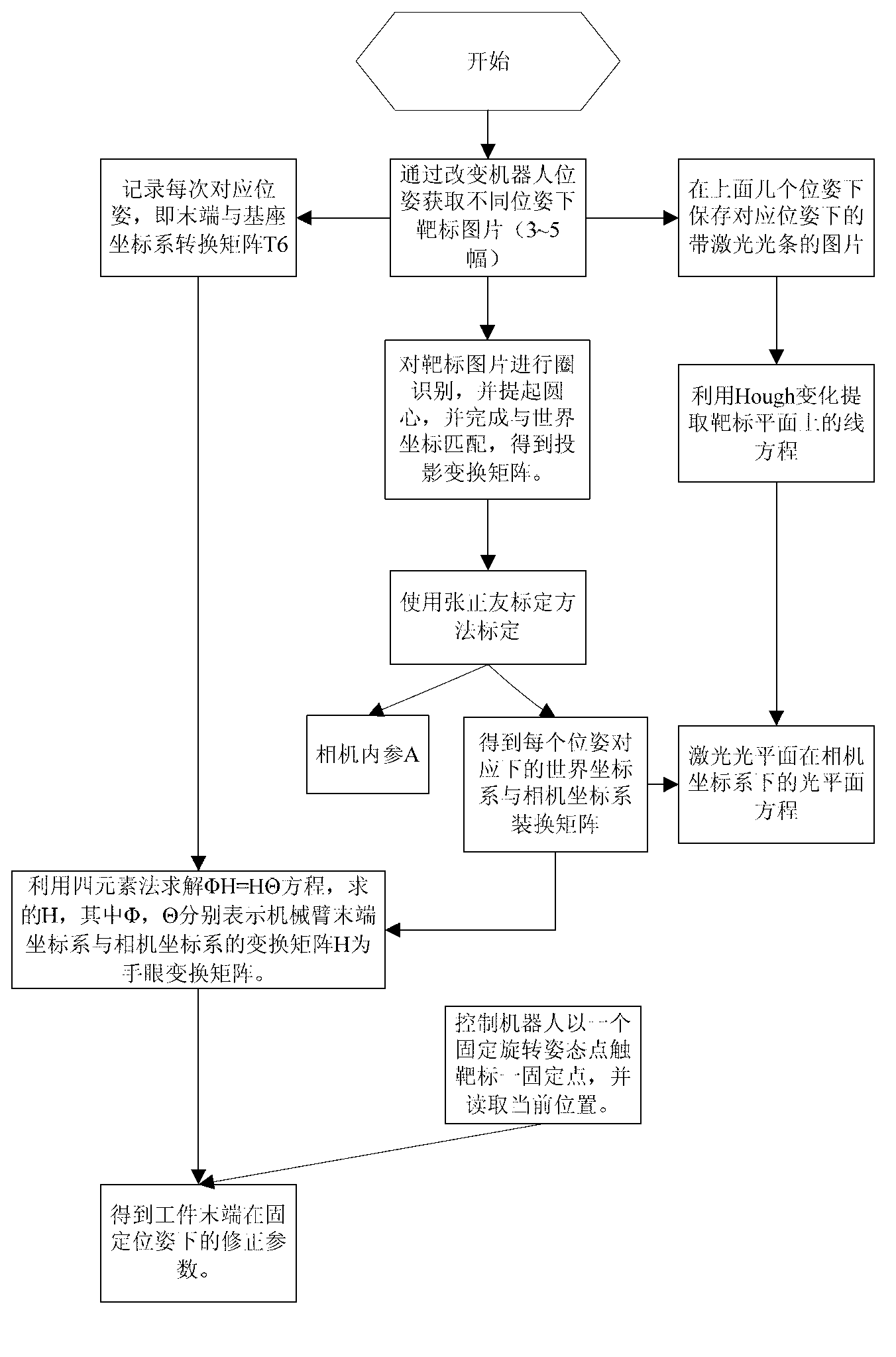

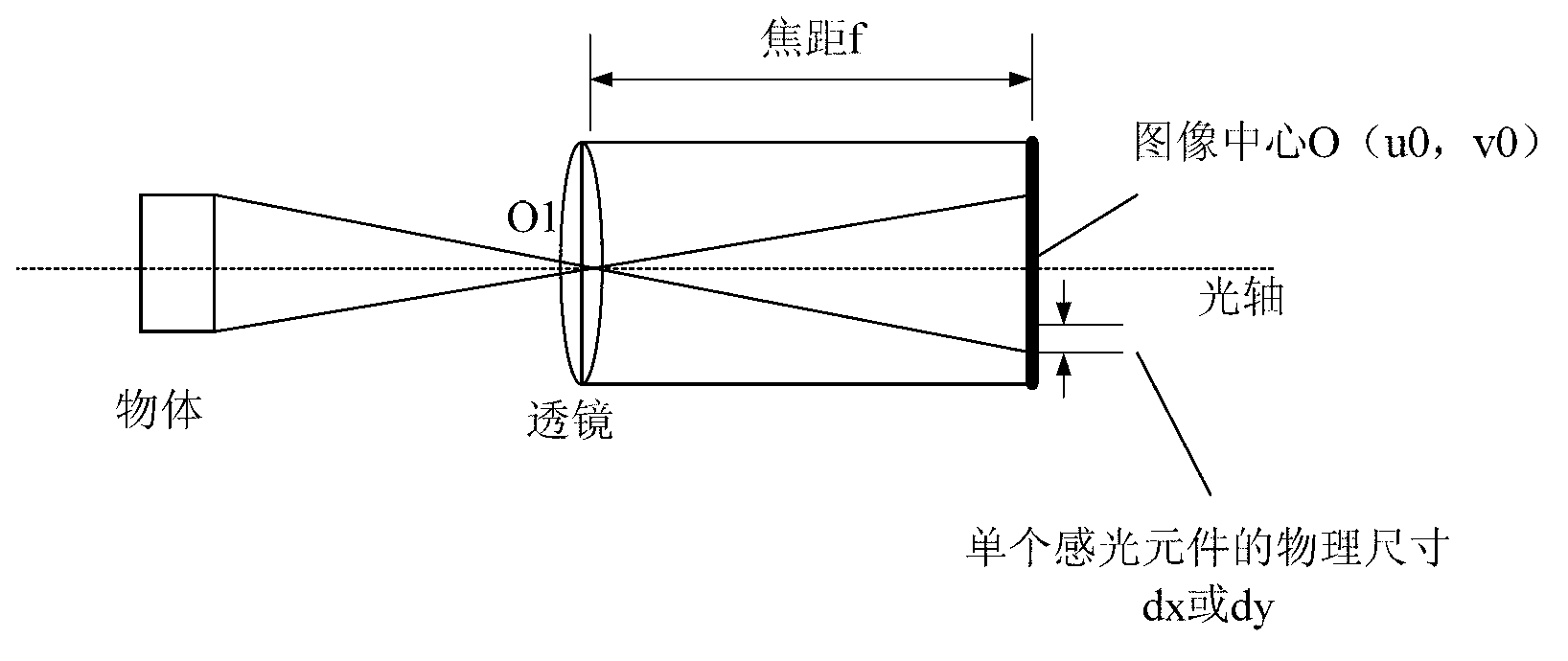

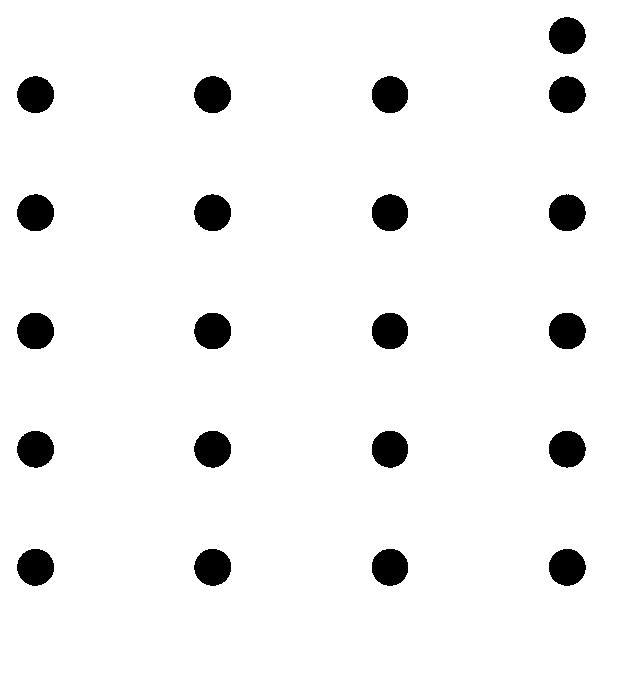

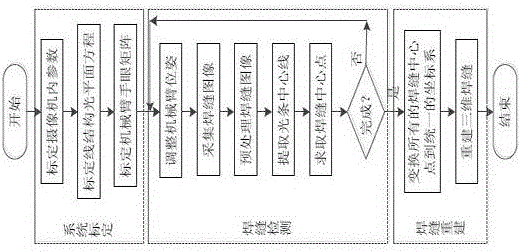

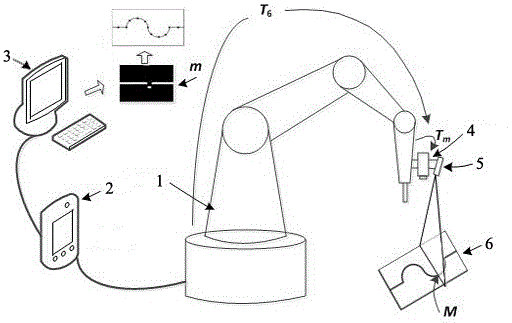

Systematic calibration method of welding robot guided by line structured light vision sensor

ActiveCN102794763AImprove tracking accuracyIncrease flexibilityProgramme-controlled manipulatorWelding/cutting auxillary devicesQuaternionEngineering

The invention relates to a systematic calibration method of a welding robot guided by a line structured light vision sensor, which comprises the following steps: firstly, controlling a mechanical arm to change pose, obtaining a round target image through a camera, accomplishing the matching of the round target image and a world coordinate, and then obtaining an internal parameter matrix and an external parameter matrix RT of the camera; secondly, solving a line equation of a line laser bar by Hough transformation, and using the external parameter matrix RT obtained in the first step to obtain a plane equation of the plane of the line laser bar under a coordinate system of the camera; thirdly, calculating to obtain a transformation matrix of a tail end coordinate system of the mechanical arm and a base coordinate system of the mechanical arm by utilizing a quaternion method; and fourthly, calculating a coordinate value of a tail end point of a welding workpiece under the coordinate of the mechanical arm, and then calculating an offset value of the workpiece in the pose combined with the pose of the mechanical arm. The systematic calibration method of the welding robot guided by the line structured light vision sensor is flexible, simple and fast, and is high in precision and generality, good in stability and timeliness and small in calculation amount.

Owner:JIANGNAN UNIV +1

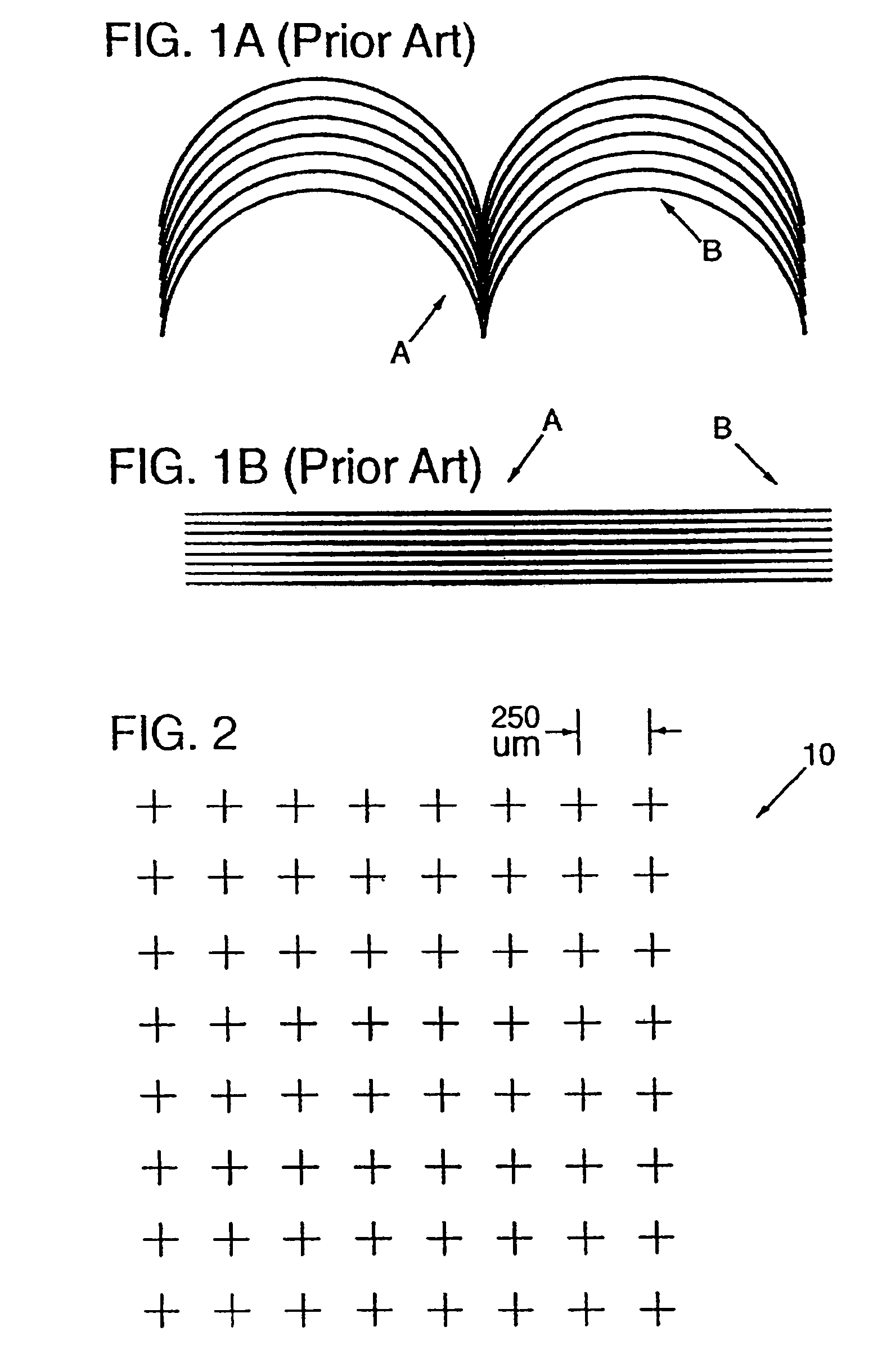

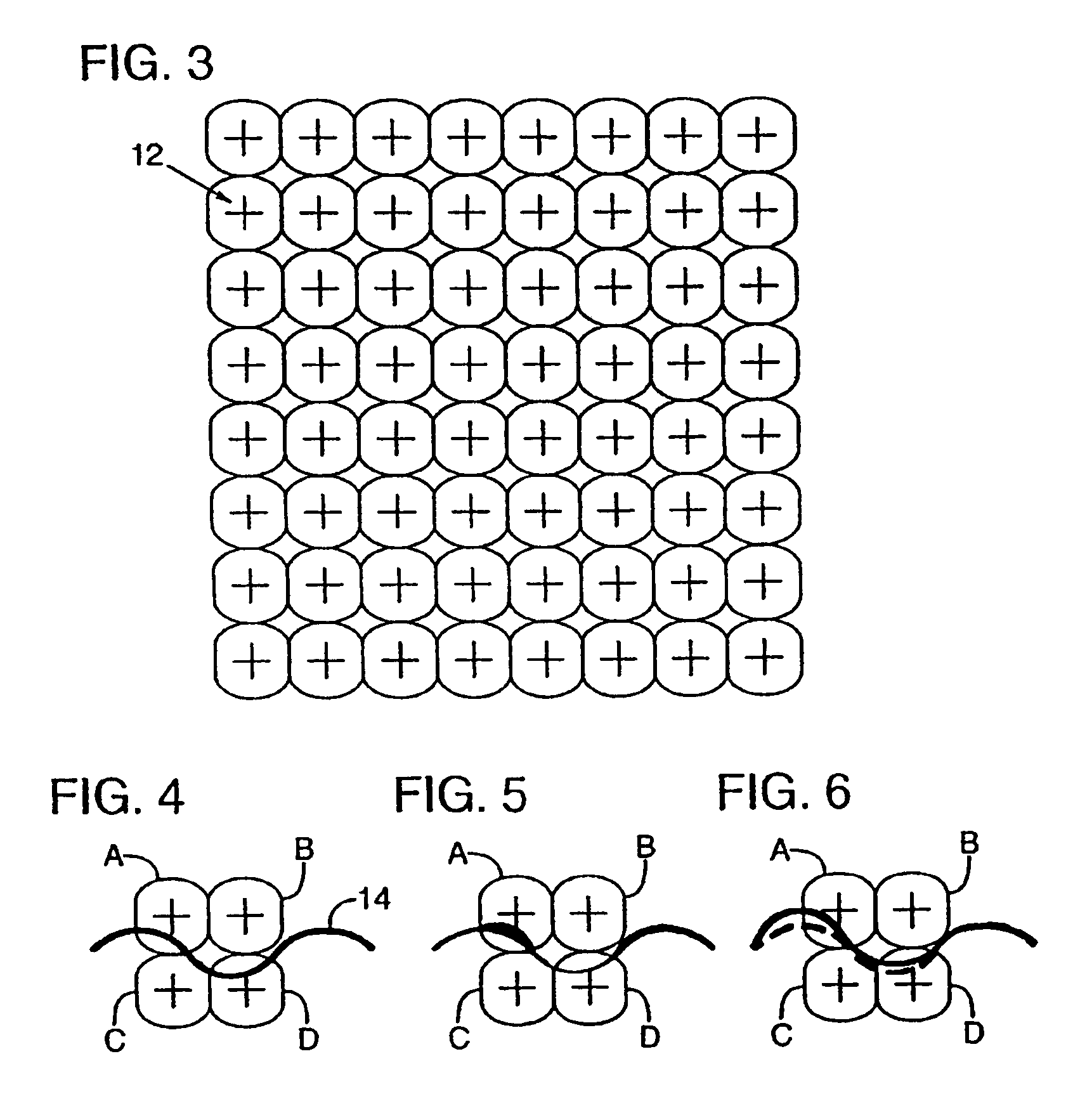

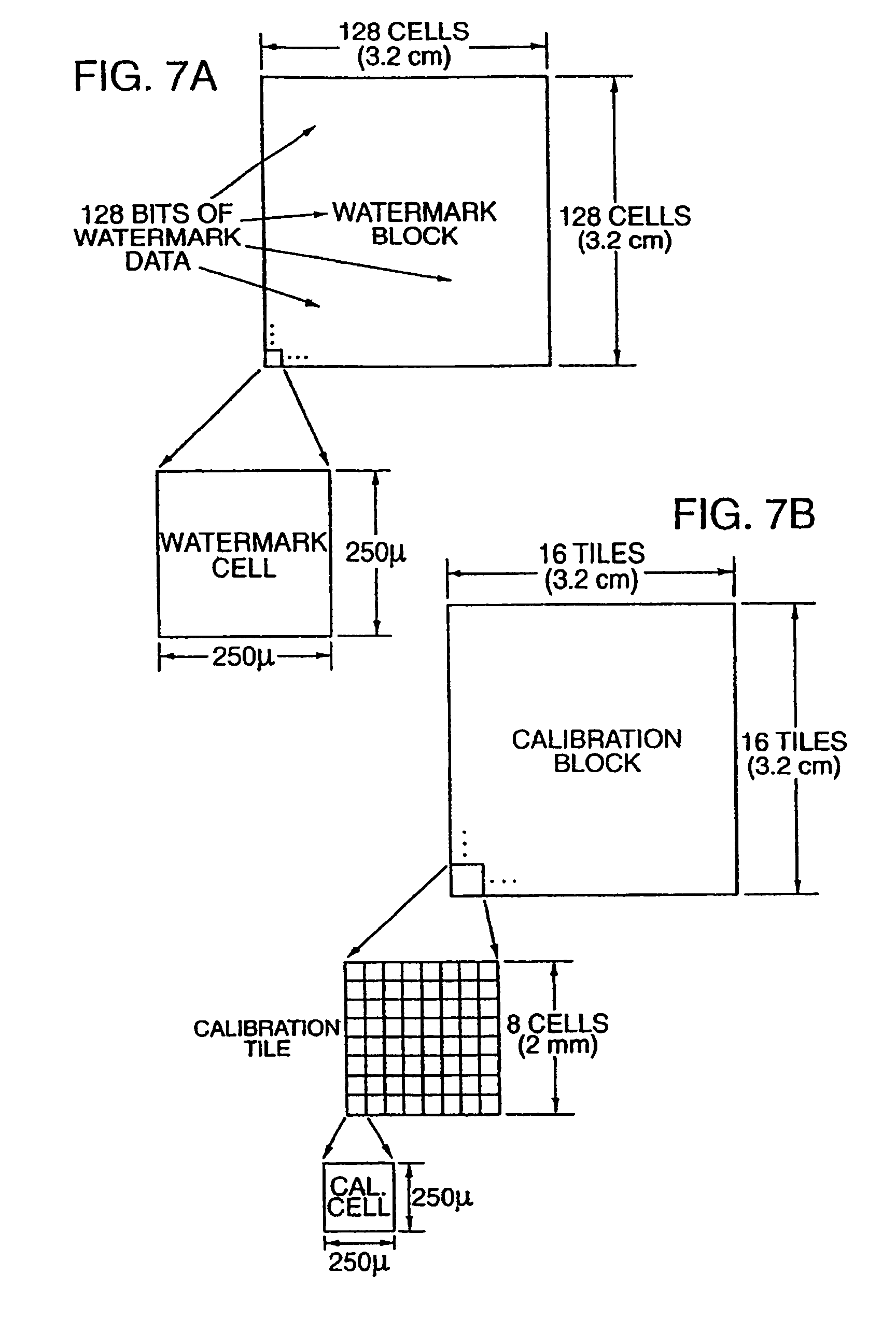

Secure documents with hidden signals, and related methods and systems

InactiveUS7555139B2Character and pattern recognitionSecret communicationPattern recognitionLine width

A security document comprising artwork including a security pattern, characterized in that the security pattern has the form of a line structure in which lines width or line spacing is adjusted to carry predefined data. The artwork is generated by the modifying at least one color of at least a part of the artwork to embed the security pattern in the artwork. Methods for detecting the security pattern include use of a frequency domain structure to detect the security pattern despite rotation and scaling of the document, use of signal tiling to improve signal detection, and use of statistical analyses to verify detection of the security pattern.

Owner:DIGIMARC CORP

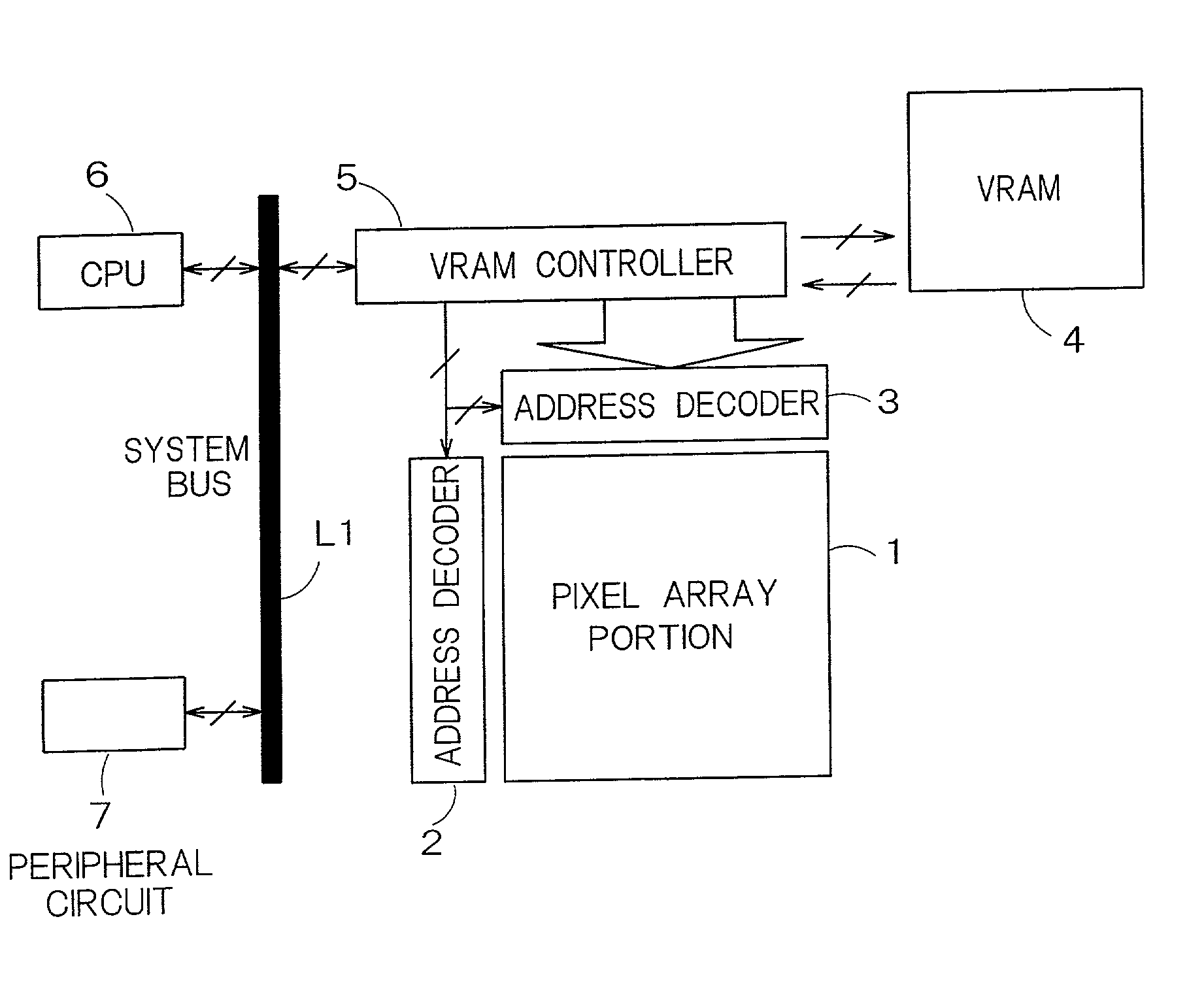

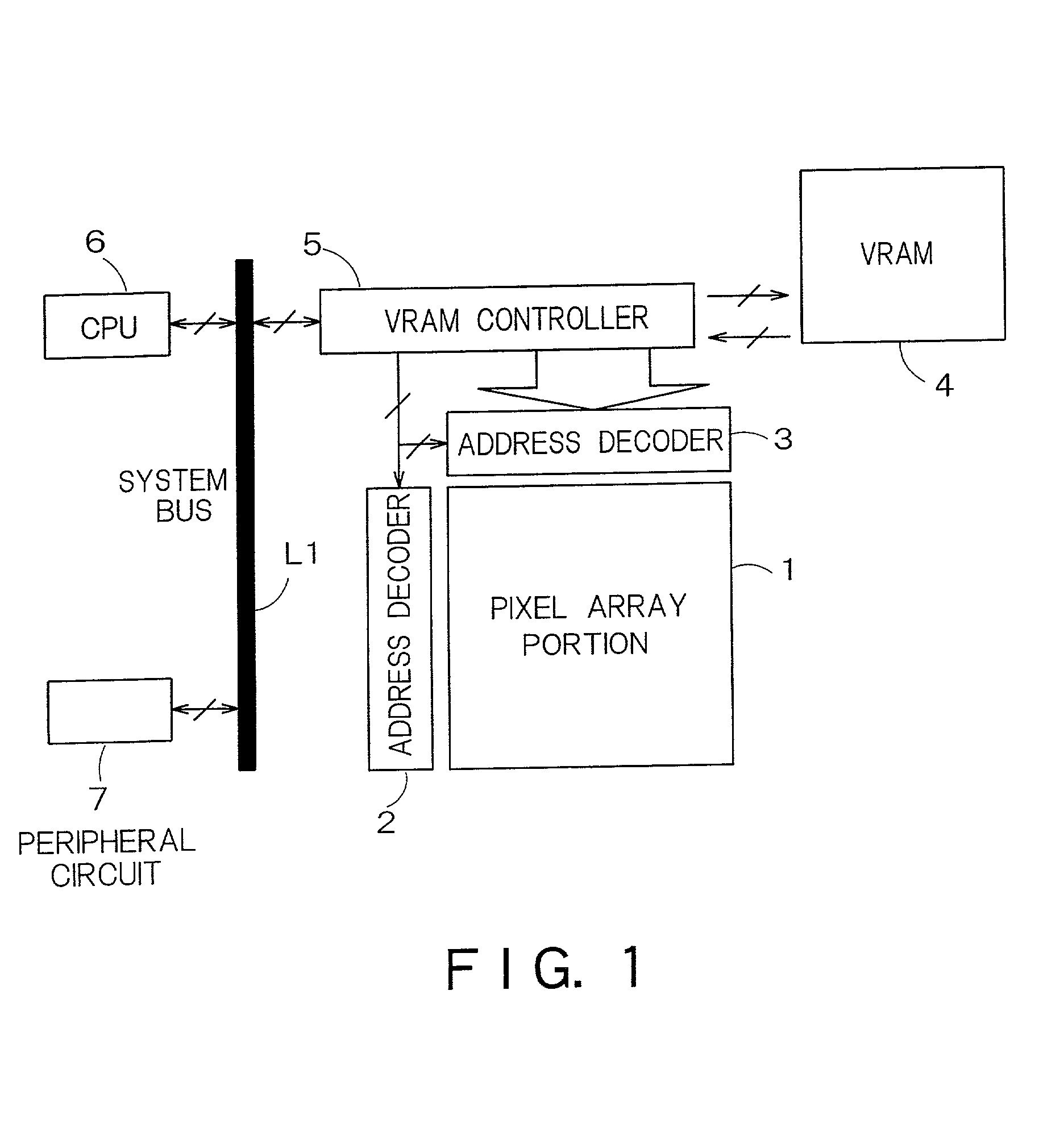

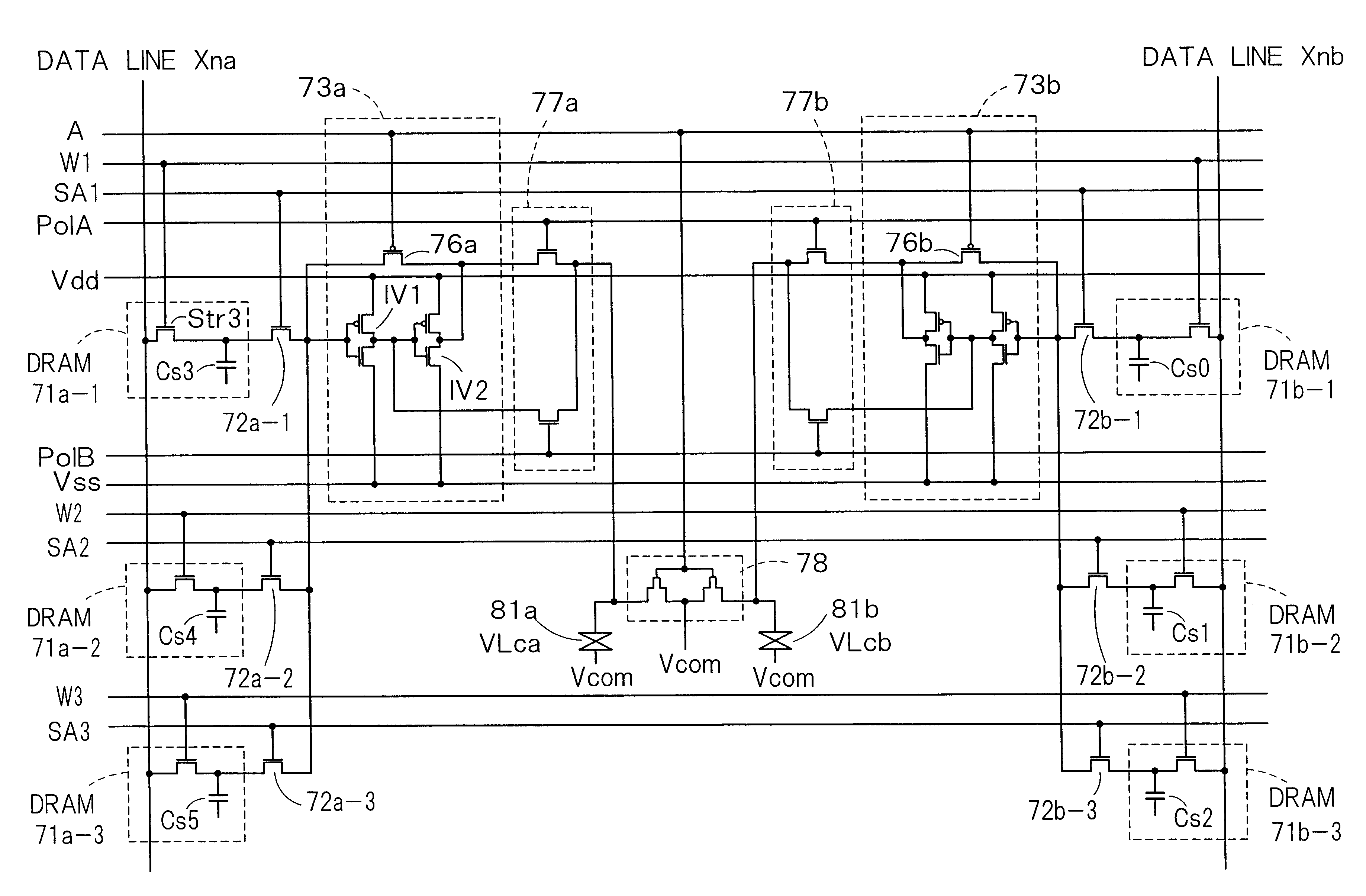

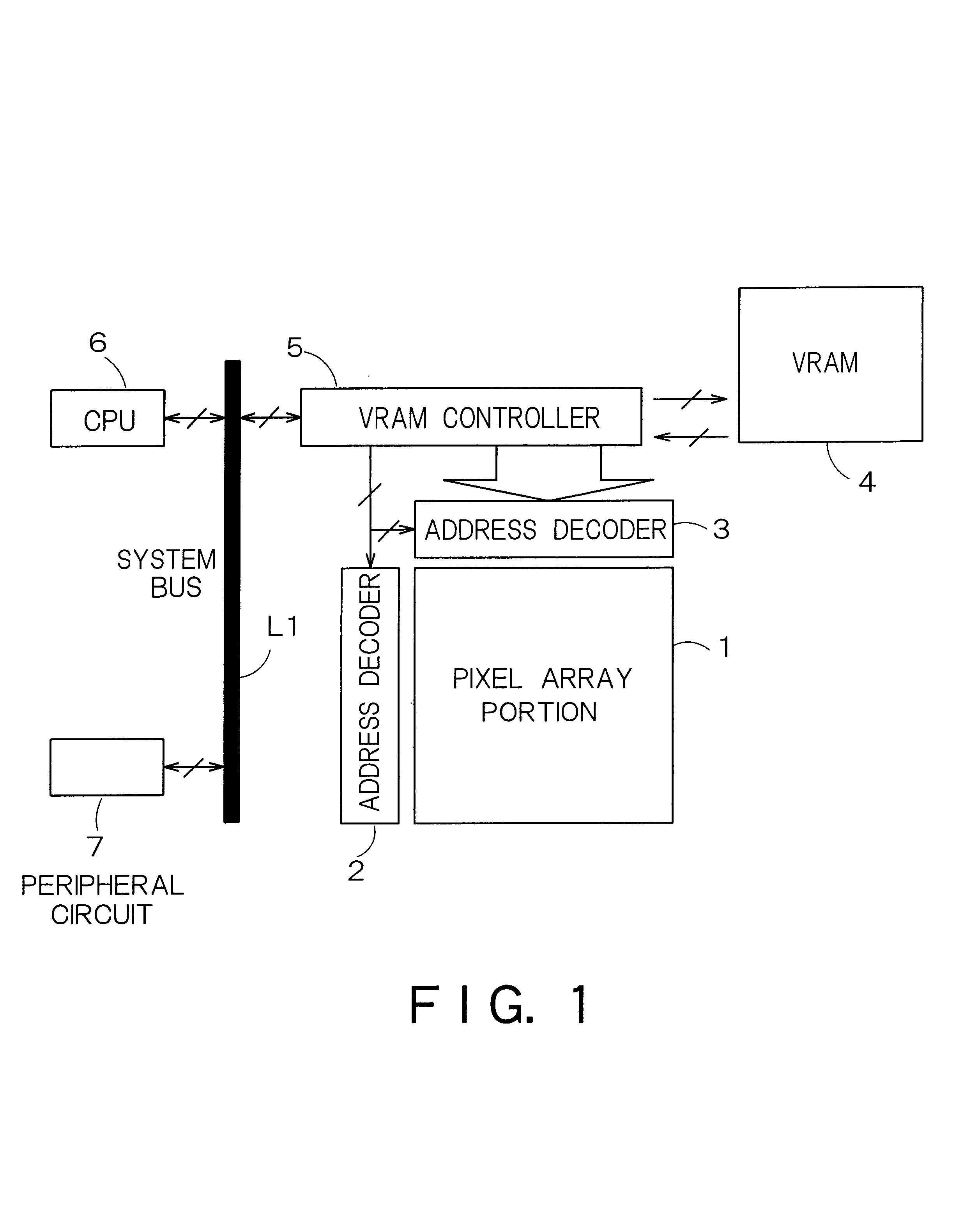

Display apparatus and driving method thereof

InactiveUS20020075211A1Static indicating devicesNon-linear opticsAddress decoderLiquid-crystal display

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:JAPAN DISPLAY CENTRAL CO LTD

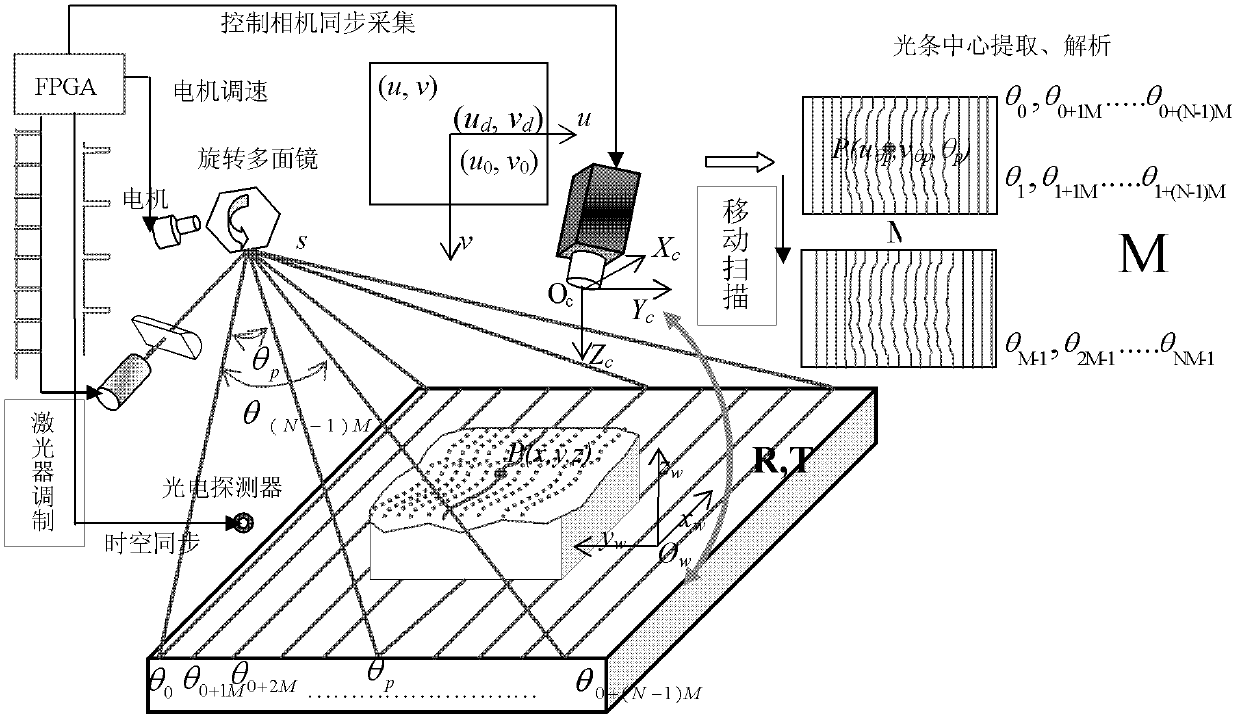

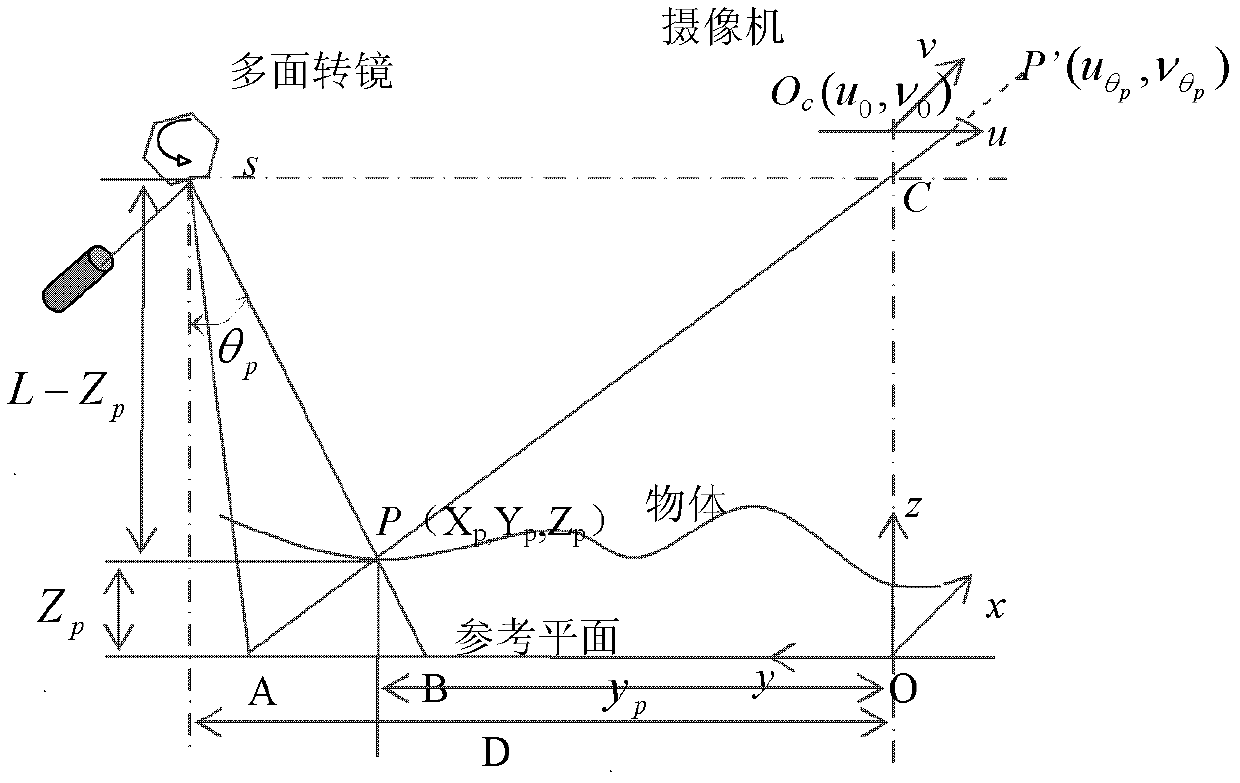

High-speed scanning and overall imaging three-dimensional (3D) measurement method

InactiveCN102589476AFast measurementLittle effect on reflectivityUsing optical meansThree dimensional measurementPrism

The invention relates to a visual inspection technology. In order to meet the requirements of fast and high-accurate surface three-dimensional (3D) topography online measurement and the detection requirements of a production line on intelligence, fastness, high accuracy and low cost, the invention adopts the technical scheme that: a high-speed scanning and overall imaging 3D measurement method comprises the following steps of: carrying out external modulation on a driving power supply by using a laser so as to control the output of a word line laser; rotating a multifaceted prism under the drive of a high-speed motor, wherein line-structured light outputted by the laser is reflected and projected to the surface of a measured object by the multifaceted prism; and placing a photoelectric detector at a position which is the limit position projected by the line-structured light during the rotating process of the multifaceted prism, carrying out exposure on an area-array CCD (Charge-Coupled Device) camera during the process that the line-structured light scans the whole area, and establishing a measurement model, wherein the 3D coordinate (xp, yp, zp) of the surface feature point of the measured object is obtained according to a formula by using an image coordinate (u[theta]p, v[theta]p) formed by the area-array CCD camera and [theta]p. The high-speed scanning and overall imaging 3D measurement method is mainly applied to the fast and high-accurate surface 3D topography online measurement.

Owner:TIANJIN UNIV

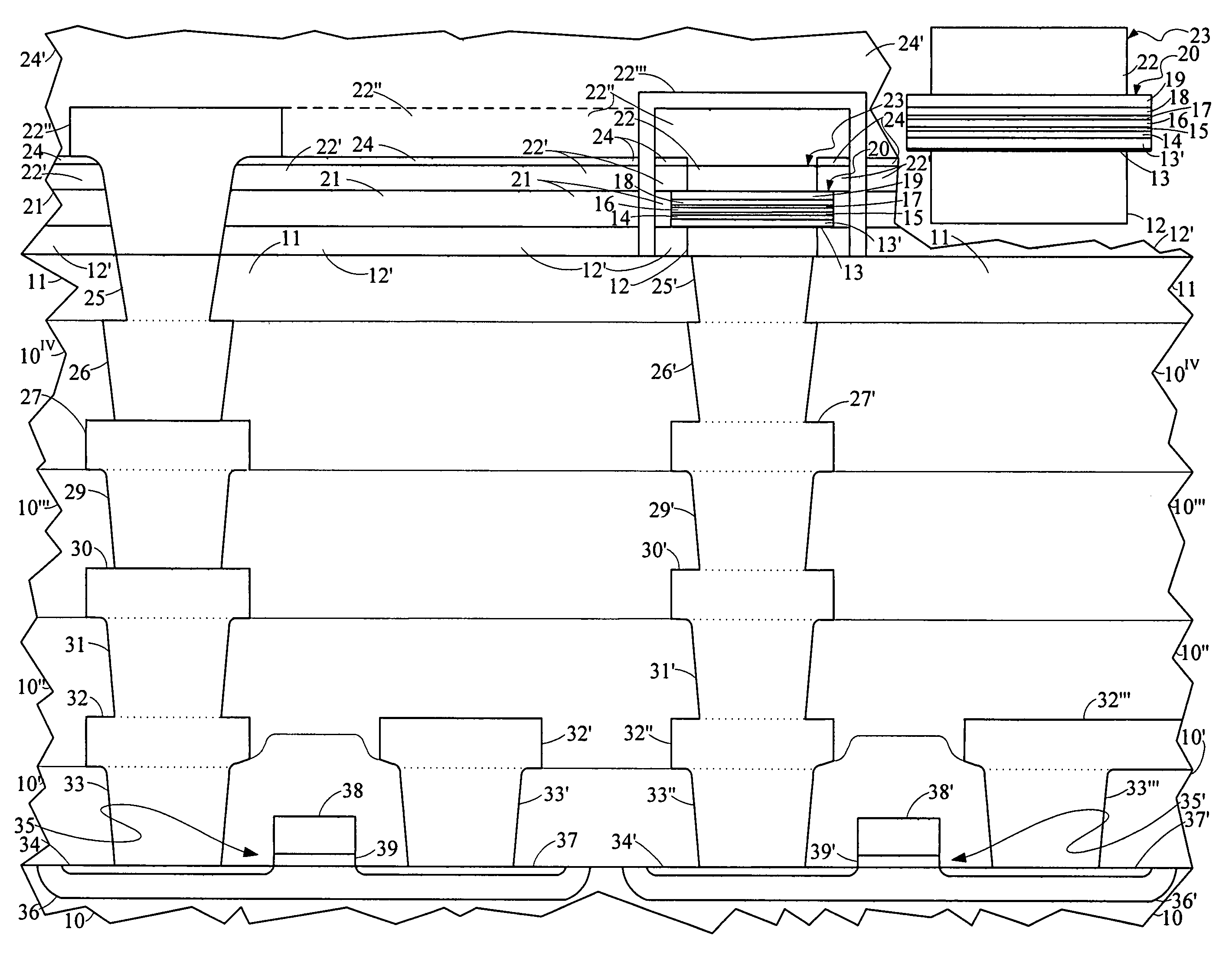

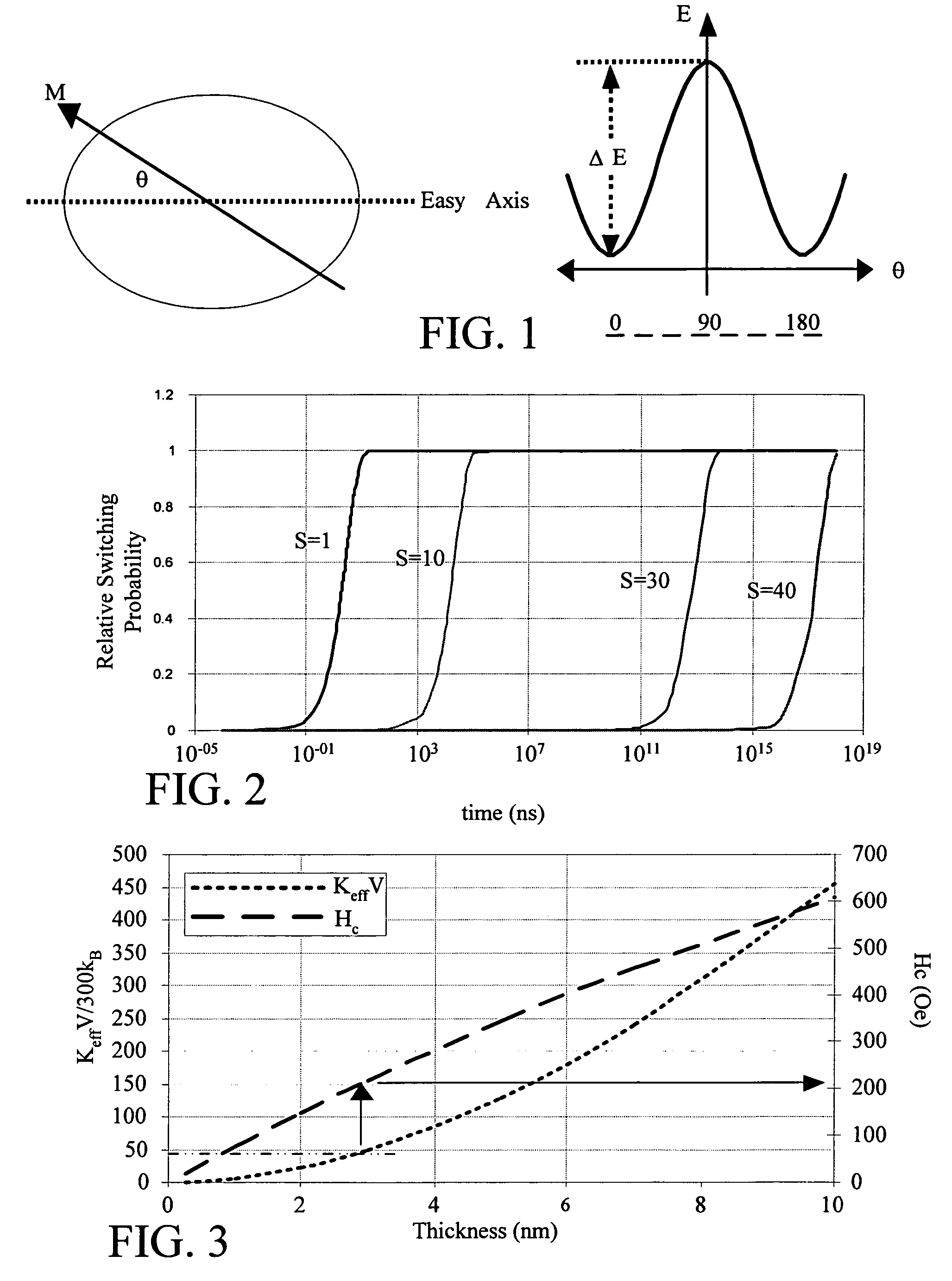

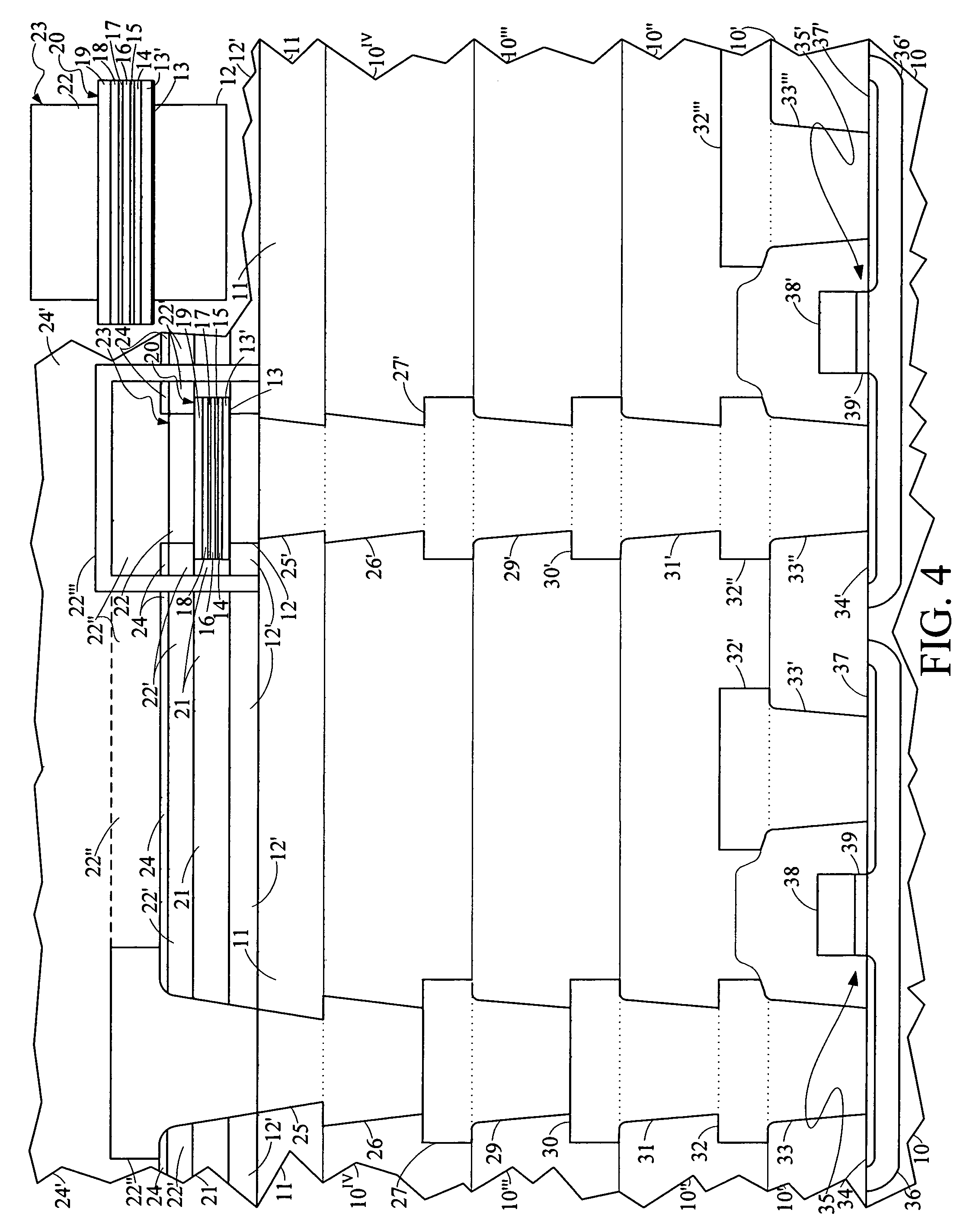

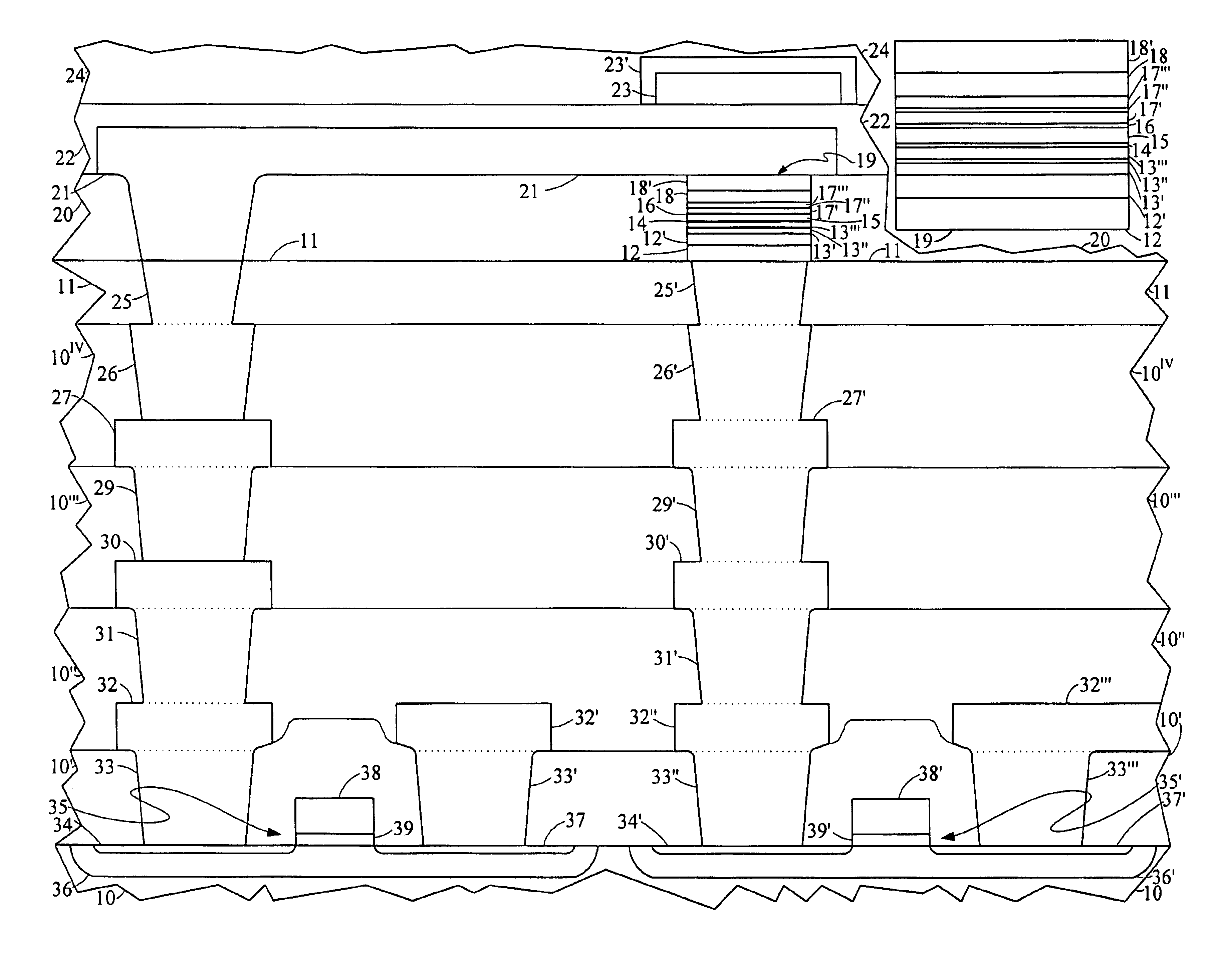

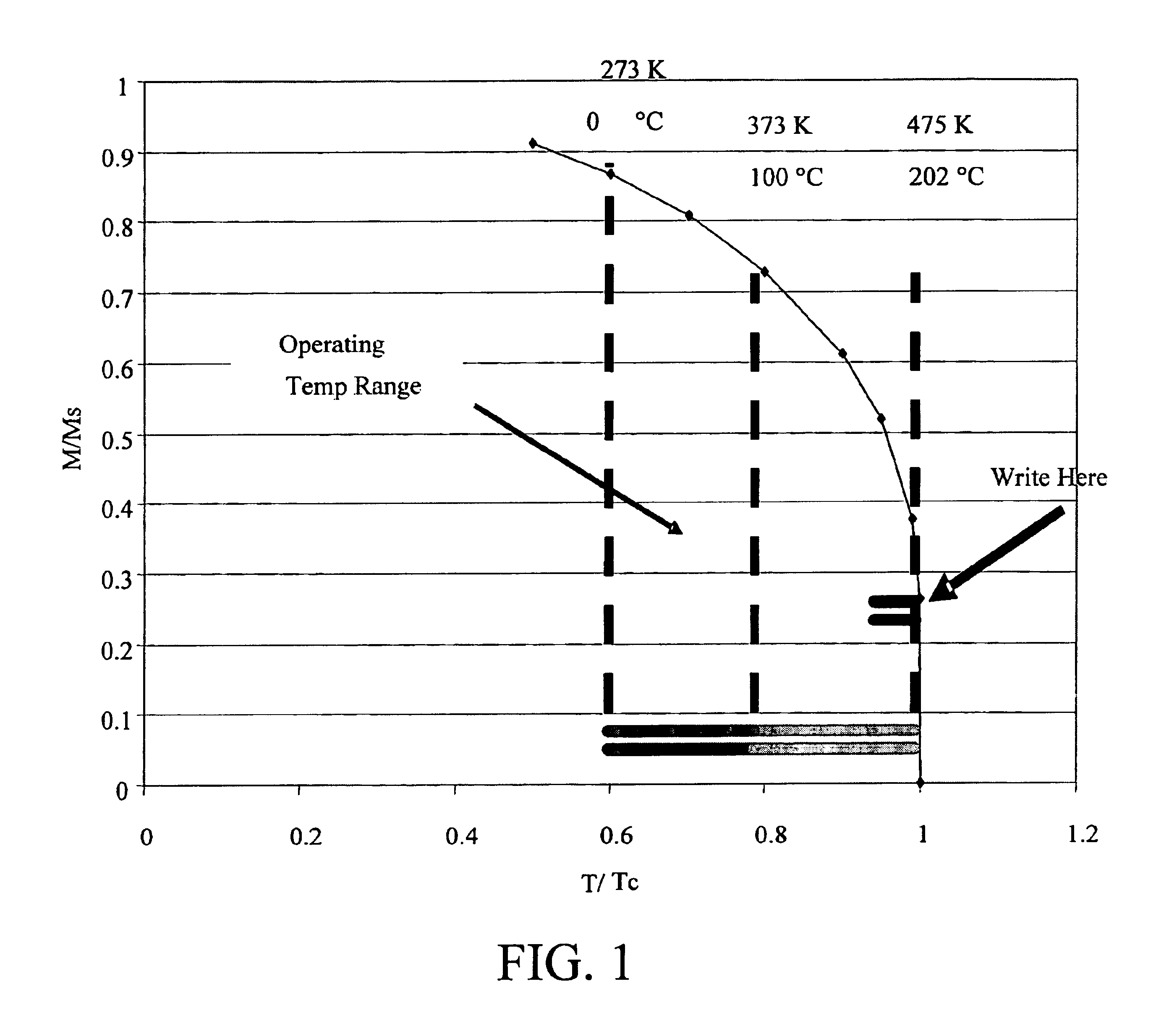

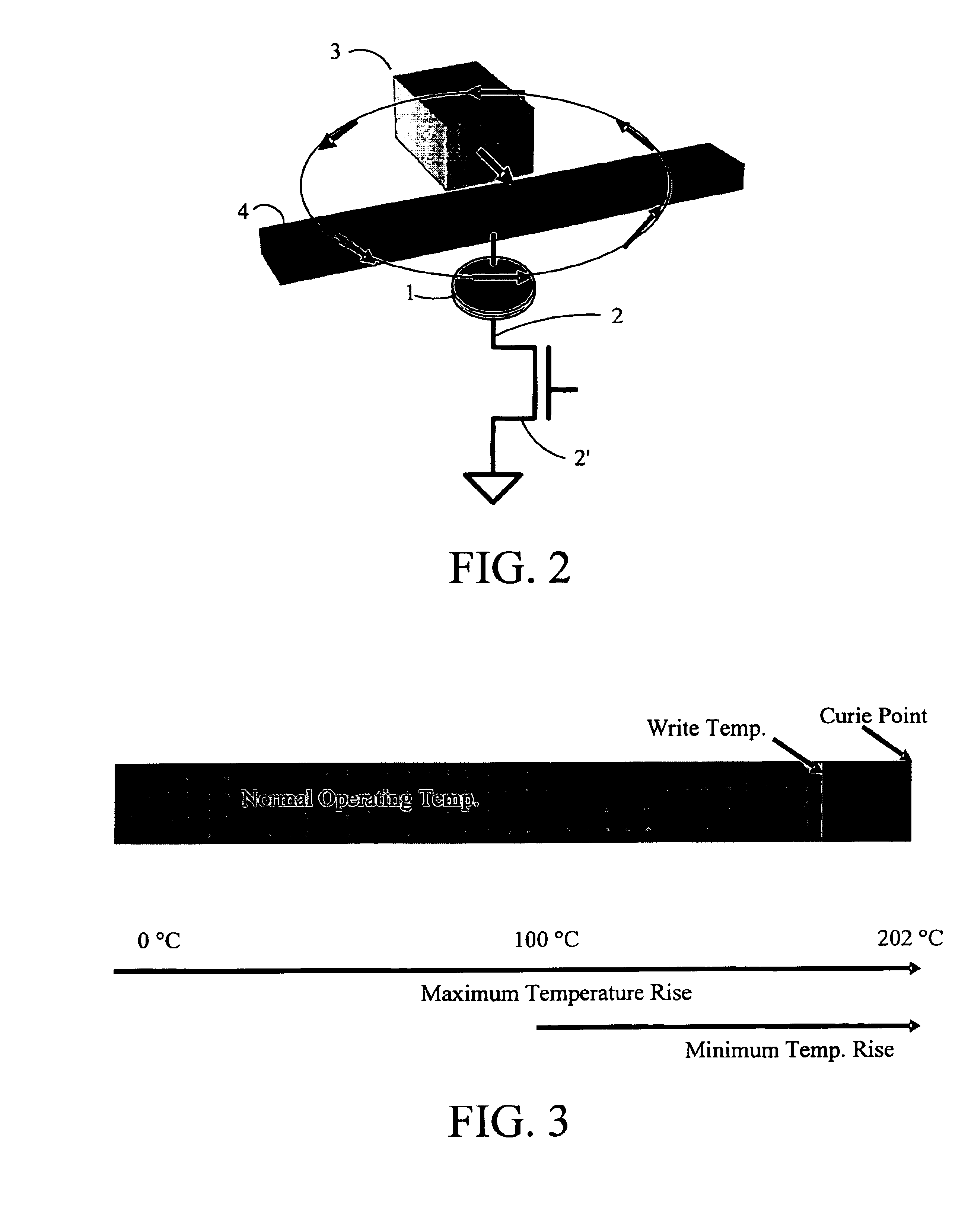

Thermomagnetically assisted spin-momentum-transfer switching memory

A ferromagnetic thin-film based digital memory having a substrate supporting bit structures that are electrically interconnected with information storage and retrieval circuitry and having first and second oppositely oriented relatively fixed magnetization layers and a ferromagnetic material film in which a characteristic magnetic property is substantially maintained below an associated critical temperature above which such magnetic property is not maintained. This ferromagnetic material film is separated from the first and second fixed magnetization films by corresponding layers of a nonmagnetic materials one being electrically insulative and that one remaining being electrically conductive. Each bit structure has an interconnection structure providing electrical contact thereto at a contact surface thereof substantially parallel to the intermediate layer positioned between the first contact surface and the substrate. A plurality of word line structures located across from a corresponding one of the bit structures on an opposite side. Electrical current selectively drawn through each of these bit structures and its interconnection structure can cause substantial heating of that bit structure to raise temperatures thereof while being above temperatures of at least an adjacent said bit structure because of sufficient thermal isolation.

Owner:NVE CORP

On-Chip RF Shields with Backside Redistribution Lines

ActiveUS20100078776A1Semiconductor/solid-state device detailsSolid-state devicesResistConductive materials

Structures of a system on chip and methods of forming a system on chip are disclosed. In one embodiment, a method of fabricating the system on chip includes forming a through substrate opening from a back surface of a substrate, the through substrate opening disposed between a first and a second region, the first region comprising devices for RF circuitry and the second region comprising devices for other circuitry. The method further includes forming patterns for redistribution lines on a photo resist layer, the photo resist layer disposed under the back surface, and filling the through substrate opening and the patterns for redistribution lines with a conductive material.

Owner:INFINEON TECH AG

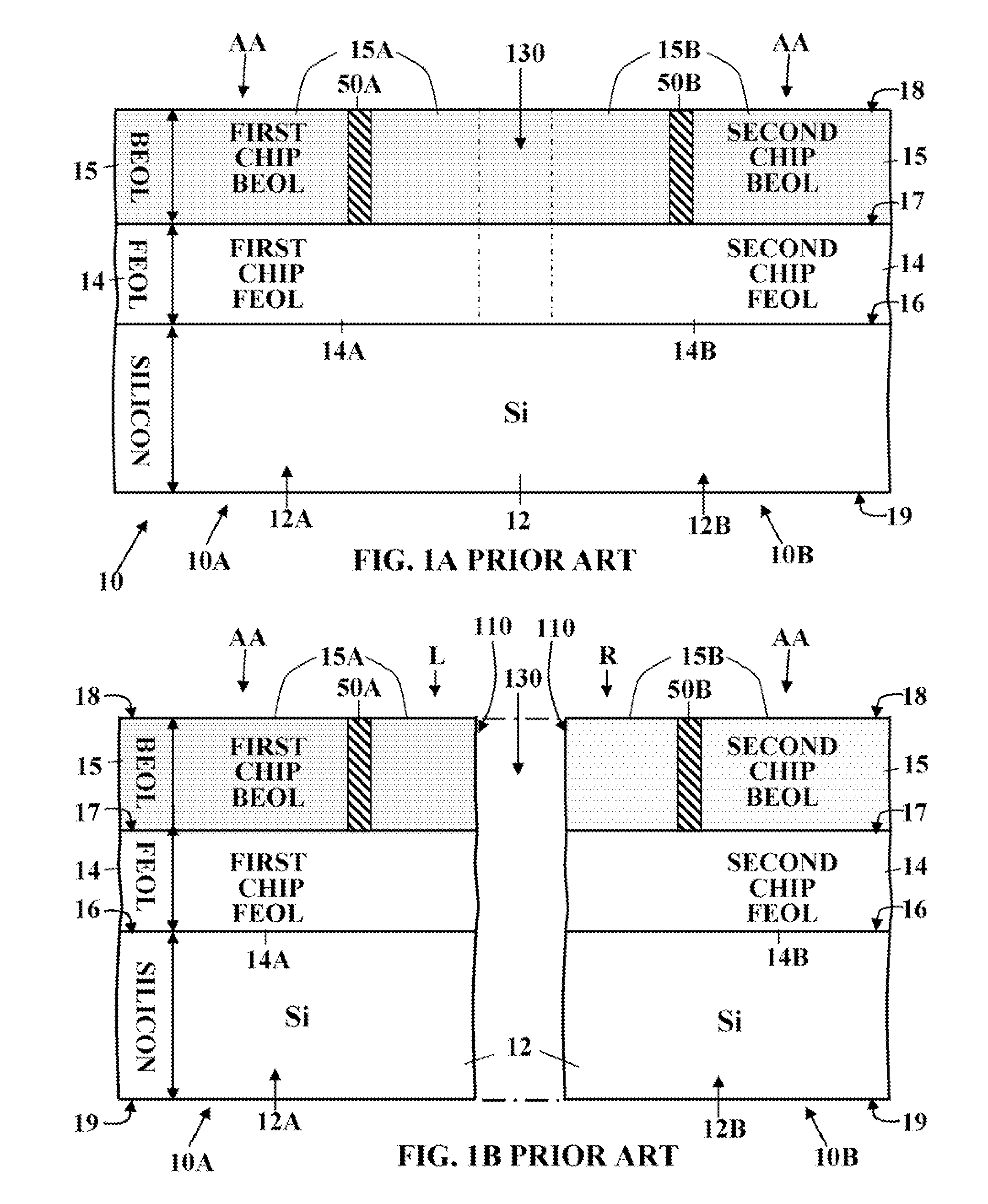

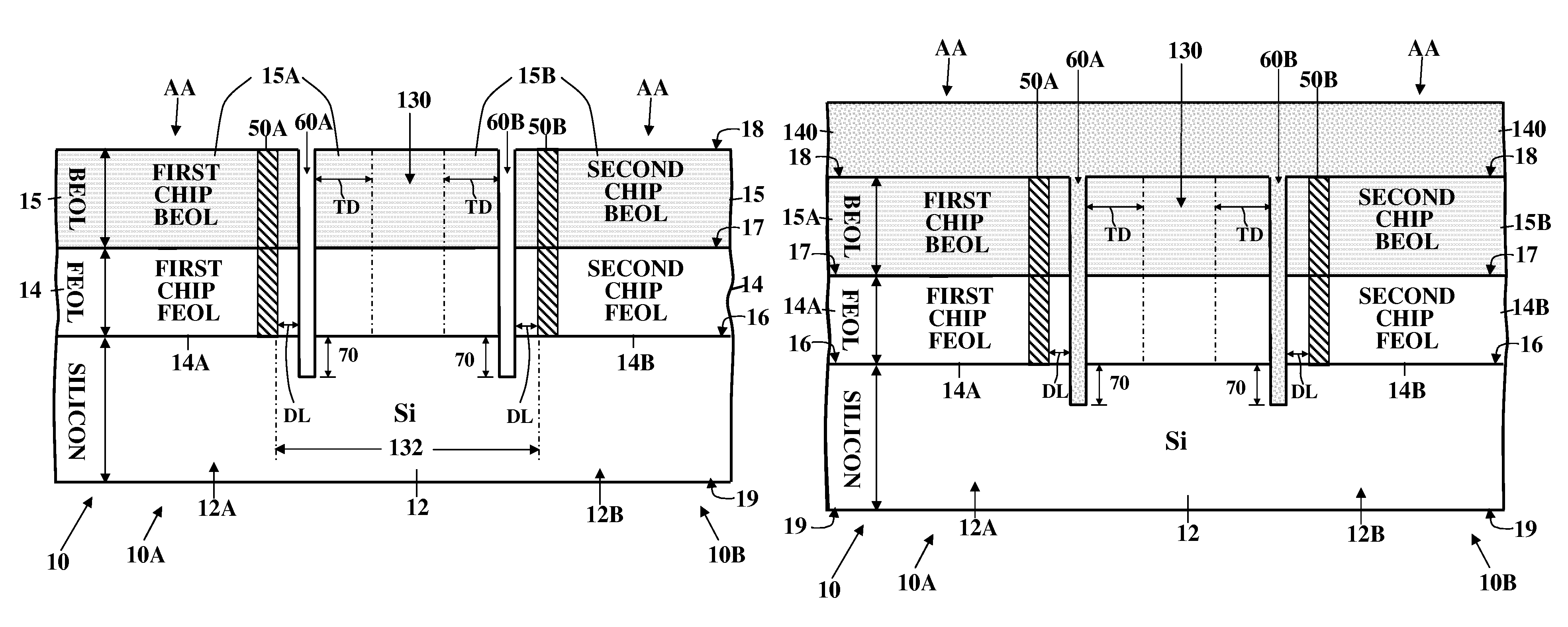

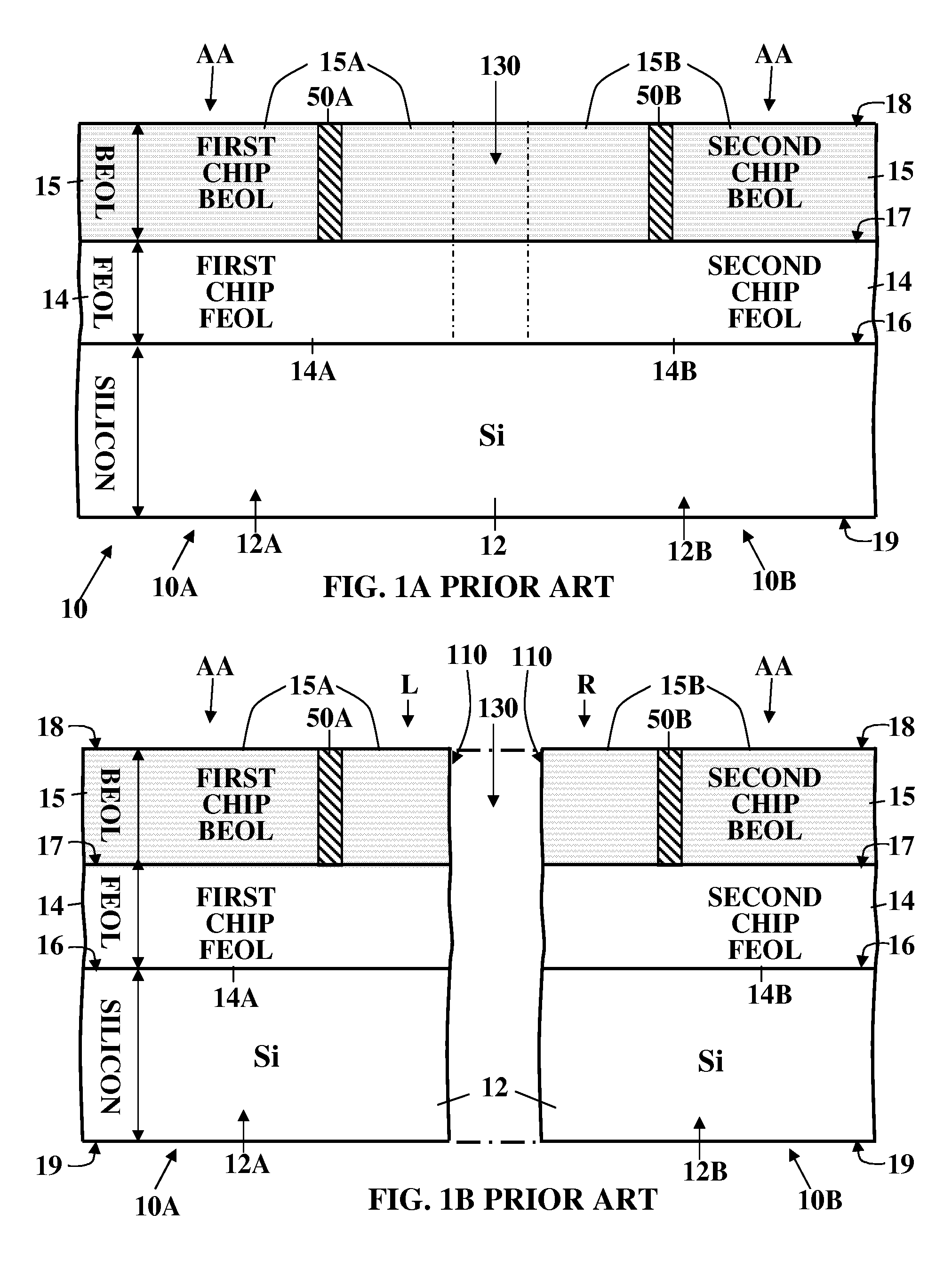

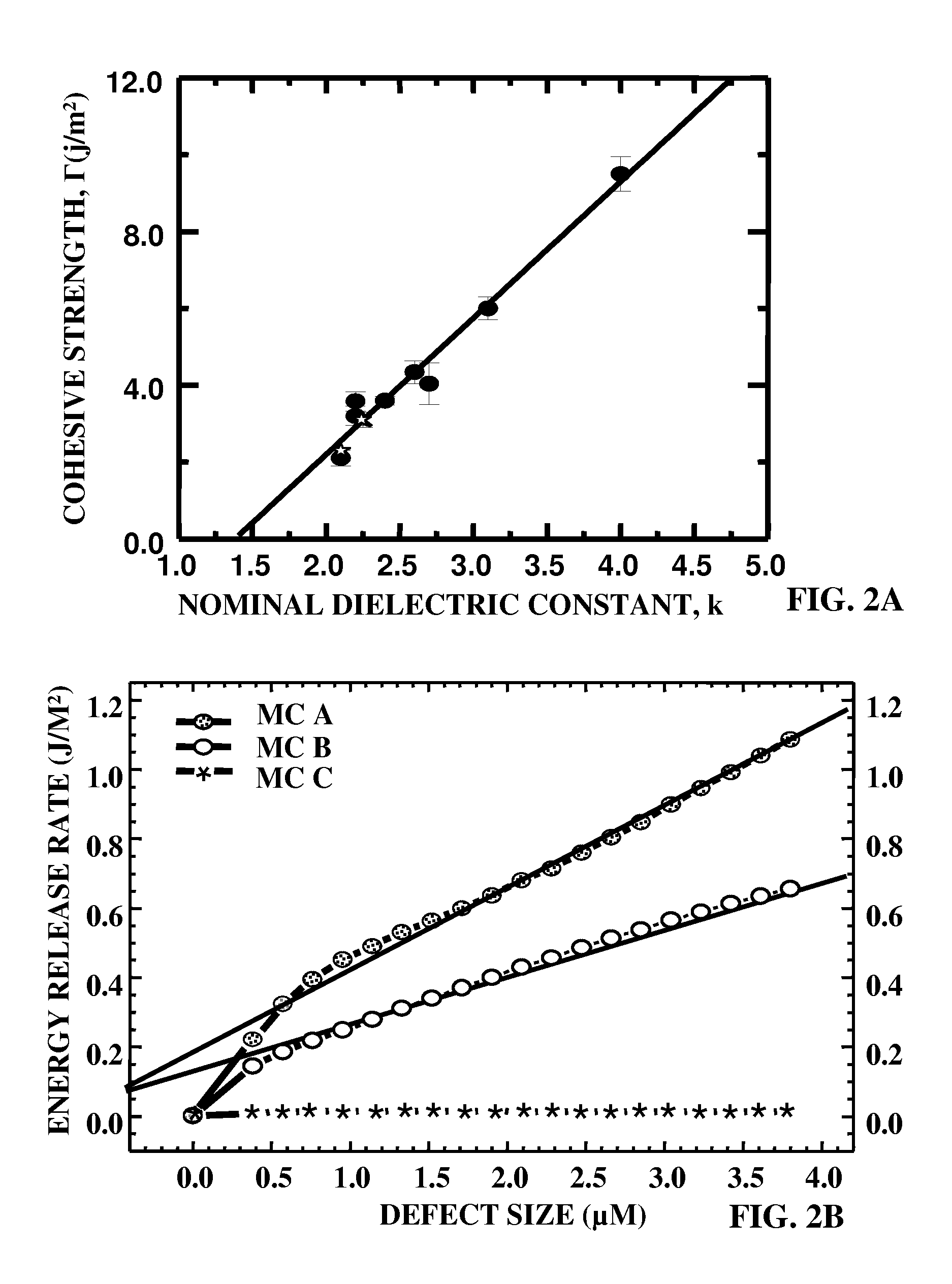

Inhibiting damage from dicing and chip packaging interaction failures in back end of line structures

ActiveUS20080277765A1Low dielectric constantAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor chip

A semiconductor product comprises a semiconductor substrate having a top surface and a bottom surface including a semiconductor chip. The semiconductor substrate has a top surface and a perimeter. A barrier is formed in the chip within the perimeter. An Ultra Deep Isolation Trench (UDIT) is cut in the top surface of the chip extending down therein between the perimeter and the barrier. A ILD structure with low-k pSICOH dielectric and hard mask layers is formed over the substrate prior to forming the barrier and the UDIT. The ILD structure interconnection structures can be recessed down to the substrate aside from the UDIT.

Owner:GLOBALFOUNDRIES US INC

Using crack arrestor for inhibiting damage from dicing and chip packaging interaction failures in back end of line structures

ActiveUS7955955B2Avoid crackingAvoid damageSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor chip

A semiconductor product comprises a semiconductor substrate having a top surface and a bottom surface including a semiconductor chip. The semiconductor substrate has a top surface and a perimeter. A barrier is formed in the chip within the perimeter. An Ultra Deep Isolation Trench (UDIT) is cut in the top surface of the chip extending down therein between the perimeter and the barrier. A ILD structure with low-k pSICOH dielectric and hard mask layers is formed over the substrate prior to forming the barrier and the UDIT. The ILD structure interconnection structures can be recessed down to the substrate aside from the UDIT.

Owner:GLOBALFOUNDRIES U S INC

Display device and driving method thereof

InactiveUS6873320B2Reduce consumptionSmall sizeCathode-ray tube indicatorsNon-linear opticsAddress decoderLiquid-crystal display

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:KK TOSHIBA

Three-dimensional semiconductor devices

Provided are a three-dimensional semiconductor device and a method of operating the same. The three-dimensional semiconductor device includes: a plurality of word line structures on a substrate; active semiconductor patterns between the plurality of word line structures; and information storage elements between the plurality of word line structures and the active semiconductor patterns. Each of the plurality of word line structures includes a plurality of word lines spaced apart from each other and stacked, and the active semiconductor patterns include electrode regions and channel regions, the electrode regions and the channel regions having different conductive types and being alternately arranged.

Owner:SAMSUNG ELECTRONICS CO LTD

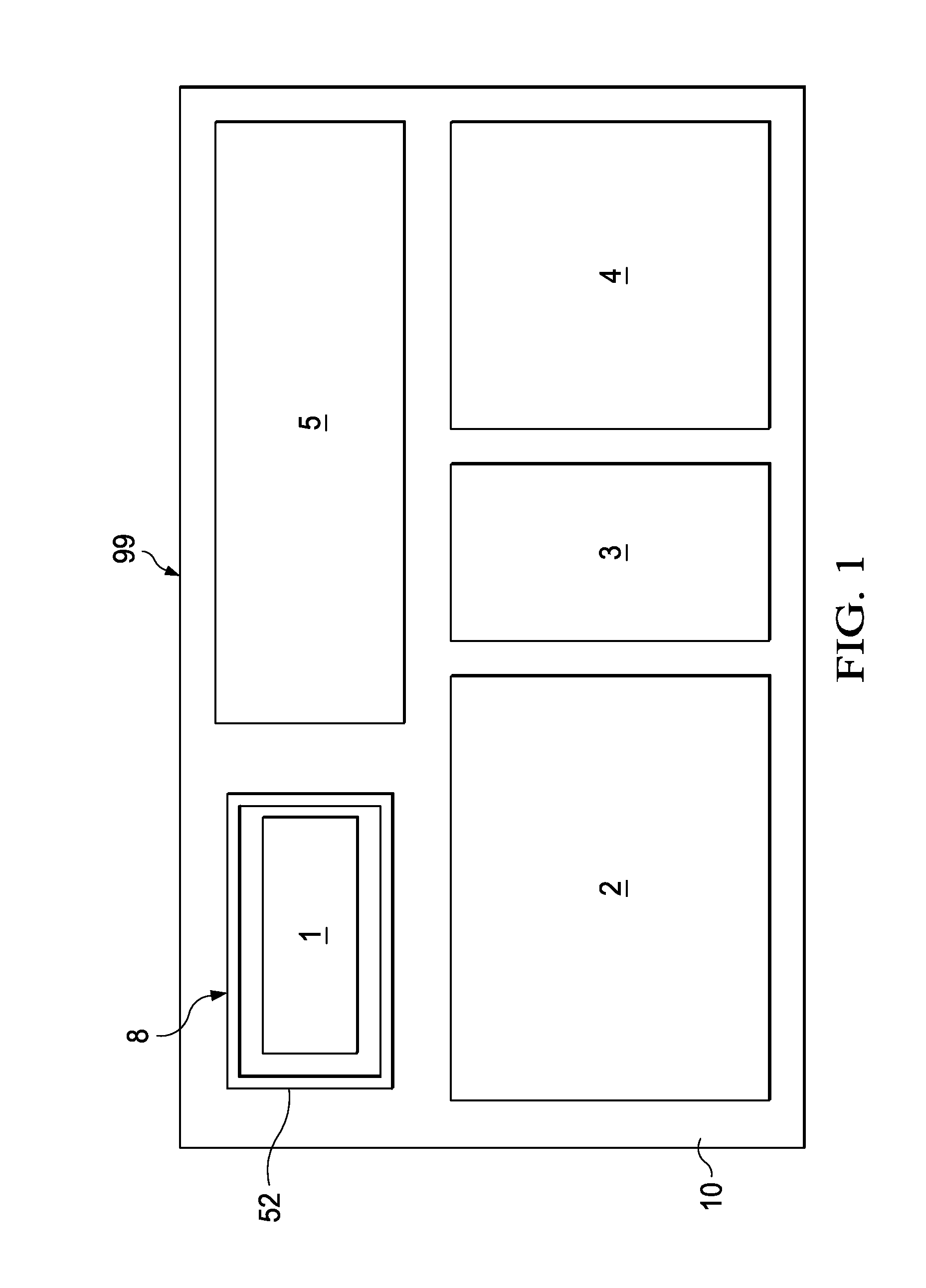

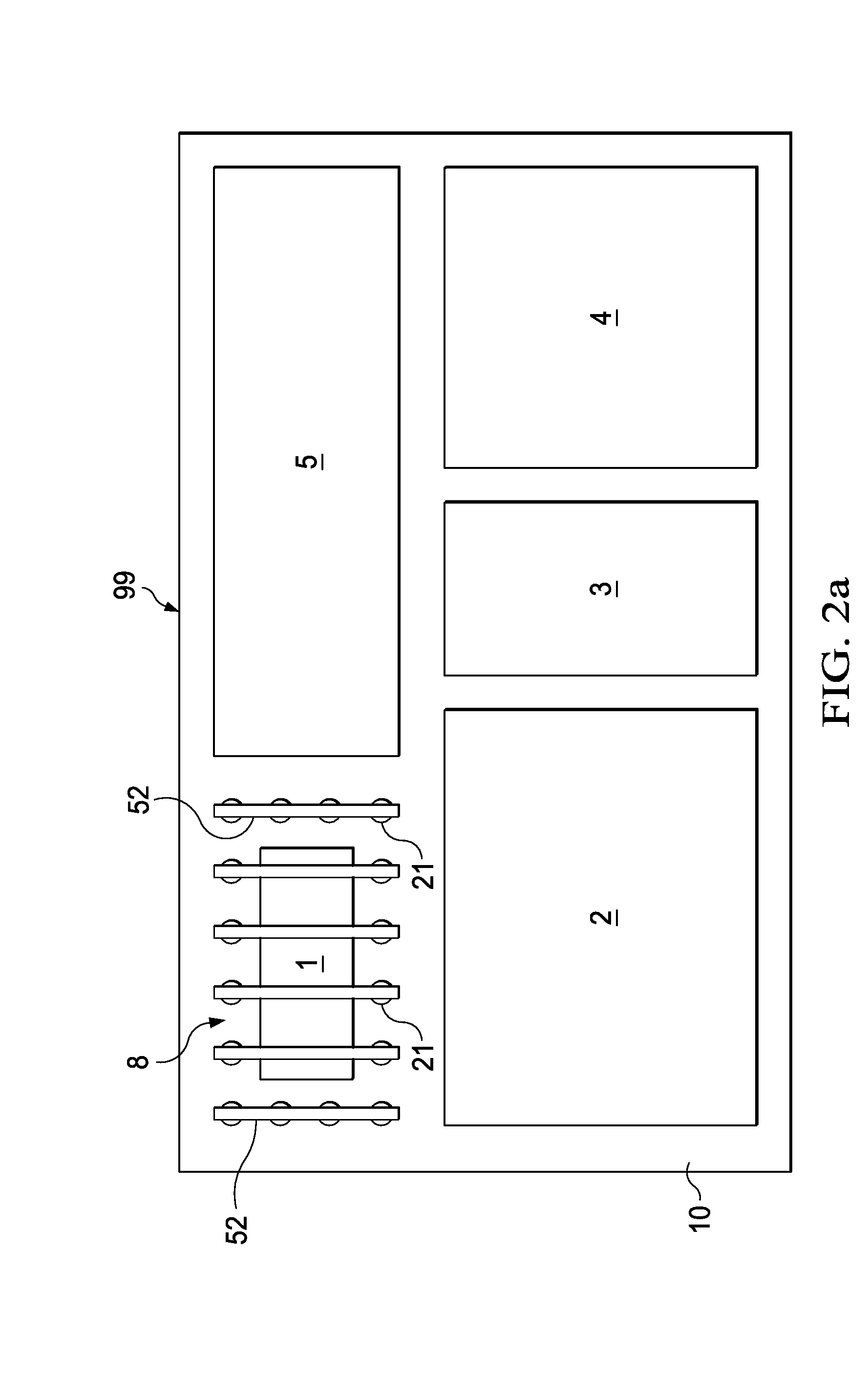

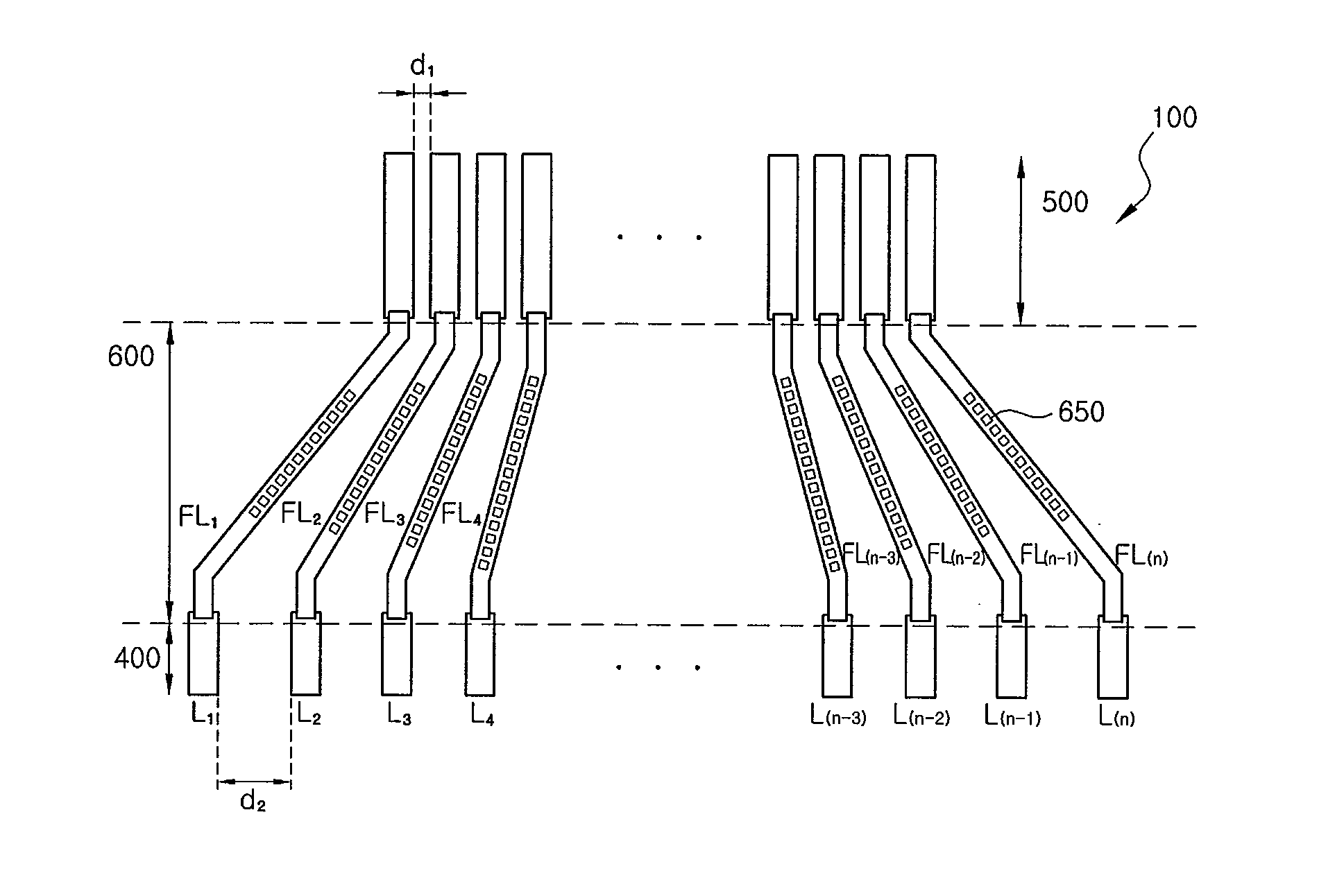

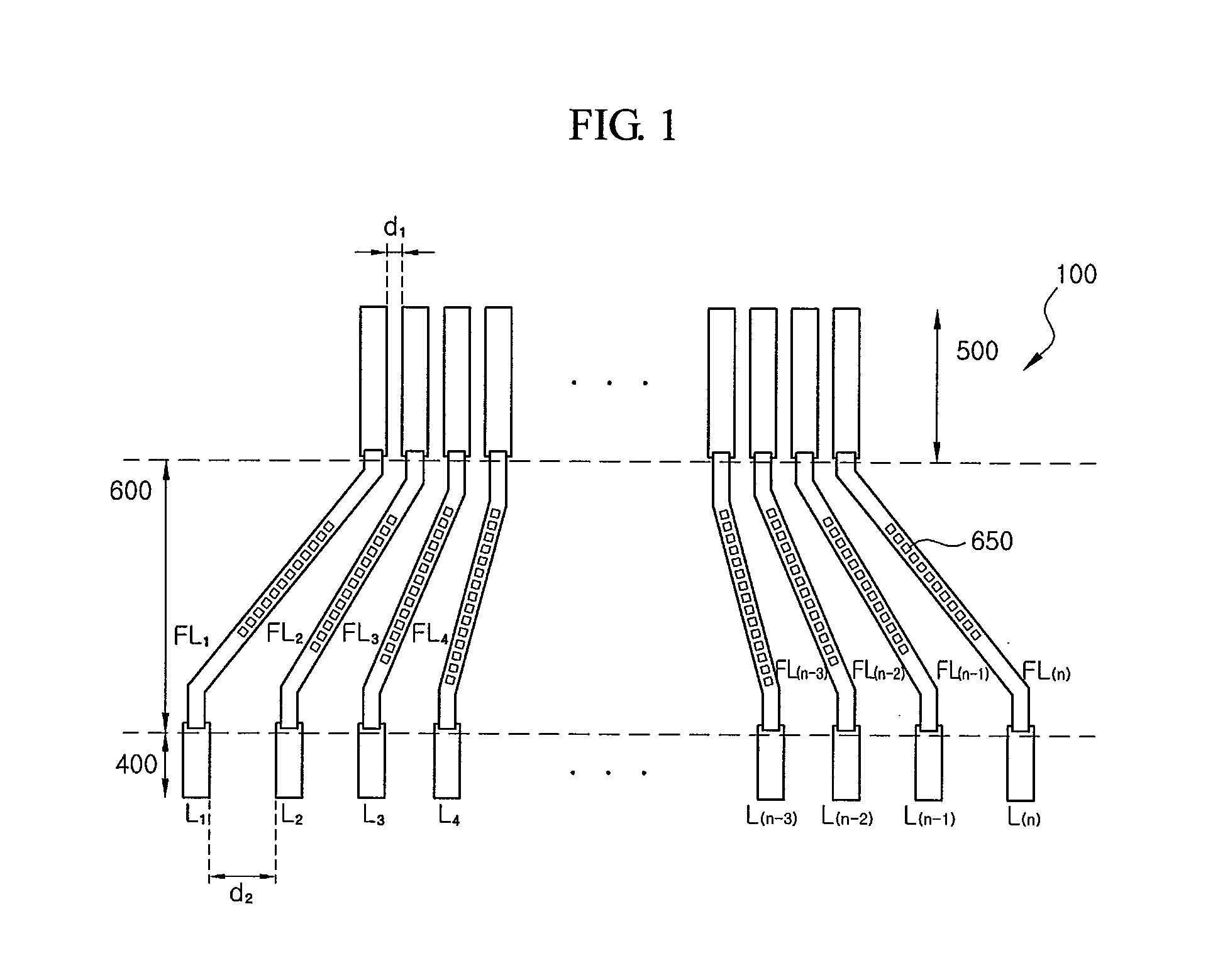

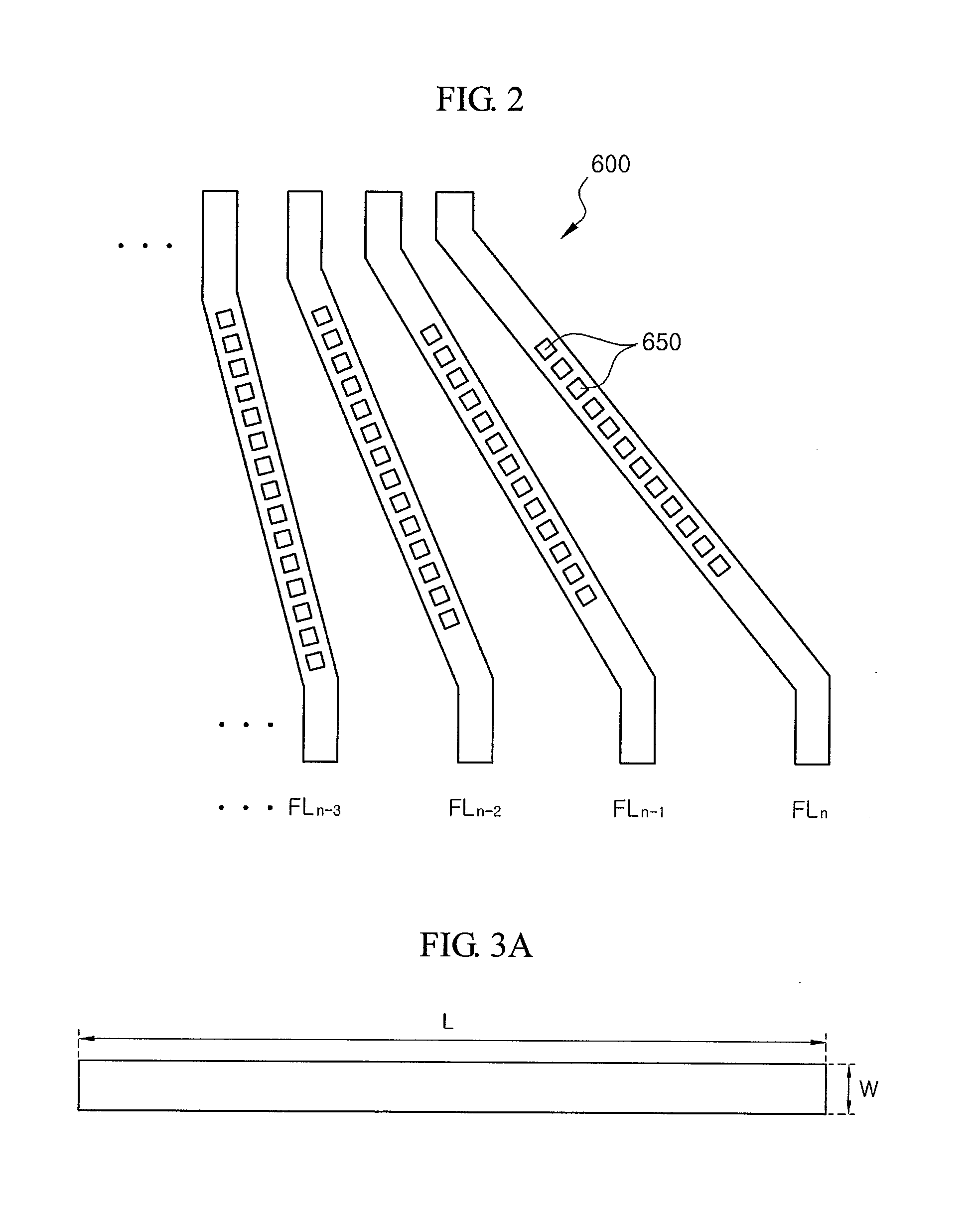

Fanout line structure and flat display device including fanout line structure

InactiveUS20080137016A1Reduce the differenceNon-linear opticsLogic circuit coupling/interface arrangementsLiquid-crystal displayImaging quality

A fanout line structure and a liquid crystal display panel and a liquid crystal display including the fanout line structure are presented. The fanout line structure connects a signal line to a bonding pad, and includes a plurality of fanout lines that are positioned apart from each other. The plurality of fanout lines are formed to have different lengths, and a hole pattern is formed in at least one of the plurality of fanout lines to reduce the difference in resistance levels between the fanout lines. The fanout structure significantly reduces any deterioration in image quality stemming from different resistance levels among the fanout lines.

Owner:SAMSUNG DISPLAY CO LTD

Thermally operated switch control memory cell

Owner:NVE CORP

Security Document Carrying Machine Readable Pattern

InactiveUS20100163629A1Easy to detectImage data processing detailsOther printing apparatusDocumentationLine structure

The present invention relates generally to security documents (e.g., banknotes, ID documents, certificates, packaging, etc.). One claim recites a security document including a security pattern provided thereon. The security pattern includes a line structure in which lines width or line spacing is adjusted to convey a predefined, machine-readable pattern in a frequency transform domain. Another claim recites a security document including a security pattern provided thereon. The security pattern is provided in the security document through modifications to a color provided on the security document. The security pattern conveys a predefined, machine-readable pattern in a frequency transform domain. Of course, additional combinations and claims are provided as well.

Owner:DIGIMARC CORP

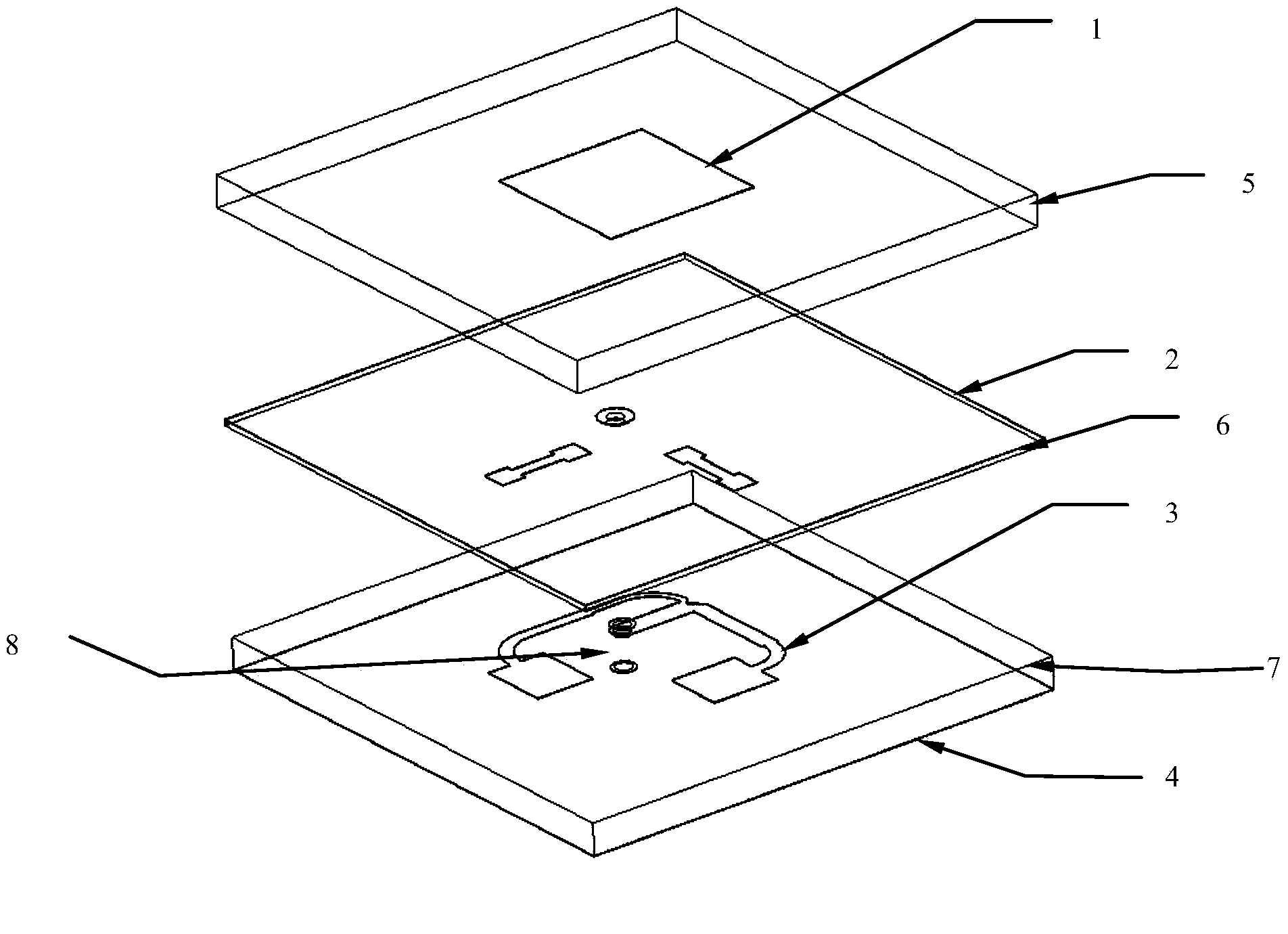

Low-cost microwave- and millimeter-wave polarized antenna of multi-layer PCB (Printed circuit board) process

InactiveCN104103906AImproving Impedance BandwidthSmall structure sizeRadiating elements structural formsSlot antennasAxial ratioDielectric substrate

The invention discloses a low-cost microwave- and millimeter-wave polarized antenna of the multi-layer PCB (Printed circuit board) process. The polarized antenna is of a multi-layer structure and comprises a quadrate radiating metal patch, an upper dielectric substrate, a metal floor equipped with an H-shaped coupling gap, a medium dielectric substrate, a feed metal plate with power division network, a lower dielectric substrate and a bottom metal floor; the quadrate radiating metal patch is coupled with the floor equipped with the H-shaped coupling gap to realize feed; the feed network of a microstrip line structure is positioned below the floor; the metal floor equipped with the H-shaped coupling gap is connected with the bottom metal floor through a metal through hole; the feed metal plate with the power division network is connected with the bottom metal floor through a second metal through hole to form a coaxial microstrip line conversion structure by which feeding from the bottom part of the antenna is realized. The antenna has the characteristics that the frequency band is wide, the size is small, the cost is low, the manufacturing and processing are simple, and the axial ratio feature is great.

Owner:SOUTHEAST UNIV

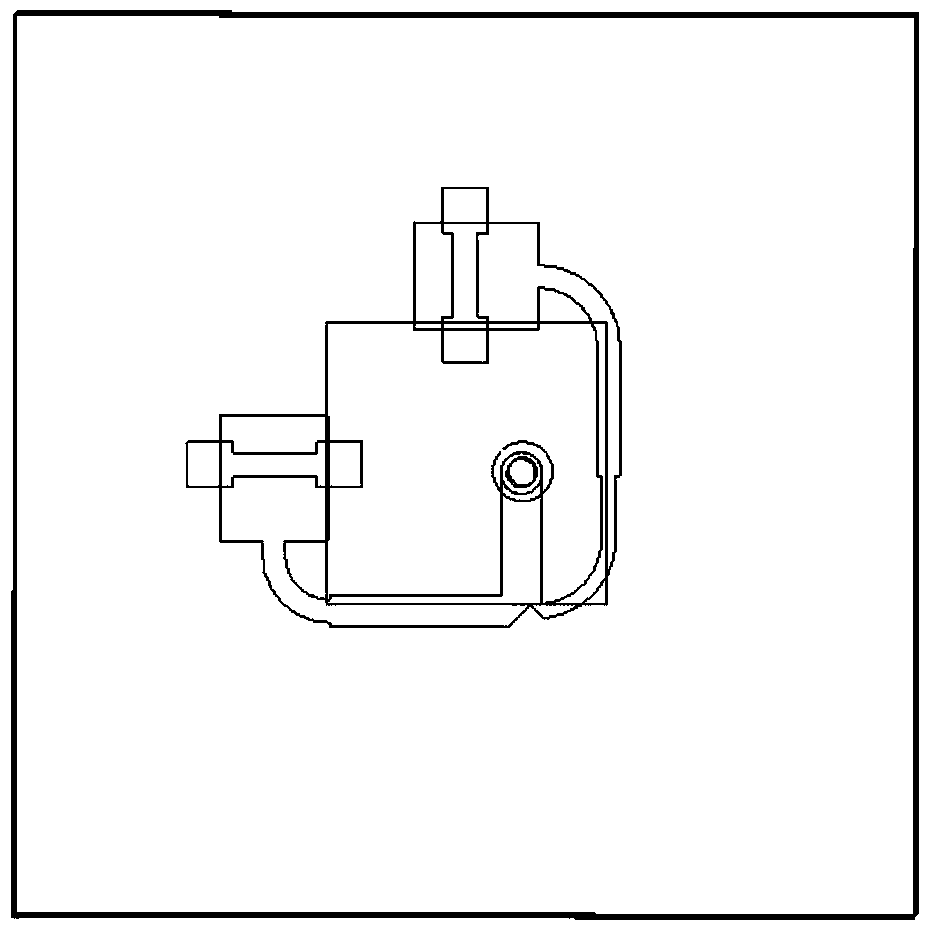

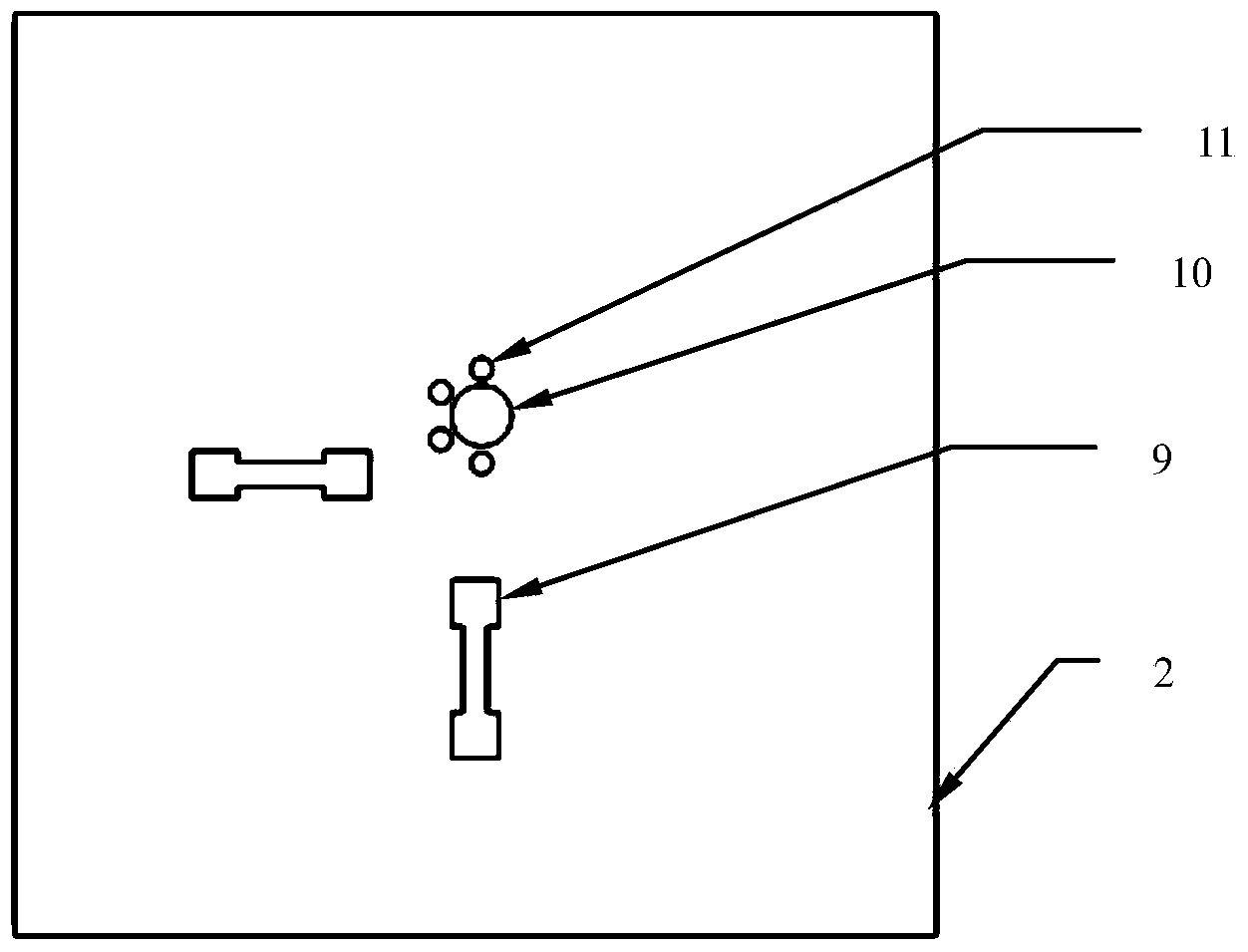

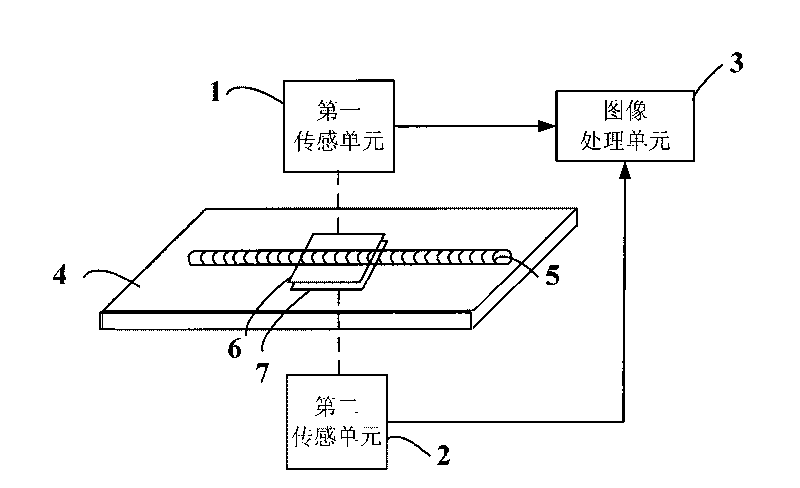

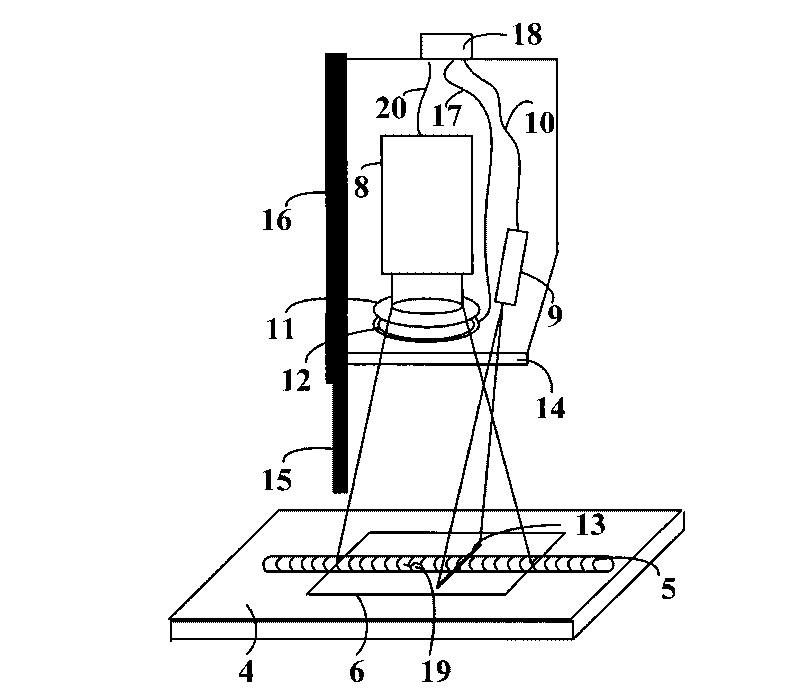

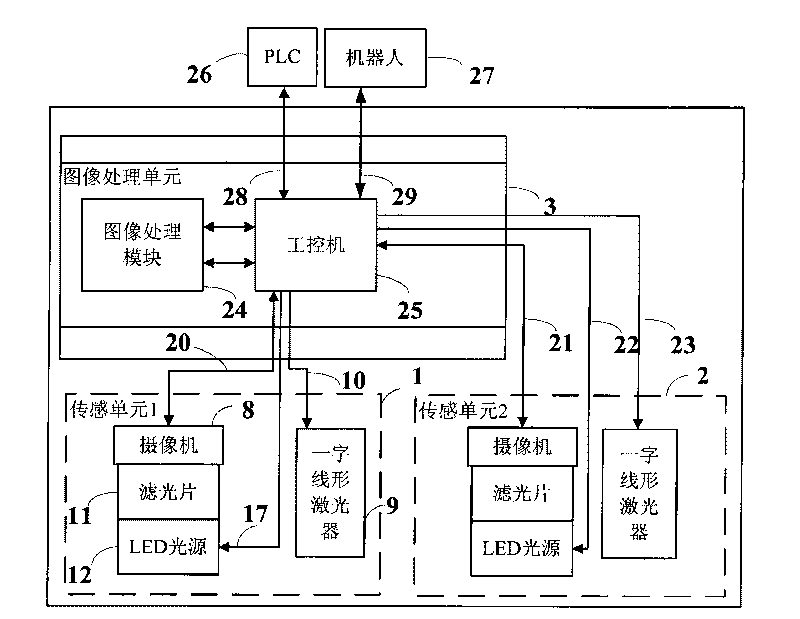

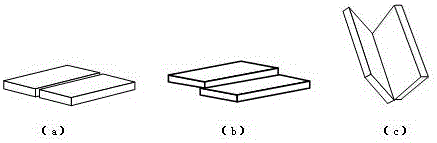

Visual welding seam surface quality detection sensor based on line structure light

InactiveCN101750416AIncrease autonomyImprove the level of intelligenceOptically investigating flaws/contaminationCamera lensWeld seam

The invention discloses a visual welding seam surface quality real-time on-line detection sensor based on line structure light, comprising sensing units and an image processing unit, wherein two sensing units are respectively vertically installed at two sides of the upper and lower surfaces of the welding seam and connected with the image processing unit; the sensing units comprise a video camera for receiving the welding seam surface gray scale image including laser stripe formed on the welding work piece; a straight linear laser for generating laser structure light stripe on the welding work piece; an optical filter in front of the video camera lens; and an LED annular light source coaxially provided with the video camera and positioned in front of the optical filter. The invention uses the straight linear laser to project onto the upper and lower surfaces of the welding seam to generate the laser stripes; the camera collects the welding seam surface gray scale image including laser stripes to finally realize automatic quality detection of the upper and lower surfaces of the welding seam; and the precision of surface quality detection of the welding seam is improved. The sensor can be widely applied to the fields such as robot automatic welding.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

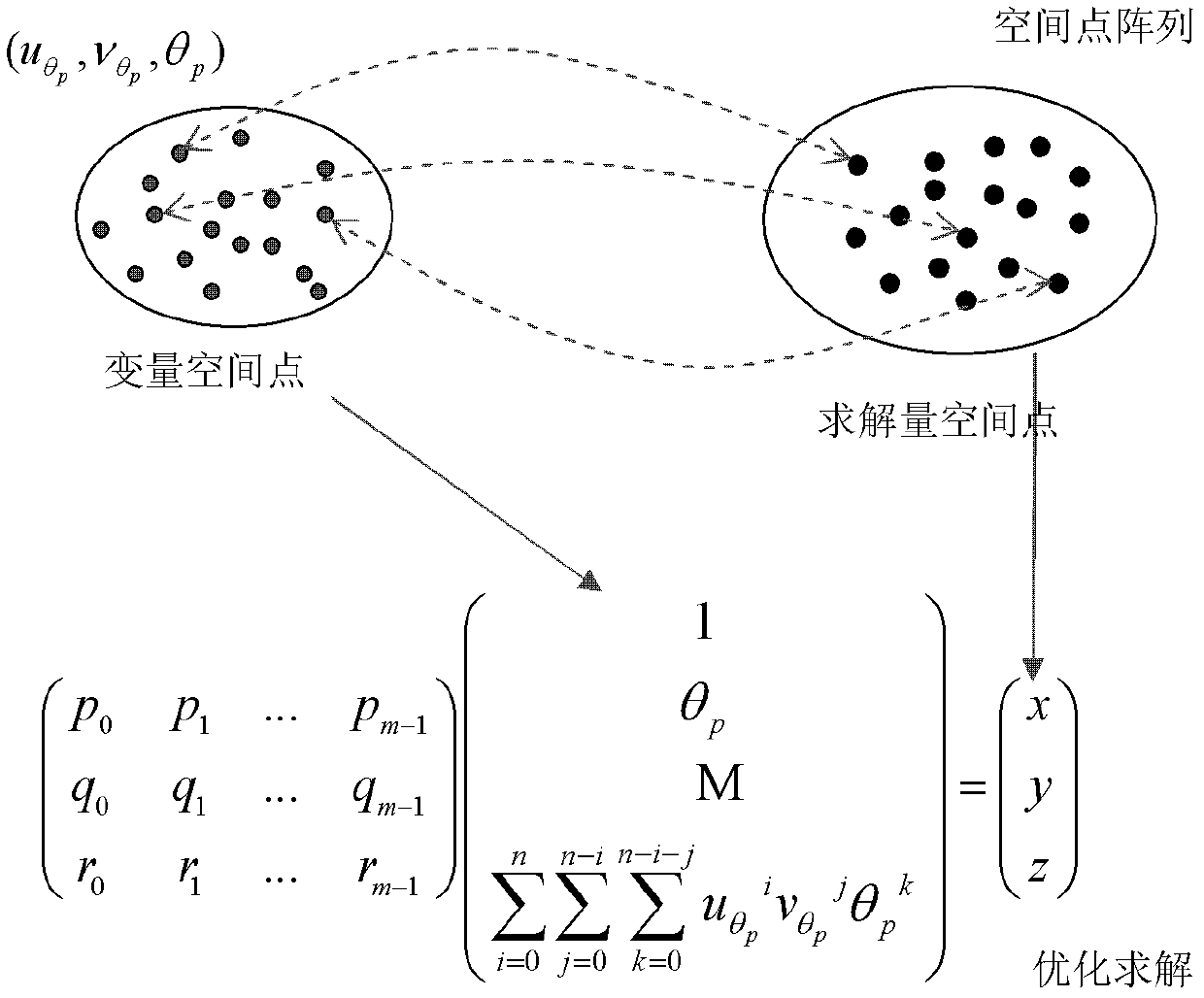

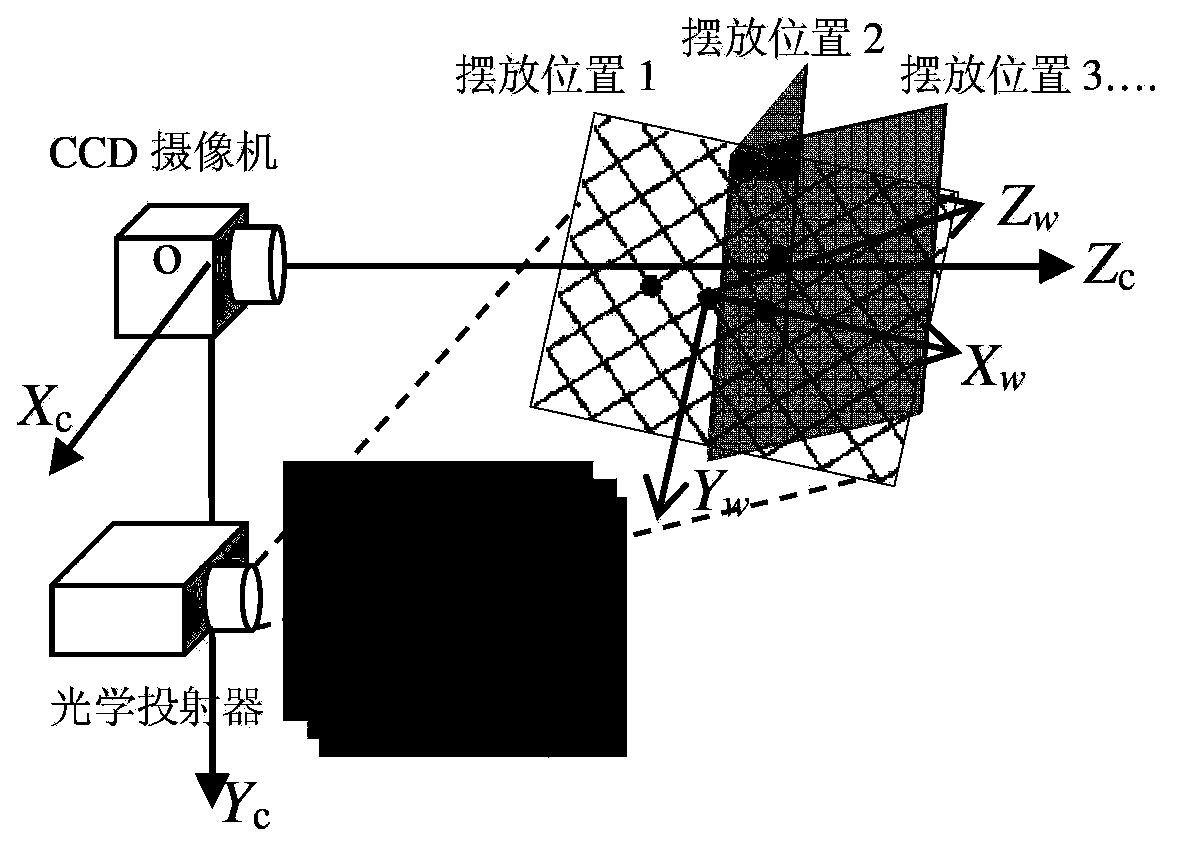

Fast calibration method of multiple line structured light visual sensor

InactiveCN103411553AEasy to completeSuitable for on-site calibrationUsing optical meansVirtual spaceBack calculation

The invention belongs to the technical field of visual detection, and provides a calibration method which is convenient and fast to use and accurate. The fast calibration method aims to make full use of characteristics of the multiple line structured light visual sensor in the aspect of three-dimensional shape measurement so as to be applied to on-line three-dimensional detection of industrial products. According to the technical scheme, the fast calibration method of the multiple line structured light visual sensor comprises the steps that a three-dimensional measurement model of the multiple line structured light visual sensor is built, wherein a measurement coordinate system is set in a world coordinate system where virtual space feature points are calibrated through the three-dimensional measurement model; according to the measurement model, due to the adoption of the Zhang calibration method that visual angles are not determined, a plurality of coplanar positions are placed through the visual sensor (namely, a plane target) to acquire virtual space feature point arrays so as to carry out camera calibration; three-dimensional point arrays on each light plane are acquired according to camera calibration results and the cross ration invariability theory to finish light plane calibration; the three-dimensional shape of a measured object is worked out in a back calculation mode through the measurement model. The fast calibration method of the multiple line structured light visual sensor is mainly used for visual detection.

Owner:TIANJIN UNIV

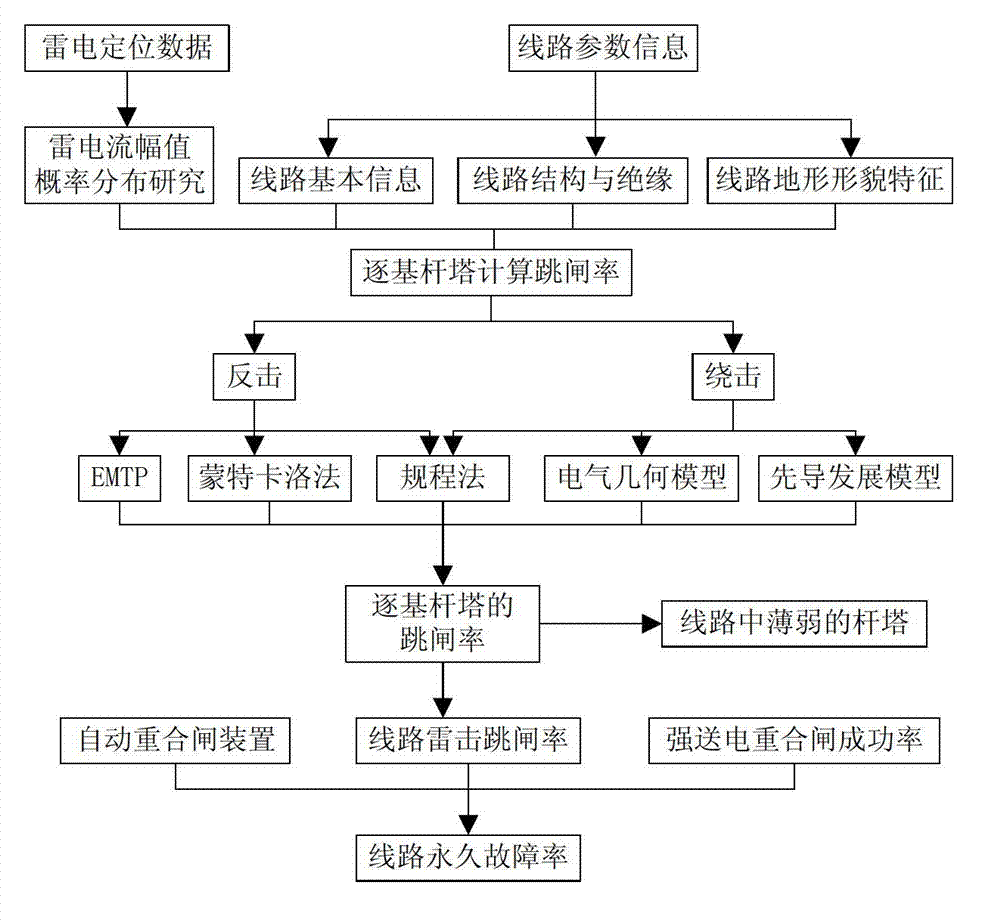

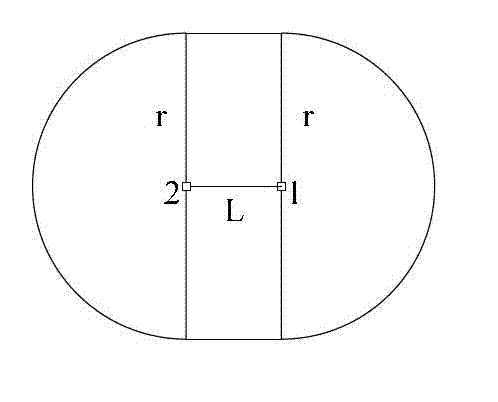

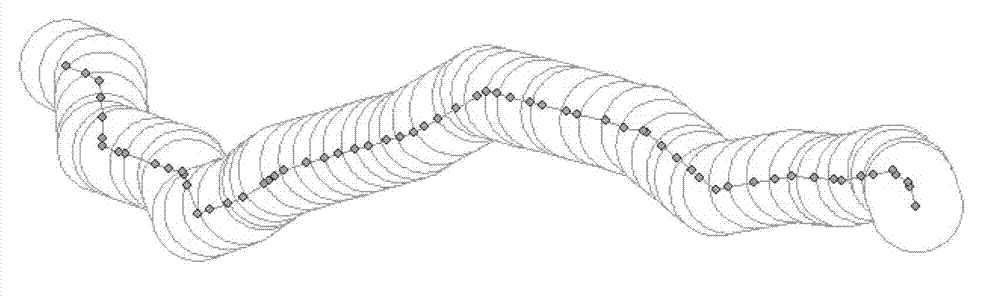

Method for assessing lightning flashover risks of regional power grid lines

ActiveCN102854415AComprehensive and detailed evaluation resultsElectrical testingFailure rateLightning strike

The invention discloses a method for assessing the lightning flashover risks of regional power grid lines, which comprises the following steps that: through calculating the lightning-resistant level of each base rod tower and combining with a probability distribution function of lightning current amplitudes of a region, the lightning trip-out rate of each rod tower is obtained, and the average lightning trip-out rate of a line is calculated; then, through combining with an automatic reclosing failure rate and a failure rate of manual forced energization, a permanent failure rate of the line is obtained; and through considering the weight coefficient of the line in a power grid structure, the permanent failure load loss coefficient of the line at the specific time of a power grid and in an specific operation mode of the power grid, and the risk occurrence probability of other influencing factors, a lightning flashover risk assessment model of a regional power transmission grid is established. According to the invention, the shortcoming that the absolute numerical value of the lightning trip-out rate can not really reflect the lightning disaster risk level of each line is overcome, and the lightning flashover risk level of each rod tower of lines is assessed through comprehensively considering the differences among the lightning motions, topographical features, line structures, insulation configuration, lightning protection measures and the like of each line corridor in the power grid, so that more comprehensive and thorough assessment results are obtained.

Owner:GUANGDONG POWER GRID CO LTD DONGGUAN POWER SUPPLY BUREAU +1

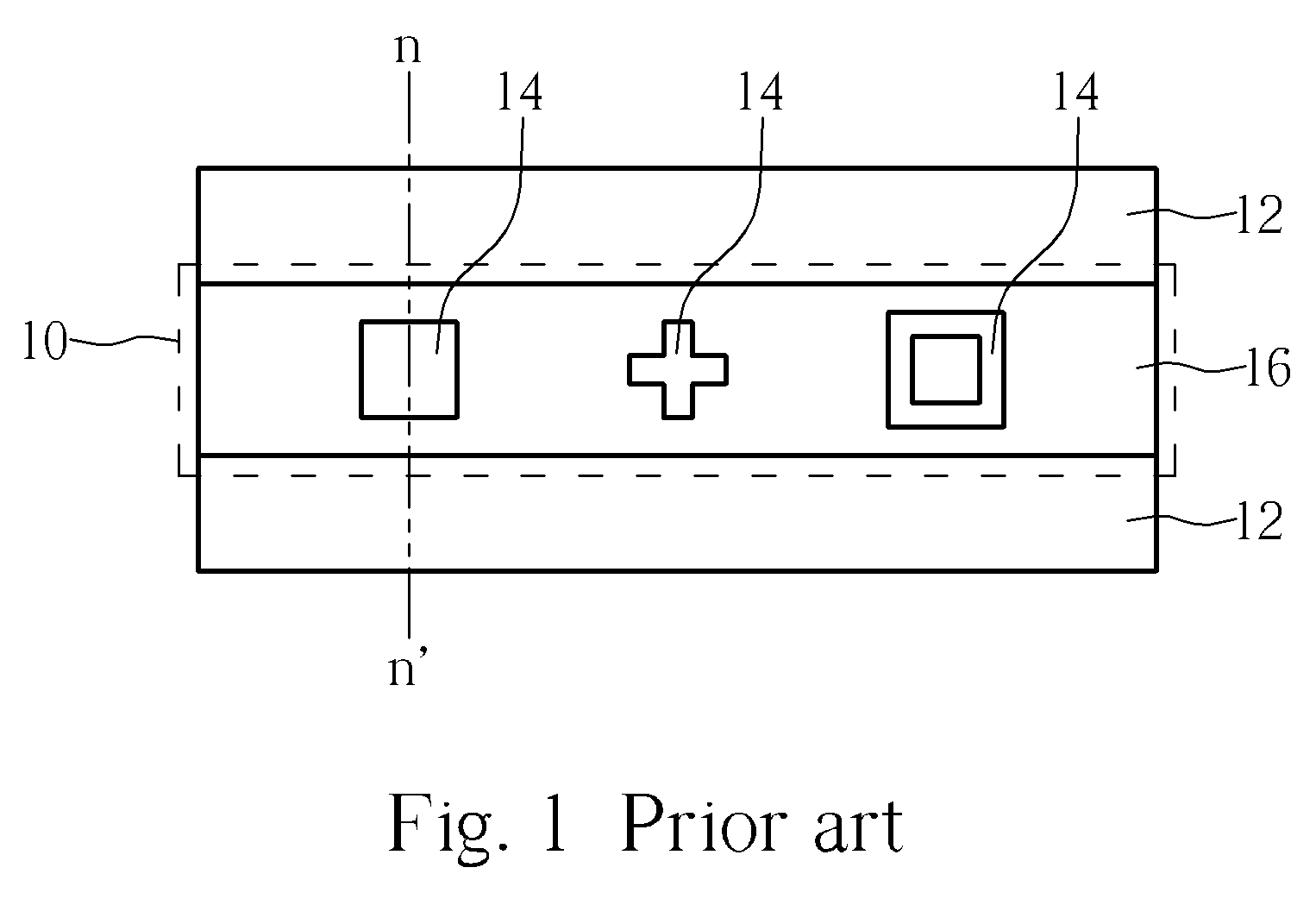

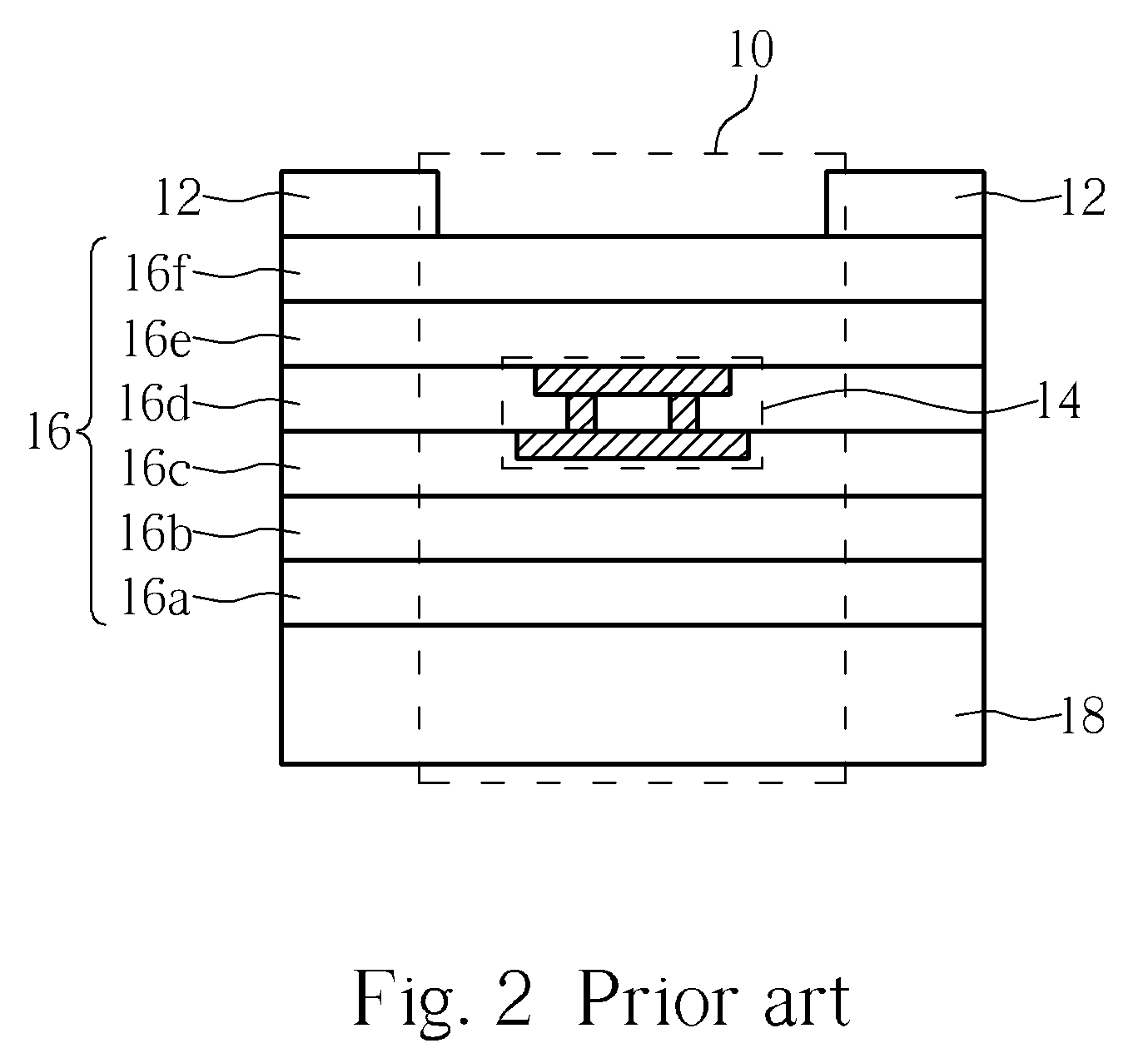

Scribe line structure

InactiveUS20060022195A1Avoid crackingIncrease productionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMetallic materialsDielectric layer

The present invention provides a scribe line structure, which includes a substrate, a plurality of dielectric layers of low dielectric constant materials formed on the substrate, at least a process monitor pattern made of materials of metal formed between the dielectric layers, and a dummy metal structure connected to the process monitor pattern. The dummy metal structure includes a plurality of dummy metal layers and a plurality of dummy vias. The dummy metal structure is formed on the surface of the substrate and is exposed in the region of the scribe line, thus facilitating heat dissipation and energy release from the scribe line structure.

Owner:UNITED MICROELECTRONICS CORP

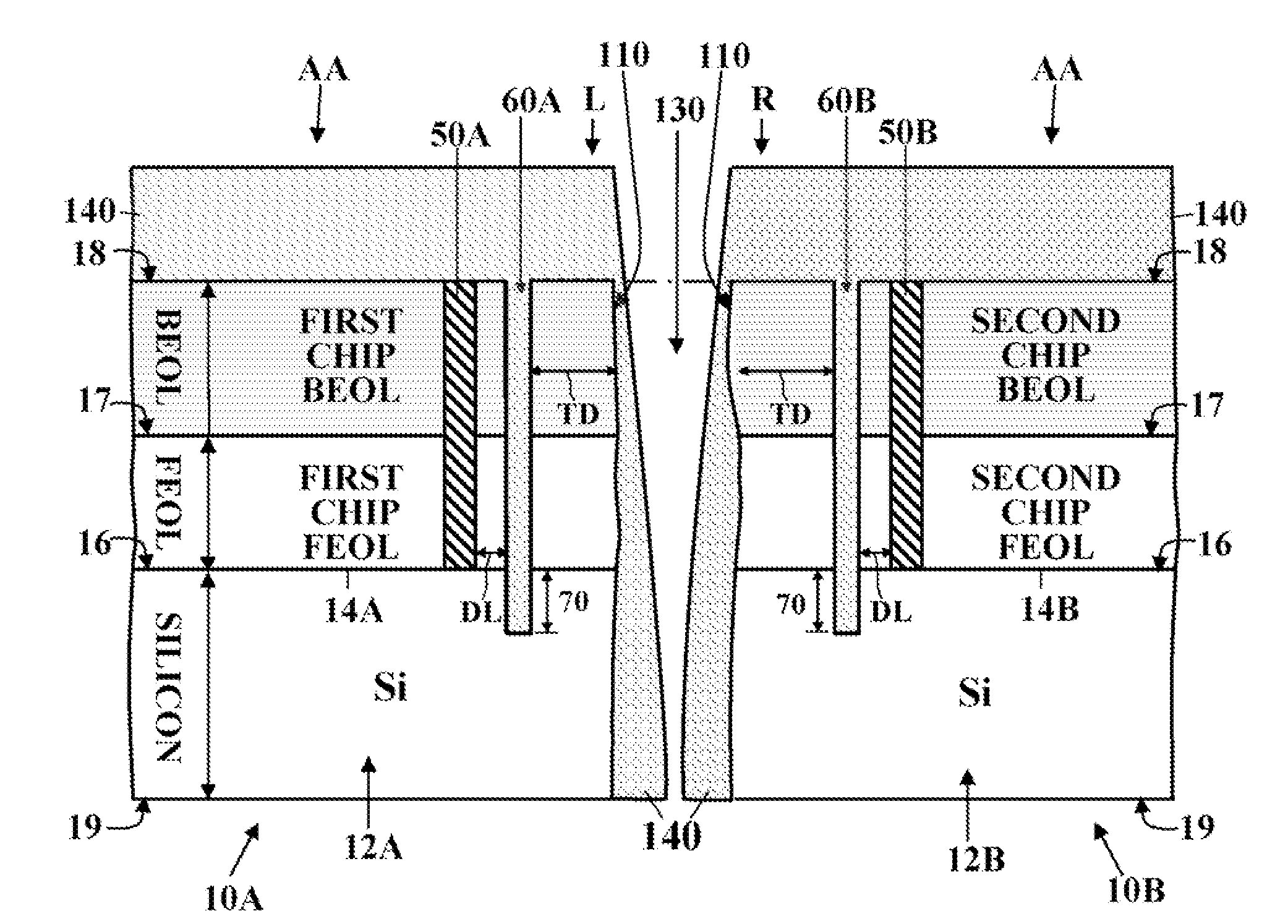

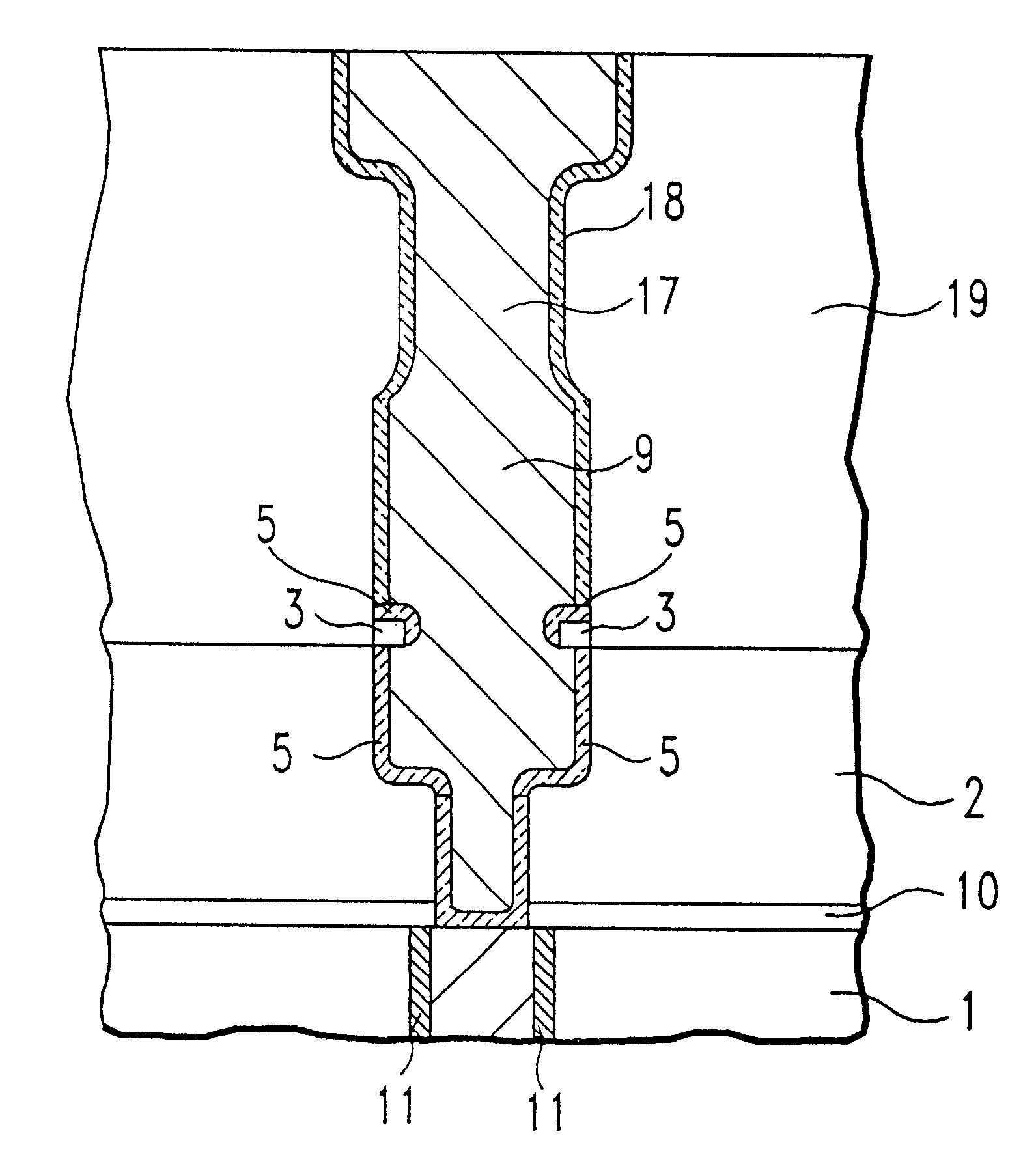

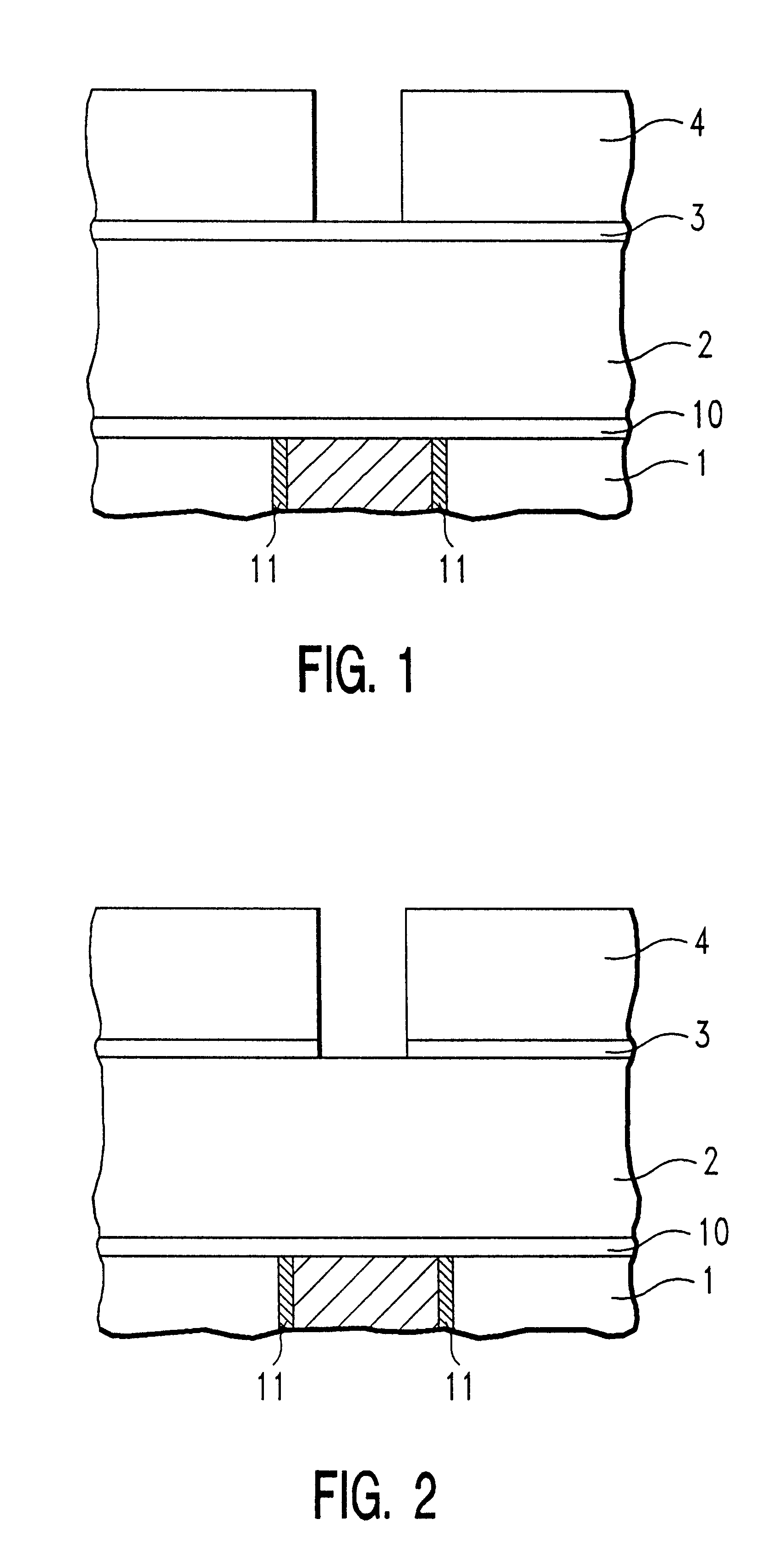

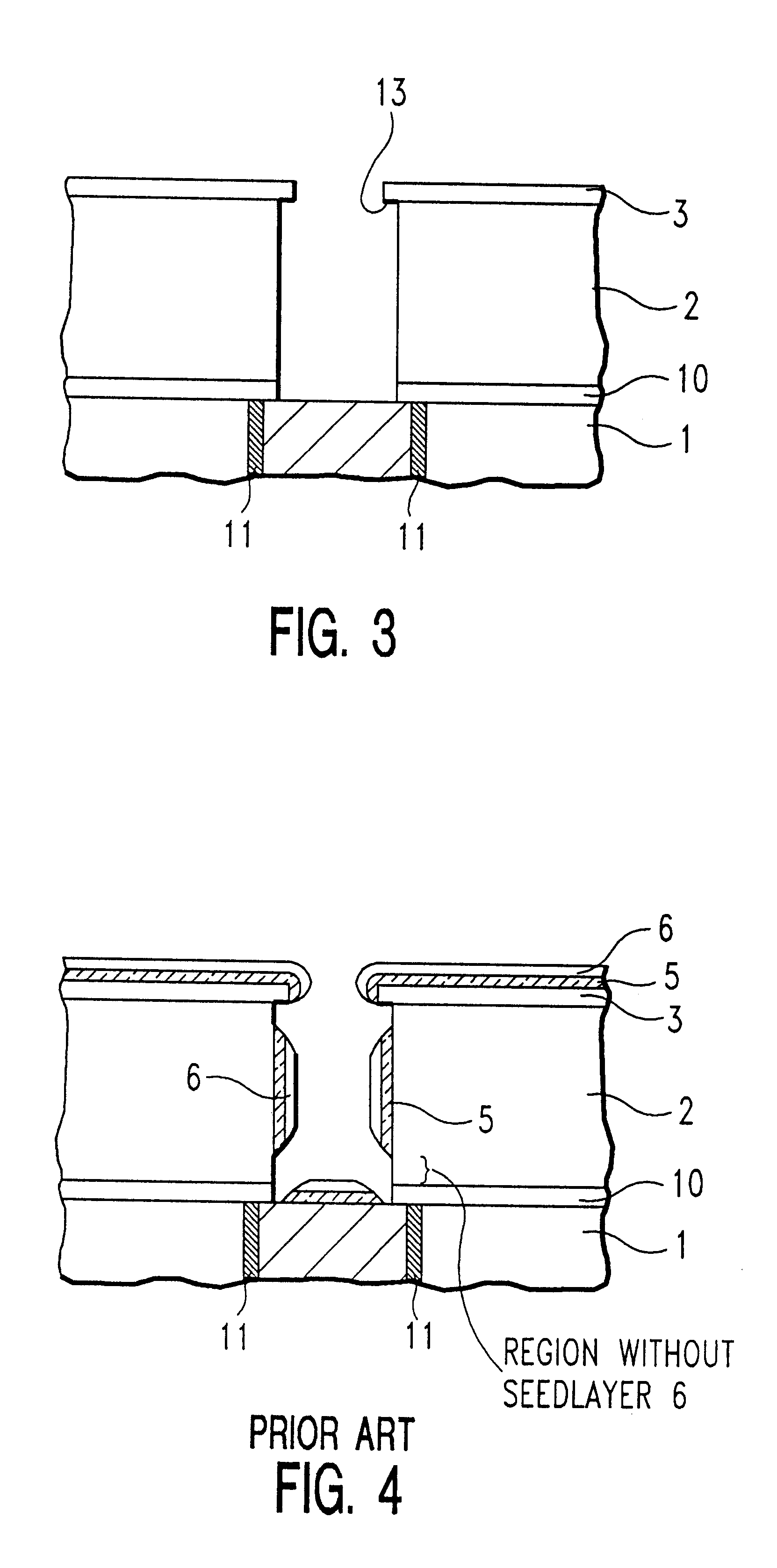

Process and structure for an interlock and high performance multilevel structures for chip interconnects and packaging technologies

InactiveUS6333560B1Semiconductor/solid-state device detailsSolid-state devicesDielectric layerLine structure

Method and structures for making a highly reliable metal interlock structure with continuous via and line structures. The absence of barrier layers between vias and lines or absence of interlevel dielectric layer is used to enhance chip performance.

Owner:IBM CORP

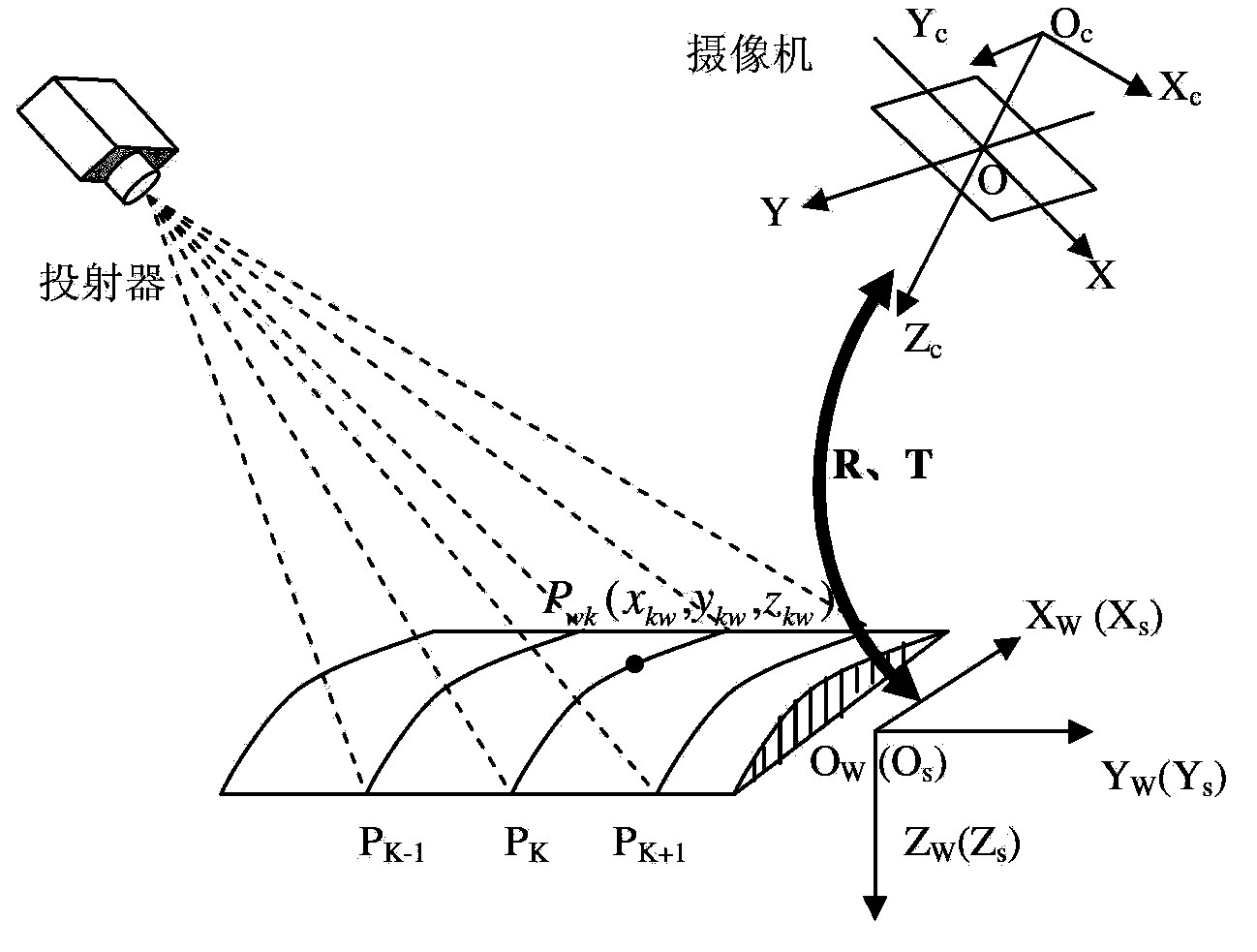

Curve-welding-seam three-dimensional reconstruction method based on line structure light vision detection

The invention provides a curve-welding-seam three-dimensional reconstruction method based on line structure light vision detection. By using the method, various kinds of welding seams can be effectively detected, reliability is high, the method is simple and detection efficiency is high. A mechanical arm and a line structure light vision system are included. A controller controls and is connected to the mechanical arm. The line structure light vision system comprises a camera and a line structure light projector. The camera is fixed to a tail end of the mechanical arm. The line structure light projector is fixed to one side of the camera and is projected to a surface of a workpiece to be welded. The curve-welding-seam three-dimensional reconstruction method comprises the steps of system calibration, welding seam detection and welding seam reconstruction so that a complete three-dimensional curve welding seam is reconstructed.

Owner:WUXI PROFESSIONAL COLLEGE OF SCI & TECH

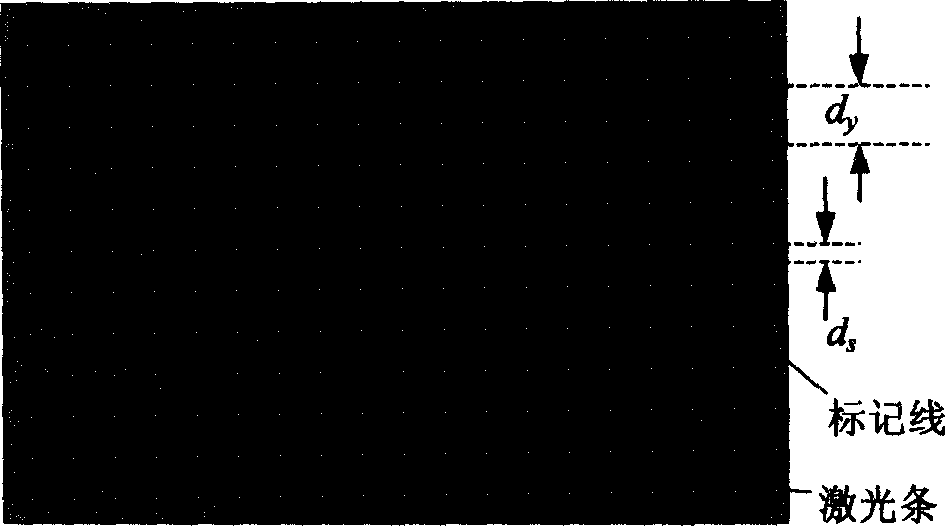

Compatible and accurate calibration method for double eye line structure photo-sensor and implementing apparatus

InactiveCN1595054AAccurate Light Plane ParametersUsing optical meansMathematical modelIntersection of a polyhedron with a line

This invention relates to laser high-accuracy three-dimensional coordinate measurement, which in detail relates to a binocular structure photo-sensor compatibility calibration and its operation apparatus. In order to calibrate the photo plane parameters of the binocular structure photo-sensor, it unites the space coordinates measured of the left and right cameras. The technique project adopted in this invention is the following: the operation apparatus comprises left and right cameras, laser machine, and target and also movable guide rail with the target fixed on; the target plane is vertical to the moving direction of the guide rail which ensures the plane is vertical to the project laser plane. Besides, it is to identify the axis coordinates in the space coordinate system of the cross points of the each lines and photo bars in the target and brings the coordinates to the photo-sensor mathematical model for computation and get sensor parameters.

Owner:TIANJIN UNIV

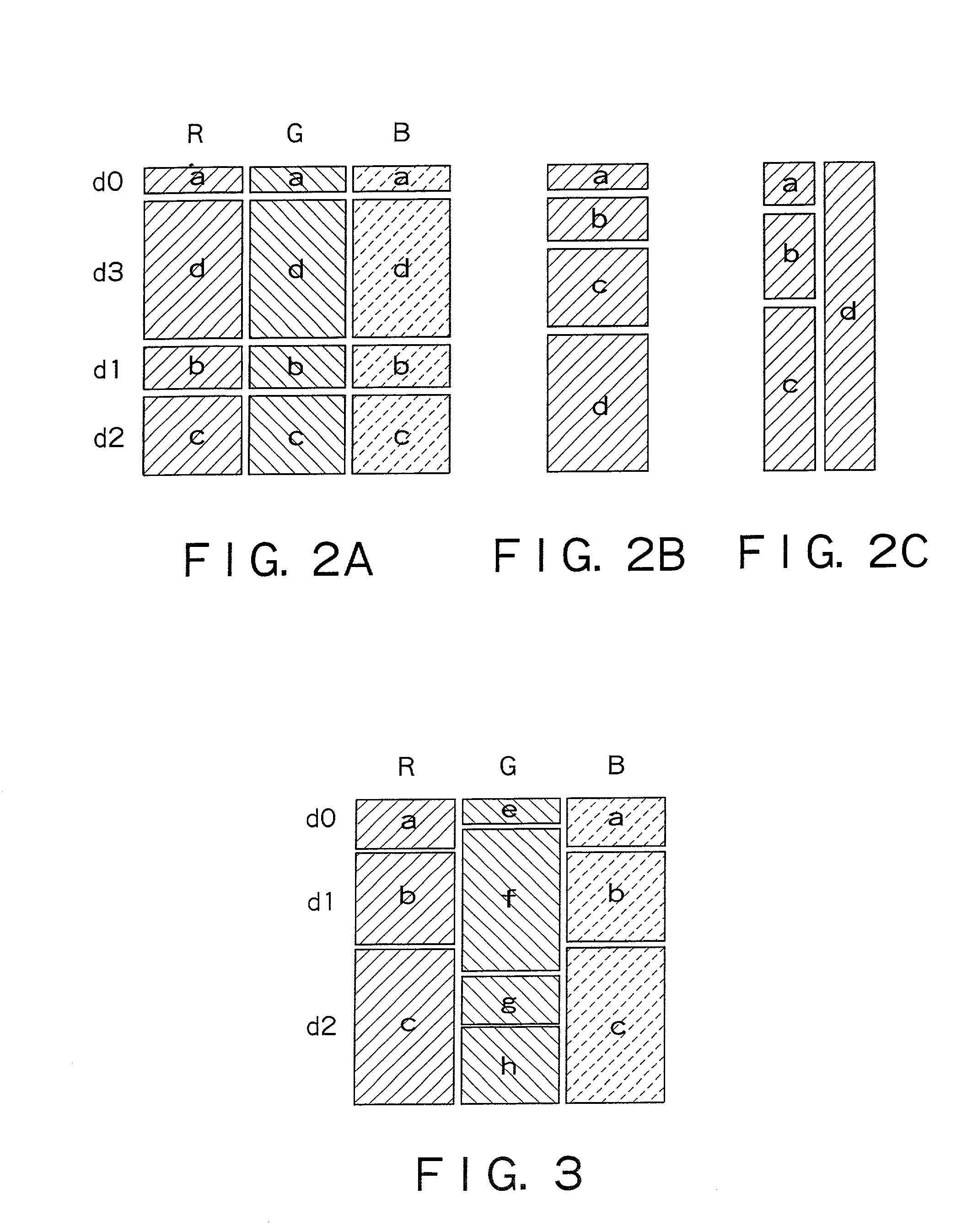

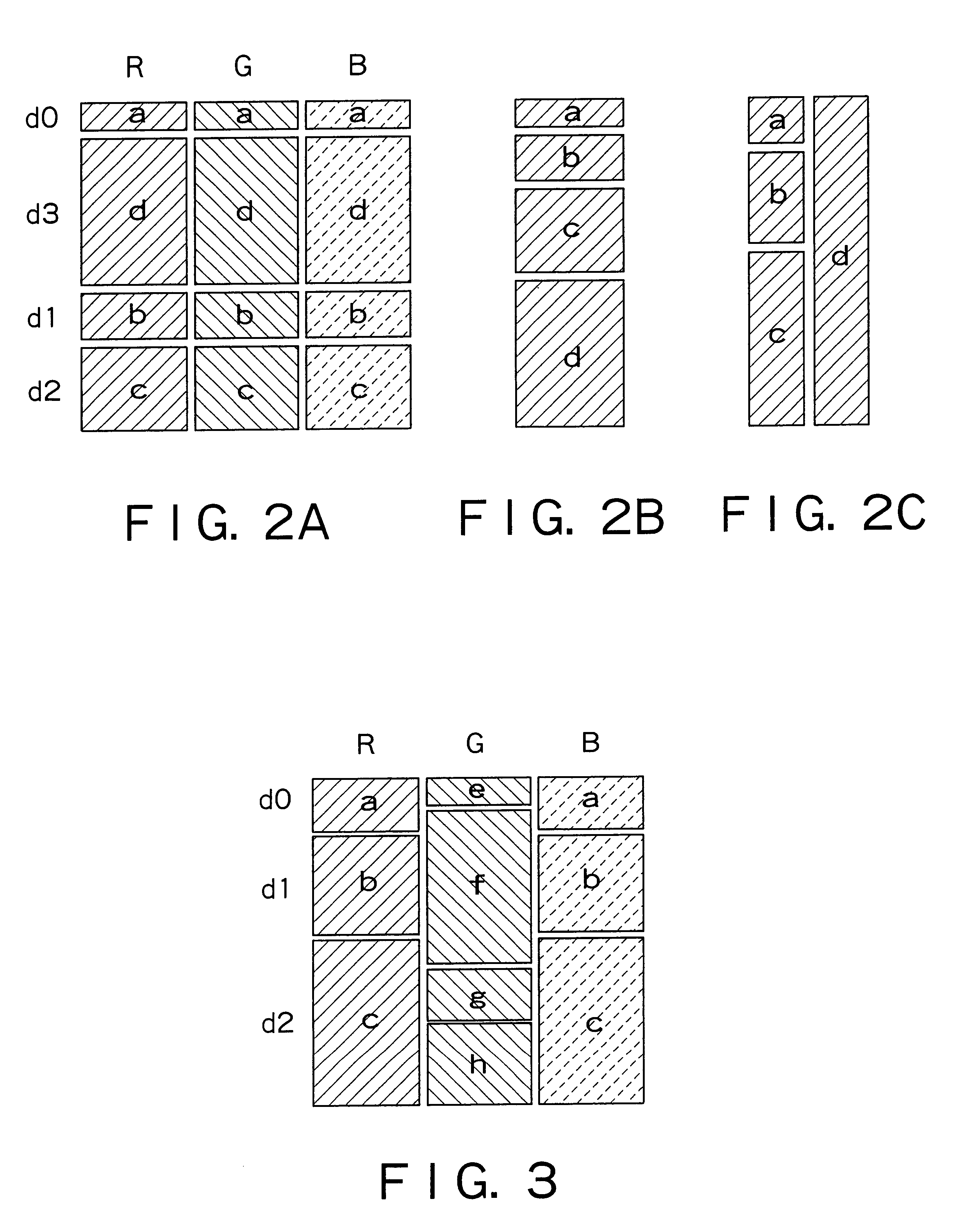

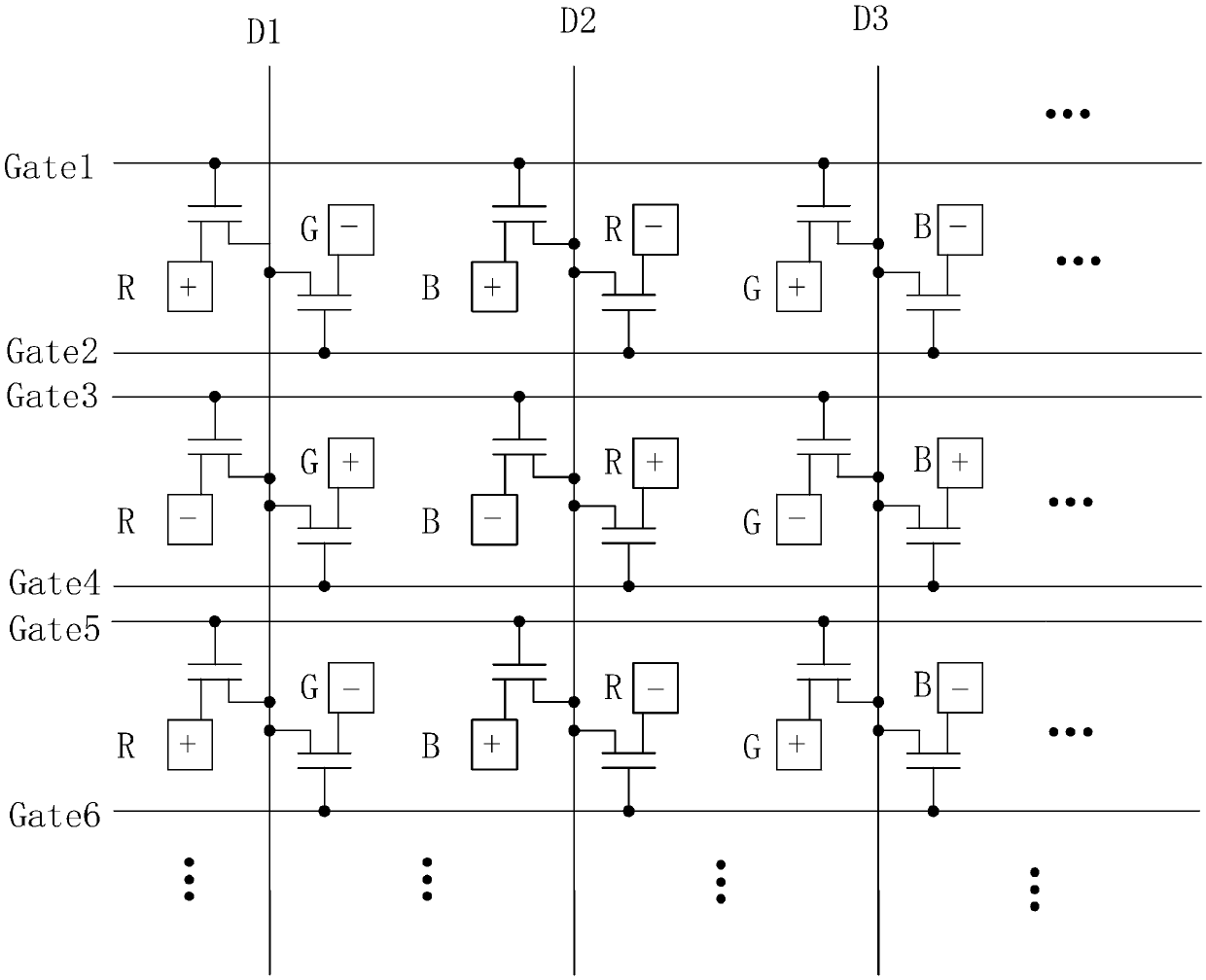

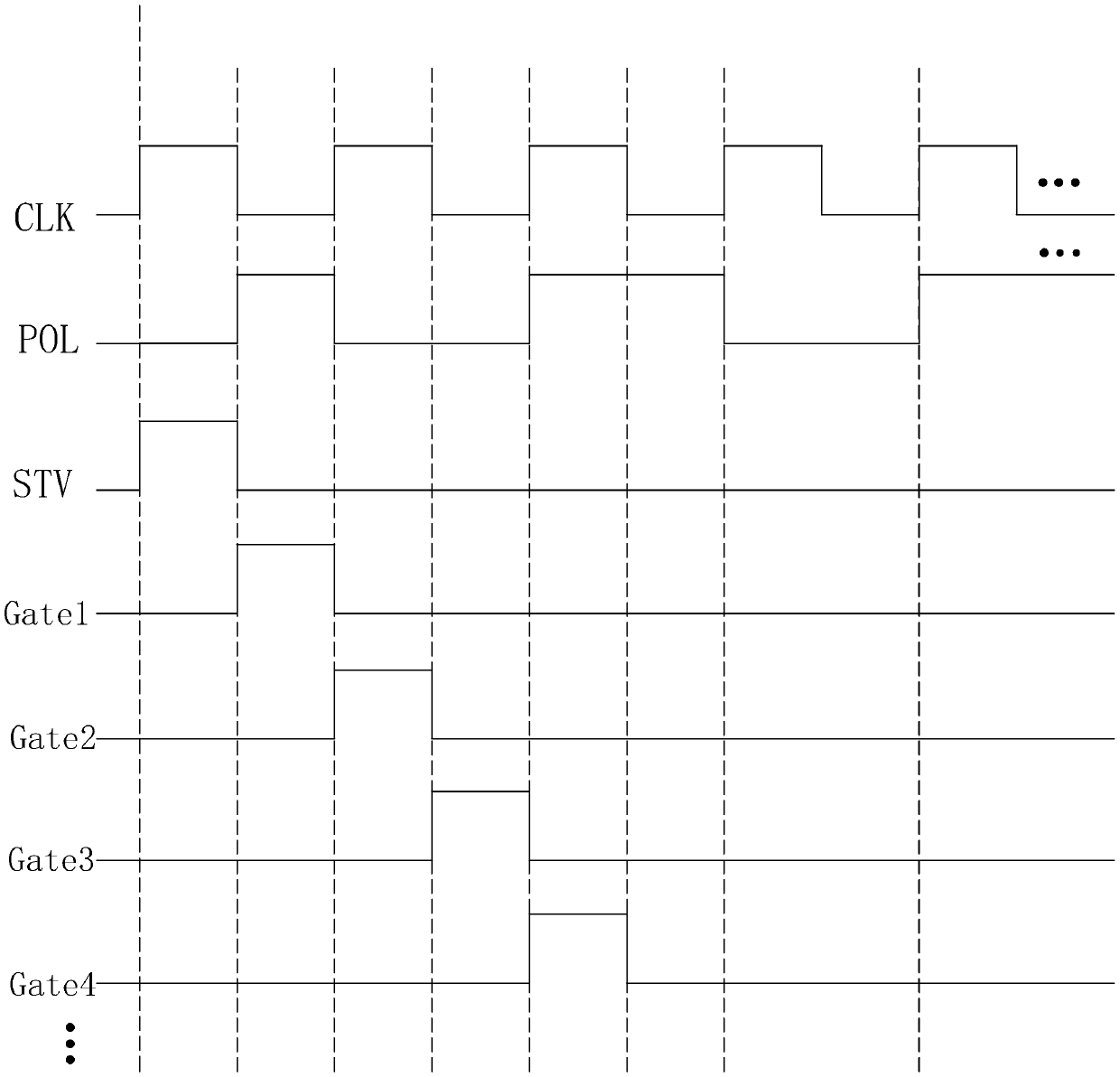

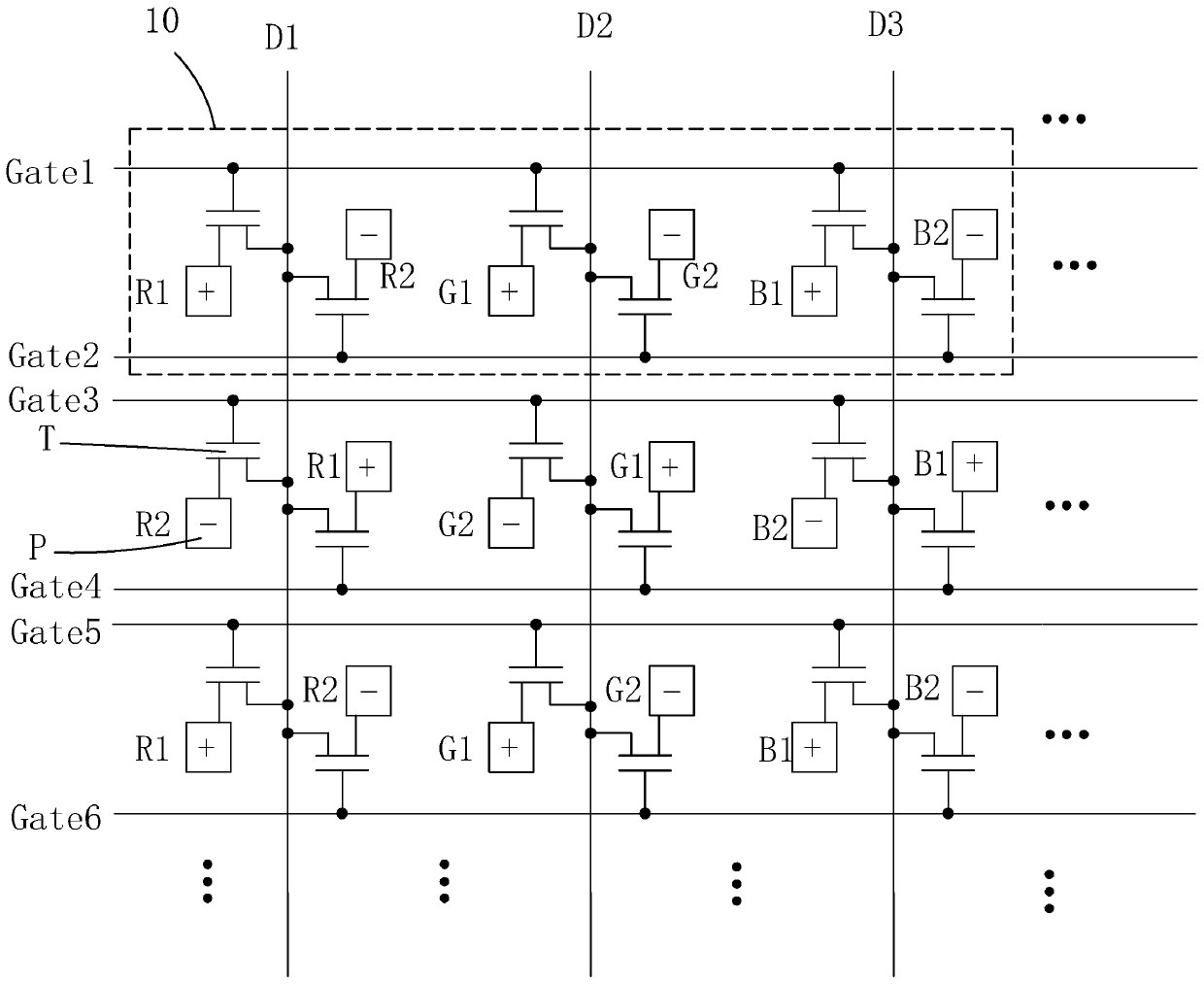

Liquid crystal display panel and driving method thereof

ActiveCN105511184AGuaranteed charging effectThe frequency of the inverted signal is reducedStatic indicating devicesNon-linear opticsLiquid-crystal displayData signal

The invention provides a liquid crystal display panel and a driving method thereof. The 4j grid scanning line and the (4j-3) grid scanning line are set to be odd-number frame grid scanning lines, the (4j-1) grid scanning line and the (4j-2) grid scanning line are set to be even-number frame grid scanning lines, first red subpixels (R1), first green subpixels (G1) and first blue subpixels (B1) are electrically connected to the odd-number frame grid scanning lines, second red subpixels (R2), second green subpixels (G2) and second blue subpixels (B2) are electrically connected to the even-number frame grid scanning lines, odd-number frame scanning and even-number frame scanning are conducted by the odd-number frame grid scanning lines and the even-number frame grid scanning lines respectively, data signal delay can be effectively weakened, the charging effect of all the subpixels is ensured, light fringes of the liquid crystal display panel of the double grid line structure in the display process are eliminated, signal inversion frequency and the driving power consumption of the liquid crystal display panel are reduced.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD